Patents

Literature

41 results about "General-purpose programming language" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer software, a general-purpose programming language is a programming language designed to be used for writing software in the widest variety of application domains (a general-purpose language). A general-purpose programming language has this status because it does not include language constructs designed to be used within a specific application domain.

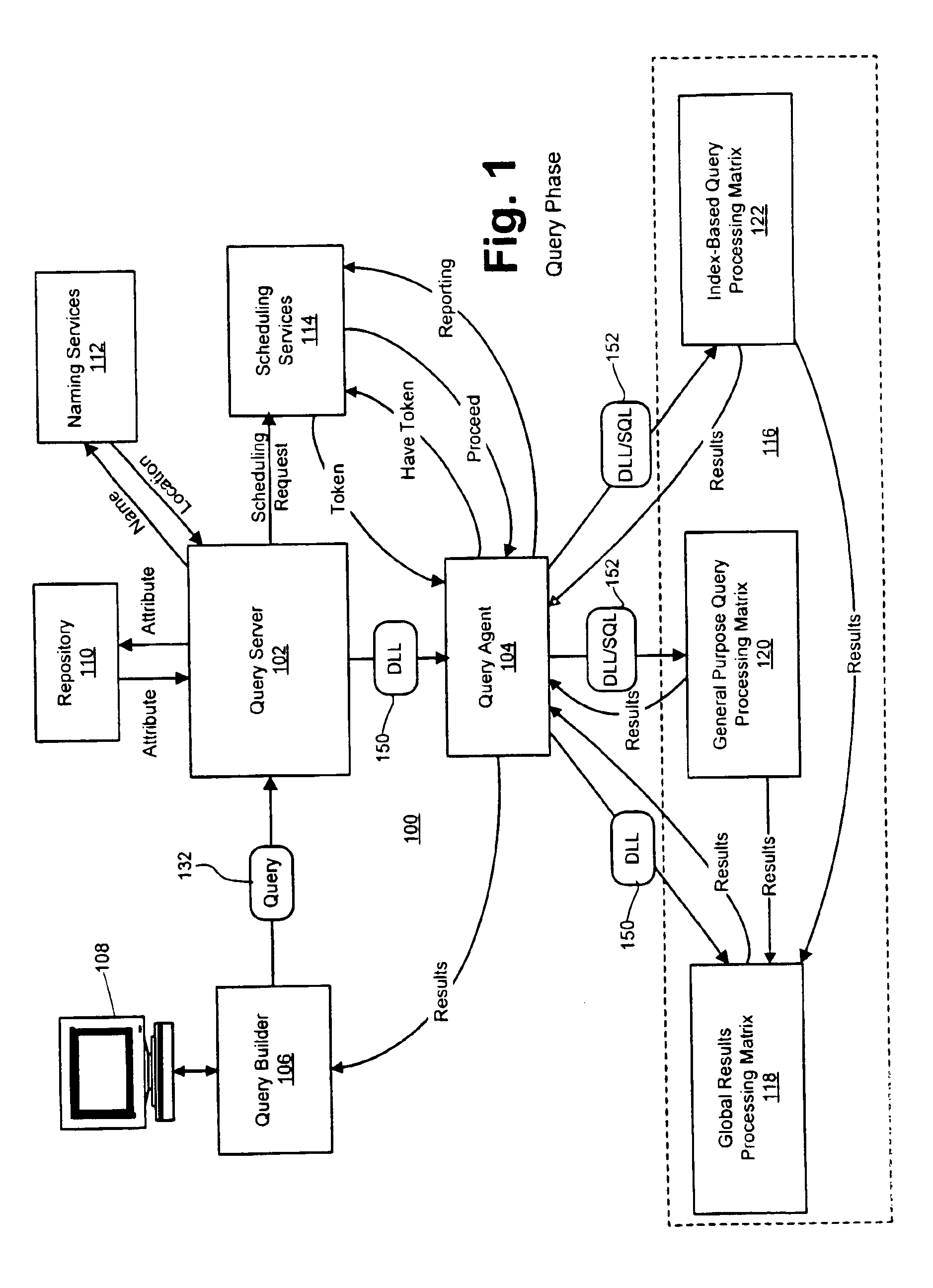

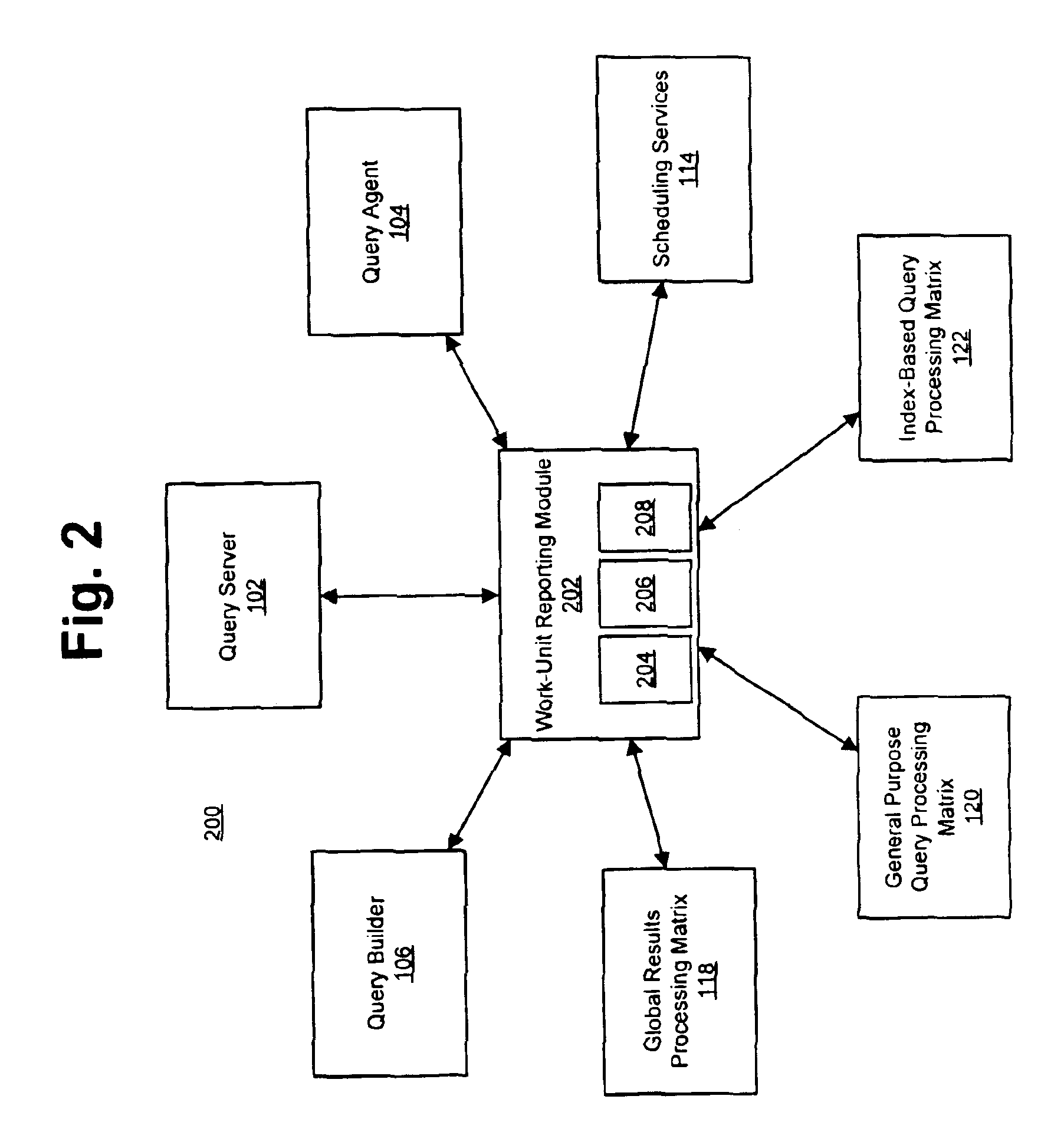

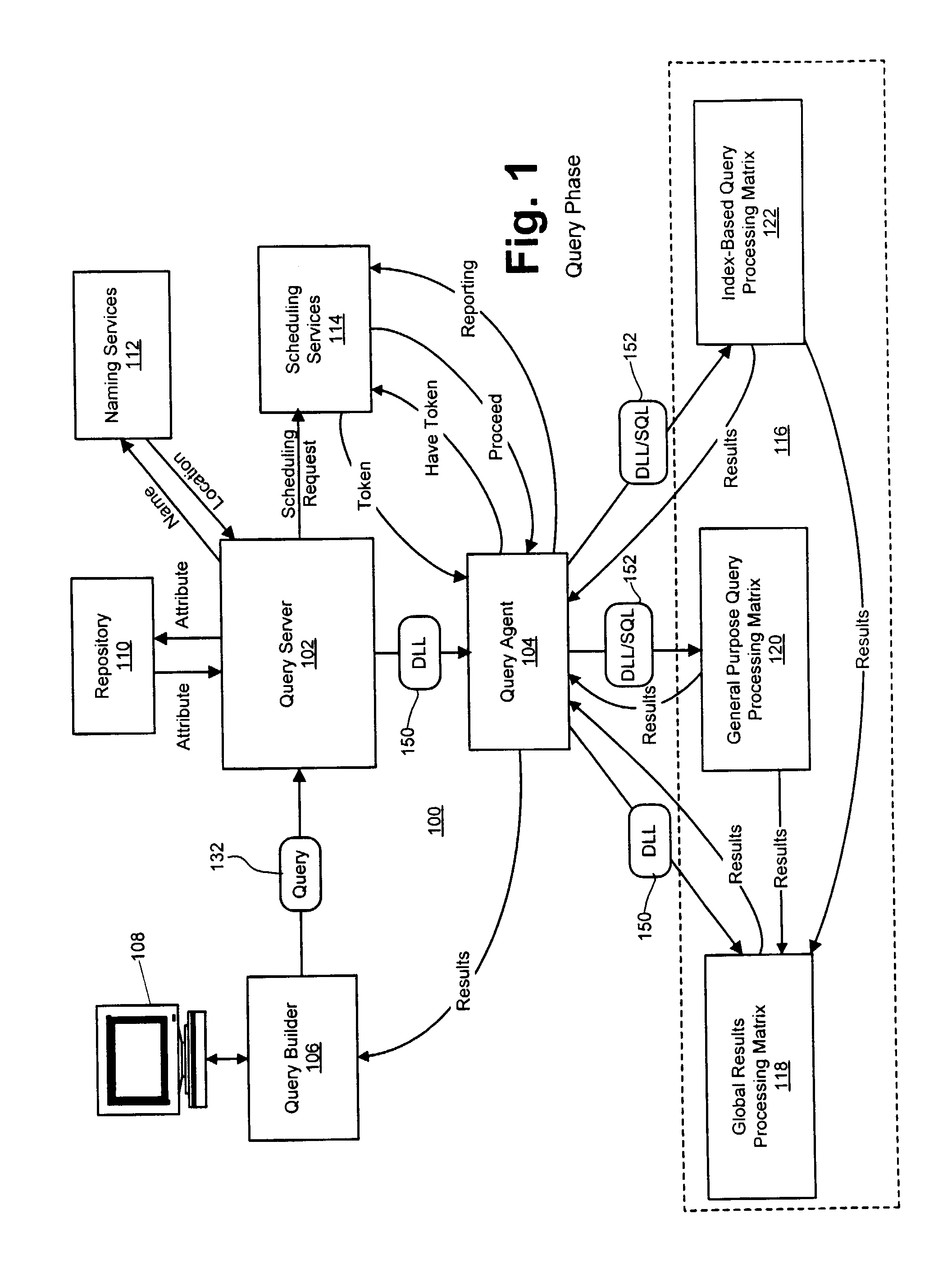

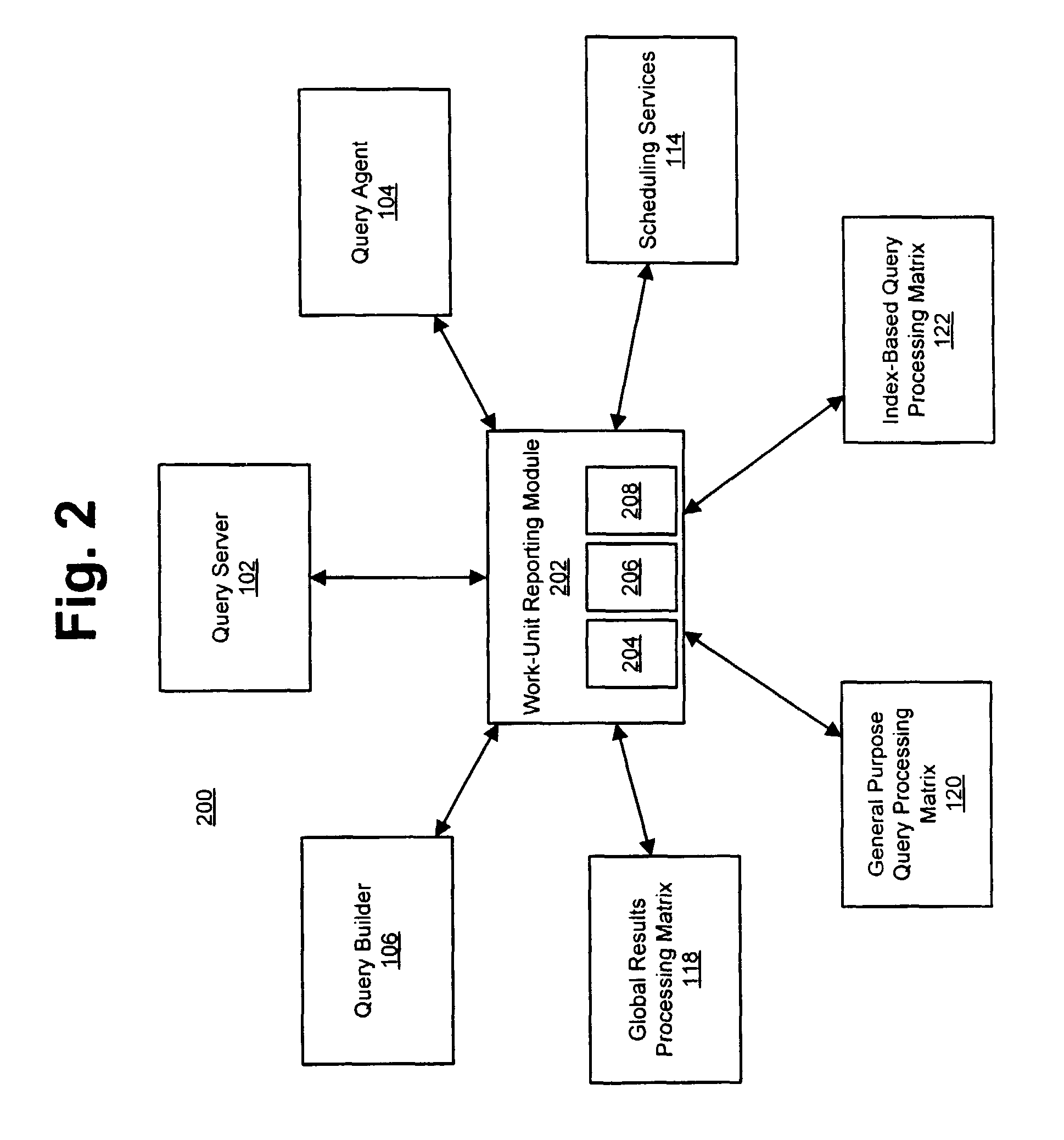

Method and system for parallel processing of database queries

ActiveUS6968335B2Transparent operationLow costData processing applicationsDigital data information retrievalTheoretical computer scienceHigh-level programming language

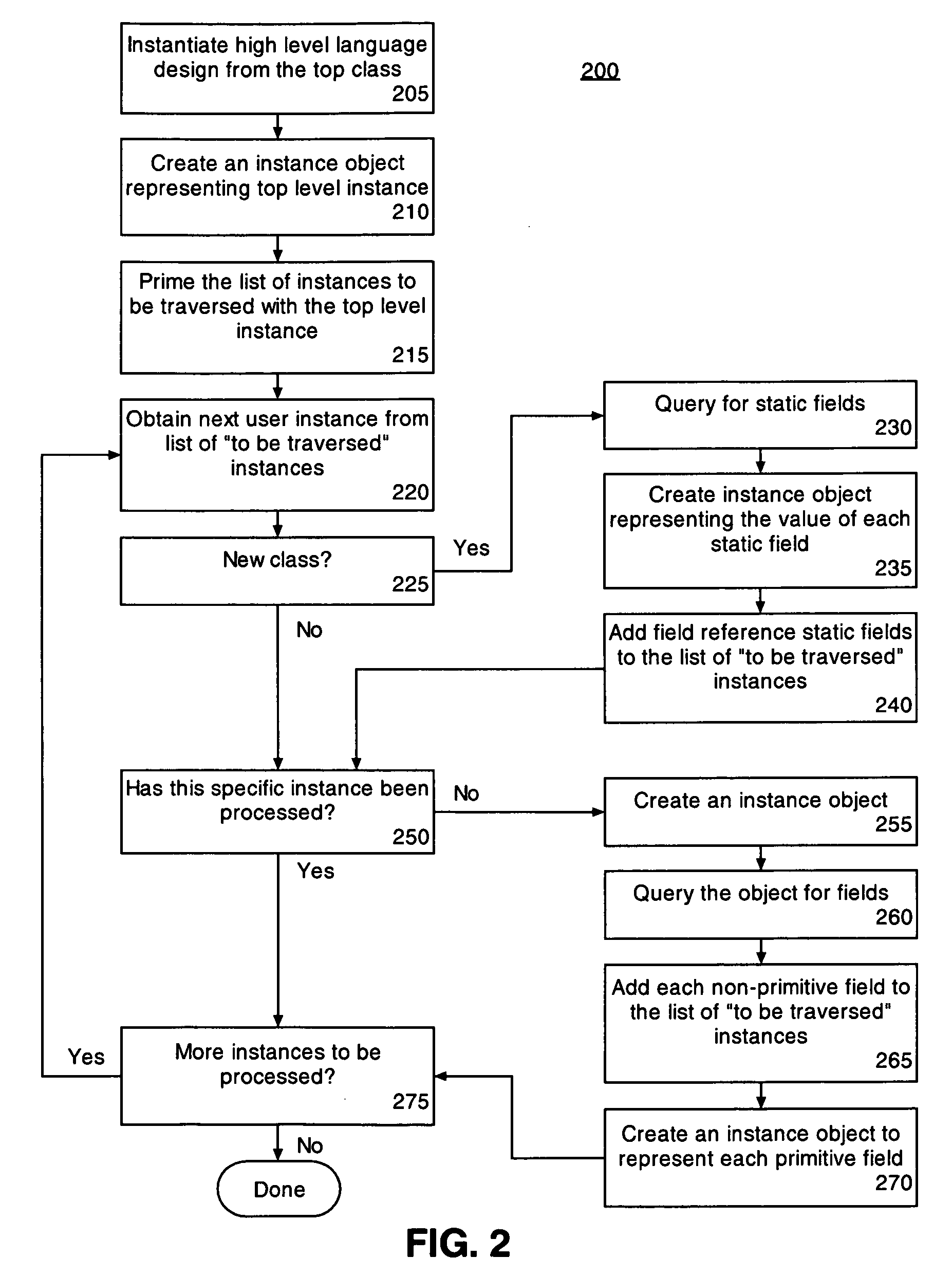

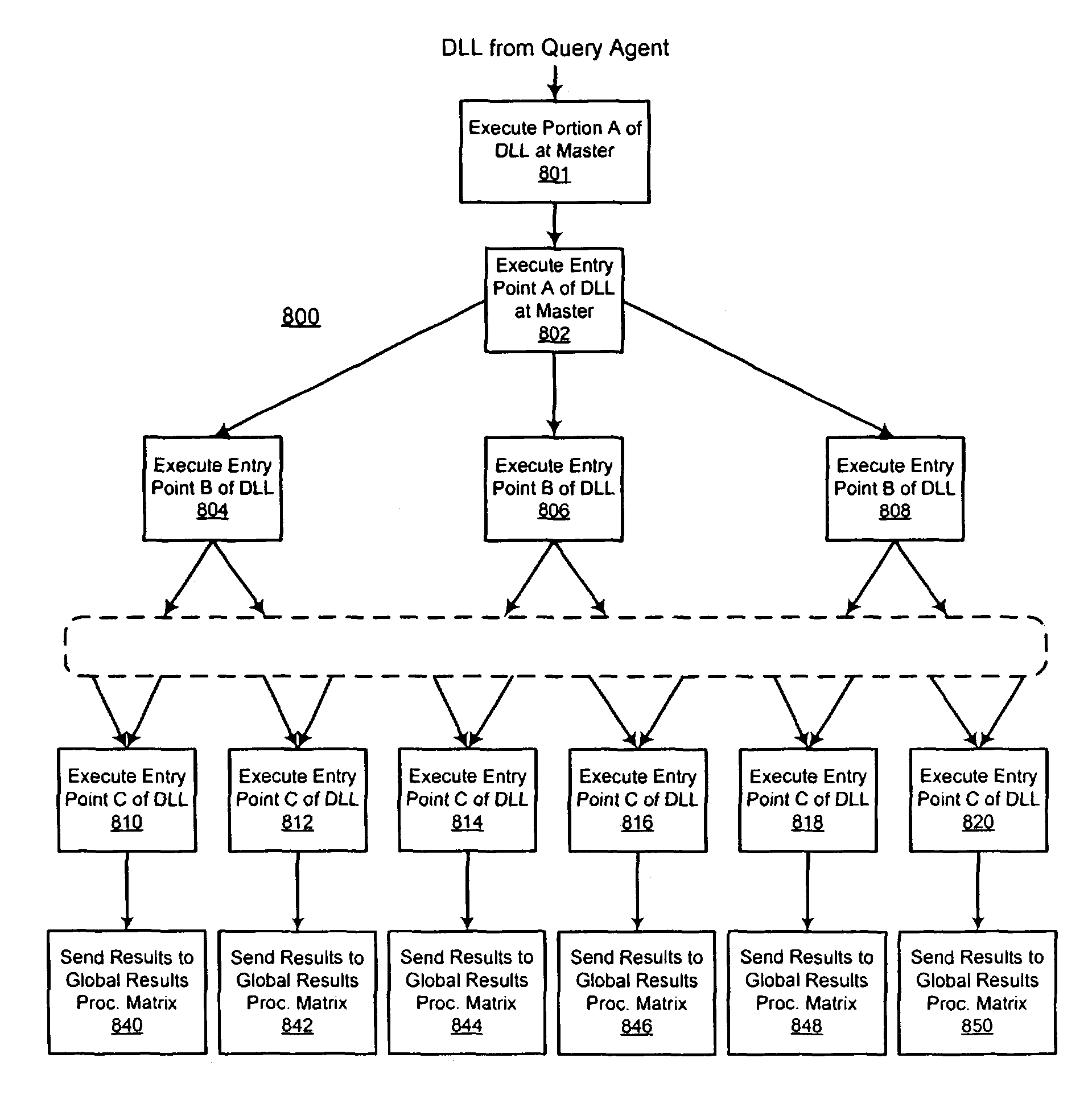

A system and methods for parallel processing of queries to one or more databases are described herein. One or more databases may be distributed among a subset of slave nodes of a global-results processing matrix. A query to the database may be generated using a query-based high-level programming language. The query-based source code then may be converted to intermediary source code in a common programming language and then compiled into a dynamic link library (DLL) or other type of executable. The DLL is then distributed among the slave nodes of the processing matrix, whereupon the slave nodes execute related portions of the DLL substantially in parallel to generate initial query results. The initial query results may then be provided to master node of the global-results processing matrix for additional processing, whereby the master node is adapted to execute one or more associated portions of the DLL on the initial query results.

Owner:LEXISNEXIS RISK DATA MANAGEMENT

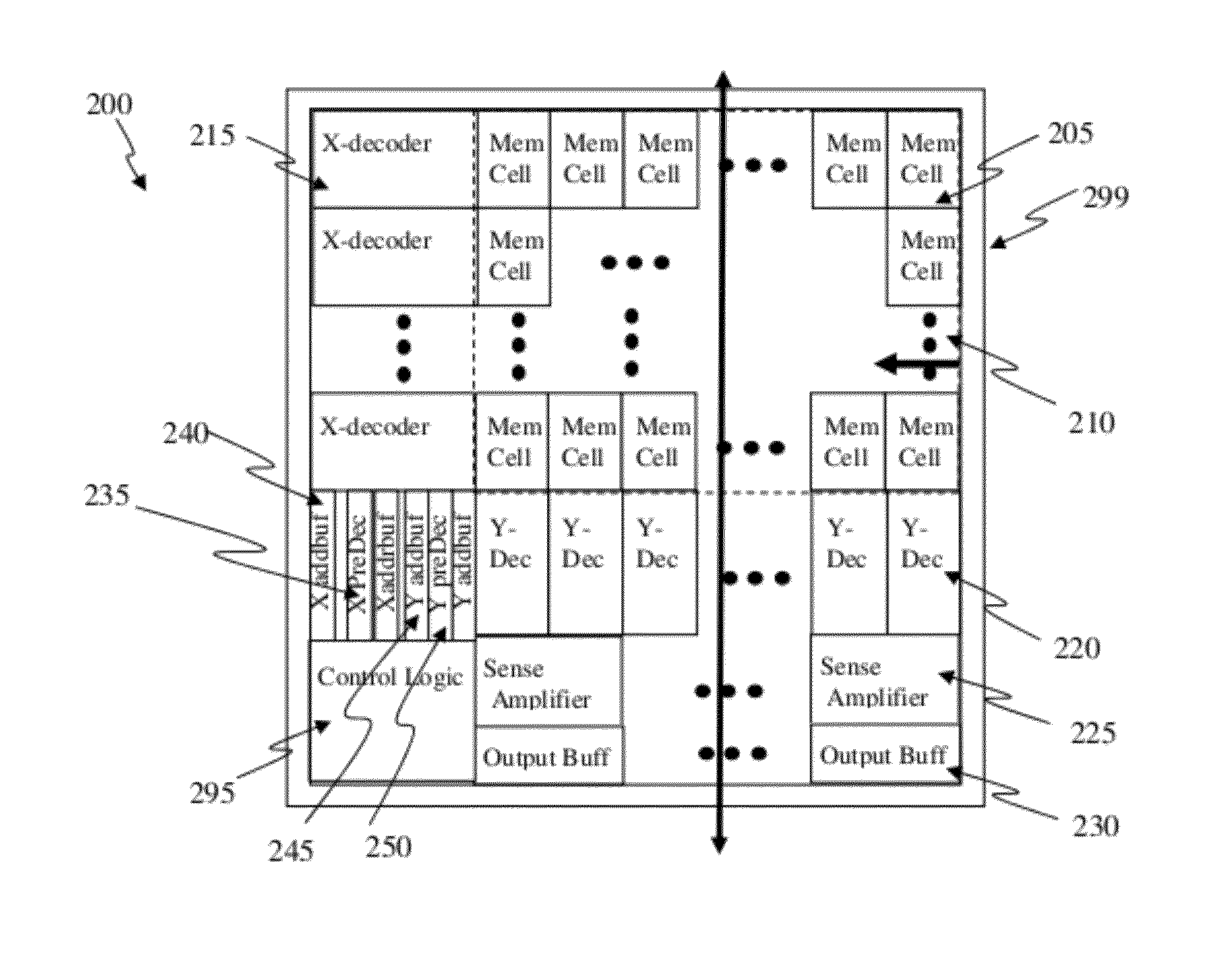

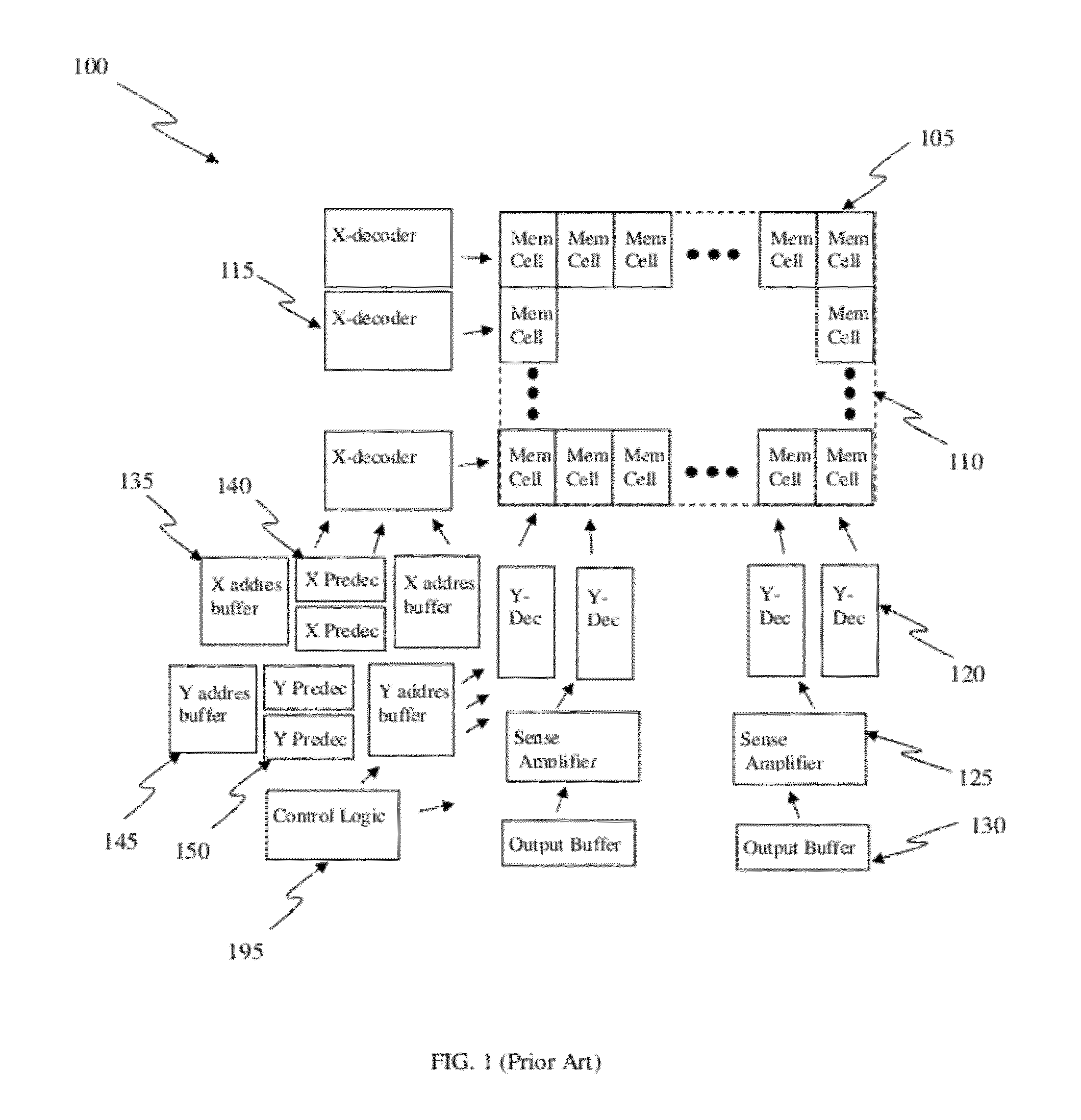

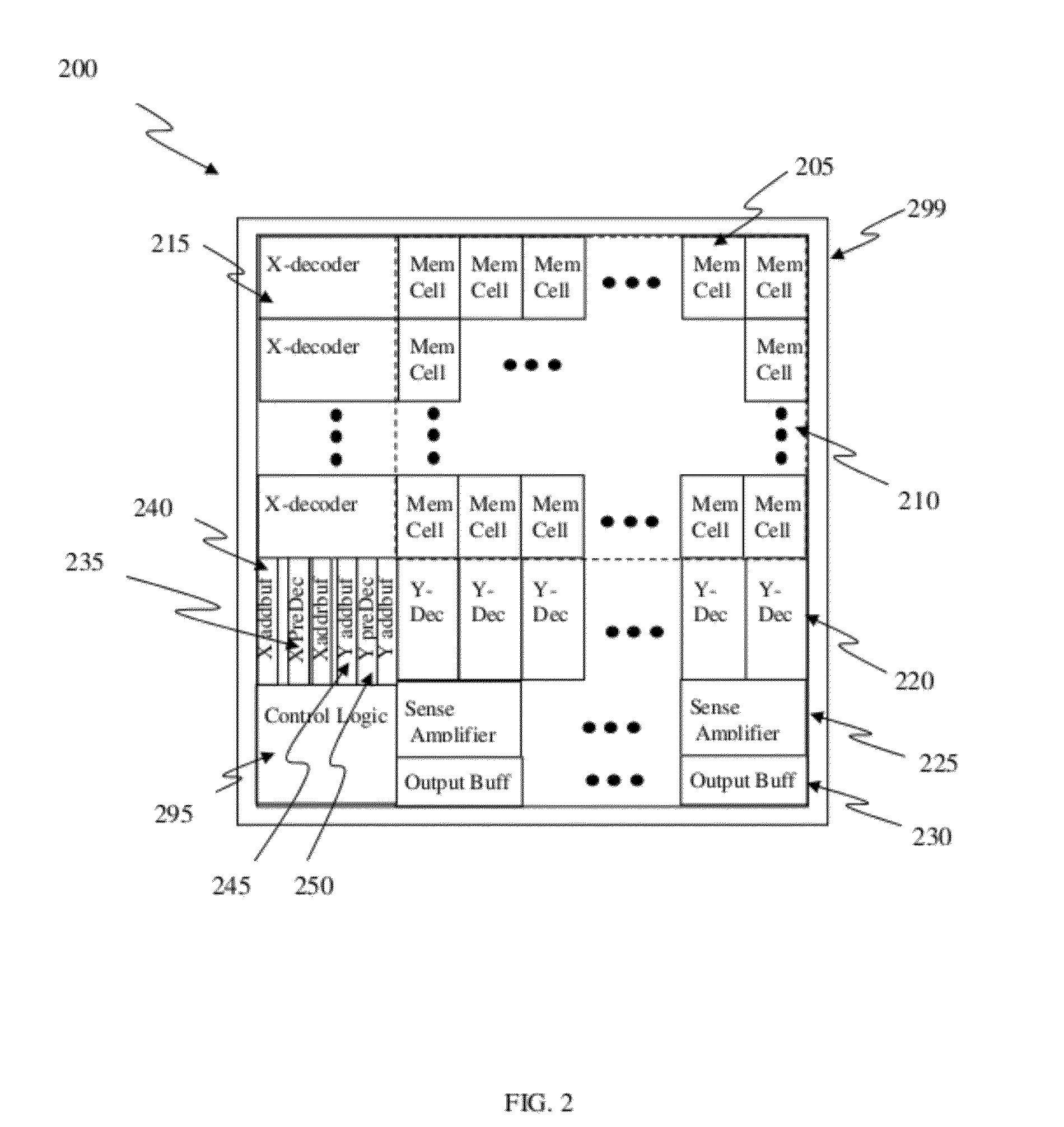

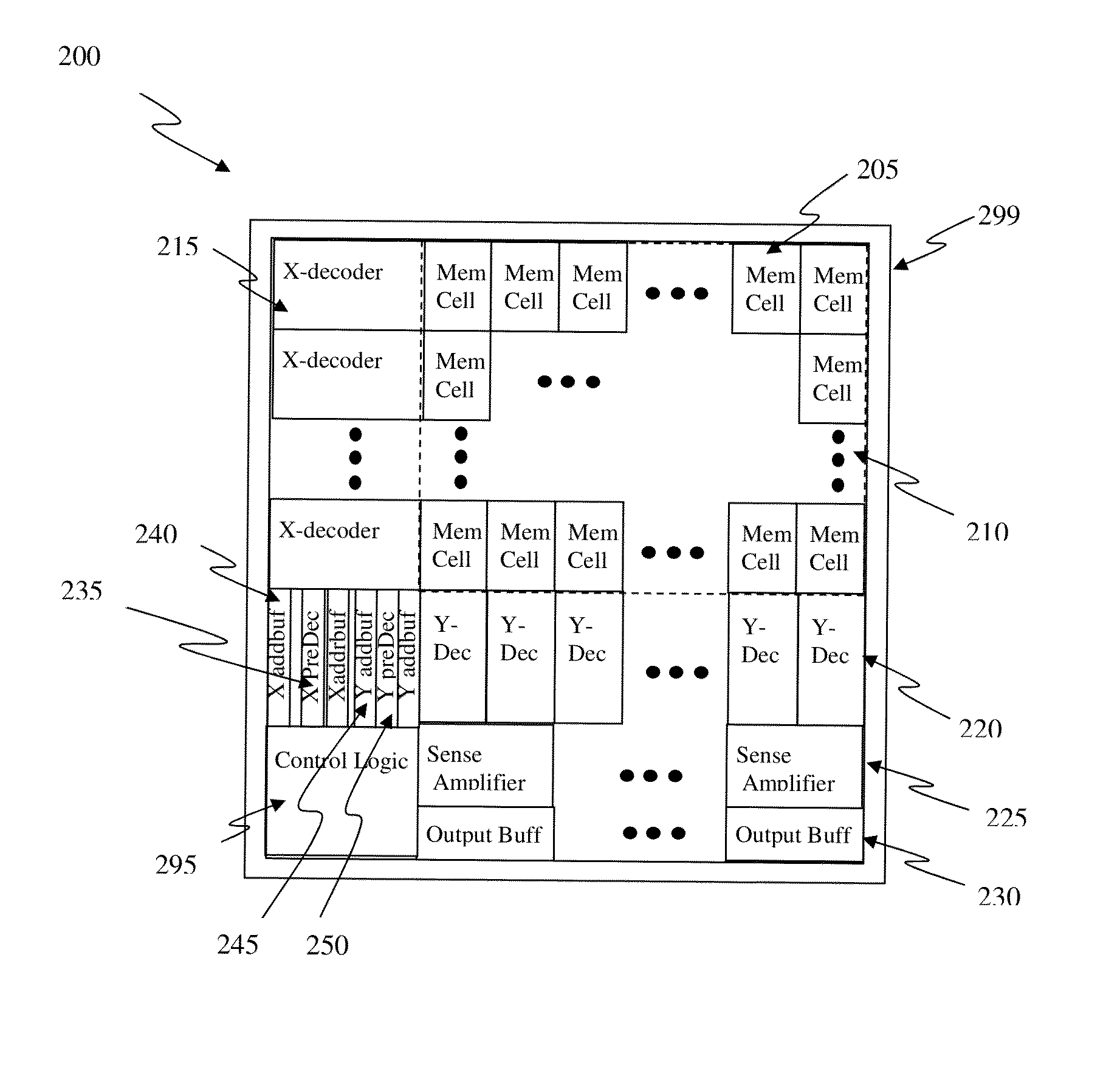

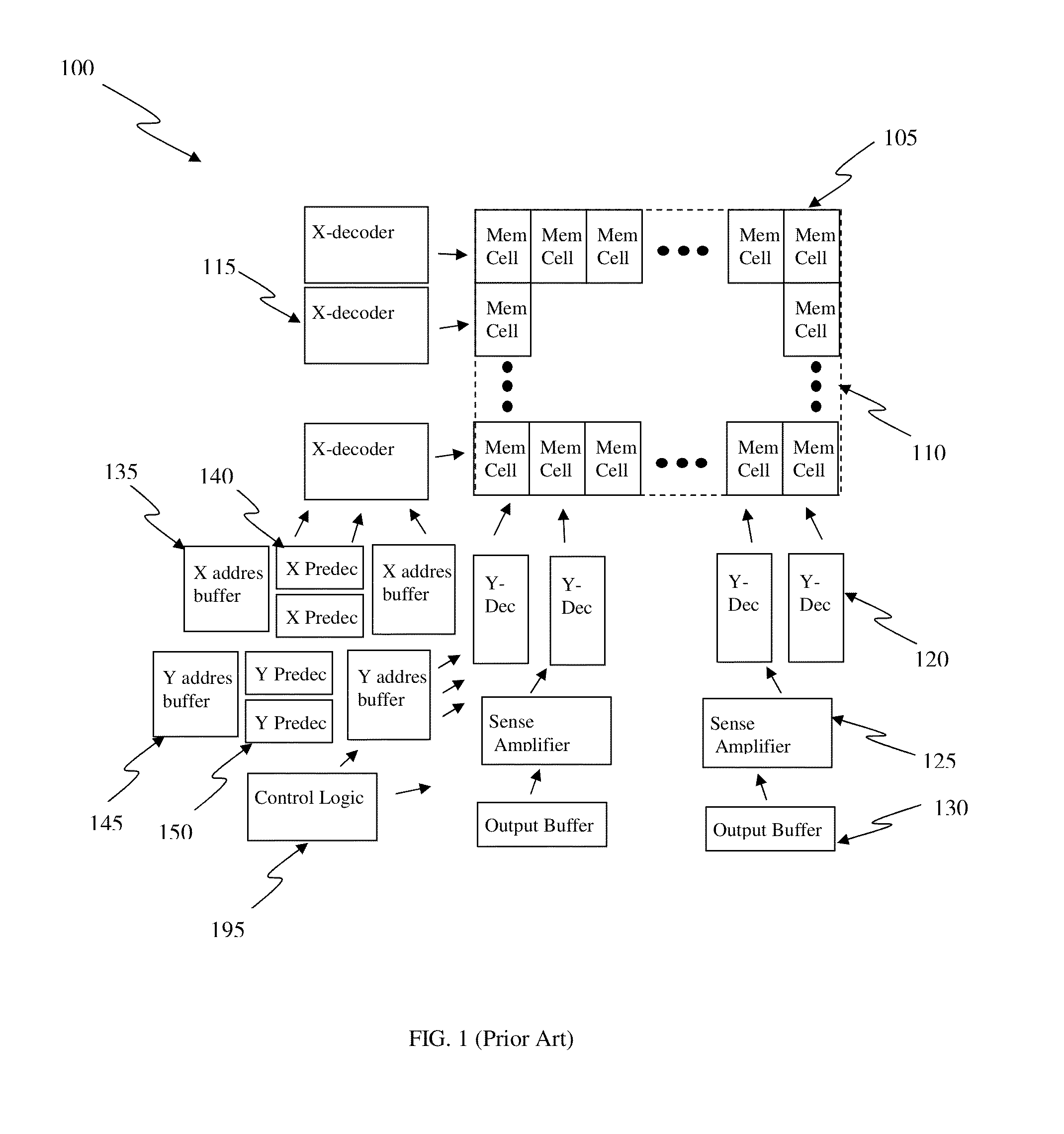

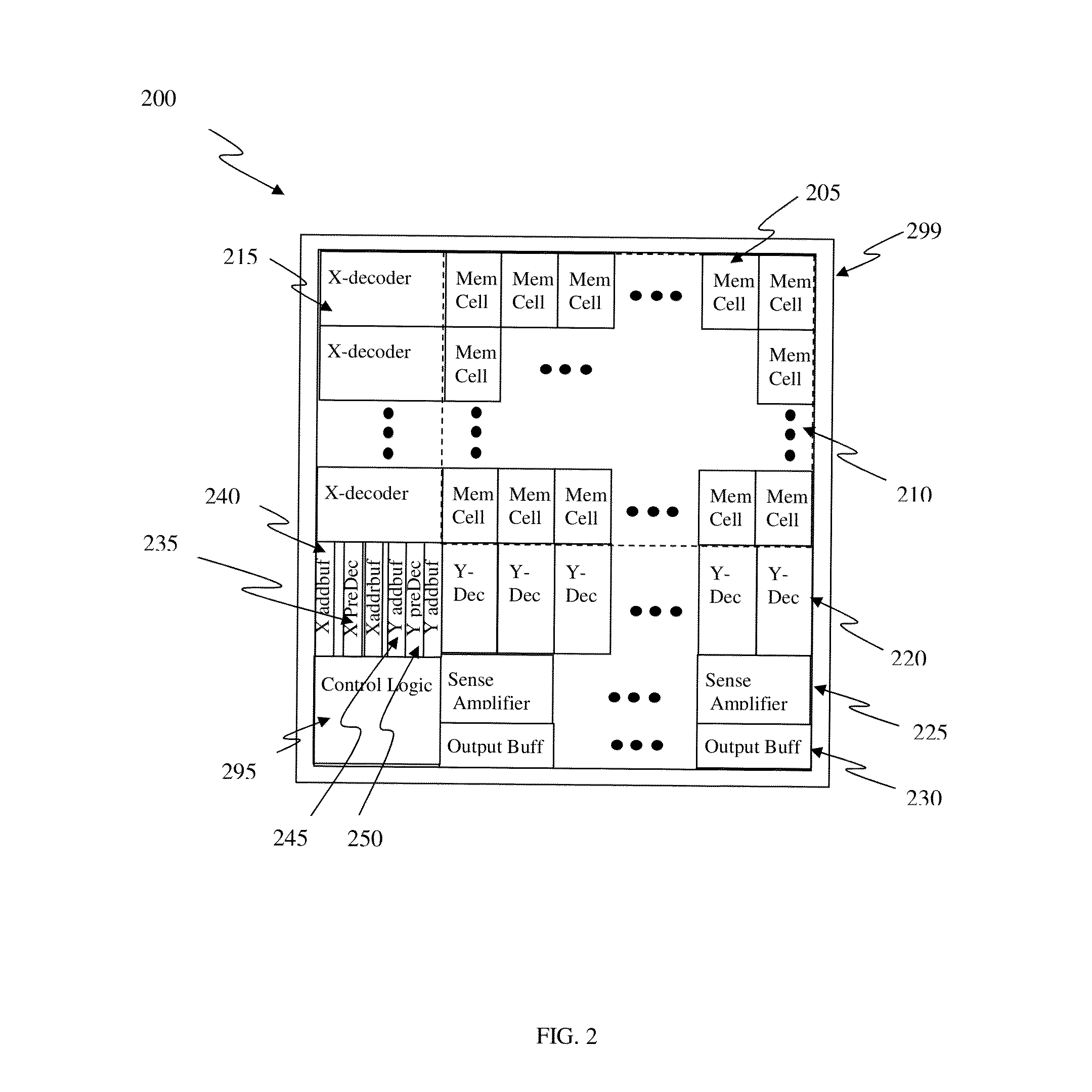

Circuit and Method of a Memory Compiler Based on Subtraction Approach

ActiveUS20120209888A1Digital data processing detailsMemory adressing/allocation/relocationDatasheetParallel computing

A memory compiler to generate a set of memories is based on a subtraction approach from a set of templates (memory templates), including at least one layout database and auxiliary design databases, by software. The software can be based on general-purpose programming language or a layout-specific language. The compiled memories can be generated by reducing the memory array sizes in row and / or column directions by moving, deleting, adding, sizing, or stretching the layout objects, and disabling the high order addresses, etc. from the memory template by software. The new auxiliary design databases, such as layout phantom, behavior model, synthesis view, placement-and-routing view or datasheet, can also be generated by modifying some parameters from the memory template by software. One-time programmable memory using junction diode, polysilicon diode, or isolated active-region diode as program selector in a cell can be generated accordingly.

Owner:ATTOPSEMI TECH CO LTD

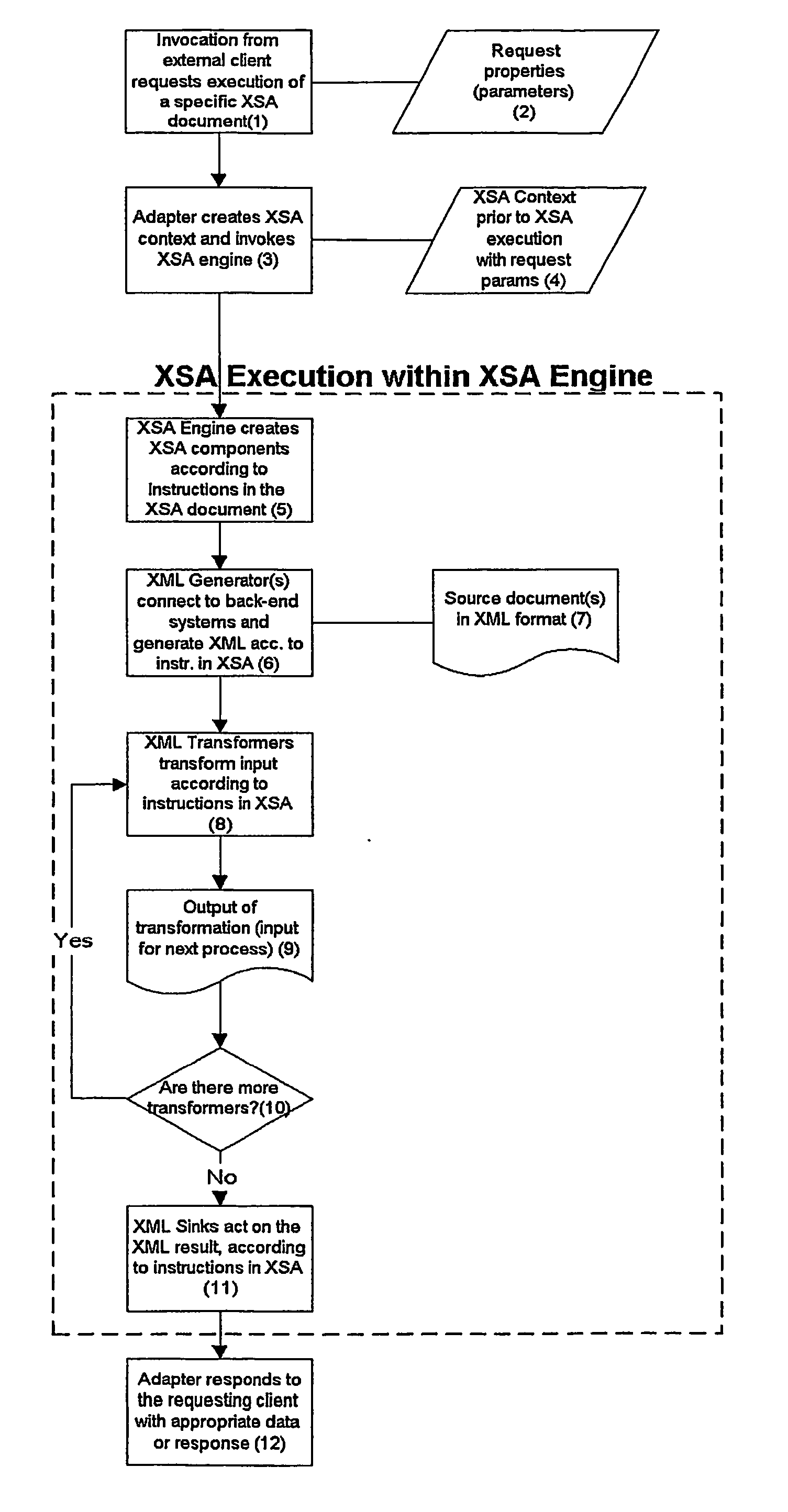

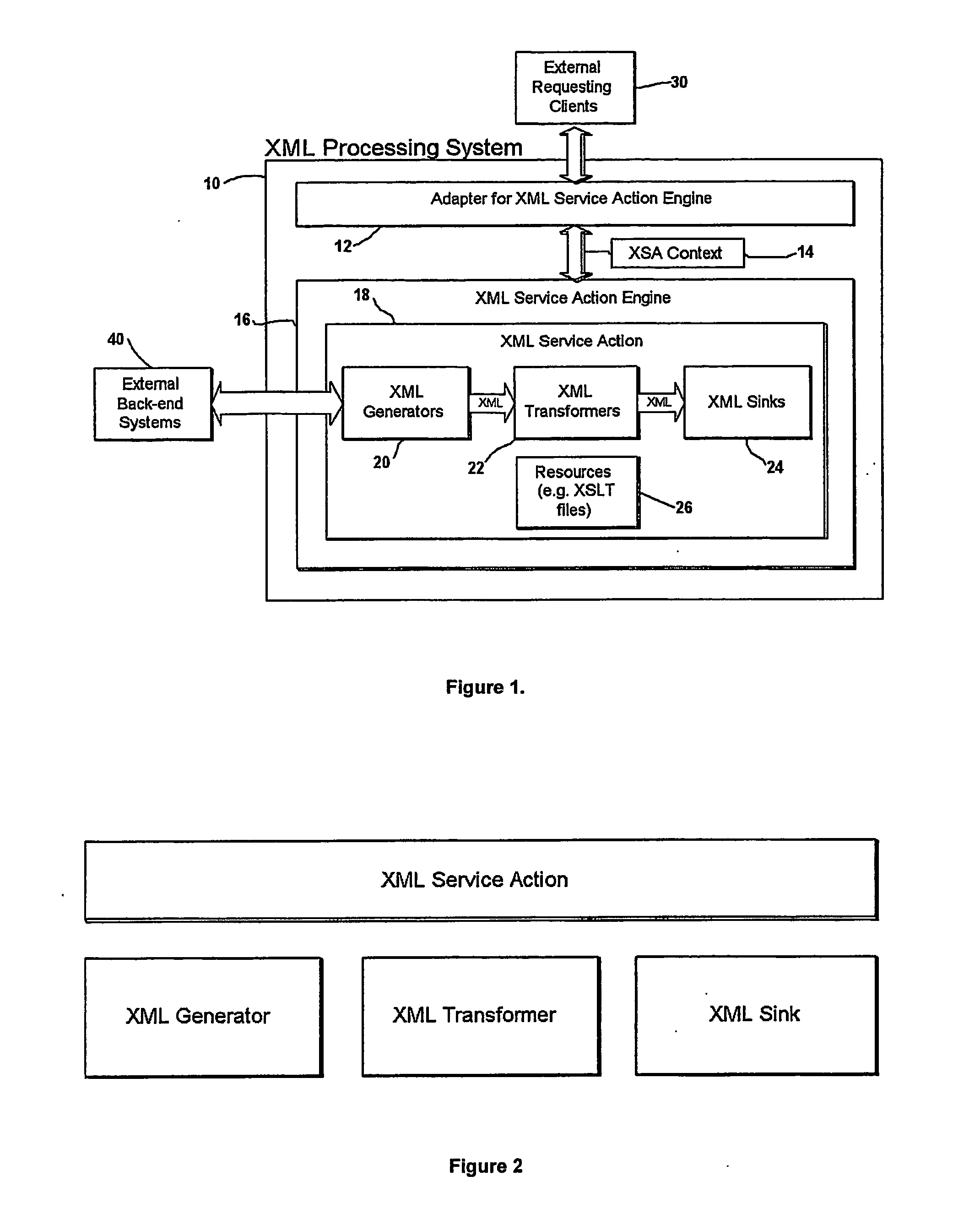

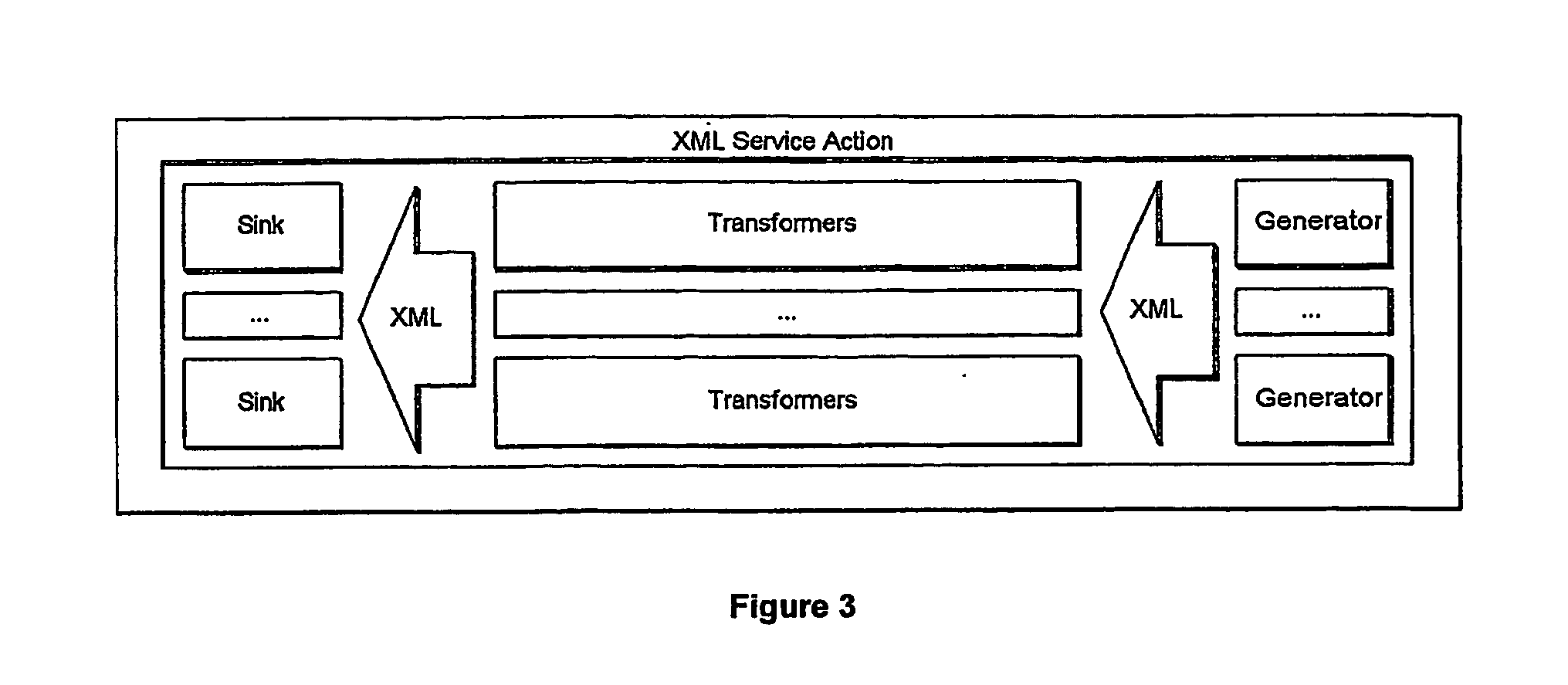

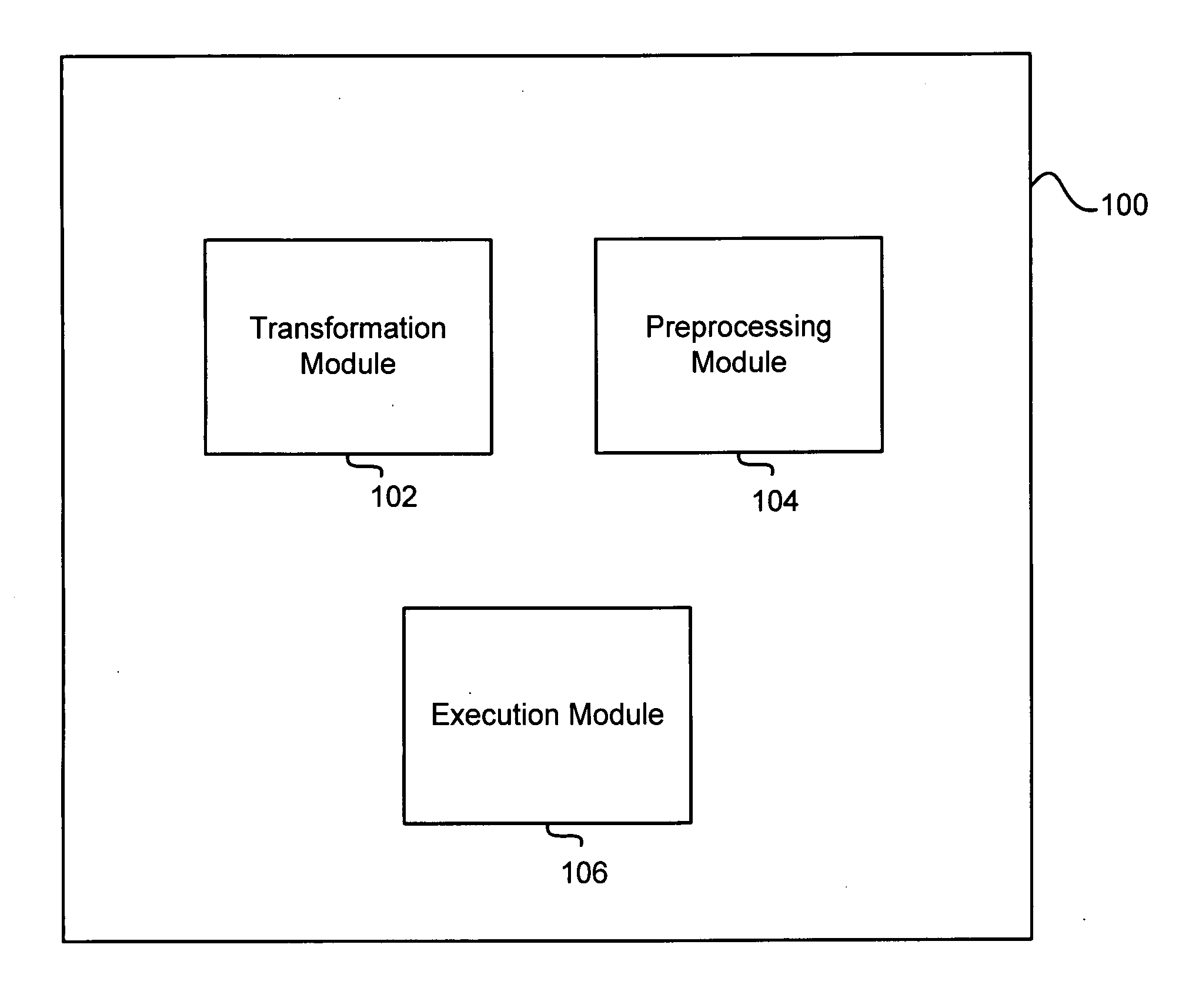

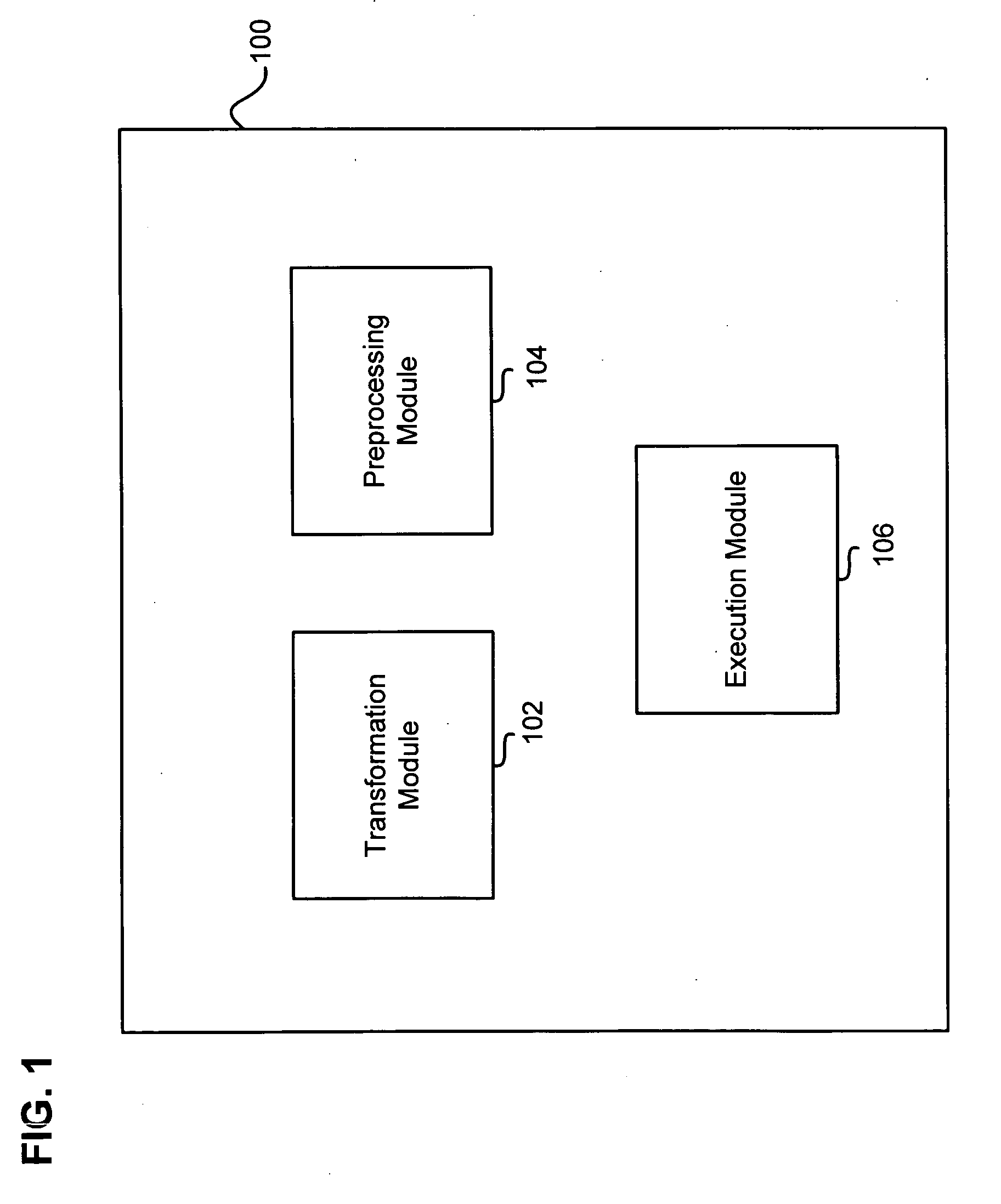

System and method for a context-independent framework for management and execution of xml processing tasks

InactiveUS20060155529A1Diminishes and even needReduce needNatural language data processingSpecial data processing applicationsGeneral purposeElectronic document

A system for a context-independent framework for management and execution of XML processing tasks is provided. The XML processing tasks are executed by a module, herein referred to as the XSA Engine, according to a predefined set of instructions provided as electronic documents written in a special purpose, XML-based, programming language. The instruction sets contain references to, and control the execution of, instances of three classes of processing modules, which independently accomplish an XML processing subtask and jointly accomplish an XML processing task. The framework is decoupled from any specific execution context, meaning that standardized XML processing can be applied in almost any desired application. The special purpose programming language enhances productivity for development of XML processing tasks as compared to using general purpose programming languages, and diminishes the need for writing custom code to link different types of XML processing subtasks to accomplish an XML processing task.

Owner:TEAMWARE GROUP

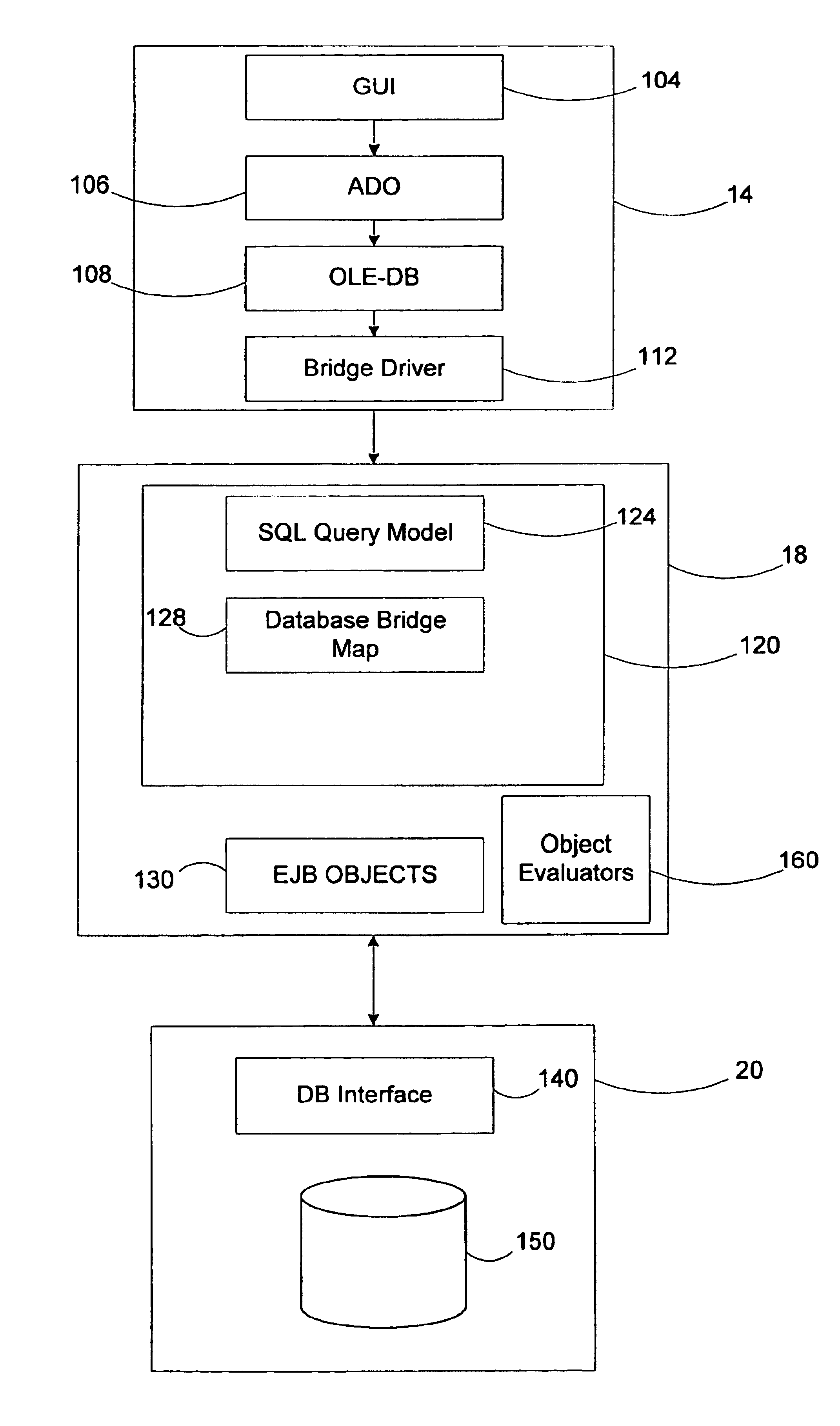

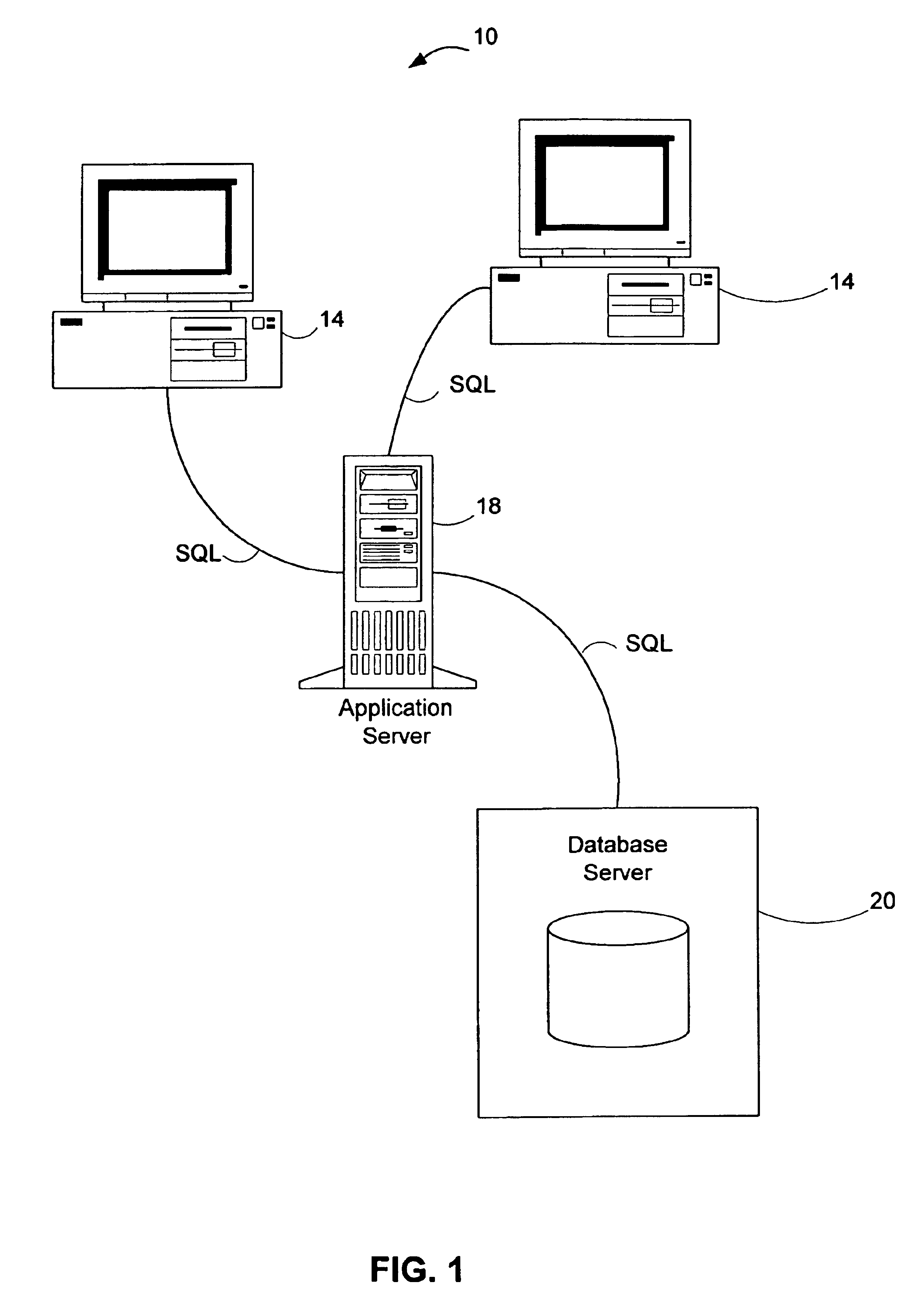

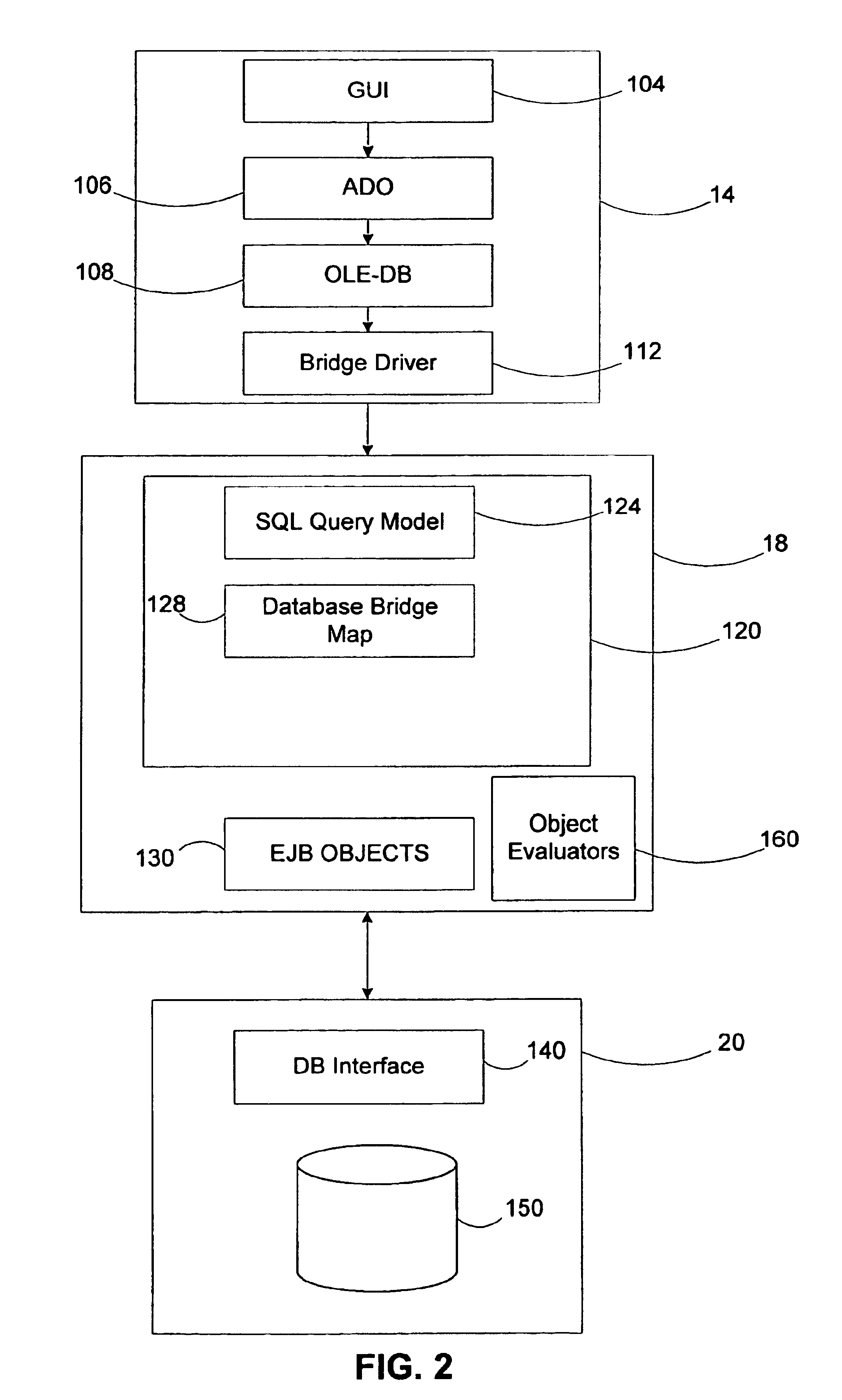

Database access bridge system and process

InactiveUS6889227B1Data processing applicationsDigital data information retrievalApplication serverGeneral purpose computer

A system or method enables a two tier computer application to operate in a three tier computer environment without specific programming for the three tier environment. Such a system or method receives a database call at a computer system and maps the database call to a general programming language call of a computer application. The general programming language call is executed to invoke functions of the computer application that correspond to functions of the database call. The general programming language call may be an Enterprise Java Bean (EJB) call. An application server receives the database call and maps the database call to the general programming language call. In response to executing the general programming language call, the application server generates a second database call to the database that may either correspond directly or indirectly to the database call received at the application server. The database calls may both be SQL calls. The general computer programming language may have EJB components that are analyzed to determine the correspondence between the database elements and the elements of the components that access the database elements. Methods of the EJB components may be identified for use in determining the correspondence. The methods may be identified by searching for a method of the form <command prefix>XXX, where the prefix is a “get” or “set” method.

Owner:ORACLE INT CORP

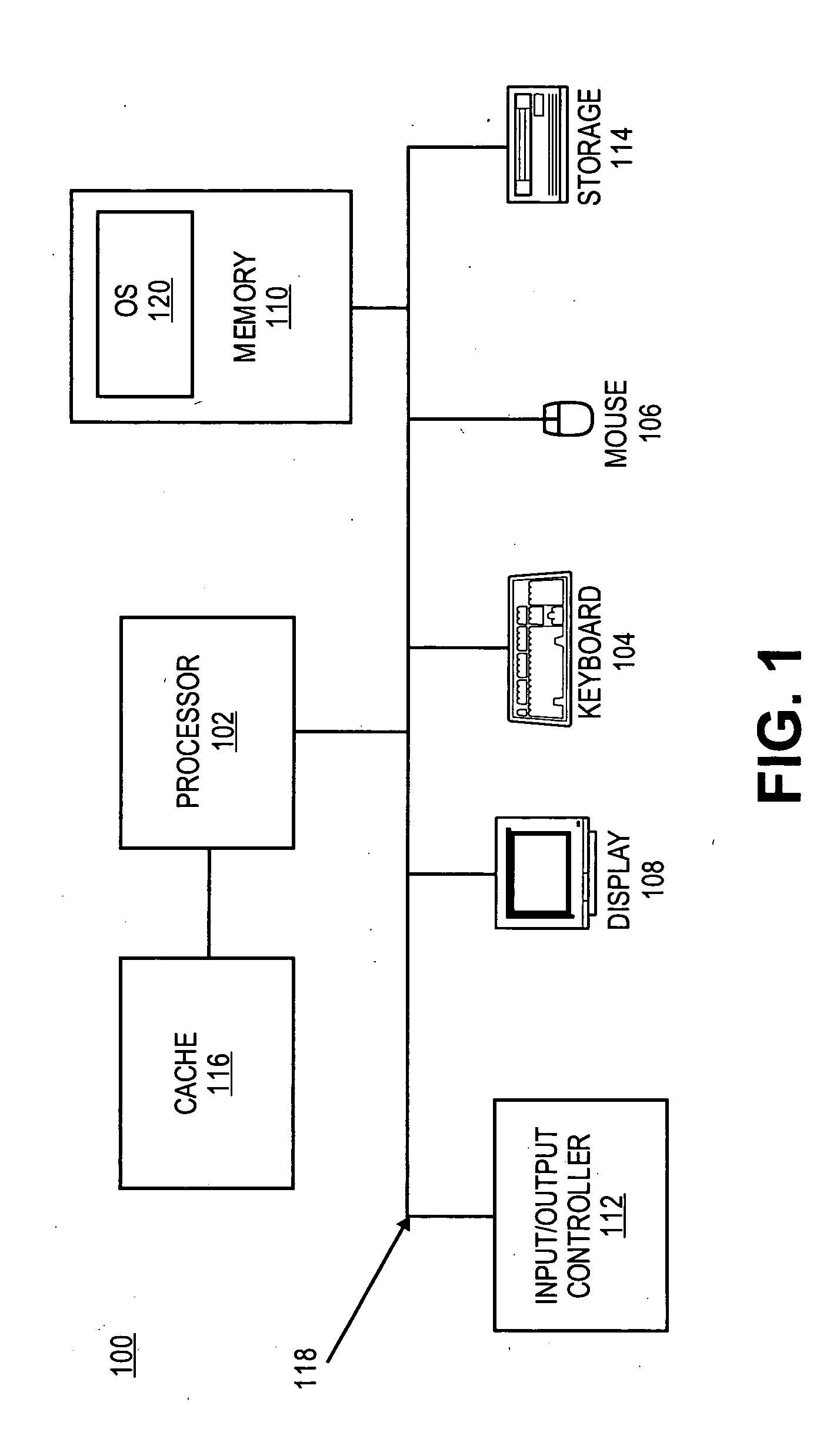

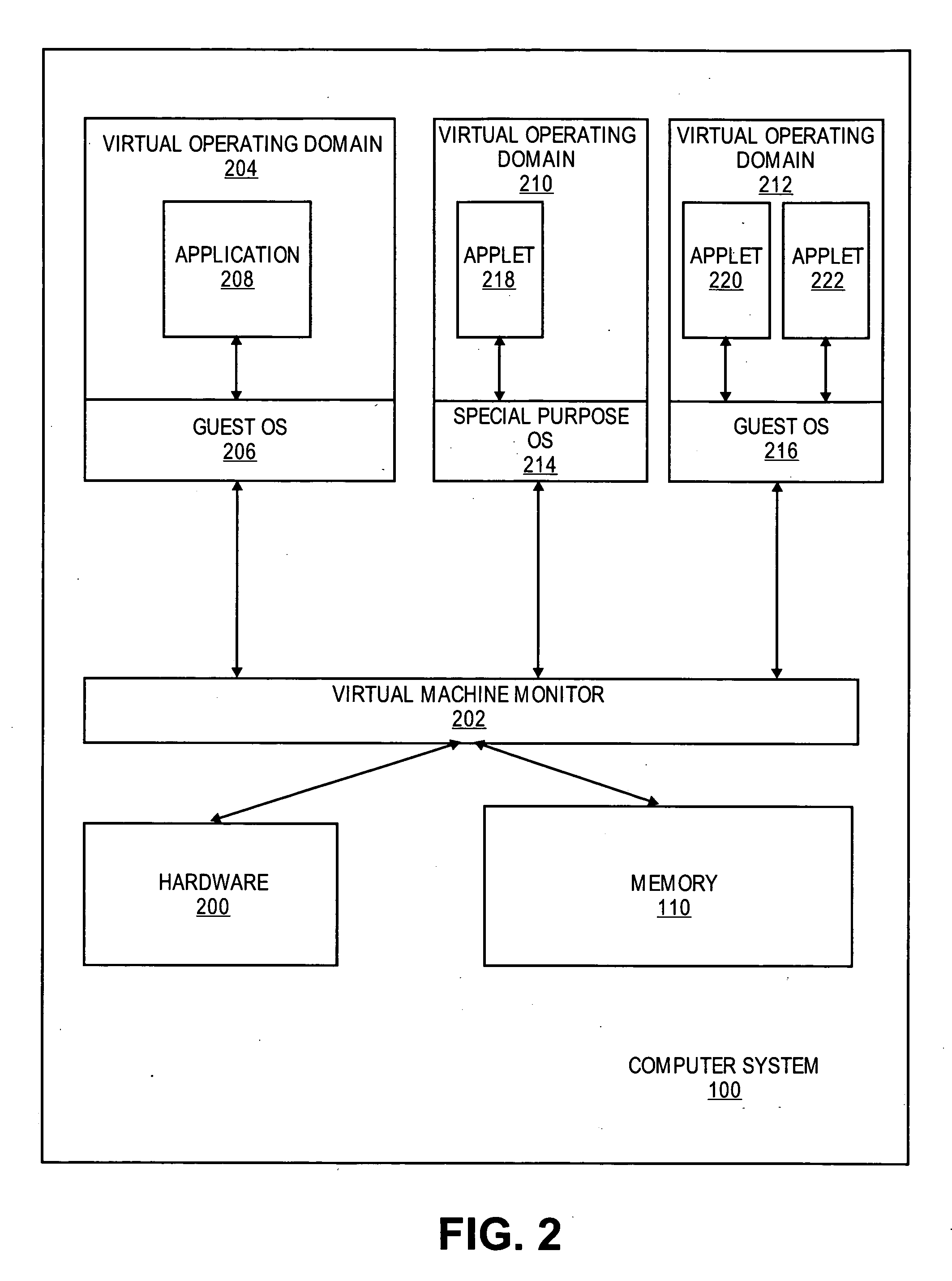

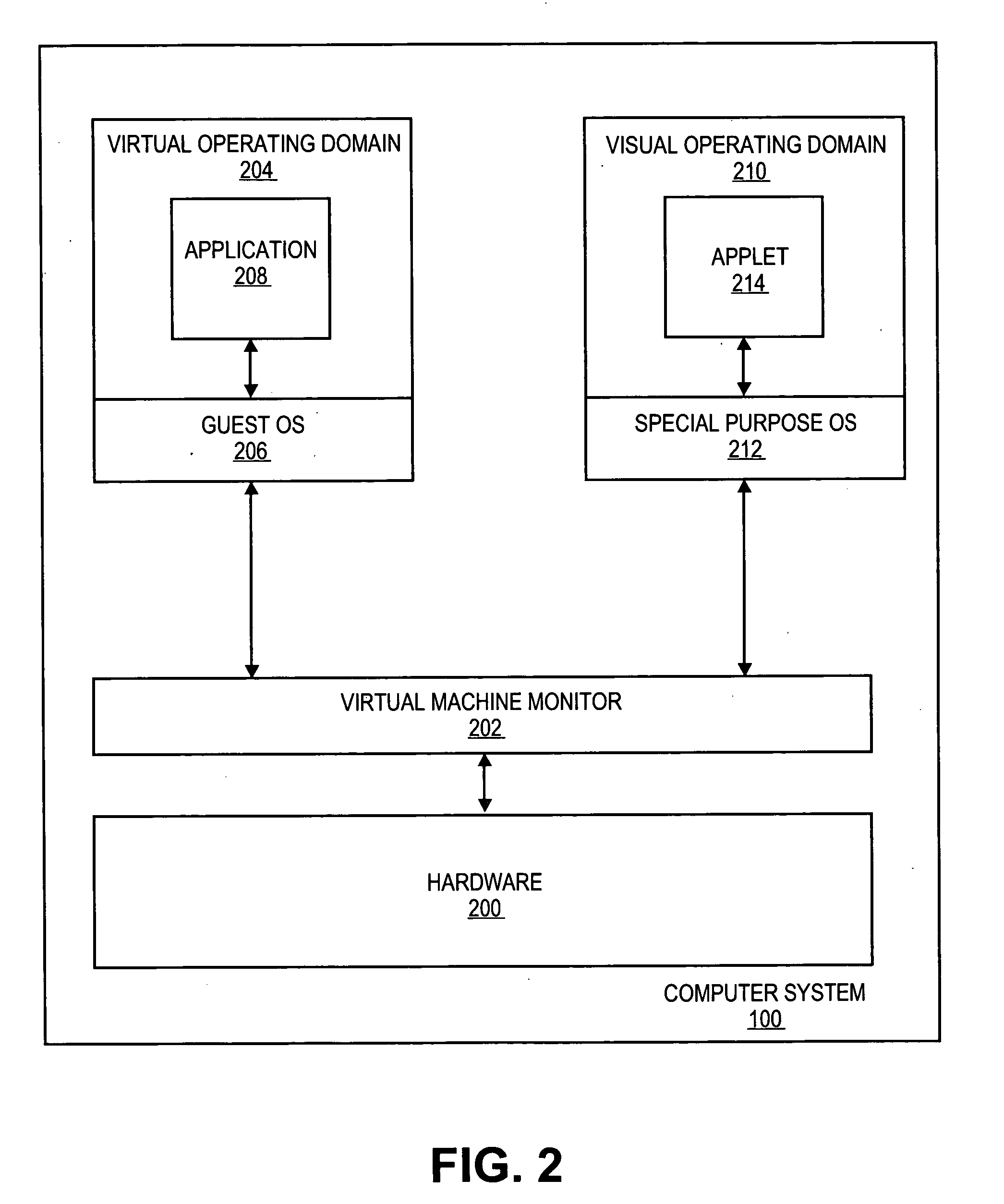

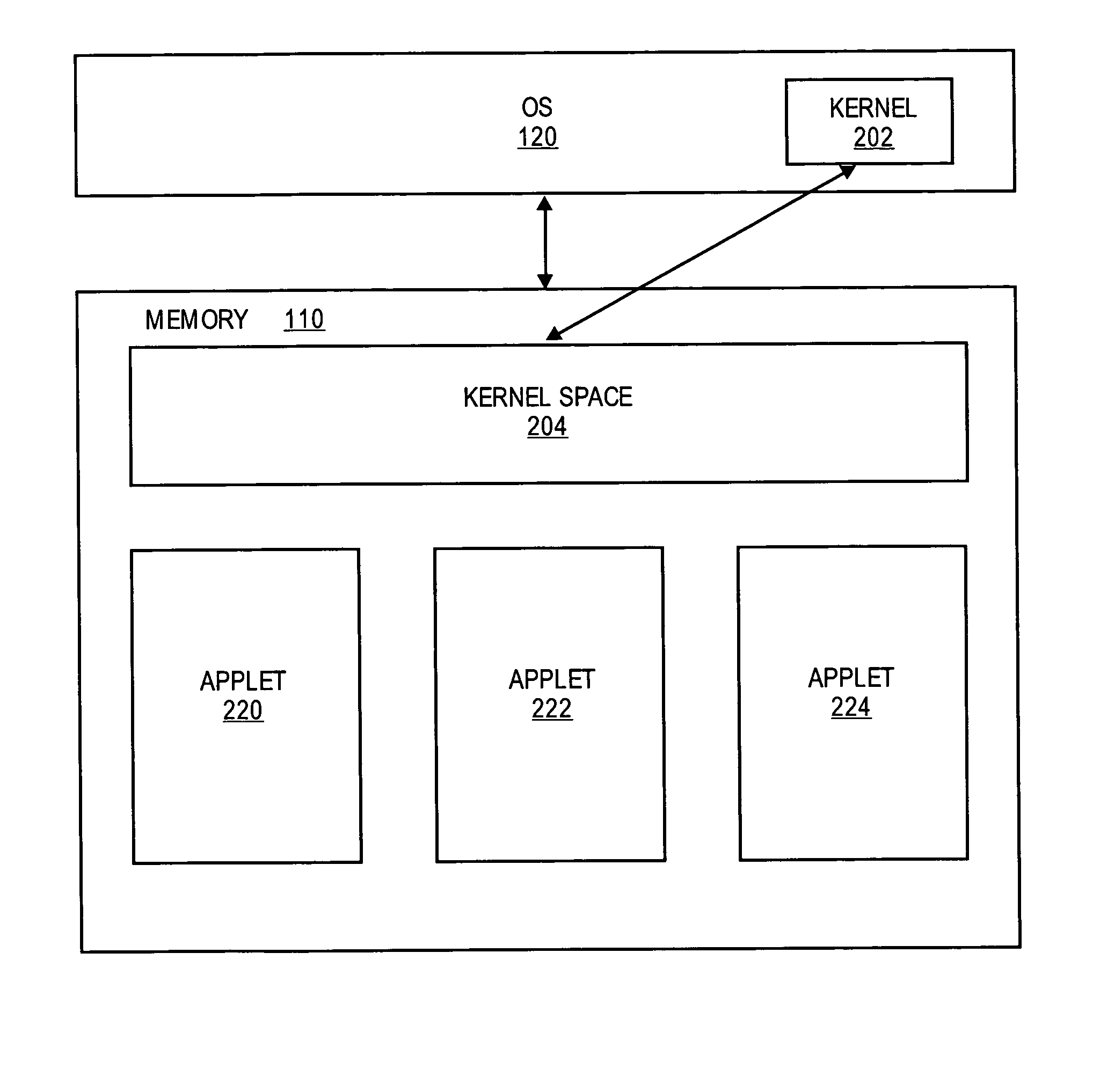

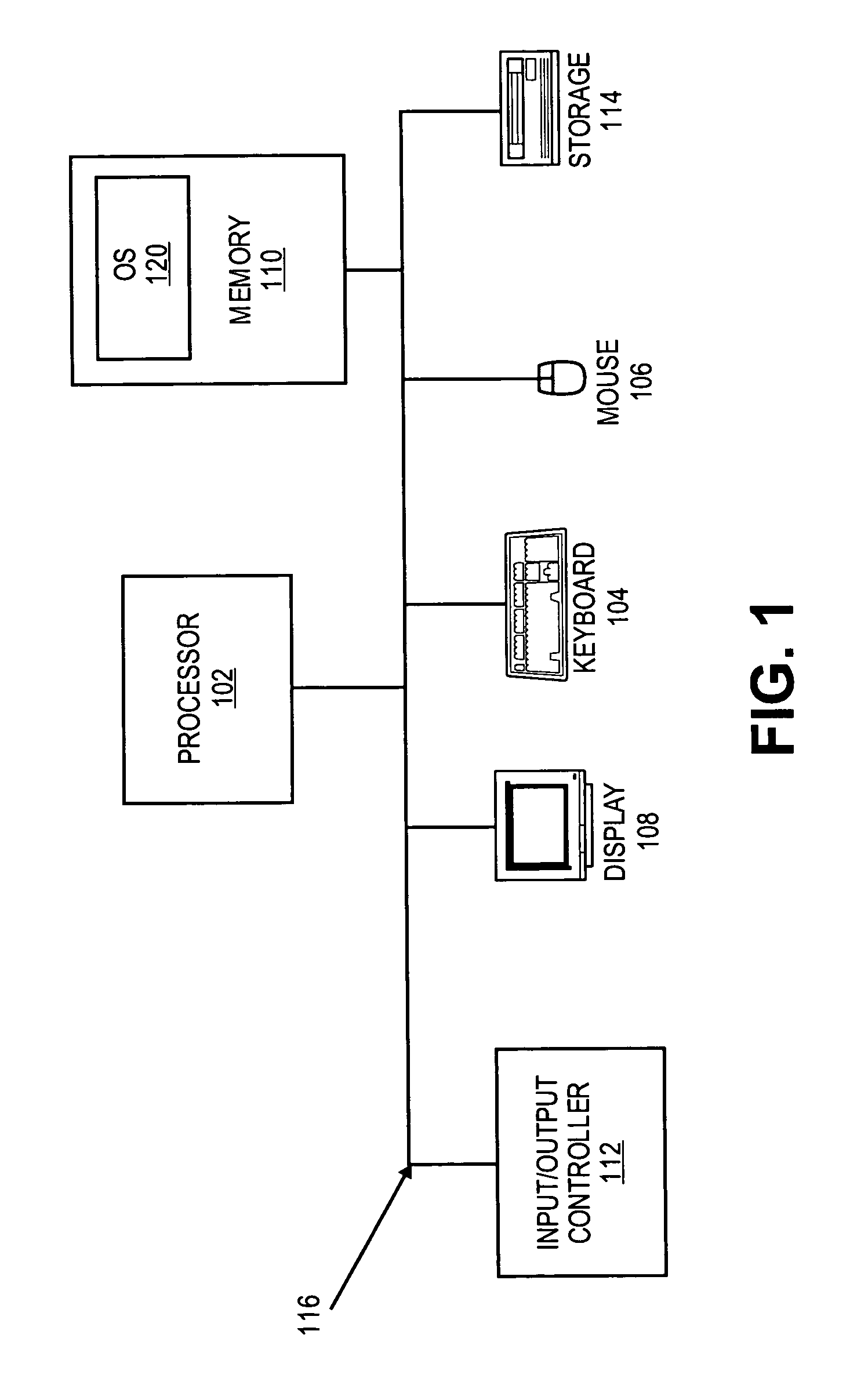

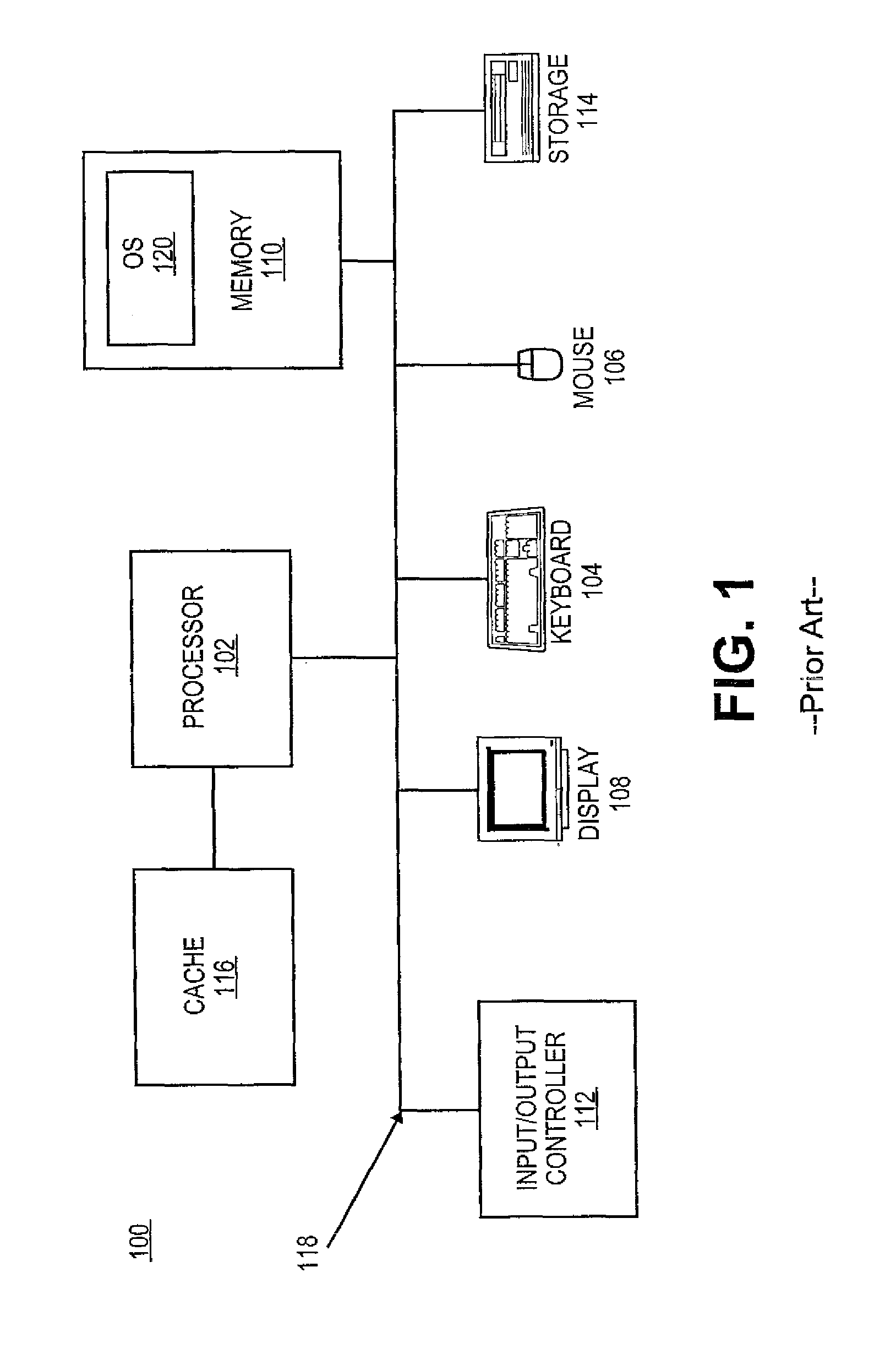

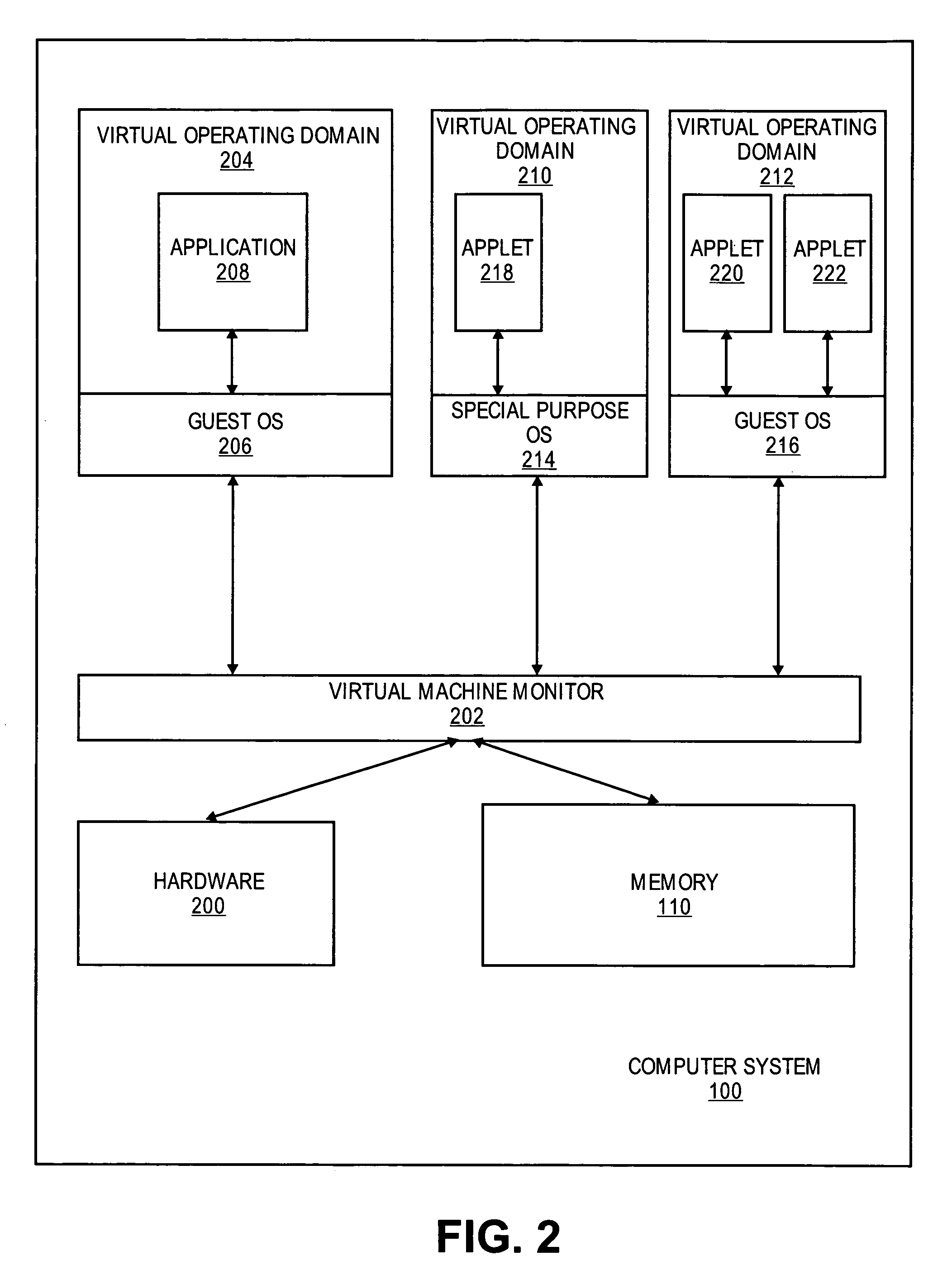

Purpose domain for in-kernel virtual machine for low overhead startup and low resource usage

ActiveUS20070169024A1Software simulation/interpretation/emulationMemory systemsOperational systemAnalog computer

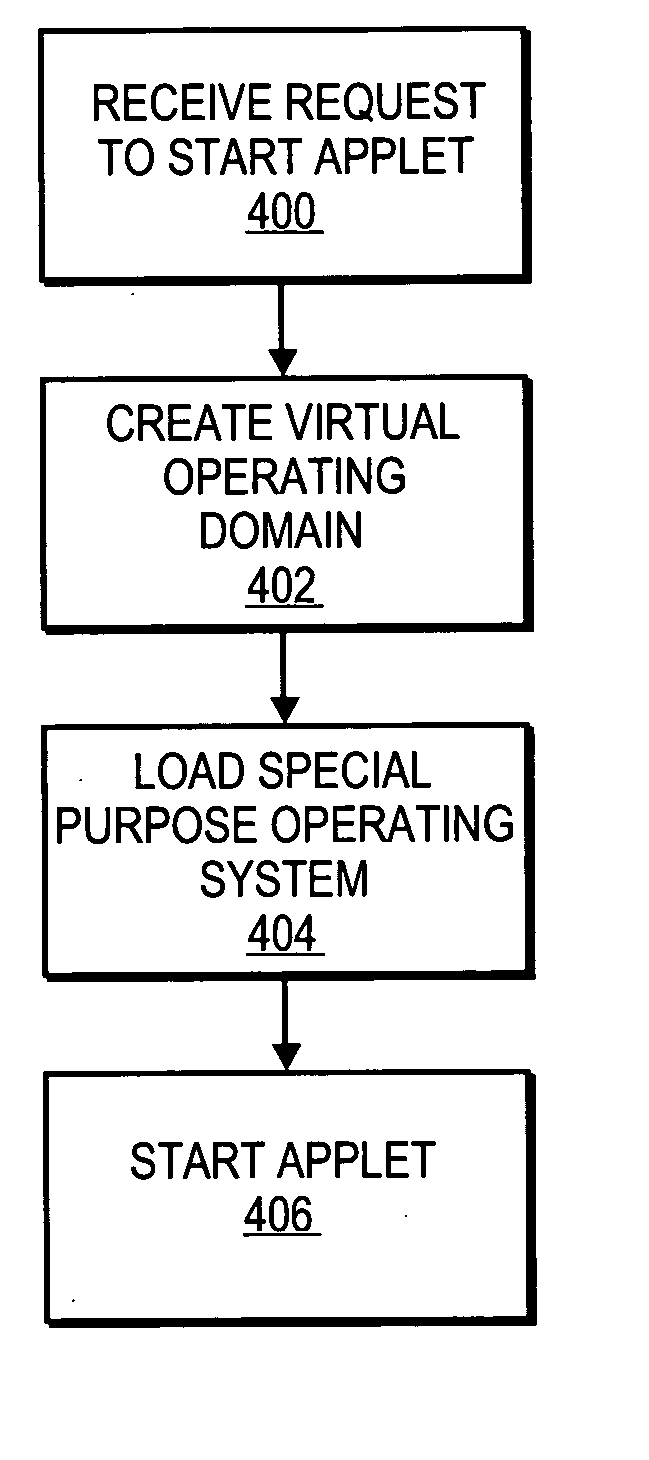

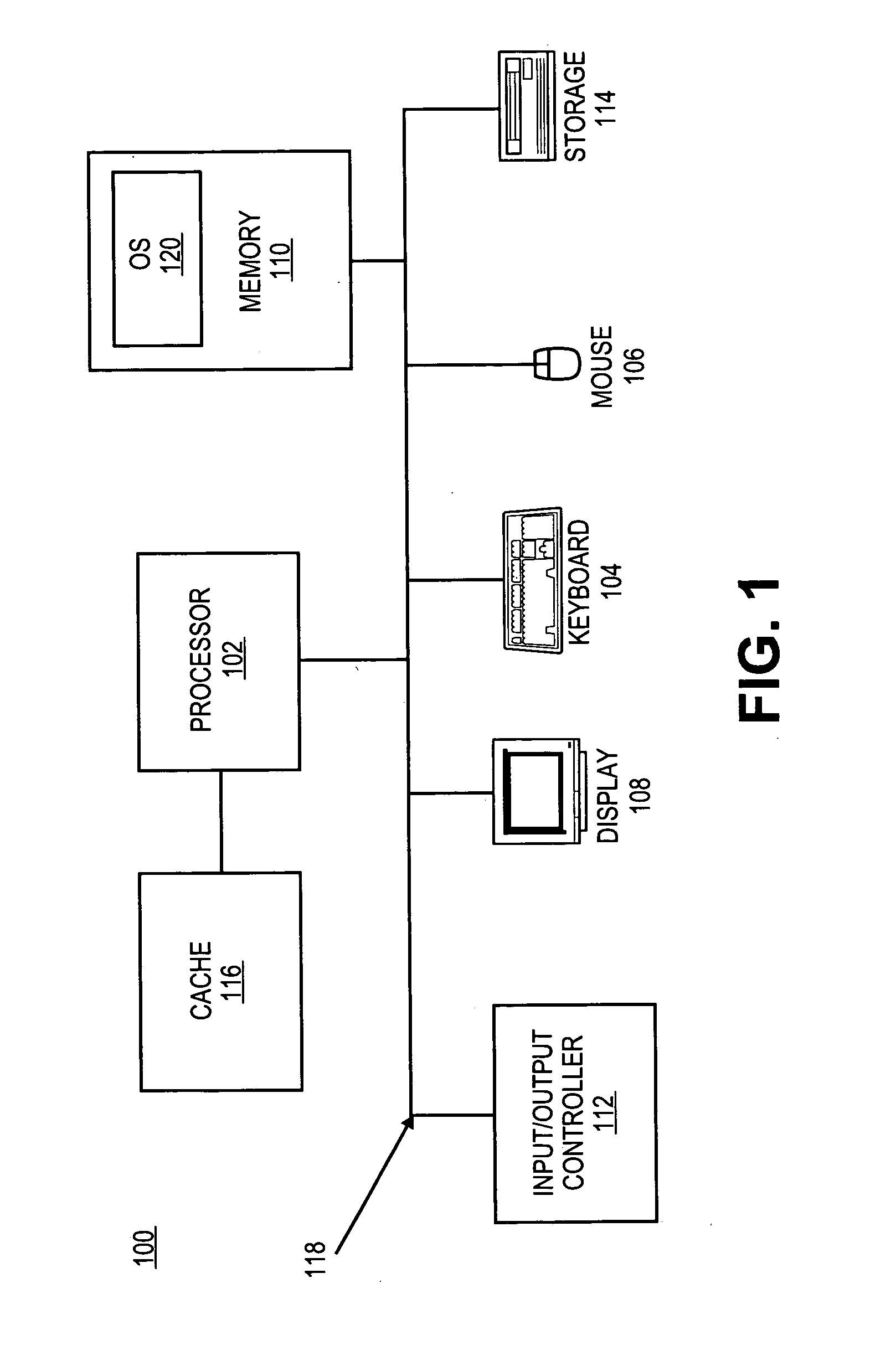

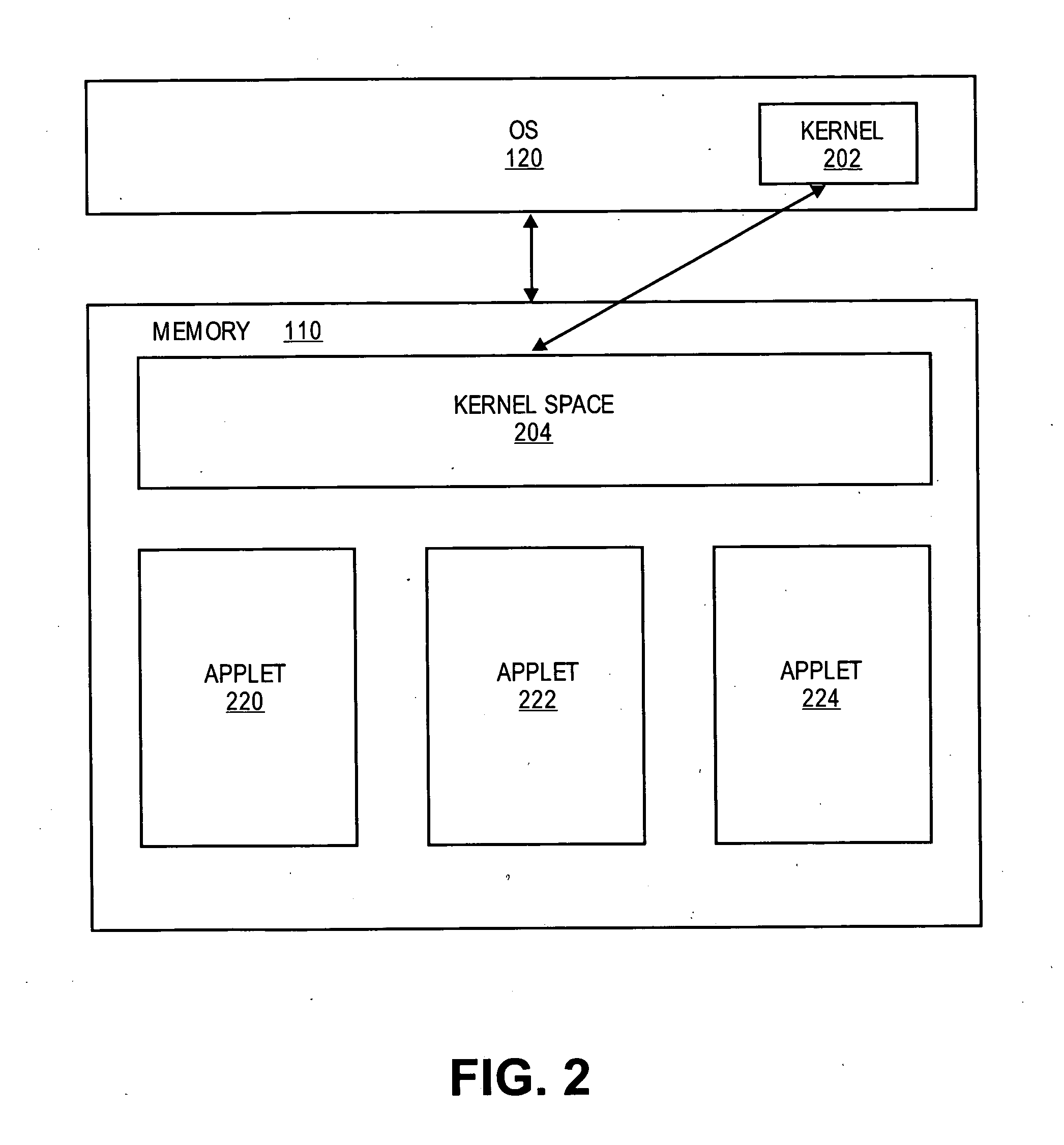

Embodiments of the present invention provide an architecture for securely and efficiently executing byte code generated from a general programming language. In particular, a computer system is divided into a hierarchy comprising multiple types of virtual machines. A thin layer of software, known as a virtual machine monitor, virtualizes the hardware of the computer system and emulates the hardware of the computer system to form a first type of virtual machine. This first type of virtual machine implements a virtual operating domain that allows running its own operating system. Within a virtual operating domain, a byte code interpreter may further implement a second type of virtual machine that executes byte code generated from a program written in a general purpose programming language. The byte code interpreter is incorporated into the operating system running in the virtual operating domain. The byte code interpreter implementing the virtual machine that executes byte code may be divided into a kernel component and one or more user level components. The kernel component of the virtual machine is integrated into the operating system kernel. The user level component provides support for execution of an applet and couples the applet to the operating system. In addition, an operating system running in a virtual operating domain may be configured as a special purpose operating system that is optimized for the functions of a particular byte code interpreter.

Owner:RED HAT

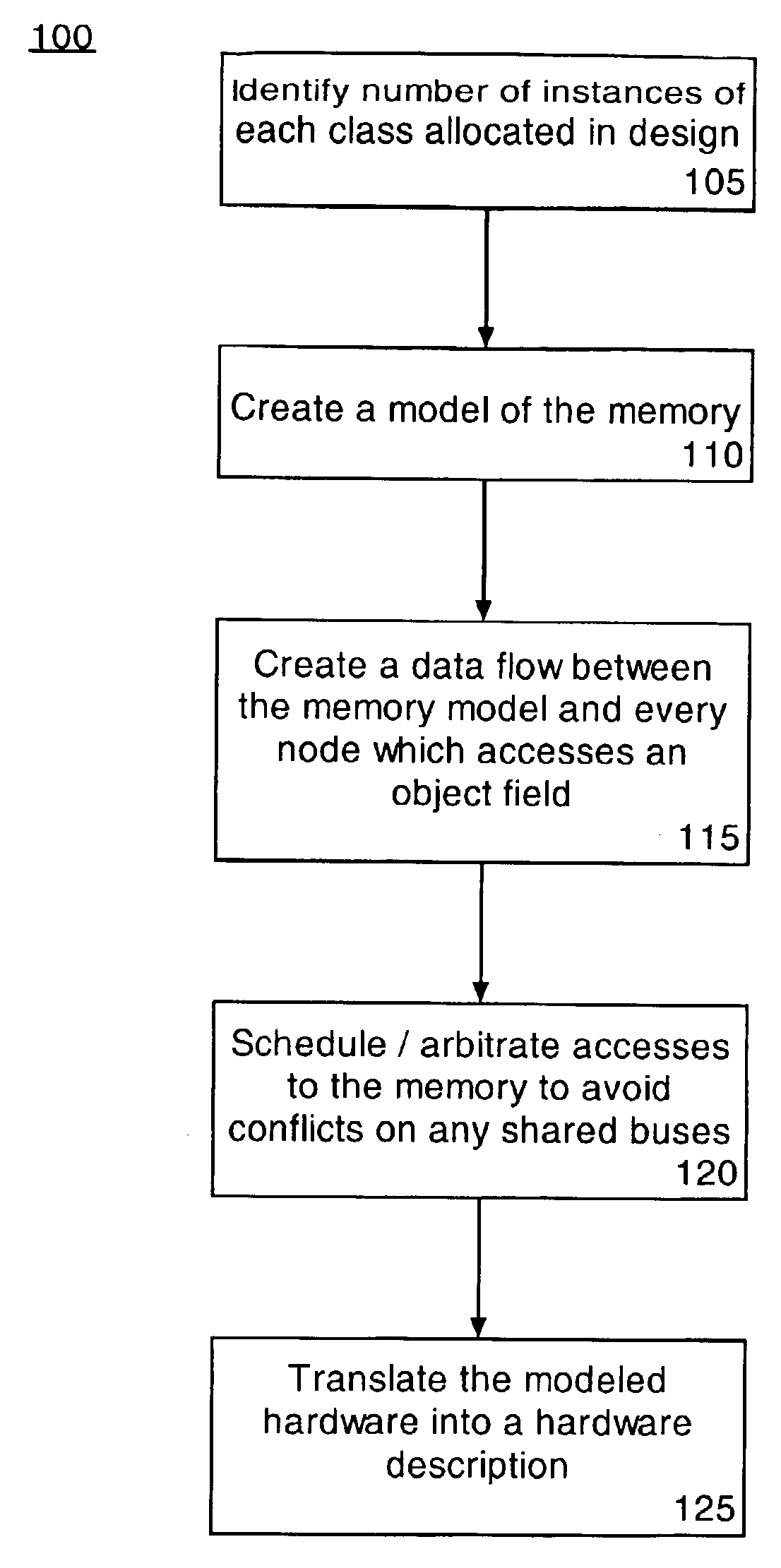

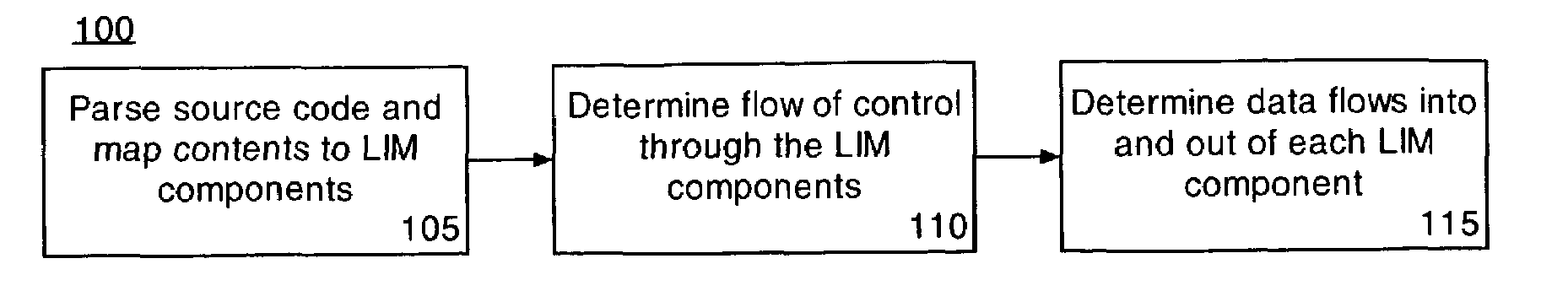

Method of transforming software language constructs to functional hardware equivalents

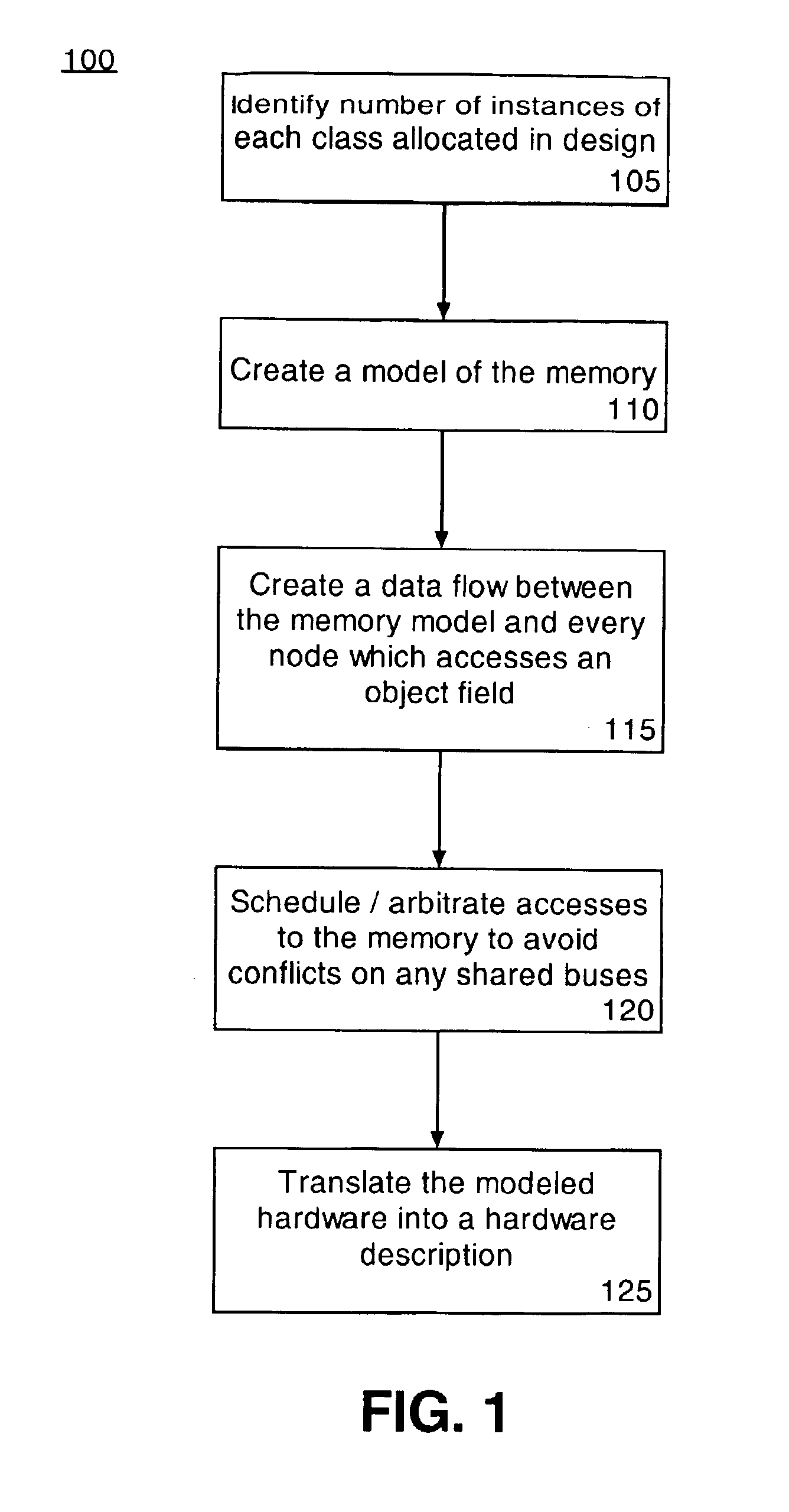

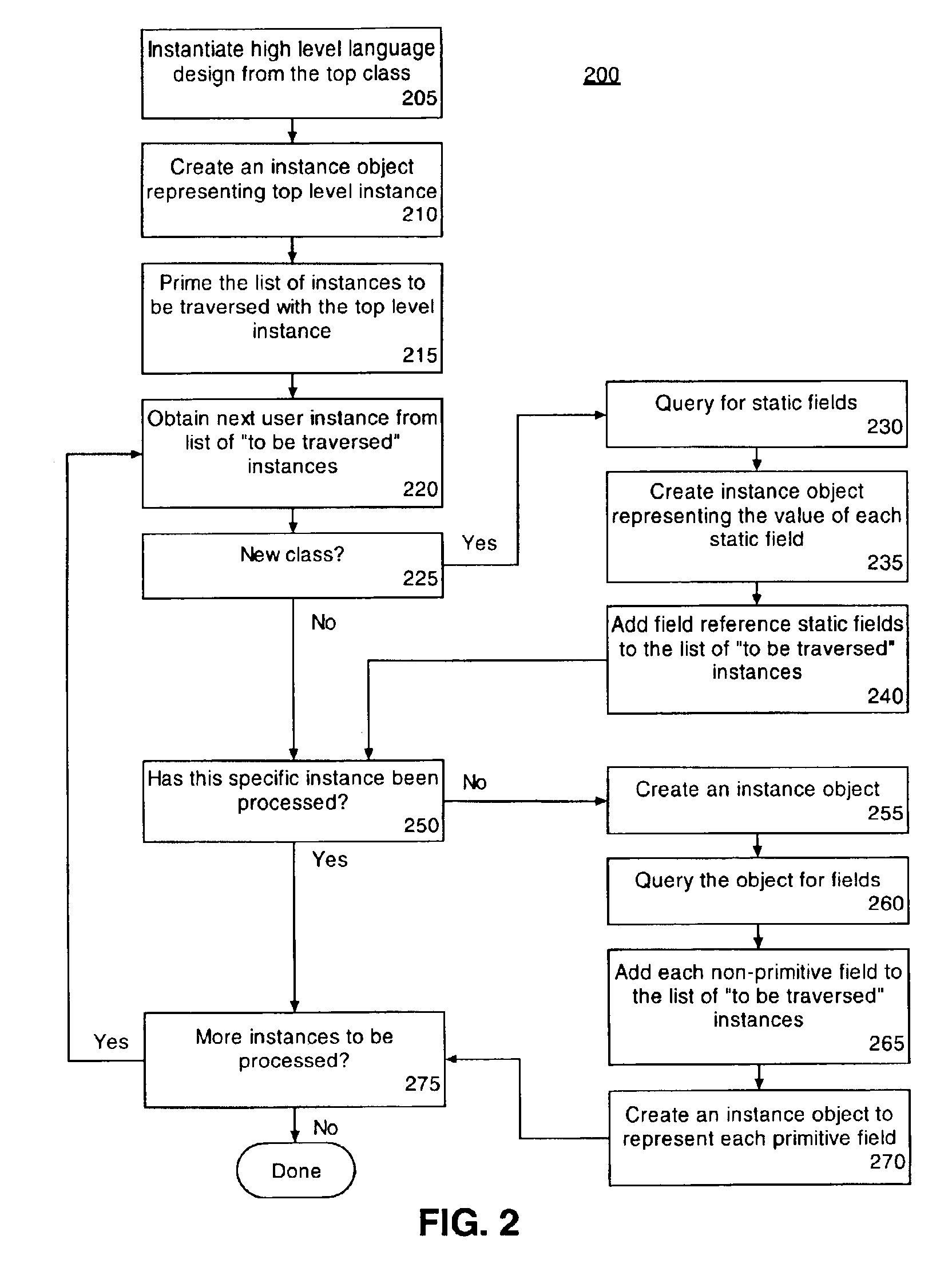

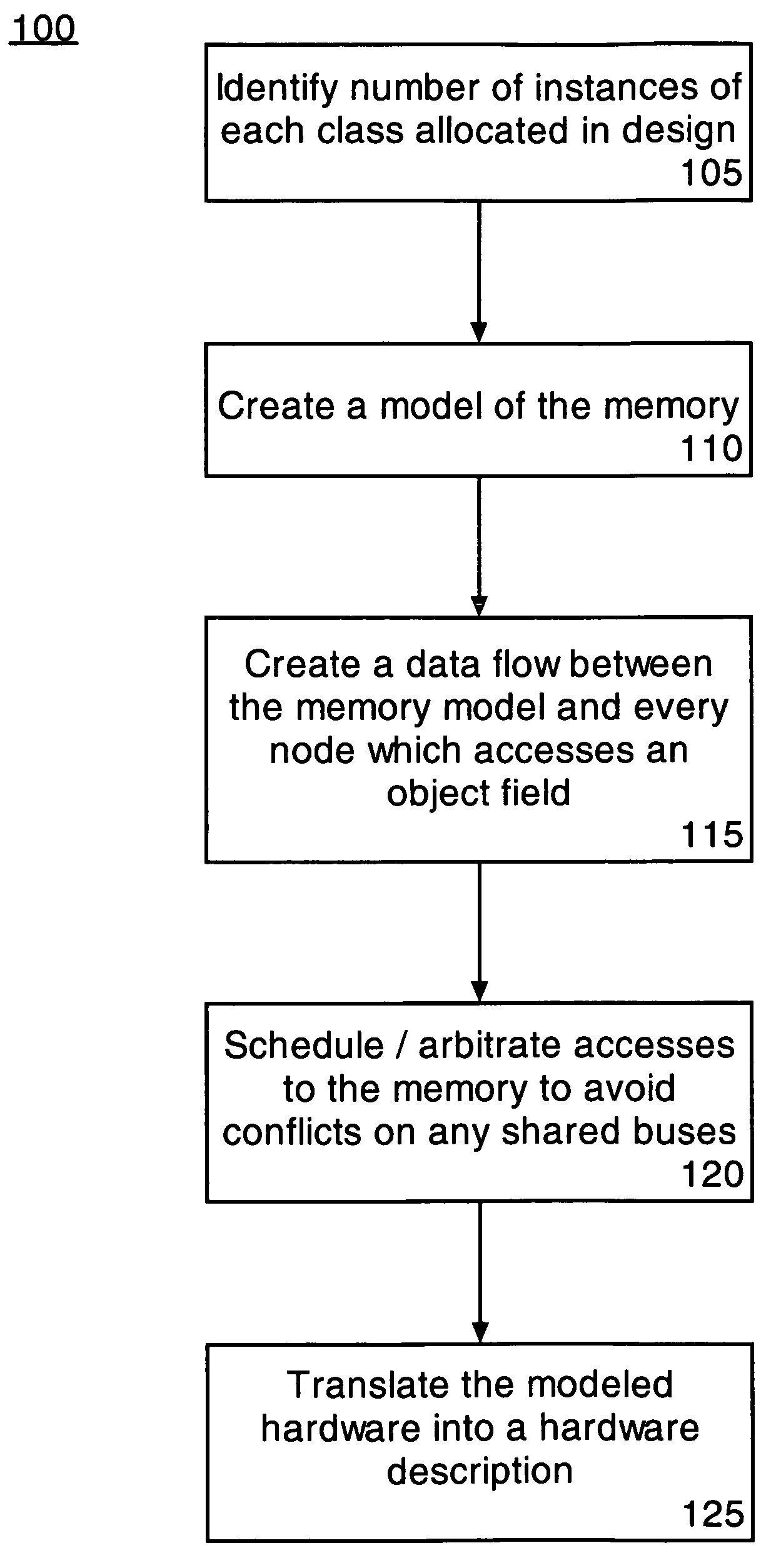

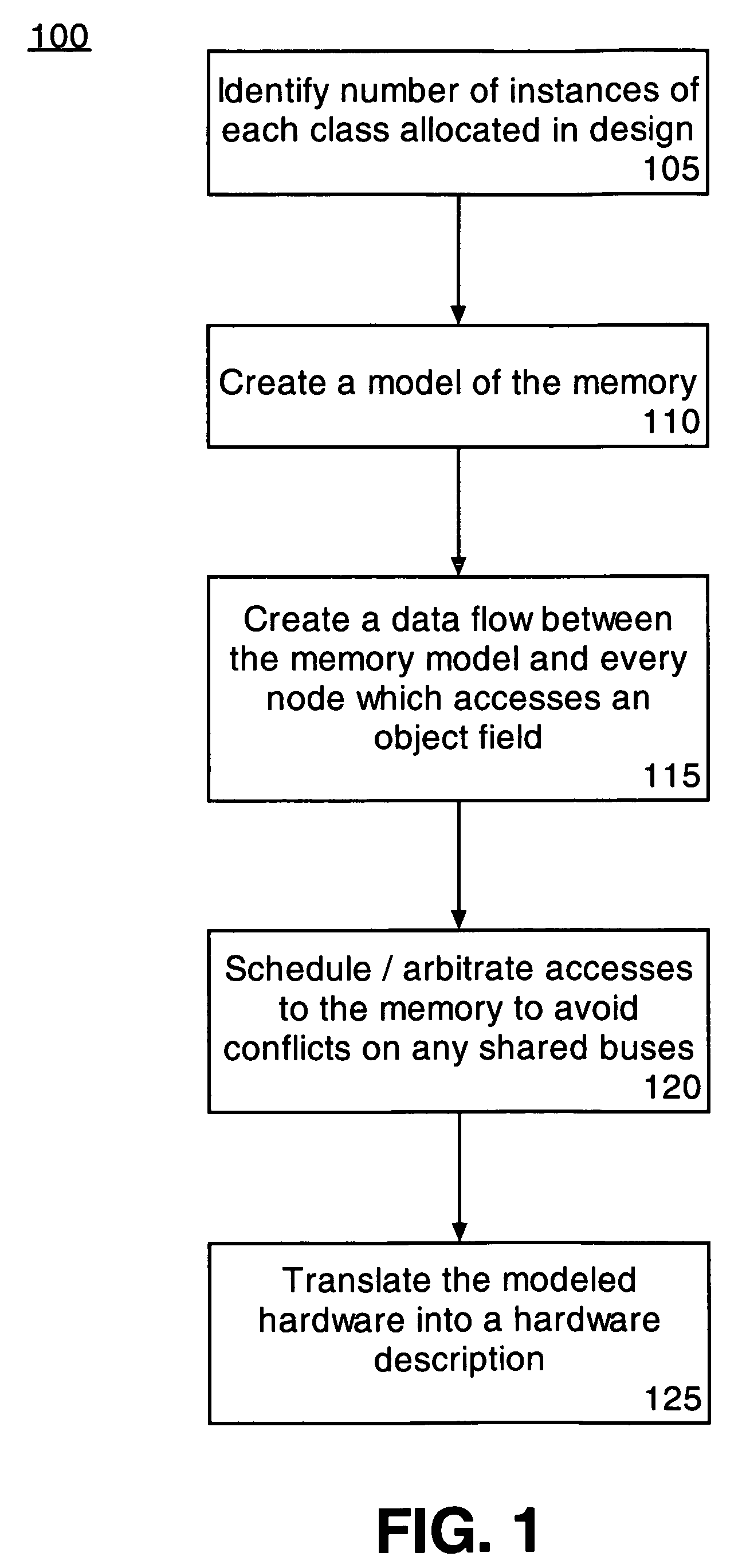

A method of designing an integrated circuit using a general purpose programming language can include identifying (105) a number of instances of each class allocated in a programmatic design implemented using the general purpose programming language and modeling (110) the global memory of the programmatic design. A data flow between the modeled global memory and instructions of the programmatic design which access object fields can be determined (115) and access to the modeled global memory can be scheduled (120). The programmatic design can be translated (125) into a hardware description of the integrated circuit using the modeled global memory, the data flow, and the scheduled memory access.

Owner:XILINX INC

Purpose domain for low overhead virtual machines

InactiveUS20070169005A1Multiprogramming arrangementsSoftware simulation/interpretation/emulationOperational systemAnalog computer

Embodiments of the present invention provide an architecture for securely and efficiently executing byte code generated from a general programming language. In particular, a computer system is divided into a hierarchy comprising multiple types of virtual machines. A thin layer of software, known as a virtual machine monitor, virtualizes the hardware of the computer system and emulates the hardware of the computer system to form a first type of virtual machine. This first type of virtual machine implements a virtual operating domain that allows running its own operating system. Within a virtual operating domain, a byte code interpreter may further implement a second type of virtual machine that executes byte code generated from a program written in a general purpose programming language. The byte code interpreter is incorporated into the operating system running in the virtual operating domain. In addition, an operating system running in a virtual operating domain may be configured as a special purpose operating system that is optimized for the functions of a particular byte code interpreter.

Owner:RED HAT

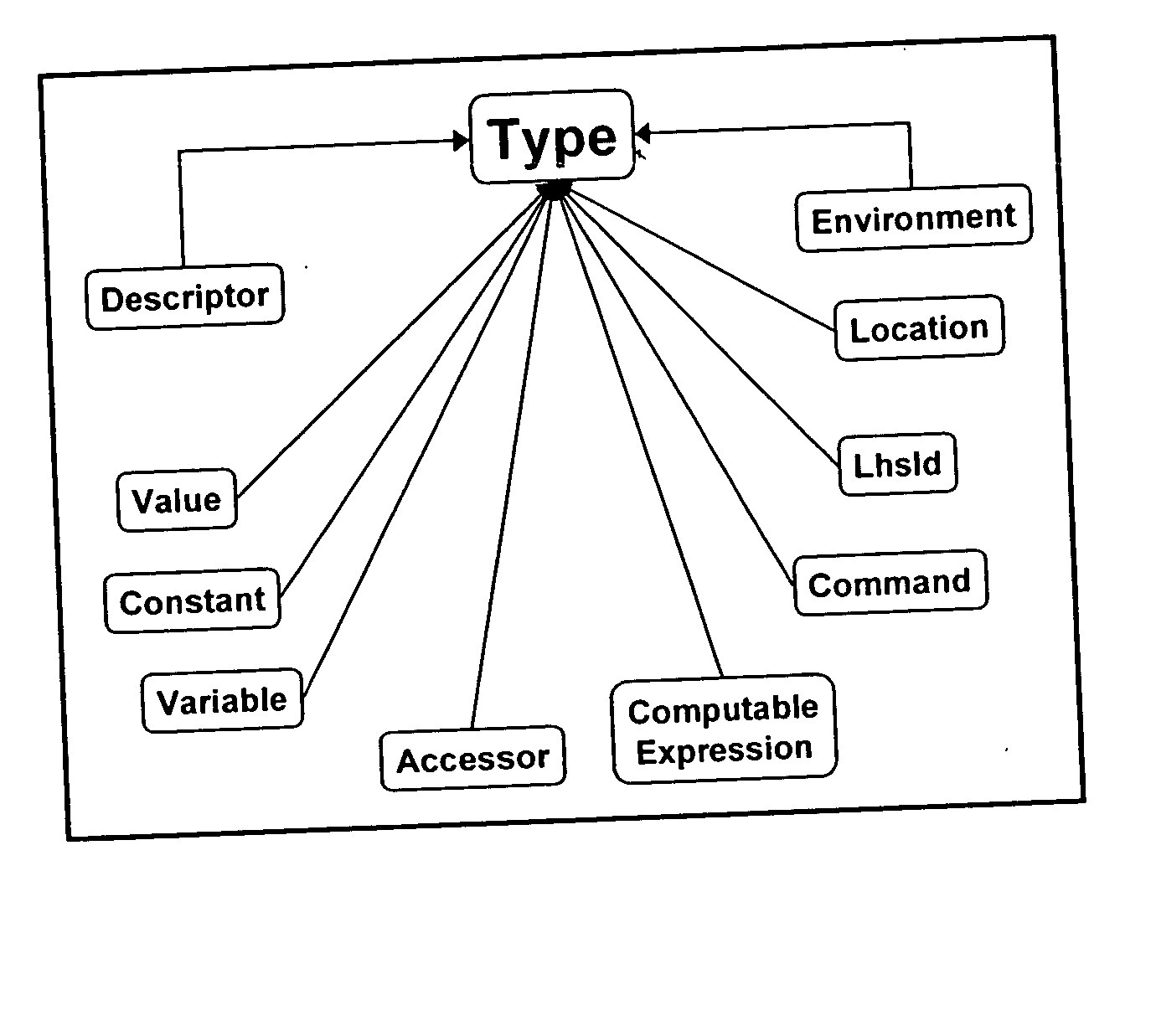

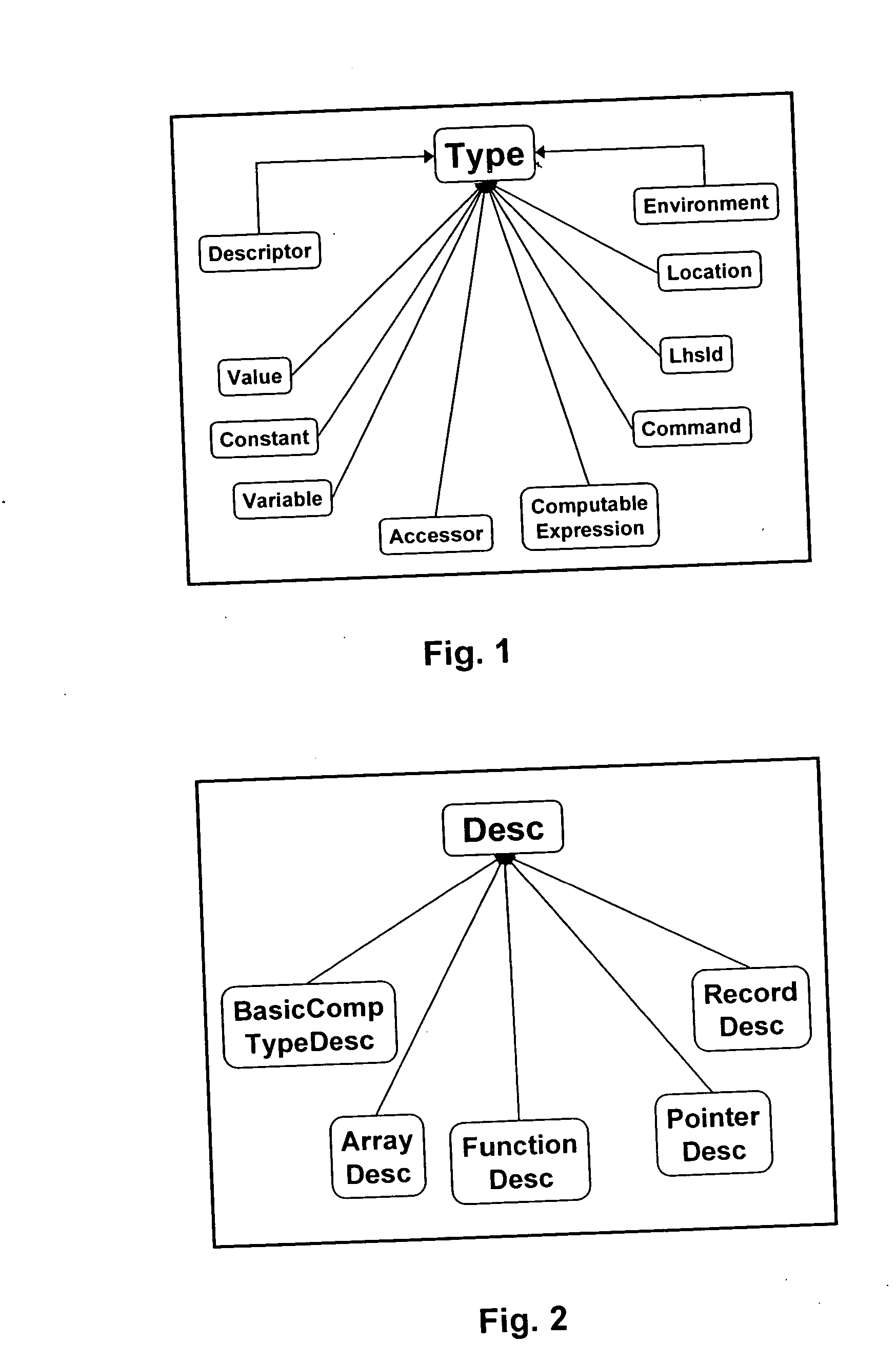

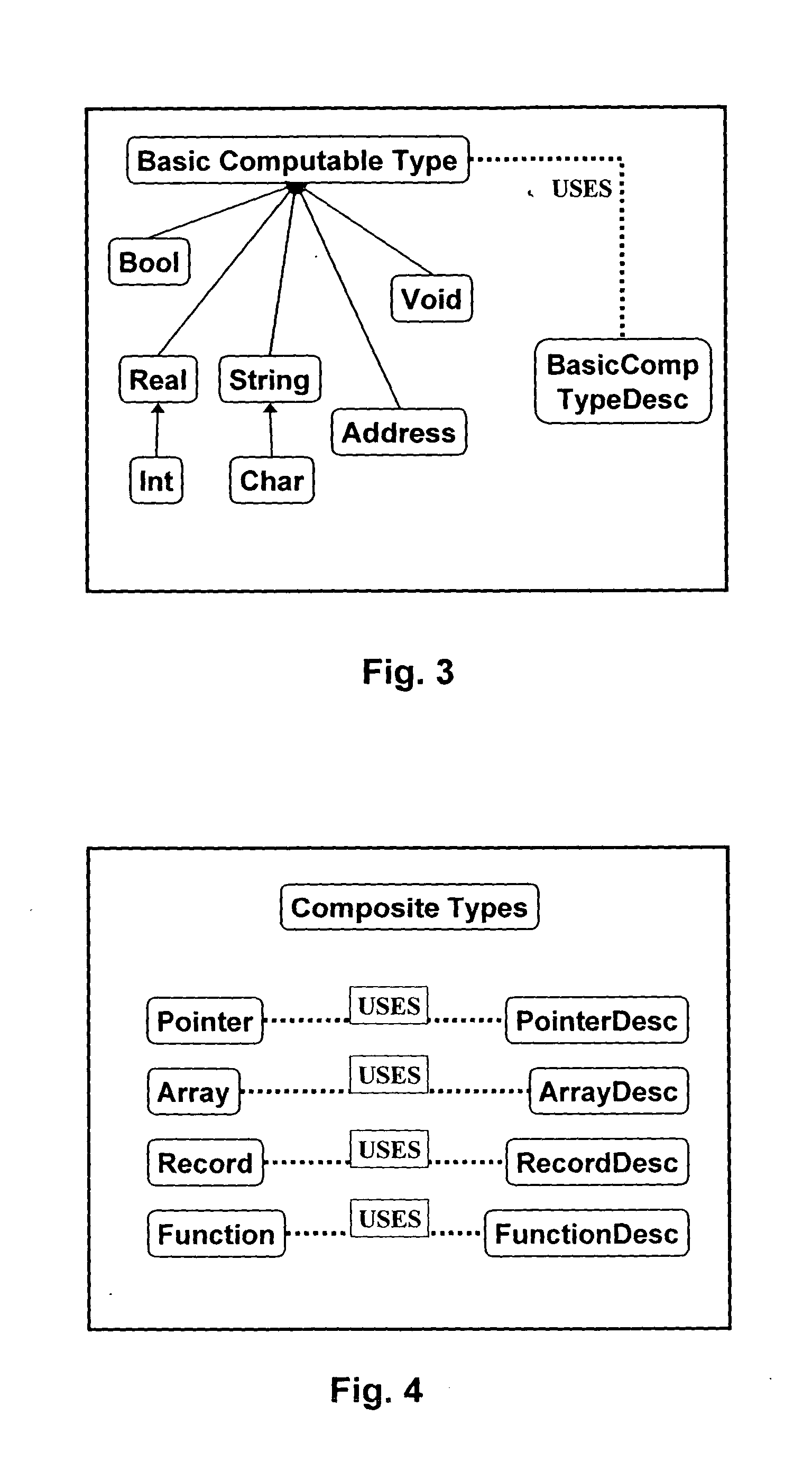

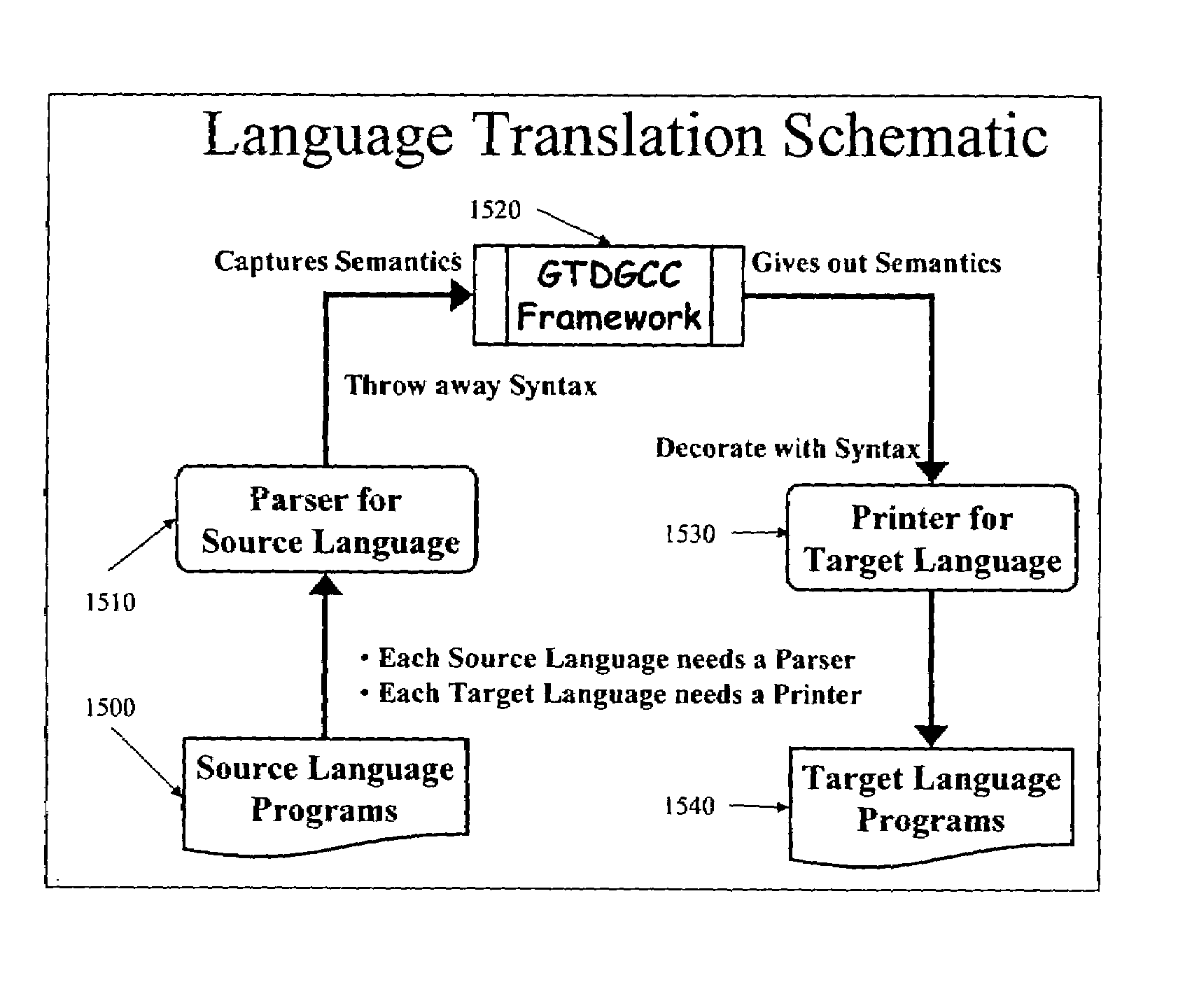

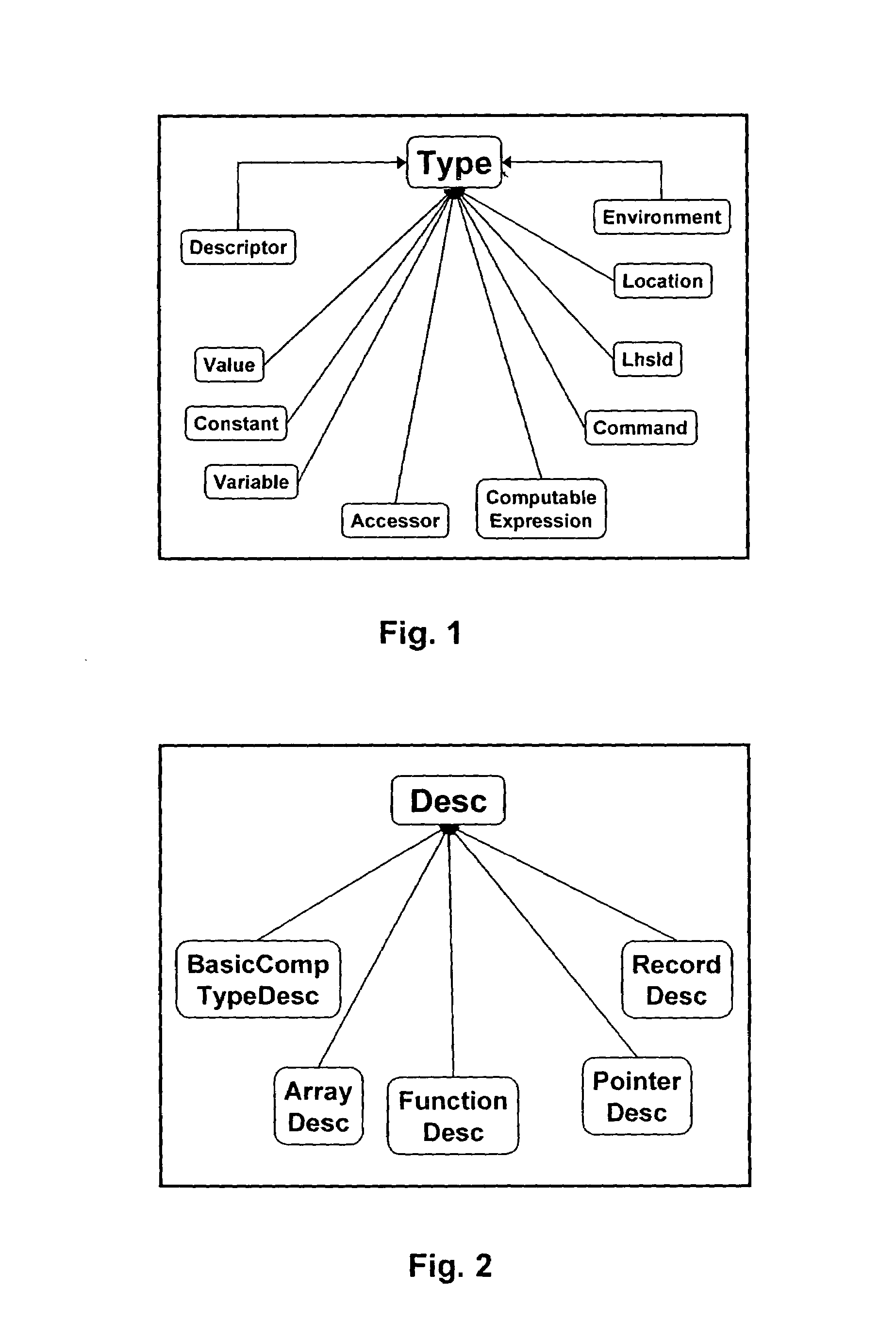

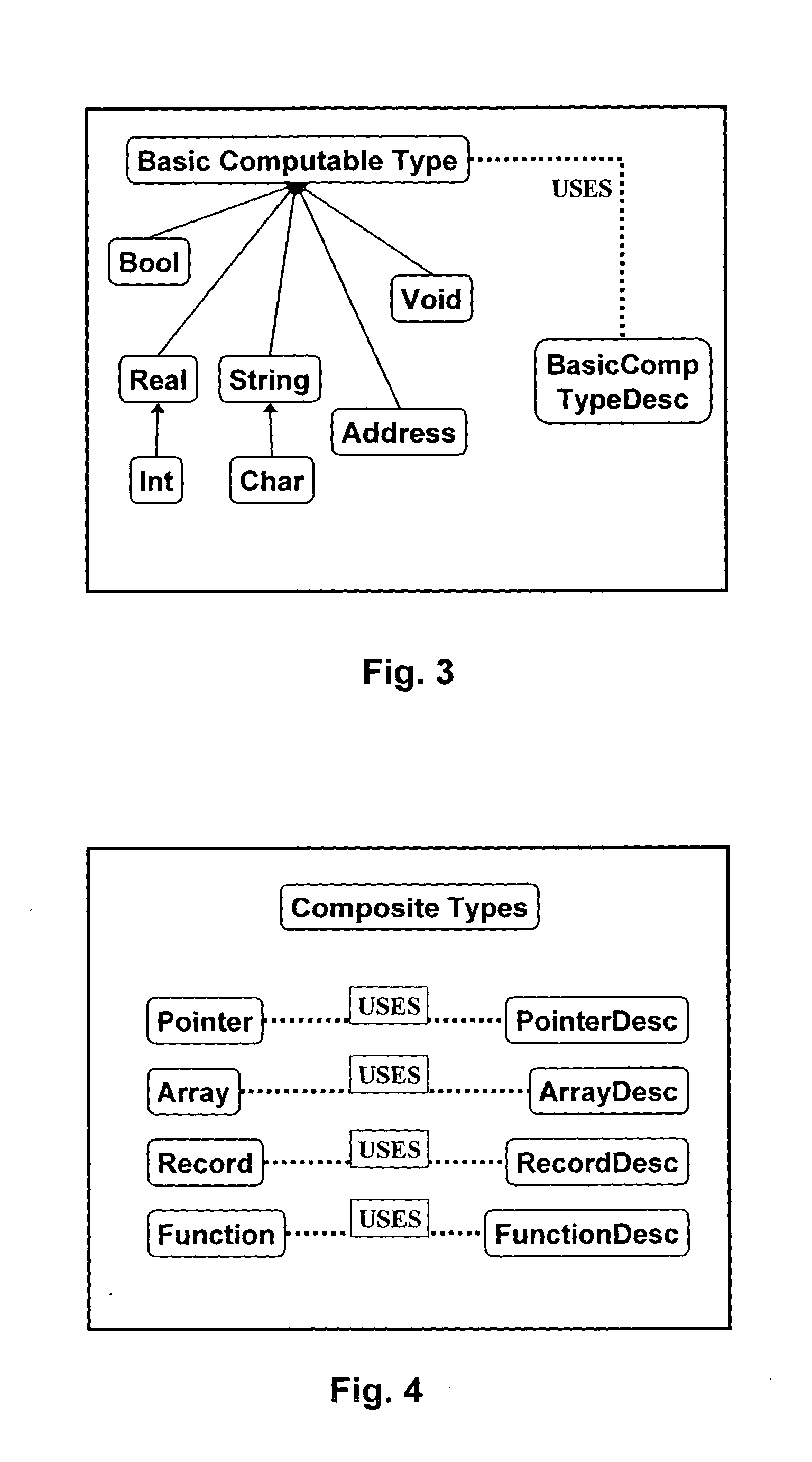

System and method of universal programming language conversion

InactiveUS20050050525A1Specific program execution arrangementsMemory systemsSemantic representationGoal programming

An apparatus and method for universal programming language conversion between two different sequential programming languages, e.g., sequential procedural and sequential object oriented programming languages. In particular, conversion is between a source program in a first programming language and a target program in a second programming language. Initially, the source program in the first programming language is parsed using a parsing interface specific to the first programming language. All syntax from the parsed source program is then stripped or removed. Classes in a framework are instantiated to capture semantics of the parsed source program independent of syntax and execution model of the sequential programming languages. The classes are C++ classes representing fundamental core constructs of all sequential programming languages. A semantic representation of the parsed source program without any syntax is produced. The semantic representation is received at a printer interface specific to the second programming language and syntax of the target program in the second programming language is added. This same process can be used for either high-level conversion or compilation depending on whether the target programming language is high level or low level, respectively.

Owner:TECH MAHINDRA INDIA

System and method of universal programming language conversion

InactiveUS7272821B2Specific program execution arrangementsMemory systemsSemantic representationSequential programming

An apparatus and method for universal programming language conversion between two different sequential programming languages, e.g., sequential procedural and sequential object oriented programming languages. In particular, conversion is between a source program in a first programming language and a target program in a second programming language. Initially, the source program in the first programming language is parsed using a parsing interface specific to the first programming language. All syntax from the parsed source program is then stripped or removed. Classes in a framework are instantiated to capture semantics of the parsed source program independent of syntax and execution model of the sequential programming languages. The classes are C++ classes representing fundamental core constructs of all sequential programming languages. A semantic representation of the parsed source program without any syntax is produced. The semantic representation is received at a printer interface specific to the second programming language and syntax of the target program in the second programming language is added. This same process can be used for either high-level conversion or compilation depending on whether the target programming language is high level or low level, respectively.

Owner:TECH MAHINDRA INDIA

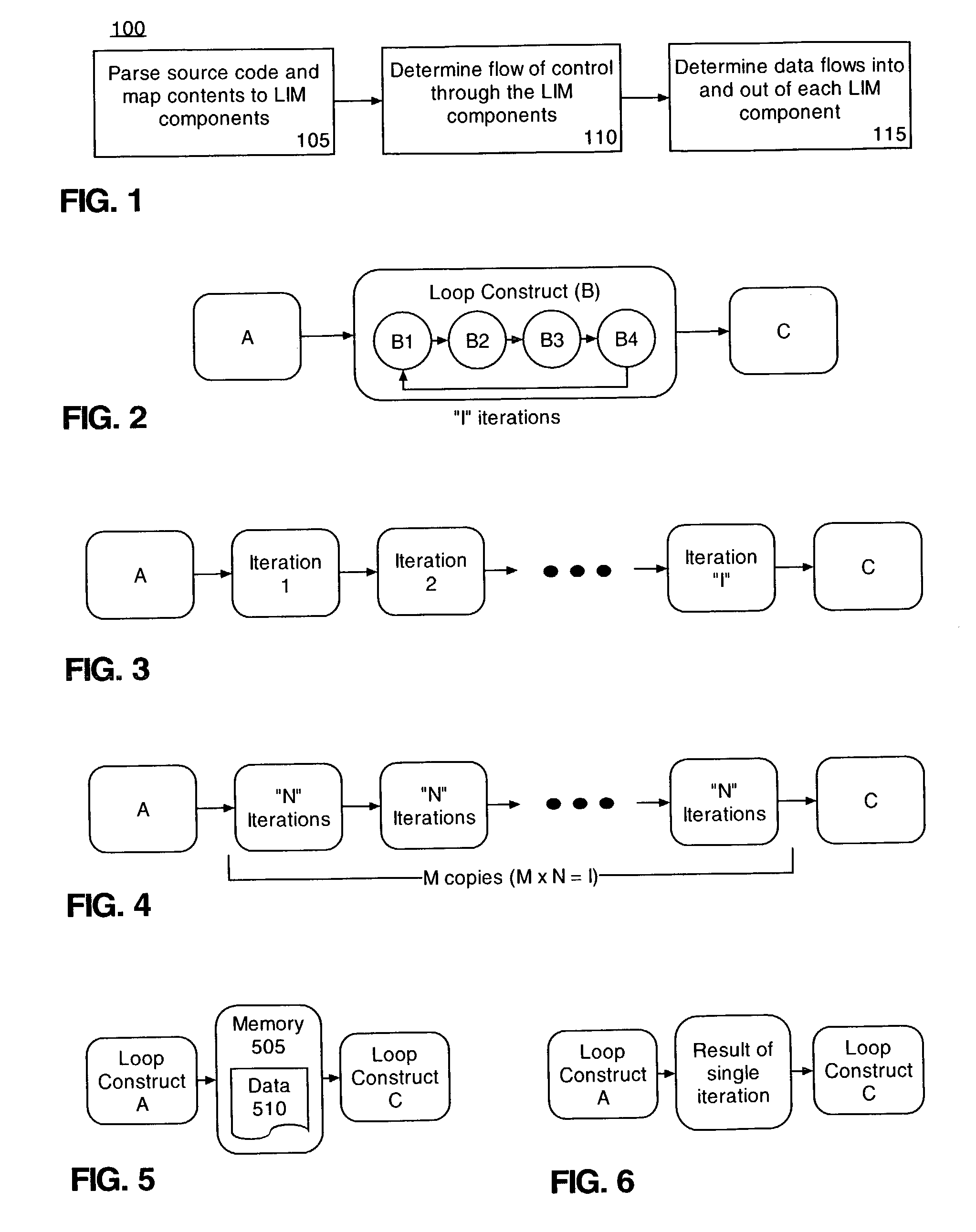

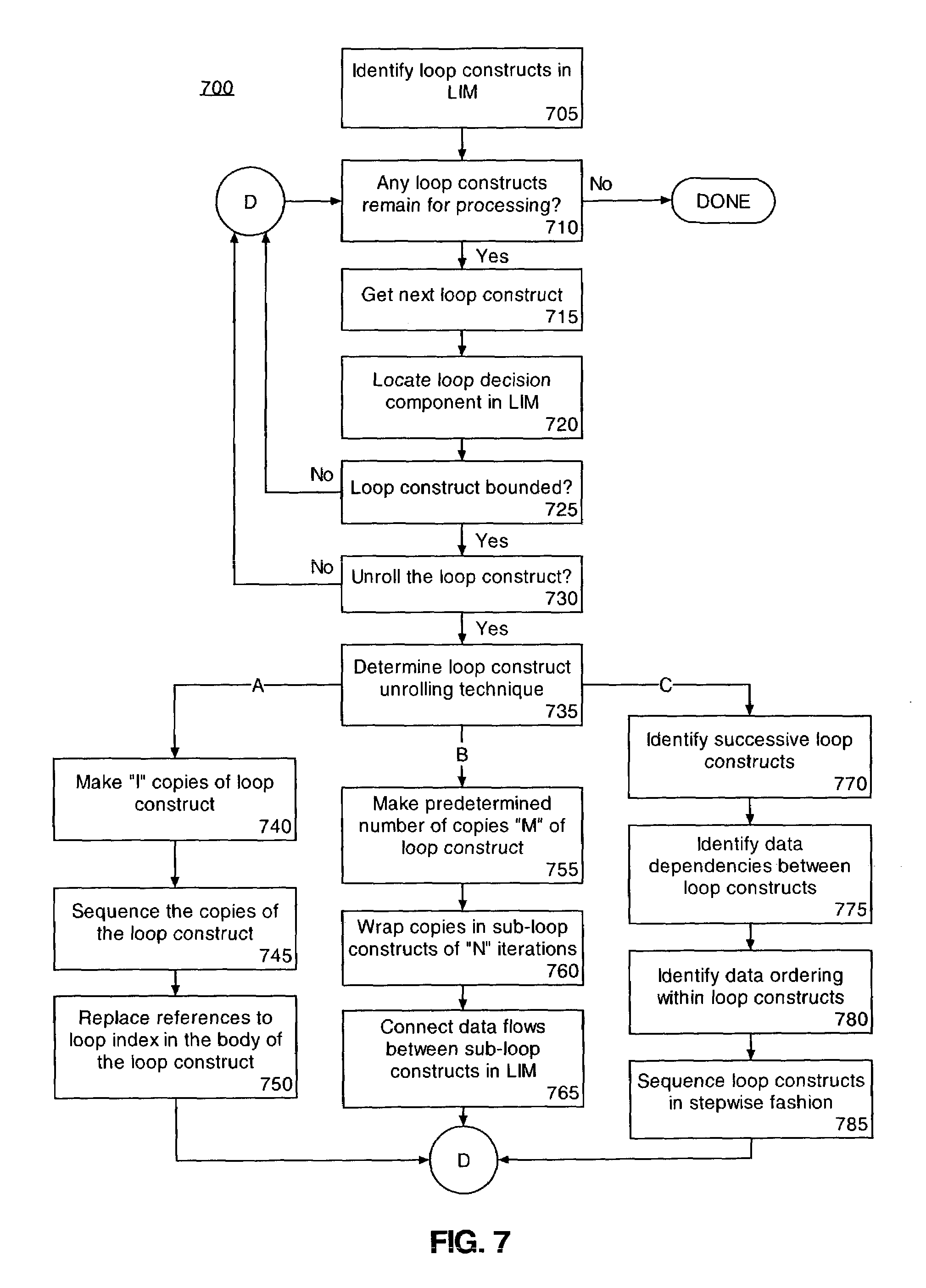

Determining hardware generated by high level language compilation through loop optimizations

ActiveUS7086047B1Accurate data inputData is availableSoftware engineeringCAD circuit designLoop optimizationGeneral-purpose programming language

A method of processing a program written in a general purpose programming language to determine a hardware representation of the program can include generating a language independent model of the program written in a general purpose programming language (100) and identifying a loop construct within the language independent model (705). A determination can be made as to whether the loop construct is bounded (725). If so, a loop processing technique can be selected for unrolling the loop construct according to stored user preferences 735). The loop construct can be replicated in the language independent model as specified by the selected loop processing technique (740, 755).

Owner:XILINX INC

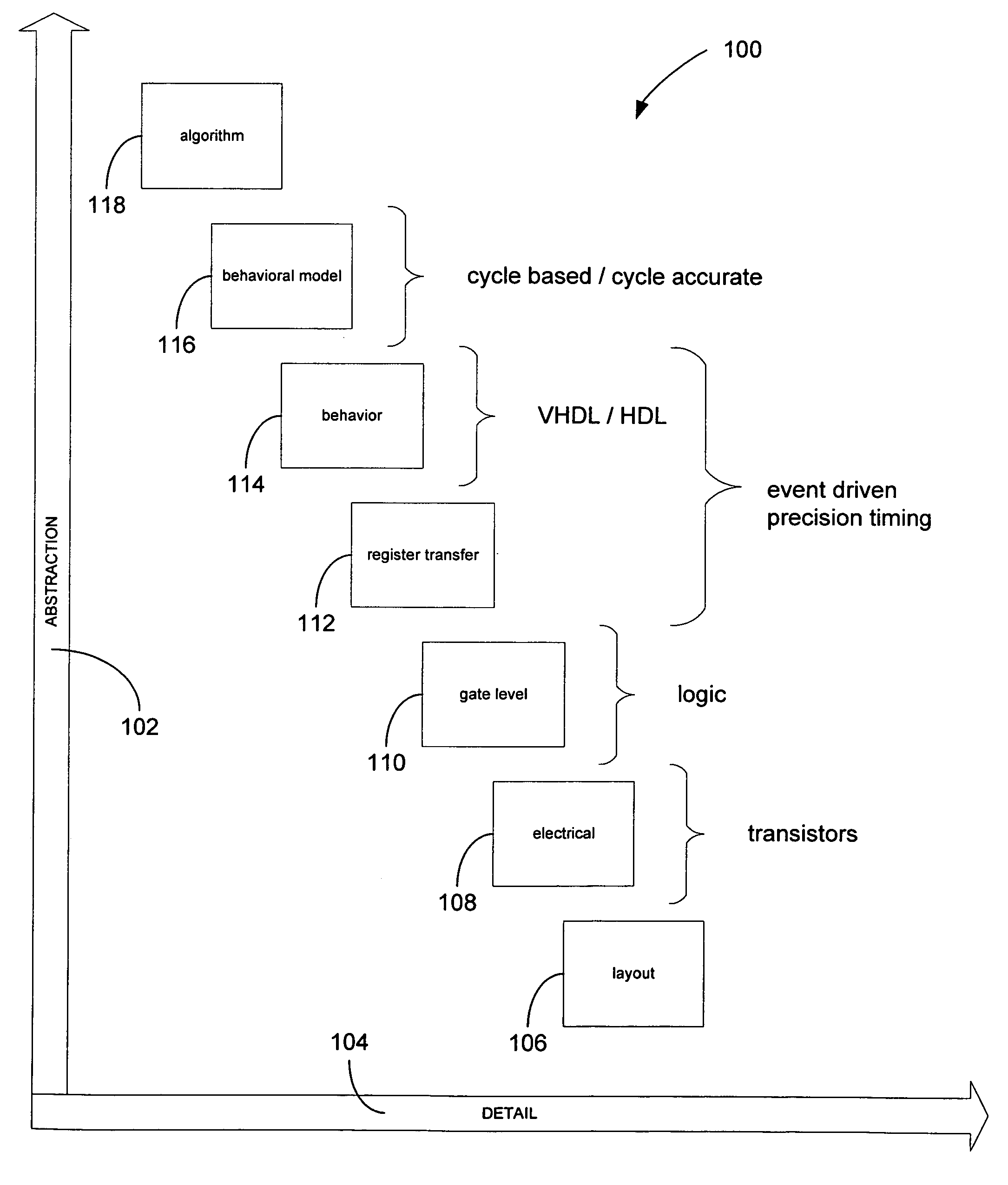

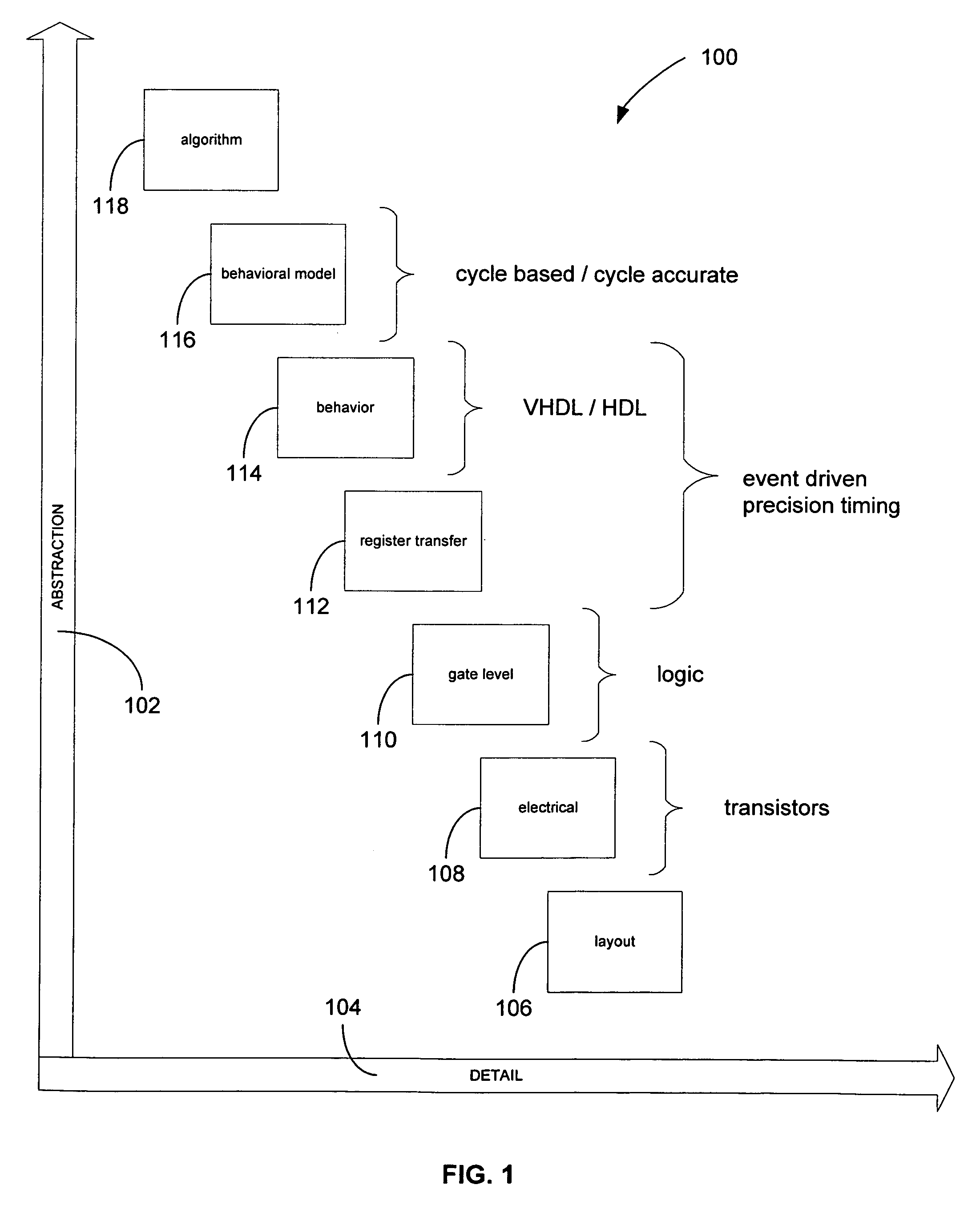

Method and apparatus for accelerating hardware simulation

InactiveUS7050958B1Reduce in quantityFunction increaseAnalogue computers for electric apparatusCAD circuit designCommunication interfaceSystems design

A method for accelerating hardware simulation is presented wherein cycle based simulations of digital system designs are generated by raising the level of abstraction in a hardware simulation environment. Behavioral models of the digital system components are created in a high level general purpose programming language. Function calls created in a high level general purpose programming language provide a transaction based communication interface. During a simulation of the system design, the behavioral models communicate with each other through the transaction based communication interface. Additionally, the behavioral models employ an execute and update method of instruction processing that generates cycle accurate information for the simulation.

Owner:ARM LTD

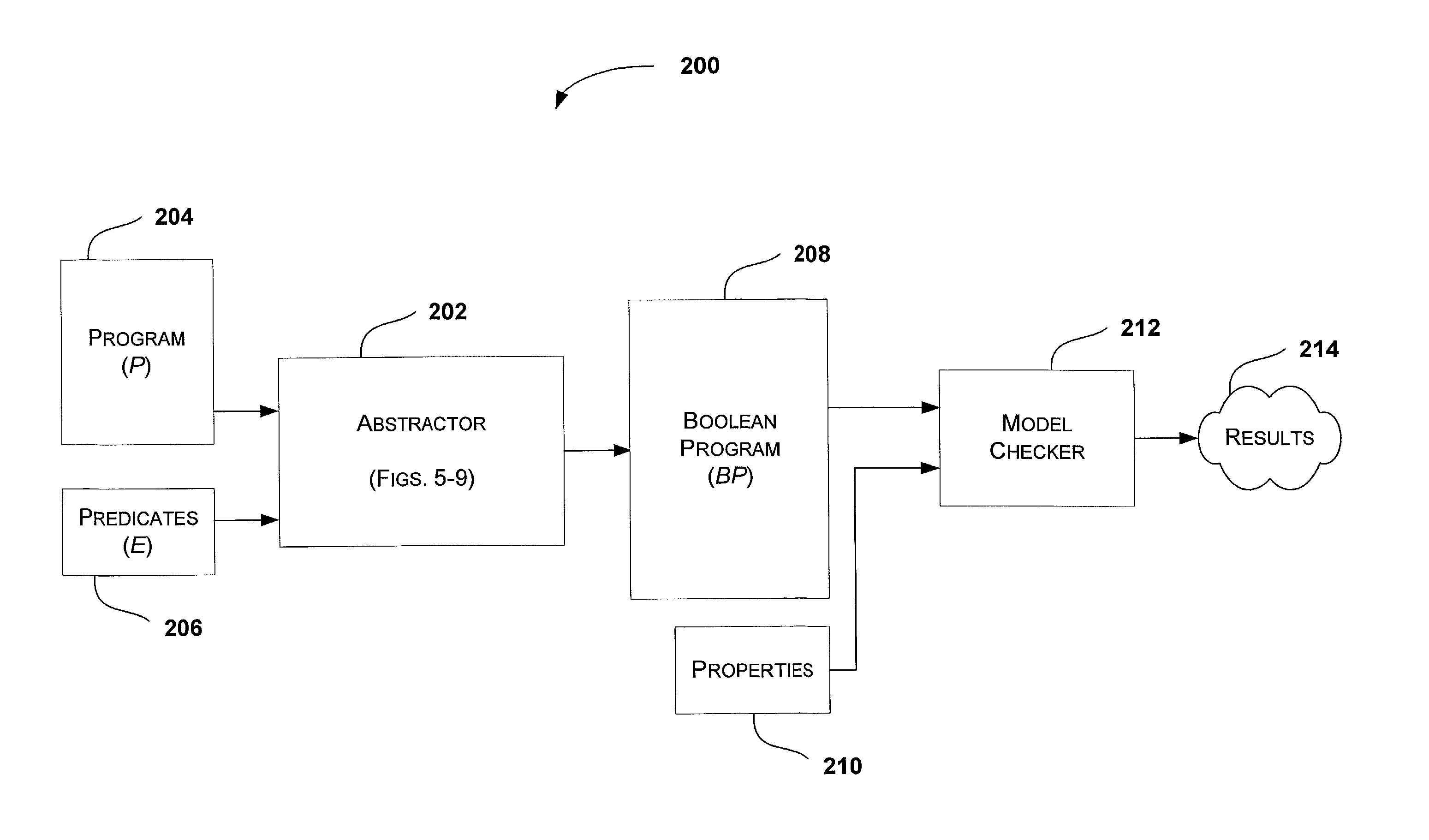

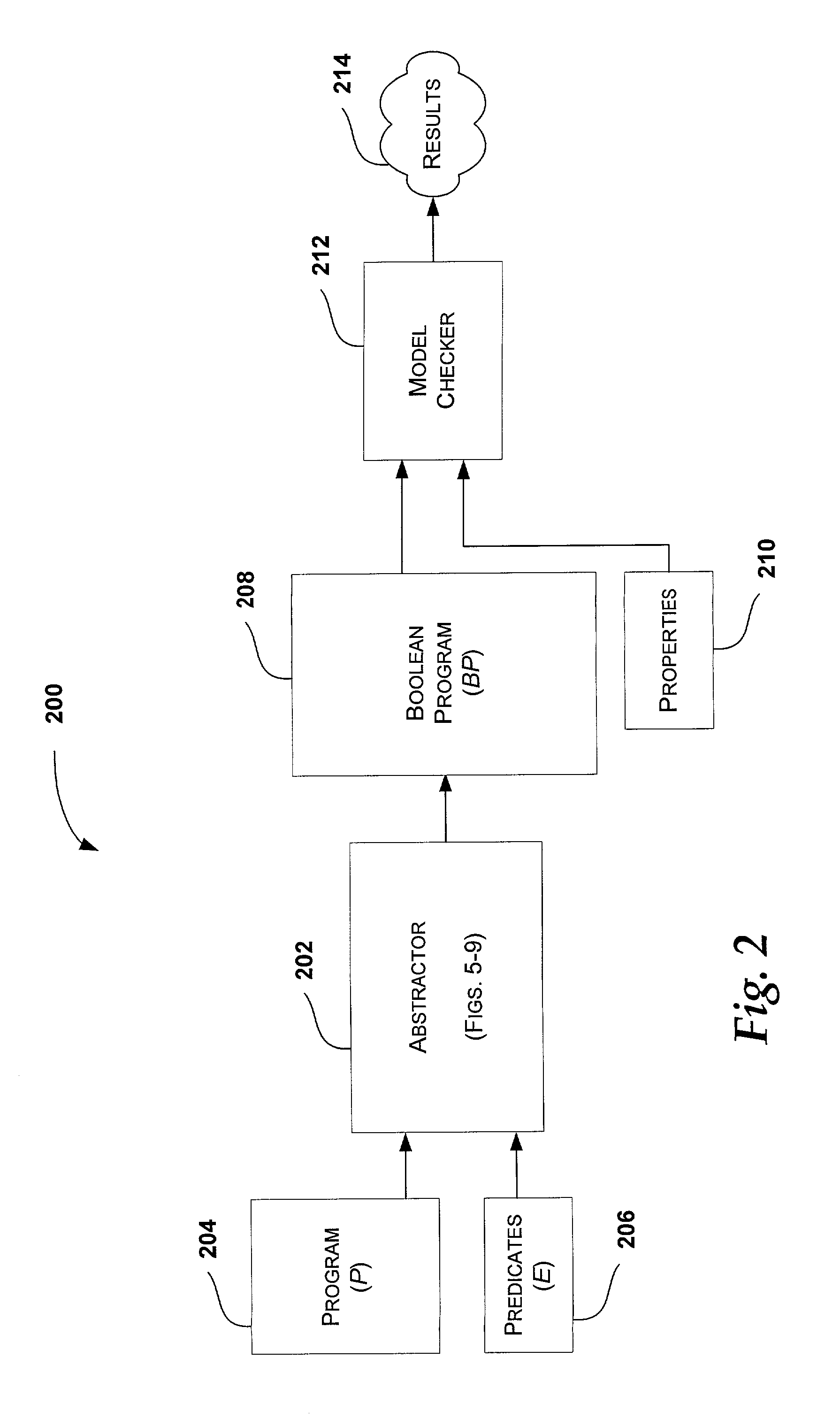

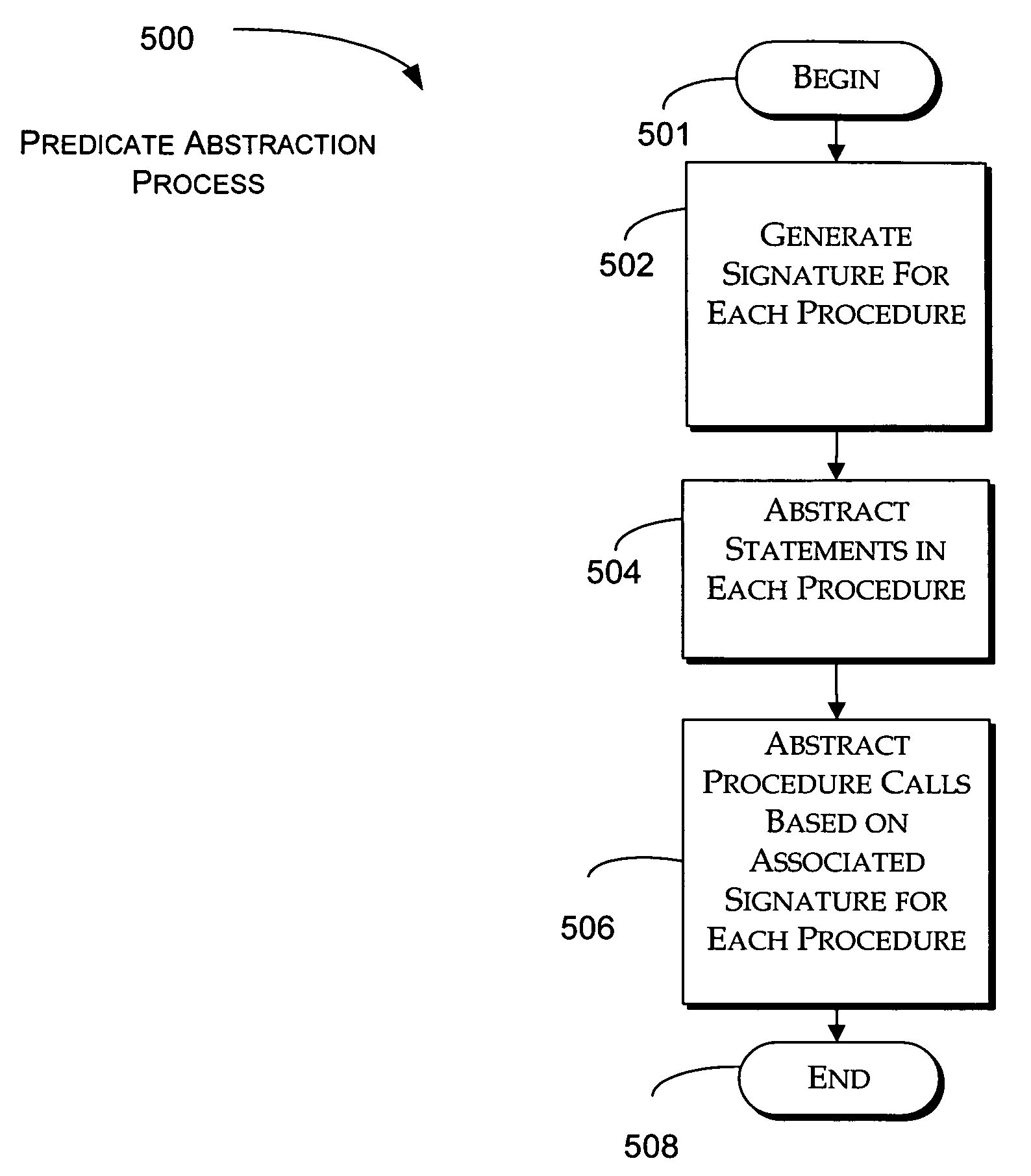

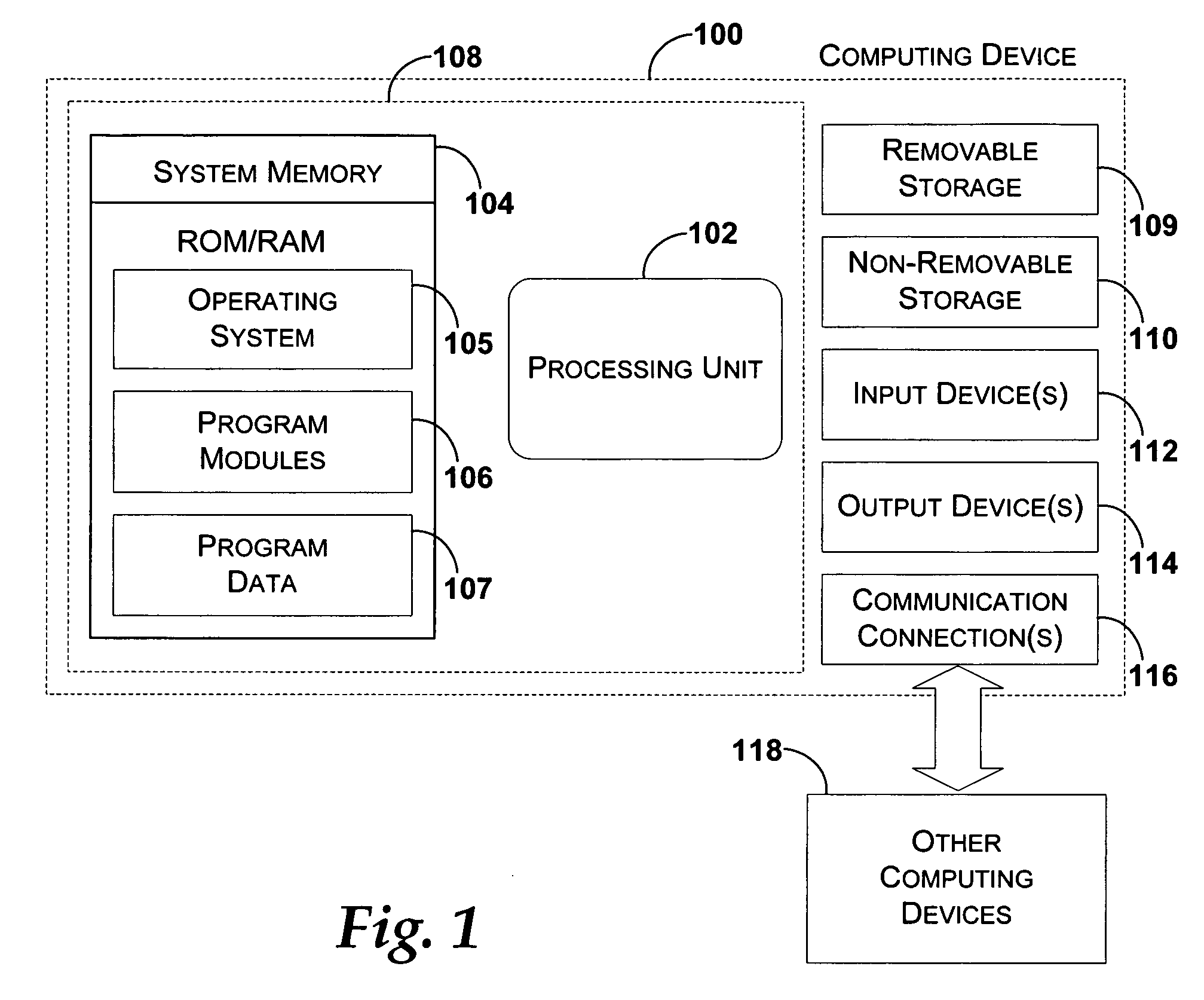

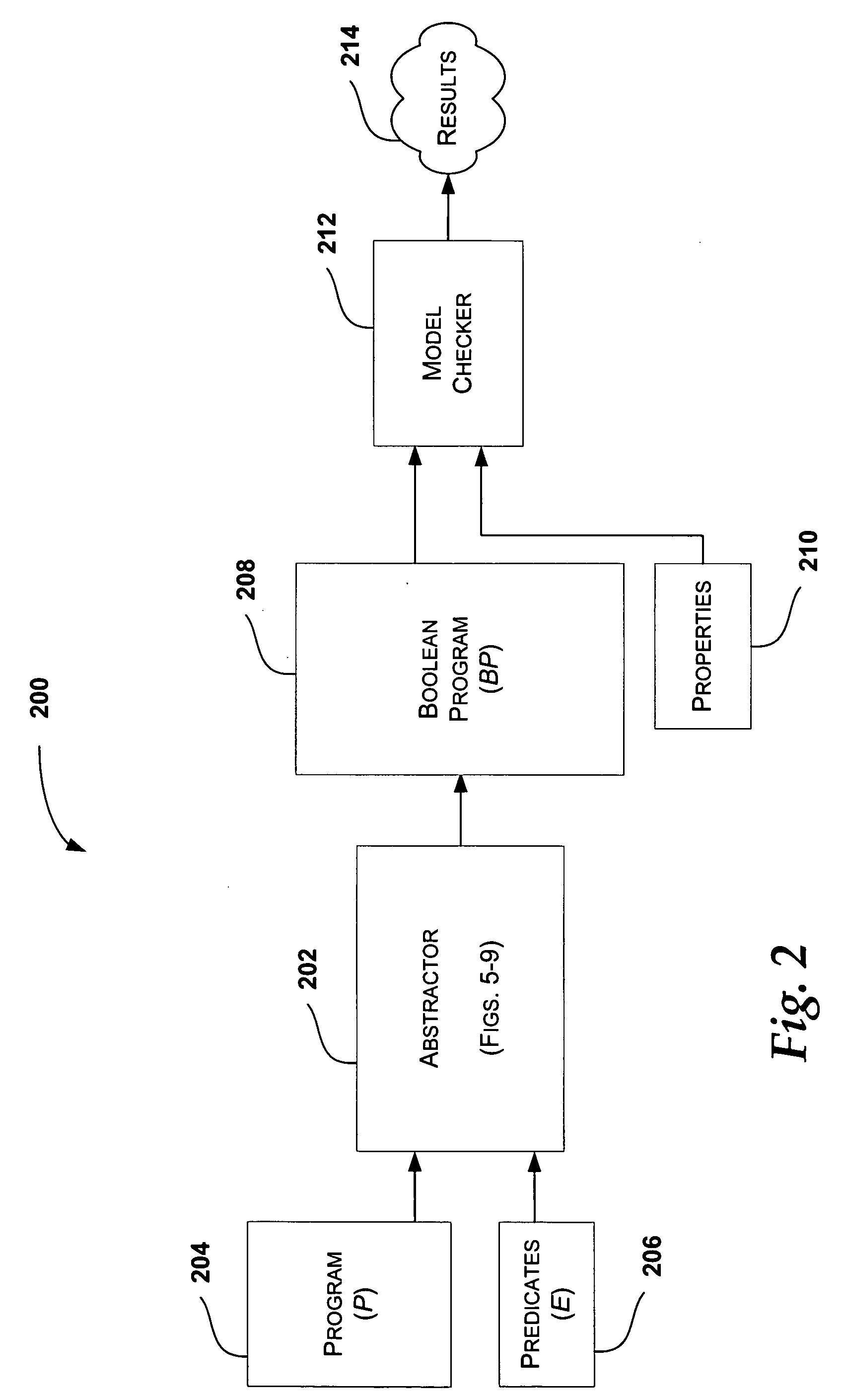

System and method for generating a predicate abstraction of a program

InactiveUS7058925B2Error detection/correctionEmergency protective arrangements for automatic disconnectionAbstract programProcedure calls

Described is a method that enables the automatic generation of a boolean program that is a predicate abstraction of a program written using a general programming language. The method is capable of abstracting code statements within the program that include procedure calls, assignments, goto statements, conditionals, and pointers. In accordance with the invention, predicates of interest are identified for each code statement in the program. For each particular code statement, the process generates predicate statements that describe an effect that the statement has on the predicates of interest. If the effect of a particular code statement is indeterminable, non-deterministic predicate statements are included in the boolean program to model the indeterminable nature of the code statement. In addition, if a particular code statement includes a procedure call, the arguments and return value of the procedure call are translated to associated predicates in the calling context.

Owner:MICROSOFT TECH LICENSING LLC

Method of transforming software language constructs to functional hardware equivalents

InactiveUS7143388B1CAD circuit designSoftware simulation/interpretation/emulationData streamTheoretical computer science

A method of designing an integrated circuit using a general purpose programming language can include identifying a number of instances of each class allocated in a programmatic design implemented using the general purpose programming language and modeling the global memory of the programmatic design. A data flow between the modeled global memory and instructions of the programmatic design which access object fields can be determined and access to the modeled global memory can be scheduled. The programmatic design can be translated into a hardware description of the integrated circuit using the modeled global memory, the data flow, and the scheduled memory access.

Owner:XILINX INC

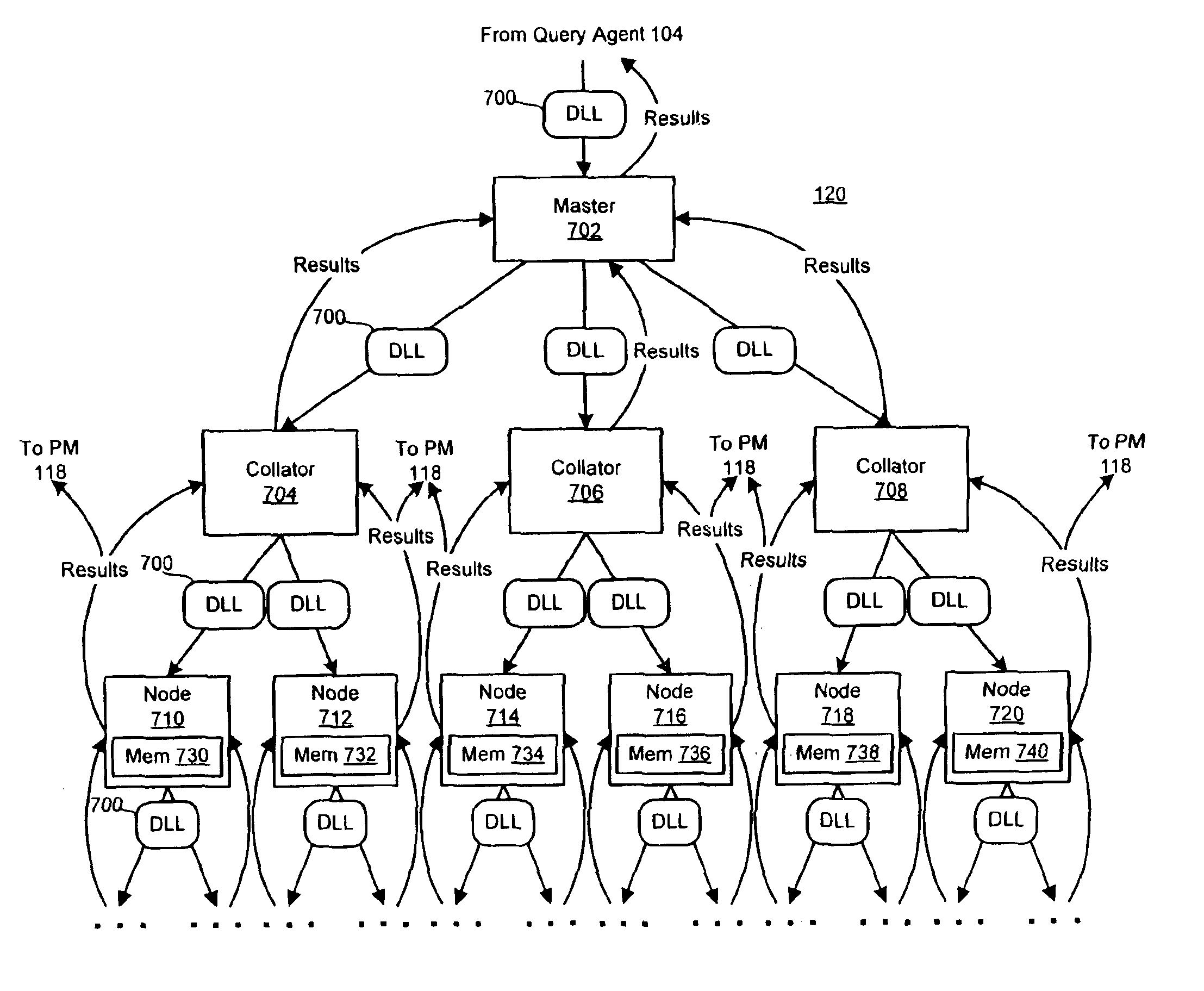

Global-results processing matrix for processing queries

ActiveUS7945581B2Improve economyTransparent operationDigital data information retrievalDigital data processing detailsTheoretical computer scienceHigh-level programming language

A system and methods for parallel processing of queries to one or more databases are described herein. One or more databases may be distributed among a subset of slave nodes of a global-results processing matrix. A query to the database may be generated using a query-based high-level programming language. The query-based source code then may be converted to intermediary source code in a common programming language and then compiled into a dynamic link library (DLL) or other type of executable. The DLL is then distributed among the slave nodes of the processing matrix, whereupon the slave nodes execute related portions of the DLL substantially in parallel to generate initial query results. The initial query results may then be provided to a master node of the global-results processing matrix for additional processing, whereby the master node is adapted to execute one or more associated portions of the DLL on the initial query results.

Owner:LEXISNEXIS RISK DATA MANAGEMENT

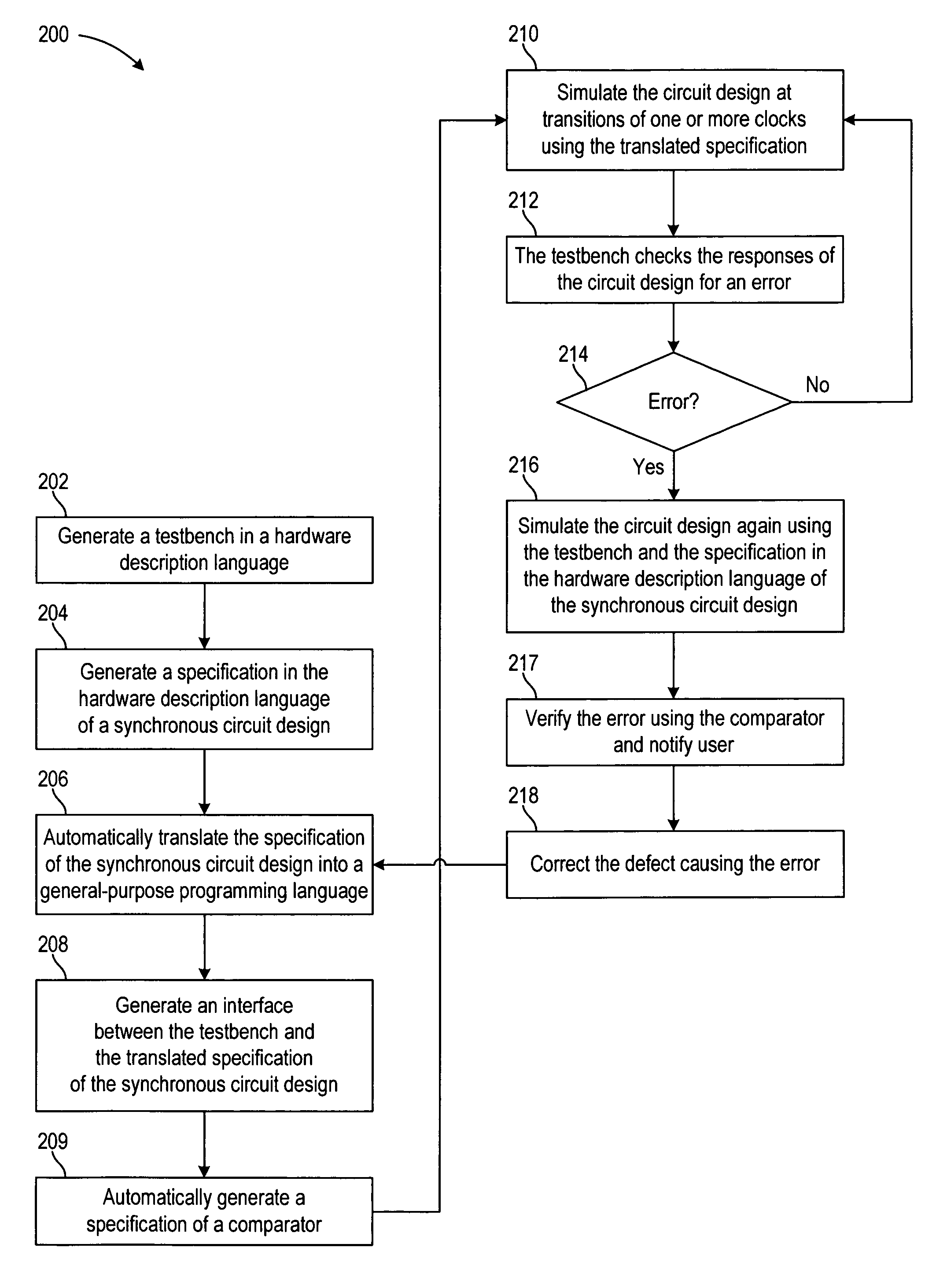

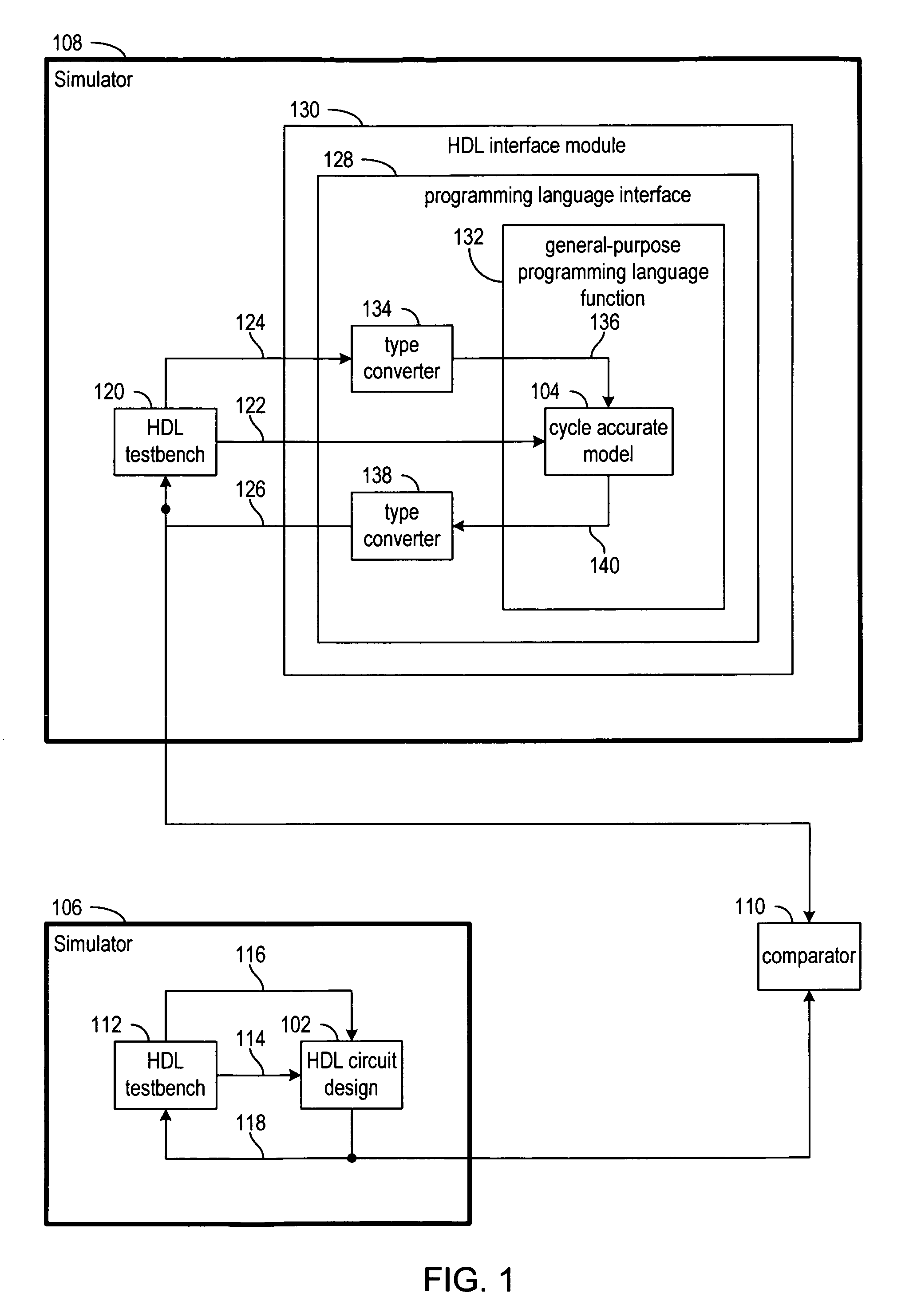

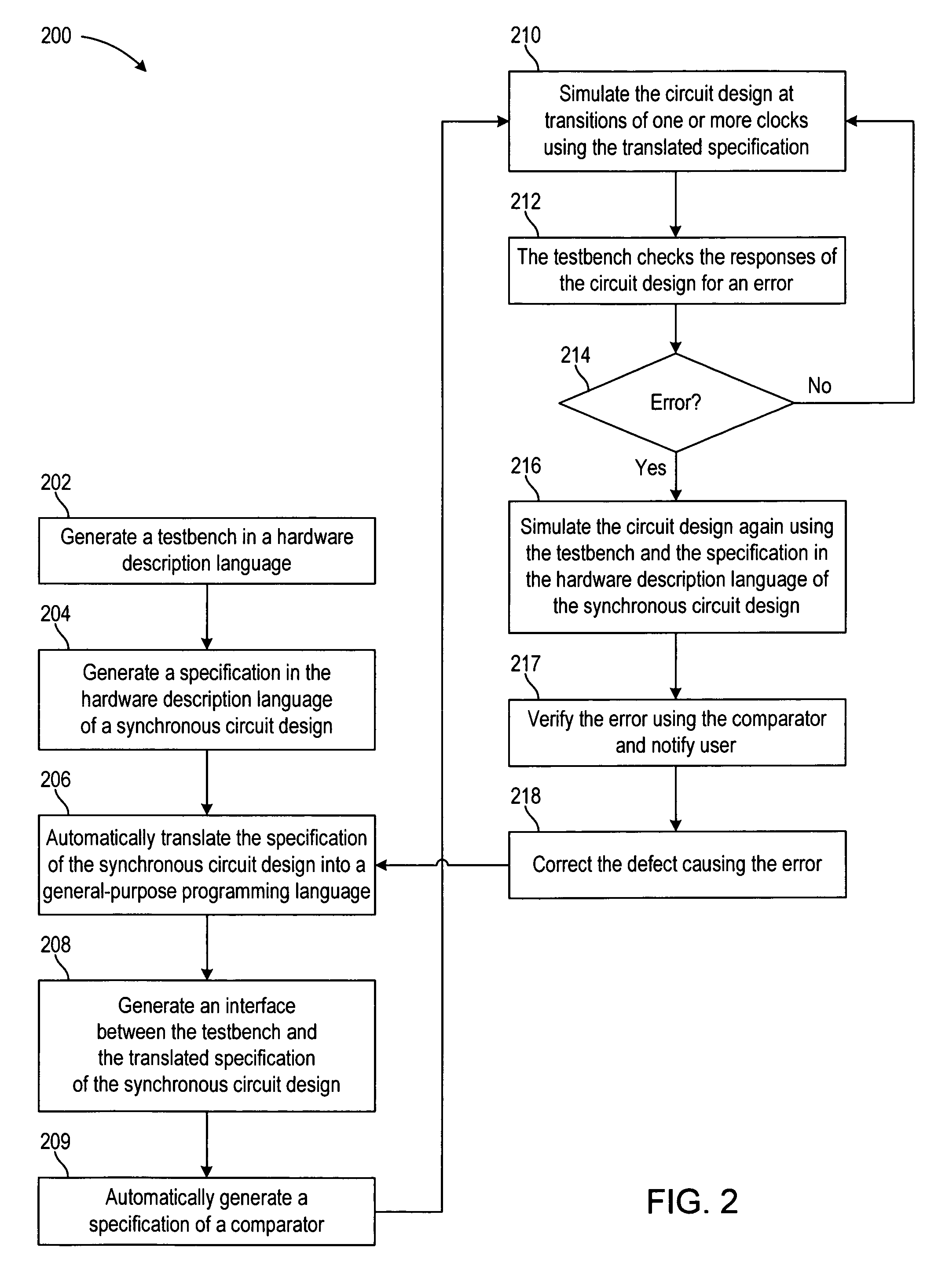

Simulation of a programming language specification of a circuit design

ActiveUS7437701B1CAD circuit designSpecial data processing applicationsAnalog circuit designTheoretical computer science

Various approaches for simulating a circuit design are disclosed. In one approach, a first specification of a testbench and a second specification of the circuit design are generated in a hardware description language. The circuit design is synchronous to at least one clock signal. The second specification of the circuit design is automatically translated into a third specification in a general-purpose programming language, and the third specification specifies the behavior of the circuit design at transitions of the at least one clock signal. A fourth specification of an interface between the first specification of the testbench and the third specification of the circuit design is automatically generated. A first behavior of the circuit design is simulated using the first and third specifications linked by the fourth specification and the stimuli from the test bench.

Owner:XILINX INC

System and method for generating a predicate abstraction of a program

InactiveUS20050235257A1Error detection/correctionEmergency protective arrangements for automatic disconnectionAbstract programProcedure calls

Described is a method that enables the automatic generation of a boolean program that is a predicate abstraction of a program written using a general programming language. The method is capable of abstracting code statements within the program that include procedure calls, assignments, goto statements, conditionals, and pointers. In accordance with the invention, predicates of interest are identified for each code statement in the program. For each particular code statement, the process generates predicate statements that describe an effect that the statement has on the predicates of interest. If the effect of a particular code statement is indeterminable, non-deterministic predicate statements are included in the boolean program to model the indeterminable nature of the code statement. In addition, if a particular code statement includes a procedure call, the arguments and return value of the procedure call are translated to associated predicates in the calling context.

Owner:MICROSOFT TECH LICENSING LLC

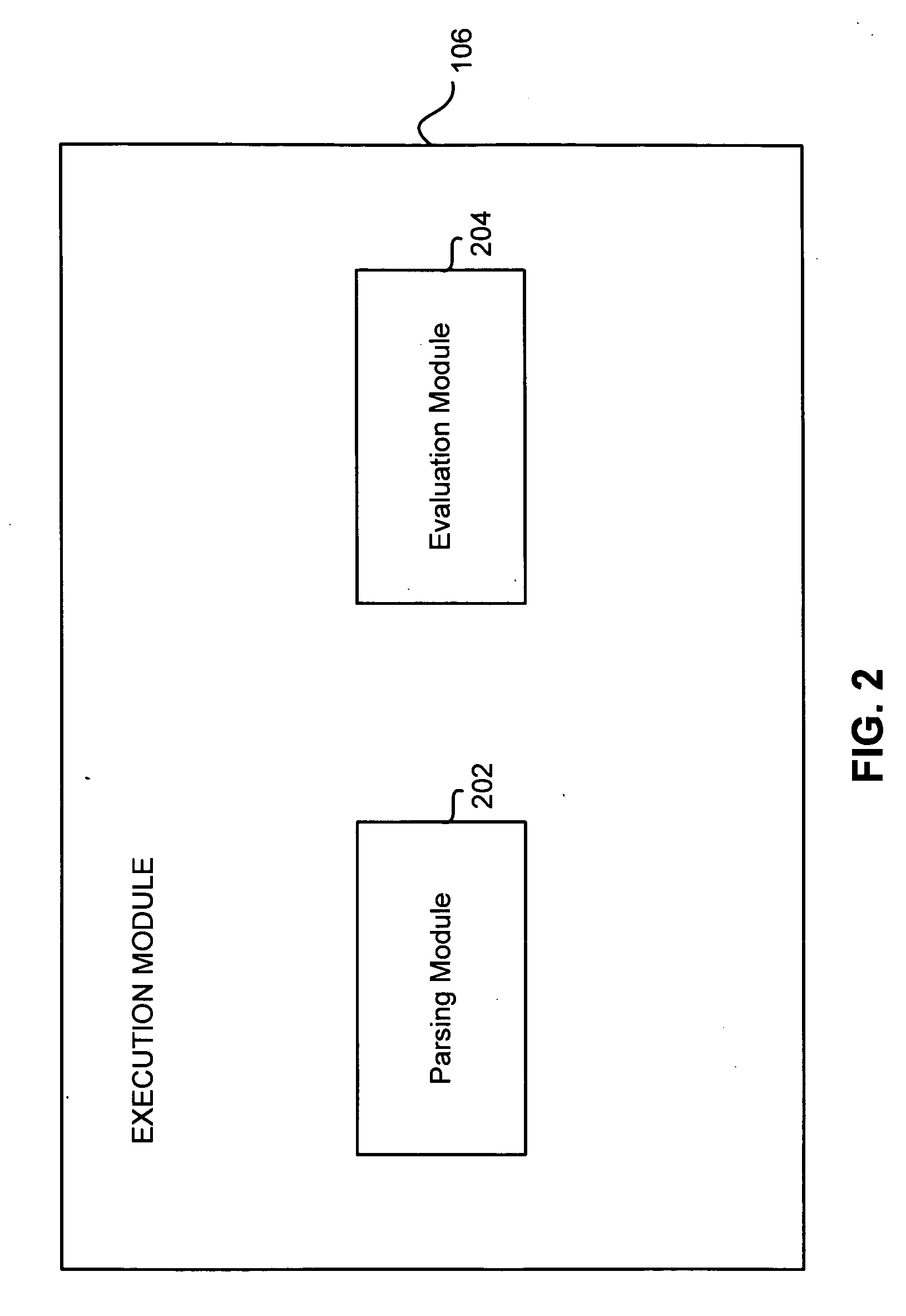

Evaluation of a temporal description within a general purpose programming language

InactiveUS20060277534A1Program controlComputer aided designTheoretical computer scienceTime expression

A translation module translates a temporal description into a temporal expression. The translation module is adapted to translate a temporal description in the form of an extended syntax or a preprocessing macro to the temporal expression. The temporal expression includes a native expression of a general purpose programming language. The temporal expression may also include one or more construct functions. A parsing module parses the temporal expression to generate a data structure that represents the temporal expression without evaluating the native expression. An evaluation module evaluates the data structure to execute the temporal expression including the native expression.

Owner:JEDA TECHNOLOGIES

Circuit and method of a memory compiler based on subtractive approach

ActiveUS8607019B2Digital data processing detailsMemory adressing/allocation/relocationDatasheetTheoretical computer science

A memory compiler to generate a set of memories is based on a subtraction approach from a set of templates (memory templates), including at least one layout database and auxiliary design databases, by software. The software can be based on general-purpose programming language or a layout-specific language. The compiled memories can be generated by reducing the memory array sizes in row and / or column directions by moving, deleting, adding, sizing, or stretching the layout objects, and disabling the high order addresses, etc. from the memory template by software. The new auxiliary design databases, such as layout phantom, behavior model, synthesis view, placement-and-routing view or datasheet, can also be generated by modifying some parameters from the memory template by software. One-time programmable memory using junction diode, polysilicon diode, or isolated active-region diode as program selector in a cell can be generated accordingly.

Owner:ATTOPSEMI TECH CO LTD

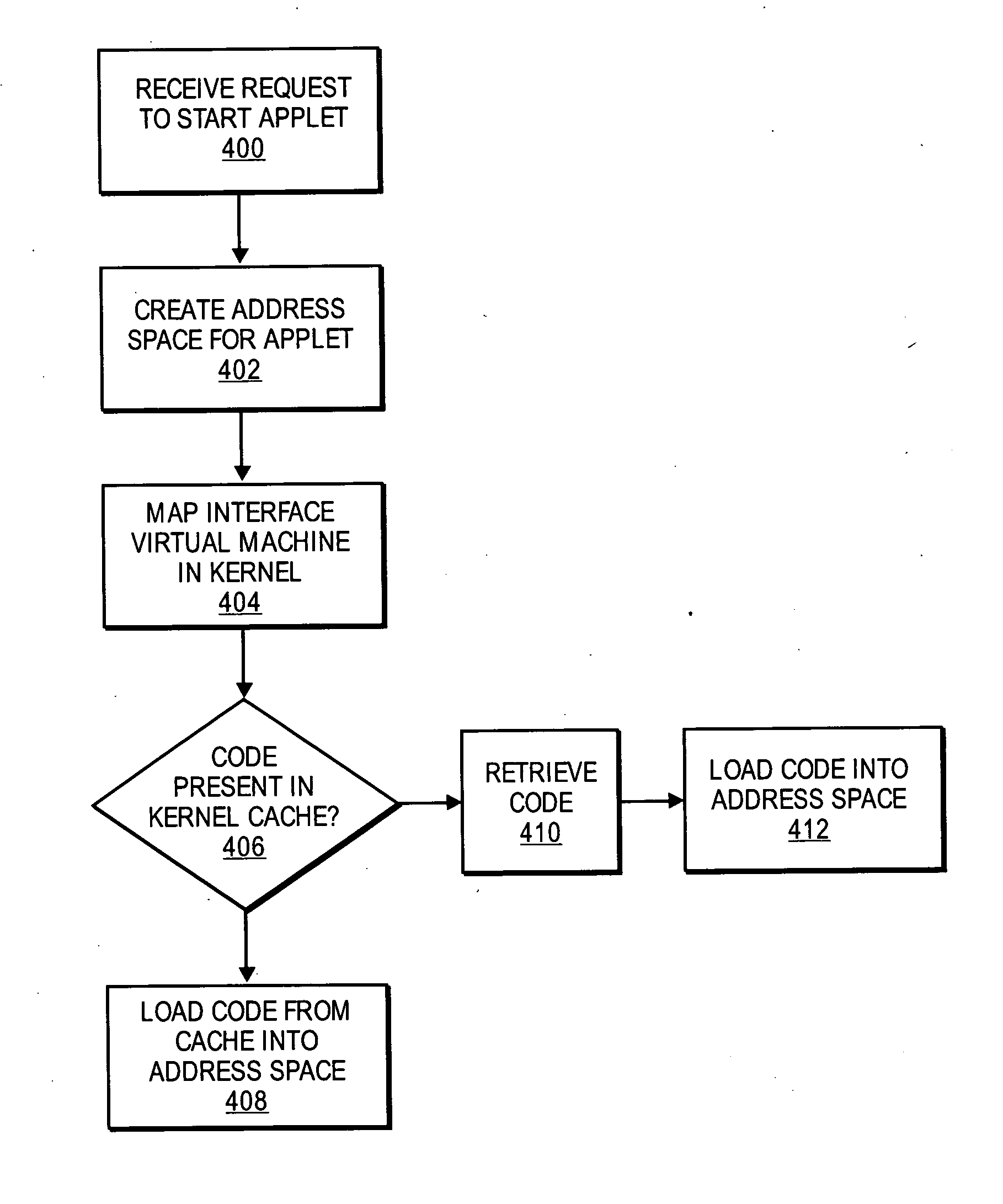

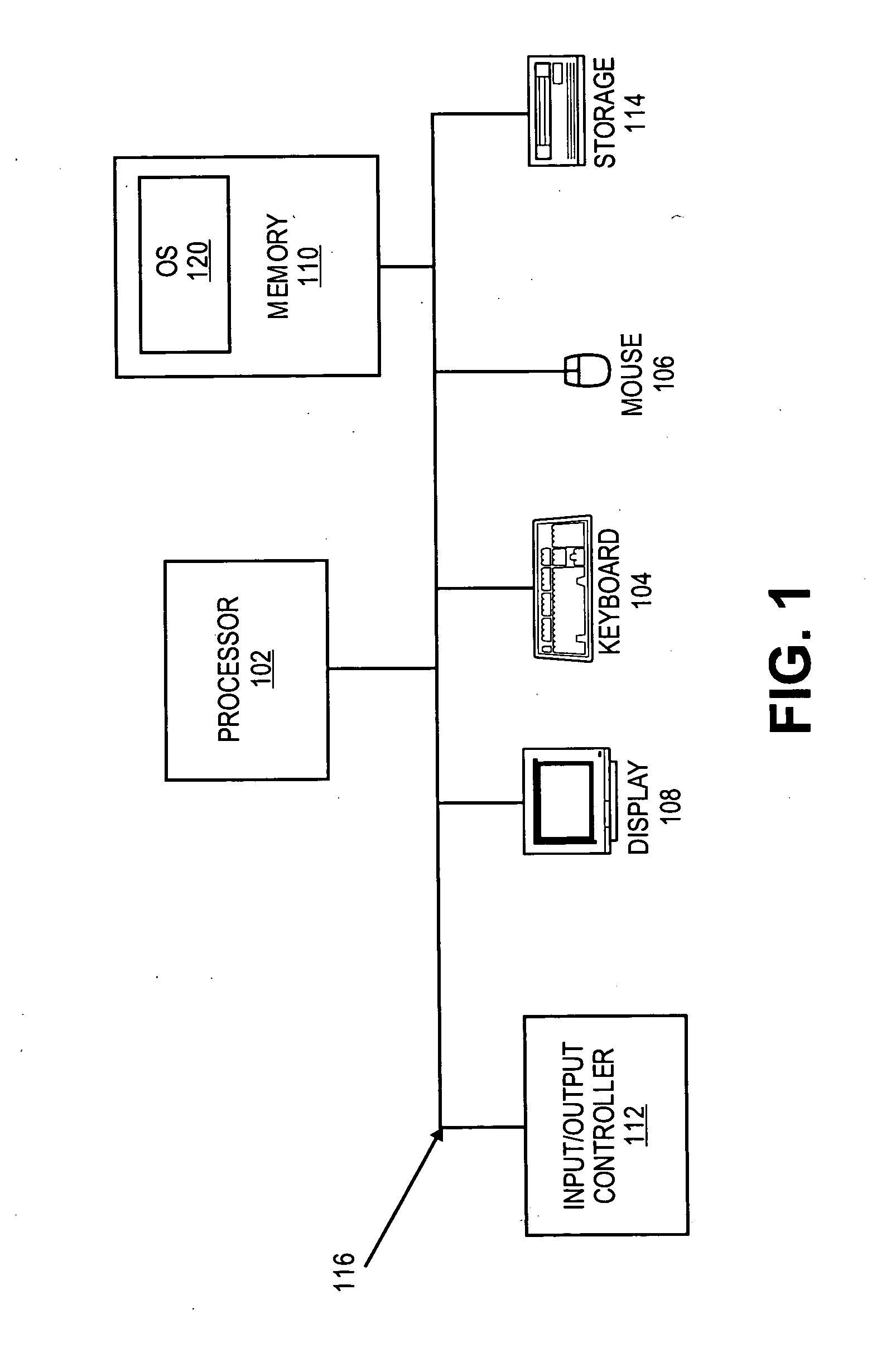

In-kernel virtual machine for low overhead startup and low resource usage

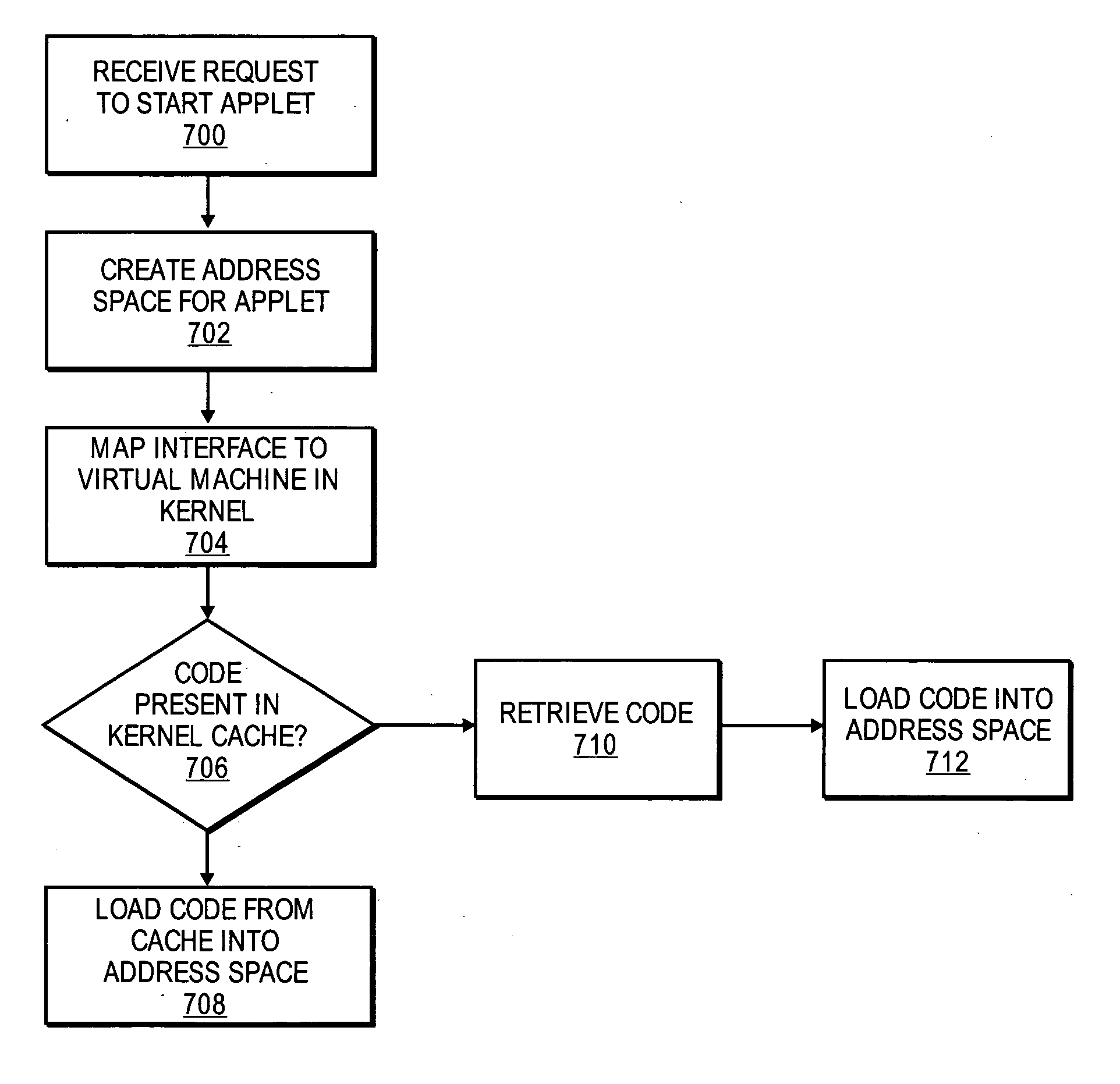

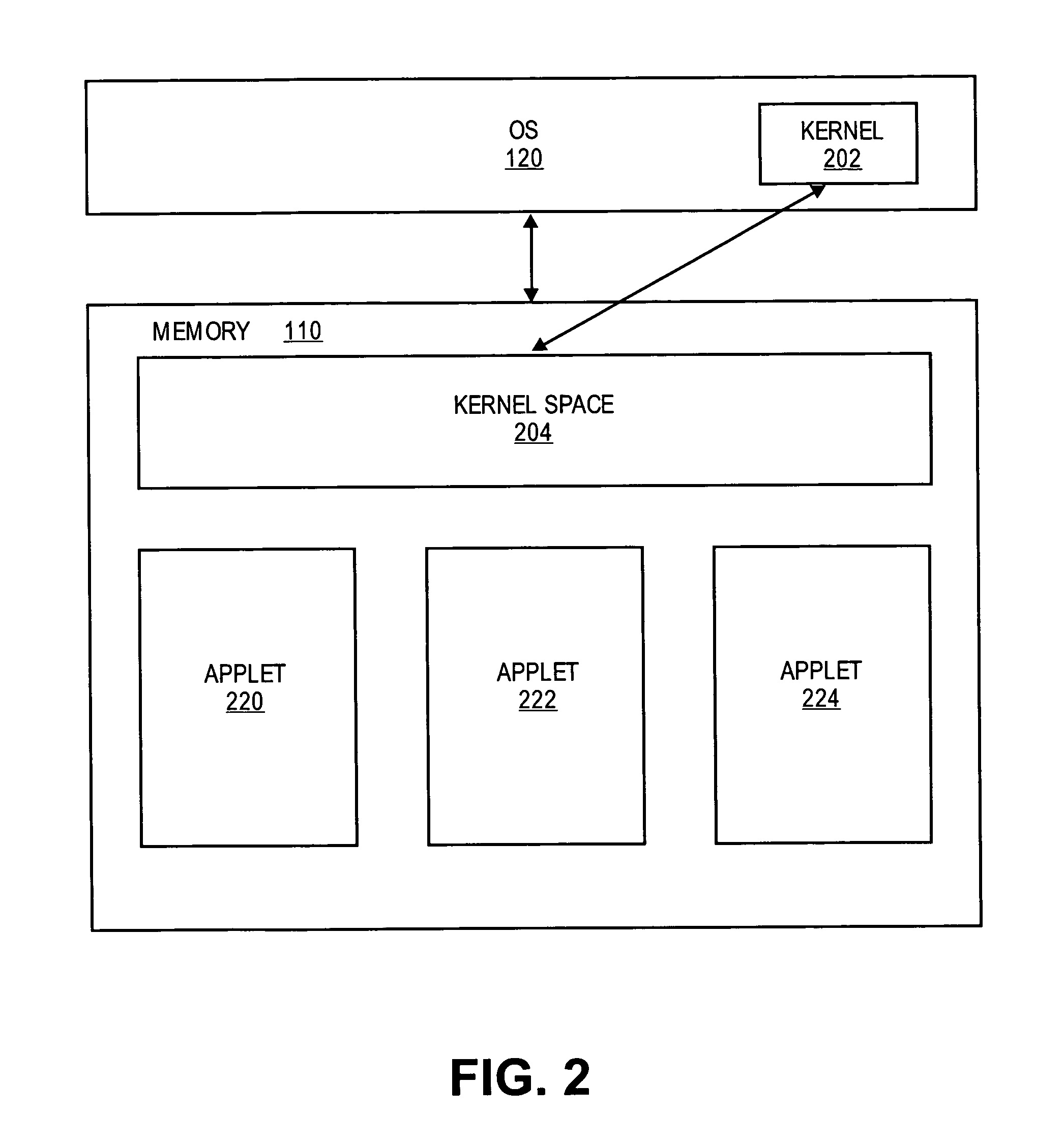

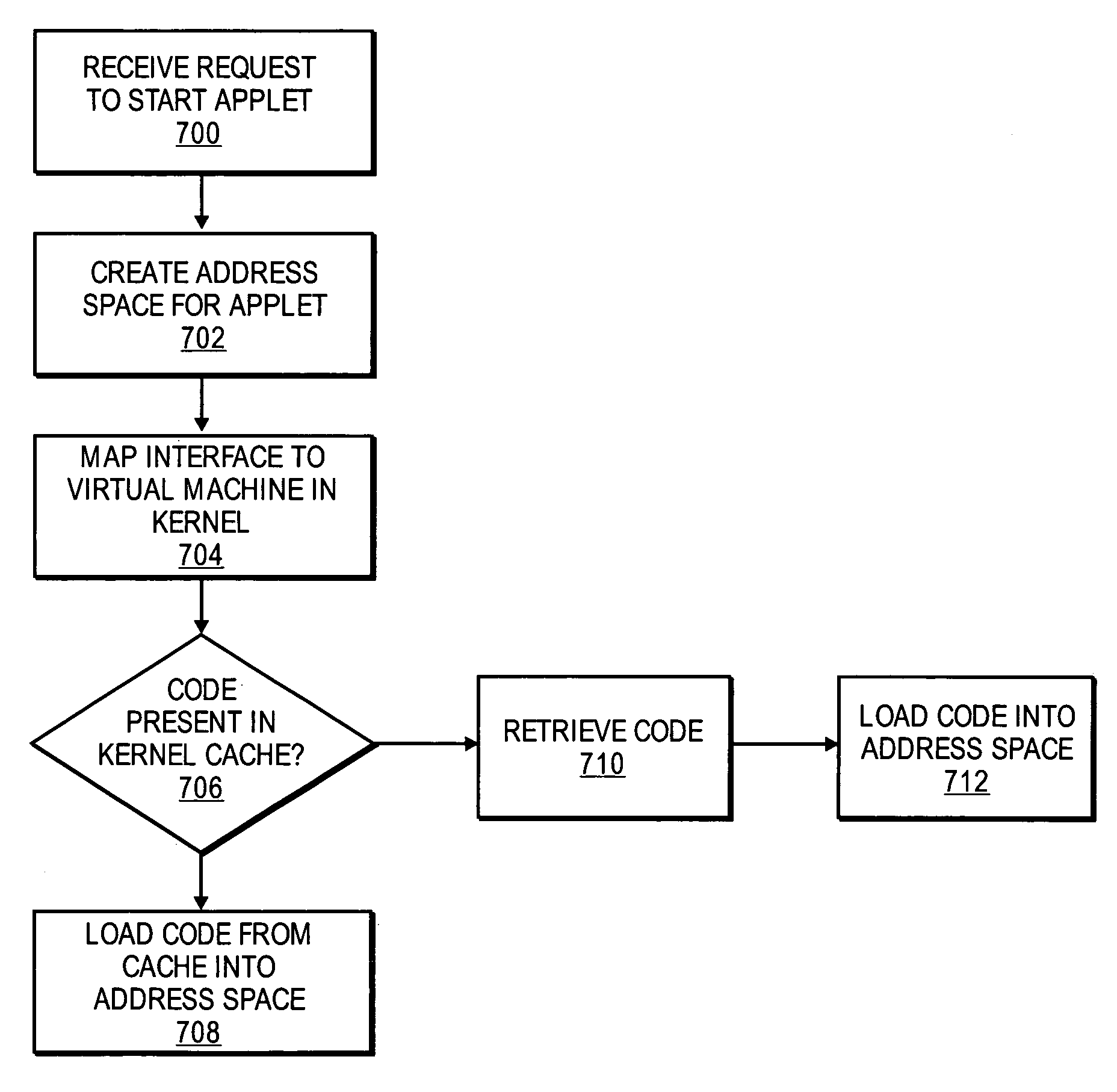

ActiveUS20070169070A1TransmissionSpecific program execution arrangementsOperational systemHuman language

Embodiments of the present invention provide an architecture for efficiently loading and executing byte code generated from a general programming language. In particular, a byte code interpreter implements a virtual machine that executes the byte code and is divided into a kernel component and one or more user components. The kernel component of the virtual machine is integrated into the operating system kernel. The user component runs in the same virtual address space as the applet, provides support for executing an applet and couples the applet to the operating system. In addition, the kernel component of the virtual machine may share code with multiple user components.

Owner:RED HAT

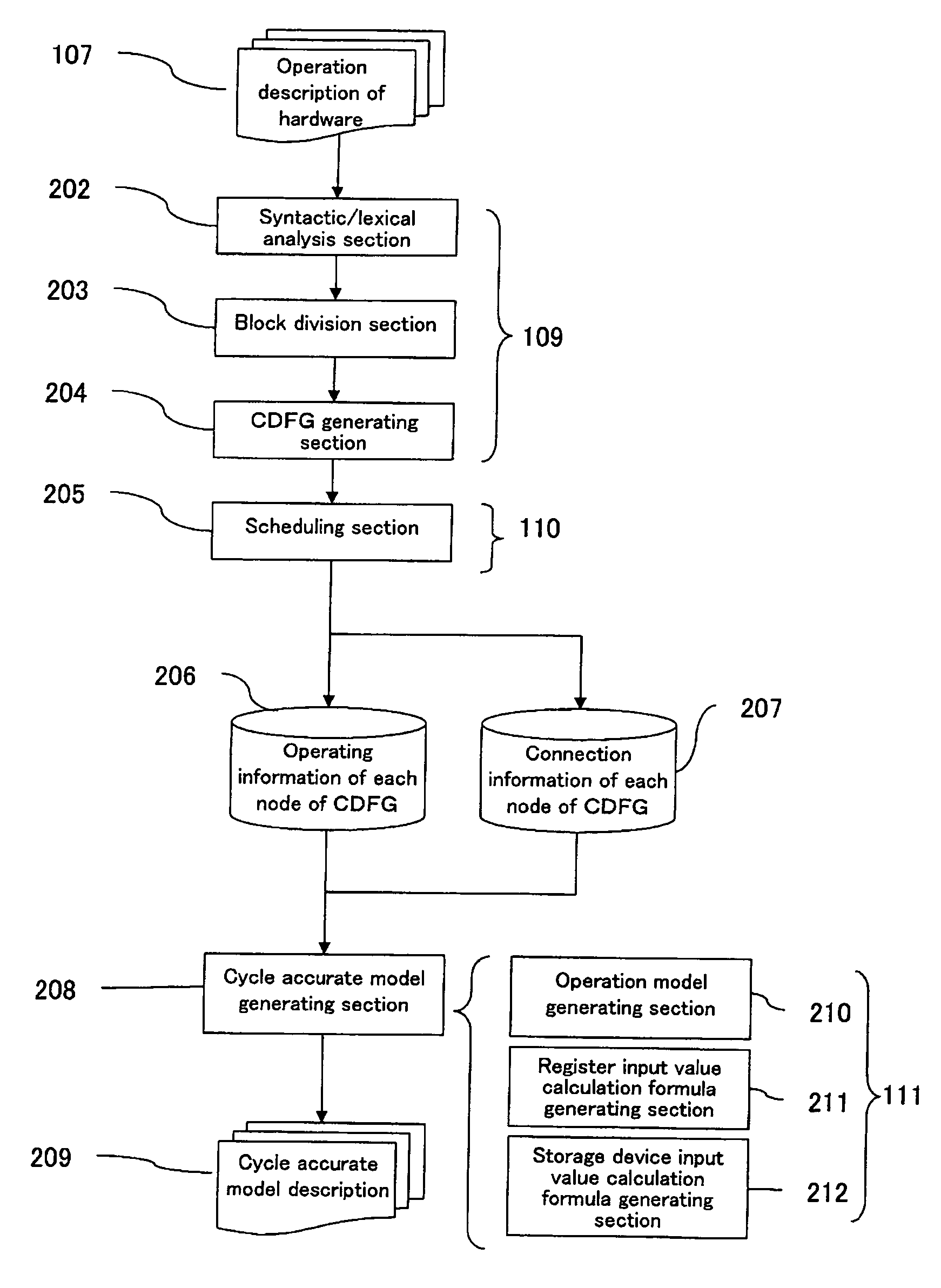

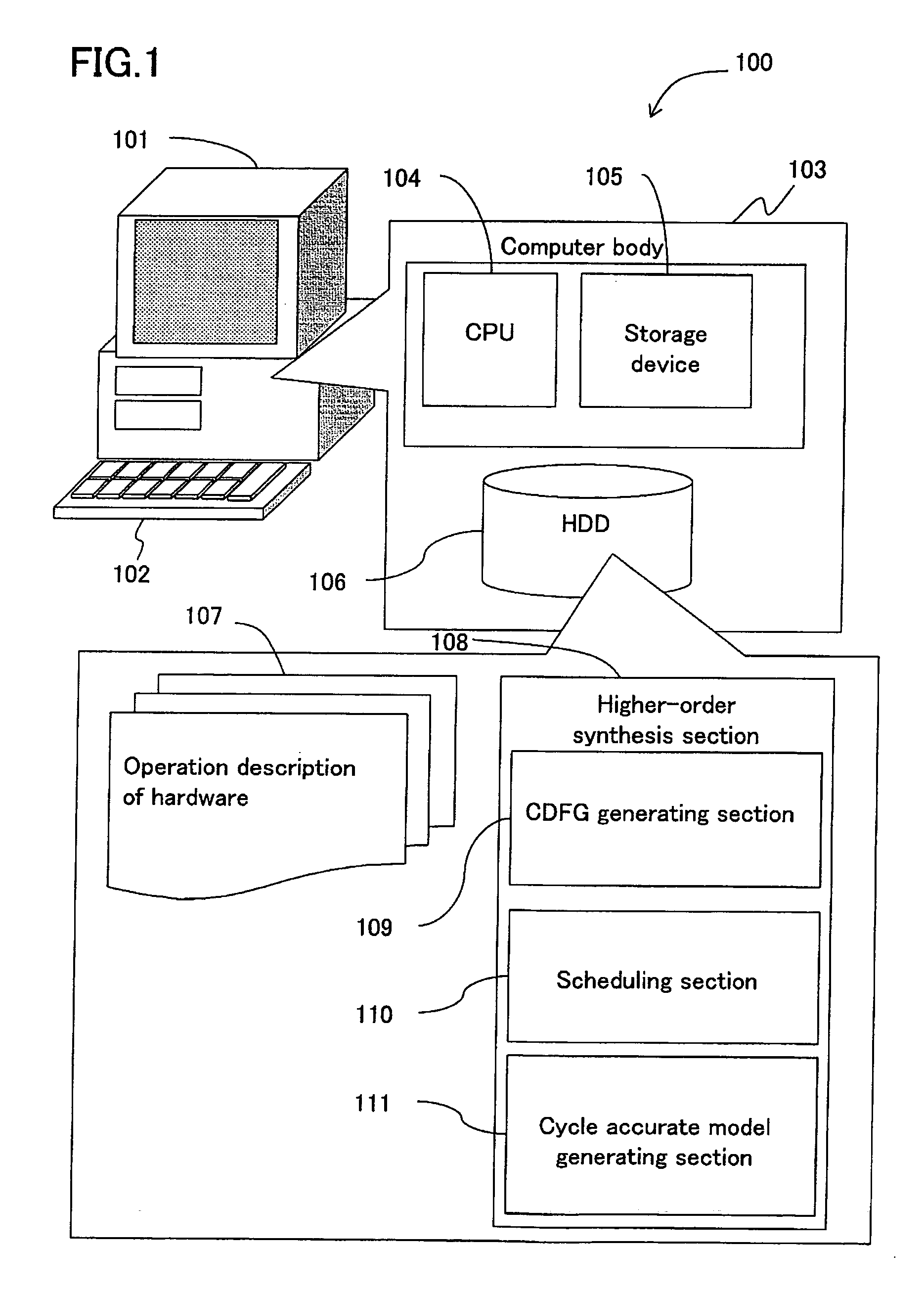

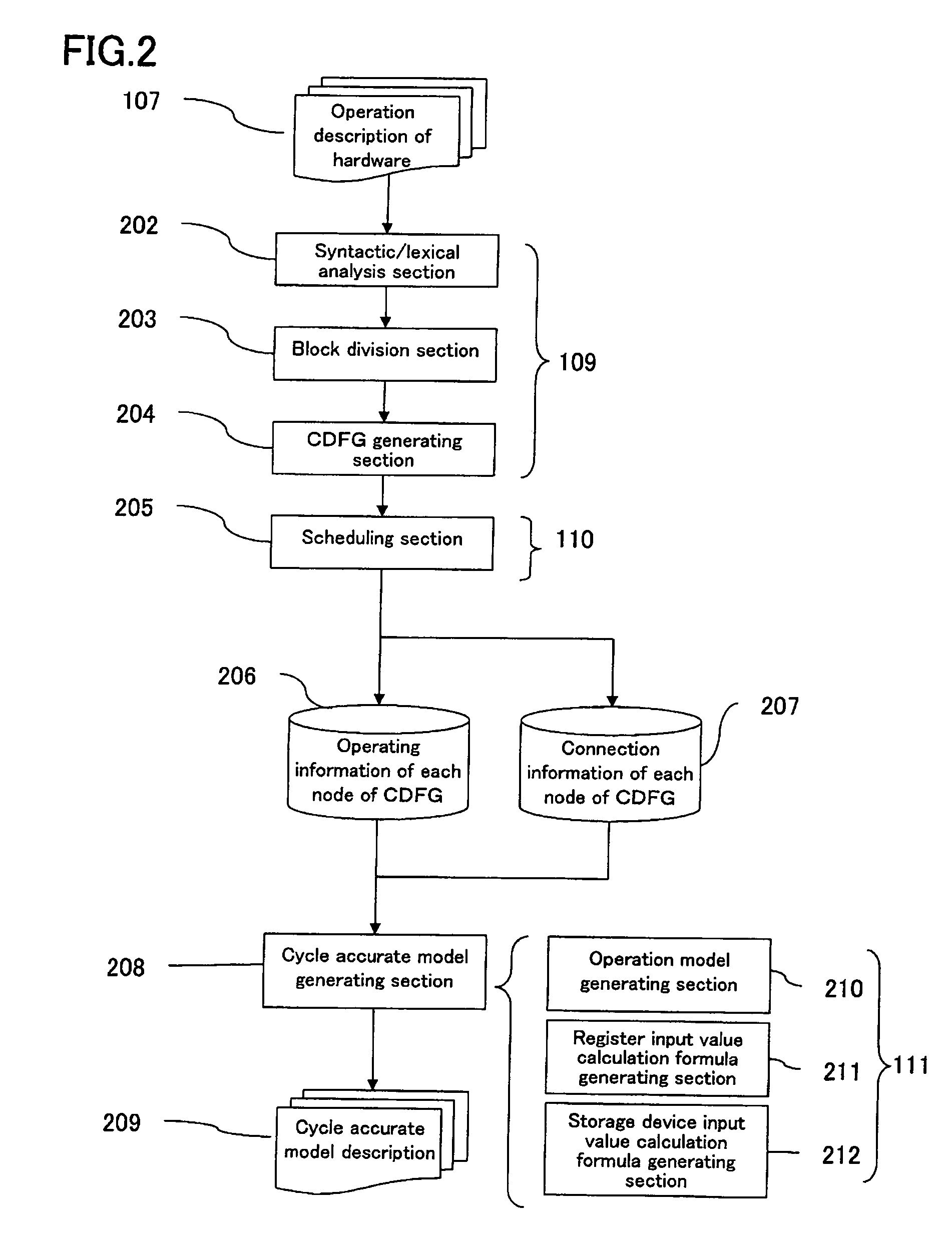

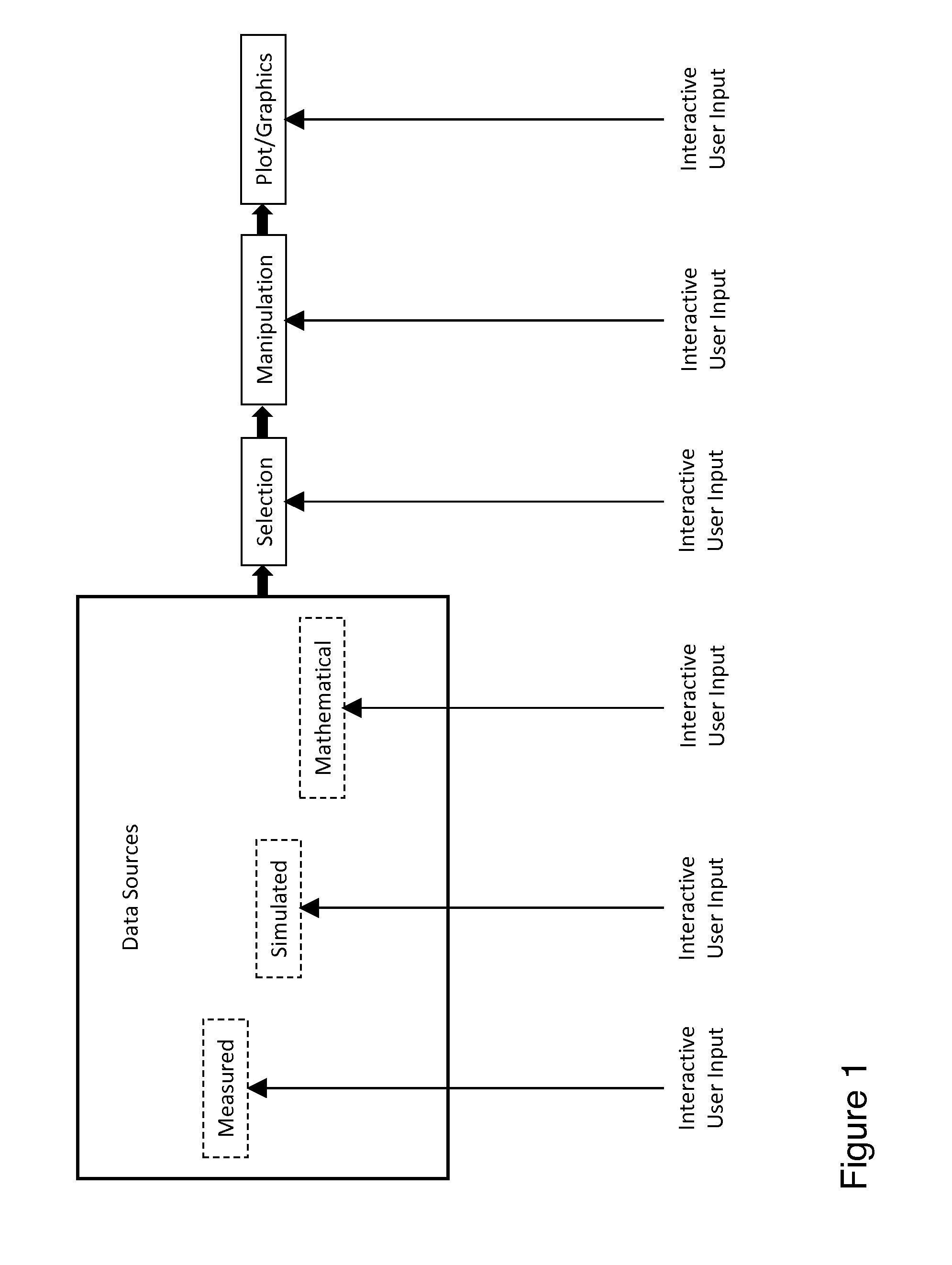

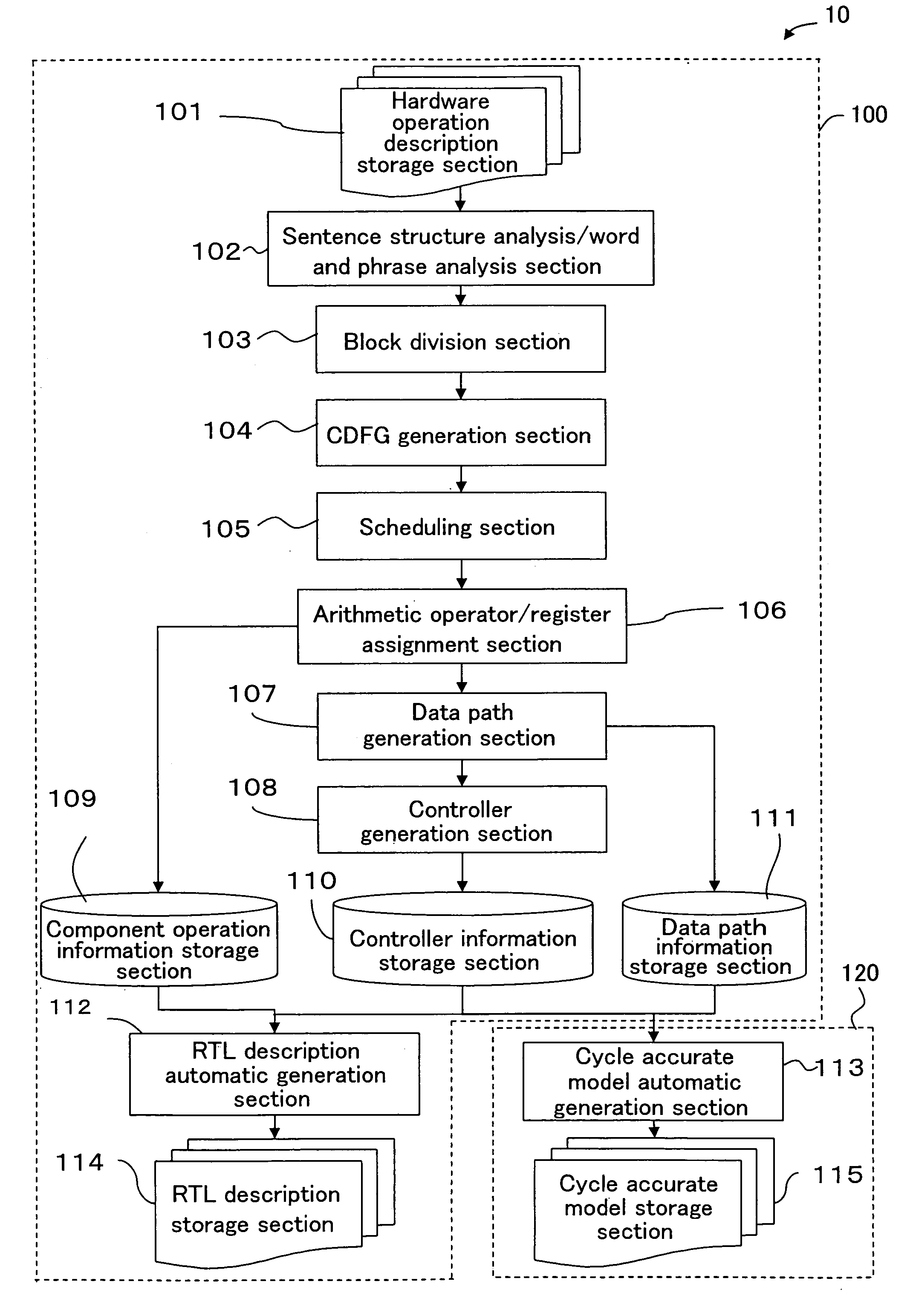

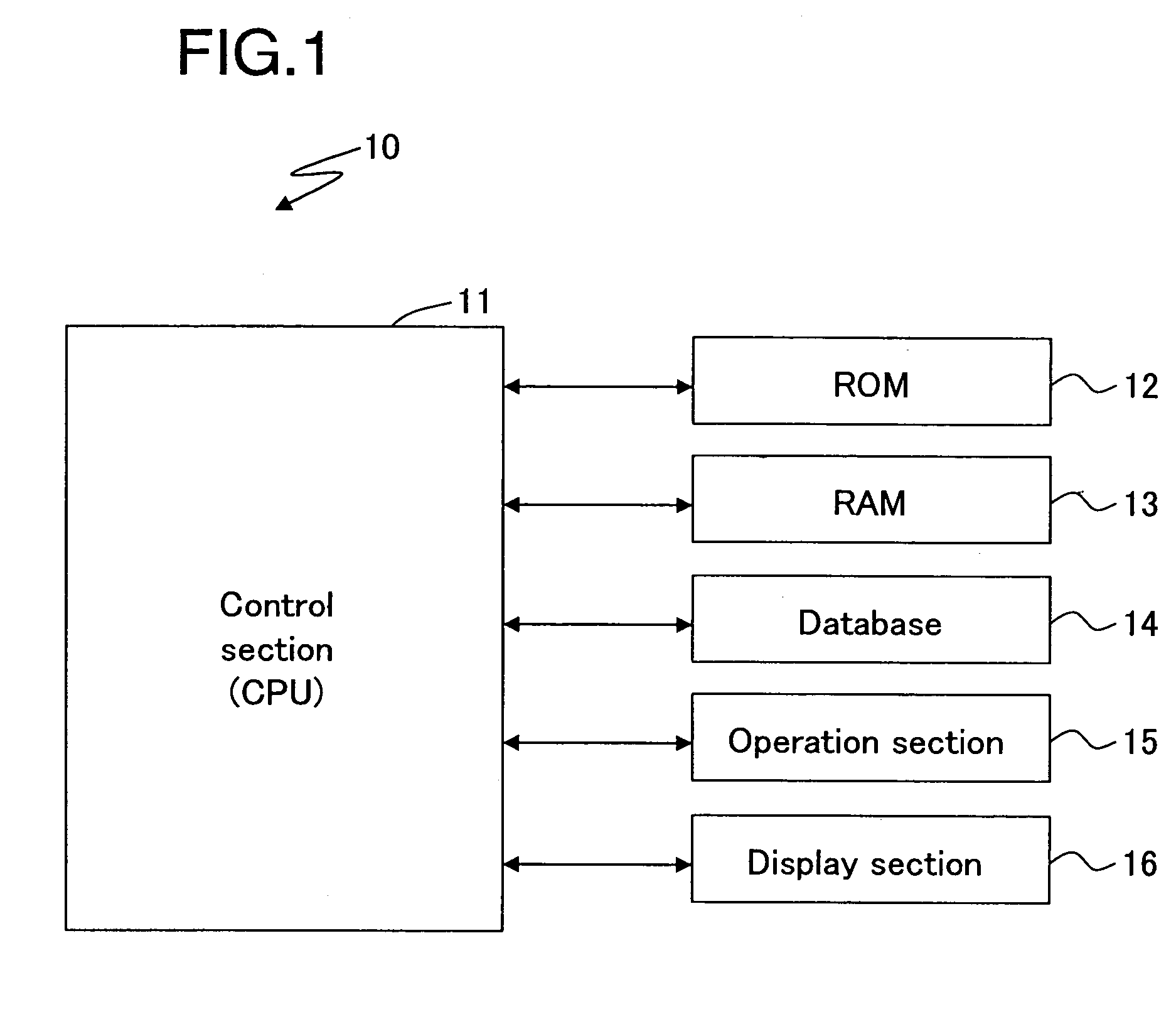

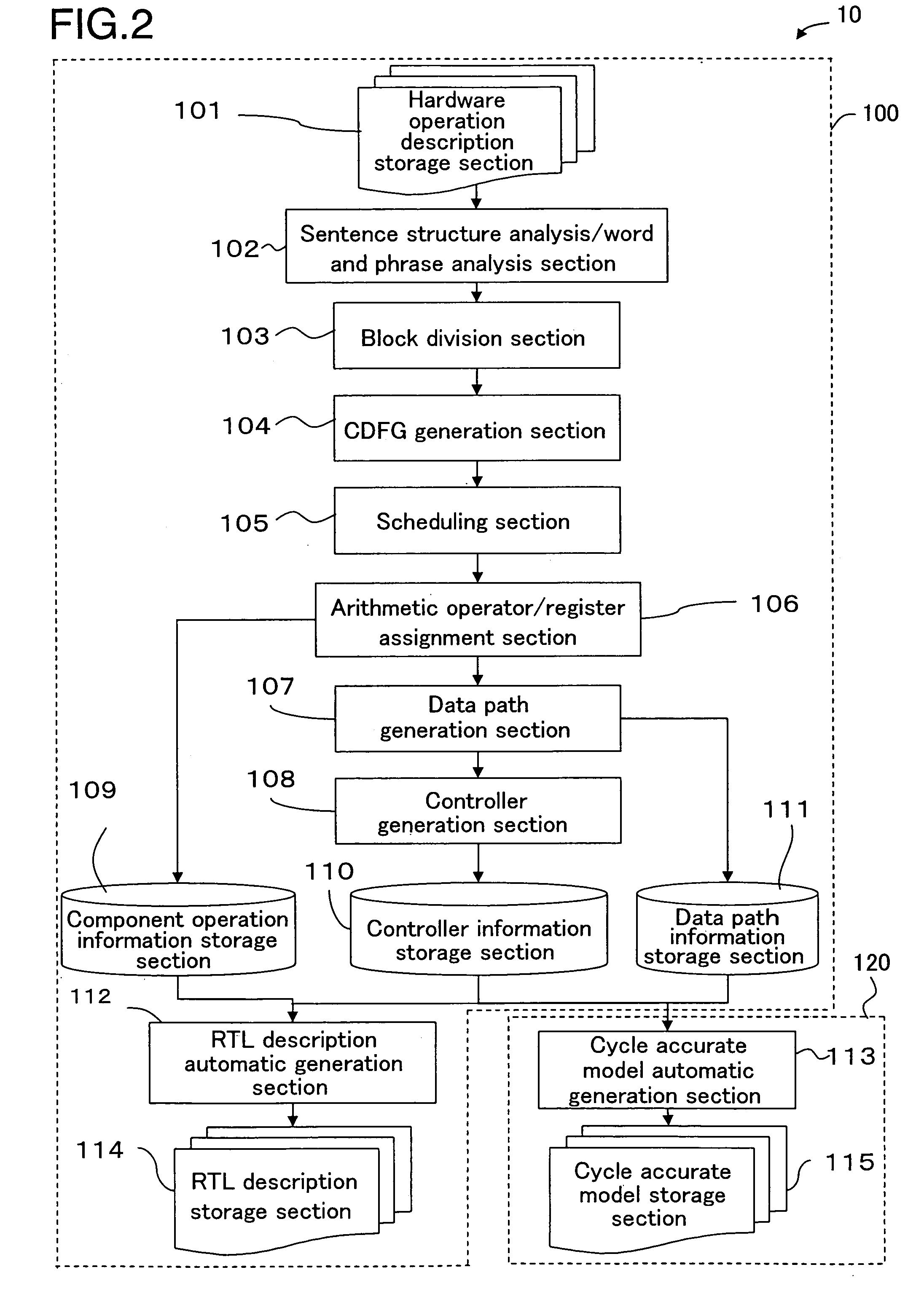

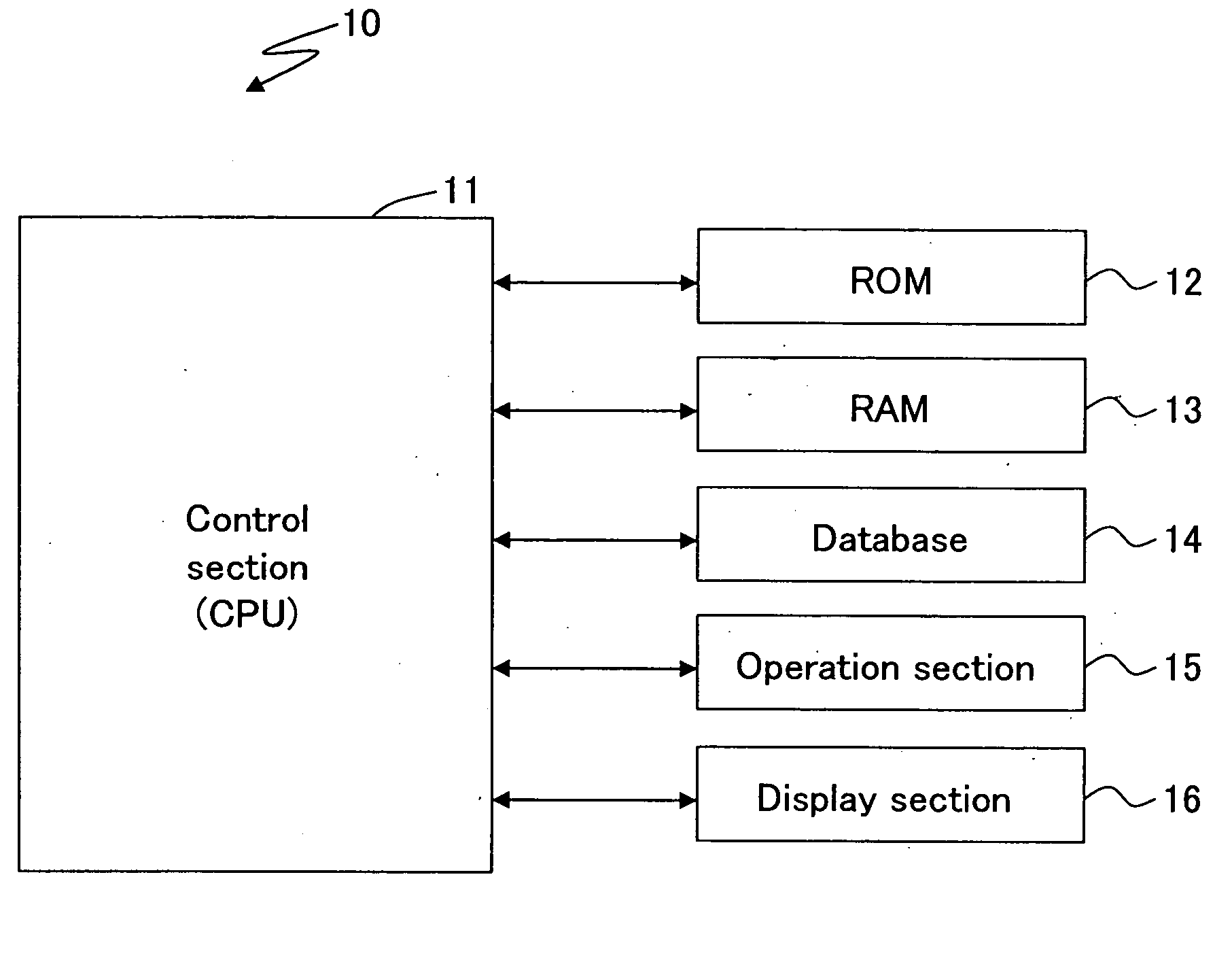

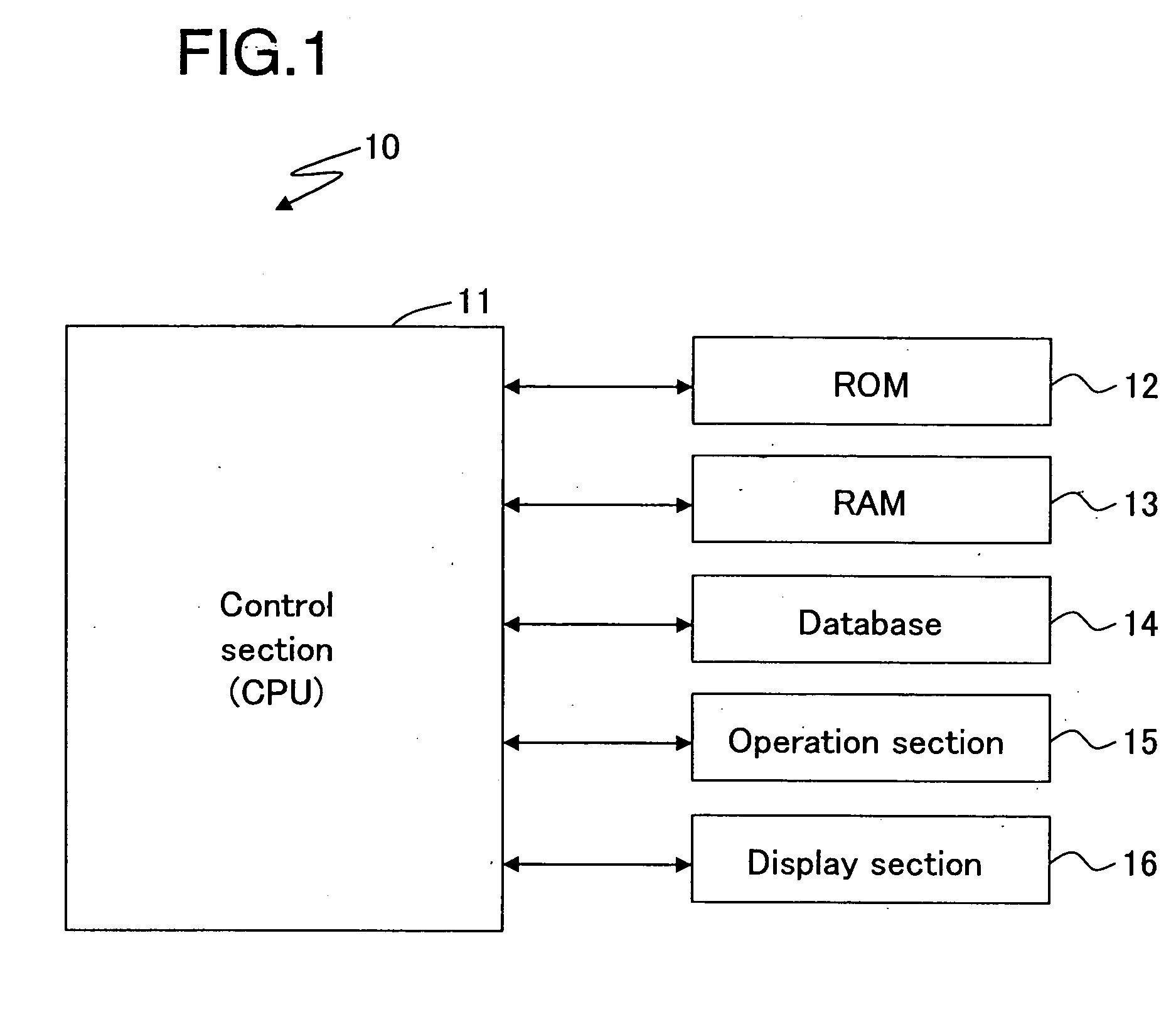

Programming language model generating apparatus for hardware verification, programming language model generating method for hardware verification, computer system, hardware simulation method, control program and computer-readable storage medium

InactiveUS20060130029A1Efficient executionLow costCAD circuit designProgram controlOperating instructionTheoretical computer science

The CDFG is generated by the CDFG generating section 109 based on the operation description of hardware 107, the CDFG is scheduled by the scheduling section 110 at an operation frequency required as the specification of the hardware and is assigned to each state, and the operation model of the hardware is generated by the cycle accurate model generating section 111 for each state as a description represented by a general-purpose programming language. The model which can be simulated for each state is generated by generating the operation model of each node using the operation information of the nodes included in the CDFG, and by determining the order in which the operation model of each node is calculated using the connection information of the nodes. As a result, it is possible to generate a model for verification described in a general-purpose programming language, which is capable of verifying hardware at a cycle accurate level at a lower cost and at a higher speed, with a smaller amount of calculation compared with the conventional method.

Owner:SHARP KK

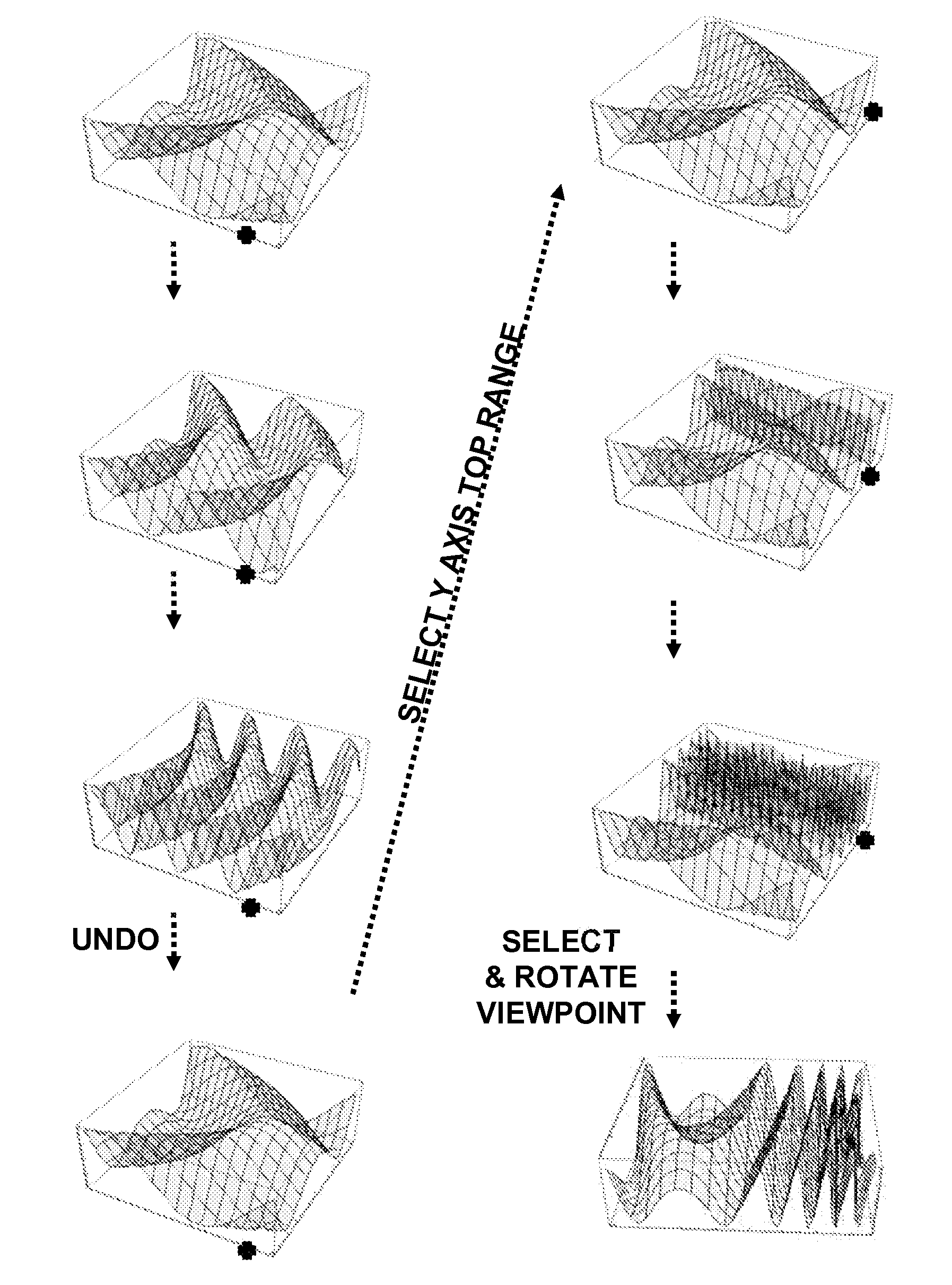

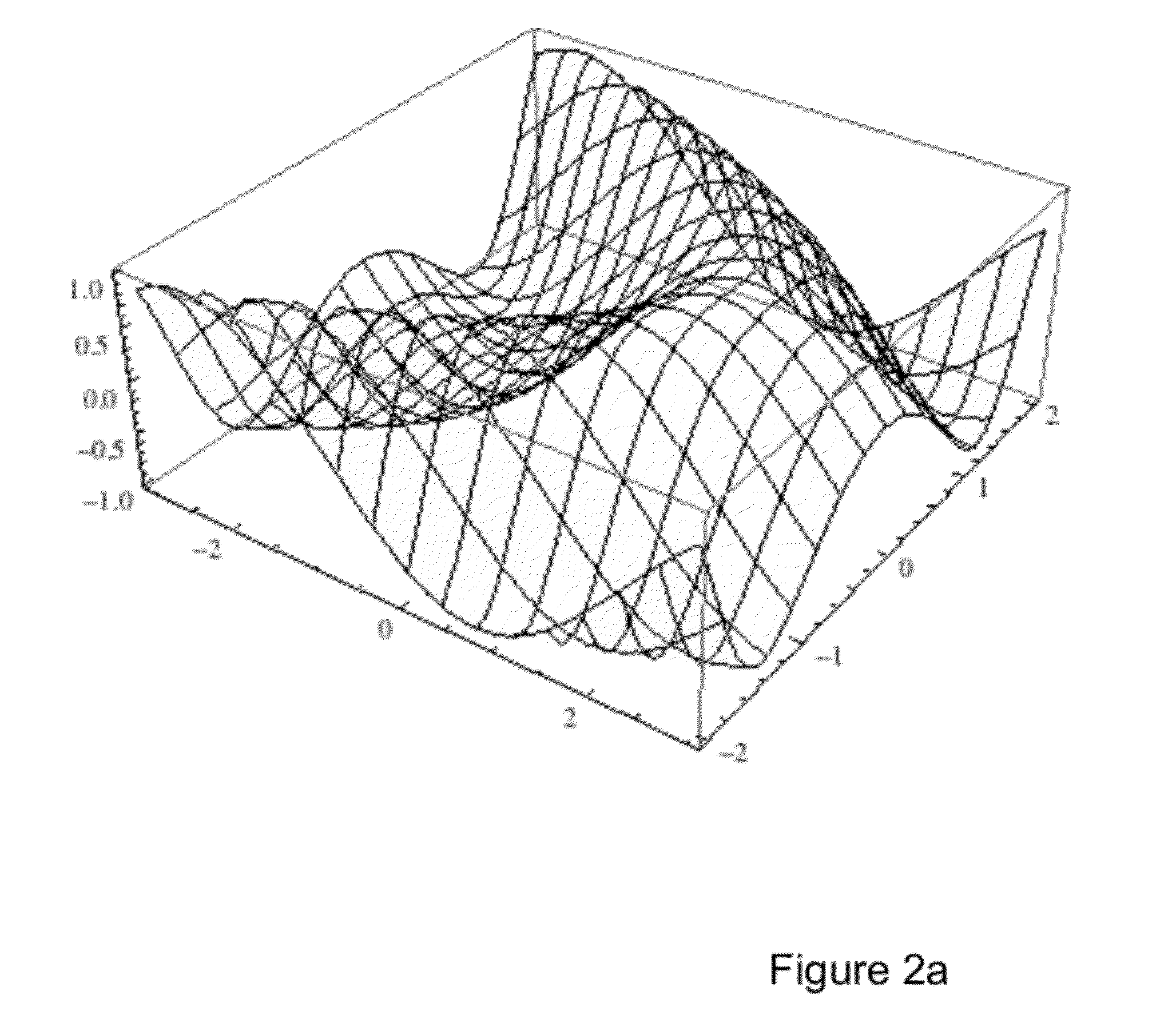

Interactive wysiwyg control of mathematical and statistical plots and representational graphics for analysis and data visualization

InactiveUS20120317509A1Full adjustmentIncrease the number of2D-image generationComplex mathematical operationsRolloverHigh dimensional

The invention provides interactive adjustment of plot and data visualization through clicks, rollovers, menus, and other familiar types of rapid user-machine interaction. In an implementation, such interactive adjustments also modify associated software code used to generate the underlying plot or data visualization. In some implementations this feature may be always active. In other embodiments, this feature can be enabled, disabled, overridden, precluded, etc. The invention supports simple mice and their equivalents, advanced mice, gesture-based touch interfaces advanced High-Dimensional Touch Pads and associated touch screens, game controllers, 6D-mice, and extended hyperlink objects. The invention can be implemented in the context of web browsers and spreadsheets, and can be used for Business intelligence, simple plots, and a wide range of data visualization applications. The invention also provides related features to more general programming languages not involved in plots or visualization, allowing programmers on software code and invoke various options via interactive GUIs.

Owner:NRI R&D PATENT LICENSING LLC

High level synthesis device, method for generating a model for verifying hardware, method for verifying hardware, control program, and readable recording medium

ActiveUS7266791B2Improve performanceSimple designCAD circuit designSoftware simulation/interpretation/emulationComputer hardwareHigh-level synthesis

A high level synthesis device includes a high level synthesis section and a cycle accurate model. The high level synthesis section may perform high level synthesis of hardware including a plurality of components and a controller for controlling the plurality of components. The cycle accurate model may be configured to verify a state of at least one of the plurality of components and the controller at a cycle accurate level, with a general-purpose programming language.

Owner:SHARP KK

In-kernel virtual machine for low overhead startup and low resource usage

Embodiments of the present invention provide an architecture for efficiently loading and executing byte code generated from a general programming language. In particular, a byte code interpreter implements a virtual machine that executes the byte code and is divided into a kernel component and one or more user components. The kernel component of the virtual machine is integrated into the operating system kernel. The user component runs in the same virtual address space as the applet, provides support for executing an applet and couples the applet to the operating system. In addition, the kernel component of the virtual machine may share code with multiple user components.

Owner:RED HAT

Purpose domain for in-kernel virtual machine for low overhead startup and low resource usage

ActiveUS8104034B2Multiprogramming arrangementsSoftware simulation/interpretation/emulationOperational systemAnalog computer

Embodiments of the present invention provide an architecture for securely and efficiently executing byte code generated from a general programming language. In particular, a computer system is divided into a hierarchy comprising multiple types of virtual machines. A thin layer of software, known as a virtual machine monitor, virtualizes the hardware of the computer system and emulates the hardware of the computer system to form a first type of virtual machine. This first type of virtual machine implements a virtual operating domain that allows running its own operating system. Within a virtual operating domain, a byte code interpreter may further implement a second type of virtual machine that executes byte code generated from a program written in a general purpose programming language. The byte code interpreter is incorporated into the operating system running in the virtual operating domain. The byte code interpreter implementing the virtual machine that executes byte code may be divided into a kernel component and one or more user level components. The kernel component of the virtual machine is integrated into the operating system kernel. The user level component provides support for execution of an applet and couples the applet to the operating system. In addition, an operating system running in a virtual operating domain may be configured as a special purpose operating system that is optimized for the functions of a particular byte code interpreter.

Owner:RED HAT

High level synthesis device, method for generating a model for verifying hardware, method for verifying hardware, control program, and readable recording medium

ActiveUS20050010387A1Increase speedSimple designCAD circuit designSoftware simulation/interpretation/emulationComputer hardwareHigh-level synthesis

A high level synthesis device includes a high level synthesis section for performing high level synthesis of hardware including a plurality of components and a controller for controlling the plurality of components; and a cycle accurate model generation section for generating a cycle accurate model, capable of verifying a state of at least one of the plurality of components and the controller at a cycle accurate level, with a general-purpose programming language.

Owner:SHARP KK

Method and apparatus for automated conversion of software applications

InactiveUS20150020051A1Enrich parsing contextEnrich the parsing contextSoftware testing/debuggingSpecific program execution arrangementsLanguage constructInterface (computing)

The invention relates to data processing apparatus and methods for automated conversion of software applications between computing platforms when said platforms do not support common set of programming languages. The Conversion System (CS) consists of several components. The Converter is a computer system that translates source application's code into target application's code. It uses set of methods to create in the target system's programming language constructs that represent source system language's constructs and that the Run Time Library (RTL) implements and supports at run time. The RTL also provides for supporting multiple target computing platforms as it insulates converted code from each target platform's specifics. The CS converts legacy applications' source code in the manner that preserves applications' structure, “look and feel”, interfaces between components, and processing flows, and thus allows to reuse test data and testing approaches that have been used with the legacy applications before conversion.

Owner:RABINOVITCH YURI G +1

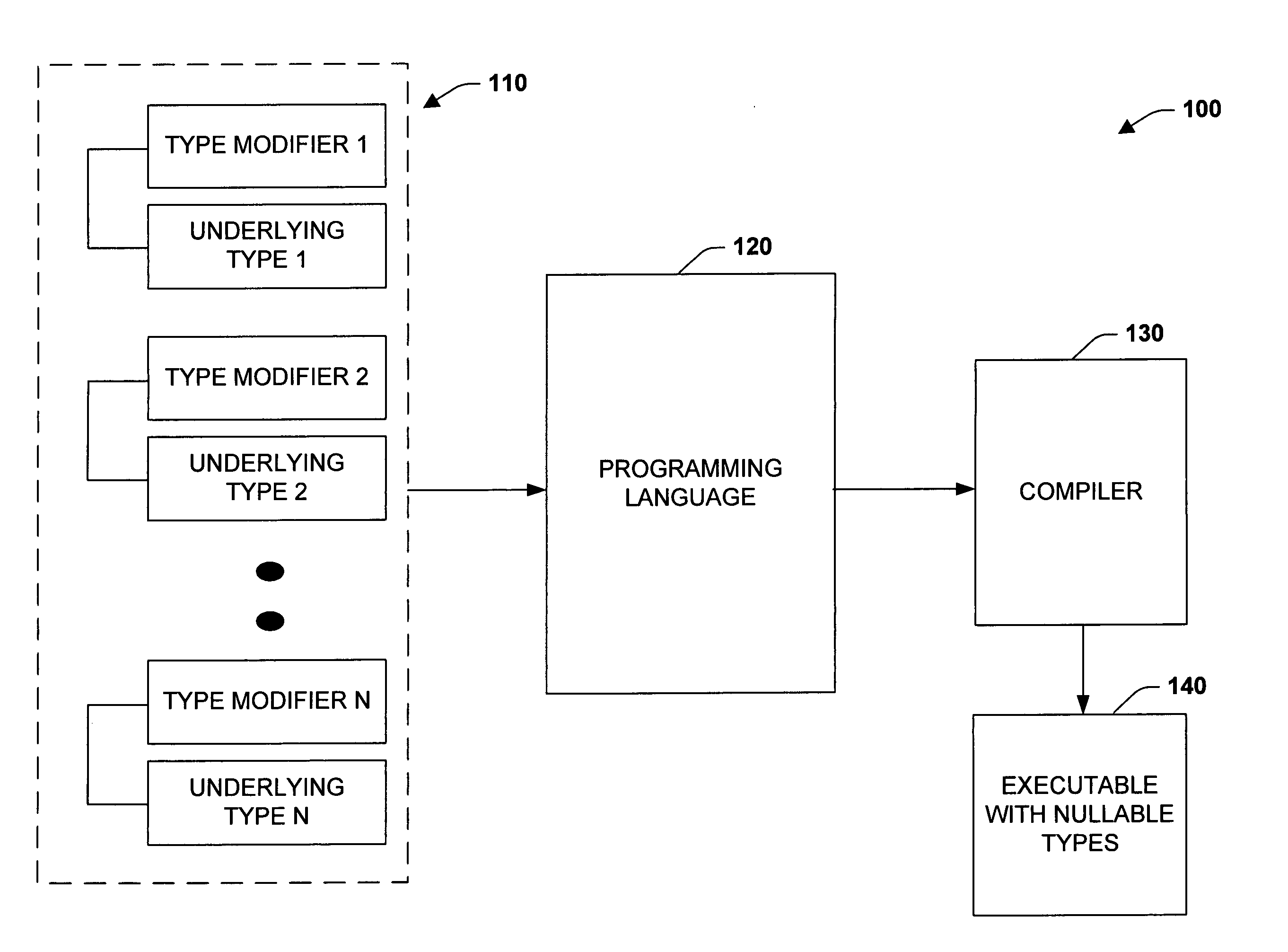

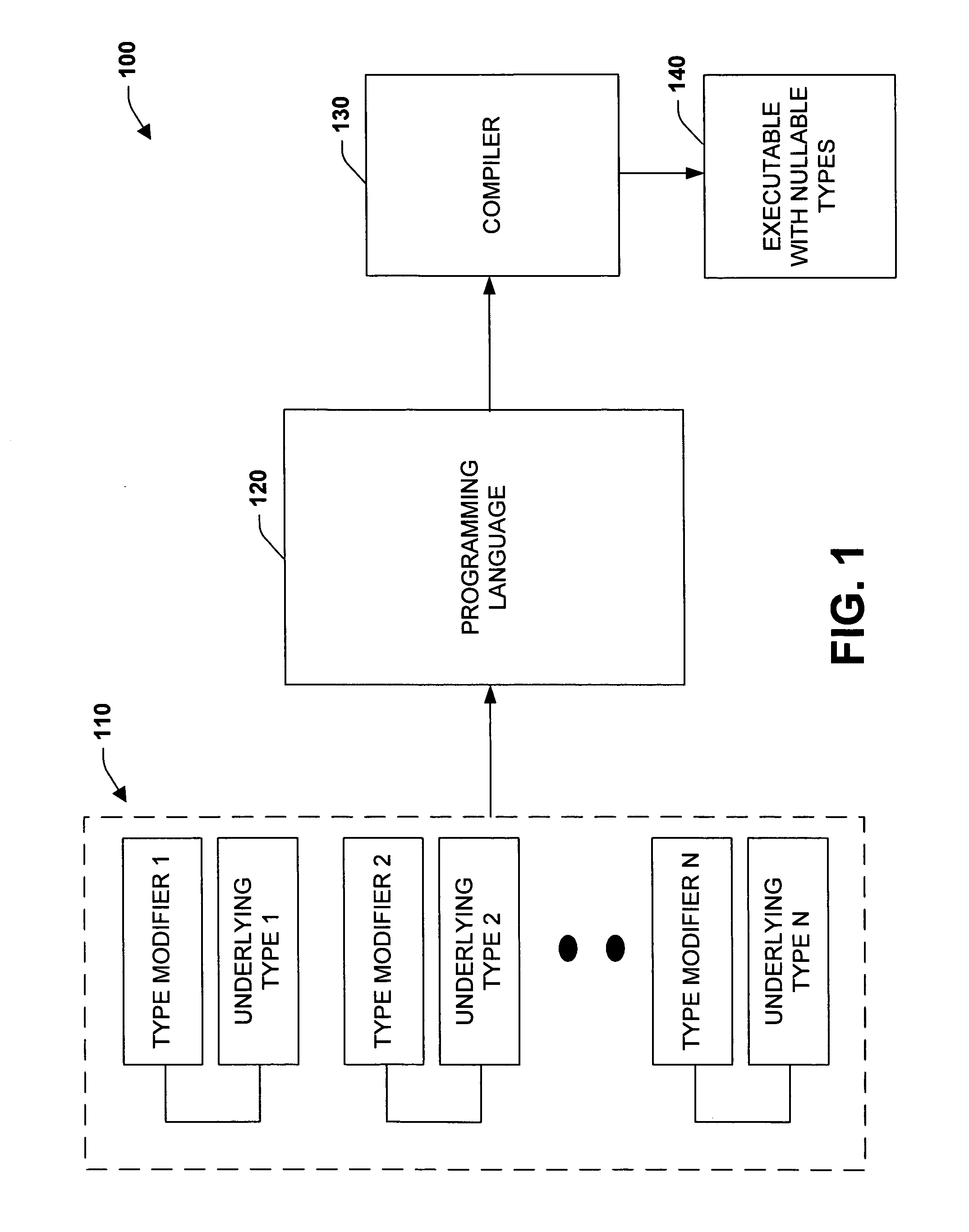

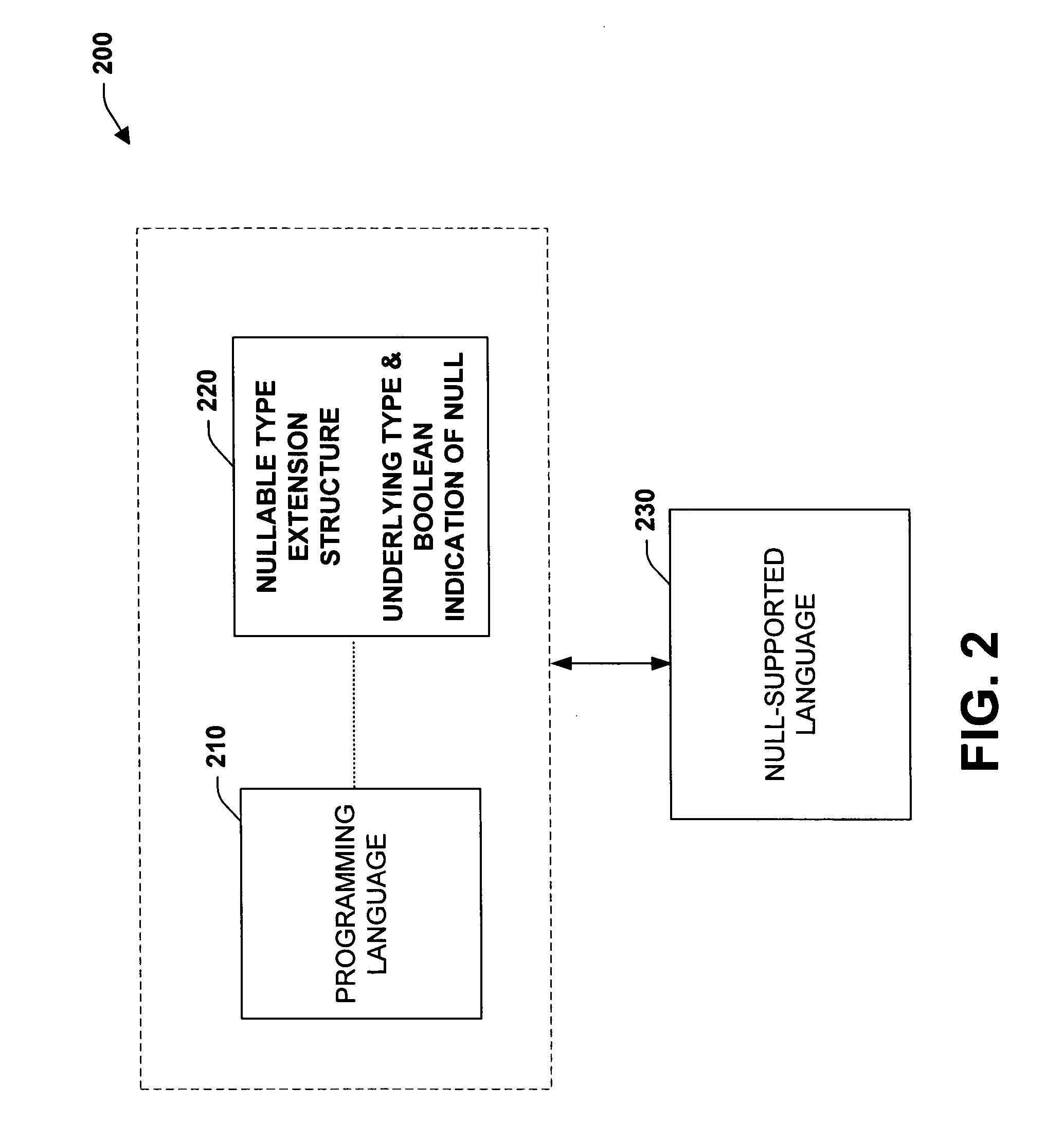

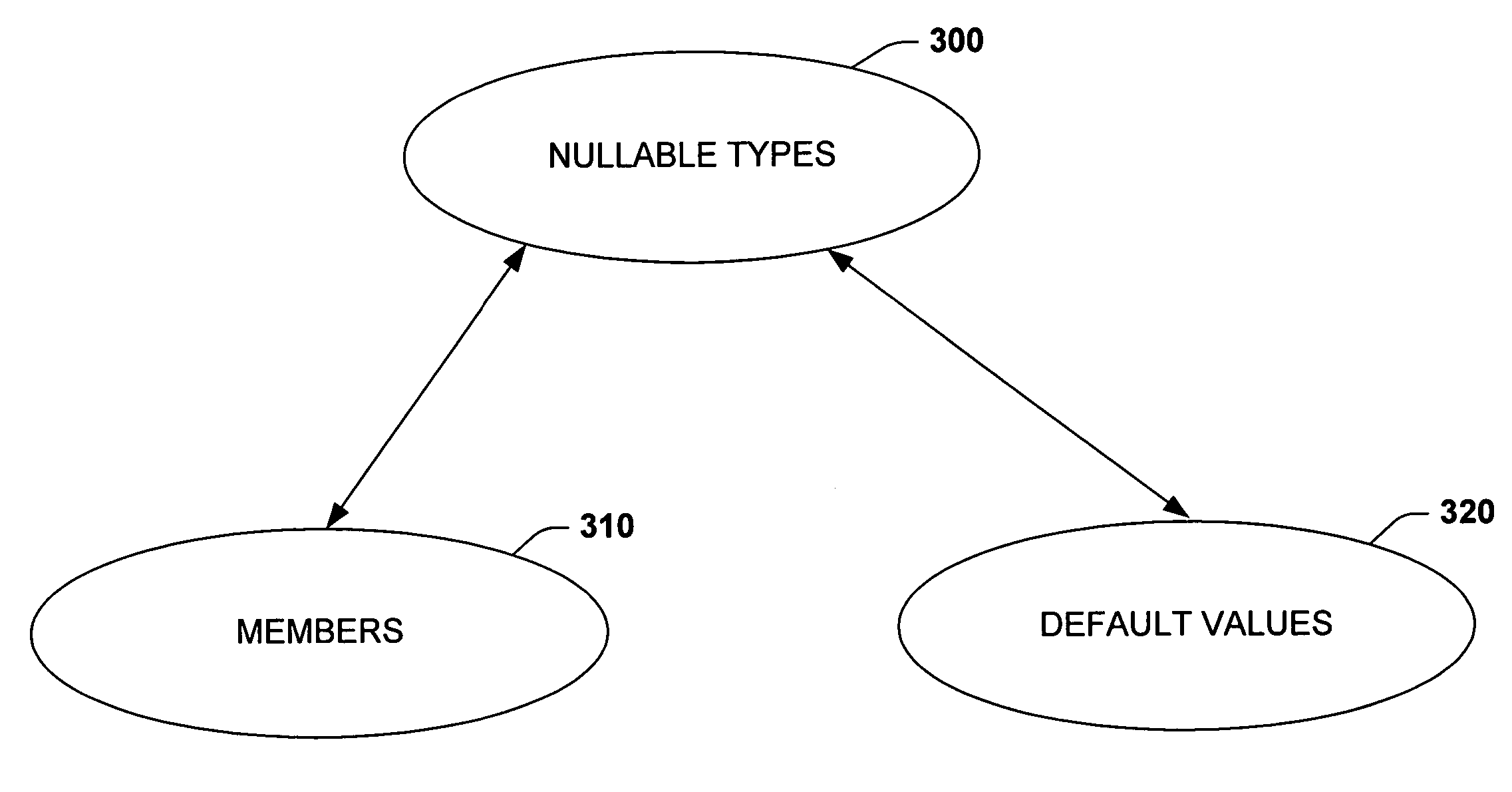

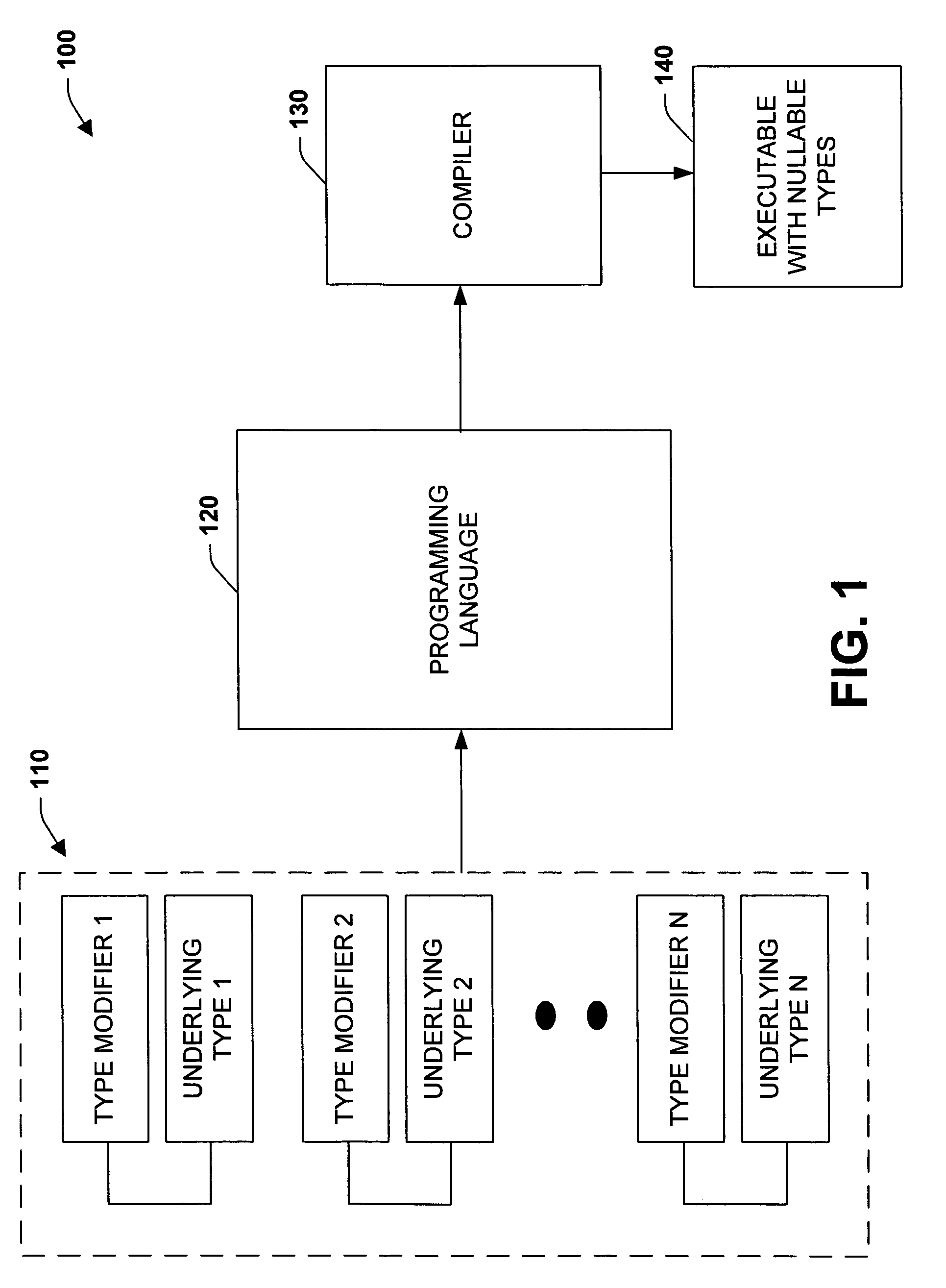

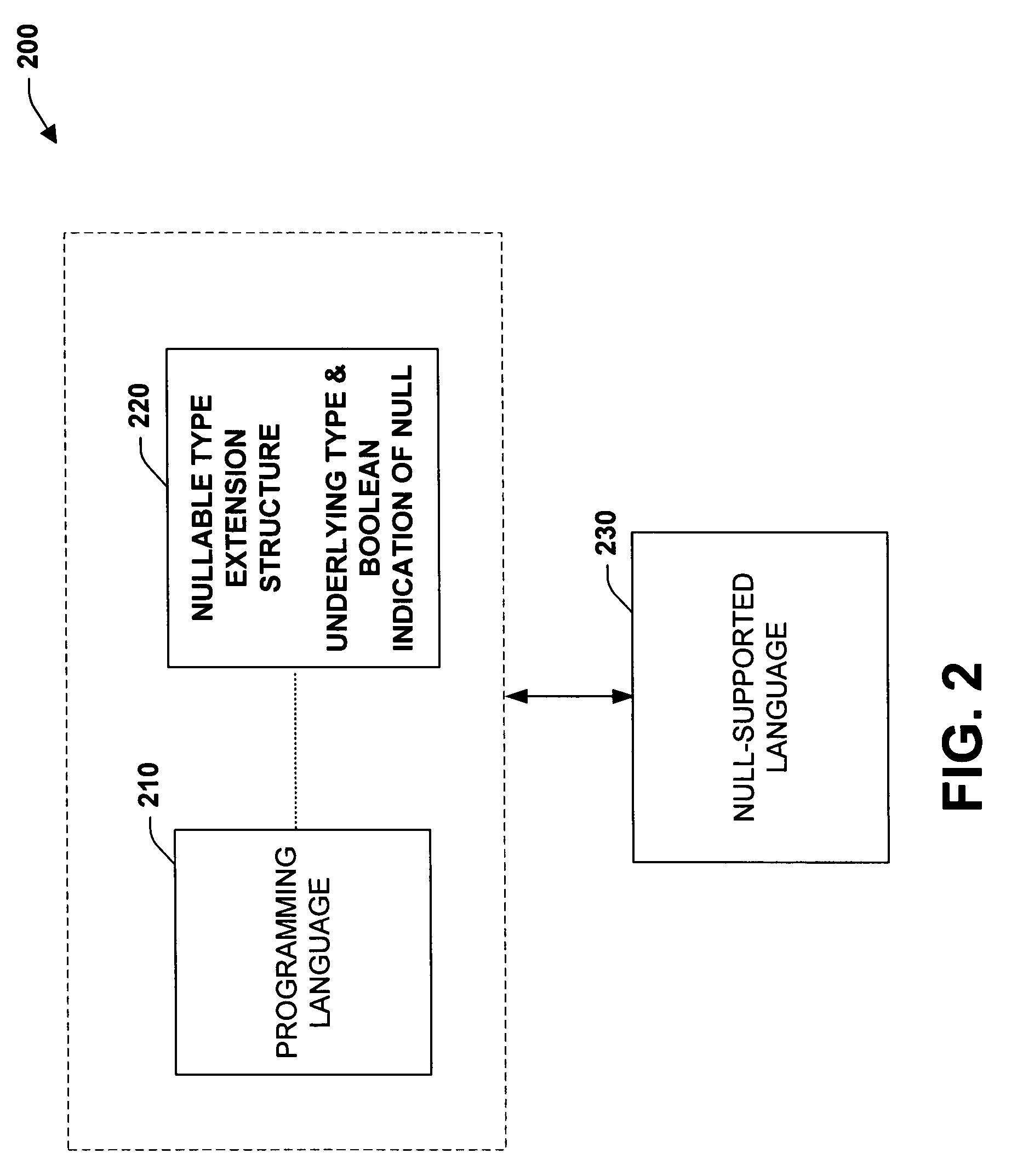

General programming language support for nullable types

InactiveUS20060053131A1Easy to handlePotential problemDigital data processing detailsProgramming languages/paradigmsMulti elementGeneral-purpose programming language

The subject invention relates to systems and methods that provide null capabilities within the context of programming languages. In one aspect, a system is provided that facilitates null-support in various programming languages. The system includes one or more types associated with at least one programming language. A type modifier is provided to signal that the type is nullable. The type modifier enables a multi-element structure to be automatically created in association with the type wherein, the multi-element structure includes the type and a Boolean element indicating whether or not the variable is null.

Owner:MICROSOFT TECH LICENSING LLC

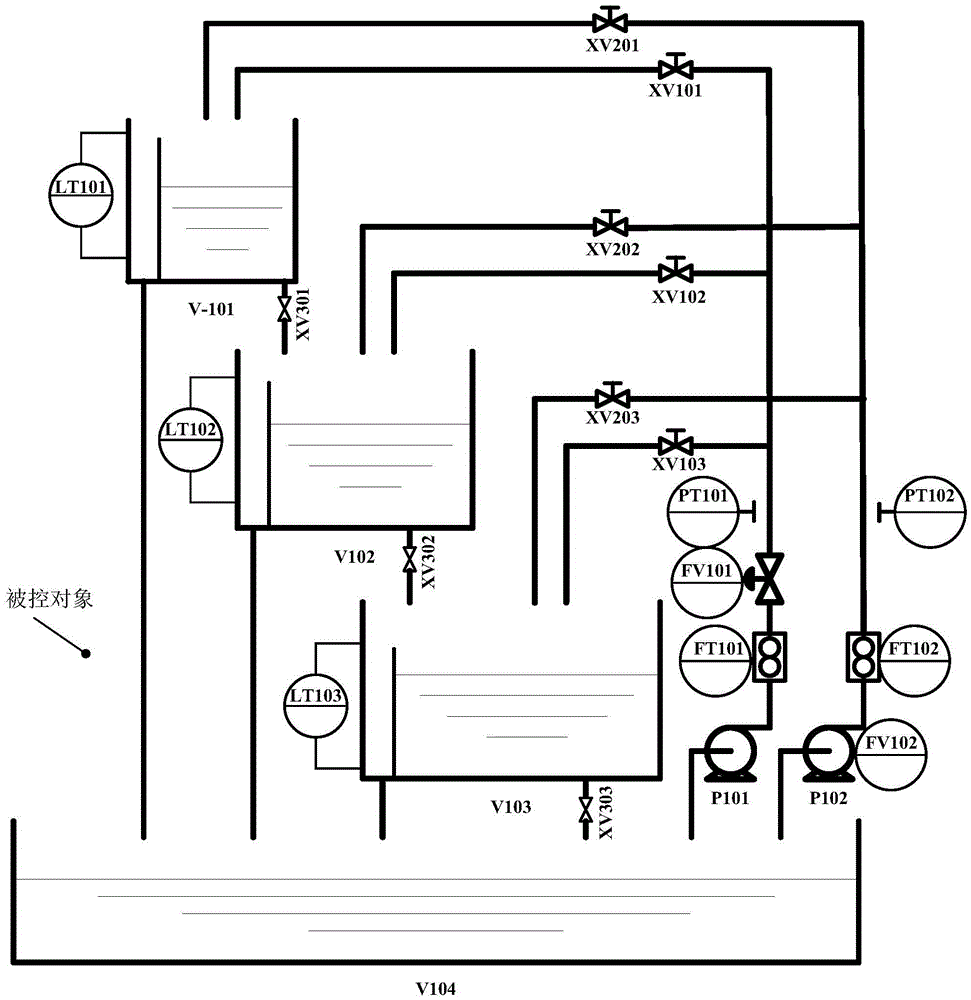

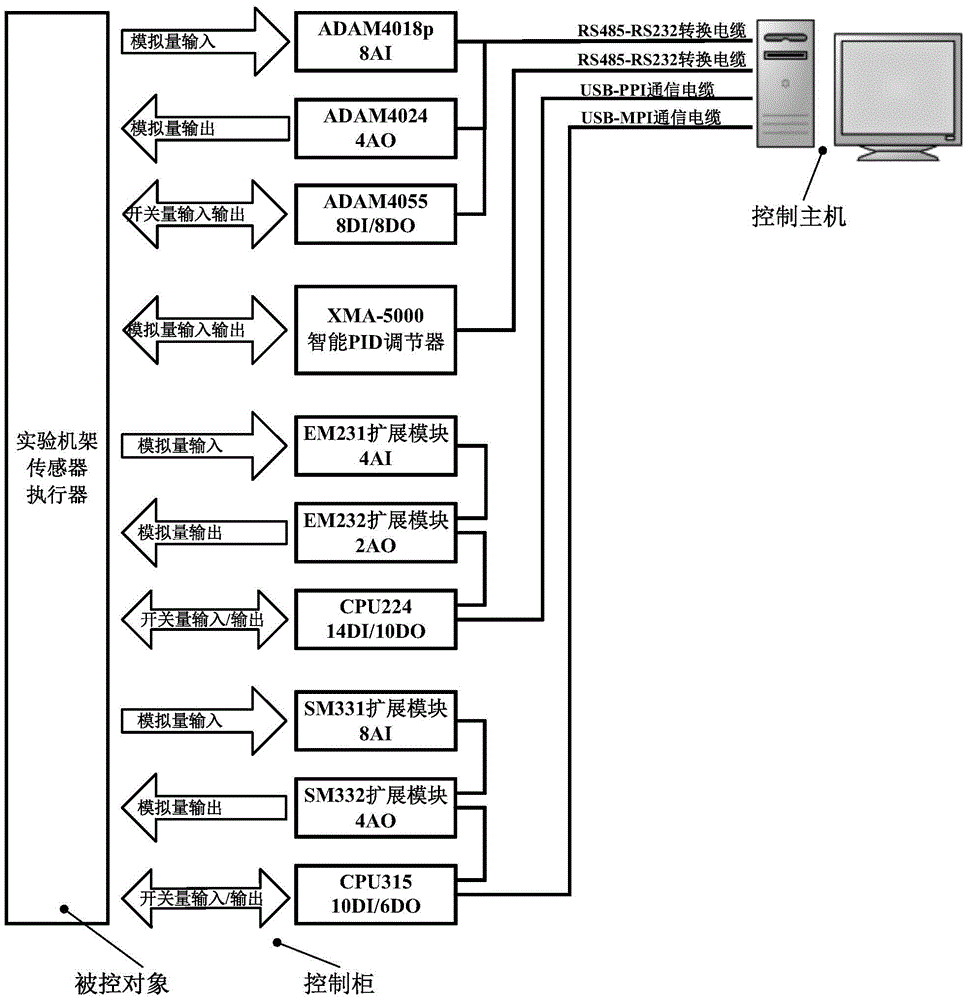

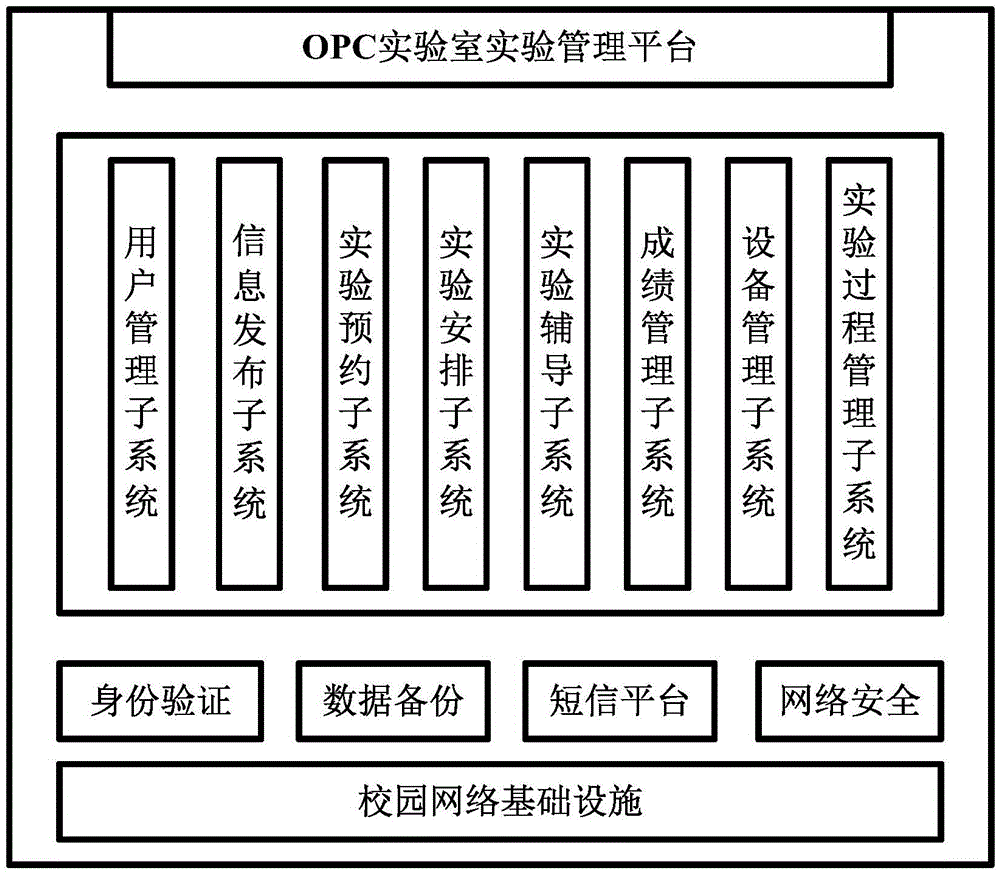

Industrial-control practical training apparatus based on OPC

An industrial-control practical training apparatus based on OPC is disclosed. The apparatus is formed by a controlled object, a control cabinet and a control host. A water tank, a water pump and an allocated pipeline are taken as experiment objects. Industrial control equipment of an on-site instrument, an intelligent IO module, an intelligent PID controller, a PLC and the like are equipped so as to carry out various kinds of control on parameters in processes of pressure, a flow, a liquid level and the like. Based on the OPC, an industrial control instrument is integrated with Matlab software, industrial control configuration software, even VB and other general programming languages. The apparatus can complete a traditional general instrument control and also can form customized control taking a customized soft controller in the Matlab or the VB as a core, an application environment is provided for a student to be familiar with an automatic control theory, learn and practice a new control algorithm and an experiment platform is provided for teh student to learn and apply the OPC. Through using experiment management software exploited based on the VB and the OPC, a good support can be provided for local management, remote monitoring and grade evaluation of the experiment.

Owner:JINLING INST OF TECH

General programming language support for nullable types

InactiveUS7647580B2Efficiently handled and processedDigital data processing detailsProgramming languages/paradigmsMulti elementGeneral-purpose programming language

Owner:MICROSOFT TECH LICENSING LLC

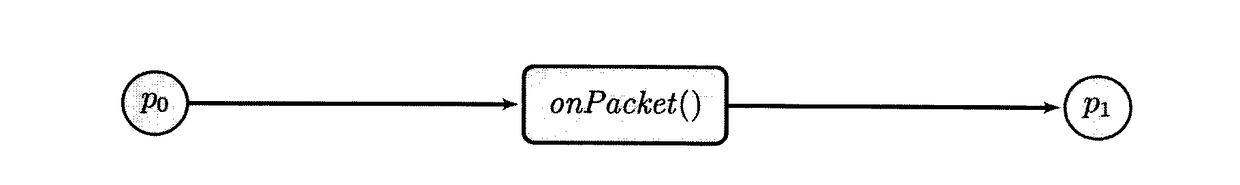

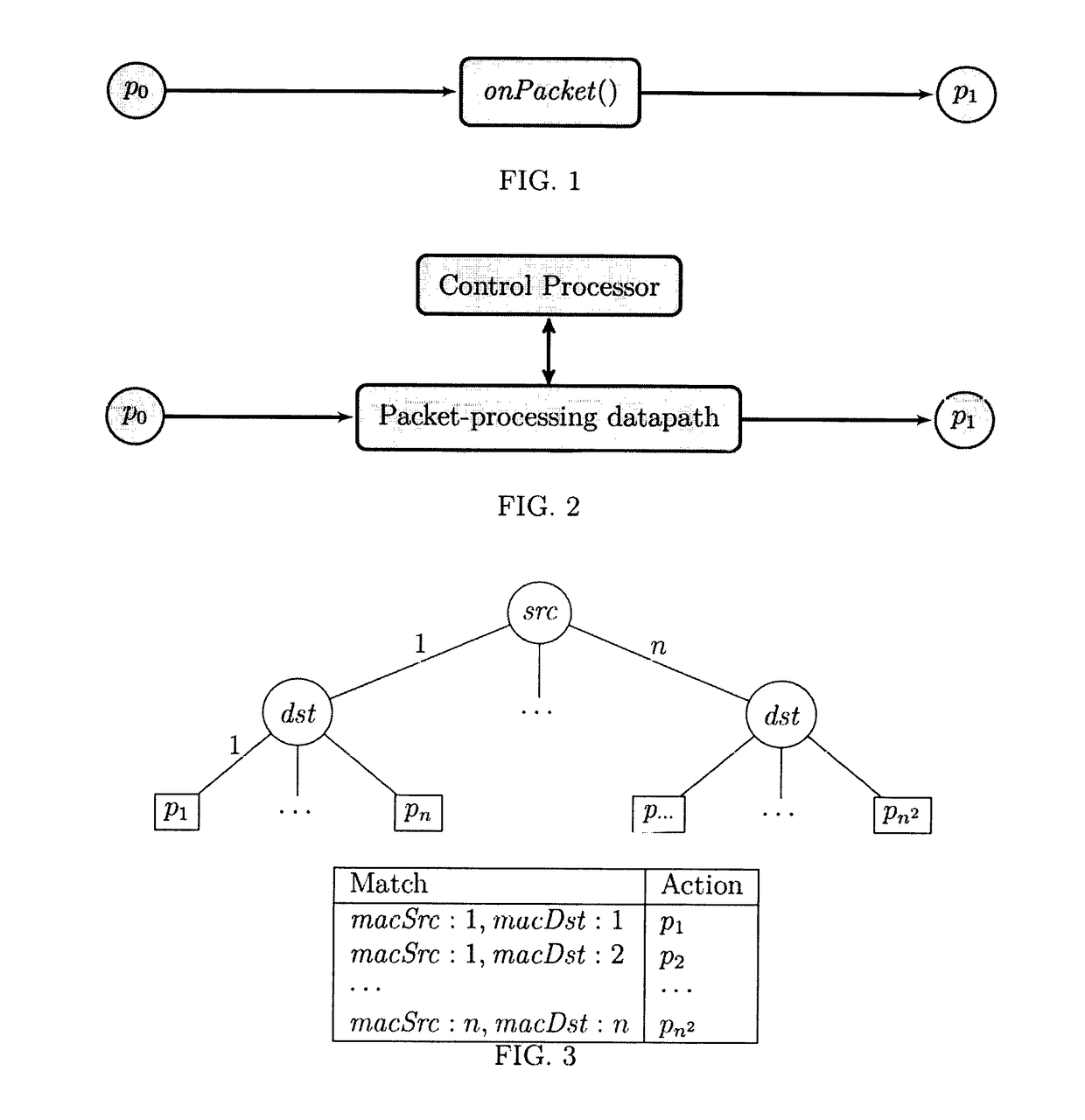

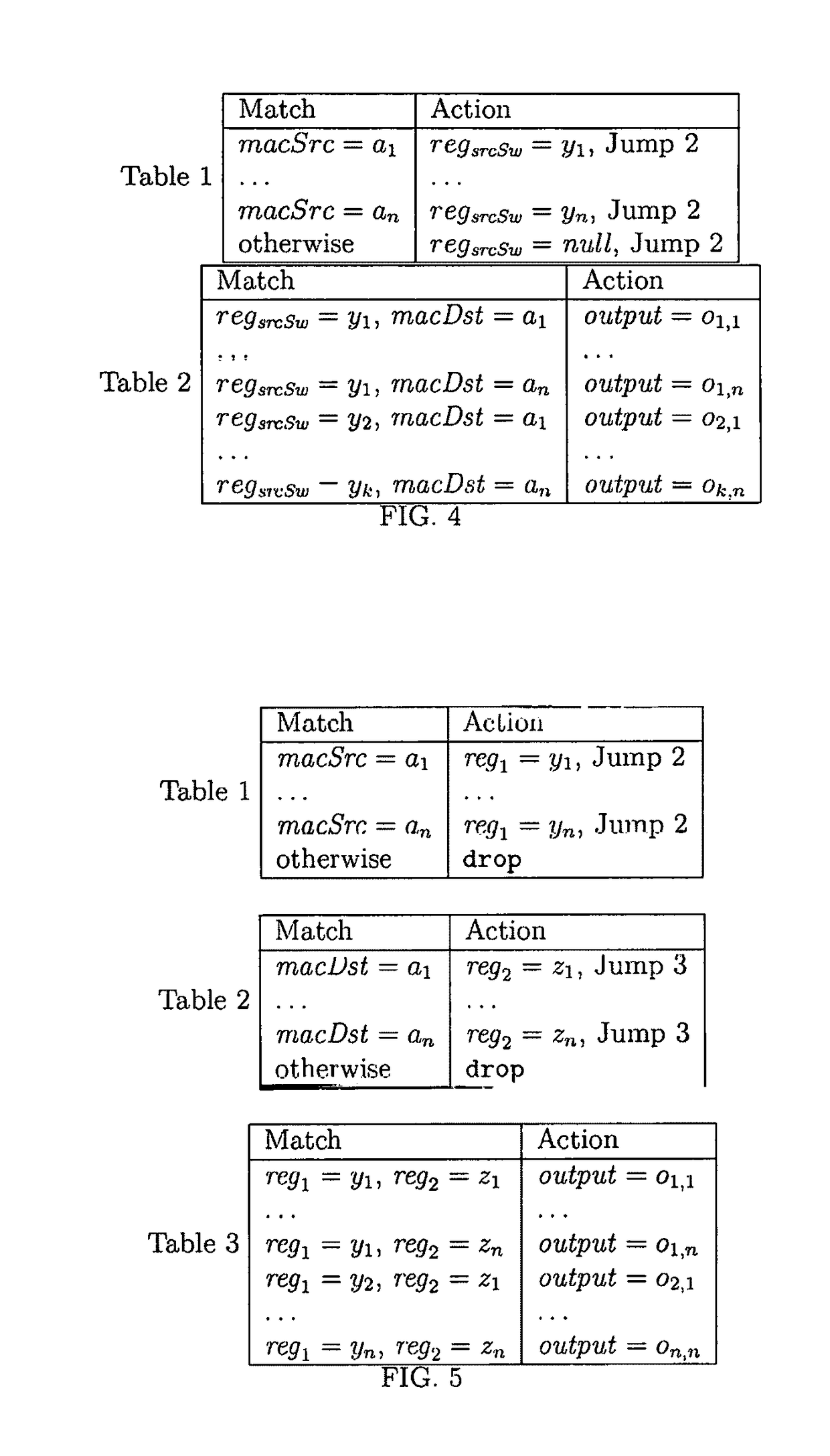

Compilation and runtime methods for executing algorithmic packet processing programs on multi-table packet forwarding elements

ActiveUS20170102943A1Reduce the burden onEfficient implementationProgramming languages/paradigmsSoftware testing/debuggingGeneral purposeDatapath

The invention pertains to a method of implementing packet-processing devices on multi-table datapath processors, comprising of a high-level, Turing-complete programming language that permits programmers to express time-invariant or time-variant packet-processing behavior using general-purpose programming languages, suitable compilation and analysis methods to transform a given input program into a datapath design, and a runtime control program to be executed on a general-purpose processor which can communicate with a configurable datapath element and which configures the datapath element according to the compiled datapath design and which implements appropriate dynamic control (e.g. flow table population) for the configured datapath element.

Owner:VOELLMY ANDREAS