Patents

Literature

38results about How to "Improve protection characteristics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

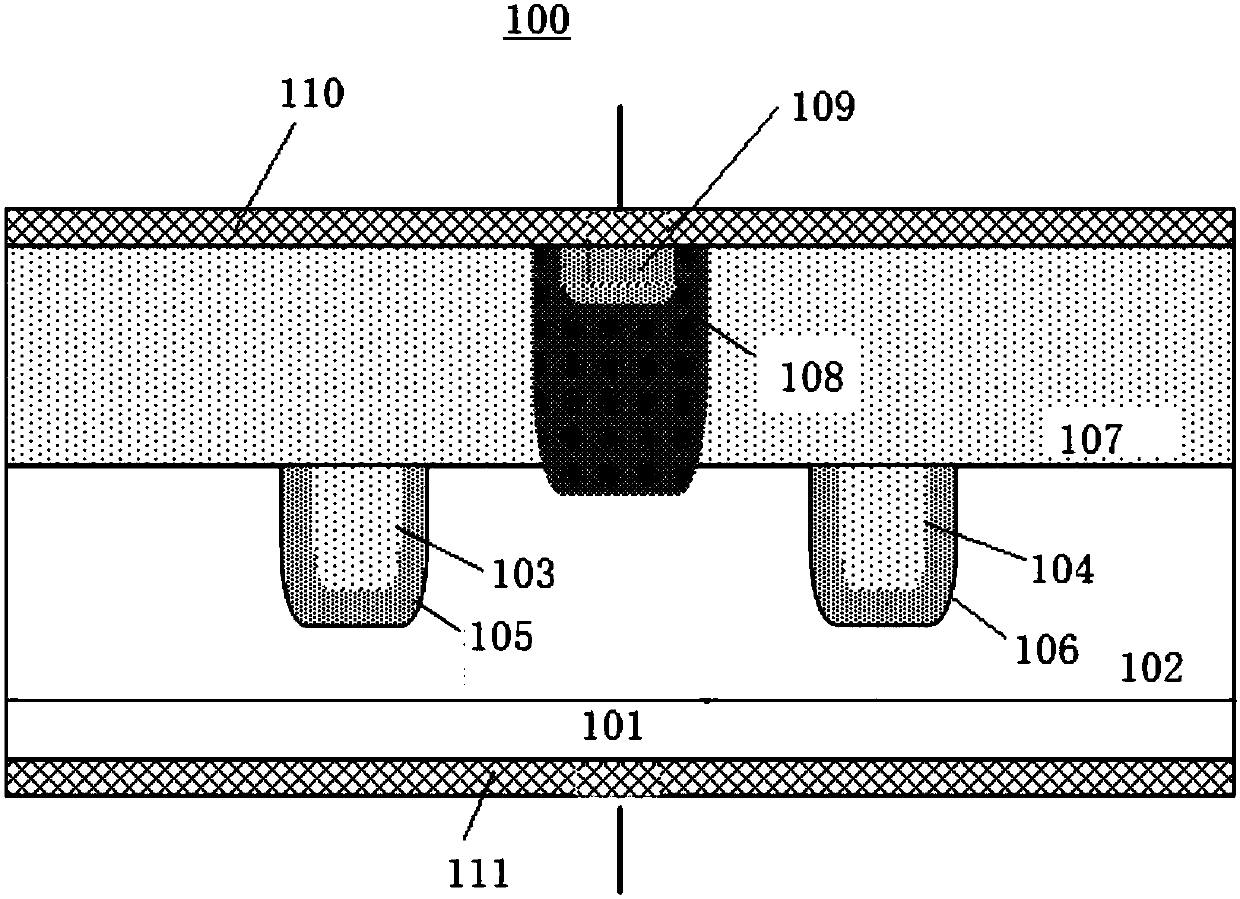

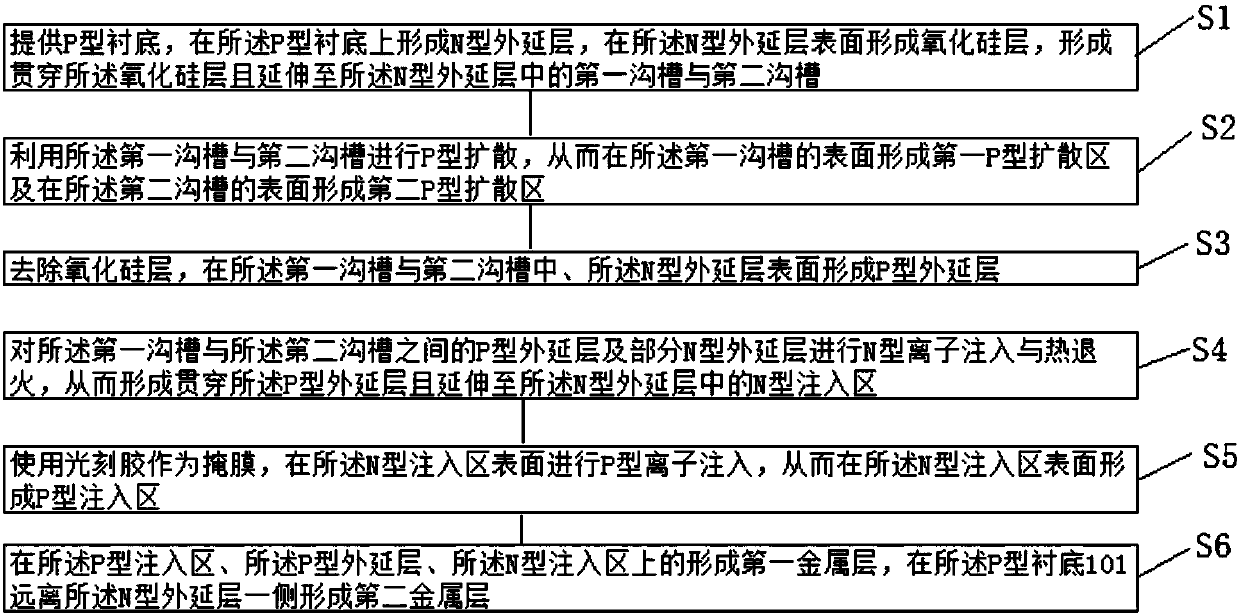

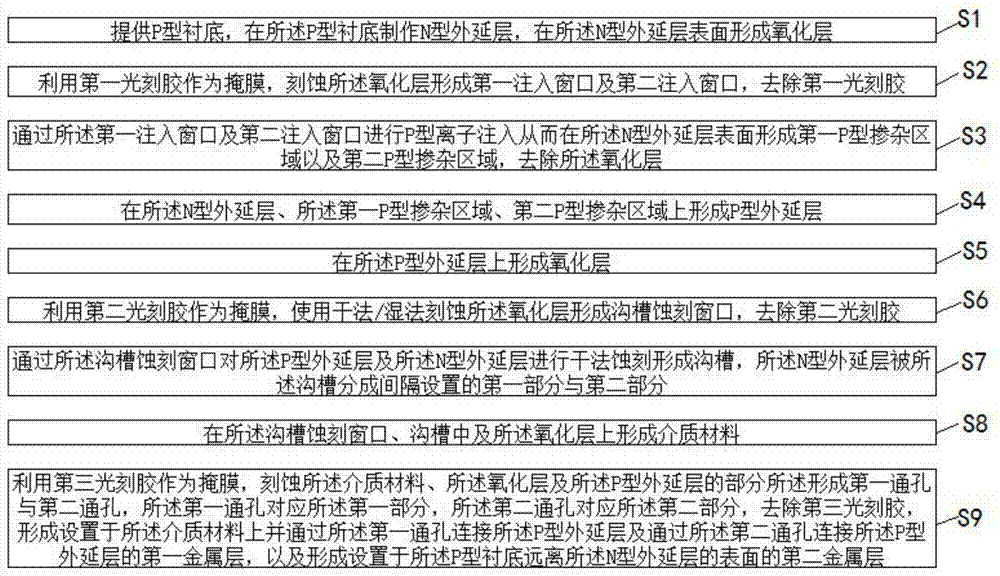

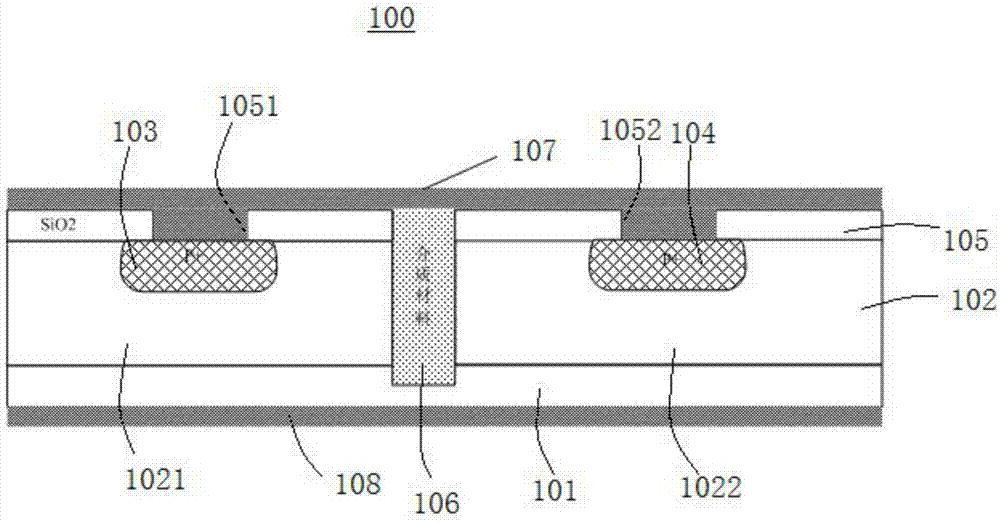

Transient voltage suppressor and fabrication method thereof

InactiveCN108054164AReduce device areaReduce process difficultySolid-state devicesSemiconductor/solid-state device manufacturingTransient voltage suppressorEngineering

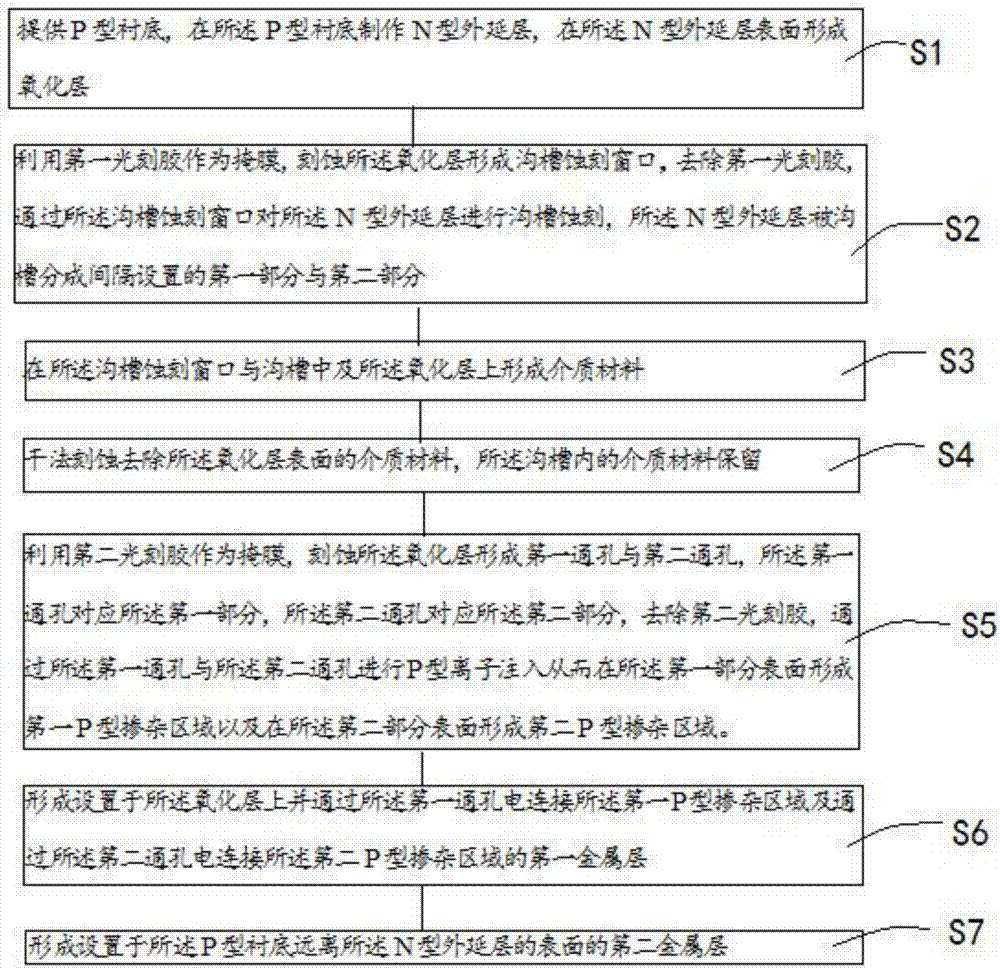

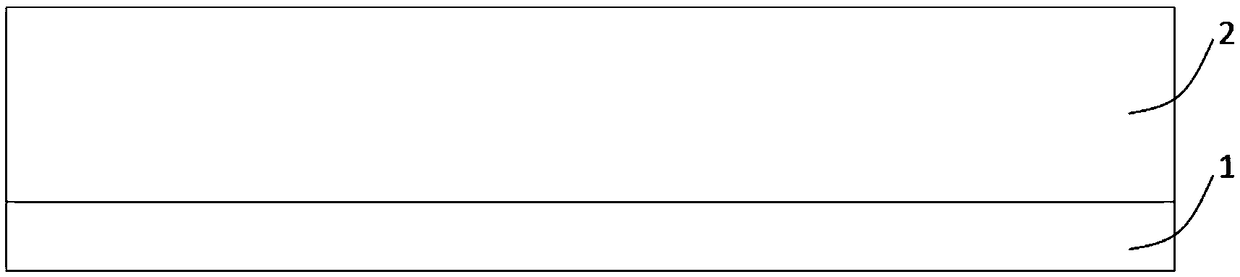

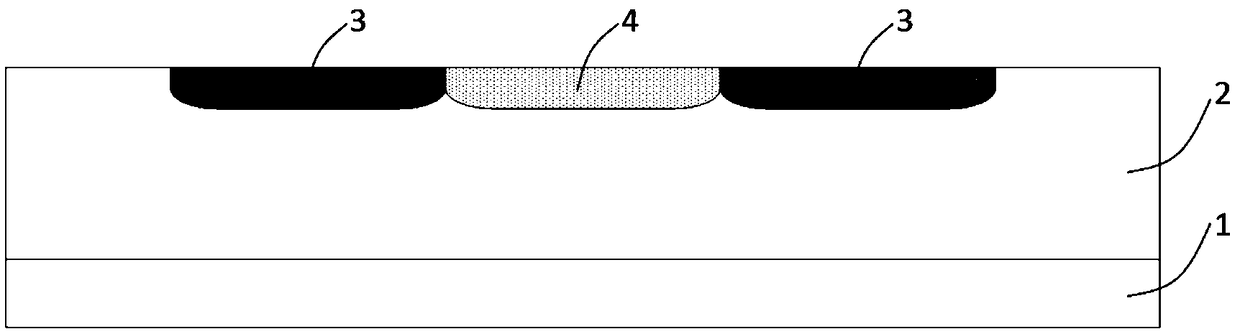

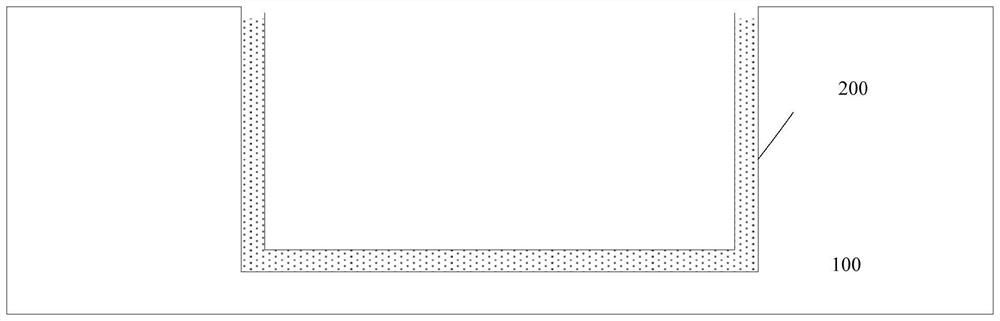

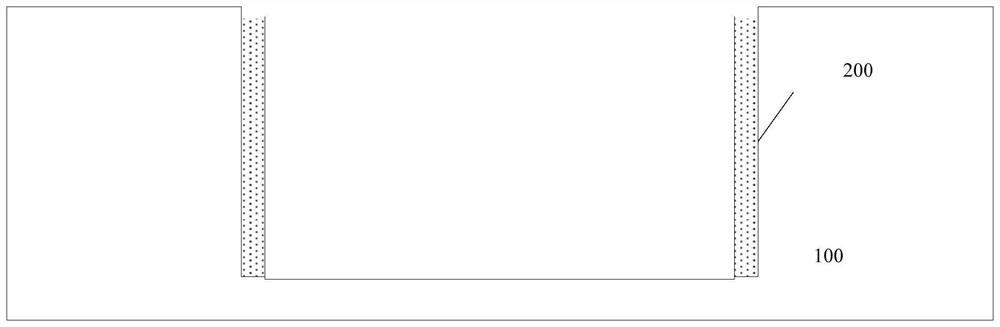

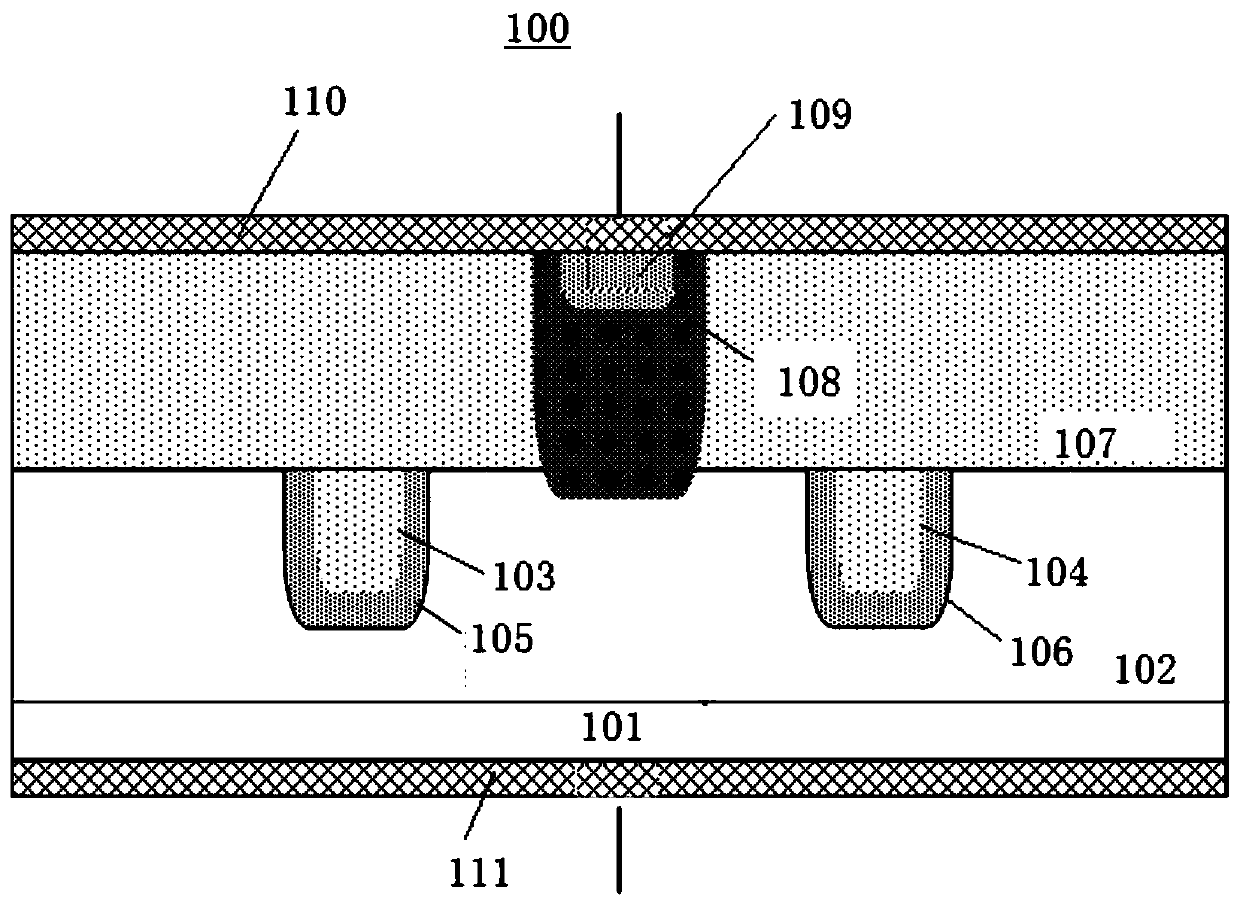

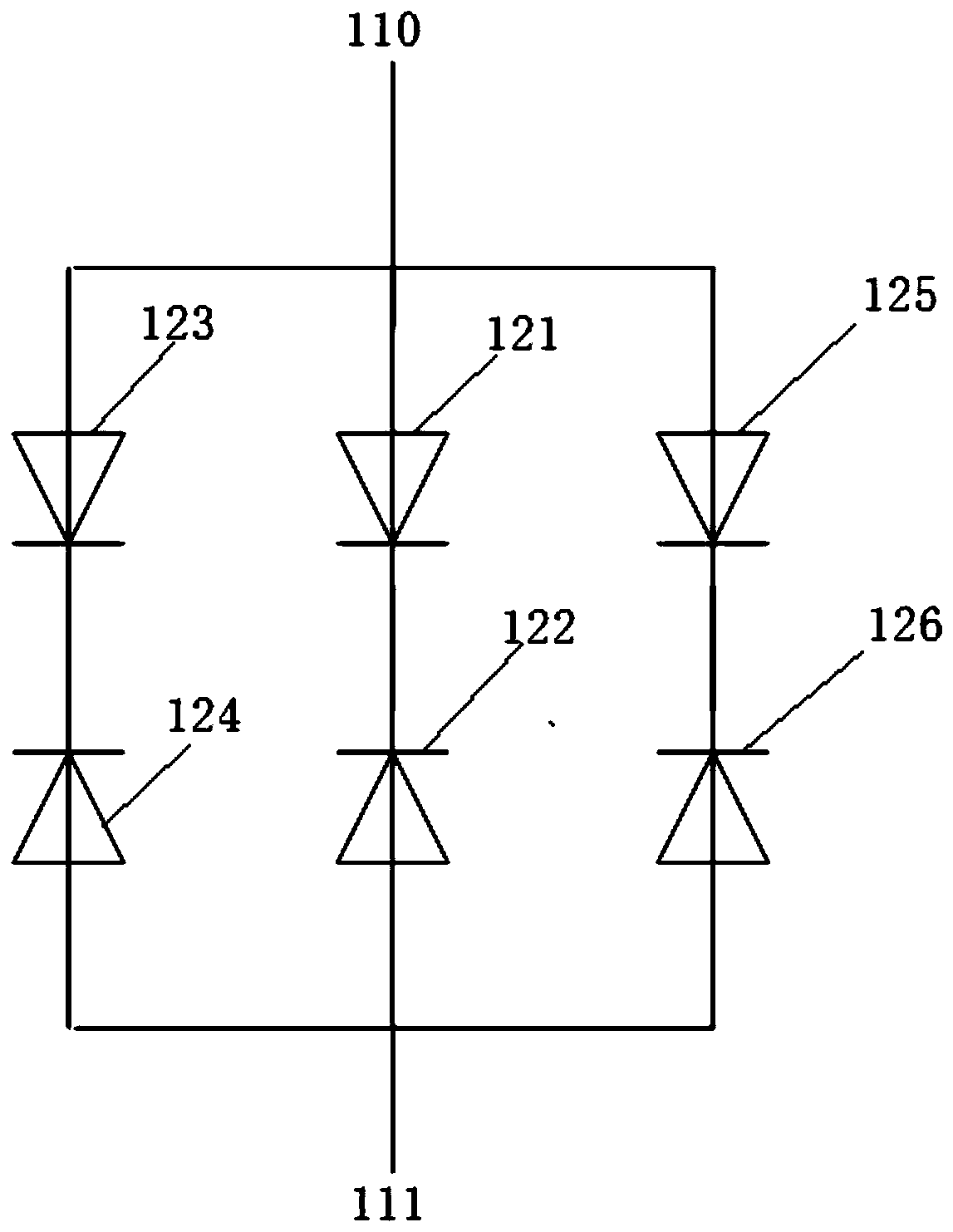

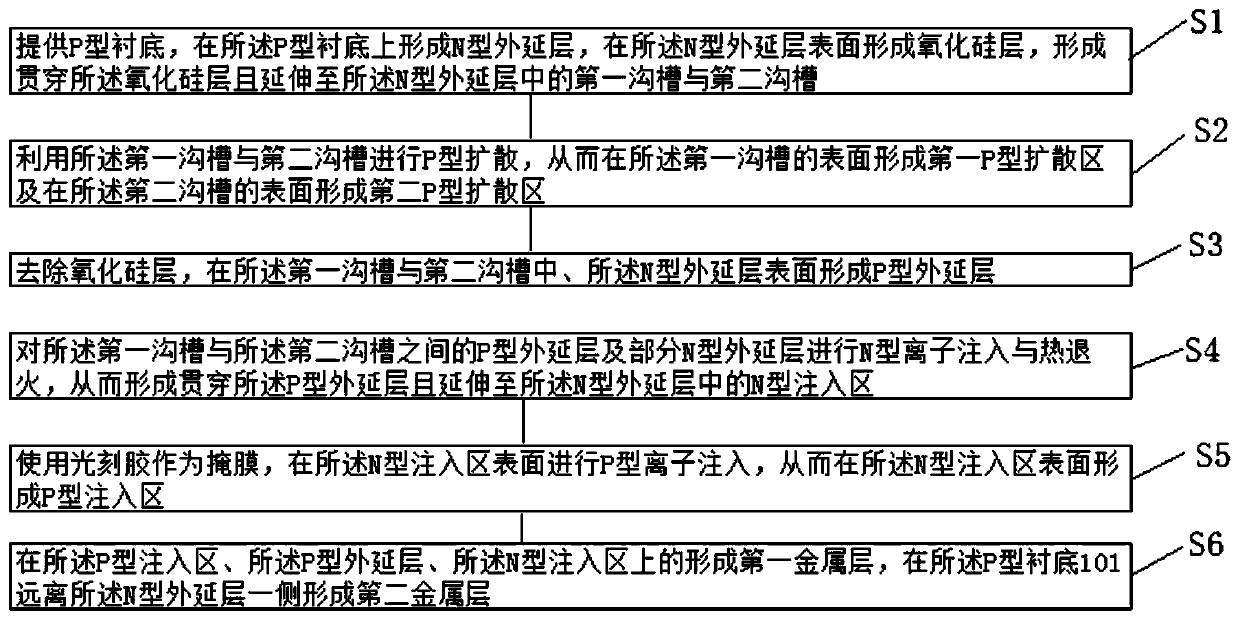

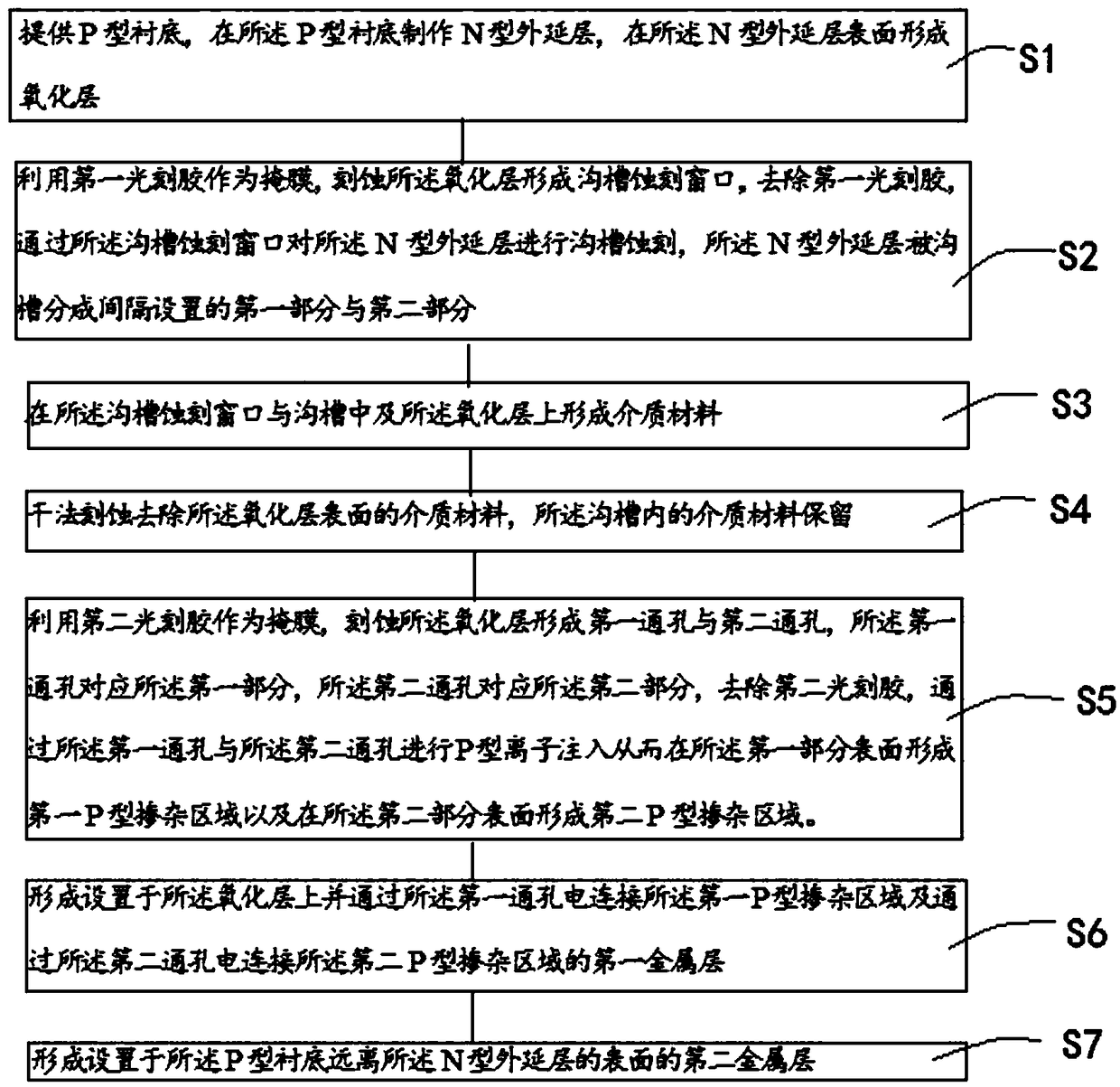

The invention provides a transient voltage suppressor and a fabrication method thereof. The transient voltage suppressor comprises a P-type substrate, an N-type epitaxial layer, a first groove, a second groove, a first P-type diffusion region, a second P-type diffusion region, P-type epitaxial layers, an N-type injection region and a P-type injection region, wherein the N-type epitaxial layer is formed on the P-type substrate, the first groove and the second groove are formed in a surface of the N-type epitaxial layer, the first P-type diffusion region is formed on a surface of the first groove, the second P-type diffusion region is formed on a surface of the second groove, the P-type epitaxial layers are formed in the first groove and the second groove and on the N-type epitaxial layer, the N-type injection region penetrates through the P-type epitaxial layer and extends to the N-type epitaxial layer between the first groove and the second groove, and the P-type injection region is formed on a surface of the N-type injection region.

Owner:NANJING LISHUI HIGH-TECH VENTURE CAPITAL MANAGEMENT CO LTD

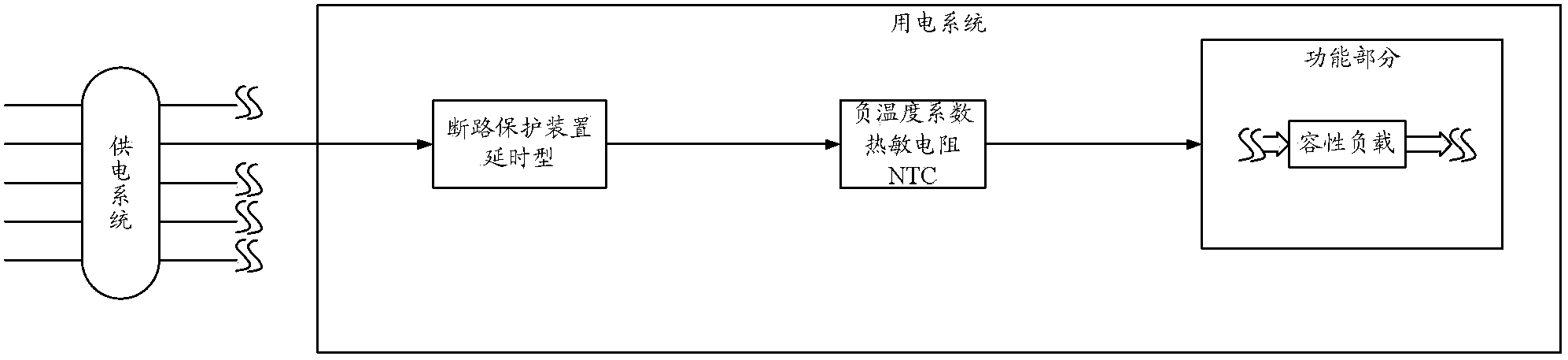

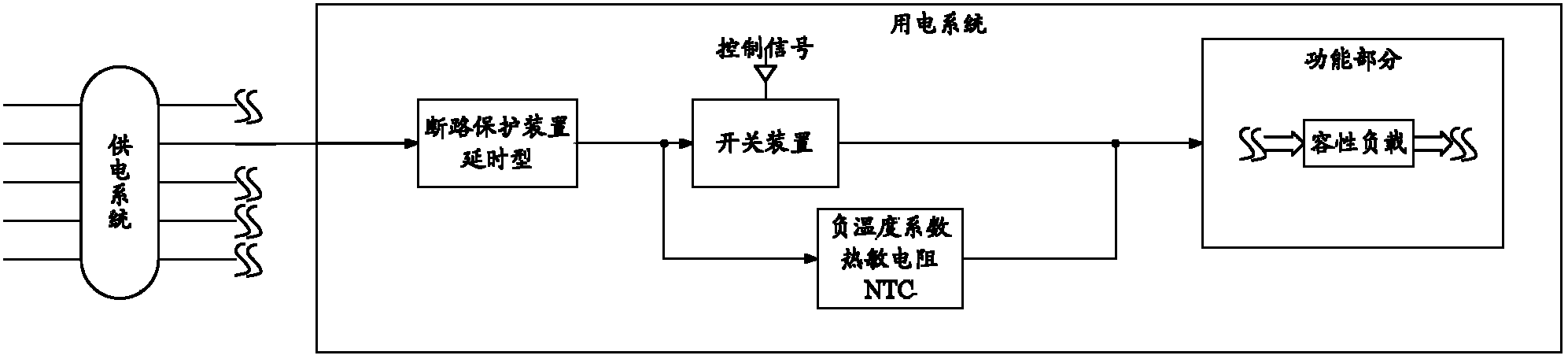

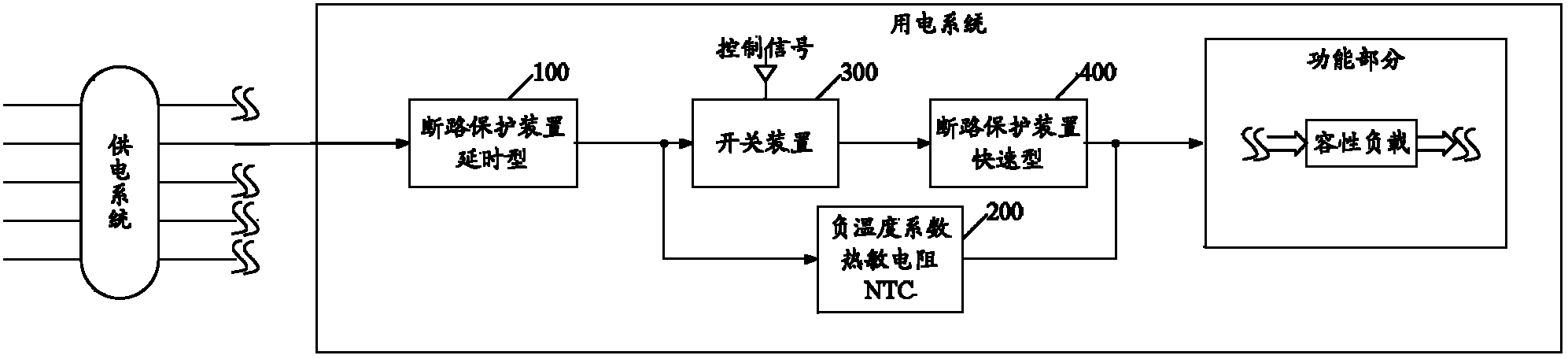

Protective device for electric system

ActiveCN103427392AAvoid impact damageImprove protection characteristicsArrangements responsive to excess currentElectrical resistance and conductanceNegative temperature

The invention relates to a protective device for an electric system. The protective device for the electric system comprises a delay type open circuit protective circuit, a negative temperature coefficient, a control switch and a rapid open circuit protective circuit, wherein the delay type open circuit protective circuit is used for carrying out open circuit protection on a circuit when the electric system has a short-circuit fault, and cannot carry out false operation on instant surge current of the electric system when the electric system is started normally, the negative temperature coefficient is used for restraining the surge current brought by charging of the capacitive load at the moment of starting, the control switch is turned off at the moment of starting of the electric system, is turned on after the starting of the electric system is accomplished, and is used for improving the surge current and eliminating influence caused by the negative temperature coefficient on conversion efficiency, and the rapid open circuit protective circuit can timely carry out operation to be opened when the electric system has the short-circuit fault, and enables the peak value of short-circuit fault current to be effectively restrained through the negative temperature coefficient. According to the protective device for the electric system, when a switch device has a short-circuit fault, the rapid open circuit protective circuit can also be timely opened to avoid impact damage caused by the surge current to devices of other portions, the protective characteristic of a power utilization system is comprehensively improved, and the defects of an existing electric power protective device are overcome.

Owner:长城电源技术有限公司

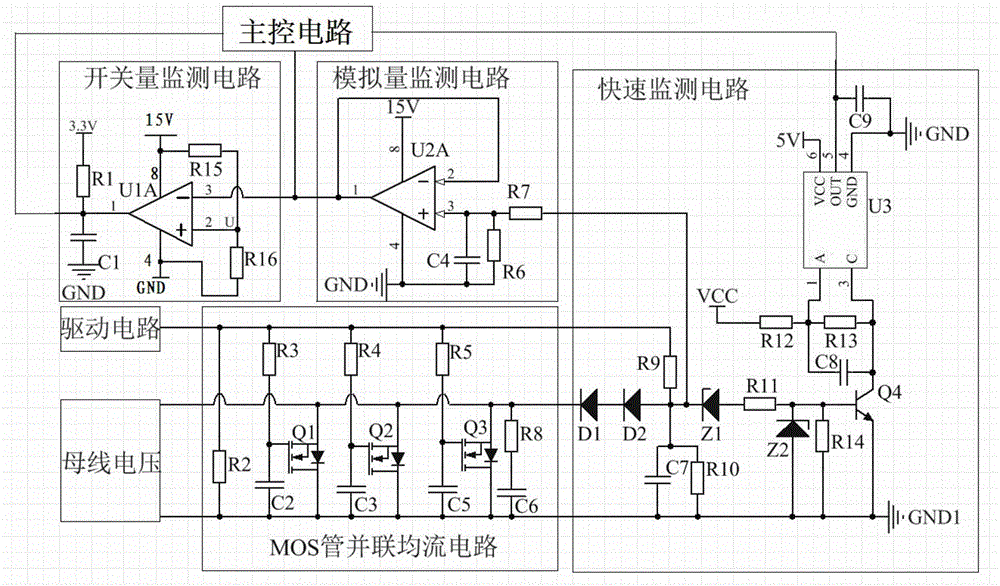

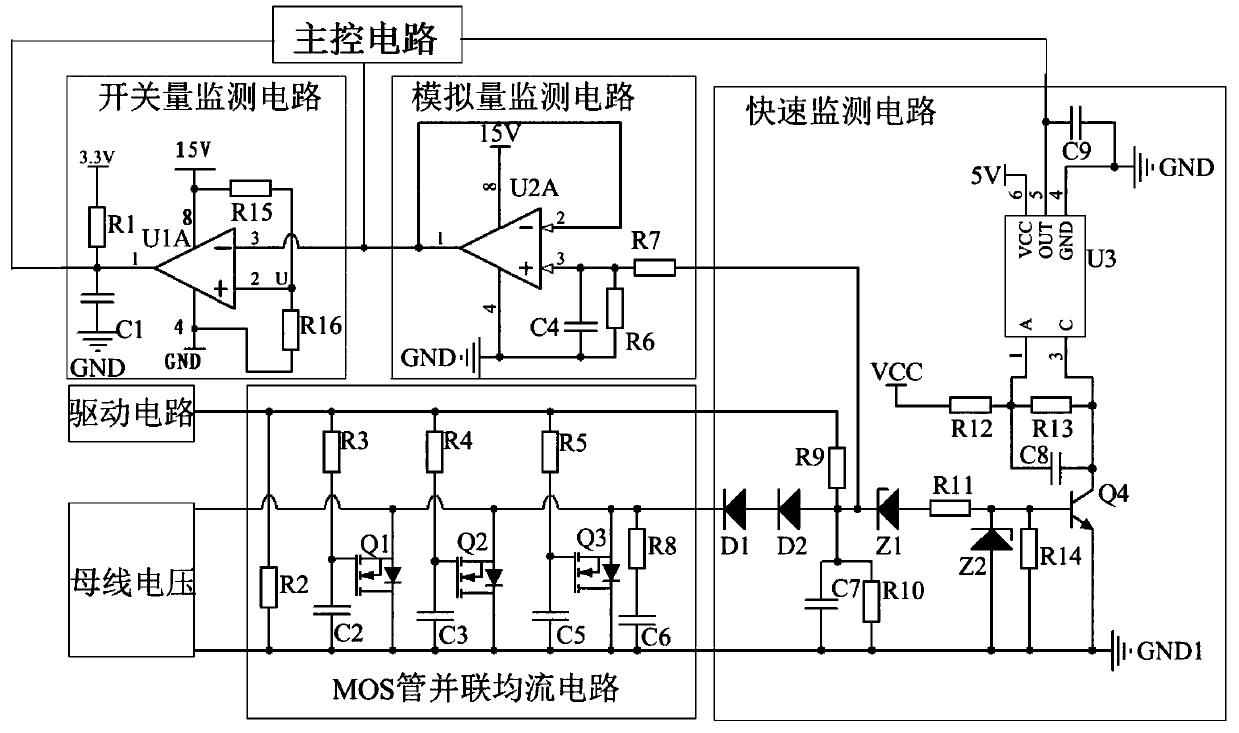

Parallel MOS transistor current sharing and short circuit protection circuit

ActiveCN107181396AImprove securityEfficient detectionElectronic switchingPower conversion systemsDriver circuitShort circuit protection

The invention discloses a parallel MOS transistor current sharing and short circuit protection circuit, and relates to the technical fields of electronic circuits and power electronics. The parallel MOS transistor current sharing and short circuit protection circuit comprises a switching value monitoring circuit, an analog quantity monitoring circuit, a fast monitoring circuit, an MOS transistor parallel current sharing circuit, a driving circuit and a main control circuit, wherein one end of the switching value monitoring circuit is connected with the main control circuit; the other end of the switching value monitoring circuit is connected with the main control circuit and one end of the analog quantity monitoring circuit; the other end of the analog quantity monitoring circuit is connected with the fast monitoring circuit; the fast monitoring circuit is connected with the main control circuit and one end of the MOS transistor parallel current sharing circuit; and the MOS transistor parallel current sharing circuit is connected with the driving circuit and external bus voltage. The parallel MOS transistor current sharing and short circuit protection circuit realizes that each MOS transistor is equal in flowing current and switching speed, and can detect the current operating state of each MOS transistor quickly and effectively; and the parallel MOS transistor current sharing and short circuit protection circuit is simple and reliable in circuit construction and small in PCB occupation area.

Owner:BEIJING RES INST OF PRECISE MECHATRONICS CONTROLS

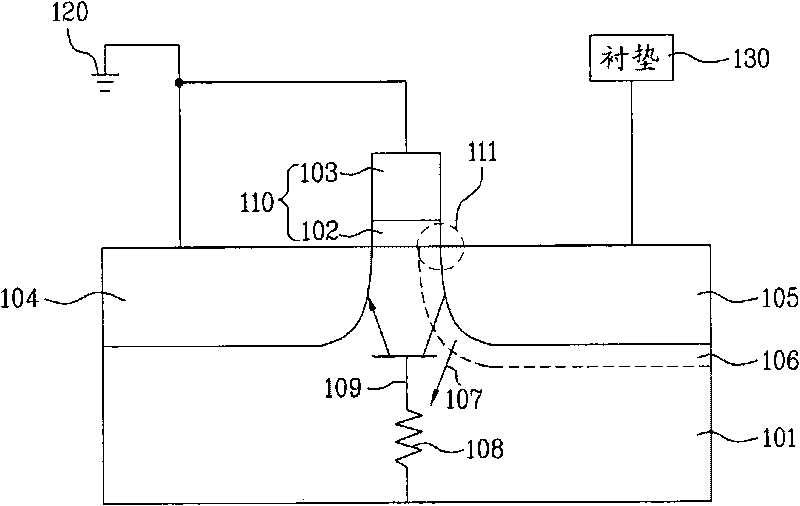

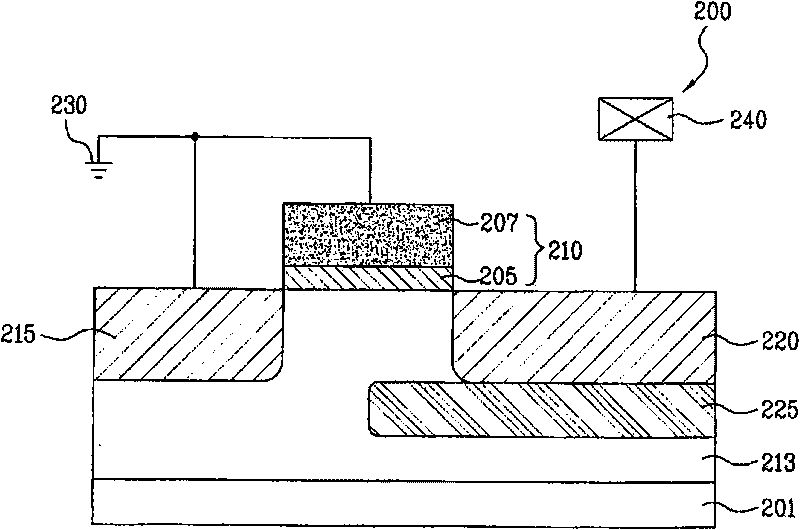

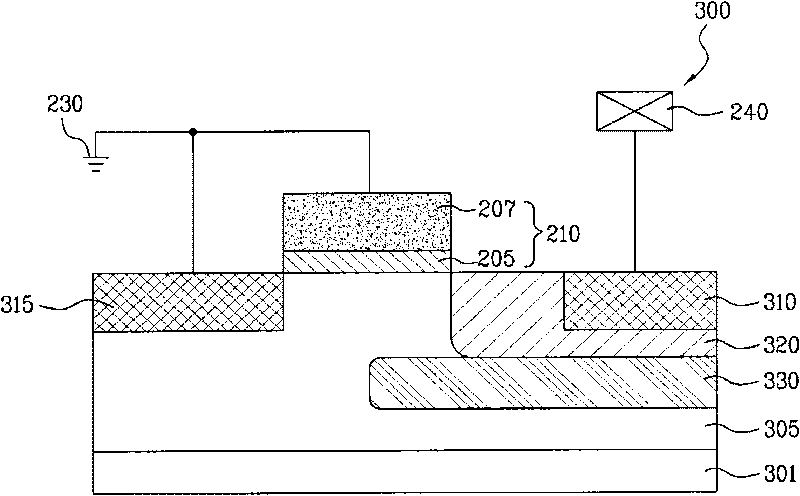

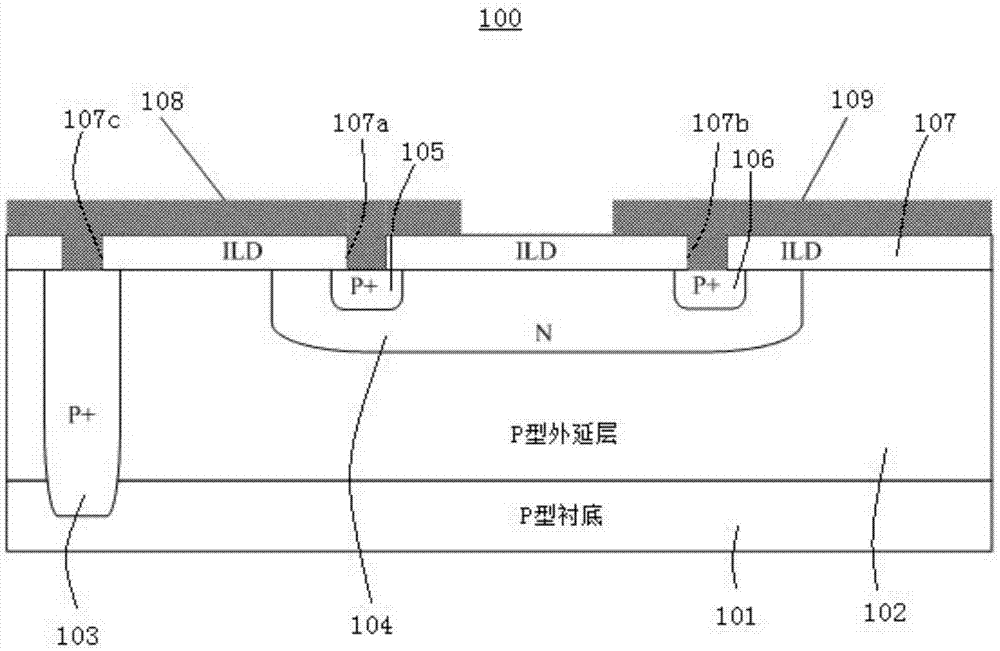

Electrostatic discharge protection semiconductor device and method for mafacturing the same

InactiveCN101714575AAvoid damageImprove protection characteristicsSemiconductor/solid-state device detailsSolid-state devicesElectrostatic discharge protectionEngineering

An electrical device, including a semiconductor device such an electrostatic discharge protection semiconductor device, and a method for manufacturing the same. An electrostatic discharge protection semiconductor device may include a substrate and a gate in and / or over the substrate. The gate may be multi-layered, and may include a gate oxide layer and a gate electrode. An electrostatic discharge protection semiconductor device may include a source region formed in and / or over a predetermined area of the substrate on a side of the gate, and a plurality of drain regions which may be sequentially multi-layered in and / or over the substrate on an opposing side of the gate in a vertical direction. At least one drain region may be overlapped with the gate in a horizontal direction.

Owner:DONGBU HITEK CO LTD

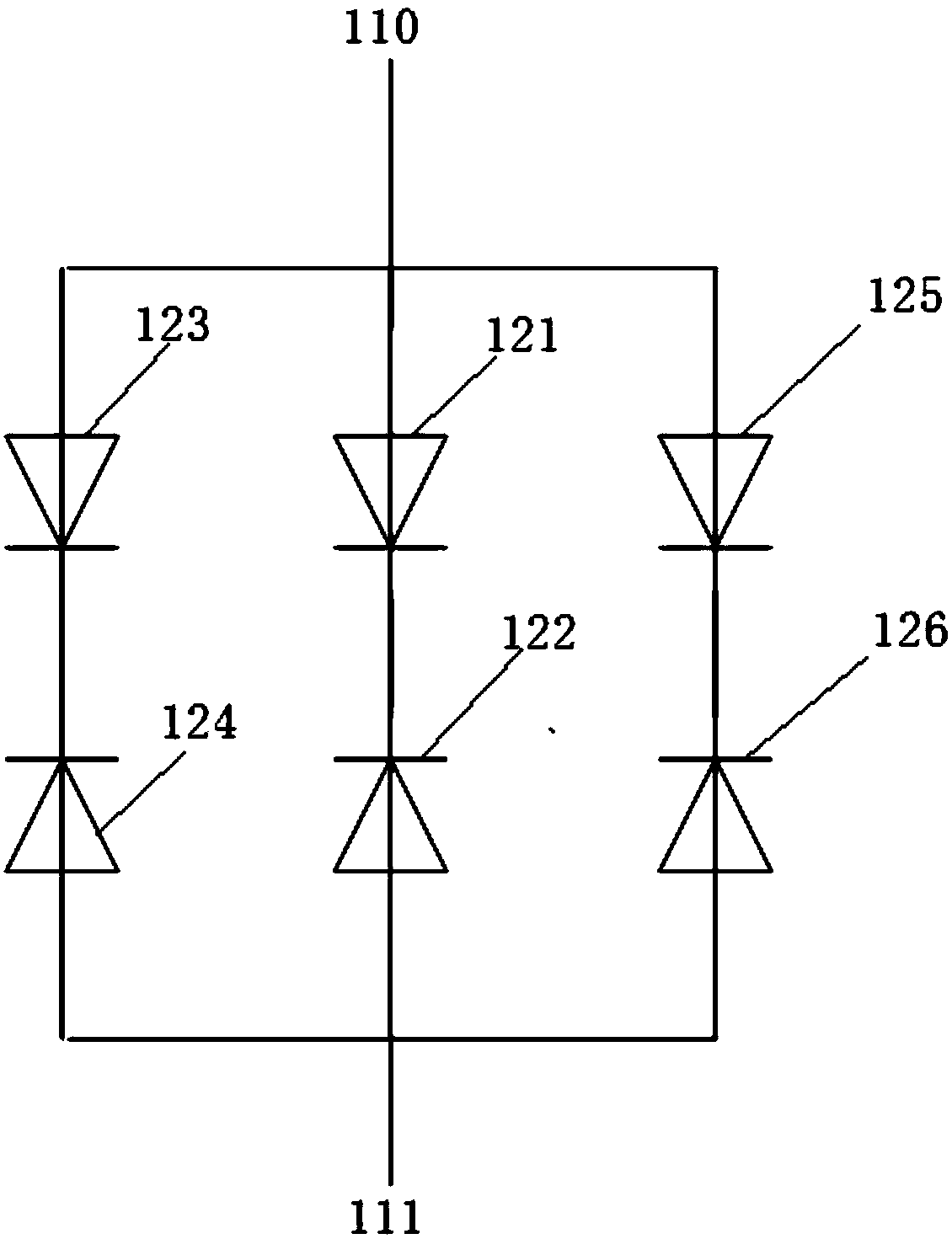

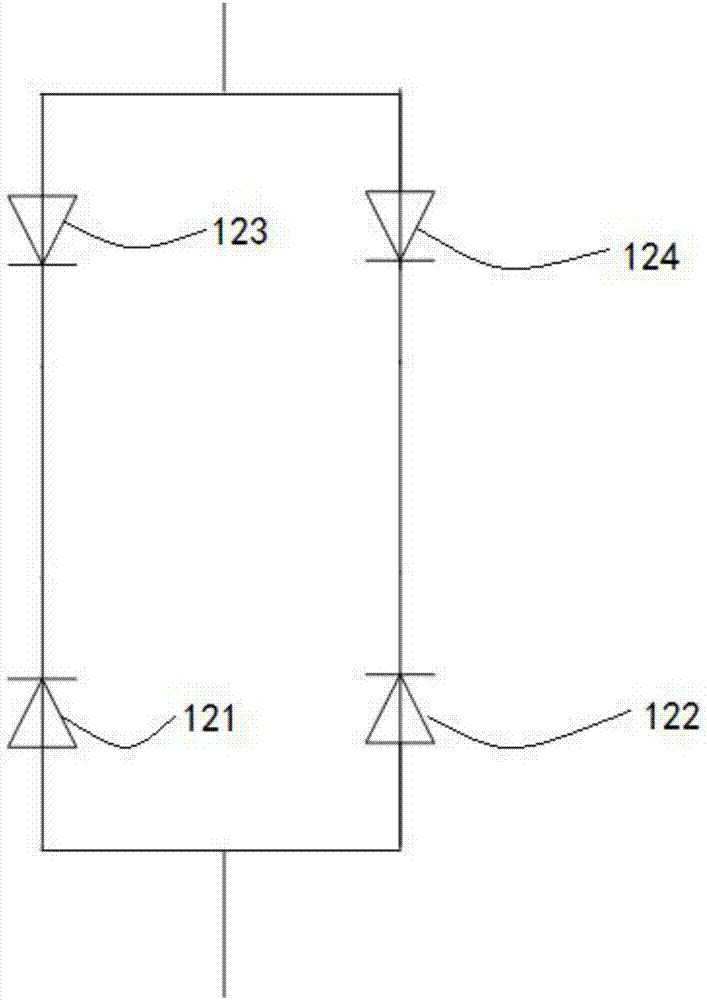

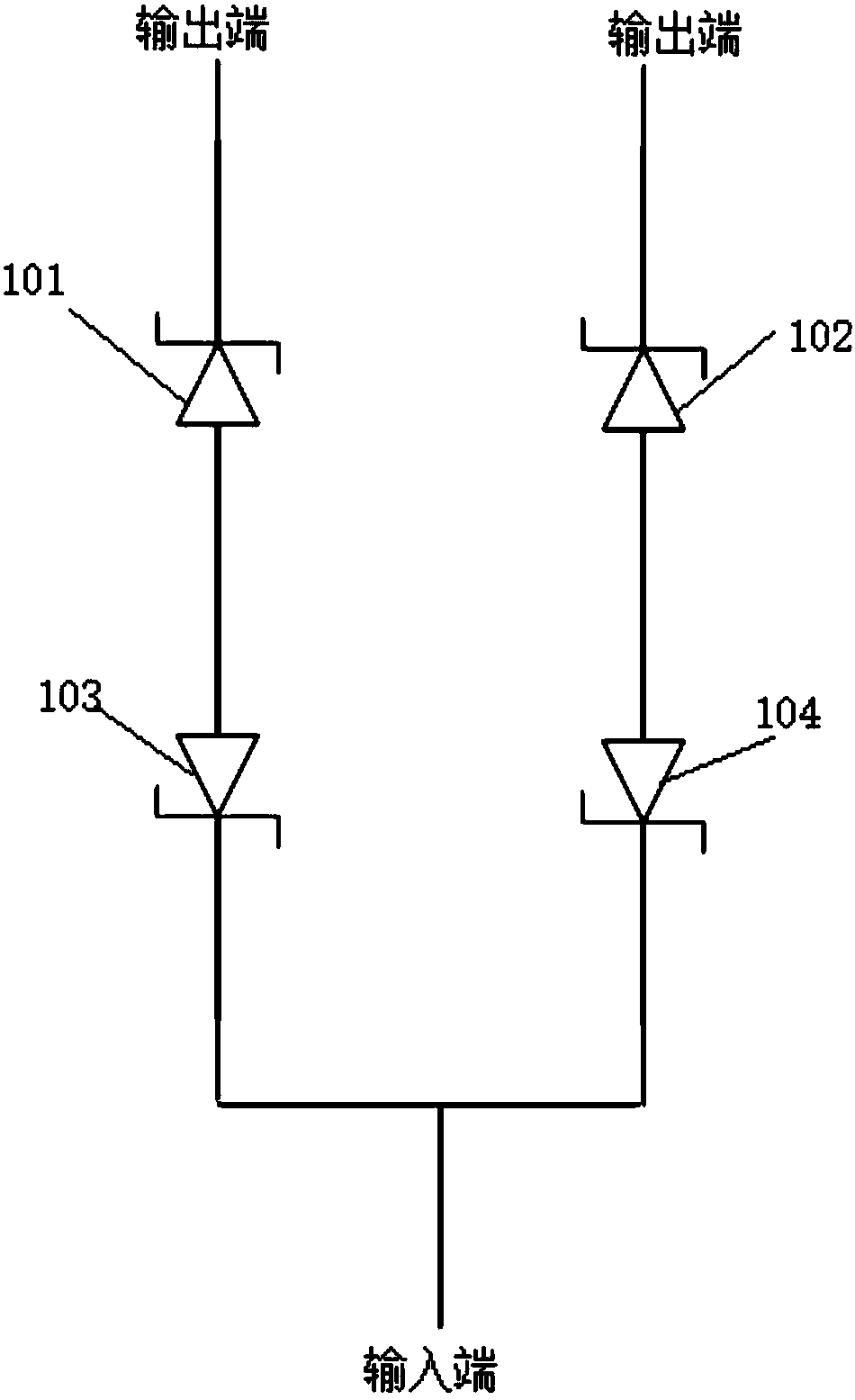

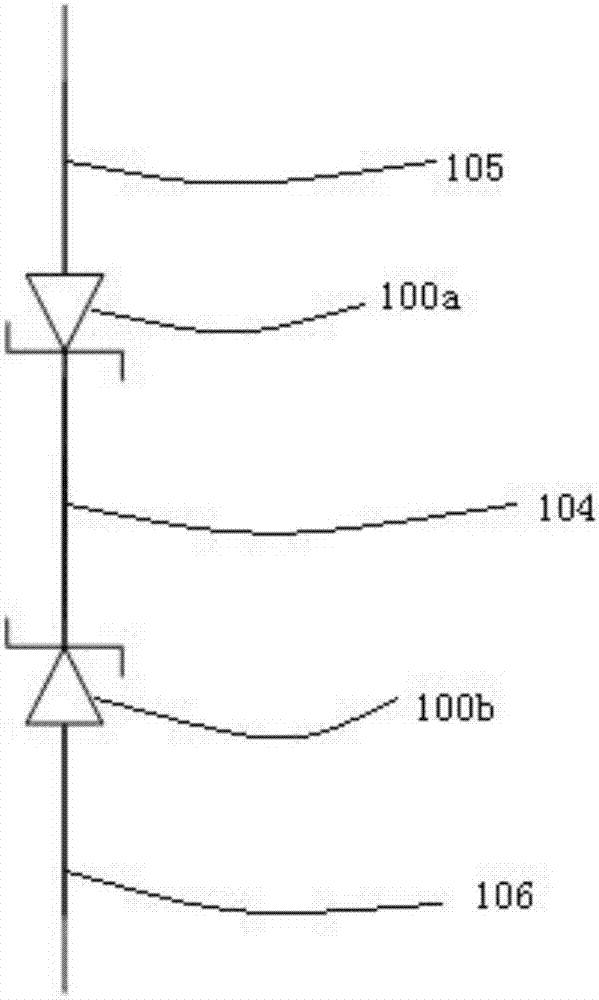

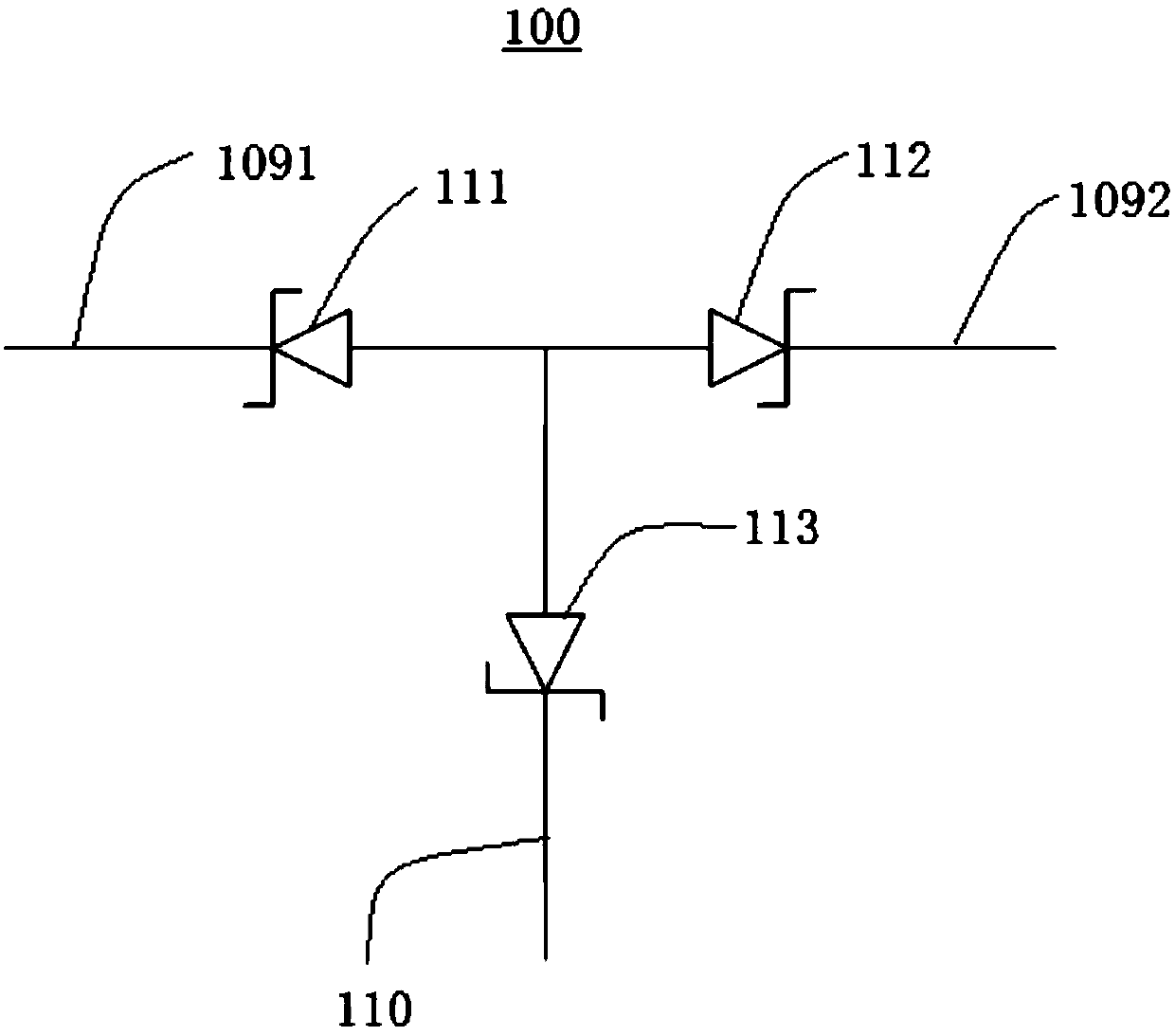

Transient voltage suppressor and manufacturing method thereof

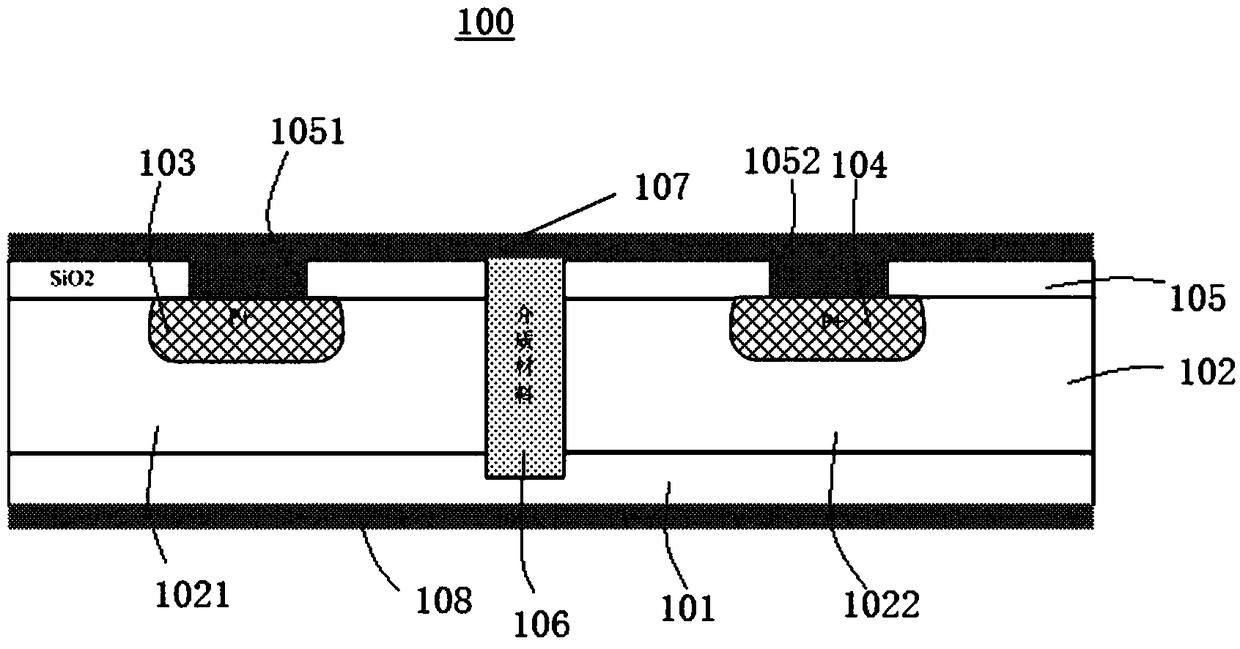

ActiveCN107301995AImprove protection characteristicsImprove protection reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingTransient voltage suppressorP type doping

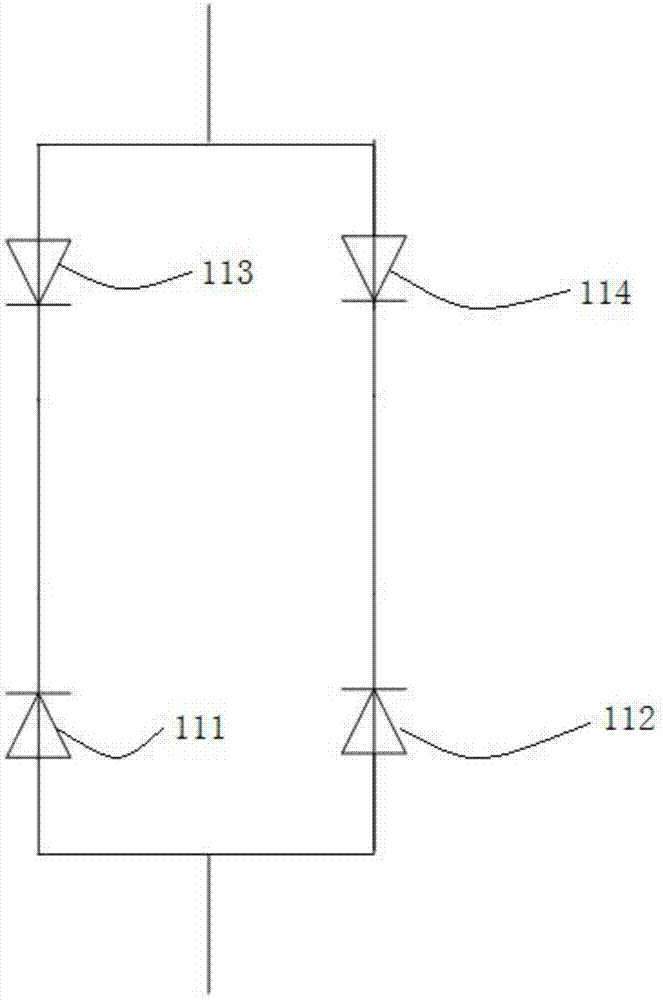

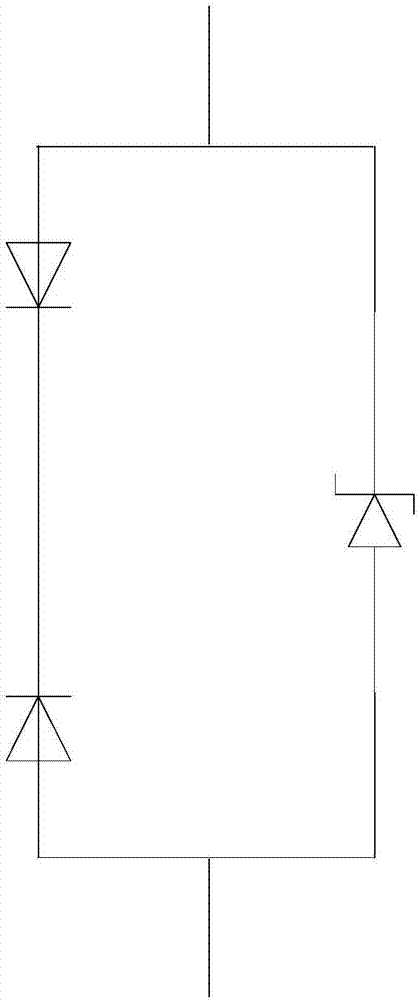

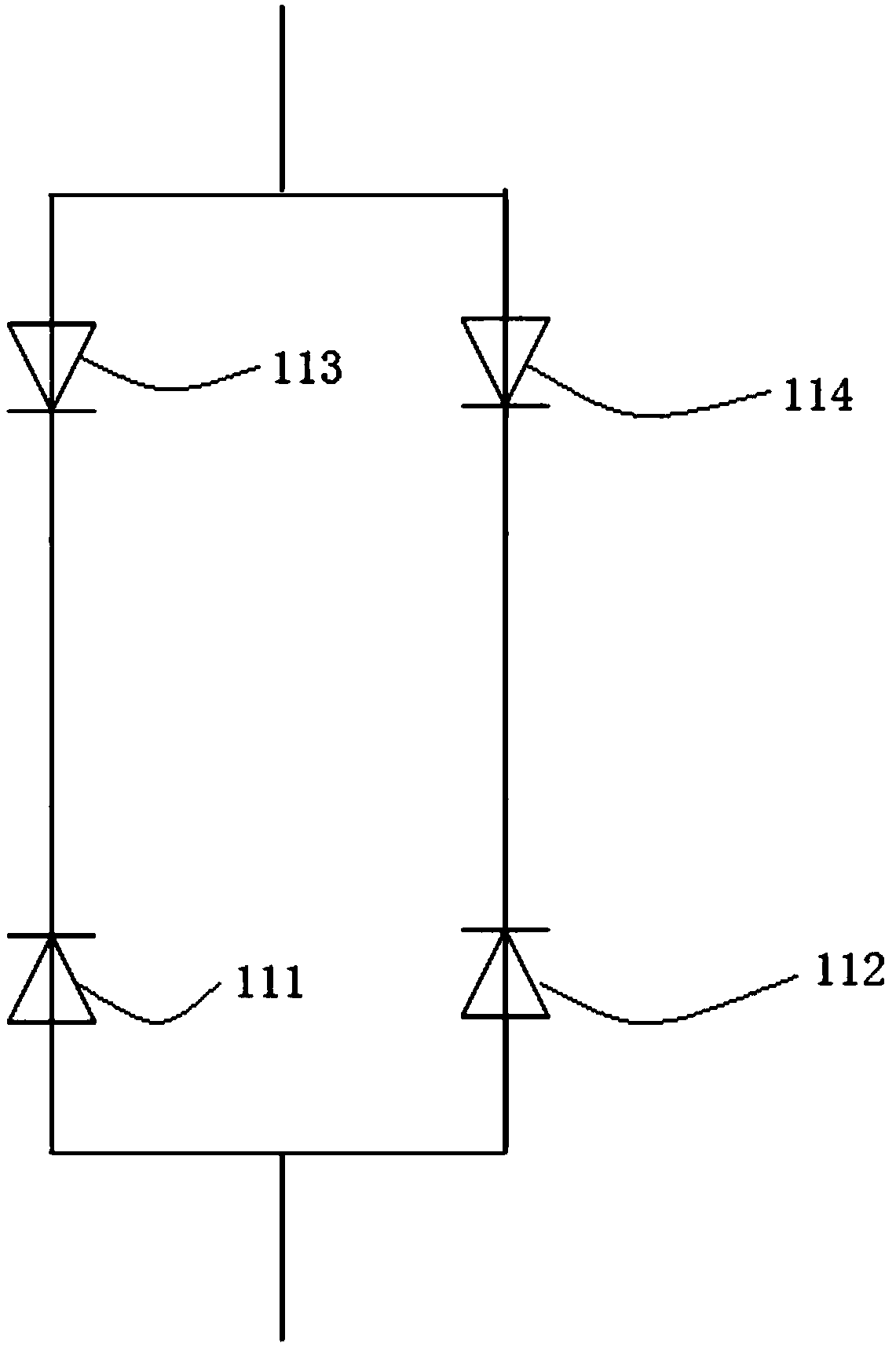

The invention provides a transient voltage suppressor which includes a P type substrate and an N type epitaxial layer. The N type epitaxial layer comprises a first part and a second part. The transient voltage suppressor also comprises a first P type doping area formed at the surface of a first part, a second P type doping area formed at the surface of a second part, and a P type epitaxial layer formed on the N type epitaxial layer, the first P type doping area and the second P type doping area. A first diode is formed by the P type substrate and the first part, a second diode is formed by the P type substrate and the second part, a third diode connected to the first diode is formed by the first part and the first P type doping area, a fourth diode connected to the second diode is formed by the second part and the second P type doping area, the negative electrode of the first diode is connected to the negative electrode of the second diode, and the negative electrode of the third diode is connected to the negative electrode of the fourth diode.

Owner:嘉兴市晨阳箱包有限公司

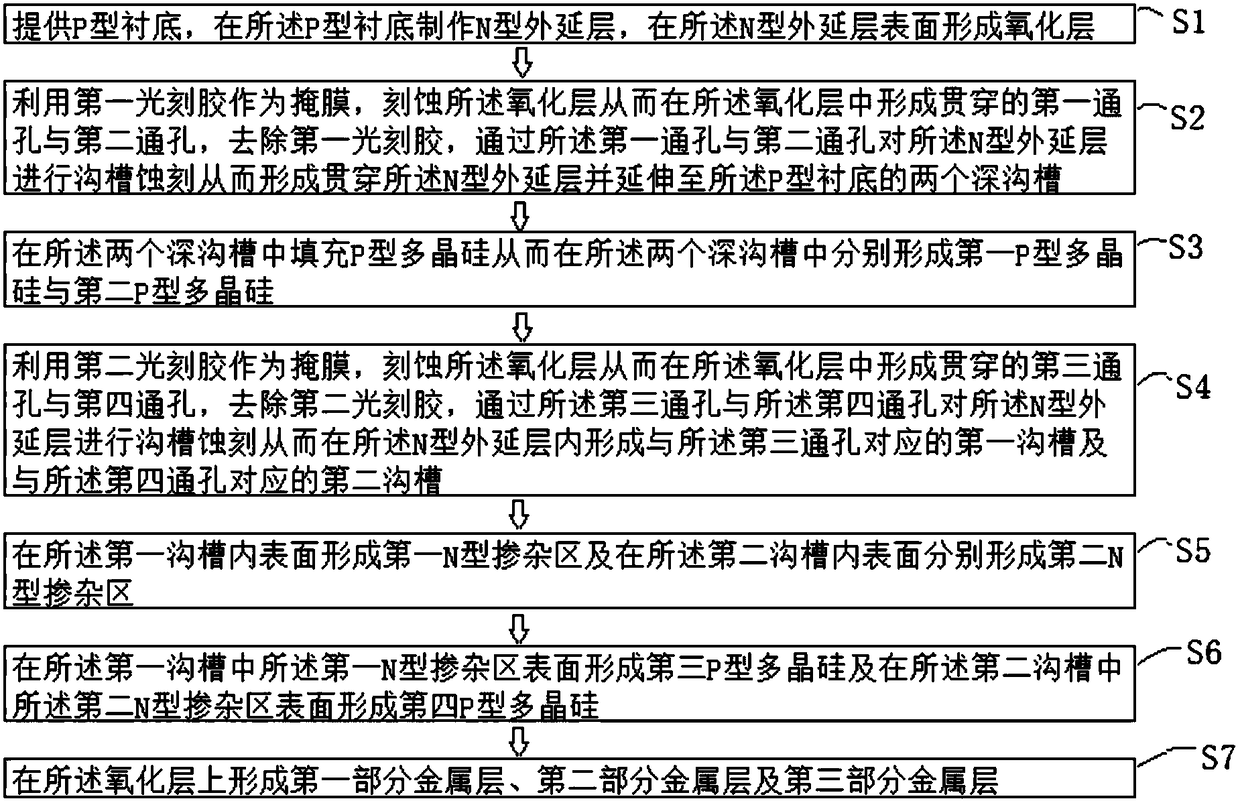

Transient voltage inhibitor and manufacturing method thereof

ActiveCN108063138AReduce parasitic capacitanceReduce areaSolid-state devicesDiodeTransient voltage suppressor

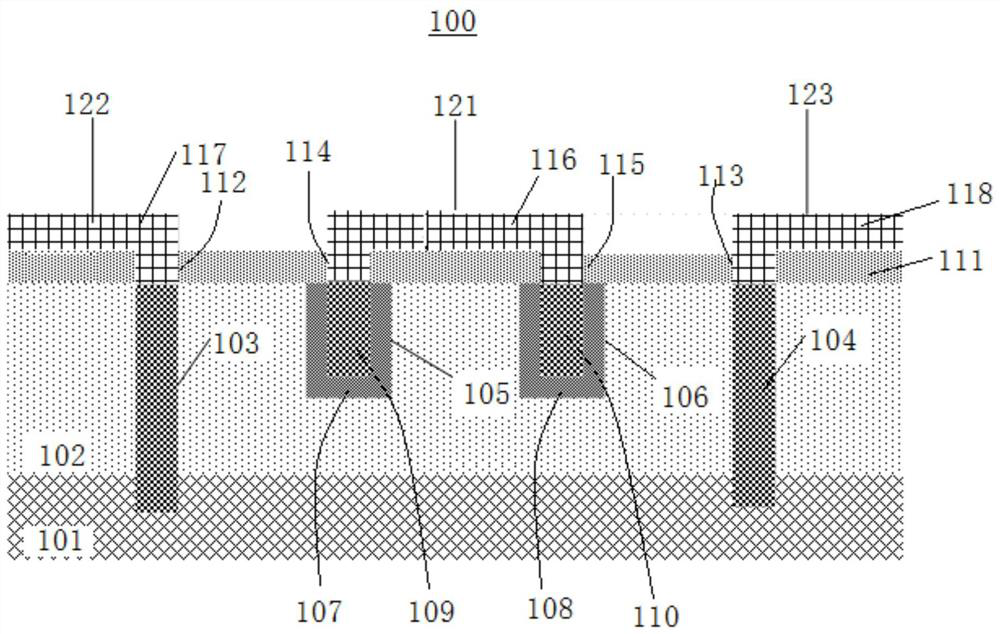

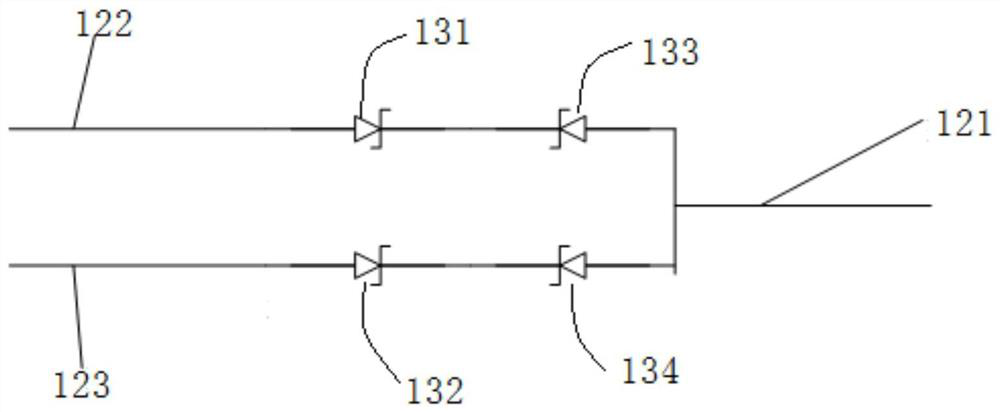

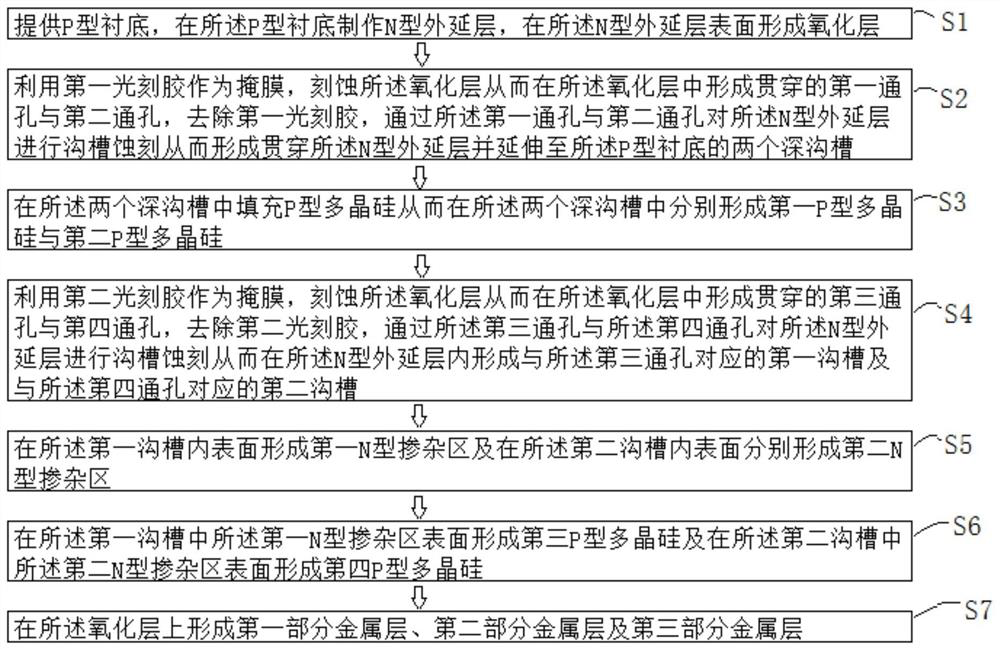

The invention provides a transient voltage inhibitor and a manufacturing method thereof. The transient voltage inhibitor includes a P type substrate, an N type epitaxial layer formed on the P type substrate, a first P type polysilicon, a second P type polysilicon, a first groove, a second groove, a first N type doped region formed on the inner surface of the first groove, a second N type doped region formed on the inner surface of the second groove, a third P type polysilicon formed on the surface of the first N type doped region in the first groove, and a fourth P type polysilicon formed on the surface of the second N type doped region in the second groove, wherein the first P type polysilicon and the second P type polysilicon penetrate through the N type epitaxial layer and extend to theP type substrate; the first groove and the second groove are formed on the surface, far away from the P type substrate, of the N type epitaxial layer; and the third P type polysilicon is also connected with the fourth P type polysilicon. The transient voltage inhibitor has the advantages of small device area, low process difficulty, low manufacturing cost, and higher protection performance and reliability.

Owner:嘉兴市龙锋市政建设有限公司

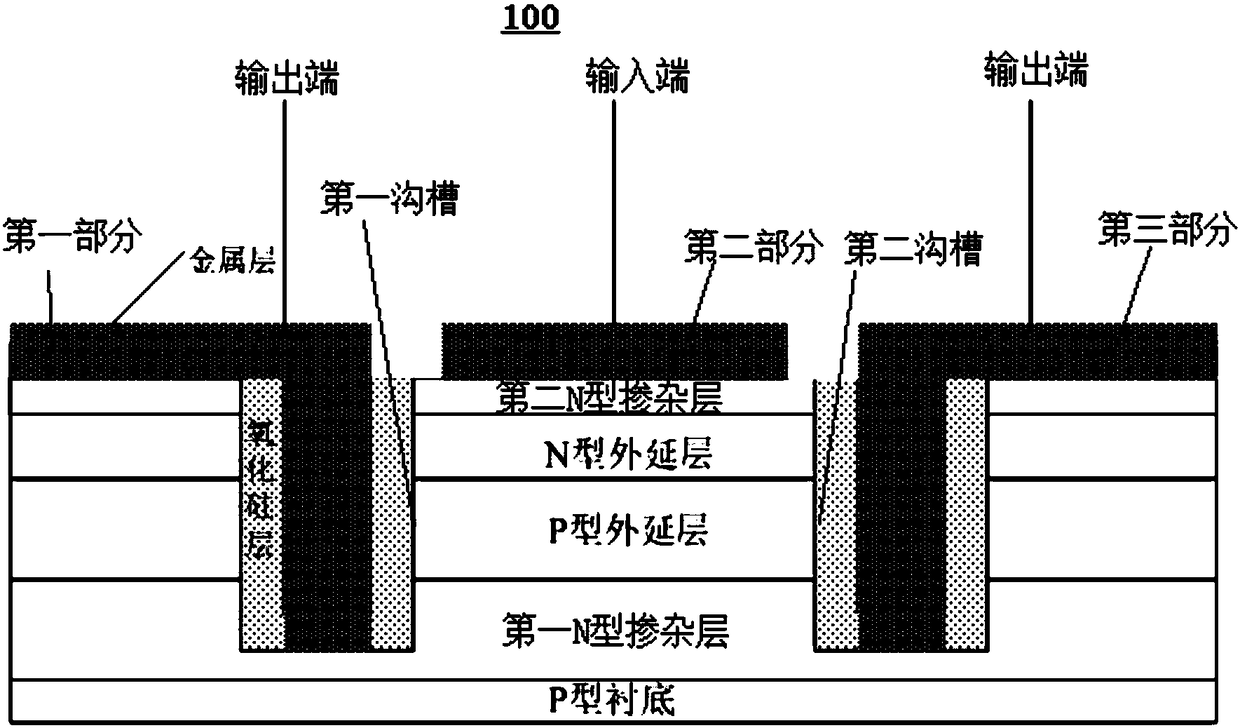

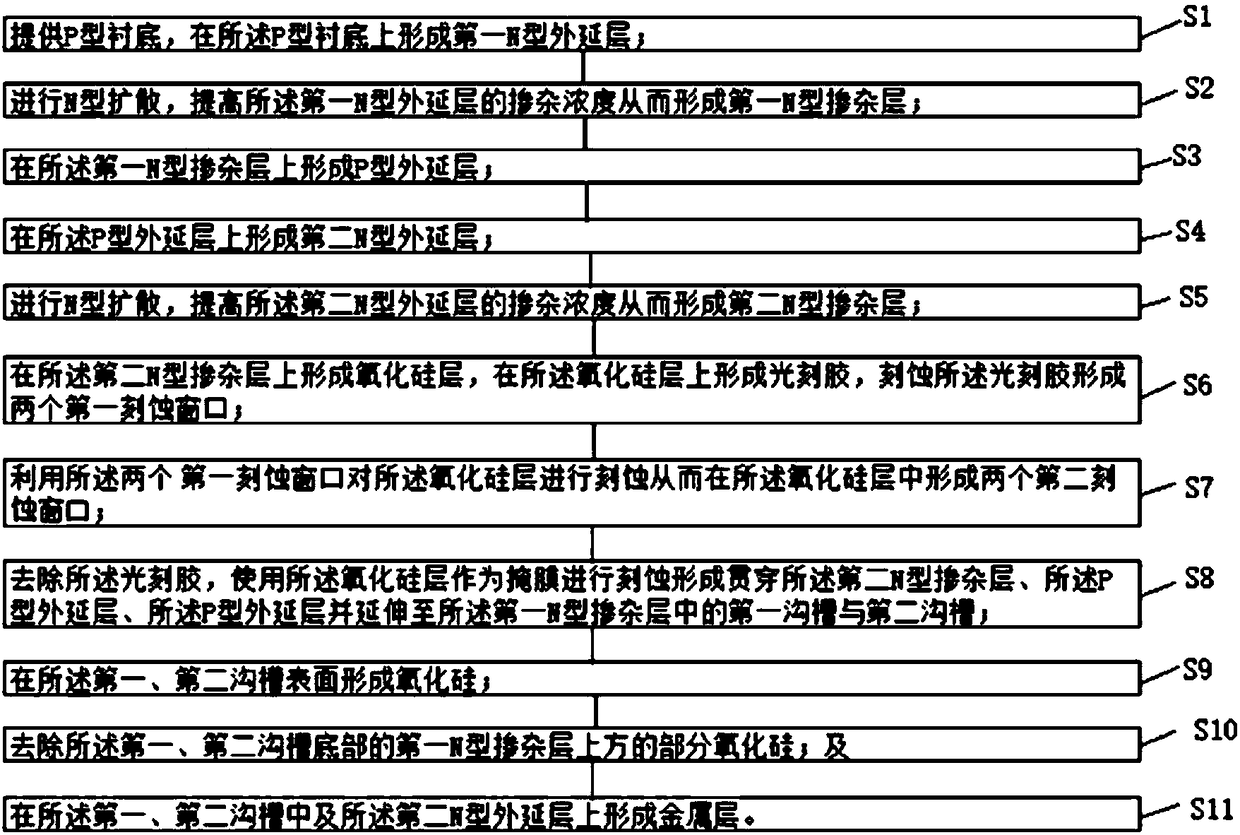

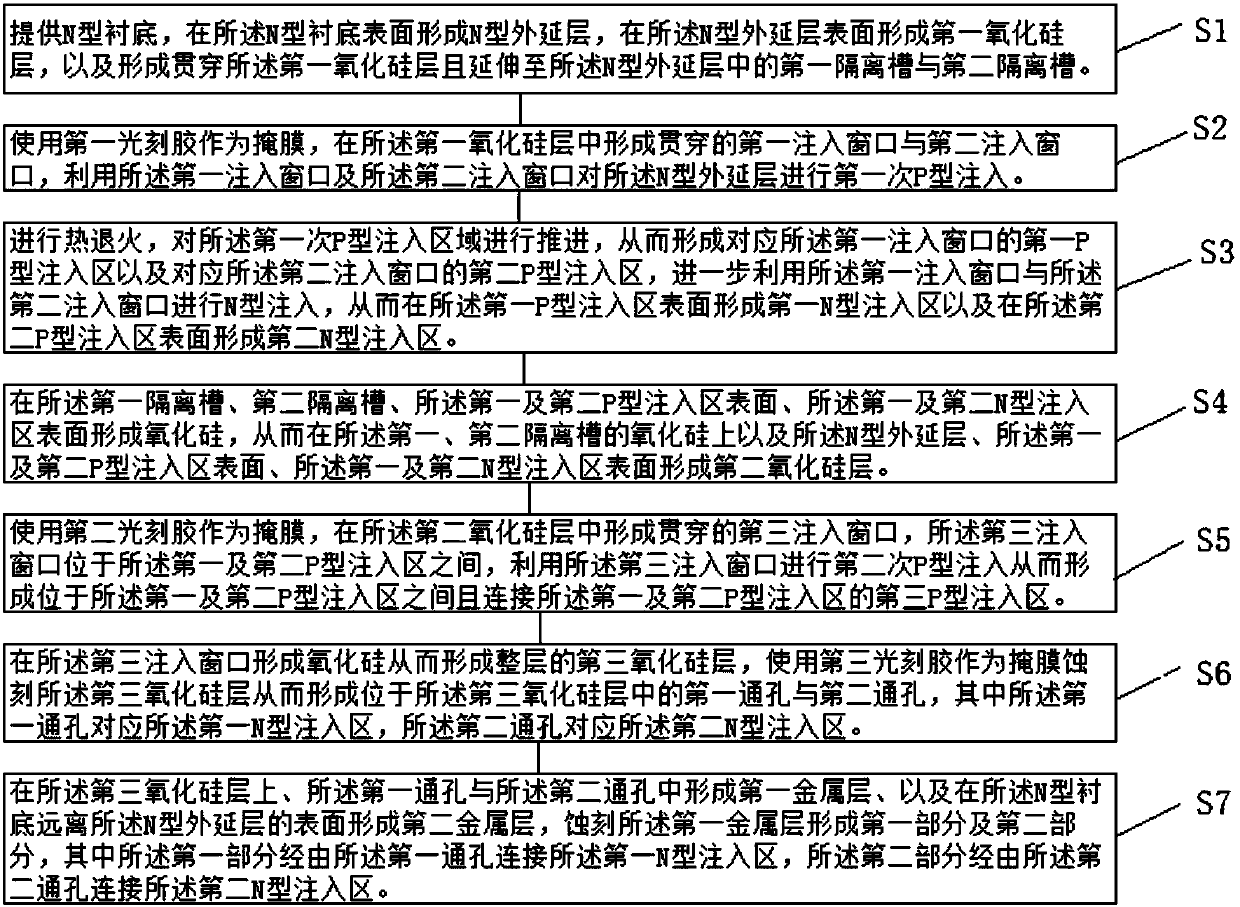

Transient voltage suppressor and making method thereof

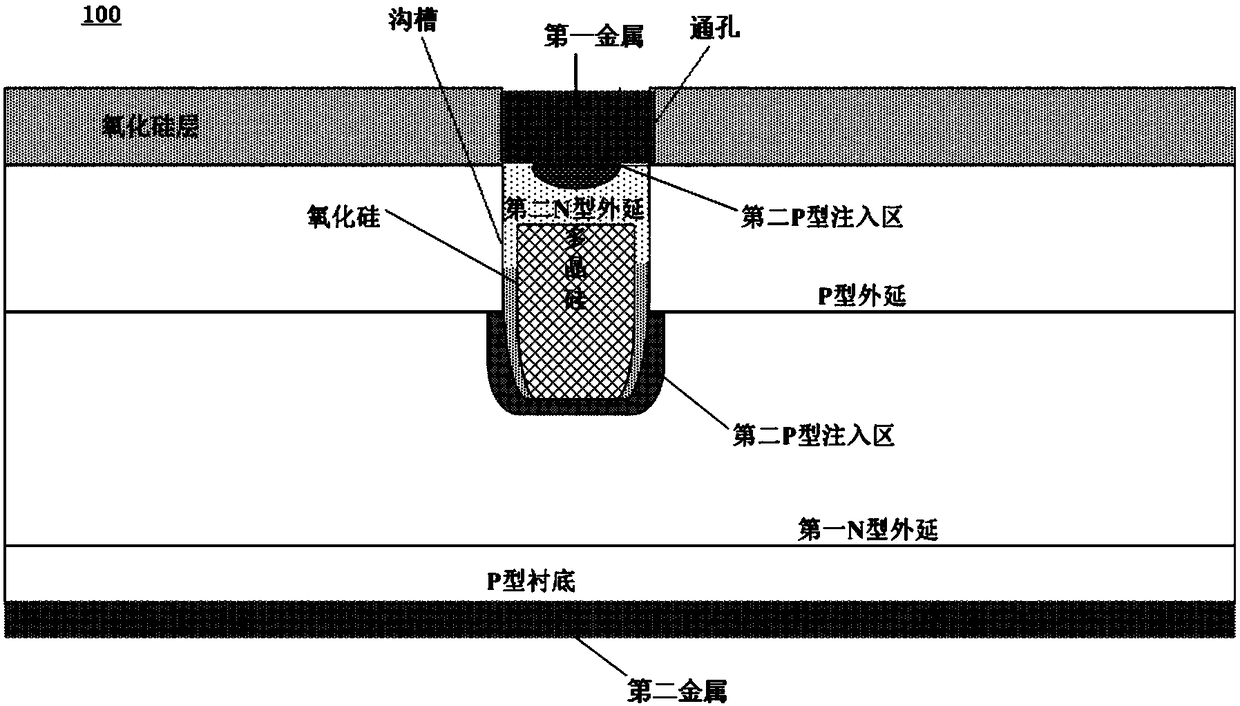

InactiveCN108063135AReduce areaNo manufacturing costSolid-state devicesSemiconductor/solid-state device manufacturingOptoelectronicsSilicon oxide

A transient voltage suppressor comprises a P-type substrate, a first N-type doping layer formed on the P-type substrate, a P-type epitaxial layer formed on the first N-type doping layer, an N-type epitaxial layer formed on the P-type epitaxial layer, a second N-type doping layer formed on the N-type epitaxial layer, a first groove and a second groove passing through the second N-type doping layer,the N-type epitaxial layer and the P-type epitaxial layer and extending to the first N-type doping layer, silicon oxide layers formed on the side walls of the first groove and the second groove, anda metal layer formed in the first groove and the second groove and on the second N-type doping layer, wherein the metal layer comprises a first part formed in the first groove and connected with the first N-type doping layer, a second part formed in the second groove and connected with the first N-type doping layer and a third part adjacent to the second N-type doping layer between the first groove and the second groove.

Owner:SHENZHEN JINGTE INTELLIGENT MFG TECH CO LTD

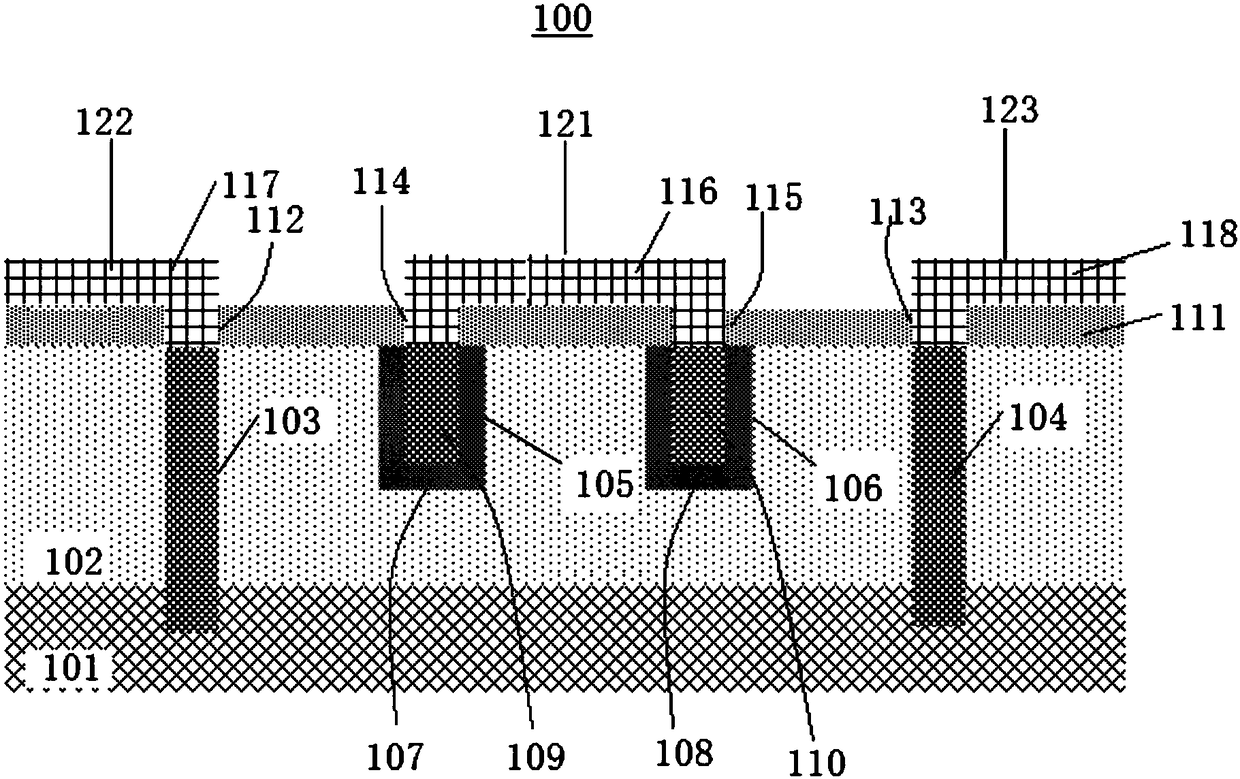

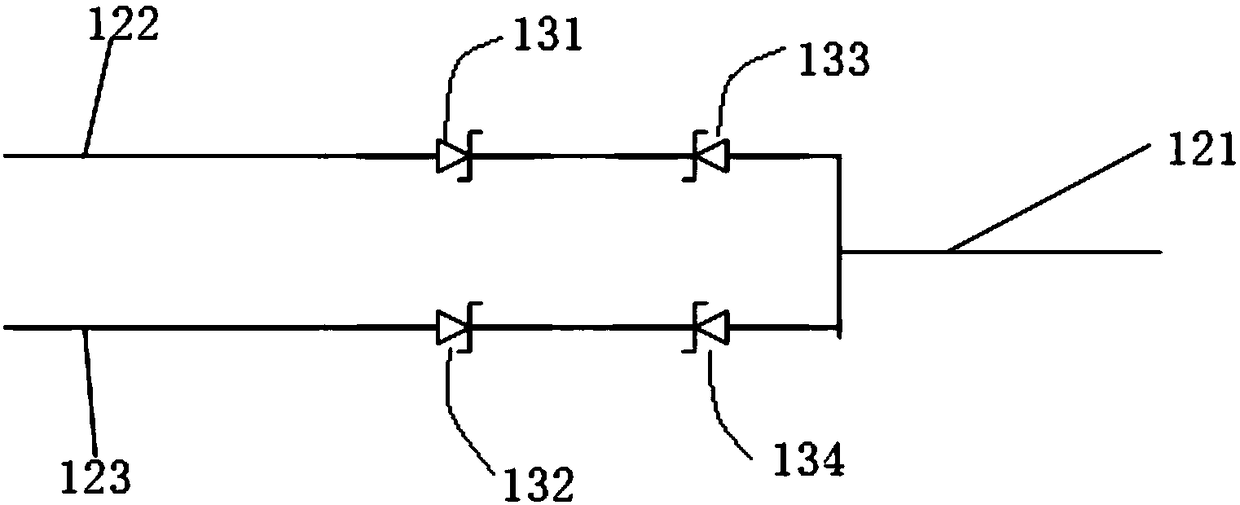

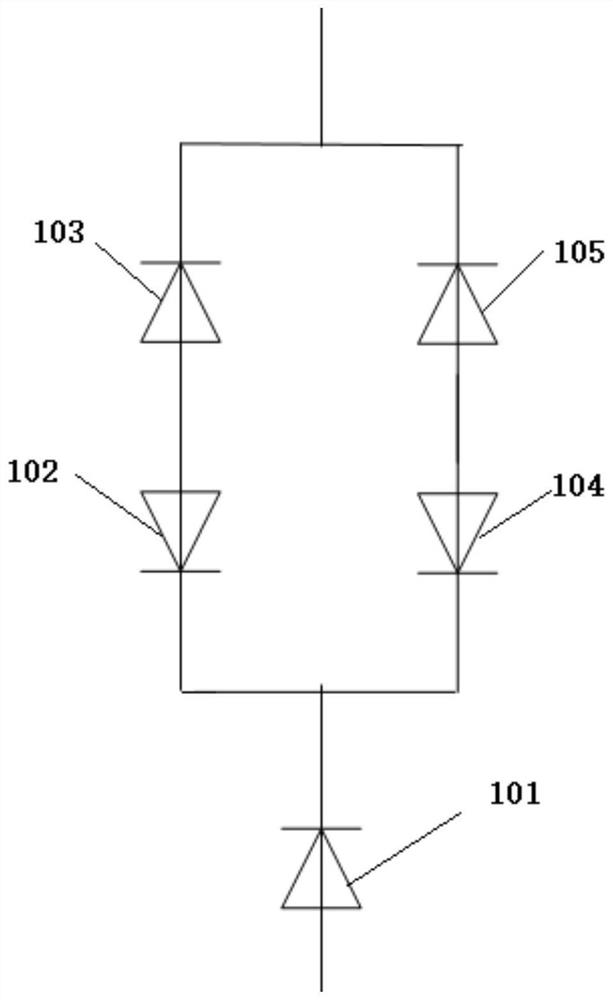

Transient voltage suppressor and fabricating method thereof

ActiveCN107316864AImprove protection characteristicsImprove protection reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingTransient voltage suppressorPhysics

The invention provides a transient voltage suppressor and a fabricating method thereof. The transient voltage suppressor comprises a P-type substrate, an N-type epitaxial layer, a first P-type doped region and a second P-type doped region, wherein the N-type epitaxial layer comprises a first part and a second part which are arranged at an interval; the first P-type doped region is formed on the surface of the first part; the second P-type doped region is formed on the surface of the second part; the P-type substrate and the first part form a first diode; the P-type substrate and the second part form a second diode; the first part and the first P-type doped region also form a third diode abutted with the first diode; the second part and the second P-type doped region also form a fourth diode abutted with the second diode; a cathode of the first diode is connected with a cathode of the second diode; and a cathode of the third diode is connected with a cathode of the fourth diode.

Owner:伯芯半导体科技(天津)有限公司

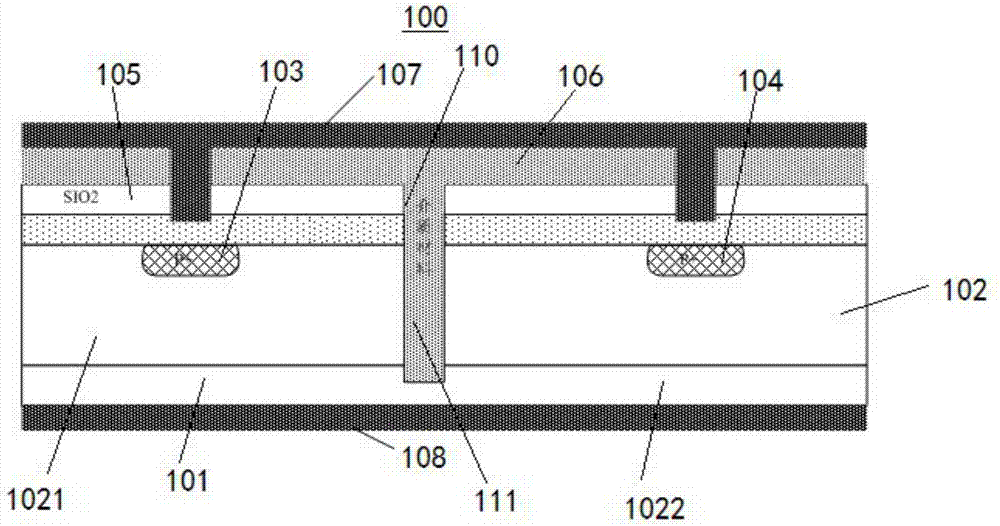

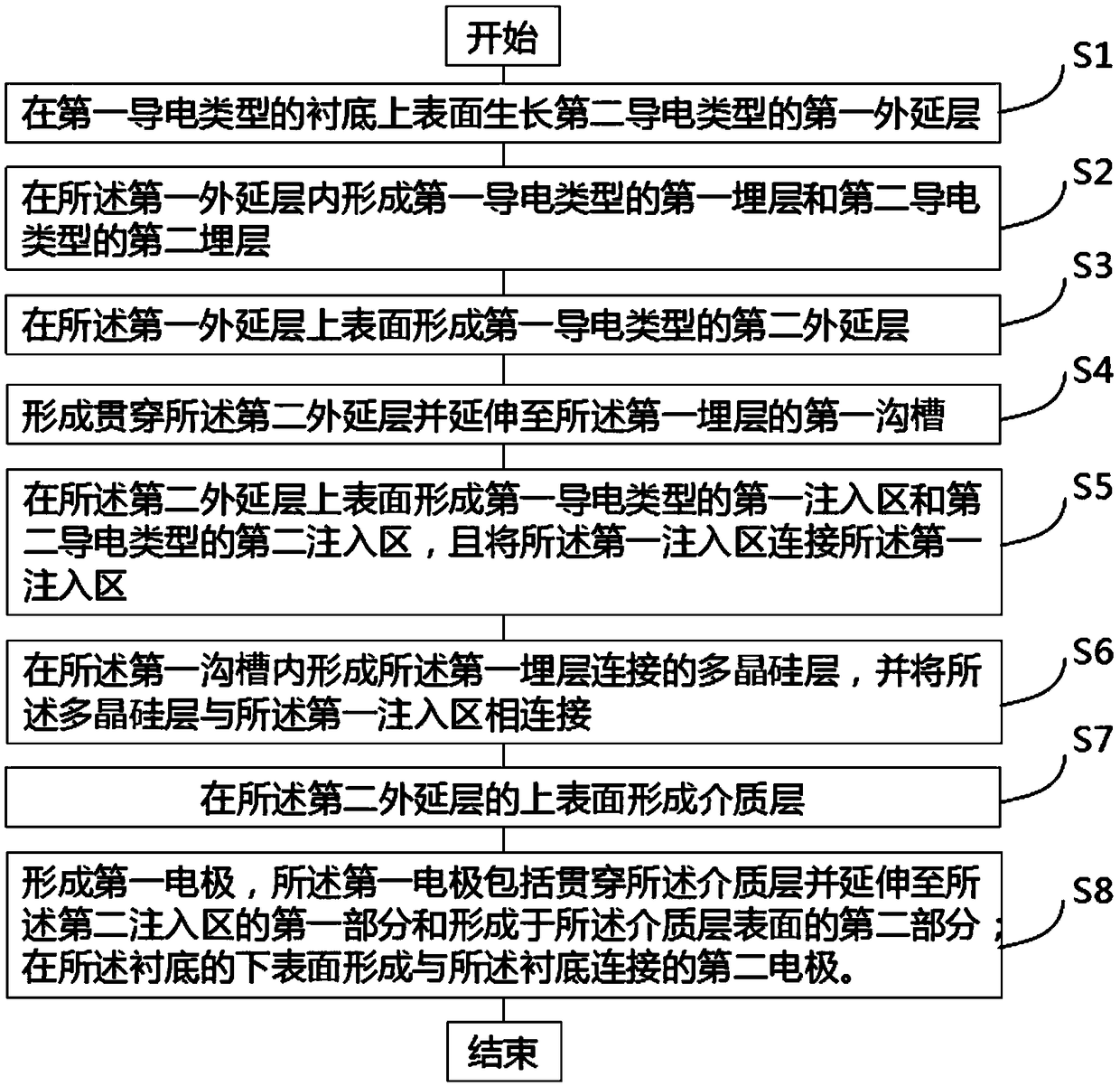

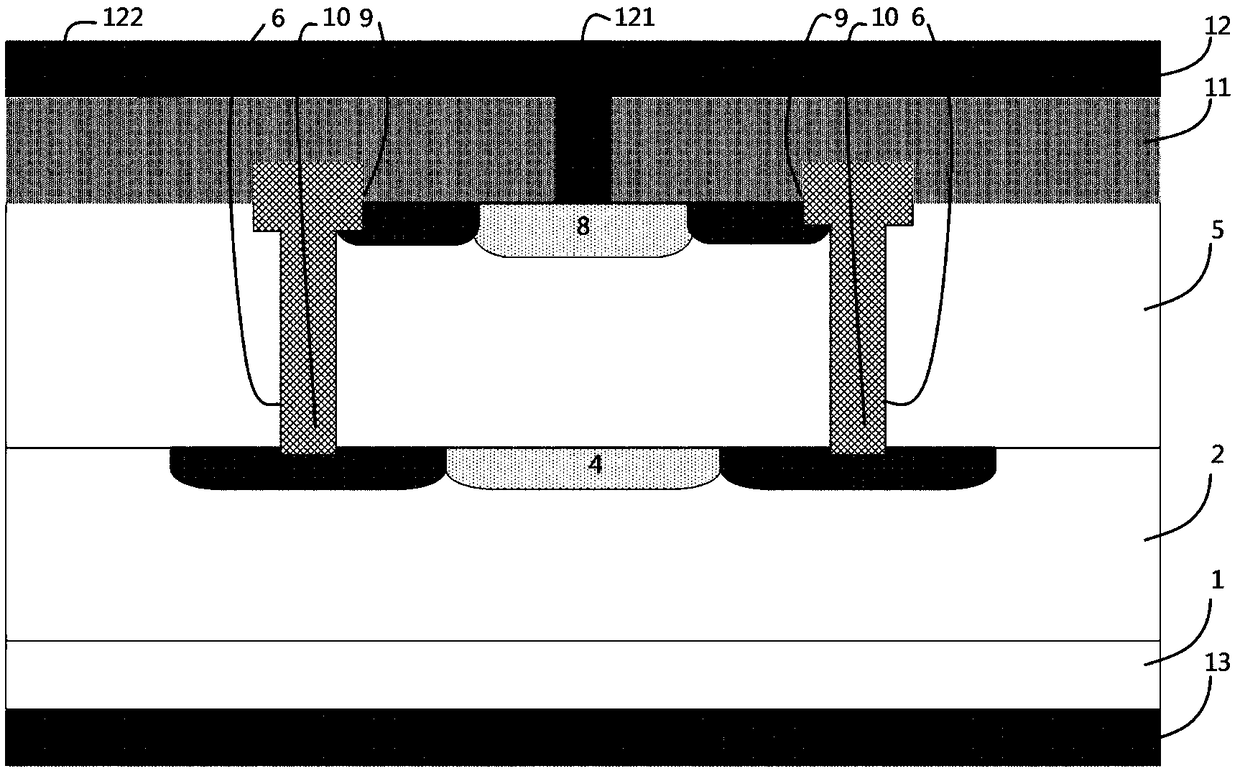

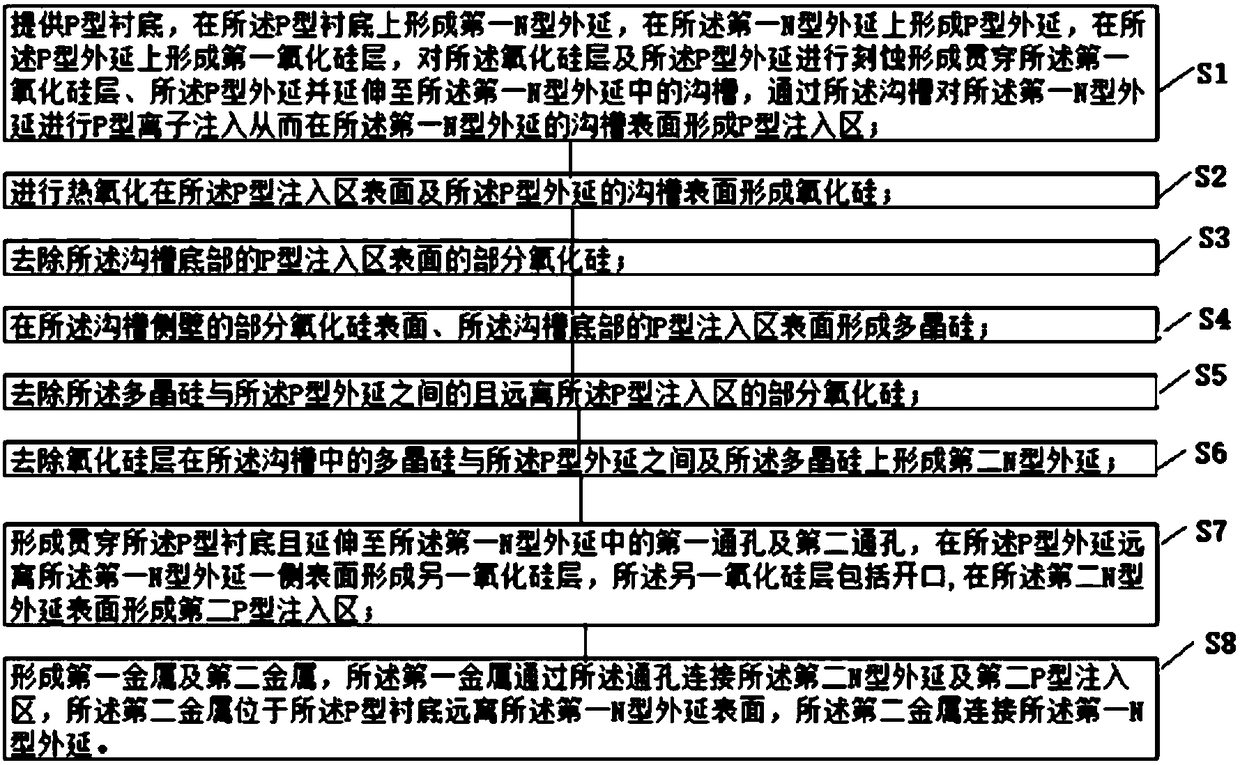

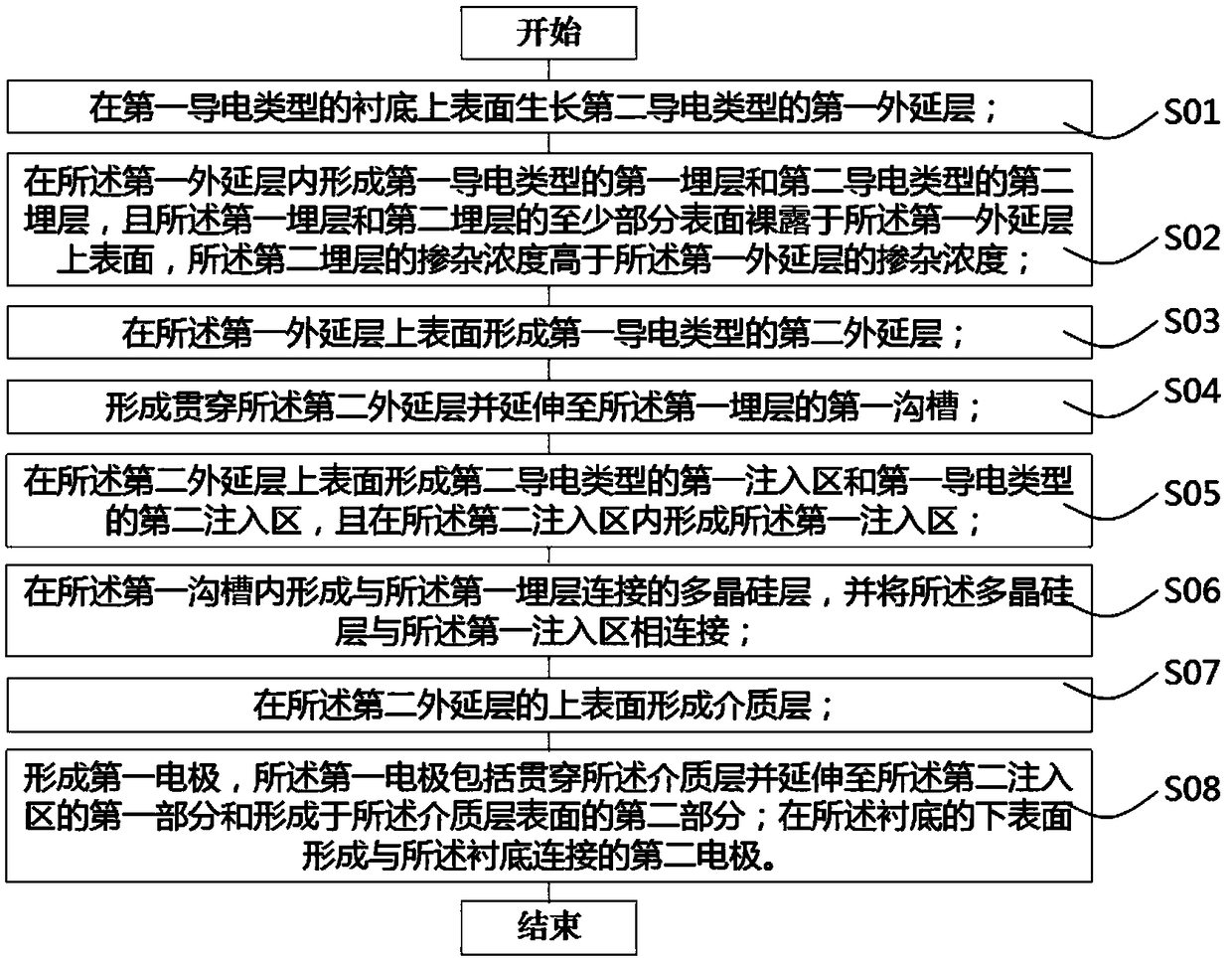

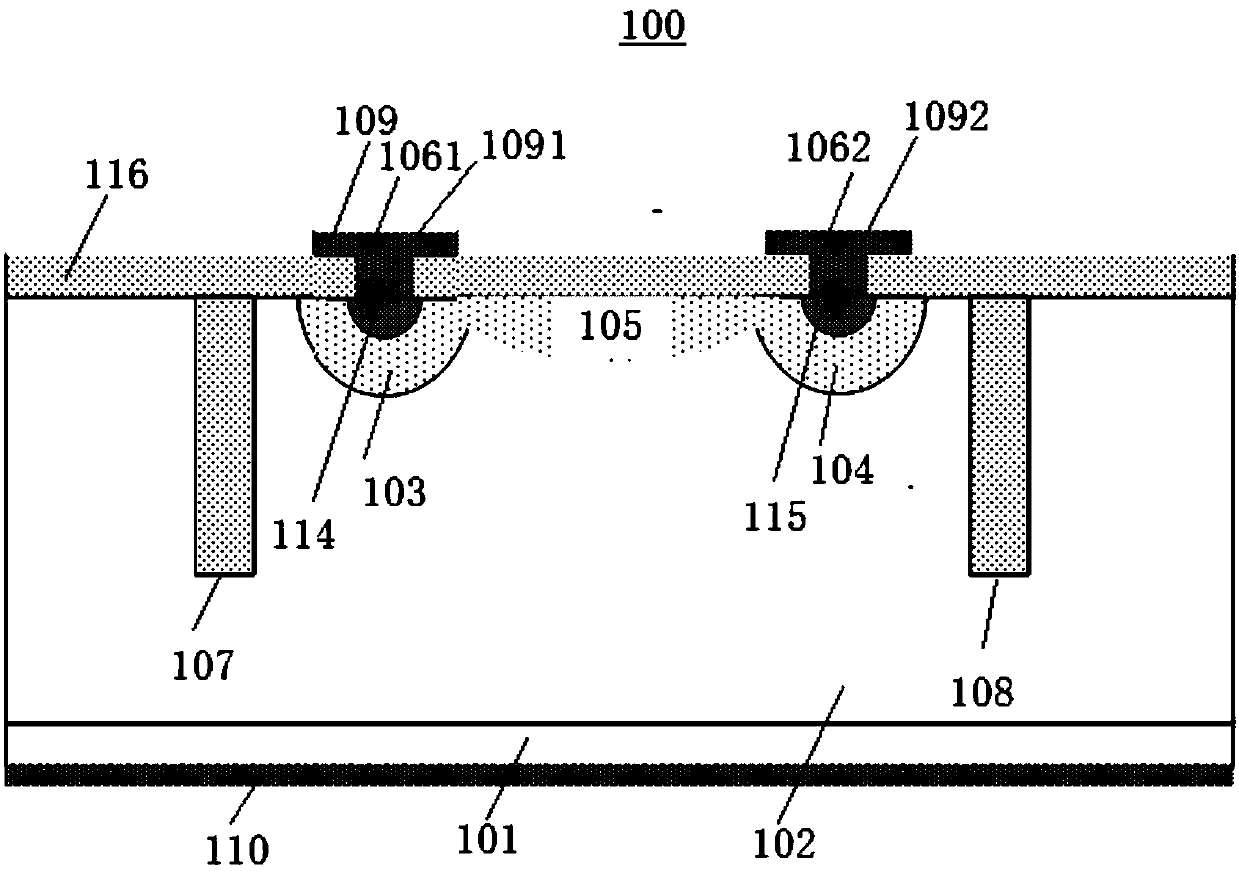

A power device protection chip and a manufacturing method thereof

InactiveCN109037206AIncrease the doping concentrationReduce the difficulty of manufacturing processSolid-state devicesDiodePolycrystalline siliconOptoelectronics

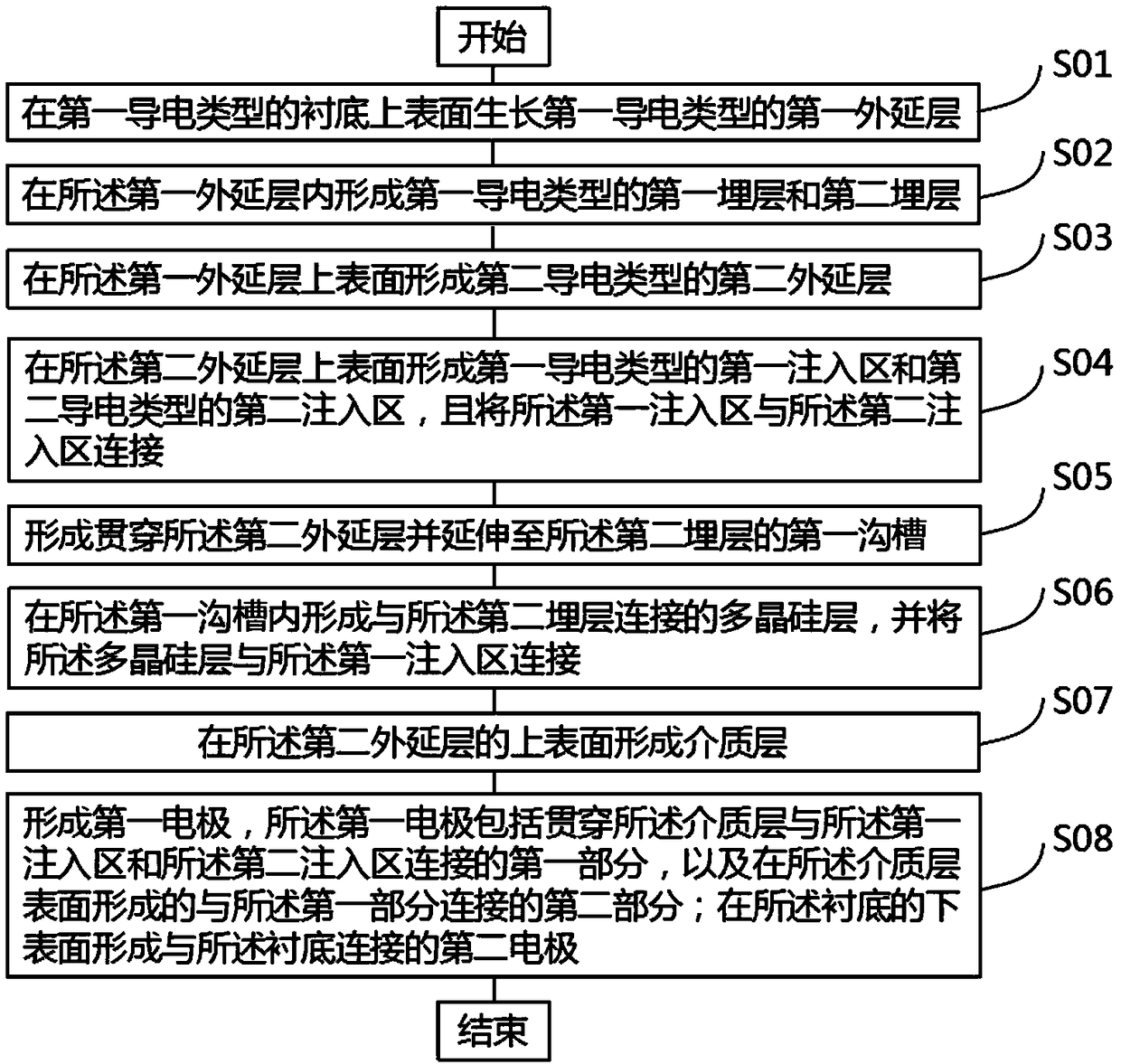

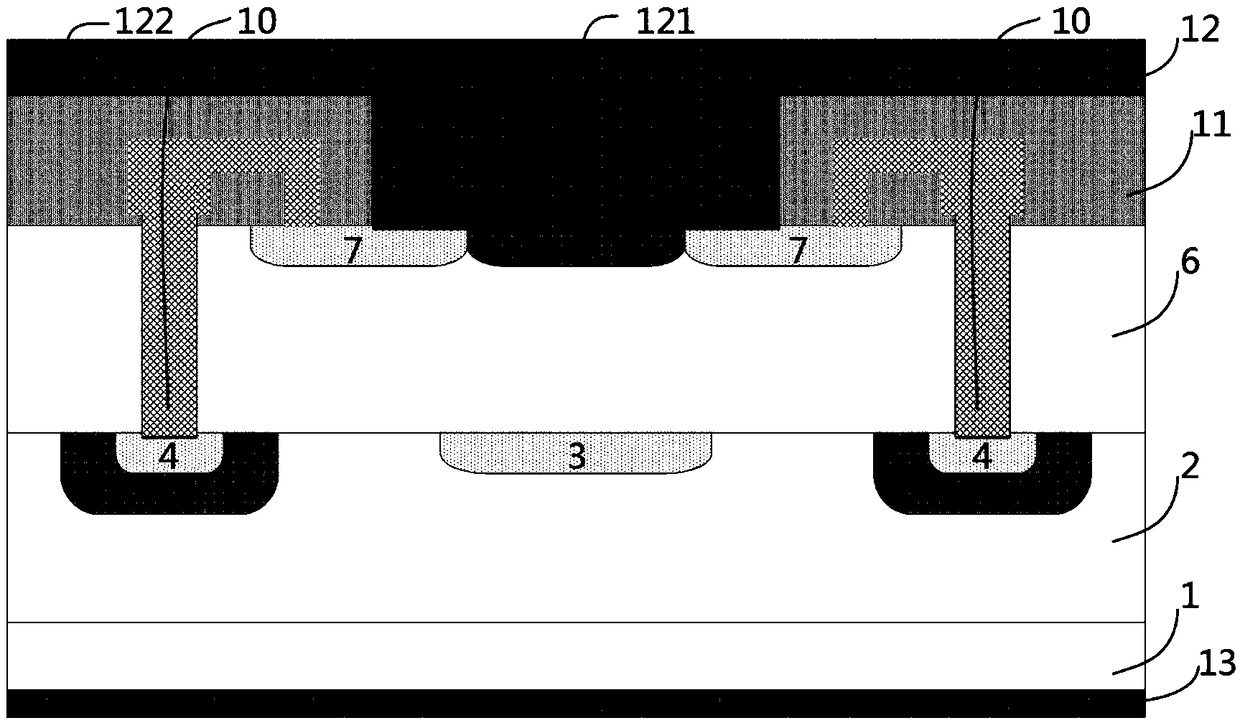

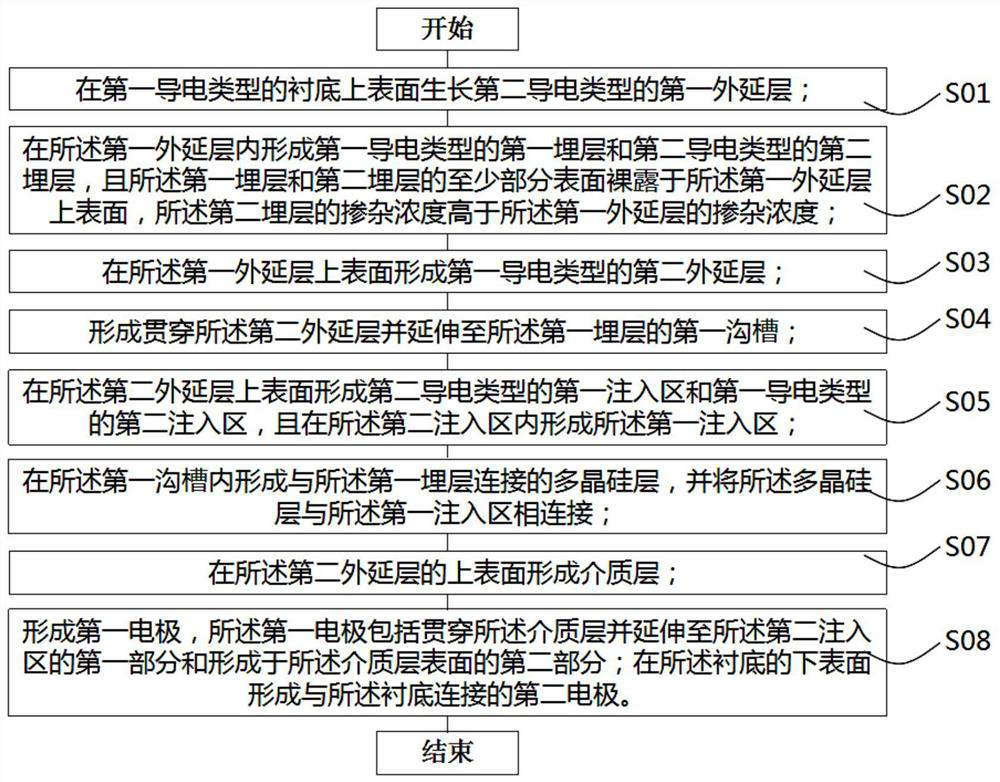

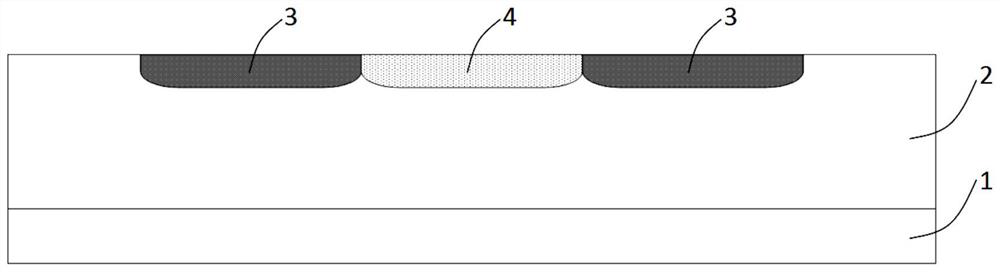

The invention provides a power device protection chip and a manufacturing method thereof, the chip comprising the following steps: a substrate of a first conductivity type; A first epitaxial layer ofa second conductivity type; A first buried layer of a first conductivity type and a second buried layer of a second conductivity type, formed in the first epitaxial layer; A second epitaxial layer ofthe first conductivity type; A first injection region of a first conductivity type and a second injection region of a second conductivity type formed on an upper surface of the second epitaxial layer,and the first injection region is connected to the second injection region; A polycrystalline silicon layer penetrating the second epitaxial layer and connected to the first implanted region and thefirst buried layer, respectively; A dielectric layer formed on an upper surface of the second epitaxial layer; A first electrode including a first portion penetrating the dielectric layer and extending to the second implantation region and a second portion formed on a surface of the dielectric layer; A second electrode formed on a lower surface of the substrate. The invention can improve device performance and reduce device cost.

Owner:深圳市华安半导体有限公司

Low-capacitance TVS (transient voltage suppressor) diode and manufacture method thereof

InactiveCN106898656AReduce parasitic capacitanceReduce areaSemiconductor/solid-state device manufacturingSemiconductor devicesParasitic capacitanceTransient voltage suppressor

The invention discloses a low-capacitance TVS (transient voltage suppressor) diode and a manufacture method thereof; the low-capacitance TVS diode is characterized in that three TVSs are integrated and connected in parallel through process modifications based on traditional TVSs, parasitic capacitance of a device is reduced, the device has small area, the process has low difficulty, and device manufacturing cost is reduced; the modified TVS device has improved protective property and reliability.

Owner:罗灿

Transient voltage suppressor and manufacturing method thereof

InactiveCN108109995AImprove discharge performanceImprove protection characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingTransient voltage suppressorEngineering

The invention relates to a transient voltage suppressor and a manufacturing method thereof. The transient voltage suppressor comprises a P-type substrate, a first N-type epitaxy formed on the P-type substrate, a second P-type epitaxy formed on the surface of the first N-type epitaxy, a trench which penetrates through the P-type epitaxy and extends into first N-type epitaxy, a first P-type injection region formed on the surface of the trench of the first N-type epitaxy, silicon oxide formed on the surface of the first P-type injection region on the side wall of the trench and extending to the surface of the side wall of the trench of the P-type epitaxy, polycrystalline silicon formed on the first P-type injection region at the bottom of the trench and the surface of the silicon oxide, a second N-type epitaxy formed in the trench and on the polycrystalline silicon and a second P-type injection region is formed on the surface of the second N-type epitaxy.

Owner:SHENZHEN JINGTE INTELLIGENT MFG TECH CO LTD

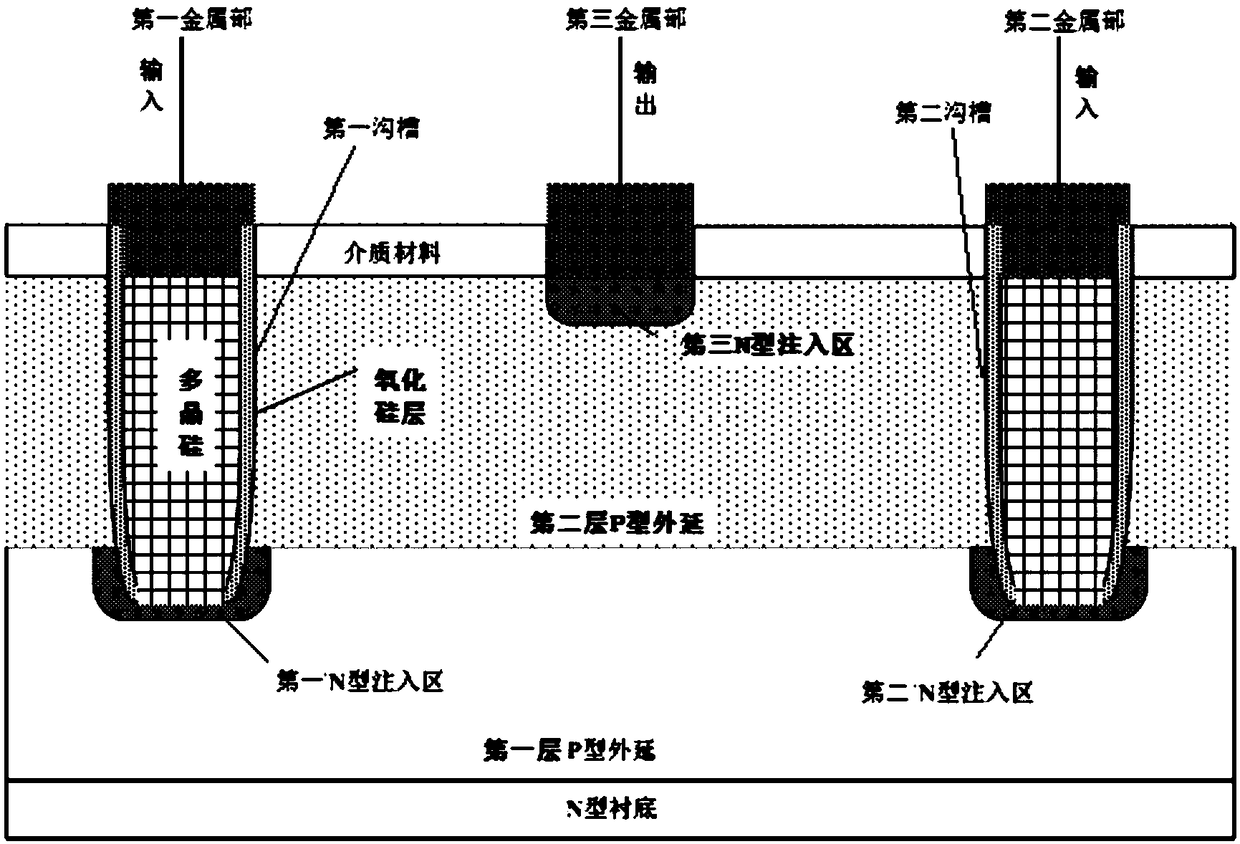

Transient voltage suppressor and manufacturing method thereof

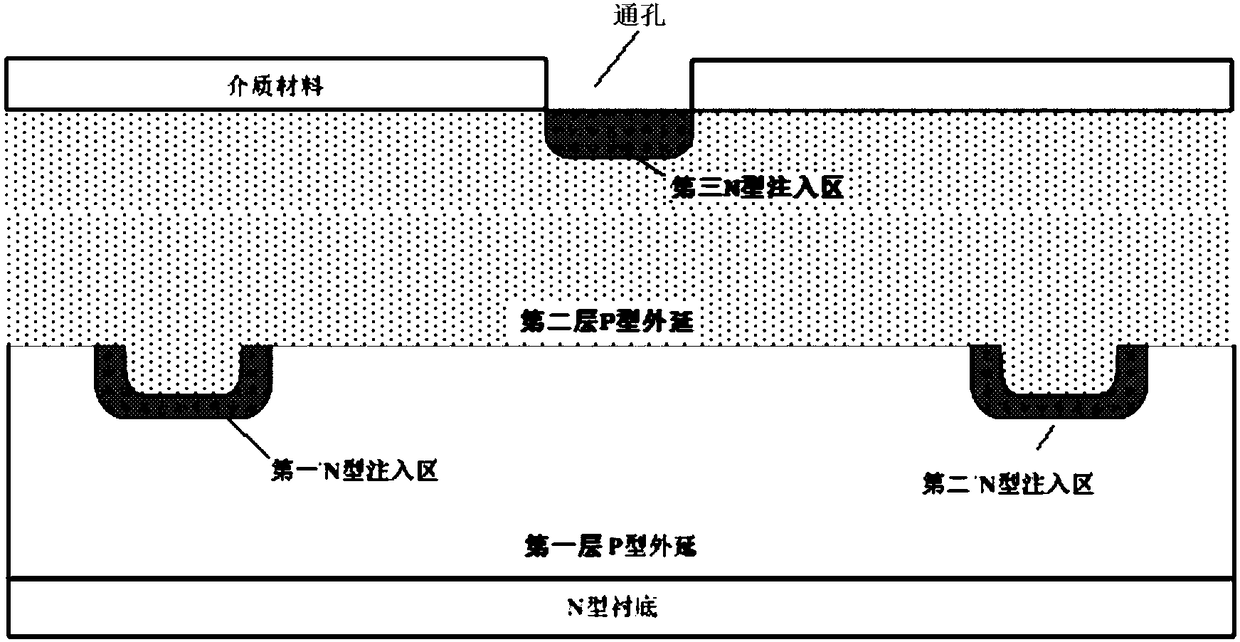

InactiveCN108063136AReduce areaNo manufacturing costSolid-state devicesSemiconductor/solid-state device manufacturingSilicon oxideTransient voltage suppressor

The invention provides a transient voltage suppressor which includes an N-type substrate, a first layer of P-type epitaxy on the N-type substrate, a first N-type injection region and a second N-type injection region on the surface of the first layer of P-type epitaxy, a second layer of P-type epitaxy on the first layer of P-type epitaxy and the first and second N-type injection regions, a third N-type injection region formed on the surface of the second layer of P-type epitaxy, a dielectric material formed on the second layer of P-type epitaxy, a first trench which passes through the dielectric material and the second layer of P-type epitaxy and extends to the first N-type injection region, a second trench which passes through the dielectric material and the second layer of P-type epitaxyand extends to the second N-type injection region, a through hole which passes through the dielectric material is corresponding to the third N-type injection region, silicon oxide formed on a first trench sidewall and a second trench sidewall, and polysilicon on the surfaces of the silicon oxide of the first trench and the silicon oxide of the second trench.

Owner:SHENZHEN JINGTE INTELLIGENT MFG TECH CO LTD

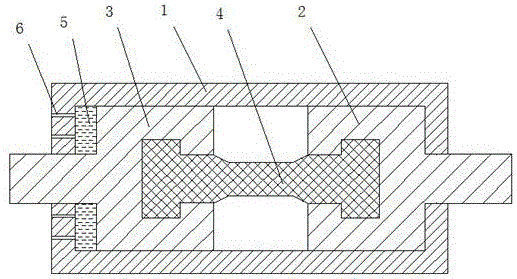

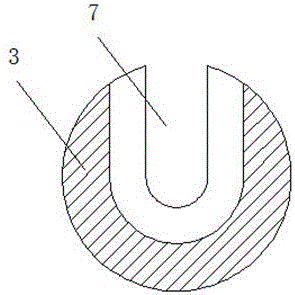

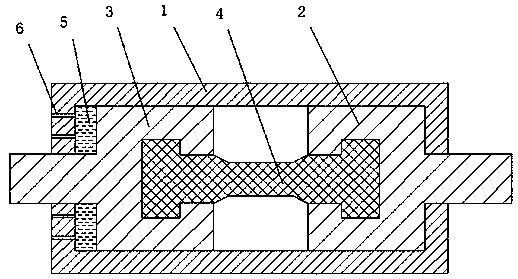

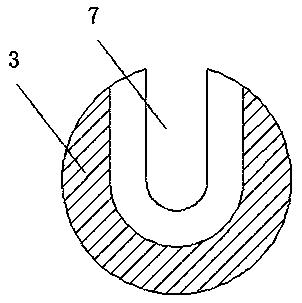

Mooring rope protector for building

ActiveCN106480759AEnsure safetyImprove protection characteristicsTextile cablesMarine engineeringOverpressure

The invention relates to a device for observing overpressure of a mooring rope for constructional engineering, belongs to the field of buildings, and particularly relates to a mooring rope protector for a building. The mooring rope protector for the building comprises a shell, a first connecting piece, a second connecting piece and a snapping piece, wherein the first connecting piece is connected with the second connecting piece through the snapping piece; the shell sleeves the outsides of the first connecting piece, the second connecting piece and the snapping piece; and after the snapping piece is snapped off, the shell bears a tensile force between the first connecting piece and the second connecting piece. By the design of the snapping piece which can be snapped off, use safety of the mooring rope can be guaranteed effectively, before the tensile force reaches a rated snapping-off force of the mooring rope, the snapping piece is snapped off at first, then whether the mooring rope is used in an overload manner can be observed effectively, and the protective feature of the mooring rope is improved. By the design of a weak link arranged on the mooring rope, whether the mooring rope is in an overpressure state or not when used can be judged, and therefore, the service life of the mooring rope in a using process can be judged.

Owner:CHENGDU 90 DEGREE IND PROD DESIGN CO LTD

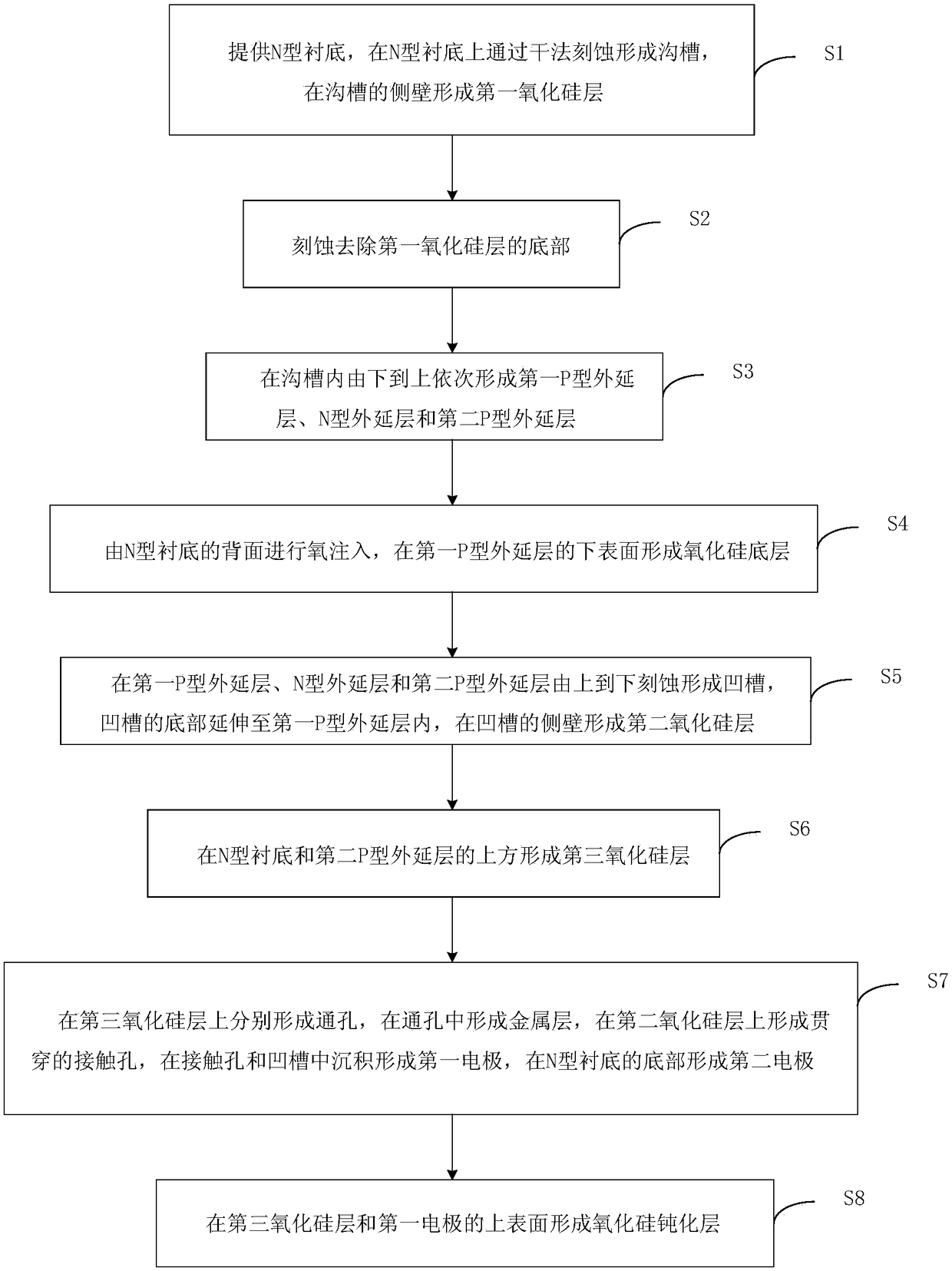

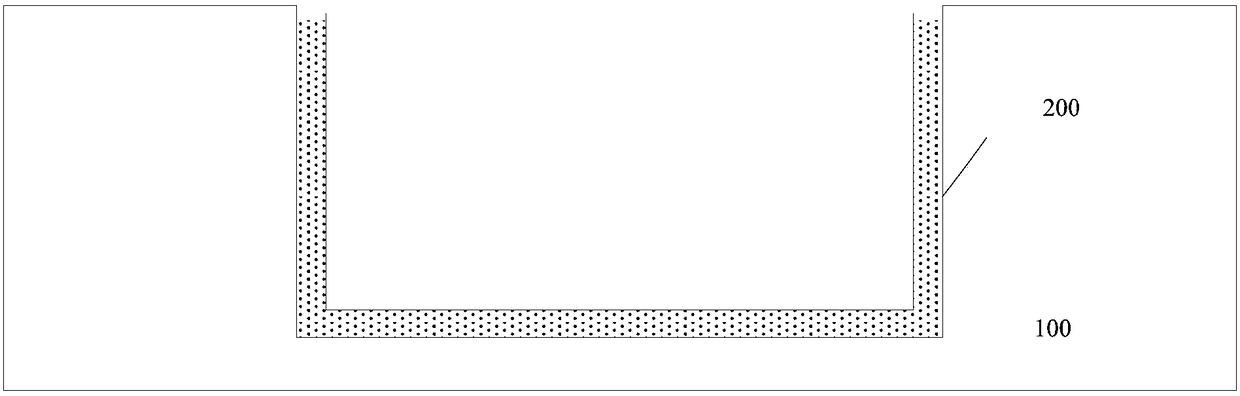

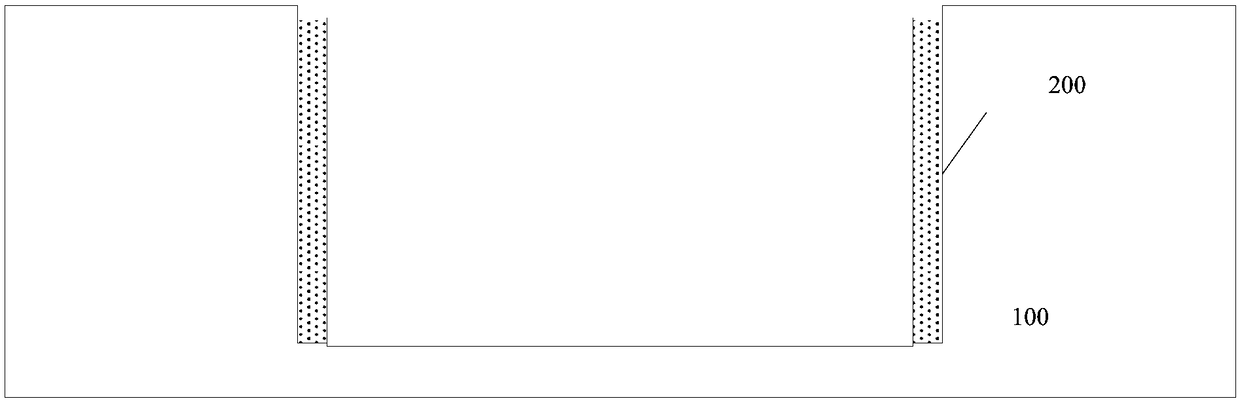

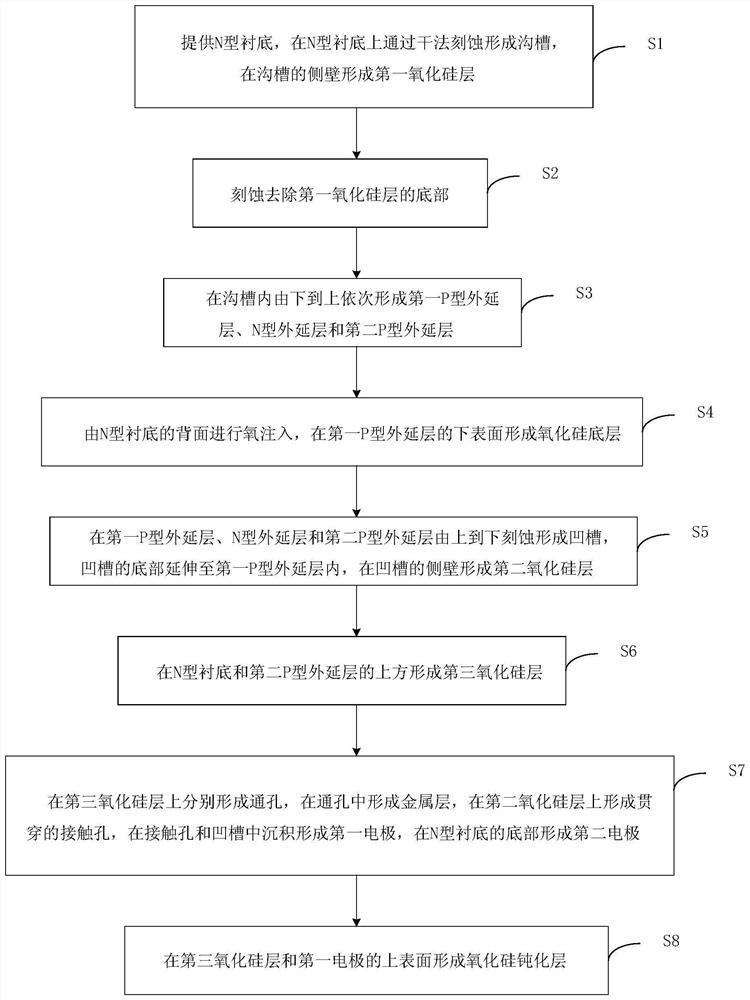

Protection device for power component, and manufacturing method thereof

ActiveCN108417534AReduce parasitic capacitanceImprove anti-surge performanceSolid-state devicesSemiconductor/solid-state device manufacturingSilicon oxidePower component

The invention provides a protection device for a power component and a manufacturing method thereof, and relates to the technical field of semiconductor devices. The method comprises firstly, providing an N-type substrate in which a first silicon oxide layer is formed, and removing the bottom of the first silicon oxide layer by etching; secondly, successively forming a first P-type epitaxial layer, an N-type epitaxial layer and a second P-type epitaxial layer, forming a silicon oxide underlayer on a lower surface of the first P-type epitaxial layer; forming a second silicon oxide layer on thesidewalls of grooves in the first P-type epitaxial layer, the N-type epitaxial layer and the second P-type epitaxial layer; then forming a third silicon oxide layer and a metal layer to form a first electrode and a second electrode; and finally, forming a silicon oxide passivation layer on the surface. The method realizes the integration of TVS by using a buried layer process, improves the anti-surge capability of a device, reduces the area of the device, realizes the small-sized package of a high-end IC, and solves the low anti-surge capability and large device area in the prior art.

Owner:NANJING HENGZHONG MECHANISM TECH

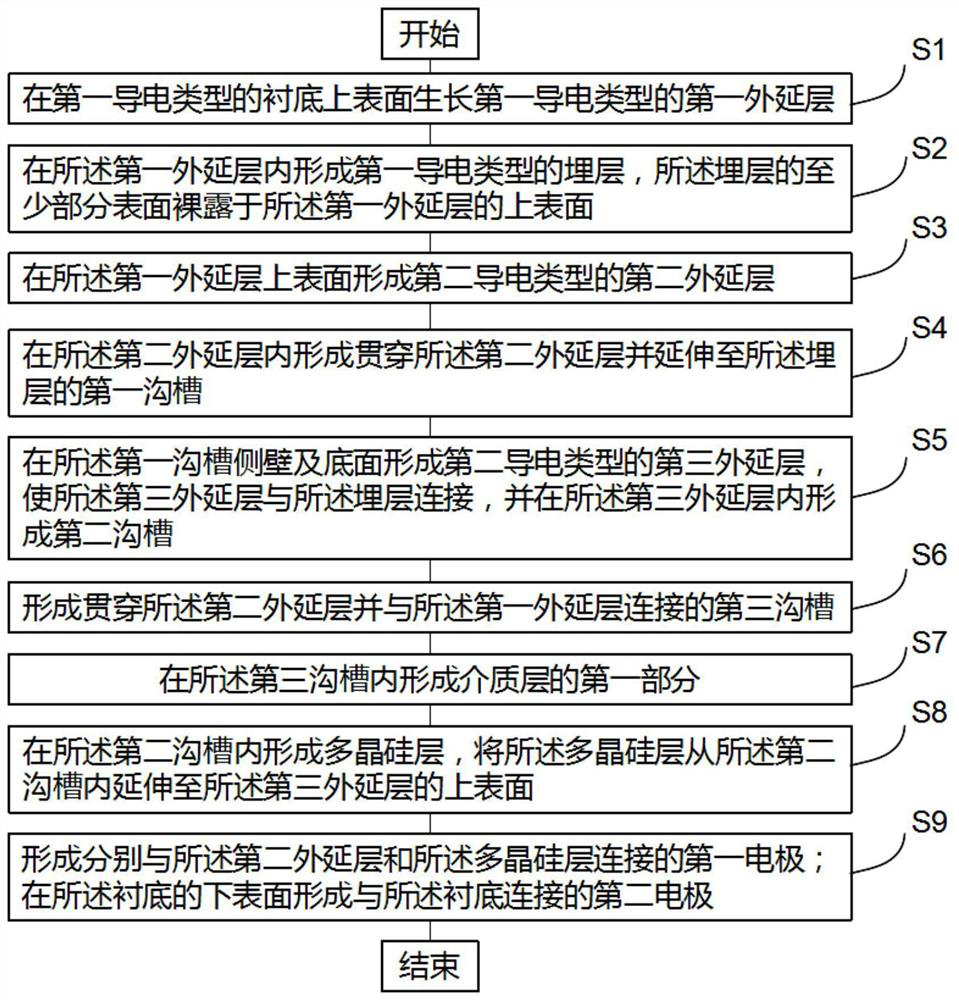

A current protection chip and a manufacturing method thereof

ActiveCN108987389AReduce the difficulty of manufacturing processImprove protection characteristicsSolid-state devicesDiodeDielectric layerSilicon

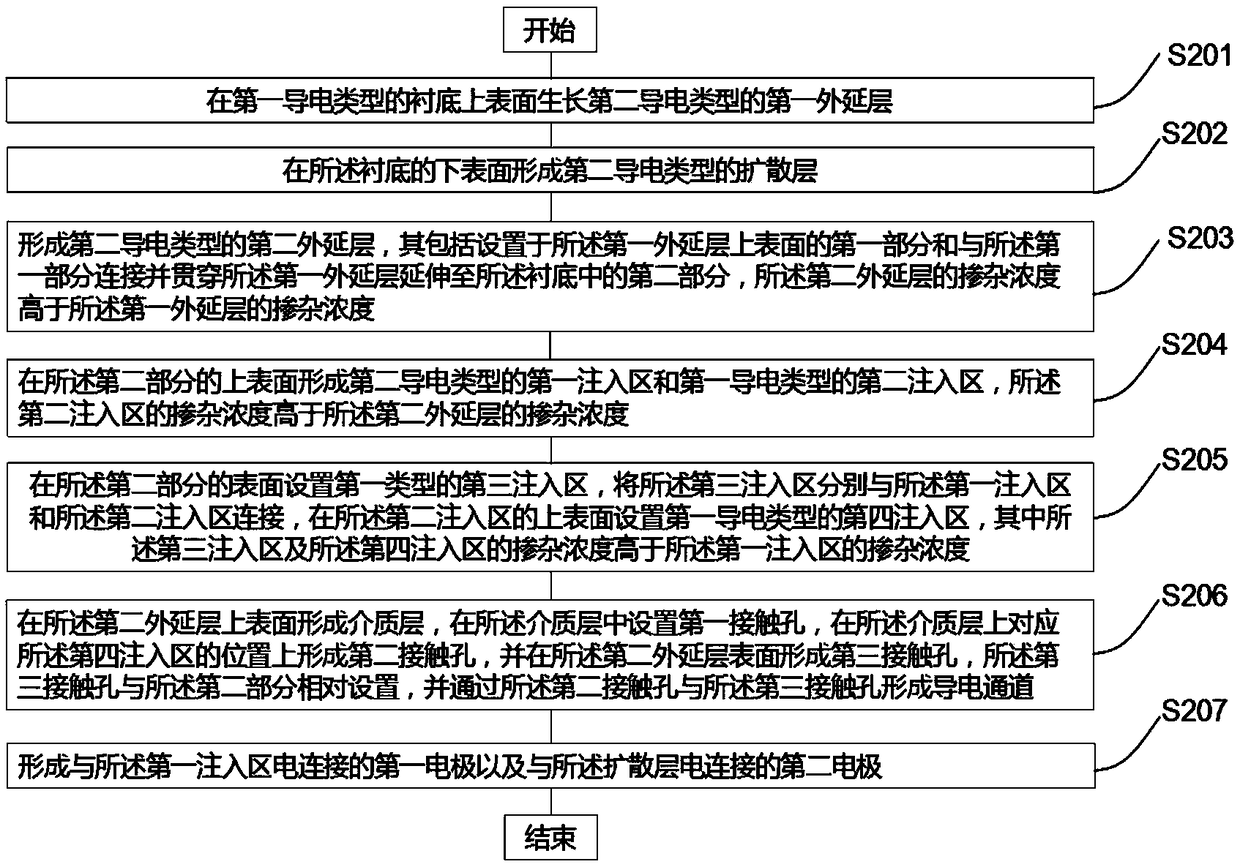

The invention provides a current protection chip and a manufacturing method thereof. The current protection chip comprises a substrate of a first conductivity type; afirst epitaxial layer of a secondconductivity type; afirst buried layer of a first conductivity type and a second buried layer of a second conductivity type, formed in the first epitaxial layer; asecond epitaxial layer of a first conductivity type formed on a surface of the first epitaxial layer; afirst injection region of a second conductivity type and a second injection region of the first conductivity type, formed on a surfaceof the second epitaxial layer, and the second injection region is located in the first injection region; apolycrystalline silicon layer connected to the first implantation region and the first buriedlayer, respectively; adielectric layer formed on an upper surface of the second epitaxial layer; afirst electrode including a first portion penetrating the dielectric layer and extending to the second implantation region and a second portion formed on a surface of the dielectric layer; asecond electrode formed on a lower surface of the substrate and connected to the substrate. The invention can improve device performance and reduce device cost.

Owner:佛山市劲电科技有限公司

A current protection chip and a manufacturing method thereof

InactiveCN109065634AImprove protection characteristicsImprove protection reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingPolycrystalline siliconOptoelectronics

The invention provides a current protection chip and a manufacturing method thereof, comprising the following steps: a substrate of a first conductivity type; A first epitaxial layer of a first conductivity type; A first buried layer and a second buried layer of a first conductivity type formed in the first epitaxial layer; A second epitaxial layer of a second conductivity type formed on an uppersurface of the first epitaxial layer; A first injection region of a first conductivity type and a second injection region of a second conductivity type, and the first injection region is connected tothe second injection region; A polycrystalline silicon layer penetrating the second epitaxial layer and connected to the first implanted region and the second buried layer, respectively; A dielectriclayer formed on an upper surface of the second epitaxial layer; A first electrode including a first portion connected to the first injection region and the second injection region through the dielectric layer, and a second portion formed on a surface of the dielectric layer; A second electrode formed on a lower surface of the substrate. The invention can improve device performance and reduce device cost.

Owner:深圳市熙电科技有限公司

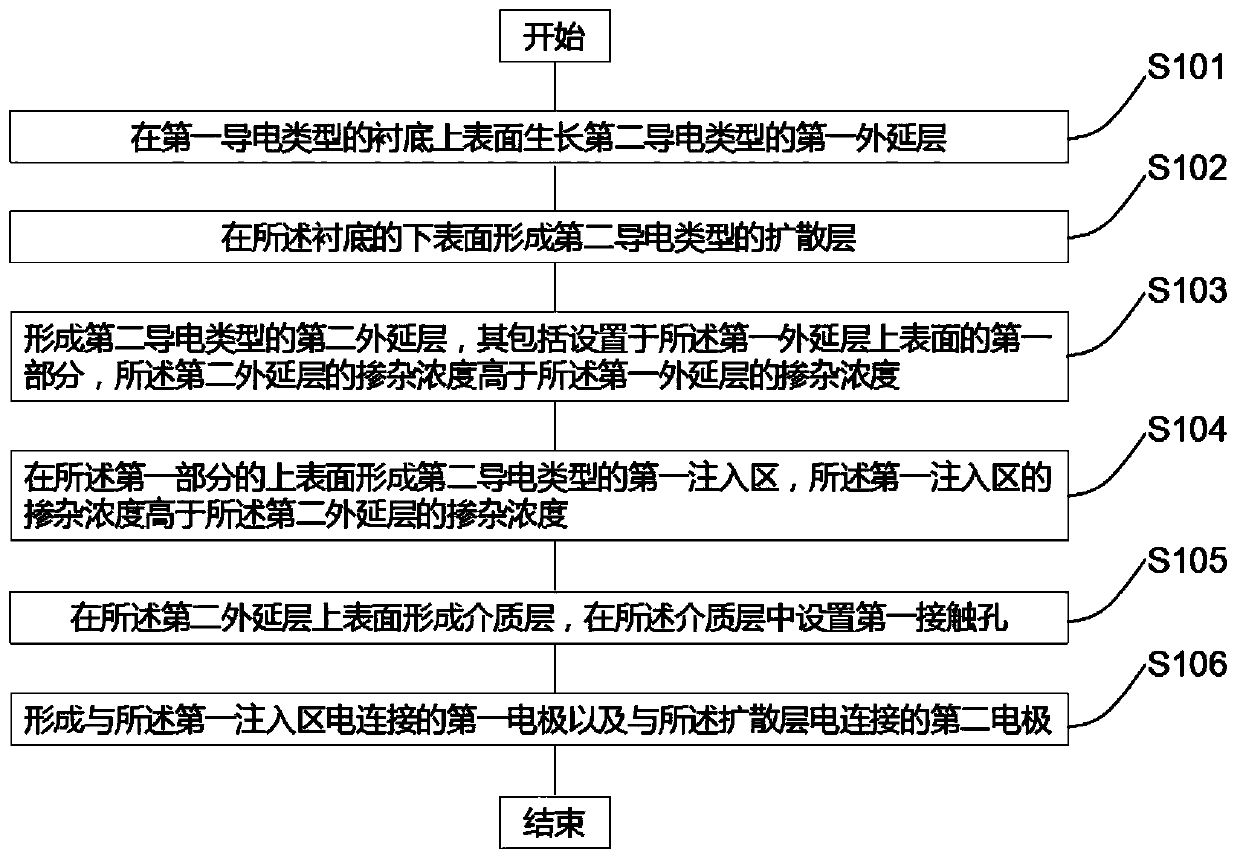

A kind of transient voltage suppressor and its manufacturing method

InactiveCN108987461BImprove protection characteristicsImprove protection reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsTransient voltage suppressor

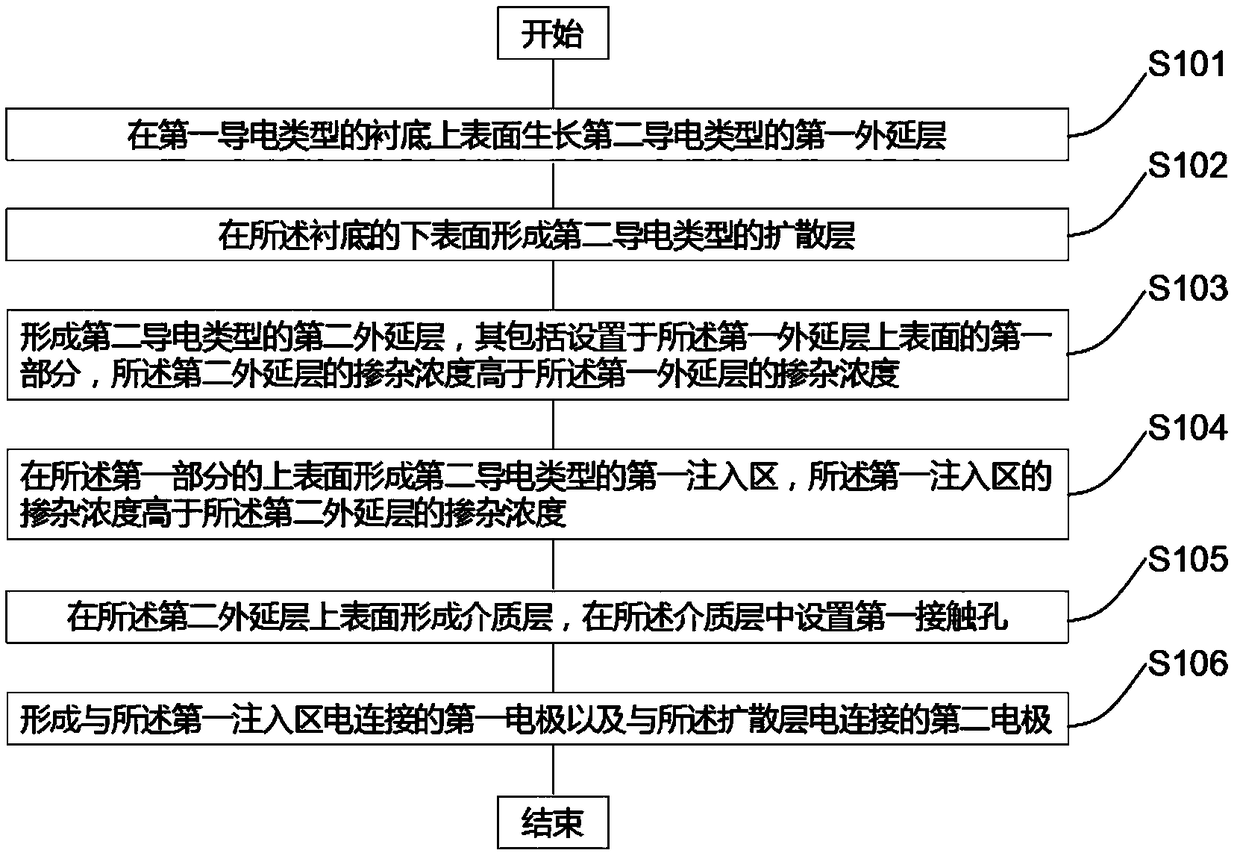

The invention provides a transient voltage suppressor and a manufacturing method thereof. The suppressor includes a substrate of a first conductivity type; afirst epitaxial layer of a second conductivity type grown on an upper surface of the substrate; adiffusion layer of a second conductivity type formed on a lower surface of the substrate; asecond epitaxial layer of a second conductivity type including a first portion disposed on an upper surface of the first epitaxial layer, the doping concentration of the second epitaxial layer being higher than the doping concentration of the first epitaxial layer; afirst implantation region of a second conductivity type formed on an upper surface of the first portion, the doping concentration of the first implantation region being higher than the doping concentration of the second epitaxial layer; afirst electrode electrically connected to the first injection region; and a second electrode electrically connected to the diffusion layer. This scheme can improve device performance and reduce device cost.

Owner:江苏韩力新材料有限公司

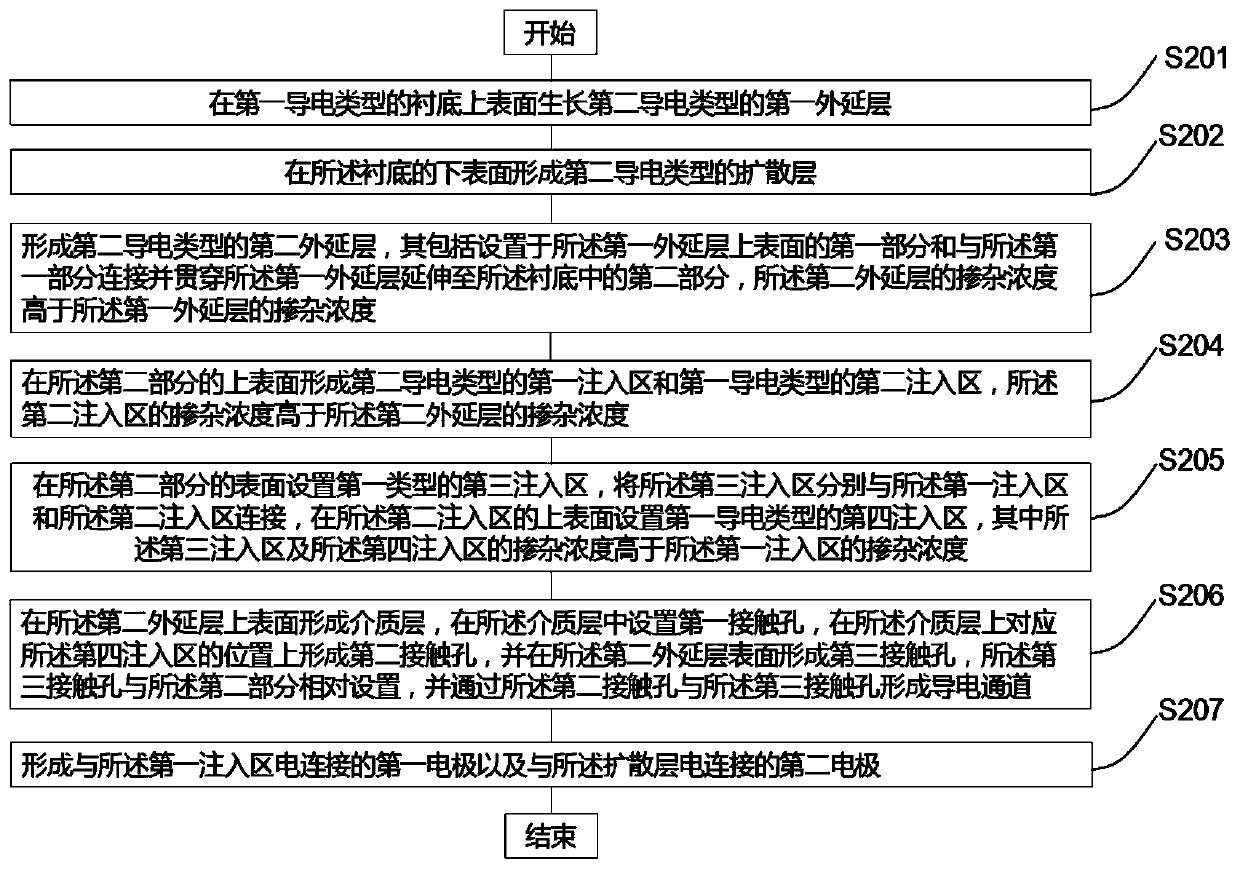

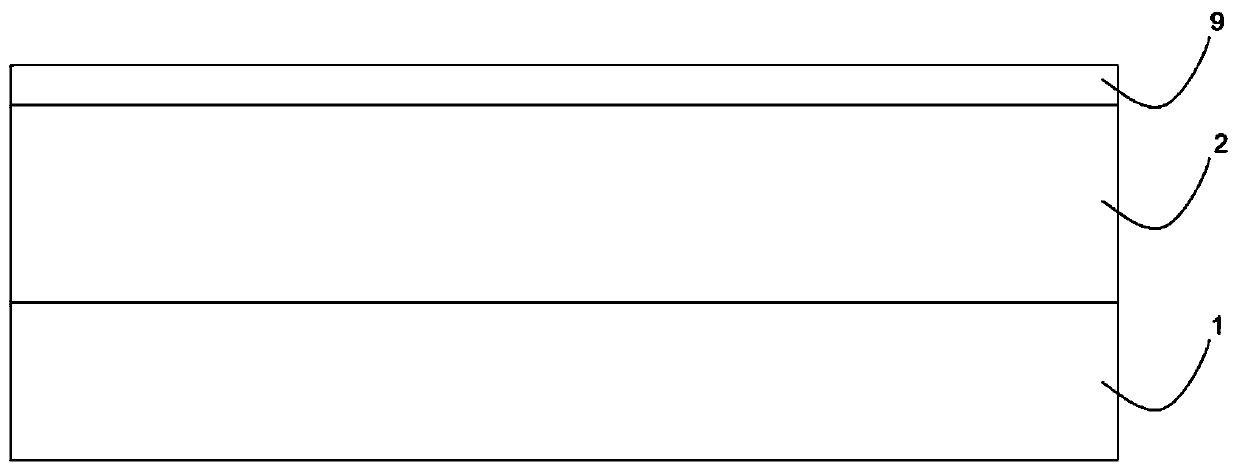

A power device protection chip and its manufacturing method

ActiveCN108922925BImprove protection characteristicsImprove protection reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesDielectric layerCondensed matter physics

The invention provides a power device protection chip and a manufacturing method thereof, comprising: a substrate of the first conductivity type; a first epitaxial layer of the first conductivity type grown on the upper surface of the substrate; a buried layer of the first conductivity type layer, formed in the first epitaxial layer; a second epitaxial layer of the second conductivity type, formed on the upper surface of the first epitaxial layer; a third epitaxial layer of the second conductivity type, penetrating through the second epitaxial layer and connected to the buried layer; the first injection region of the first conductivity type is formed in the second epitaxial layer and connected to the buried layer and the third epitaxial layer; a dielectric layer, the dielectric layer comprising a first portion located on the upper surface of the second epitaxial layer connected to the first portion and extending through the second epitaxial layer to a second portion of the first epitaxial layer; a polysilicon layer extending through the first portion to within the third epitaxial layer. The invention can improve device performance and reduce device cost.

Owner:深圳物芯半导体有限公司

A protection device for power components and its manufacturing method

ActiveCN108417534BReduce parasitic capacitanceImprove anti-surge performanceSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

Owner:NANJING HENGZHONG MECHANISM TECH

Groove-type transient voltage suppressor and manufacturing method thereof

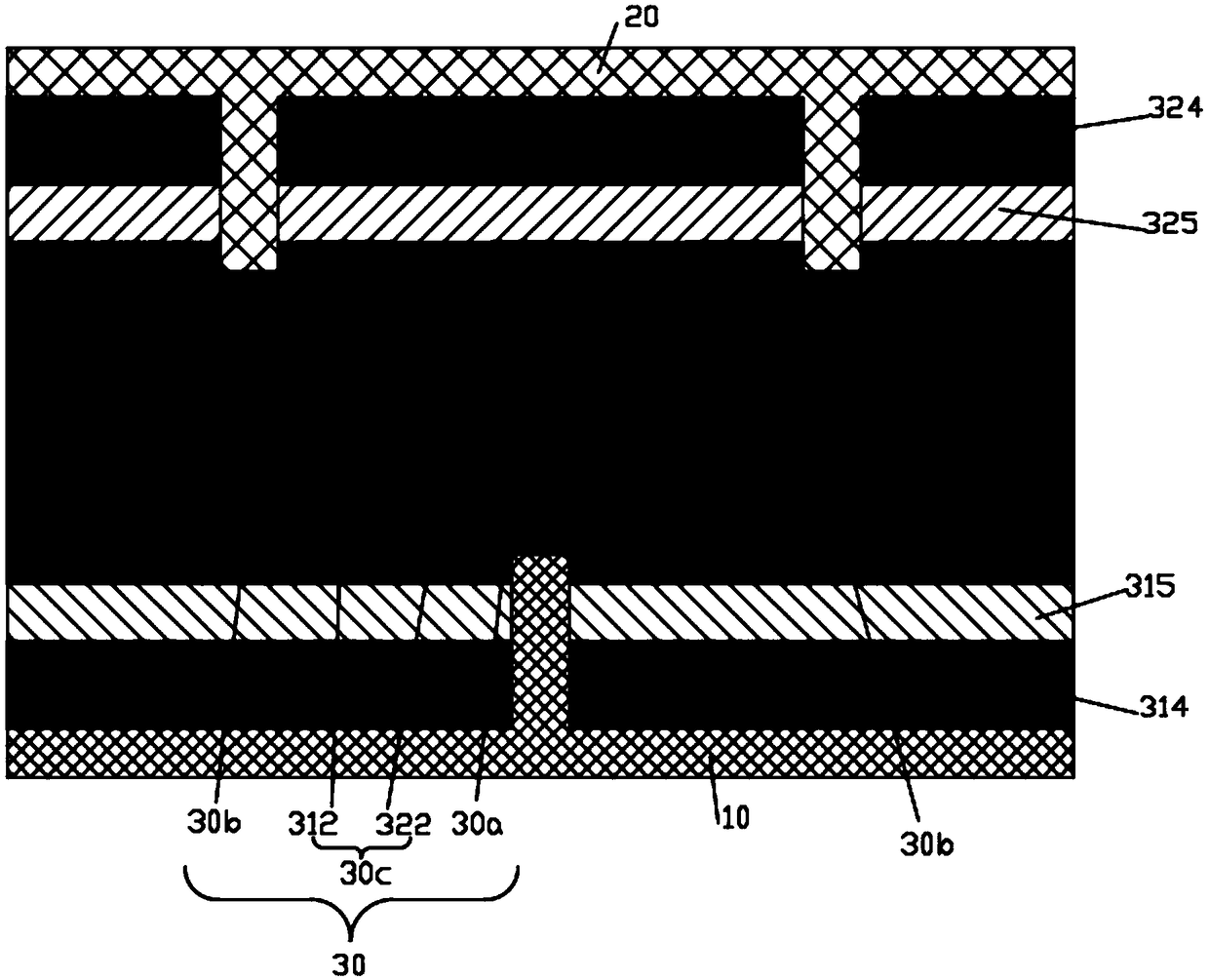

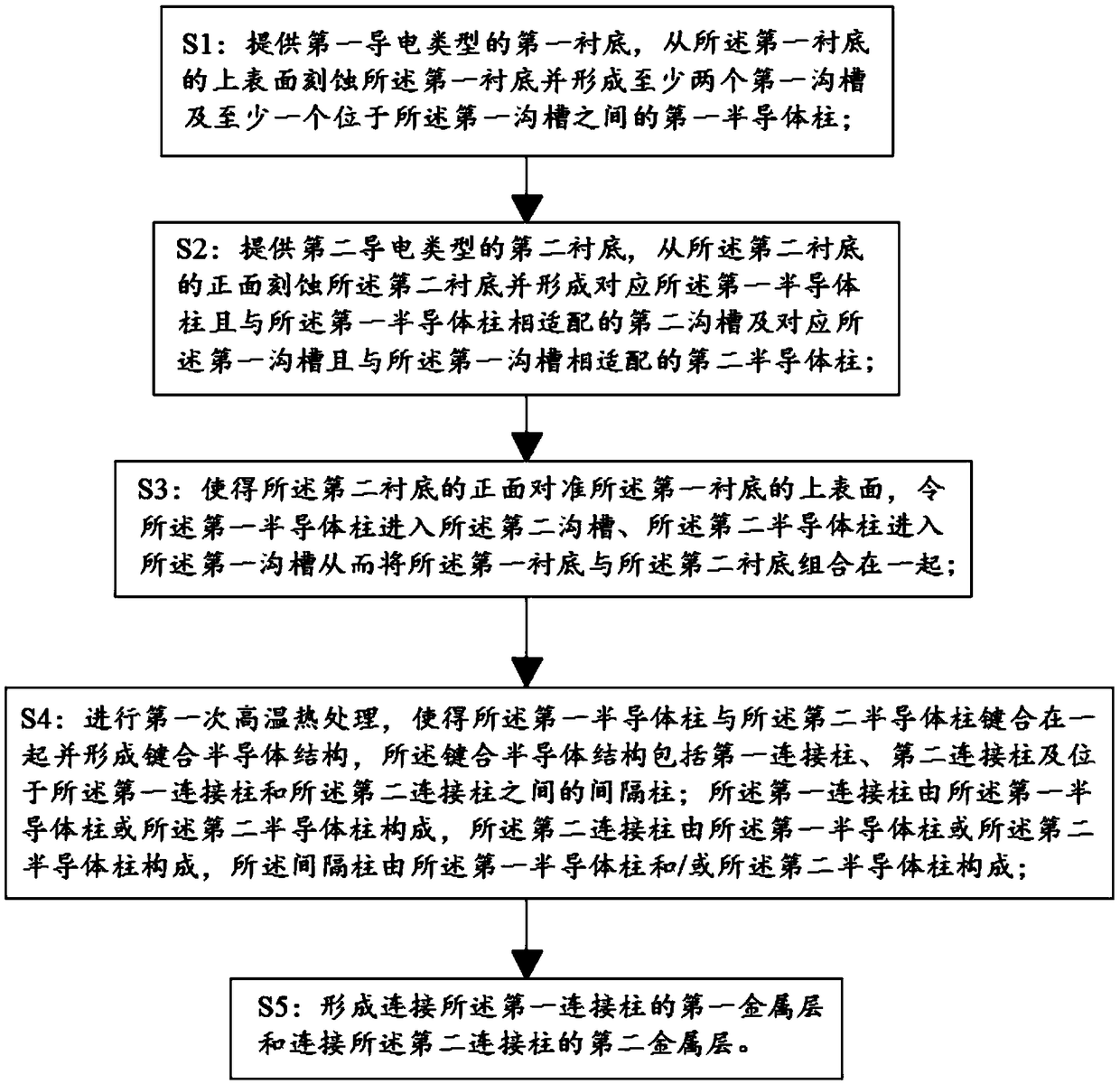

ActiveCN109360823AReduce leakageImprove protection characteristicsSolid-state devicesDiodeSemiconductor structureTransient voltage suppressor

The invention discloses a groove-type transient voltage suppressor and a manufacturing method thereof. According to the manufacturing method, a first substrate of a first conduction type and a secondsubstrate of a second conduction type are etched and heated to form a bonding semiconductor structure, the bonding semiconductor structure comprises at least three binding semiconductor columns, conduction types of two adjacent semiconductor columns are opposite, the semiconductor columns comprise first connecting columns, second connecting columns and interval columns, the first connecting columns are used for connecting with first metal layers, the second connecting columns are used for connecting with second metal layers, and the interval columns are positioned among the first connecting columns and the second connecting columns. The groove-type transient voltage suppressor at least comprises two serially connected and abutted diodes, so that a bi-directional protection function is achieved. A PN knot interface shortcoming of the bonding semiconductor structure is less, so that electric leakage of the groove-type transient voltage suppressor is low, and the protective characteristics and the reliability of the groove-type transient voltage suppressor are effectively improved.

Owner:江苏埃盾电磁科技有限公司

A kind of parallel MOS tube current sharing and short circuit protection circuit

ActiveCN107181396BImprove securityEfficient detectionElectronic switchingPower conversion systemsEngineeringShort circuit protection

Owner:BEIJING RES INST OF PRECISE MECHATRONICS CONTROLS

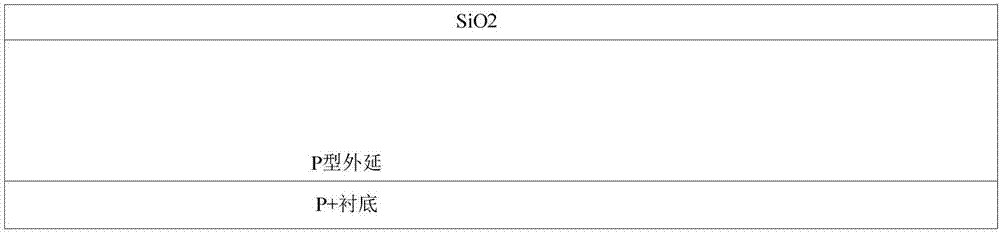

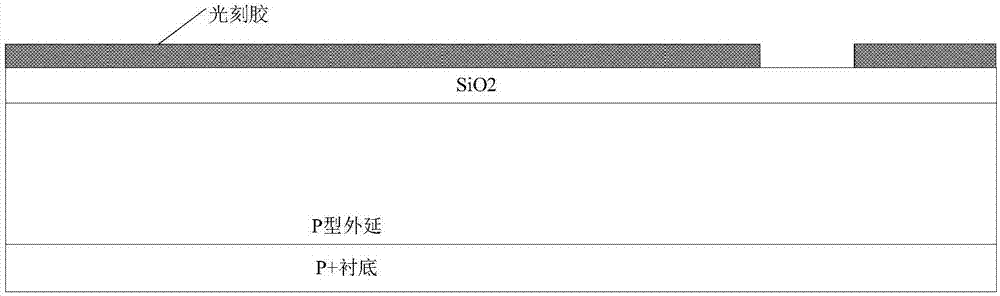

Transient voltage inhibitor and manufacturing method thereof

ActiveCN107342283AReduce processing difficultyReduce areaSolid-state devicesSemiconductor/solid-state device manufacturingZener diodeTransient voltage suppressor

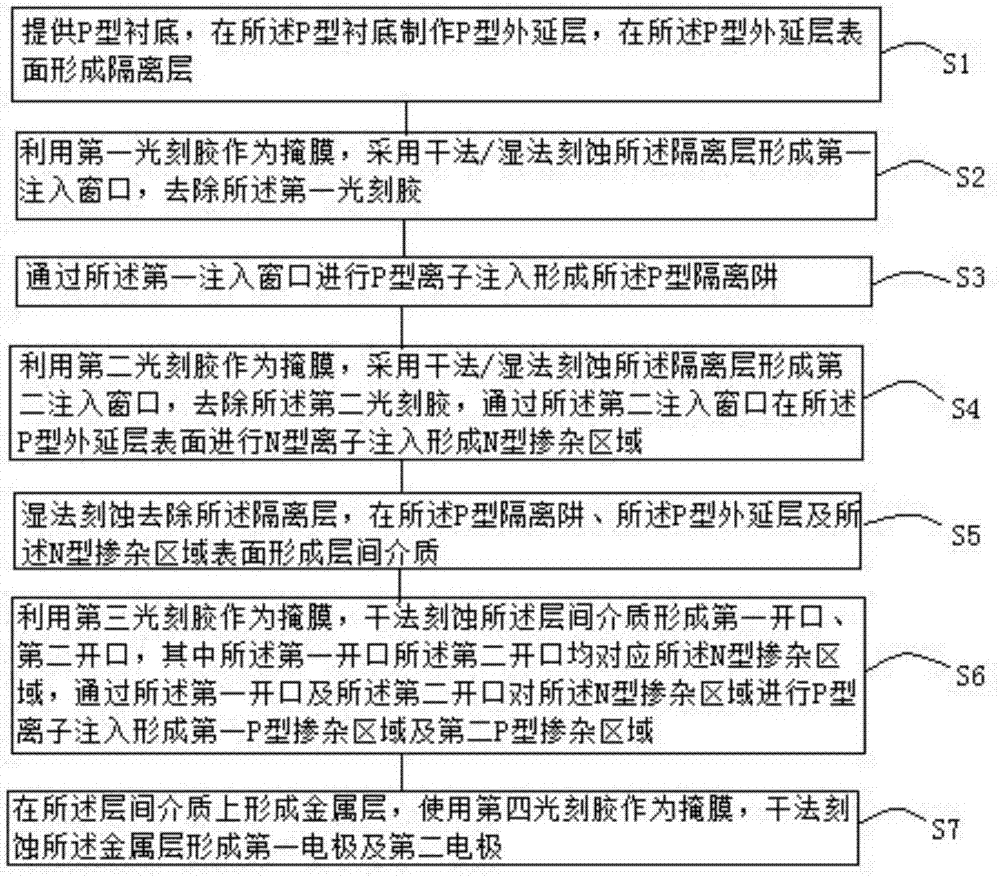

The invention relates to a transient voltage inhibitor and a manufacturing method thereof. The transient voltage inhibitor comprises a P-type substrate, a P-type epitaxial layer formed on the P-type substrate, a P-type isolation well formed in the P-type epitaxial layer, an N-type doping region formed at a surface of the P-type epitaxial layer, and a first P-type doping region and a second P-type doping region formed on a surface of the N-type doping region, wherein the first P-type doping region and the second P-type doping region are arranged at two ends of the N-type doping region, the first P-type doping region and the N-type doping region form a first Zener diode, and the second P-type doping region and the N-type doping region form a second Zener diode. The transient voltage inhibitor is advantaged in that the device area is small, process difficulty is low, manufacturing cost is low, and protection characteristics and reliability are relatively high.

Owner:绍兴市秀臻新能源科技有限公司

A current protection chip and its manufacturing method

ActiveCN108987389BReduce the difficulty of manufacturing processImprove protection characteristicsSolid-state devicesDiodeEngineeringDielectric layer

Owner:佛山市劲电科技有限公司

Transient voltage suppressor and method of making the same

InactiveCN108054164BReduce areaReduce processing difficultySolid-state devicesSemiconductor/solid-state device manufacturingTransient voltage suppressorMaterials science

The invention provides a transient voltage suppressor and a fabrication method thereof. The transient voltage suppressor comprises a P-type substrate, an N-type epitaxial layer, a first groove, a second groove, a first P-type diffusion region, a second P-type diffusion region, P-type epitaxial layers, an N-type injection region and a P-type injection region, wherein the N-type epitaxial layer is formed on the P-type substrate, the first groove and the second groove are formed in a surface of the N-type epitaxial layer, the first P-type diffusion region is formed on a surface of the first groove, the second P-type diffusion region is formed on a surface of the second groove, the P-type epitaxial layers are formed in the first groove and the second groove and on the N-type epitaxial layer, the N-type injection region penetrates through the P-type epitaxial layer and extends to the N-type epitaxial layer between the first groove and the second groove, and the P-type injection region is formed on a surface of the N-type injection region.

Owner:NANJING LISHUI HIGH-TECH VENTURE CAPITAL MANAGEMENT CO LTD

Transient voltage suppressor and method of making the same

ActiveCN107316864BImprove protection characteristicsImprove protection reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringTransient voltage suppressor

The invention provides a transient voltage suppressor and a fabricating method thereof. The transient voltage suppressor comprises a P-type substrate, an N-type epitaxial layer, a first P-type doped region and a second P-type doped region, wherein the N-type epitaxial layer comprises a first part and a second part which are arranged at an interval; the first P-type doped region is formed on the surface of the first part; the second P-type doped region is formed on the surface of the second part; the P-type substrate and the first part form a first diode; the P-type substrate and the second part form a second diode; the first part and the first P-type doped region also form a third diode abutted with the first diode; the second part and the second P-type doped region also form a fourth diode abutted with the second diode; a cathode of the first diode is connected with a cathode of the second diode; and a cathode of the third diode is connected with a cathode of the fourth diode.

Owner:伯芯半导体科技(天津)有限公司

A transient voltage suppressor and a manufacturing method thereof

InactiveCN108987461AImprove protection characteristicsImprove protection reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSuppressorOptoelectronics

The invention provides a transient voltage suppressor and a manufacturing method thereof. The suppressor includes a substrate of a first conductivity type; afirst epitaxial layer of a second conductivity type grown on an upper surface of the substrate; adiffusion layer of a second conductivity type formed on a lower surface of the substrate; asecond epitaxial layer of a second conductivity type including a first portion disposed on an upper surface of the first epitaxial layer, the doping concentration of the second epitaxial layer being higher than the doping concentration of the first epitaxial layer; afirst implantation region of a second conductivity type formed on an upper surface of the first portion, the doping concentration of the first implantation region being higher than the doping concentration of the second epitaxial layer; afirst electrode electrically connected to the first injection region; and a second electrode electrically connected to the diffusion layer. This scheme can improve device performance and reduce device cost.

Owner:江苏韩力新材料有限公司

Transient voltage suppressor and method of making the same

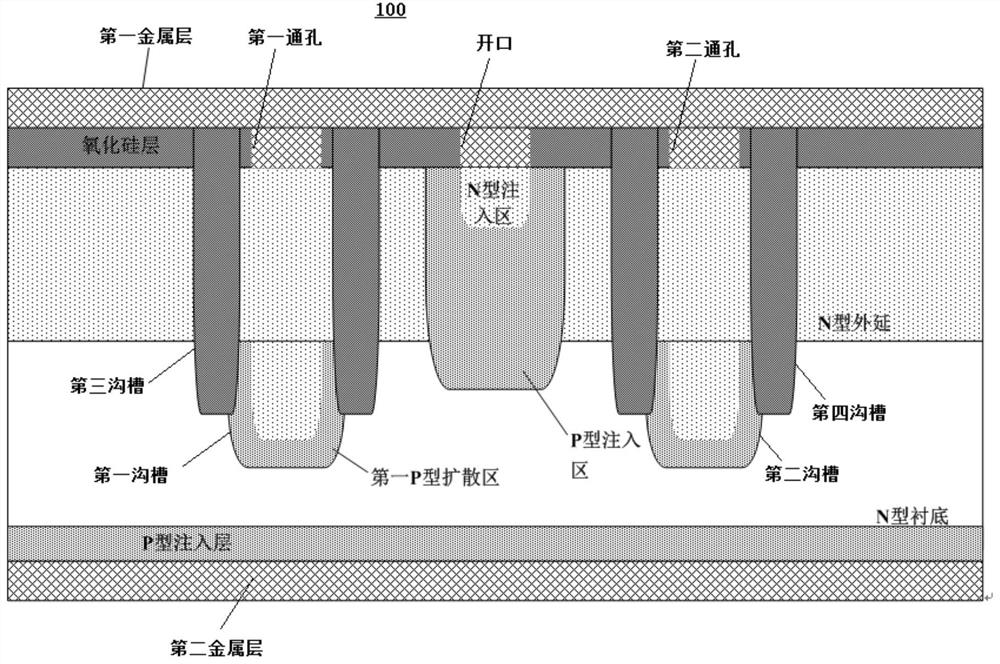

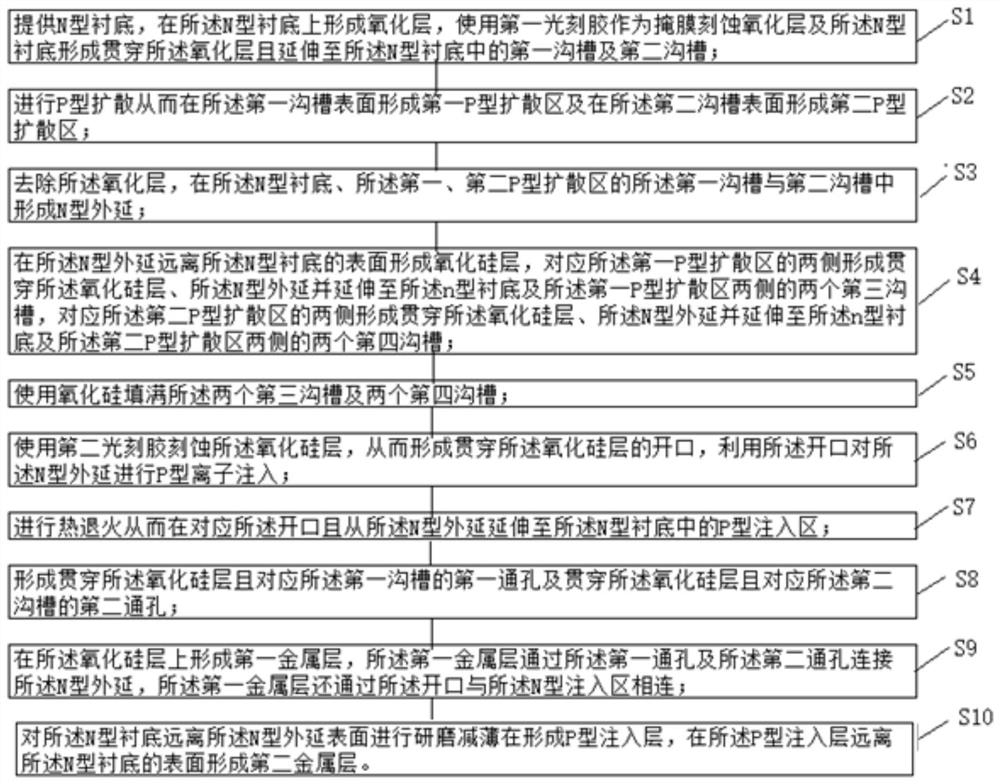

InactiveCN108063137BReduce capacitanceImprove protection characteristicsSolid-state devicesDiodeSilicon oxideTransient voltage suppressor

The invention relates to a transient voltage suppressor and a manufacturing method thereof. The transient voltage suppressor includes an N-type substrate, a first trench and a second trench formed onthe surface of the N-type substrate, first and second P-type diffusion regions formed on the surfaces of the first trench and the second trench, an N-type epitaxy formed on the surfaces of the N-typesubstrate and the first and second P-type diffusion regions, a silicon oxide layer formed on the N-type epitaxy, two third trenches which pass through the N-type epitaxy and extends to the N-type substrate and two sides of the first P-type diffusion region, two fourth trenches which pass through the N-type epitaxy and extends to the N-type substrate and two sides of the second P-type diffusion region, silicon oxide in the third and the fourth trenches, a first through hole corresponding to the first trench, a second through hole corresponding to the second trench, a P-type injection region which is formed at the surface of the N-type epitaxy, an N-type injection region formed on the surface of the P-type injection region, an opening corresponding to the N-type injection region, and a P-type injection layer formed at the other side of the N-type substrate.

Owner:NANJING LISHUI HIGH-TECH VENTURE CAPITAL MANAGEMENT CO LTD

Transient voltage suppressor and method of making the same

ActiveCN108063138BReduce parasitic capacitanceReduce areaSolid-state devicesDiodeEngineeringTransient voltage suppressor

The invention provides a transient voltage inhibitor and a manufacturing method thereof. The transient voltage inhibitor includes a P type substrate, an N type epitaxial layer formed on the P type substrate, a first P type polysilicon, a second P type polysilicon, a first groove, a second groove, a first N type doped region formed on the inner surface of the first groove, a second N type doped region formed on the inner surface of the second groove, a third P type polysilicon formed on the surface of the first N type doped region in the first groove, and a fourth P type polysilicon formed on the surface of the second N type doped region in the second groove, wherein the first P type polysilicon and the second P type polysilicon penetrate through the N type epitaxial layer and extend to theP type substrate; the first groove and the second groove are formed on the surface, far away from the P type substrate, of the N type epitaxial layer; and the third P type polysilicon is also connected with the fourth P type polysilicon. The transient voltage inhibitor has the advantages of small device area, low process difficulty, low manufacturing cost, and higher protection performance and reliability.

Owner:嘉兴市龙锋市政建设有限公司

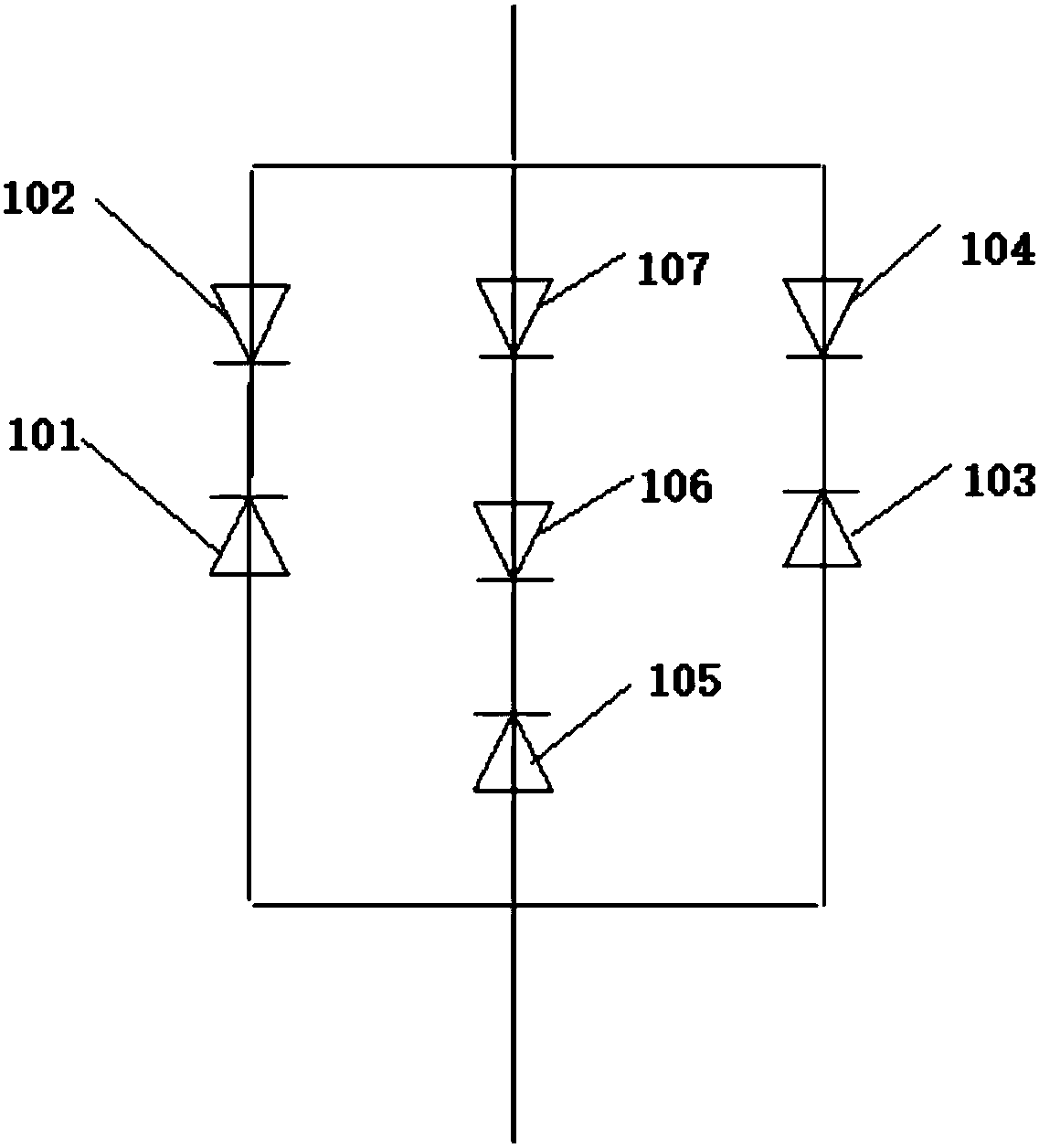

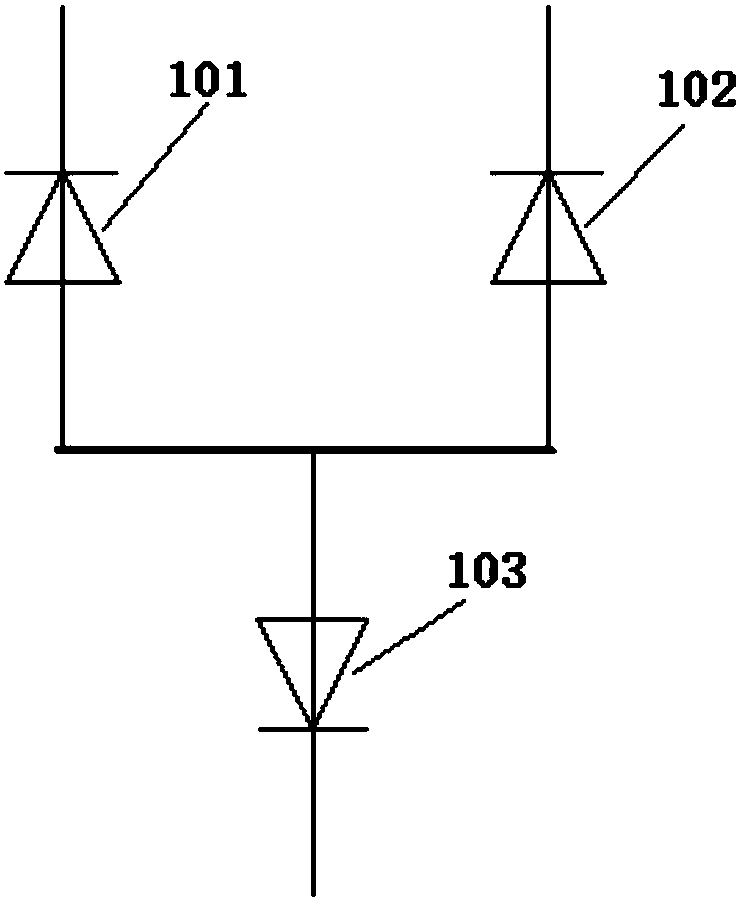

Transient-voltage suppressor and manufacturing method thereof

InactiveCN108054165AReduce areaReduce processing difficultySolid-state devicesSemiconductor/solid-state device manufacturingTransient voltage suppressorExternal circuit

The invention provides a transient-voltage suppressor and a manufacturing method thereof. The transient-voltage suppressor comprises an N-type substrate, an N-type epitaxial layer formed on the N-typesubstrate, a first P-type injection region, a second P-type injection region, a third P-type injection region, a first N-type injection region and a second N-type injection region, wherein the firstP-type injection region, the second P-type injection region and the third P-type injection region are formed on the surface of the N-type epitaxial layer; the first N-type injection region is formed on the surface of the first P-type injection region; the second N-type injection region is formed on the surface of the second P-type injection region; the third P-type injection region is located between the first P-type injection region and the second P-type injection region and connected with the first P-type injection region and the second P-type injection region; the first P-type injection region and the first N-type injection region form a first diode; the second P-type injection region and the second N-type injection region form a second diode; the third P-type injection region, the N-type epitaxial layer and the N-type substrate form a third diode; positive electrodes of the three diodes are connected; and negative electrodes of the three diodes are used for being connected to an external circuit.

Owner:SHENZHEN JINGTE INTELLIGENT MFG TECH CO LTD

A cable protector for construction

ActiveCN106480759BEnsure safetyImprove protection characteristicsTextile cablesArchitectural engineeringOverpressure

The invention relates to a device for observing overpressure of a mooring rope for constructional engineering, belongs to the field of buildings, and particularly relates to a mooring rope protector for a building. The mooring rope protector for the building comprises a shell, a first connecting piece, a second connecting piece and a snapping piece, wherein the first connecting piece is connected with the second connecting piece through the snapping piece; the shell sleeves the outsides of the first connecting piece, the second connecting piece and the snapping piece; and after the snapping piece is snapped off, the shell bears a tensile force between the first connecting piece and the second connecting piece. By the design of the snapping piece which can be snapped off, use safety of the mooring rope can be guaranteed effectively, before the tensile force reaches a rated snapping-off force of the mooring rope, the snapping piece is snapped off at first, then whether the mooring rope is used in an overload manner can be observed effectively, and the protective feature of the mooring rope is improved. By the design of a weak link arranged on the mooring rope, whether the mooring rope is in an overpressure state or not when used can be judged, and therefore, the service life of the mooring rope in a using process can be judged.

Owner:CHENGDU 90 DEGREE IND PROD DESIGN CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com