Patents

Literature

269results about "Discontinuously variable inductances/transformers" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

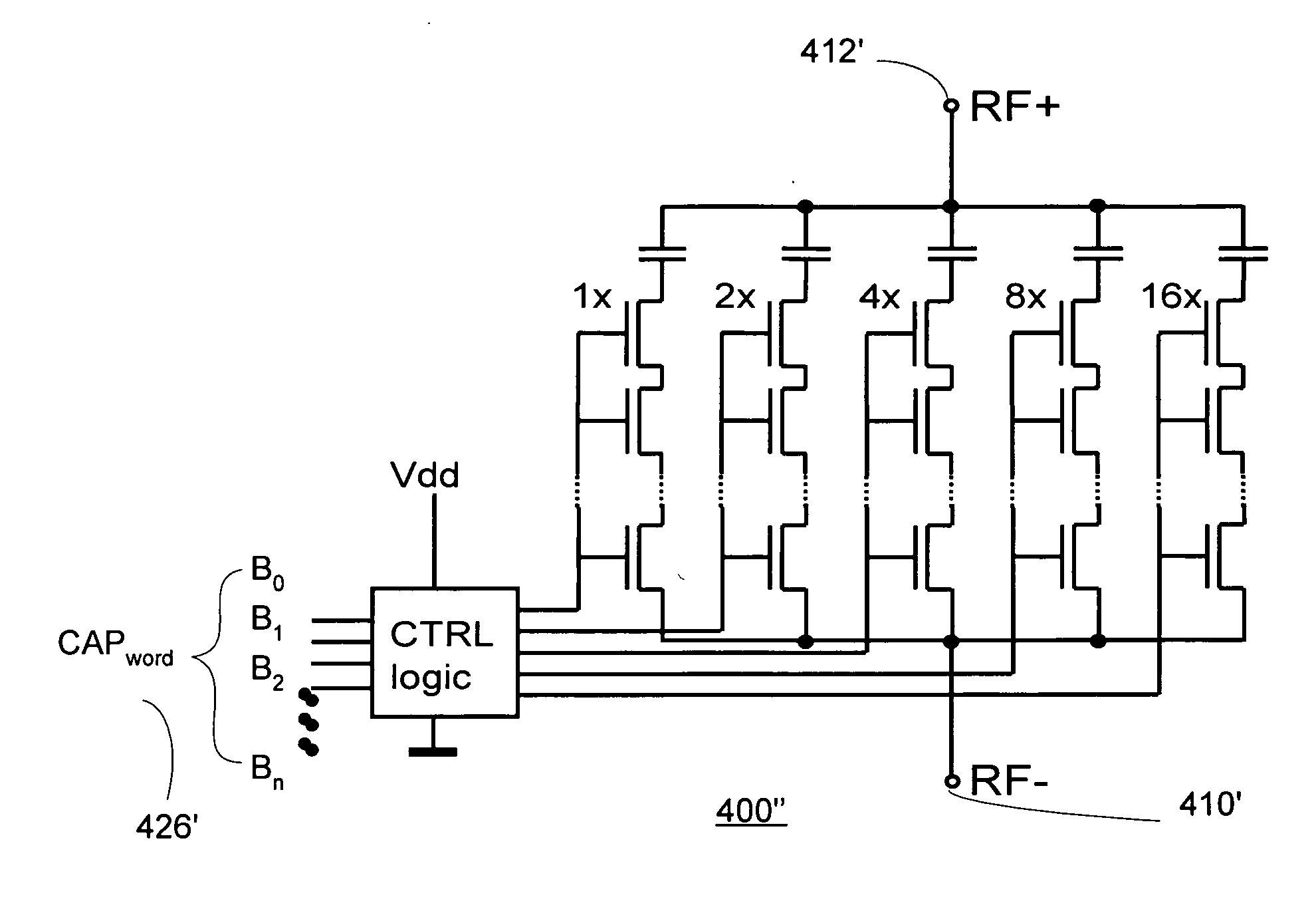

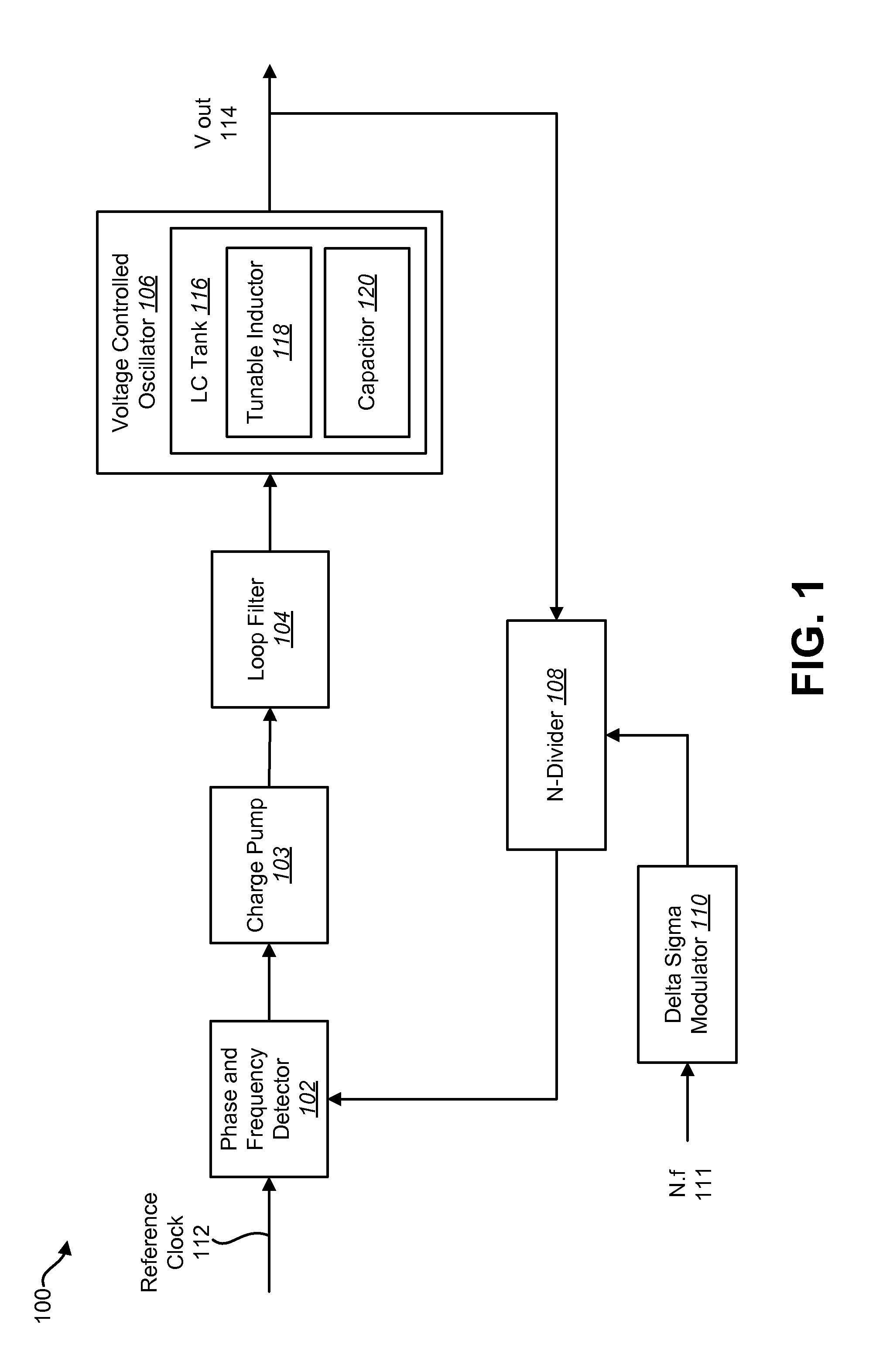

Method and apparatus for use in digitally tuning a capacitor in an integrated circuit device

ActiveUS20110002080A1Easy to controlHigh Power Handling CapabilityAnalogue/digital conversionImpedence matching networksCapacitanceLeast significant bit

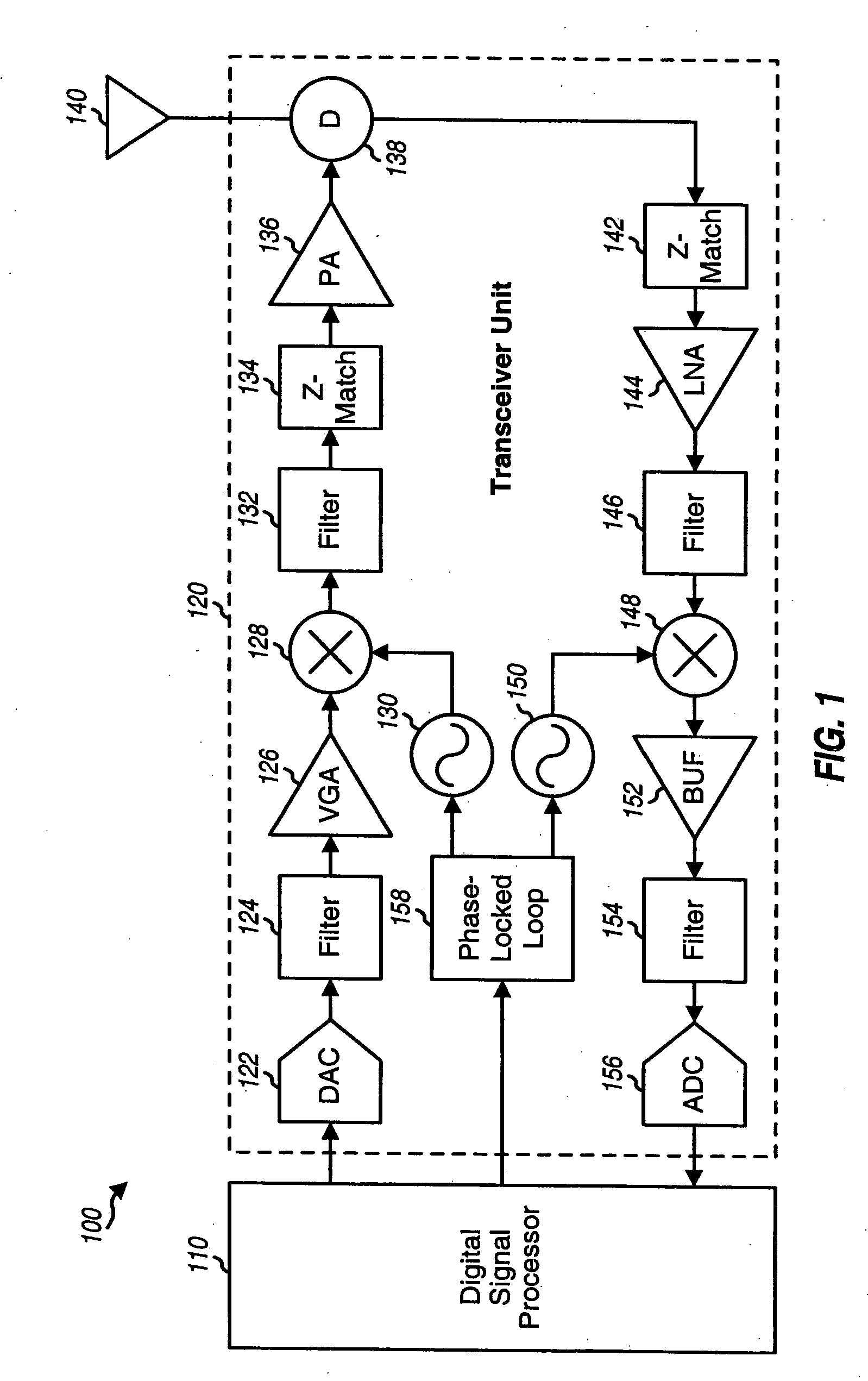

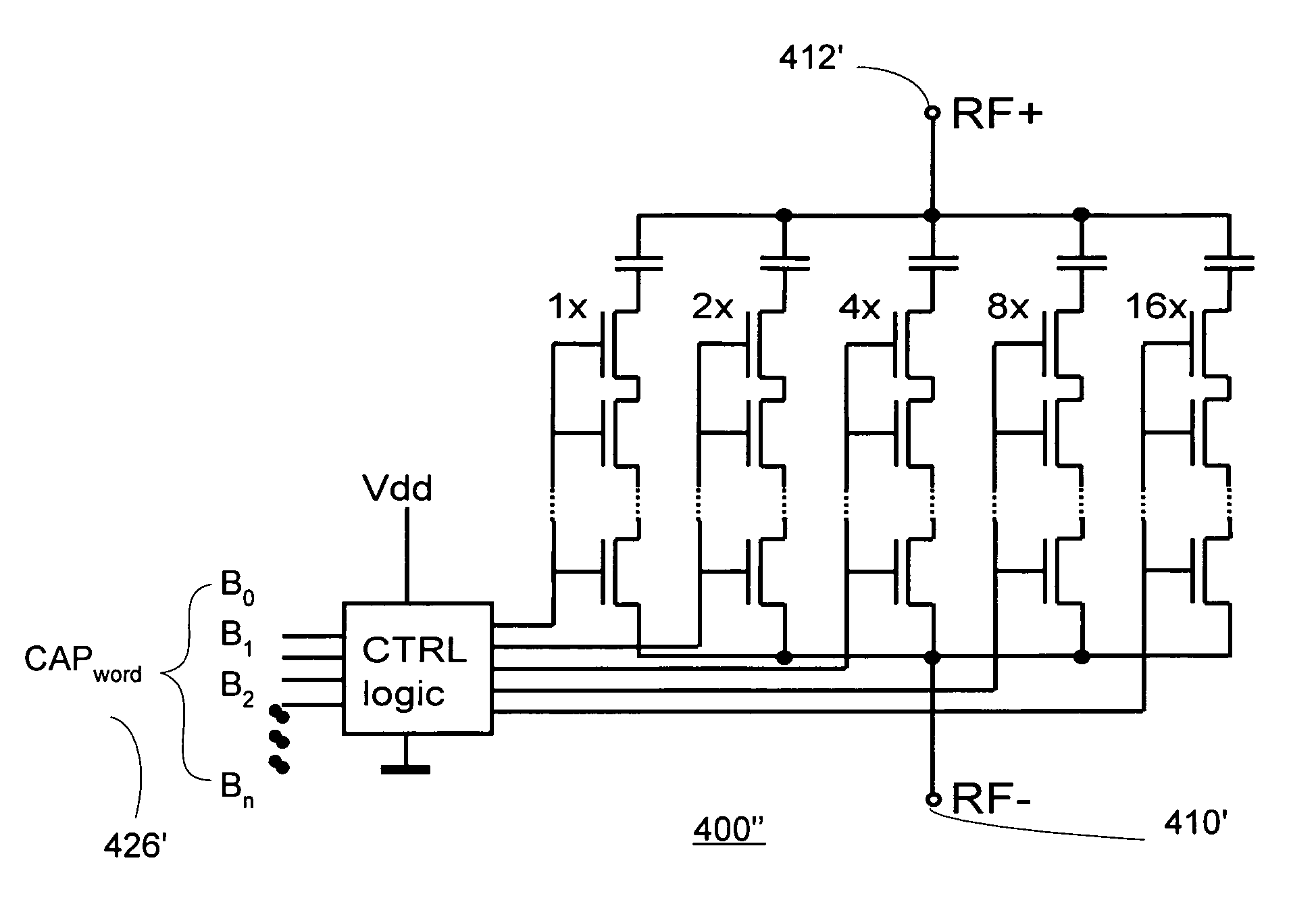

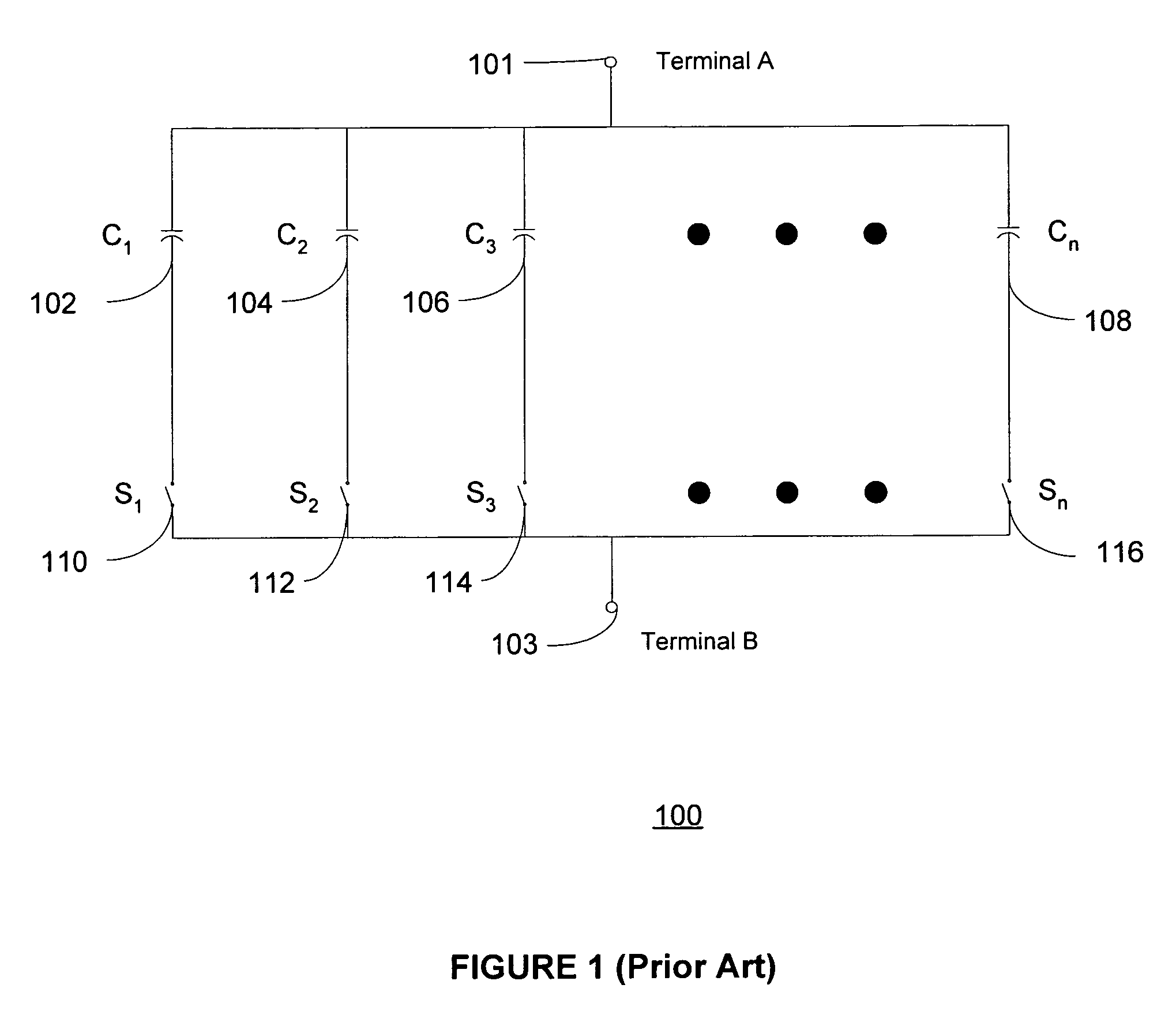

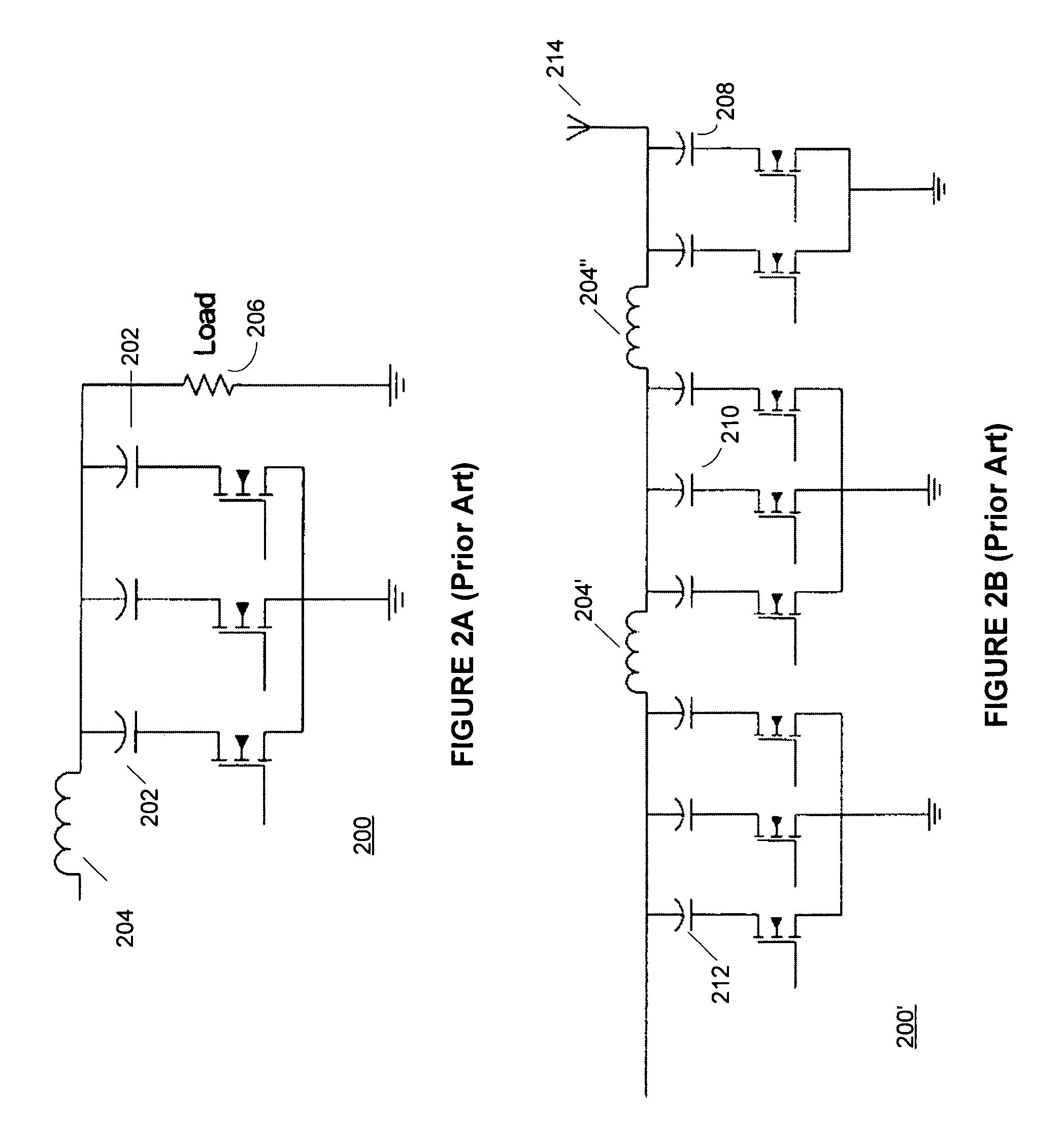

A method and apparatus for use in a digitally tuning a capacitor in an integrated circuit device is described. A Digitally Tuned Capacitor DTC is described which facilitates digitally controlling capacitance applied between a first and second terminal. In some embodiments, the first terminal comprises an FW+ terminal and the second terminal comprises an RF terminal. In accordance with some embodiments, the DTCs comprises a plurality of sub-circuits ordered in significance from least significant bit (LSB) to most significant bit (MSB) sub-circuits, wherein the plurality of significant bit sub-circuits are coupled together in parallel, and wherein each sub-circuit has a first node coupled to the first RF terminal, and a second node coupled to the second FW terminal. The DTCs further include an input means for receiving a digital control word, wherein the digital control word comprises bits that are similarly ordered in significance from an LSB to an MSB.

Owner:PSEMI CORP

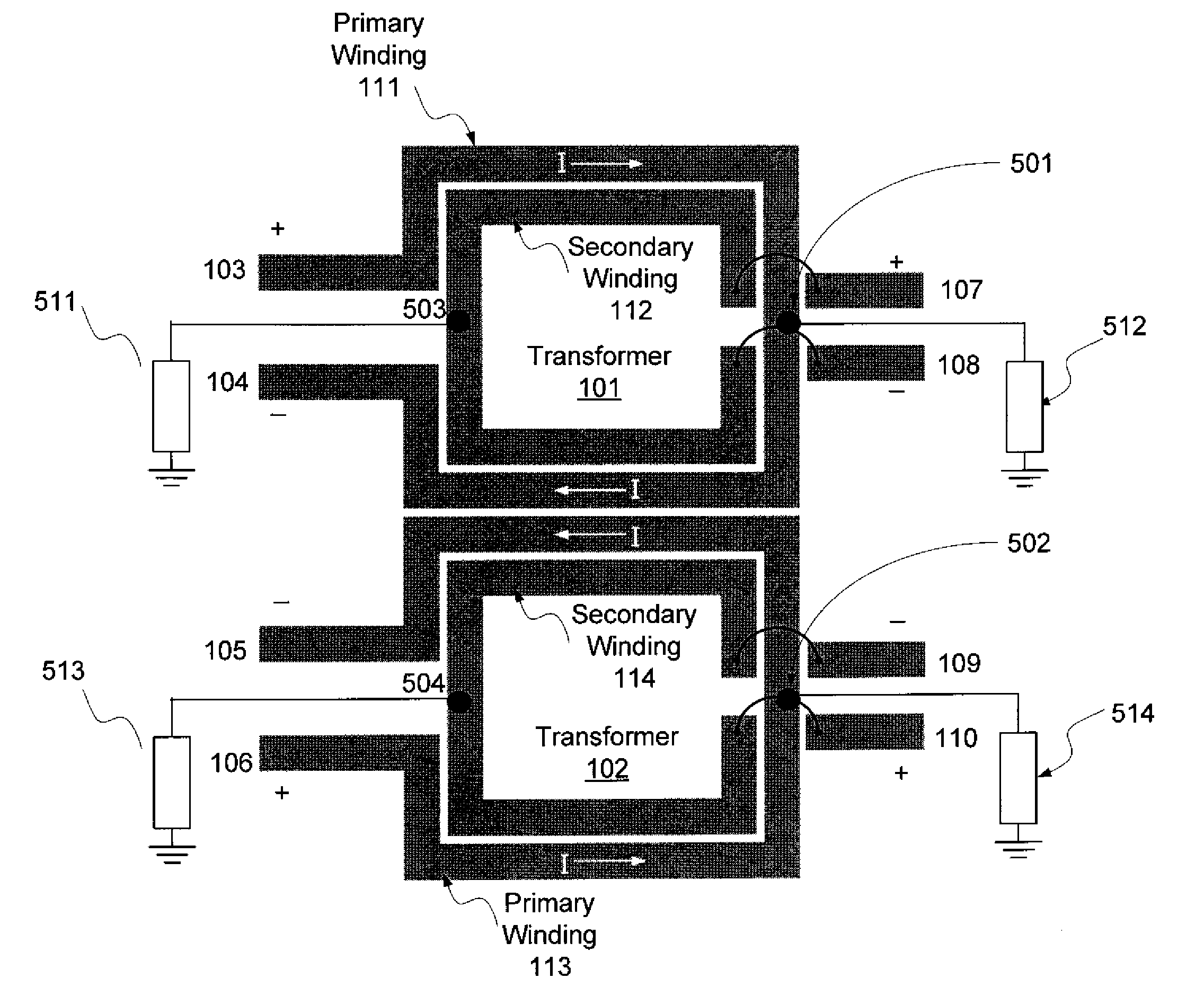

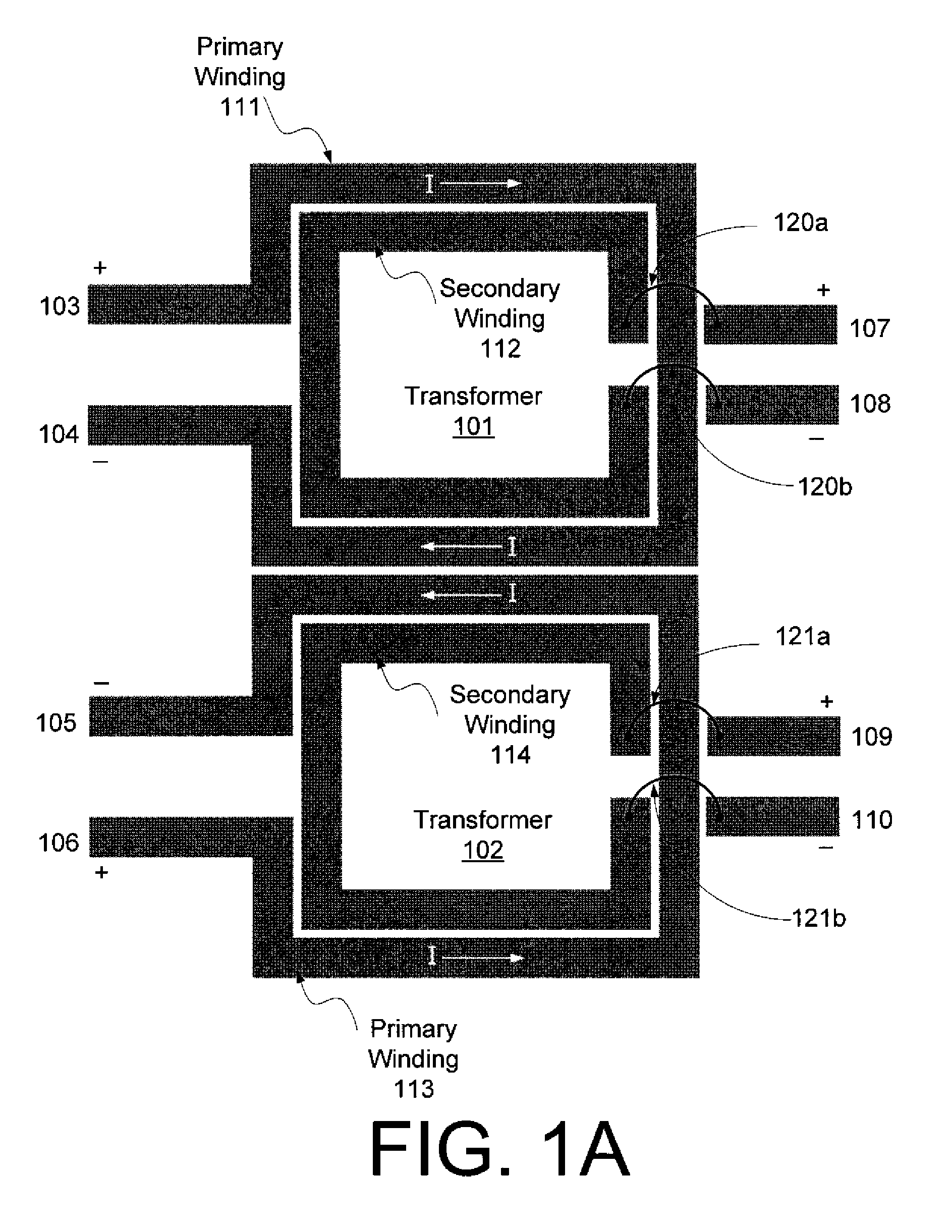

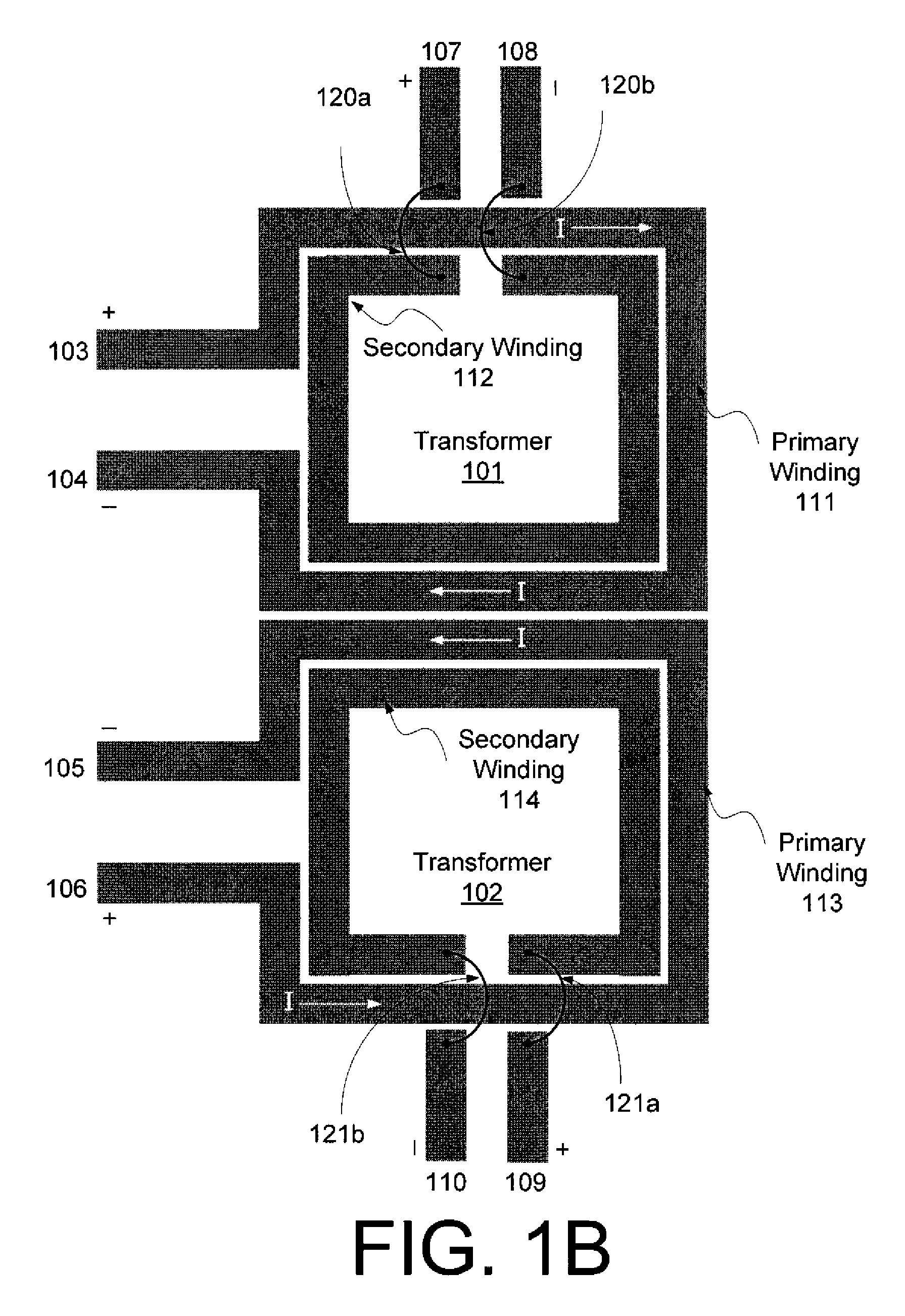

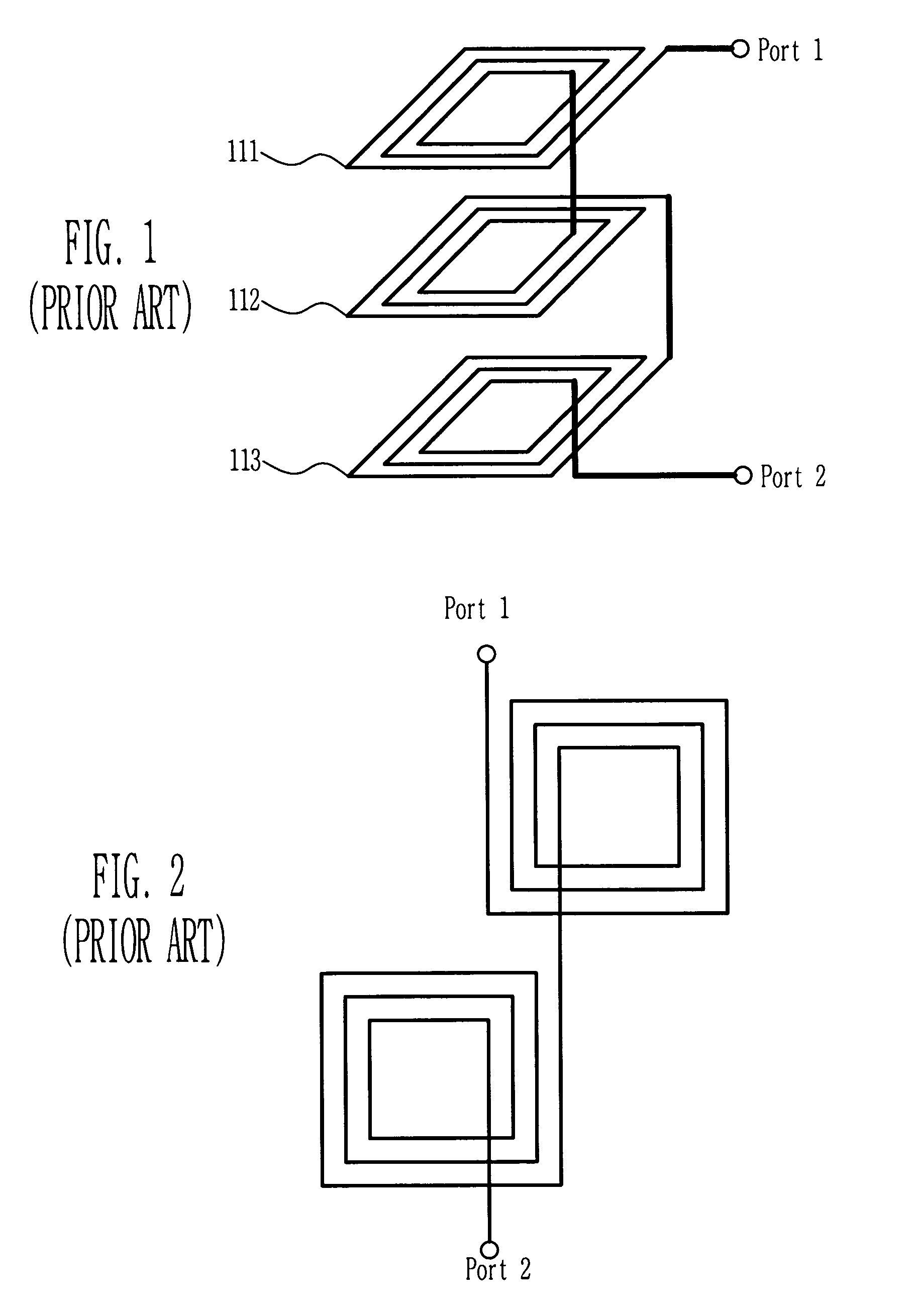

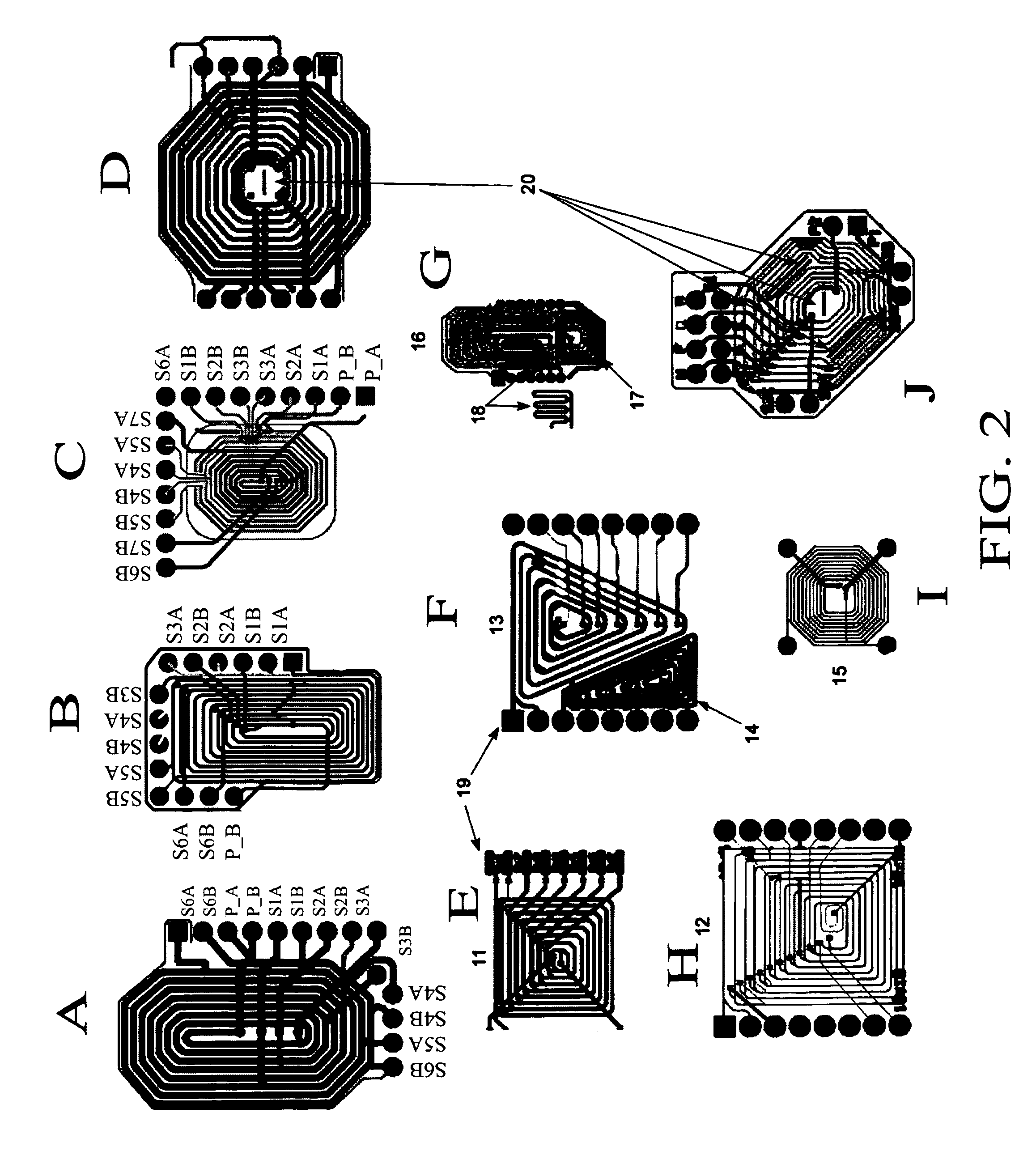

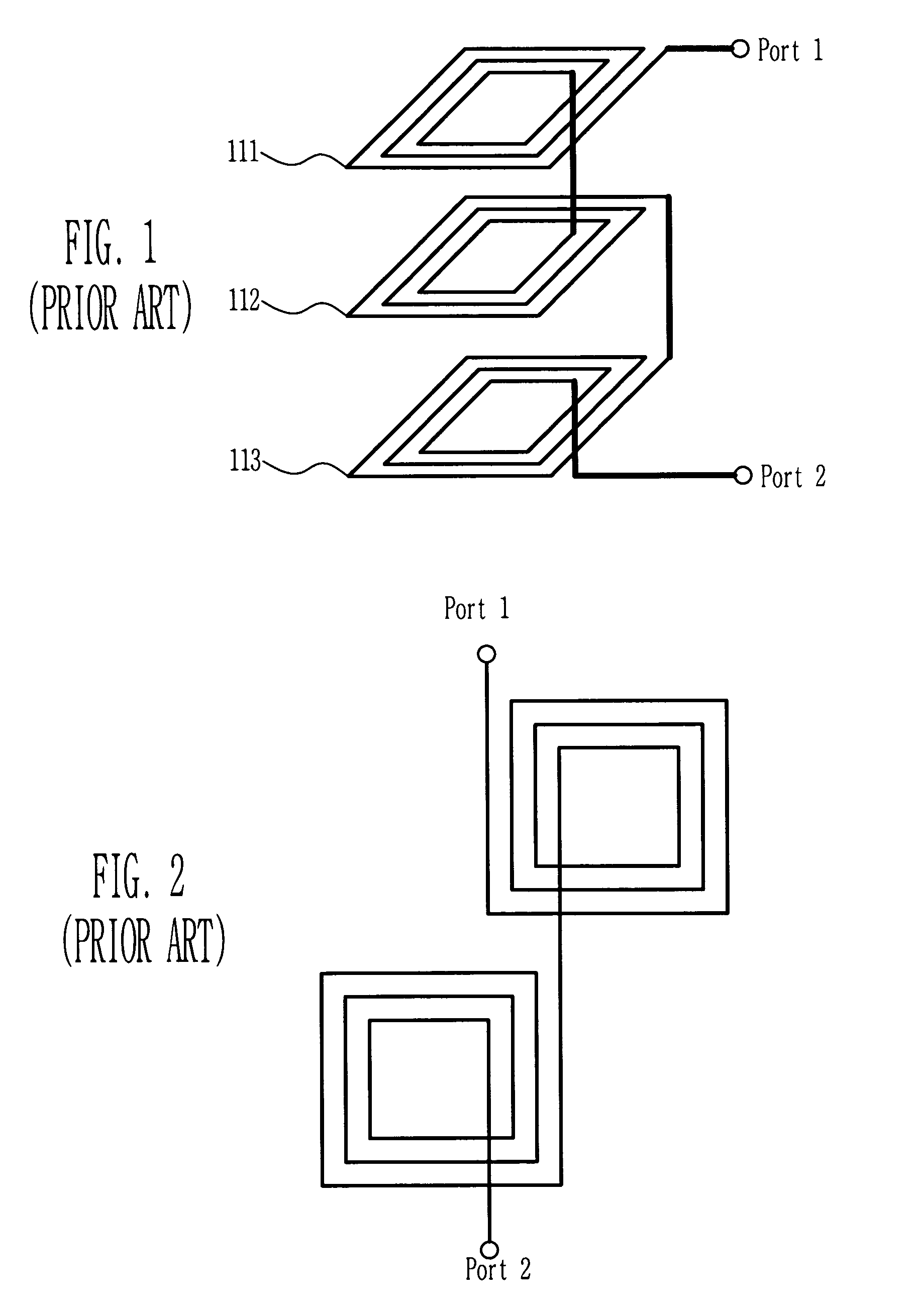

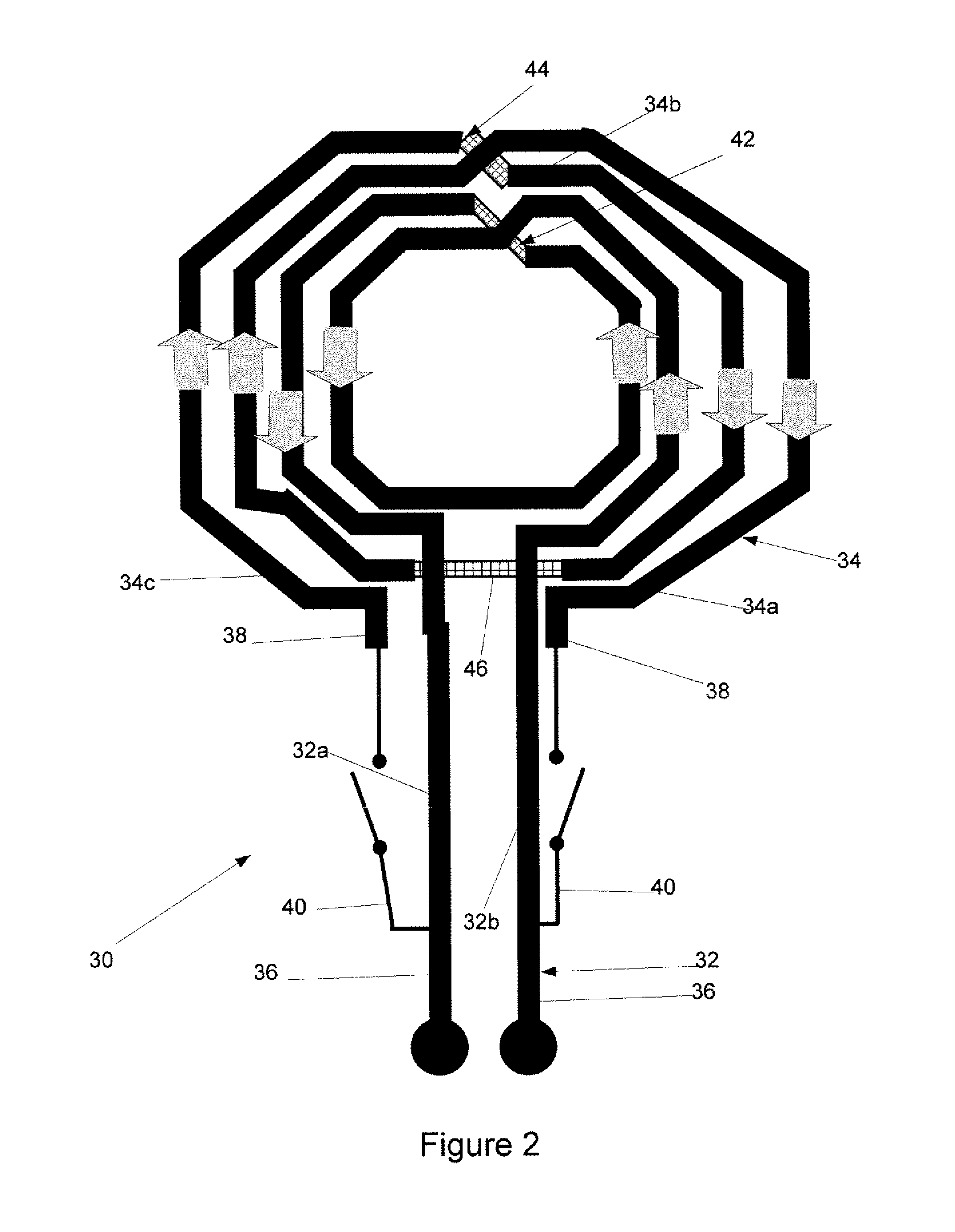

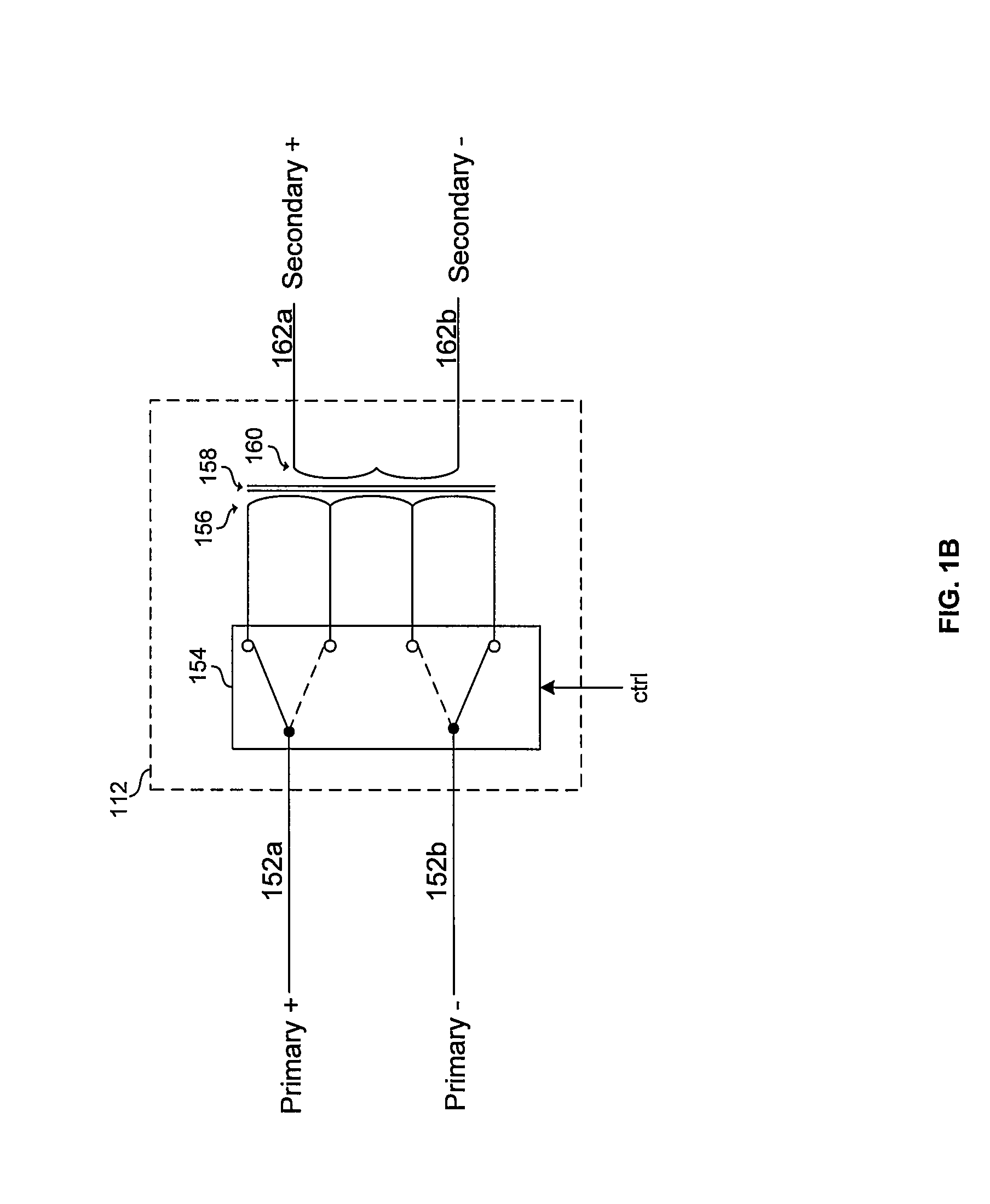

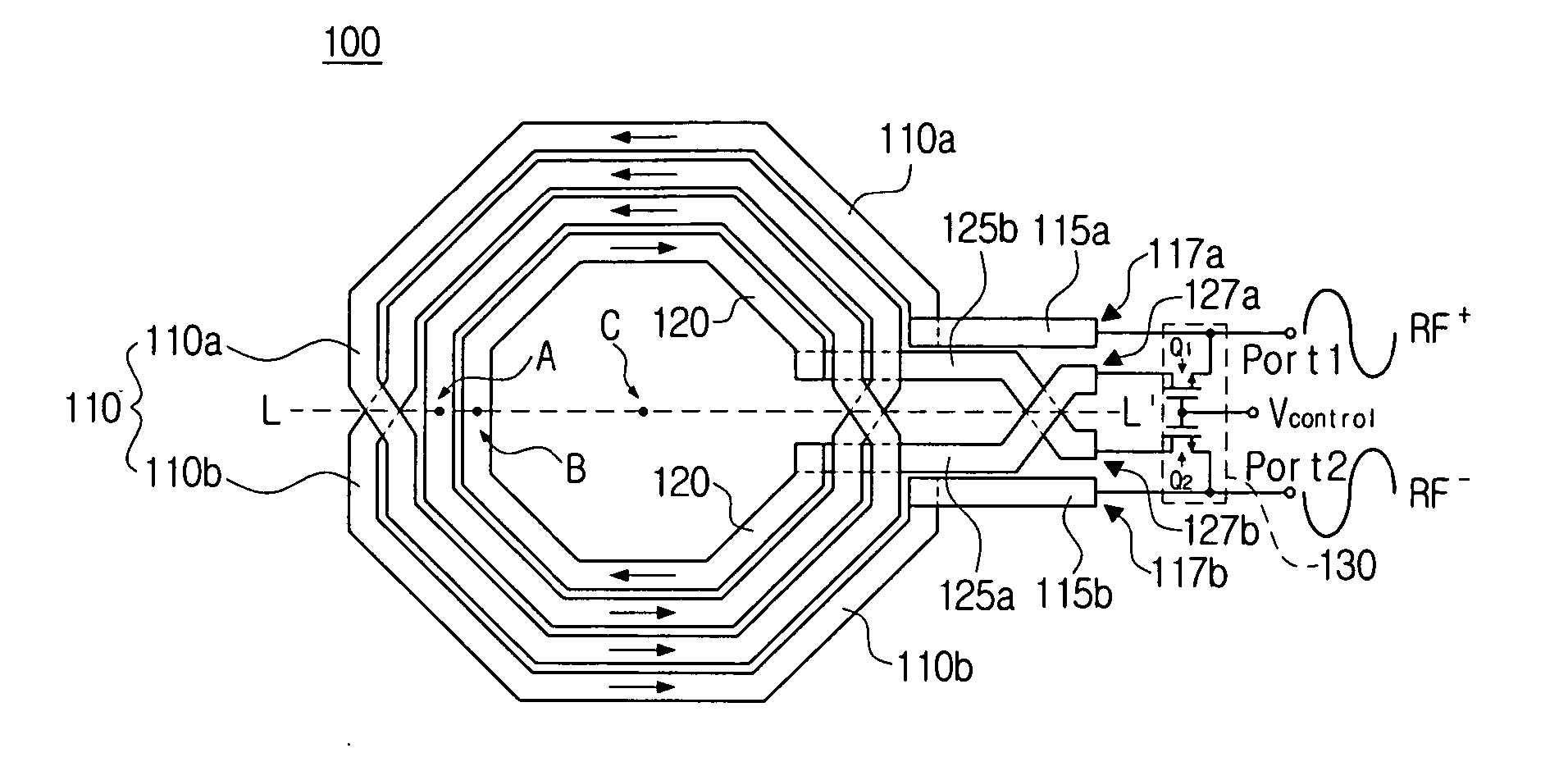

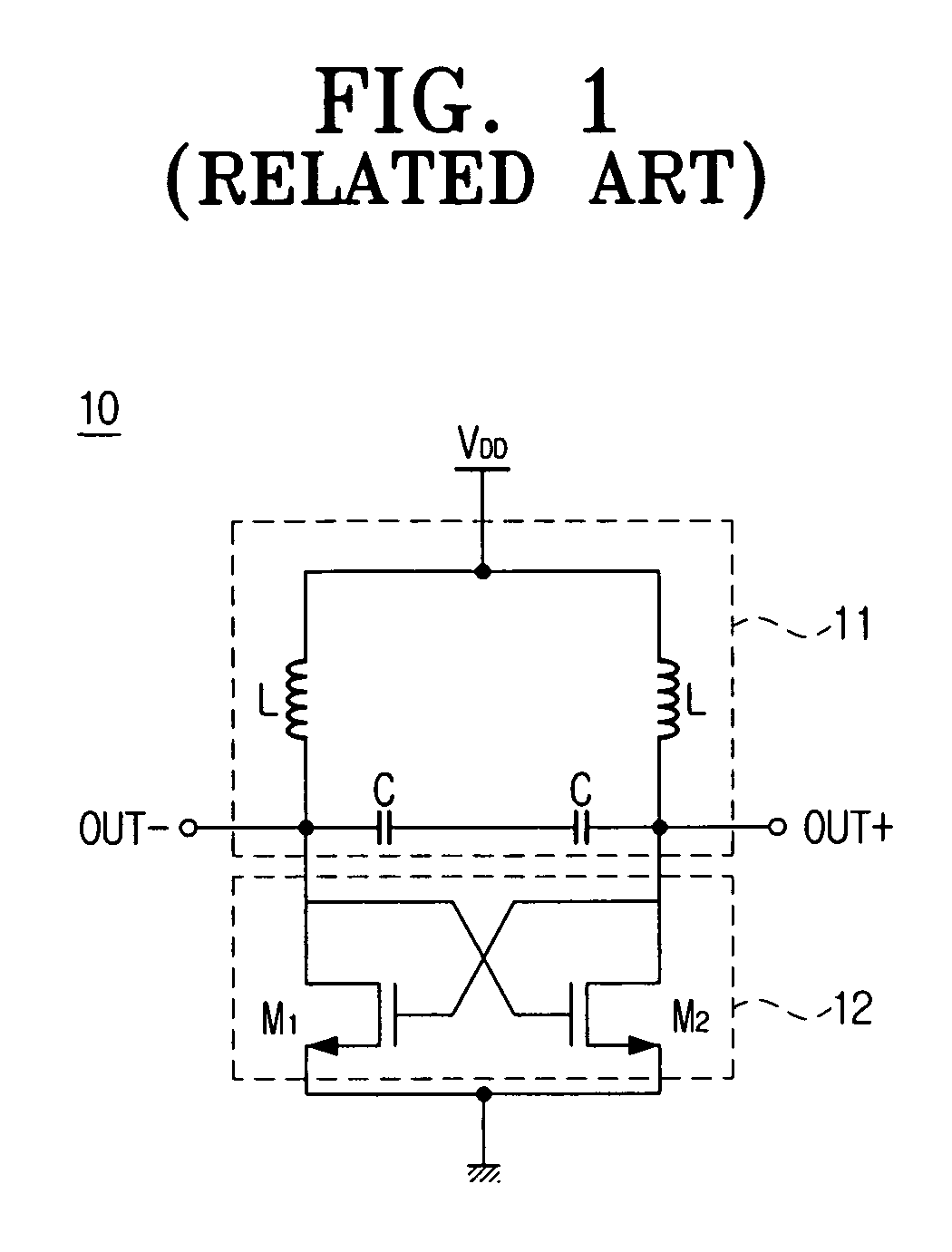

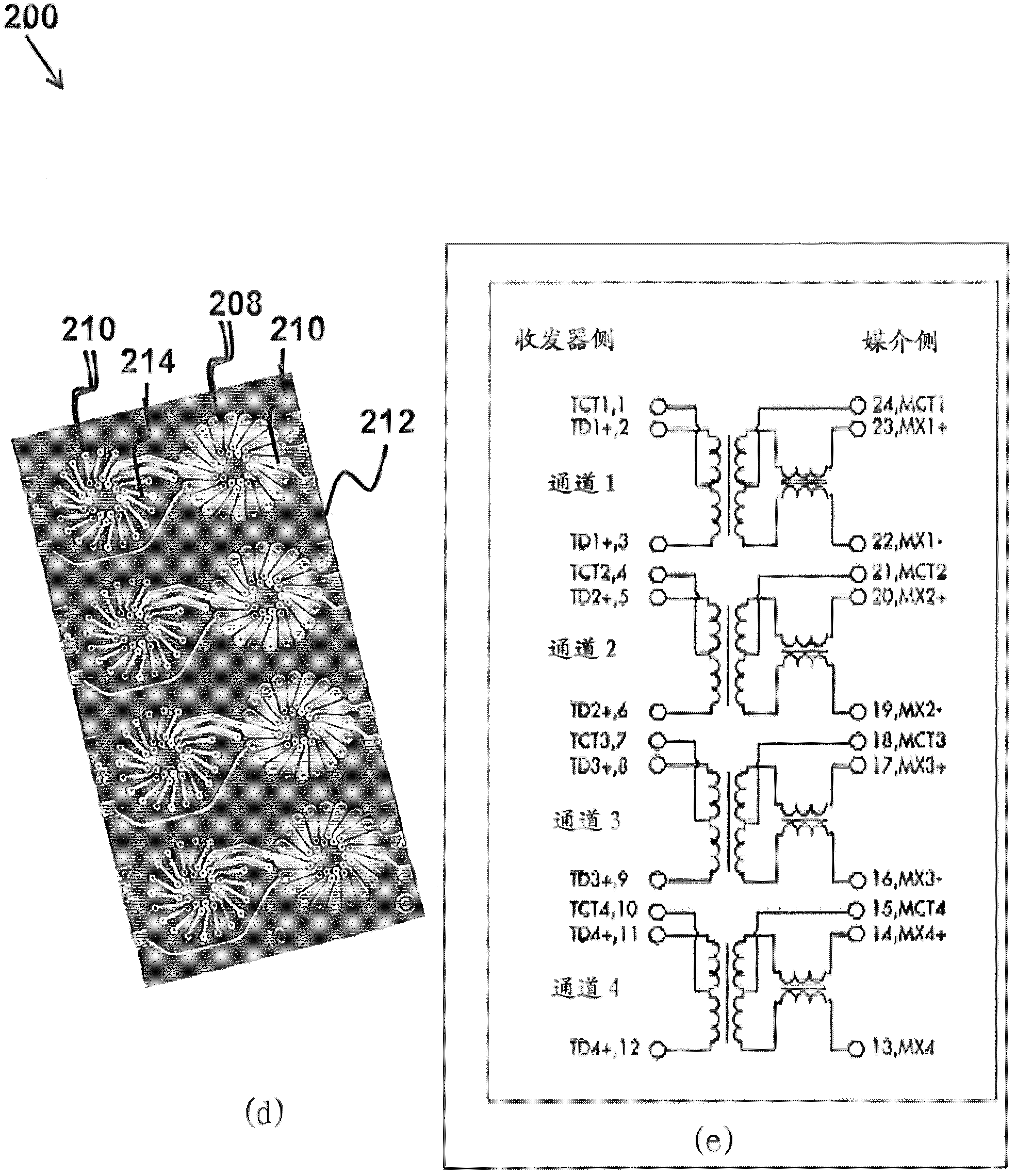

Compact multiple transformers

InactiveUS7812701B2Increase magnetic flux and inductance and quality factorTransformersTransformers/inductances coils/windings/connectionsTransformerEngineering

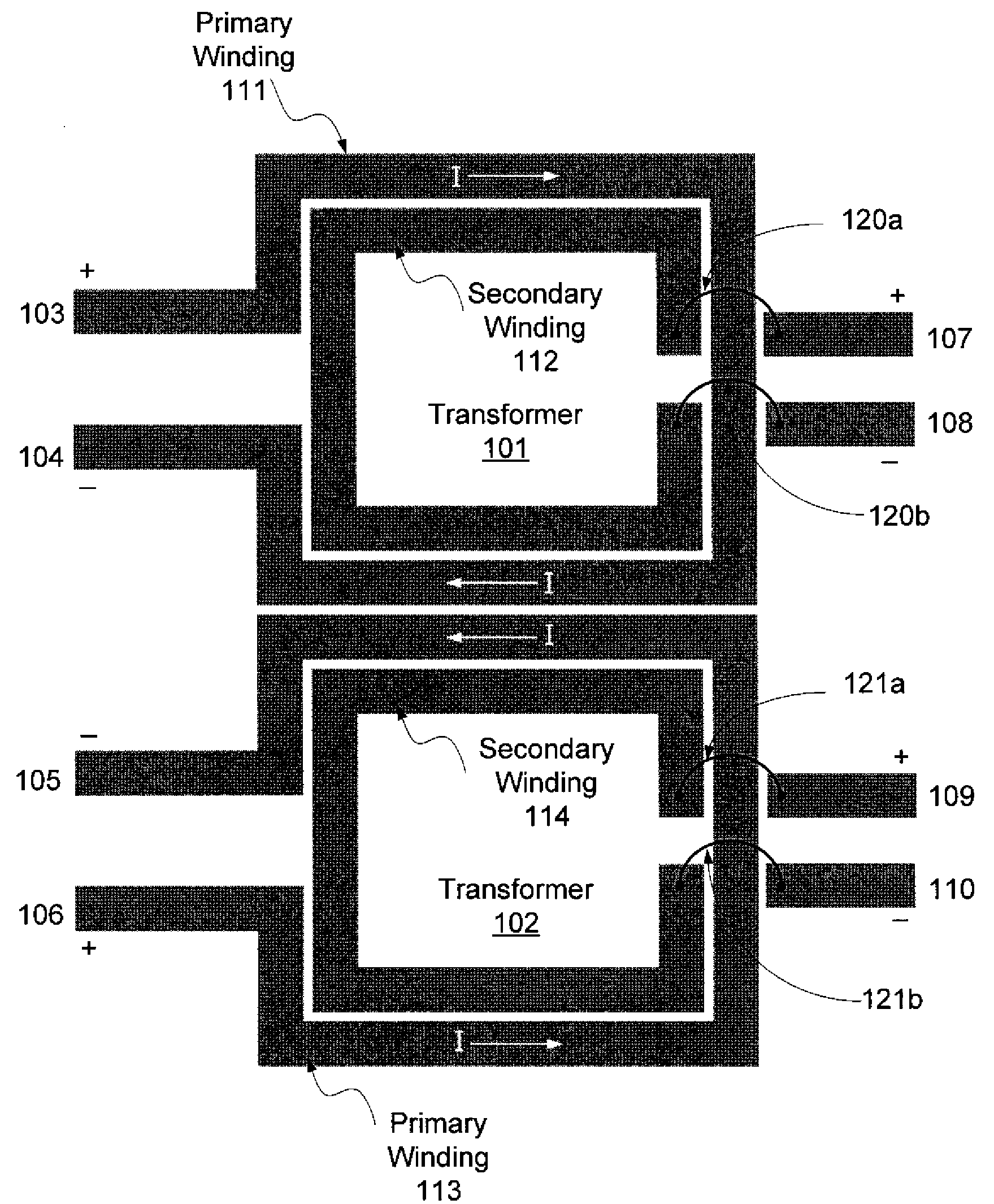

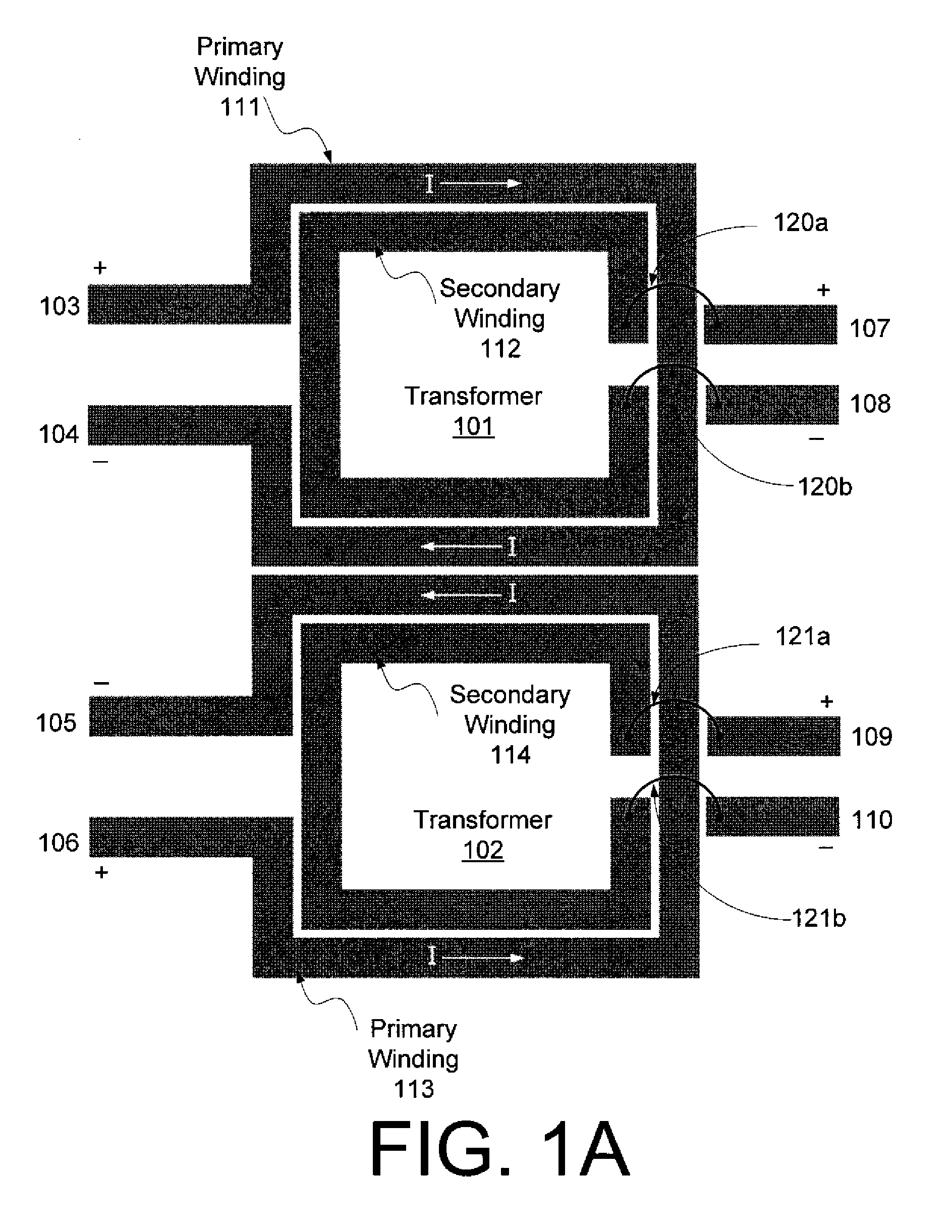

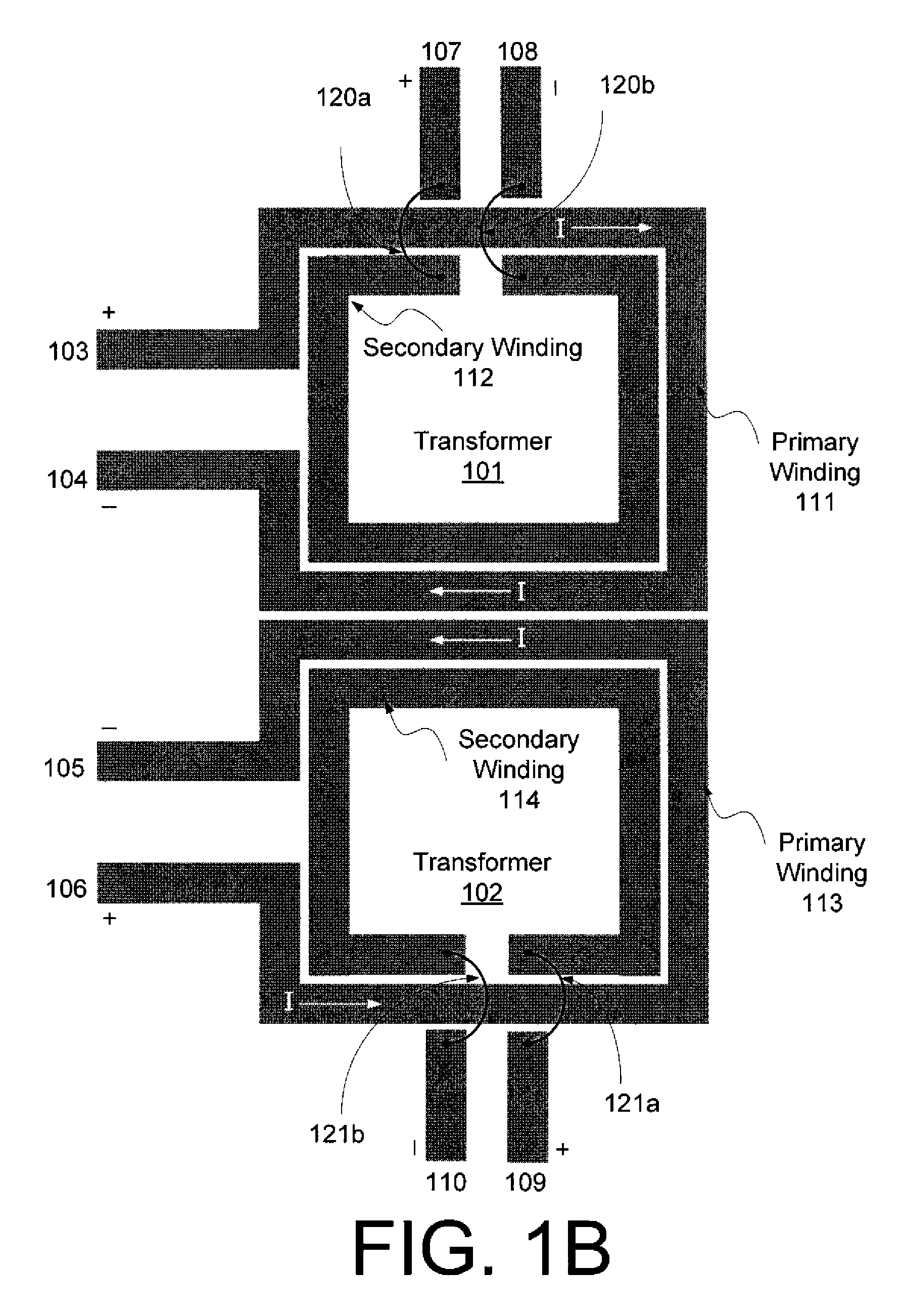

Example embodiments of the invention may provide systems and methods for multiple transformers. The systems and methods may include a first transformer that may include a first primary winding and a first secondary winding, where the first primary winding may be inductively coupled to the first secondary winding, where the first transformer may be associated with a first rotational current flow direction in the first primary winding. The systems and methods may further include a second transformer that may include a second primary winding and a second secondary winding, where the second primary winding may be inductively coupled to the second secondary winding, where the second transformer may be associated with a second rotational current flow direction opposite the first rotational current flow direction in the second primary winding, where a first section of the first primary winding may be positioned adjacent to a second section of the second primary winding, and where the adjacent first and second sections may include a substantially same first linear current flow direction.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD +1

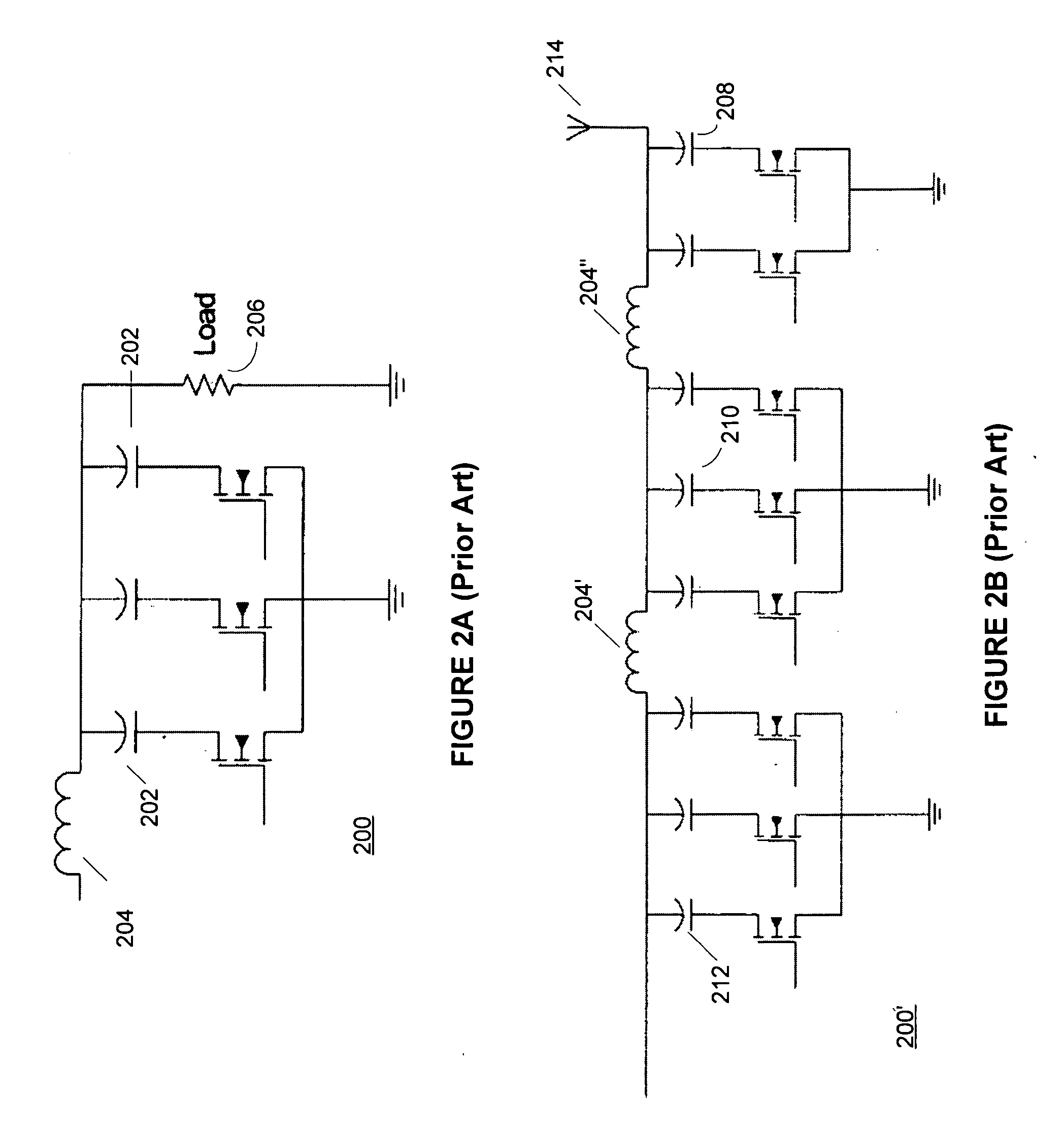

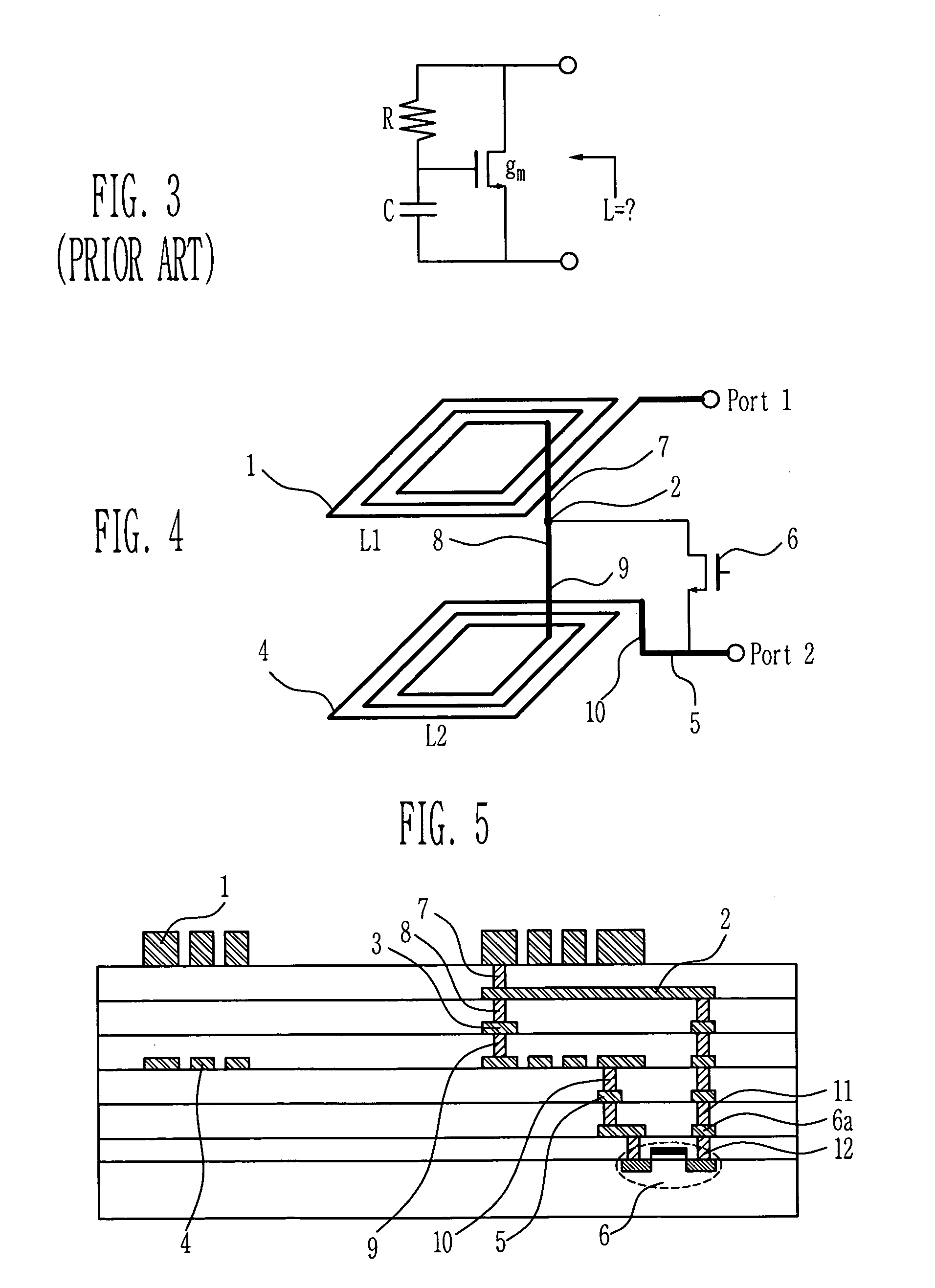

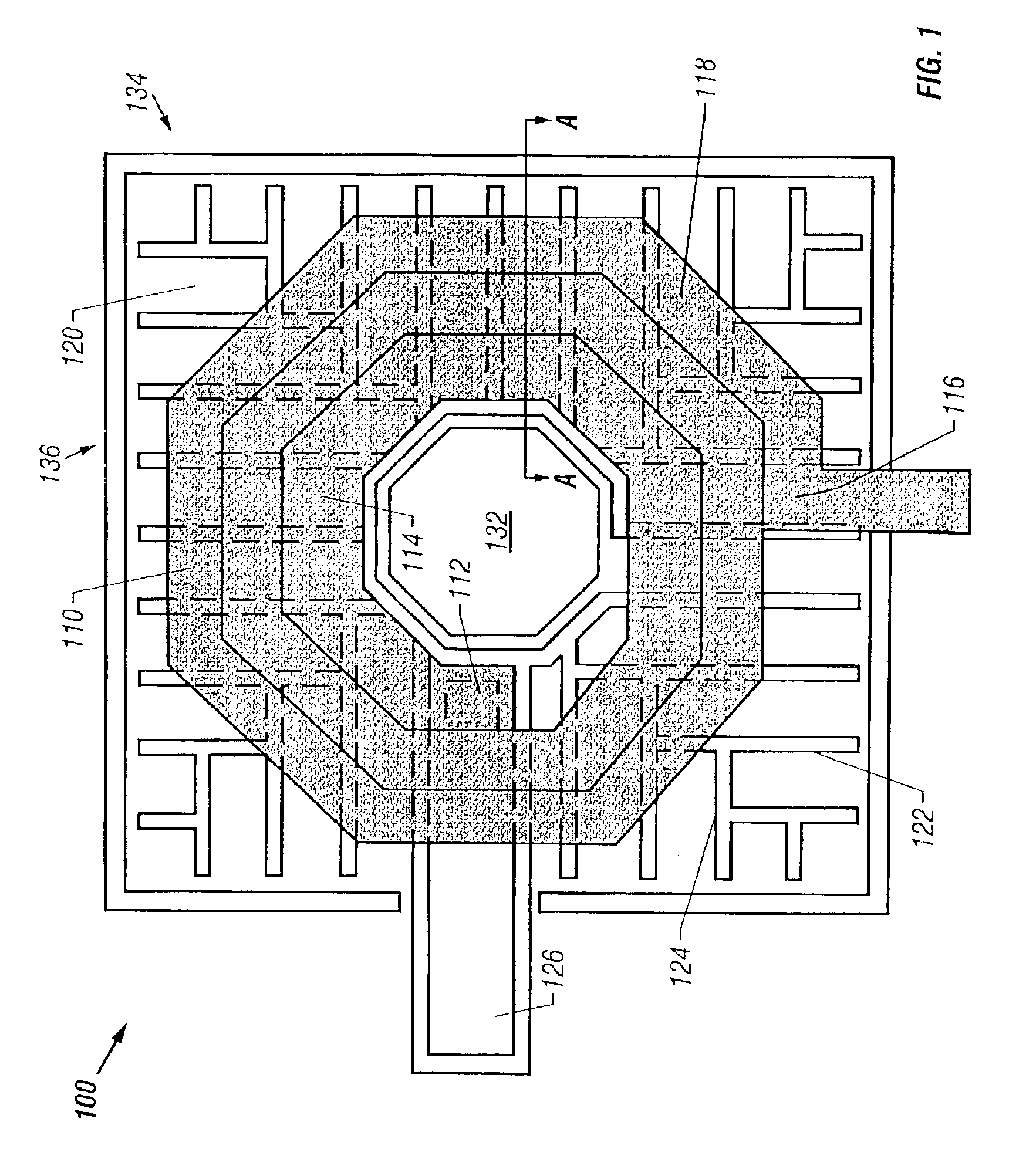

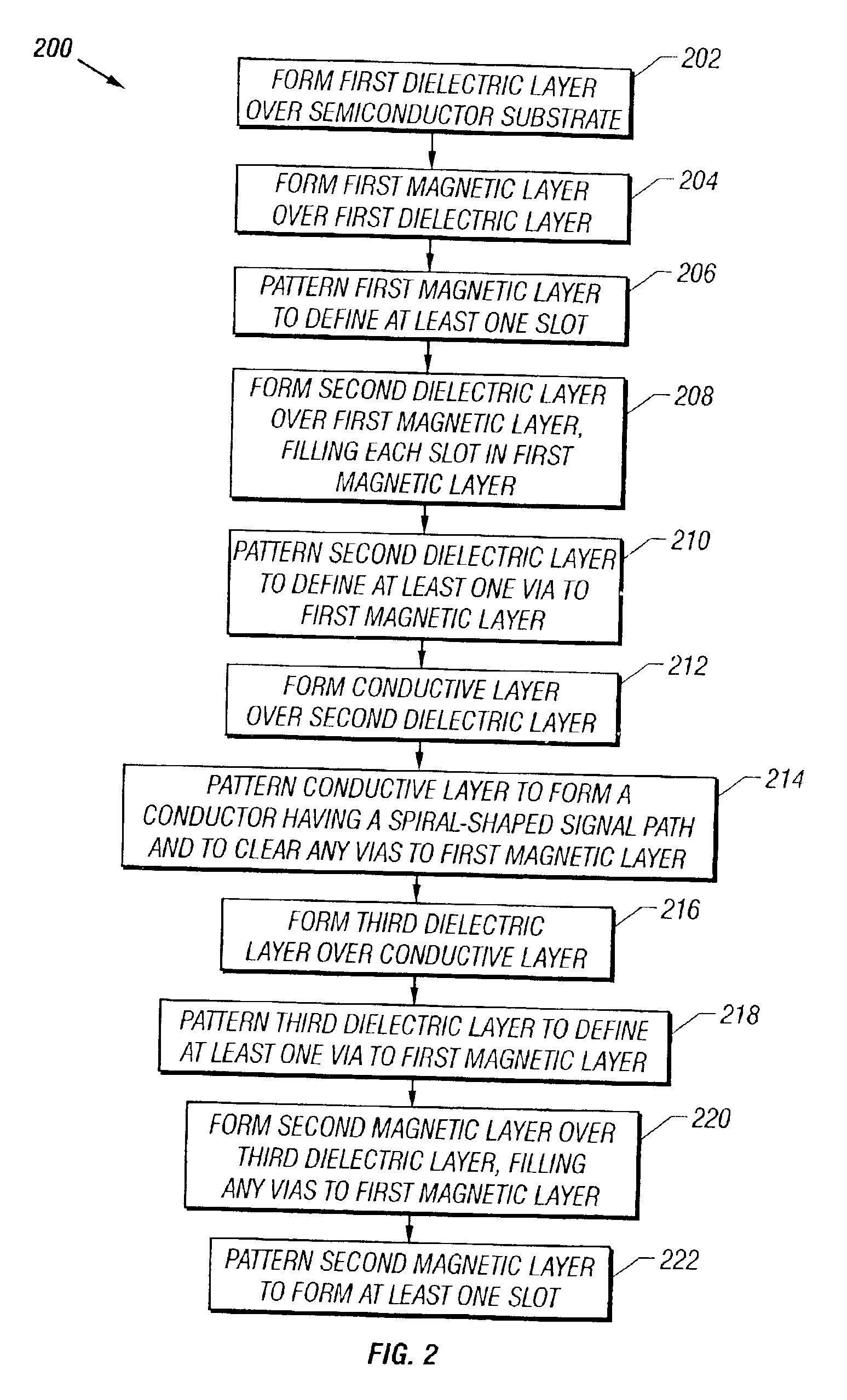

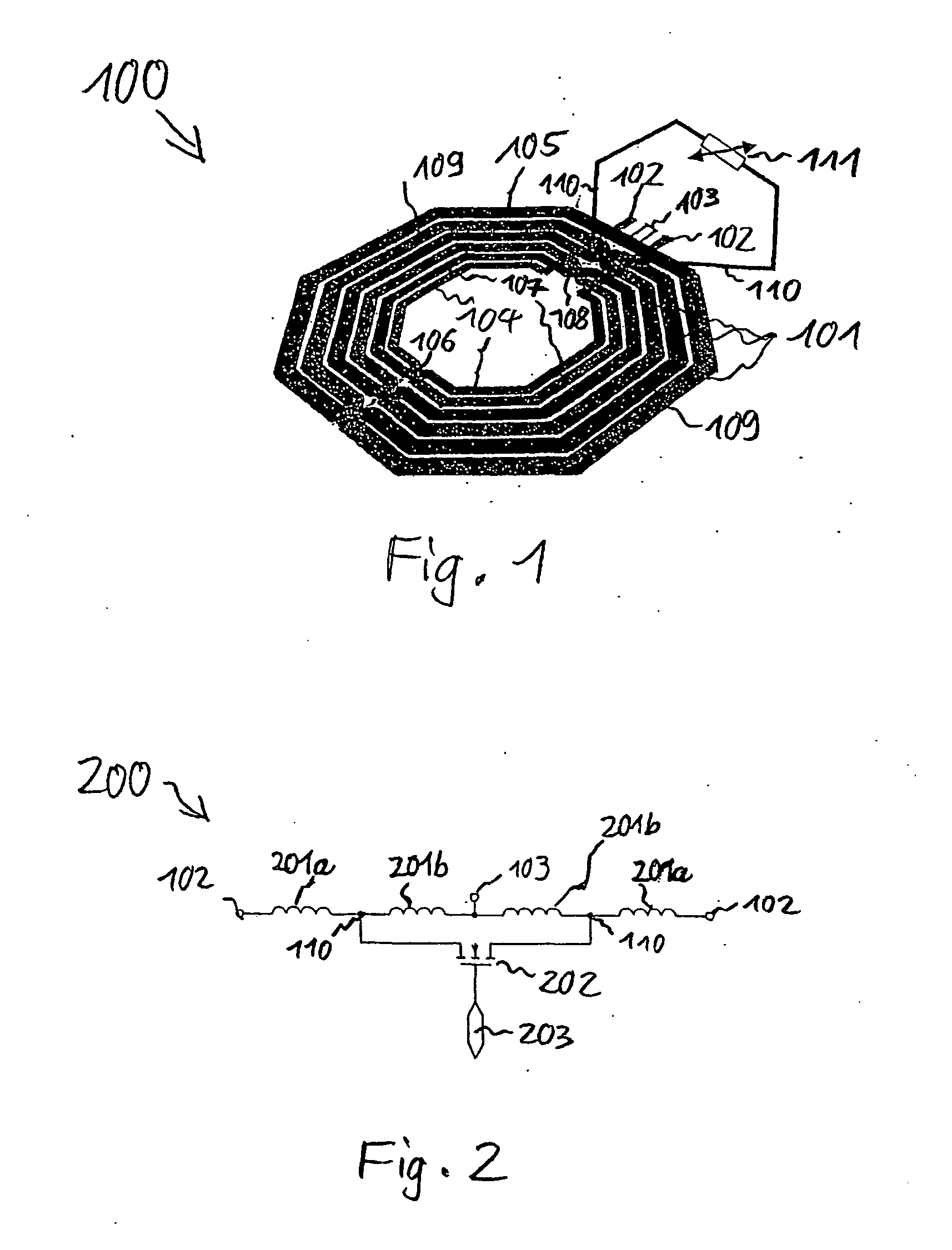

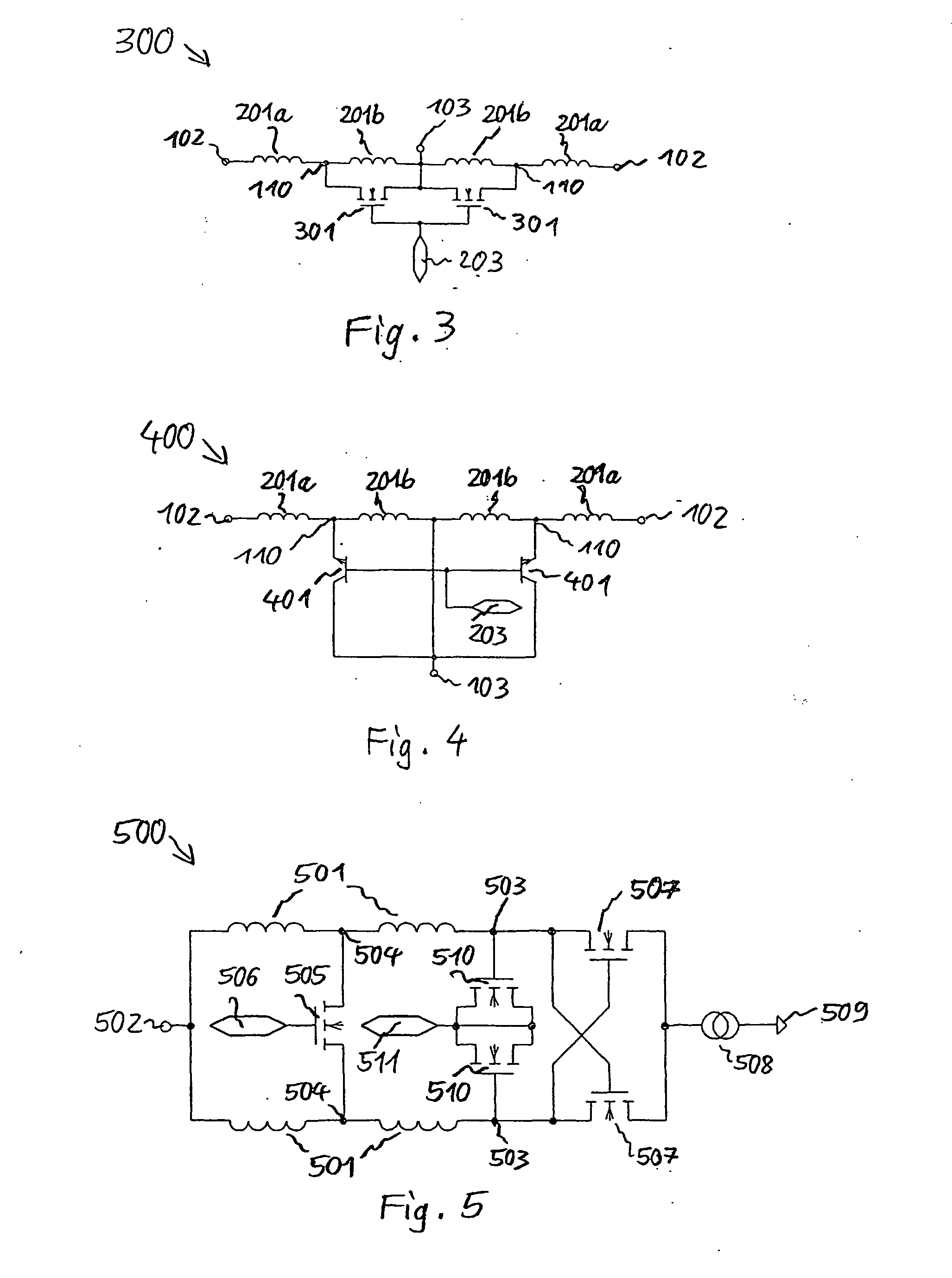

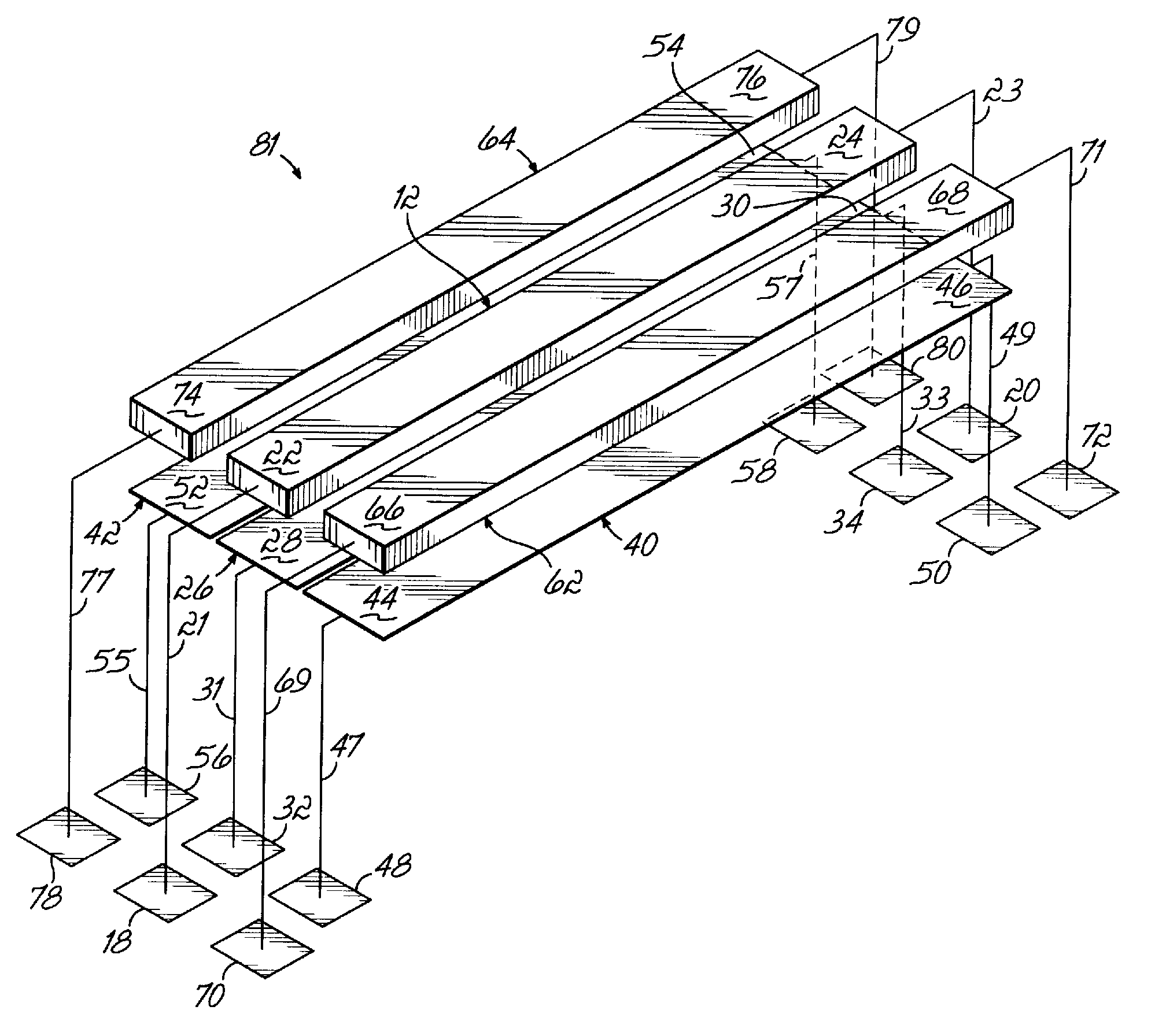

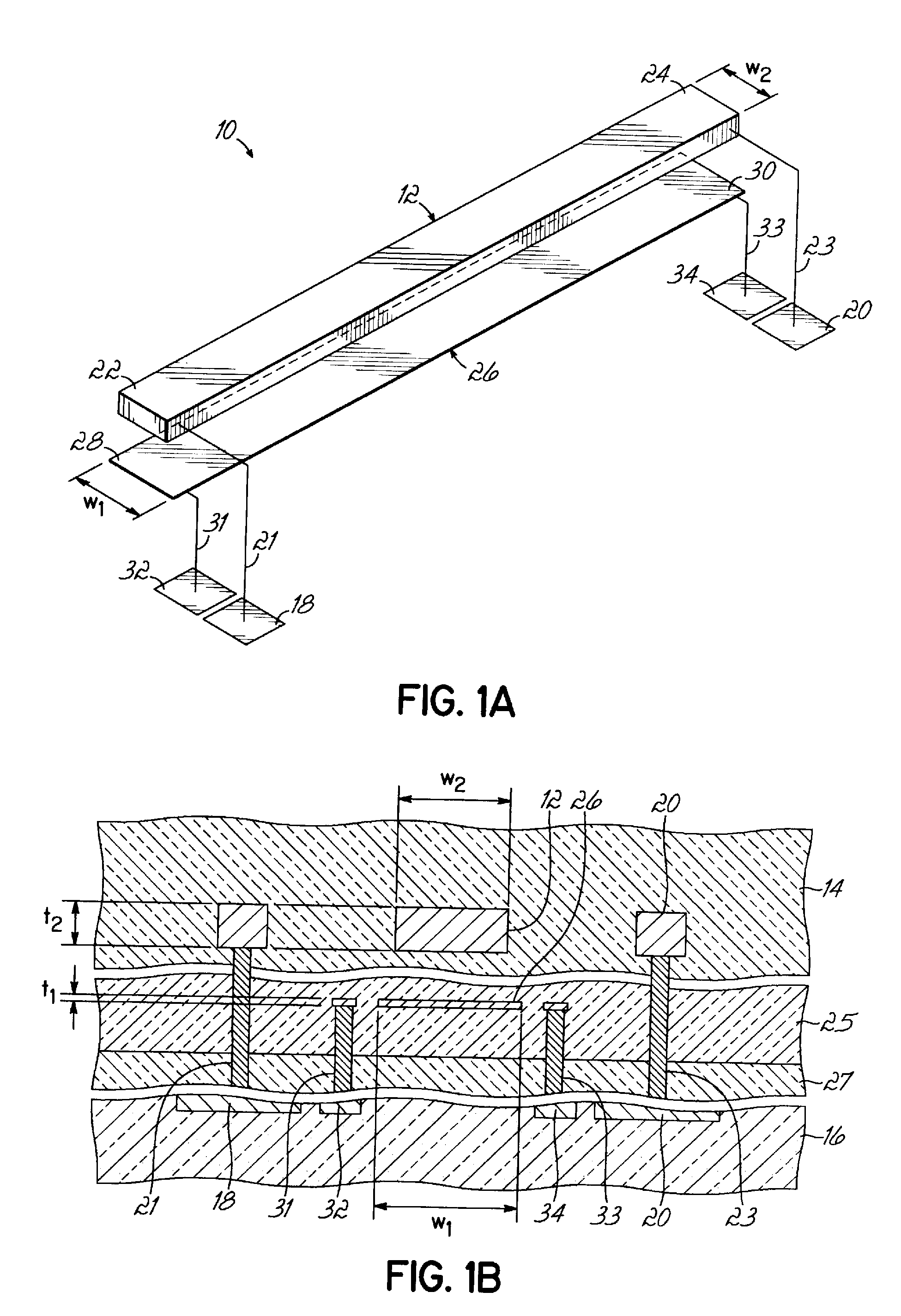

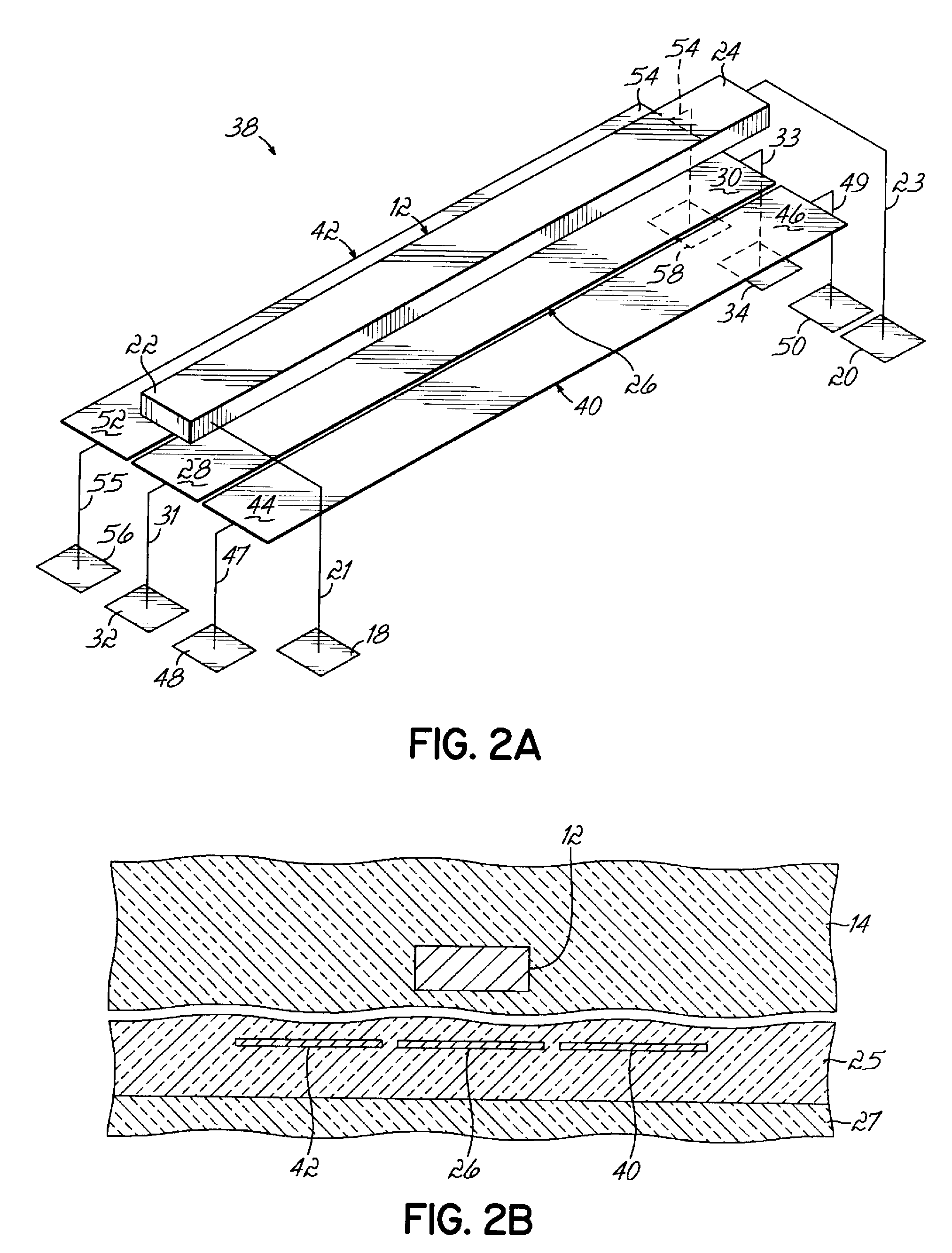

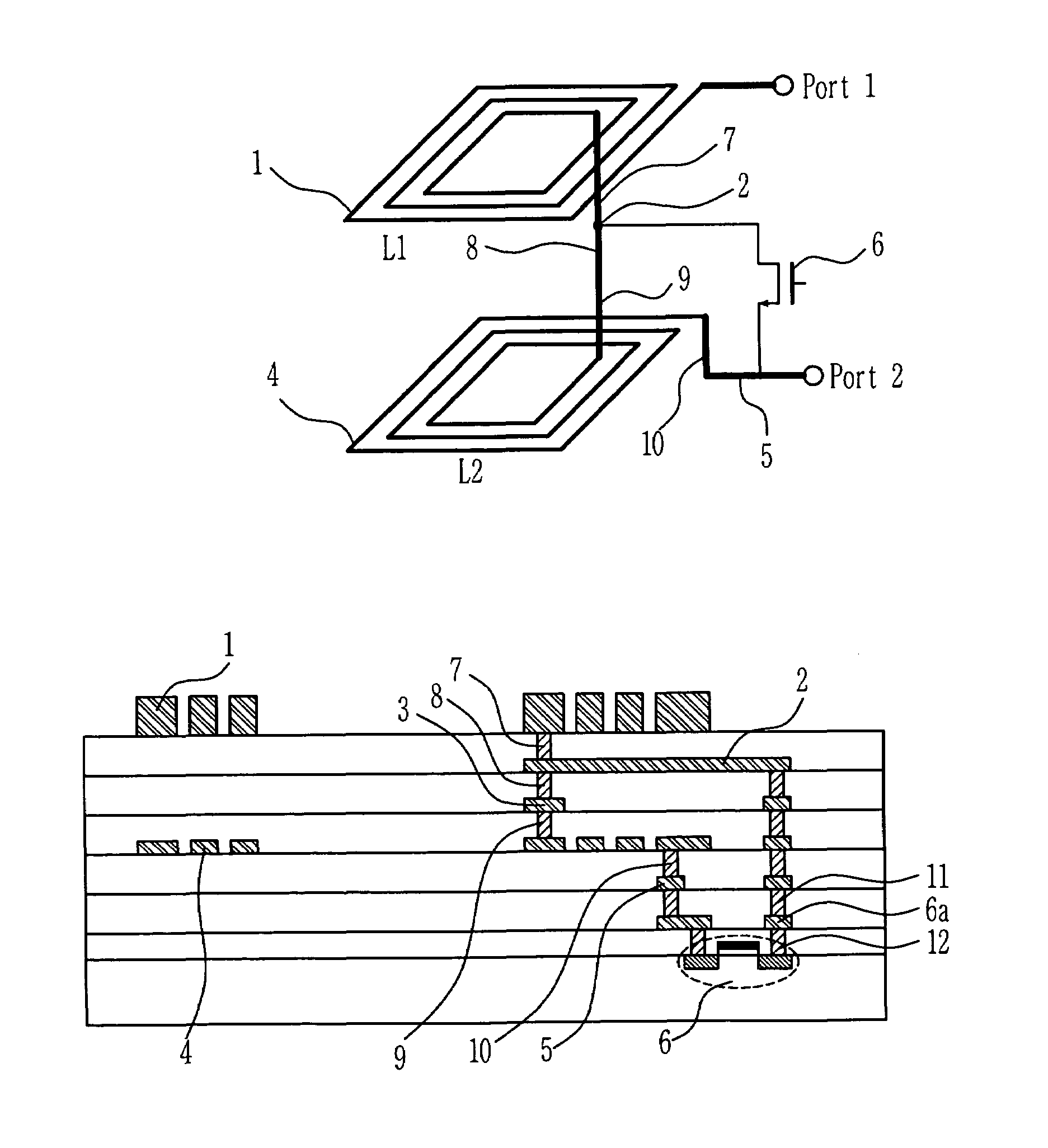

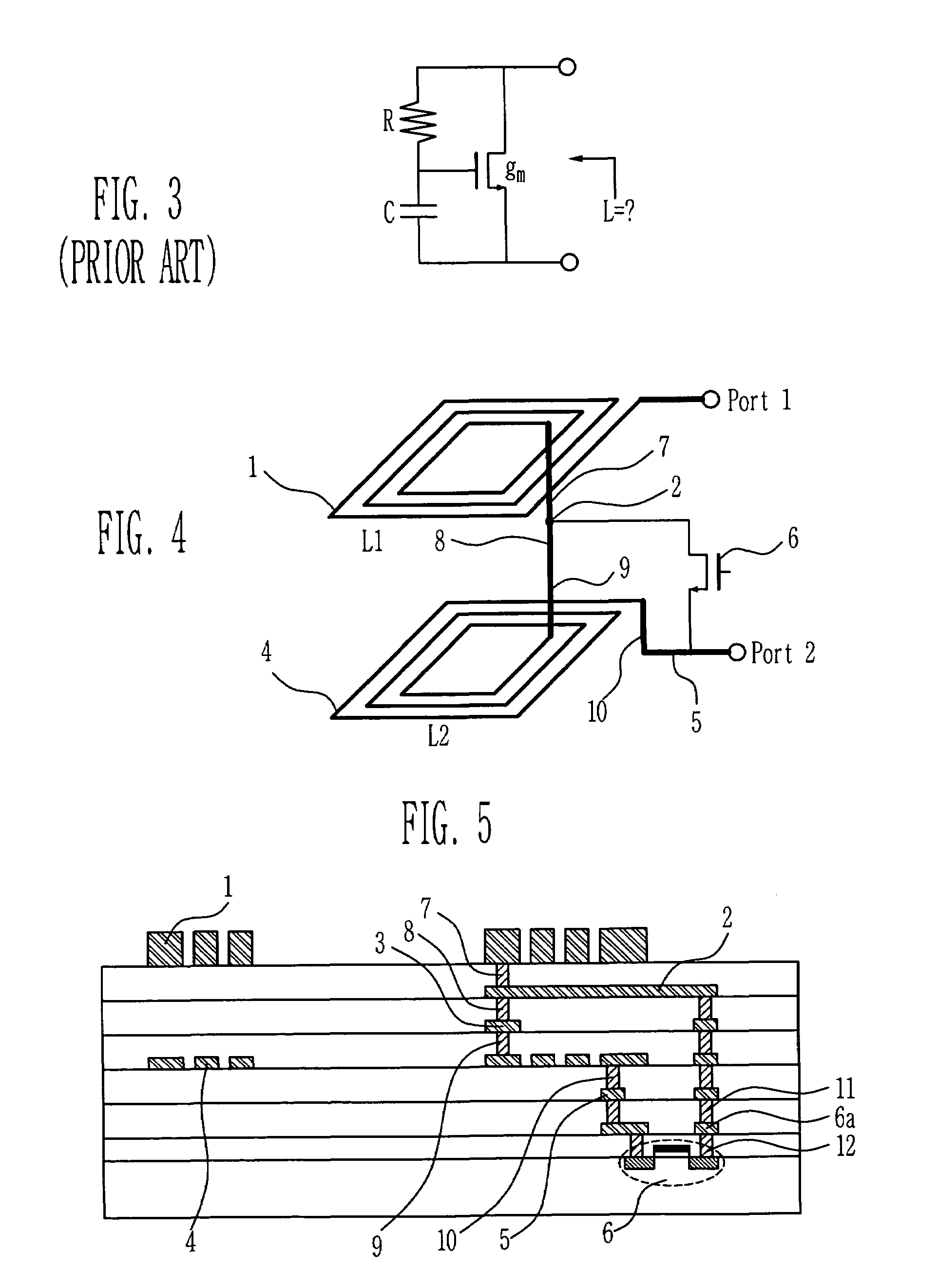

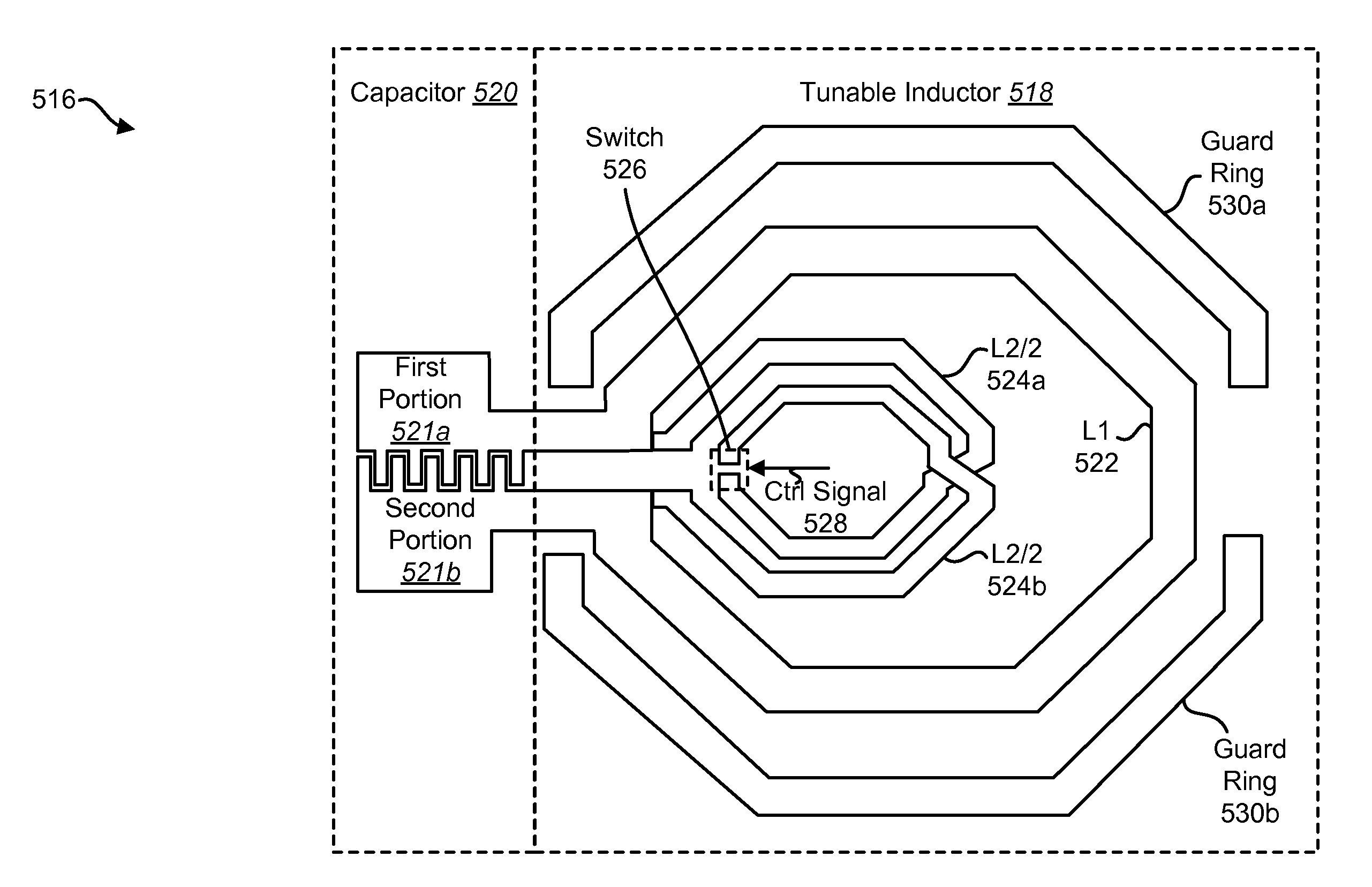

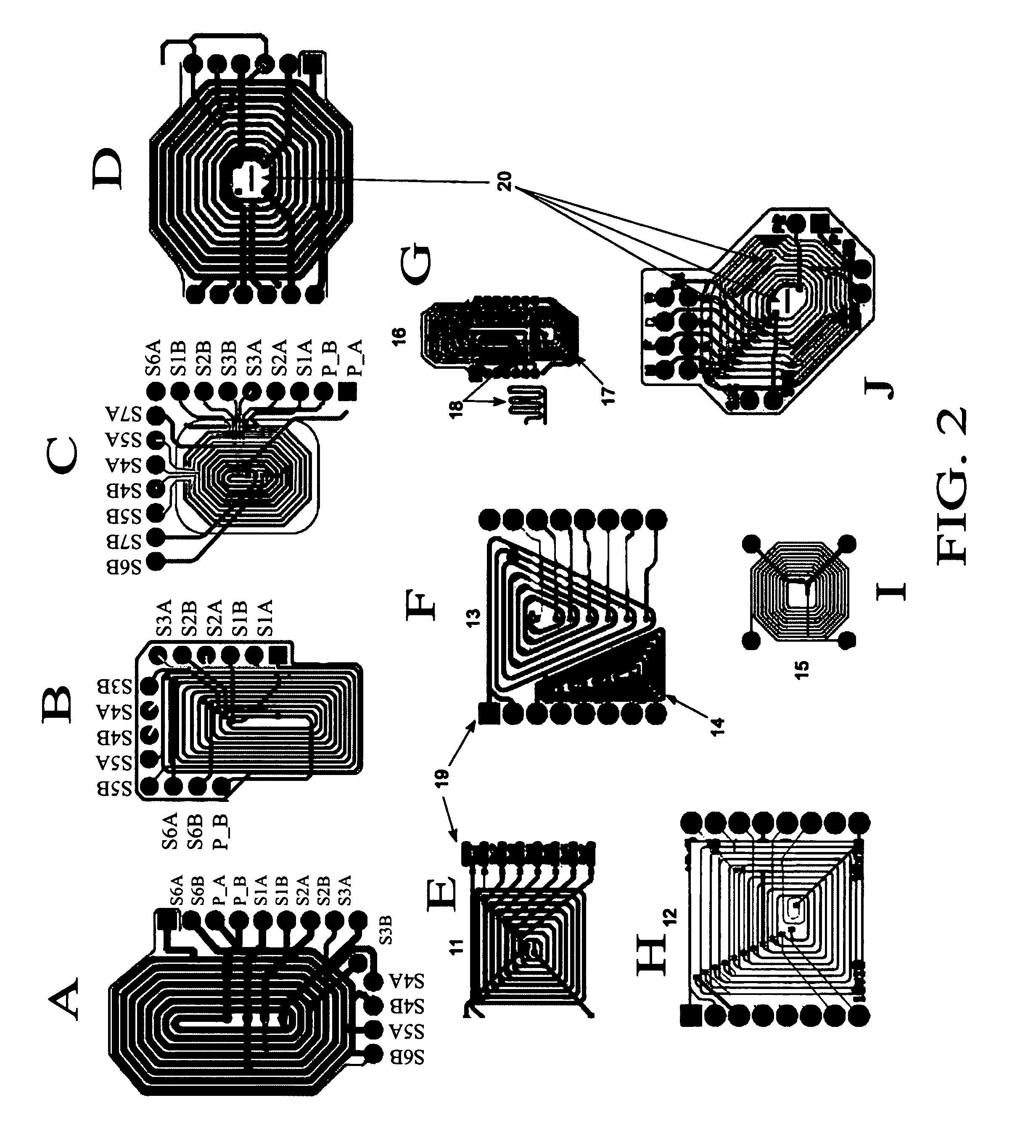

Tunable embedded inductor devices

ActiveUS7884697B2Transformers/inductances coils/windings/connectionsInductances/transformers/magnets manufactureCouplingDielectric substrate

The invention provides tunable embedded high frequency inductor devices. The inductor device comprises a dielectric substrate. A first conductive line is disposed on a first surface of the dielectric substrate. A second conductive line is disposed on a second surface of the dielectric substrate. An interconnection is disposed perforating the dielectric substrate and connecting the first conductive line with the second conductive line. A coupling region is defined between the first and the second conductive lines. A conductive plug connecting the first conductive line and the second line is disposed in the coupling region. Alternatively, an opening is disposed in the first and second conductive lines to tune inductance of the inductor.

Owner:IND TECH RES INST

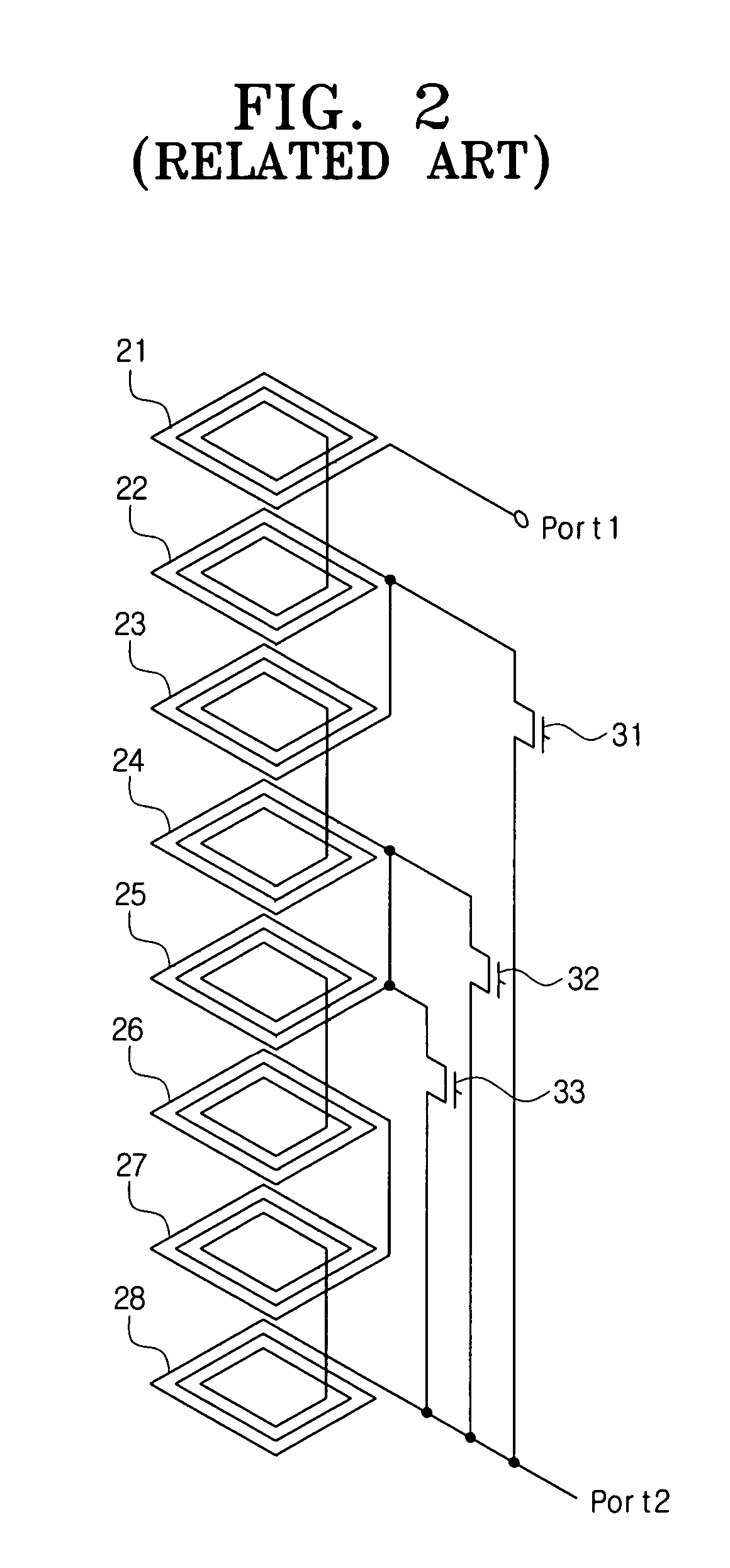

Stacked variable inductor

Disclosed is a stacked variable inductors manufactured by stacking M (M>=2) metal layers on a semiconductor substrate, and provides stacked variable inductors comprising, 1 to N inductors continuously connected in serial, wherein each of said inductors is formed on N (N<=M) metal layers that are different each other; first and second ports each connected to the highest positioned inductor and to the lowest positioned inductor among said 1 to N inductors; and at least one MOSFET, and wherein one terminal of at least one MOSFET is connected to one of the first and second ports, and the other one is connected to one of adjacent terminals connected in serial between 1 to N inductors.

Owner:ELECTRONICS & TELECOMM RES INST

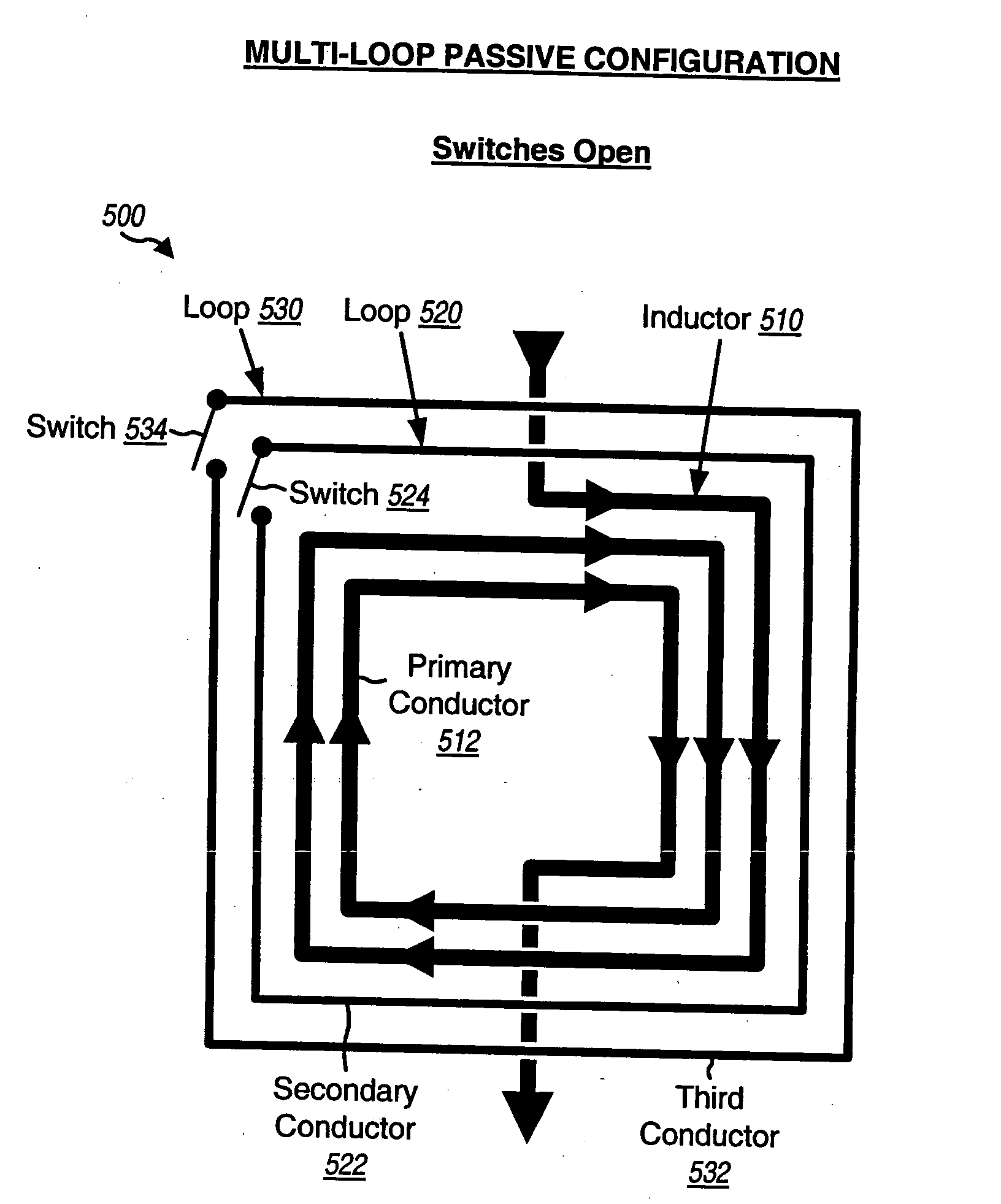

Variable inductor for integrated circuit and printed circuit board

InactiveUS20050068146A1Conveniently fabricatedImprove RF performanceResonant circuit tuningSemiconductor/solid-state device detailsElectrical conductorImpedance matching

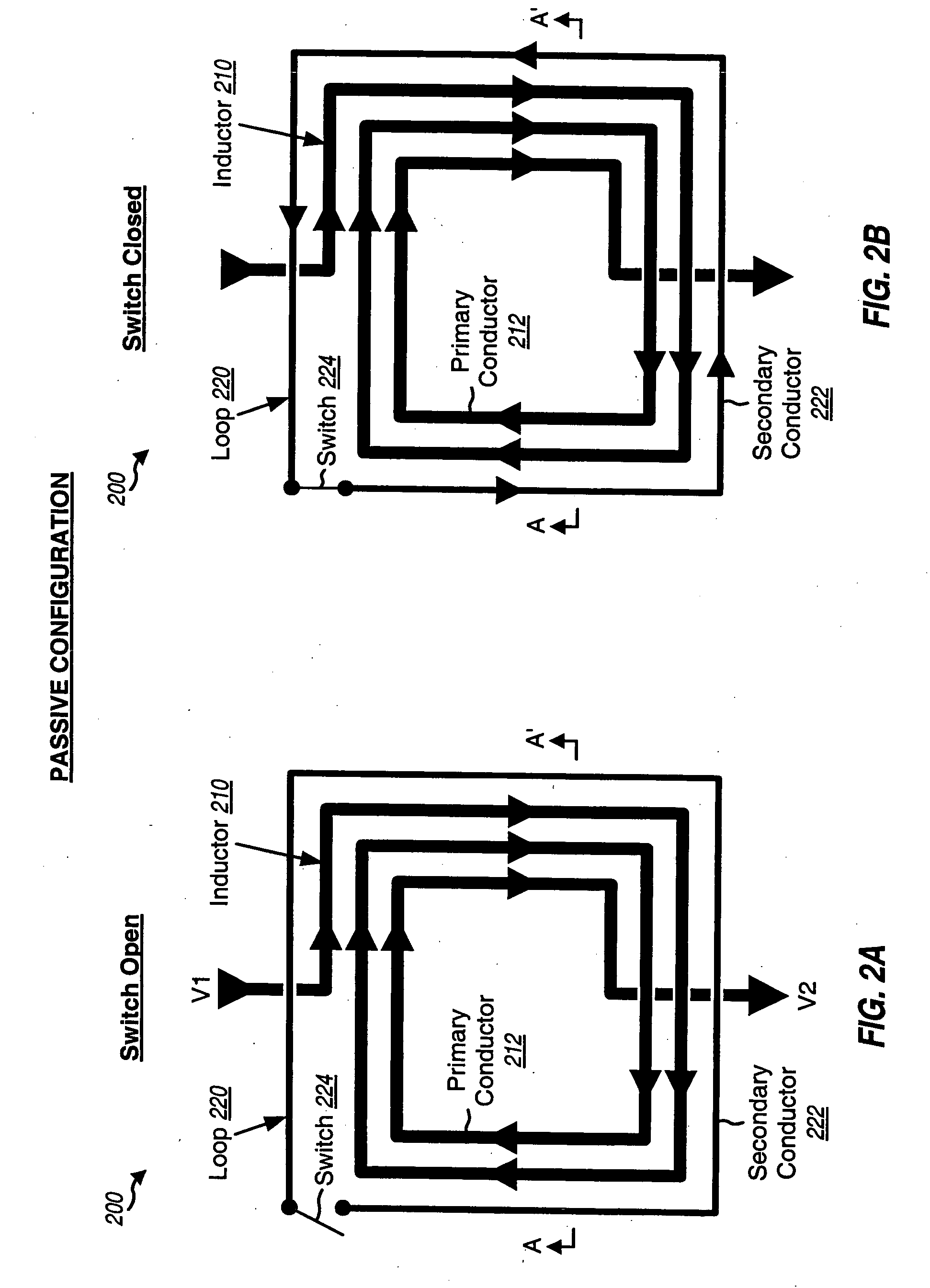

A variable inductor can be formed on an integrated circuit with a primary conductor, a secondary conductor, and a switch. The primary conductor implements an inductor and may be formed in various patterns (e.g., a spiral). The secondary conductor forms a loop in proximity to (e.g., on the outside of) the primary conductor. The switch couples in series with the secondary conductor and opens or closes the loop. The inductance of the inductor is varied by closing and opening the loop with the switch. A current source may also be coupled in series with the secondary conductor and used to control the current flow in the secondary conductor to either increase or decrease the inductance. Multiple loops may be formed to change the inductance in more than two discrete steps. The variable inductor may be used for various applications such as filters, VCOs, and impedance matching networks.

Owner:QUALCOMM INC

Method and apparatus for use in digitally tuning a capacitor in an integrated circuit device

ActiveUS9024700B2Easy to controlHigh Power Handling CapabilityMultiple-port networksImpedence matching networksCapacitanceLeast significant bit

Owner:PSEMI CORP

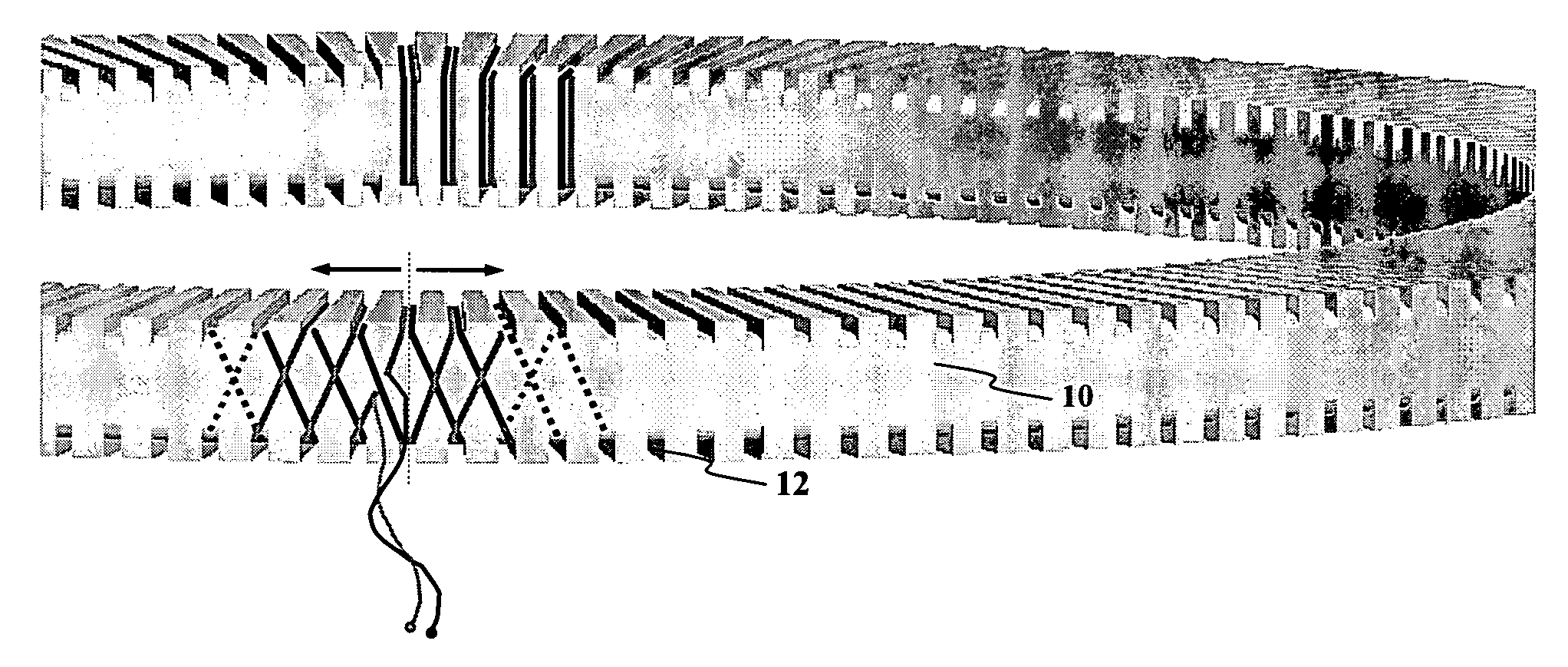

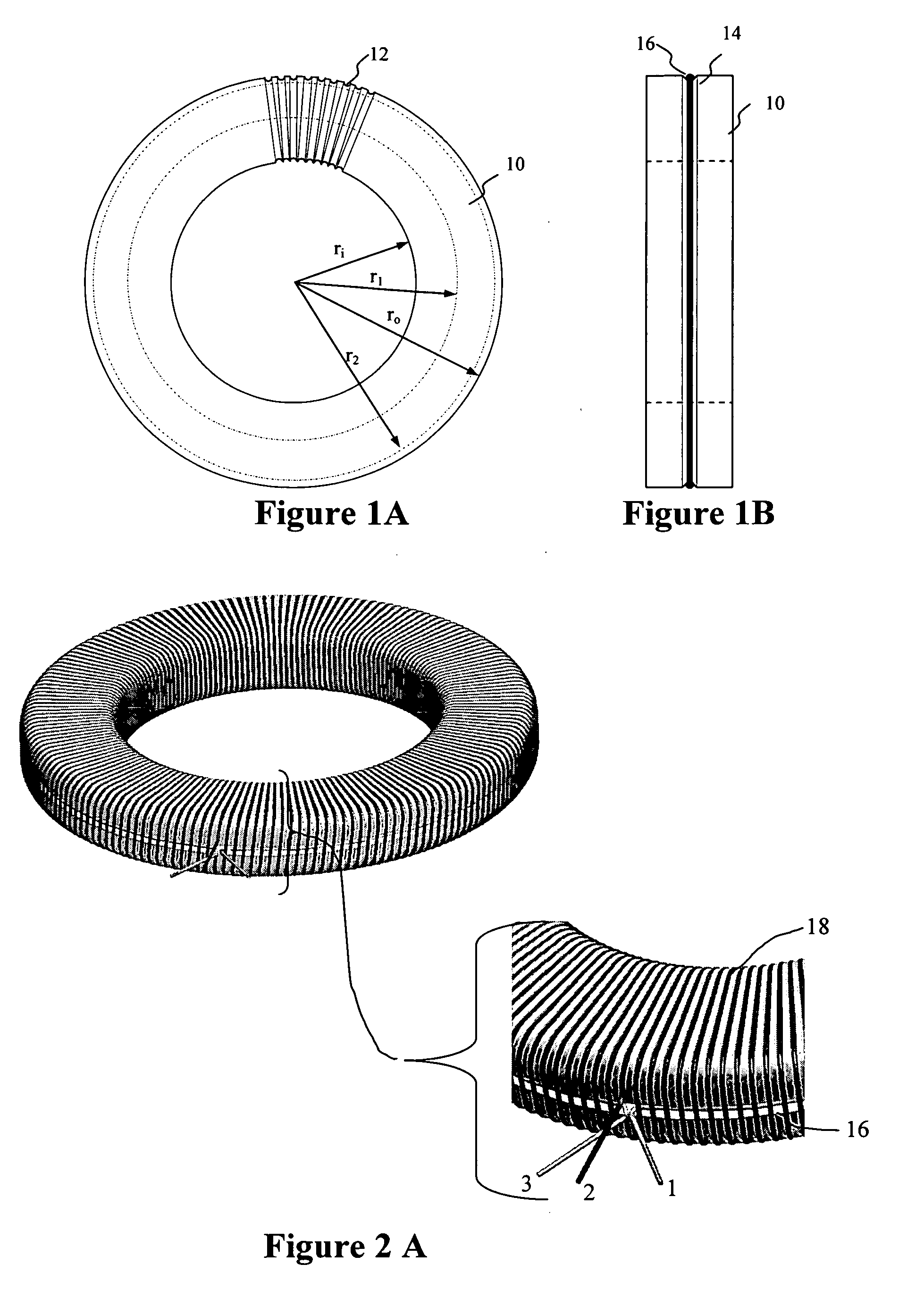

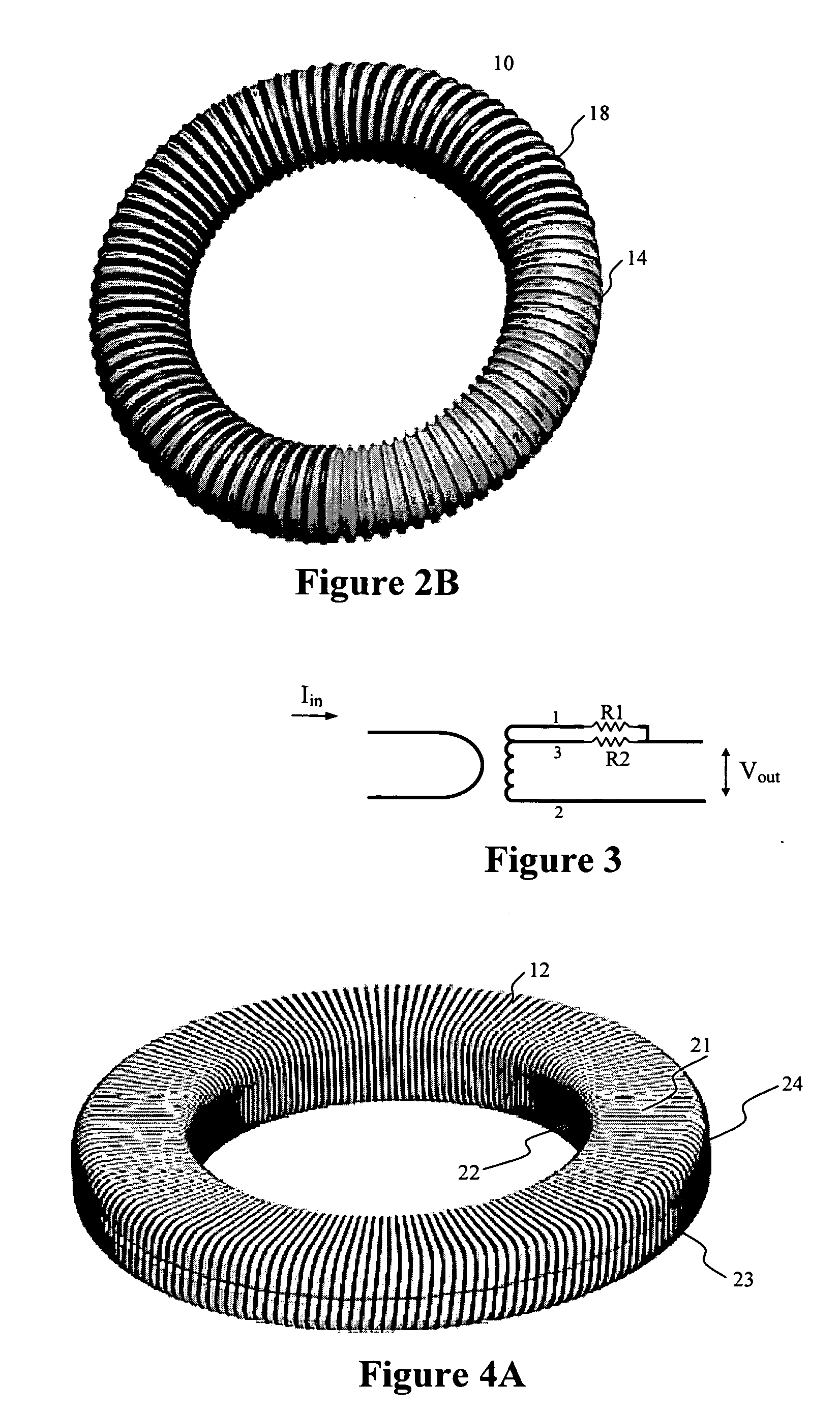

Precision Rogowski coil and method for manufacturing same

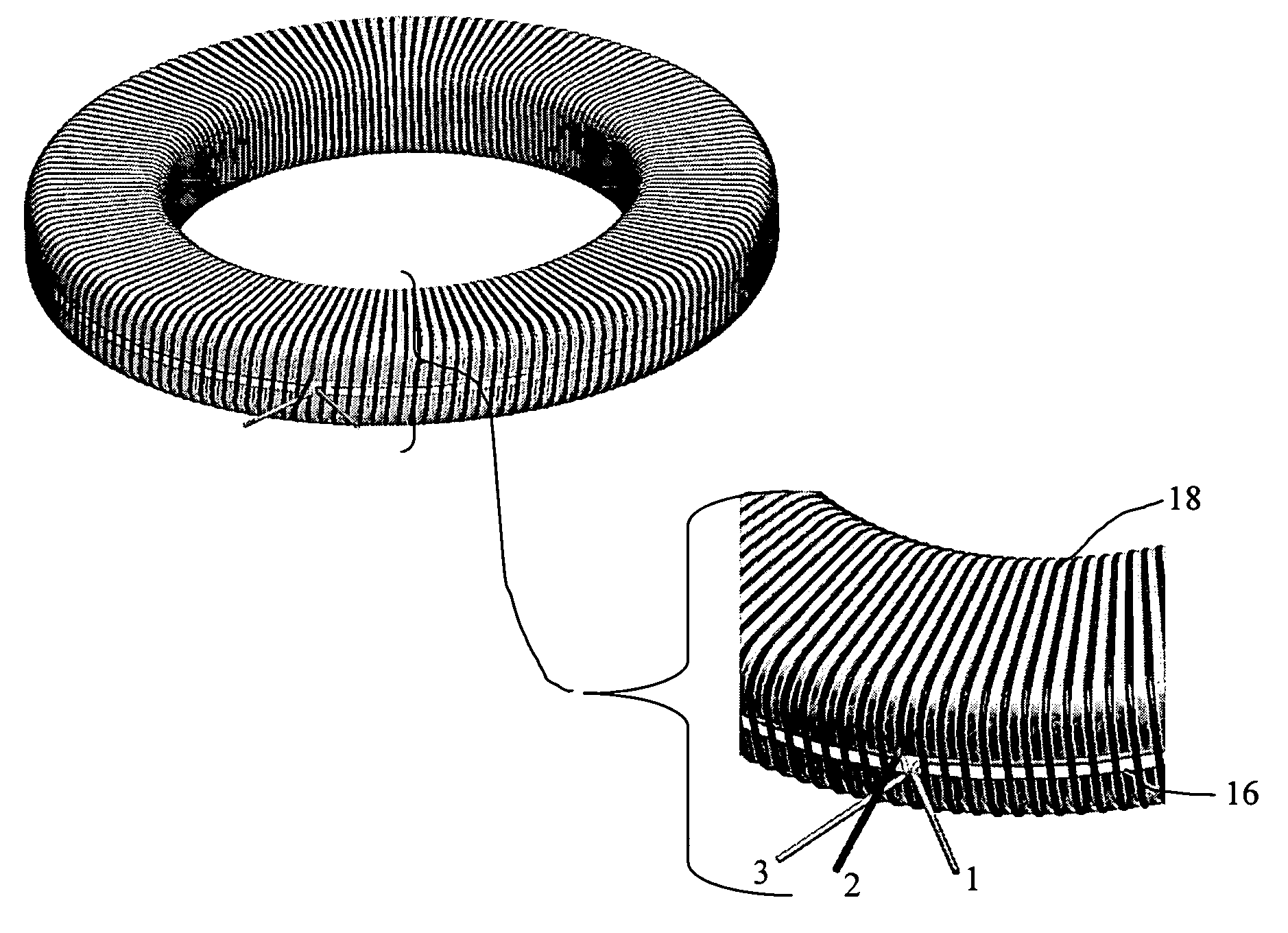

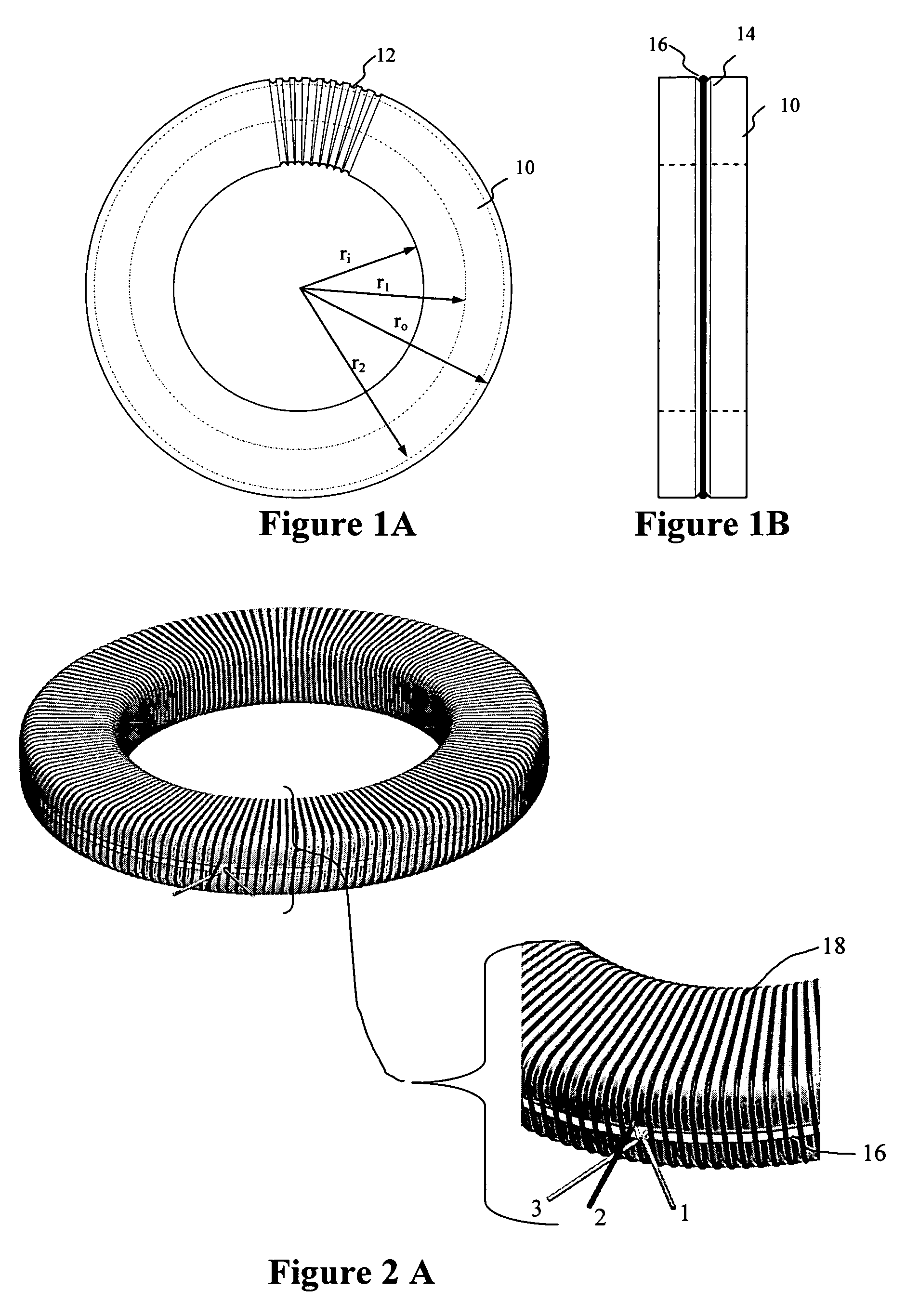

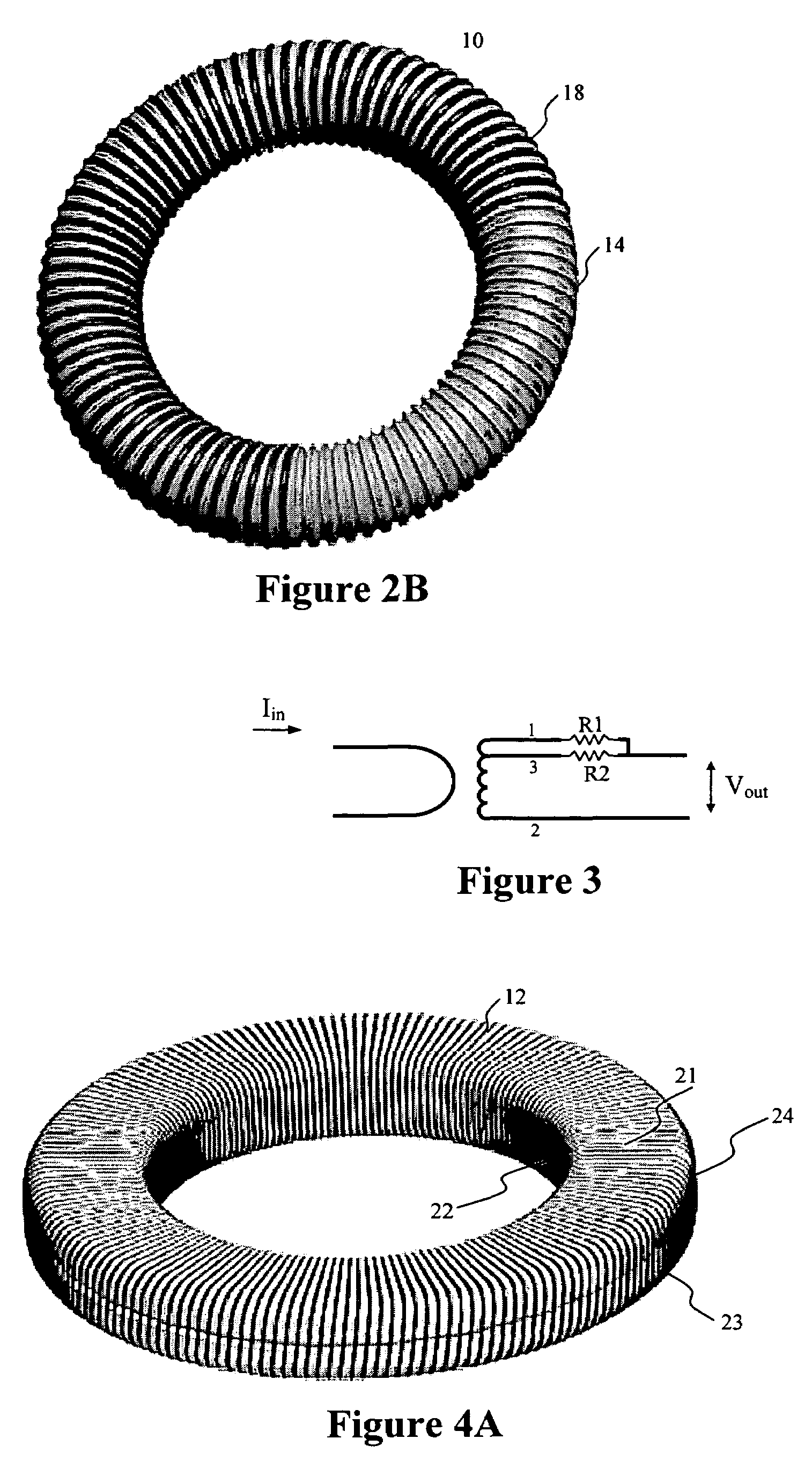

InactiveUS7227441B2Transformers/inductances coils/windings/connectionsElectrical measurementsThermoplasticElectrical resistance and conductance

An improved Rogowski coil is formed on a toroidal core made of a thermoplastic or other moldable material, the core having a preferably continuous groove or grooves extending around the core. The grooves correspond in size to magnet wire which registers within the grooves, thus controlling the specific location of the wires. The grooving may be helical. A return loop can be provided for return path cancellation, or a reverse winding can be added in a direction opposite to the direction of advancement of the main coil. In using the return loop, a resistive network can be added to improve the cancellation of the return path due to the effect of geometries. In addition, it can compensate for thermal and other variations.

Owner:SCHWEITZER ENGINEERING LABORATORIES

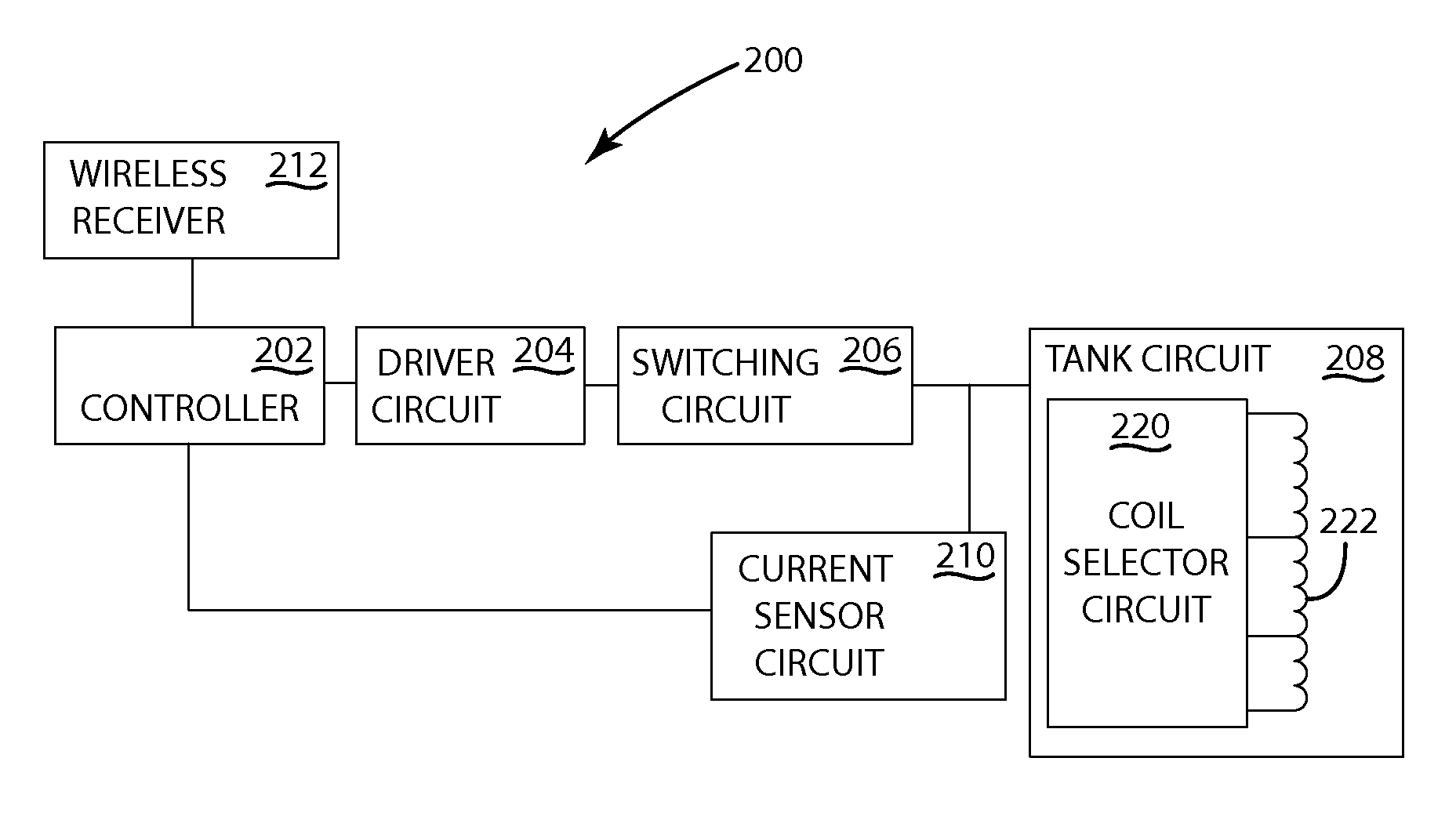

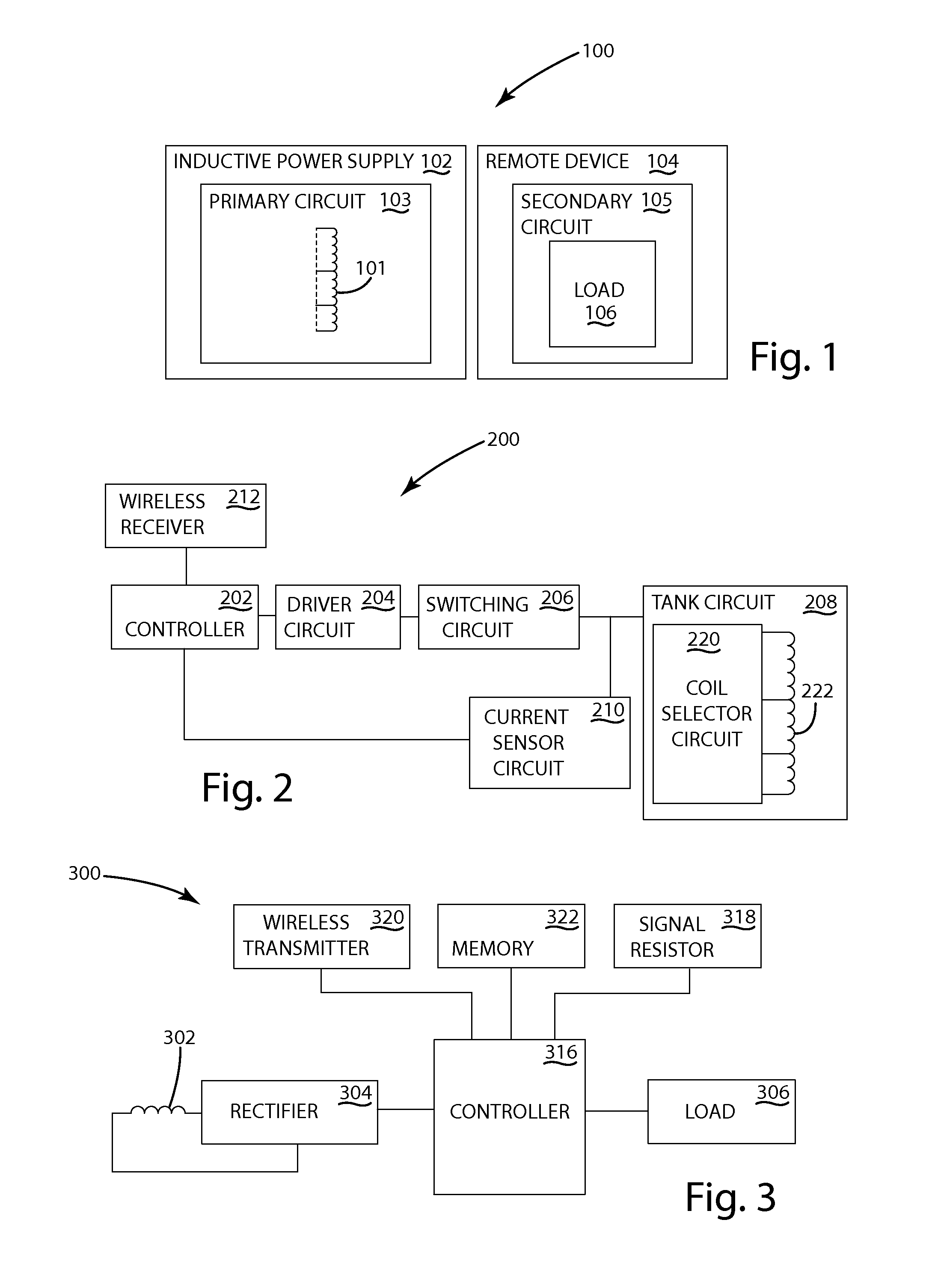

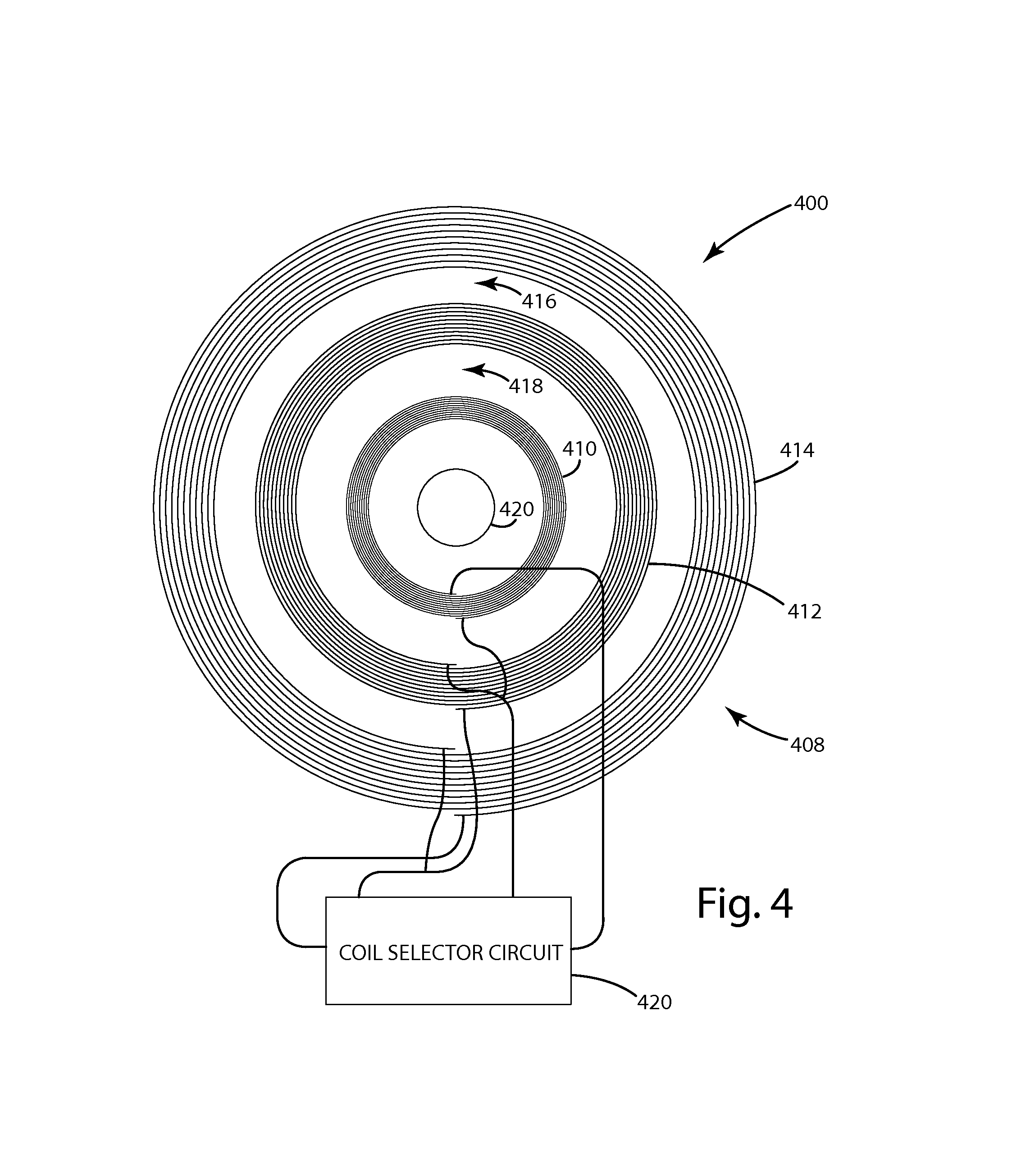

Inductive power supply system with multiple coil primary

ActiveUS8338990B2Save energyIncrease powerTransformersCircuit arrangementsCommunications systemEngineering

An inductive power supply including multiple tank circuits and a controller for selecting at least one of the tank circuits in order to wirelessly transfer power based on received power demand information. In addition, a magnet may be used to align multiple remote devices with the inductive power supply. In one embodiment, different communication systems are employed depending on which coil is being used to transfer wireless power.

Owner:PHILIPS IP VENTURES BV

Integrated transformer

InactiveUS6856226B2Transformers/inductances casingsSemiconductor/solid-state device detailsElectrical conductorSemiconductor materials

A transformer comprises a substrate comprising a semiconductor material, a first conductor over the substrate, a second conductor over the substrate, and a magnetic layer over the substrate. The first conductor defines a generally spiral-shaped signal path having at least one turn. The second conductor defines a generally spiral-shaped signal path having at least one turn.

Owner:INTEL CORP

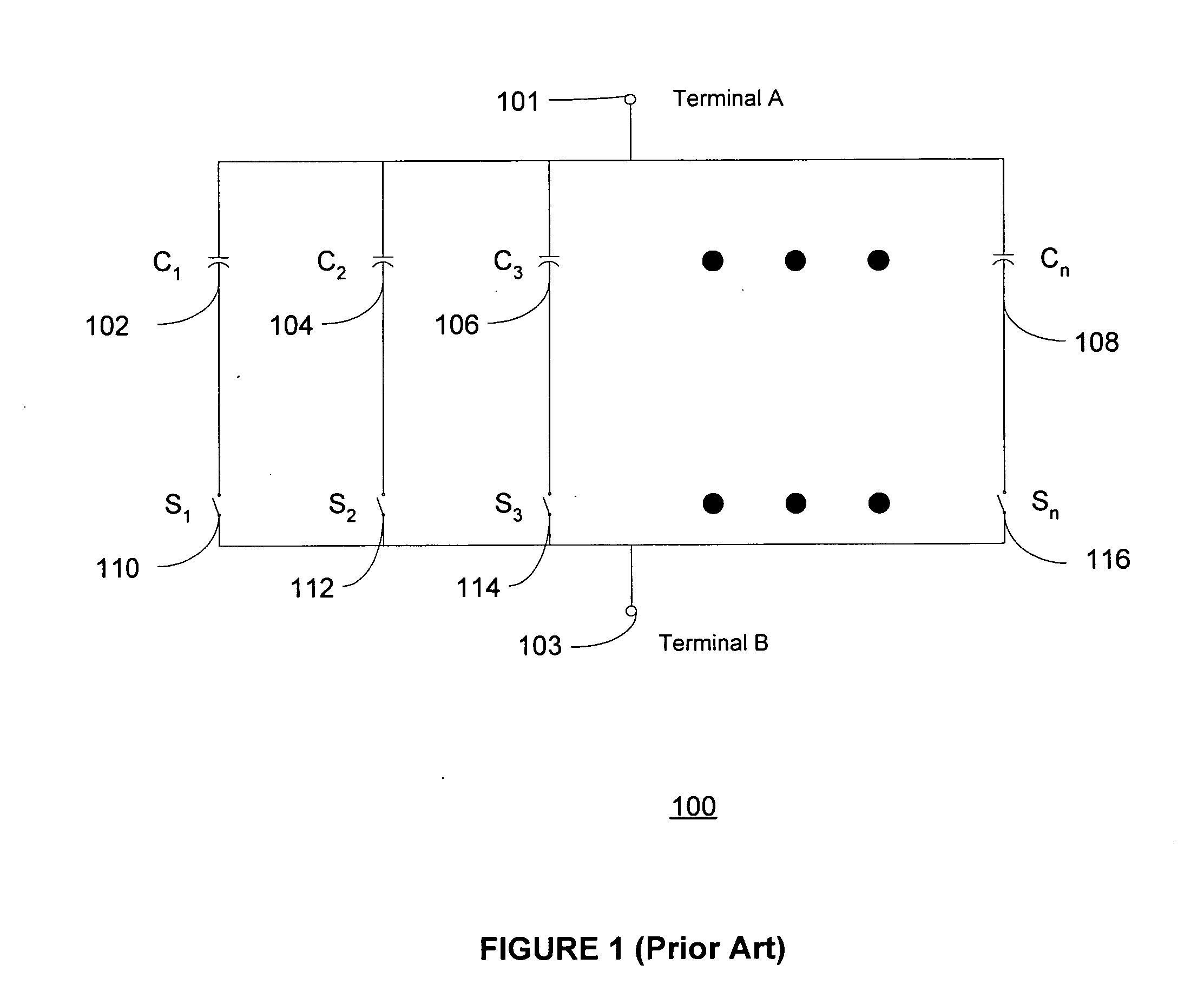

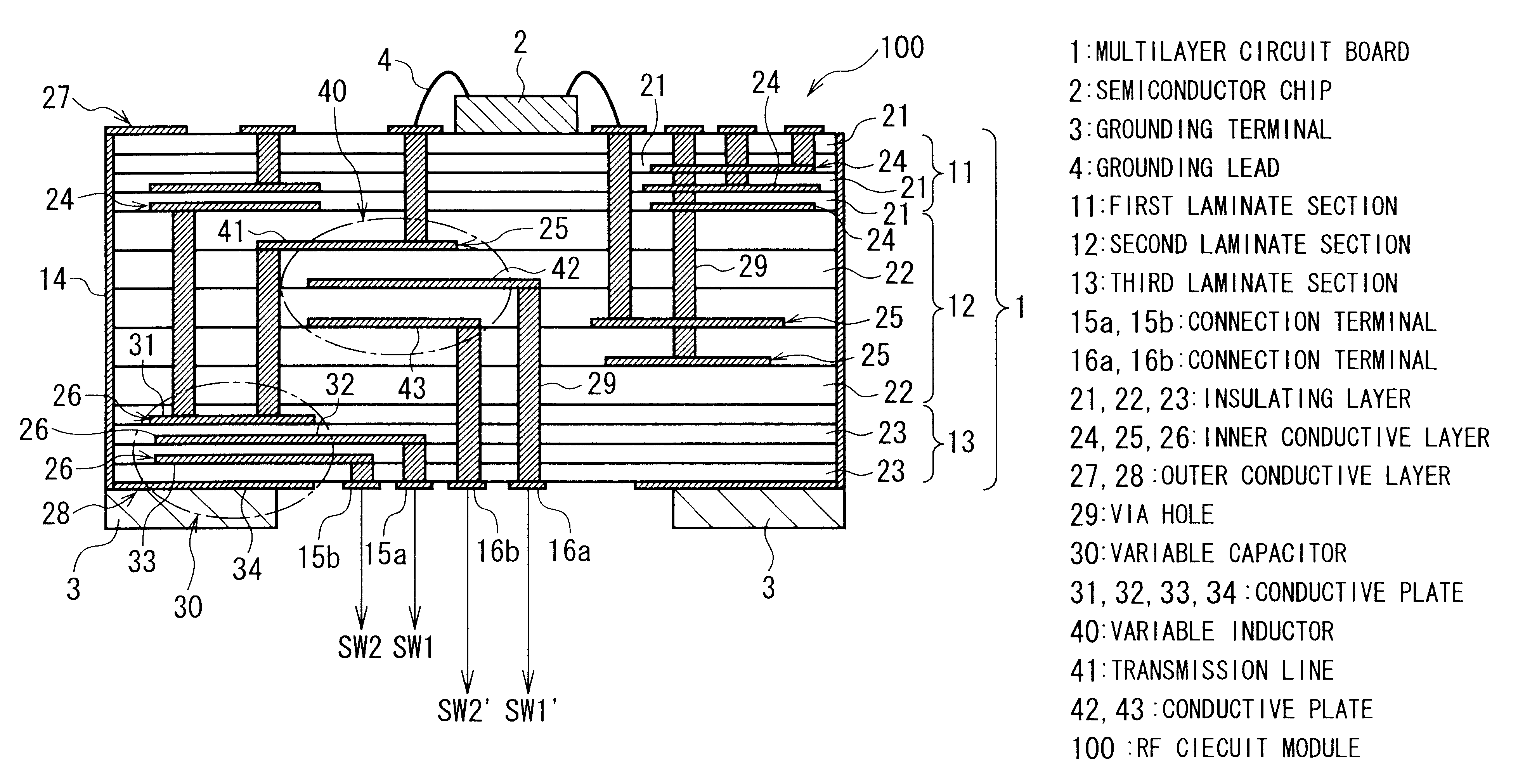

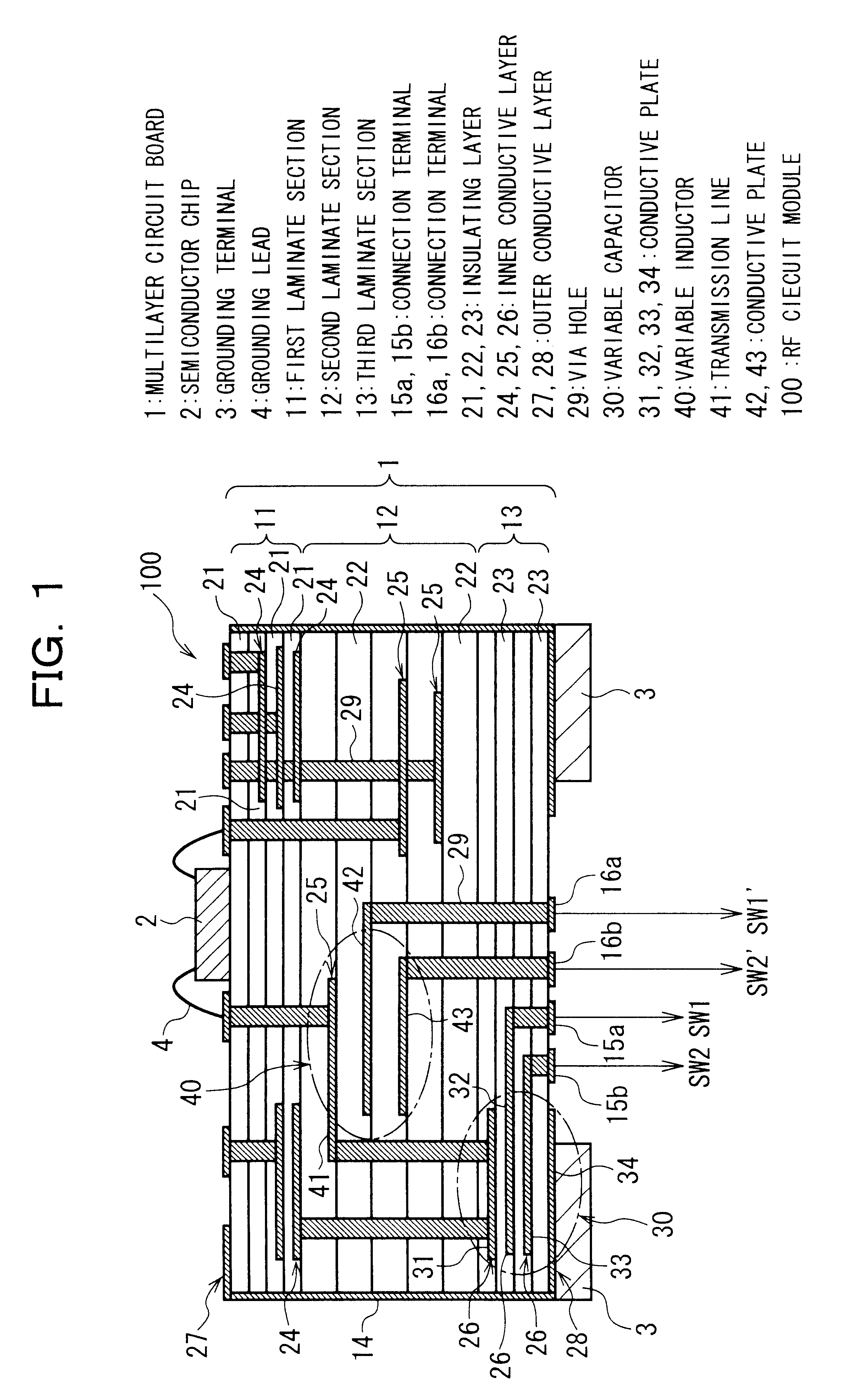

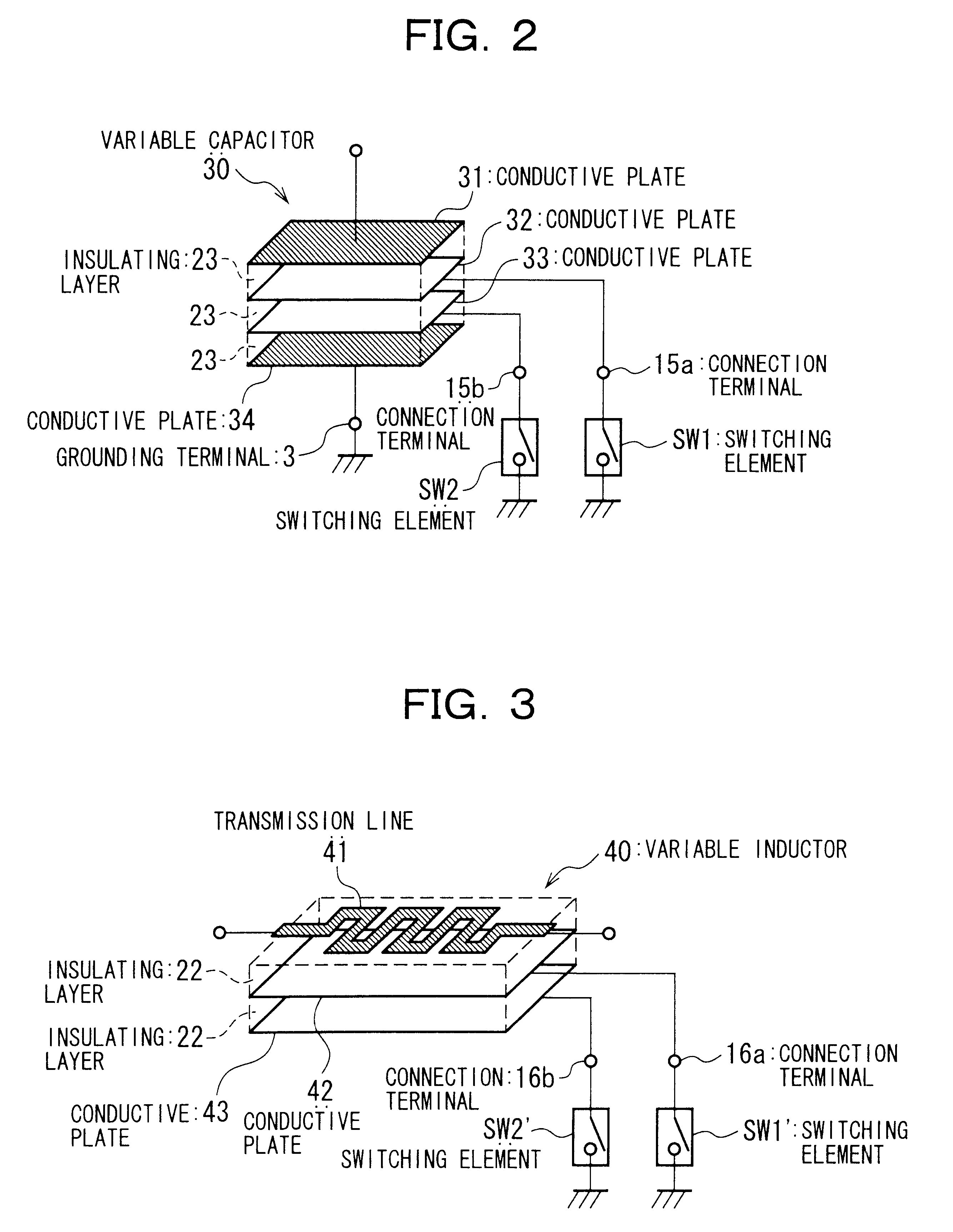

Variable capacitor and a variable inductor

InactiveUS6556416B2Compact implementationEasy to adjustMultiple-port networksHigh frequency amplifiersEngineeringInductor

A variable capacitor is formed by a multilayer circuit board having a plurality of dielectric layers; a first conductive plate, provided within the multilayer circuit board, for serving as one electrode of the variable capacitor; a second conductive plate, provided within the multilayer circuit board, for serving as the other electrode of the variable capacitor; a plurality of third conductive plates provided between the first conductive plate and the second conductive plate; and a plurality of switching means provided for grounding the third conductive plates selectively.

Owner:NEC CORP

Precision rogowski coil and method for manufacturing same

InactiveUS20060176140A1The location is limitedTransformers/inductances coils/windings/connectionsElectrical measurementsThermoplasticElectrical resistance and conductance

An improved Rogowski coil is formed on a toroidal core made of a thermoplastic or other moldable material, the core having a preferably continuous groove or grooves extending around the core. The grooves correspond in size to magnet wire which registers within the grooves, thus controlling the specific location of the wires. The grooving may be helical. A return loop can be provided for return path cancellation, or a reverse winding can be added in a direction opposite to the direction of advancement of the main coil. In using the return loop, a resistive network can be added to improve the cancellation of the return path due to the effect of geometries. In addition, it can compensate for thermal and other variations.

Owner:SCHWEITZER ENGINEERING LABORATORIES

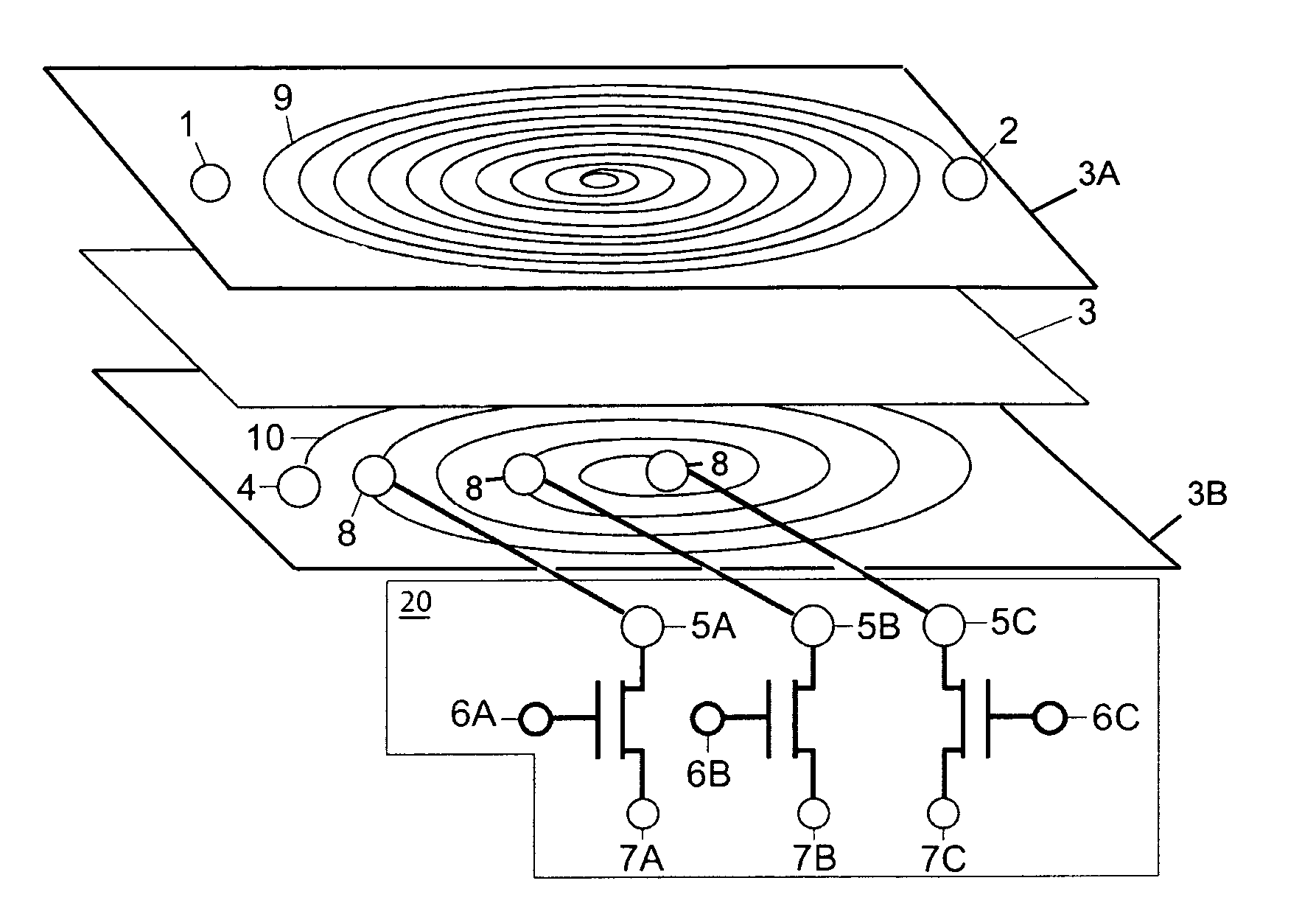

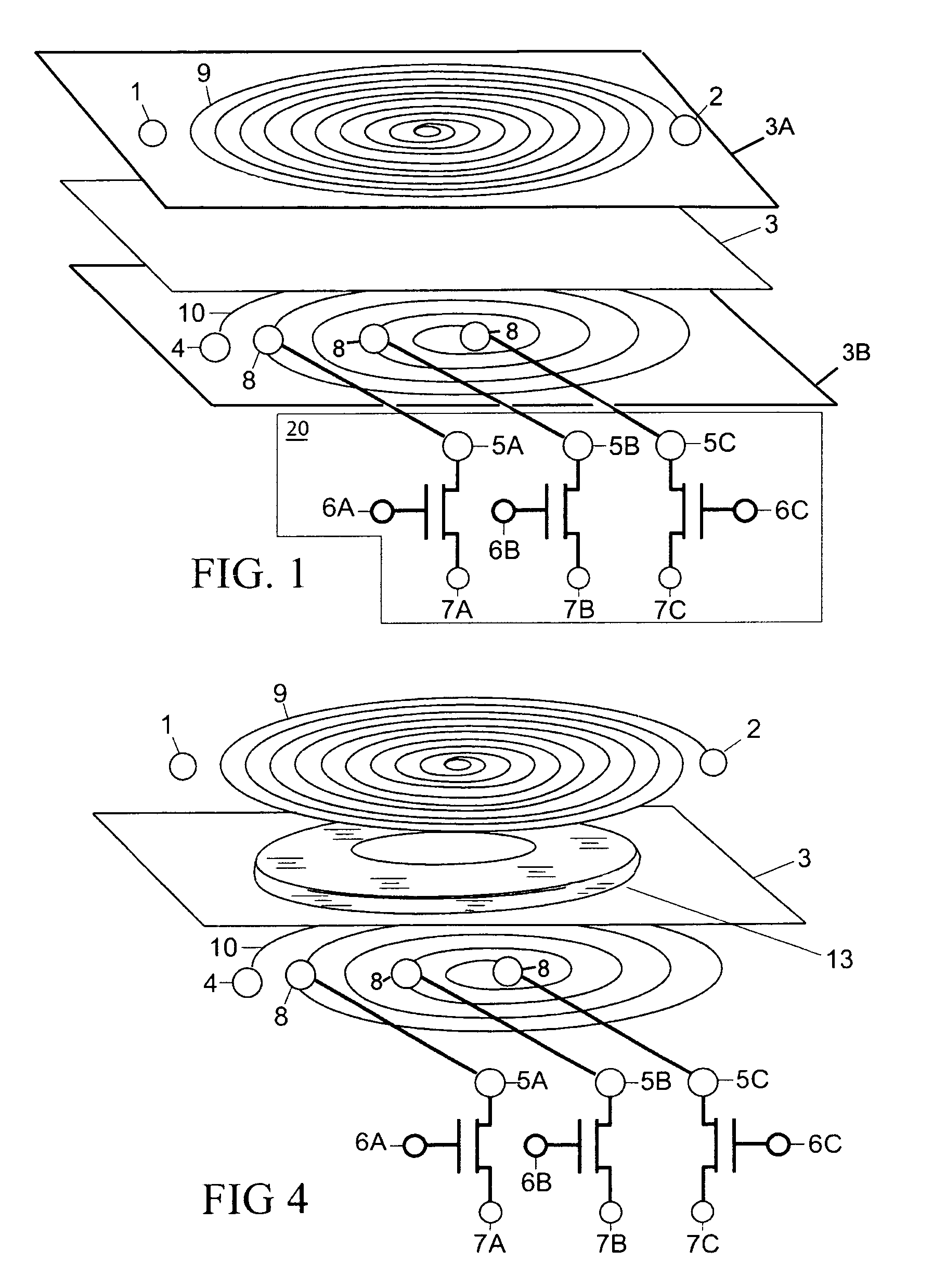

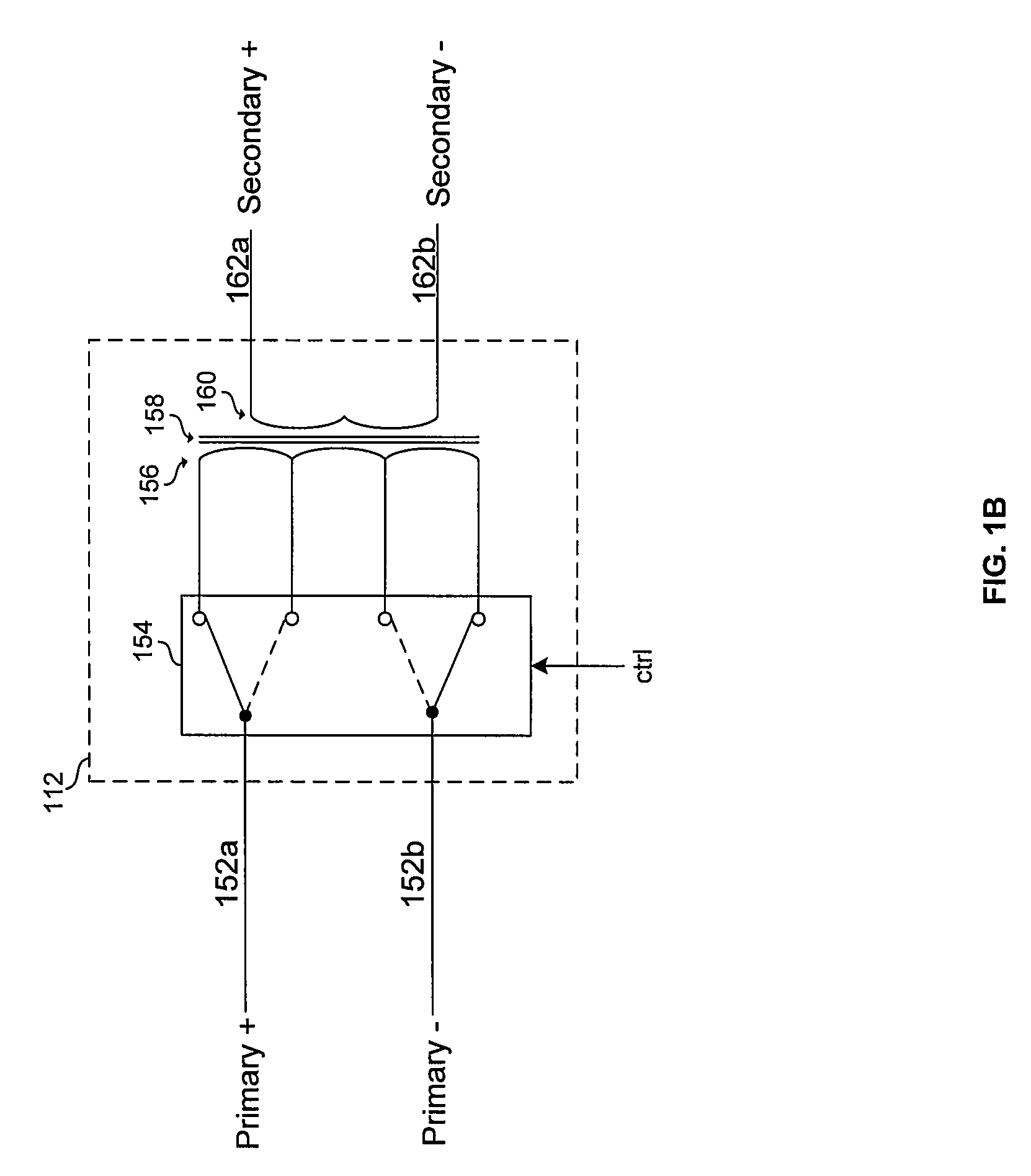

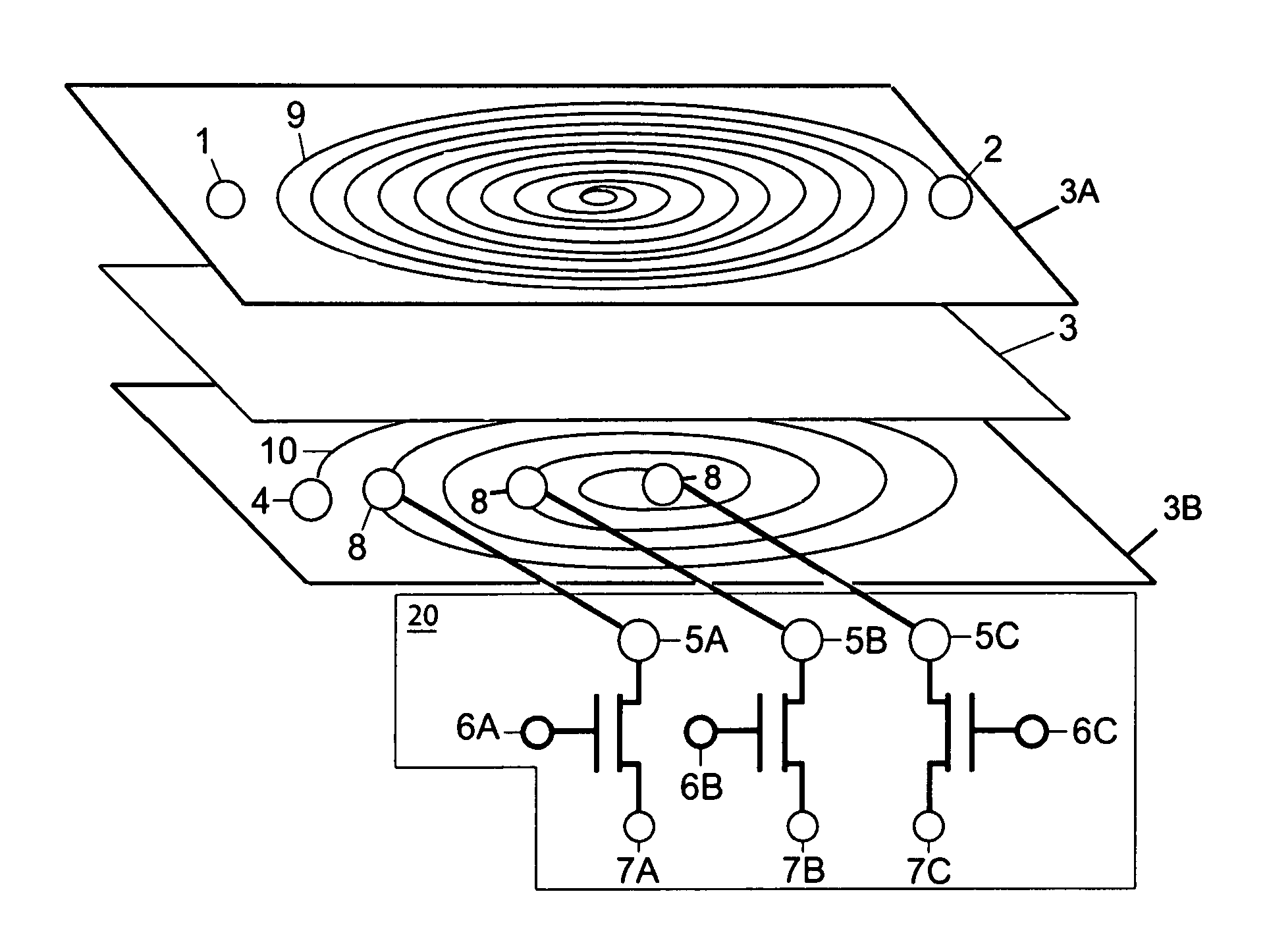

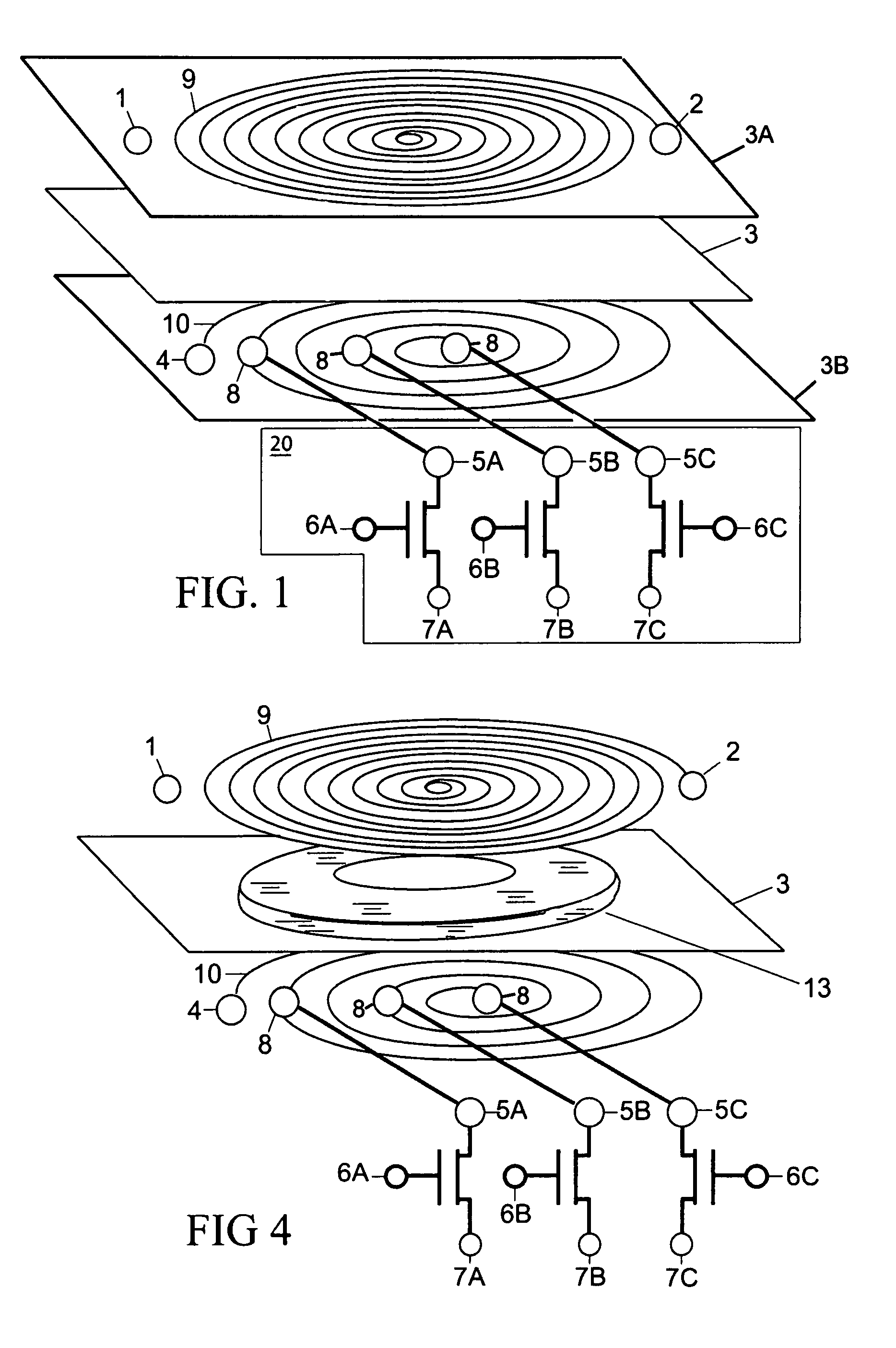

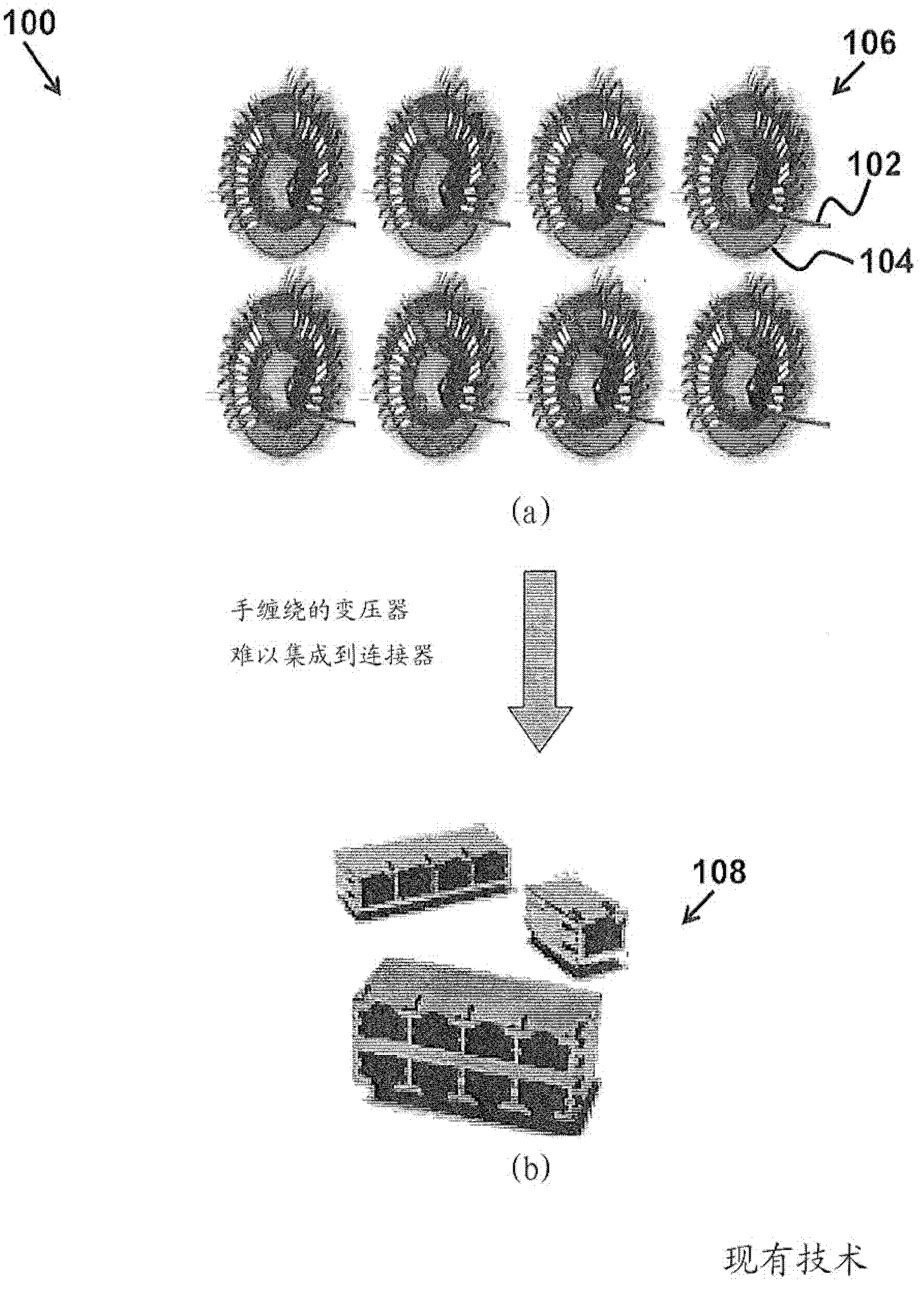

Programmable microtransformer

InactiveUS7298238B1Good suitReduce and eliminate magnetic core materialTransformers/inductances coils/windings/connectionsElectronic switchingCMOSConductor Coil

A programmable transformer incorporating windings embedded in a thin film substrate. The windings are flat wire traces embedded into the substrate, primary on one side and secondary on the other. The secondary windings may be planar or different coils spatially arrayed throughout a thickness of the substrate. The secondary winding may include multiple tap points, effectively providing multiple secondary coils referenced to the single primary coil. Each tap point is bridged to a field effect or CMOS transistor path by which a digital controls permit dynamic adjustment of the turns ratio. The final secondary output depends on the activated transistor paths. Multiple secondary outputs from a single secondary coil and a digitally programmable turns ratio are available aspects.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

Inductive component

InactiveUS20050052272A1Add series resistanceIncrease resistanceSemiconductor/solid-state device detailsTransformers/inductances coils/windings/connectionsElectrical conductorEngineering

Inductive component including precisely one coil having a total inductance and a plurality of spiral turns which are realized in the form of conductor tracks having a conductor track width that tapers toward the center of the plurality of spiral turns, two tapping contacts at the coil, and a control circuit which is connected between the two tapping contacts and alters effective inductance of the coil.

Owner:INFINEON TECH AG

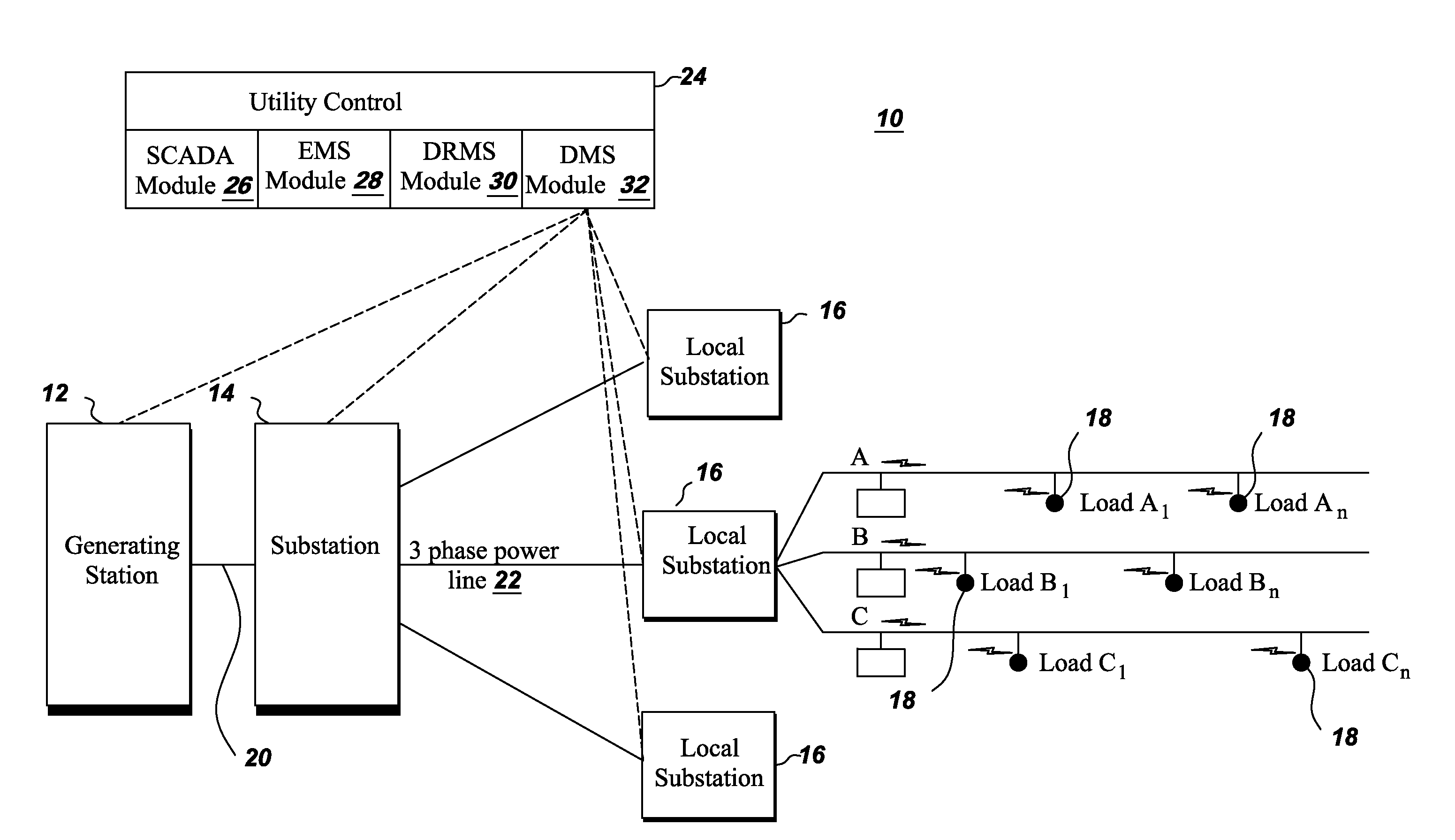

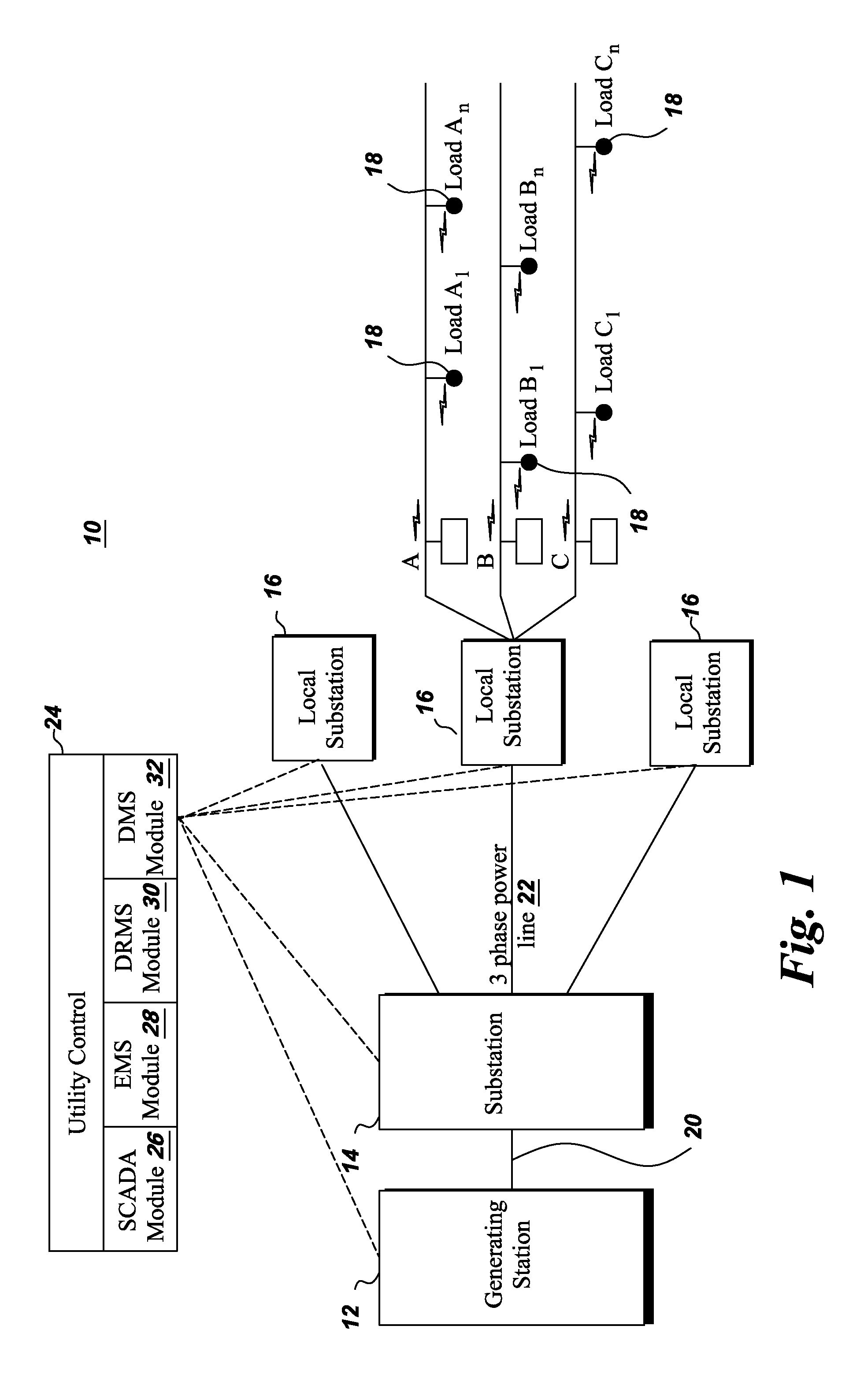

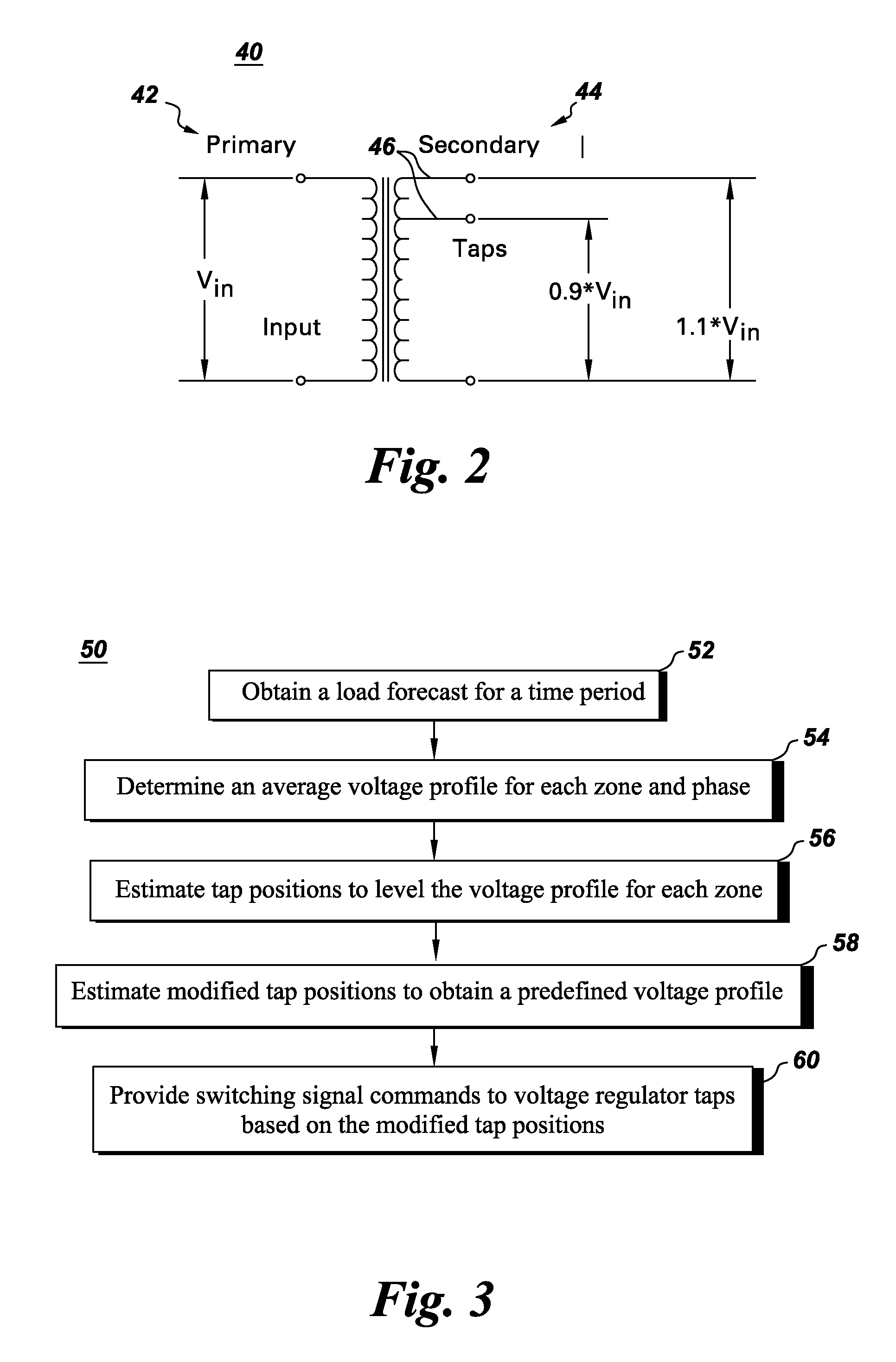

System and method for operating a tap changer

A method of operating a tap changer of a transformer or a voltage regulator in a power grid includes obtaining a load forecast for a time period. An average voltage profile is determined for the time period based on the load forecast. The method further includes estimating tap positions of the tap changer for leveling the average voltage profile during the time period. Switching signal commands are provided to the tap changer based on the estimated tap positions.

Owner:GENERAL ELECTRIC CO

On-chip integrated voltage-controlled variable inductor, methods of making and tuning such variable inductors, and design structures integrating such variable inductors

InactiveUS20090189725A1Multiple-port networksTransformers/inductances coils/windings/connectionsInductorVoltage control

On-chip integrated variable inductors, methods of making and tuning an on-chip integrated variable inductor, and design structures embodying a circuit containing the on-chip integrated variable inductor. The inductor generally includes a signal line configured to carry an electrical signal, a ground line positioned in proximity to the signal line, and at least one control unit electrically coupled with the ground line. The at least one control unit is configured to open and close switch a current path connecting the ground line with a ground potential so as to change an inductance of the signal line.

Owner:GLOBALFOUNDRIES INC

Stacked variable inductor

ActiveUS6992366B2Reduce areaEffective characterizationSemiconductor/solid-state device detailsSolid-state devicesMOSFETInductor

Disclosed is a stacked variable inductors manufactured by stacking M (M≧2) metal layers on a semiconductor substrate, and provides stacked variable inductors comprising, 1 to N inductors continuously connected in serial, wherein each of said inductors is formed on N (N≦M) metal layers that are different each other; first and second ports each connected to the highest positioned inductor and to the lowest positioned inductor among said 1 to N inductors; and at least one MOSFET, and wherein one terminal of at least one MOSFET is connected to one of the first and second ports, and the other one is connected to one of adjacent terminals connected in serial between 1 to N inductors.

Owner:ELECTRONICS & TELECOMM RES INST

Variable inductor

InactiveUS20080129434A1Reduce disadvantagesVariable inductancesTransformers/inductances detailsInductorInductance

The present invention is directed at an inductor which is capable of providing a variable inductance. The variable inductor is typically mounted / stored on an integrated circuit chip to provide continuous or multiple variable inductor values for wireless applications and the like.

Owner:SIRIFIC WIRELESS CORP

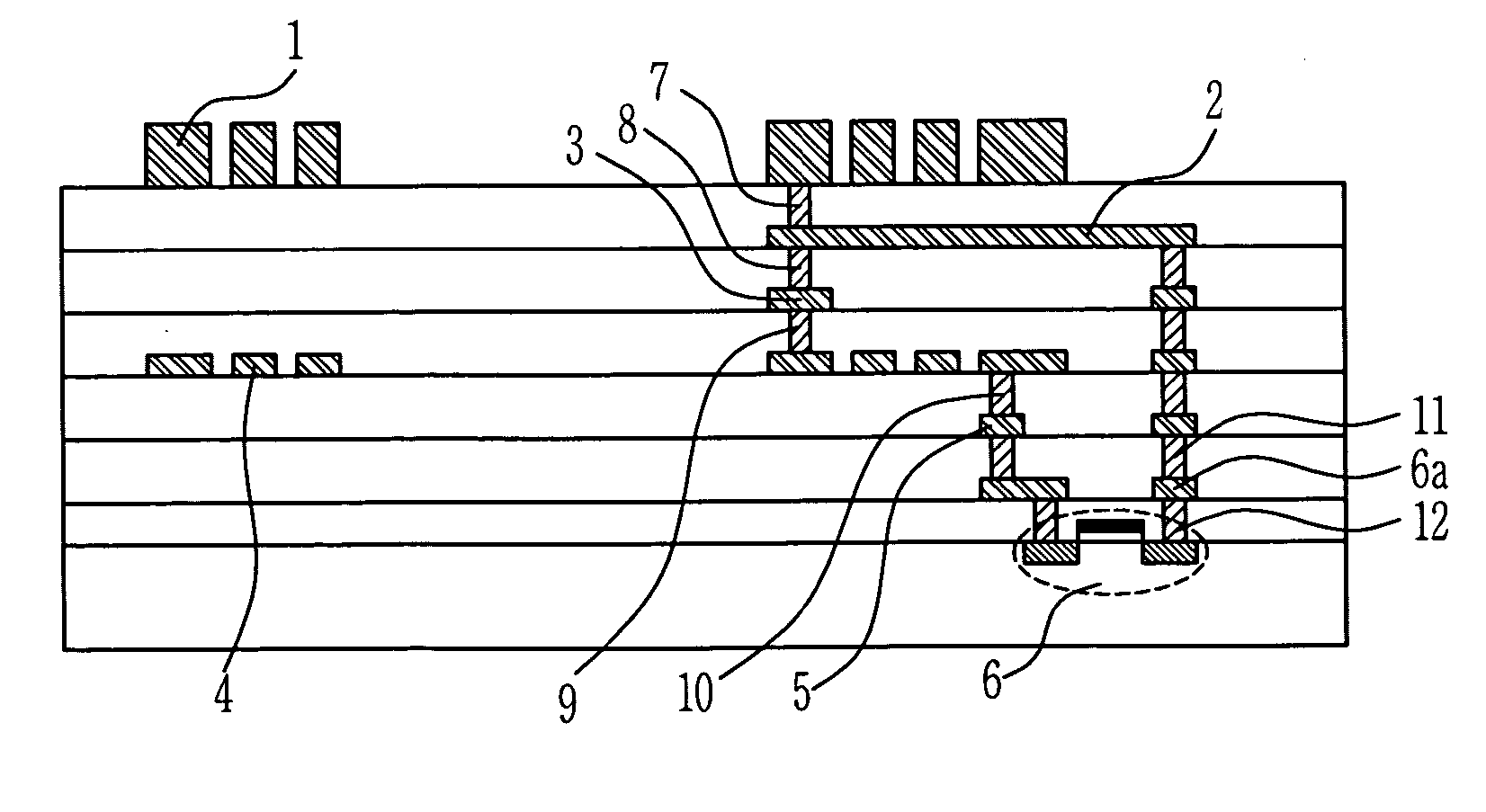

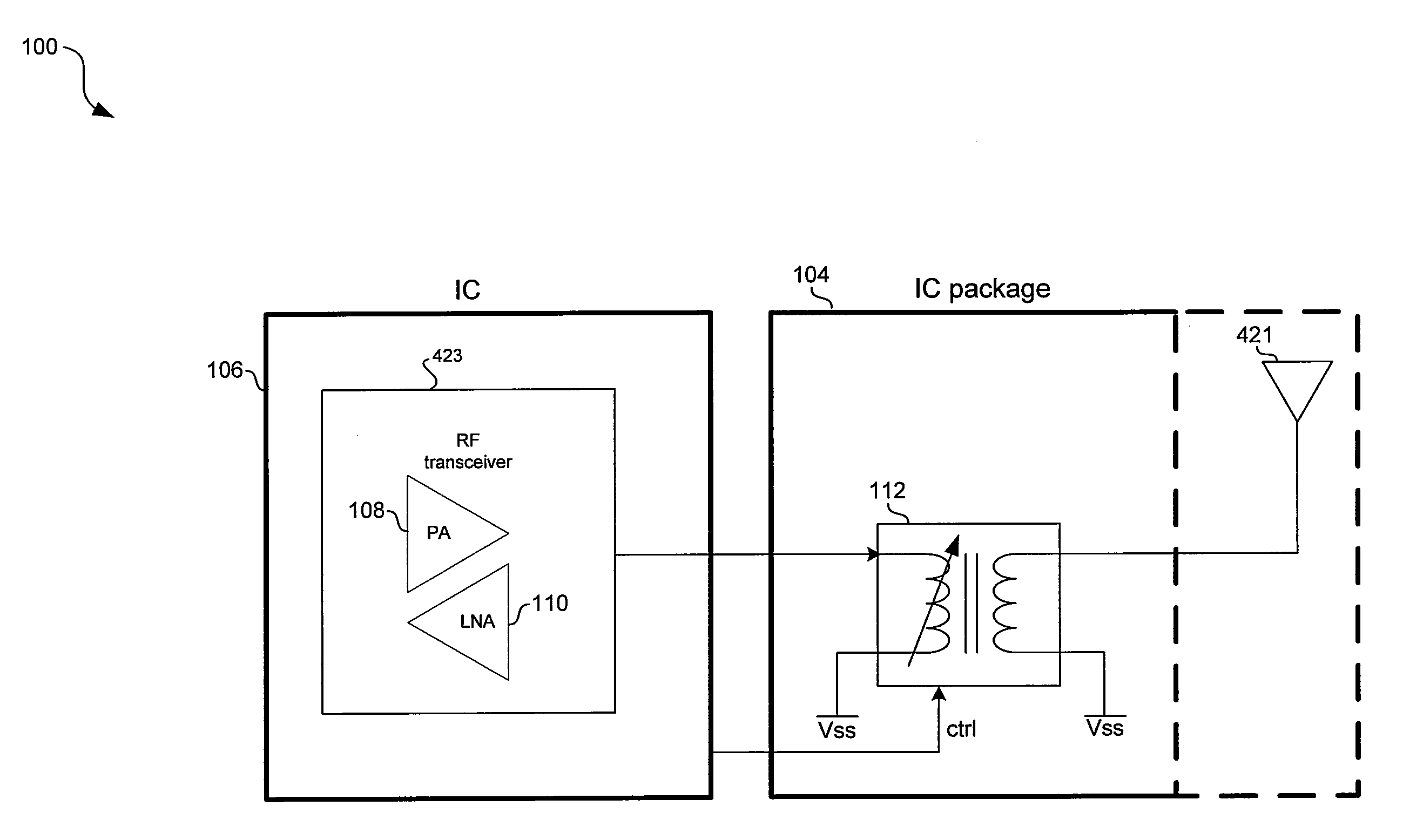

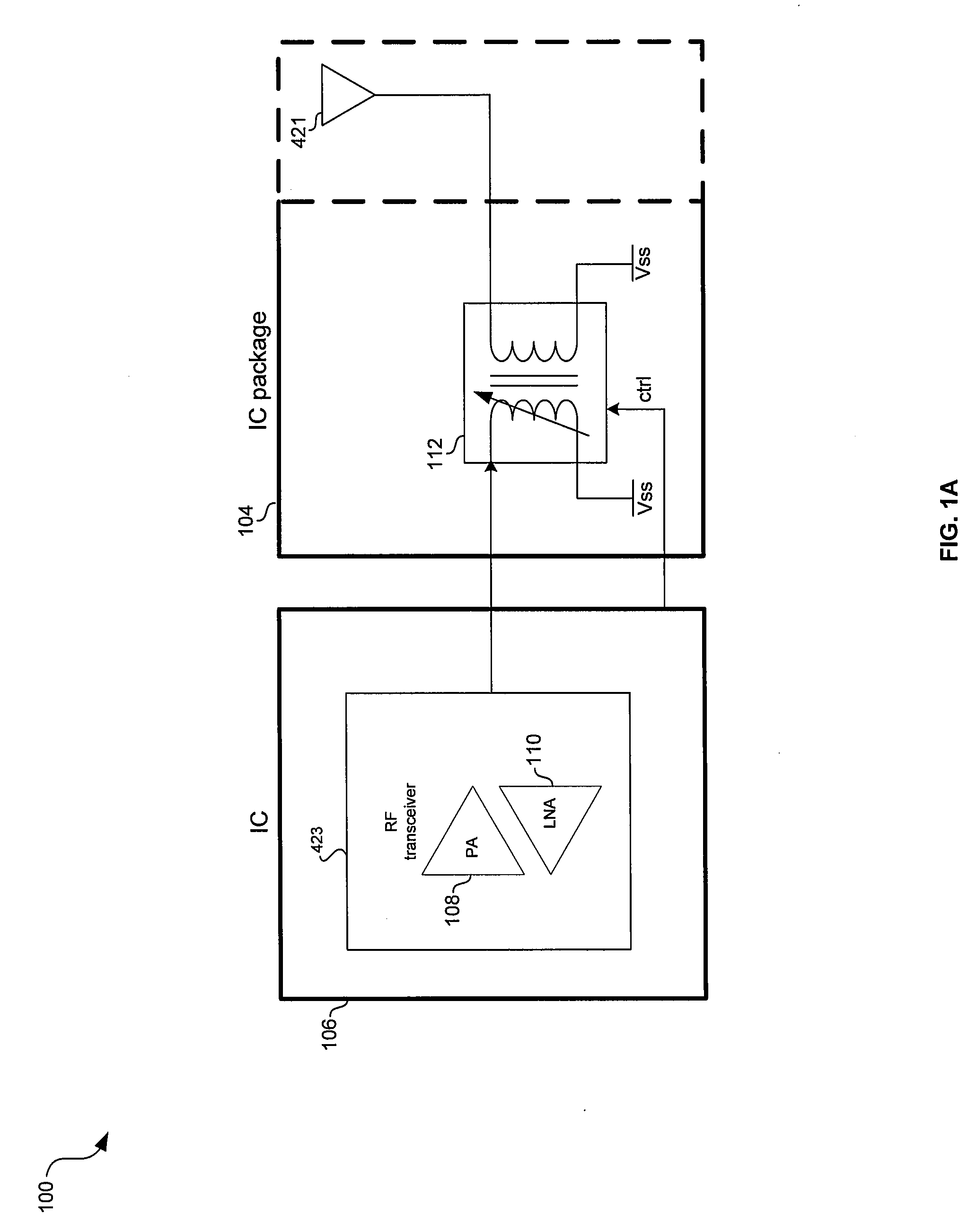

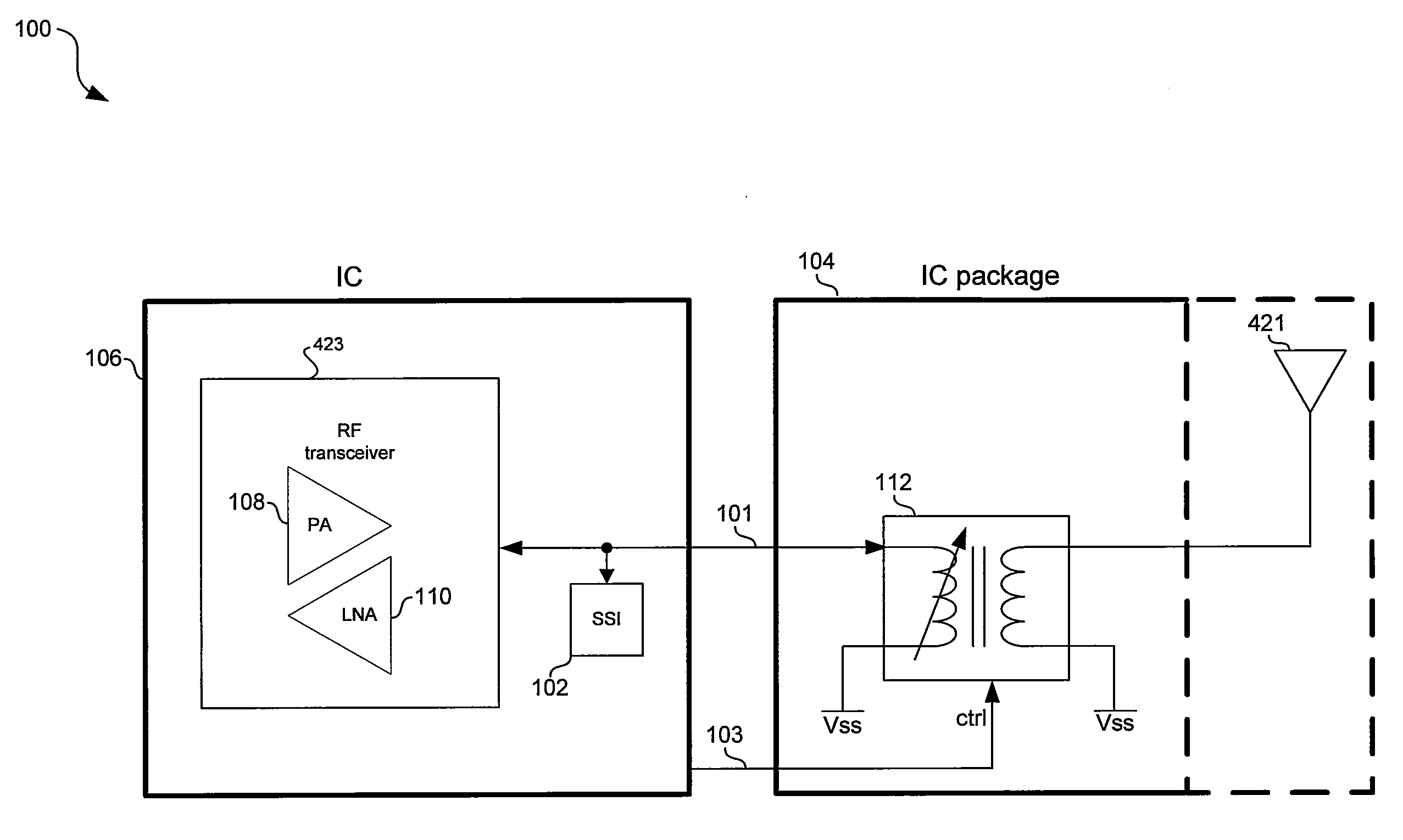

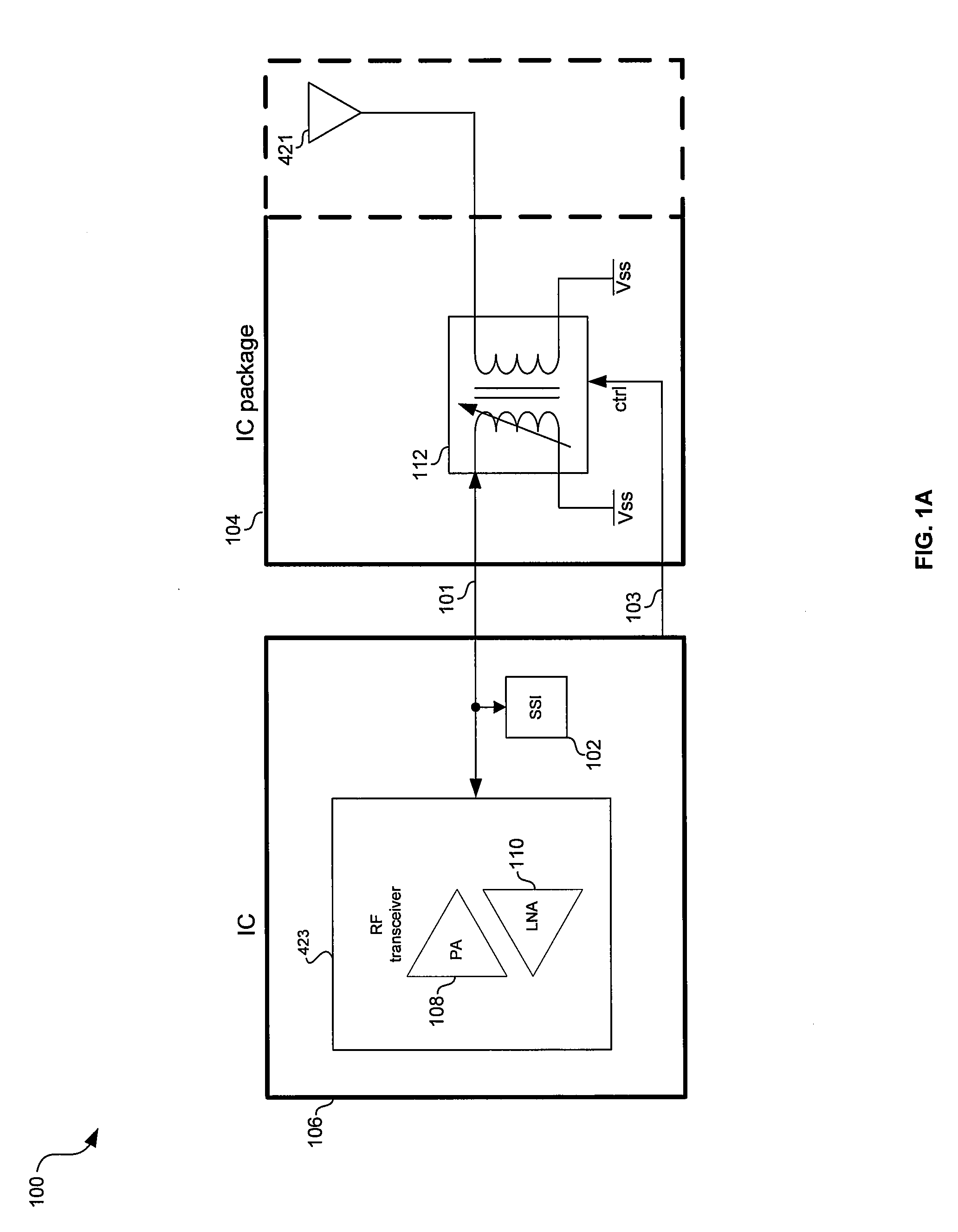

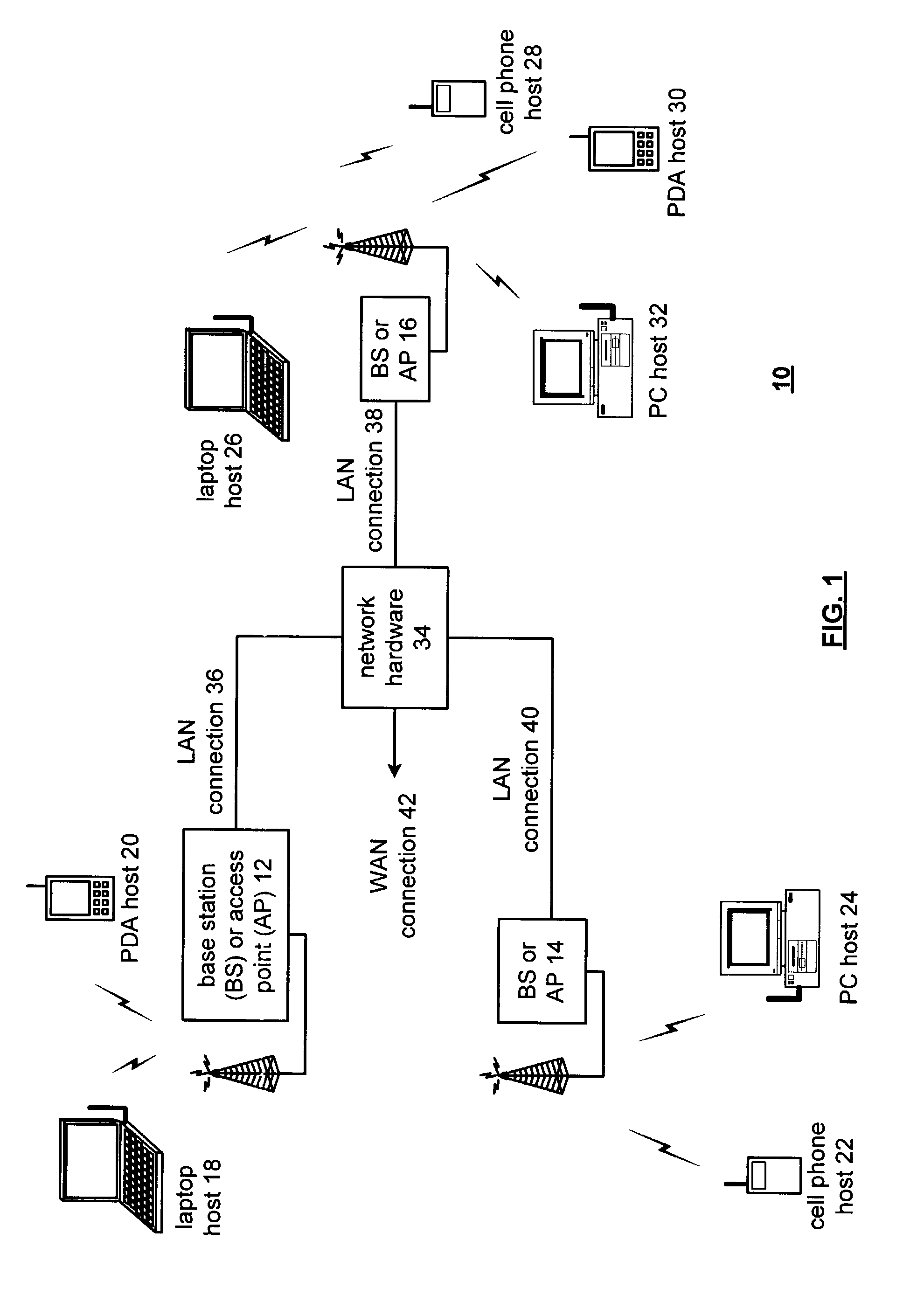

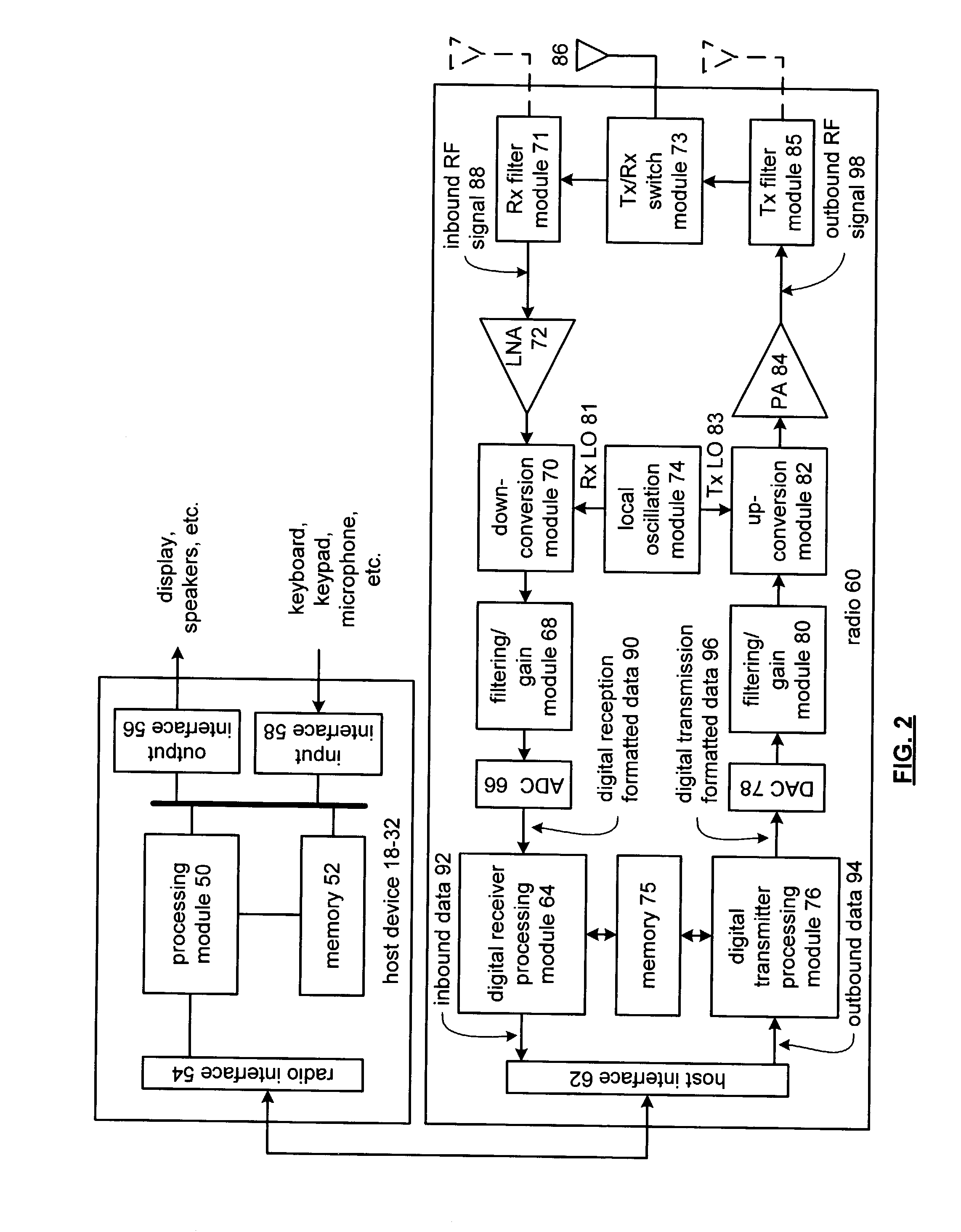

Method and system for a transformer in an integrated circuit package

ActiveUS20090156157A1One-port networksSemiconductor/solid-state device detailsTransformerEngineering

Aspects of a method and system for a transformer in an integrated circuit package are provided. In this regard, signals may be transmitted and / or received via an antenna communicatively coupled to a transformer embedded in multi-layer integrated circuit package. The windings ratio of the transformer may be configured based on an impedance of the antenna, an impedance of a transmitter coupled to the transformer, an impedance of an LNA coupled to the transformer, and / or a power level of the received and / or transmitted signals. The windings ratio may be configured via one or more switching elements which may be MEMS switches embedded in the multi-layer IC package. The transformer may comprise a plurality of loops fabricated on a corresponding plurality of metal layers in the multi-layer IC package, and the loops may be communicatively coupled with one or more vias. The multi-layer IC package may comprise ferromagnetic and / or ferromagnetic materials.

Owner:AVAGO TECH INT SALES PTE LTD

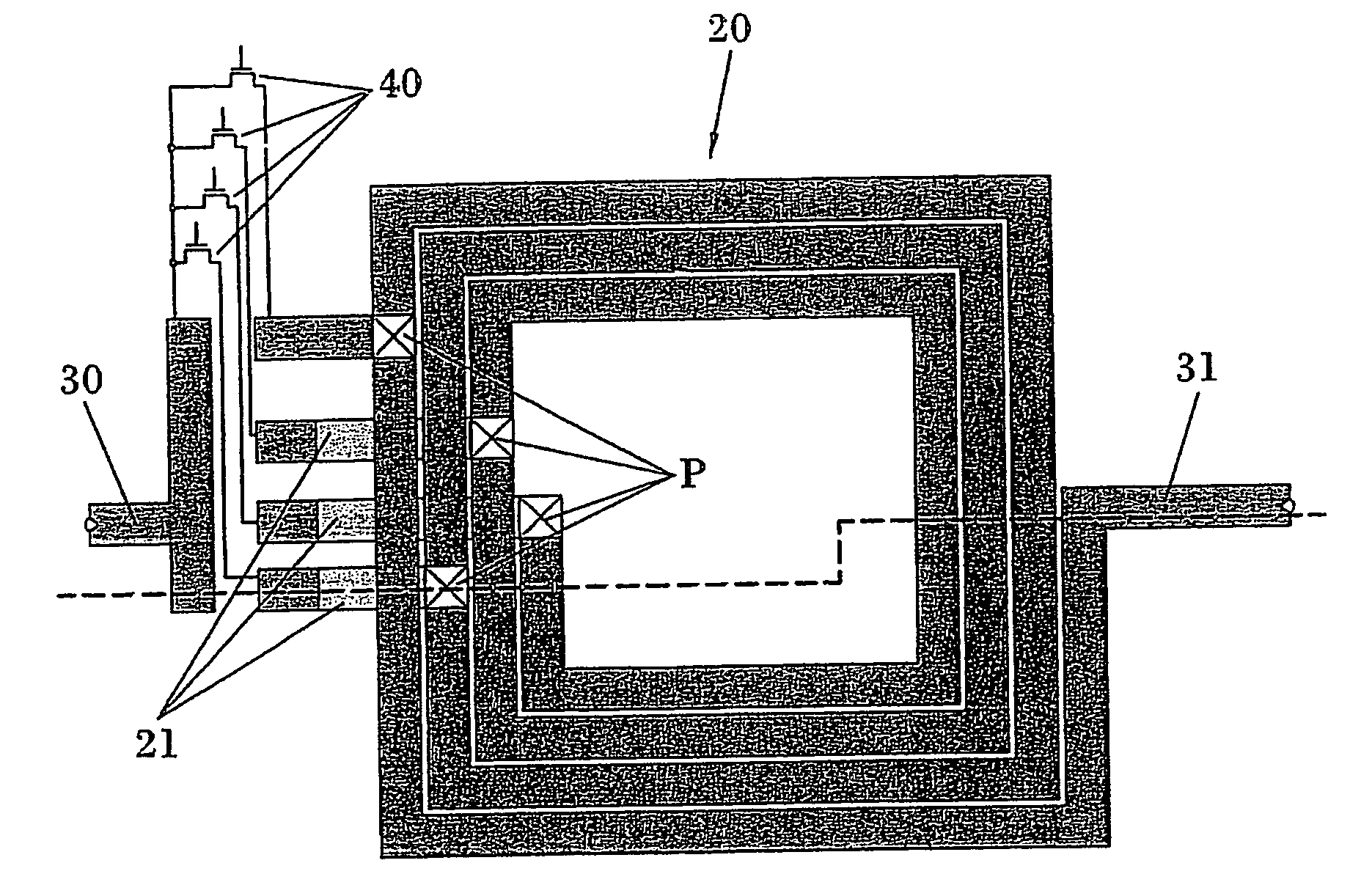

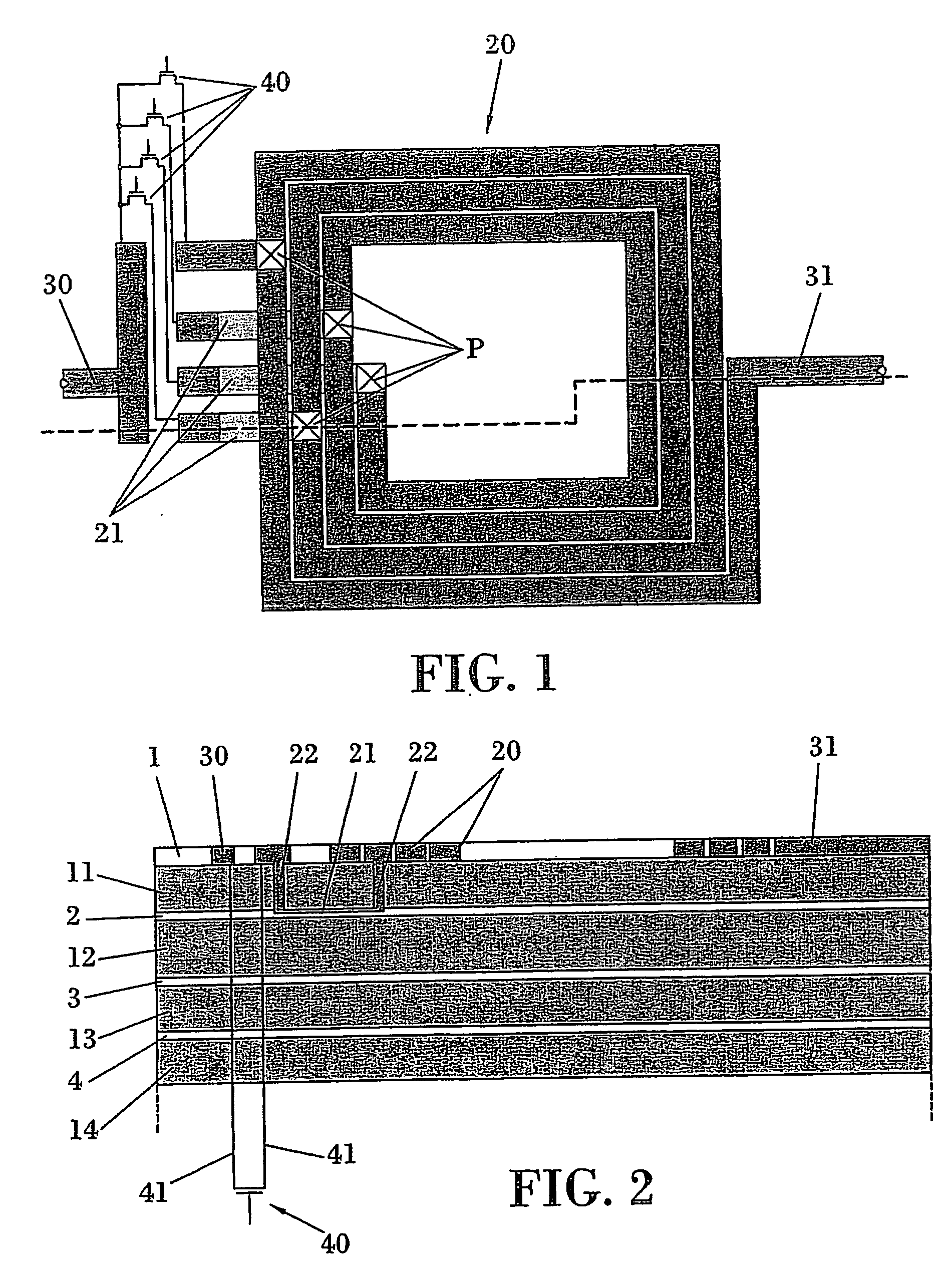

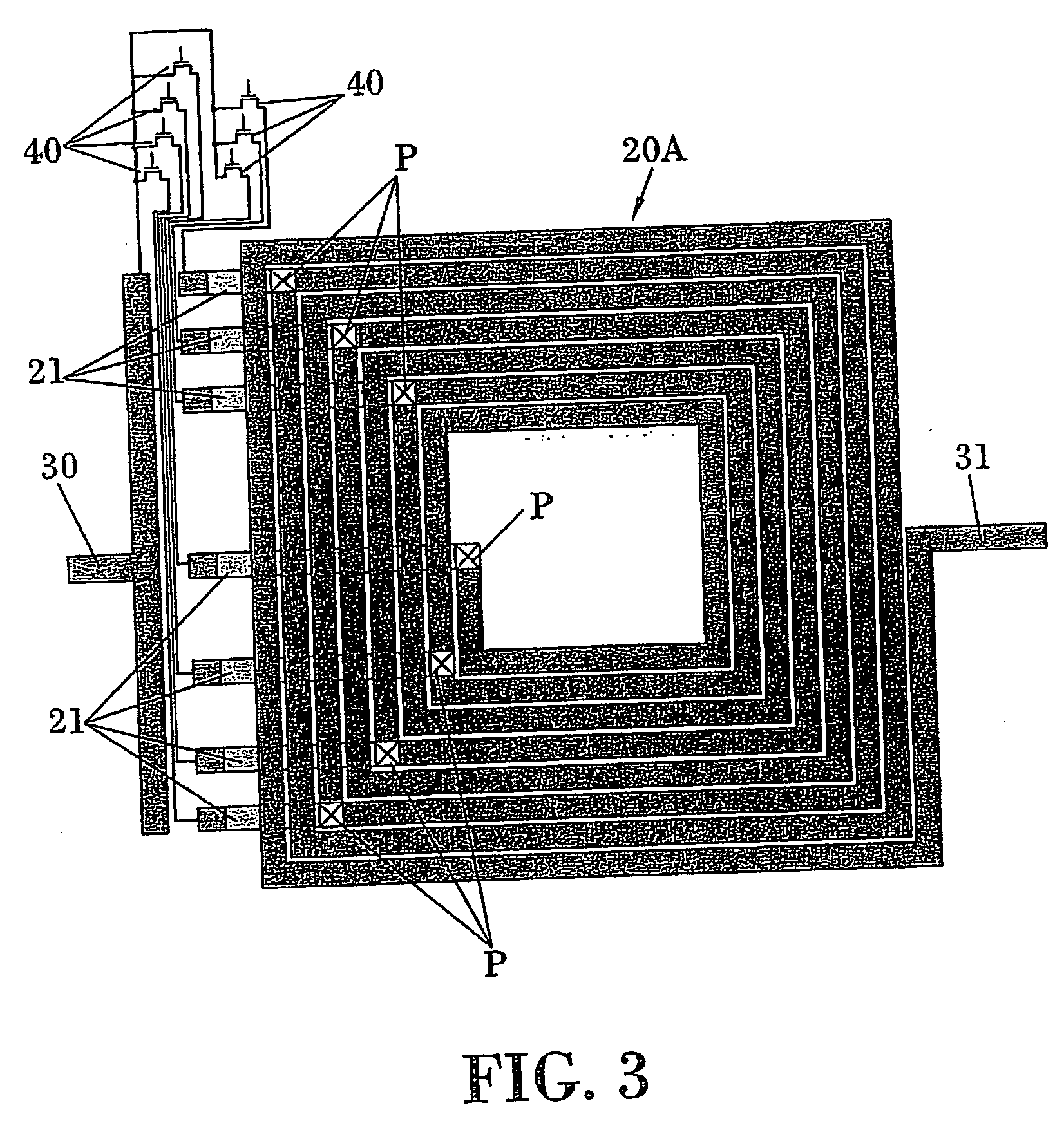

Multilayer circuit with variable inductor, and method of manufacturing it

InactiveUS20070115086A1Easy to implementSemiconductor/solid-state device detailsSolid-state devicesInductorInductance

The multilayer circuit comprising a plurality of electrically conductive layers separated from each other by respective dielectric layers, wherein at least one variable inductor is provided that comprises: a conductive coil structure following a coil path in a single and thickest one of said conductive layers; two ports connected to said coil structure; and a switch arrangement comprising at least one switch for selectively connecting at least one of said ports to one of a plurality of specific positions of said coil structure along said coil path in said one of said conductive layers, thus providing for a corresponding selective inductance value of the variable inductor, between said two ports. The invention also relates to a method of manufacturing the circuit.

Owner:SEIKO EPSON CORP

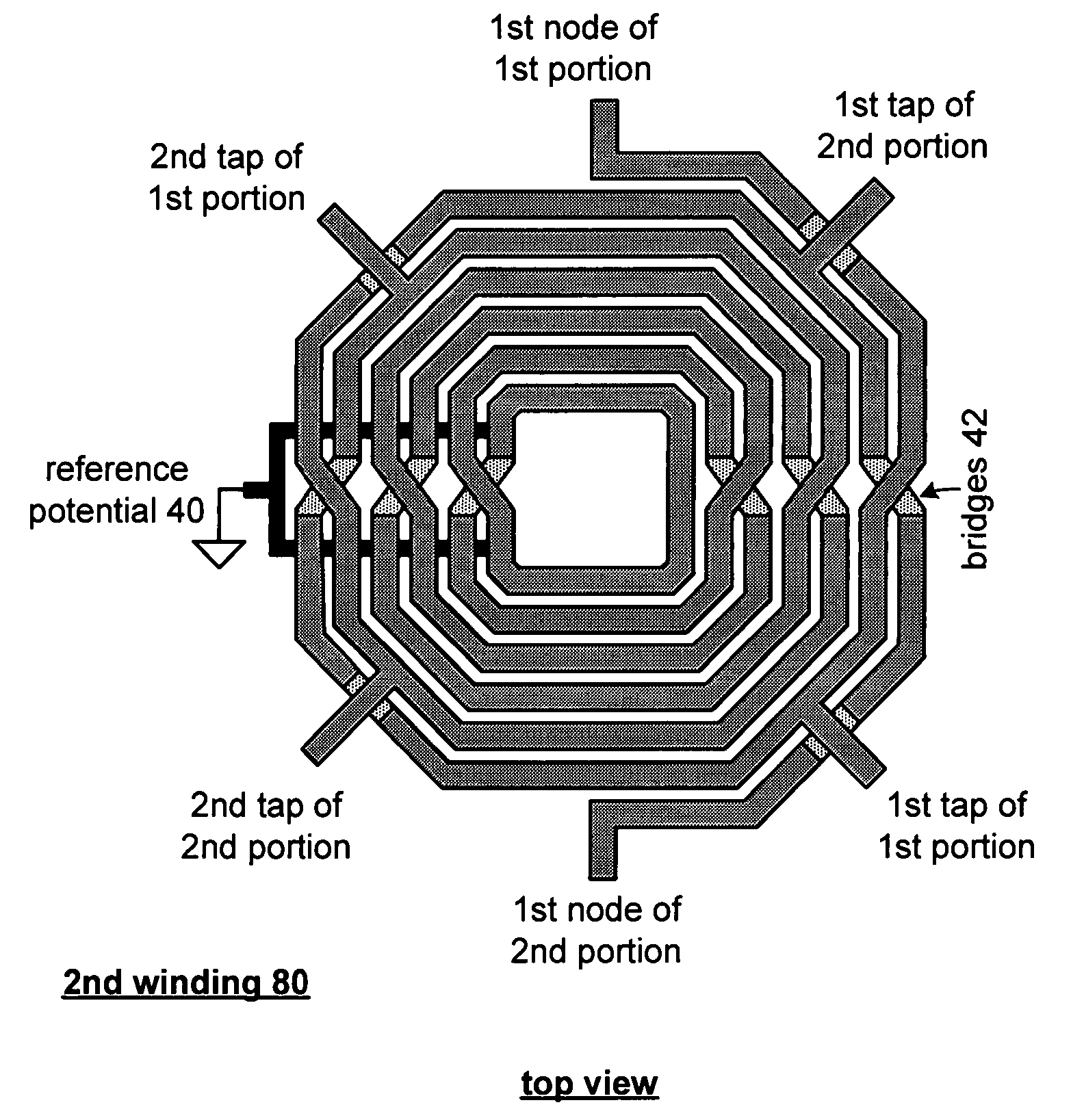

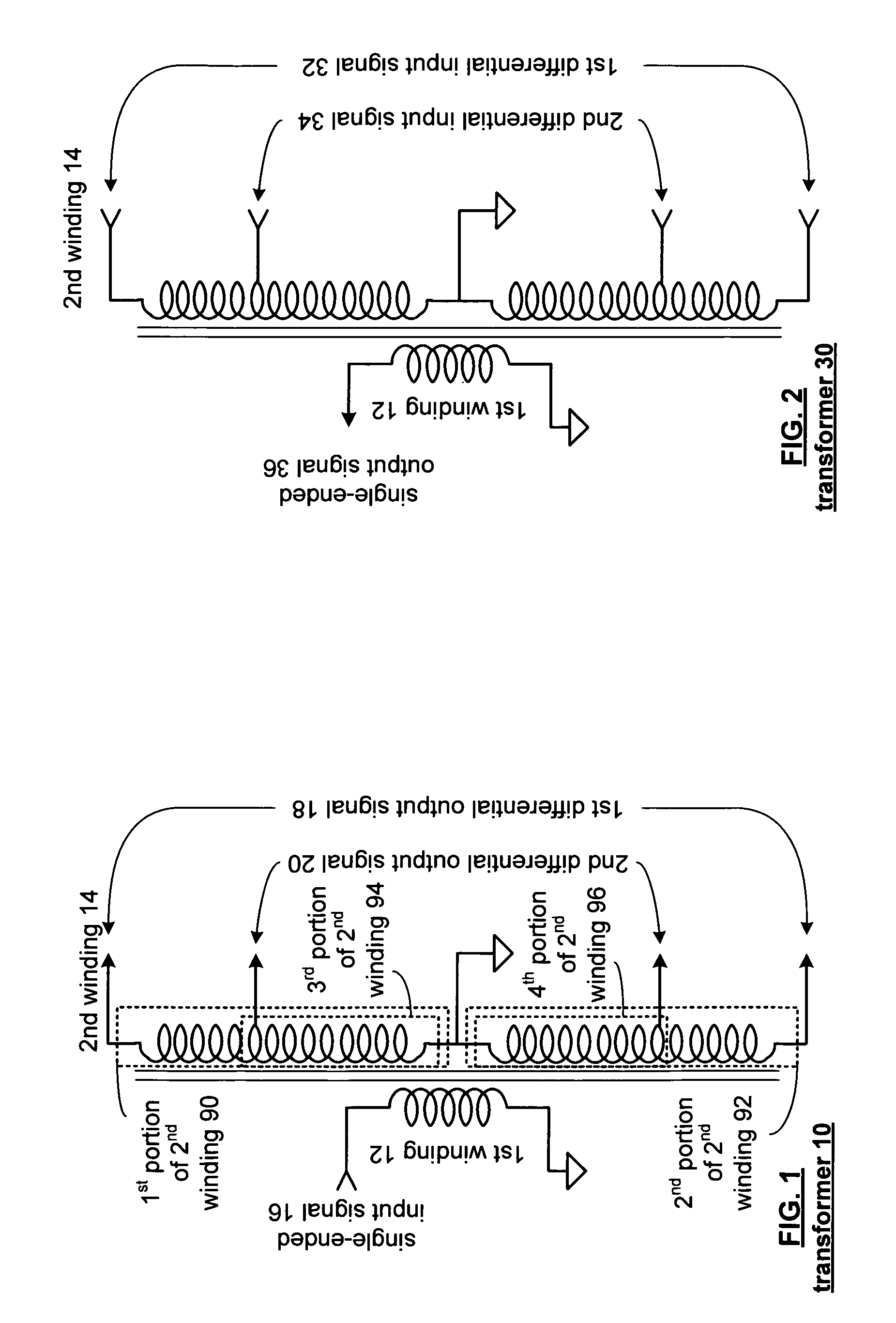

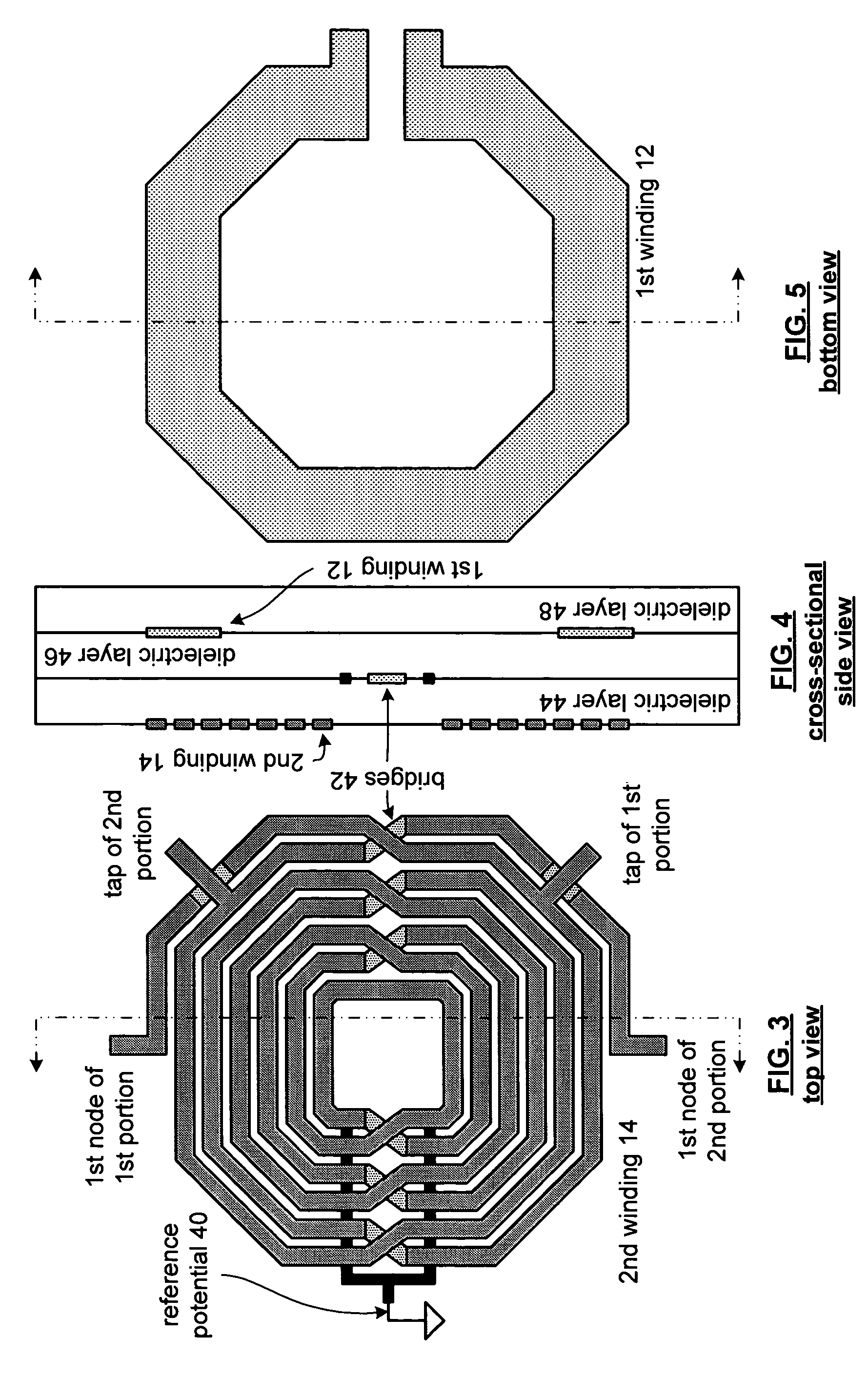

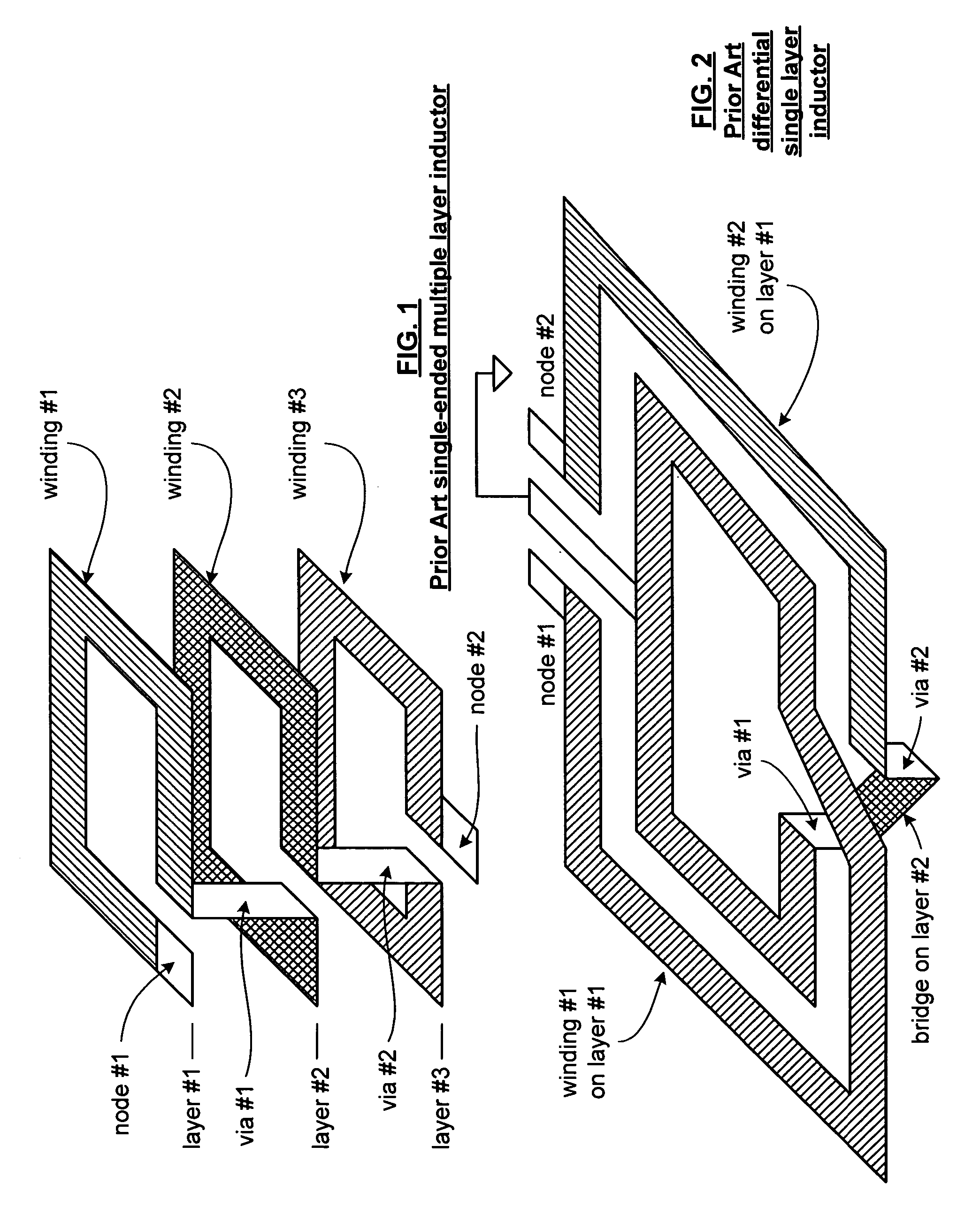

On-chip multiple tap transformer and inductor

An on-chip multiple tap transformer balun includes a 1st winding and a 2nd winding having two portions. The 1st winding is on a 1st layer of an integrated circuit and is operably coupled for a single ended signal. The 1st and 2nd portions of the 2nd winding are on a 2nd layer of the integrated circuit. The 1st portion of the 2nd winding includes a 1st node, a 2nd node, and a tap. The 1st node is operably coupled to receive a 1st leg of a 1st differential signal and the 2nd node is coupled to a reference potential. The tap of the 1st portion is operably coupled for a 1st leg of a 2nd differential signal. The 2nd portion of the 2nd winding includes a 1st node, 2nd node, and tap. The 1st node is operably coupled to receive a 2nd leg of the 1st differential signal and the 2nd node is operably coupled to the reference potential. The tap of the 2nd portion is coupled for a 2nd leg of the 2nd differential signal. The 1st and 2nd portions of the 2nd winding are symmetrical with respect to the 1st and 2nd nodes and with respect to the tap nodes.

Owner:AVAGO TECH INT SALES PTE LTD

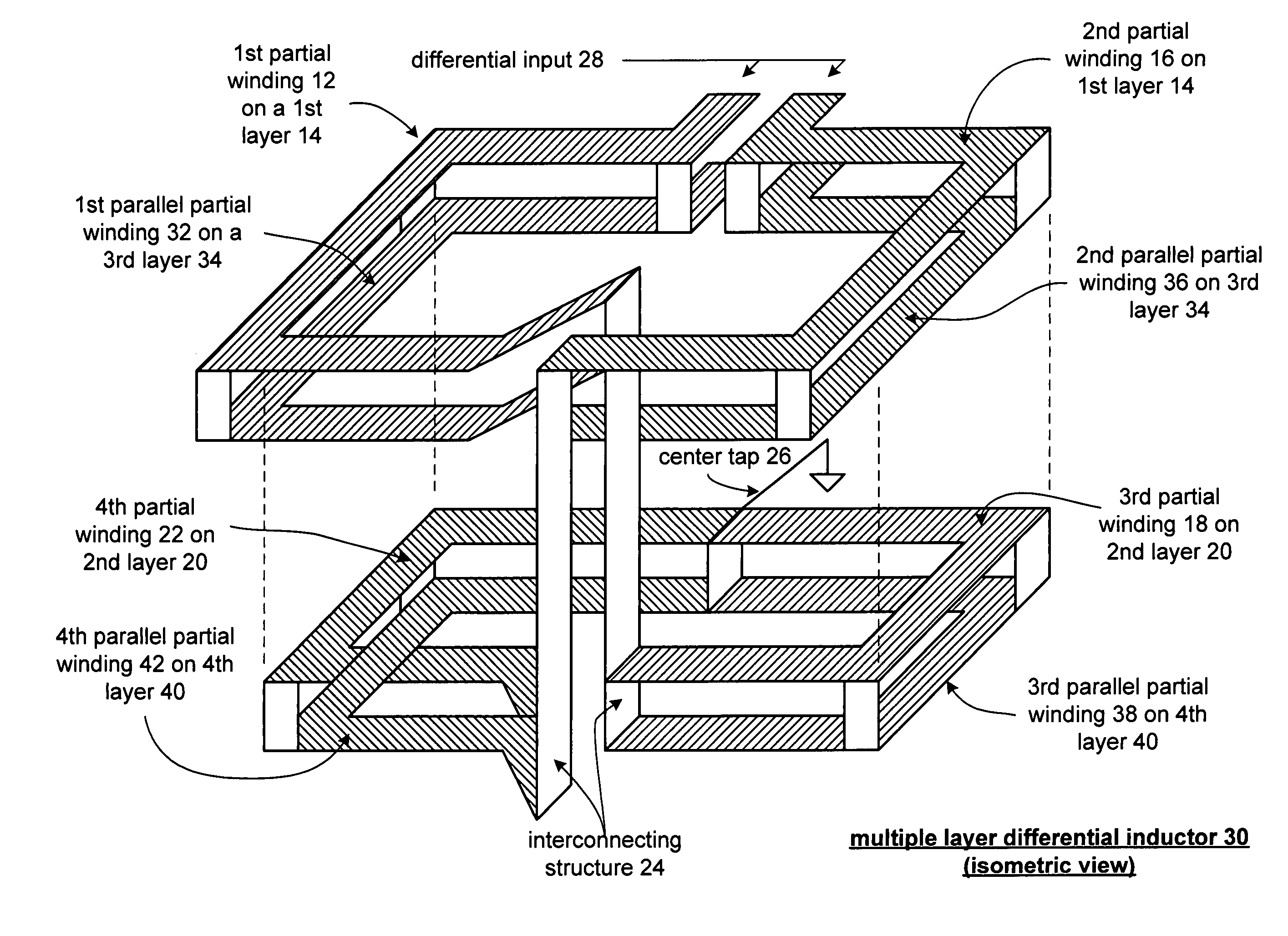

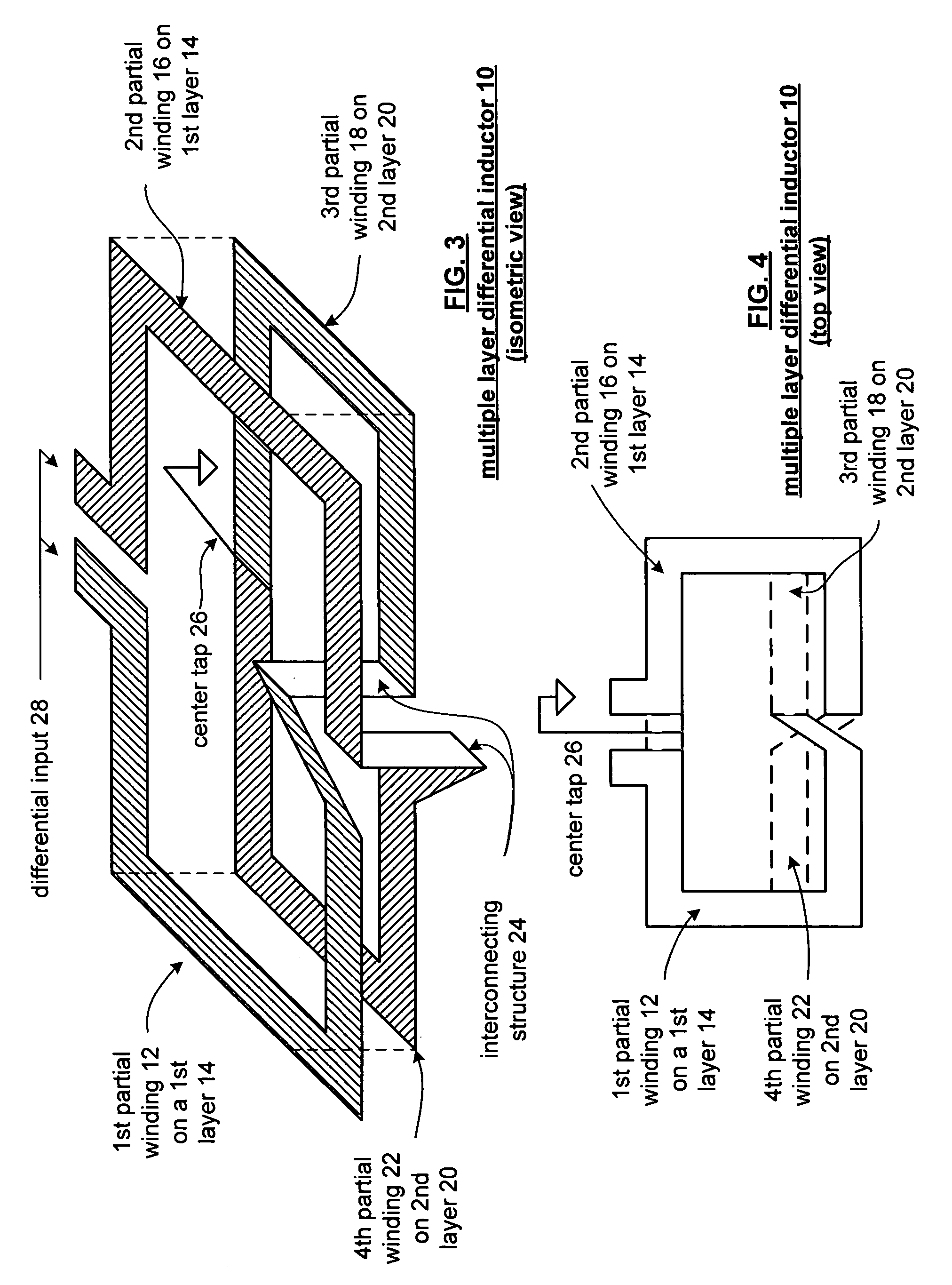

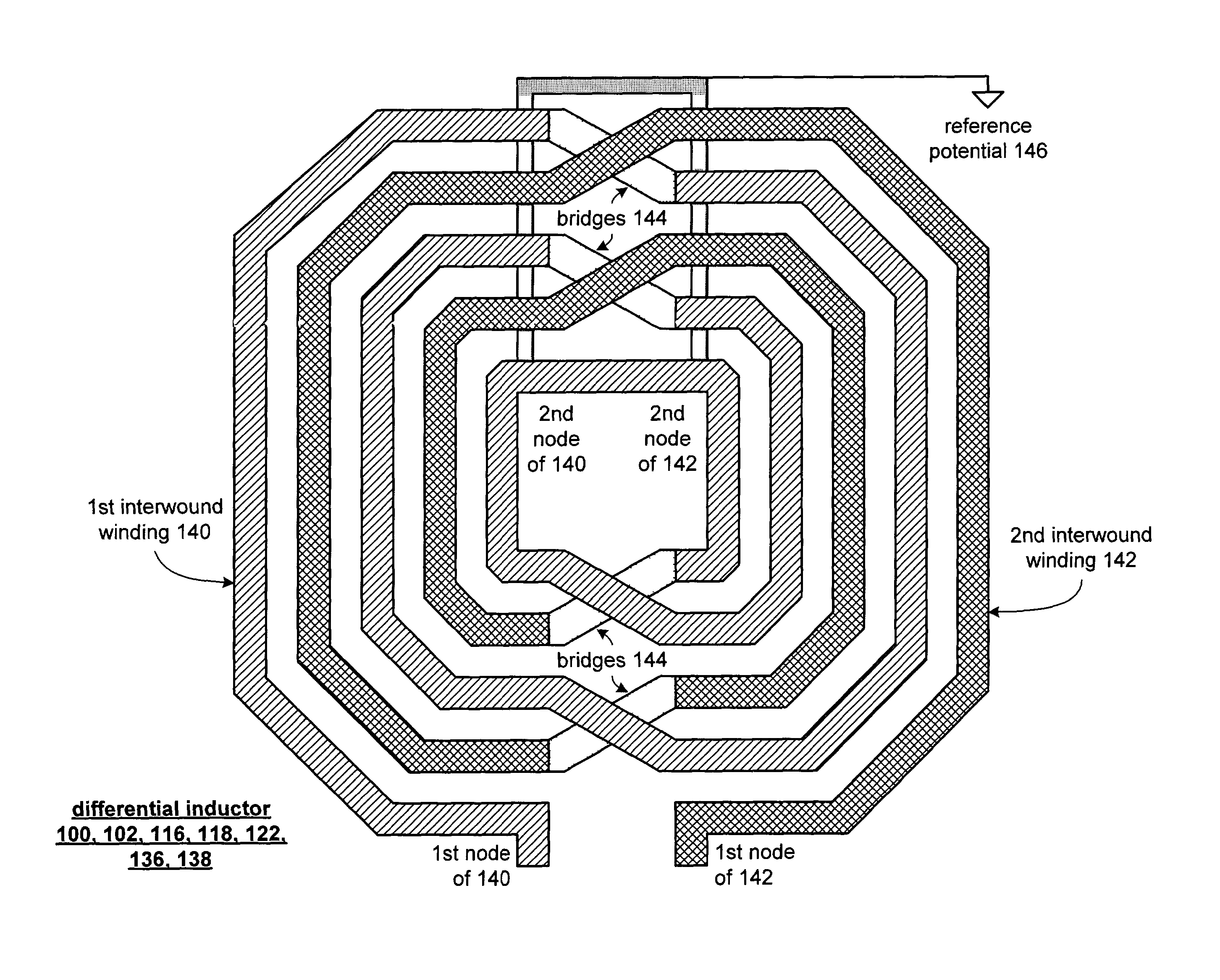

On-chip differential multi-layer inductor

InactiveUS7091814B2Improve manufacturing yieldUse minimizedSemiconductor/solid-state device detailsSolid-state devicesCapacitanceEngineering

An on-chip differential multi-layer inductor includes a 1st partial winding on a 1st layer, a 2nd partial winding on the 1st layer, a 3rd partial winding on a 2nd layer, a 4th partial winding on the 2nd layer, and an interconnecting structure. The 1st and 2nd partial windings on the 1st layer are operably coupled to receive a differential input signal. The 3rd and 4th partial windings on the 2nd layer are each operably coupled to a center tap. The interconnecting structure couples the 1st, 2nd, 3rd and 4th partial windings such that the 1st and 3rd partial windings form a winding that is symmetrical about the center tap with a winding formed by the 2nd and 4th partial windings. By designing the on-chip differential multi-layer inductor to have a desired inductance value, a desired Q factor, and a desired operating rate, a desired resonant frequency and corresponding desired capacitance value can be determined. Having determined the electrical parameters of the multi layer established, the geometric shapes of the windings, number of windings, number of layers to support the inductor, and the interconnecting structure may be determined.

Owner:AVAGO TECH INT SALES PTE LTD

Method and system for configuring a transformer embedded in a multi-layer integrated circuit (IC) package

ActiveUS20090243767A1Near-field transmissionSemiconductor/solid-state device detailsCouplingTransformer

Aspects of a method and system for configuring a transformer embedded in a multi-layer integrated circuit package are provided. In this regard, a windings ratio of a transformer embedded in a multi-layer IC package bonded to an IC may be configured, via logic, circuitry, and / or code in the IC, based on signal levels at one or more terminals of the transformer. The transformer may comprise a plurality of inductive loops fabricated in transmission line media. The integrated circuit may be flip-chip bonded to the multi-layer package. The IC may comprise a signal strength indicator enabled to measure signal levels input to or output by the transformer. The windings ratio may be configured via one or more switches in the IC and / or in the multi-layer package. The IC and / or the multi-layer package may comprise ferromagnetic material which may improve magnetic coupling of the transformer.

Owner:AVAGO TECH INT SALES PTE LTD

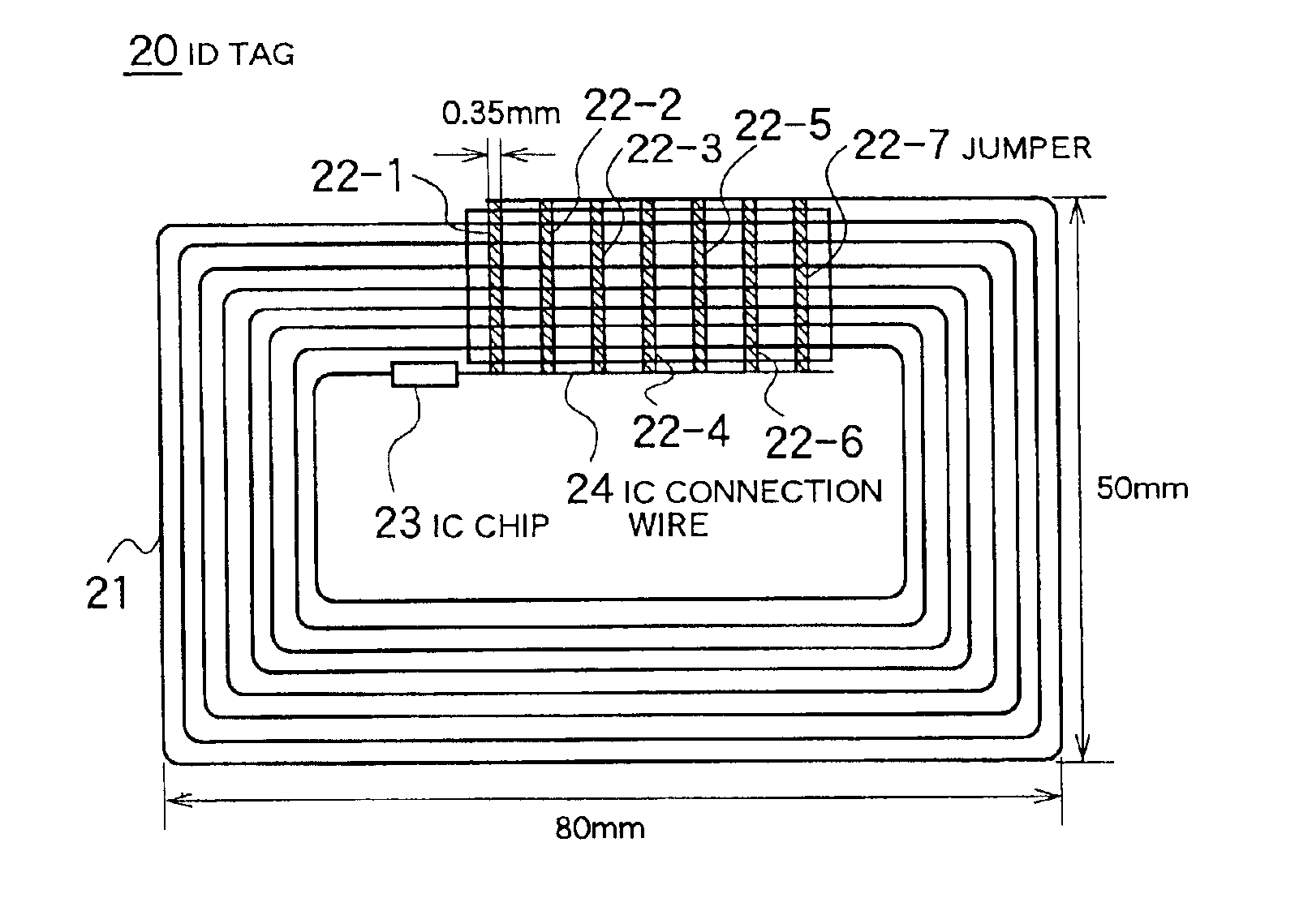

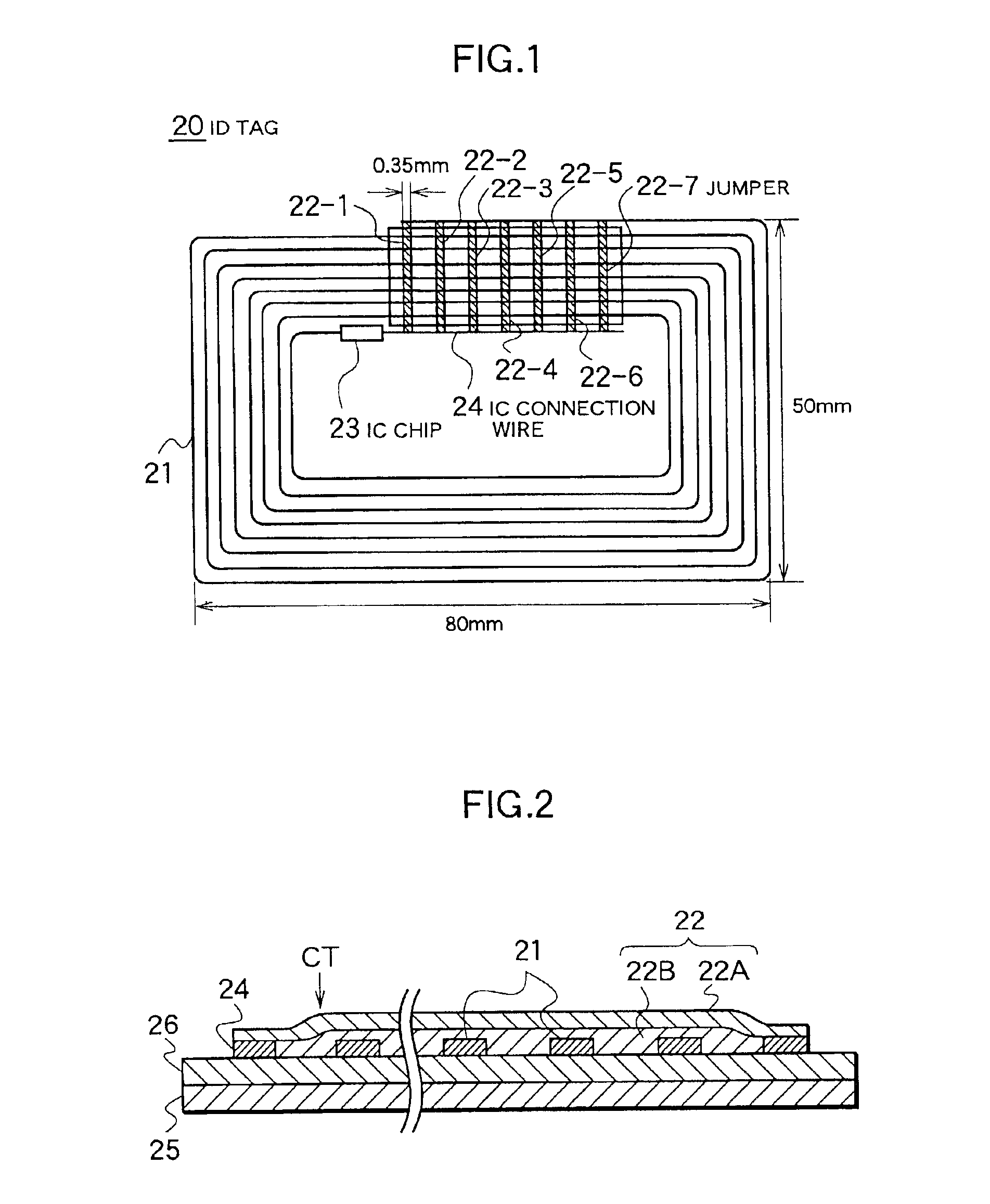

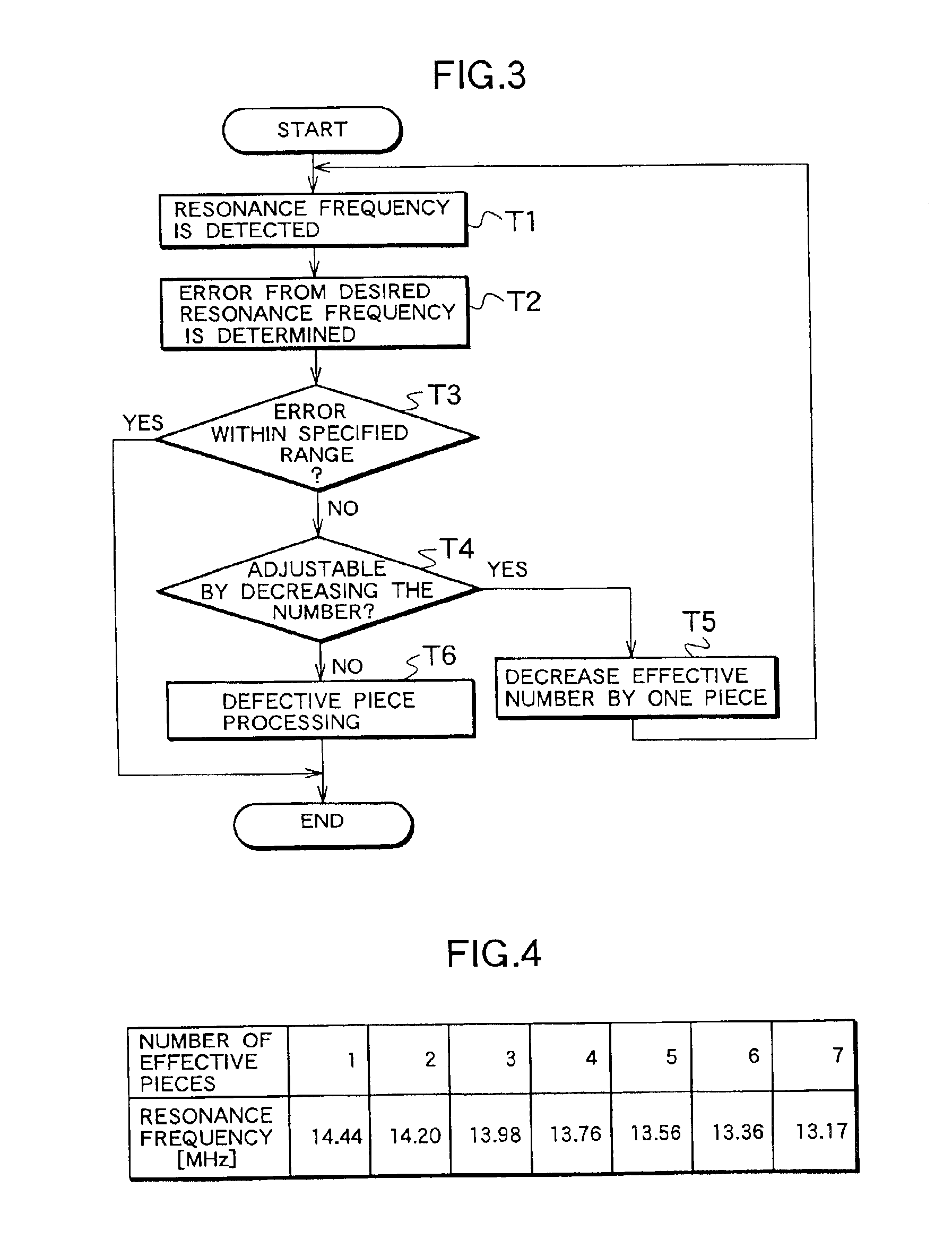

Flat coil component, characteristic adjusting method of flat coil component, ID tag, and characteristic adjusting method of ID tag

To present the ID tag including flat coil component, and characteristic adjusting method of ID tag capable of suppressing product fluctuations about the desired characteristic. The flat coil component of the ID tag of the invention comprises a flat coil composed of a conductive material provided continuously and spirally on an insulating substrate, and a jumper disposed on the flat coil with insulation, from one of inner end or outer end of this flat coil to the outside or inside of the flat coil where other end is positioned, in which the jumper is composed of a plurality of jumpers variable in the number of pieces in arrangement. The characteristic is adjusted by varying the number of effective pieces for forming the parallel arrangement.

Owner:LINTEC CORP

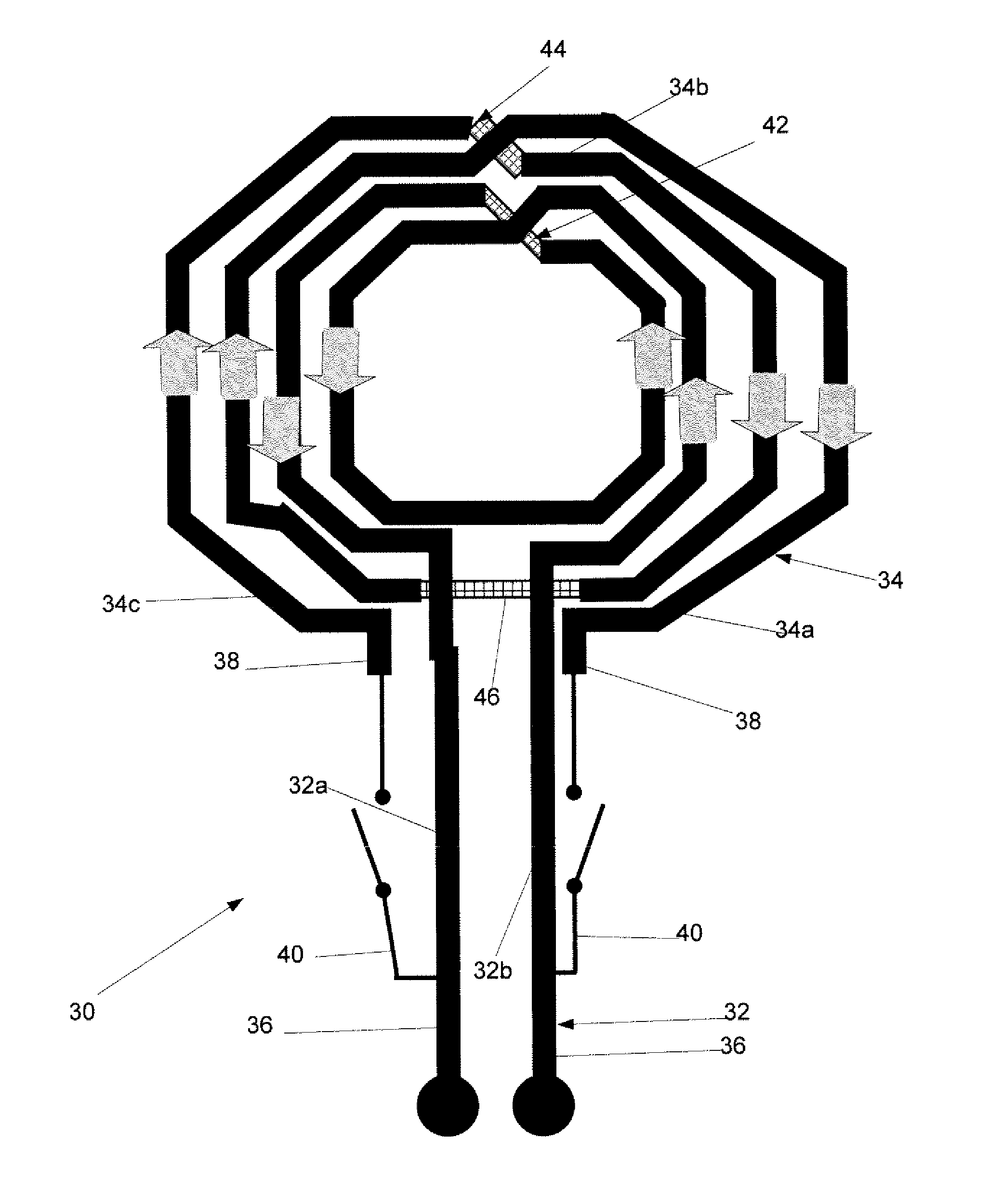

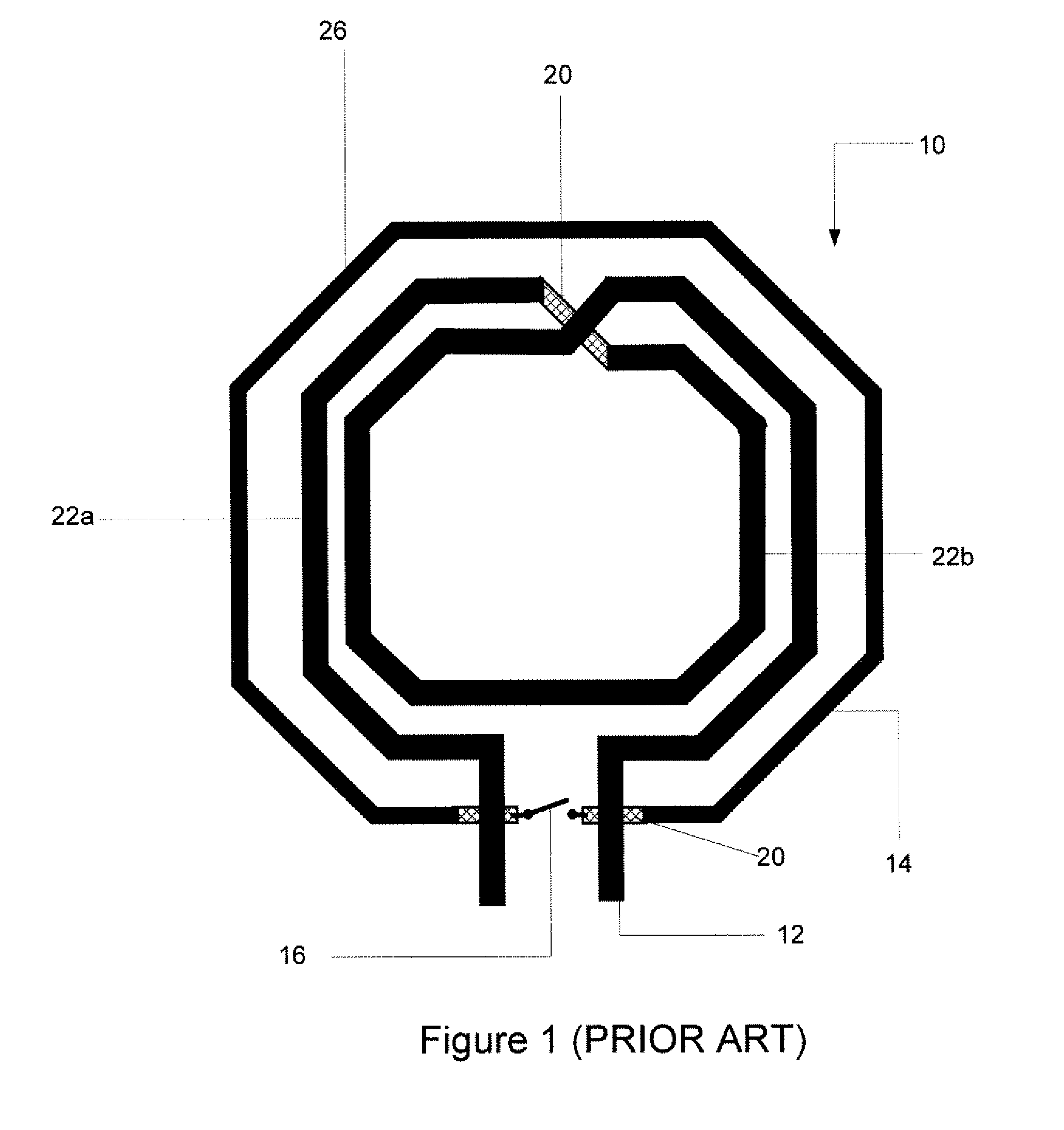

On-chip differential inductor and applications thereof

ActiveUS7039381B2Optimal integrated circuit layoutHigh quality factorSemiconductor/solid-state device detailsSolid-state devicesEngineeringInductor

An on-chip differential inductor includes a 1st interwound winding having a substantially octagonal shape, or rectangular octagonal shape, and a 2nd interwound winding having a substantially octagonal shape, or rectangular octagonal shape, that is interwound with the 1st interwound winding. Both the 1st and 2nd interwound windings are on the same layer of the integrated circuit. Each interwound winding includes two nodes; one of node of each winding is commonly coupled to a reference potential. The other node of each winding is operably coupled to receive a respective leg of a differential signal.

Owner:AVAGO TECH INT SALES PTE LTD

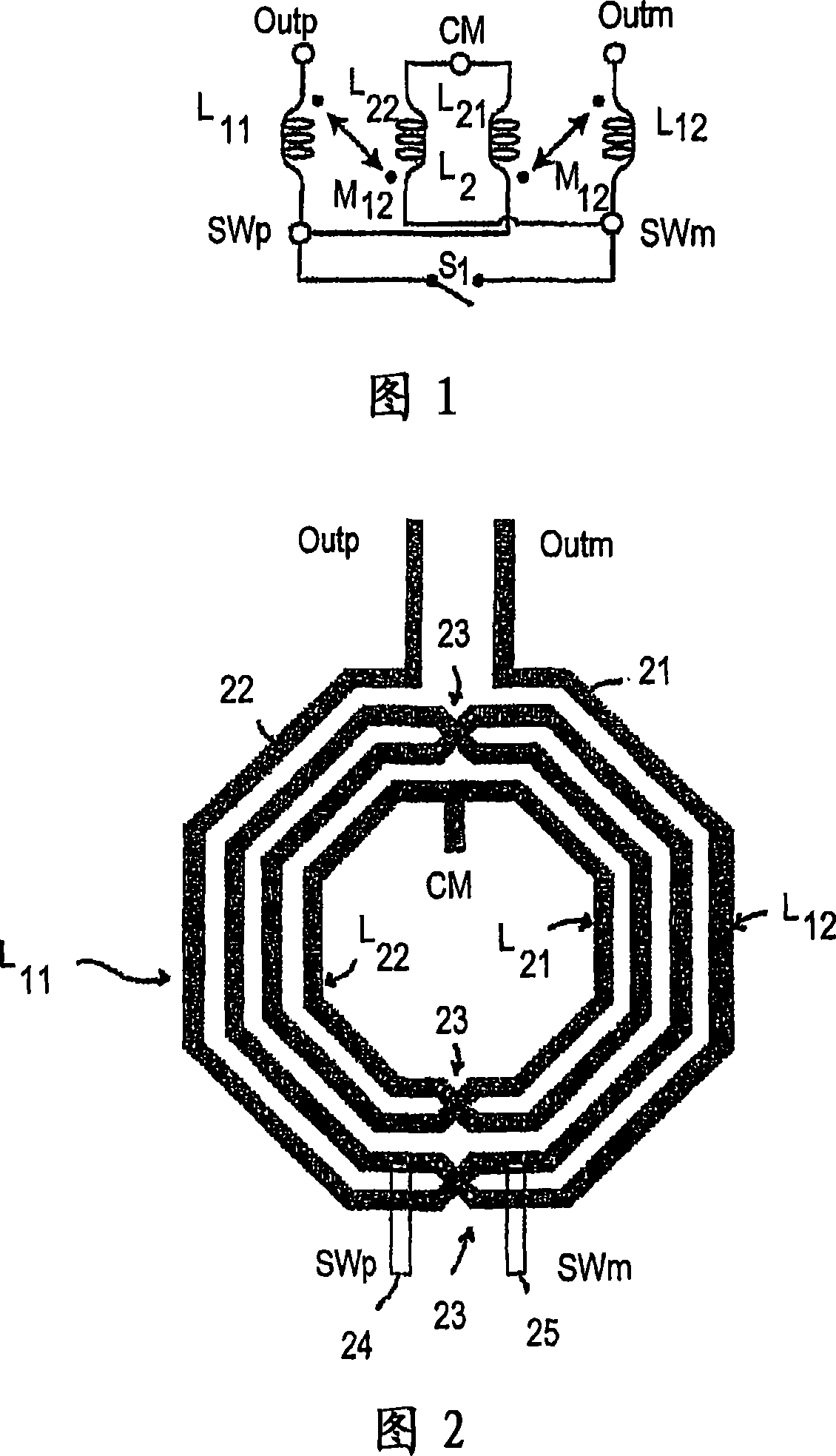

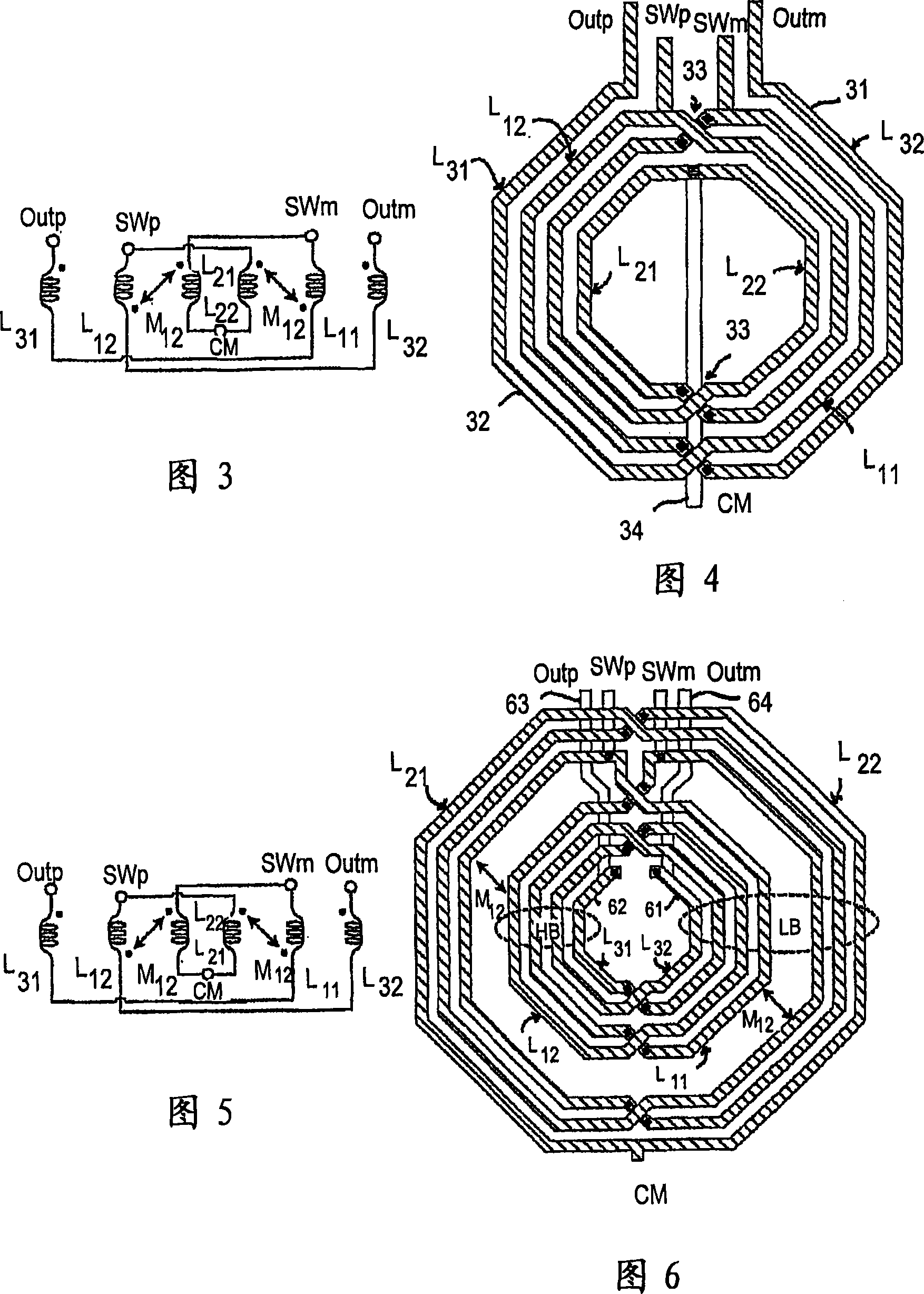

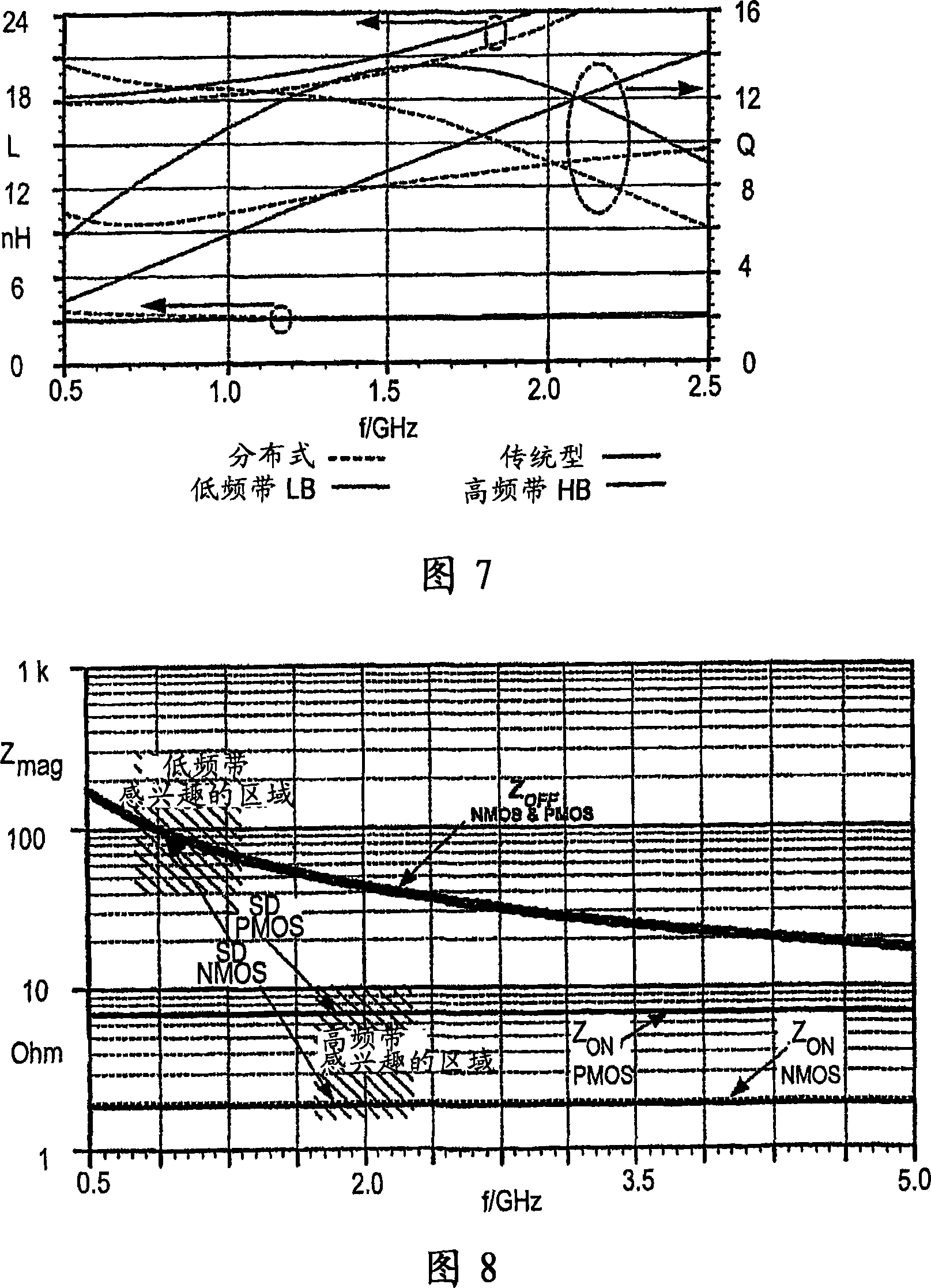

Inductor device for multiband radio frequency operation

InactiveCN101253586AOperation steps can be controlledEasy to operateTransformers/inductances coils/windings/connectionsAmplifier with semiconductor-devices/discharge-tubesAudio power amplifierPlanar inductor

Owner:NOKIA CORP

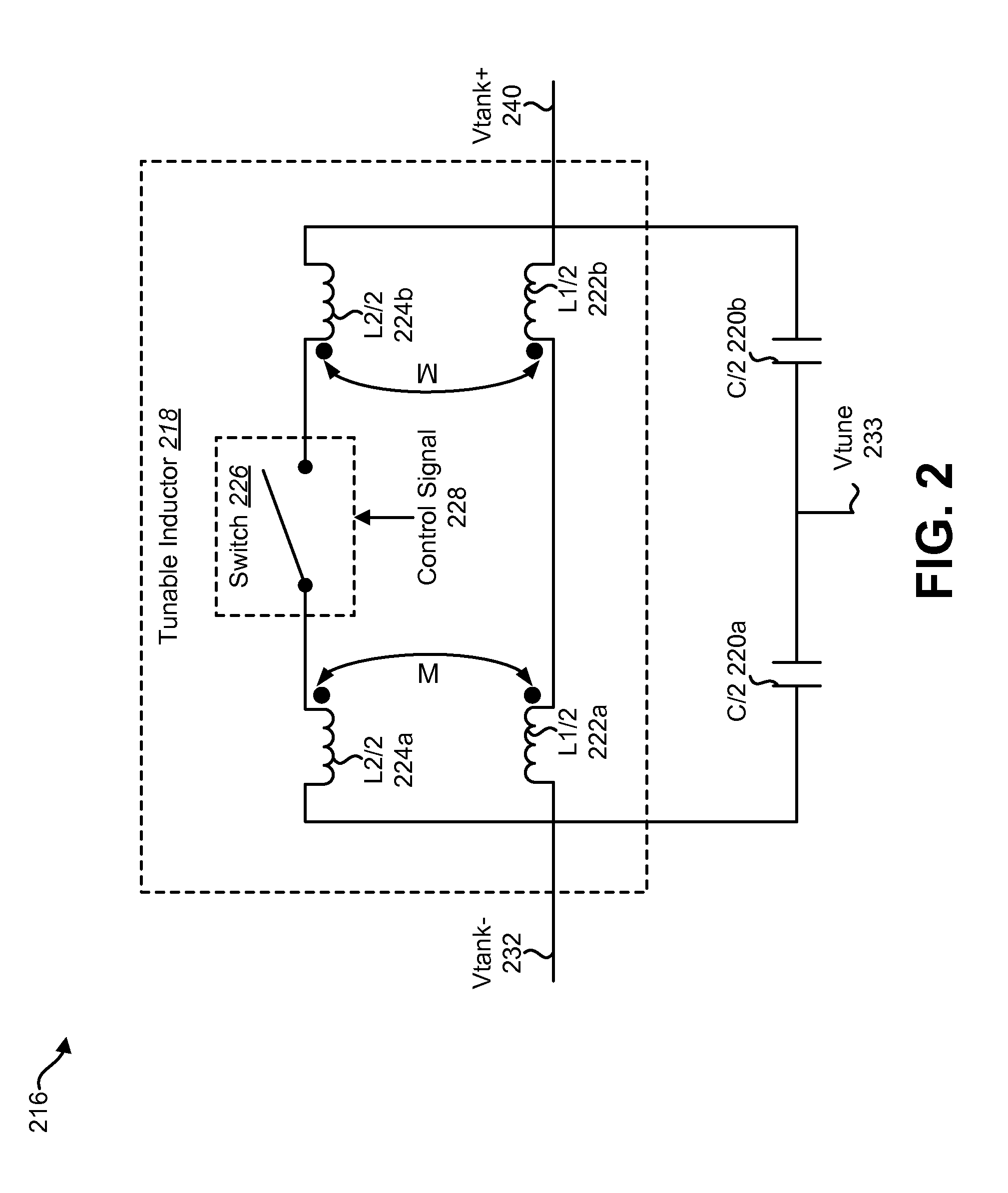

Tunable inductor circuit

A tunable inductor circuit is disclosed. The tunable inductor circuit includes a first inductor. The tunable inductor circuit also includes a second inductor in parallel with the first inductor. The tunable inductor circuit also includes a switch coupled to the second inductor. A resistance of the switch is added in parallel to the first inductor based on operation of the switch.

Owner:QUALCOMM INC

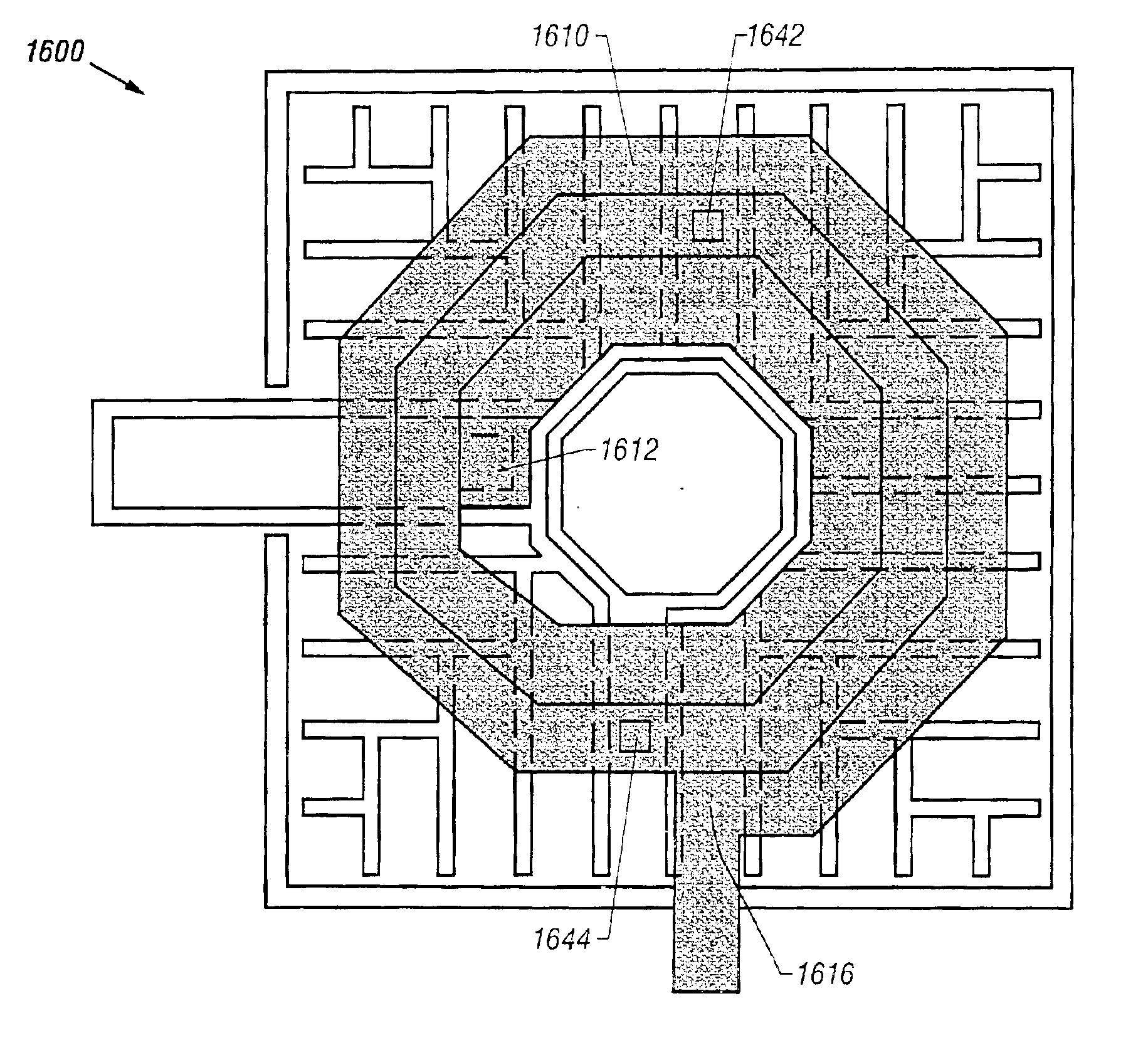

Compact Multiple Transformers

InactiveUS20090174515A1Increase magnetic fluxIncrease inductanceTransformersTransformers/inductances coils/windings/connectionsTransformerEngineering

Example embodiments of the invention may provide systems and methods for multiple transformers. The systems and methods may include a first transformer that may include a first primary winding and a first secondary winding, where the first primary winding may be inductively coupled to the first secondary winding, where the first transformer may be associated with a first rotational current flow direction in the first primary winding. The systems and methods may further include a second transformer that may include a second primary winding and a second secondary winding, where the second primary winding may be inductively coupled to the second secondary winding, where the second transformer may be associated with a second rotational current flow direction opposite the first rotational current flow direction in the second primary winding, where a first section of the first primary winding may be positioned adjacent to a second section of the second primary winding, and where the adjacent first and second sections may include a substantially same first linear current flow direction.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD +1

Programmable microtransformer

InactiveUS7456722B1Reduce and eliminate magnetic core materialGood suitElectronic switchingTransformers/inductances detailsCMOSConductor Coil

A programmable transformer incorporating windings embedded in a thin film substrate. The windings are flat wire traces embedded into the substrate, primary on one side and secondary on the other. The secondary windings may be planar or different coils spatially arrayed throughout a thickness of the substrate. The secondary winding may include multiple tap points, effectively providing multiple secondary coils referenced to the single primary coil. Each tap point is bridged to a field effect or CMOS transistor path by which a digital controls permit dynamic adjustment of the turns ratio. The final secondary output depends on the activated transistor paths. Multiple secondary outputs from a single secondary coil and a digitally programmable turns ratio are available aspects.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

Variable inductor

ActiveUS20070052512A1Maximizes variation rateTransformers/inductances coils/windings/connectionsSolid-state devicesControl signalInductor

A variable inductor is provided, which includes a first lead having both ends to receive a pair of difference signals, a second lead having both ends to receive a pair of the difference signals, and a switch selectively supplying a pair of the difference signals to the second lead by turning on / off according to a control signal. Accordingly, a variable inductor can be implemented that is compact and maximizes the variation rate of inductance.

Owner:SAMSUNG ELECTRONICS CO LTD

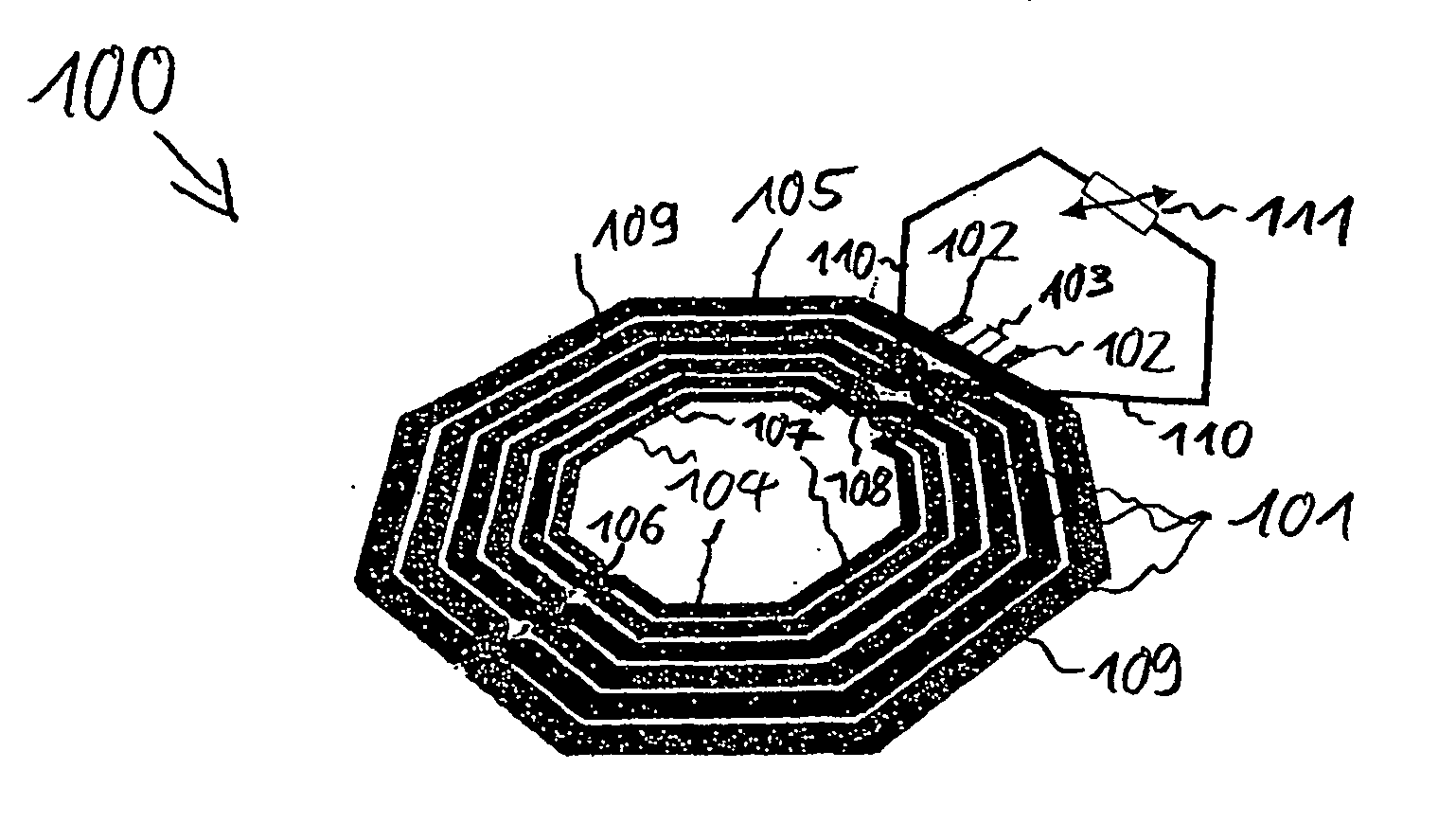

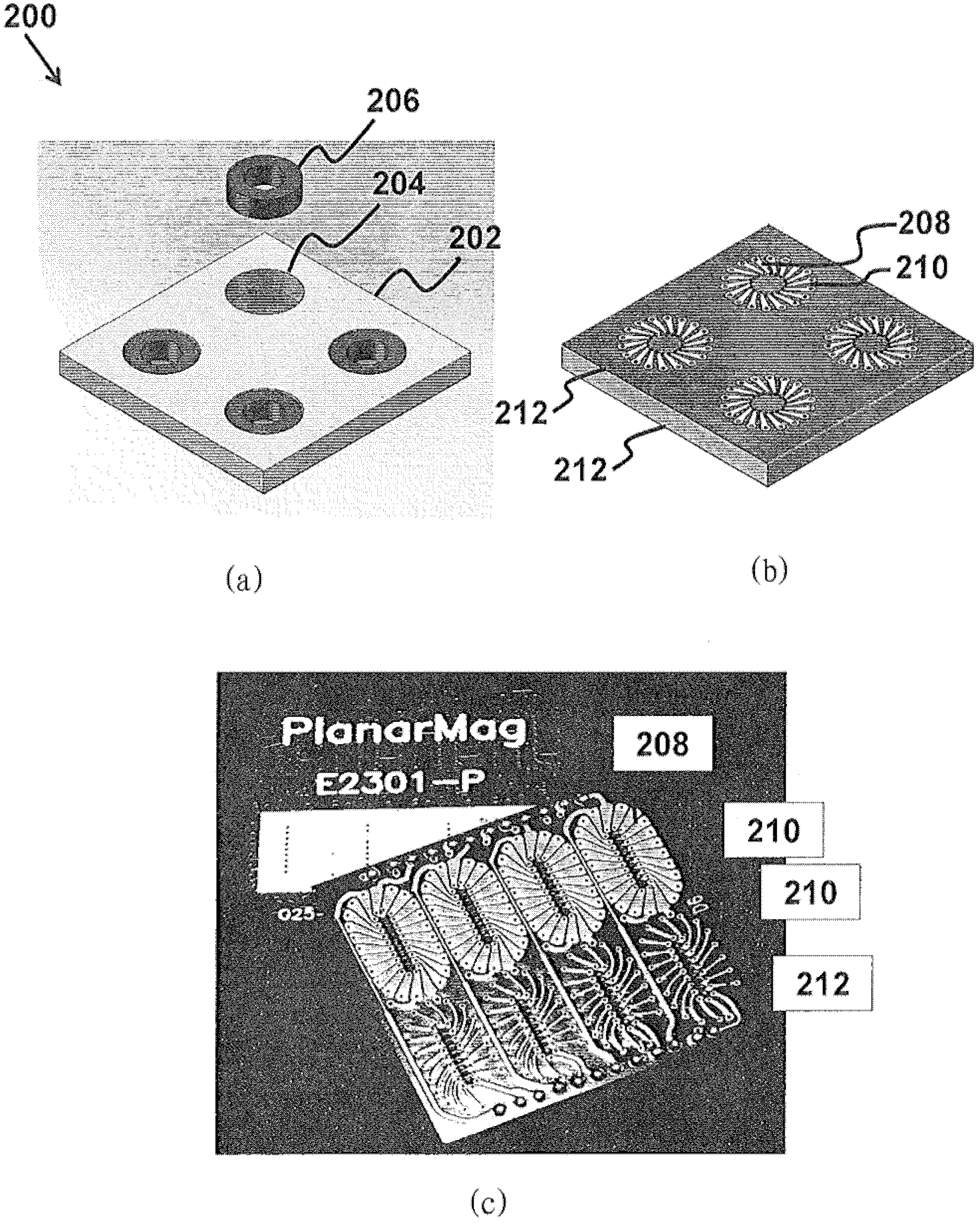

An integrated planar variable transformer with embedded magnetic core

ActiveCN102308346ATransformers/inductances coolingCoupling for high frequencyAdhesivePlanar substrate

The current invention provides an integrated planar transformer and electronic component that includes at least one wideband planar transformer disposed in a planar substrate, where each wideband planar transformer includes a planar substrate in a fully-cured and rigid state, a ferrite material embedded in the planar substrate, where the ferrite material is enveloped in an elastic and non-conductive material, inter-wound conductors disposed around the embedded ferrite material, where top and bottom conductors are bonded by an insulating adhesive. The top and bottom conductors are connected in an inter-connected pattern by conductive vias disposed on each side of the ferrite material and span through the layers to the conductors. The planar transformer further includes at least one center tap connected to at least one inter-wound conductor. The integrated planar transformer and electronic component further includes at least one electronic component connected to at least one terminal of the wide-band planar transformer.

Owner:PLANARMAG