Patents

Literature

78results about "H-bridge head driver circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

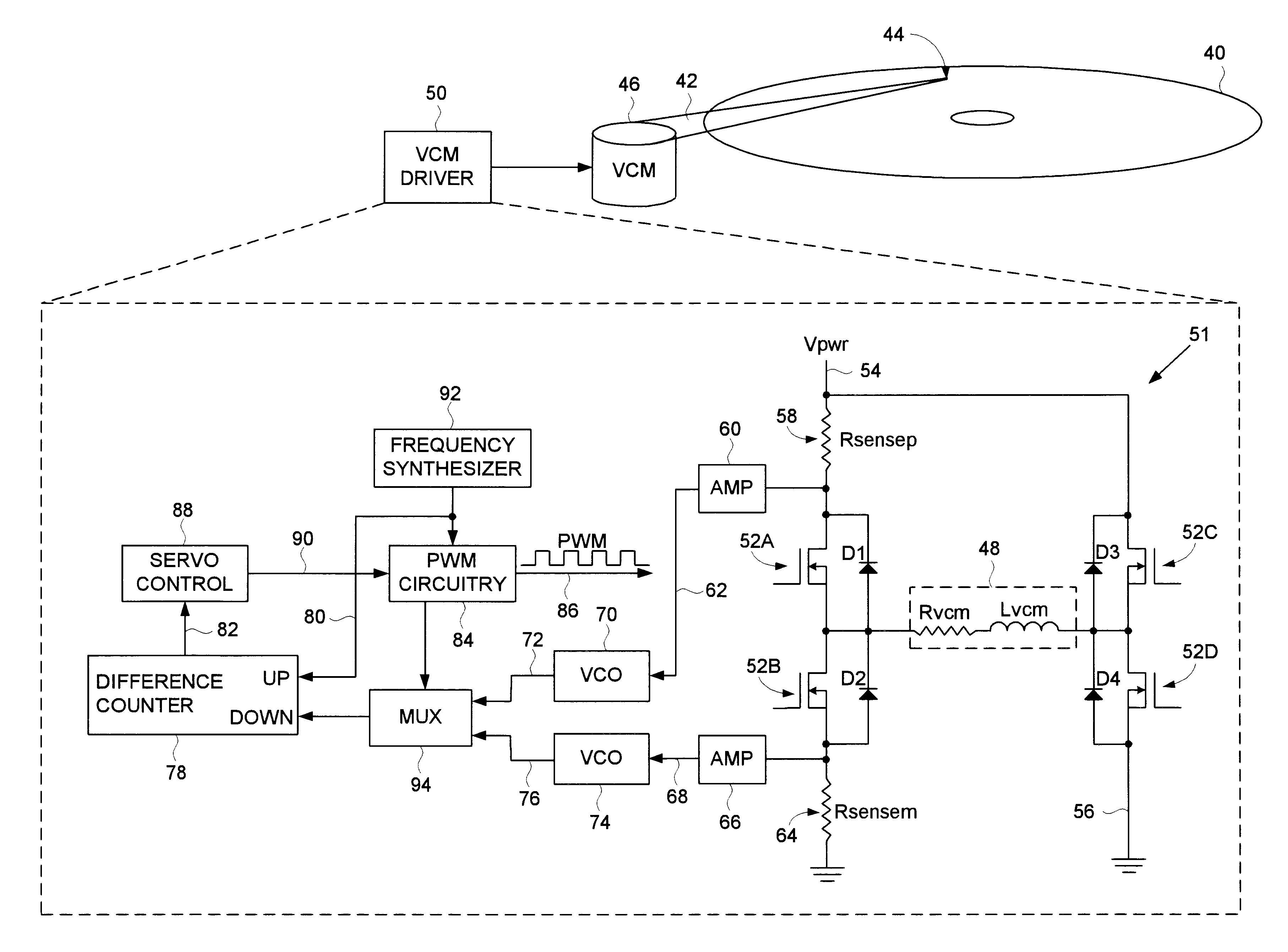

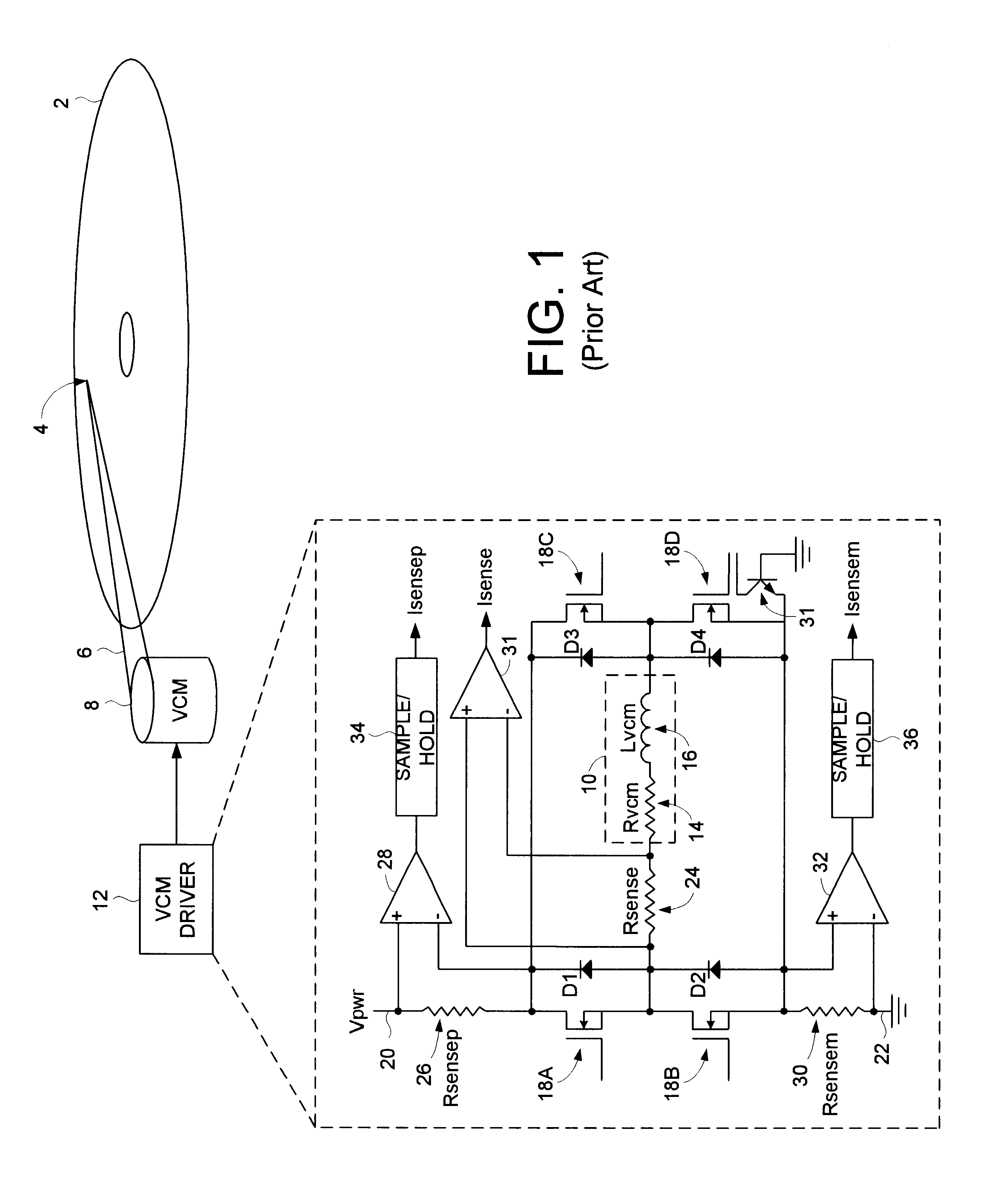

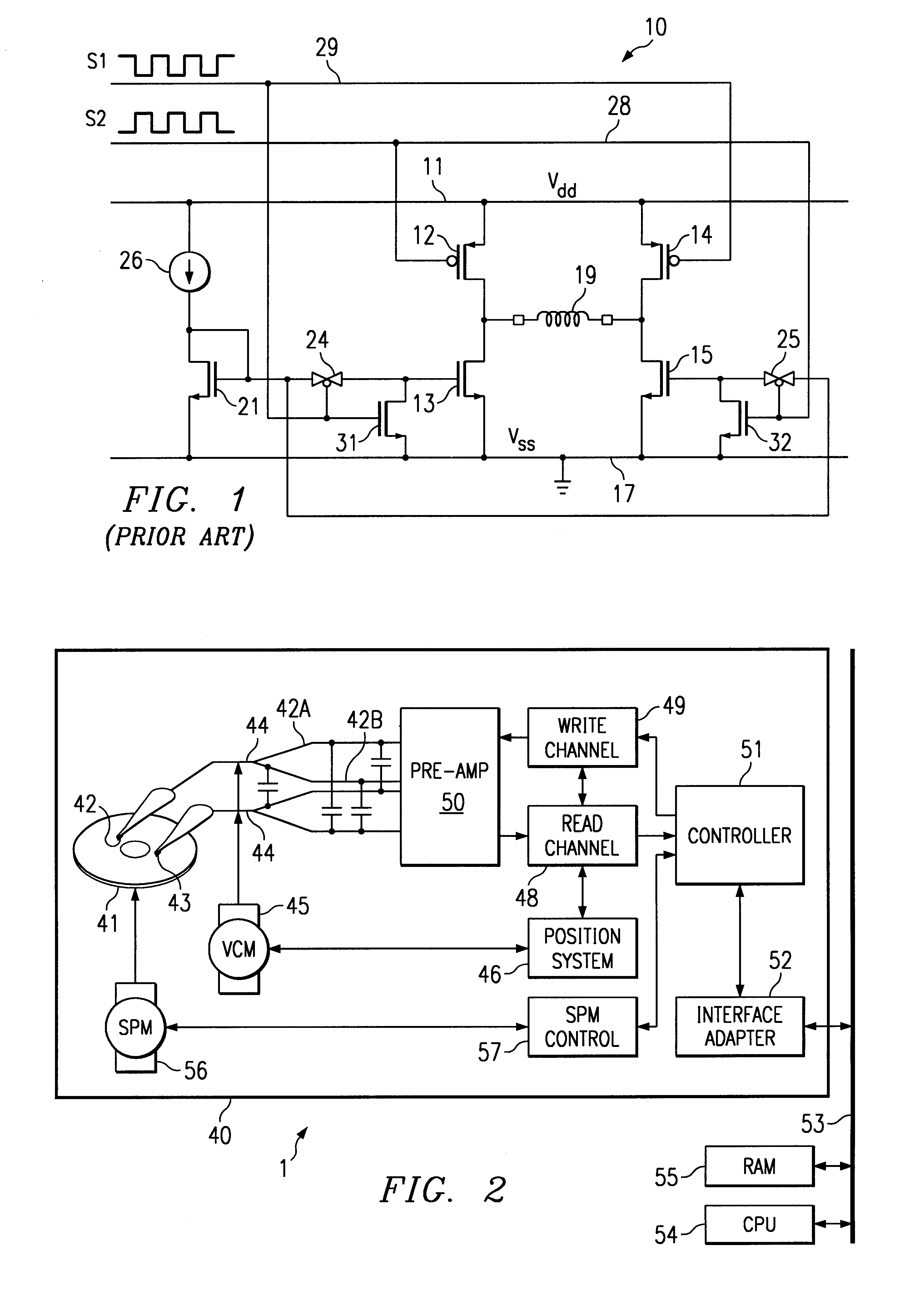

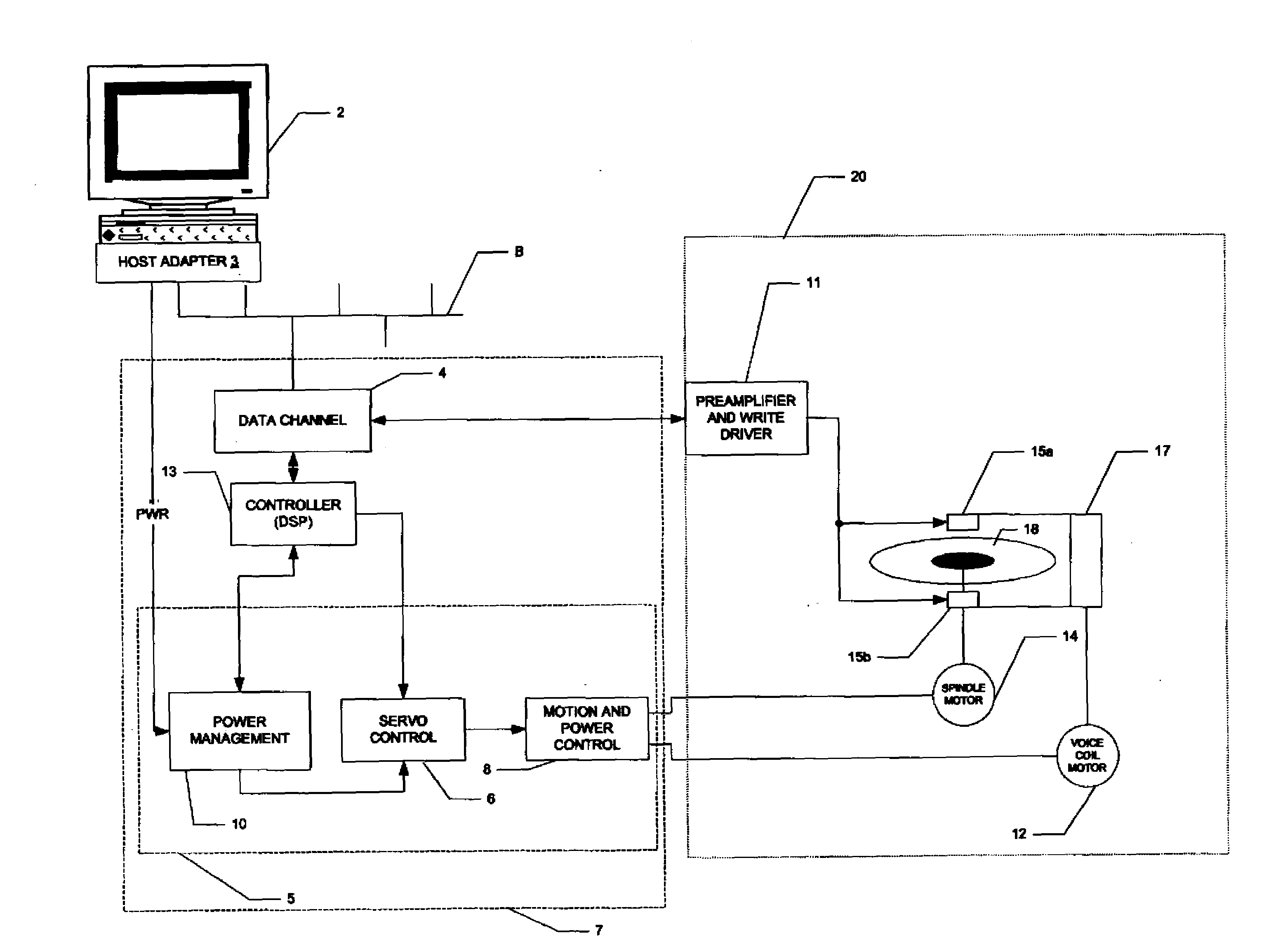

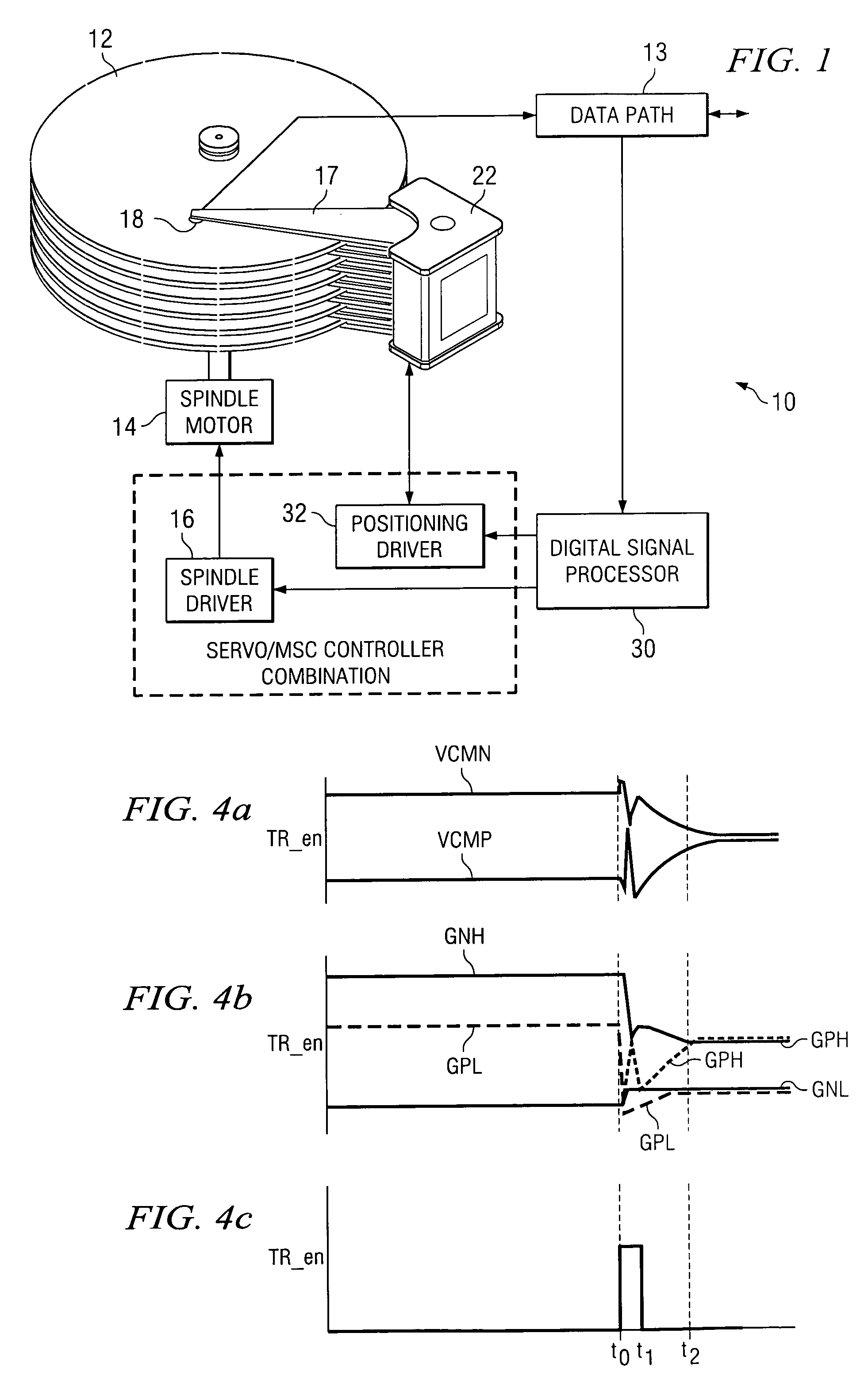

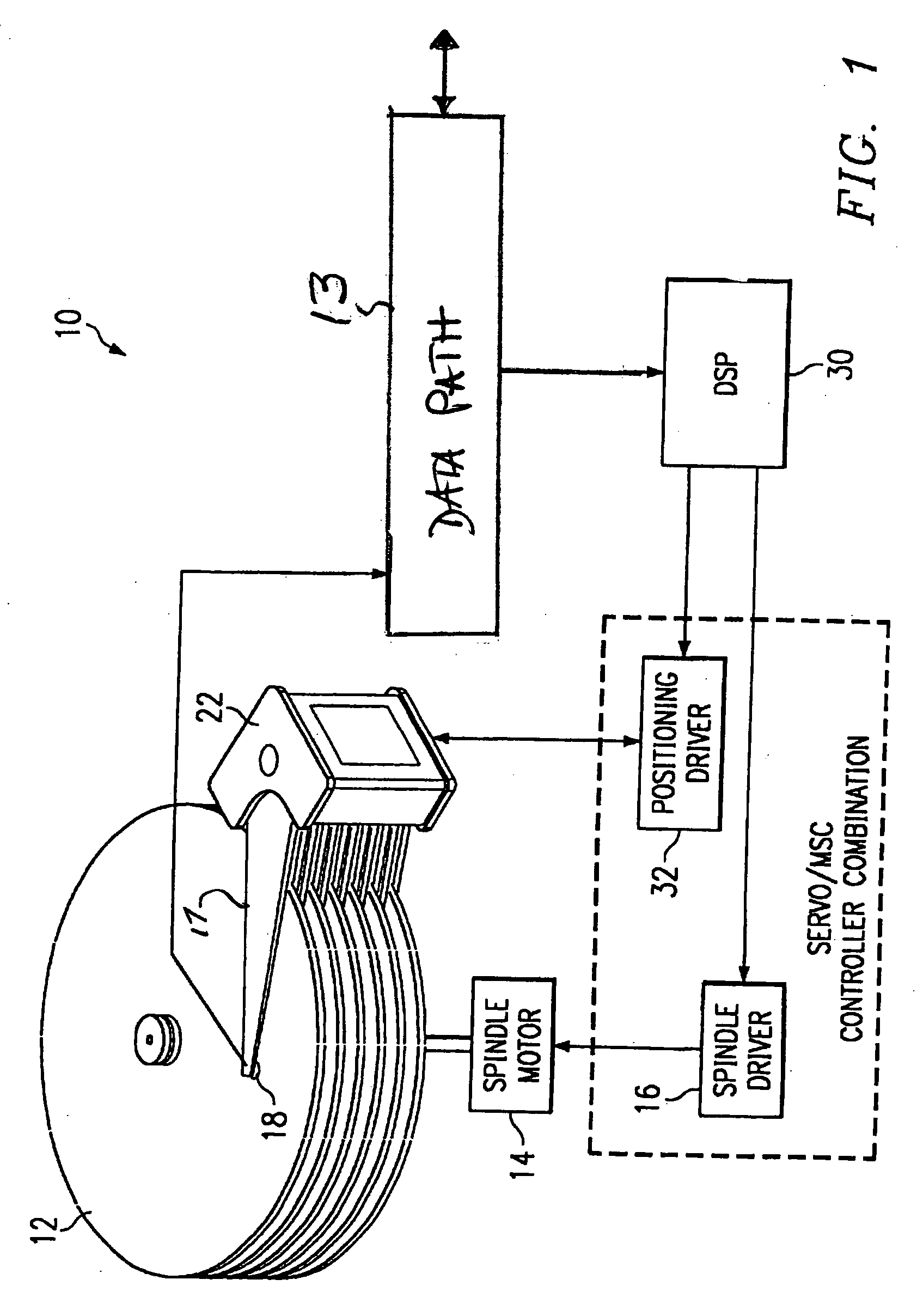

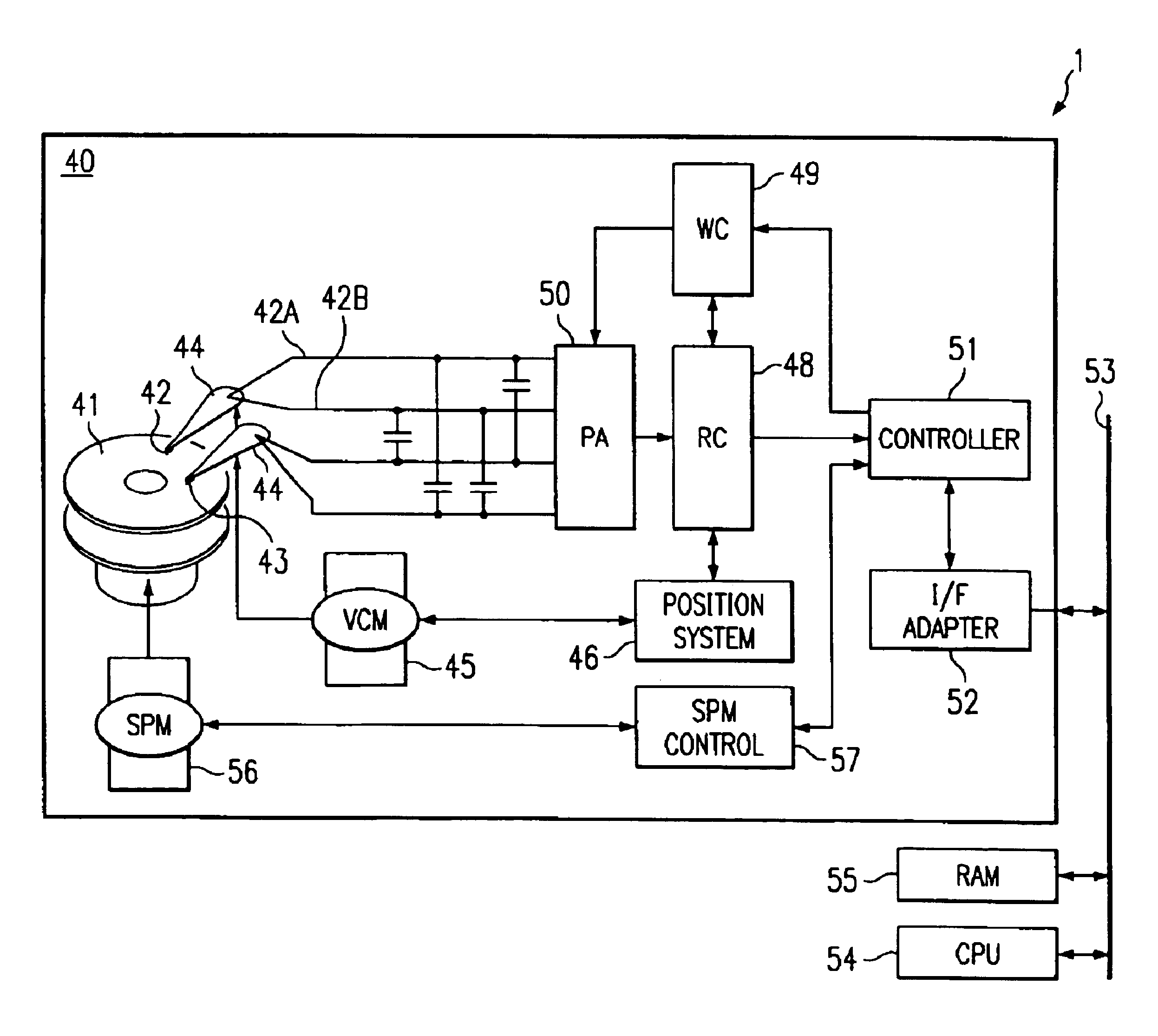

Disk drive comprising oscillators and counters for sensing current in a voice coil motor

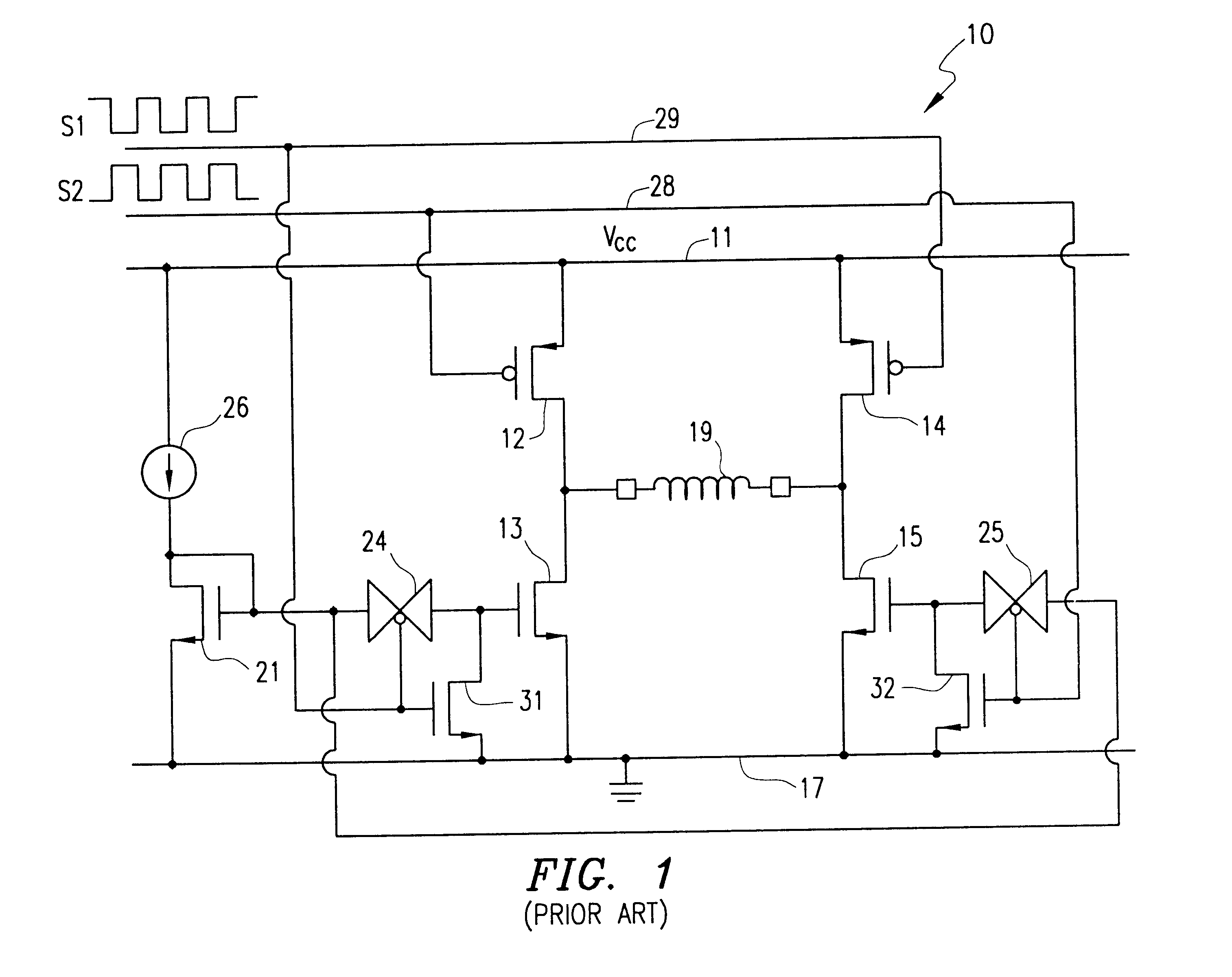

ActiveUS6850384B1Driving/moving recording headsH-bridge head driver circuitAudio power amplifierElectric machine

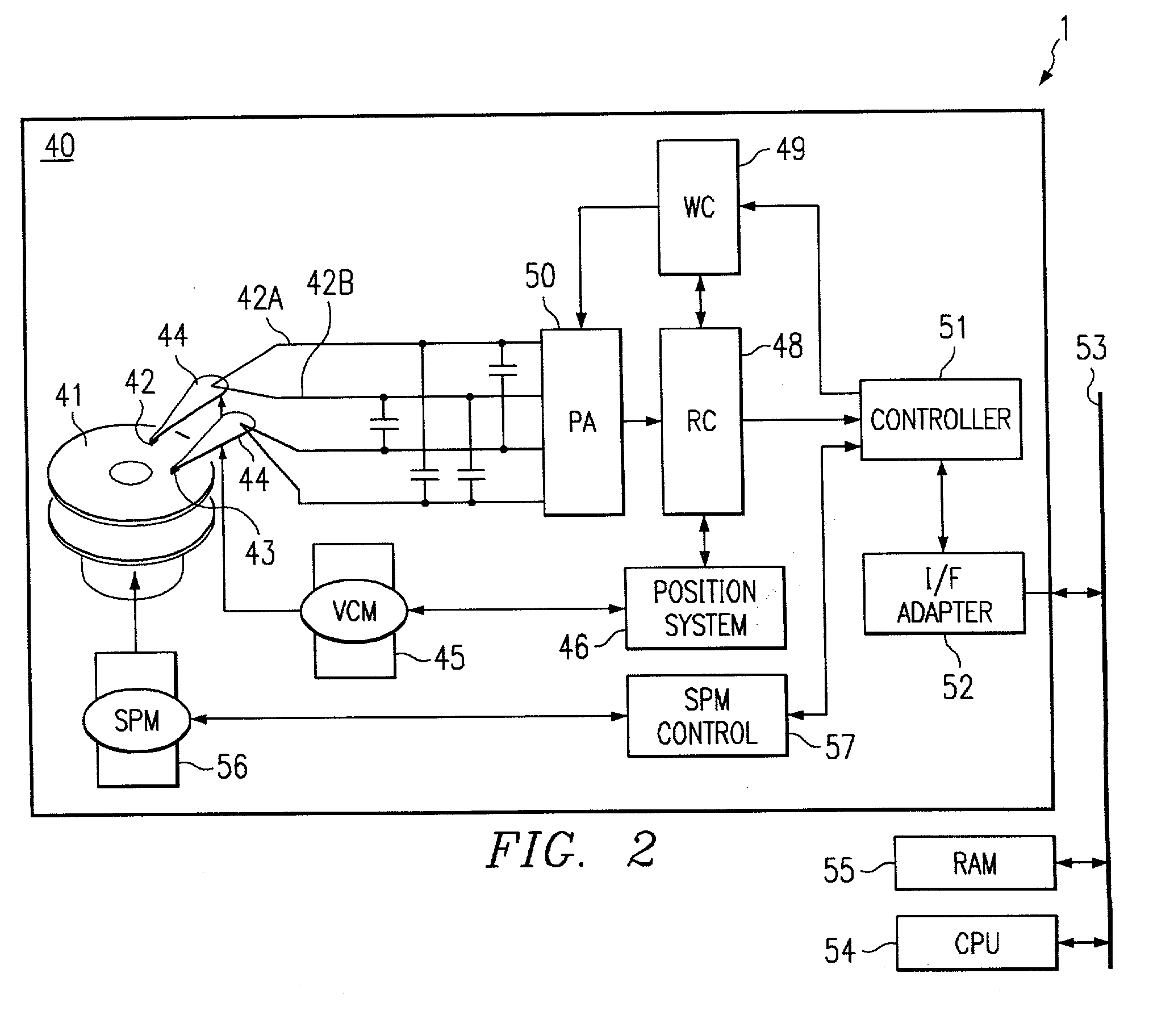

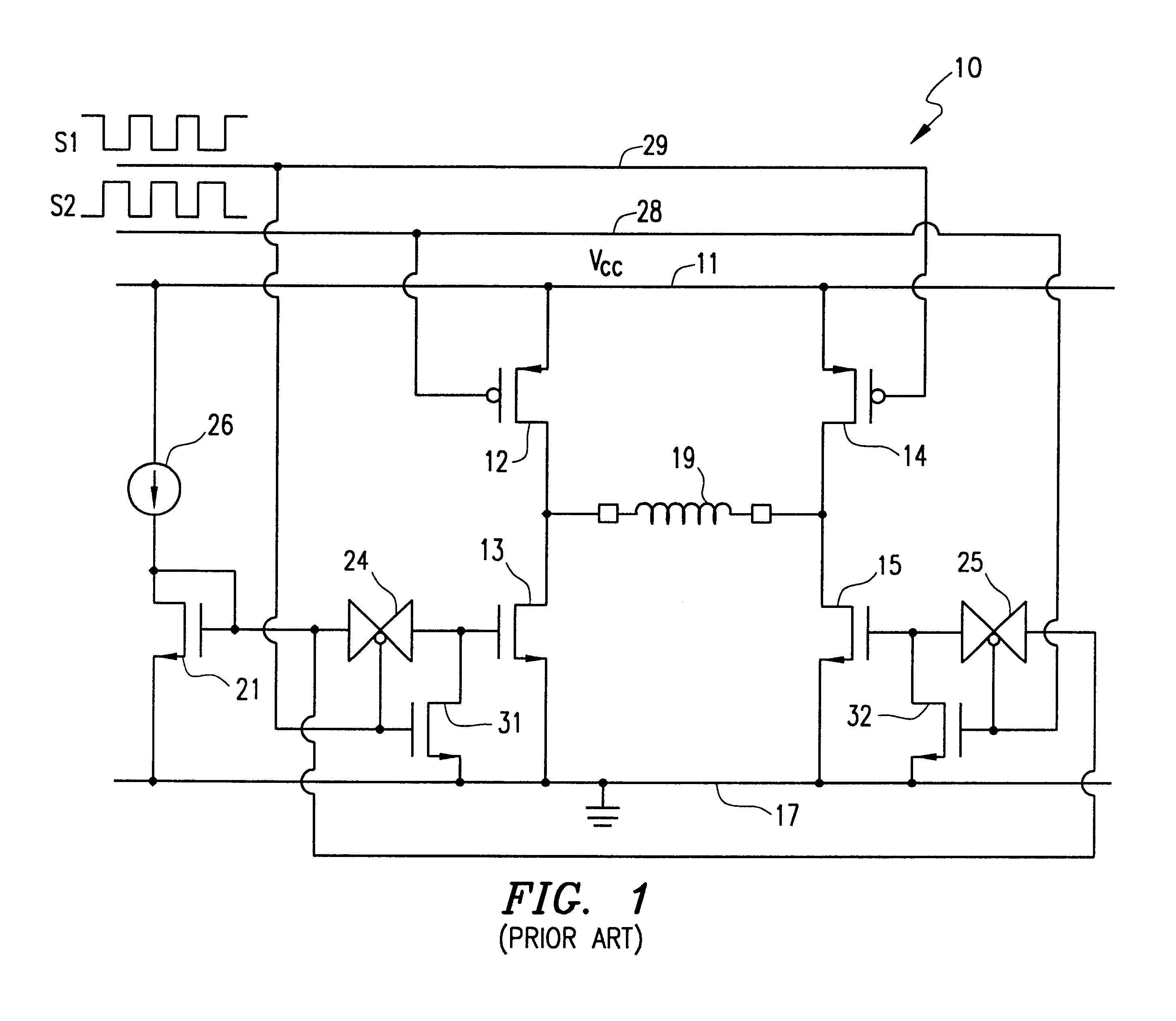

A disk drive is disclosed comprising a voice coil motor (VCM) driver including an H-bridge driver having a first sense resistor connected in series with a supply voltage and a second sense resistor connected in series with ground. First and second amplifiers amplify the voltages across the first and second sense resistors, wherein the output of the amplifiers drive respective first and second oscillators. A counter processes the frequency signals output by the oscillators to generate a digital representation of the current flowing through the voice coil of the VCM.

Owner:WESTERN DIGITAL TECH INC

Circuit and method for writing to a memory disk with a boosted voltage

A method and circuit are disclosed for controlling the write head of a magnetic disk storage device. The circuit includes a pull-up device coupled to a terminal of the write head, a current sink circuit which is coupled to the write head terminal and a bootstrap circuit coupled to the current sink circuit. When reversing the direction of current flow through the write head so that current is drawn from the write head from the write head terminal, the bootstrap circuit and the current sink circuit are activated. When the current in the write head nears and / or slightly surpasses the desired destination current level, the bootstrap circuit is deactivated and the pull-up device is thereafter immediately activated for a predetermined period of time.

Owner:STMICROELECTRONICS SRL

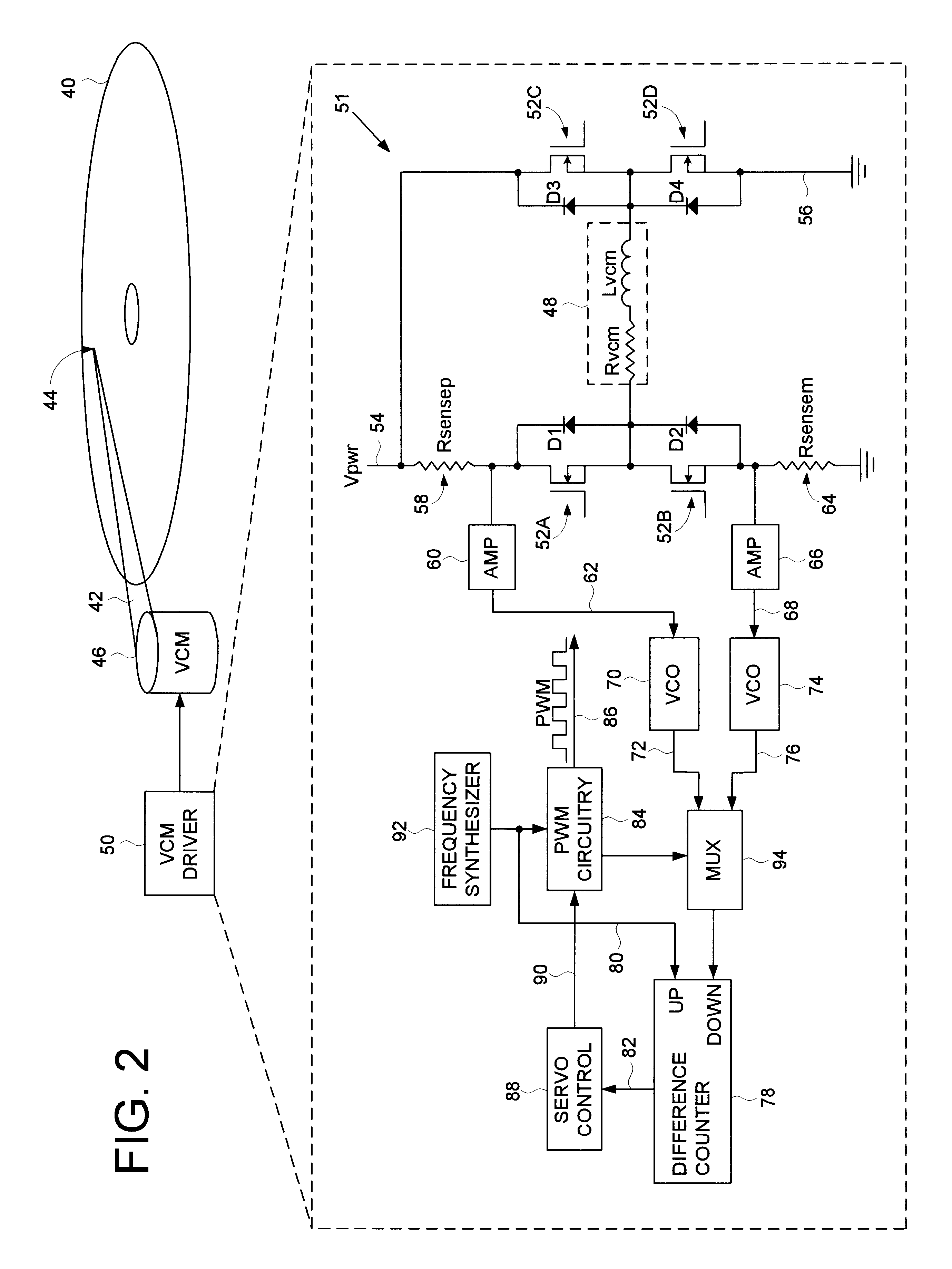

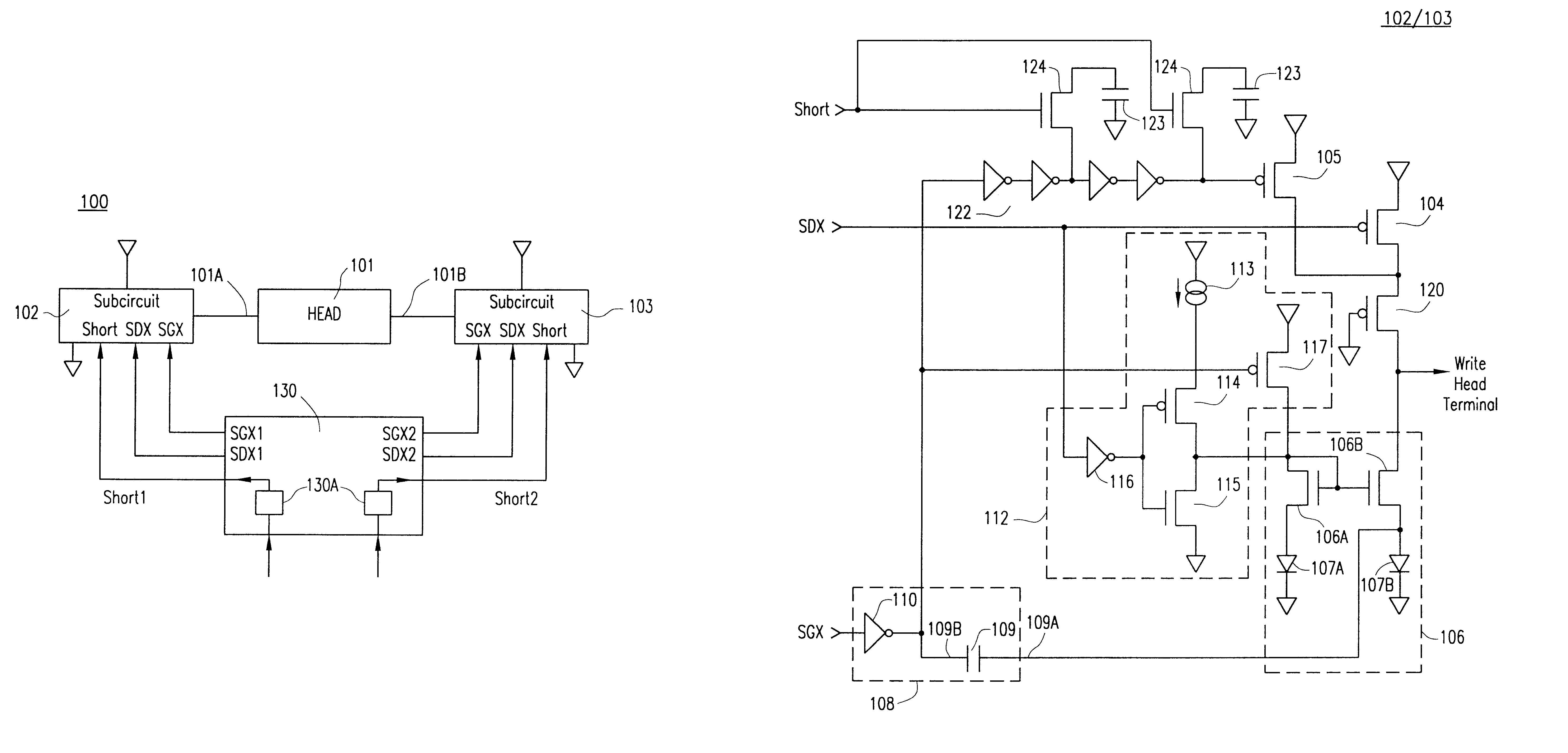

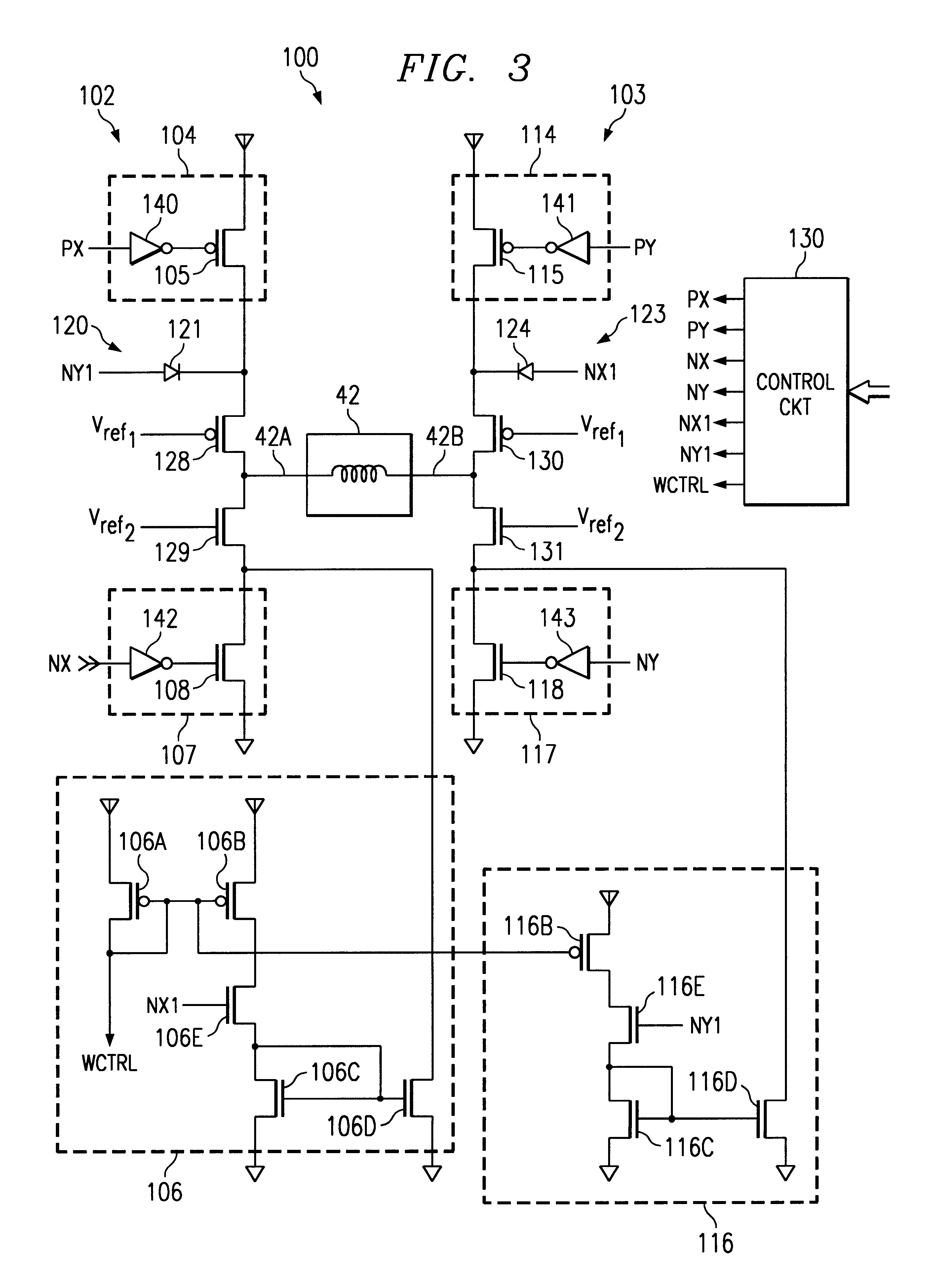

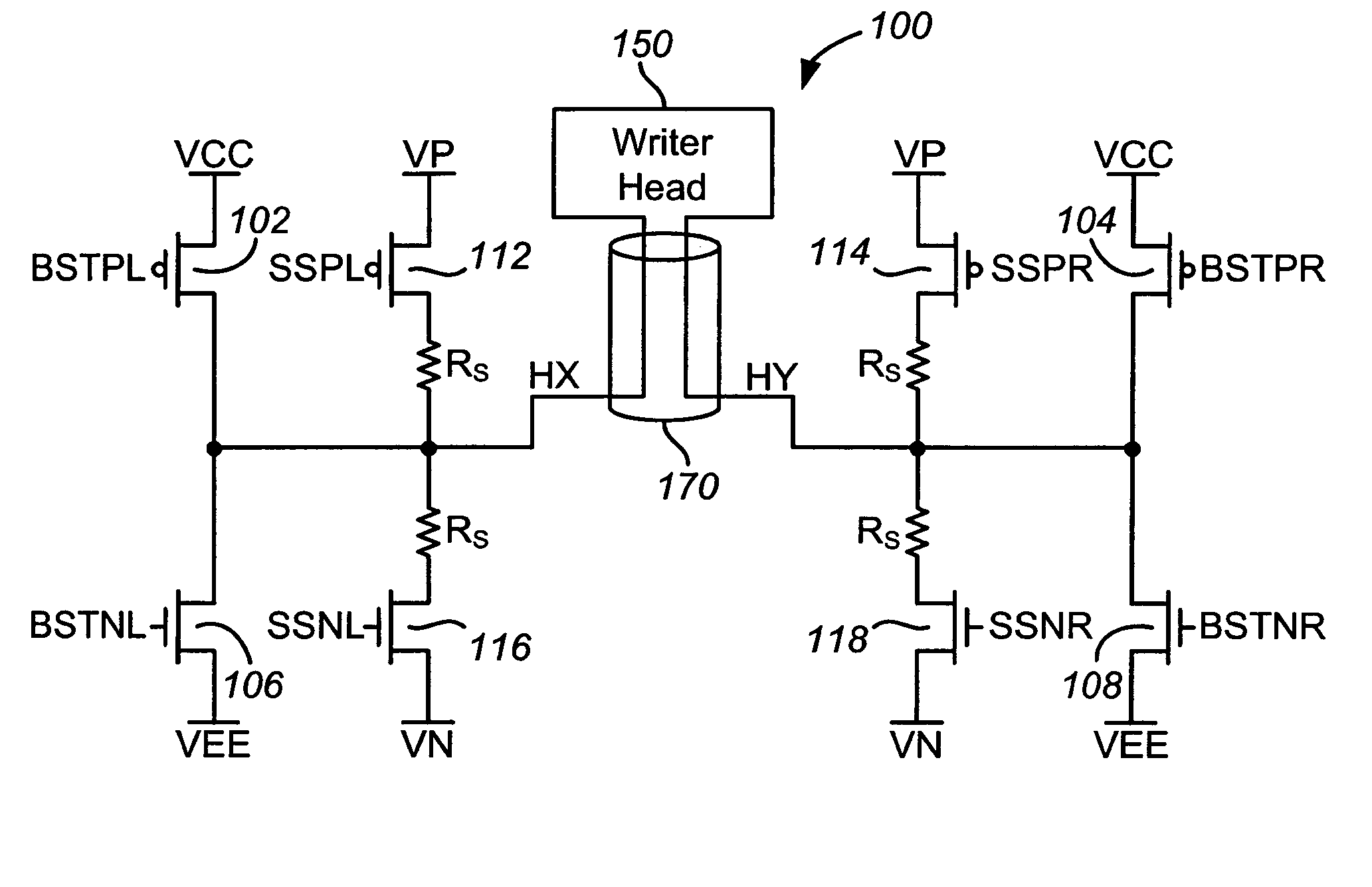

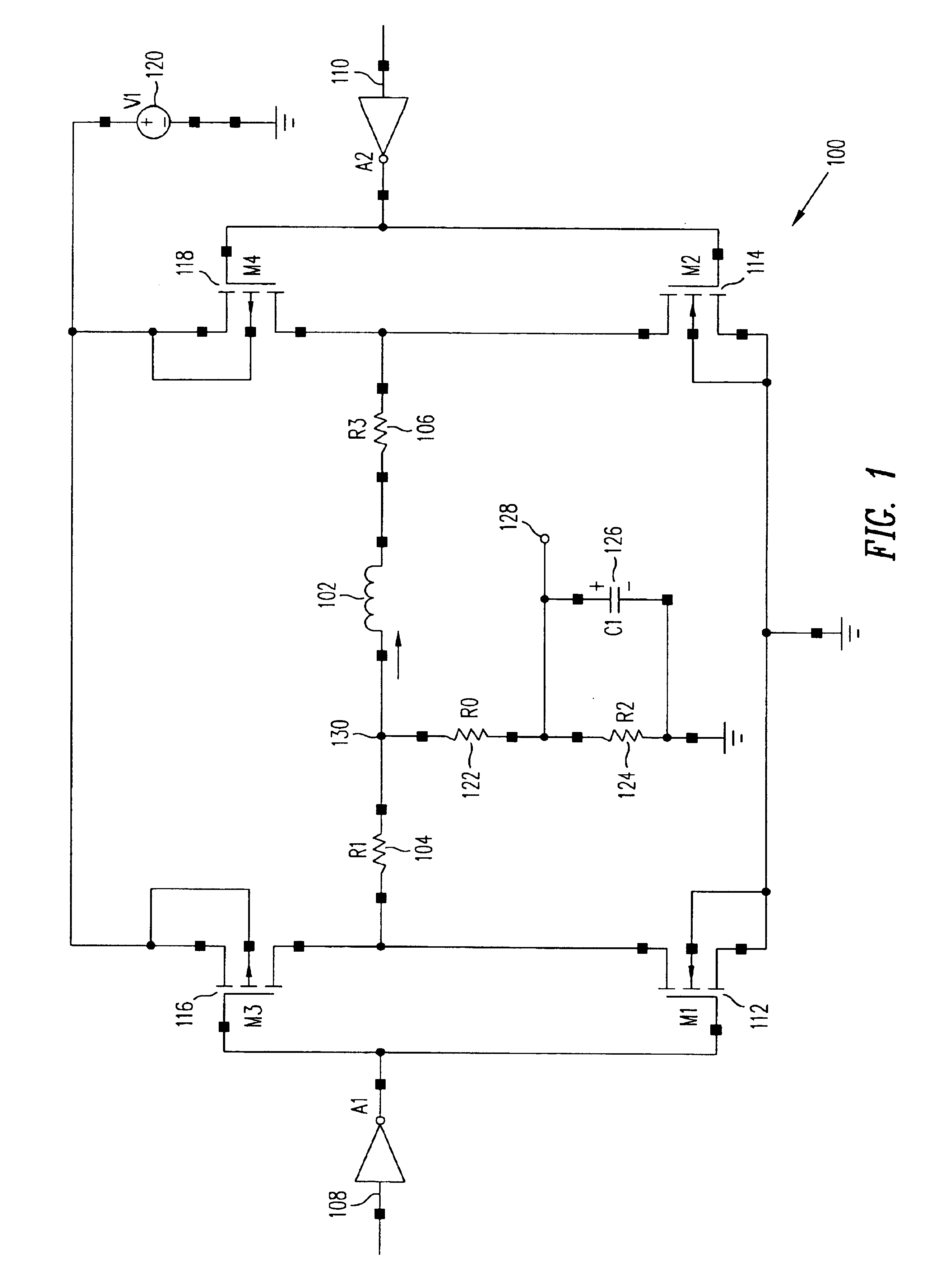

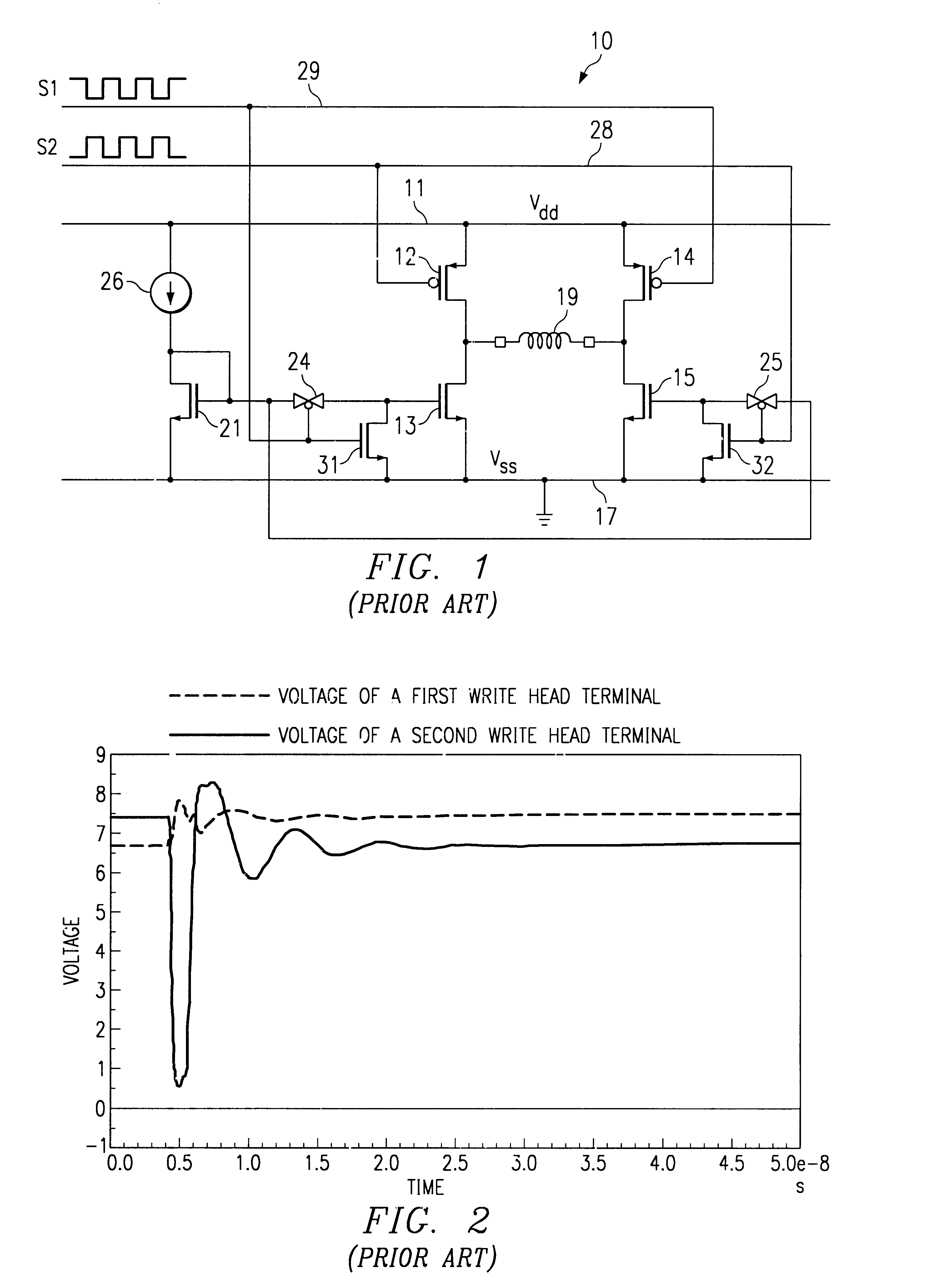

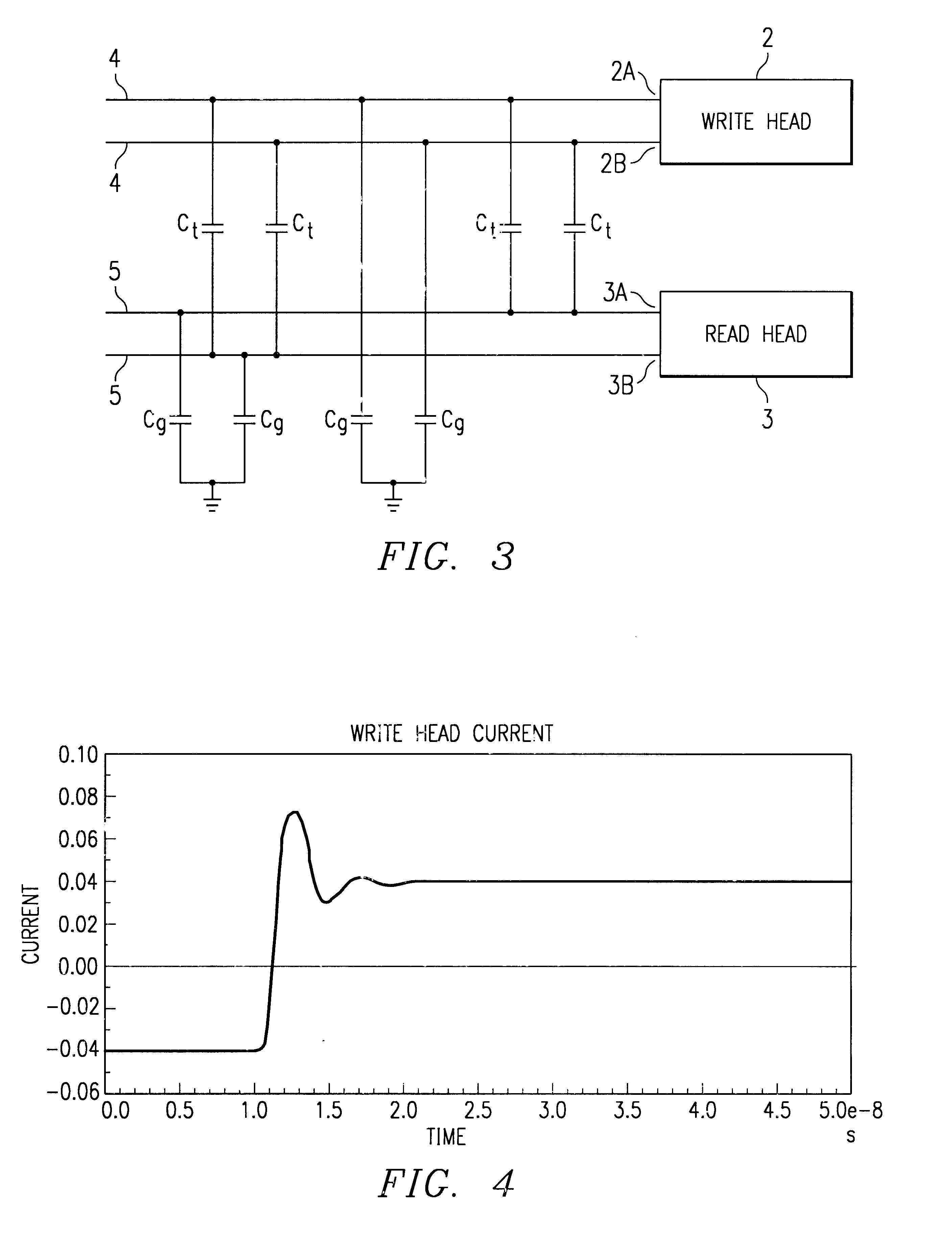

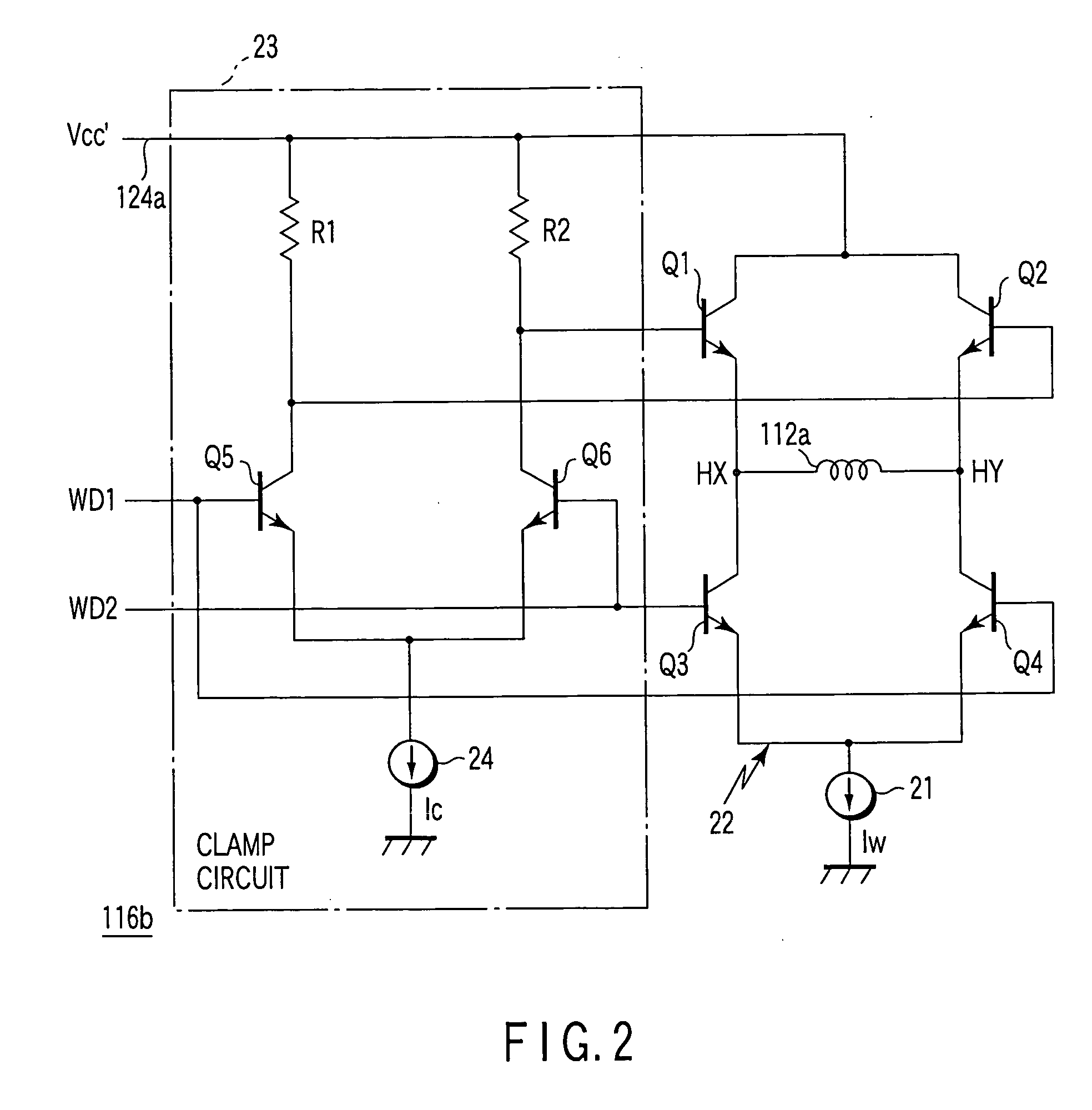

Write head driver circuit and method for writing to a memory disk

InactiveUS6504666B1H-bridge head driver circuitRecord information storageDriver circuitHemt circuits

A method and circuit are disclosed for controlling the write head of a magnetic disk storage device. The circuit includes a pull-up device and a current sink circuits coupled to each terminal of the write head, for selectively sourcing current to and sinking current from the write head, respectively. A clamp device is coupled to each write head terminal to selectively clamp the write head terminals to steady state intermediate voltage levels. The circuit further includes a control circuit for individually activating the pull-up devices, the current sink circuits and the clamp devices. In particular, when reversing the direction of current flow through the write head from a first direction in which current is provided to the write head via the write head terminal to a second direction in which current is drawn from the write head from the write head terminal, the appropriate pull-up device is activated for a predetermined period of time. The clamp device coupled to the temporarily activated pull-up device is thereafter activated to clamp the corresponding write head terminals to the steady state intermediate voltage levels.

Owner:STMICROELECTRONICS SRL

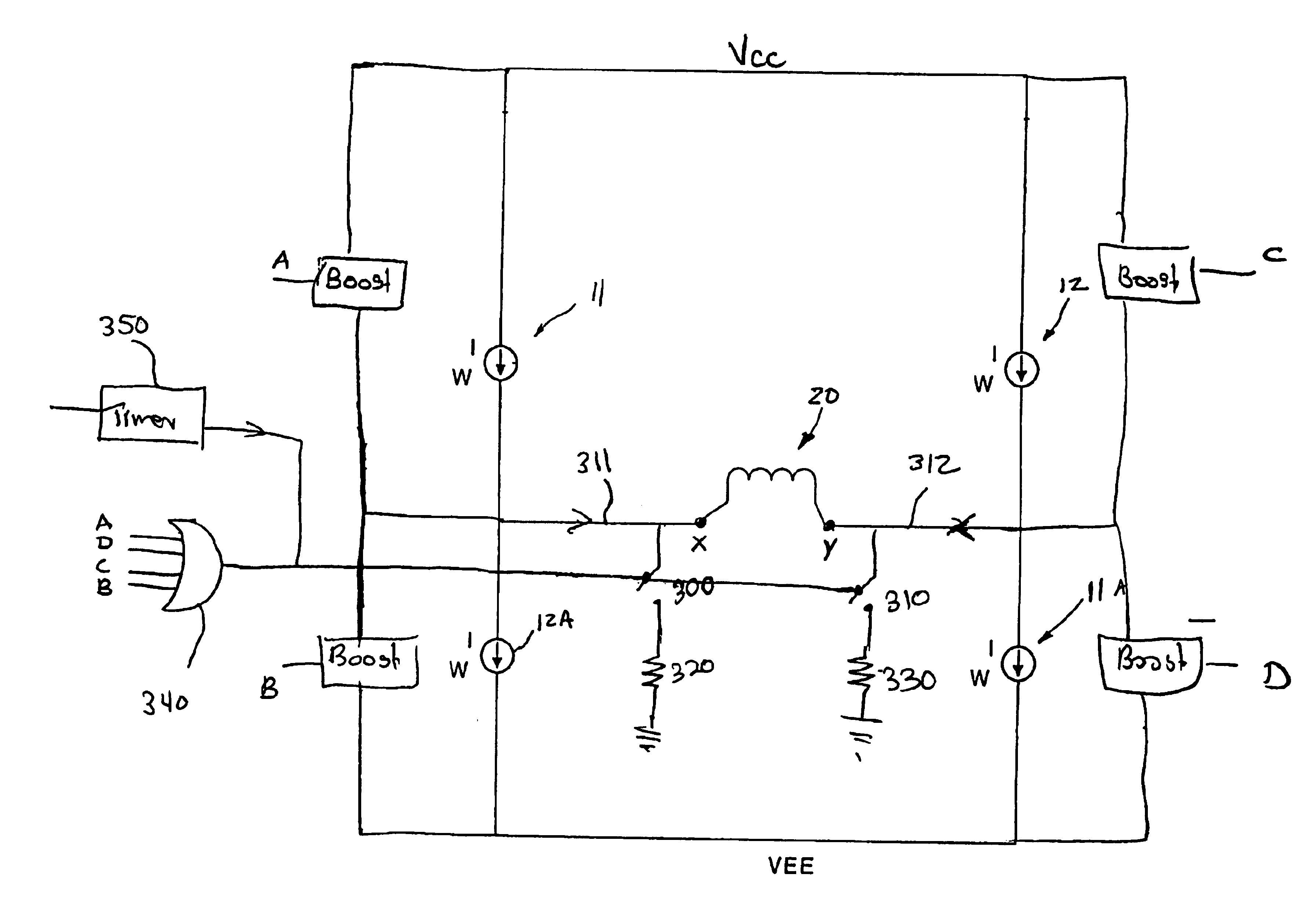

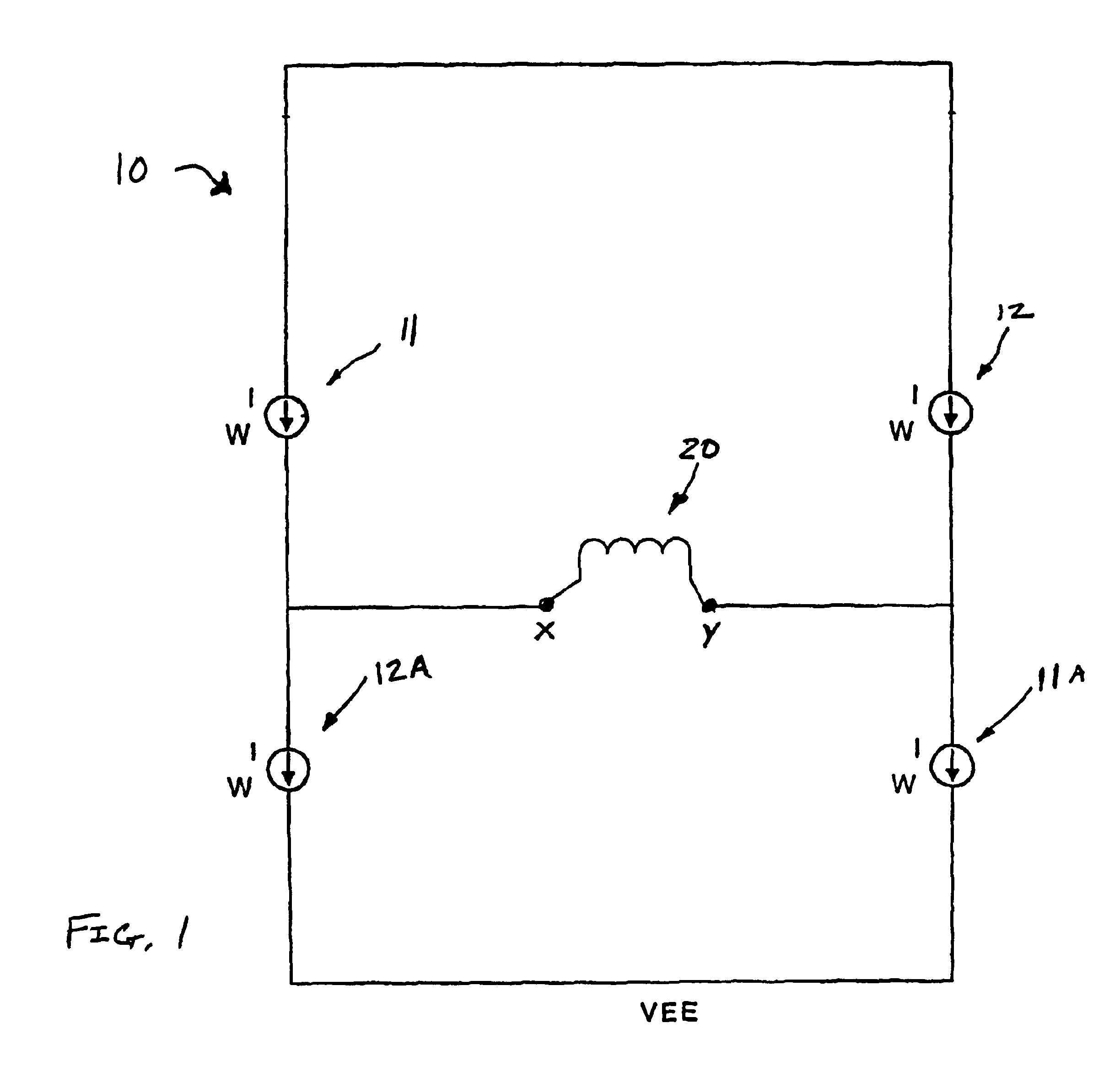

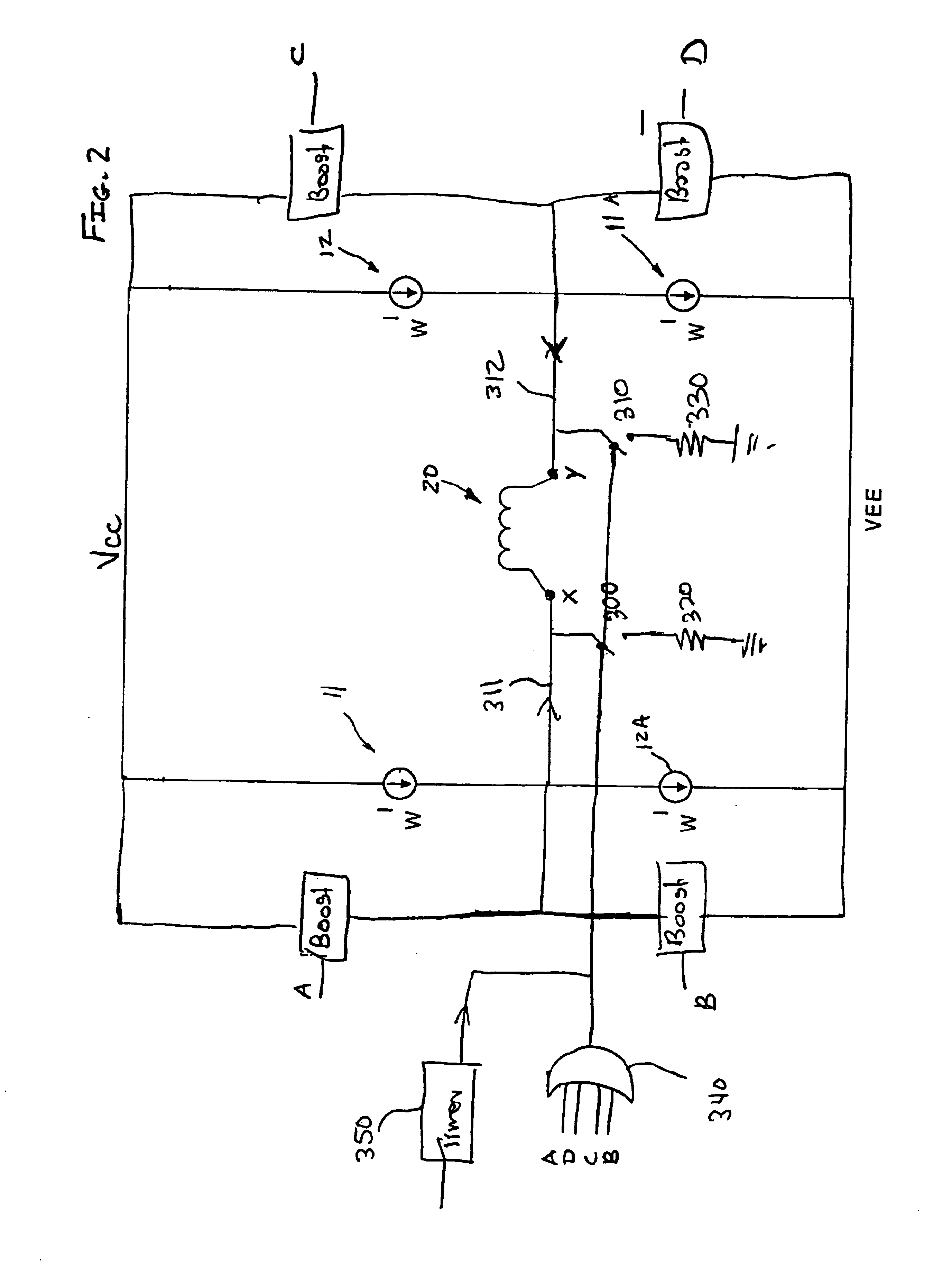

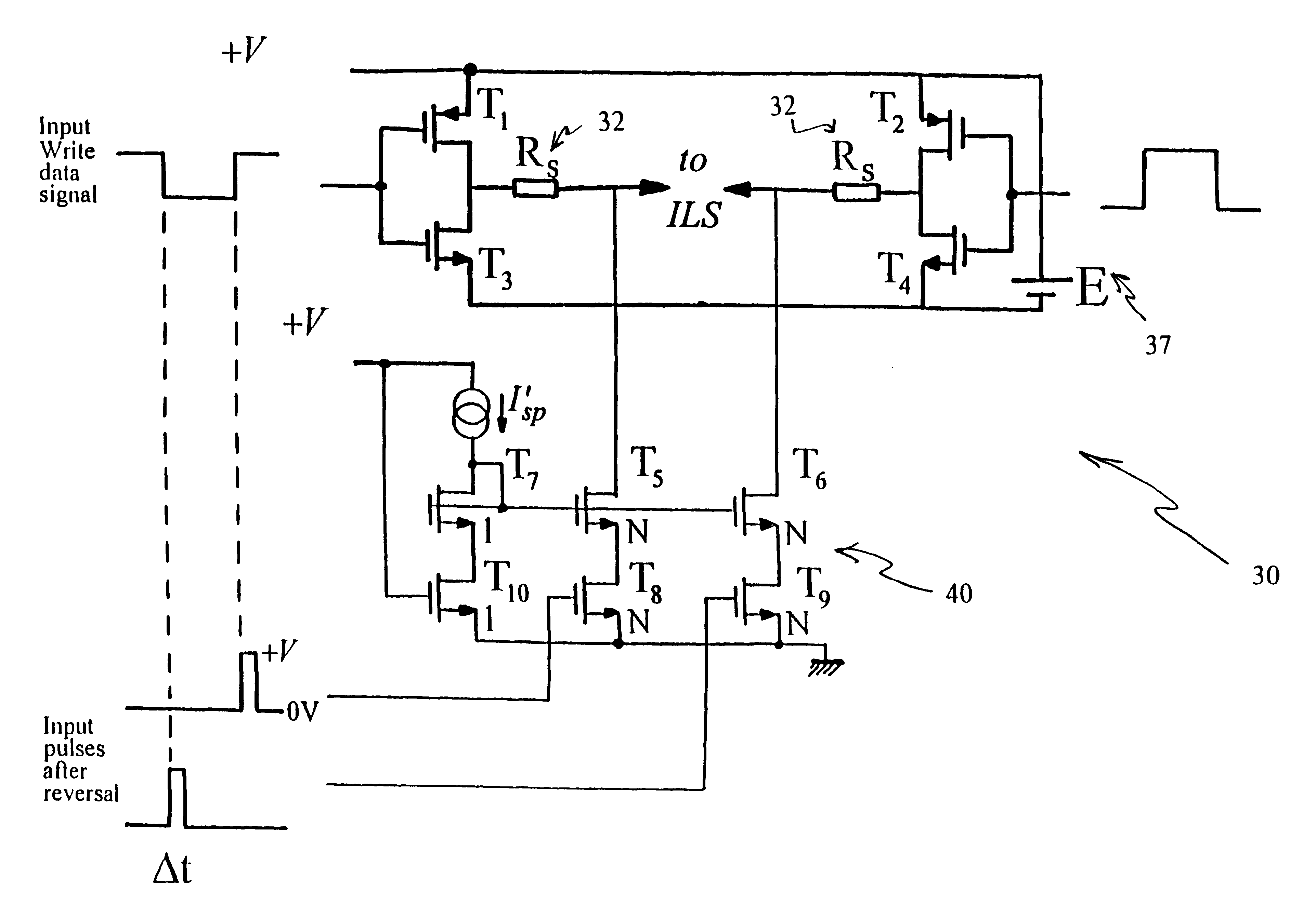

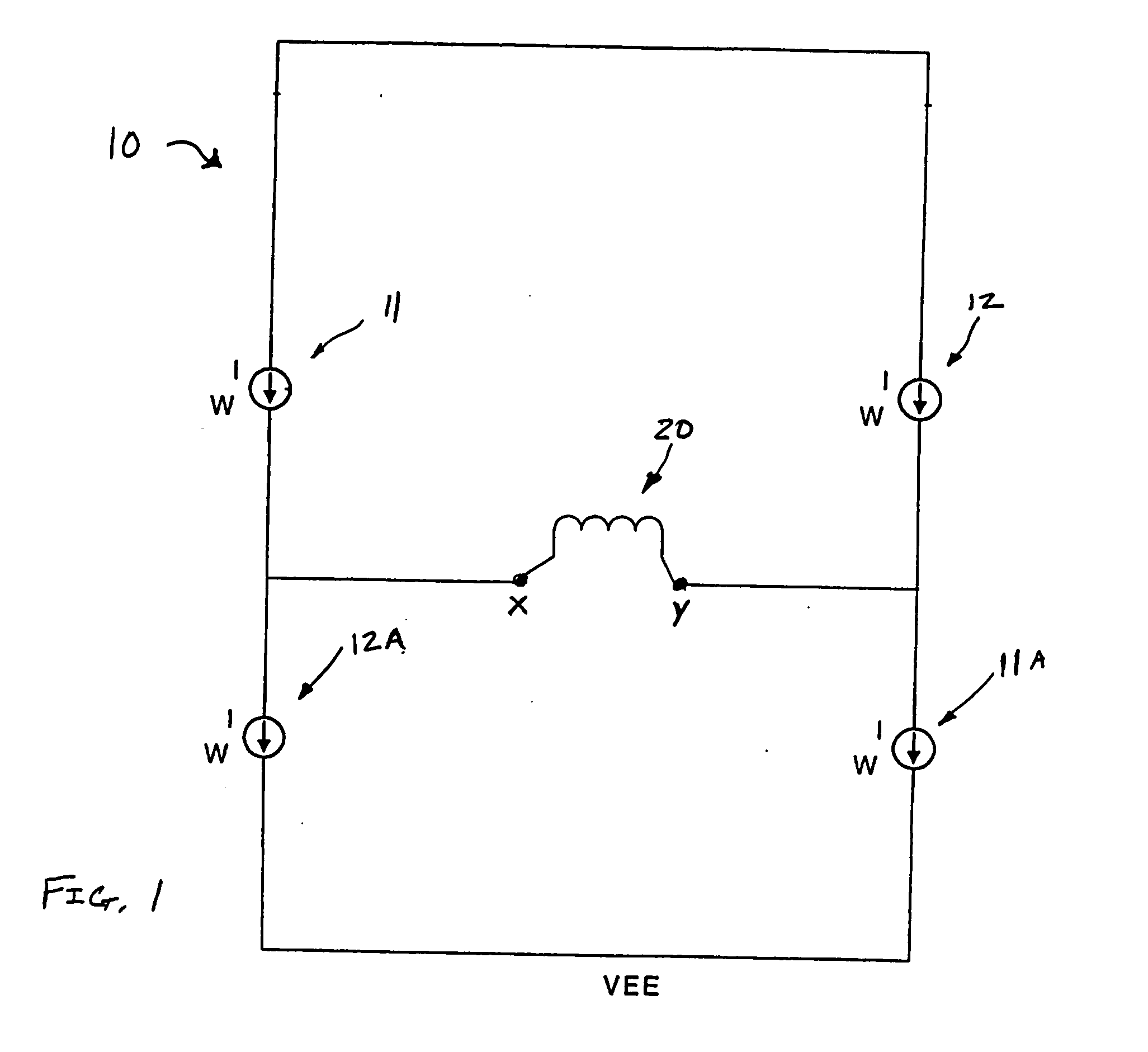

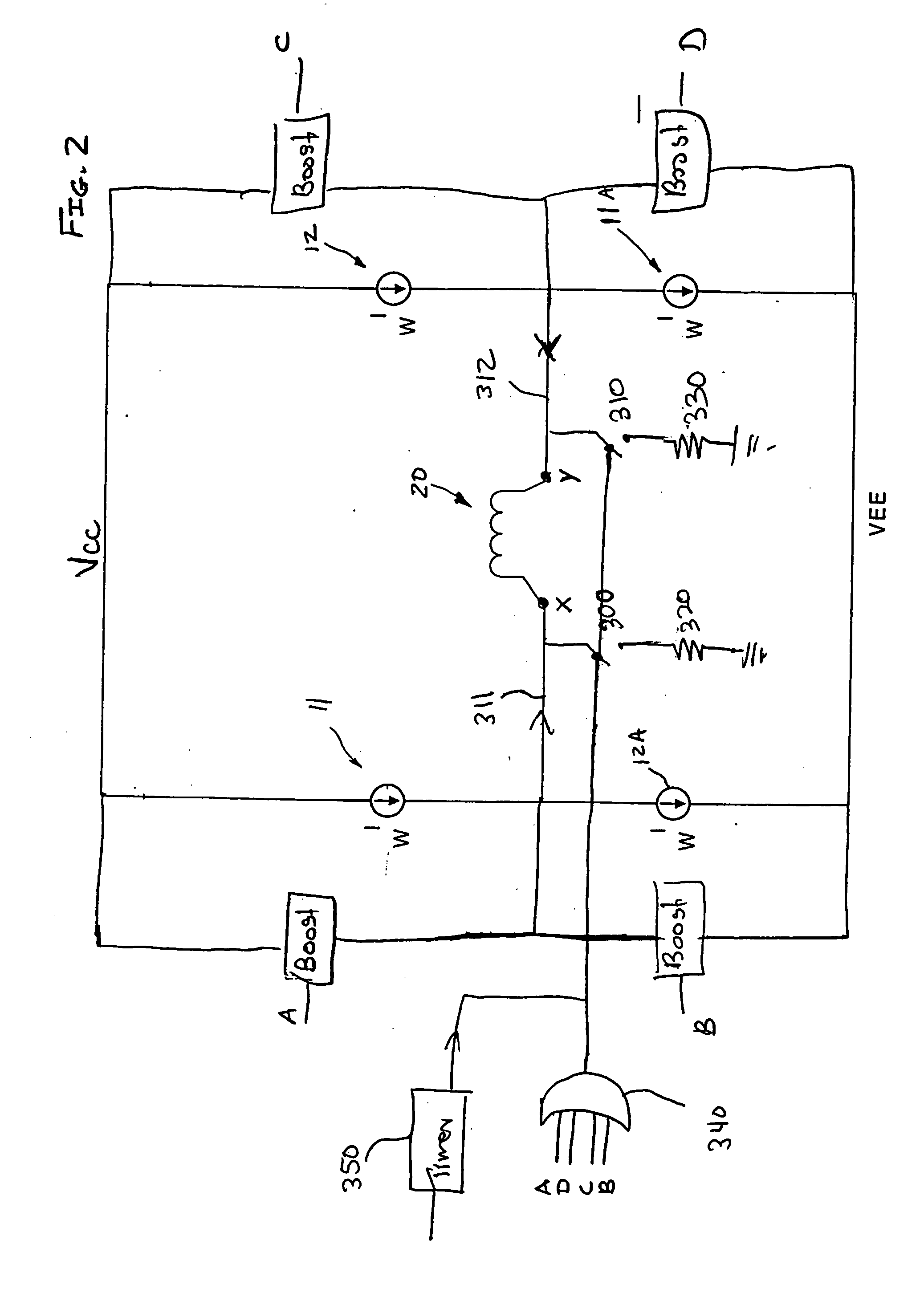

Damping resistor boost writer architecture

ActiveUS6917484B2H-bridge head driver circuitRecord information storageHard disc driveMagnetic storage

A write driver apparatus and corresponding method for an inductive head element (20) in a magnetic storage medium, such as a hard disk drive, having an H-bridge type circuit (10) which is capable of driving a current through the inductive head element (20) and having a boost circuit (250, 260) which is coupled with the H-bridge (10) and which is operable for delivering another current during a predetermined period to the head element (20), wherein a sum of the currents provides the write current for the head element (20) of the hard disk drive. Further, a resistive element (210, 320, 330) is selectively coupled with the head element (20) for providing impedance matching in which the resistive element (210, 320, 330) is decoupled from the head element (20) during delivery of the current from the boost circuit (250, 260).

Owner:TEXAS INSTR INC

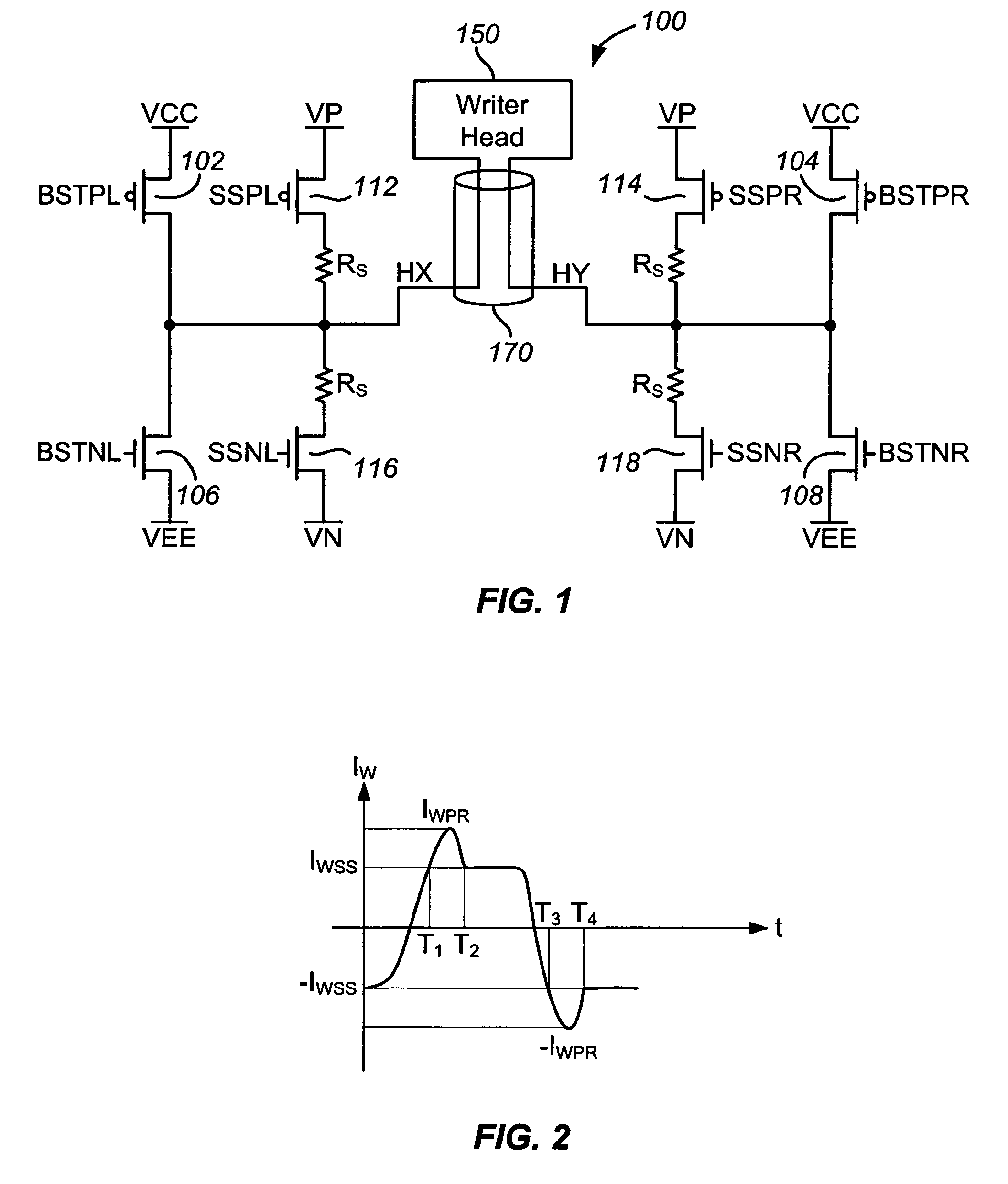

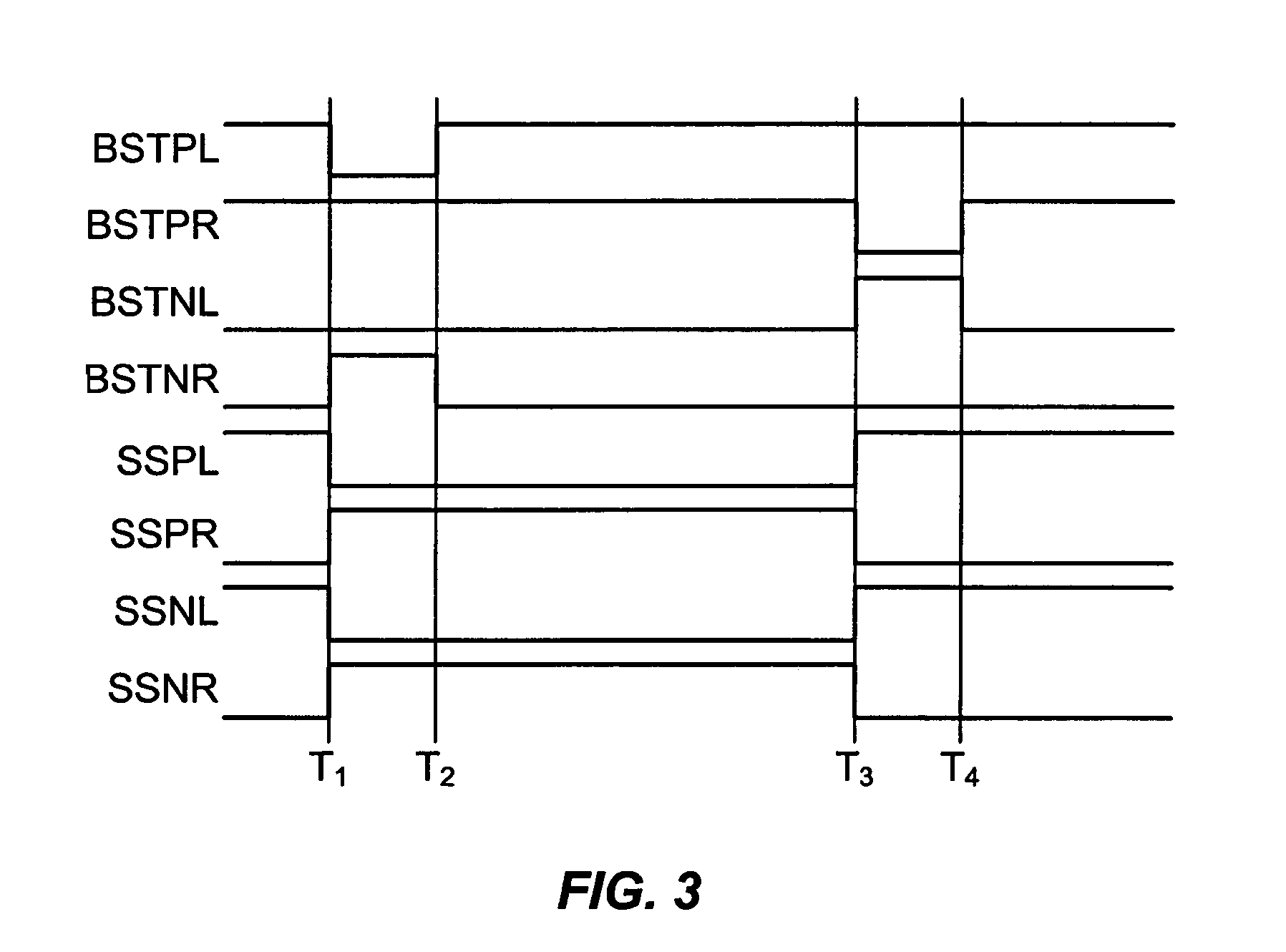

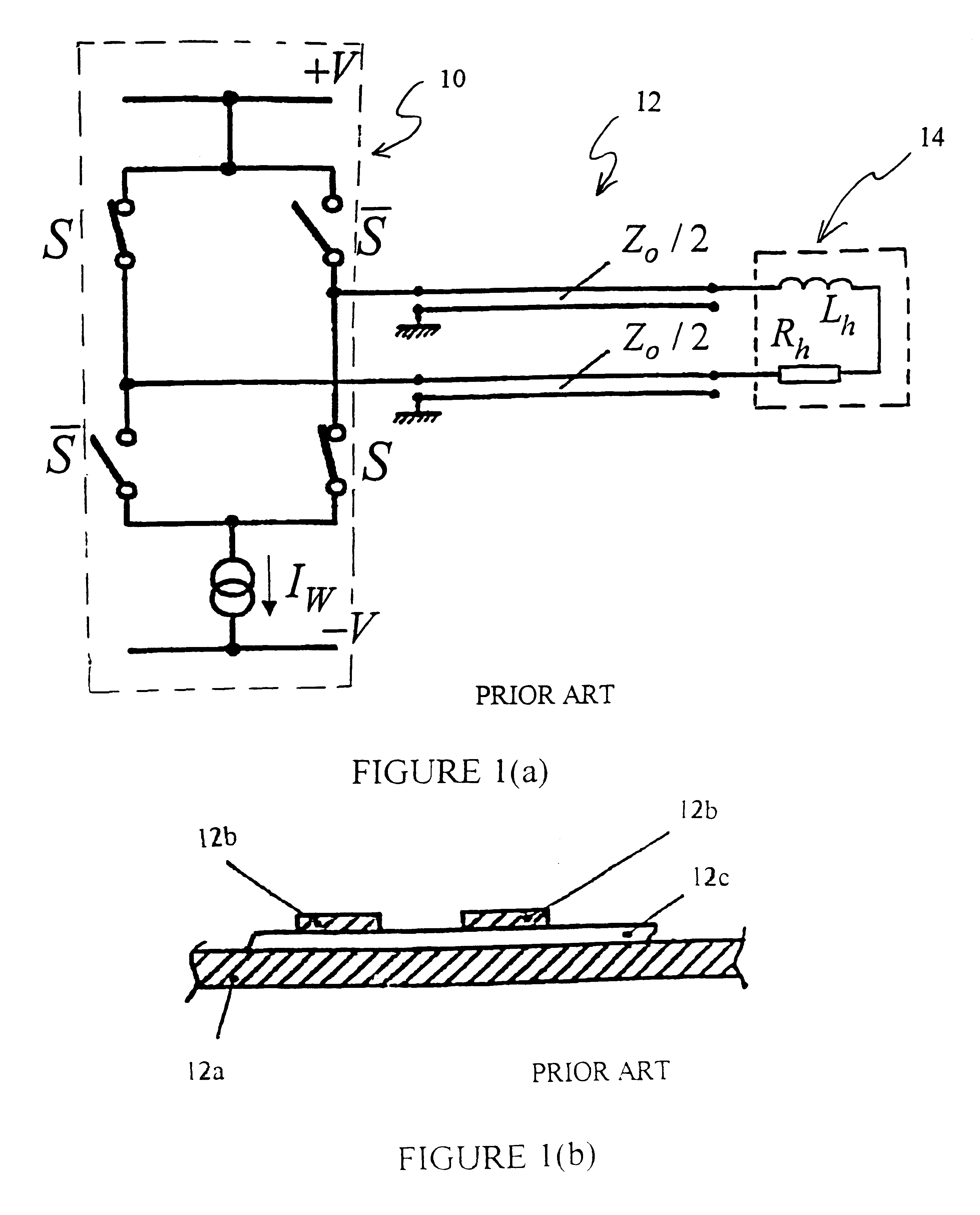

Low power preamplifier writer architecture

ActiveUS7408313B1DC motor speed/torque controlH-bridge head driver circuitAudio power amplifierEngineering

A circuit is adapted to activate a writer head of a data storage media drive during both the boost periods as well as the steady state periods. The current supplied to the writer head during the boost periods exceeds the steady state current and flows between positive and negative voltage supplies so as to provide the required magnetic flux change in the inductor disposed in the write head. During the steady state periods, a switch circuit is turned on to provide a second current path across the writer head. During the steady state periods, the current flows between the positive voltage supply and the ground to reduce power consumption. The switch circuit is turned off during the boost periods.

Owner:MARVELL ASIA PTE LTD

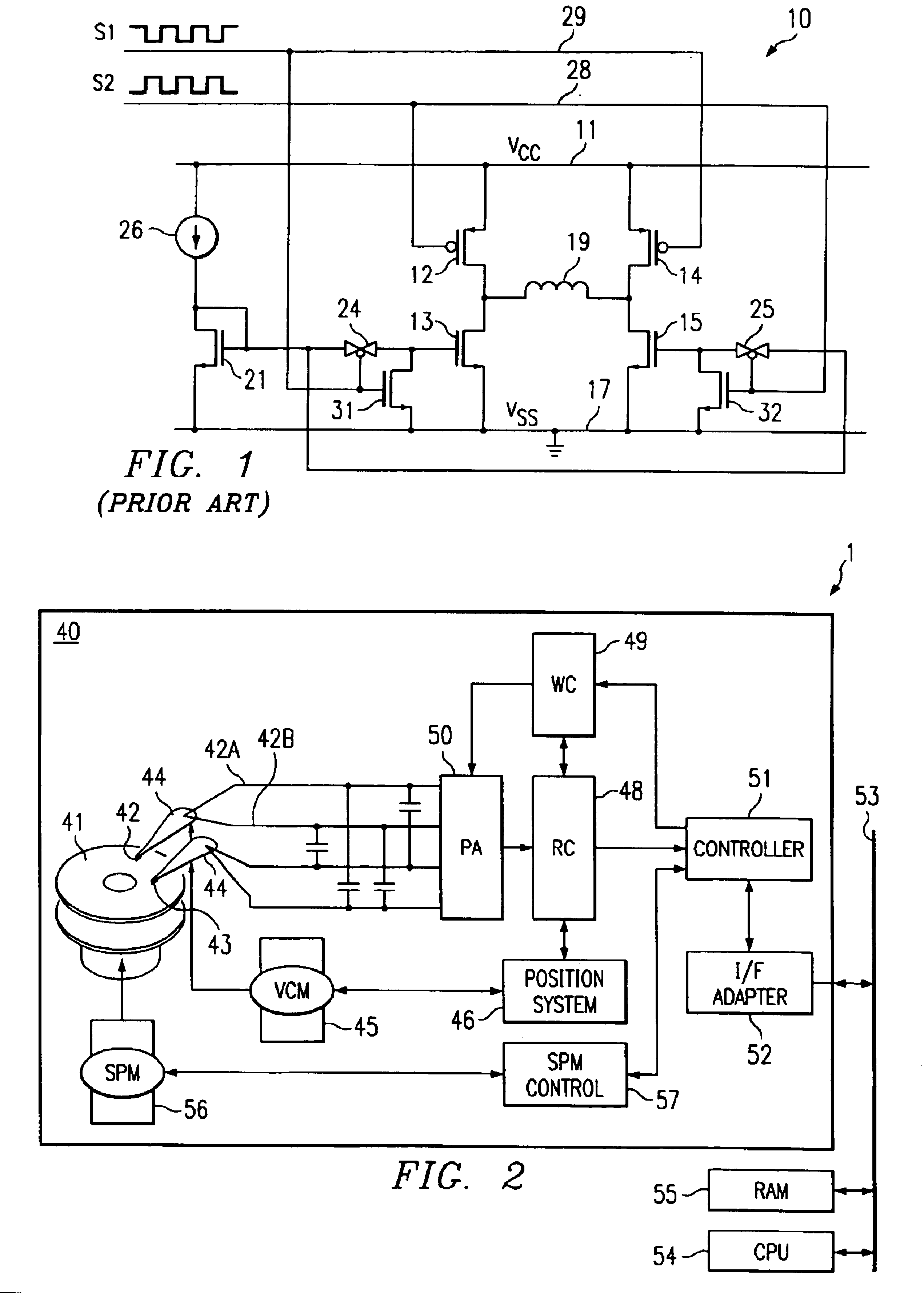

Low Power Write Driver for a Magnetic Disk Drive

InactiveUS20080204914A1Reduces steady-state power dissipationReduce power consumptionH-bridge head driver circuitRecord information storageElectrical currentWrite current

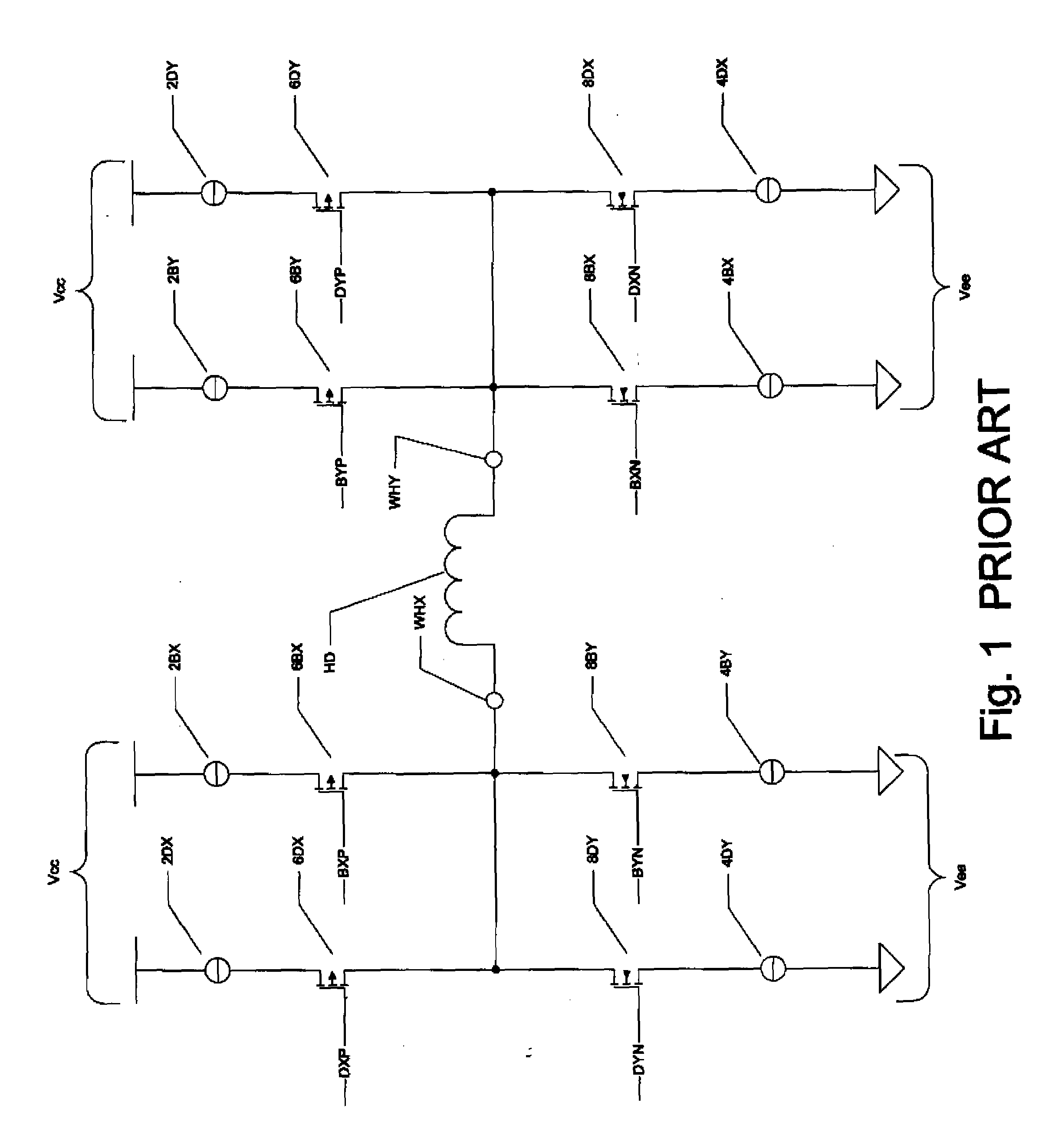

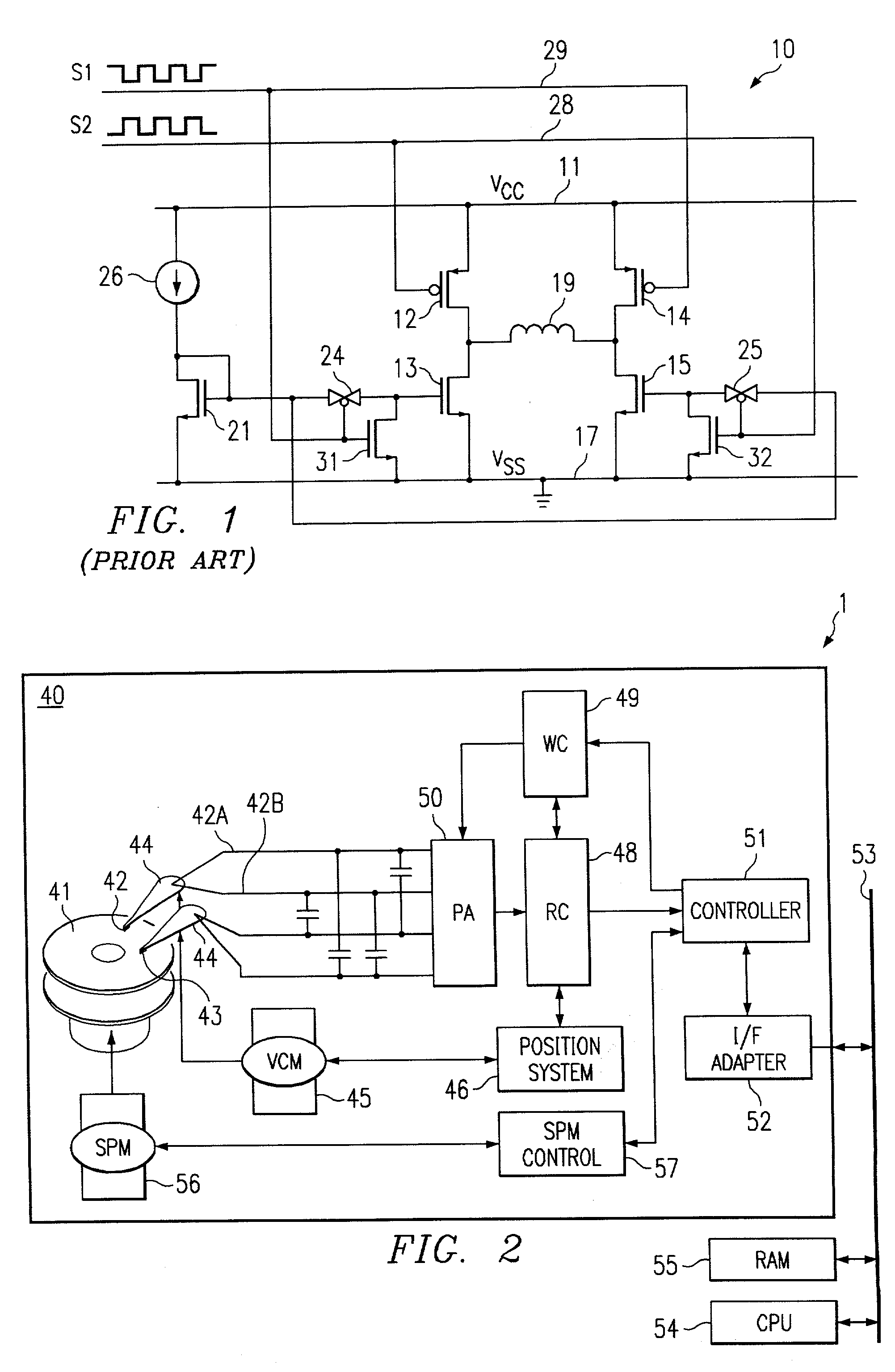

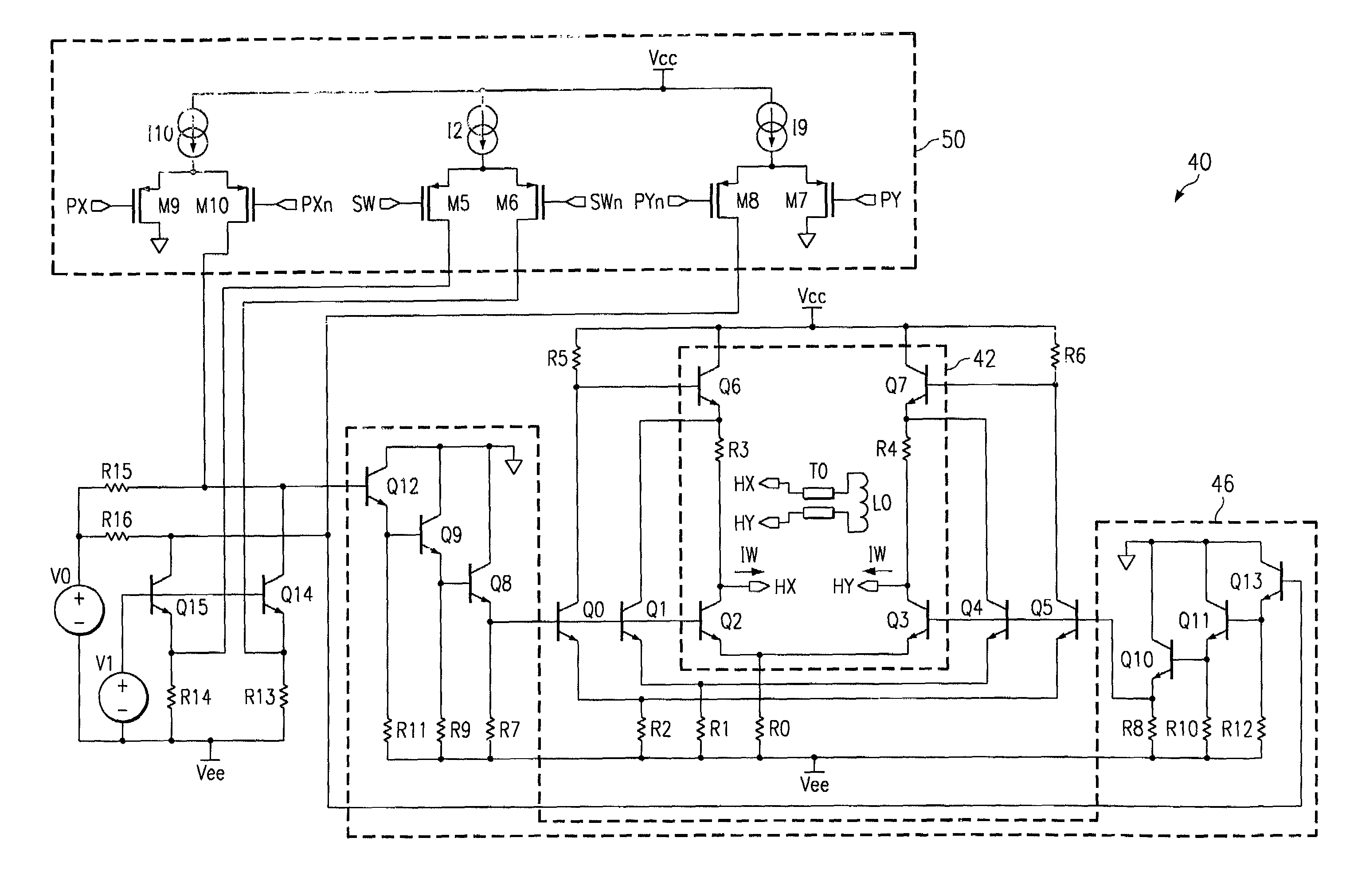

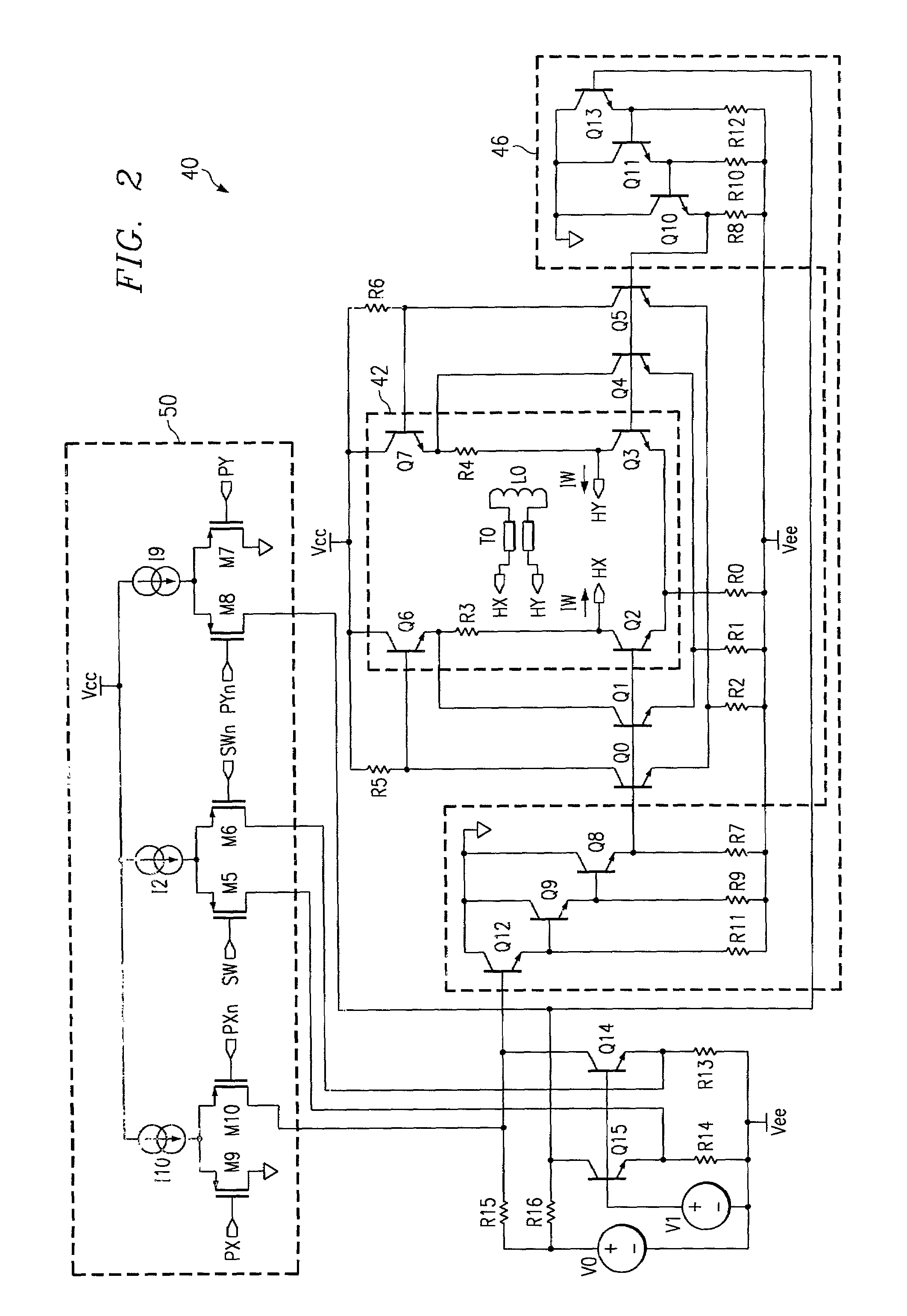

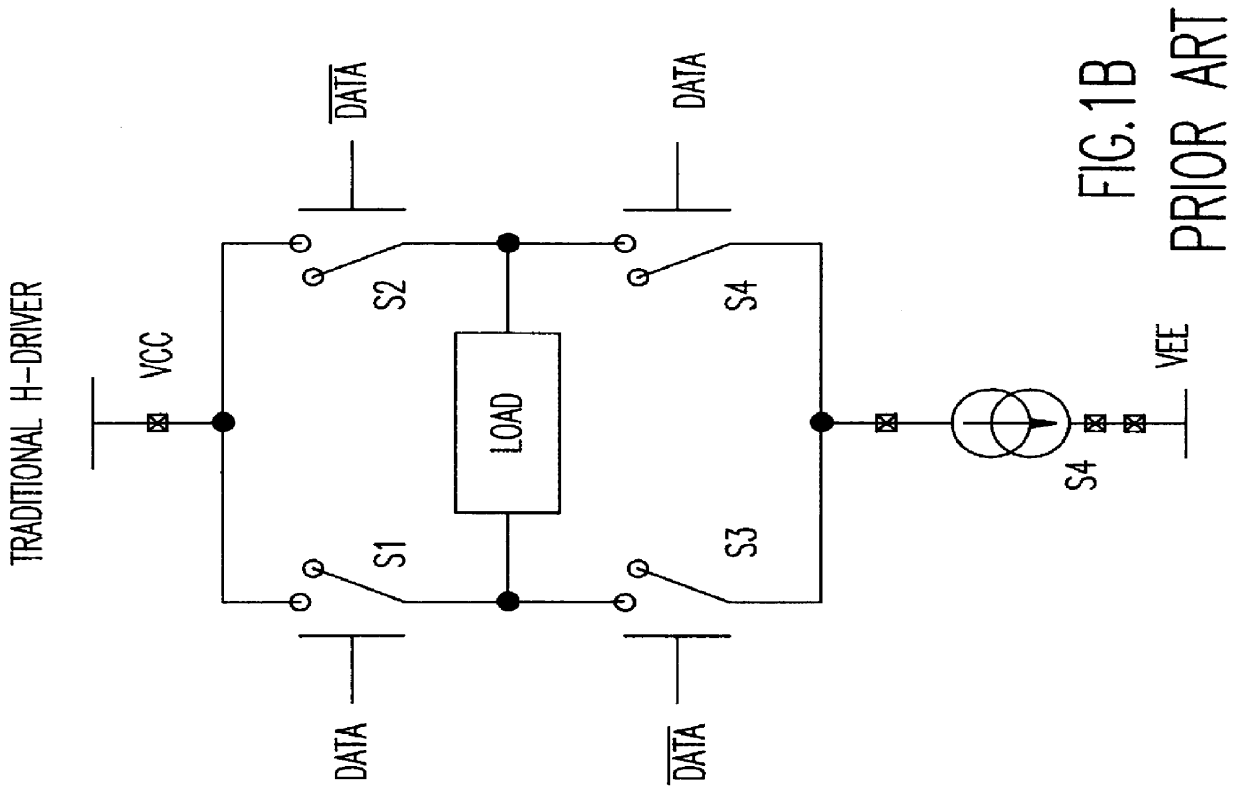

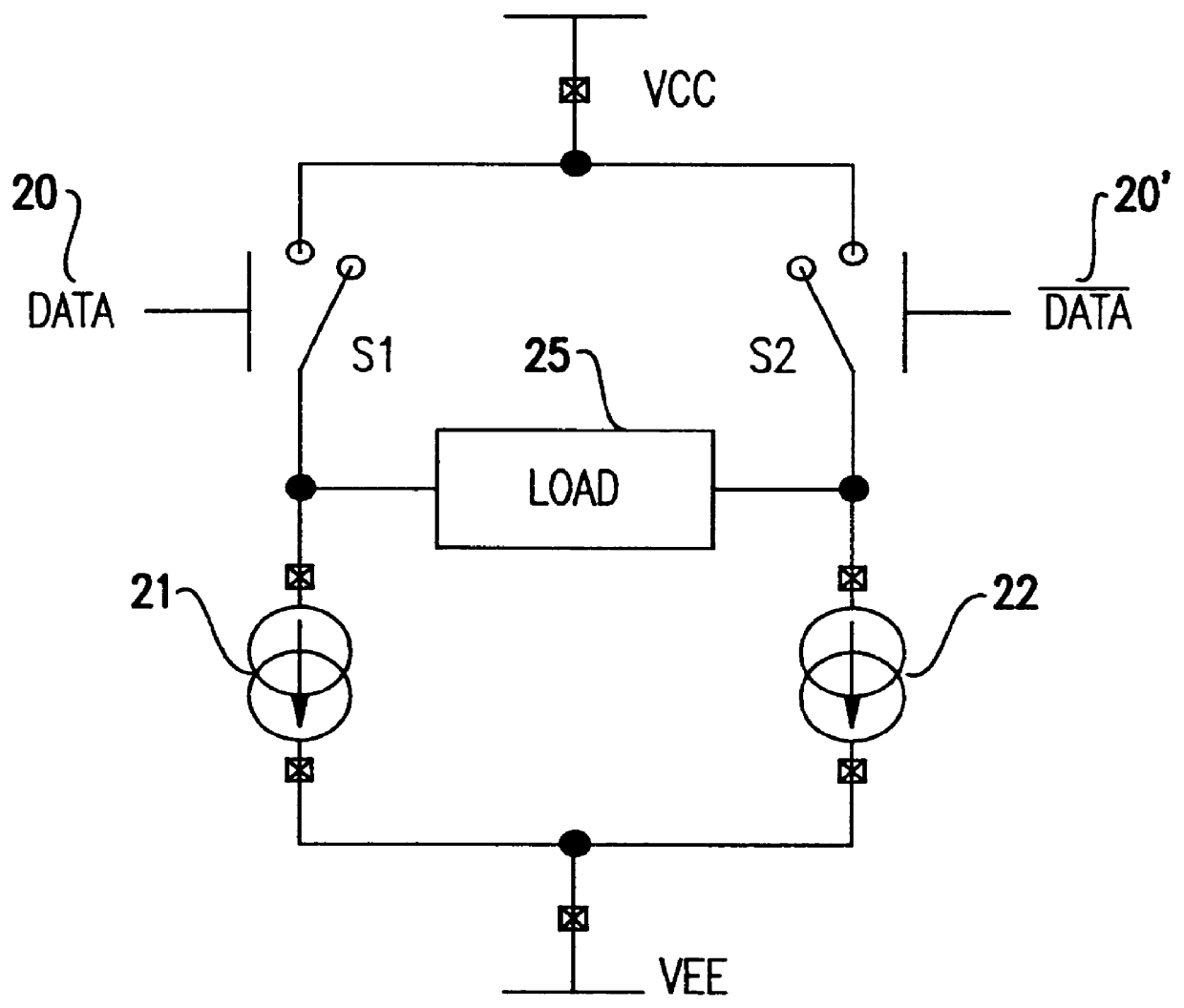

A write driver (11) for a disk drive system is disclosed. The write driver (11) includes a normal H-bridge drive circuit (30) and a boost H-bridge drive circuit (32). The normal and boost H-bridge drive circuits (30, 32) are both biased from a Vcc power supply; however, system ground (GND) biases the normal H-bridge drive circuit (30), while a Vee power supply voltage, which is negative relative to system ground (GND), biases the boost H-bridge drive circuit (32). Diodes (46Y, 46X) are provided in the pull-down paths of the normal H-bridge drive circuit (30). During the boost portion of the write cycle, both of the normal and boost H-bridge drive circuits (30, 32) are on, and the pull-down current from the write head (HD) is conducted to the Vee power supply voltage. After the boost portion of the cycle, and thus after the desired overshoot current has been applied, only the normal H-bridge drive circuit (30) drives the steady-state write current, which is conducted to system ground (GND).

Owner:TEXAS INSTR INC

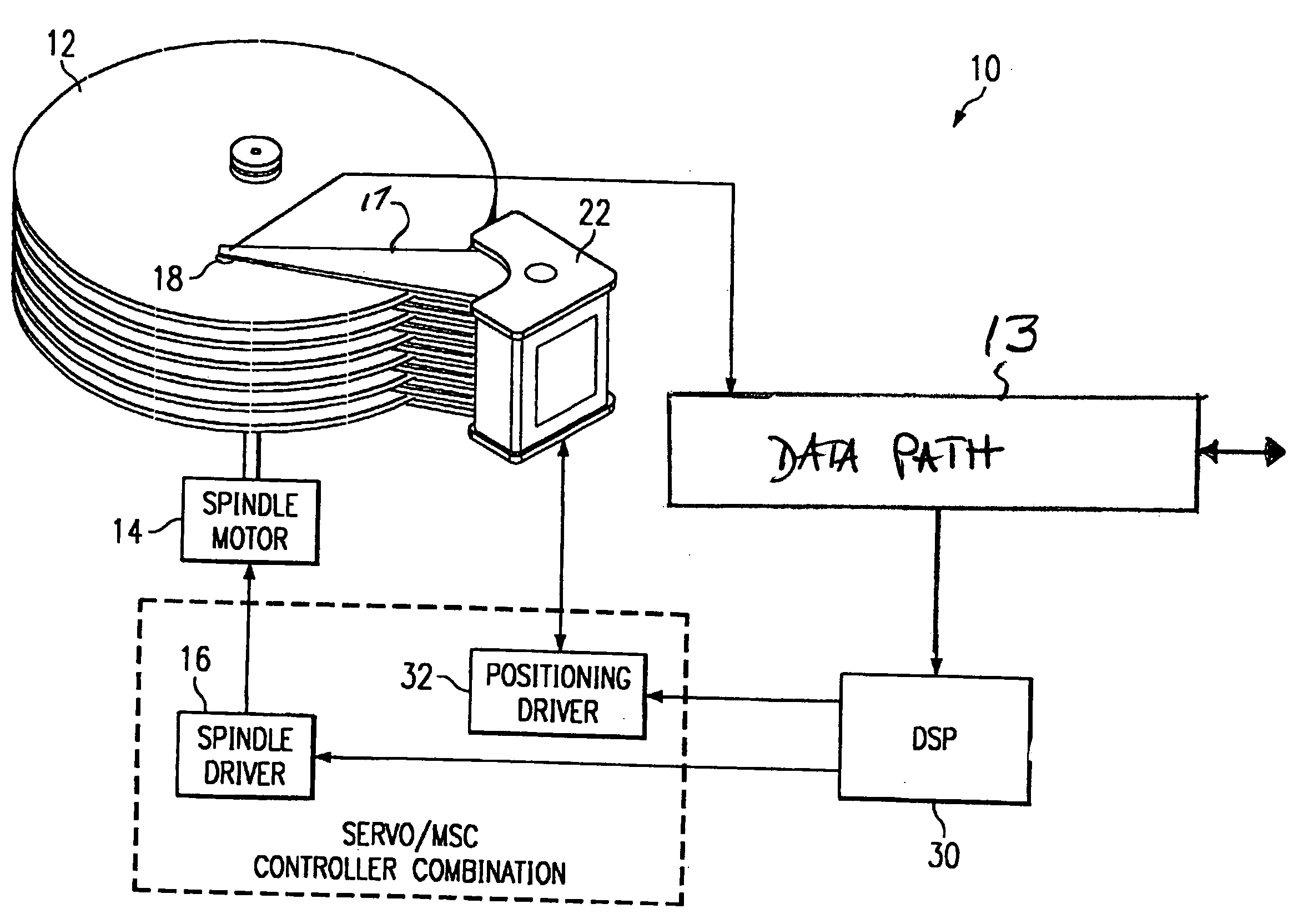

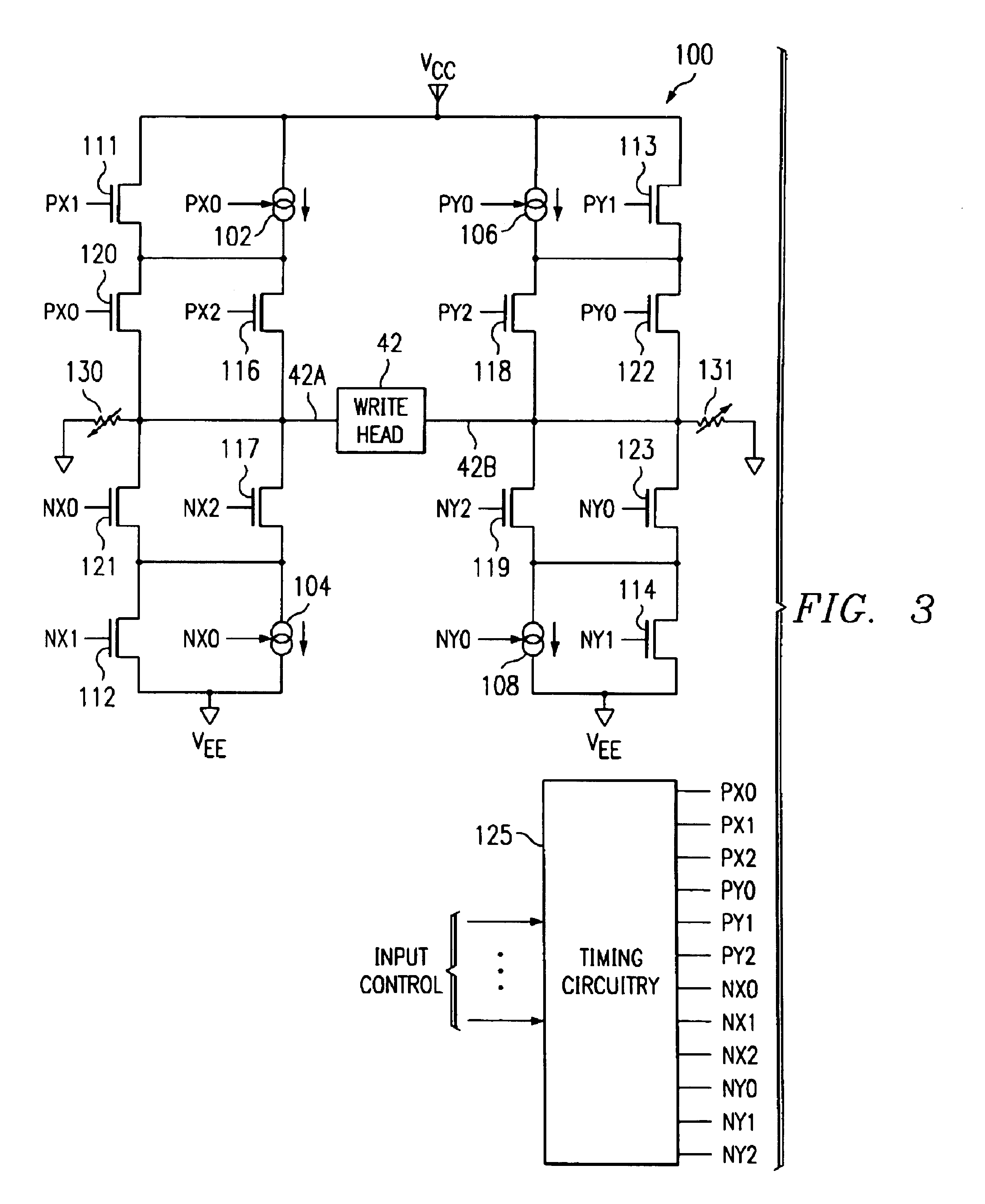

Write head driver circuit and method for writing to a memory disk

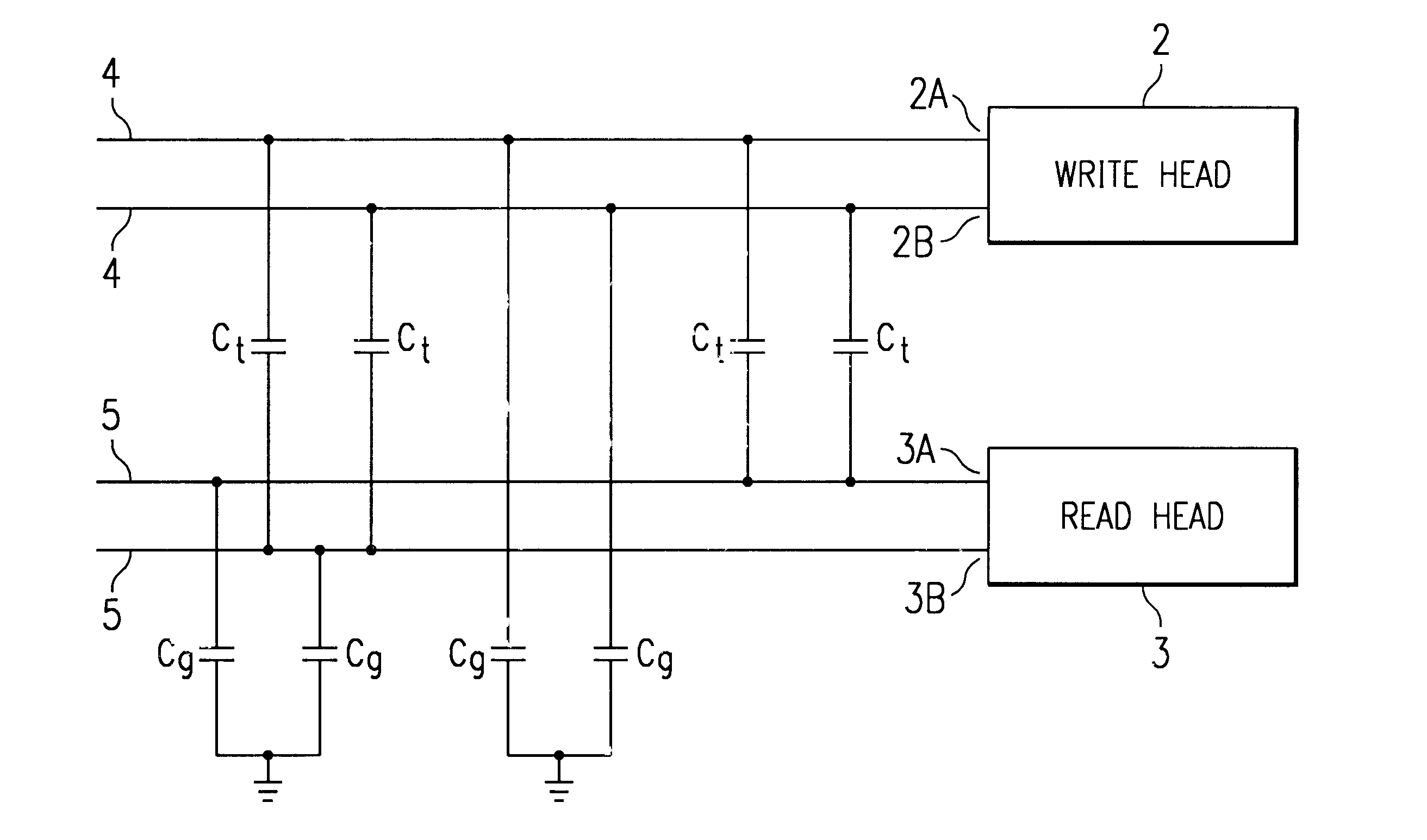

InactiveUS20030090828A1Filamentary/web carriers operation controlH-bridge head driver circuitCapacitanceControl signal

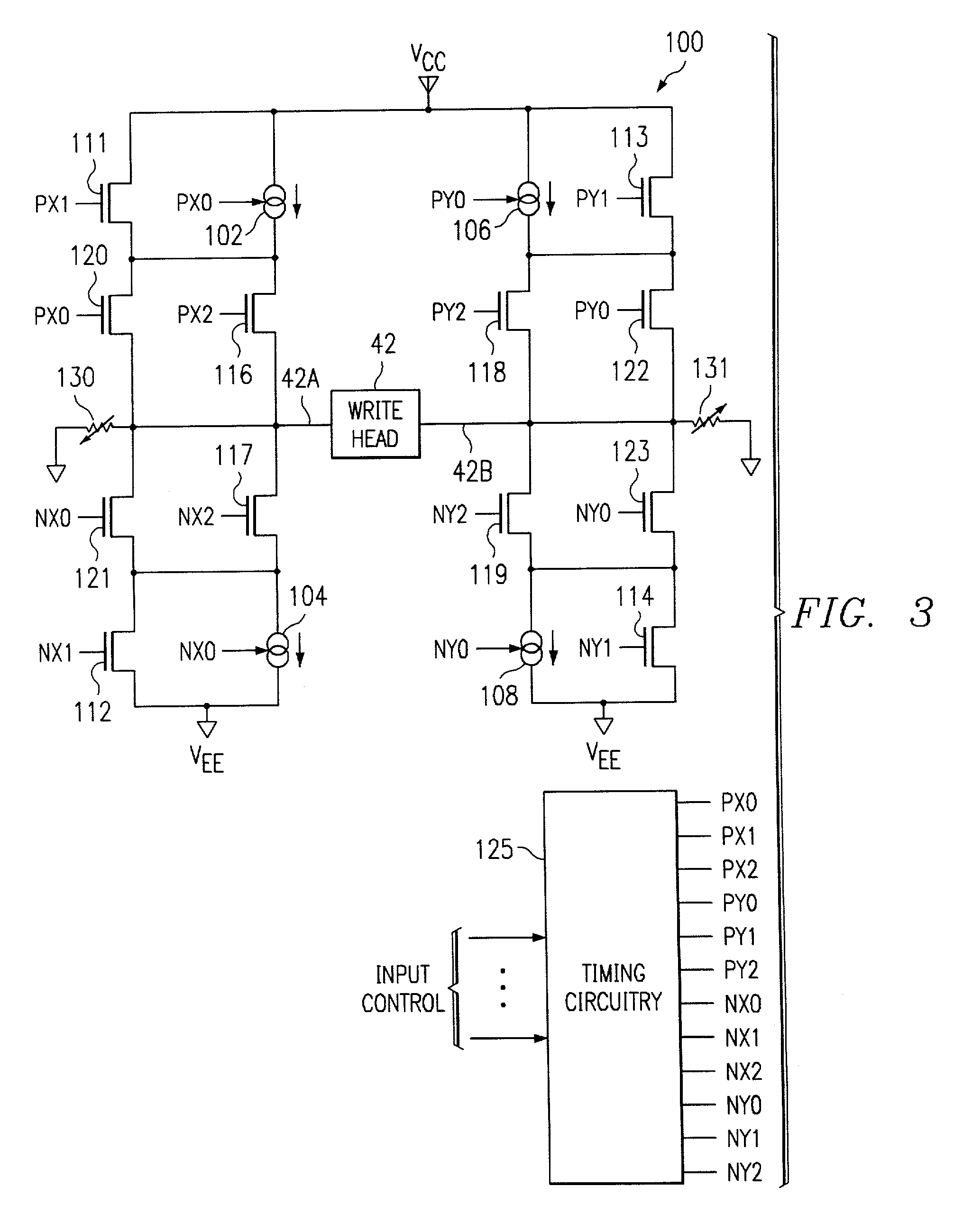

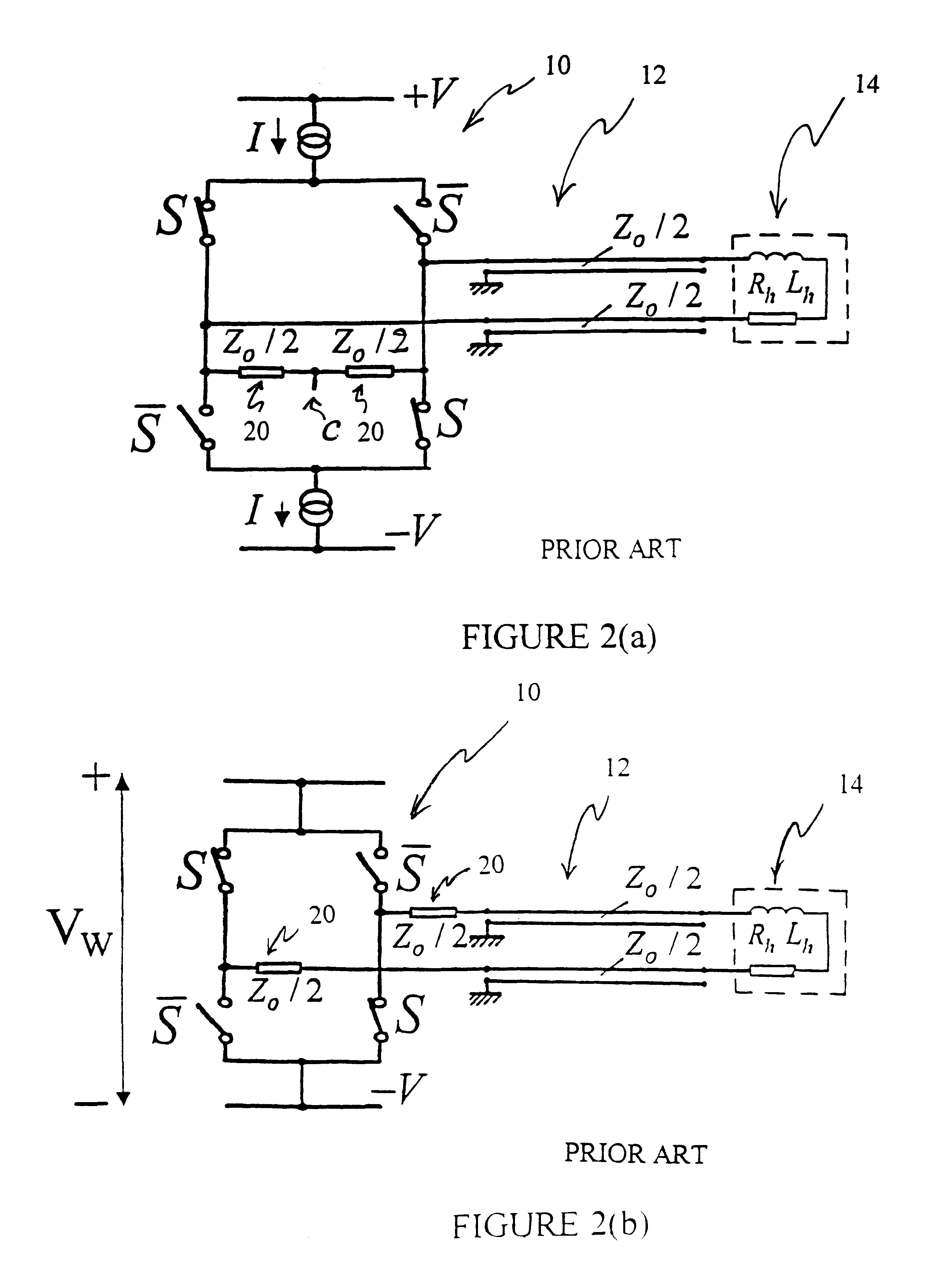

A circuit and method are disclosed for relatively rapidly causing the current flowing through a write head to transition between steady states without generating an appreciable amount of capacitively-coupled noise. Embodiments of the present invention generally provide drive voltage signals to the write head that have no common mode voltage levels during transitions between steady state current levels in the write head. In other words, the drive voltage signals applied to the write head are substantially entirely differential during write head current transitions. In an exemplary embodiment of the present invention, a driver circuit includes switching circuitry connected between the terminals of the write head and reference voltage supplies, such as positive and negative voltage supplies. The driver circuit further includes timing circuitry that generates control signals for controlling the switching circuitry.

Owner:STMICROELECTRONICS SRL

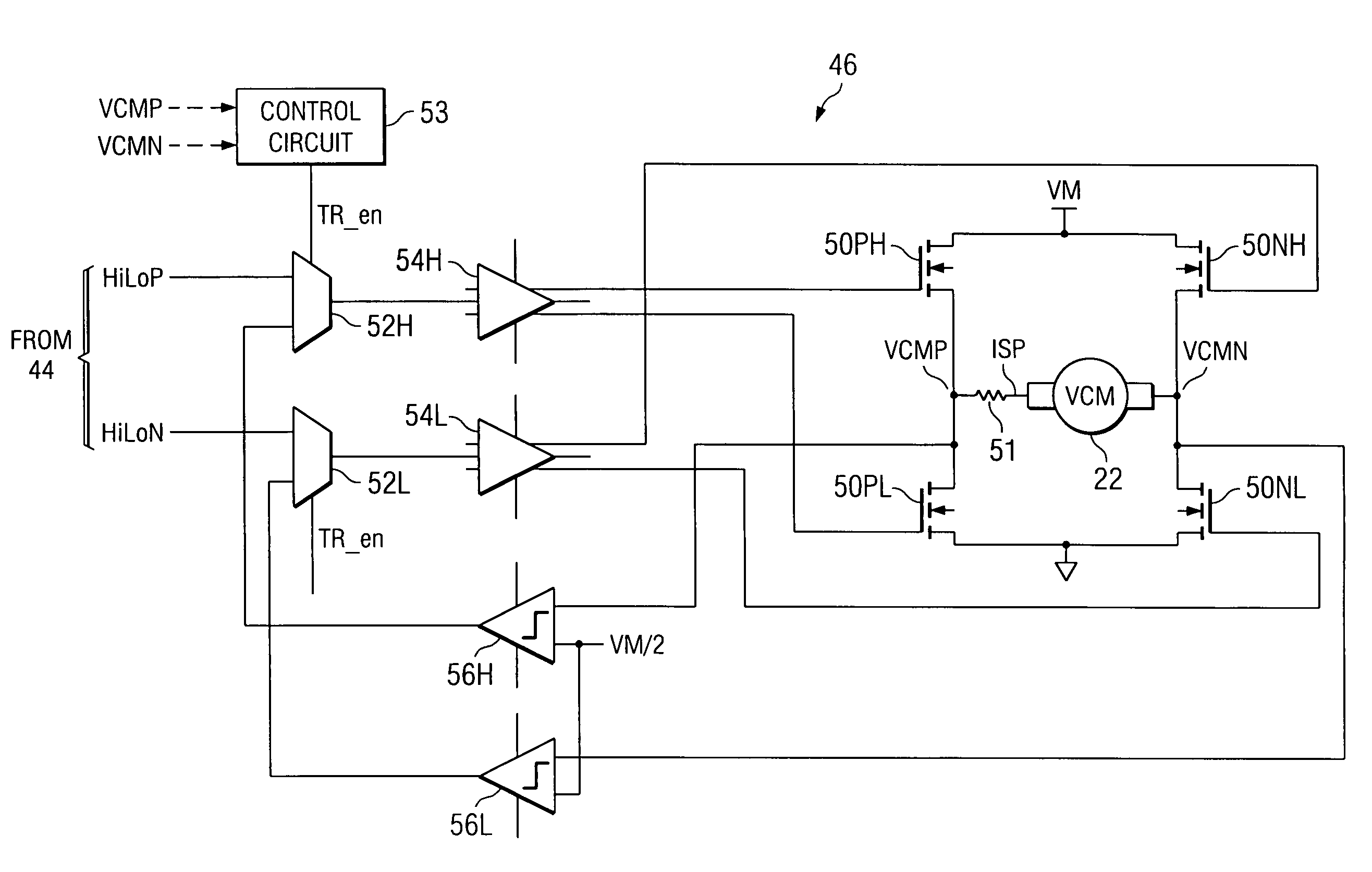

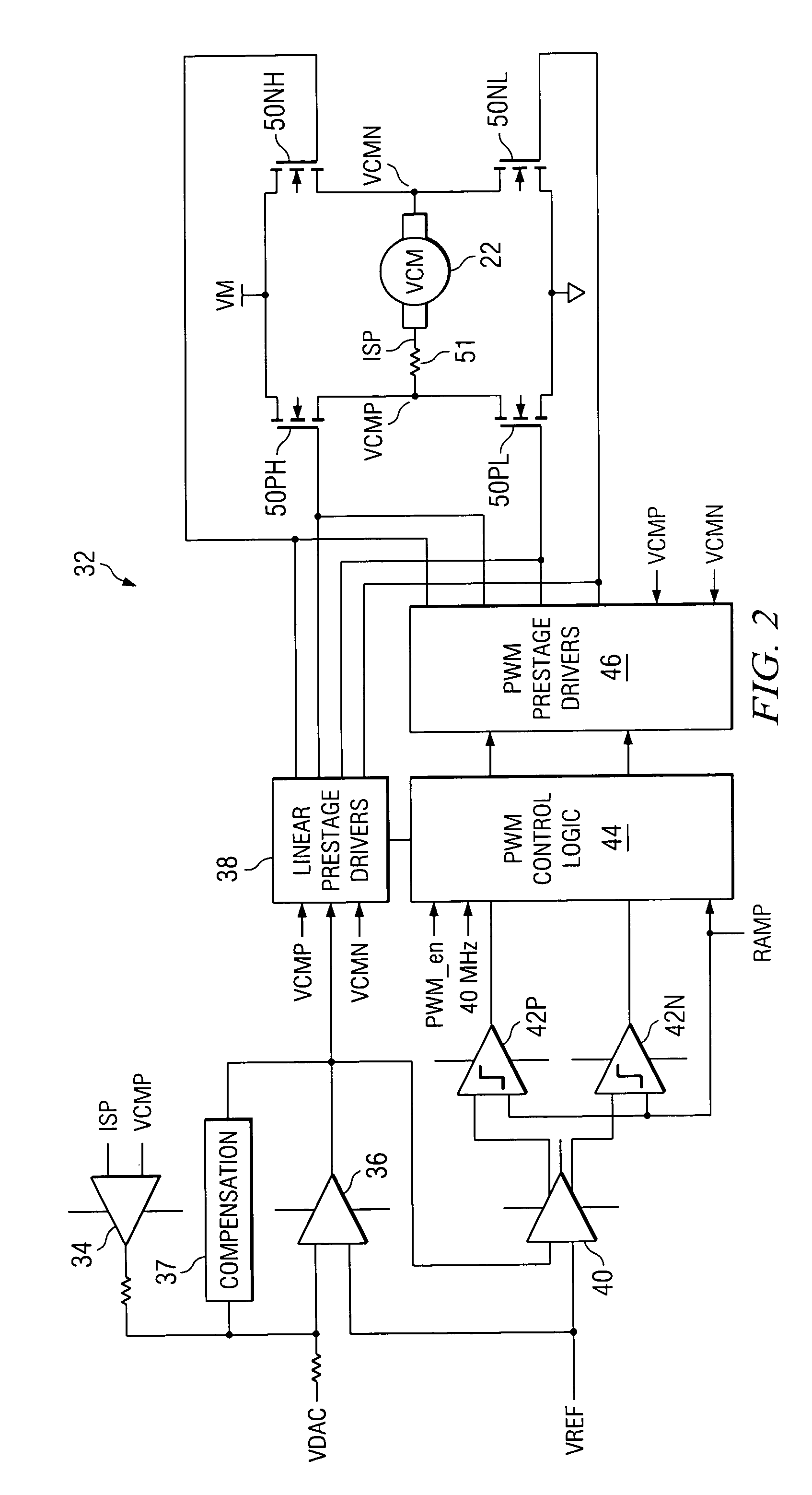

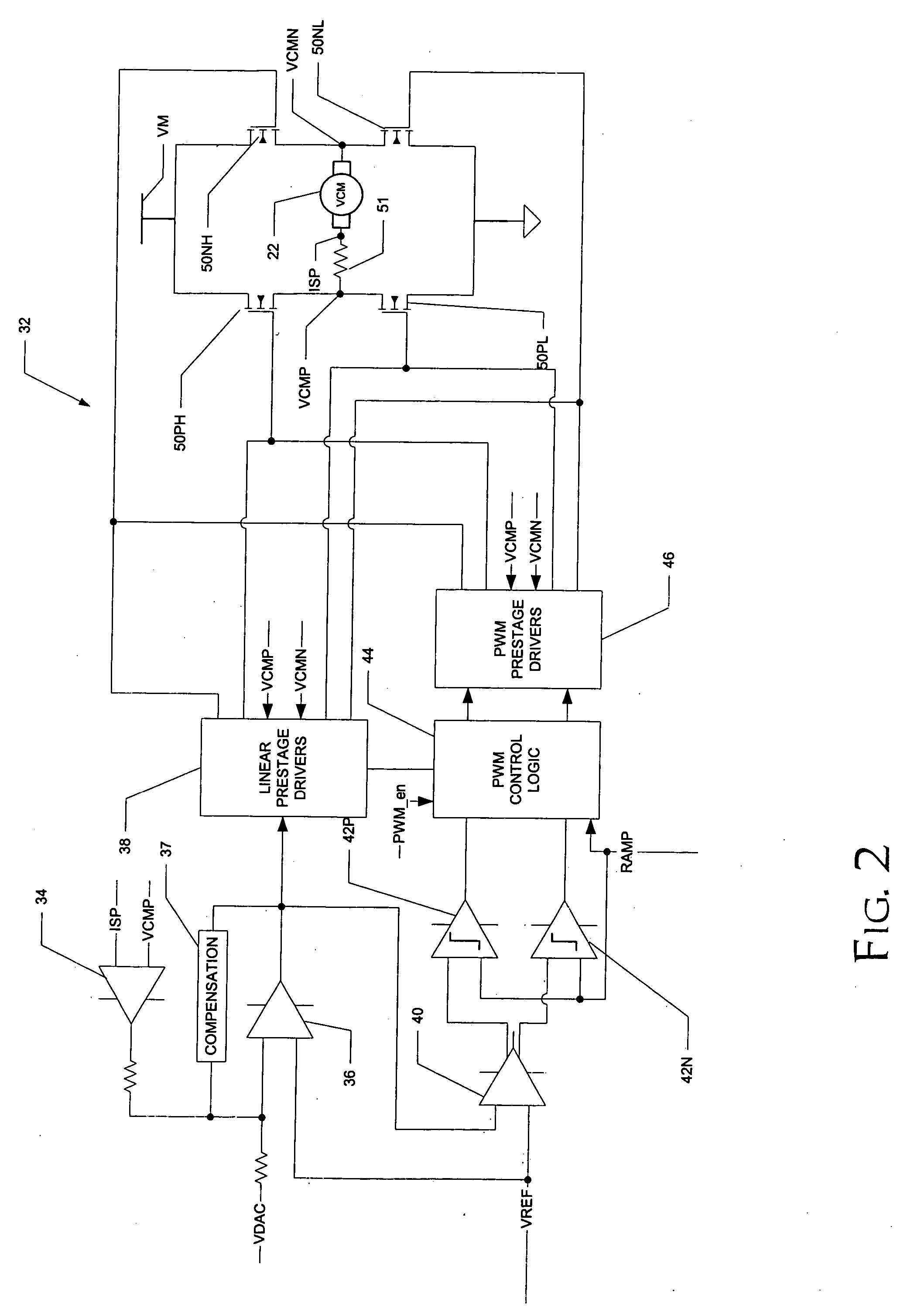

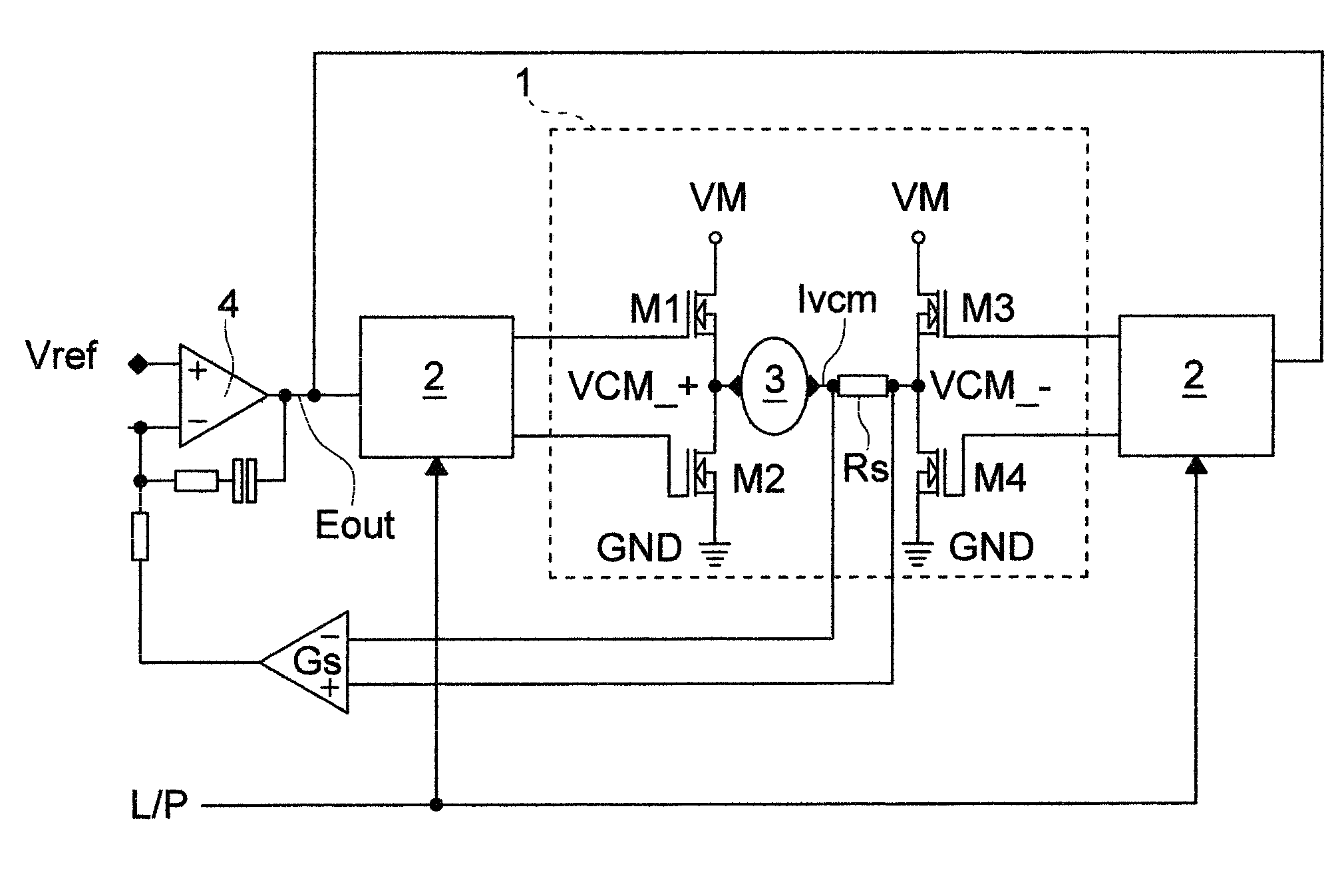

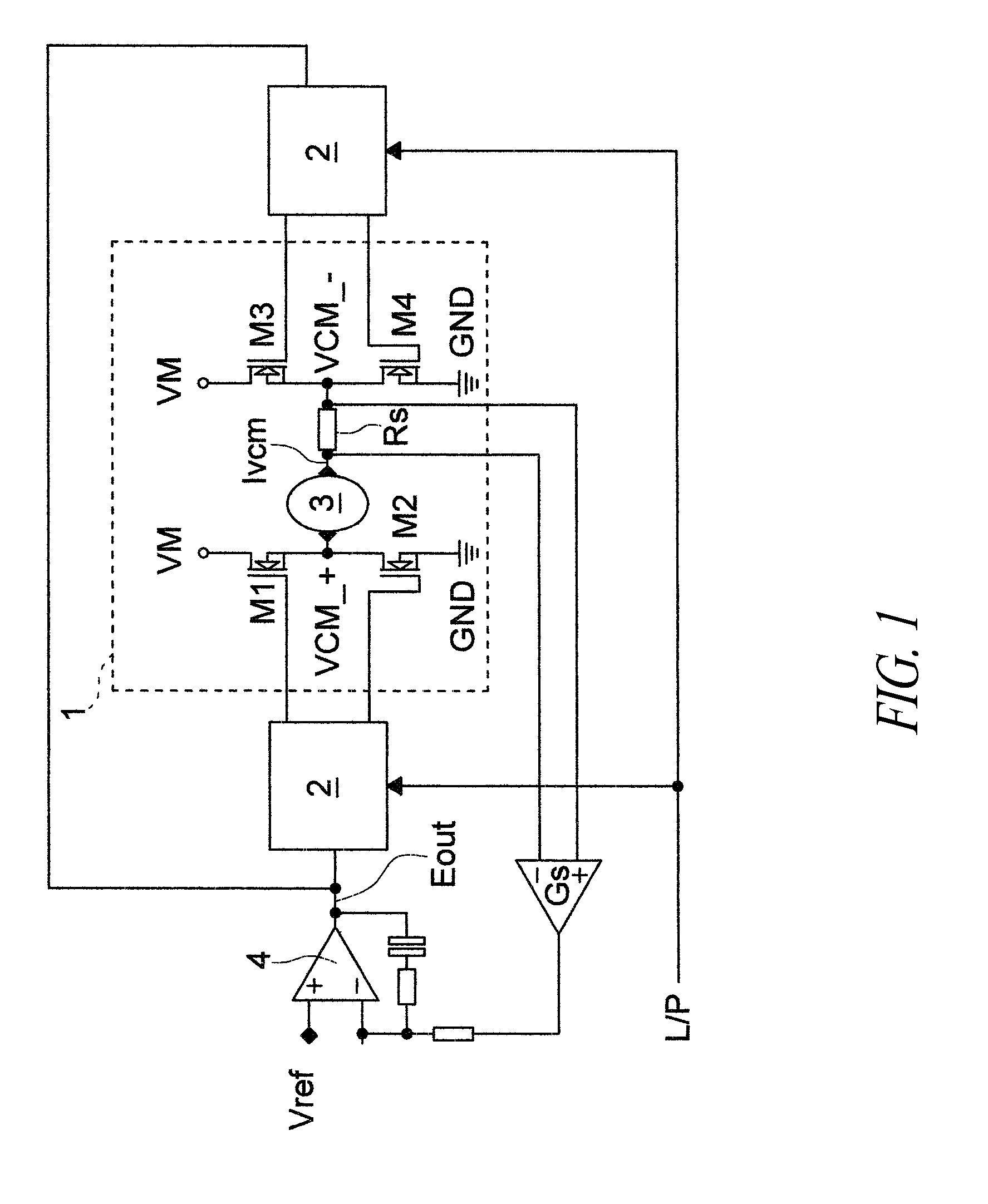

Efficient transition from class D to linear operation in dual-mode voice coil motor controllers

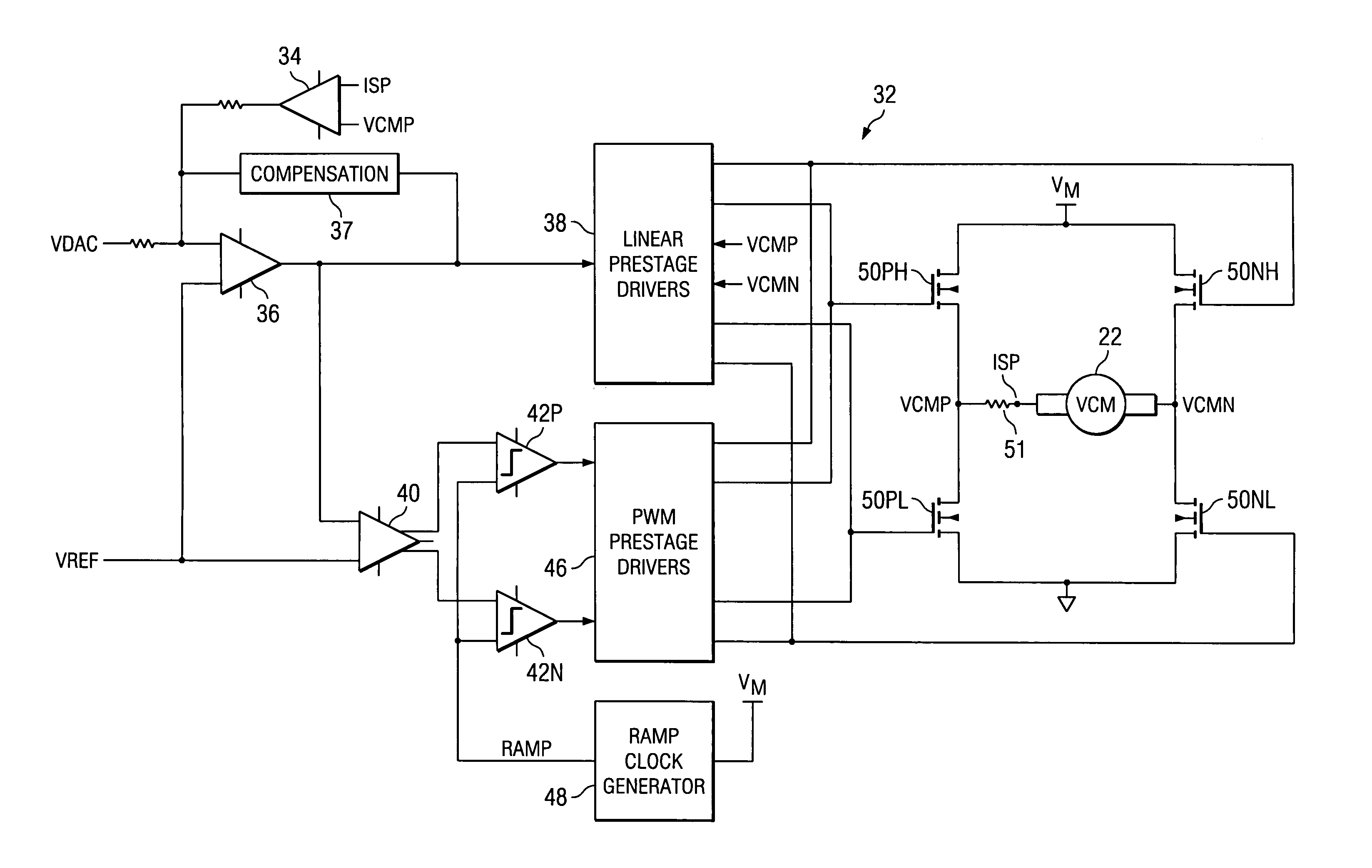

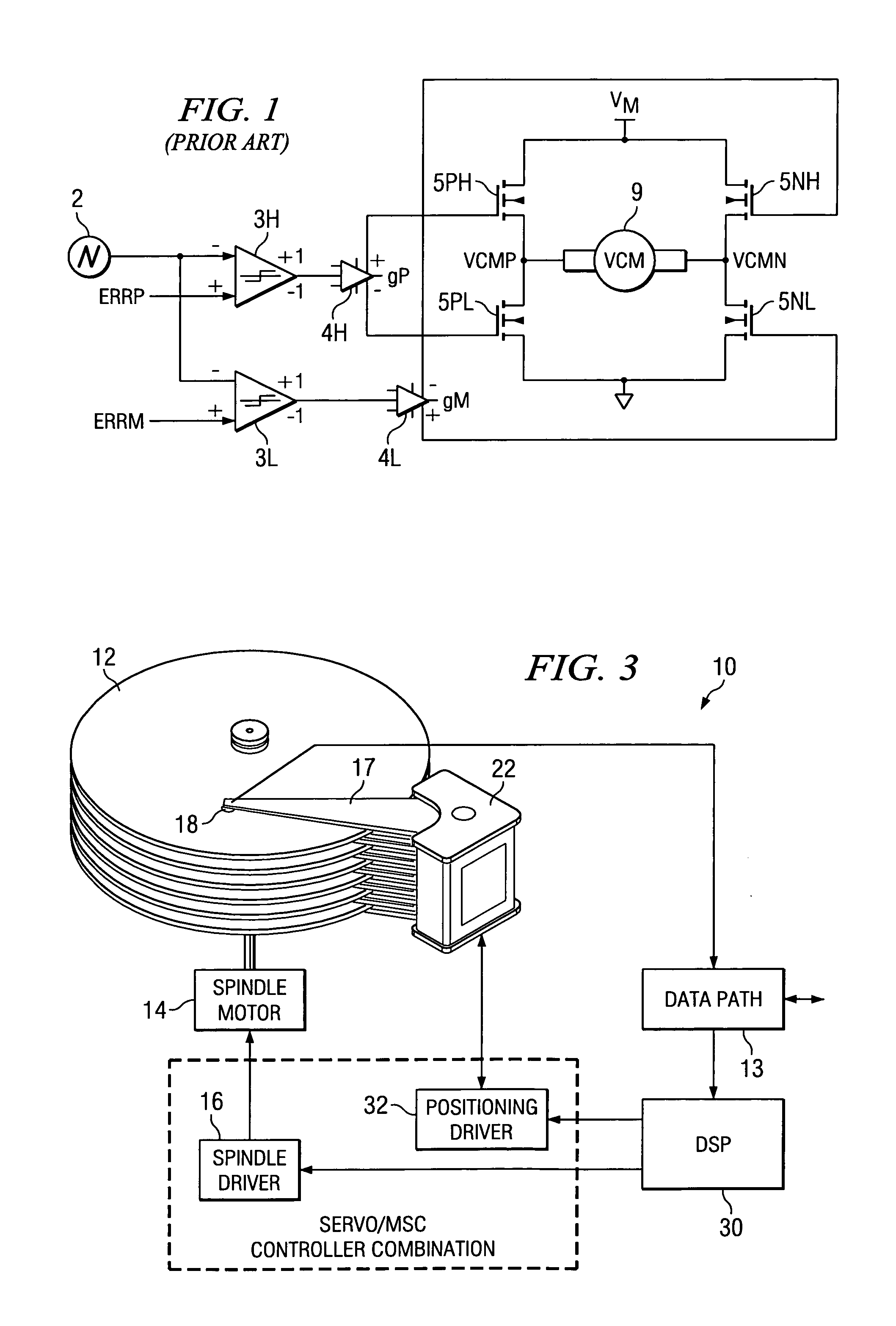

ActiveUS6989955B2Drive mode to a linear drive mode are greatly reducedReduce discontinuityDriving/moving recording headsH-bridge head driver circuitDual modeVoltage reference

A dual-mode positioning driver for a voice coil motor in a disk drive system is disclosed. Linear prestage drivers and pulse-width-modulated prestage drivers are both coupled to power transistors arranged in an “H” bridge for driving the voice coil motor. The positioning driver is thus operable to drive the power transistors in either a linear mode or a pulse-width-modulated class D mode. In a transition period while switching from the pulse-width-modulated mode to linear mode, comparators compare the phase voltages in the “H” bridge with a reference voltage. The outputs of the comparators are applied to the PWM output amplifiers to drive the power transistors, so that the phase voltages are preconditioned toward their linear bias points. Discontinuities in the drive current through the voice coil motor are minimized as a result.

Owner:TEXAS INSTR INC

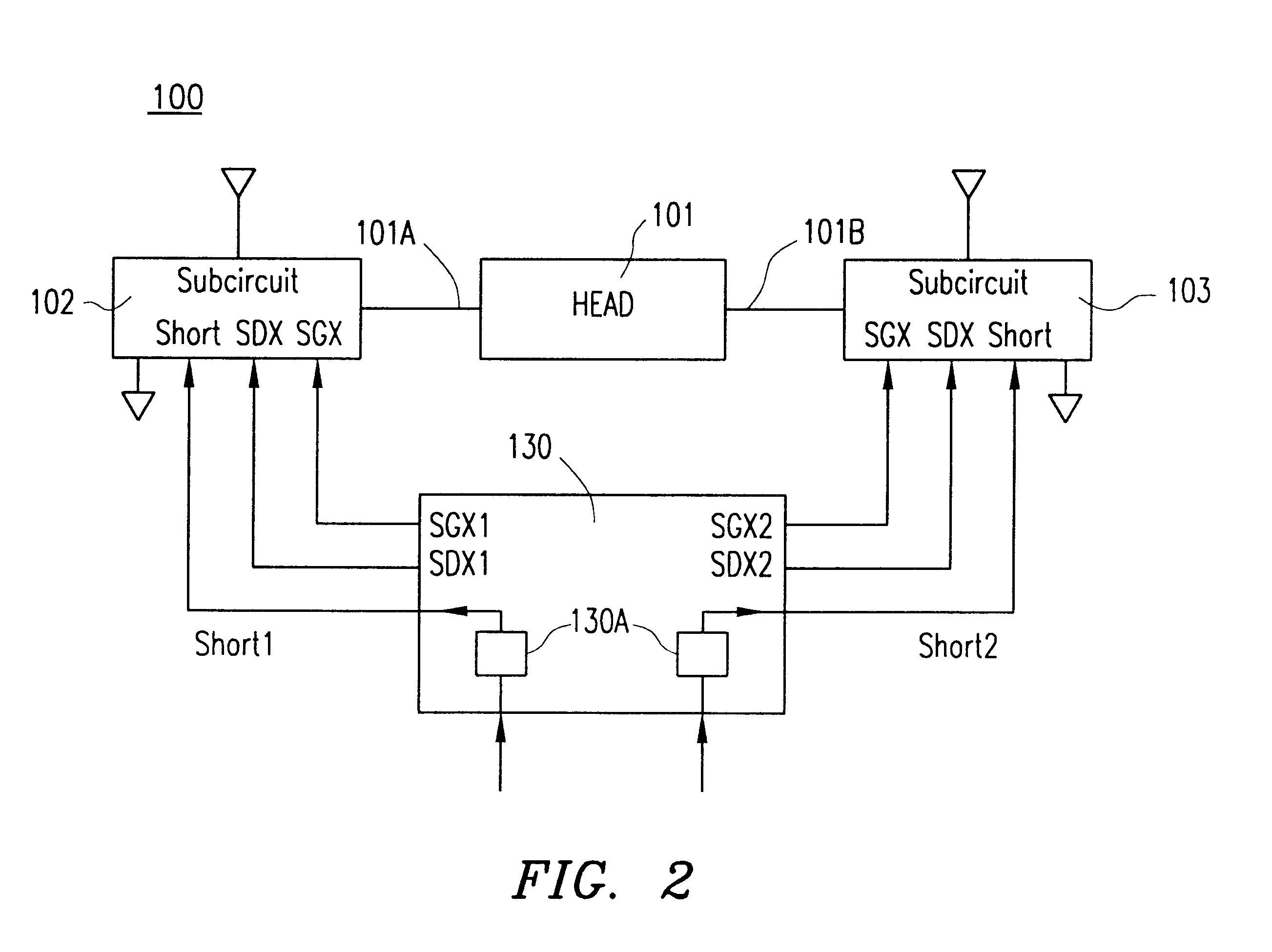

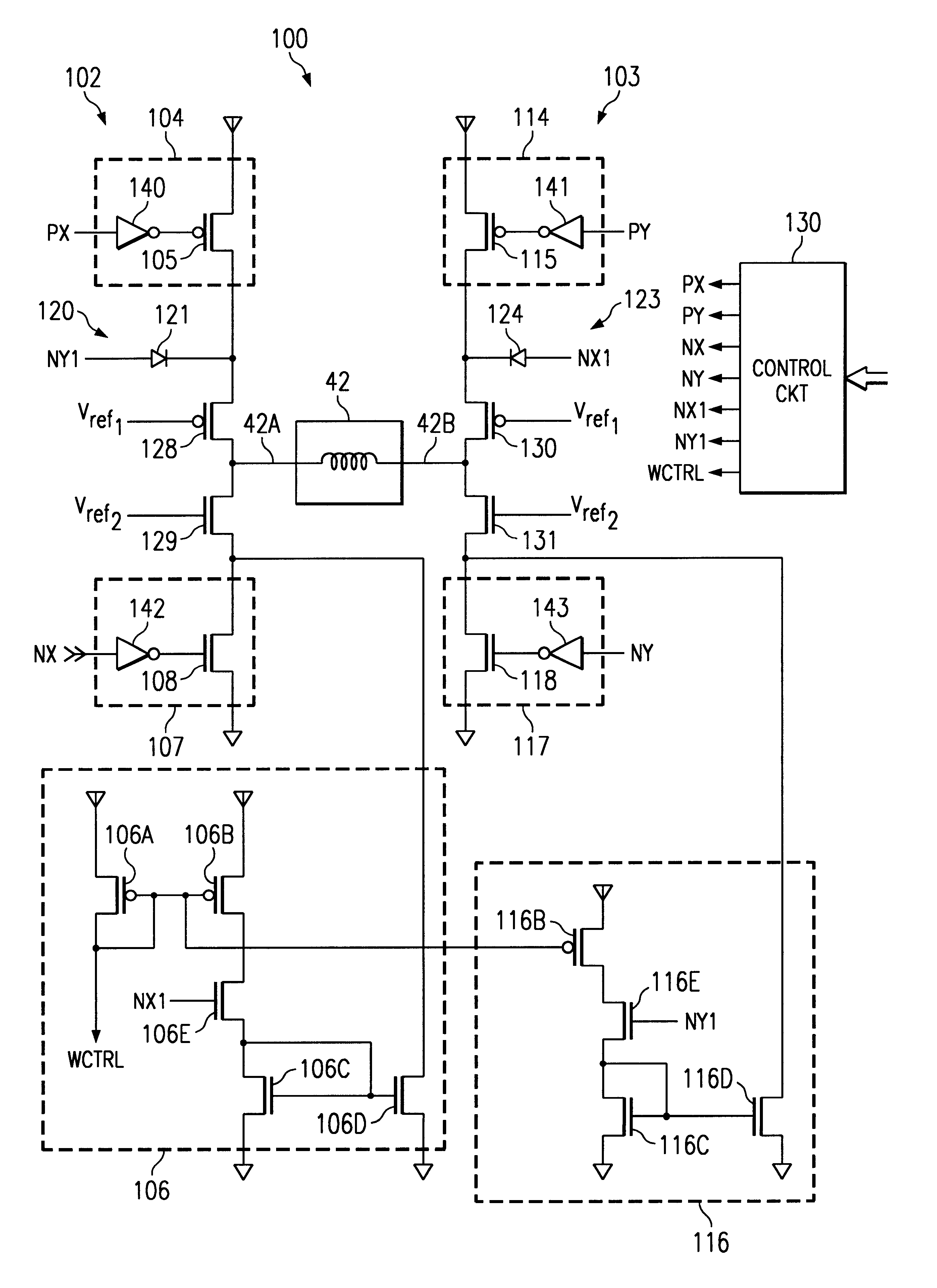

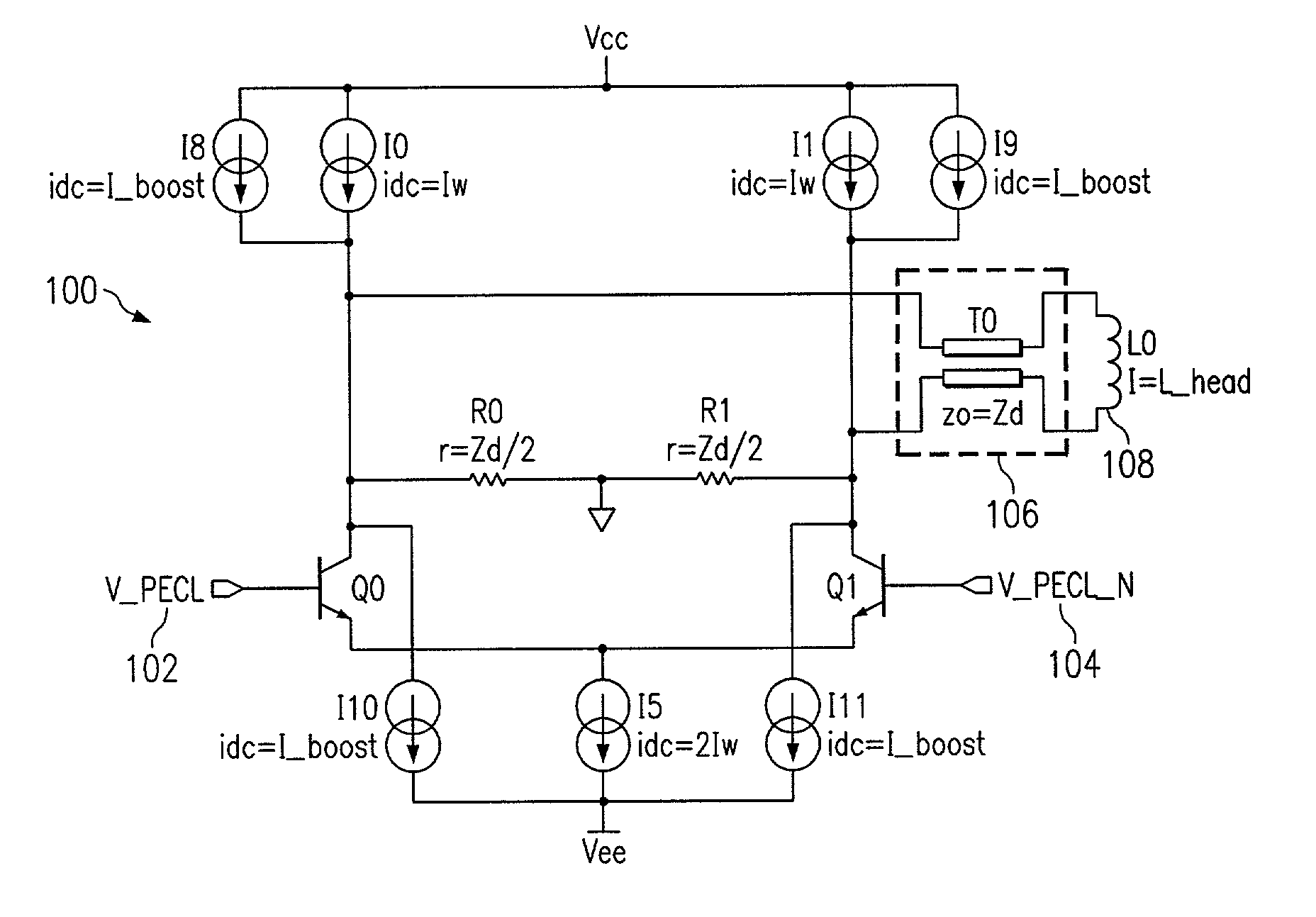

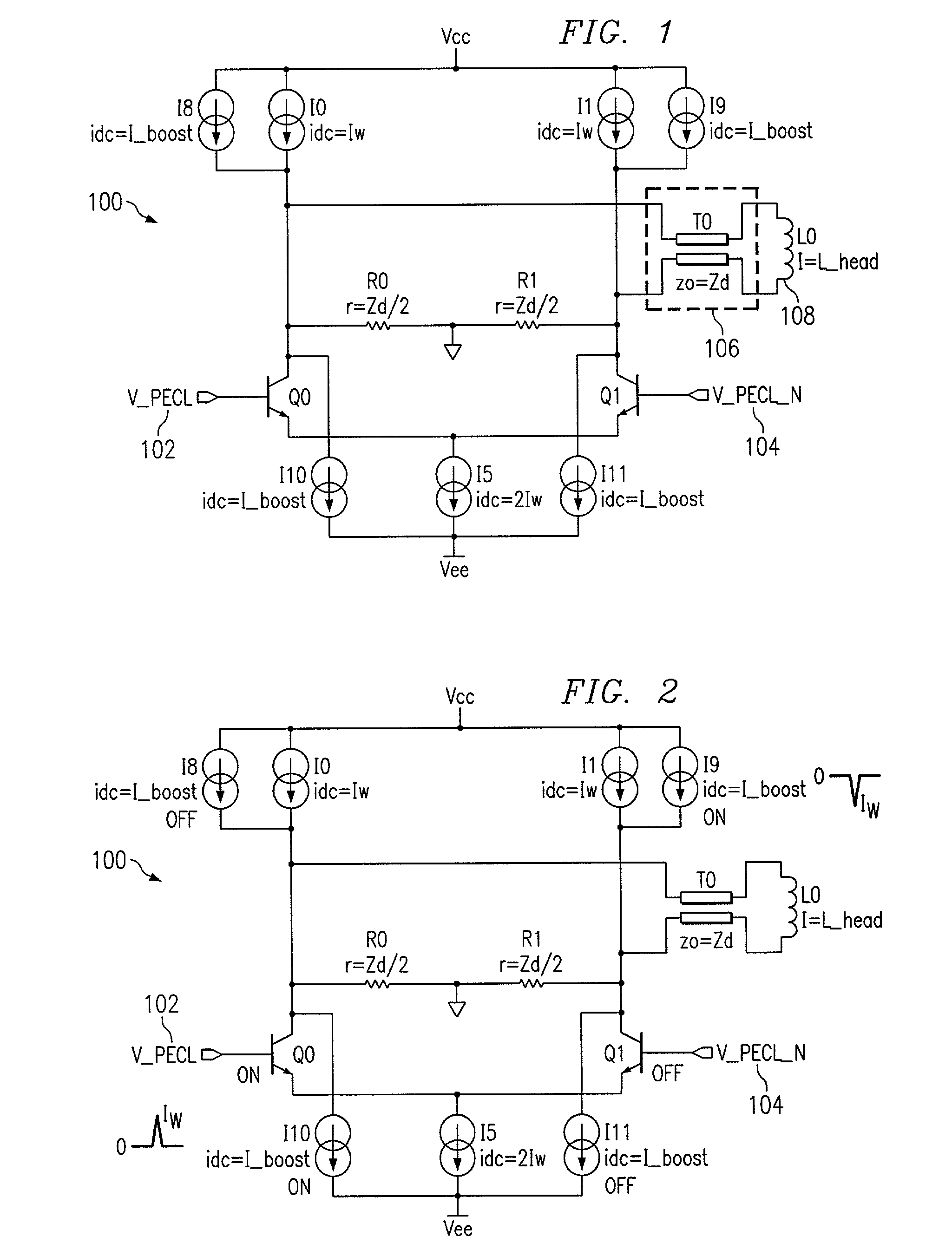

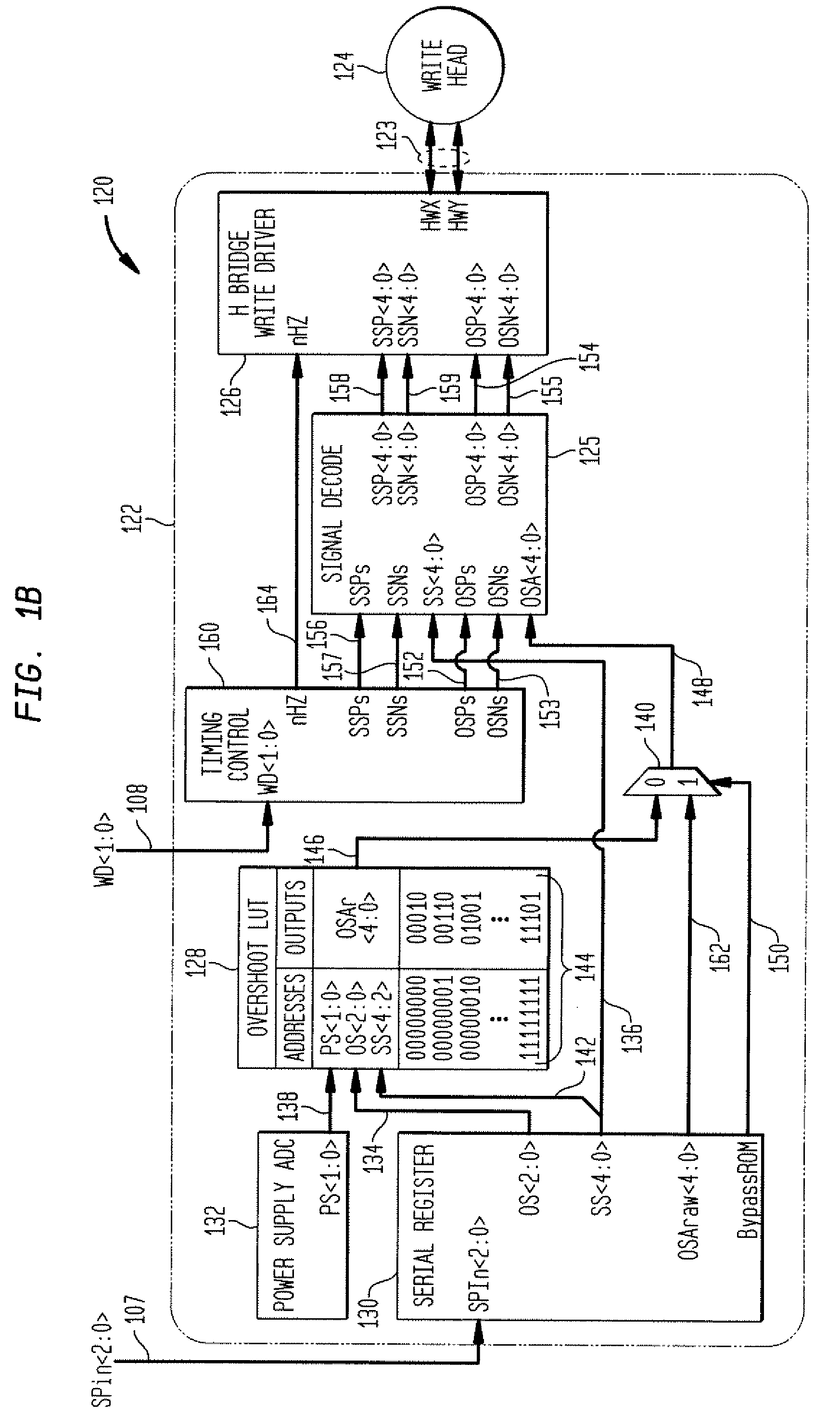

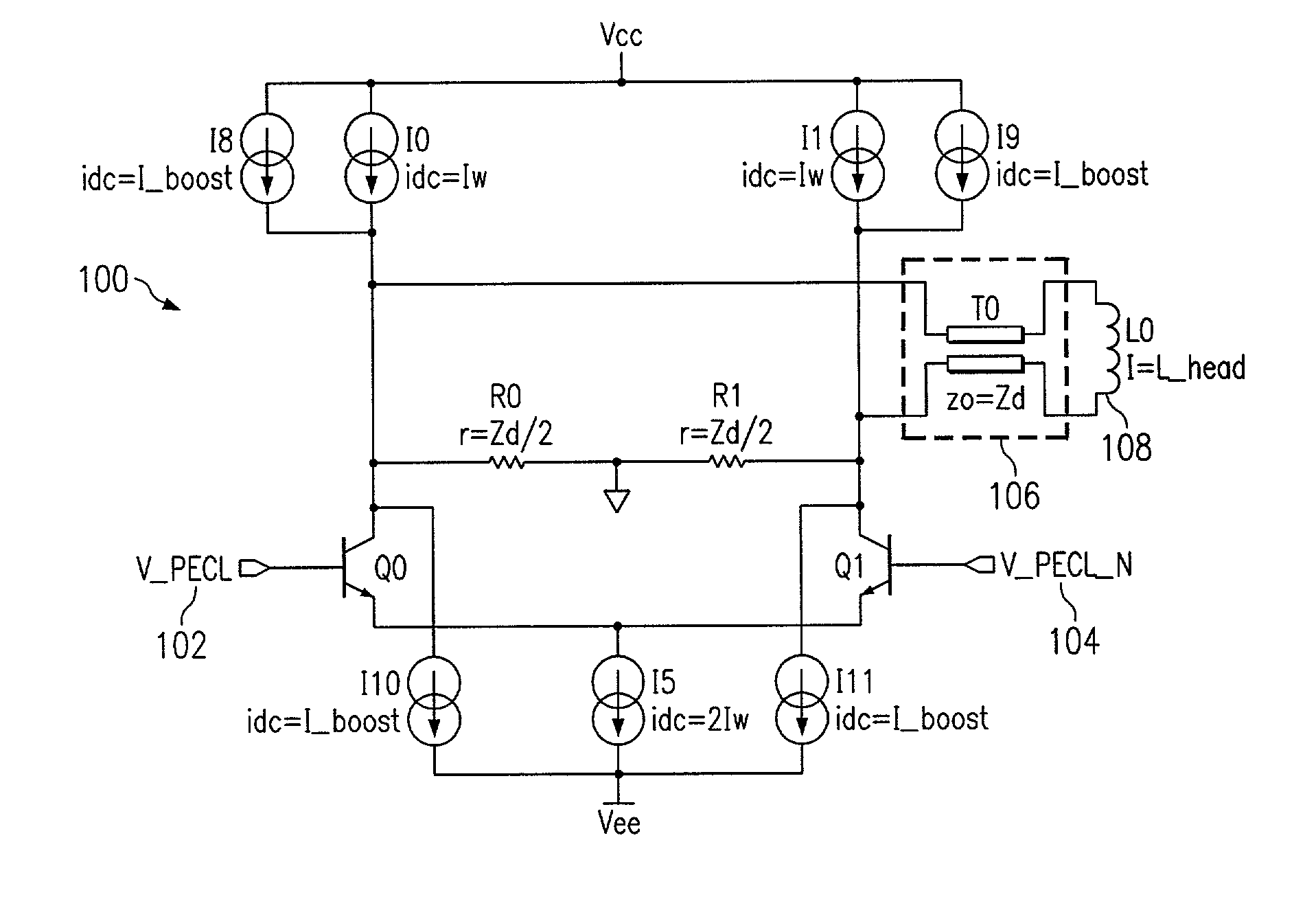

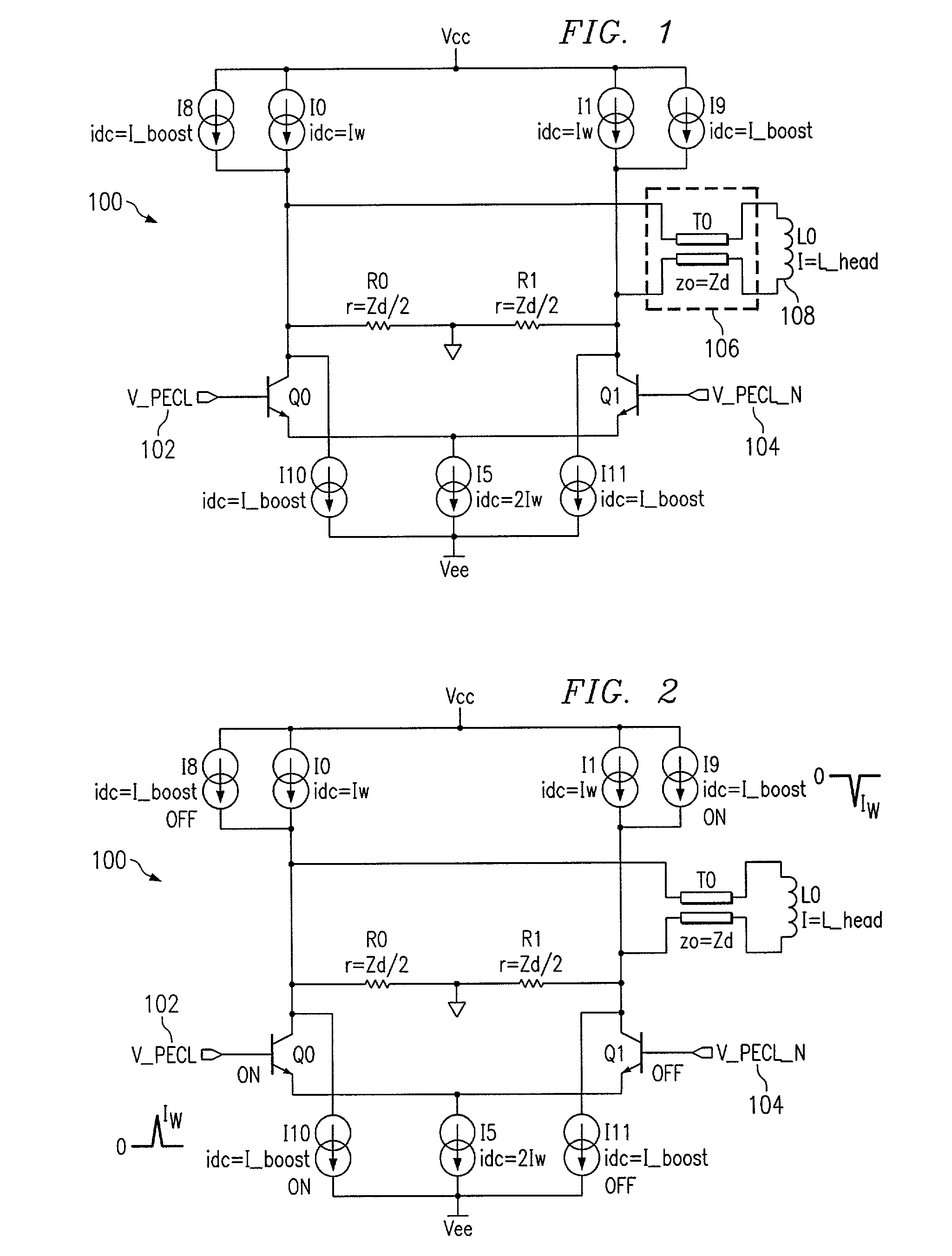

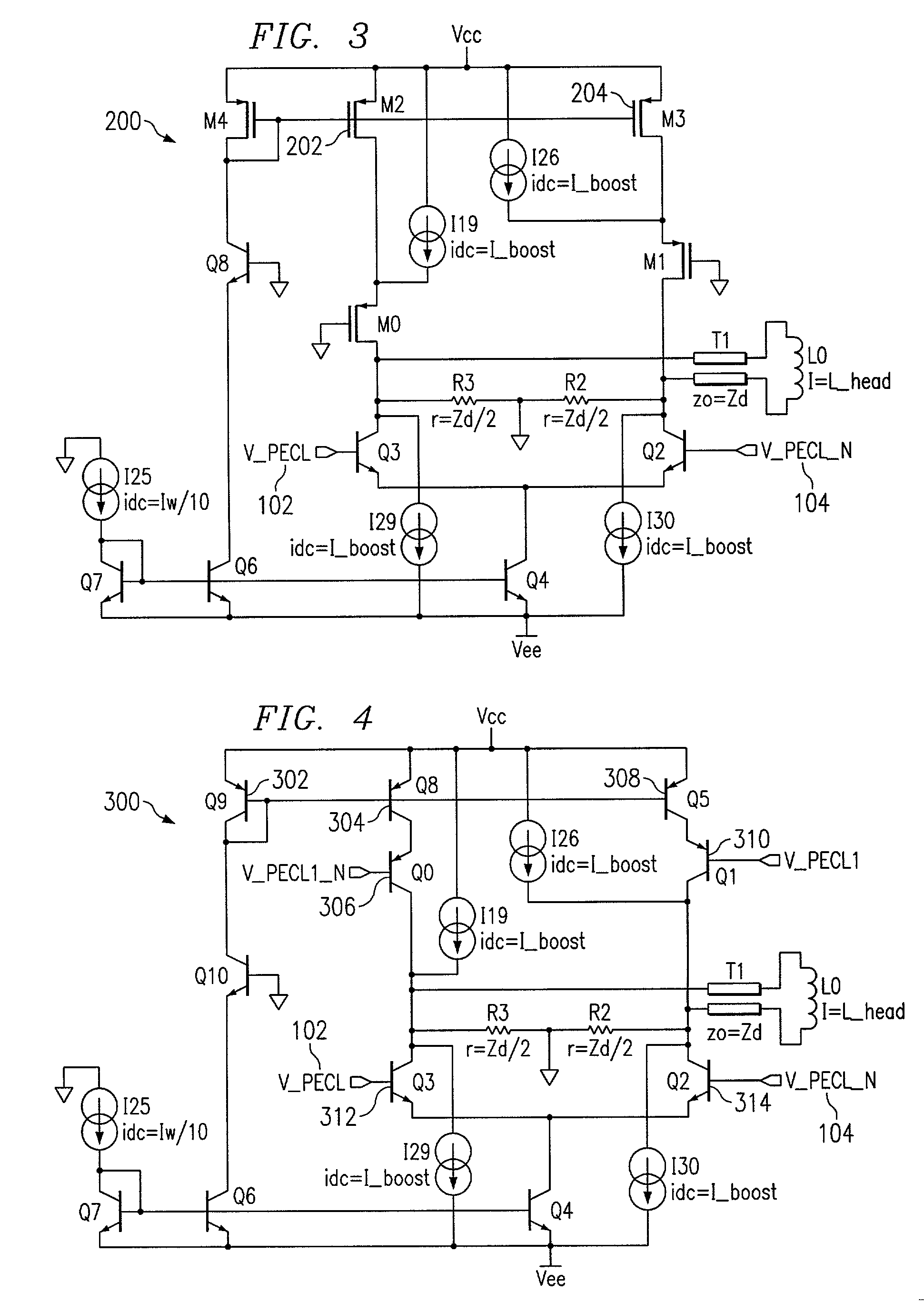

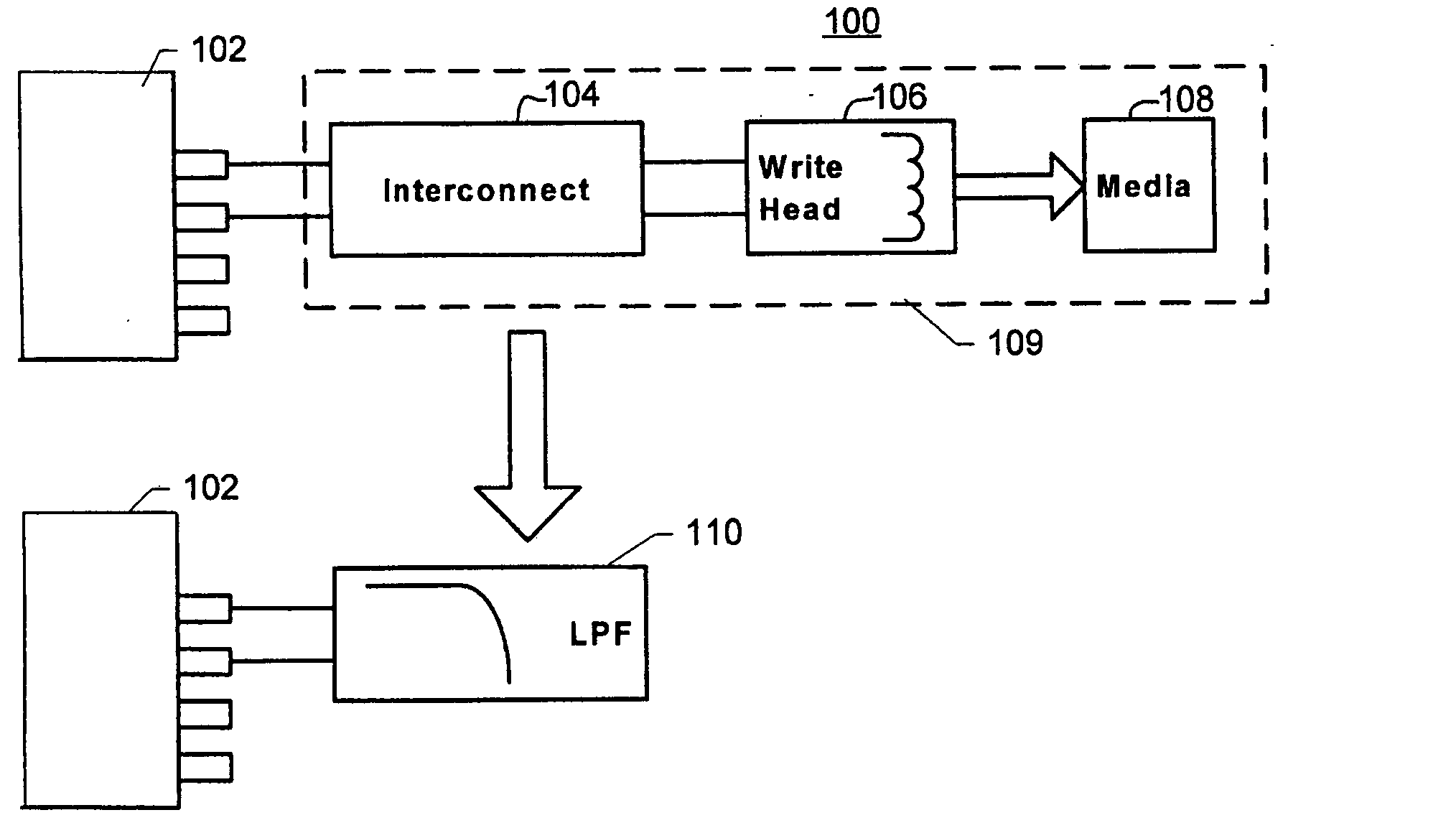

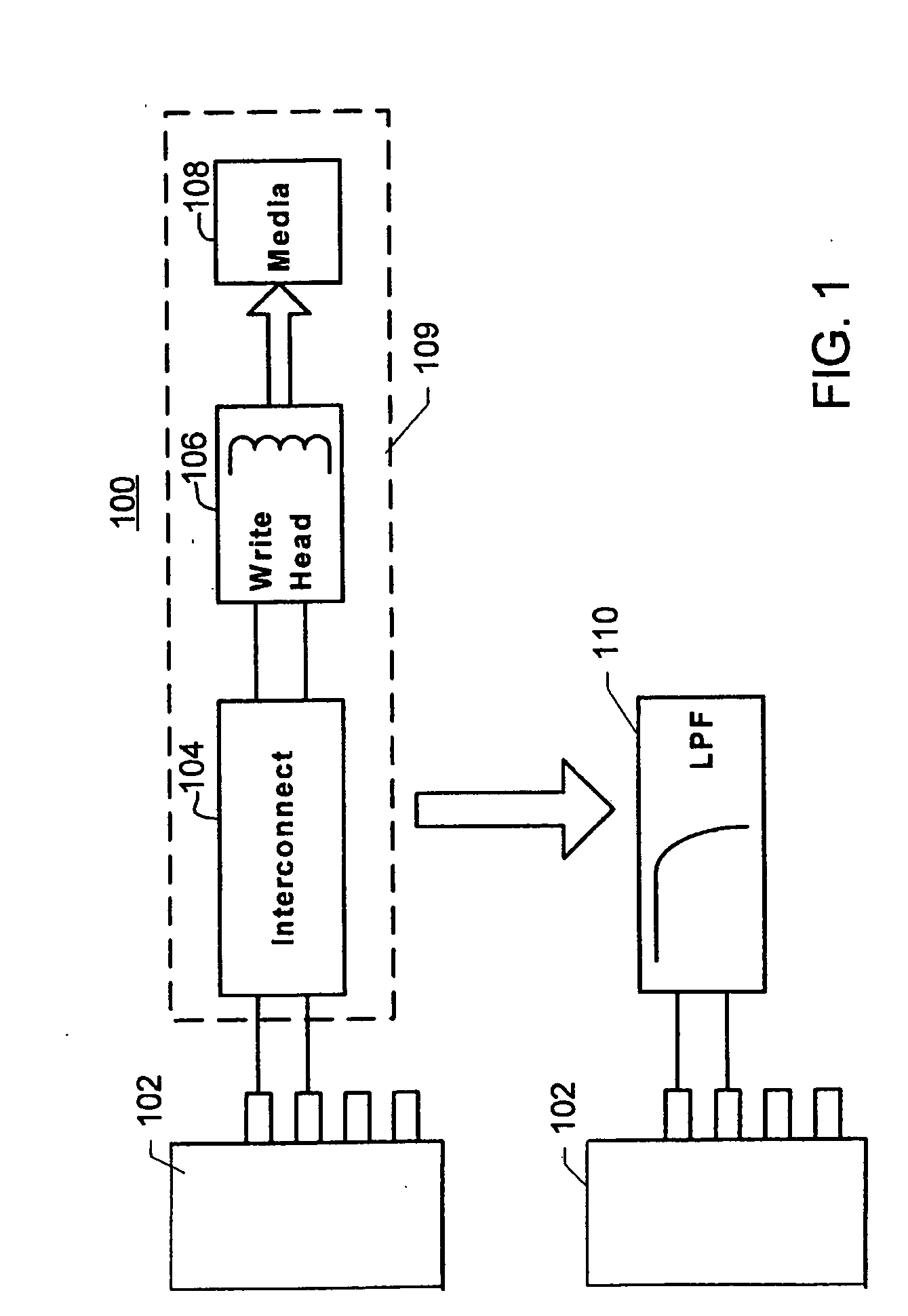

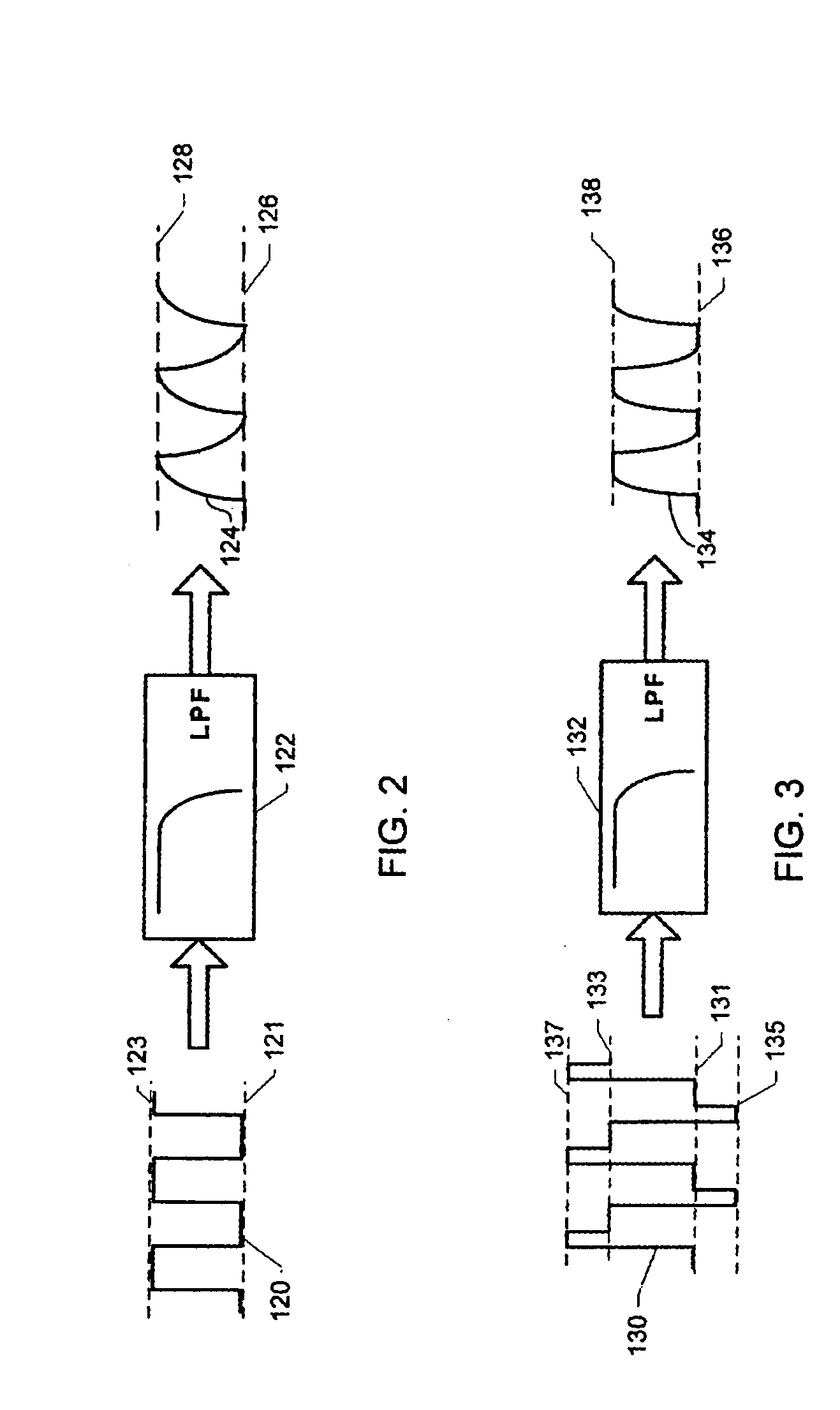

Circuit and method to match common mode flex impedance and to achieve symmetrical switching voltage outputs of write driver

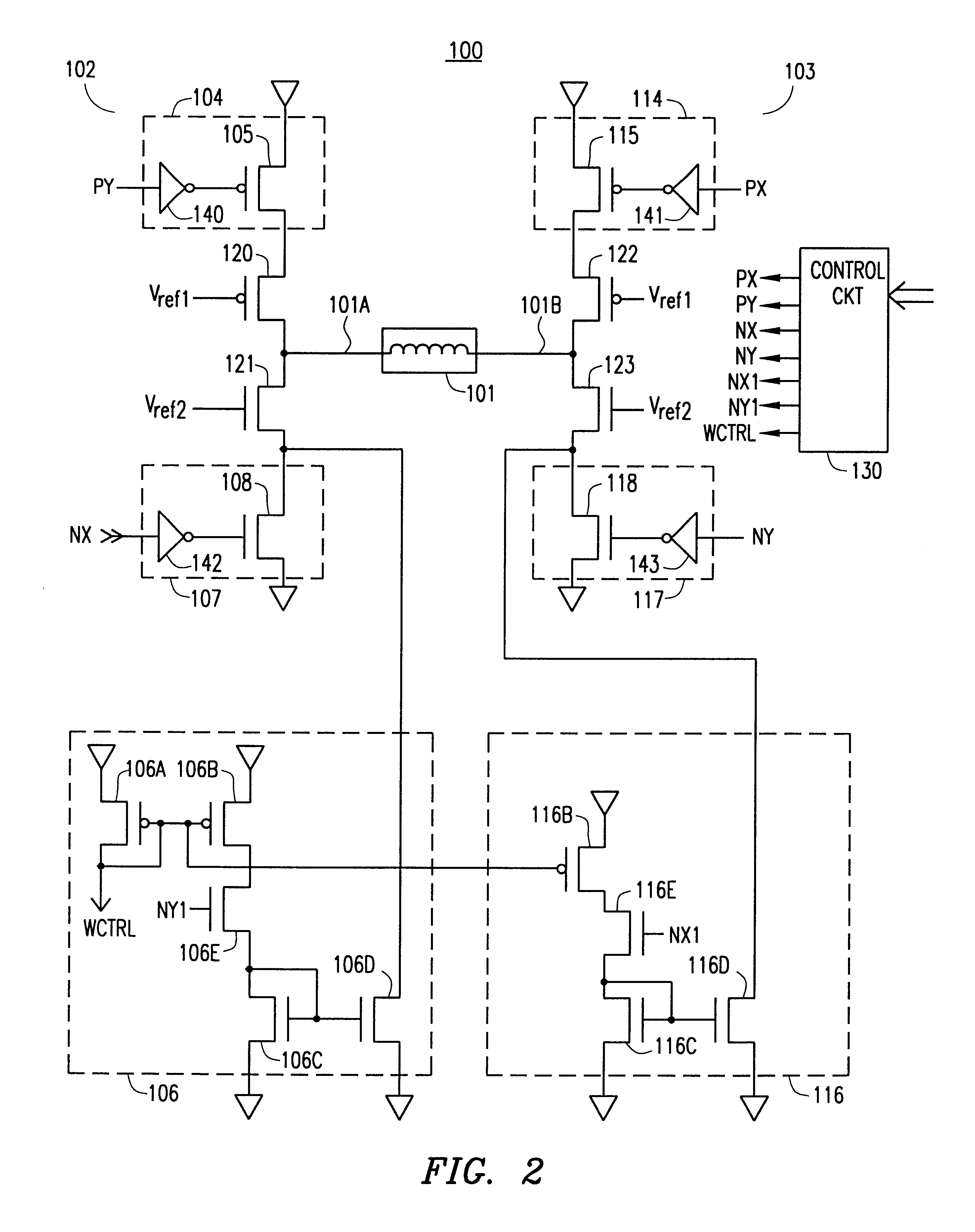

InactiveUS7006313B2Minimal signal reflectionIncrease data rateTransistorH-bridge head driver circuitCMOSConstant power

A write driver 100, 200, 300 is implemented to provide near-ground common mode output voltages to produce a more symmetrical head voltage swing (i.e. ±0.4V from ground to ±5V supply voltages). These features help to reduce the effects of common mode impedance associated with the interconnection to the disk drive head to improve overall performance. Lower jitter at high data rates can be achieved when compared to prior art techniques for implementing current mode write drivers. Further, the matched impedance between the write driver 100 and the interconnection 106 eliminates unwanted reflections. ECL level voltage swings (200–500 mV) have replaced more conventional CMOS level voltage swings (5V) to further reduce overall power dissipation associated with the write driver. The small ECL level switching further maintains constant power dissipation with changes in operating frequency and results in less NTLS effects due to quieter supplies.

Owner:TEXAS INSTR INC

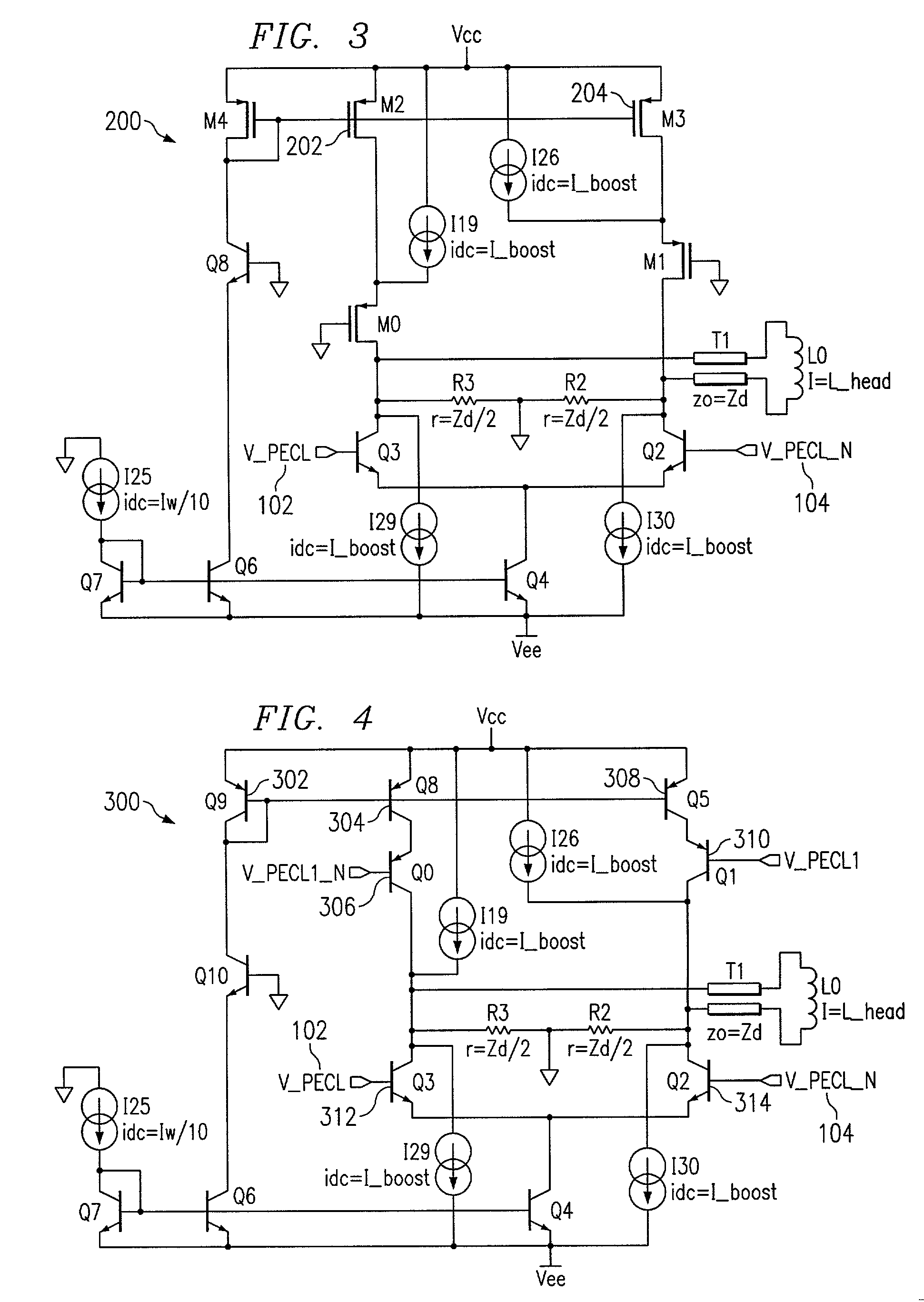

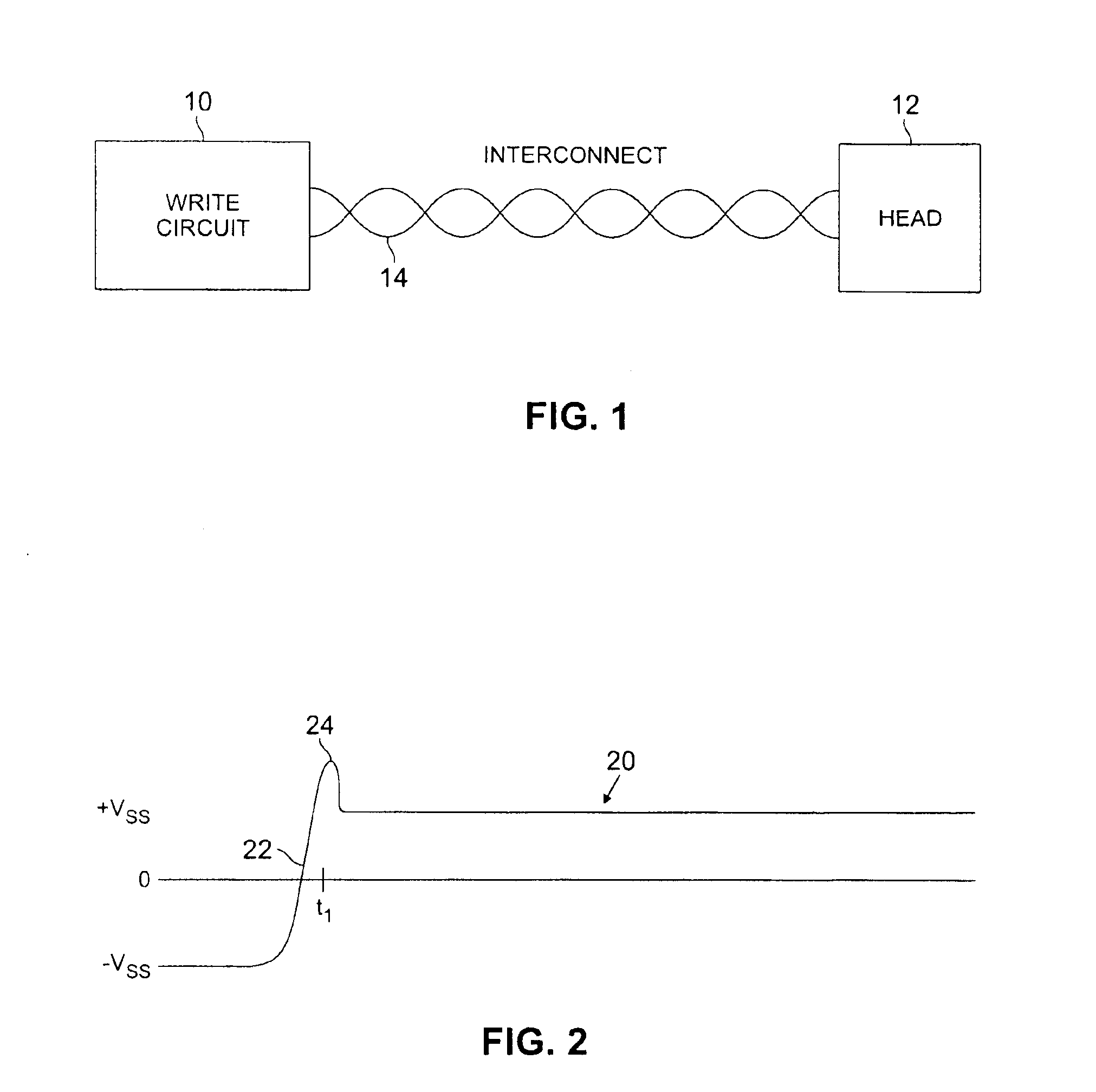

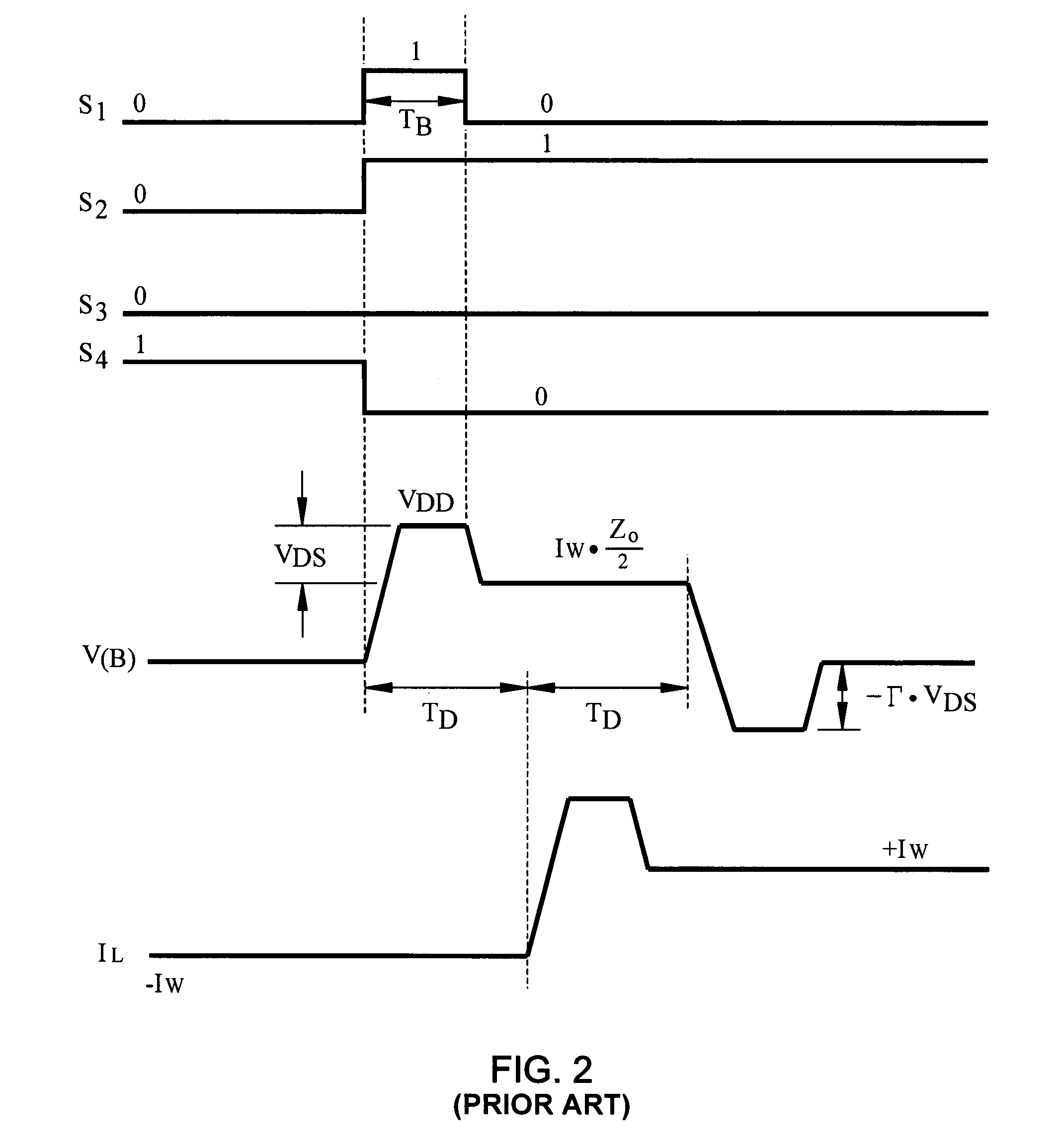

Characteristically terminated write driver with compensation for magnetic response and method therefor

InactiveUS6671113B2Filamentary/web carriers operation controlH-bridge head driver circuitElectrical polarityMagnetic response

A method (and magnetic recording circuit structure) for write drivers to reduce the reversal time for the current through the inductive recording head, includes a write driver output stage providing a write signal output with a write signal source strength SO, a magnetic write head with a write signal input essentially equal to strength SO, and an interconnect circuit having a characteristic impedance ZO coupled to the write signal output of the write driver output stage and the magnetic write head. The write driver output stage preferably includes a source-side termination circuit having output impedance ZS, wherein the source-side termination circuit output impedance ZS is substantially equal to ZO and the source strength SO of the write driver at the input of the interconnect circuit is temporarily enlarged after every polarity reversal of the write signal for a predetermined time duration Deltat.

Owner:INT BUSINESS MASCH CORP

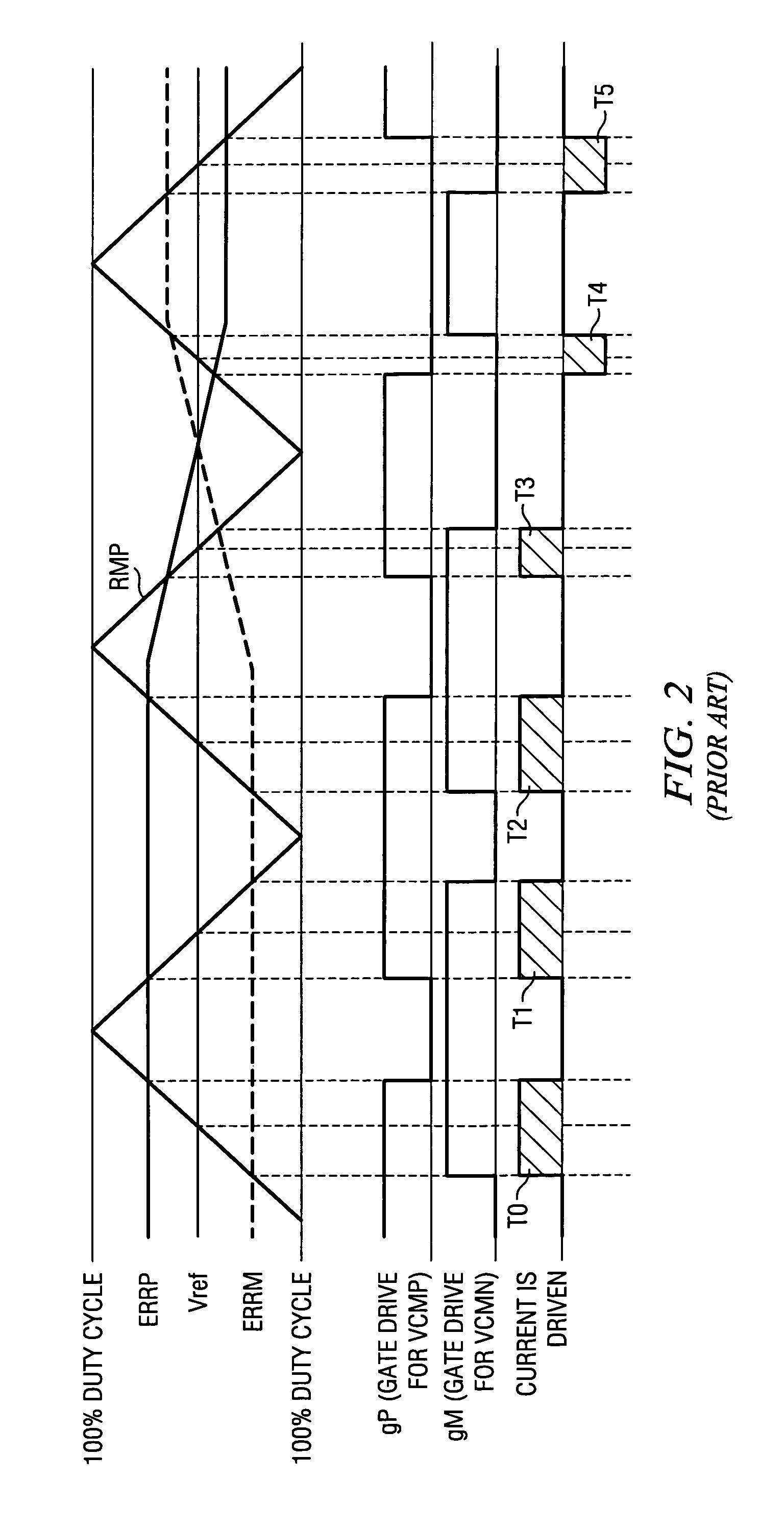

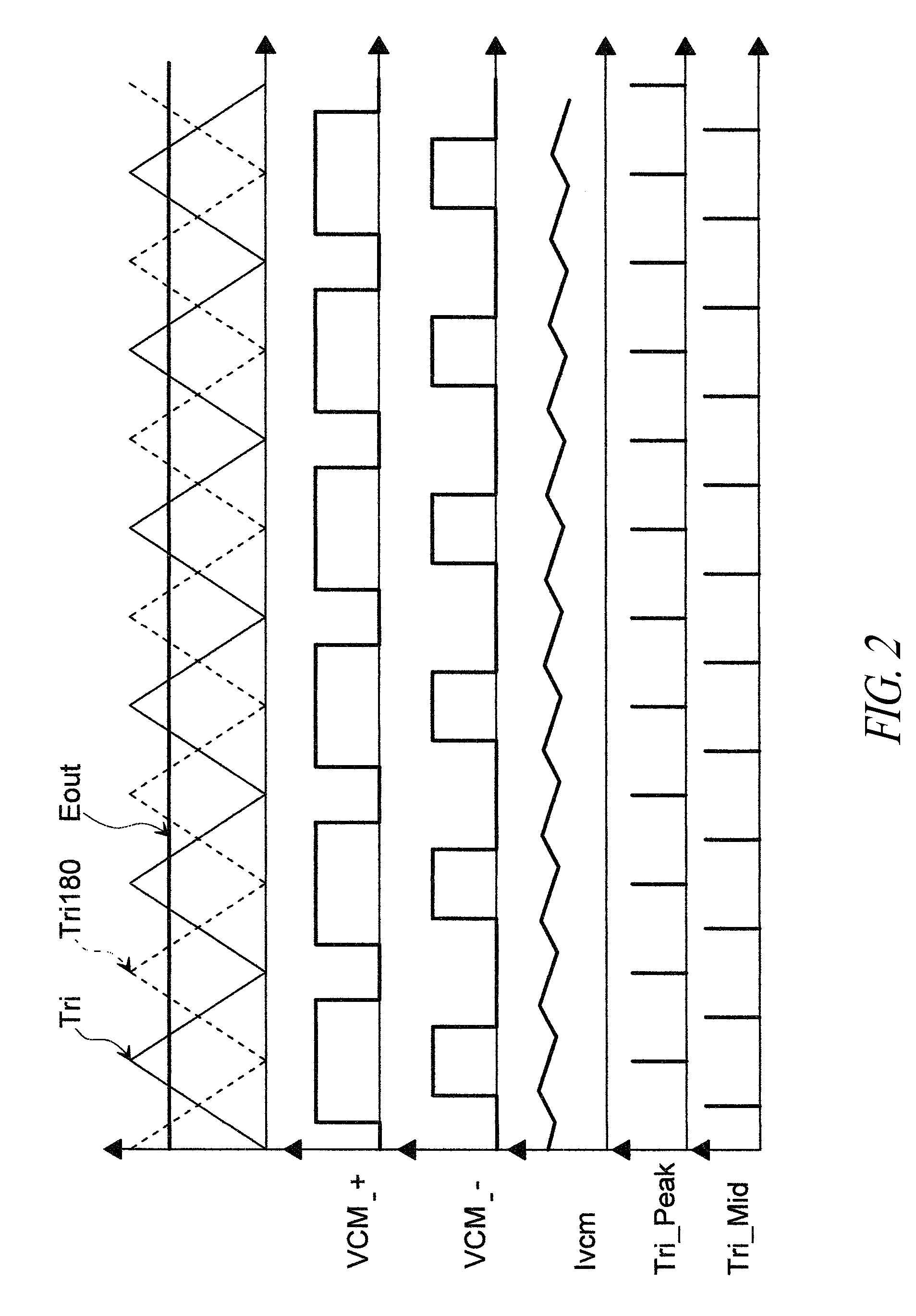

Rejection of power supply variations for gain error cancellation in pulse-width-modulated motor controllers

A positioning driver (32) for a voice coil motor (22) in a disk drive system (10) is disclosed. Pulse-width-modulated prestage drivers (46) are coupled to power transistors (50) arranged in an “H” bridge for driving the voice coil motor (22), biased with a power supply voltage (VM). The pulse-width-modulated prestage drivers (46) drive the power transistors (50) according to a comparison between an error signal from an error amplifier (36) and a ramp clock signal (RMP) generated by a ramp clock generator (46). The ramp clock generator (46) includes a control circuit (68) that modulates the high and low limits of the ramp clock signal (RMP) in response to variations in the power supply voltage (VM). This modulation of the high and low limits compensates for variations in the gain of the power transistors (50) resulting from variations in the power supply voltage (VM). The control circuit (68) may also modulate the slope of the ramp clock signal (RMP) according to variations in the power supply voltage (VM), for example to maintain a constant frequency.

Owner:TEXAS INSTR INC

Circuits to achieve high data rate writing on thin film transducer

InactiveUS7035027B2High speed data transmissionTotal current dropH-bridge head driver circuitRecord information storageHemt circuitsTransducer

Owner:TEXAS INSTR INC

Circuit and method for writing to a memory disk

A method and circuit is disclosed for controlling the write head of a magnetic disk storage device. The circuit includes a pull-up device coupled to a terminal of the write head, for selectively providing a current to the write head through the terminal. The circuit further includes parallel-connected first and second current sink circuits, each of which is coupled to the write head terminal and selectively activated to draw current from the write head via the write head terminal. The circuit further includes a control circuit for individually activating the pull-up device and the first and second current sink circuits. In particular, when reversing the direction of current flow through the write head from a first direction in which current is provided to the write head via the write head terminal to a second direction in which current is drawn from the write head from the write head terminal, both the first and second current sink circuits are activated by the control circuit. When the current in the write head nears the desired destination current level, the second current sink circuit is deactivated and the pull-up device is thereafter immediately activated for a predetermined period of time. The pull-up device is deactivated as the current in the write head approaches a constant value. Due to the deactivation of the second current sink circuit and the temporary activation of the pull-up device, current overshoot and undershoot of the write head current is minimized.

Owner:STMICROELECTRONICS SRL

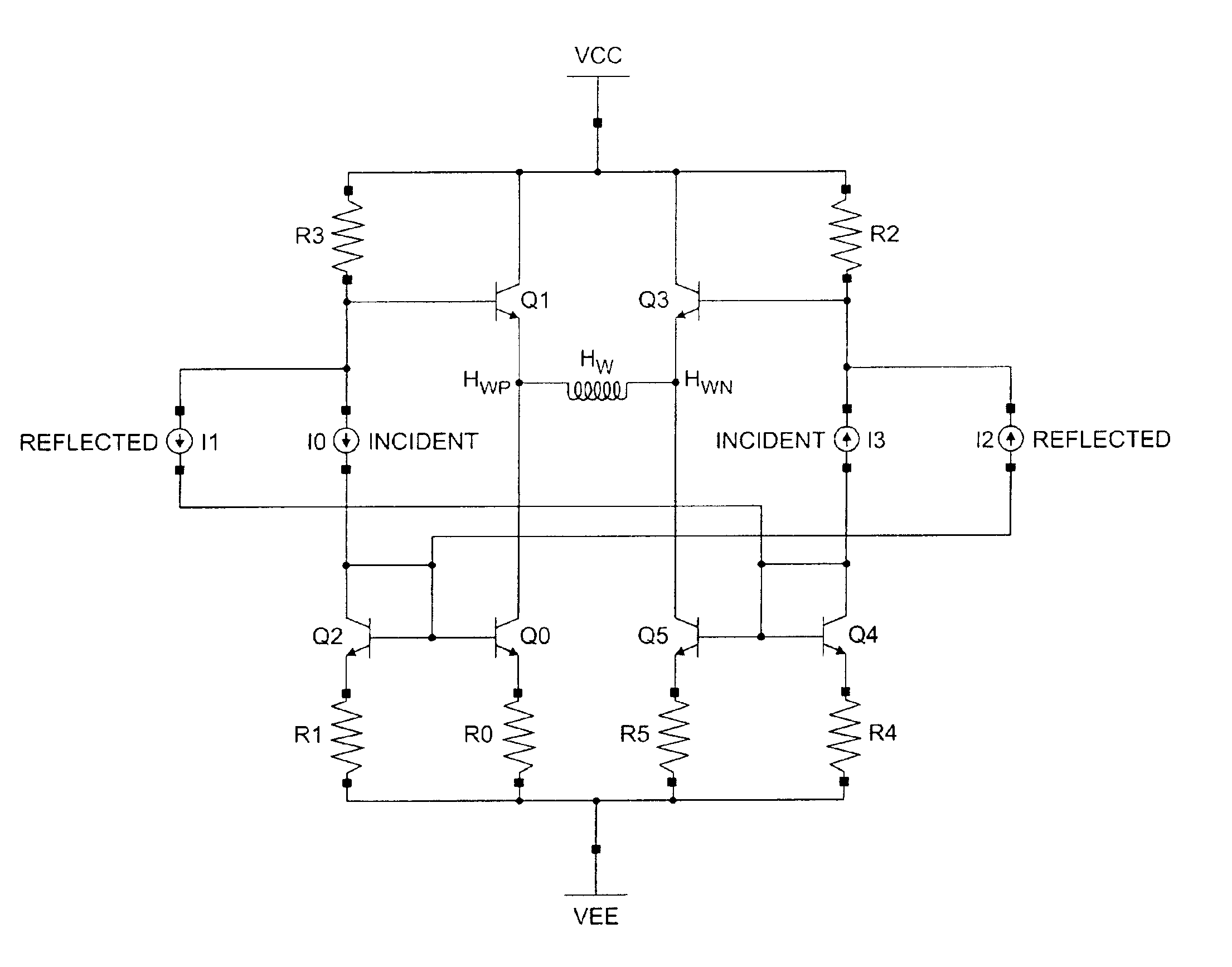

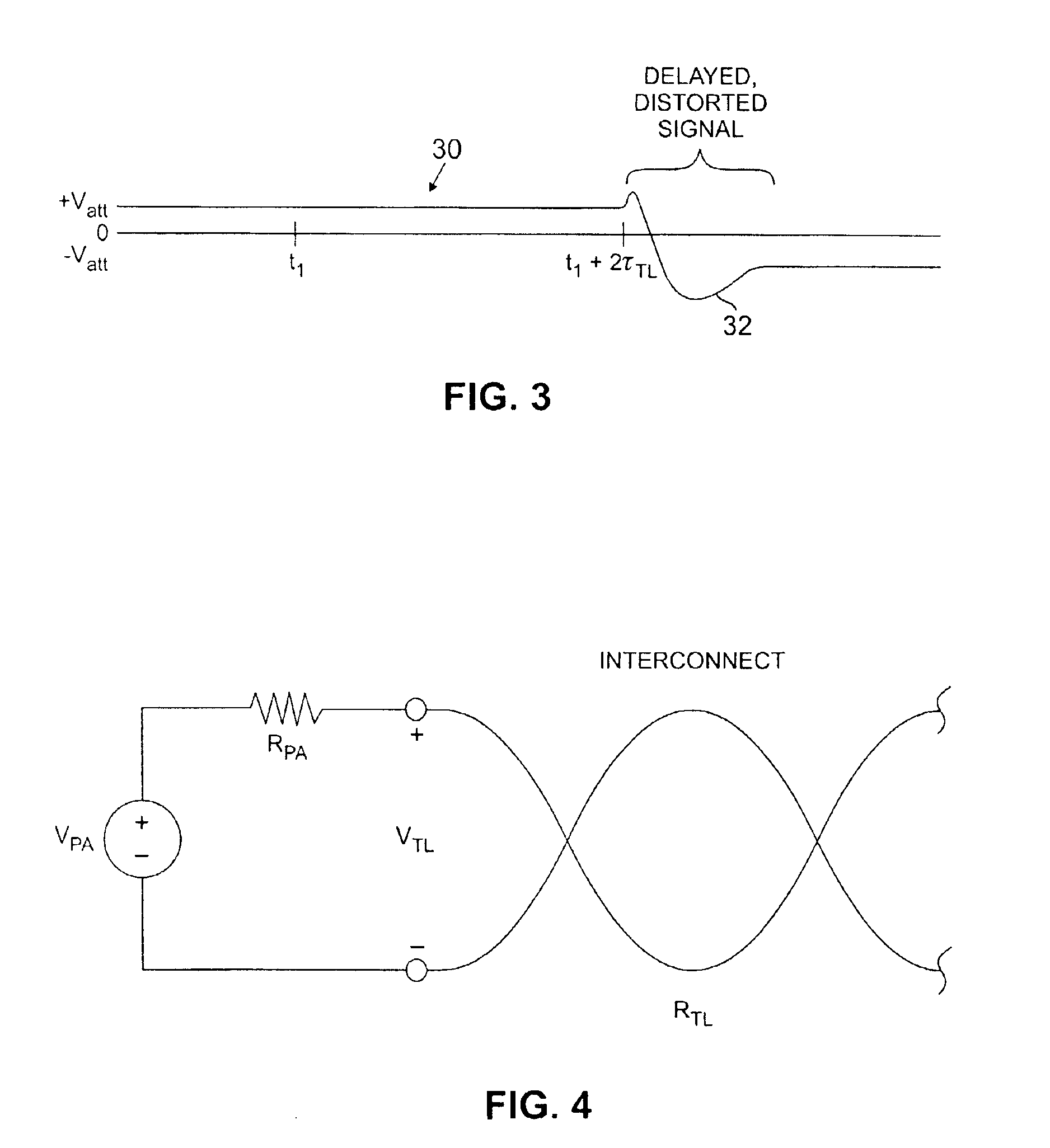

Disk drive writer with active reflection cancellation

InactiveUS6879456B2H-bridge head driver circuitRecord information storageDriver circuitHemt circuits

A write driver circuit selectively provides a write current through a write head in first and second opposite directions. The write driver circuit is connected to the write head through an interconnect. The write driver circuit provides an incident write current signal through the interconnect to the write head, and also provides a reflection cancellation signal through the interconnect to the write head. In an exemplary embodiment, the incident write current signal is provided by providing an incident voltage signal across the write head, and the reflection cancellation signal is provided by providing a reflection cancellation voltage signal across the write head. In an exemplary embodiment, the reflection cancellation signal is a delayed and filtered version of the incident write current signal that cancels a reflected signal that is reflected at the interface between the interconnect and the write head due to impedance mismatching.

Owner:AVAGO TECH INT SALES PTE LTD

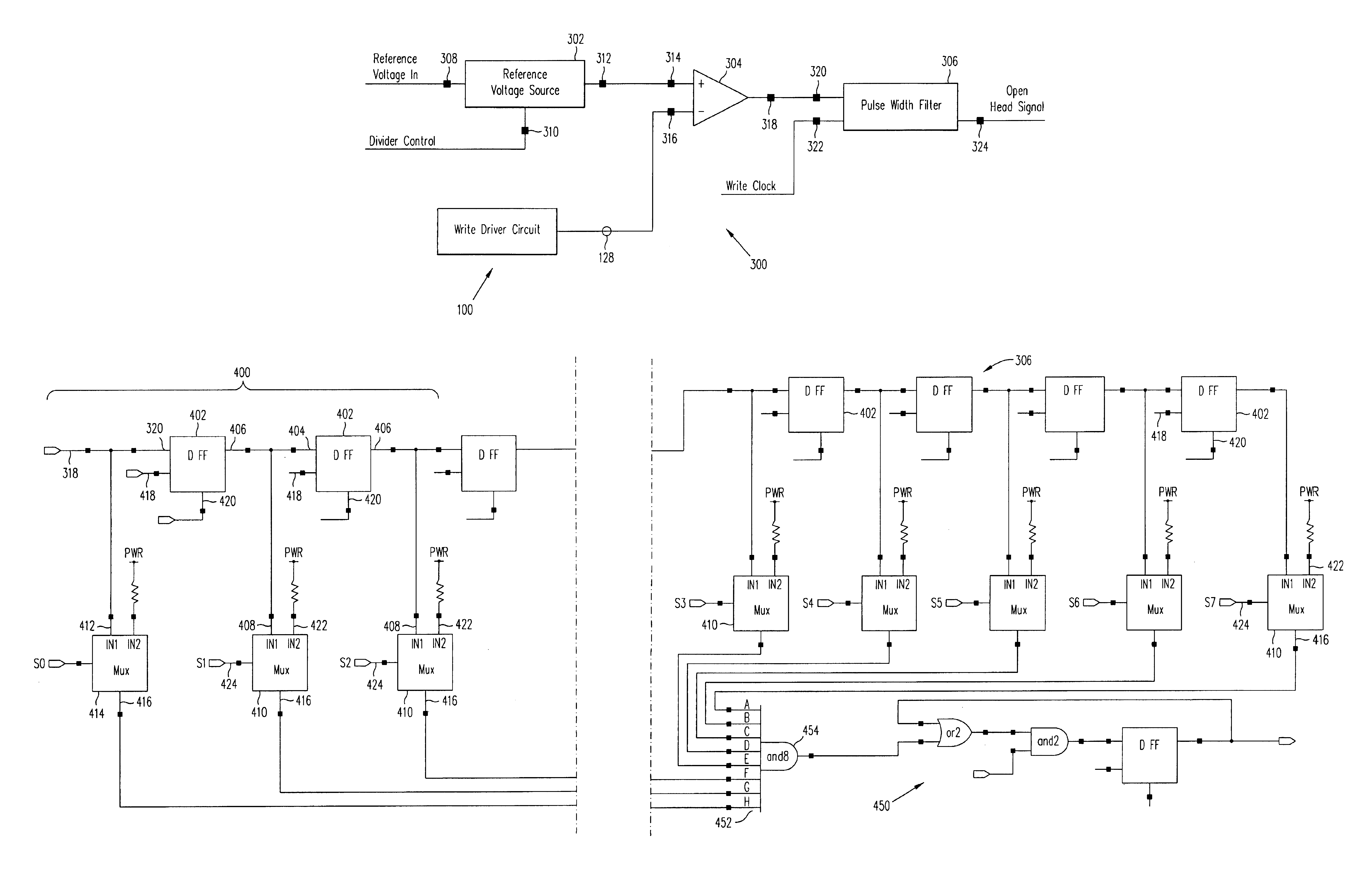

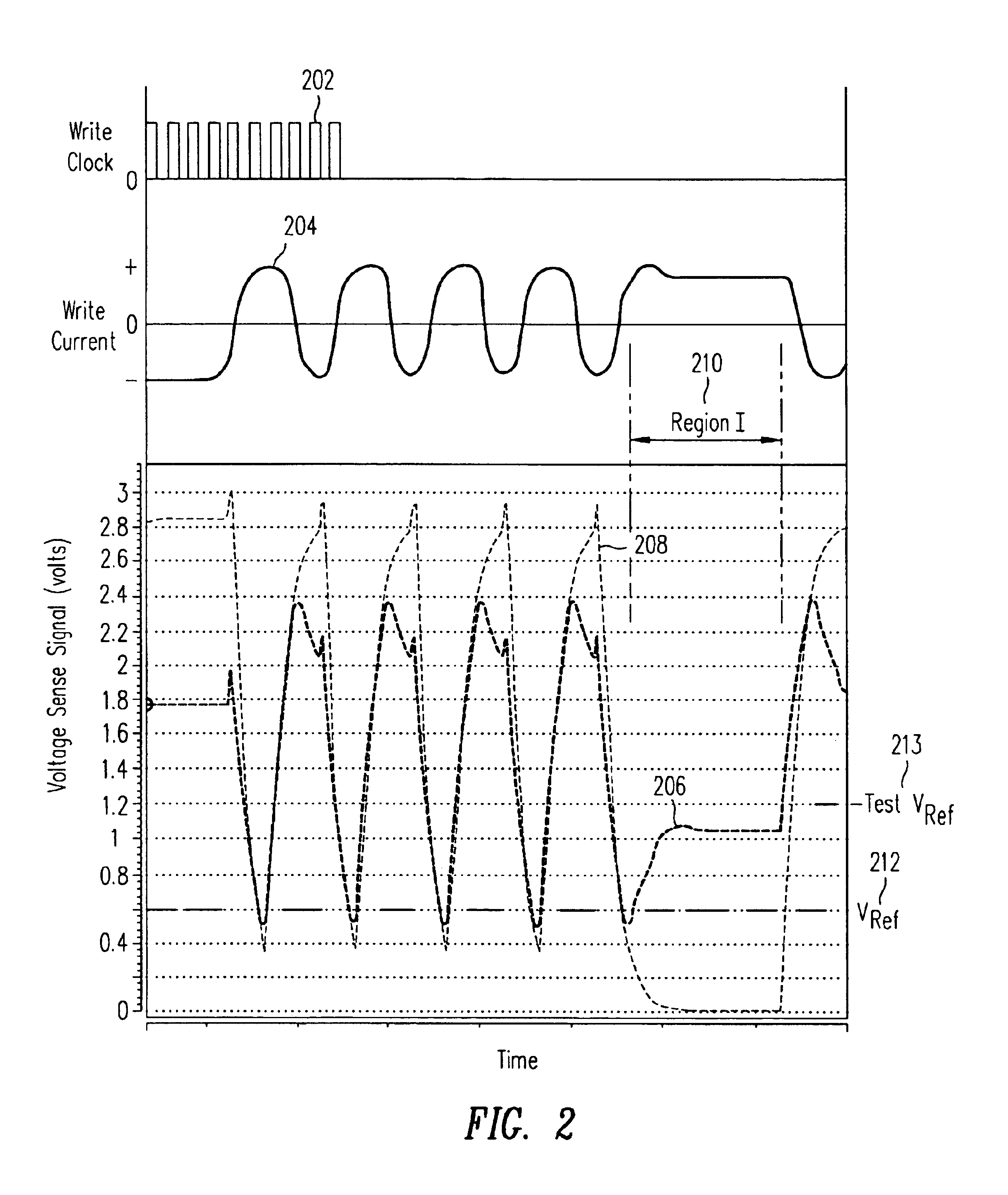

Open head detection circuit and method in a voltage or current mode driver

InactiveUS6952316B2Disc-shaped record carriersH-bridge head driver circuitDriver circuitHemt circuits

An open write head detection circuit is provided comprising a write head driver circuit, a programmable reference voltage source, a comparator and a pulse width filter. The write head driver circuit generates an voltage sense signal. The comparator compares the voltage sense signal with a reference voltage from the programmable reference voltage source and generates a comparator output signal indicative of whether the voltage sense signal is greater than or less than the reference voltage. The comparator output signal is input to the pulse width filter which generates a latched open head signal in response the voltage sense signal being less than the reference level for a predetermined time measured as a programmable number of write clock cycles.

Owner:IBM CORP

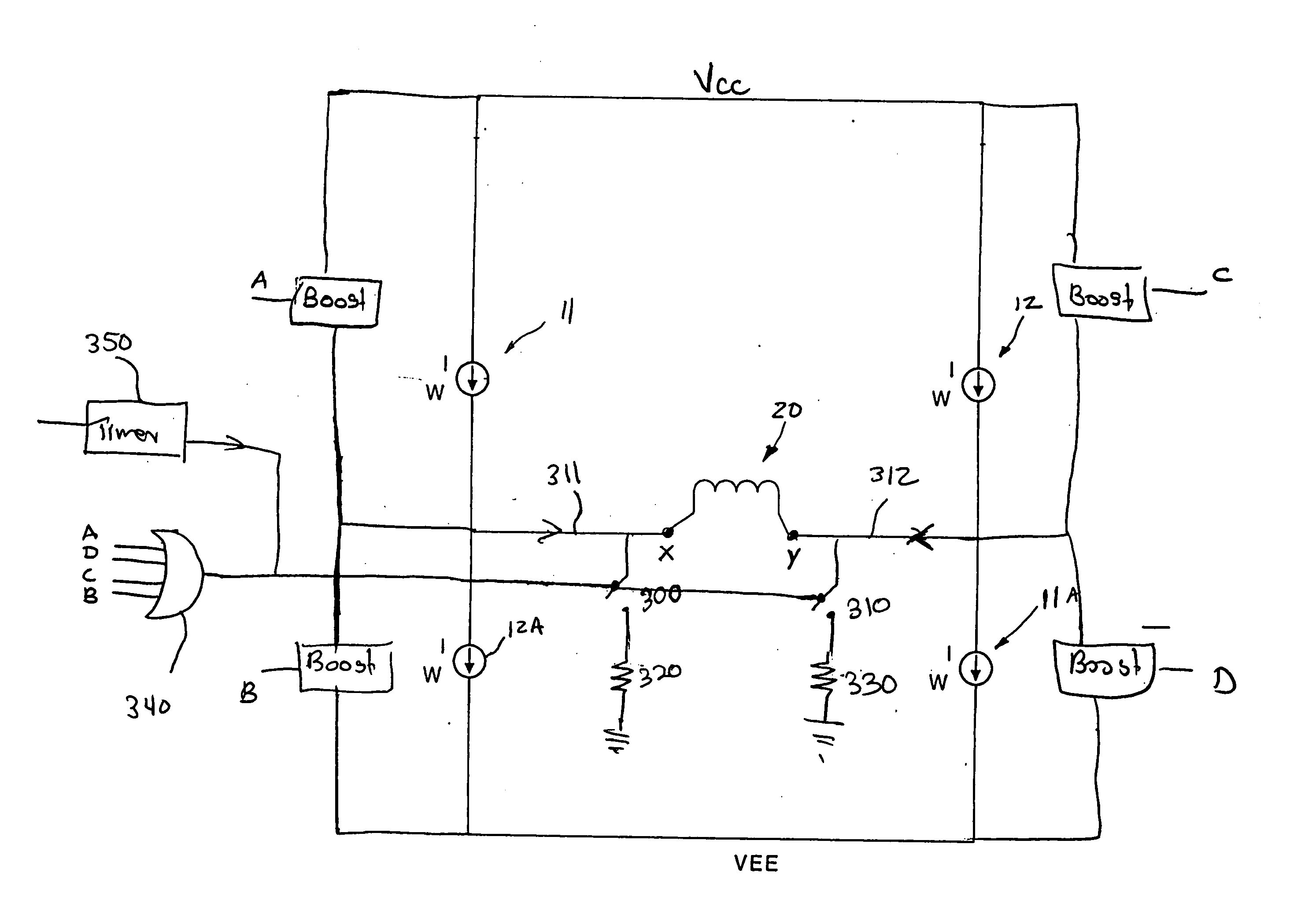

Damping resistor boost writer architecture

ActiveUS20050117244A1H-bridge head driver circuitRecord information storageHard disc driveMagnetic storage

A write driver apparatus and corresponding method for an inductive head element (20) in a magnetic storage medium, such as a hard disk drive, having an H-bridge type circuit (10) which is capable of driving a current through the inductive head element (20) and having a boost circuit (250, 260) which is coupled with the H-bridge (10) and which is operable for delivering another current during a predetermined period to the head element (20), wherein a sum of the currents provides the write current for the head element (20) of the hard disk drive. Further, a resistive element (210, 320, 330) is selectively coupled with the head element (20) for providing impedance matching in which the resistive element (210, 320, 330) is decoupled from the head element (20) during delivery of the current from the boost circuit (250, 260).

Owner:TEXAS INSTR INC

Method for differentially writing to a memory disk

InactiveUS6512649B1H-bridge head driver circuitRecord information storageVoltage referenceEngineering

A method is disclosed for controlling the write head of a magnetic disk storage device. The method includes sinking current from the first terminal of the write head and sourcing current to the second terminal of the write head substantially simultaneously with sinking current from the first terminal so that a first steady state voltage level appears on the first terminal of the write head and a second steady state voltage level appears on the second terminal thereof that are approximately at a midpoint between a high reference voltage level and a low reference voltage level. The common mode voltage of the write head is substantially constant over time.

Owner:STMICROELECTRONICS SRL +1

Efficient transition from class d to linear operation in dual-mode voice coil motor controllers

ActiveUS20050264920A1Drive mode to a linear drive mode are greatly reducedReduce discontinuityDriving/moving recording headsH-bridge head driver circuitDriving currentAudio power amplifier

A dual-mode positioning driver (32) for a voice coil motor (22) in a disk drive system (10) is disclosed. Linear prestage drivers (38) and pulse-width-modulated prestage drivers (46) are both coupled to power transistors (50) arranged in an “H” bridge for driving the voice coil motor (22). The positioning driver (32) is thus operable to drive the power transistors (50) in either a linear mode or a pulse-width-modulated class D mode. In a transition period while switching from the pulse-width-modulated mode to linear mode, comparators (56H, 56L) compare the phase voltages in the “H” bridge with a reference voltage. The outputs of the comparators (56H, 56L) are applied to the PWM output amplifiers (54H, 54L) to drive the power transistors (50), so that the phase voltages are preconditioned toward their linear bias points. Discontinuities in the drive current through the voice coil motor (22) are minimized as a result.

Owner:TEXAS INSTR INC

Write head driver circuit and method for writing to a memory disk

InactiveUS6970316B2Small noise levelEfficient driveFilamentary/web carriers operation controlH-bridge head driver circuitCapacitanceControl signal

A circuit and method are disclosed for relatively rapidly causing the current flowing through a write head to transition between steady states without generating an appreciable amount of capacitively-coupled noise. Embodiments of the present invention generally provide drive voltage signals to the write head that have no common mode voltage levels during transitions between steady state current levels in the write head. In other words, the drive voltage signals applied to the write head are substantially entirely differential during write head current transitions. In an exemplary embodiment of the present invention, a driver circuit includes switching circuitry connected between the terminals of the write head and reference voltage supplies, such as positive and negative voltage supplies. The driver circuit further includes timing circuitry that generates control signals for controlling the switching circuitry.

Owner:STMICROELECTRONICS SRL

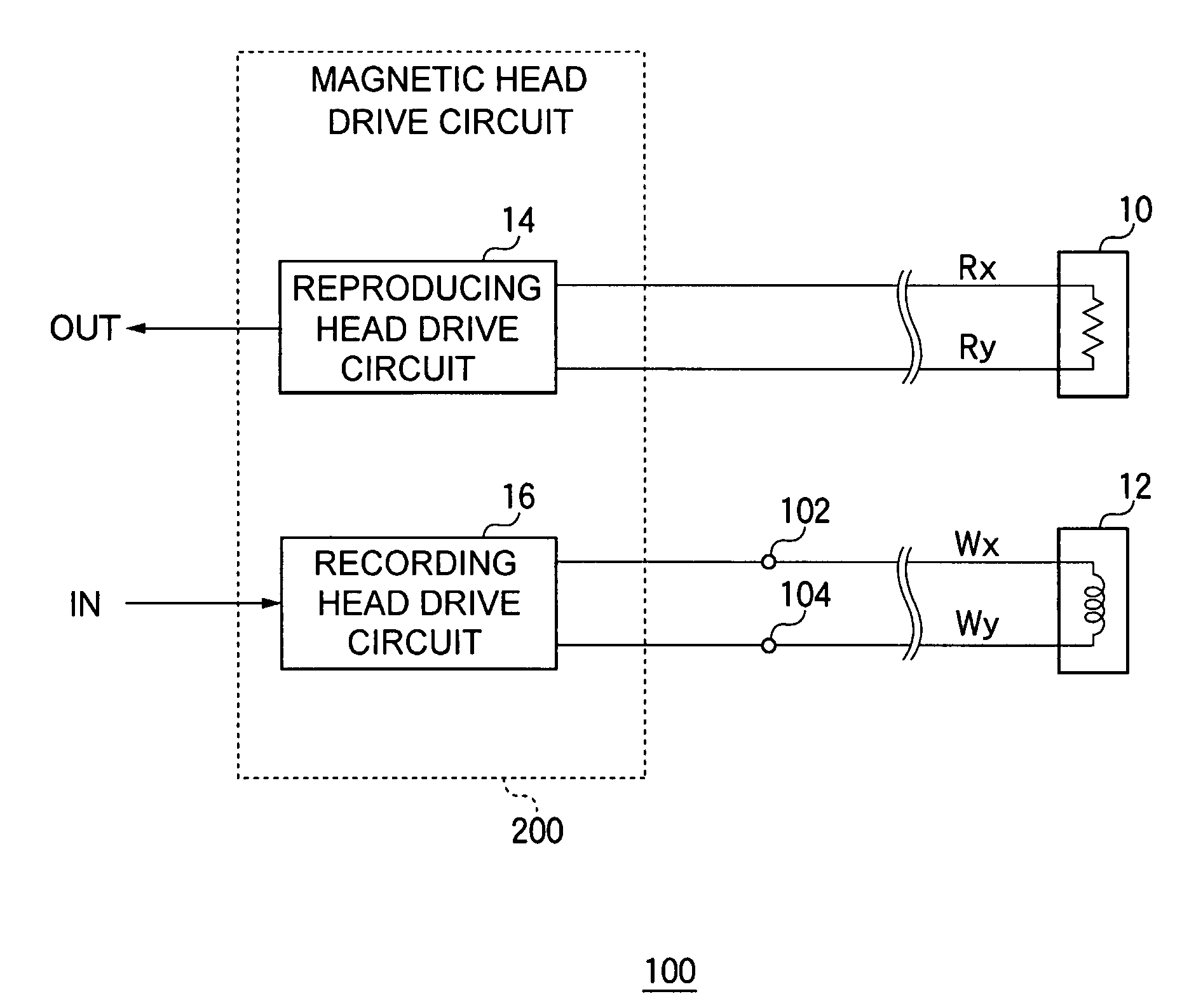

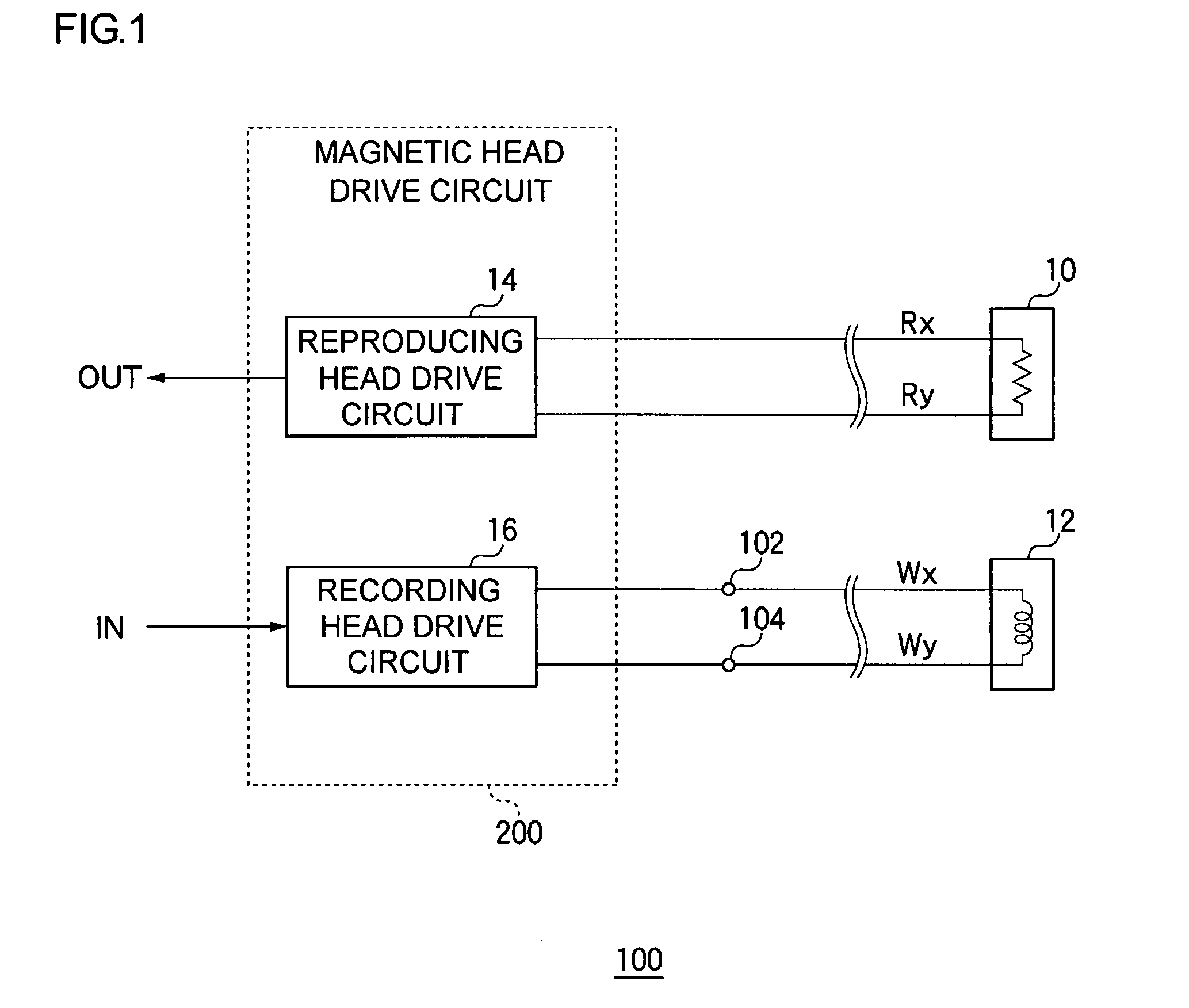

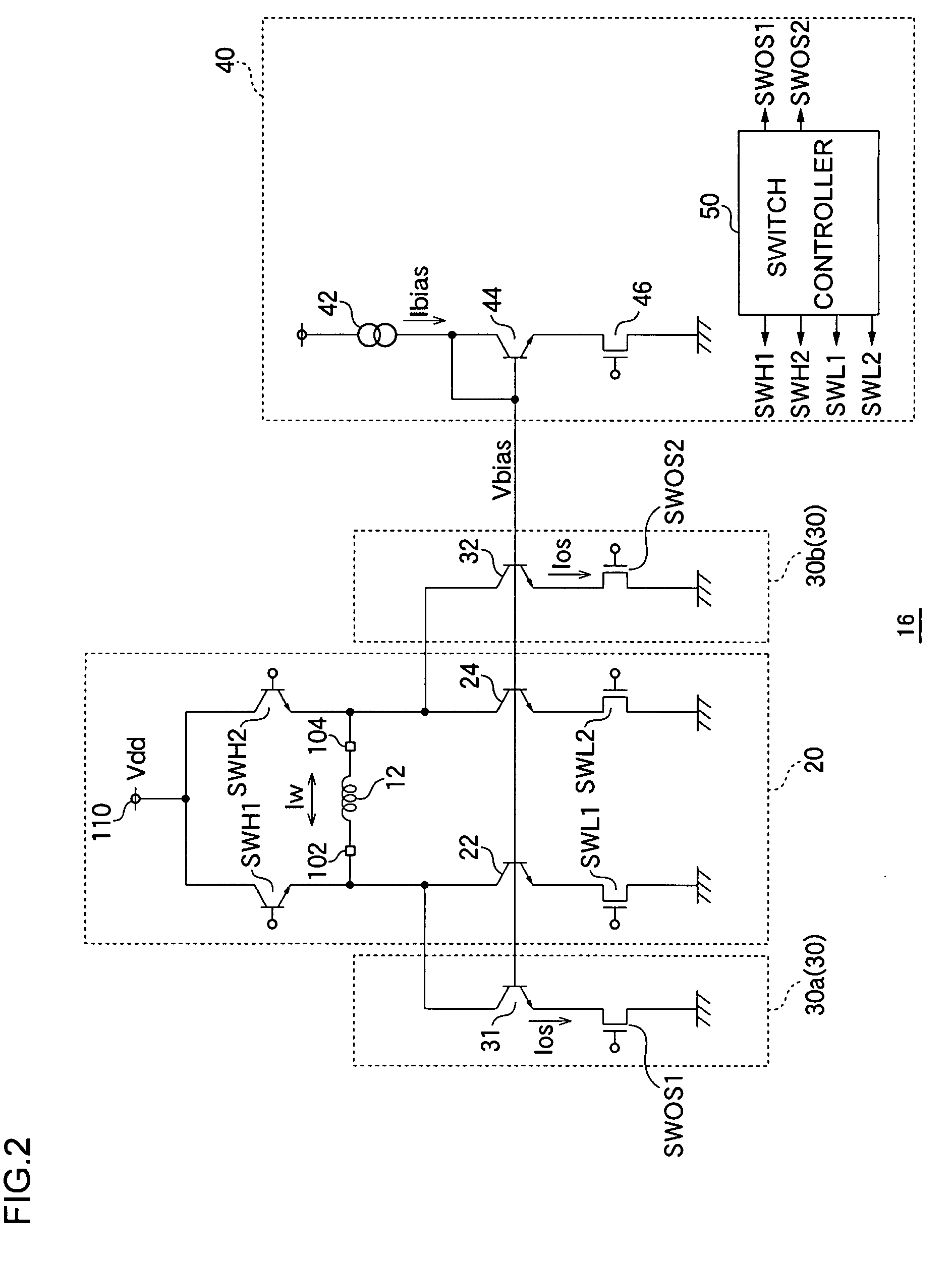

Magnetic head drive circuit

InactiveUS20070206306A1Maintain uniformity of propertyReduce circuit areaFilamentary/web carriers operation controlH-bridge head driver circuitHemt circuitsEngineering

A recording head drive circuit drives a recording head that records information on a magnetic recording medium. A switching circuit is a H-bridge circuit which includes a plurality of transistors. The switching circuit switches direction of a write current (Iw) flowing in the recording head, in accordance with a conduction state of each transistor. A write current controller controls the write current (Iw) in the recording head. An overshoot control circuit adds an overshoot current (Ios), proportional to the write current (Iw), to the write current (Iw) flowing in the recording head, in a predetermined overshoot time period.

Owner:ROHM CO LTD

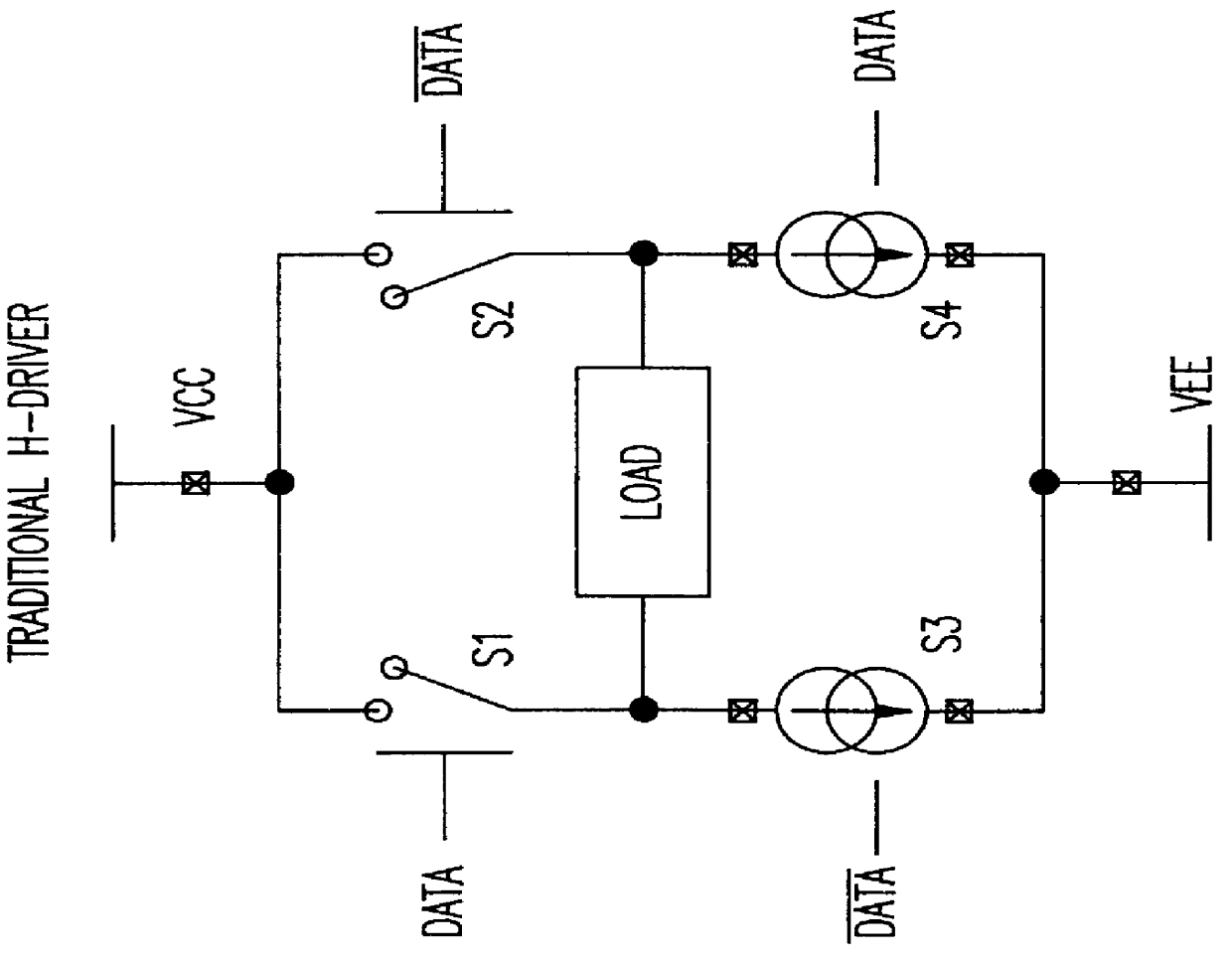

High speed write driver for magnetic inductive write head using a half-switched H-driver

Owner:IBM CORP

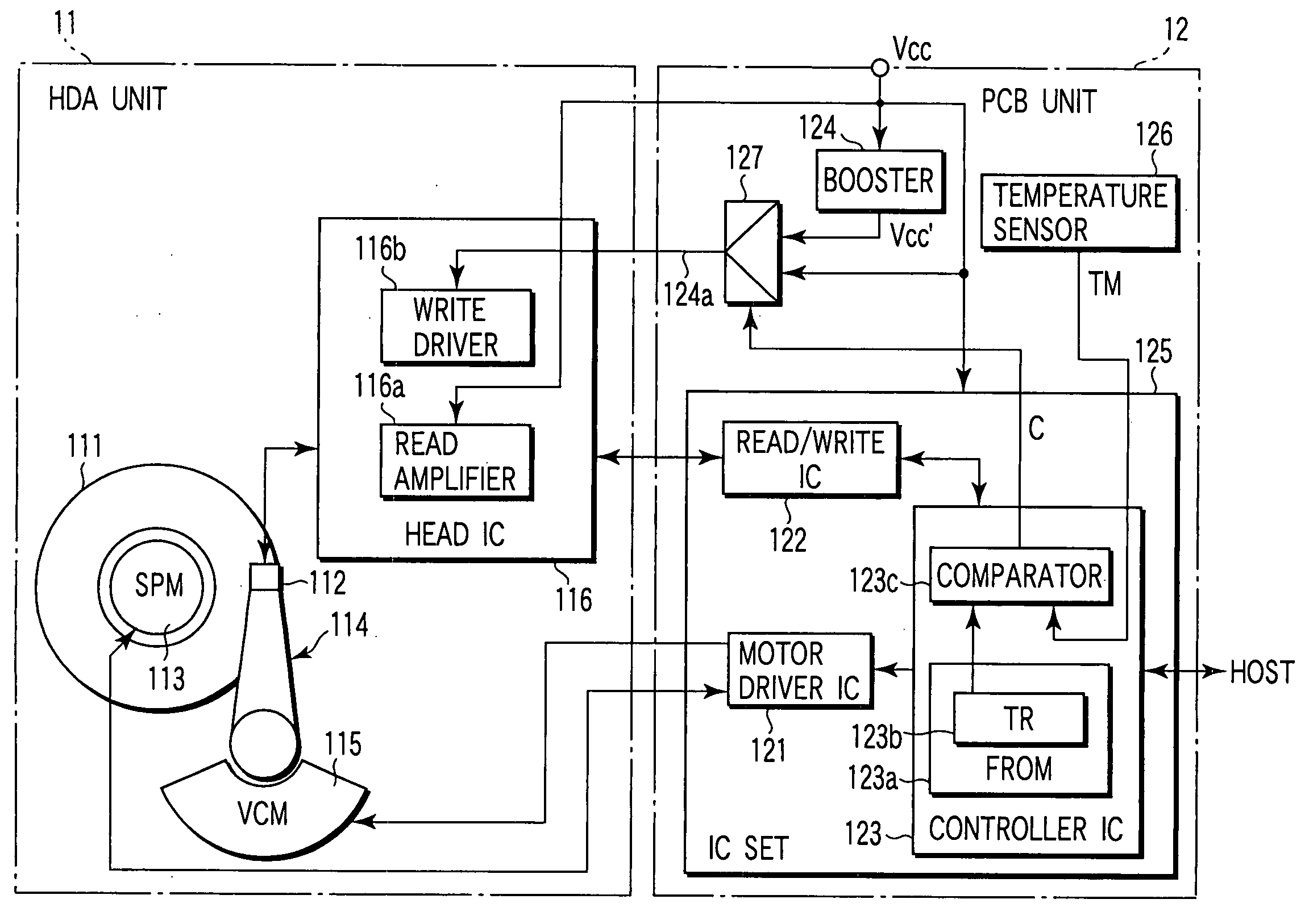

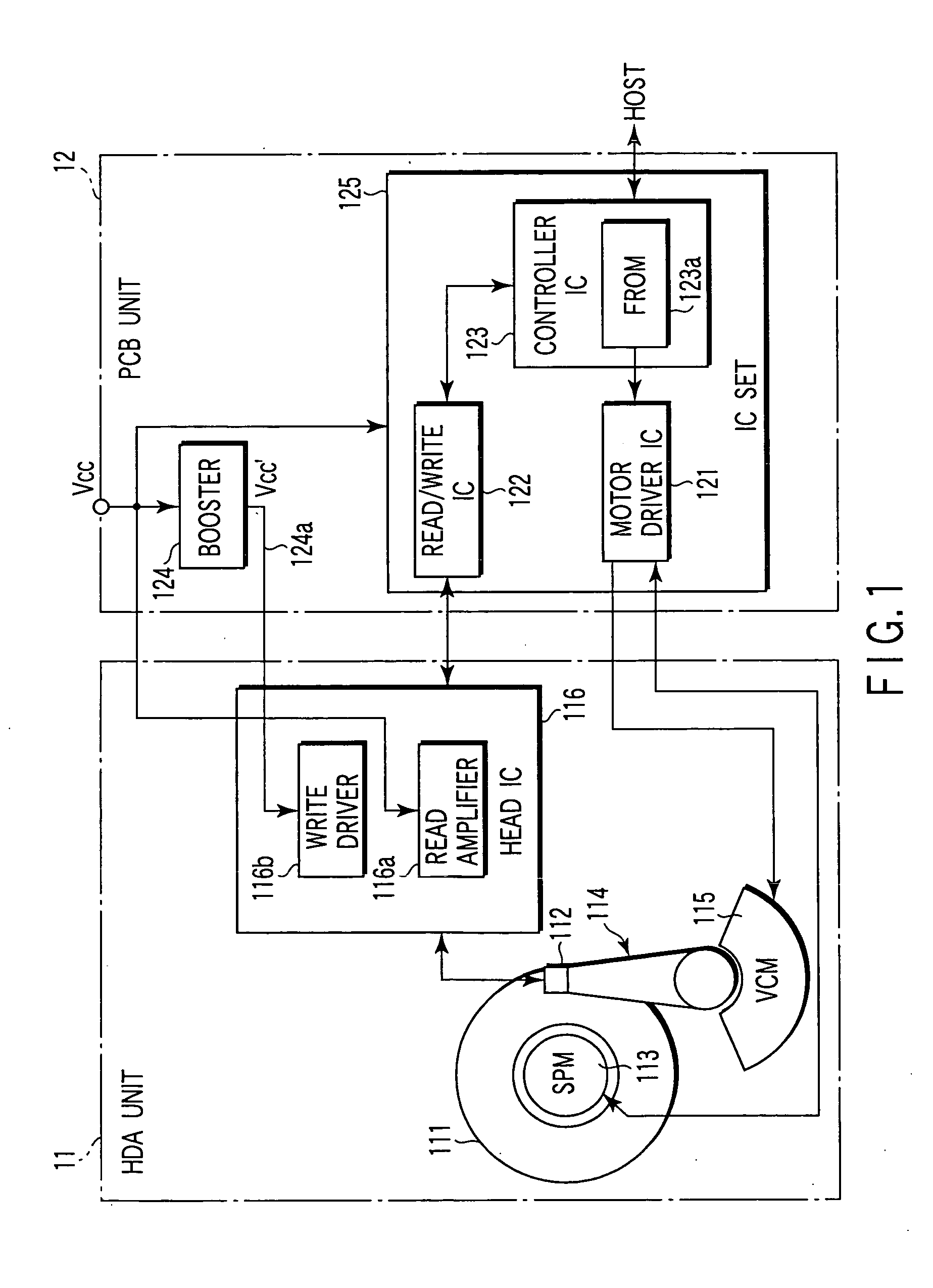

Apparatus controlling write current supplied to head and method for the apparatus

InactiveUS20050063084A1Filamentary/web carriers operation controlH-bridge head driver circuitAudio power amplifierEngineering

A booster boosts a power voltage of a disk storage apparatus. The voltage obtained by boosting the power voltage is applied to a write driver in a head IC via a power line as a power voltage for the write driver. The power voltage of the disk storage apparatus is applied to a read amplifier in the head IC.

Owner:KK TOSHIBA

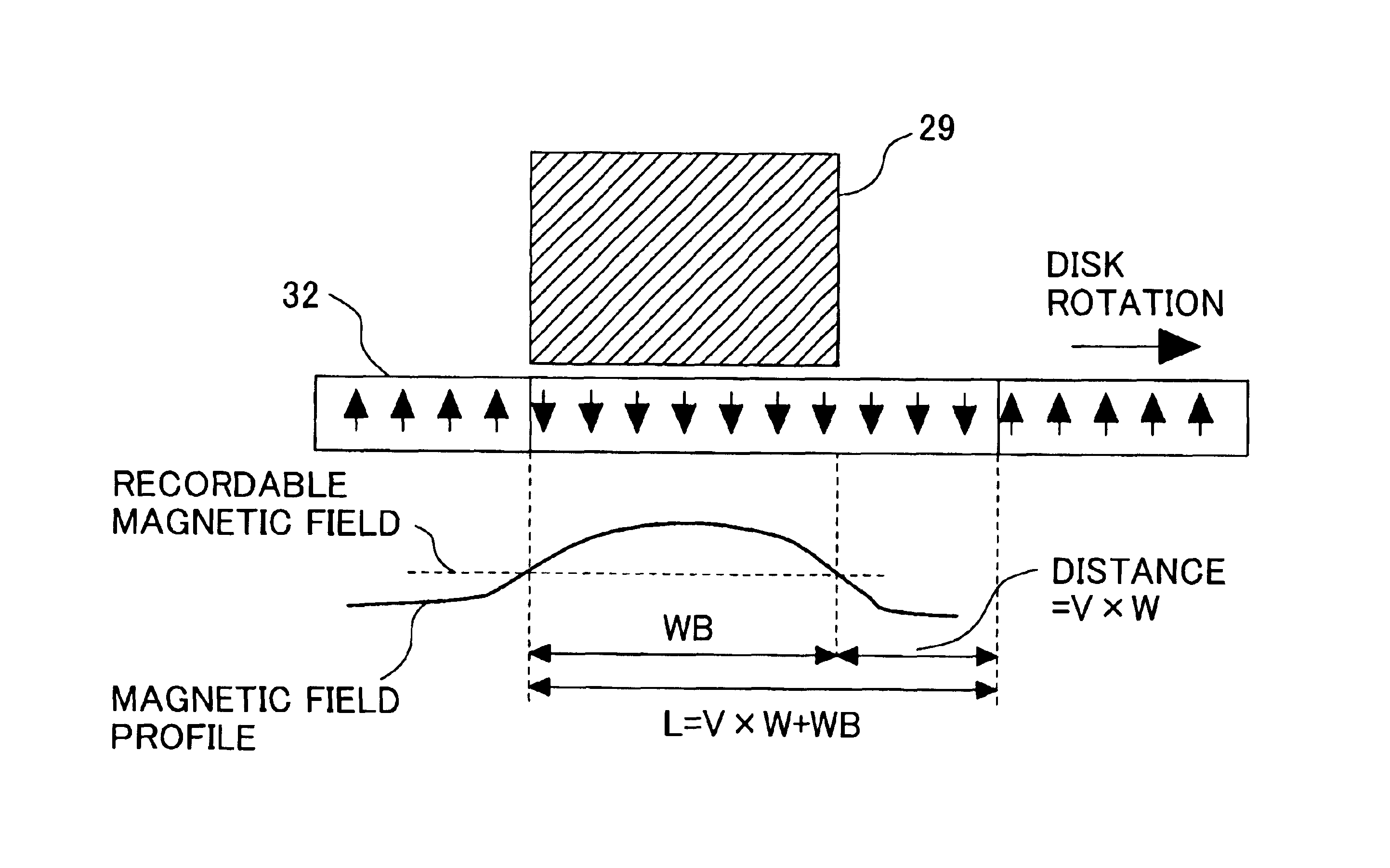

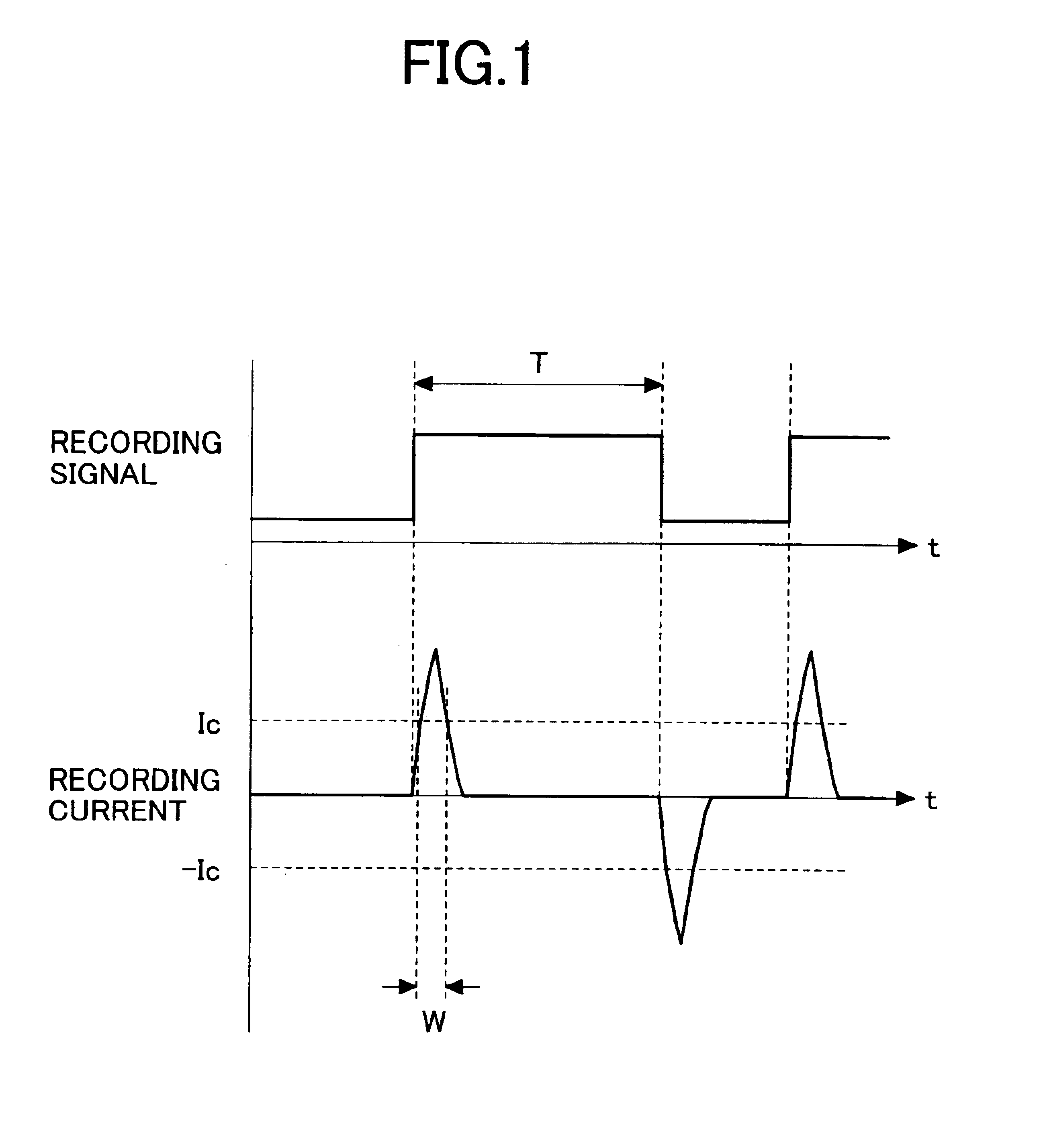

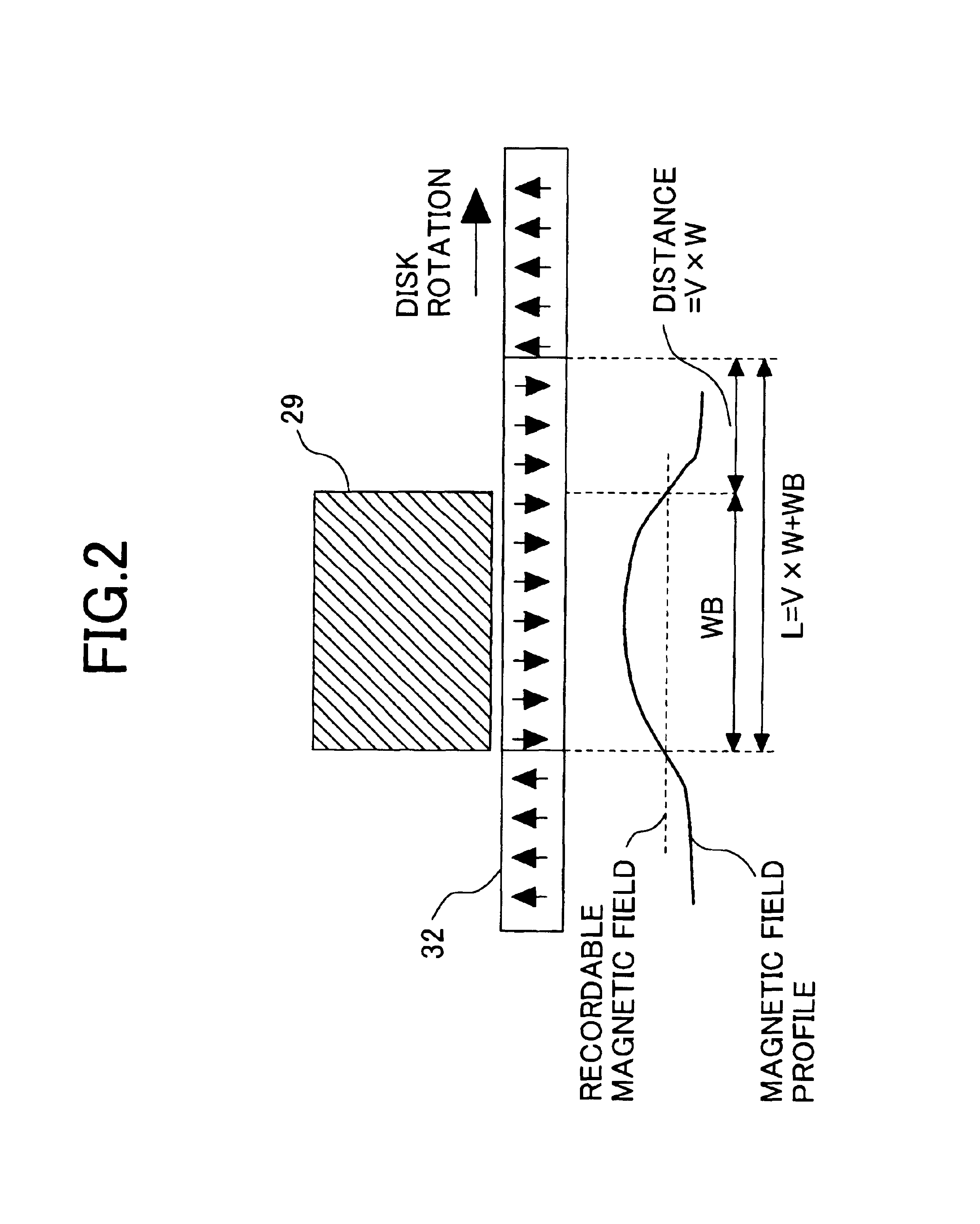

Magnetic recording apparatus and system for driving a magnetic recording medium

InactiveUS6930846B2Avoid excessive magnetizationContributes to high-density recordingH-bridge head driver circuitRecord information storageHigh densityEngineering

A magnetic recording apparatus suitable for high-density and high-frequency magnetic recording includes a recording head to the coil of which a recording current is supplied, the recording current having a waveform such that the conducting time length is shorter than the time length of a recording pattern.

Owner:HITACHI GLOBAL STORAGE TECH JAPAN LTD

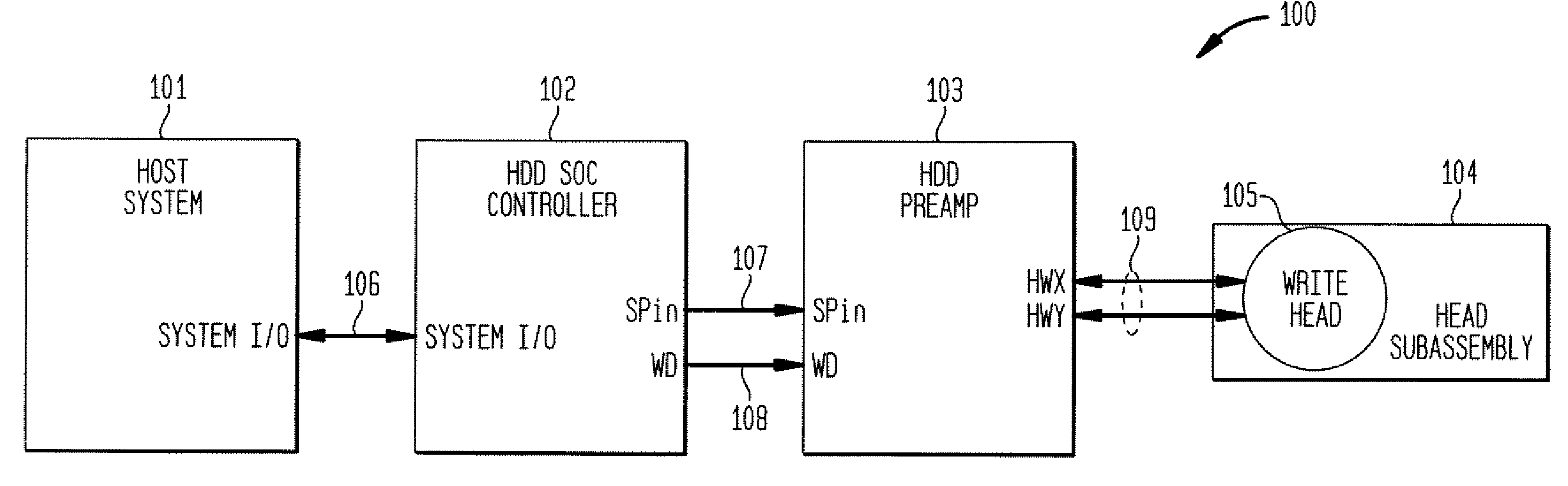

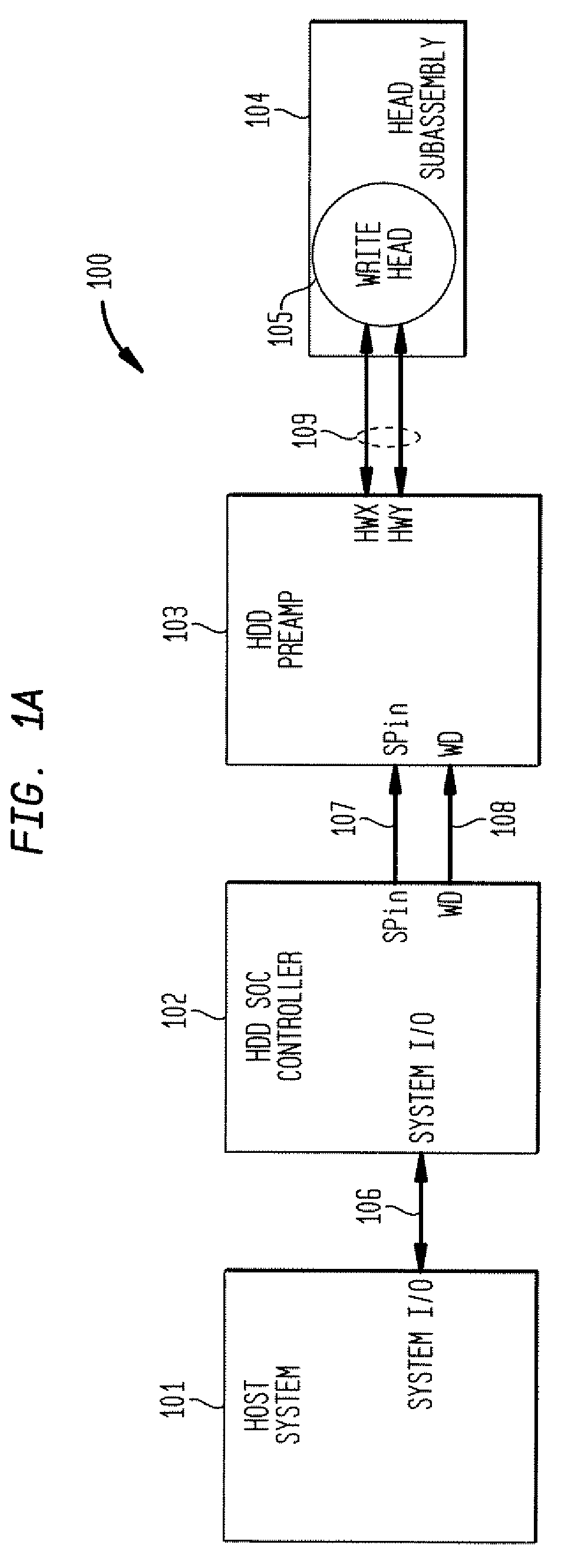

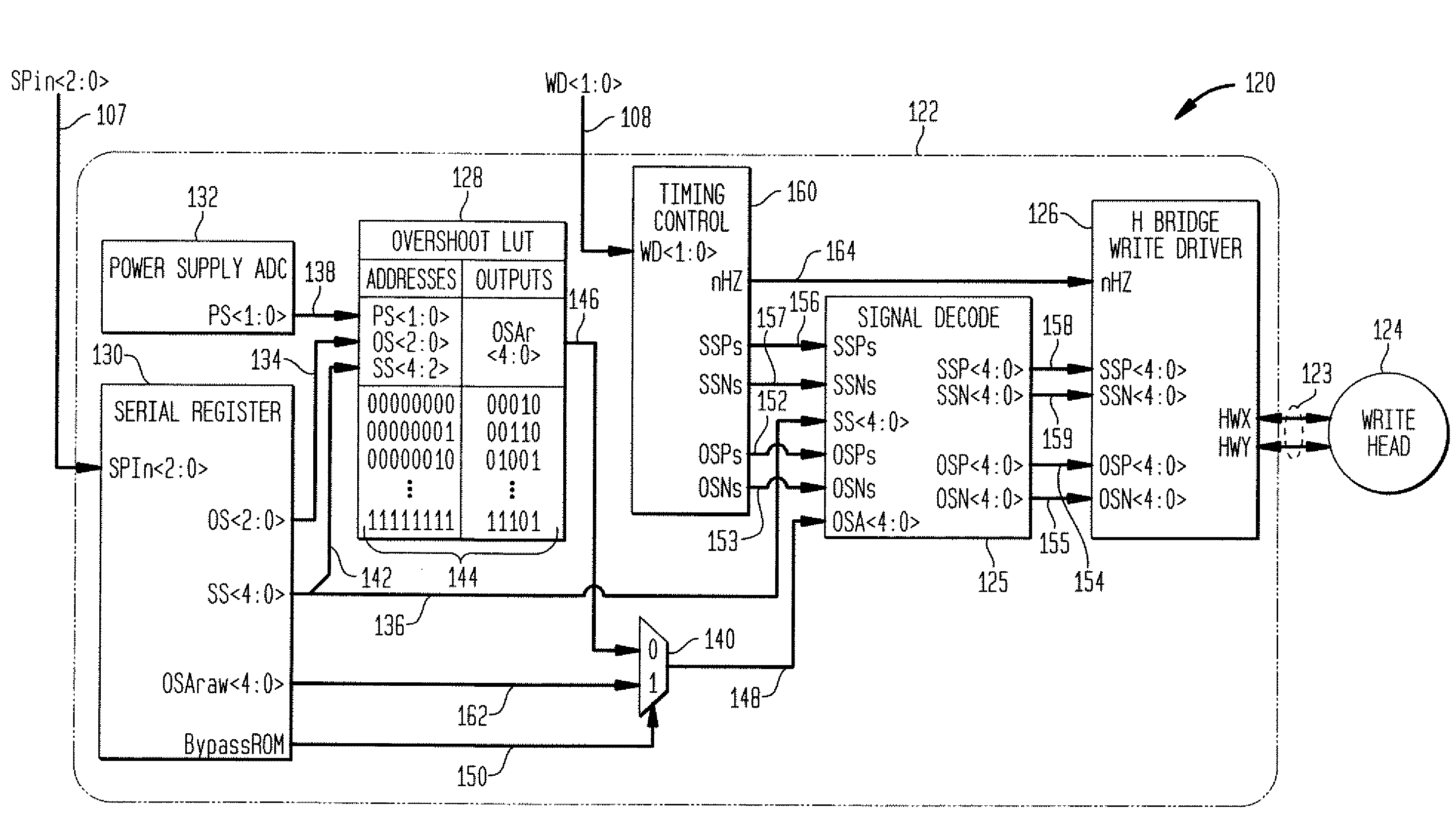

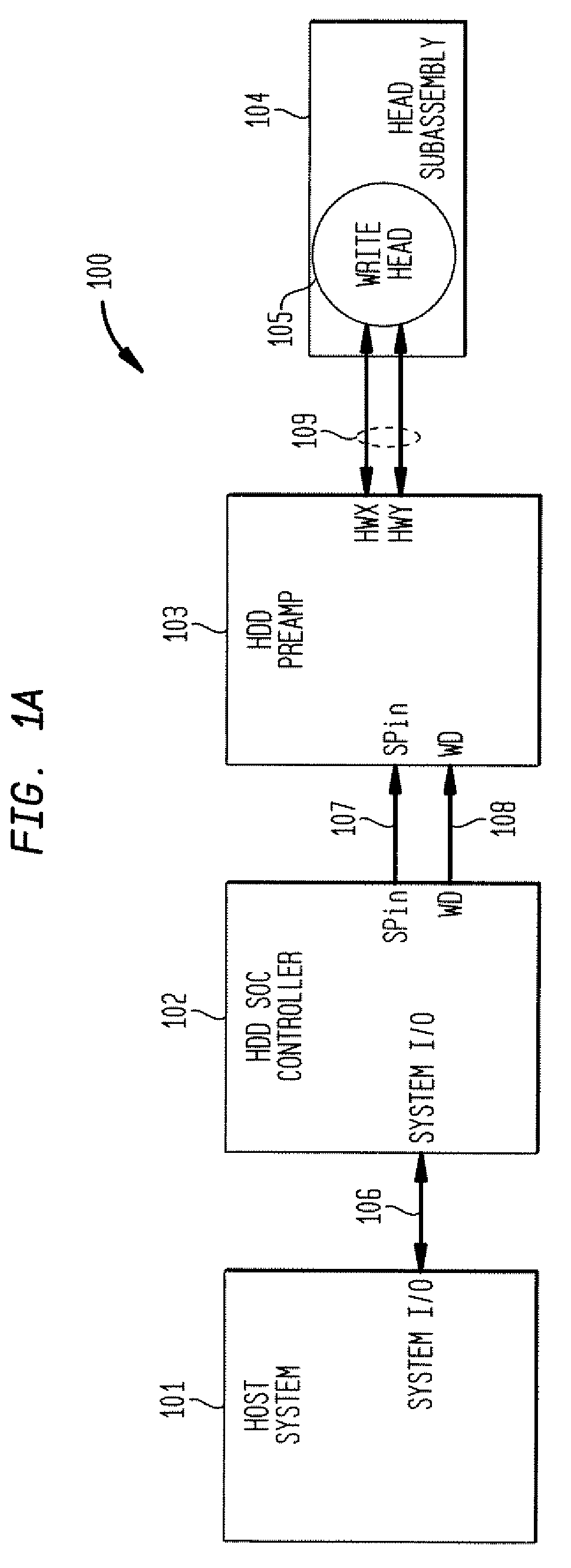

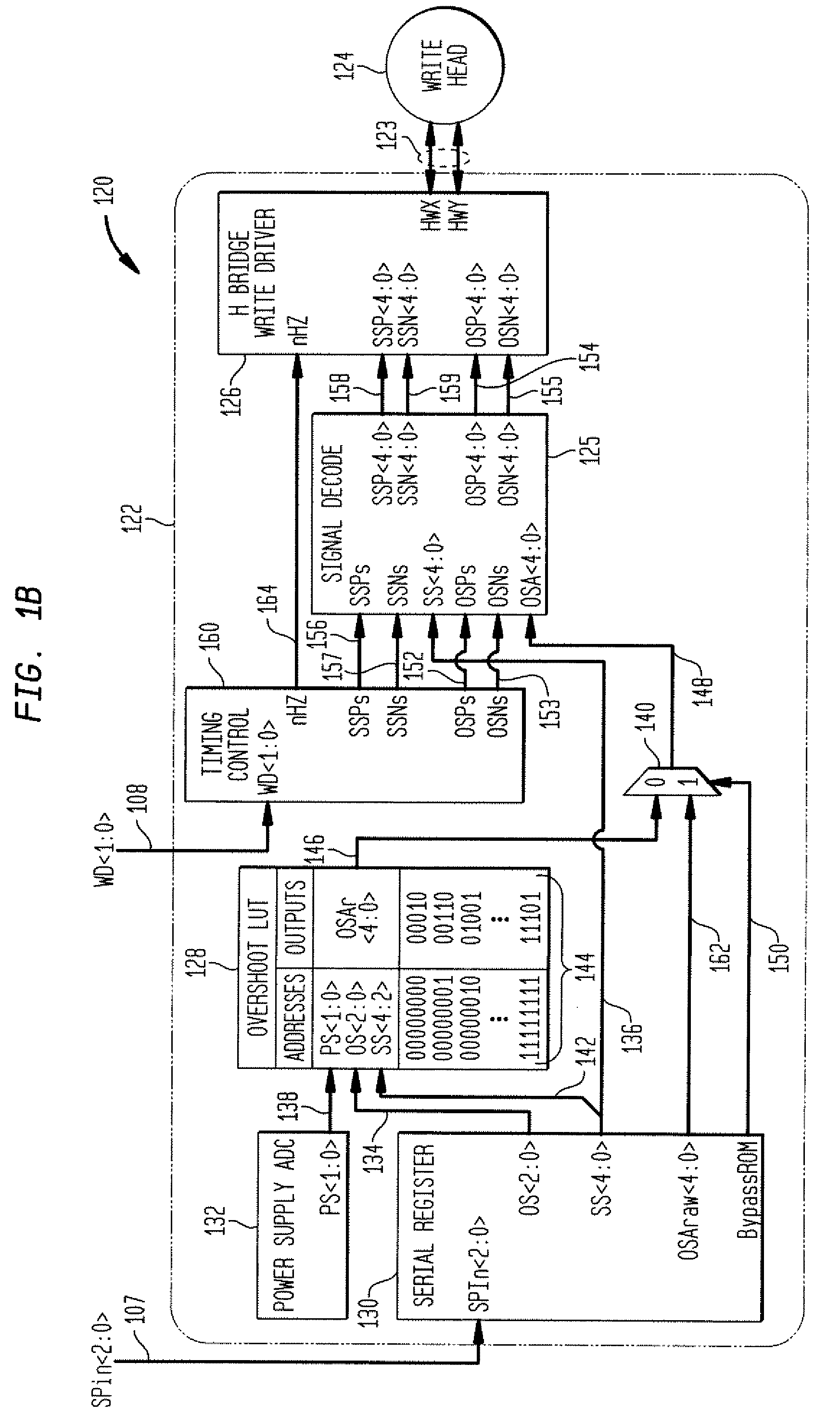

Methods and Apparatus for Controlling Write Driver Current

InactiveUS20090116134A1Widen the optionsShorten design timeH-bridge head driver circuitFilamentary/web record carriersHard disc driveDriver circuit

A hard disk drive write driver circuit is described that can change the output impedance of the write driver by use of a lookup table of control values. A control value is selected from the lookup table by using an address based on a dynamic system variable and a program controlled value. The dynamic system variable is converted to a digital representation. The digital representation and a portion of the program controlled value are used as an address to the lookup table to select a control value. The write driver is responsive to the selected control value to control overshoot current. A method to digitally program the output impedance of a preamp write driver based on realistic operating data is also discussed. An additional approach to controlling overshoot current in a write driver through digital control of overshoot duration is also described.

Owner:BROADCOM INT PTE LTD +1

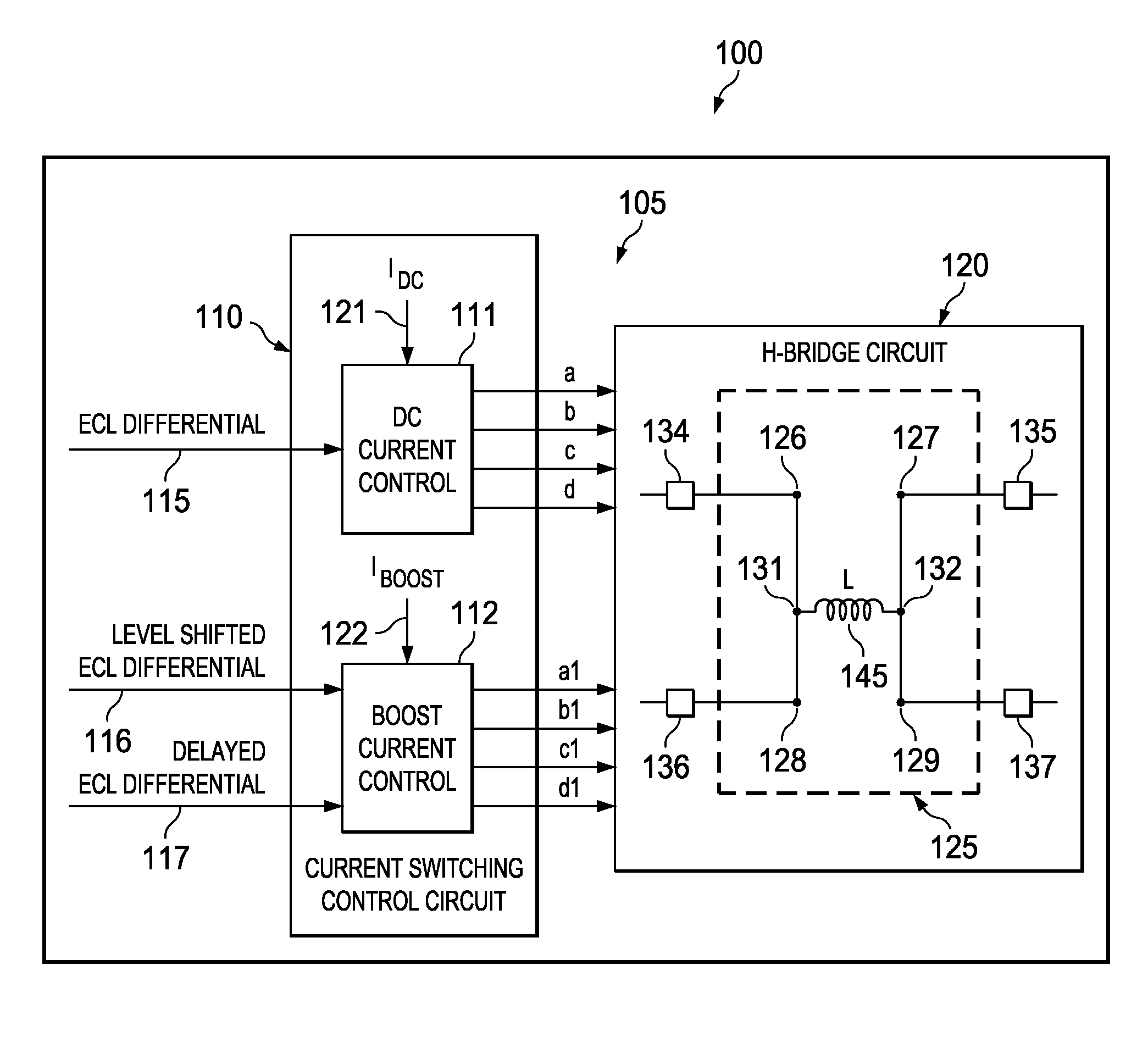

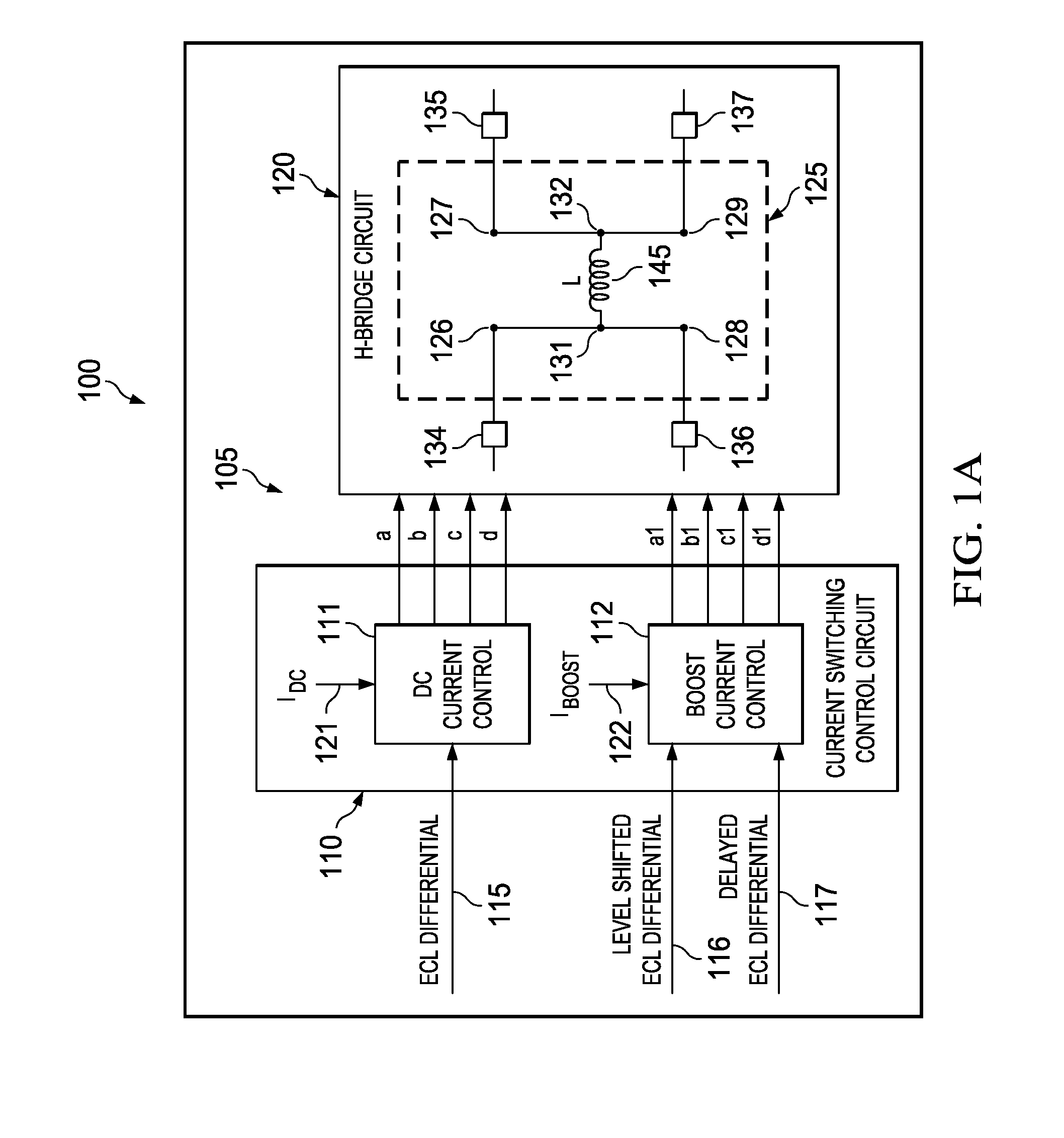

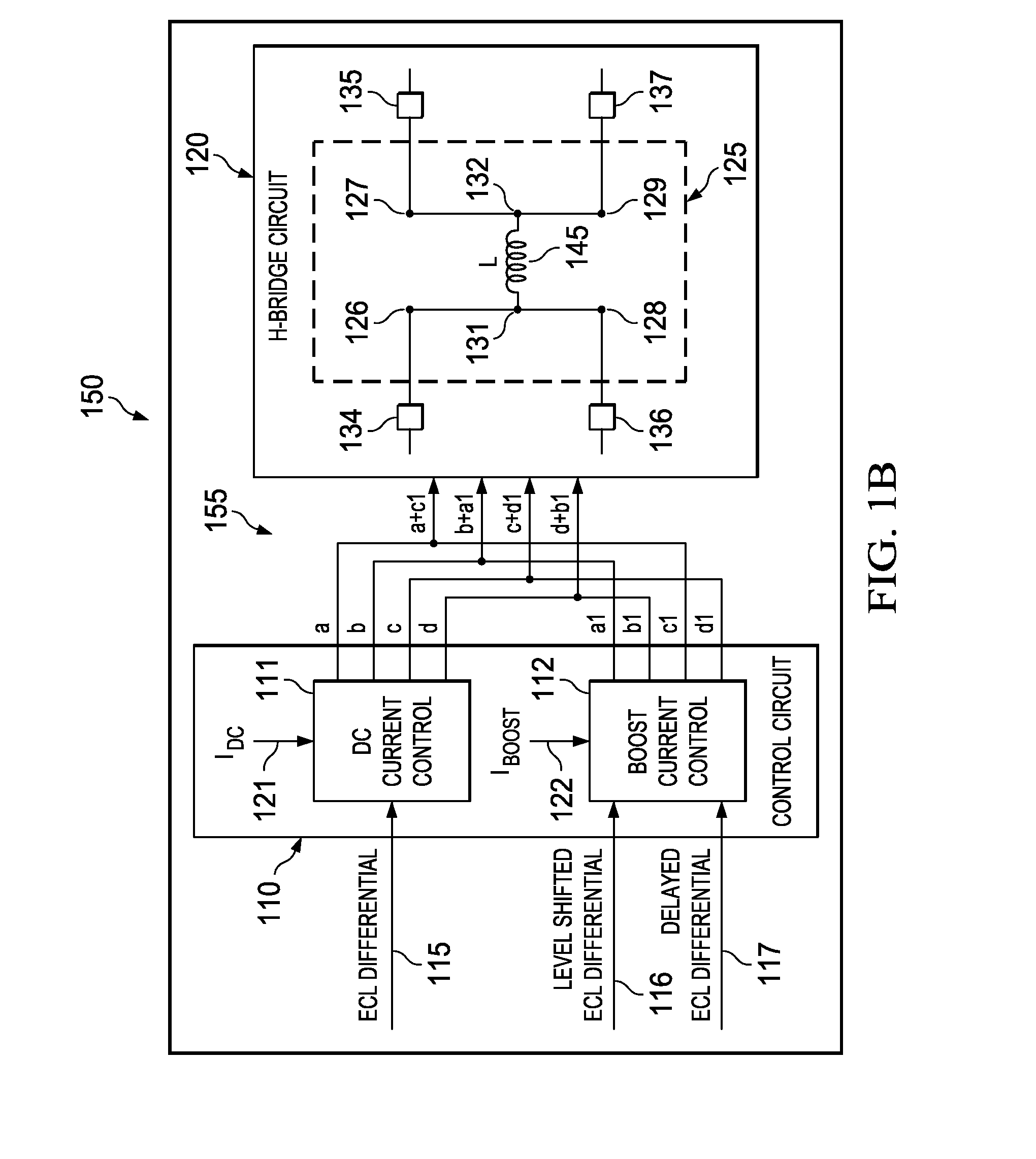

Circuit and method to match common mode flex impedance and to achieve symmetrical switching voltage outputs of write driver

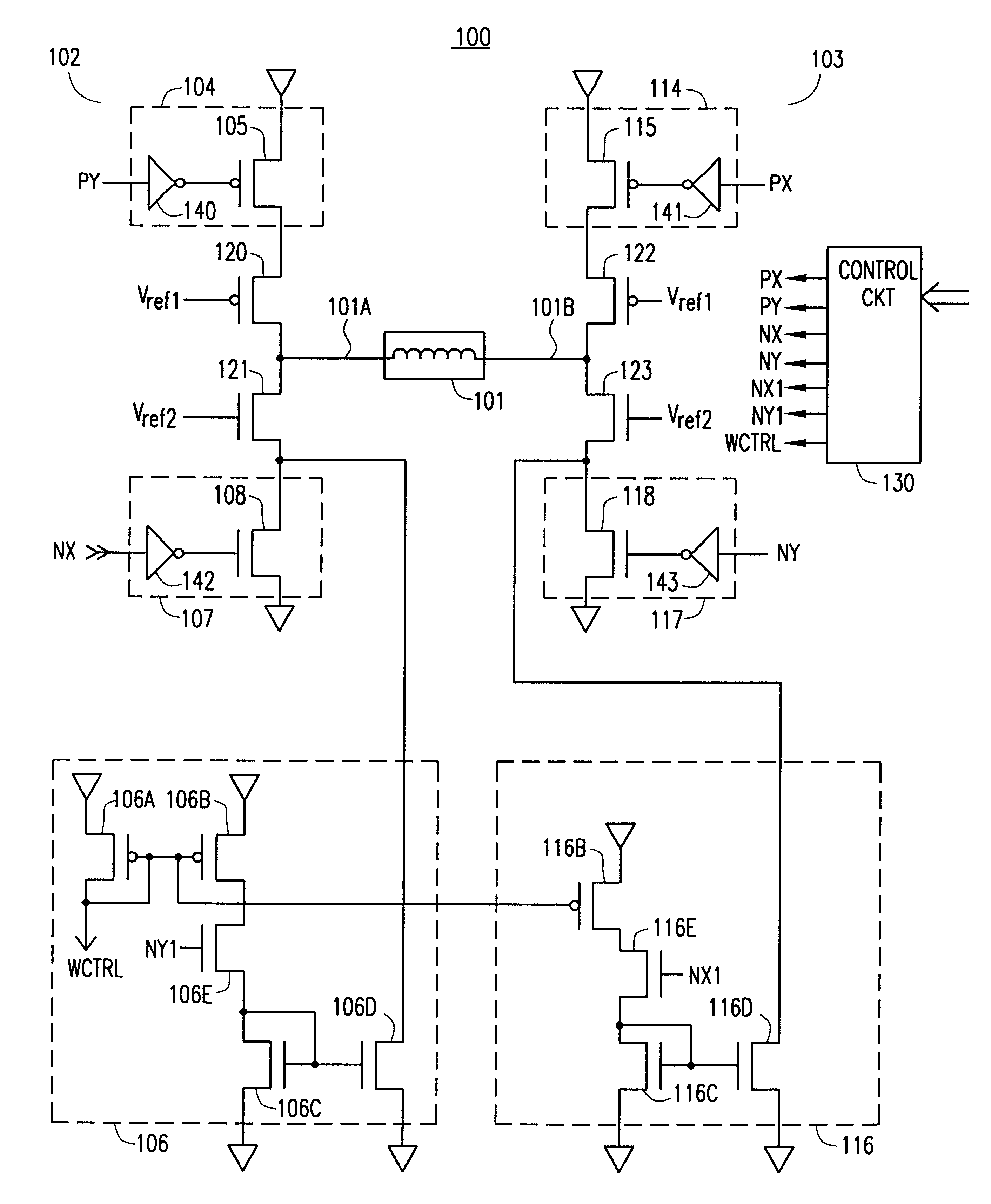

A write driver 100, 200, 300 is implemented to provide near-ground common mode output voltages to produce a more symmetrical head voltage swing (i.e. ±0.4V from ground to ±5V supply voltages). These features help to reduce the effects of common mode impedance associated with the interconnection to the disk drive head to improve overall performance. Lower jitter at high data rates can be achieved when compared to prior art techniques for implementing current mode write drivers. Further, the matched impedance between the write driver 100 and the interconnection 106 eliminates unwanted reflections. ECL level voltage swings (200-500 mV) have replaced more conventional CMOS level voltage swings (5V) to further reduce overall power dissipation associated with the write driver. The small ECL level switching further maintains constant power dissipation with changes in operating frequency and results in less NTLS effects due to quieter supplies.

Owner:TEXAS INSTR INC

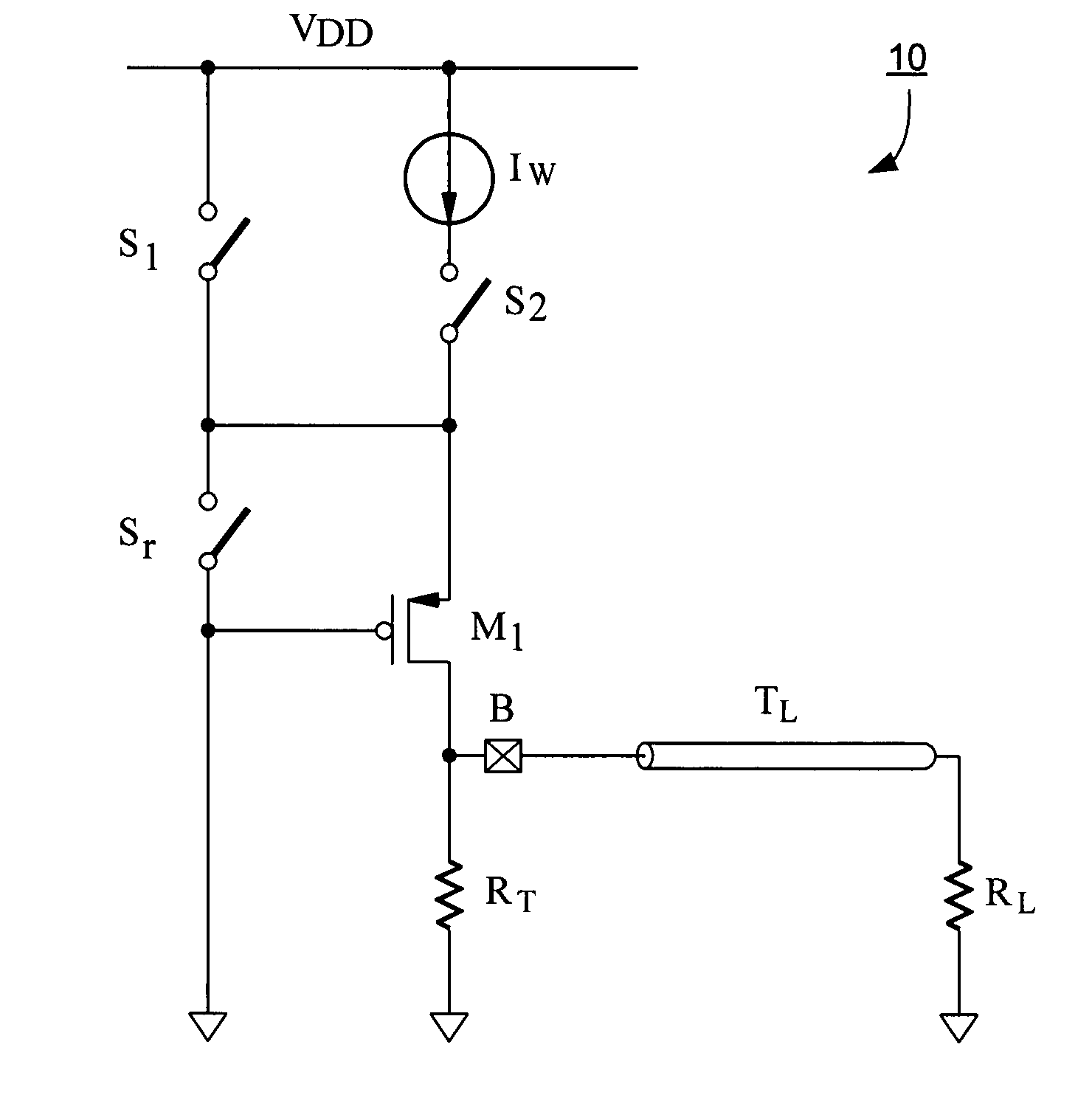

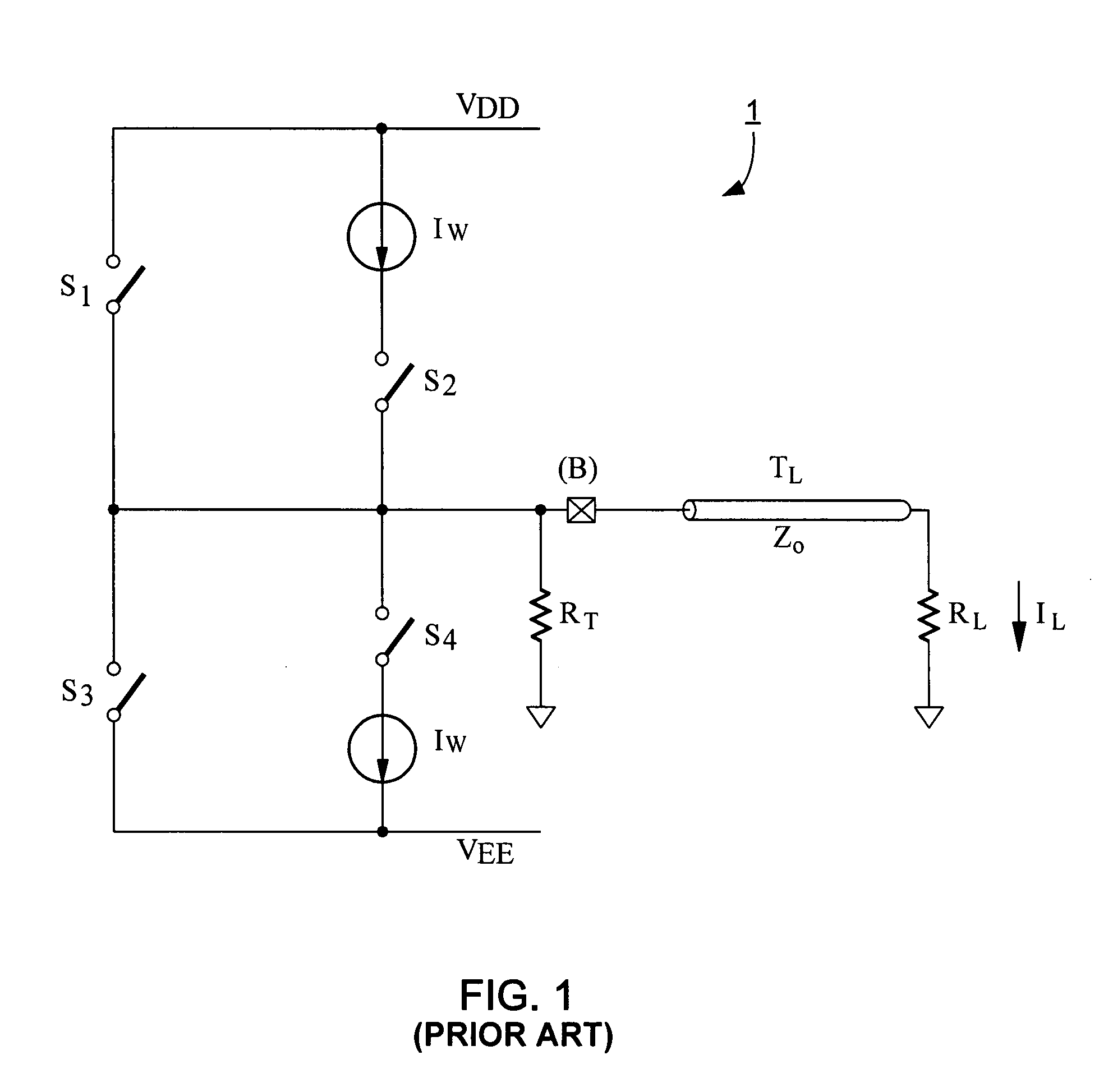

Boosted write driver for transmission line with reduction in parasitic effect of protection devices

InactiveUS7848038B1Reduce parasitic effectsH-bridge head driver circuitRecord information storageHard disc driveEngineering

A driver for driving a load over a transmission line, such as driving the magnetic head of a hard disk drive. The driver includes a signal switch for switching the signal to the load during a signal period, and a boost switch for boosting the signal during a boost period, so as to decrease rise time of the signal at the load by deliberately injecting an overshoot. A switchable protection device protects the signal switch and the boost switch. The protection device includes a reflection-suppression switch which is pulsed during a time corresponding to the expected return of a reflection corresponding to the overshoot signal, so as to force the protection device into saturation mode. Since the protection device is in the saturation mode during the return reflection of the boost signal, the returned reflection sees a matched impedance and thus reduces a re-reflection back to the load.

Owner:MARVELL INT LTD

High speed current mode write driver

ActiveUS7642819B1Fast switching speedLow power operationH-bridge head driver circuitElectric pulse generatorDc currentEngineering

Owner:TEXAS INSTR INC

Methods and apparatus for controlling write driver current

InactiveUS7660064B2Add optionsOptimizationH-bridge head driver circuitRecord information storageHard disc driveDriver circuit

A hard disk drive write driver circuit is described that can change the output impedance of the write driver by use of a lookup table of control values. A control value is selected from the lookup table by using an address based on a dynamic system variable and a program controlled value. The dynamic system variable is converted to a digital representation. The digital representation and a portion of the program controlled value are used as an address to the lookup table to select a control value. The write driver is responsive to the selected control value to control overshoot current. A method to digitally program the output impedance of a preamp write driver based on realistic operating data is also discussed. An additional approach to controlling overshoot current in a write driver through digital control of overshoot duration is also described.

Owner:BROADCOM INT PTE LTD +1

Hard disk drive preamplifier write driver

InactiveUS20050007686A1H-bridge head driver circuitRecord information storageHard disc driveElectrical polarity

The present invention discloses an apparatus (160) comprising a common mode generator circuit (162) coupled to a current directing circuit adapted to provide current to a first write head connection node (170) and to a second write head connection node (172). The common mode generator circuit (162) is adapted to provide additional current to the first write head connection node (170) and to the second write head connection node (172), wherein the first write head connection node (170) is adapted to produce a first write signal, wherein the second write head connection node (172) is adapted to produce a second write signal, wherein the current and the additional current are adapted to establish a voltage across the first write head connection node (170) and the second write head connection node (172), wherein the voltage is adapted to be pulled toward a first polarity based on the first write signal and toward a second polarity based on the second write signal, and wherein the voltage pulled toward the first polarity and the voltage pulled toward the second polarity are substantially centered about a common mode voltage.

Owner:TEXAS INSTR INC

Device to synchronize the change of the driving mode of an electromagnetic load

ActiveUS20100244761A1Minimizes time required to change driving modalitySuppress mutationAC motor controlSynchronous motors startersVoltage referenceElectromagnetic shielding

A device for the change of the driving mode of an electromagnetic load from a first operating mode with pulse width modulation to a second operating mode that is linear by means of switching circuits. During a first operating mode, each of two outputs has a voltage value ranging from a first reference voltage to a second reference voltage. The device adapted to synchronize a change command signal from a first operating mode to a second operating mode of the electromagnetic load with the signal representative of the flow of current circulating within the load at substantially its average value and adapted to generate a first command signal in response to the synchronization.

Owner:STMICROELECTRONICS SRL