Patents

Literature

37 results about "Delta delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In VHDL simulations, all signal assignments occur with some infinitesimal delay, known as delta delay. Technically, delta delay is of no measurable unit, but from a hardware design perspective one should think of delta delay as being the smallest time unit one could measure, such as a femtosecond (fs).

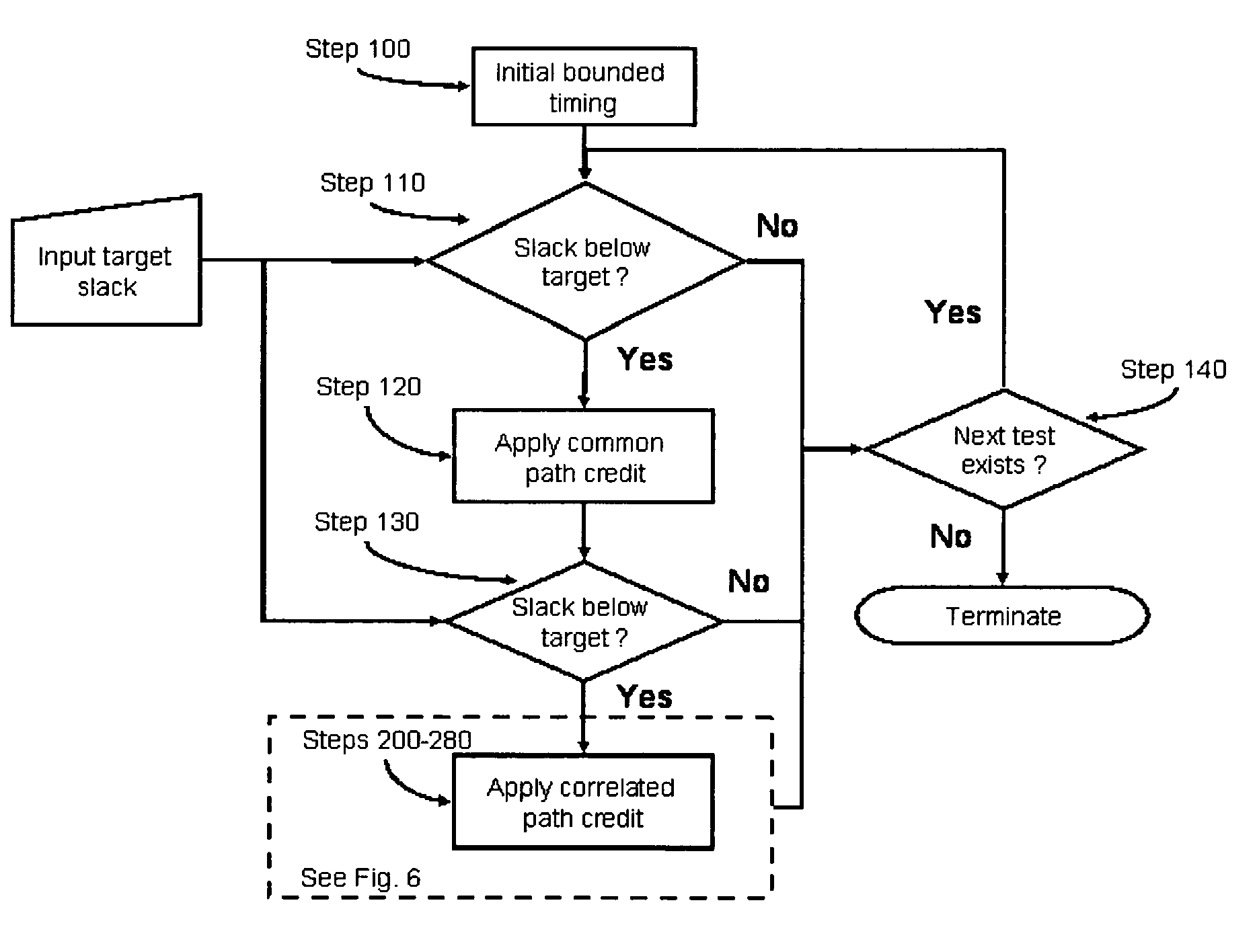

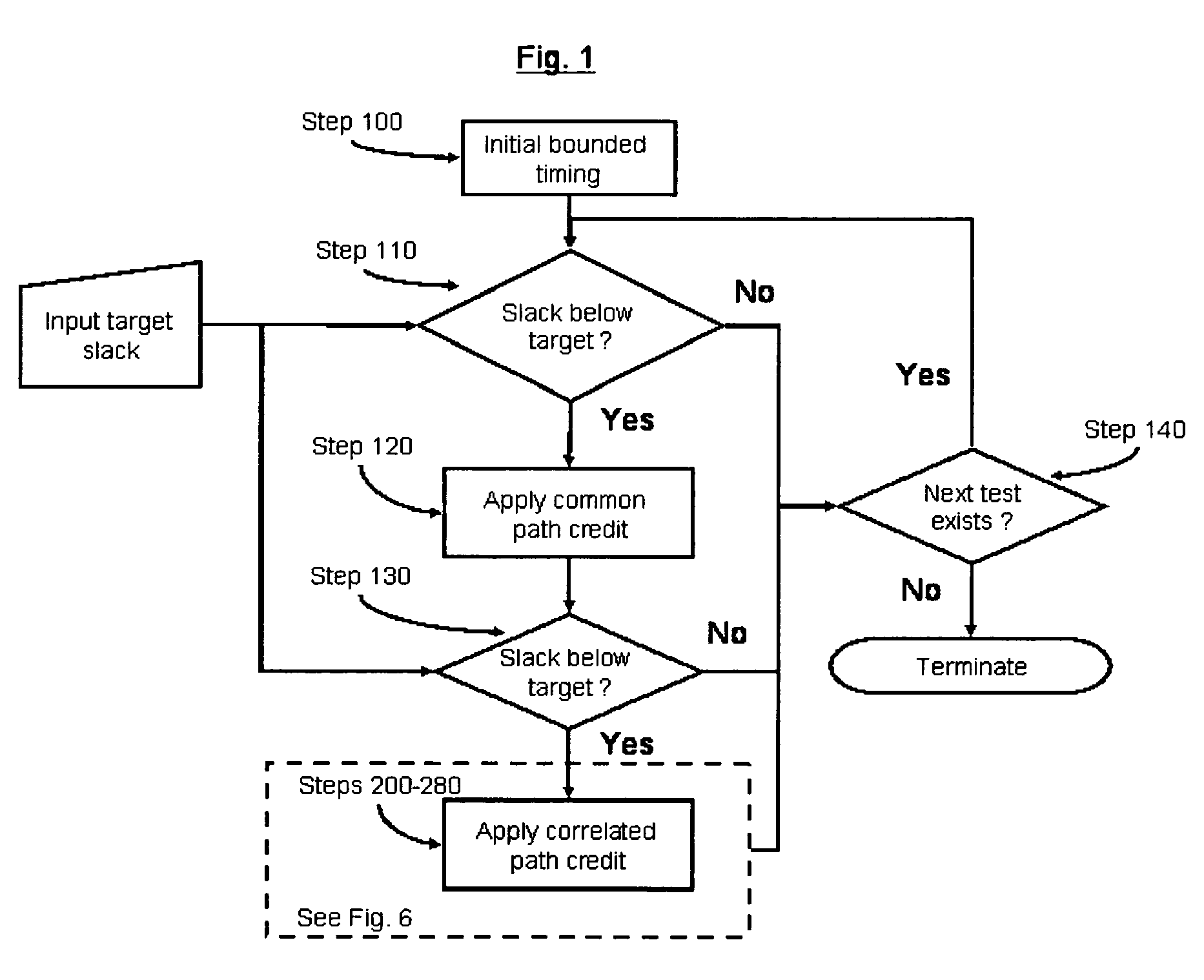

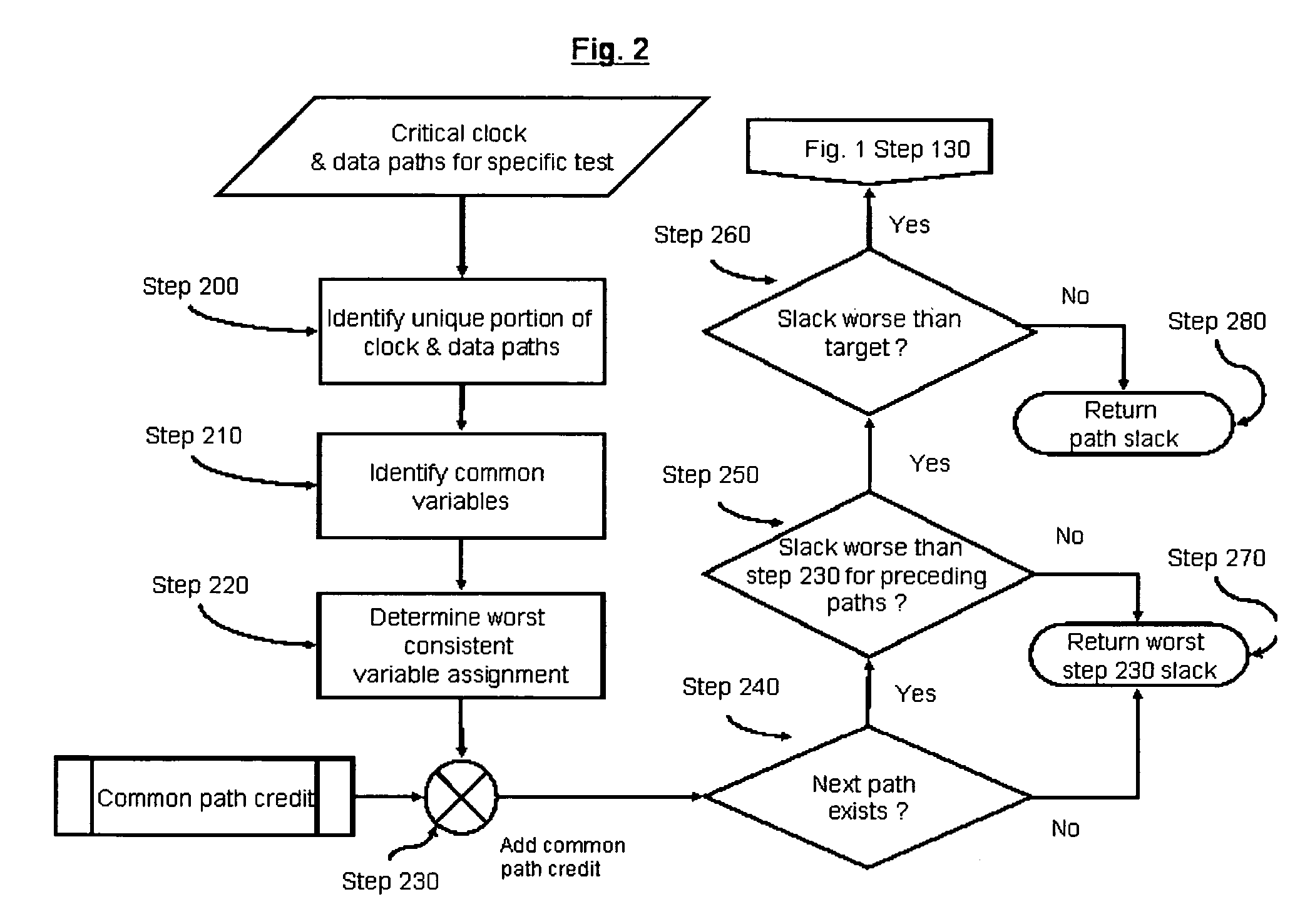

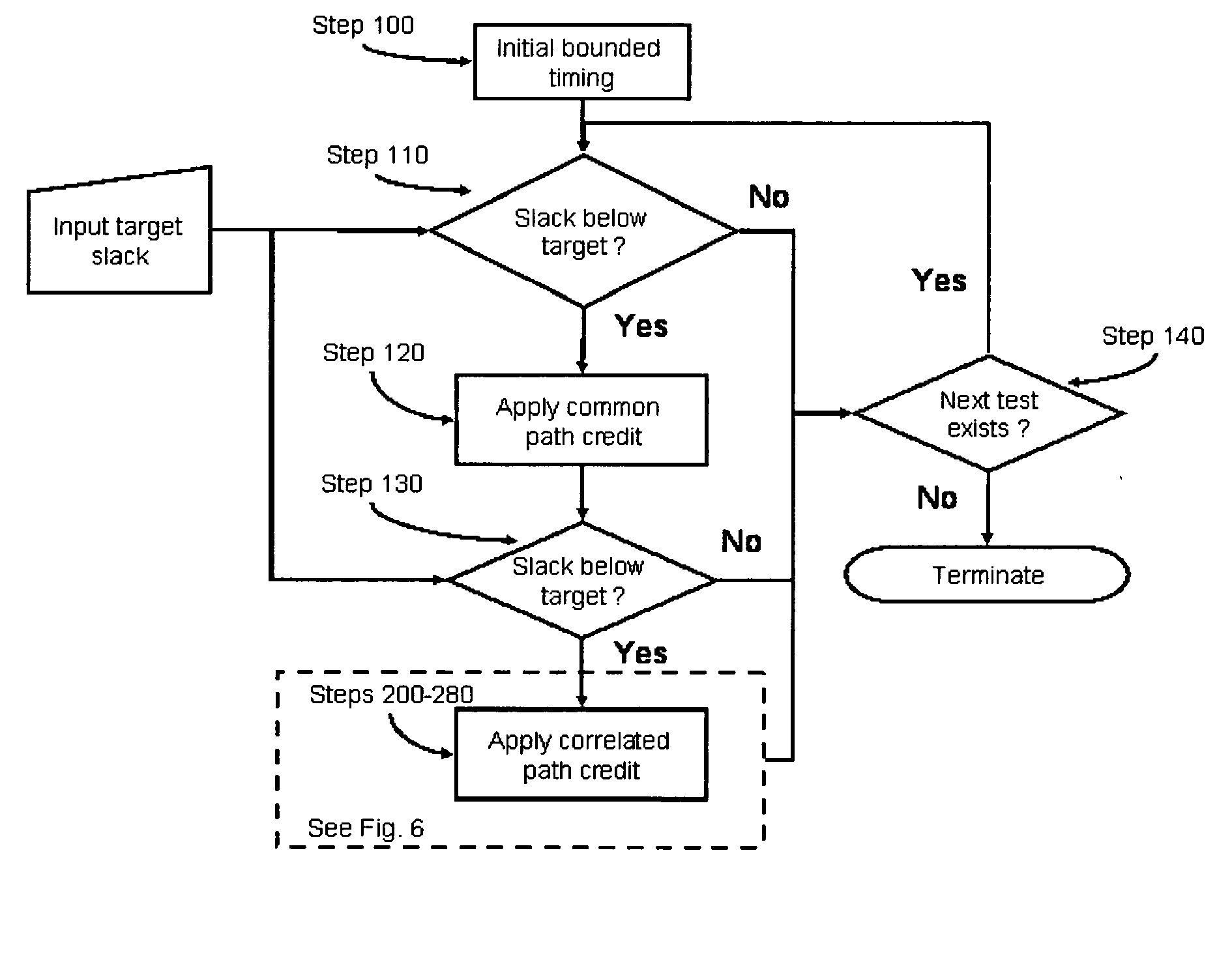

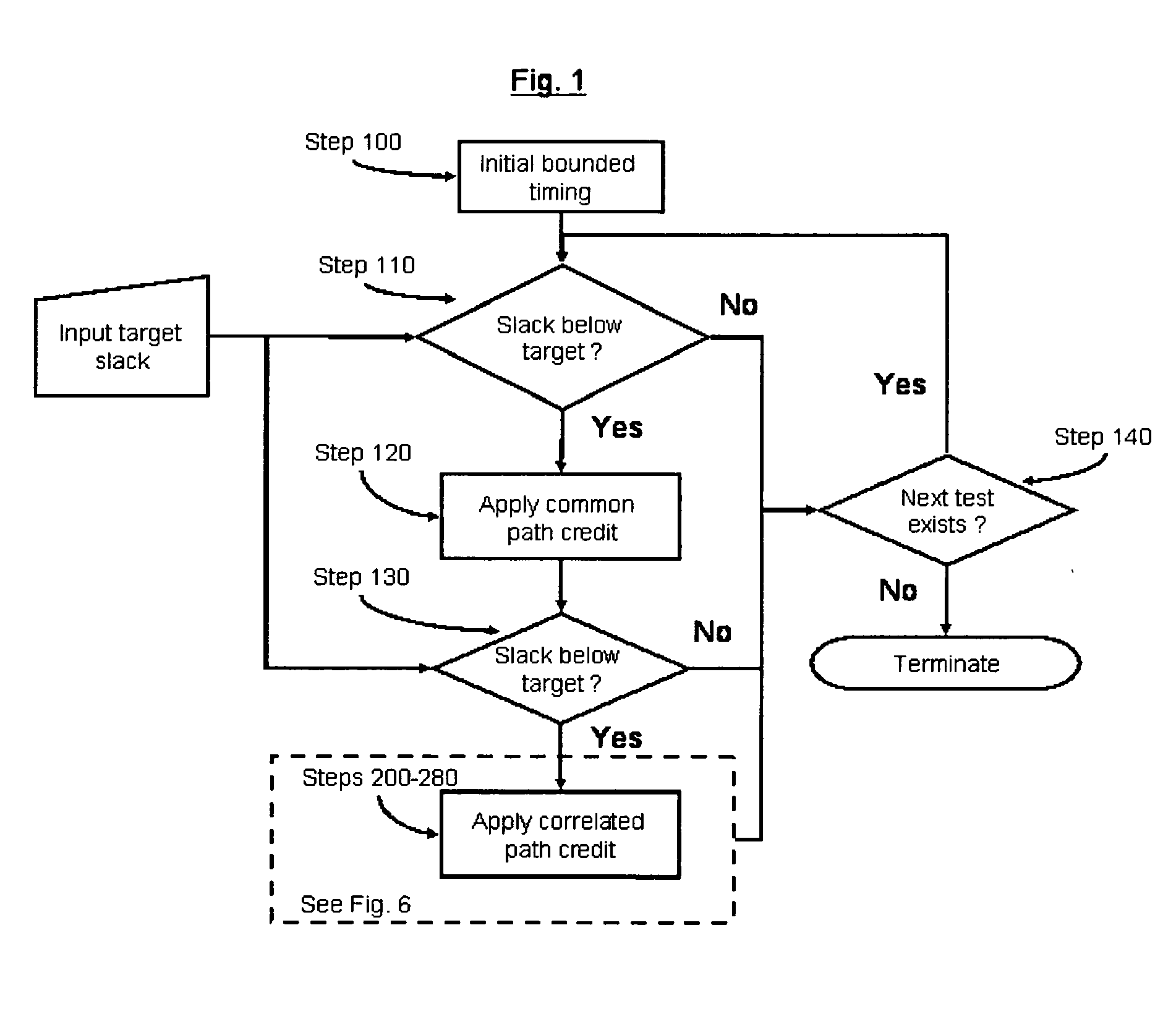

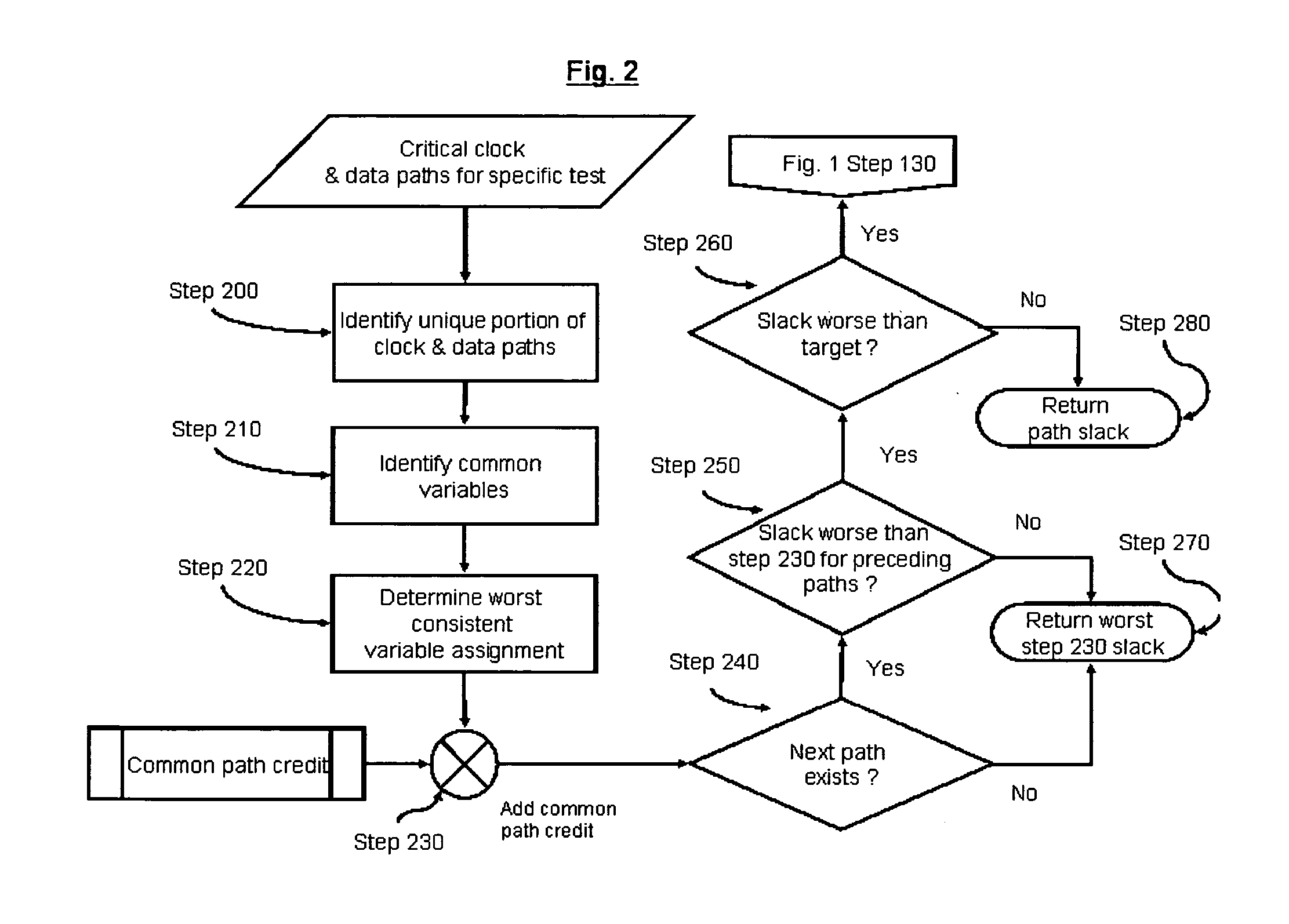

System and method for correlated process pessimism removal for static timing analysis

InactiveUS7117466B2Reduce pessimismComputer aided designSoftware simulation/interpretation/emulationStatic timing analysisAngular point

A method of removing pessimism in static timing analysis is described. Delays are expressed as a function of discrete parameter settings allowing for both local and global variation to be taken in to account. Based on a specified target slack, each failing timing test is examined to determine a consistent set of parameter settings which produces the worst possible slack. The analysis is performed on a path basis. By considering only parameters which are in common to a particular data / clock path-pair, the number of process combinations that need to be explored is reduced when compared to analyzing all combinations of the global parameter settings. Further, if parameters are separable and linear, worst-case variable assignments for a particular clock / data path pair can be computed in linear time by independently assigning each parameter value. In addition, if available, the incremental delay change with respect to each physically realizable process variable may be used to project the worst-case variable assignment on a per-path basis without the need for performing explicit corner enumeration.

Owner:GLOBALFOUNDRIES INC

System and method for correlated process pessimism removal for static timing analysis

InactiveUS20050066297A1Reduce pessimismRemove pessimismComputer aided designSoftware simulation/interpretation/emulationDelta delayDatapath

A method of removing pessimism in static timing analysis is described. Delays are expressed as a function of discrete parameter settings allowing for both local and global variation to be taken in to account. Based on a specified target slack, each failing timing test is examined to determine a consistent set of parameter settings which produces the worst possible slack. The analysis is performed on a path basis. By considering only parameters which are in common to a particular data / clock path-pair, the number of process combinations that need to be explored is reduced when compared to analyzing all combinations of the global parameter settings. Further, if parameters are separable and linear, worst-case variable assignments for a particular clock / data path pair can be computed in linear time by independently assigning each parameter value. In addition, if available, the incremental delay change with respect to each physically realizable process variable may be used to project the worst-case variable assignment on a per-path basis without the need for performing explicit corner enumeration.

Owner:GLOBALFOUNDRIES INC

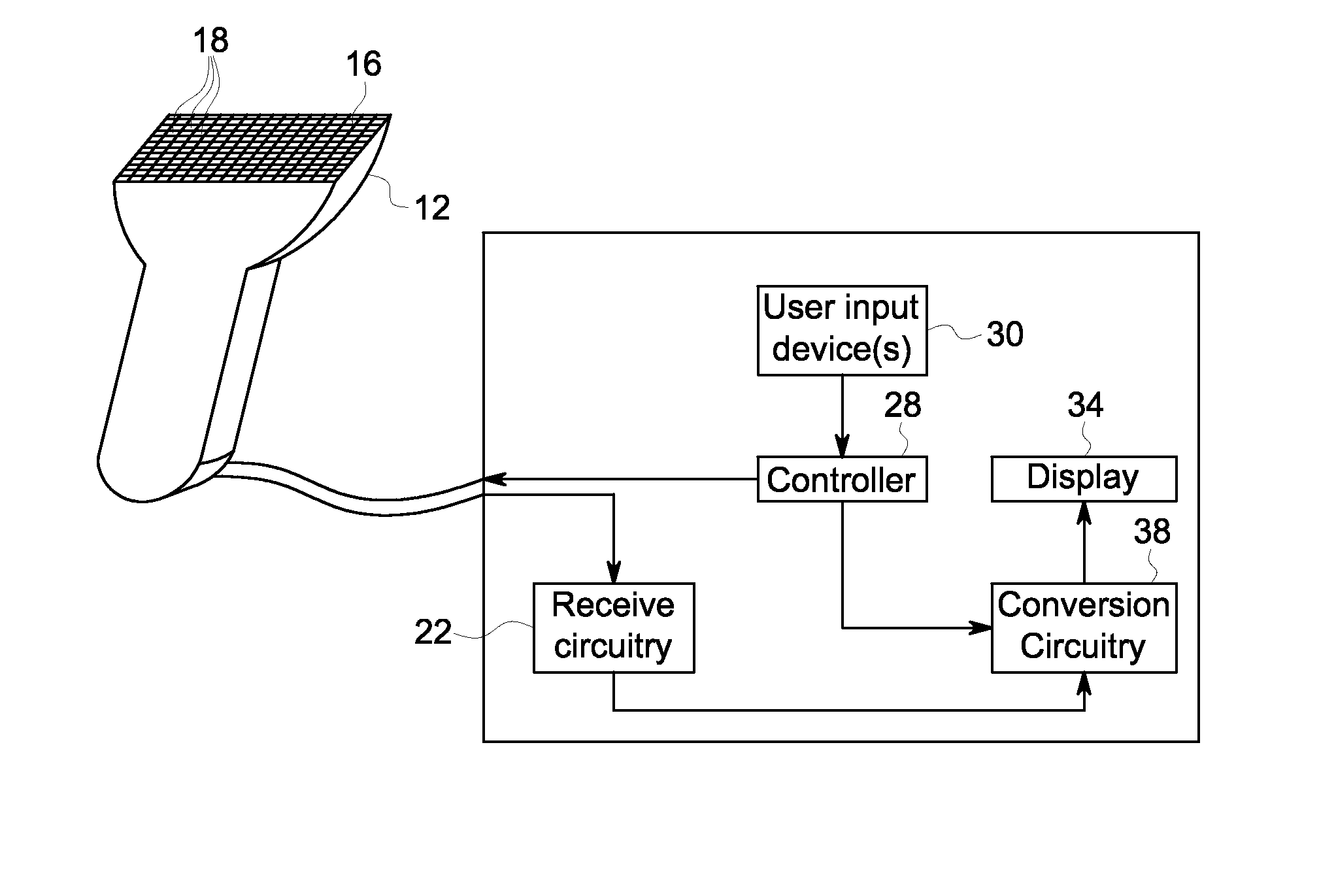

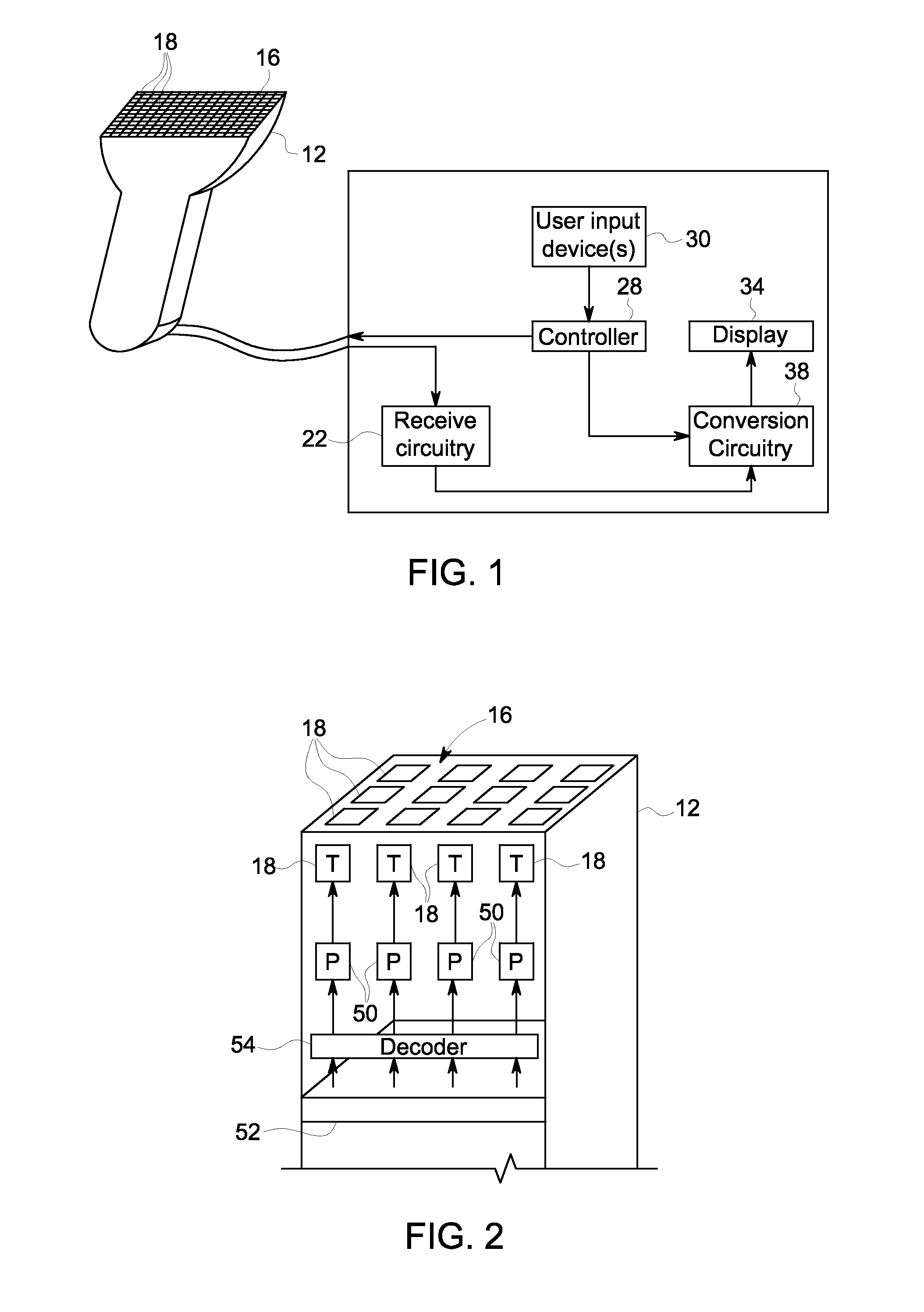

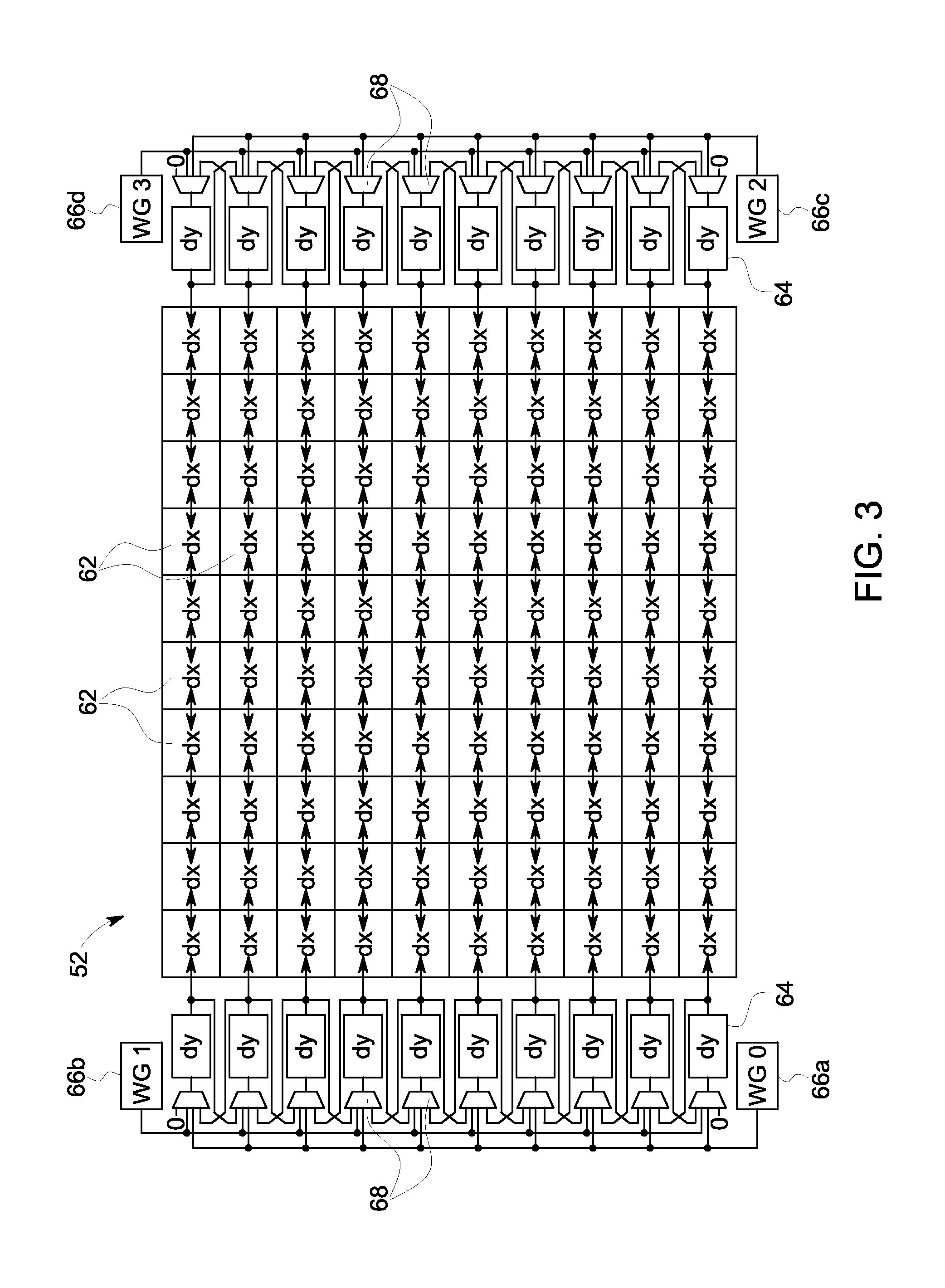

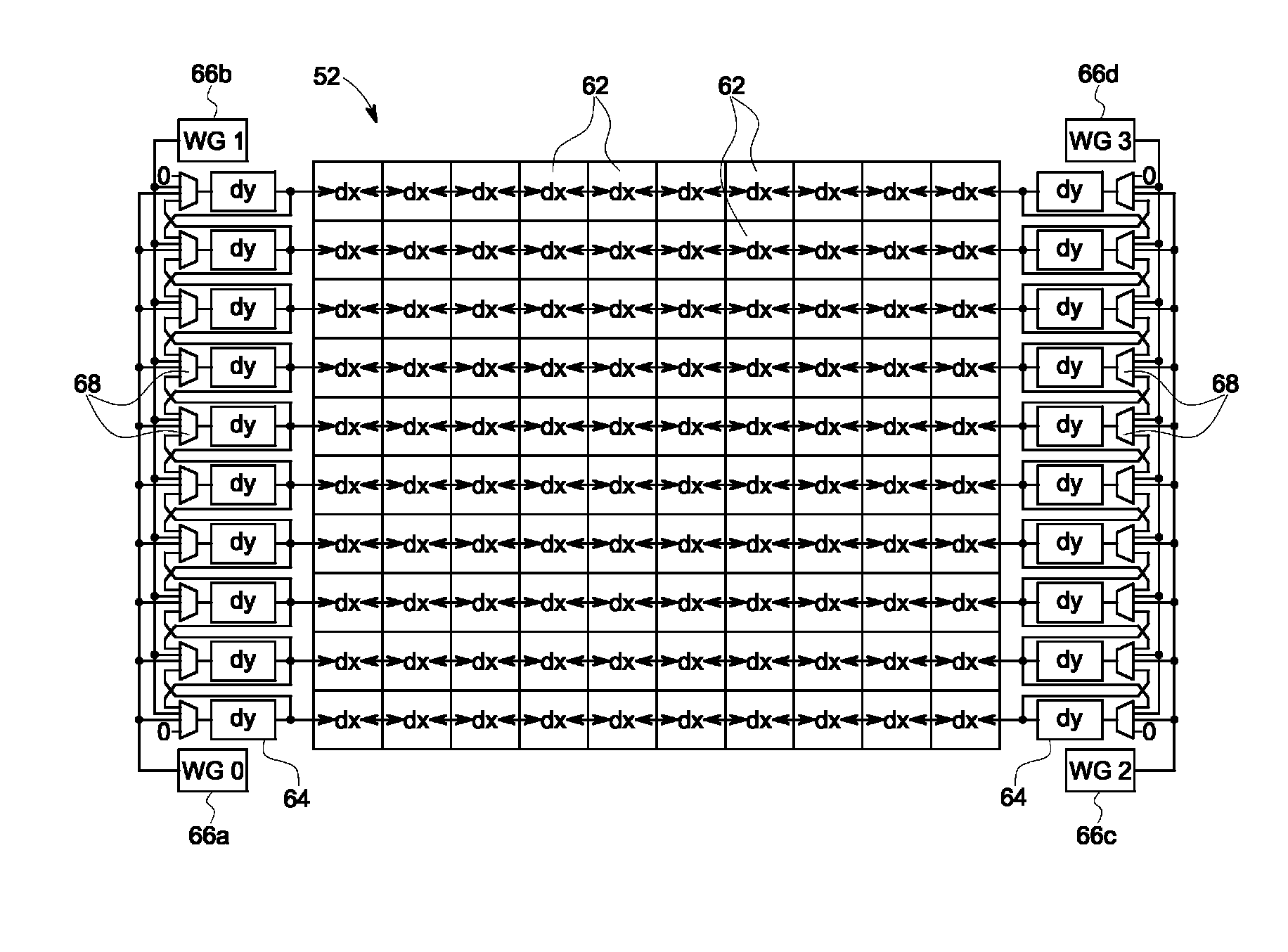

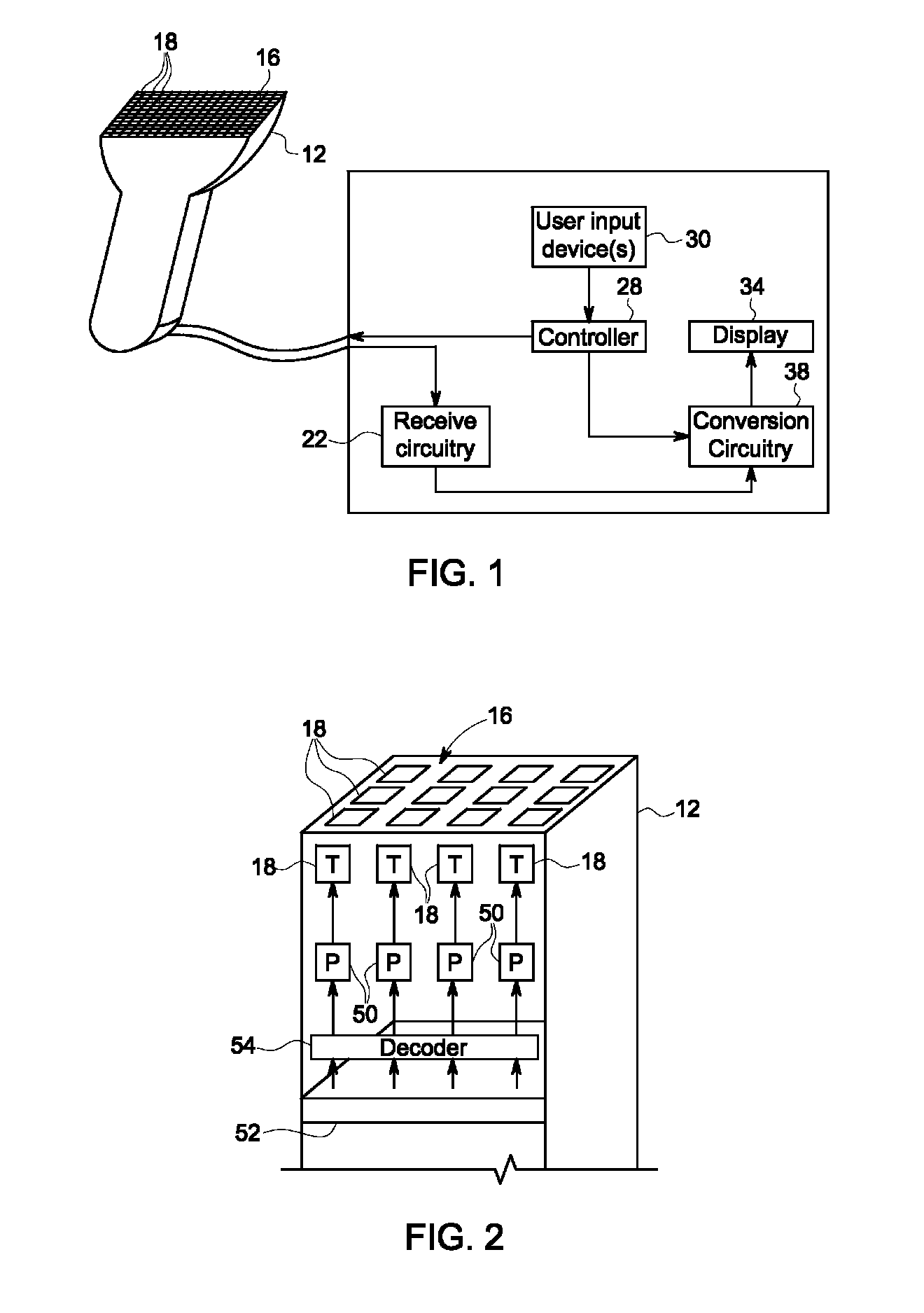

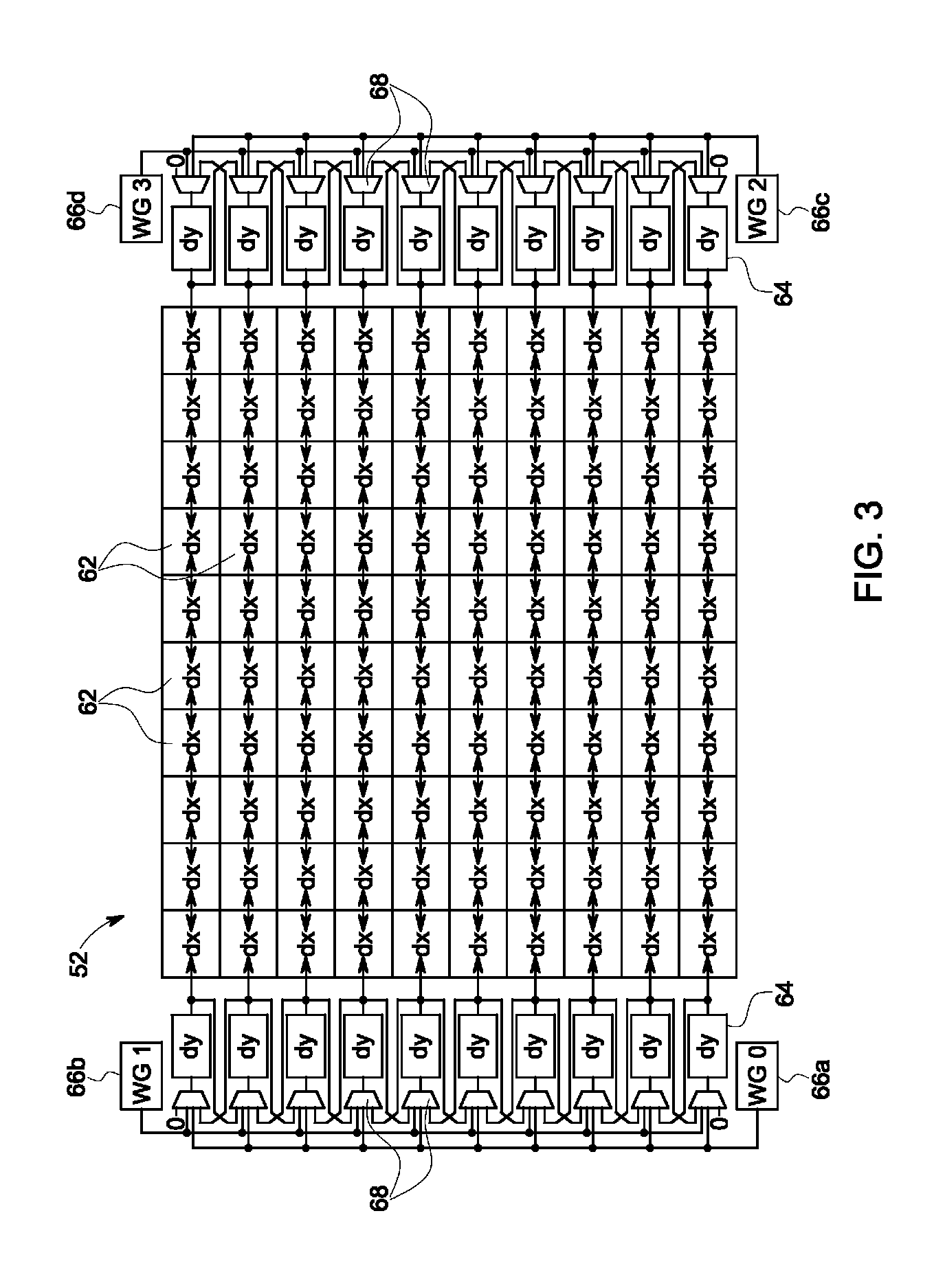

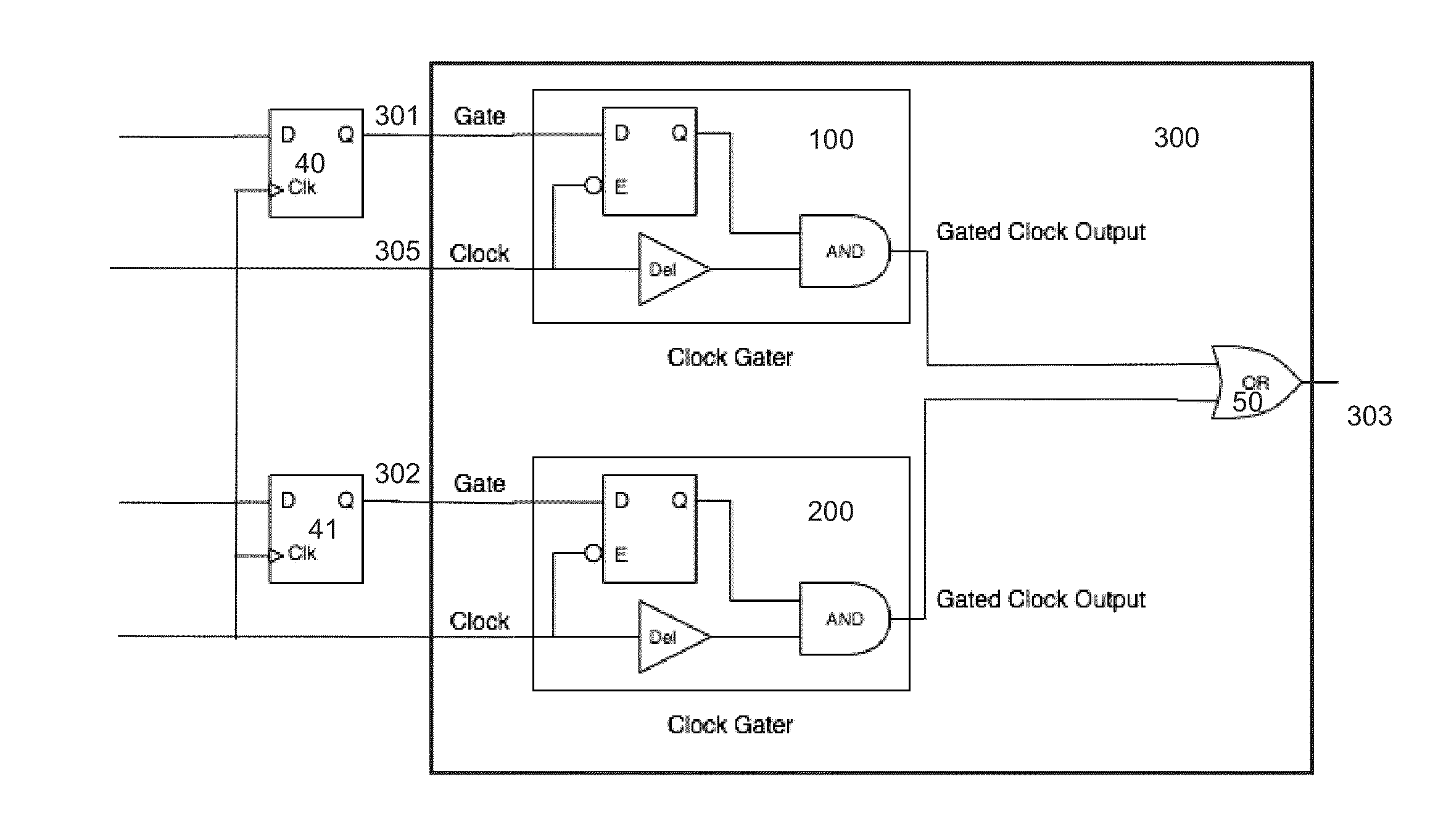

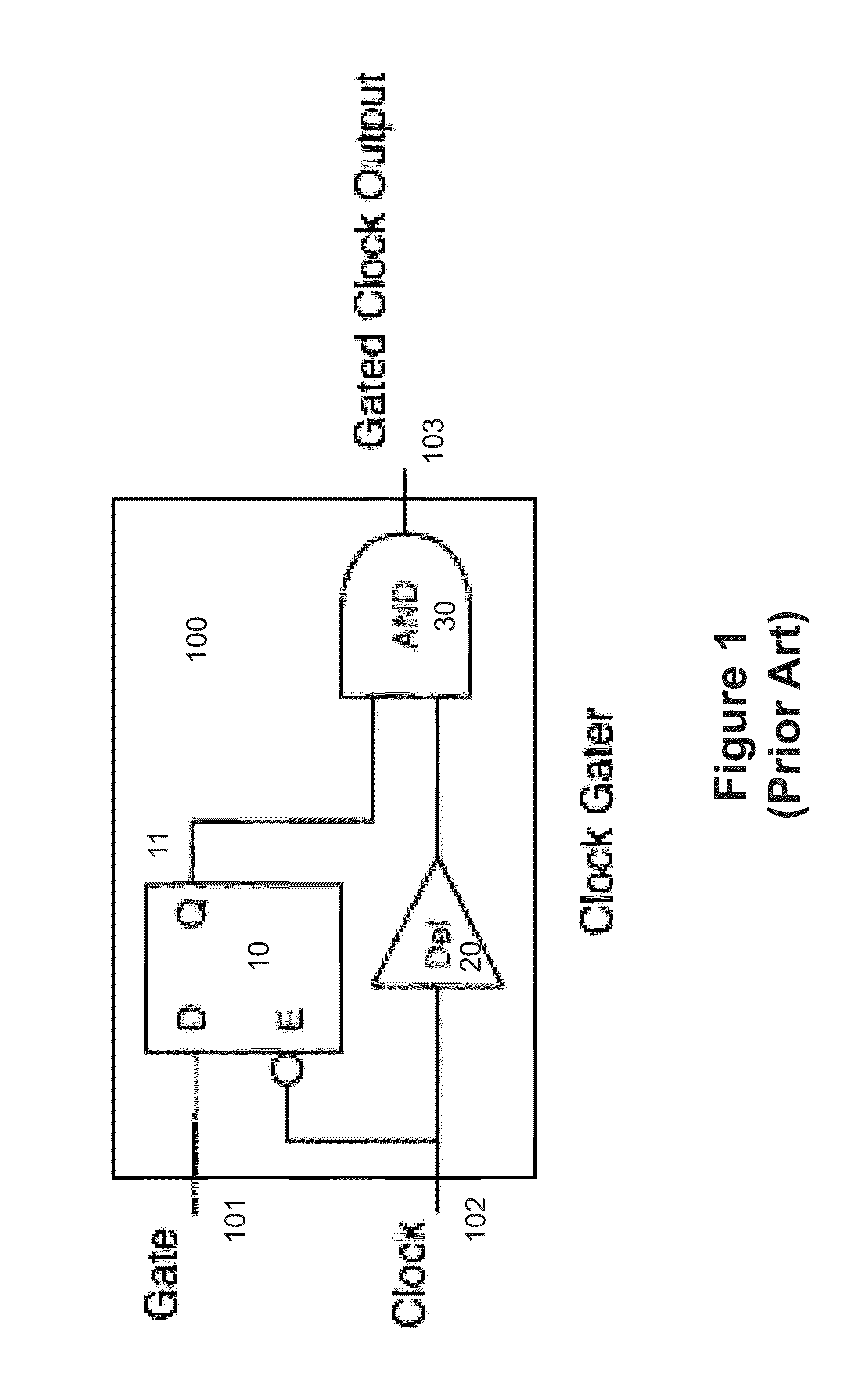

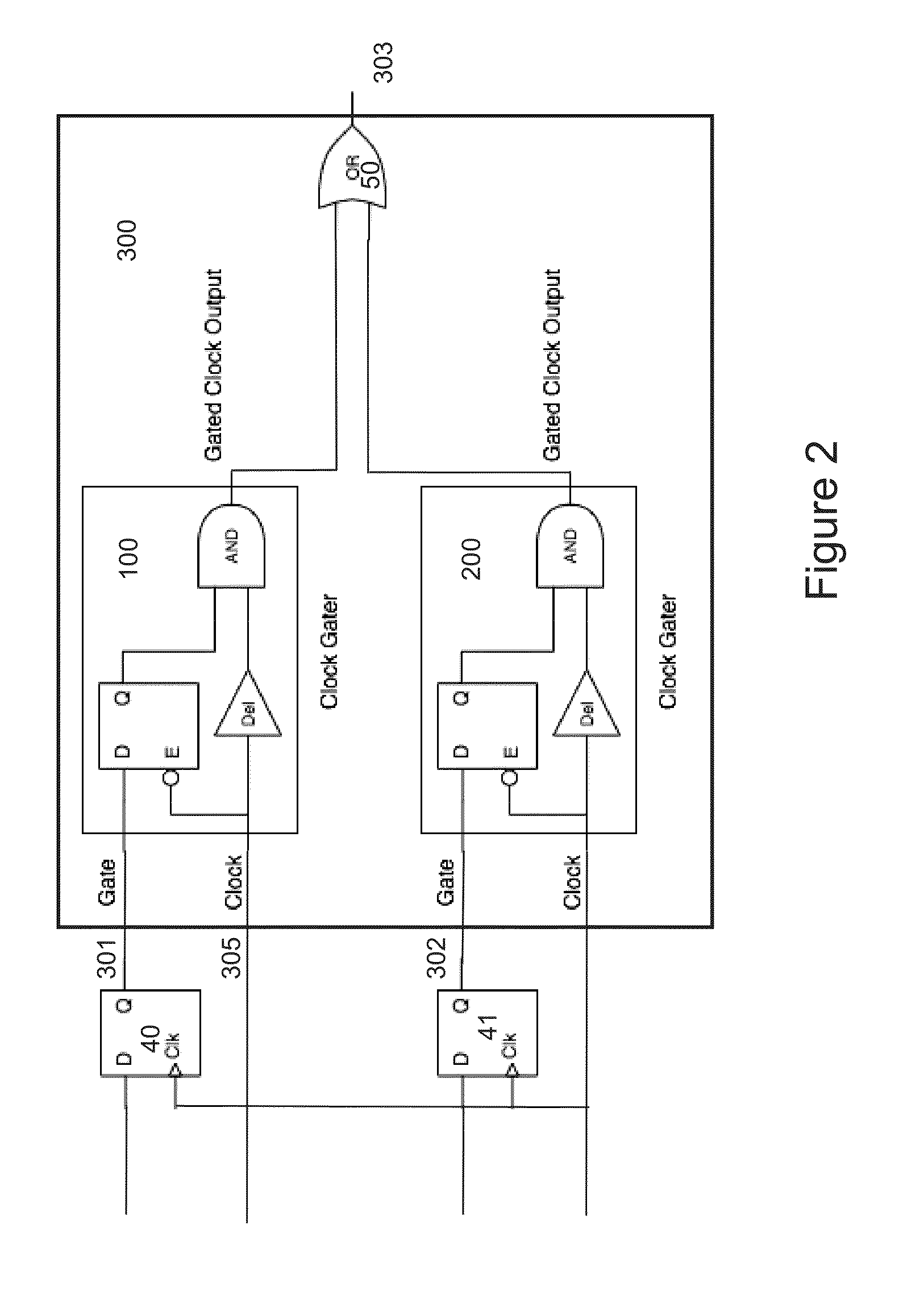

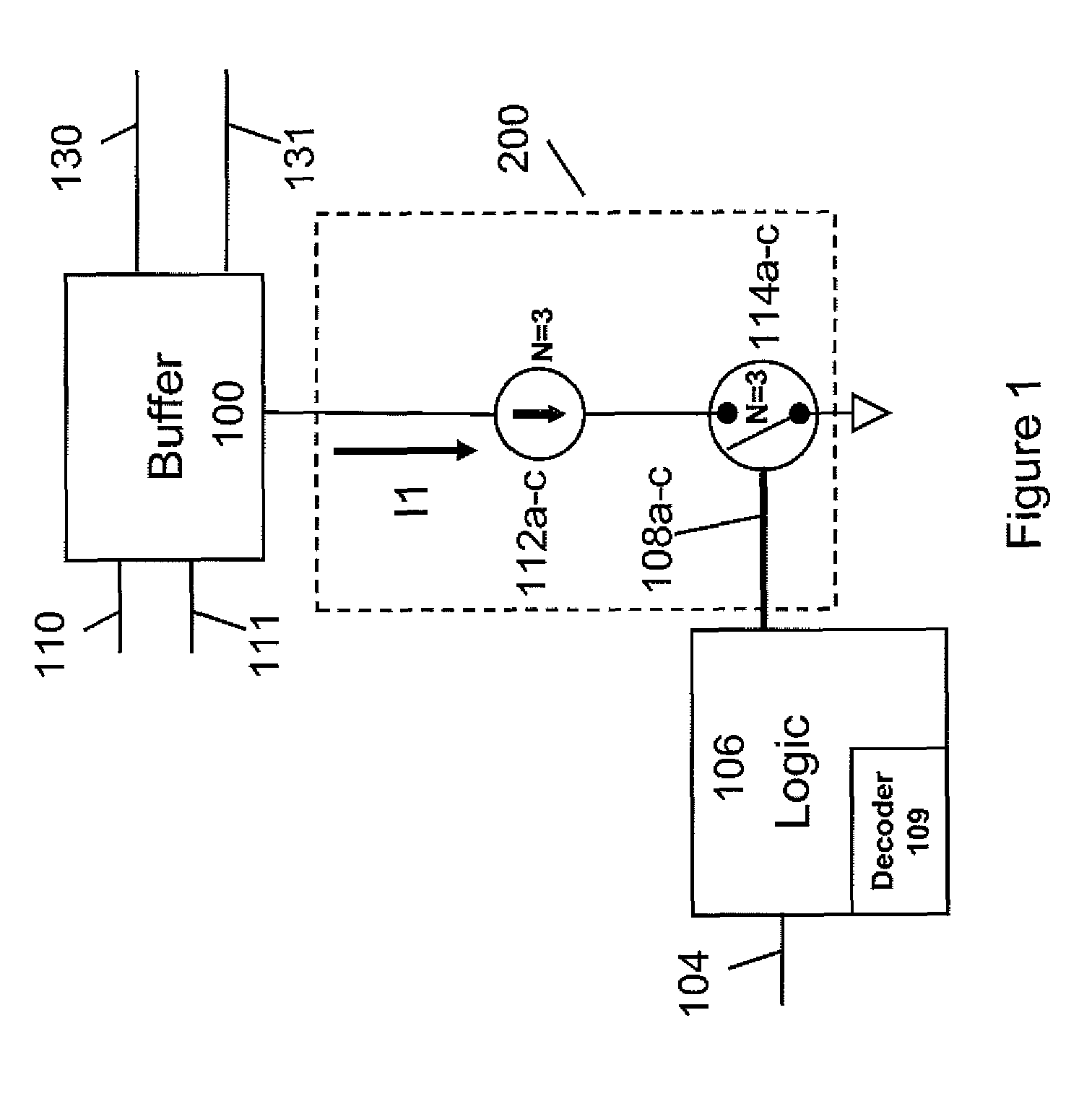

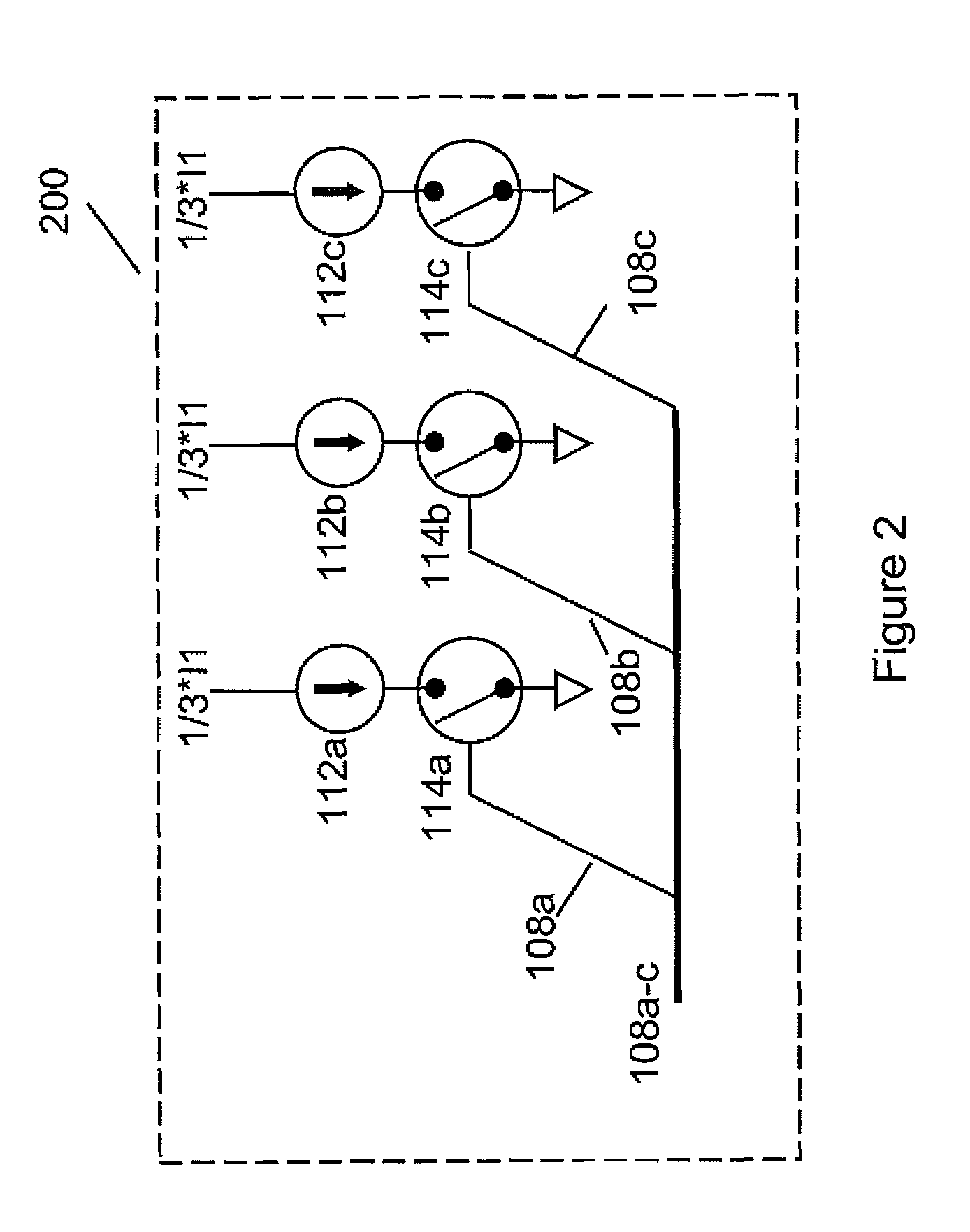

Delta delay approach for ultrasound beamforming on an asic

ActiveUS20140243676A1Ultrasonic/sonic/infrasonic diagnosticsInfrasonic diagnosticsTransducerEngineering

Systems are disclosed for ultrasound beamforming on an application specific integrated circuit (ASIC). In certain embodiments, the system includes an ultrasound probe that includes a plurality of transducer elements electrically coupled to an ASIC. The ASIC includes a plurality of waveform generators electrically coupled to a plurality of delay units. Each delay unit receives a waveform from a waveform generator or an adjacent delay unit, applies a delay to the waveform, and outputs the waveform to adjacent delay units, one or more of the plurality of transducer elements, or both. The delays that are provided to waveforms before being output to a transducer element determine the beamforming characteristics of the ultrasonic pulses generated by the ultrasound probe.

Owner:GENERAL ELECTRIC CO

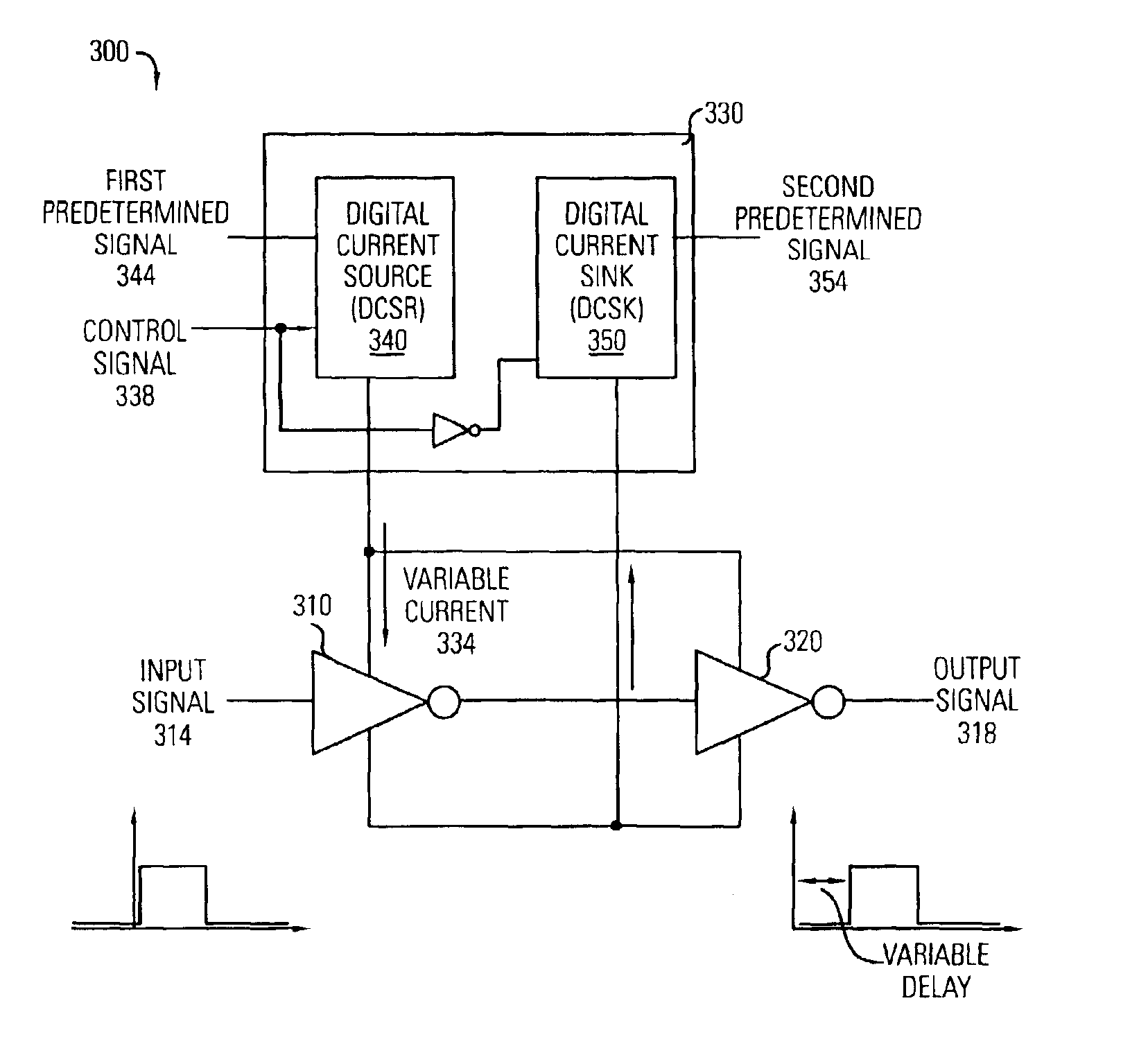

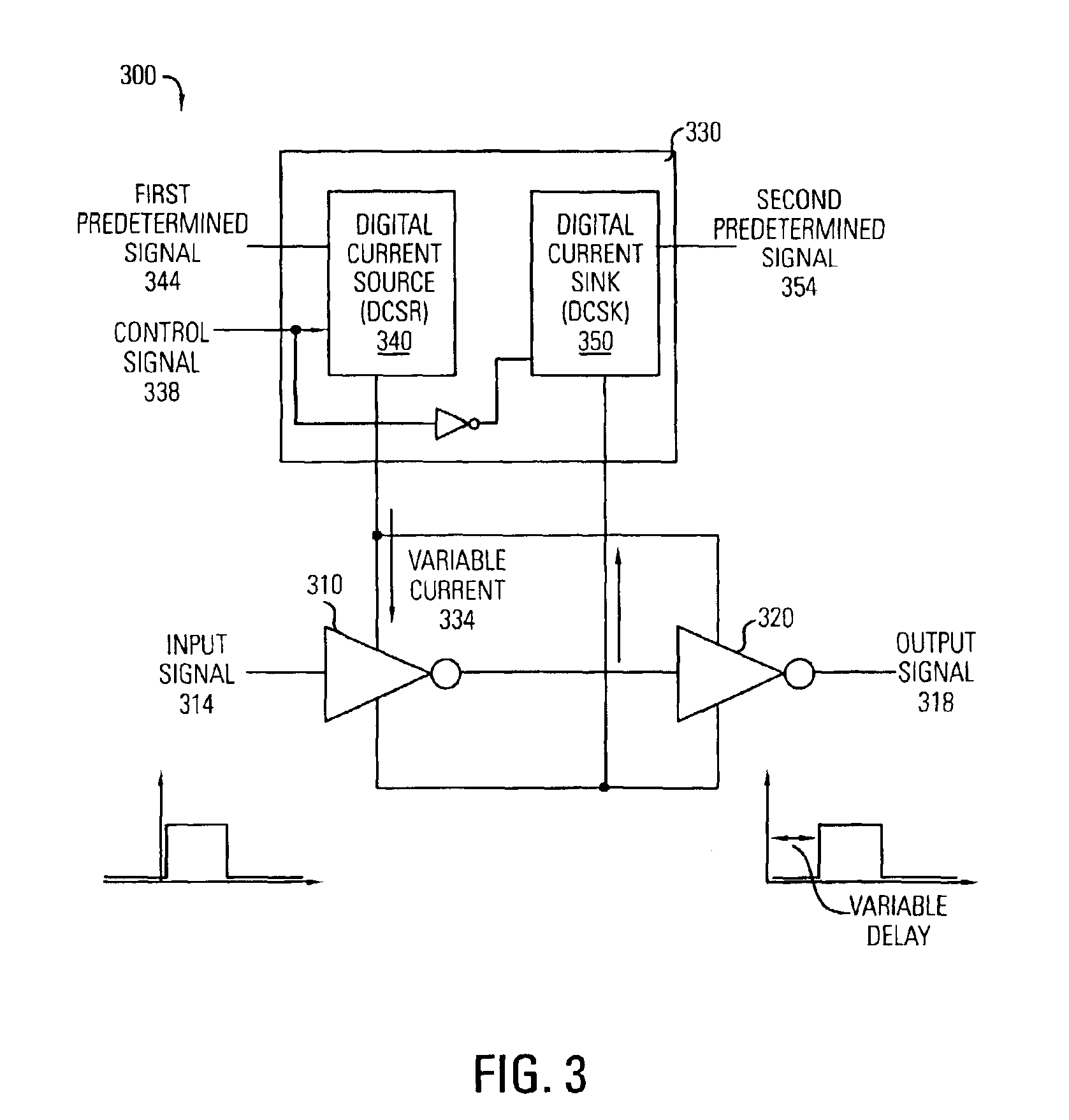

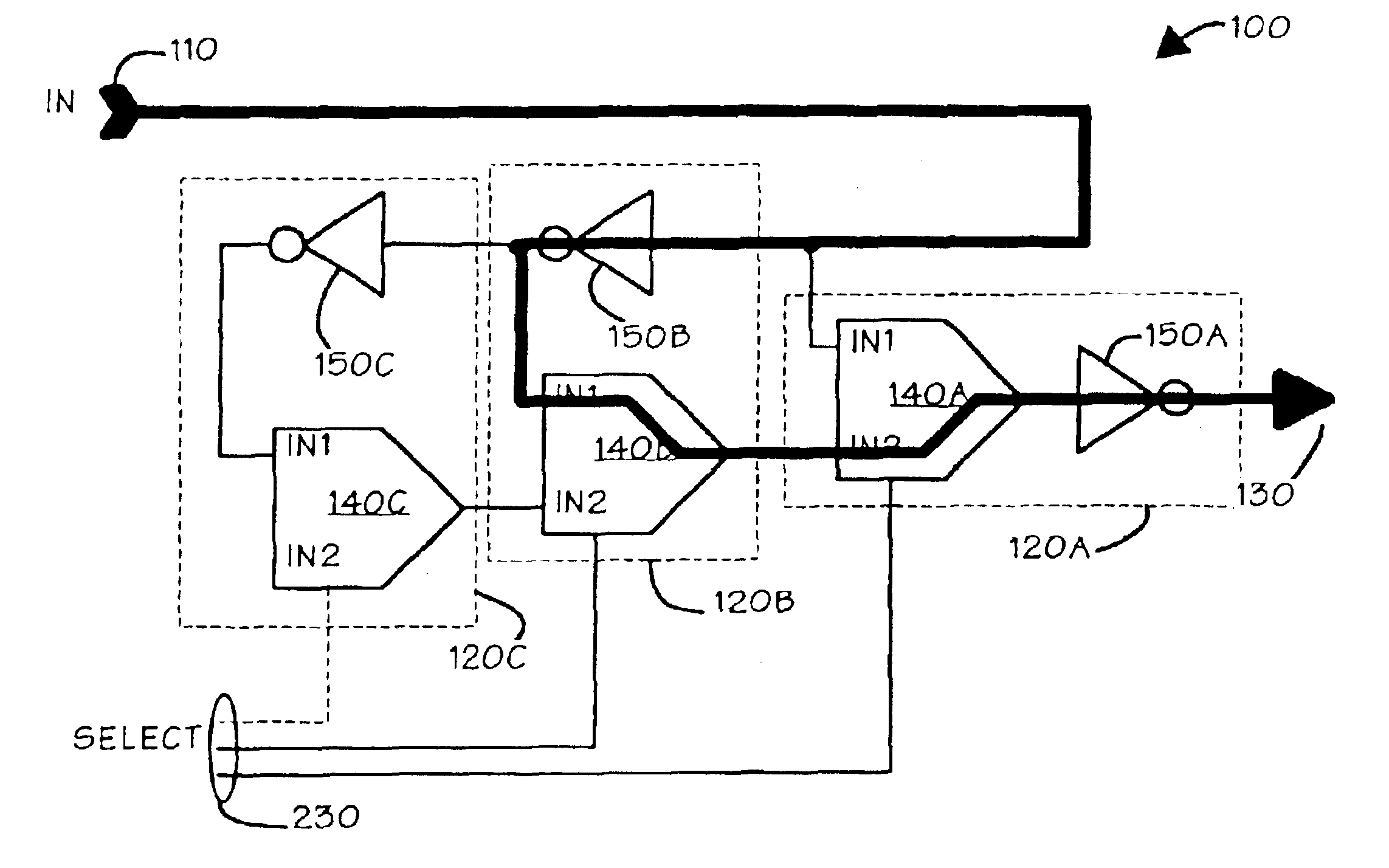

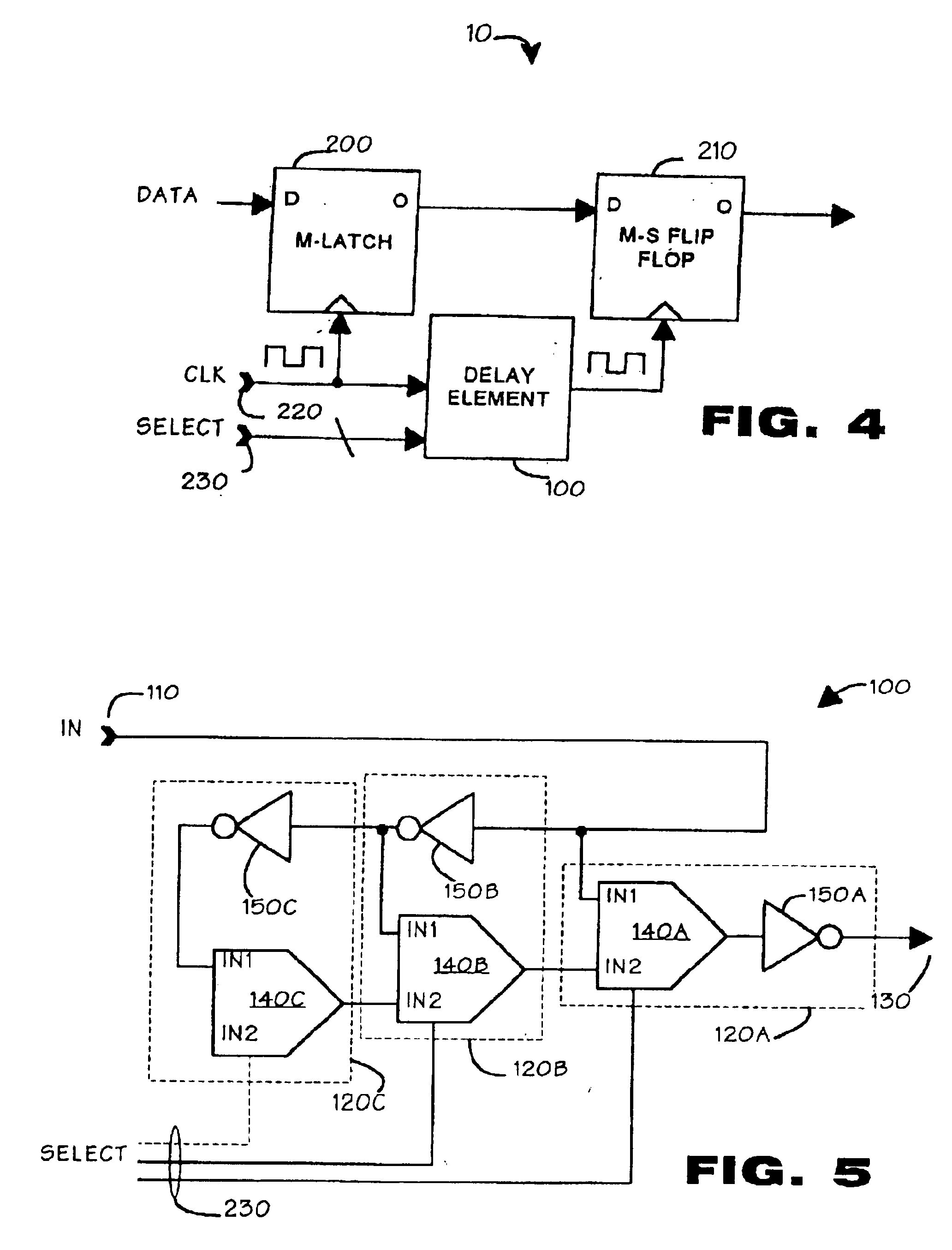

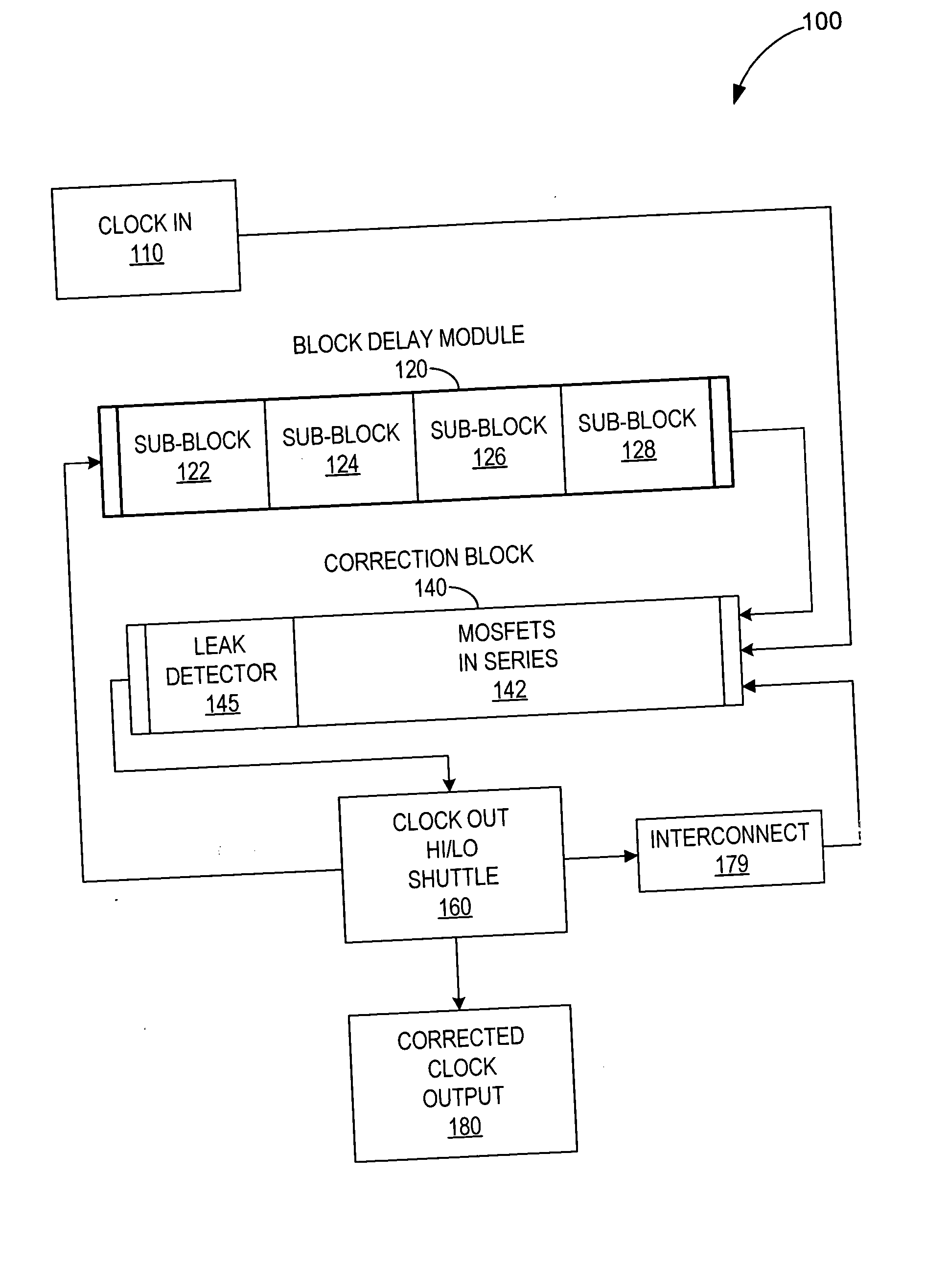

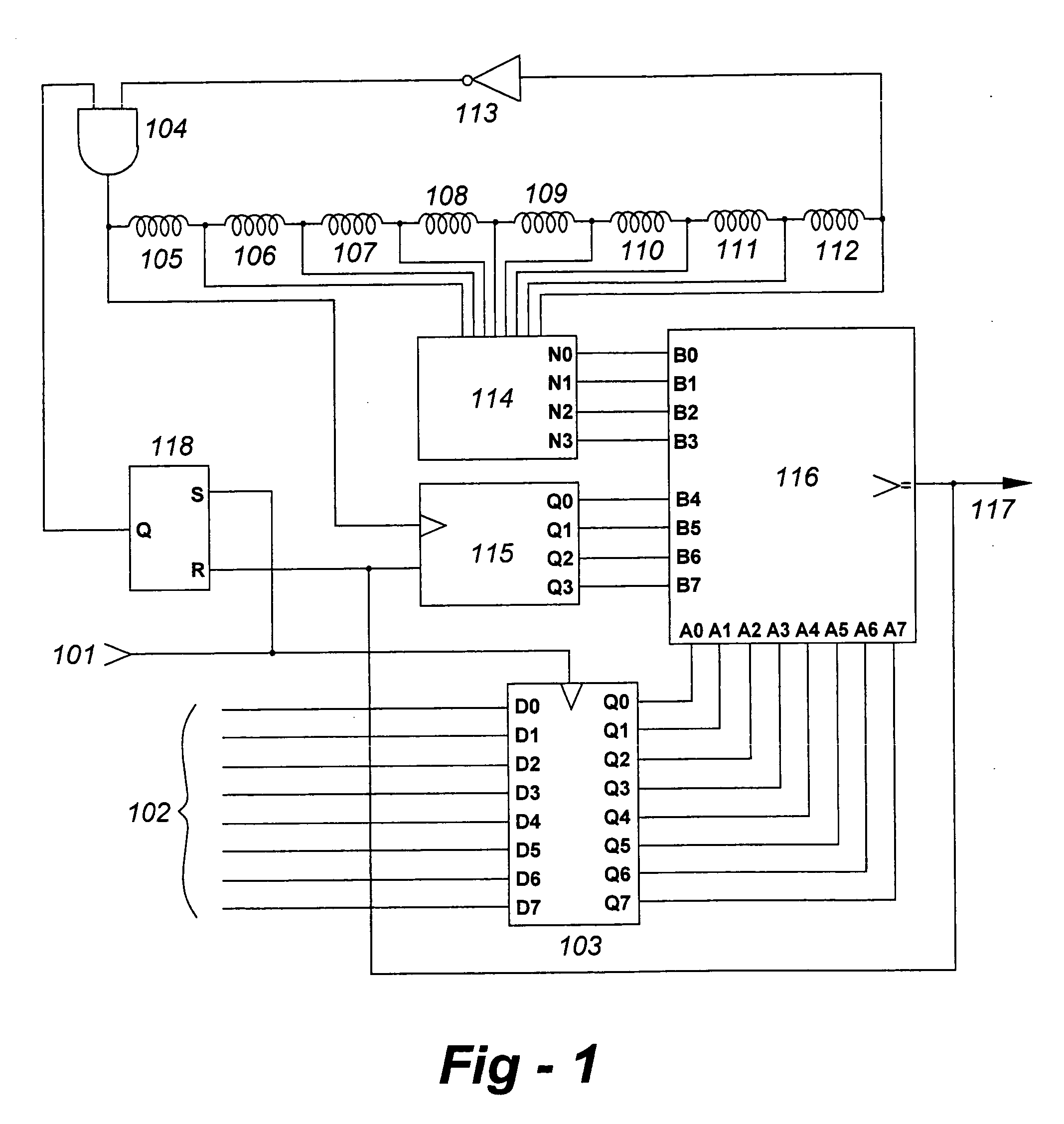

Balanced programmable delay element

Balanced programmable delay element that has a variable incremental delay. A first inverter is provided that has a first electrode for receiving an input signal, a second electrode, a third electrode, and a fourth electrode for providing an output signal and that has a propagation delay that is dependent on a first current. A second inverter is provided that has a first electrode coupled to the fourth electrode of the first inverter for receiving the output signal of the first inverter, a second electrode, a third electrode, and a fourth electrode for providing an output signal and that has a propagation delay that is dependent on a second current. A current switch is coupled to the first inverter, the second inverter, receives at least two control signals, and responsive thereto, selectively varies the incremental delay of the delay element.

Owner:BROADCOM INT PTE LTD

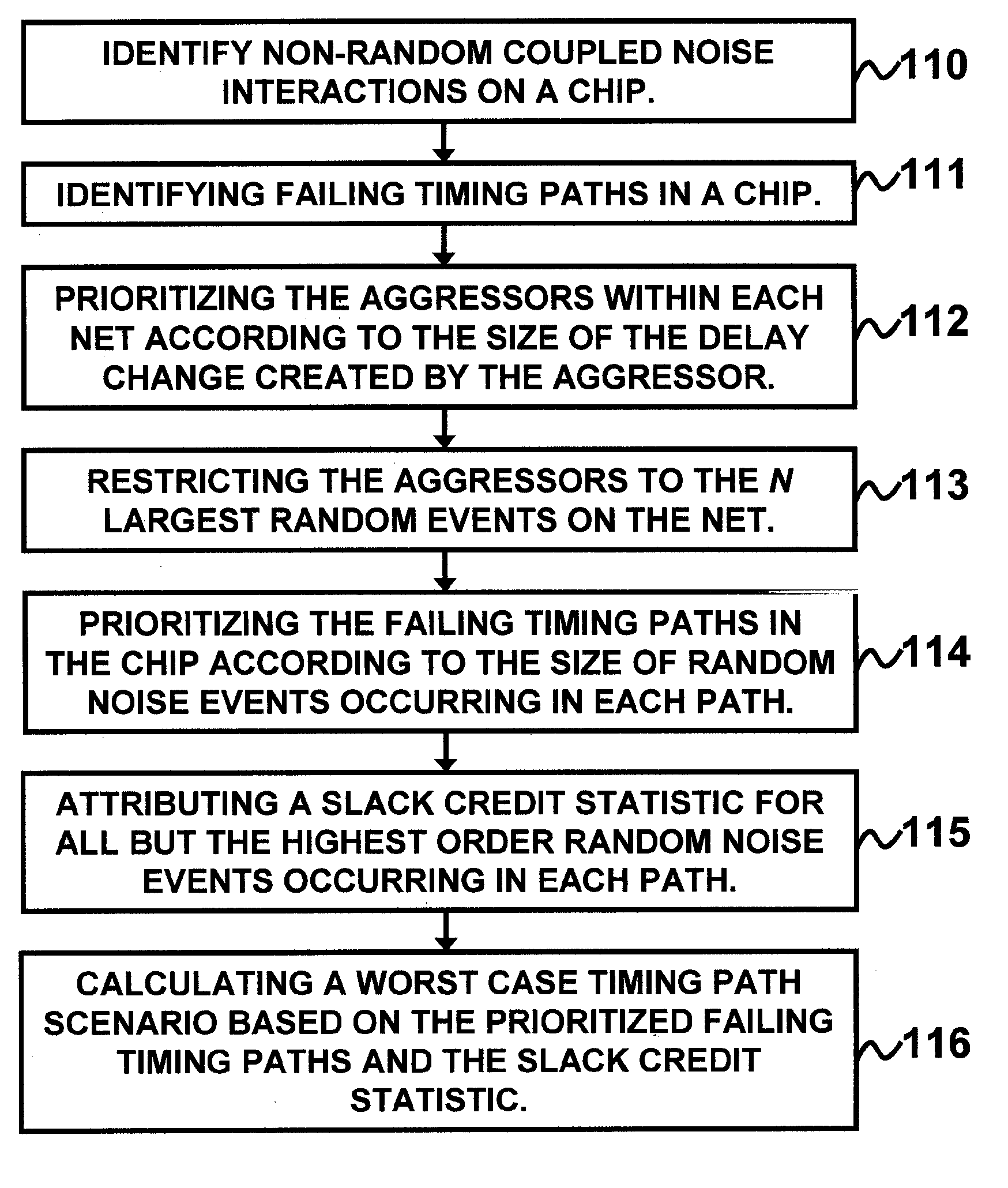

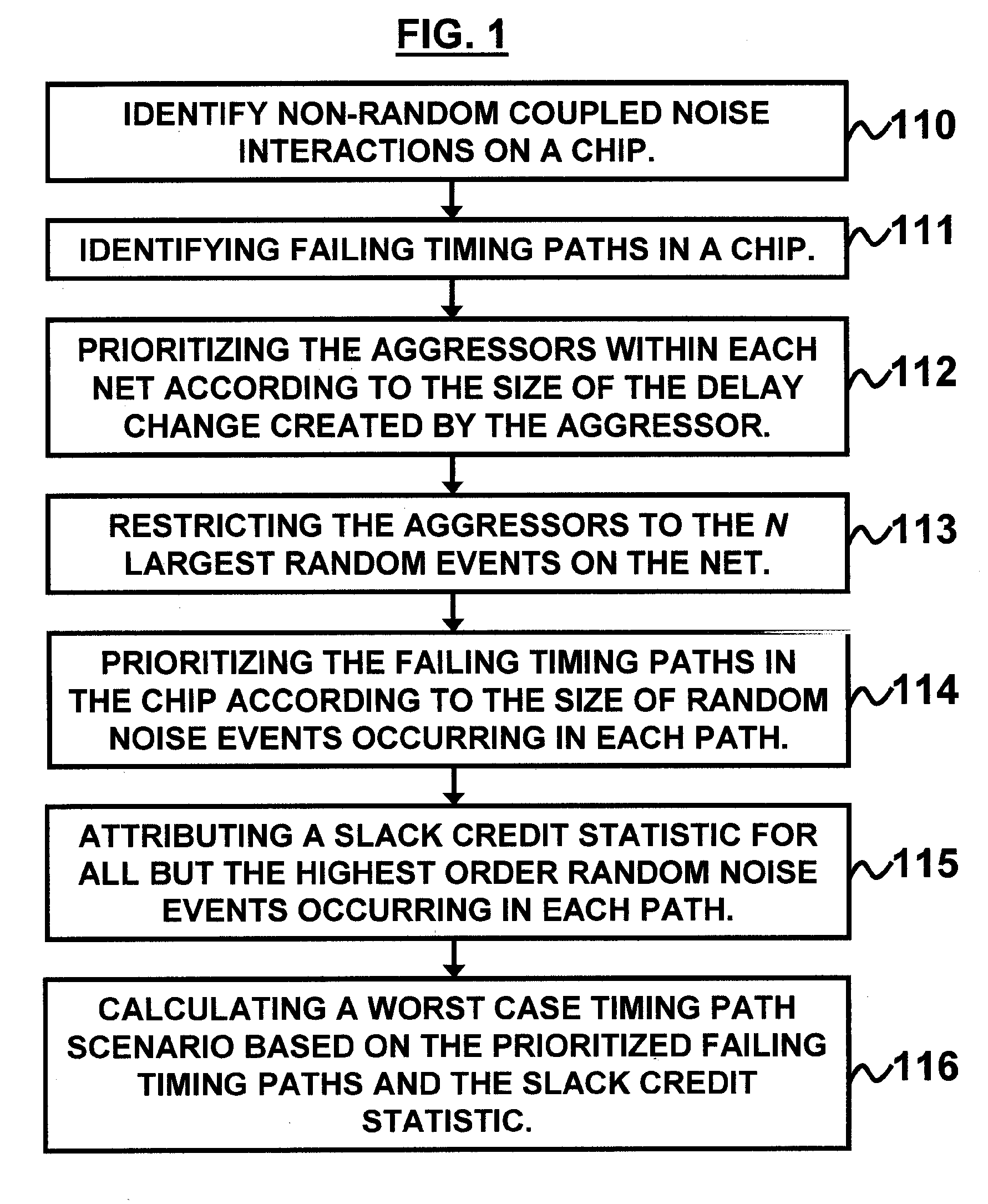

Priortizing of nets for coupled noise analysis

InactiveUS20060248485A1Computer aided designSoftware simulation/interpretation/emulationRandom noiseComputer science

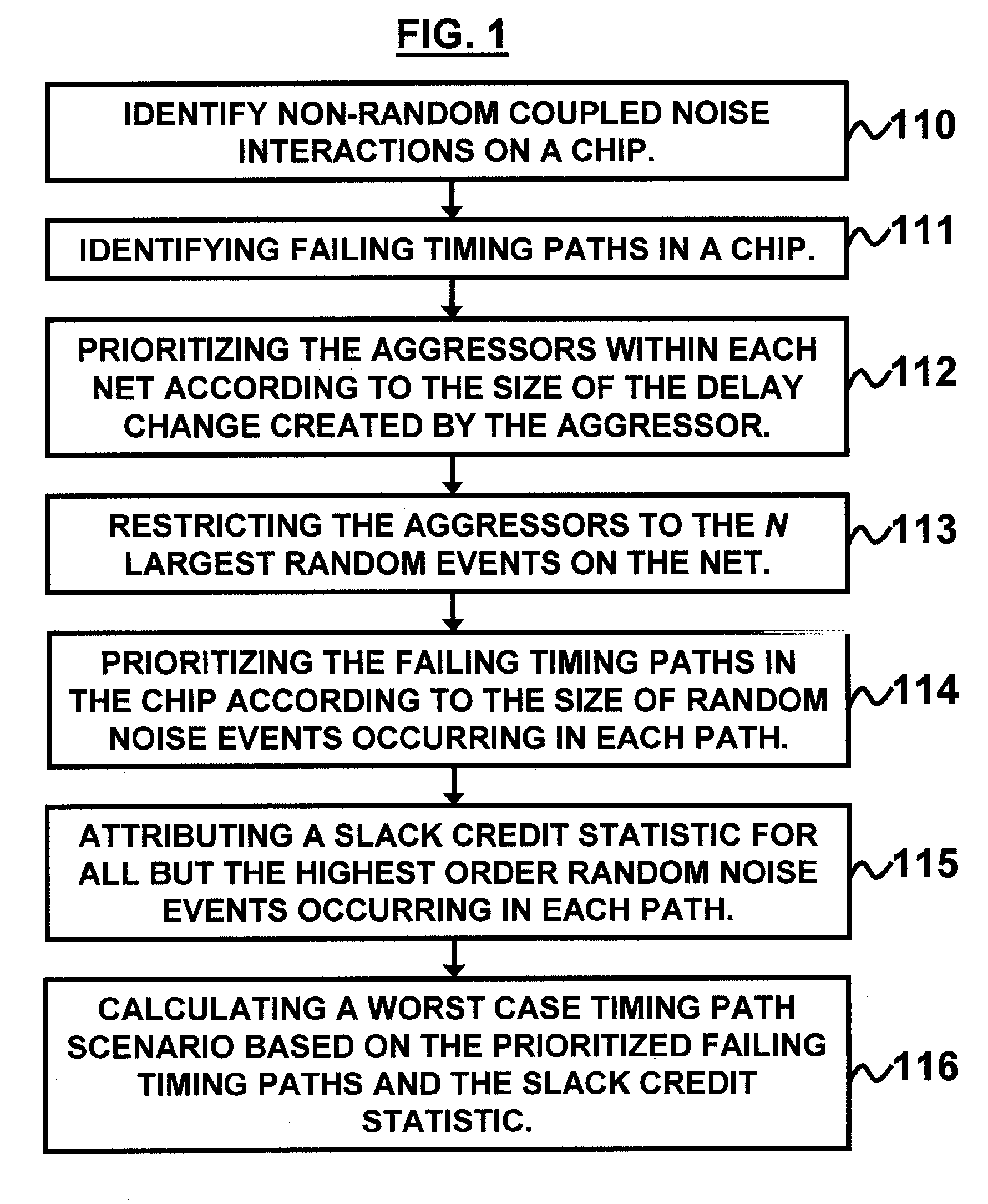

A system and method of performing microelectronic chip timing analysis, wherein the method comprises identifying failing timing paths in a chip; prioritizing the failing timing paths in the chip according to a size of random noise events occurring in each timing path; attributing a slack credit statistic for all but highest order random noise events occurring in each timing path; and calculating a worst case timing path scenario based on the prioritized failing timing paths and the slack credit statistic. Preferably, the random noise events comprise non-clock events. Moreover, the random noise events may comprise victim / aggressor net groups belonging to different regularity groups. Preferably, the size of random noise events comprises coupled noise delta delays due to the random noise events occurring in the chip.

Owner:IBM CORP

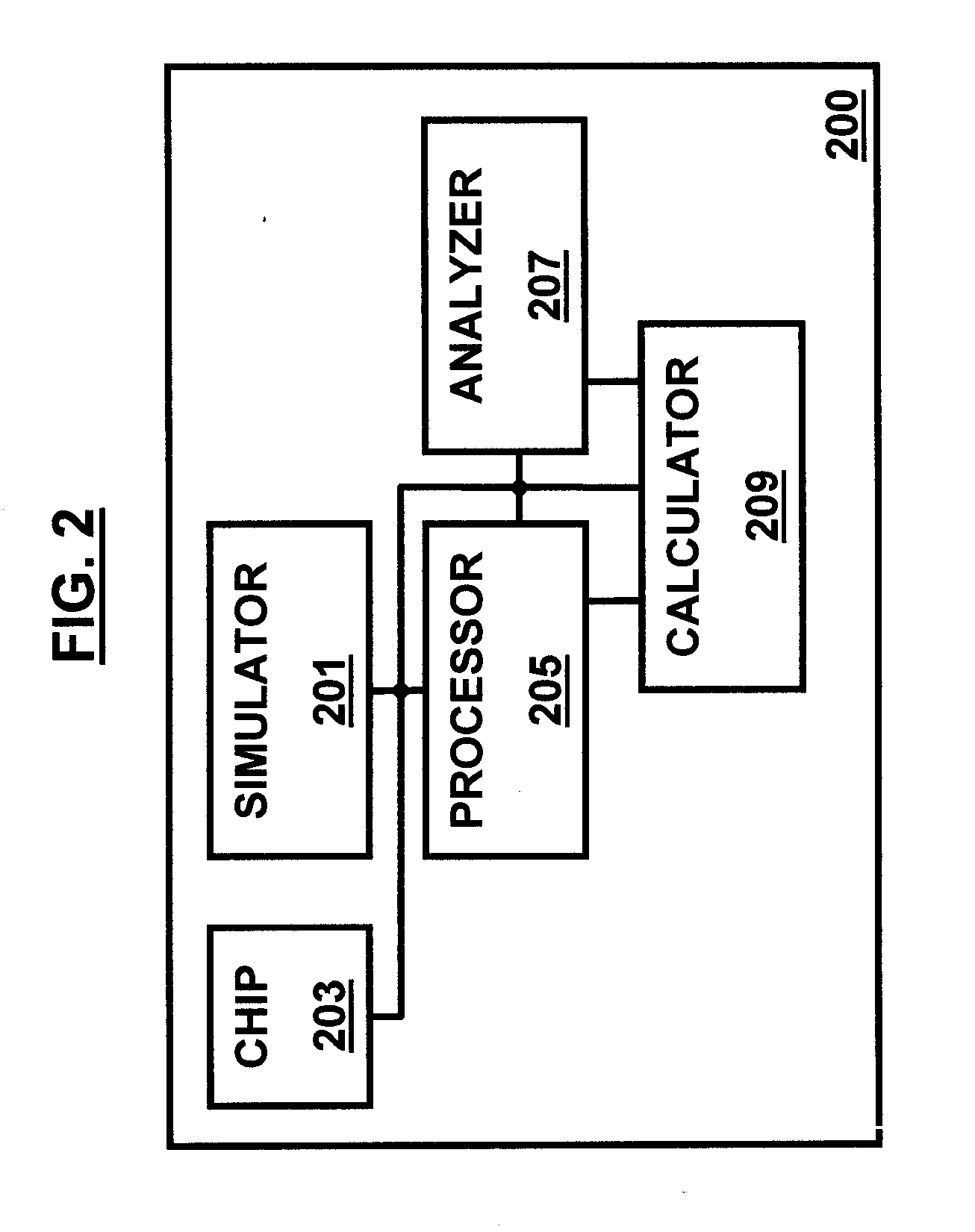

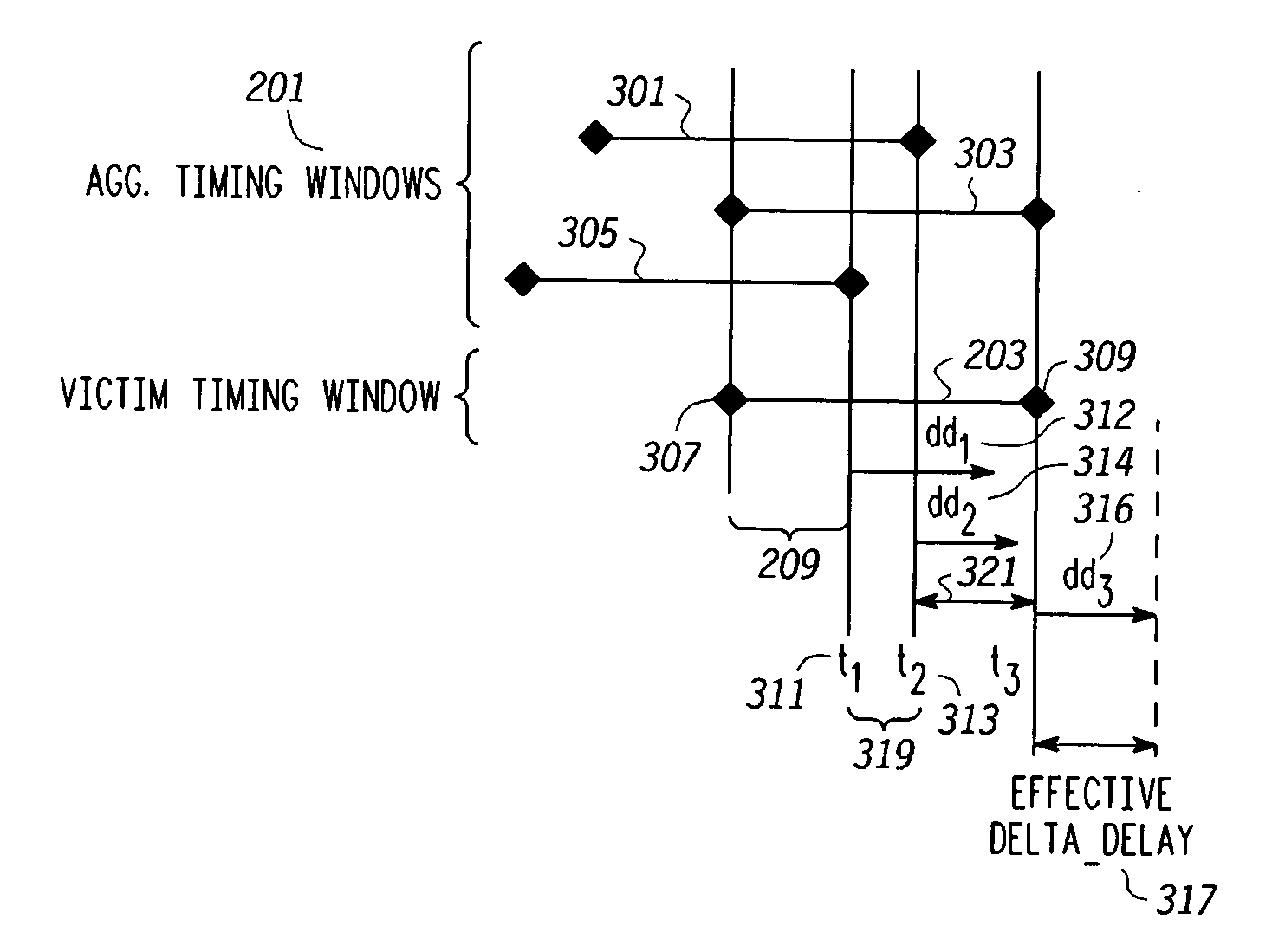

Pessimism reduction in crosstalk noise aware static timing analysis

InactiveUS20060112359A1Computer aided designSoftware simulation/interpretation/emulationEngineeringFalse path

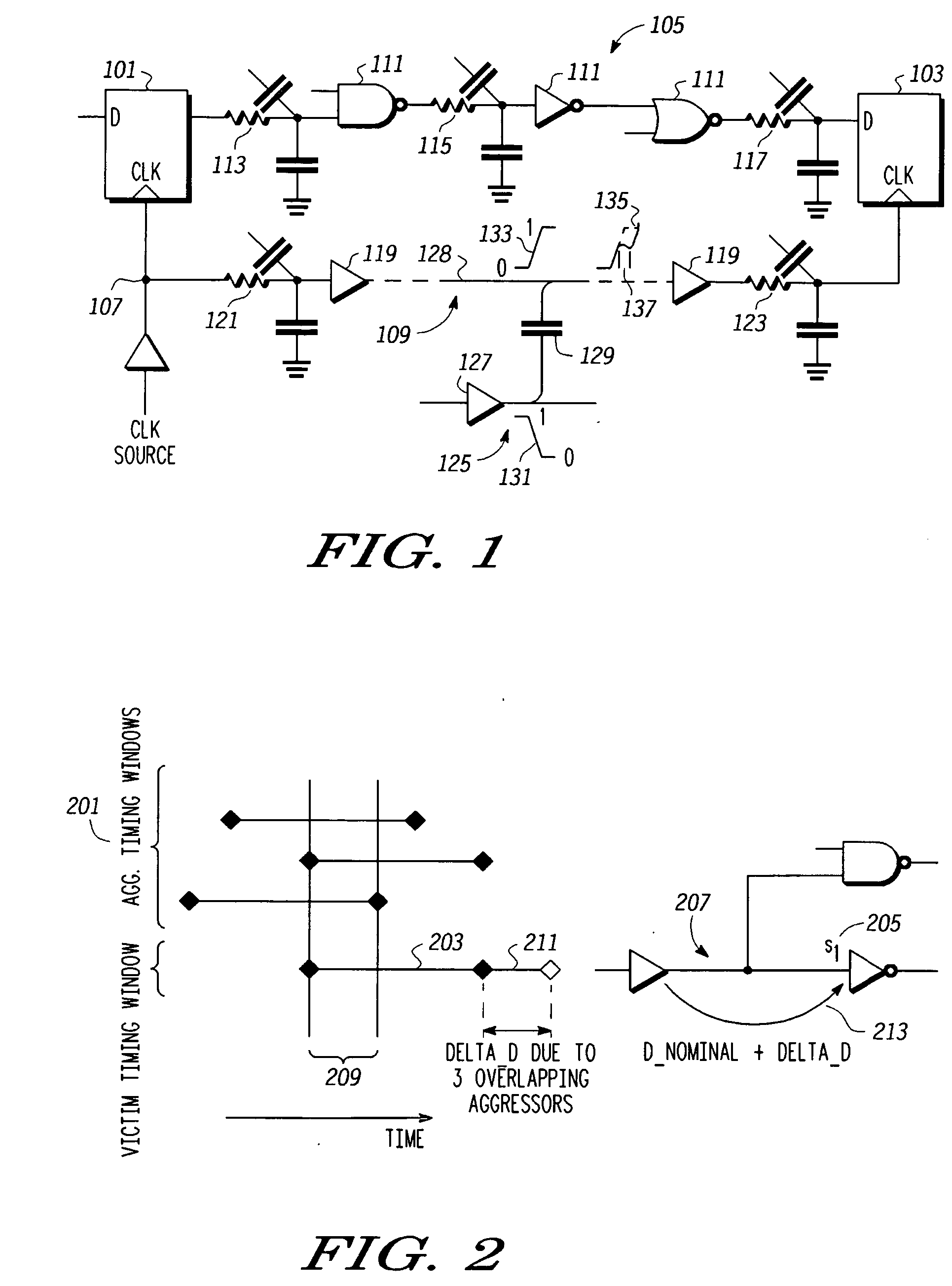

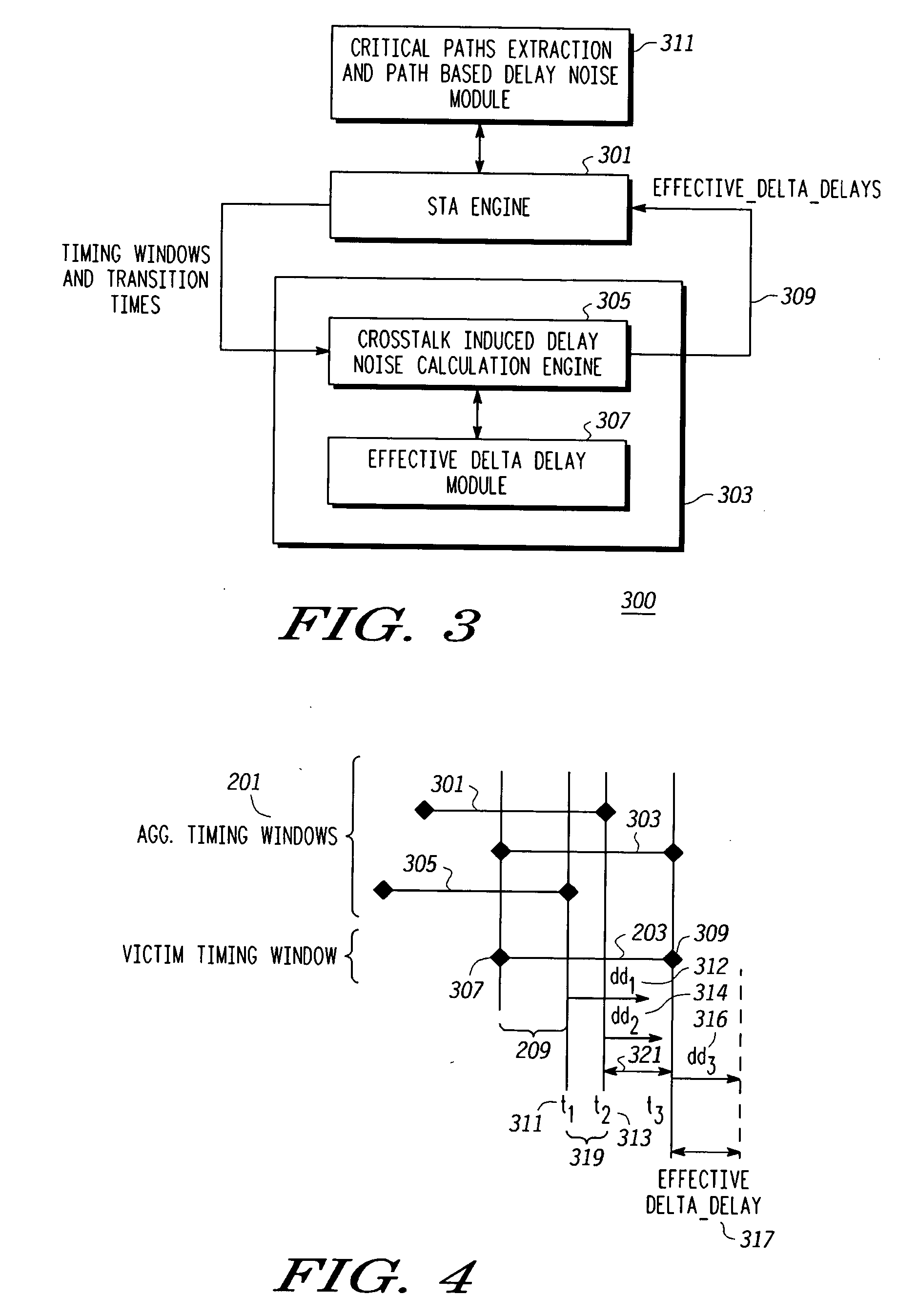

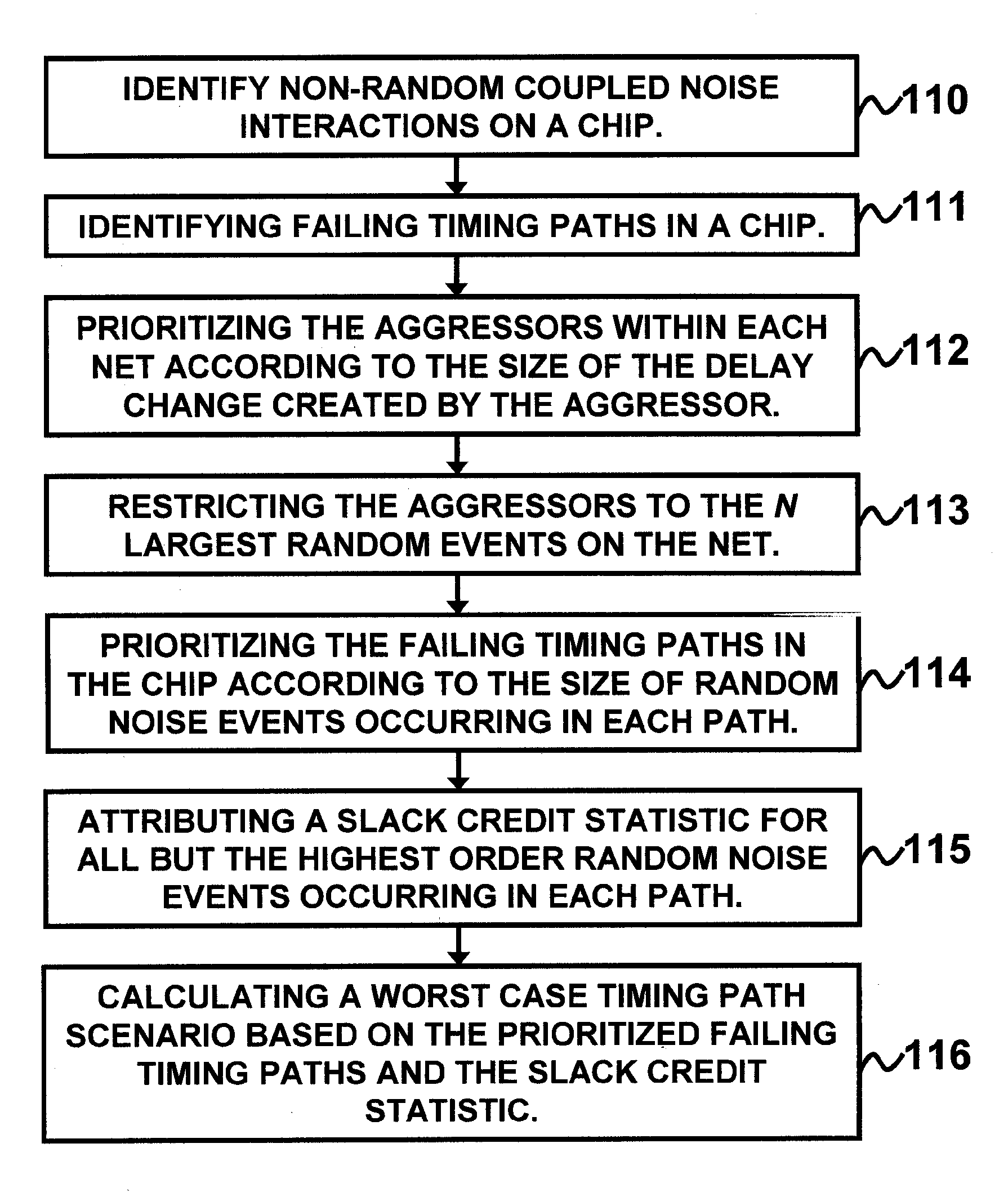

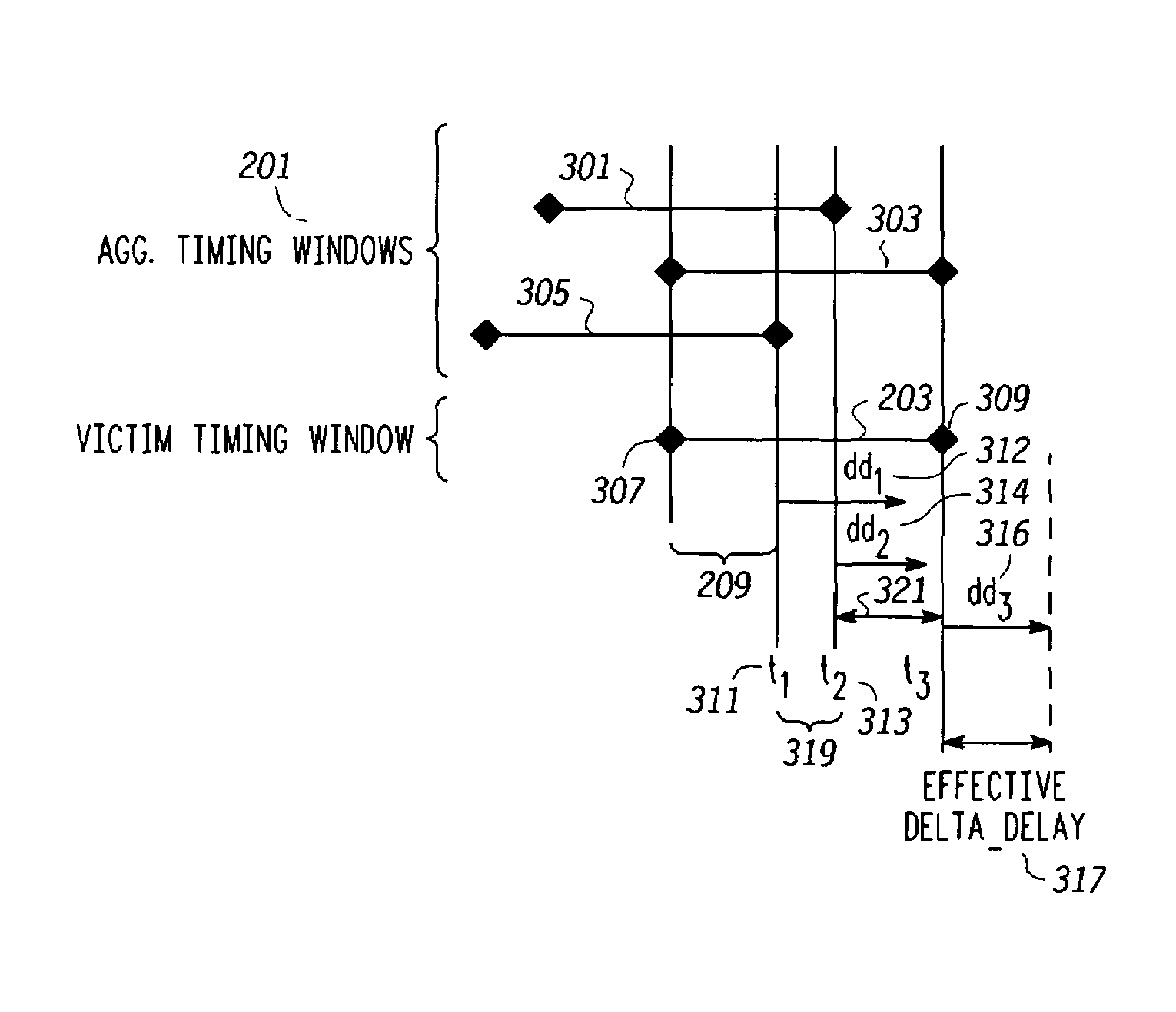

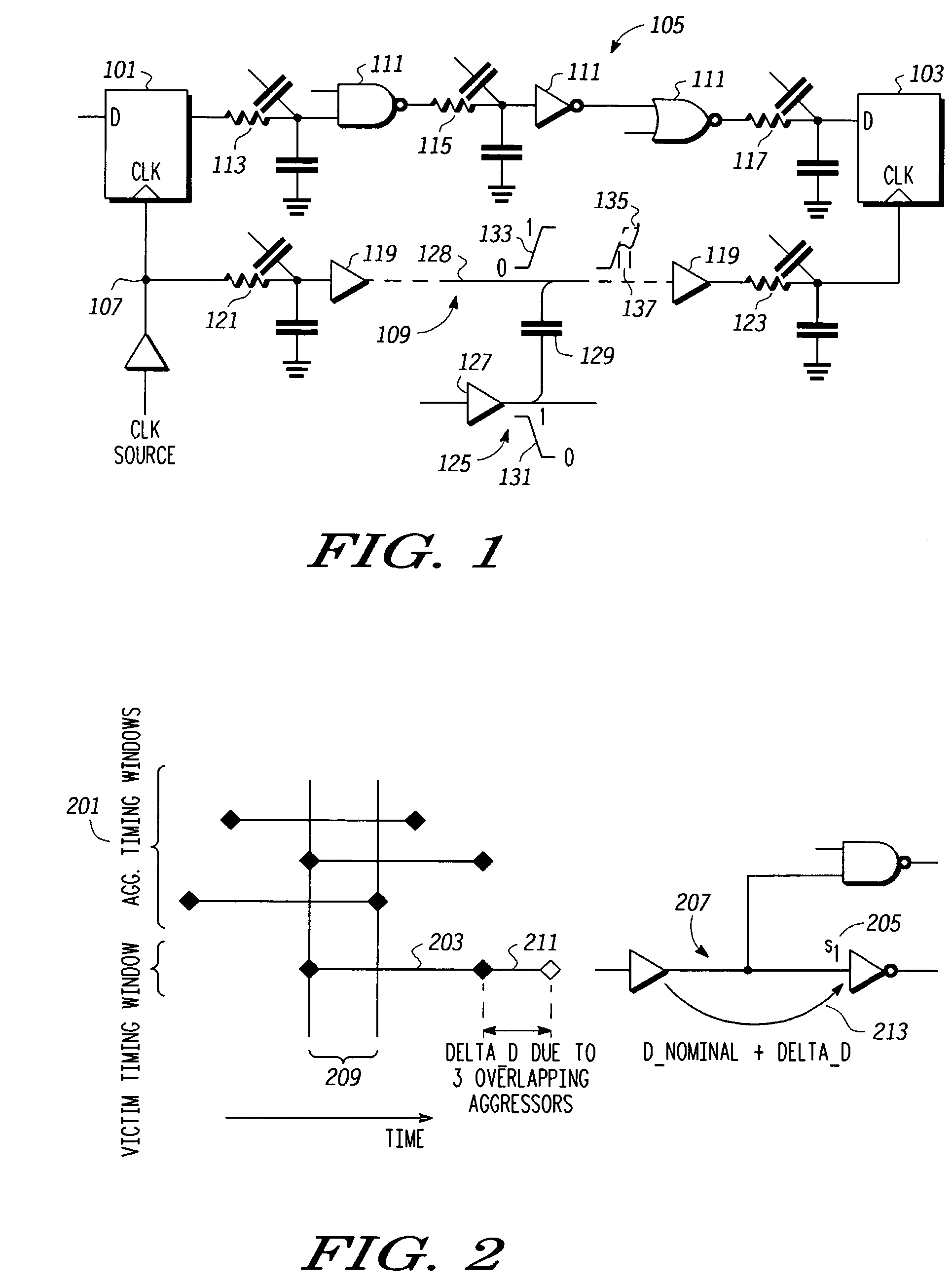

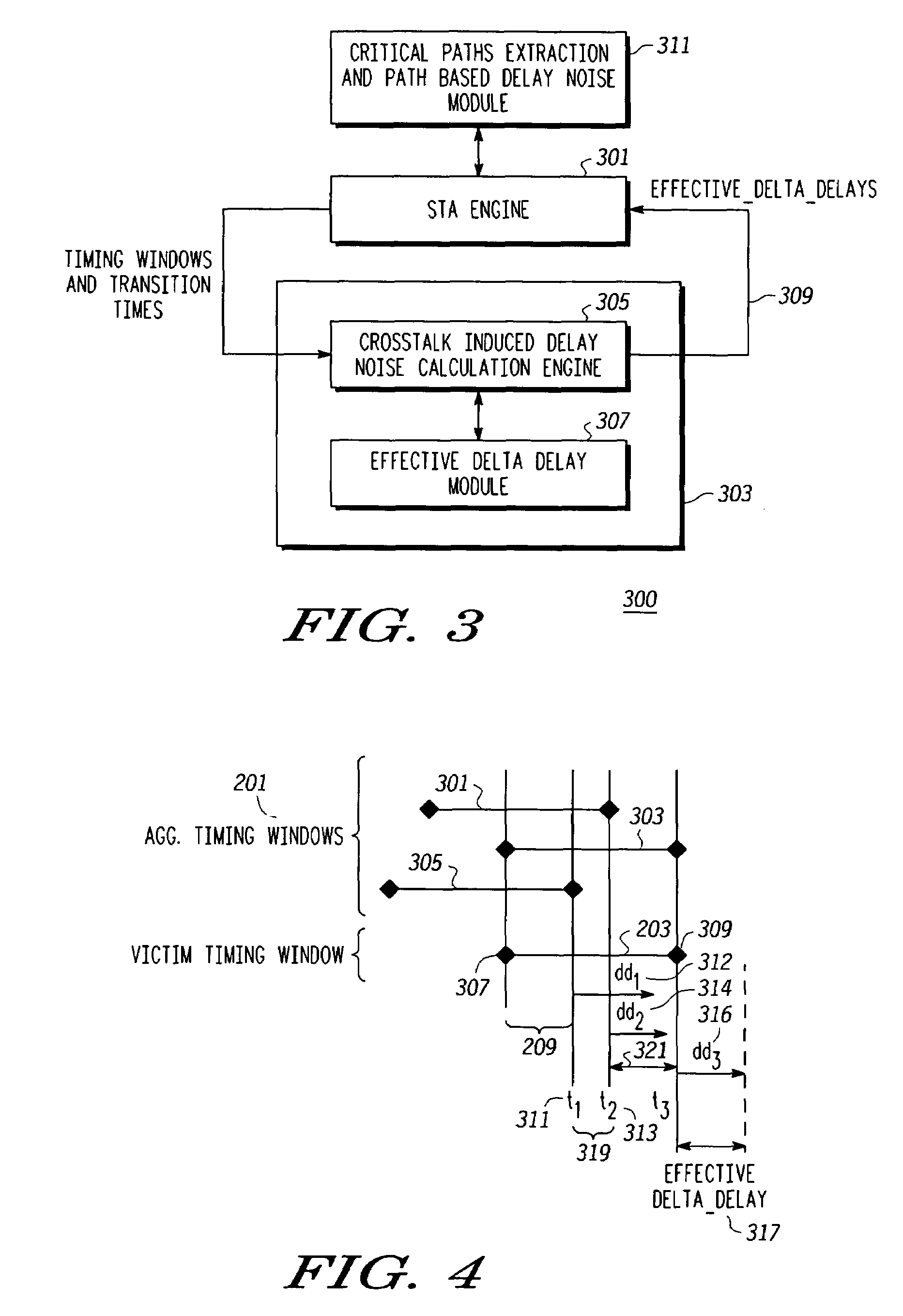

Processes and systems (300) for reducing pessimism in cross talk noise aware static timing analysis and thus resulting false path failures use either or both of effective delta delay noise (307) and path based delay noise (311) analysis. Effective delta delay determines an impact (312, 314, 316) on victim timing of an action by aggressors that occur during a region (209, 319, 321) where victim and aggressor timing windows overlap and determines an effective delta delay 317 corresponding to any portion 316 of the impact on victim timing that extends beyond the victim timing window. The effective delta delay is used to adjust the victim timing window. Path based delta delay determines an uncertainty (627, 637) in a switching time corresponding to a particular path for a victim resulting from an action (switching) by aggressors that occurs at the switching time 607, 613, i.e. during a switching time window (a2 to a2+u1) (613, 625) when uncertainty is included.

Owner:FREESCALE SEMICON INC

Prioritizing of nets for coupled noise analysis

InactiveUS7181711B2Computer aided designSoftware simulation/interpretation/emulationRandom noiseComputer science

A system and method of performing microelectronic chip timing analysis, wherein the method comprises identifying failing timing paths in a chip; prioritizing the failing timing paths in the chip according to a size of random noise events occurring in each timing path; attributing a slack credit statistic for all but highest order random noise events occurring in each timing path; and calculating a worst case timing path scenario based on the prioritized failing timing paths and the slack credit statistic. Preferably, the random noise events comprise non-clock events. Moreover, the random noise events may comprise victim / aggressor net groups belonging to different regularity groups. Preferably, the size of random noise events comprises coupled noise delta delays due to the random noise events occurring in the chip.

Owner:INT BUSINESS MASCH CORP

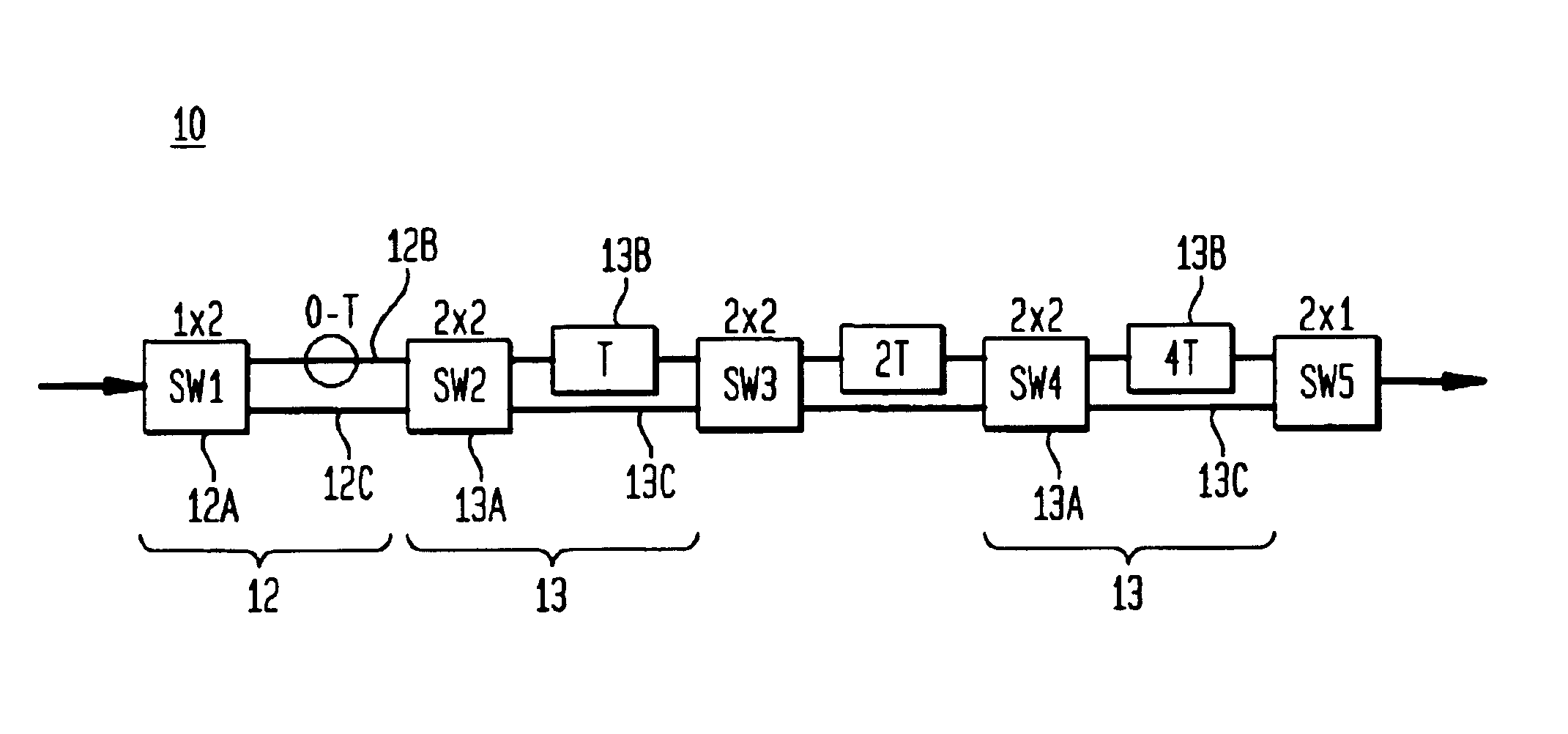

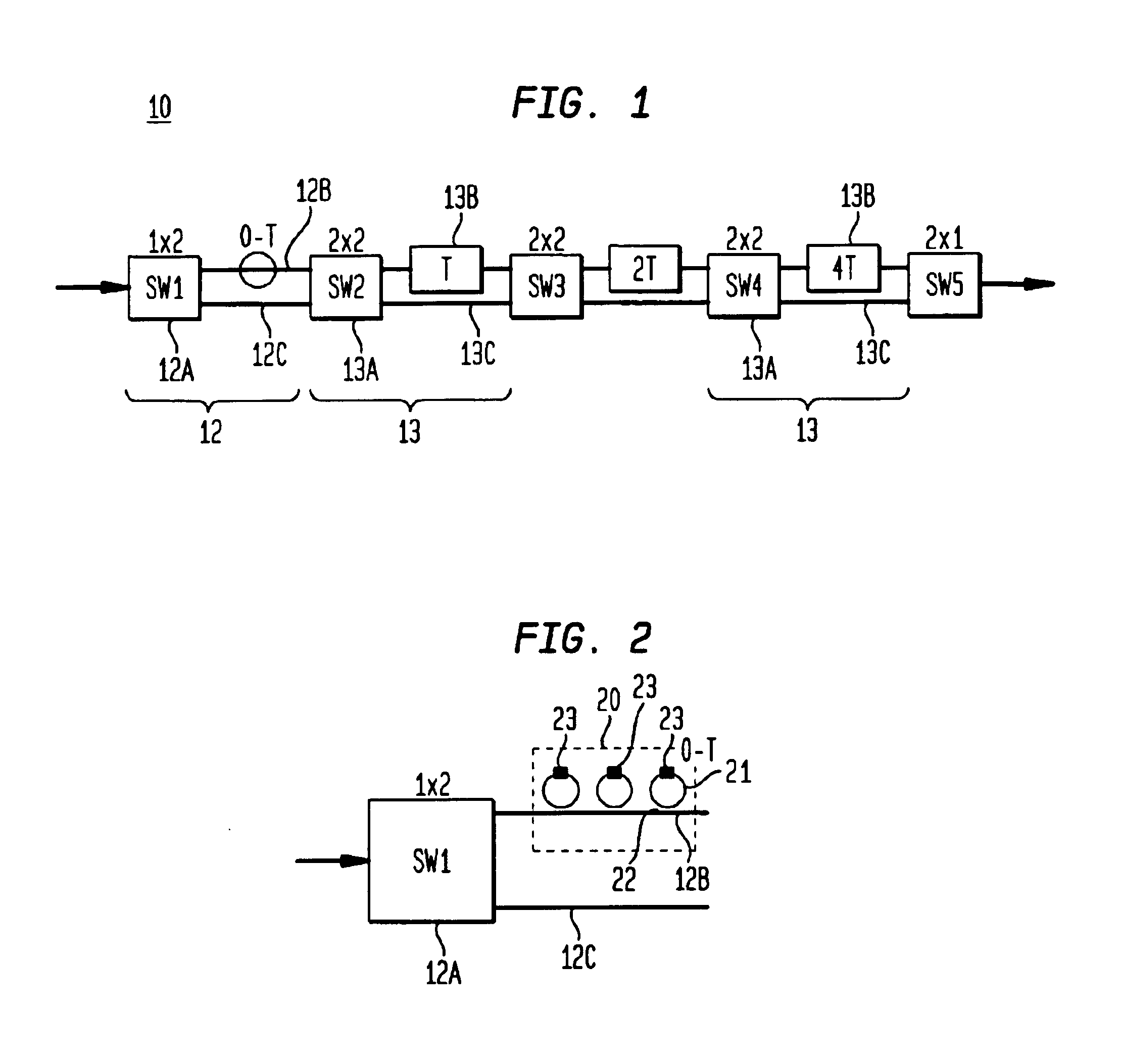

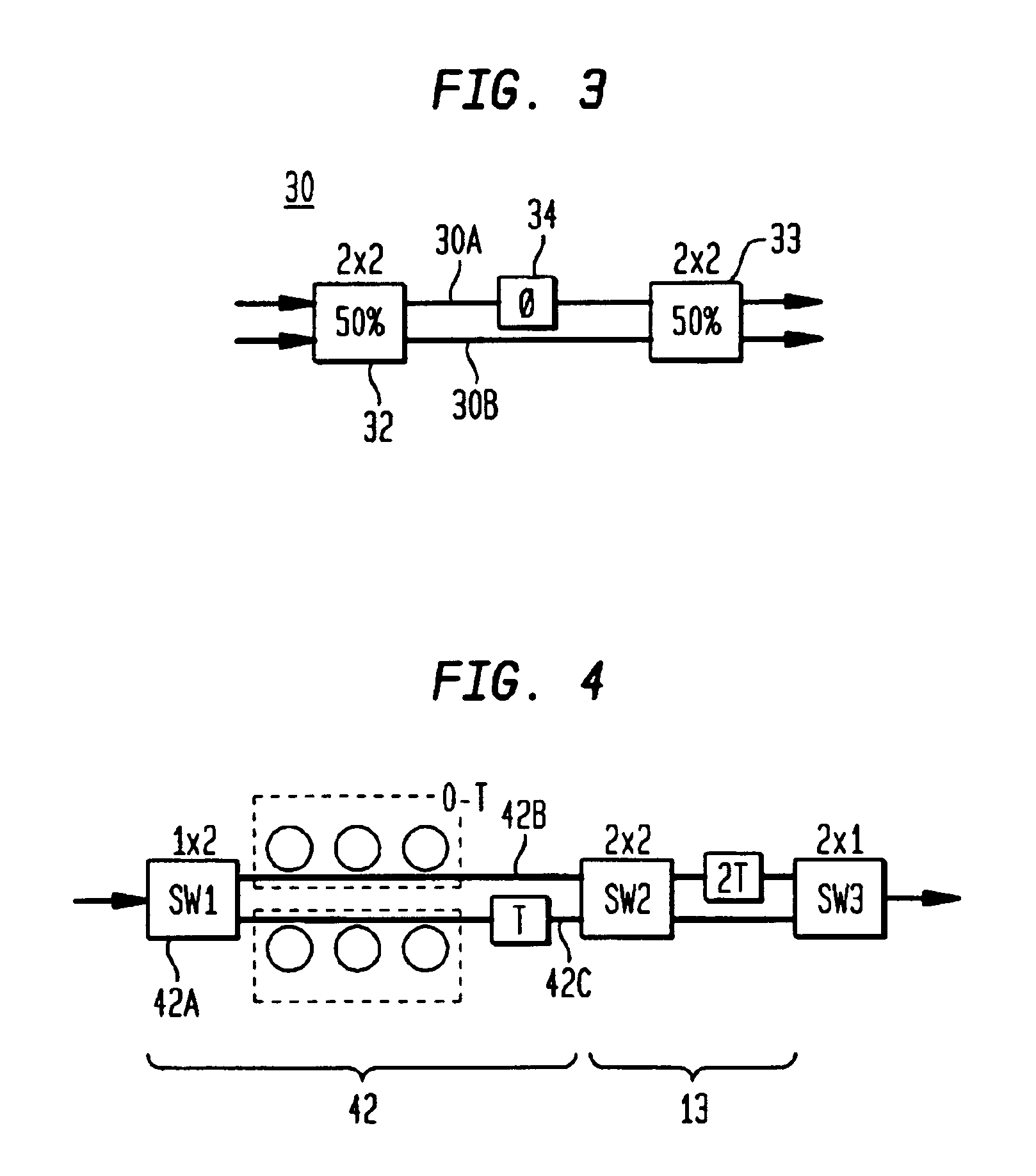

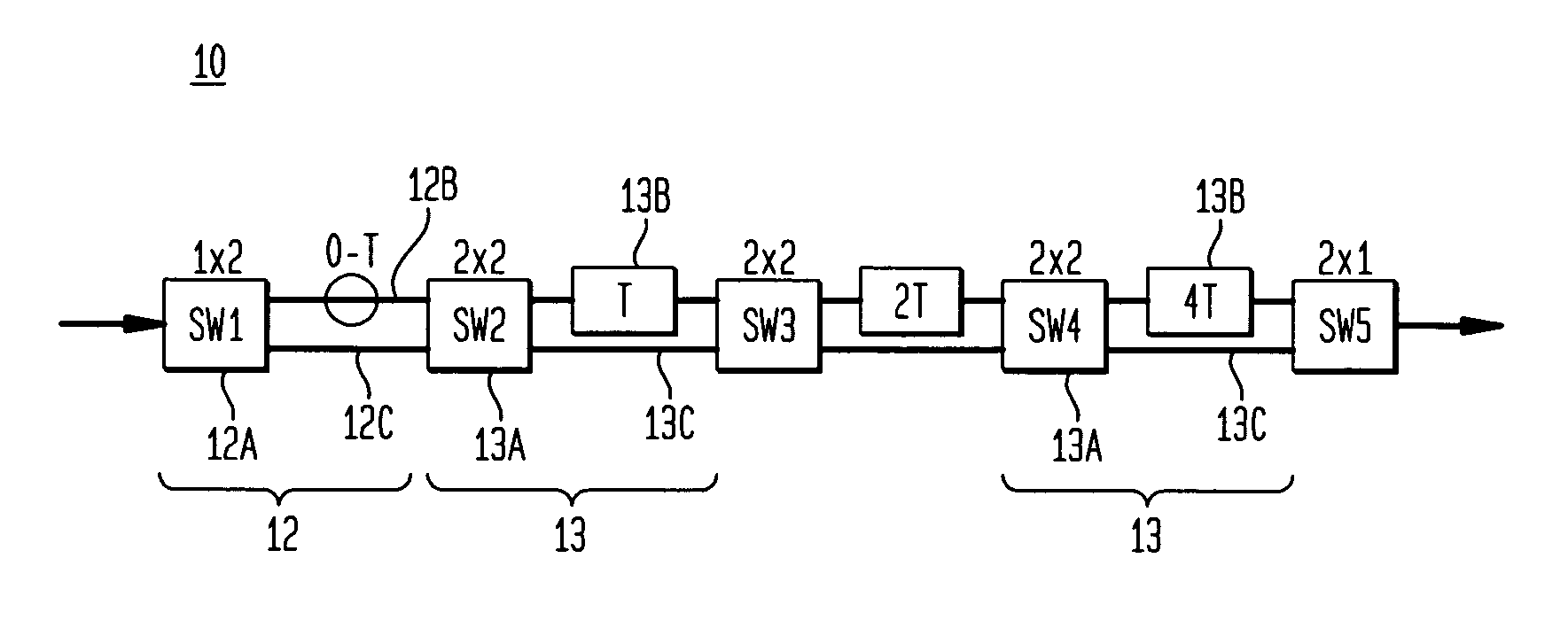

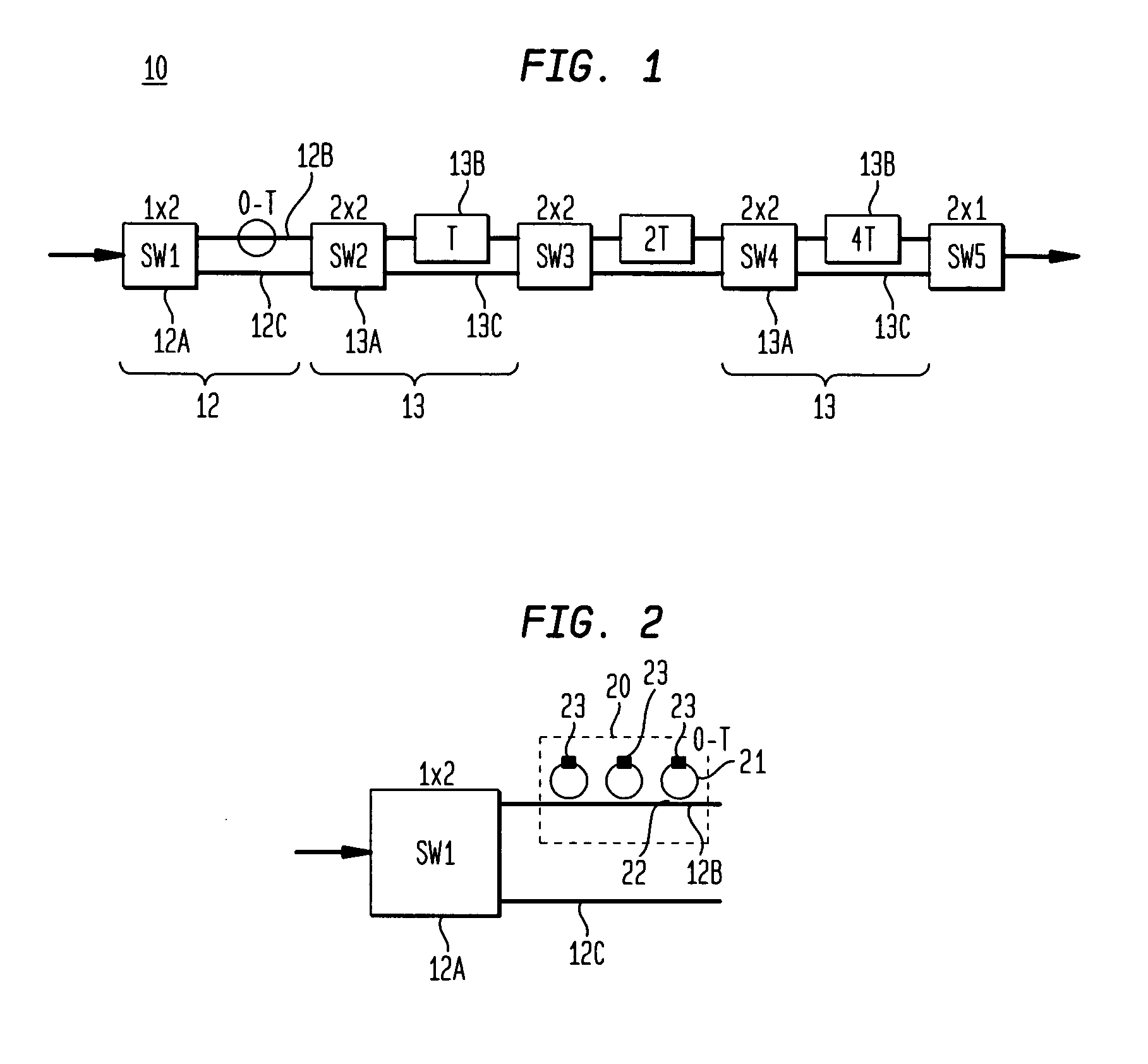

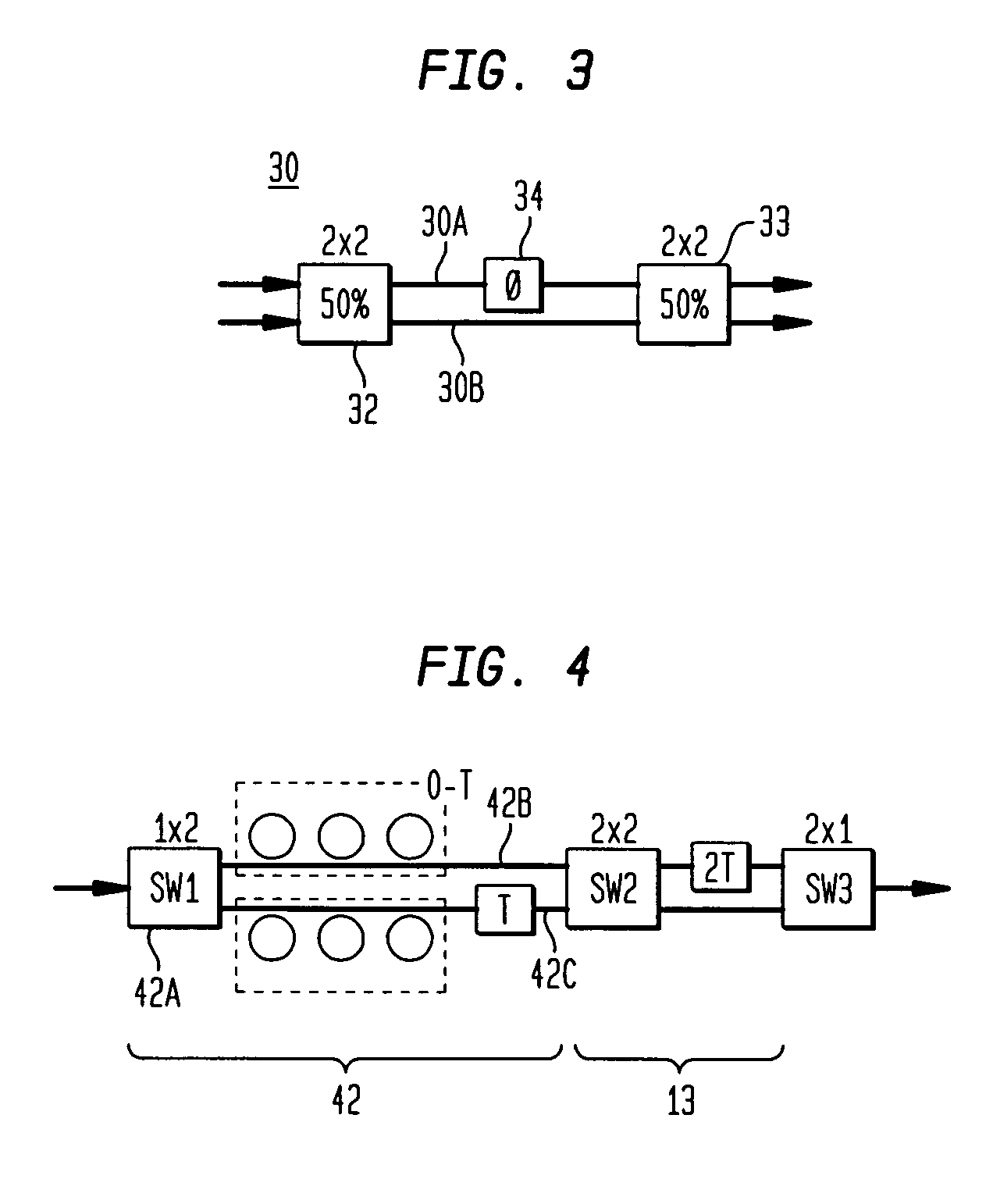

Compact solid-state variable optical delay line with a large continuous tuning range

In accordance with the invention, a variable delay line with continuous tuning comprises an optical path providing at least one continuous delay element coupled to a series of switchable binary fixed delays. The series of switchable delays can be configured to select a delay among a plurality of incremental delays, and the continuous delay can set a continuous delay in a range encompassing the delay increment of the binary series. In a preferred embodiment, the variable delay element comprises a tunable all pass filter (APF) with delay tunable from essentially 0 to a time T and the switchable binary fixed delays form a series (0,T), (0, 2T), (0, 4T), . . . , [0, (2n+1)], where n is an integer ≧0. The switches are preferably Mach-Zehnder switches. In an alternative embodiment, the continuous delay element comprises a suitable pair of APF arms. The path and all components can be fabricated as an integrated planar waveguide (solid state) device.

Owner:ALCATEL-LUCENT USA INC +1

Pessimism reduction in crosstalk noise aware static timing analysis

InactiveUS7251797B2Computer aided designSoftware simulation/interpretation/emulationFalse pathSwitching time

Processes and systems (300) for reducing pessimism in cross talk noise aware static timing analysis and thus resulting false path failures use either or both of effective delta delay noise (307) and path based delay noise (311) analysis. Effective delta delay determines an impact (312, 314, 316) on victim timing of an action by aggressors that occur during a region (209, 319, 321) where victim and aggressor timing windows overlap and determines an effective delta delay 317 corresponding to any portion 316 of the impact on victim timing that extends beyond the victim timing window. The effective delta delay is used to adjust the victim timing window. Path based delta delay determines an uncertainty (627, 637) in a switching time corresponding to a particular path for a victim resulting from an action (switching) by aggressors that occurs at the switching time 607, 613, i.e. during a switching time window (a2 to a2+u1) (613, 625) when uncertainty is included.

Owner:FREESCALE SEMICON INC

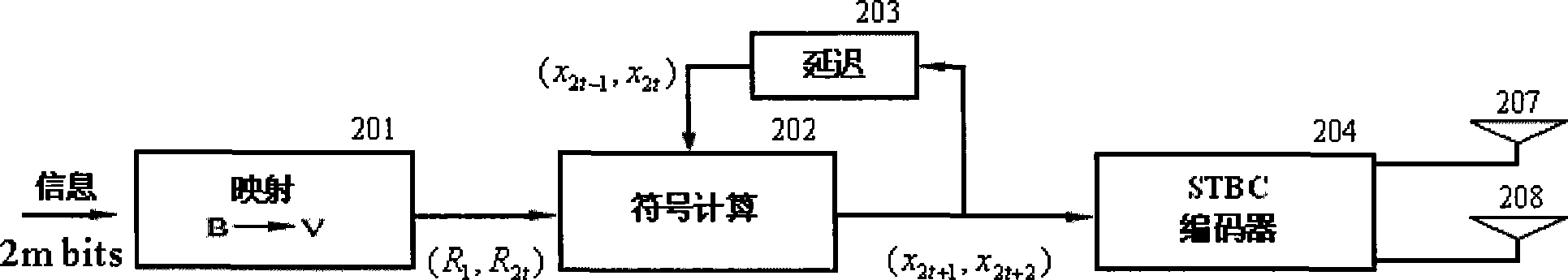

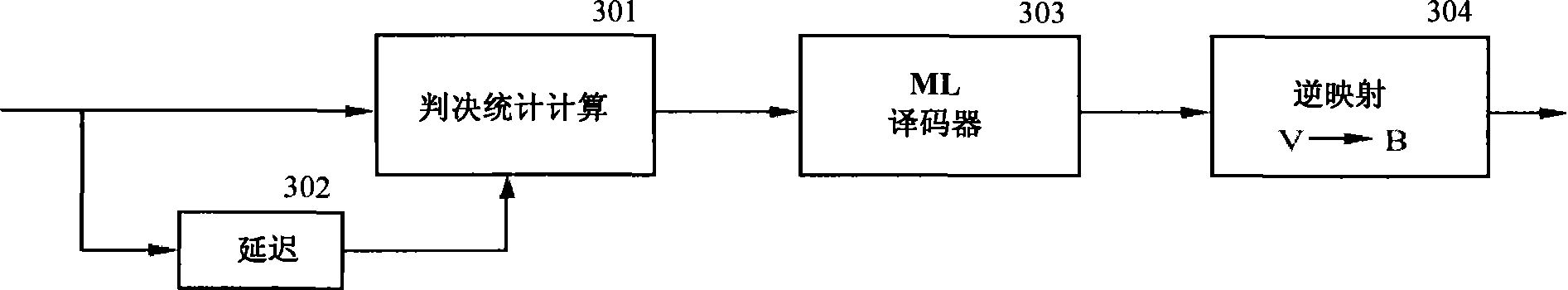

Differential space-time transmission diversity system in multi-carrier modulation system and implementing method

InactiveCN101453257AImprove spectral efficiencyDiversity gain at altitudeSpatial transmit diversityMulti-frequency code systemsCarrier signalCyclic prefix

The invention provides a system for a differential space time transmit diversity in a multicarrier modulation system and an implement method thereof, wherein the implement method comprises the following steps: A, a modulation signal is subjected to differential coding by a differential space time coder and is output to two paths; and B, one path of signal in the step A passes through an OFDM modulator and a cyclic prefix insertion device and is transmitted by an antenna, the other path of coding signal passes through another OFDM modulator and is transmitted to a time delay delta unit, after the signal is subjected to cyclic time delay with delta delayed time, the signal is transmitted to the cyclic prefix insertion device, inserted with cyclic prefix and transmitted by an antenna. On the premise of ensuring the transmission speed, the system can obtain high space time diversity gain and effectively improve system performance.

Owner:ACAD OF BROADCASTING SCI SARFT

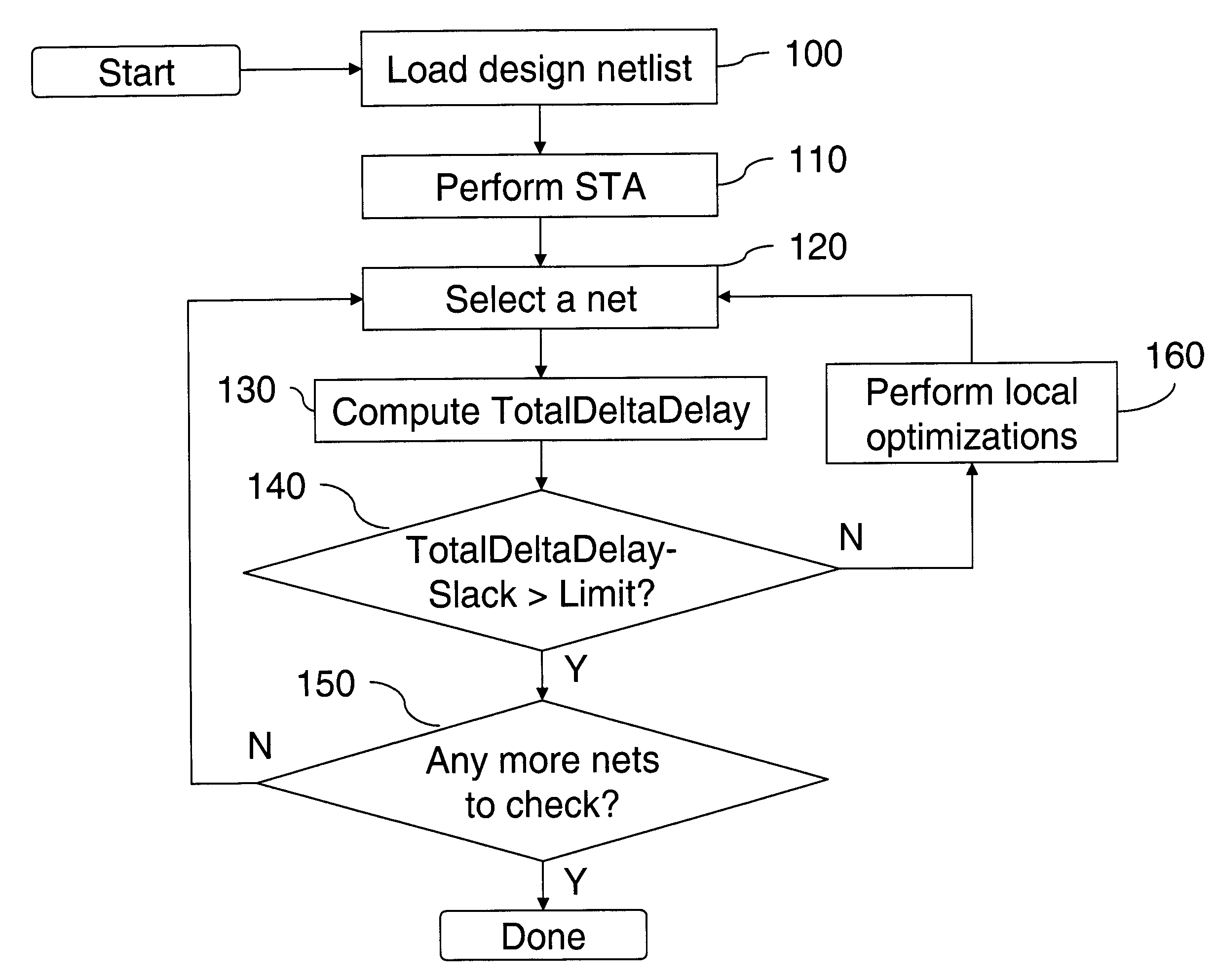

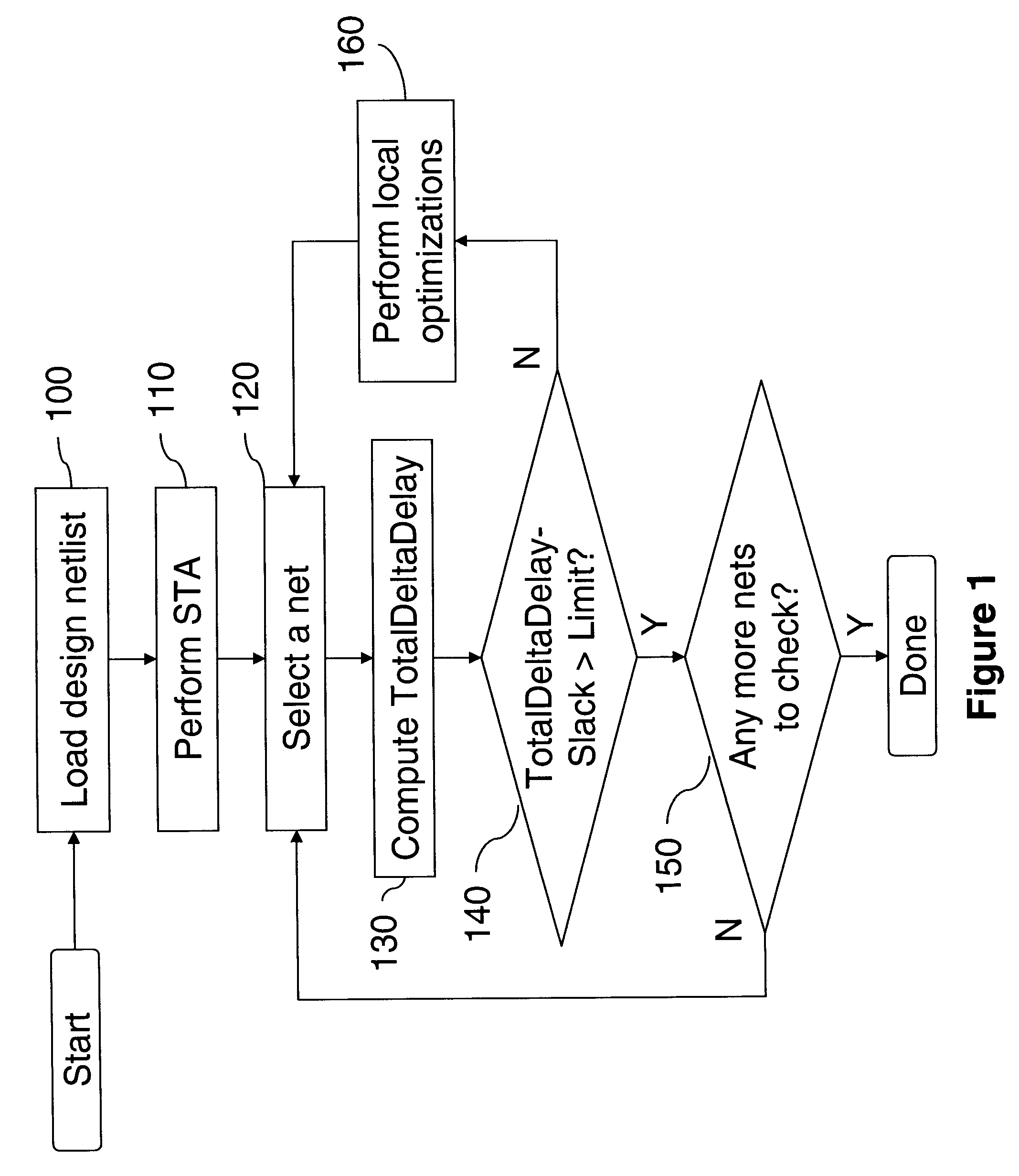

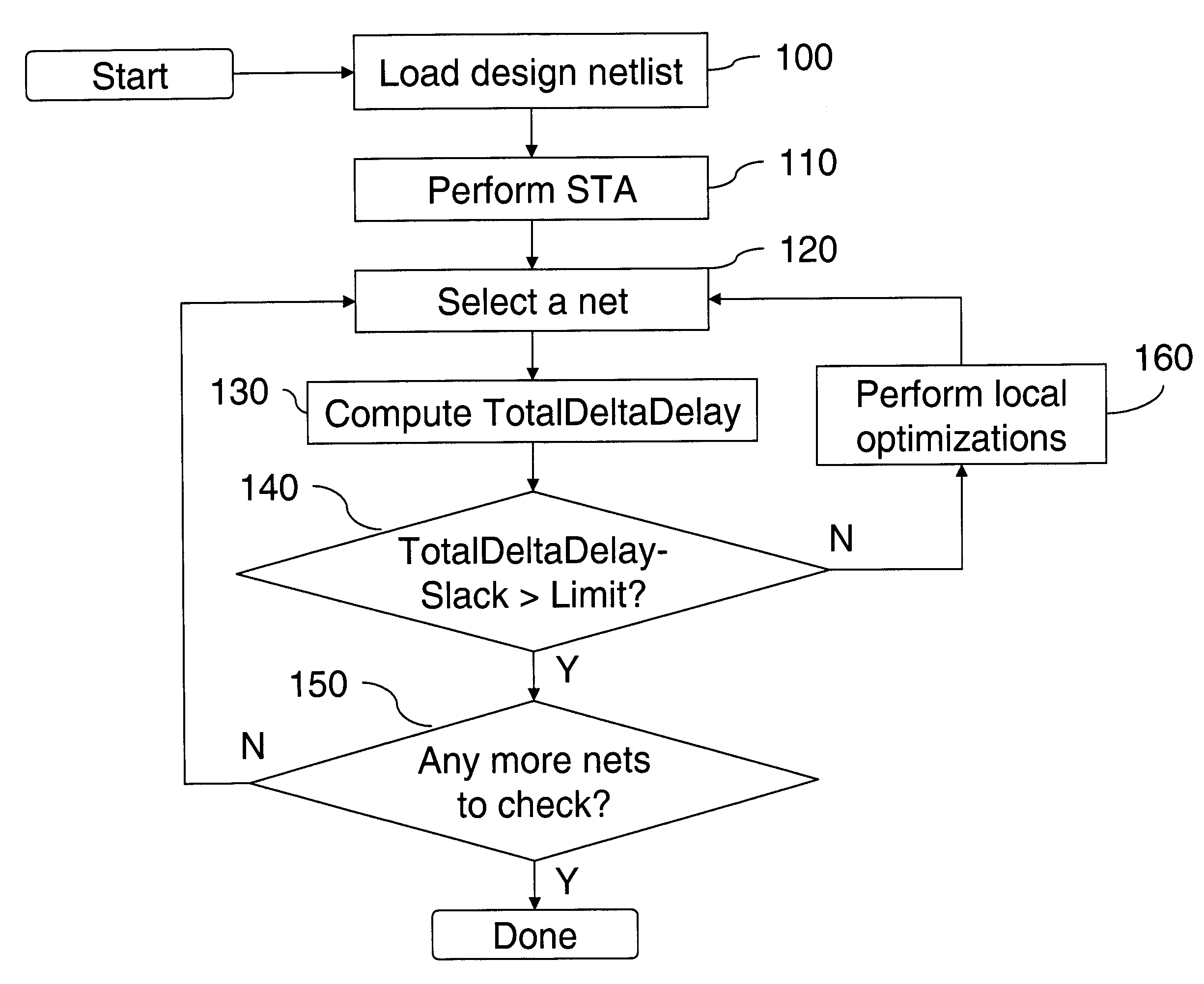

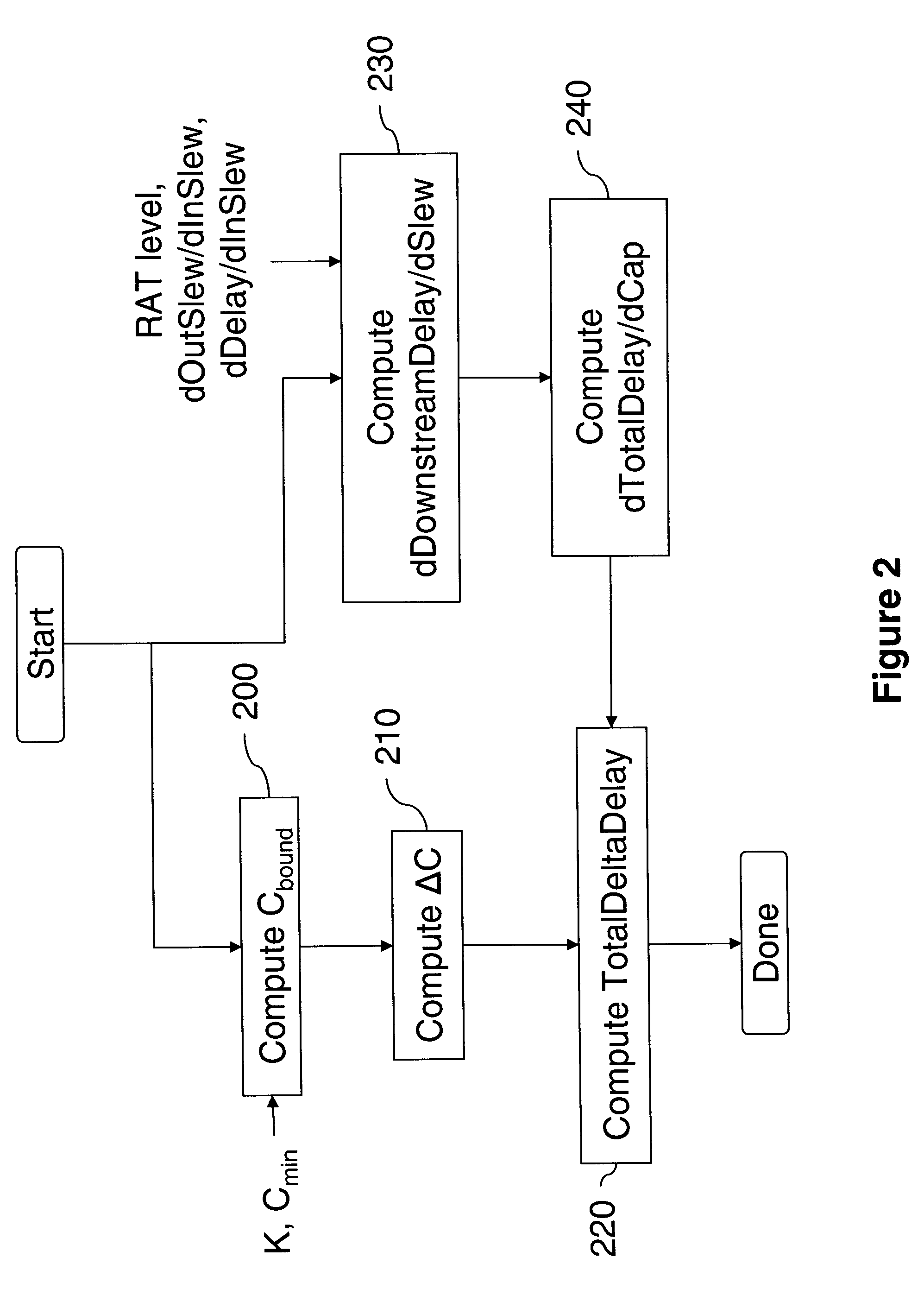

Method for optimizing an unrouted design to reduce the probability of timing problems due to coupling and long wire routes

InactiveUS7895556B2Simple designMinimizing sensitivityCAD circuit designSoftware simulation/interpretation/emulationCapacitanceComputer science

A method and a system is described to predict effects of coupling on timing by estimating the delta delay and delta slack that can occur due to coupling on any net, for optimization to minimize the sensitivity of slack to potential coupling violations. The invention protects against other unexpected increases in effective load capacitance, such as those due to unexpectedly long wire routes. It also estimates the delay impact of a single ‘fault’ or ‘event’, such as a coupling event or unexpectedly long wires routes, including the impact of slew propagation.

Owner:GLOBALFOUNDRIES INC

Delta delay approach for ultrasound beamforming on an ASIC

ActiveUS9439625B2Ultrasonic/sonic/infrasonic diagnosticsInfrasonic diagnosticsElectricitySonification

Systems are disclosed for ultrasound beamforming on an application specific integrated circuit (ASIC). In certain embodiments, the system includes an ultrasound probe that includes a plurality of transducer elements electrically coupled to an ASIC. The ASIC includes a plurality of waveform generators electrically coupled to a plurality of delay units. Each delay unit receives a waveform from a waveform generator or an adjacent delay unit, applies a delay to the waveform, and outputs the waveform to adjacent delay units, one or more of the plurality of transducer elements, or both. The delays that are provided to waveforms before being output to a transducer element determine the beamforming characteristics of the ultrasonic pulses generated by the ultrasound probe.

Owner:GENERAL ELECTRIC CO

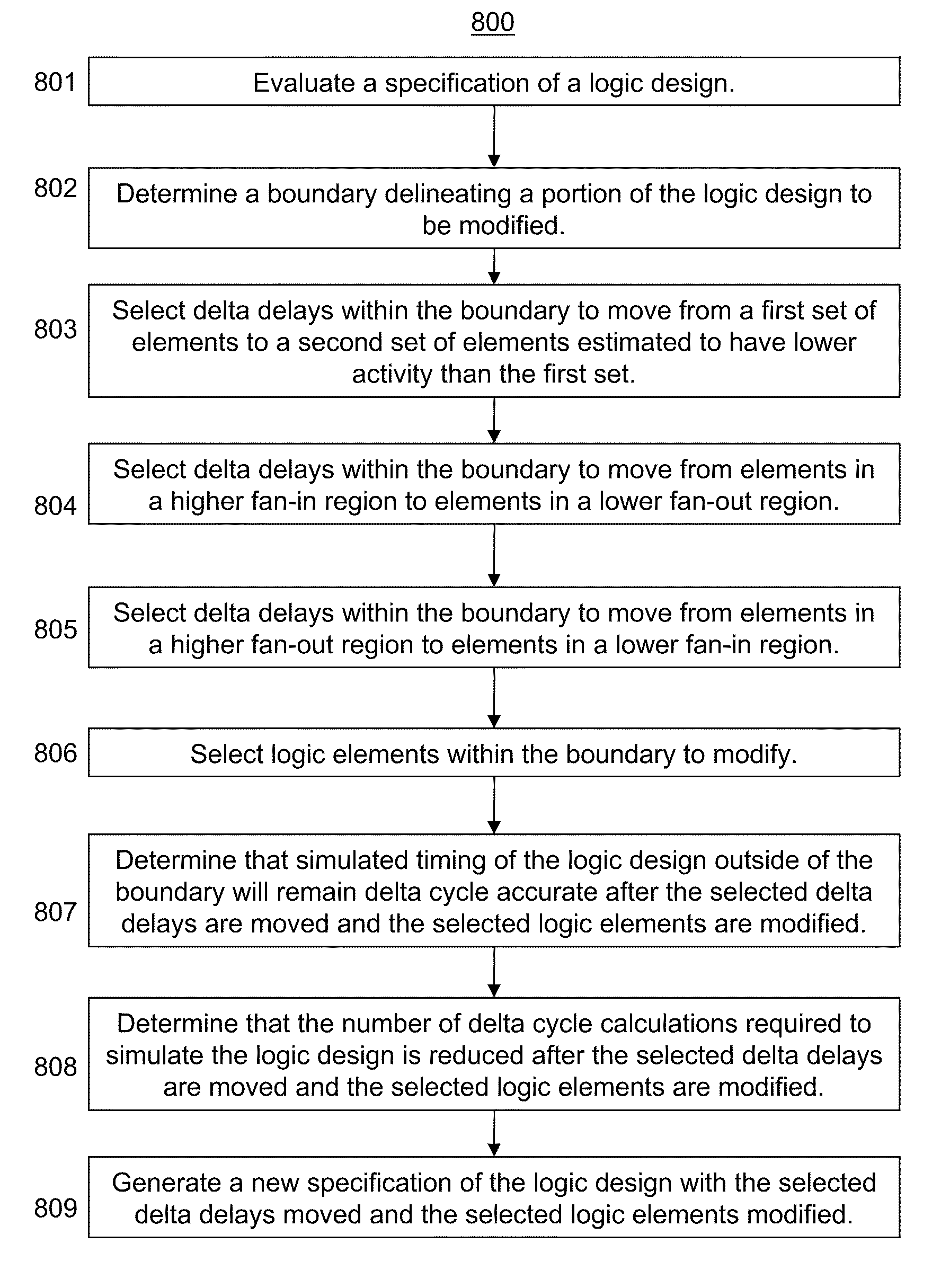

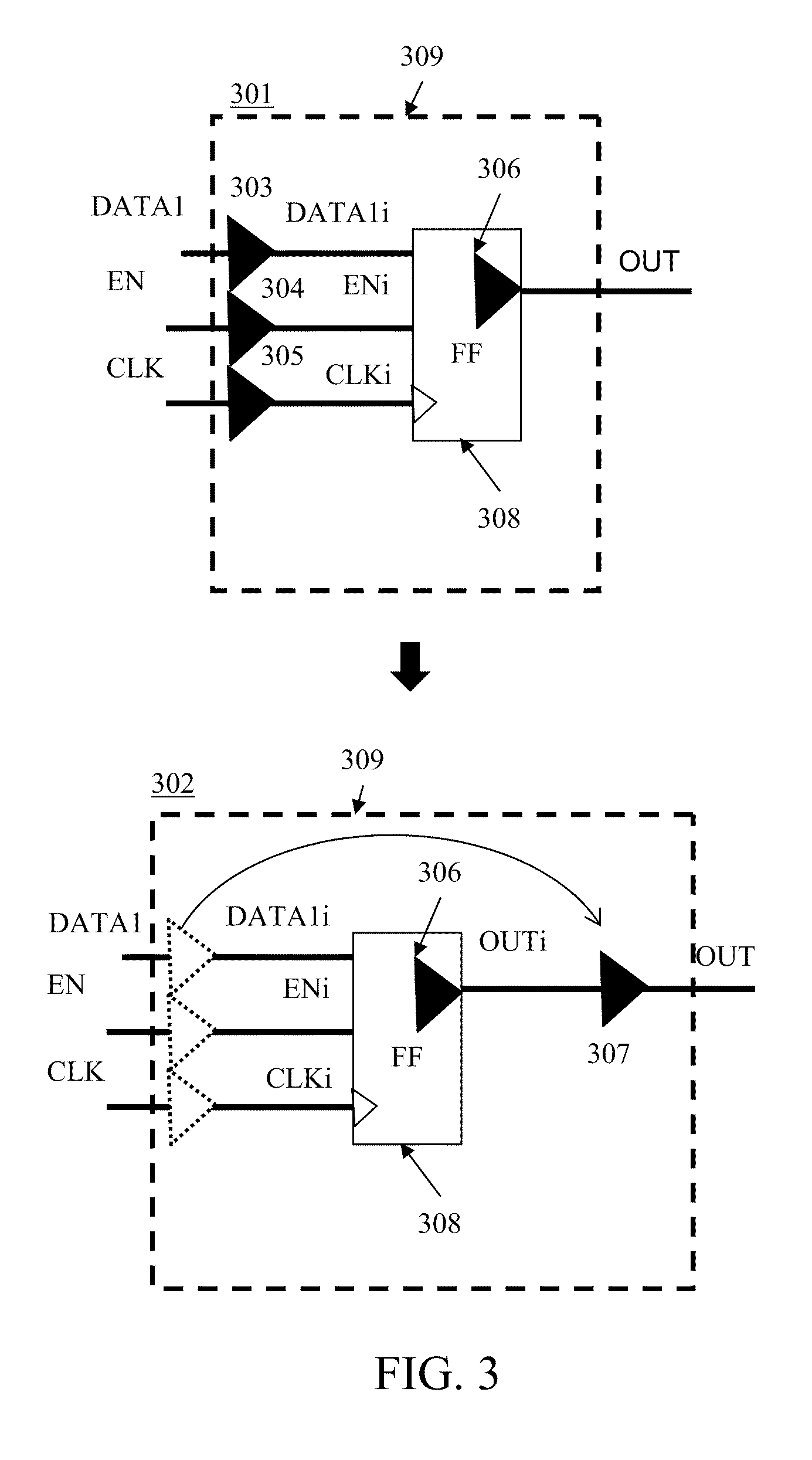

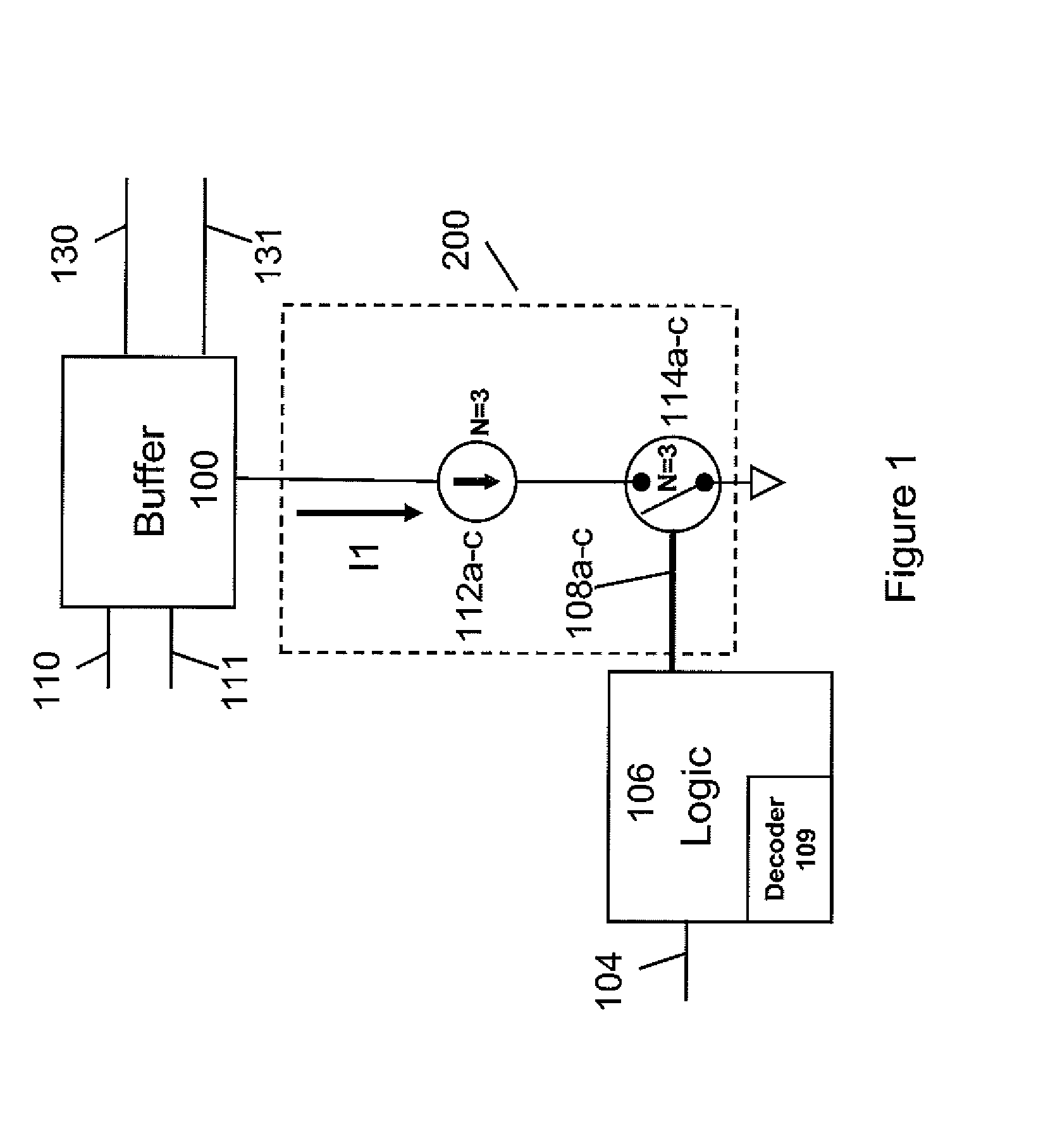

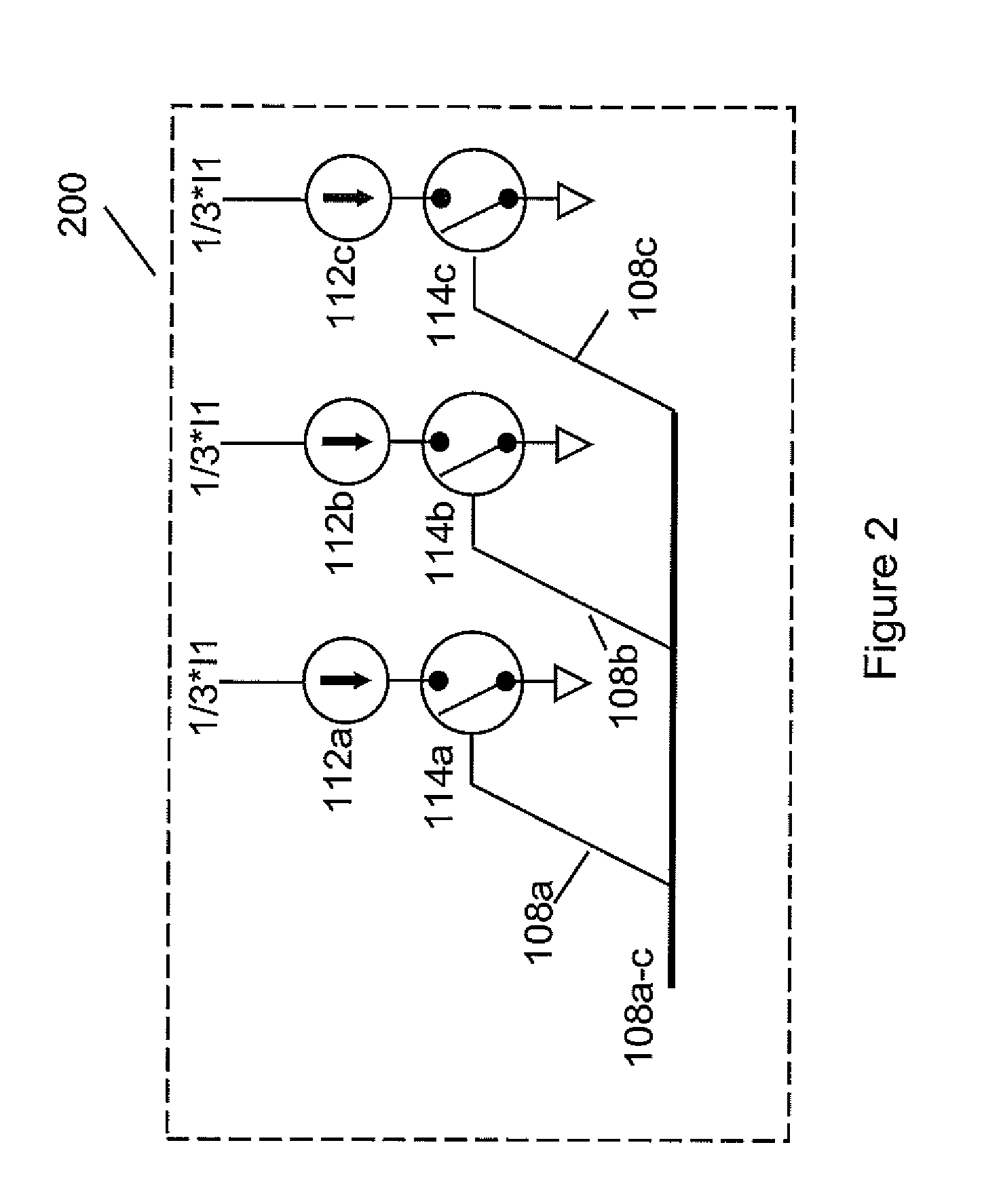

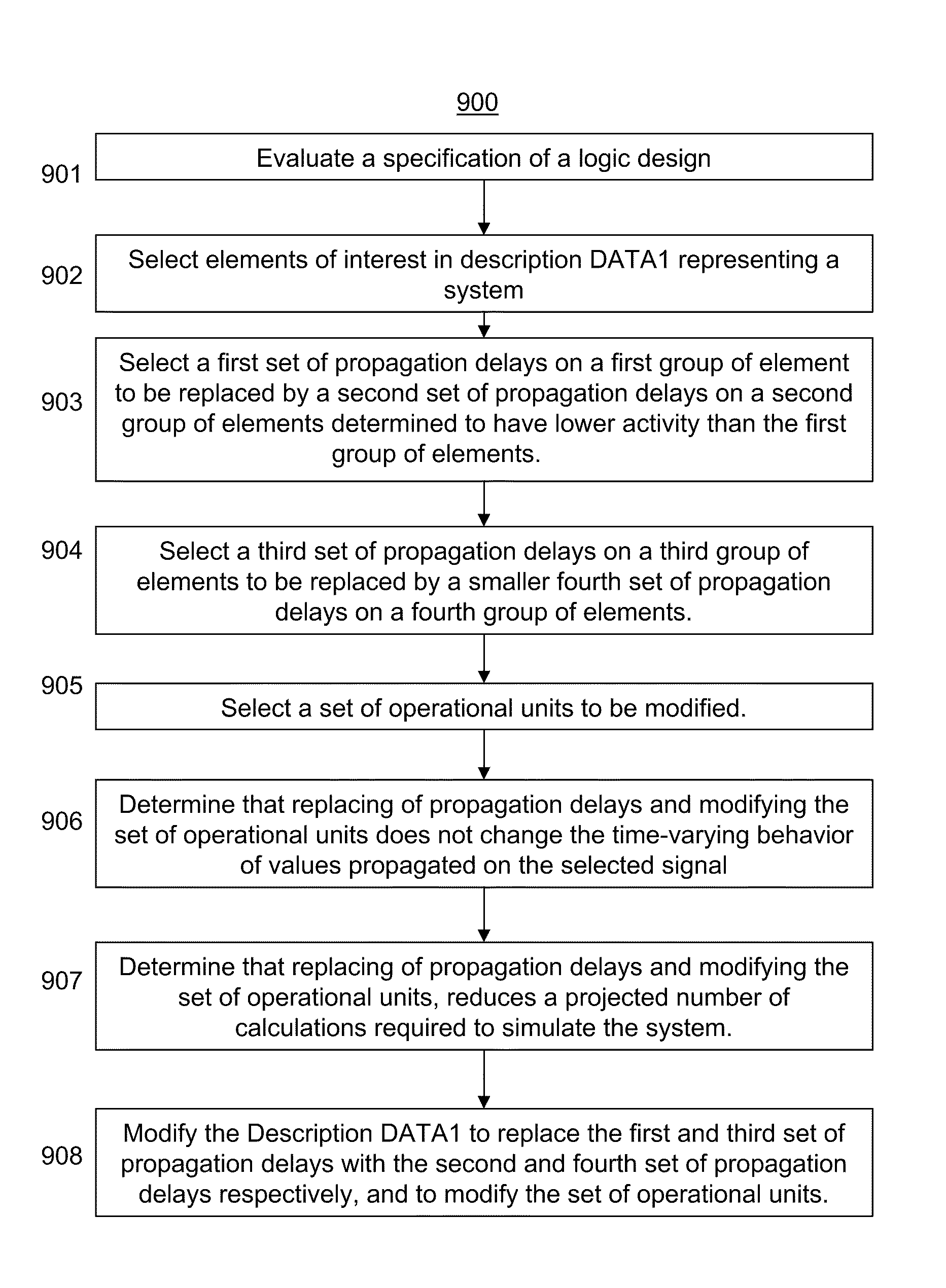

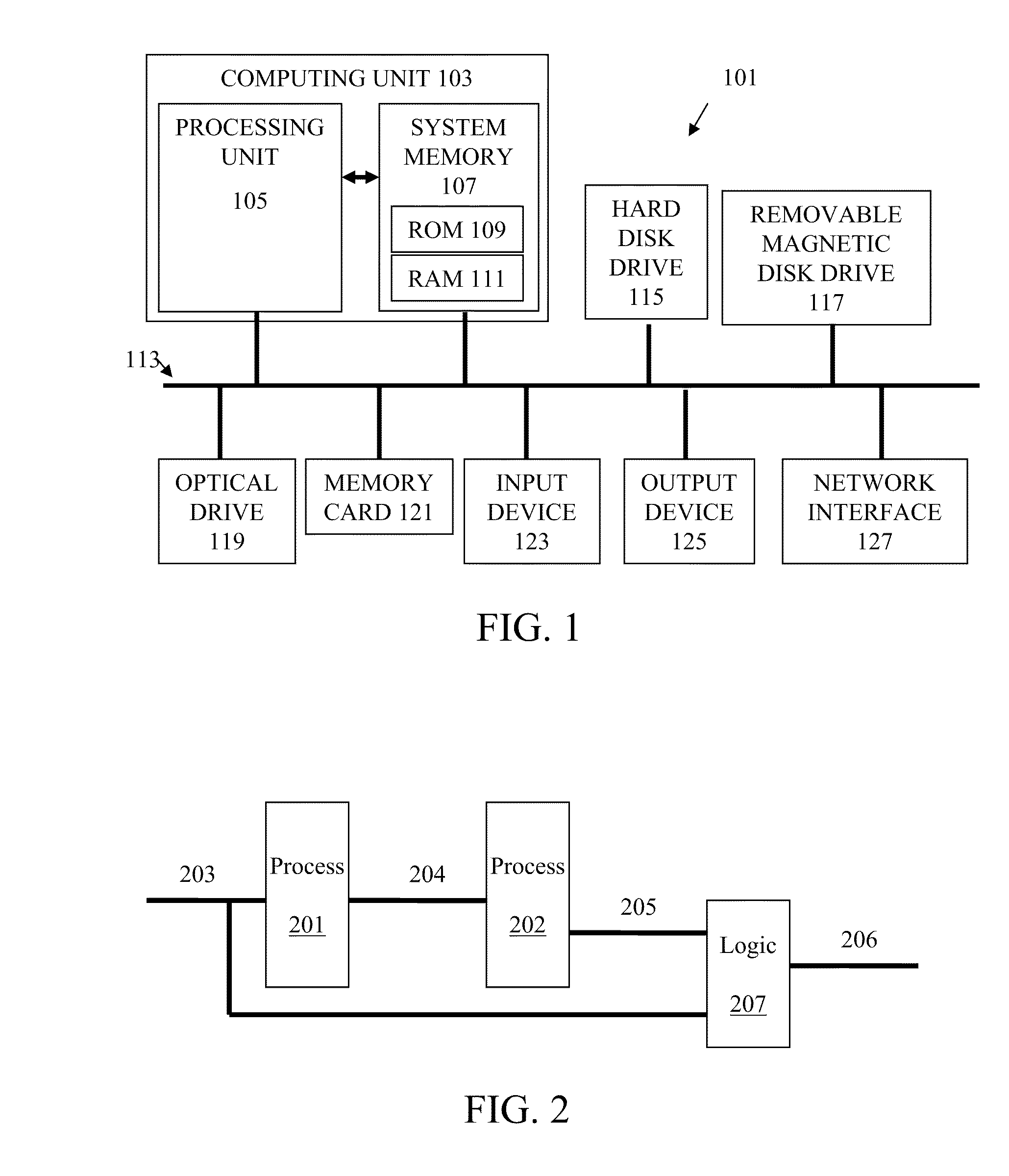

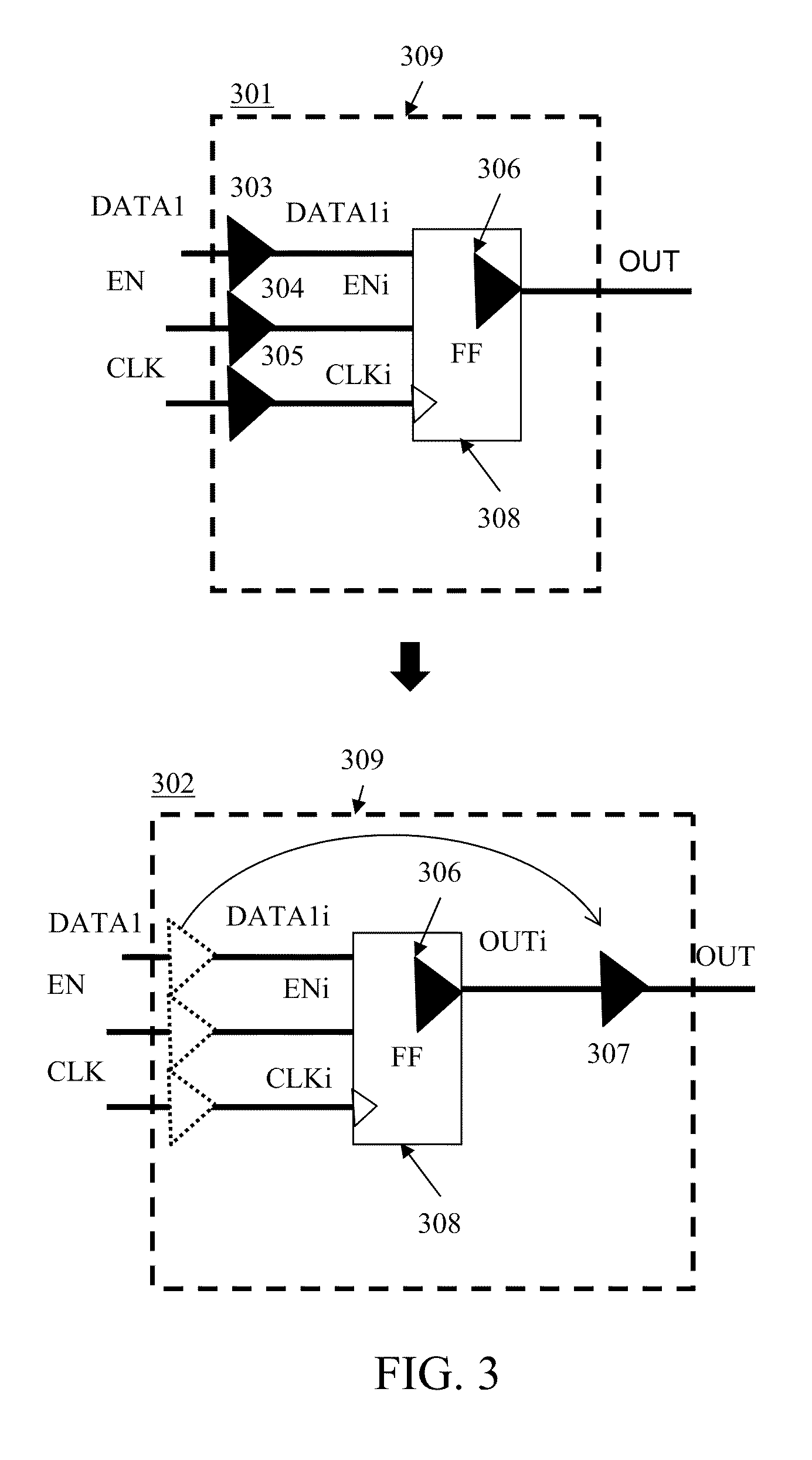

Delta retiming in logic simulation

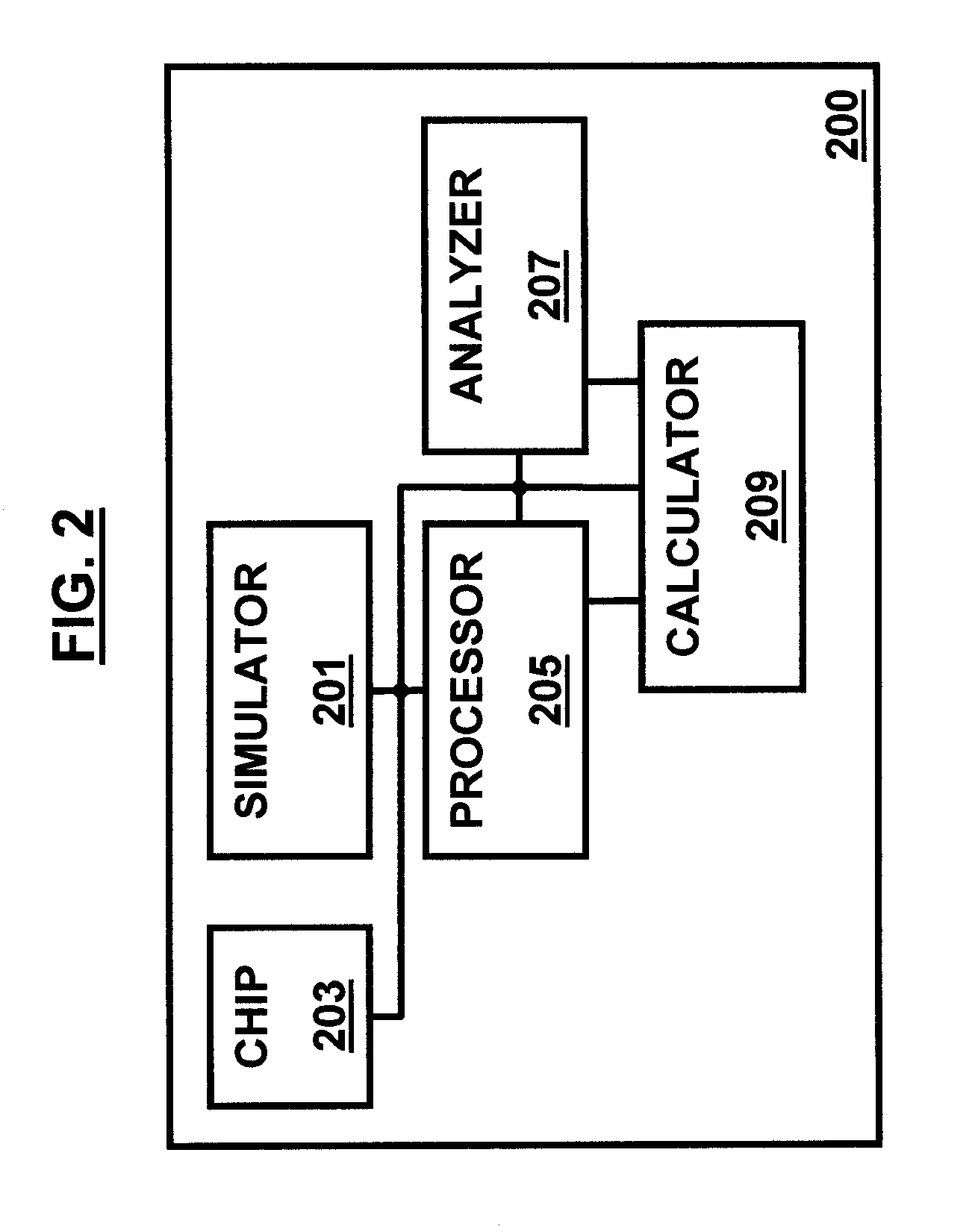

ActiveUS20110161066A1Reduce run time penaltyEfficient designAnalogue computers for electric apparatusDesign optimisation/simulationLow activityEngineering

Aspects of the present invention are directed to improving the speed of event-driven simulation by manipulating delta delays in a system model to reduce delta cycle executions. The manipulation is performed in a manner that preserves delta cycle accurate timing on selected signals of the system, which may be of interest to a designer. Methods and systems are provided for identifying the signals of interest, and for determining portions of the design that may have delta delays retimed. Preserving the timing on the signals of interest ensures that race conditions and glitches present in the design on the signals of interest are still viewable by the designer. To reduce simulation time, delta delays may be moved from high activity signals to low activity signals, the total number of delta delays may be reduced, or a number of processes executed may be reduced.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

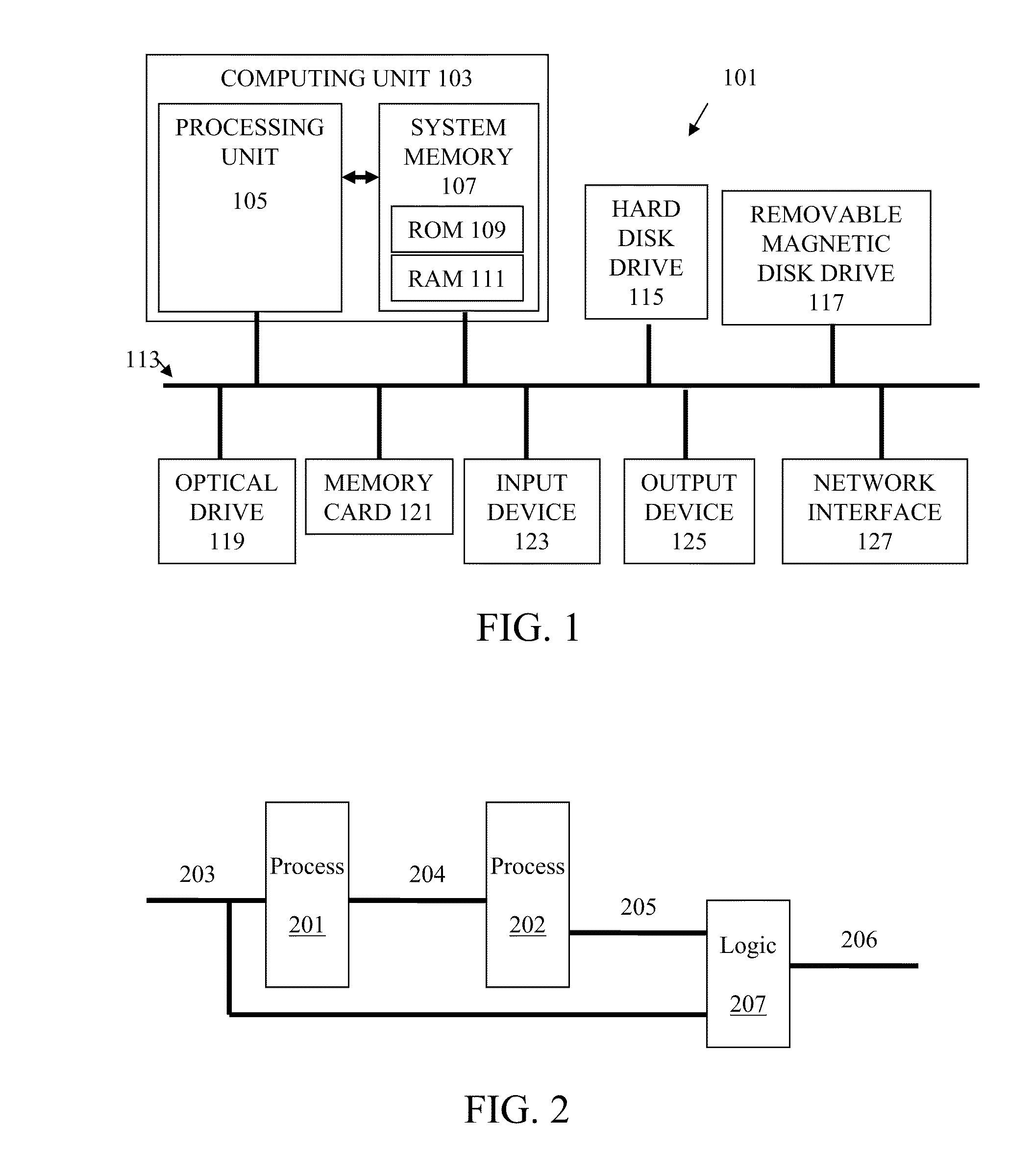

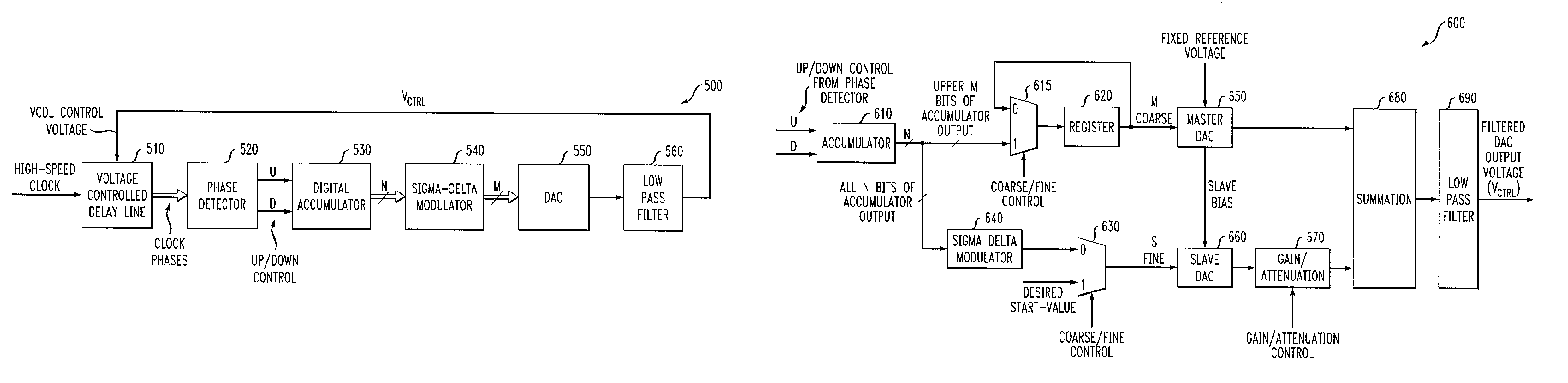

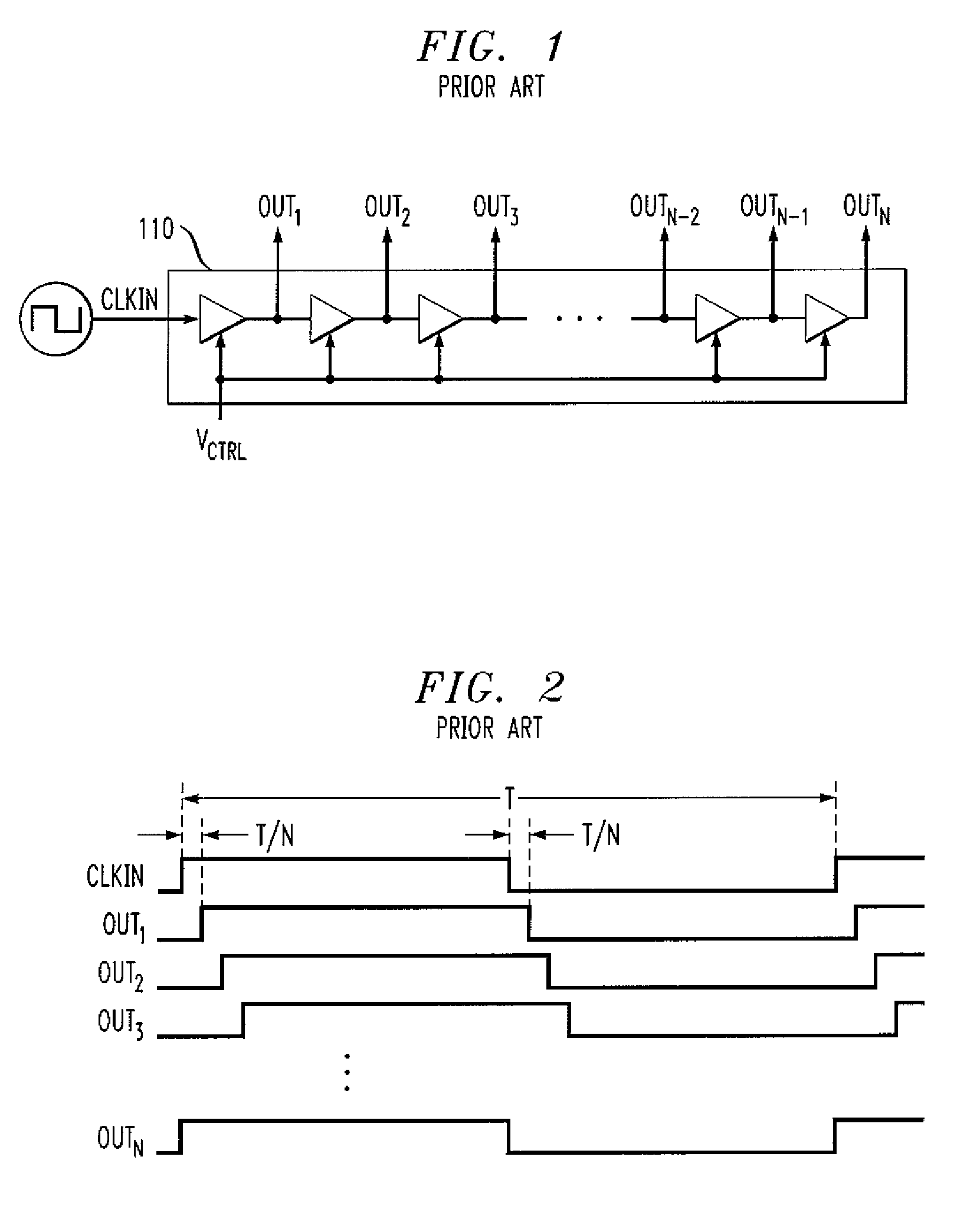

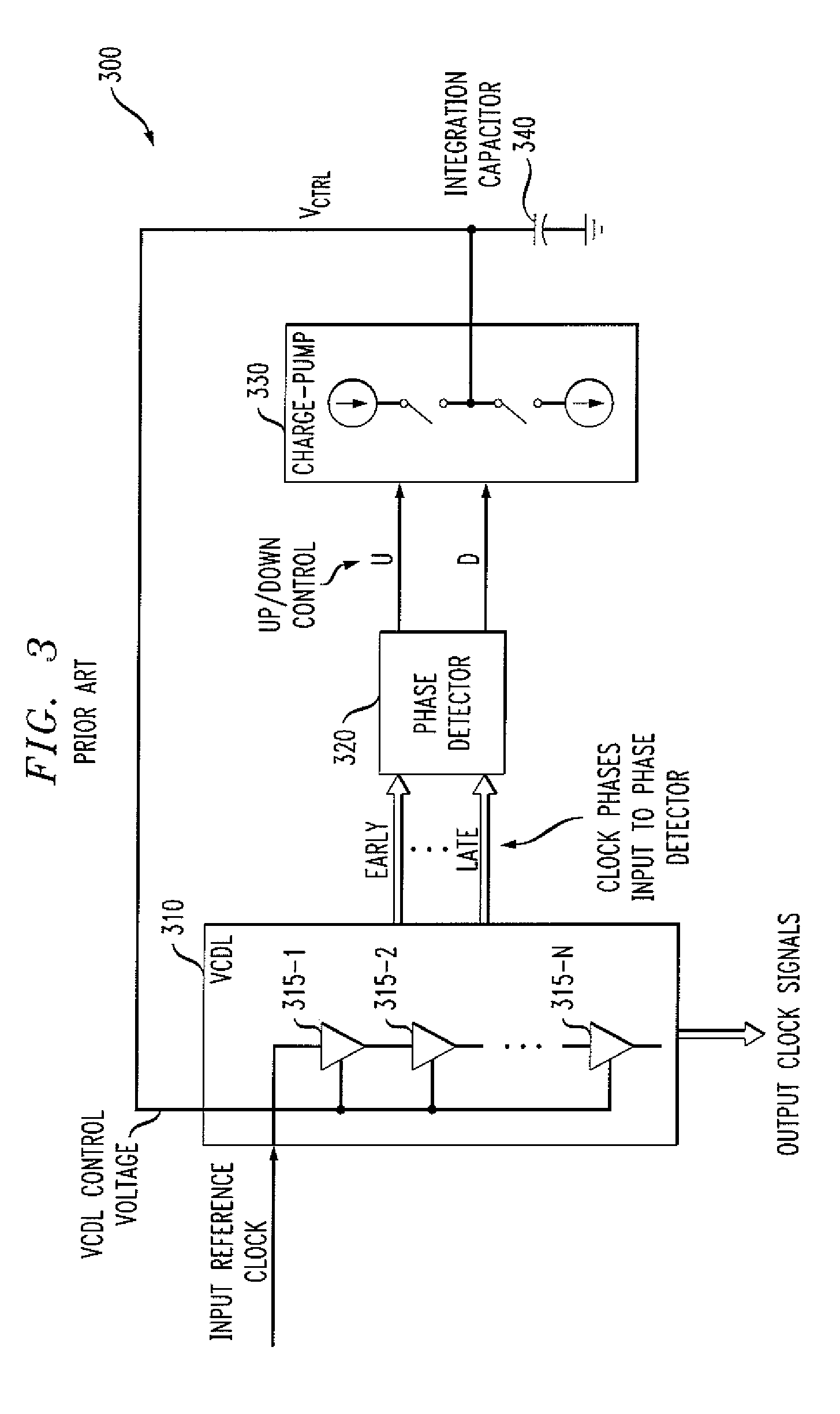

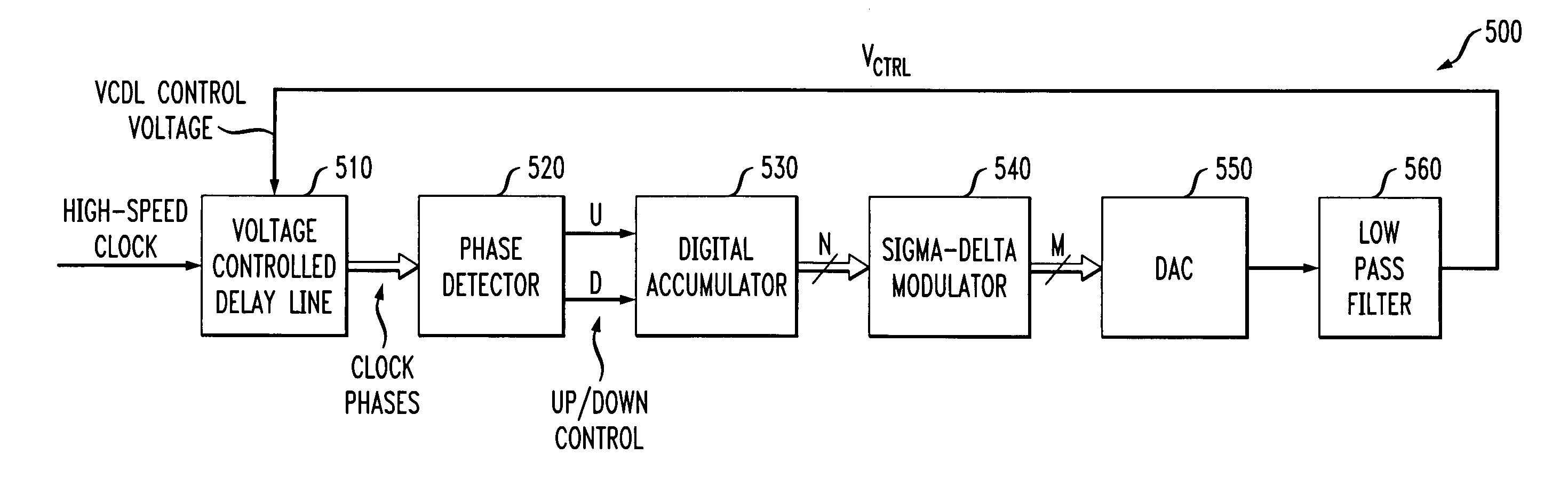

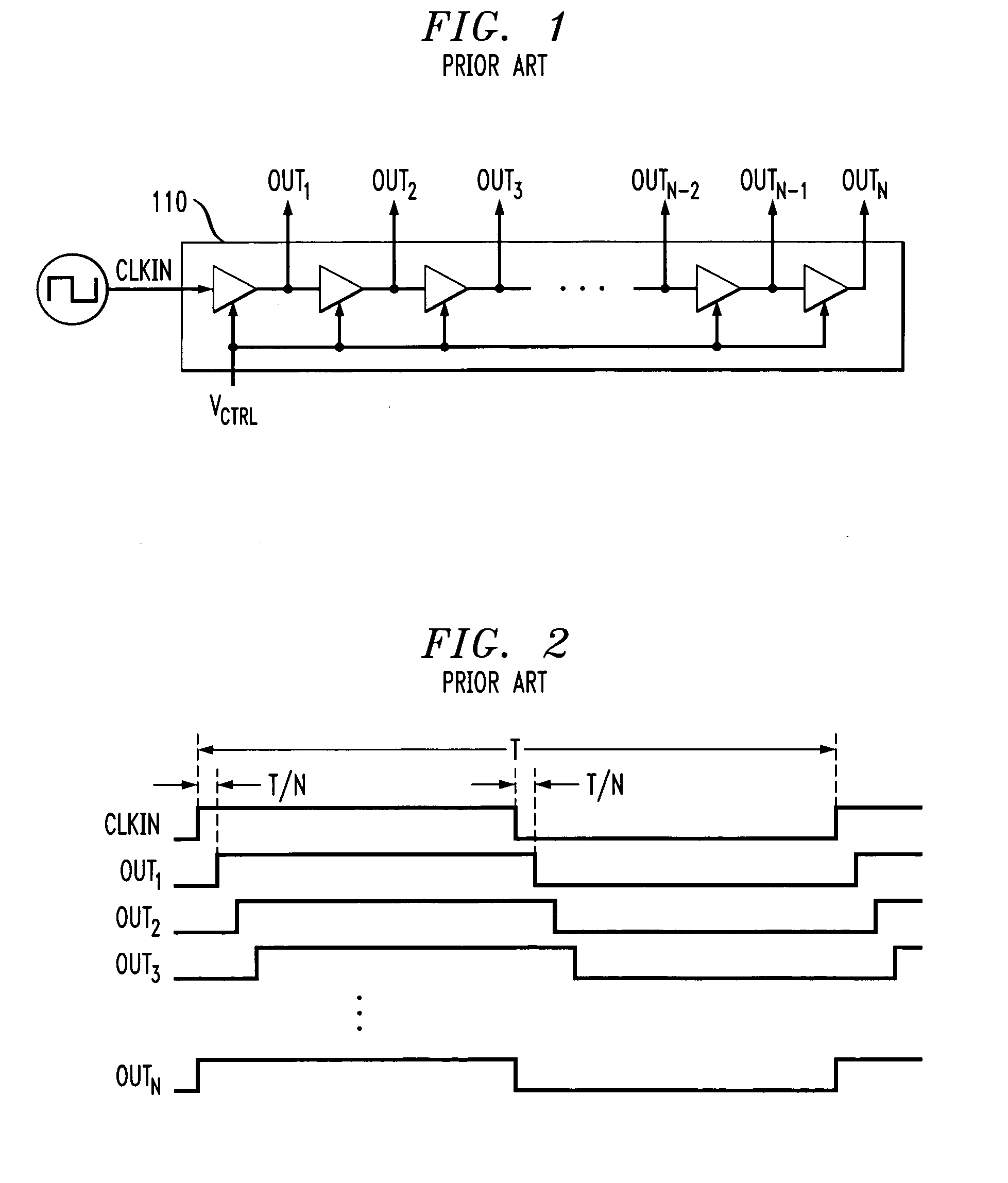

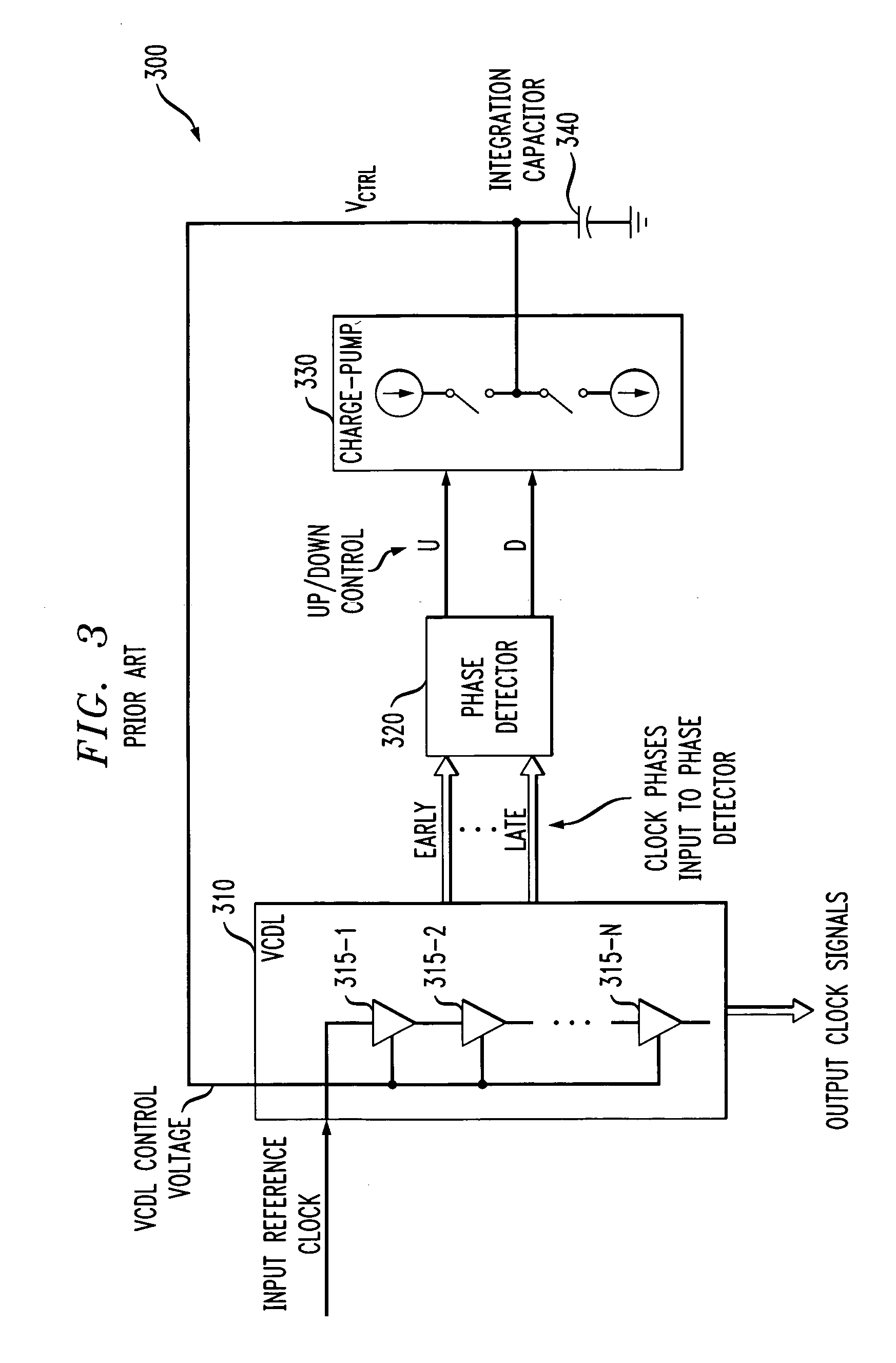

Method and apparatus for sigma-delta delay control in a delay-locked-loop

Methods and apparatus are provided for sigma-delta delay control in a Delay-Locked-Loop that employs a delay line to generate a clock signal based on a reference signal. A first value is generated if a clock signal has a time lead relative to a reference signal; and a second value is generated if a clock signal has a time lag relative to a reference signal. The first and second values are accumulated to generate an N bit digital word; and the N bit digital word is reduced to an M bit digital word, where M is less than N. Thereafter, the M bit digital word can be converted to an analog bias signal. The reducing step can be performed, for example, by a sigma-delta modulator. The high frequency quantization noise generated by the sigma-delta modulator can be filtered using a low pass filter. The converting step can be performed by a digital-to-analog converter, such as a master / slave digital-to-analog converter.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Method and apparatus for sigma-delta delay control in a Delay-Locked-Loop

Methods and apparatus are provided for sigma-delta delay control in a Delay-Locked-Loop that employs a delay line to generate a clock signal based on a reference signal. A first value is generated if a clock signal has a time lead relative to a reference signal; and a second value is generated if a clock signal has a time lag relative to a reference signal. The first and second values are accumulated to generate an N bit digital word; and the N bit digital word is reduced to an M bit digital word, where M is less than N. Thereafter, the M bit digital word can be converted to an analog bias signal. The reducing step can be performed, for example, by a sigma-delta modulator. The high frequency quantization noise generated by the sigma-delta modulator can be filtered using a low pass filter. The converting step can be performed by a digital-to-analog converter, such as a master / slave digital-to-analog converter.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

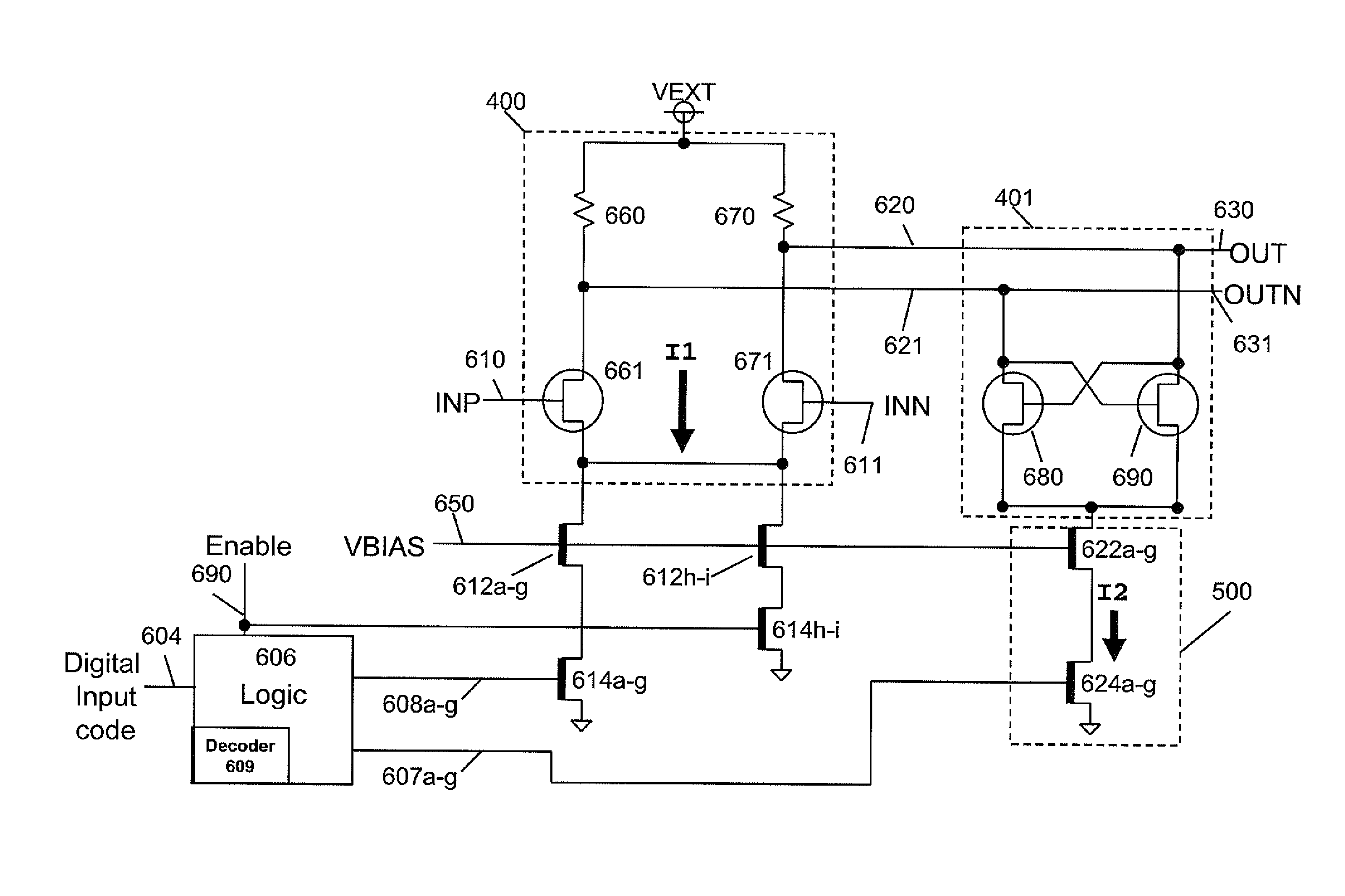

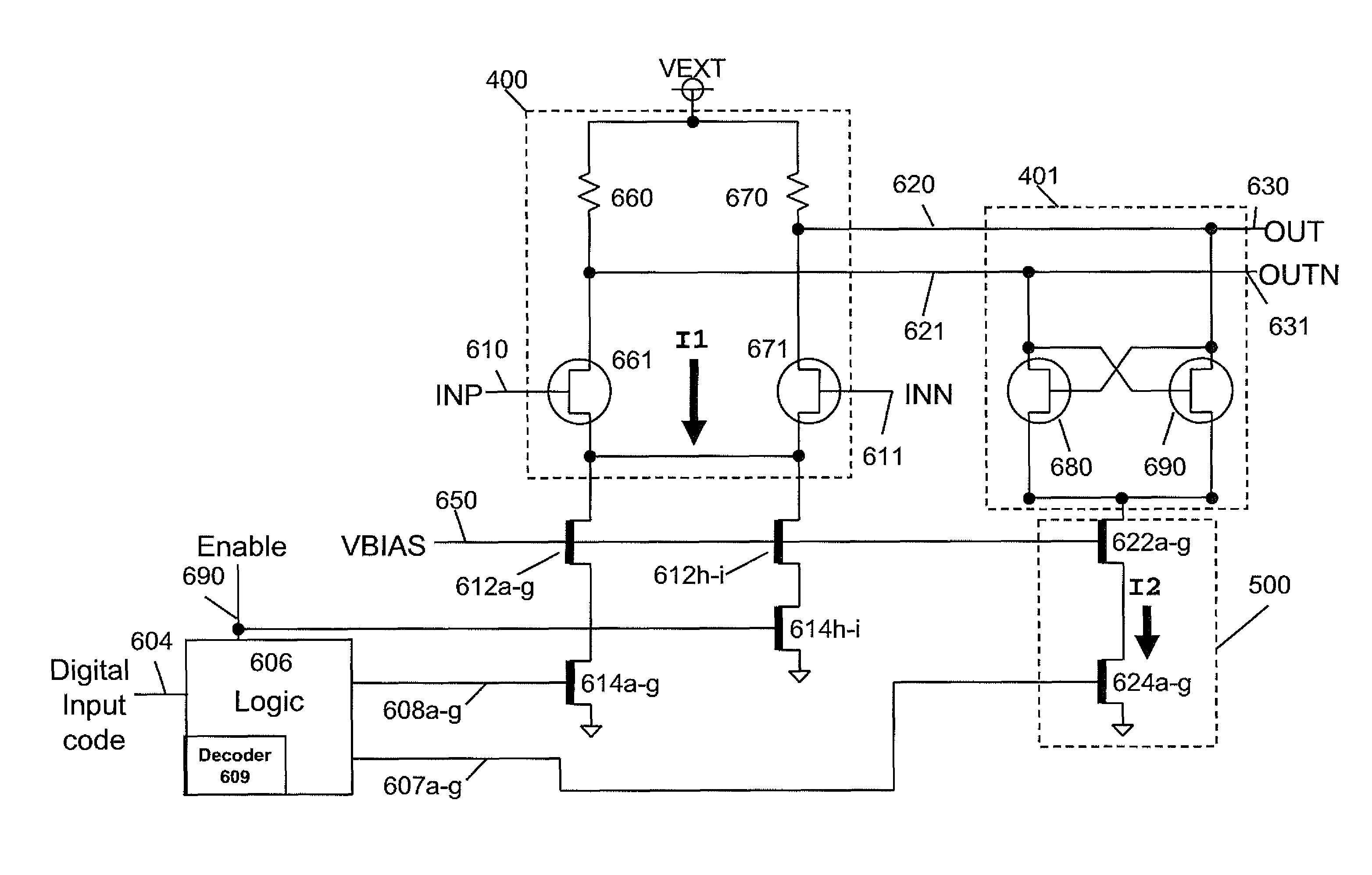

Digitally Controlled CML Buffer

Techniques and corresponding circuits for achieving programmable delay of a current mode logic delay buffer are provided. The techniques provide for incremental delay with substantially equal increments Delay may be achieved through the use of a circuit arrangement that allows biasing current to be controlled effect the response time of the circuit by digital control.

Owner:POLARIS INNOVATIONS

Delta retiming in logic simulation

ActiveUS8346529B2Reduce run time penaltyEfficient designAnalogue computers for electric apparatusAnalogue computers for nuclear physicsLow activitySignal of interest

Aspects of the present invention are directed to improving the speed of event-driven simulation by manipulating delta delays in a system model to reduce delta cycle executions. The manipulation is performed in a manner that preserves delta cycle accurate timing on selected signals of the system, which may be of interest to a designer. Methods and systems are provided for identifying the signals of interest, and for determining portions of the design that may have delta delays retimed. Preserving the timing on the signals of interest ensures that race conditions and glitches present in the design on the signals of interest are still viewable by the designer. To reduce simulation time, delta delays may be moved from high activity signals to low activity signals, the total number of delta delays may be reduced, or a number of processes executed may be reduced.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

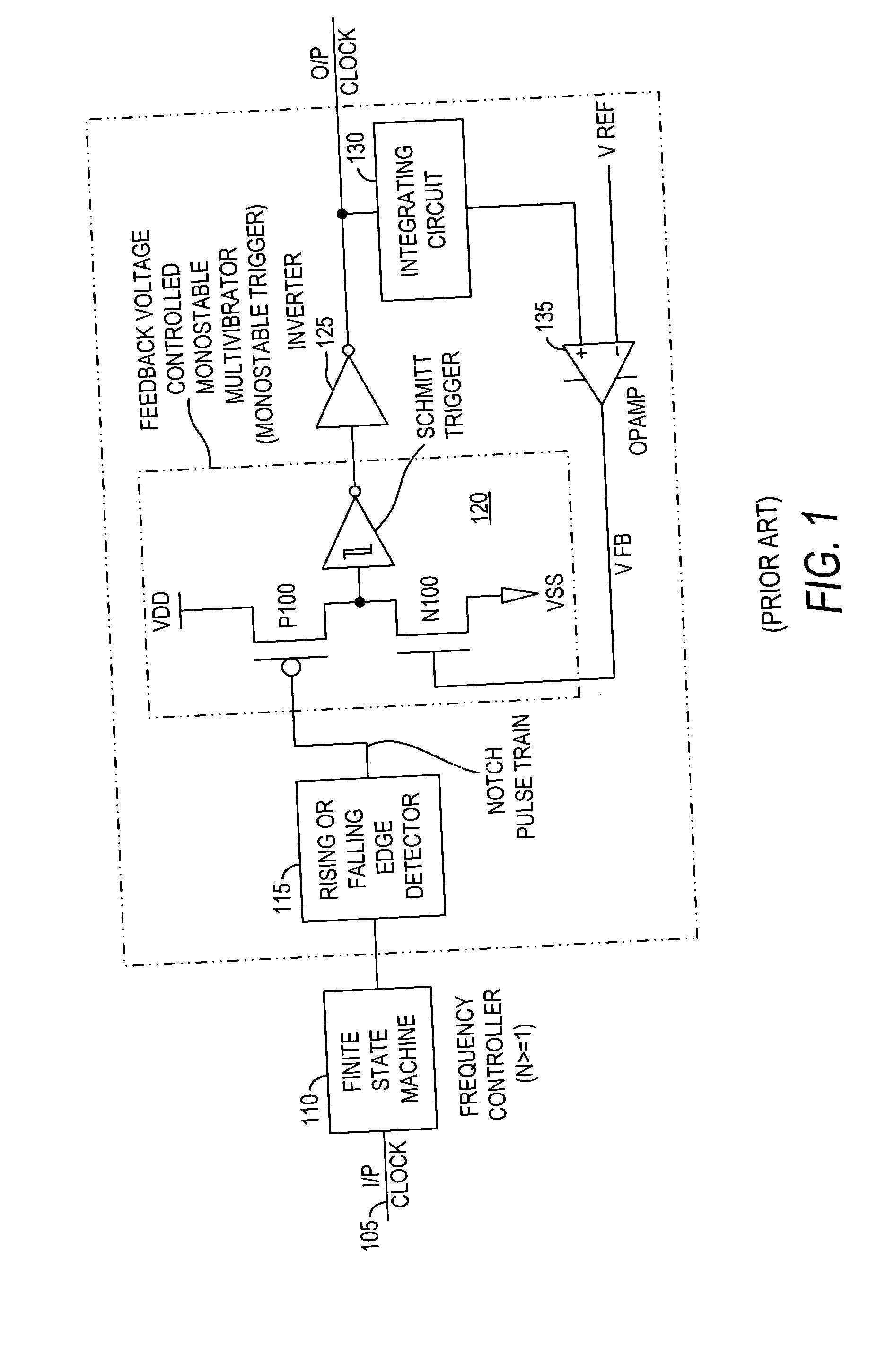

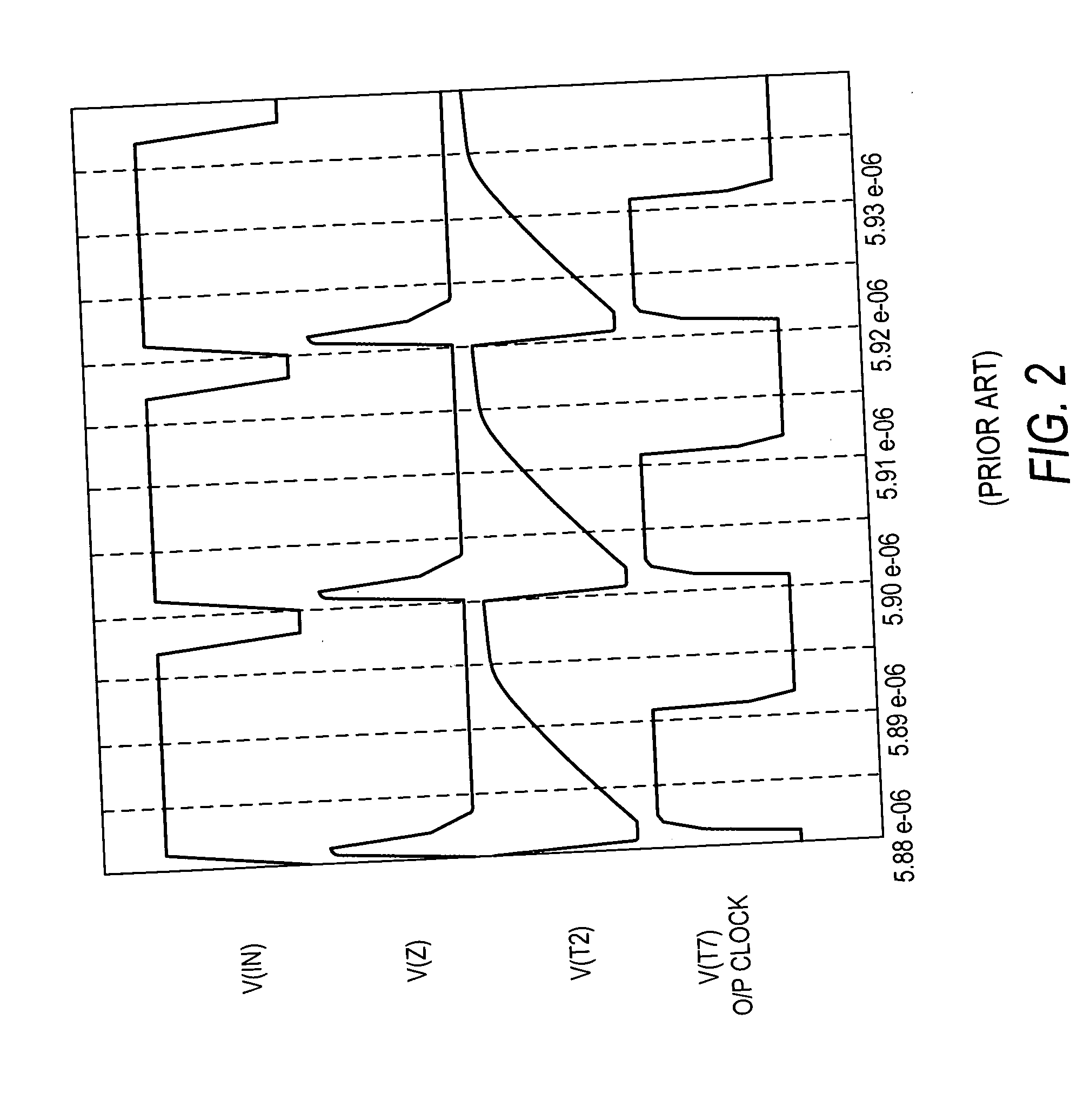

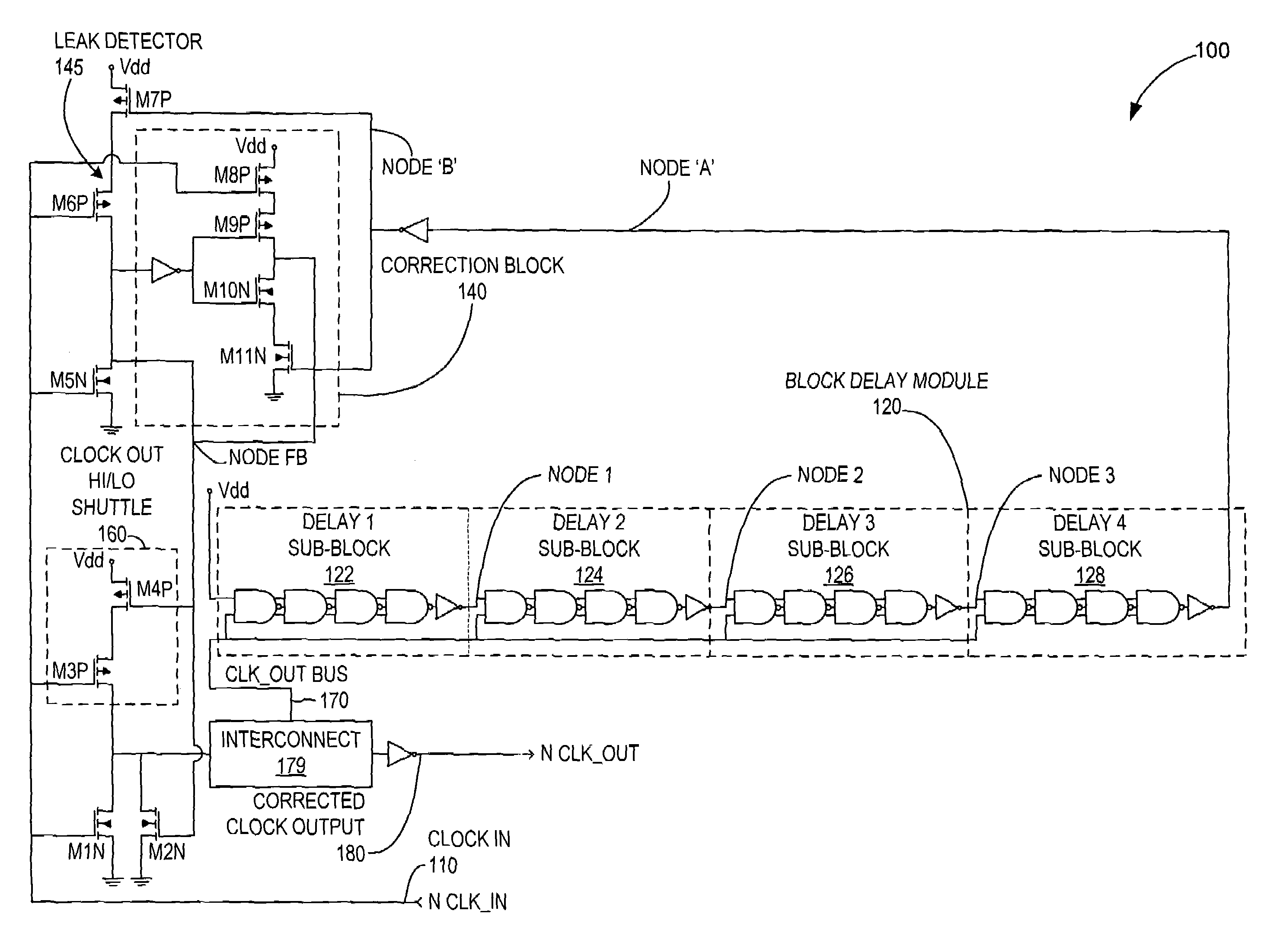

Simplified method for limiting clock pulse width

InactiveUS20050091620A1Continuous to patterned pulse manipulationElectric pulse generatorTotal delayEngineering

The present invention provides for correcting excessive pulse widths using incremental delays. The pulse width is evaluated through a correction block and leak detector. An acceptable pulse passes through an interconnect directly to the clock output. Unacceptable pulses are sent through a block delay module that incorporates a series of delay sub-blocks that disconnect and reset in accordance with a pre-programmed total delay time. The conditioned clock pulse is resent through a node to the correction block and leak detector where it is reevaluated. If the pulse is acceptable, it is sent to the clock output. If the pulse is found unacceptable, it is recycled again. A high low clock pulse shuttle determines and alters the high or low state of the clock pulse to ensure a correct output to downstream dependent devices.

Owner:GOOGLE LLC

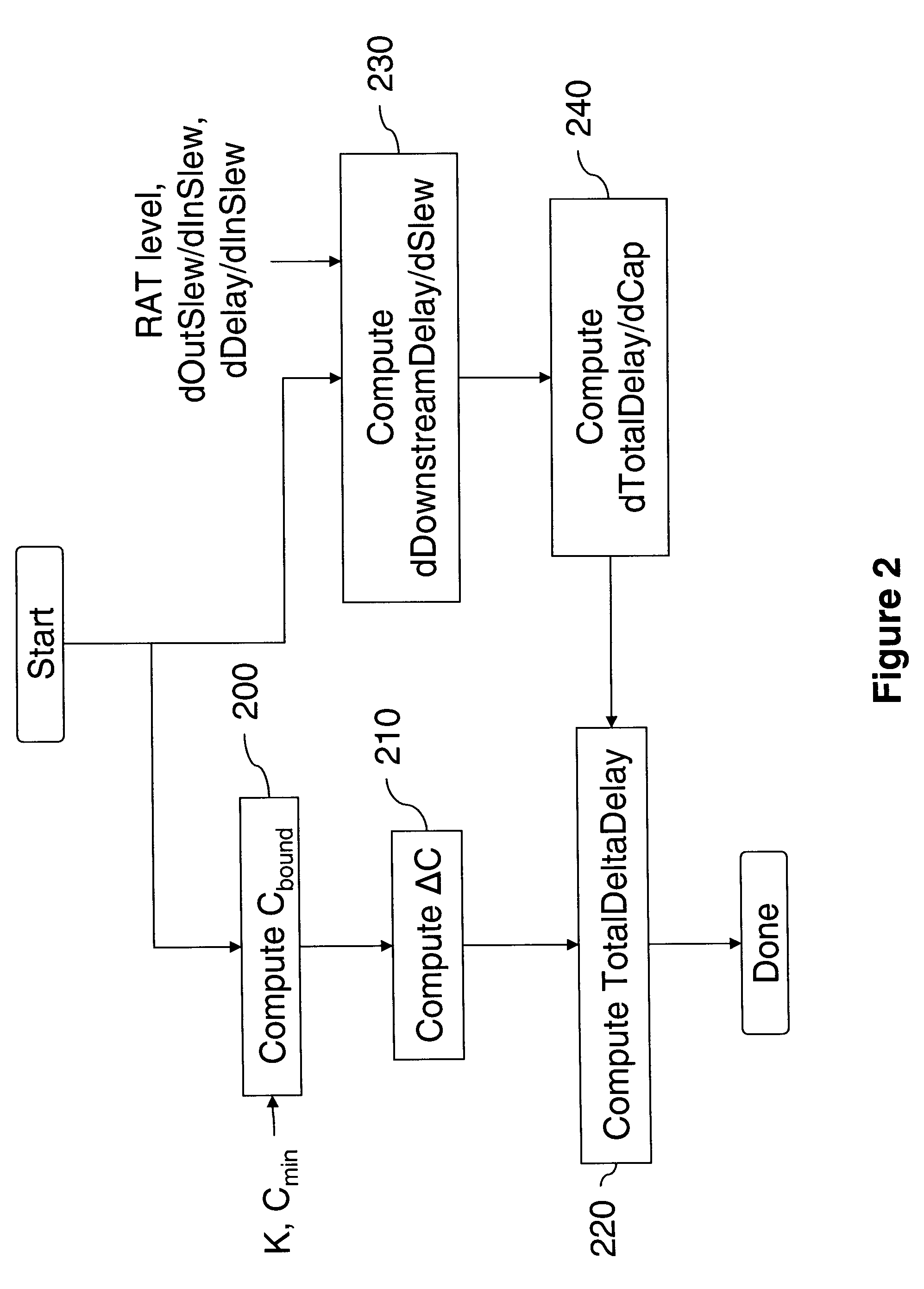

Method for optimizing an unrouted design to reduce the probability of timing problems due to coupling and long wire routes

InactiveUS20090132982A1Decreasing TotalDeltaDelayEasy to relaxCAD circuit designSoftware simulation/interpretation/emulationCapacitanceCoupling

A method and a system is described to predict effects of coupling on timing by estimating the delta delay and delta slack that can occur due to coupling on any net, for optimization to minimize the sensitivity of slack to potential coupling violations. The invention protects against other unexpected increases in effective load capacitance, such as those due to unexpectedly long wire routes. It also estimates the delay impact of a single ‘fault’ or ‘event’, such as a coupling event or unexpectedly long wires routes, including the impact of slew propagation.

Owner:GLOBALFOUNDRIES INC

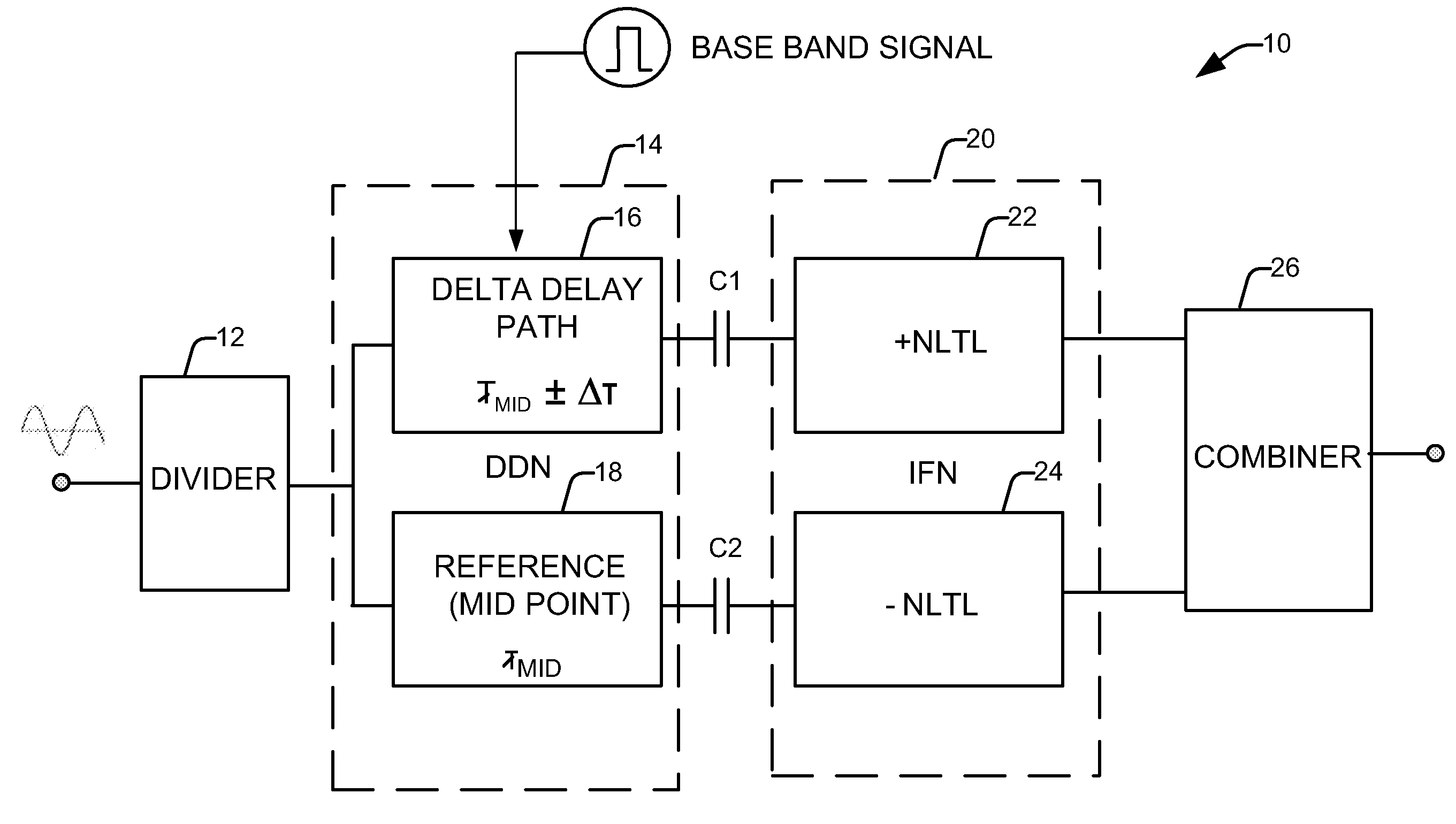

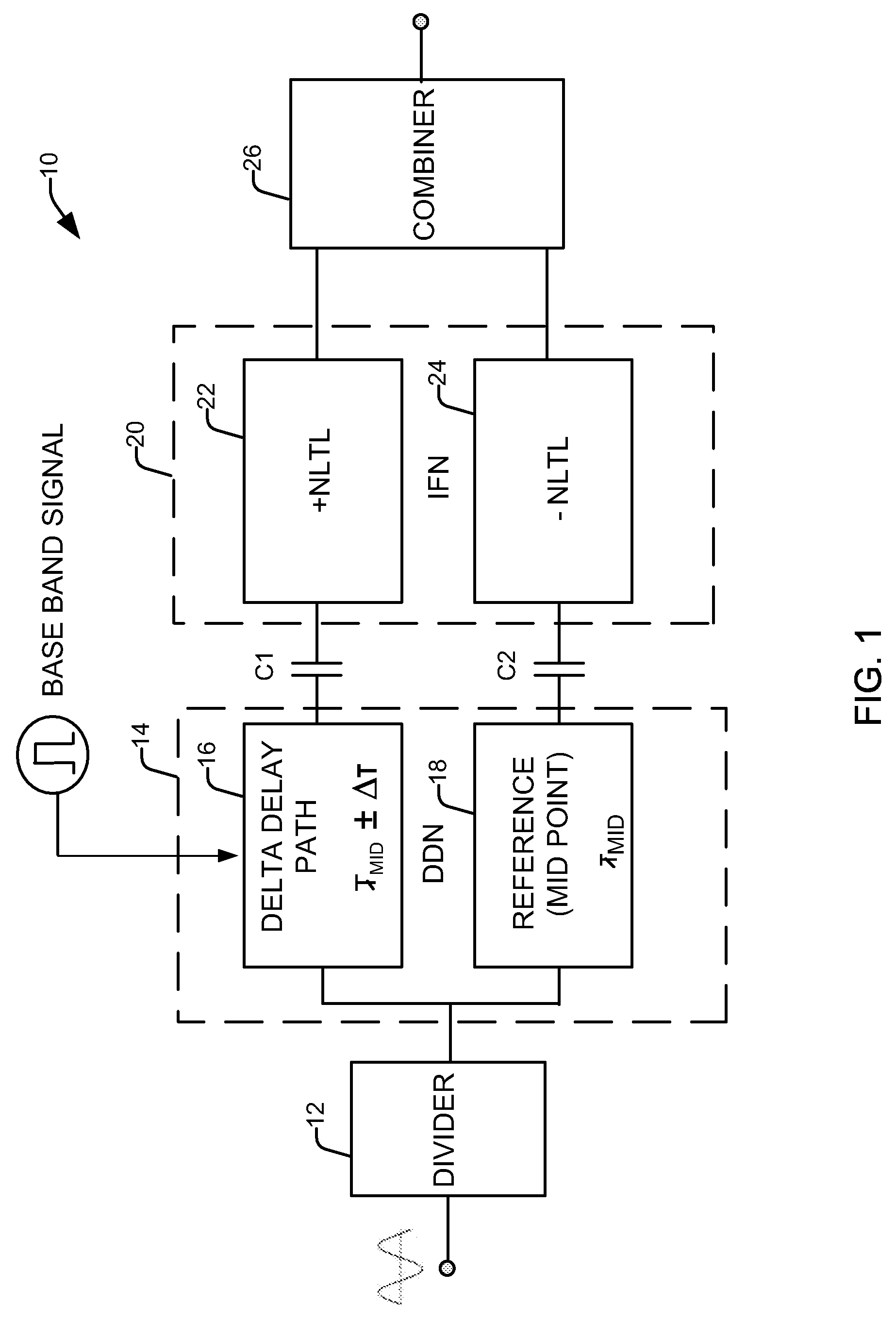

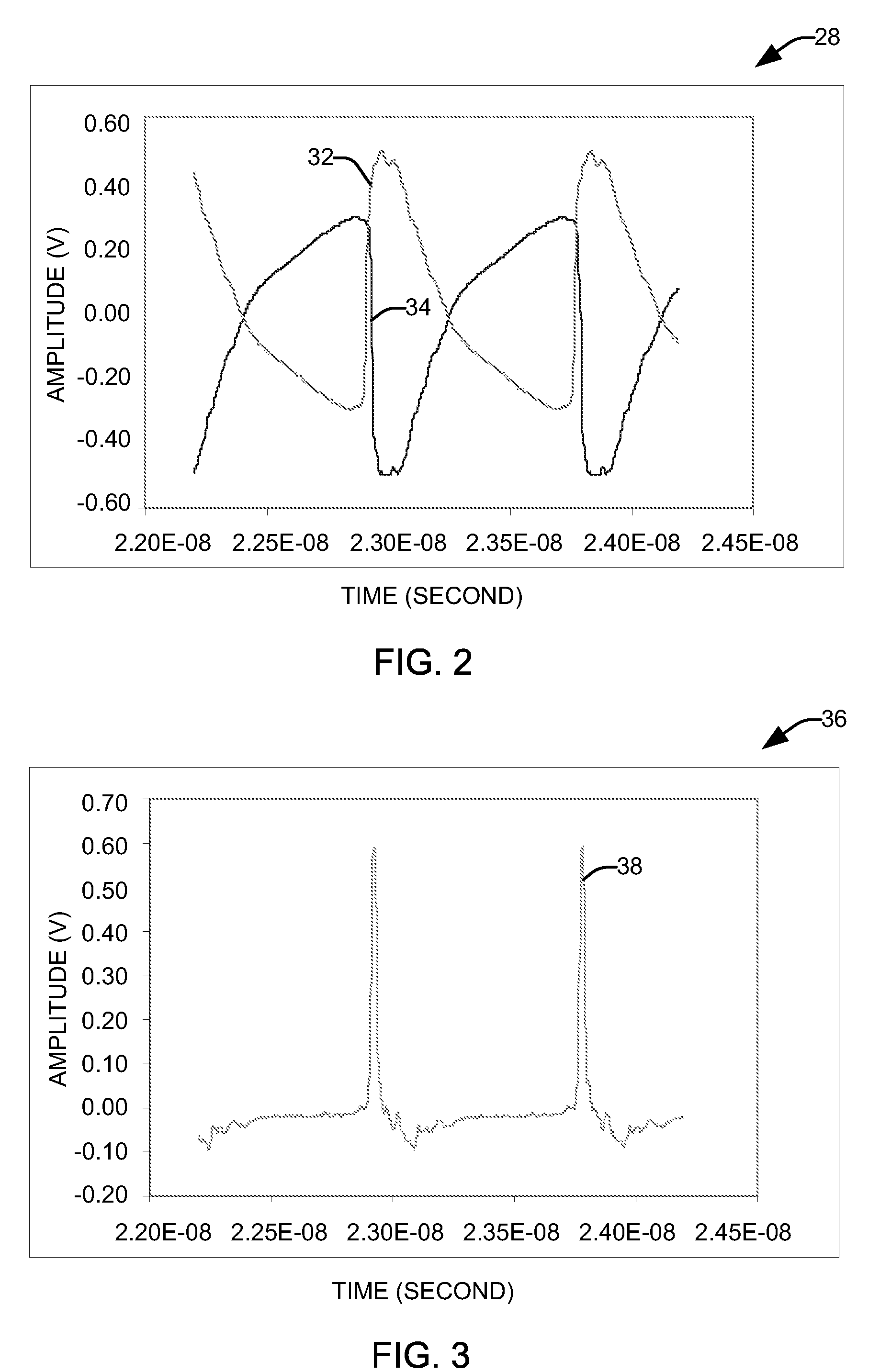

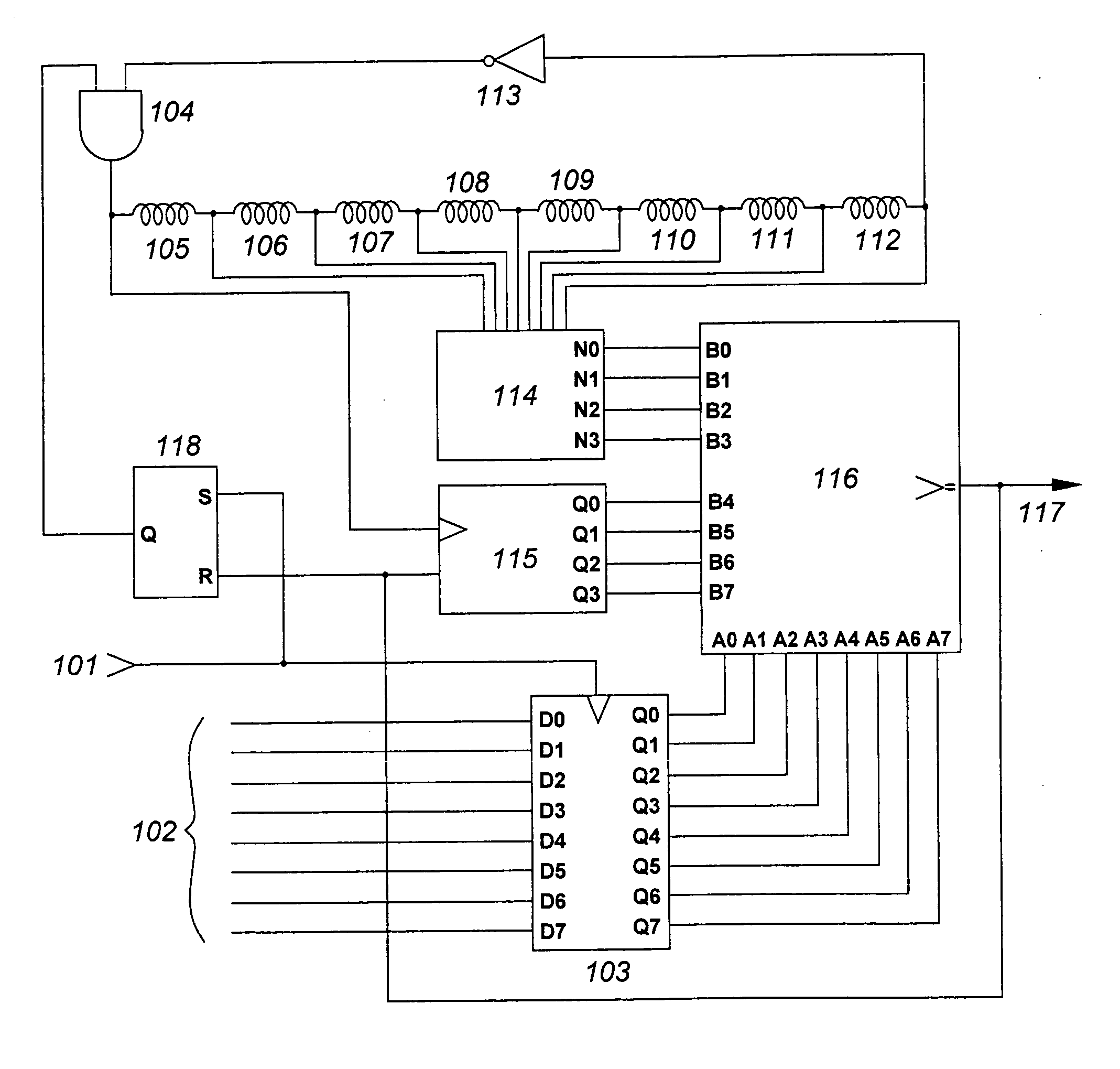

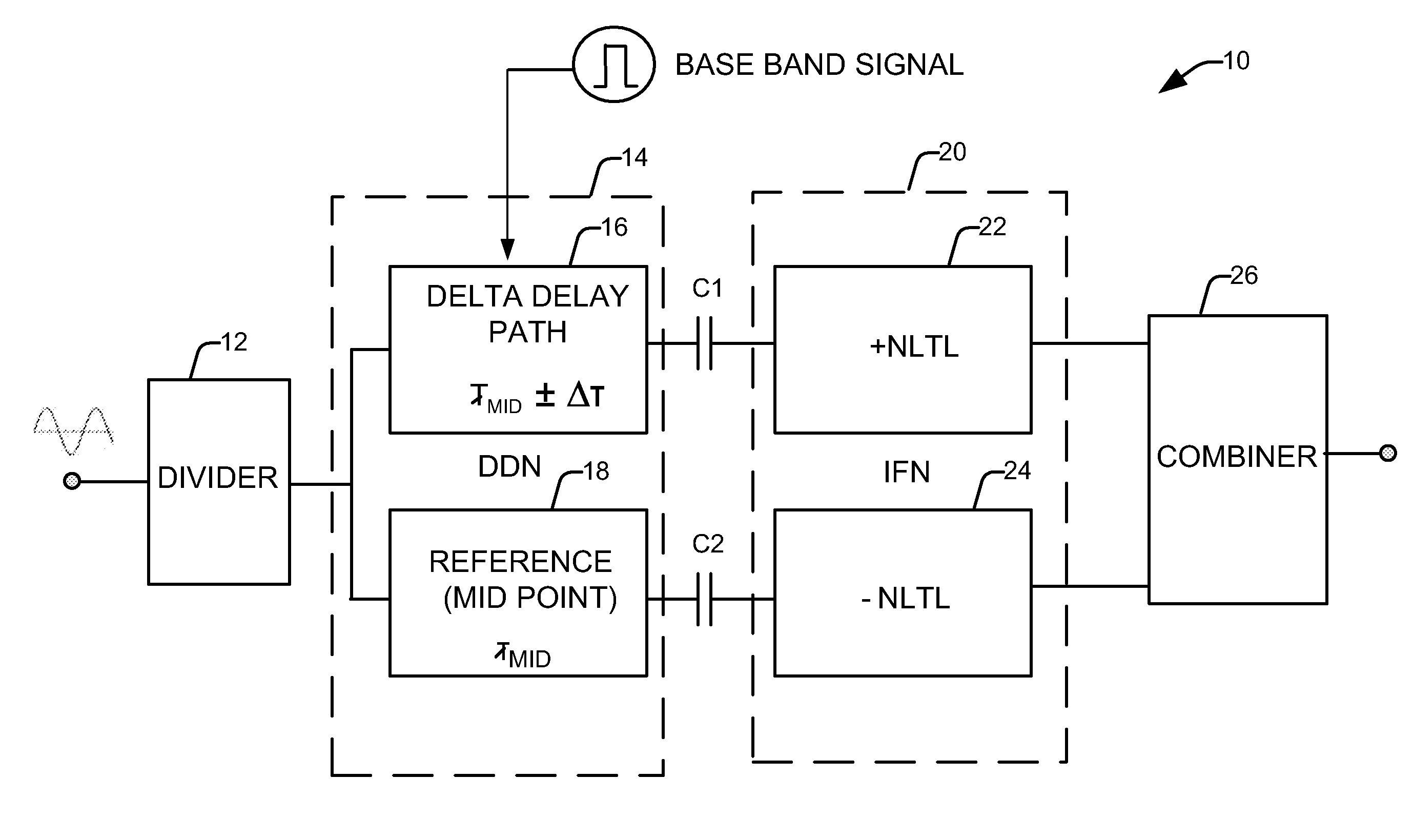

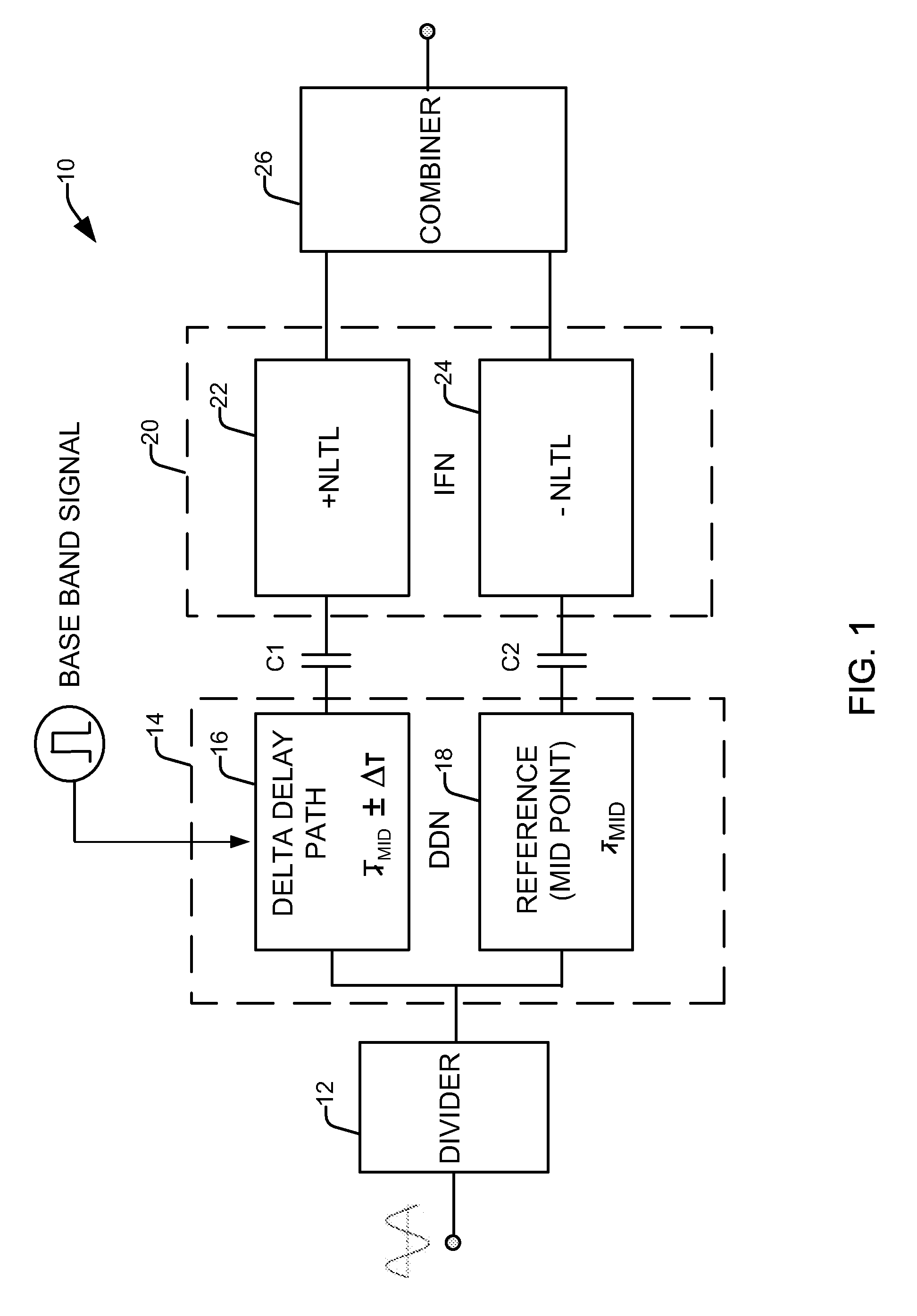

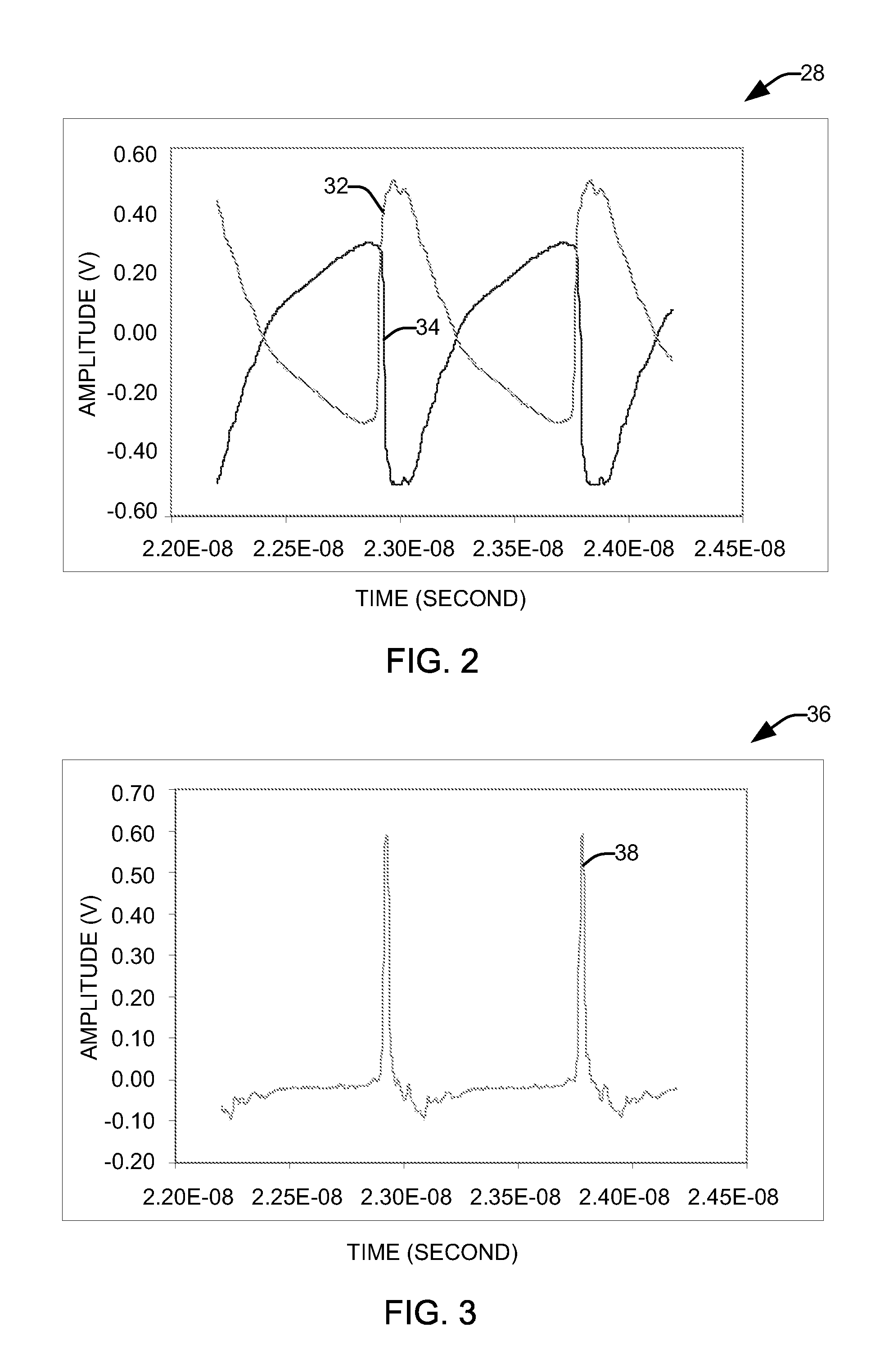

Nonlinear transmission line modulator

ActiveUS7733194B2Transmission control/equlisationPulse duration/width modulationPulse forming networkPower combiner

A modulator is provided that comprises a nonlinear transmission line (NLTL) that is bias modulated by a baseband signal. A given logic state of the baseband signal determines a delay amount of a first carrier signal through the NLTL. The modulator further comprises an impulse forming network (IFN) that includes a first NLTL that receives the first carrier signal delayed by the determined delay amount and a second NLTL that receives a second carrier signal having a fixed delay amount. The first NLTL and second NLTL within the IFN have opposite diode polarity configurations. The modulator further comprises a power combiner that converts a delta delay of the first carrier signal relative to the second carrier signal to a sharp impulse that represents the given logic state of the baseband signal.

Owner:NORTHROP GRUMMAN SYST CORP

Synchronous delay-line amplification technique

ActiveUS20060077011A1Digital data processing detailsAmplifier with semiconductor-devices/discharge-tubesAudio power amplifierEngineering

An open-loop switching amplifier achieves synchronous operation using a ring oscillator based upon a tapped delay line. A counter is clocked from the ring oscillator, periodically comparing incoming more significant data to the value of the counter to form a pulsewidth modulated output waveform. Modulating the effective width of the output waveform in incremental delay line taps is equivalent to incoming less significant data. This technique then effects time-period summation of coarse and fine resolution clocked data.

Owner:JM MGMT GRP LTD LLC

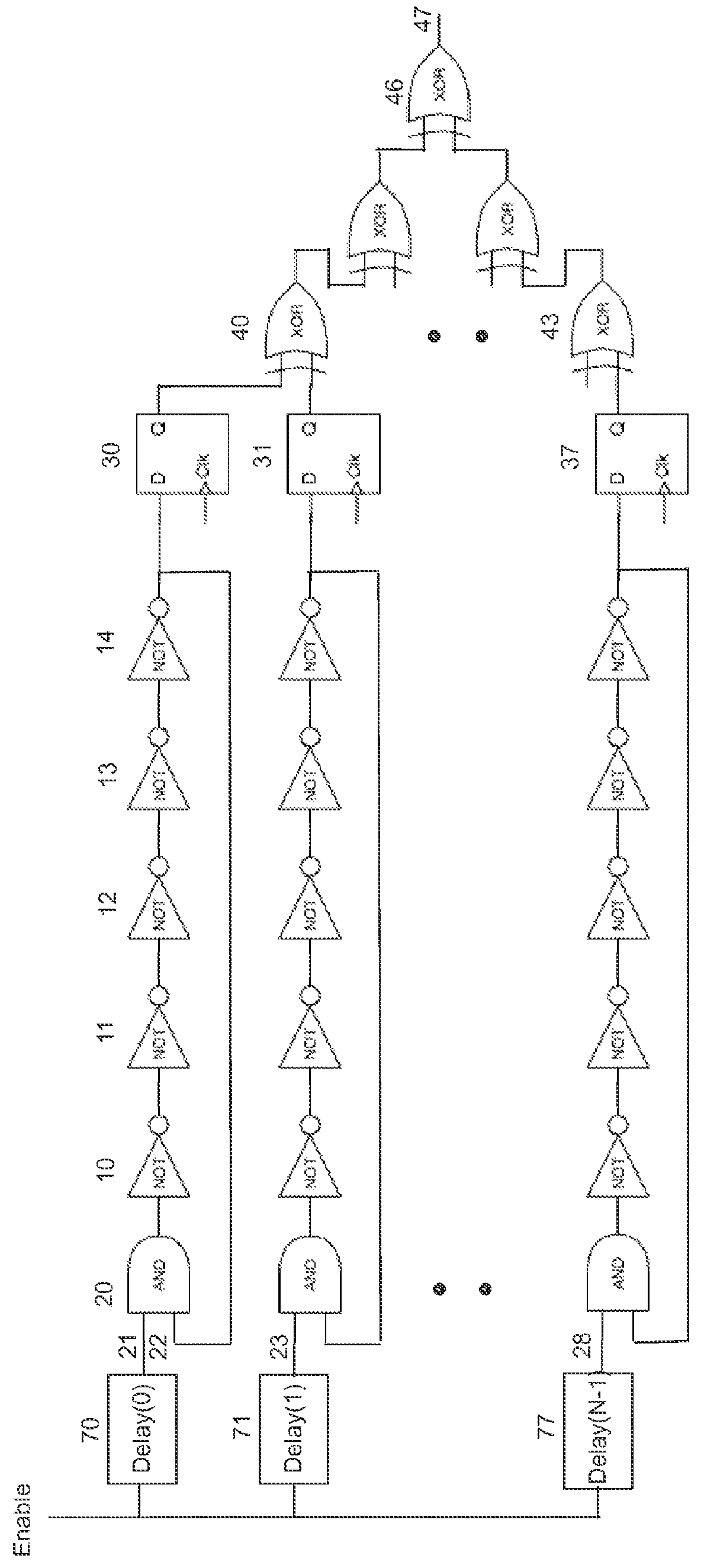

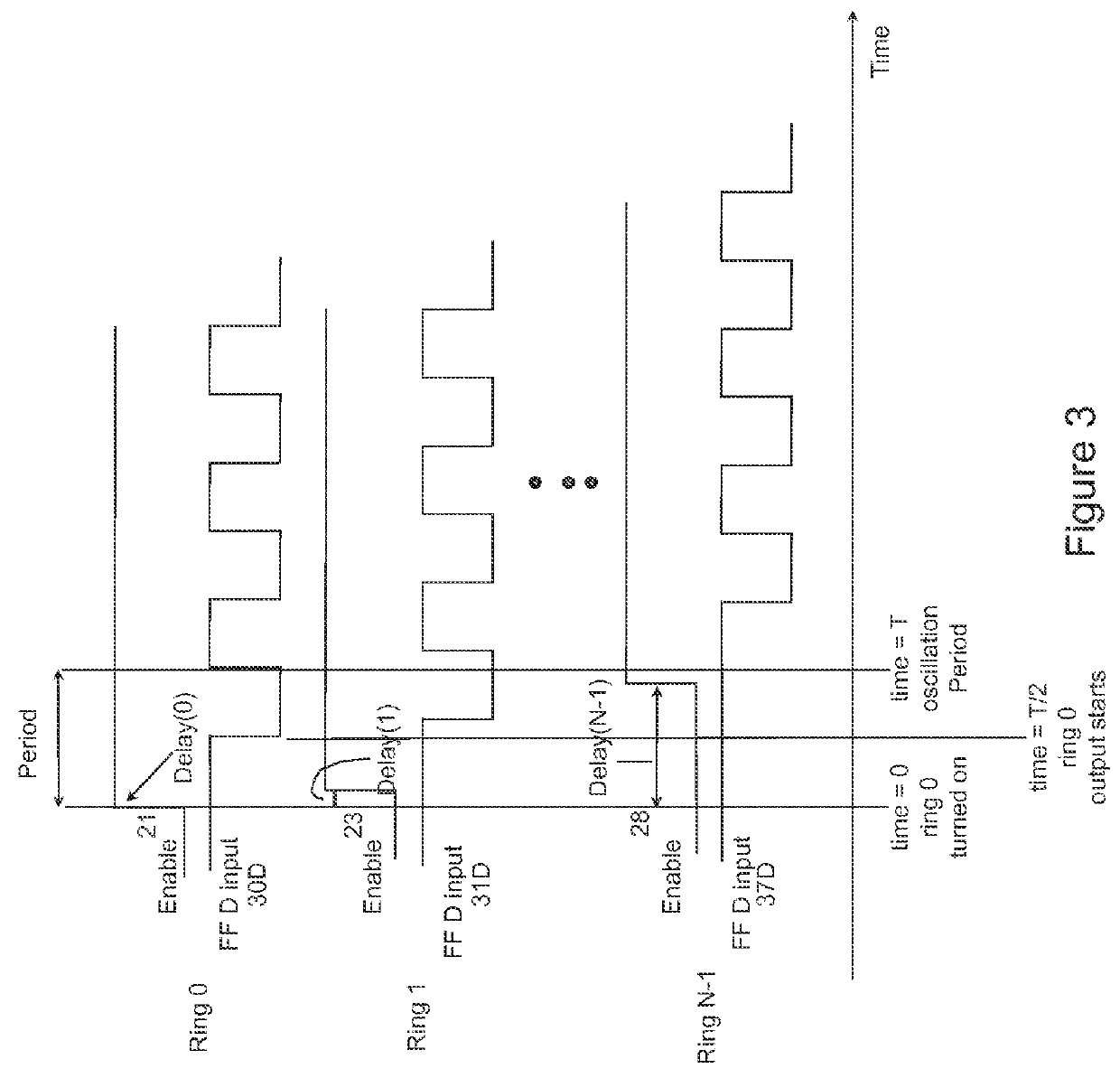

Random Number Generator Using Ring Oscillators With Initial Delay

ActiveUS20150193208A1Overcome limitationsRandom number generatorsPulse generation by logic circuitsStart timeNumber generator

Apparatus and method for a ring oscillator based random number generator with intentional startup delays timed for each ring to provide a uniform initial spreading of the ring oscillator transition edges. This invention adds a controlled incremental delay in the startup of each individual ring within the ring oscillator random number generator. Typically the delay units used in the ring oscillators themselves can be used to get a course delay between the start times of each ring. A subset of the rings start up with a particular course delay and different fine delays such that the transition edges of all the rings are spread out over the oscillation period. This spreading of the transition edges ensures the output of the random number generator are not a predictable sequence of ones and zeros based on a simultaneous startup of all rings at the same time.

Owner:THE UNITED STATES OF AMERICA AS REPRESETNED BY THE SEC OF THE AIR FORCE

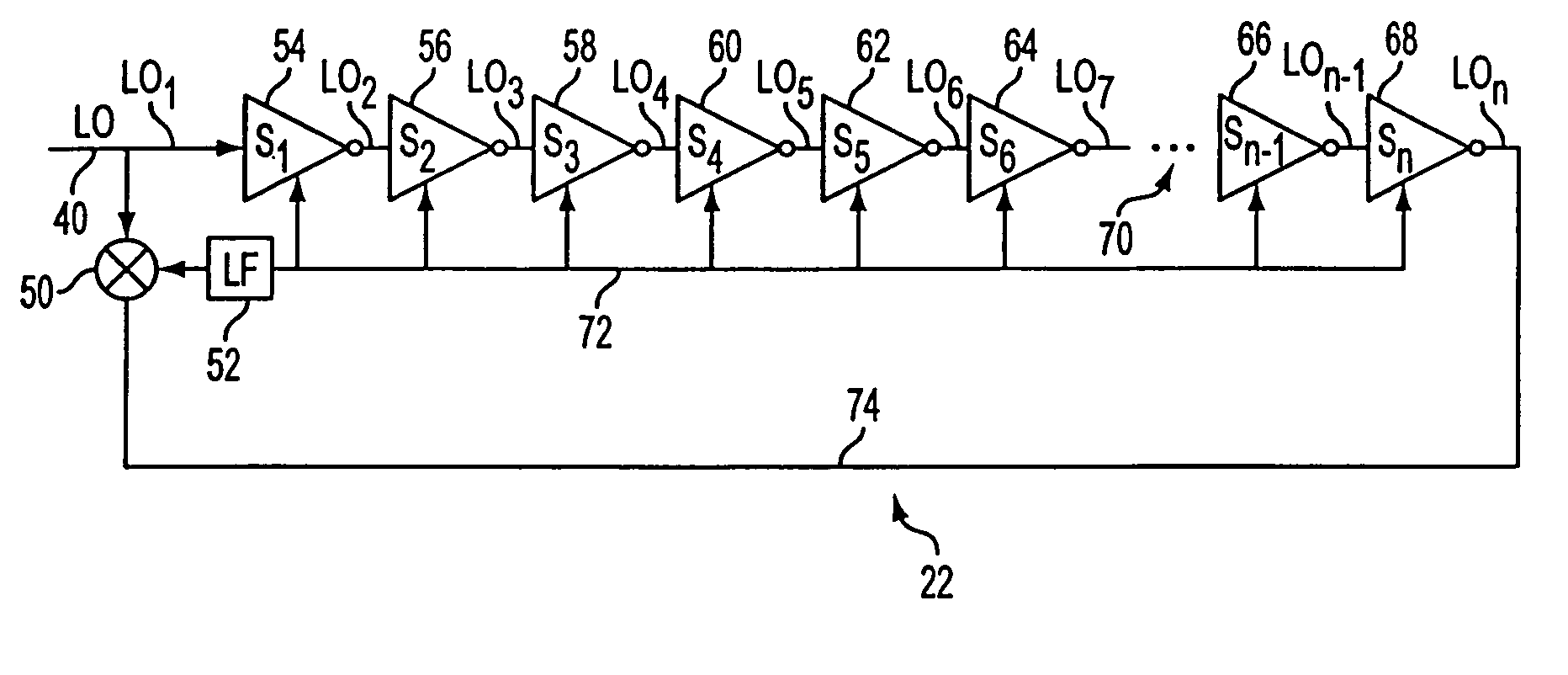

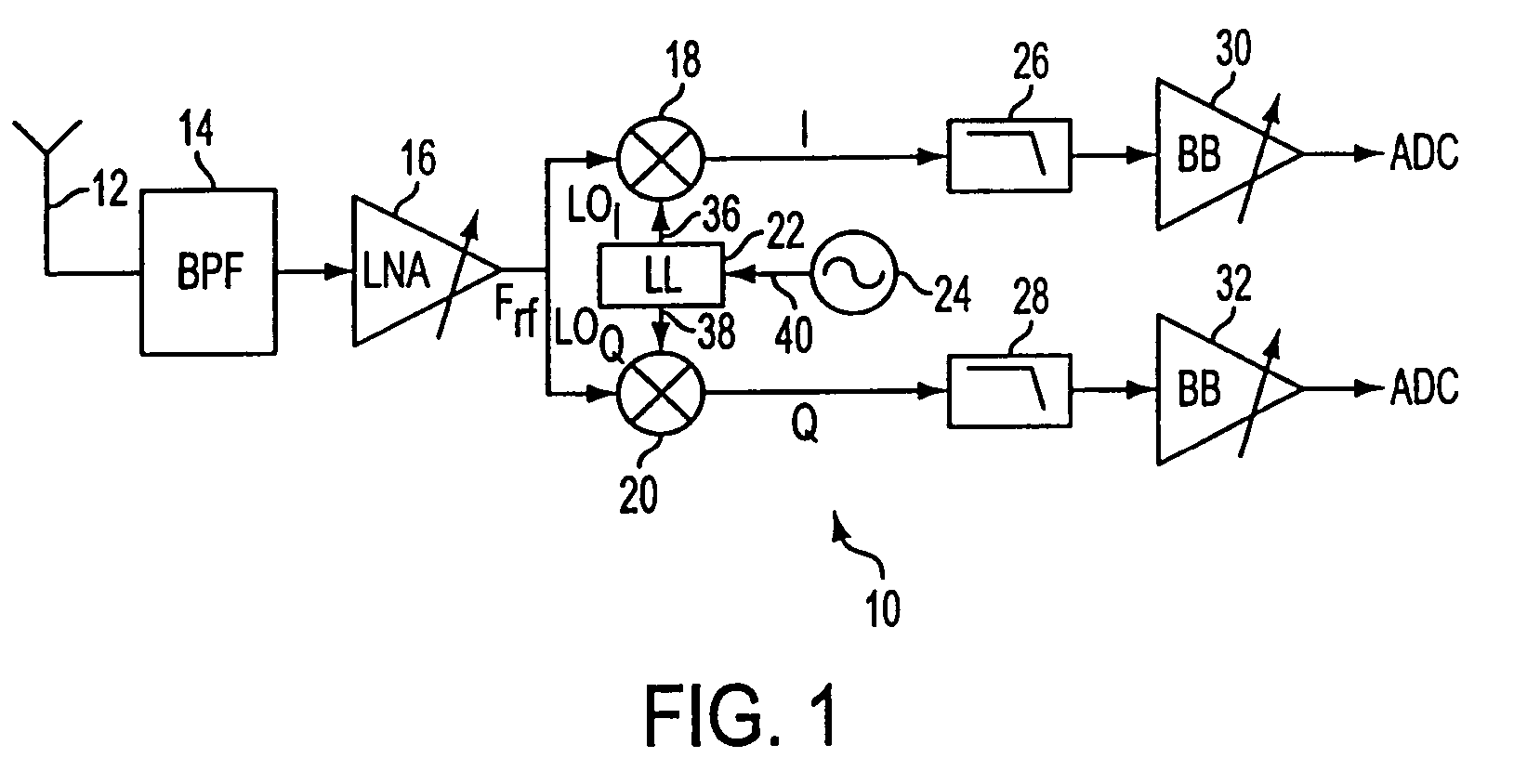

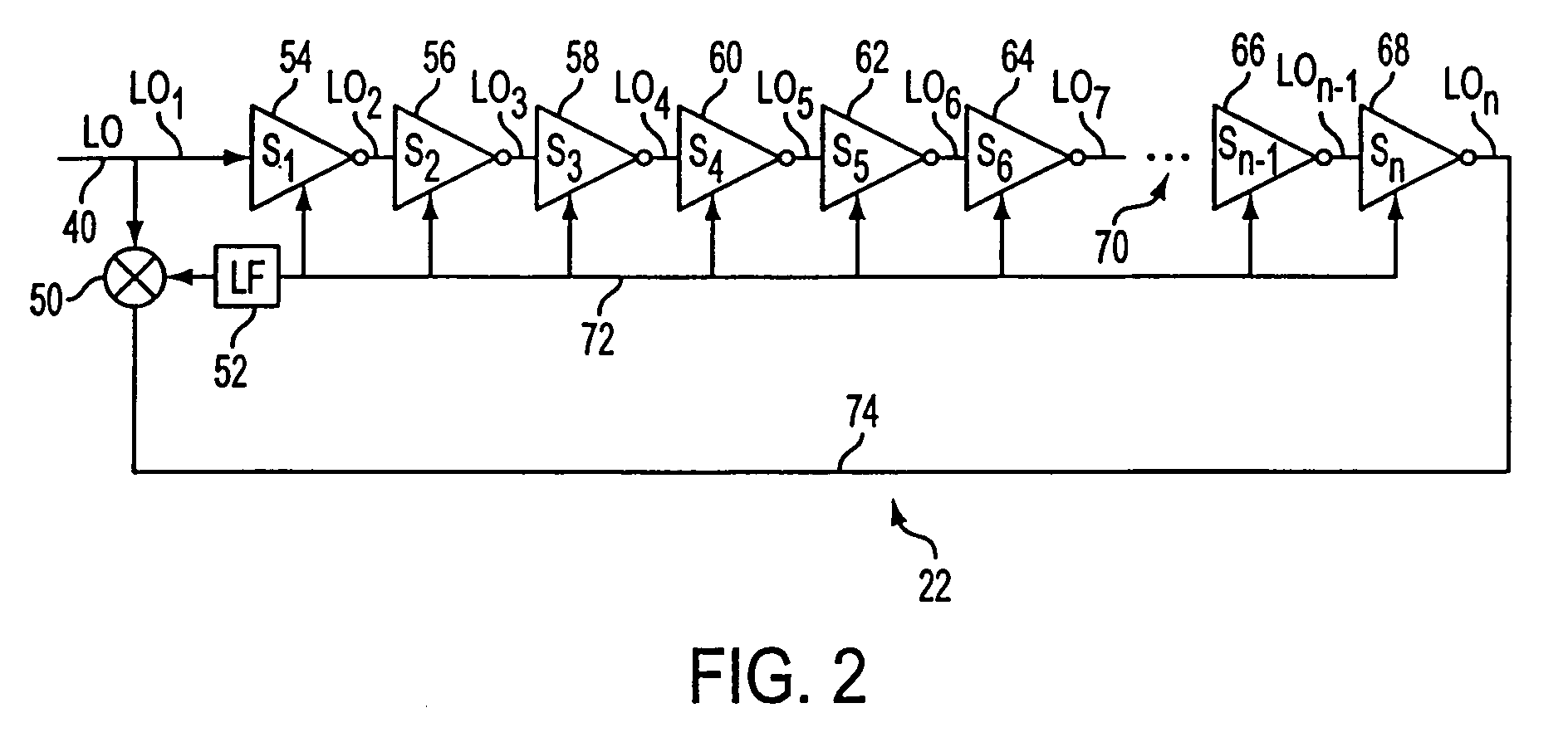

Method and apparatus for multiple phase splitting for dual band IQ subharmonic mixer drive chains

InactiveUS7145963B2Amplitude demodulationMultiple carrier systemsLocal oscillator signalPhase splitting

A method and apparatus are provided for generating first and second modulation signals from a local oscillator signal for quadrature subharmonic modulation of a quadrature amplitude modulated information signal. The method includes the steps of delaying the local oscillator signal in a plurality of incremental odd and even delay steps to form respective sets of odd and even modulator signals, said odd set of modulator signals together forming the first modulation signal and said even set forming the second modulation signal for quadrature subharmonic modulation of the quadrature amplitude modulated information signal and controlling a magnitude of the incremental delays based upon a predetermined phase offset between the local oscillator signal and a last delay step of the incremental delay steps.

Owner:SKYWORKS SOLUTIONS INC

Nonlinear Transmission Line Modulator

ActiveUS20090115545A1Transmission control/equlisationPulse duration/width modulationPulse forming networkPower combiner

A modulator is provided that comprises a nonlinear transmission line (NLTL) that is bias modulated by a baseband signal. A given logic state of the baseband signal determines a delay amount of a first carrier signal through the NLTL. The modulator further comprises an impulse forming network (IFN) that includes a first NLTL that receives the first carrier signal delayed by the determined delay amount and a second NLTL that receives a second carrier signal having a fixed delay amount. The first NLTL and second NLTL within the IFN have opposite diode polarity configurations. The modulator further comprises a power combiner that converts a delta delay of the first carrier signal relative to the second carrier signal to a sharp impulse that represents the given logic state of the baseband signal.

Owner:NORTHROP GRUMMAN SYST CORP

Digitally controlled CML buffer

Owner:POLARIS INNOVATIONS LTD

Compact solid-state variable optical delay line with a large continuous tuning range

In accordance with the invention, a variable delay line with continuous tuning comprises an optical path providing at least one continuous delay element coupled to a series of switchable binary fixed delays. The series of switchable delays can be configured to select a delay among a plurality of incremental delays, and the continuous delay can set a continuous delay in a range encompassing the delay increment of the binary series. In a preferred embodiment, the variable delay element comprises a tunable all pass filter (APF) with delay tunable from essentially 0 to a time T and the switchable binary fixed delays form a series (0,T), (0, 2T), (0, 4T), . . . , [0, (2n+1)], where n is an integer ≧0. The switches are preferably Mach-Zehnder switches. In an alternative embodiment, the continuous delay element comprises a suitable pair of APF arms. The path and all components can be fabricated as an integrated planar waveguide (solid state) device.

Owner:ALCATEL-LUCENT USA INC +1

Random number generator using ring oscillators with initial delay

ActiveUS9361066B2Overcome limitationsRandom number generatorsPulse generation by logic circuitsStart timeNumber generator

Apparatus and method for a ring oscillator based random number generator with intentional startup delays timed for each ring to provide a uniform initial spreading of the ring oscillator transition edges. This invention adds a controlled incremental delay in the startup of each individual ring within the ring oscillator random number generator. Typically the delay units used in the ring oscillators themselves can be used to get a course delay between the start times of each ring. A subset of the rings start up with a particular course delay and different fine delays such that the transition edges of all the rings are spread out over the oscillation period. This spreading of the transition edges ensures the output of the random number generator are not a predictable sequence of ones and zeros based on a simultaneous startup of all rings at the same time.

Owner:THE UNITED STATES OF AMERICA AS REPRESETNED BY THE SEC OF THE AIR FORCE

Simplified method for limiting clock pulse width

InactiveUS7242233B2Continuous to patterned pulse manipulationElectric pulse generatorTotal delayComputer module

The present invention provides for correcting excessive pulse widths using incremental delays. The pulse width is evaluated through a correction block and leak detector. An acceptable pulse passes through an interconnect directly to the clock output. Unacceptable pulses are sent through a block delay module that incorporates a series of delay sub-blocks that disconnect and reset in accordance with a pre-programmed total delay time. The conditioned clock pulse is resent through a node to the correction block and leak detector where it is reevaluated. If the pulse is acceptable, it is sent to the clock output. If the pulse is found unacceptable, it is recycled again. A high low clock pulse shuttle determines and alters the high or low state of the clock pulse to ensure a correct output to downstream dependent devices.

Owner:GOOGLE LLC

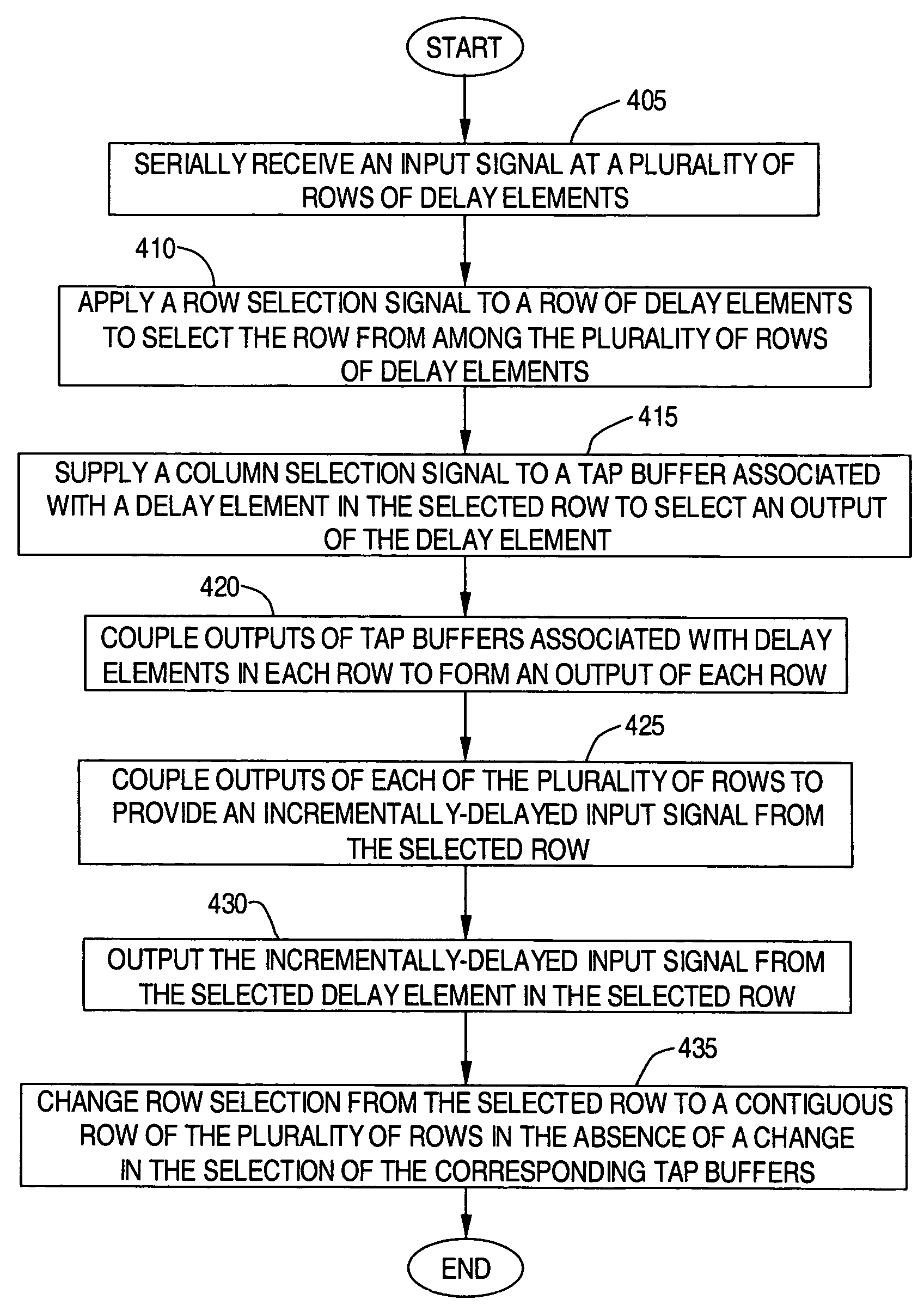

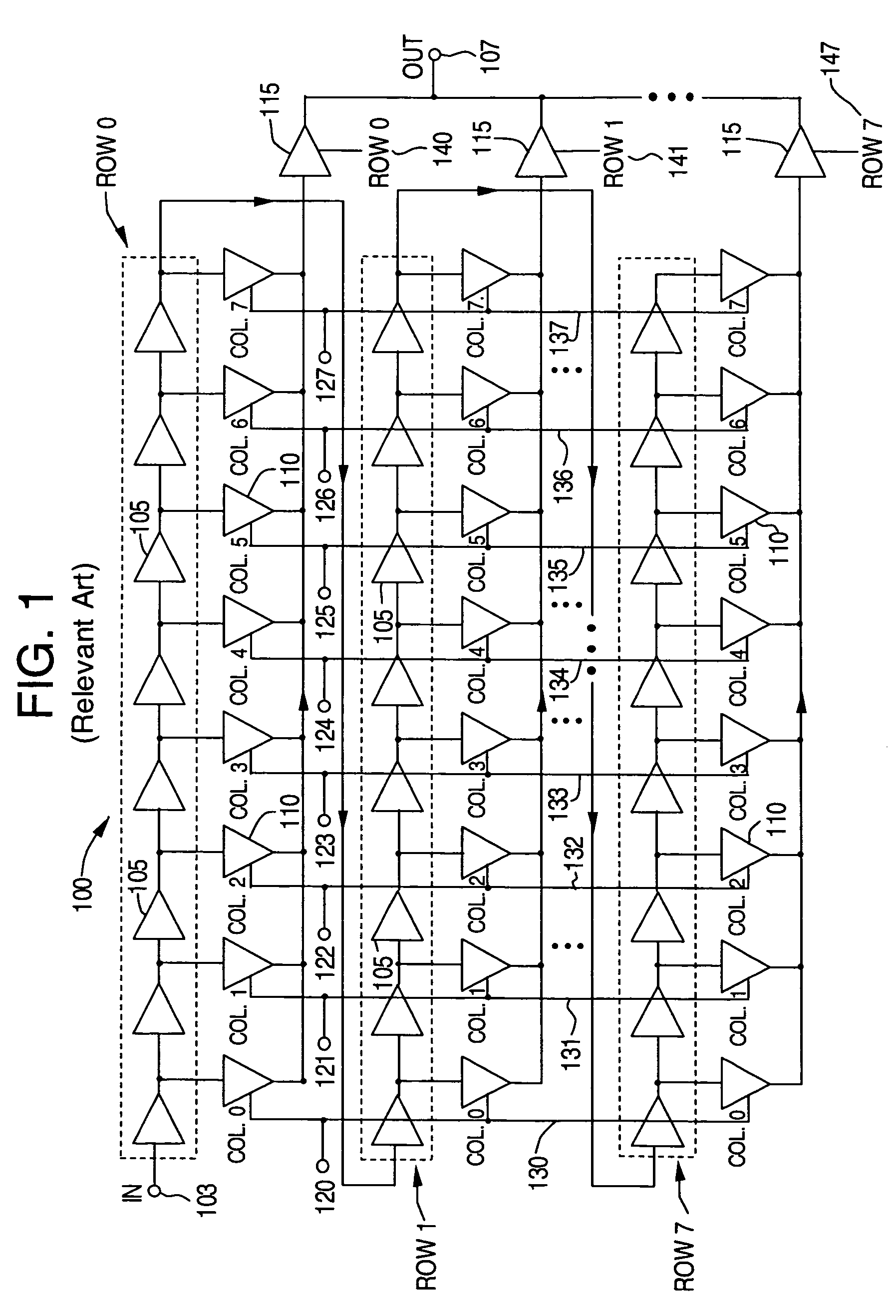

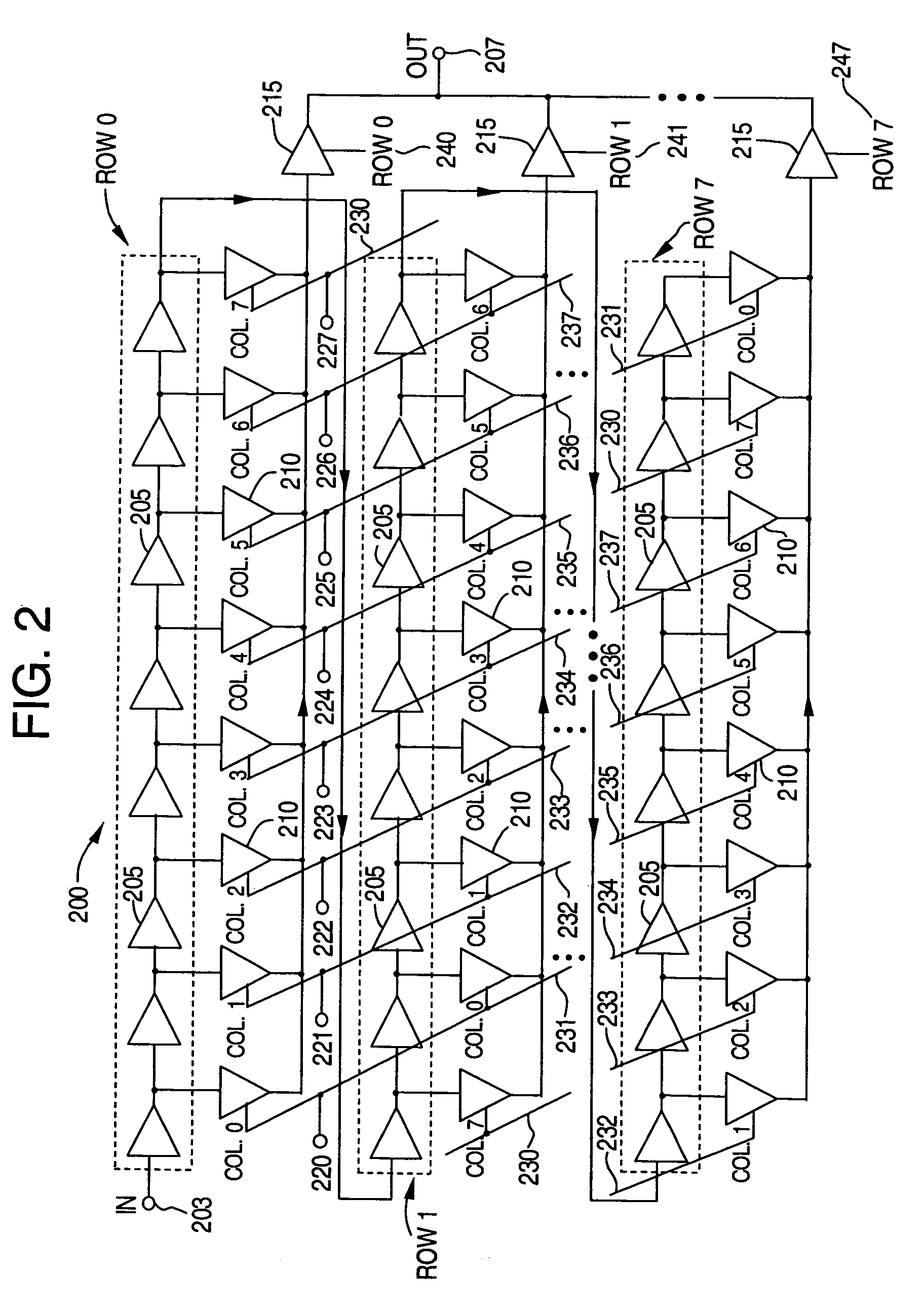

Diagonal matrix delay

InactiveUS7405983B1Digital storagePulse manipulationDiagonal matrixElectrical and Electronics engineering

A method of delaying an input signal comprises serially receiving the input signal at a plurality of rows of delay elements; applying a row selection signal to a row of delay elements to select the row from the plurality of rows; supplying a column selection signal to a tap buffer associated with a delay element in the selected row to select an output of the delay element; coupling outputs of tap buffers associated with delay elements in each row to form an output of each row; coupling outputs of each of the plurality of rows to provide an incrementally-delayed input signal from the selected row; outputting the incrementally-delayed input signal from the selected delay element in the selected row; and changing row selection from the selected row to a contiguous row of the plurality of rows in the absence of a change in the selection of the corresponding tap buffers.

Owner:MARVELL ISRAEL MISL