Patents

Literature

97results about "Hierarchy auxillary PCBs" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

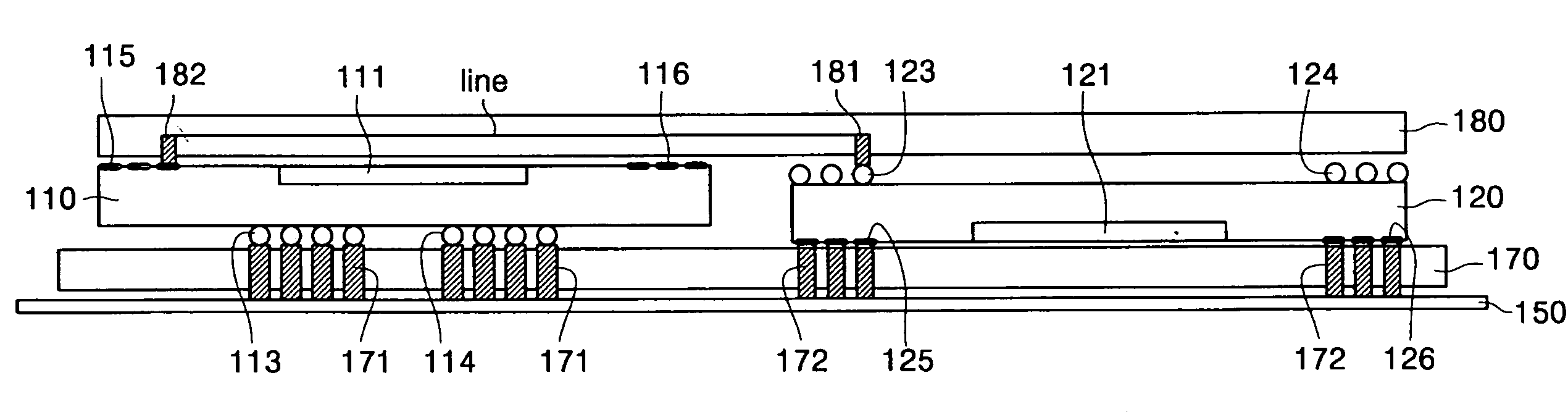

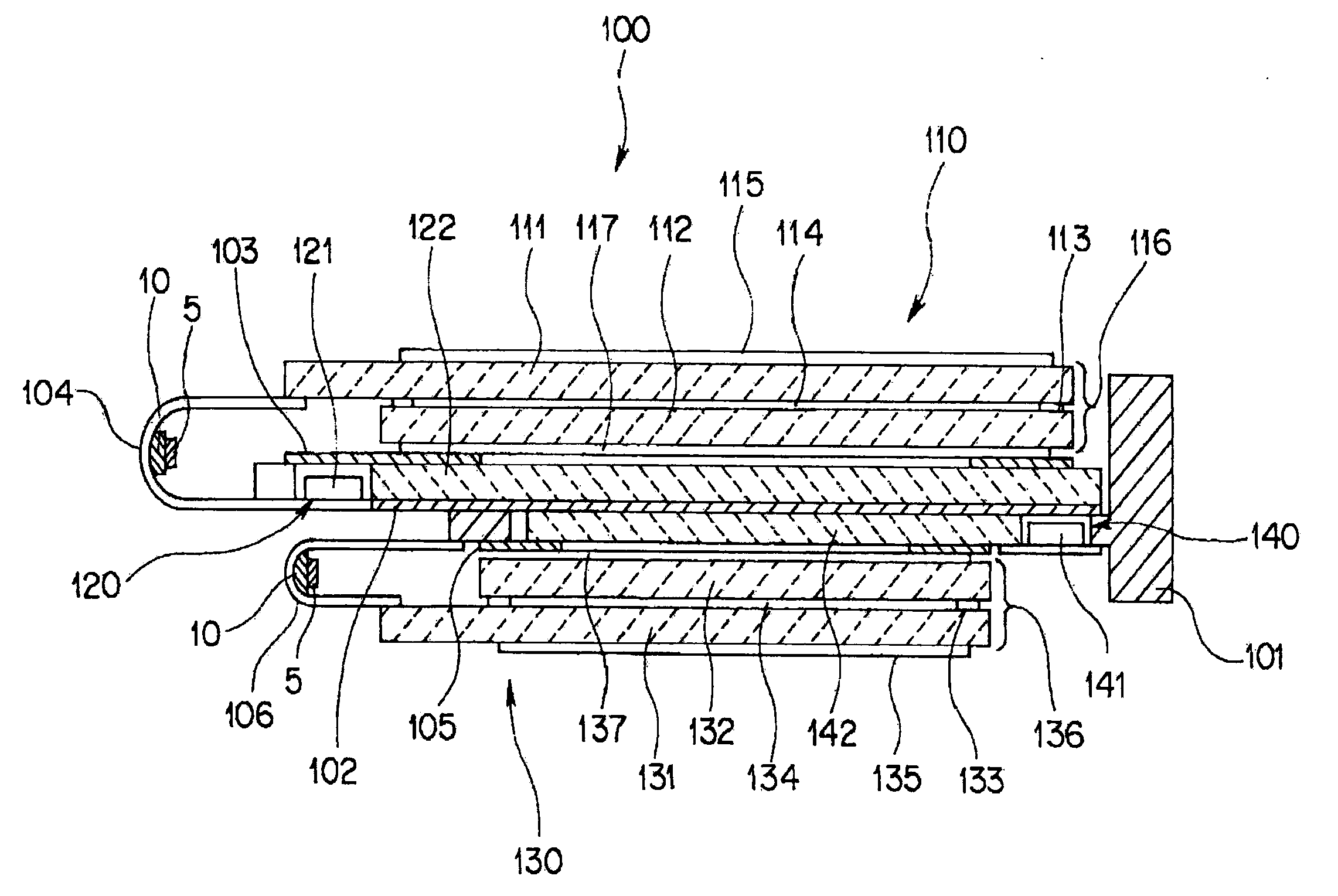

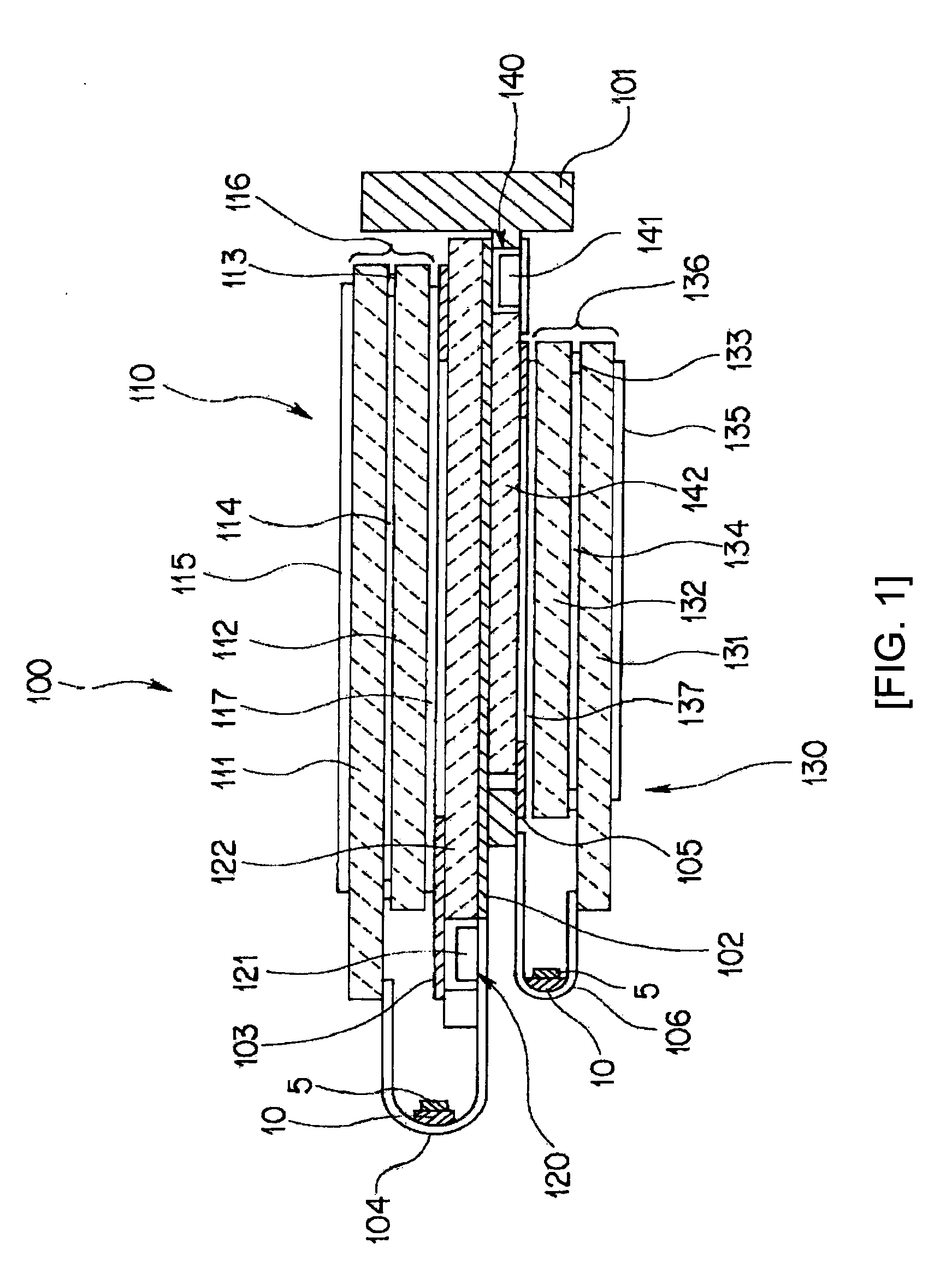

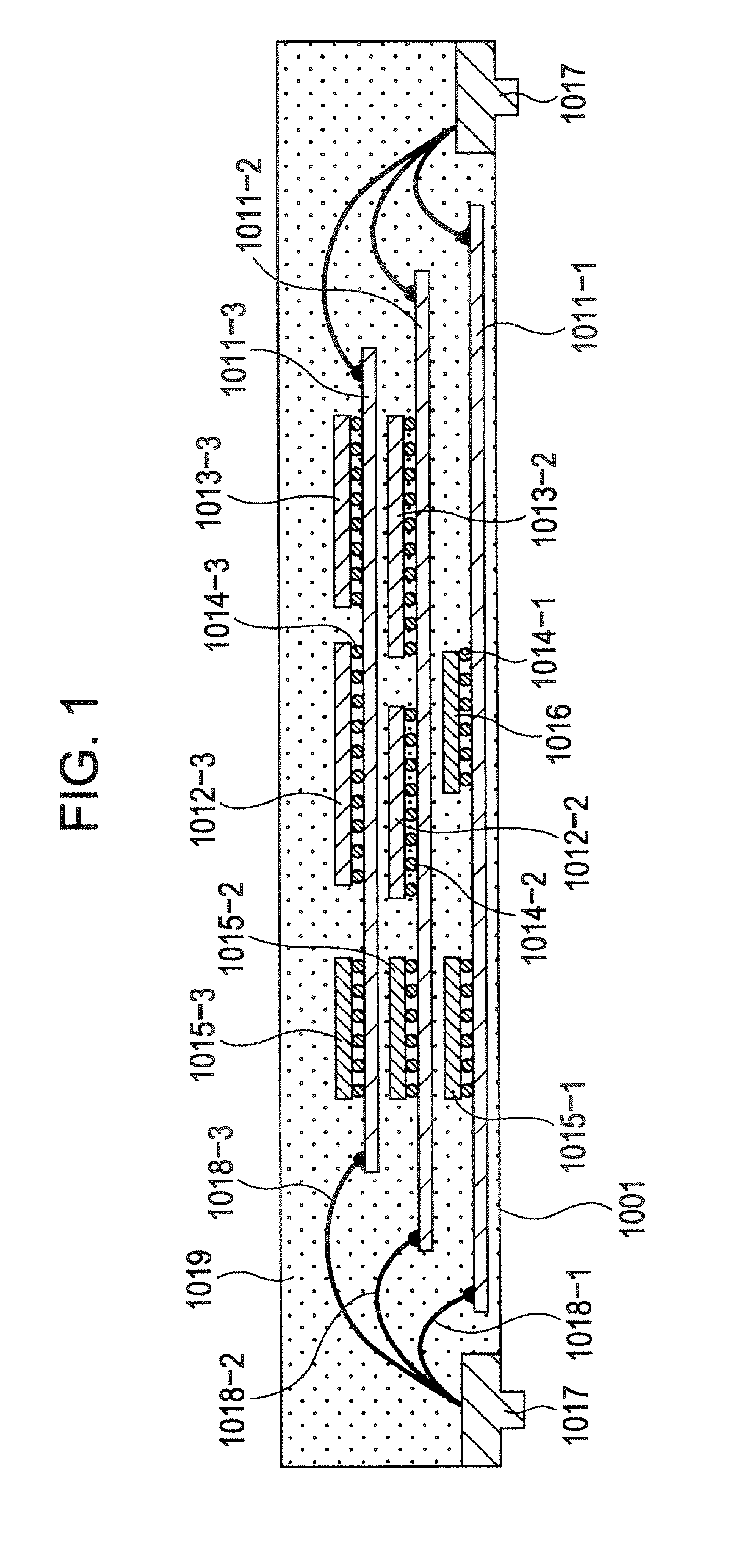

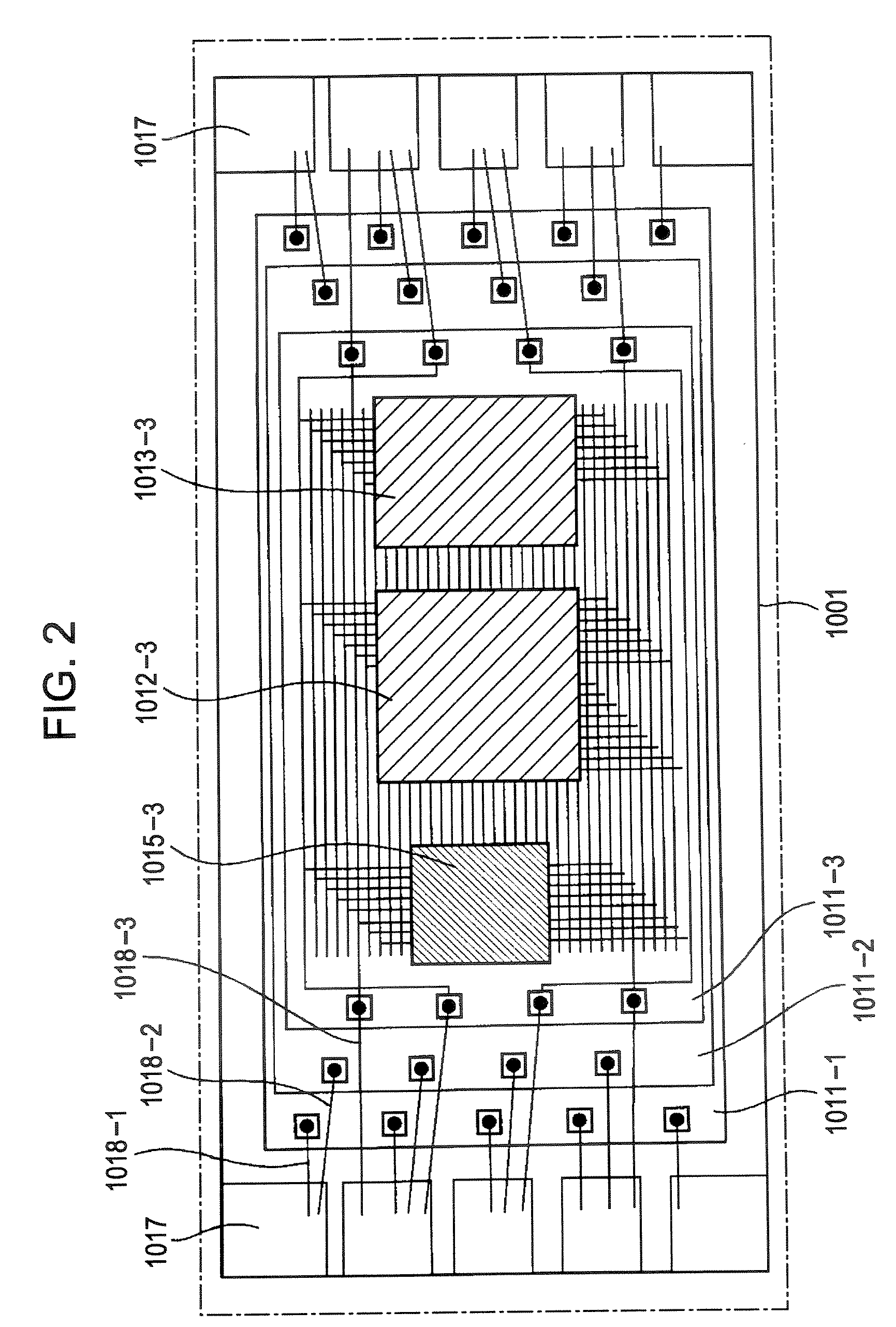

Stacked semiconductor device

ActiveUS7049692B2Eliminate the problemPrinted circuit assemblingSemiconductor/solid-state device detailsGeneral purposeEngineering

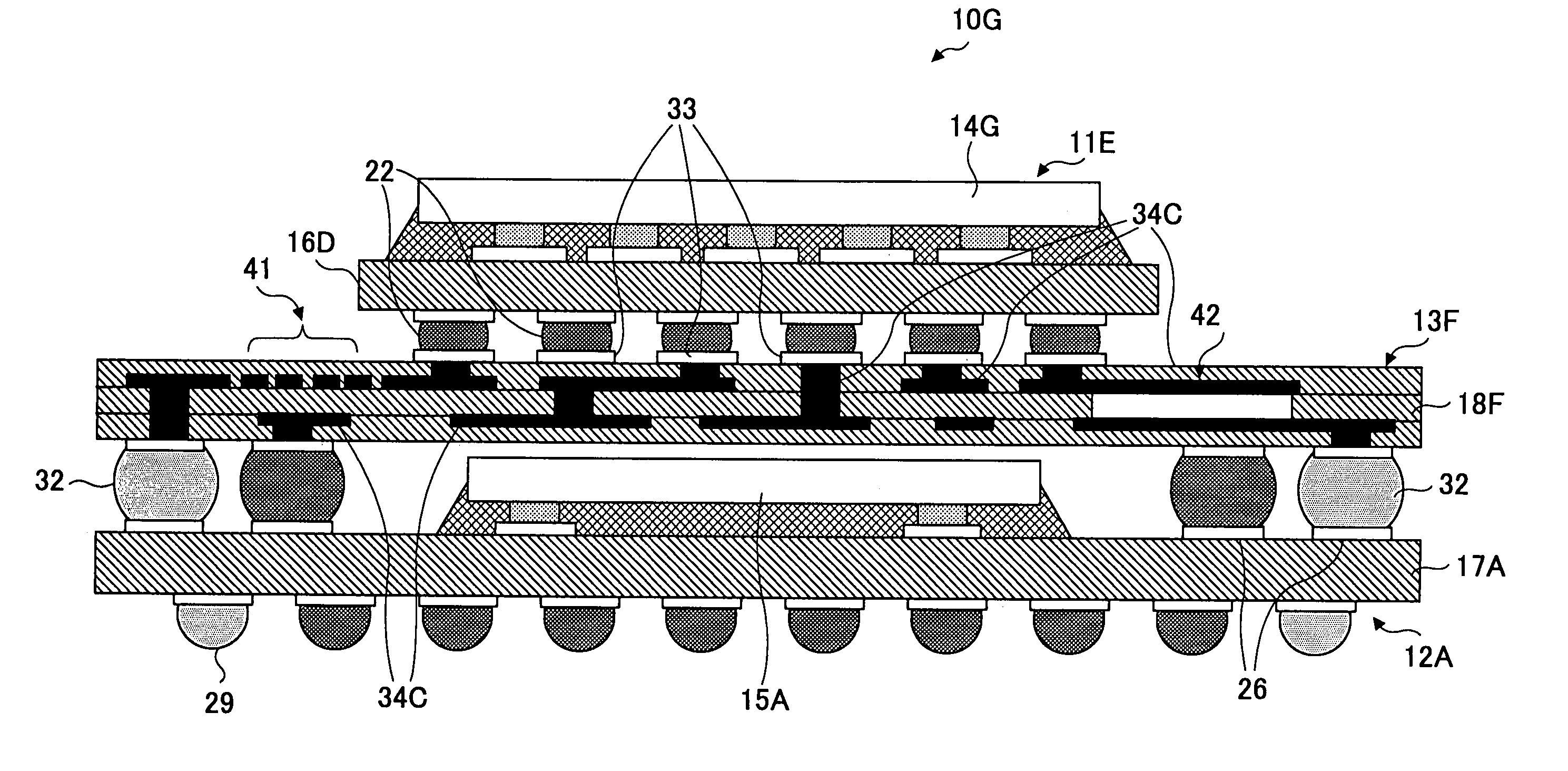

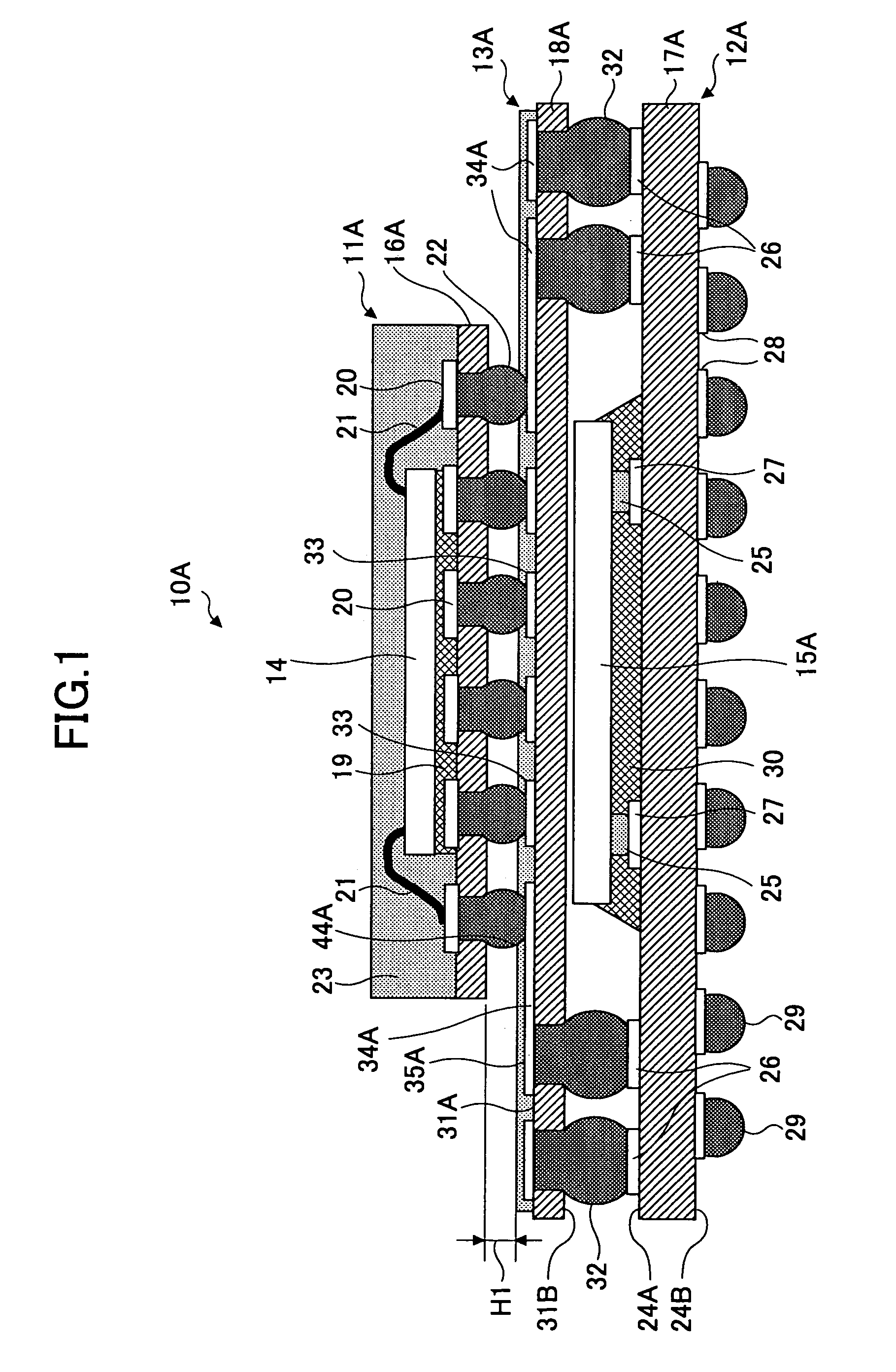

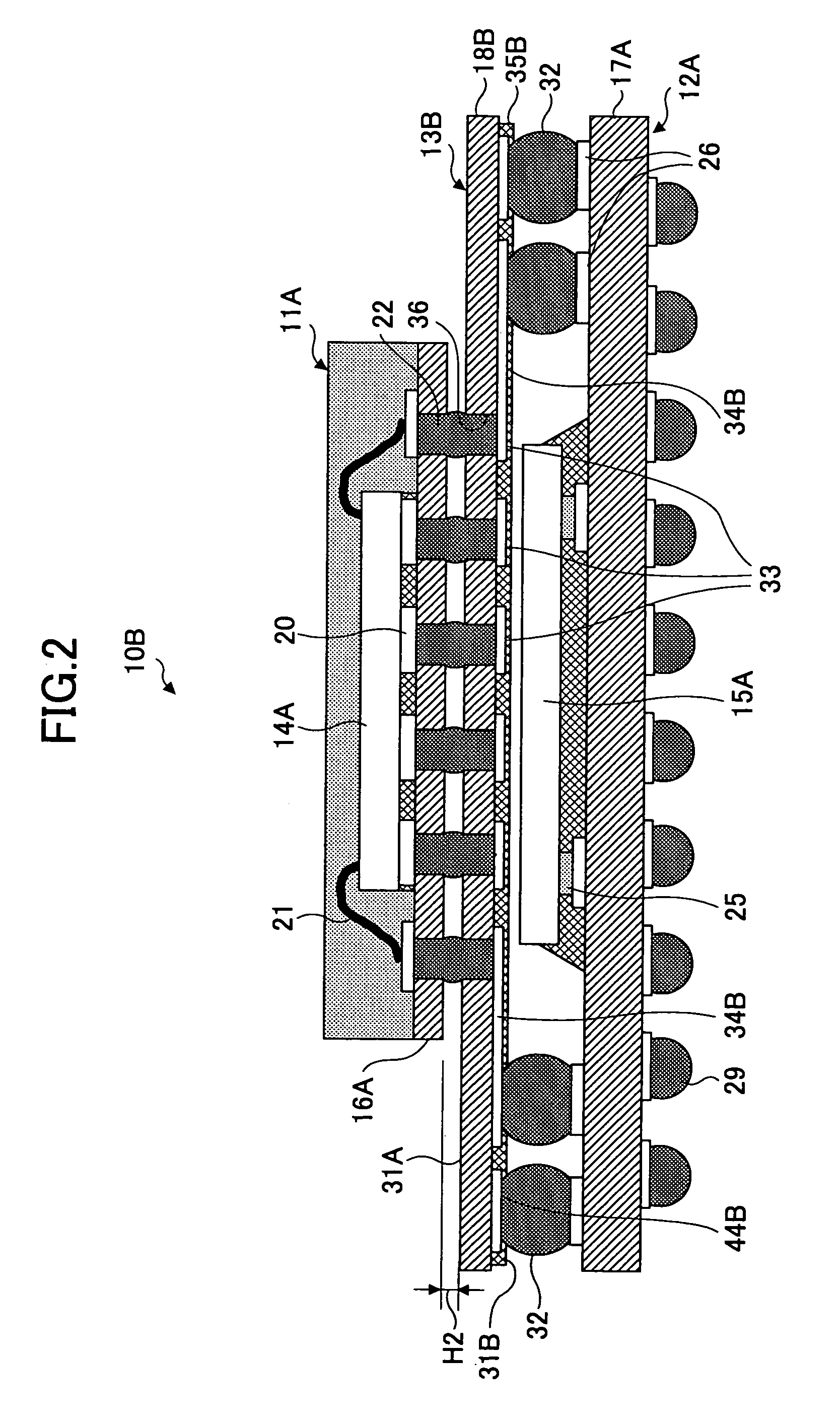

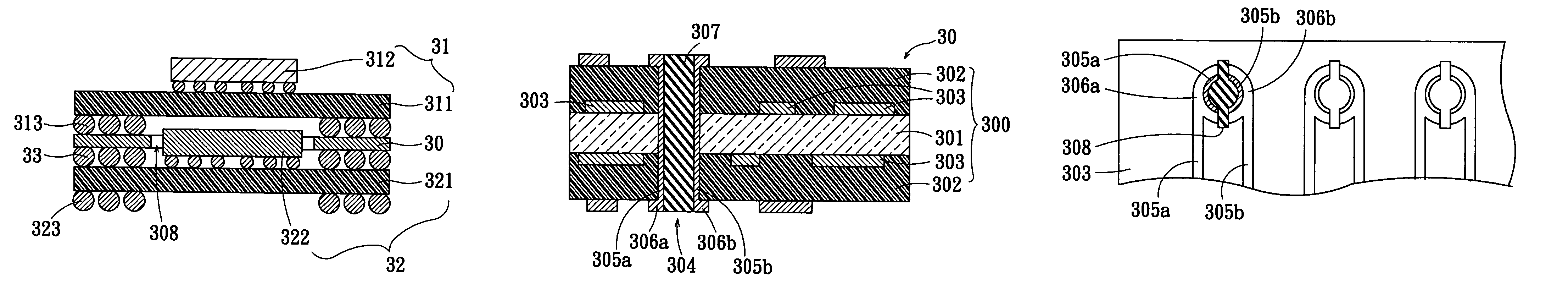

A stacked semiconductor device is disclosed that has a three-dimensional structure using general-purpose semiconductor device units (semiconductor devices) that are stacked with an interposer substrate being provided between an upper device unit and a lower device unit. The upper device unit includes a semiconductor device, a first wiring substrate, and an external connection terminal. The lower device unit includes a semiconductor device, a second wiring substrate, and a connection electrode that is prepared on the upper surface of the second wiring substrate. The interposer substrate includes a circuit board, a first conductive material connecting to the connection electrode, a second conductive material formed in a form position of the external connection terminal that is electrically connected to the second conductive material, and a third conductive material for electrically connecting the first conductive material and the second conductive material.

Owner:SOCIONEXT INC

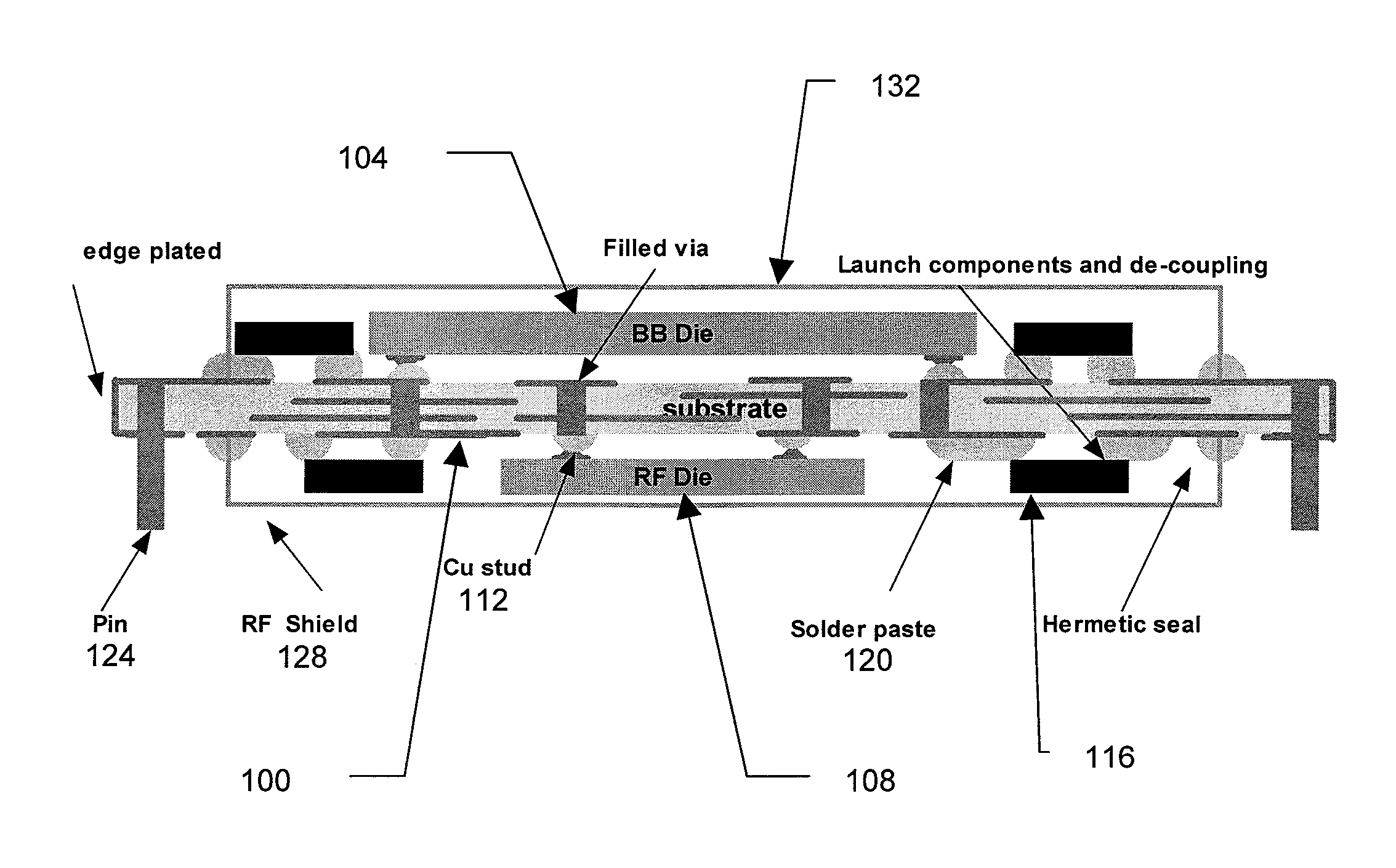

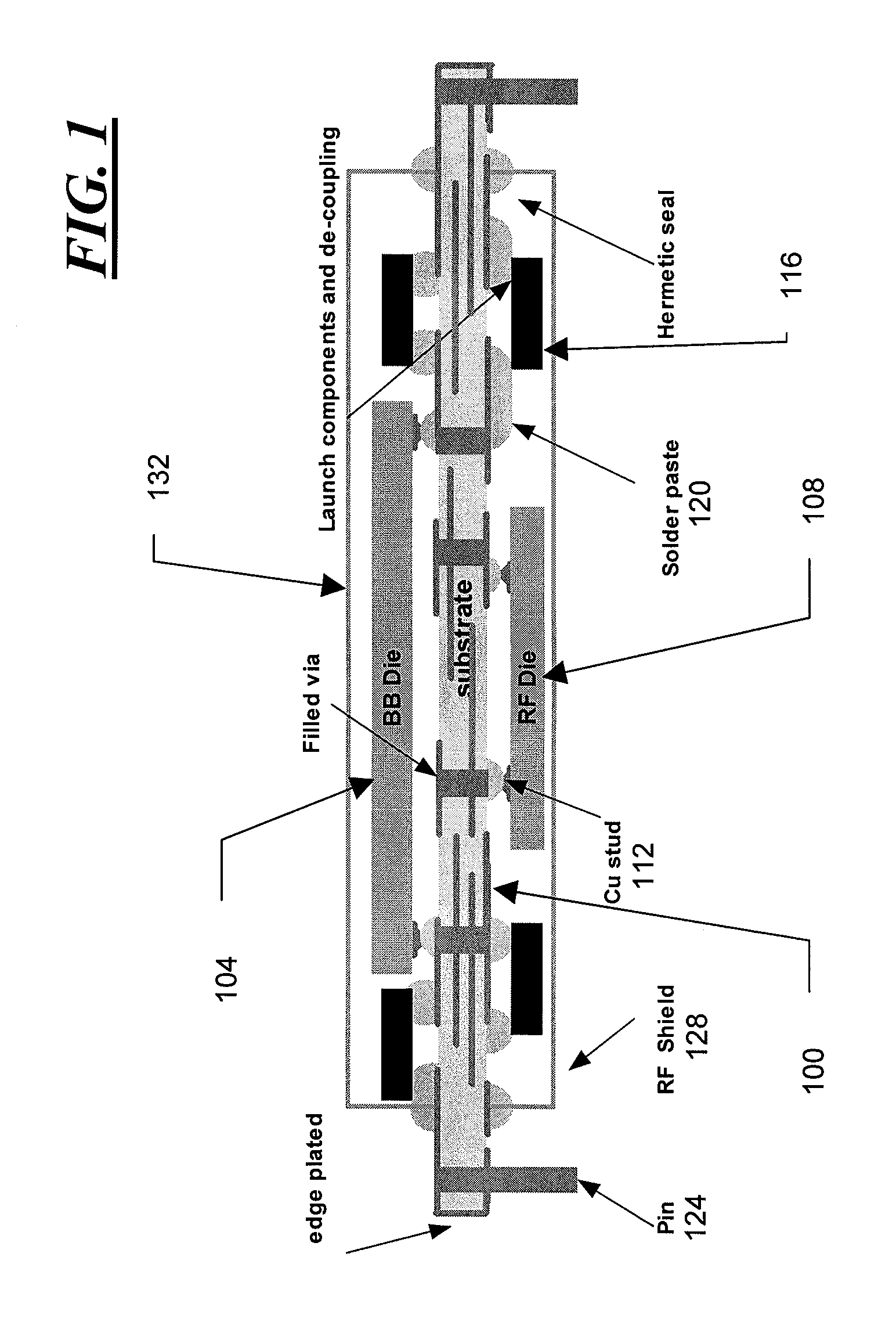

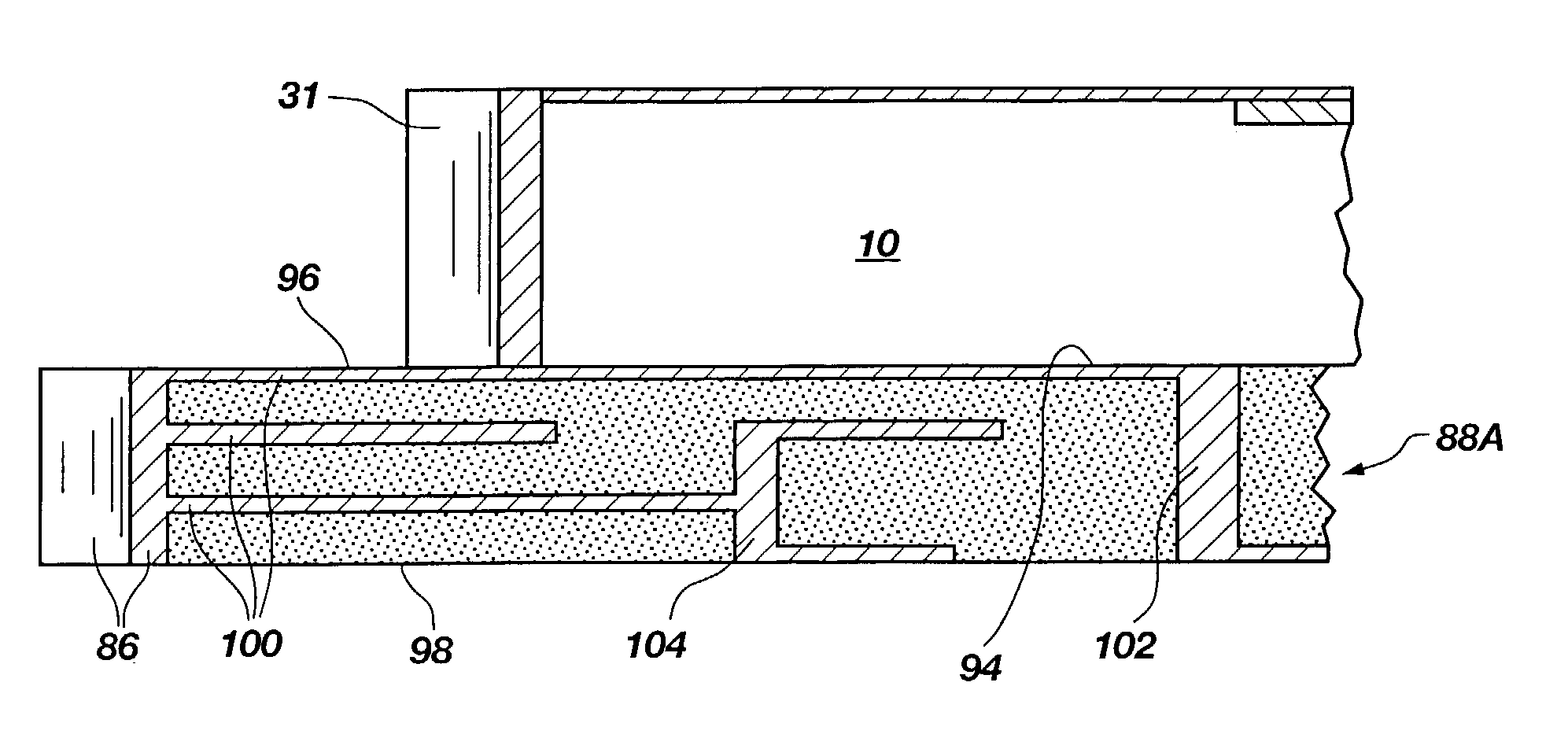

Methods for assembling multiple semiconductor devices

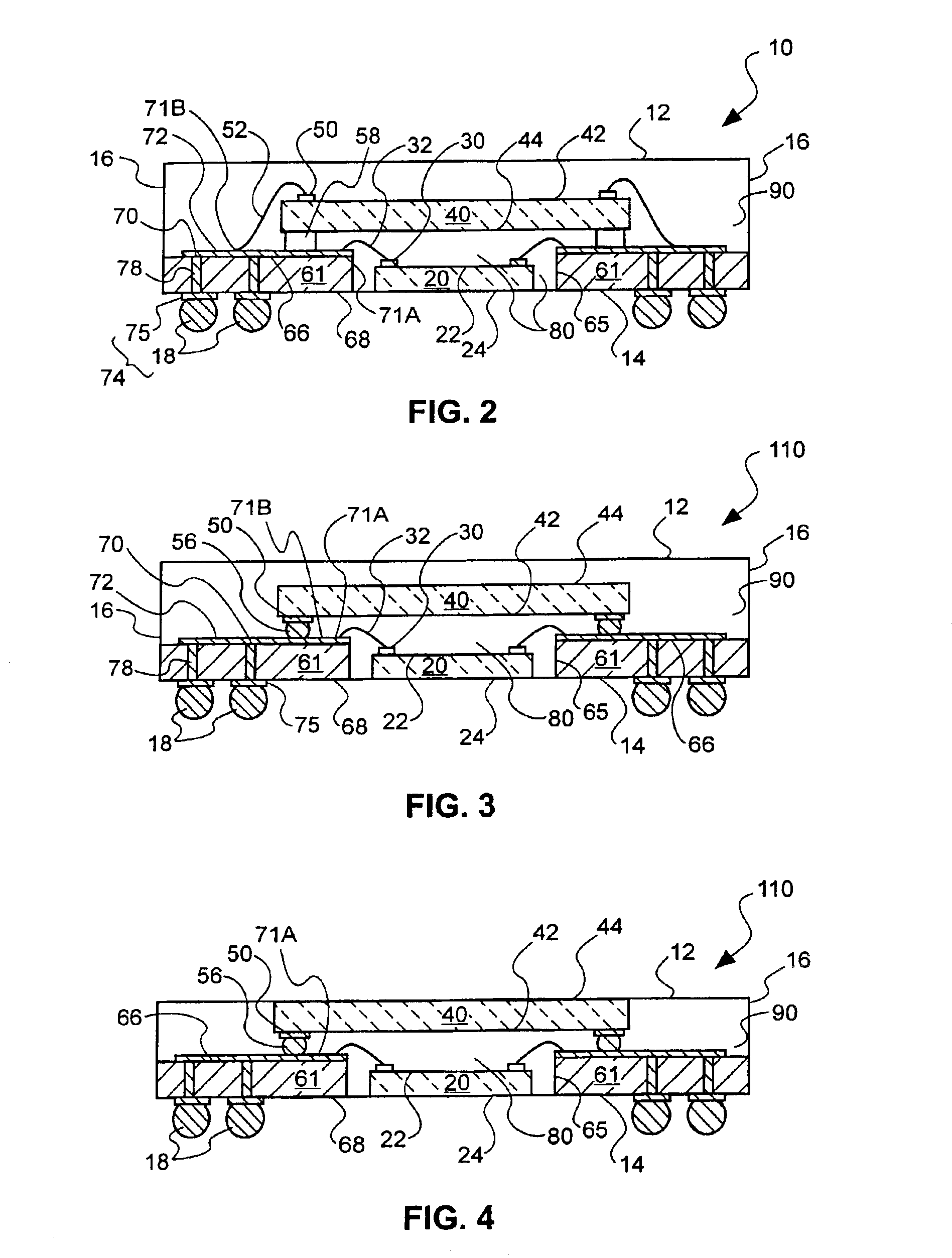

InactiveUS7198980B2Reduce area requirementsHelp positioningPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorElectrical connection

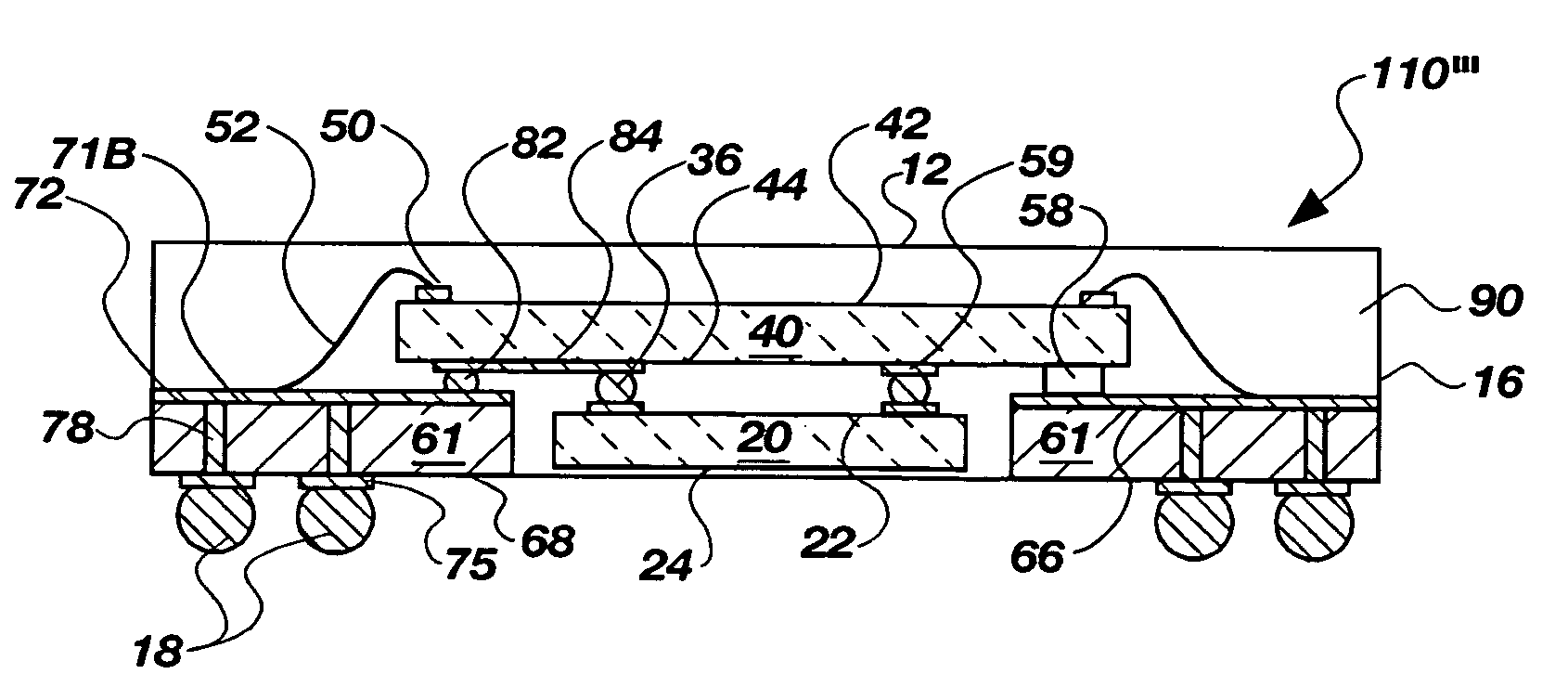

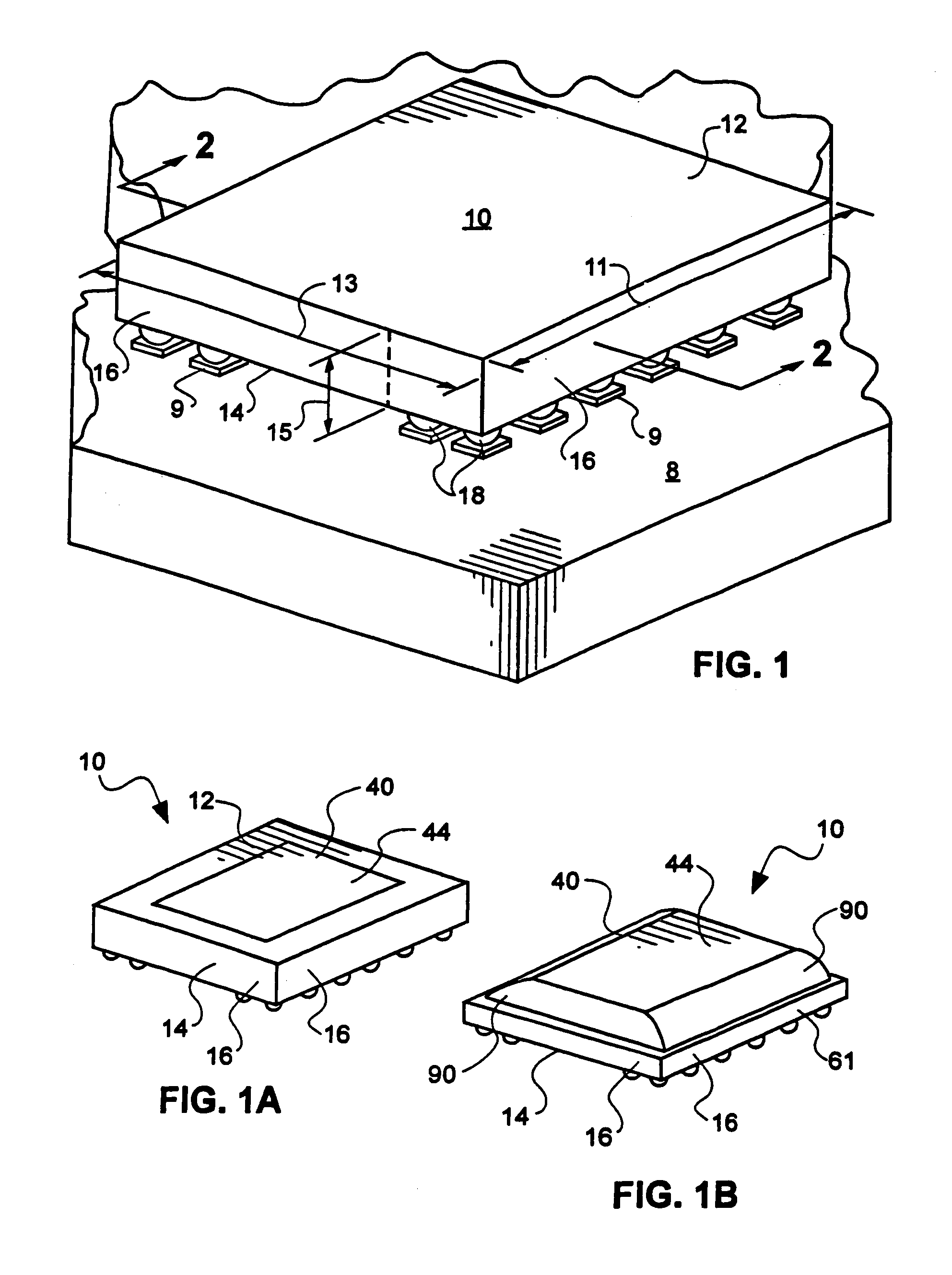

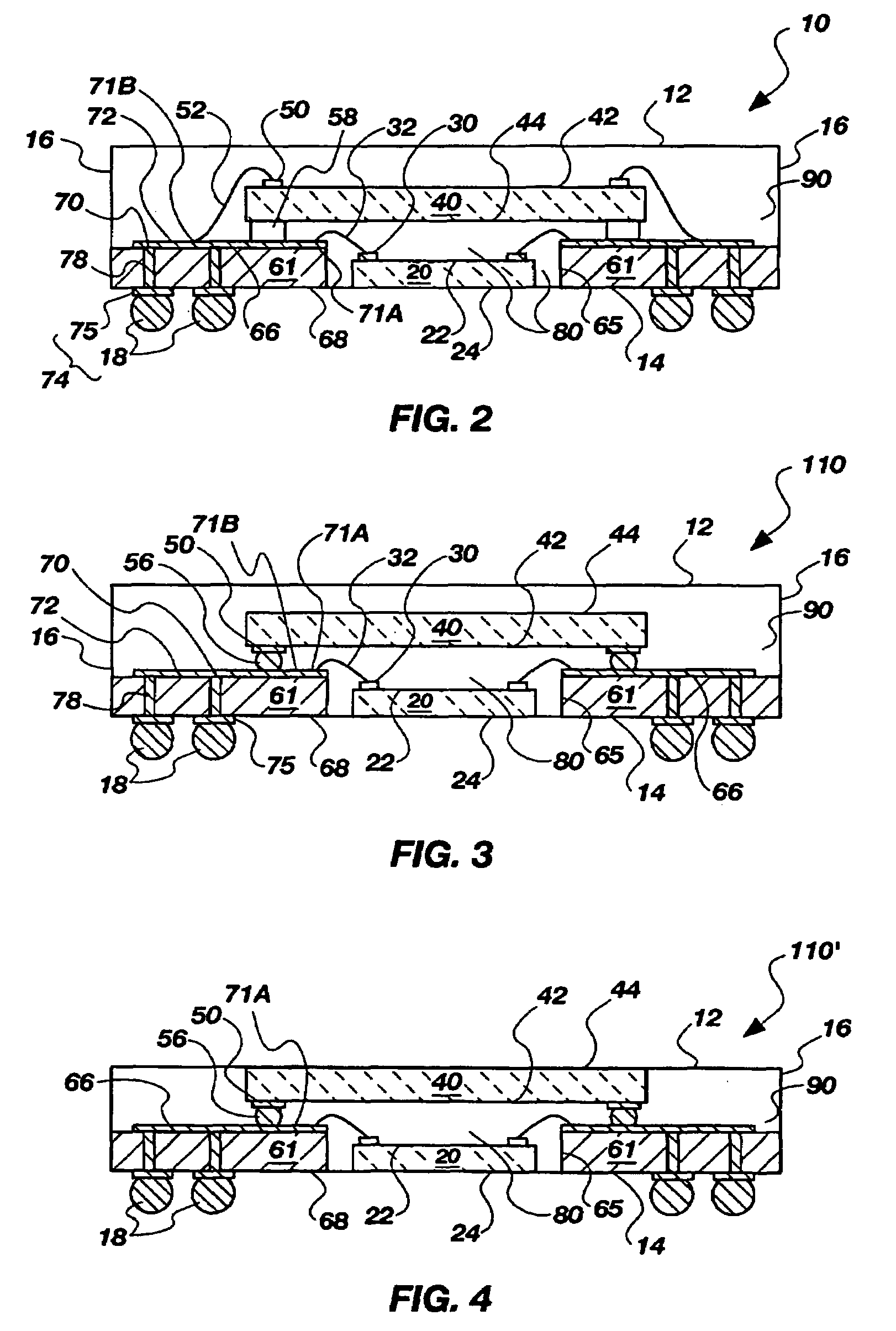

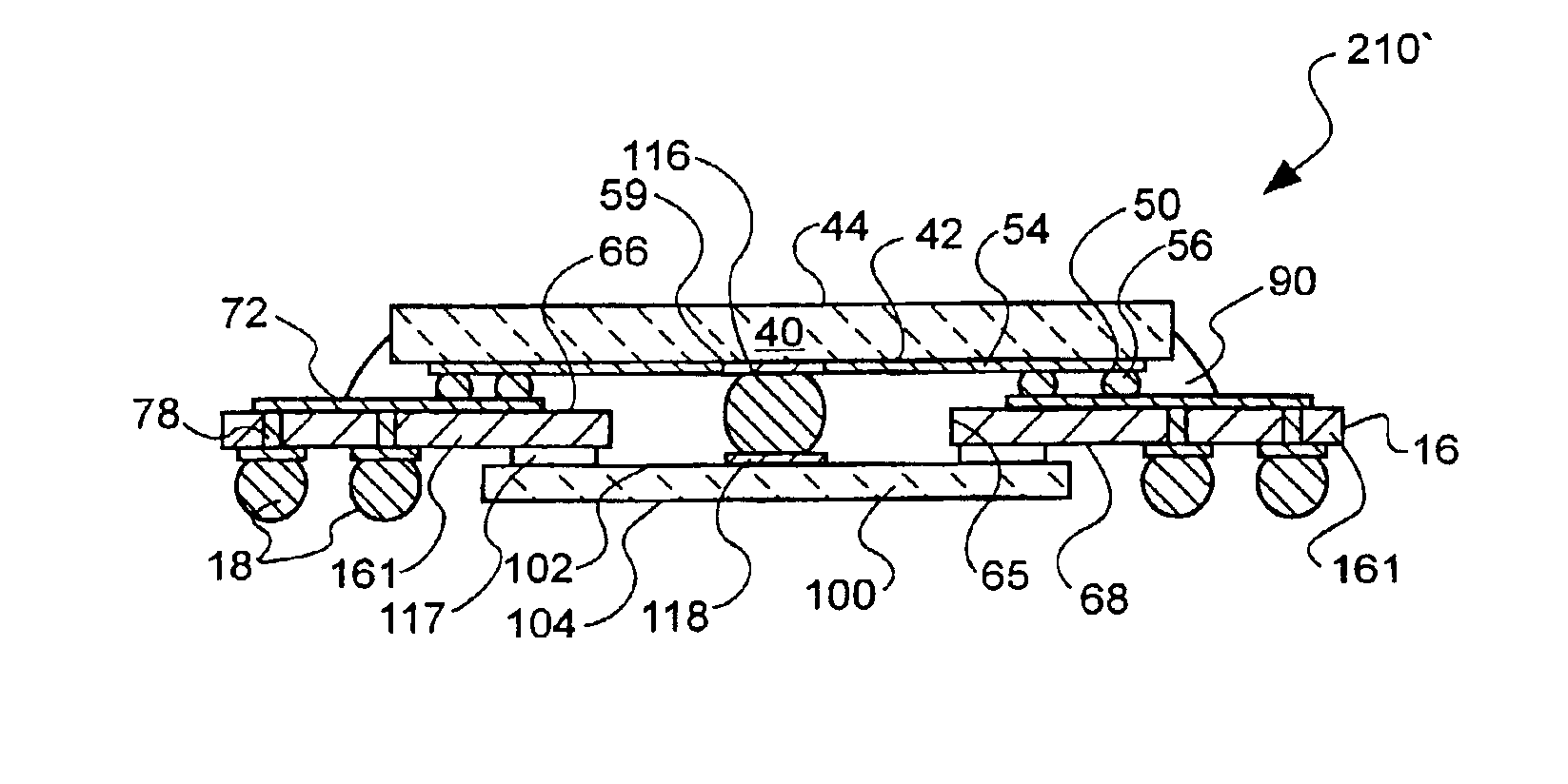

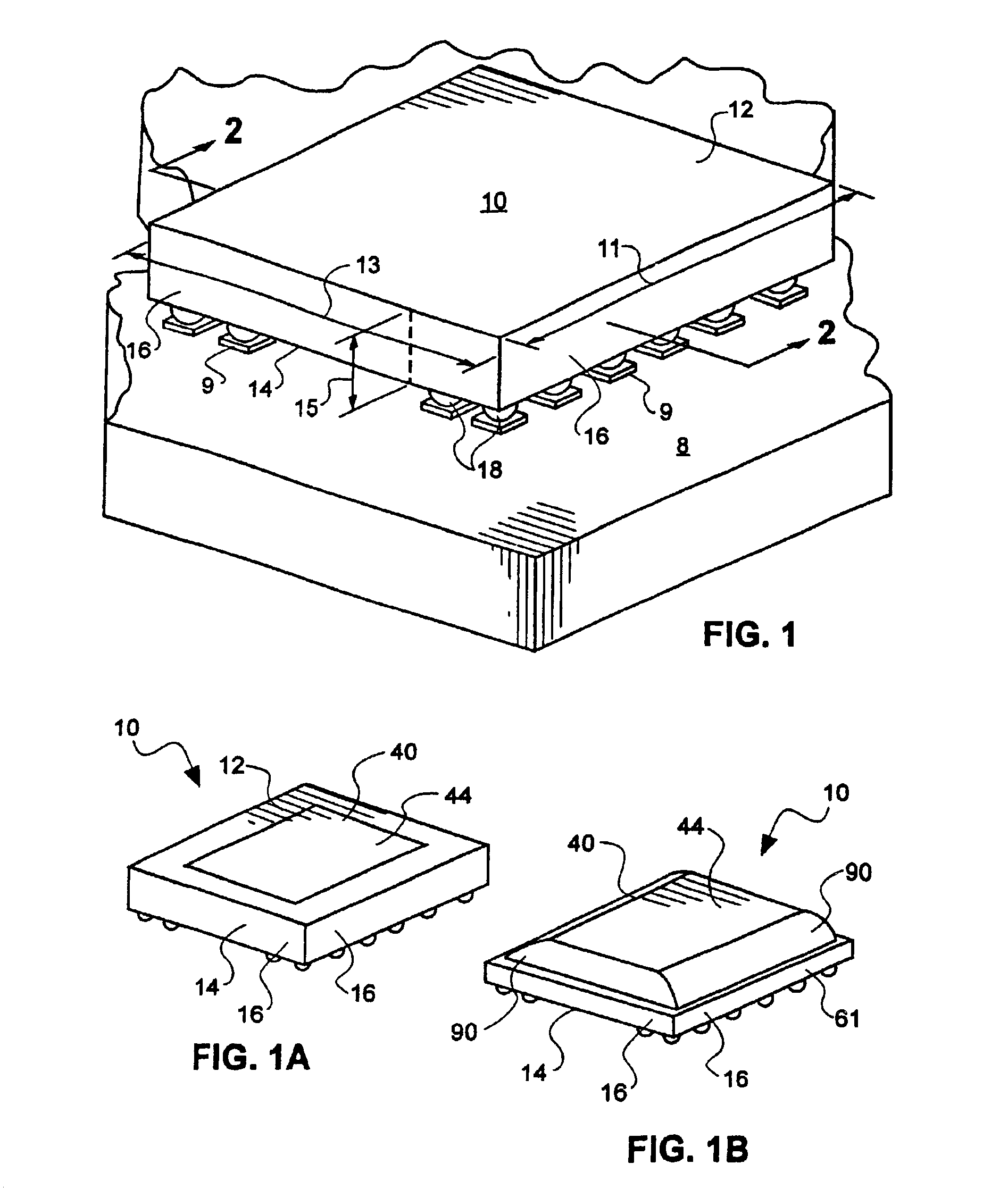

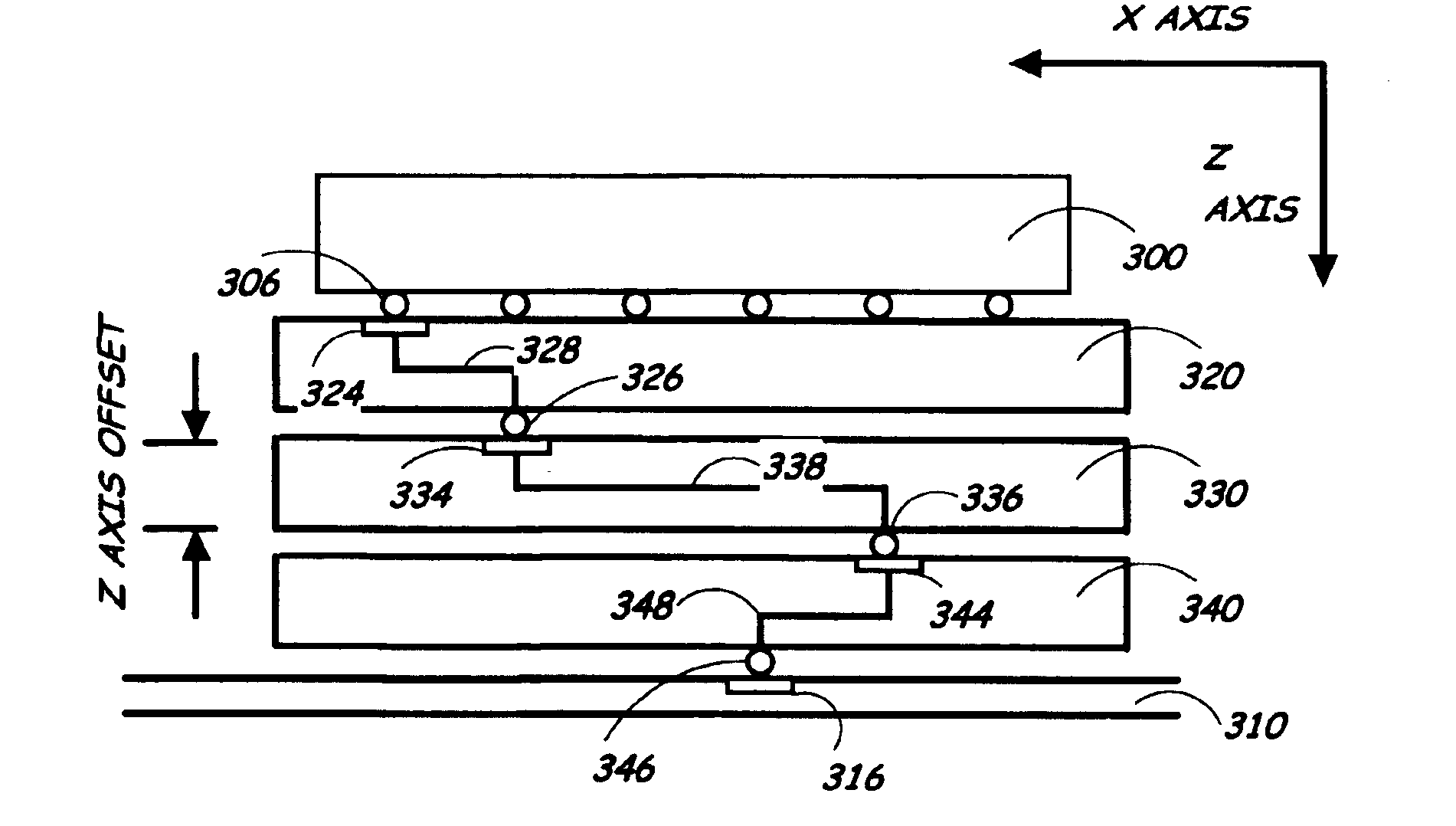

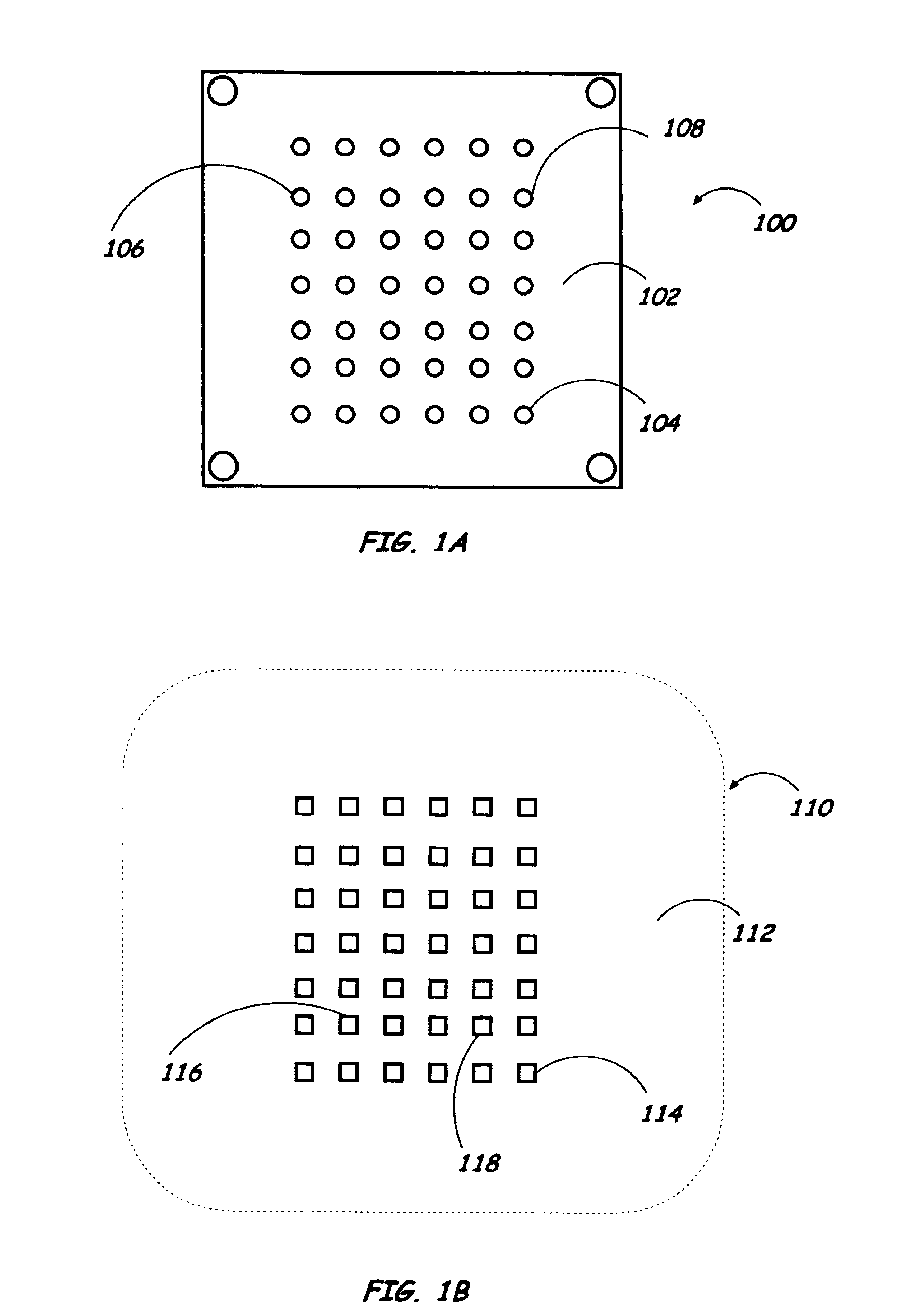

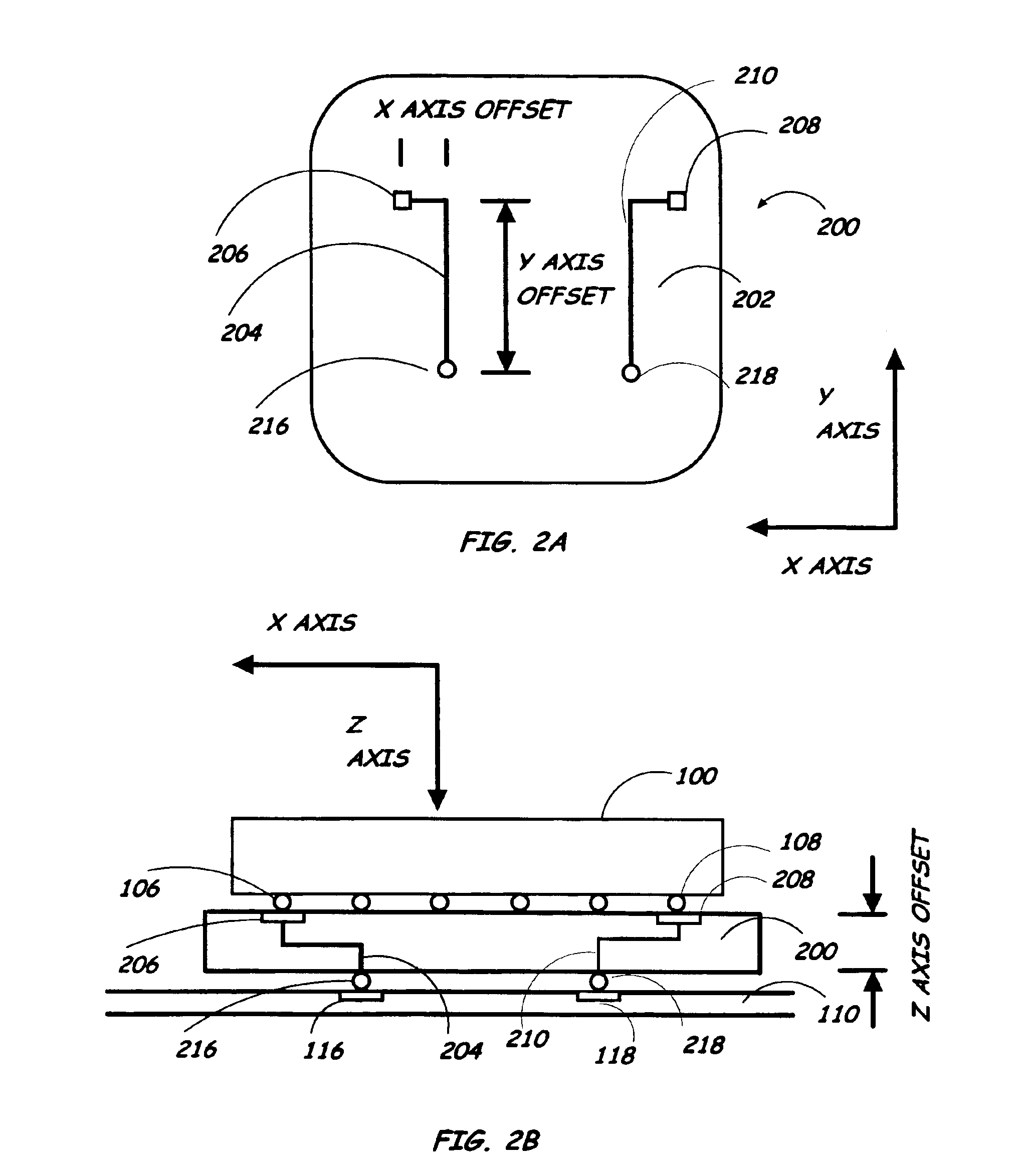

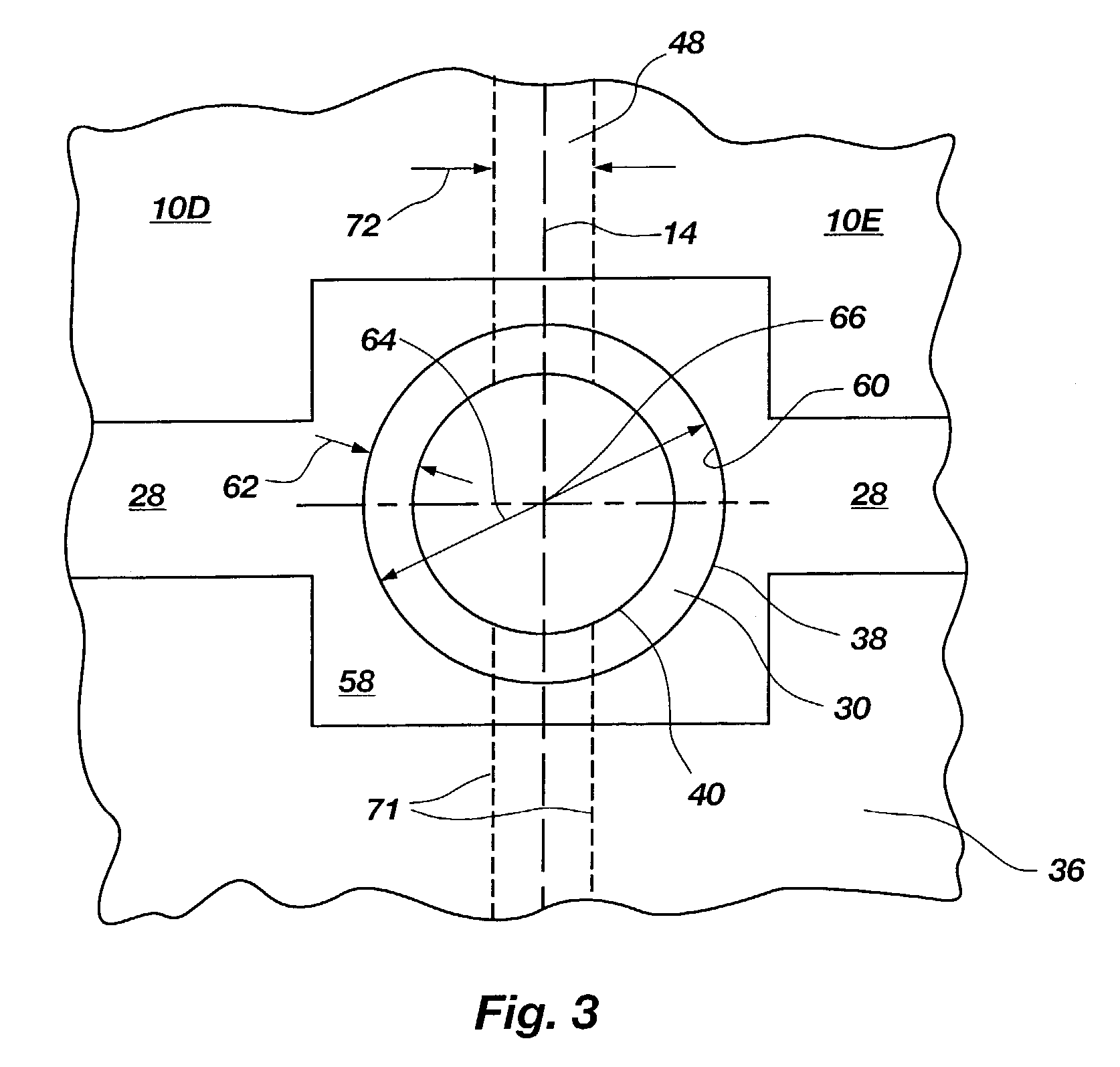

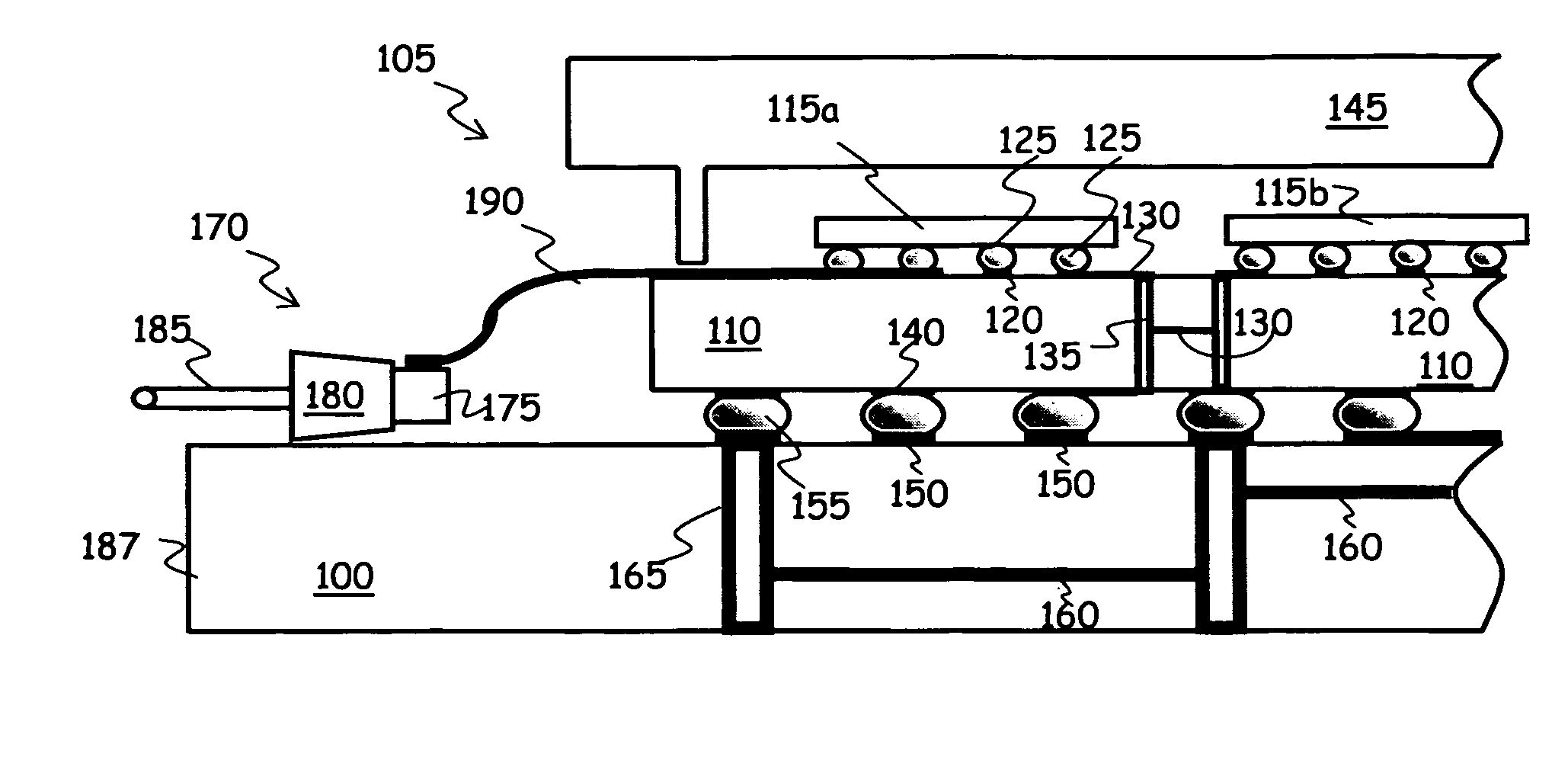

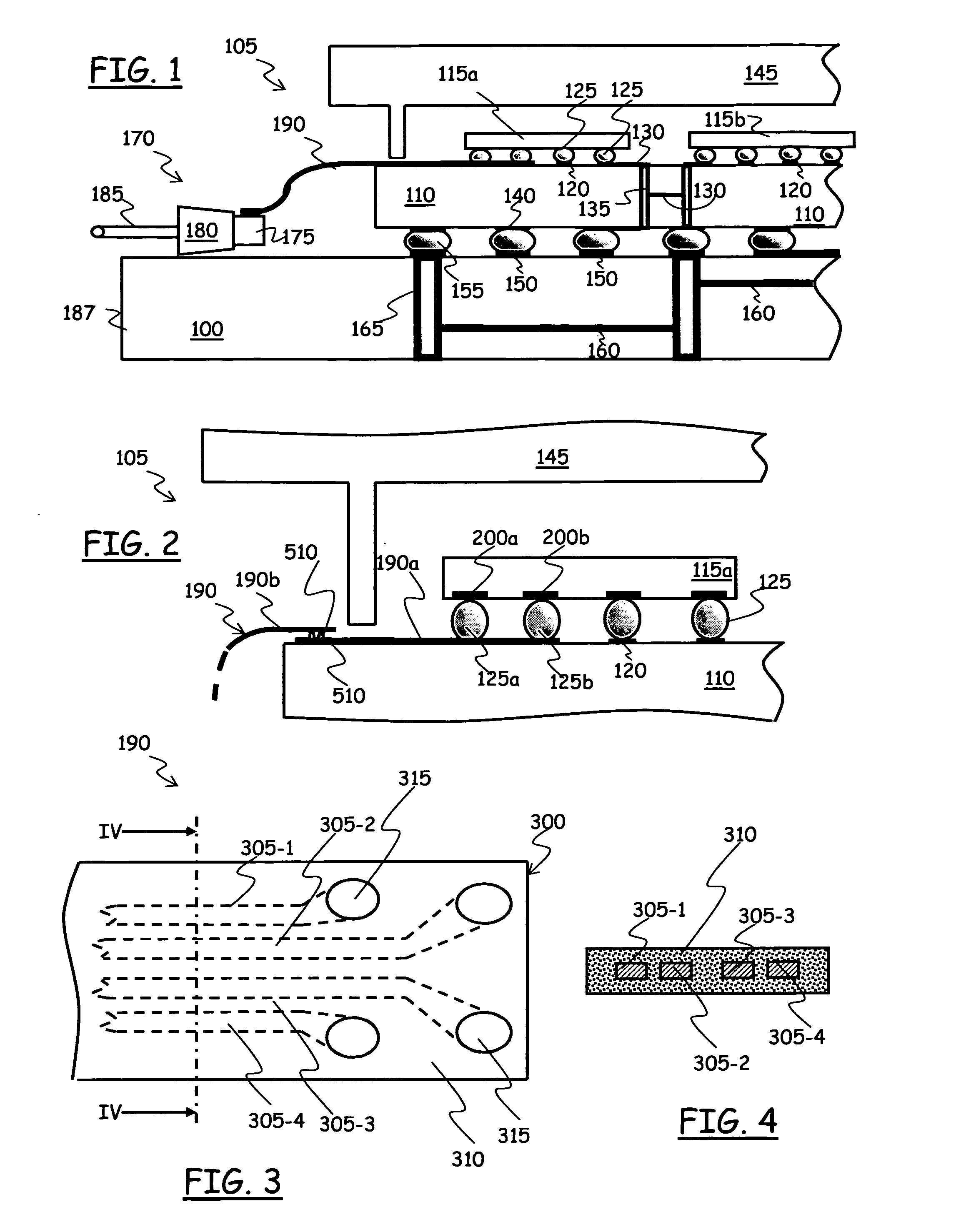

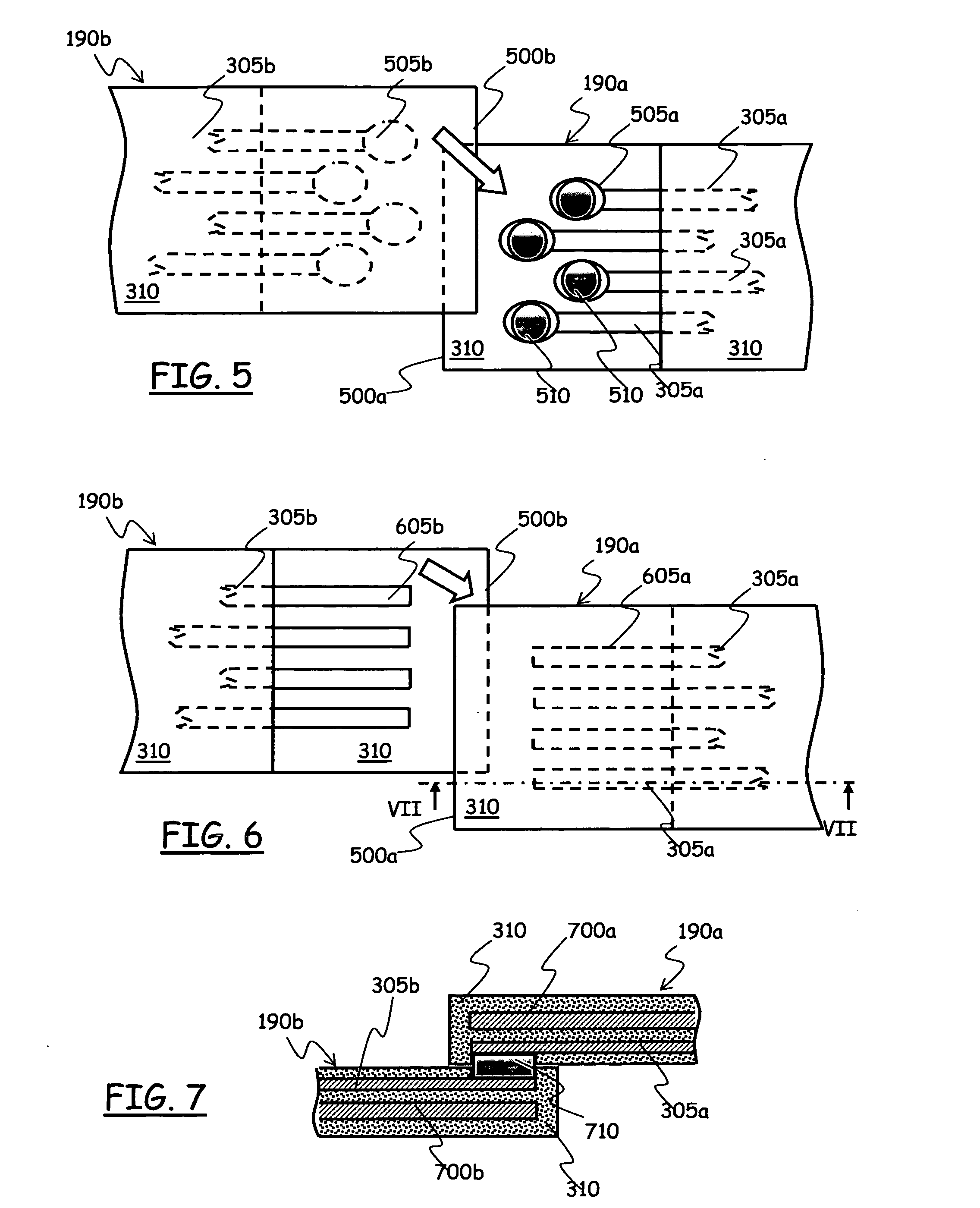

A multidie semiconductor device (MDSCD) package includes a generally planar interposer comprising a substrate with a central receptacle, upper surface conductors, and outer connectors on the lower surface of the interposer. Conductive vias connect upper surface conductors with outer connectors. One or more semiconductor devices may be mounted in the receptacle and one or more other semiconductor devices mounted above and / or below the interposer and attached thereto. The package may be configured to have a footprint not significantly larger than the footprint of the largest device and / or a thickness not significantly greater than the combined thickness of included devices. Methods for assembling and encapsulating packages from multidie wafers and multi-interposer sheets or strips are disclosed. Methods for combining a plurality of packages into a single stacked package are disclosed. The methods may include use of somewhat laterally extending intermediate conductive elements, flip-chip style electrical connection, or both within the same package.

Owner:MICRON TECH INC

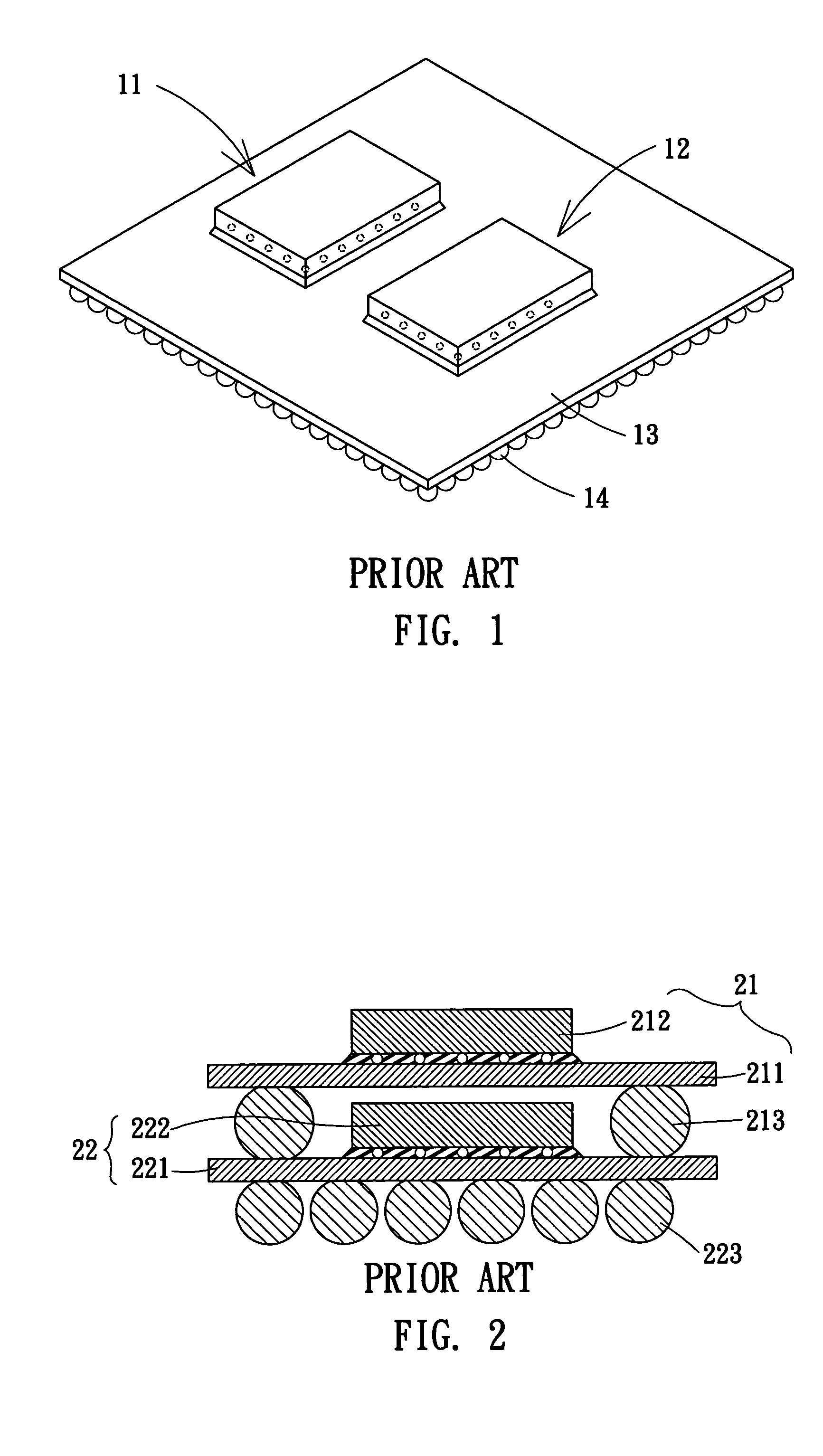

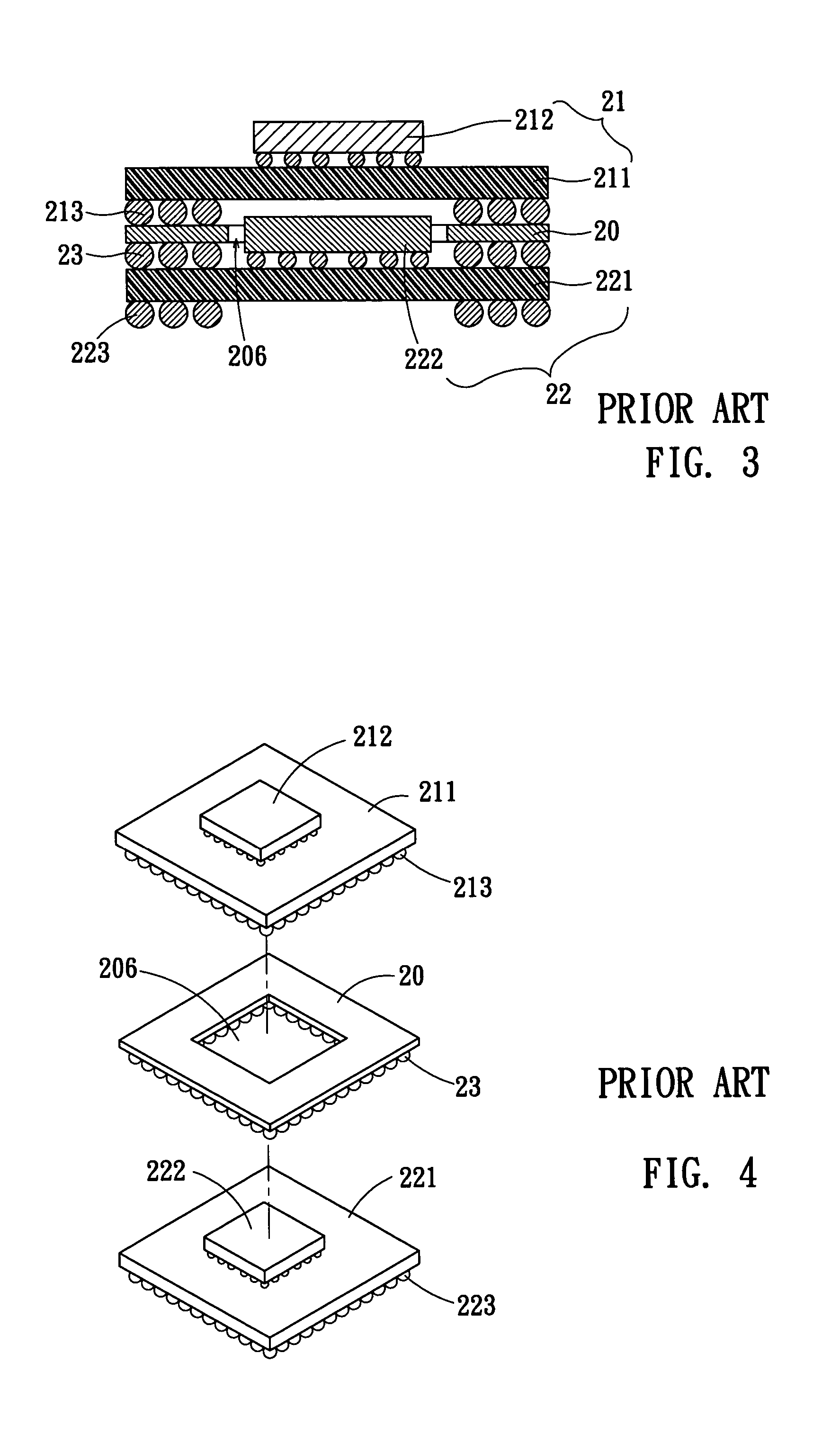

Semiconductor device assemblies and packages including multiple semiconductor devices and methods

InactiveUS6906415B2Reduce area requirementsHelp positioningPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorElectrical connection

A multidie semiconductor device (MDSCD) package includes a generally planar interposer comprising a substrate with a central receptacle, upper surface conductors, and outer connectors on the lower surface of the interposer. Conductive vias connect upper surface conductors with outer connectors. One or more semiconductor devices may be mounted in the receptacle and one or more other semiconductor devices mounted above and / or below the interposer and attached thereto. The package may be configured to have a footprint not significantly larger than the footprint of the largest device and / or a thickness not significantly greater than the combined thickness of included devices. Methods for assembling and encapsulating packages from multidie wafers and multi-interposer sheets or strips are disclosed. Methods for combining a plurality of packages into a single stacked package are disclosed. The methods may include use of somewhat laterally extending intermediate conductive elements, flip-chip style electrical connection, or both within the same package.

Owner:MICRON TECH INC

Multi-chips module assembly package

ActiveUS7015571B2Increase the number ofPrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringElectrical and Electronics engineering

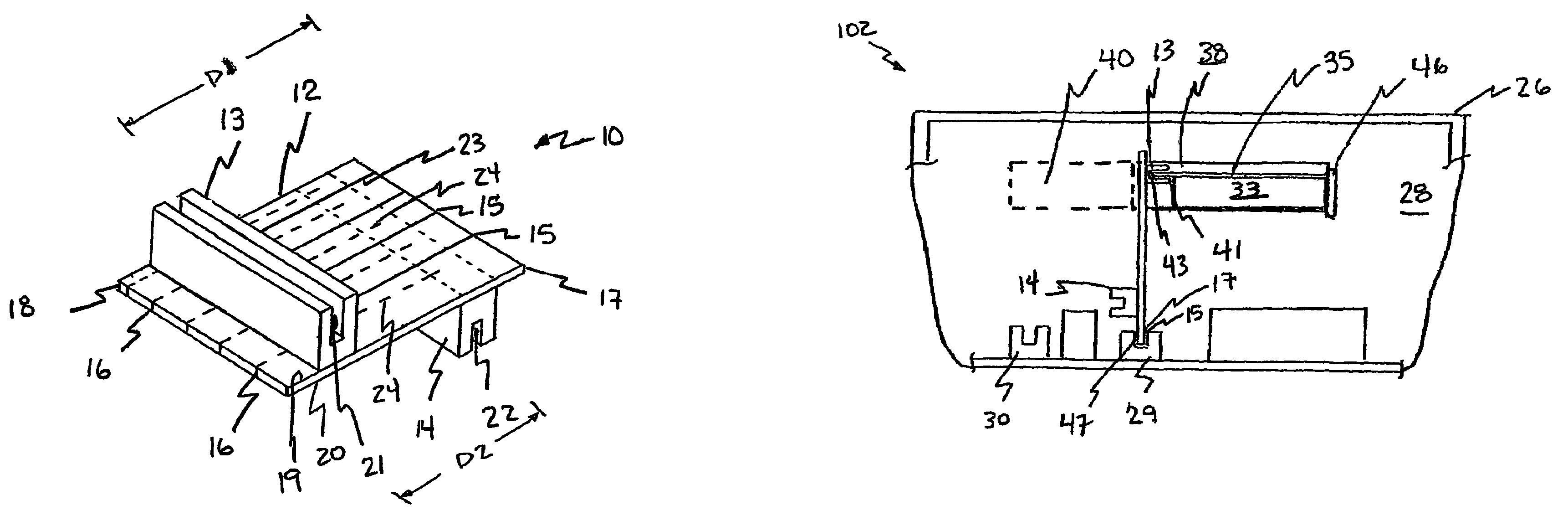

A multi-chips module assembly package mainly comprises a first package, a second package and an intermediate substrate. The intermediate substrate includes an opening, at least a via and a plurality of circuit layers, wherein the second package is accommodated in the opening. The via has an inner wall, and a plurality of separated electrically conductive layers, which is formed on the inner wall and connected with the corresponding circuit layers. The first package electrically connects with the second package through the intermediate substrate, and the intermediate substrate is interposed between the first package and the second package. At least an insulator is formed in the via, and the separated electrically conductive layers are separated from each other. After the intermediate substrate is interposed between the first package and the second package, there will be not enough space between the intermediate substrate, the first package and the second package for disposing conductive devices therein. Therefore, the first package will be electrically connected to the second package through the separated electrically conductive layers of the intermediate substrate for providing more conductive devices disposed and interposed between the intermediate substrate, the first package and the second package.

Owner:ADVANCED SEMICON ENG INC

Converter device

InactiveUS6914786B1Printed circuit assemblingSemiconductor/solid-state device detailsIntegrated circuitEngineering

The present invention is directed to a converter device. In a first aspect of the present invention, a converter device includes a board having a first side and a second side. The first side includes a first set of contacts suitable for electrically contacting an integrated circuit having a first configuration. The second side includes a second set of contacts suitable for electrically contacting a circuit board having a second configuration. The second set of contacts is communicatively coupled to the first set of contacts.

Owner:BELL SEMICON LLC

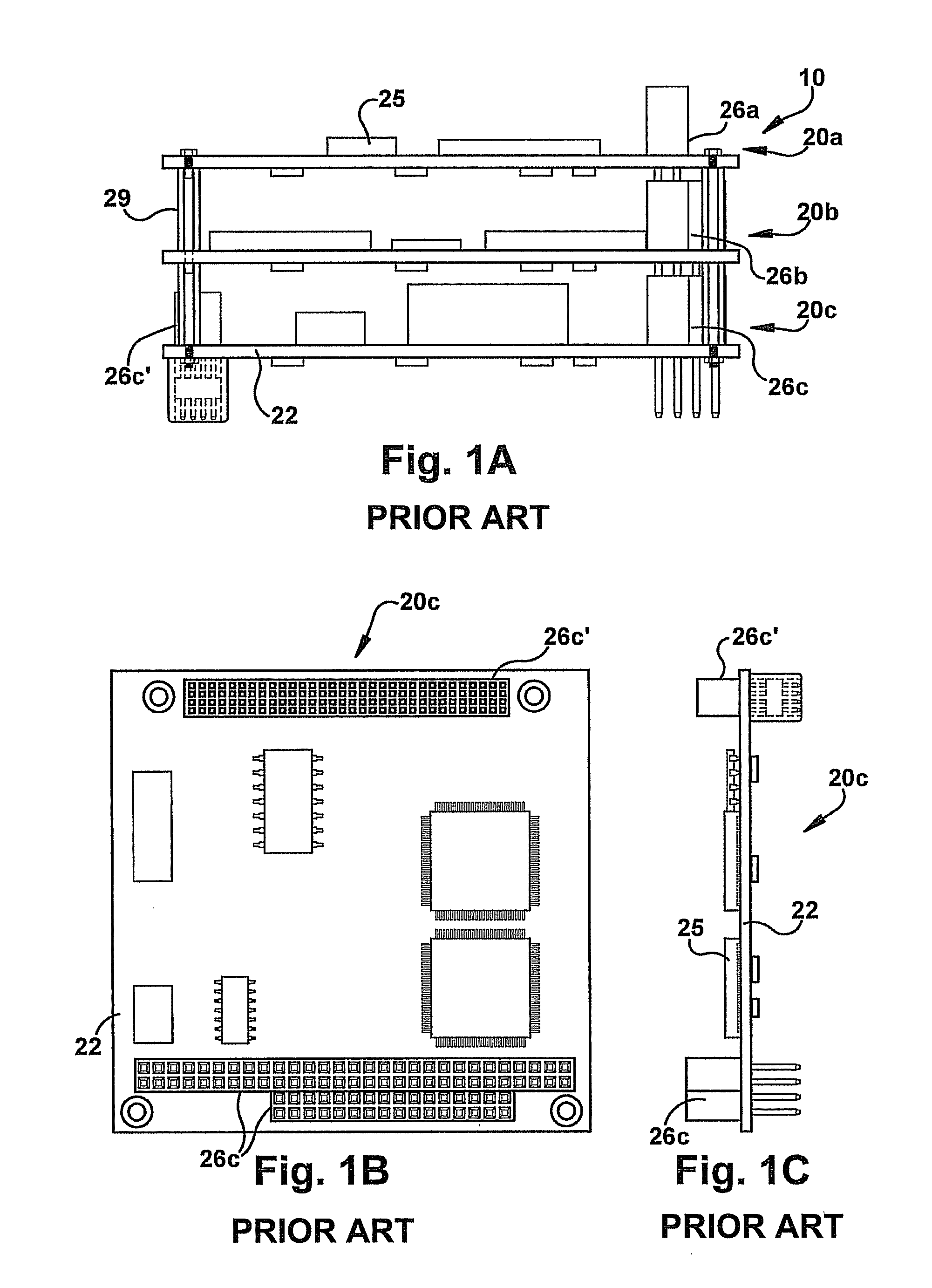

Circuit board riser for volume sharing peripheral cards

A substantially rigid card having a first side and an opposing second side, a first connector end adapted to mate with a first expansion connector on a circuit board and a second connector end adapted to mate with a second expansion connector on the board. A first peripheral card connector is connected to the first side and electrically connected to the first connector end, wherein the first connector is of a first form factor and adapted to mate with a first peripheral card. A second peripheral card connector is connected to the second side and electrically connected to the second connector end, wherein the second connector is of a second form factor different from the first form factor and matable with a second peripheral card. The first peripheral card connector is spaced from the first connector end a distance approximately the same as the distance the second peripheral card connector is spaced from the second connector end such that the peripheral card carried by the riser card shares approximately the same region whether the riser card is in a first or a second orientation.

Owner:LENOVO PC INT

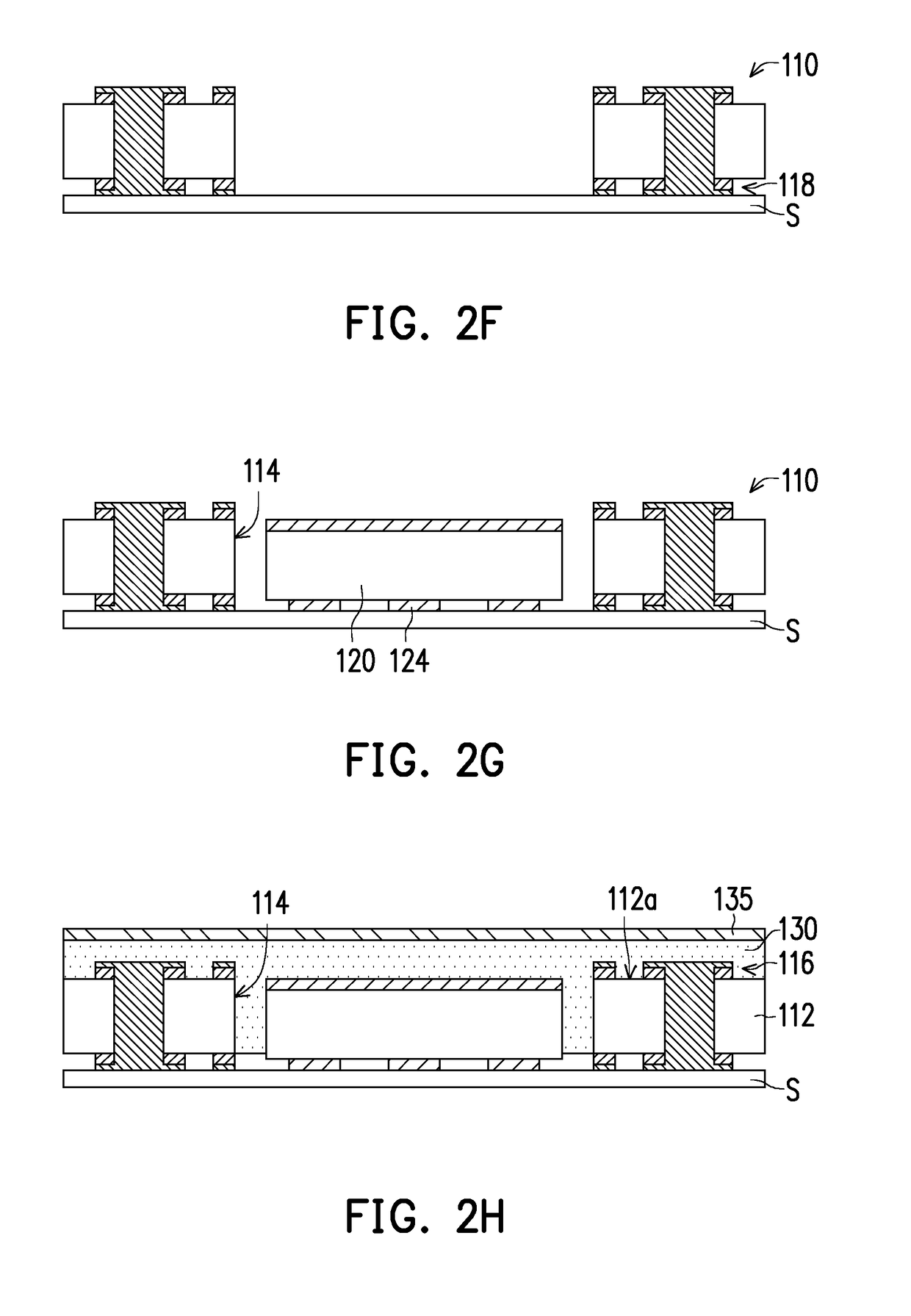

Component embedded package carrier and manufacturing method thereof

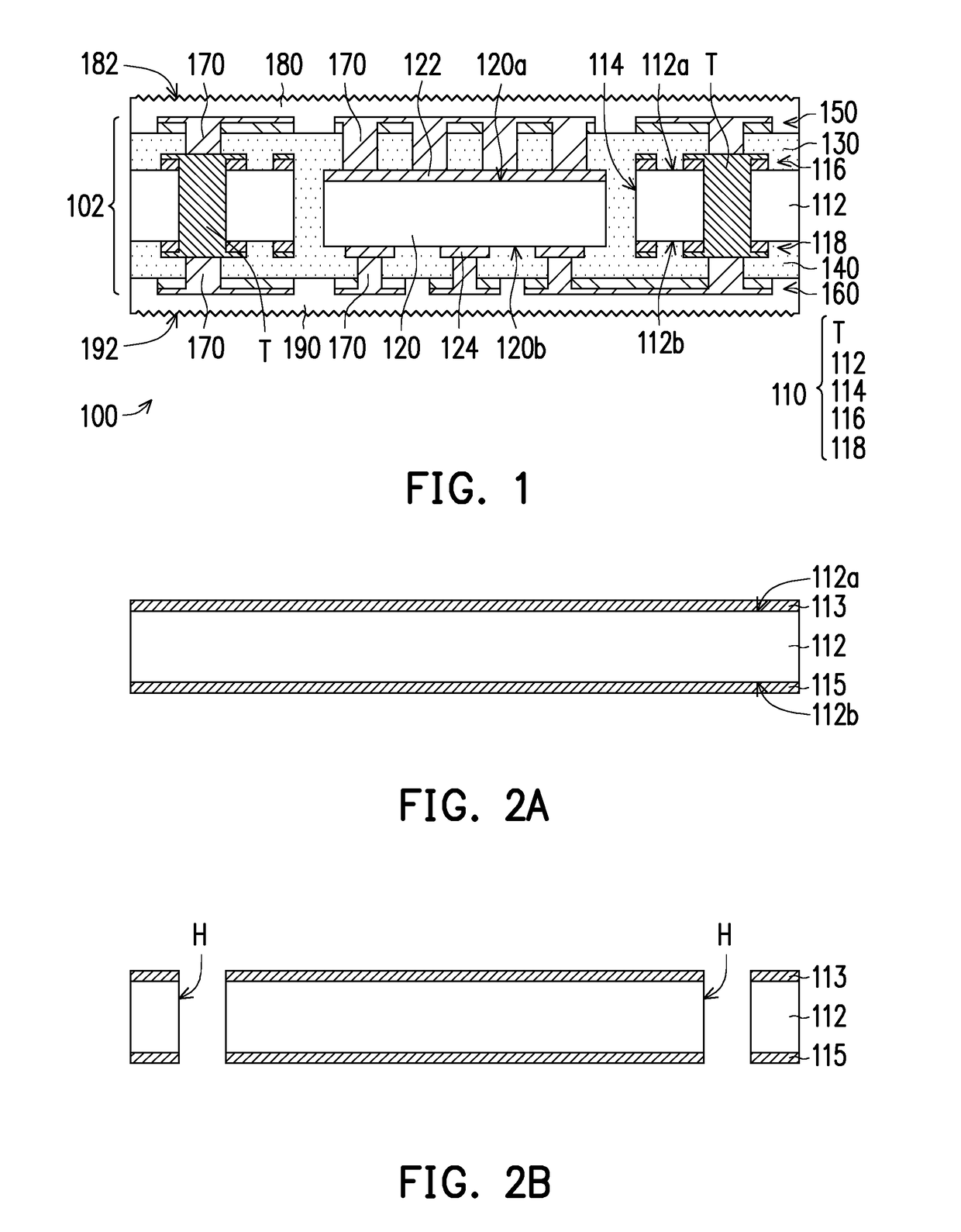

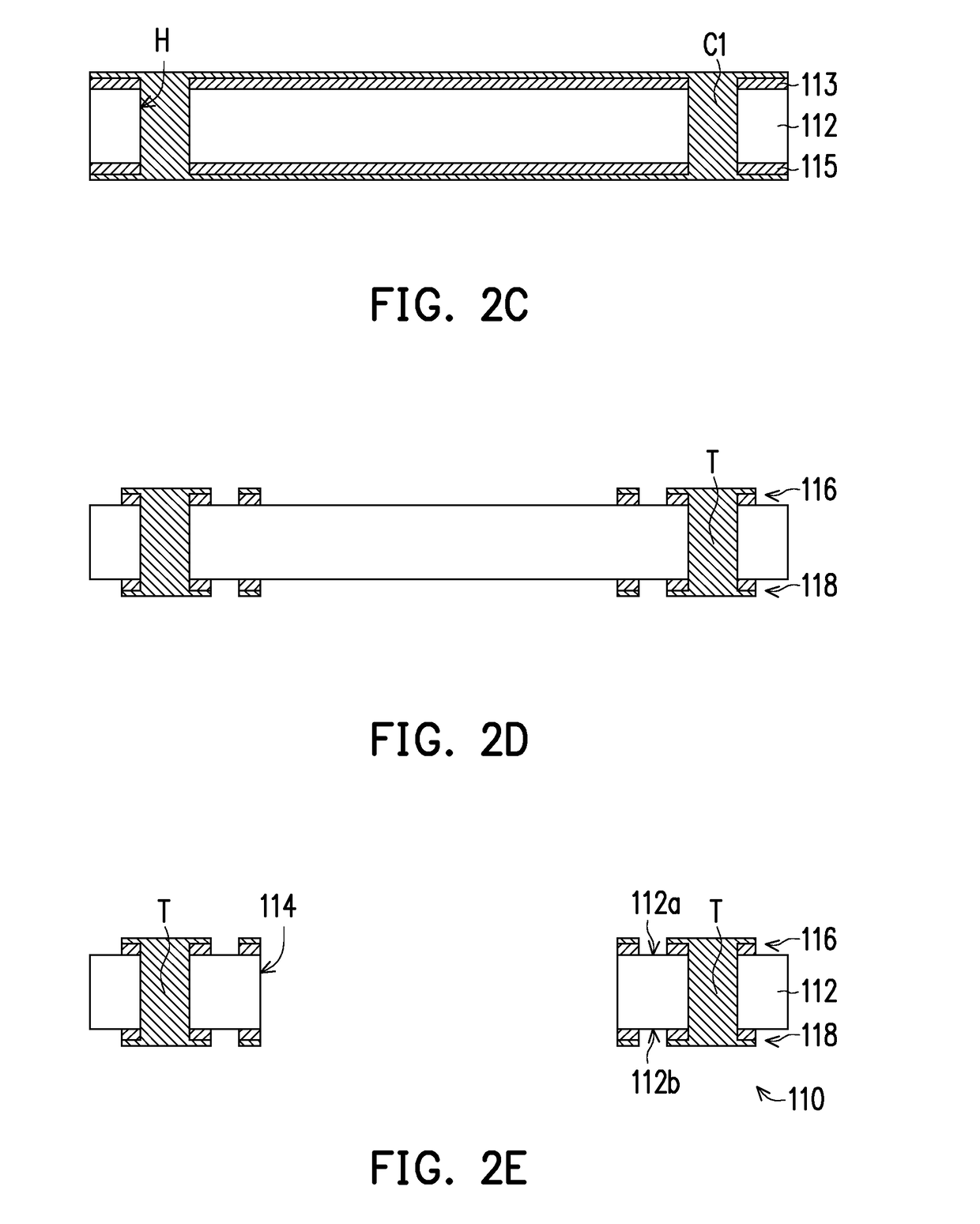

ActiveUS20180352658A1Small package thicknessImprove performancePrinted circuit assemblingSemiconductor/solid-state device detailsElectronic component

A component embedded package carrier includes a core layer, at least one electronic component, a first insulating layer, a second insulating layer, a third patterned conductive layer, a fourth patterned conductive layer, a plurality of conductive blind via structures, a first protecting layer and a second protecting layer. The electronic component is disposed inside an opening of the core layer. The first and second insulating layers completely fill the opening and completely encapsulate the electronic component. The conductive blind via structures connect the third and fourth patterned conductive layers with a plurality of conductive through hole structures of the core layer, and connect the third and fourth patterned conductive layers with the electronic component. The first protecting layer covers the third patterned conductive layer and has a first roughness surface. The second protecting layer covers the fourth patterned conductive layer and has a second roughness surface.

Owner:SUBTRON TECH

Electronic device

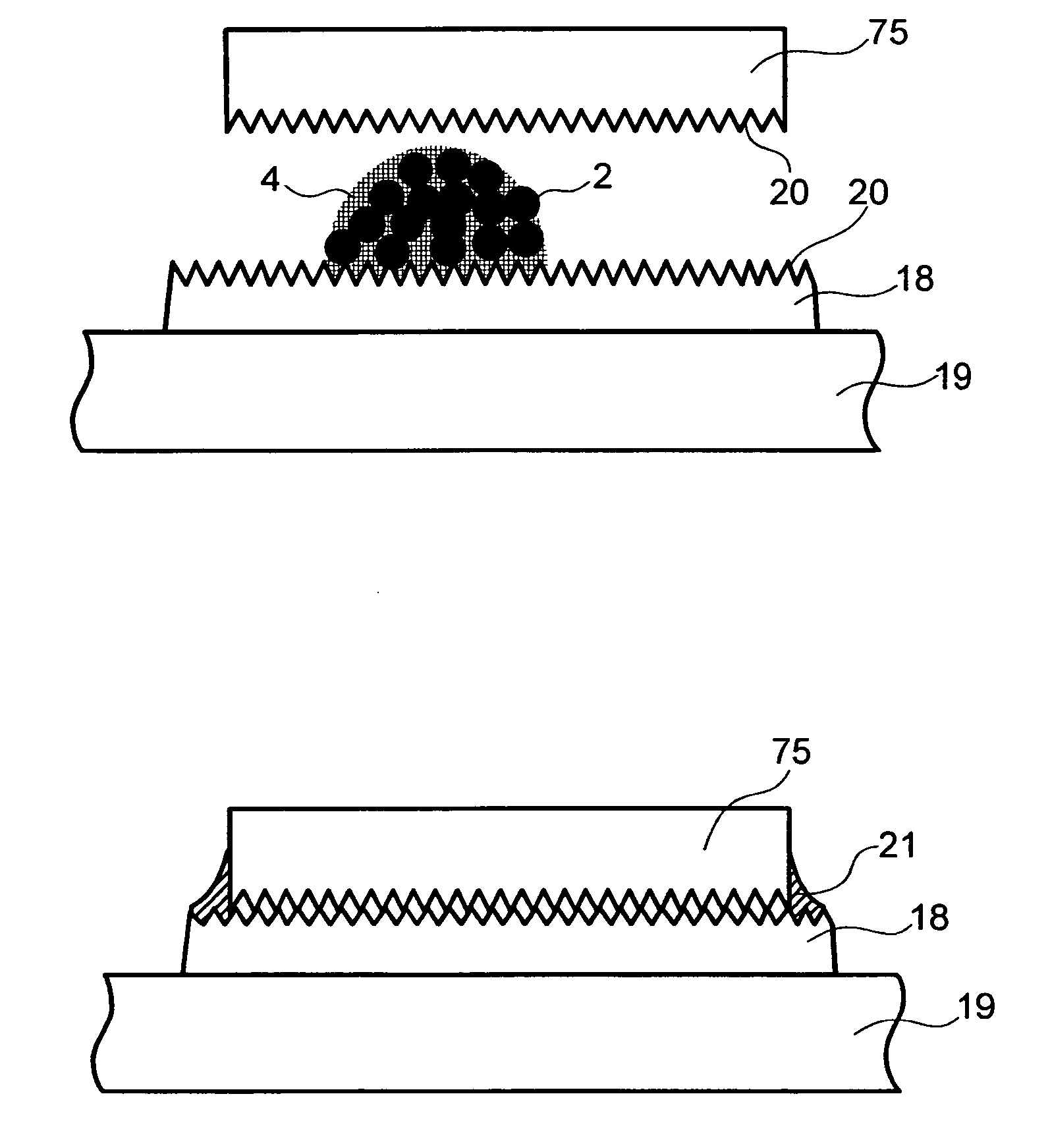

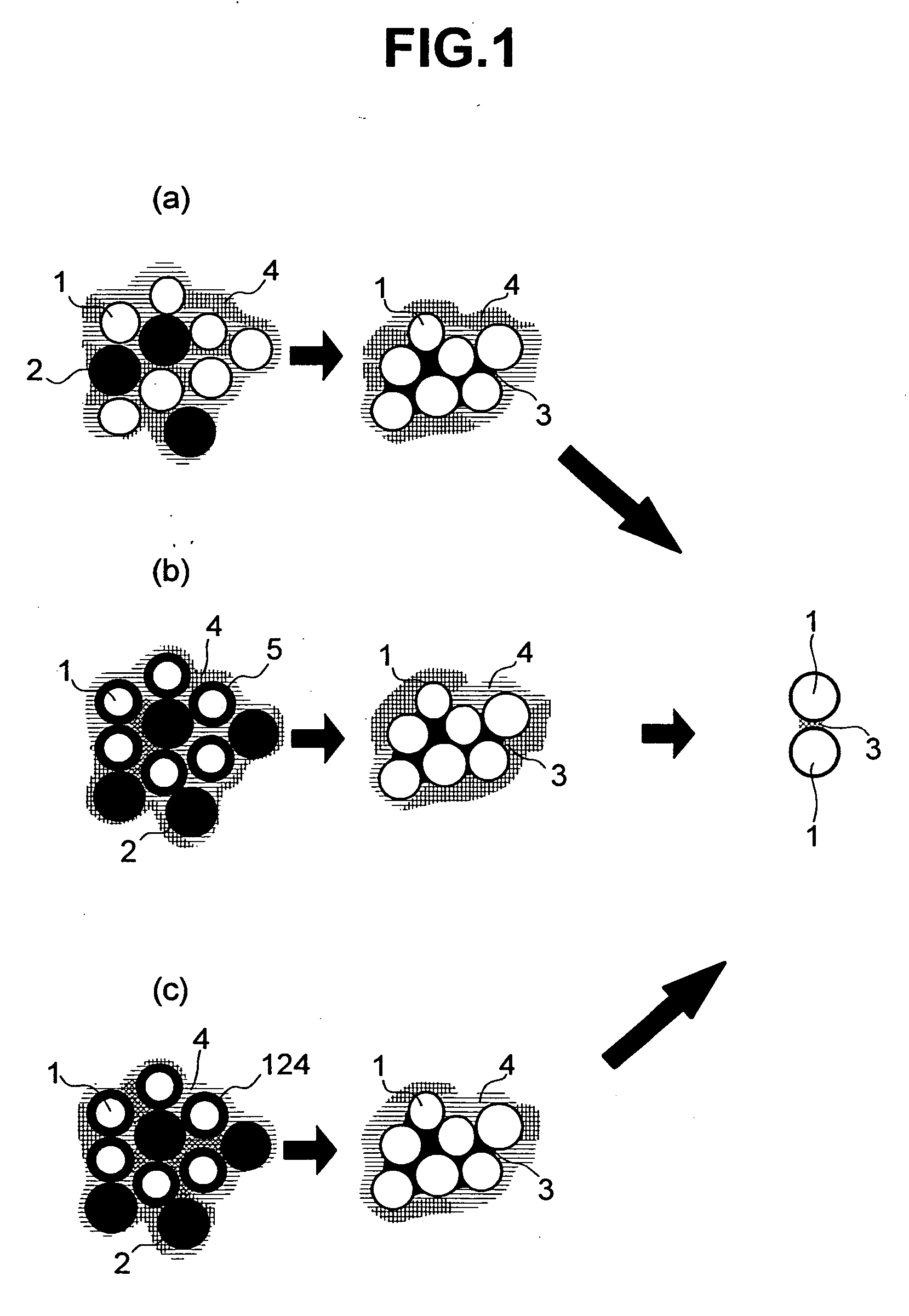

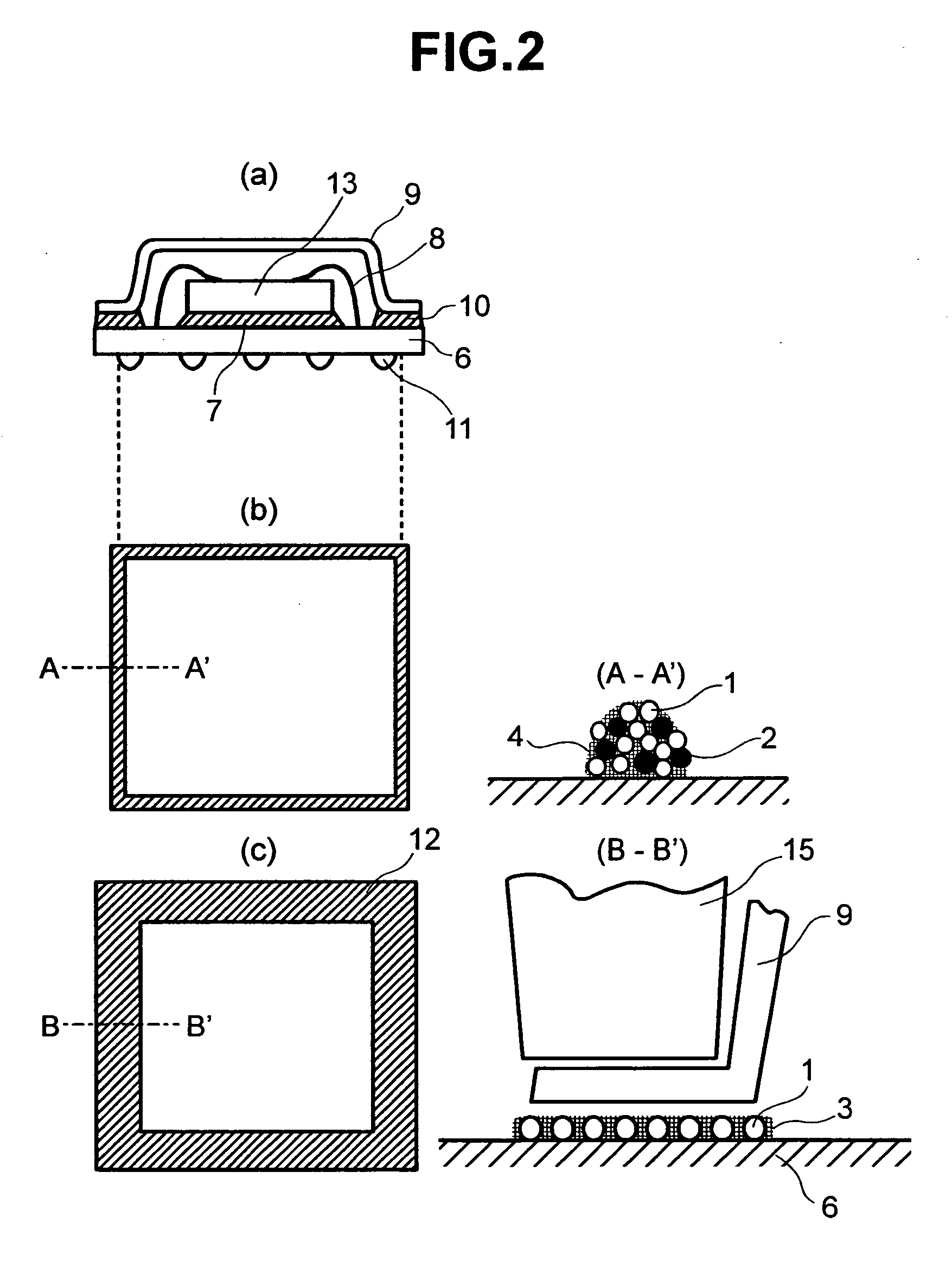

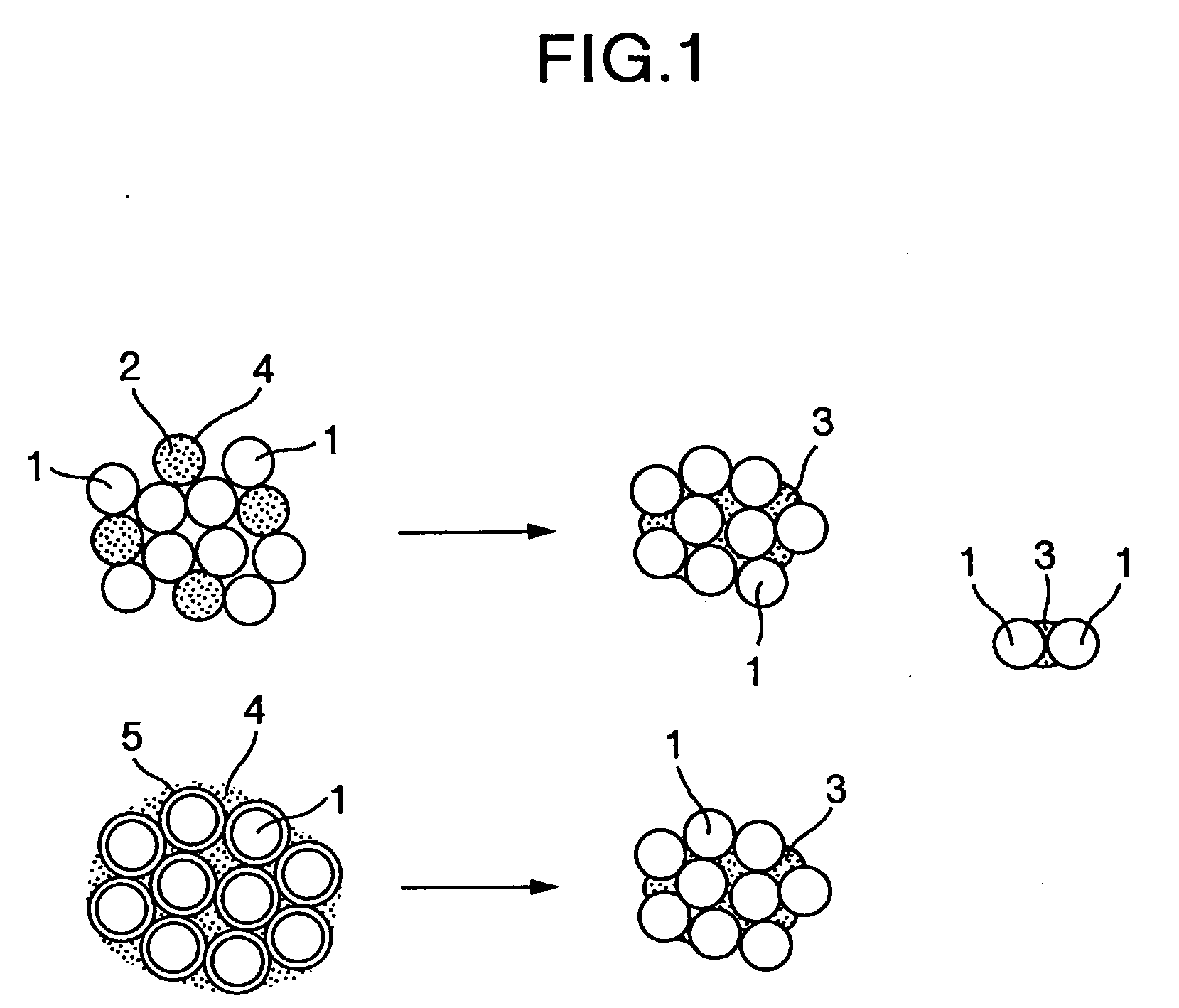

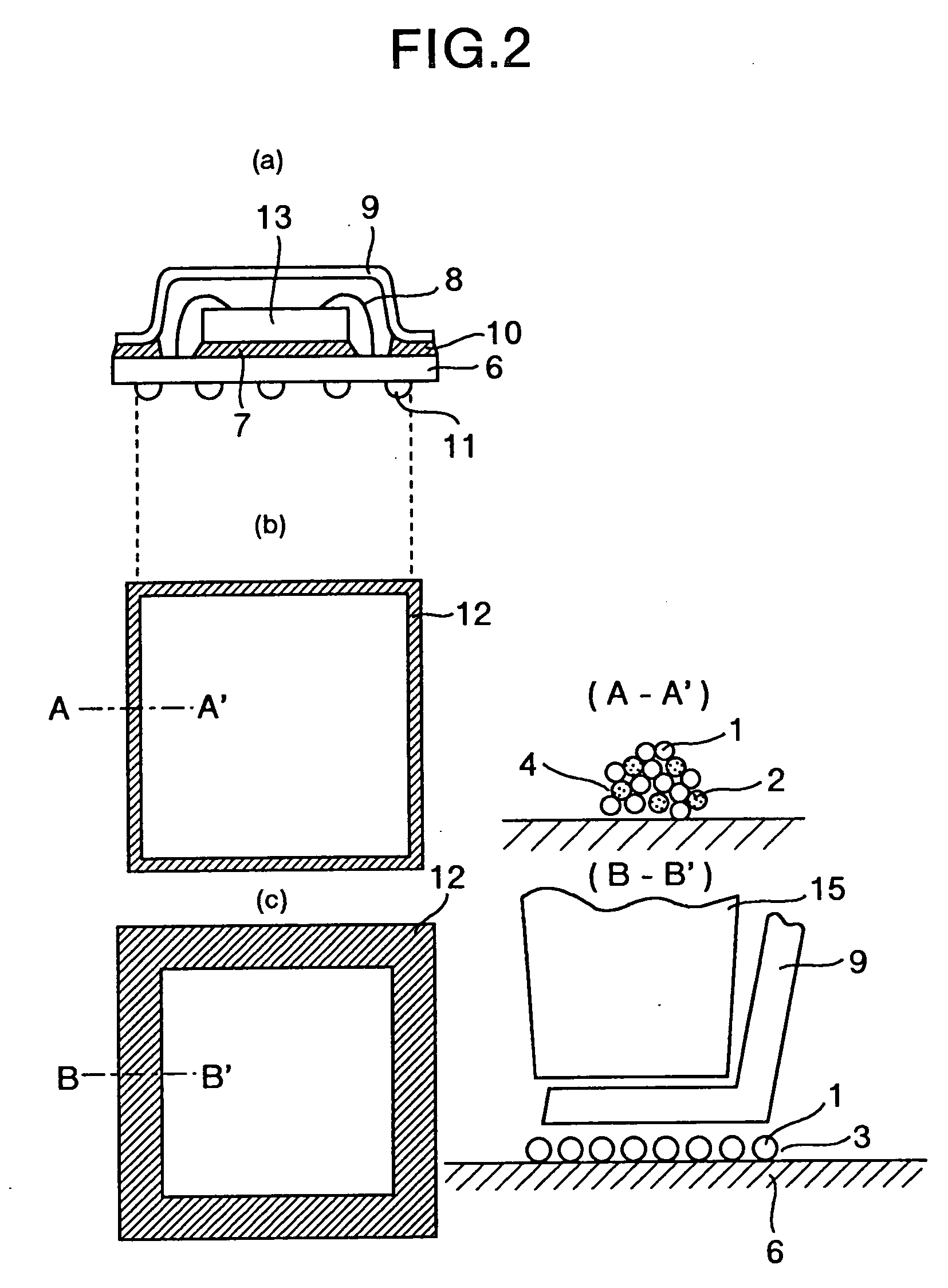

InactiveUS20060145352A1Reduce the possibilityEasy to cutPrinted circuit assemblingFinal product manufactureDevice materialSemiconductor

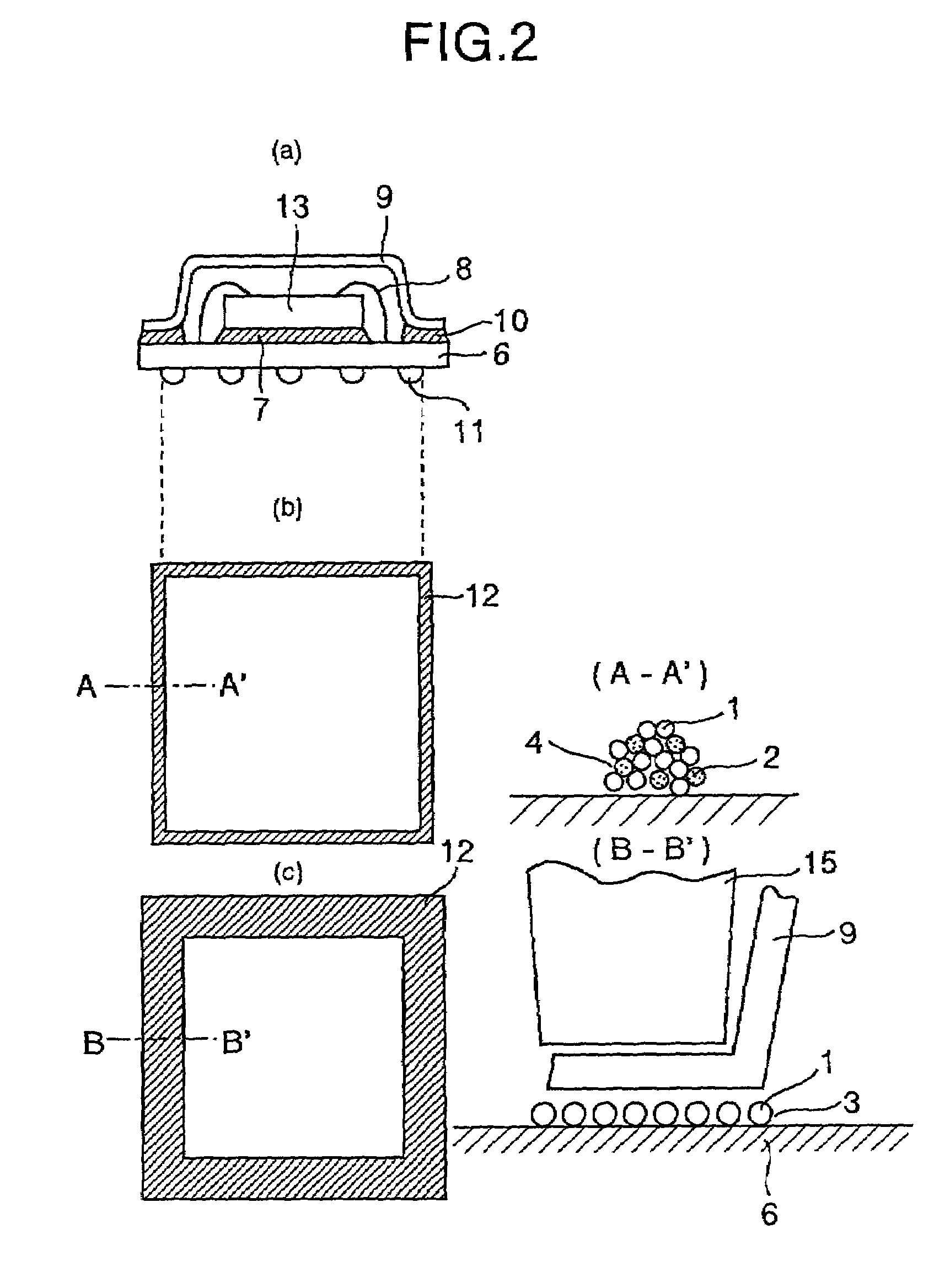

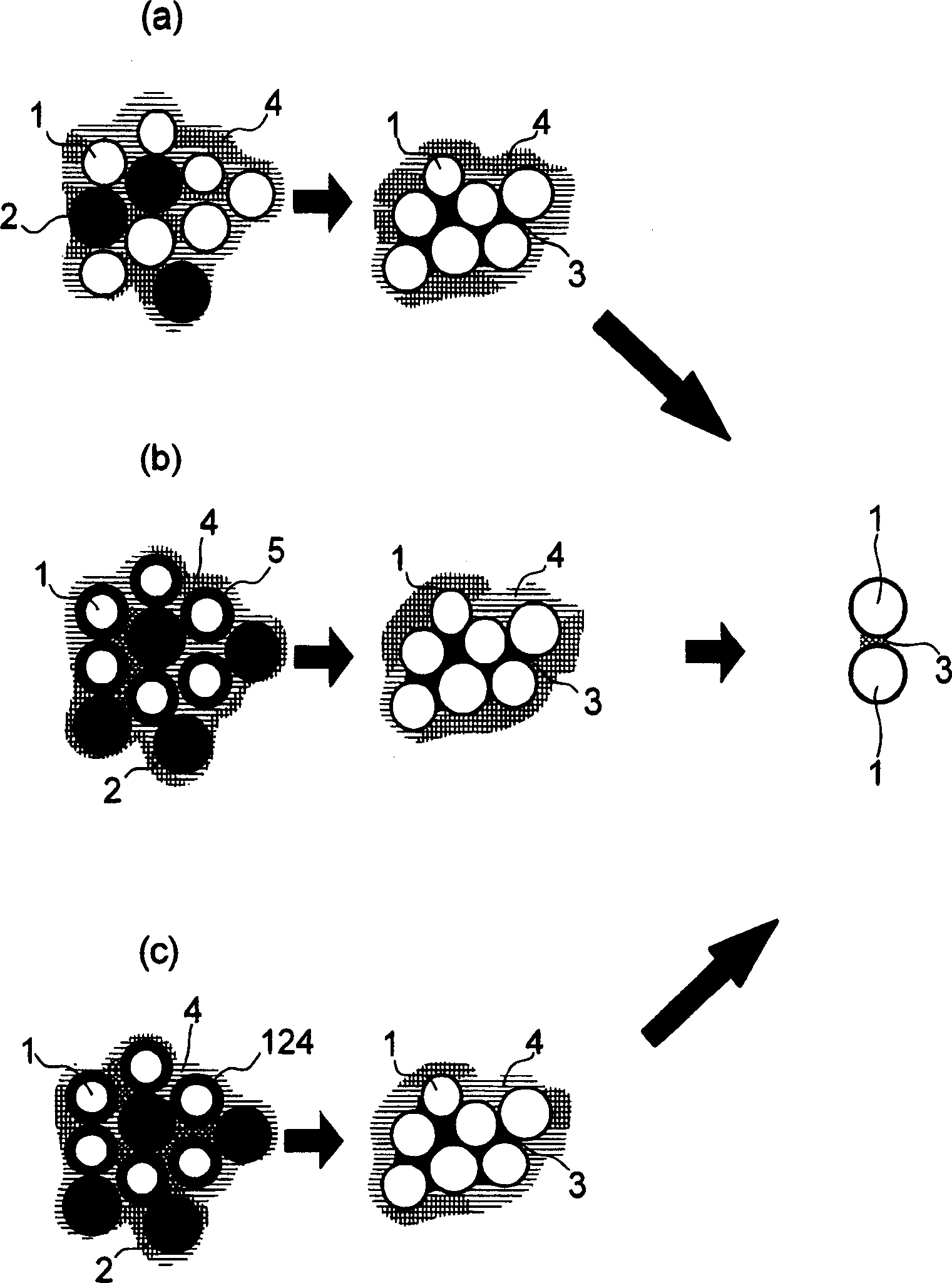

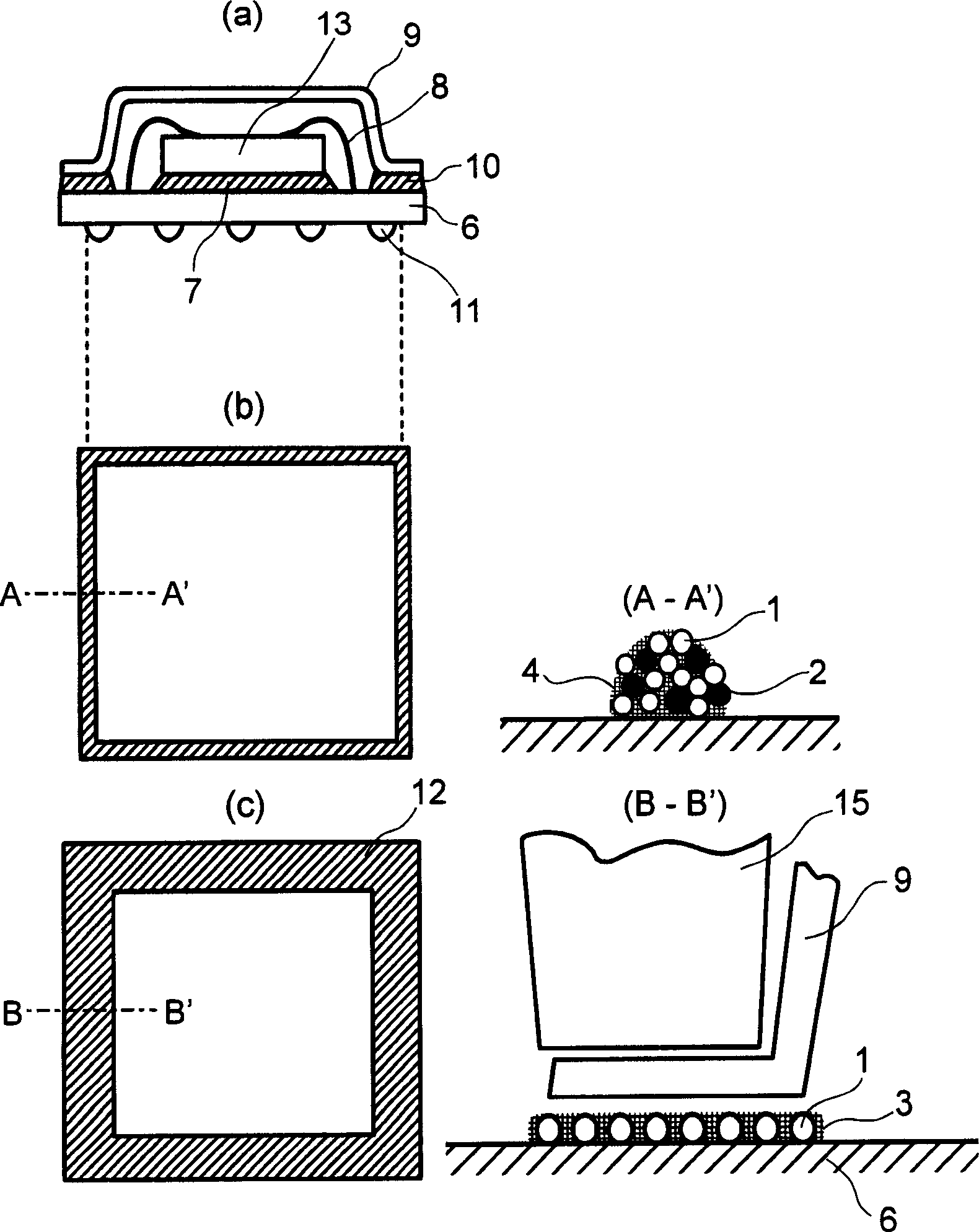

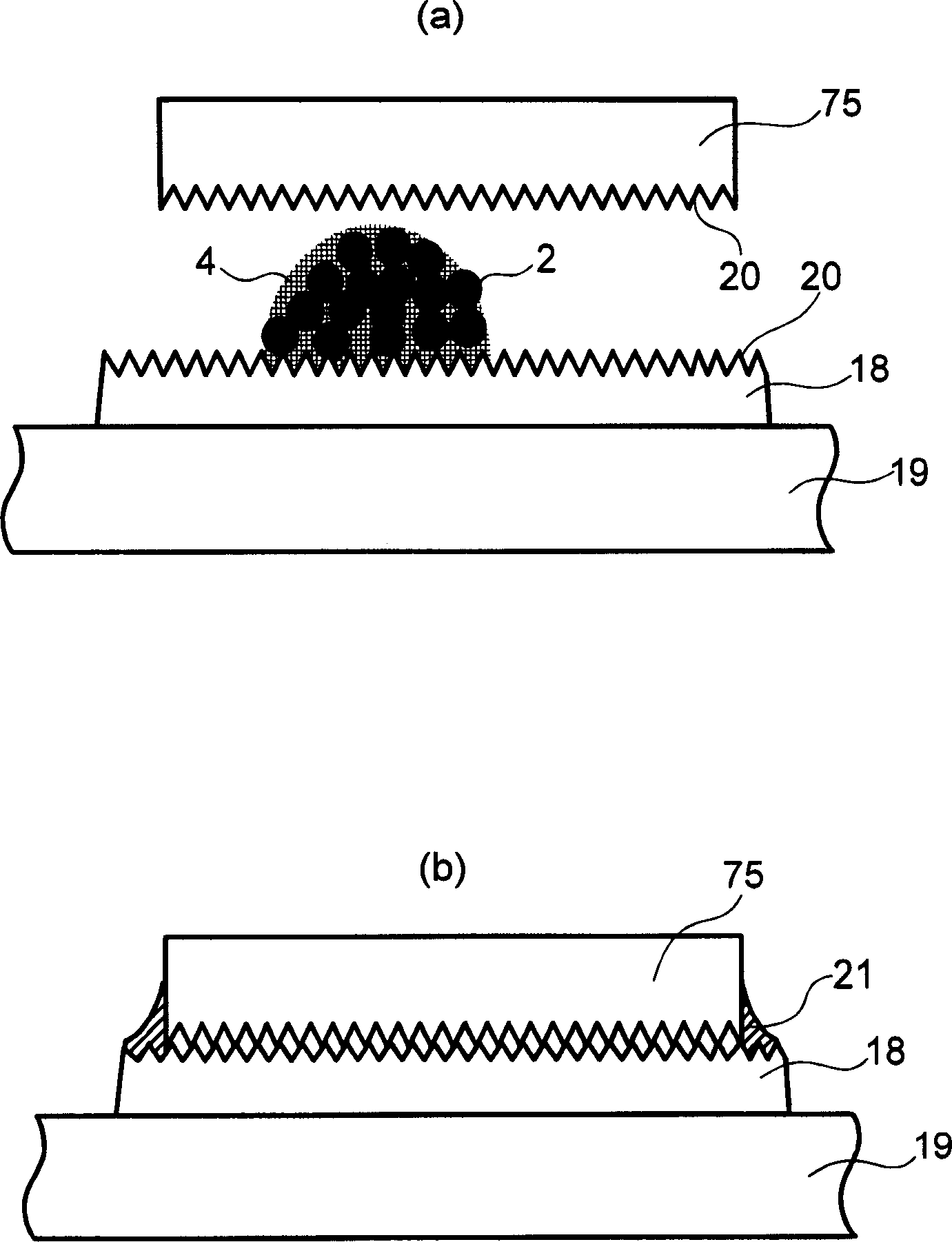

In an electronic device which realizes high-temperature-side solder bonding in temperature-hierarchical bonding, a bonding portion between a semiconductor device and a substrate is formed of metal balls made of Cu, or the like, and compounds formed of metal balls and Sn, and the metal balls are bonded together by the compounds.

Owner:HITACHI LTD

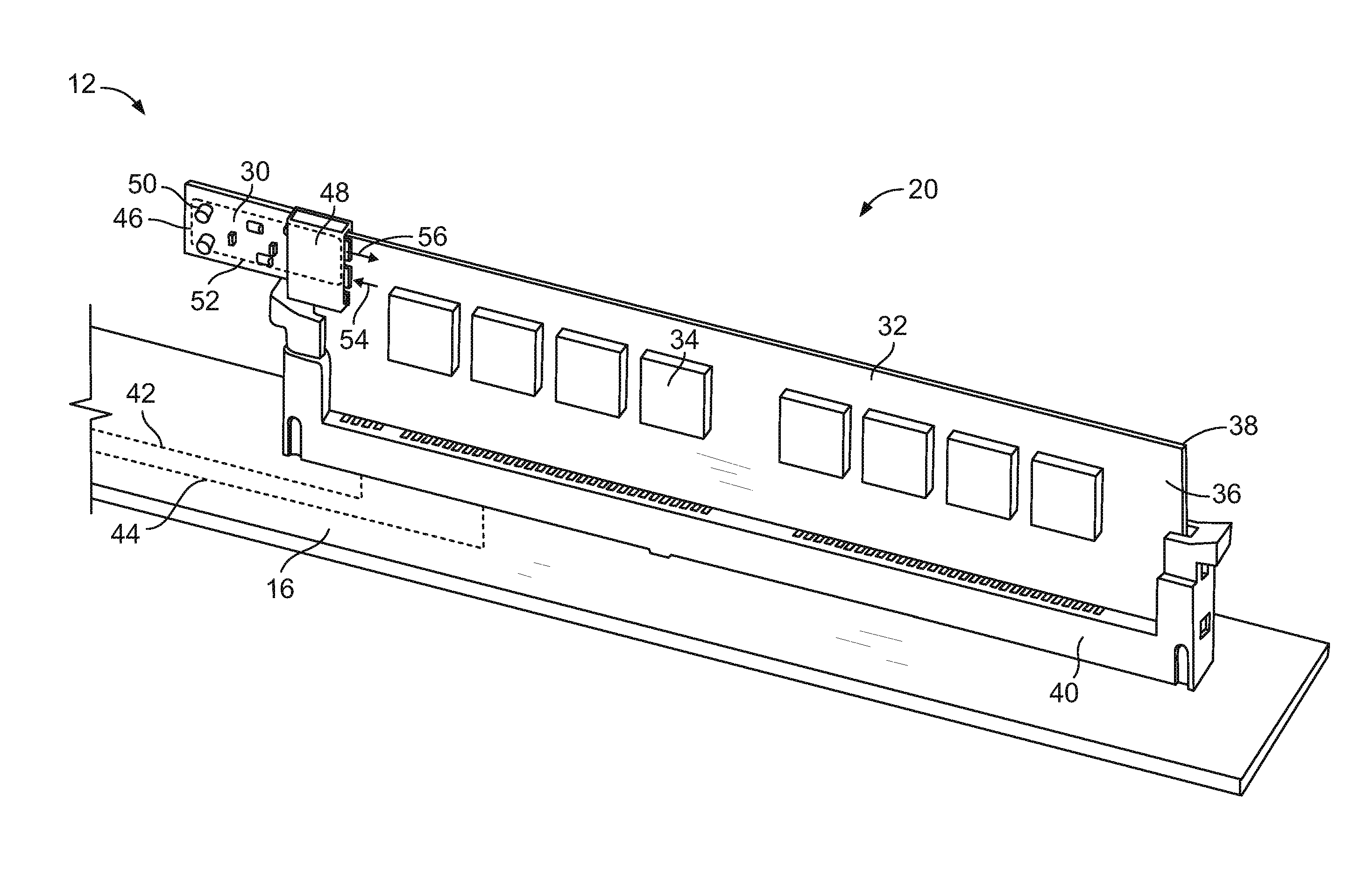

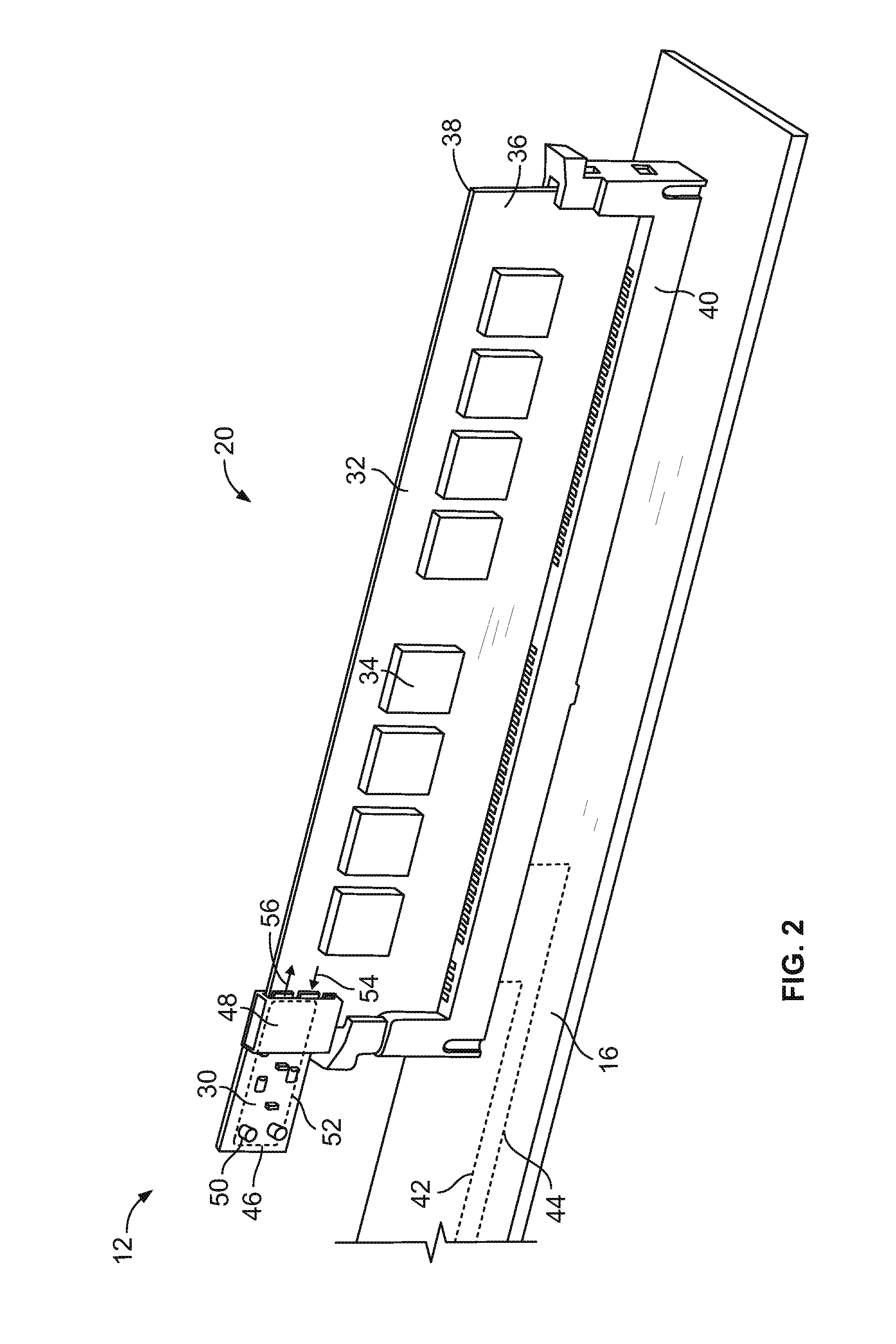

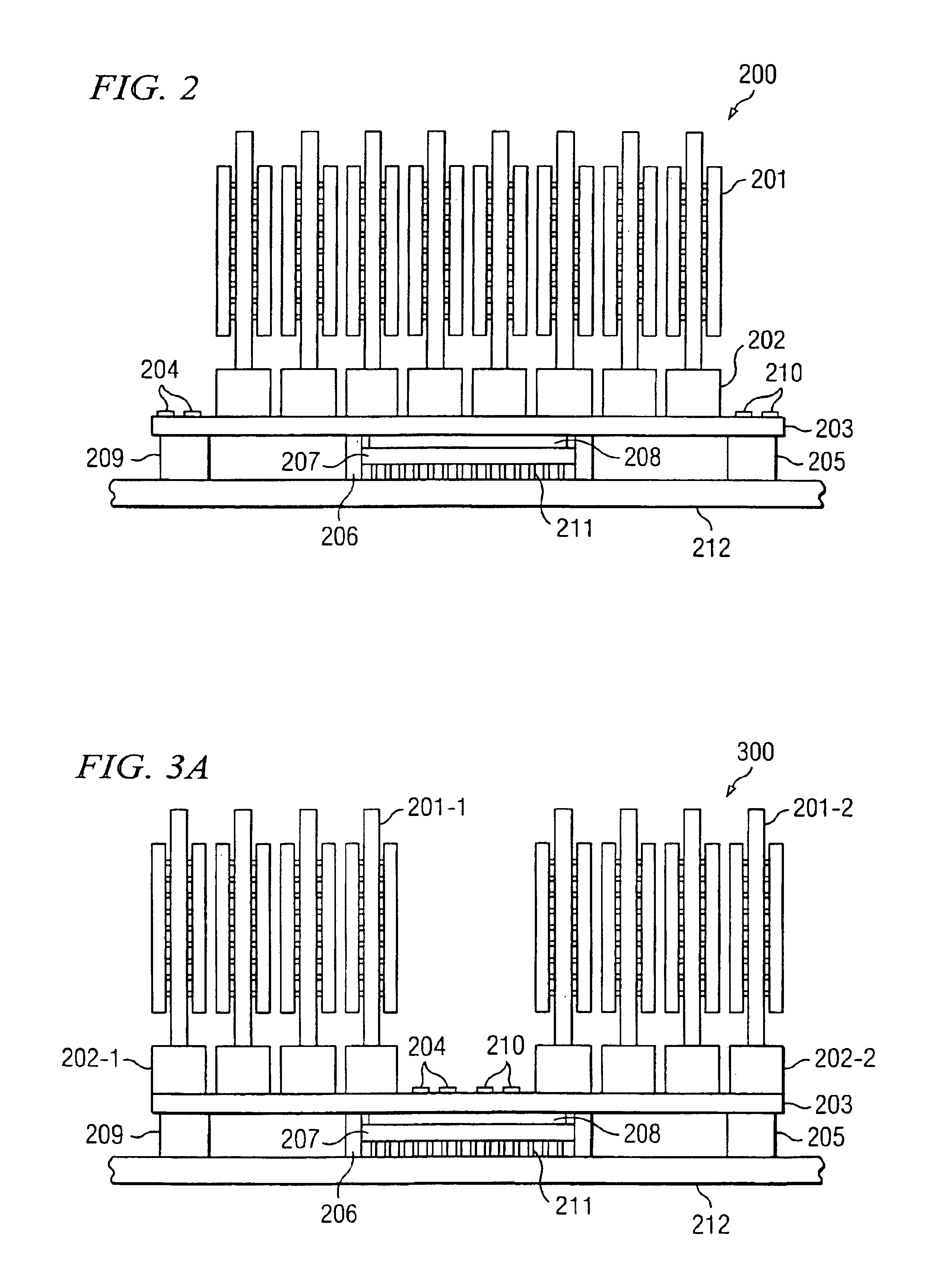

Memory module having voltage regulator module

InactiveUS20100128447A1High voltage circuit adaptationsPrinted circuit manufactureVoltage regulator moduleEngineering

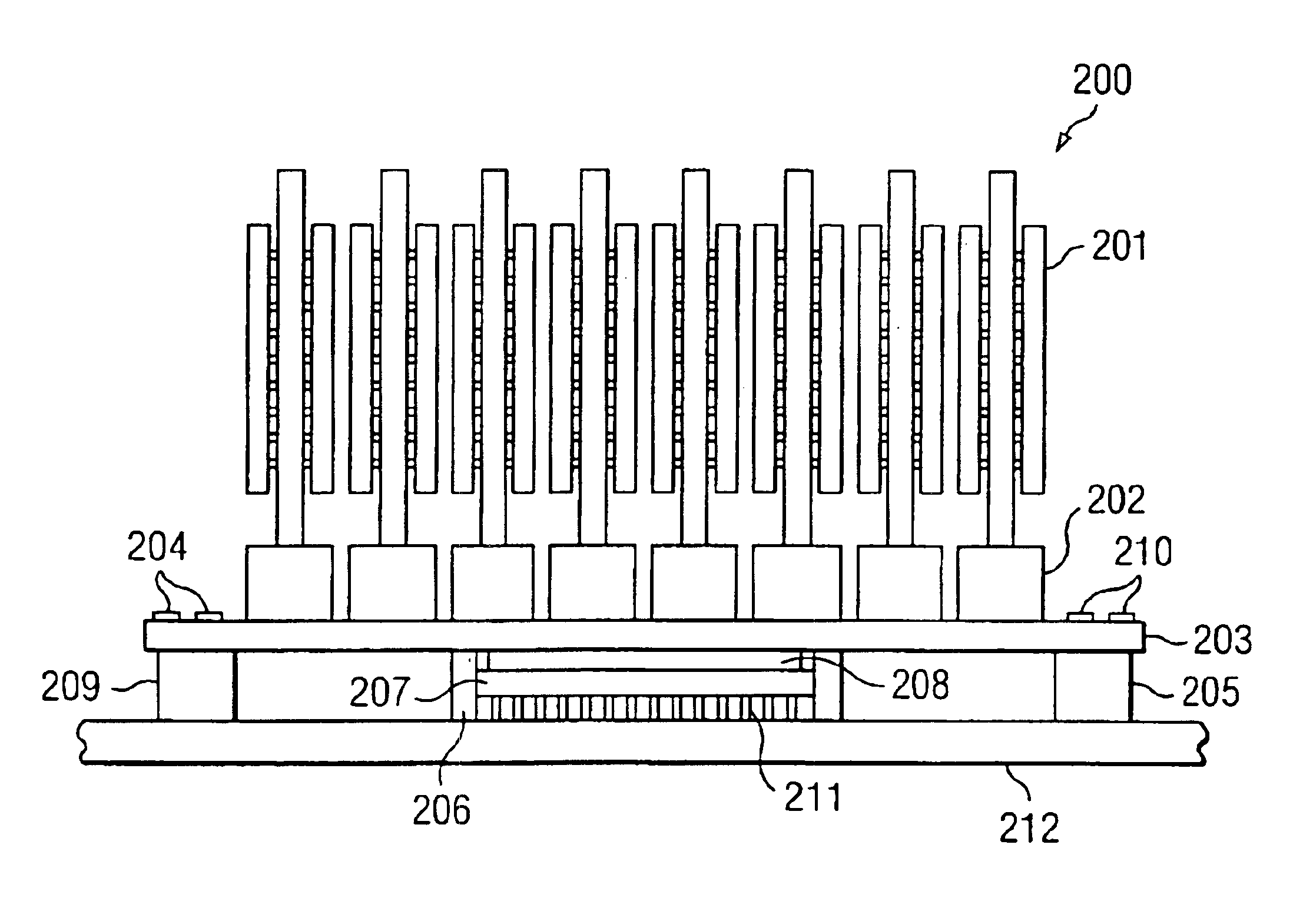

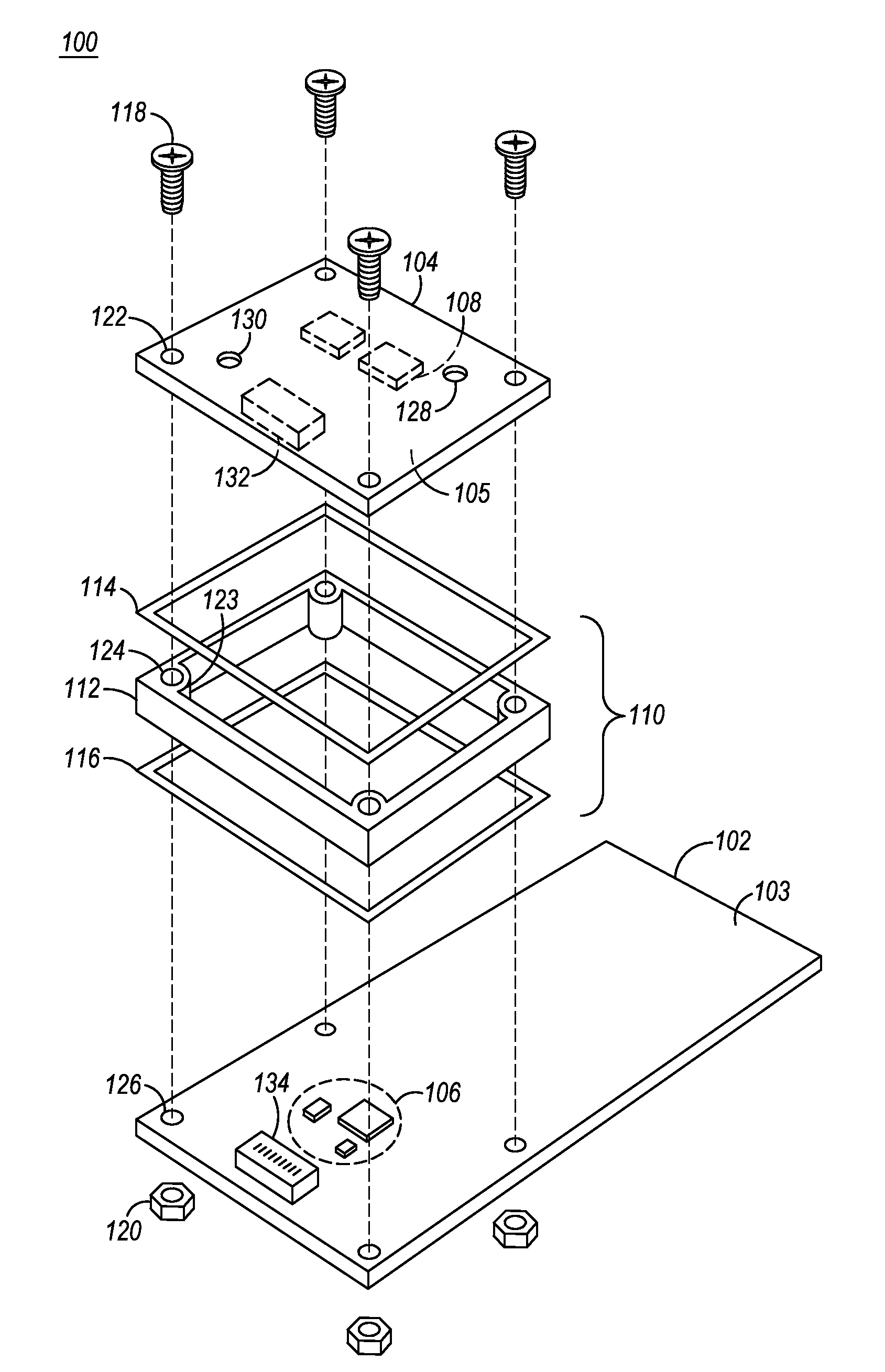

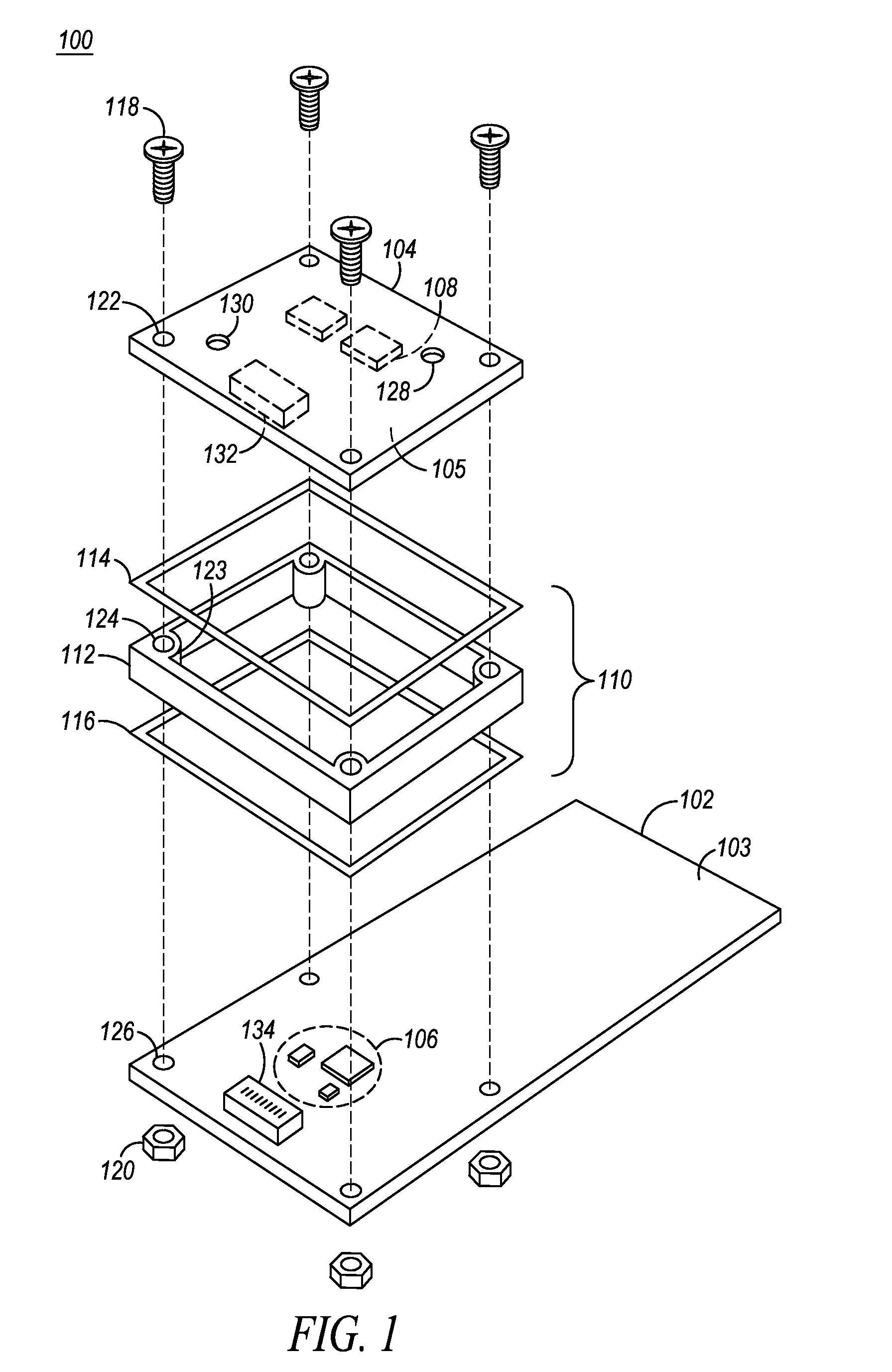

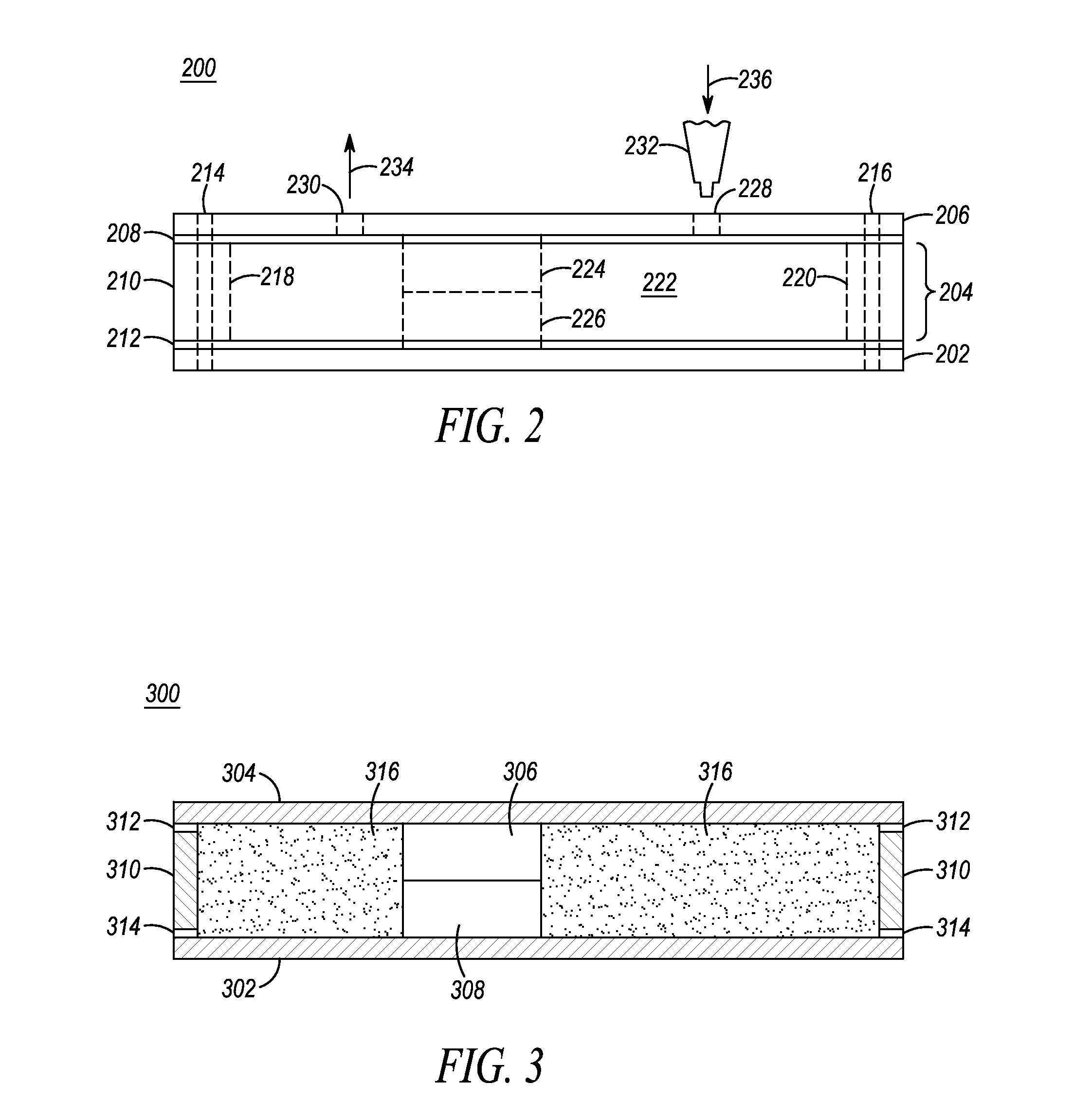

A memory module includes a circuit board having socket mating contacts at a socket interface and VRM contacts at a VRM interface. Memory devices are coupled to the circuit board. The memory devices are electrically connected to corresponding socket mating contacts and the memory devices are electrically connected to corresponding VRM contacts. A voltage regulator module is coupled to the circuit board at the VRM interface. The voltage regulator module is electrically connected to the VRM contacts.

Owner:TE CONNECTIVITY CORP

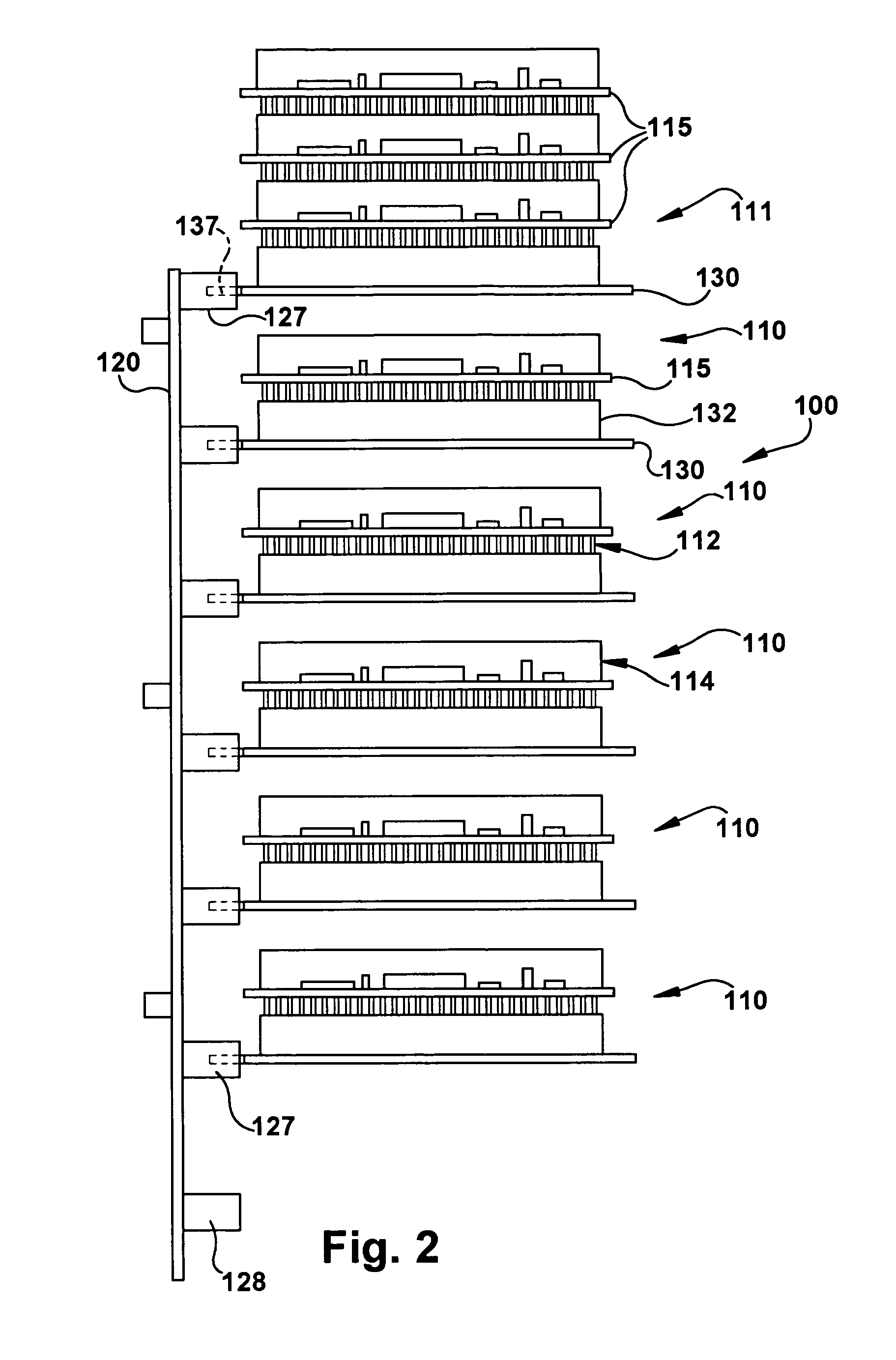

Systems for electrically connecting circuit board based electronic devices

InactiveUS7848115B2Limited interconnectivityConflicting signalOrthogonal PCBs mountingRack/frame constructionEngineeringElectric power

In one exemplary embodiment, a system for supplying electrical connectivity to one or more circuit board based devices includes a backplane and at least one module. The backplane includes a mounting surface having a plurality of modular power connectors. The at least one module includes an interface portion, a power connection portion, and a circuit board. The power connection portion is configured to connect with the corresponding one of the plurality of modular power connectors. The circuit board includes a plurality of power-related electrical contacts and a plurality of data-related electrical contacts. At least one of the plurality of power-related electrical contacts is connected with the power connection portion, and at least one of the plurality of data-related electrical contacts is connected with the interface portion. The backplane is configured to connect with a power supply, such that the power supply supplies power to the at least one module through one of the modular power connectors when the at least one module is connected with the corresponding modular power connector.

Owner:ICI NETWORKS

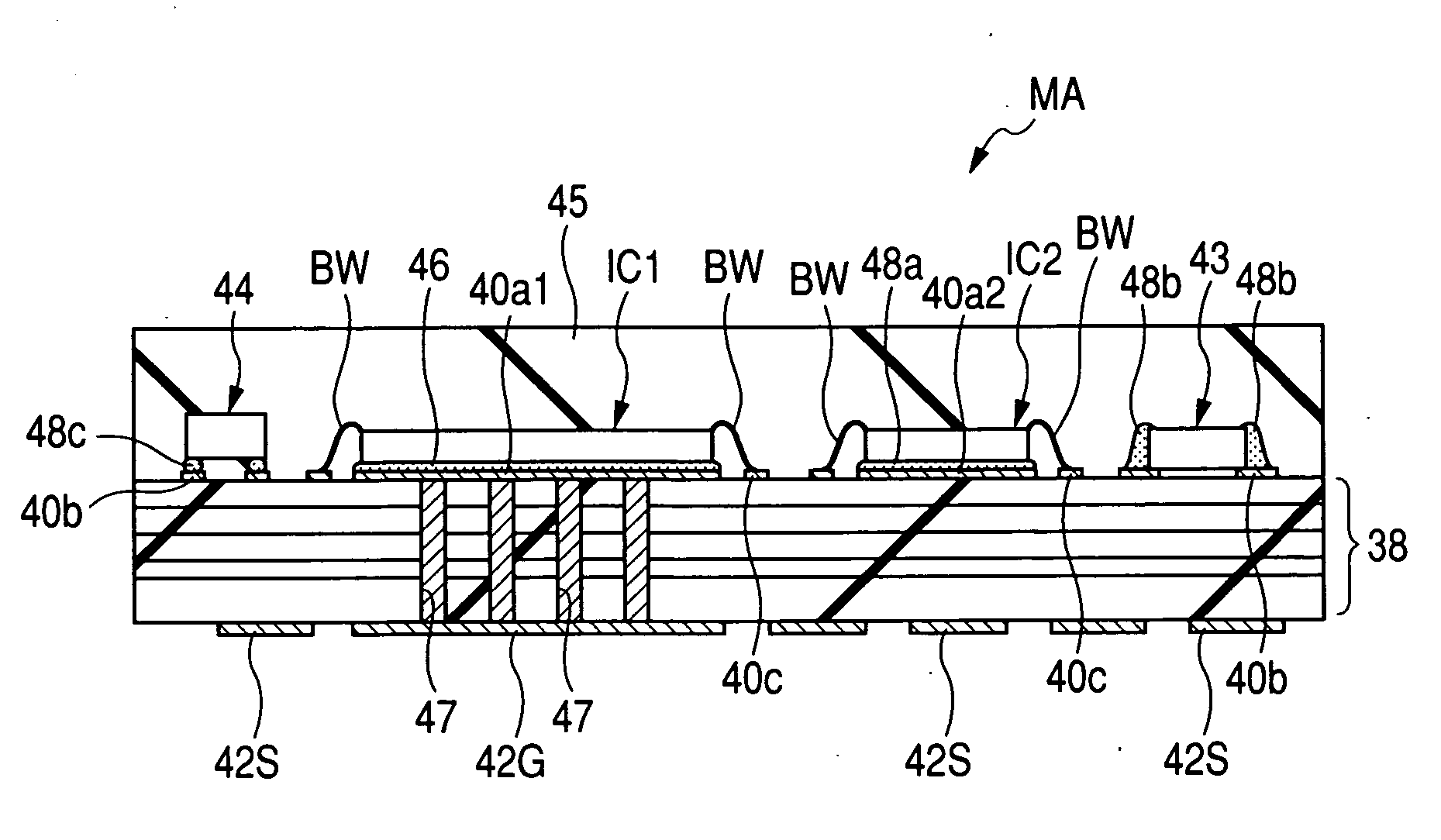

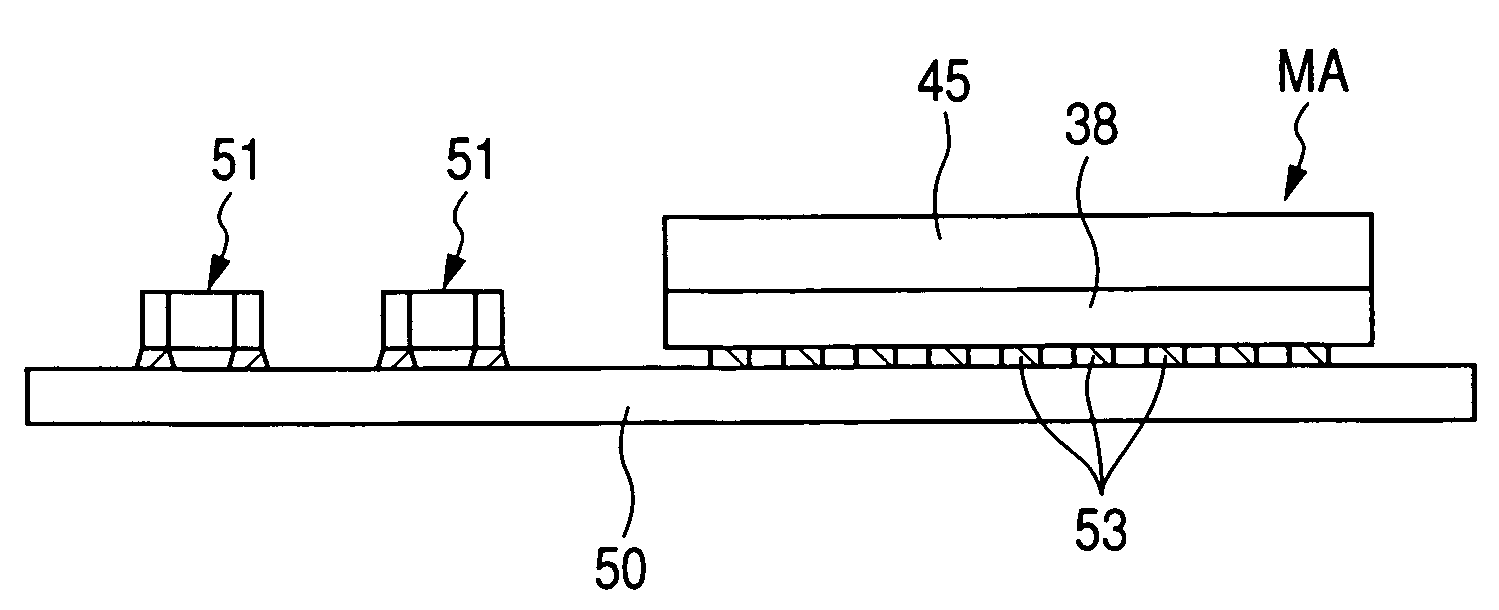

Electronic device and manufacturing method of the same

InactiveUS20060110859A1High bonding strengthPreventing connection terminalTransistorPrinted circuit assemblingResistSemiconductor chip

A technique that makes it possible to enhance the reliability of a module using PCB as its module substrate is provided. Solder connection of a single-chip component 43, an integrated chip component 44, and a semiconductor chip IC2 by Pb-free solder is carried out by heat treatment at a temperature below 280° C. using a heat block. Solder connection of a semiconductor chip IC1 by high-melting point solder is carried out by heat treatment at a temperature of 280° C. or higher using a hot jet. Thus, the semiconductor chip IC1 can be solder connected to PCB 38 using high-melting point solder without the following troubles: damage to the PCB 38 due to heat, for example, burning of solder resist; and peeling of prepreg from a core material. Therefore, the semiconductor chip IC1 can be mounted over the PCB 38 with high connection strength.

Owner:RENESAS ELECTRONICS CORP

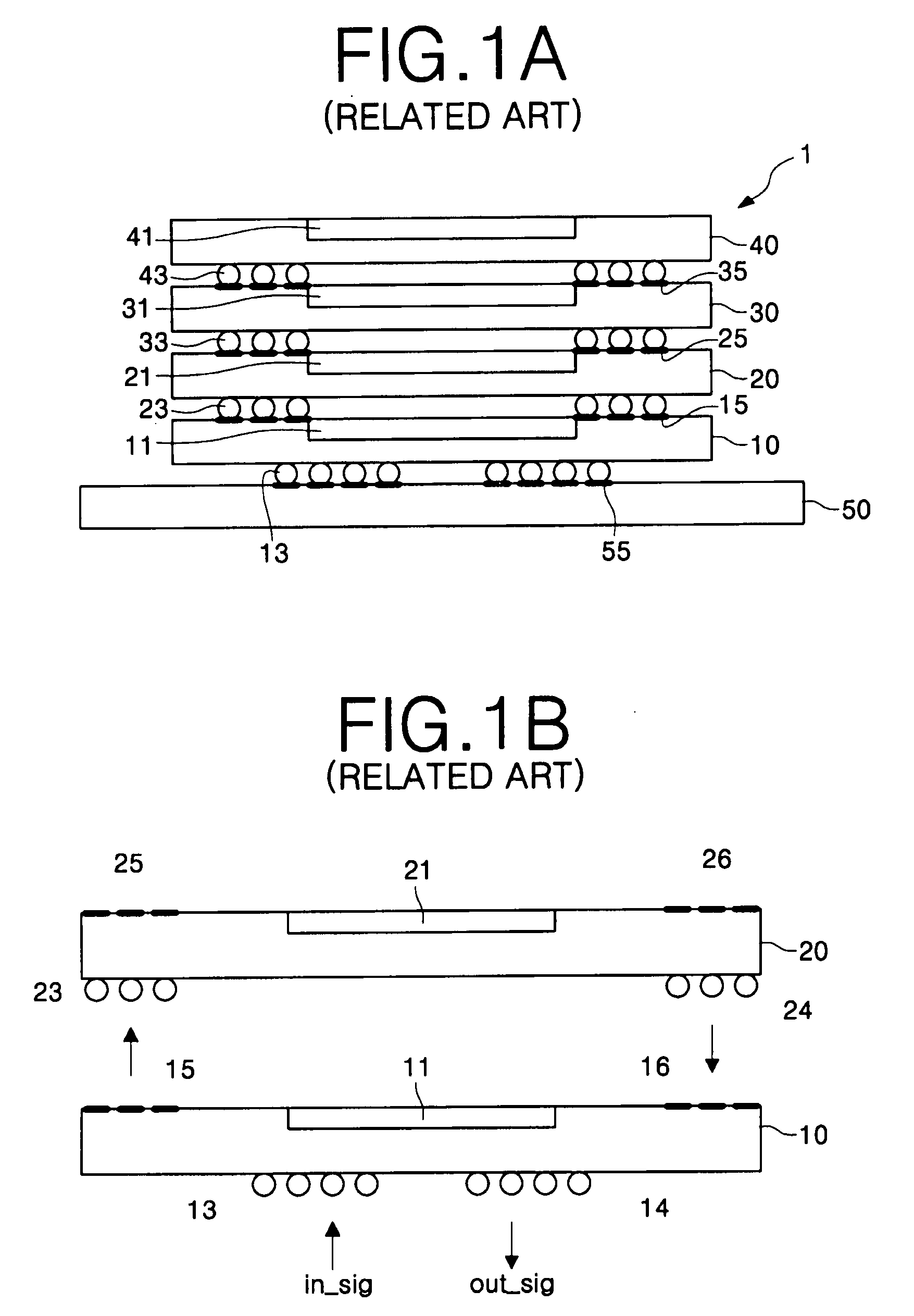

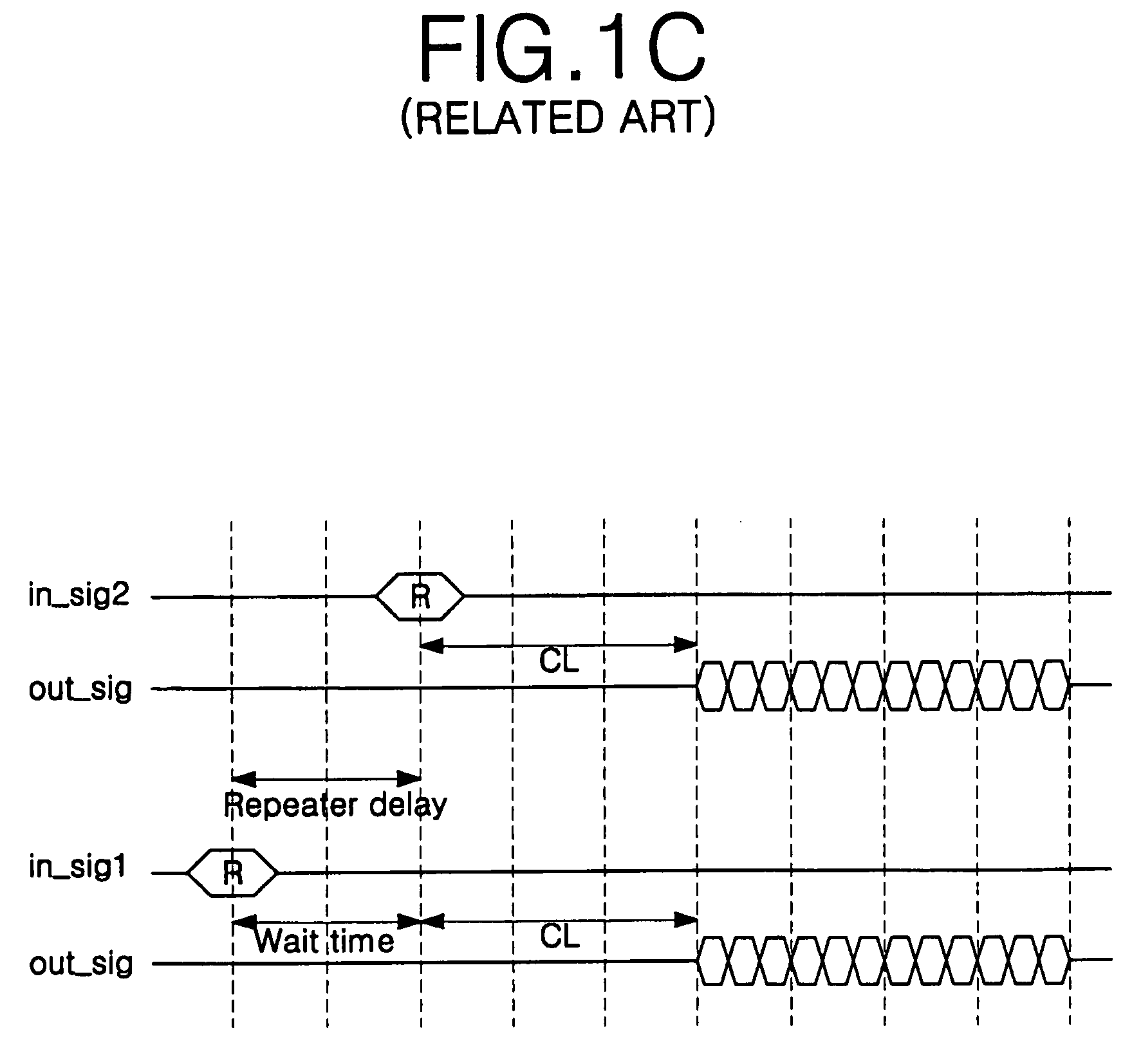

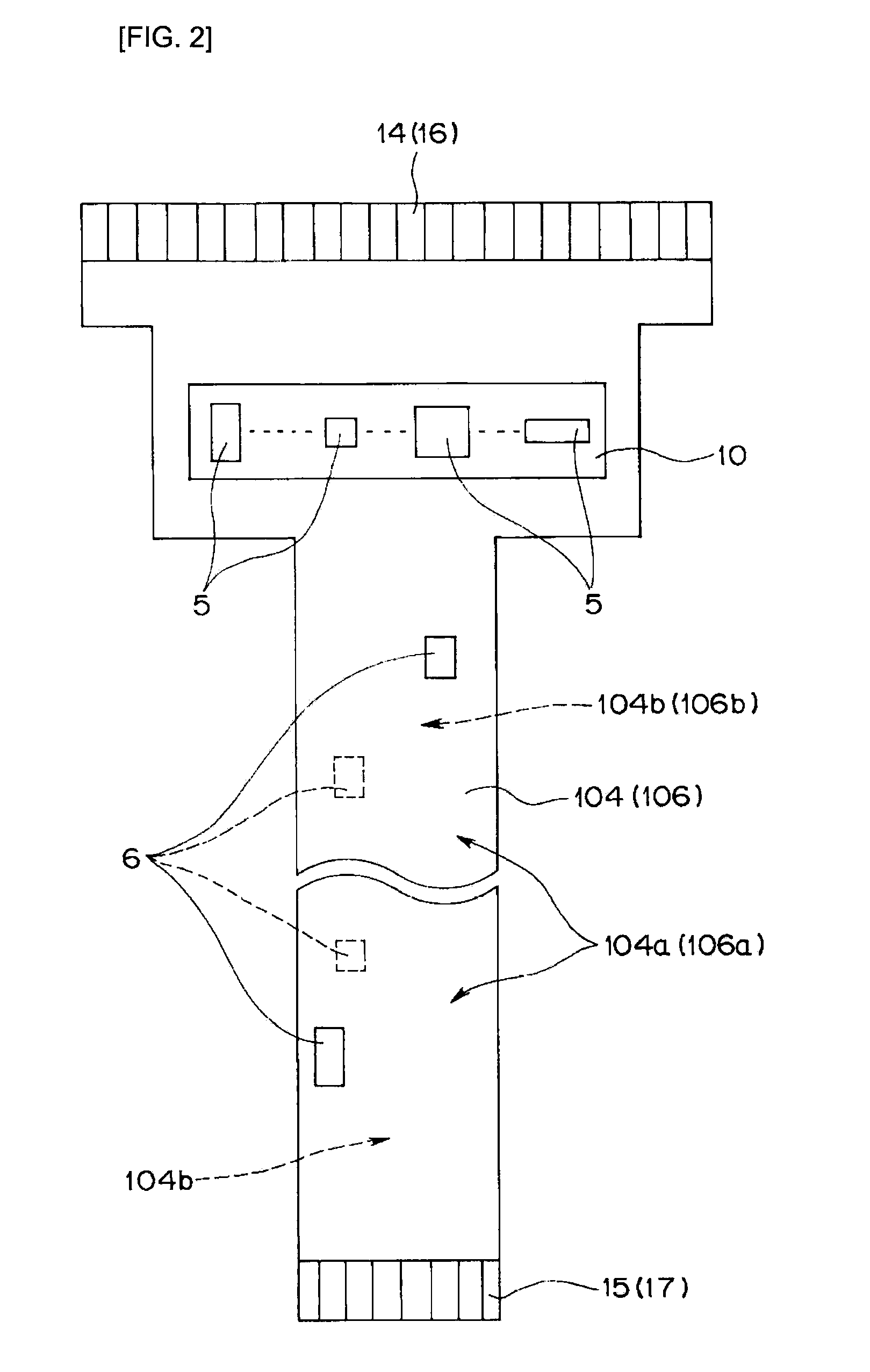

Stack-type semiconductor package sockets and stack-type semiconductor package test systems

ActiveUS20080094086A1Electrical measurement instrument detailsSemiconductor/solid-state device detailsSemiconductor packagePrinted circuit board

A stack-type semiconductor package socket may include: a first package connection portion for connection with leads of a lowermost package of a stack-type semiconductor package; a second package connection portion for connection between pads of an odd-numbered package and leads of an even-numbered package, wherein the odd-numbered package and the even-numbered package are adjacent to each other; a lower case for fixing the first package connection portion; and an upper case for fixing the second package connection portion. A stack-type semiconductor package test system may include: a stack-type semiconductor package socket that includes first and second package connection portions; a printed circuit board electrically connected to leads of the lowermost package through the first package connection portion; and a test controller for receiving, outputting, or receiving and outputting signals from, to, or from and to the stack-type semiconductor package through the PCB and the stack-type semiconductor package socket.

Owner:SAMSUNG ELECTRONICS CO LTD

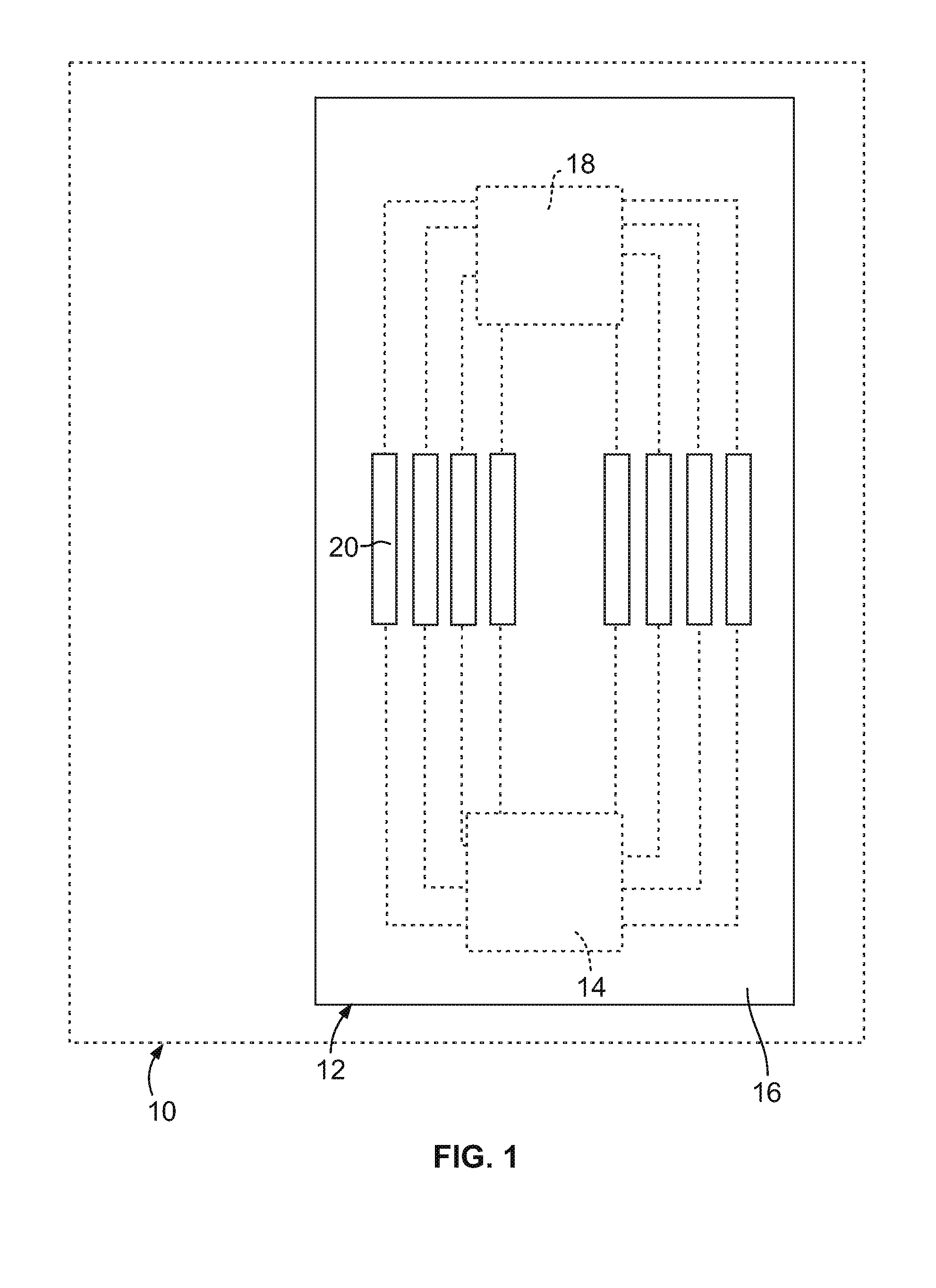

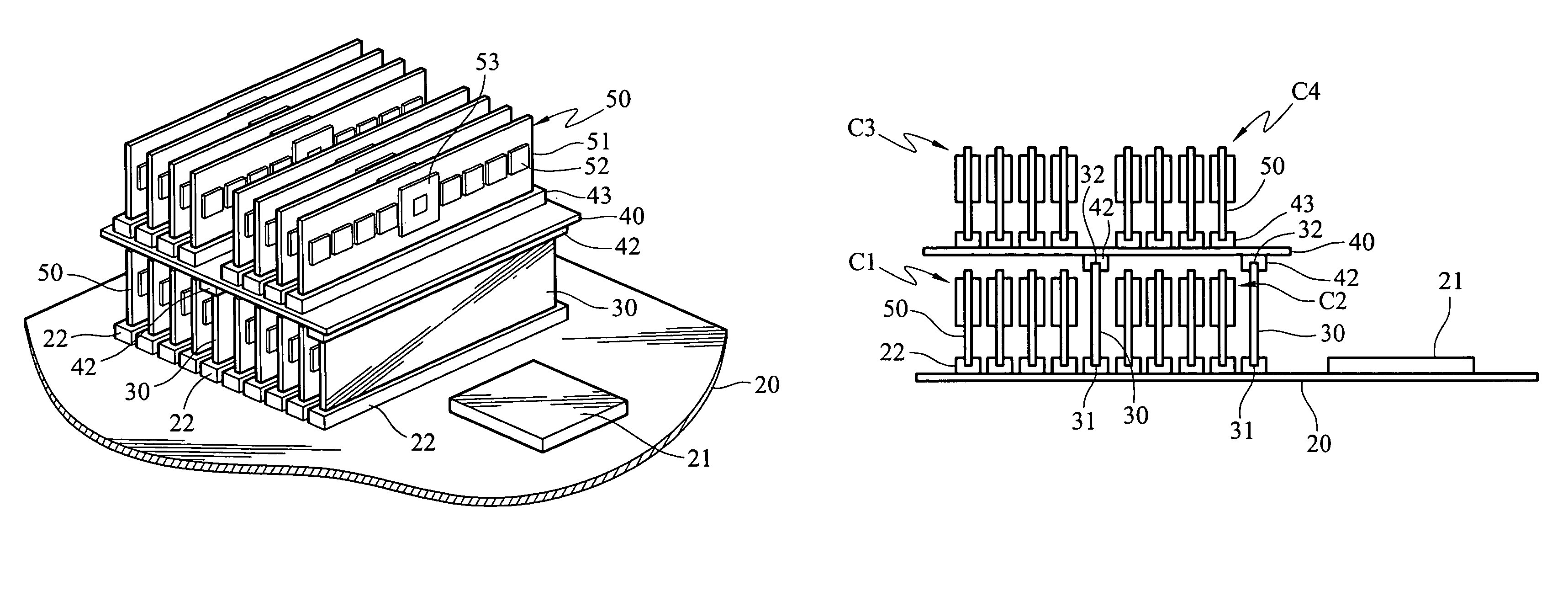

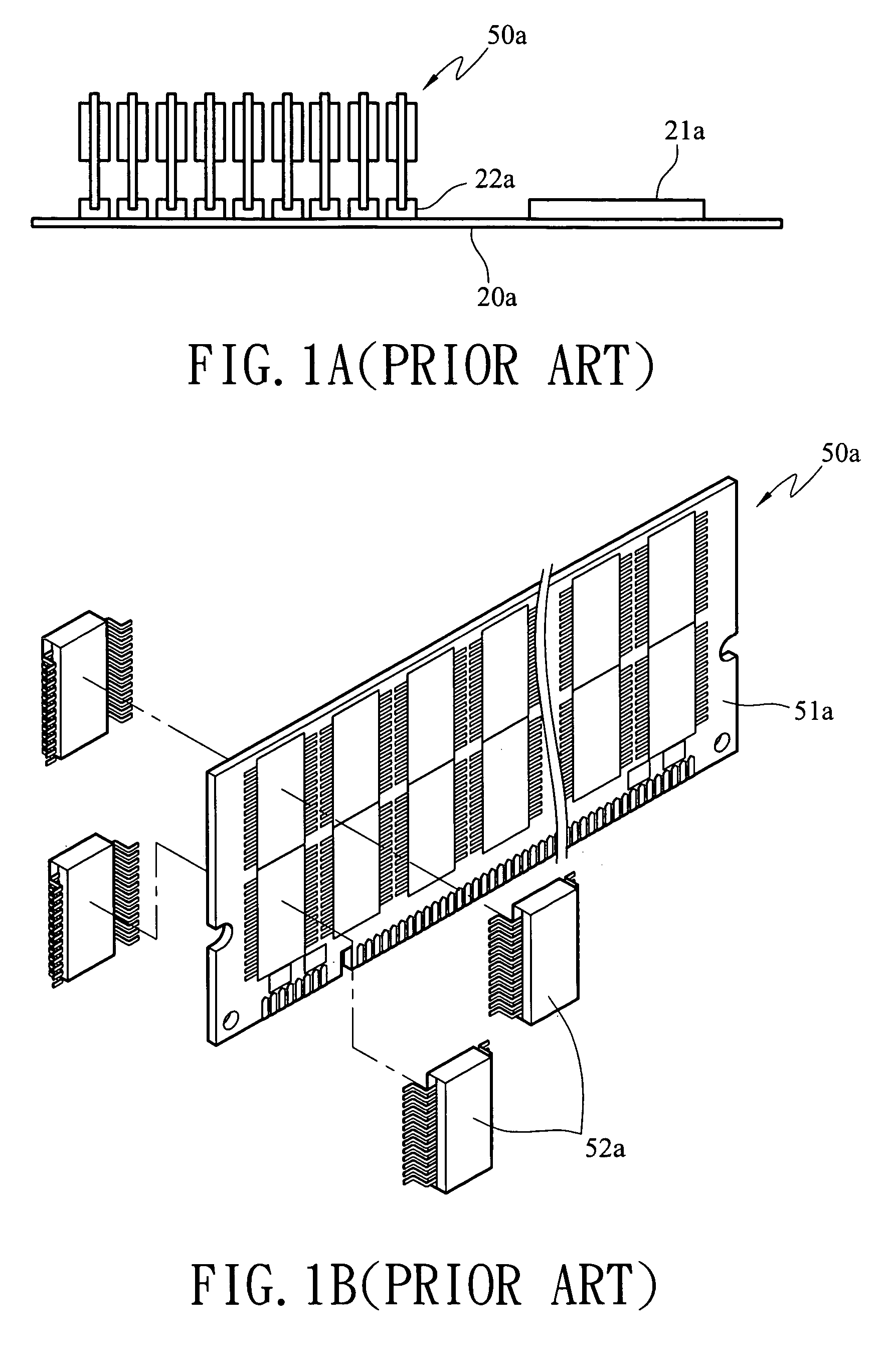

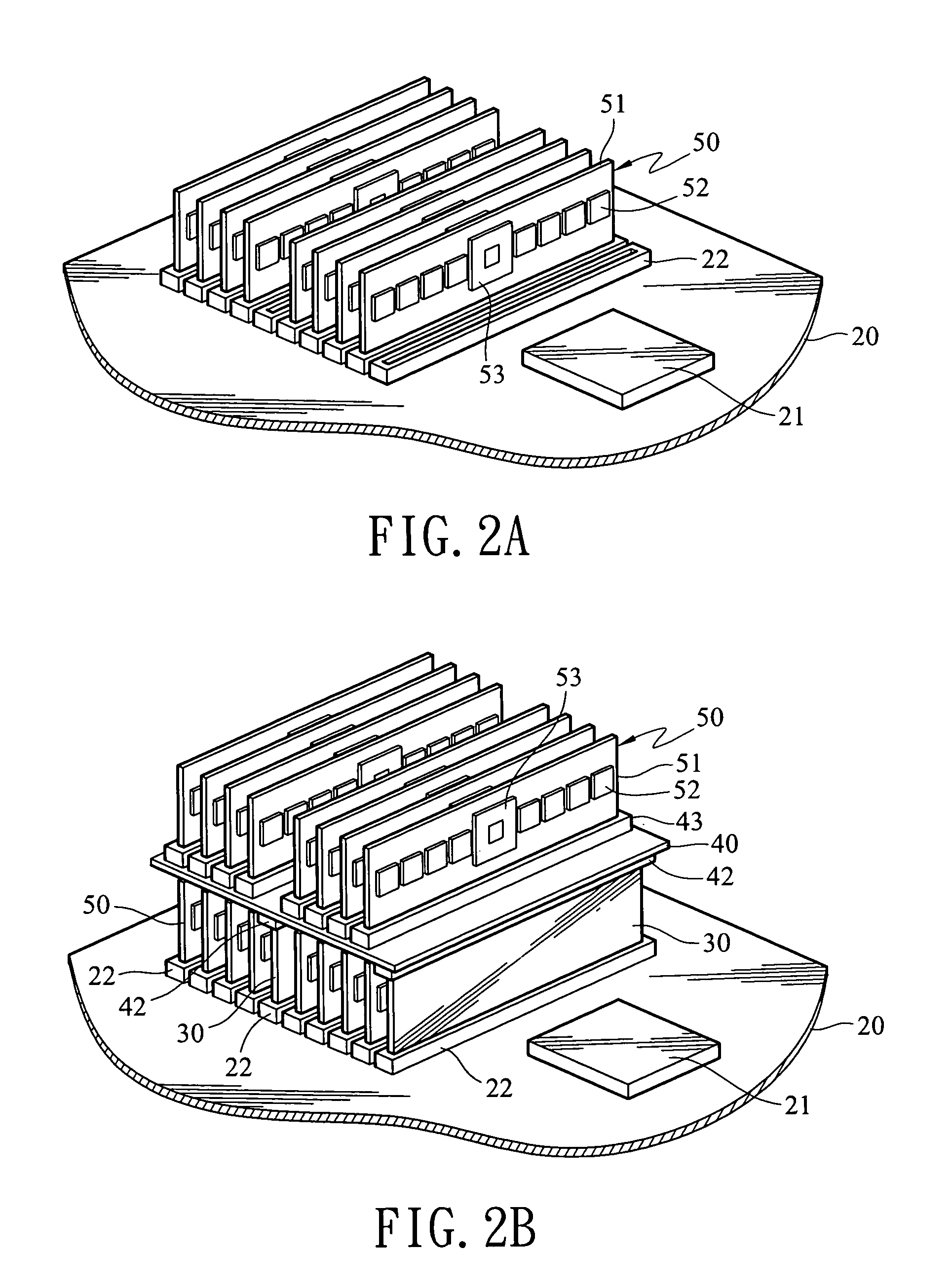

Expansion structure of memory module slot

InactiveUS7298625B1Small surface areaReduce manufacturing costDigital data processing detailsSemiconductor/solid-state device detailsMemory moduleMotherboard

An expansion structure of memory module slots is provided. A circuit switch board and a substrate are disposed on a motherboard, wherein a plurality of first memory module slots is disposed on the motherboard, at least one second memory module slot is disposed on one side of the substrate, and a plurality of third memory module slots is disposed on the other side of the substrate. The third memory module slots are electrically connected to the second memory module slot, and two ends of the circuit switch board are plugged into one of the first memory module slots and the second memory module slot. When memory modules are plugged in the third memory module slots, the memory modules are electrically connected to the first memory module slots respectively through the circuit switch board and then transmit data and signals with the motherboard.

Owner:INVENTEC CORP

Electronic device and manufacturing method of the same

InactiveUS7396701B2Reduce size and thicknessLow costTransistorPrinted circuit assemblingResistSemiconductor chip

A technique that makes it possible to enhance the reliability of a module using PCB as its module substrate is provided. Solder connection of a single-chip component 43, an integrated chip component 44, and a semiconductor chip IC2 by Pb-free solder is carried out by heat treatment at a temperature below 280° C. using a heat block. Solder connection of a semiconductor chip IC1 by high-melting point solder is carried out by heat treatment at a temperature of 280° C. or higher using a hot jet. Thus, the semiconductor chip IC1 can be solder connected to PCB 38 using high-melting point solder without the following troubles: damage to the PCB 38 due to heat, for example, burning of solder resist; and peeling of prepreg from a core material. Therefore, the semiconductor chip IC1 can be mounted over the PCB 38 with high connection strength.

Owner:RENESAS ELECTRONICS CORP

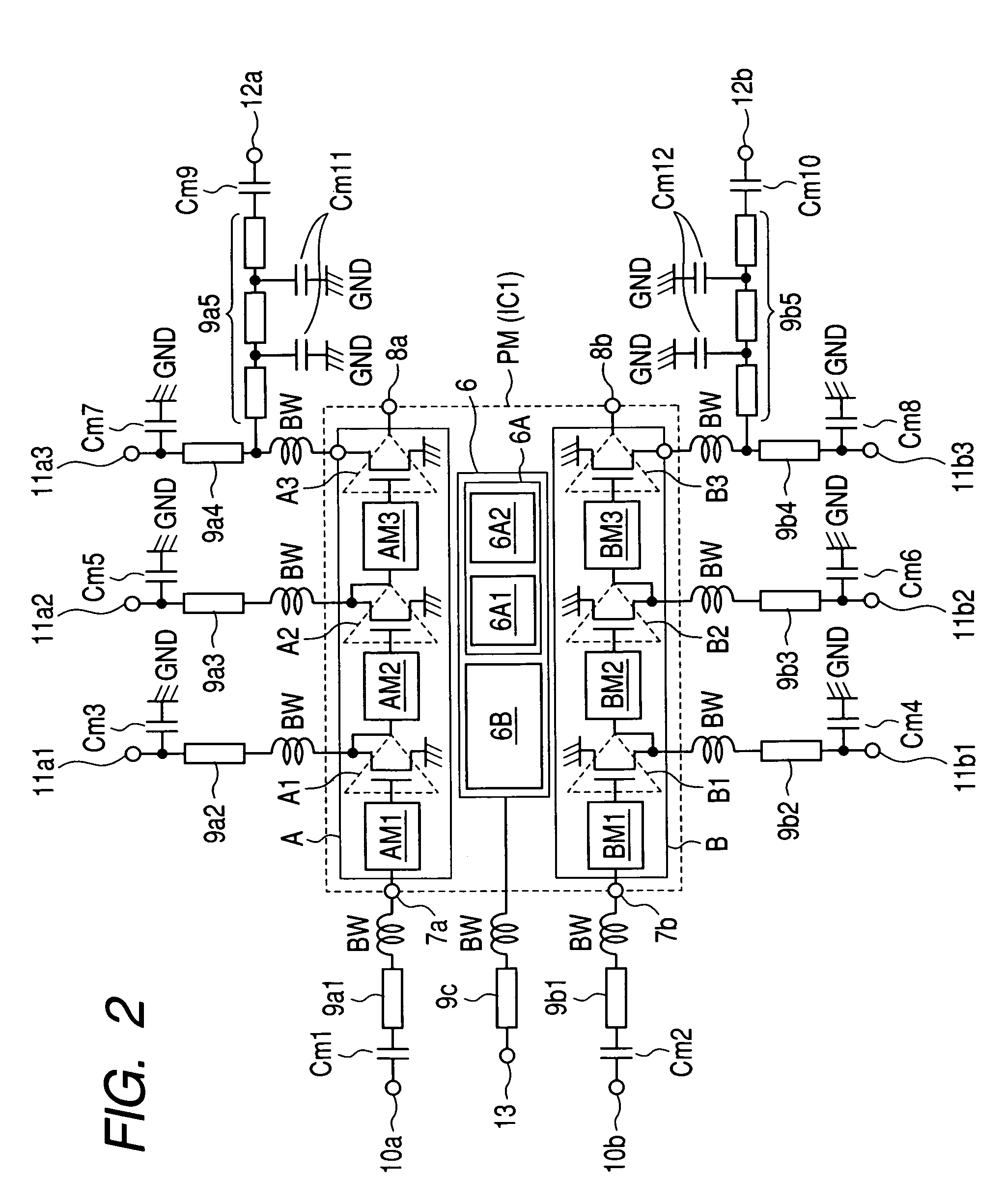

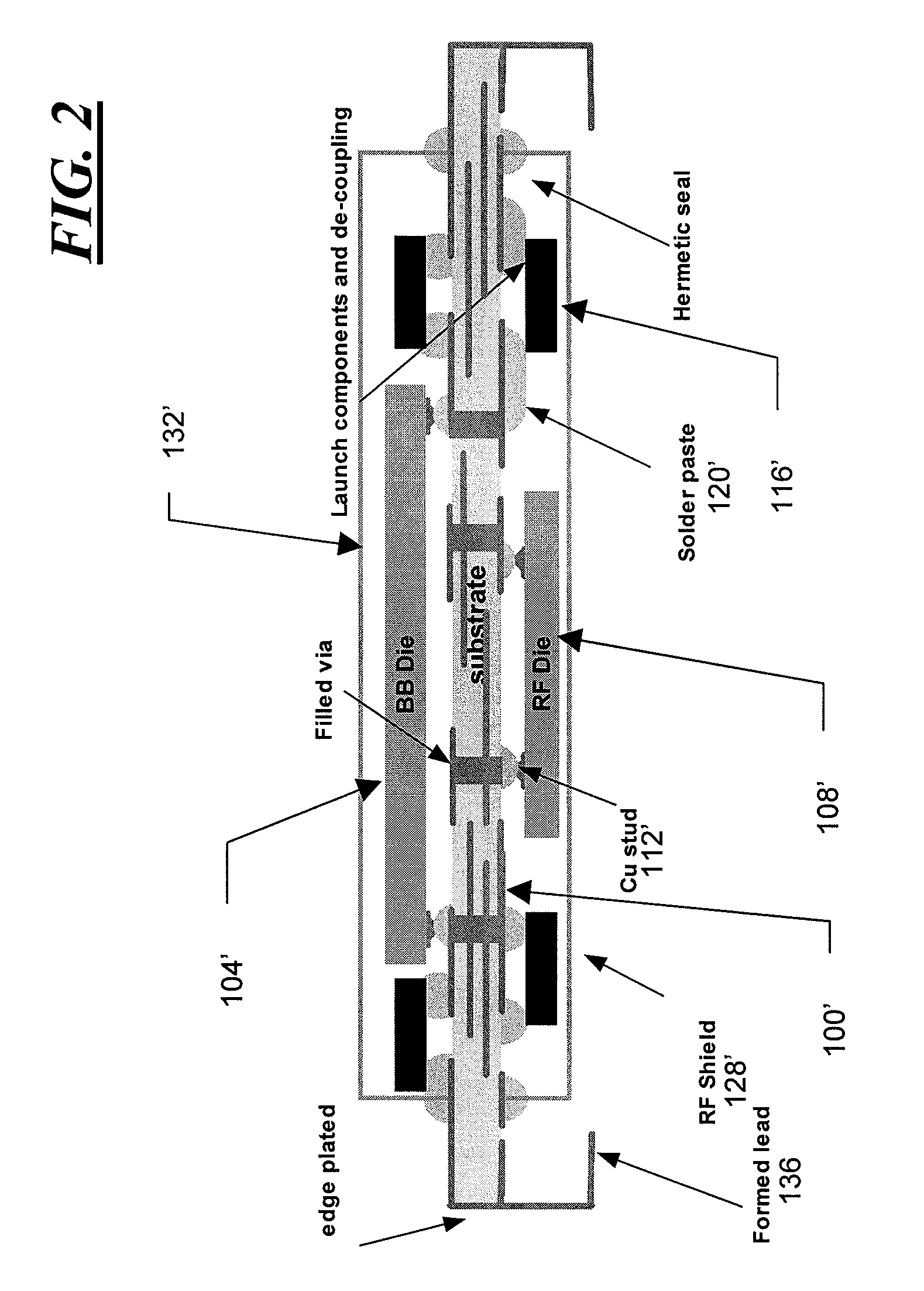

Methods and apparatus for multichip module packaging

InactiveUS20080157295A1Improve performanceCross-talk/noise/interference reductionSemiconductor/solid-state device detailsEngineeringElectrical and Electronics engineering

Owner:CUSTOM ONE DESIGN

Printable 3D electronic structure

ActiveUS20180042110A1Reduce failureSimple and inexpensiveMultiple fixed capacitorsThin/thick film capacitorElectronic structureContact pad

A printable electronic component includes a component substrate and a circuit disposed in or on the component substrate. One or more electrically conductive connection posts protrude from the component substrate. One or more electrically conductive component contact pads are exposed on or over the component substrate on a side of the component substrate opposite the one or more connection posts. The one or more component contact pads and the one or more electrically conductive connection posts are both electrically connected to the circuit. The components can be printed onto a destination substrate and electrically connected to contact pads on the destination substrate through the connection posts. The components can also be printed onto other components and electrically connected through the connection posts and component contact pads to form a three-dimensional electronic structure.

Owner:X DISPLAY CO TECH LTD

Component-containing module and method for producing the same

InactiveUS20070170582A1Improve reliabilityLow costFinal product manufactureCross-talk/noise/interference reductionEngineeringElectrical and Electronics engineering

Owner:MURATA MFG CO LTD

Solder composition for electronic devices

InactiveUS20070031279A1Prevent a solder outflowLow costPrinted circuit assemblingFinal product manufactureDevice materialSemiconductor

Each of junctions formed between a semiconductor device and a substrate comprises metal balls of Cu, or other materials and compounds of Sn and the metal balls, and the metal balls are bonded together by the compounds.

Owner:RENESAS ELECTRONICS CORP

Electronic device

InactiveUS7075183B2High bonding strengthHigh melting pointPrinted circuit assemblingFinal product manufactureMetallurgySemiconductor

Each of junctions formed between a semiconductor device and a substrate comprises metal balls of Cu etc. and compounds of Sn and the metal balls, and the metal balls are bonded together by the compounds.

Owner:RENESAS ELECTRONICS CORP

Electronic device

InactiveCN1444273ACut wellSmall volume expansionPrinted circuit assemblingFinal product manufactureMetallurgyElectron

In an electronic device realizing high-temperature terminal solder bonding in temperature-level bonding, the bonding portion between the semiconductor device and the substrate is formed by metal balls composed of Cu or the like and a compound composed of the metal balls and Sn, and Metal balls are held together by compounds.

Owner:RENESAS ELECTRONICS CORP

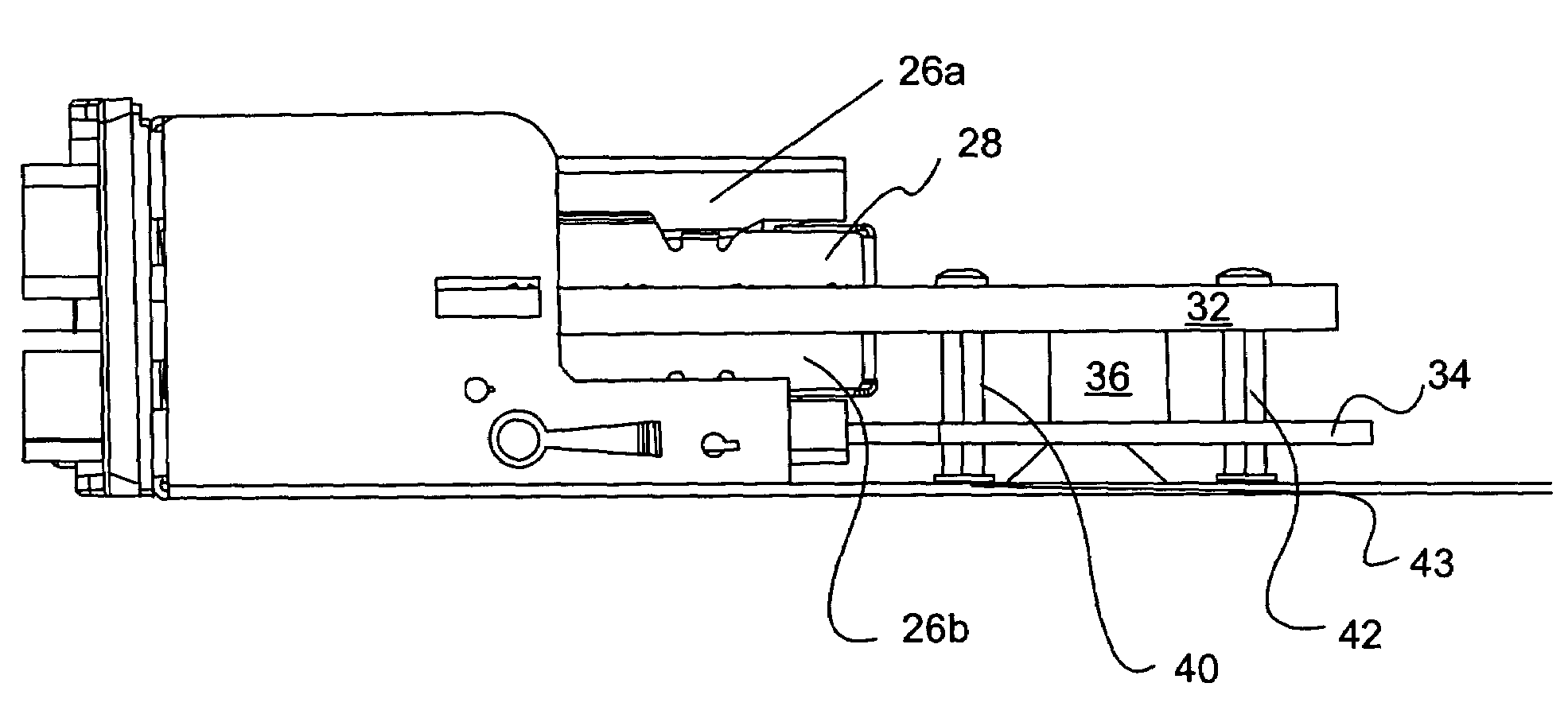

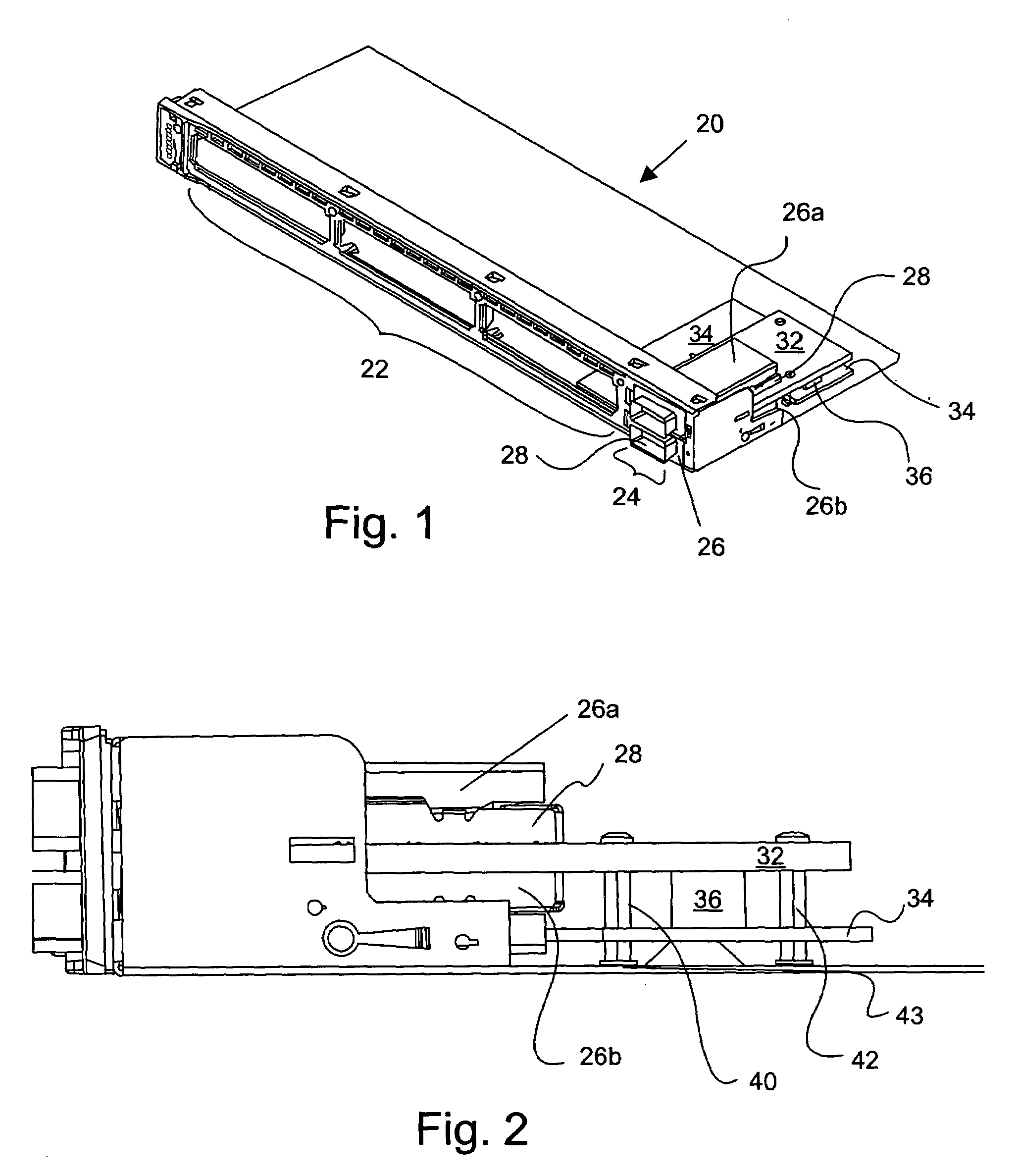

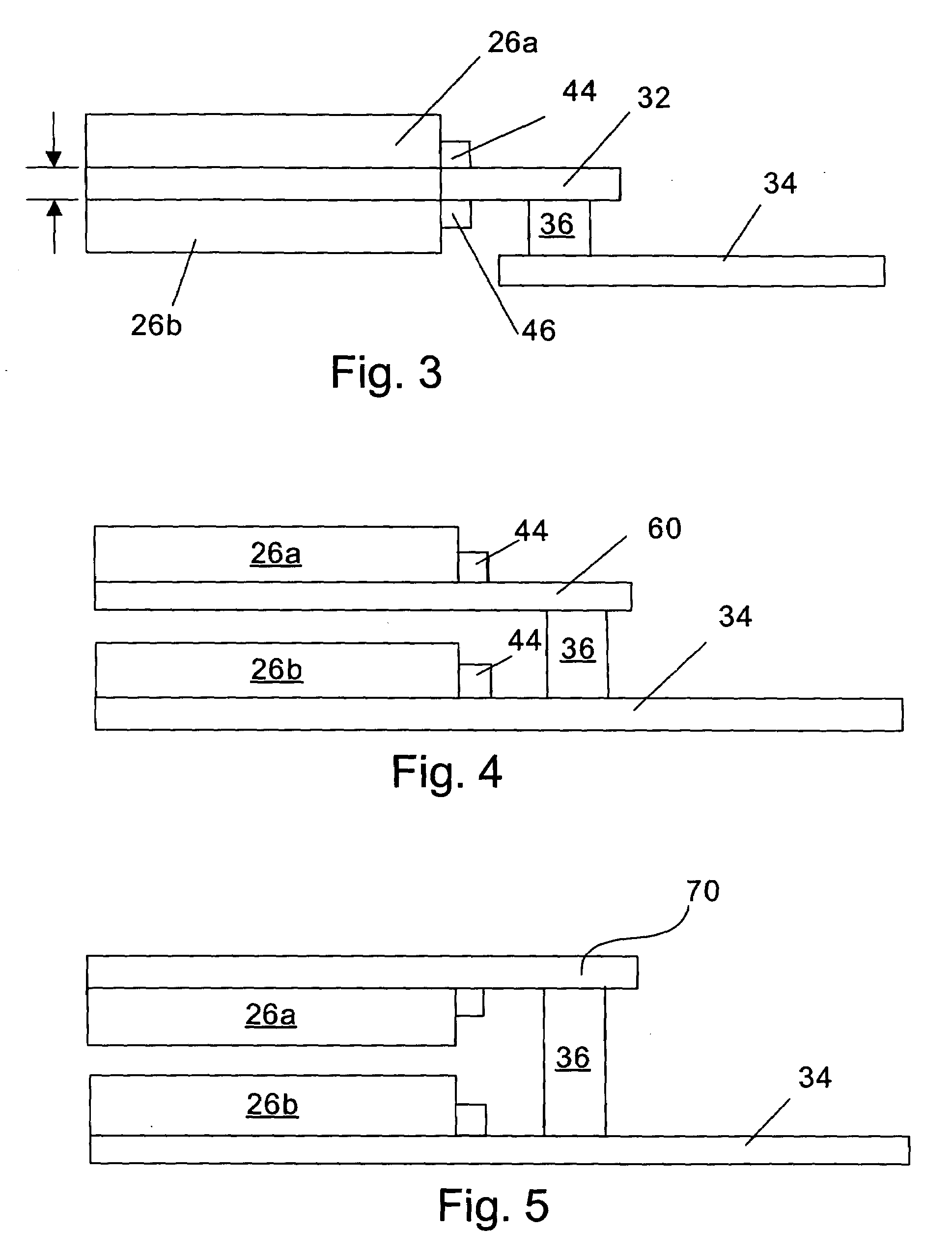

Dual-stacked 10 Gigabit X2 uplinks in a single rack unit switch

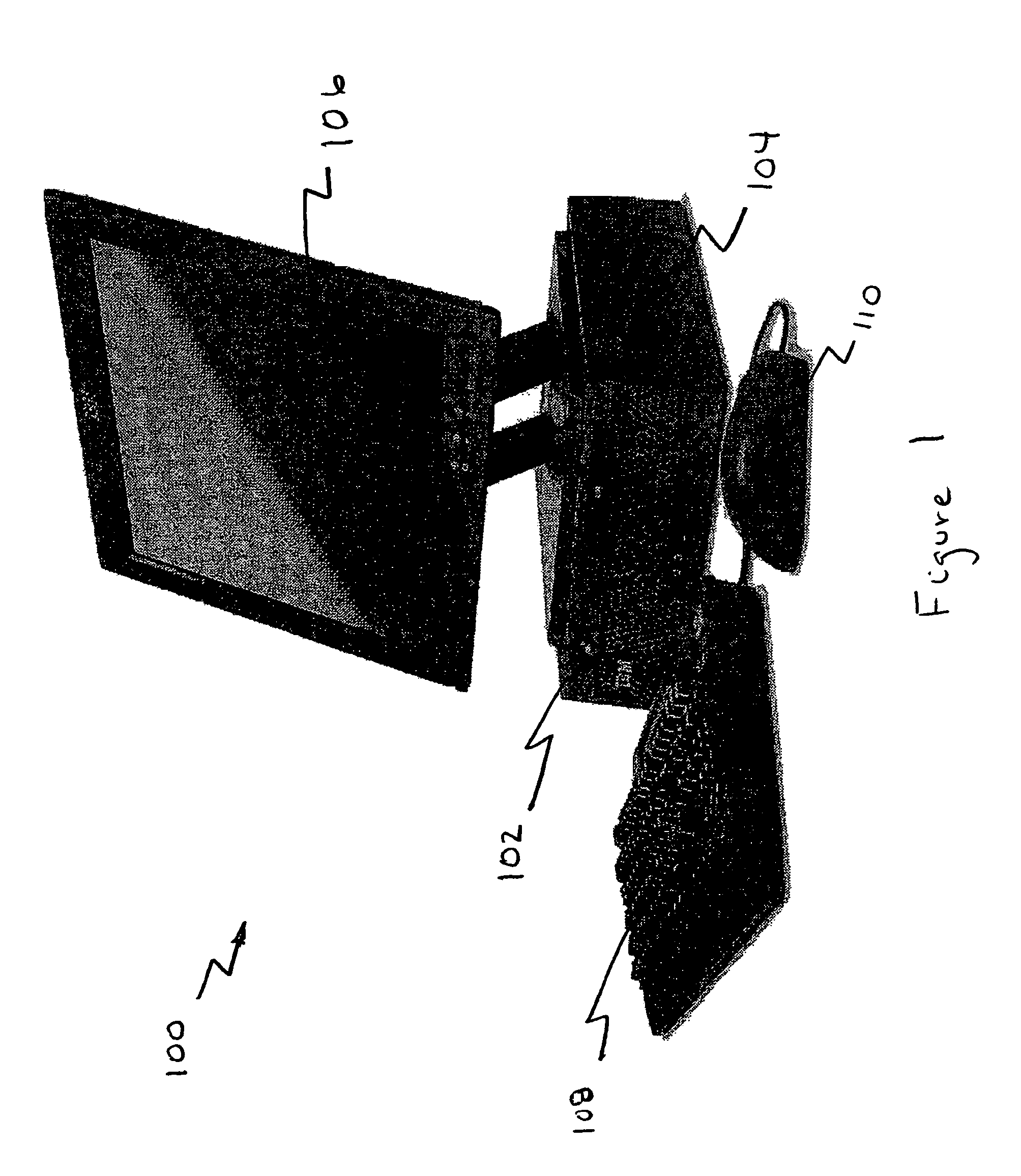

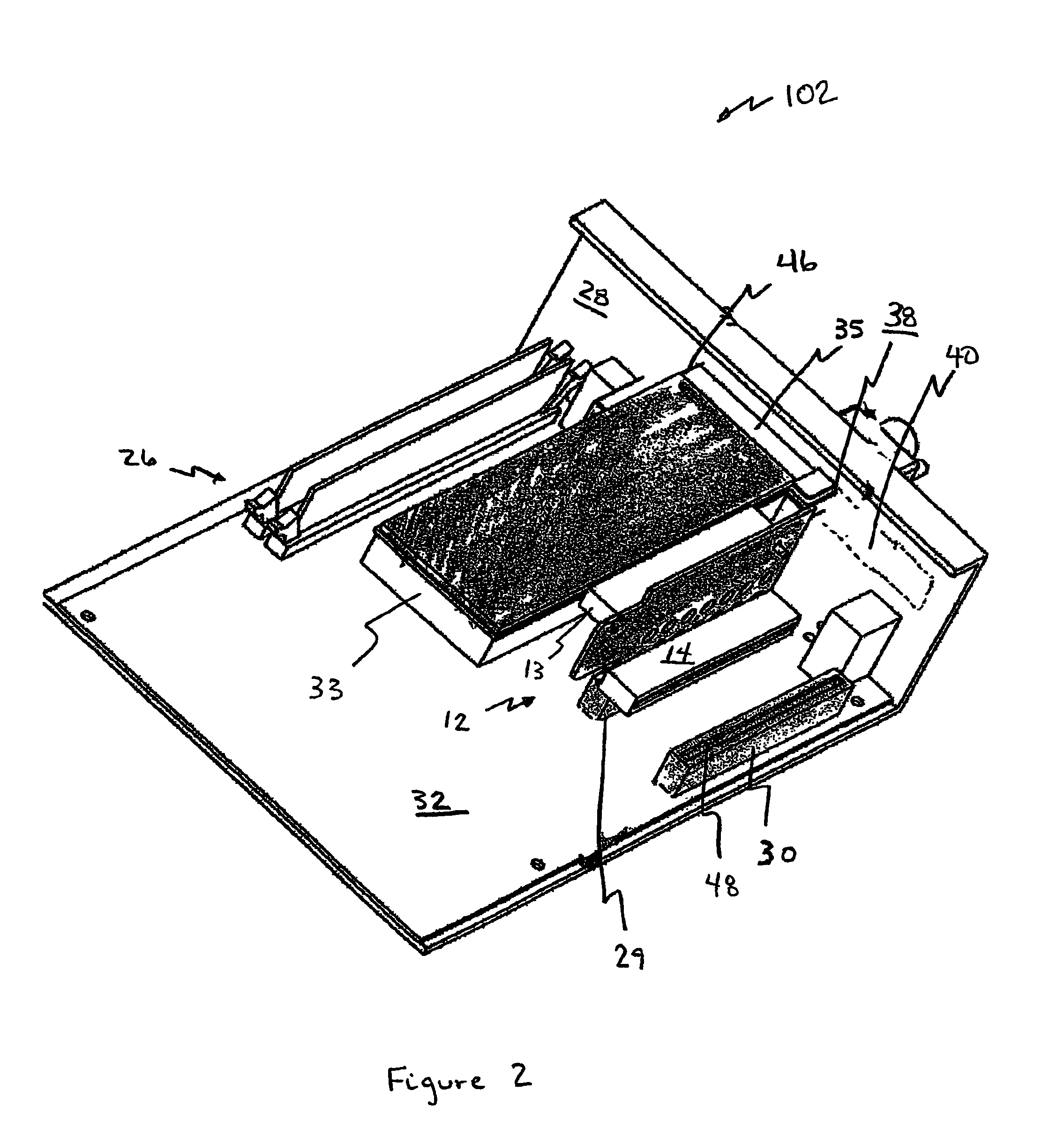

InactiveUS7136289B2Provide supportSubstation/switching arrangement detailsDigital data processing detailsRack unitGigabit

A system for providing dual 10 GB uplinks in the front side of a single rack unit switch that stacks two MSA X2 I / O devices in a limited space. In one embodiment the two X2 I / O devices are mounted on opposite sides of a single circuit board positioned above the motherboard.

Owner:CISCO TECH INC

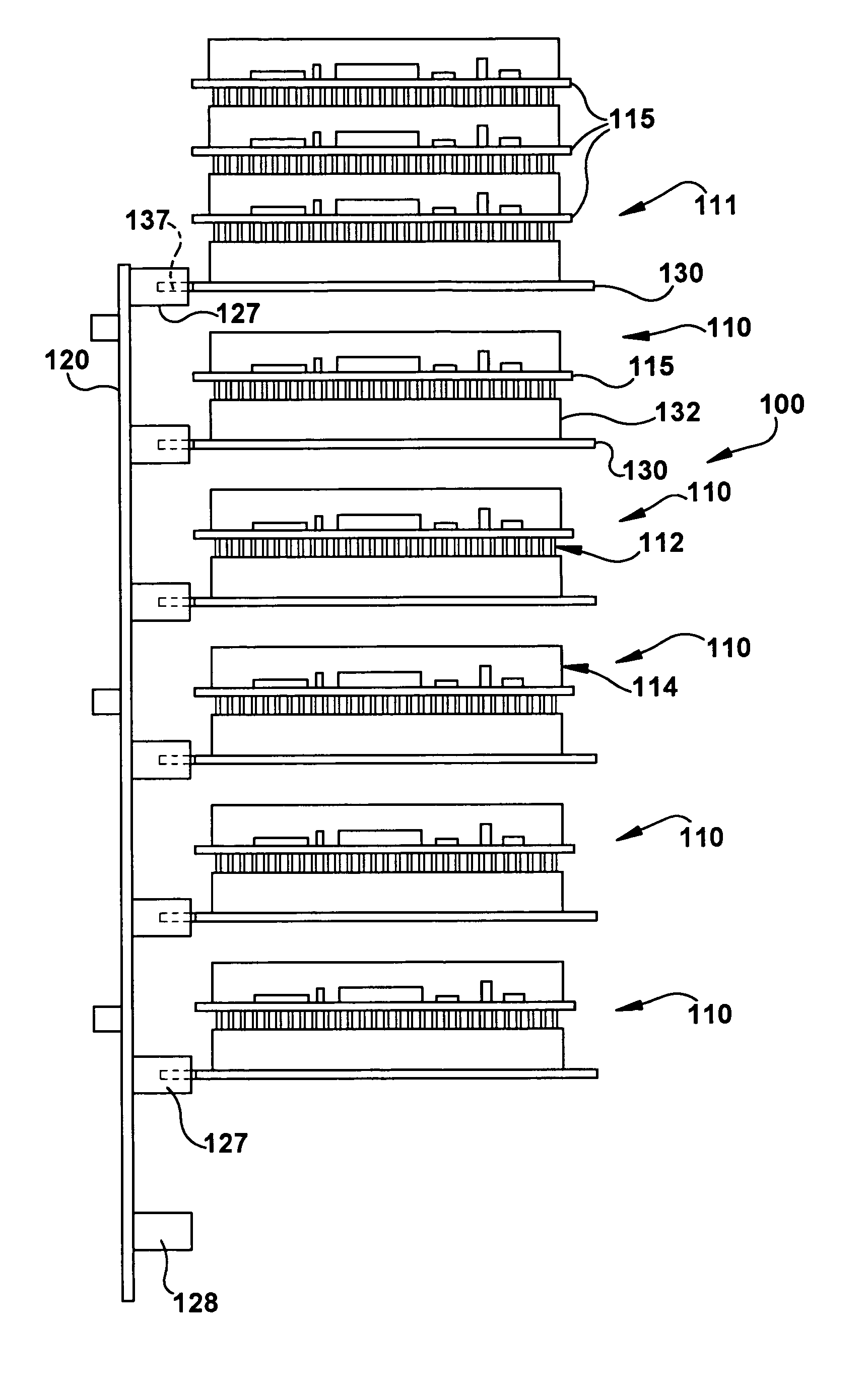

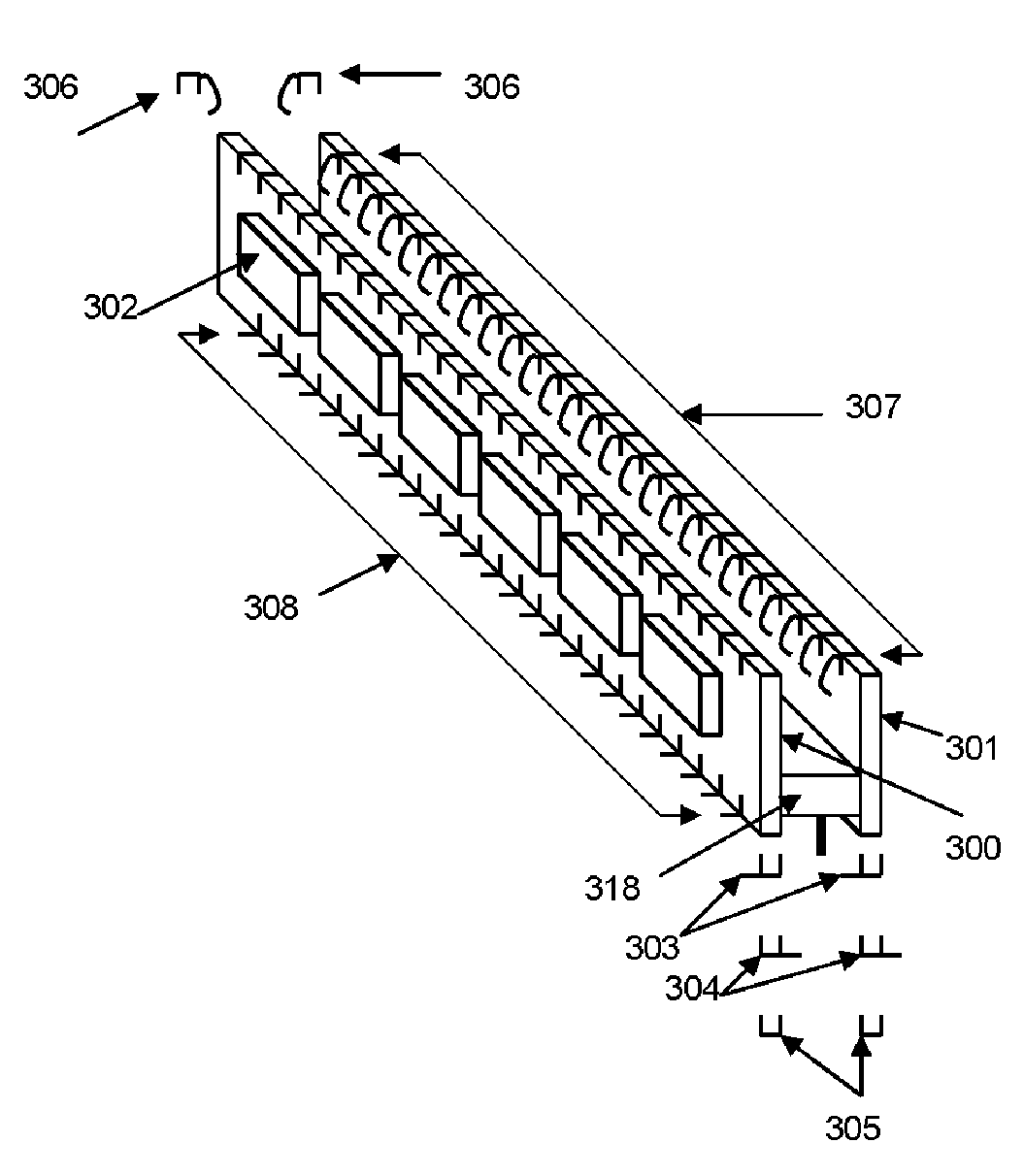

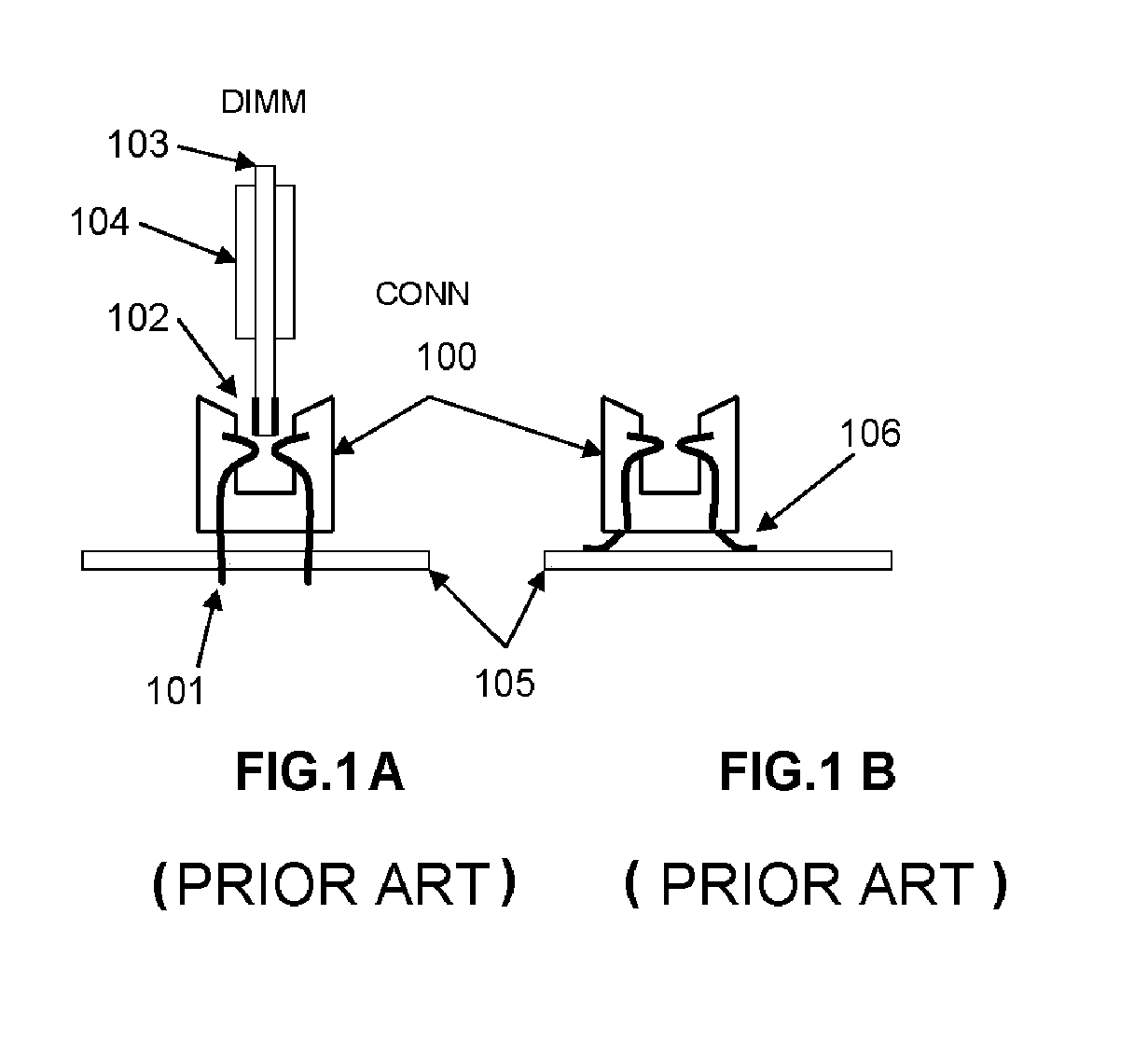

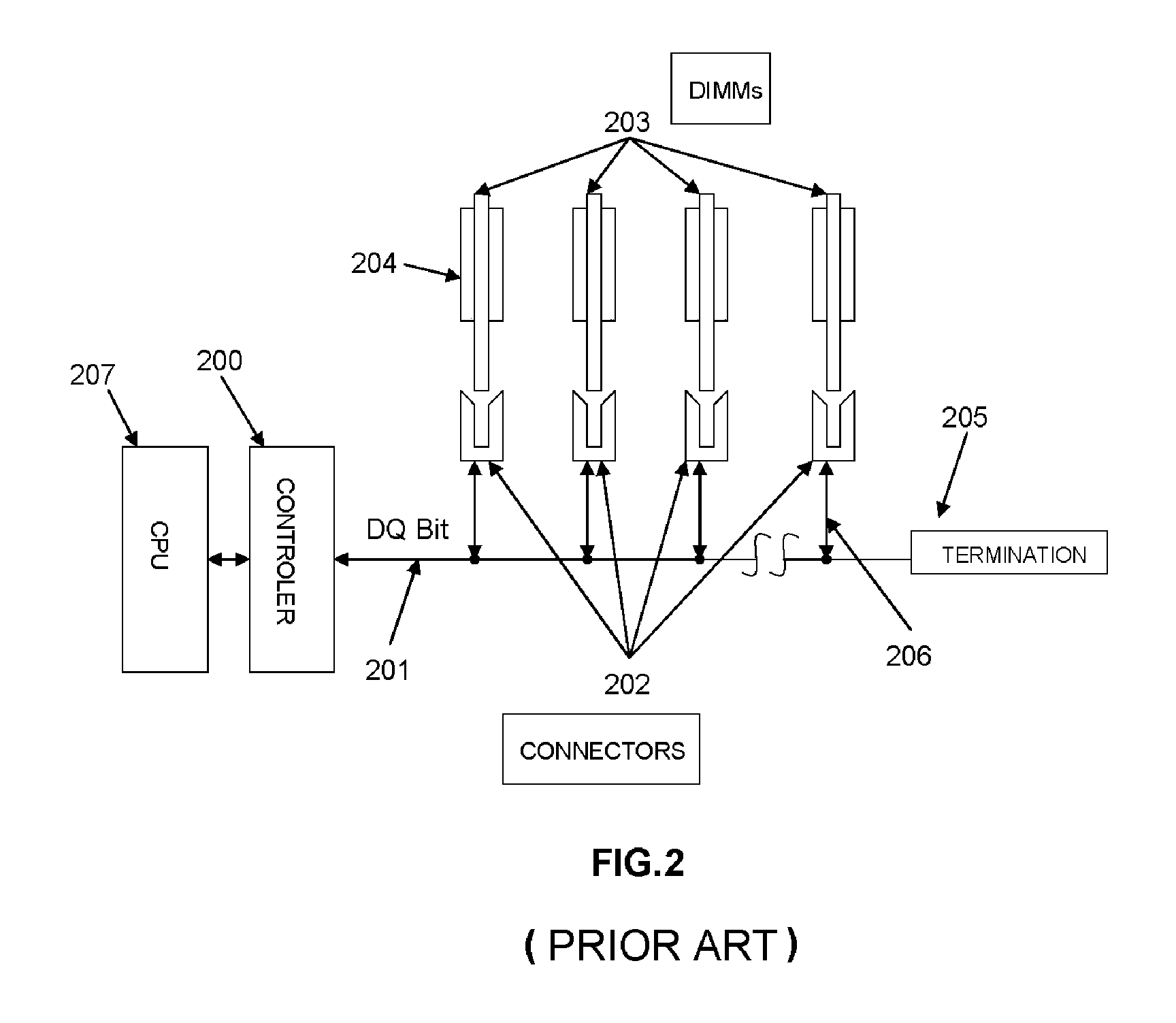

Active Dual in Line Memory Module Connector with Re-driven Propagated Signals

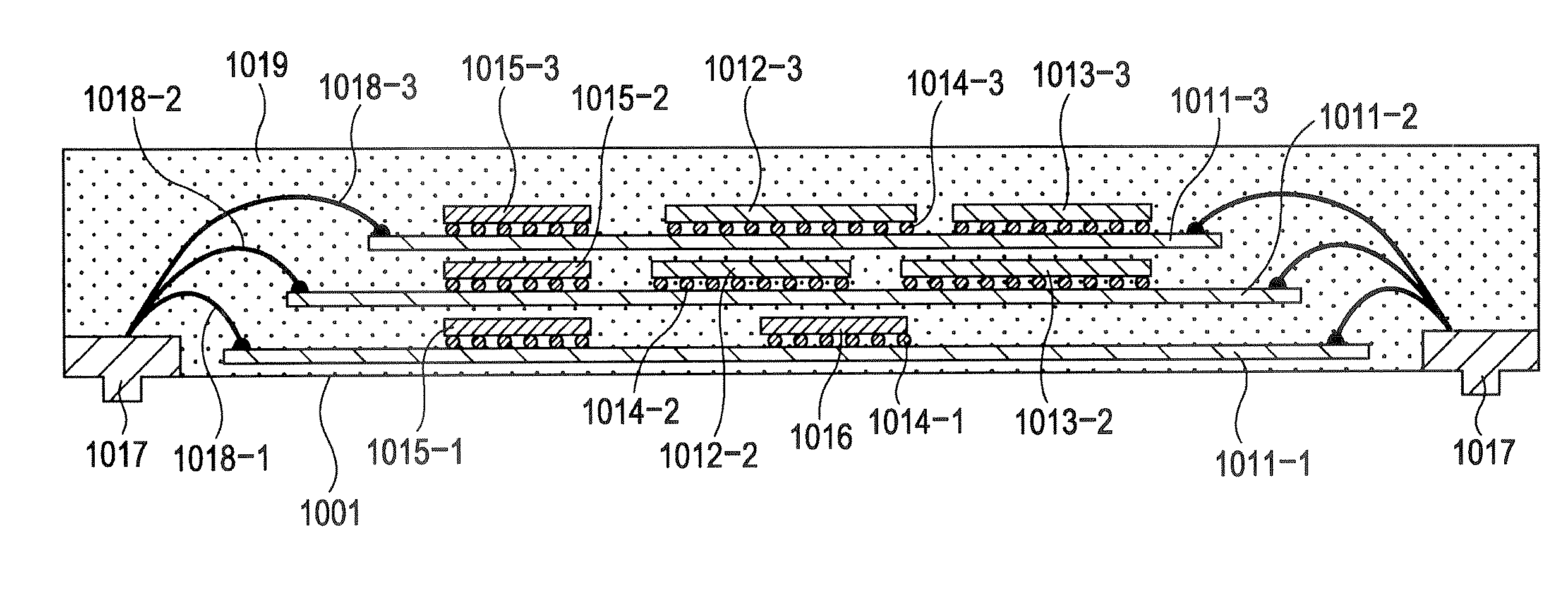

ActiveUS20110143579A1High densityData rateCoupling device detailsPrinted circuit manufactureActive edgeComputer module

An Active edge connector for memory modules has a base including two PCB sides and a spacer separating the sides, with driver chips mounted on each side of each side, printed wiring electrically connecting a first set of electrical signals from each of the driver chips to a mother board on which the connector is mounted, and printed wiring for electrically connecting a second set of electrical signals from each of the driver chips to a memory module inserted in the edge connector. When a group of connectors are mounted on a mother board, electrical signals arriving at the first connector are routed to its driver chips, producing re-driven signals to the next connector, and so on. A decoder circuit provides addressing signals determining the last such connector to which the signals are intended, and which prevents the signals from going to any connectors containing memories not addressed.

Owner:CALLAHAN CELLULAR L L C

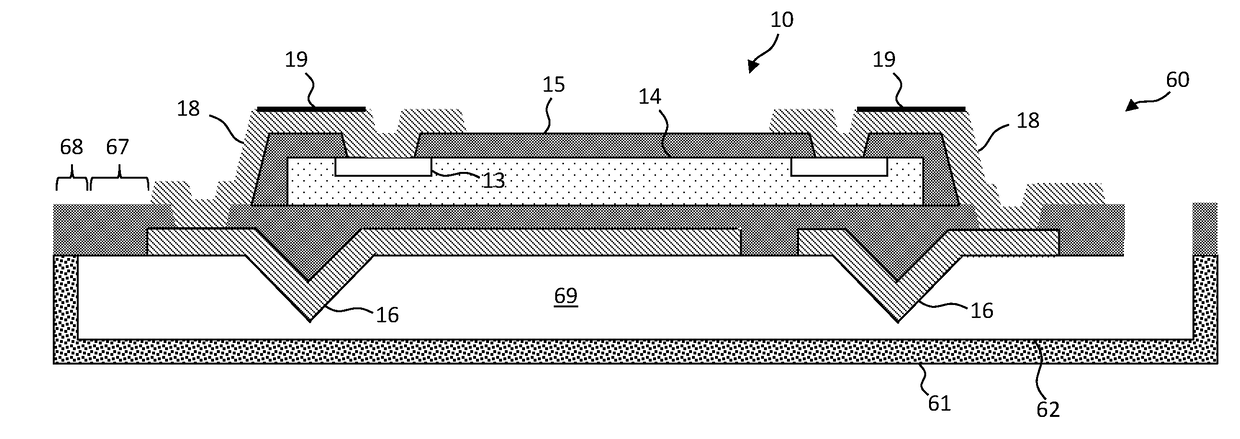

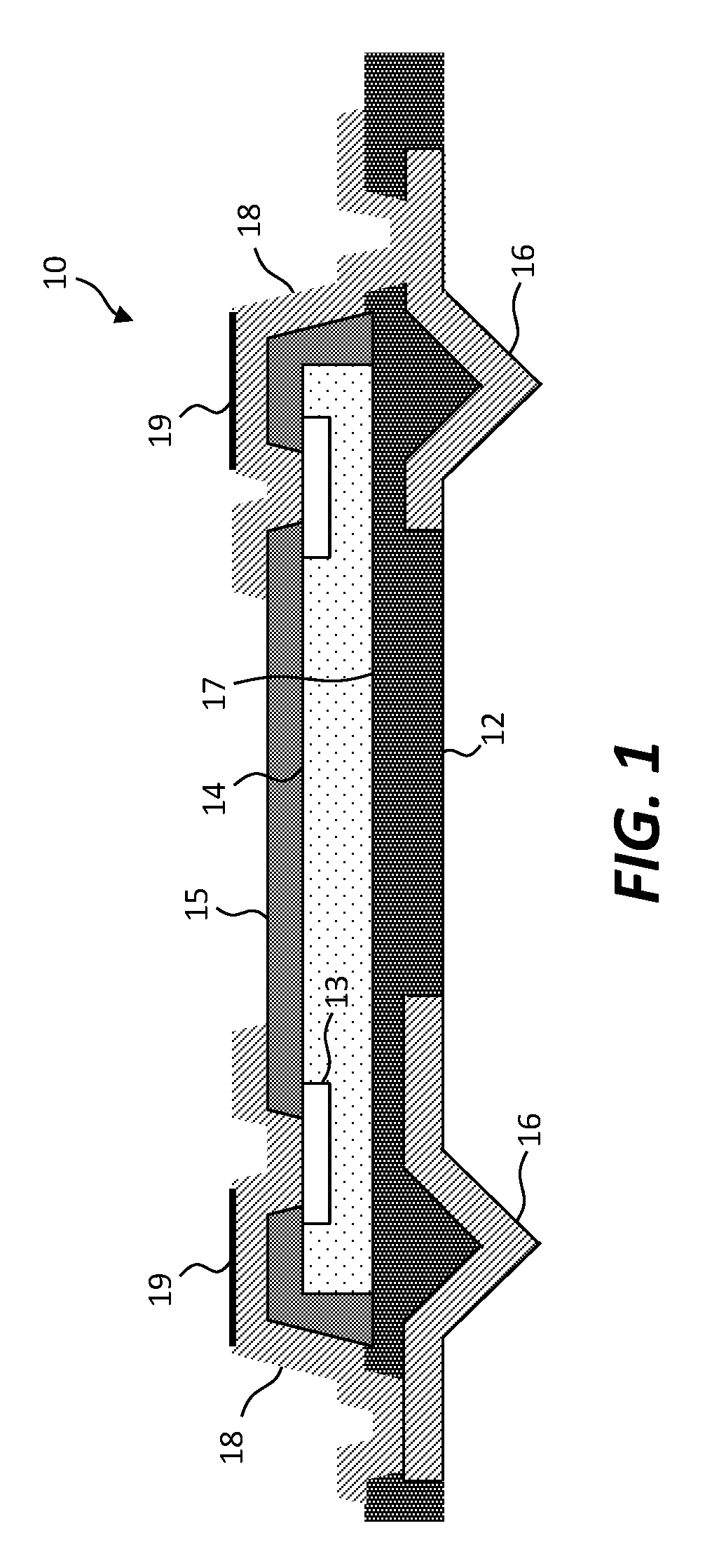

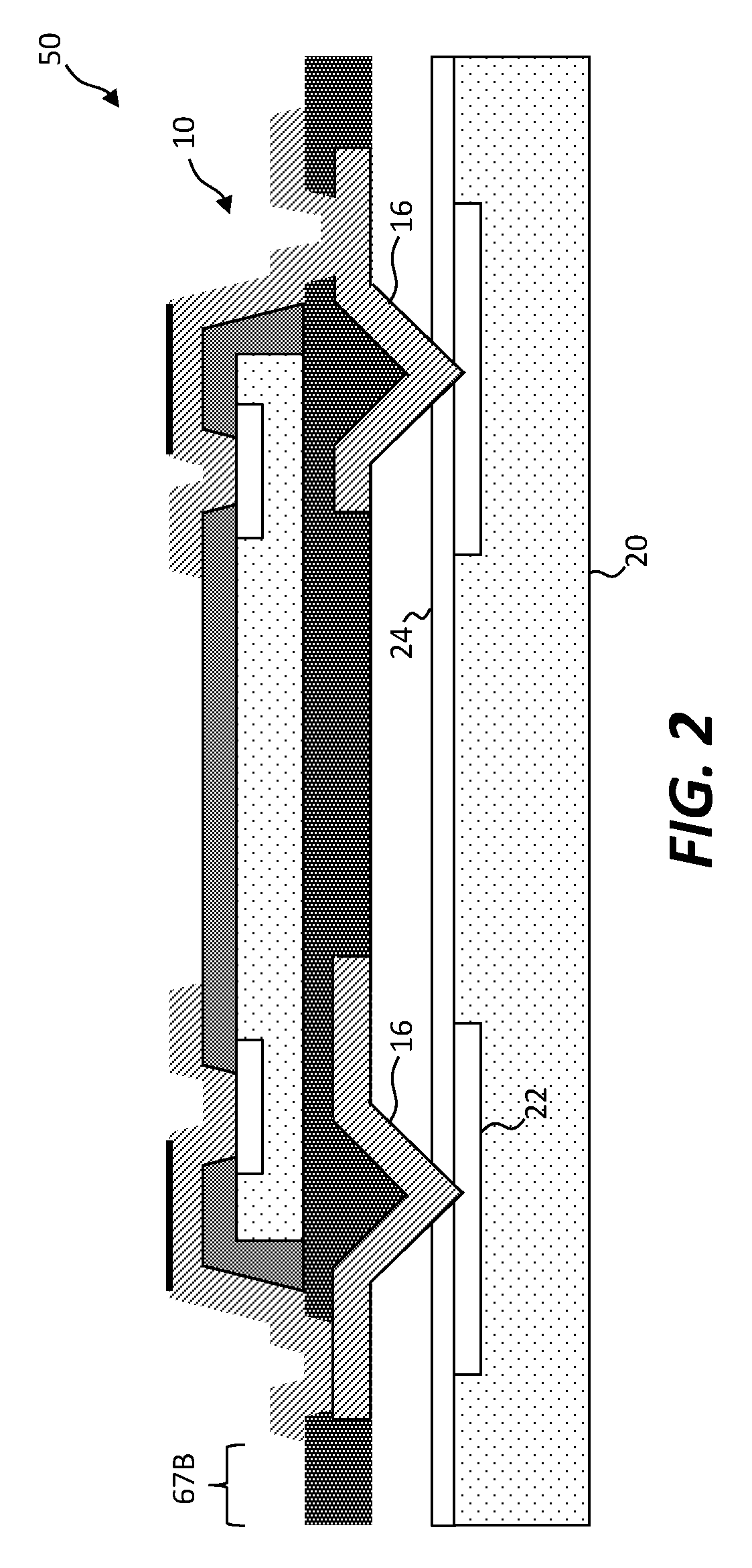

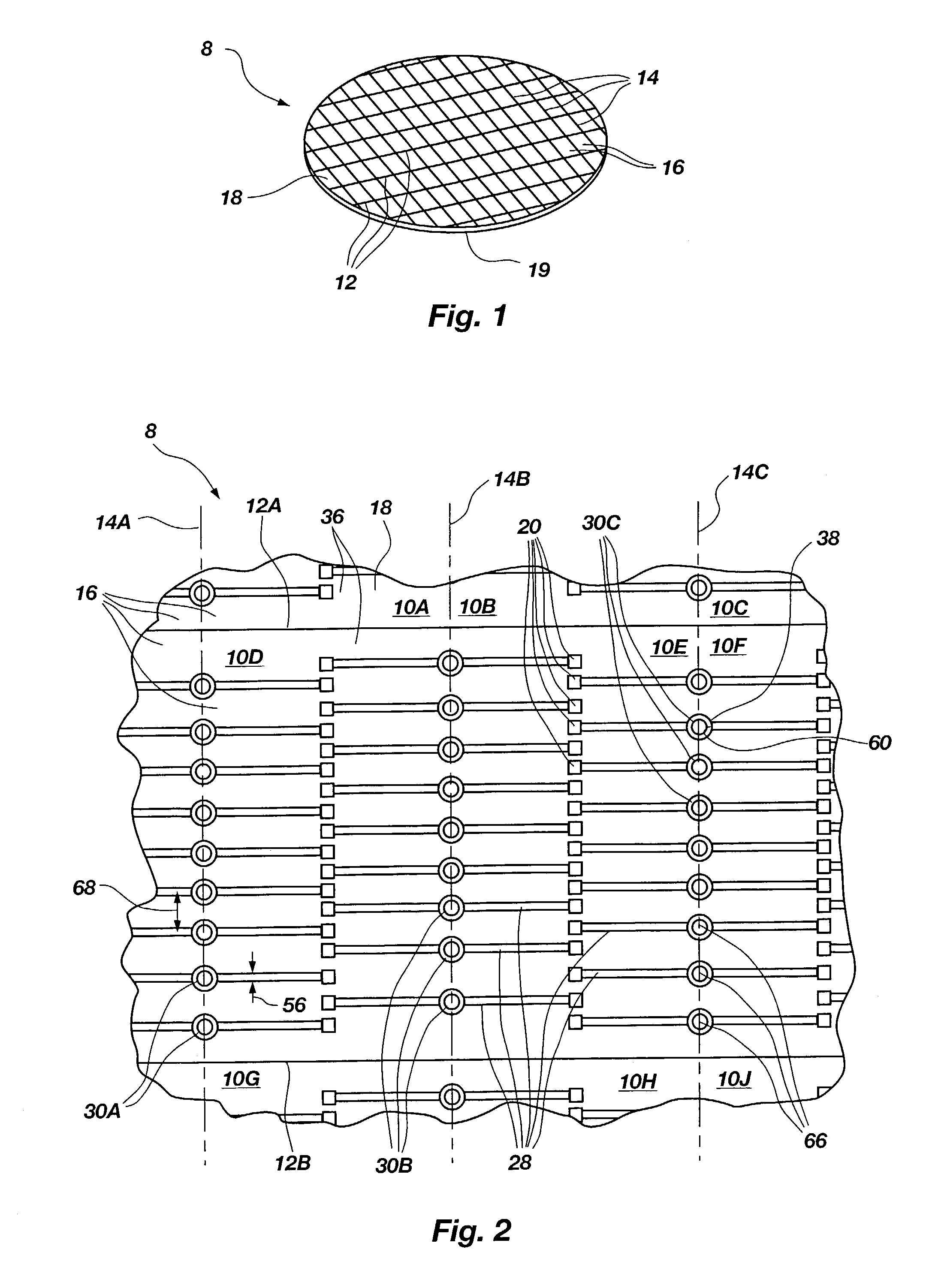

Semiconductor devices and semiconductor device components with peripherally located, castellated contacts, assemblies and packages including such semiconductor devices or packages and associated methods

InactiveUS7226809B2Printed circuit assemblingSemiconductor/solid-state device detailsConductive materialsElectroplating

A multichip assembly includes semiconductor devices or semiconductor device components with outer connectors on peripheral edges thereof. The outer connectors are formed by creating via holes along boundary lines between adjacent, unsevered semiconductor devices, or semiconductor device components, then plating or filling the holes with conductive material. When adjacent semiconductor devices or semiconductor device components are severed from one another, the conductive material in each via between the semiconductor devices is bisected. The semiconductor devices and components of the multichip assembly may have different sizes, as well as arrays of outer connectors with differing diameters and pitches. Either or both ends of each outer connector may be electrically connected to another aligned outer connector or contact area of another semiconductor device or component. Assembly in this manner provides a low-profile stacked assembly.

Owner:MICRON TECH INC

Method of assembling electronic components of an electronic system, and system thus obtained

InactiveUS20060267176A1Reduce in quantitySemiconductor/solid-state device detailsSolid-state devicesElectronic systemsElectrical connection

An electronic system comprising: an electronic system support substrate for the attachment of components of the electronic system, the electronic system support substrate including electric signal propagation paths for the propagation of electric signals between the system components; at least a first and a second electronic components wherein at least the first electronic component is part of a module in mechanical and electrical connection with the electronic system support substrate, the module comprising a module substrate to which the first electronic component is at least mechanically connected, and an electric coupling between the first and the second electronic components, for the electric coupling allowing the first and the second electronic components exchange of electric signals. The electric coupling comprises a direct electric connection particularly formed by a flexible electrical interconnection member, between the first and the second electronic components, the electric connection being independent of the electronic system support substrate.

Owner:IBM CORP

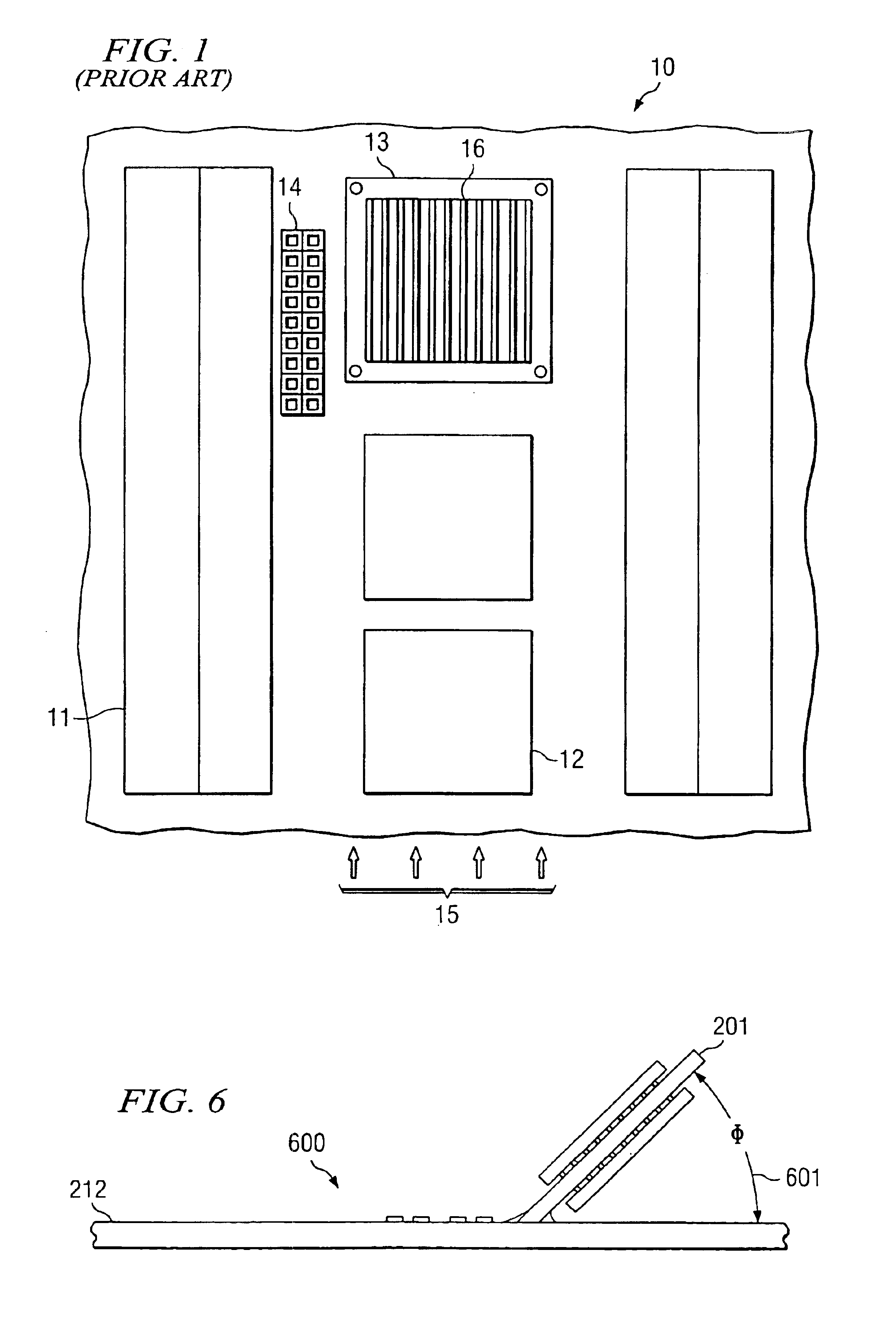

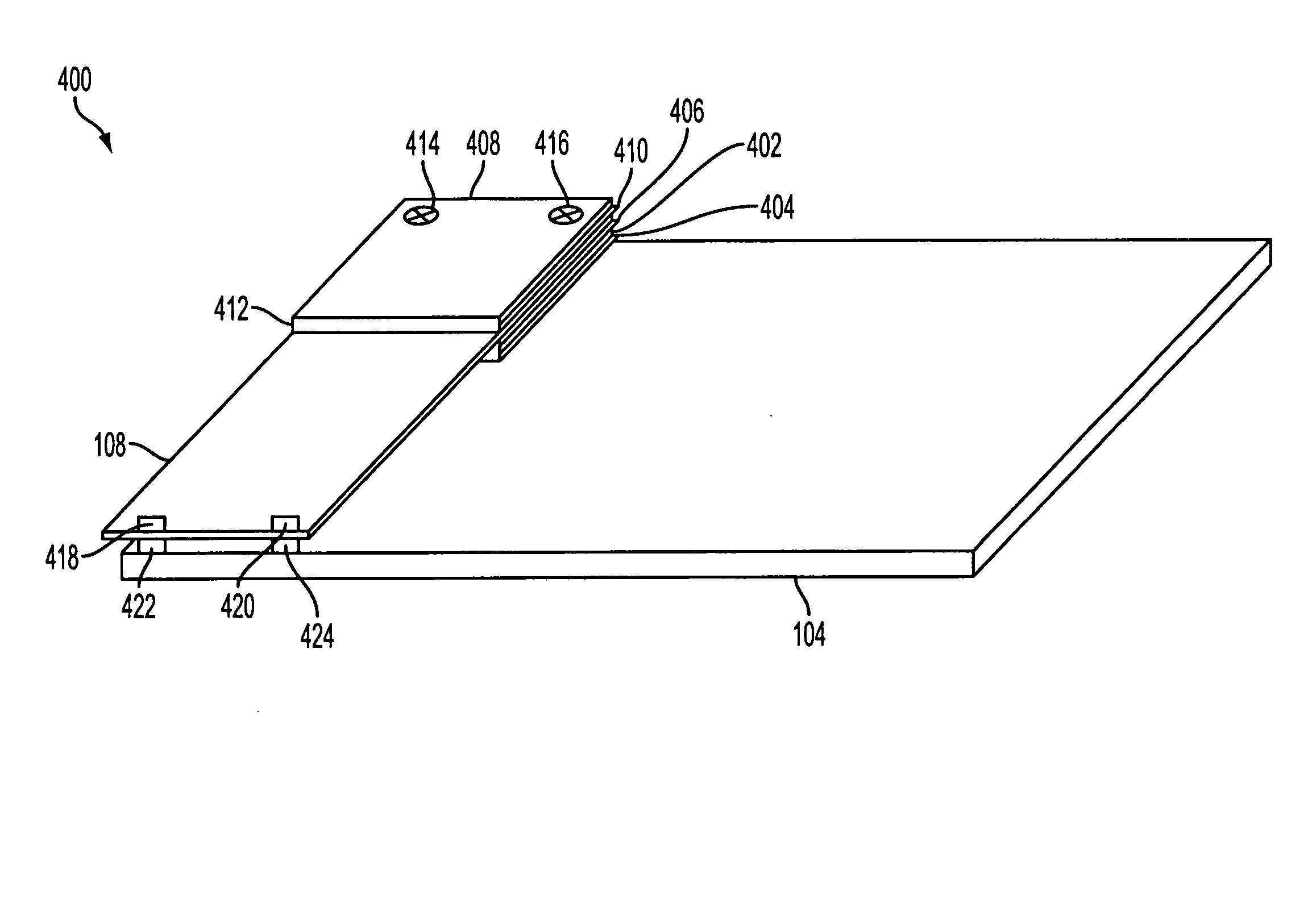

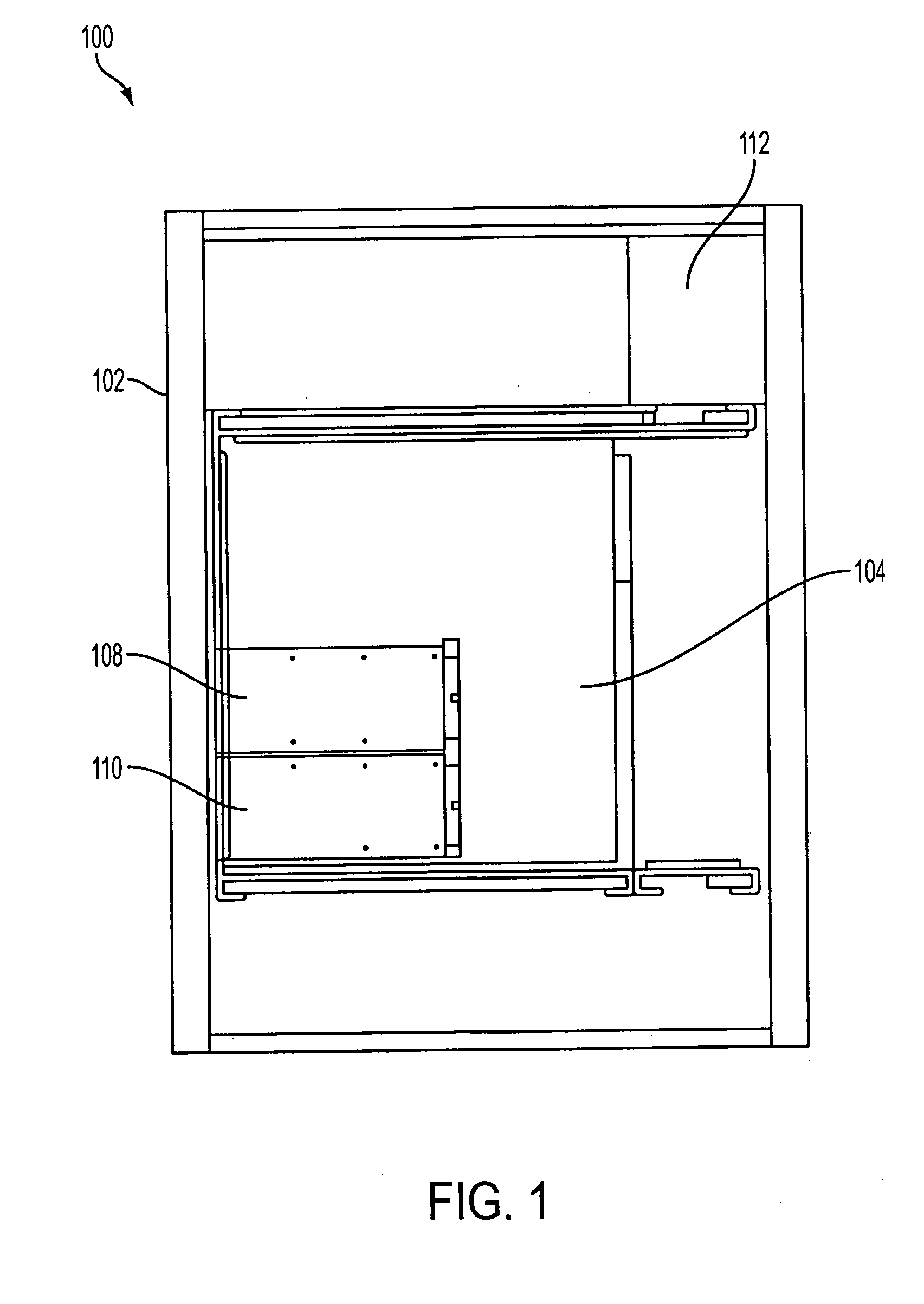

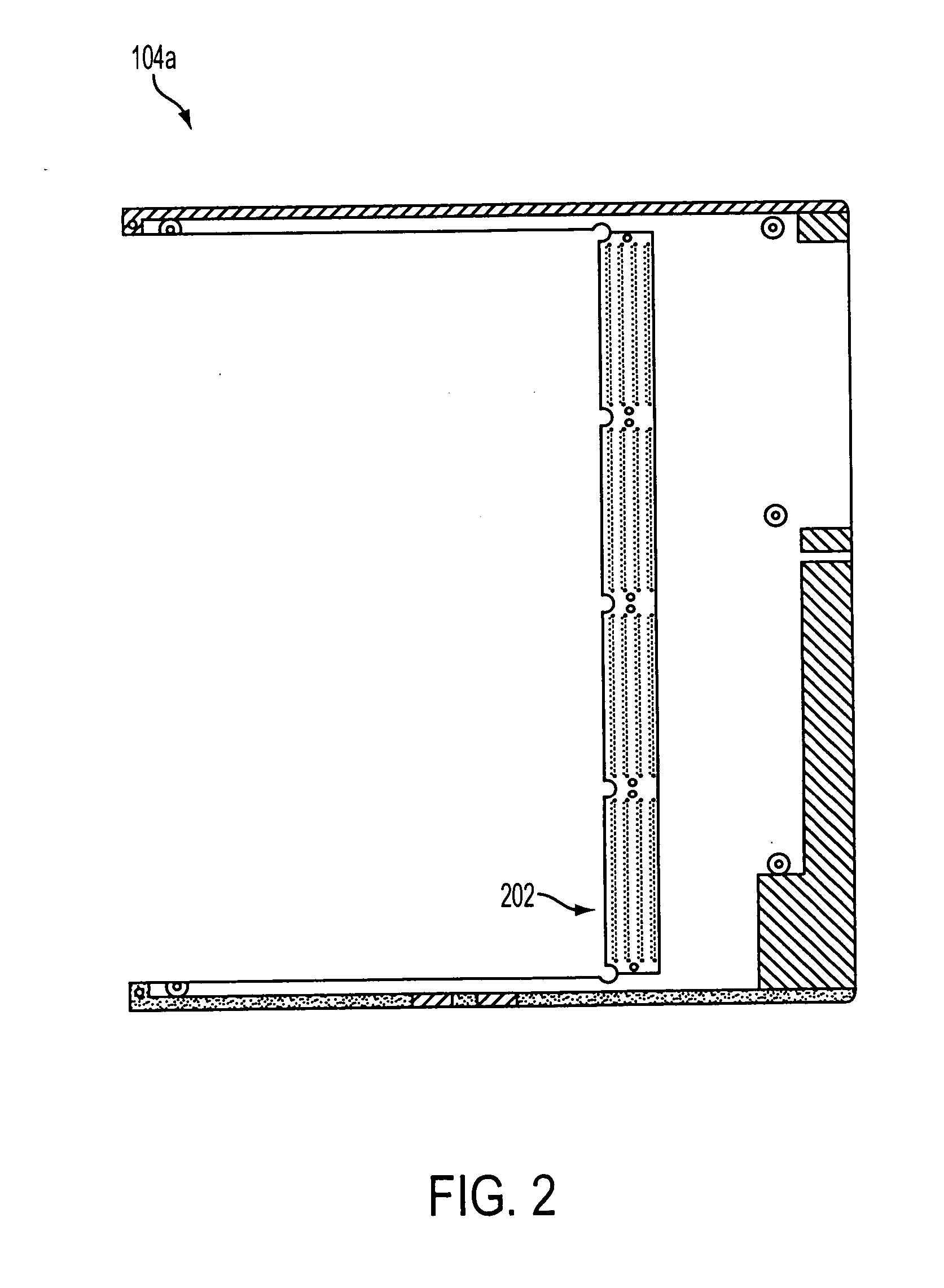

Horizontal Dual In-line Memory Modules

Horizontal dual in-line memory modules are disclosed. In one embodiment, the memory module includes a circuit board, a plurality of memory chips attached to a top surface of the circuit board, and a plurality of connector contacts disposed under a back surface of the circuit board and extending away from the memory chips, the connector contacts being electrically coupled to the memory chips, the back surface opposite the top surface of the circuit board.

Owner:POLARIS INNOVATIONS

Systems and methods that use at least one component to remove the heat generated by at least one other component

One embodiment of the invention is a system comprising a first component that generates heat, and a second component that is thermally connected to the first component, wherein the heat from the first component is transferred to a coolant through the second component, and the second component has a function in the computer system associated with an operation of the system other than transferring heat.

Owner:VALTRUS INNOVATIONS LTD +1

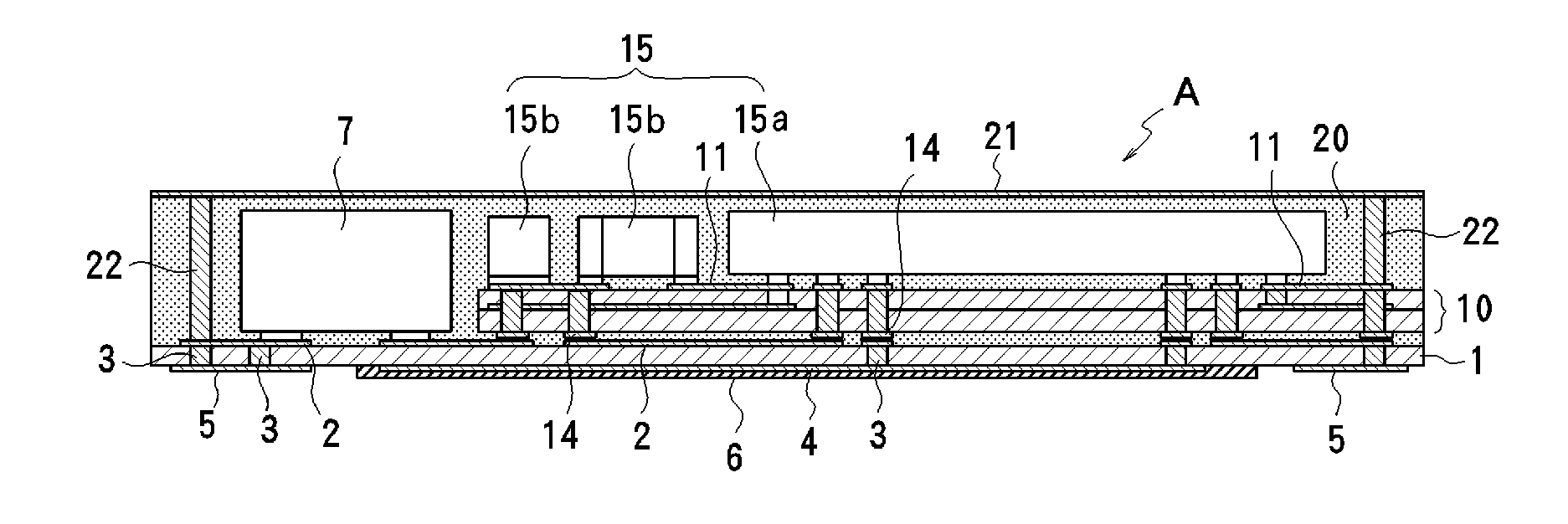

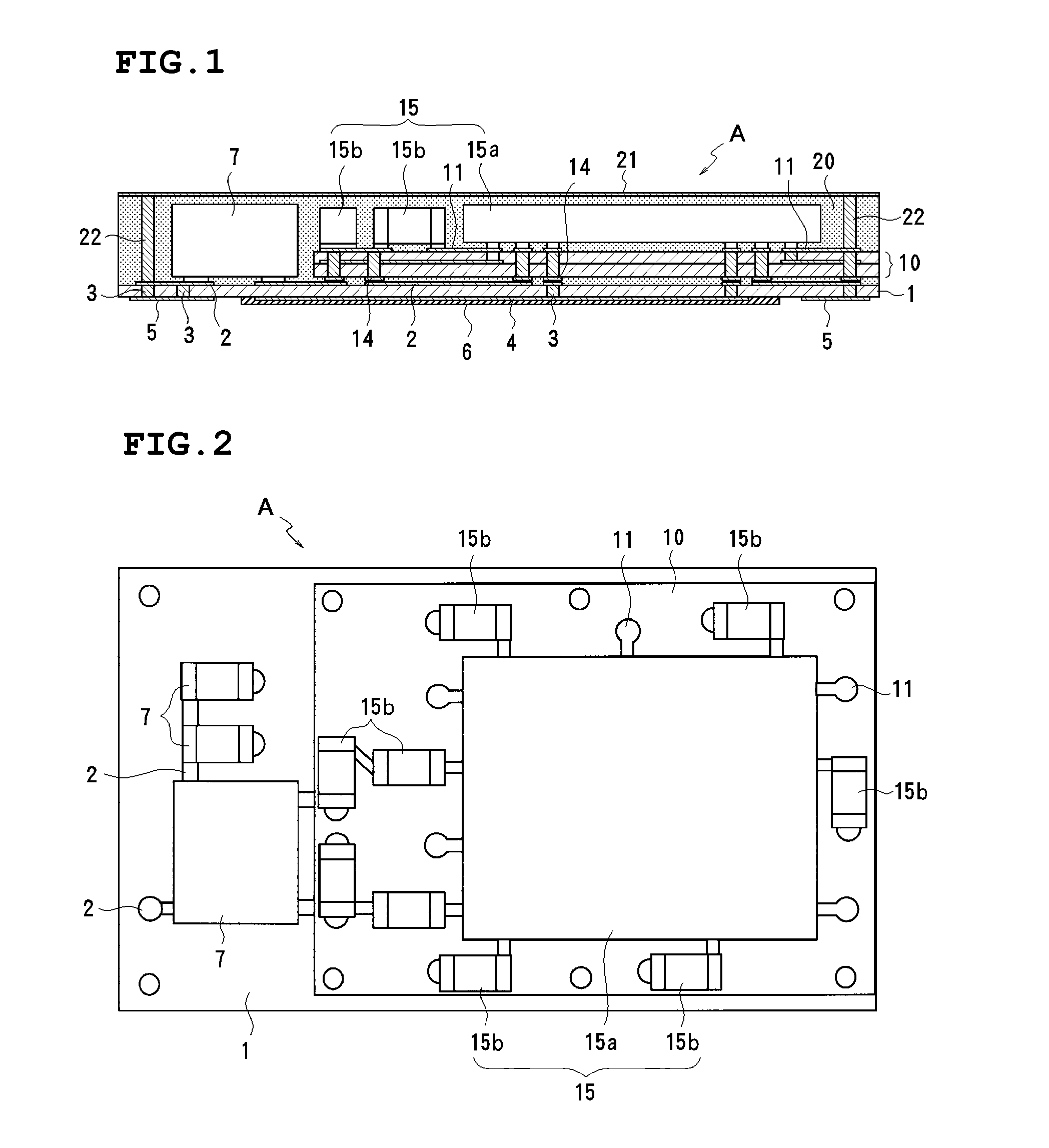

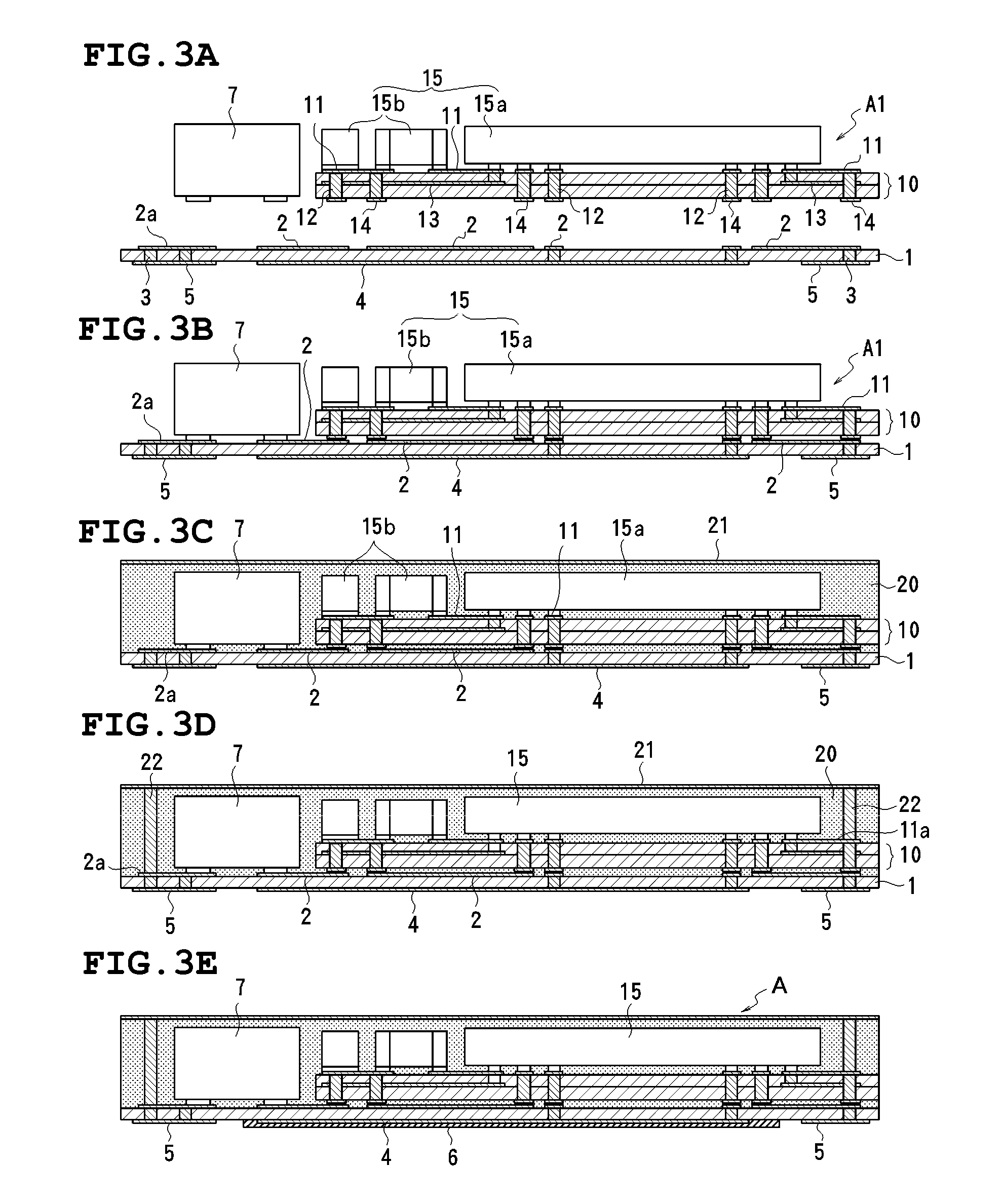

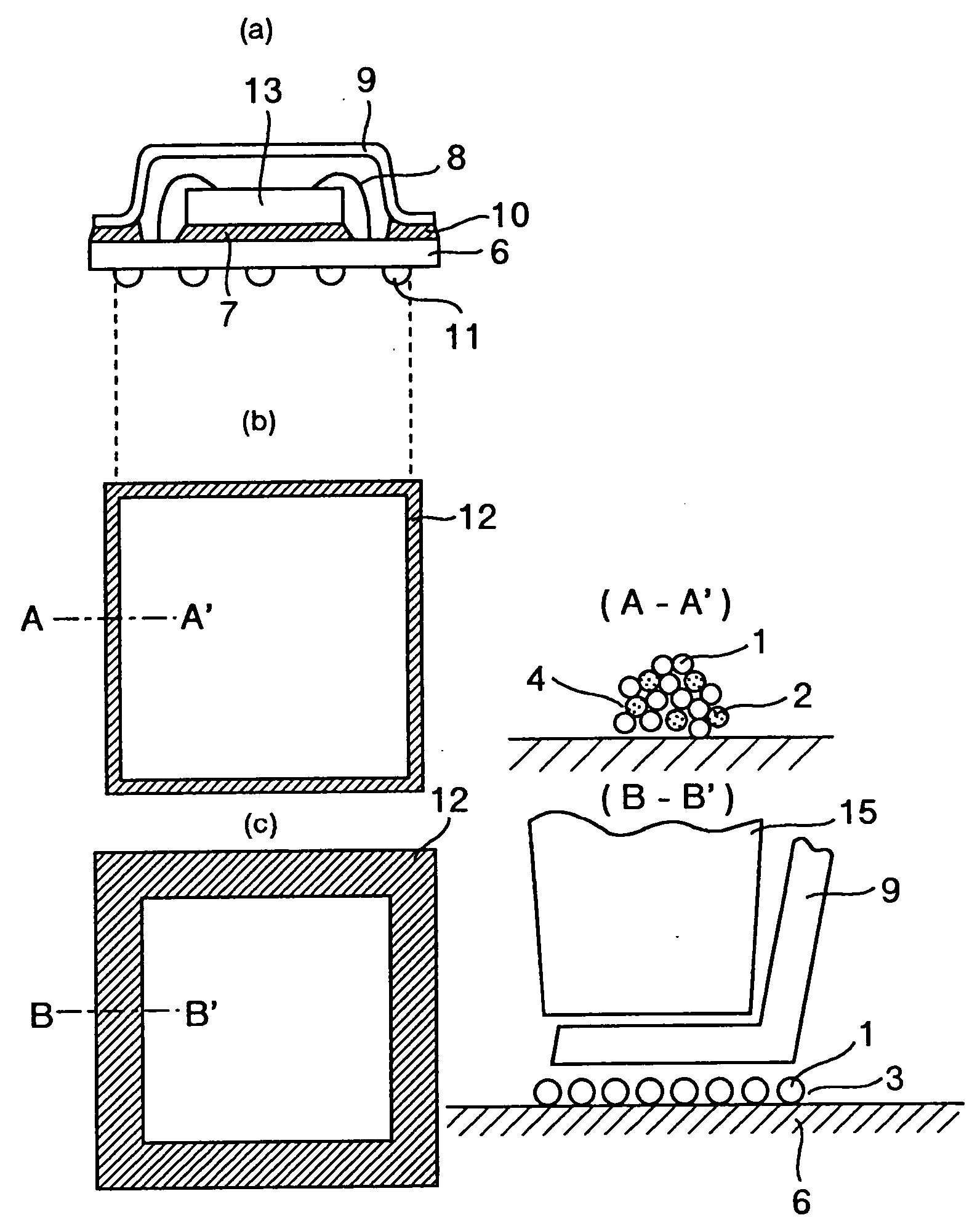

Electro-optical apparatus, flexible printed circuit board, manufacturing method for electro-optical apparatus, and electronic equipment

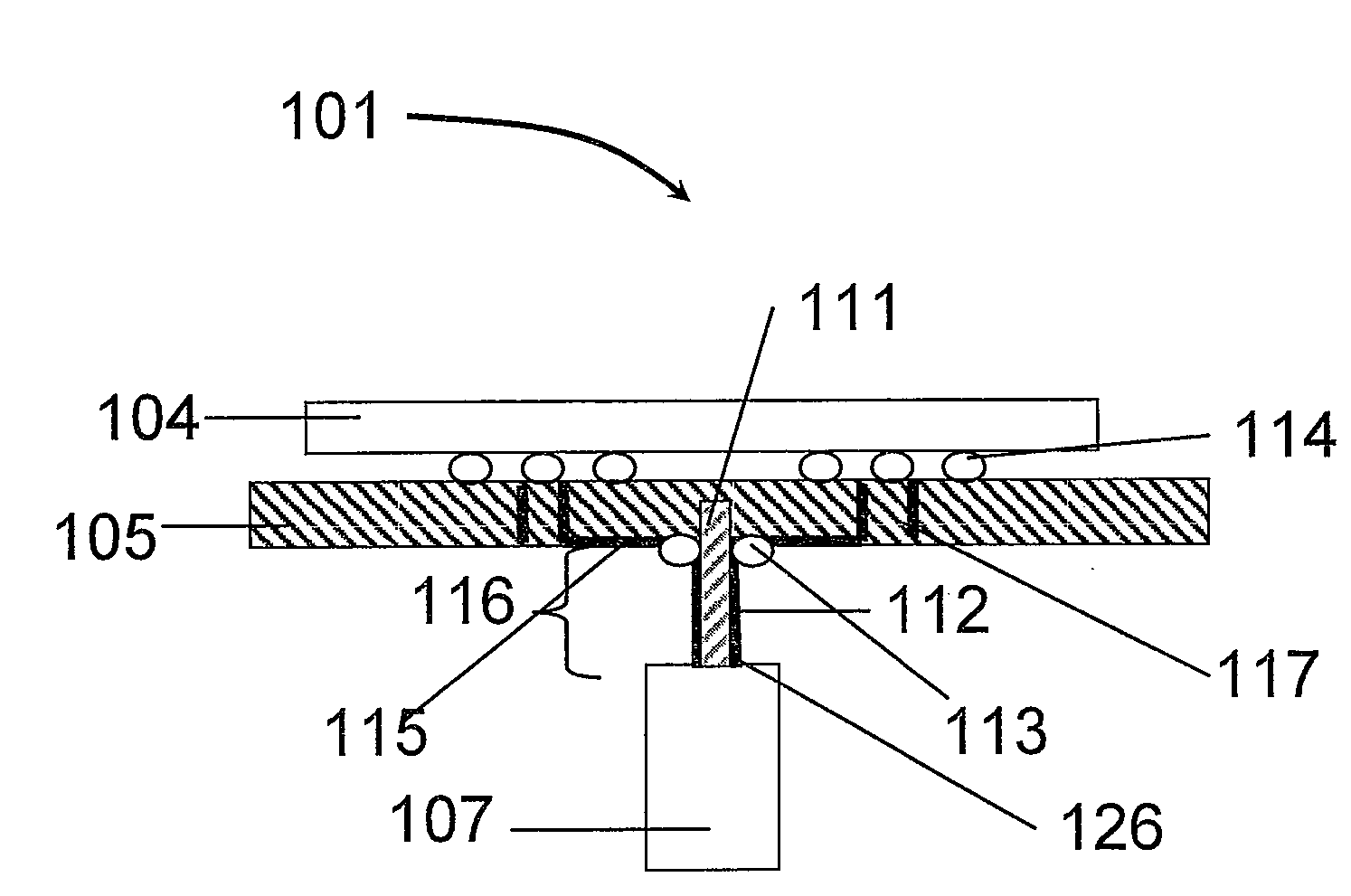

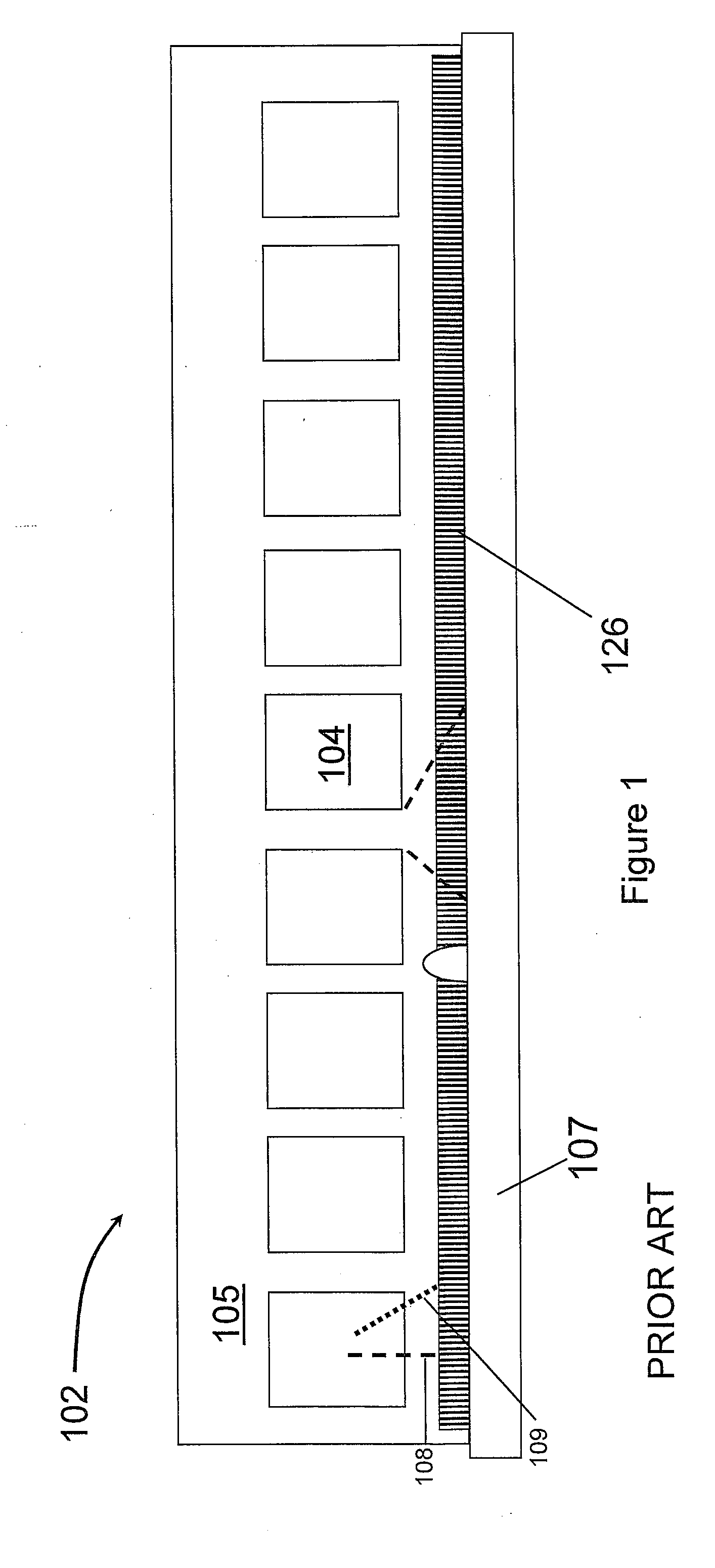

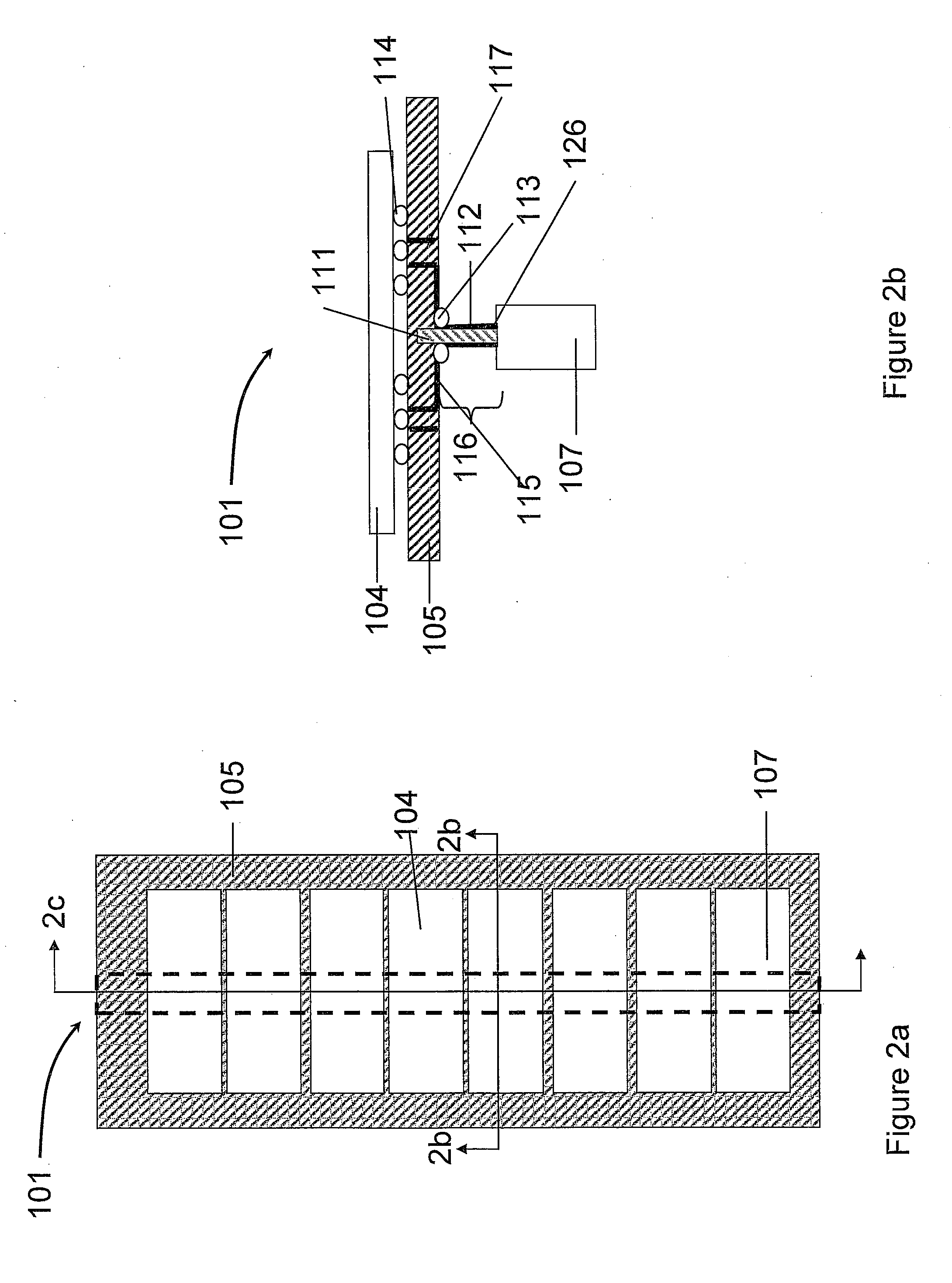

ActiveUS20110051382A1Reduce installation costsLow costPrinted circuit assemblingHierarchy auxillary PCBsElectricitySurface mounting

Owner:BOE TECH GRP CO LTD

System and method for Advanced Mezzanine Card connection

InactiveUS20060221590A1Electrically conductive connectionsDigital data processing detailsAdvanced Mezzanine CardElectrical contacts

A method according to one embodiment may include providing a circuit board having a connector footprint including a plurality of electrical contacts and providing a mezzanine card including a first plurality of conductive traces on a first side of the mezzanine card. The method of this embodiment may also include providing a first wiring board disposed between at least a portion of the circuit board and at least a portion of the mezzanine card. The first wiring board may electrically couple at least a portion of the electrical contacts of the connector footprint to at least a portion of the conductive traces of the mezzanine card. Of course, many alternatives, variations, and modifications are possible without departing from this embodiment.

Owner:RADISYS CORP

Method and apparatus for intrinsically safe circuit board arrangement for portable electronic devices

ActiveUS20160174377A1Printed circuit assemblingLine/current collector detailsIntrinsic safetyEngineering

Owner:MOTOROLA SOLUTIONS INC

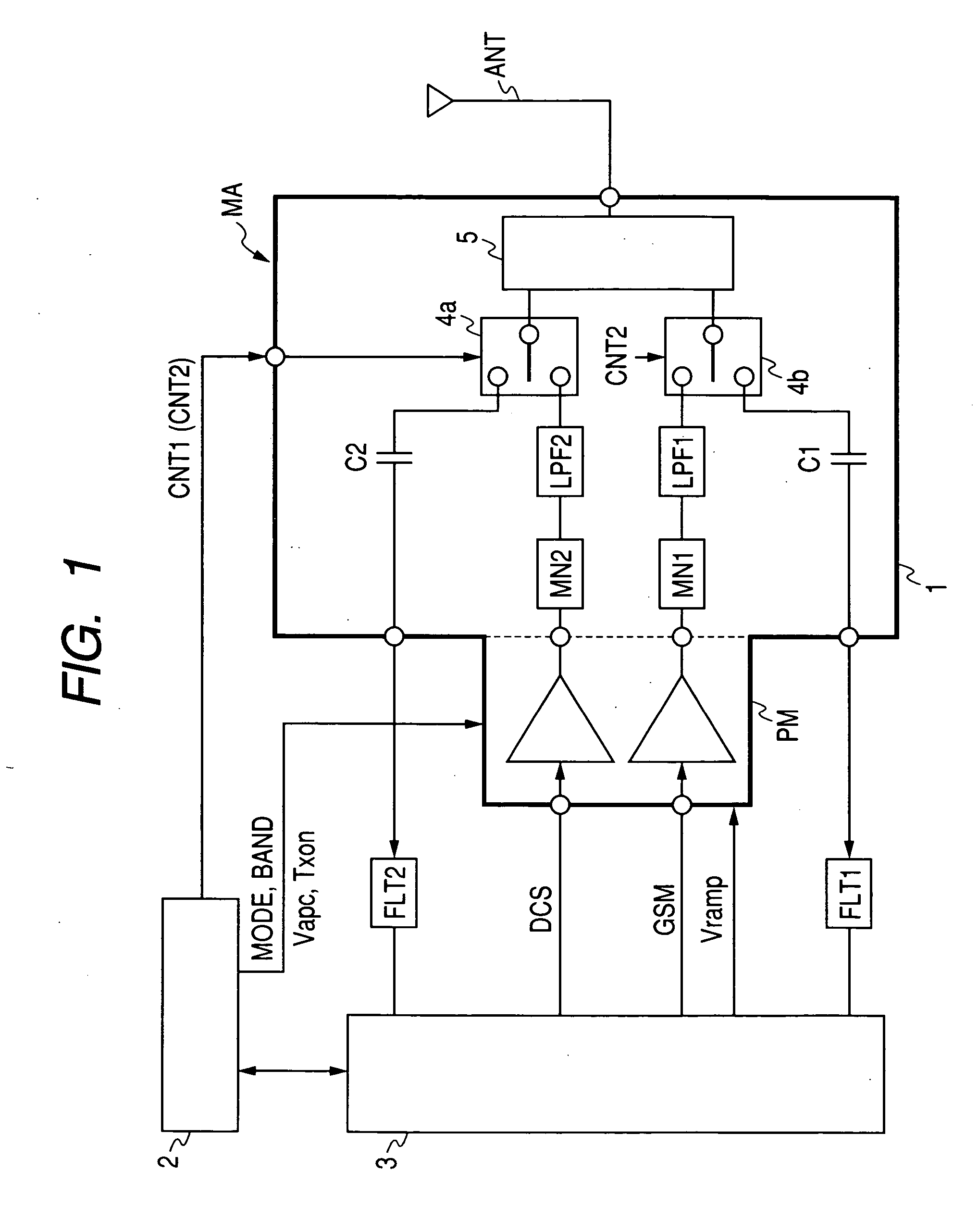

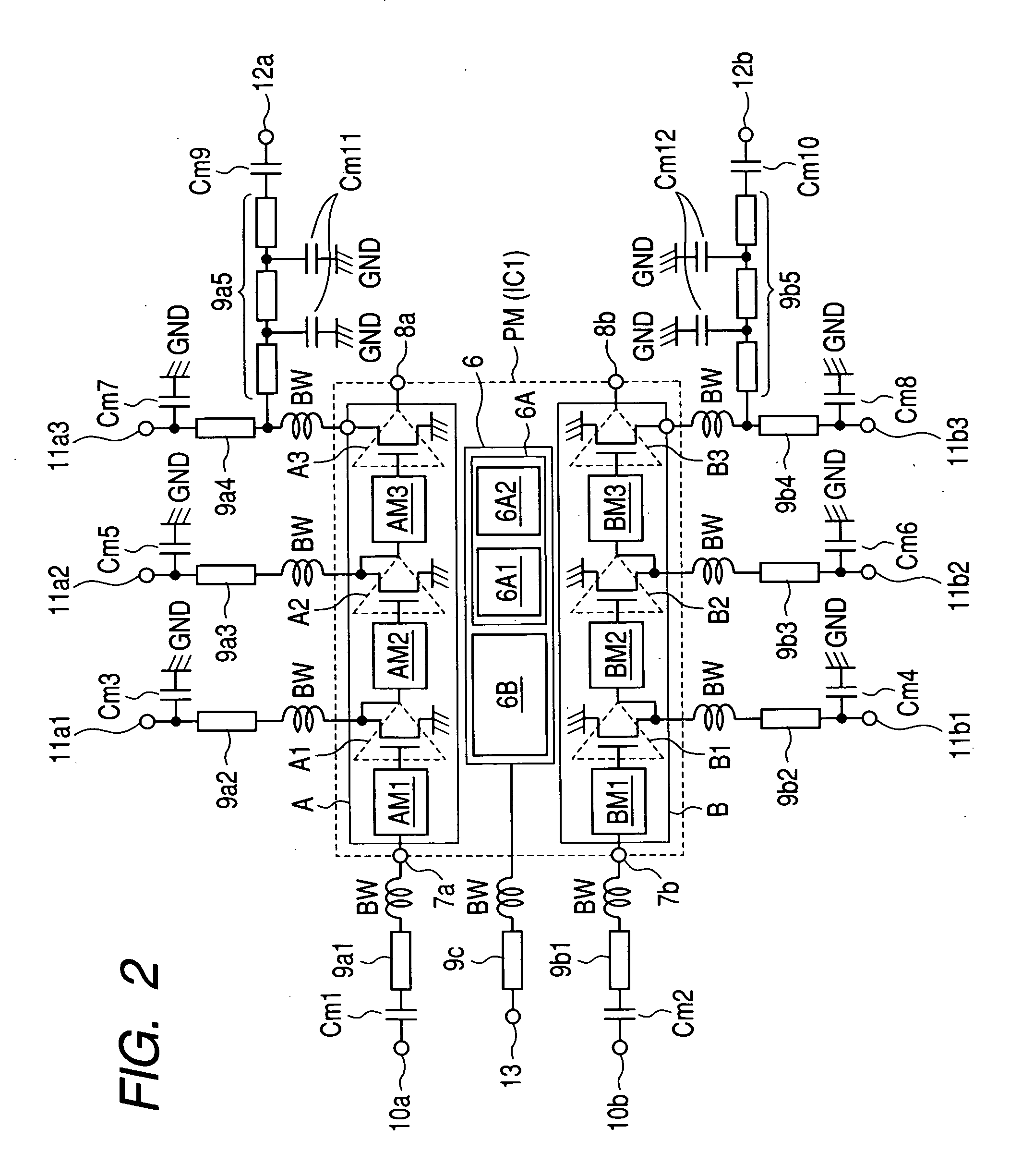

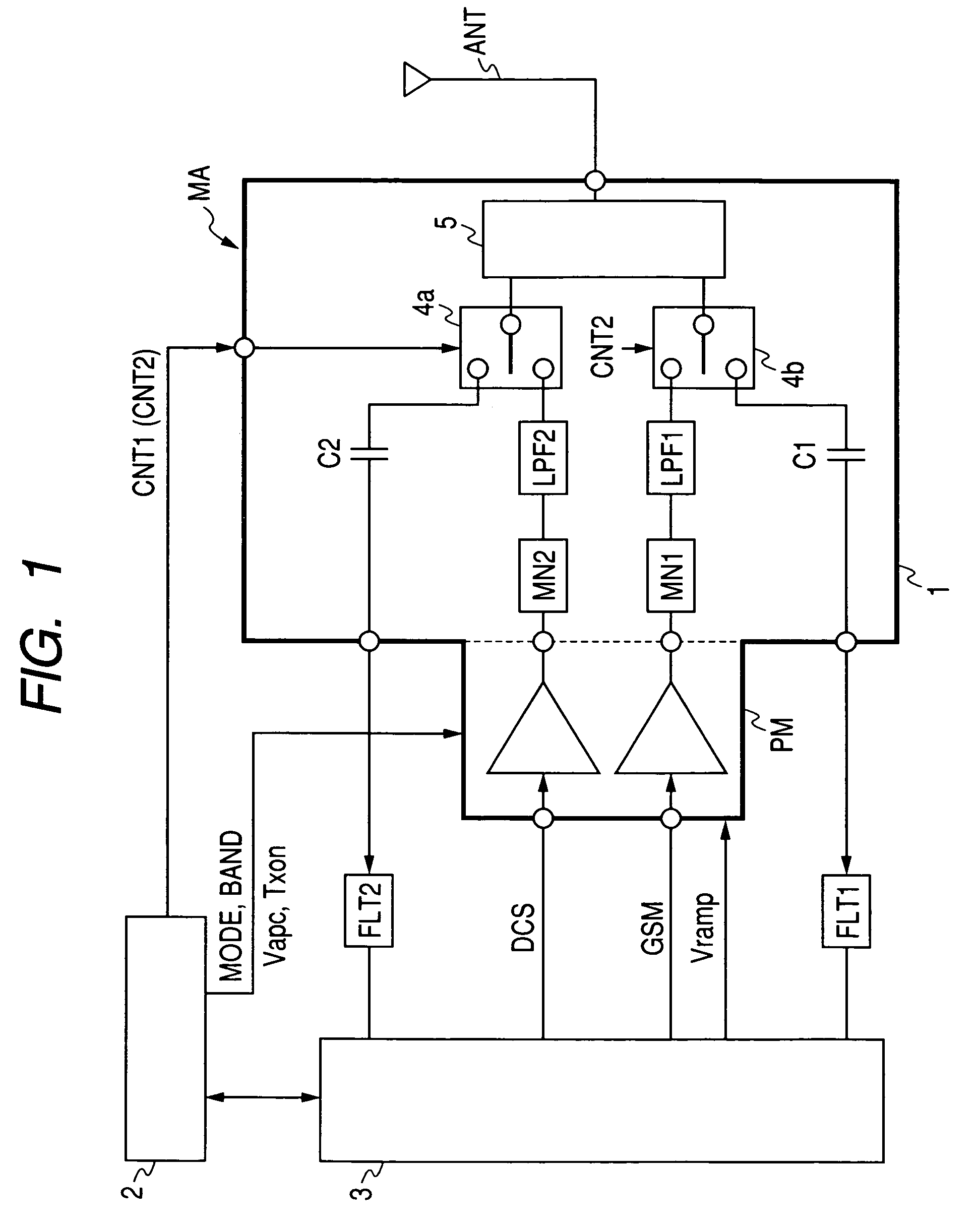

Communication semiconductor chip, calibration method, and program

InactiveUS20070120569A1Easy to implementStable communicationSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipVoltage reference

A communication semiconductor chip performs wireless communication with another communication semiconductor chip. The semiconductor chip includes a communication module and a control unit. The communication module performs the wireless communication with another communication semiconductor chip and has a receiving circuit for receiving data. The control unit supplies a reference voltage to the receiving circuit and performs a calibration operation on the reference voltage.

Owner:SONY CORP

Popular searches

Printed electric component incorporation Printed circuits structural associations Semiconductor devices Semiconductor/solid-state device manufacturing Printed element electric connection formation Electrical connection printed elements Resilient/clamping means Support structure mounting Fixed connections Printed circuit non-printed electric components association