Patents

Literature

34 results about "Multidrop bus" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A multidrop bus (MDB) is a computer bus in which all components are connected to the electrical circuit. A process of arbitration determines which device sends information at any point. The other devices listen for the data they are intended to receive.

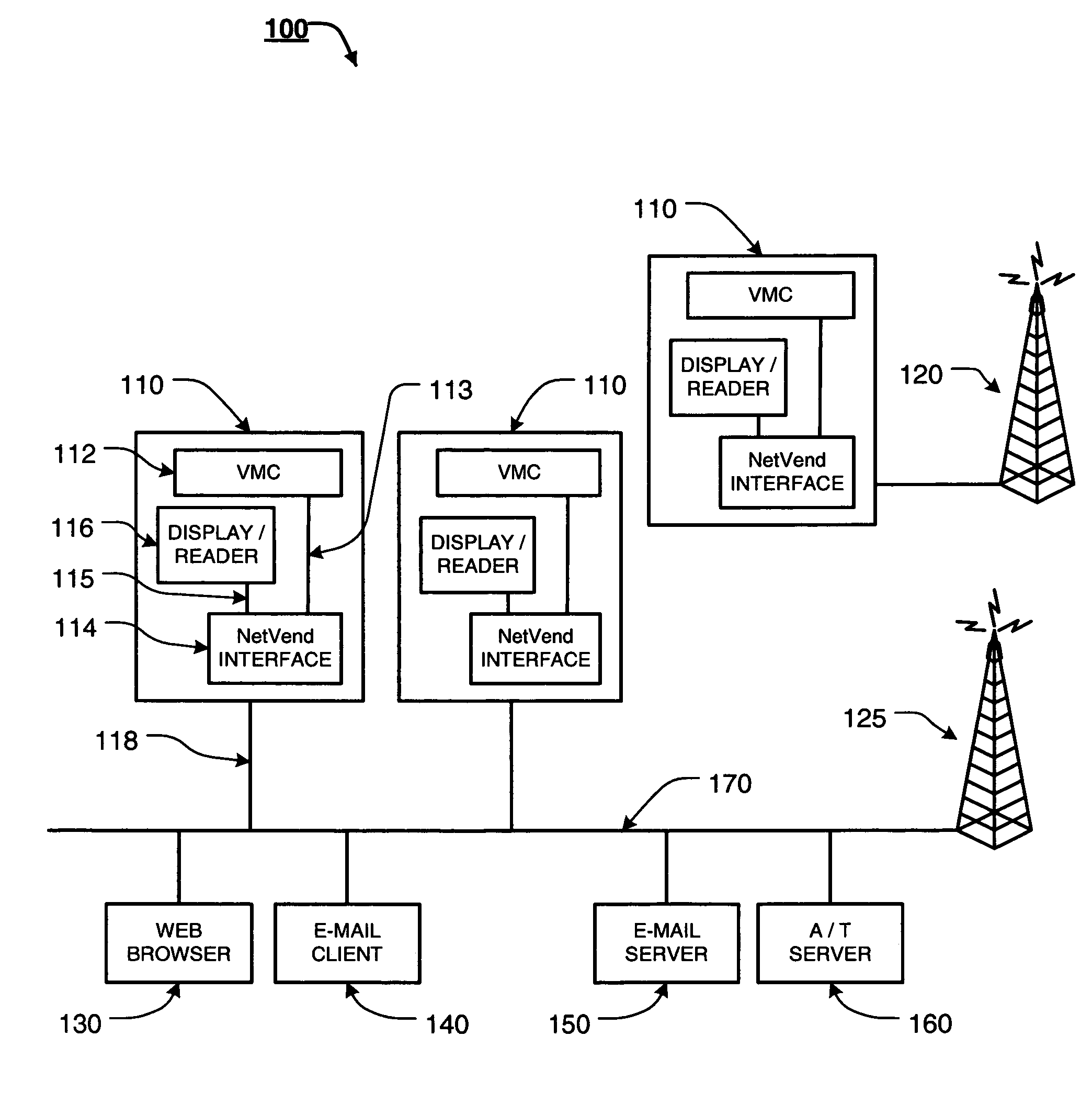

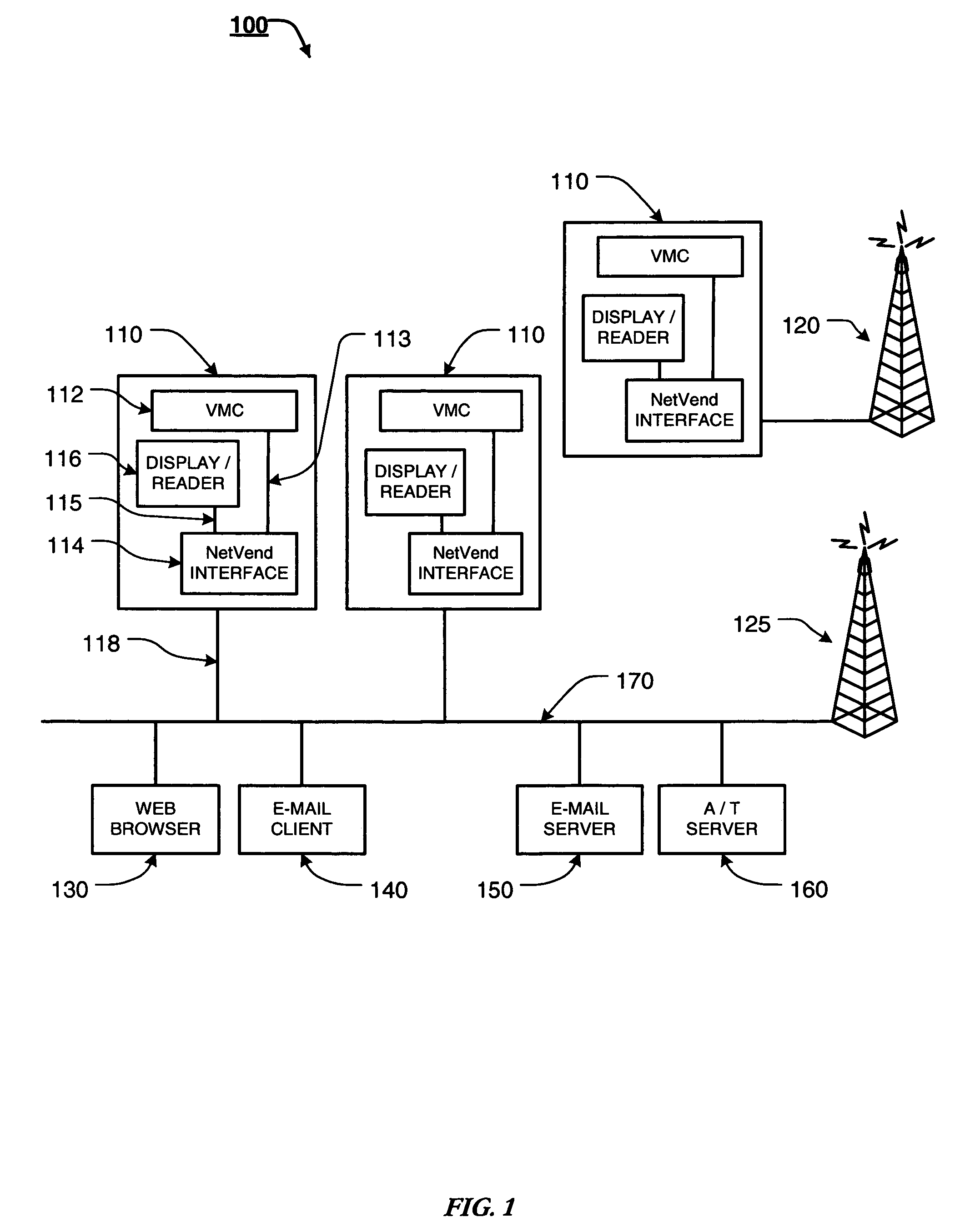

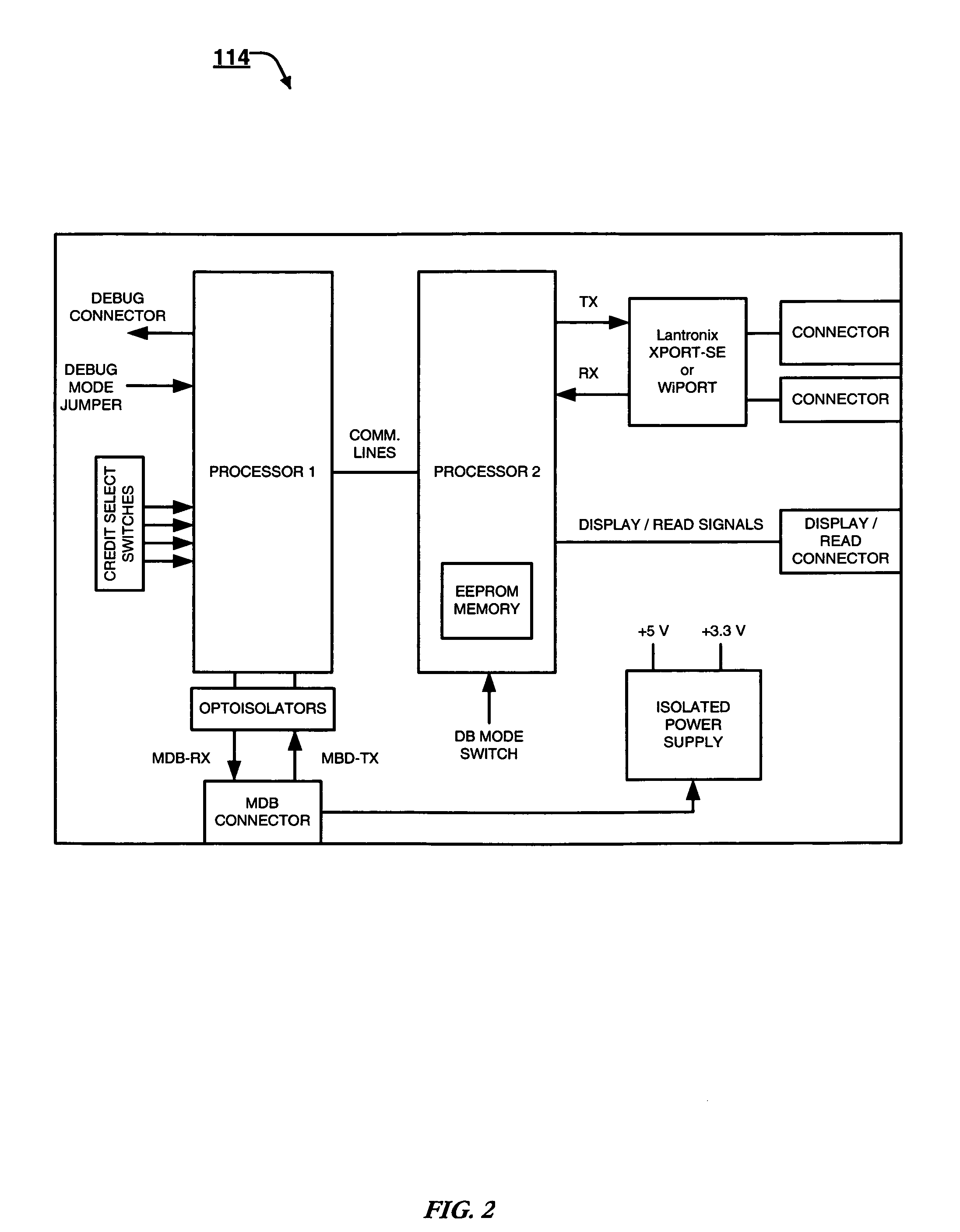

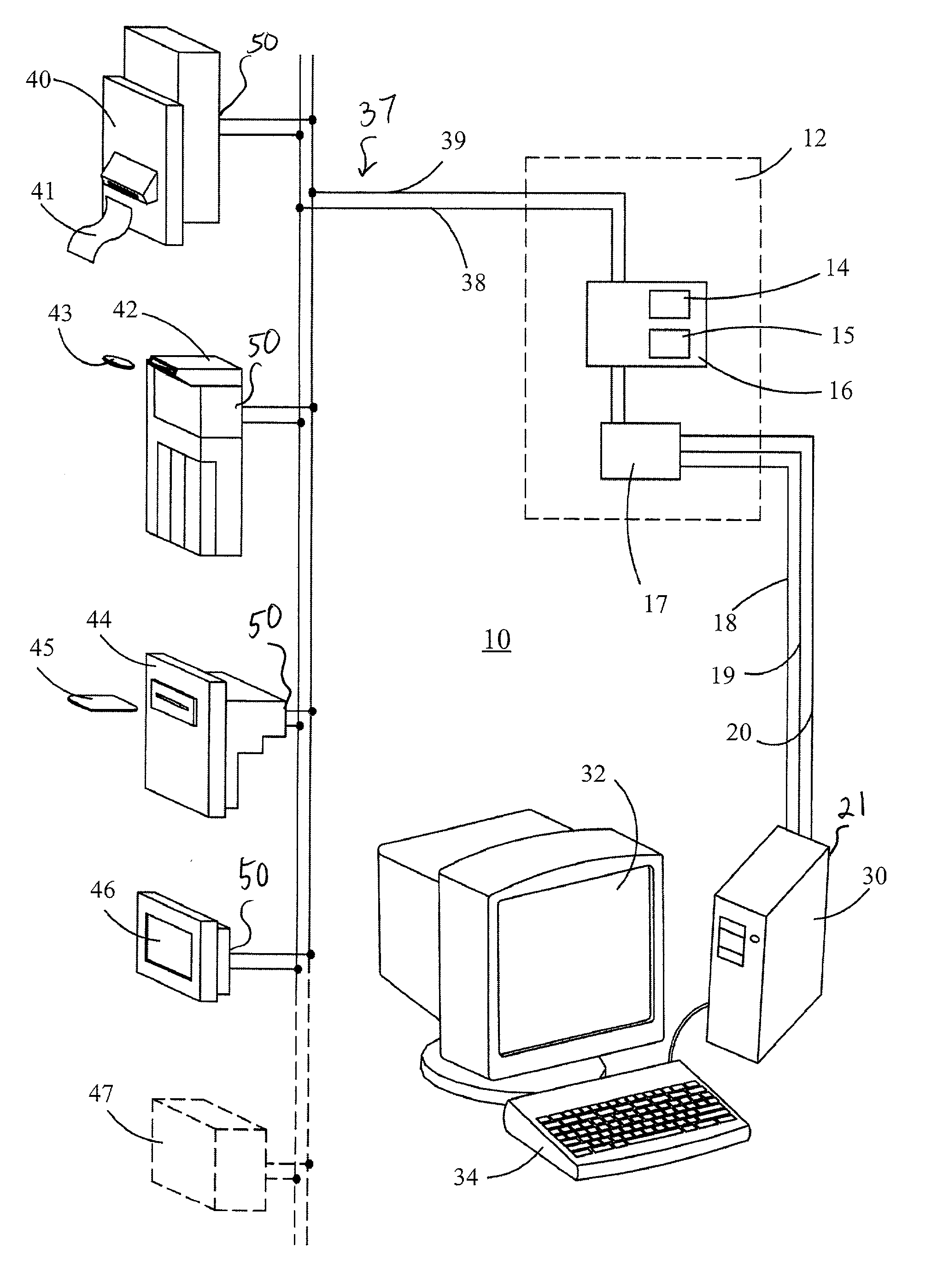

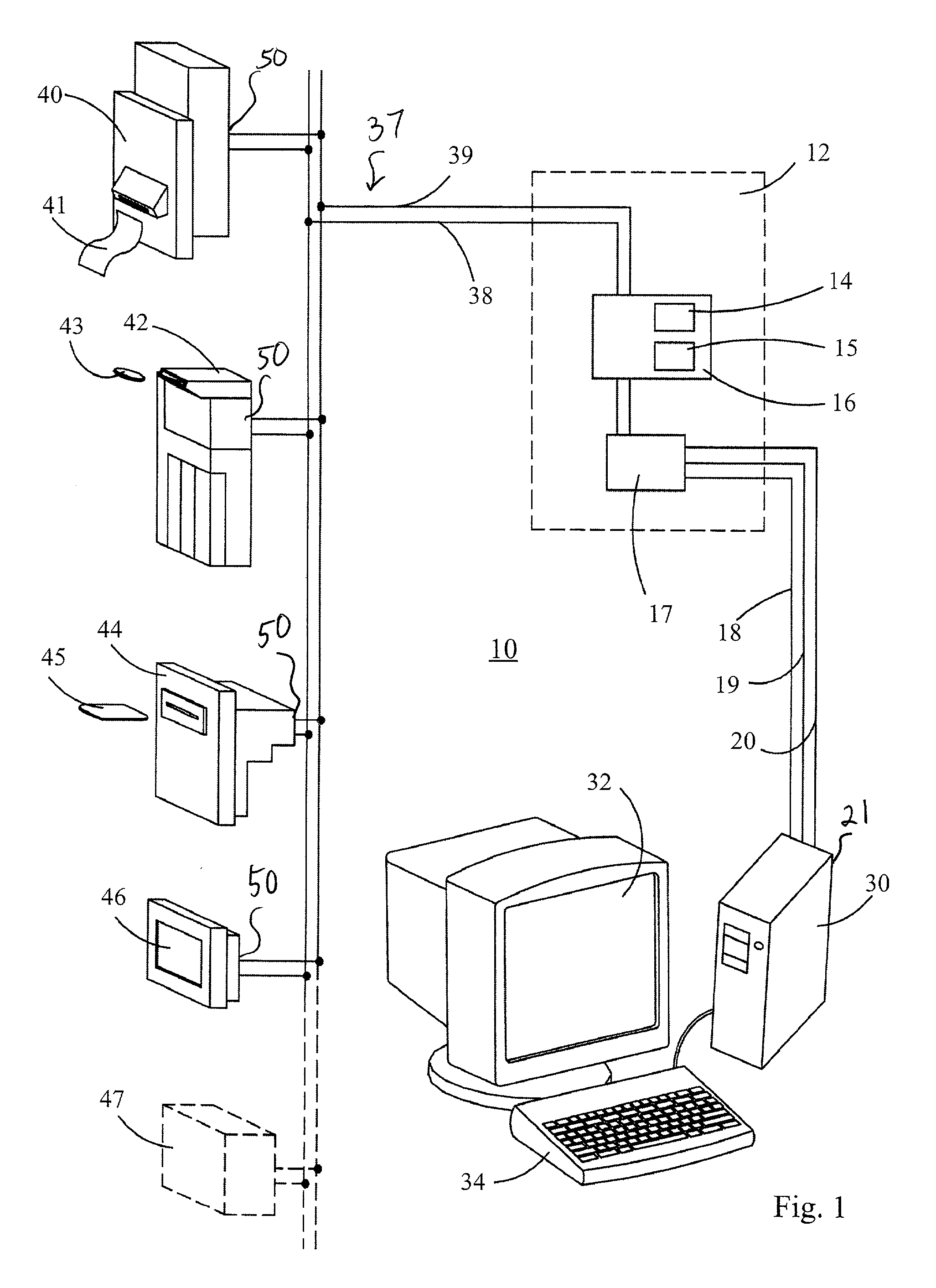

RFID-based method for a networked cashless vending system

InactiveUS7455223B1Reduce the possibilityCoin-freed apparatus detailsLiquid transferring devicesMultidrop busTransaction data

A cashless vending system, comprising, a plurality of vending machines, wherein each vending machine comprises a Vending Machine Controller that supports the international Multi-Drop Bus / Internal Communication Protocol standard; wherein each vending machine includes a NetVend interface, wherein each NetVend interface communicates, via a Multi-Drop Bus / Internal Communication Protocol interface, with the Vending Machine Controller; wherein each NetVend interface communicates with at least one central server, wherein the central server contains a database for storing user Identifiers and an associated allowable credit or available cash data for each user Identifier, wherein the central server is capable of authenticating users for granting / denying access to a vending machine, receiving transaction data, and monitoring and controlling each of the plurality of vending machines; and wherein each vending machine includes a display / reader.

Owner:BOB JONES UNIV

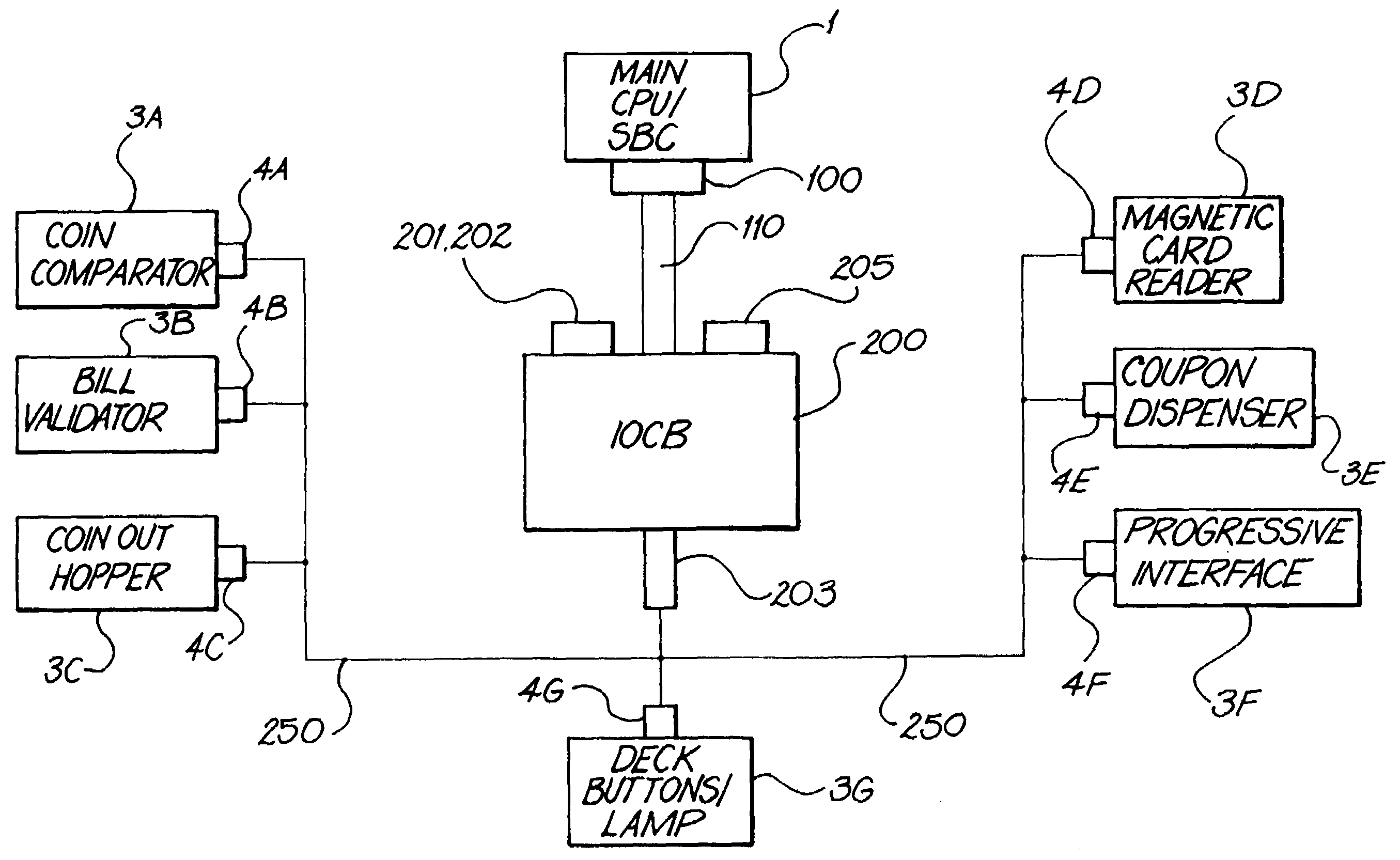

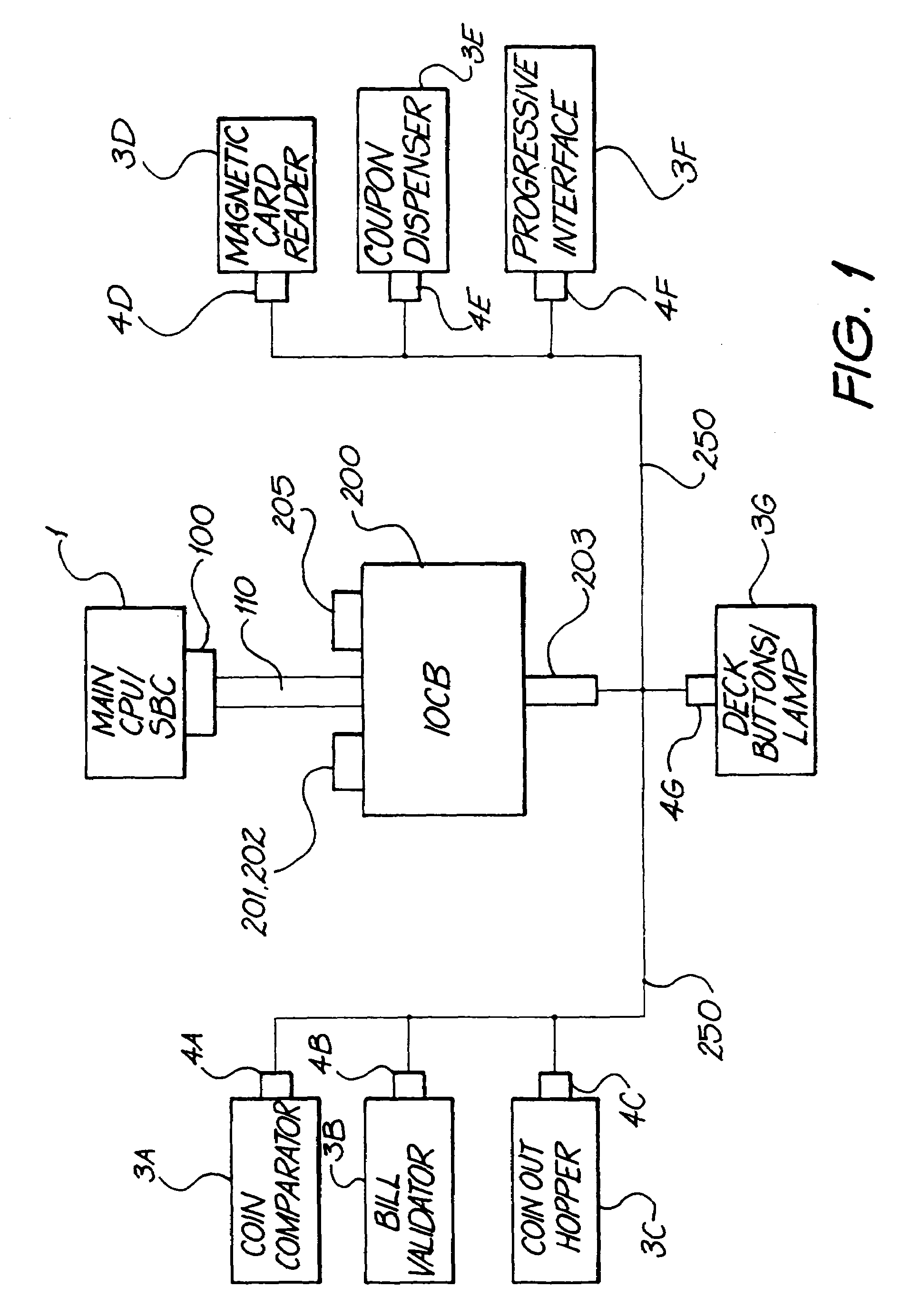

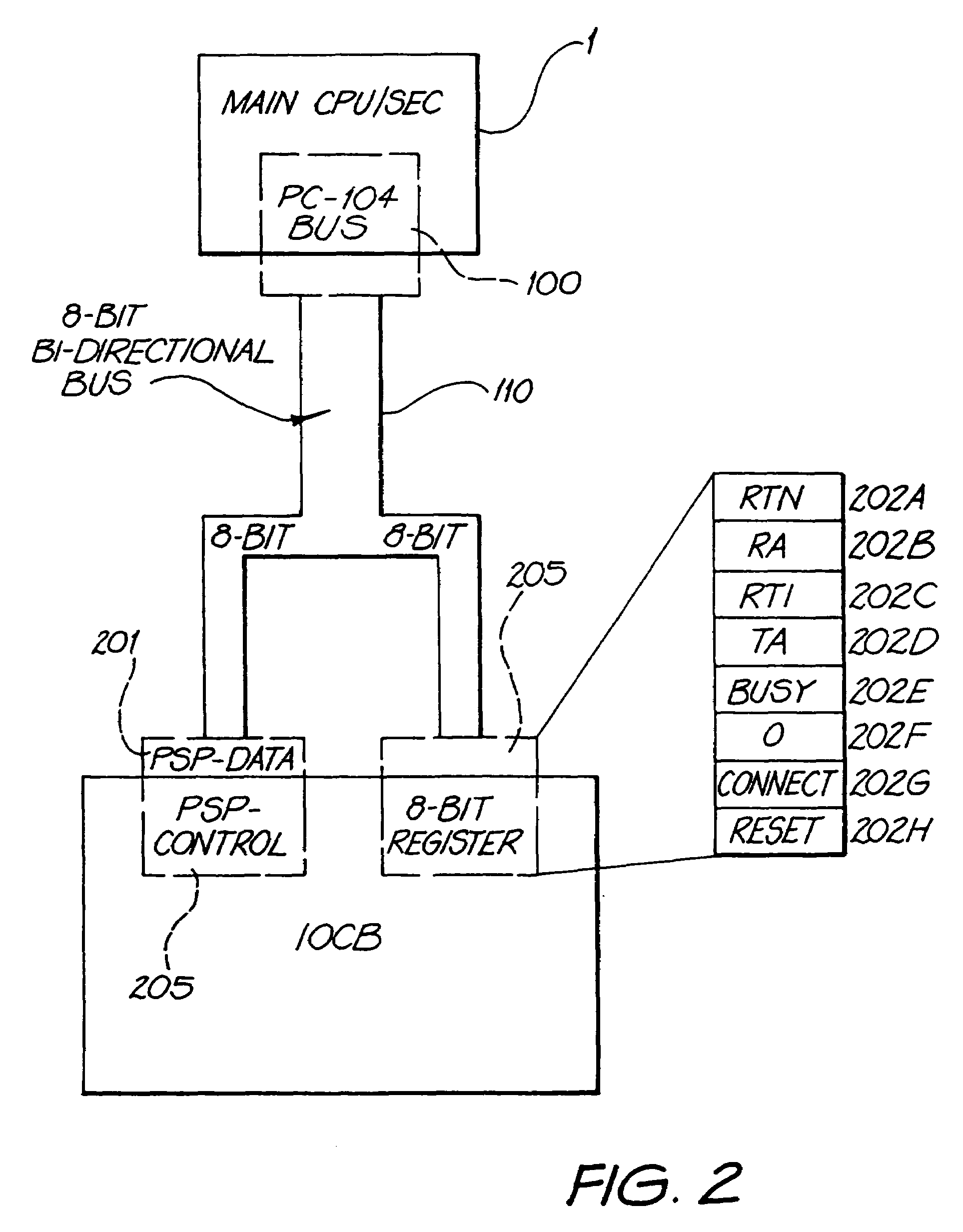

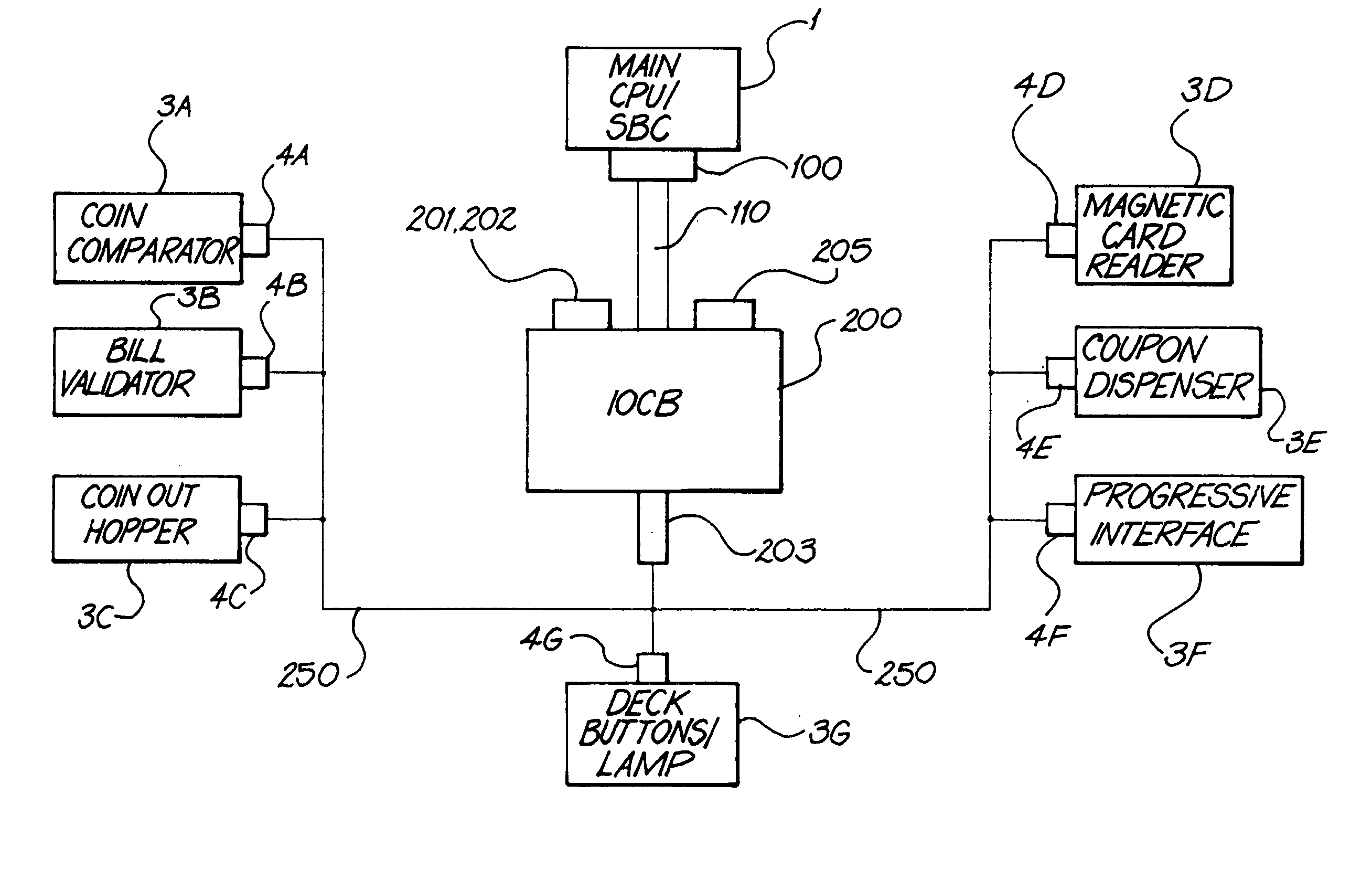

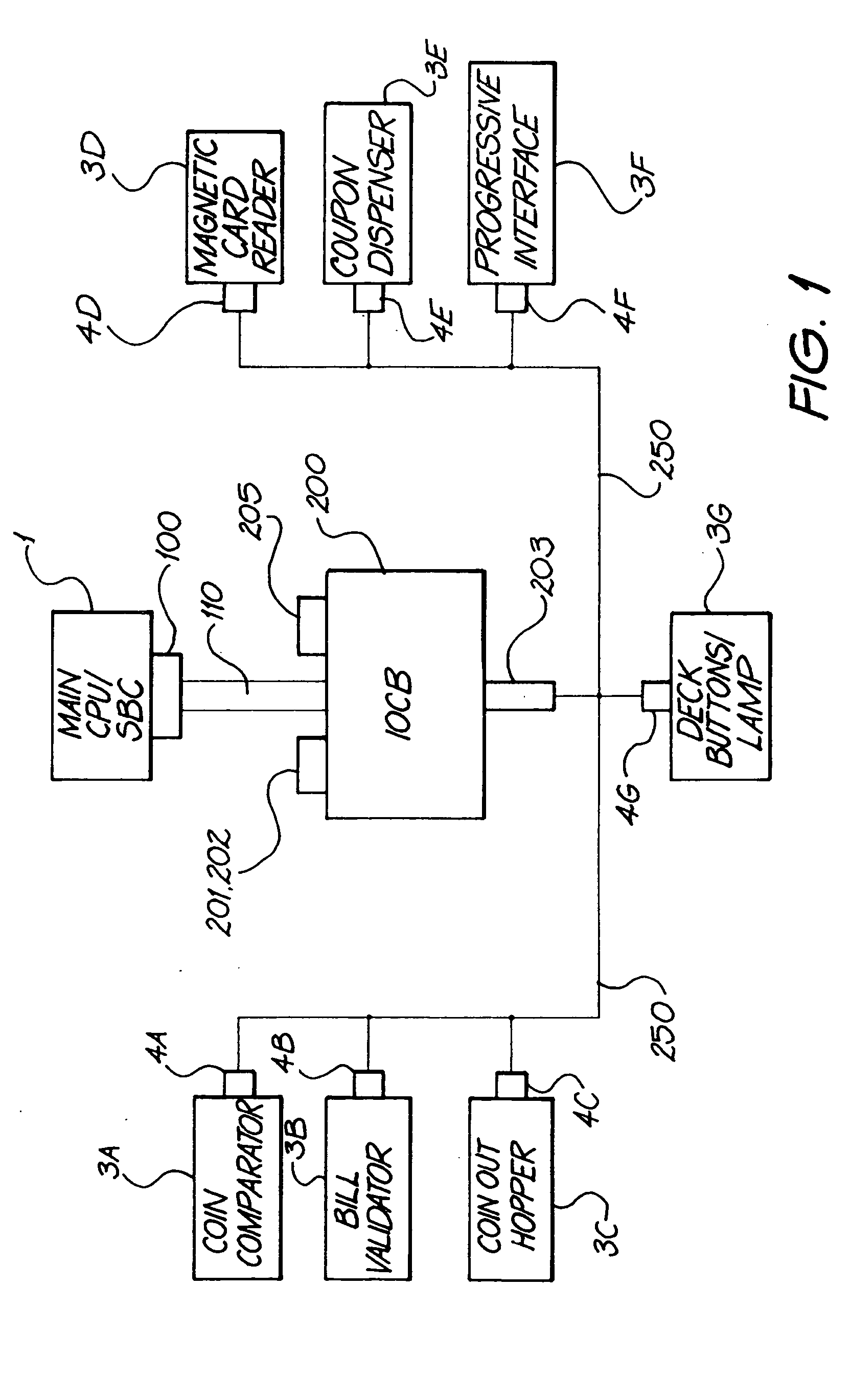

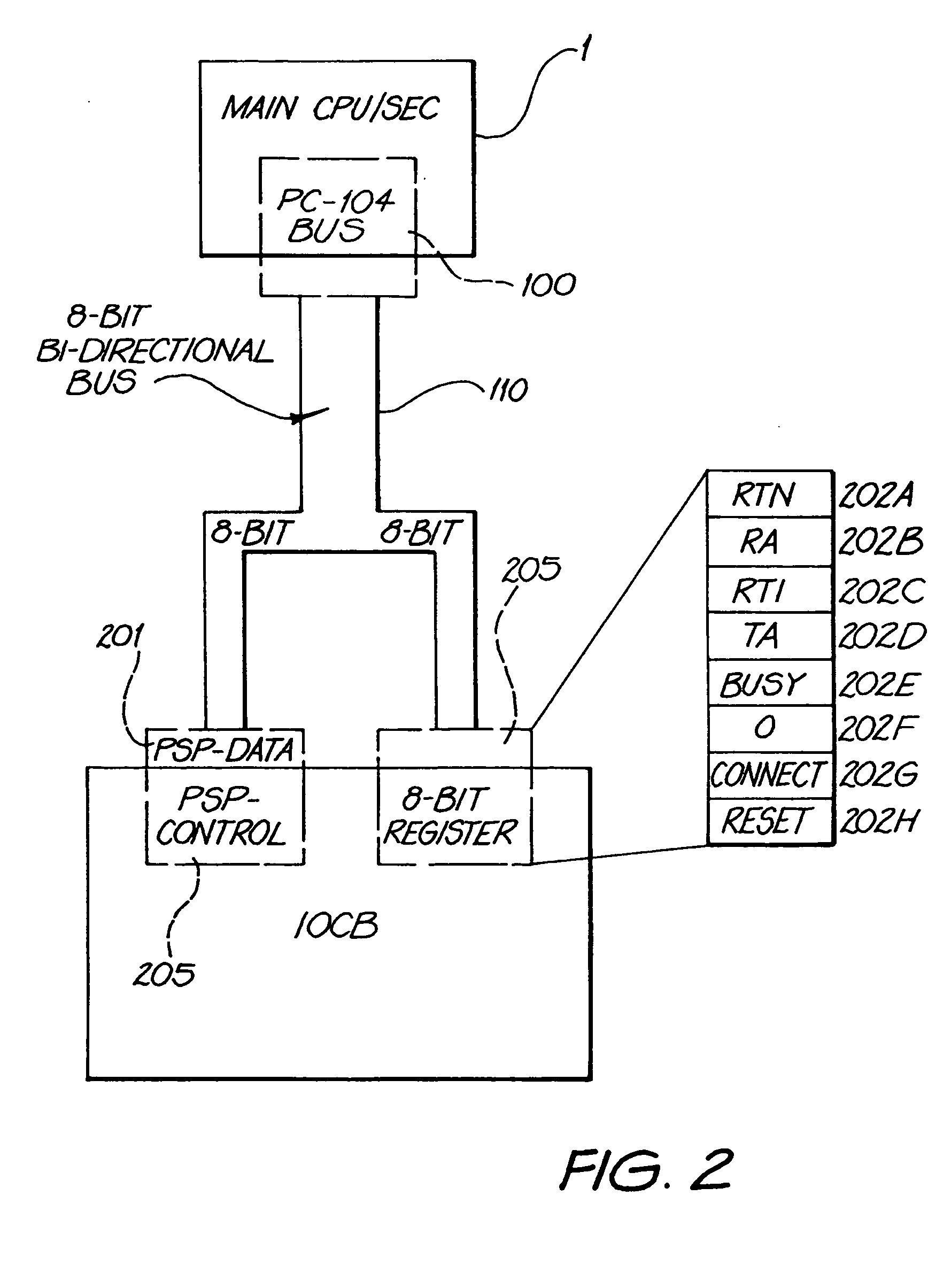

Secured inter-processor and virtual device communications system for use in a gaming system

InactiveUS7093040B1Reliable dataFacilitate communicationDigital computer detailsInternal/peripheral component protectionCommunications systemMultidrop bus

The invention comprises an electronically secured inter-processor and virtual device communications system, with an input / output controller board, a multi-drop bus interface to multiple devices, and a parallel interface to an industry standard single board computer. The invention assigns a bus address and virtual identification number to each device and controls communications between the main central processing unit and the devices through a Plug-n-Play protocol.

Owner:ARISTOCRAT TECH AUSTRALIA PTY LTD

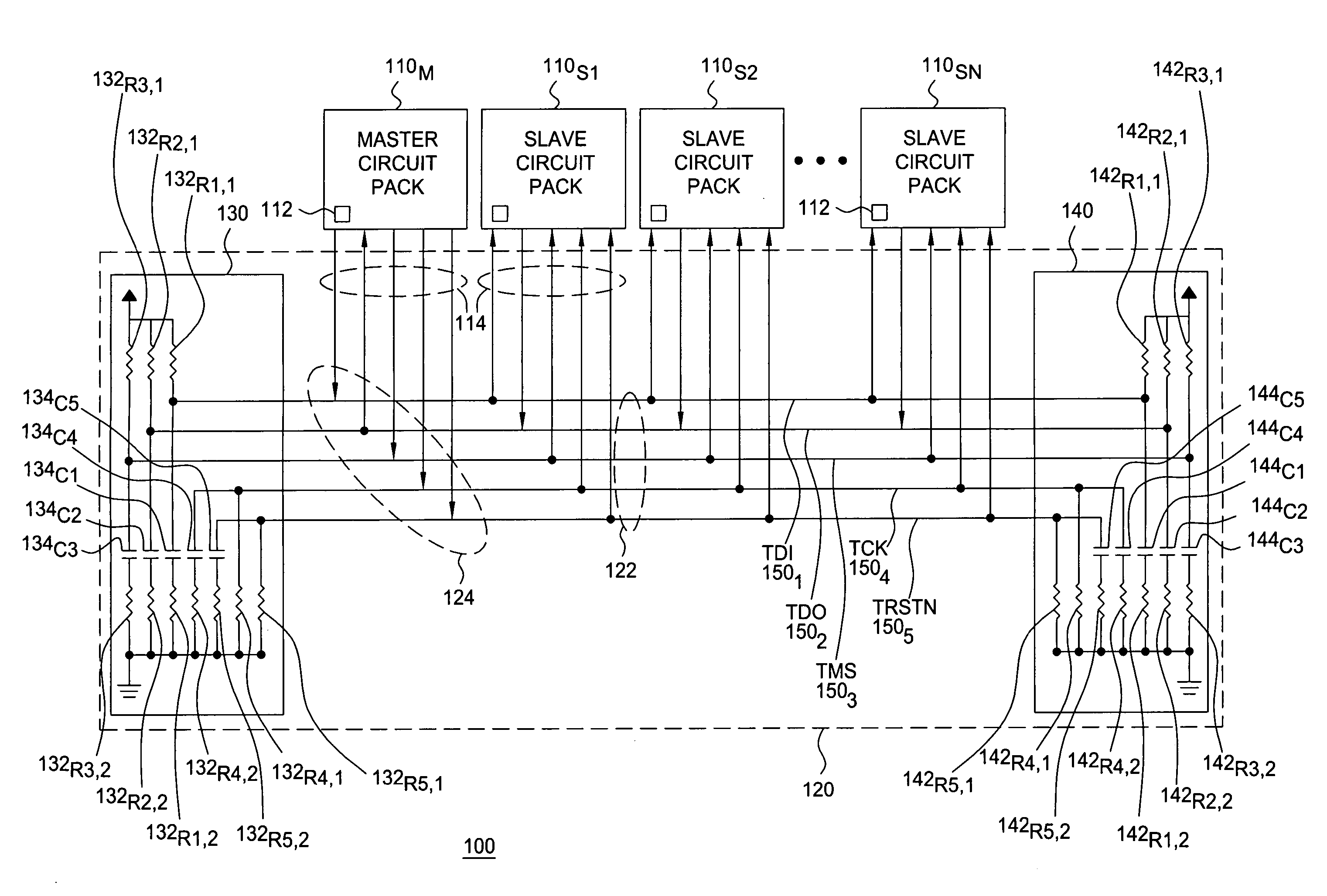

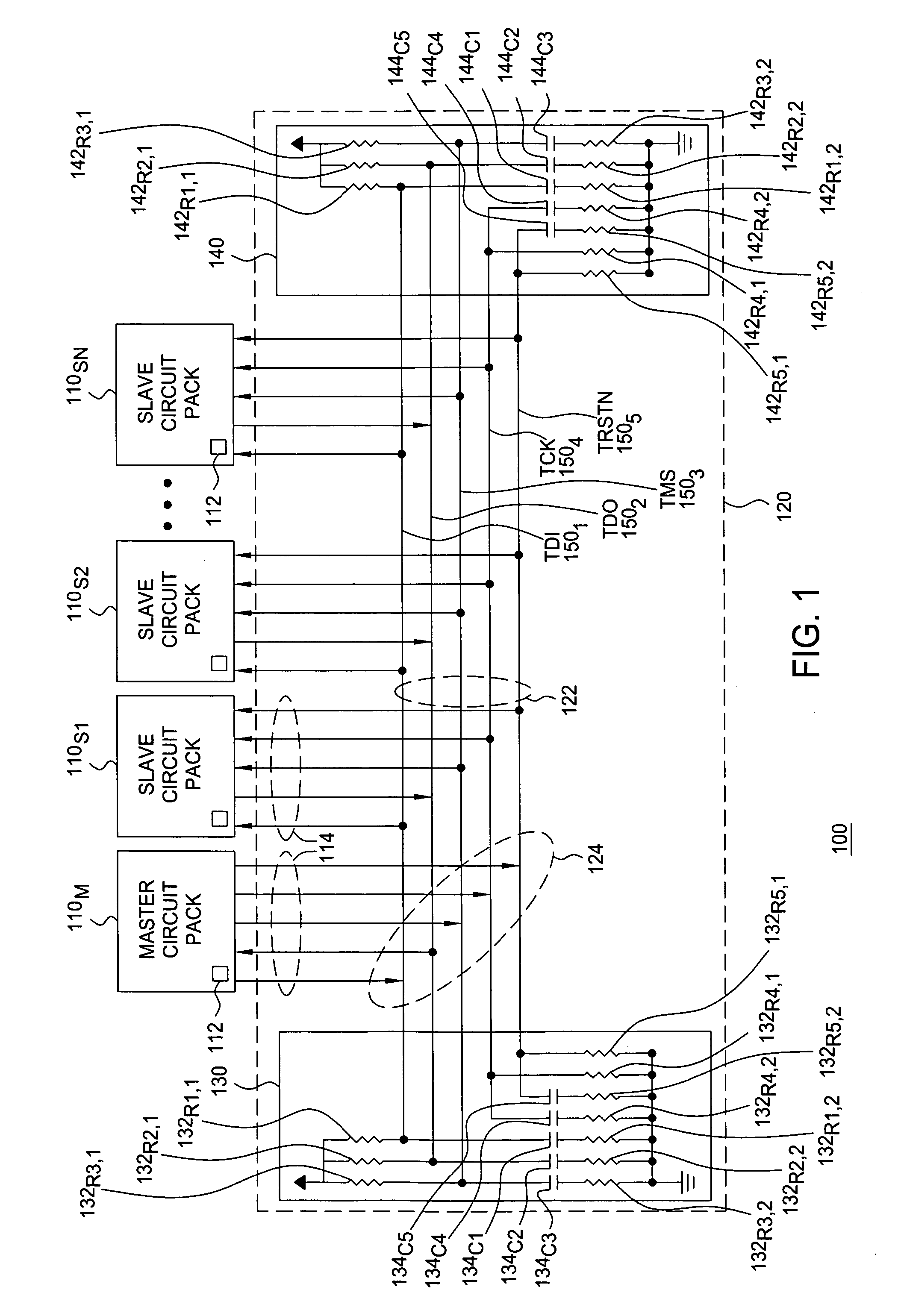

Method and apparatus for enabling multipoint bus access

The invention includes a method and apparatus for enabling multipoint bus access. In one example, the open ring-architecture bus includes a boundary scan bus including a plurality of bus access points adapted for interfacing with a plurality of circuit packs, a first termination circuit coupled to a first end of the bus, and a second termination circuit coupled to a second end of the bus. The first termination circuit and second termination circuit are adapted for terminating signaling on the boundary scan bus. The open-ring architecture bus provides a master circuit pack a multipoint access capability such that the master circuit pack may be disposed at any of the plurality of bus access points. In one example, signaling includes signaling operable for performing hierarchical system testing, including boundary scan testing. In another example, signaling includes upgrade signaling operable for performing firmware upgrades, software upgrades, and like circuit pack upgrades.

Owner:LUCENT TECH INC

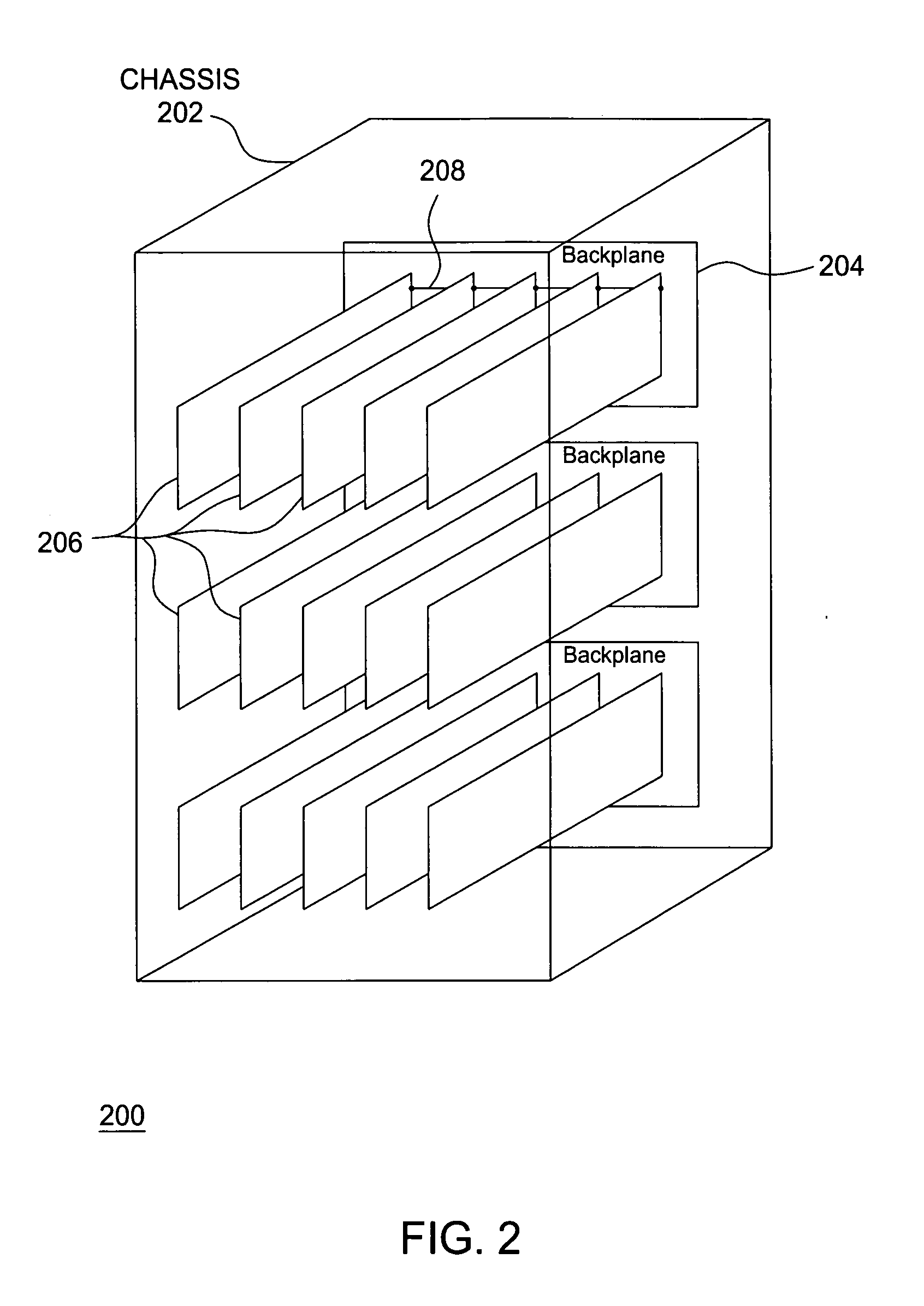

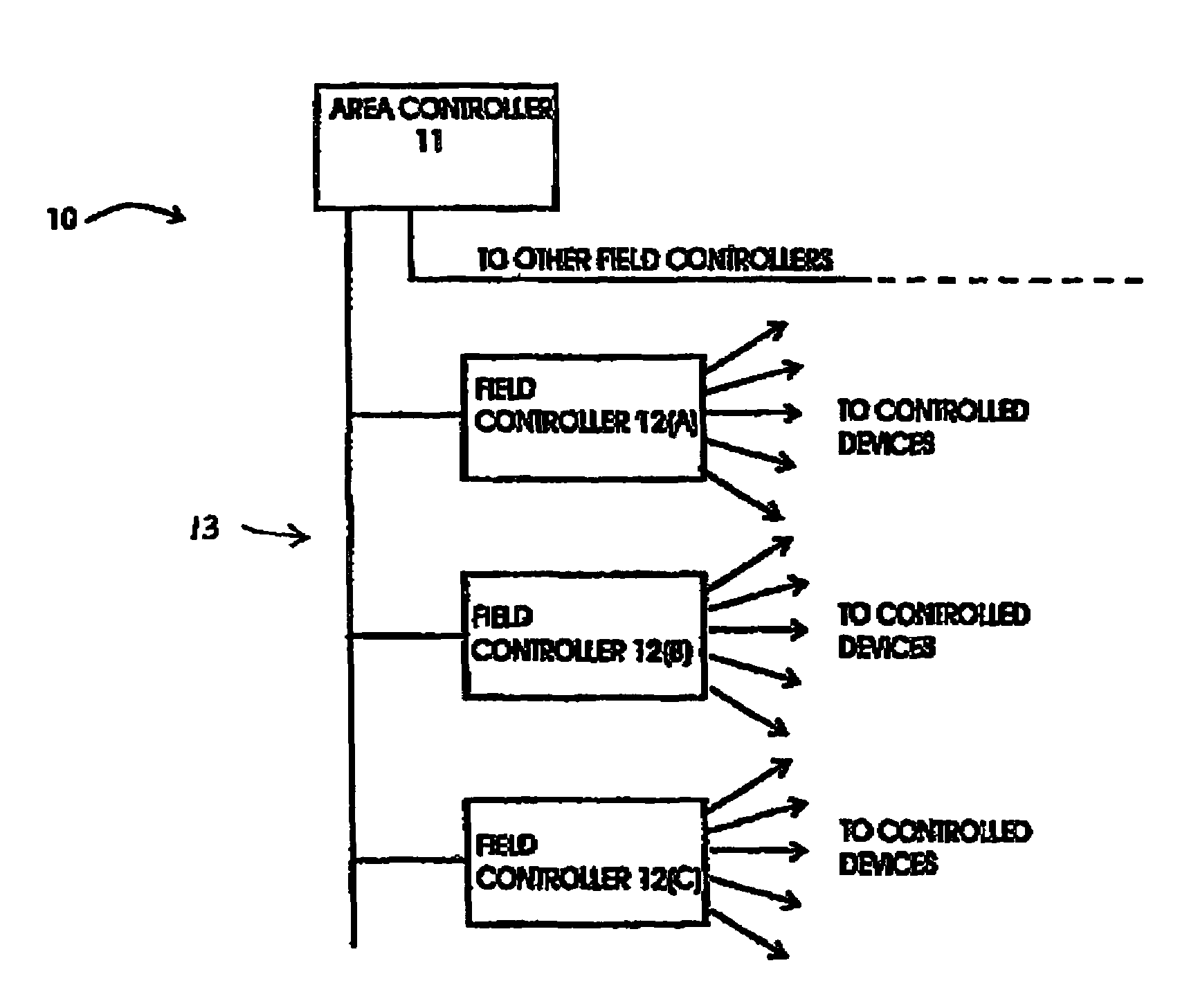

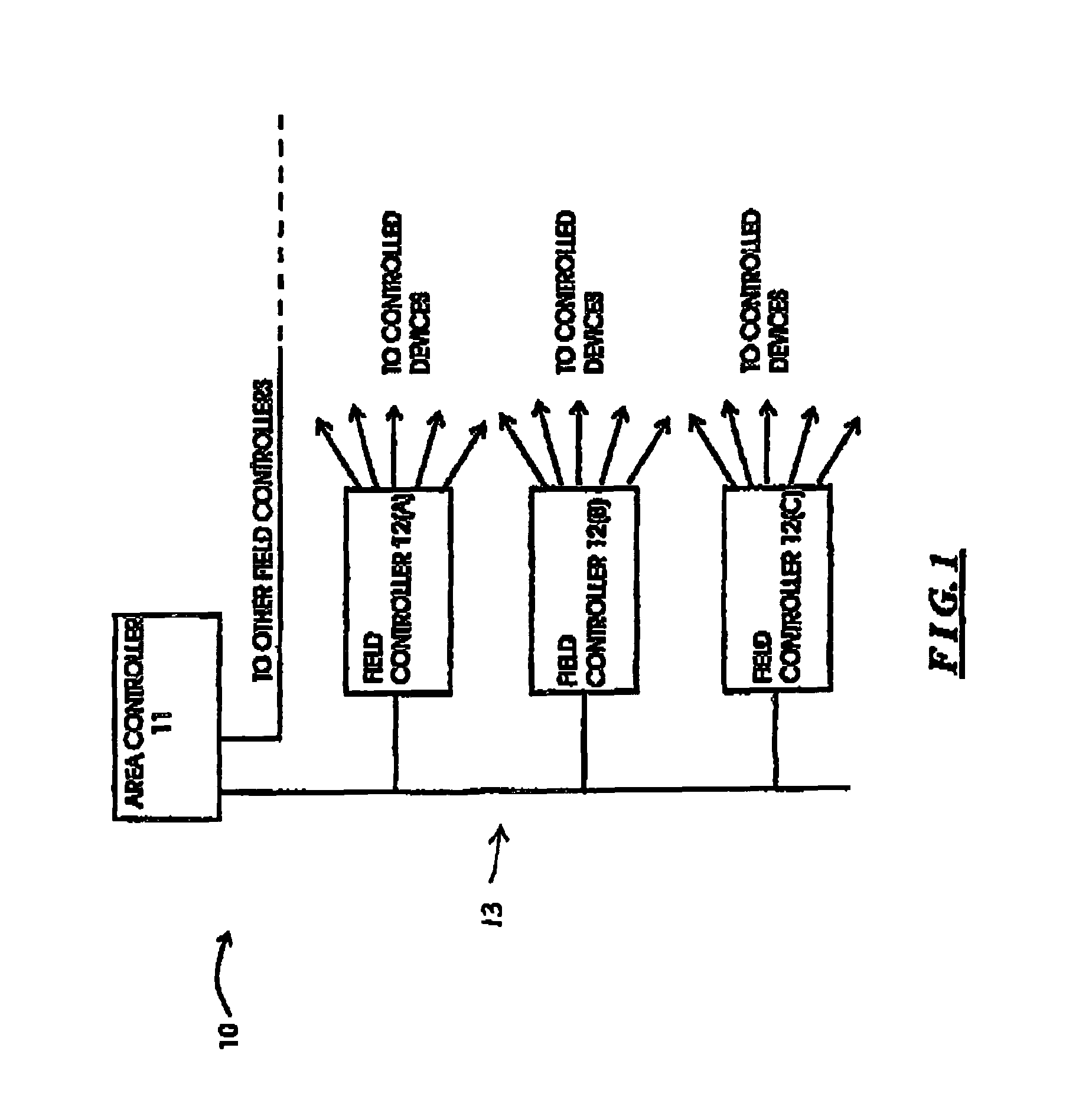

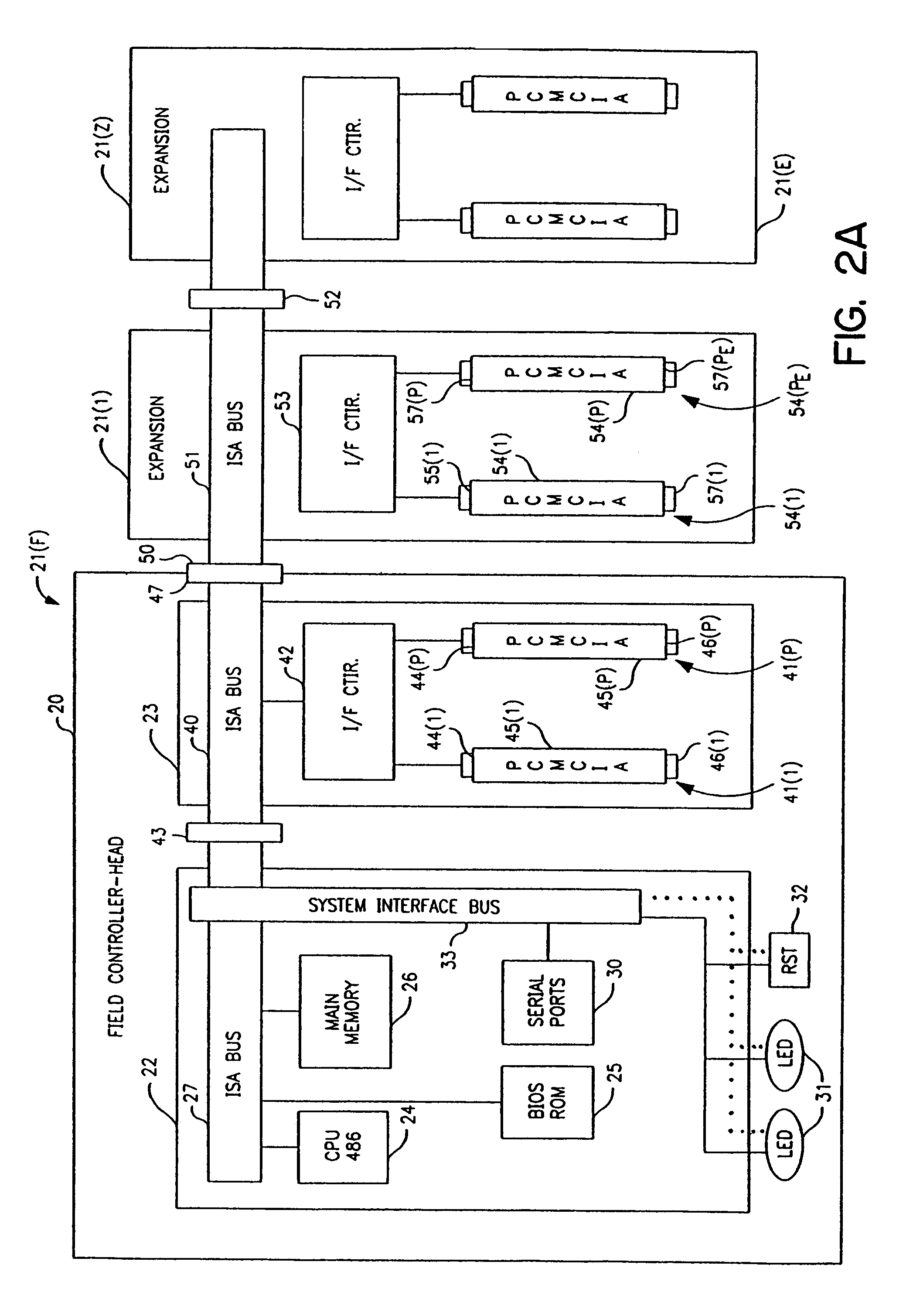

Distributed control system with multiple control levels and/or downloading

InactiveUS7337256B2Easy to controlImprove scalabilityElectrically conductive connectionsComputer controlMultidrop busDistributed control system

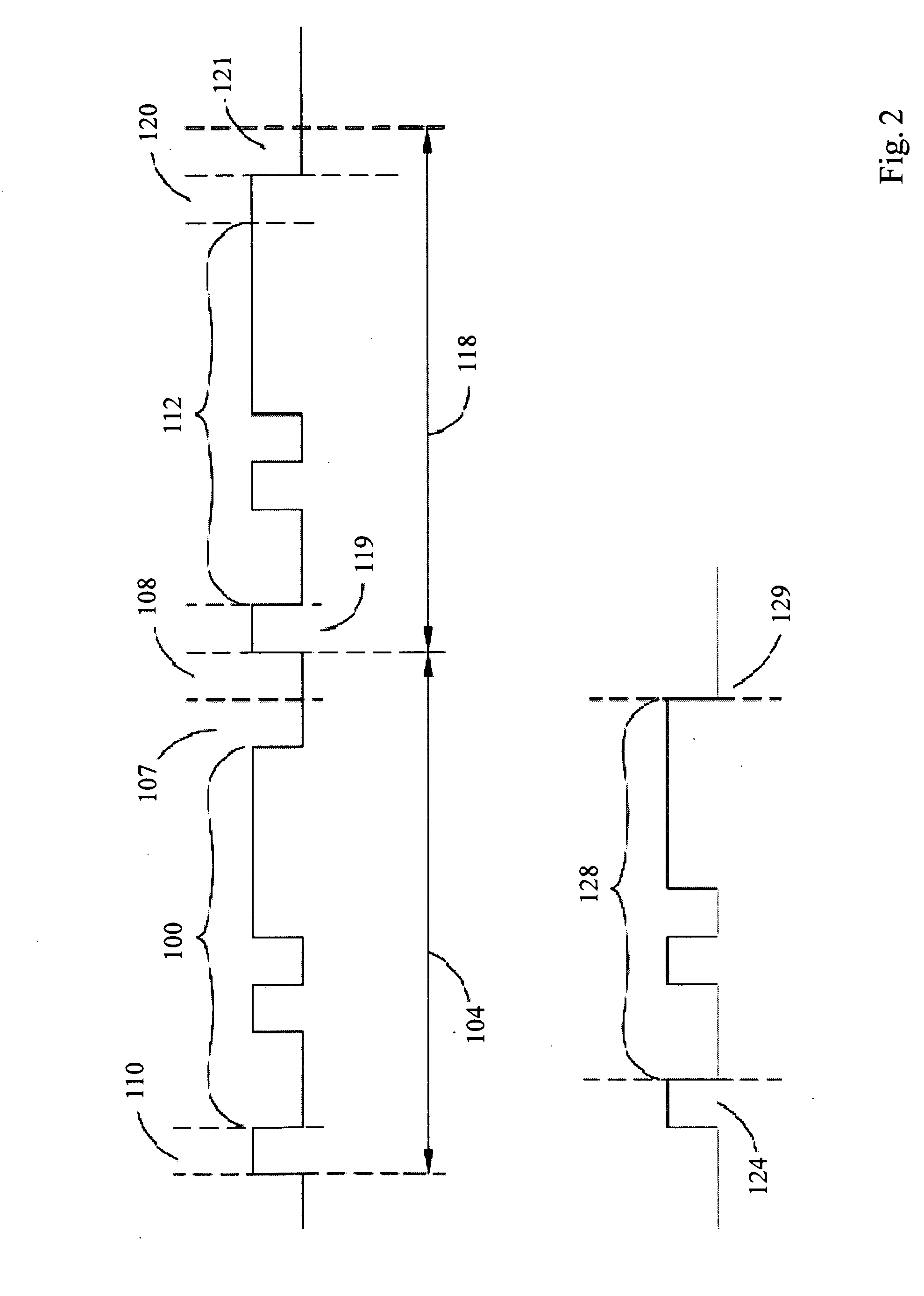

A field controller for use in a distributed control system including an area controller and at least one field controller. The field controller manages at least one controlled device in an industrial process operation. The field controller comprises a processor module segment through which it can control a selected number of devices, and it may also include one or more expansion module segments to enable it to control a larger number of controlled devices. The processor module segment includes a processor module and at least one local interface module for interfacing to a controlled device, and the expansion module segment includes interface modules for interfacing to other controlled devices. In the processor module segment, the processor module and said local interface module are interconnected by a bus segment, which is also connected to an upstream off-module connector. Each expansion module segment includes at least one interface module, and also includes a downstream off-module connector and an upstream off-module connector, which are interconnected by a bus segment. The downstream off-module connector of each expansion module segment is adapted to mate with the upstream off-module connector of the processor module segment and of other expansion module segment, so as to facilitate the interconnection of the processor module segment and a sequence of expansion module segments by establishing a unitary multi-drop bus comprising the processor module's bus segment and the bus segments of expansion module in the sequence. The processor module controls each controlled device through the respective local interface module or expansion interface module connected thereto. The processor module segment and each expansion module segment are each mounted in a housing segment which is configured to form a unitary housing when they are interconnected.

Owner:SCHNEIDER ELECTRIC SYST USA INC

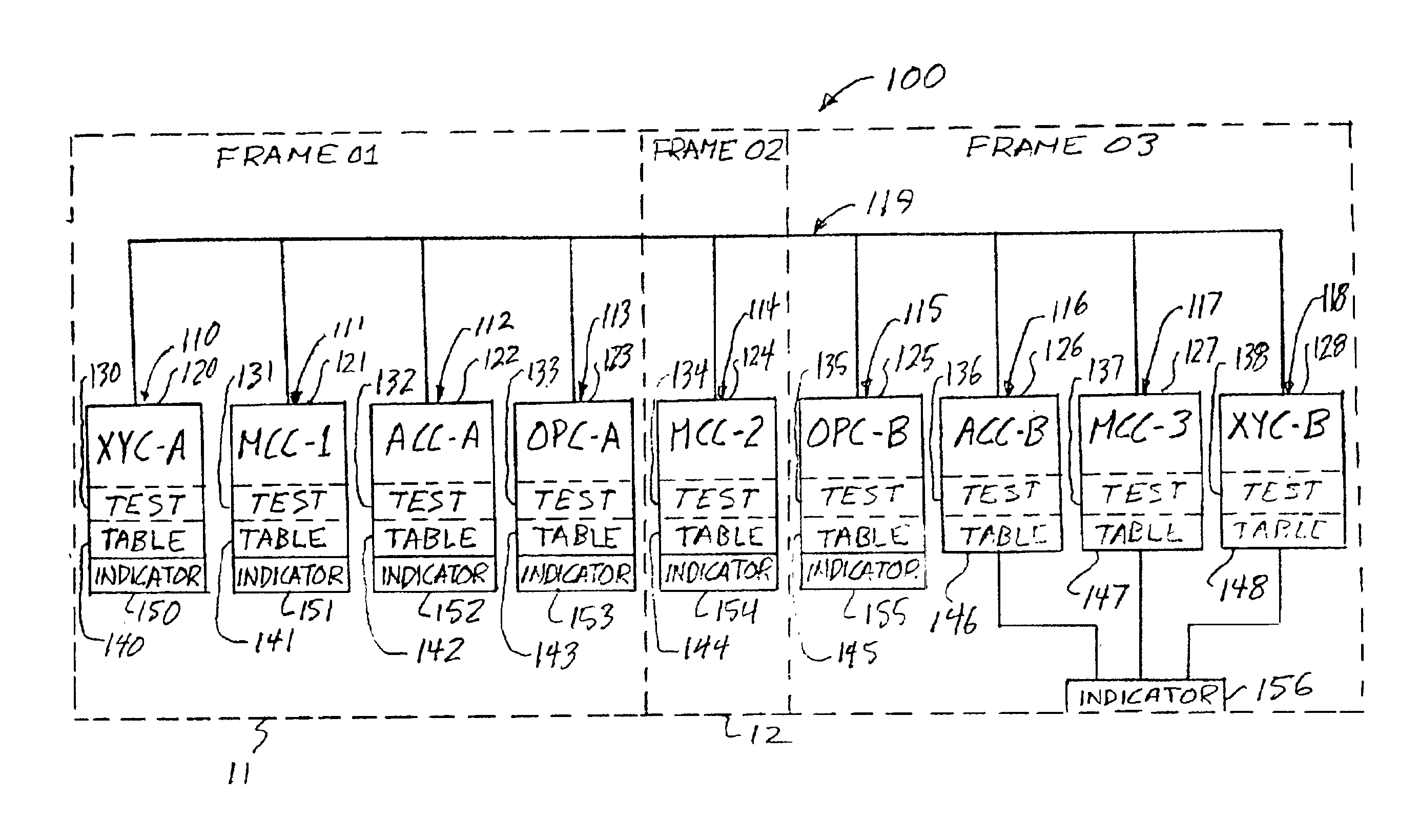

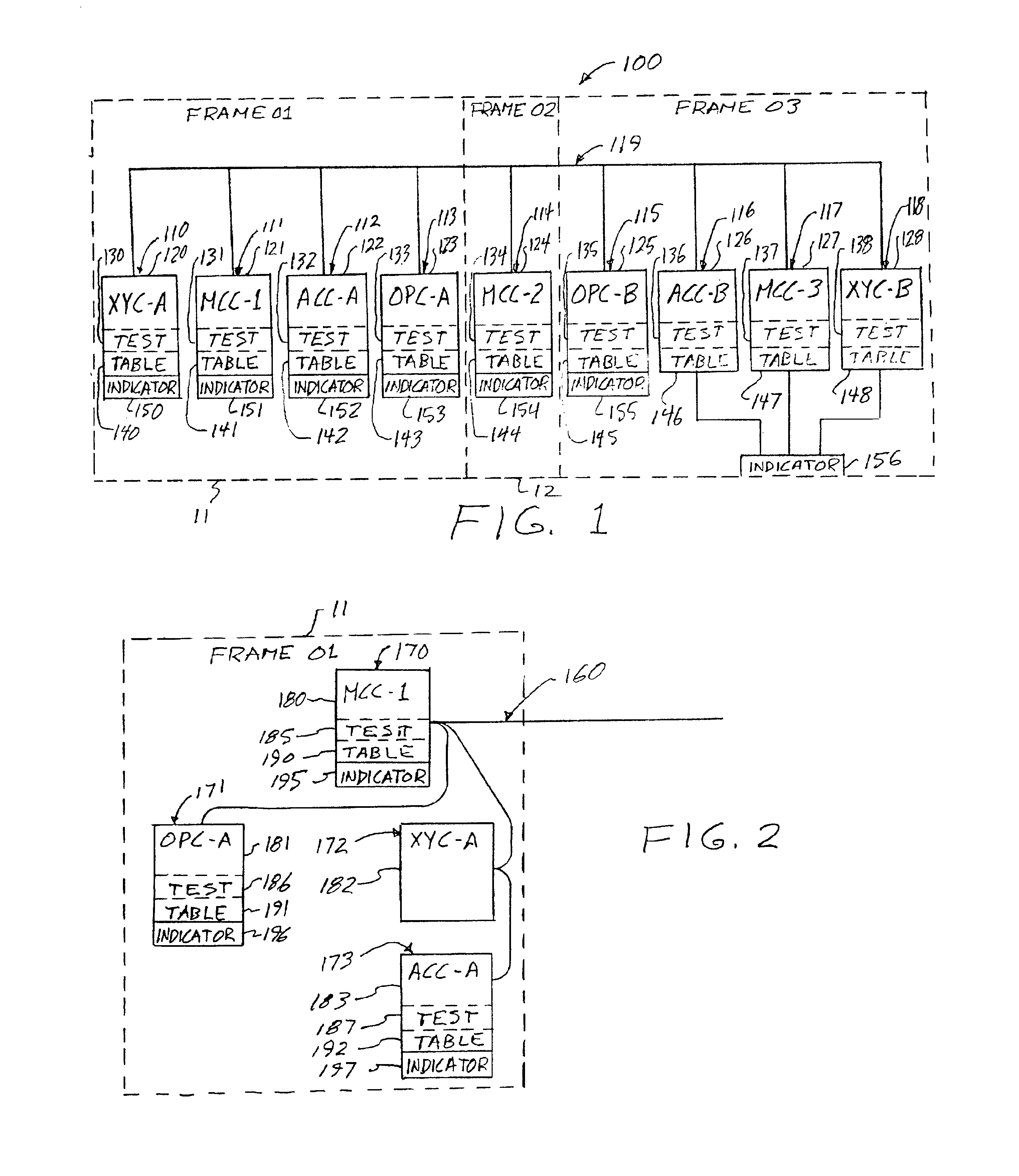

Failure isolation in a distributed processing system employing relative location information

InactiveUS6931564B2Multiple failureError preventionError detection/correctionMultidrop busProcessor node

Failure isolation in a distributed processing system of processor nodes coupled by a multi-drop bus network. The processor nodes have information of relative locations of the processor nodes on the network, and have an associated local error indicator, such as a character display. Each node independently tests access to other nodes on the network, and upon detecting a failure to access one or more nodes, determines, from the relative locations, the node having failed access which is closest. The failure detecting processor posts, at its associated local error indicator, an identifier of the closest failed access node. A user may inspect the local error indicators and thereby isolate the detected failure.

Owner:INTELLECTUAL DISCOVERY INC

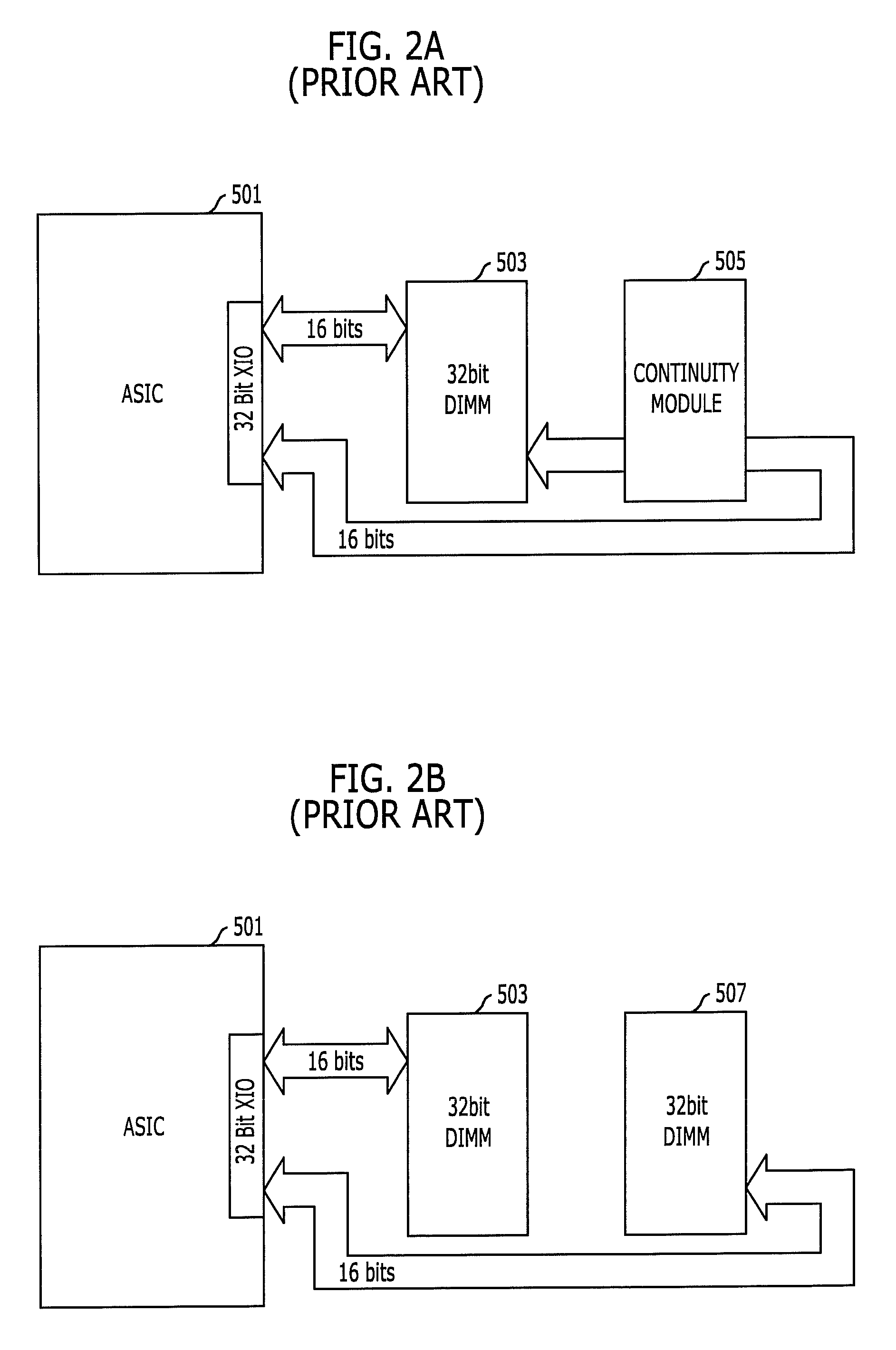

Bi-directional multi-drop bus memory system

ActiveUS20090313410A1Logic circuit coupling arrangementsReliability increasing modificationsMultidrop busEngineering

A bus system includes a plurality of stubs; a plurality of connectors, each of which is serially coupled between a corresponding one of the stubs and a corresponding one of memory modules; a plurality of first serial loads, each of which is serially coupled to a corresponding one of the connectors; and a plurality of second serial loads, each of which is serially coupled to characteristic impedance of a transmission line of a corresponding one of the stubs, wherein the first and the second serial loads are determined to be impedance matched at each transmission line terminal of the stubs.

Owner:SK HYNIX INC +1

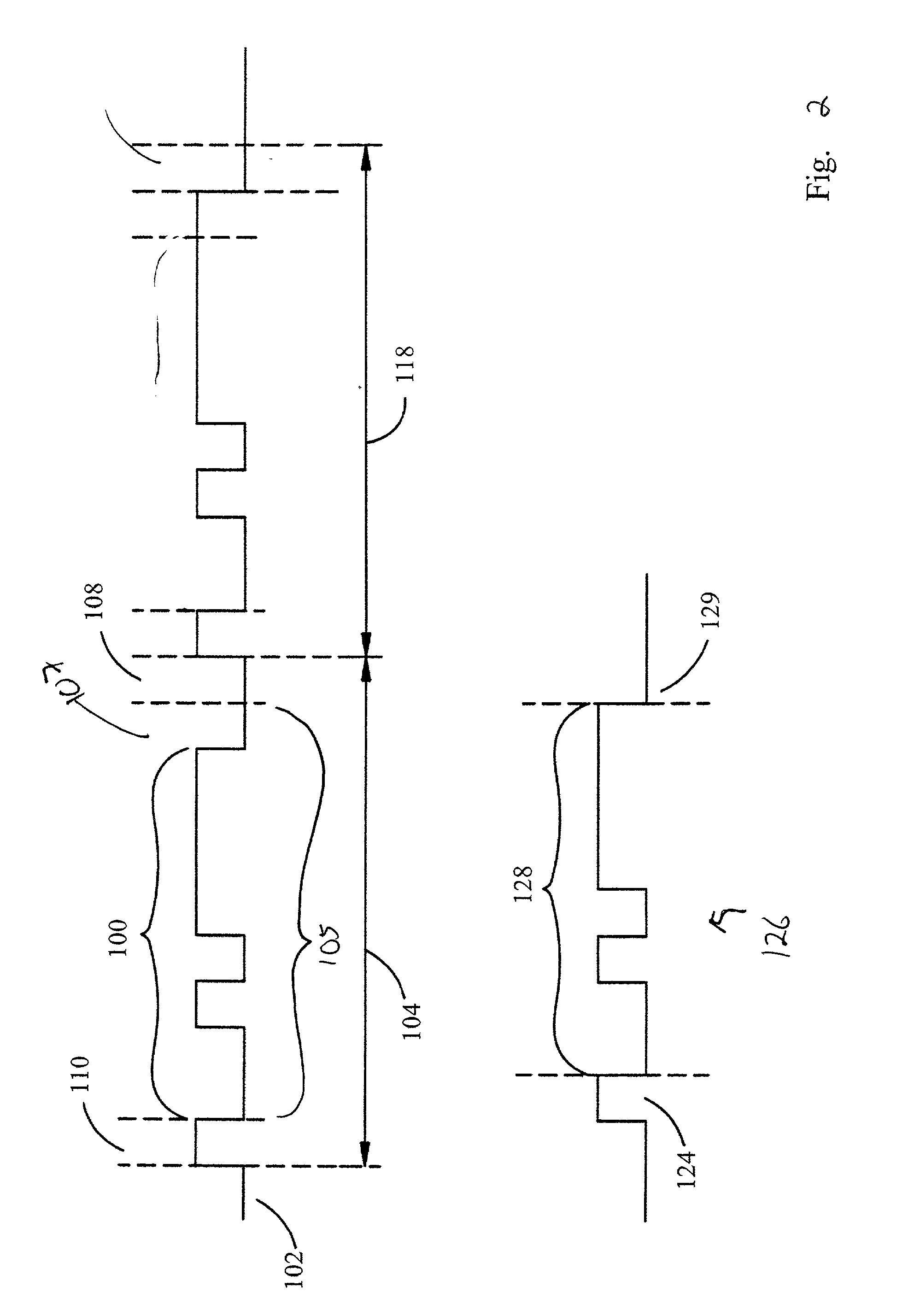

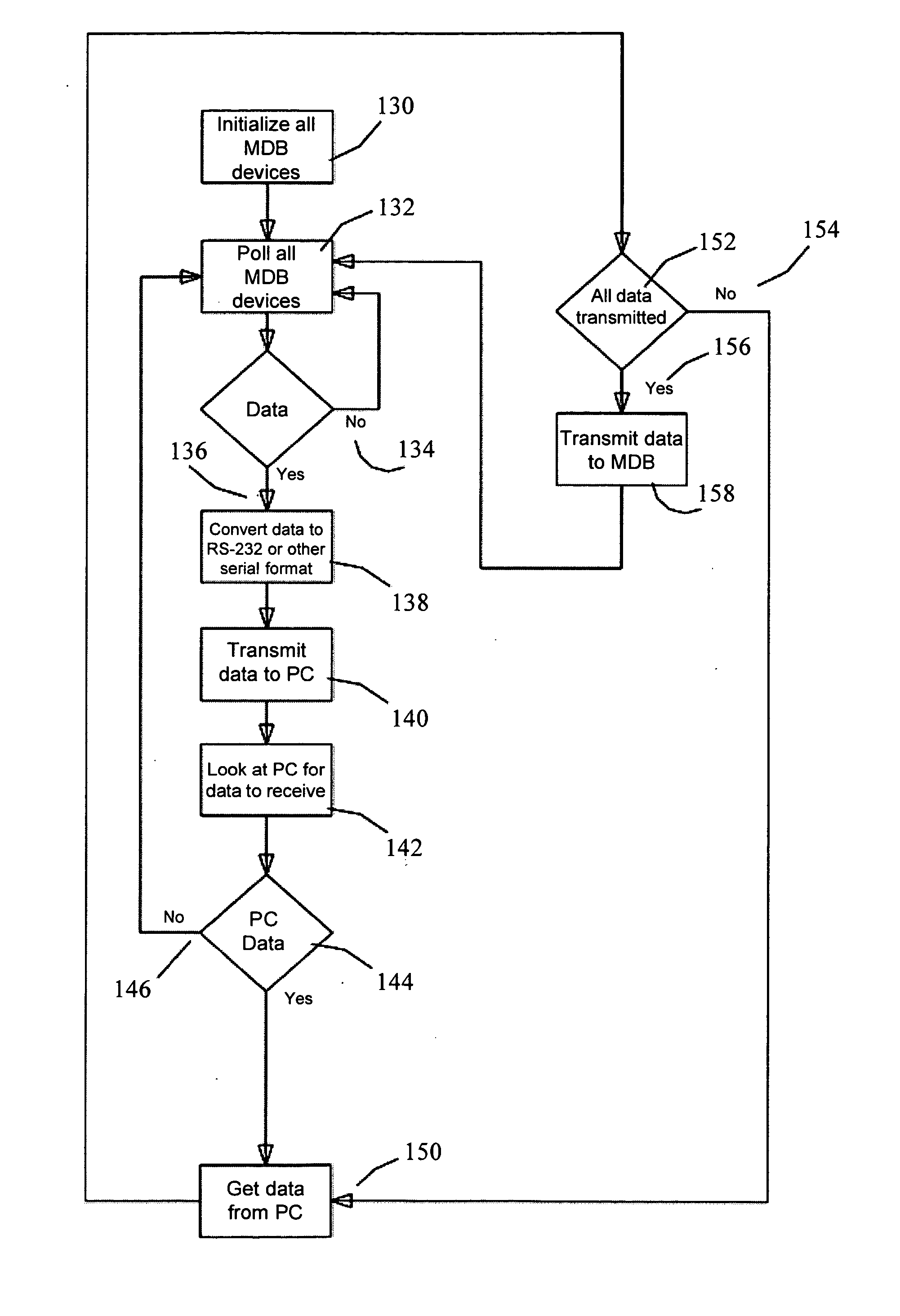

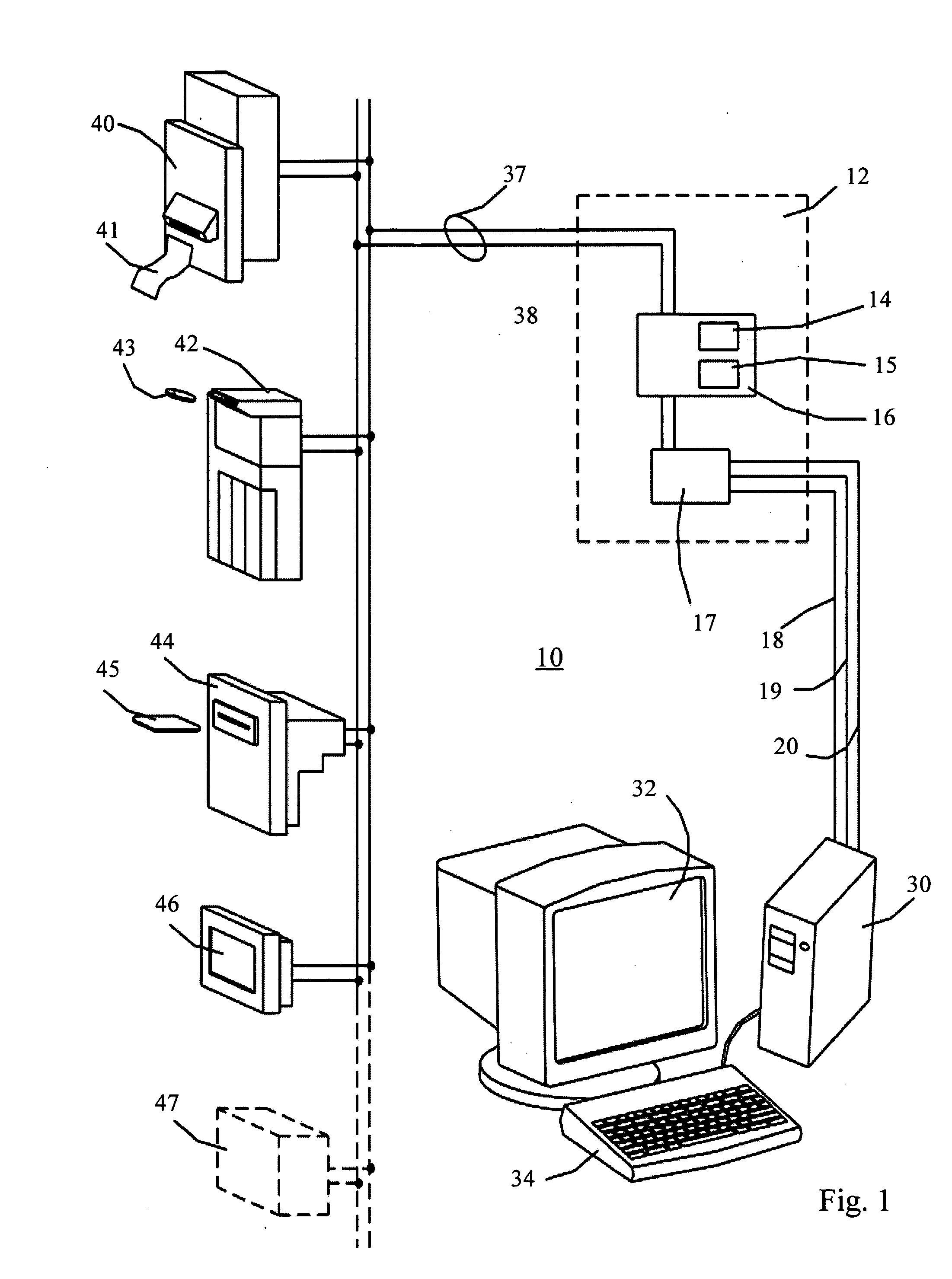

Multi-drop bus to personal computer interface

InactiveUS20030149827A1Coin/paper handlersElectric digital data processingMultidrop busPersonal computer

In a vending system there is at least one vending device which transmits data across a multidrop bus to a personal computer. The vending system data includes a start bit, a plurality of data bits, a modal bit and a stop bit. A multidrop bus to personal computer interface polls each vending device and manages and removes the modal bit, thereby freeing up the personal computer for application oriented functions.

Owner:SMOLEN CHRIS +1

Multi-drop bus to personal computer interface

InactiveUS20060047533A1Facilitate communicationData processing applicationsCoin/paper handlersMultidrop busEthernet protocol

Owner:SMOLEN CHRISTOPHER M +1

Secured inter-processor and virtual device communications system

InactiveUS20050172101A1Reliable dataFacilitate communicationGeneral purpose stored program computerInternal/peripheral component protectionBus interfaceElectronic security

The invention comprises an electronically secured inter-processor and virtual device communications system, with an input / output controller board, a multi-drop bus interface to multiple devices, and a parallel interface to an industry standard single board computer. The invention assigns a bus address and virtual identification number to each device and controls communications between the main central processing unit and the devices through a Plug-n-Play protocol.

Owner:ARISTOCRAT TECH AUSTRALIA PTY LTD

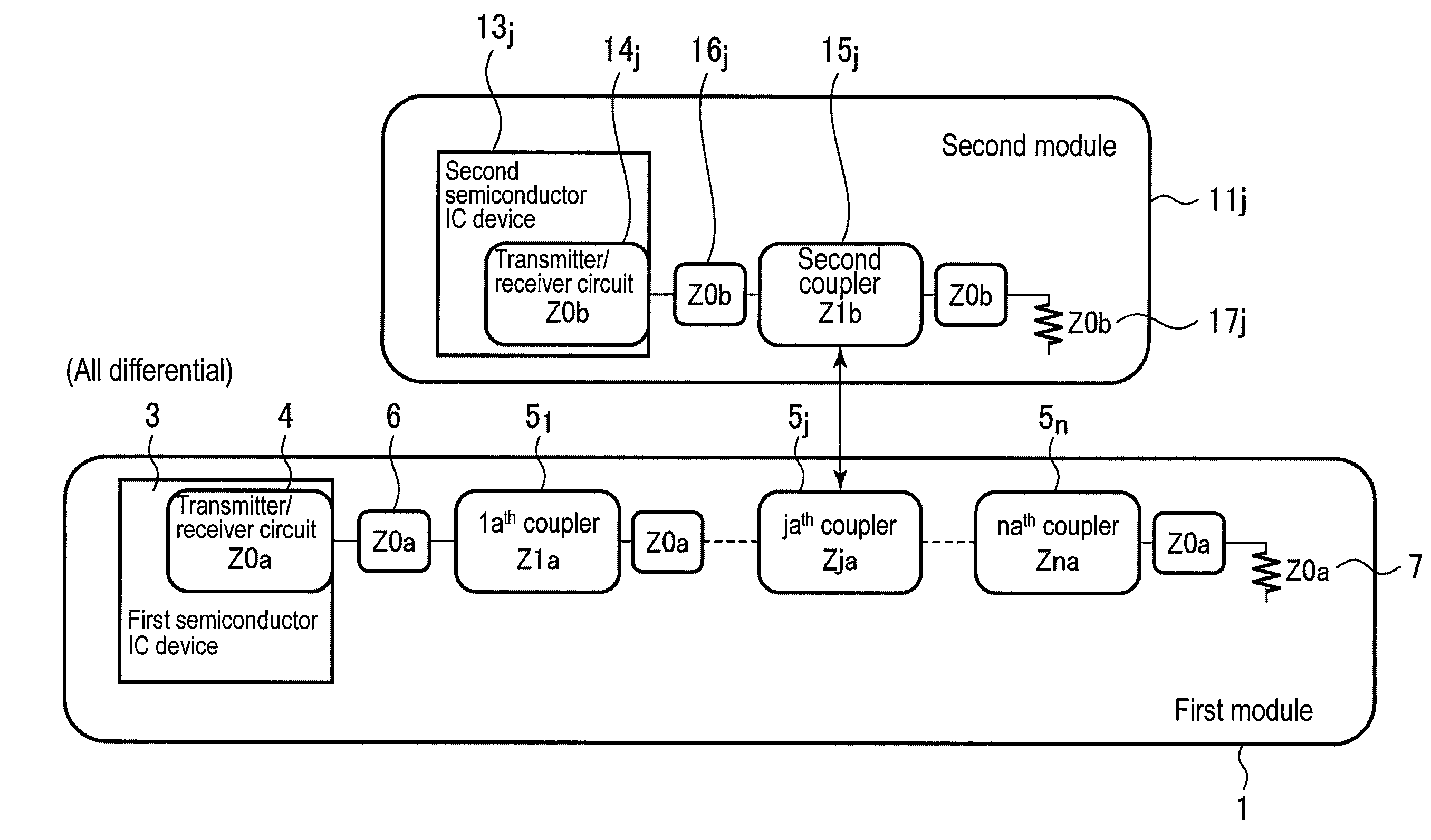

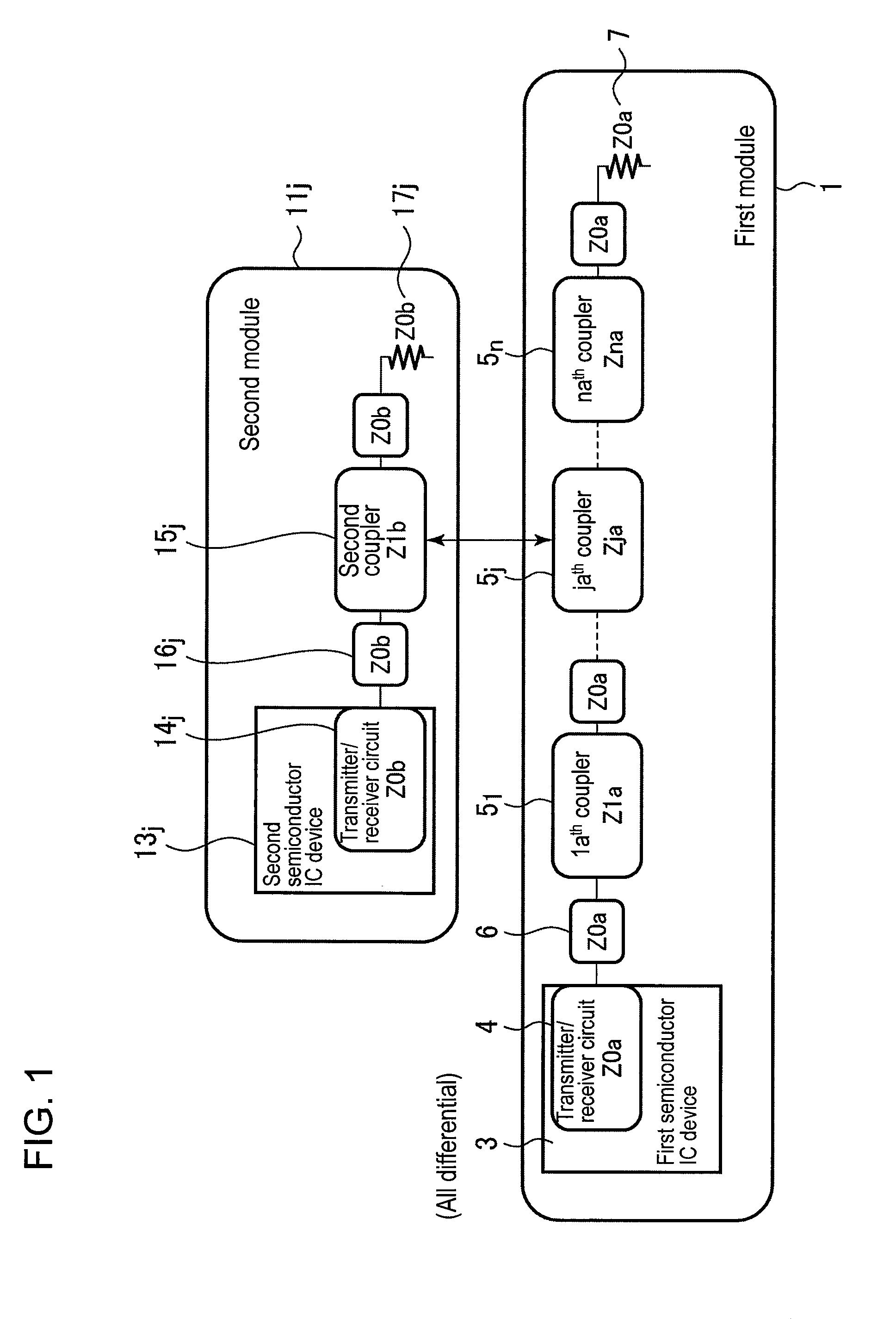

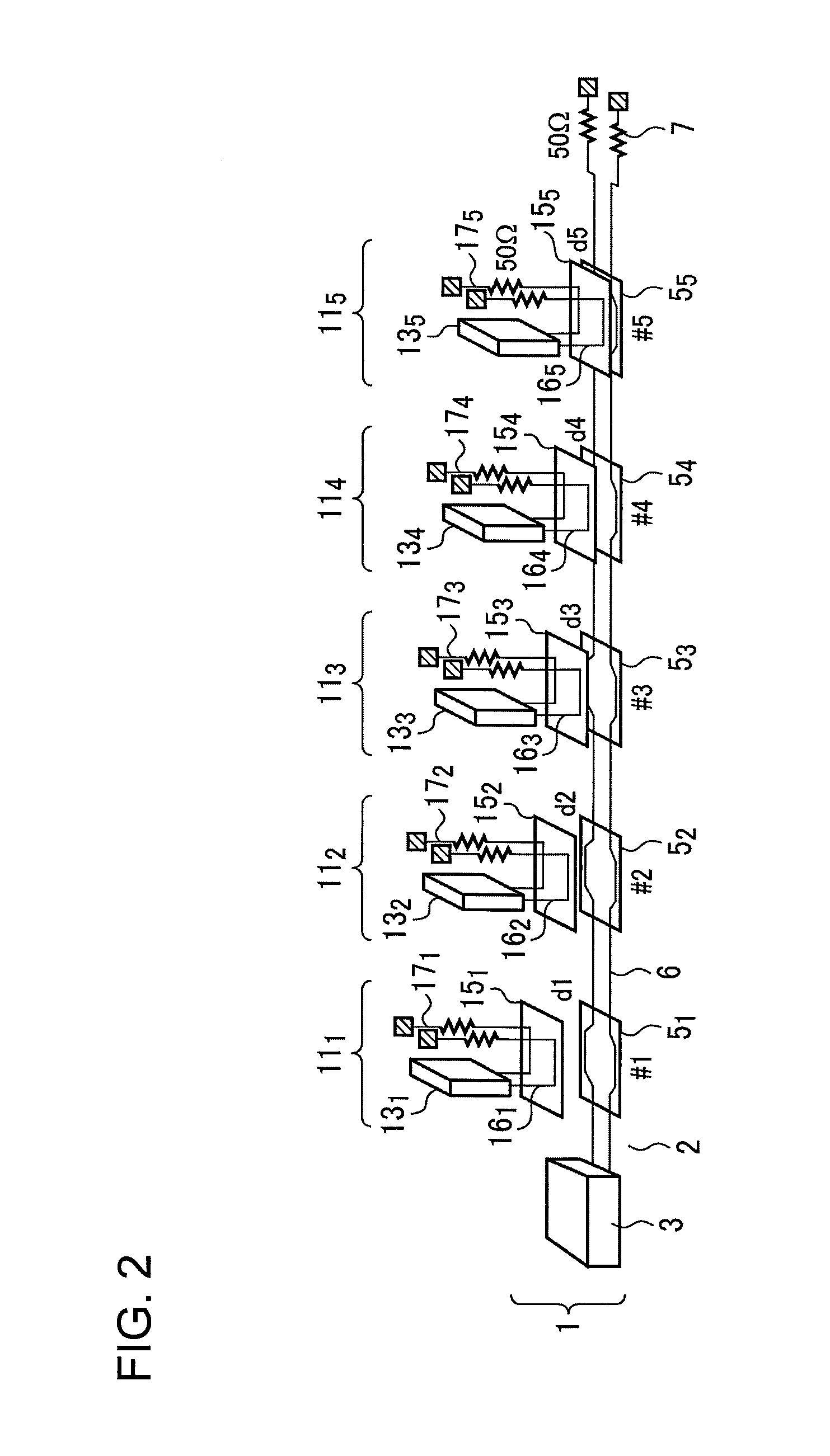

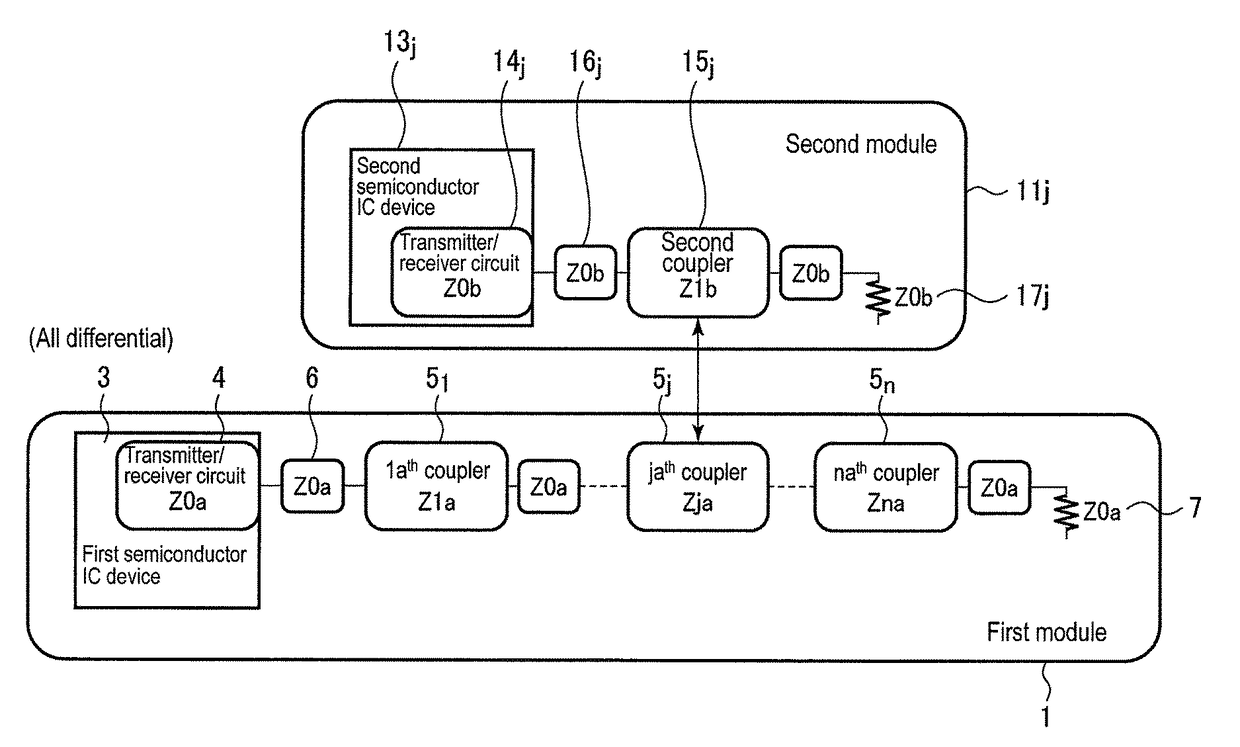

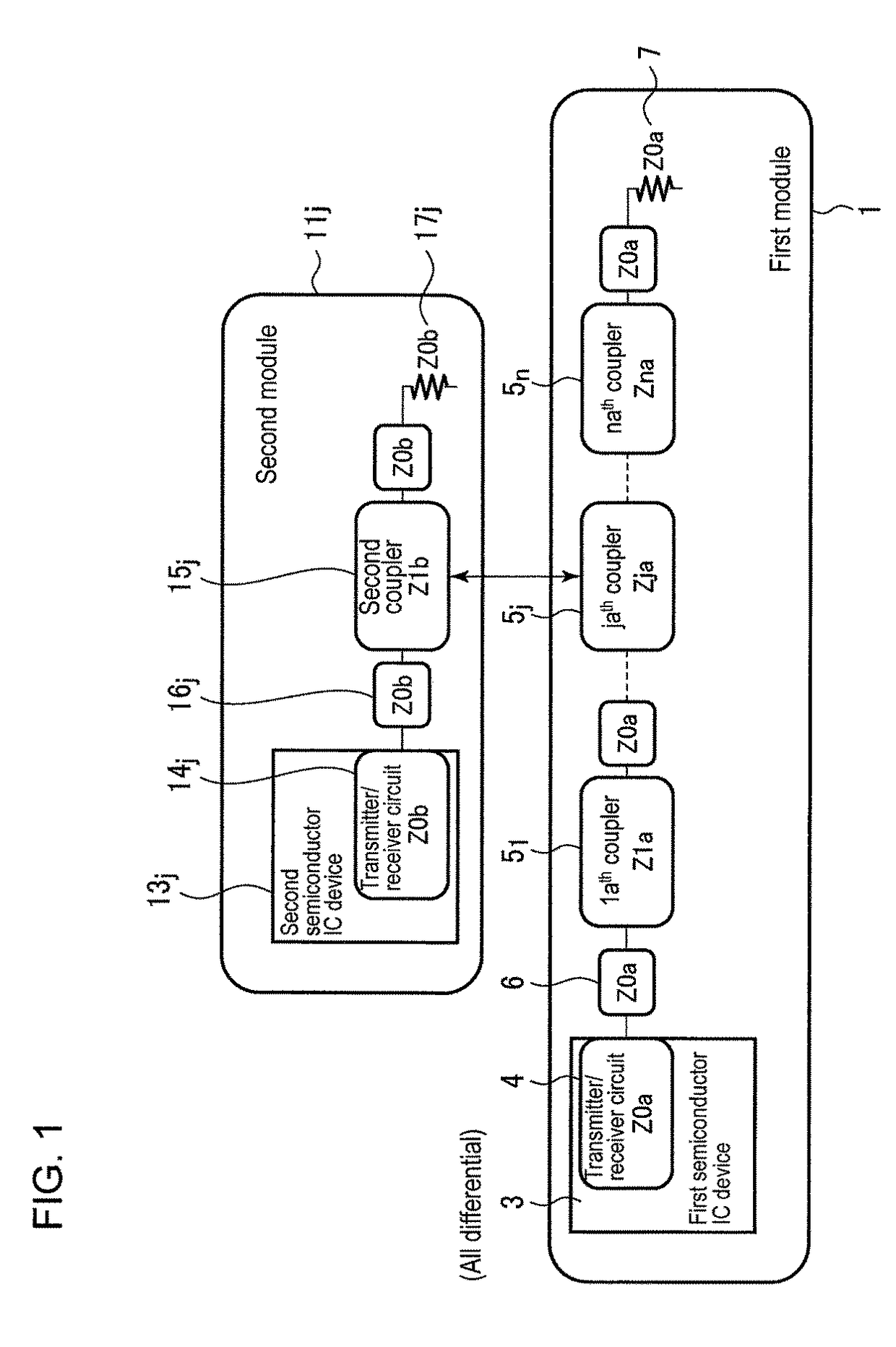

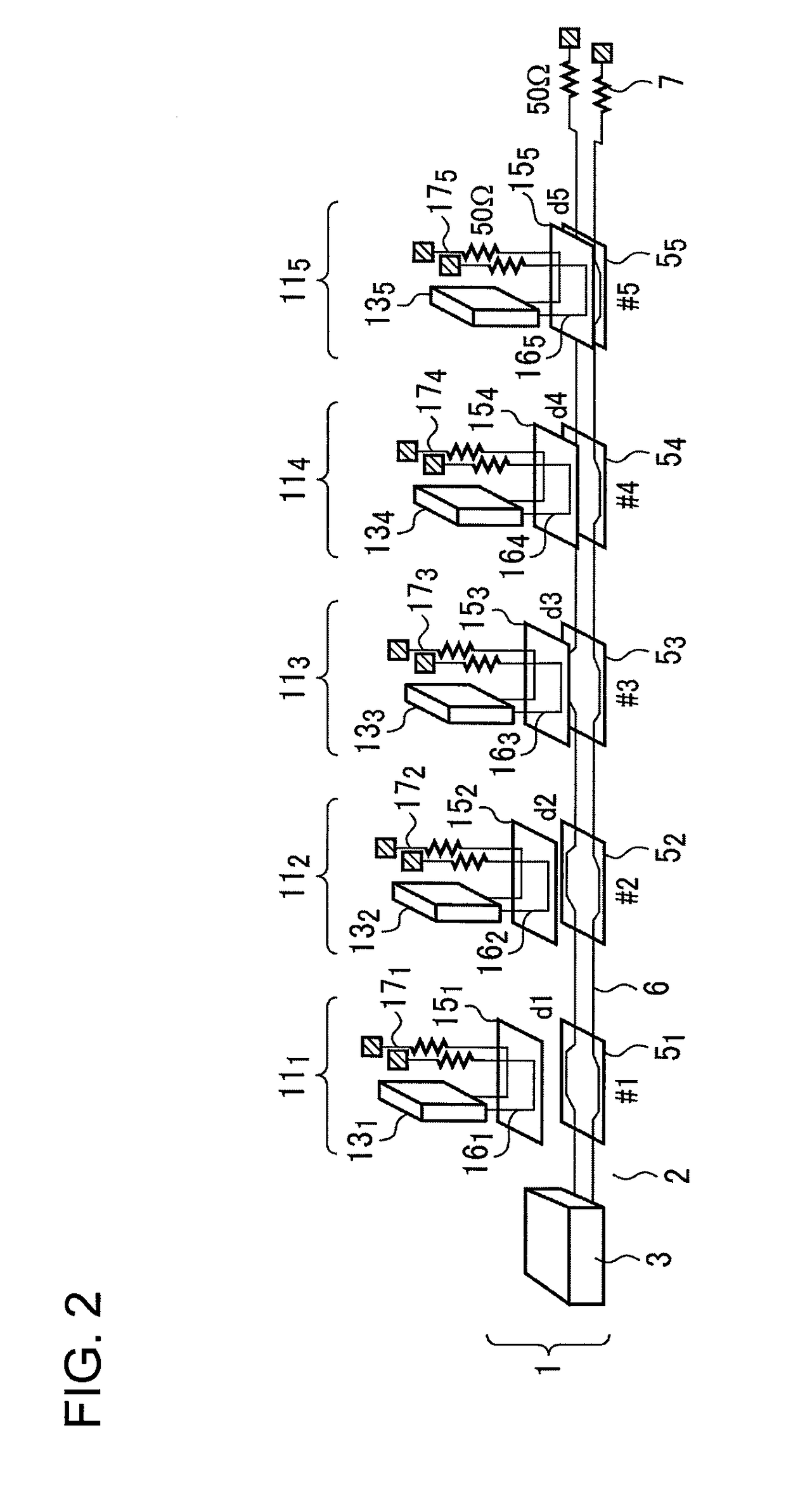

Directional coupling-type multi-drop bus

ActiveUS20140355935A1Improve signal transfer speedReduce the required powerCoupling light guidesTransmission line coupling arrangementsMultidrop busEngineering

The invention relates to a directional coupling-type multi-drop bus of which the impedance is matched with the bus at the time of coupling so that the speed is increased. A directional coupler is formed when a second module provided with a second coupler end is mounted on a first module provided with a first coupler end, and as a result, the coupling impedance where the proximity effects in the coupling state of the directional coupler are reflected is matched with the impedance of the bus.

Owner:KEIO UNIV

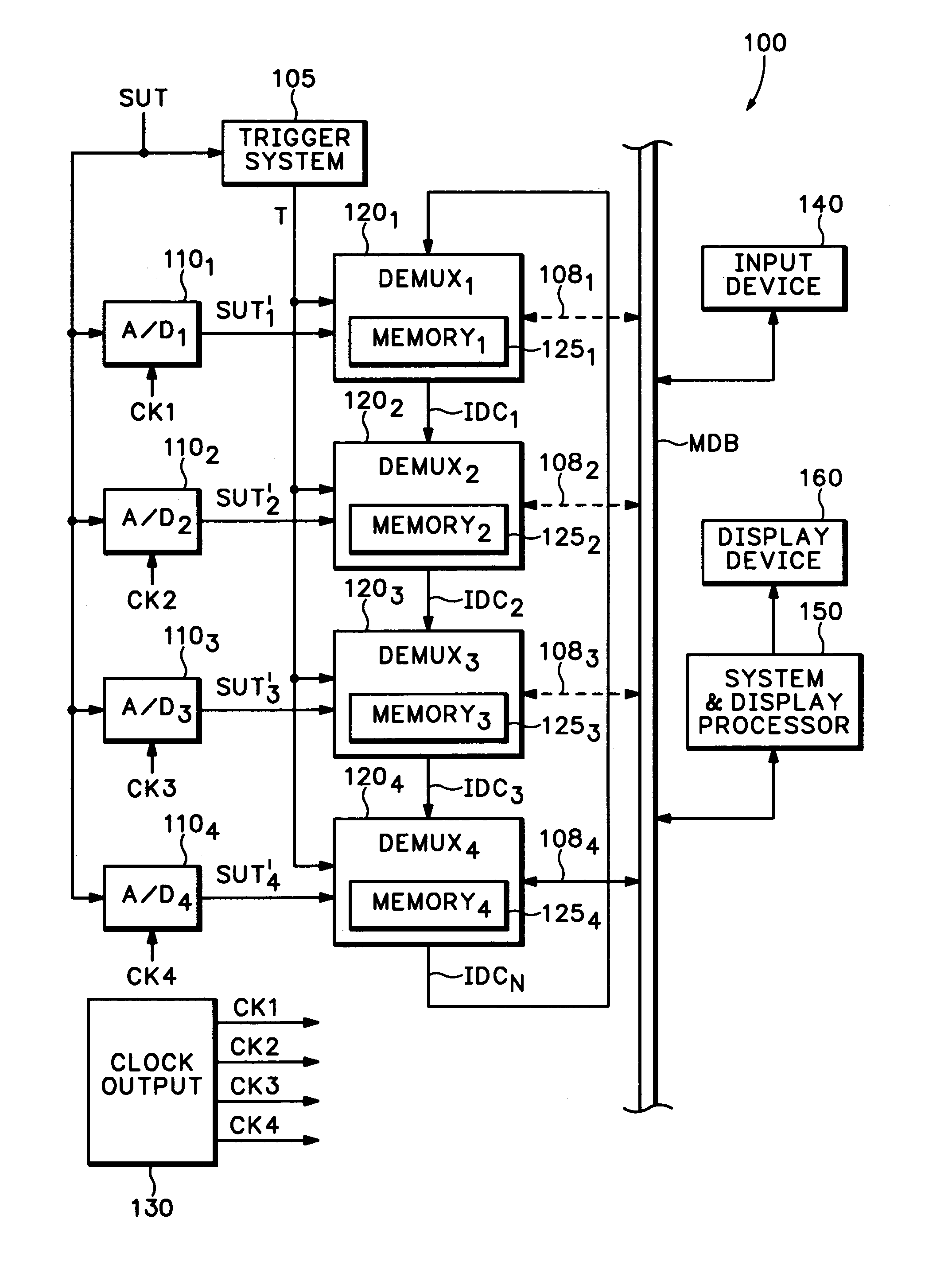

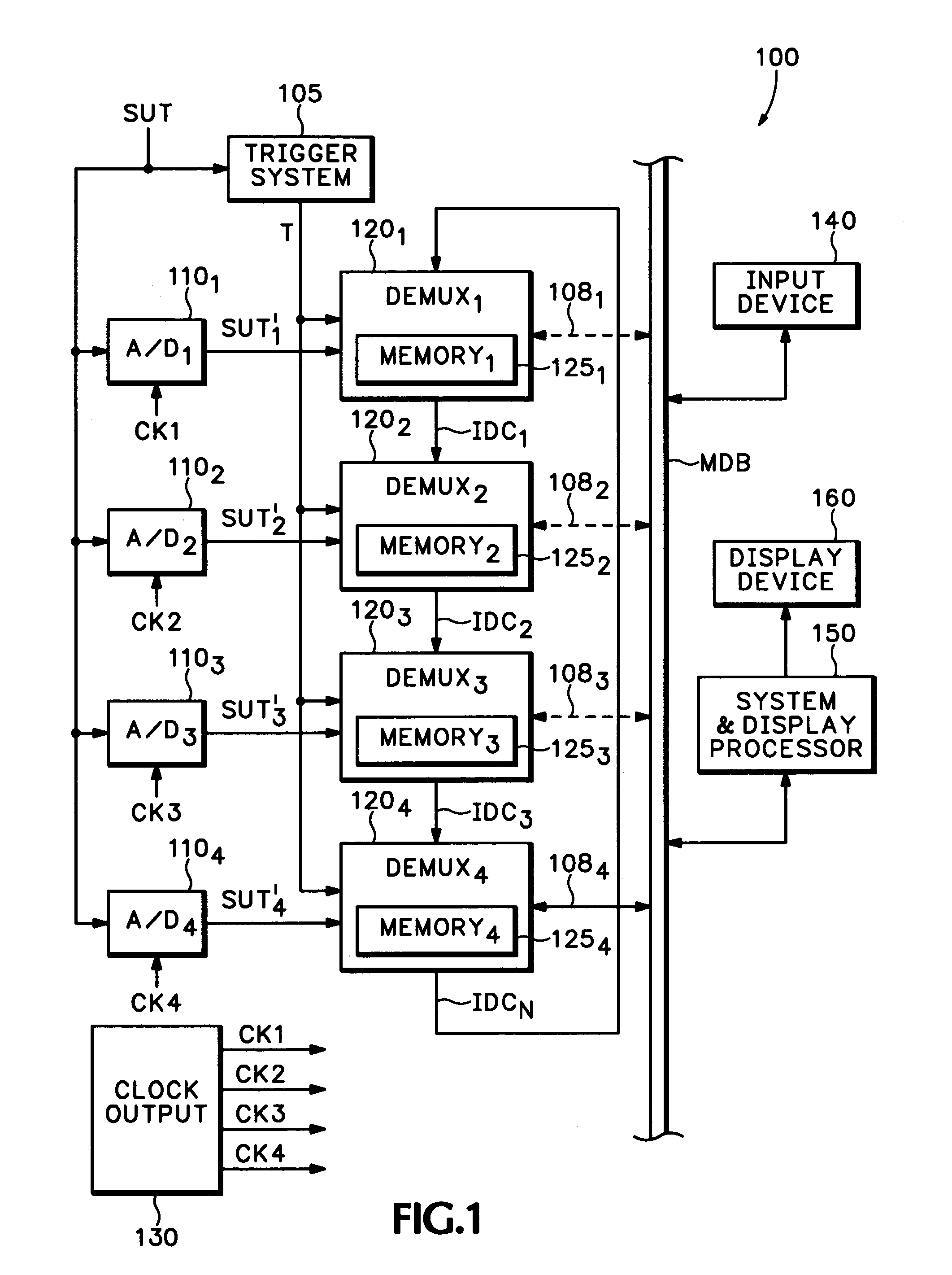

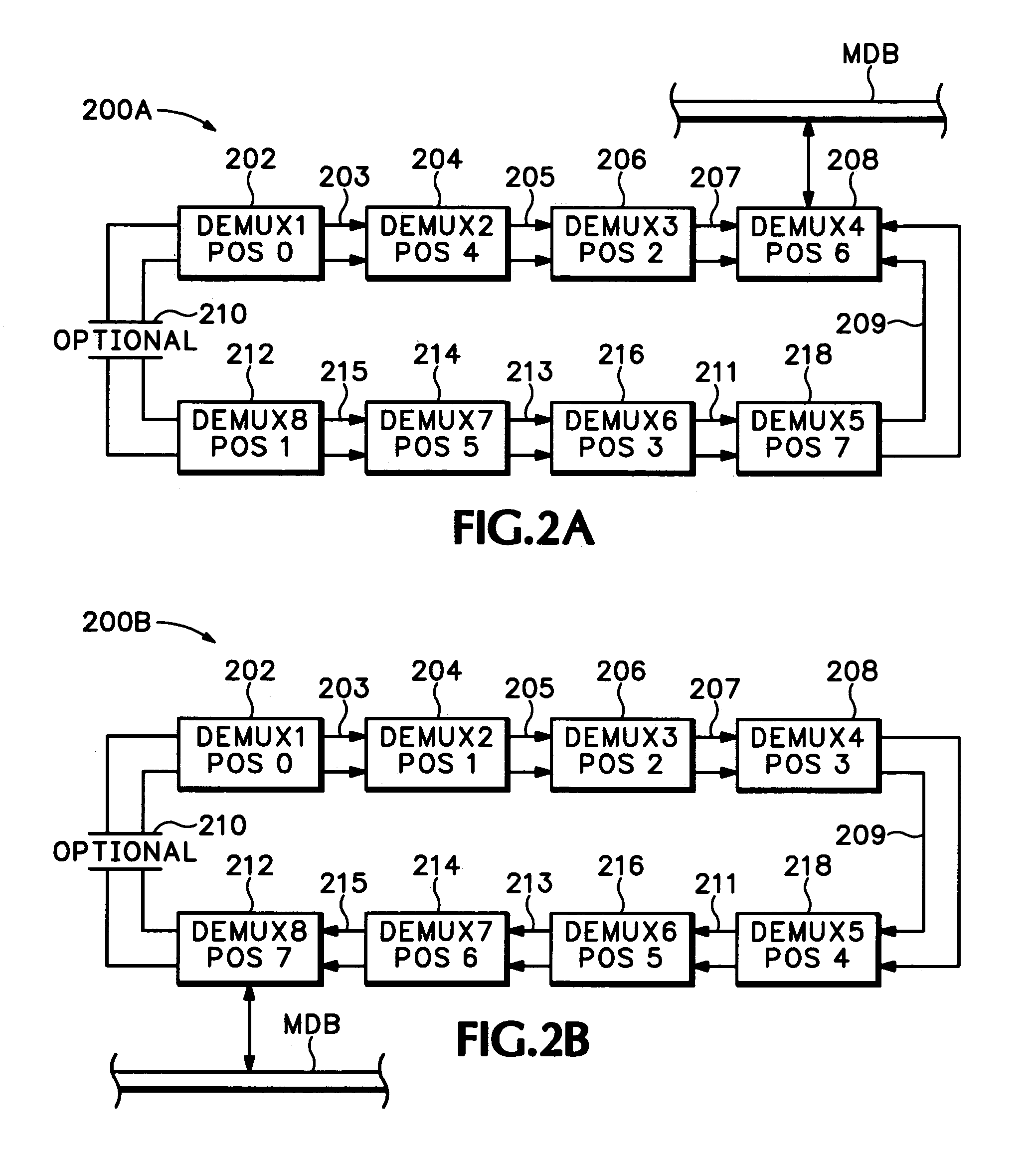

Inter-demux communication through a point to point interface

A method and apparatus in which a plurality of demux processors propagates respective received sample streams to adjacent demux processors via an inter-demux bus; and wherein a final one of the plurality of demux processors propagates all of the respective received sample streams toward a next processing element such as a multi-drop bus (MDB) or system processor within a data acquisition device.

Owner:TEKTRONIX INC

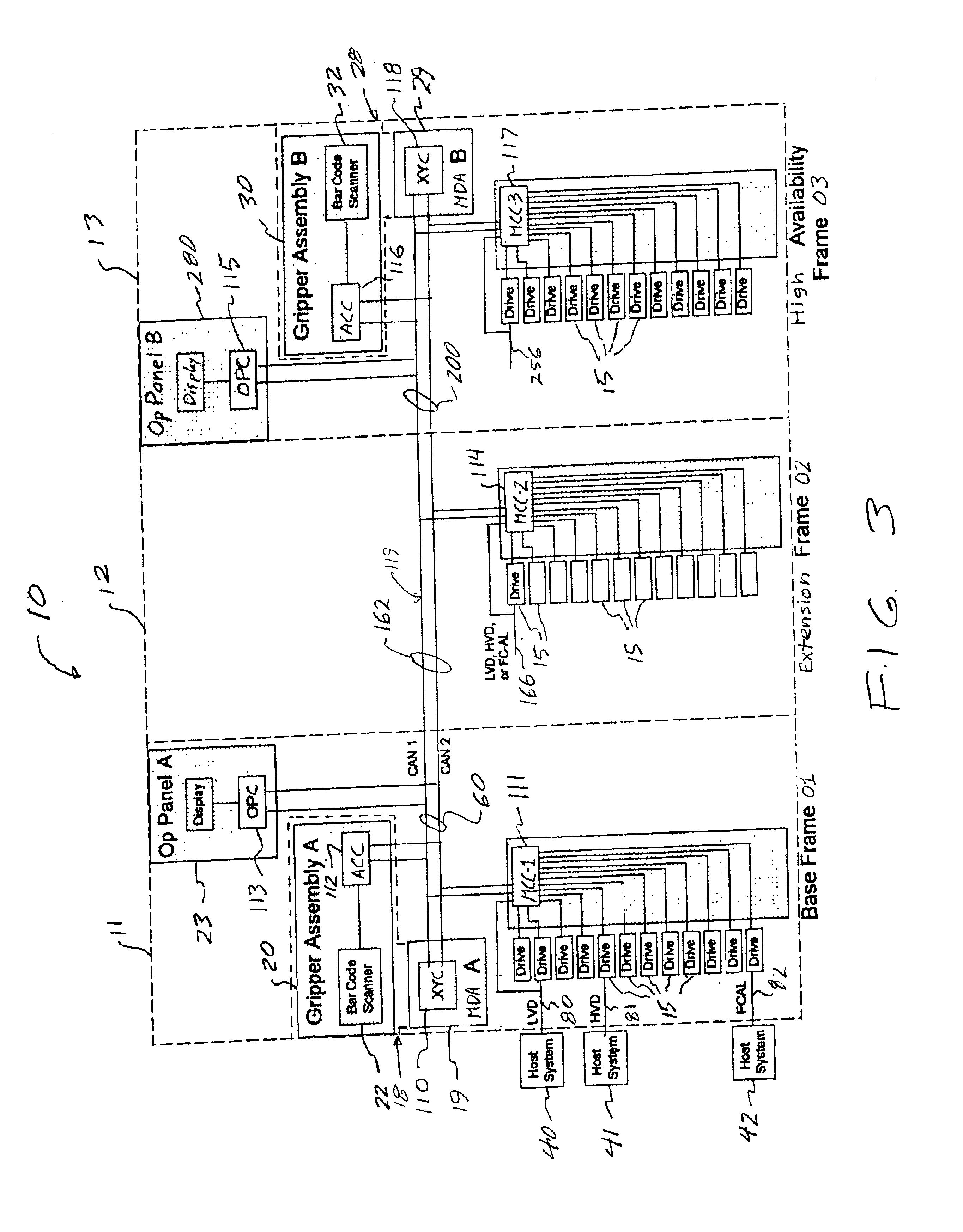

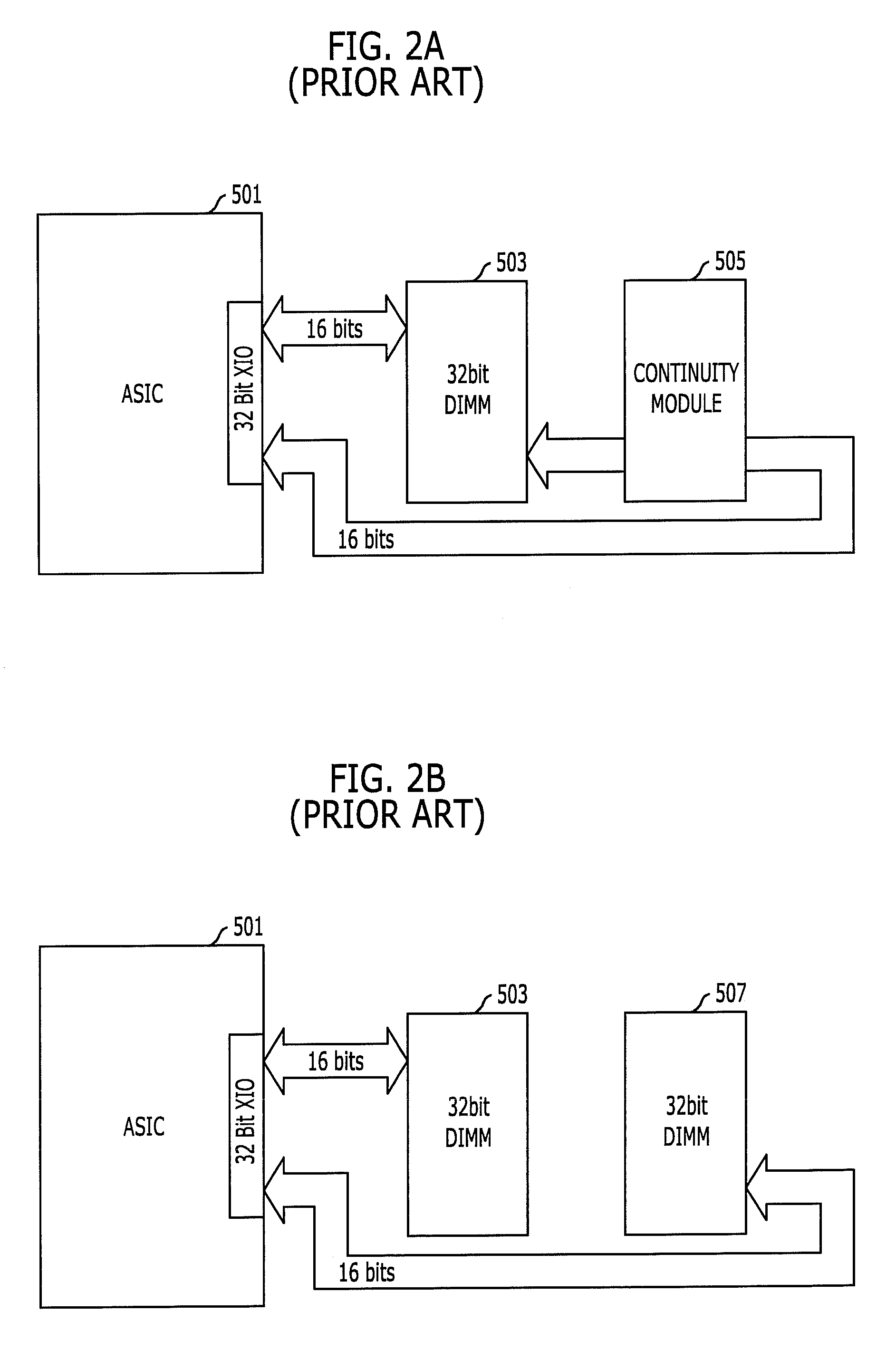

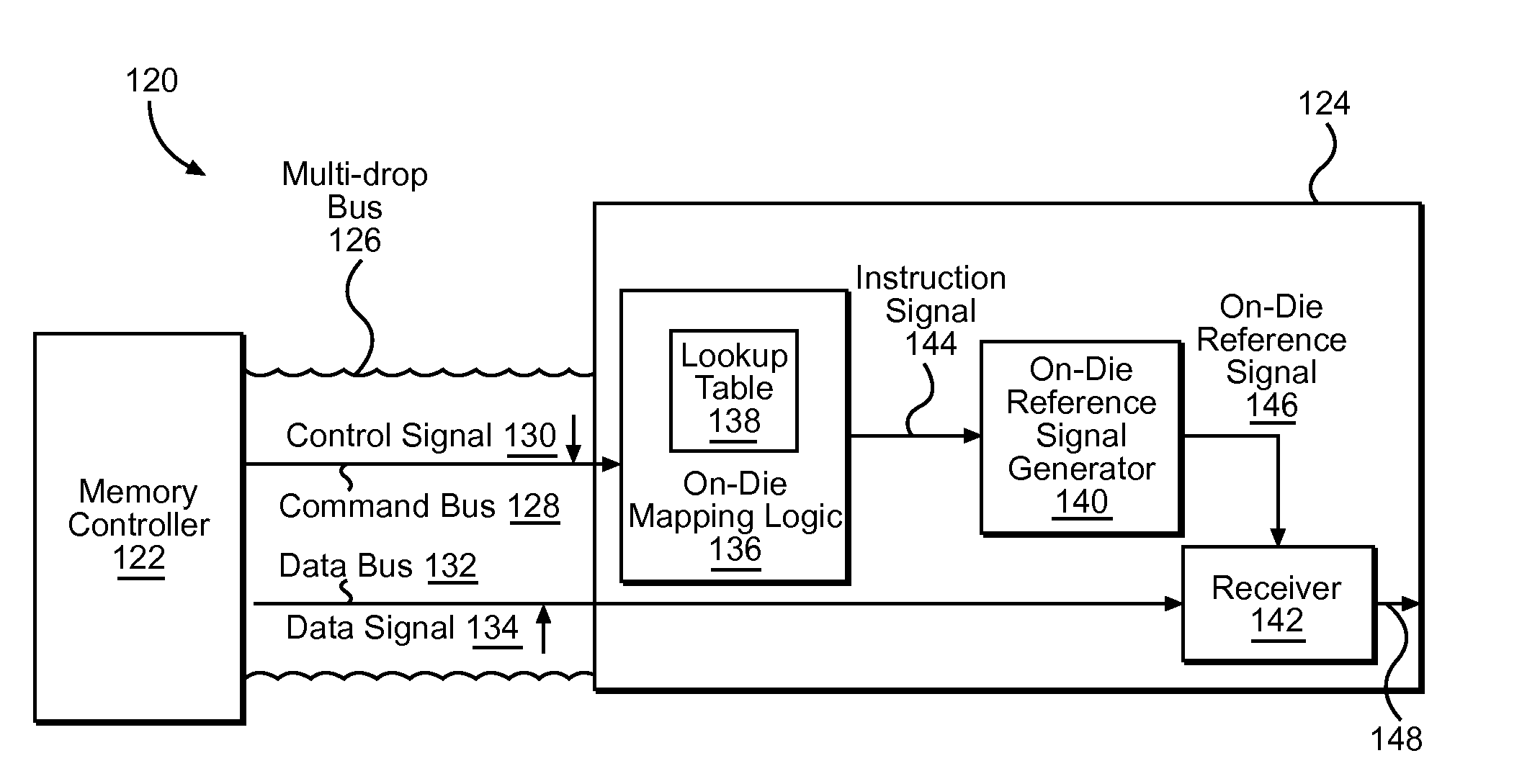

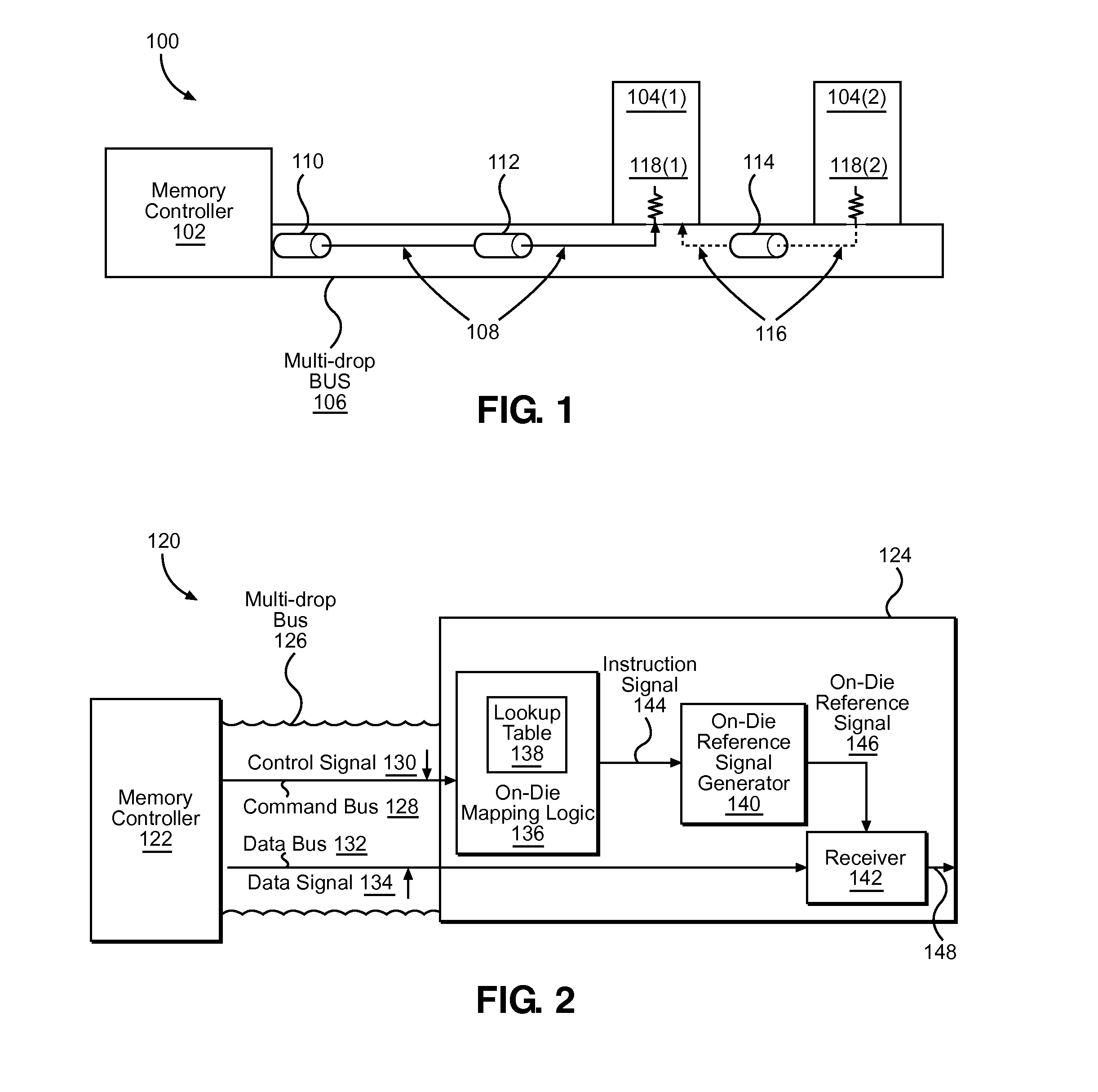

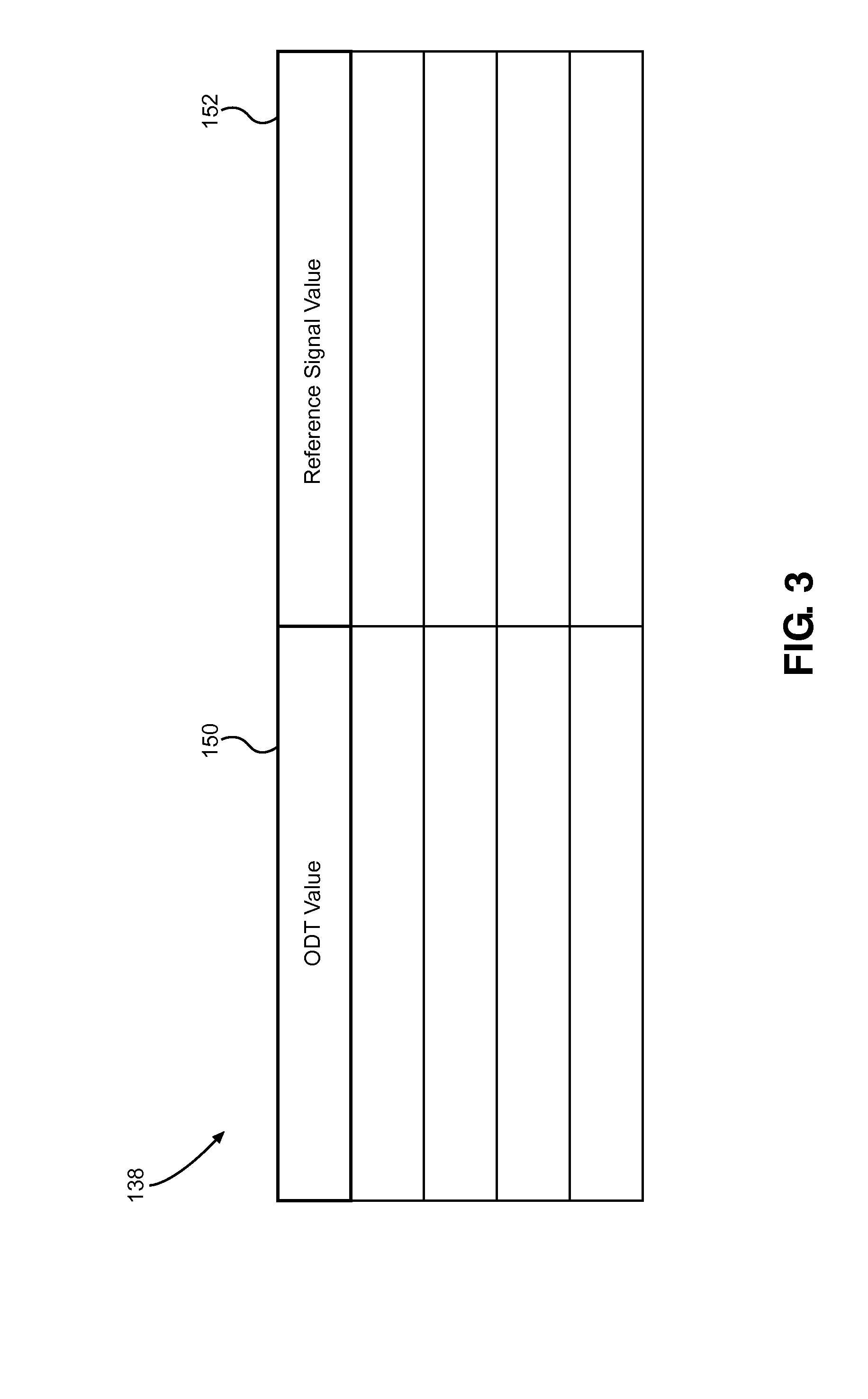

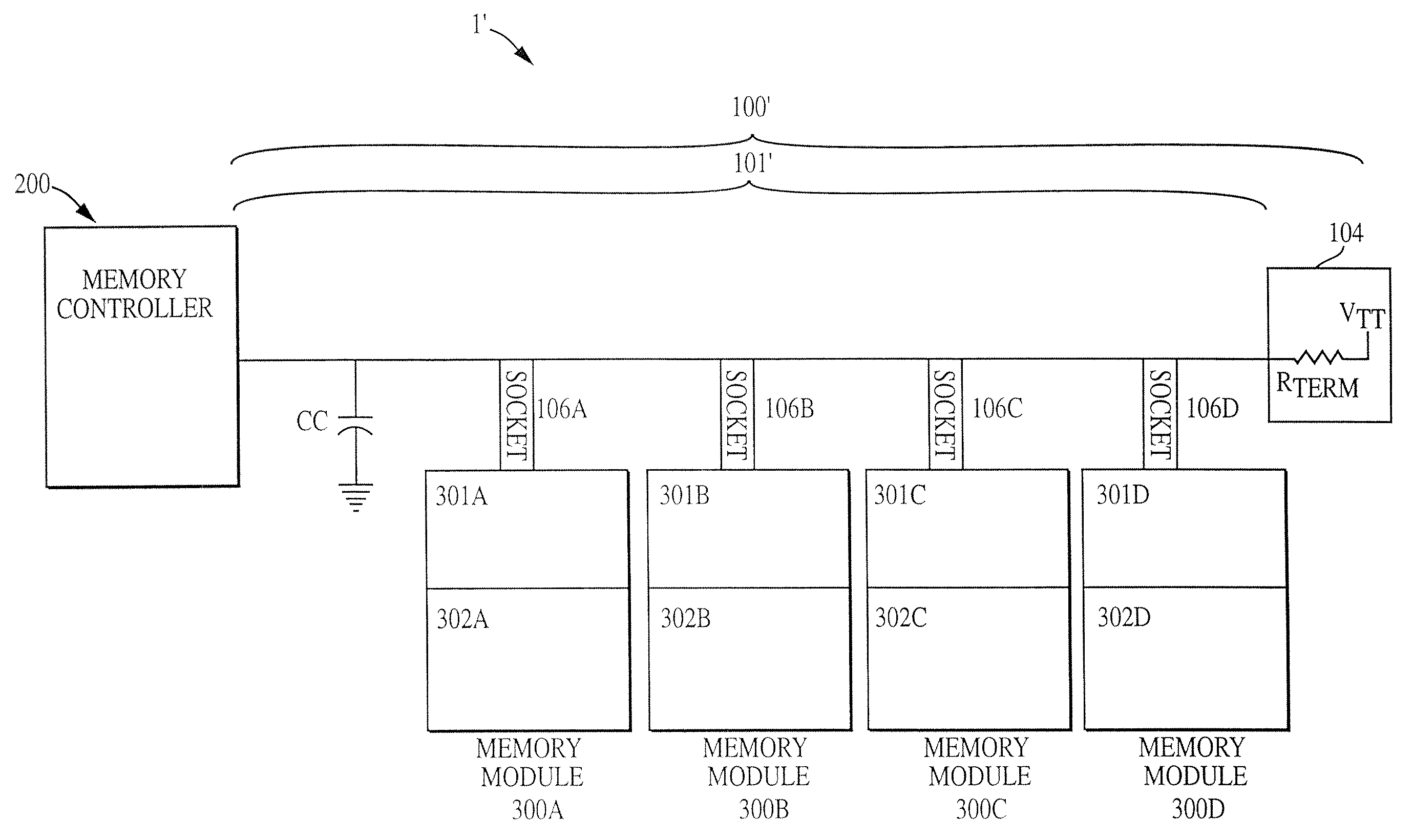

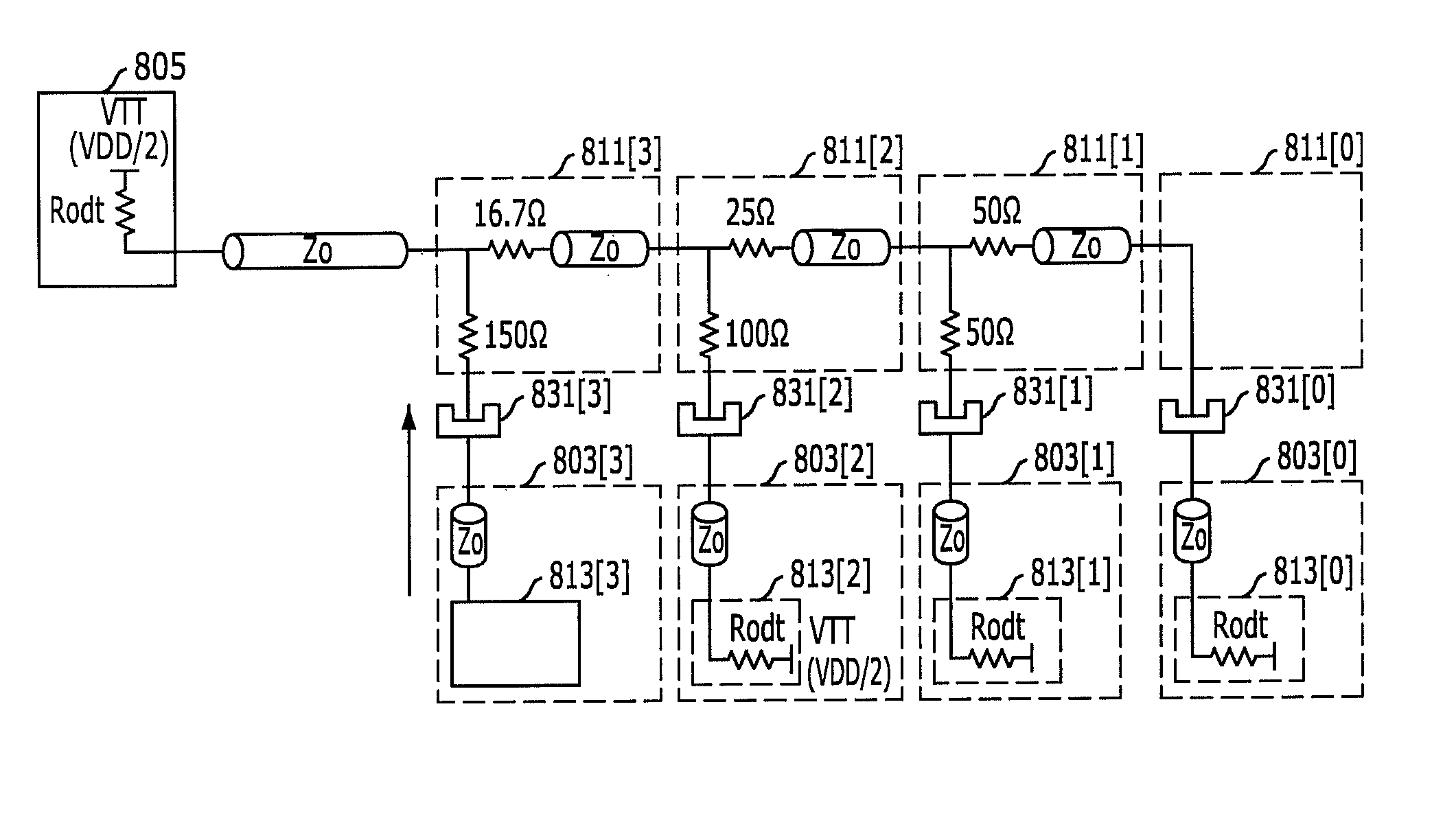

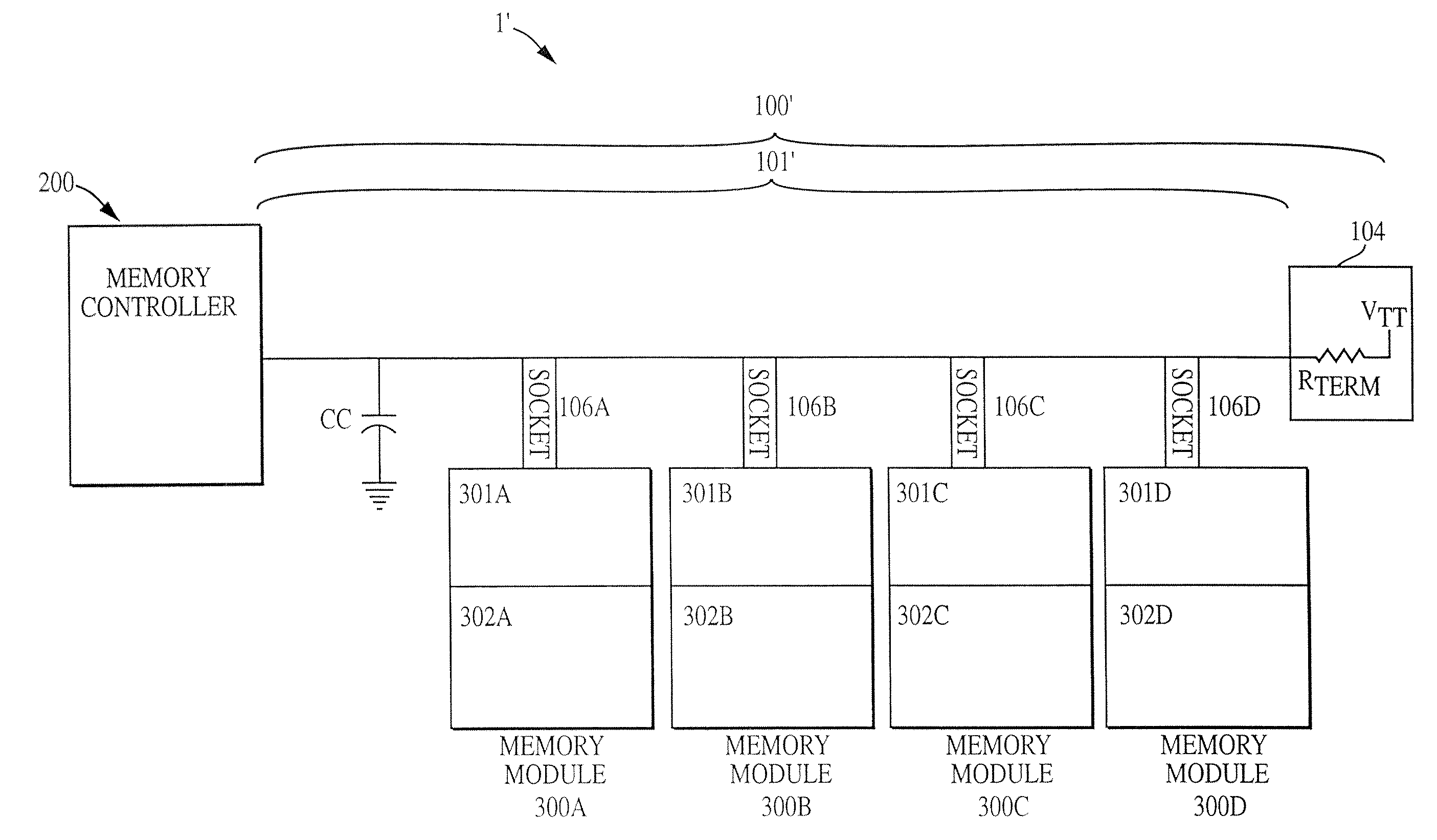

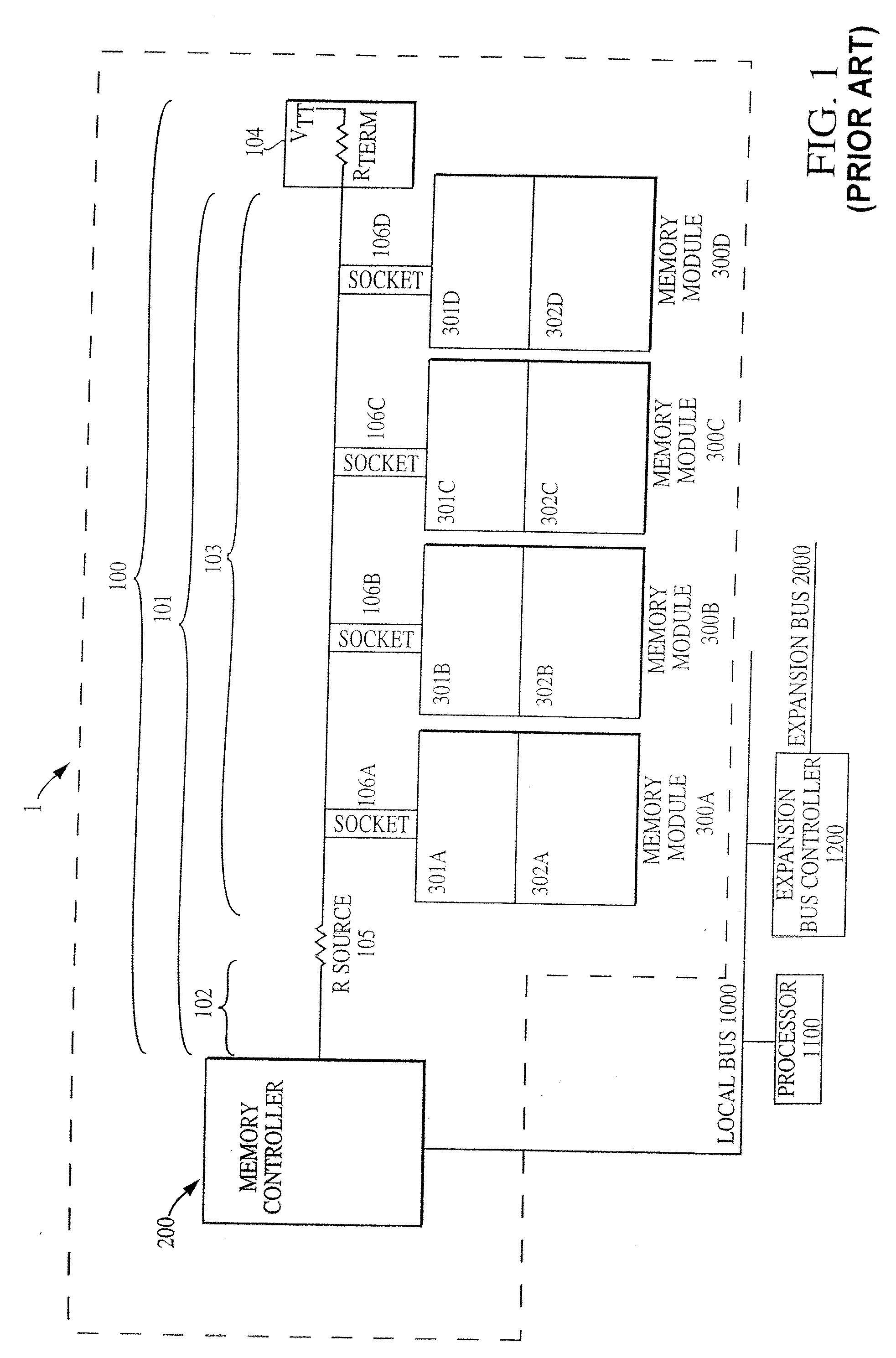

Memory circuit configuration schemes on multi-drop buses

ActiveUS20160041943A1Improved signal integrity reduces errors in writing dataMaintain signal integrityMemory adressing/allocation/relocationDigital storageMultidrop busComputer terminal

Memory circuit configuration schemes on multi-drop buses are disclosed. In aspects disclosed herein, an on-die mapping logic is provided in a memory circuit. A memory controller communicates with the on-die mapping logic over a multi-drop bus. The on-die mapping logic is configured to receive a predetermined on-die termination (ODT) value from the memory controller prior to being accessed. In response to receiving the predetermined ODT value, the memory circuit sets on-die termination to the predetermined ODT value and instructs an on-die reference signal generator to generate a predetermined reference signal associated with the predetermined ODT value. The predetermined reference signal provides an optimal reference voltage for implementing a desired equalization setting at the memory circuit, thus aiding in preserving signal integrity. Such improved signal integrity reduces errors in accessing the memory circuit, thus leading to improved efficiency and data throughput on the multi-drop bus.

Owner:QUALCOMM INC

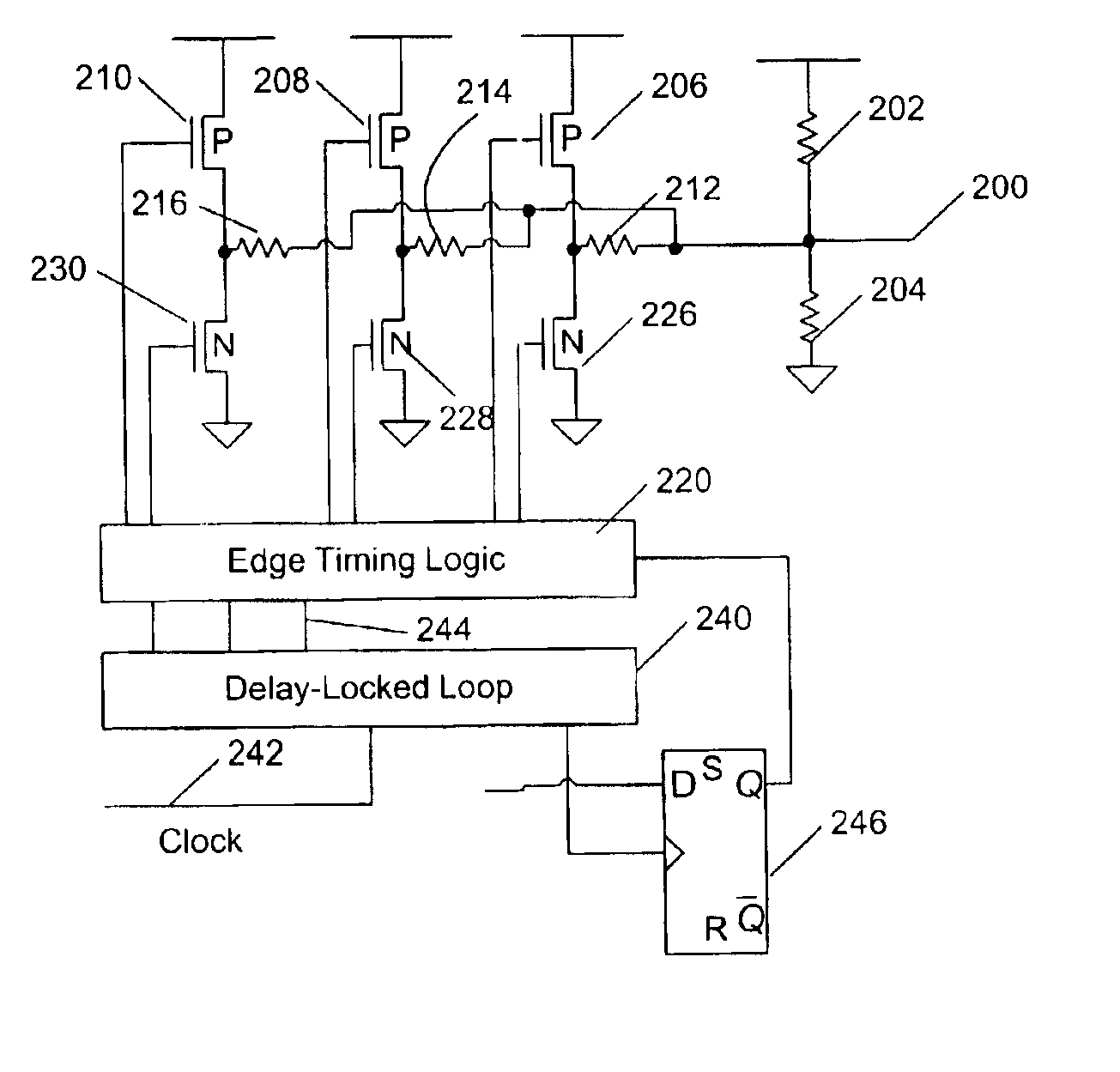

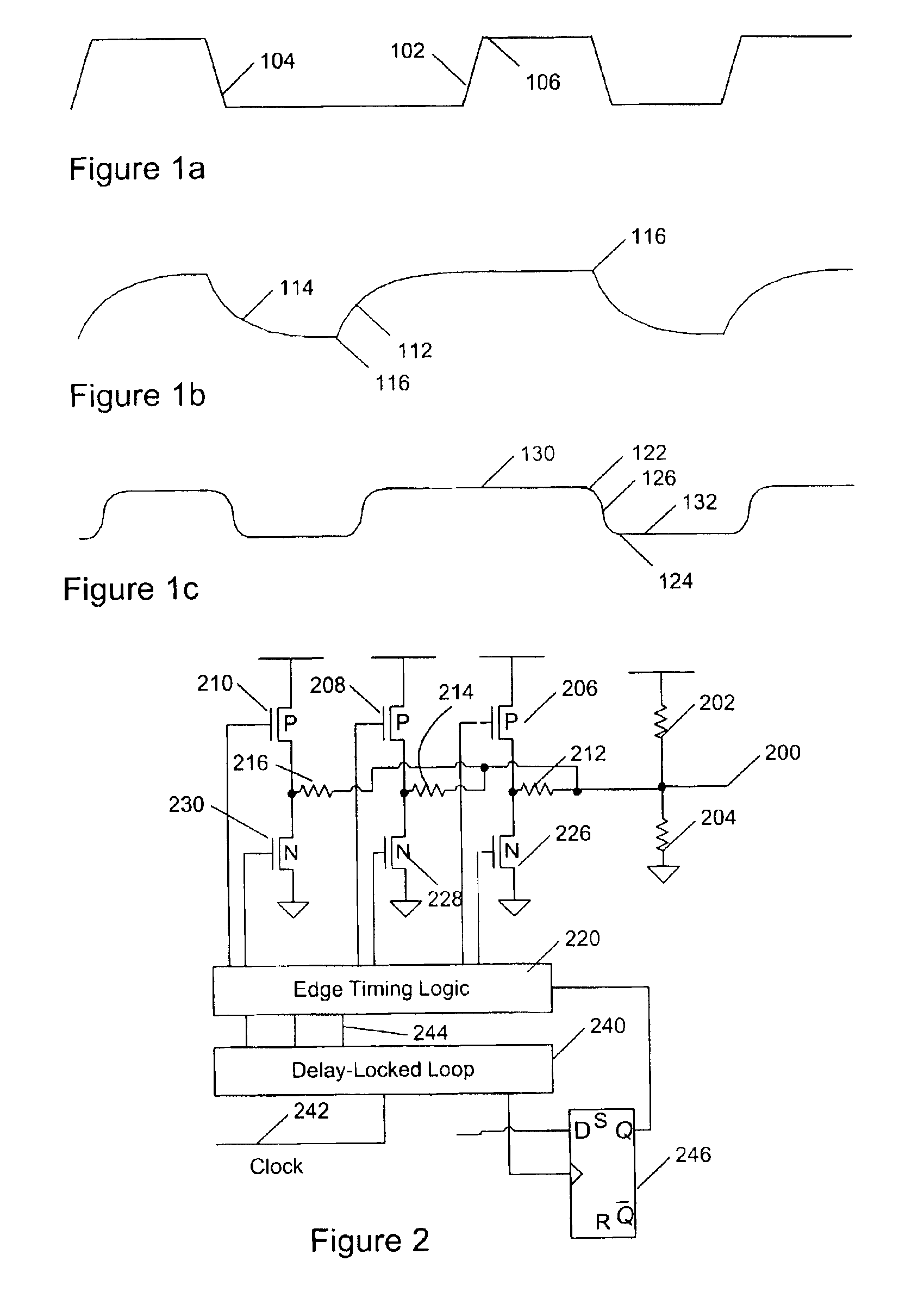

Method and apparatus for high speed bus having adjustable, symmetrical, edge-rate controlled, waveforms

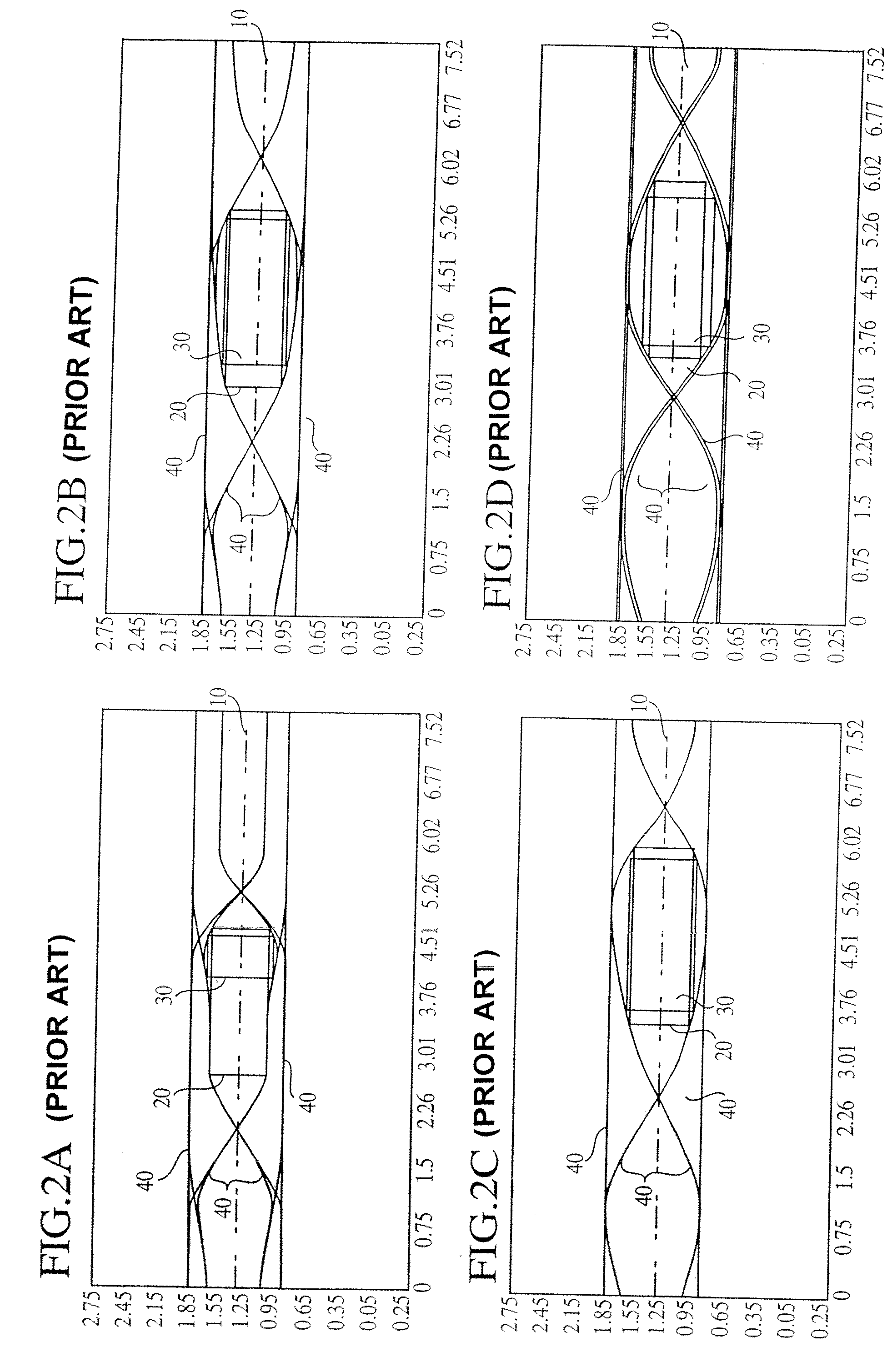

InactiveUS6876224B2Minimize harmonicQuick transitionReliability increasing modificationsElectronic switchingMultidrop busResonance

A method of enhancing noise margin on digital signal lines of a system includes steps of evaluating impedances and lengths of the digital signal lines. Resonances of each digital signal line are determined, and target waveforms for each digital signal line optimized for noise margin are determined. A configuration is generated for a programmable device driver to configure the device driver to generate the waveform optimized for noise margin. An alternative embodiment selects waveforms, and corresponding configurations, from a group of possible waveforms at boot time to ensure that data is transferred with optimum noise margins. Also claimed is apparatus embodying bus drivers capable of driving a bus with a waveform approximating blended trapezoidal and sinusoidal edge shapes, this waveform being optimum for noise margin in certain systems having multidrop busses.

Owner:VALTRUS INNOVATIONS LTD +1

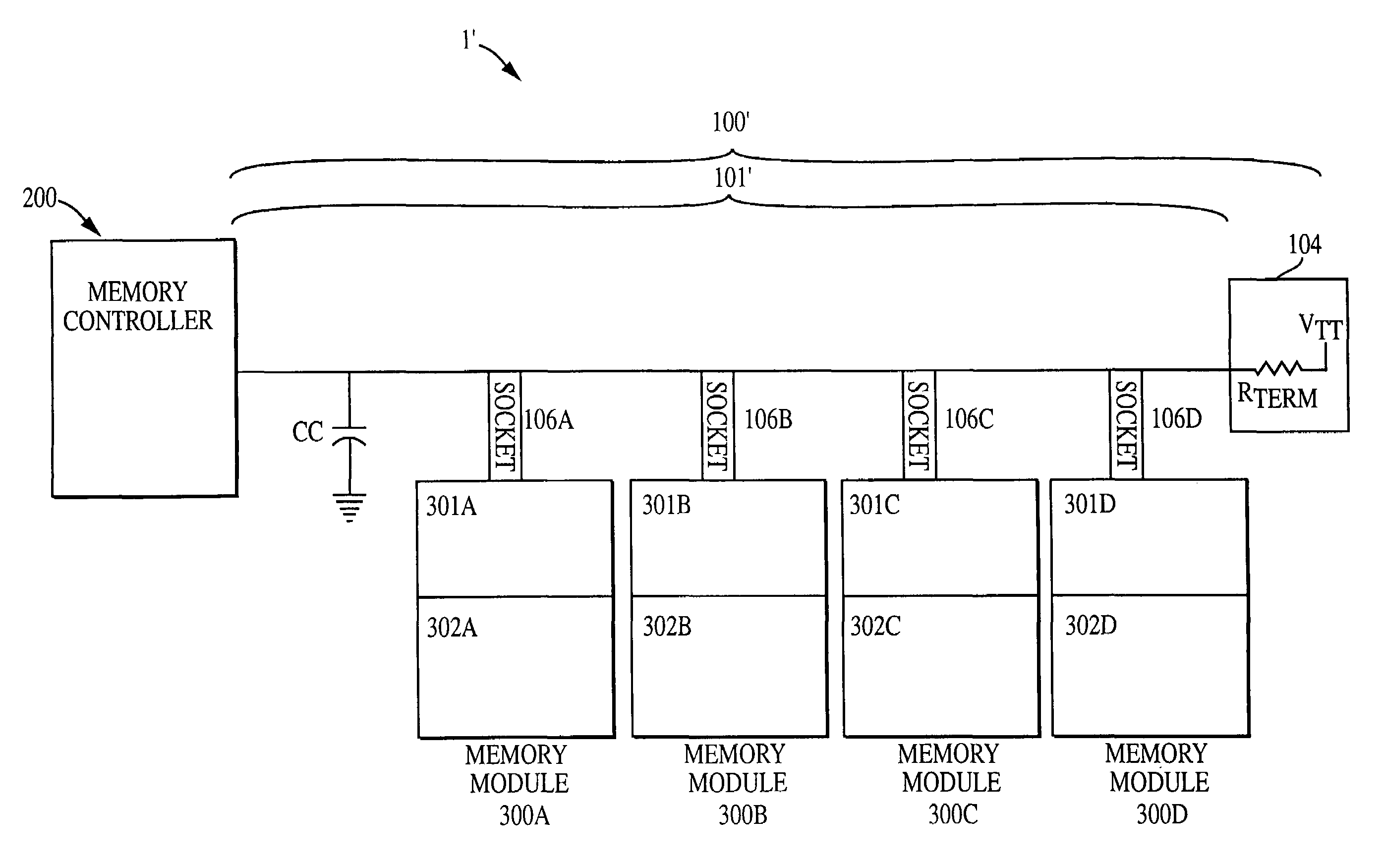

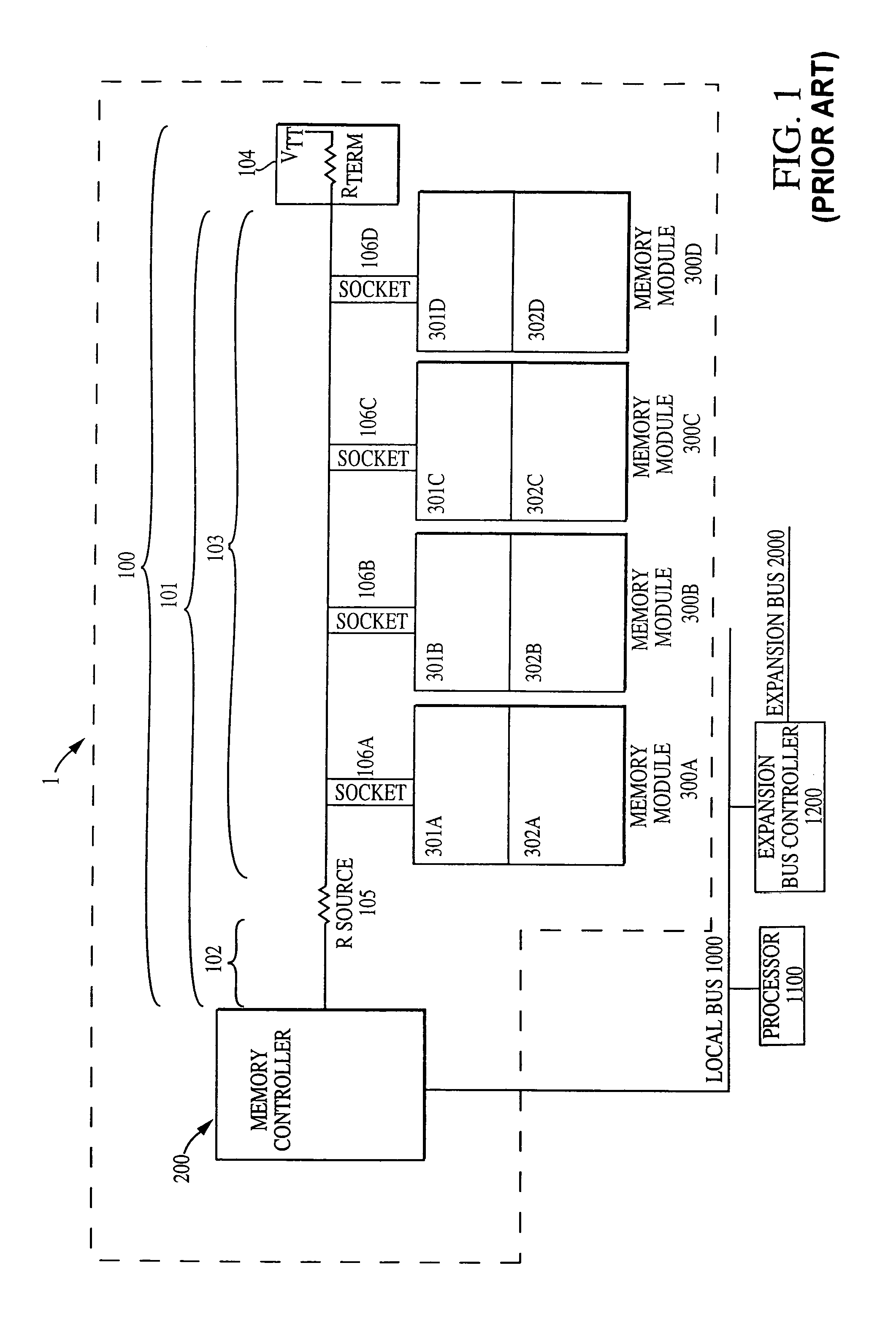

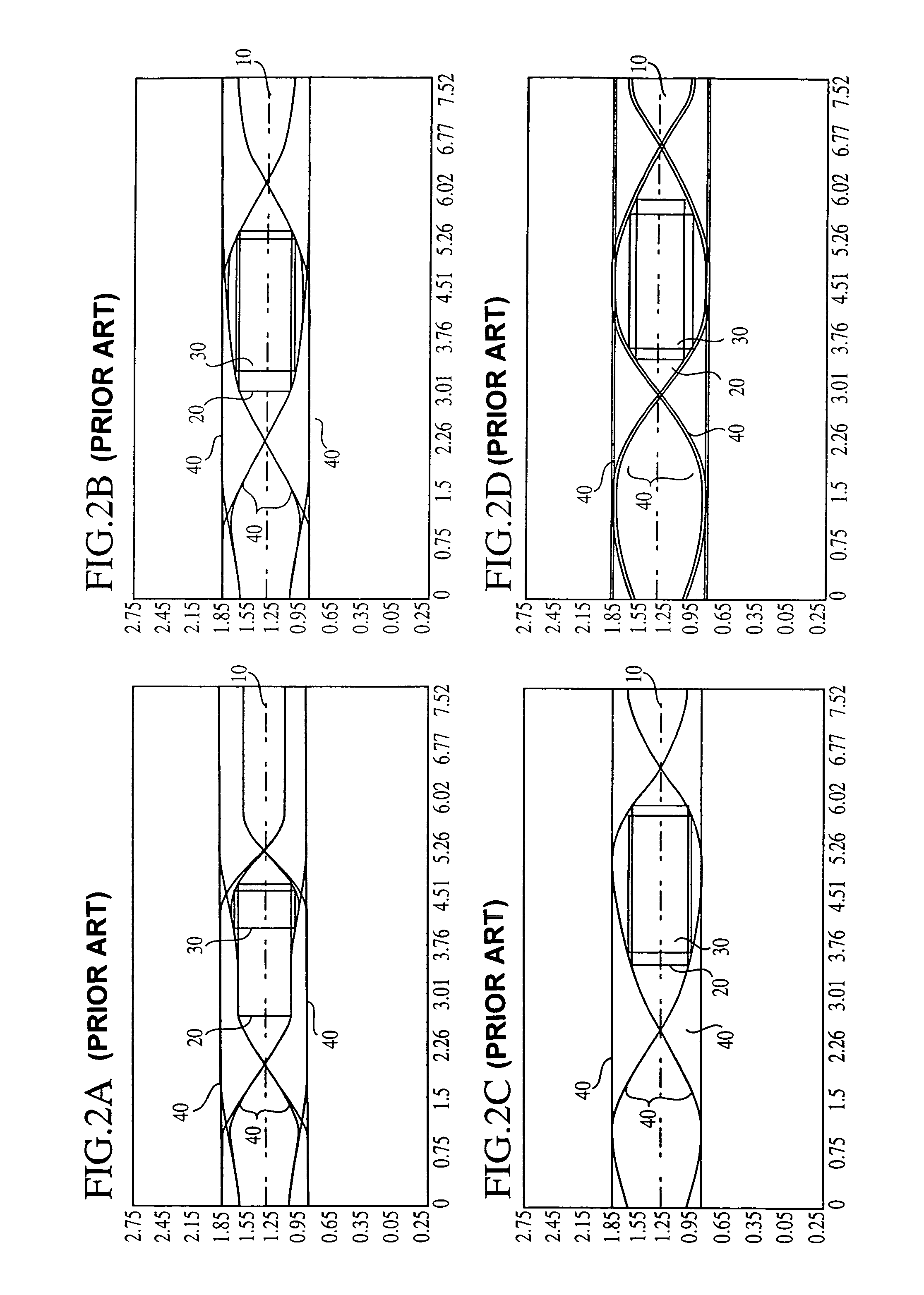

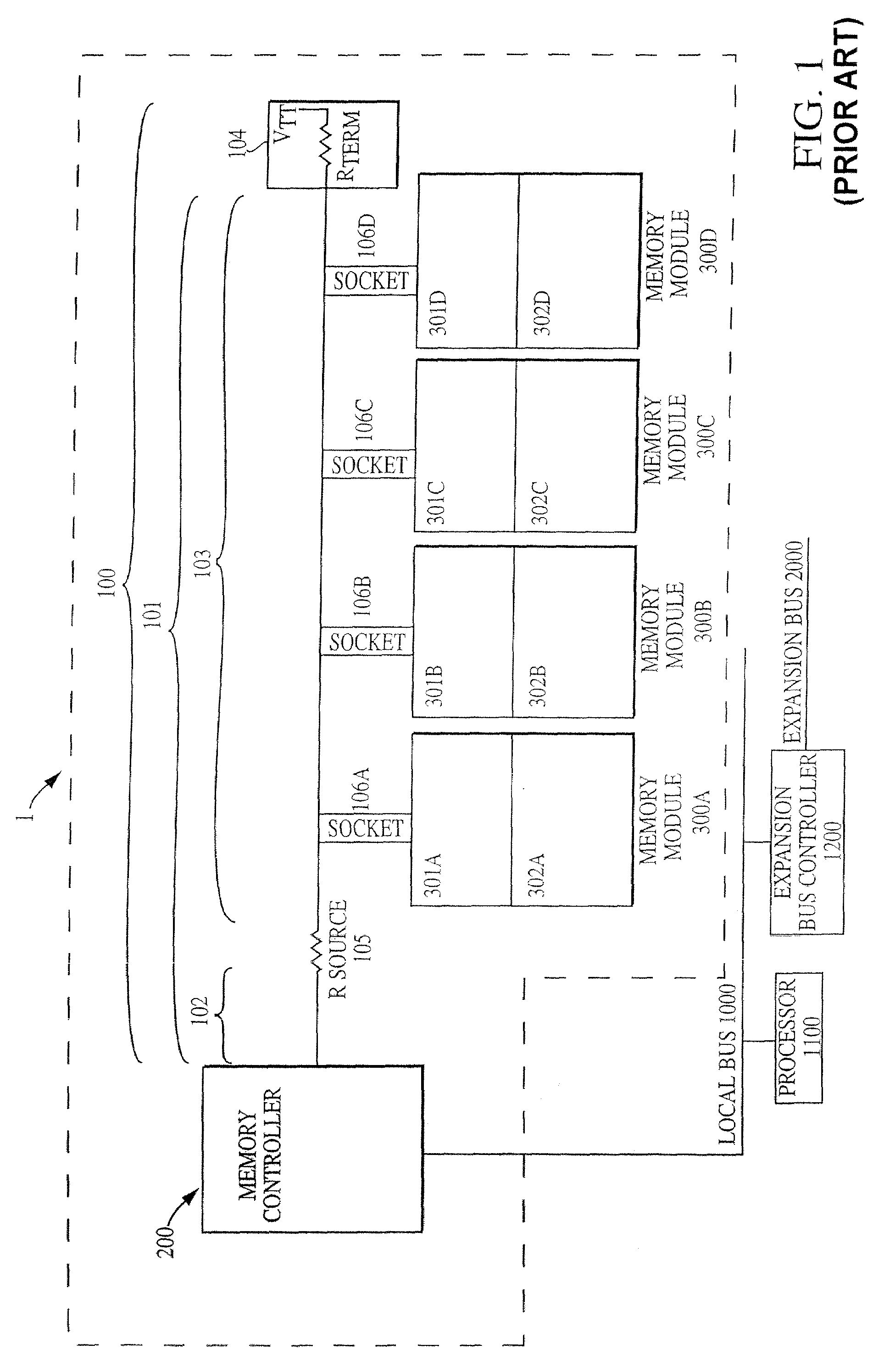

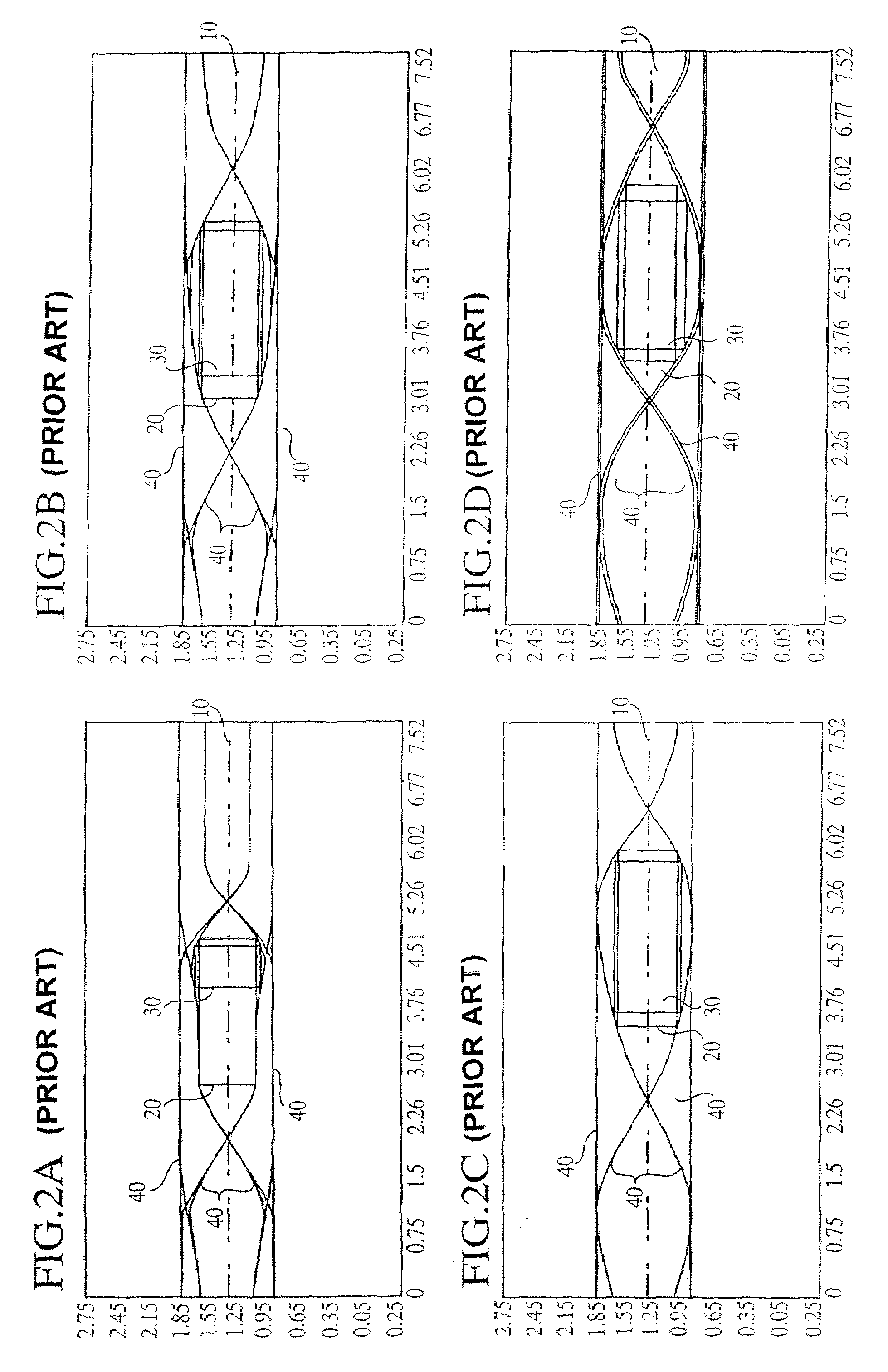

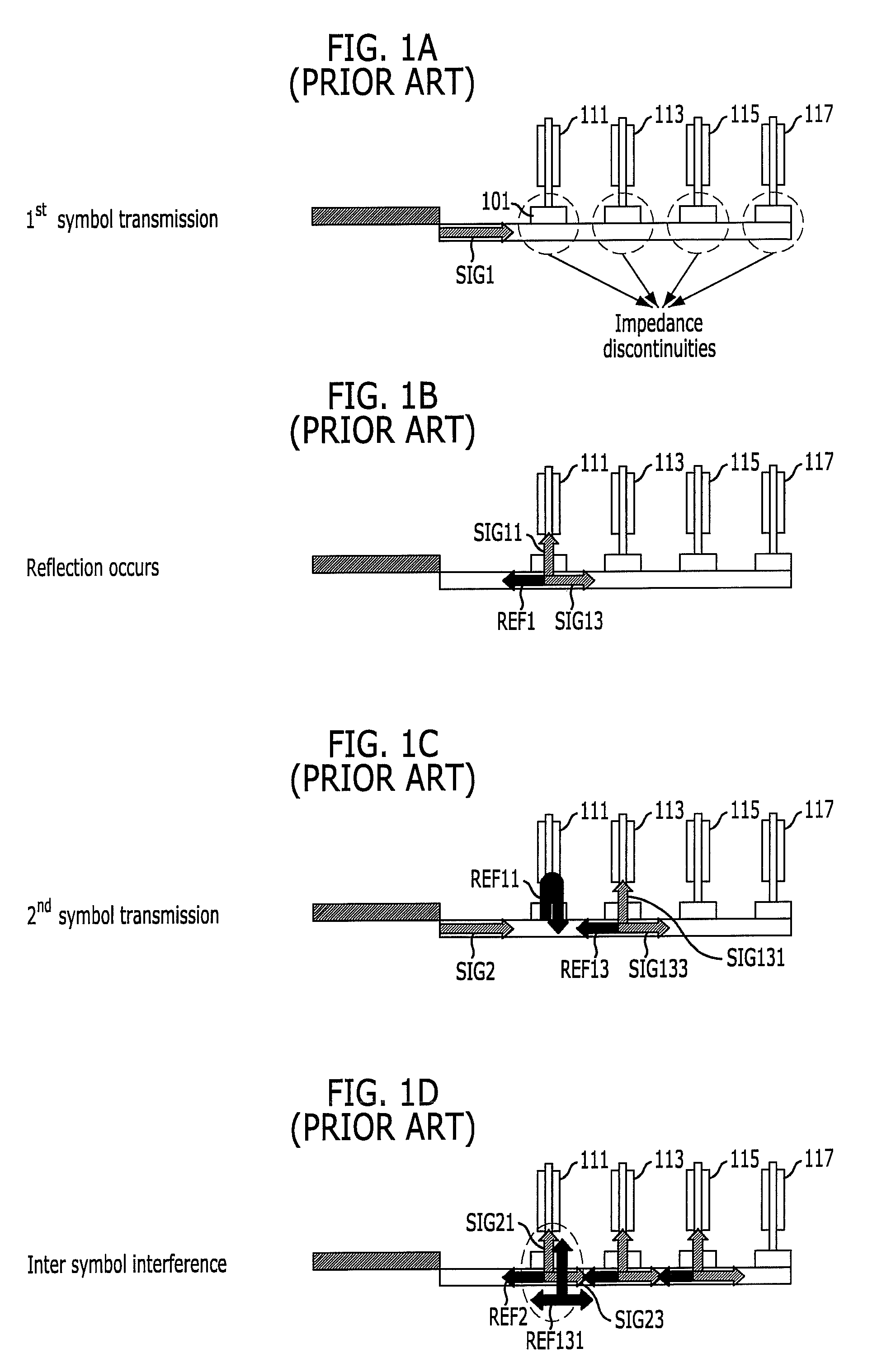

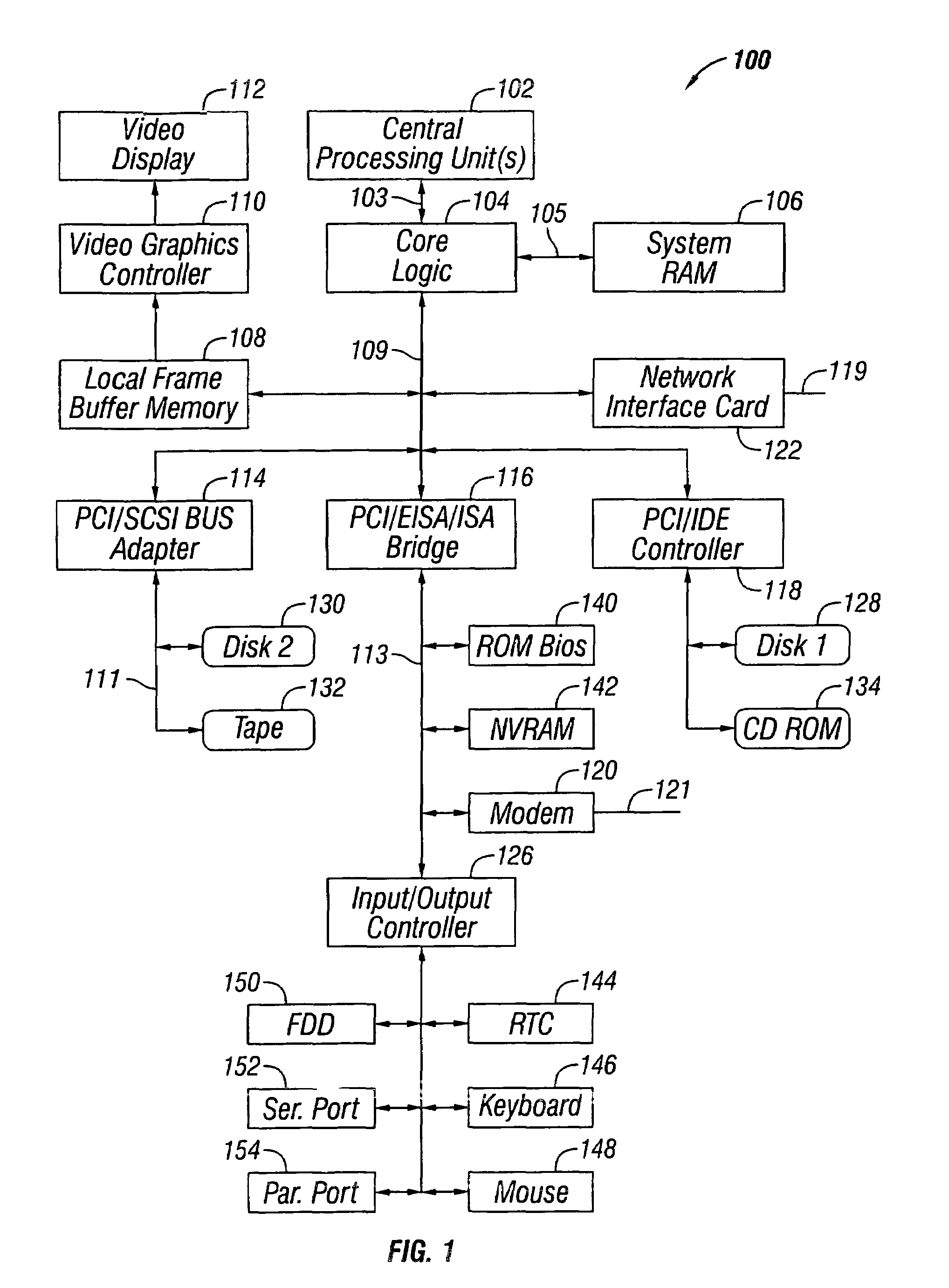

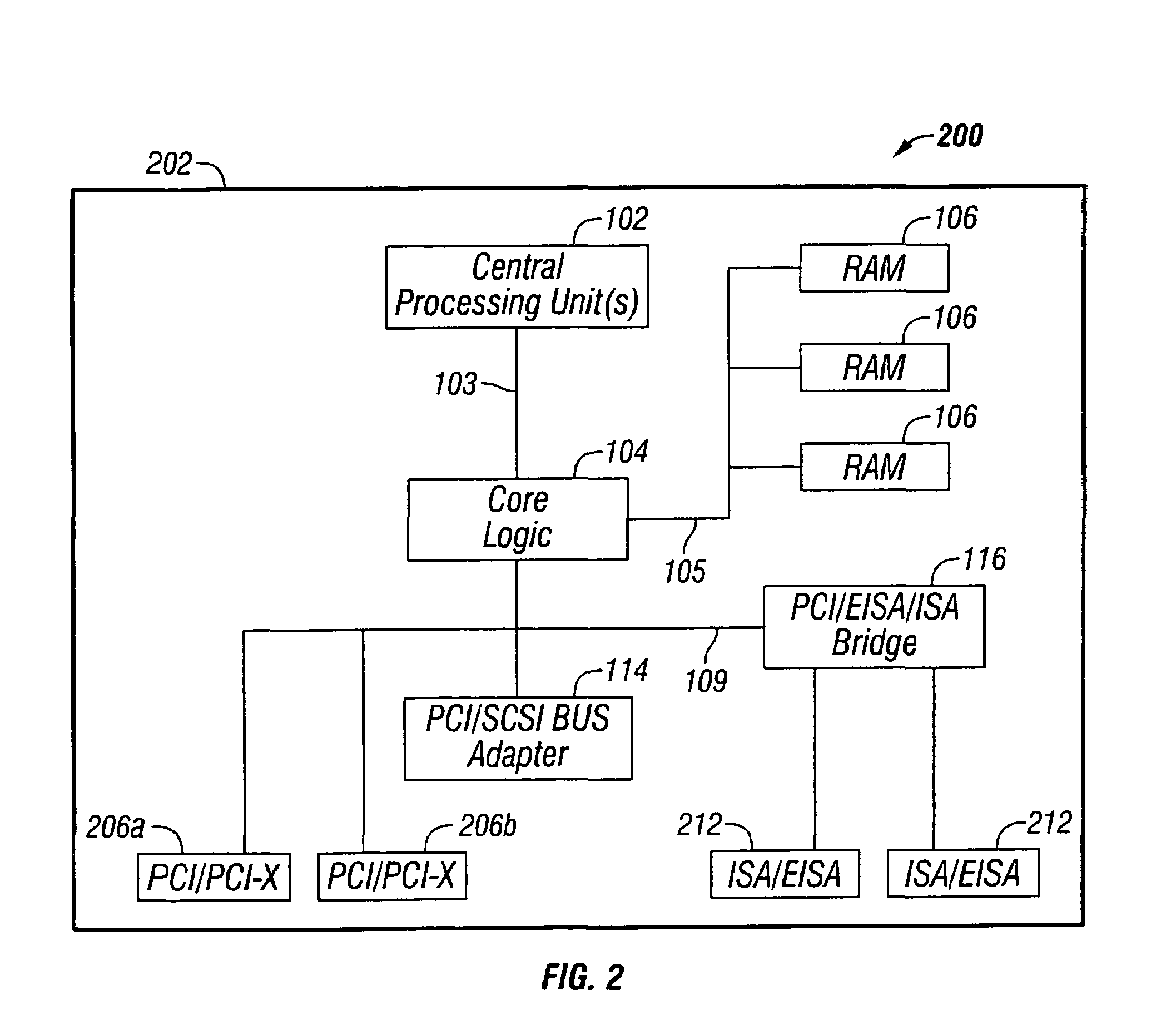

Capacitive multidrop bus compensation

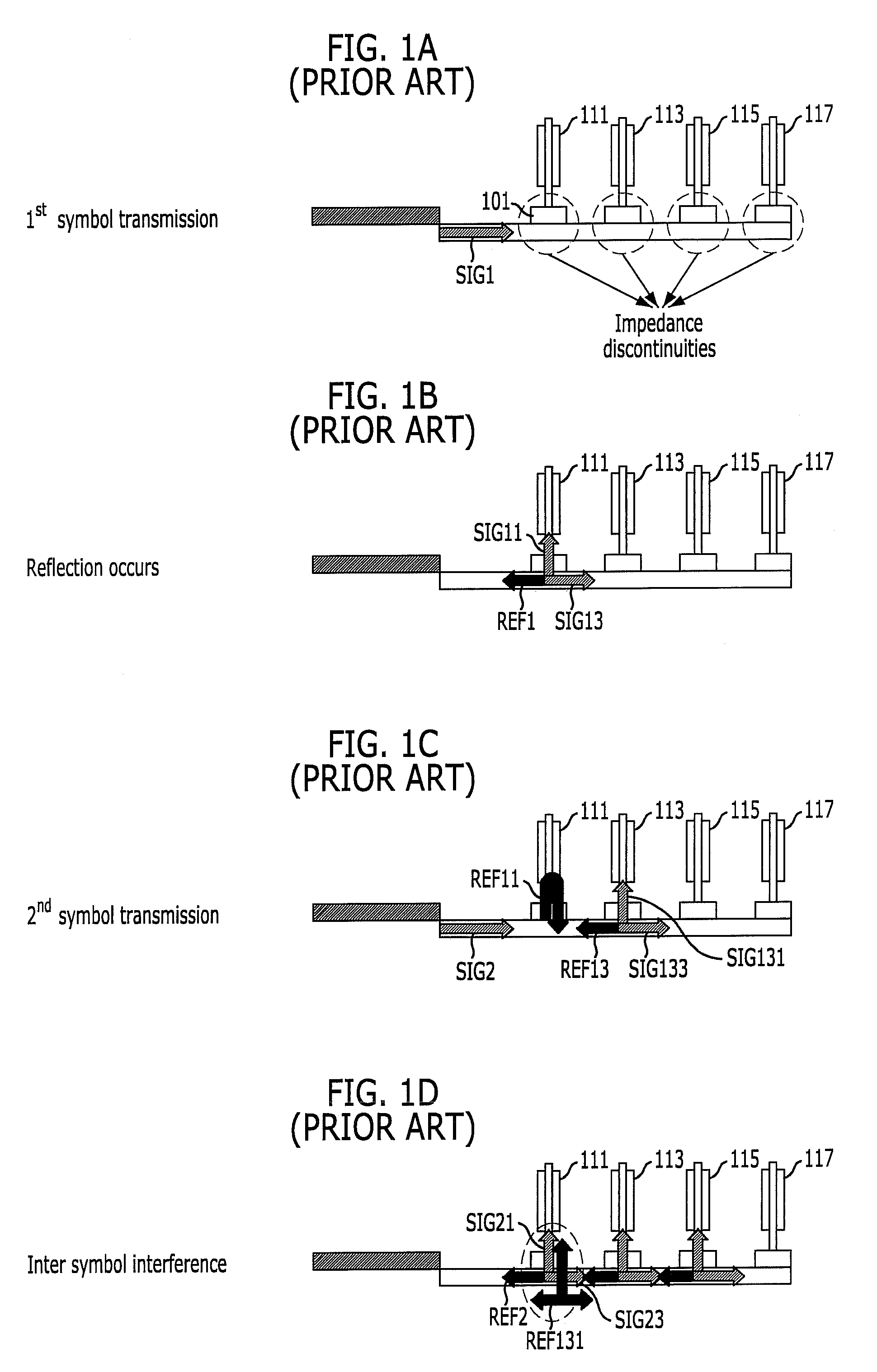

InactiveUS7287108B2Improve signal integrityIncrease volumeMultiple-port networksDigital storageEngineeringElectrical impedance

The signal integrity of a high speed heavily loaded multidrop memory bus is often degraded due the numerous impedance mismatches. The impedance mismatches causes the bus to exhibit a nonlinear frequency response, which diminishes signal integrity and limits the bandwidth of the bus. A compensating element, such as a capacitor which ties the bus to a reference plane (e.g., a ground potential), or an inductor wired in series with the bus, is located approximately midway between the memory controller and the memory slots. The use of the compensating element equalizes signal amplitudes and minimizes phase errors of signals in an interested frequency range and diminishes the amplitudes of high frequency signals which exhibit high degrees of phase error. The resulting bus structure has increased desirable harmonic content with low phase error, thereby permitting the bus to exhibit better rise time performance and permitting a higher data transfer rate.

Owner:ROUND ROCK RES LLC

Capacitive multidrop bus compensation

InactiveUS7461188B2Improve signal integrityIncrease volumeMultiple-port networksDigital storageEngineeringElectrical impedance

Owner:ROUND ROCK RES LLC

Bi-directional multi-drop bus memory system

ActiveUS8195855B2Logic circuit coupling arrangementsReliability increasing modificationsMultidrop busComputer module

A bus system includes a plurality of stubs; a plurality of connectors, each of which is serially coupled between a corresponding one of the stubs and a corresponding one of memory modules; a plurality of first serial loads, each of which is serially coupled to a corresponding one of the connectors; and a plurality of second serial loads, each of which is serially coupled to characteristic impedance of a transmission line of a corresponding one of the stubs, wherein the first and the second serial loads are determined to be impedance matched at each transmission line terminal of the stubs.

Owner:SK HYNIX INC +1

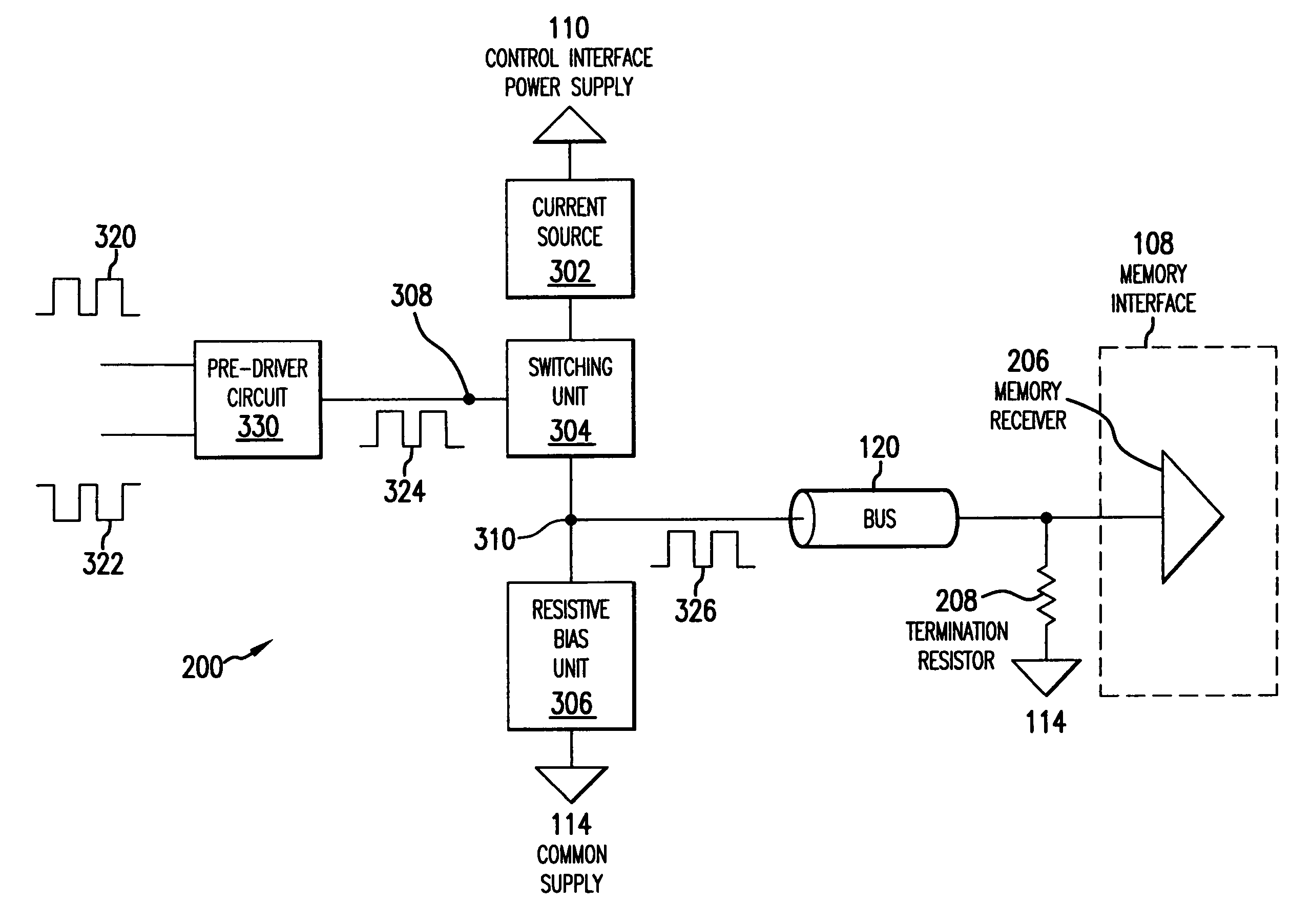

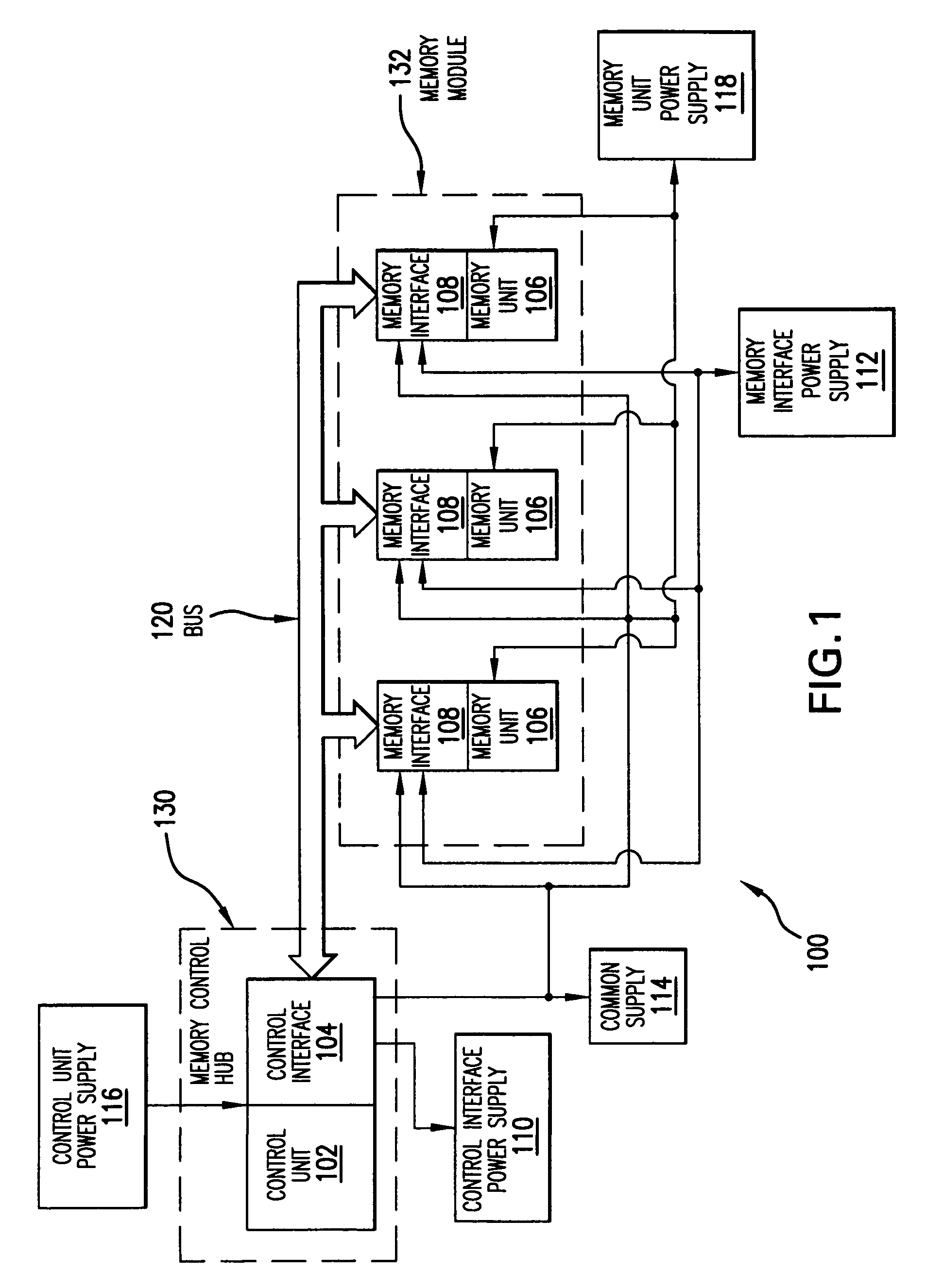

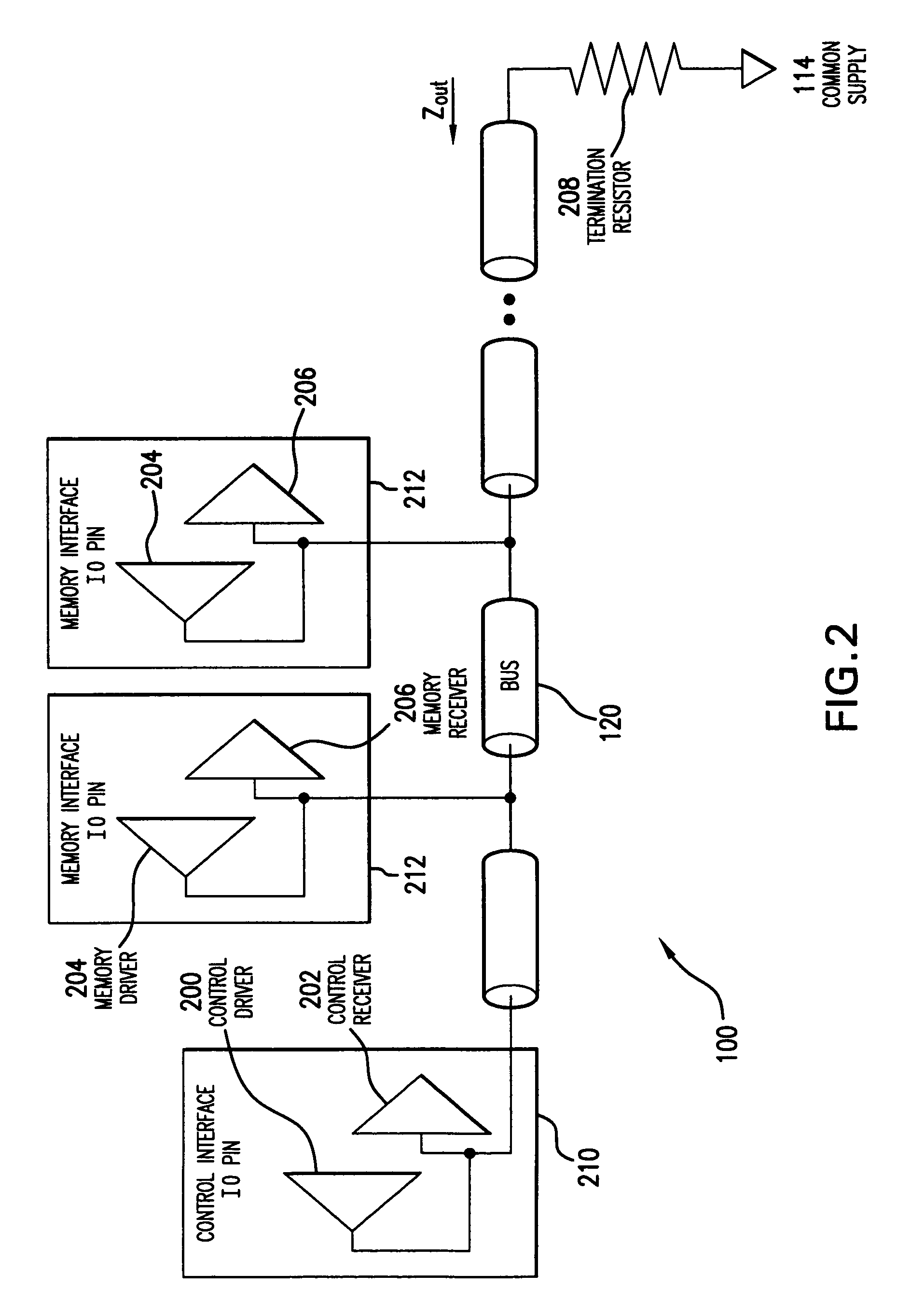

Single-ended memory interface system

InactiveUS7010637B2Reliability increasing modificationsLogic circuits coupling/interface using field-effect transistorsMultidrop busMemory interface

A system for interfacing over a multi-drop bus comprising a single-ended control interface coupled with a first power supply, and a common supply and a plurality of single-ended memory interfaces coupled with a second power supply, the common supply and coupled directly to the control interface. The control interface is configured to drive a control output signal and the memory interface is configured to drive a memory output signal. The output signals are driven to the common supply to transfer a logic low.

Owner:INTEL CORP

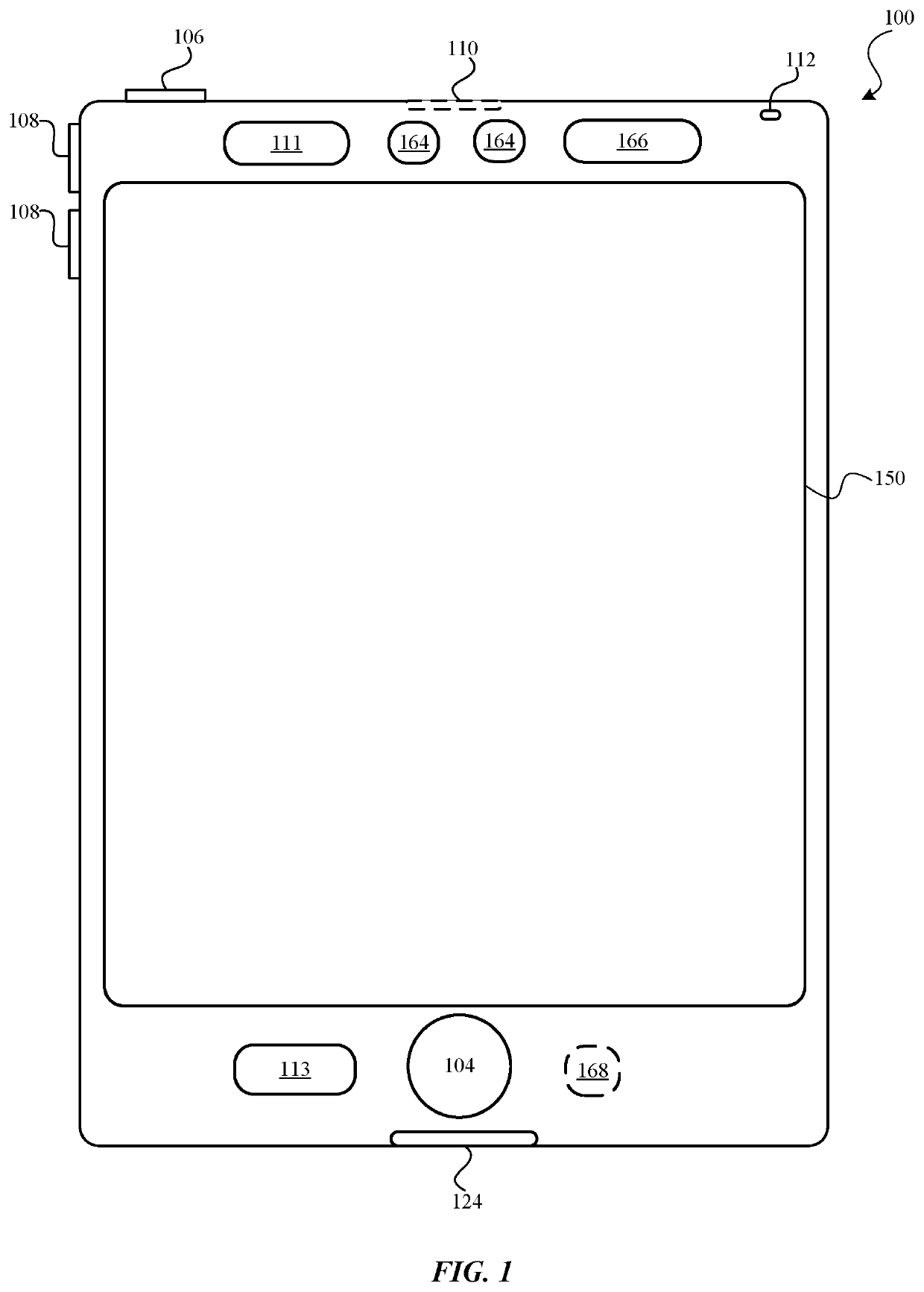

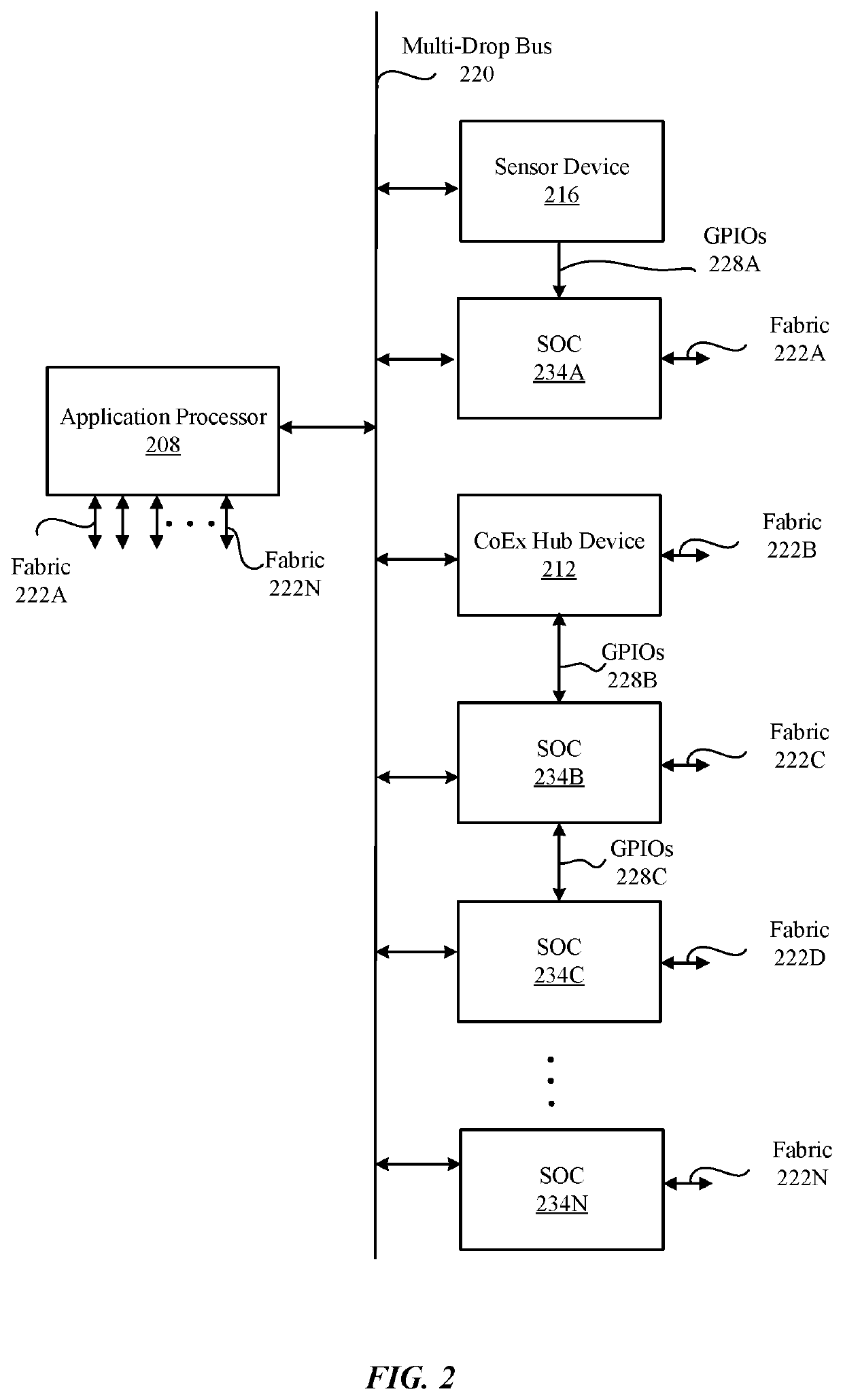

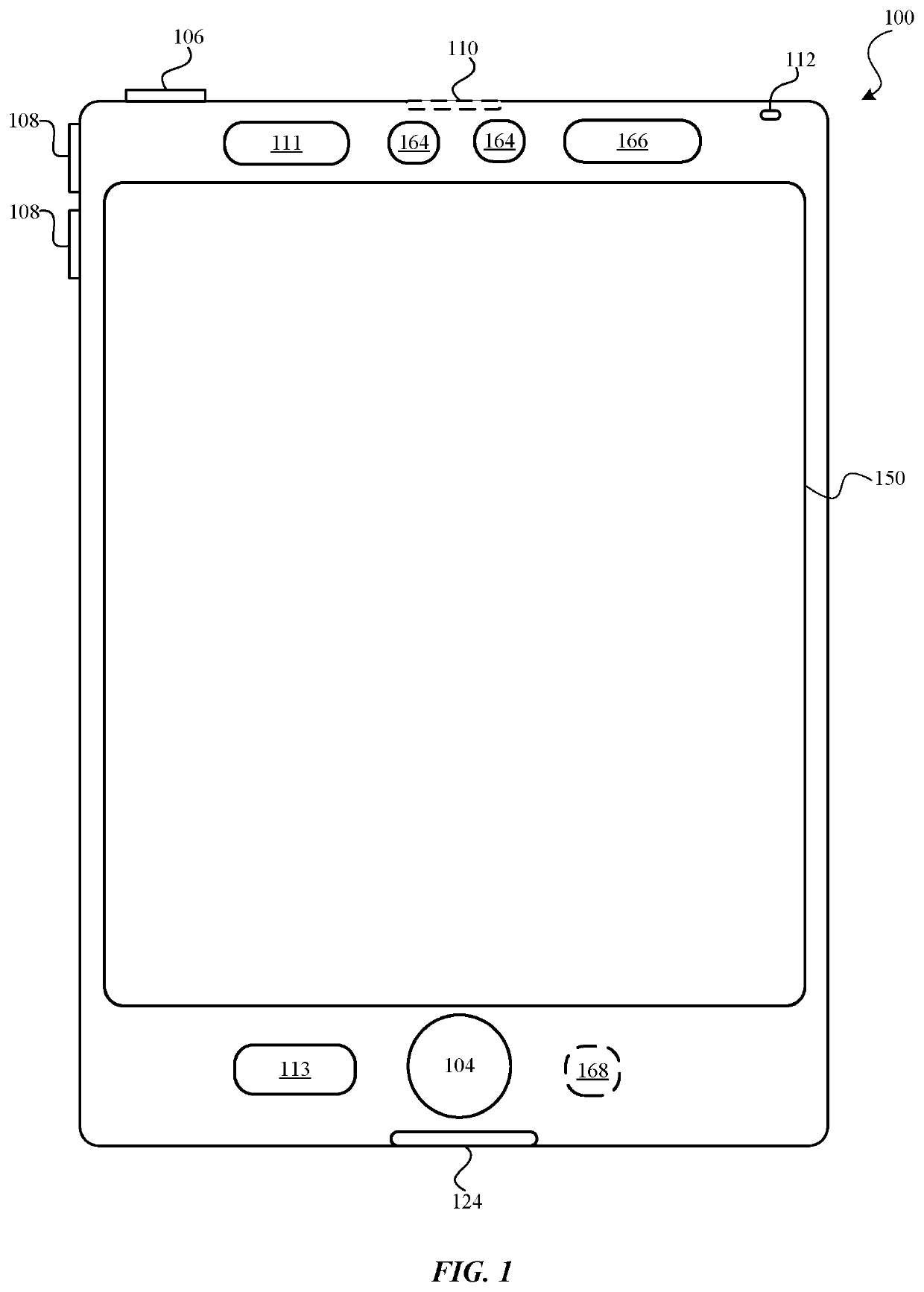

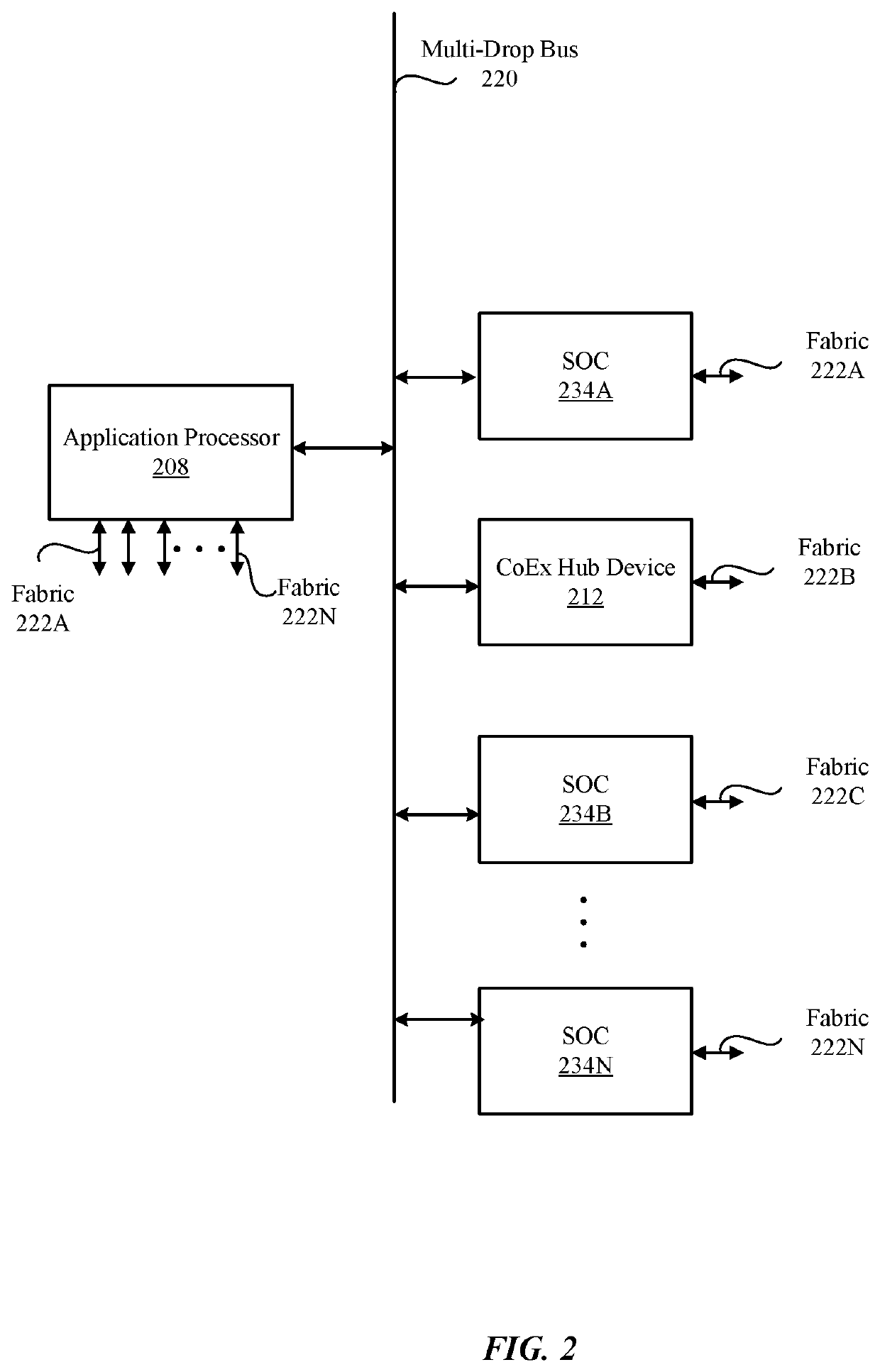

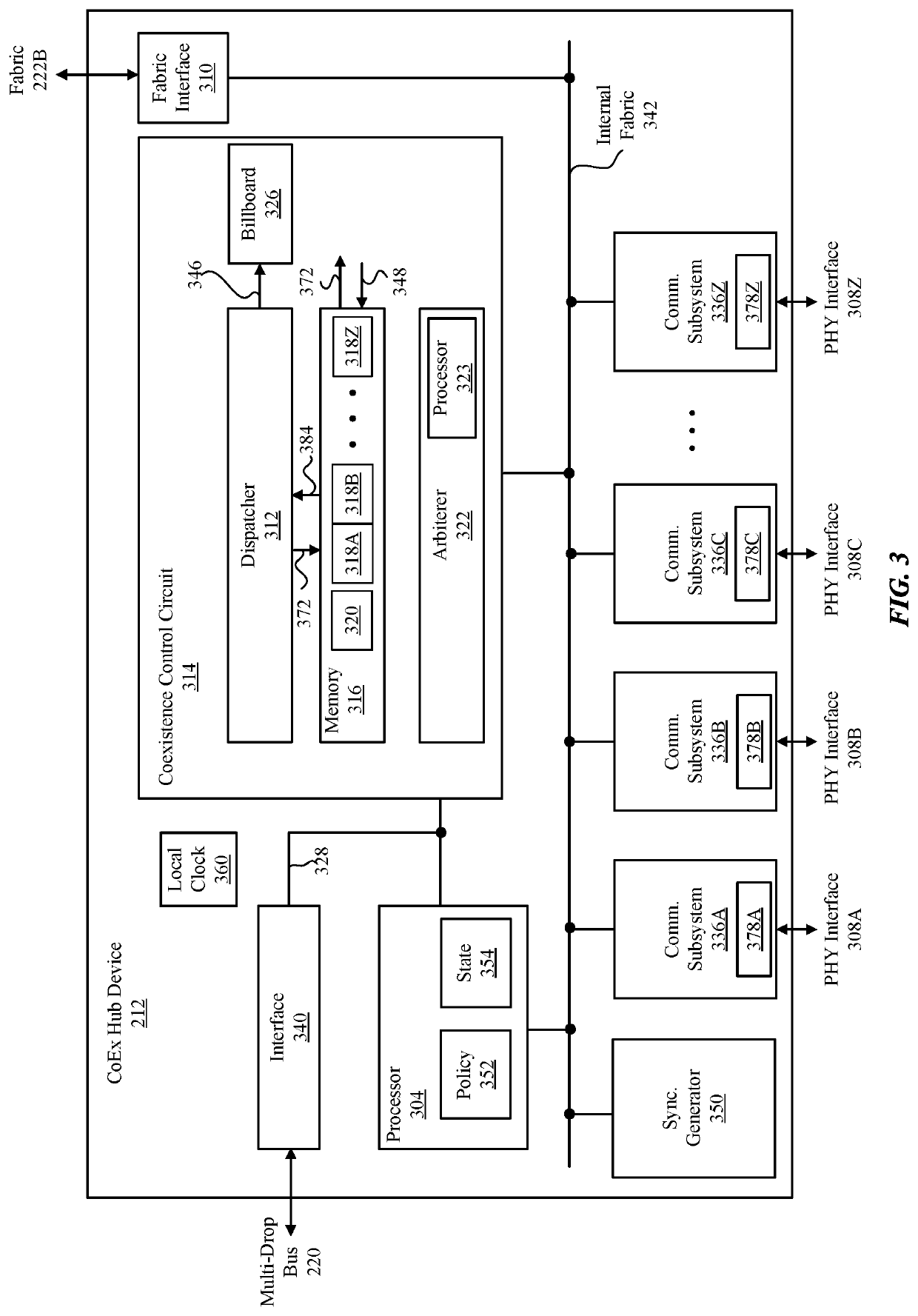

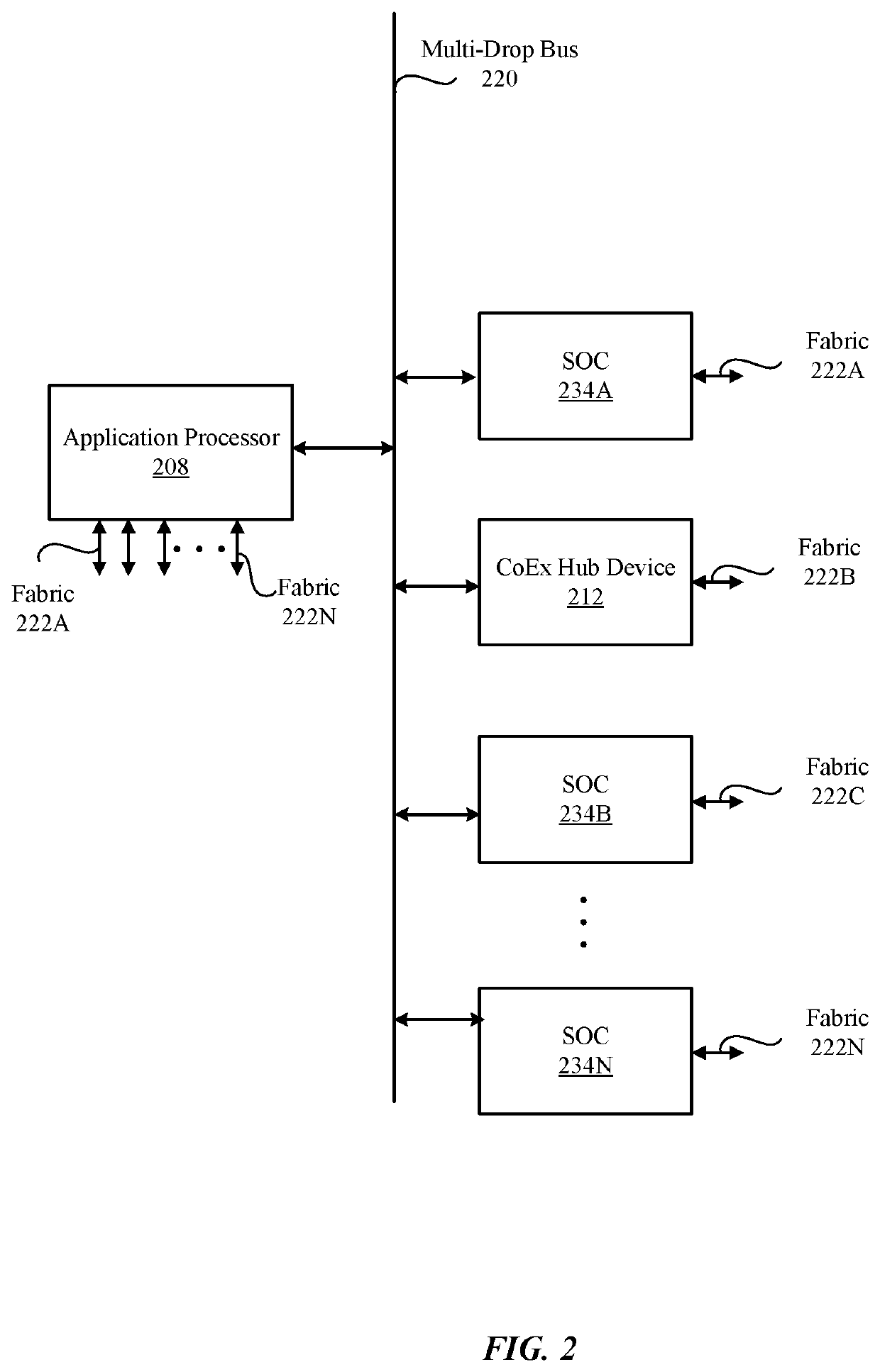

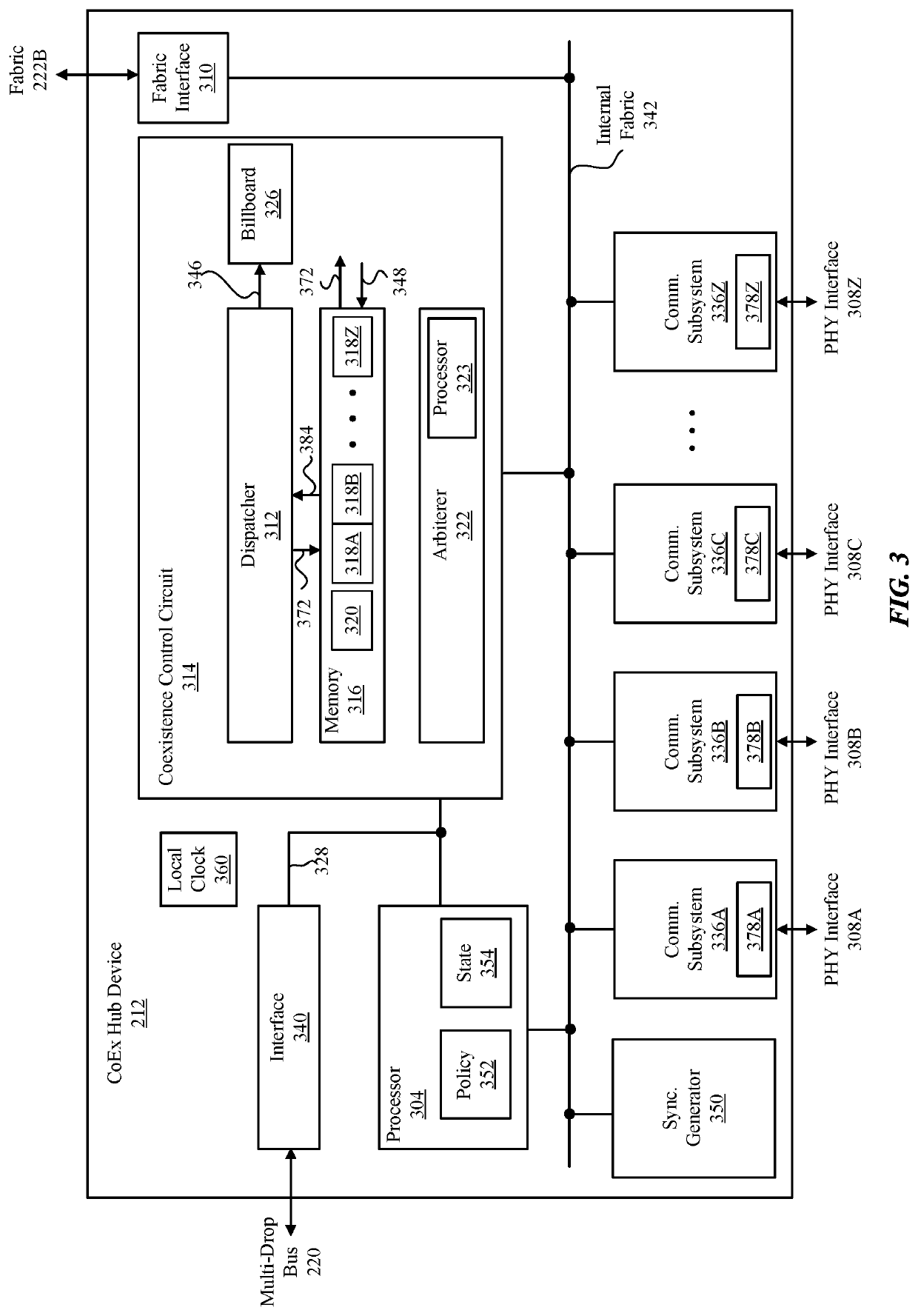

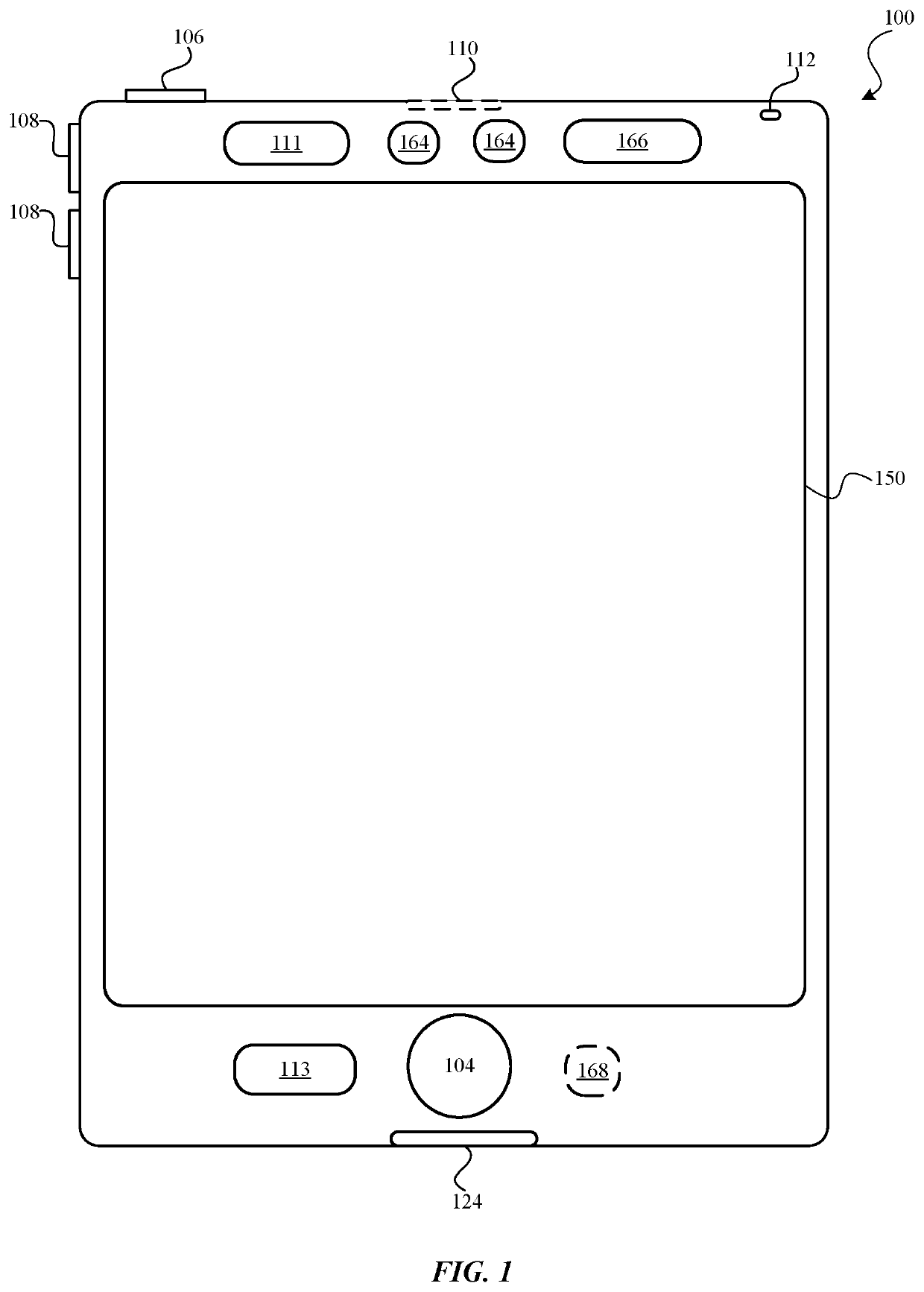

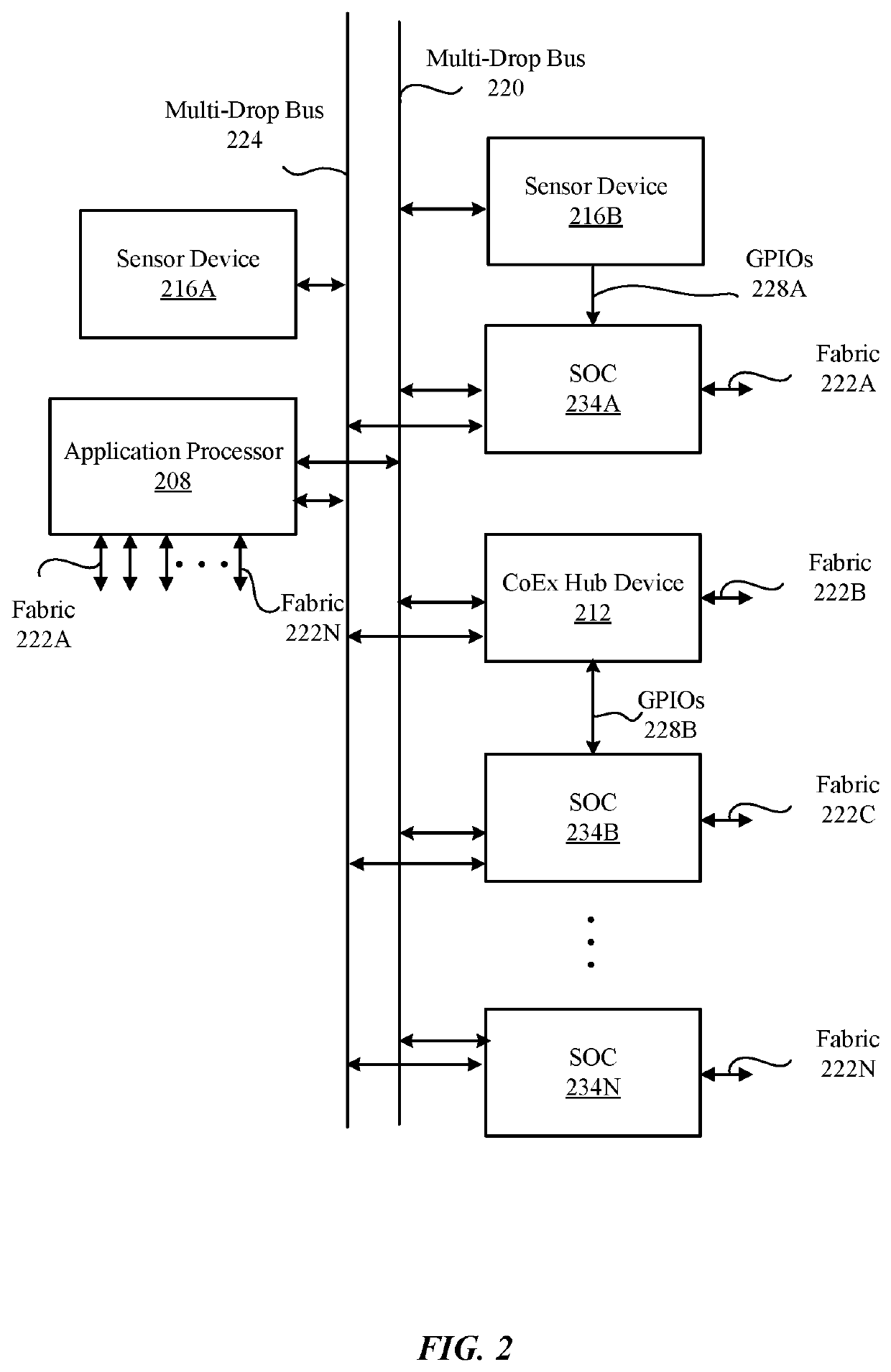

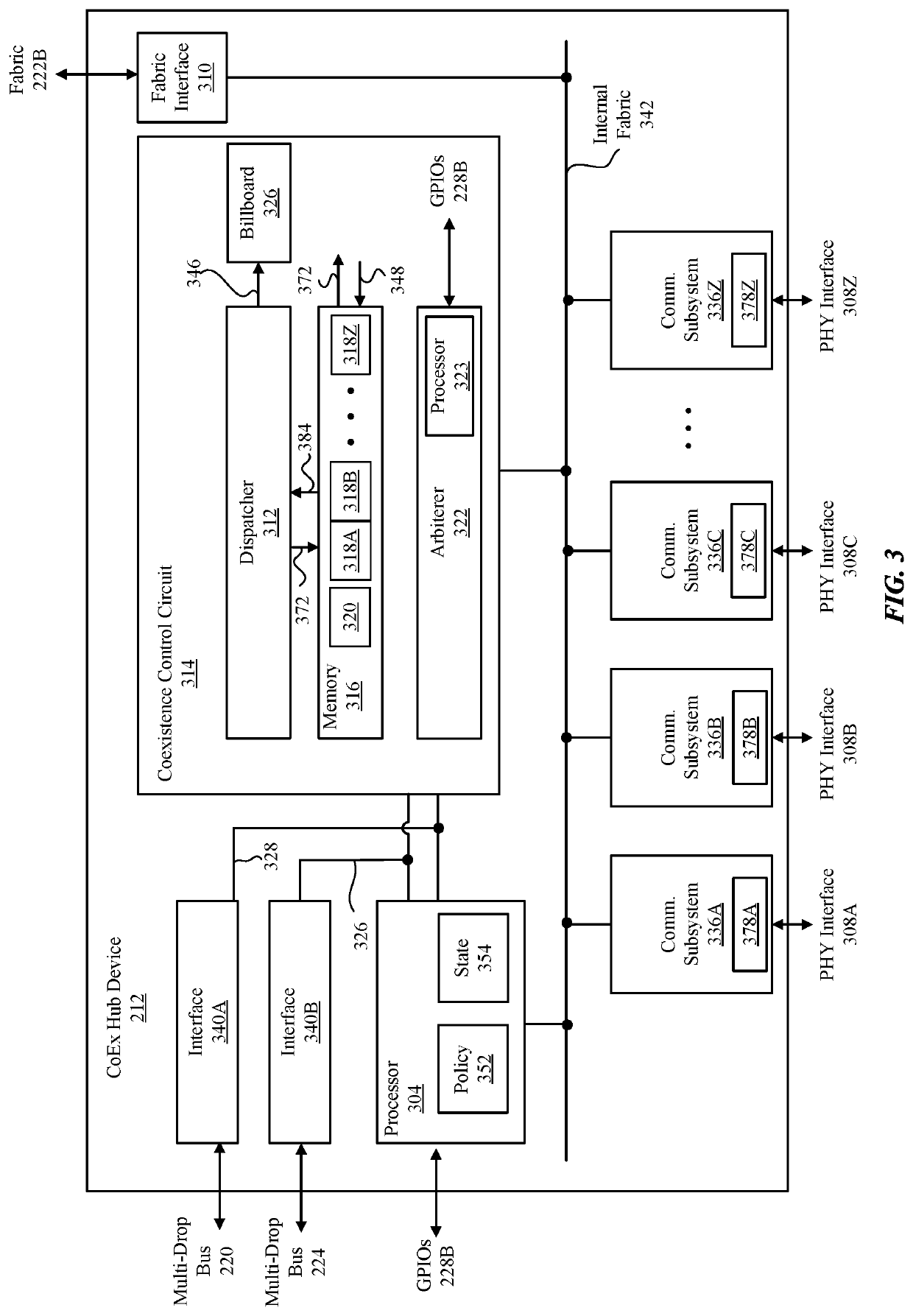

System for link management between multiple communication chips

Embodiments relate to an integrated circuit of an electronic device that coordinates activities with another integrated circuit of the electronic device. The integrated circuit includes an interface circuit and a processor circuit. The interface circuit communicates over a multi-drop bus connected to multiple electronic components. The processor circuit receives an authorization request from the integrated circuit via the interface circuit and the multi-drop bus. The received authorization request relates to authorization to perform an activity on the other integrated circuit. In response to receiving the authorization request, the processor circuit determines whether the other integrated circuit is authorized to execute the activity. In response to determining that the other integrated circuit is authorized to execute the activity, the processor circuit sends, to the other integrated circuit over a configurable direct connection, an authorization signal authorizing the other integrated circuit to execute the activity.

Owner:APPLE INC

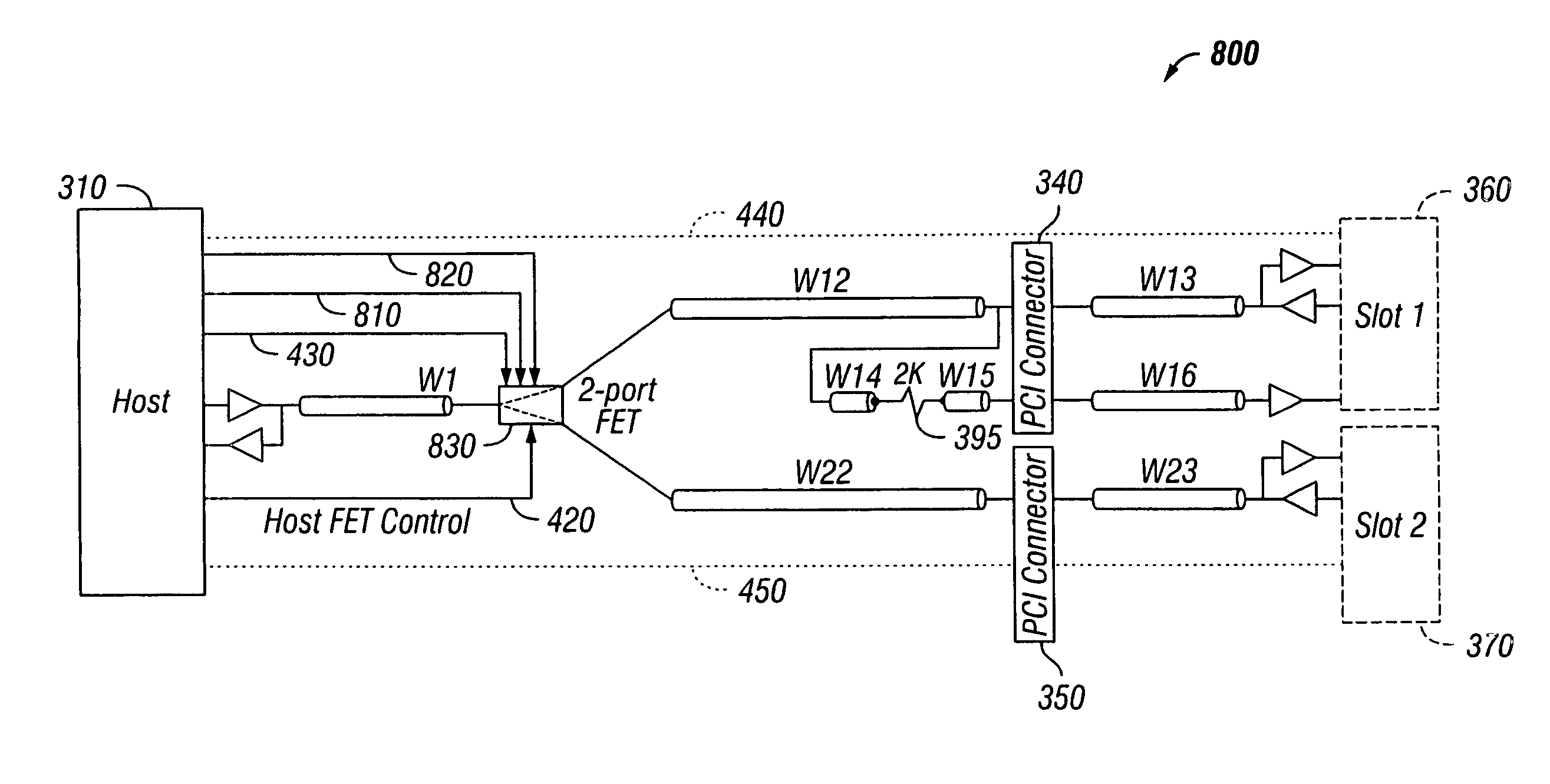

Point-to-point electrical loading for a multi-drop bus

InactiveUS7099966B2Component plug-in assemblagesElectric digital data processingElectricityMultidrop bus

A switching technique allows multiple interconnect bus devices to be connected to a single bus segment, even if the interconnect bus protocol only allows a one of the interconnect devices to be connected at any time. Each of the interconnect devices is connected to the interconnect bus segment with a switch, such that the interconnect device is electrically isolated from the interconnect bus segment when the switch is open. An interconnect sourcing agent connected to the interconnect bus segment controls the switches, closing the switch for one of the interconnect devices when a transaction is destined for that interconnect device, opening all of the other switches so that only one device is connected to the bus at any time.

Owner:HEWLETT PACKARD DEV CO LP

Signaling of time for communication between integrated circuits using multi-drop bus

Embodiments relate to including information in a data packet transmitted by a transmitting integrated circuit (e.g., SOC) to account for a time delay associated with an unsuccessful arbitration attempt to send the data packet over a multi-drop bus. The unsuccessful arbitration attempt by the integrated circuit may delay the transmission of the data packet until the multi-drop bus becomes available for the integrated circuit to send the data packet. The data packet includes a data field to include time delay information caused by the unsuccessful arbitration attempt. A receiving integrated circuit may determine the time that the data packet would have been sent out from the transmitting integrated circuit absent the unsuccessful arbitration attempt based on the delay information. Embodiments also relate to a synchronization generator circuit in an integrated circuit that generates timing signals indicating times at which periodic events occur at another integrated circuit.

Owner:APPLE INC

Signaling of time for communication between integrated circuits using multi-drop bus

Embodiments relate to including information in a data packet transmitted by a transmitting integrated circuit (e.g., SOC) to account for a time delay associated with an unsuccessful arbitration attempt to send the data packet over a multi-drop bus. The unsuccessful arbitration attempt by the integrated circuit may delay the transmission of the data packet until the multi-drop bus becomes available for the integrated circuit to send the data packet. The data packet includes a data field to include time delay information caused by the unsuccessful arbitration attempt. A receiving integrated circuit may determine the time that the data packet would have been sent out from the transmitting integrated circuit absent the unsuccessful arbitration attempt based on the delay information. Embodiments also relate to a synchronization generator circuit in an integrated circuit that generates timing signals indicating times at which periodic events occur at another integrated circuit.

Owner:APPLE INC

Capacitive multidrop bus compensation

InactiveUS20070288669A1Improve signal integrityIncrease volumeMultiple-port networksDigital storageEngineeringElectrical impedance

The signal integrity of a high speed heavily loaded multidrop memory bus is often degraded due the numerous impedance mismatches. The impedance mismatches causes the bus to exhibit a nonlinear frequency response, which diminishes signal integrity and limits the bandwidth of the bus. A compensating element, such as a capacitor which ties the bus to a reference plane (e.g., a ground potential), or an inductor wired in series with the bus, is located approximately midway between the memory controller and the memory slots. The use of the compensating element equalizes signal amplitudes and minimizes phase errors of signals in an interested frequency range and diminishes the amplitudes of high frequency signals which exhibit high degrees of phase error. The resulting bus structure has increased desirable harmonic content with low phase error, thereby permitting the bus to exhibit better rise time performance and permitting a higher data transfer rate.

Owner:ROUND ROCK RES LLC

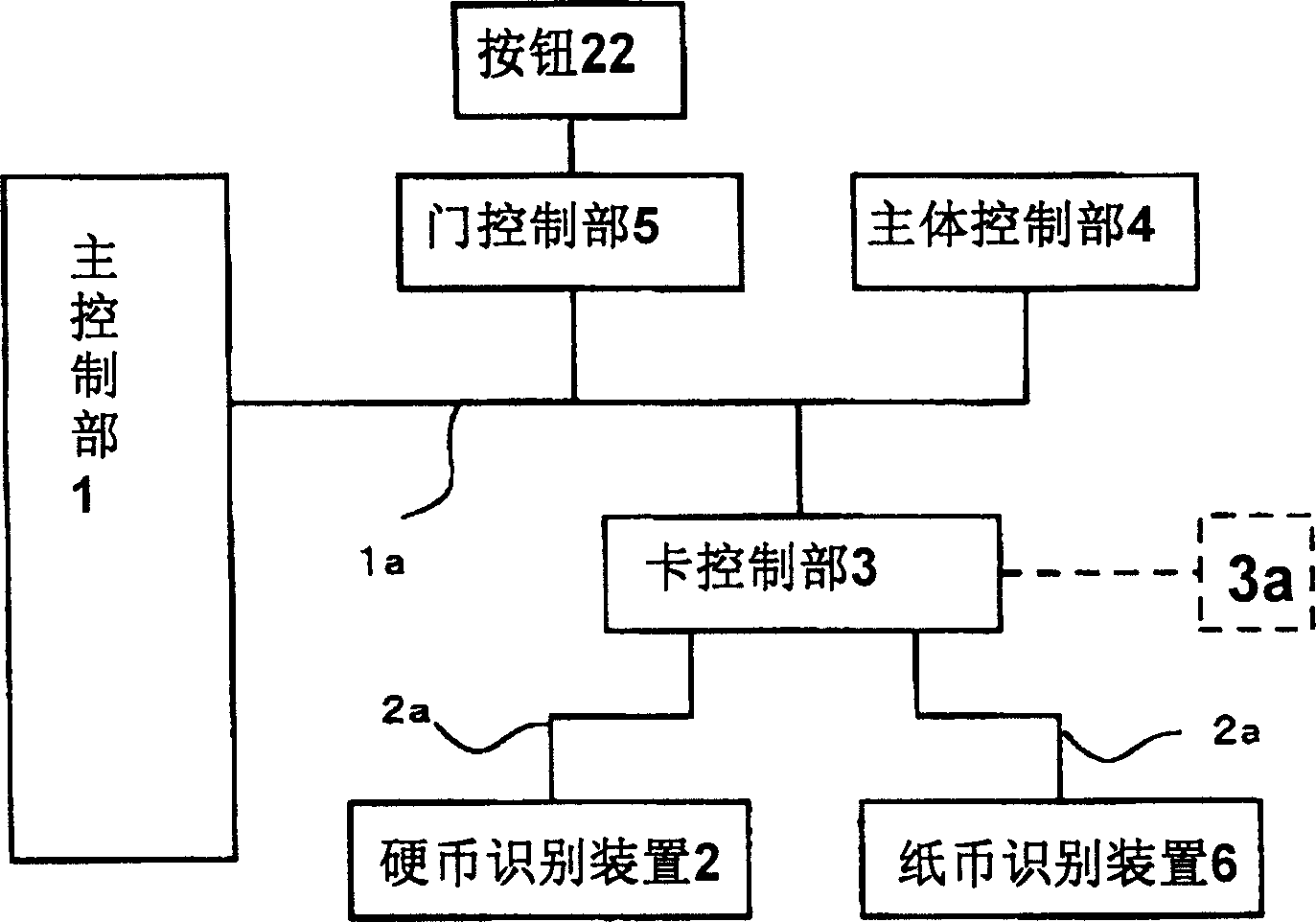

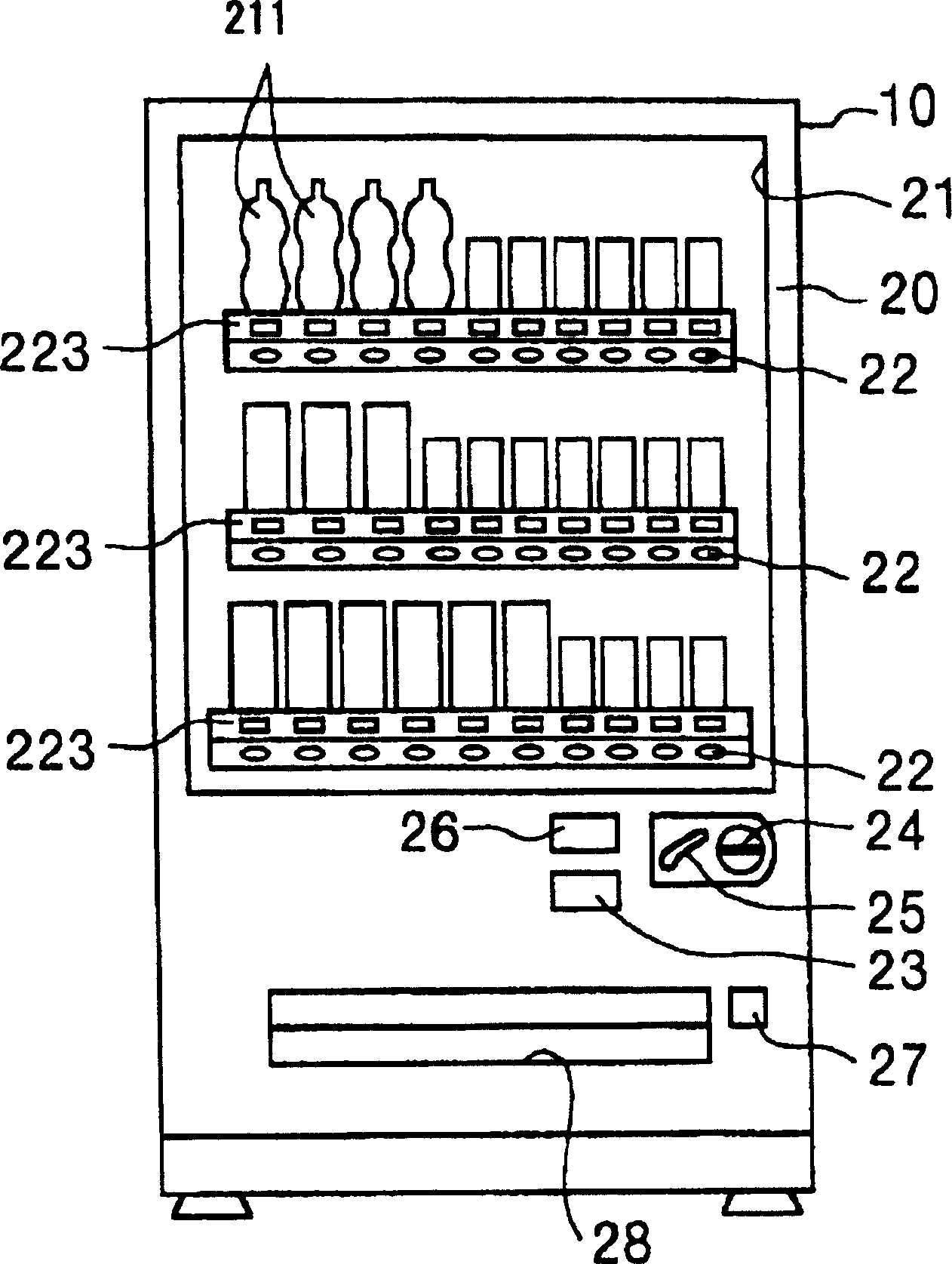

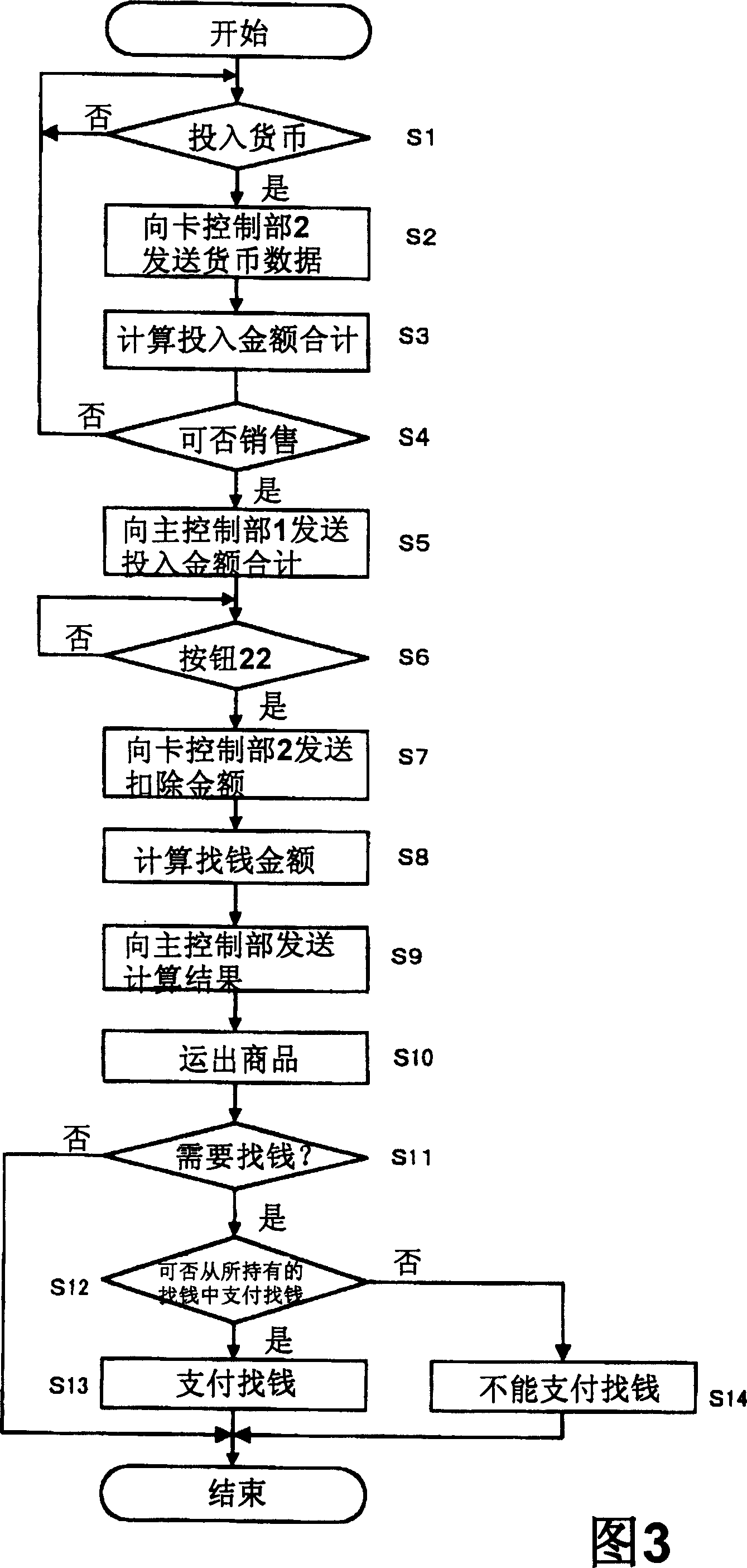

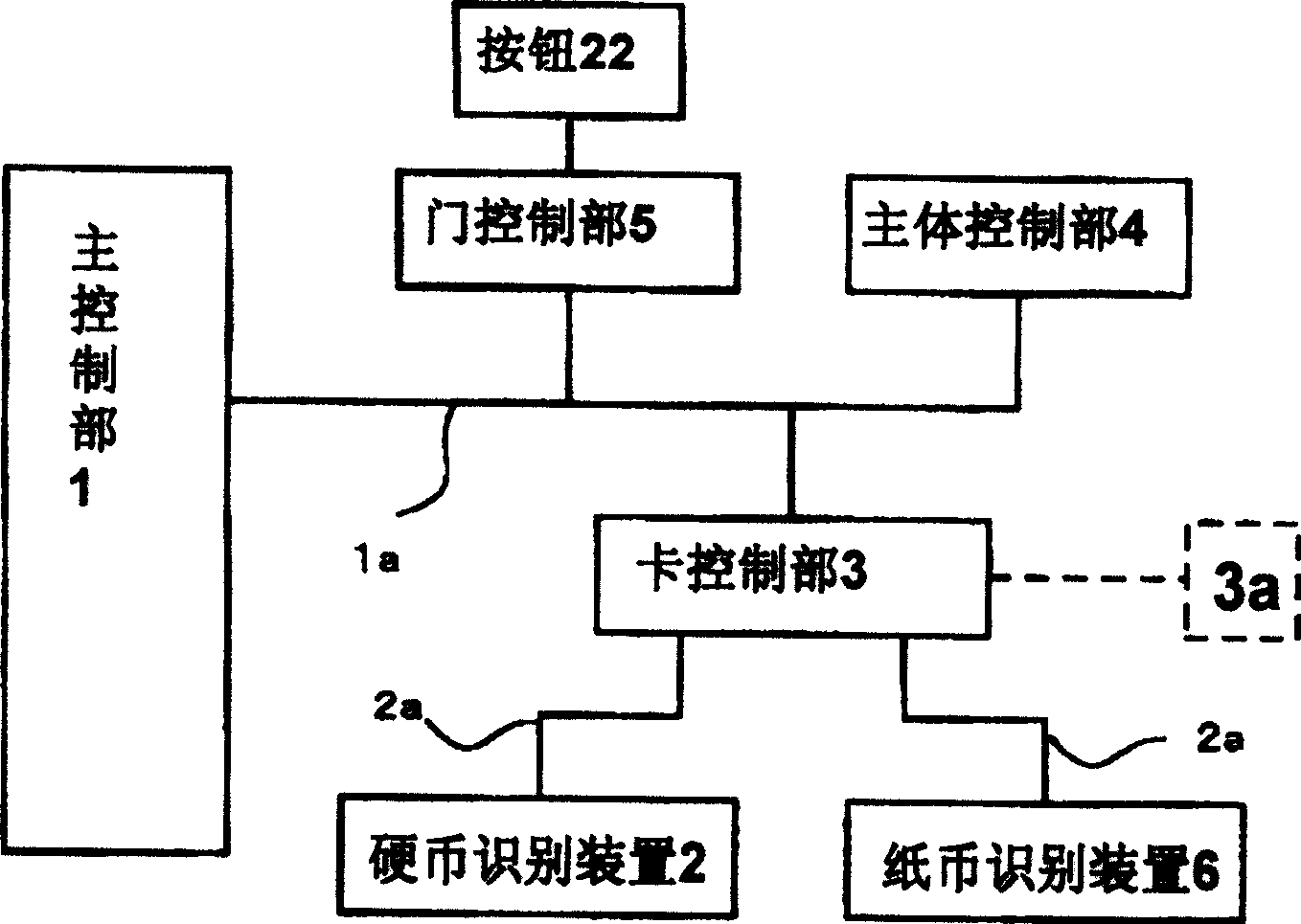

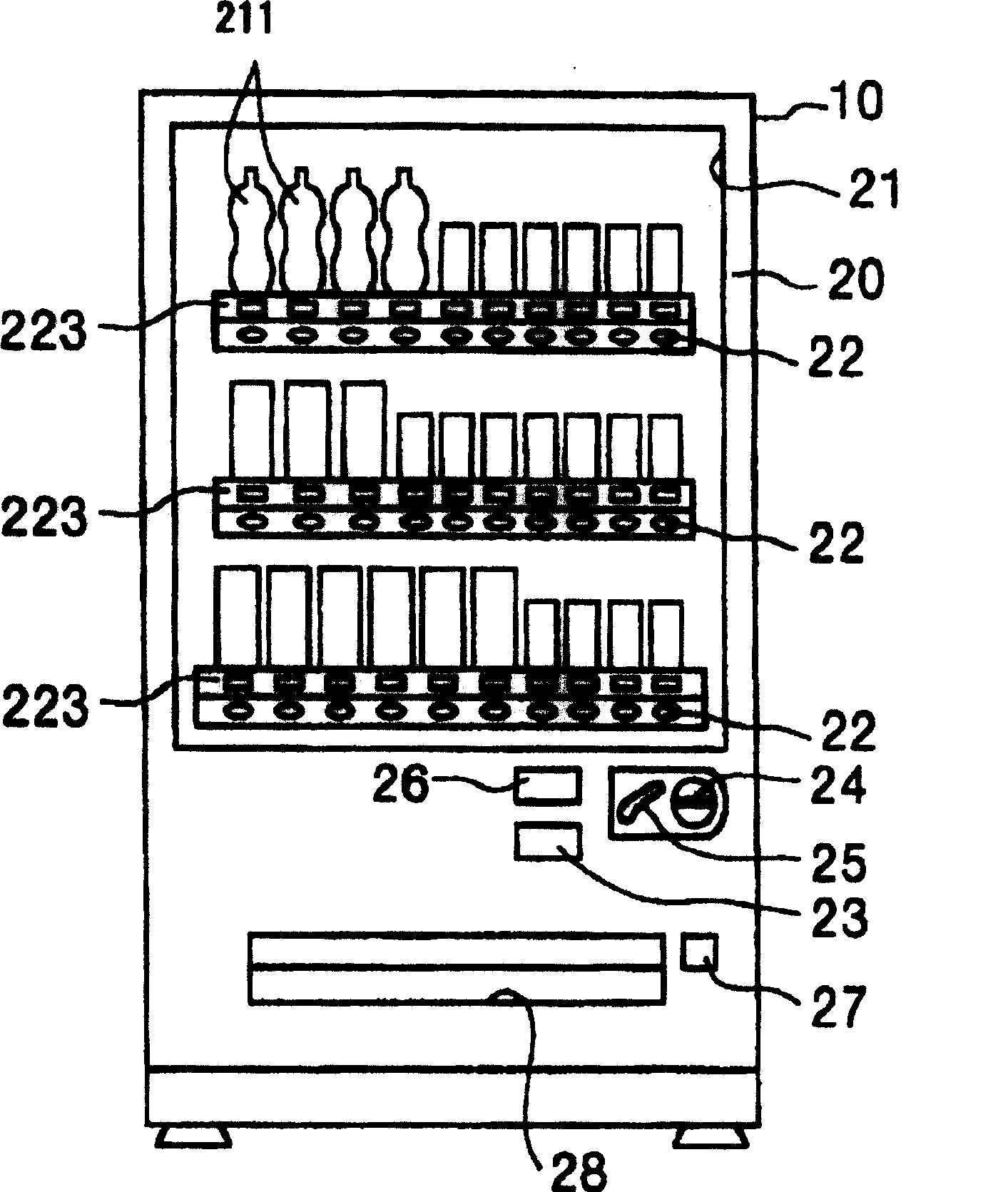

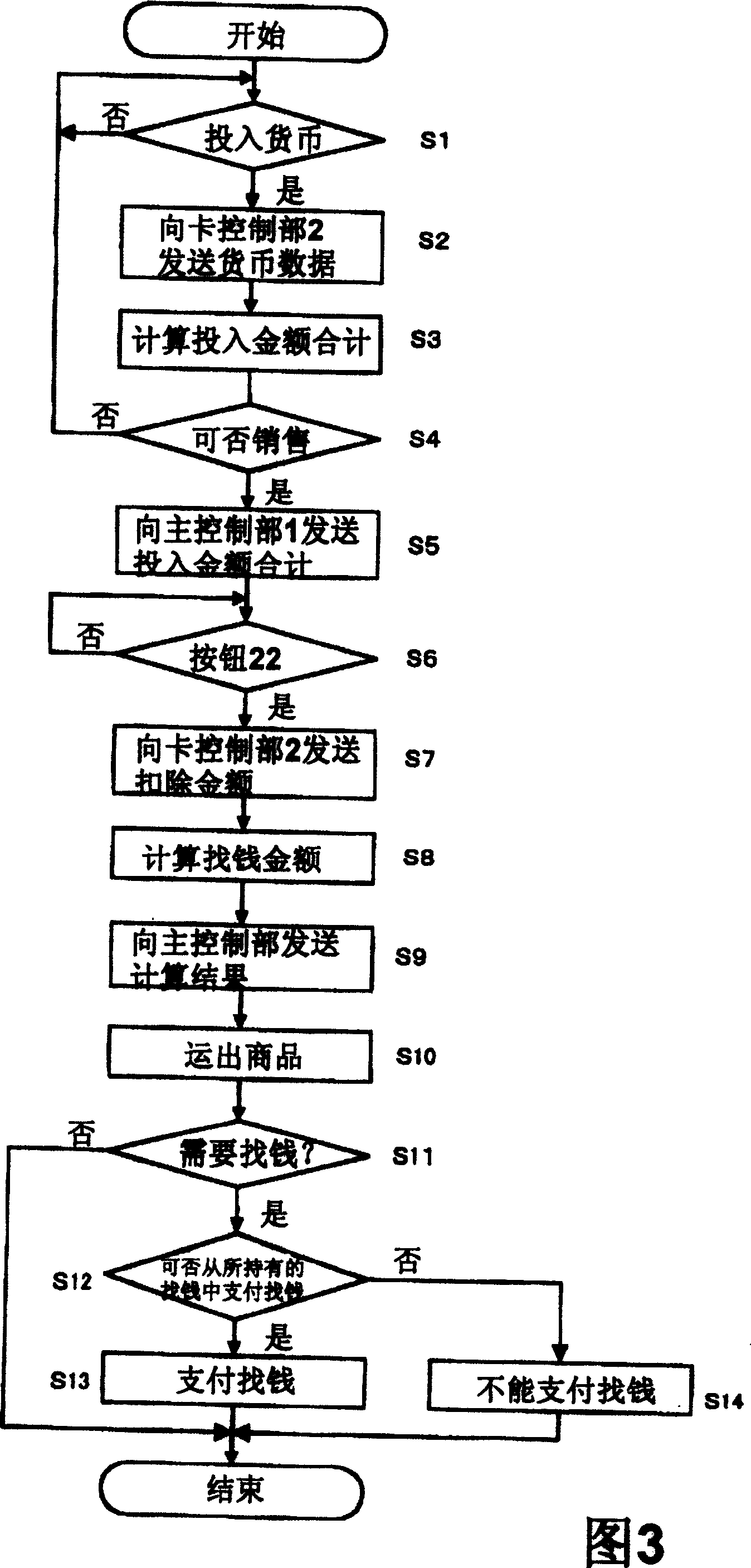

Automat and card controlling part used in automat

The purpose of the present invention is to provide a kind of automatic vending machine and the automatic vending machine in which the main control part of the automatic vending machine and the coin recognition device can easily communicate even under the situation that the communication protocol (communication standard) is different. The card control section used. In an automatic vending machine with a main control unit that controls the entire vending machine, and a currency identification device with a multi-point bus specification, there is a card control unit, and the currency identification device with a multi-point bus specification is connected to the main control unit through the card control unit. According to the communication standard of the part, as a communication from the card control part, a signal is sent to the main control part to enable communication.

Owner:FUJI ELECTRIC CO LTD

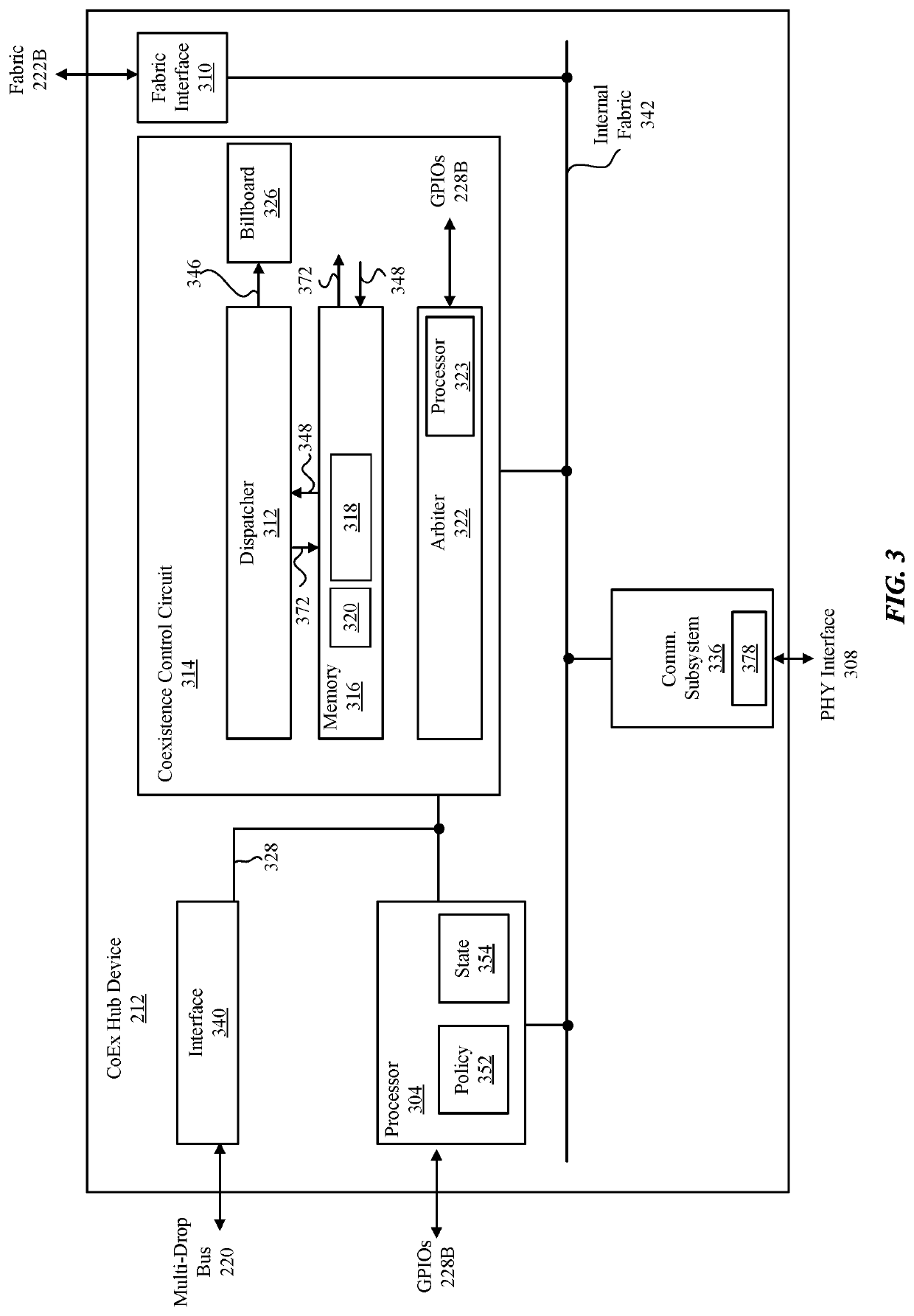

Coordinating operations of multiple communication chips via local hub device

ActiveUS11106612B2Digital computer detailsEnergy efficient computingCommunications systemMultidrop bus

Owner:APPLE INC

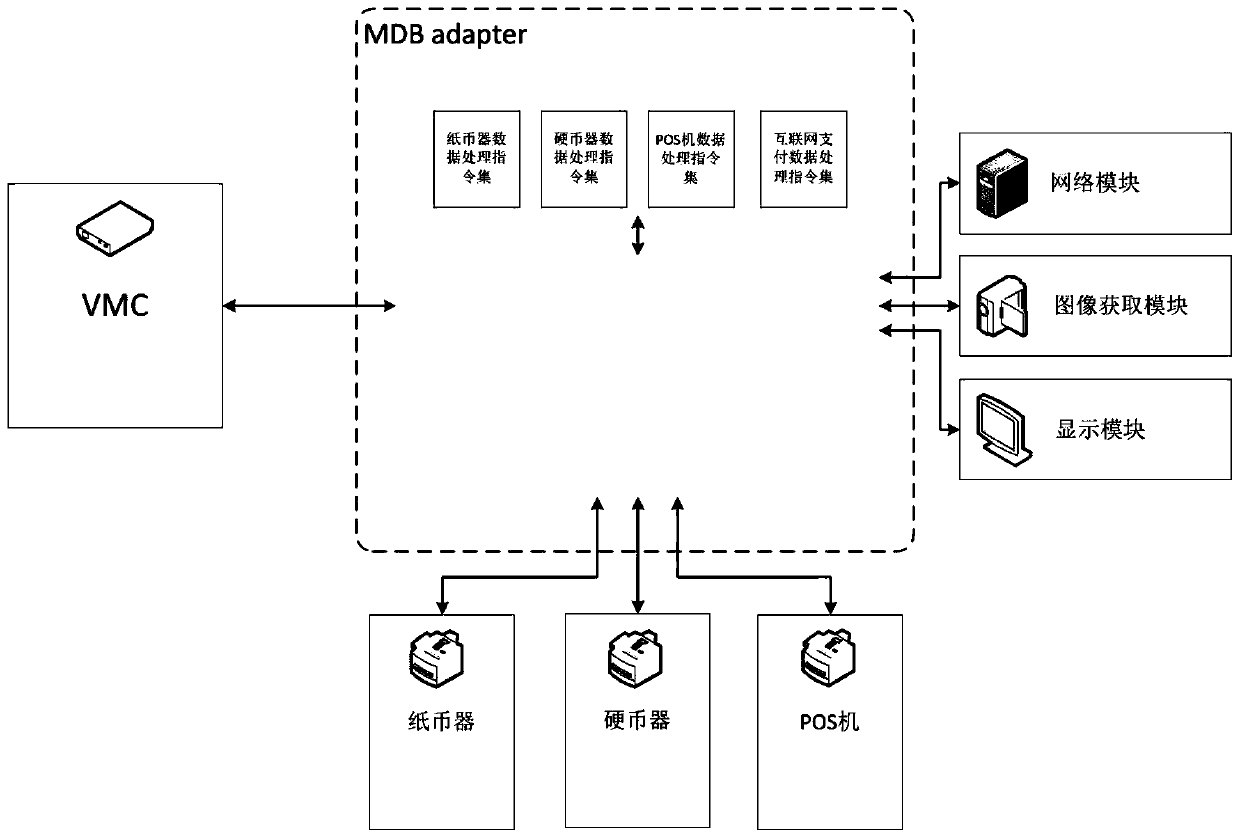

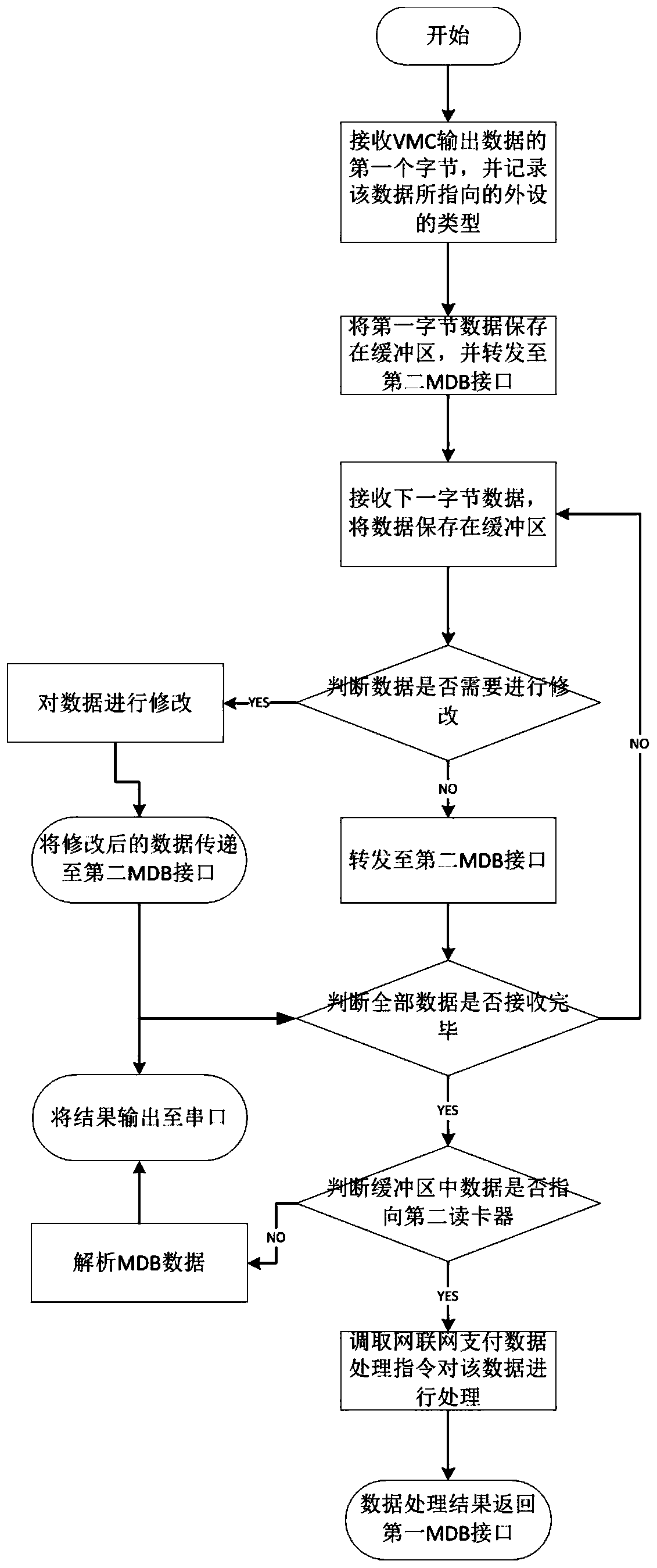

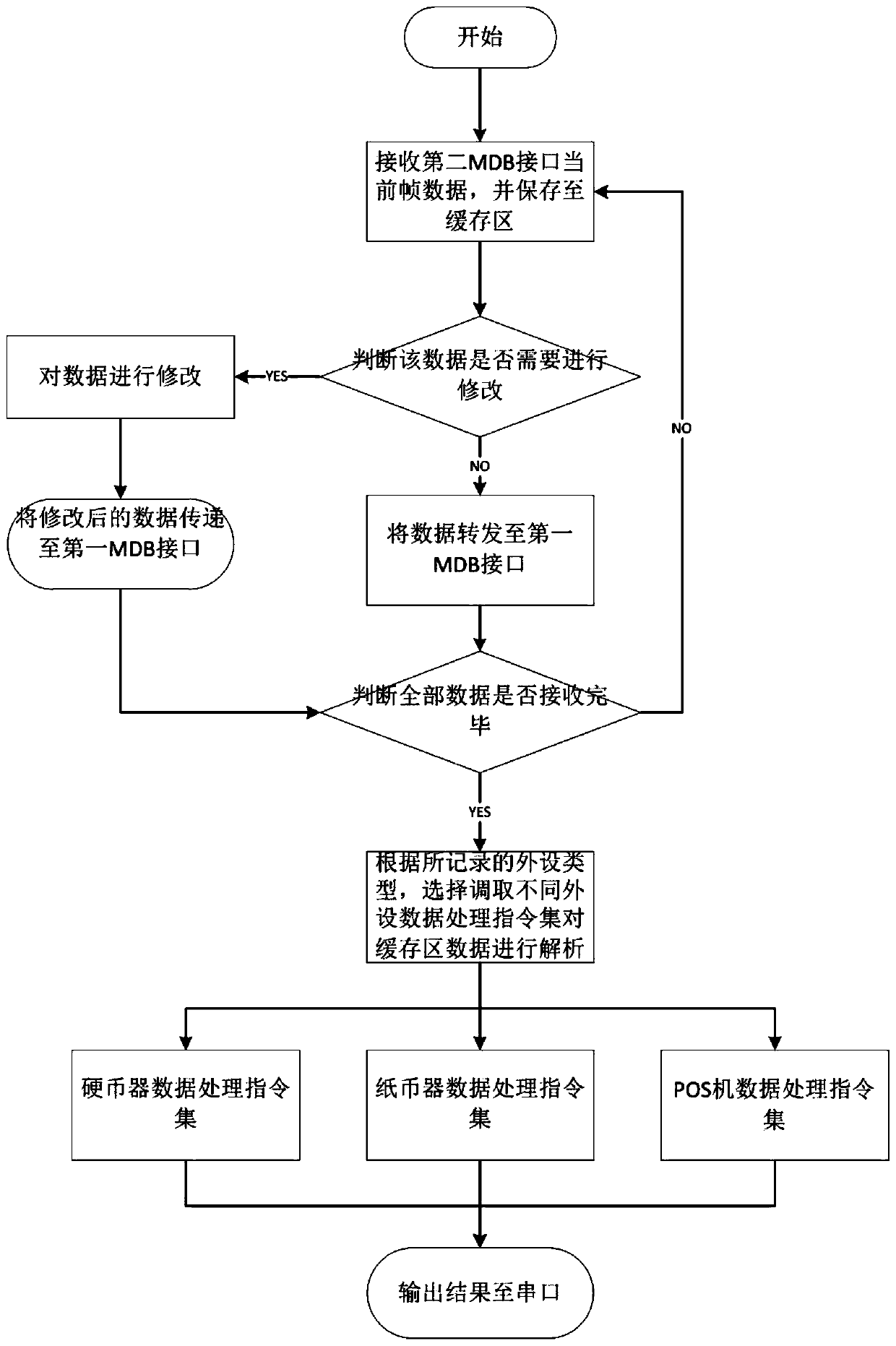

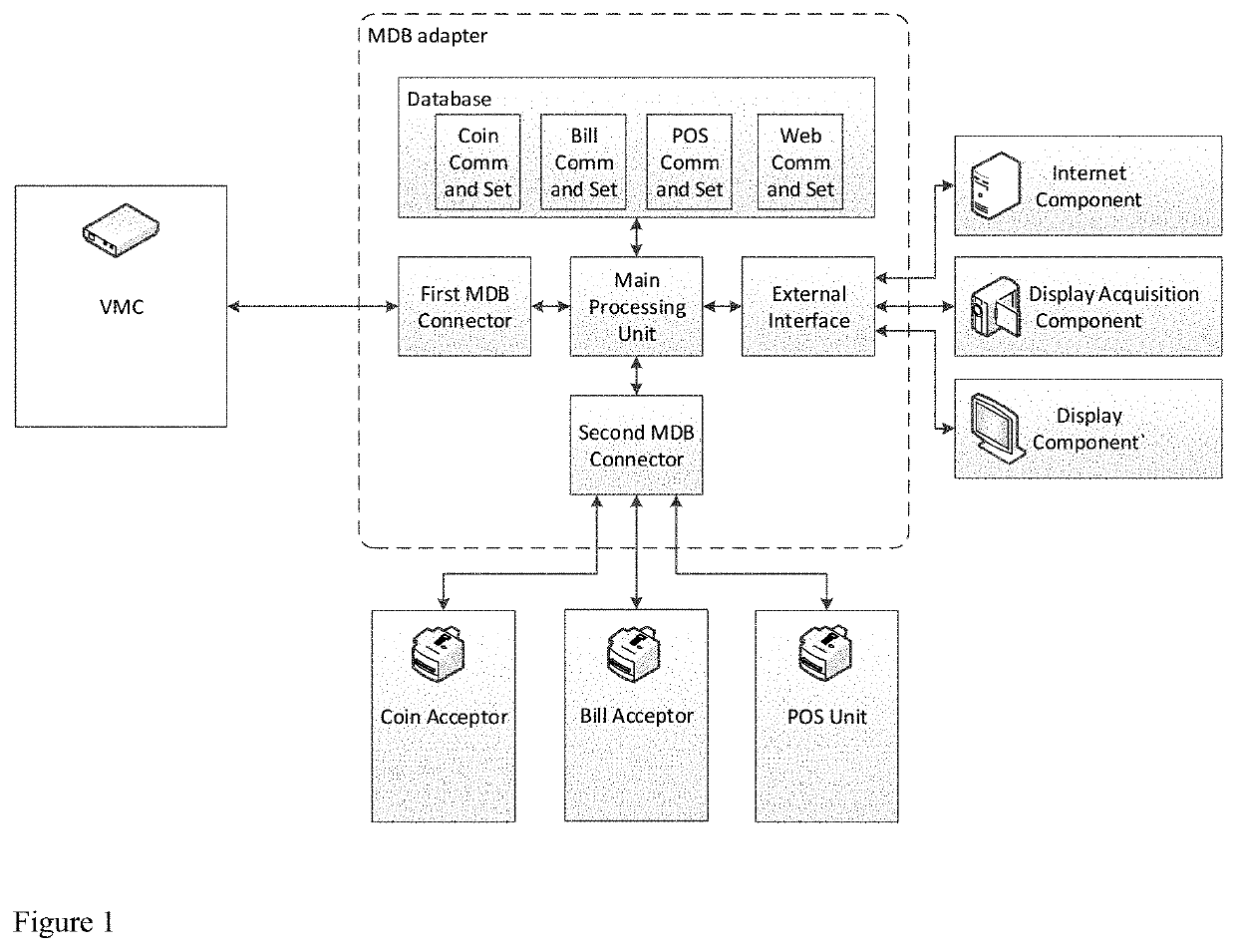

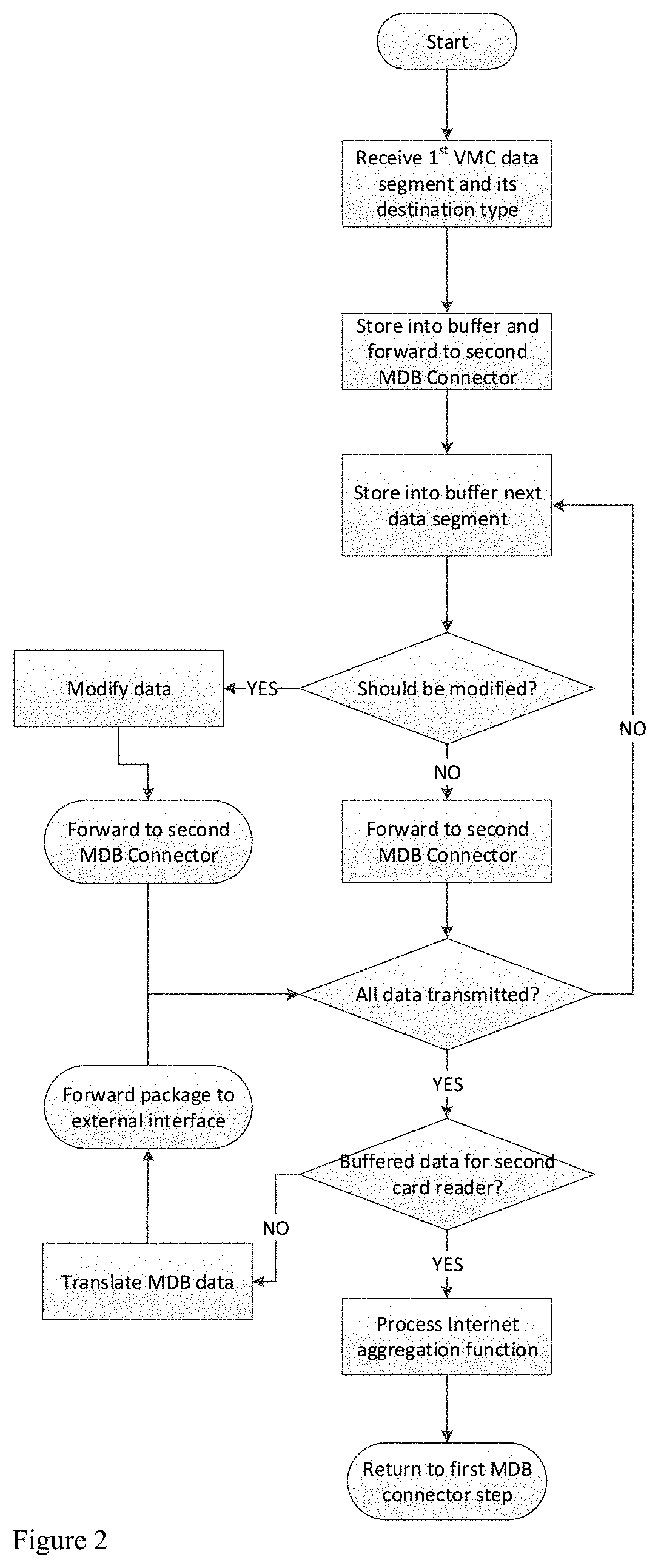

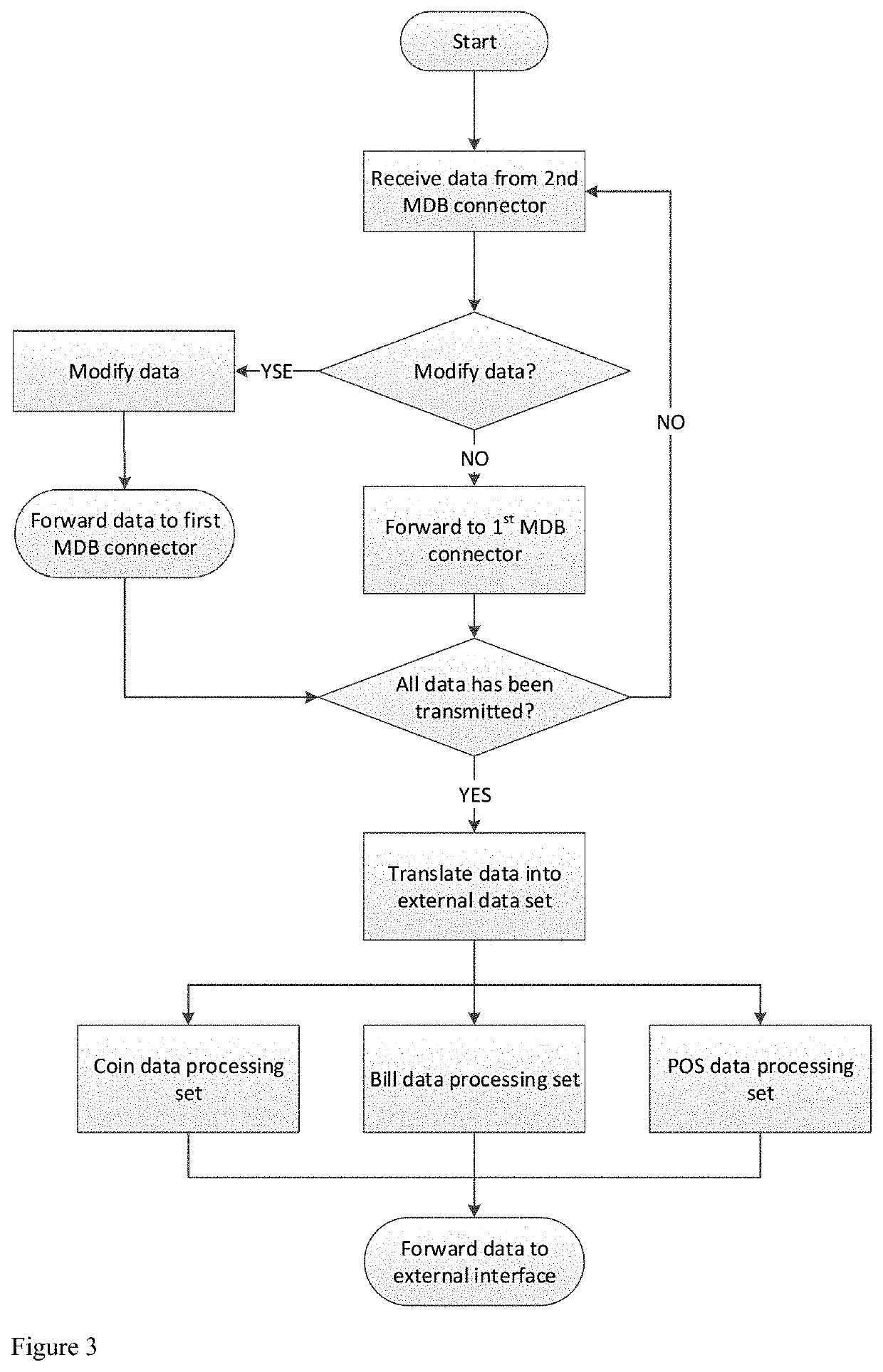

System and method for mdb data processing of vending machines

ActiveCN111373427ACoin-freed apparatus detailsBuying/selling/leasing transactionsMultidrop busControl system

The present disclosure relates to the field of vending machine technology. In particular, it involves a control system and control method implementing data processing under multidrop bus (MDB) protocol.

Owner:INHAND NETWORKS INC

Directional coupling-type multi-drop bus

ActiveUS9864143B2Increase speedMaintain performanceTransmission line coupling arrangementsOptical light guidesMultidrop busComputer module

The invention relates to a directional coupling-type multi-drop bus of which the impedance is matched with the bus at the time of coupling so that the speed is increased. A directional coupler is formed when a second module provided with a second coupler end is mounted on a first module provided with a first coupler end, and as a result, the coupling impedance where the proximity effects in the coupling state of the directional coupler are reflected is matched with the impedance of the bus.

Owner:KEIO UNIV

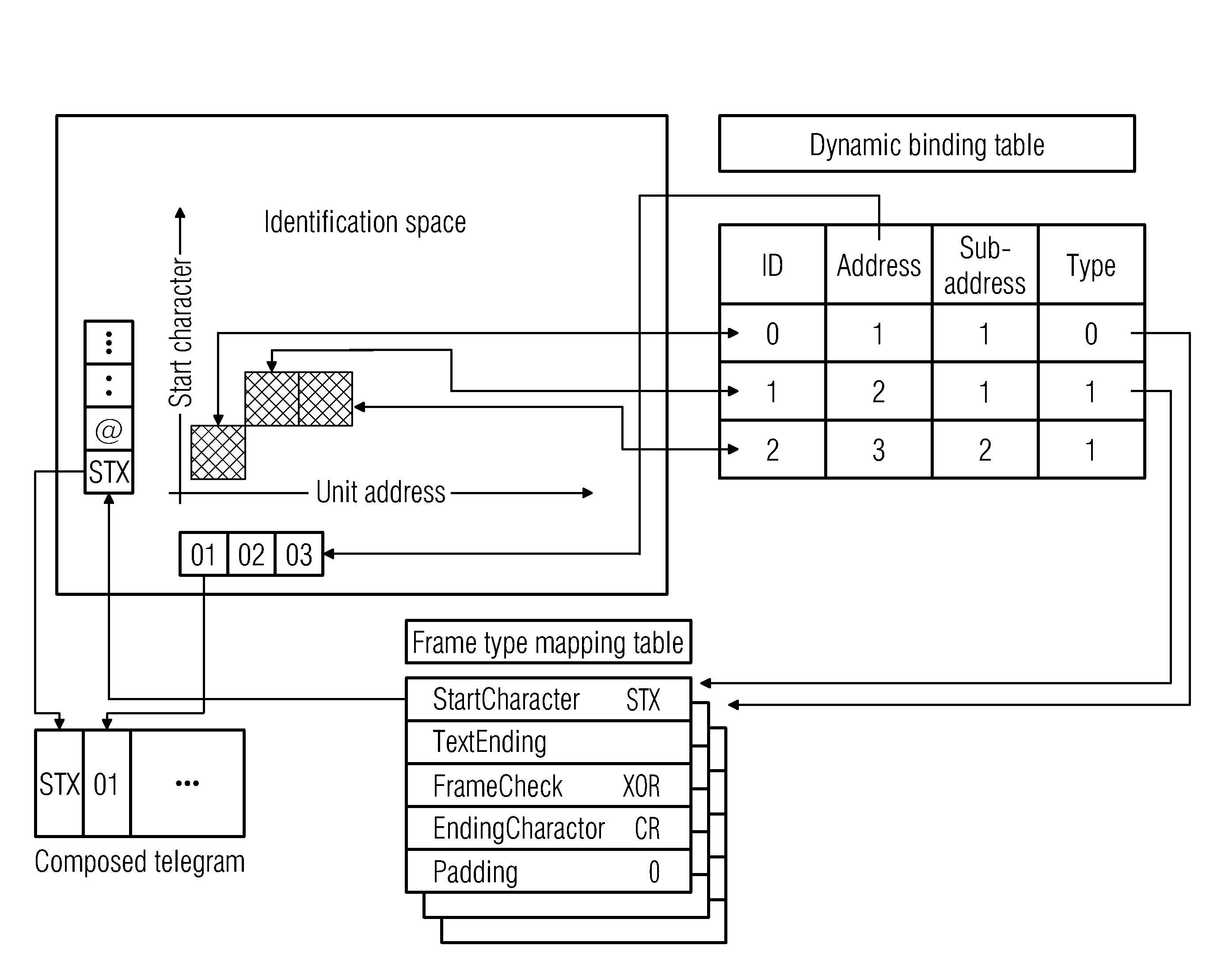

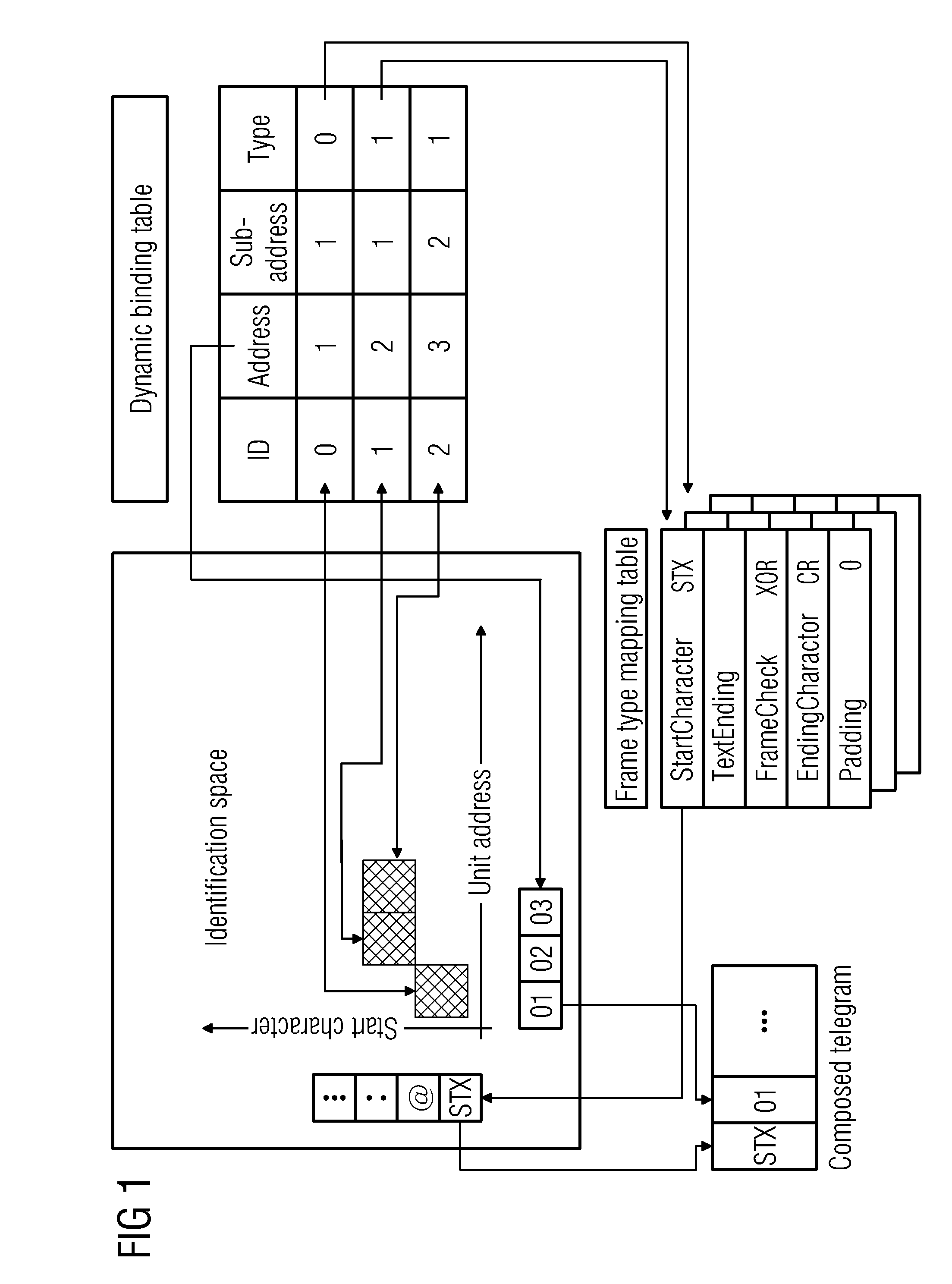

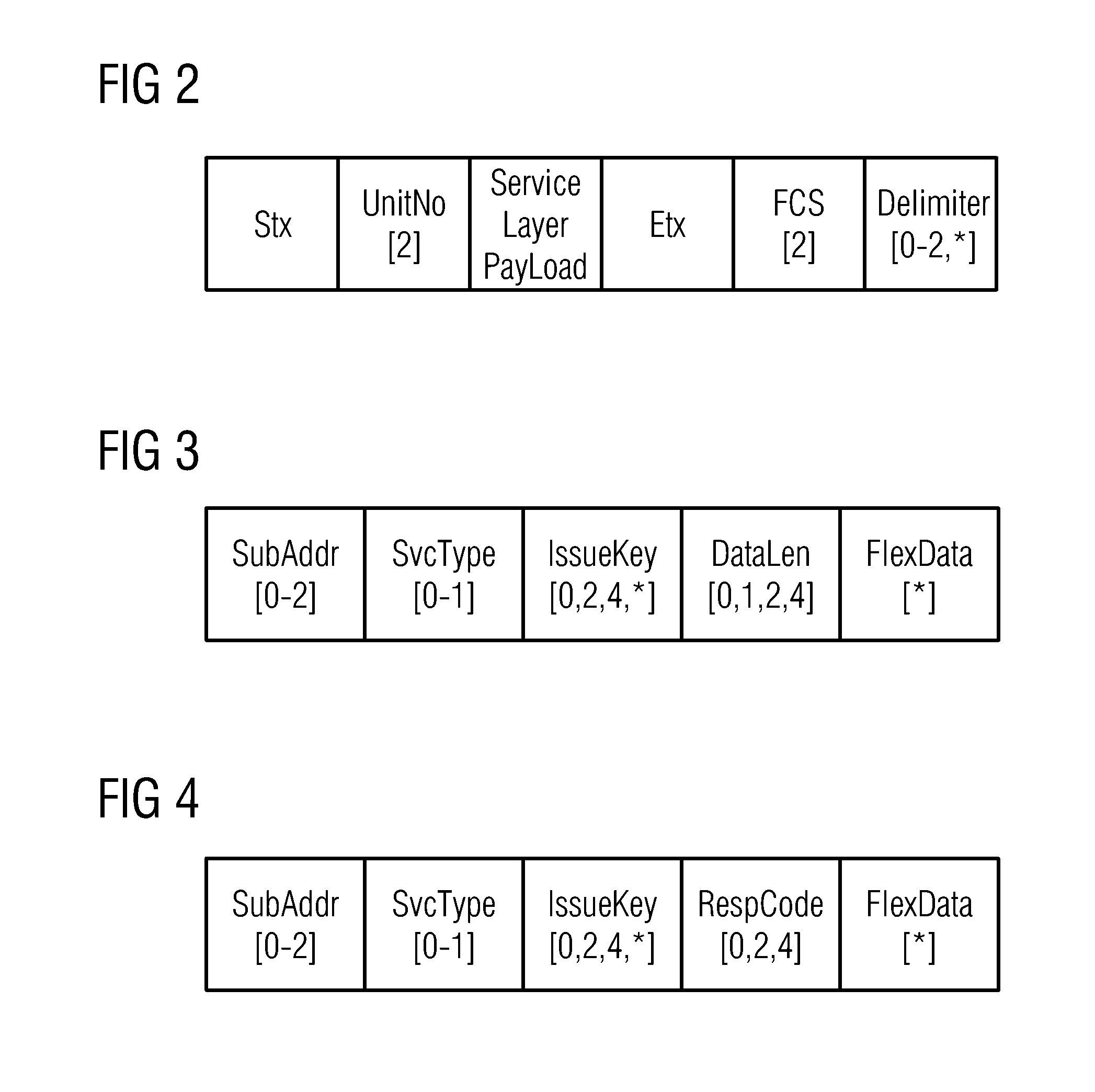

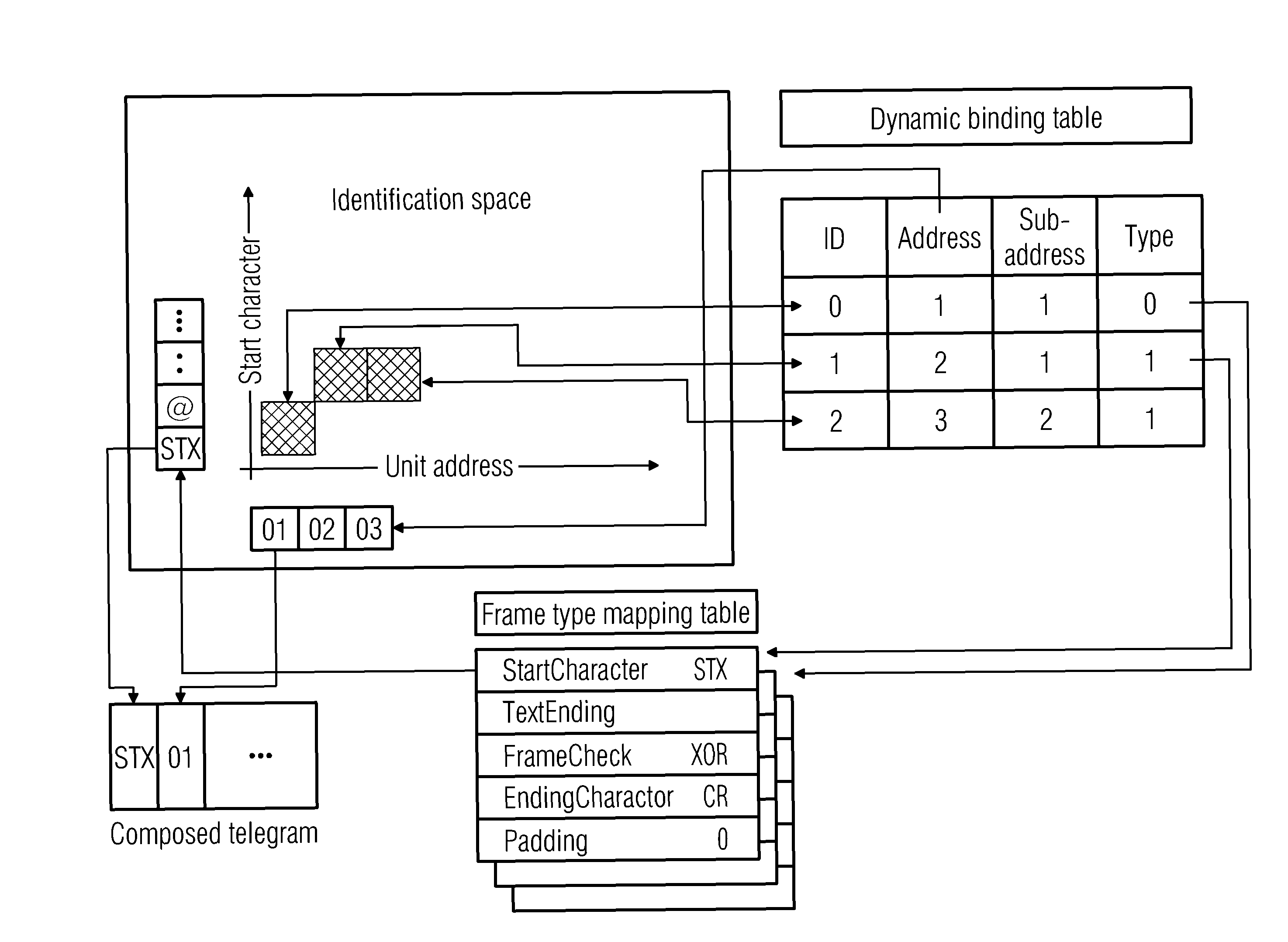

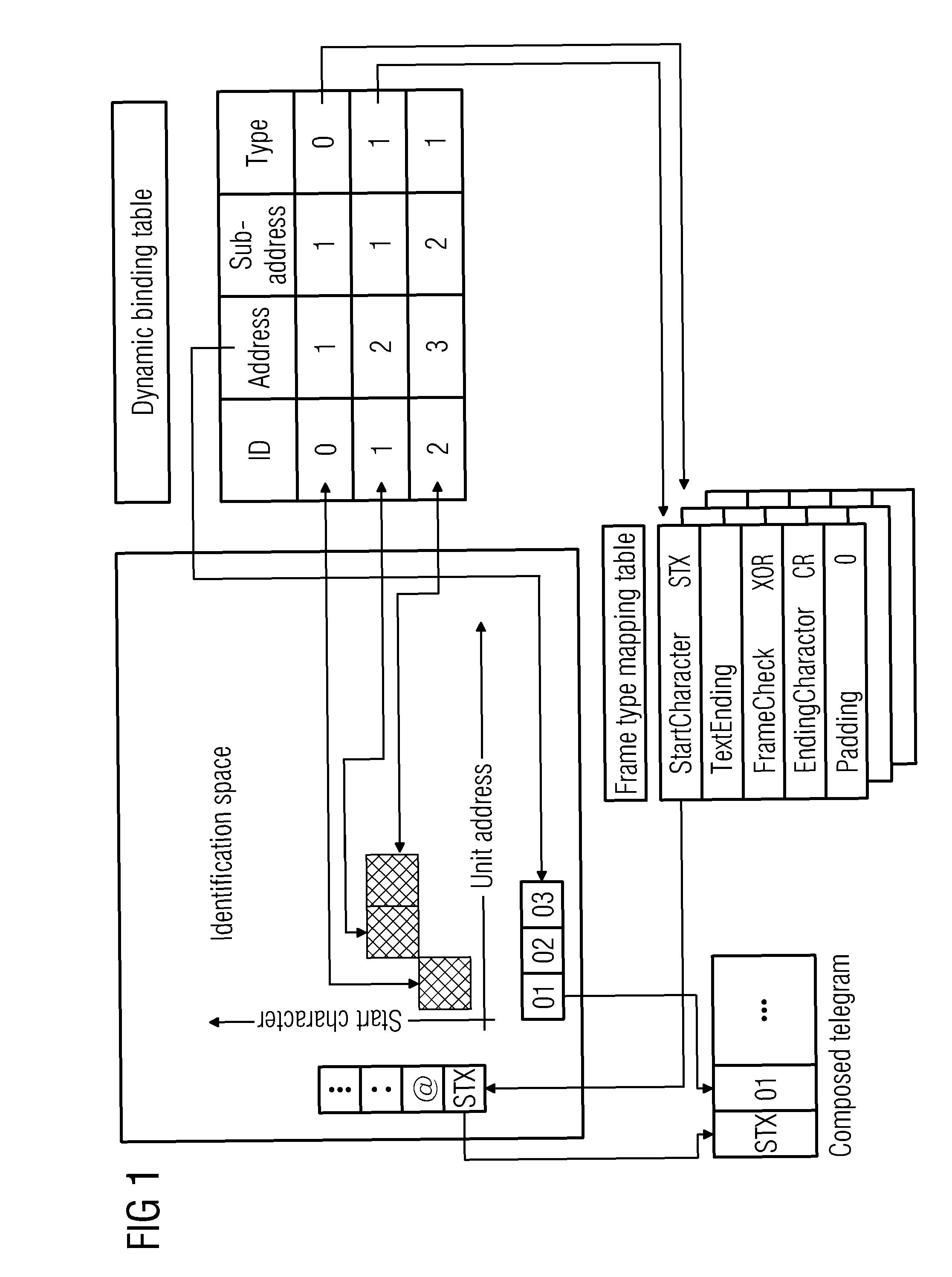

Communication method in a MRI system

InactiveUS20100199004A1Data switching networksElectric digital data processingMultidrop busResonance

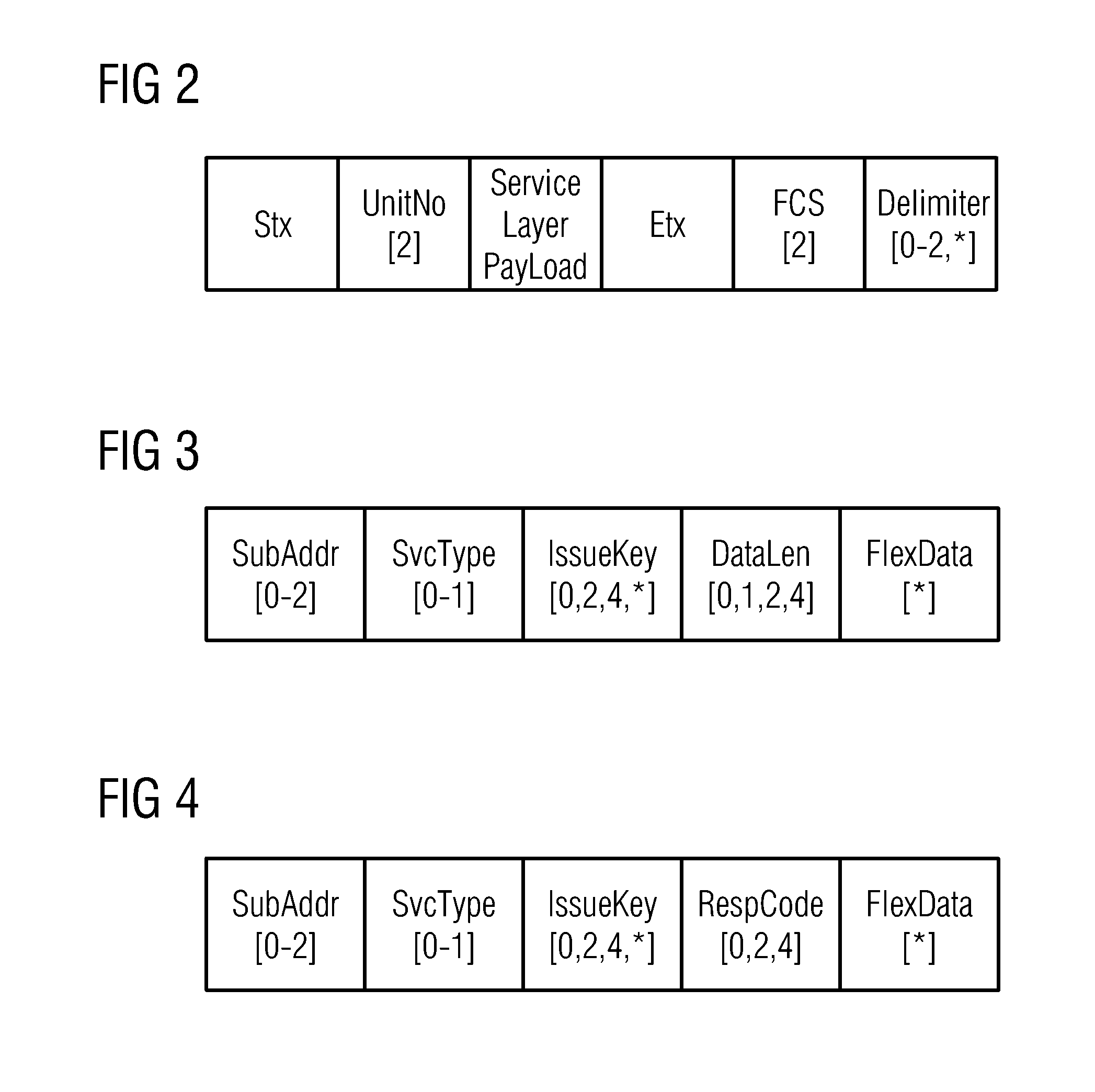

In a method of communication on a multidrop bus of a magnetic resonance system, an adaptive protocol script for telegrams on the multidrop bus is used, that implements adaptive protocol matching using telegram start characters, addresses and frame-type binding. For this purpose, a telegram frame is divided into a link layer and a service layer, the link layer being device-based and being responsible for differentiating addresses and frame types, and enabling devices that use different communication protocols to be simultaneously present on the bus. The service layer represents the load of the link layer, and its service script is operation-based, and the service layer provides, for the exterior, interfaces that are independent of the communication protocols used by the devices.

Owner:SIEMENS HEALTHCARE GMBH

Card controlling part used in automatic vending machine and the automatic vending machine

The object of the invention is to provide a vending machine for easily performing communication even when communication protocols (communication specification) are different between a main control part and a coin identifying device in the vending machine, and to provide a card control part used for the machine. The vending machine including the main control part for controlling the whole vending machine; and the coin identifying device by multi-drop bus specification comprises the card control part. Communication is achieved by transmitting the communication specification from the multi-drop bus specification coin identifying device to the main control part via the card control part to the main control part as communication from the card control part.

Owner:FUJI ELECTRIC CO LTD

System and method for mdb data processing of vending machines

ActiveUS20200258341A1Coin-freed apparatus detailsPayment architectureData processing systemMultidrop bus

The present disclosure relates to the field of vending machine technology. In particular, it involves a control system and control method implementing data processing under multidrop bus (MDB) protocol.

Owner:INHAND NETWORKS INC

Method for communication on a multidrop bus of a magnetic resonance system

In a method of communication on a multidrop bus of a magnetic resonance system, an adaptive protocol script for telegrams on the multidrop bus is used, that implements adaptive protocol matching using telegram start characters, addresses and frame-type binding. For this purpose, a telegram frame is divided into a link layer and a service layer, the link layer being device-based and being responsible for differentiating addresses and frame types, and enabling devices that use different communication protocols to be simultaneously present on the bus. The service layer represents the load of the link layer, and its service script is operation-based, and the service layer provides, for the exterior, interfaces that are independent of the communication protocols used by the devices.

Owner:SIEMENS HEALTHCARE GMBH