Patents

Literature

36results about How to "Reduce access rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and apparatus for reselecting cell in mobile communication system

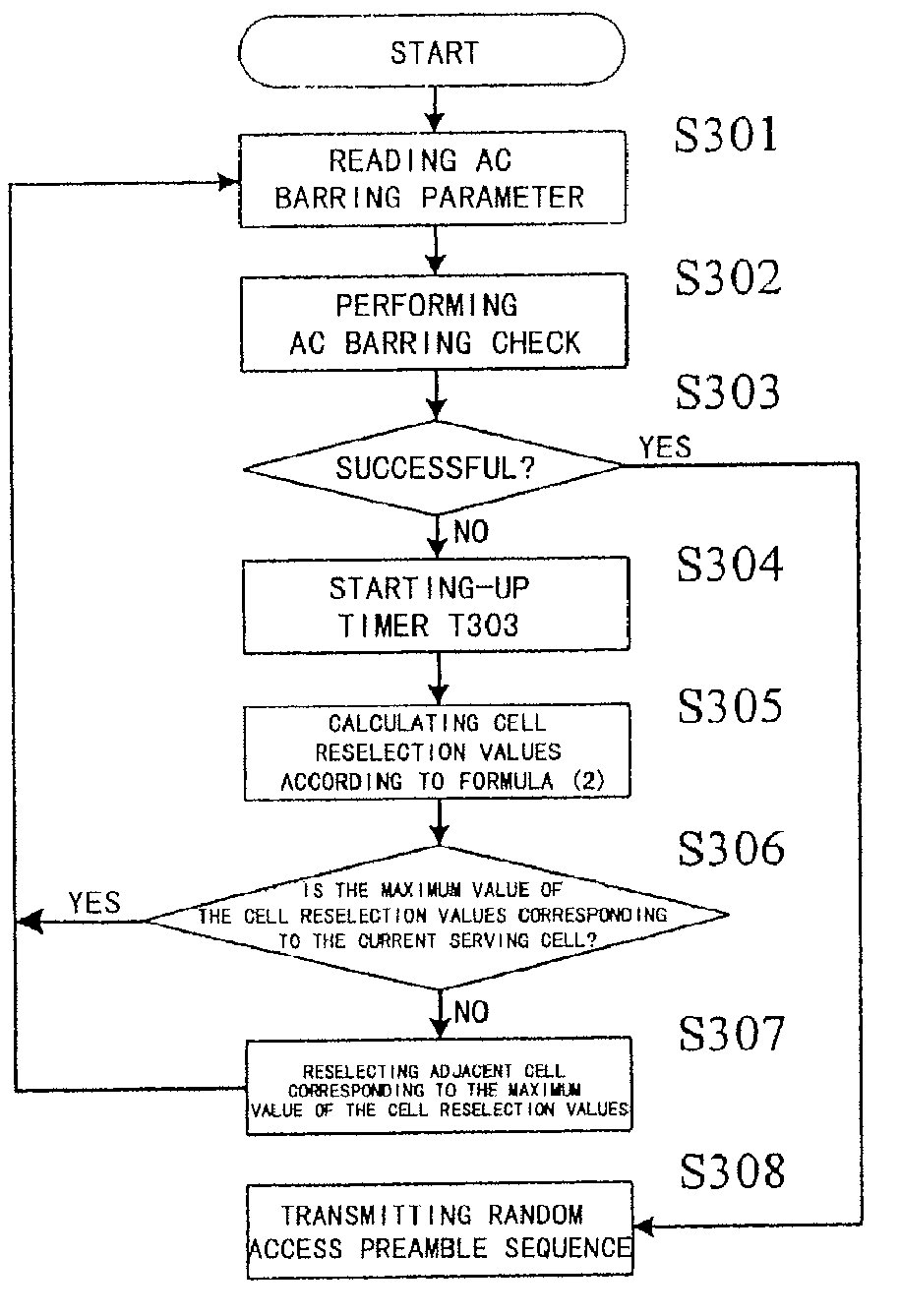

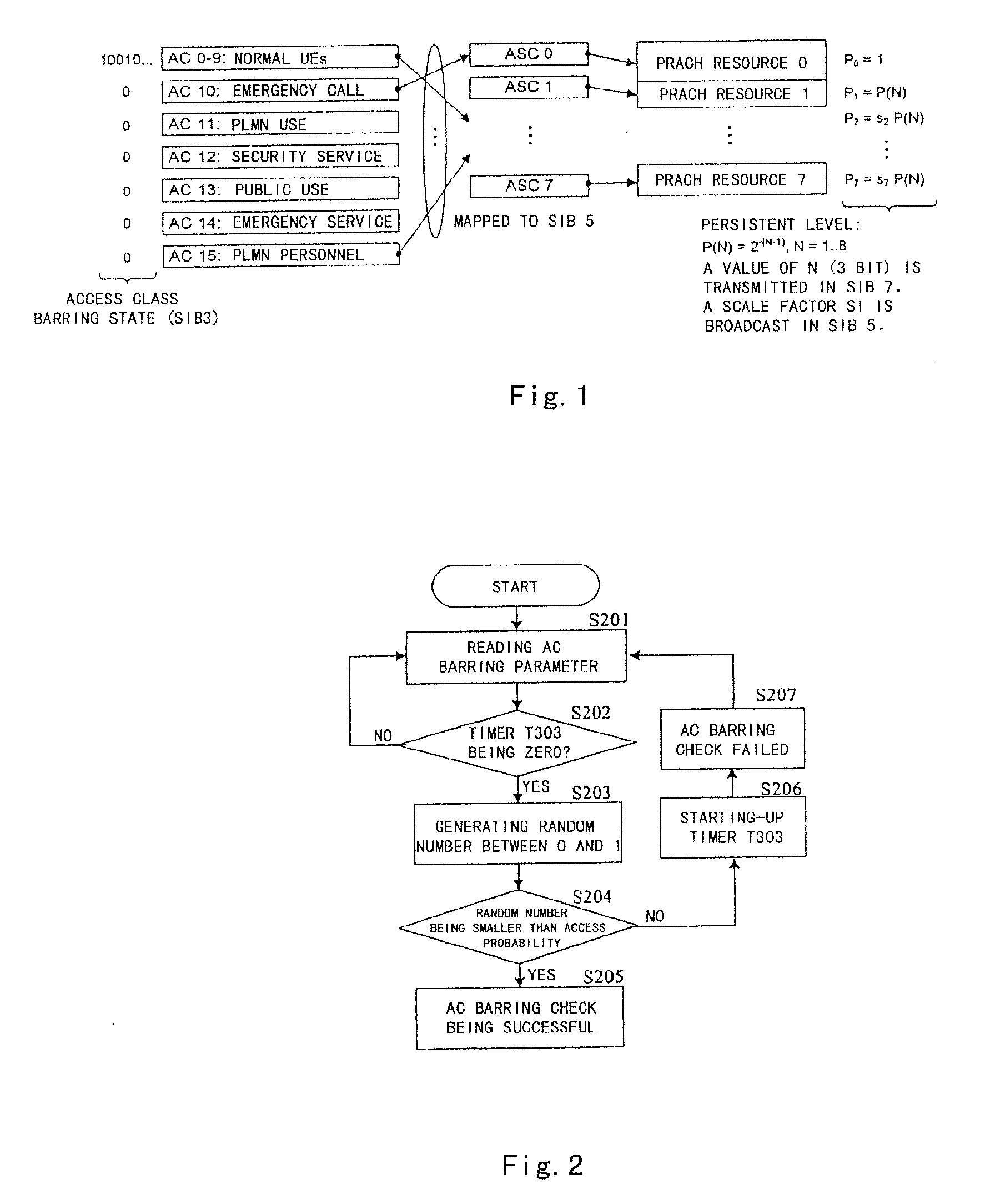

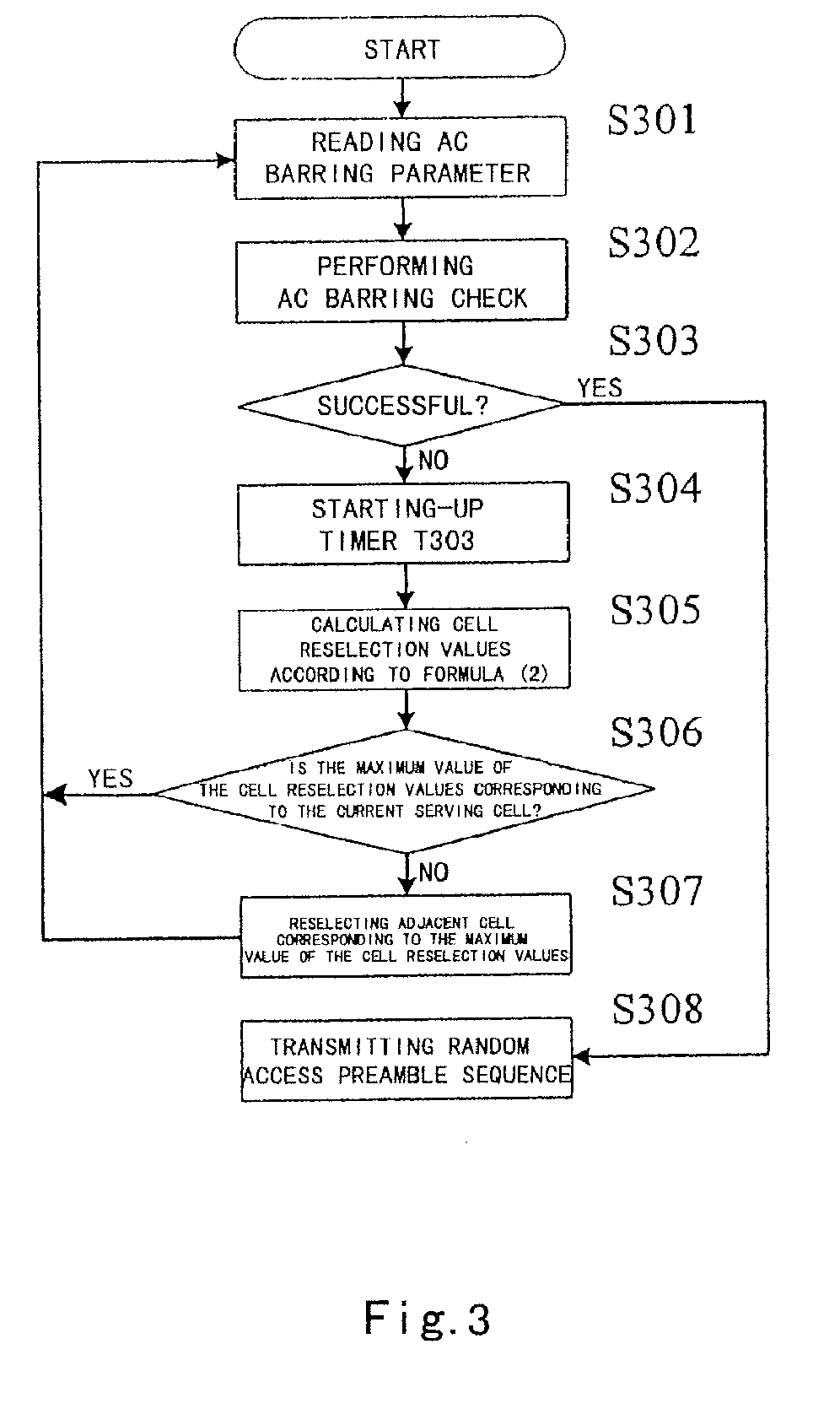

InactiveUS20090270104A1Reduce degradationReduce access rateError preventionTransmission systemsMobile communication systemsUser equipment

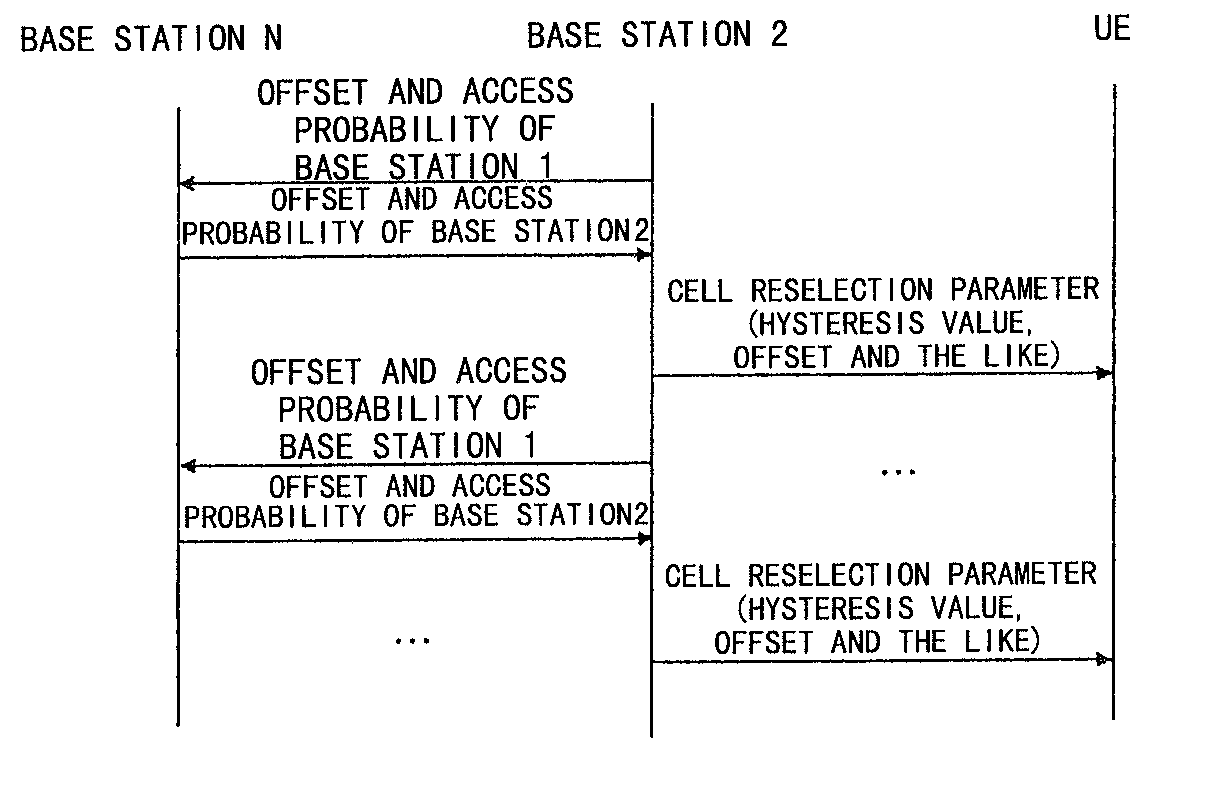

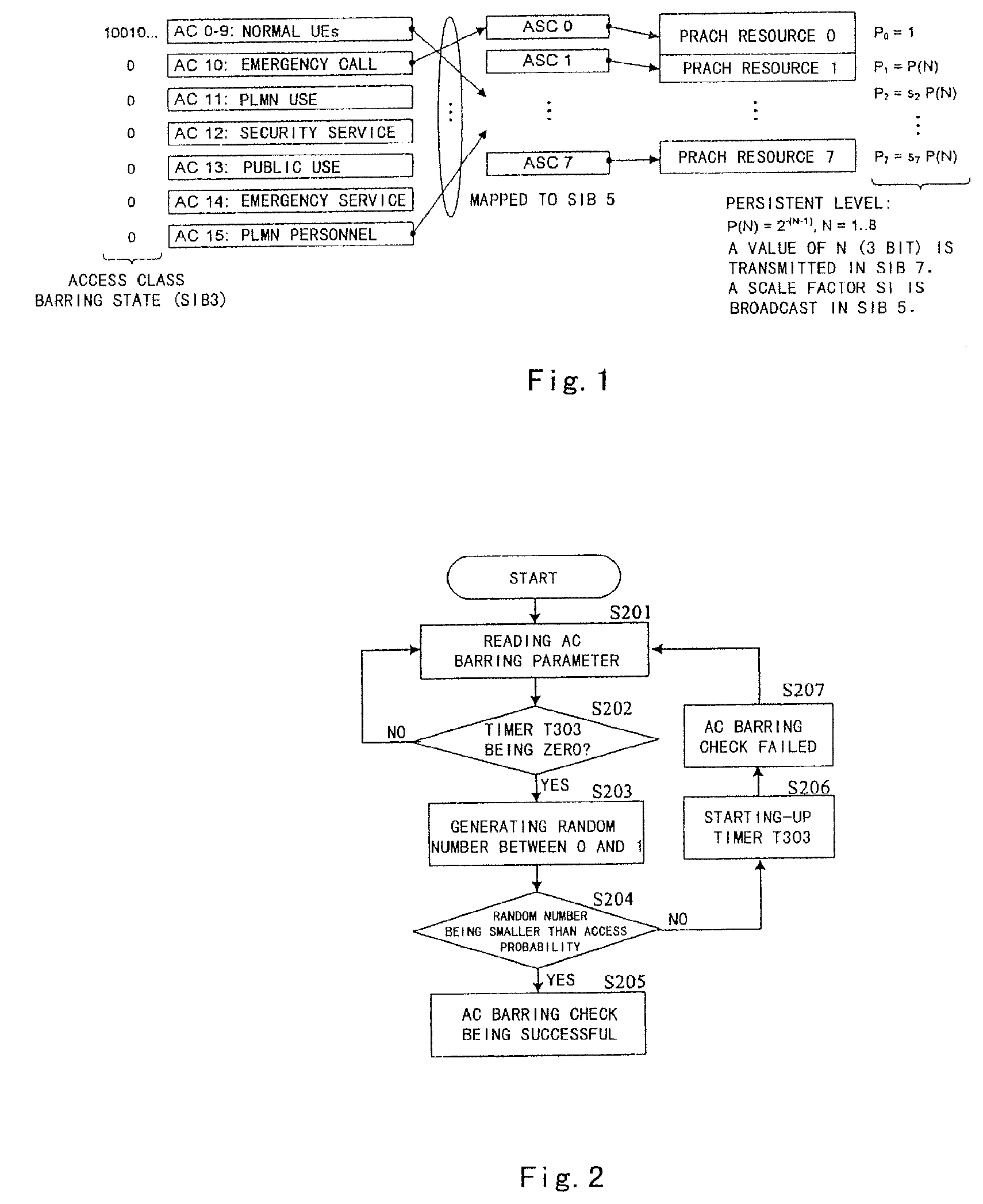

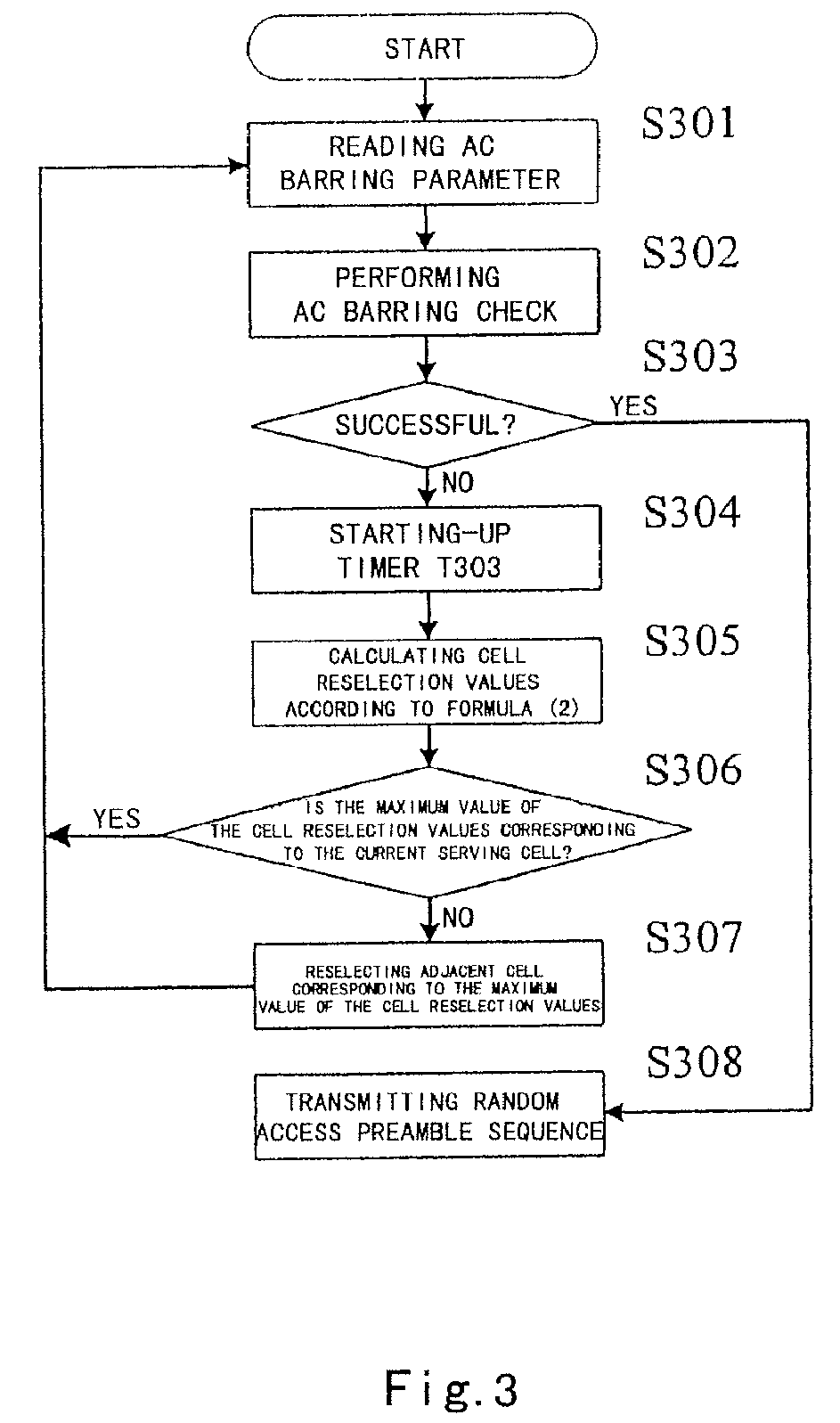

Embodiments of the present invention include a method for performing cell reselection in a mobile communication system. The method comprises the steps of reading, by a user equipment (UE), the Access Class (AC) barring parameters of the serving cell which are broadcast from a base station, and performing an AC barring check; calculating the cell reselection values of the serving cell and the adjacent cells according to the cell reselection parameters broadcast by the base station when the AC barring check fails; and ranking the calculated cell reselection values, selecting by the UE the cell corresponding to the maximum value of the calculated cell reselection values as the serving cell of the UE.

Owner:NTT DOCOMO INC

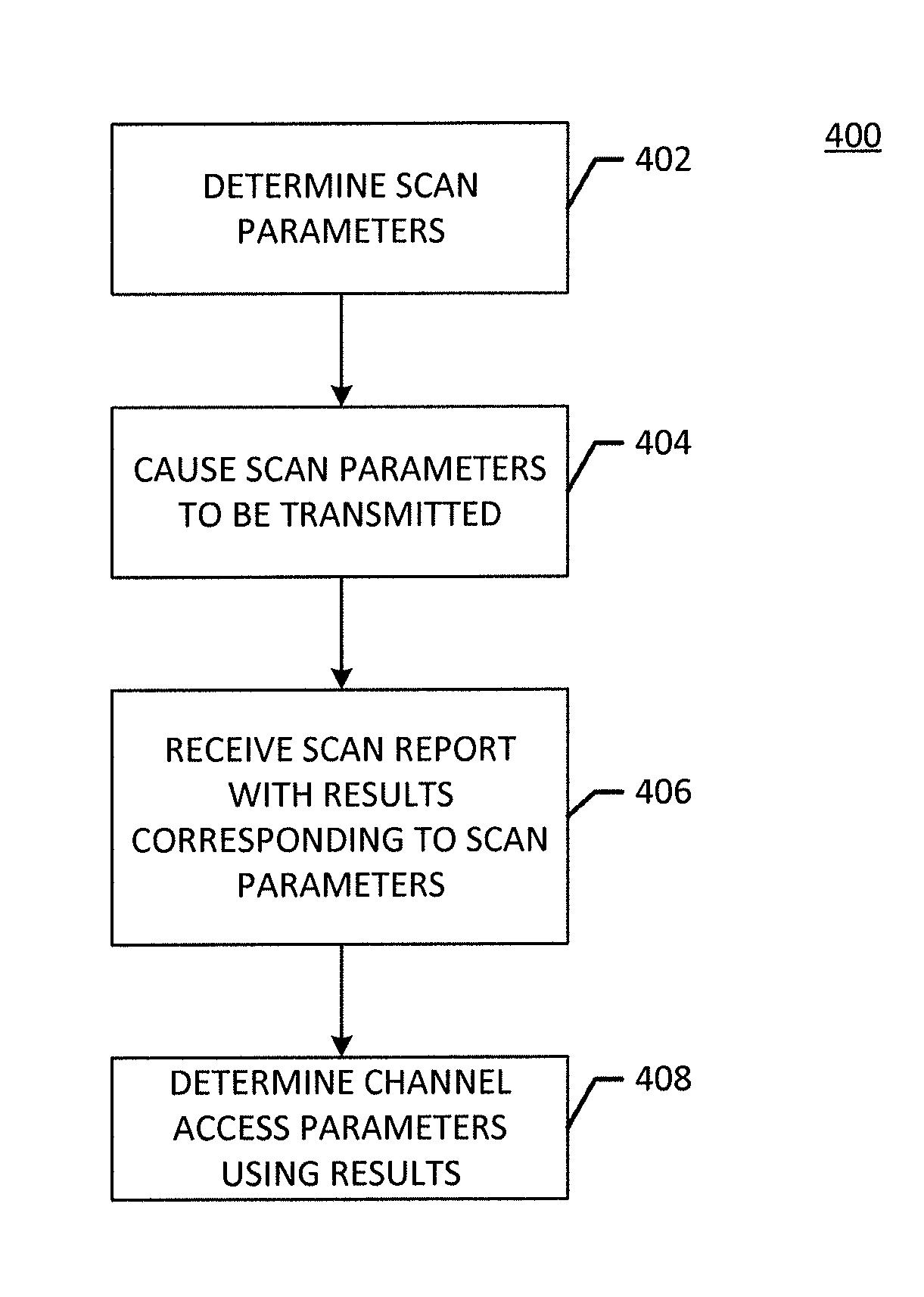

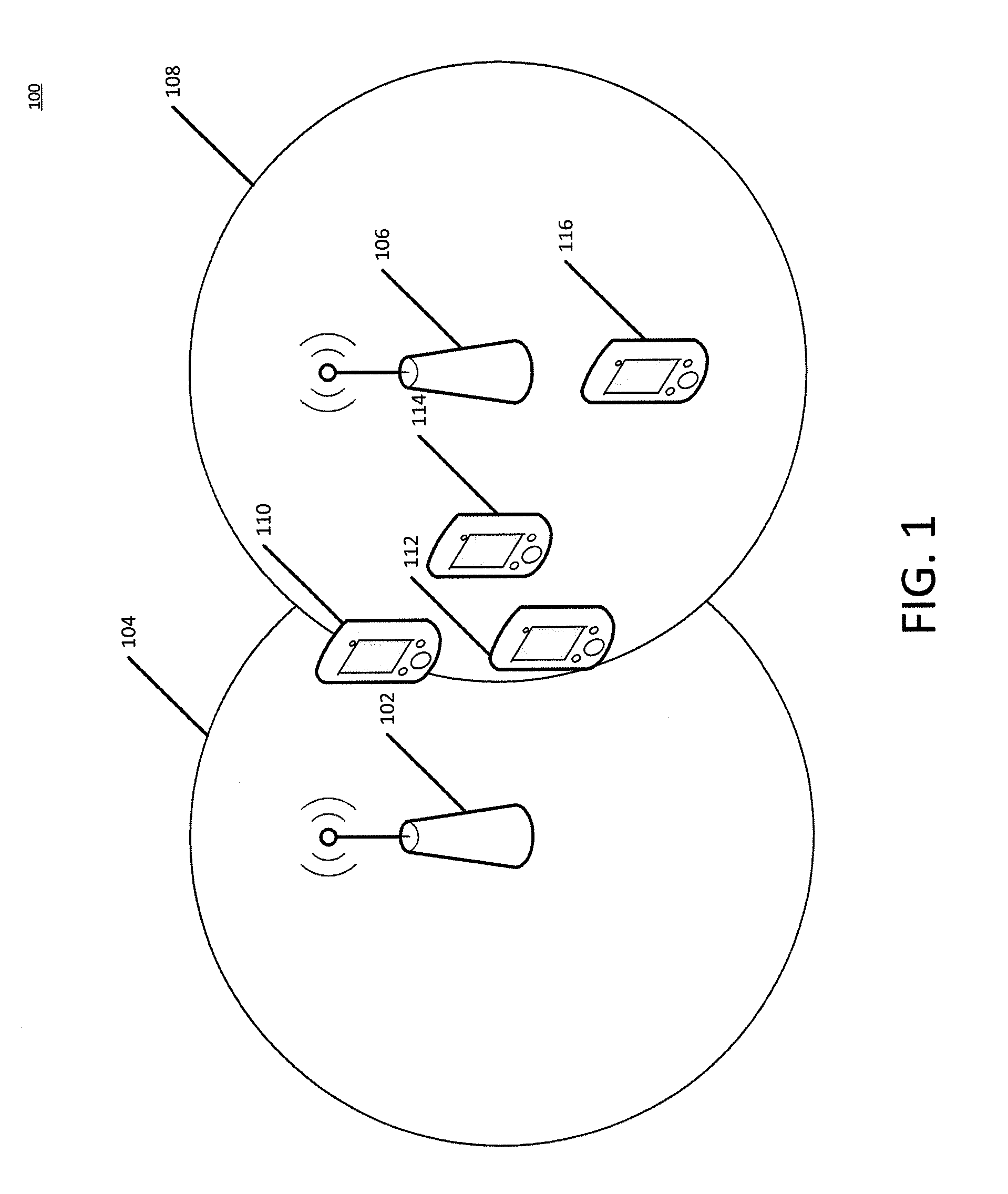

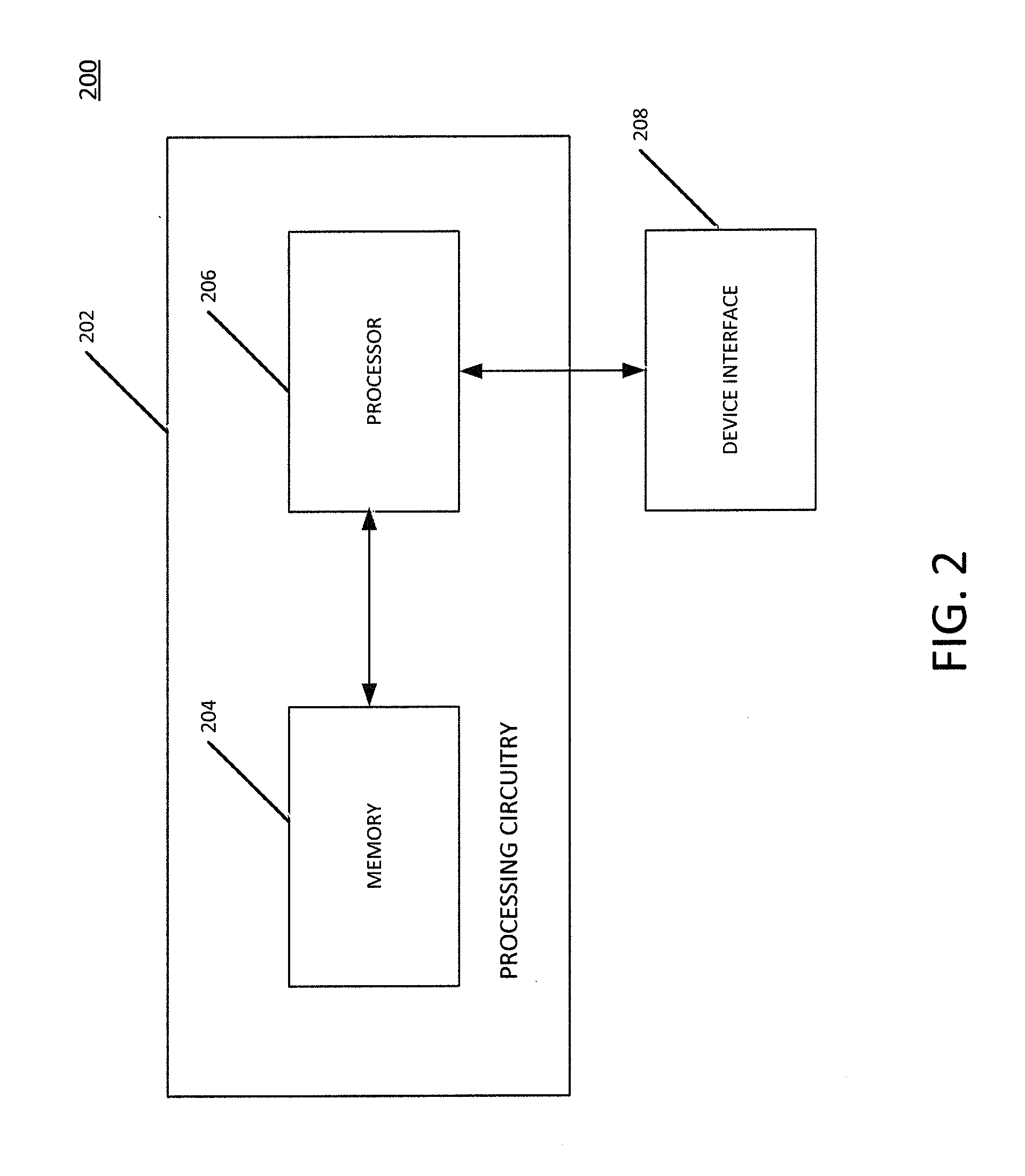

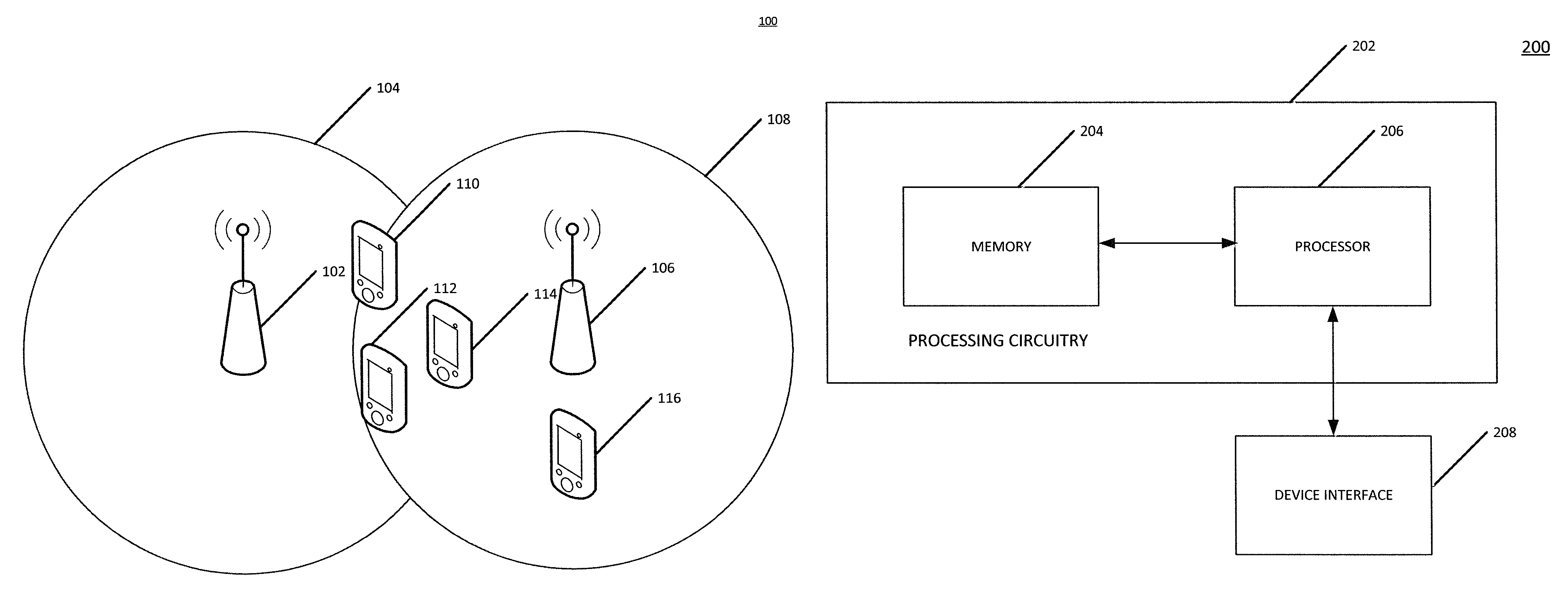

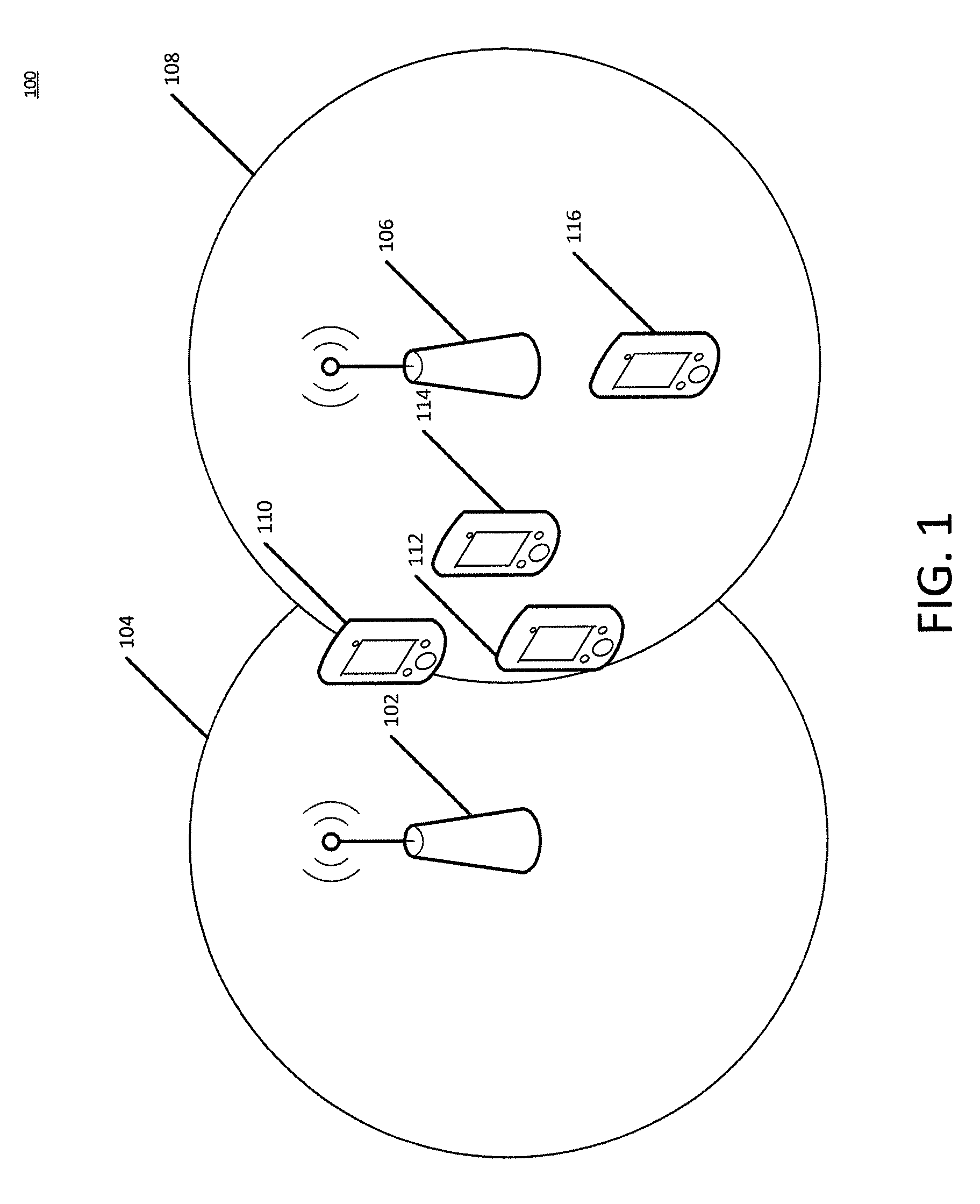

Method and apparatus for providing improved detection of overlapping networks

ActiveUS20140016478A1Minimizing bandwidthMinimizing transmission timeError preventionFrequency-division multiplex detailsTelecommunicationsWireless access point

A method, apparatus and computer program product provide improved detection of overlapping wireless networks. In this regard, the method, apparatus and computer program product may utilize a processor, such as a processor on a wireless access point, to determine one or more parameters for a scan of a wireless network to identify overlapping networks. Wireless stations may utilize the parameters to determine the content of a scan report generated from a scan of the wireless network. The wireless stations may further utilize the parameters to determine which values should be monitored and / or recorded during the scan of the network. The wireless stations may respond to the access point with results corresponding to the parameters requested by the access point, and the access point may use the results to determine channel access parameters for other devices on the network, such as the wireless stations.

Owner:AVAGO TECH INT SALES PTE LTD

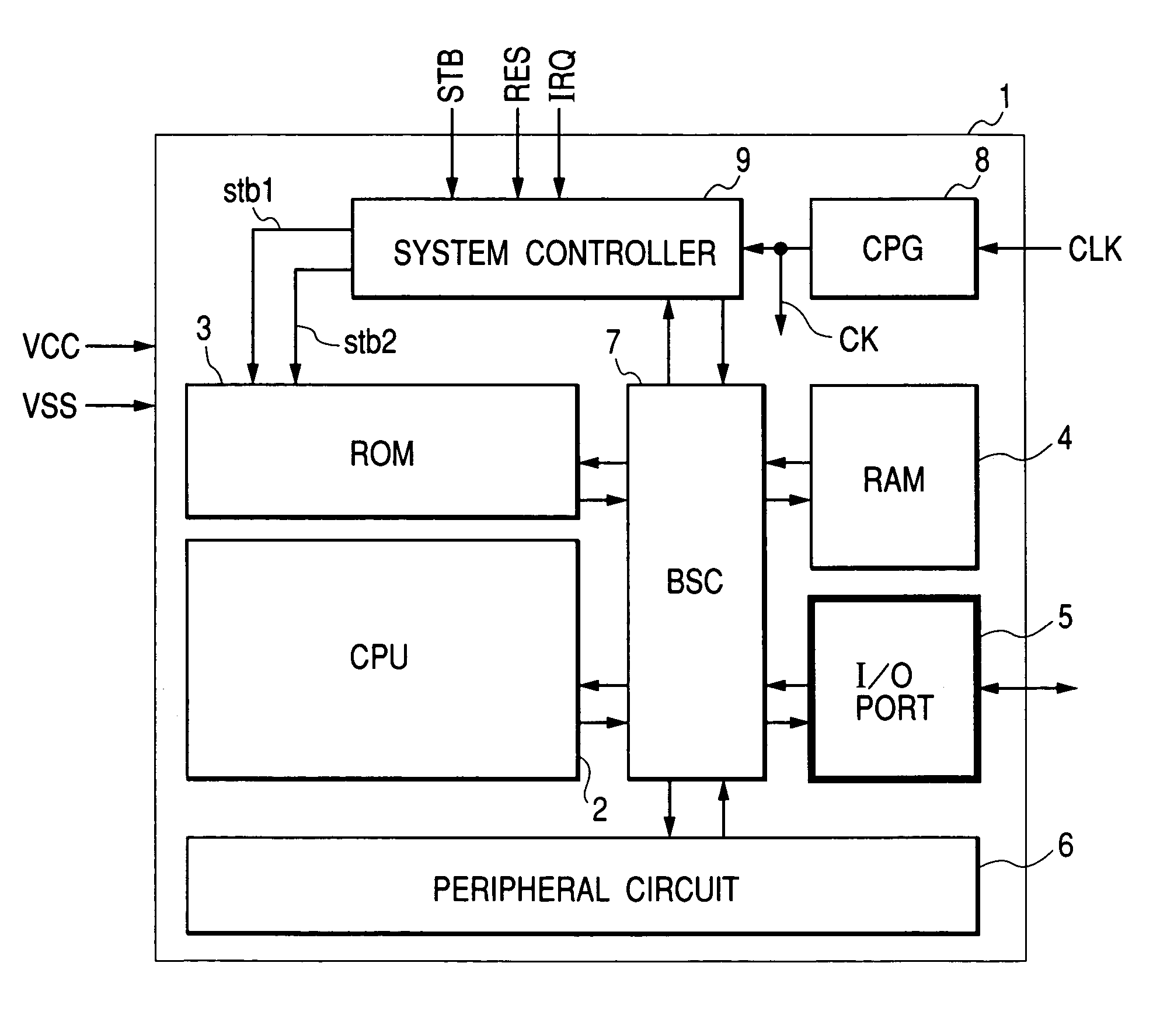

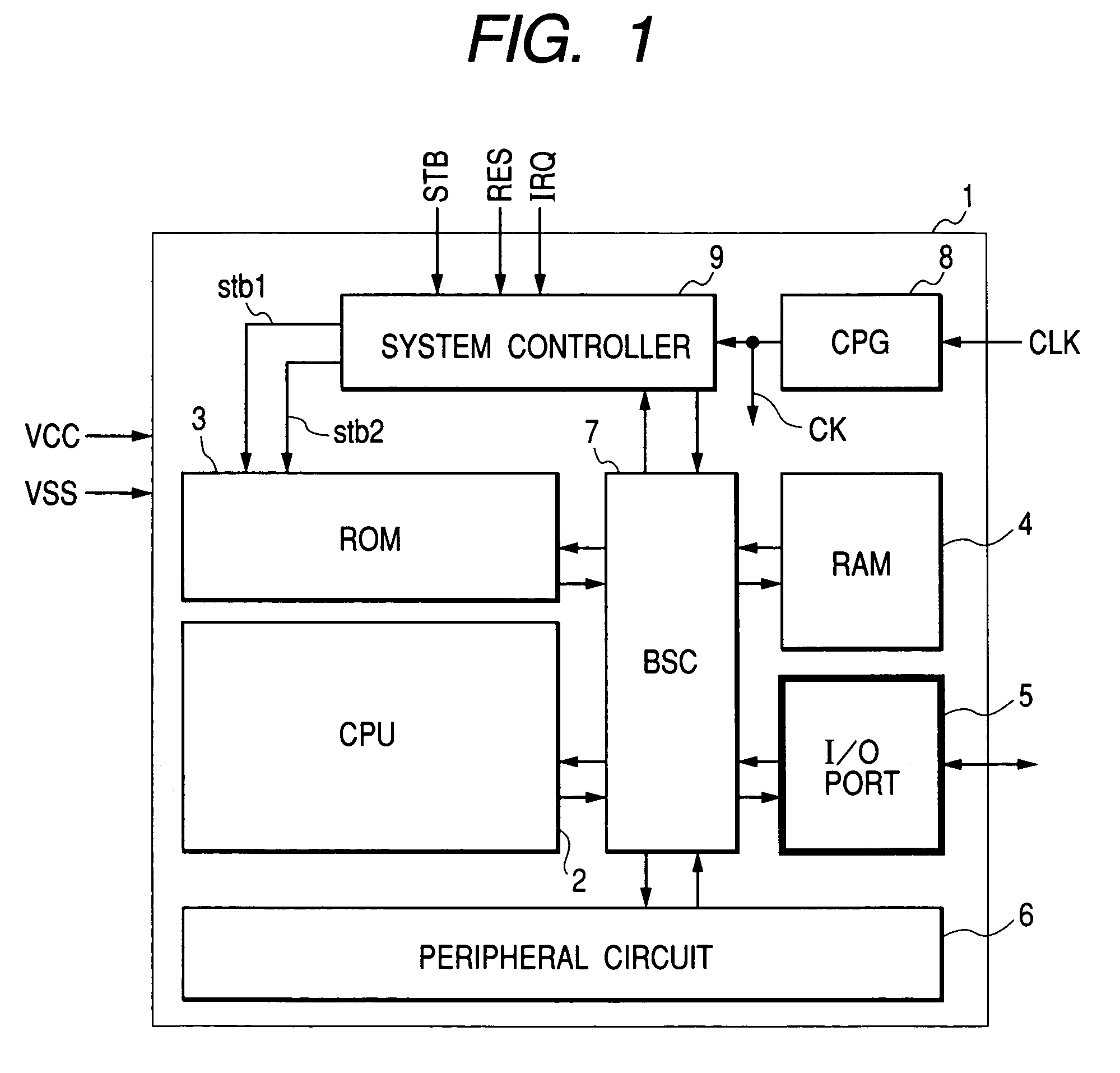

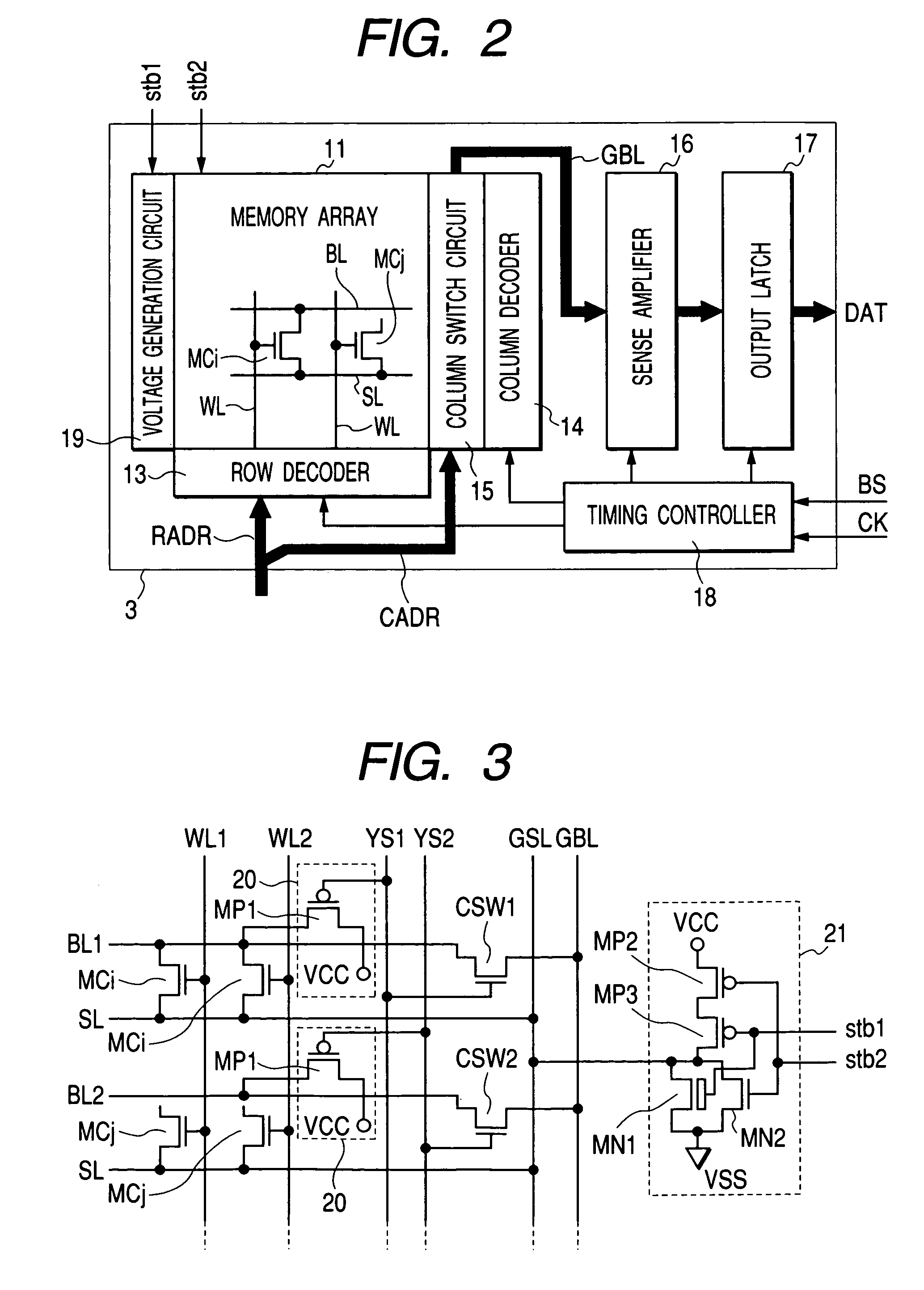

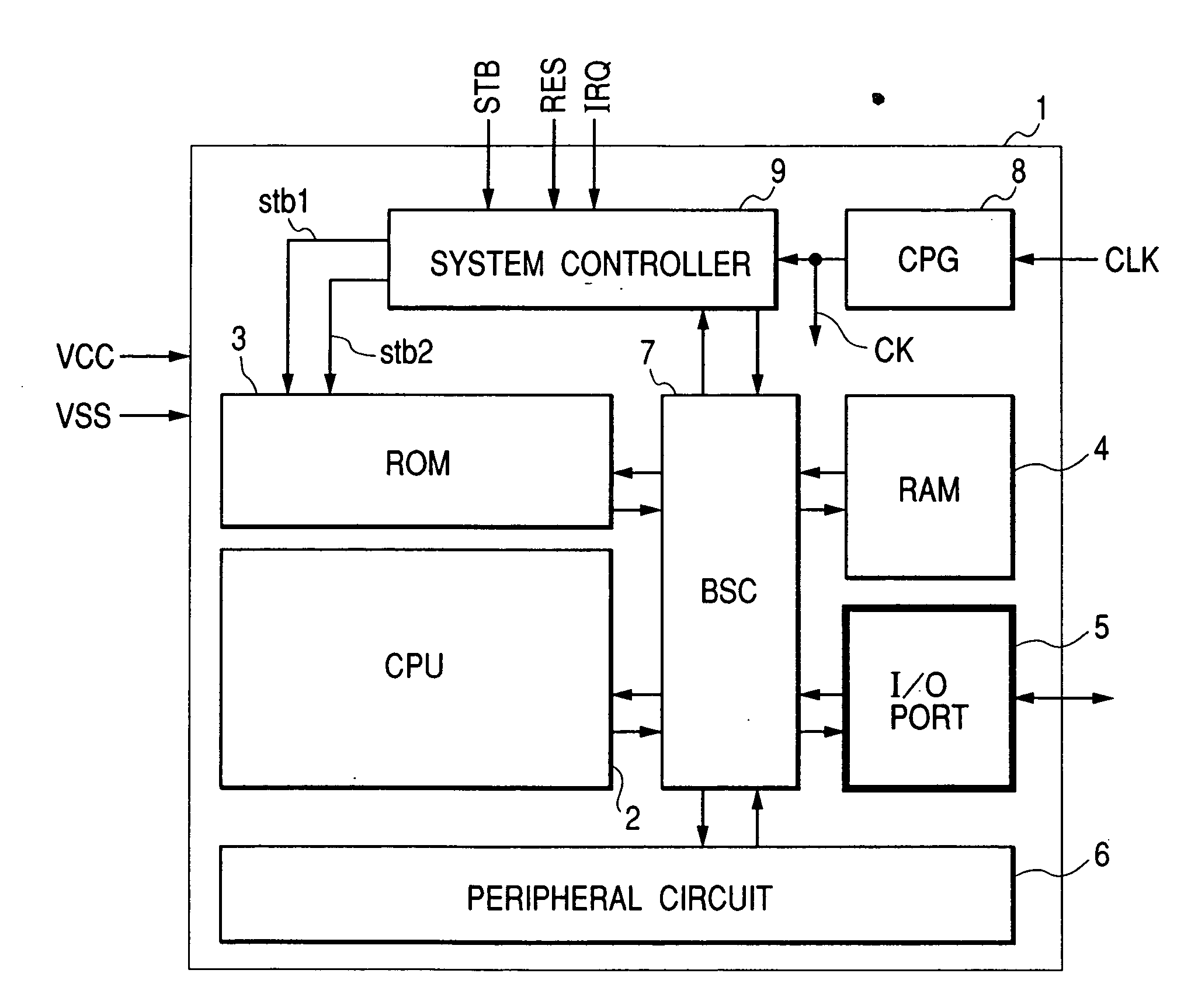

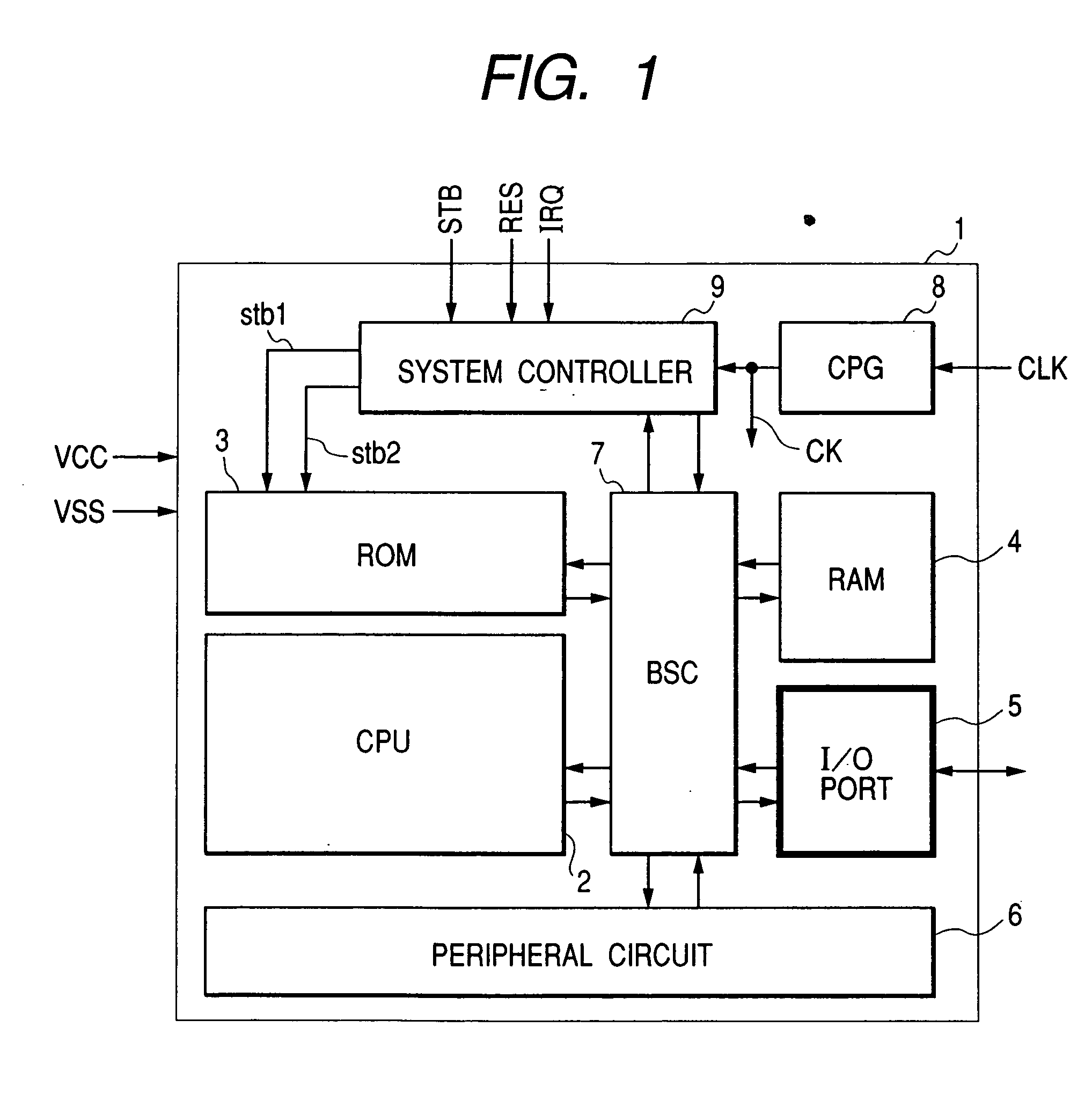

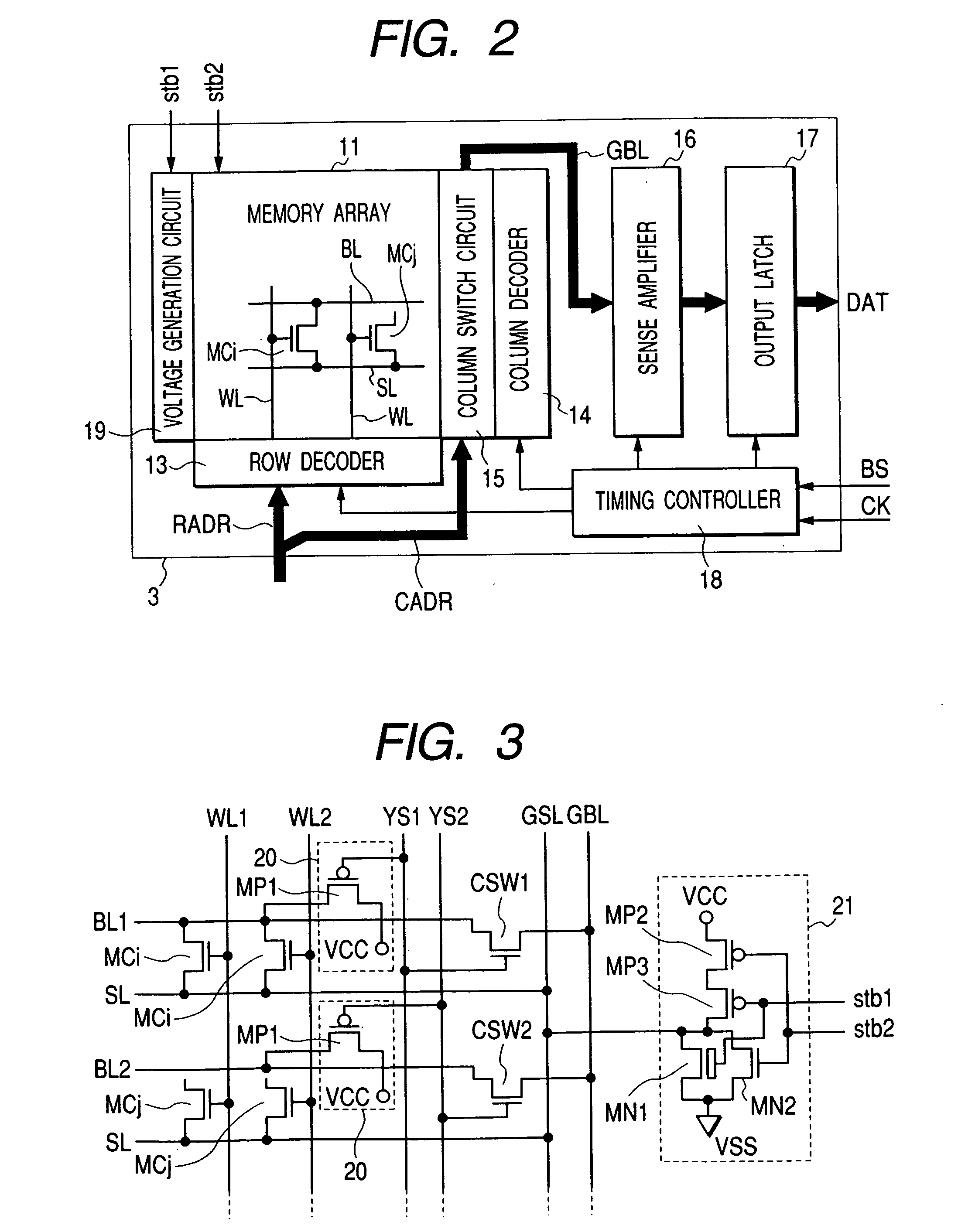

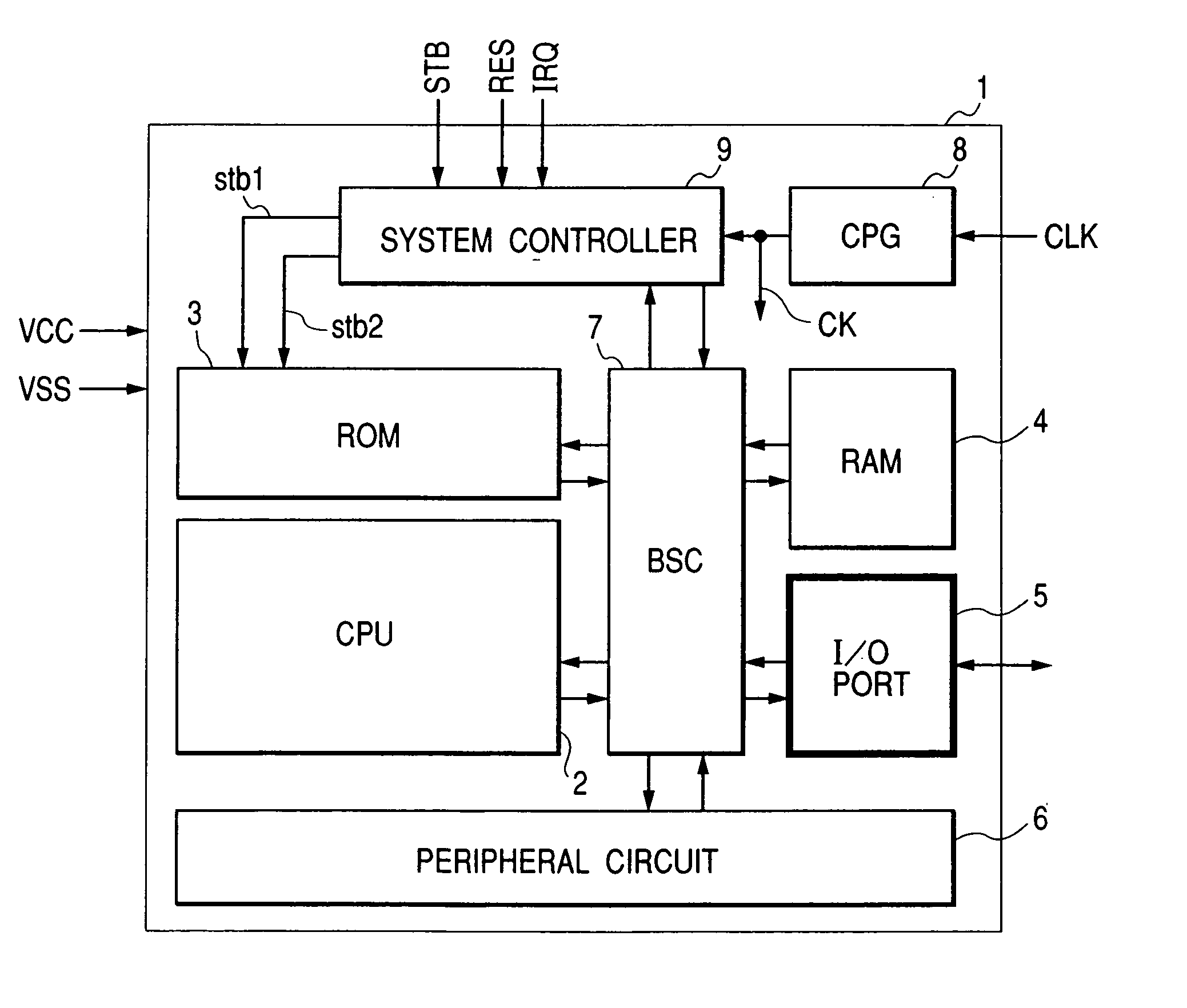

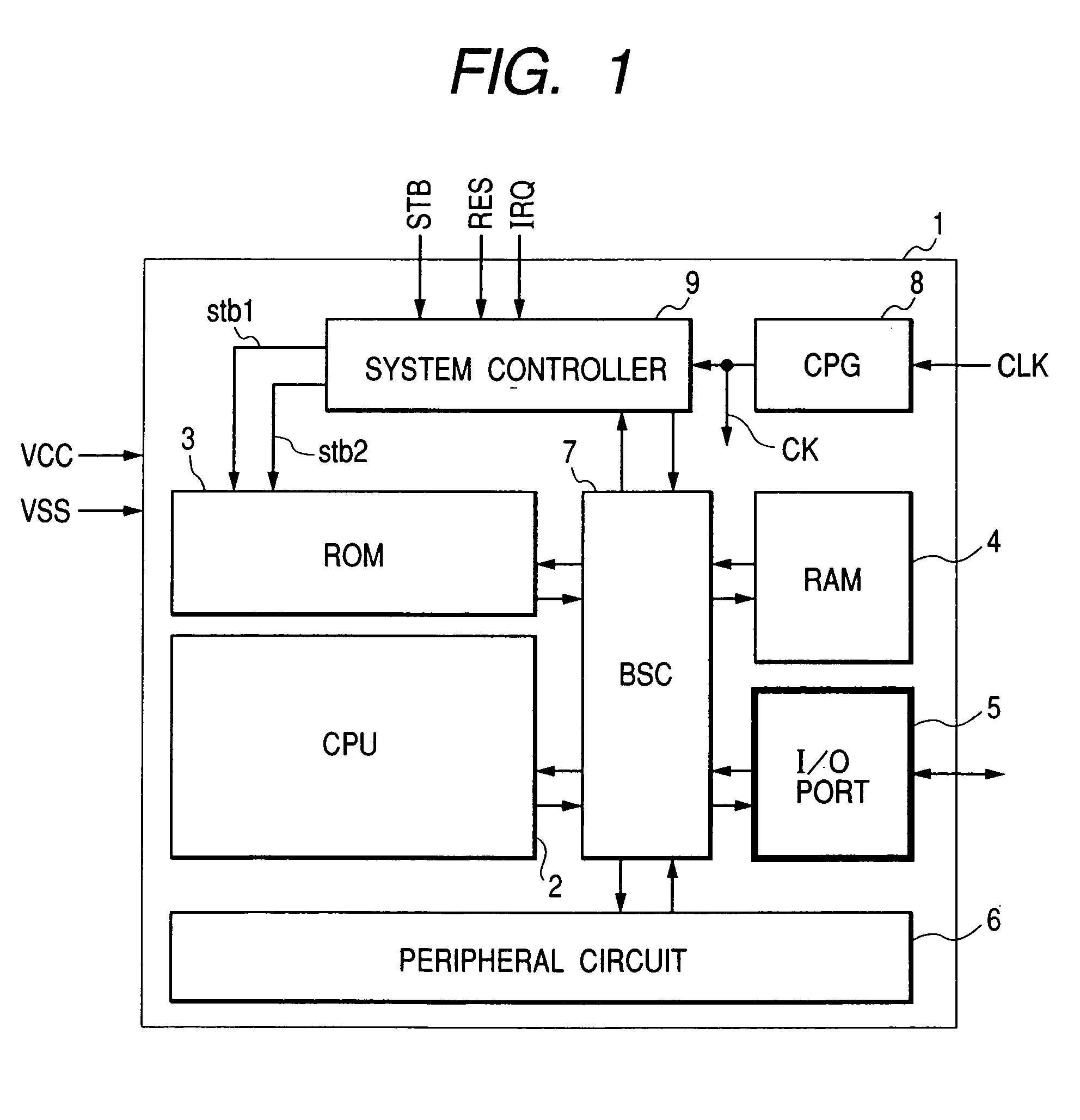

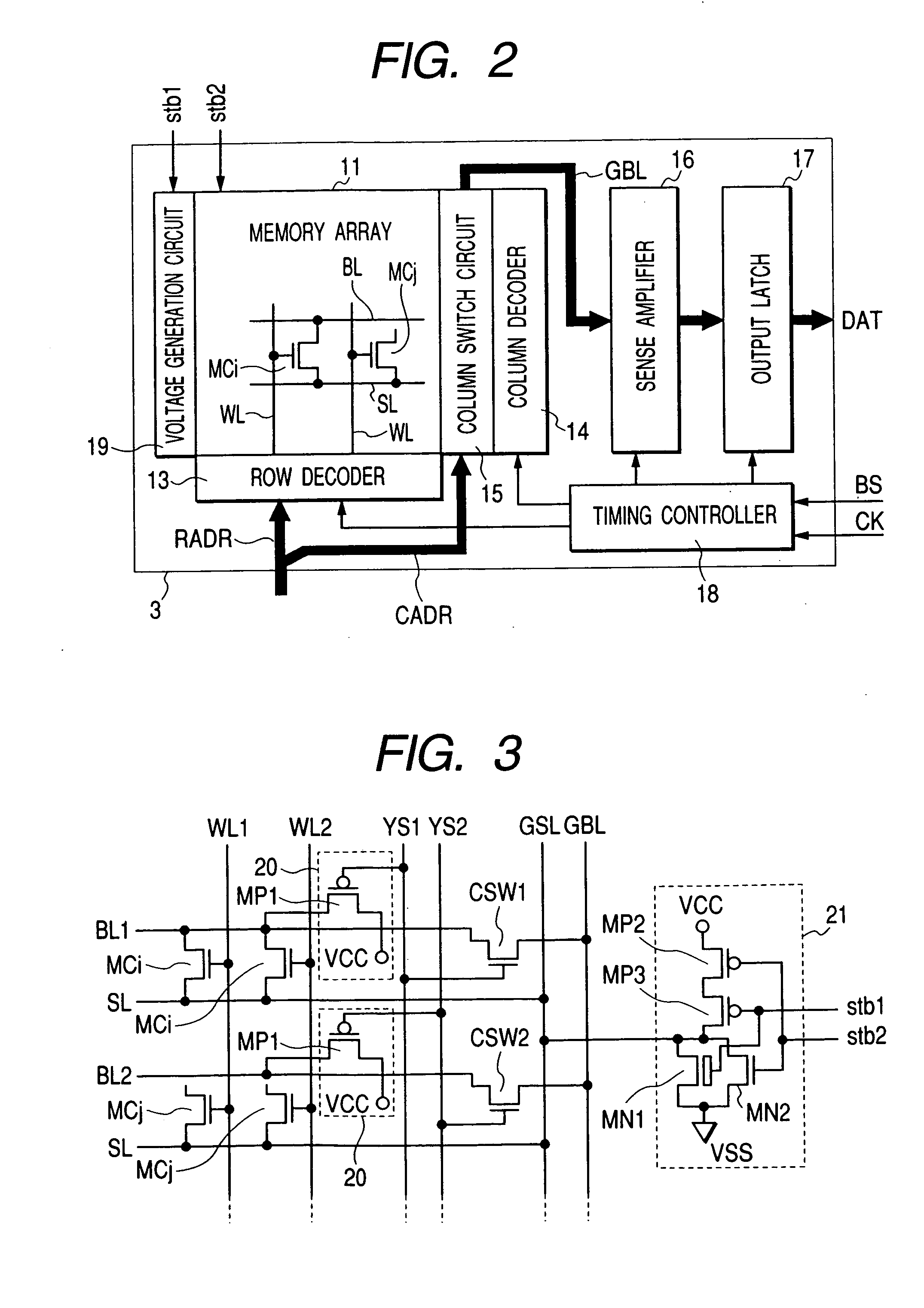

Semiconductor integrated circuit and IC card

InactiveUS7046573B2Improve discharge rateLarge noise is preventedRead-only memoriesDigital storageIntegrated circuitEngineering

A semiconductor integrated circuit has a memory which can enter active state or standby state, and the memory has voltage generation circuits for bit lines and source lines with which memory cells are connected. The voltage generation circuits make the potential of the bit lines and the potential of the source lines equal to each other in response to an instruction to transition from active state to standby state. The voltage generation circuits produce a potential difference between the bit lines and the source lines in response to an instruction to transition from standby state to active state. In standby state, the potential of the bit lines and that of the source lines are equal to each other. Therefore, sub-threshold leakage does not occur between the source and drain of each memory cell. In active state, the source line potential is not varied.

Owner:HITACHI ULSI SYST CO LTD +1

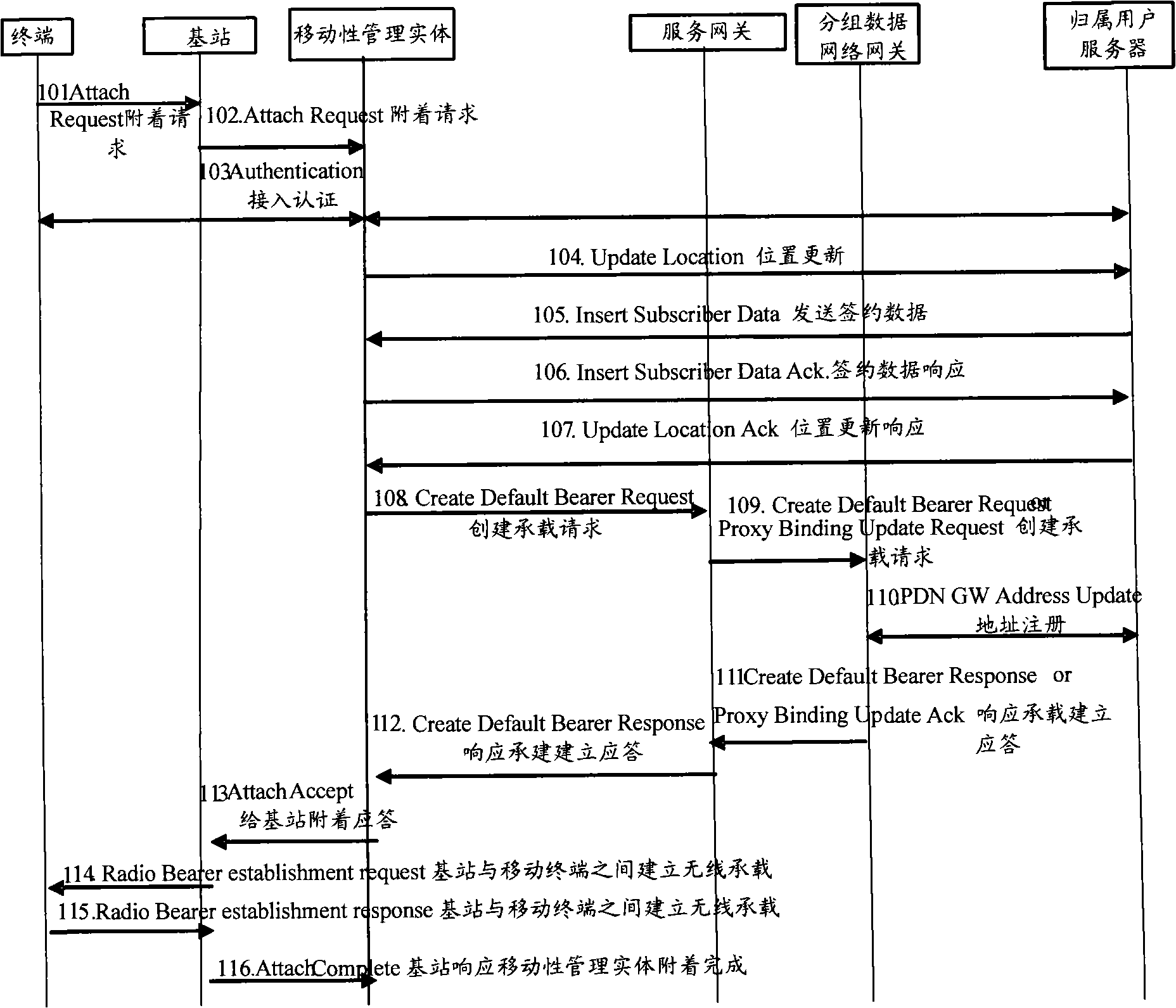

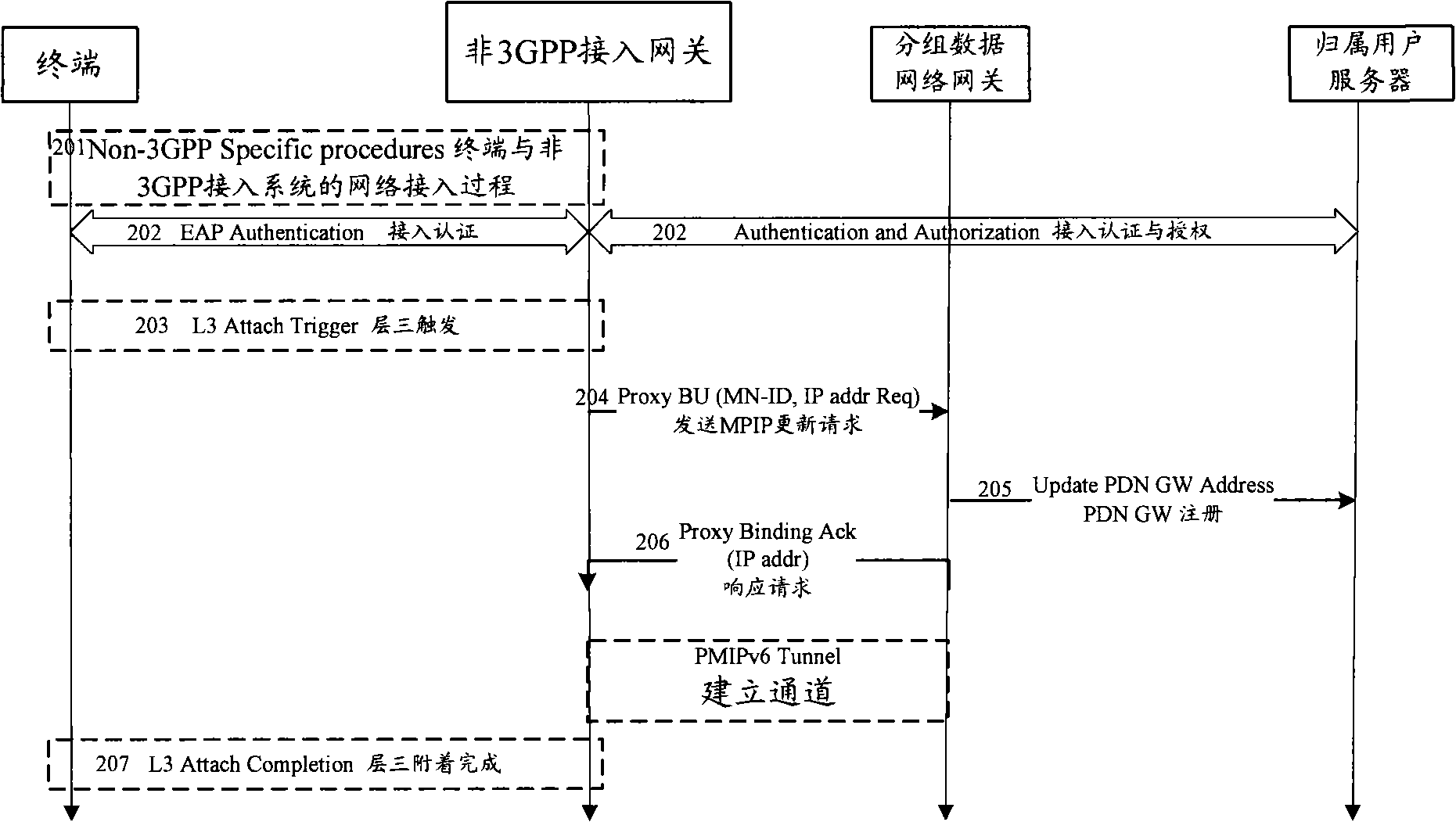

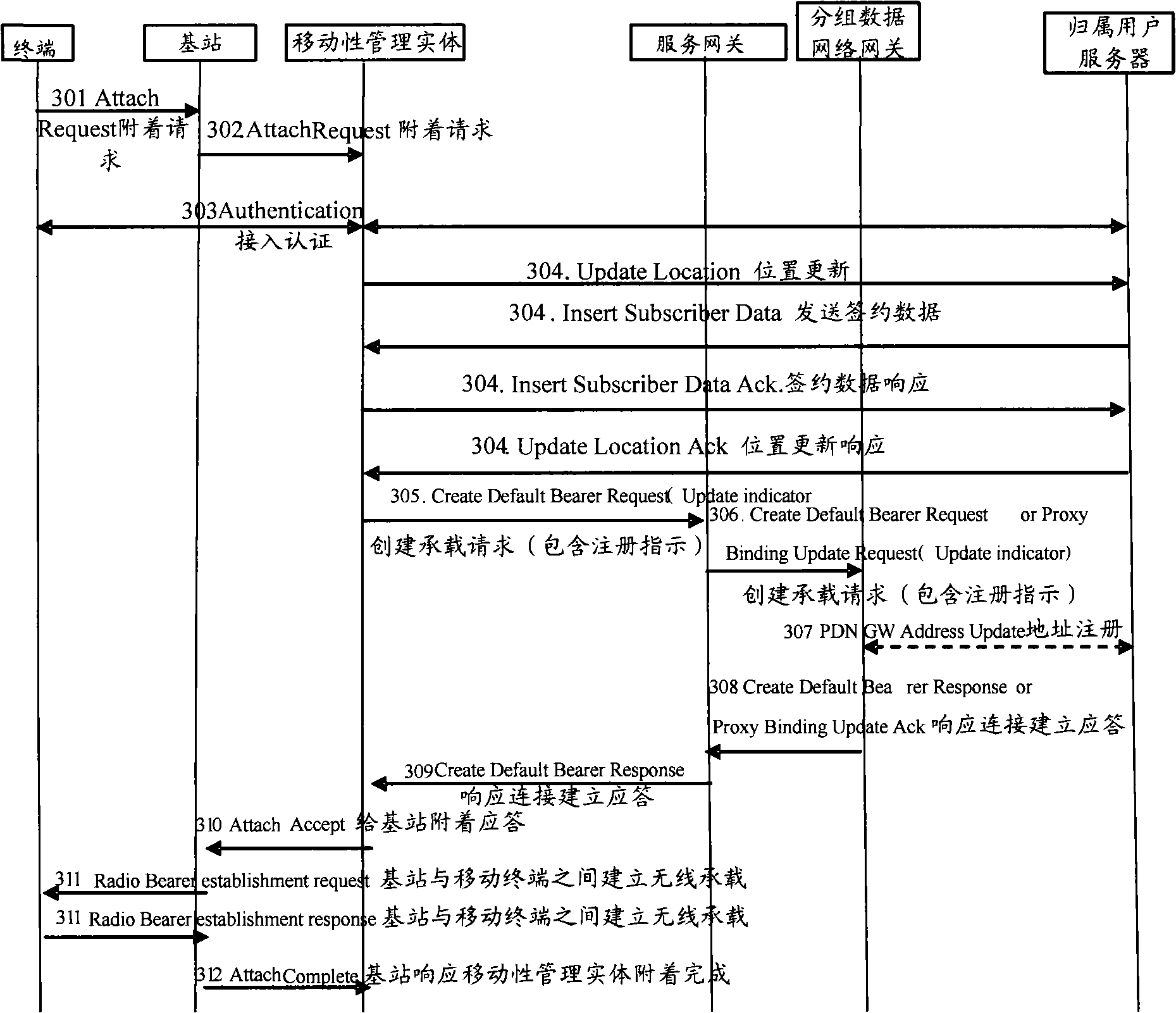

Method for registering gateway address and mobility management entity

ActiveCN101325583AReduce access rateSave storage spaceRadio/inductive link selection arrangementsNetwork connectionsSystem informationMobility management

The invention discloses a method for registering gateway address, including: judging whether a terminal is provided with the multisystem access capability and is authorized to use a plurality of wireless access system, according to currently supporting wireless access capability information and information of the wireless access system that are currently authorized to use by users; carrying register indication in connection establish request message, according to the judge result; a packet data network gateway determining whether to register updating onto an enregistering apparatus, according to the register indication; if so, the packet data network gateway initiates an address renewal request to the enregisterign apparatus; otherwise, the packet data network gateway does not initiate an address renewal request to the enregisterign apparatus. The invention also discloses a mobility management entity, a packet data network gateway and a mobile terminal.

Owner:HUAWEI TECH CO LTD

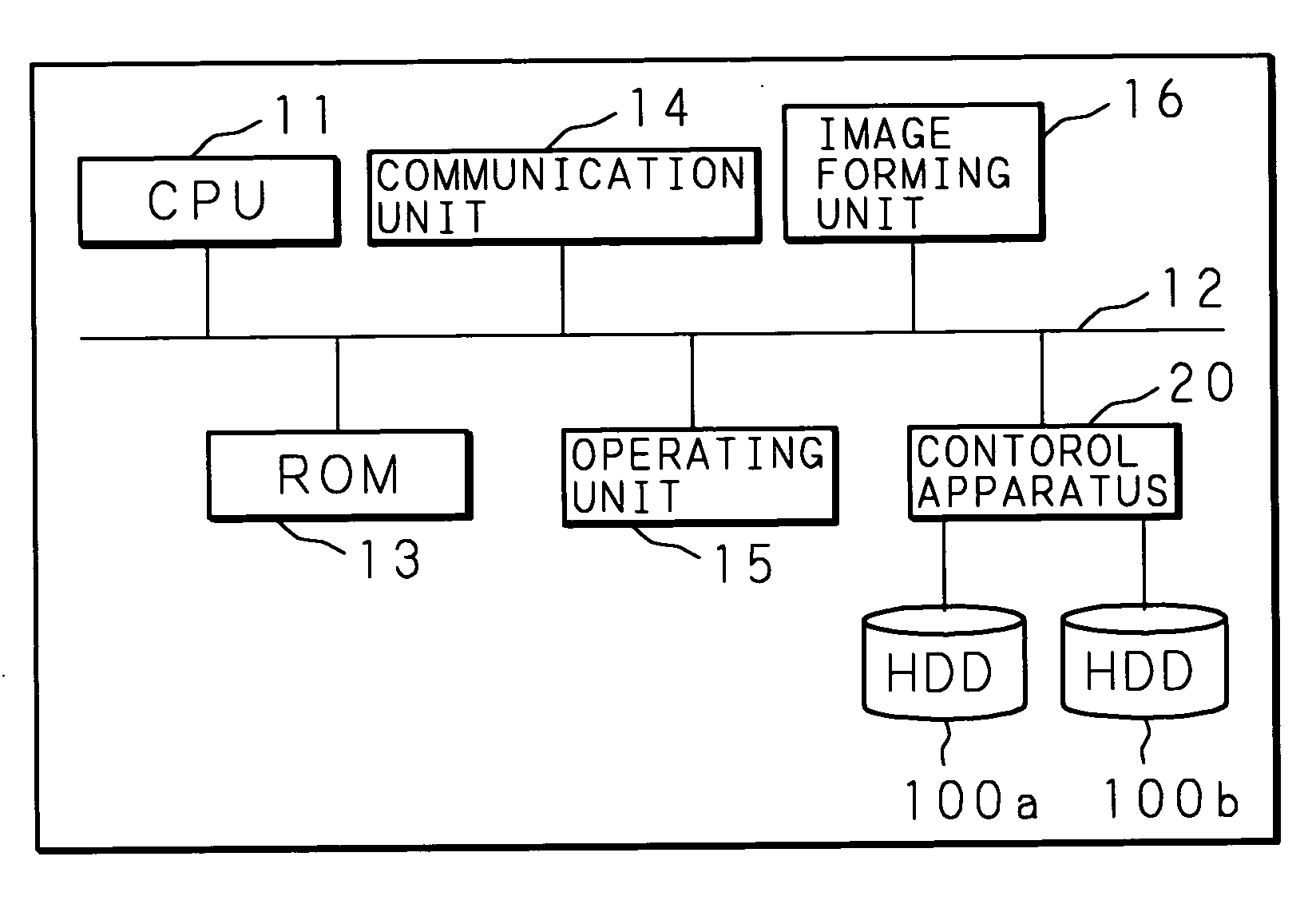

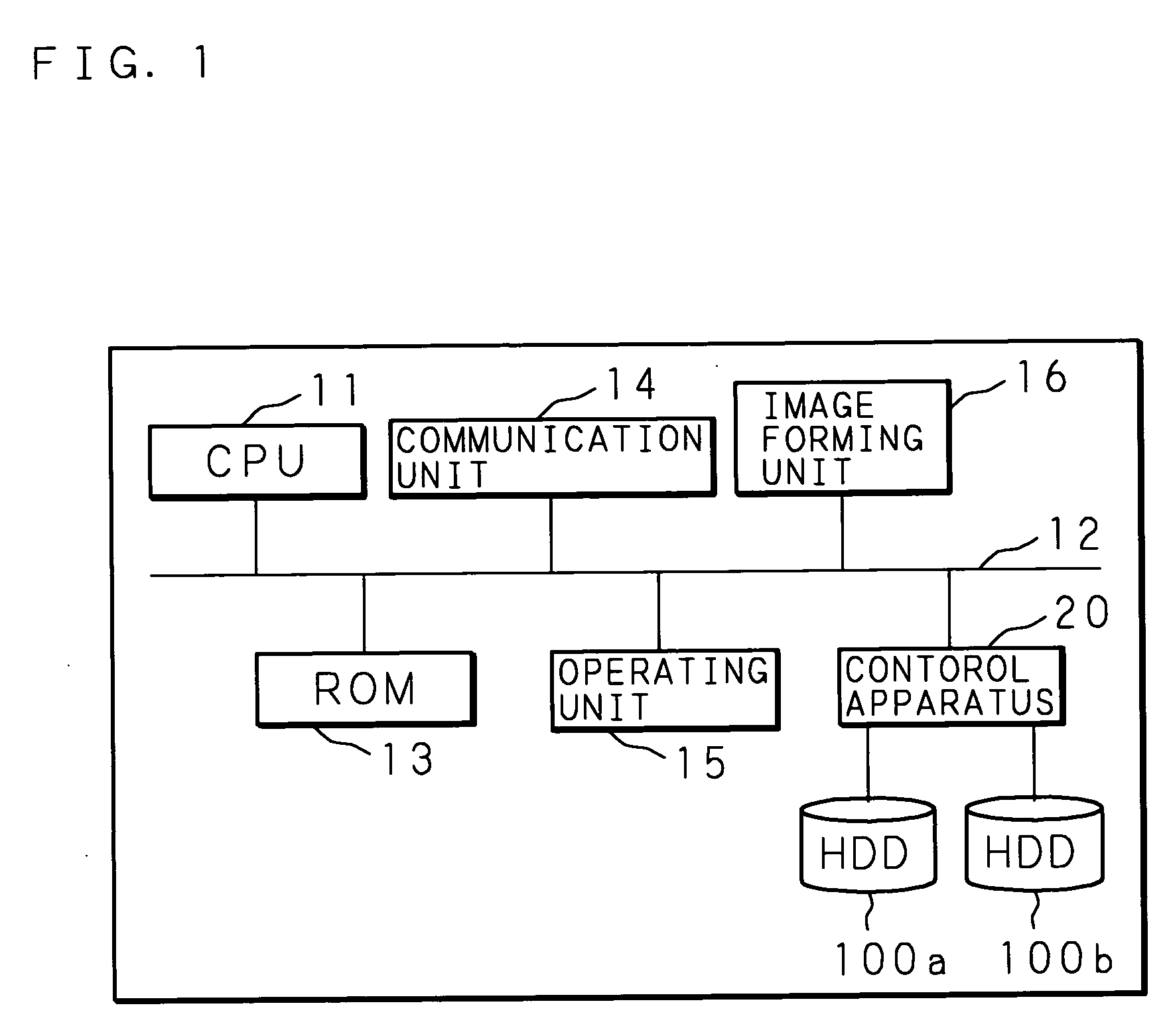

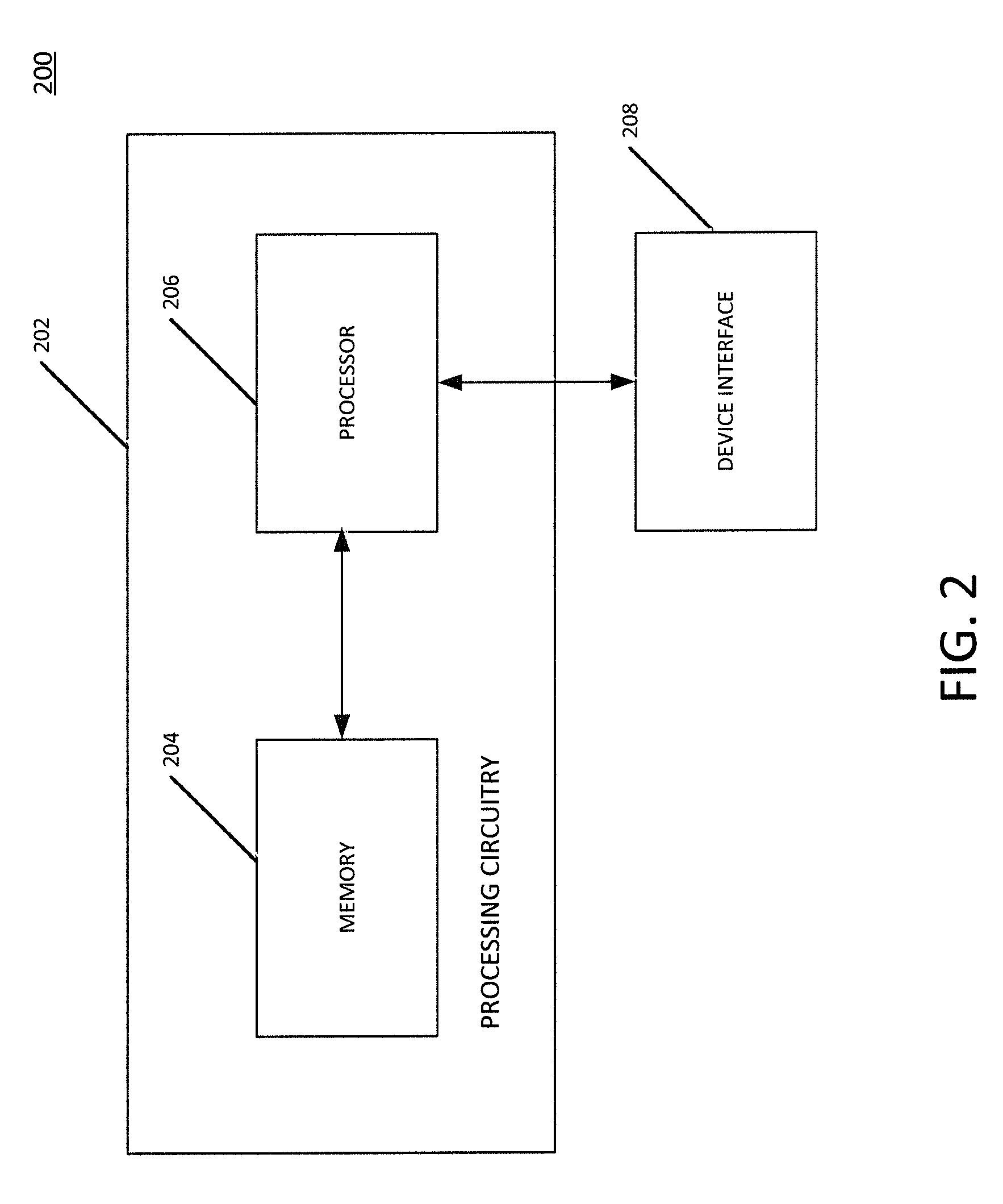

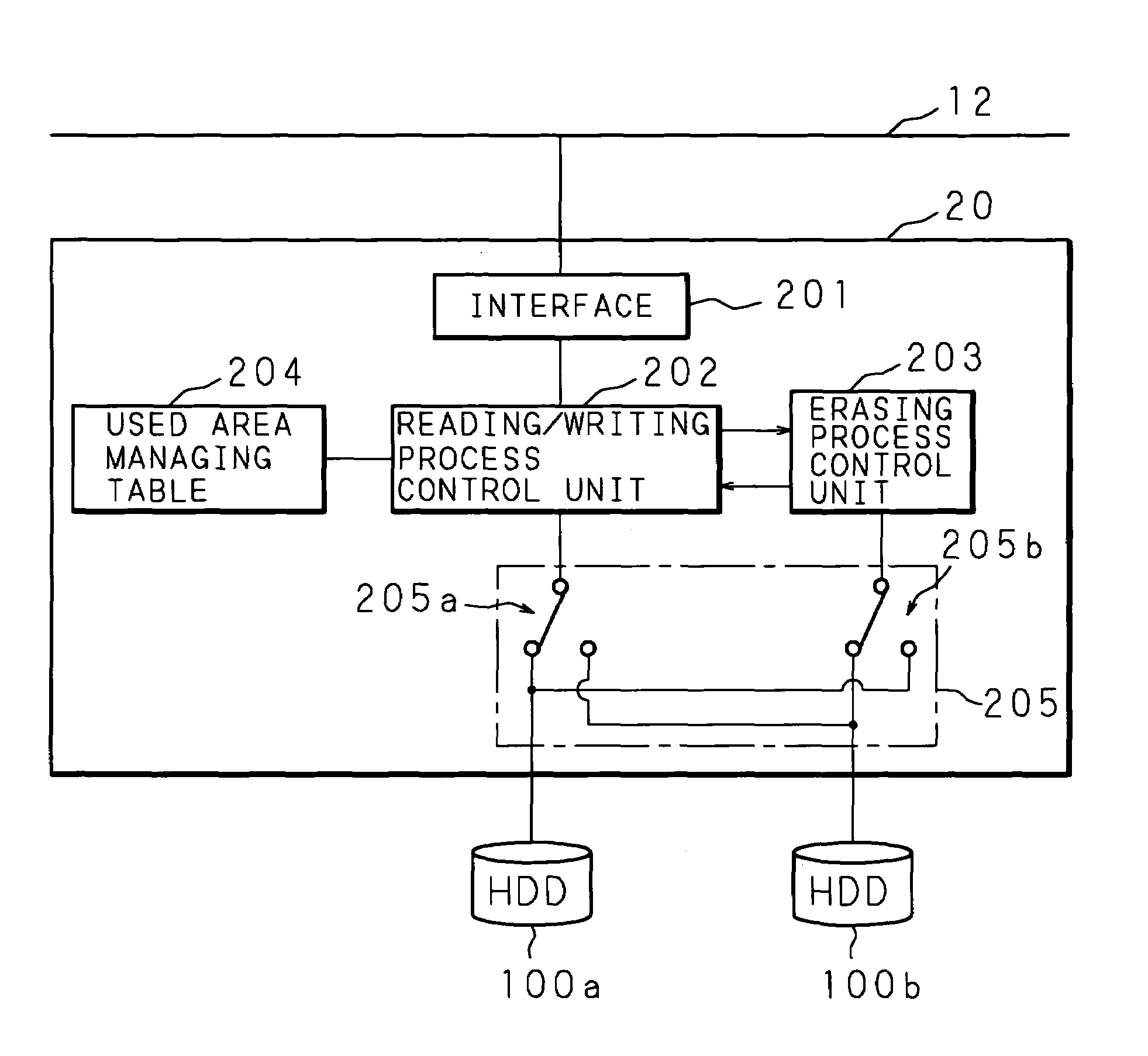

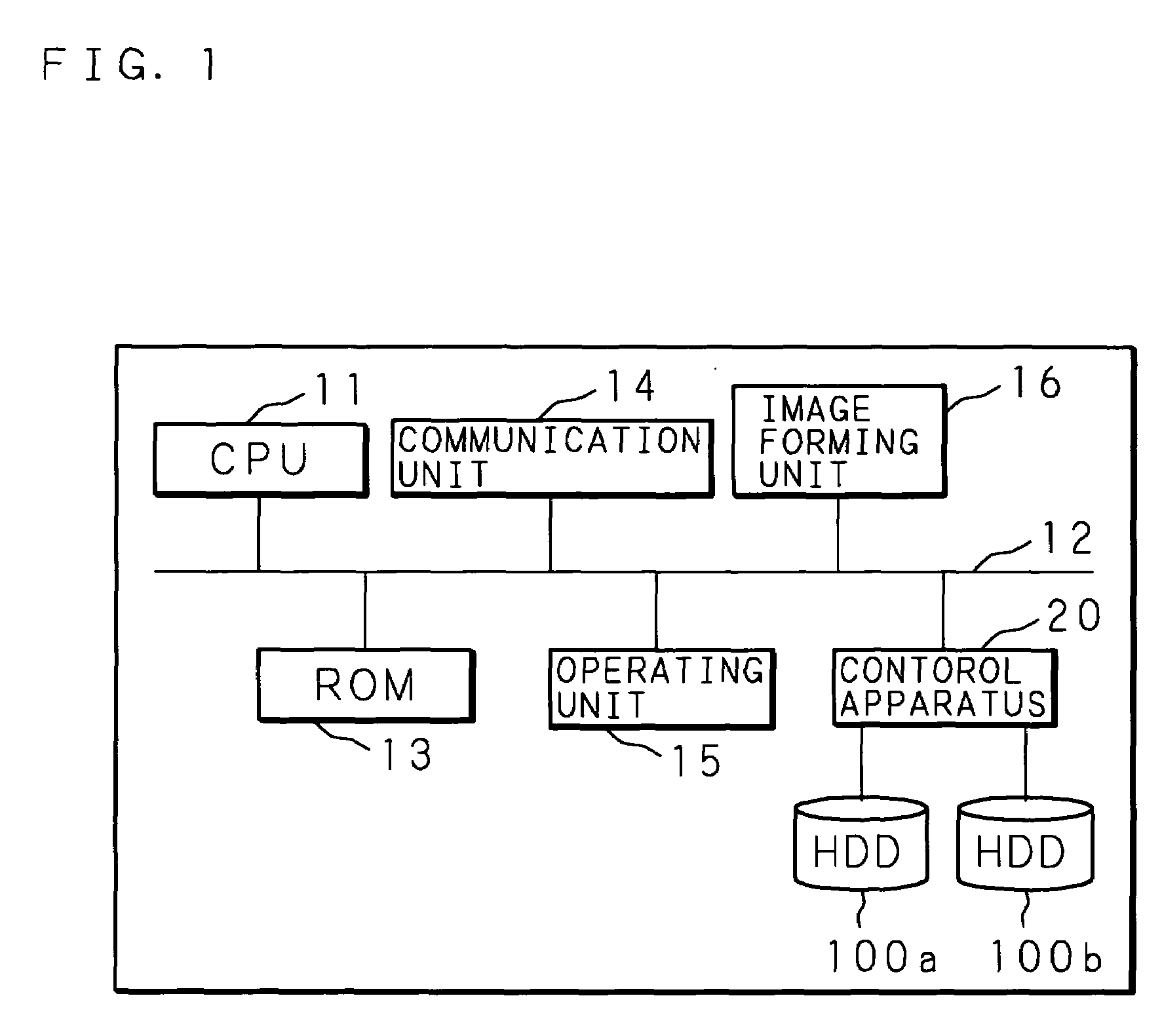

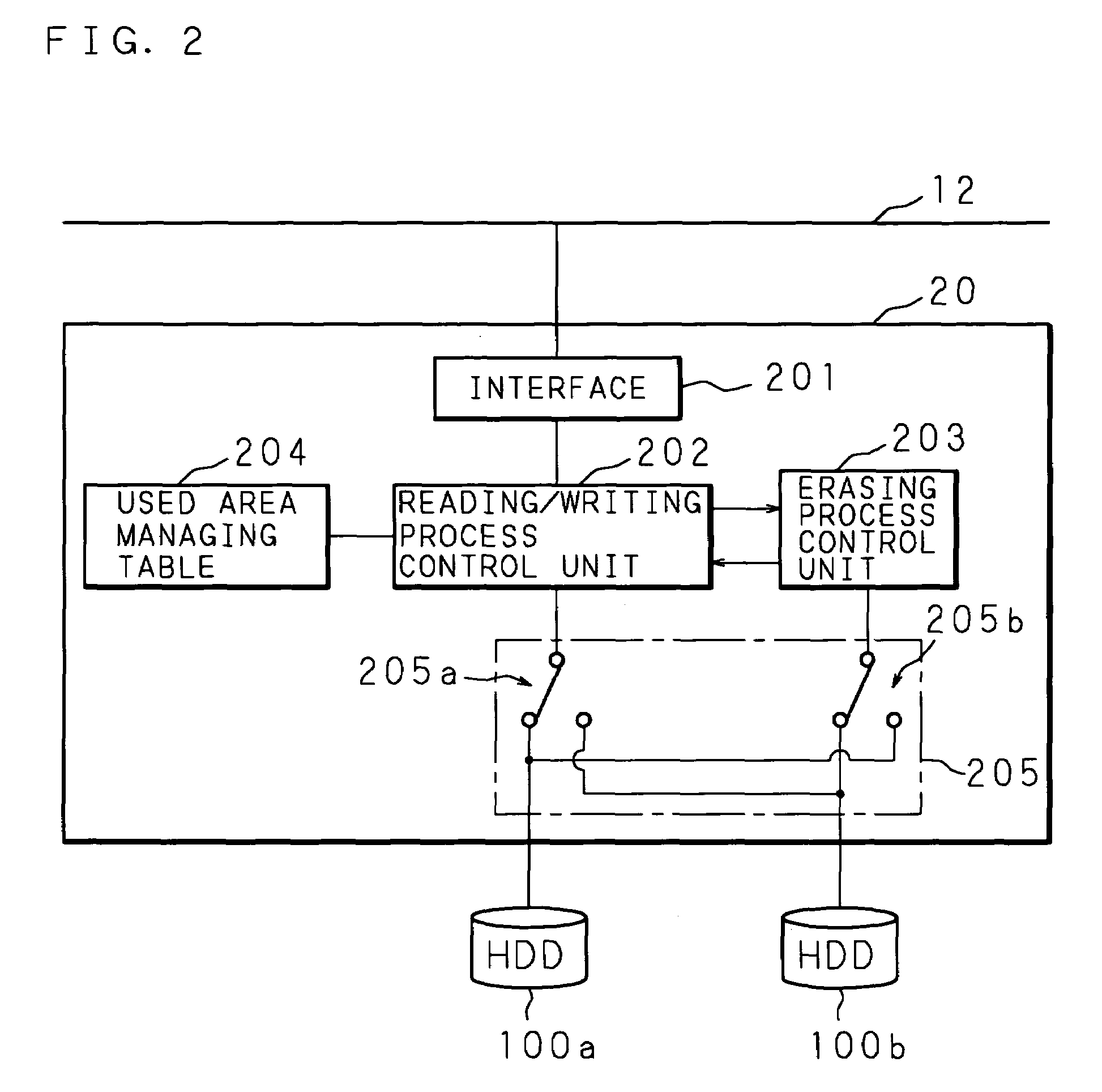

Control system; control apparatus; storage device and computer program product

ActiveUS20050219899A1Reduce access rateInput/output to record carriersRead-only memoriesControl systemEmbedded system

A reading / writing process control unit for instructing a reading / writing process and an erasing process control unit for instructing an erasing process are provided separately and each is connected with two HDDs via a switch. While the reading / writing process control unit is connected with one HDD and executing a reading / writing process, a switch is controlled to connect the erasing process control unit with another HDD to erase data of the HDD connected with the erasing process control unit. Since it is enabled to execute a data reading / writing process and a data erasing process for a storage device in parallel for different HDDs, lowering of the access rate as a whole can be prevented.

Owner:SHARP KK

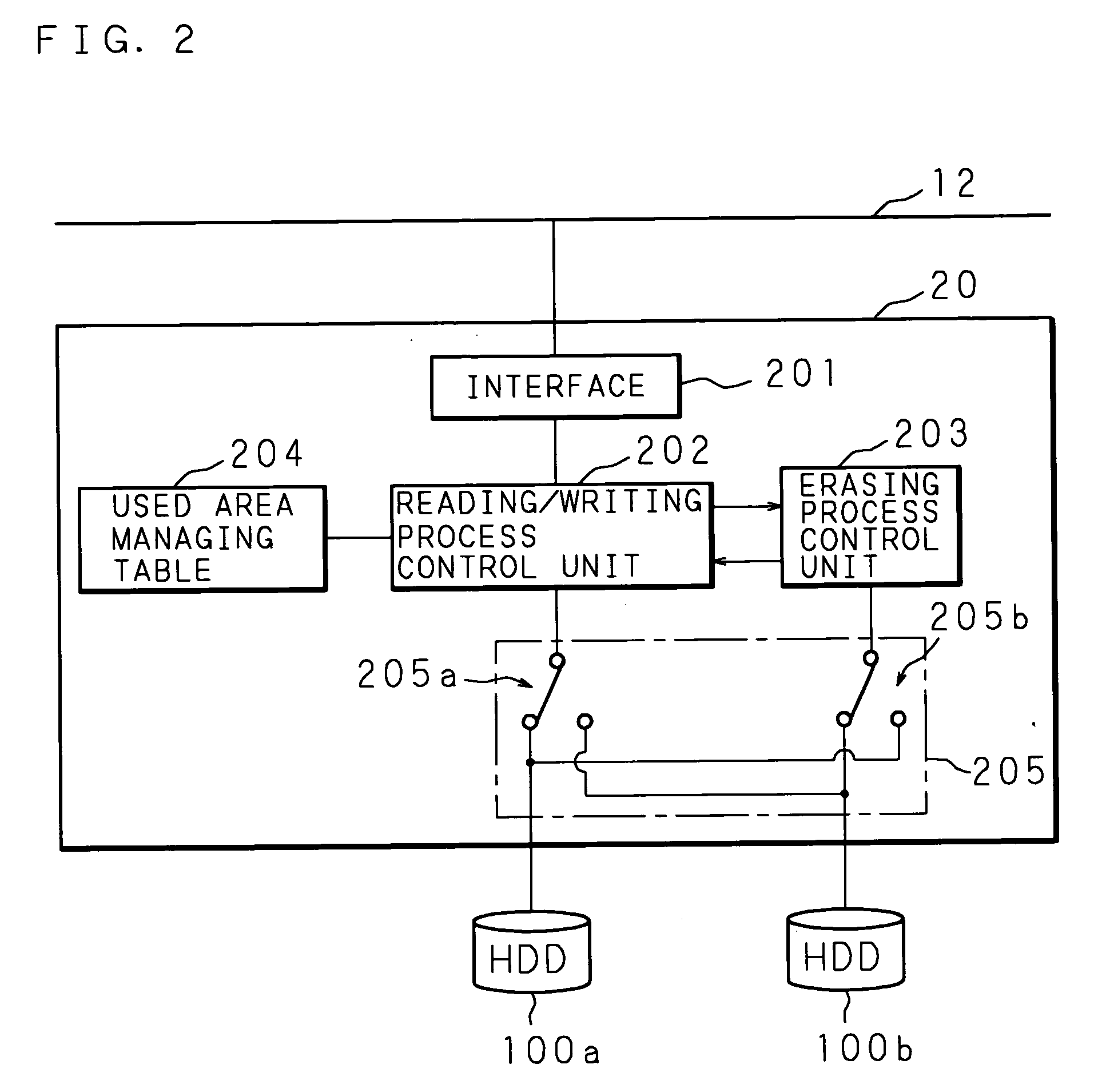

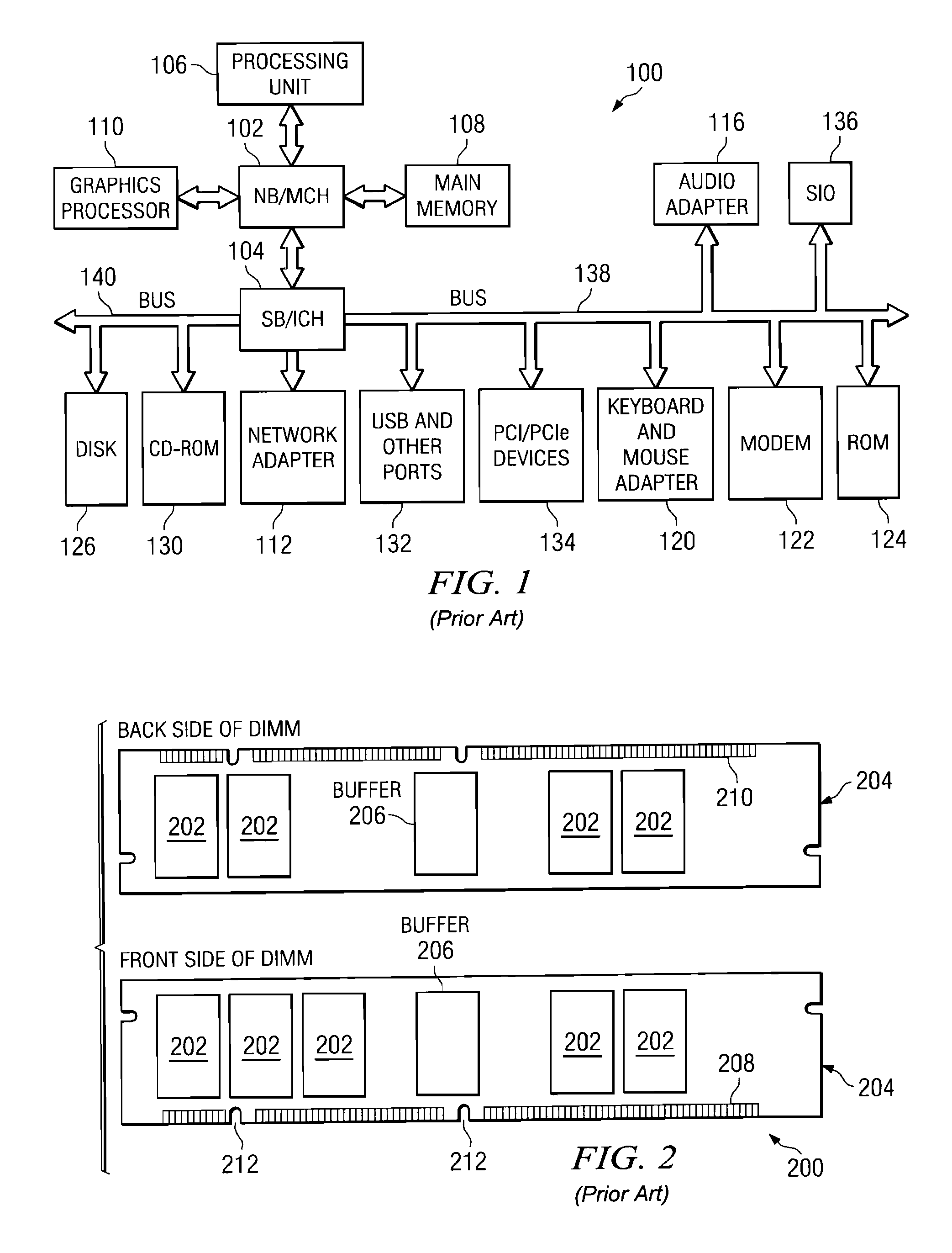

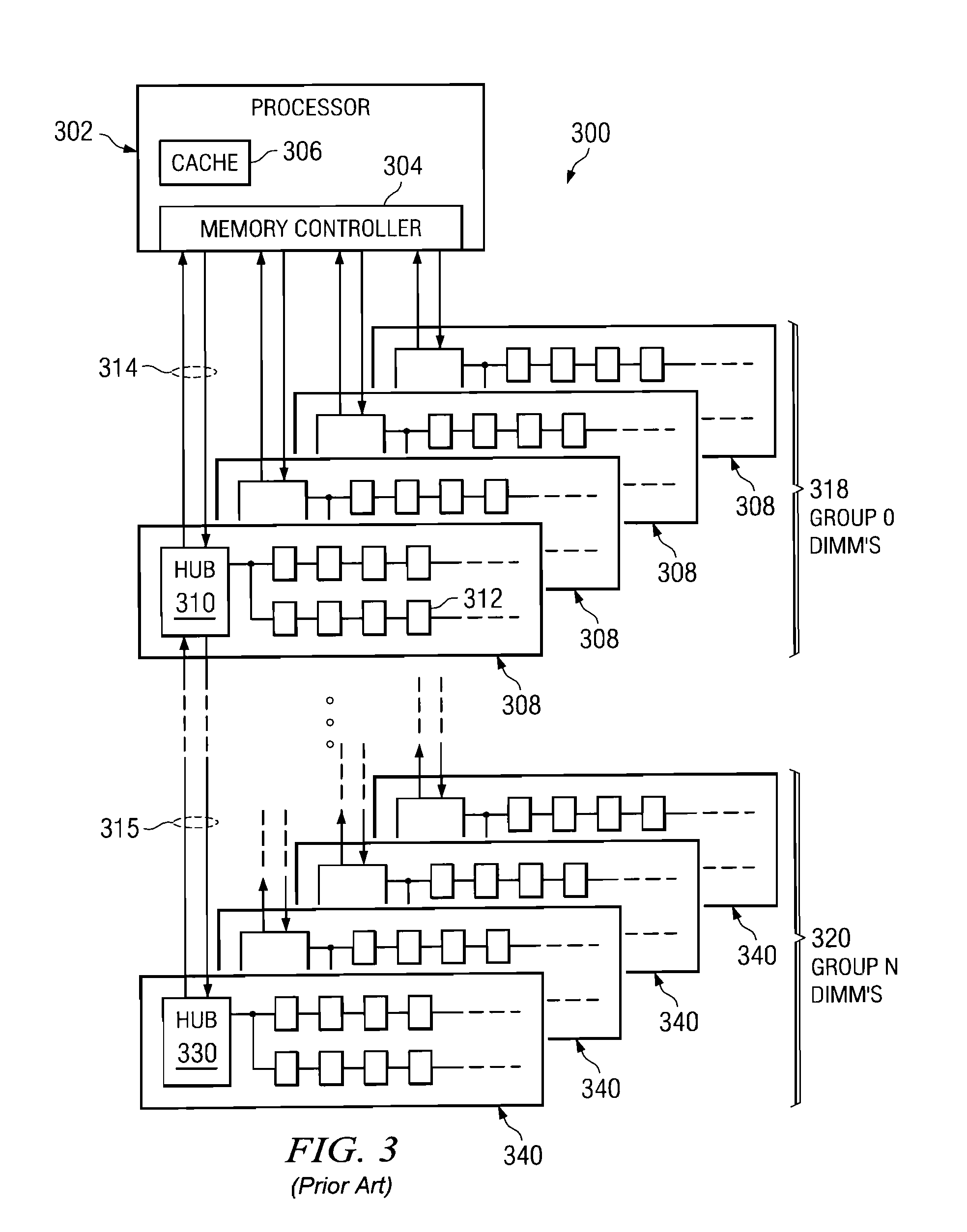

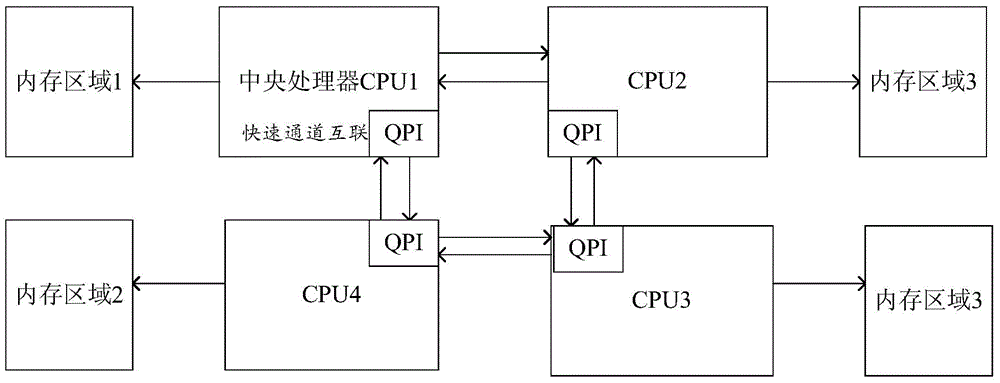

System to enable a memory hub device to manage thermal conditions at a memory device level transparent to a memory controller

InactiveUS7930470B2High bandwidthReduce operating frequencyEnergy efficient ICTDigital data processing detailsParallel computingDevice Monitor

A memory system is provided that manages thermal conditions at a memory device level transparent to a memory controller. The memory systems comprises a memory hub device integrated in a memory module, a set of memory devices coupled to the memory hub device, and a first set of thermal sensors integrated in the set of memory devices. A thermal management control unit integrated in the memory hub device monitors a temperature of the set of memory devices sensed by the first set of thermal sensors. The memory hub device reduces a memory access rate to the set of memory devices in response to a predetermined thermal threshold being exceeded thereby reducing power used by the set of memory devices which in turn decreases the temperature of the set of memory devices.

Owner:INT BUSINESS MASCH CORP

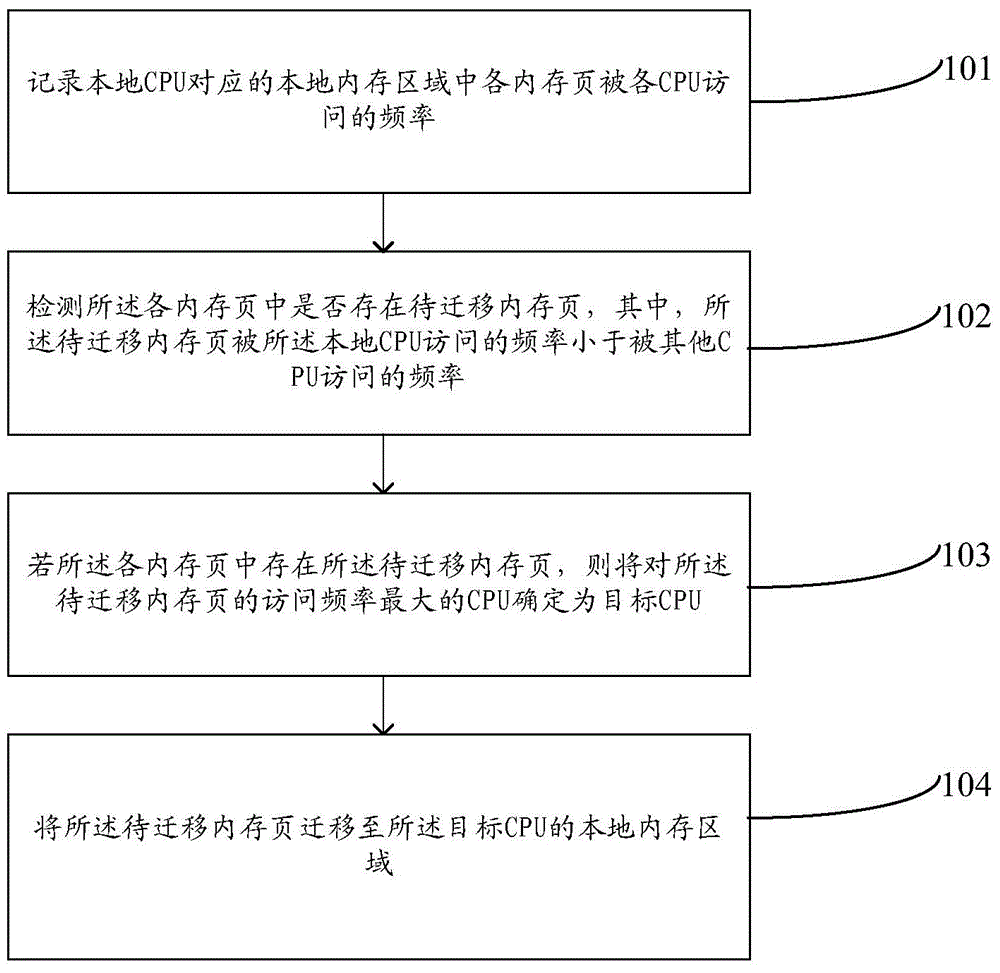

Cache management method and device

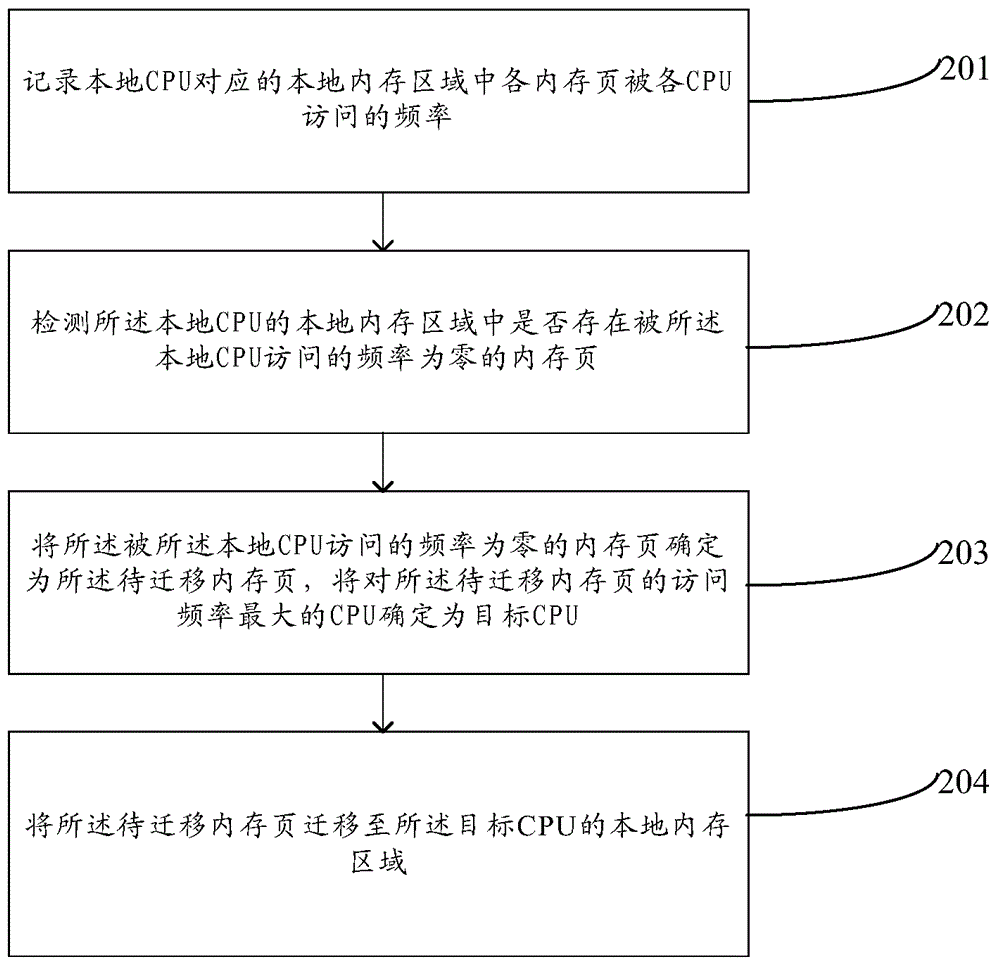

ActiveCN104156322AReduce access rateImprove access rateInput/output to record carriersMemory adressing/allocation/relocationData accessAccess frequency

The embodiment of the invention provides a cache management method and device and relates to the technical field of computer application. An internal storage page is transferred reasonably, so that data are concentrated at the local internal storage zones of CPUs as much as possible, data accessing speed lowering caused by frequent remote internal storage accessing is avoided, and data accessing speed is improved. The method comprises the steps that the accessing frequency from each CPU to each internal storage page in the local internal storage zone corresponding to a local CPU is recorded; whether an internal storage page exists in each internal storage page is detected, and if yes, a CPU with the maximum accessing frequency of the internal storage page to be accessed is determined as a target CPU; and the internal storage page to be accessed is transferred to the local internal storage zone of the target CPU.

Owner:HUAWEI TECH CO LTD

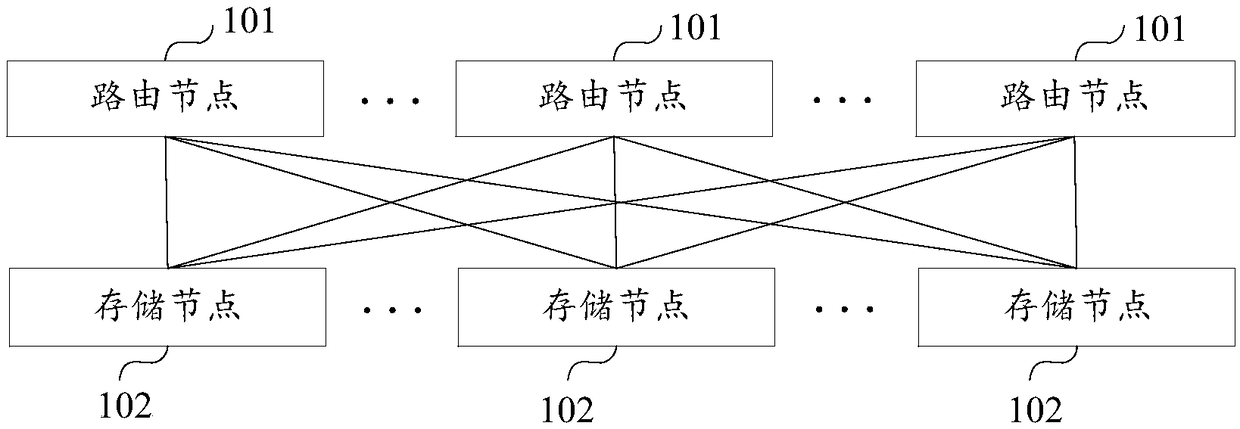

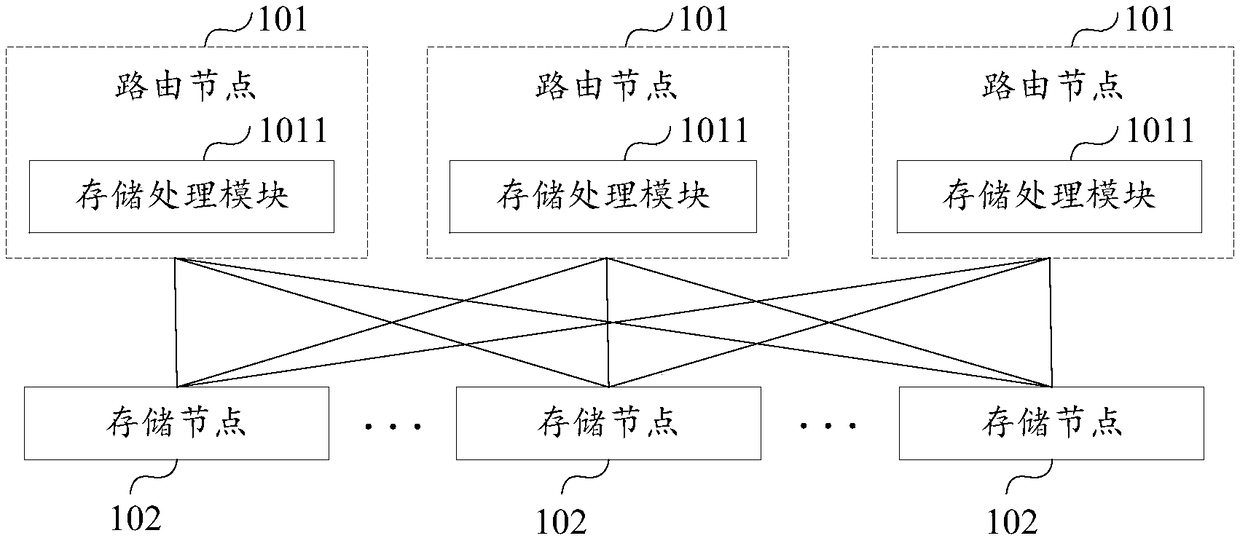

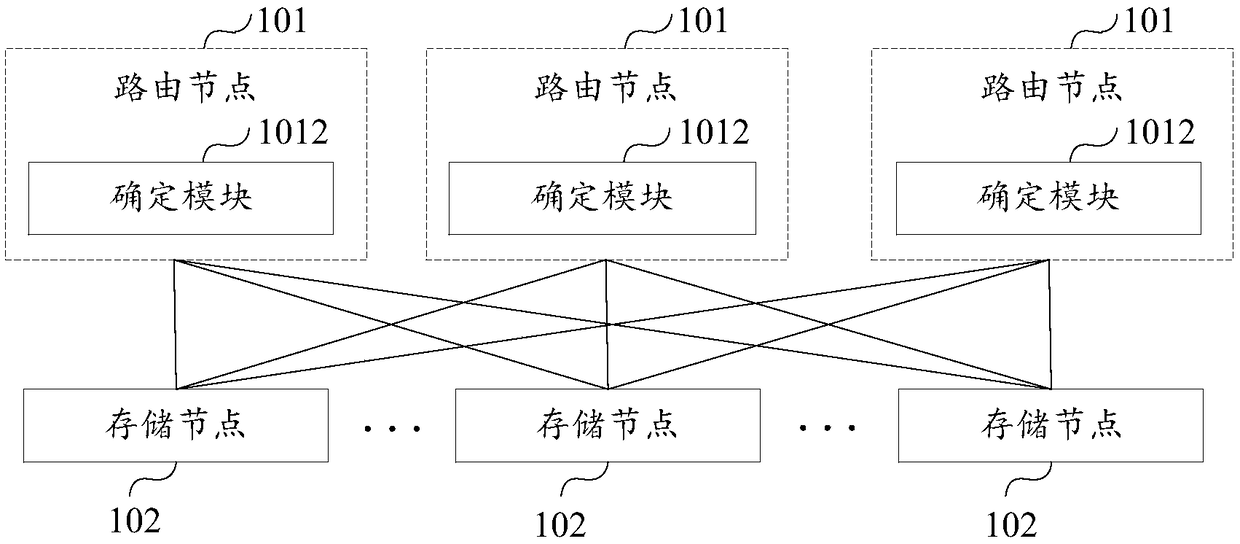

Block chain system and application method thereof

ActiveCN108664222AImprove storage efficiencyReduce access rateInput/output to record carriersComplete dataChain system

The invention provides a block chain system and an application method thereof. The block chain system comprises one or more routing nodes and one or more storage nodes; each routing node is used for determining one or more target storage nodes in one or more storage nodes when receiving data and sending the data to one or more target storage nodes; a storage condition of one or more target storagenodes for storing the data is monitored, and when it is monitored that one or more target storage nodes complete data storage, data storage task information is broadcasted; each storage node is usedfor storing the data when receiving the data sent by the routing nodes. Therefore, according to the scheme, the efficiency of storing the data can be improved.

Owner:BEIJING QIHOO TECH CO LTD

Method and apparatus for reselecting cell in mobile communication system

InactiveUS8265035B2Reduce degradationReduce access rateError preventionTransmission systemsTelecommunicationsMobile communication systems

Embodiments of the present invention include a method for performing cell reselection in a mobile communication system. The method comprises the steps of reading, by a user equipment (UE), the Access Class (AC) barring parameters of the serving cell which are broadcast from a base station, and performing an AC barring check; calculating the cell reselection values of the serving cell and the adjacent cells according to the cell reselection parameters broadcast by the base station when the AC barring check fails; and ranking the calculated cell reselection values, selecting by the UE the cell corresponding to the maximum value of the calculated cell reselection values as the serving cell of the UE.

Owner:NTT DOCOMO INC

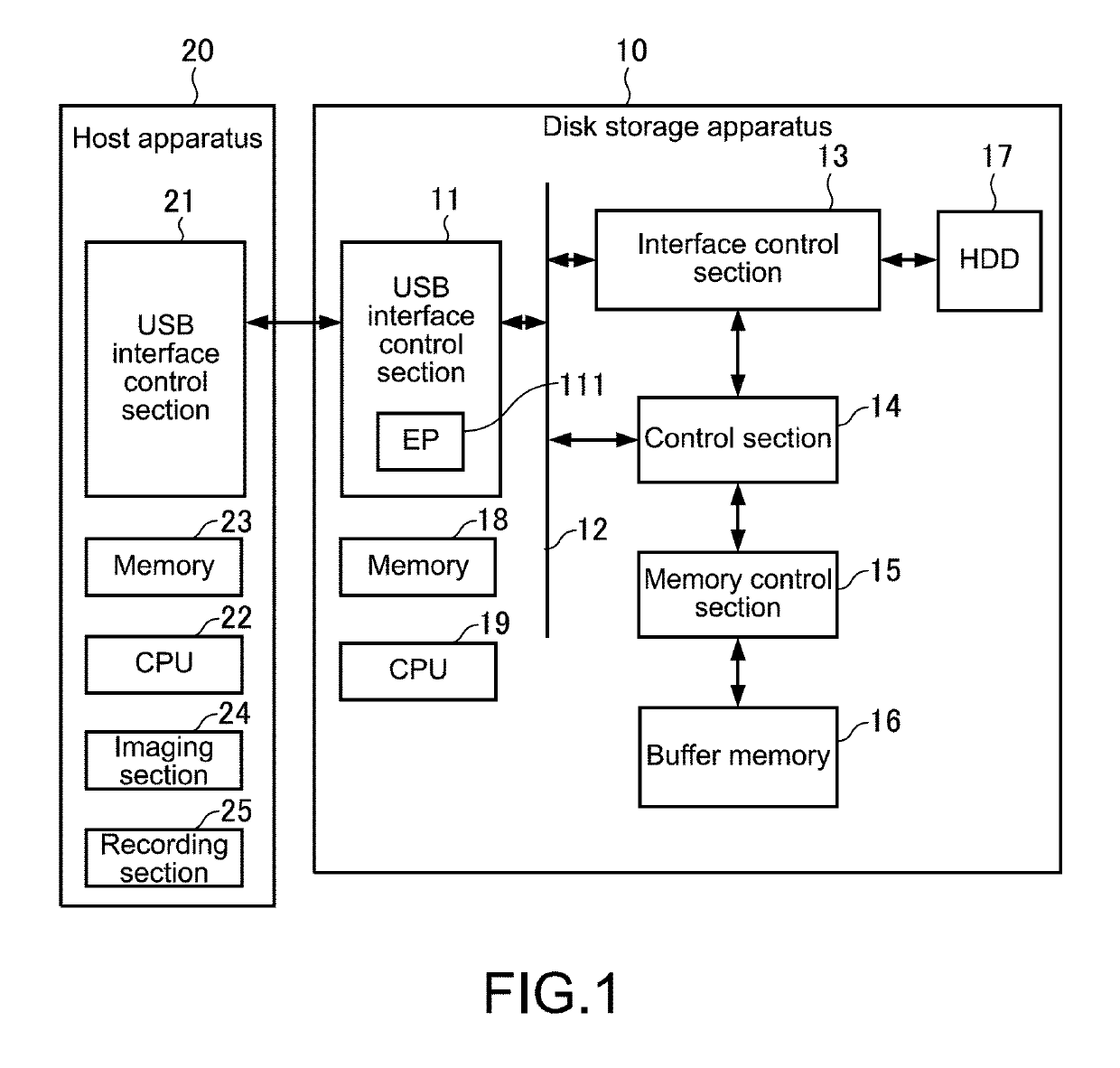

Disk storage apparatus and program

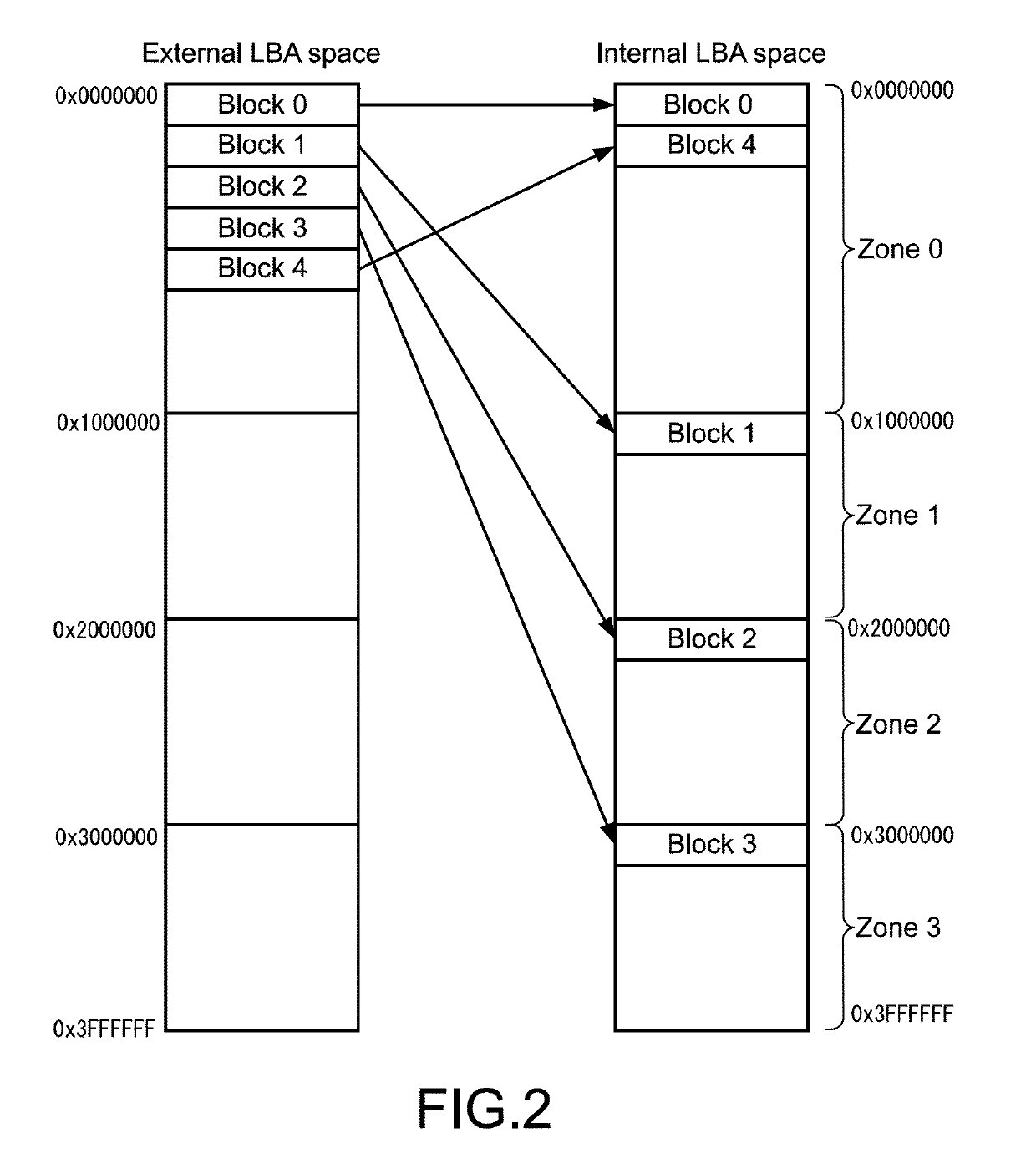

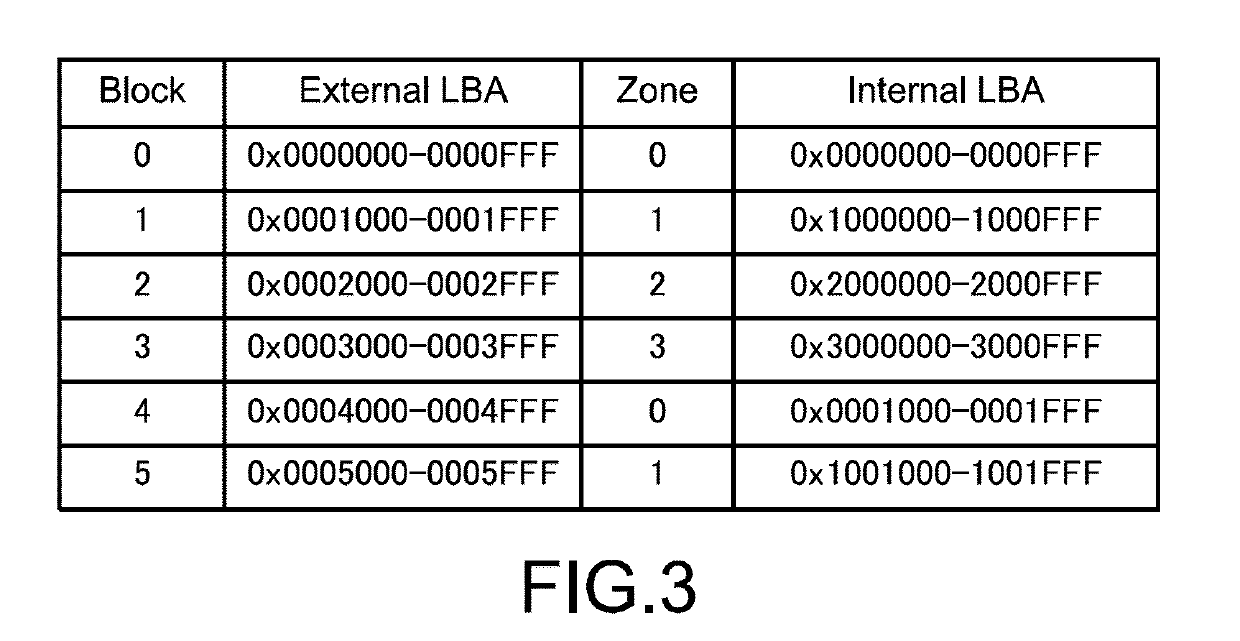

InactiveUS20090327598A1Access rate decreaseReduce access rateMemory adressing/allocation/relocationRecord information storageAddress spaceTransmission rate

Disclosed is a disk storage apparatus to control writing to a storage medium having a storage area to which a first address space is allocated and whose transfer rate spatially changes, including a command reception section and control section. The command reception section receives a write command from a host apparatus and containing an address of the first address space. The control section performs control to divide the storage area into zones, pre-define a second address space where blocks are successively allocated to the zones from a beginning address of the first address space, replace, for each of the write commands received by the command reception, an address of the first address space contained therein with an address of the second address space, select one of the zones as a write target zone by cyclical changing, and perform a writing process to the storage medium for each selected zone.

Owner:SONY CORP

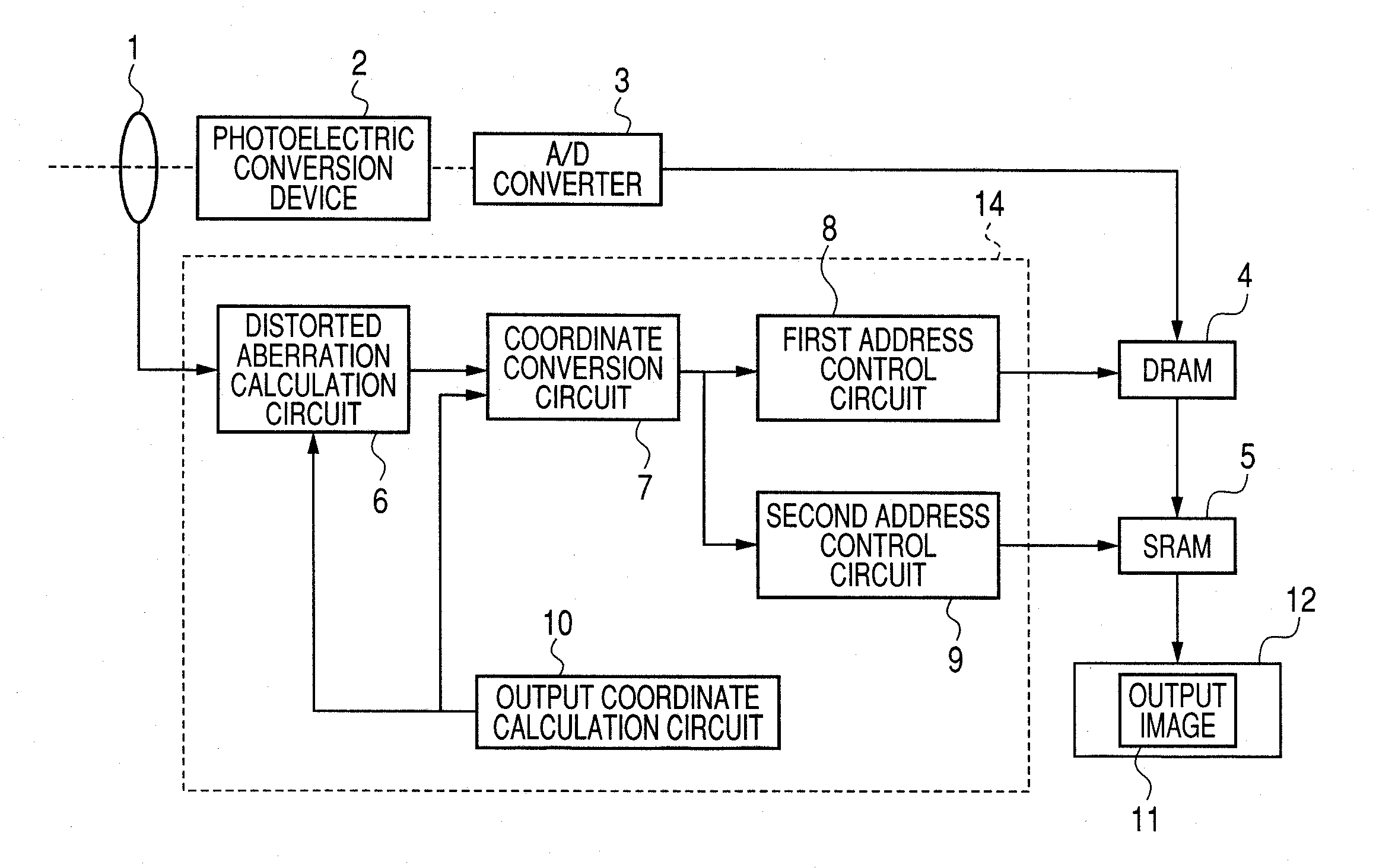

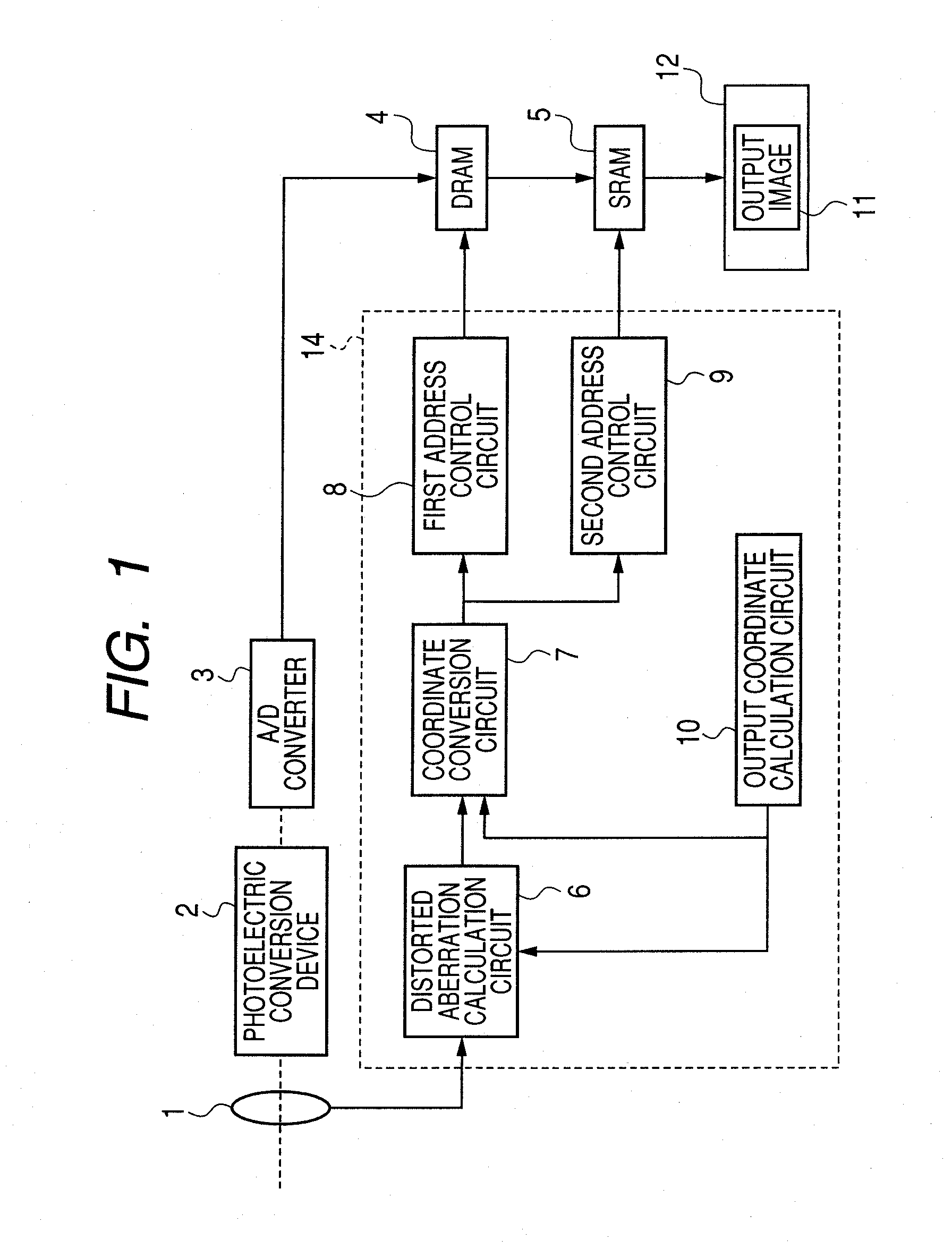

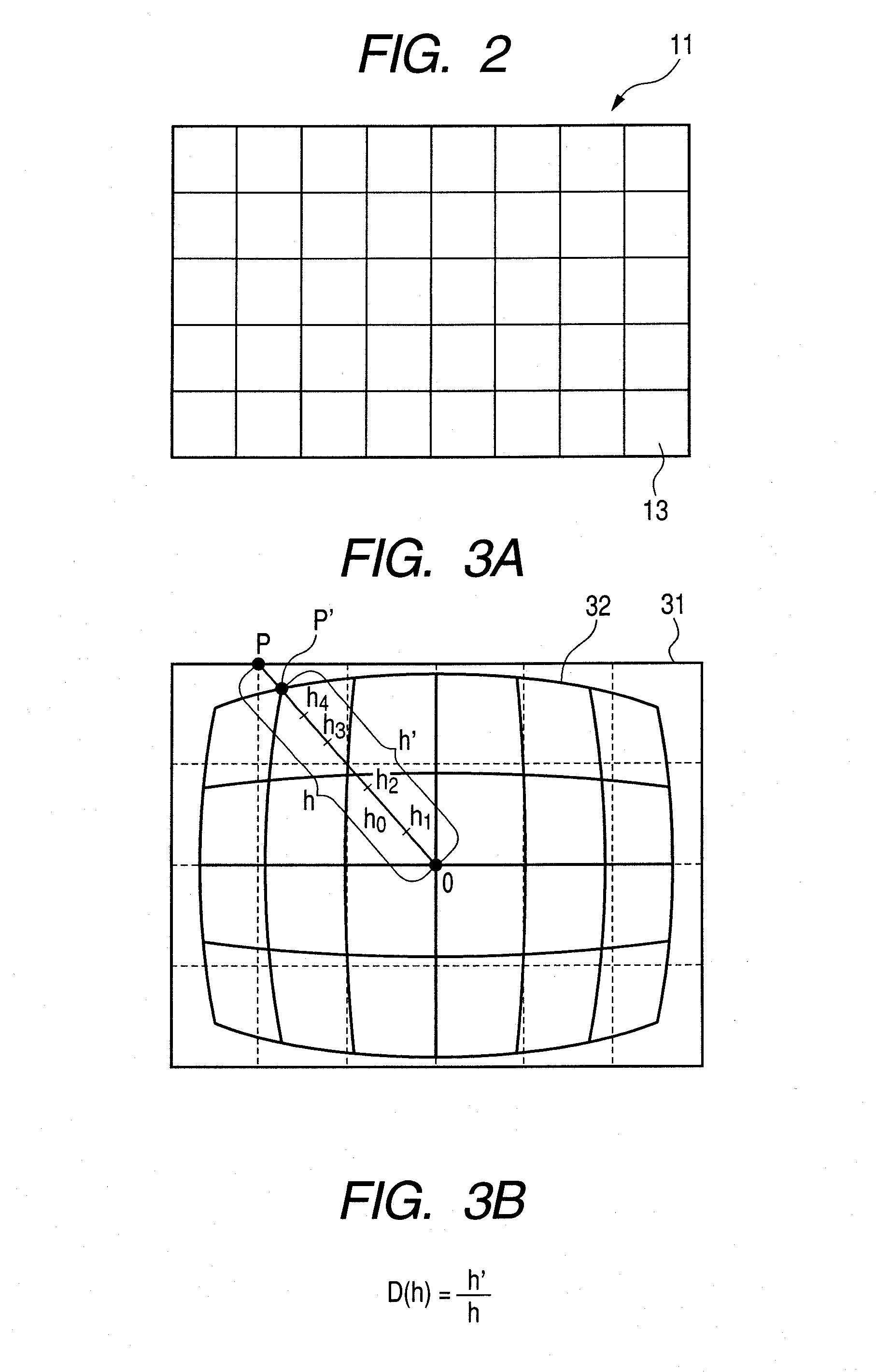

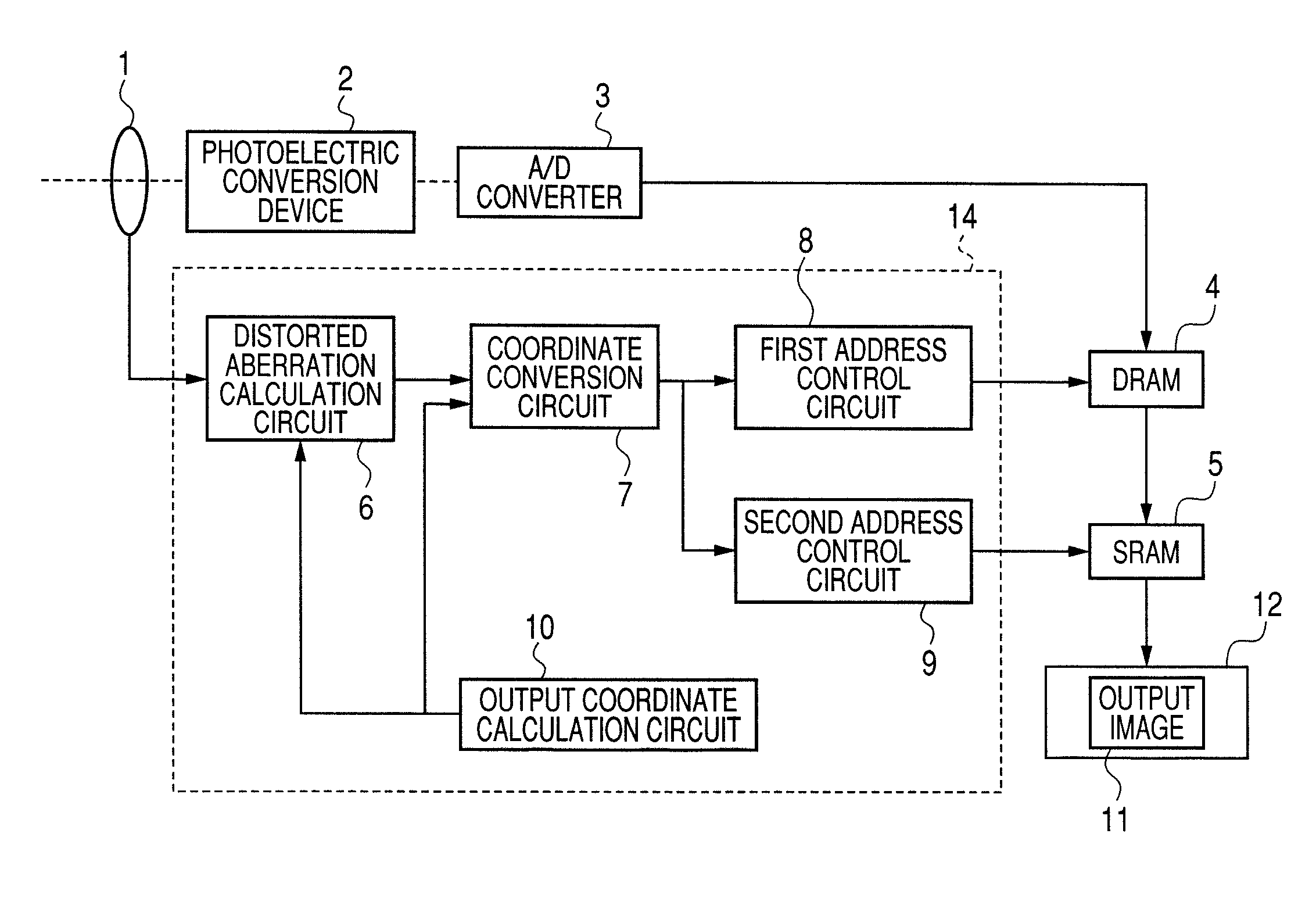

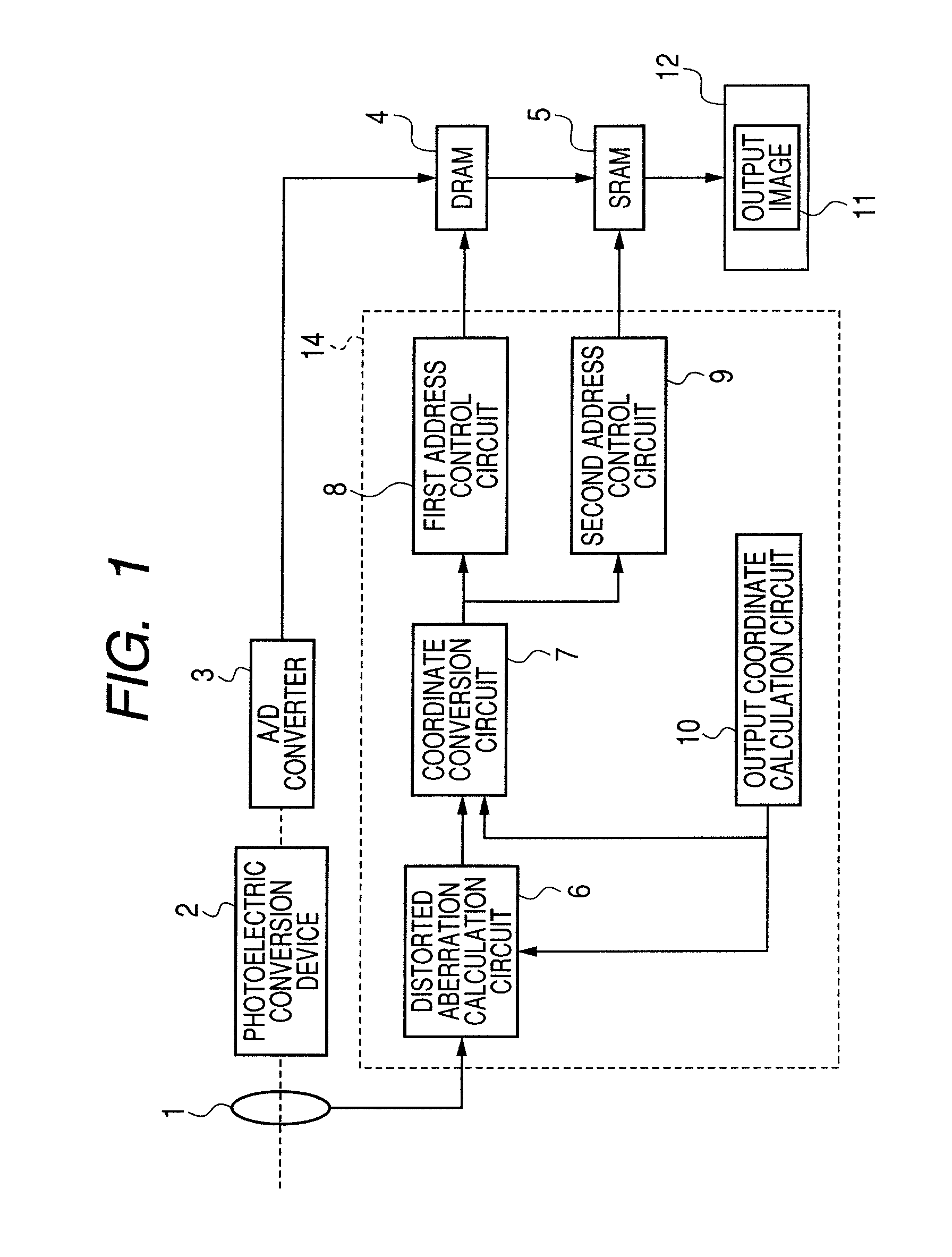

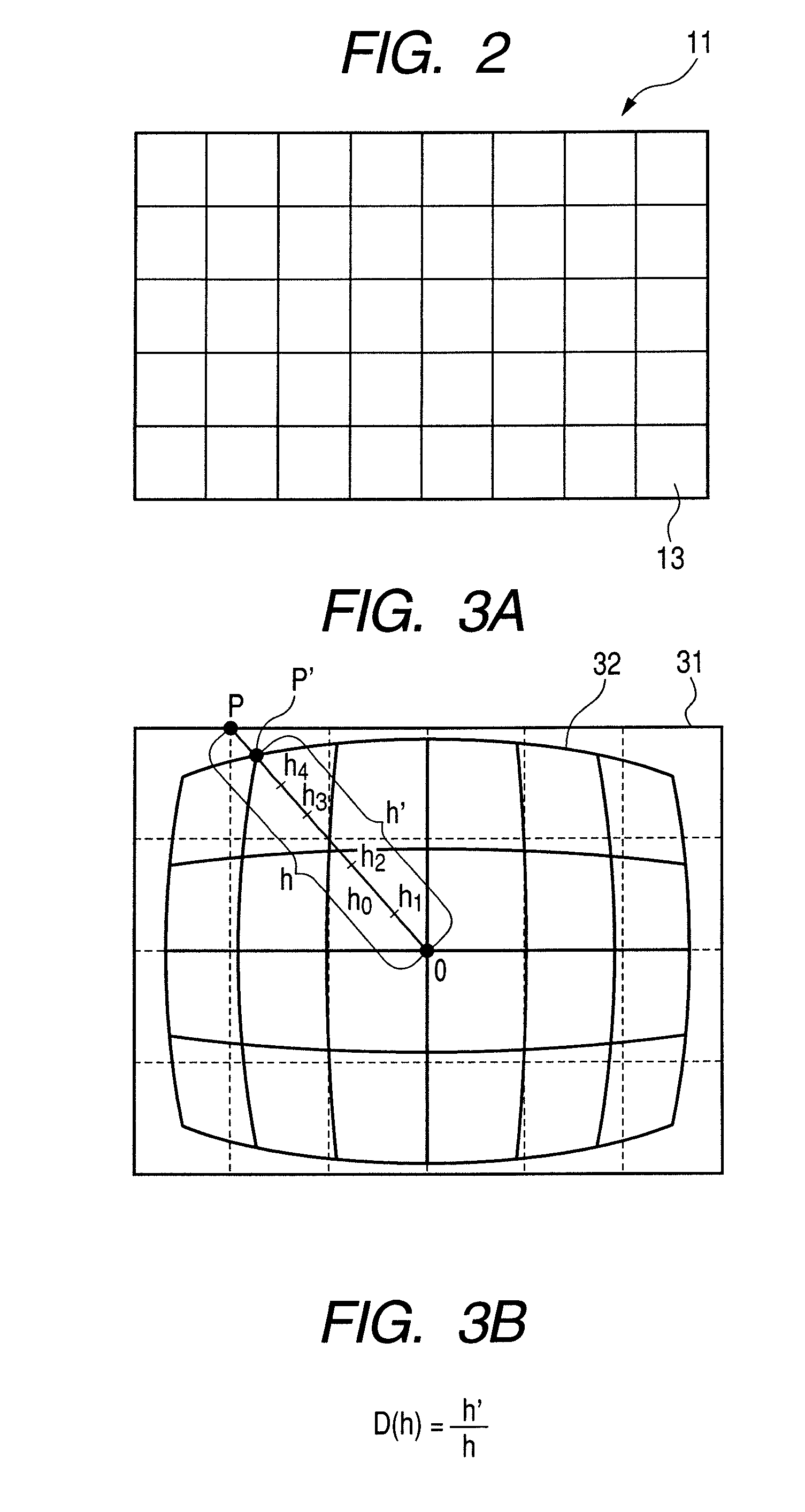

Distorted aberration correction processing apparatus

ActiveUS20080100929A1Reduce access rateAberration correctionTelevision system detailsColor signal processing circuitsAddress controlOptical aberration

A distorted aberration correction processing apparatus includes DRAM and SRAM for storing an object image from an optical system. Further, the distorted aberration correction processing apparatus includes: a first address control circuit for reading out a pixel in the DRAM on a unit basis of an area including a plurality of the pixels along a curve corresponding to a distorted aberration of an optical system and writing the read-out pixel in SRAM; and a second address control circuit for reading out a pixel in the SRAM on a pixel basis and outputting the pixel read out on a pixel basis to an output portion so as to suppress the distorted aberration of the optical system. The first address control circuit effects control so that the signal of the areas is sequentially read out in a predetermined order, and the second address control circuit effects random access control.

Owner:CANON KK

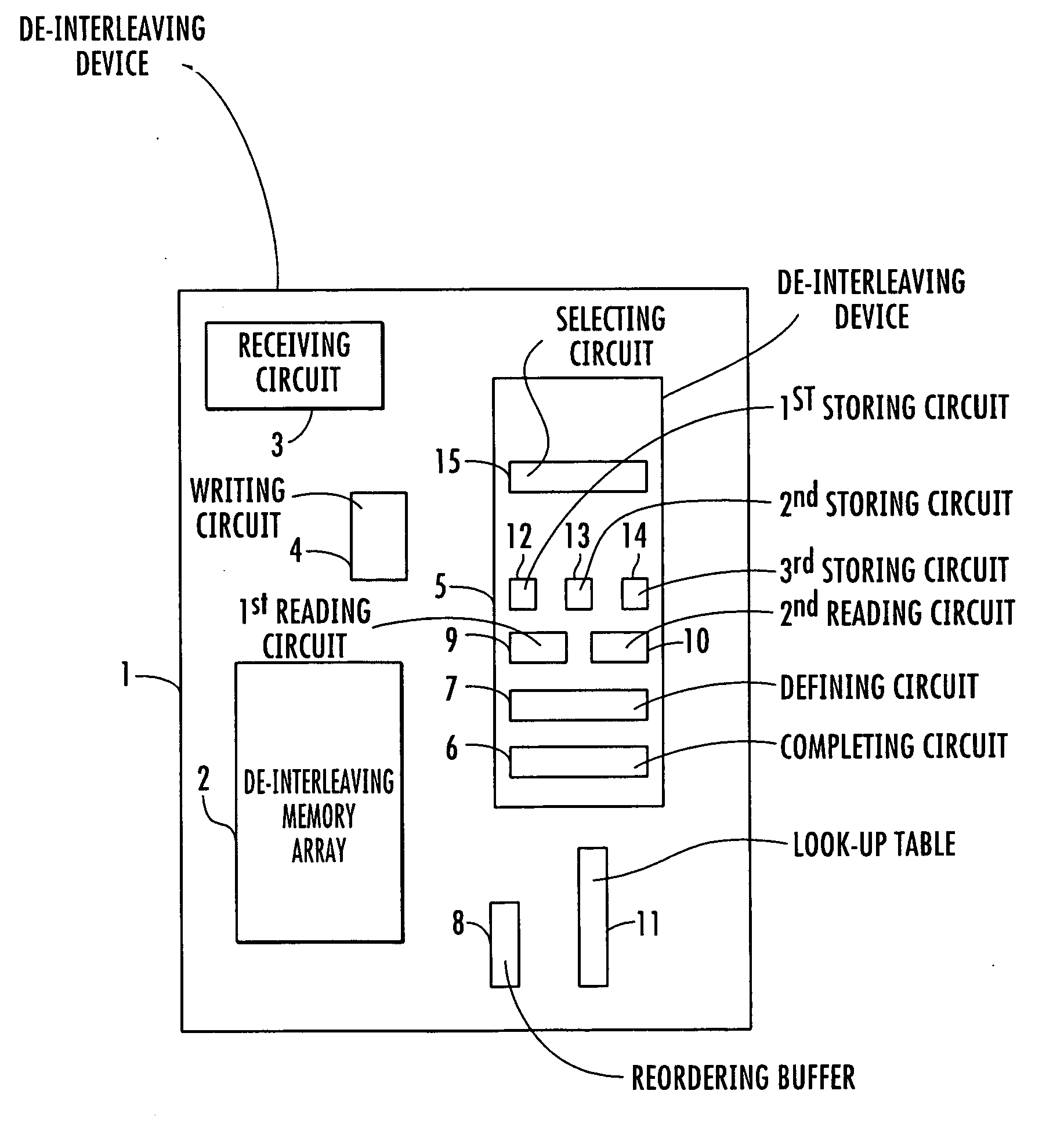

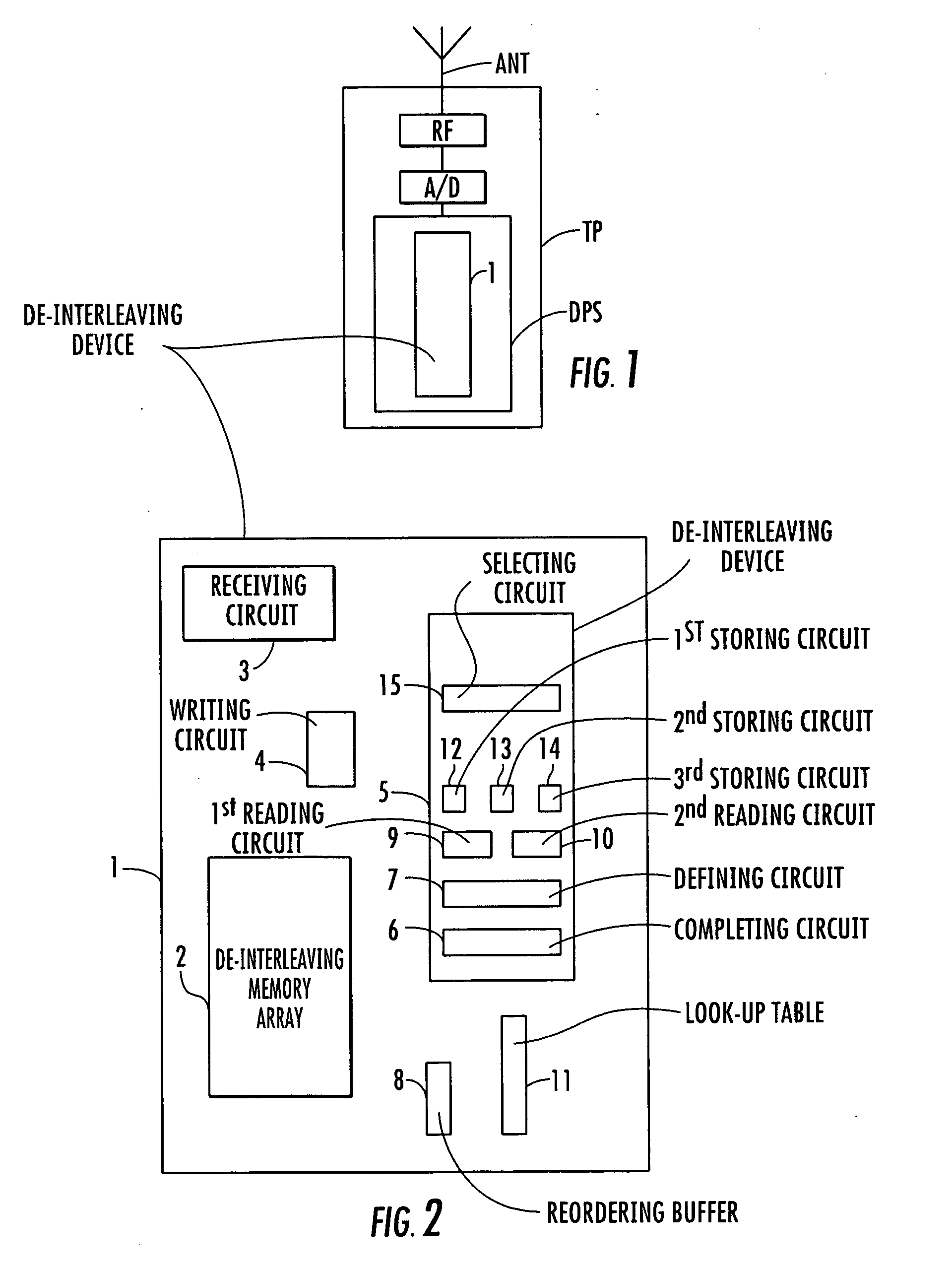

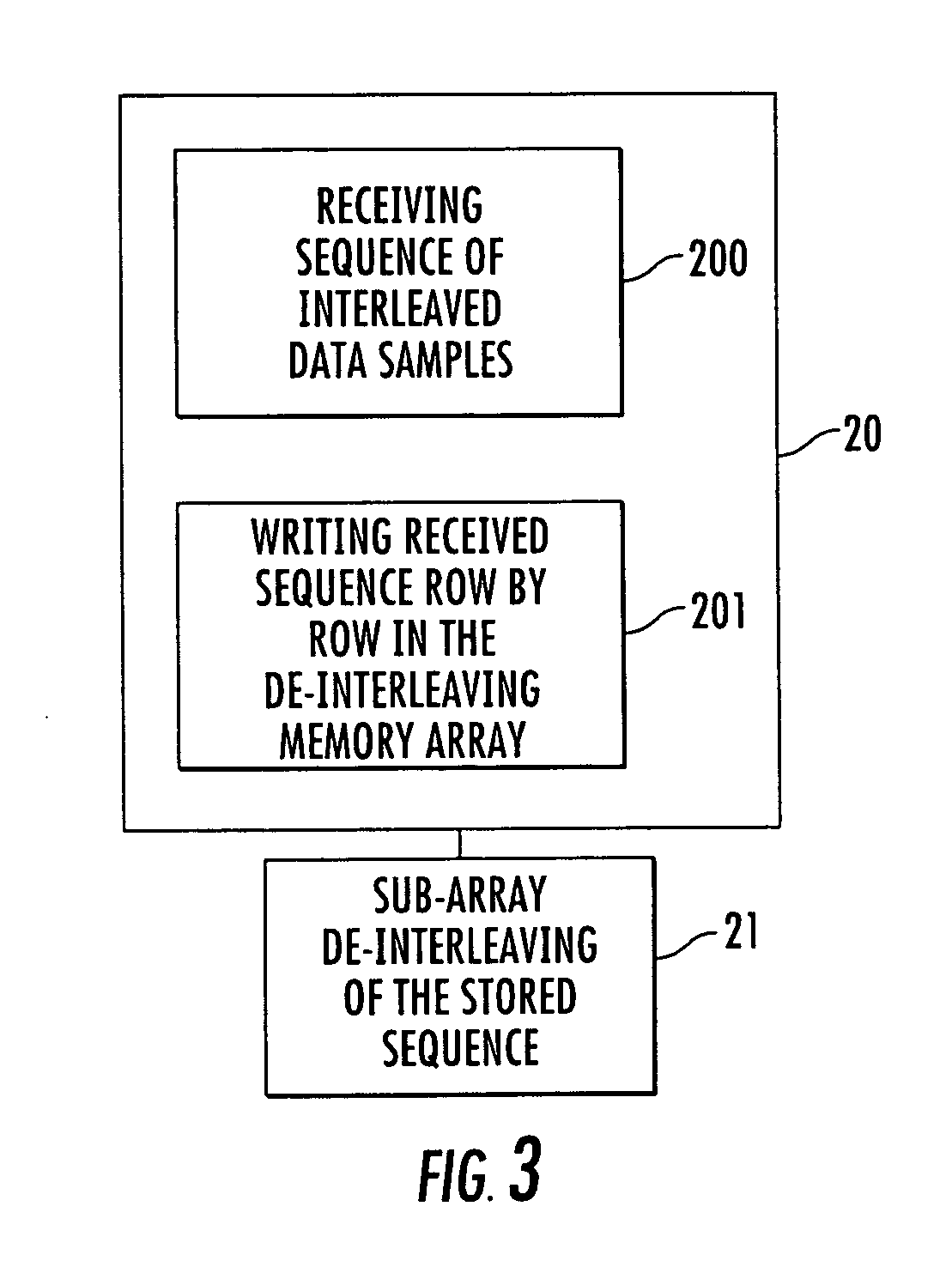

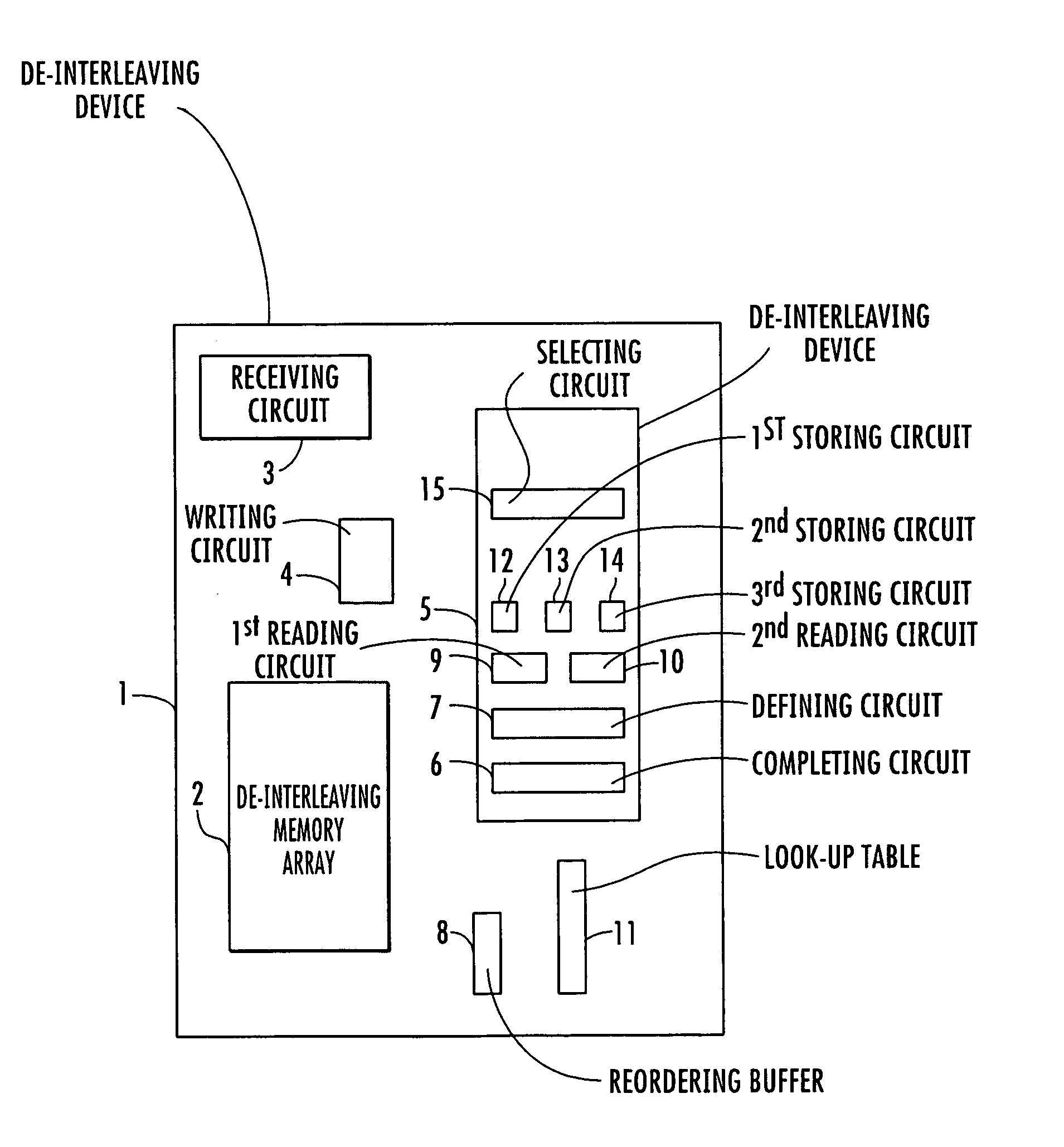

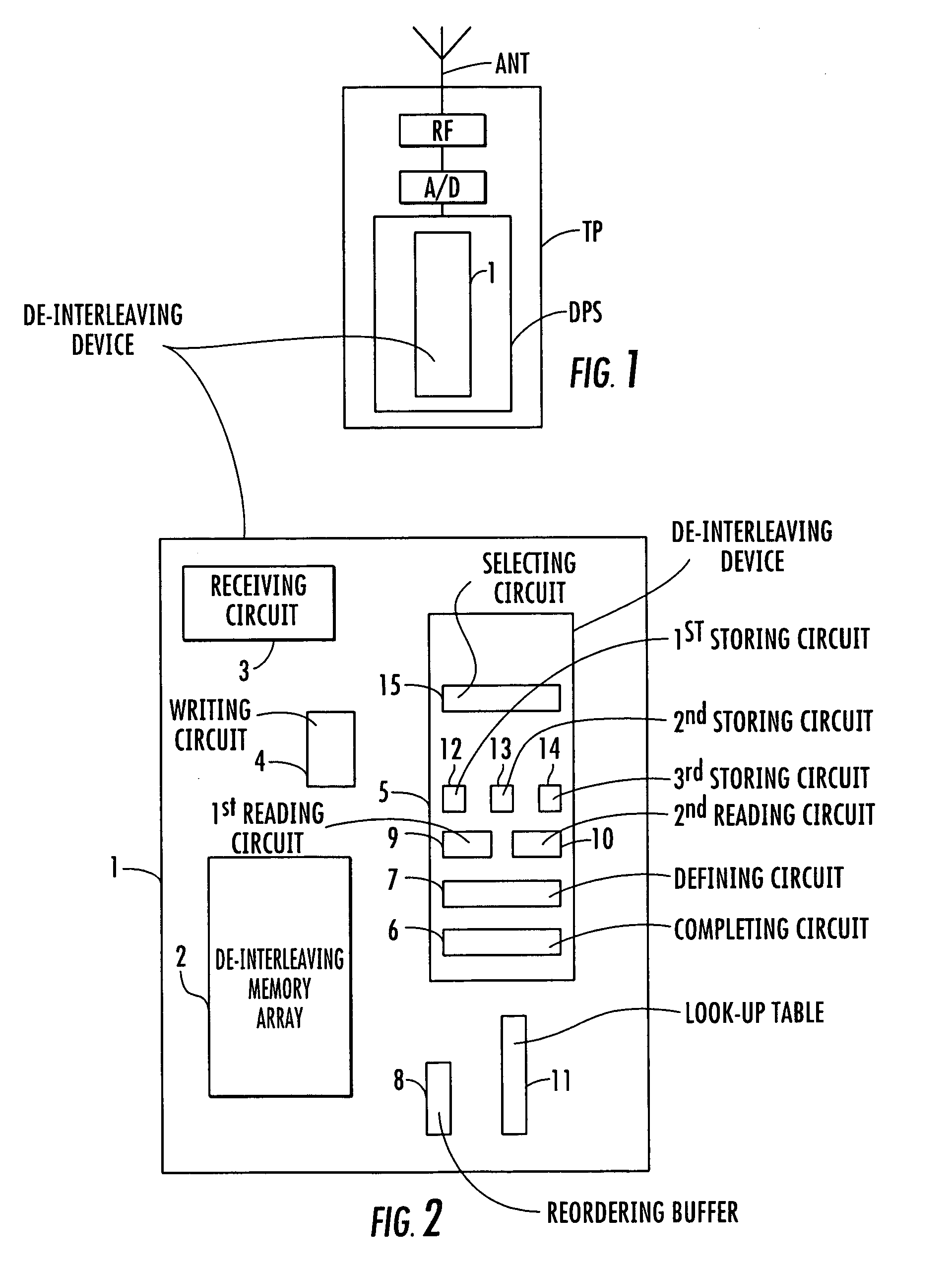

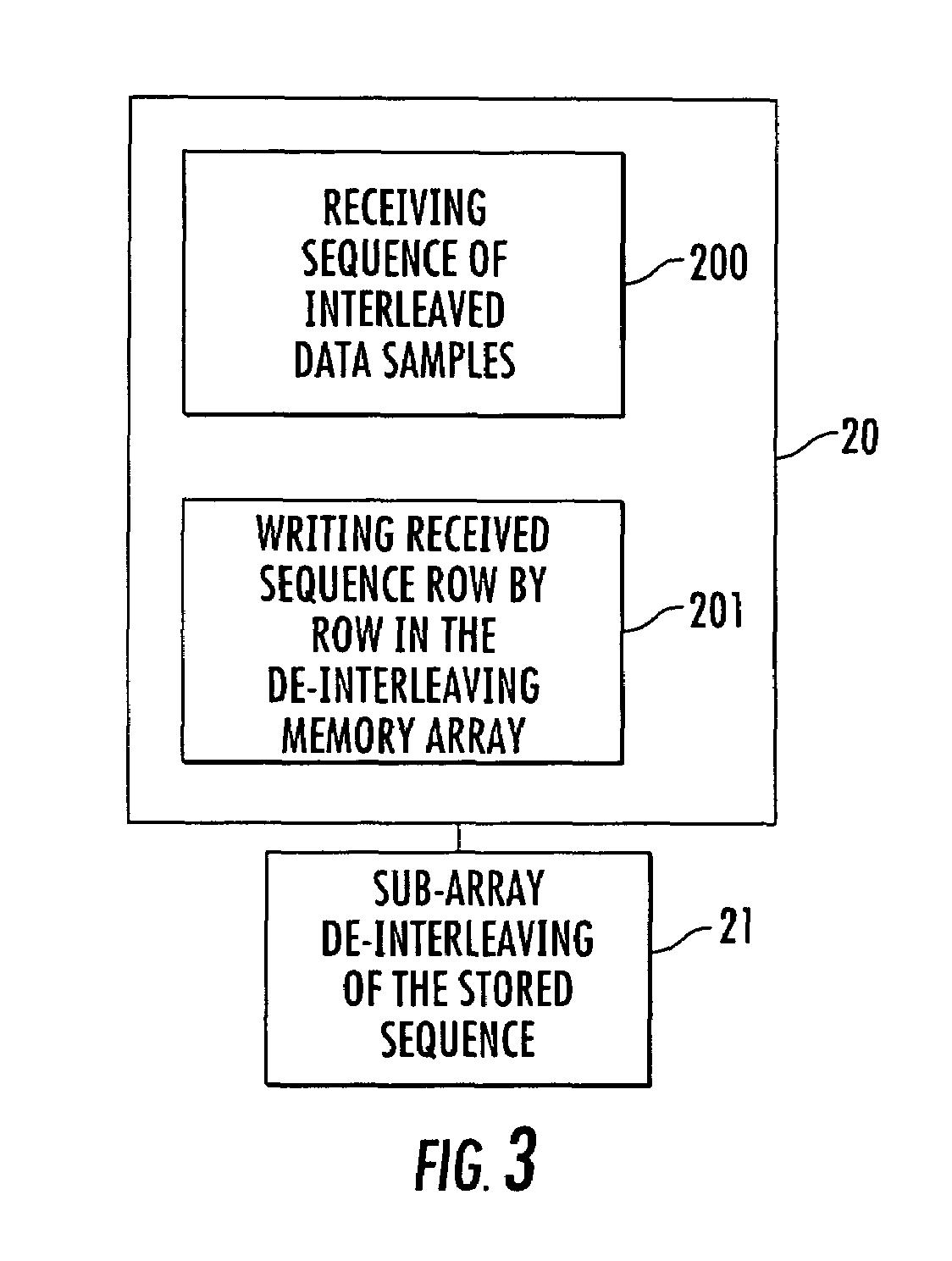

Method and device of de-interleaving successive sequences of interleaved data samples

ActiveUS20050160342A1Avoidance of memory re-use bottleneckDecrease memory access rateData representation error detection/correctionError detection/correctionVirtual memoryParallel computing

Successive sequences of interleaved data samples extracted from a virtual memory having L0 columns and C0 rows are de-interleaved. The de-interleaving includes receiving each sequence of the interleaved data samples, and writing row by row the received sequences of interleaved data samples in a de-interleaving memory array having L rows and C columns, with L being greater or equal to L0 and C being greater or equal to C0. The data samples stored in the de-interleaving memory array are de-interleaved sub-array by sub-array. Each sub-array is a square cluster array having a number SQ of rows and columns. A cluster array is a row of the square cluster array comprising SQ data samples, with the number L of rows and the number C of columns of the de-interleaving memory array being multiples of the number SQ of rows and columns.

Owner:STMICROELECTRONICS INT NV

Semiconductor integrated circuit and IC card

InactiveUS20060187734A1Reduce wasted powerReduce access rateRead-only memoriesDigital storageBit lineSub threshold

A semiconductor integrated circuit has a memory which can enter active state or standby state, and the memory has voltage generation circuits for bit lines and source lines with which memory cells are connected. The voltage generation circuits make the potential of the bit lines and the potential of the source lines equal to each other in response to an instruction to transition from active state to standby state. The voltage generation circuits produce a potential difference between the bit lines and the source lines in response to an instruction to transition from standby state to active state. In standby state, the potential of the bit lines and that of the source lines are equal to each other. Therefore, sub-threshold leakage does not occur between the source and drain of each memory cell. In active state, the source line potential is not varied.

Owner:RENESAS TECH CORP +1

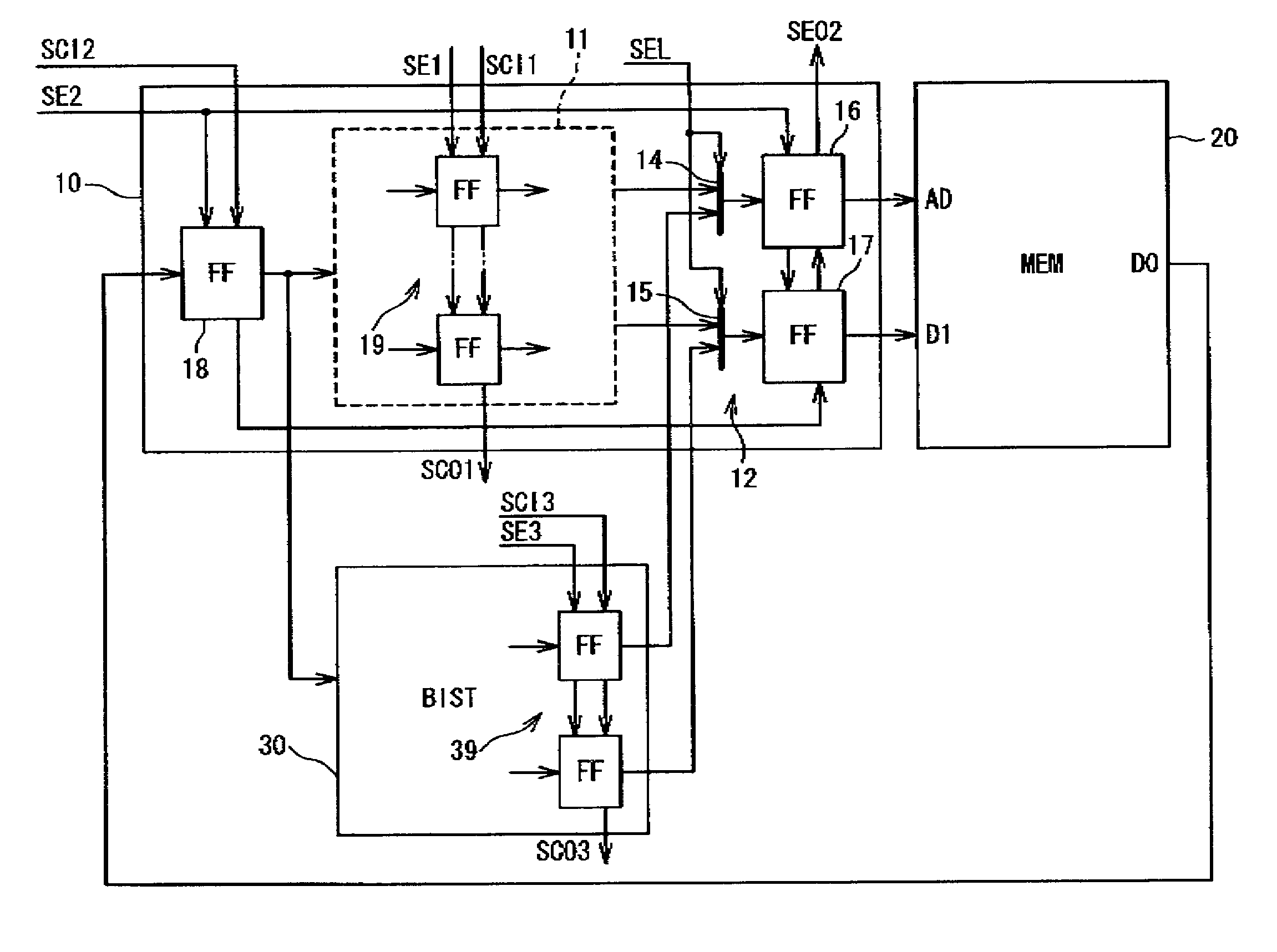

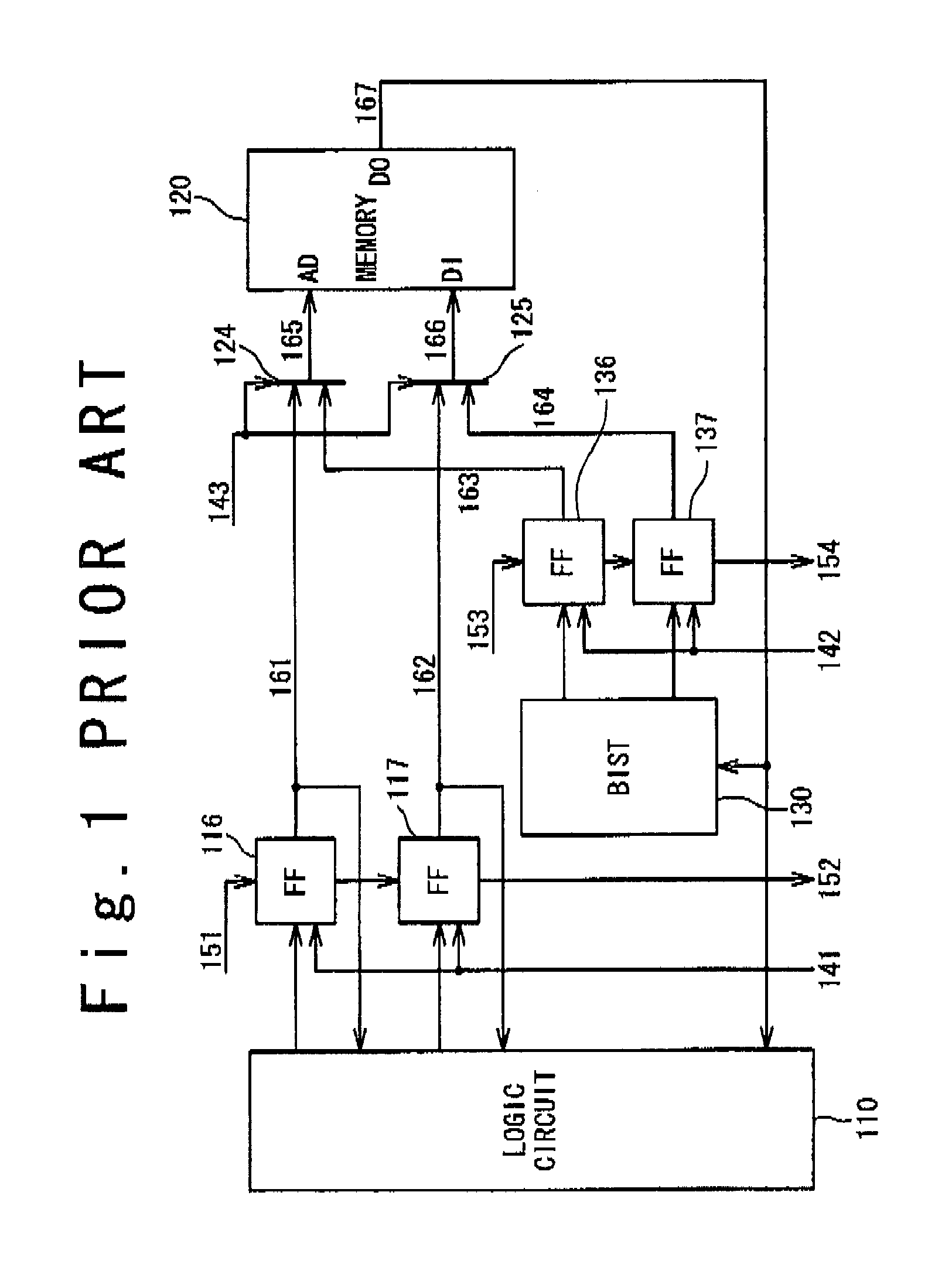

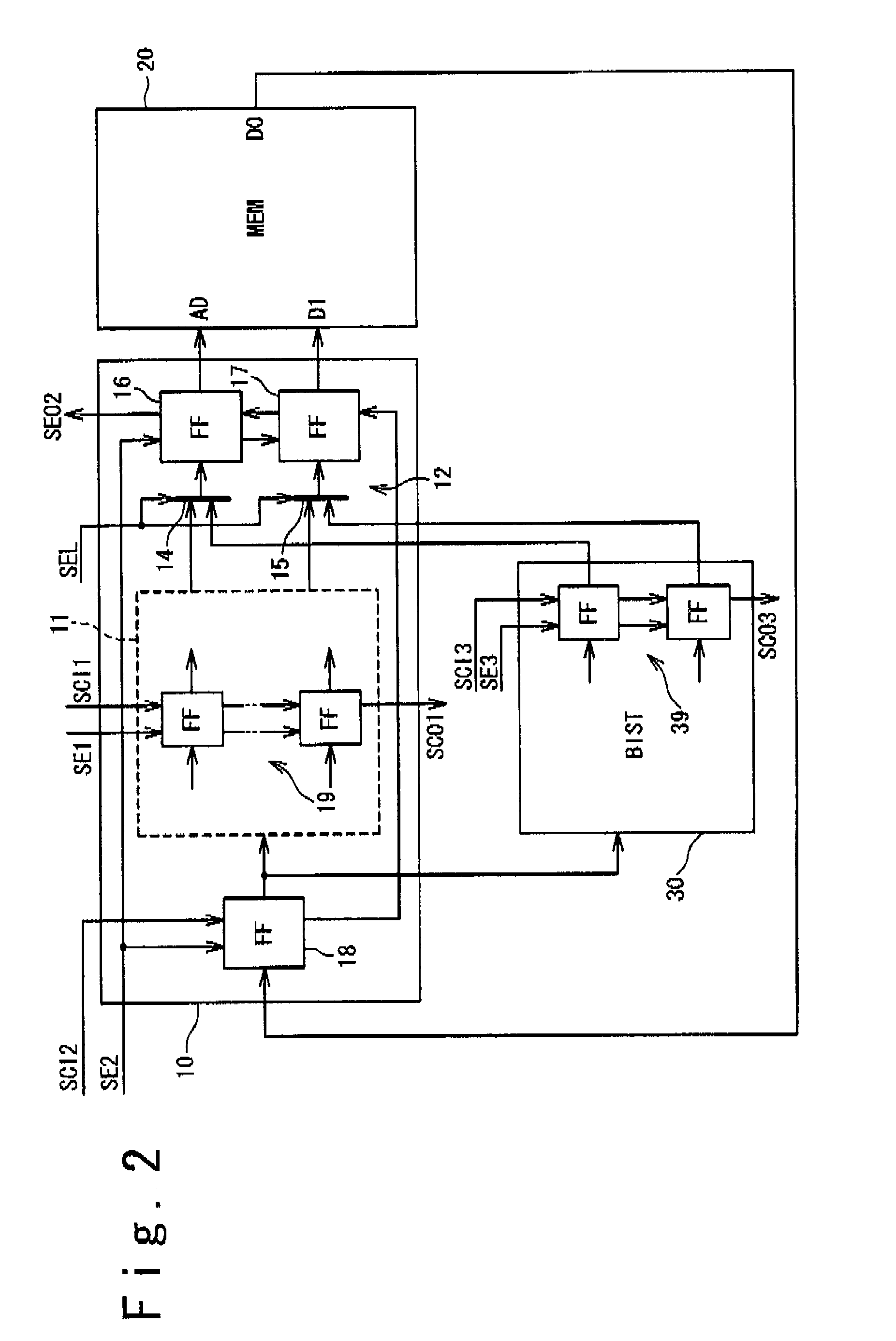

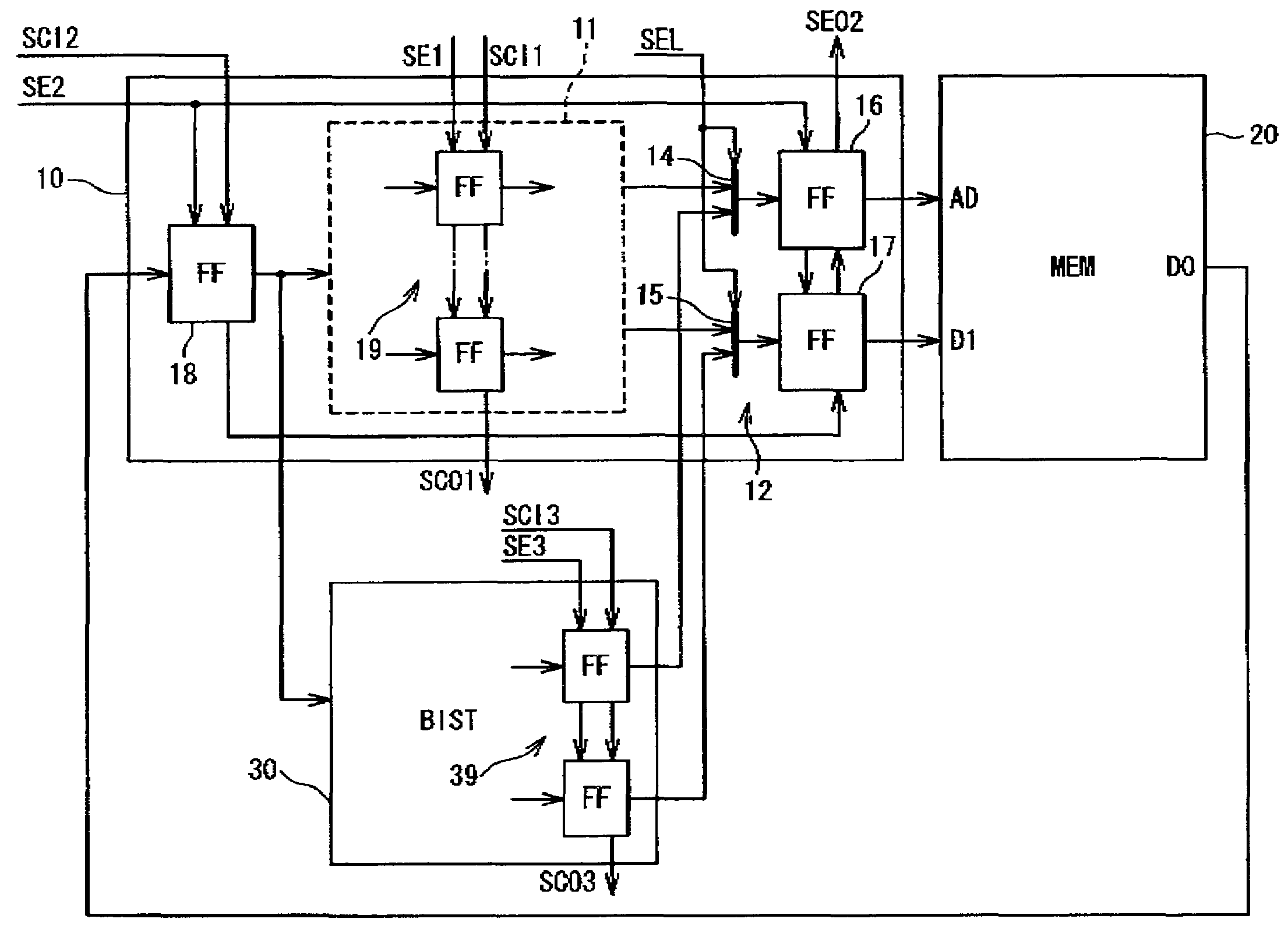

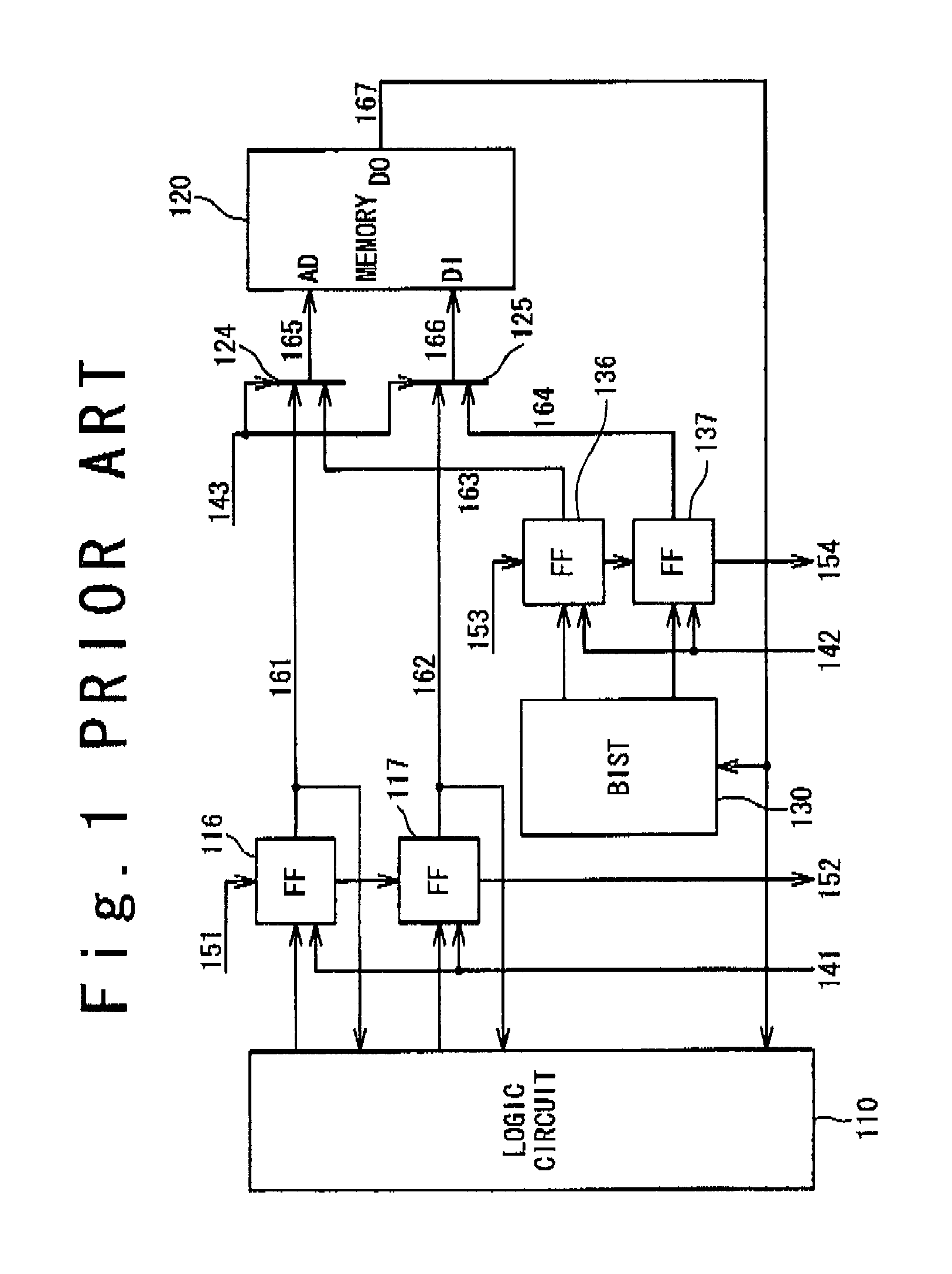

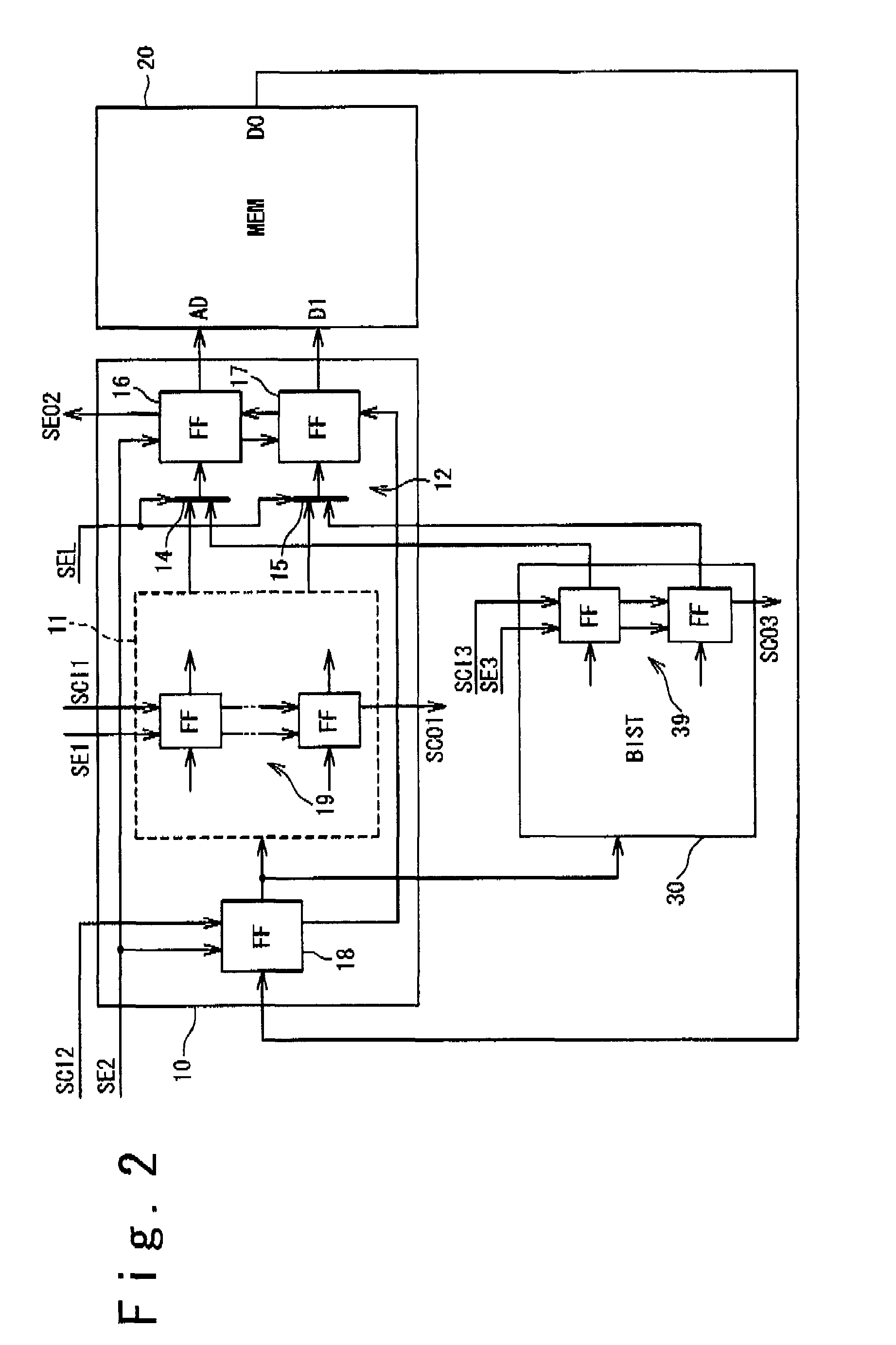

Semiconductor integrated circuit

InactiveUS20070180340A1Reduce access rateExtra stressElectronic circuit testingStatic storageShift registerEngineering

A semiconductor integrated circuit includes: a first circuit having a plurality of scan chains; a second circuit connected with input / output signals of the first circuit; and a third circuit connected with the second circuit through the first circuit. The plurality of scan chains comprises a first scan chain that contains flip-flops whose input / output signals are connected with the second circuit, and a second scan chain that does not contain any flip-flop whose input / output signal is connected with the second circuit. The flip-flops operate as a shift register at a scan path test, and when the third circuit exchanges signals with the second circuit through the flip-flops of the first scan chain, the second scan chain of the first circuit operates as a shift register.

Owner:RENESAS ELECTRONICS CORP

Method and apparatus for providing improved detection of overlapping networks

ActiveUS9001680B2Minimizing bandwidthMinimize timeError preventionTransmission systemsTelecommunicationsWireless access point

A method, apparatus and computer program product provide improved detection of overlapping wireless networks. In this regard, the method, apparatus and computer program product may utilize a processor, such as a processor on a wireless access point, to determine one or more parameters for a scan of a wireless network to identify overlapping networks. Wireless stations may utilize the parameters to determine the content of a scan report generated from a scan of the wireless network. The wireless stations may further utilize the parameters to determine which values should be monitored and / or recorded during the scan of the network. The wireless stations may respond to the access point with results corresponding to the parameters requested by the access point, and the access point may use the results to determine channel access parameters for other devices on the network, such as the wireless stations.

Owner:AVAGO TECH INT SALES PTE LTD

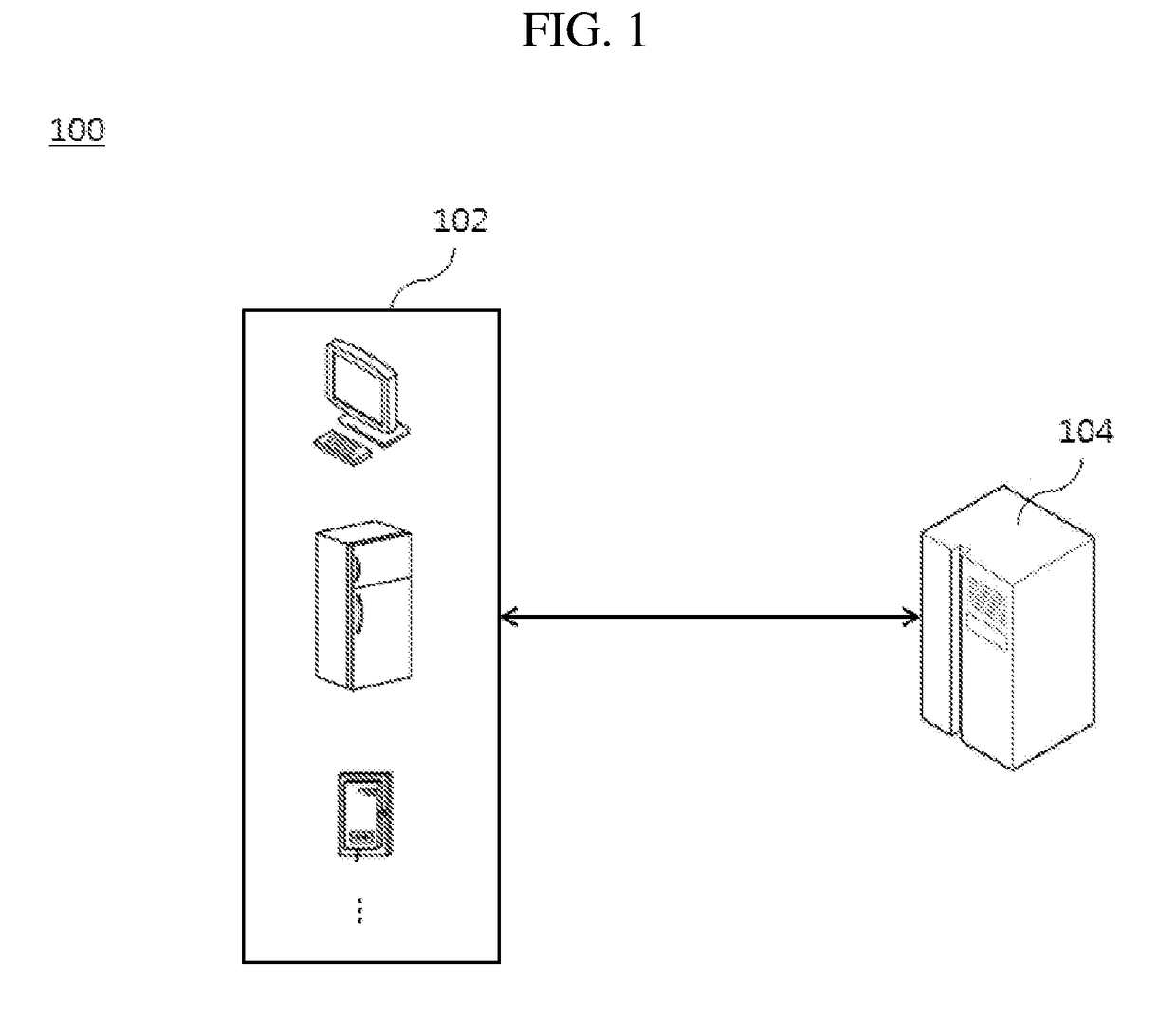

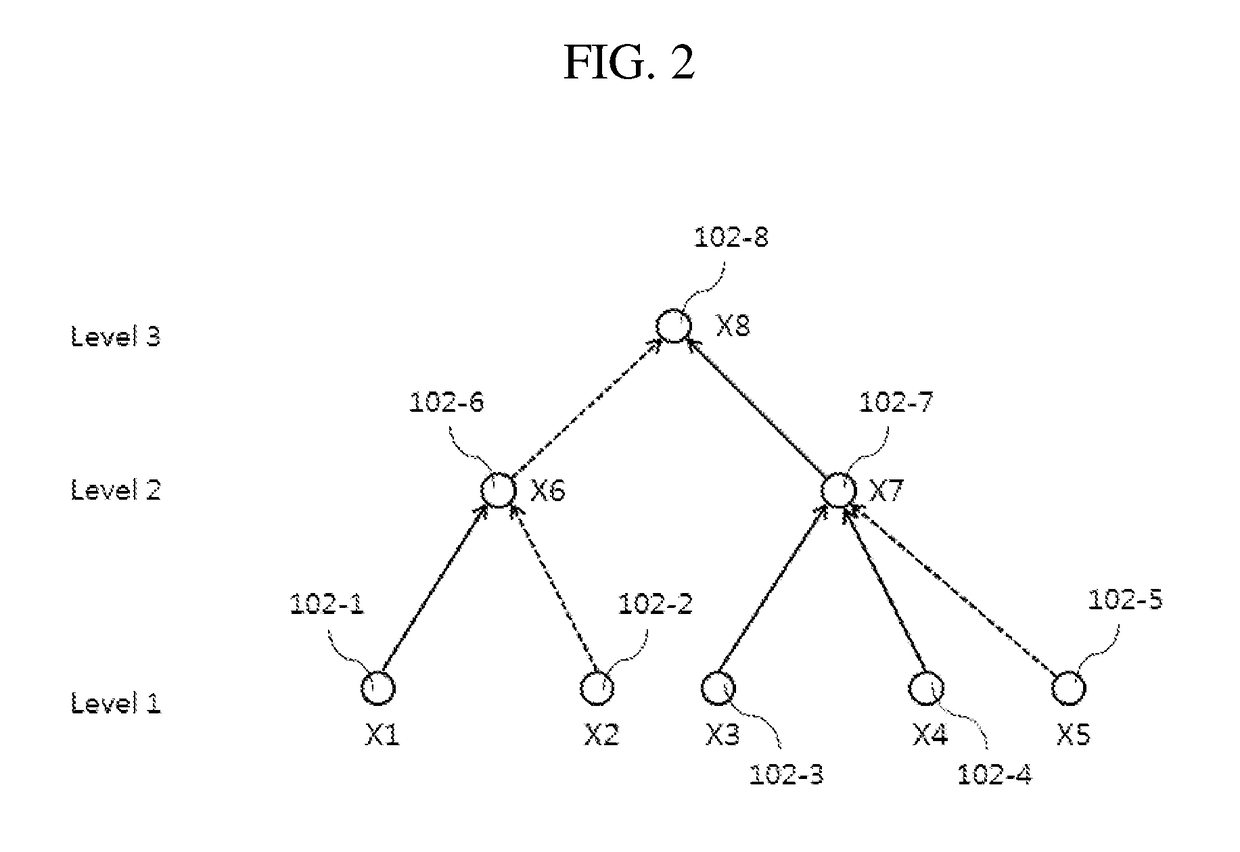

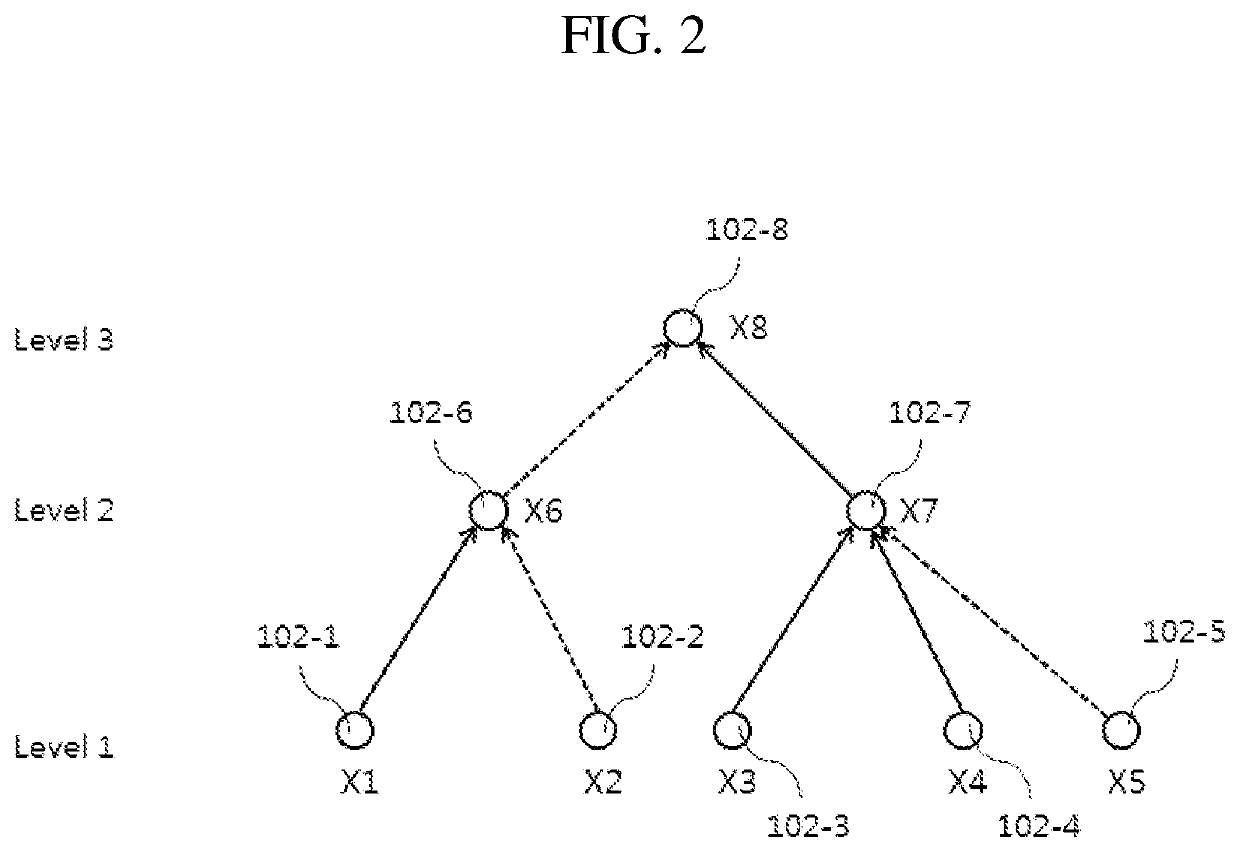

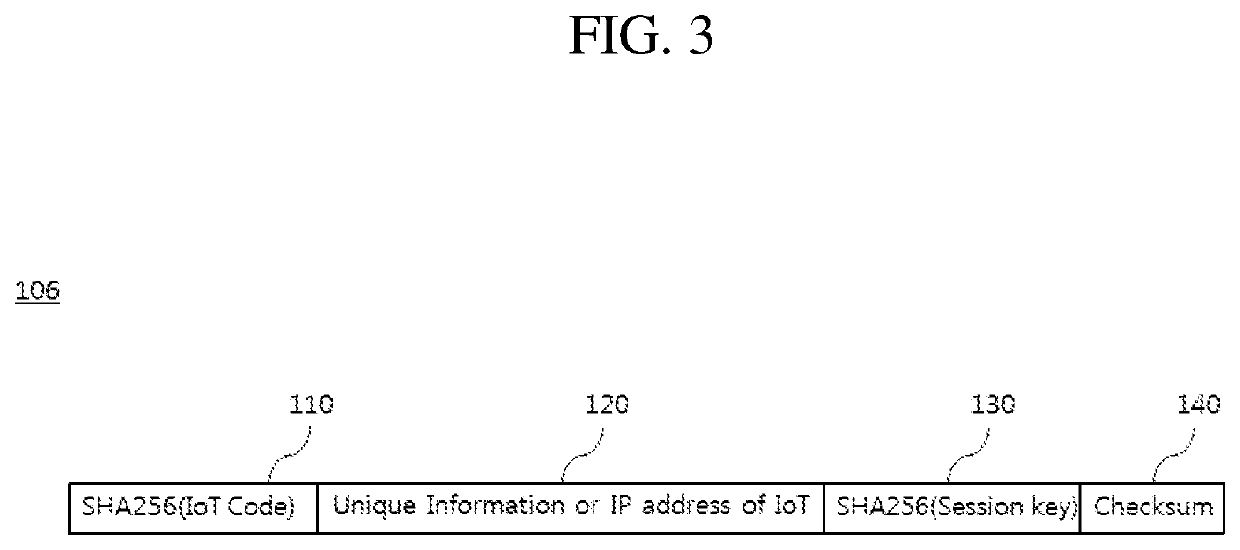

Data transmission method, authentication method, and server

ActiveUS20180124048A1Reduce access rateKey distribution for secure communicationUser identity/authority verificationStructure of Management InformationData transmission

Disclosed are a data transmission method, an authentication method, and a server. The data transmission method performed by a node among a plurality of nodes connected in a hierarchical structure includes generating a node identity (ID) comprising at least one from among a virtual address for identifying the node and a group key for identifying a group to which the node belongs, generating a signature of the node by using at least one from among the node ID and information about a previous node adjacent to the node, and transmitting a data packet to a server using a node chain formed based on signatures of the nodes.

Owner:SAMSUNG SDS CO LTD

Distorted aberration correction processing apparatus

ActiveUS8098954B2Reduce access rateAberration correctionTelevision system detailsColor signal processing circuitsOptical aberrationAddress control

A distorted aberration correction processing apparatus includes DRAM and SRAM for storing an object image from an optical system. Further, the distorted aberration correction processing apparatus includes: a first address control circuit for reading out a pixel in the DRAM on a unit basis of an area including a plurality of the pixels along a curve corresponding to a distorted aberration of an optical system and writing the read-out pixel in SRAM; and a second address control circuit for reading out a pixel in the SRAM on a pixel basis and outputting the pixel read out on a pixel basis to an output portion so as to suppress the distorted aberration of the optical system. The first address control circuit effects control so that the signal of the areas is sequentially read out in a predetermined order, and the second address control circuit effects random access control.

Owner:CANON KK

Semiconductor integrated circuit

InactiveUS7752512B2Reduce access rateExtra stressElectronic circuit testingStatic storageShift registerSemiconductor

A semiconductor integrated circuit includes: a first circuit having a plurality of scan chains; a second circuit connected with input / output signals of the first circuit; and a third circuit connected with the second circuit through the first circuit. The plurality of scan chains comprises a first scan chain that contains flip-flops whose input / output signals are connected with the second circuit, and a second scan chain that does not contain any flip-flop whose input / output signal is connected with the second circuit. The flip-flops operate as a shift register at a scan path test, and when the third circuit exchanges signals with the second circuit through the flip-flops of the first scan chain, the second scan chain of the first circuit operates as a shift register.

Owner:RENESAS ELECTRONICS CORP

Data packet transmission method, data packet authentication method, and server thereof

ActiveUS10581849B2Reduce access rateKey distribution for secure communicationUser identity/authority verificationData packData transmission

Owner:SAMSUNG SDS CO LTD

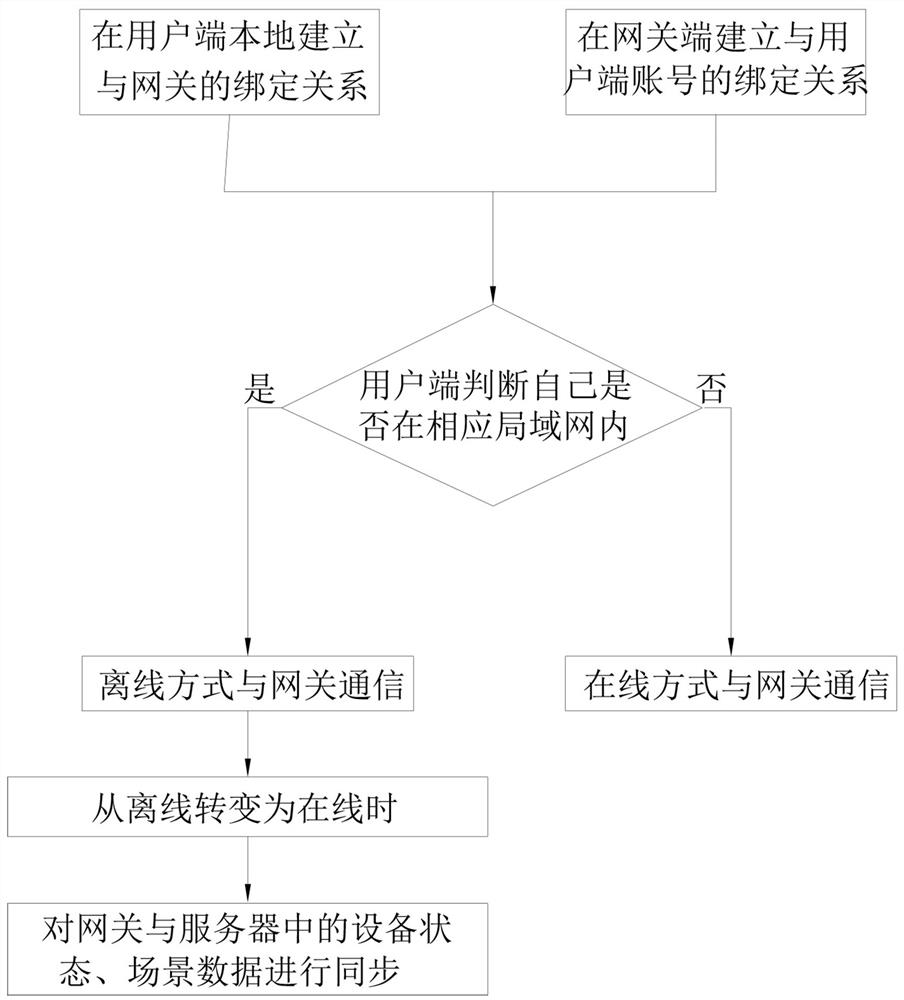

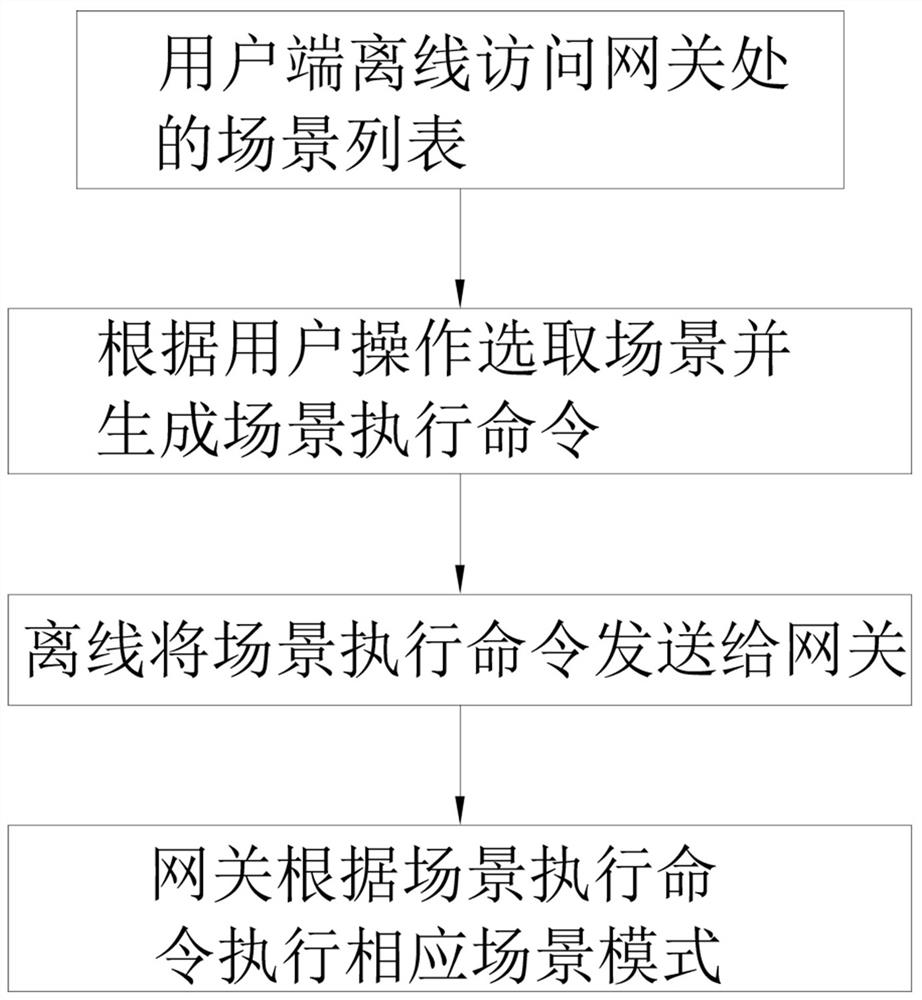

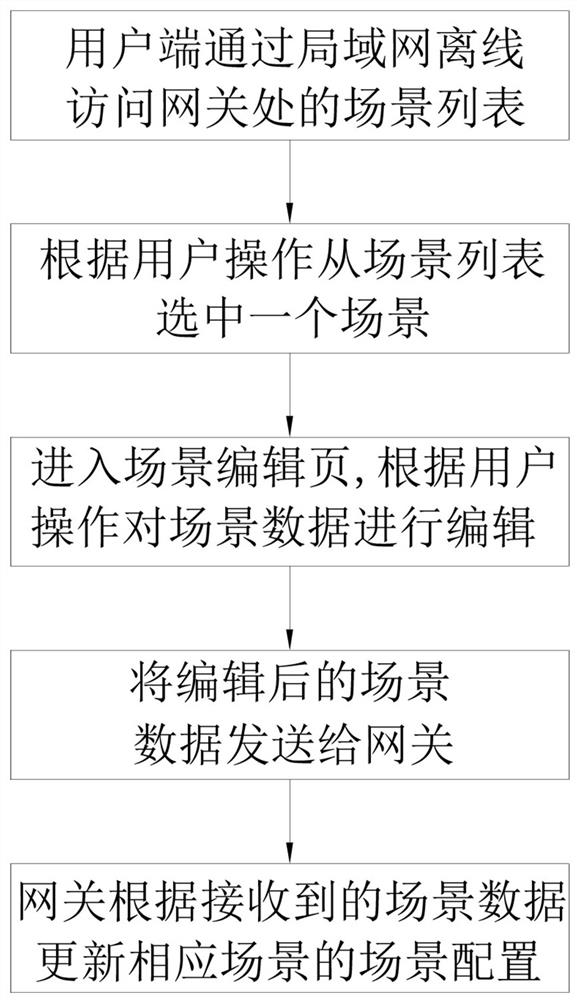

Offline control implementation method in local area network in whole-house intelligent system

InactiveCN113645084ARealize offline controlReduce access rateHome automation networksEngineeringSmart system

The invention discloses an offline control implementation method in local area network in whole-house intelligent system, which comprises the following steps of: S1, locally establishing a binding relationship with a gateway at a user side, and simultaneously establishing a binding relationship with a user side account at a gateway side; S2, when the user side communicates with the gateway, enabling the user side to firstly judge whether the user side is in the corresponding local area network or not, and if yes, enabling the user side to communicate with the gateway in a local area network off-line mode; and S3, when the offline state is changed into the online state, synchronizing the equipment state and / or scene data in the gateway and the server. According to the scheme, the account and the gateway are bound with each other, so that the account end can access the scene data and the equipment information of the bound gateway, and equipment off-line control and scene mode off-line editing and control are realized; and when the user side is located in the local area network, the offline mode based on the local area network is preferentially used to directly communicate with the gateway without depending on the network, so that the access rate of the server platform is reduced, and meanwhile, the privacy and the security can be improved.

Owner:HANGZHOU KONKE INFORMATION TECH CO LTD

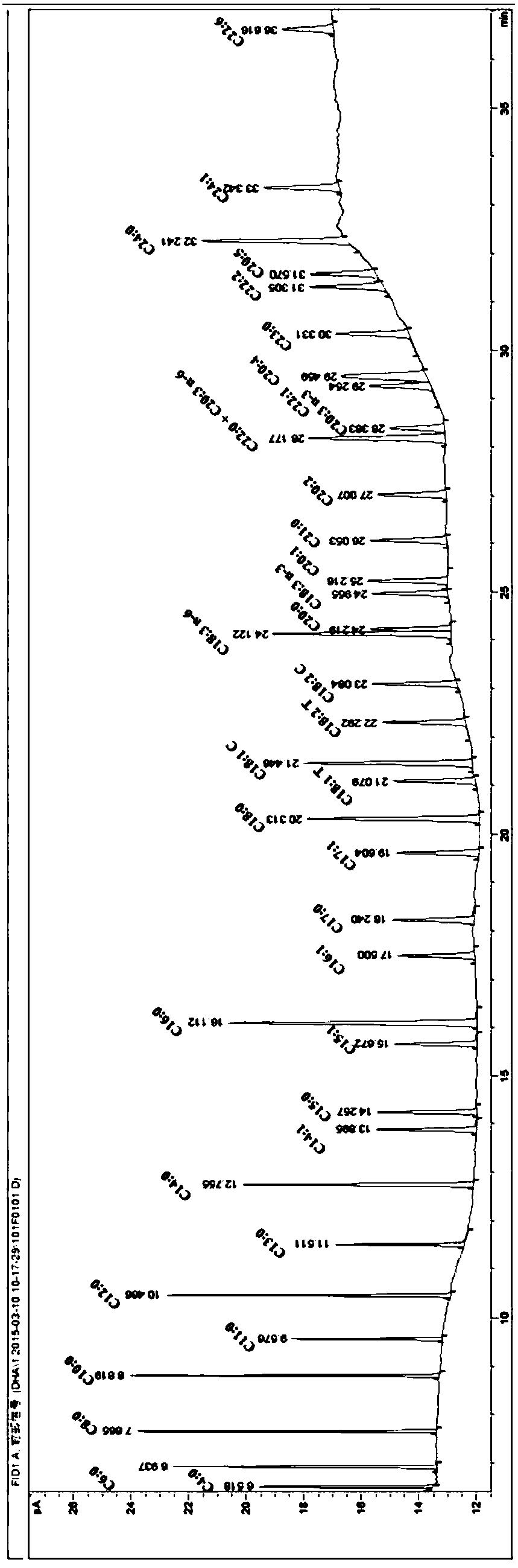

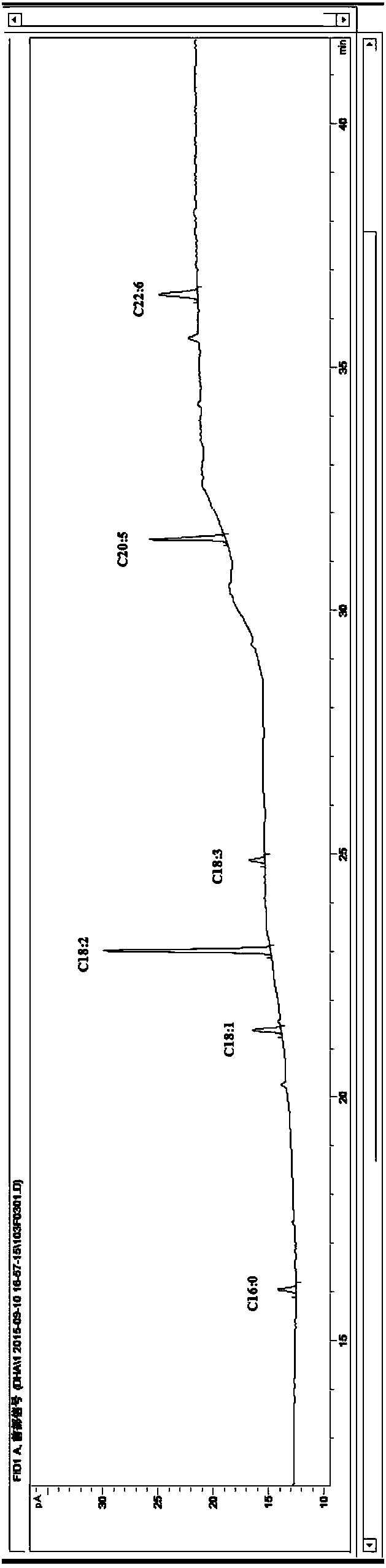

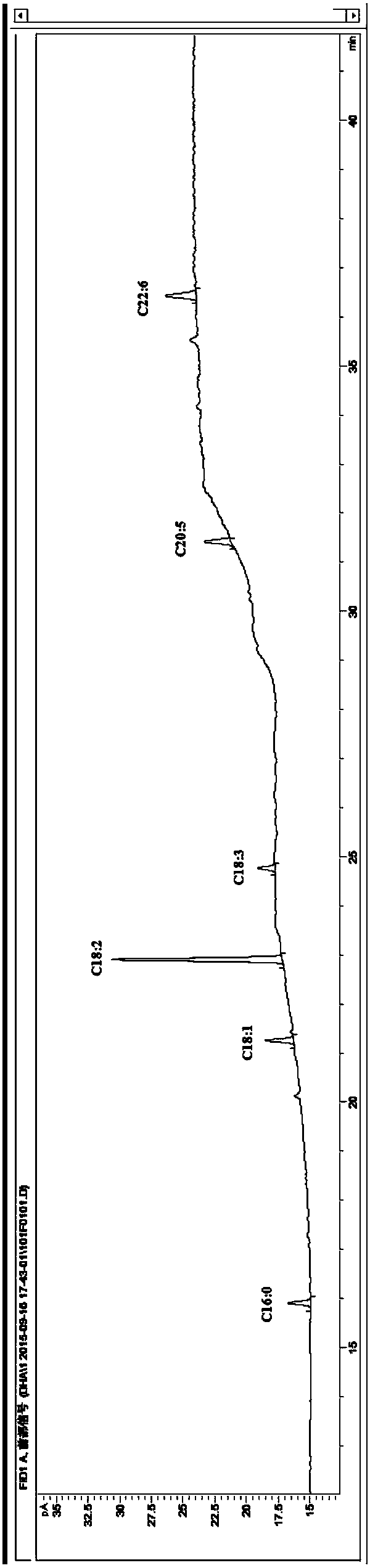

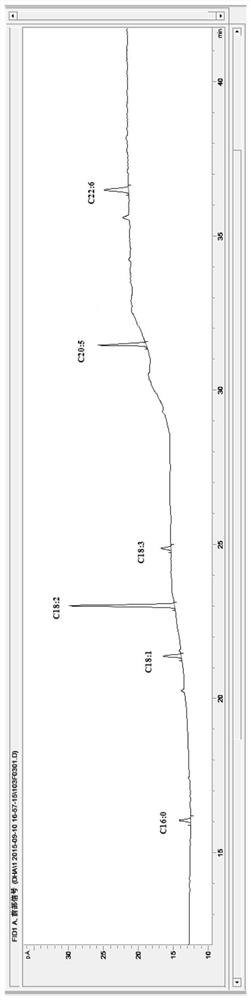

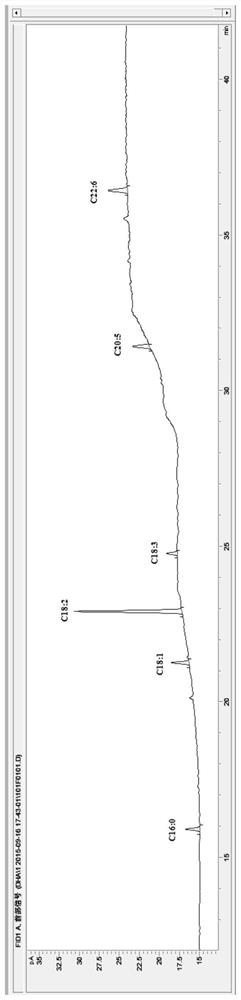

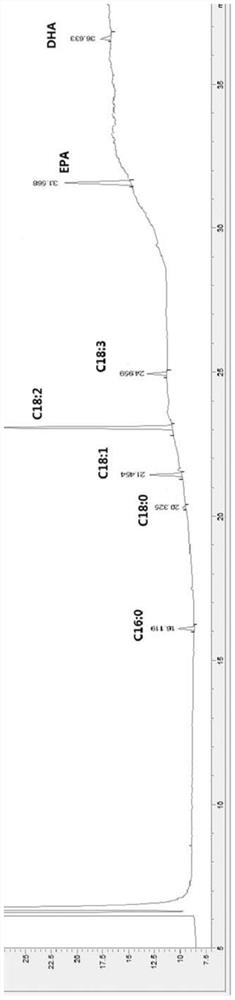

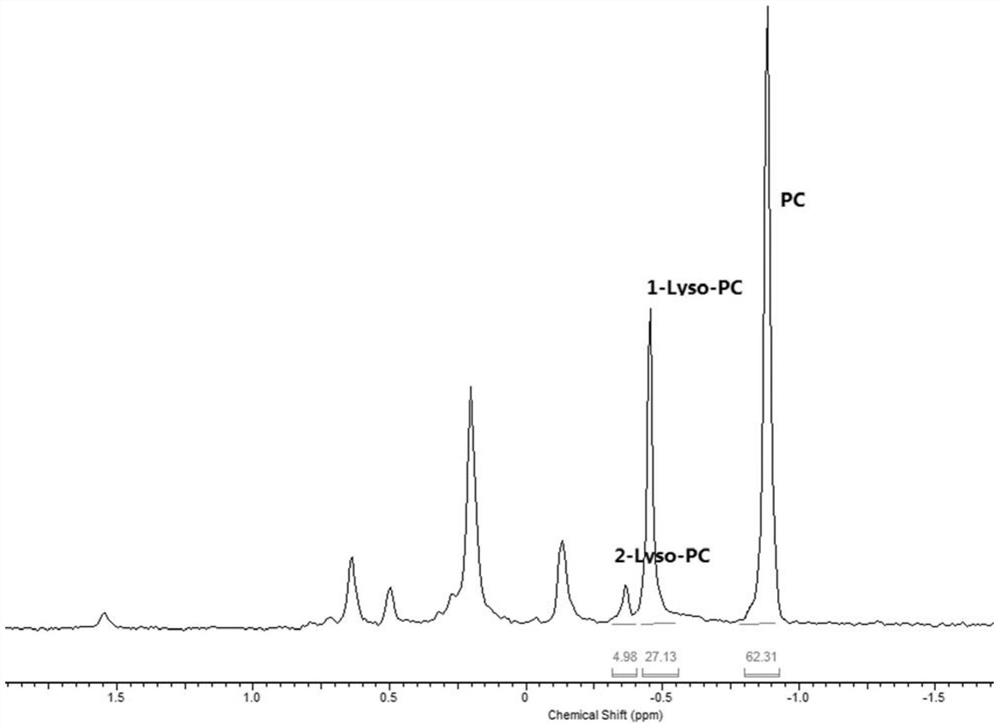

Preparation method of euphausia superba oil substitute

ActiveCN108265090AFully absorbedTake advantage ofImmobilised enzymesHydrolasesBiotechnologyEngineering

The invention discloses a preparation method of a euphausia superba oil substitute, and provides a method for preparing a fat composition containing phosphatide type DHA and phosphatide type EPA and afat composition prepared according to the method. Particularly, by accurate control over the ratio of DHA to EPA in reaction raw materials, the fat composition which contains the phosphatide type DHAand the phosphatide type EPA and is almost the same as natural euphausia superba oil is prepared.

Owner:COFCO GROUP +3

Control system; control apparatus; storage device and computer program product

ActiveUS7187593B2Reduce access rateInput/output to record carriersRead-only memoriesComputer hardwareControl system

A reading / writing process control unit for instructing a reading / writing process and an erasing process control unit for instructing an erasing process are provided separately and each is connected with two HDDs via a switch. While the reading / writing process control unit is connected with one HDD and executing a reading / writing process, a switch is controlled to connect the erasing process control unit with another HDD to erase data of the HDD connected with the erasing process control unit. Since it is enabled to execute a data reading / writing process and a data erasing process for a storage device in parallel for different HDDs, lowering of the access rate as a whole can be prevented.

Owner:SHARP KK

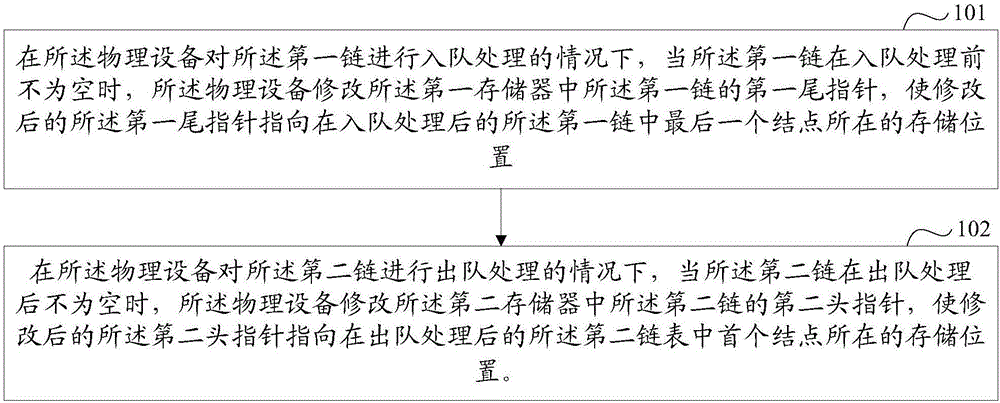

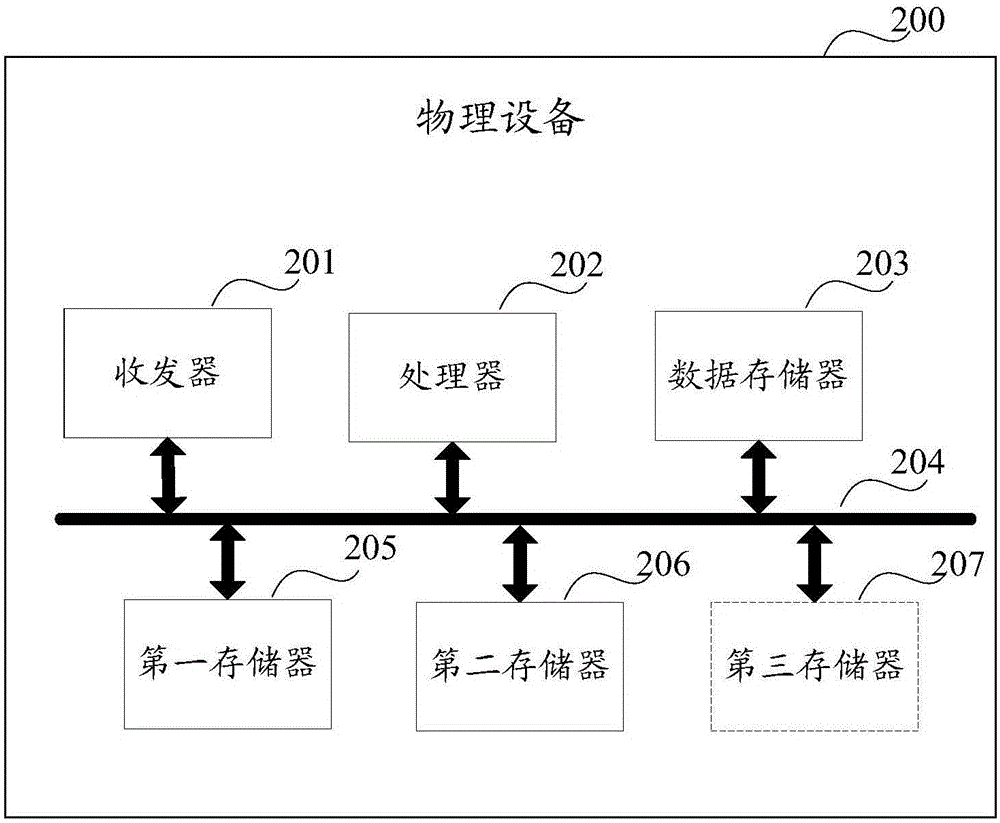

Chain management method and physical equipment

ActiveCN106528598AReduce access rateReduce areaMemory architecture accessing/allocationEnergy efficient computingComputer scienceInformation storage

The invention provides a chain management method and physical equipment, and aims to solve the problems of relatively high cost and relatively high power consumption due to the high performance requirement of a conventional management information storage in the prior art. The physical equipment comprises a first storage for storing a tail pointer of a chain and a second storage for storing a head pointer of the chain, and supports enqueueing processing and dequeueing processing in a clock period. The method comprises the following steps that: the physical equipment modifies a first tail pointer of a first chain in the first storage when the first chain is not empty before the enqueueing processing; and the physical equipment modifies a second head pointer of a second chain in the second storage when the second chain is not empty after the dequeueing processing. Thus, each management information storage only needs to have a read-once write-once capability on the premise of ensuring input and output performance of the physical equipment. Through adoption of the method, the performance requirements of the management information storages are lowered, and the cost and power consumption of the management information storages are lowered.

Owner:HUAWEI TECH CO LTD

Preparation method of Antarctic krill oil substitute

ActiveCN108265090BFully absorbedTake advantage ofImmobilised enzymesHydrolasesEngineeringPhospholipid

The invention discloses a preparation method of an Antarctic krill oil substitute. The invention provides a method for preparing an oil composition containing phospholipid DHA and phospholipid EPA and the oil composition prepared according to the method. Specifically, the present invention precisely controls the ratio of DHA and EPA in the reaction raw materials to prepare an oil composition containing phospholipid DHA and phospholipid EPA almost the same as natural Antarctic krill oil.

Owner:COFCO GROUP +3

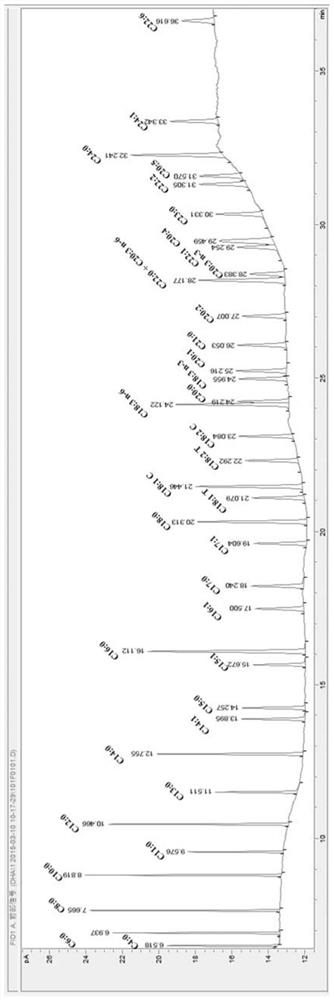

Preparation method of pla1 type n-3 polyunsaturated fatty acid phospholipid

ActiveCN106893747BImprove absorption and utilizationHigh yieldFermentationFatty acids.polyunsaturatedPhospholipid

The invention provides a method for preparing PLA1 type n-3 polyunsaturated fatty acid phospholipids and PLA1 type n-3 polyunsaturated fatty acid phospholipids prepared by the method of the invention. Compared with the effect in the prior art that the catalytic reaction at the PLA1 position is not more than 66% achieved by using commercial enzymes such as Lecitase Ultra, TL IM, and SP435, the method of the present invention greatly improves the production of PLA1-type functional phospholipids. Rate.

Owner:COFCO GROUP +2

Method and device of de-interleaving successive sequences of interleaved data samples

ActiveUS7370246B2Avoidance of memory re-use bottlenecksReduce access rateData representation error detection/correctionError detection/correctionVirtual memorySample sequence

Successive sequences of interleaved data samples extracted from a virtual memory having L0 columns and C0 rows are de-interleaved. The de-interleaving includes receiving each sequence of the interleaved data samples, and writing row by row the received sequences of interleaved data samples in a de-interleaving memory array having L rows and C columns, with L being greater or equal to L0 and C being greater or equal to C0. The data samples stored in the de-interleaving memory array are de-interleaved sub-array by sub-array. Each sub-array is a square cluster array having a number SQ of rows and columns. A cluster array is a row of the square cluster array comprising SQ data samples, with the number L of rows and the number C of columns of the de-interleaving memory array being multiples of the number SQ of rows and columns.

Owner:STMICROELECTRONICS INT NV

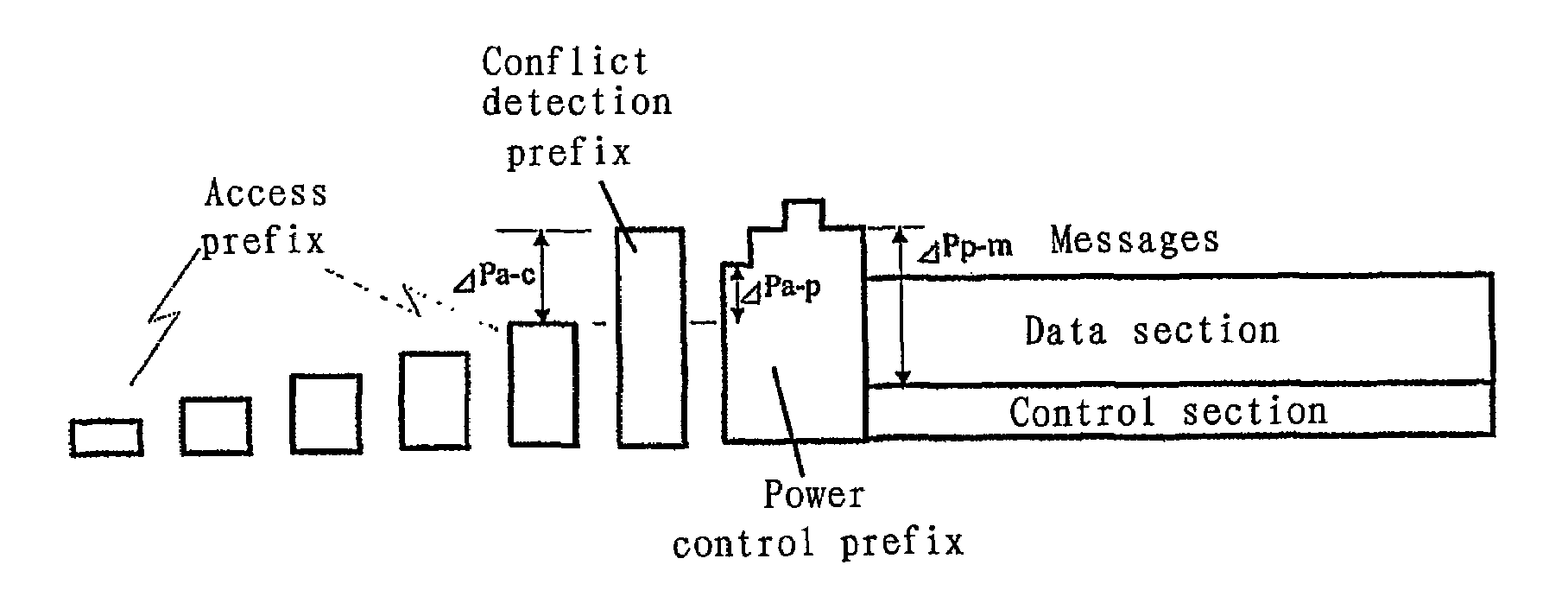

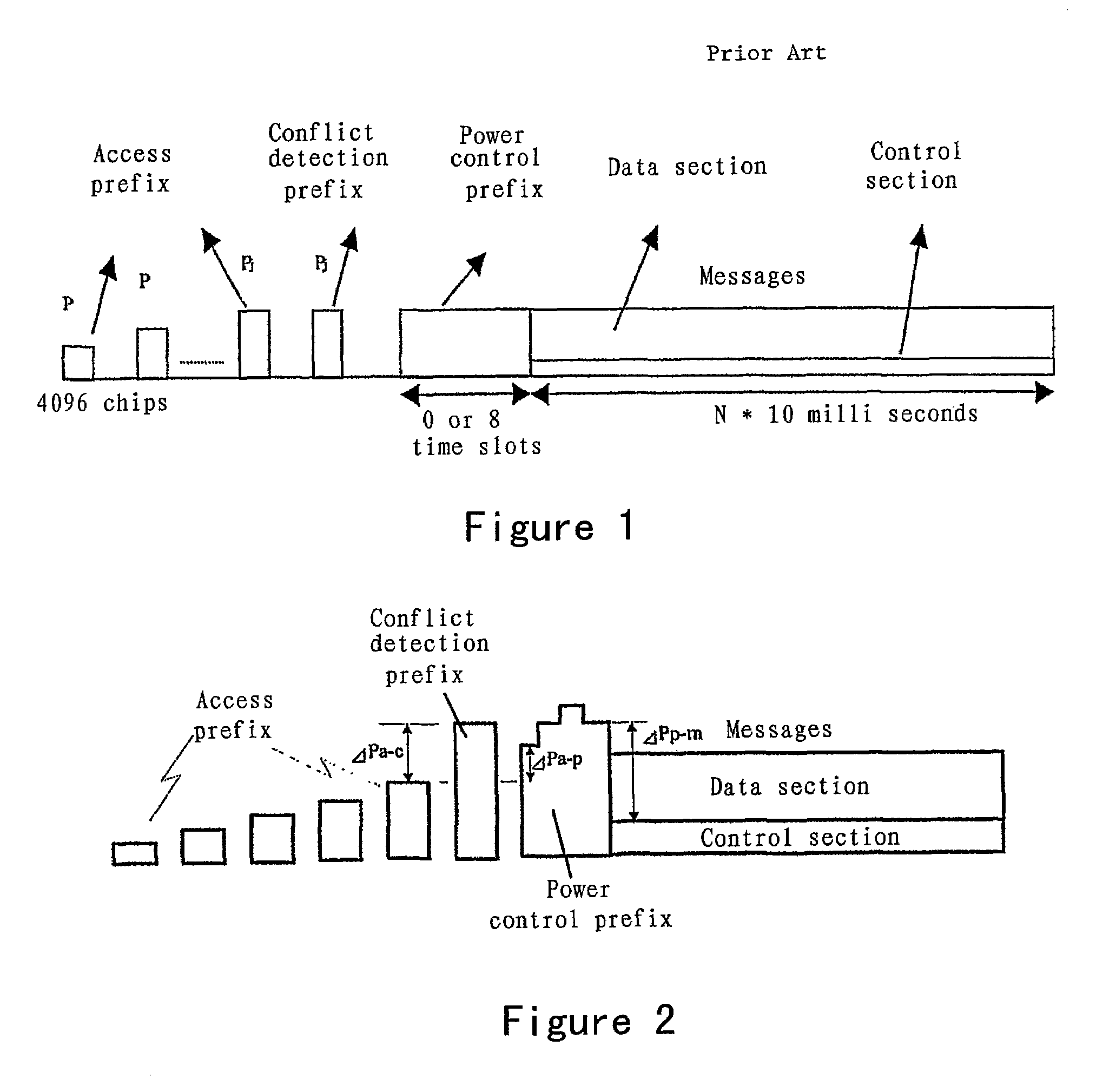

Transmission method for physical common packet channels having a power bias

ActiveUS7382761B2Reduce access ratePoor link performancePower managementTransmission control/equalisingAccess timeTransfer procedure

A transmission method for the physical common packet channels having the power bias is disclosed in the invention. The power bias magnitudes are added in the physical common channels of the said transmission method between the last successfully accessed access prefix and the conflict detection prefix, between the access prefix and the power control prefix, and between the power control prefix and the control section of the messages. By utilizing the method of the invention, the access probability in the transmission procedure of the physical common packet channels can be increased, the average access time can be shortened, the interference with the other users can be reduced, and the comprehensive performance of the link can be improved.

Owner:HUAWEI TECH CO LTD

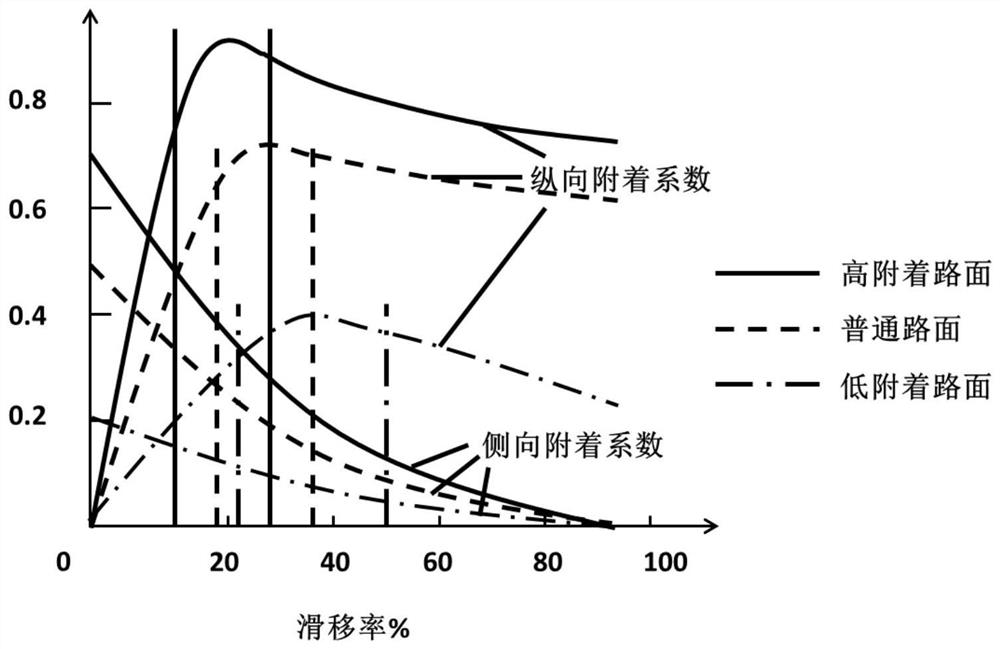

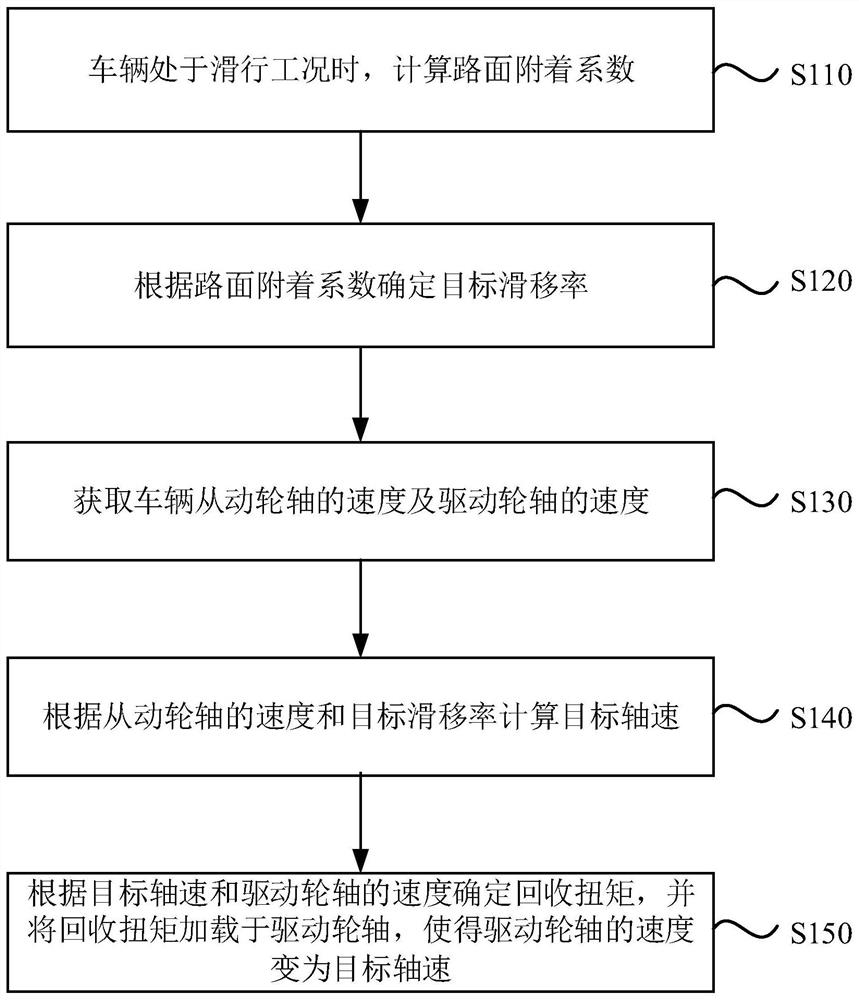

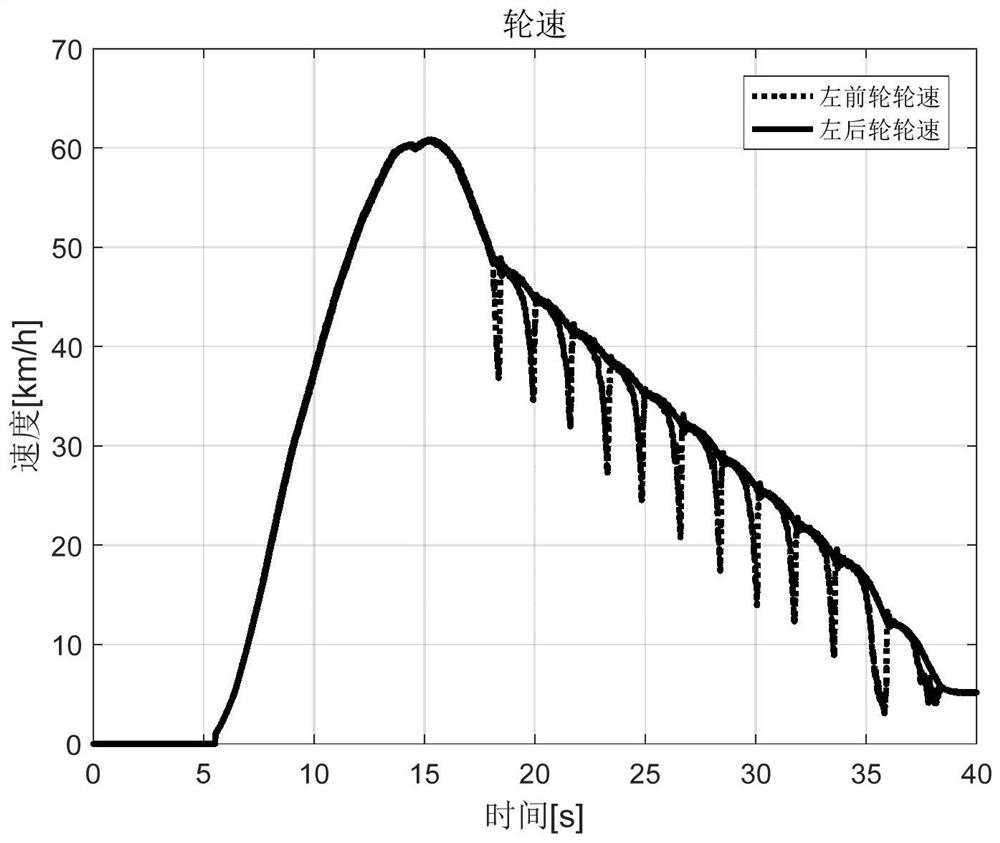

Control method, device and equipment for recycling torque and vehicle

InactiveCN112026527AImprove stabilityReduce access rateElectrodynamic brake systemsDrive wheelRoad surface

The embodiment of the invention discloses a control method, device and equipment for recycling a torque and a vehicle. The method comprises the steps of calculating a pavement adhesion coefficient when a vehicle is in a sliding condition; determining a target slip rate according to a pavement adhesion coefficient; obtaining the speed of a vehicle driven axle and the speed of a driving axle; calculating a target axle speed according to the speed of the driven axle and the target slip rate; and determining a recovery torque according to the target axle speed and the speed of the driving axle, and loading the recovery torque to the driving axle so that the speed of the driving axle is changed into the target axle speed. According to the control method for recycling the torque, when the vehicle is in the sliding working condition, the target axle speed is calculated according to the speed of the driven axle and the target slip rate, the recovery torque is determined according to the targetaxle speed and the speed of the driving axle, and the recovery torque is loaded to the driving axle so that the speed of the driving axle is changed into the target axle speed; and vehicle stabilitycan be improved while the energy recovery strength is ensured.

Owner:CHINA FIRST AUTOMOBILE

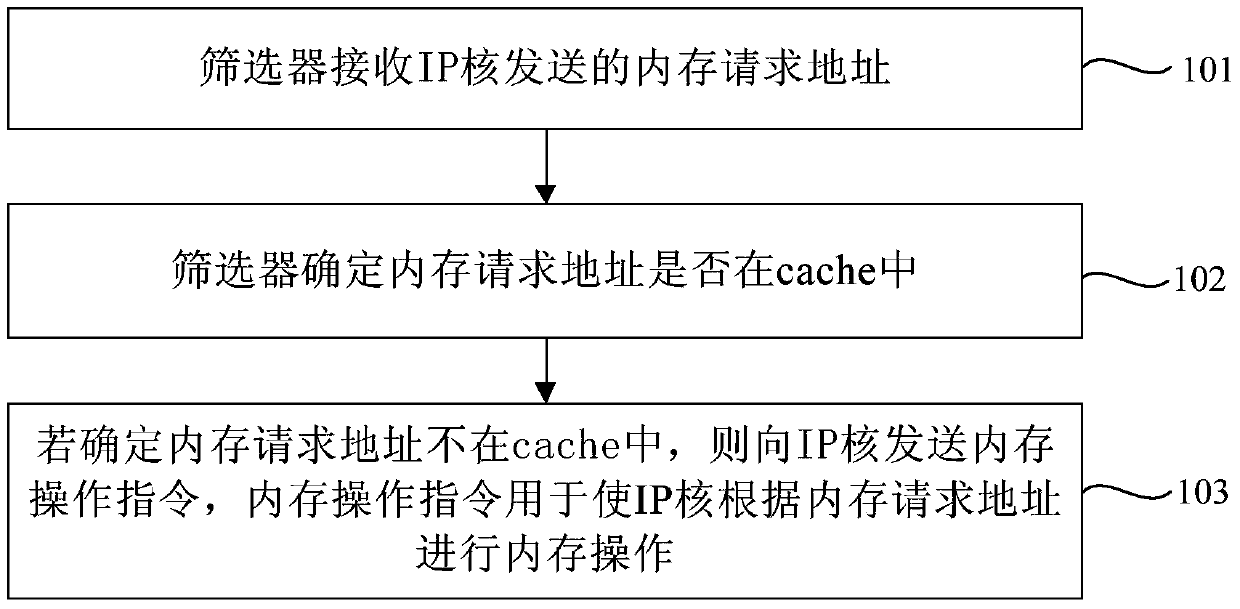

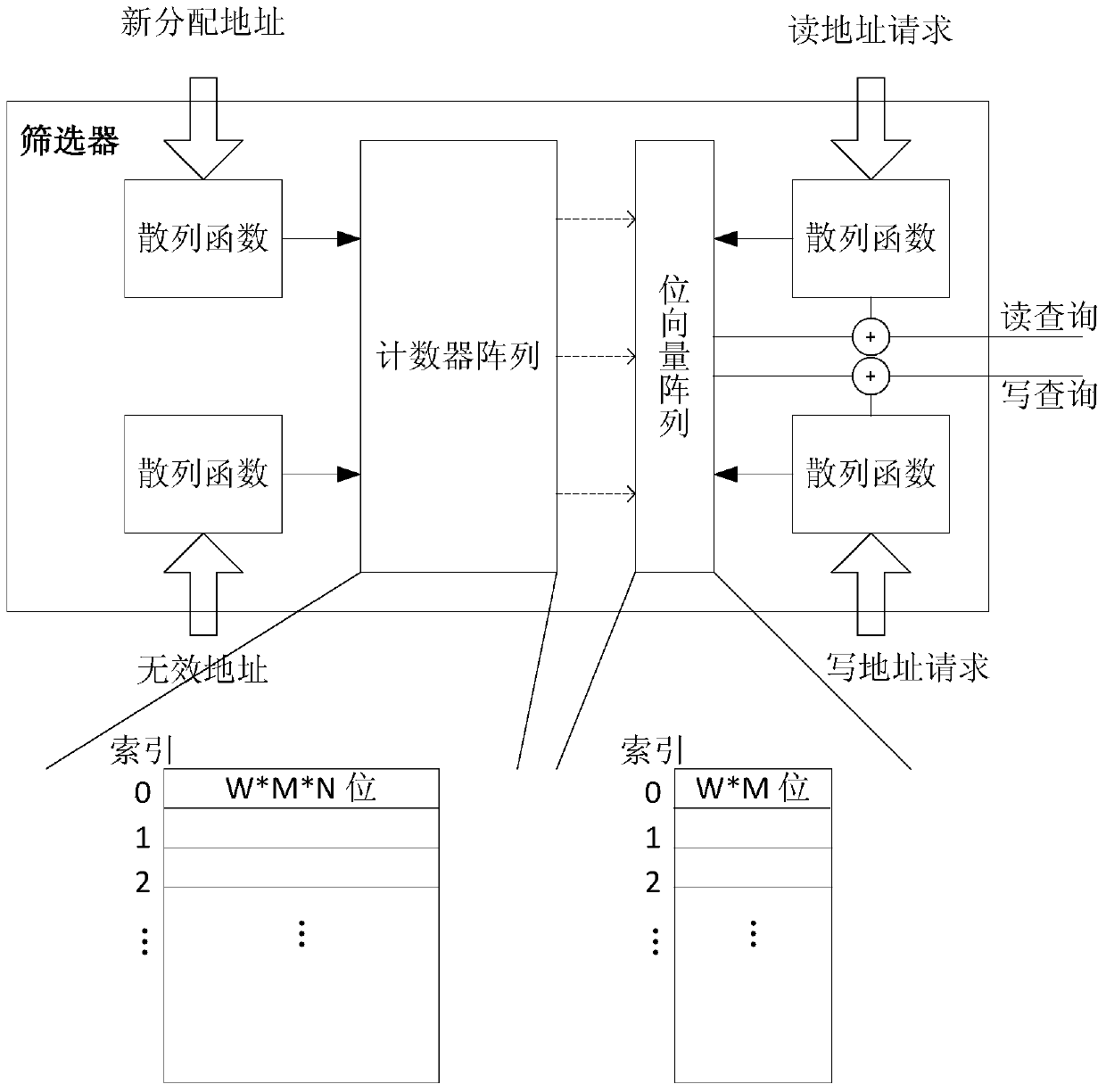

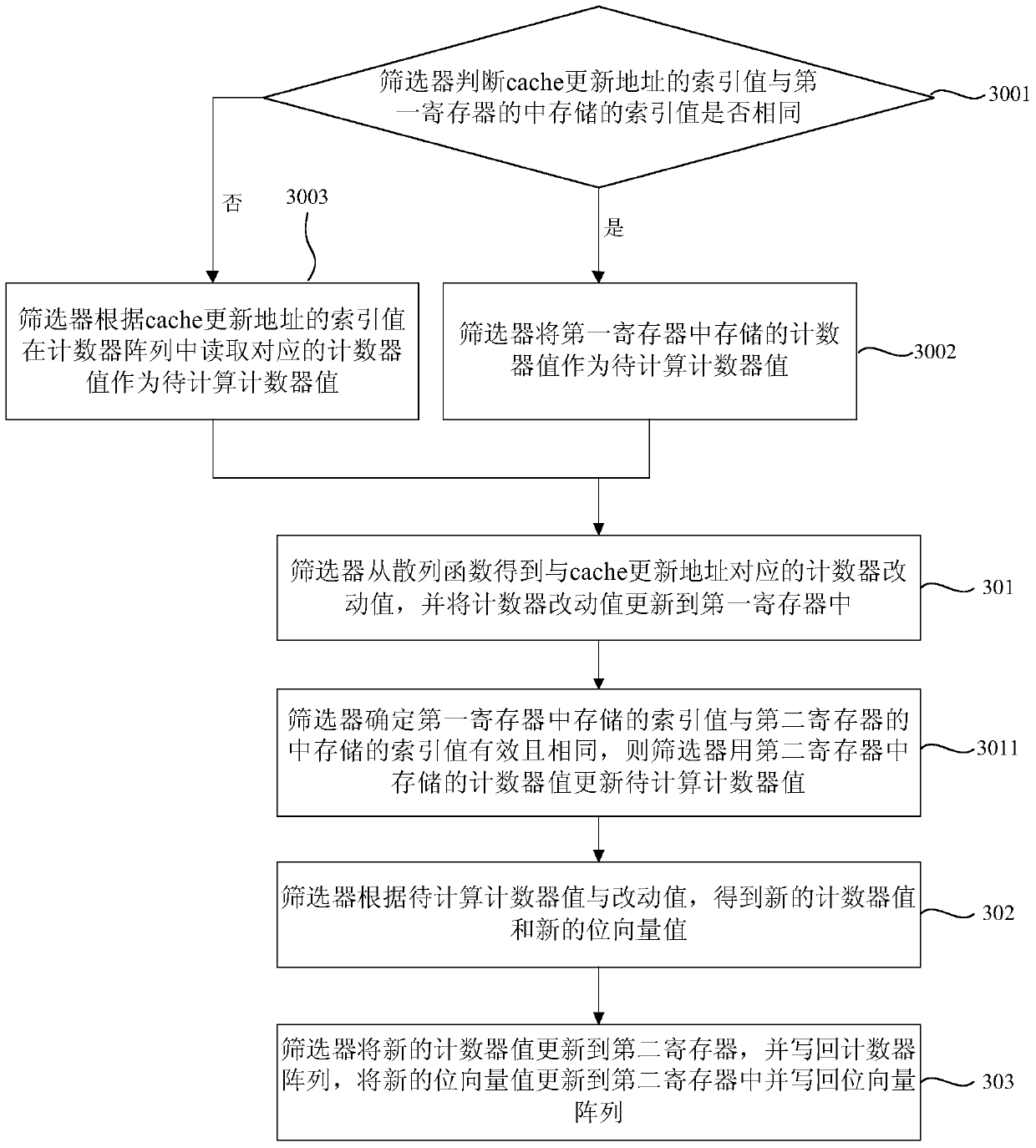

Screening method, filter and data consistency maintenance system

ActiveCN106354421BReduce access rateReduce access queuing timeInput/output to record carriersCache accessScreening method

The invention provides a screening method, a screening device and a data consistency maintenance system. The method includes the steps that the screening device receives memory request addresses sent by an IP core; the screening device determines whether the memory request addresses are in a cache or not; if it is determined that the memory request addresses are not in the cache, a memory operation instruction is sent to the IP core, wherein the memory operation instruction is used for enabling the IP core to carry out memory operation according to the memory request addresses. Screening is carried out before data consistency operation to screen out the memory request addresses not in the cache, and then the IP core carries out memory operation directly according to the memory request addressees without carrying out cache inquiry, so that the cache query frequency is greatly reduced, the cache access rate is reduced, the cache access queuing time is shortened, and the cache performance is improved.

Owner:LOONGSON TECH CORP

Semiconductor integrated circuit and IC card

InactiveUS20060164906A1Reduce wasted powerReduce access rateRead-only memoriesDigital storageBit lineSub threshold

A semiconductor integrated circuit has a memory which can enter active state or standby state, and the memory has voltage generation circuits for bit lines and source lines with which memory cells are connected. The voltage generation circuits make the potential of the bit lines and the potential of the source lines equal to each other in response to an instruction to transition from active state to standby state. The voltage generation circuits produce a potential difference between the bit lines and the source lines in response to an instruction to transition from standby state to active state. In standby state, the potential of the bit lines and that of the source lines are equal to each other. Therefore, sub-threshold leakage does not occur between the source and drain of each memory cell. In active state, the source line potential is not varied.

Owner:HITACHI ULSI SYST CO LTD +1