Patents

Literature

74 results about "Modular multiplier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Modular multiplier

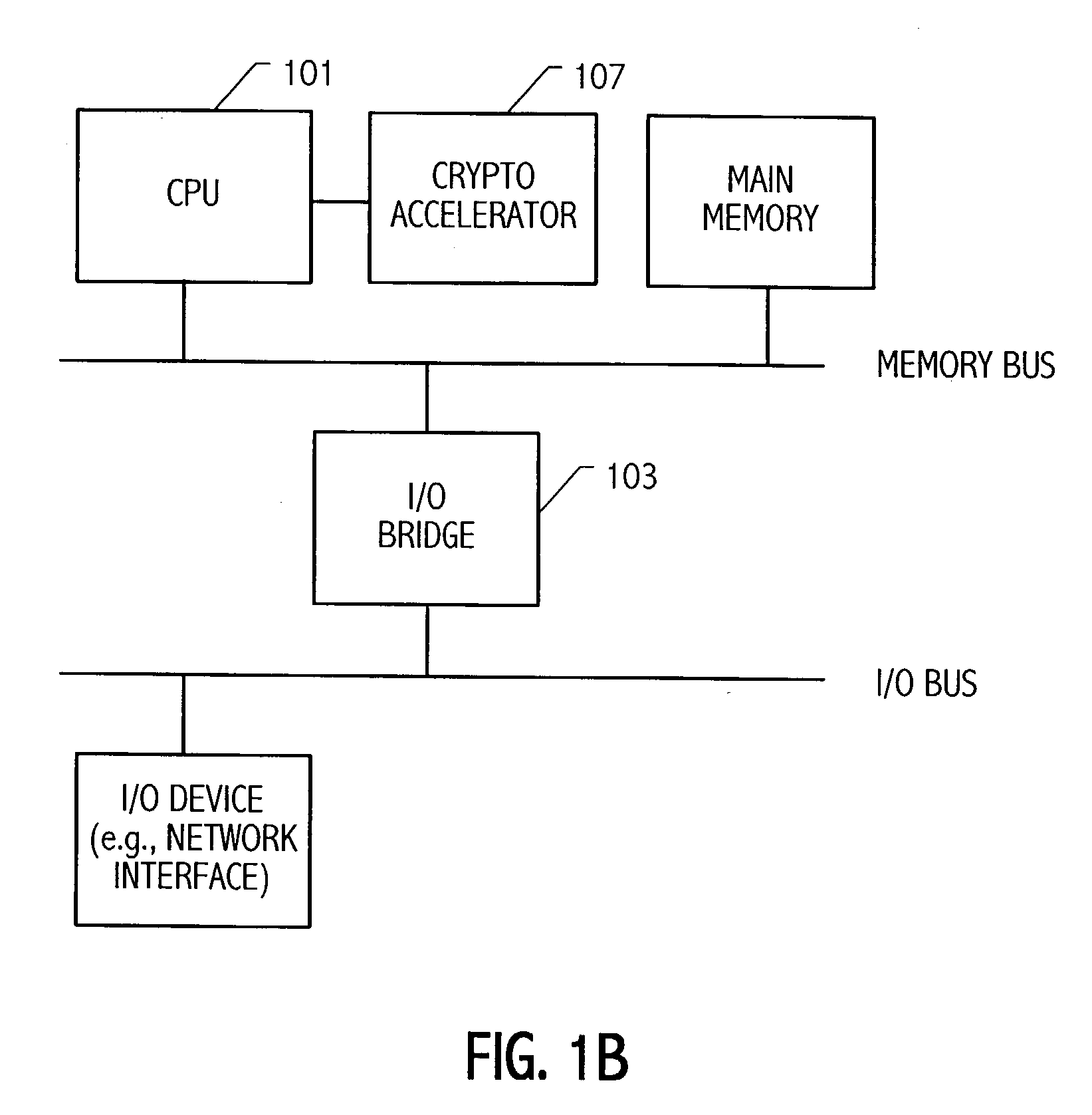

ActiveUS20030212729A1Computation using non-contact making devicesDigital computer detailsModular multiplierKaratsuba algorithm

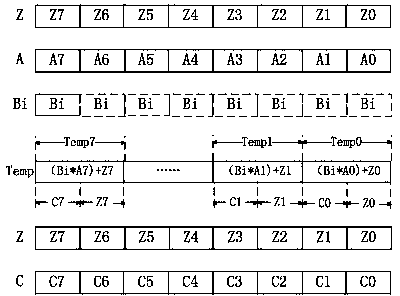

Modular multiplication of two elements X(t) and Y(t), over GF(2), where m is a field degree, may utilize field degree to determine, at least in part, the number of iterations. An extra shift operation may be employed when the number of iterations is reduced. Modular multiplication of two elements X(t) and Y(t), over GF(2), may include a shared reduction circuit utilized during multiplication and reduction. In addition, a modular multiplication of binary polynomials X(t) and Y(t), over GF(2), may utilize the Karatsuba algorithm, e.g., by recursively splitting up a multiplication into smaller operands determined according to the Karatsuba algorithm.

Owner:ORACLE INT CORP

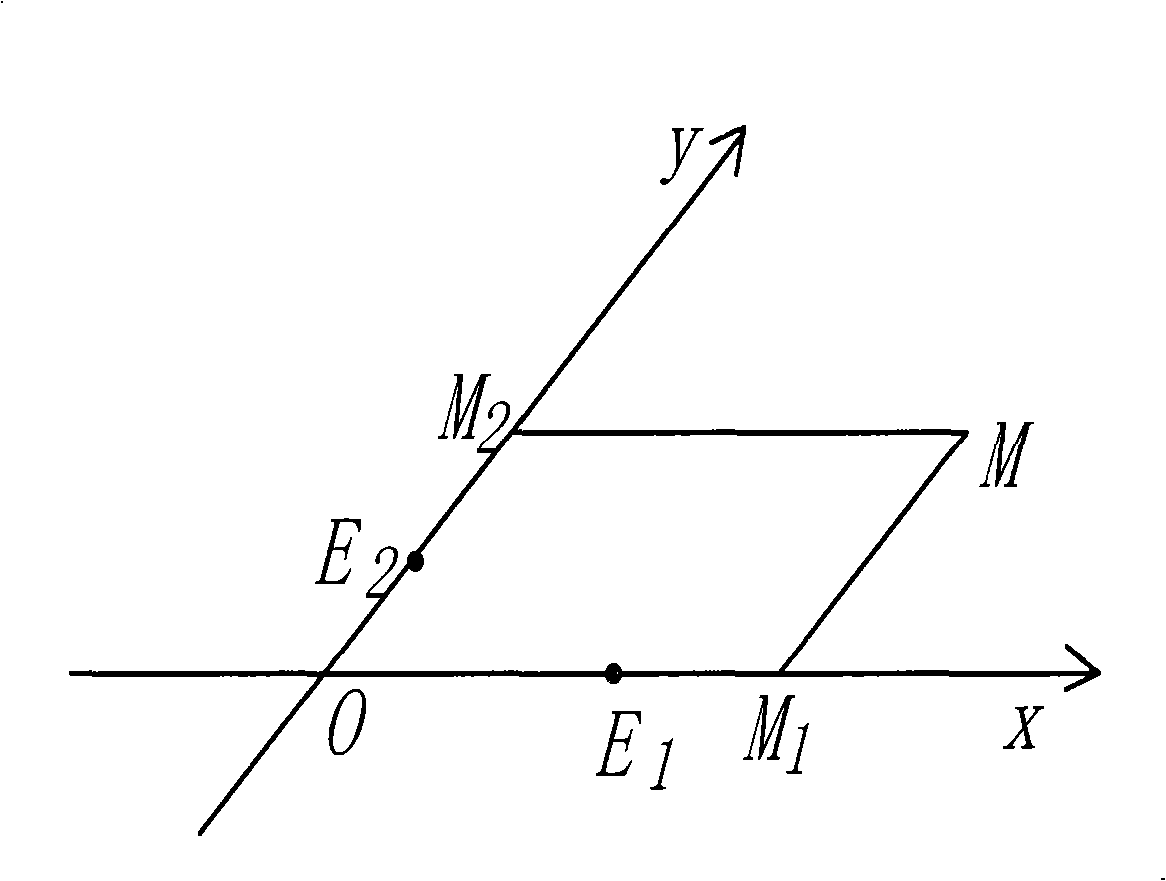

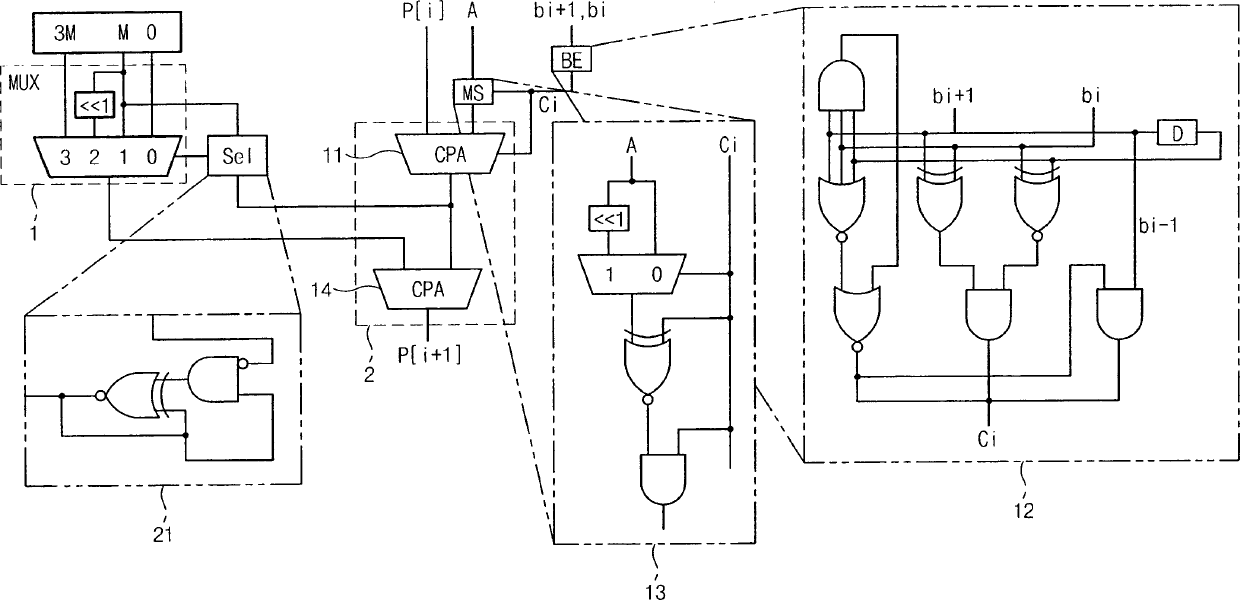

High speed arithmetic device and method of elliptic curve code

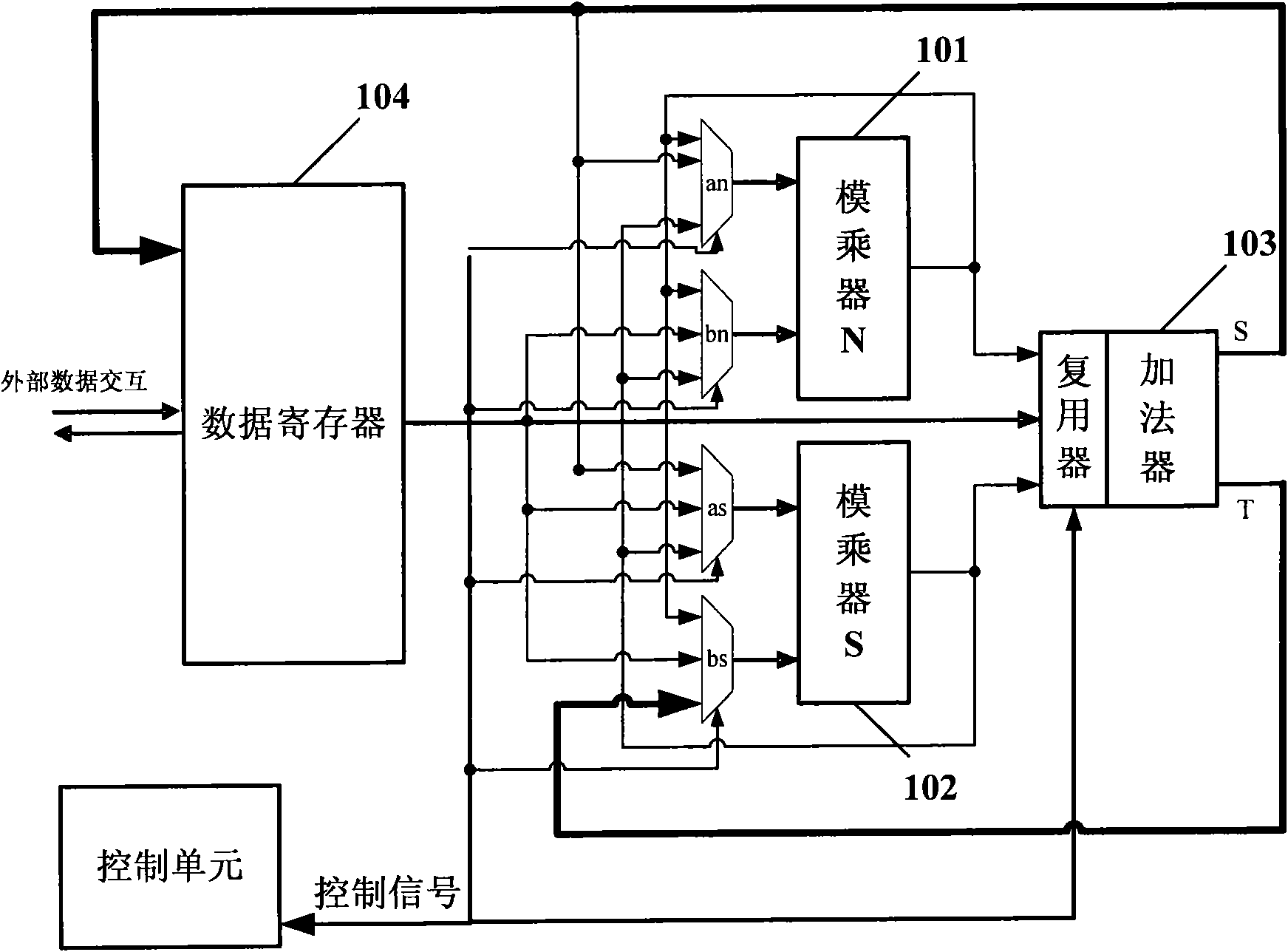

ActiveCN101782845AImprove hardware efficiencyReduced number of cycles for modular multiplicationPublic key for secure communicationComputations using residue arithmeticHardware structureModular multiplier

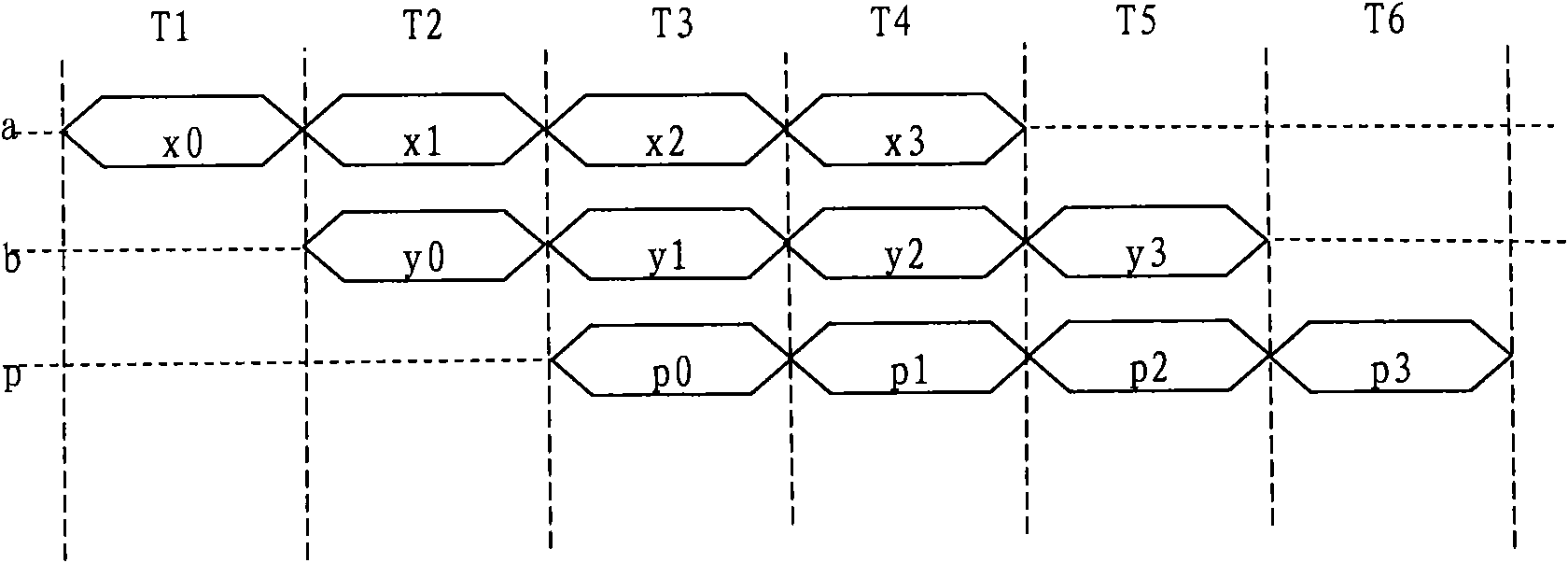

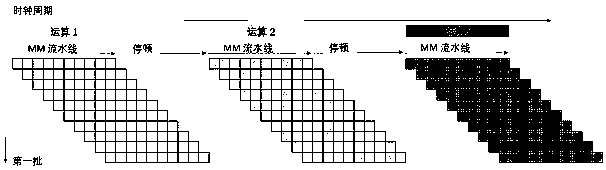

The invention relates to a high speed arithmetic device and a method of elliptic curve codes. The invention mainly aims to a master curve, the elliptic curve of which is 160-256 bit of die length and the prime field of which is on Fp. The high speed arithmetic device is a special hardware structure based on a water running pulsate double modular multiplier; the hardware structure comprises an operation part, a control part and a storage part, wherein the operation part comprises two parallel water running pulsate modular multipliers and two groups of adders. Based on the specific hardware structure, point addition and point double water running operation sequences of modified Jacobi coordinate projective joints are rearranged, and point addition and point double operations which sequentially appear in succession are connected end to end; and the vacant times of the double modular multipliers are mutually complemented, thus increasing the hardware efficiency of the water running pulsate modular multipliers and causing the point addition operation to only occupy seven modular multiplication operation cycles and the point double operation to occupy four modular multiplication operation cycles, and drastically reducing clock periodic numbers of the point addition and / or point double and point multiplication operation.

Owner:BEIJING HUADA INFOSEC TECH

Generic modular multiplier using partial reduction

ActiveUS20030206628A1Public key for secure communicationDigital computer detailsBinary multiplierParallel computing

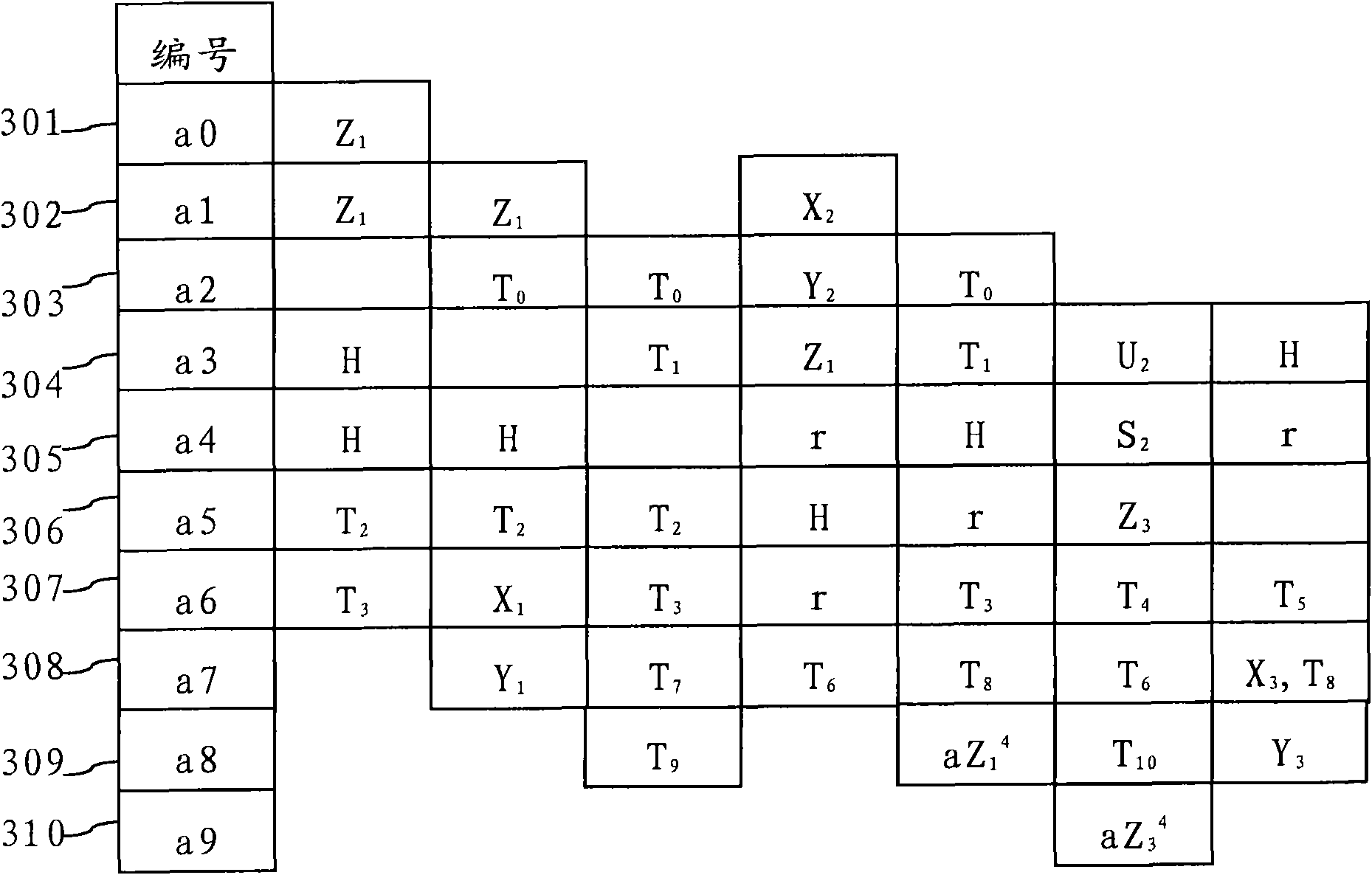

An apparatus multiplies a first and a second binary polynomial X(t) and Y(t) over GF(2), where an irreducible polynomial Mm(t)=t<m>+am-1t<m-1>+am-2t<m-2>t<m-2>+ . . . +a1t+a0, and where the coefficients ai are equal to either 1 or 0, and m is a field degree. The degree of X(t)<n, and the degree of Y(t)<n, and m<=n. The apparatus includes a digit serial modular multiplier circuit coupled to supply a multiplication result of degree >=m of a multiplication of the first and second binary polynomials. The digit serial modular multiplier circuit includes a first and second register, each being <=n bits. A partial product generator circuit multiplies a portion of digit size d of contents of the first register and contents of the second register. The partial product generator is also utilized as part of a reduction operation for at least one generic curve.

Owner:ORACLE INT CORP

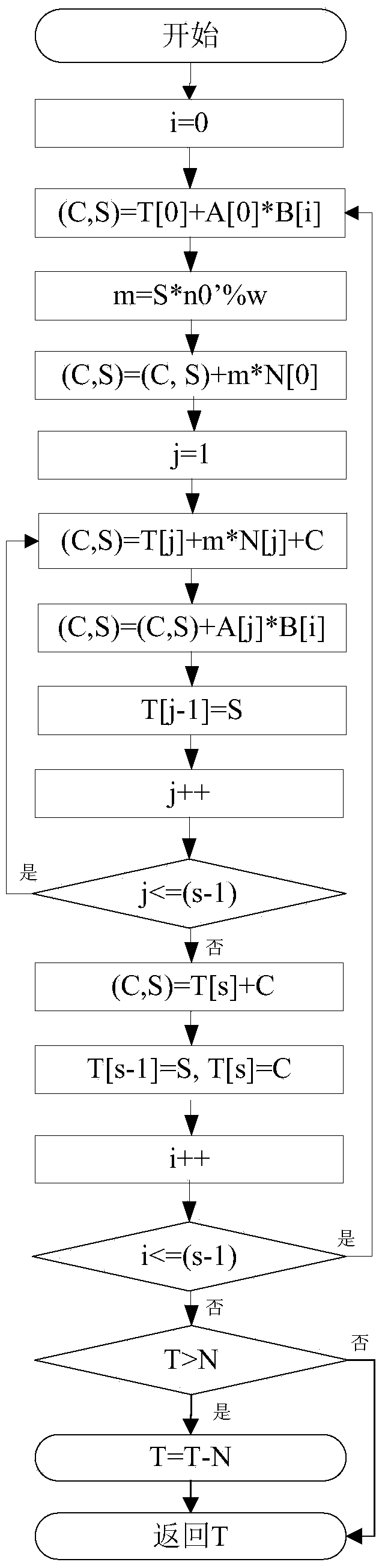

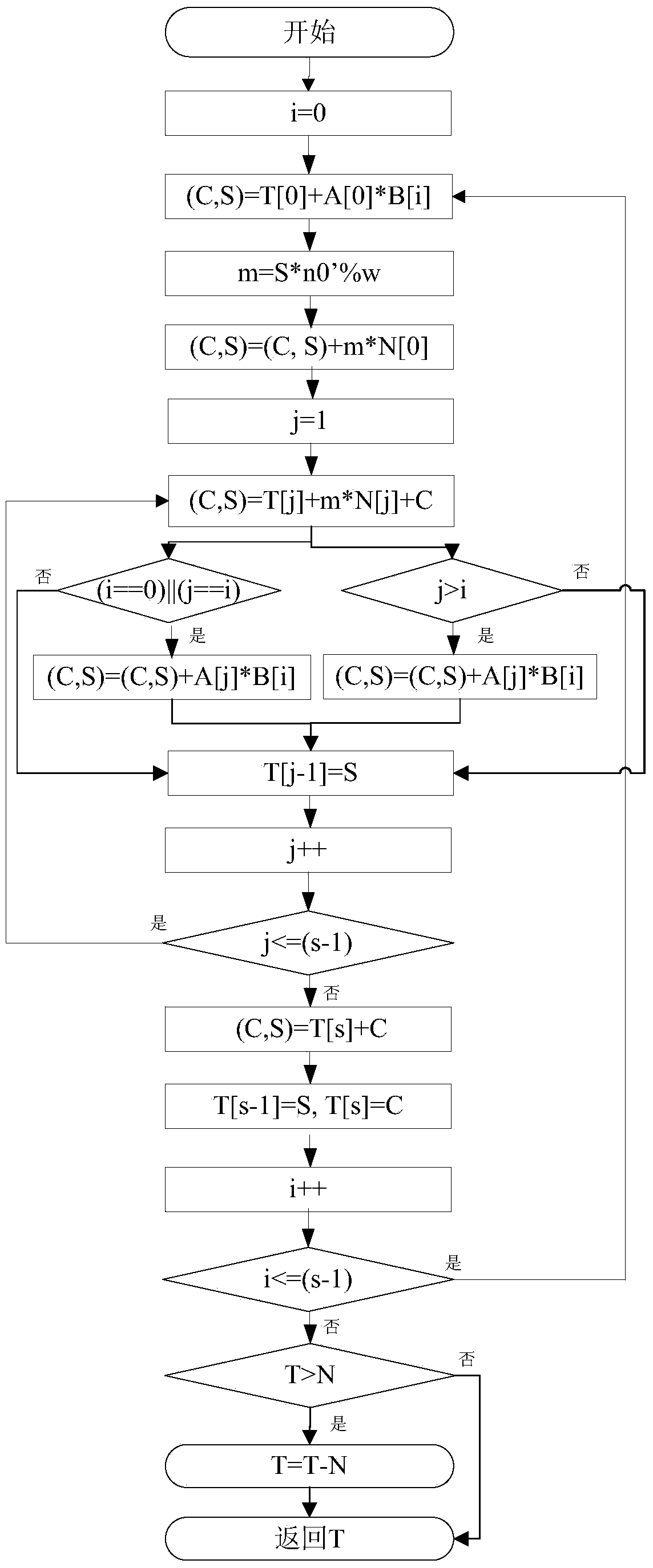

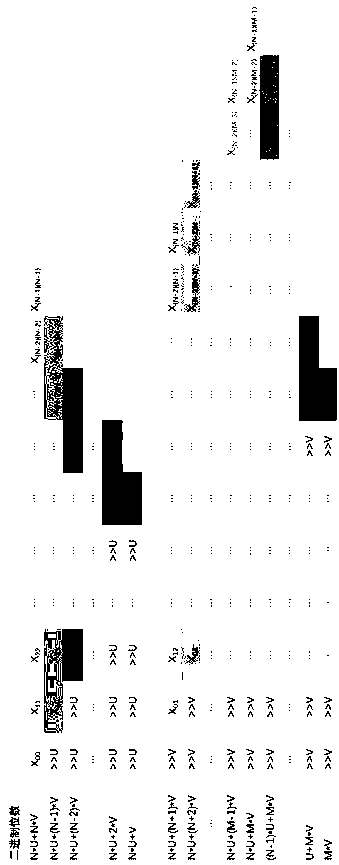

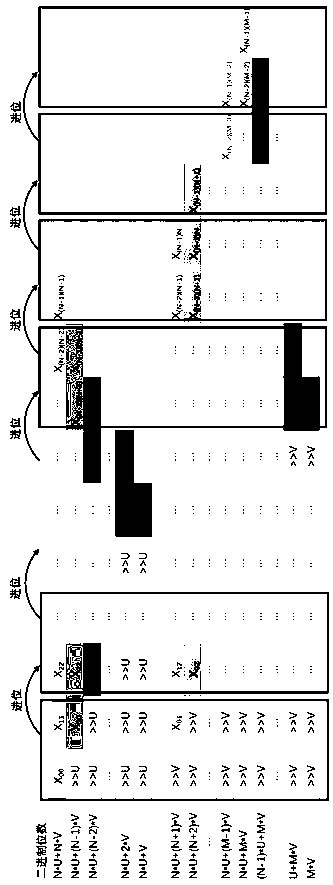

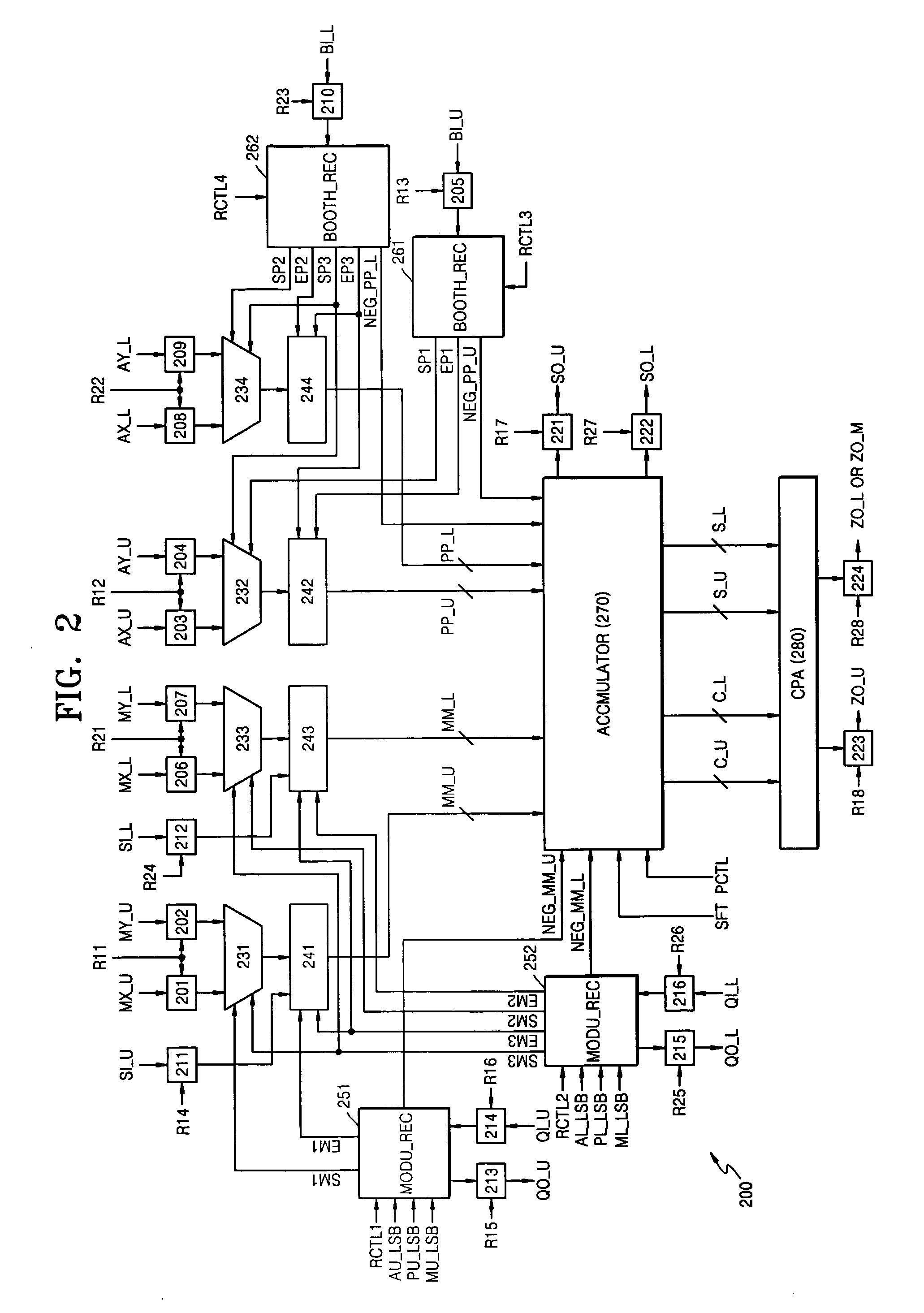

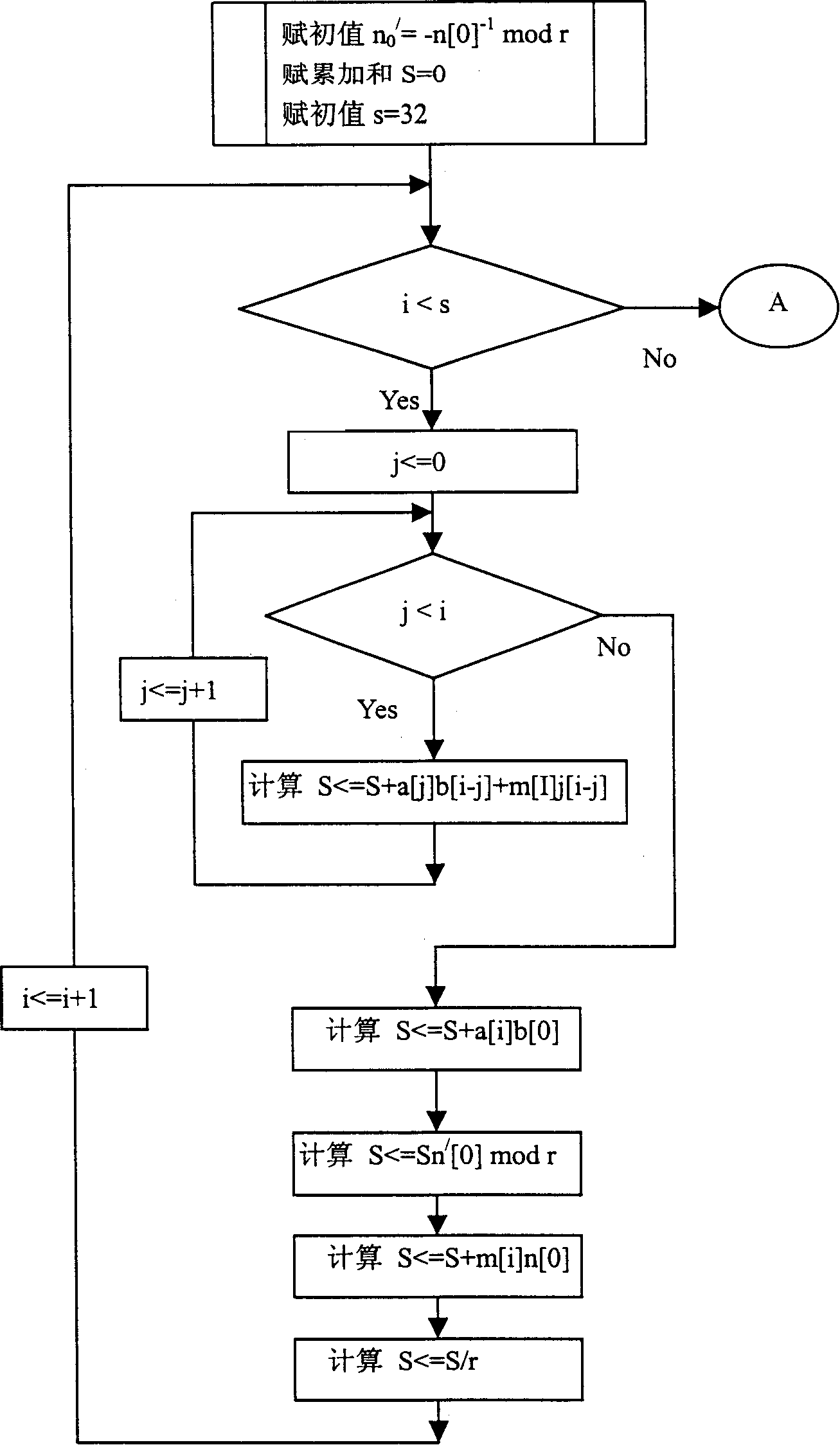

Optimized Montgomery modular multiplication method, optimized modular square method and optimized modular multiplication hardware

InactiveCN103761068AImprove computing powerReduce areaComputations using residue arithmeticBinary multiplierProcessor register

The invention discloses an optimized Montgomery modular multiplication method, an optimized modular square method and optimized modular multiplication hardware. The optimization is carried out based on an original FIOS (Finely integrated operand scanning) algorithm. The optimized modular multiplication hardware mainly comprises three single-port SRAMs, a double-port SRAM, a 32-bit multiplier, a 34-bit adder, a 4-2 compressor, a 64-bit register and six 32-bit registers. According to the optimized Montgomery modular multiplication method, the optimized modular square method and the optimized modular multiplication hardware, a high-radix modular multiplier of a two-stage parallel assembly line is adopted, the AB operation is completed through a first-stage 32-bit multiplier, the T+AB+C operation is completed through a second-stage adder, the 32-2048-bit modular multiplication operation is achieved, the area of a chip is reduced, and the modular multiplication operation performance is improved.

Owner:SHANGHAI JIAO TONG UNIV

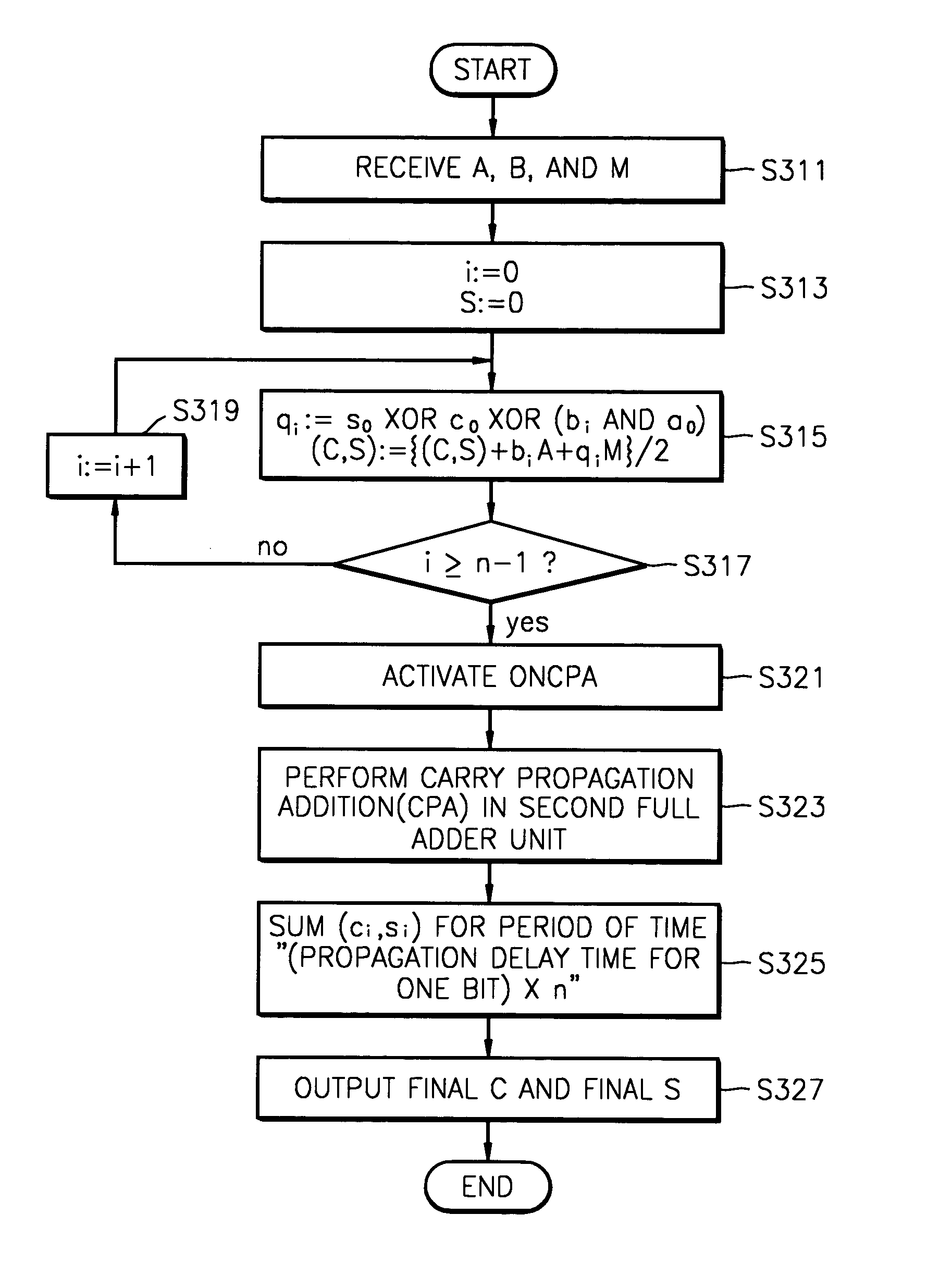

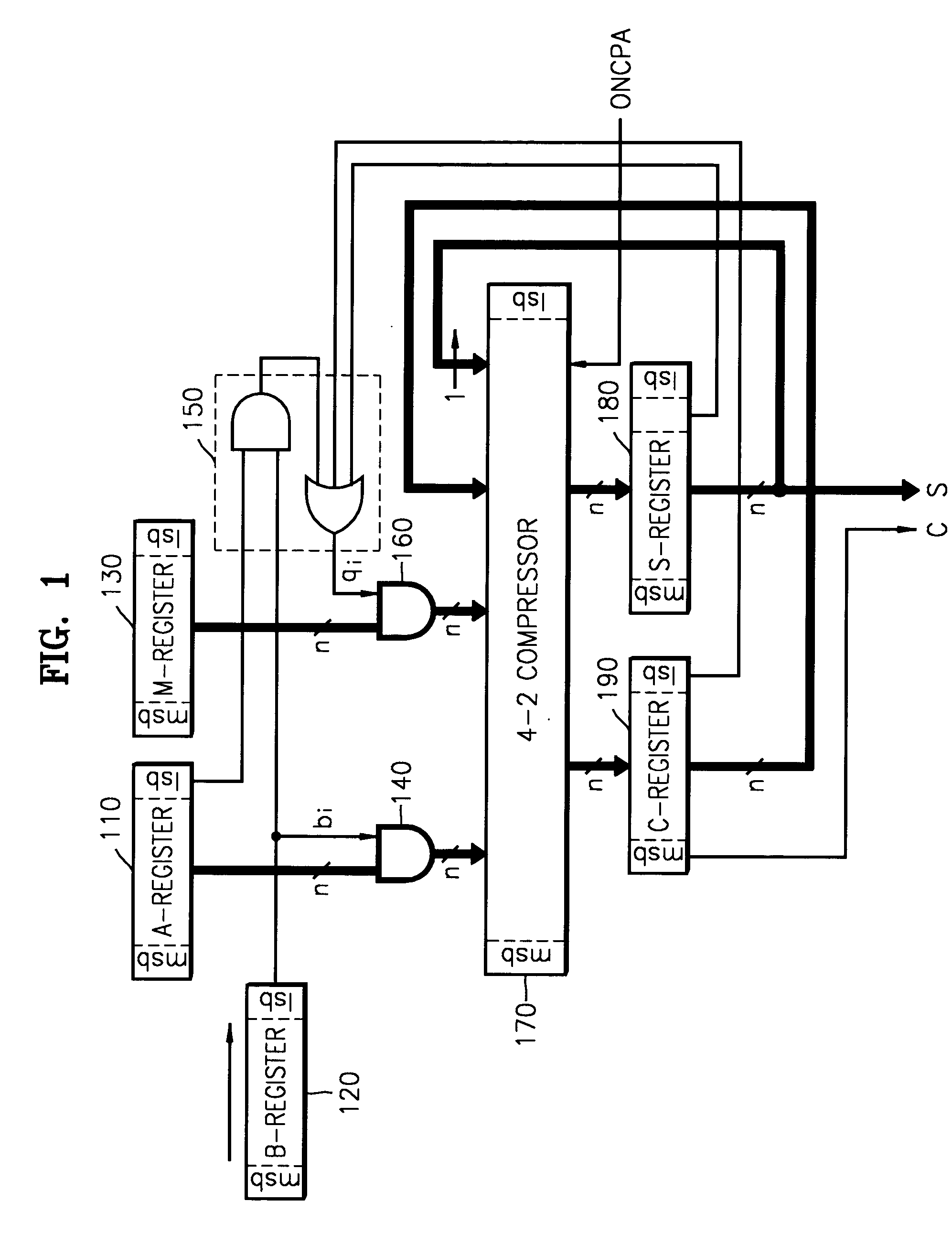

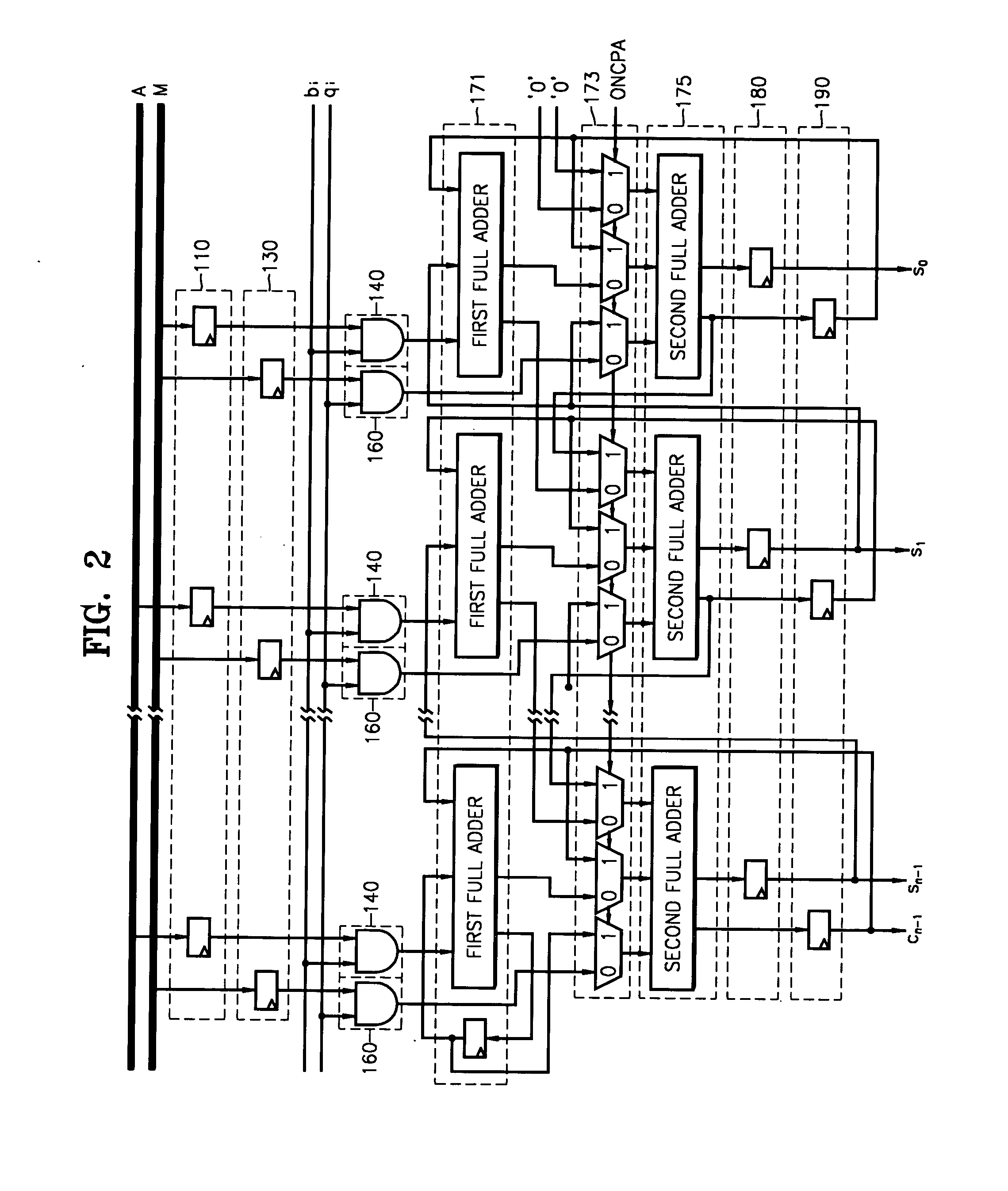

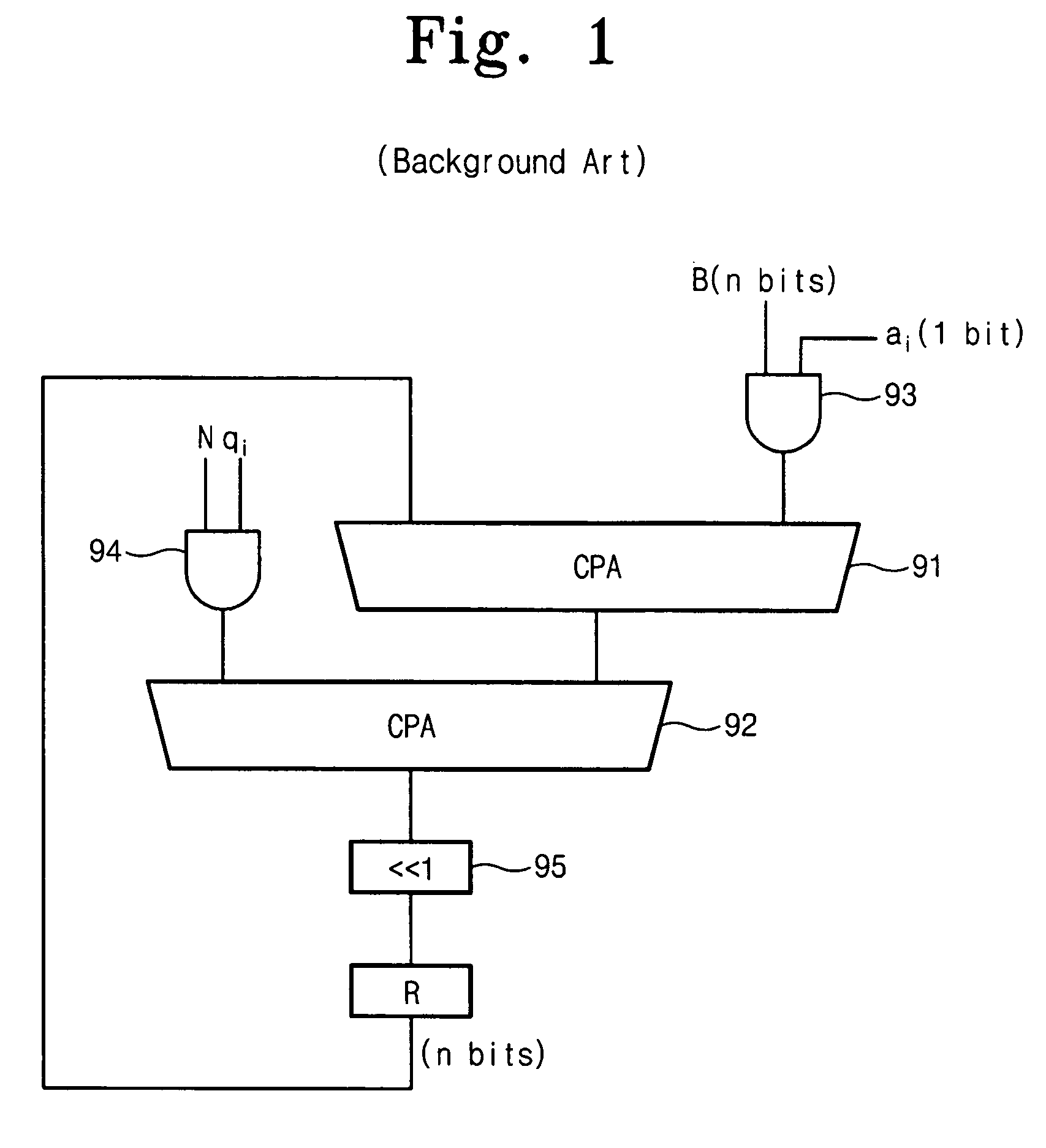

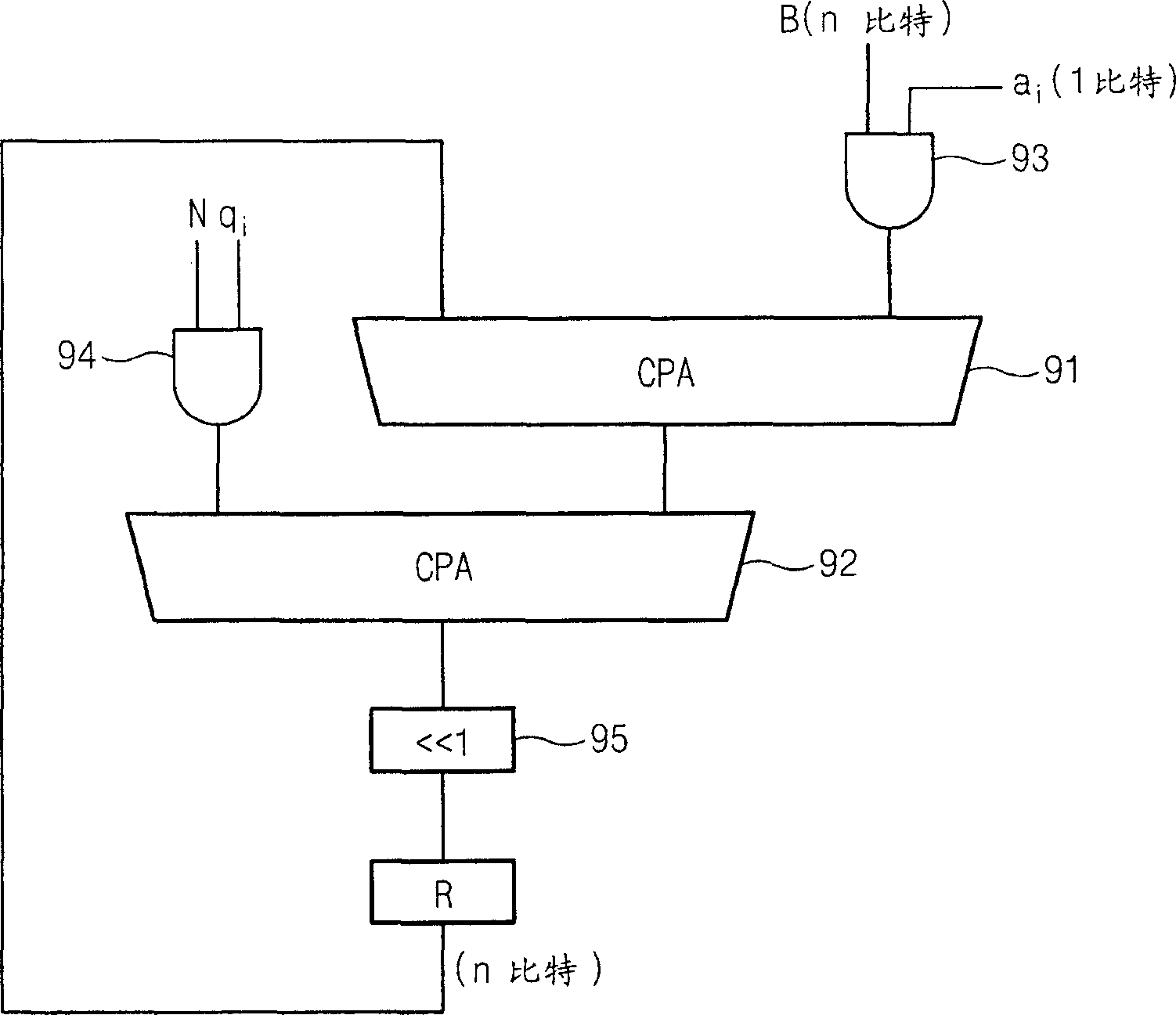

Montgomery modular multiplier and method thereof using carry save addition

InactiveUS7543011B2Reduce power consumptionIncrease speedComputation using non-contact making devicesDigital computer detailsCarry propagationModular multiplier

A method of reducing power consumption and / or enhancing computation speed in the modulus multiplication operation of a Montgomery modulus multiplication module. A coding scheme reduces the need for an adder or memory element for obtaining multiple modulus values, and the use of carry save addition with carry propagation addition enhances the computational speed of the multiplication module.

Owner:SAMSUNG ELECTRONICS CO LTD

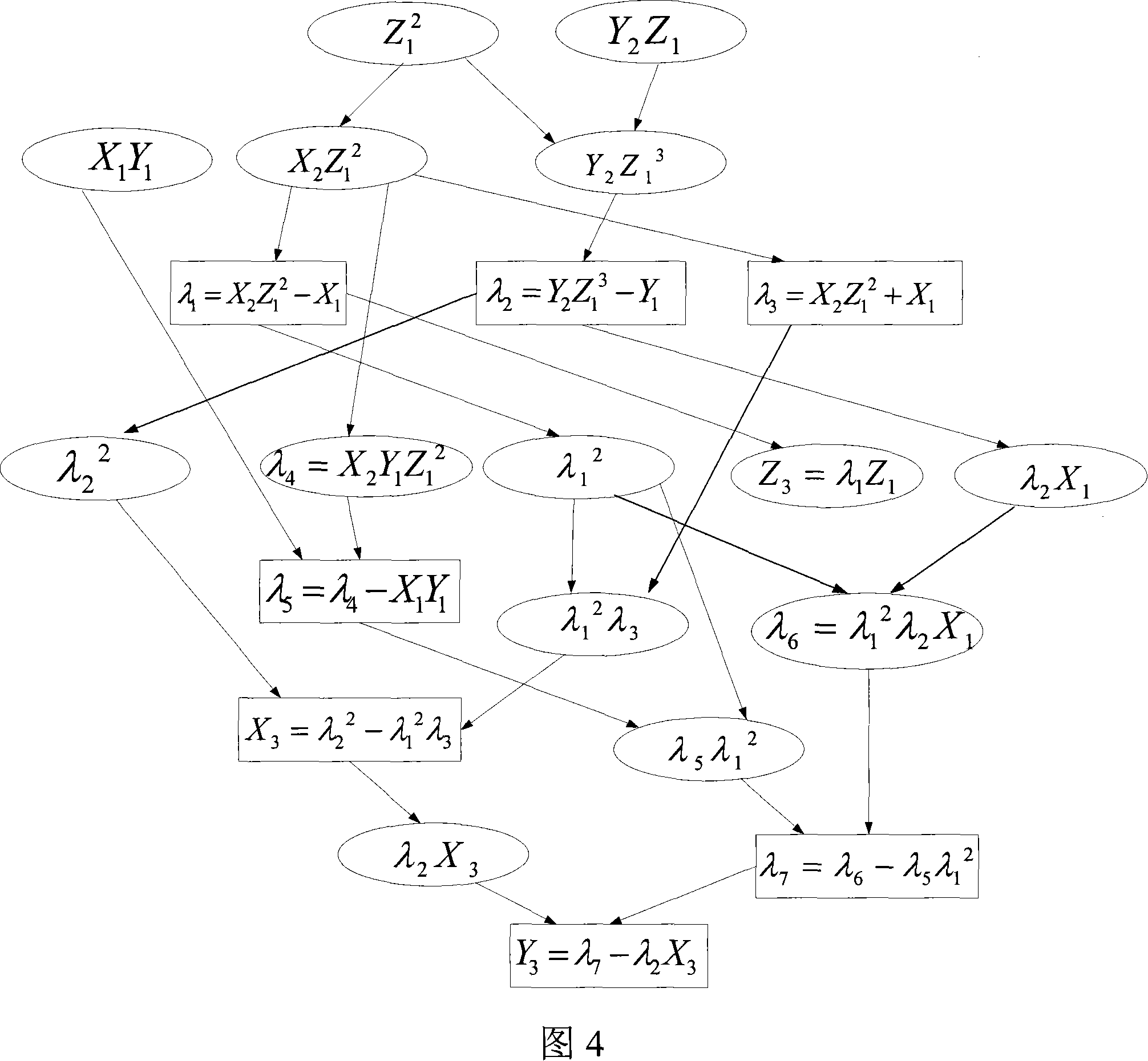

Time point system for ellipse curve password system

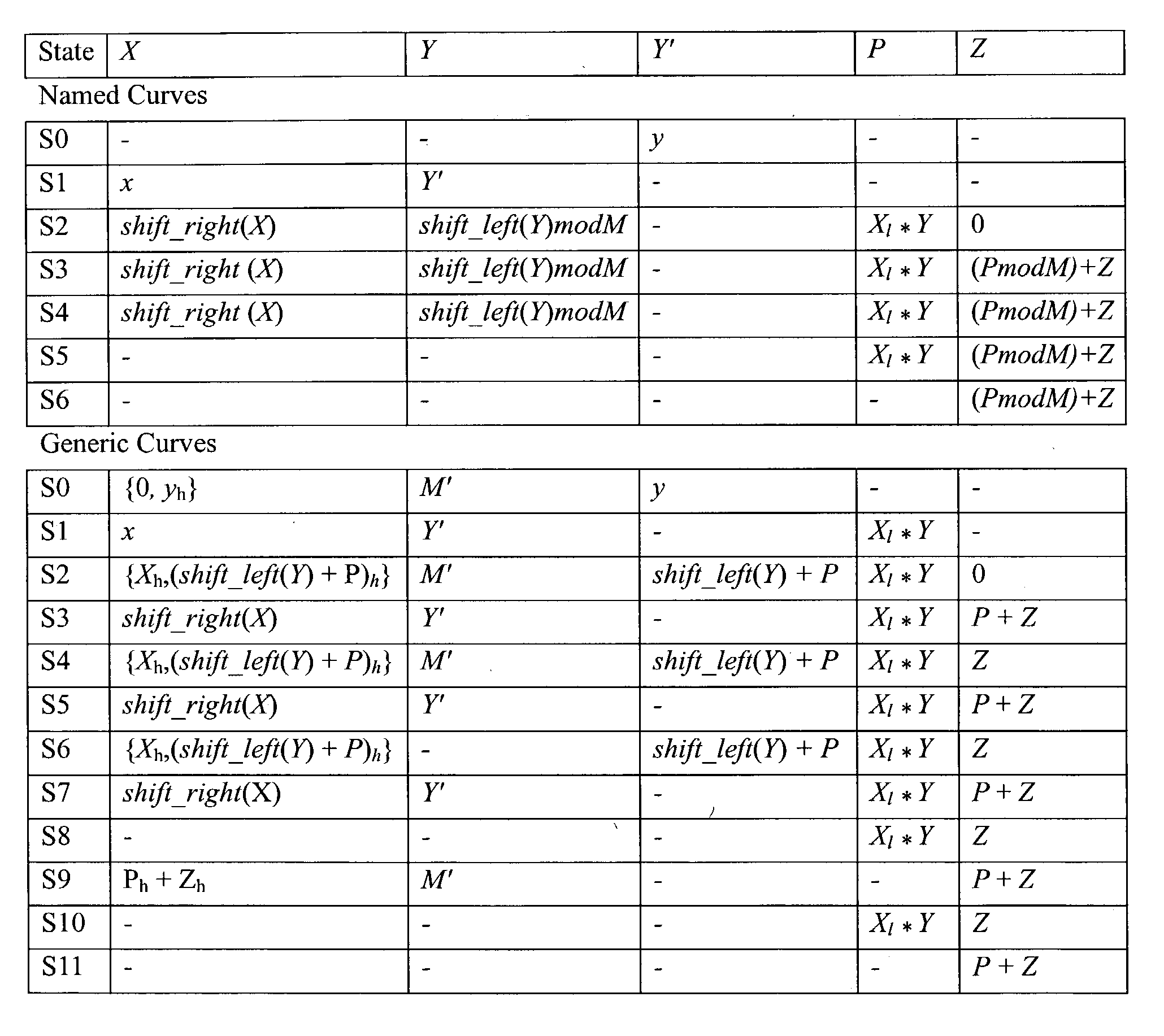

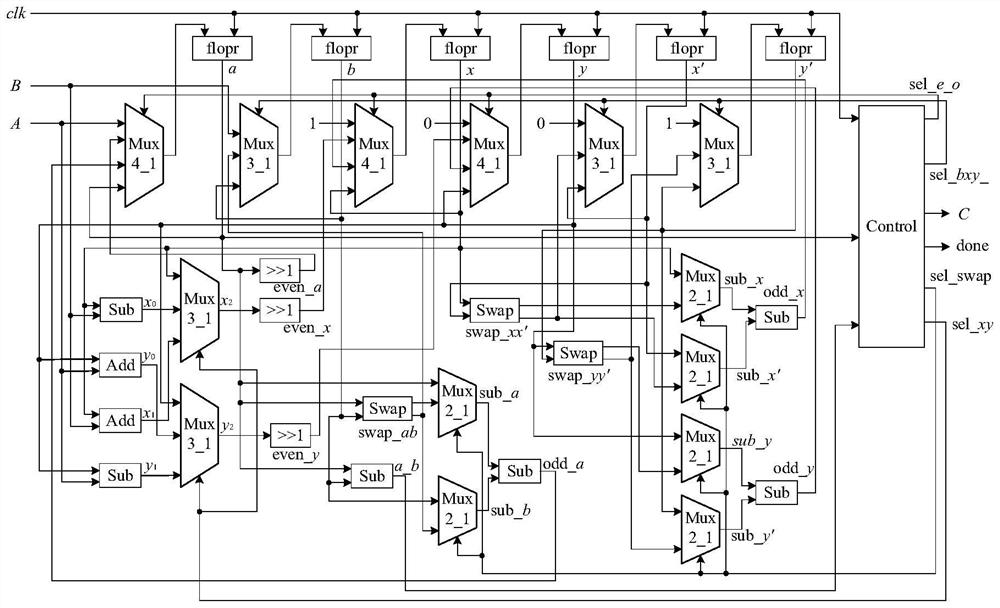

The invention relates to a point-timing system of an elliptic curve cryptosystem, which pertains to the point-timing technical field of an elliptic curve cryptosystem and is characterized in that: the invention includes a controller of a point-timing register, a point-timing multipath option controller, a first multipath selector group, a middle variable register group and a second multipath selector group; under gating control signals output by the point-timing multipath option controller and in the process of six production lines, point-timing algorithm for multipliers and addends of the second multipath selector group is carried out by a modular multiplier and a modular adder positioned outside the point-timing system. In each production line, under the control of the gating control signals, the modular multiplier and the modular adder respectively return intermediate data to the first and the second multipath selector groups; under the control of operation control signals output by the controller of the point-timing register, each multipath selector controlling the first multipath selector group outputs relevant multipliers and addends to the second multipath selector group by the middle variable register group. The point-timing system of an elliptic curve cryptosystem of the invention increases point-timing arithmetic speed, optimizes point- multiplying performance of elliptic curves under a basic level and improves data throughput rate.

Owner:TSINGHUA UNIV

Point addition system of elliptic curve cipher system

A point addition system for elliptic curve cryptosystem belongs to the elliptic curve cryptosystem point addition technical field. The present invention is characterized in that: the system comprises a point addition register controller, a point addition multi-channel selection controller, a first multi-channel selector group, an intermediate variable register group and a second multi-channel selector group; under the gating control signals output by the point addition multi-channel selection controller, in the process of six pipelines, point addition operation to the multipliers and addends output by the second multi-channel selector group is accomplished by a modular multiplier and a modular adder which are positioned outside the point addition system; in the process of each pipeline, under the control of the gating control signals, the modular multiplier and the modular adder respectively return intermediate data to the first multi-channel selector group and the second multi-channel selector group; under the control of operation control signals output by the point addition register controller, multi-channel selectors in the first multi-channel selector group are controlled to output corresponding multipliers and addends to the second multi-channel selector group through the intermediate variable register group. The present invention improves point addition operation speed, optimizes the point multiplication performance of elliptic curve in a basic aspect, and improves data throughput rate.

Owner:TSINGHUA UNIV

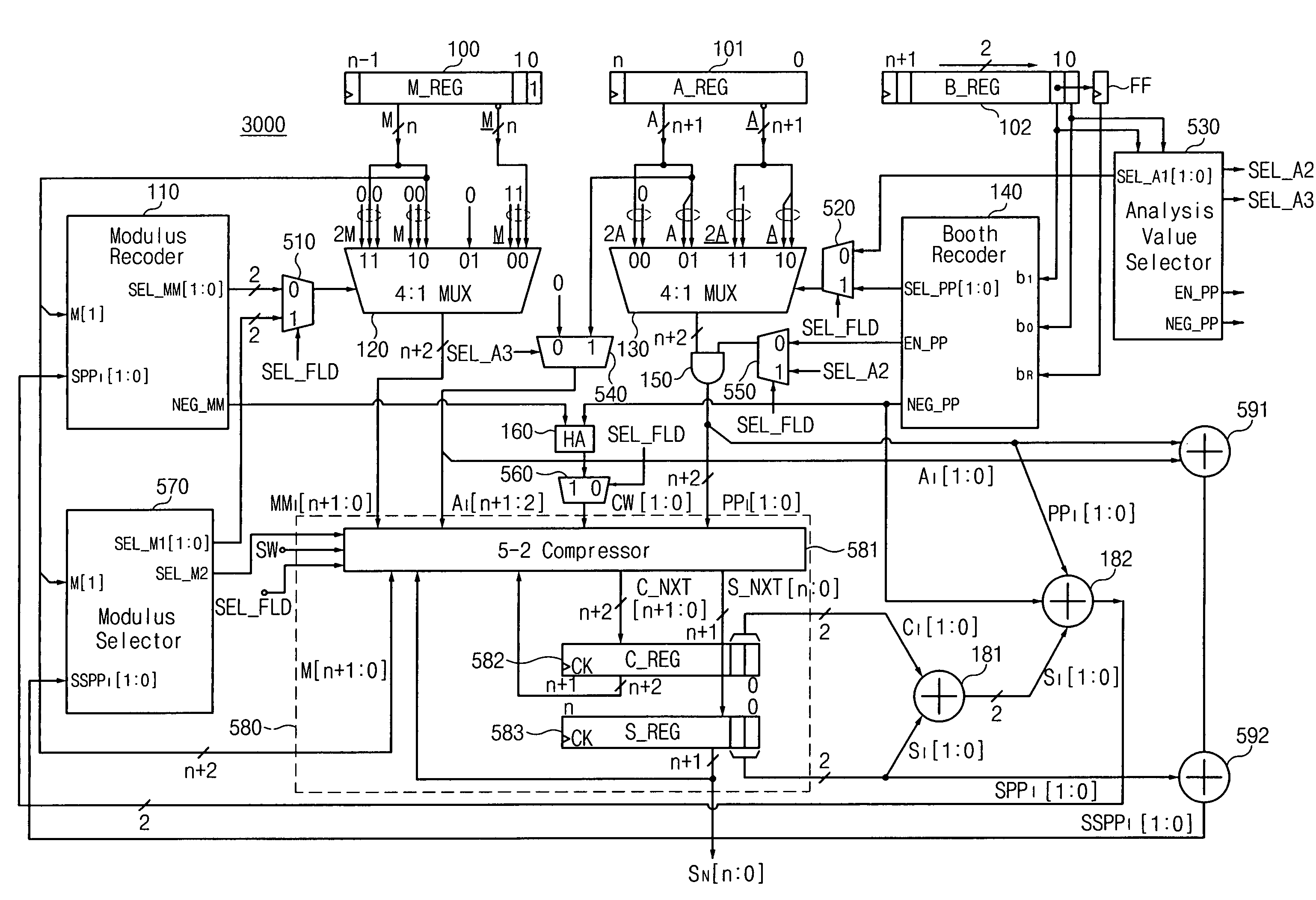

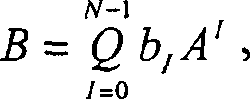

Montgomery modular multiplier using a compressor and multiplication method

ActiveUS20040125948A1Easy to disassembleHigh speedPublic key for secure communicationComputation using non-contact making devicesCarry propagationModular multiplier

A Montgomery modular multiplier receiving a multiplicand (A), a modulus (M), and a multiplier (B), using a t-s compressor, where t>3 and s>1, and a multiplication method performed in the same. In response to a carry propagation adder signal, the t-s compressor performs additions on the carry C and the sum Sand obtains the final results in a carry propagation adder structure.

Owner:SAMSUNG ELECTRONICS CO LTD

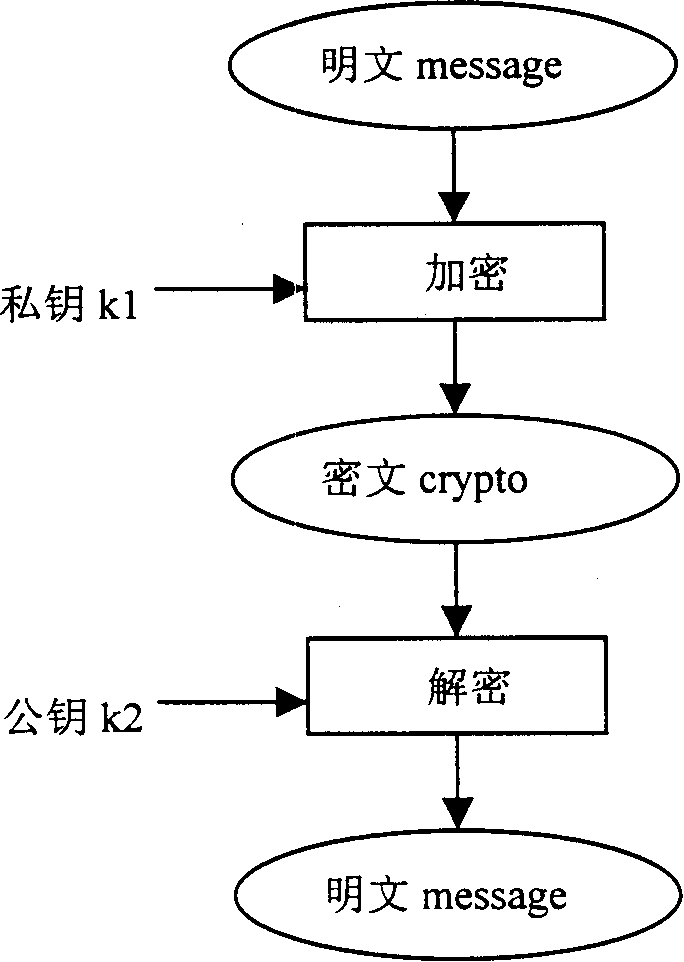

RSA (Ron Rivest, Adi Shamir and Leonard Adleman) algorithm digital signature method

ActiveCN102571342ALow costFast to marketKey distribution for secure communicationUser identity/authority verificationCoprocessorDigital signature

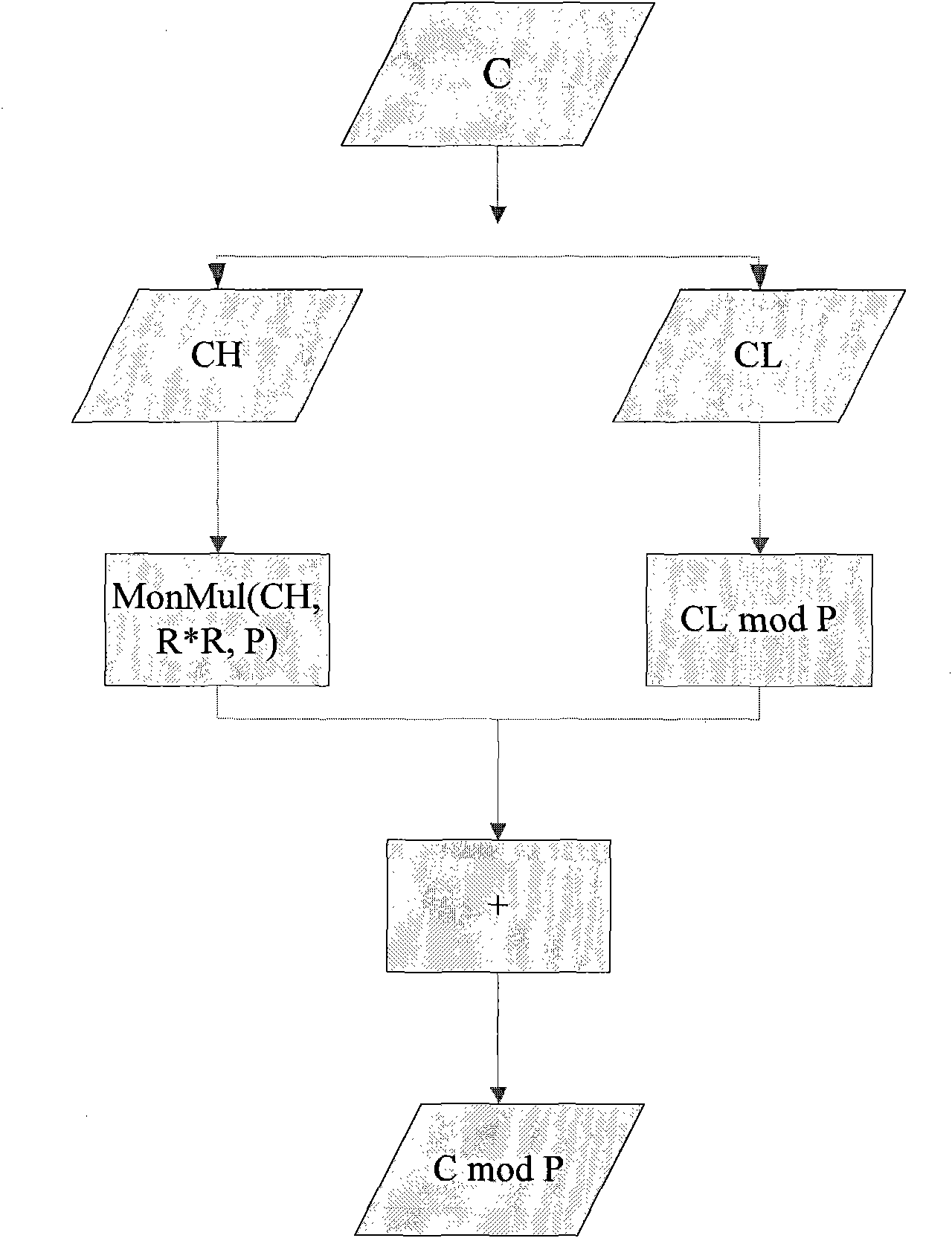

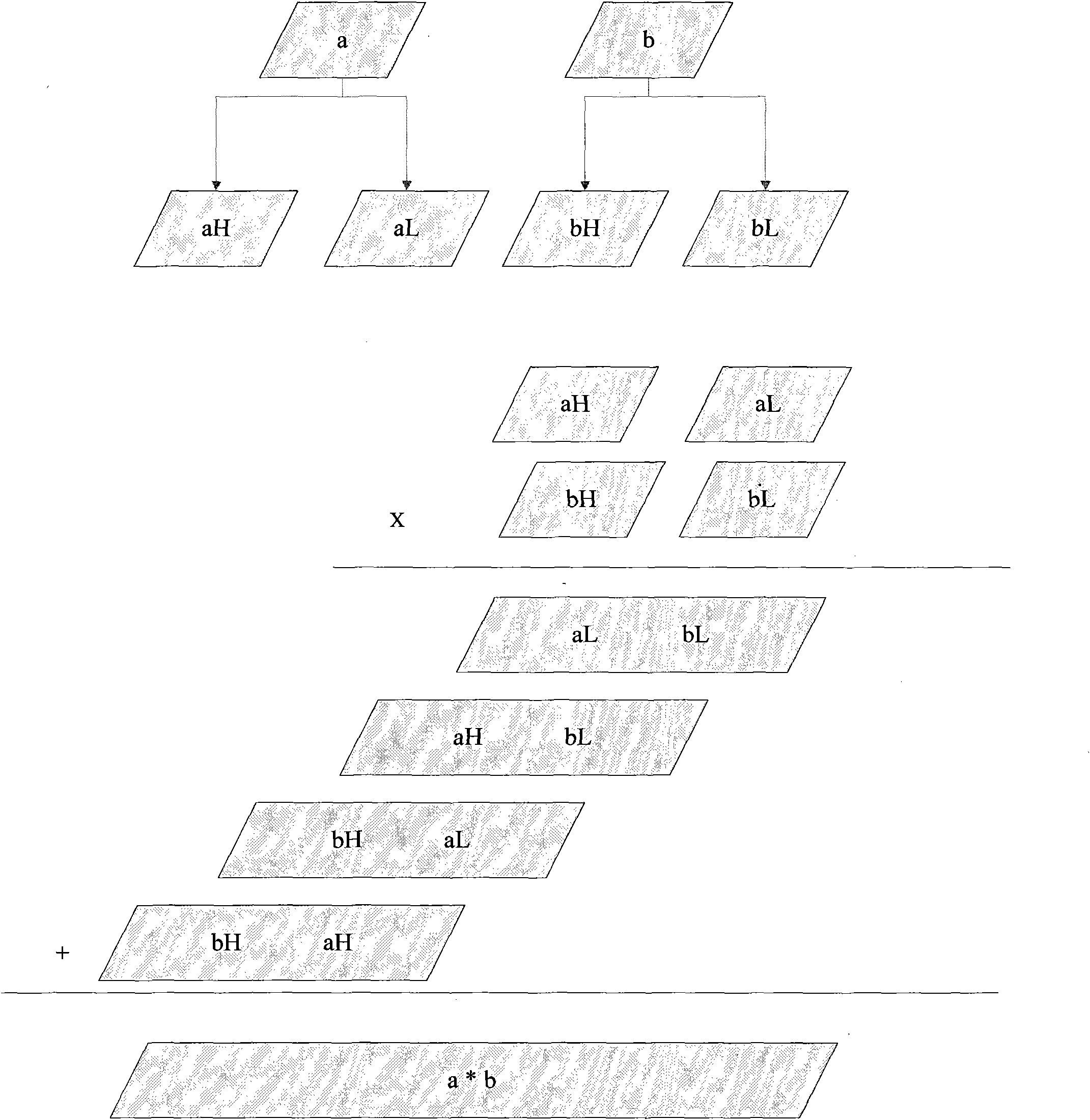

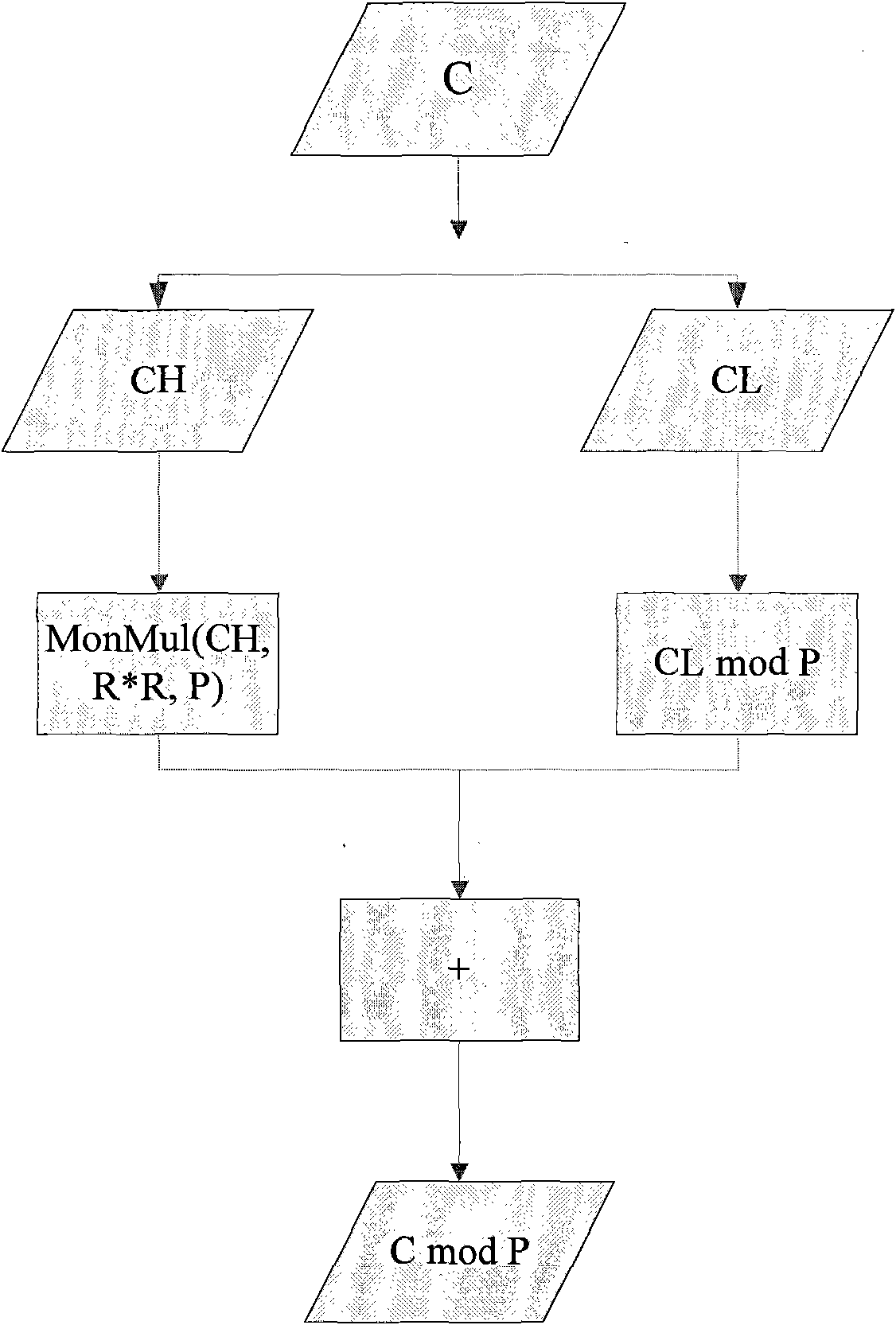

The invention designs an RSA (Ron Rivest, Adi Shamir and Leonard Adleman) algorithm digital signature method which realizes a 1408-bit RSA private key operation technology based on a 1024-bit hardware coprocessor and is mainly applied to the field of safety calculation of smart cards. A parameter in a large-bit-length RSA private key operation is calculated by utilizing a modular multiplier with small bit length, for example, a parameter in 1408-bit or 2048-bit RSA private key operation is calculated by utilizing a modular multiplier of 1024 bits. The RSA private key operation utilizes a Chinese remainder theorem and can be used for reducing the operation length of a main operation-modular exponentiation, but an operation of a key parameter, such as C mod P, C mod Q and a multiply operation, wherein the C represents a plain text, the length of the C is double the lengths of the P and the Q; and the multiply operation is accelerated by utilizing the modular multiplier, and a final result is also over the calculation capability of the modular multiplier. In the technology of the invention, the C is split into two numbers with the small bit lengths to calculate the C mod P by mainly utilizing the algorithm deformation of modular arithmetic; and the multiply operation larger than the length of the modular multiplier is calculated through a quarter multiply operation.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

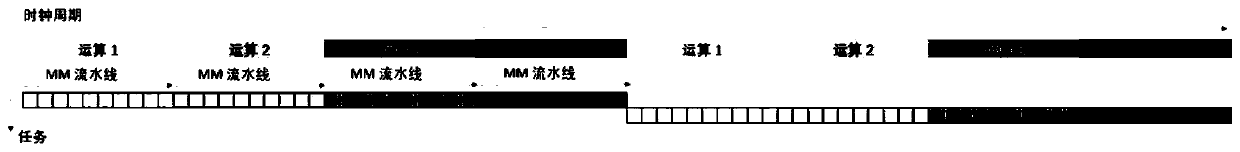

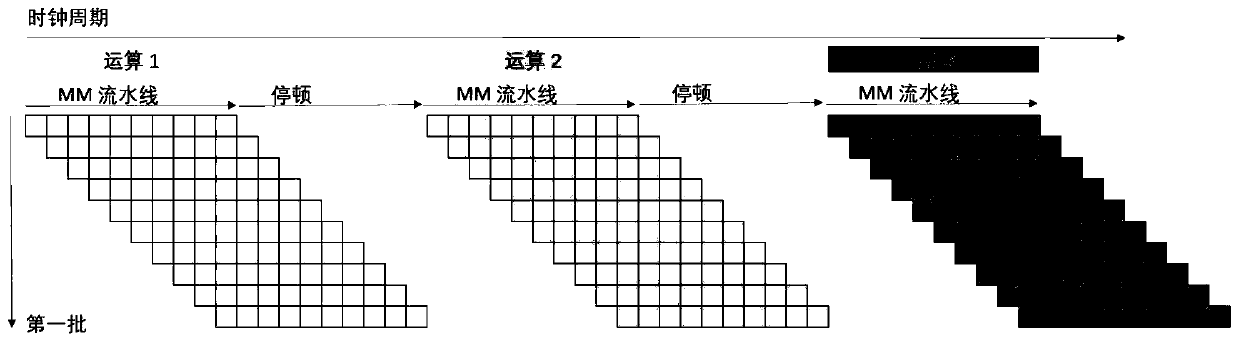

Pipelined Montgomery modular multiplication method and pipelined Montgomery modular multiplication calculation device

InactiveCN110351087AImprove throughputImprove performancePublic key for secure communicationComputations using residue arithmeticParallel computingModular multiplier

The invention discloses a pipelined Montgomery modular multiplication operation method and a pipelined Montgomery modular multiplication operation device, relates to the technical field of data cryptography algorithms, adopts a pipelined mode to improve Montgomery modular multiplication algorithm performance, increases throughput of a single Montgomery modular multiplier, and consumes less hardware resources and area than a traditional method using a plurality of Montgomery modular multipliers under the condition of the same throughput. Therefore, the modular multiplication number in unit timeis increased by dozens of times, and the Montgomery modular multiplier has higher performance / resource ratio than a non-pipelined Montgomery modular multiplier. Meanwhile, the asymmetric key algorithm hardware using the pipelined Montgomery modular multiplier can achieve higher performance with fewer hardware resources, and the throughput of Montgomery modular multiplication operation of any length is improved.

Owner:南京秉速科技有限公司

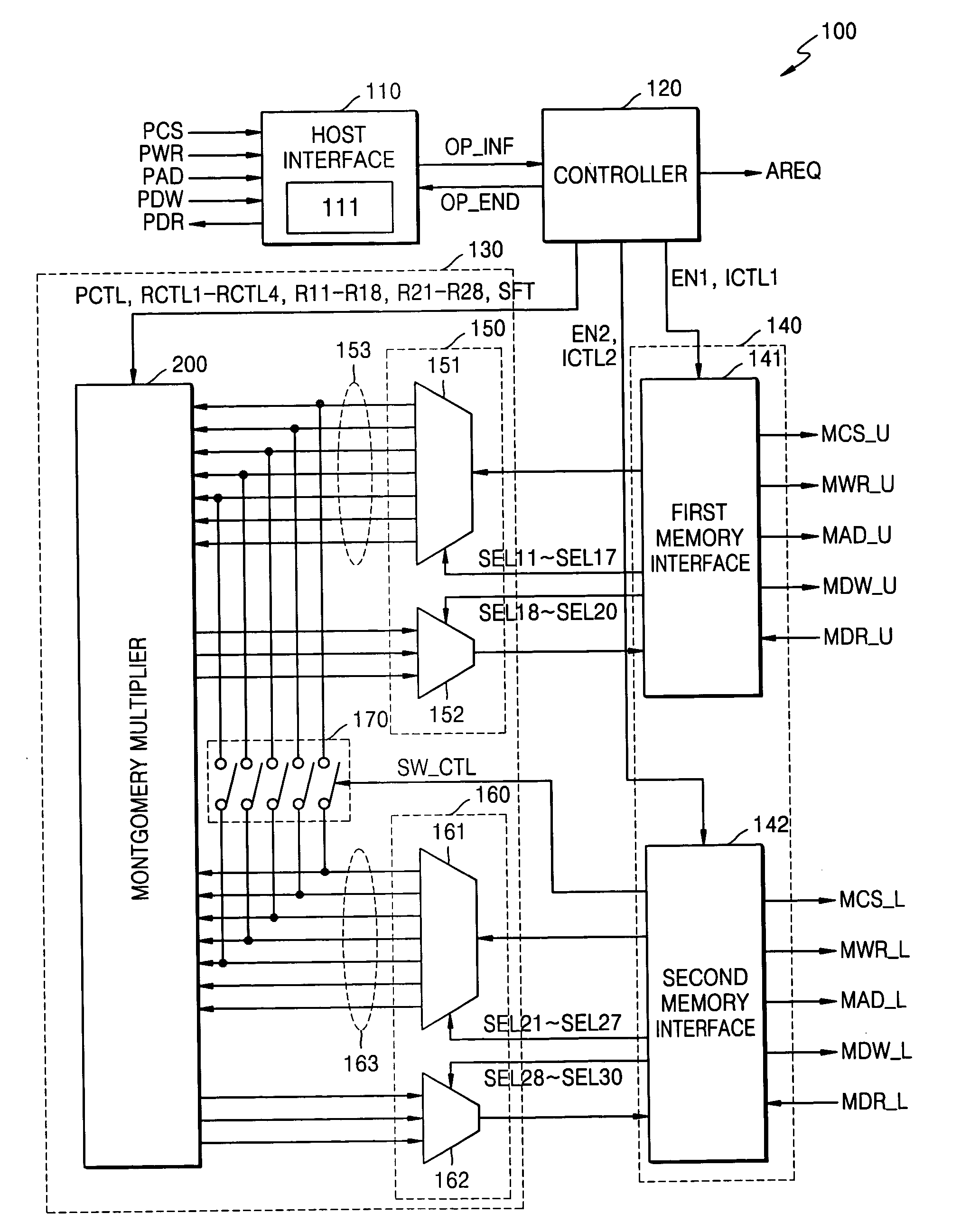

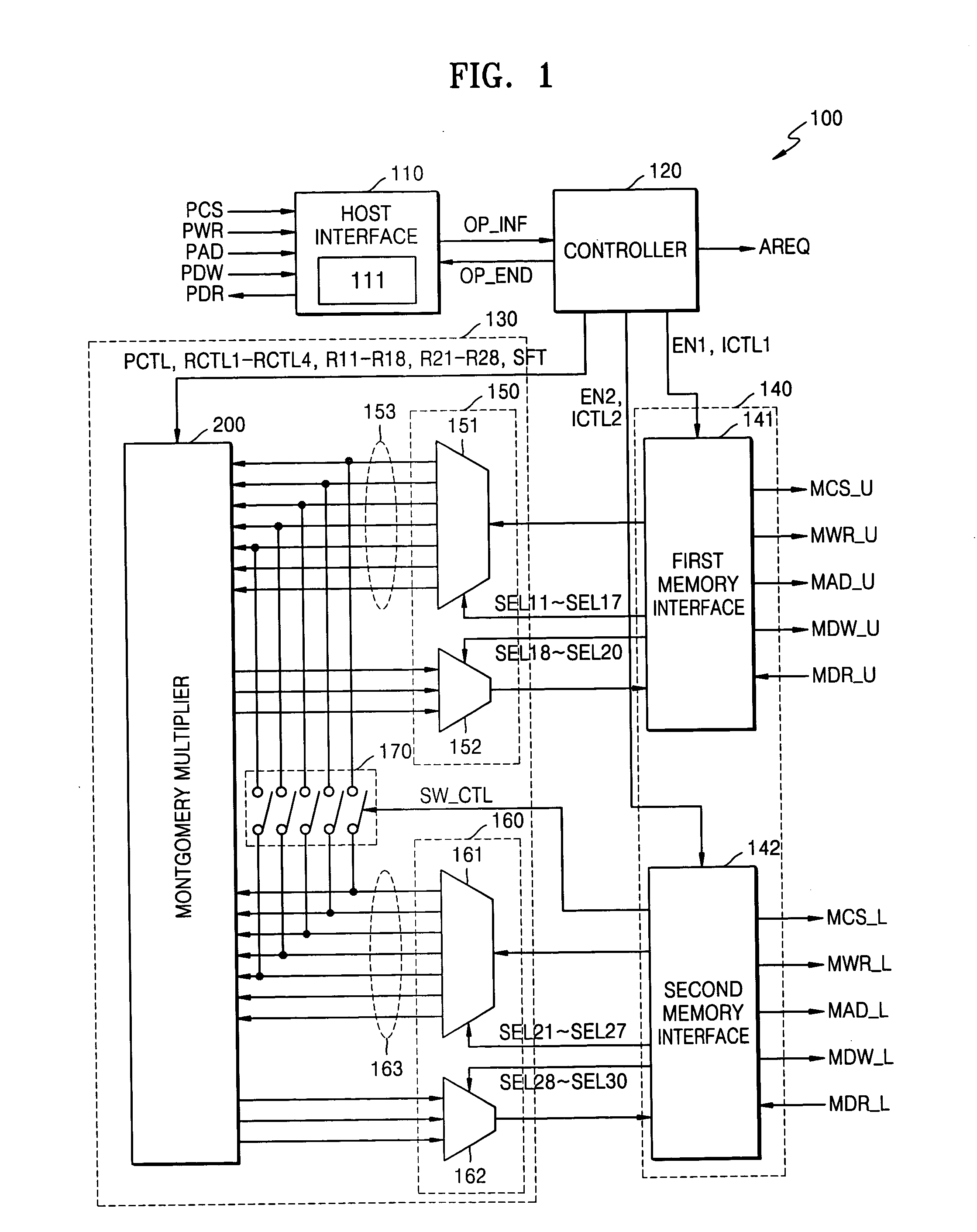

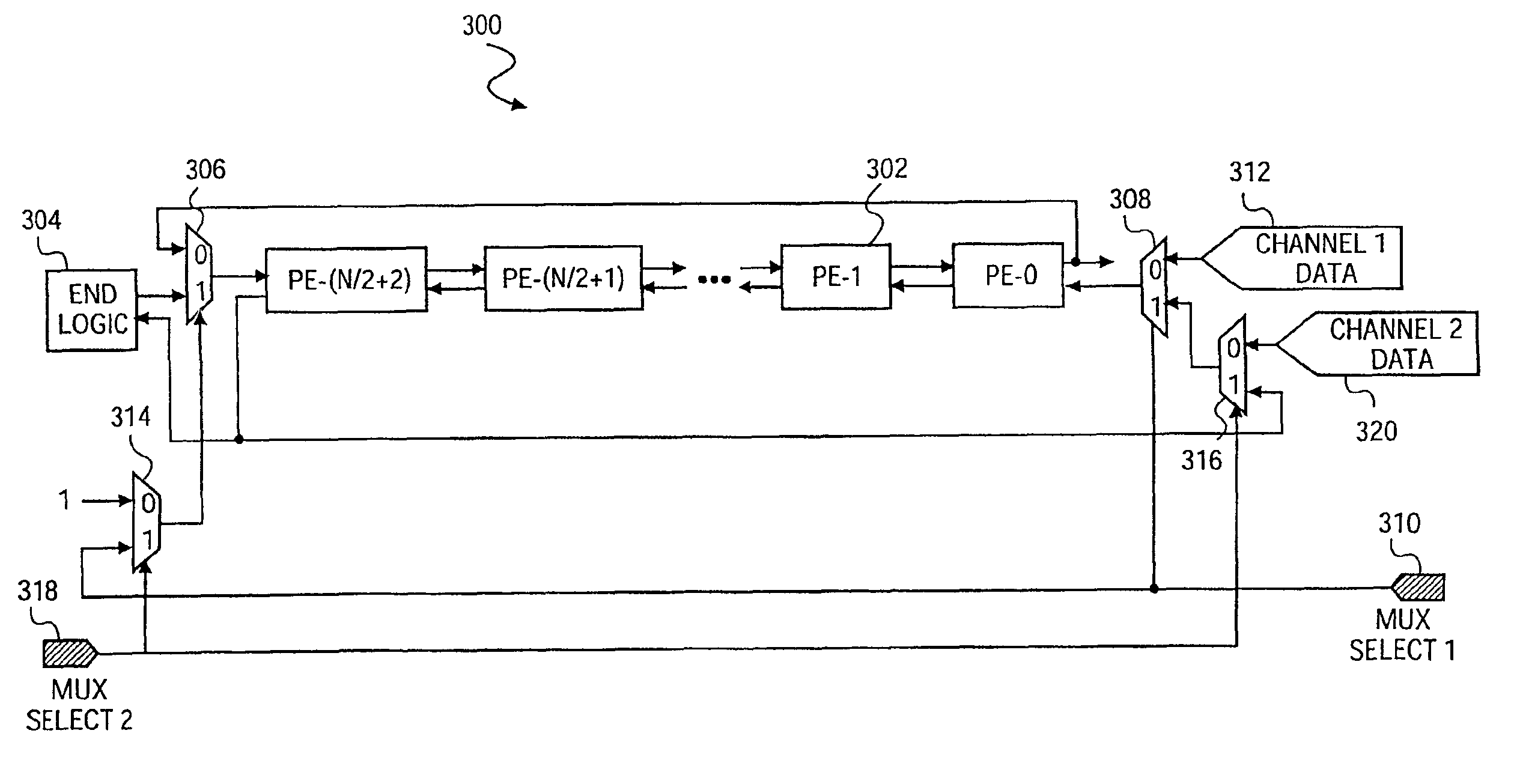

Modular multipliers having segmentable structure and cryptography systems utilizing same

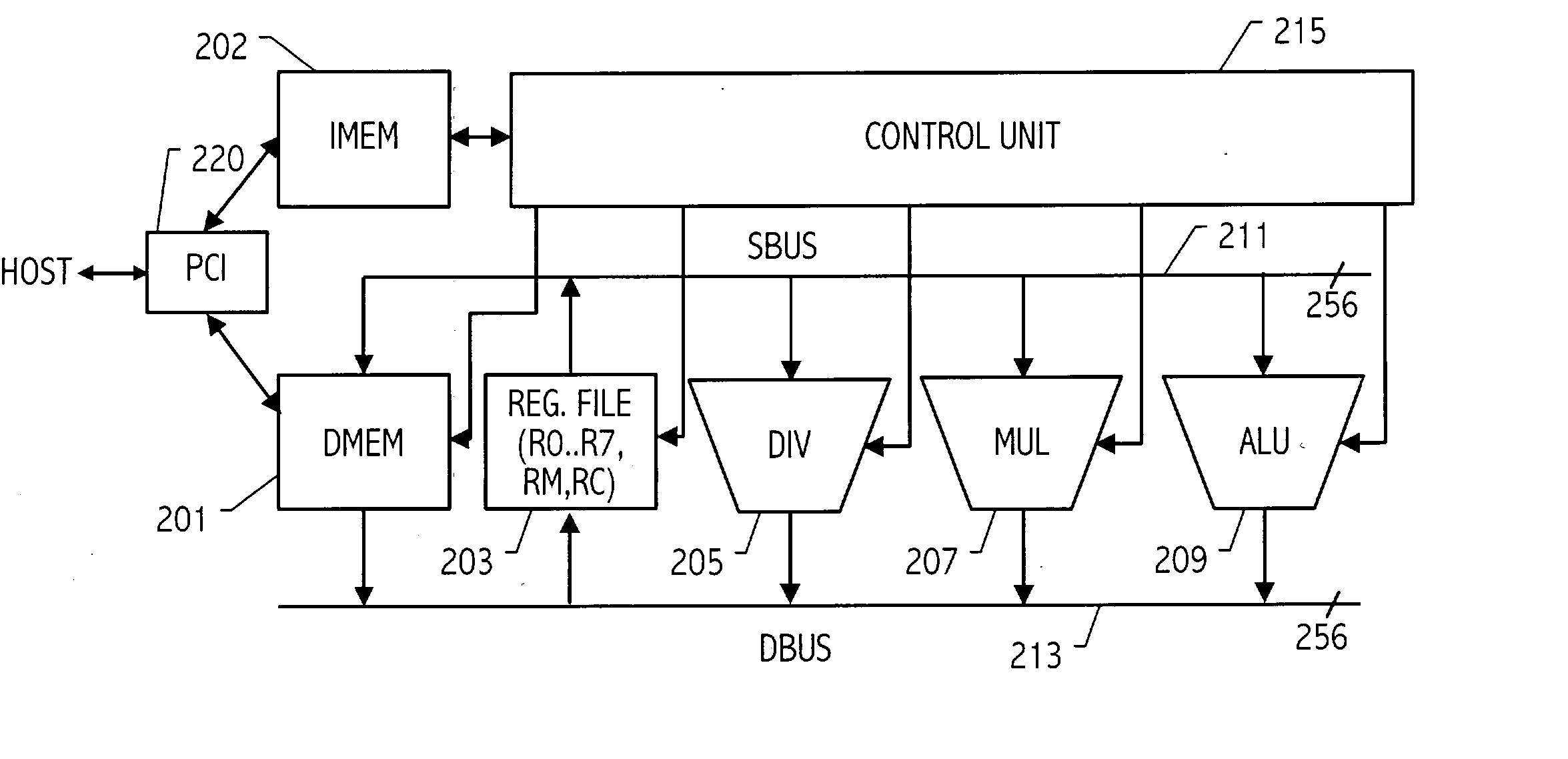

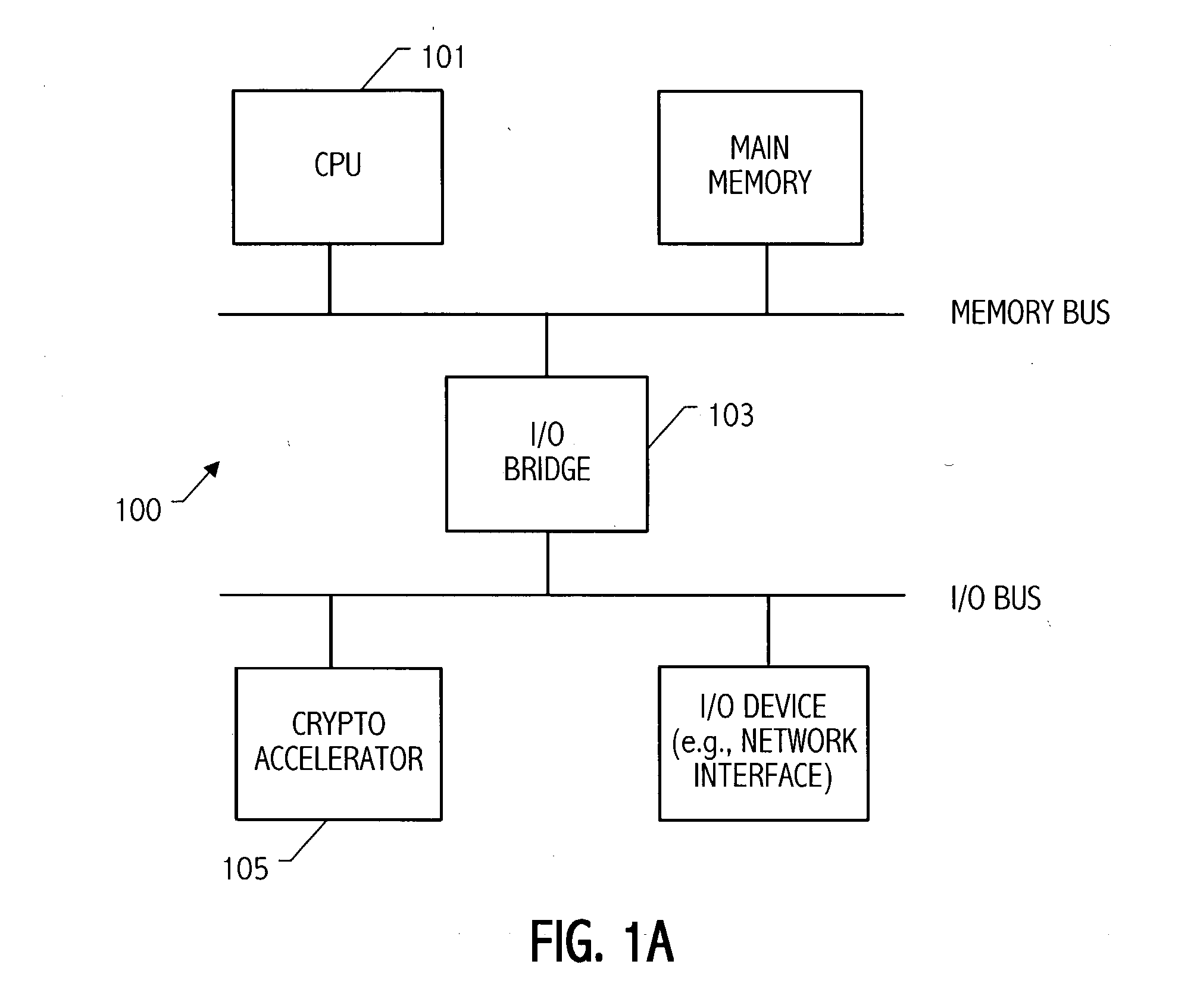

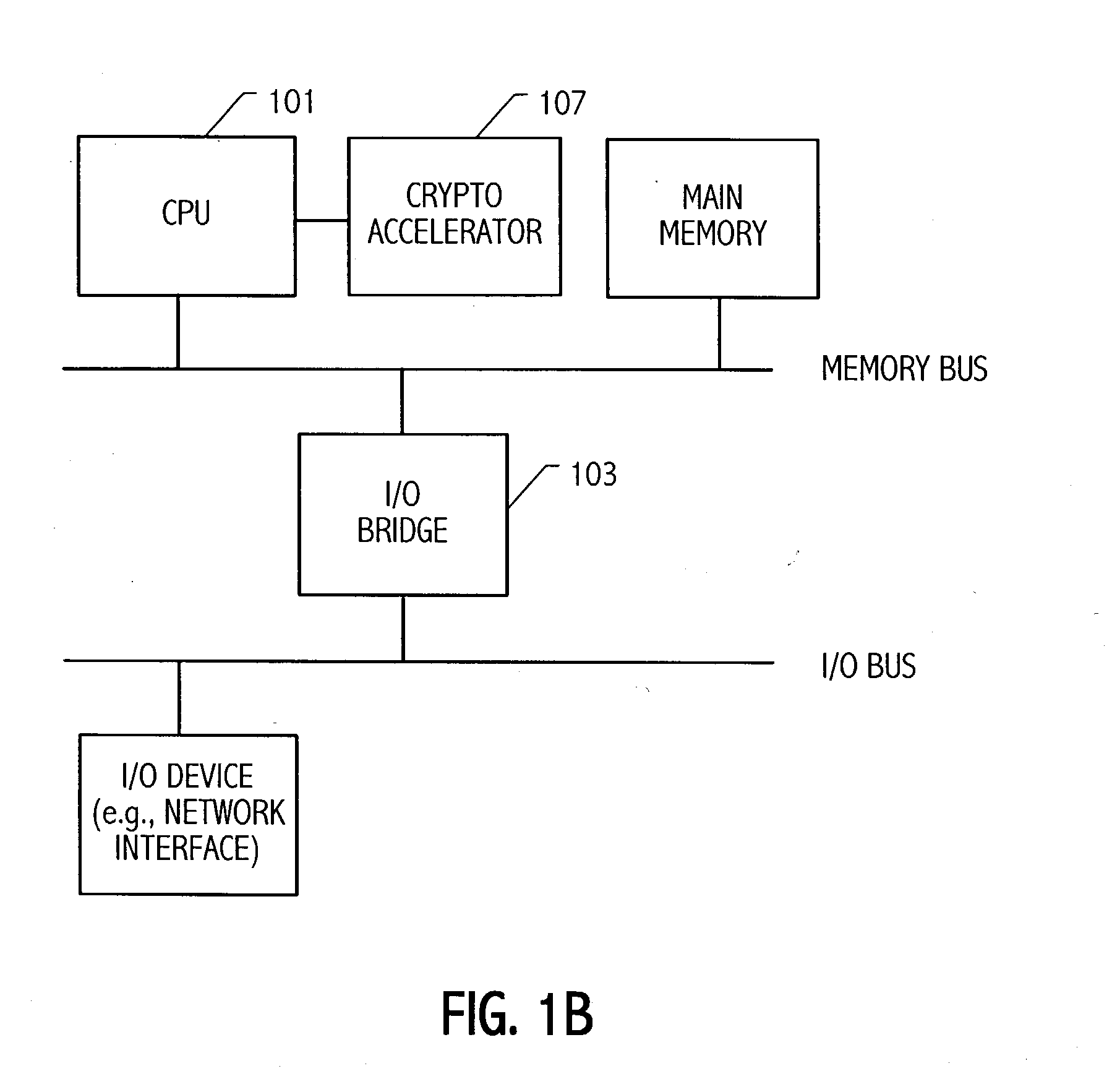

InactiveUS20060023878A1Improve securityImprove performanceComputation using non-contact making devicesSecret communicationControl signalMode control

A segmentable modular multiplier circuit includes a control circuit configured to produce a mode control signal and operation control signals in response to a control signal and a calculator circuit configured to perform modular multiply operations on first and second bit length operands in respective first and second modes responsive to the mode control signal and the operation control signals. The control circuit may include a host interface unit configured to produce an operation information signal in response to a control data signal received from a host and a controller configured to produce the mode control signal and the operation control signals in response to the operation information signal.

Owner:SAMSUNG ELECTRONICS CO LTD

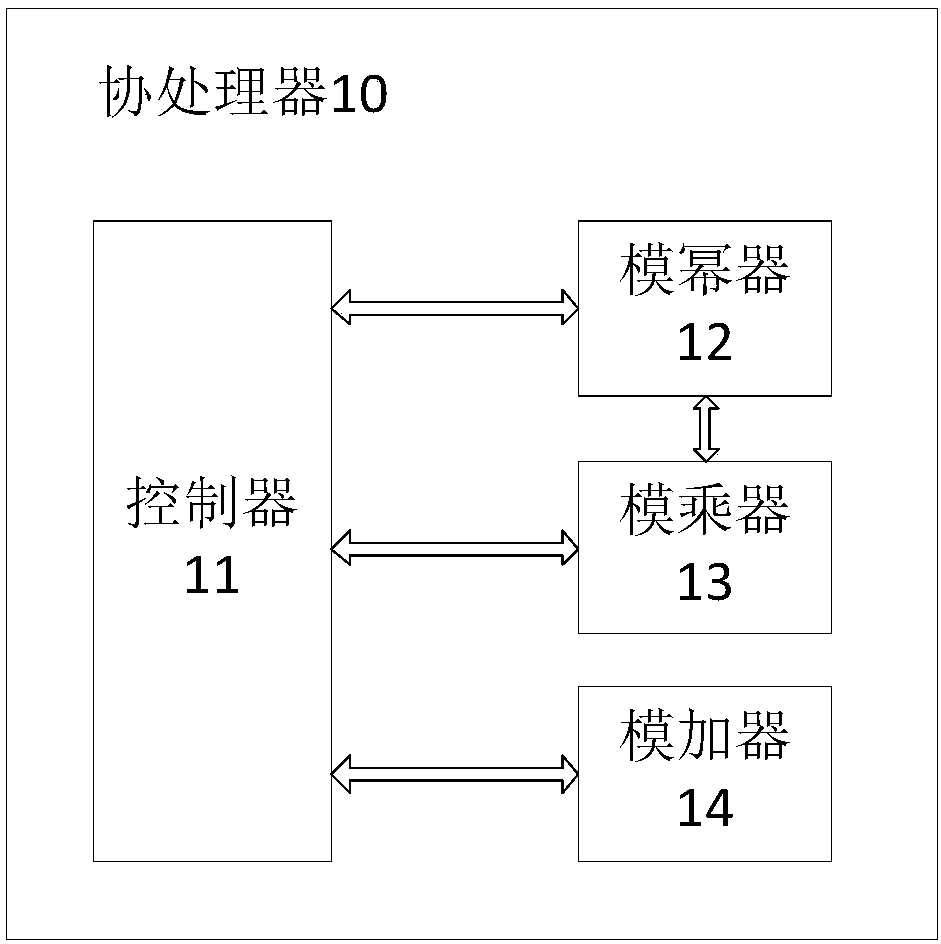

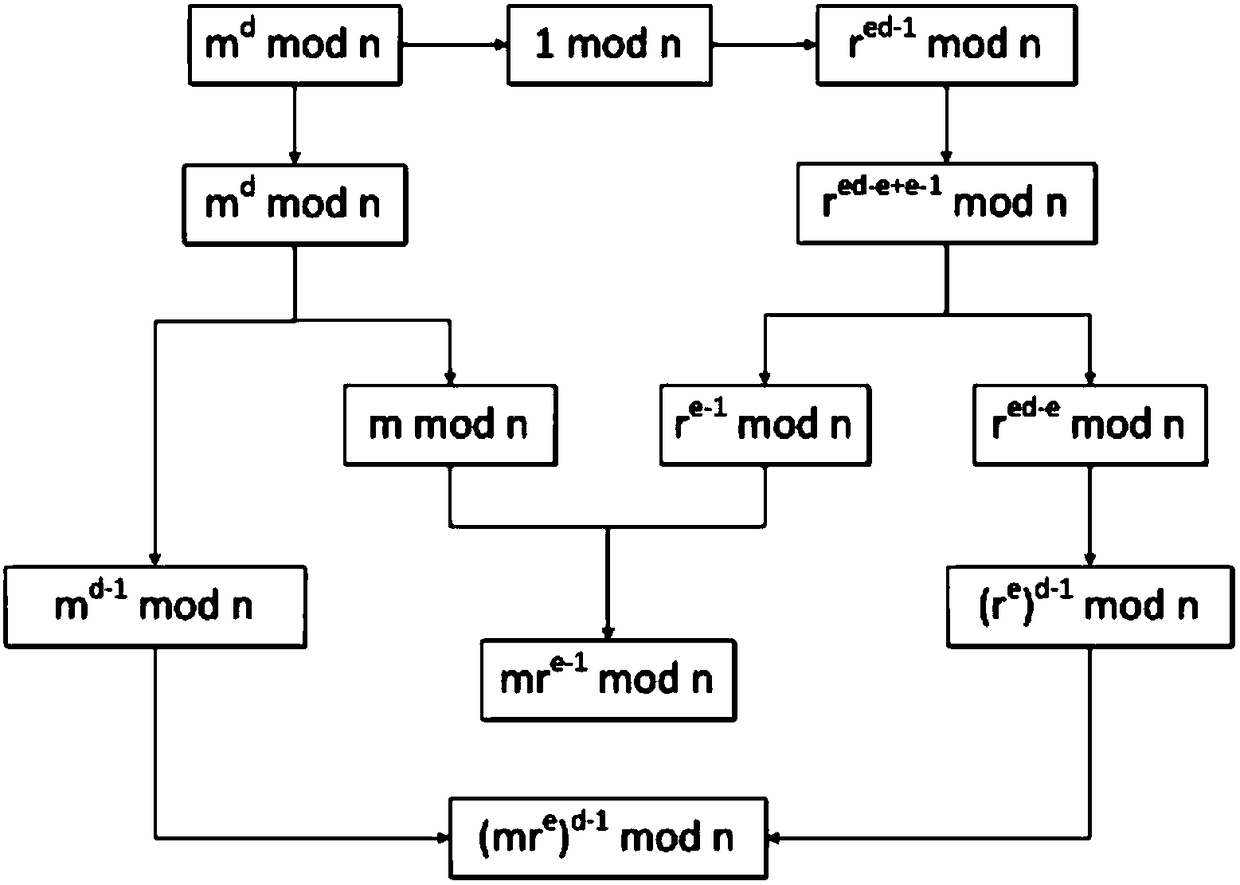

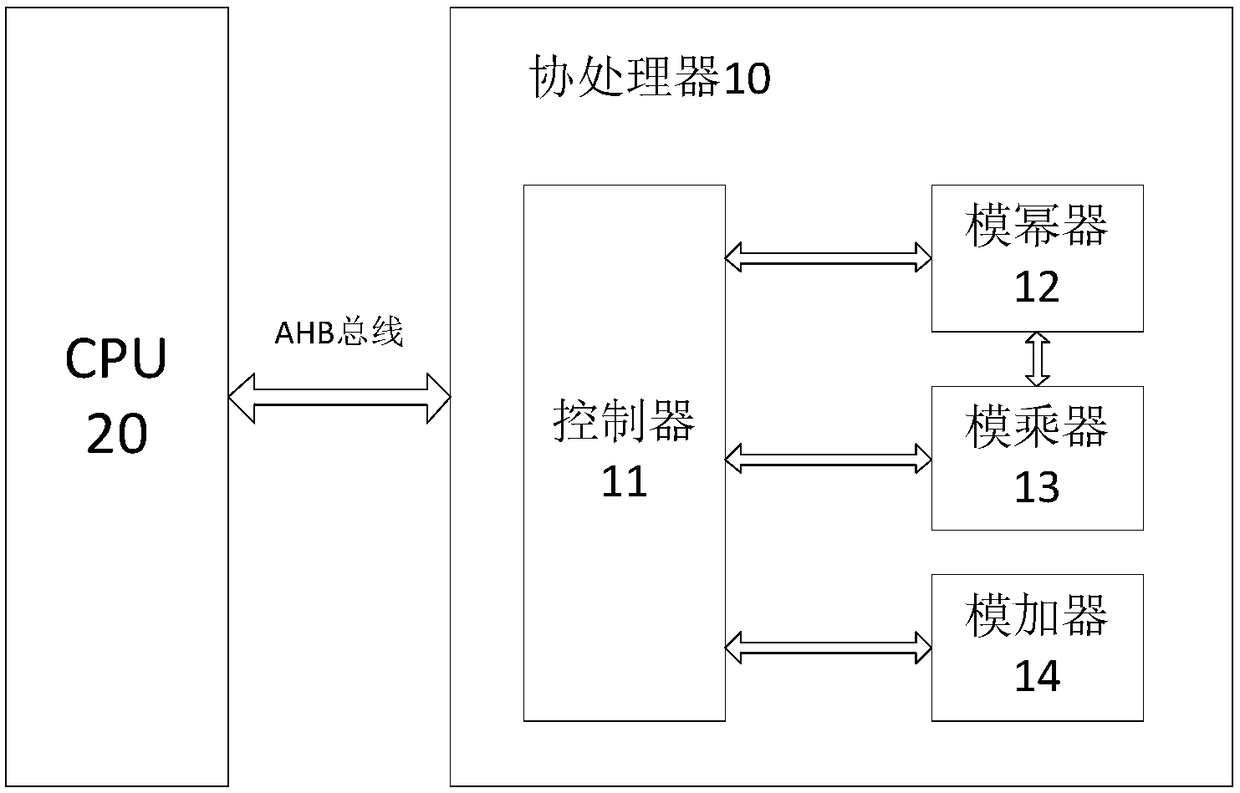

RSA private key mask operation method, coprocessor and RSA arithmetic device

InactiveCN108111309APrevent inversionLower cover costPublic key for secure communicationCryptographic attack countermeasuresCoprocessorModular multiplier

The invention provides a RSA private key mask operation method, a coprocessor and a RSA arithmetic device, wherein when a controller receives a start operation instruction sent by a master processor,the controller acquires a to-be-decrypted content m, a random number r, a public key e, a private key d and a modulus n of a RSA algorithm, and sends the decrypted content to the master processor; a modular adder calculates e-1 and calculates d-1; a modular exponentiation device calculates r<e-1>modn based on the e-1, calculates (mr<e>)<d-1>modn based on the mr<e>modn and the d-1; a modular multiplier calculates mr<e-1>modn based on the r<e-1>modn, calculates mr<e-1>.rmodn based on the mr<e-1>modn to obtain mr<e>modn, and calculates (mr<e>)<d-1>.mr<e-1>modn based on the (mr<e>)<d-1>modn and the mr<e-1>modn to obtain m<d>modn, and sends the decrypted content of the m<d>modn to the controller, thus, technical effects of reducing mask base cost, having relatively higher security in aspects, such as resisting side channel attacks and resisting fault attacks, are achieved.

Owner:北京融通高科微电子科技有限公司

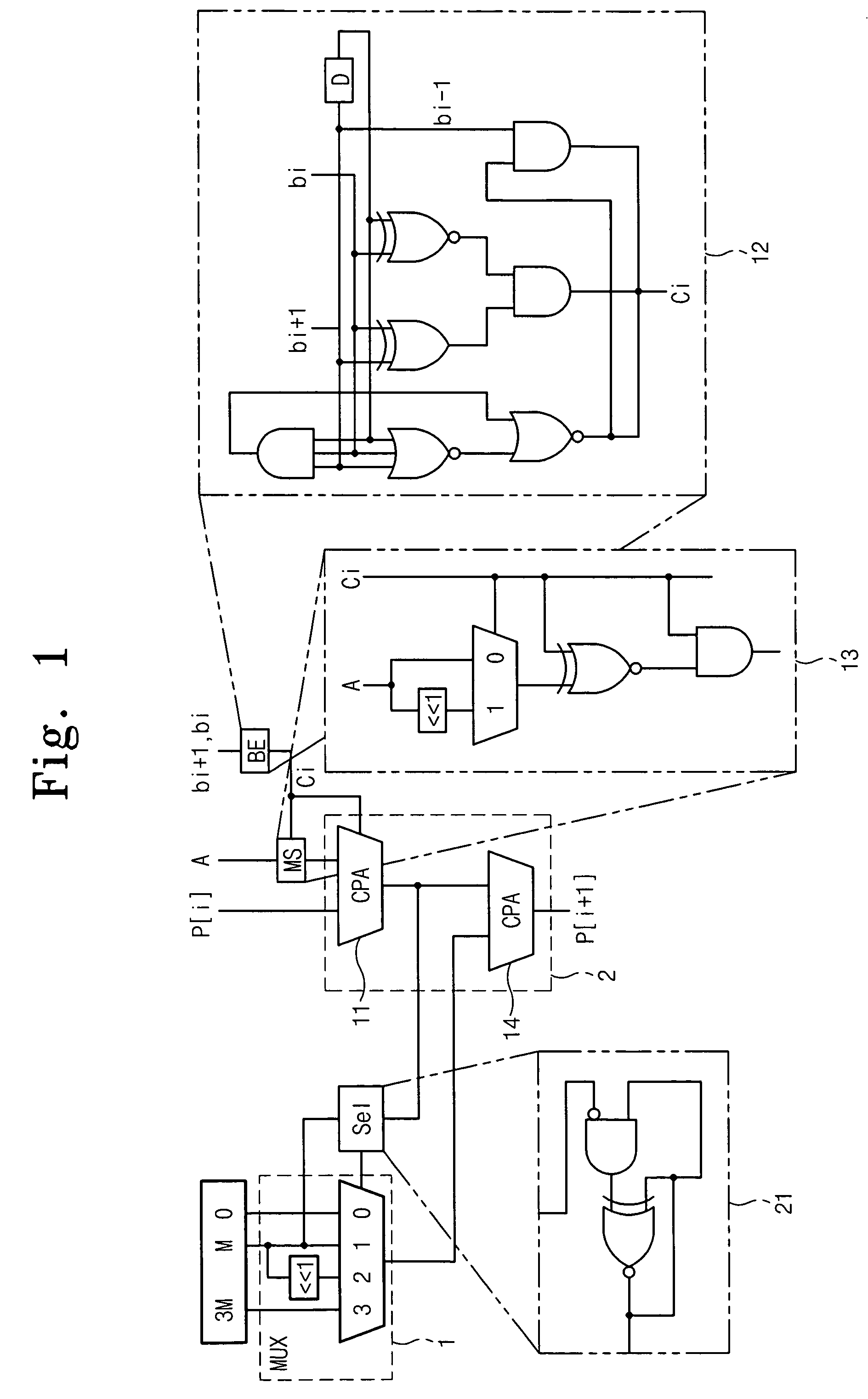

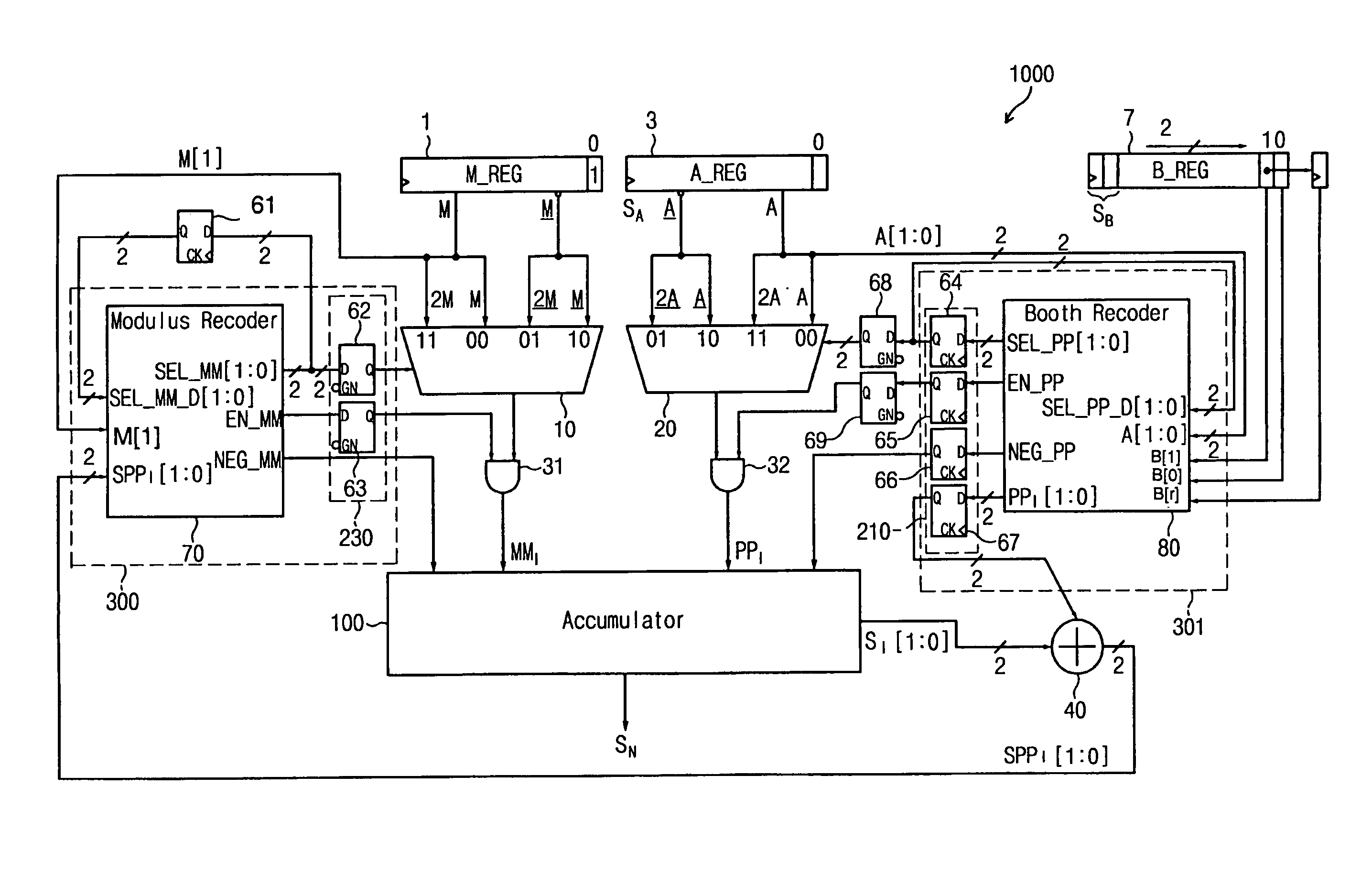

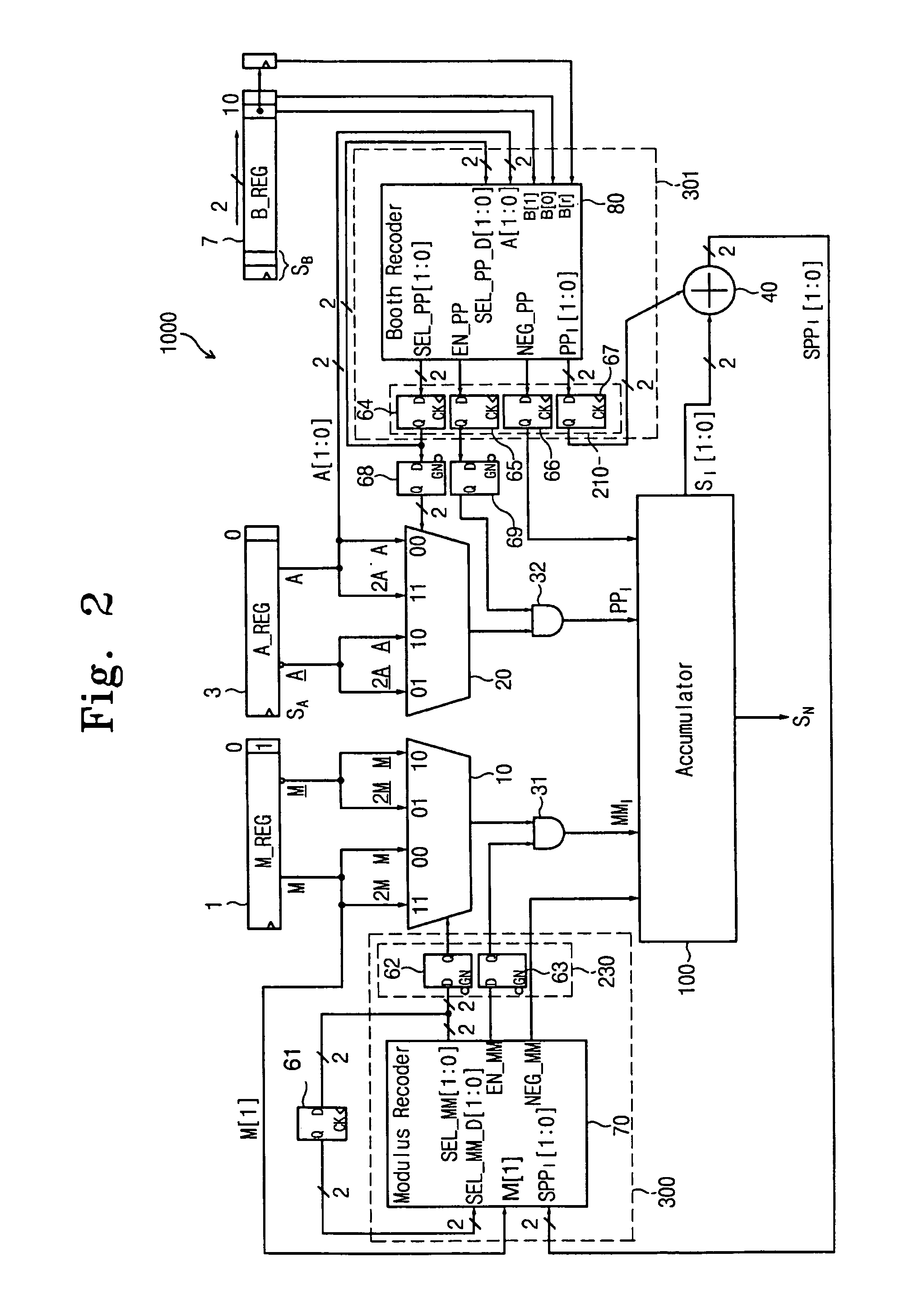

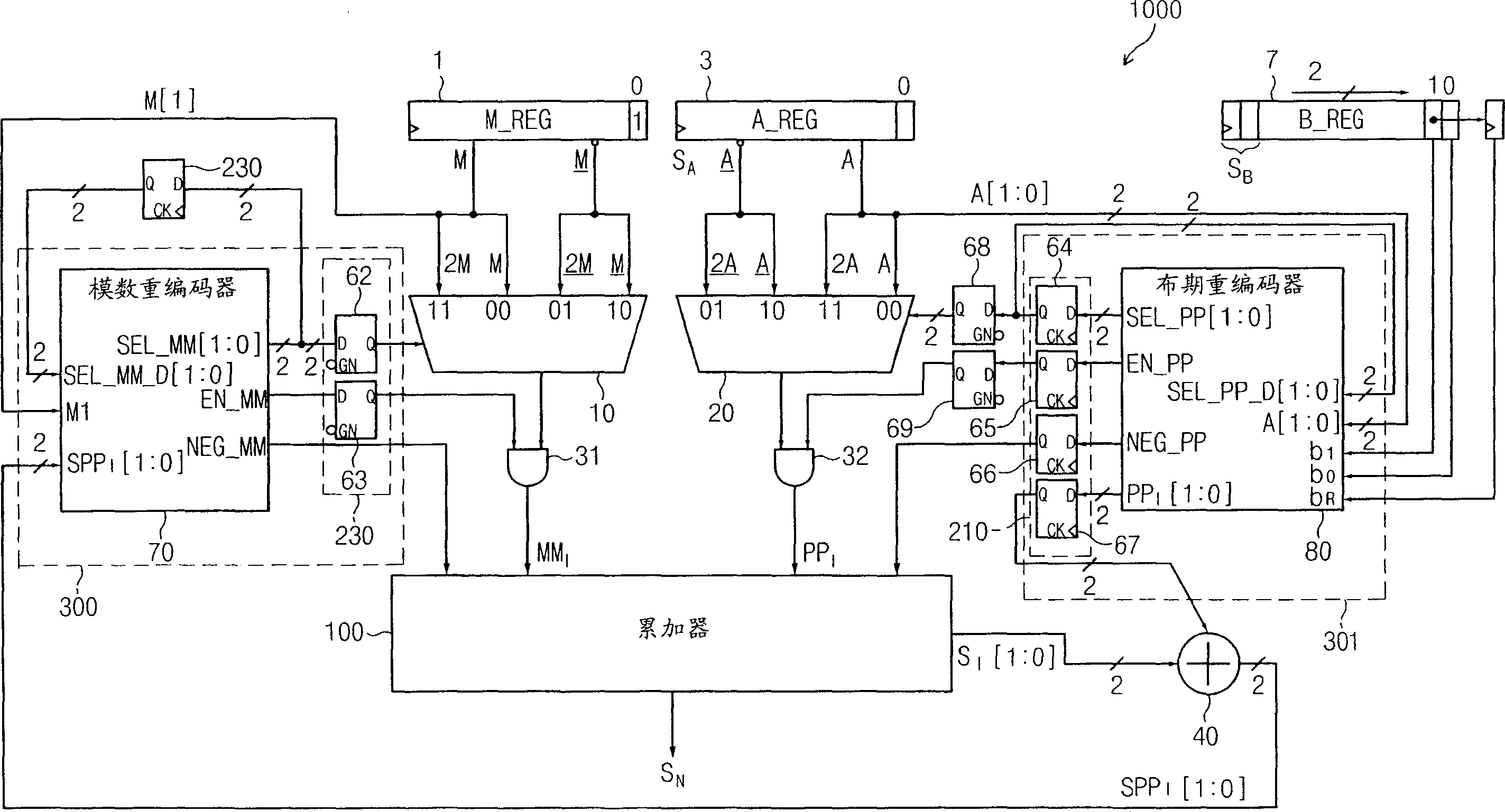

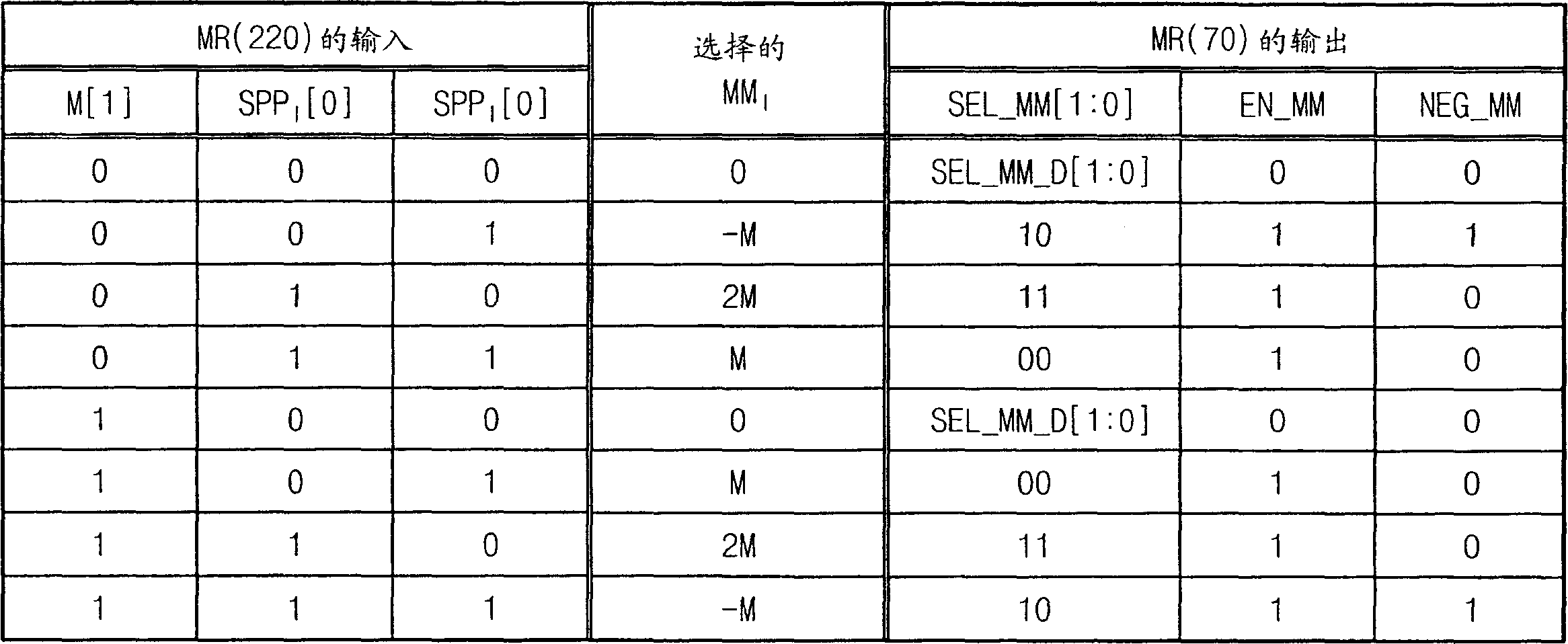

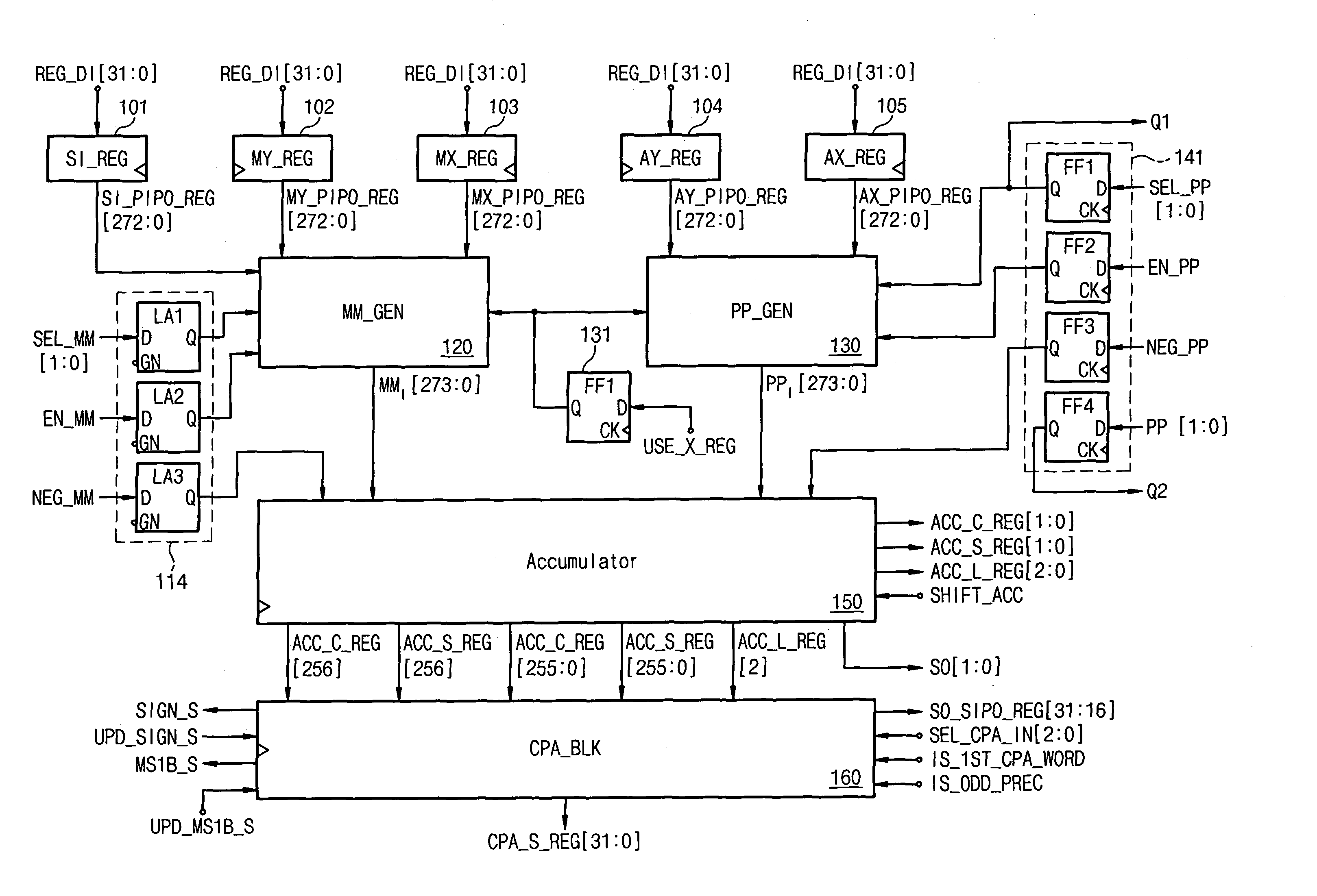

Montgomery modular multiplier and method thereof

ActiveUS7552163B2Increase speedReduce power consumptionComputation using non-contact making devicesDigital computer detailsParallel computingModular multiplier

A method for power reduction and increasing computation speed for a Montgomery modulus multiplication module for performing modulus multiplication. A coding scheme reduces the hamming distance for partial product and multiple modulus selection, reducing MUX operations and power consumption. Synchronization registers synchronize partial product and multiple modulus values input to an accumulator reducing glitch and / or increase computation speed. Registers provide storage of previous values and reduce the need to obtain the values from a MUX, reducing MUX operations and / or reducing power consumption.

Owner:SAMSUNG ELECTRONICS CO LTD

Montgomery modular multiplier and method thereof

InactiveCN1550975AReduce calculationsReduce power consumptionComputation using non-contact making devicesComputations using residue arithmeticMultiplexingParallel computing

A method for power reduction and increasing computation speed for a Montgomery modulus multiplication module for performing modulus multiplication. A coding scheme reduces the hamming distance for partial product and multiple modulus selection, reducing MUX operations and power consumption. Synchronization registers synchronize partial product and multiple modulus values input to an accumulator reducing glitch and / or increase computation speed. Registers provide storage of previous values and reduce the need to obtain the values from a MUX, reducing MUX operations and / or reducing power consumption.

Owner:SAMSUNG ELECTRONICS CO LTD

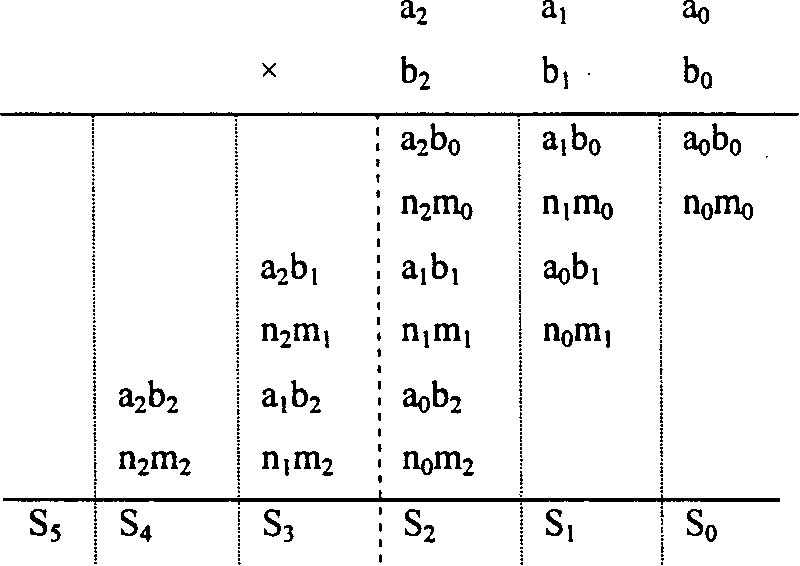

Montgomery analog multiplication algorithm for VLSI and VLSI structure of intelligenjt card analog multiplier

InactiveCN1392472ADigital data processing detailsSecuring communicationBinary multiplierVlsi implementations

The present invention relates to the encryption and decryption technology and features that it is one algorithm with high degree of parallelism and suitable for VLSI implementation. The thrice large number multiplications of primary montgomery analog multiplication are decomposed into 2ss+s times small number multiplications. The VLSI structur for the intelligent card analog multiplifier is one high-order analog multiplier, which has 32 bit multiplier to complete 1024 bit analog multiplication and three stage parallel flow water structure in the data passage. Compared with available structure, the present invention has reduced chip area and analog multiplication clock number and can realize digital signature and confirmation of RSM algorithm in intelligent card.

Owner:TSINGHUA UNIV

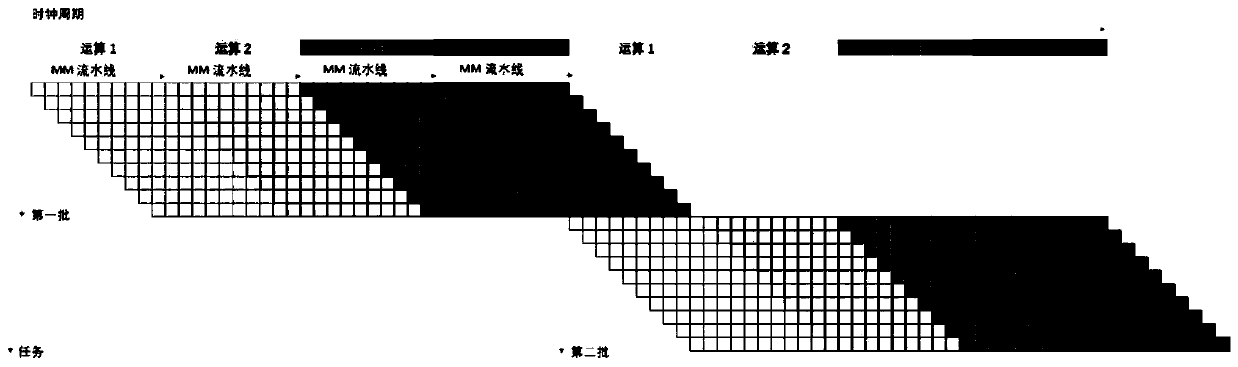

High-speed point addition operation method and device for elliptic curve password

PendingCN110460443AAvoid Time to Improve Performance PitfallsImprove performancePublic key for secure communicationBatch processingMultiple point

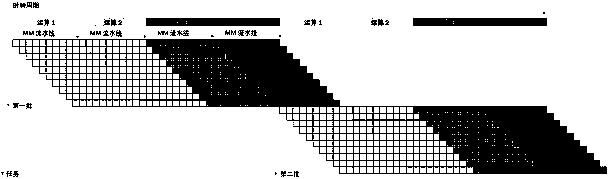

The invention discloses a high-speed point addition operation method and a device for elliptic curve cryptography, which are realized by matching a pipelined Montgomery modular multiplier with a modular adder, and 16 modular multiplication operations are executed by one point addition operation; according to the point addition circuit using one or more modular multipliers, each modular multiplication operation executes an operation request of one batch, and the system can calculate N operations at the same time, so that the overall performance of the system is improved by N times. According tothe method, the pipelined characteristics of the pipelined Montgomery modular multiplier are utilized, a bottom pipelined hardware circuit is ingeniously multiplexed, multiple point addition operations are executed at the same time in a batch processing mode, and the throughput of the whole system is improved by several orders of magnitudes. Therefore, the performance / hardware resource ratio andthe performance / energy consumption ratio of the method are improved by several times or even dozens of times compared with those of the prior art. Meanwhile, the optimal number of Montgomery modular multipliers and modular adders is selected by analyzing the characteristics of the point addition algorithm, and the optimal configuration of performance and resource use is achieved.

Owner:南京秉速科技有限公司

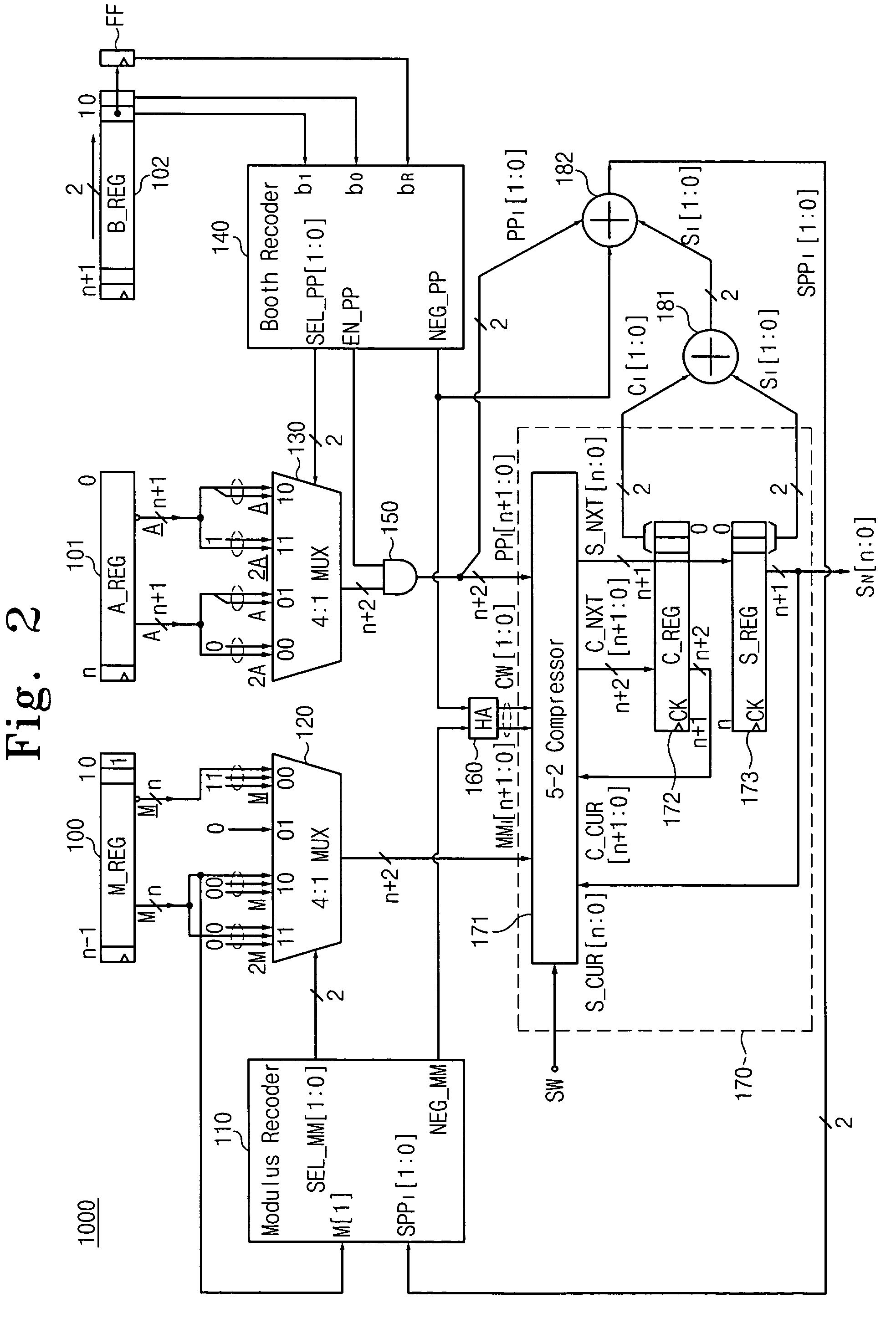

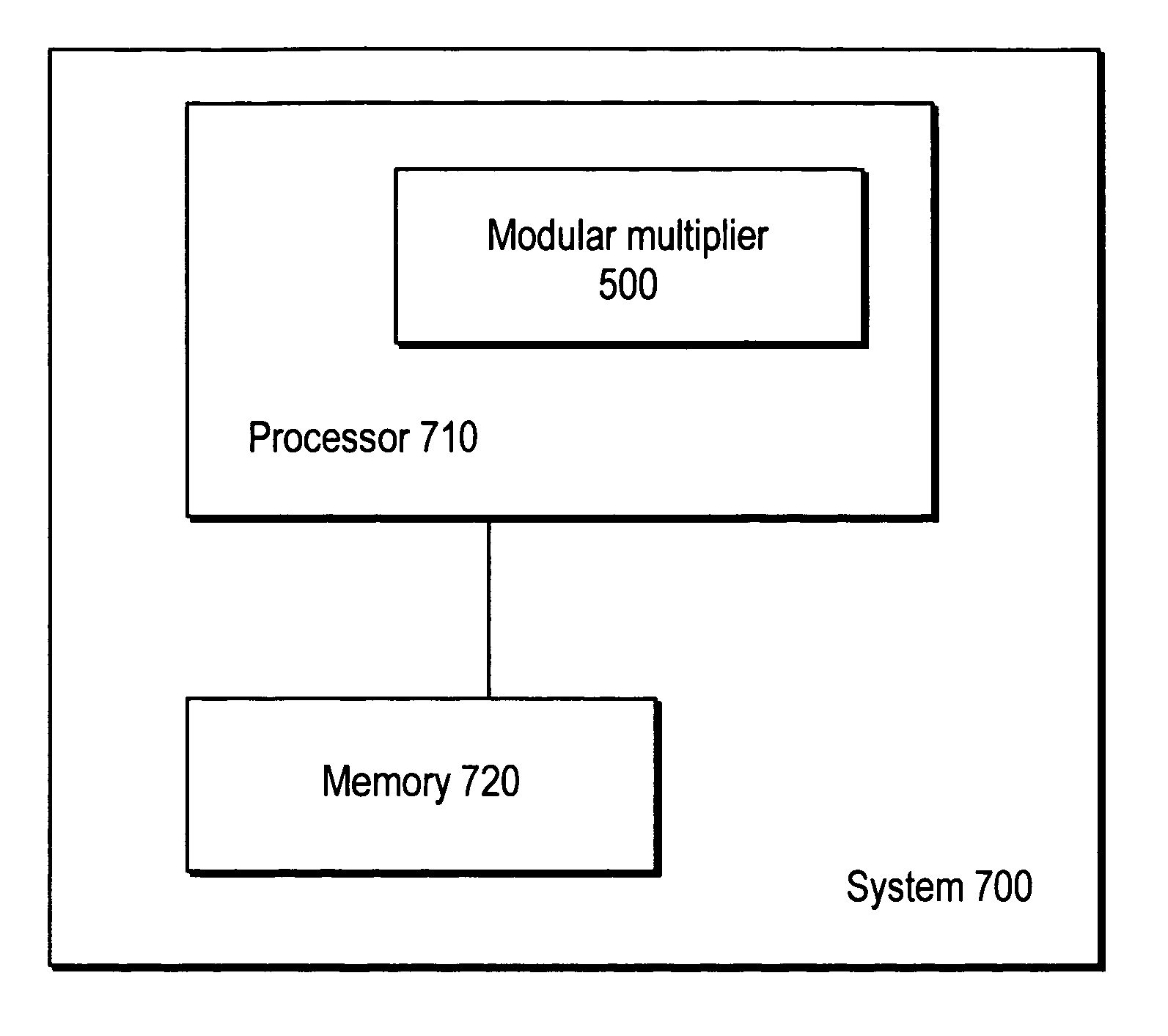

Montgomery modular multiplier

ActiveUS7805478B2Computations using contact-making devicesComputation using non-contact making devicesControl signalModular multiplier

In a Montgomery multiplier, a modulus product generator may select a modulus product from a plurality of selectable n-bit modulus numbers M, a given modulus number M being formed from a currently input extended chunk of bits among the n-bit modulus numbers. A partial product generator may select a multiplicand number from a plurality of selectable n-bit multiplicands A as a partial product, a given multiplicand A being formed from a currently input extended chunk of bits among the n-bit multiplicands. An accumulator may accumulate the selected modulus product and partial product to generate a multiplication result. The Montgomery multiplier may be part of an operation unit that may include a memory and host, and may be adapted to perform a Montgomery multiplication operation and a normal multiplication operation based on a logic state of a control signal input thereto.

Owner:SAMSUNG ELECTRONICS CO LTD

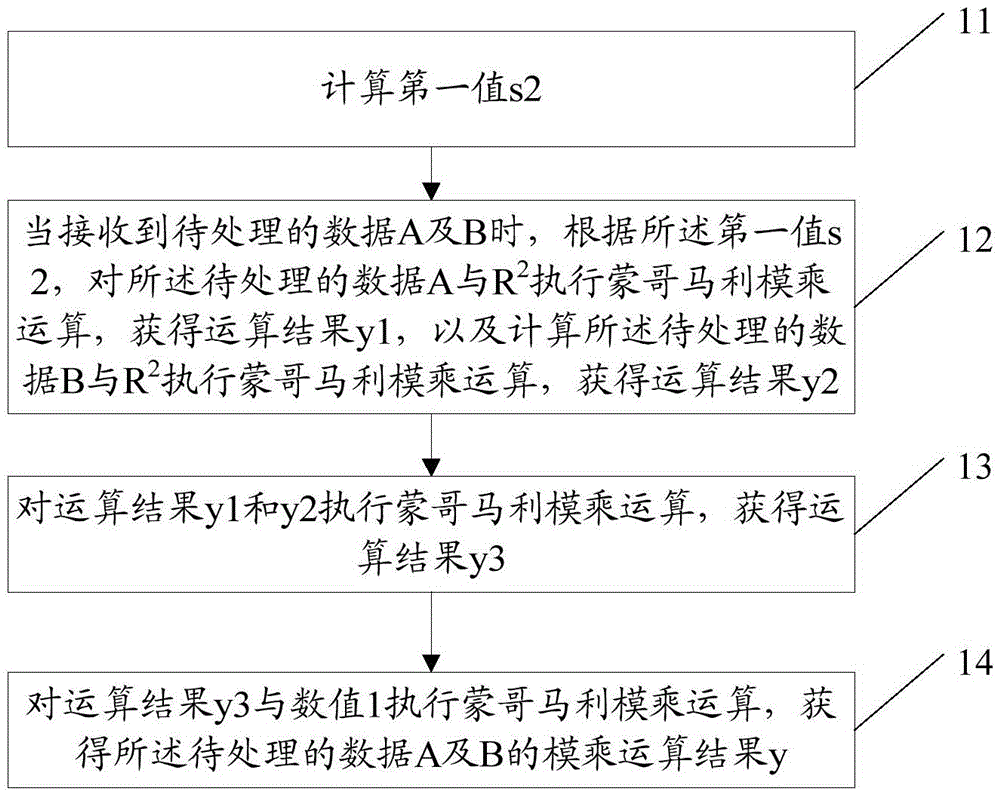

Data processing method and modular multiplication operation method and apparatus based on Montgomery modular-multiplication

ActiveCN106681691ASmall amount of calculationImprove computing efficiencyComputations using residue arithmeticSimulationModular multiplier

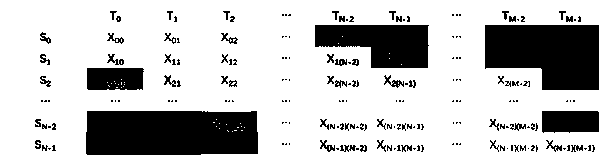

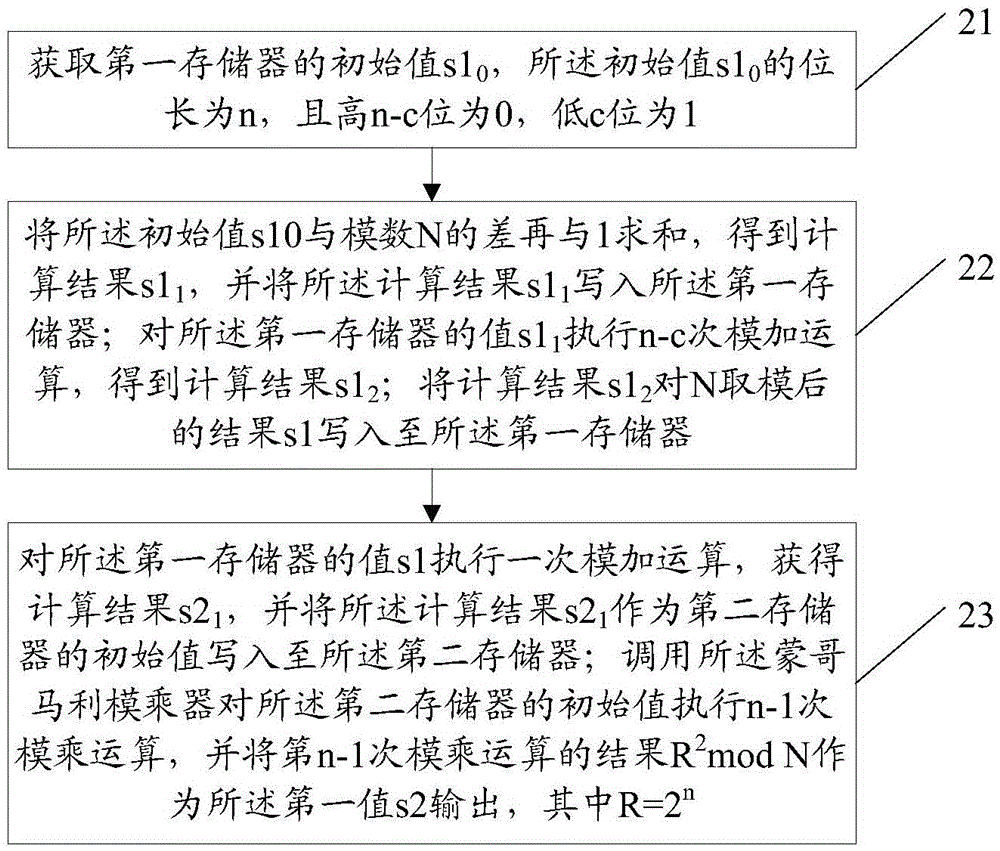

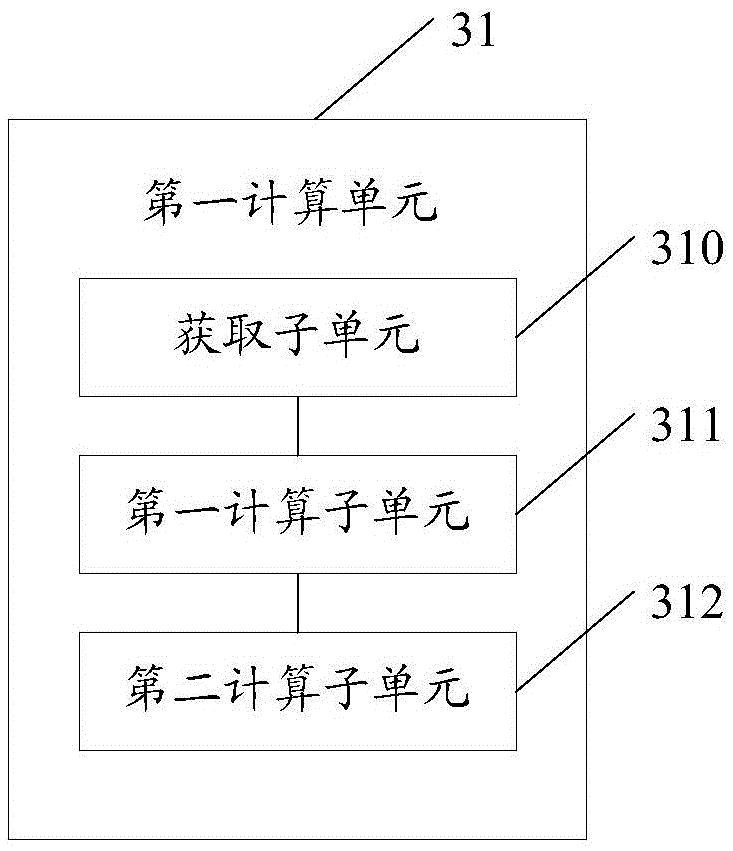

The invention provides a data processing method and a modular multiplication operation method and an apparatus based on the Montgomery modular-multiplication. The data processing method based on the Montgomery modular-multiplication comprises the steps of using the following steps to calculate a first value S2: acquiring an initial value s10 of a first memory, wherein the initial value s10 is an n-digit number, the digit n plus n-c is 0, the digit n-c is 1; the calculation is made to let s10 be subtracted by a modular number N, and the result is made to be added by 1 to get a result s11, which is written in the first memory; n-c times of modular addition is made to the s11 in the first memory to get a calculated result s1n-c+1; the calculated result s1n-c+1 takes a modular from N, the result s1 is written in the first memory, the Montgomery modular multiplier is called to implement n-1 times of modular multiplication to the initial value of a second memory, the result R2mod N of the n-1th time of modular multiplication is treated as a first value s2 to be exported. The data processing method and the modular multiplication operation method based on Montgomery modular-multiplication can be used for reducing the calculation amount of the Montgomery modular multiplier calculation, and enhance the calculation efficiency.

Owner:SHANGHAI FUDAN MICROELECTRONICS GROUP

High-speed radix-16 Montgomery modular multiplier VLSI (very large scale integrated circuit)

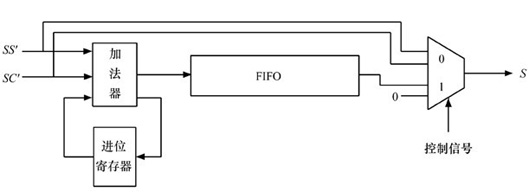

InactiveCN101986261AOptimize overheadGood expensesComputations using residue arithmeticVery large scale integrated circuitsData selection

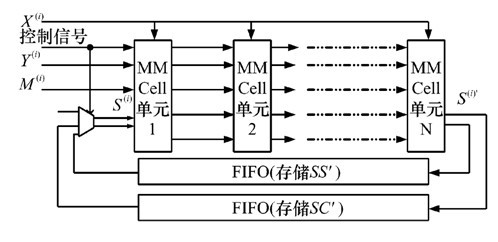

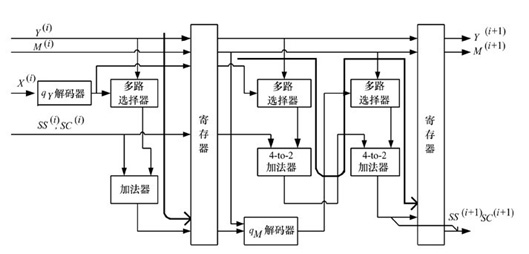

The invention discloses a high-speed radix-16 Montgomery modular multiplier VLSI (very large scale integrated circuit) which comprises N-numbered MMCell arithmetic elements, an FIFO (first in first out) storage unit and an alternative data selection unit. The high-speed radix-16 Montgomery modular multiplier VLSI overcomes the defects of low average behavior, low clock frequency, large hardware expenditure, poor practicability and the like in the prior art, thus achieving the advantages of high average behavior, high clock frequency, small hardware expenditure and good practicability.

Owner:WUXI GAOZHEN S&T

Montgomery modular multiplier and method thereof using carry save addition

InactiveCN1570848AGuaranteed normal operationApplicability is clearComputation using non-contact making devicesComputations using residue arithmeticCarry propagationModular multiplier

A method of reducing power consumption and / or enhancing computation speed in the modulus multiplication operation of a Montgomery modulus multiplication module. A coding scheme reduces the need for an adder or memory element for obtaining multiple modulus values, and the use of carry save addition with carry propagation addition enhances the computational speed of the multiplication module.

Owner:SAMSUNG ELECTRONICS CO LTD

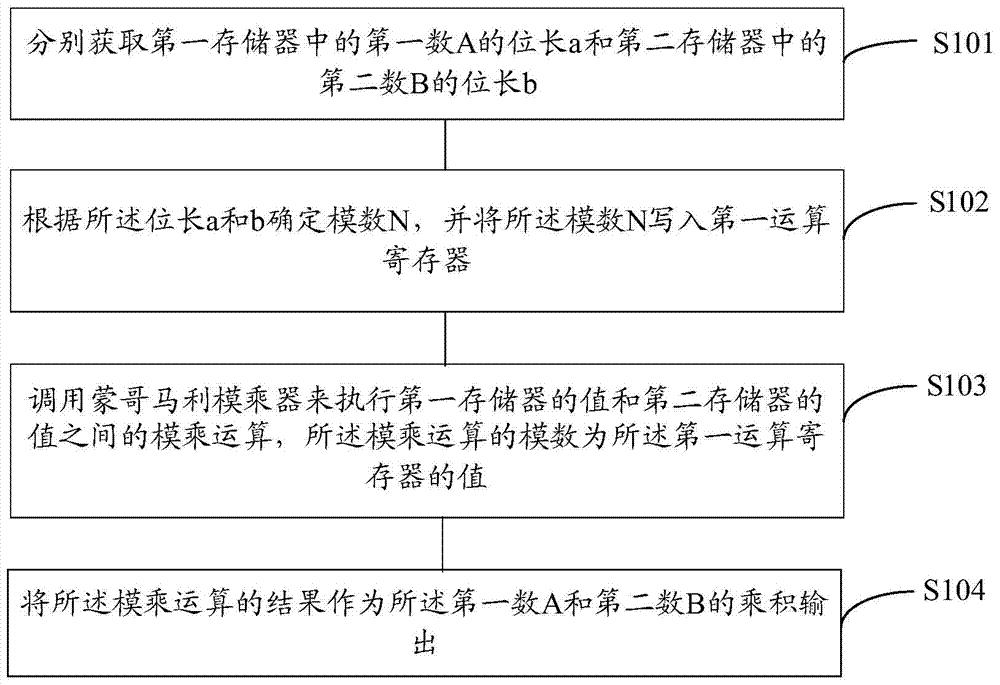

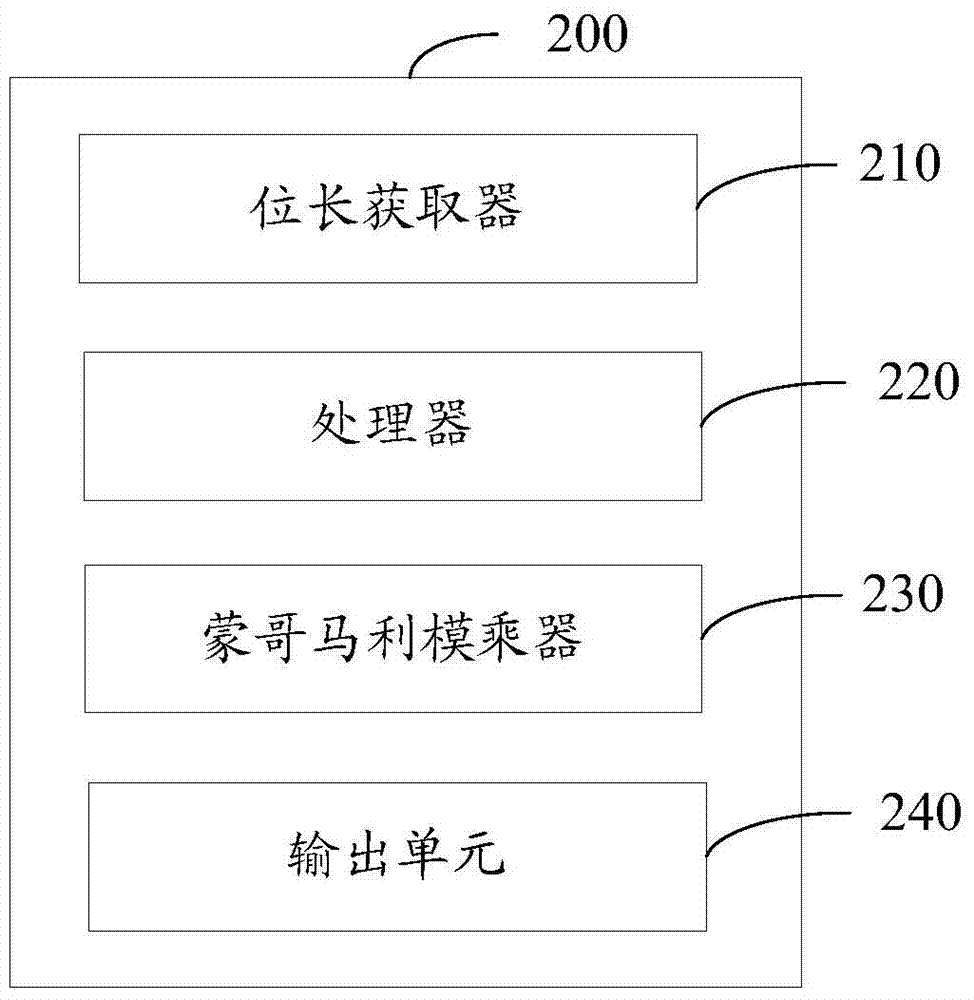

Method and device for processing data on basis of Montgomery modular multiplication

ActiveCN104750455AAvoid product operationsShorten the timeDigital data processing detailsProcessor registerModular multiplier

The invention provides a method and a device for processing data on the basis of Montgomery modular multiplication. The method includes respectively acquiring bit lengths a of first numbers A in first storages and bit lengths b of second numbers B in second storages; determining module numbers N according to the bit lengths a and b and writing the module numbers N into first arithmetic registers; calling Montgomery modular multipliers to execute modular multiplication on values of the first storages and values of the second storages; outputting products of the first numbers A and the second numbers B. Bit lengths n of the module numbers N are larger than or equal to the sums of the bit lengths a and b. Module numbers of modular multiplication are values of the first arithmetic registers. The products of the first numbers A and the second numbers B are results of modular multiplication. The method and the device have the advantage that the encryption processing efficiency can be improved by the aid of the method and the device.

Owner:SHANGHAI FUDAN MICROELECTRONICS GROUP

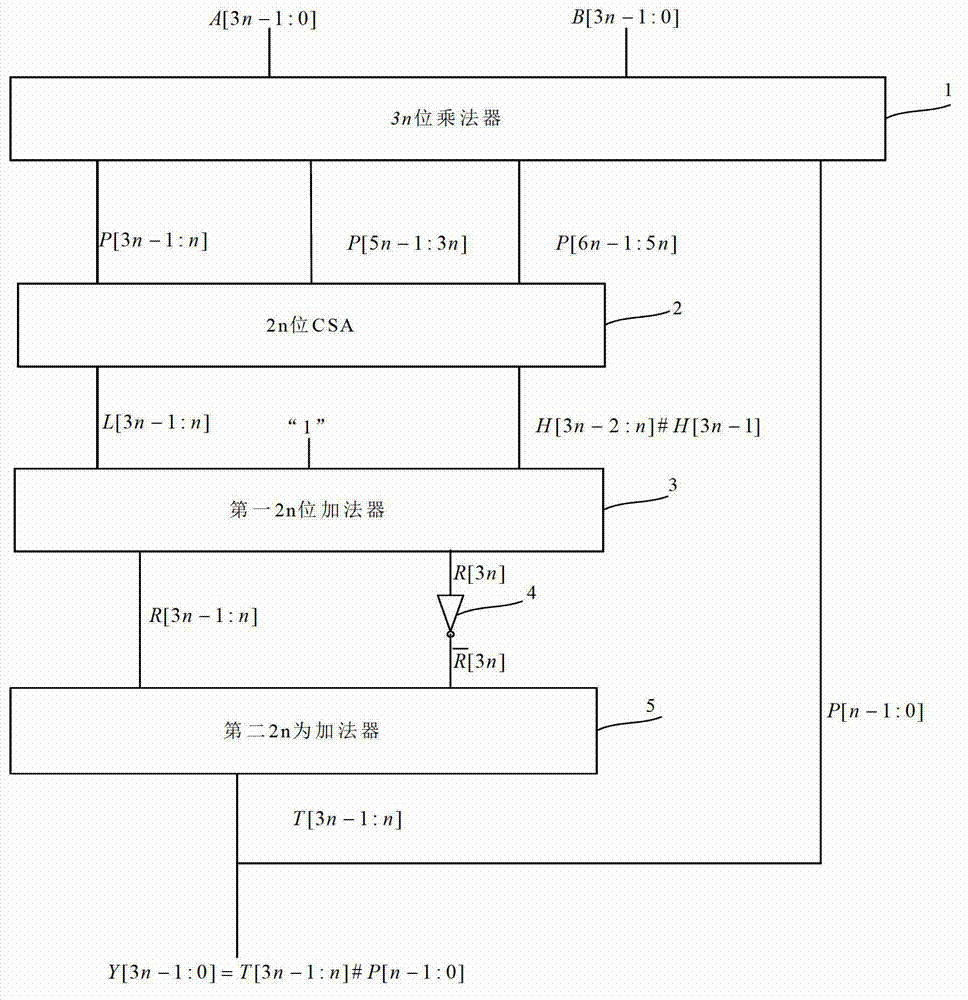

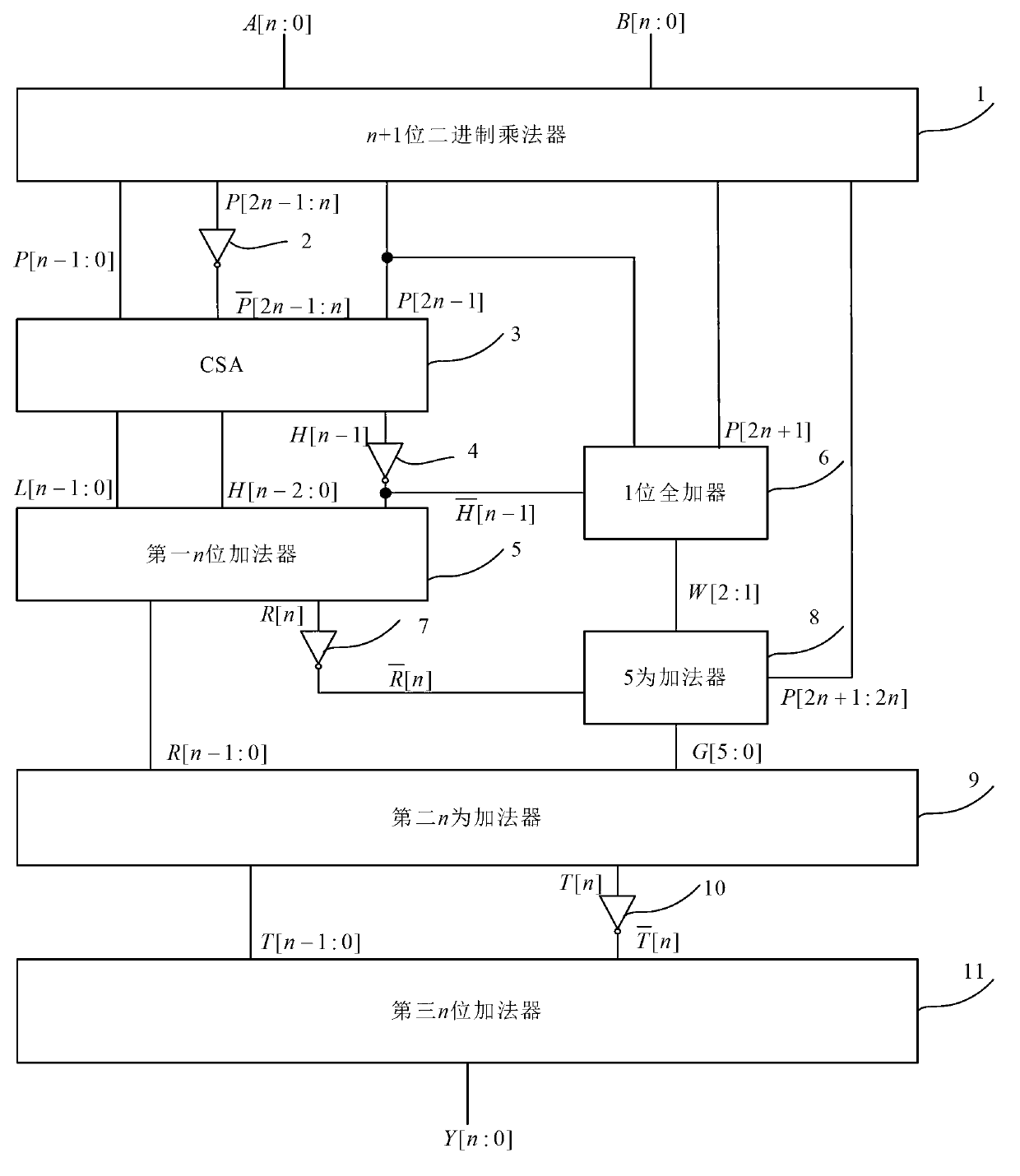

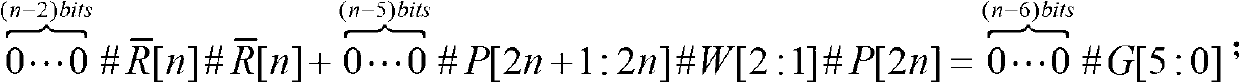

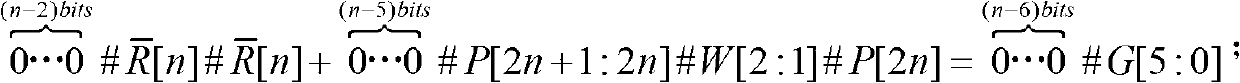

Modular multiplier

InactiveCN102955682AFast operationDigital data processing detailsBinary multiplierModular multiplier

The invention discloses a modular (2<3n>-2<n>) multiplier, which comprises a 3n-bit binary multiplier, a 2n-bit CSA (Carry Save Adder) compressor array, a first 2n-bit binary adder, a one-bit phase inverter and a second 2n-bit binary adder. In the modular (2<3n>-2<n>) multiplier disclosed by the invention, the result P of binary multiplication is taken as an operand for reprocessing, and modulo addition operation is corrected in a way of adding 1 in advance, so that the operation speed is increased greatly. Compared with the prior art, the modular (2<3n>-2<n>) multiplier has the advantages that a multiplier and a combined logic circuit are reduced on resource cost; and on a key path, a multiplier is reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

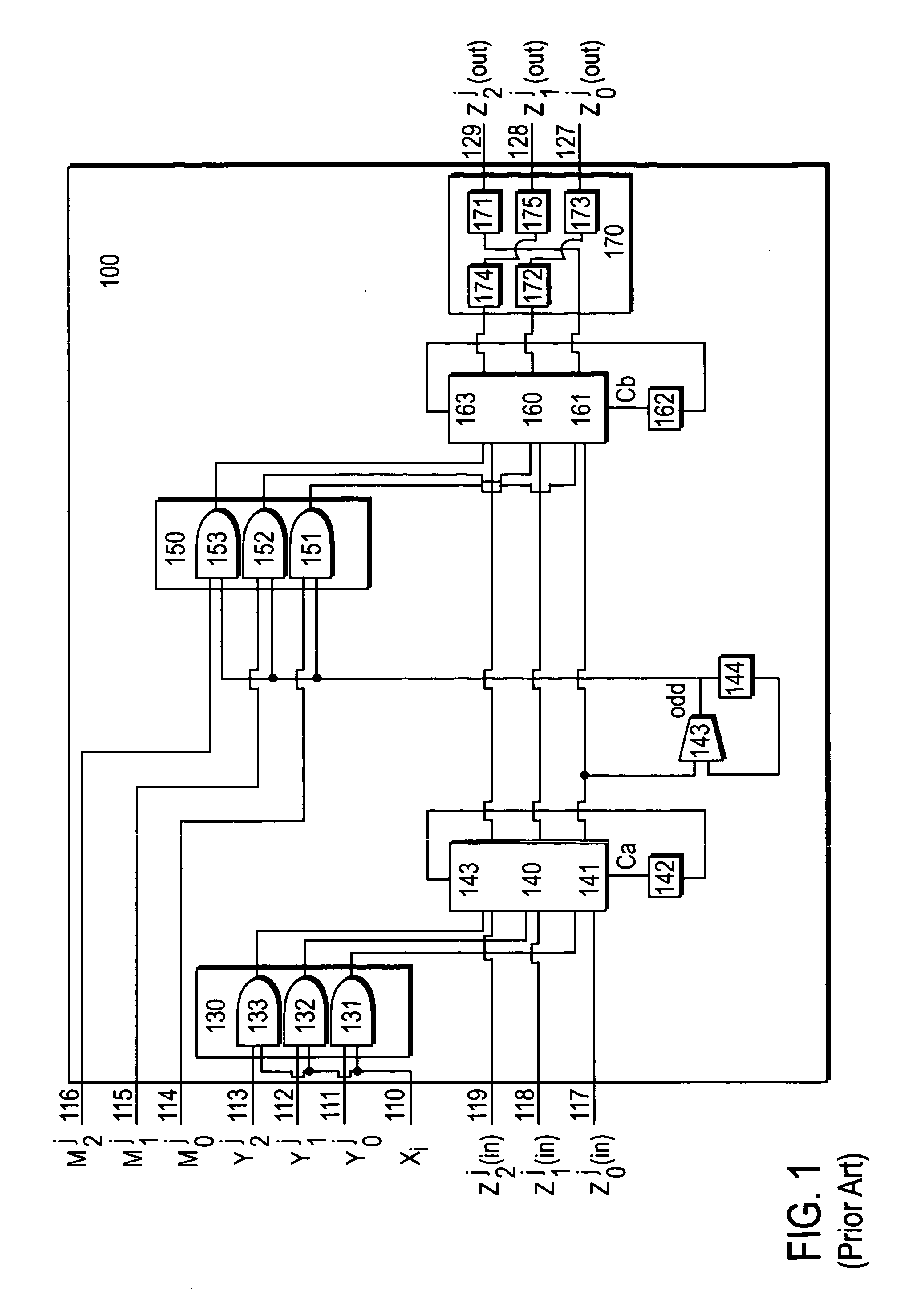

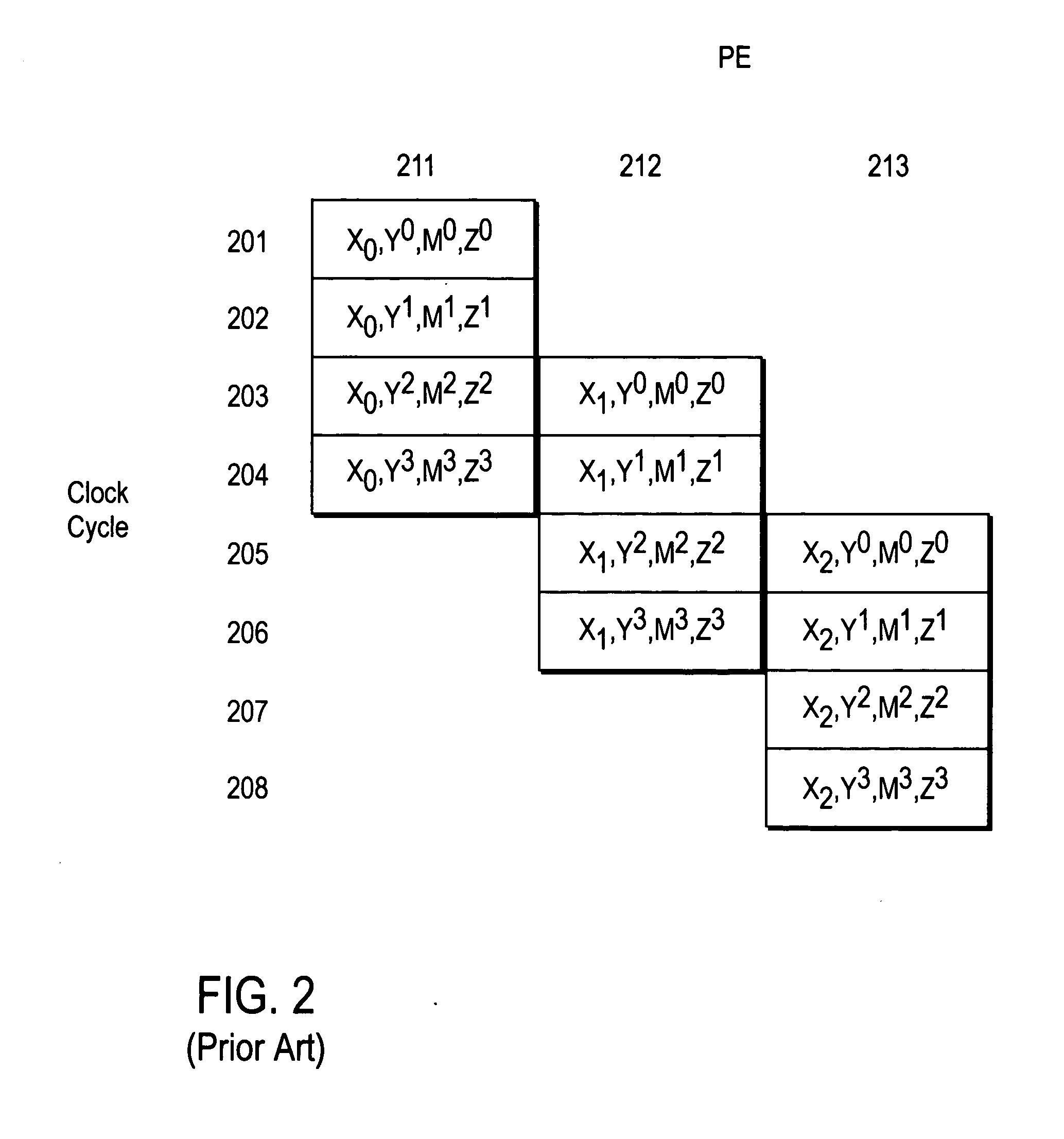

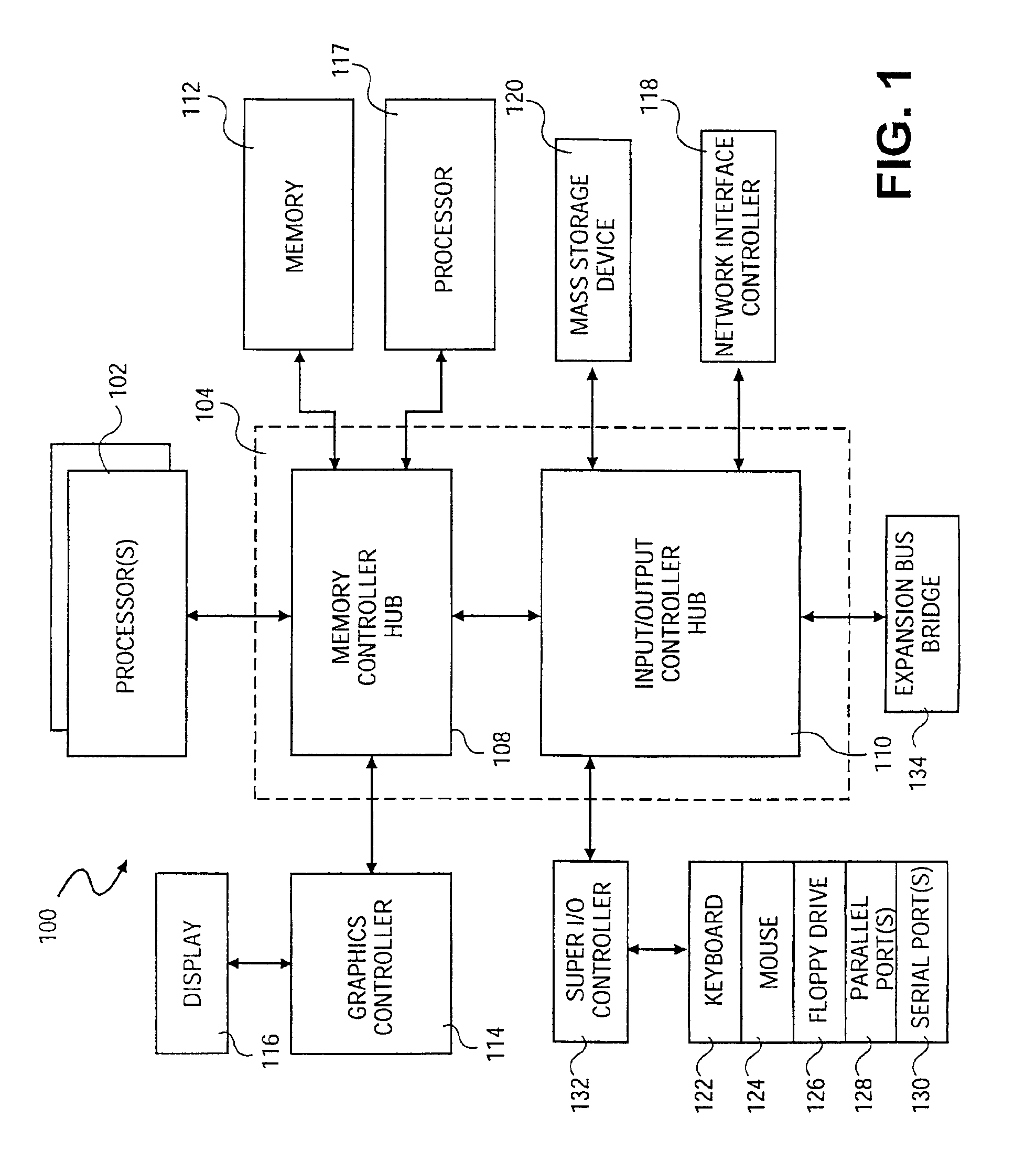

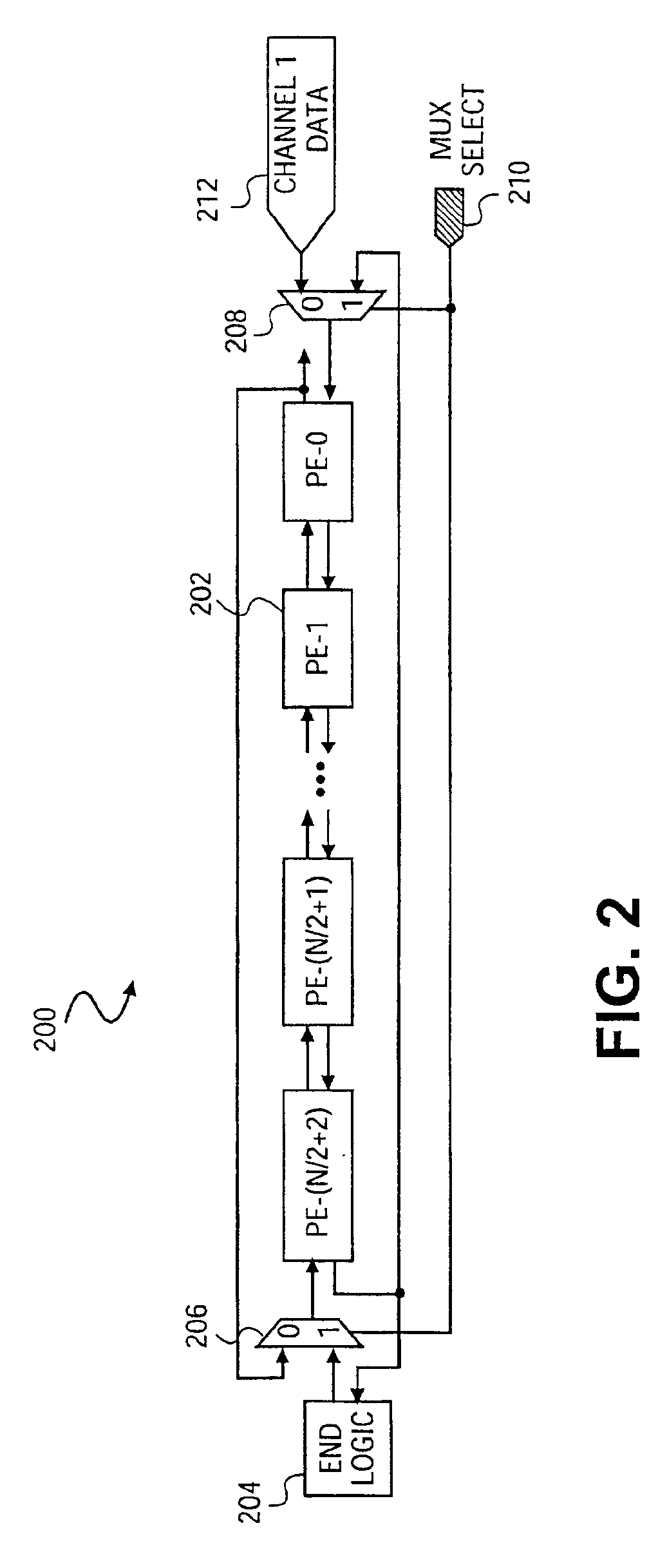

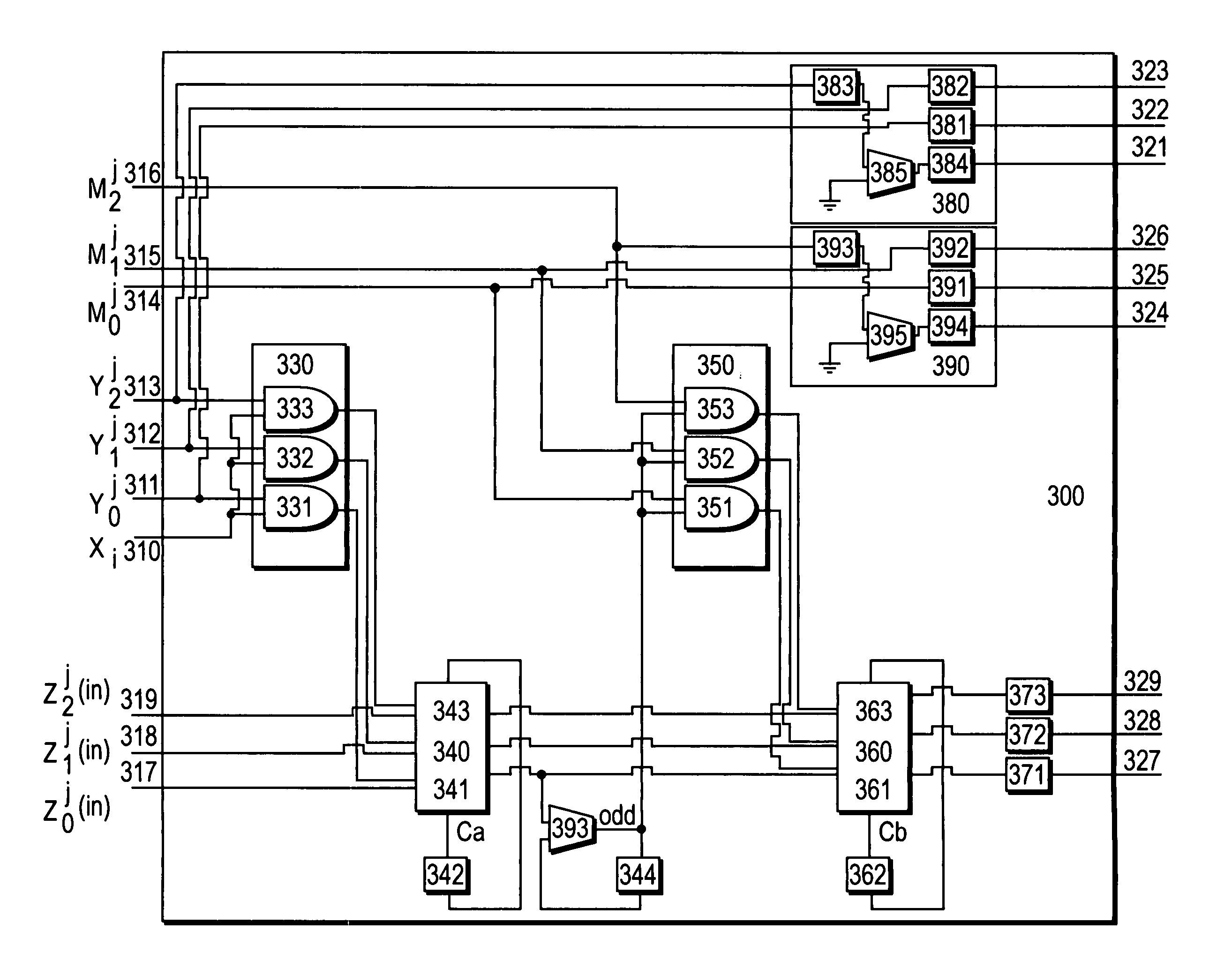

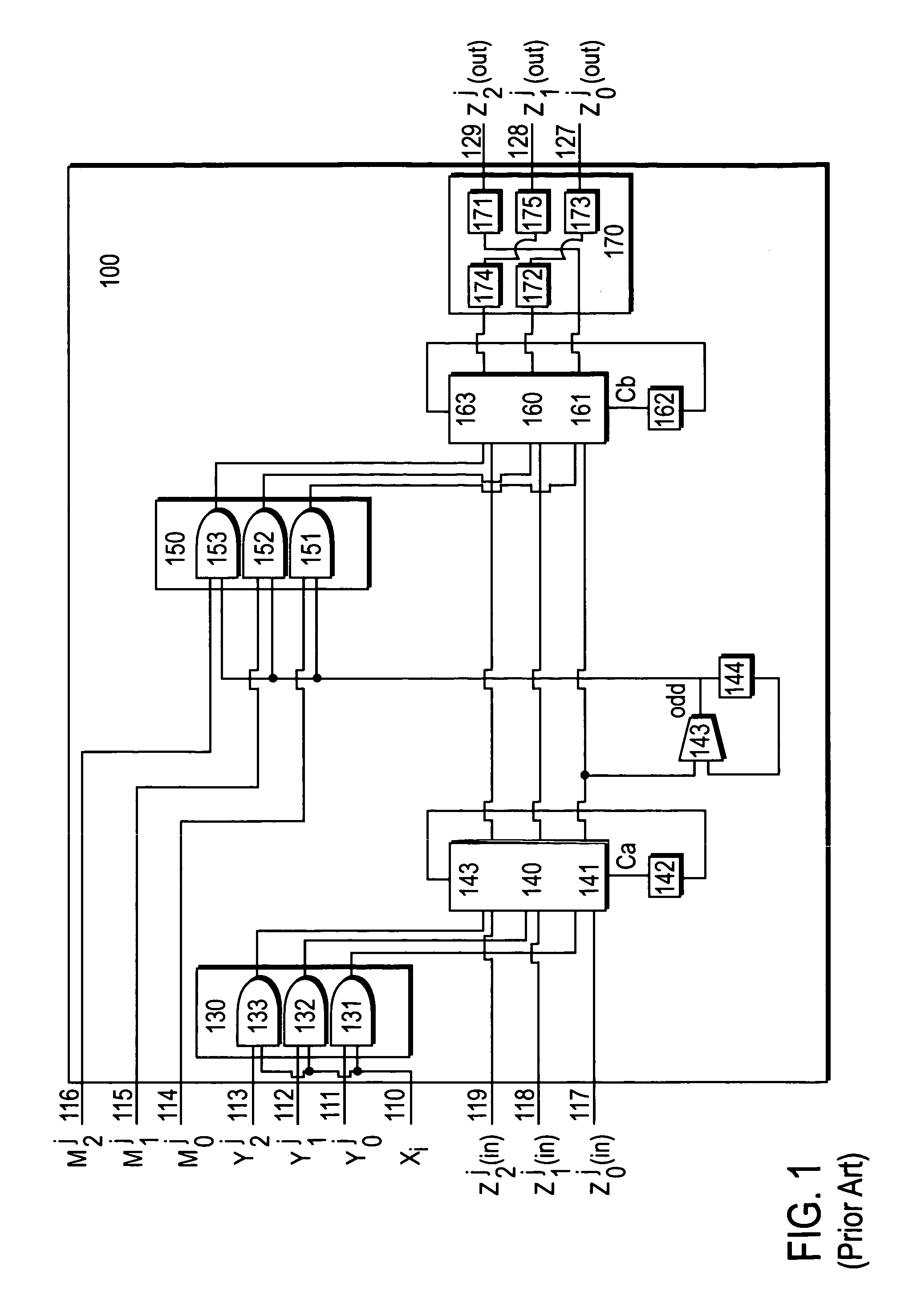

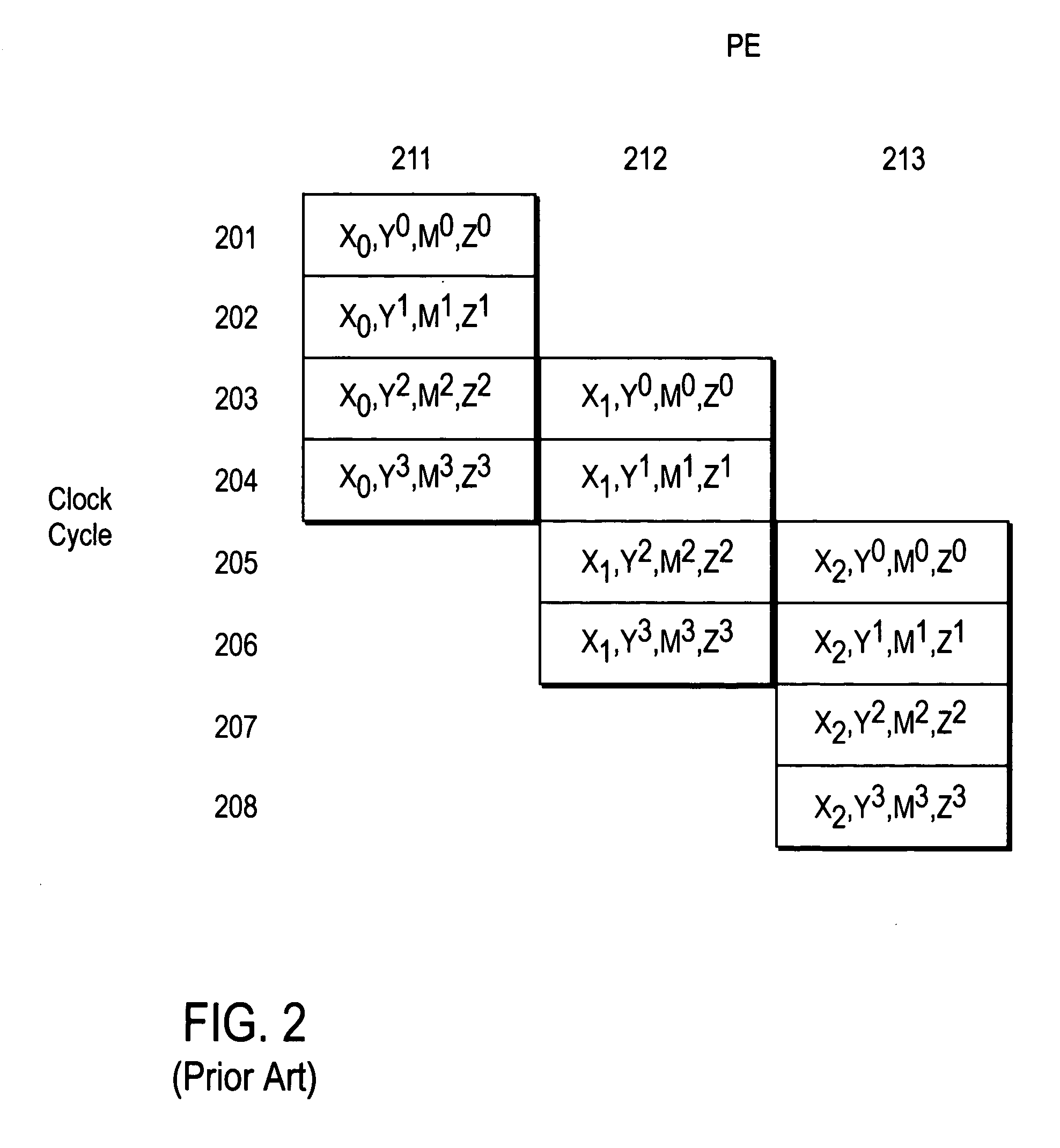

Multiplicand shifting in a linear systolic array modular multiplier

InactiveUS20070203961A1Data conversionComputation using denominational number representationBinary multiplierParallel computing

Embodiments of apparatuses and methods for multiplicand shifting in a linear systolic array modular multiplier are disclosed. In one embodiment, an apparatus includes two processing elements of a linear systolic array. One processing element includes multiplication logic, multiplicand shift logic, an adder, modulus logic, and modulus shift logic. The multiplication logic is to multiply a word of the multiplicand and a bit of the multiplier to generate a product. The multiplicand shift logic is to shift the word of the multiplicand. The adder is to add the product to a first running sum to generate a second running sum. The modulus logic is to conditionally add a word of a modulus and the second running sum. The modulus shift logic is to shift the word of the modulus. The next processing element includes logic to multiply the shifted word of the multiplicand and the next bit of the multiplier.

Owner:INTEL CORP

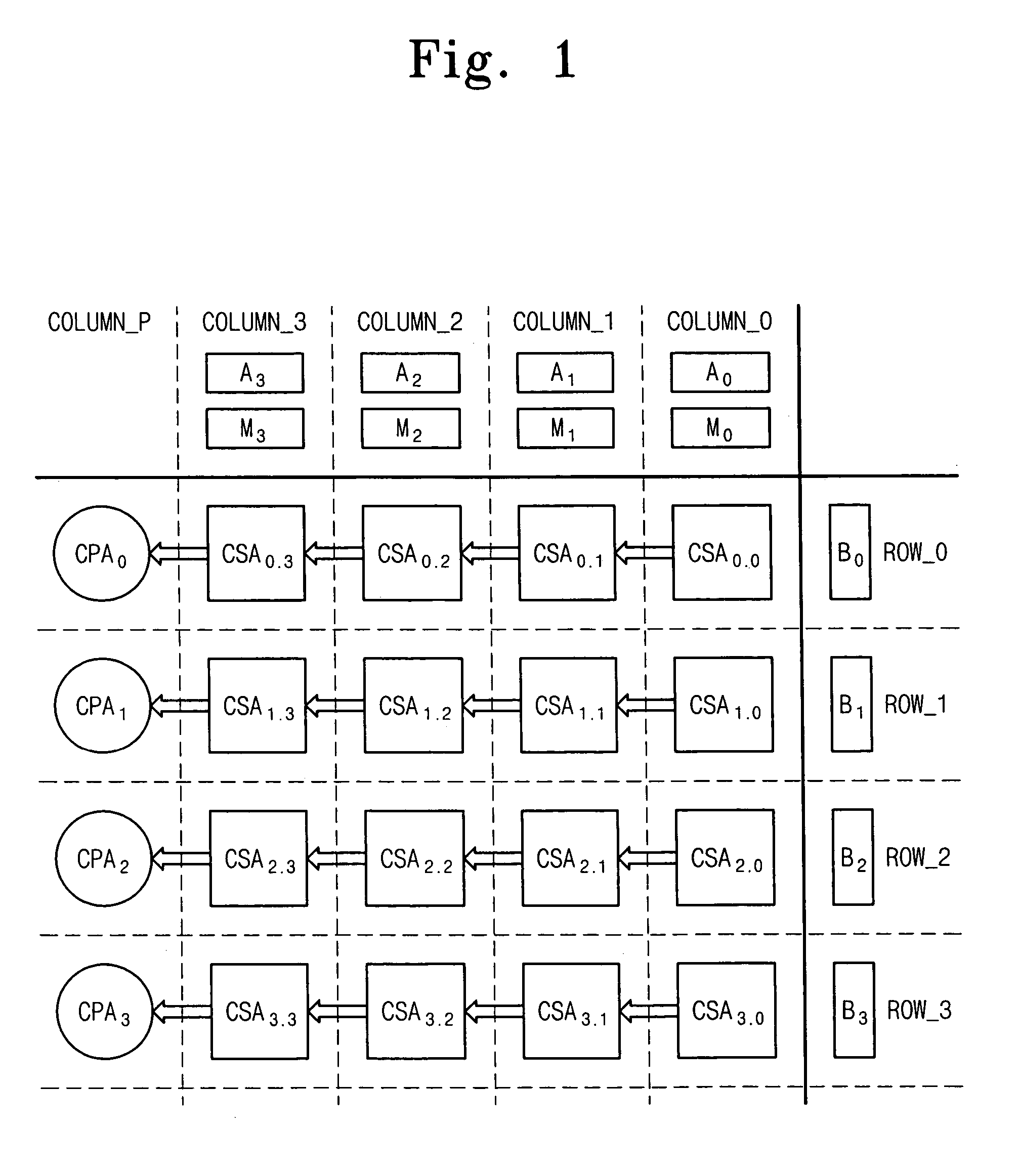

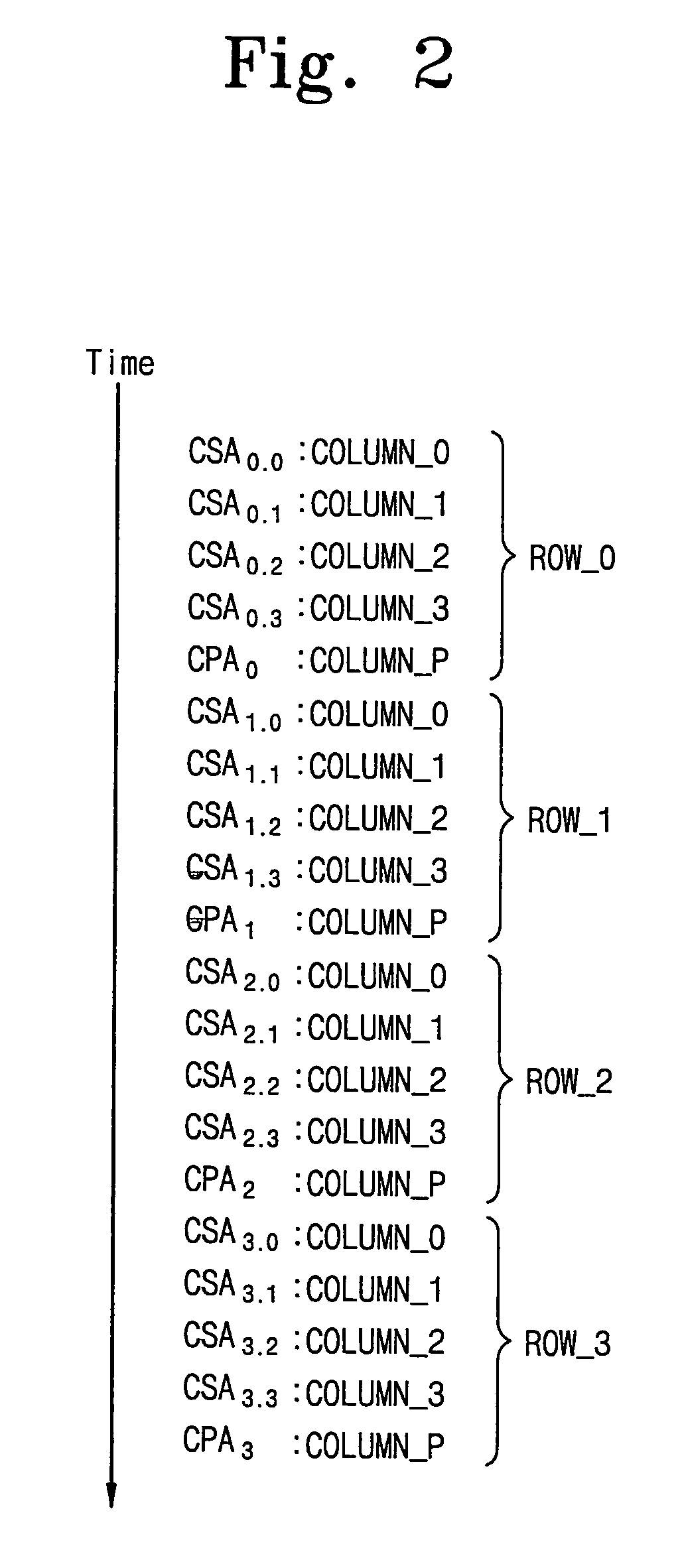

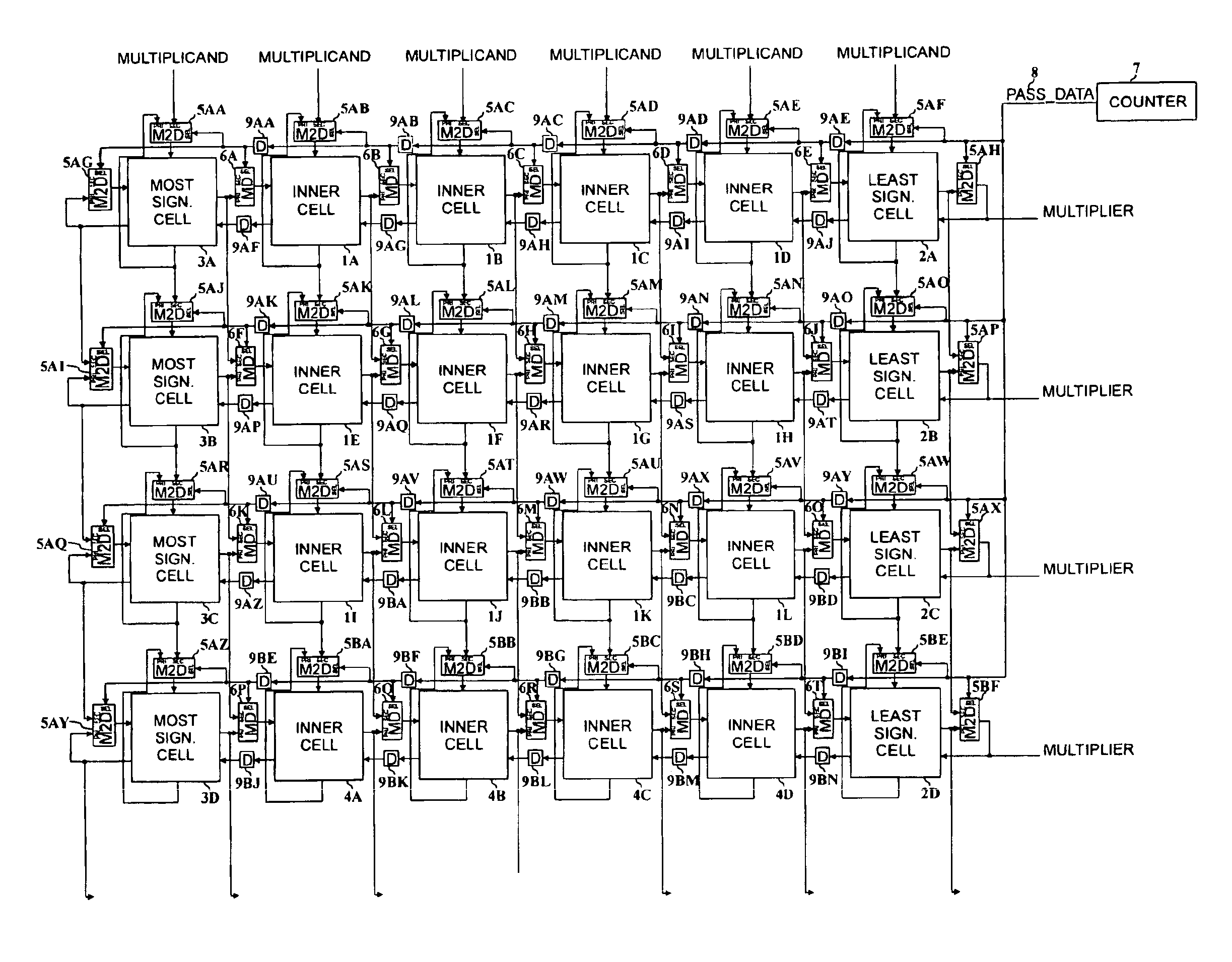

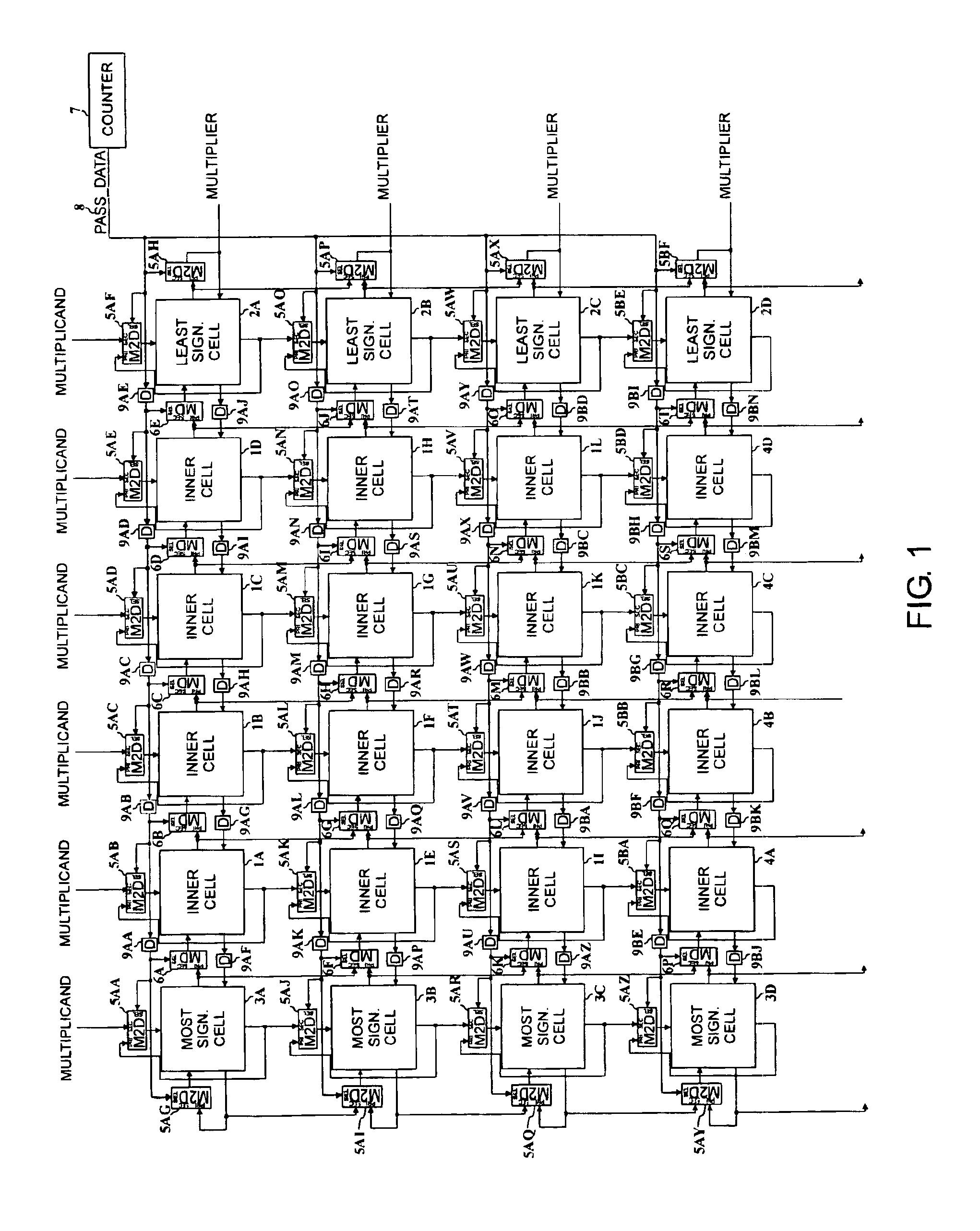

Fast parallel cascaded array modular multiplier

InactiveUS6892215B2Fast parallel processingOptimal systolic clock rateComputation using non-contact making devicesComputations using residue arithmeticBinary multiplierClock rate

A fast, parallel modular multiplier is presented which is scalable according to available hardware resources. Linear throughput increases with respect to consumed resources is achieved. Multiple independent data streams may be processed simultaneously, and optimal clock rates are attained by virtue of limited fan-out of all signal paths and nearest neighbor interconnections. Integrated circuit implementation is benefited by the potential for signal sharing among input and output busses and a common control interface for all independent data streams.

Owner:FREKING WILLIAM L

High-speed multiple-point operation method for elliptic curve passwords

InactiveCN110232289AImprove performanceReduce resource usageDigital data processing detailsDigital data protectionPasswordModular multiplier

The invention discloses a high-speed multiple-point operation method for elliptic curve passwords, which is realized by adopting an assembly line type Montgomery modular multiplier matched with an adder, executing N clock periods by one modular multiplier to obtain a result, and sending N different operations to the modular multiplier in N continuous clock periods; and in the previous clock periodof the first operation result, sending the input of the Nth operation into the modular multiplier. The invention utilizes the flow characteristics of the pipelined Montgomery modular multiplier, subtly multiplexes the underlying pipelined hardware circuit, and simultaneously performs multiple multiplication operations in a batch manner, and the throughput of a whole system is improved by severalorders of magnitude.Therefore, the performance / hardware resource ratio and the performance / energy consumption ratio are improved by several times or even dozens of times compared with those in the prior art. Meanwhile, the optimal number of Montgomery modular multipliers and modular adders is selected by analyzing the characteristics of a multiple point algorithm, and the optimal configuration ofperformance and resource use is achieved.

Owner:南京秉速科技有限公司

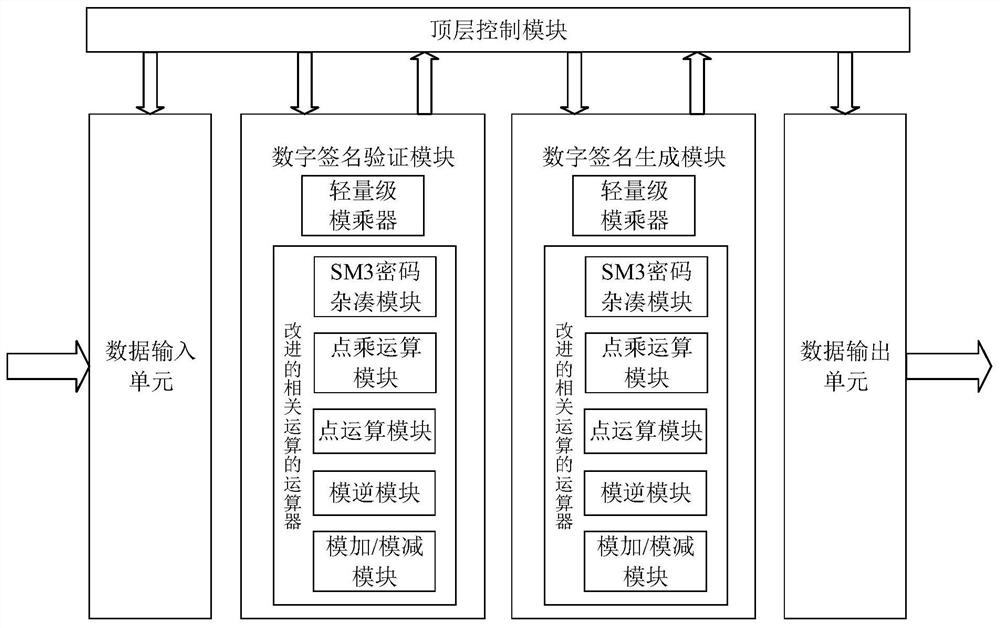

SM2 digital signature generation and verification device based on lightweight modular multiplication

ActiveCN113193962AReduce space complexityReduce resource areaUser identity/authority verificationHigh level techniquesParallel computingDigital Signature Algorithm

The invention provides an SM2 digital signature generation and verification device based on lightweight modular multiplication. The device at least comprises a top layer control module, a data input unit, a data output unit, a lightweight modular multiplier, an SM2 digital signature generation module, an SM2 digital signature verification module and a set of improved arithmetic units for correlation operation. According to the method, a complex modular multiplication algorithm is simplified into common addition, subtraction and shifting operations by utilizing the idea of simultaneous multiplication and modular multiplication of the staggered modular multiplication algorithm, so that the resource area is consumed as little as possible while the modular multiplication speed is increased, and the efficiency of an upper-layer algorithm is further influenced; and a quicker way is provided for the finally constructed SM2 digital signature algorithm of the application layer.

Owner:ANHUI NORMAL UNIV

Modular multiplier

InactiveCN102929575AConsume less resourcesFast operationDigital data processing detailsBinary multiplierResource consumption

The invention discloses a modular multiplier, which comprises (n+1)-bit binary multiplier, an n-bit inverter array, an n-bit CSA compressor array, a first n-bit binary adder, a 1-bit full adder, a 5-bit adder, a first 1-bit inverter, a second 1-bit inverter, a third 1-bit inverter, a second n-bit binary adder and a third n-bit binary adder. According to a modular (2n+3) multiplier, the result of binary multiplication serves as an operation number and is reprocessed, so that repeated correction of the traditional modular (2n+3) multiplier is changed into one-step correction, the resource consumption of the modular (2n+3) multiplier is greatly reduced, and the operation speed is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Method and apparatus for performing modular multiplication

InactiveUS6922717B2Computation using non-contact making devicesDigital computer detailsBinary multiplierControl signal

A method and apparatus for performing modular multiplication is disclosed. An apparatus in accordance with one embodiment of the present invention includes a modular multiplier including a plurality of independent computation channels, where the plurality of independent computation channels includes a first computation channel and a second computation channel, and a coupling device interposed between the first computation channel and the second computation channel to receive a control signal and to couple the first computation channel to the second computation channel in response to a receipt of the control signal.

Owner:TAHOE RES LTD

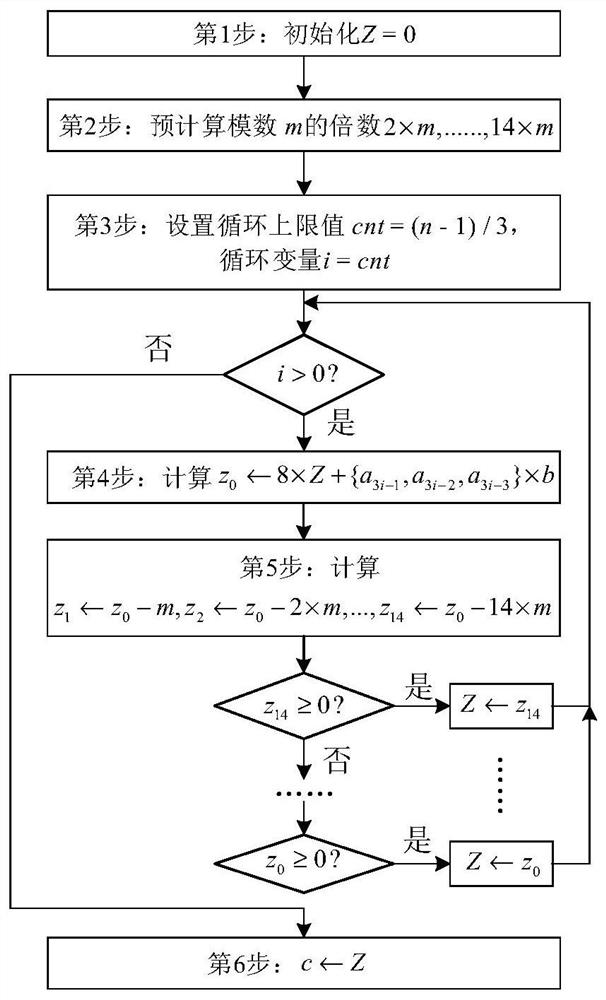

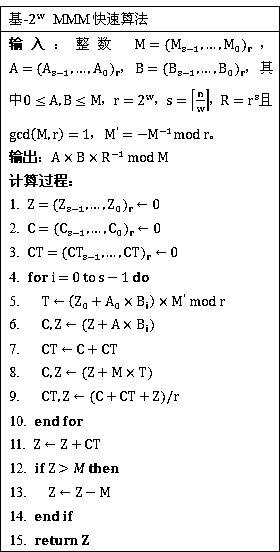

Vectorized Montgomery modular multiplier design method based on NEON engine

ActiveCN104951279AReduce accumulationNo dependenciesProgram controlMemory systemsModular multiplierParallel processing

The invention discloses a vectorized Montgomery modular multiplier design method based on an NEON engine. The method comprises the steps that 1, data are input; 2, the data are initialized; data iterative computation is carried out; 4, Z and CT are accumulated for updating the Z value according to the iterative results; 5, overflow judging and processing are carried out on the computing result Z. The carry data are cached independently, accumulation of each iteration for the carry data is reduced, and the carry data are accumulated at a time only after the last iteration is finished, so that high data calculation and low data calculation do not depend on each other, vectorized data parallel processing can be carried out through the NEON engine, specifically, the operation speed of the MMM based on an ARM Cortex-A series chip can be improved, and the overall performance of a public key encryption system is improved.

Owner:成都三零嘉微电子有限公司

Multiplicand shifting in a linear systolic array modular multiplier

InactiveUS7693925B2Computations using residue arithmeticData conversionBinary multiplierModular multiplier

Embodiments of apparatuses and methods for multiplicand shifting in a linear systolic array modular multiplier are disclosed. In one embodiment, an apparatus includes two processing elements of a linear systolic array. One processing element includes multiplication logic, multiplicand shift logic, an adder, modulus logic, and modulus shift logic. The multiplication logic is to multiply a word of the multiplicand and a bit of the multiplier to generate a product. The multiplicand shift logic is to shift the word of the multiplicand. The adder is to add the product to a first running sum to generate a second running sum. The modulus logic is to conditionally add a word of a modulus and the second running sum. The modulus shift logic is to shift the word of the modulus. The next processing element includes logic to multiply the shifted word of the multiplicand and the next bit of the multiplier.

Owner:INTEL CORP