Patents

Literature

42results about How to "Reduce image lag" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

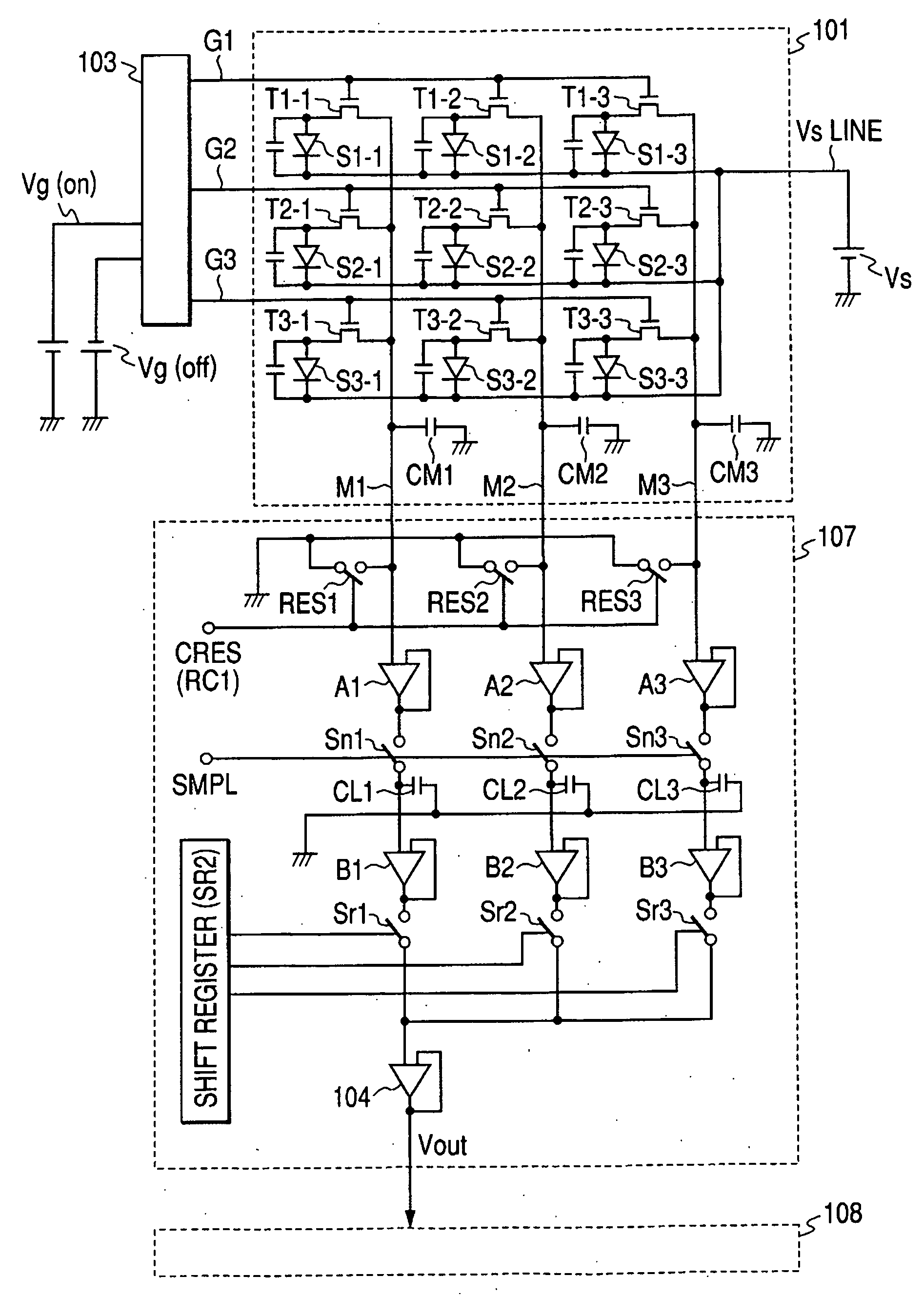

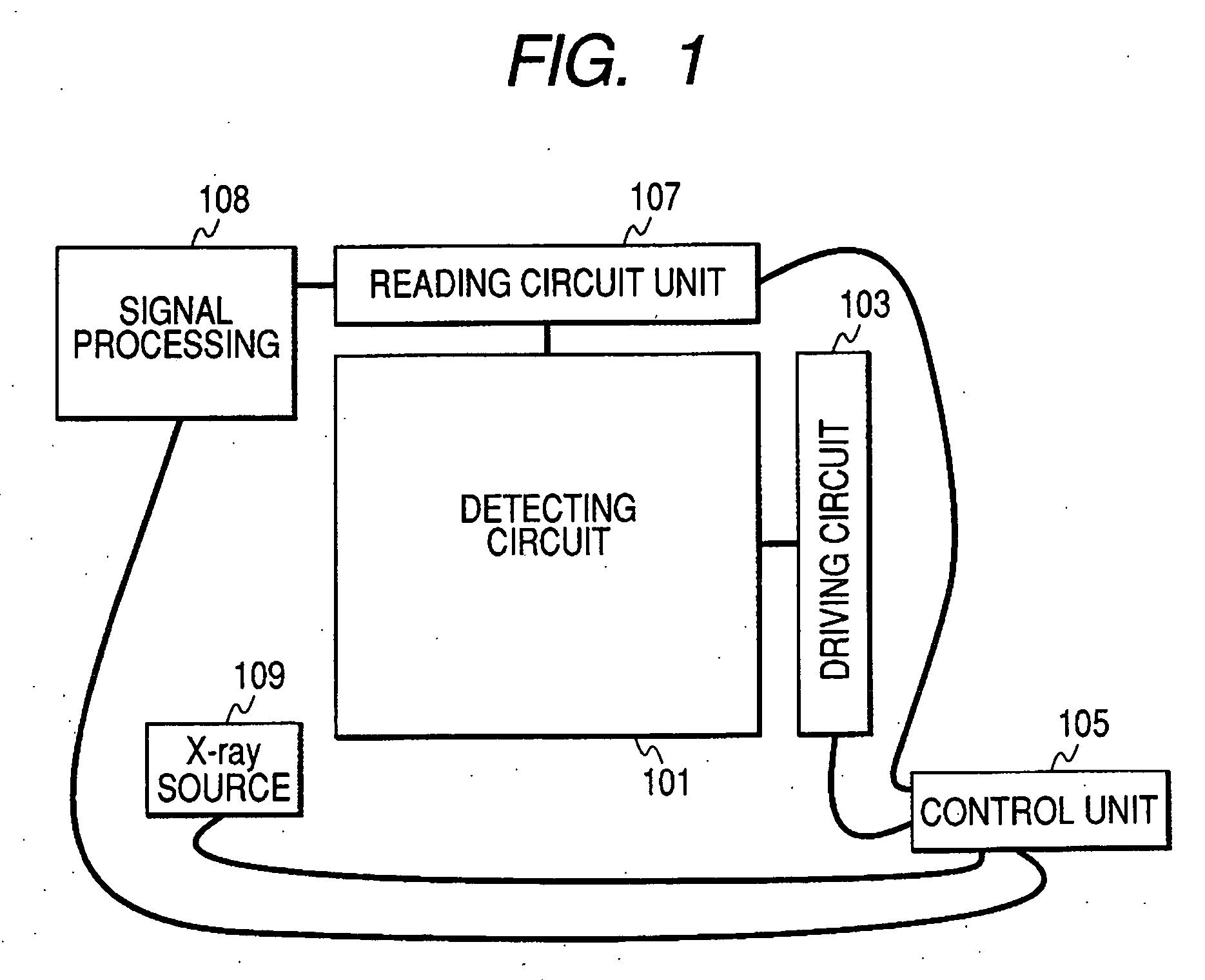

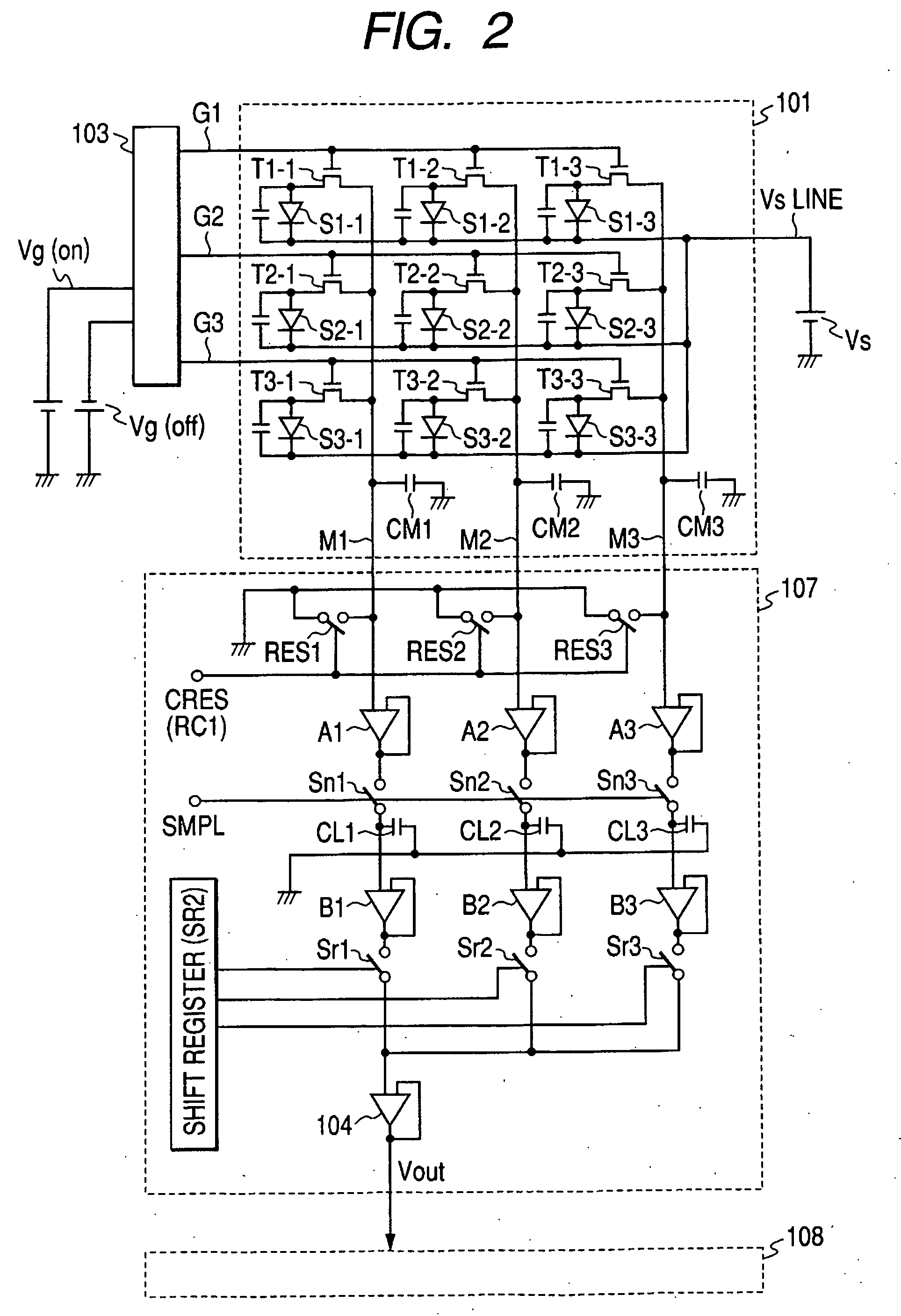

Radiation image pickup apparatus, radiation image pickup system, their control method and their control program

InactiveUS20070040099A1Improve image qualityImprove reliabilityTelevision system detailsSolid-state devicesRandom noiseRadiation exposure

A radiation image pickup apparatus which selectively executes a first reading operation driving a detection unit irradiated with the radiation to read a first signal value, a second reading operation driving the detection unit without being irradiated with any radiations before the first reading operation to read a second signal value, and a third reading operation driving the detection unit without being irradiated with any radiations after the first reading operation to read a third signal value, and subtracts a signal value produced by the processing of the second signal value and the third signal value from the first signal value, thereby reducing an offset component and random noises without lowering a frame rate and its control method are provided.

Owner:CANON KK

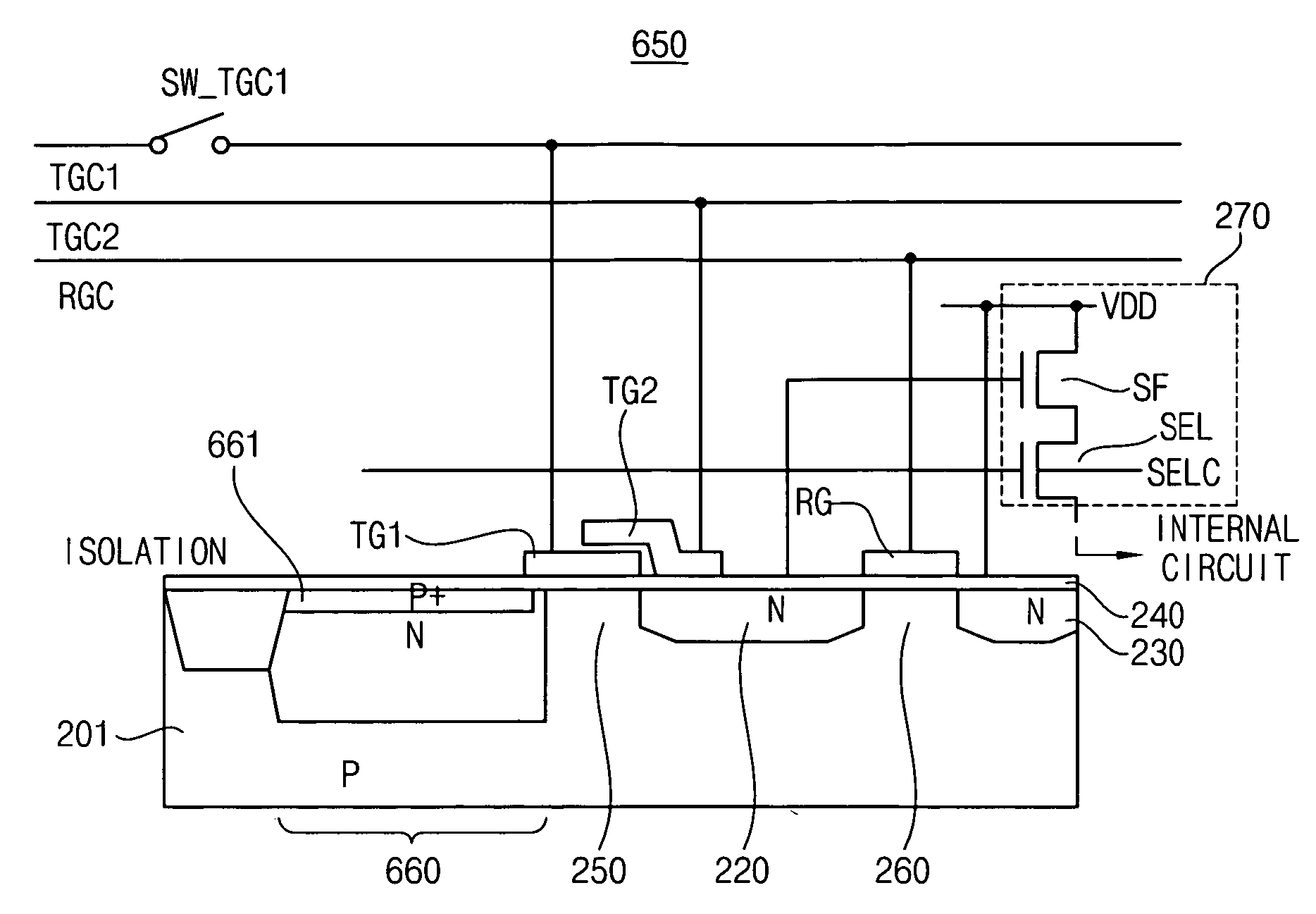

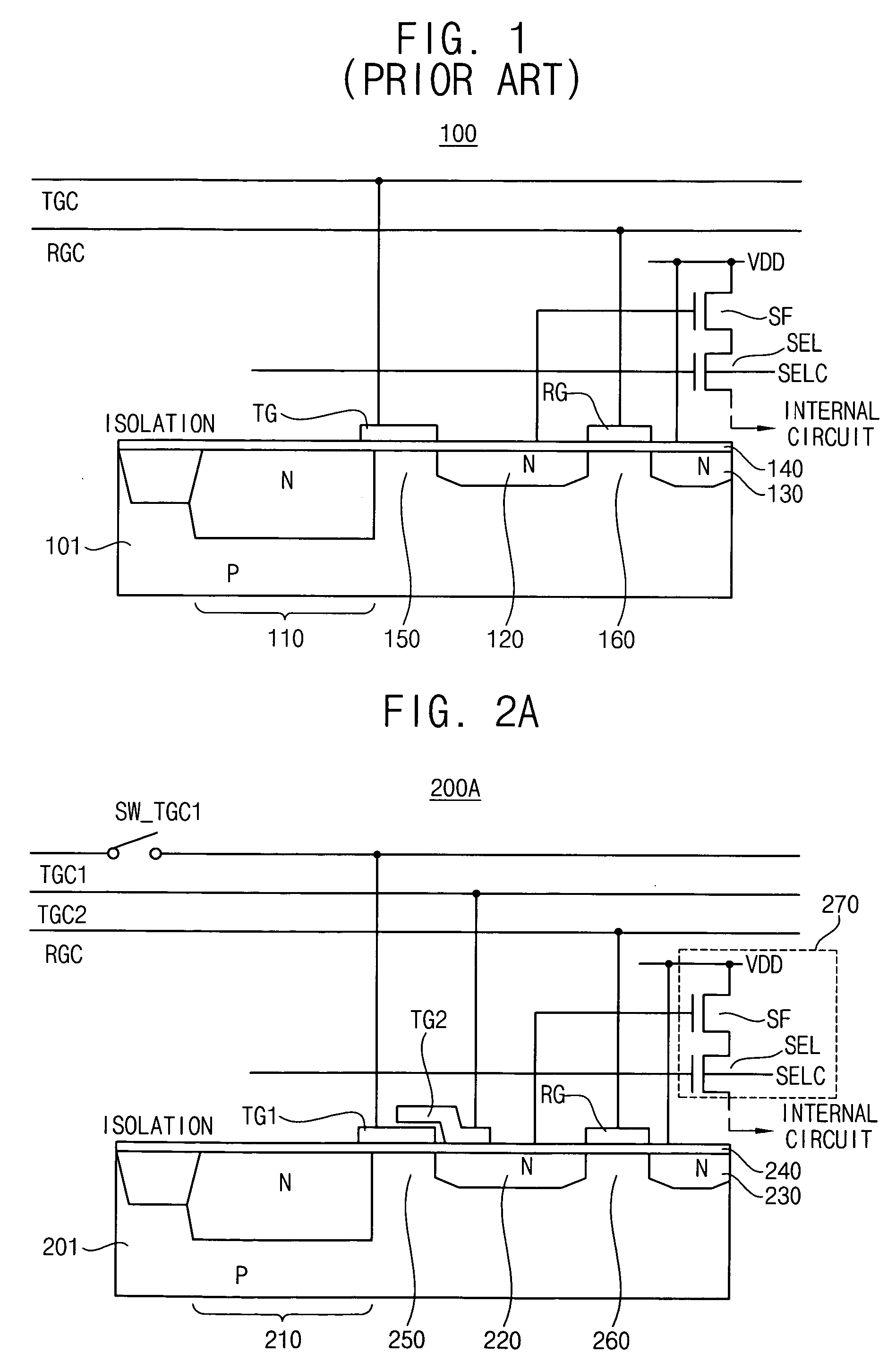

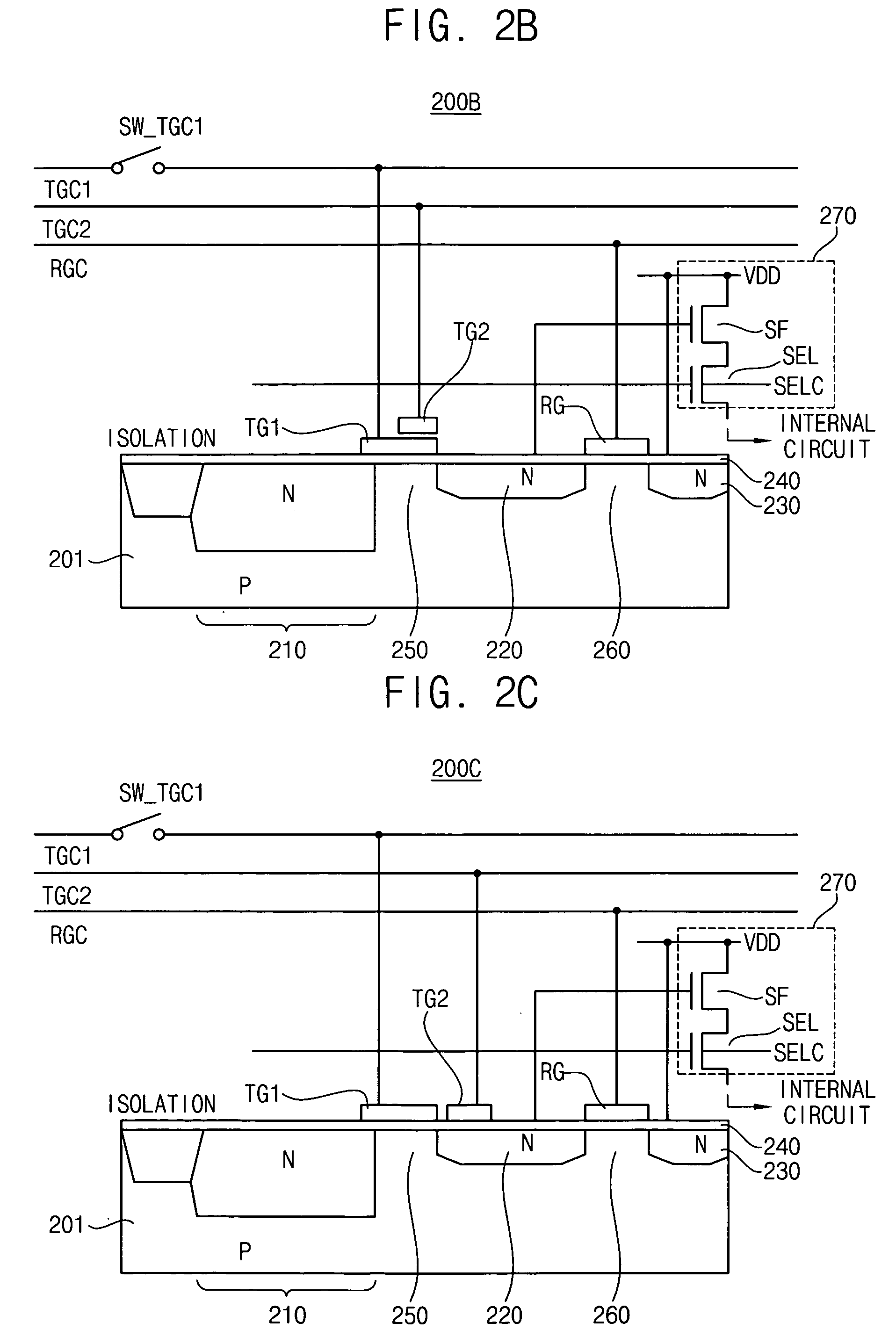

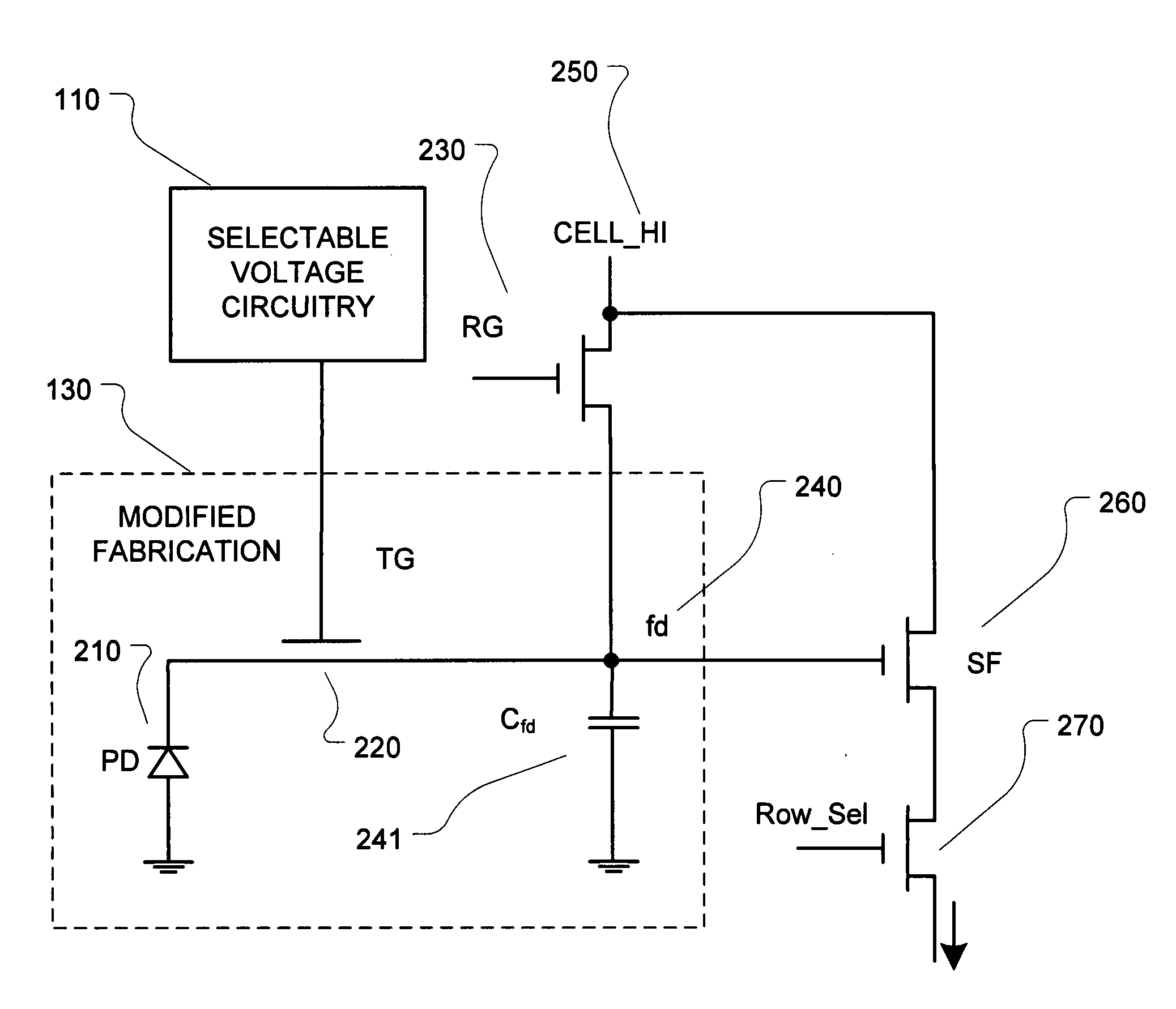

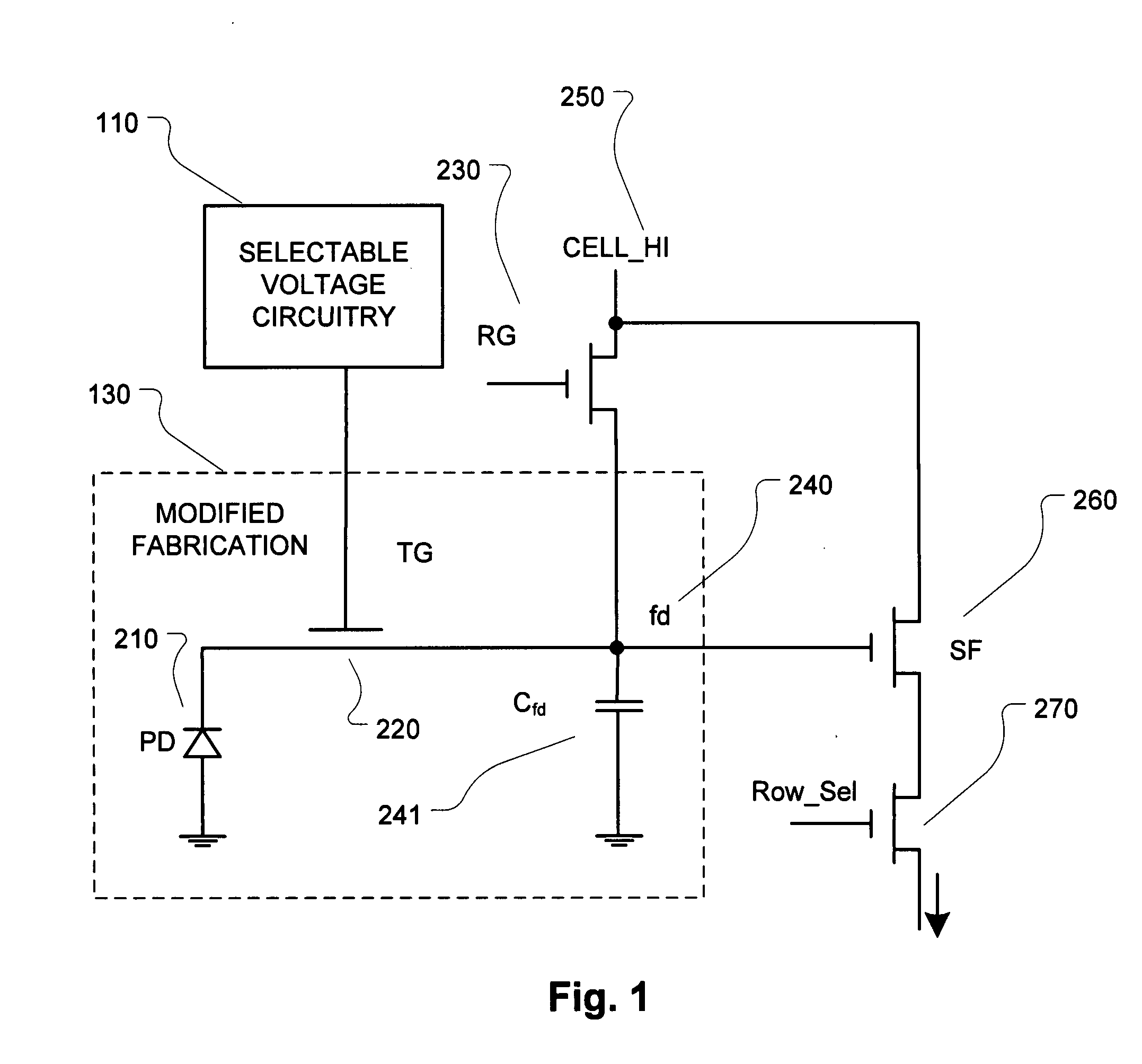

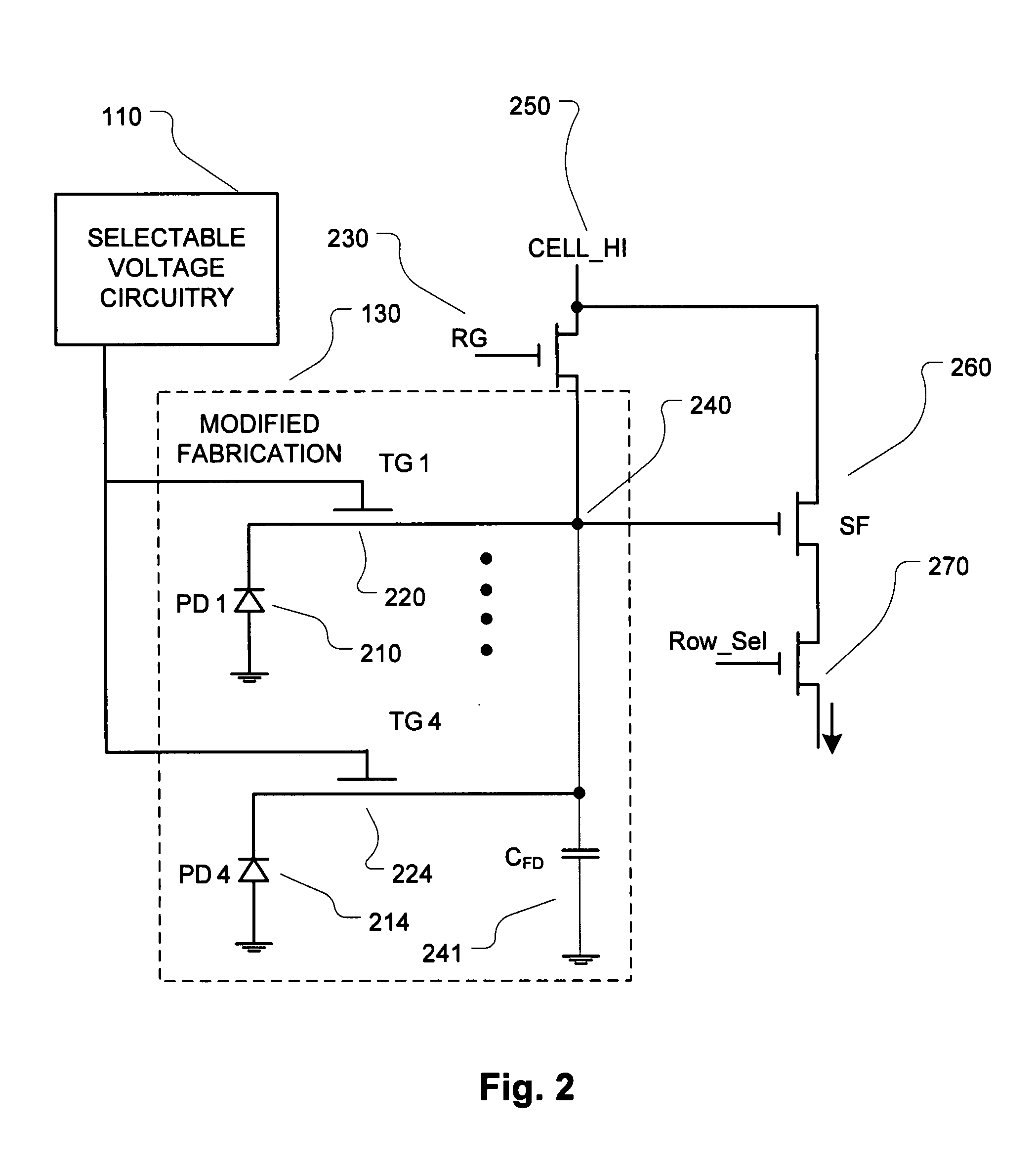

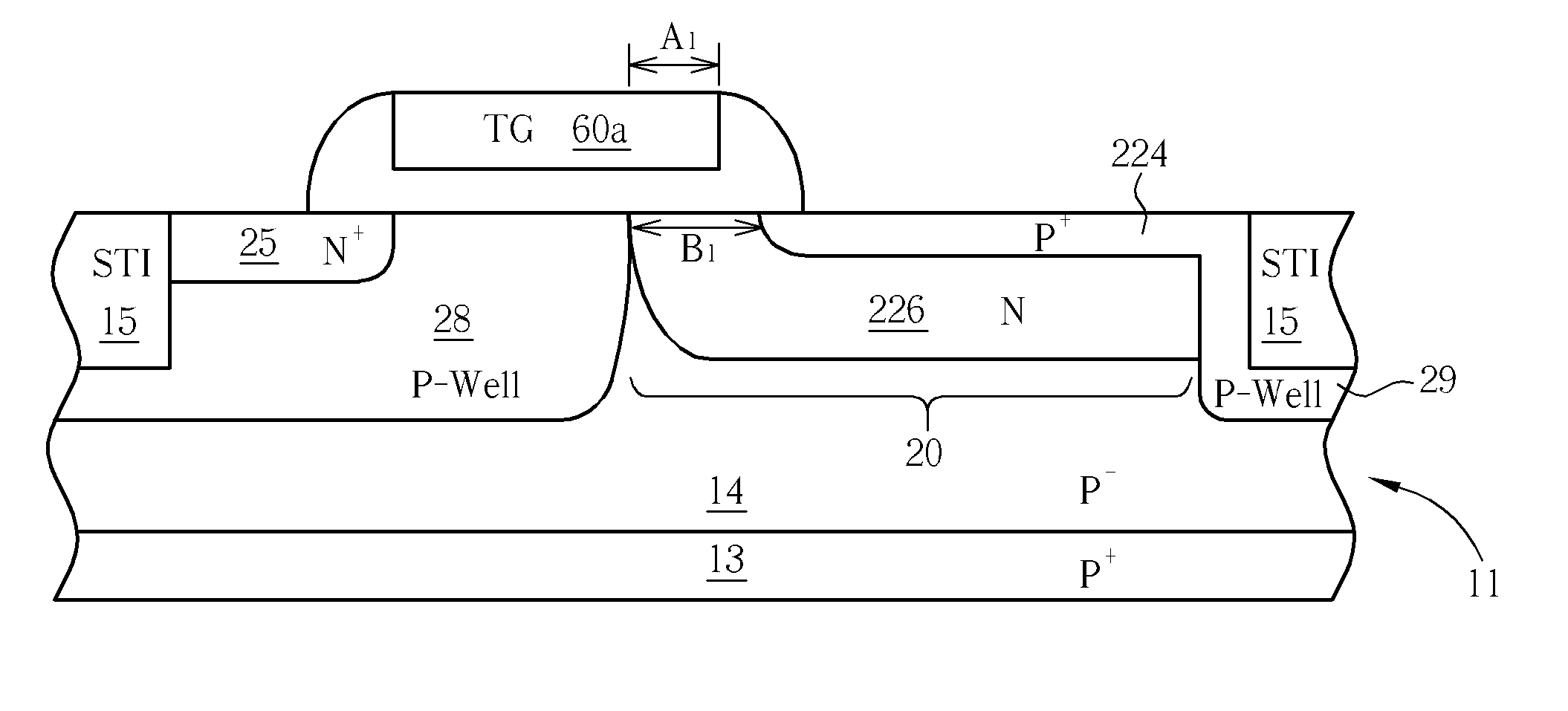

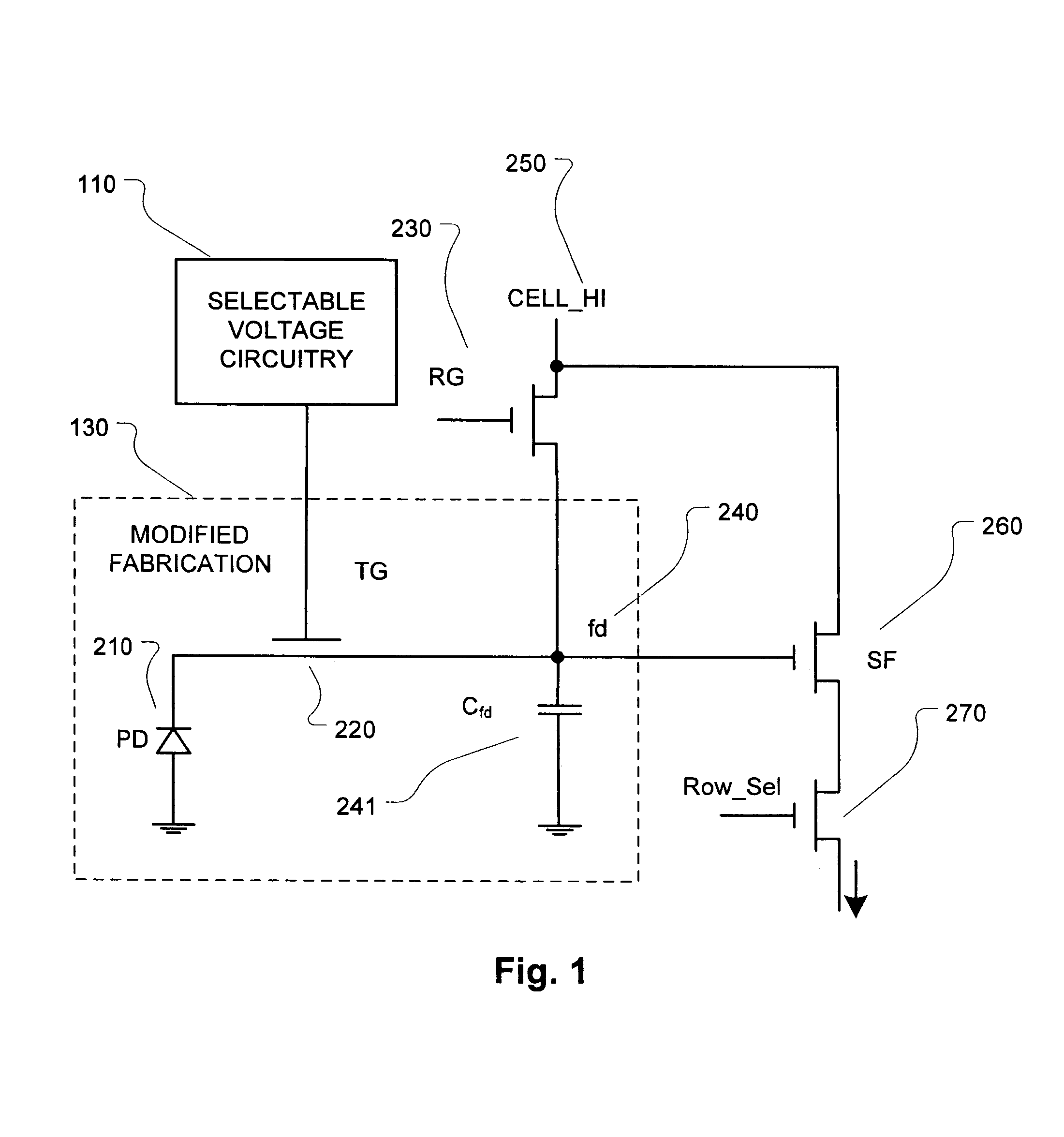

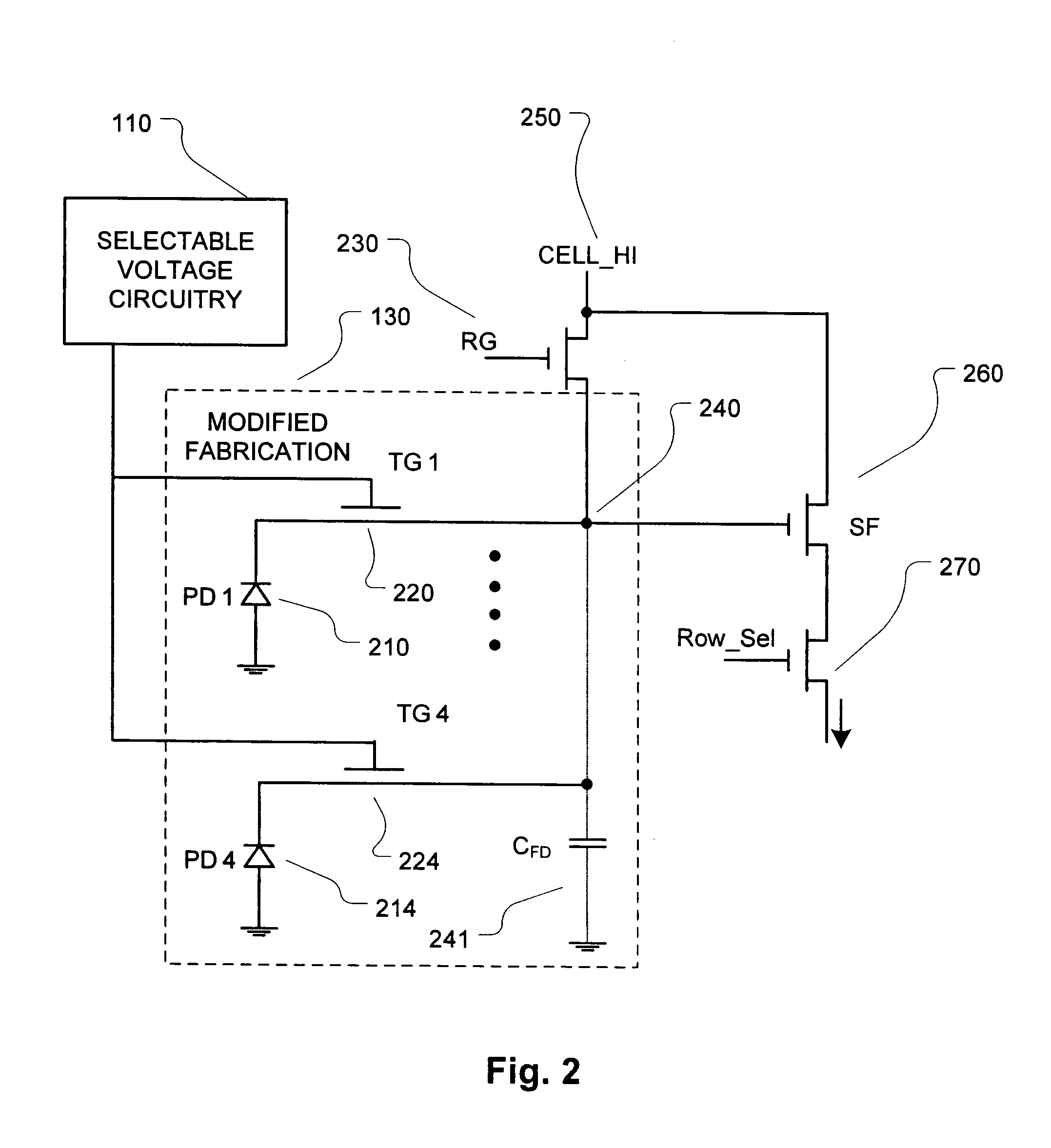

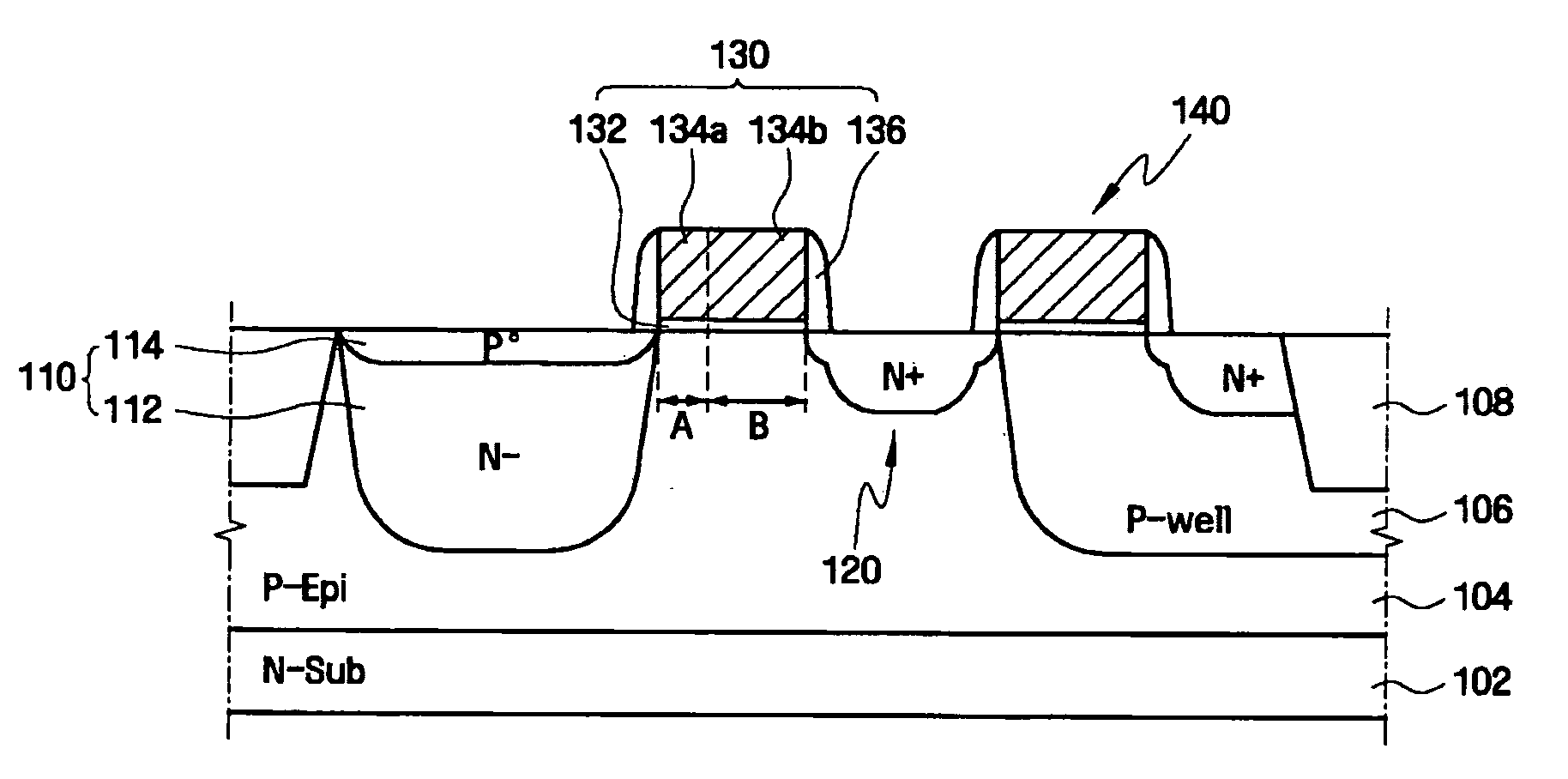

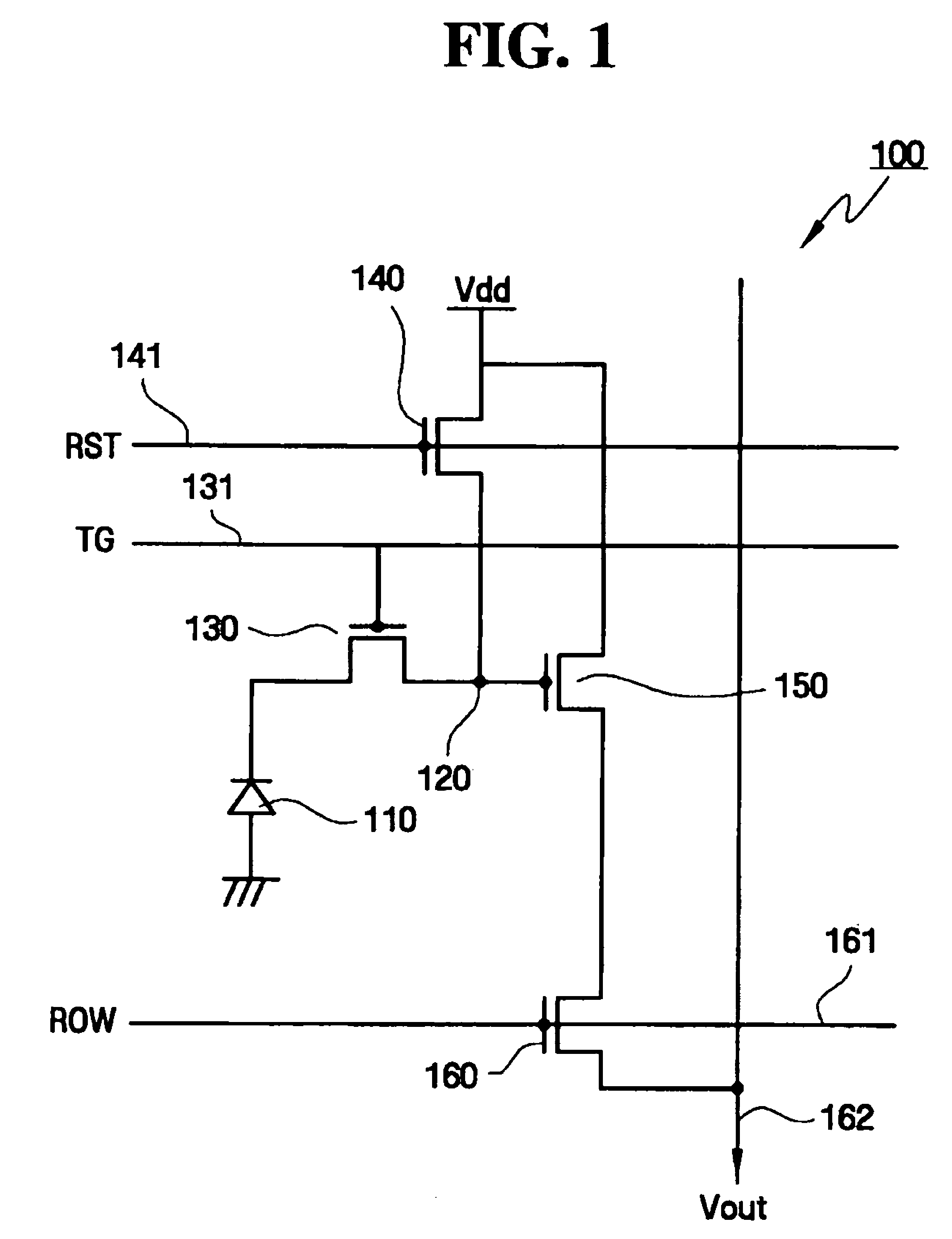

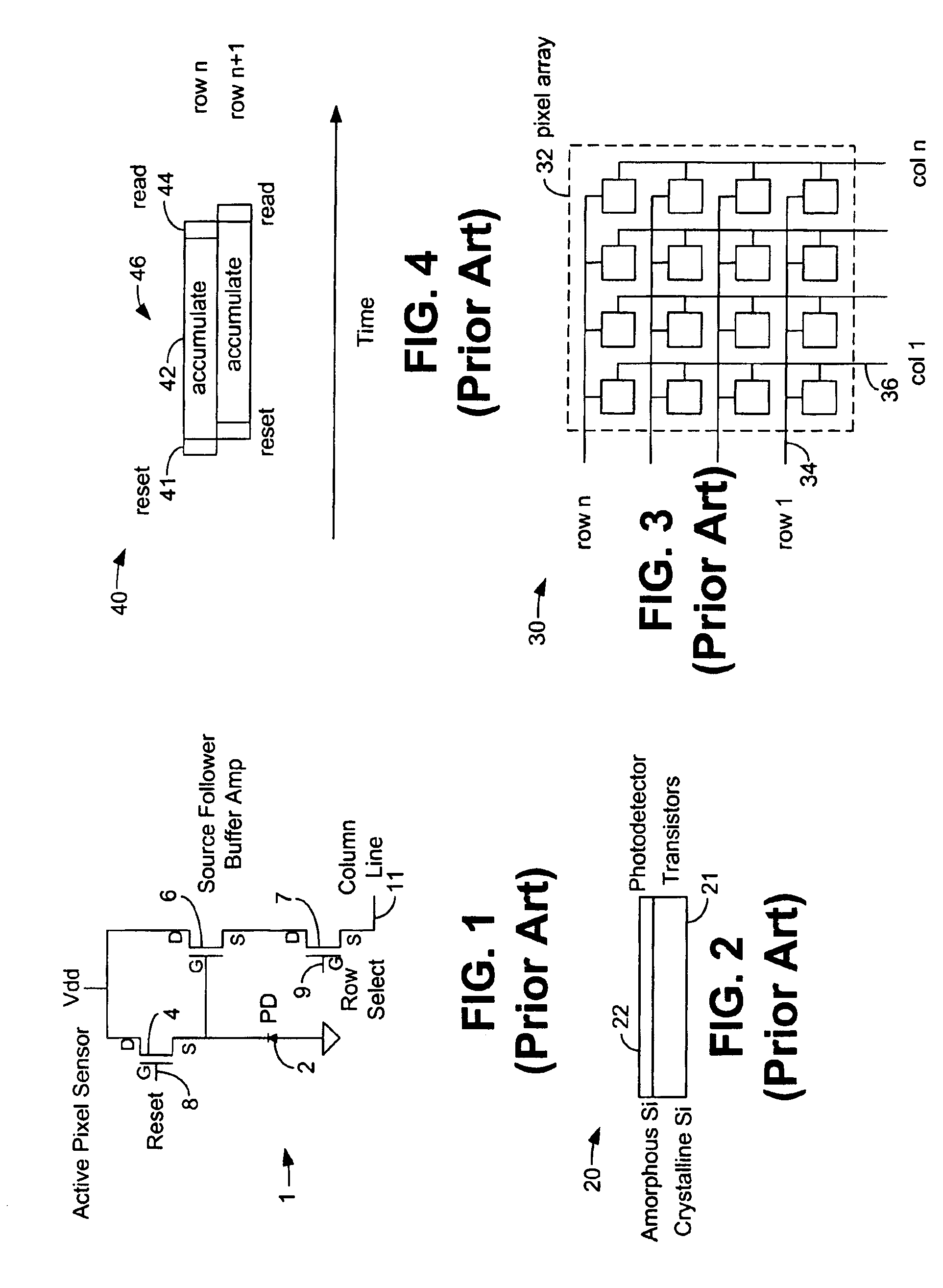

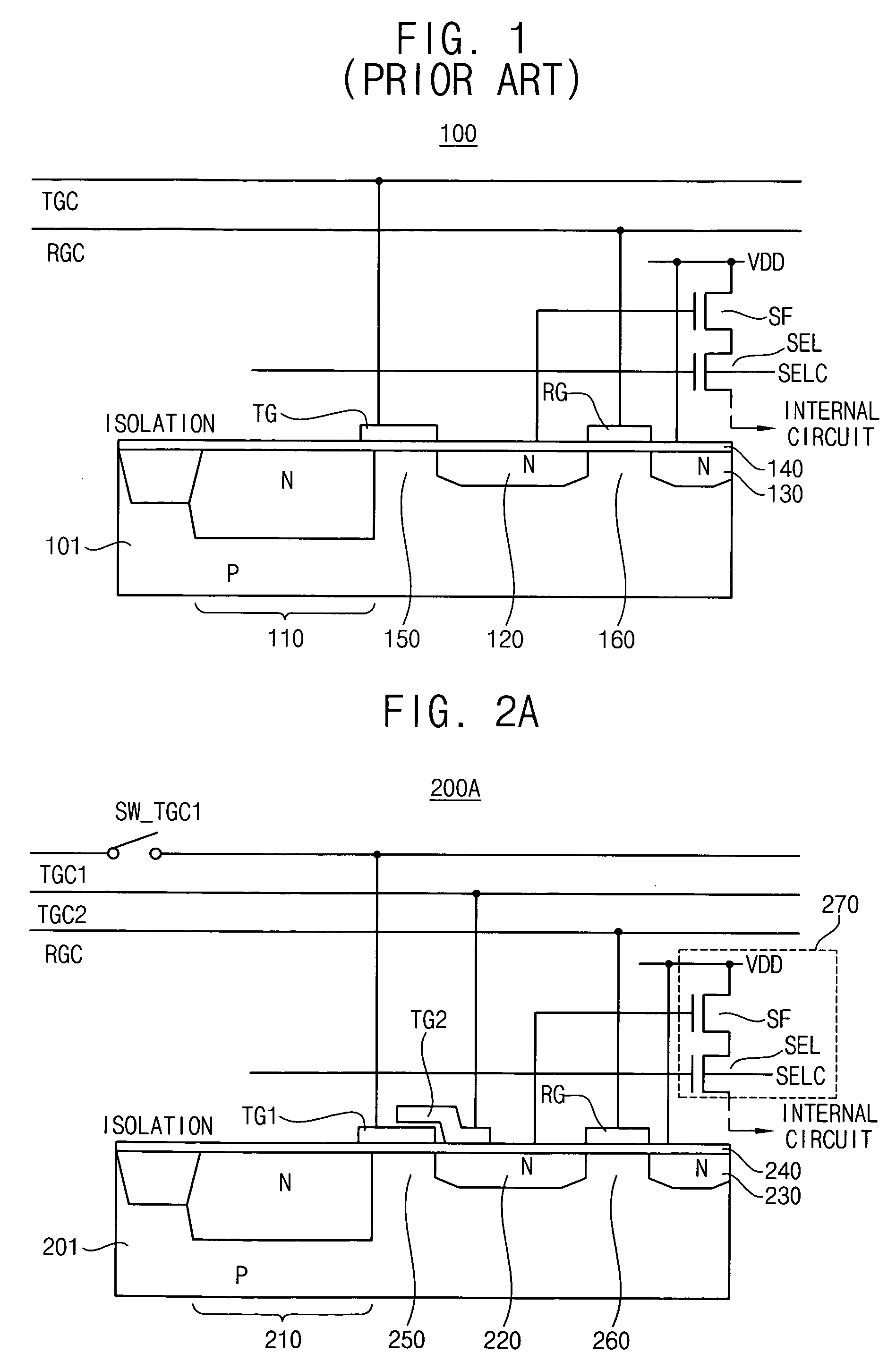

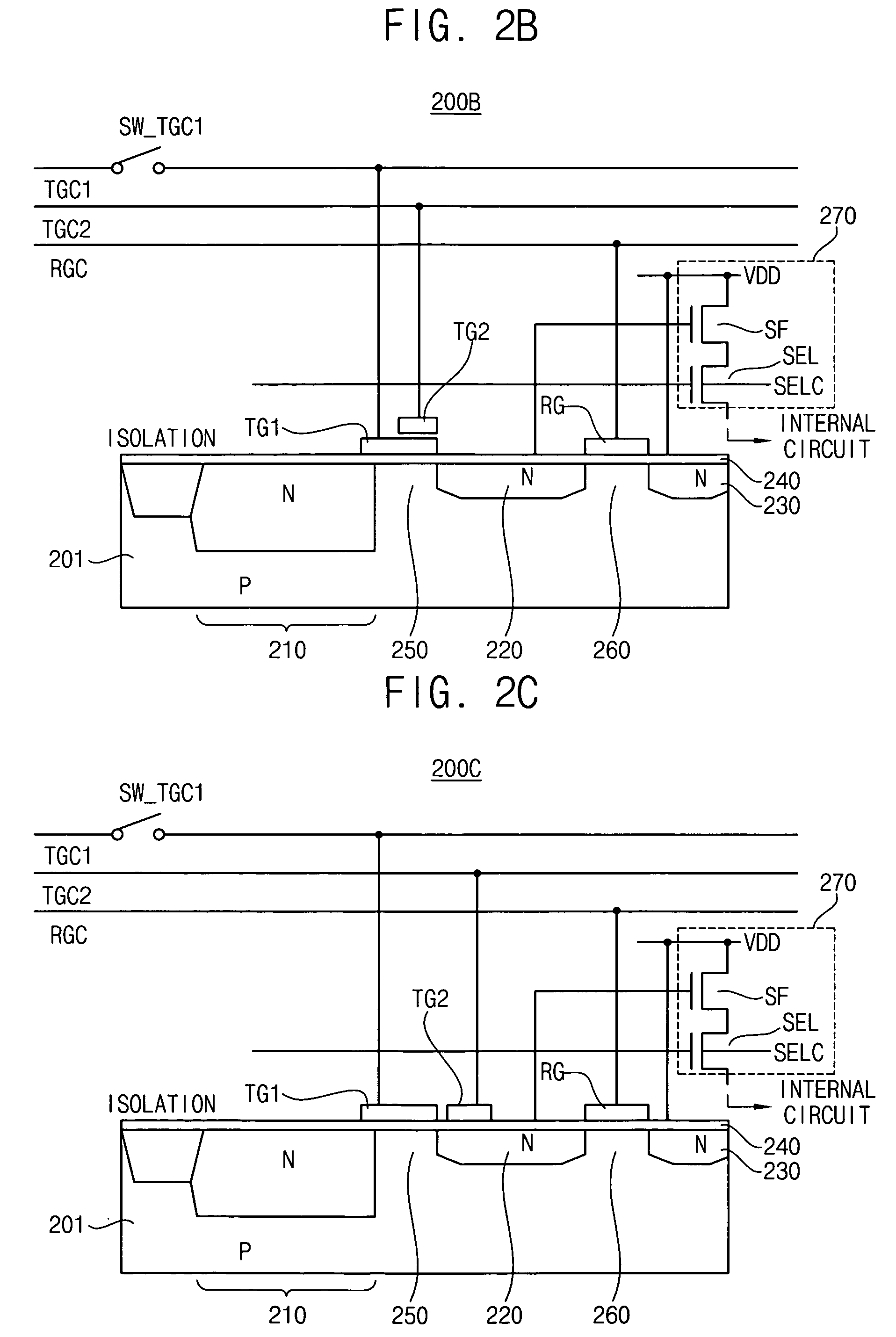

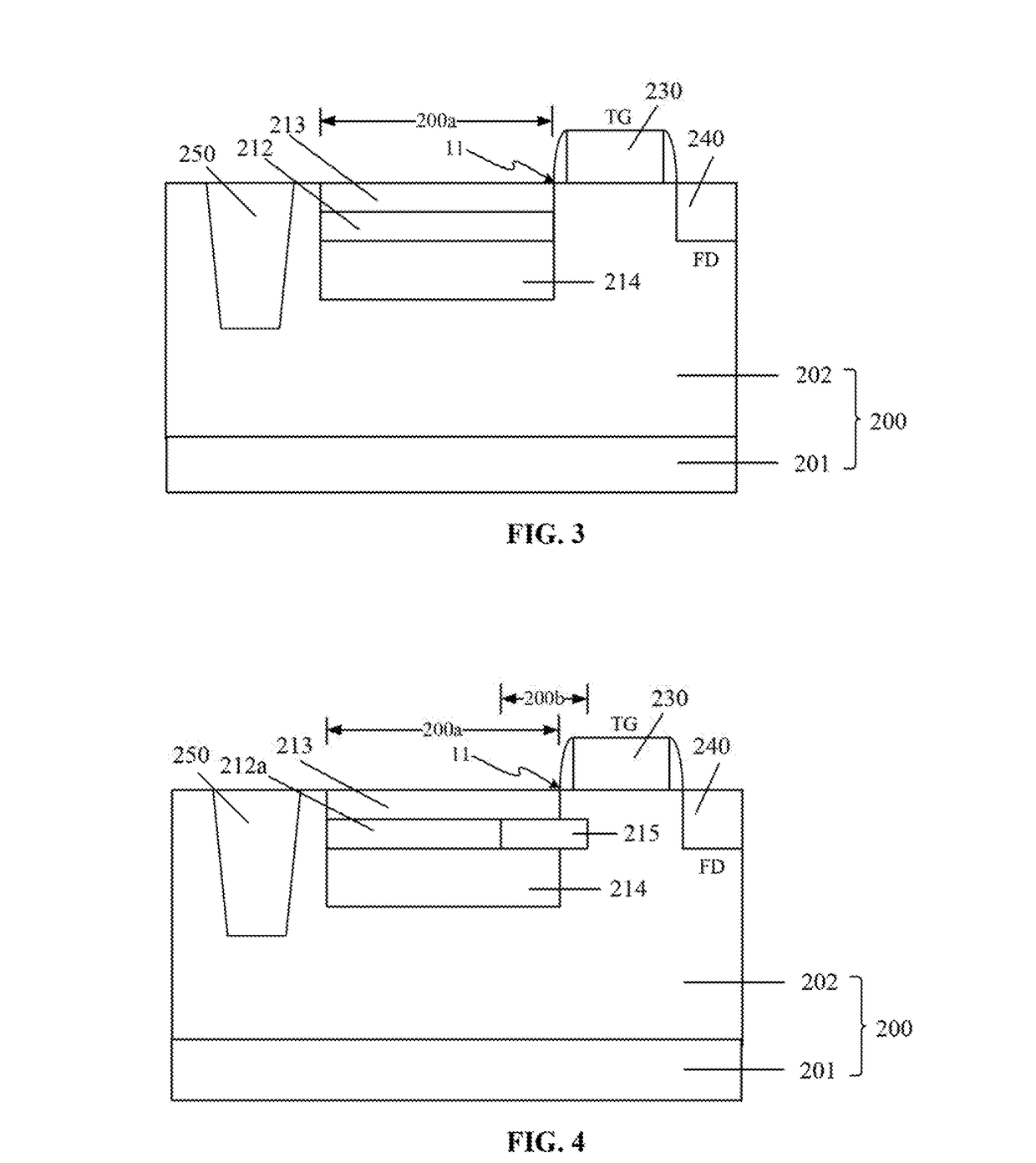

Active pixel sensor with coupled gate transfer transistor

ActiveUS20060138489A1Improve dynamic rangeReduce image lagTelevision system detailsTelevision system scanning detailsEngineeringFloating diffusion

A complementary metal-oxide semiconductor (CMOS) active pixel sensor includes a photodiode, a transfer transistor with a coupled gate, a reset transistor and a signal transfer circuit, where the photodiode generates electric charges in response to incident light, the transfer transistor transfers the electric charges integrated in the photodiode to a floating diffusion node, wherein the transfer transistor has a first transfer gate and a second transfer gate, and the first and second transfer gates have a coupled gate structure, the reset transistor resets a potential level of the floating diffusion node by a given voltage level, the signal transfer circuit transfers the potential level of the floating diffusion node to an internal circuit in response to a selection signal, and the CMOS active pixel sensor with the coupled gate may increase a capacity of the photodiode and reduce an image lag by using a voltage coupling effect of the coupled gate.

Owner:SAMSUNG ELECTRONICS CO LTD

Radiation image pickup apparatus, radiation image pickup system, their control method and their control program

InactiveUS7573038B2Lower frame rateReduce componentsTelevision system detailsSolid-state devicesFluenceRandom noise

A radiation image pickup apparatus which selectively executes a first reading operation driving a detection unit irradiated with the radiation to read a first signal value, a second reading operation driving the detection unit without being irradiated with any radiations before the first reading operation to read a second signal value, and a third reading operation driving the detection unit without being irradiated with any radiations after the first reading operation to read a third signal value, and subtracts a signal value produced by the processing of the second signal value and the third signal value from the first signal value, thereby reducing an offset component and random noises without lowering a frame rate and its control method are provided.

Owner:CANON KK

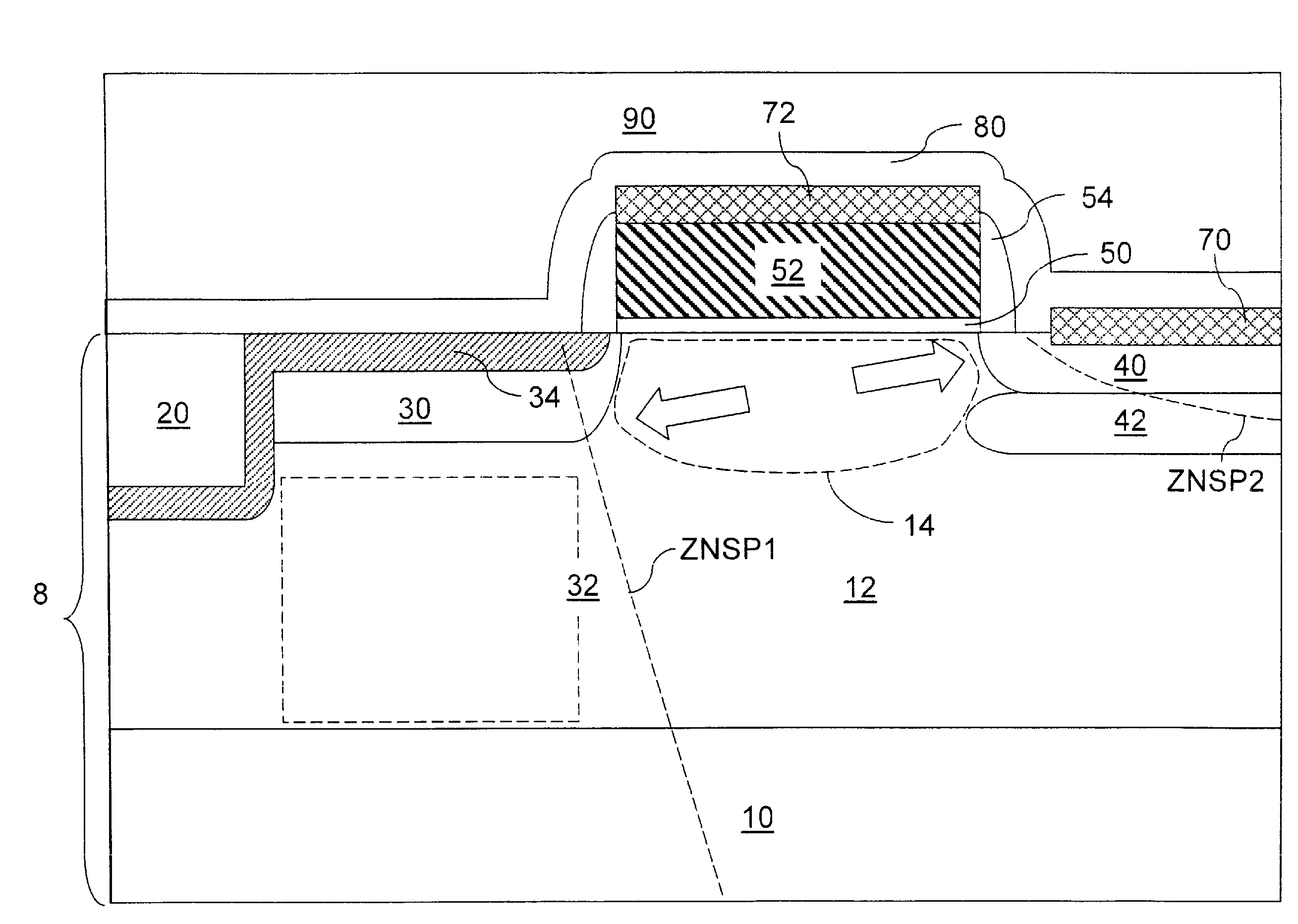

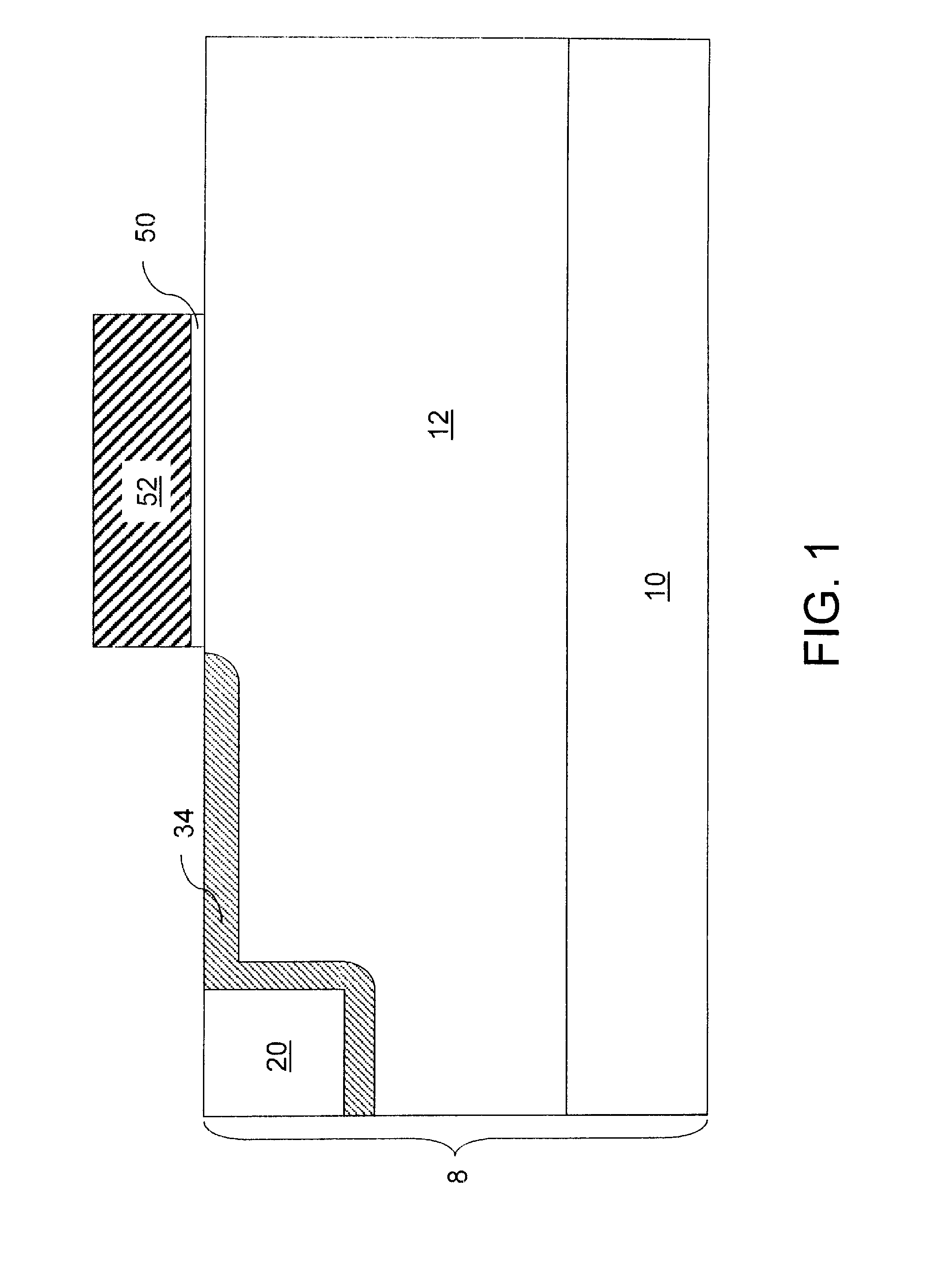

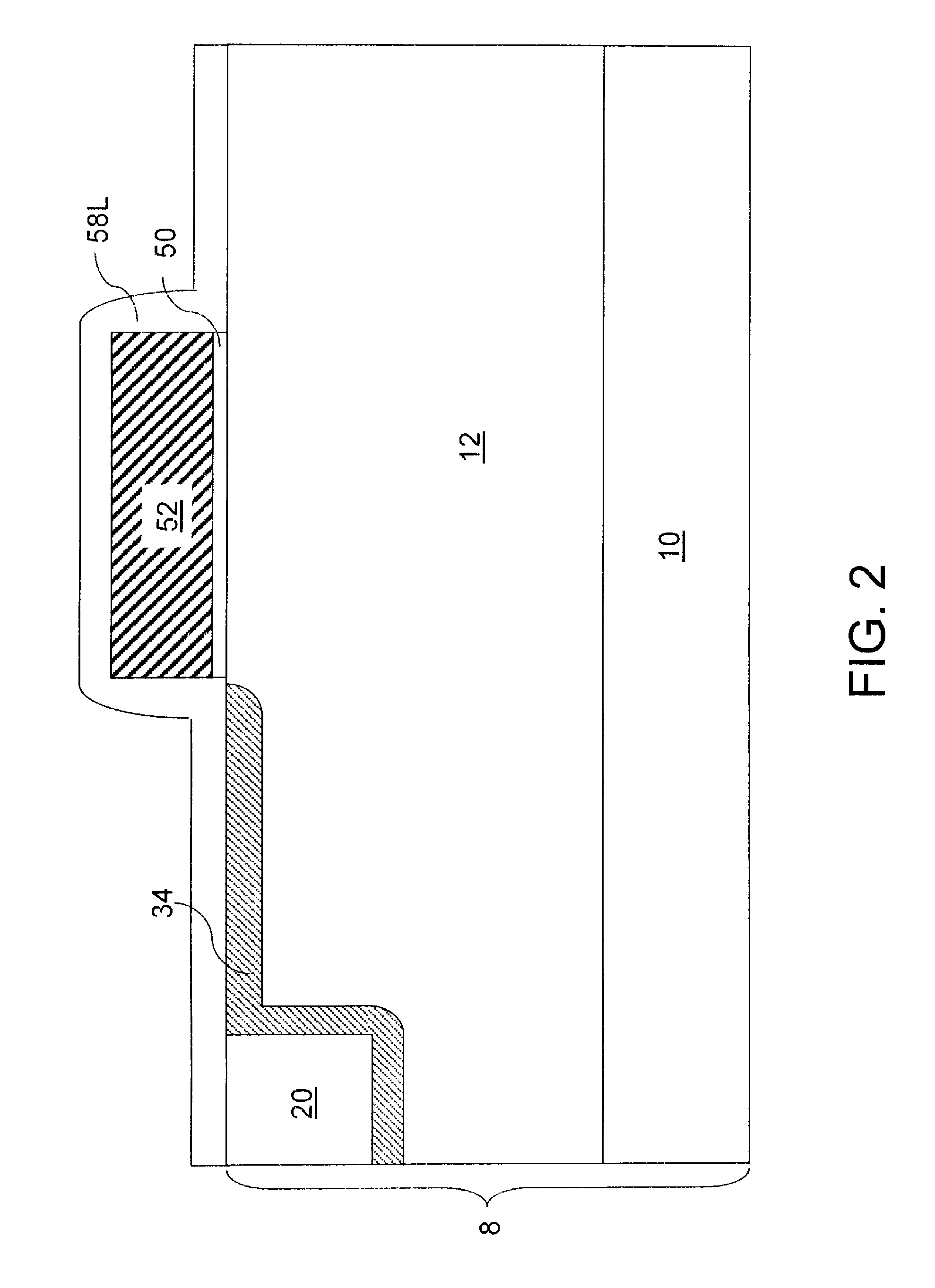

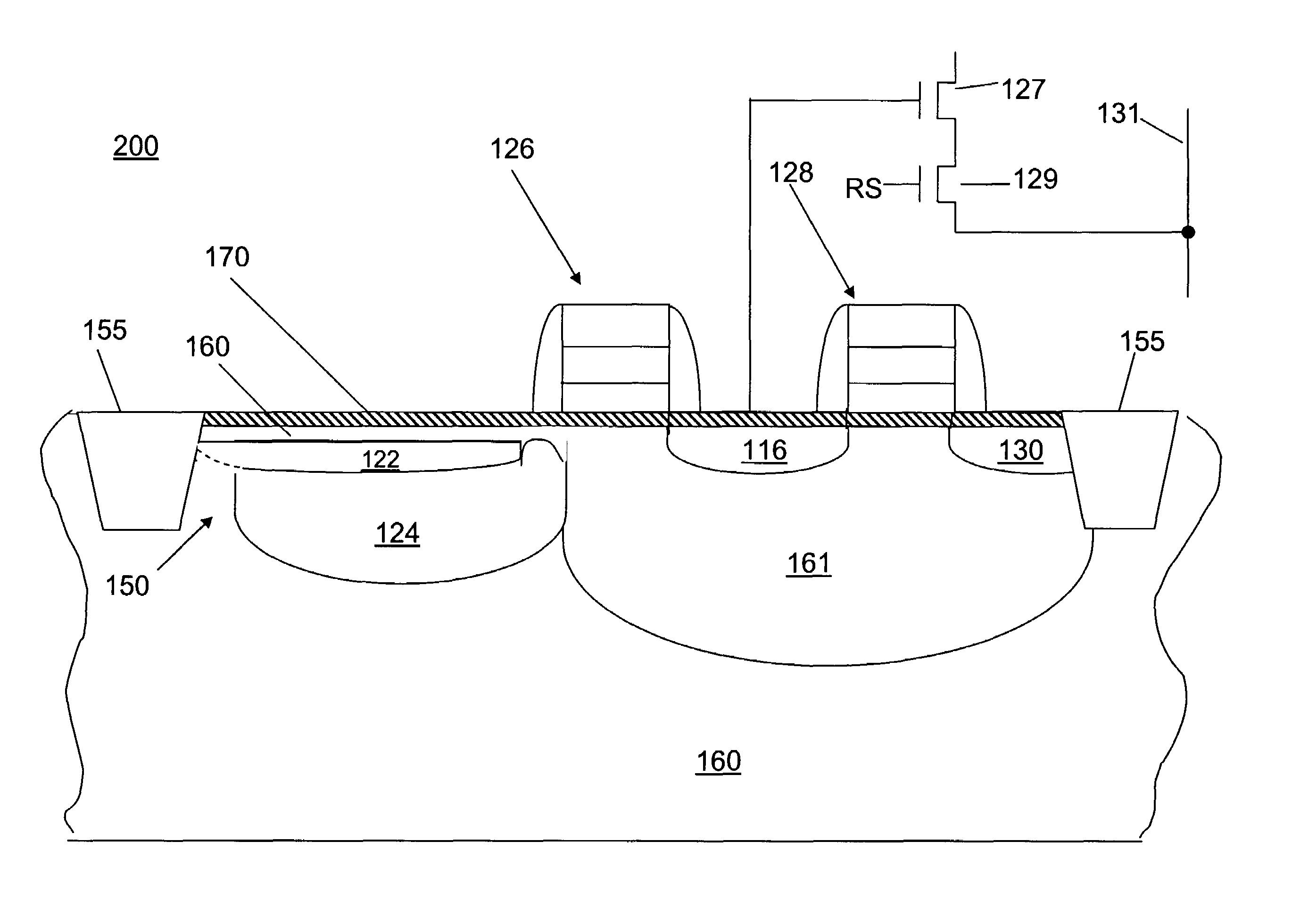

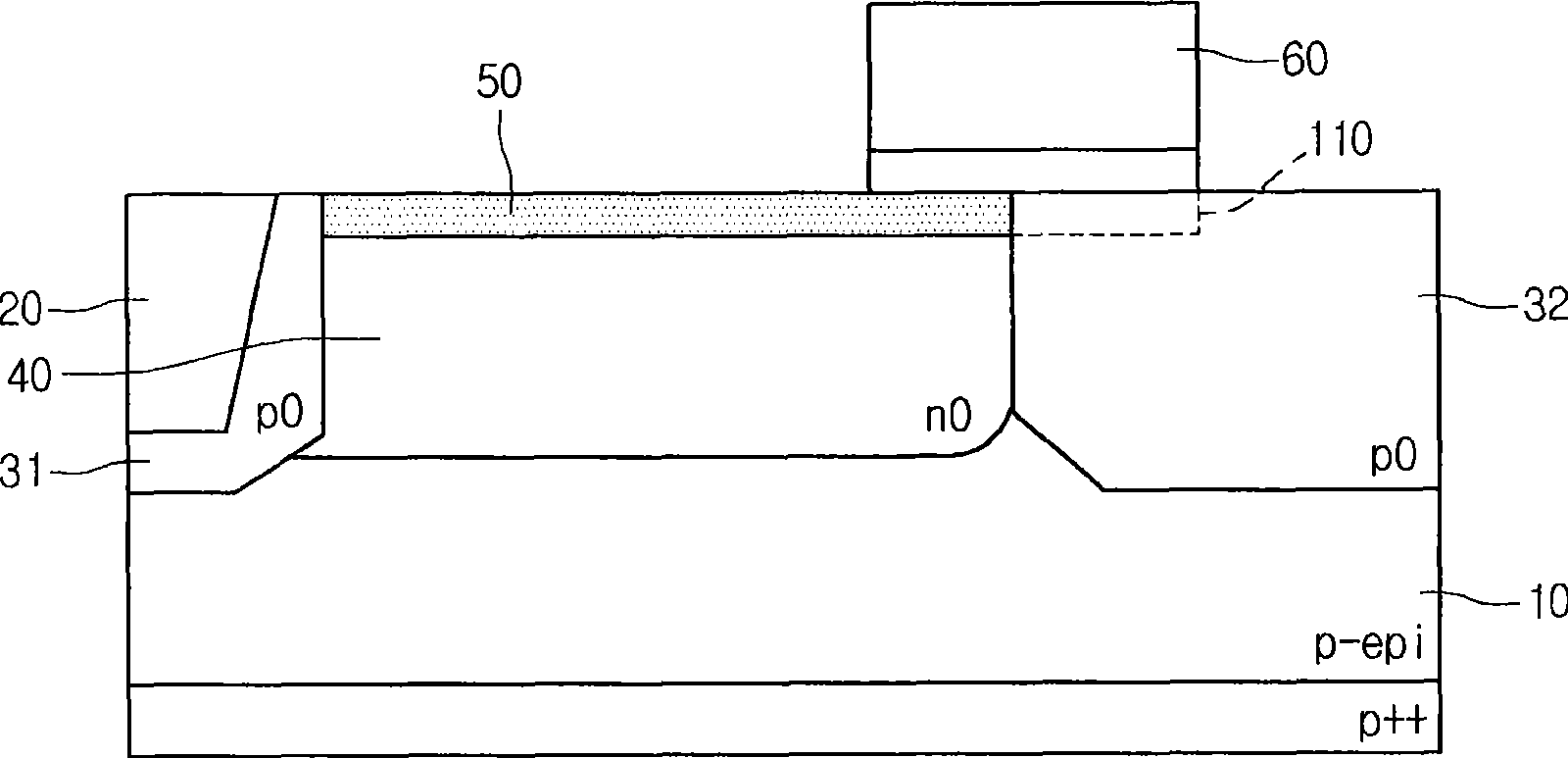

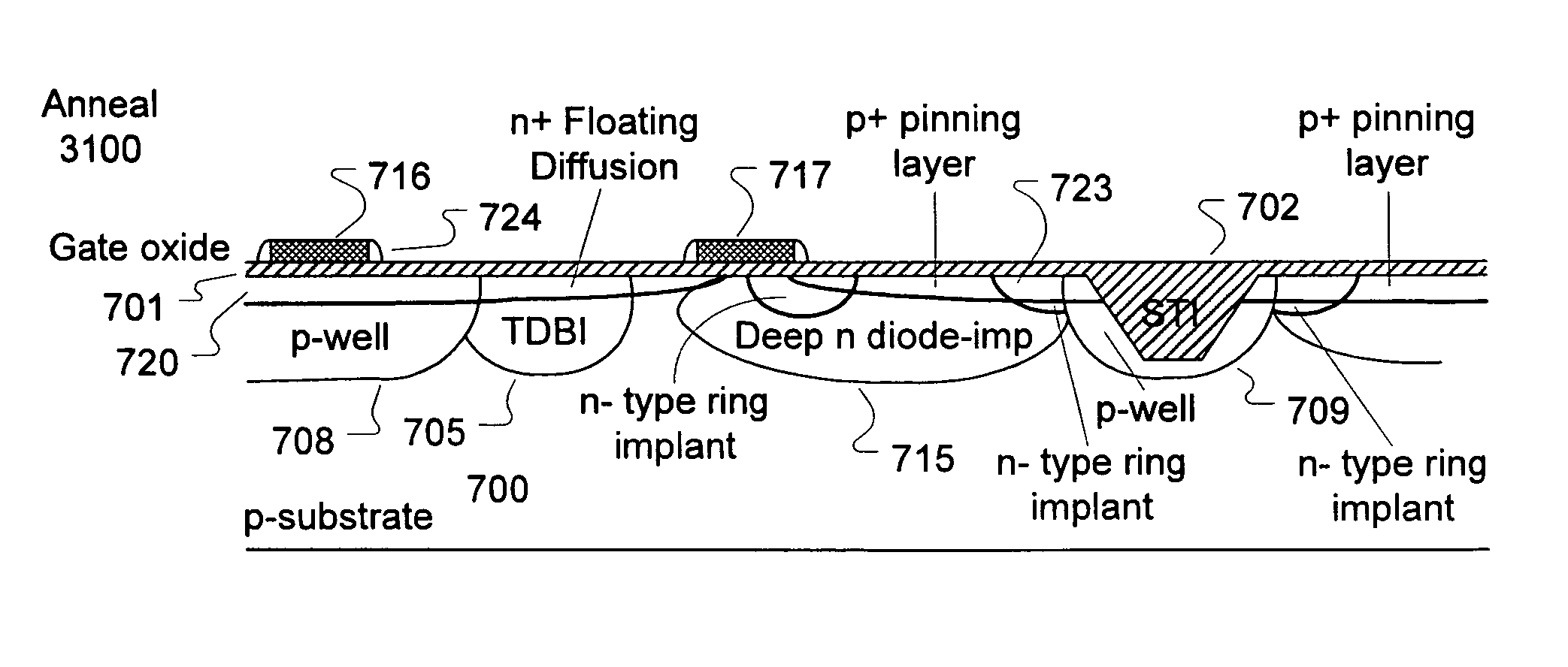

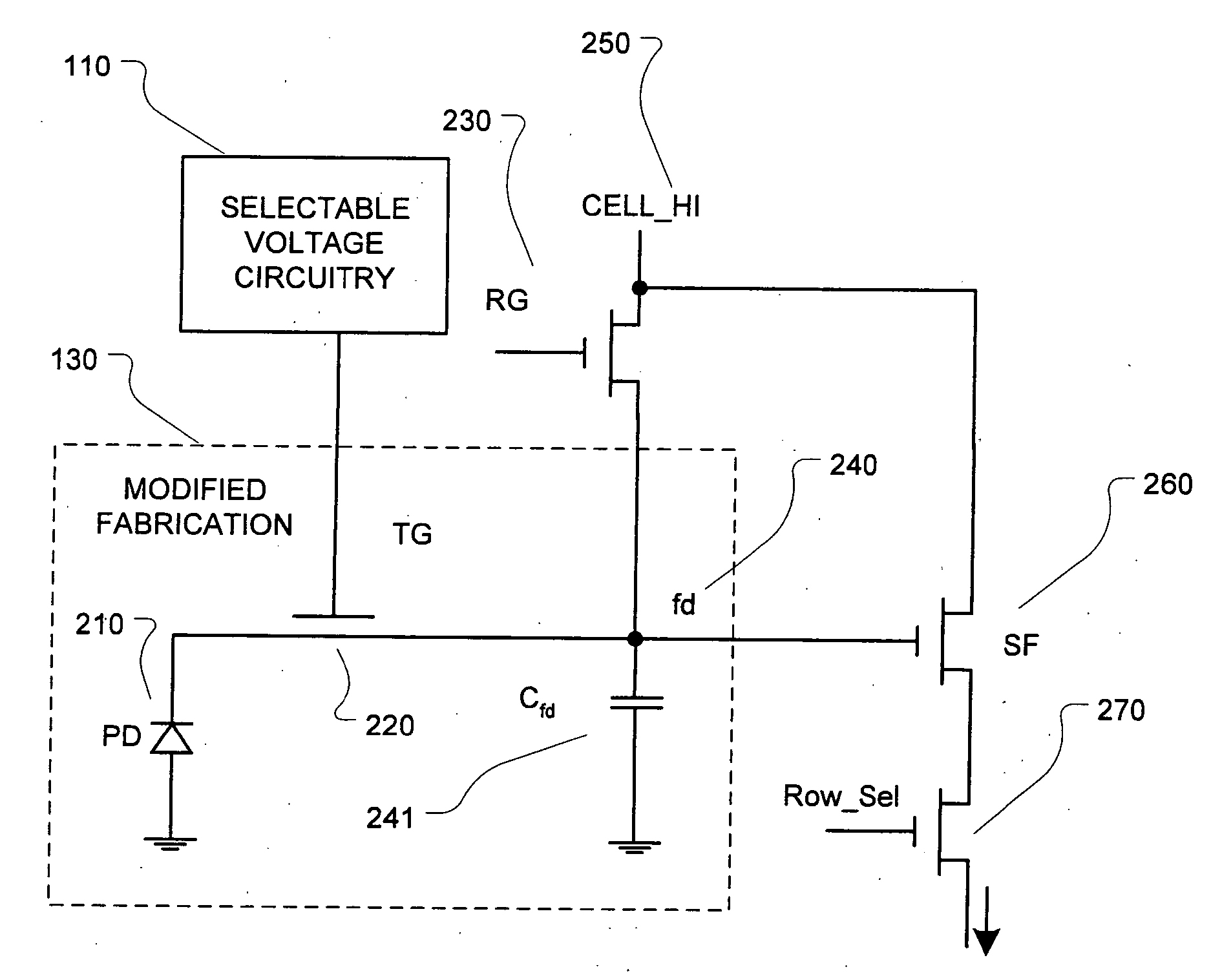

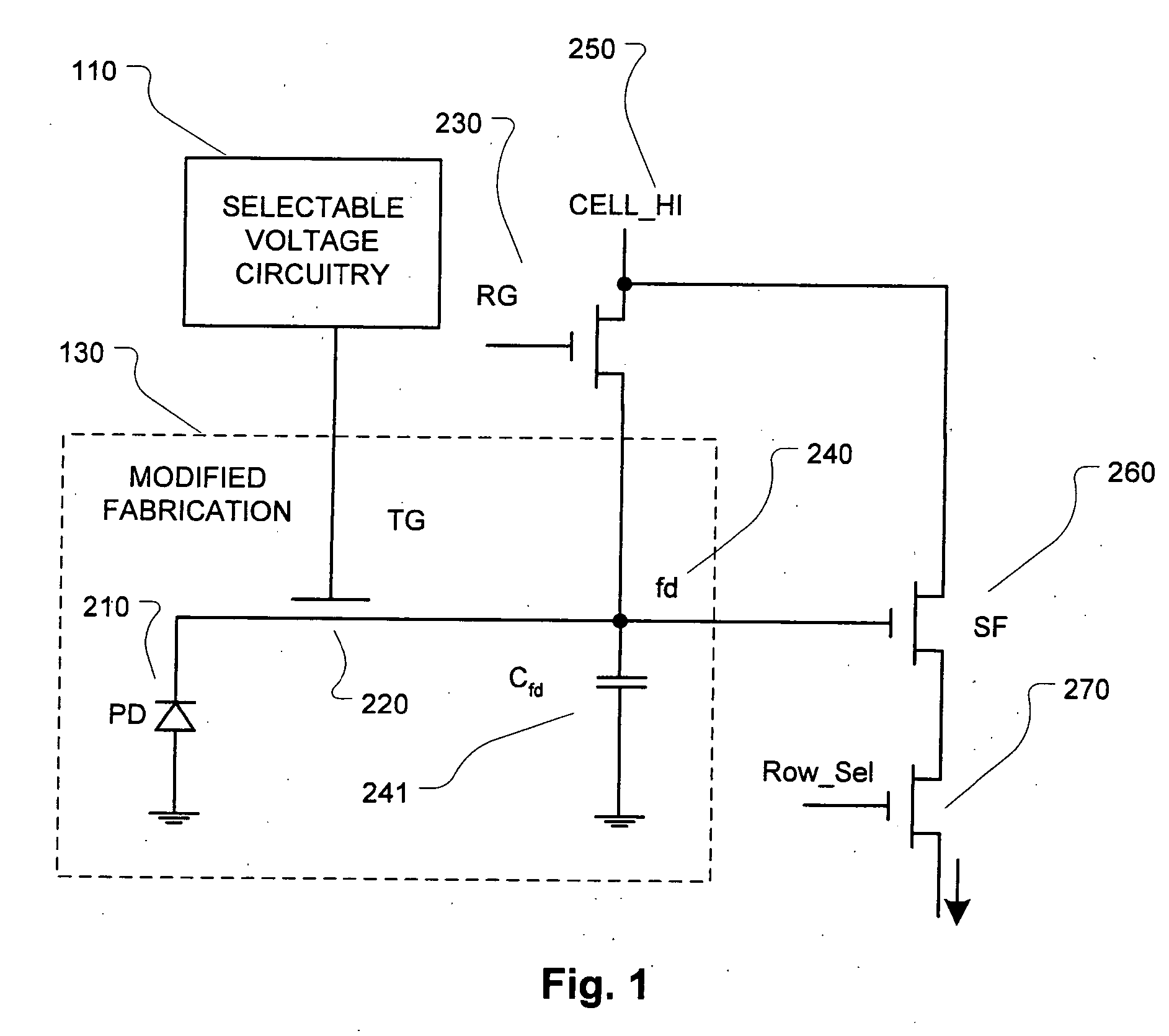

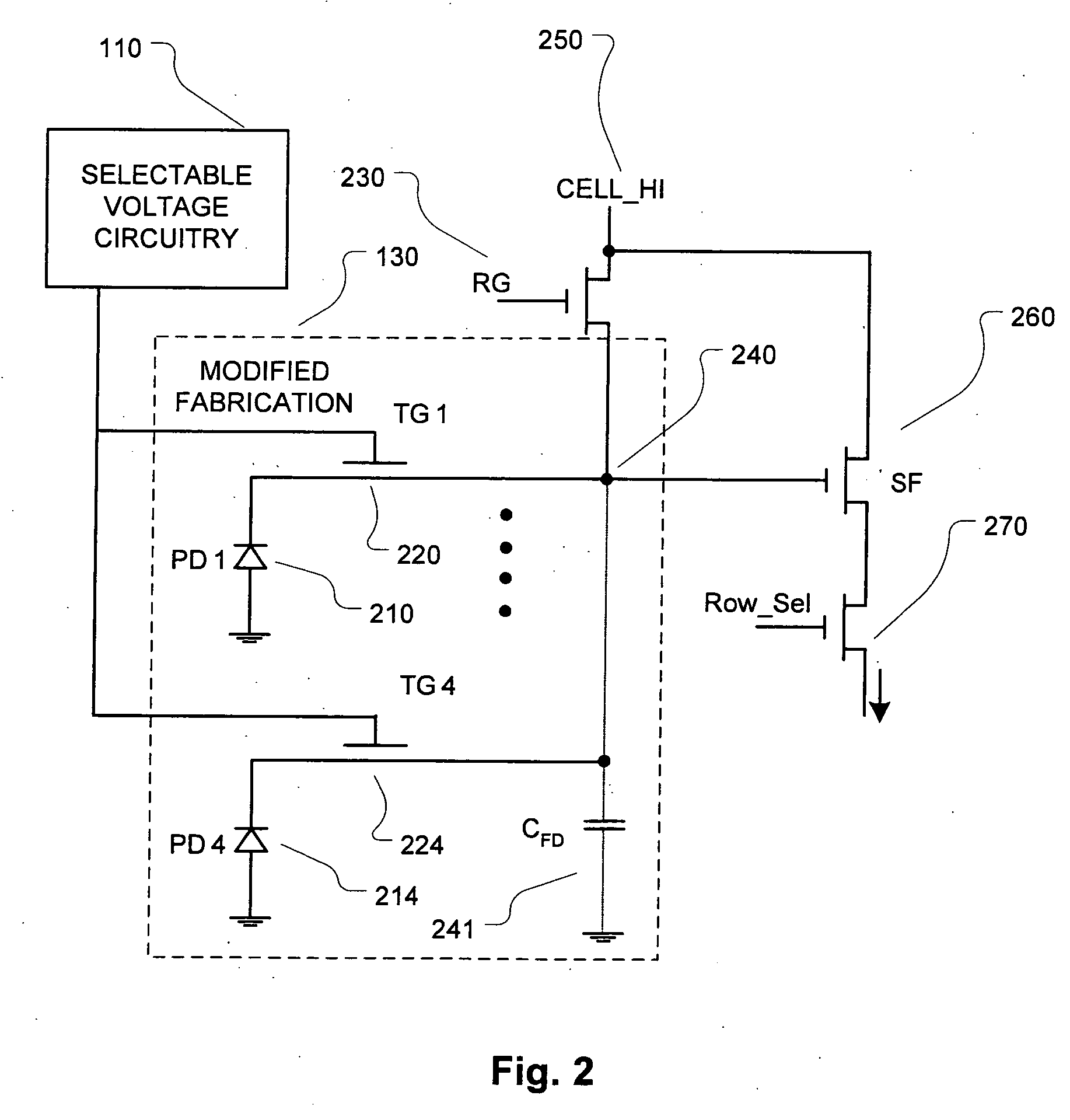

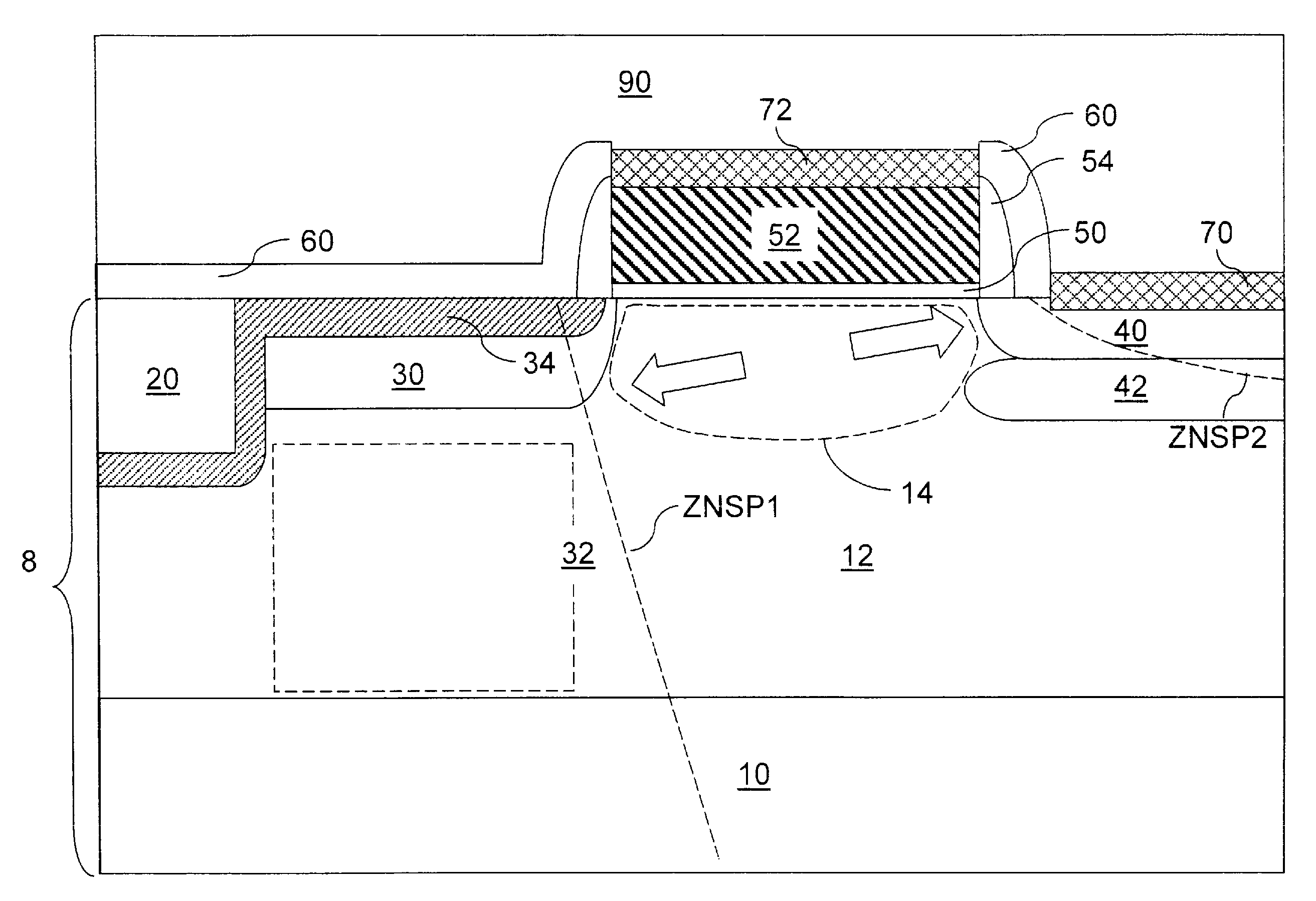

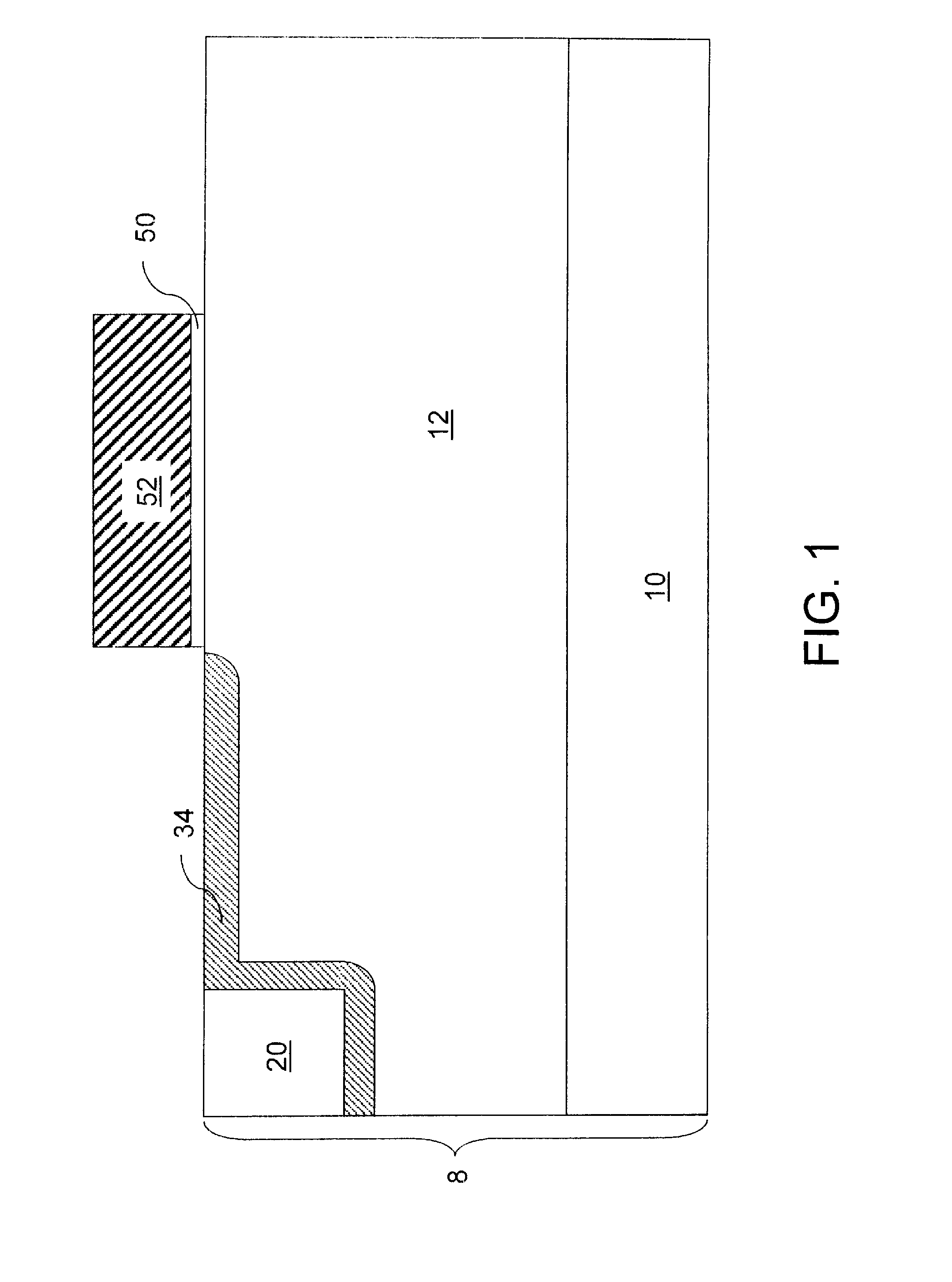

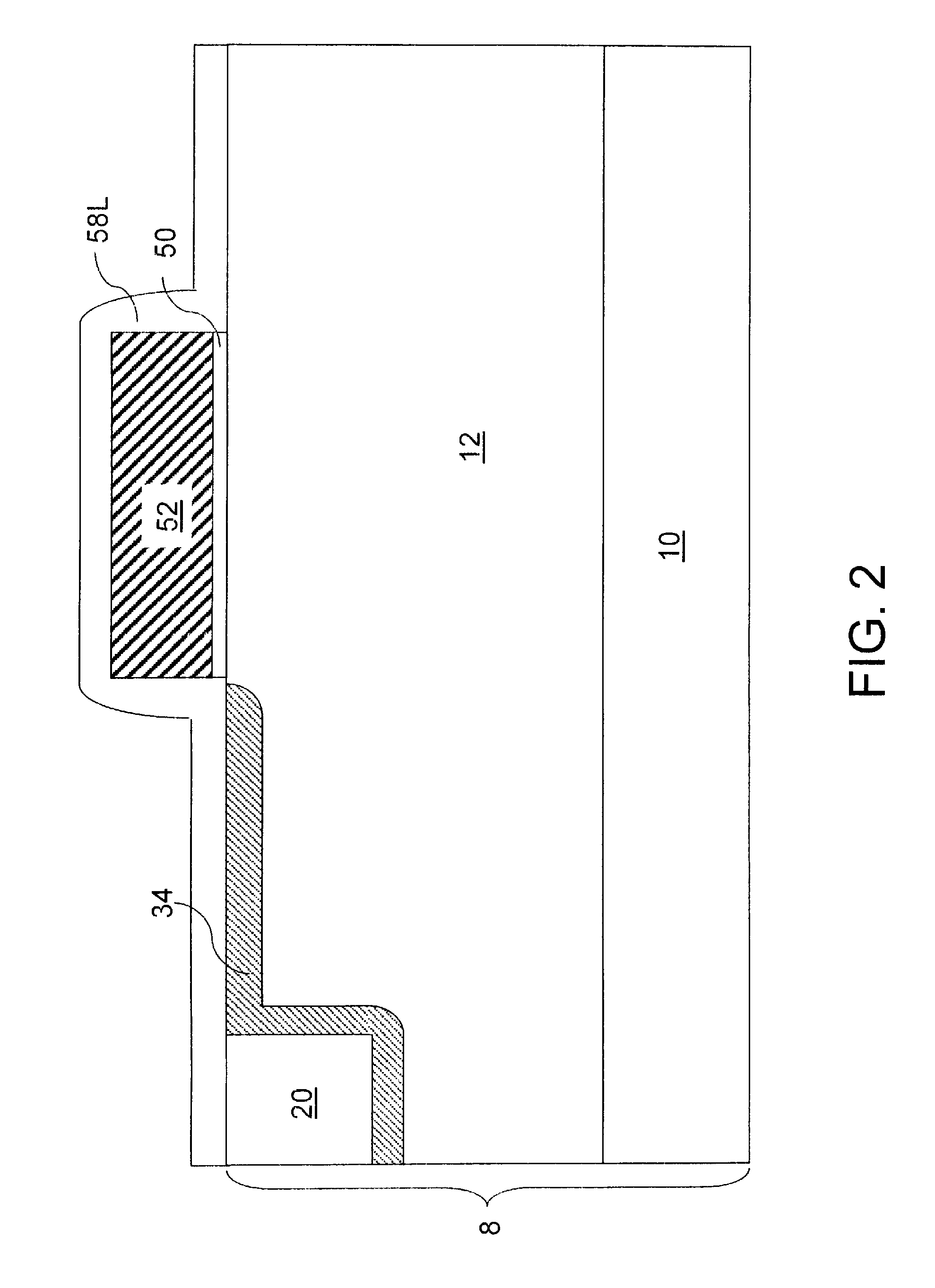

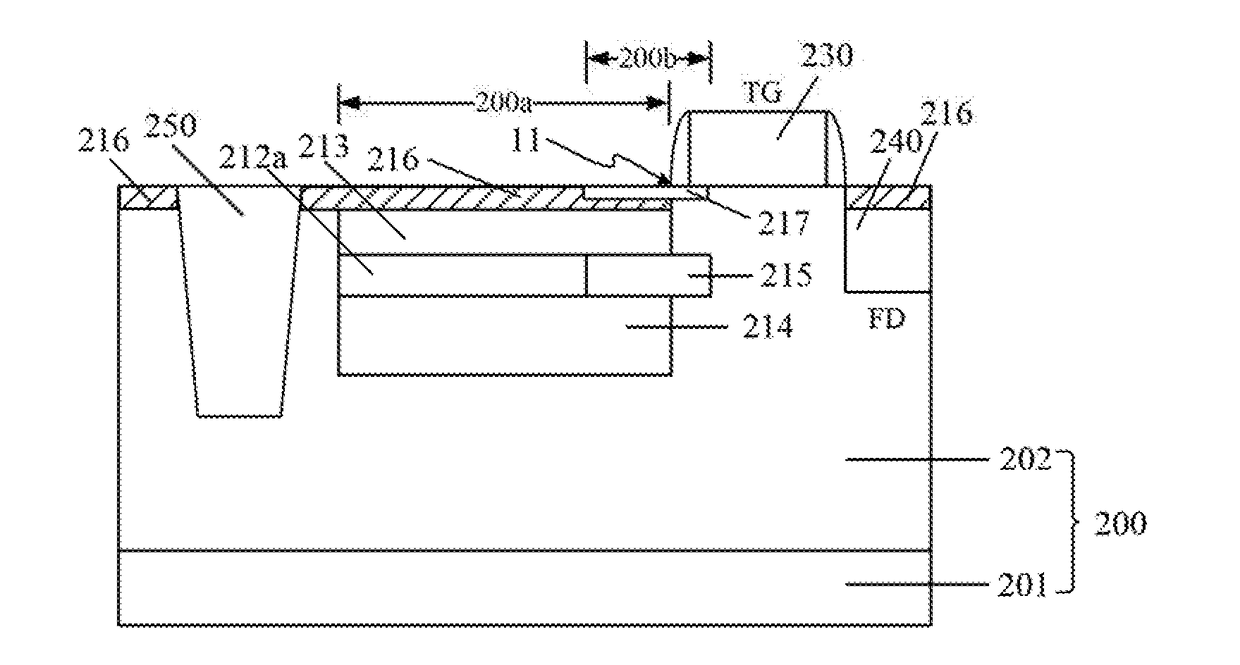

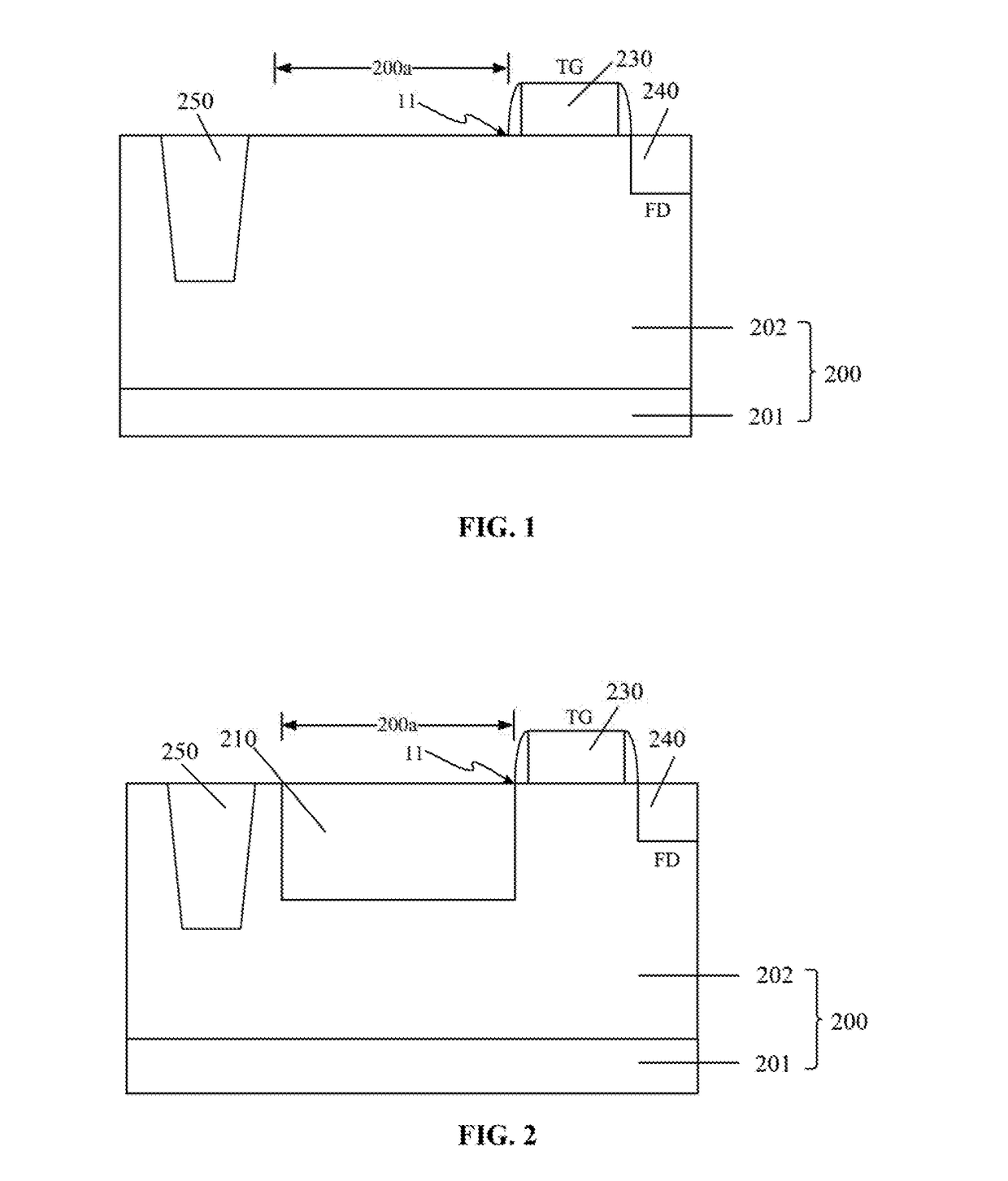

Pixel sensor with reduced image lag

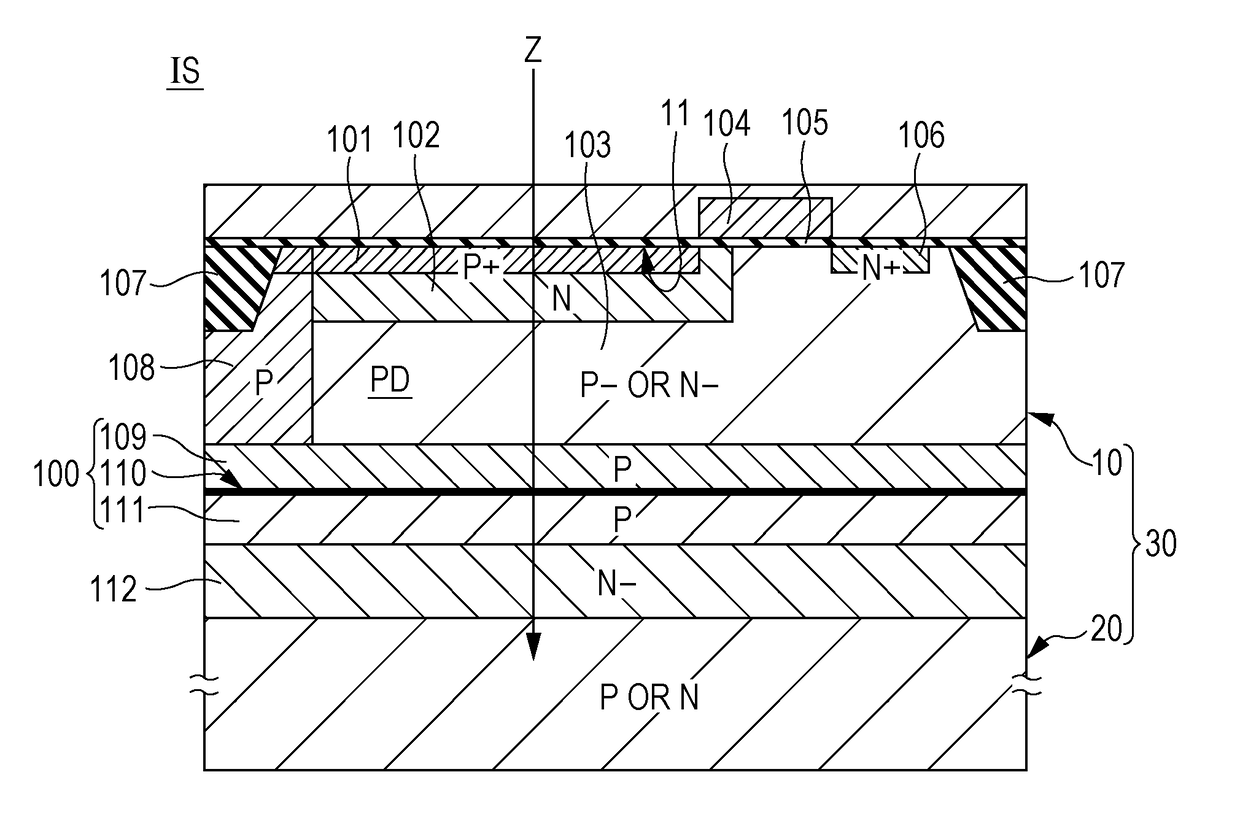

ActiveUS20090250733A1Lower a potential barrierLower potential barrierSolid-state devicesSemiconductor/solid-state device manufacturingCMOSLag

A tensile-stress-generating structure is formed above a gate electrode in a CMOS image sensor to apply a normal tensile stress between a charge collection well of a photodiode, which is also a source region of a transfer transistor, and a floating drain in the direction connecting the source region and the floating drain. The tensile stress lowers the potential barrier between the source region and the body of the transfer transistor to effect a faster and more through transfer of the electrical charges in the source region to the floating drain. Image lag is thus reduced in the CMOS image sensor. Further, charge capacity of the source region is also enhanced due to the normal tensile stress applied to the source region.

Owner:GLOBALFOUNDRIES US INC

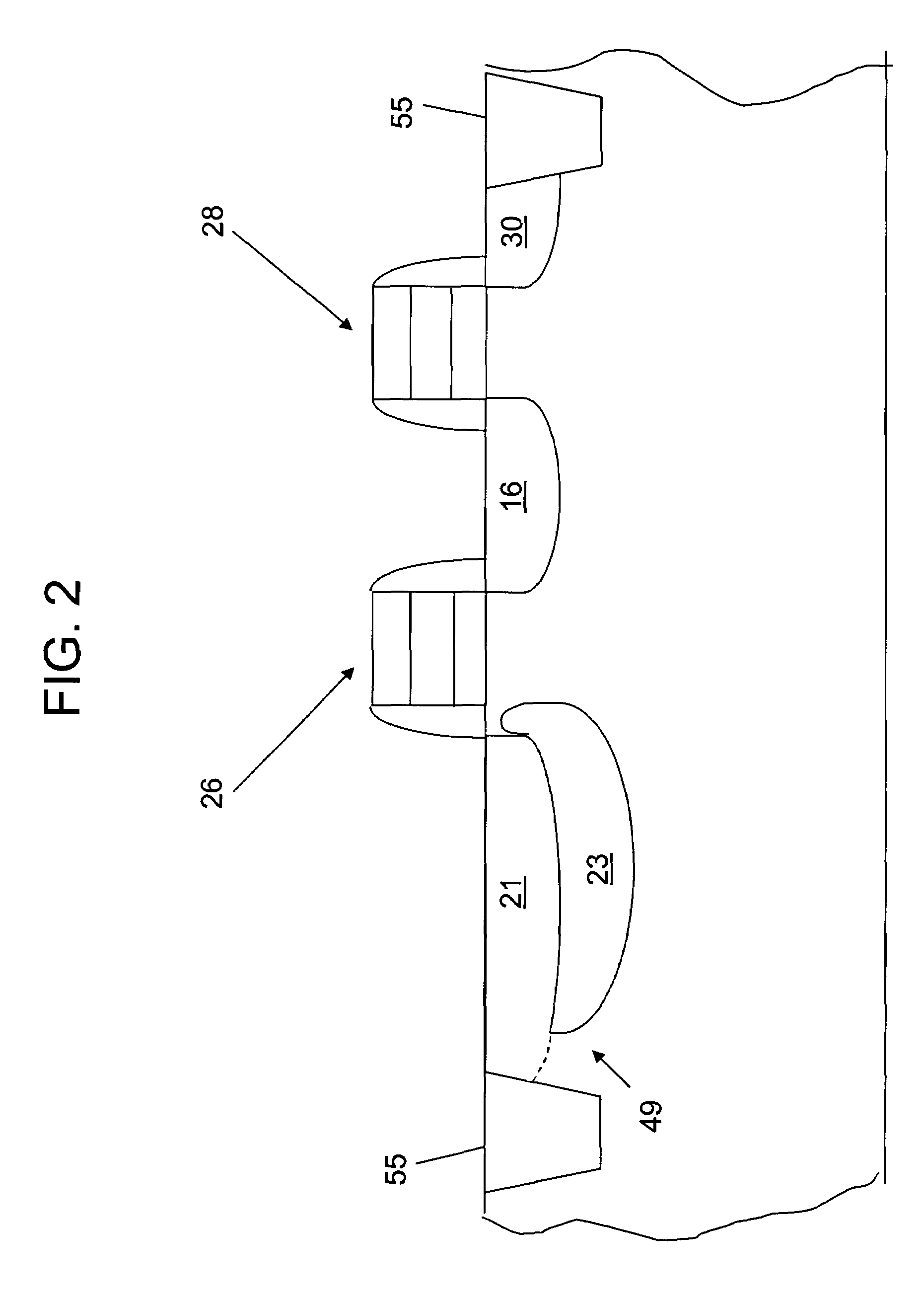

Pixel with strained silicon layer for improving carrier mobility and blue response in imagers

ActiveUS7164182B2Improve responseImprove charge transfer efficiencySolid-state devicesSemiconductor/solid-state device manufacturingCharge carrier mobilityStrained silicon

An imager having a pixel cell having an associated strained silicon layer. The strained silicon layer increases charge transfer efficiency, decreases image lag, and improves blue response in imaging devices.

Owner:MICRON TECH INC

Method and apparatus for removing electrons from CMOS sensor photodetectors

InactiveUS20070152292A1Reduce noiseLow costTelevision system detailsSolid-state devicesCMOS sensorPhotovoltaic detectors

An improved CMOS sensor integrated circuit is disclosed, along with methods of making the circuit and computer readable descriptions of the circuit.

Owner:RE SECURED NETWORKS LLC

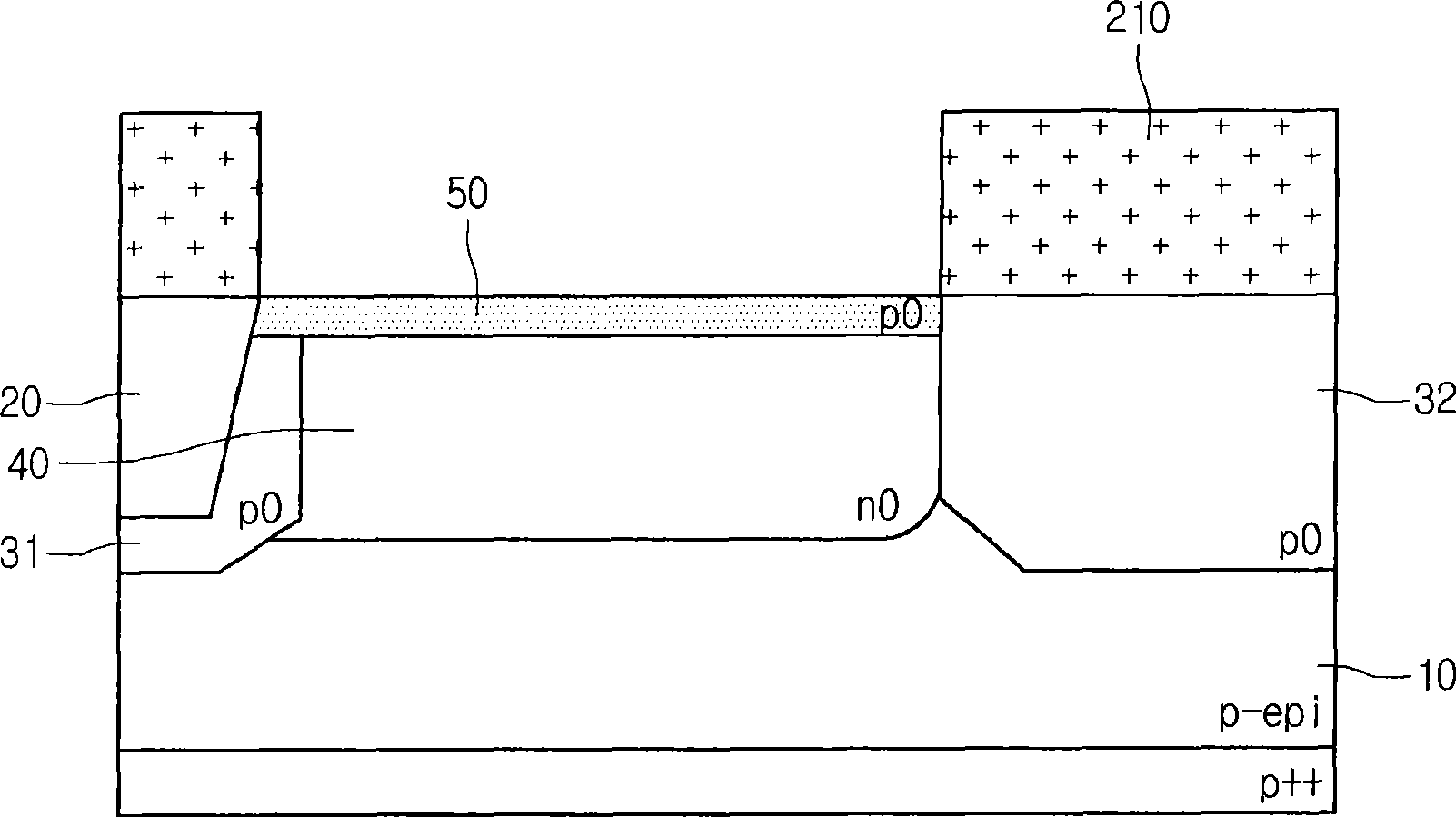

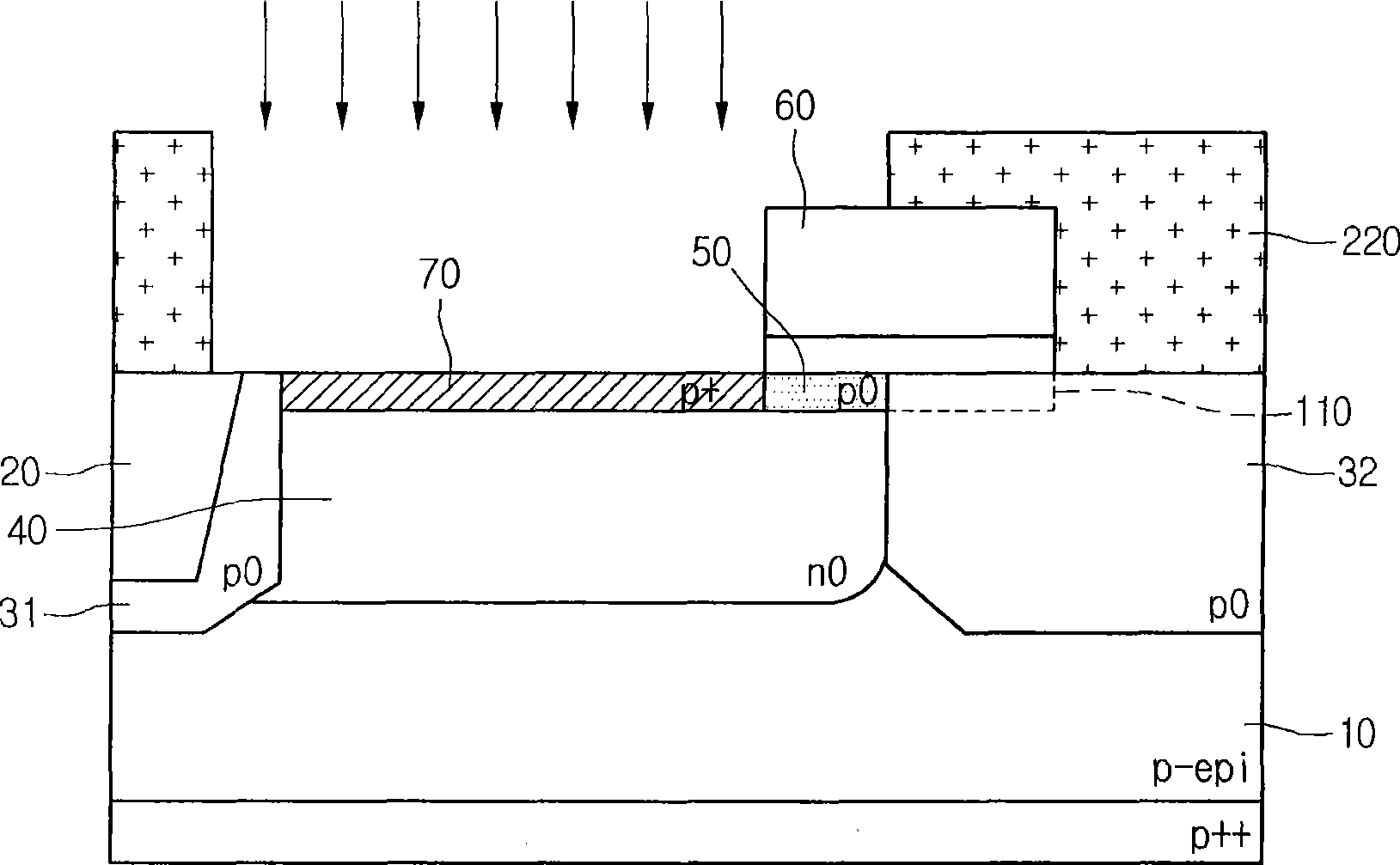

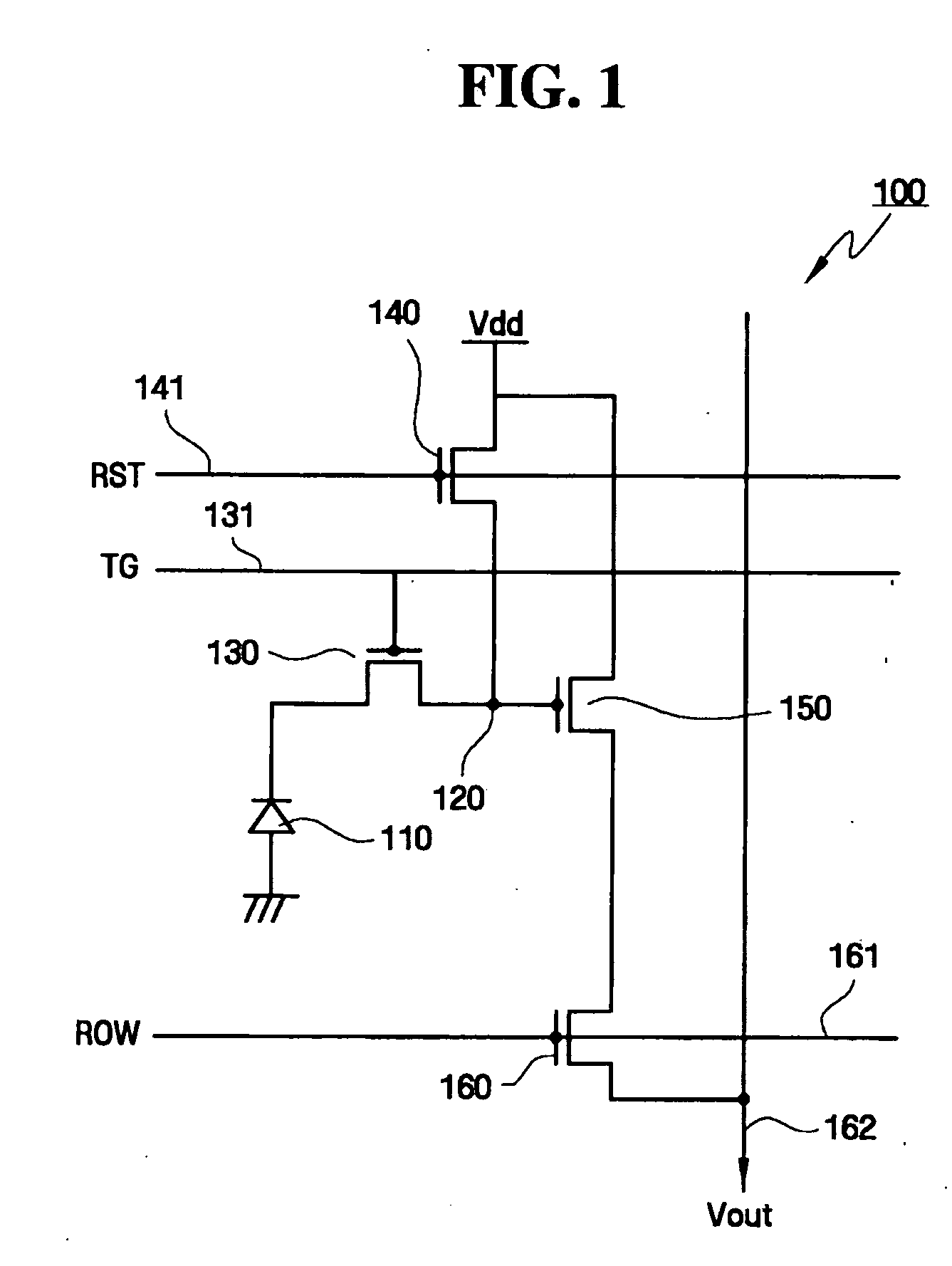

Image sensor and method for manufacturing the sensor

InactiveCN101471360AReduce noiseReduce image lagSolid-state devicesSemiconductor/solid-state device manufacturingFloating diffusionPhotodiode

An image sensor and manufacturing method thereof are provided. The image sensor can include a gate on a semiconductor substrate, first and second p-type doping areas below the gate, a third p-type doping area adjacent to the first p-type doping area, and a fourth p-type doping area adjacent to the third p-type doping area. An n-type doping area can be provided in the semiconductor substrate such that at least a portion of the n-type doping area is disposed below the first, third, and fourth p-type doping areas. A floating diffusion area can be provided adjacent to the second p-type doping area. The invention can prevent the electrons of the channel area from flowing back toward the photodiode, so that noise and image lagging can be reduced.

Owner:DONGBU HITEK CO LTD

CMOS image sensor

ActiveUS20070102739A1Reducing clock feedthroughReduce image lagSolid-state devicesDiodeCMOSLight sensing

A CMOS image sensor includes a semiconductor substrate; a pinned photodiode formed in a light-sensing region of the semiconductor substrate, the pinned photodiode comprising a charge-accumulating diffusion region and a surface pinning diffusion region overlying the charge-accumulating diffusion region; a transfer transistor, wherein the transfer transistor has a transfer gate comprising a protruding first gate segment with a first gate dimension and a second gate segment with a second gate dimension that is smaller than the first gate dimension. A first overlapping portion between the protruding first gate segment and the charge-accumulating diffusion region is greater than a second overlapping portion between the second gate segment and the charge-accumulating diffusion region.

Owner:SK HYNIX INC

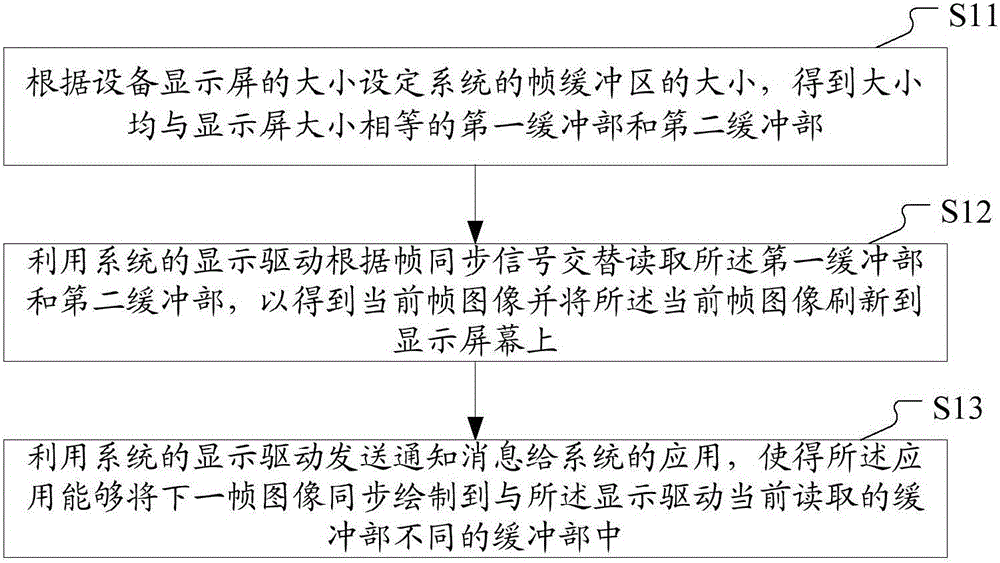

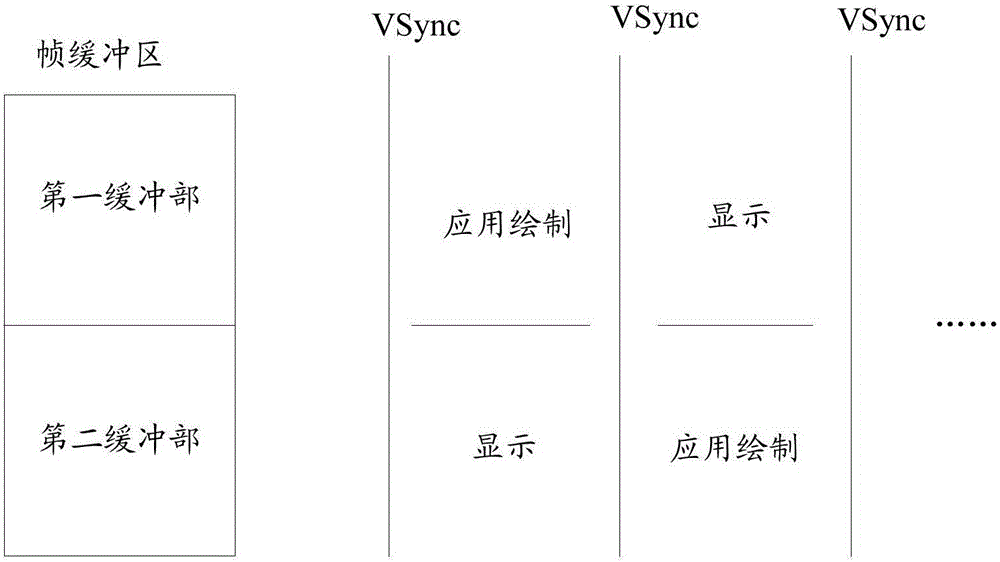

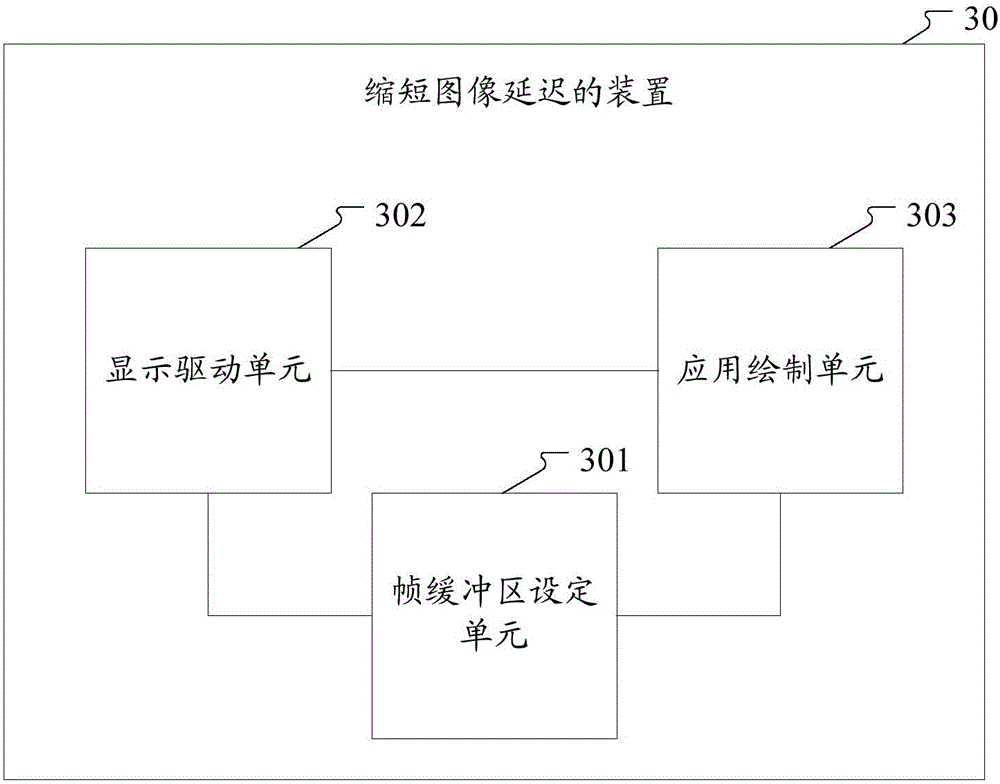

Method and device for shortening image delay

ActiveCN106098022AReduce processing timeAvoid tearingCathode-ray tube indicatorsFrame synchronizationReal-time computing

The invention discloses a method and device for shortening image delay. The method comprises steps of setting a size of a frame buffer area of a system according to a size of a device display screen, obtaining a first buffer part and a second buffer part which have same sizes with size of the display screen, using a display driver of the system to alternatively read the first buffer part and the second buffer part according to a frame synchronization signal in order to obtain a current frame image and refresh the current frame image onto the display screen, and using the display driver of the system to transmit notification information to applications of the system and making the application synchronically draw the image of the next frame into a buffer part different from the buffer part that the display driver reads currently. The method and the device arrange the first buffer part and the second buffer part, so that the display driver can alternatively display contents of the two buffer parts, and the application can directly draw the image into the two buffer parts so as to shorten delay of the image from rendering to display and optimize user experience.

Owner:BEIJING PICO TECH

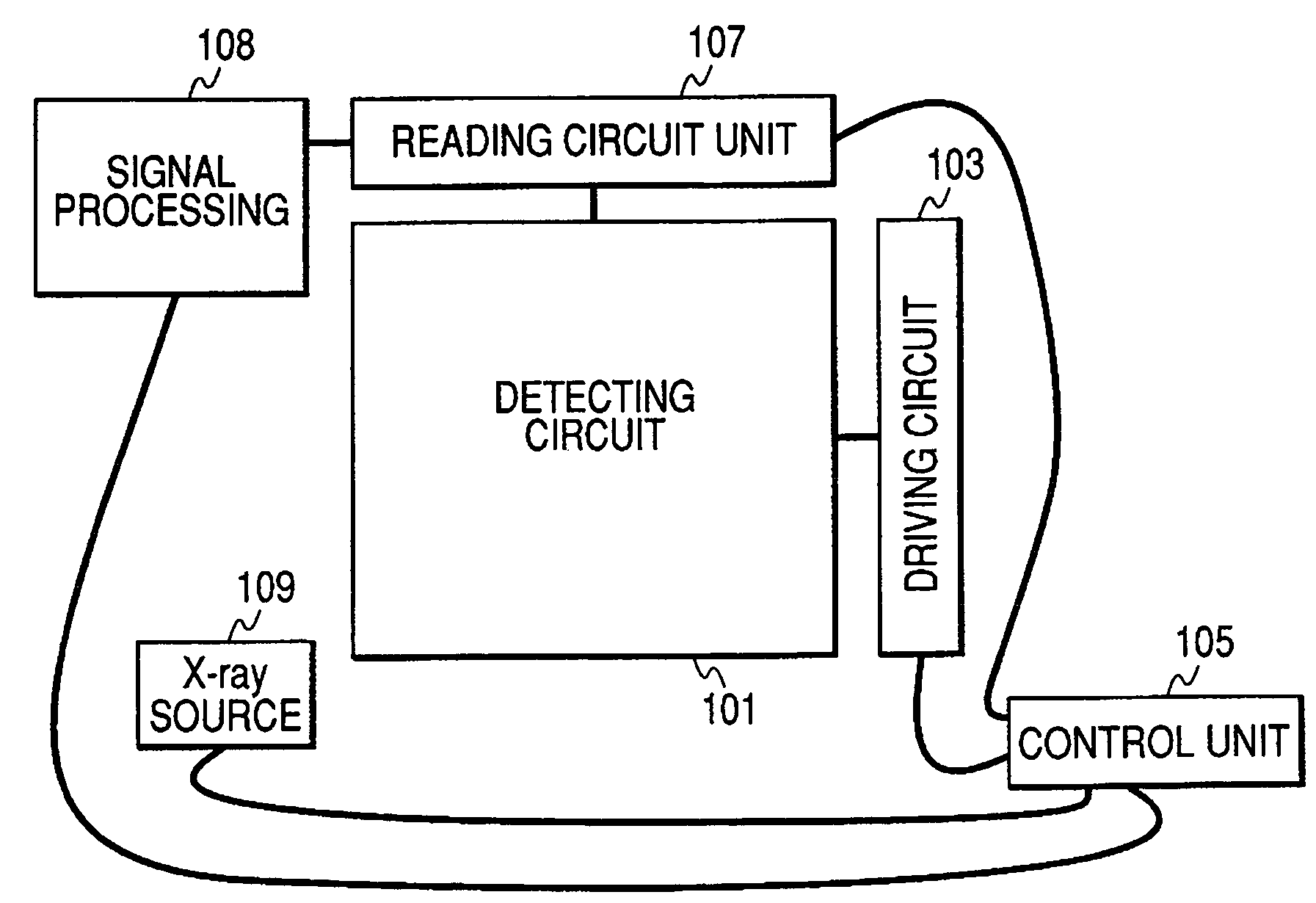

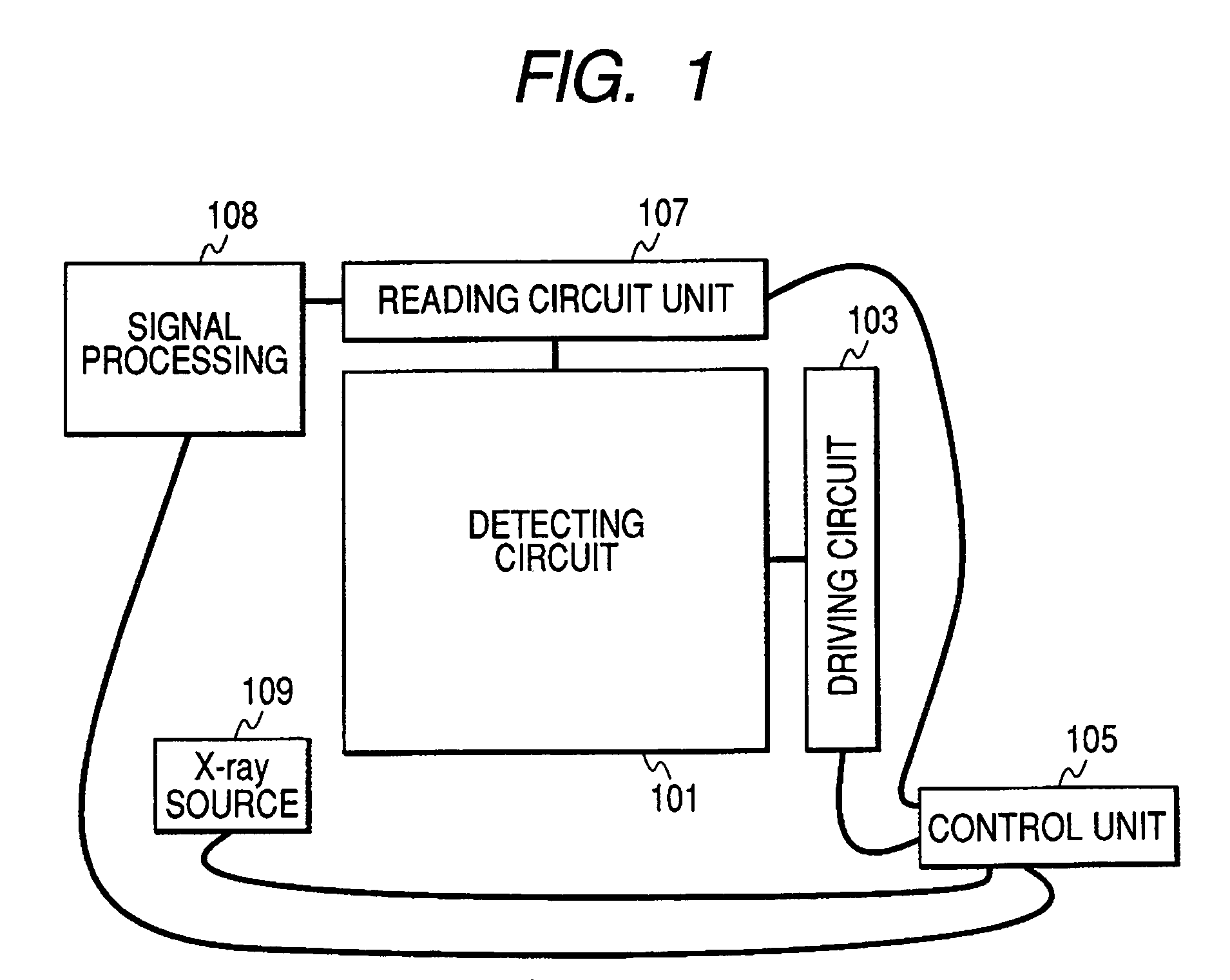

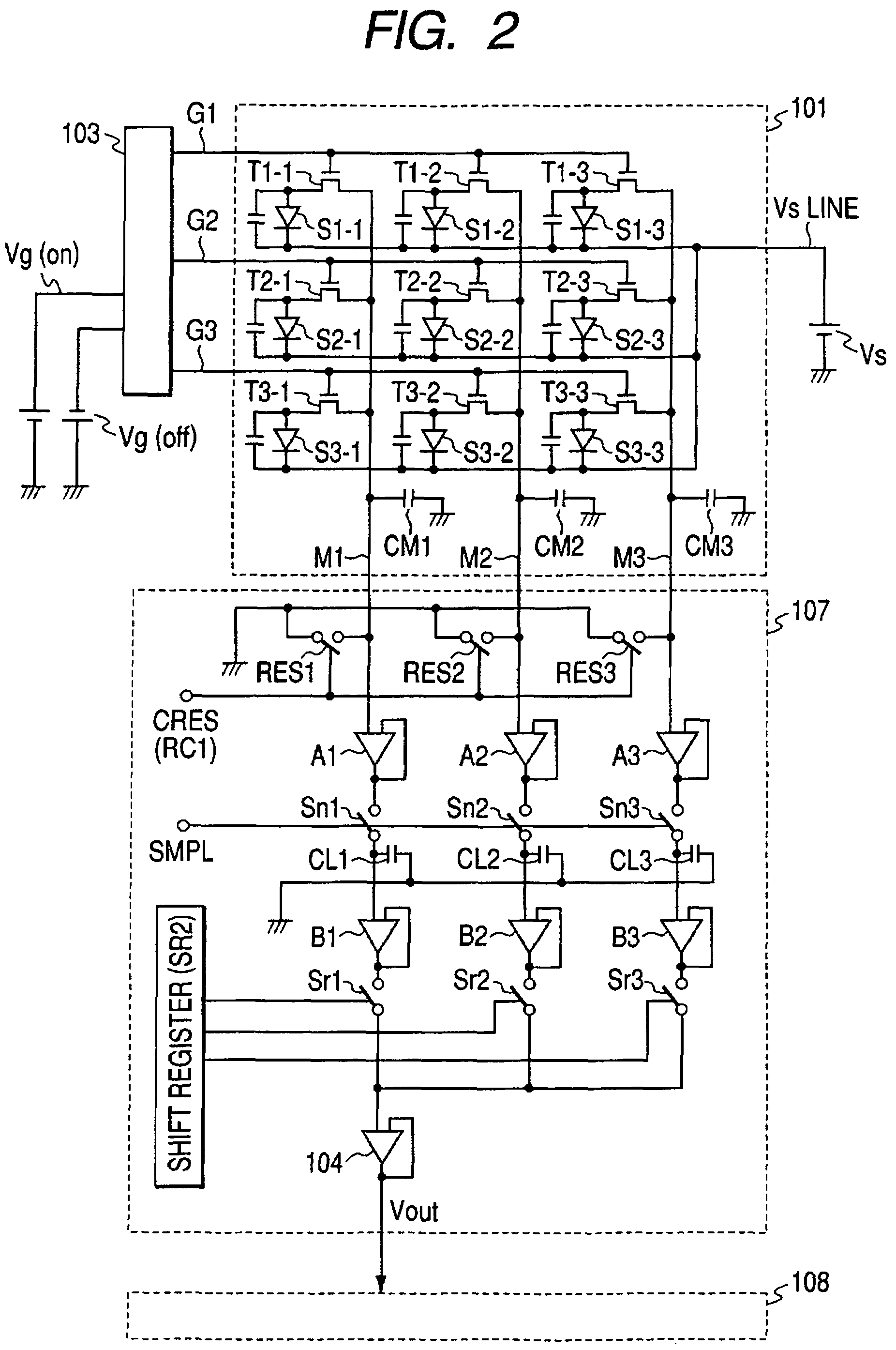

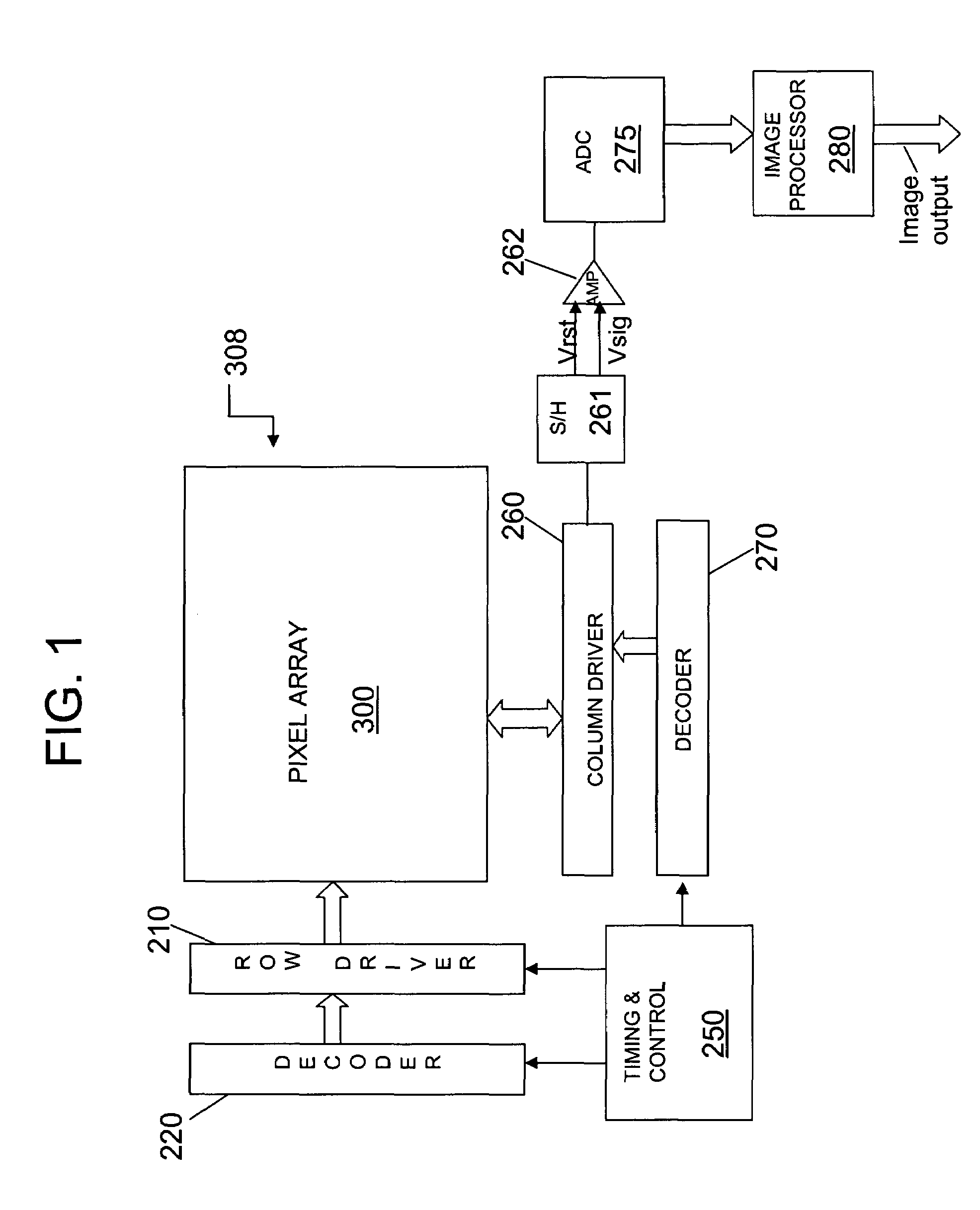

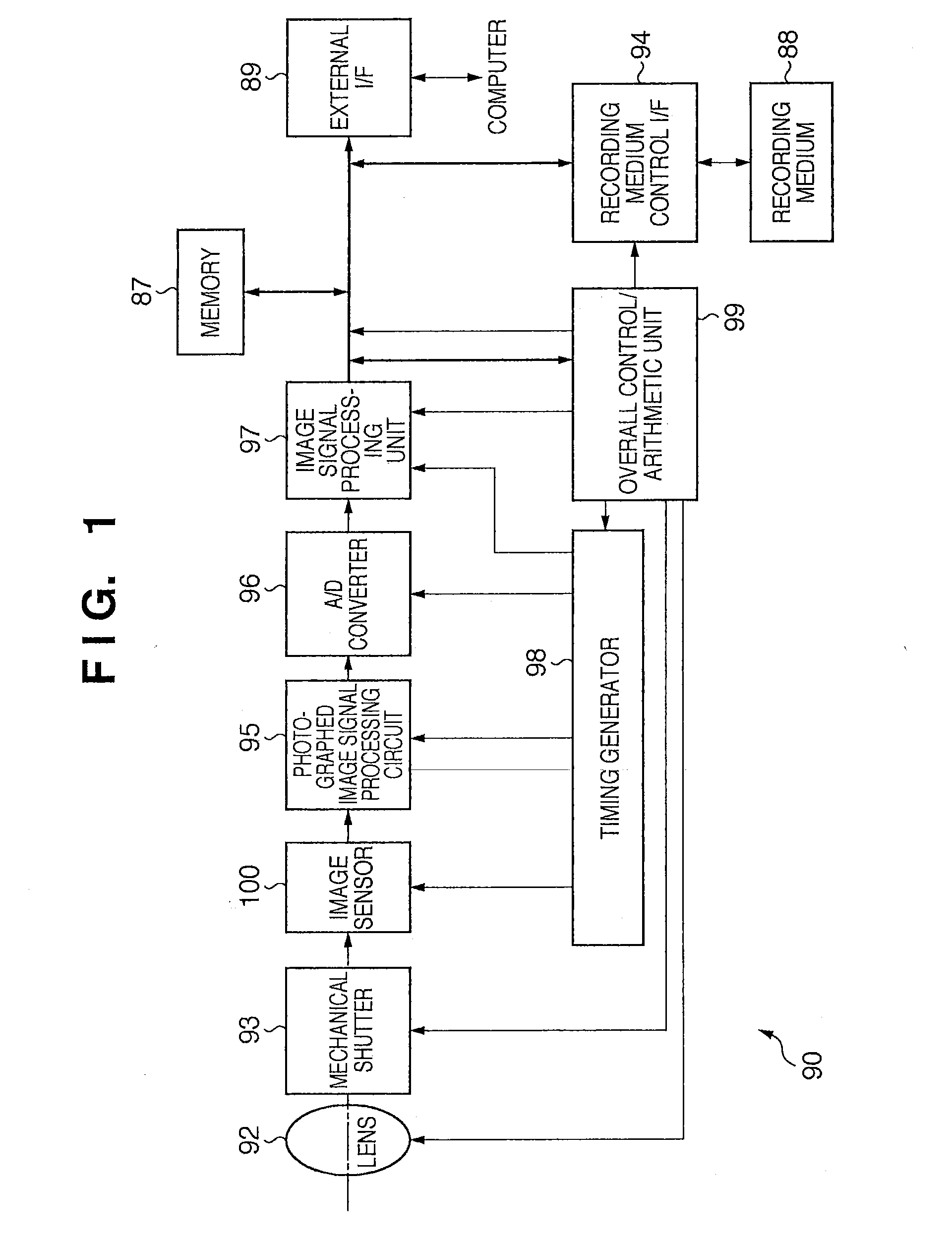

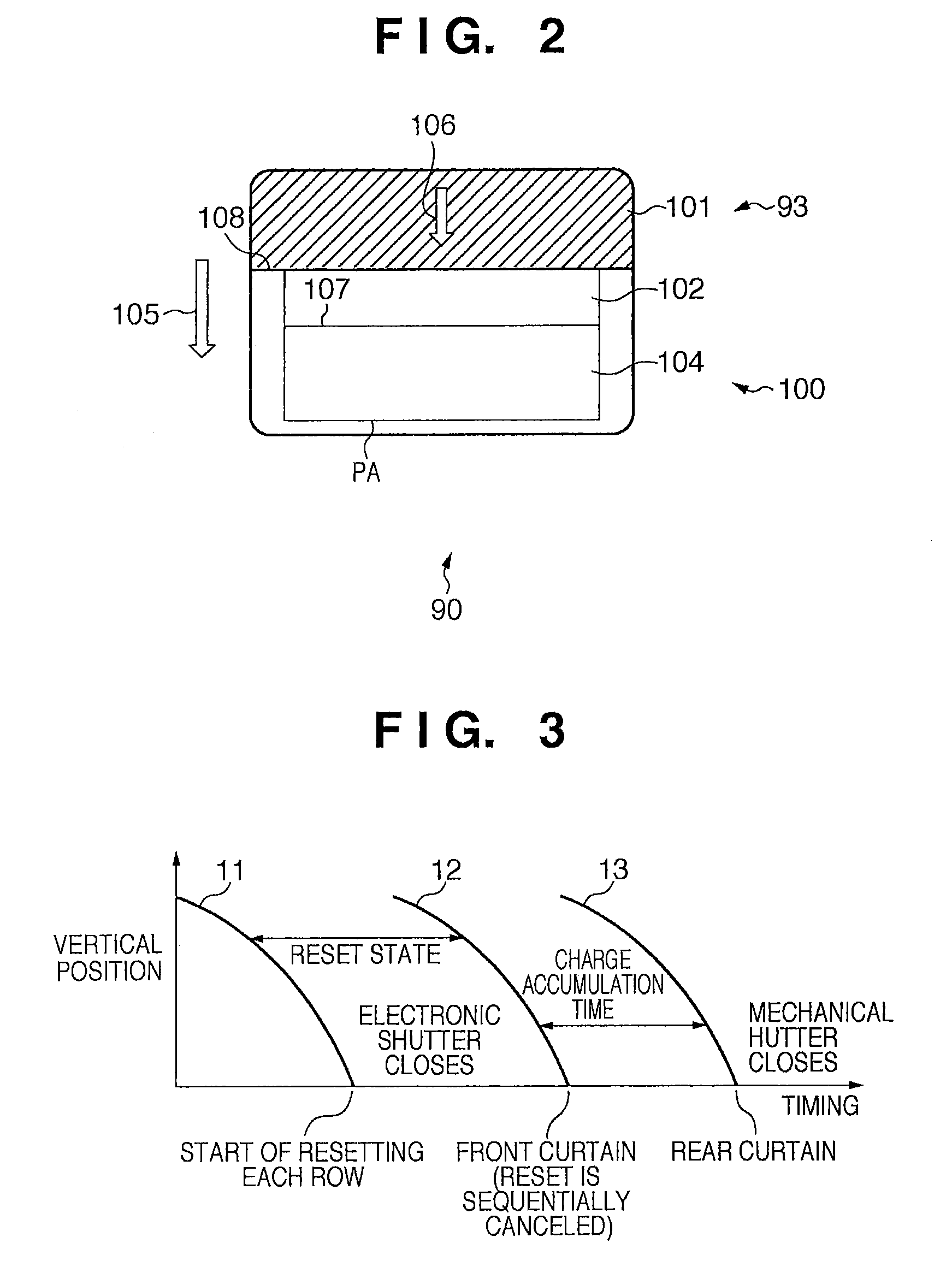

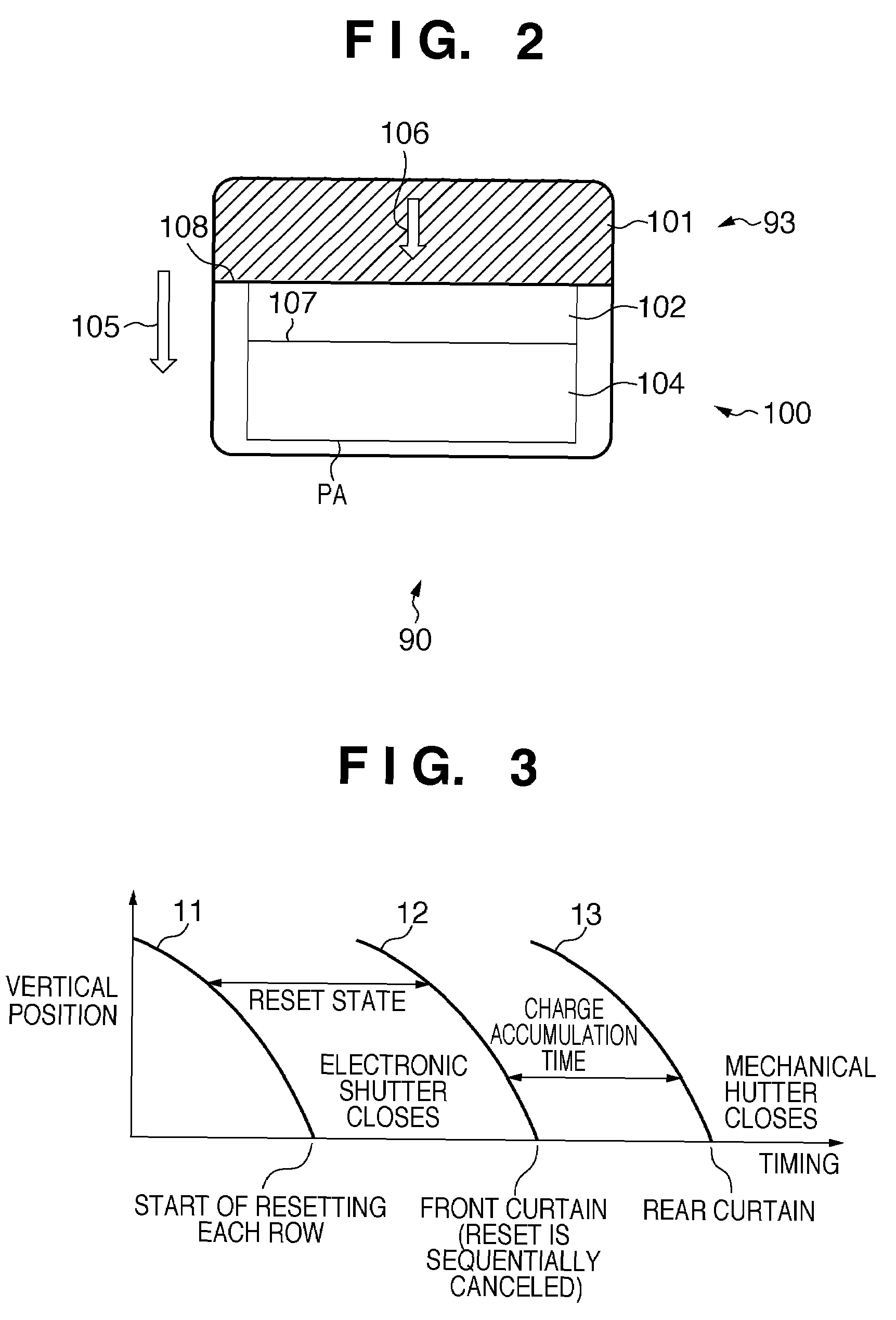

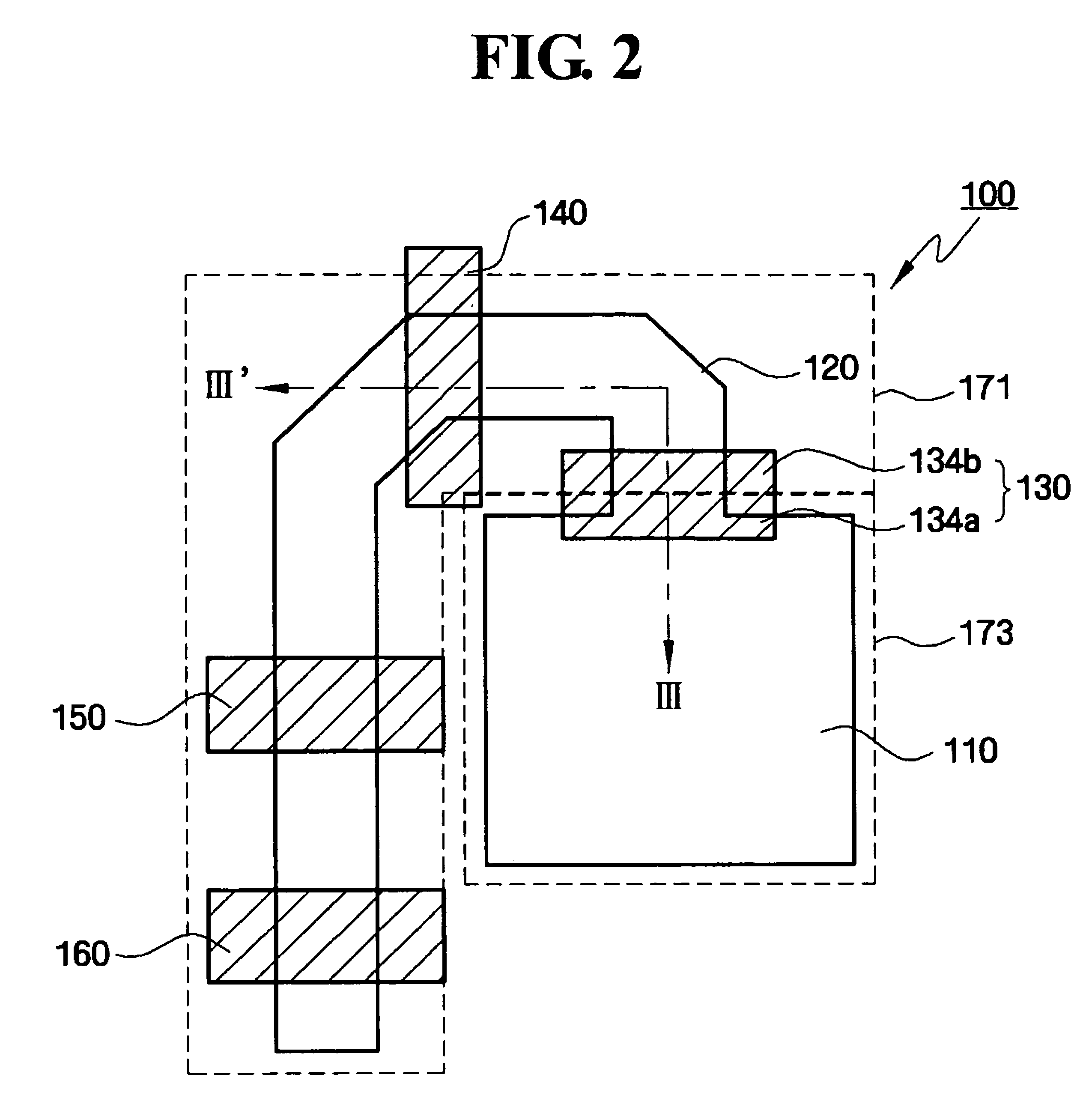

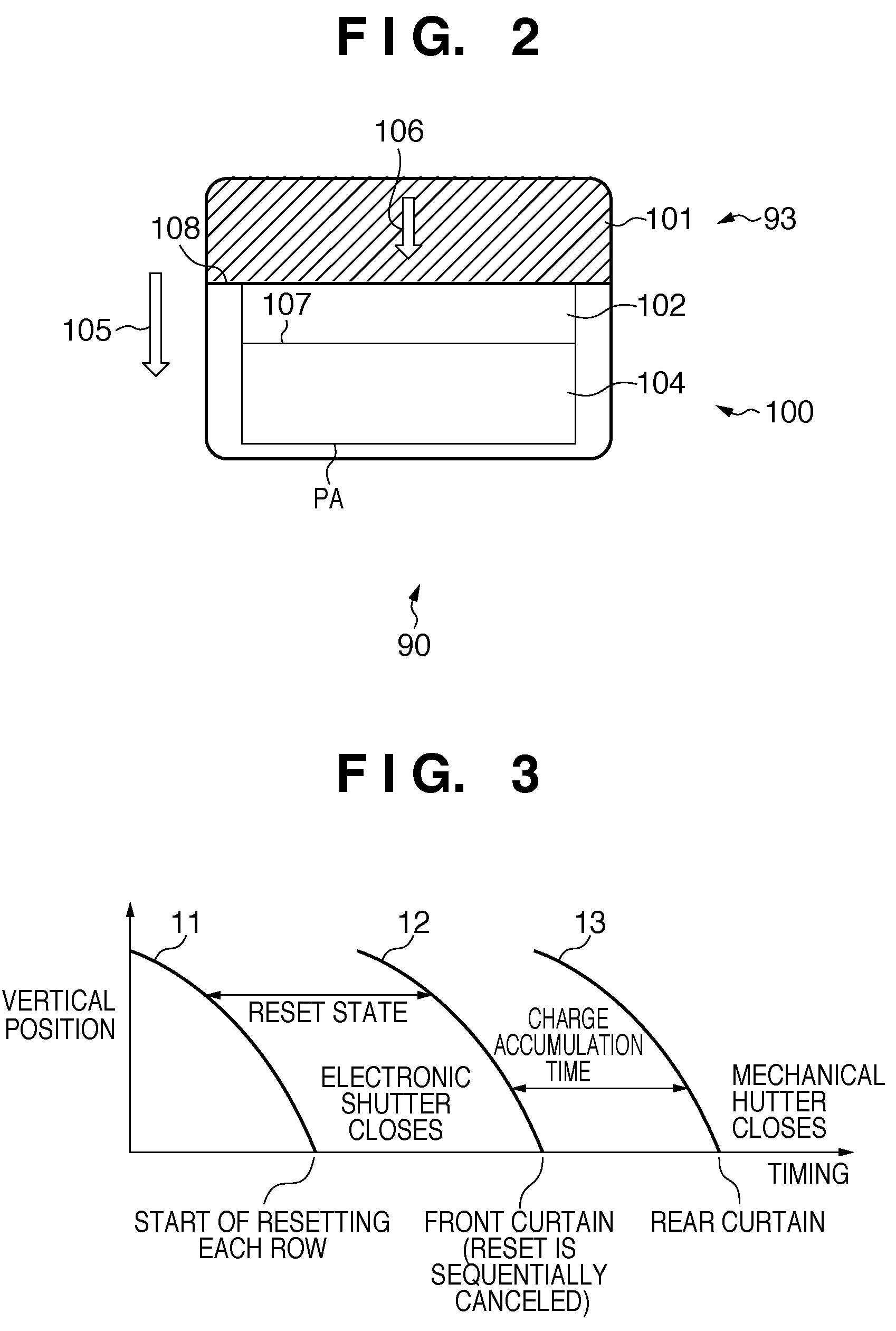

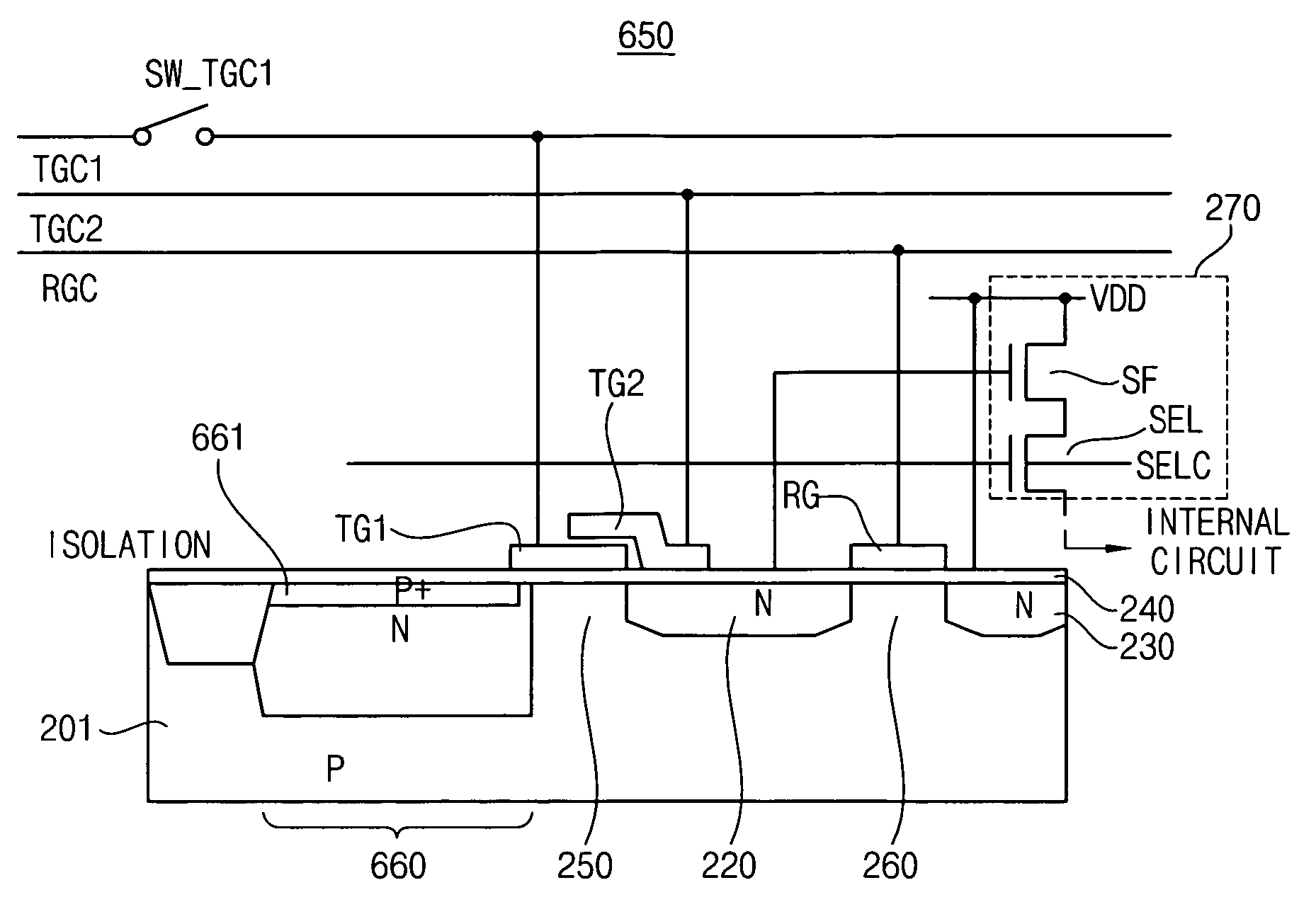

Imaging system, image sensor, and method of controlling imaging system

ActiveUS20090268083A1Reduce generationReduce image lagTelevision system detailsTelevision system scanning detailsPixel arrayImage system

Owner:CANON KK

Method and apparatus for removing electrons from CMOS sensor photodetectors

InactiveUS7250665B1Reduce noiseLow costTelevision system detailsSolid-state devicesCMOS sensorPhotovoltaic detectors

An improved CMOS sensor integrated circuit is disclosed, along with methods of making the circuit and computer readable descriptions of the circuit.

Owner:RE SECURED NETWORKS LLC

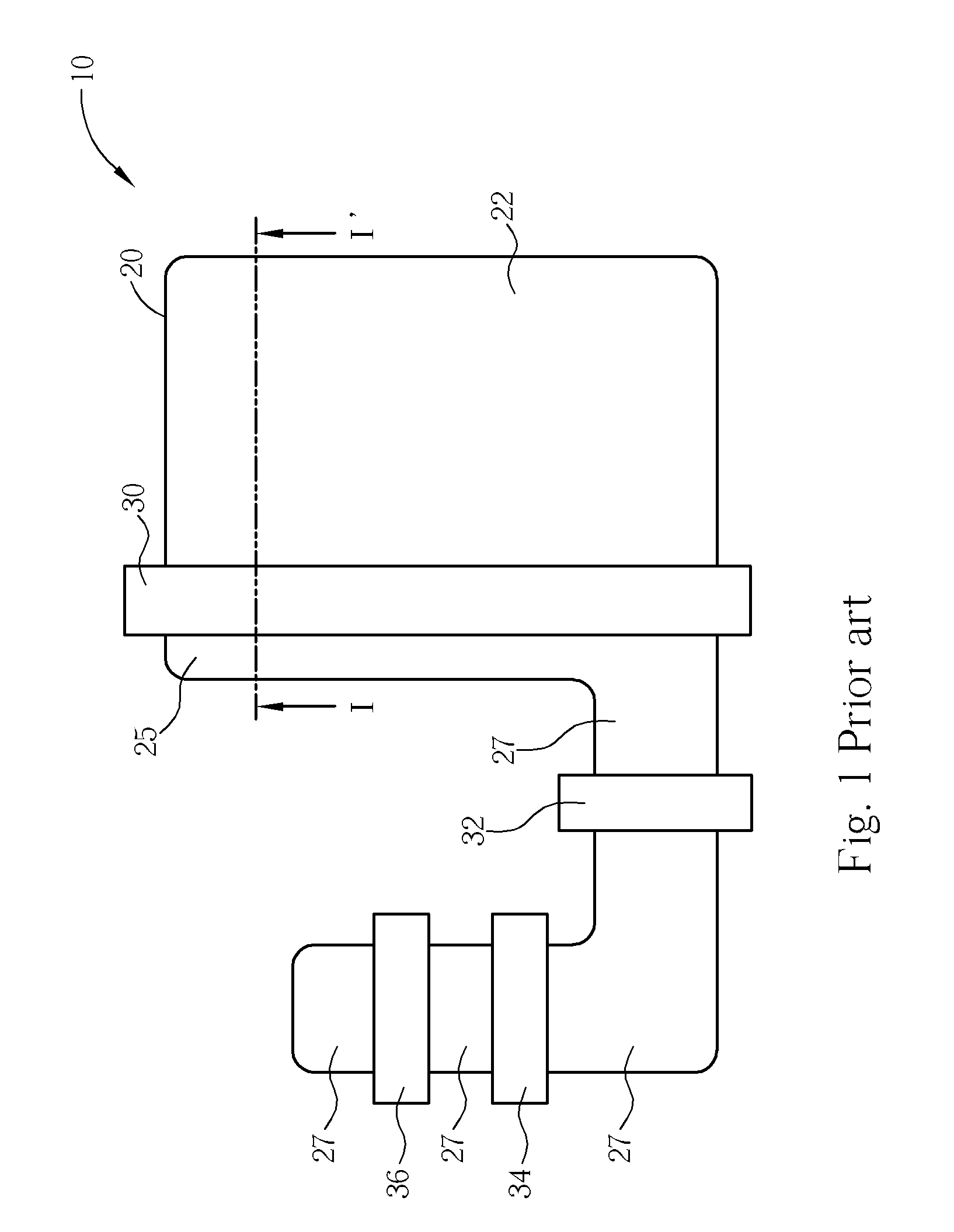

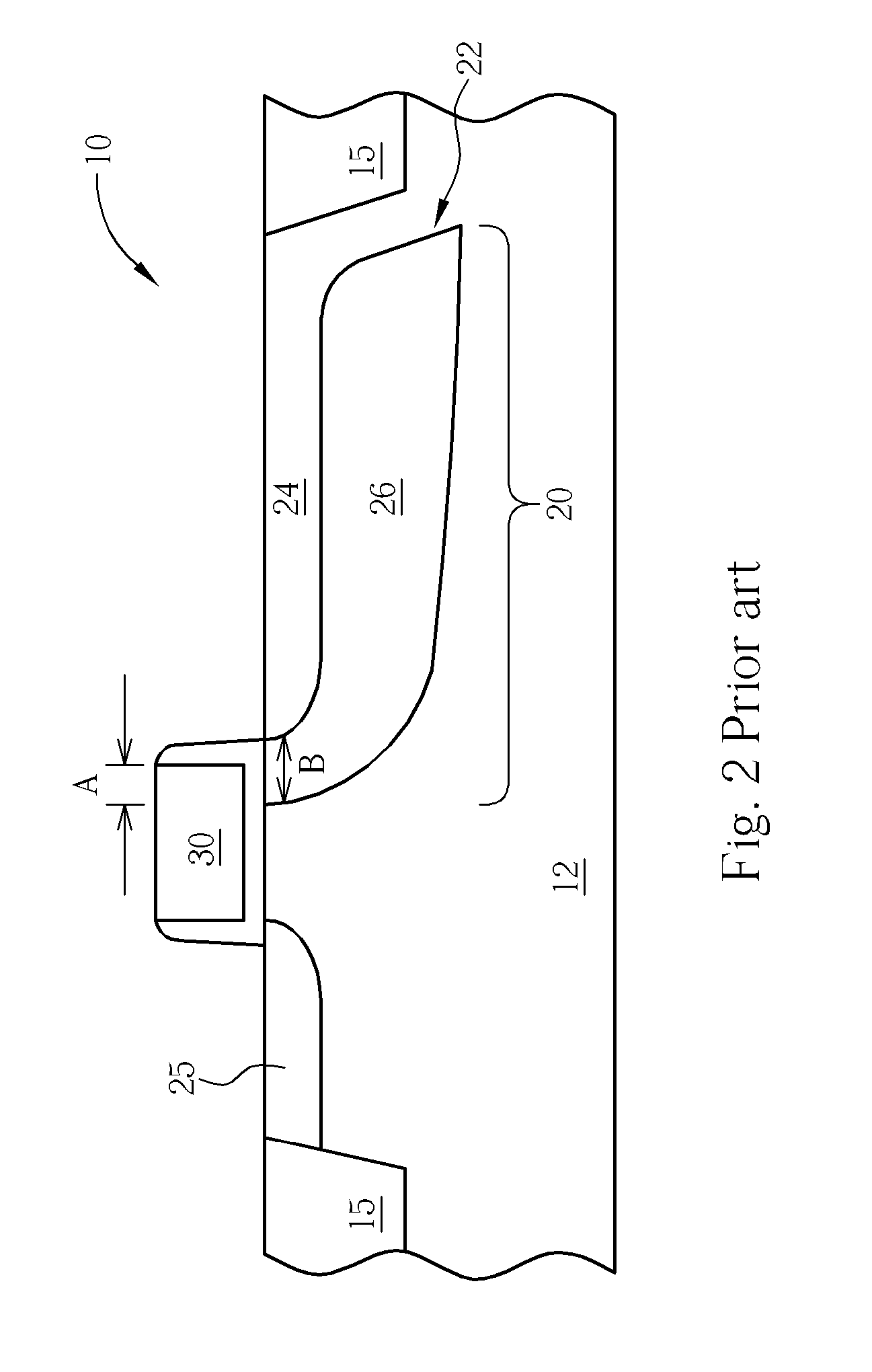

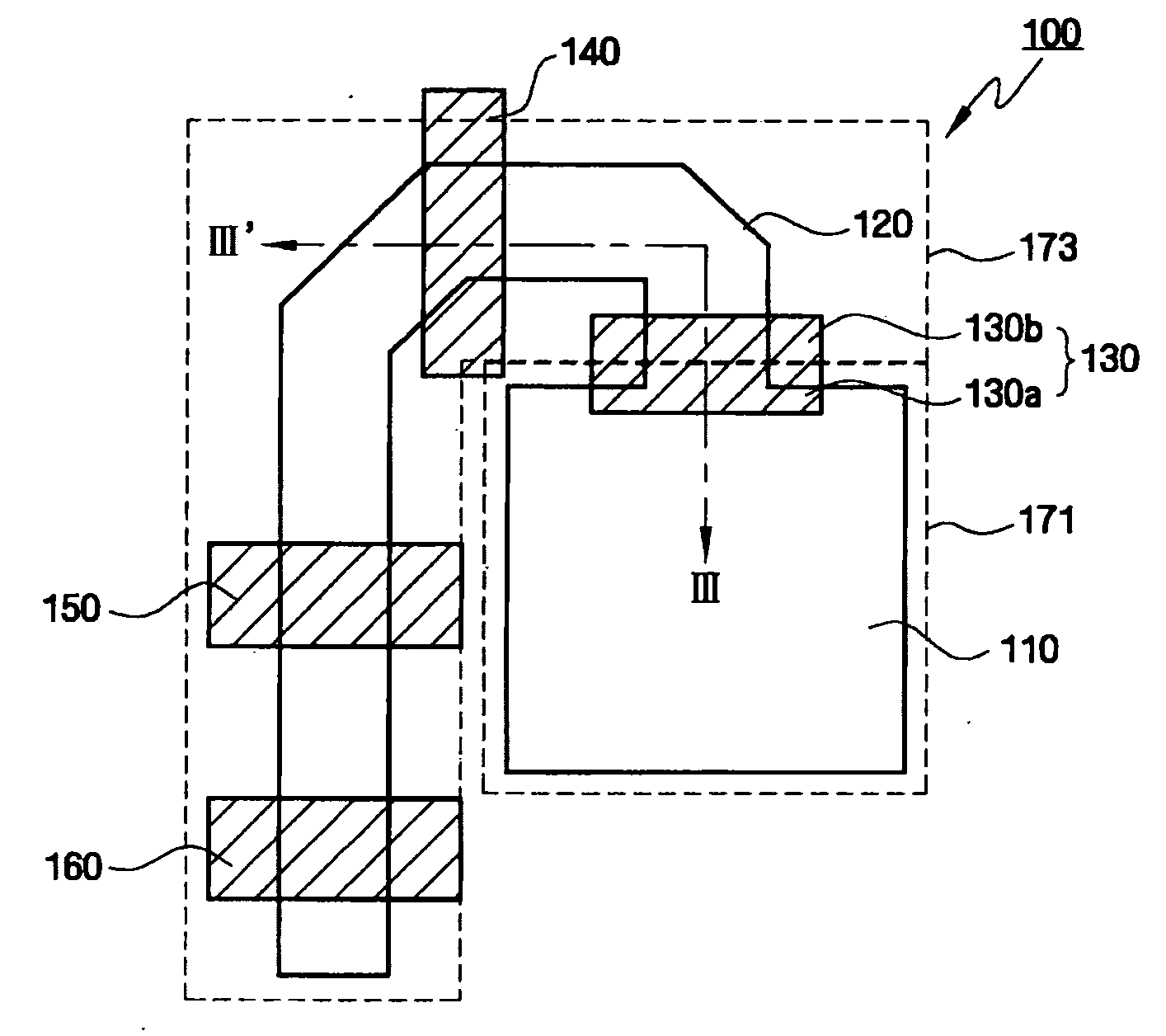

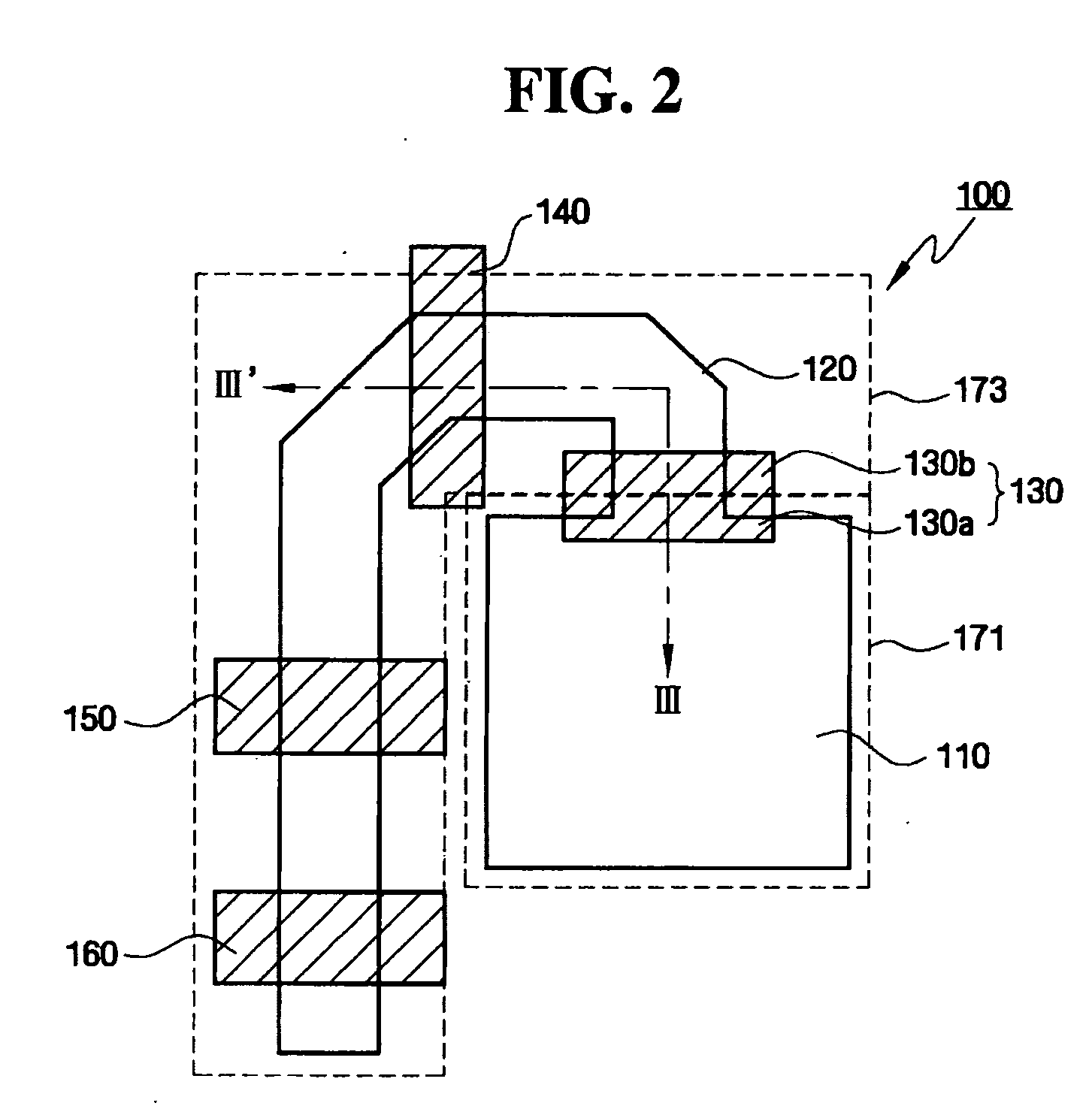

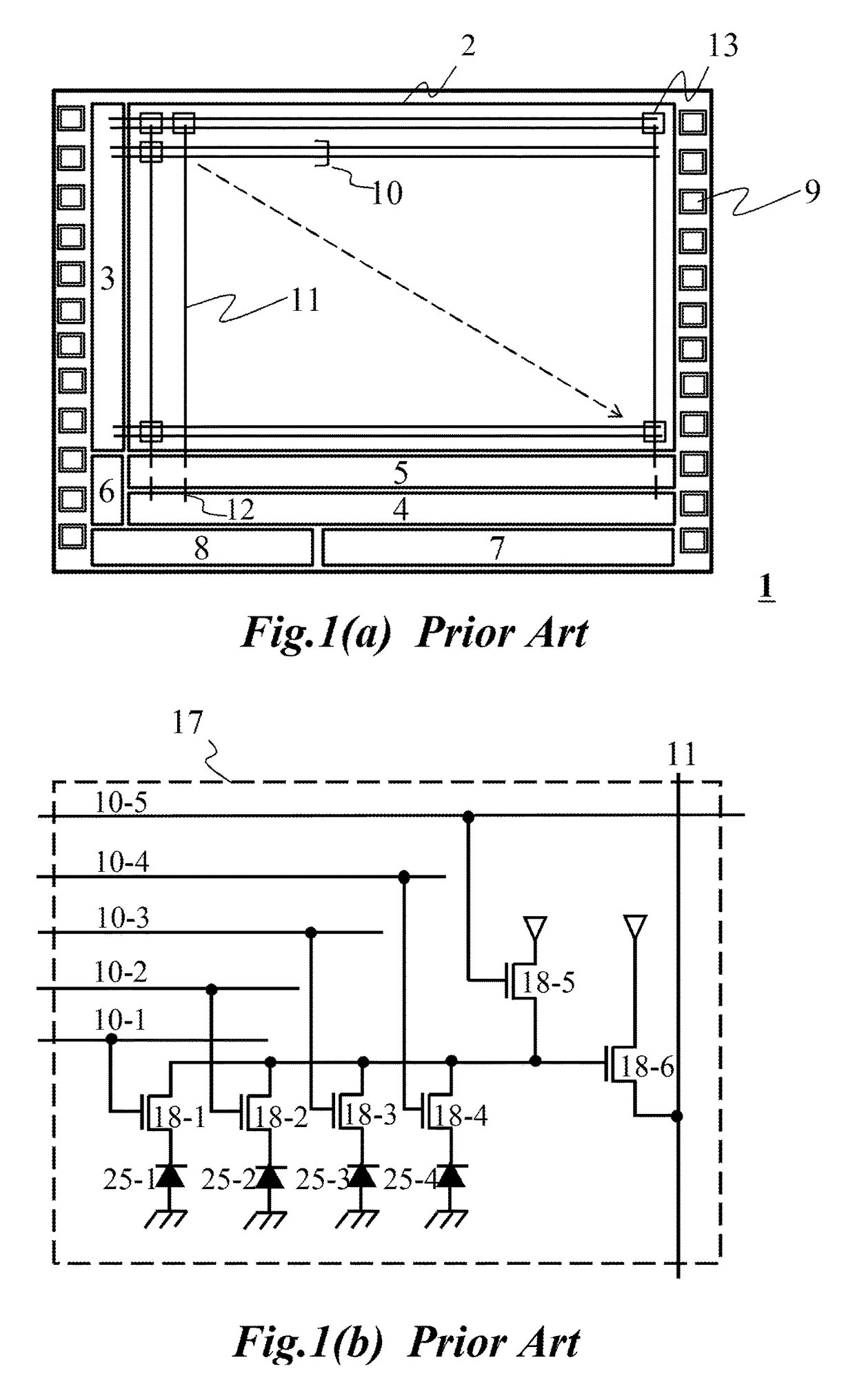

Image sensor and method of manufacturing the same

InactiveUS20070161140A1Reduce lagReduce image lagRoller bearingsSolid-state devicesImage sensorEngineering

Example embodiments disclose an image sensor capable of preventing or reducing image lag and a method of manufacturing the same. Example methods may include forming a gate insulating film and a gate conductive film doped with a first-conductive-type dopant on a semiconductor substrate; forming a transfer gate pattern by patterning the gate insulating film and the gate conductive film; and fabricating a transfer gate electrode by forming a first-conductive-type photodiode in the semiconductor substrate adjacent to one region of the transfer gate pattern, by forming a second-conductive-type photodiode on the first-conductive-type photodiode, and by forming a first-conductive-type floating diffusion region in the semiconductor substrate adjacent to the other region of the transfer gate pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

Method and apparatus for controlling charge transfer in CMOS sensors with a graded transfer gate work function

ActiveUS20060146156A1Reduce noiseLow costTelevision system detailsTelevision system scanning detailsCMOS sensorWork function

An improved CMOS sensor integrated circuit is disclosed, along with methods of making the circuit and computer readable descriptions of the circuit.

Owner:RE SECURED NETWORKS LLC

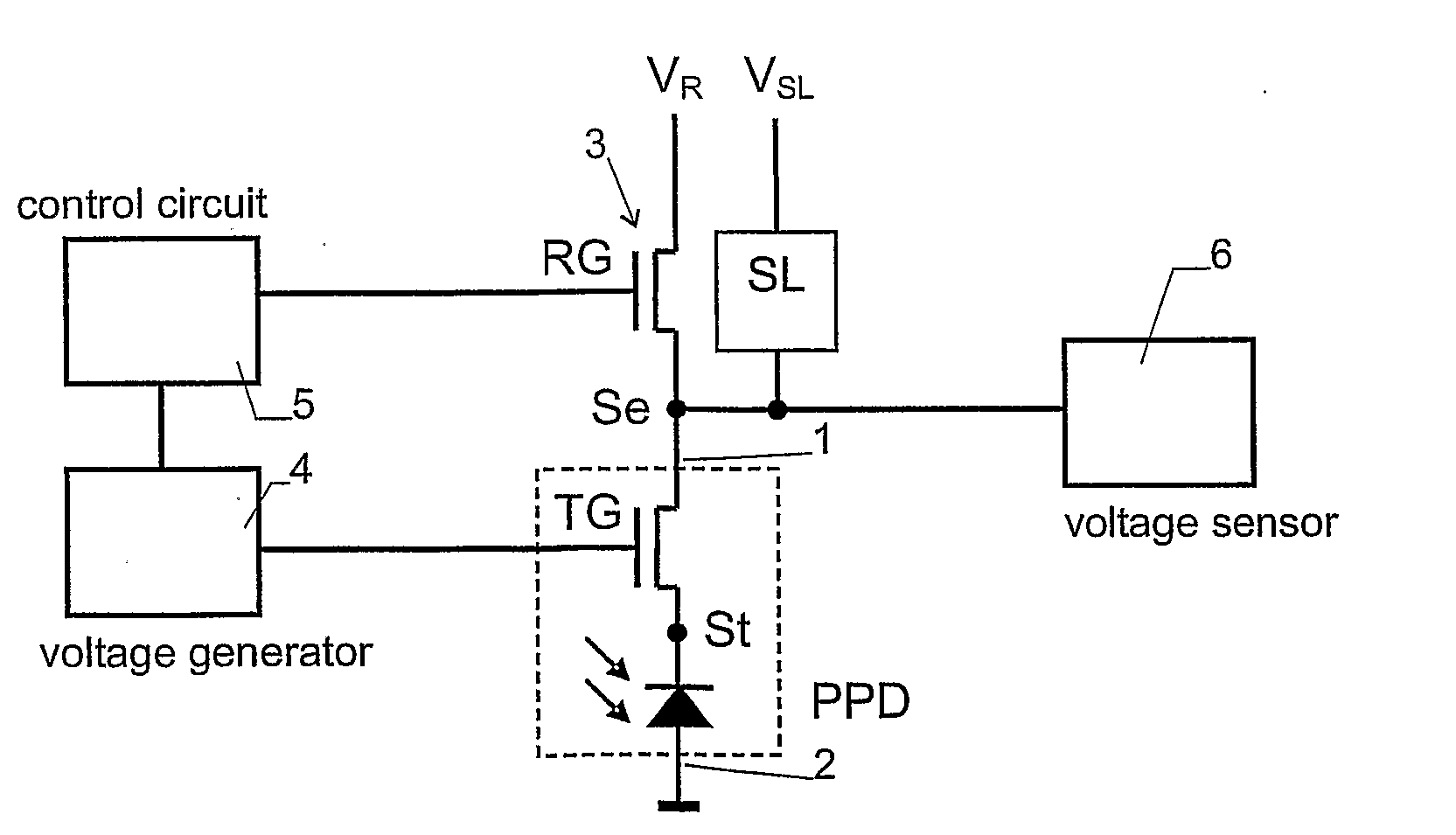

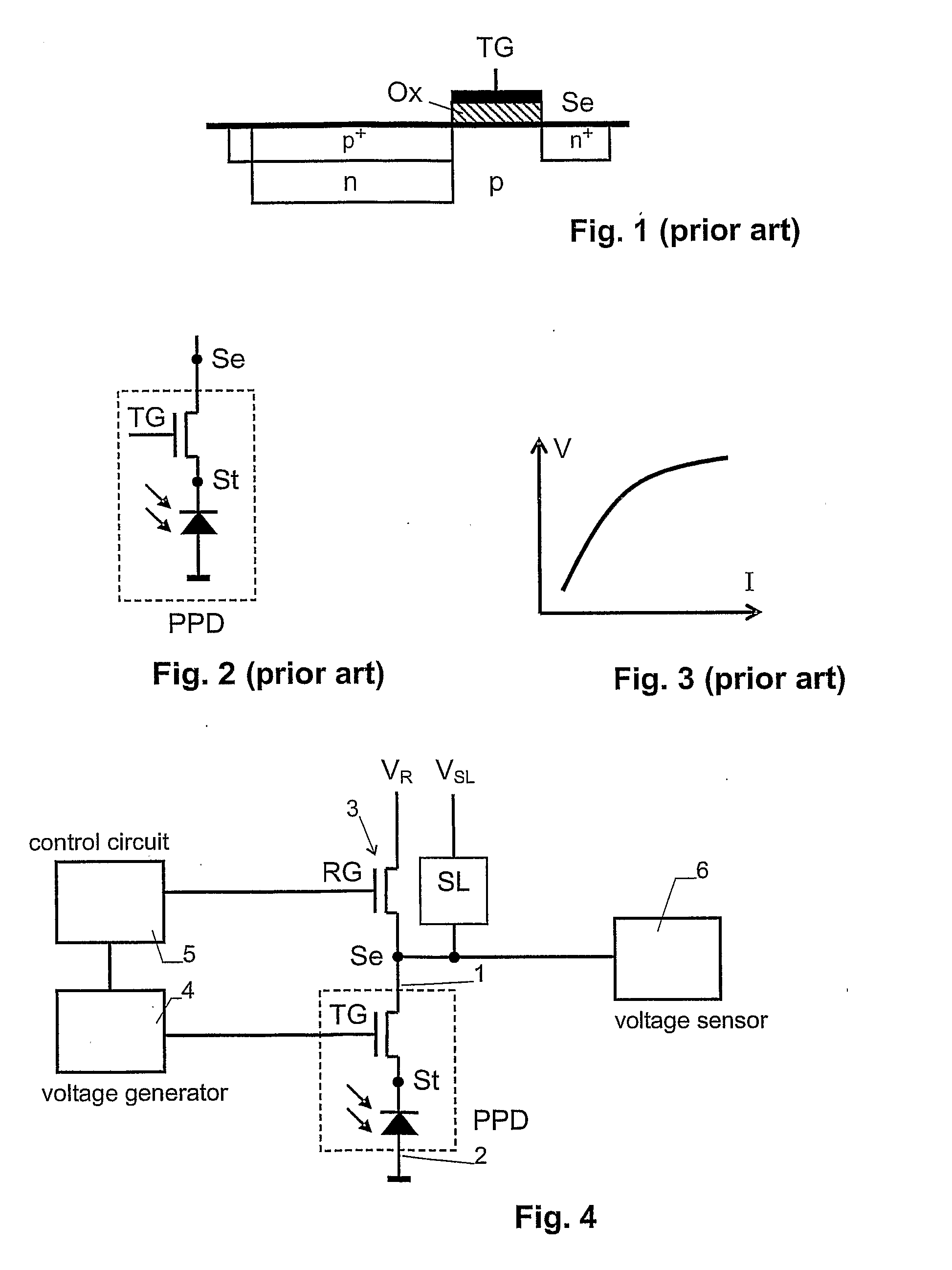

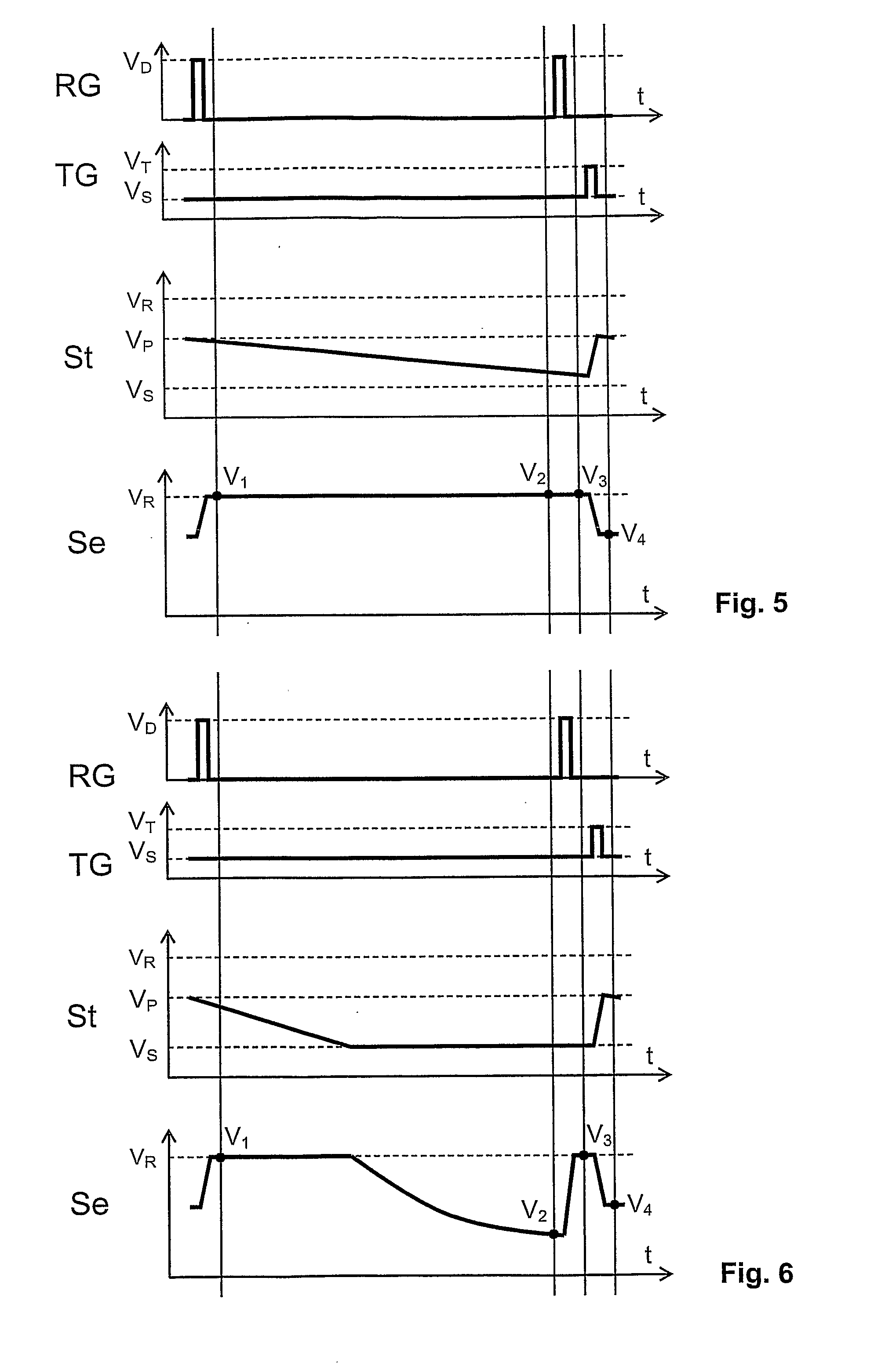

Photo Sensor With Pinned Photodiode and Sub-Linear Response

InactiveUS20100224765A1Improve dynamic rangeReduce noiseTelevision system scanning detailsMaterial analysis by optical meansCMOSImage sensor

A photo sensor exhibiting low noise, low smear, low dark current and high dynamic range consists of a pinned (or buried) photodiode (PPD) with associated transfer gate (TG), a reset circuit (3) and a device (SL) with sub-linear voltage-to-current characteristic. The exposure cycle is started by reverse biasing the buried photodiode to its pinning potential and by setting the transfer gate (TG) to a non-zero skimming potential. Photo-generated charge carriers start to fill the buried photodiode; if illumination intensity is high, excessive photocharges are flowing over the transfer gate (TG) to the sensing node. Because of the sub-linear device (SL) connected to the sensing node, the voltage at the sensing node is a sub-linear function of the illumination intensity, and hence the dynamic range of the pixel is increased. The voltage at the sensing node (Se) is read four times, namely before exposure, with the spilled-over photocharge, after reset, and after the photocharge in the buried photodiode has been transferred to the sensing node. This allows correlated multiple sampling techniques to be employed for eliminating reset noise. Because of its compact size, the photo sensor can be employed in one- and two-dimensional image sensors fabricated with industry-standard CMOS or CCD technologies.

Owner:CSEM CENT SUISSE DELECTRONIQUE & DE MICROTECHNIQUE SA RECH & DEV

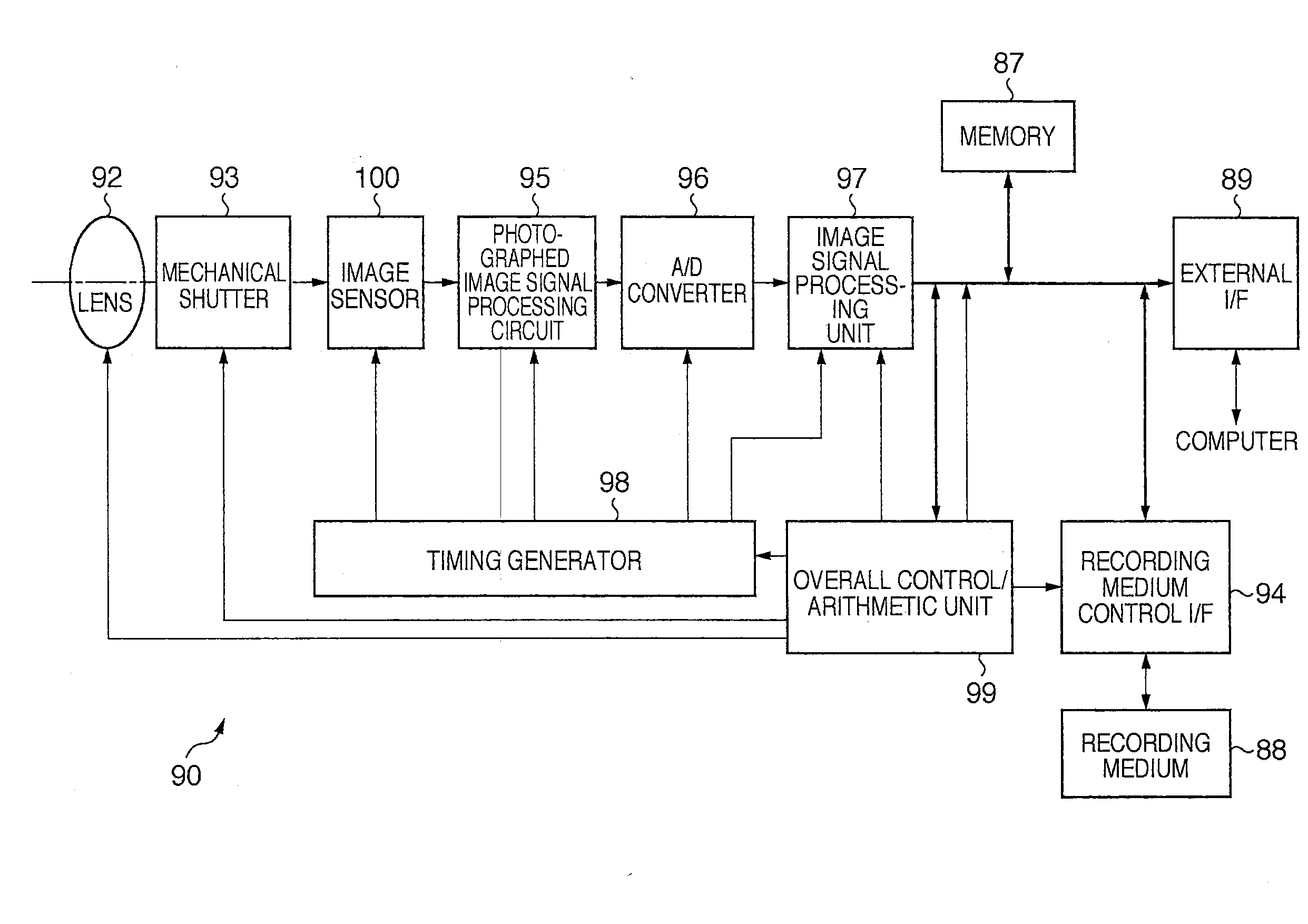

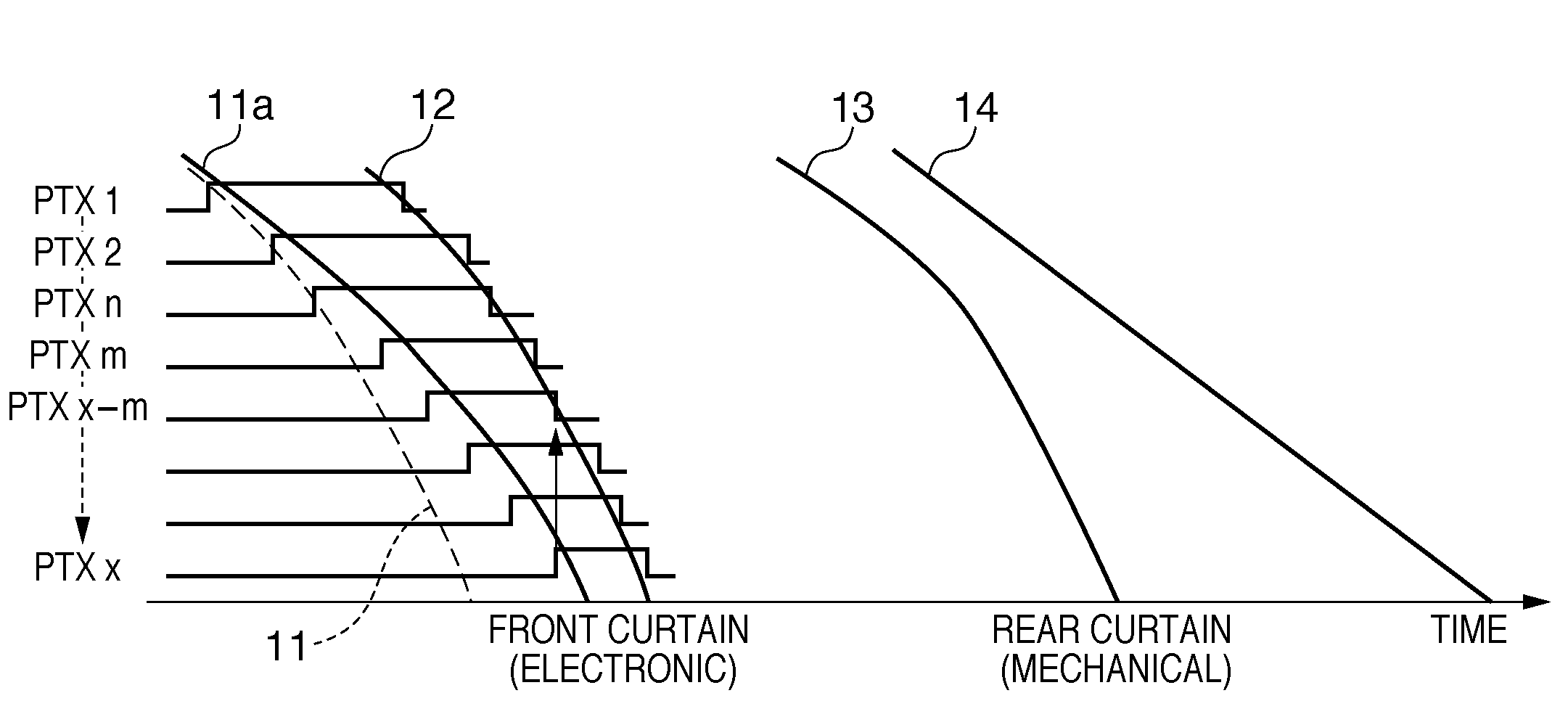

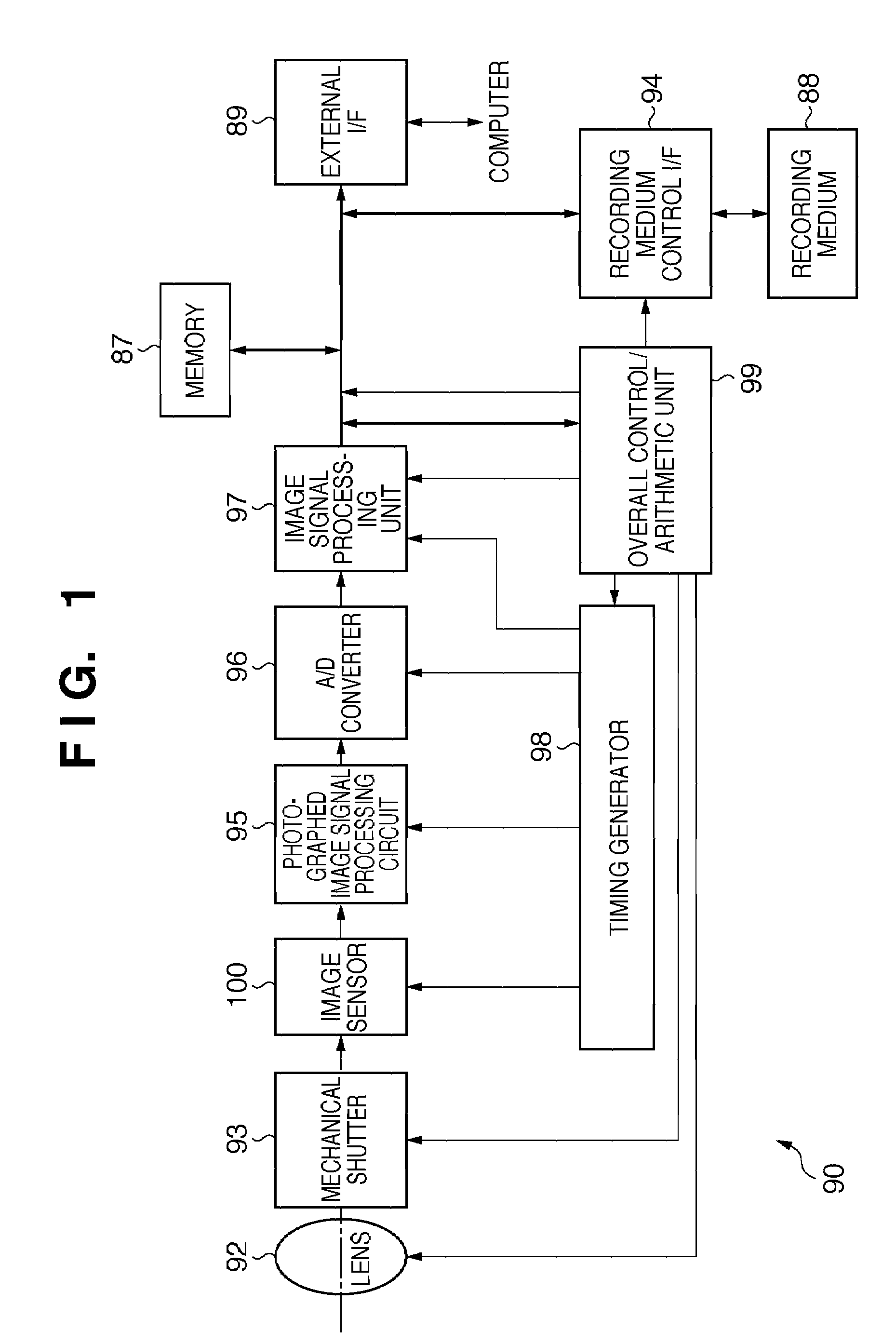

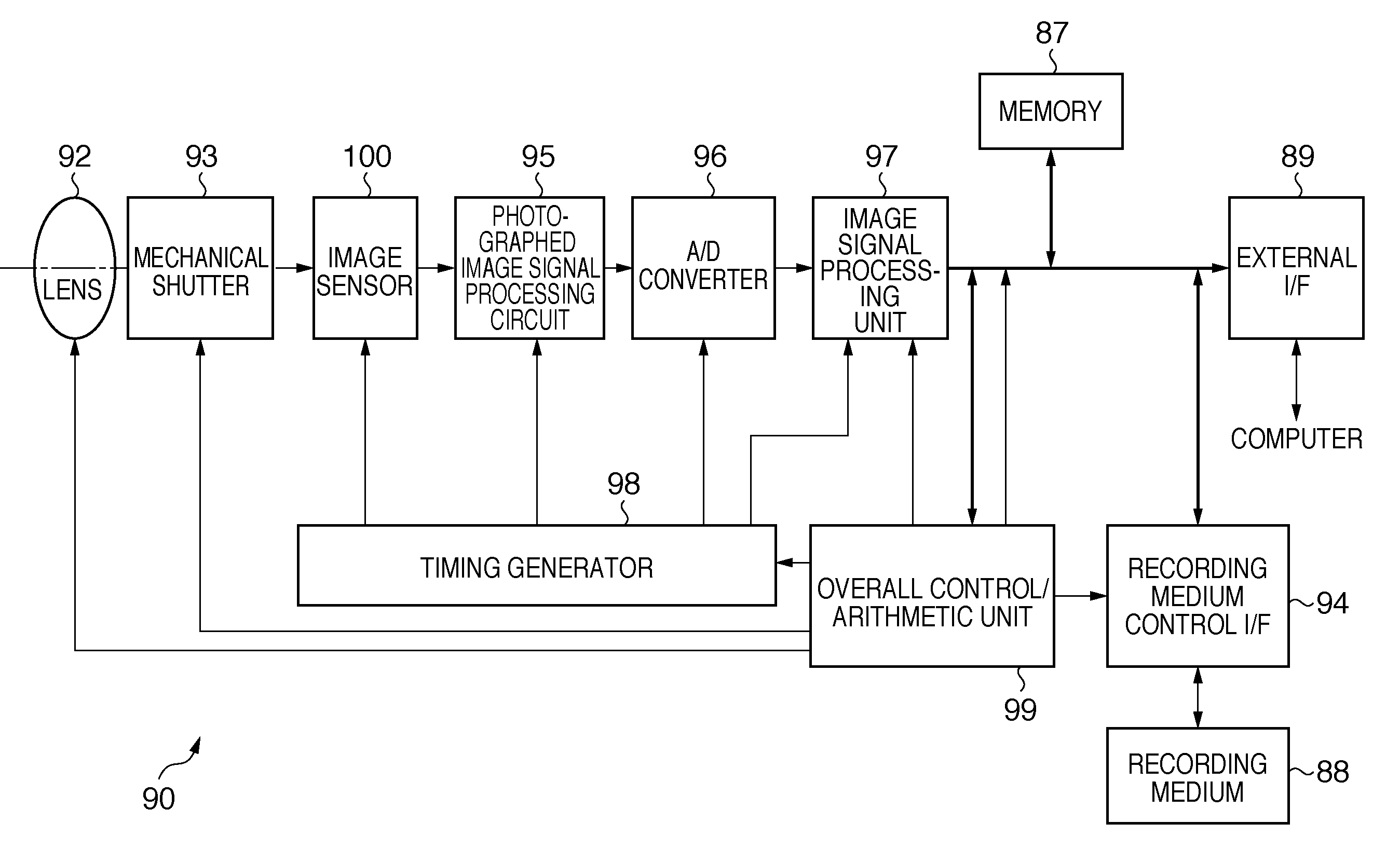

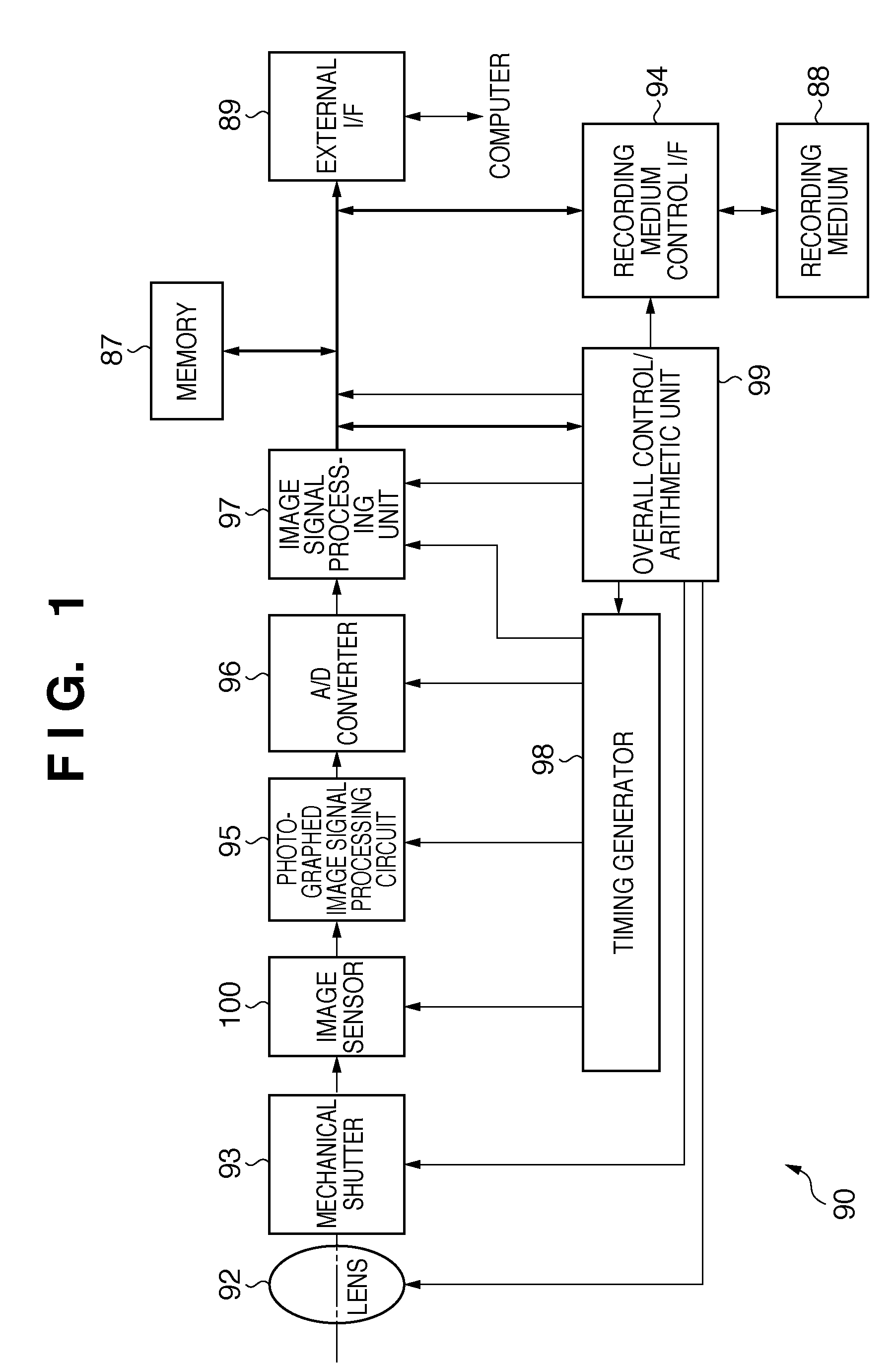

Imaging system, image sensor, and method of controlling imaging system

InactiveUS7630009B2Reduce generationReduce image lagTelevision system detailsTelevision system scanning detailsImage systemPixel array

An imaging system includes an image sensor and a mechanical shutter which controls the termination of exposure of the image sensor. The image sensor includes a pixel array in which a plurality of pixels are arrayed in a matrix, and a vertical scanning unit which scans the pixel array for each row. The vertical scanning unit executes in parallel some of the reset operations of pixels on at least two adjacent rows of the pixel array. The charge accumulation operation of pixels starts upon completion of the reset operation and terminates in response to light shielding by the mechanical shutter.

Owner:CANON KK

Image sensor and method of manufacturing the same

Example embodiments disclose an image sensor capable of preventing or reducing image lag and a method of manufacturing the same. Example methods may include forming a gate insulating film and a gate conductive film doped with a first-conductive-type dopant on a semiconductor substrate; forming a transfer gate pattern by patterning the gate insulating film and the gate conductive film; and fabricating a transfer gate electrode by forming a first-conductive-type photodiode in the semiconductor substrate adjacent to one region of the transfer gate pattern, by forming a second-conductive-type photodiode on the first-conductive-type photodiode, and by forming a first-conductive-type floating diffusion region in the semiconductor substrate adjacent to the other region of the transfer gate pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

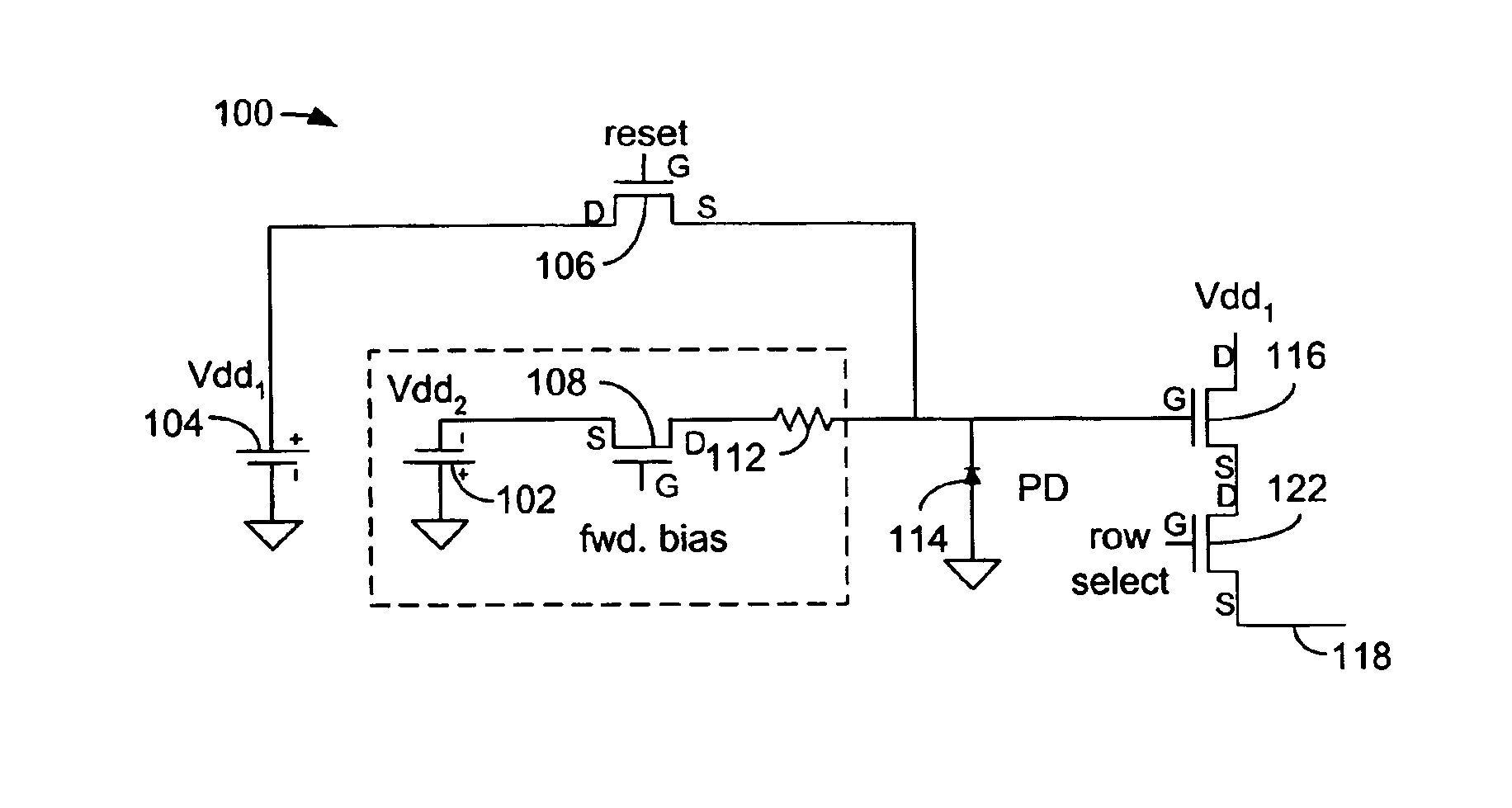

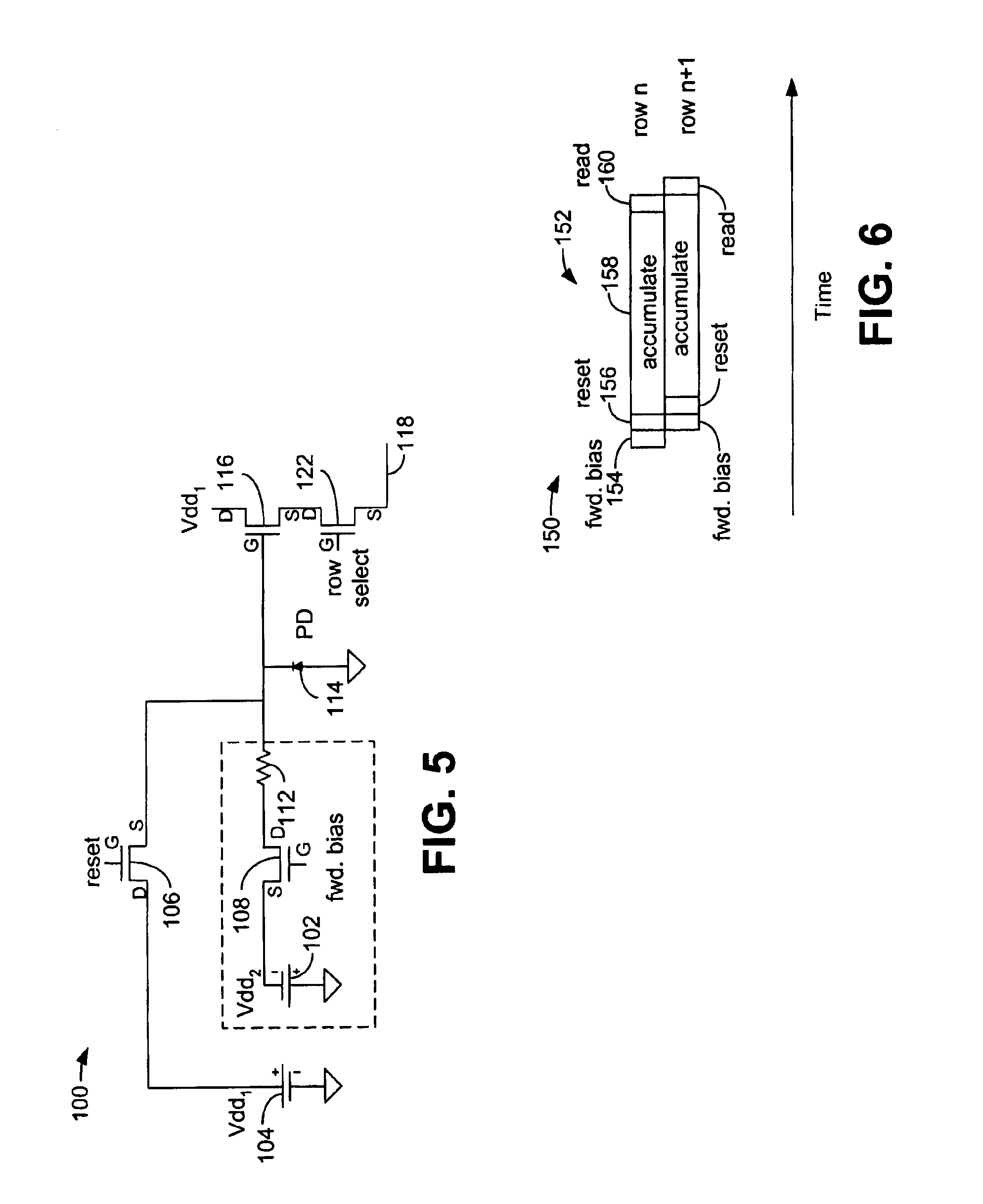

System and method for reducing trapped charge effects in a CMOS photodetector

ActiveUS6914230B2Reduce the impactReduce charge effectTelevision system detailsSolid-state devicesCMOSPhotovoltaic detectors

A system and method for reducing image lag in a complementary metal oxide semiconductor (CMOS) photodetector is disclosed. In one embodiment, the invention is a a method for reducing image lag in an array of complementary metal oxide semiconductor (CMOS) photodetectors by forward biasing the photodetectors during a first time period to charge charge traps in the photodetectors, and reverse biasing the photodetectors during a second time period to remove charge from the photodetectors except the charge trapped in the charge traps.

Owner:APTINA IMAGING CORP

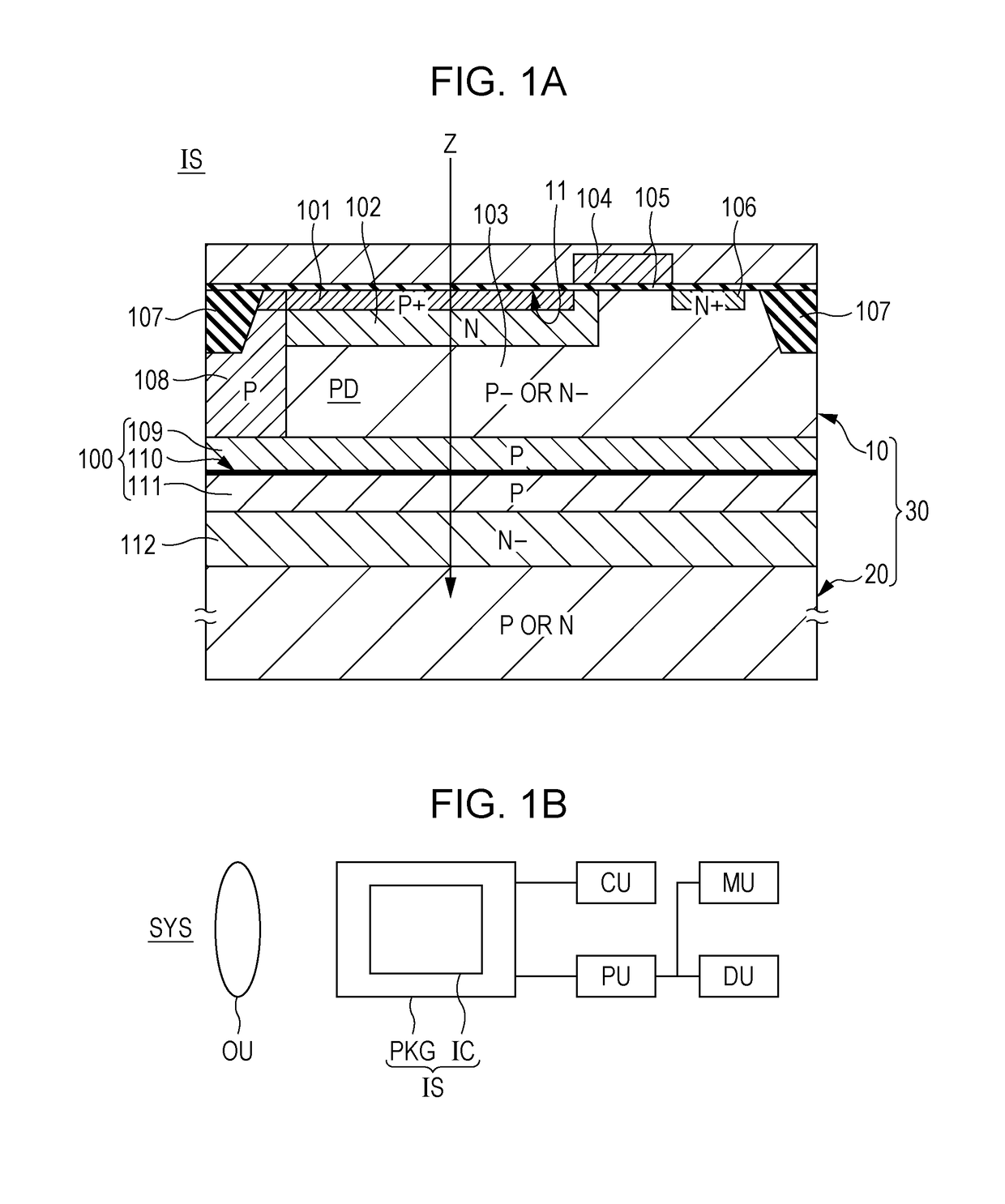

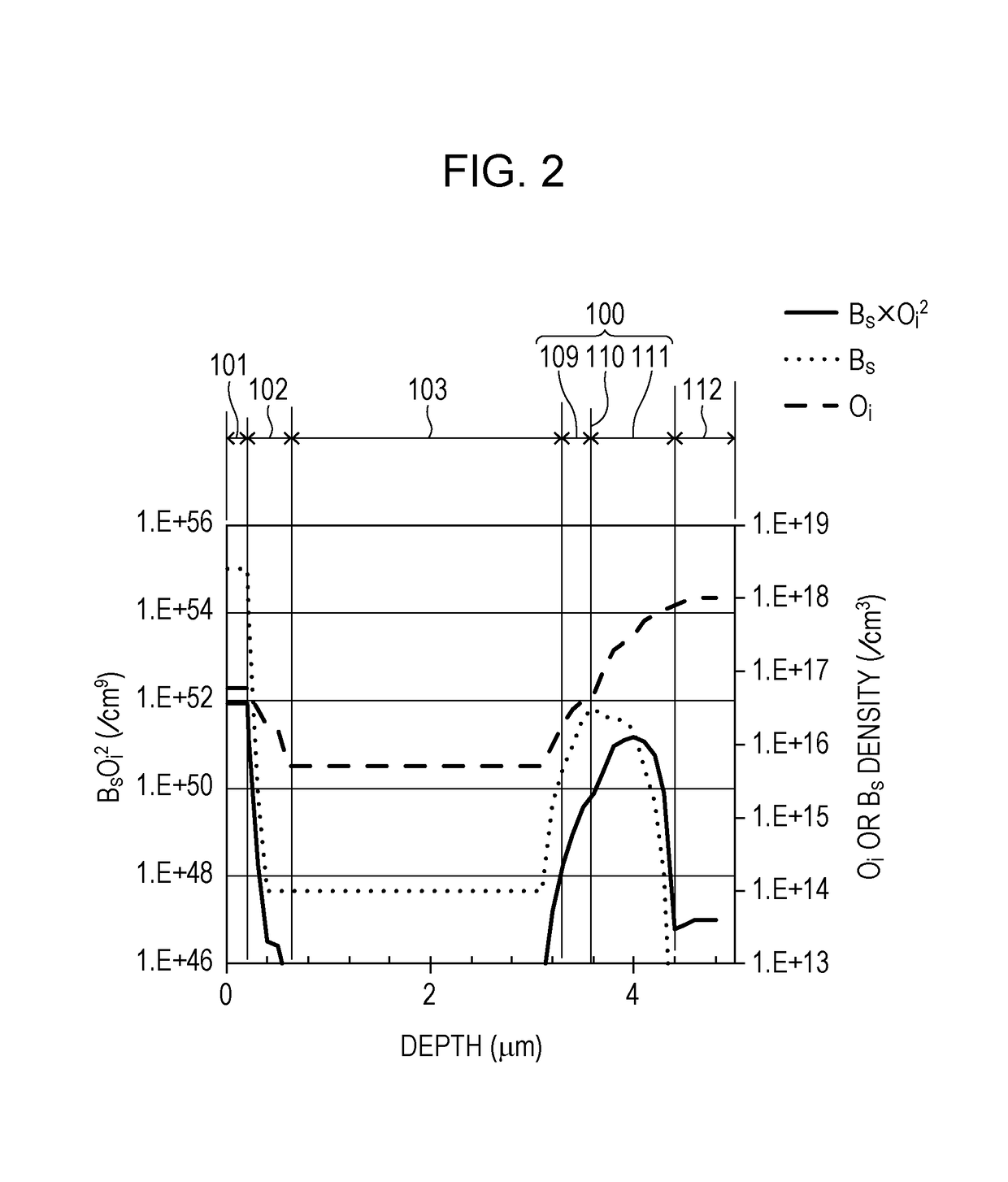

Photoelectric conversion device and imaging system

InactiveUS20180061872A1Improve image qualityReduce image lagTelevision system detailsSolid-state devicesPhotoelectric conversionDepth direction

A photoelectric conversion device includes a photoelectric conversion portion in a silicon layer having a light-receiving surface. The silicon layer includes a P-type impurity region including a base portion having an atomic boron concentration Ba that is the highest of the portions opposite the light-receiving surface with respect to a charge accumulation region and an atomic oxygen concentration Oa, and a deep portion located opposite the charge accumulation region in the depth direction with respect to the base portion and having an atomic boron concentration Bb and an atomic oxygen concentration Ob. The impurity region satisfies Ba×Oa2<Bb×Ob2.

Owner:CANON KK

Imaging system, image sensor, and method of controlling imaging system

InactiveUS20080309806A1Degrading image can be generatedReduce generationTelevision system detailsTelevision system scanning detailsPixel arrayImage system

An imaging system includes an image sensor and a mechanical shutter which controls the termination of exposure of the image sensor. The image sensor includes a pixel array in which a plurality of pixels are arrayed in a matrix, and a vertical scanning unit which scans the pixel array for each row. The vertical scanning unit parallelly executes some of the reset operations of pixels on at least two adjacent rows of the pixel array. The charge accumulation operation of pixels starts upon completion of the reset operation and terminates in response to light shielding by the mechanical shutter.

Owner:CANON KK

Active pixel sensor with coupled gate transfer transistor

ActiveUS7888715B2Improve dynamic rangeReduce image lagTelevision system detailsTelevision system scanning detailsEngineeringFloating diffusion

A complementary metal-oxide semiconductor (CMOS) active pixel sensor includes a photodiode, a transfer transistor with a coupled gate, a reset transistor and a signal transfer circuit, where the photodiode generates electric charges in response to incident light, the transfer transistor transfers the electric charges integrated in the photodiode to a floating diffusion node, wherein the transfer transistor has a first transfer gate and a second transfer gate, and the first and second transfer gates have a coupled gate structure, the reset transistor resets a potential level of the floating diffusion node by a given voltage level, the signal transfer circuit transfers the potential level of the floating diffusion node to an internal circuit in response to a selection signal, and the CMOS active pixel sensor with the coupled gate may increase a capacity of the photodiode and reduce an image lag by using a voltage coupling effect of the coupled gate.

Owner:SAMSUNG ELECTRONICS CO LTD

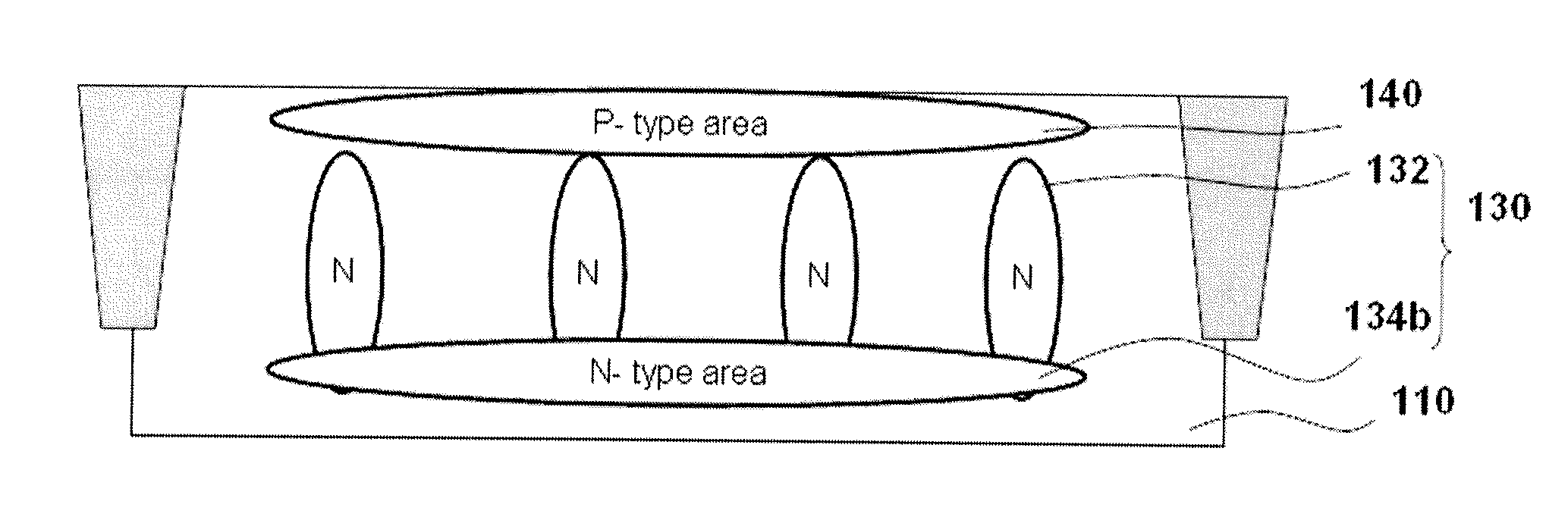

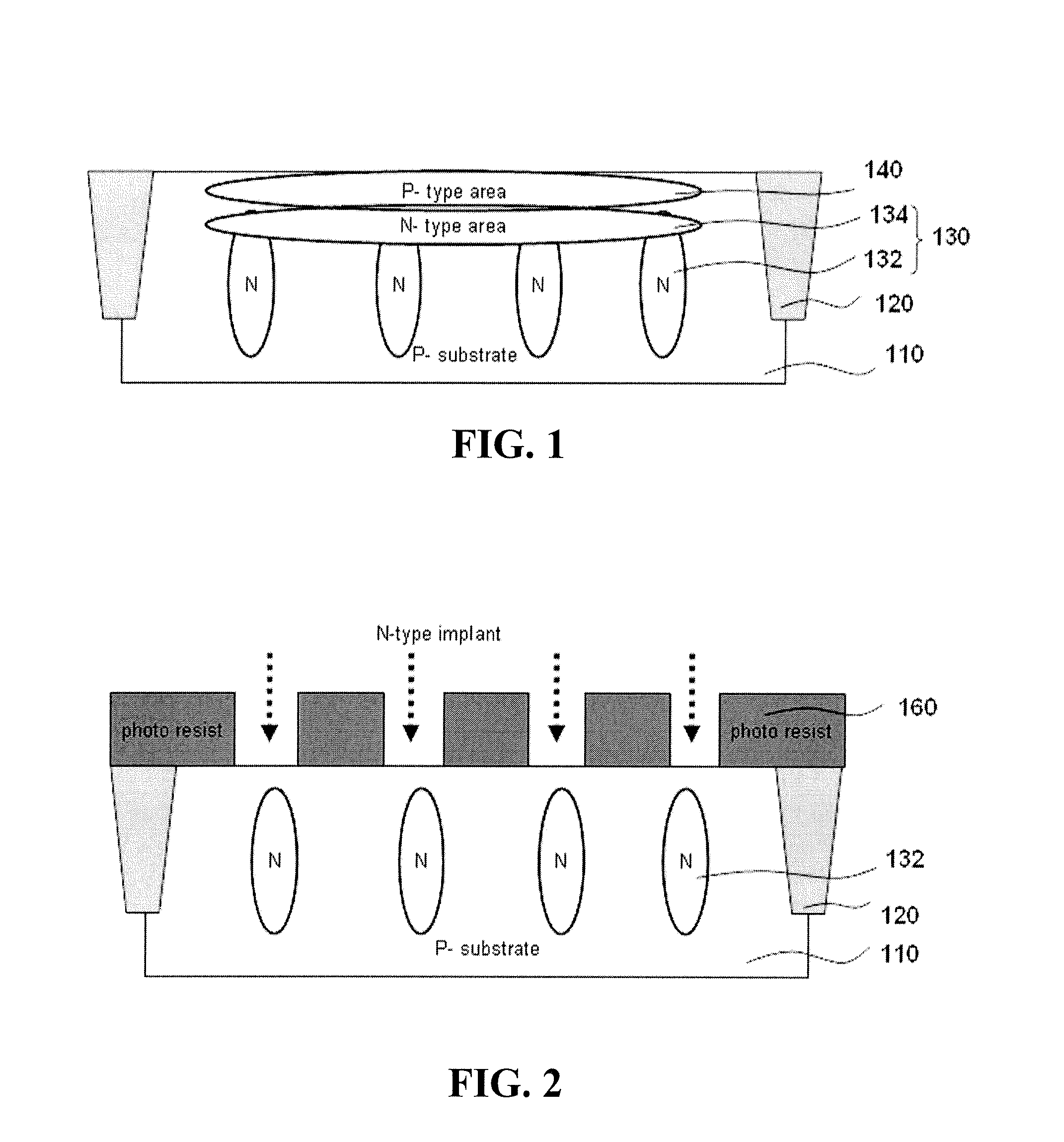

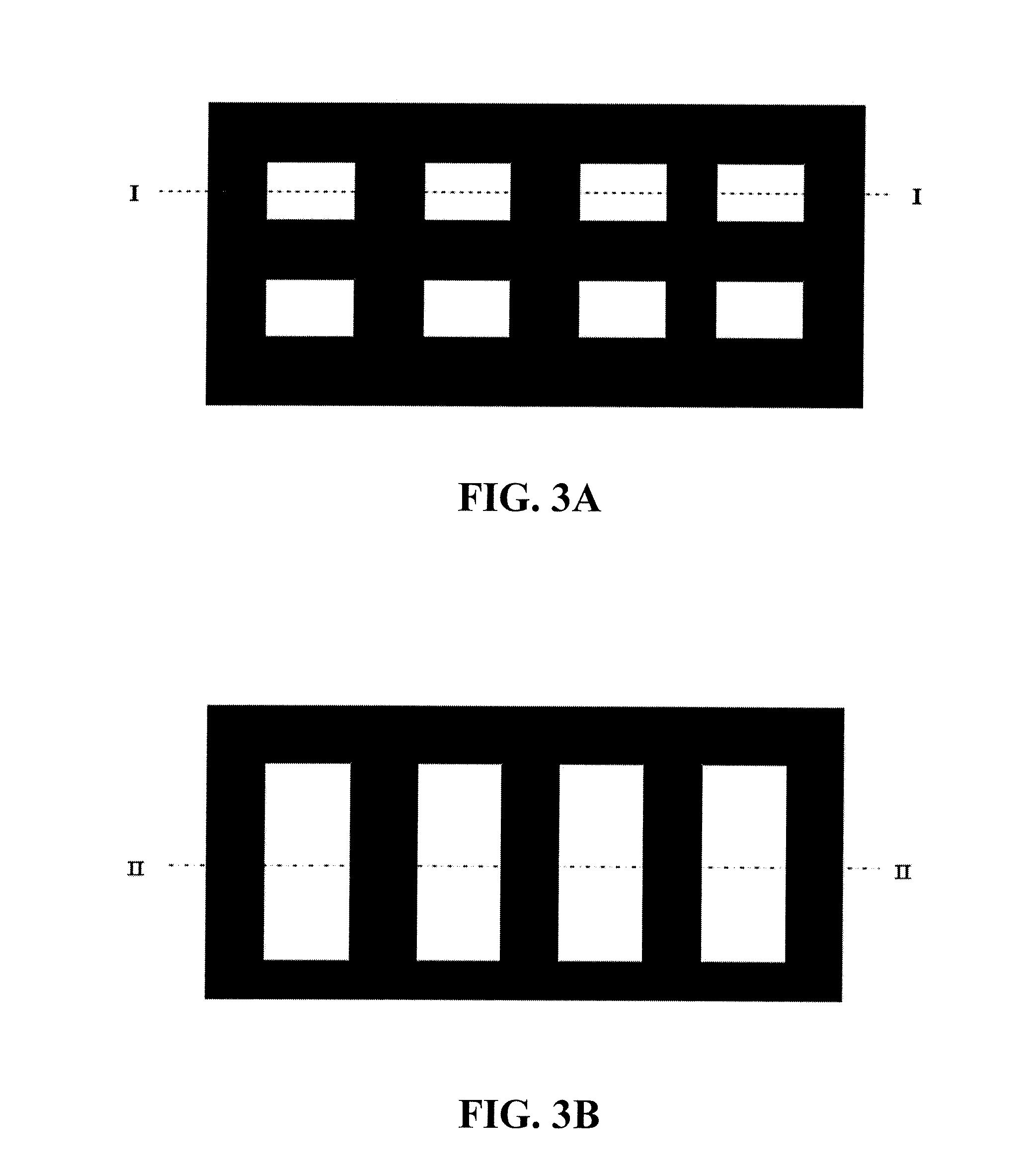

Image Sensor and Method for Manufacturing the Same

InactiveUS20080042229A1Maximize depletionSimple processSolid-state devicesSemiconductor/solid-state device manufacturingIsolation layerSemiconductor

An image sensor is provided incorporating a first conductive type semiconductor substrate including an active area defined by a device isolation layer; a second conductive type first ion implant area formed as multiple regions in the active area; a second conductive type second ion implant area connecting the multiple regions of the second conductive type first ion implant area; and a first conductive type ion implant area formed on the second conductive type second ion implant area. The multiple regions of the second conductive type first ion implant area can be formed deeply in the substrate. The second conductive type second ion implant can be formed in the substrate at an upper region of the first ion implant area, a middle region of the first ion implant area, or a lower region of the first ion implant area.

Owner:DONGBU HITEK CO LTD

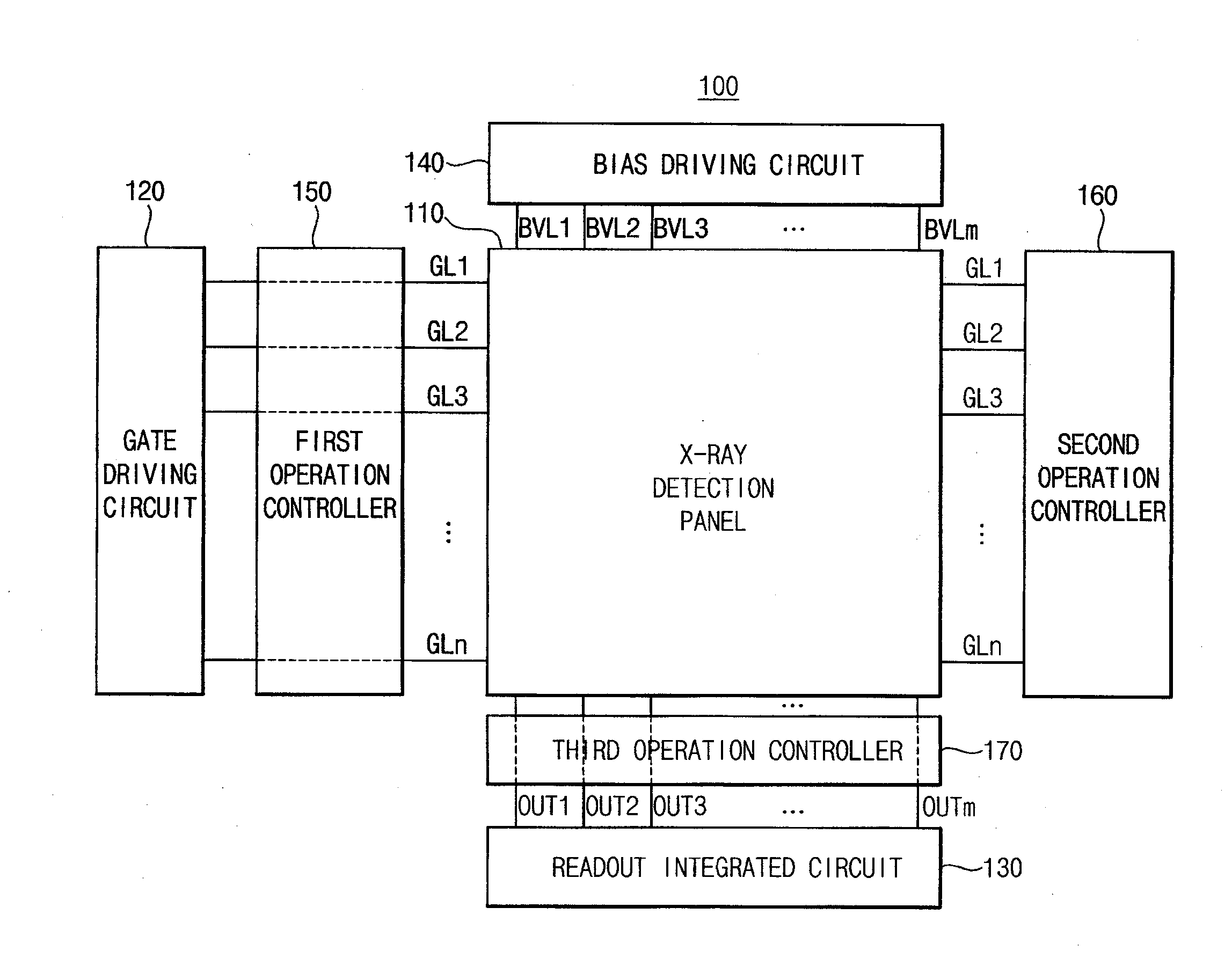

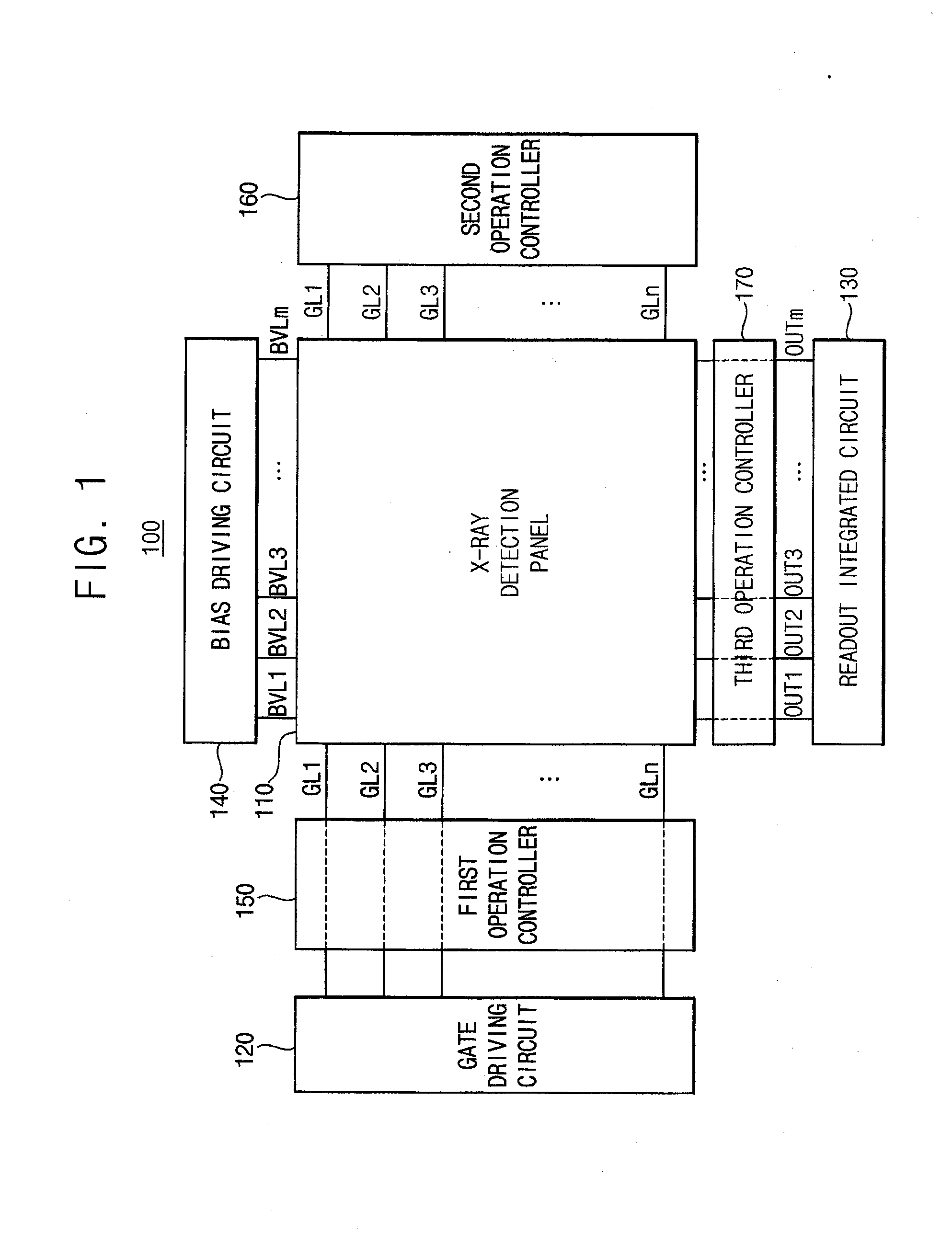

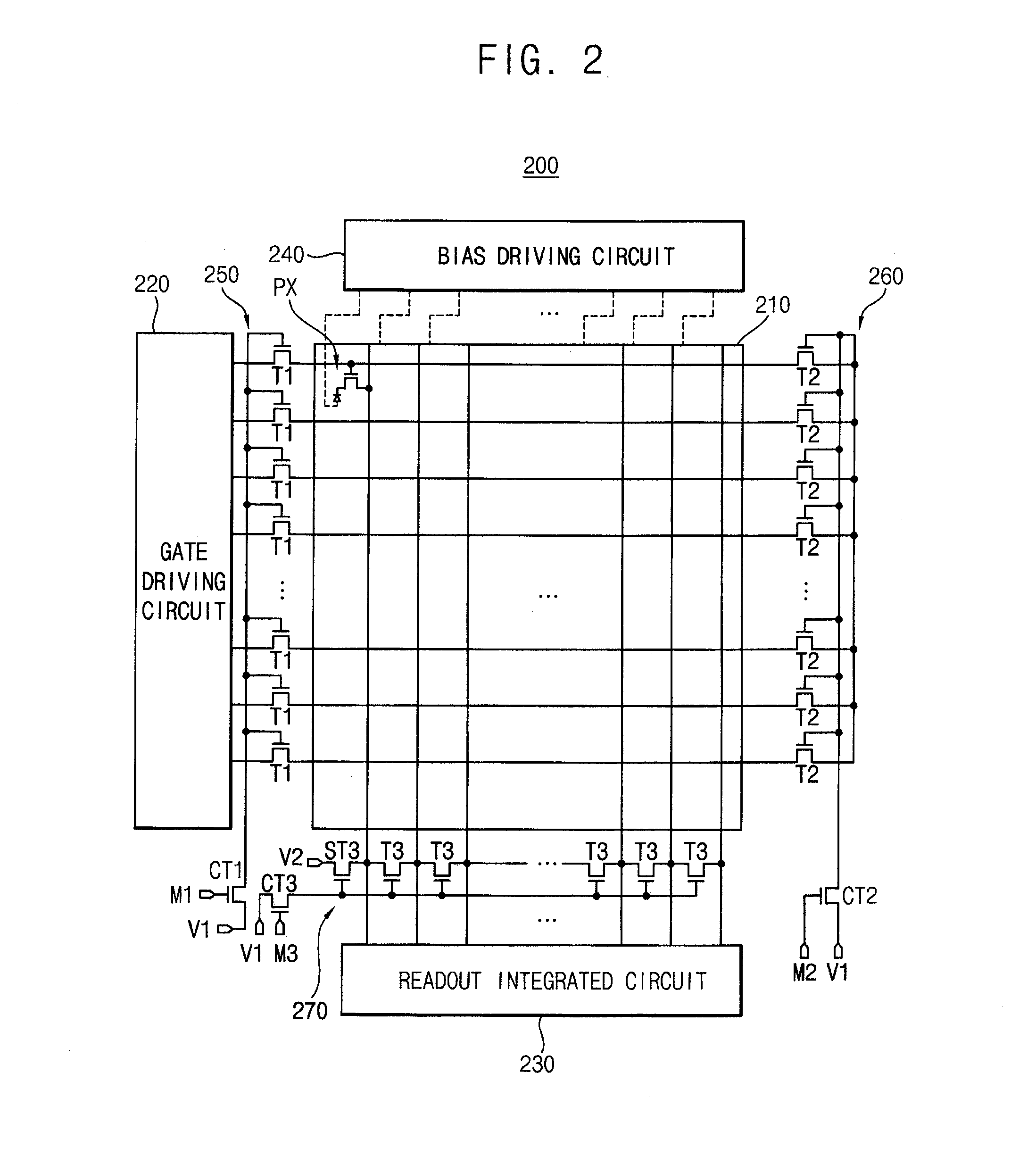

X-ray detection device and method of driving an x-ray detection panel

ActiveUS20140124675A1Reduce image lagLower frame rateTelevision system detailsSolid-state devicesSoft x rayX-ray

An X-ray detection device includes an X-ray detection panel having a plurality of gate-lines, a plurality of data-lines, a plurality of bias-lines, a plurality of pixel circuits, a gate driving circuit that sequentially provides a gate signal to the pixel circuits via the gate-lines when an X-ray detecting operation is performed, a readout integrated circuit that performs a readout operation of a detection signal that is output from the pixel circuits via the data-lines when the X-ray detecting operation is performed, a bias driving circuit that provides a forward-bias voltage or a reverse-bias voltage to the pixel circuits via the bias-lines, and an operation control circuit that controls a forward-biasing operation and an initializing operation to be simultaneously performed on the pixel circuits.

Owner:SAMSUNG DISPLAY CO LTD

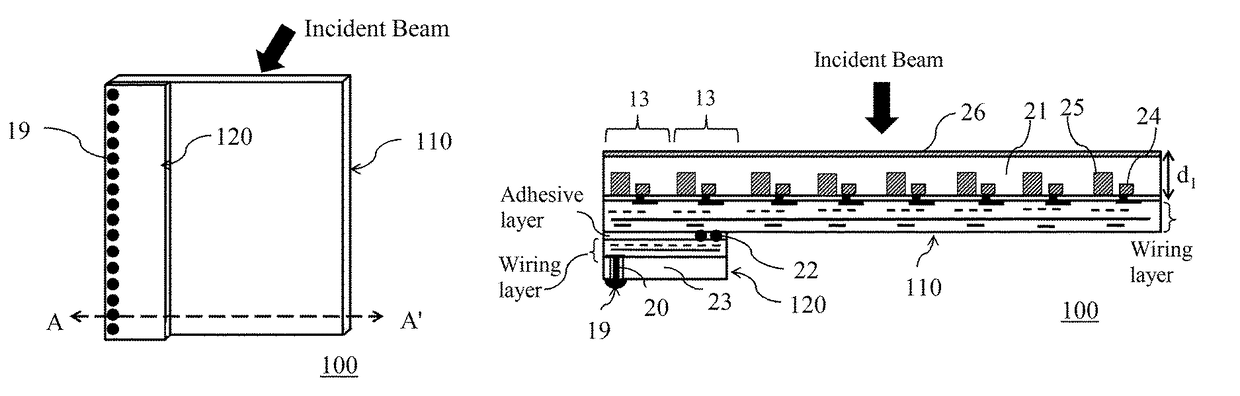

Solid-state image sensor and imaging apparatus including the same

ActiveUS9808159B2Large image sensing areaPreventing and limiting radiation damageSolid-state devicesDiagnostic recording/measuringSemiconductor chipOptoelectronics

An image sensor includes a first semiconductor chip including first and second surfaces; a second semiconductor chip including first and second surfaces; and a first adhesive layer between the second surface of the first semiconductor chip and the second surface of the second semiconductor chip, the first semiconductor chip being stacked on the second semiconductor chip via the first adhesive layer such that a footprint of the first semiconductor chip is larger than a footprint of the second semiconductor chip with respect to a plan view of the image sensor, the first semiconductor chip including an array of unit pixels configured to capture light corresponding to an image and to generate image signals based on the captured light, the second semiconductor chip including first peripheral circuits configured to control the array of unit pixels and receive the generated image signals.

Owner:SHIZUKUISHI MAKOTO

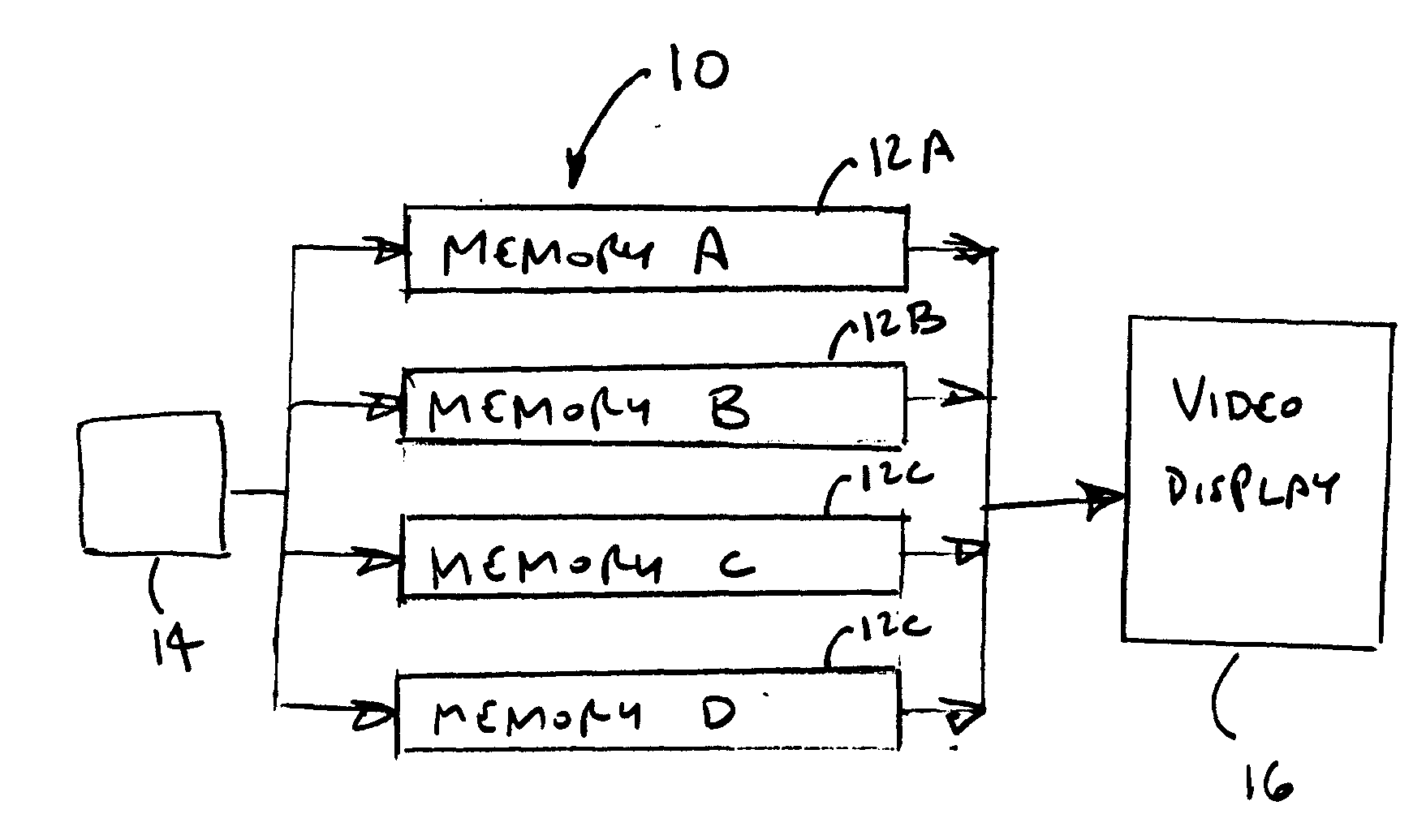

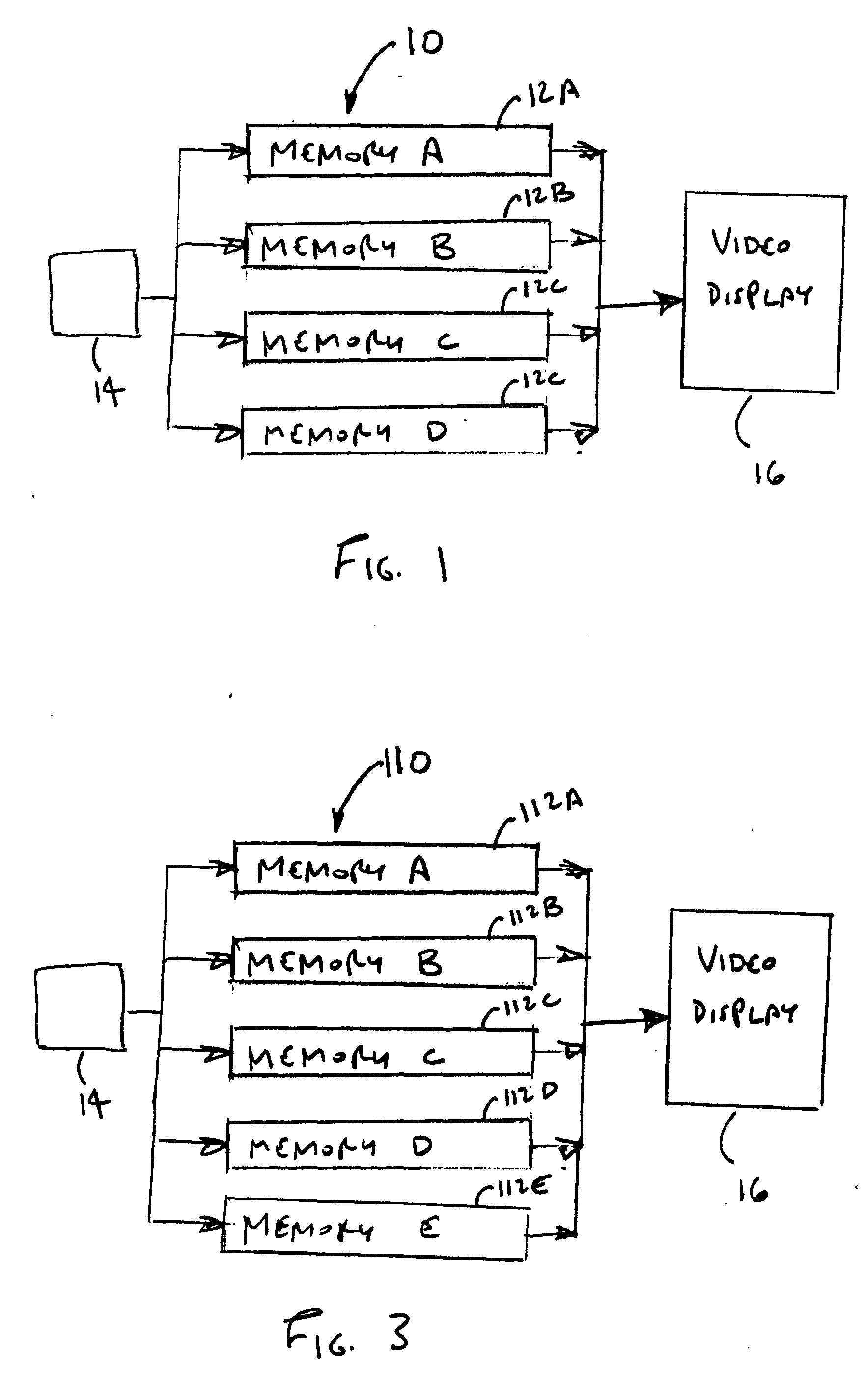

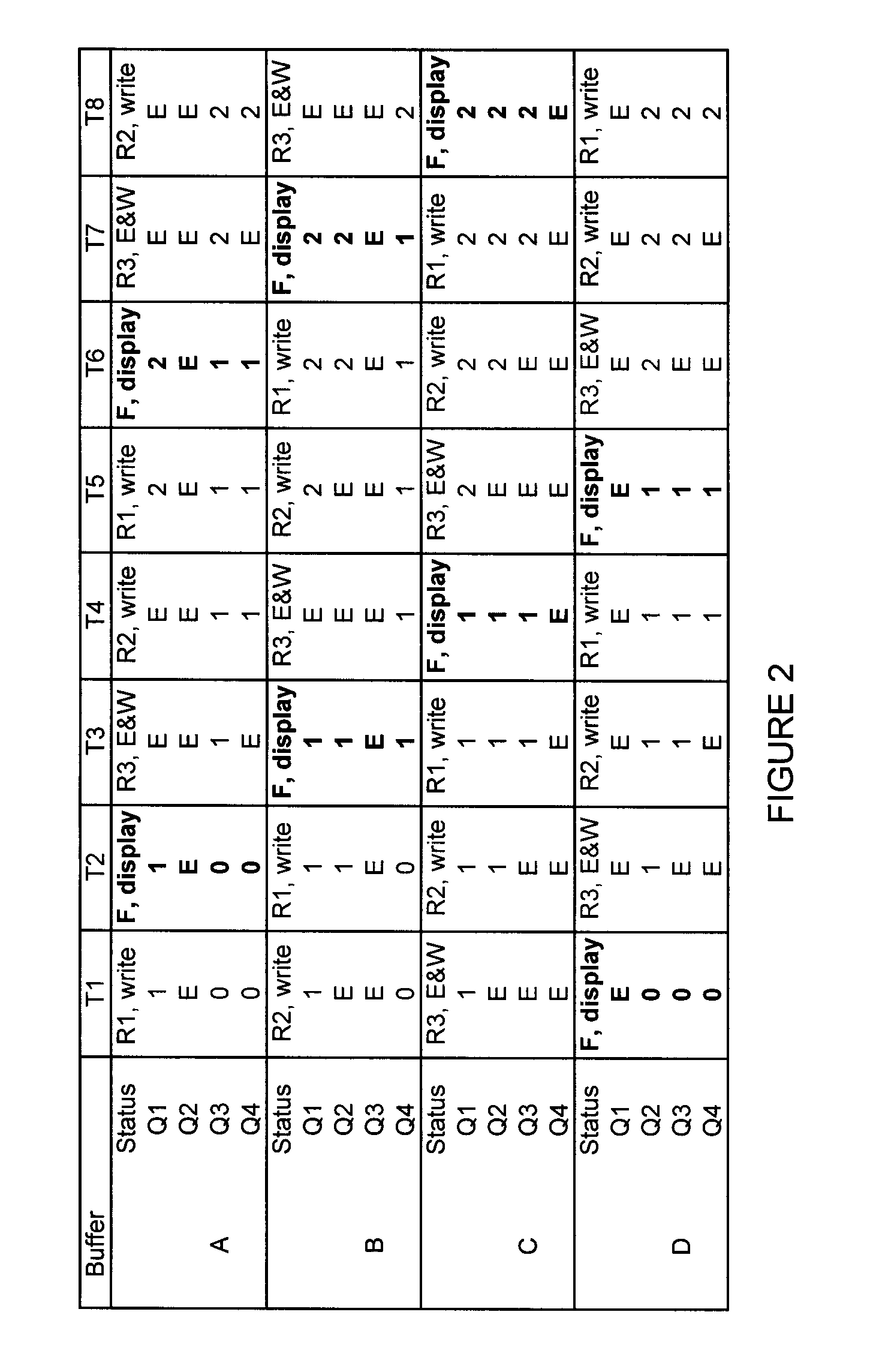

Method for reducing video image latency

ActiveUS20090256851A1Reduce image lagImage degradationCathode-ray tube indicatorsInput/output processes for data processingVideo imageImaging data

Image latency is reduced in a video display system where an image is displayed for a stroke video frame period. The system has a display device and a plurality of memory buffers, each of which is adapted to receive image data (in a receiving condition) or to display data to the display device (in a display condition). The stroke video frame period is divided into at least two time periods and the number of memory buffers provided is at least the number of time periods per stroke video frame period. One of the memory buffers is in the display condition for a first time period, with the remaining memory buffers in the receiving condition. At the end of the time period, the memory buffers are rotated so that the displayed memory buffer moves to the receiving condition and one of the receiving buffers moves into the display condition.

Owner:MERCURY MISSION SYST LLC

Pixel sensor with reduced image lag

ActiveUS7732845B2Lower a potential barrierLower potential barrierSolid-state devicesSemiconductor/solid-state device manufacturingCMOSEngineering

Owner:GLOBALFOUNDRIES U S INC

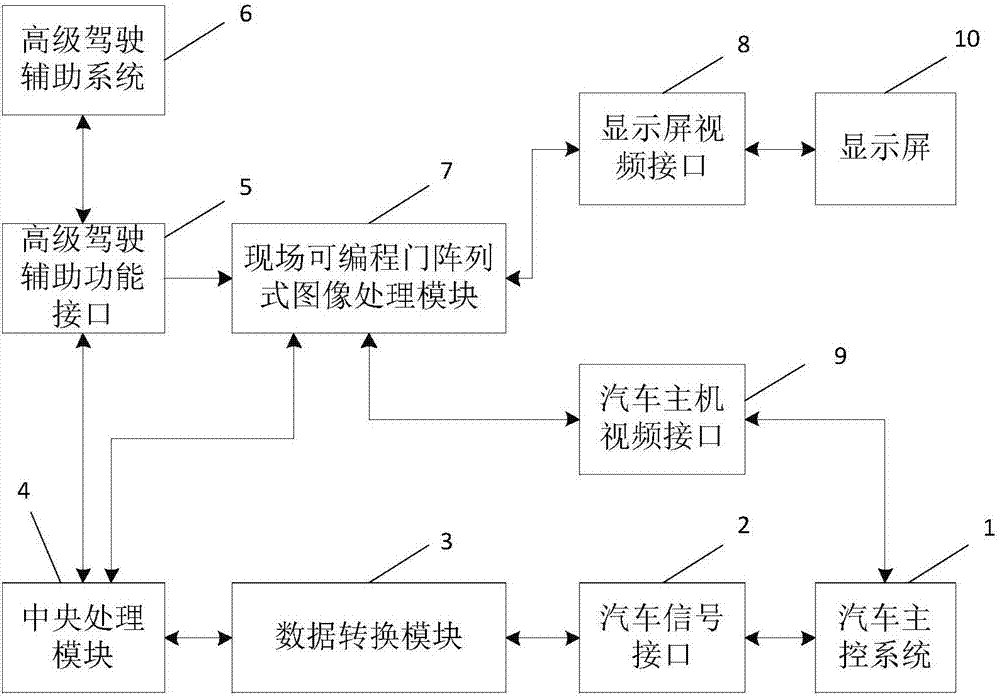

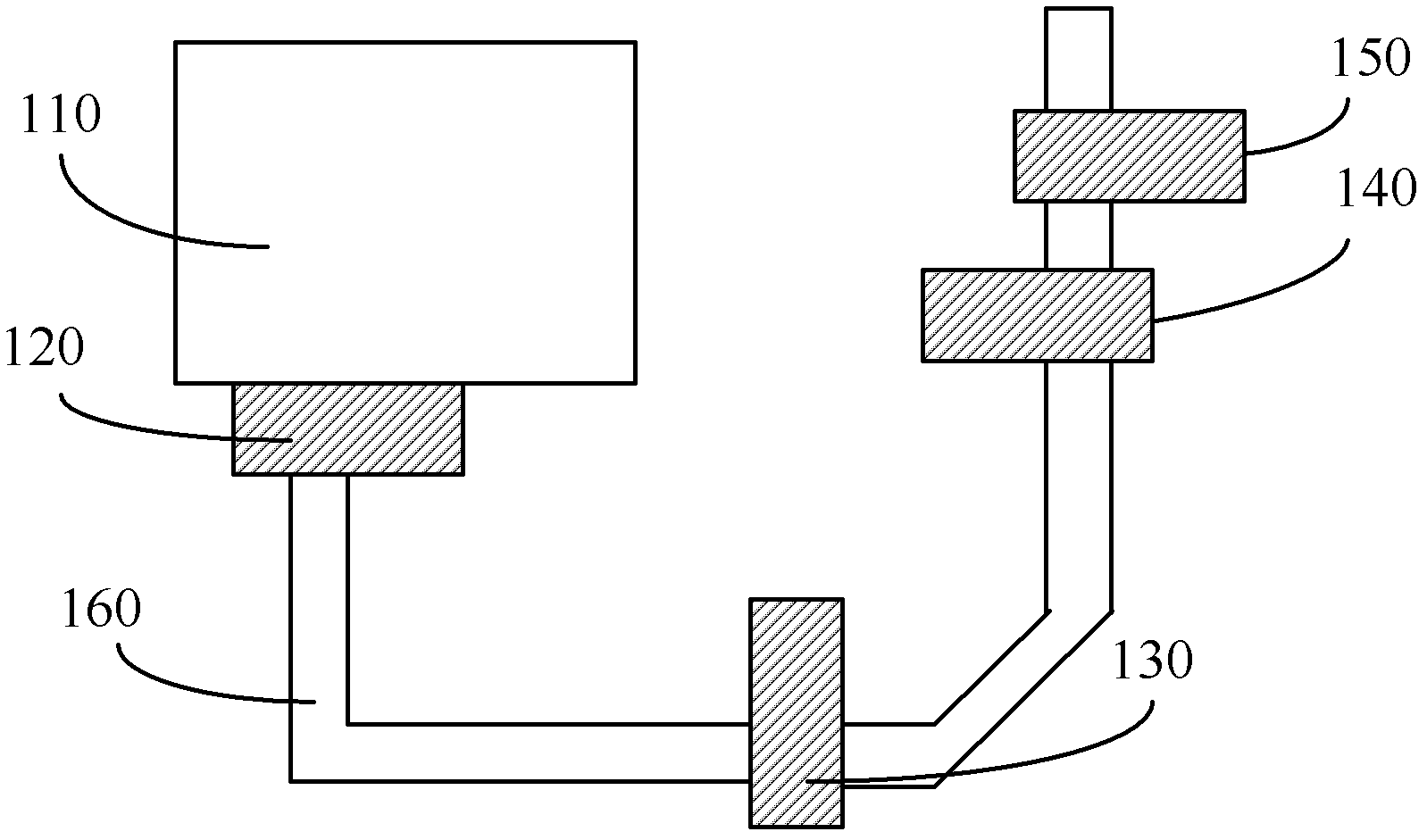

Advanced driving-assistance function upgrading system

PendingCN106864393AReduce image lagReduce image stuttering and flickeringElectric/fluid circuitInput/output processes for data processingEmbedded systemCar driving

The invention relates to the technical field of vehicle driving assistance, in particular to an advanced driving-assistance function upgrading system. The advanced driving-assistance function upgrading system comprises a vehicle signal interface, a data conversion module, a central processing module, an advanced driving assistance function interface, a field-programmable gate array picture processing module, a display screen video interface, and a vehicle main engine video interface. By using the high-speed central processing module and the field-programmable gate array picture processing module to conduct quick analysis processing on CAN bus data and picture-text signals and picture signals respectively, the picture delay can be effectively lowered, picture jamming, stopping and flickering are relieved, and the user experience is improved.

Owner:SHENZHEN KLLEN AUTIAN NAVIGATION TECH CO LTD

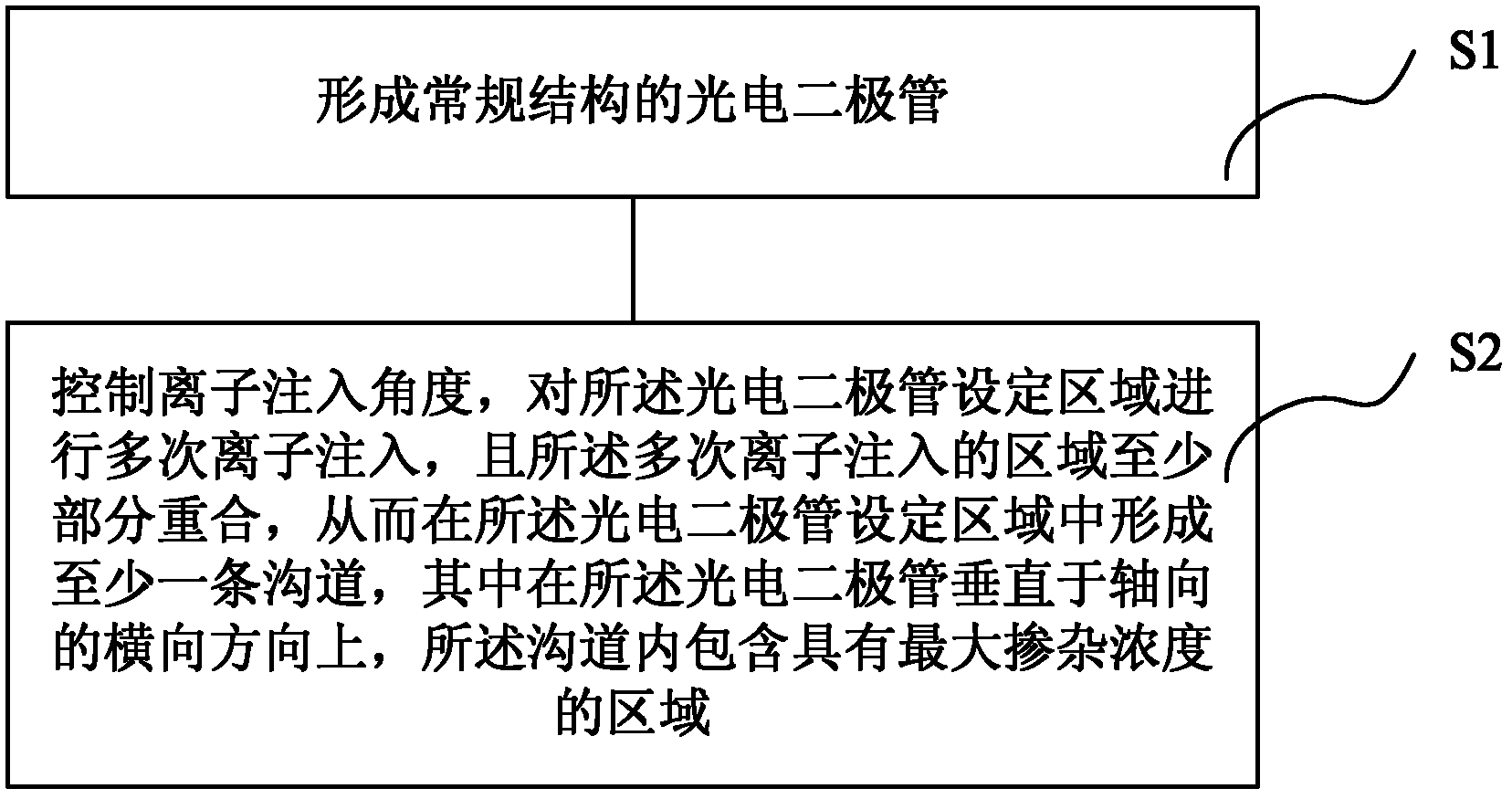

Method for manufacturing CMOS (complementary metal-oxide-semiconductor transistor) image sensor

InactiveCN102222680AReduce in quantityImprove collection efficiencyRadiation controlled devicesCMOSEngineering

The invention relates to a method for manufacturing a CMOS (complementary metal-oxide-semiconductor transistor) image sensor, wherein the method comprises the steps of: forming a photodiode with a common structure; and controlling an ion injecting angle, carrying out a plurality of times of ion injection on set areas of the photodiode, wherein the areas subjected to the plurality of times of ion injection are partially overlapped, so that at least one trench is formed among the set areas of the photodiode and the trench comprises areas with maximal doping concentration in transverse directions of the photodiode vertical to an axial direction. In the method for manufacturing the CMOS image sensor, the plurality of times of ion injection are carried out on the photodiode and the ion injecting angle is adjusted, thus the trench with the doping concentration greater than of that of the other areas of the photodiode is formed in the photodiode; and the trench comprises the areas with the maximal doping concentration, so that photoelectrons are effectively driven to move, the quantity of the delayed photoelectrons is reduced, the transfer efficiency of the photodiode is improved, and the phenomenon of image delay or information loss is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

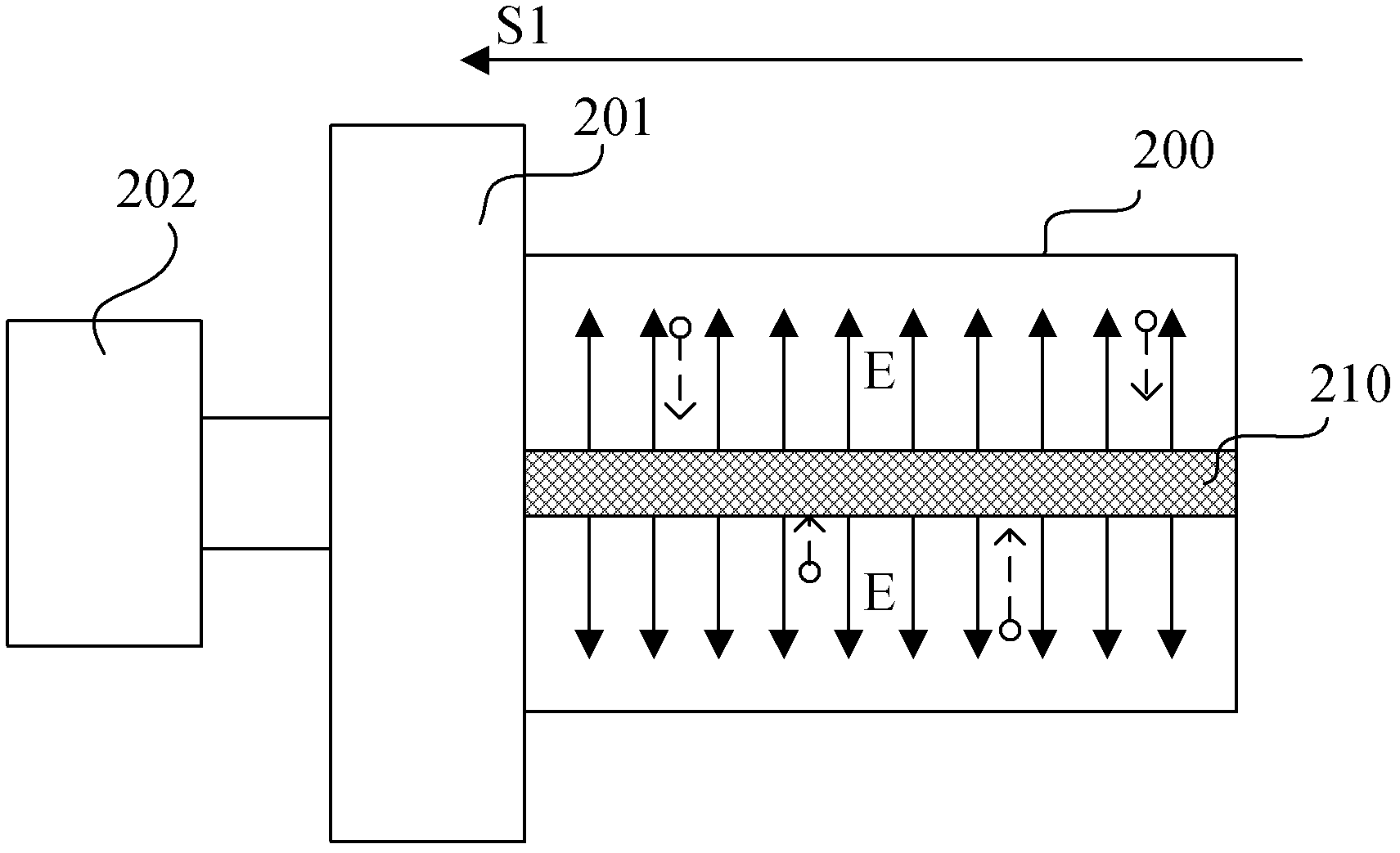

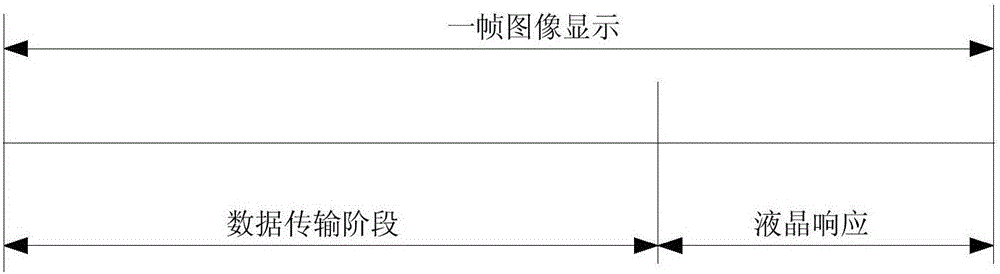

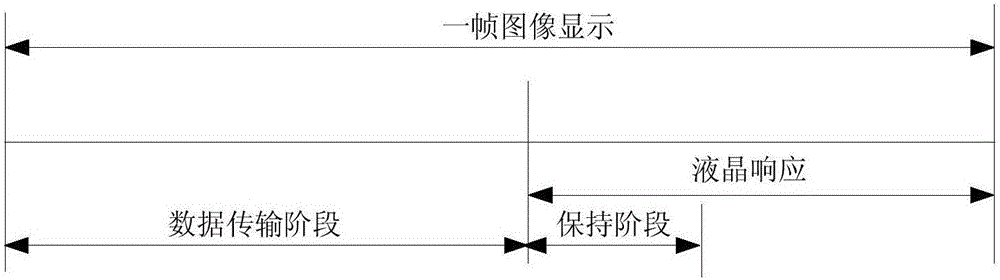

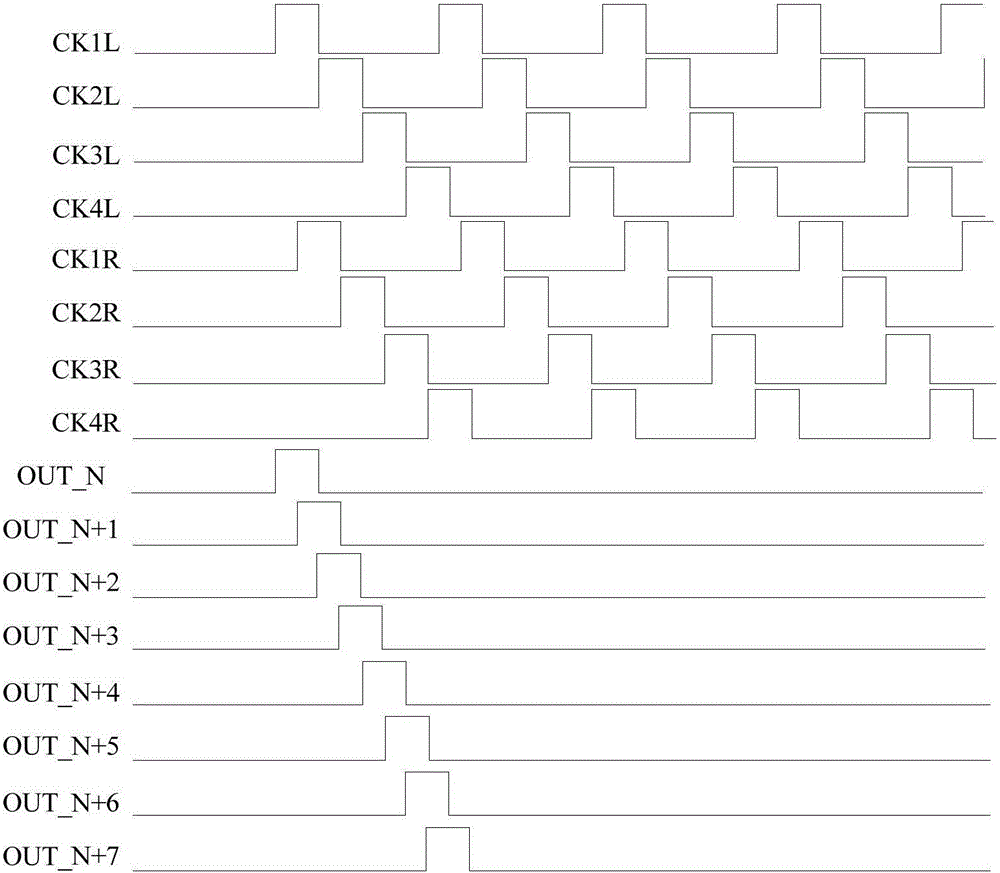

Driving method of liquid crystal display panel and liquid crystal display panel

ActiveCN106205525ASolve dizzinessOffset response timeStatic indicating devicesLiquid-crystal displayData transmission

The invention belongs to the technical field of display and particularly relates to a driving method of a liquid crystal display panel and the liquid crystal display panel. The driving method of the liquid crystal display panel is used to display images frame by frame, the display process of each frame of image includes a data transmission stage including successively turning on the control element of each pixel, transmitting the image data to each pixel, and turning off the control element of each pixel after the image data is transmitted to each pixel; and a maintaining stage including maintaining the control elements of all of the pixels at the off state after the data of the whole frame of image is transmitted. The driving method of the liquid crystal display panel can at least solve the dizziness problem of virtual reality VR application, guarantees the touch control effect, and moreover, with respect to high refreshing frequency, the power consumption is reduced, and the application value of a display screen is greatly improved.

Owner:BOE TECH GRP CO LTD +1

CMOS image sensor and fabrication method thereof

ActiveUS20170200758A1Increase full well capacityReduce image lagTransistorSolid-state devicesCMOSBiomedical engineering

The present disclosure provides CMOS image sensors and fabrication methods thereof. An exemplary fabrication process of a CMOS image sensor includes providing a substrate having a first region and a second region connecting with the first region at a first end of the first region: forming a transfer transistor on surface of the substrate in the second region; forming a first implanting region in the substrate in the first region using a first mask; forming a second implanting region in the first implanting region by, the first implanting region being separated into a third implanting region on the second implanting region and a fourth implanting region under the second implanting region; forming a fifth region in the second region at the first end using a second mask, connecting the third implanting region with the fourth implanting region.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

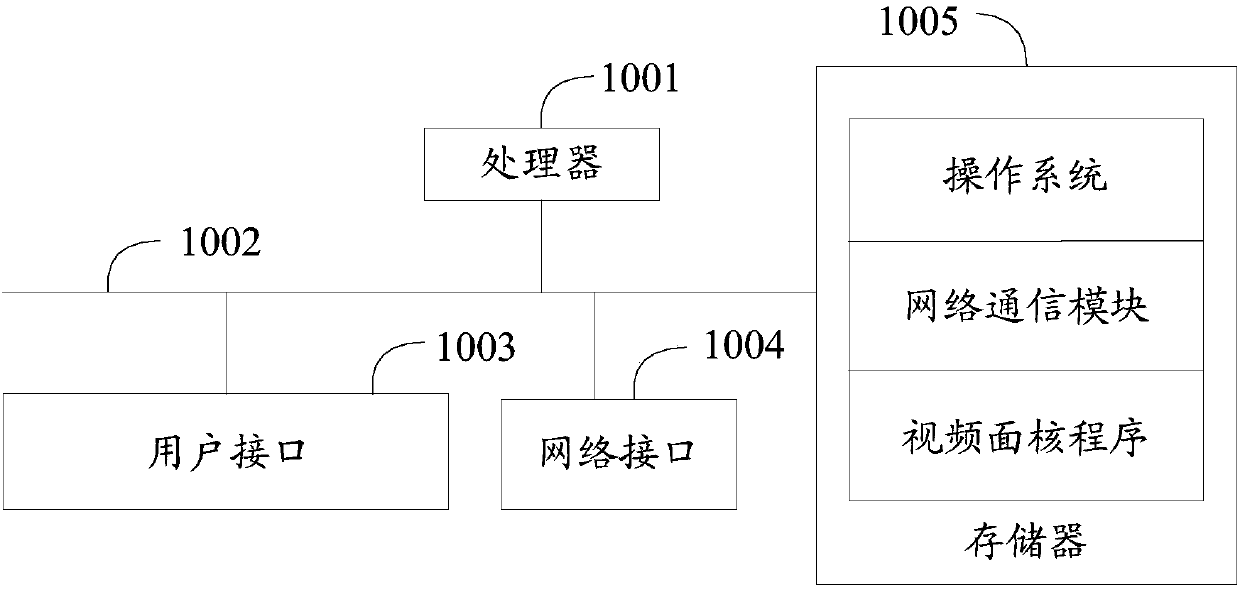

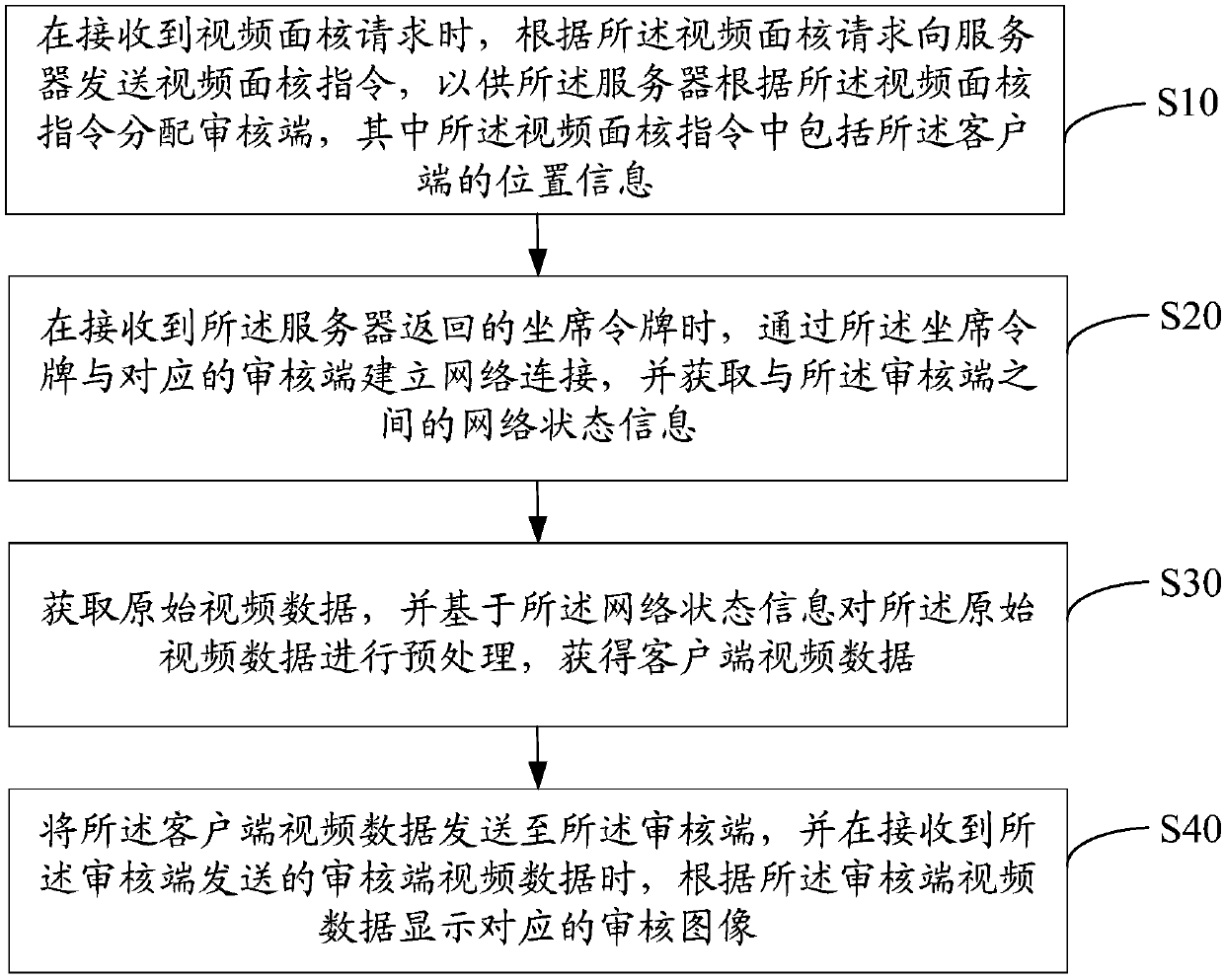

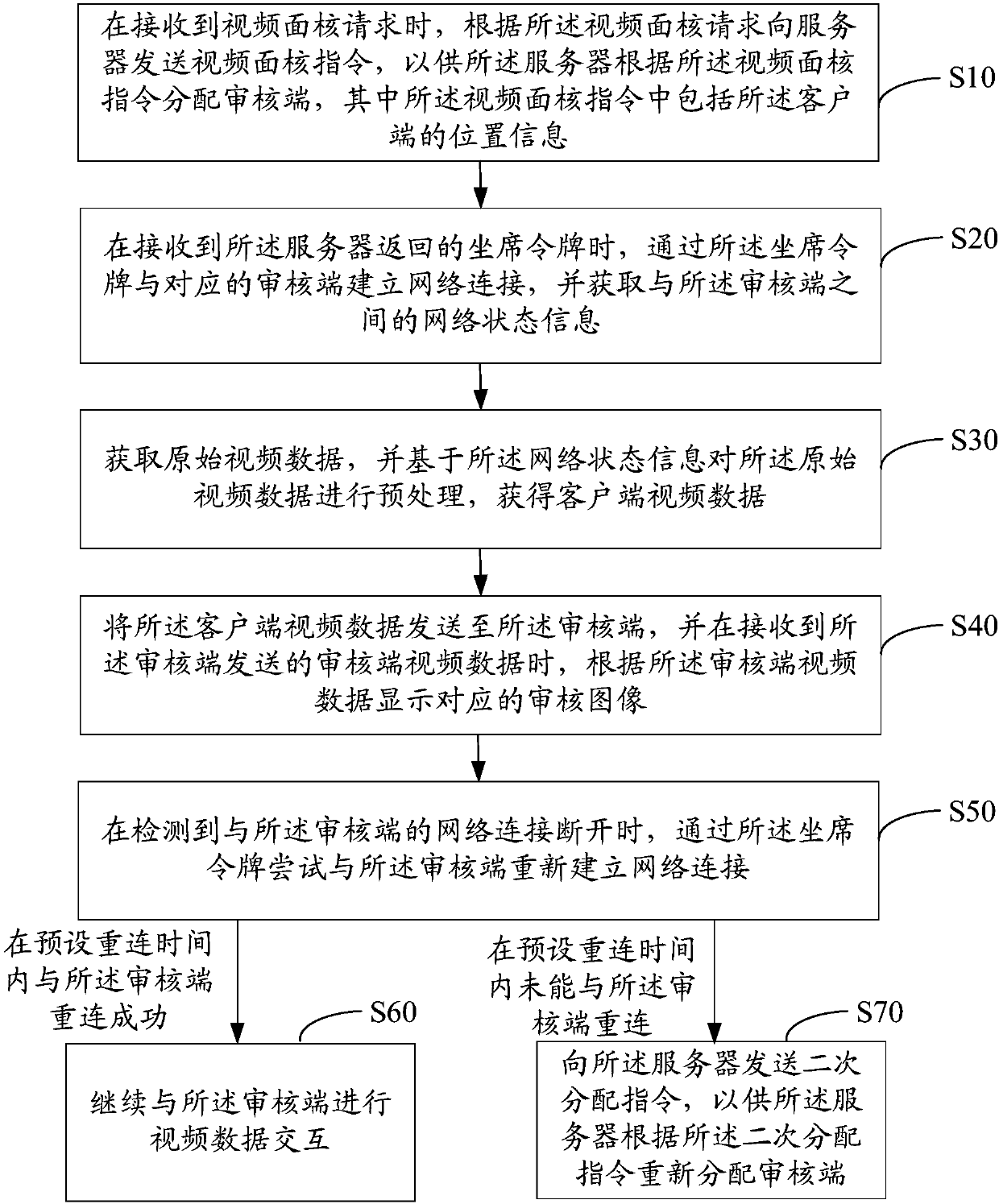

Video face kernel method, client, server and computer readable storage medium

InactiveCN109756701AImplementation delayAchieve jitterFinanceClosed circuit television systemsKernel methodNetwork connection

The invention provides a video face check method, which comprises the following steps that: when receiving a video face check request, a client sends a video face check instruction to a server, so that the server distributes a check end; When the agent token returned by the server is received, establishing a network connection with a corresponding audit end, and obtaining network state informationbetween the agent token and the audit end; obtaining original video data, and preprocessing the original video data based on the network state information to obtain client video data; and sending theclient video data to the auditing terminal, and displaying a corresponding auditing image when receiving the auditing terminal video data. The invention also provides a client, a server and a computer readable storage medium. According to the method, when the video face check is carried out, image jamming caused by a network problem in the video face check process can be reduced, the fluency andthe stability of the real-time video in the video face check process are improved, and the video face check process is guaranteed to be carried out smoothly.

Owner:ONE CONNECT SMART TECH CO LTD SHENZHEN