Patents

Literature

73results about How to "Optimal utilisation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

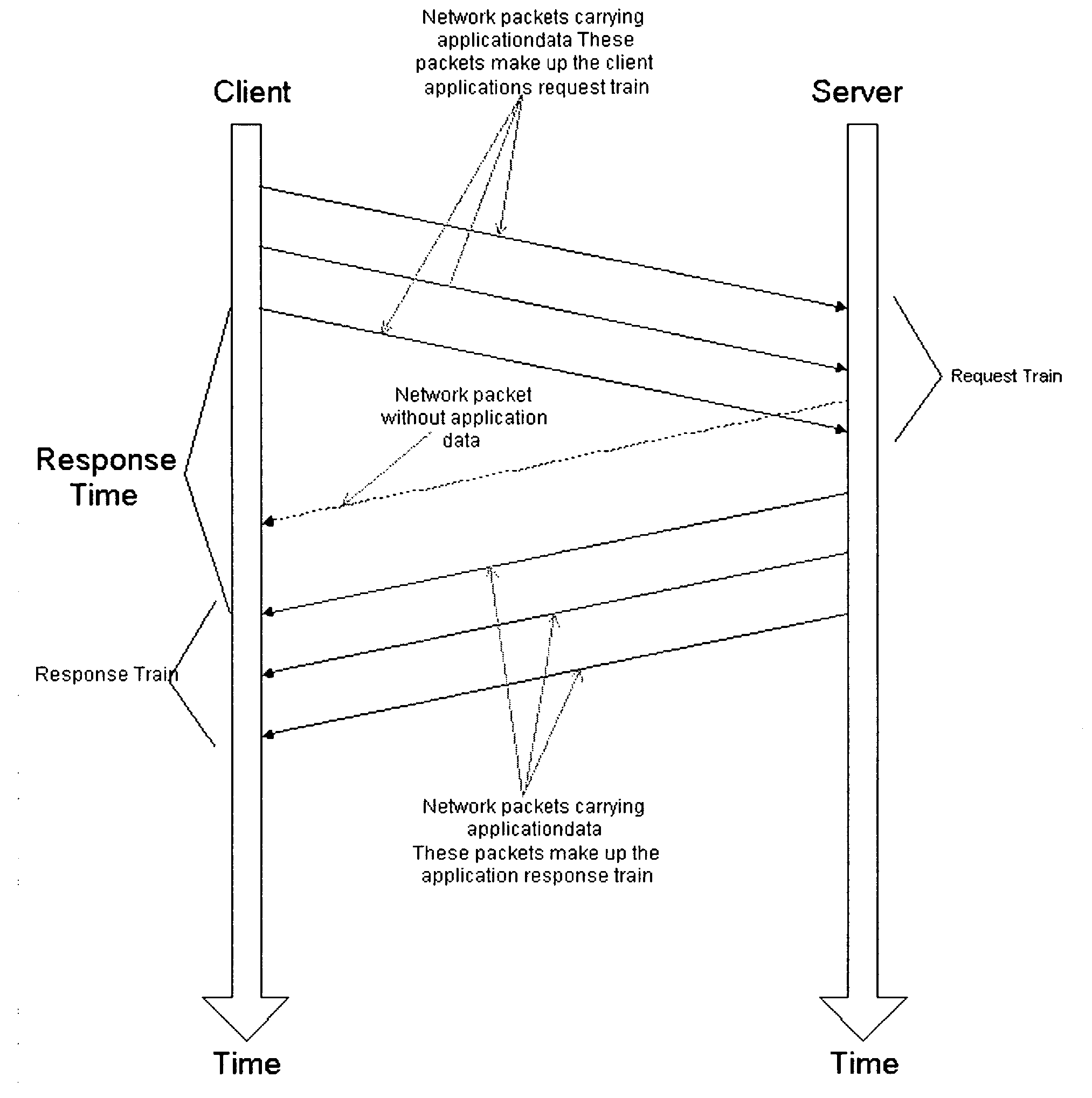

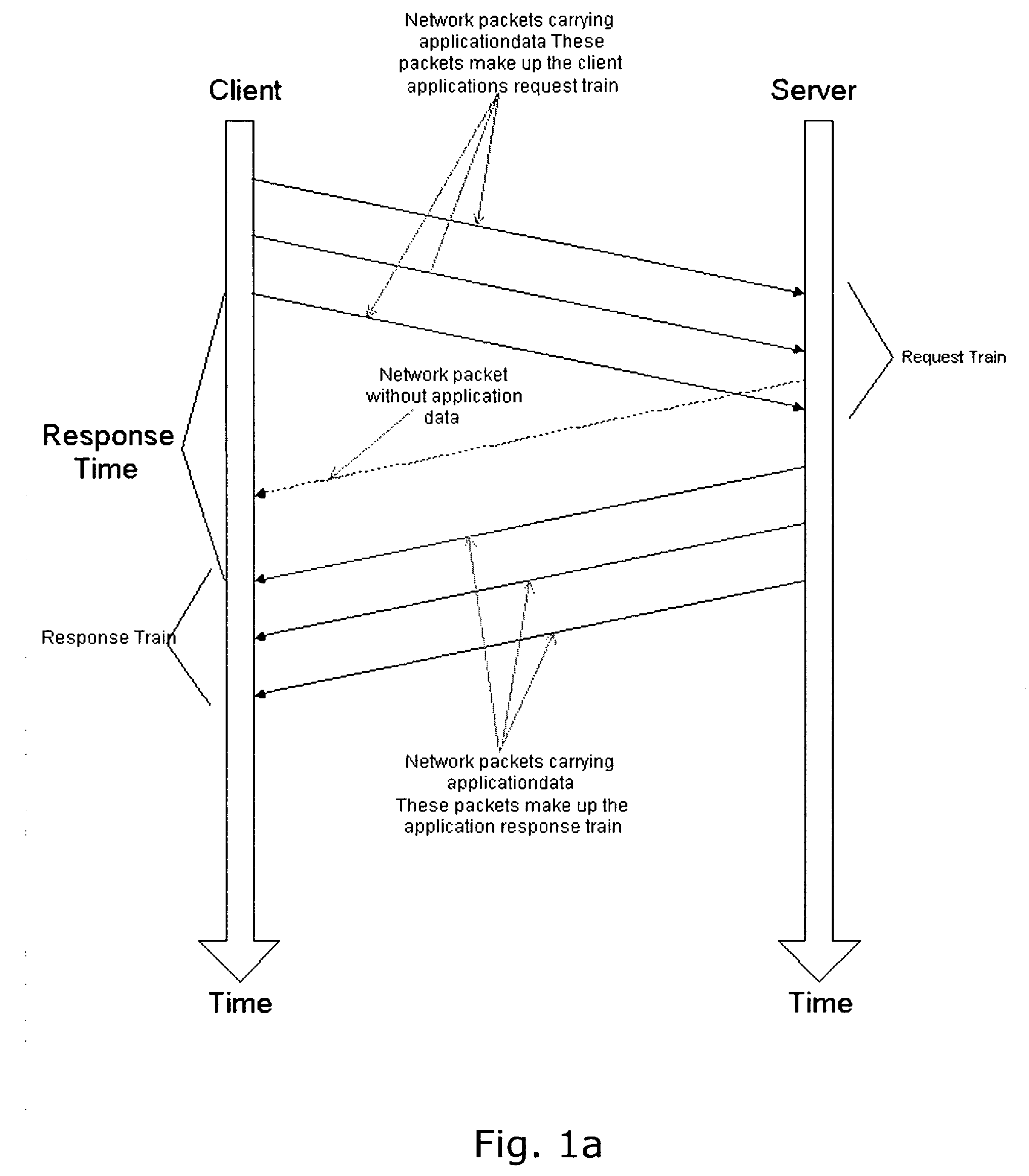

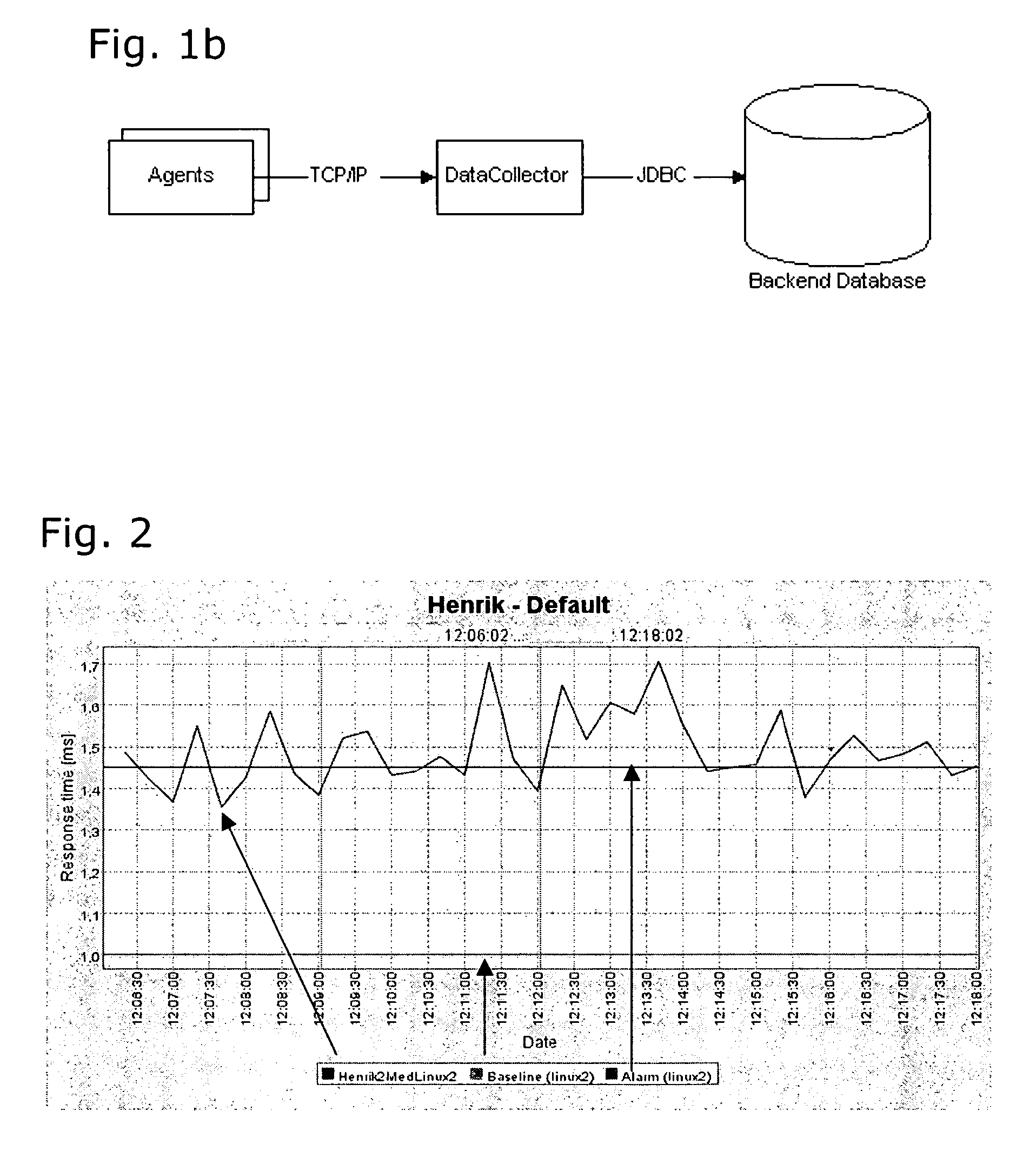

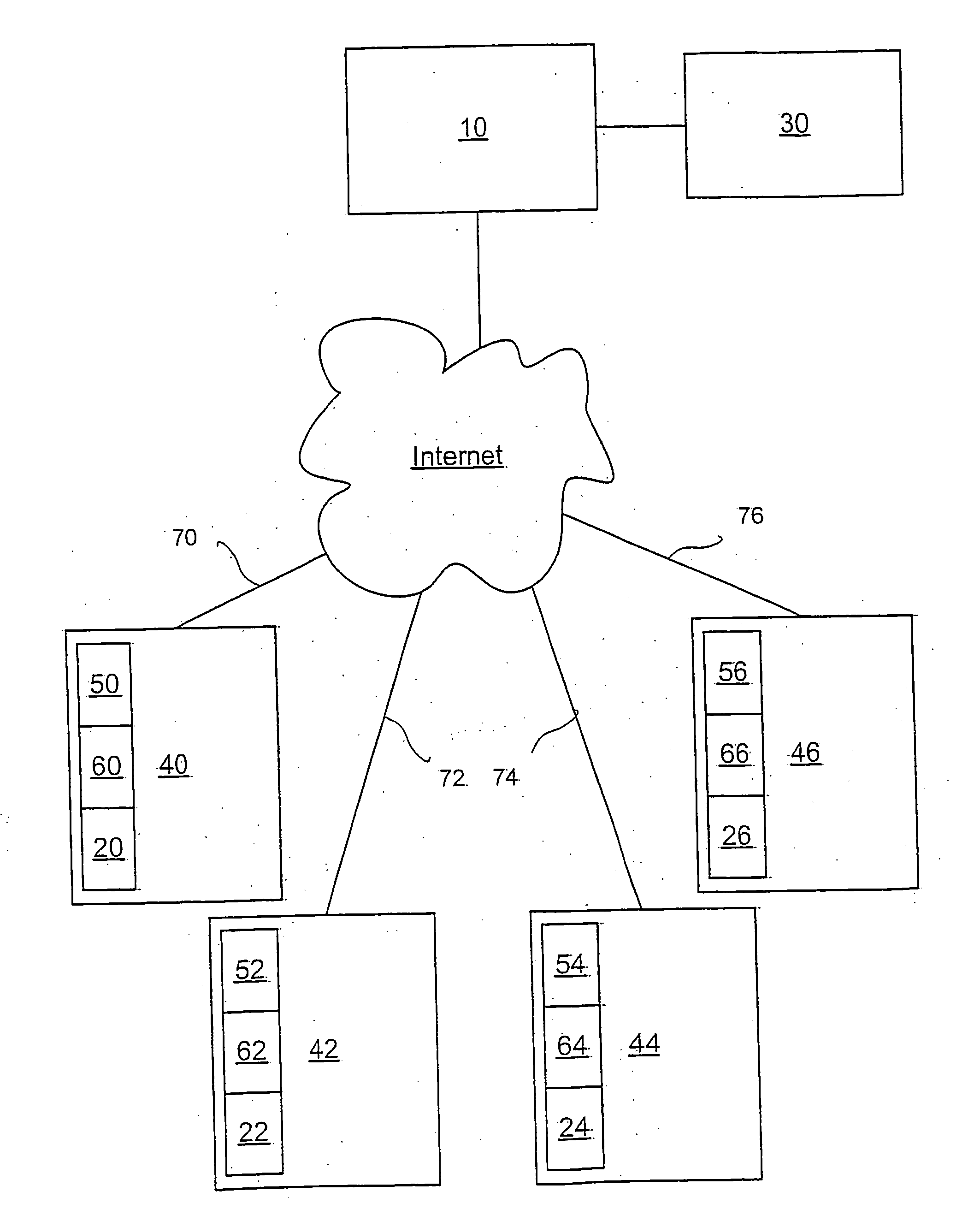

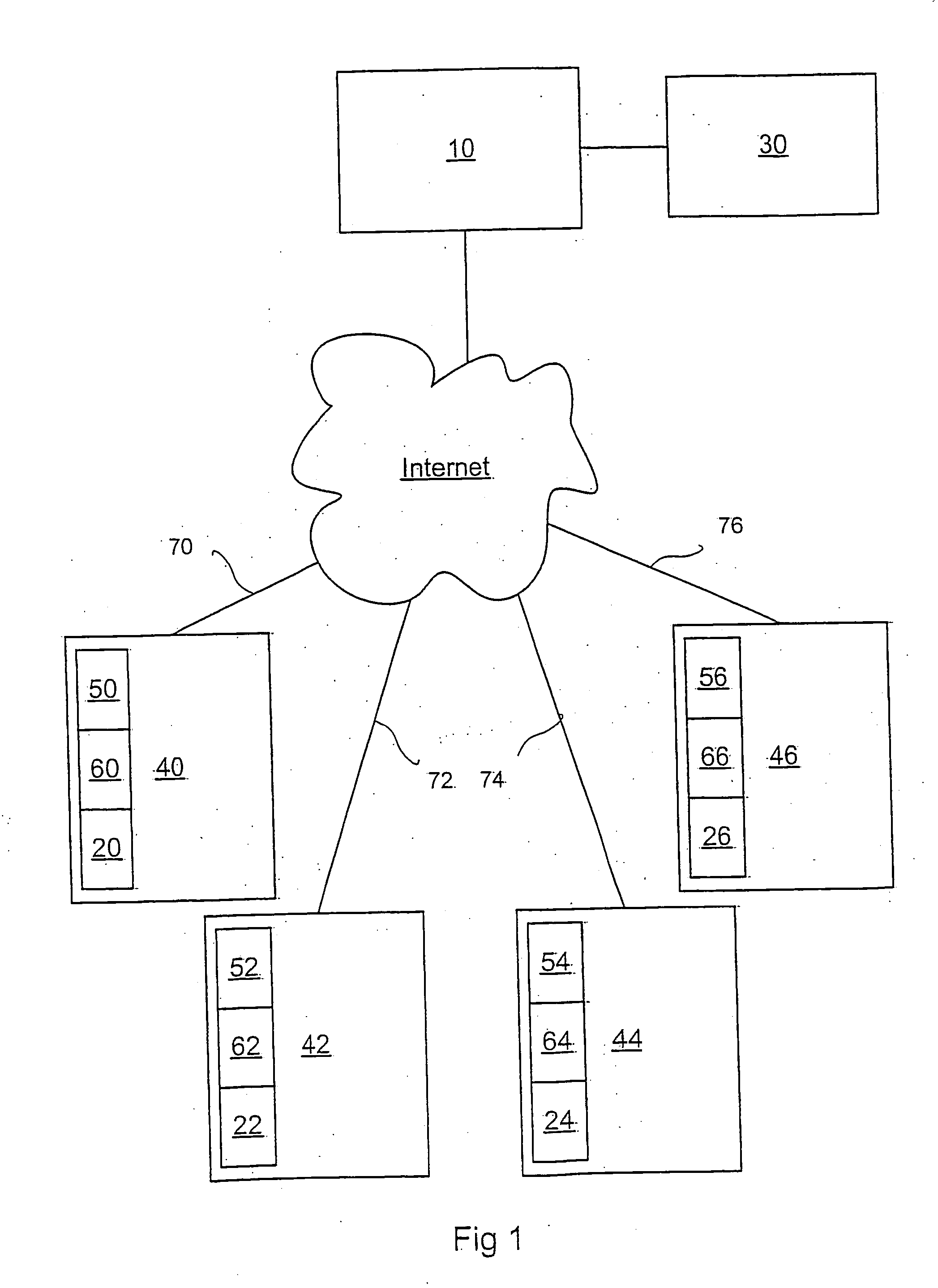

System and method for measuring and monitoring performance in a computer network

InactiveUS20050027858A1Efficient error detectionOptimal utilisationDigital computer detailsData switching networksNetwork connectionClient-side

A method and a computer program product for measuring and monitoring performance in a computer network environment that includes multiple clients and one or more servers providing one or more services is disclosed. The method includes monitoring the performance at each client based on true requests send to the servers over a network connection. The performance at each client is collected at a performance monitor database, where the collected performance data can be extracted to yield the performance of e.g. specific servers or services towards a specific client or a group of clients or the performance of a connection between a server and a client. The system performance is thereby measured at the clients where the system performance is actually utilized. The present invention thereby provides a more realistic scenario of the actual system performance than prior art systems based on monitoring server performance at the servers or through simulated clients.

Owner:PREMITECH

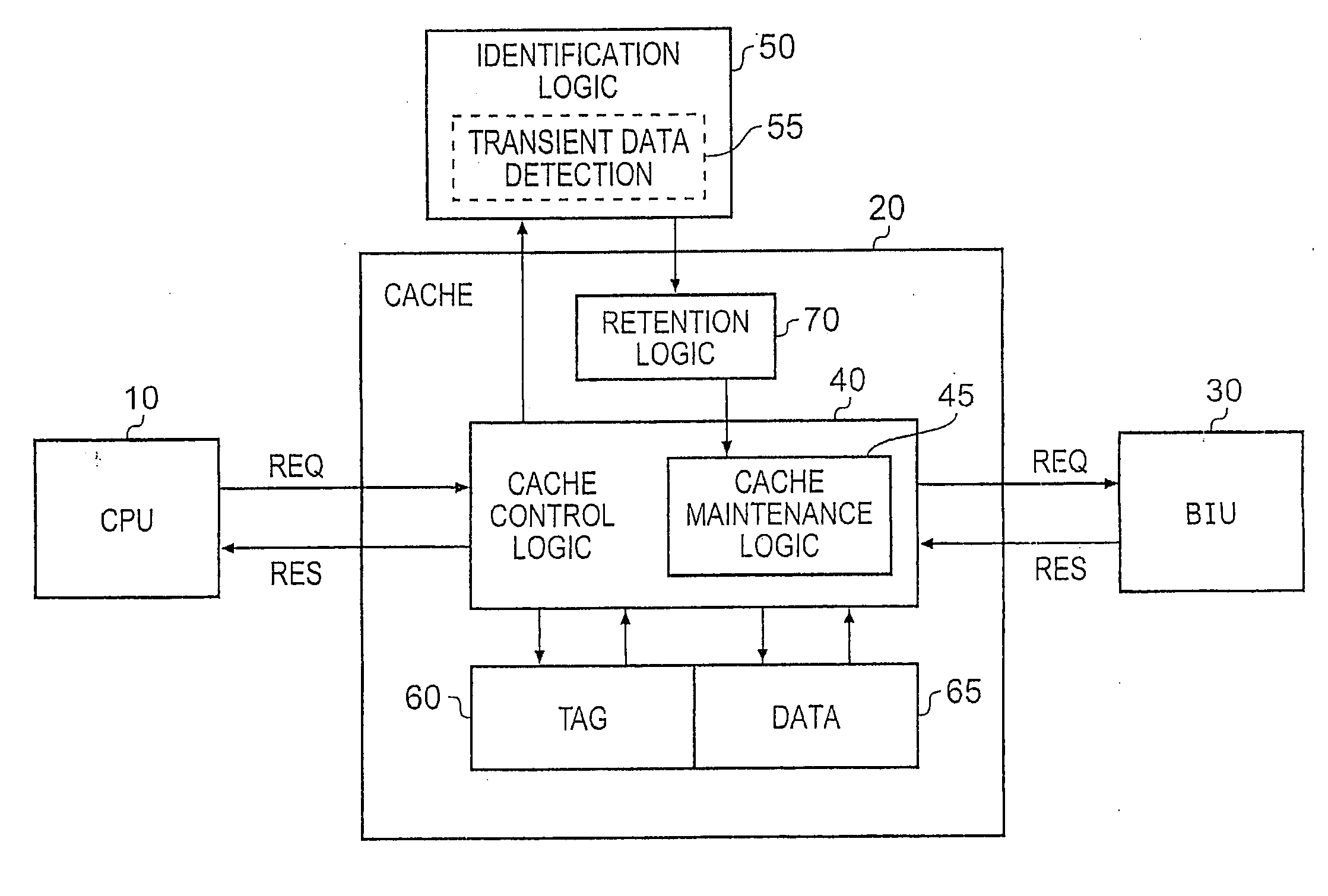

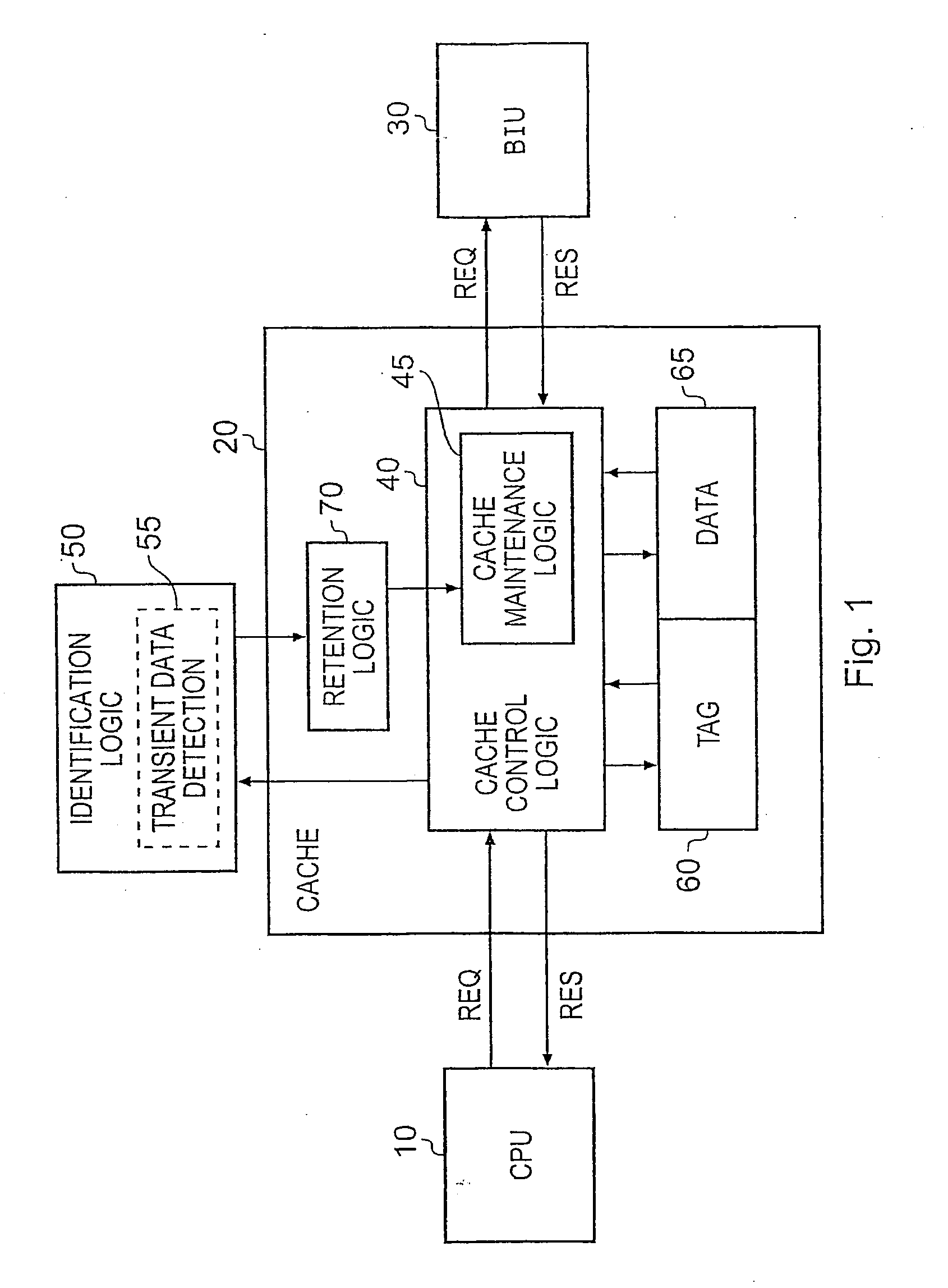

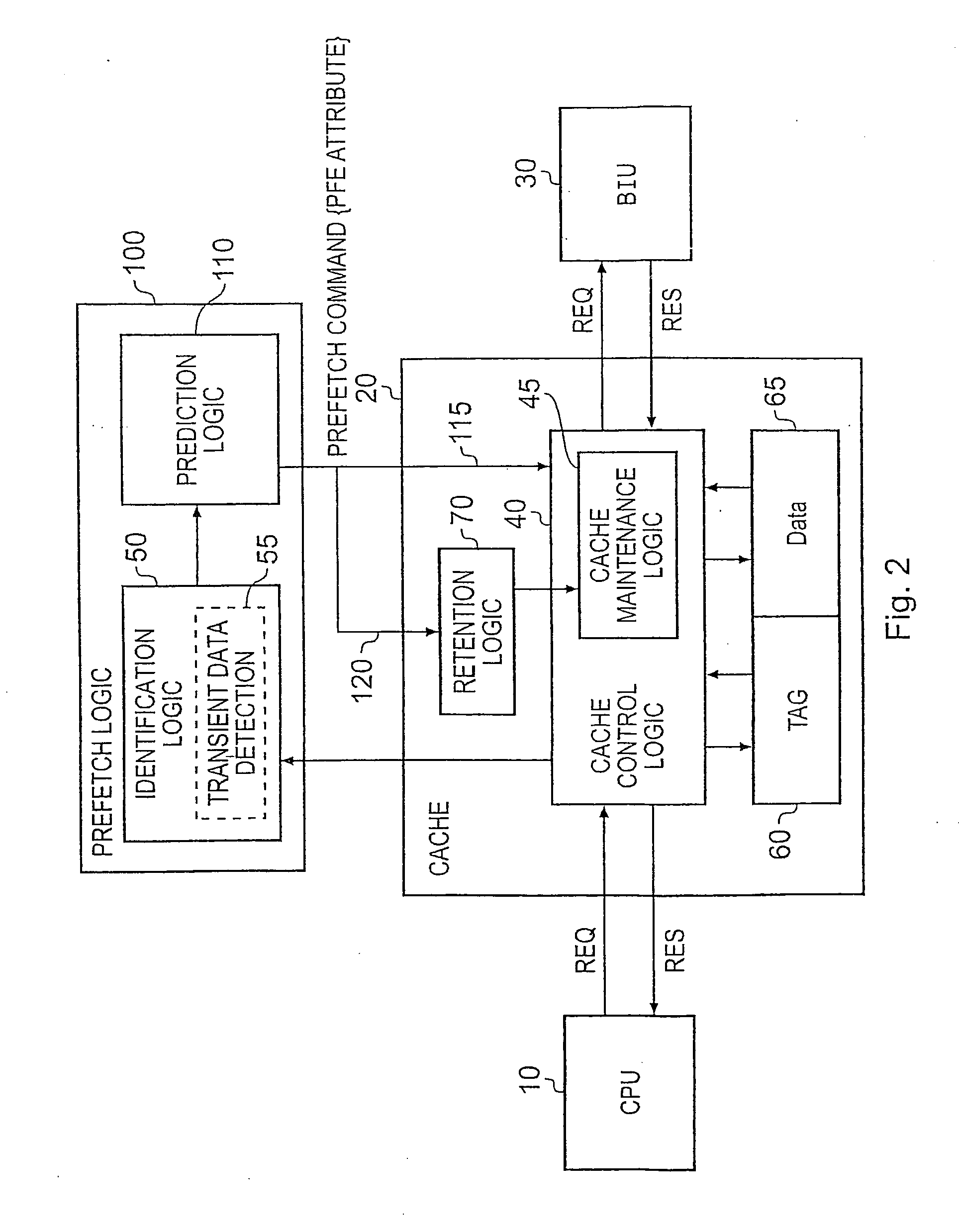

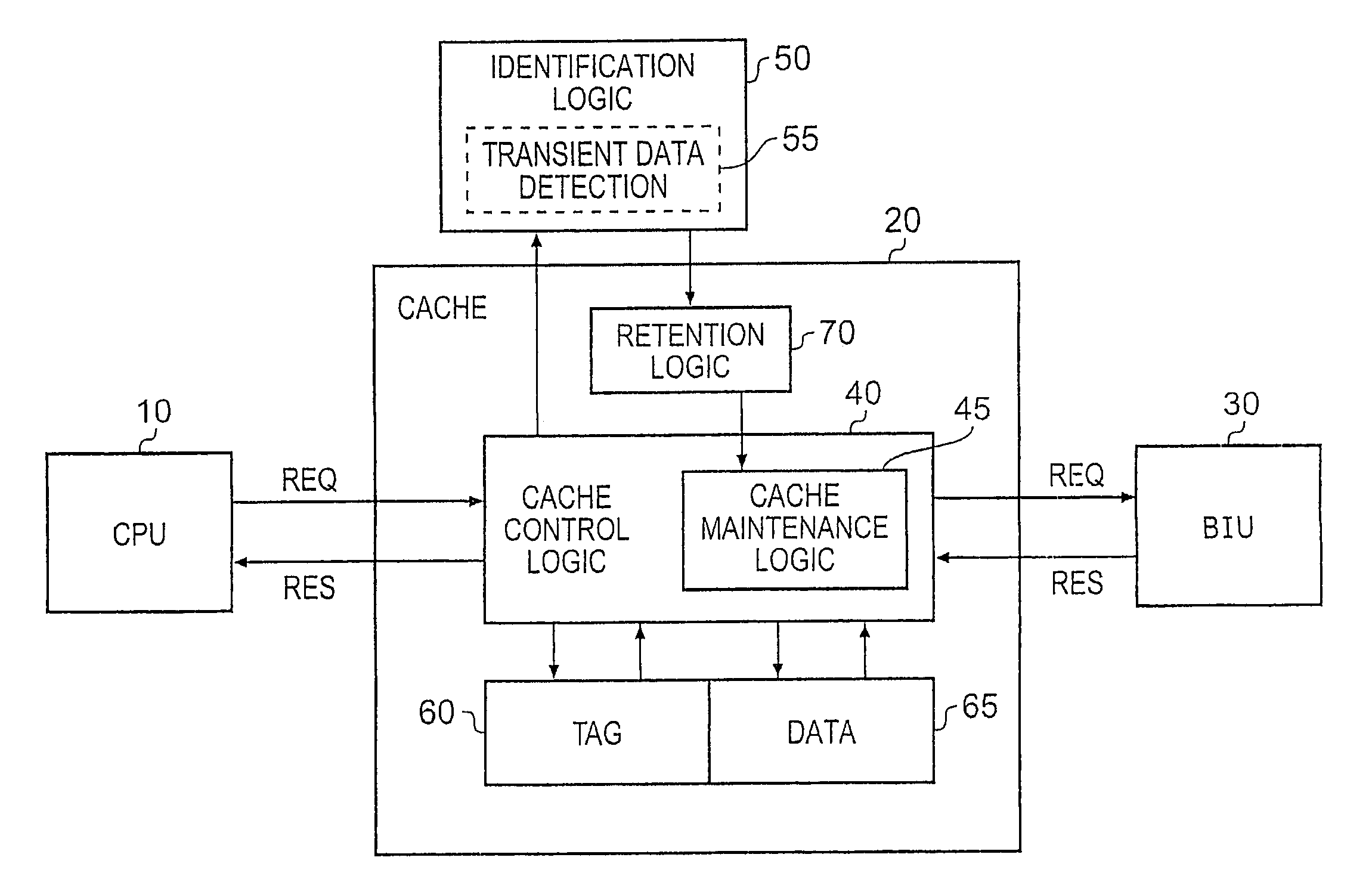

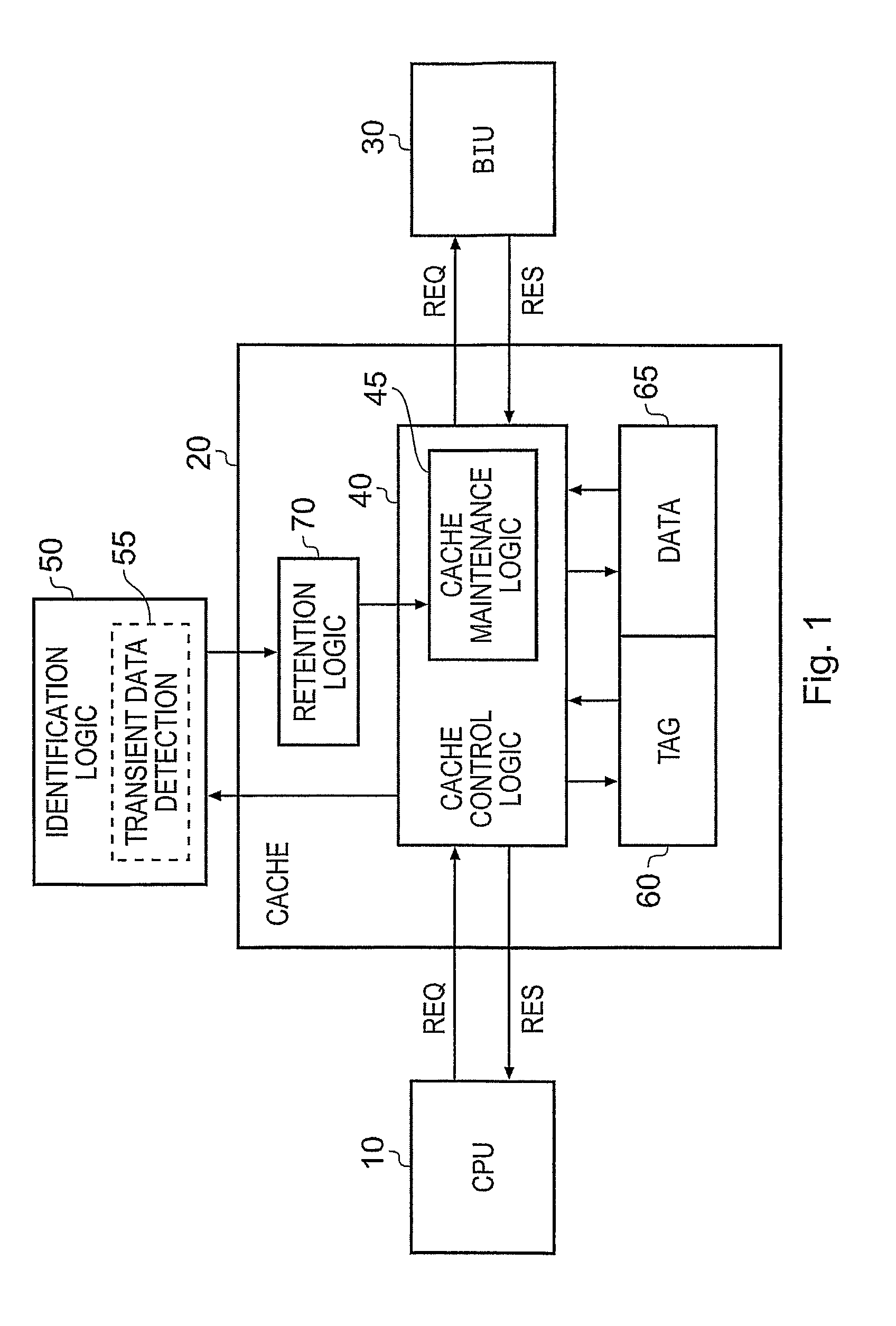

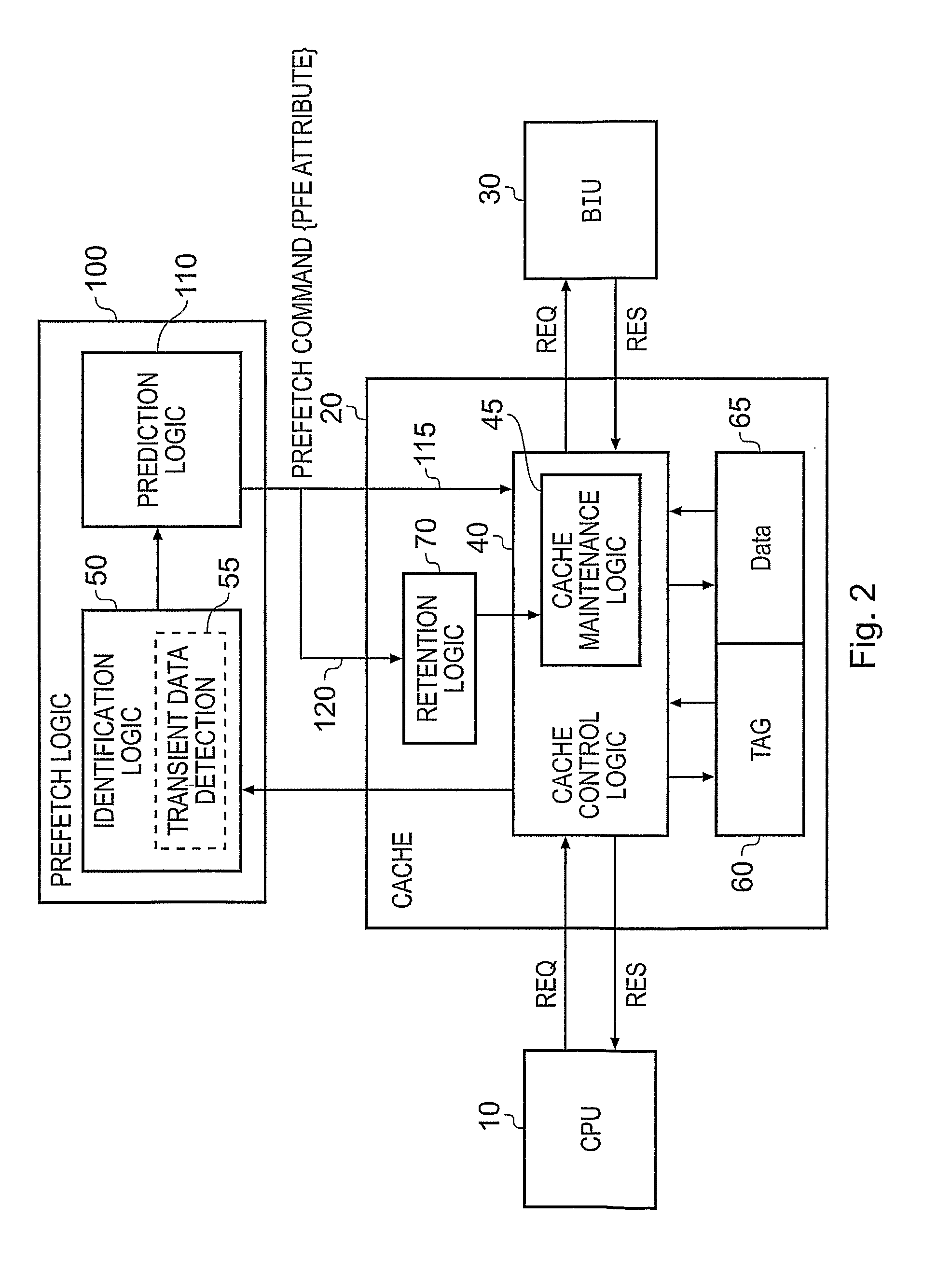

Cache Management Within A Data Processing Apparatus

ActiveUS20100235579A1Optimal utilisationProvide flexibilityMemory adressing/allocation/relocationTraffic capacityParallel computing

A data processing apparatus, and method of managing at least one cache within such an apparatus, are provided. The data processing apparatus has at least one processing unit for executing a sequence of instructions, with each such processing unit having a cache associated therewith, each cache having a plurality of cache lines for storing data values for access by the associated processing unit when executing the sequence of instructions. Identification logic is provided which, for each cache, monitors data traffic within the data processing apparatus and based thereon generates a preferred for eviction identification identifying one or more of the data values as preferred for eviction. Cache maintenance logic is then arranged, for each cache, to implement a cache maintenance operation during which selection of one or more data values for eviction from that cache is performed having regard to any preferred for eviction identification generated by the identification logic for data values stored in that cache. It has been found that such an approach provides a very flexible technique for seeking to improve cache storage utilisation.

Owner:ARM LTD

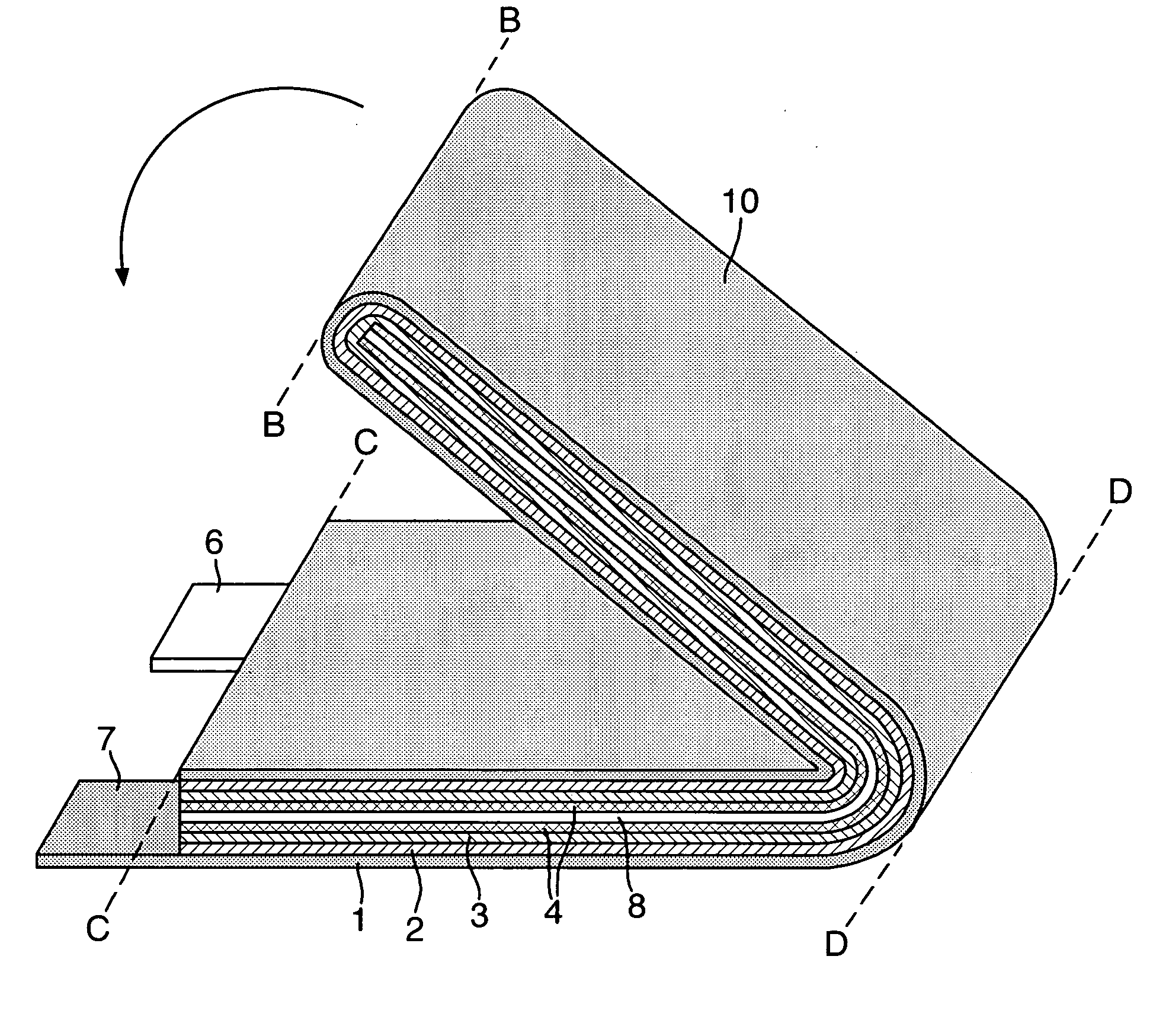

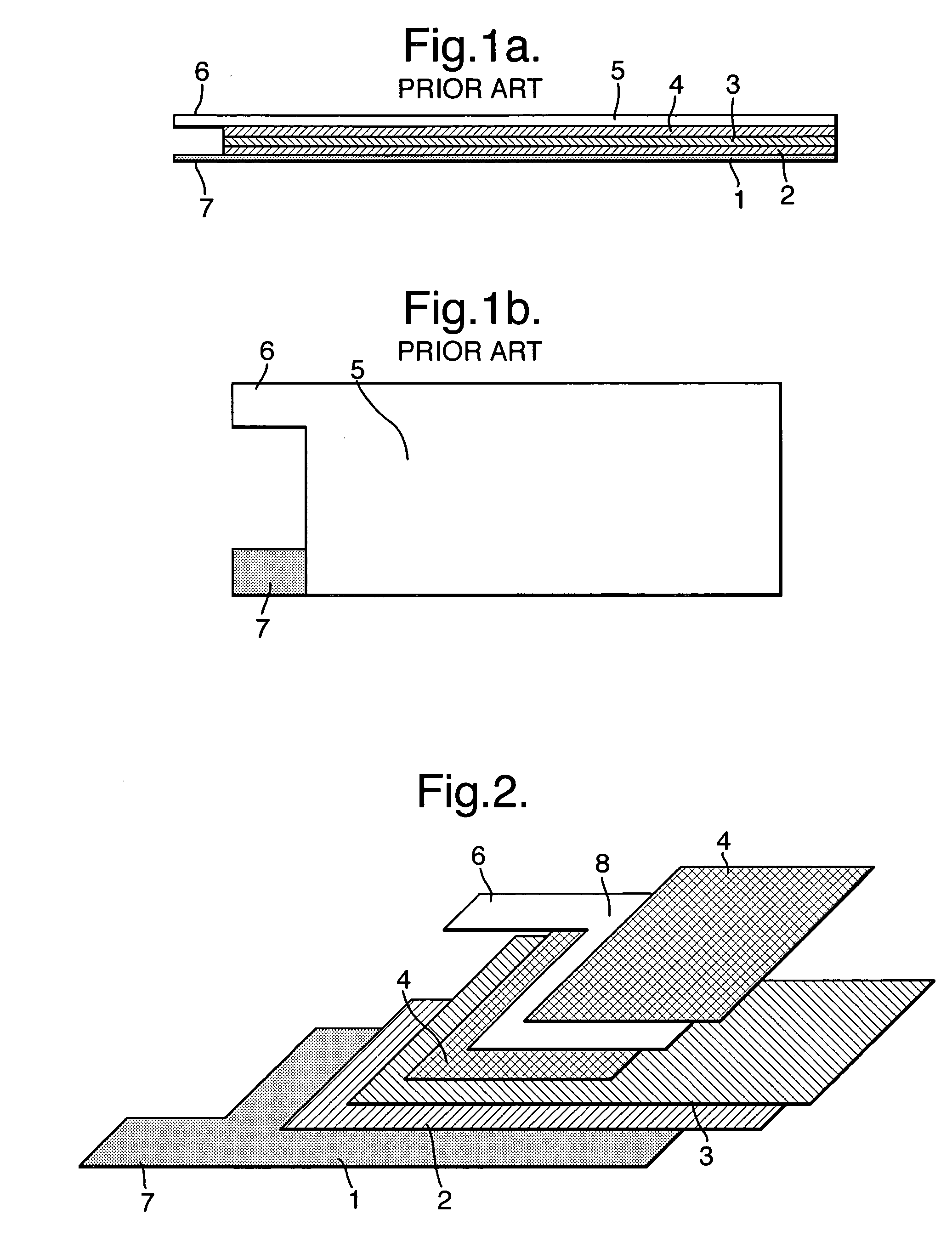

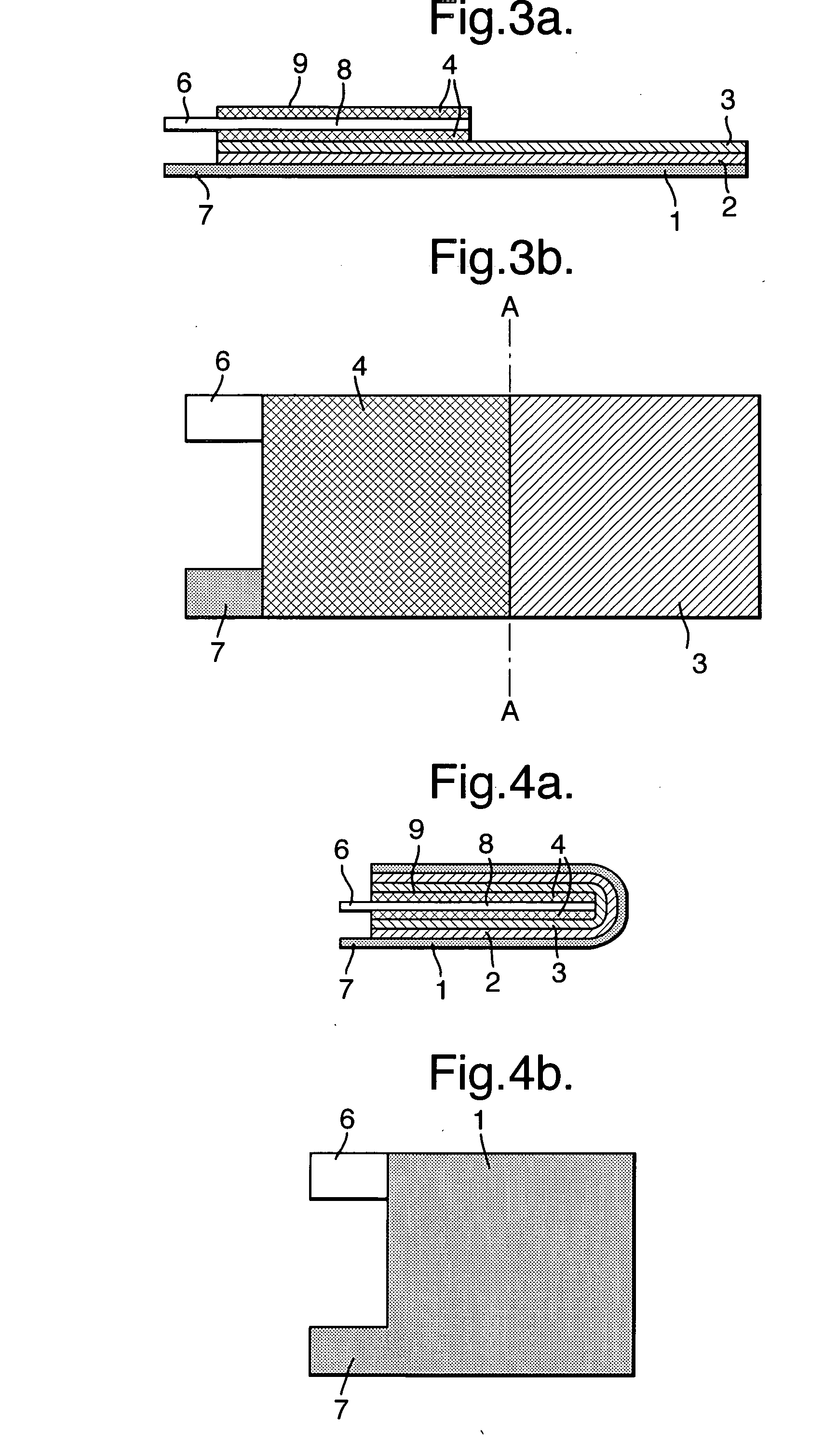

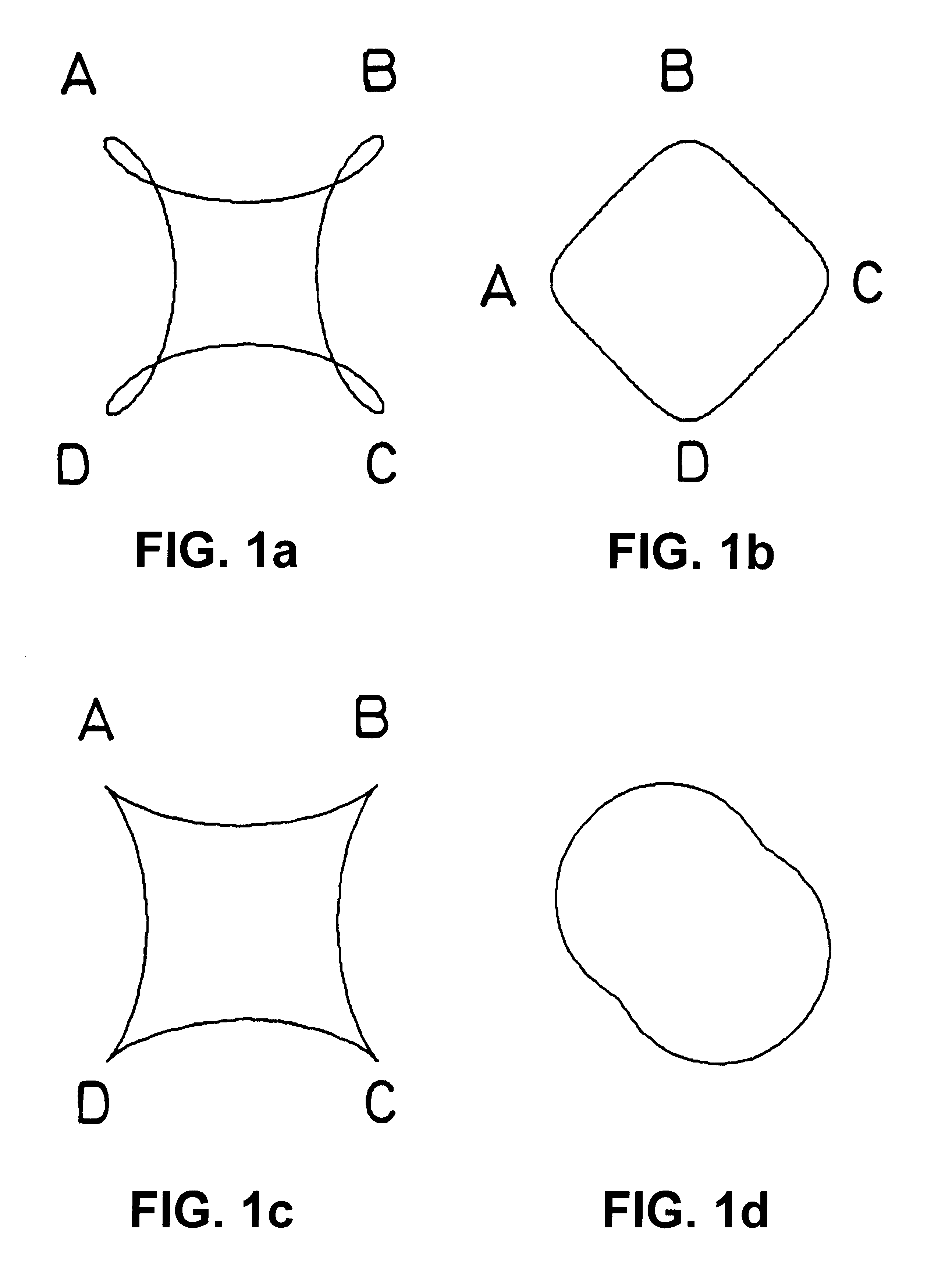

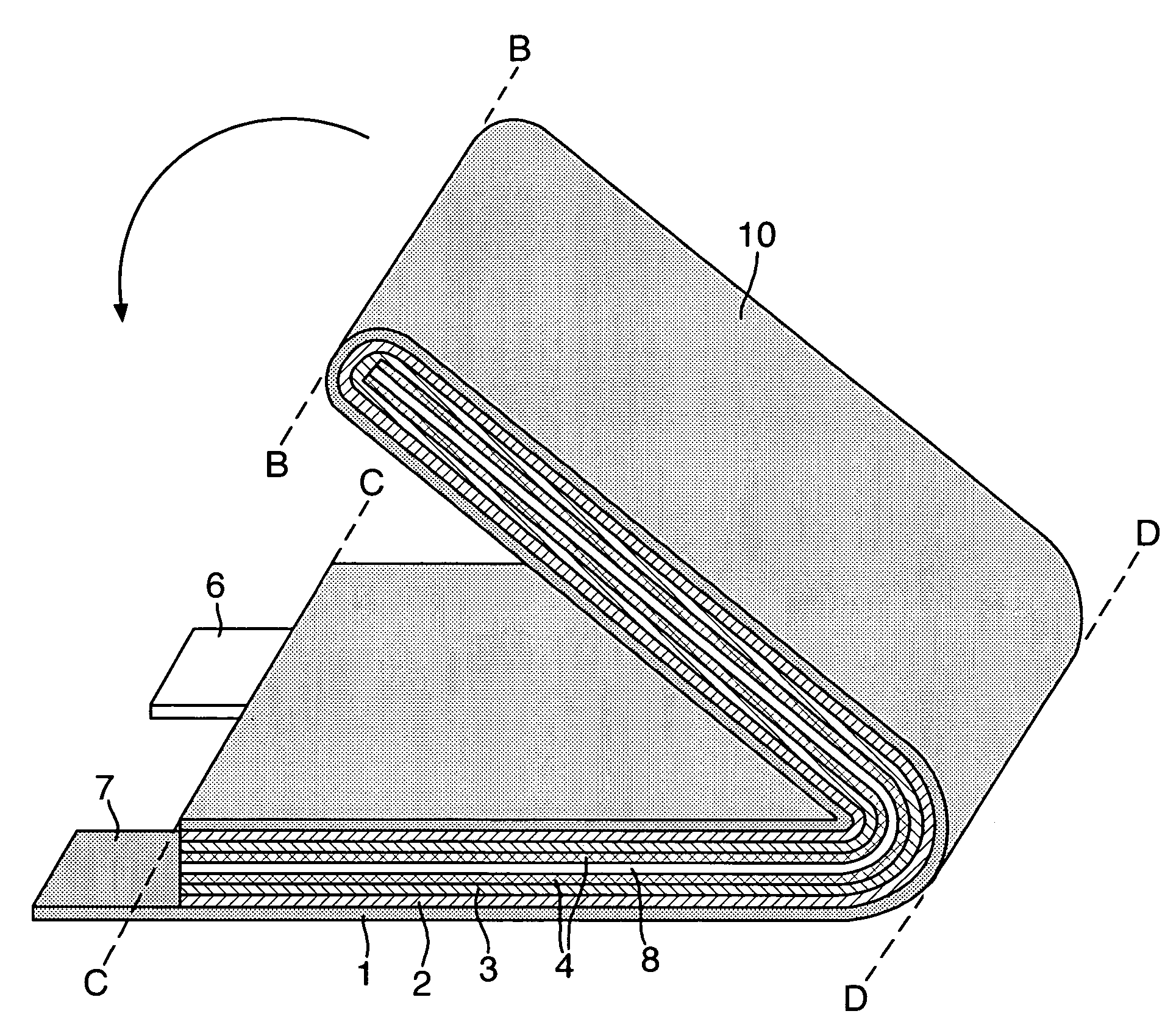

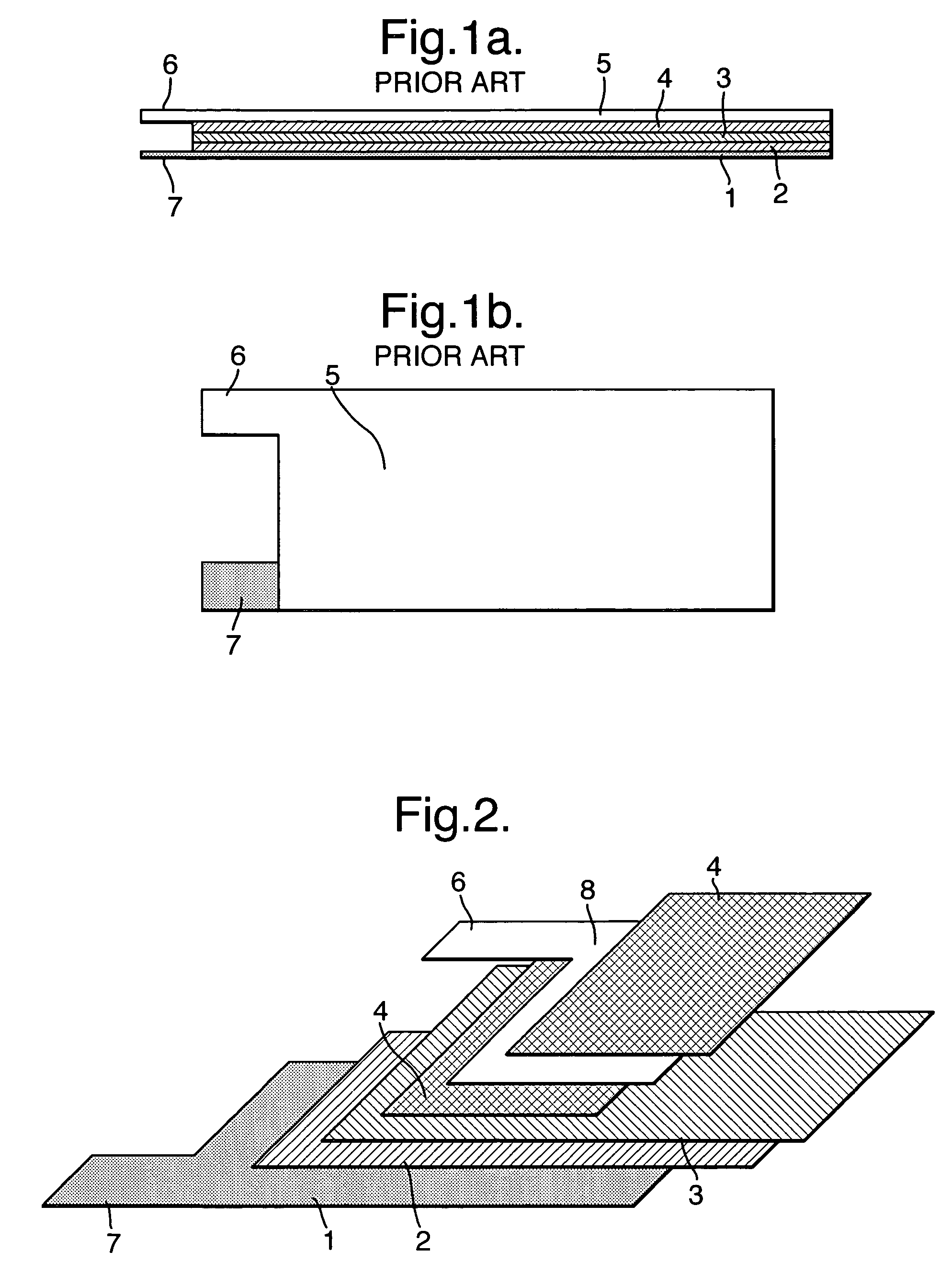

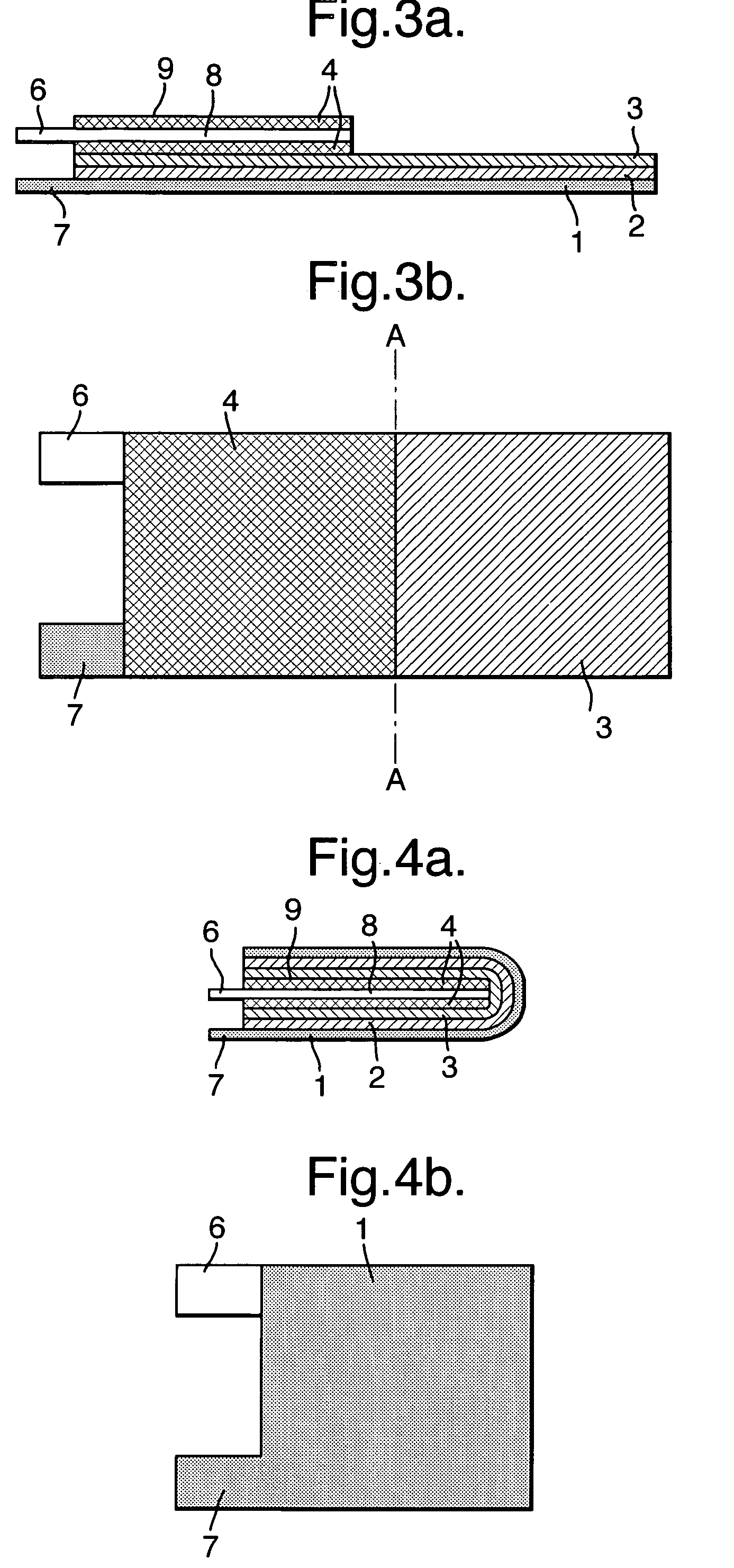

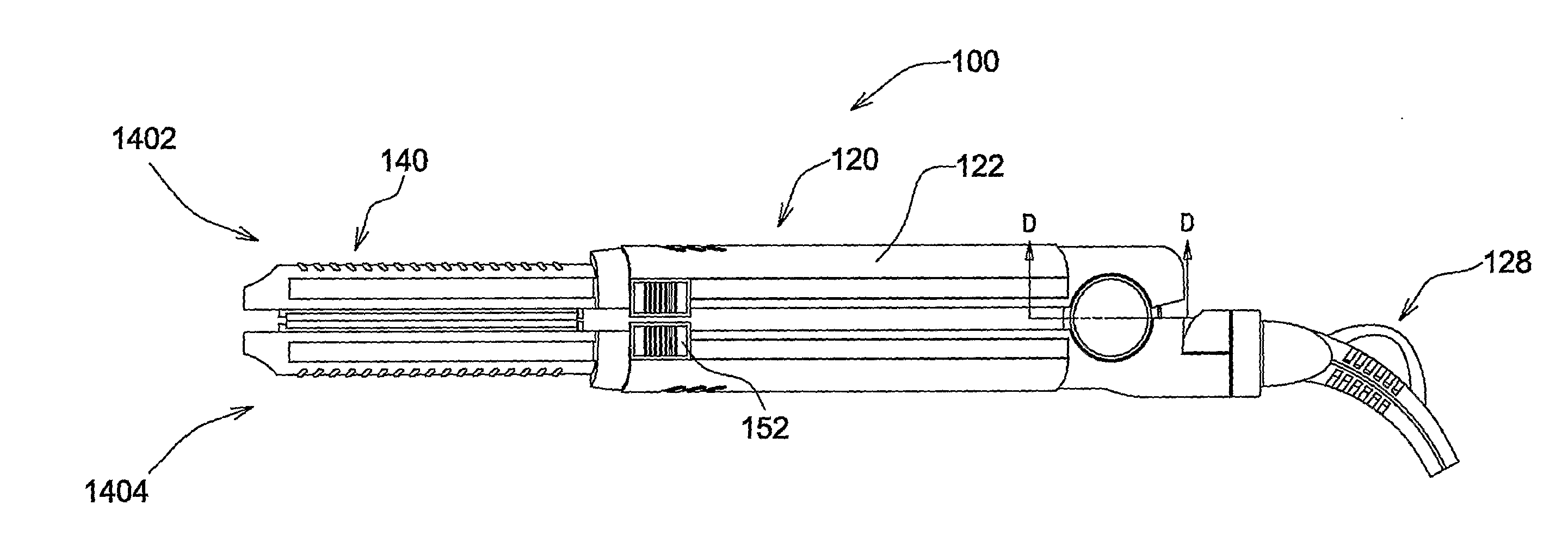

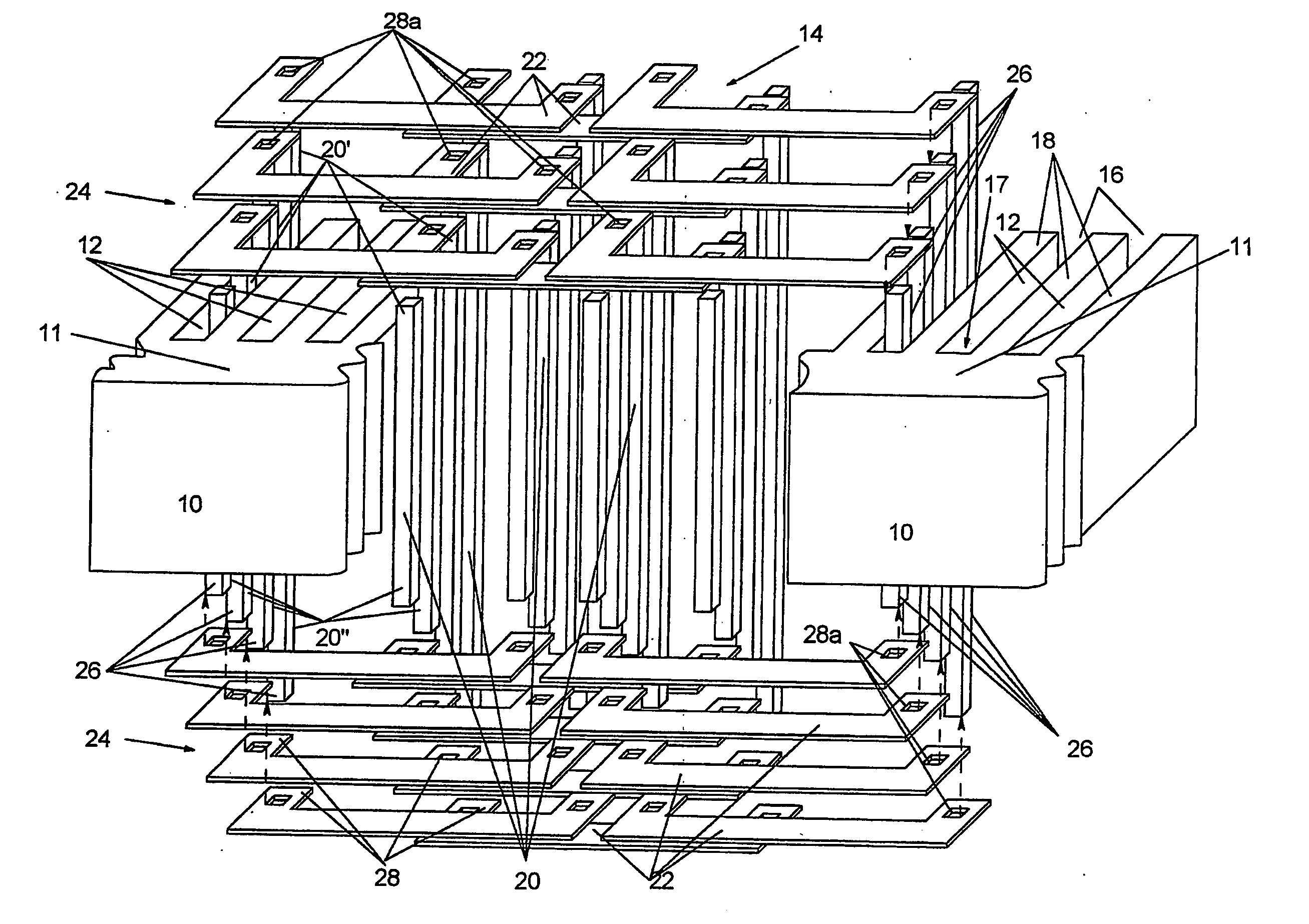

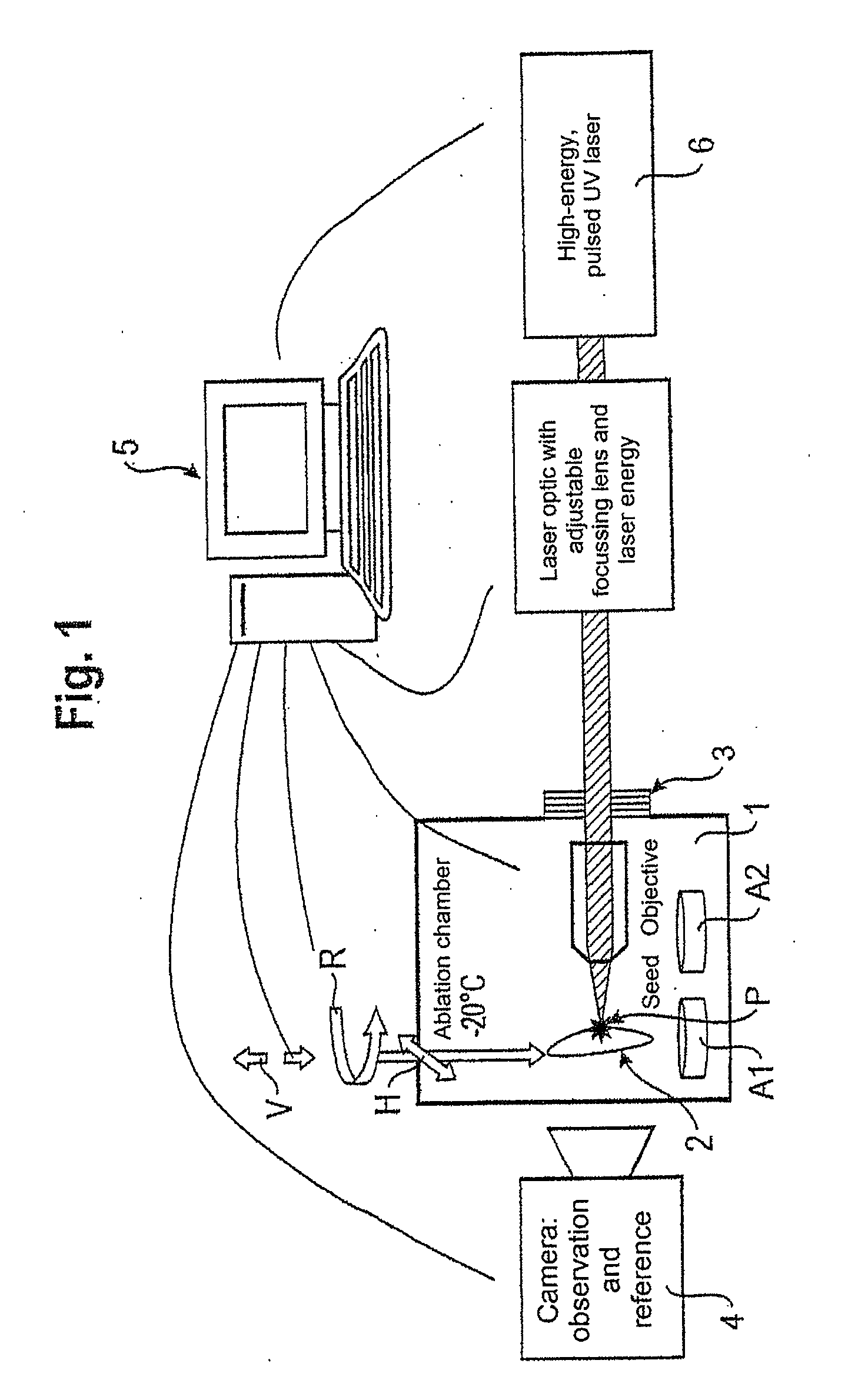

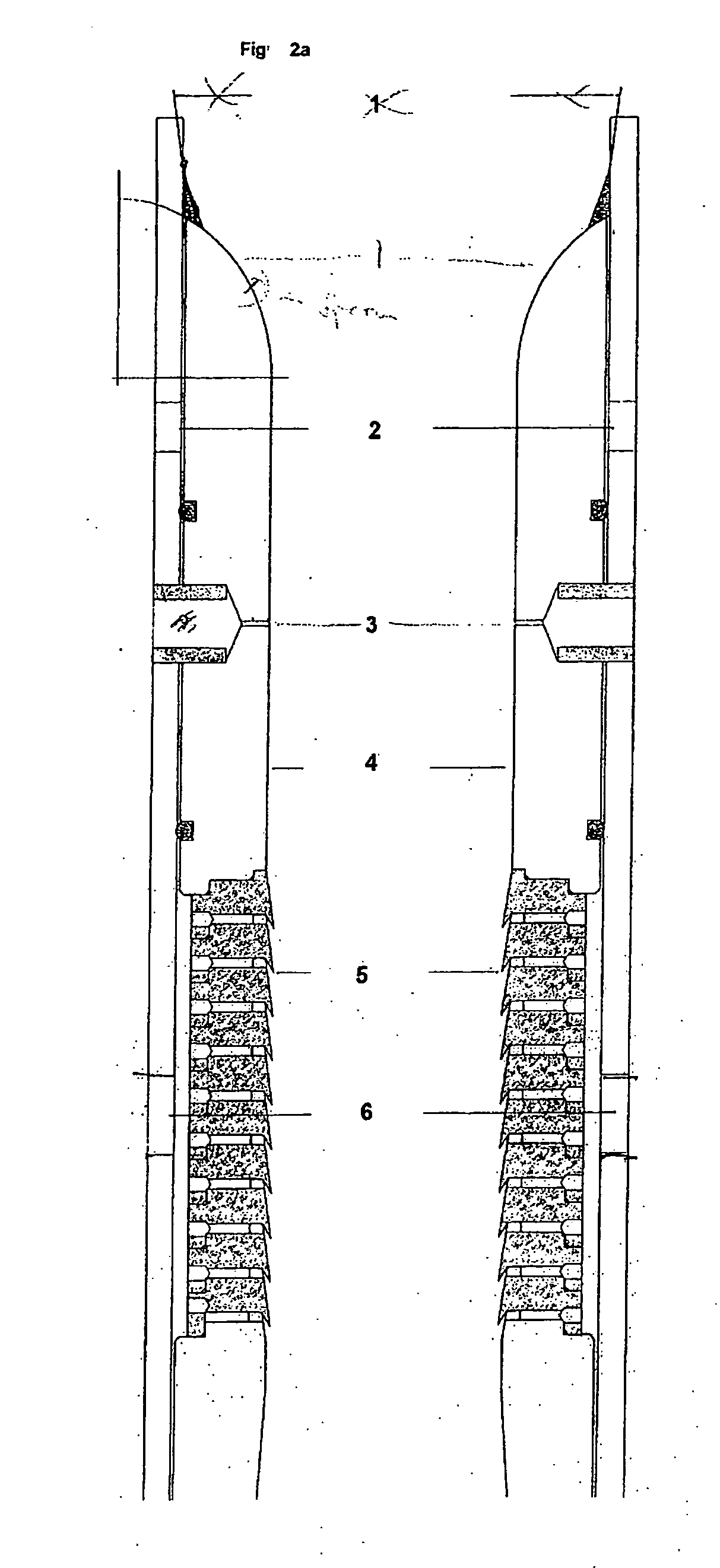

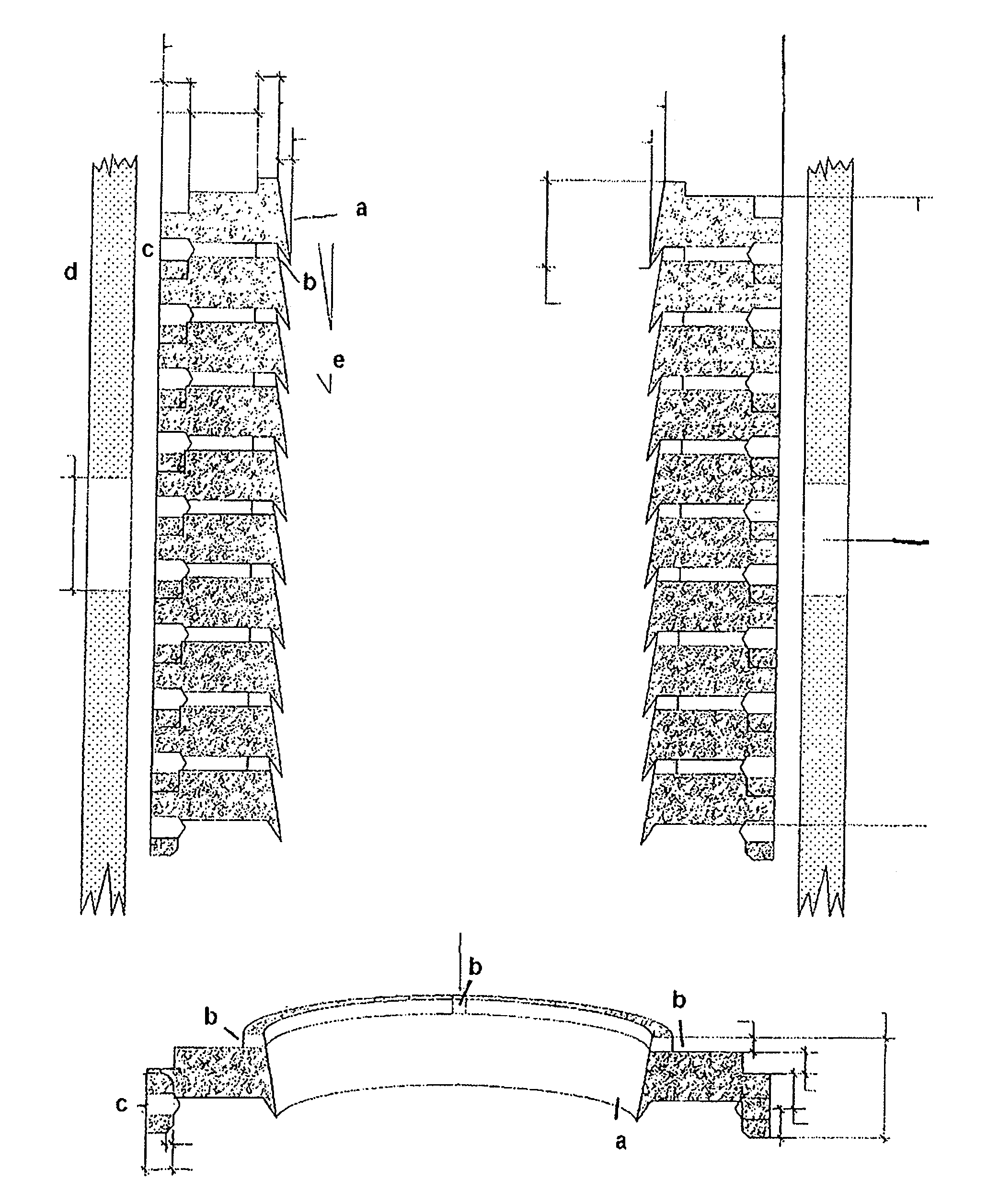

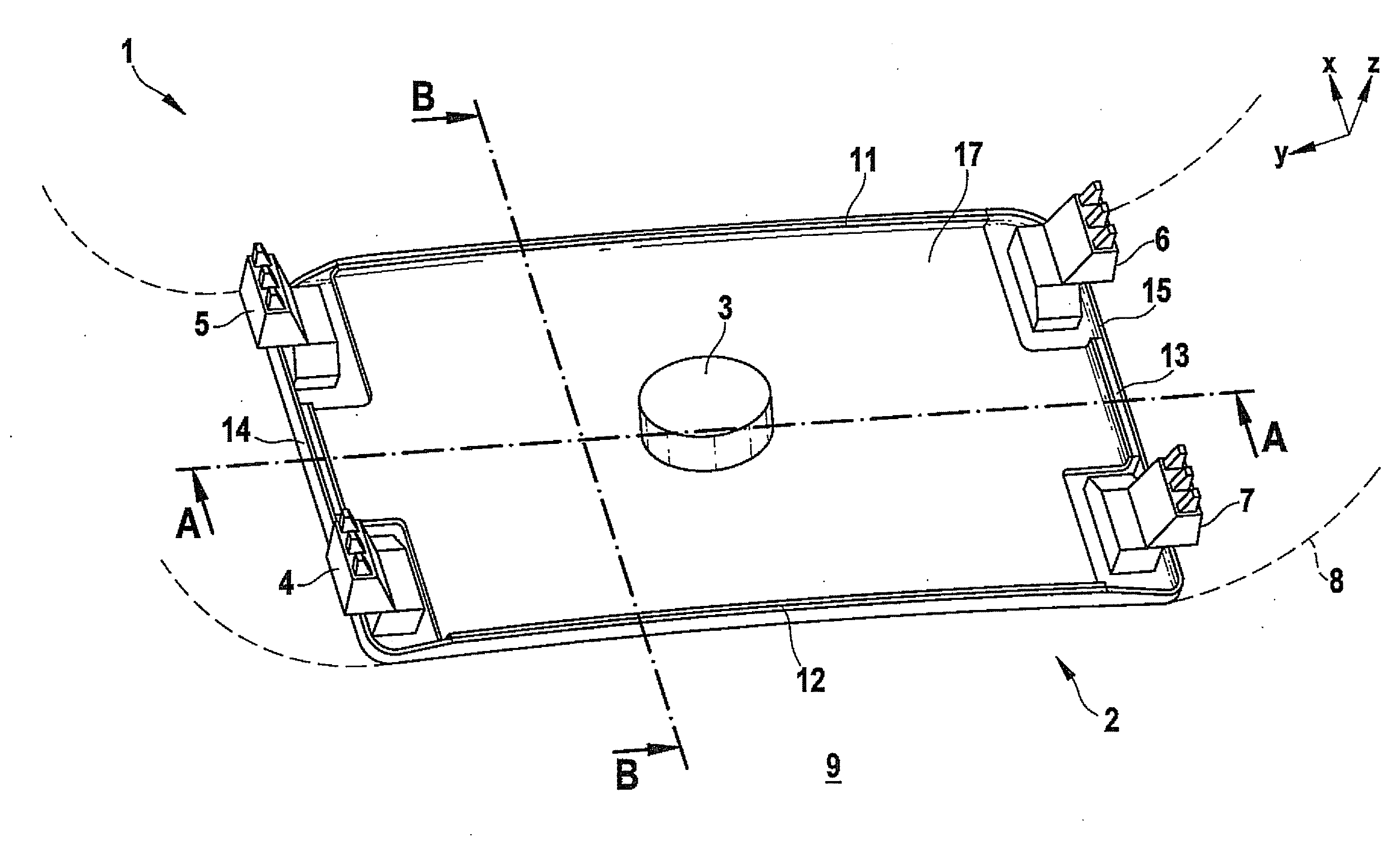

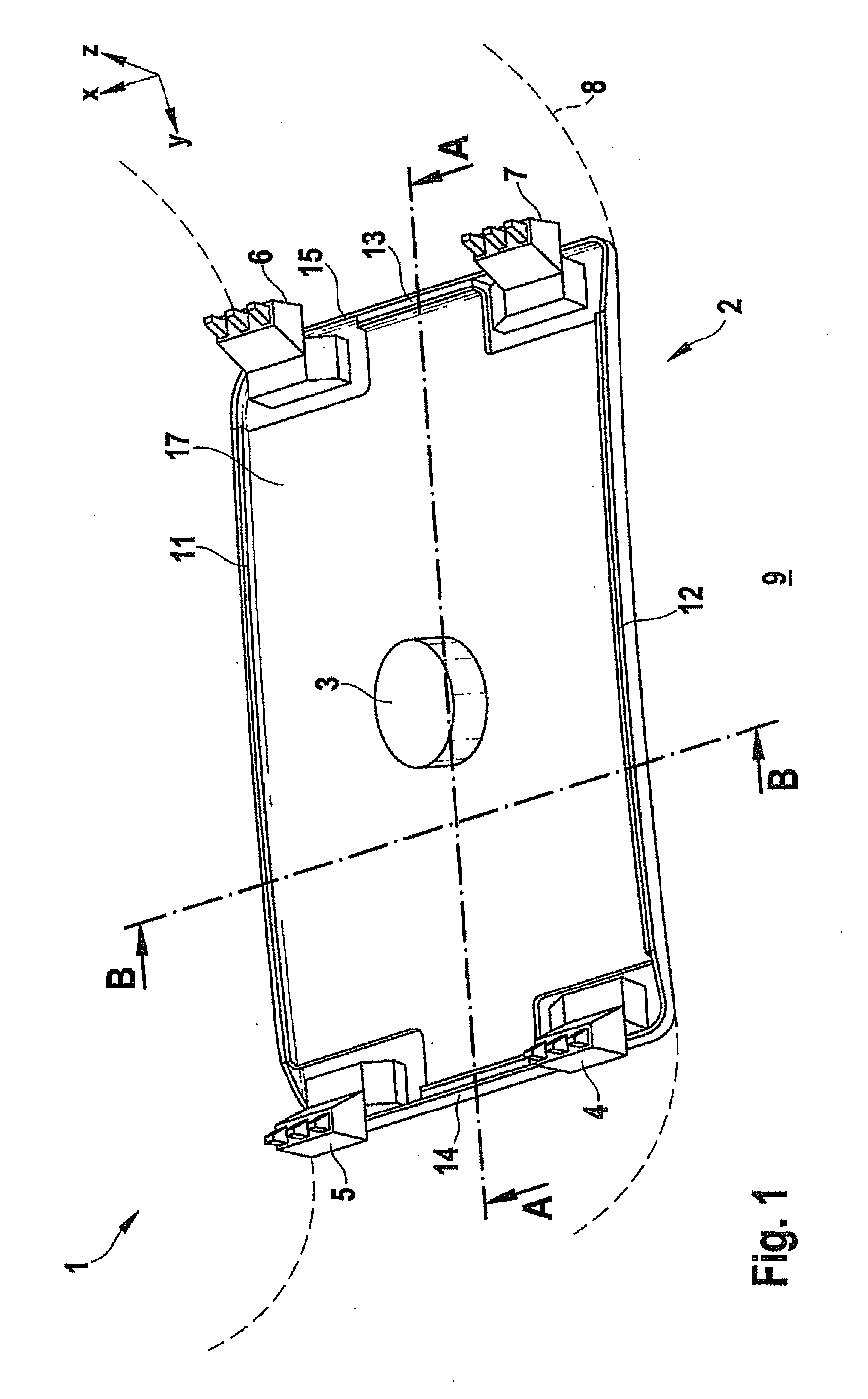

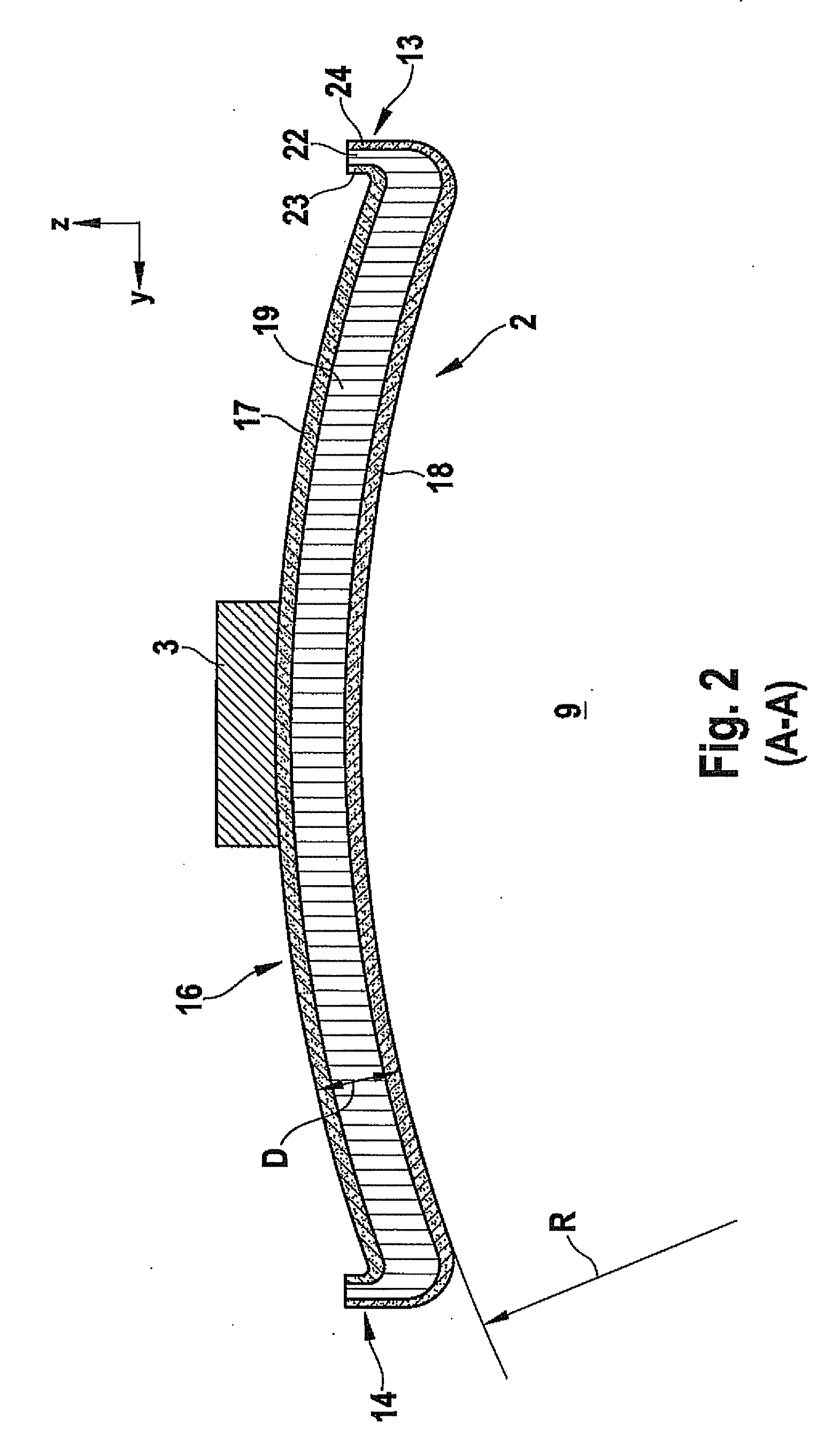

Electrode assembly

ActiveUS20050191545A1Increase energy densityReduce resistancePrimary cell maintainance/servicingFinal product manufactureEngineeringPrimary battery

An electrode assembly is formed by respectively overlaying a sheet cathode 1, a sheet separator 3 and a double-sided sheet anode 8 to form a stacked structure 10, and subjecting the stacked structure to multiple folds, wherein the initial fold comprises folding the cathode in half around the double-sided anode so as to surround the respective upper and lower active anode surfaces thereof. The multiple folds may comprise one or more subsequent parallel folds made with the fold line D-D extending perpendicular to the original length of the stacked structure such that its overall length is halved at each fold. A pouch battery comprising said electrode assembly has improved safety and performance characteristics. The pouch battery construction has especial application to lithium primary batteries.

Owner:QINETIQ LTD

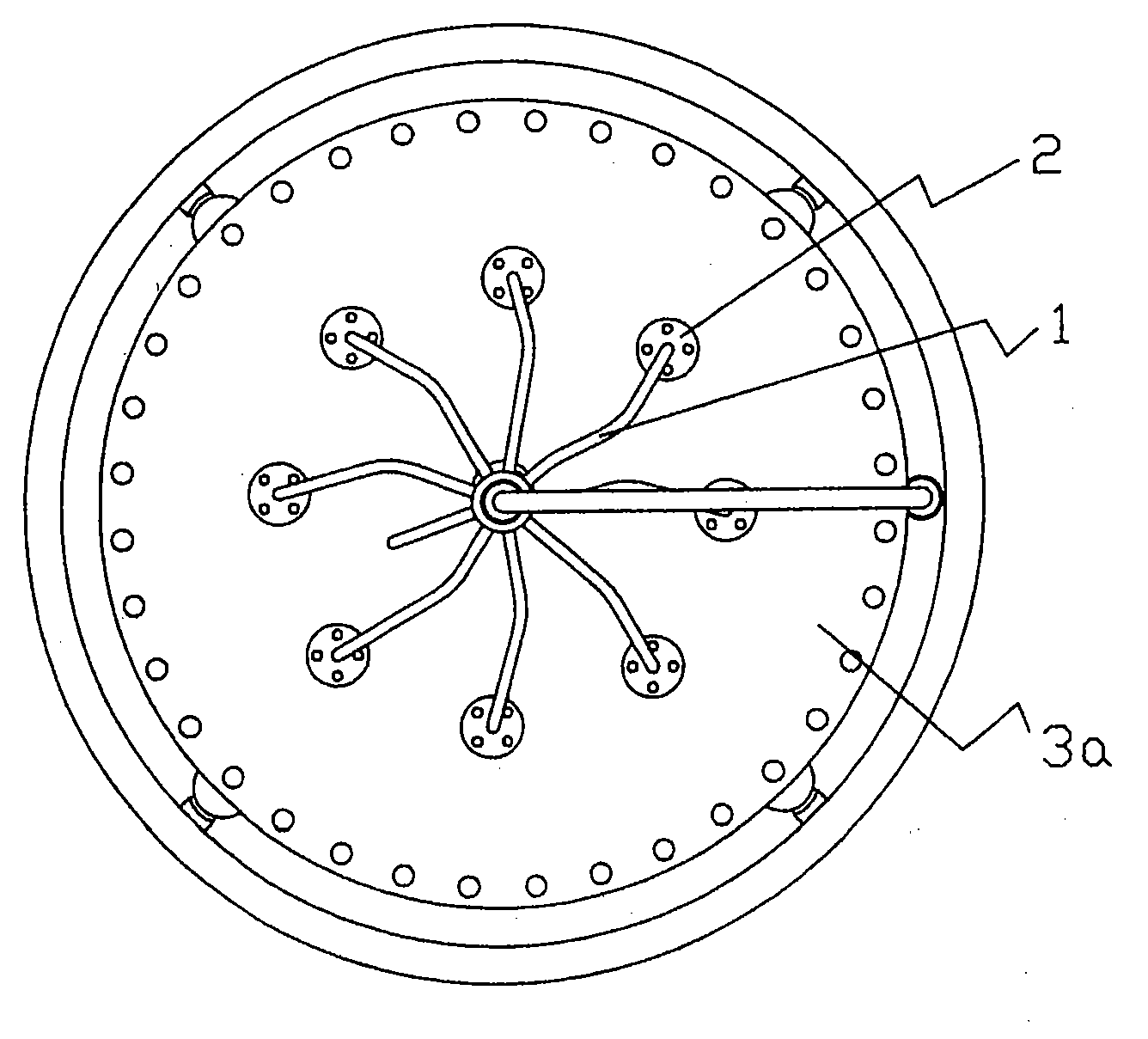

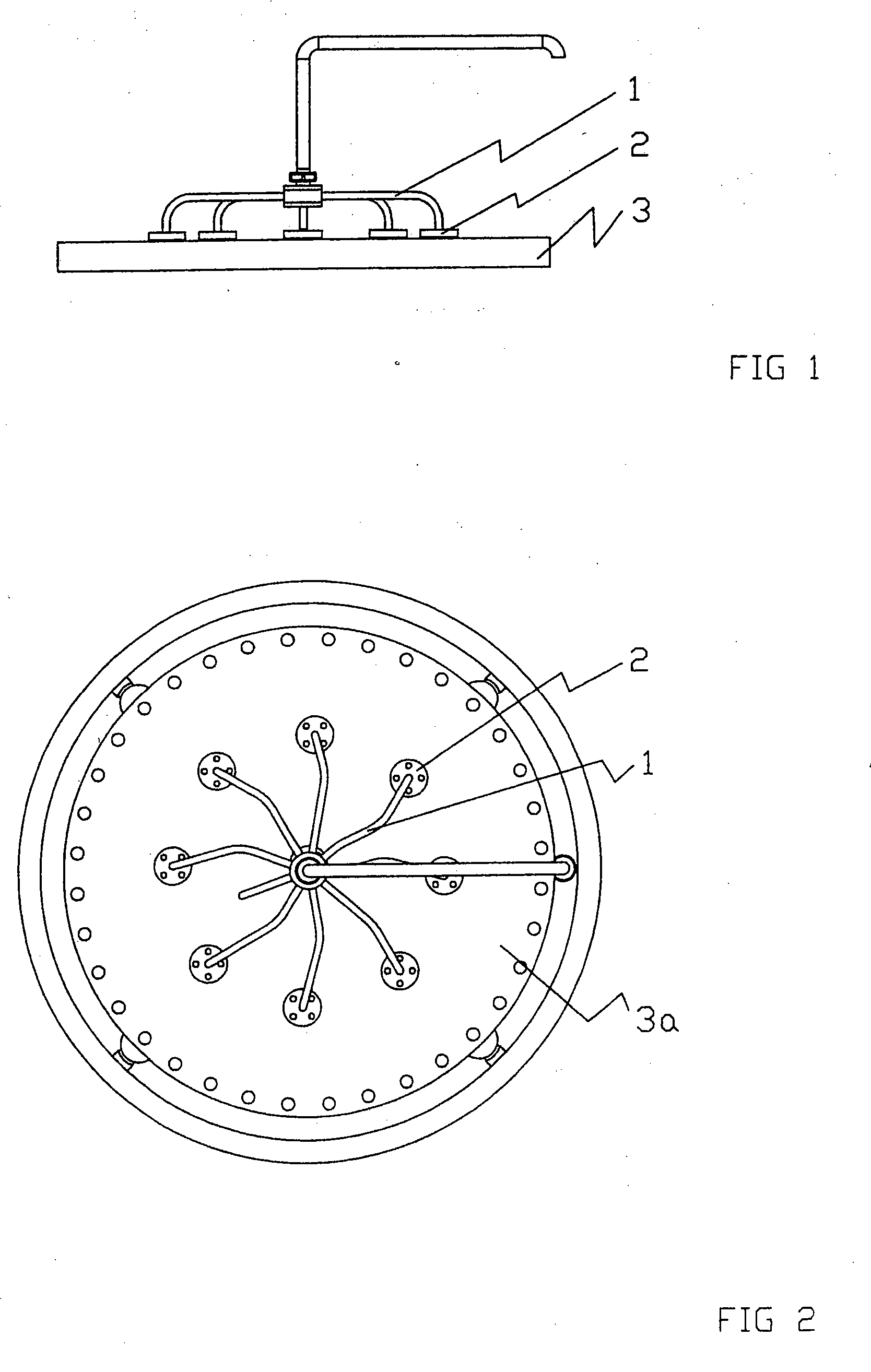

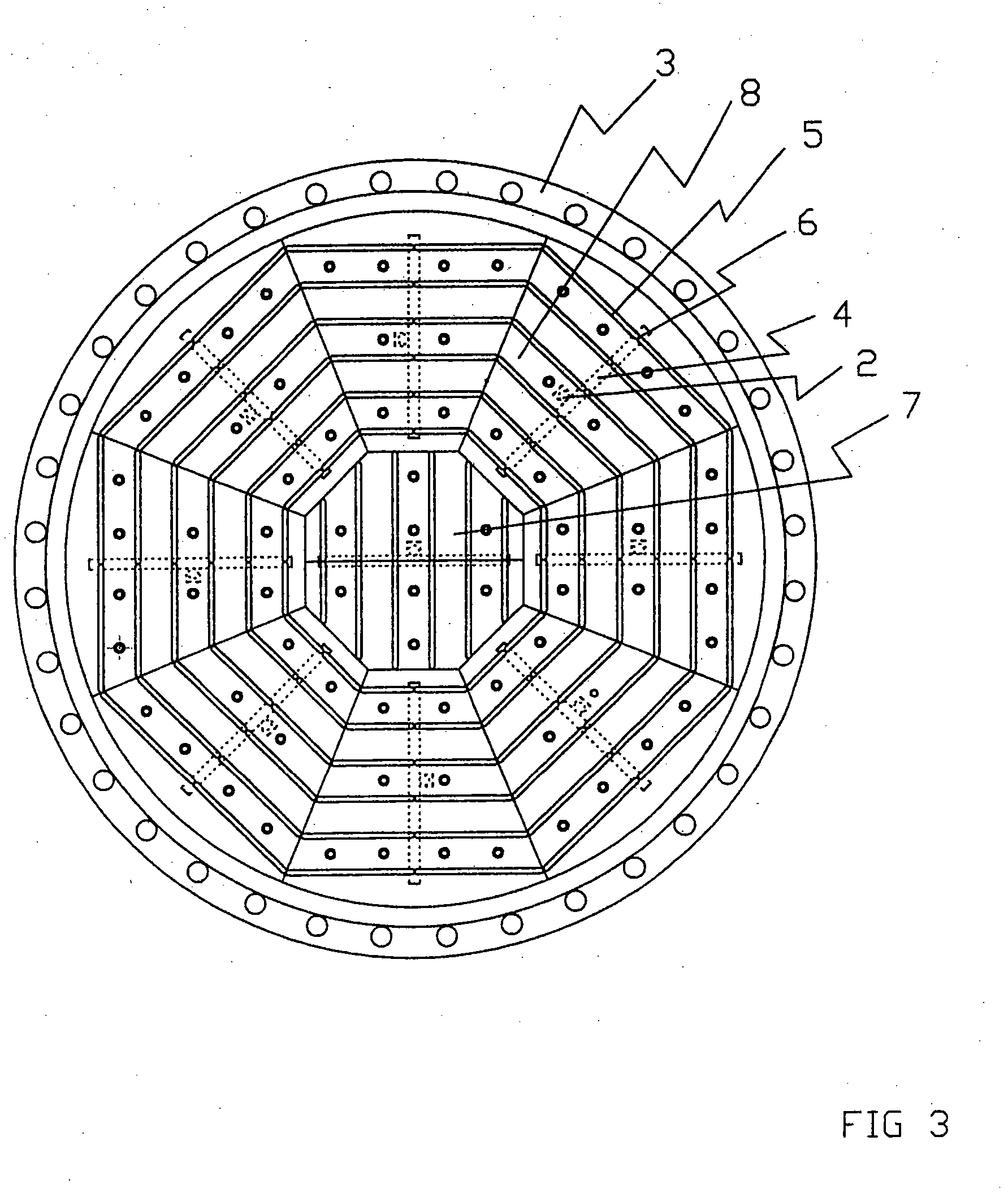

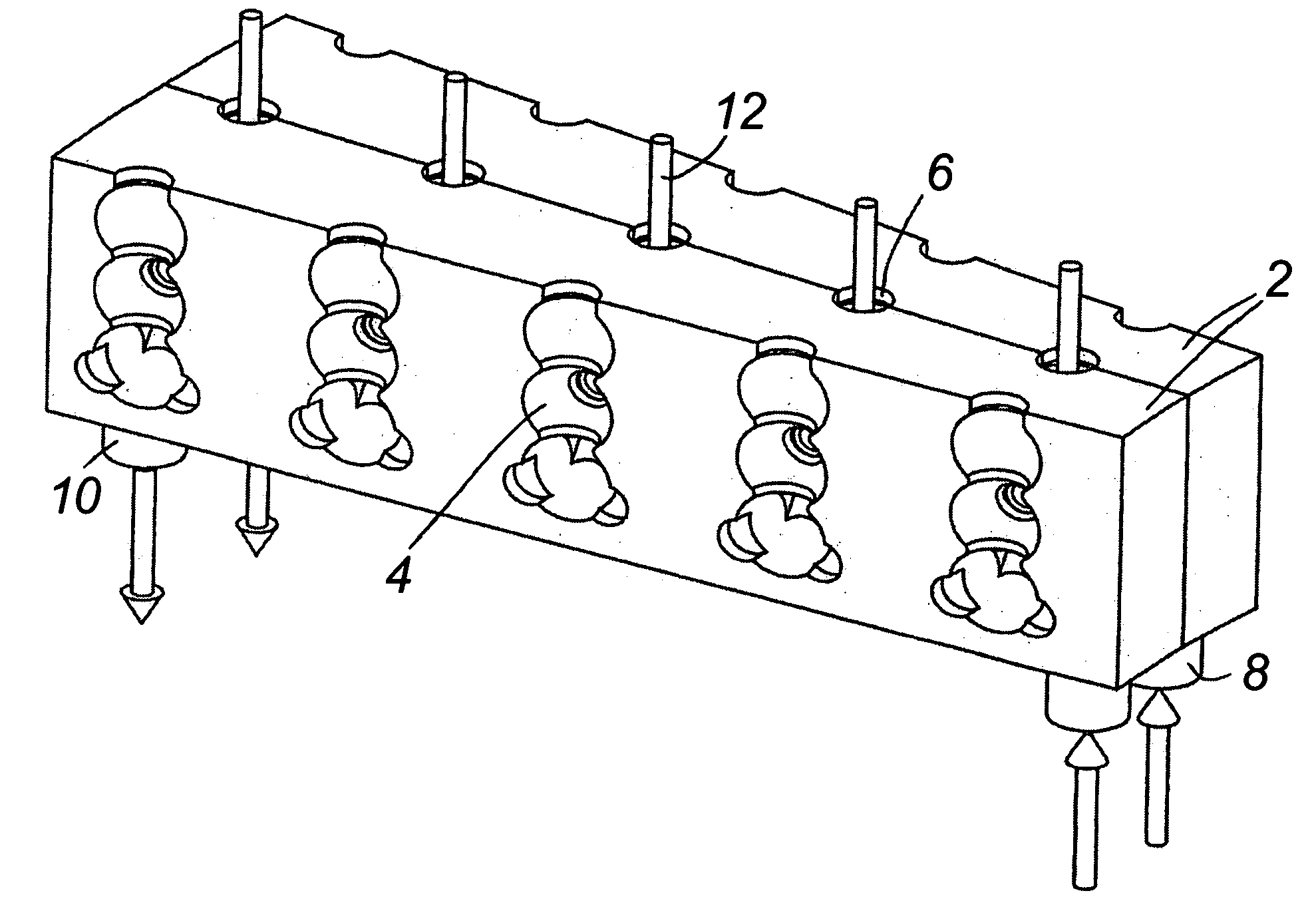

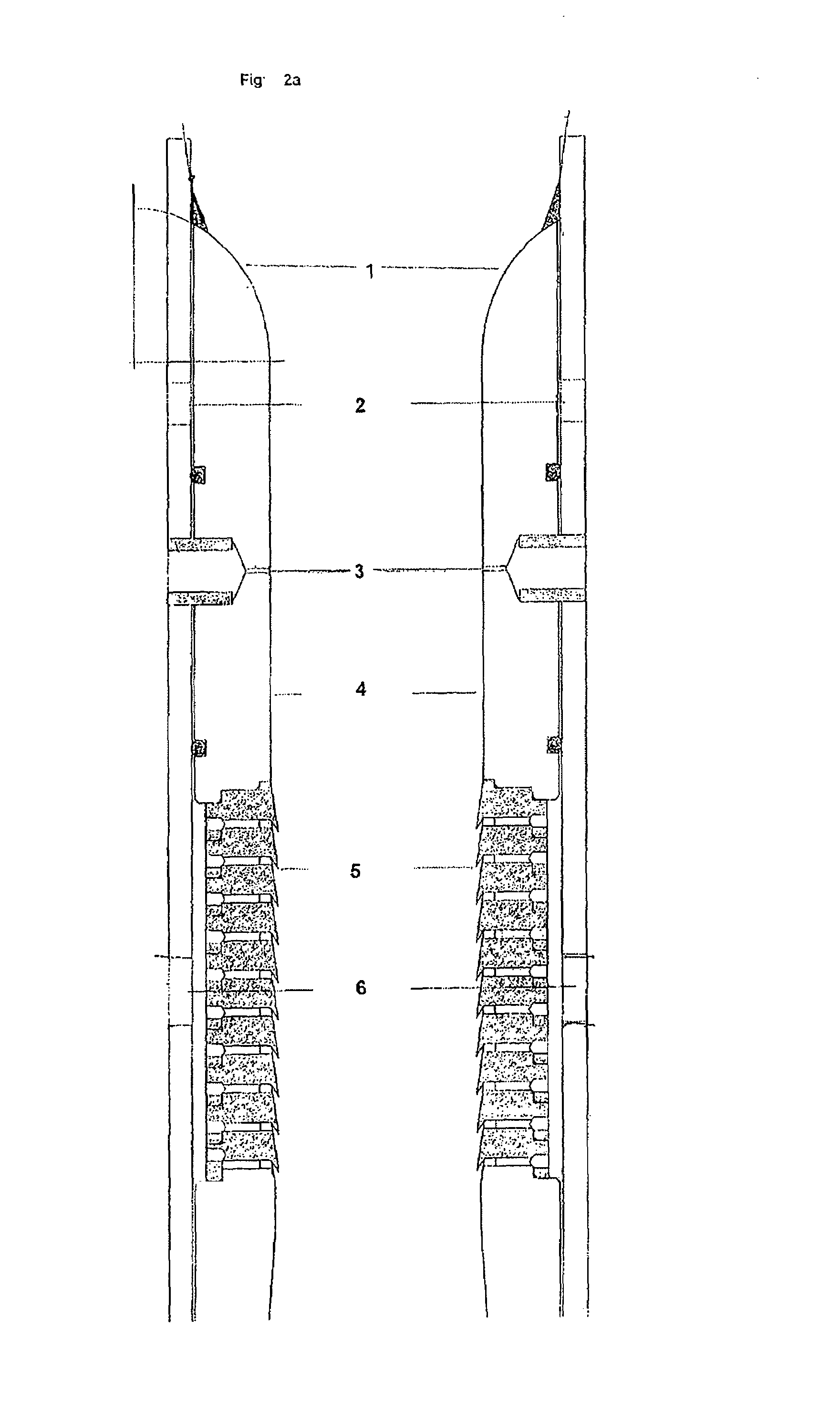

Erosion compensated magnetron with moving magnet assembly

InactiveUS6416639B1Simple profileOptimal utilisationCellsElectric discharge tubesClosed loopRace track

A magnetron including a target (2) for sputtering onto a substrate in described. The magnetron comprises a magnetic field generator (4) for generating a closed loop magnetic field adapted to generate a plasma race-track above the target (2) and a driving device for establishing relative substantially translational movement between the race-track and the target (2) and adapted to influence the magnetic field generated by the magnetic field generator (4) at least during part of the relative substantially translational movement, the distance between any point on the race track and the momentarily closest part of the one or more pieces (50) of ferromagnetic material varying in accordance with the relative substantially translational movement of the race-track and the target (2).

Owner:BEKAERT ADVANCED COATINGS

Method

InactiveUS20080063783A1Accumulation is reduced and eliminatedIncreased amount of free fatty acidMilk preparationDough treatmentMonoglycerideGlycerol

A method for the in situ production of an emulsifier in a foodstuff, wherein a lipid acyltransferase is added to the foodstuff. Preferably the emulsifier is produced without an increase or without a substantial increase in the free fatty acid content of the foodstuff. Preferably, the lipid acyltransferase is one which is capable of transferring an acyl group from a lipid to one or more of the following acyl acceptors: a sterol, a stanol, a carbohydrate, a protein or a sub-unit thereof, glycerol. Preferably, in addition to an emulsifier one or more of a stanol ester or a stanol ester or a protein ester or a carbohydrate ester or a diglyceride or a monoglyceride may be produced. One or more of these may function as an additional emulsifier.

Owner:DUPONT NUTRITION BIOSCIENCES APS

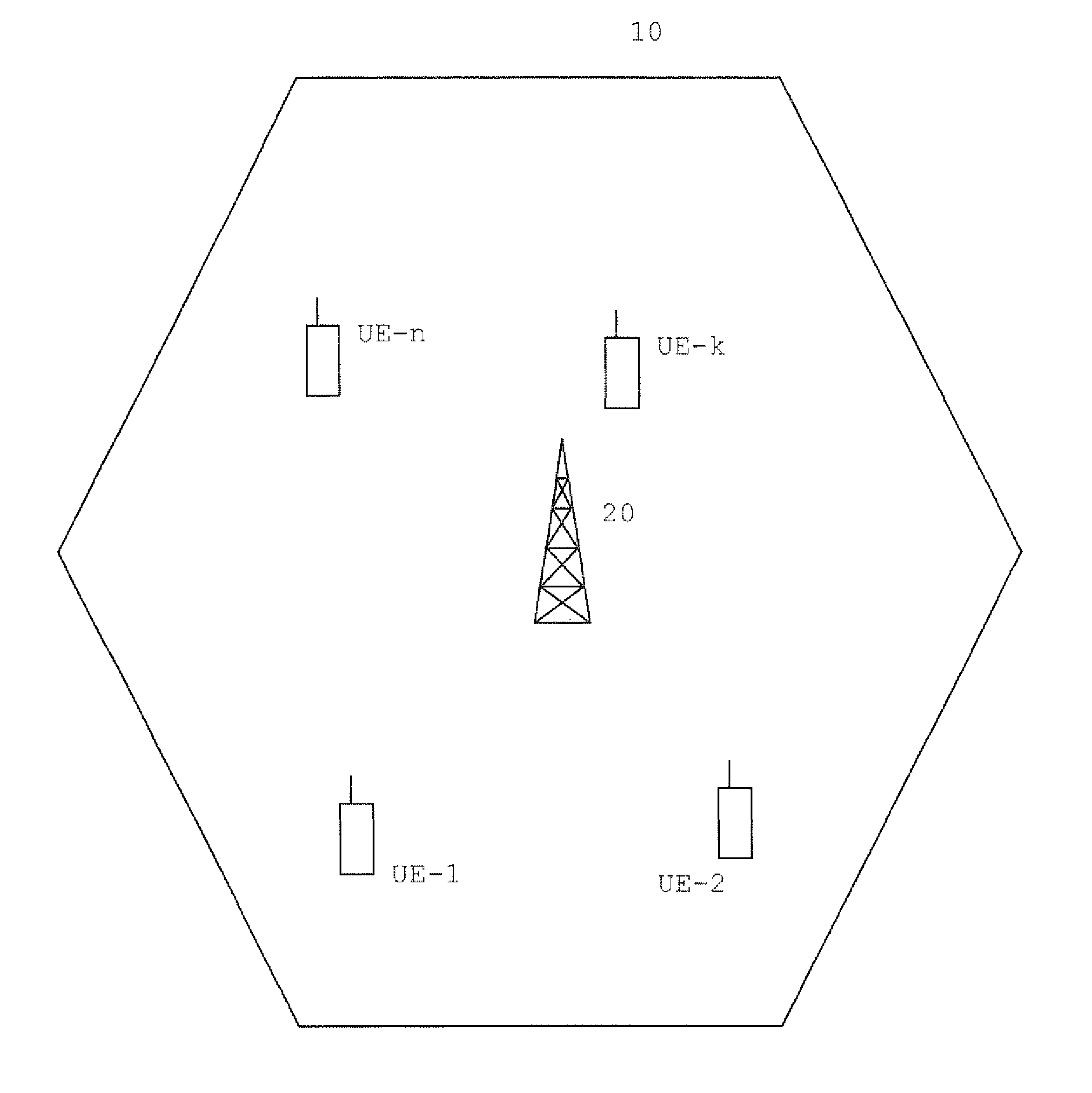

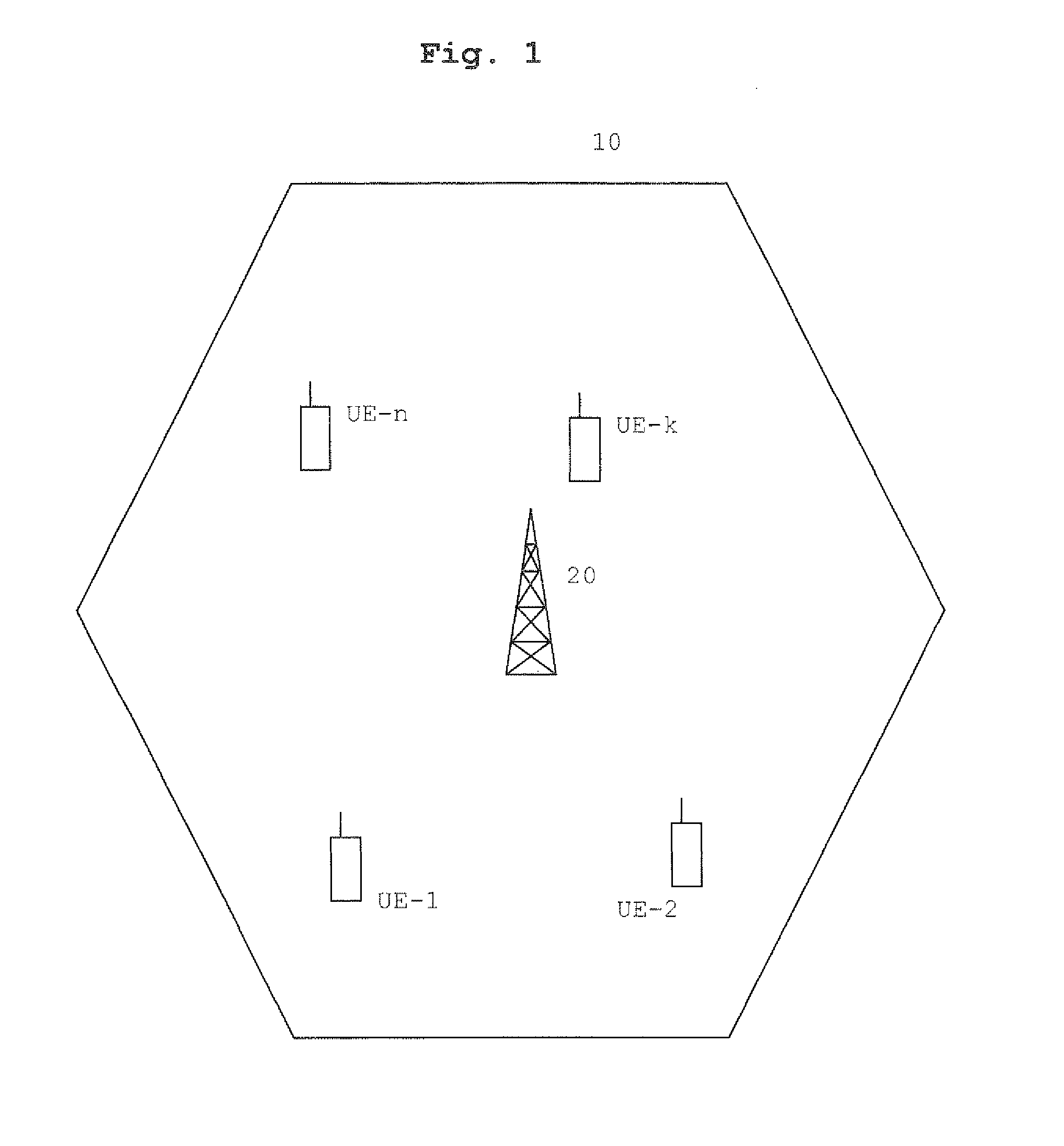

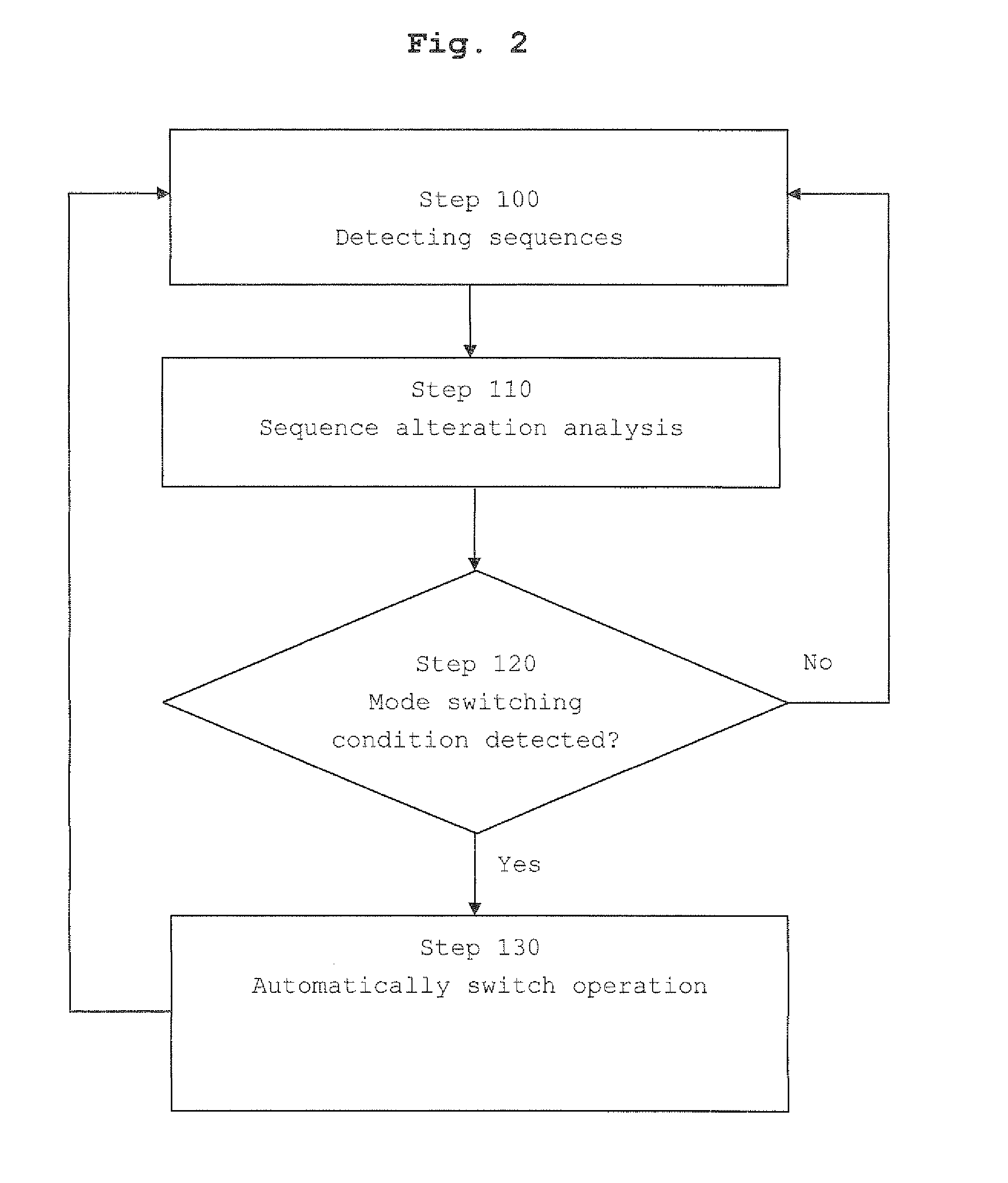

Random Access Mode Control Method and Entity

InactiveUS20110086658A1Flexible managementOptimal utilisationModulated-carrier systemsCode division multiplexRandom access memoryMode control

A method of controlling a random access mode in a cell of a cellular communication system, said cell being operable in a first random access mode associated with a first set of random access identification sequences or in a second random access mode associated with a second set of random access identification sequences / said random access identification sequences to be used by terminals (UEI . . . UEn) performing a random access operation in said cell, where said second set of random access identification sequences is arranged for avoiding misidentifications due to sequence alterations occurring in transmissions from said terminals (UEI . . . -UEn), the method comprising: performing a sequence alteration analysis based on the an output of a random access identification sequence detector in a network entity, and if a mode switching condition is determined on the basis of the sequence alteration analysis, automatically switching operation of said cell from one of said random access modes to the other of said random access modes.

Owner:TELEFON AB LM ERICSSON (PUBL)

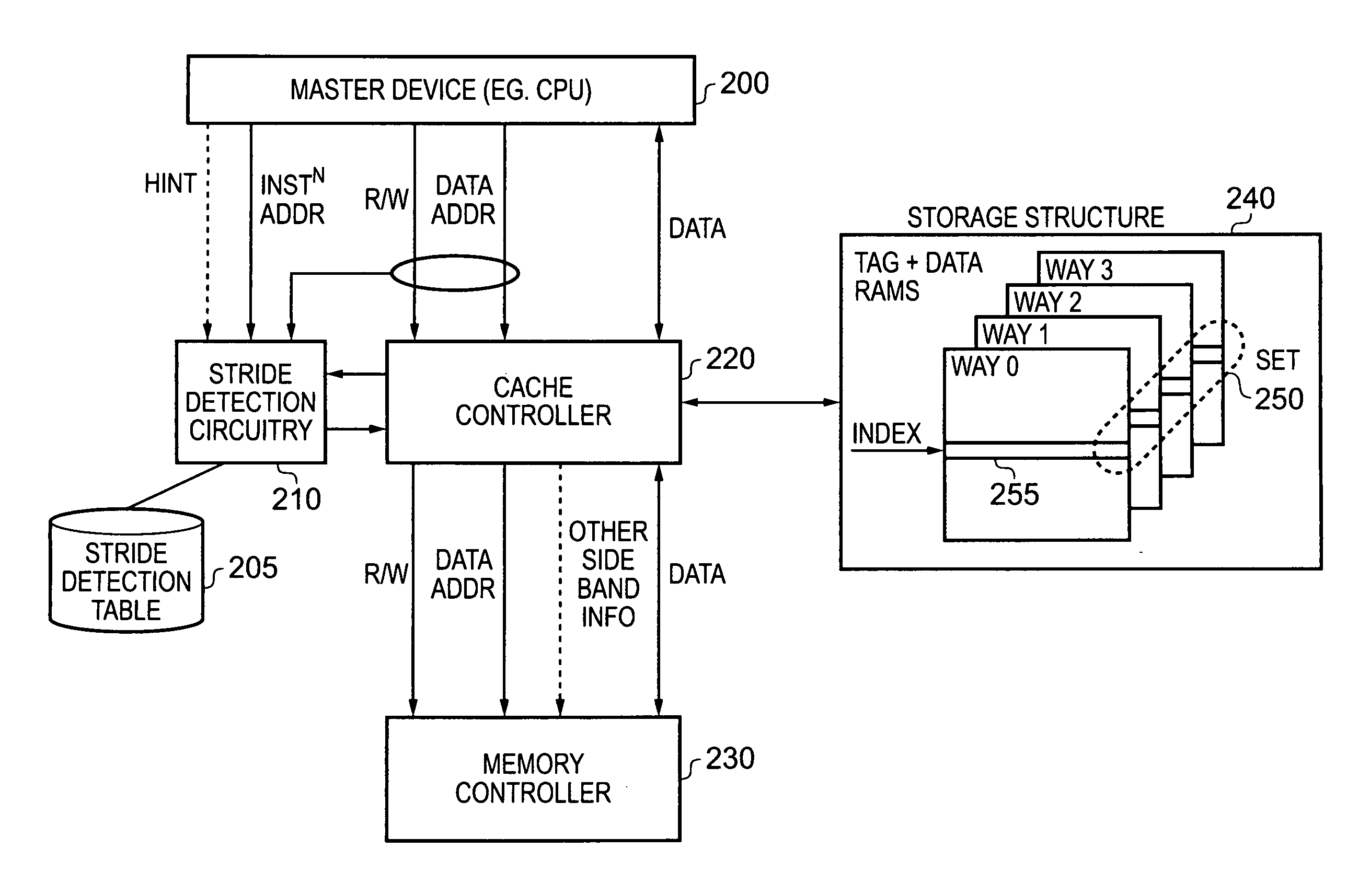

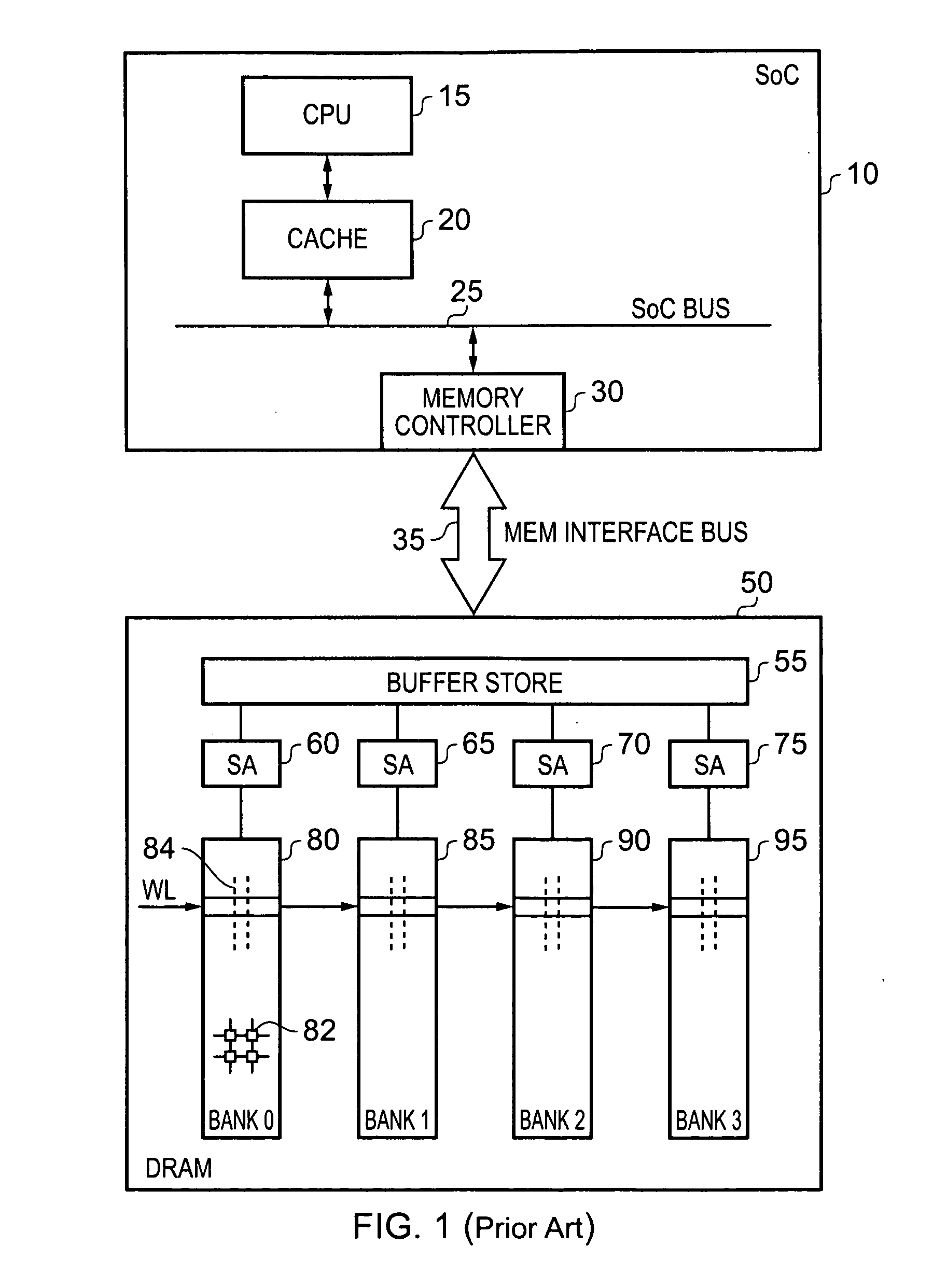

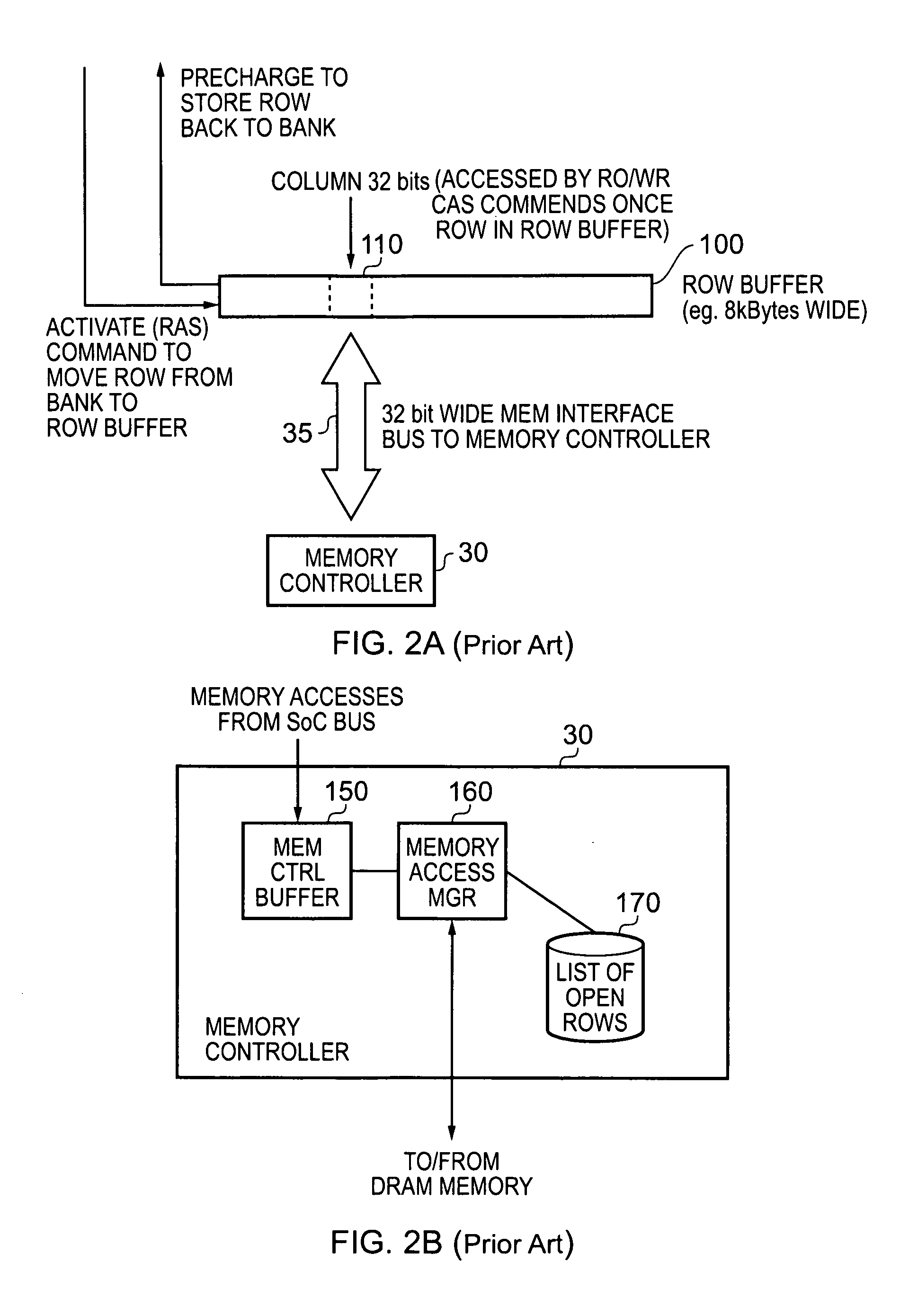

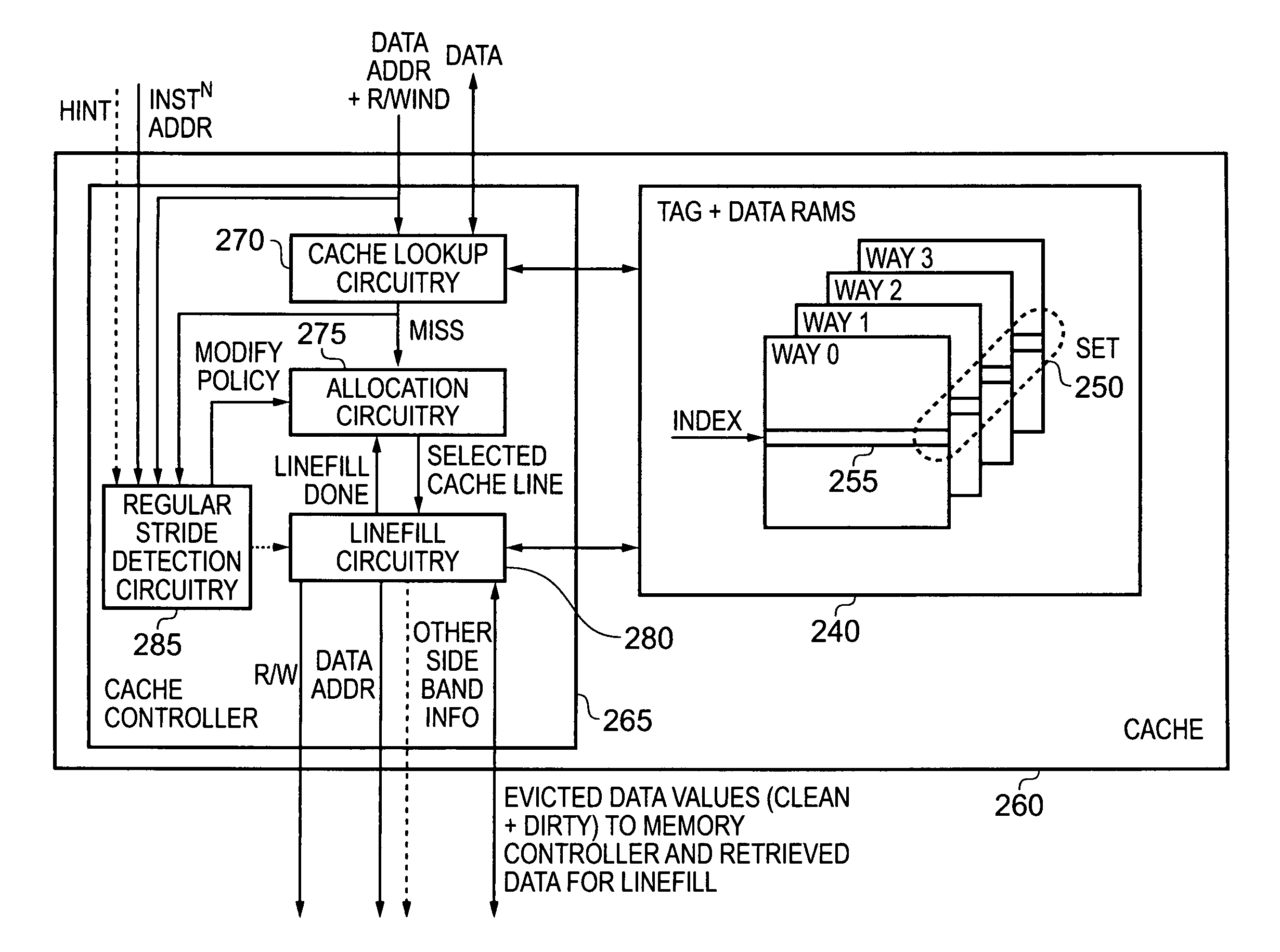

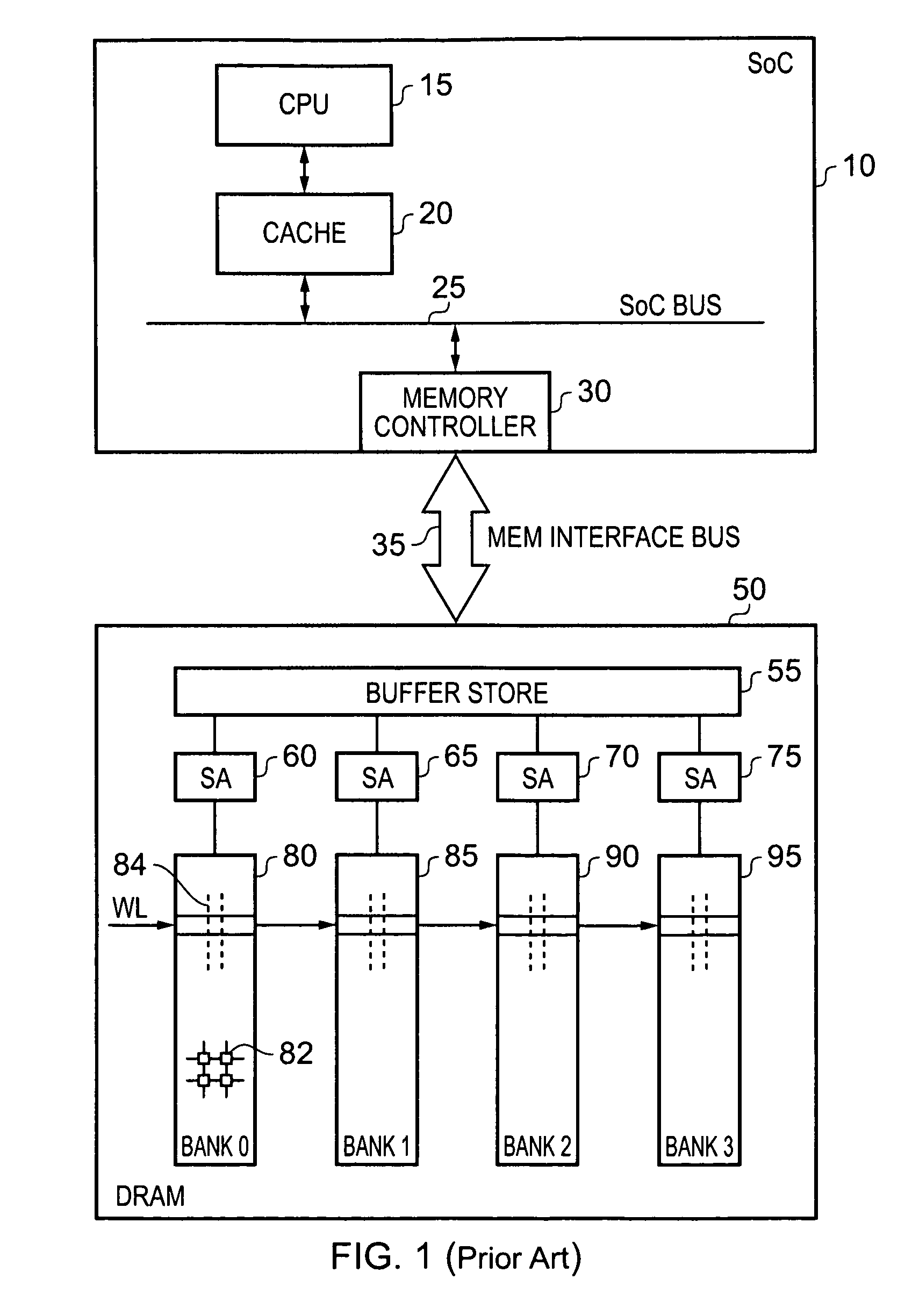

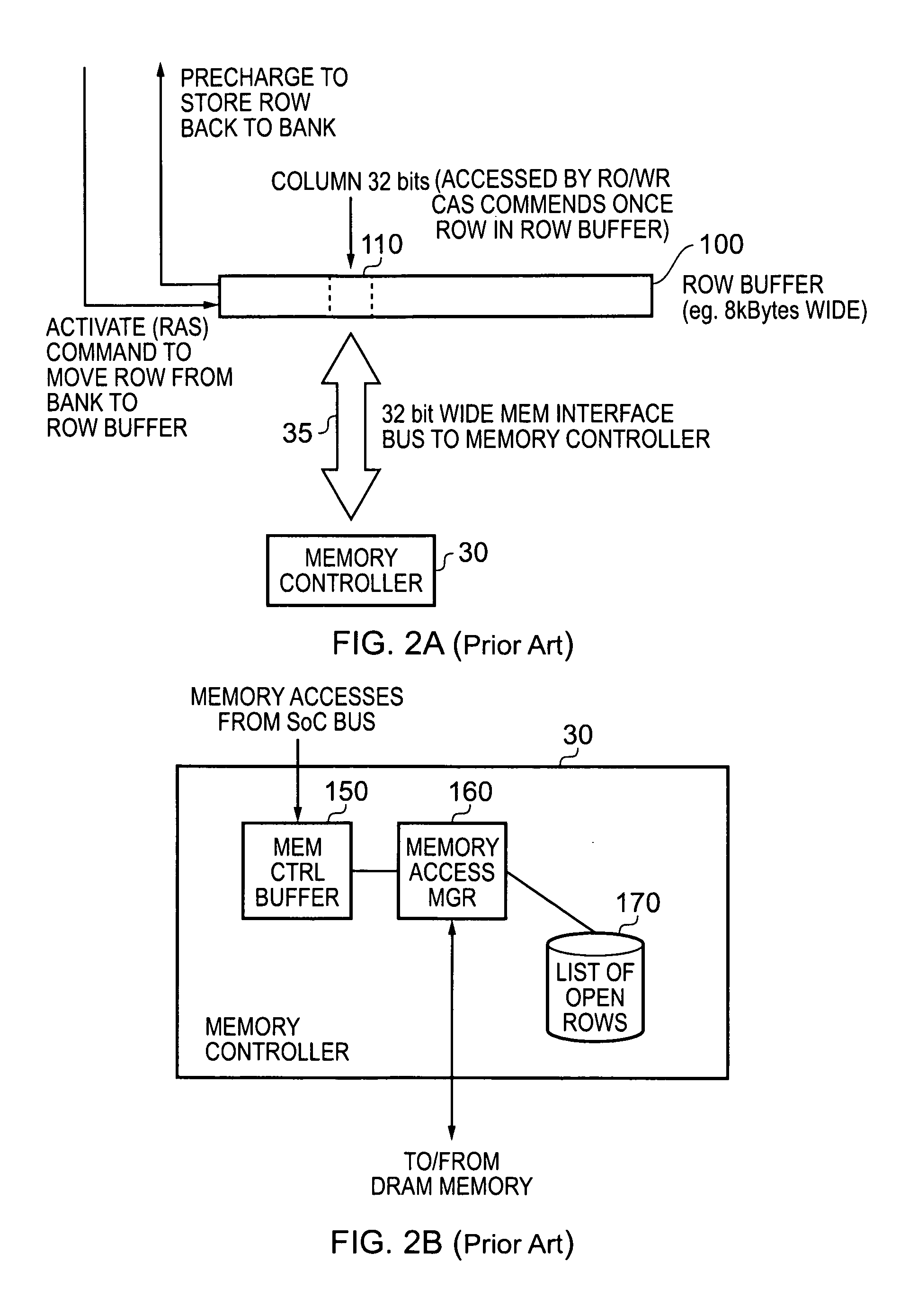

Cache device for coupling to a memory device and a method of operation of such a cache device

ActiveUS20110307664A1Number of time blockRaise the possibilityEnergy efficient ICTMemory adressing/allocation/relocationRegular patternData value

A cache device is provided for use in a data processing apparatus to store data values for access by an associated master device. Each data value has an associated memory location in a memory device, and the memory device is arranged as a plurality of blocks of memory locations, with each block having to be activated before any data value stored in that block can be accessed. The cache device comprises regular access detection circuitry for detecting occurrence of a sequence of accesses to data values whose associated memory locations follow a regular pattern. Upon detection of such an occurrence of a sequence of accesses by the regular access detection circuitry, an allocation policy employed by the cache to determine a selected cache line into which to store a data value is altered with the aim of increasing a likelihood that when an evicted data value output by the cache is subsequently written to the memory device, the associated memory location resides within an already activated block of memory locations. Hence, by detecting regular access patterns, and altering the allocation policy on detection of such patterns, this enables a reuse of already activated blocks within the memory device, thereby significantly improving memory utilisation, thereby giving rise to both performance improvements and power consumption reductions.

Owner:ARM LTD

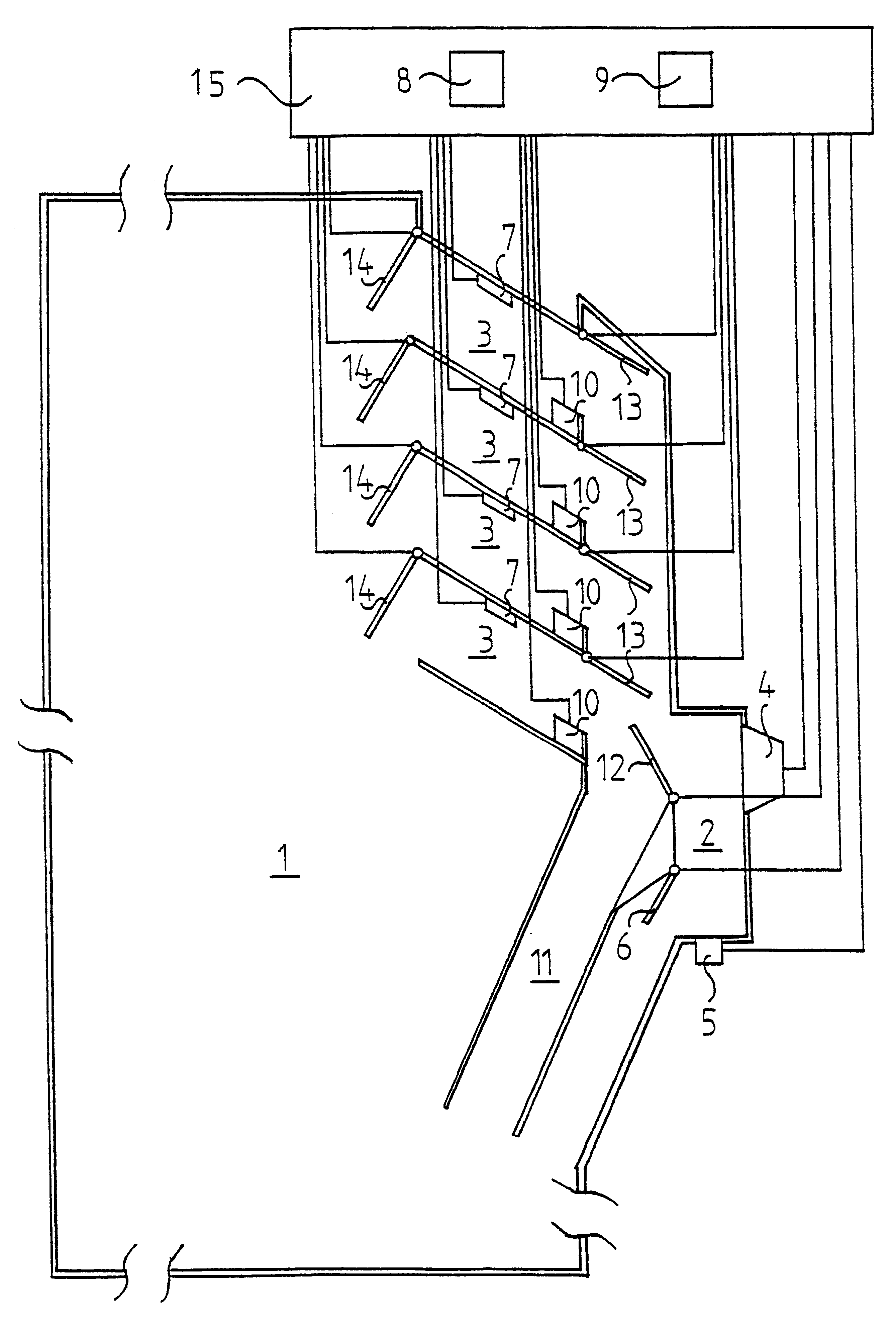

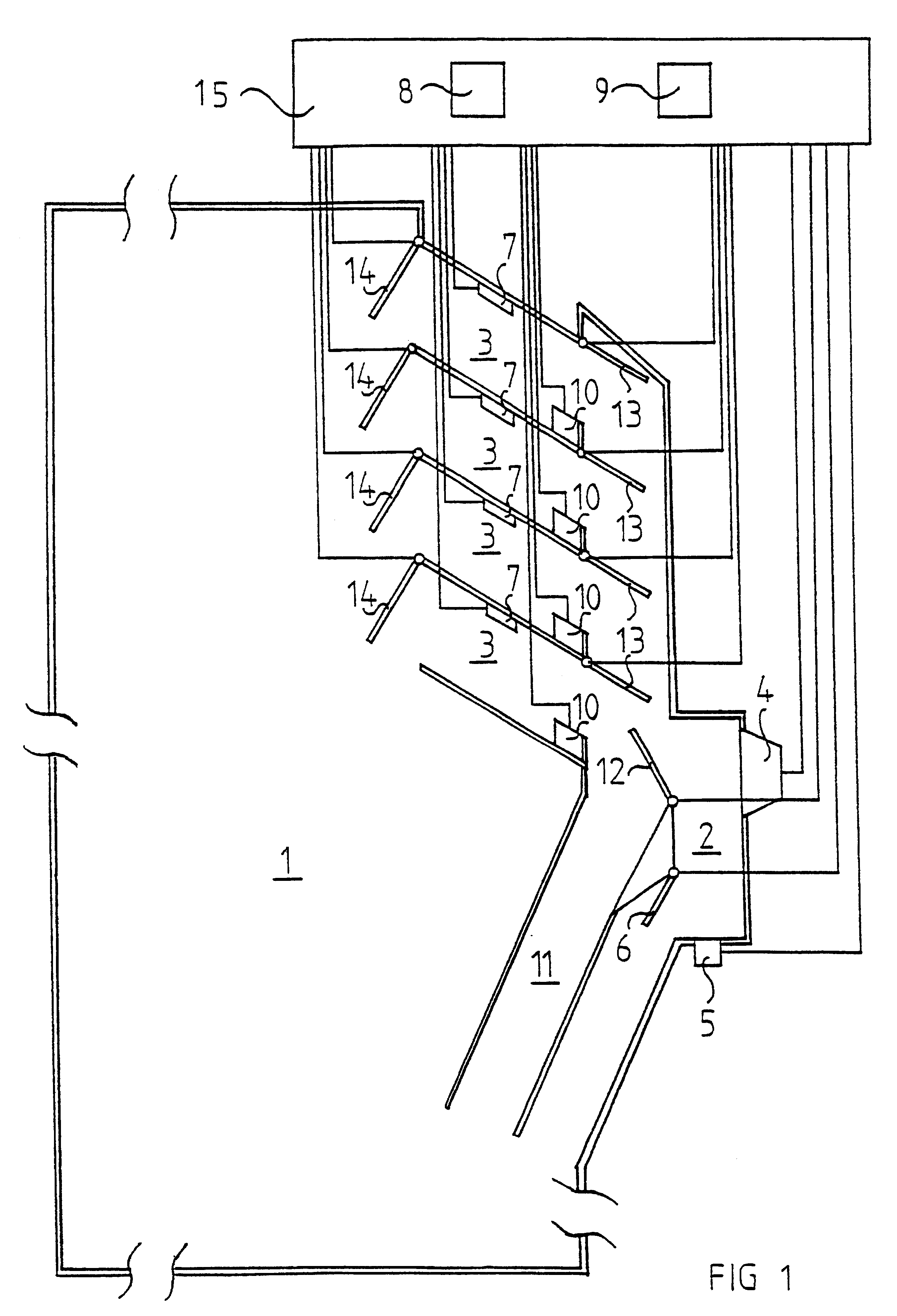

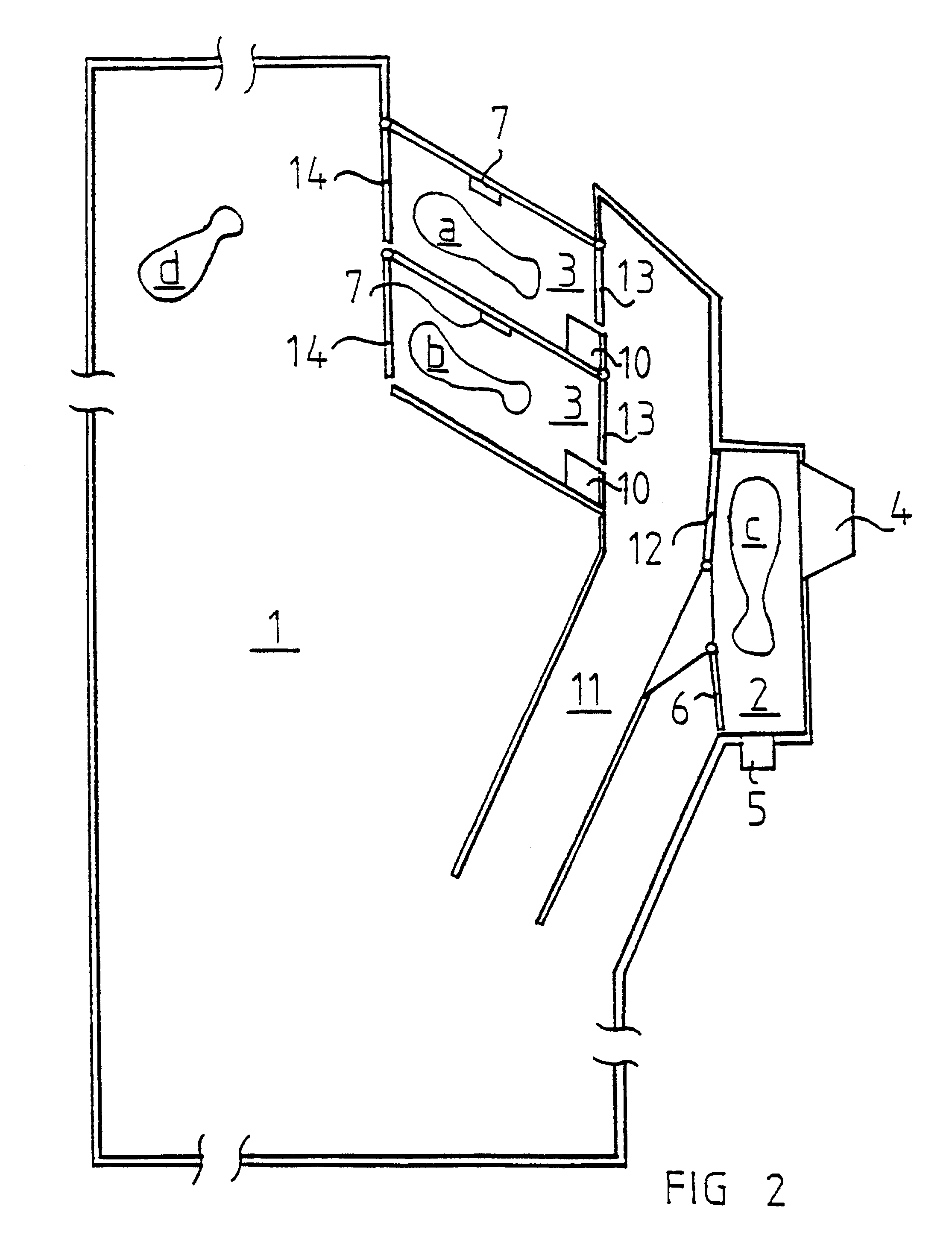

Arrangement for managing a herd of freely walking animals

An arrangement for managing a herd of freely walking animals includes an area (1) for receiving the animals, a milking station (2) and a plurality of waiting station (3) leading from the receiving area (1) to at least the milking station (2). The waiting station (3) is arranged to receive one animal and comprises one identification device (7) for identifying the animal entering the waiting station (3). The arrangement comprises a memory device (8) arranged to provide a value of a parameter related to the milk production of an animal identified by the identification device (7) and present in the waiting station (3) and by an analyzer (9) for analyzing the parameter and determining if the animal is to be milked in response to the value.

Owner:DELAVAL HLDG AB

Method

InactiveUS20060078648A1Accumulation is reduced and eliminatedIncreased amount of free fatty acidFatty acid esterificationHydrolasesMonoglycerideGlycerol

A method for the in situ production of an emulsifier in a foodstuff, wherein a lipid acyltransferase is added to the foodstuff. Preferably the emulsifier is produced without an increase or without a substantial increase in the free fatty acid content of the foodstuff. Preferably, the lipid acyltransferase is one which is capable of transferring an acyl group from a lipid to one or more of the following acyl acceptors: a sterol, a stanol, a carbohydrate, a protein or a sub-unit thereof, glycerol. Preferably, in addition to an emulsifier one or more of a stanol ester or a stanol ester or a protein ester or a carbohydrate ester or a diglyceride or a monoglyceride may be produced. One or more of these may function as an addition emulsifier.

Owner:DUPONT NUTRITION BIOSCIENCES APS

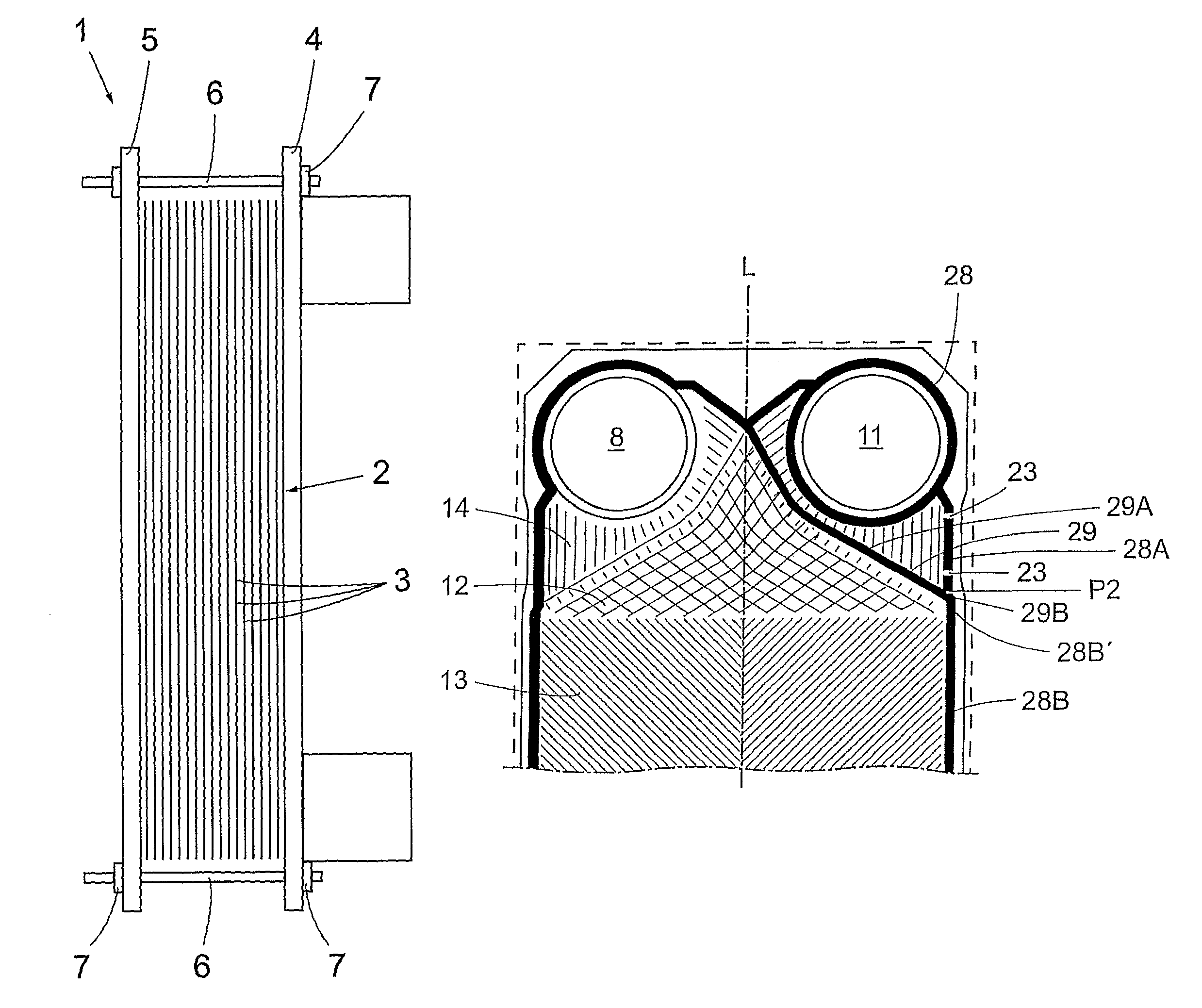

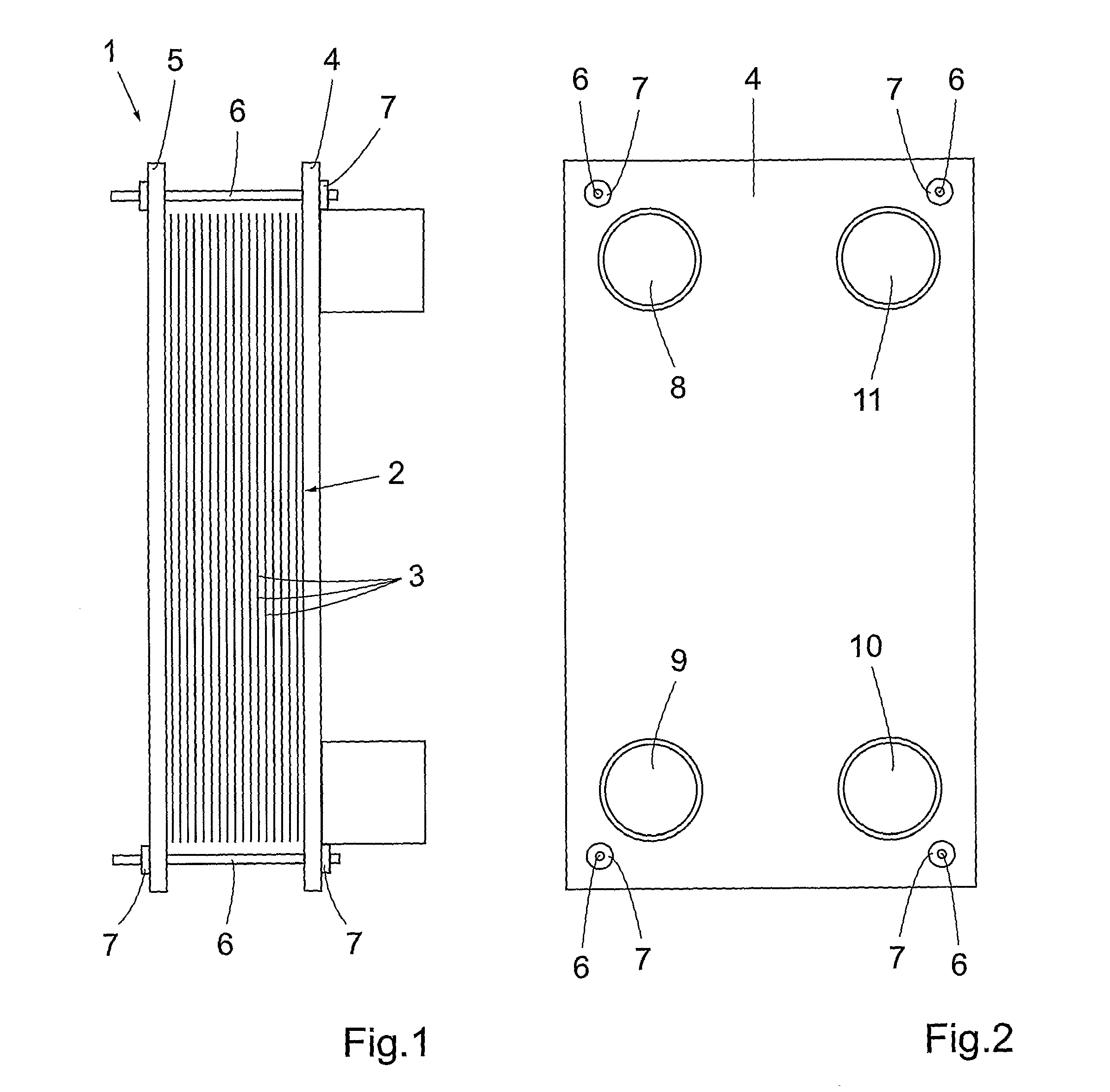

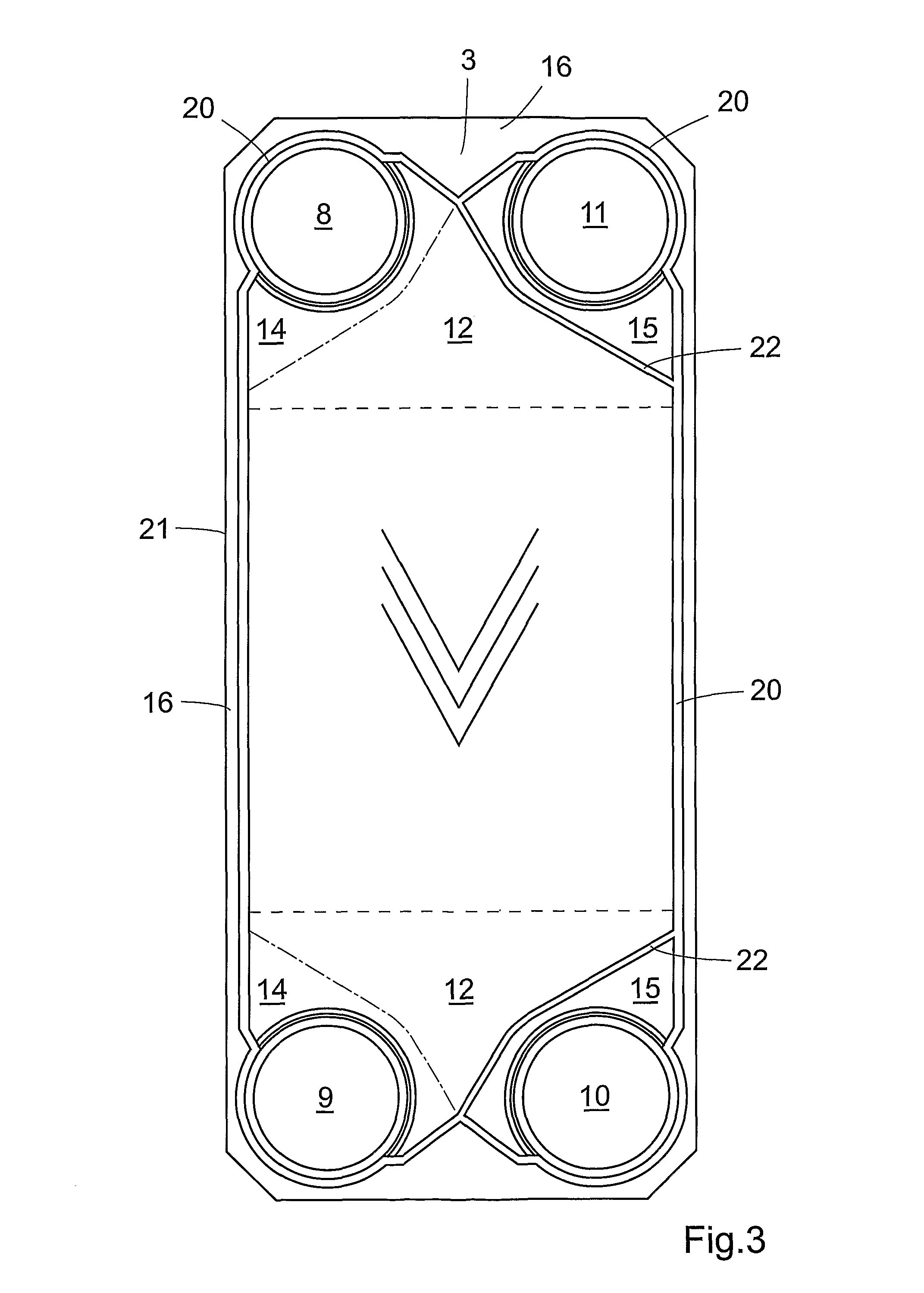

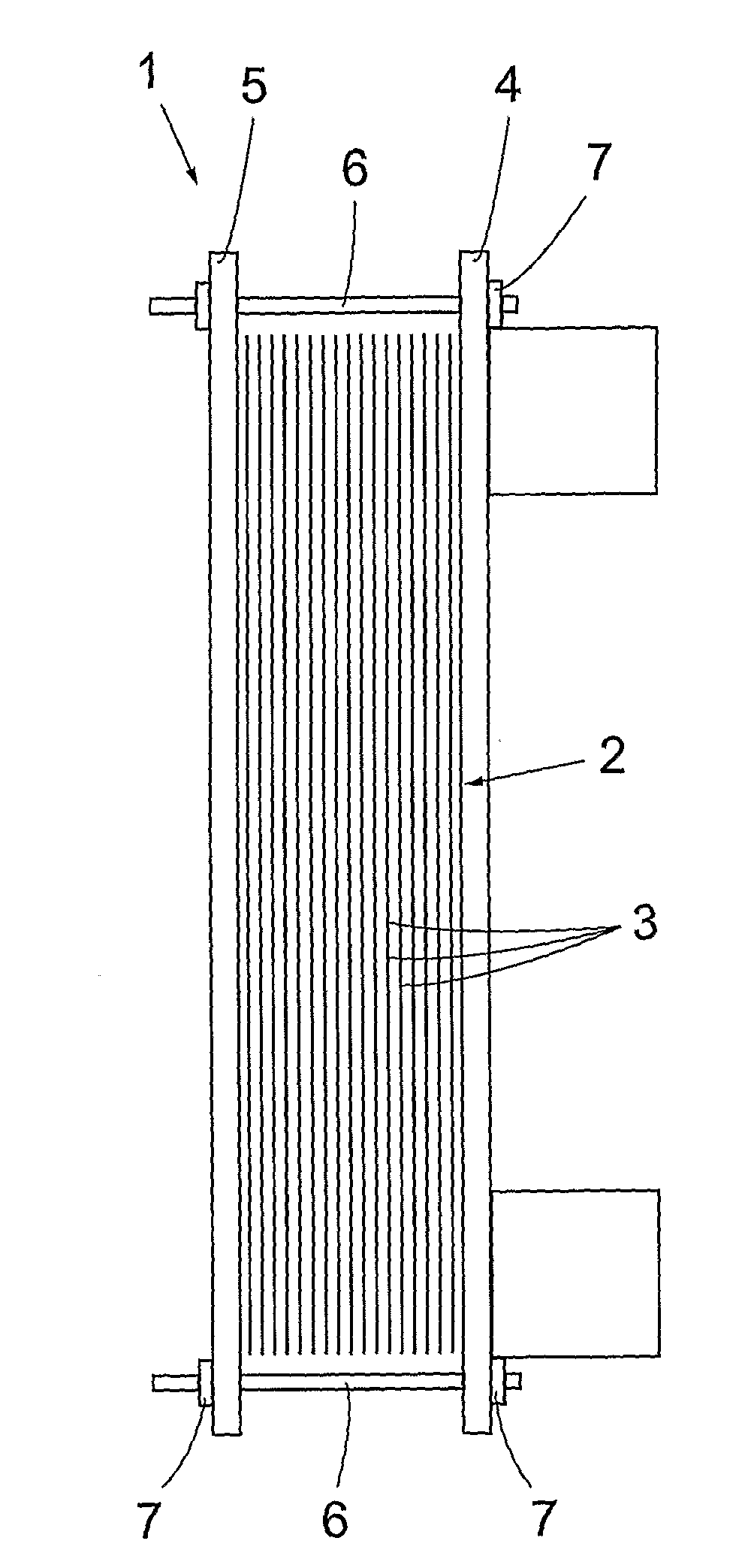

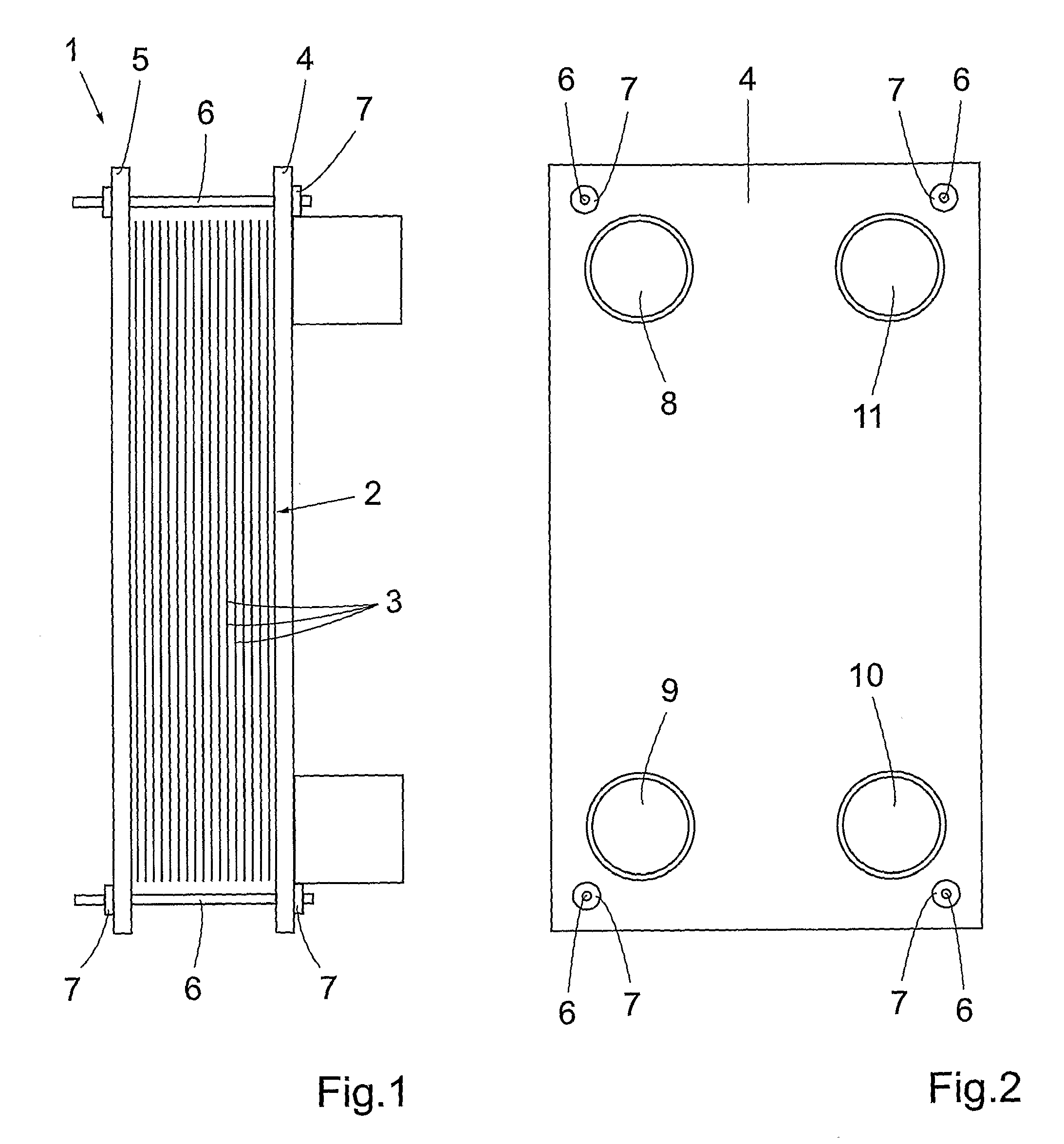

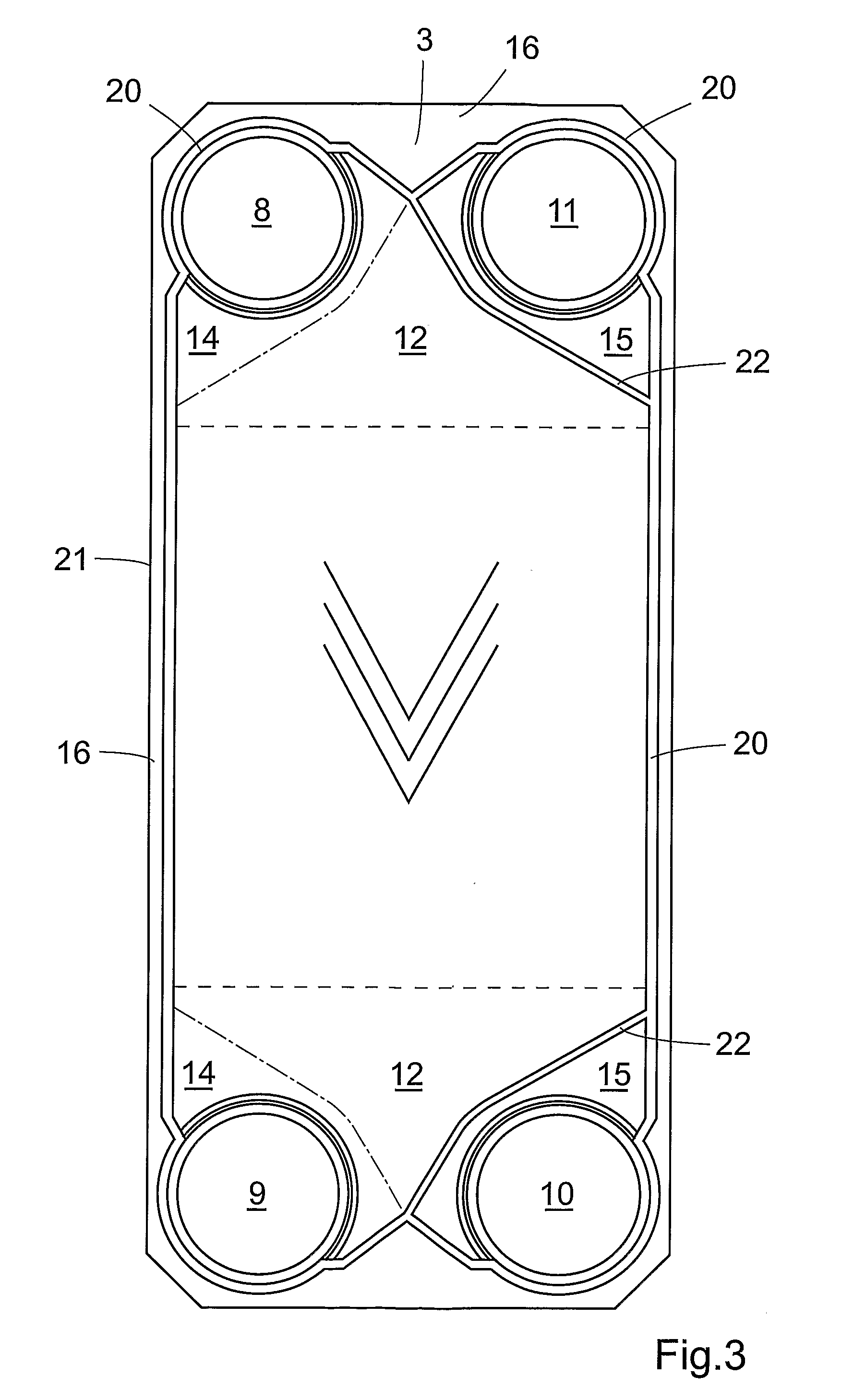

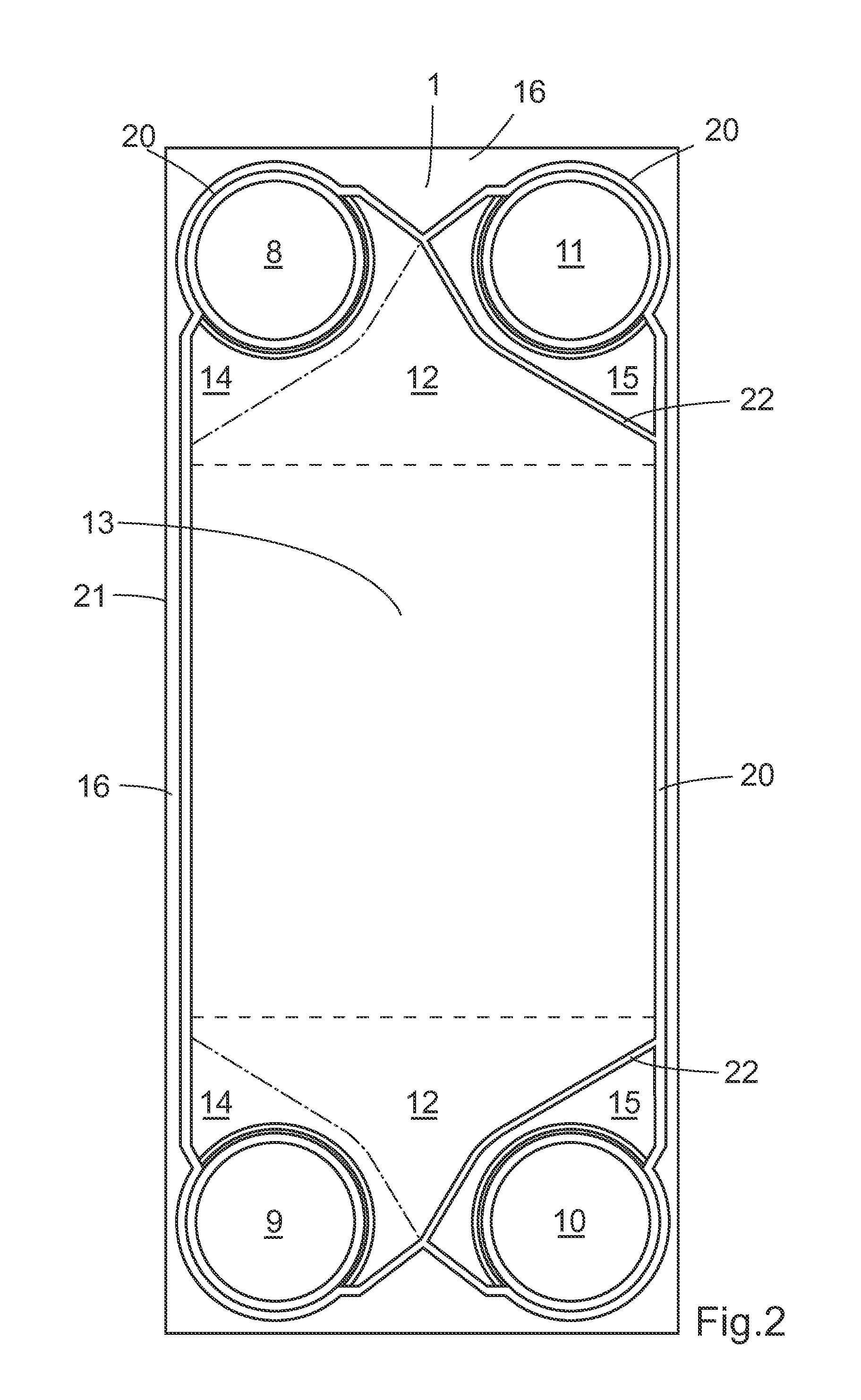

Plate and gasket for plate heat exchanger

ActiveUS8646517B2Optimal utilisationImprove performanceHeat exhanger sealing arrangementHeat exchanger casingsPlate heat exchangerEngineering

The invention relates to a heat exchanger plate for a plate heat exchanger, which plate has a number of ports, a distribution region, a heat transfer region, a first adiabatic region, a second adiabatic region and an edge area that extends outside the ports and the regions, which plate has a first gasket groove extending in the edge area outside the regions and around the ports, and a second gasket groove extending between the adiabatic region and the adjacent distribution region, whereby the gasket grooves are connected together to accommodate a gasket for sealing abutment against an adjacent heat exchanger plate in the plate heat exchanger. The invention further relates to a gasket for a heat exchanger plate and a plate heat exchanger having a package of heat exchanger plates and gaskets.

Owner:ALFA LAVAL CORP AB

Pouch cell construction

ActiveUS7629077B2Increase energy densityReduce resistancePrimary cell maintainance/servicingFinal product manufactureEngineeringPouch cell

An electrode assembly is formed by respectively overlaying a sheet cathode 1, a sheet separator 3 and a double-sided sheet anode 8 to form a stacked structure 10, and subjecting the stacked structure to multiple folds, wherein the initial fold comprises folding the cathode in half around the double-sided anode so as to surround the respective upper and lower active anode surfaces thereof. The multiple folds may comprise one or more subsequent parallel folds made with the fold line D-D extending perpendicular to the original length of the stacked structure such that its overall length is halved at each fold. A pouch battery comprising said electrode assembly has improved safety and performance characteristics. The pouch battery construction has especial application to lithium primary batteries.

Owner:QINETIQ LTD

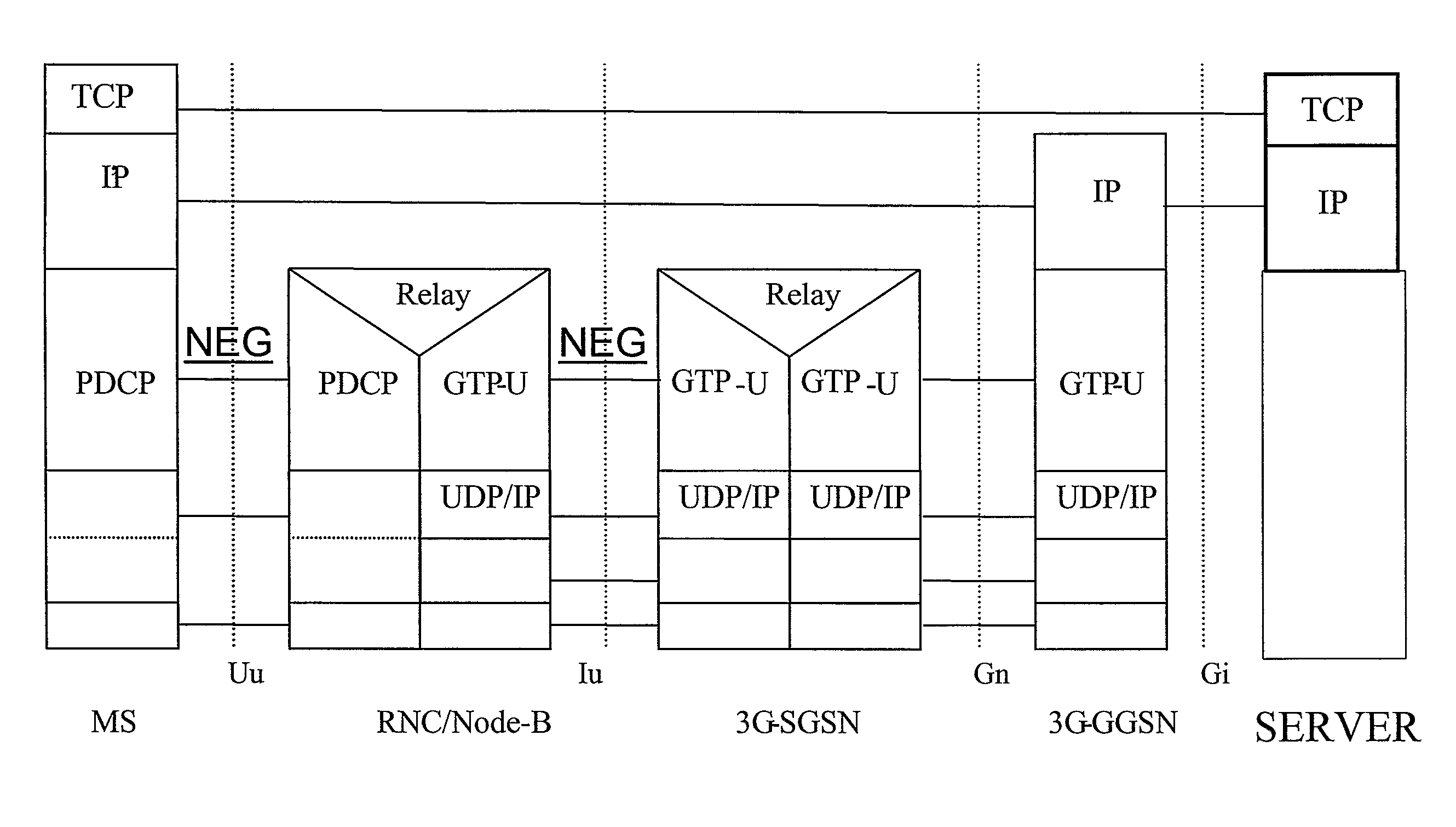

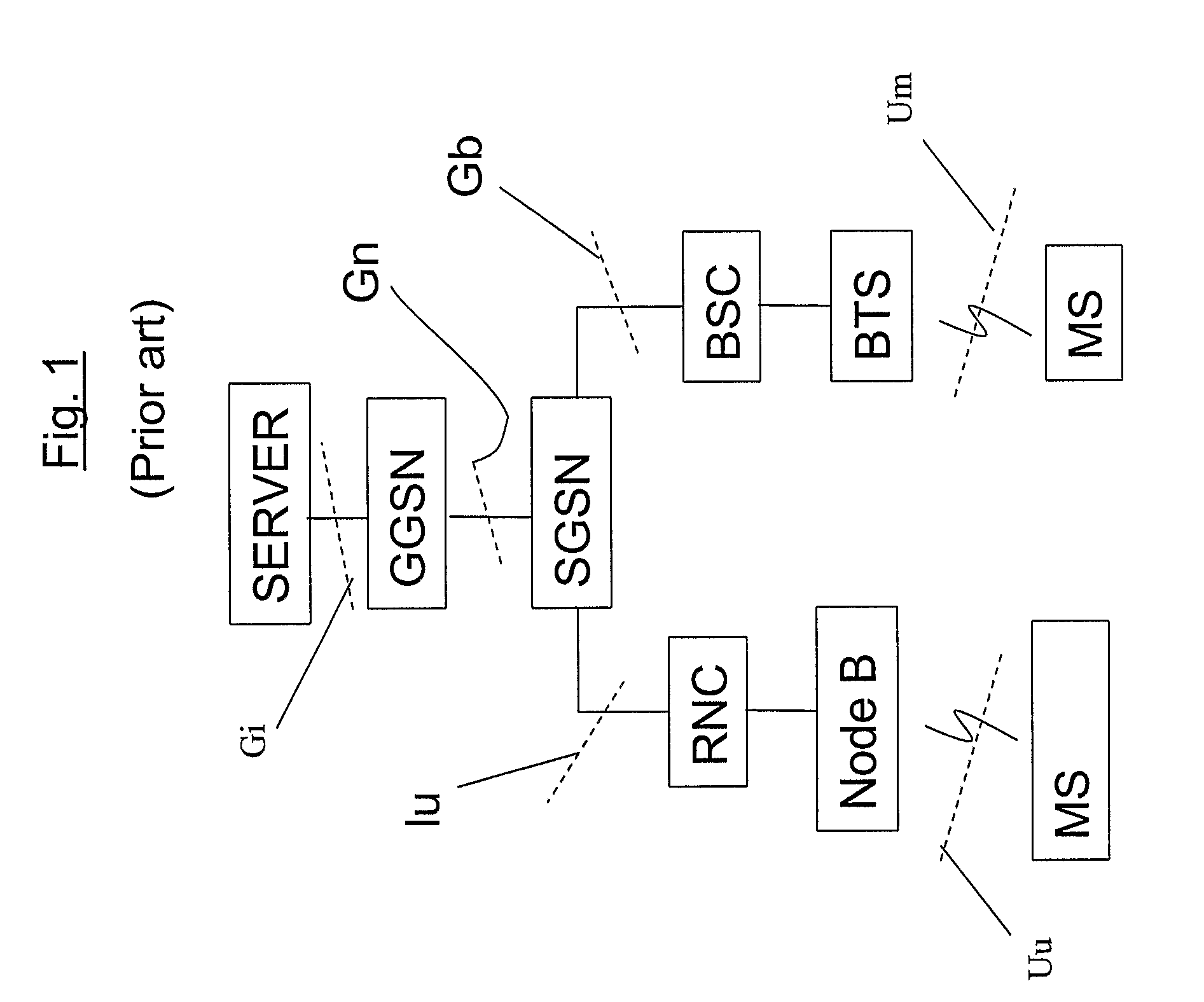

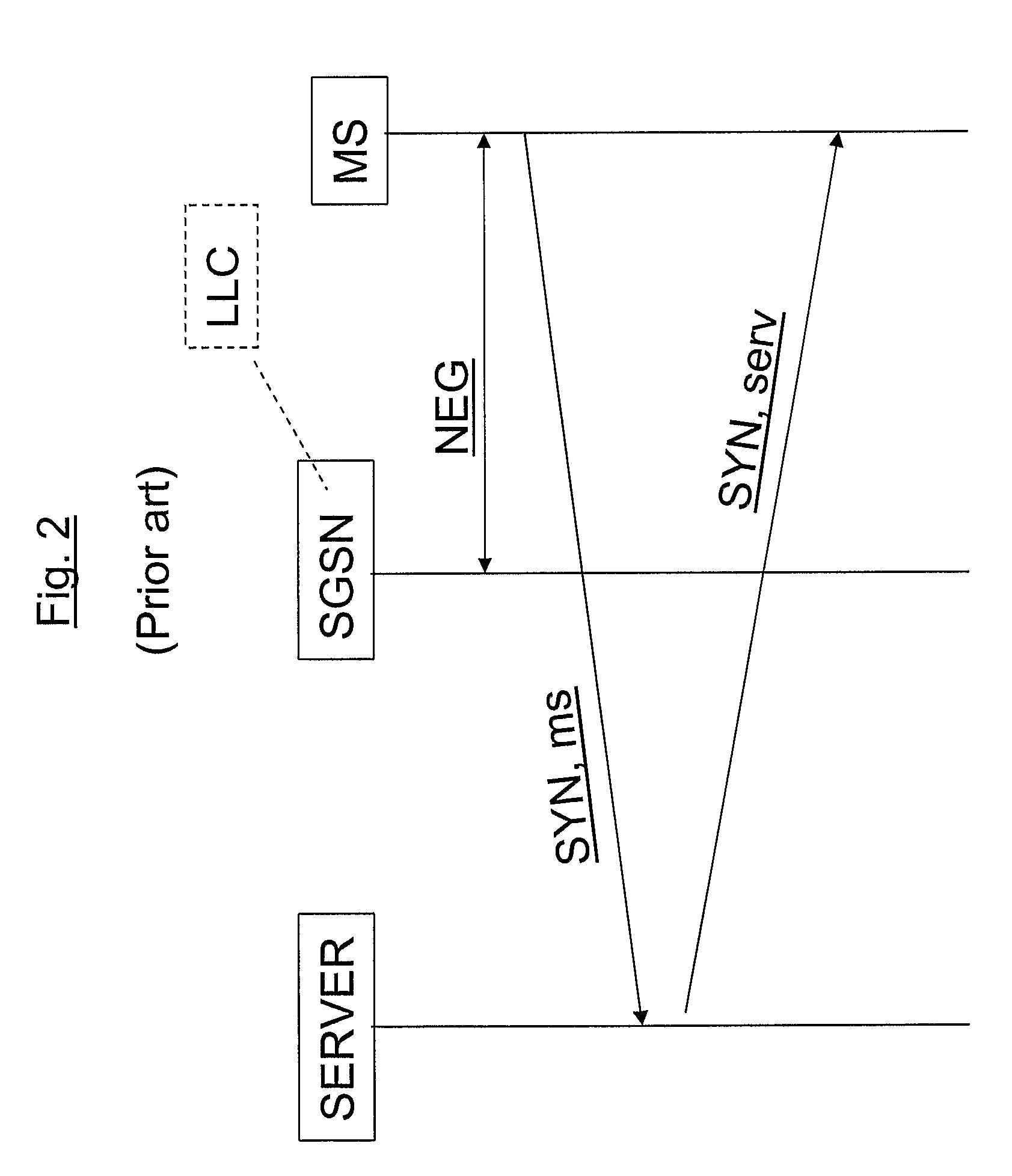

Method for Modifying Mss

InactiveUS20080107026A1Optimal utilisationGood utilisation and performanceError preventionFrequency-division multiplex detailsClient-sideRadio networks

The invention refers to a method for optimising the data communication in a network comprising a wireless radio network using connection oriented protocol (TCP) over internet protocol (IP). The network comprises a router (SGSN) intervening the connection oriented setup between a host (SERVER) and a client (MS), and changing the maximum segment size (MSS, ms) into a maximum segment size (MSS, sgsn) based on the router's (SGSN) knowledge about the radio network.

Owner:TELEFON AB LM ERICSSON (PUBL)

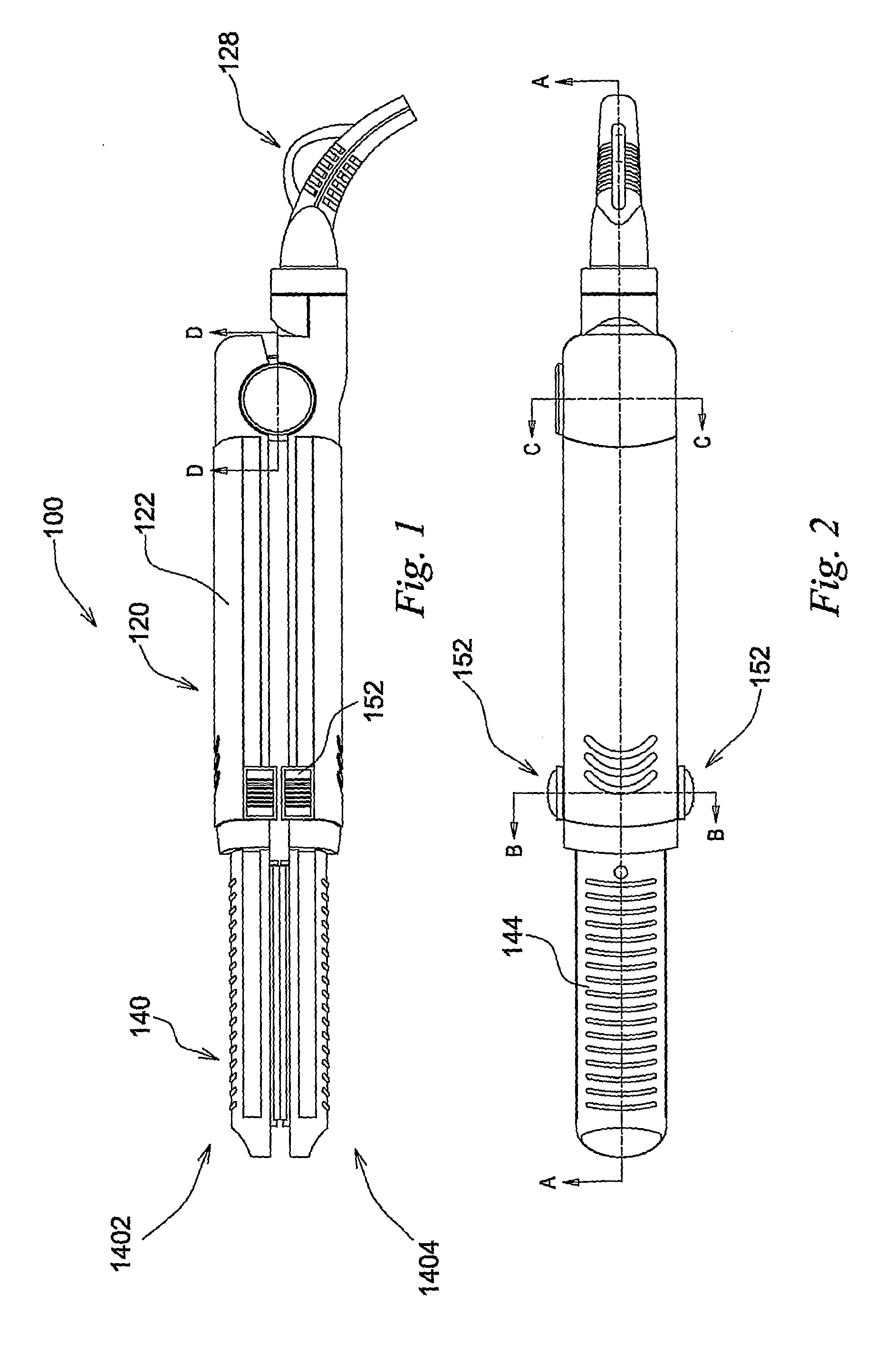

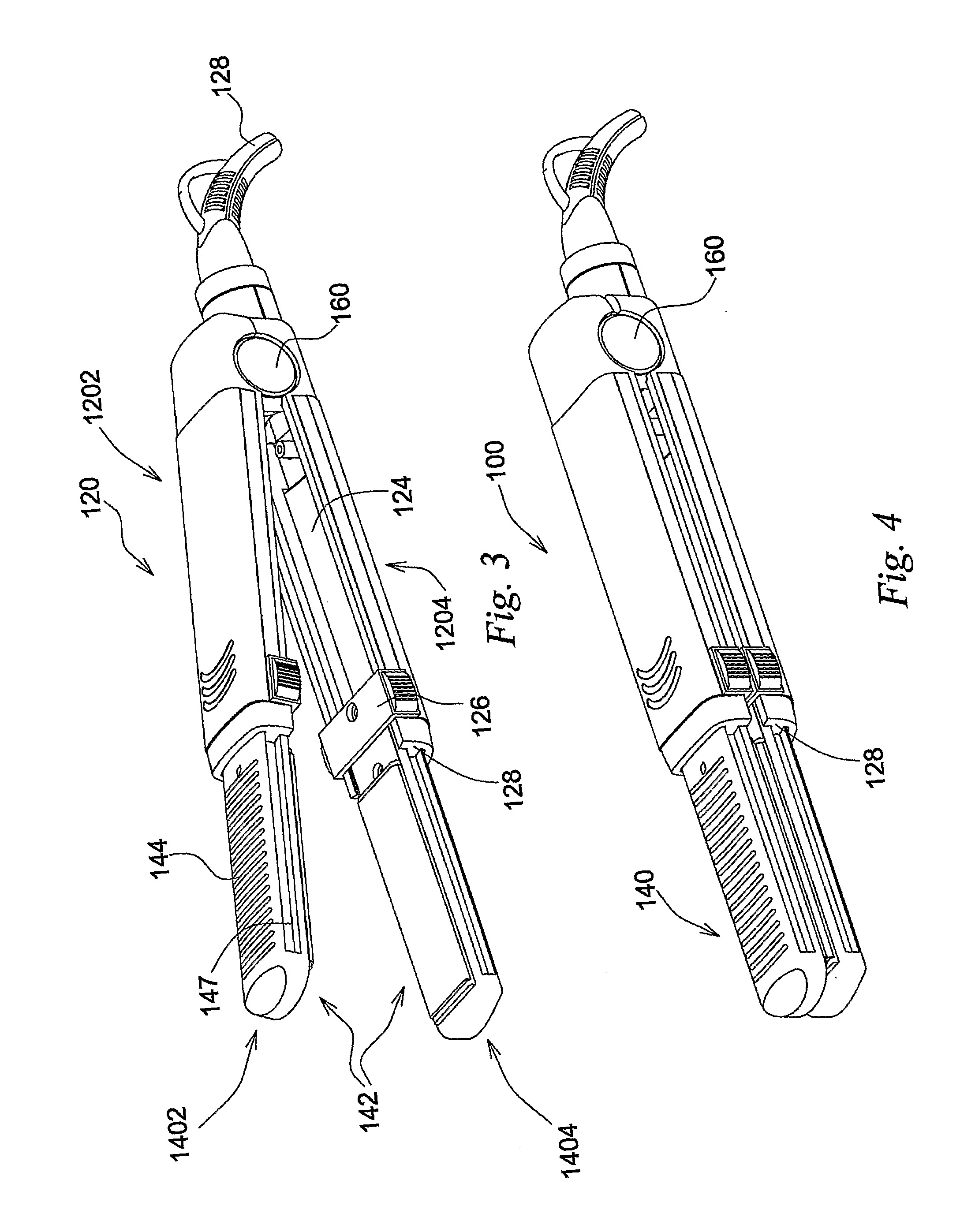

Hair styling apparatus with retractable styling heads

InactiveUS20090260651A1Reduce riskConducive to compact designCurling-ironsCurling-tongsEngineeringMechanical engineering

A hair styling apparatus includes a handle, a styling head and a heater. The handle has a pair of pivotally joined arms, and the head includes a pair of styling members which cooperate to form styling surfaces of the styling head. Each styling member is extendable from and retractable into the handle.

Owner:DICKSON IND CO LTD

Cache management within a data processing apparatus

ActiveUS8041897B2Optimal utilisationProvide flexibilityMemory adressing/allocation/relocationParallel computingCache management

A data processing apparatus, and method of managing at least one cache within such an apparatus, are provided. The data processing apparatus has at least one processing unit for executing a sequence of instructions, with each such processing unit having a cache associated therewith, each cache having a plurality of cache lines for storing data values for access by the associated processing unit when executing the sequence of instructions. Identification logic is provided which, for each cache, monitors data traffic within the data processing apparatus and based thereon generates a preferred for eviction identification identifying one or more of the data values as preferred for eviction. Cache maintenance logic is then arranged, for each cache, to implement a cache maintenance operation during which selection of one or more data values for eviction from that cache is performed having regard to any preferred for eviction identification generated by the identification logic for data values stored in that cache. It has been found that such an approach provides a very flexible technique for seeking to improve cache storage utilisation.

Owner:ARM LTD

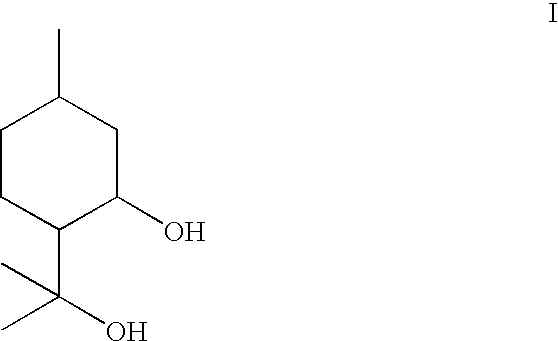

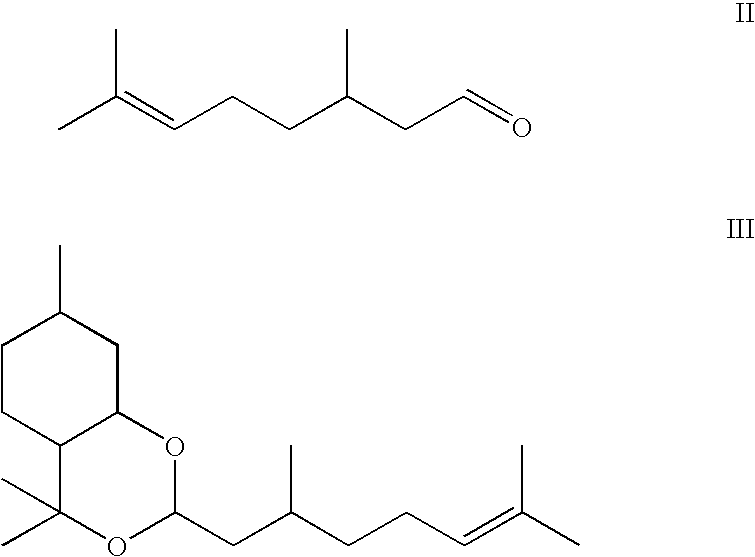

Composition containing p-menthane-3, 8-diol and its use as insect repellant

ActiveUS20100278755A1Good curative effectCosts associated with methodBiocideCosmetic preparationsDiolInsect repellent

An economical and simple method of producing para-menthane-3,8-diol in relatively high yield is disclosed. The product is useful as a repellent against noxious insects and other arthropods.

Owner:DELL IAN THOMAS

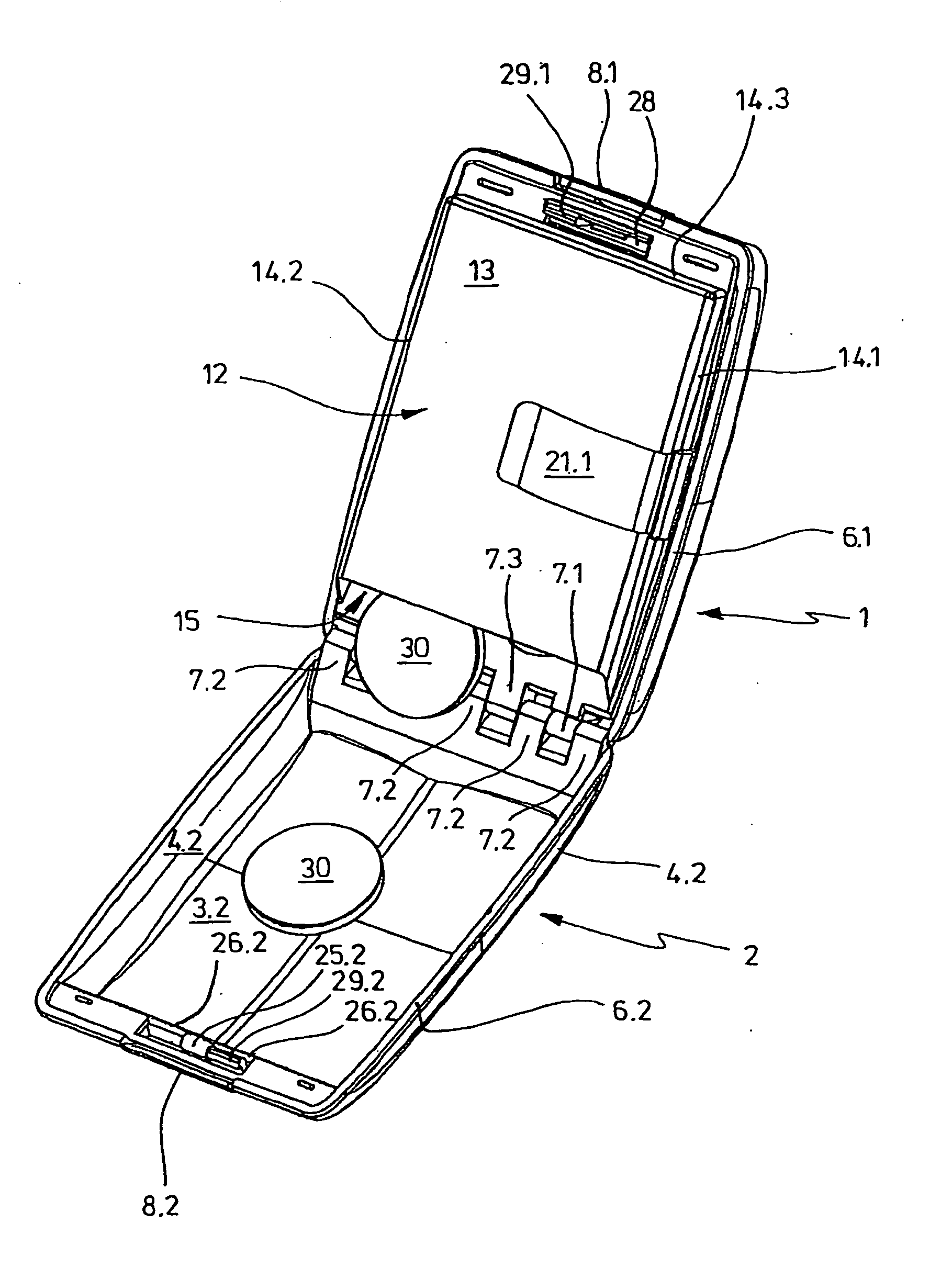

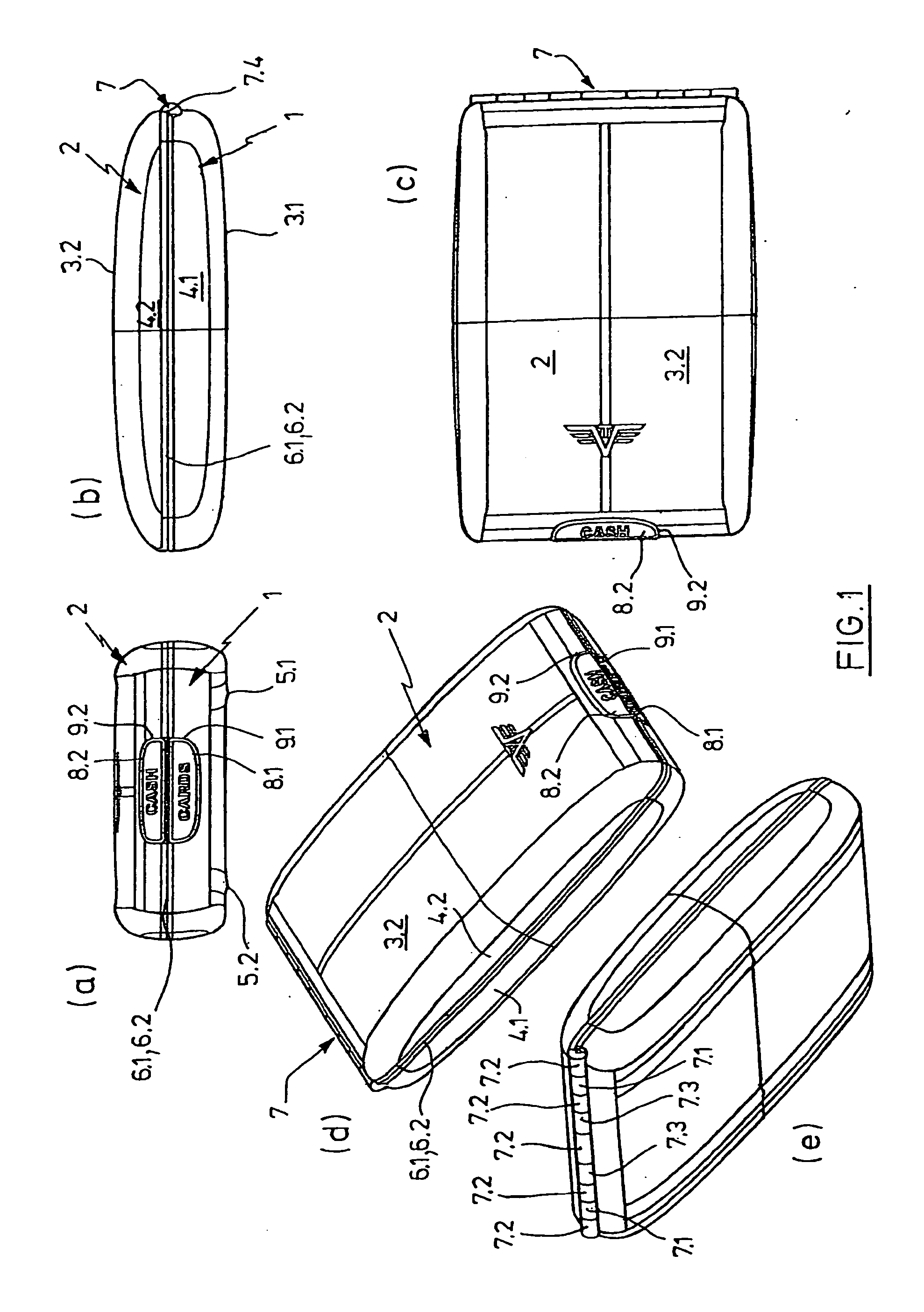

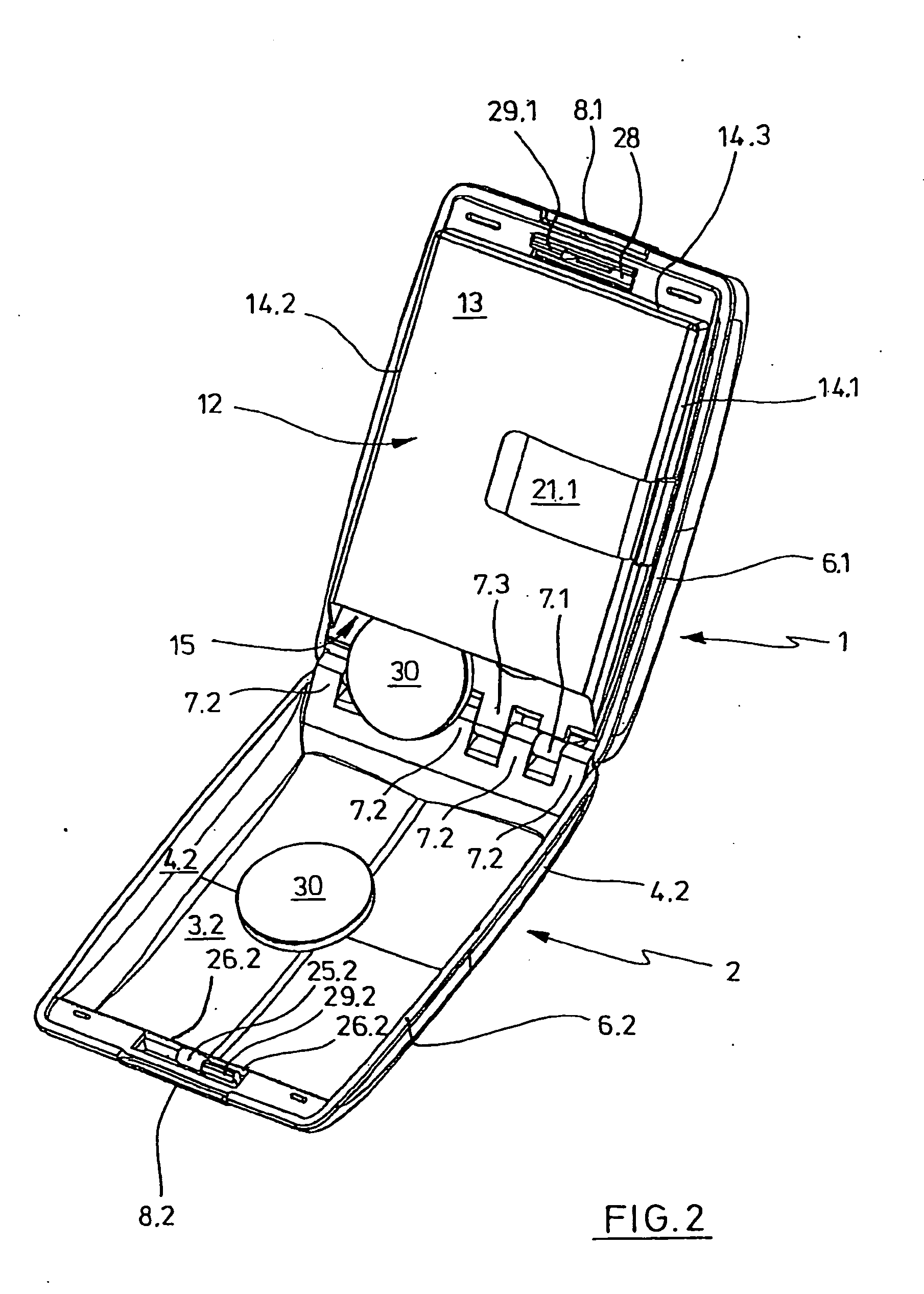

Case for Coins and/or Plastic Cards

Owner:WINGERTER THOMAS +1

Plate And Gasket For Plate Heat Exchanger

ActiveUS20090159251A1Cost savingLarge impactHeat exhanger sealing arrangementHeat exchanger casingsEdge regionEngineering

The invention relates to a heat exchanger plate for a plate heat exchanger, which plate has a number of ports, a distribution region, a heat transfer region, a first adiabatic region, a second adiabatic region and an edge area that extends outside the ports and the regions, which plate has a first gasket groove extending in the edge area outside the regions and around the ports, and a second gasket groove extending between the adiabatic region and the adjacent distribution region, whereby the gasket grooves are connected together to accommodate a gasket for sealing abutment against an adjacent heat exchanger plate in the plate heat exchanger. The invention further relates to a gasket for a heat exchanger plate and a plate heat exchanger having a package of heat exchanger plates and gaskets.

Owner:ALFA LAVAL CORP AB

Apparatus and method for adaptive data transmission

InactiveUS20060235654A1Optimal utilisationImprove securityDigital computer detailsNuclear monitoringData streamThe Internet

An apparatus and method for adjusting bandwidth utilisation between a group of different participating users accessing client terminals in a common media event in a computer network. The apparatus includes a distributing unit which distributes address information and bandwidth limitation to the users connectable via the computer network to the media event from their respective client terminals. The distributing unit is hosted from a central administration entity and connecting links connect each client terminals of participating users via the Internet or other global interconnecting network to the distributing unit. Measurement elements are provided in association with the client terminals to measure incoming data streams from other users. The distributed bandwidth limitation is provided to the client terminals to allow them to compare incoming data streams, in response to which the terminals autonomously adjust their amount of transmission to a level that allows for optimal utilisation of available resources during transmission.

Owner:MARRATECH

Travelling field machine

InactiveUS20070052315A1Guaranteed maximum utilizationOptimal utilisationSynchronous generatorsMagnetic circuitElectrical conductorStator coil

A travelling field machine with a stator and a rotor which are separated by an air gap and each of which comprises at least one stator coil or one rotor coil, with the stator or the rotor, respectively, comprising a soft magnetic iron body with a stator or rotor back, in which spaced grooves are formed, generating teeth, and in each of the grooves several conductor bars of the stator coil or the rotor coil, respectively, are arranged in series comprising end connectors arranged at the faces of the stator or the rotor, respectively, which connect the conductor bars extending across at least one groove, with the conductor bars comprising conductor portions of different length projecting beyond the faces of the stator or rotor, respectively, and the end connectors being arranged in a stacked fashion in the axial direction at the faces of the stator or the rotor.

Owner:COMPACT DYNAMICS

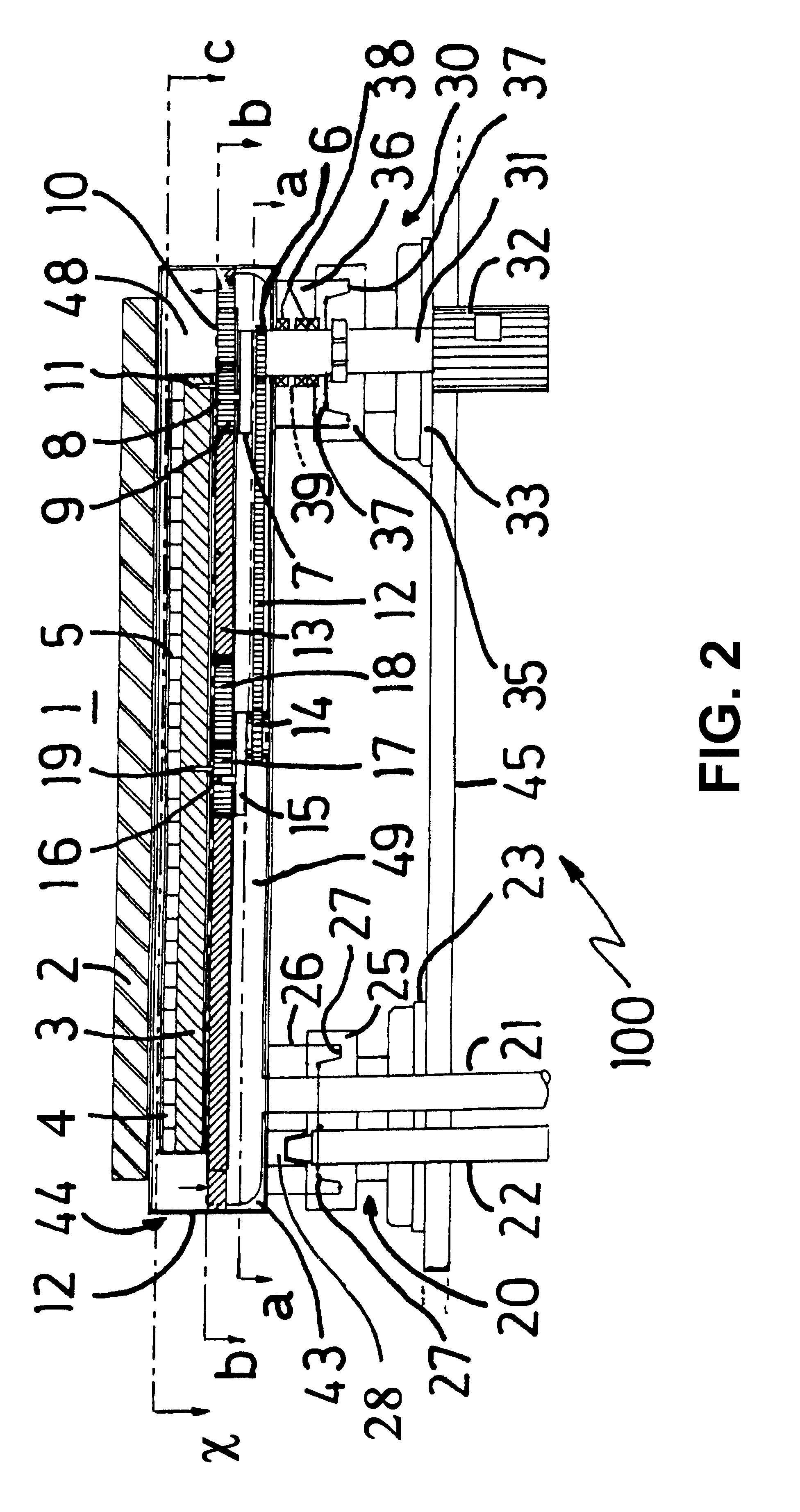

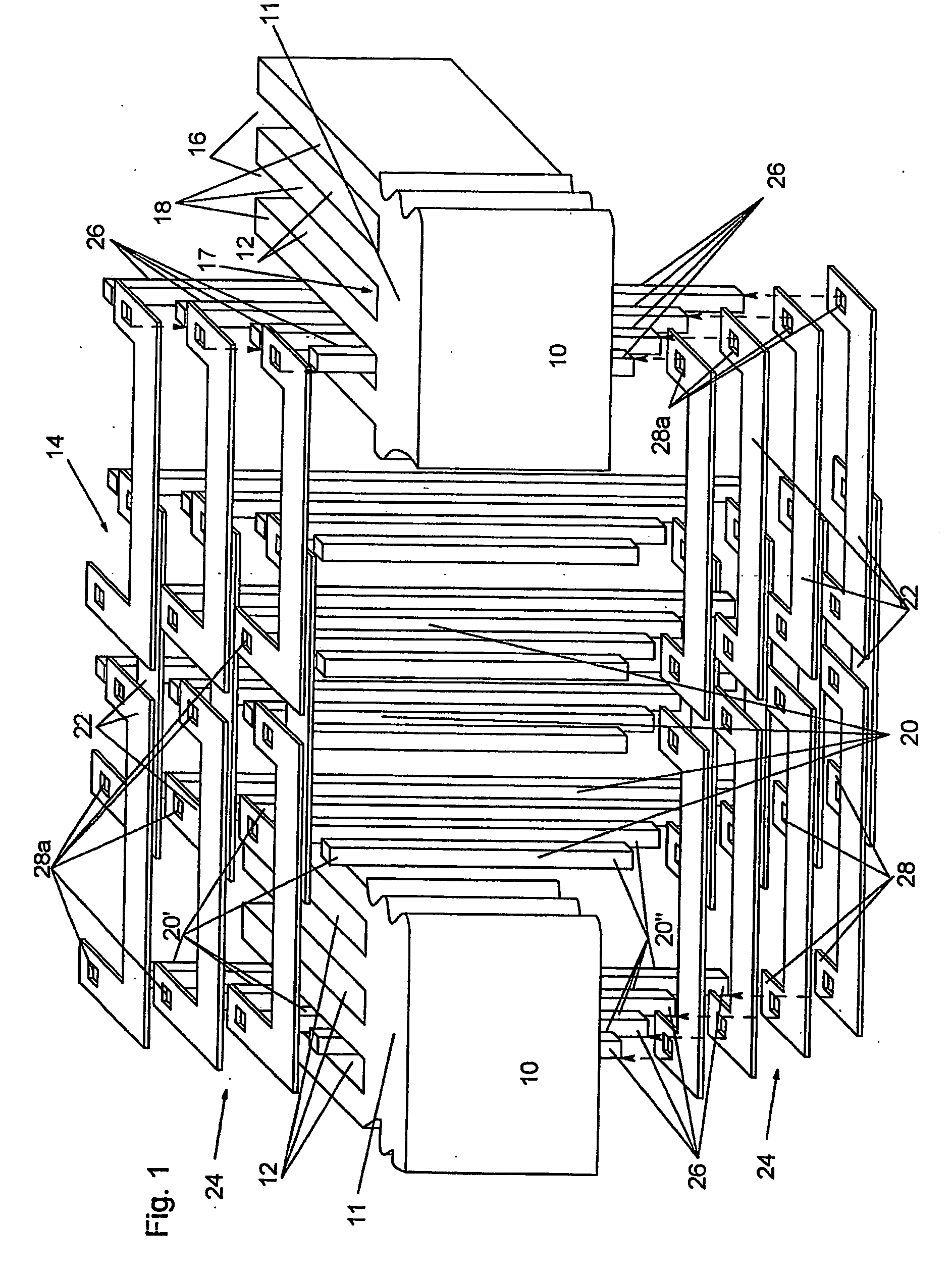

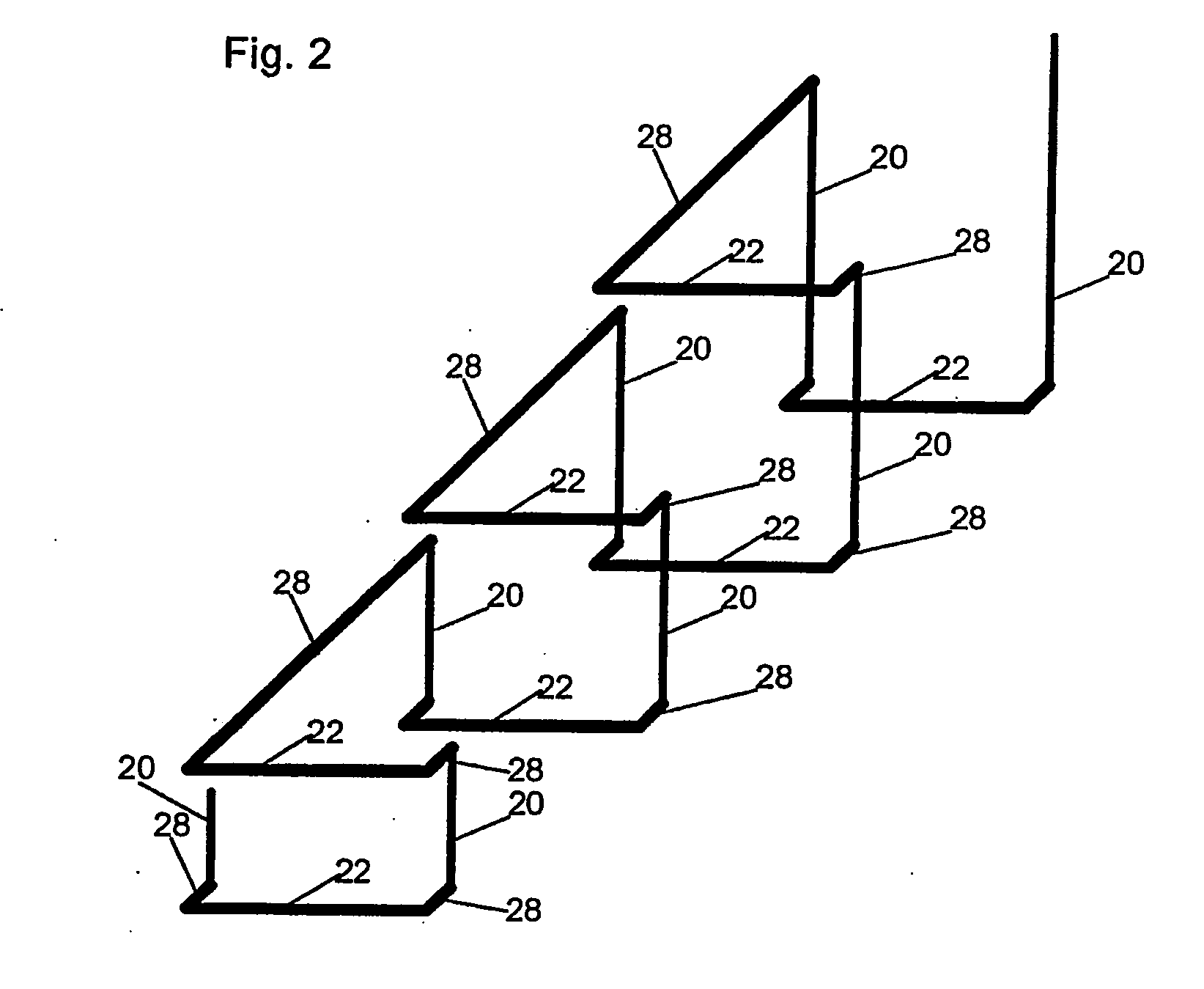

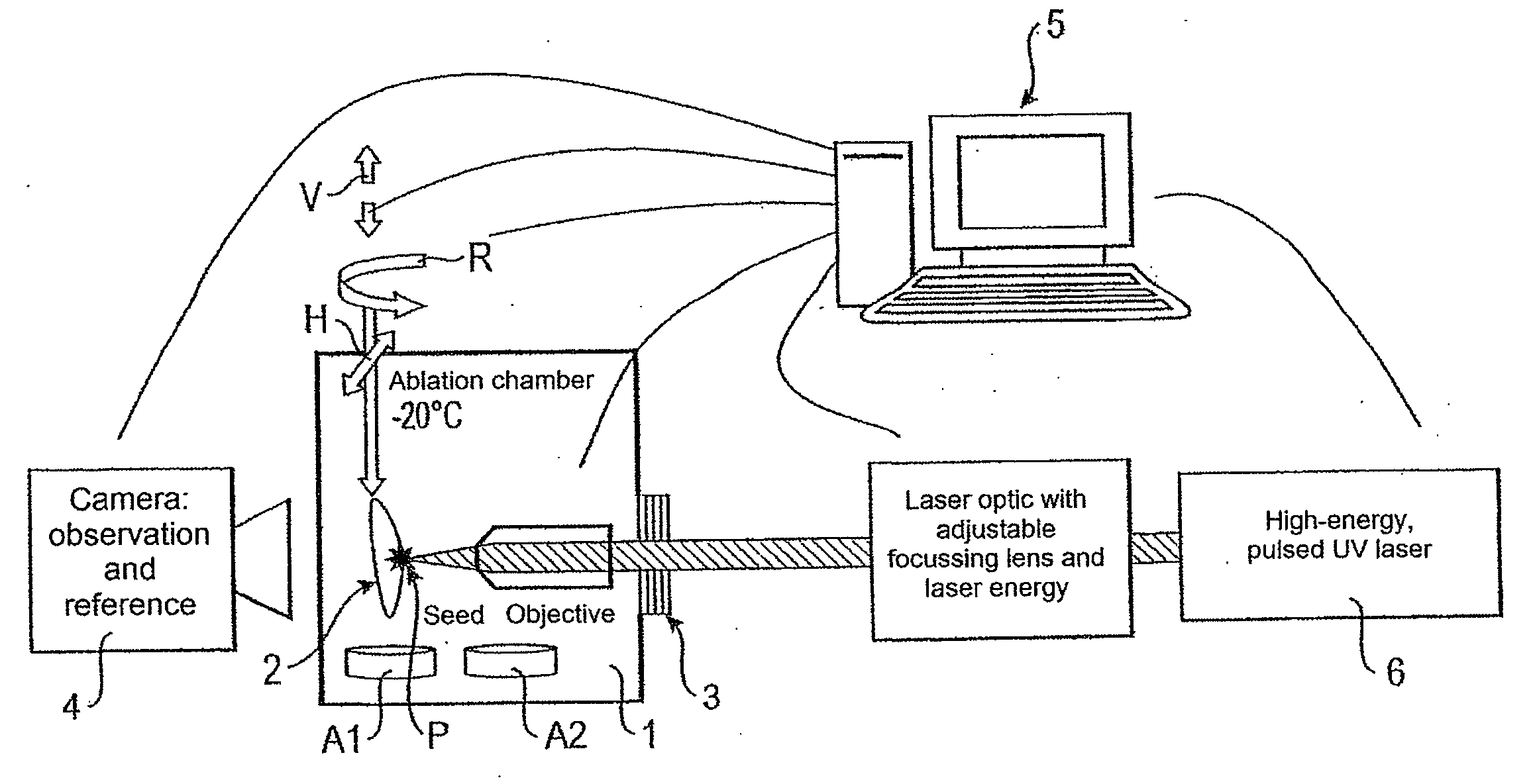

Method and device for three dimensional microdissection

ActiveUS20090140169A1High precisionSimple calculationWithdrawing sample devicesPreparing sample for investigationPhysicsCorneal ablation

A method for three-dimensional microdissection for the separation of defined structures in the sub-millimeter range by means of cold laser ablation or by means of multi-photon absorption, whereby exposure of the structures to be separated is performed using directional information in all spatial directions. In addition, a 3D microdissection system for the separation of defined, three-dimensional structures from a sample, having: a control unit (5); an ablation chamber (1) with a sample holder provided therein, on which the sample to be processed is to be mounted and which is movable along a linear axis V and rotatable about a rotary axis R, whereby the sample holder is provided with positioning devices that are connected to the control unit which can cause the positioning devices to move the sample holder along another linear axis H and to rotate it about rotary axis R, and a laser device (6), which is introduced into the ablation chamber at least partially through a laser window (3) that is provided in the ablation chamber. The ablation chamber is connected to the control unit and has an adjustable optic, which can be adjusted by means of the control unit such that the laser beam is focussed in the region of the sample.

Owner:MMI MOLECULAR MACHINES & INDS

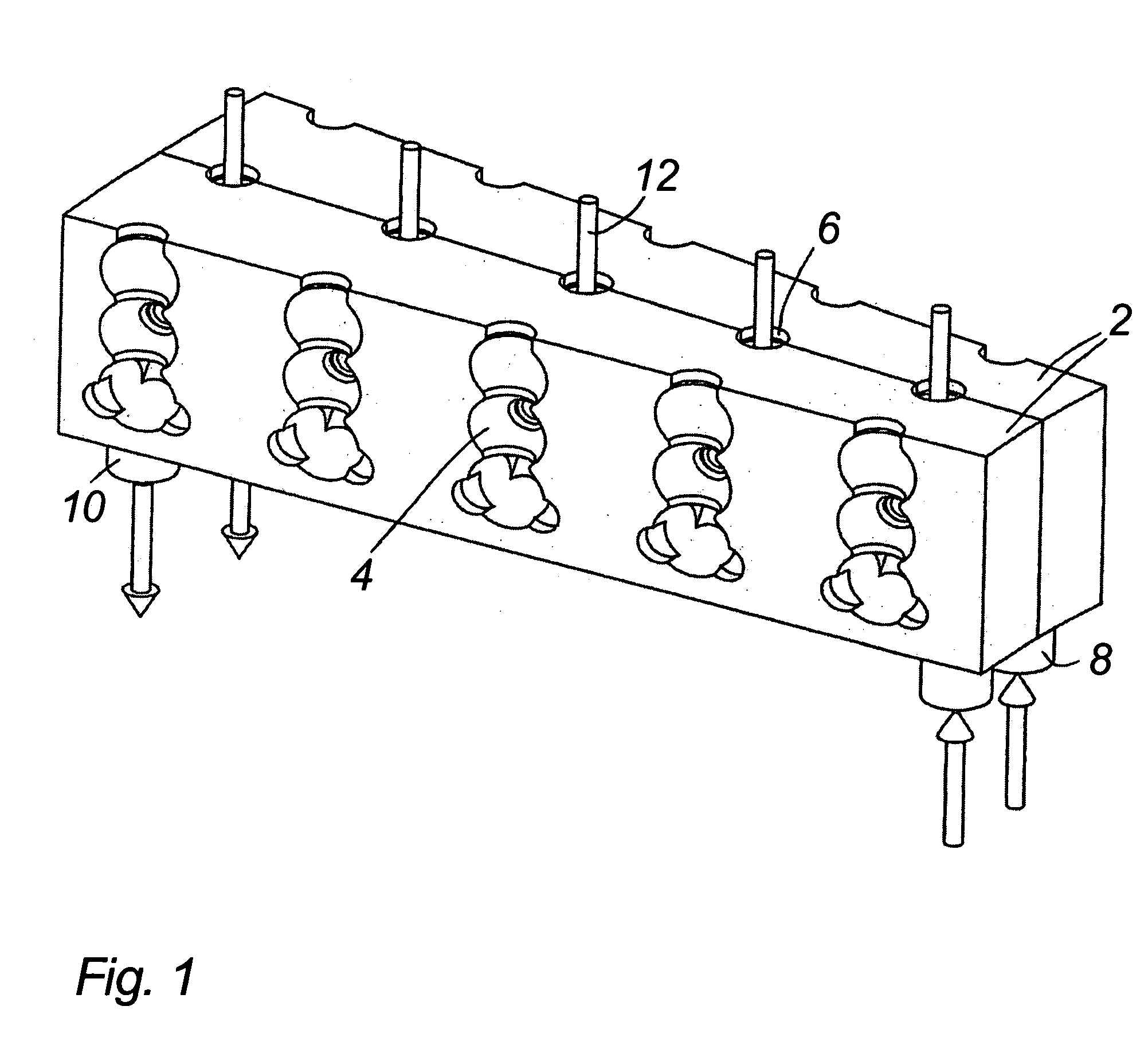

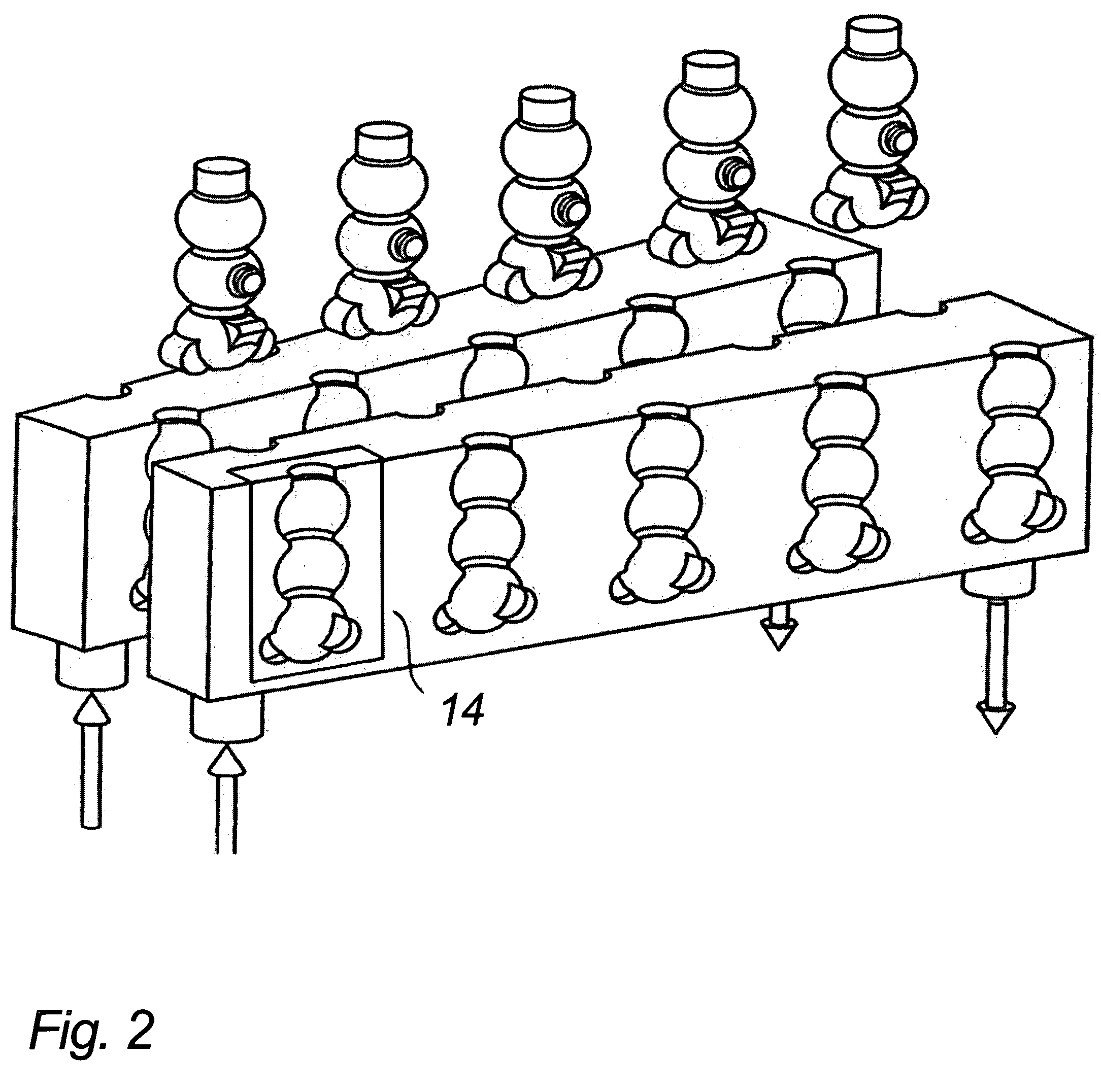

Distributing or Collecting Device

InactiveUS20060124550A1Easy to separateOptimal utilisationIon-exchange process apparatusComponent separationChromatographic separationFluidized bed

Owner:FINPHIDE

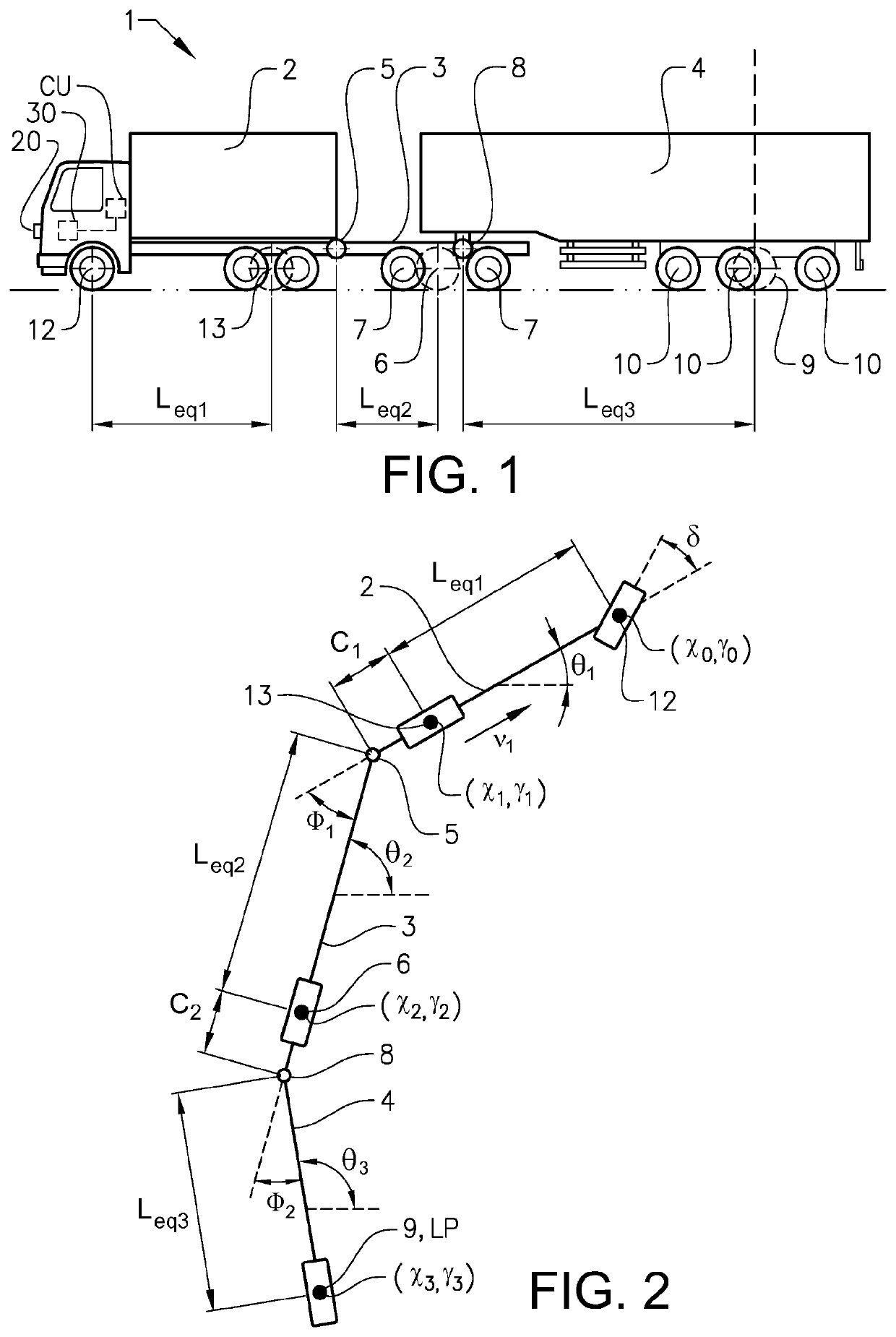

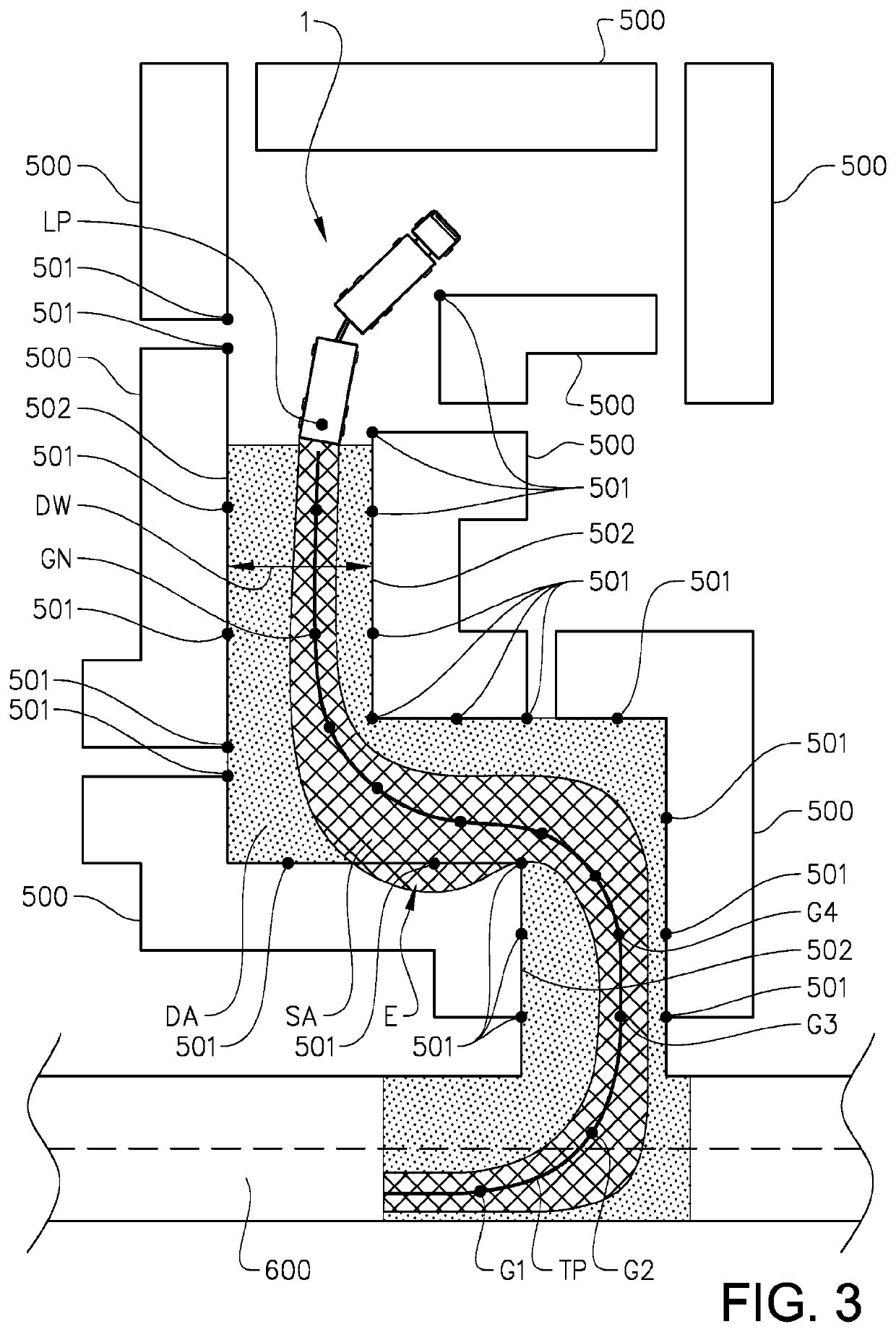

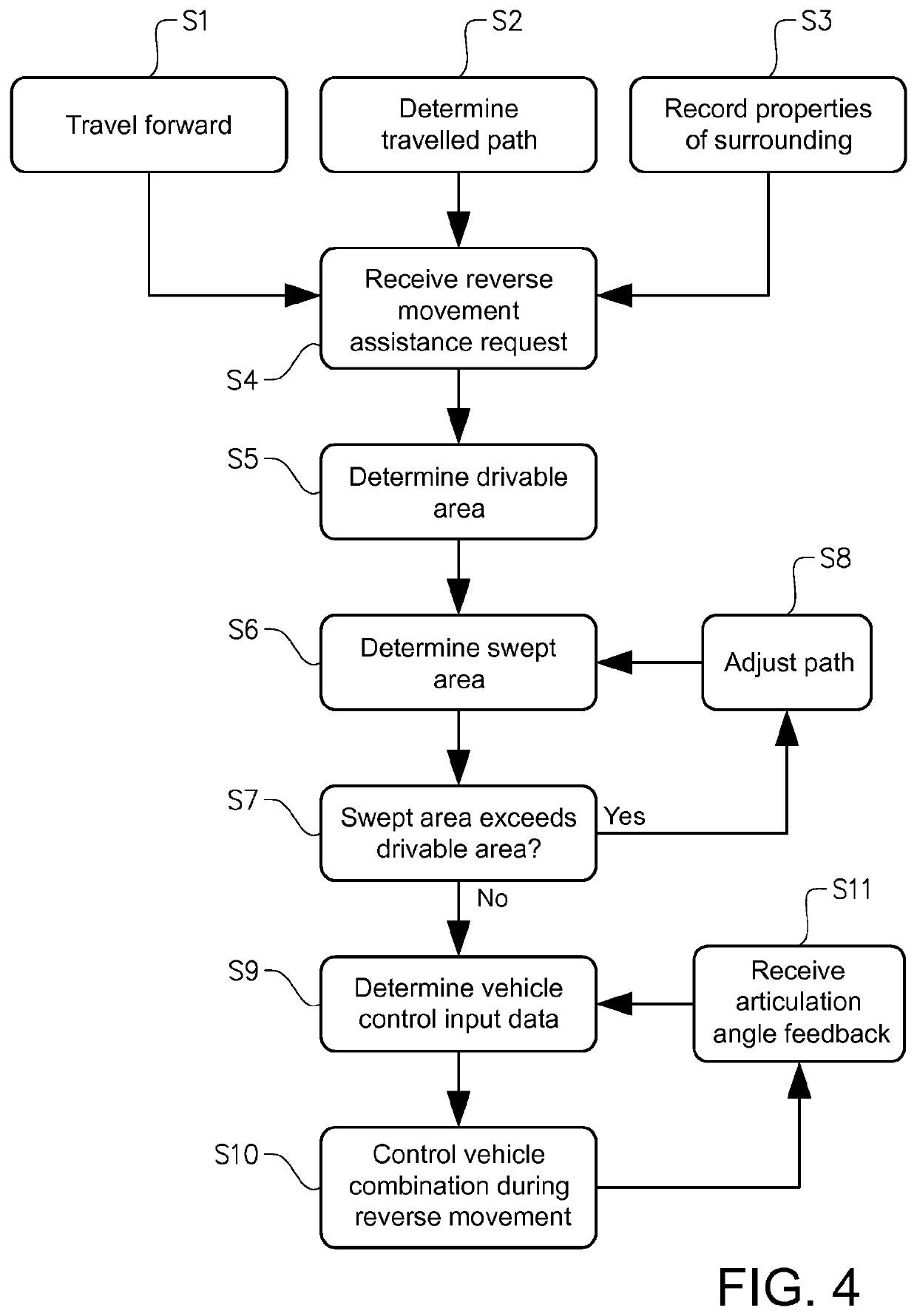

A device and a method for reversing an articulated vehicle combination

ActiveUS20200180691A1Auxiliary judgmentGuaranteed execution efficiencyCharacter and pattern recognitionExternal condition input parametersControl engineeringControl cell

A device for reversing an articulated vehicle combination that has at least two vehicle units interconnected via at least one articulated join includes an arrangement for recording and storing a plurality of global positions of a local position of the vehicle combination, at least one sensor, mounted on the vehicle combination, for recording data representing a plurality properties of the surroundings, and a control unit arranged to determine, based at least partly on a plurality of dimensions of the vehicle combination, a set of global positions recorded when the vehicle combination is moving forward, and a set of data representing properties of the surroundings recorded during the forward movement, vehicle control input data for control of the vehicle combination during a reverse movement of the vehicle combination.

Owner:VOLVO LASTVAGNAR AB

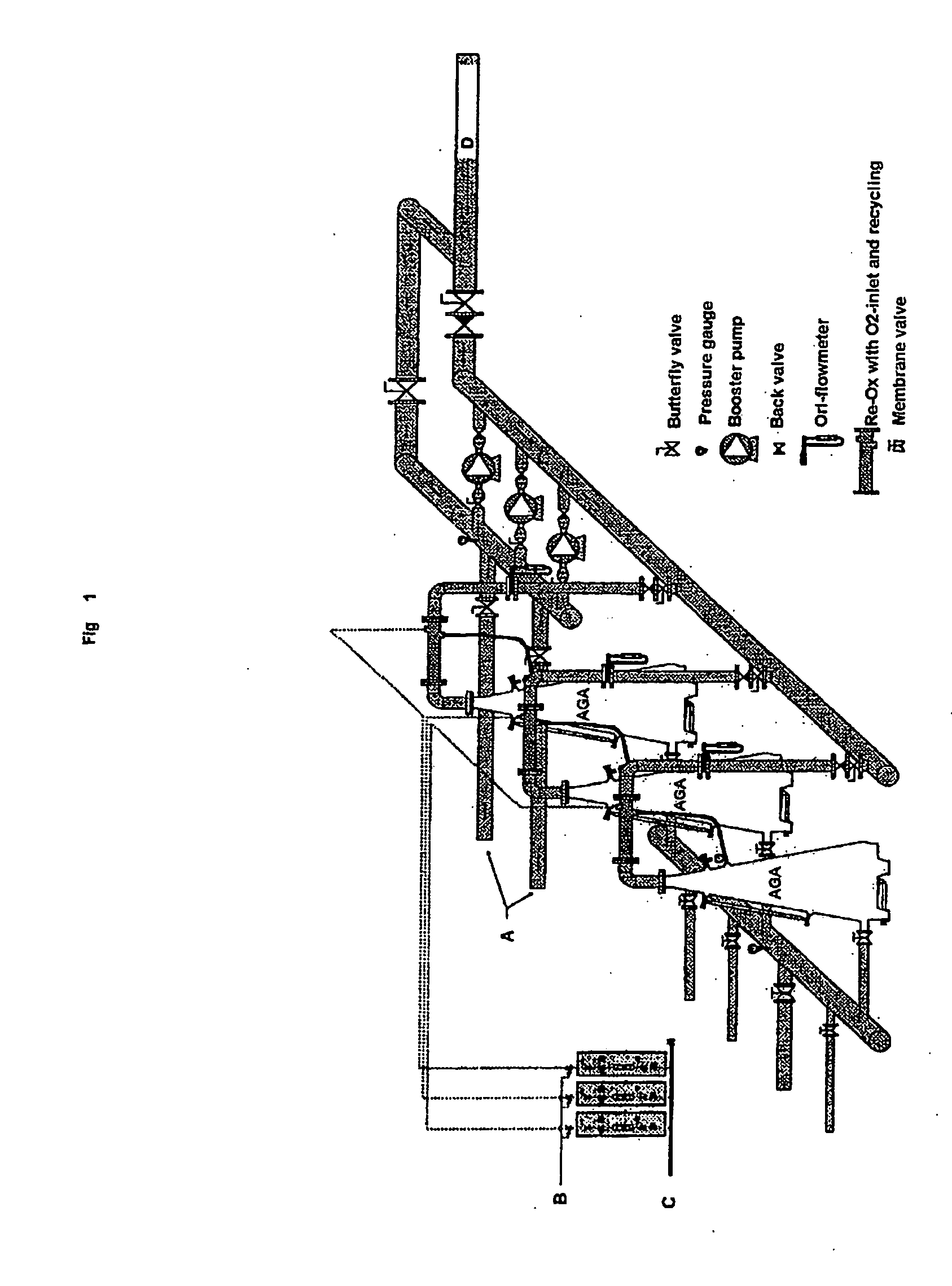

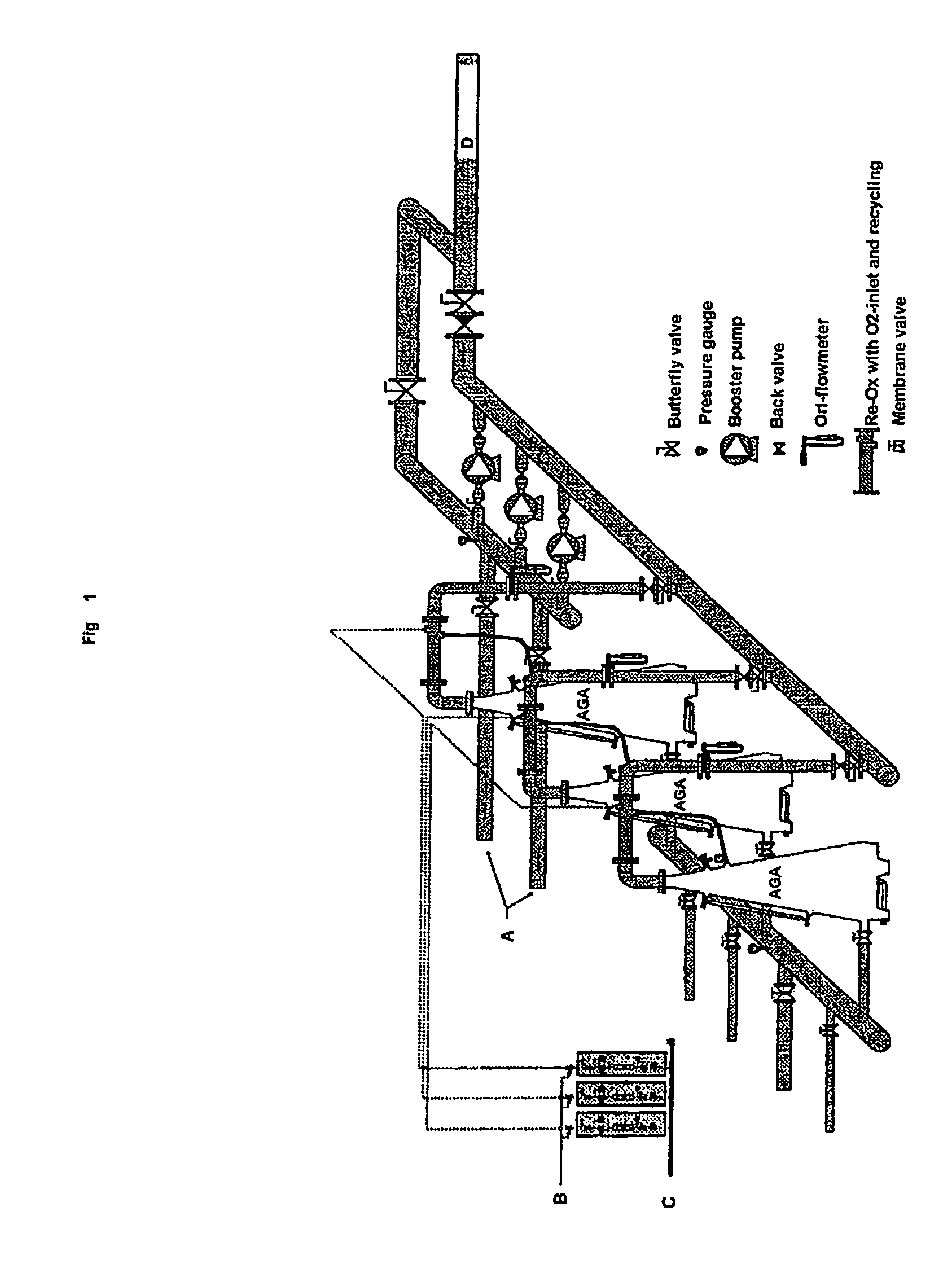

Oxygenating nozzle

ActiveUS20050275119A1Optimal utilisationIncrease consumptionFlow mixersTransportation and packagingEngineeringOxygen

The present invention relates to a nozzle unit for the supply of gas into a liquid comprising two or more annular nozzles one after the other in the direction of flow. The nozzles are angled to give a restriction in the direction of flow, and each nozzle overlaps the following nozzle. Each nozzle has one or more apertures for the supply of gas at the overlap.

Owner:MESSER IND USA INC

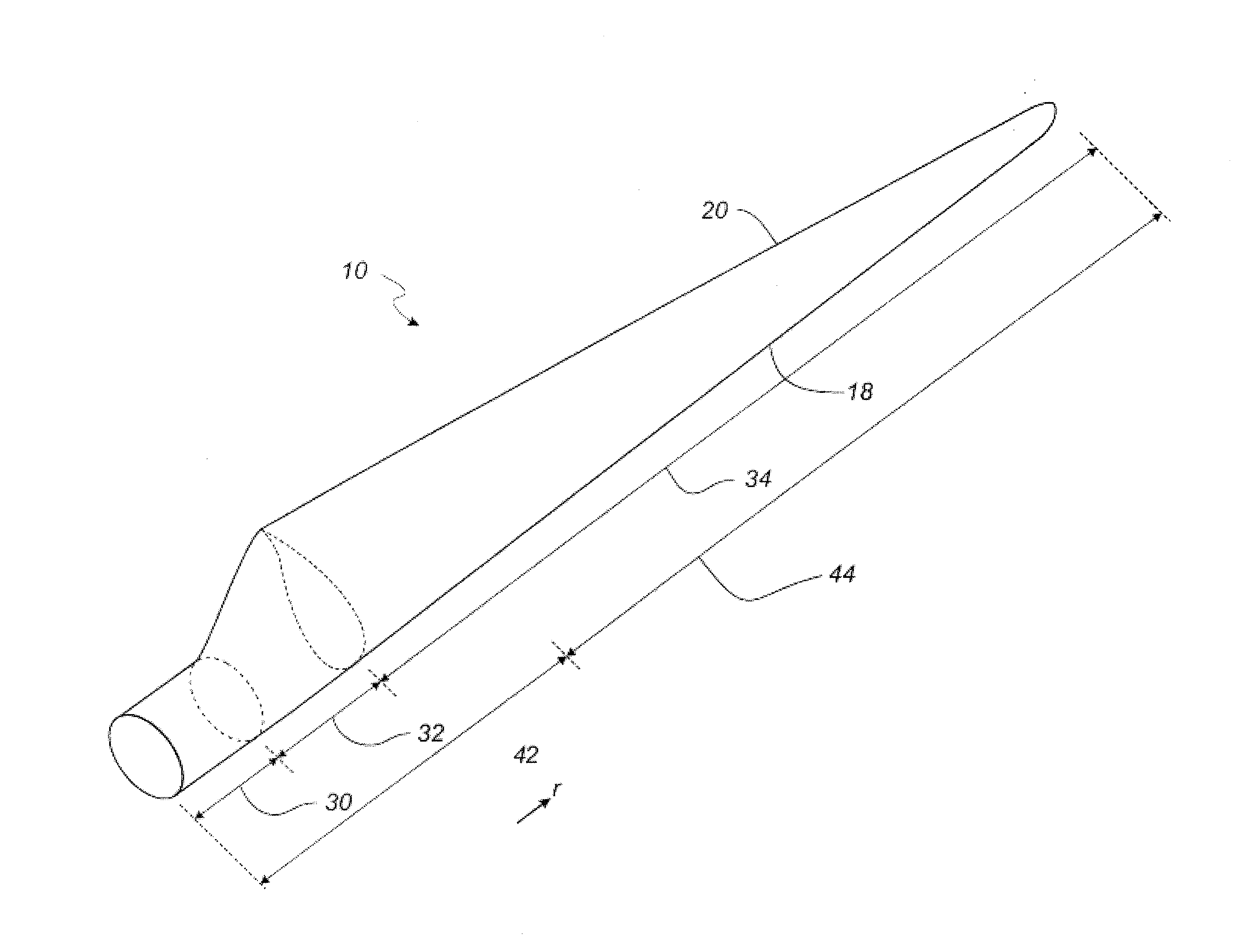

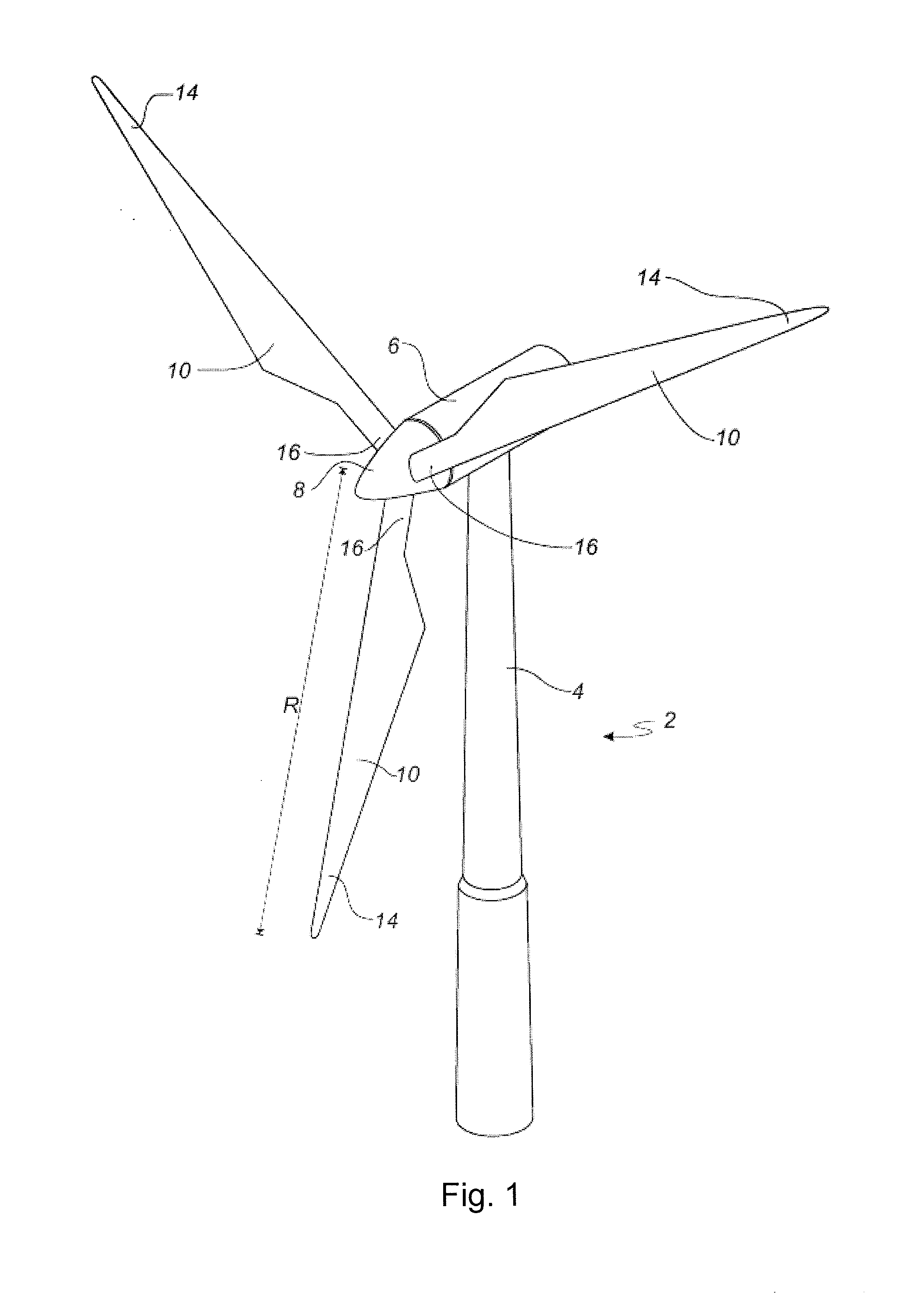

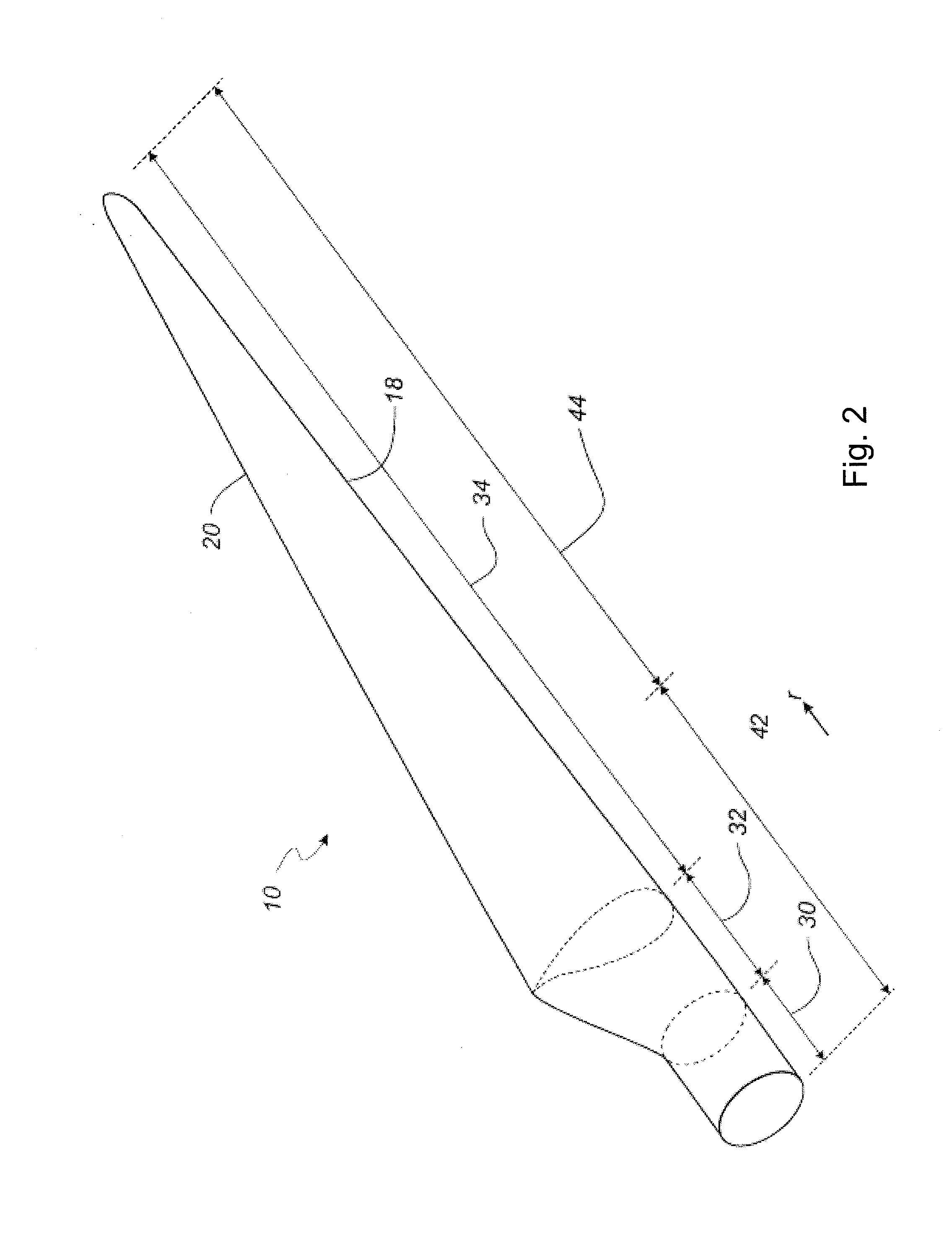

A Post-Moulding Station and an Associated Method of Manufacture of a Wind Turbine Blade

ActiveUS20150056081A1Expand accessOptimal utilisationPropellersMechanical working/deformationProduction rateTurbine blade

A post-moulding station is described which is used in the manufacturing of a wind turbine blade. A blade shell forming part of a wind turbine blade is initially moulded in a blade mould, the blade shell subsequently transferred to a post-moulding station which allows for various post-moulding operations to be carried out on the blade shell away from the mould, thereby increasing the productivity of the blade mould in the manufacturing process. The post-moulding station may be operable to perform the closing of first and second blade shells to form a wind turbine blade, and may be formed from an adjustable structure which can provide relatively easy access to the contained blade shell for working thereon. Accordingly, the manufacturing equipment may be of reduced cost, combined with an increase in the overall productivity of the manufacturing system.

Owner:LM WP PATENT HLDG

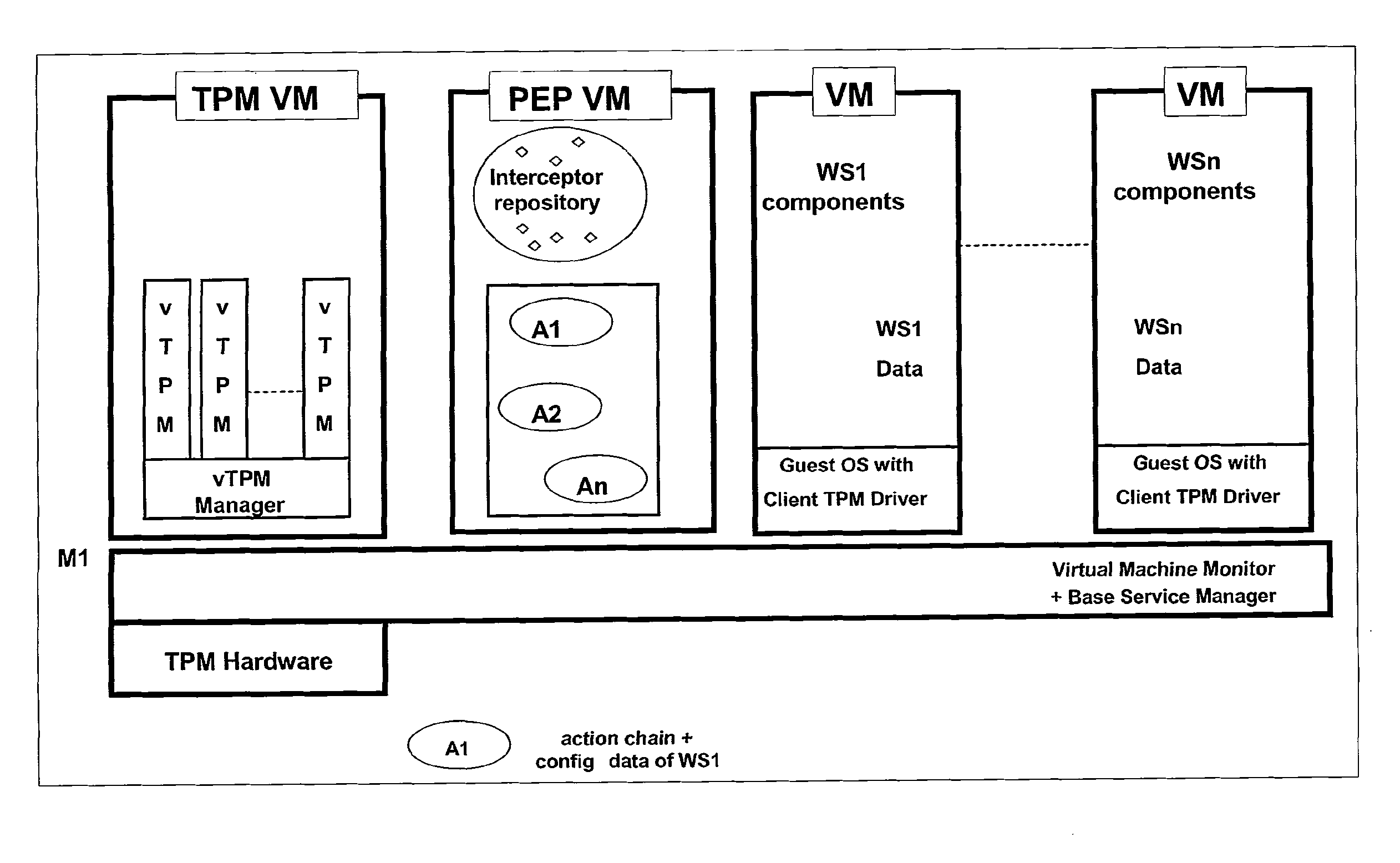

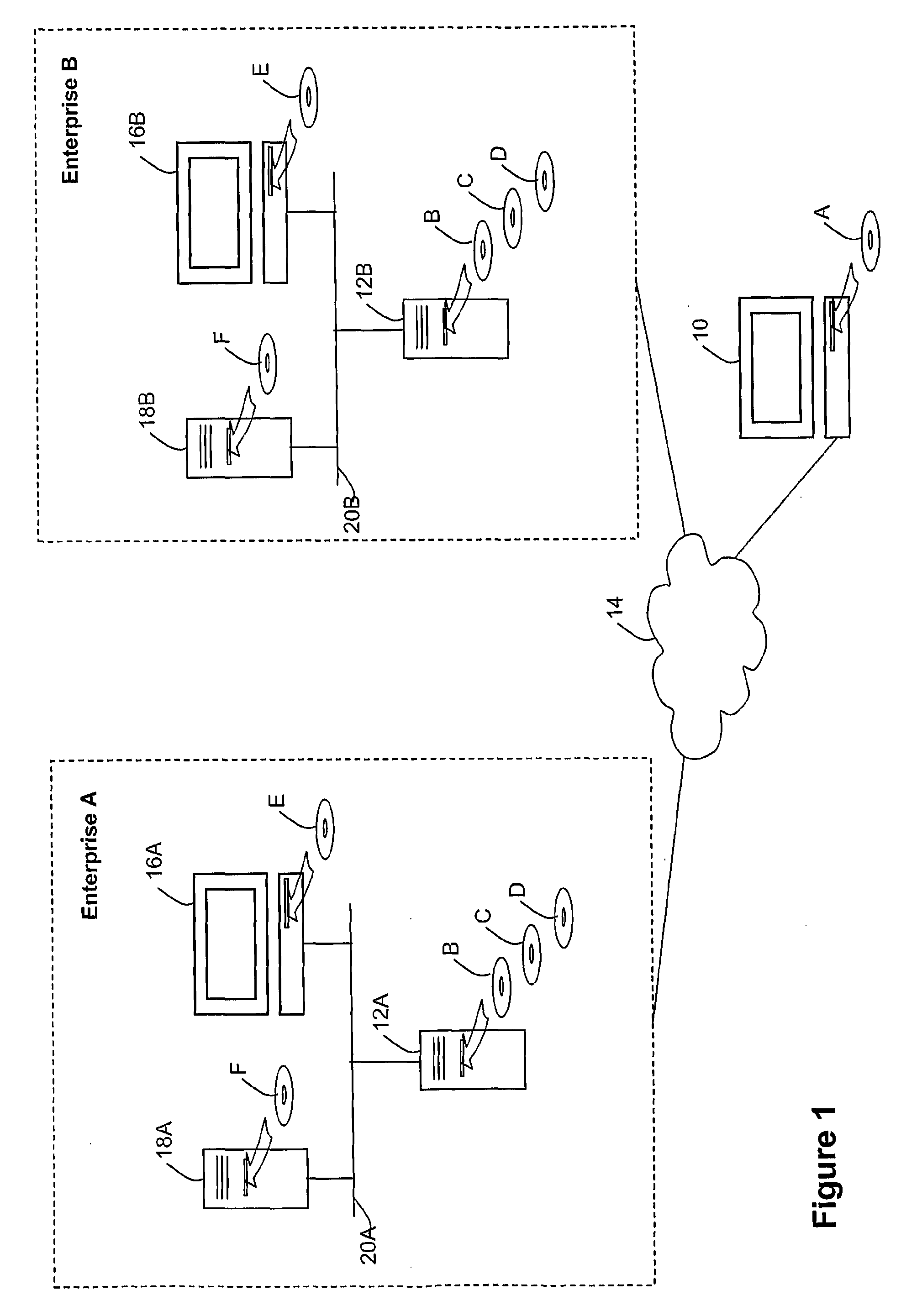

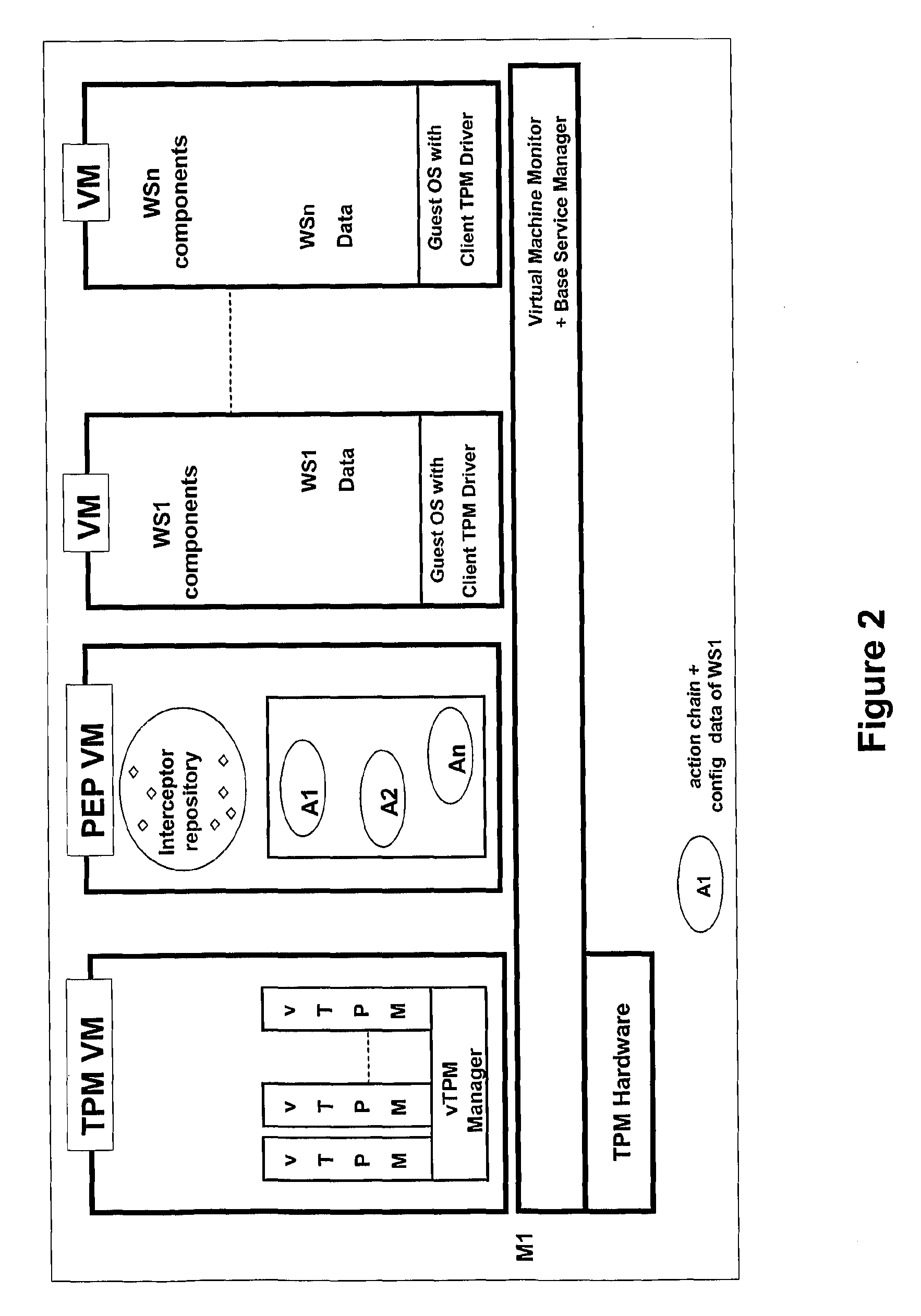

Distributed computing network using multiple local virtual machines

ActiveUS8595480B2Improve safetyOptimal utilisationUnauthorized memory use protectionHardware monitoringWeb serverApplication software

A distributed computer system is disclosed in which computers co-operate with one another by sending messages over a network such as the Internet in order to perform a distributed application. In order to improve the security of such system, each web service involved in the distributed application runs in a separate virtual machine. Furthermore, the virtual machines on a web server dedicated to respective web service instances utilise the same policy enforcement point—running in another virtual machine on the web-server—in order to handle messages for or from the web server. To increase security still further, each virtual machine provides virtual cryptoprocessor functionality which is used in the processing of messages sent in the performance of the distributed application.

Owner:BRITISH TELECOMM PLC

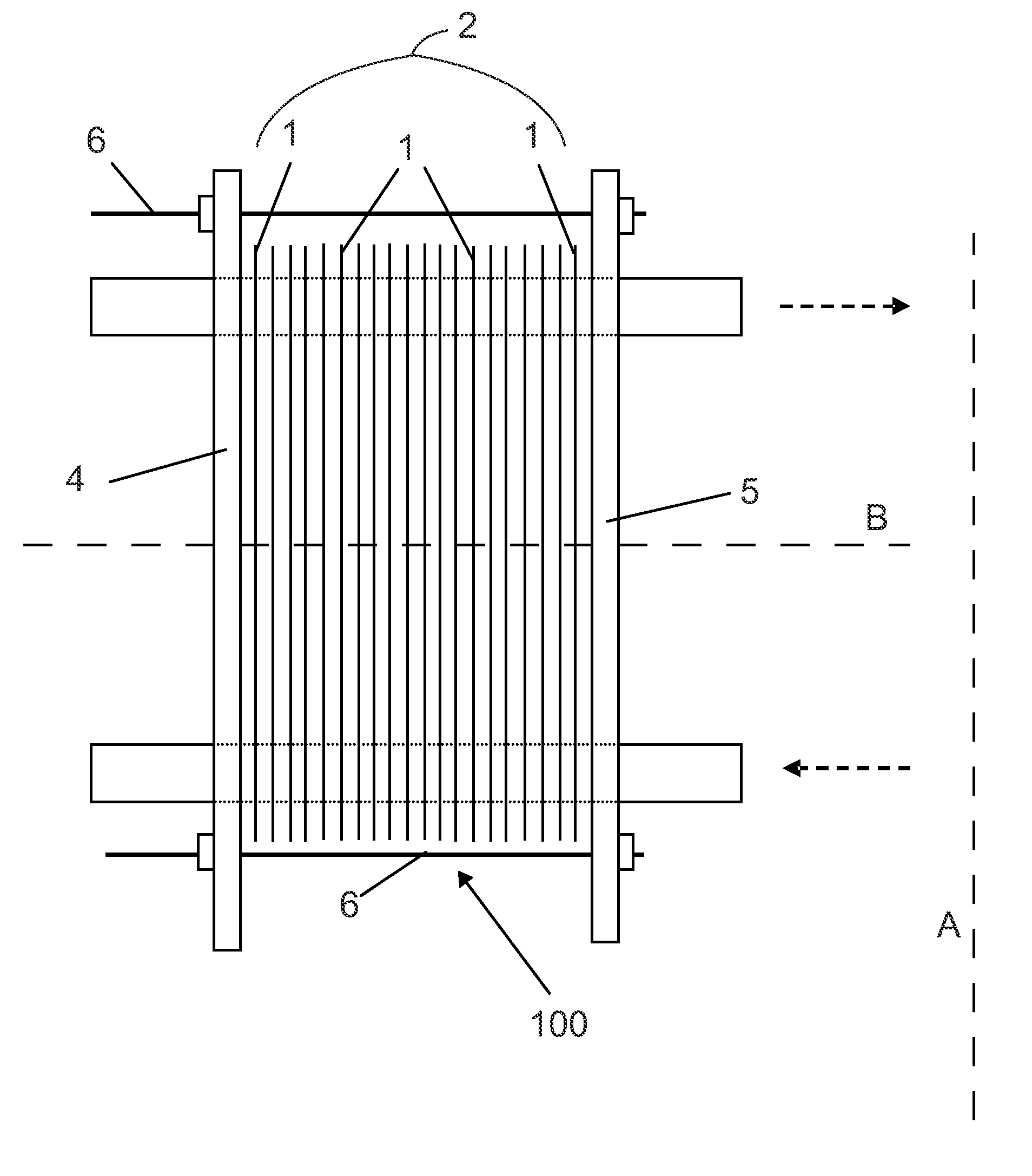

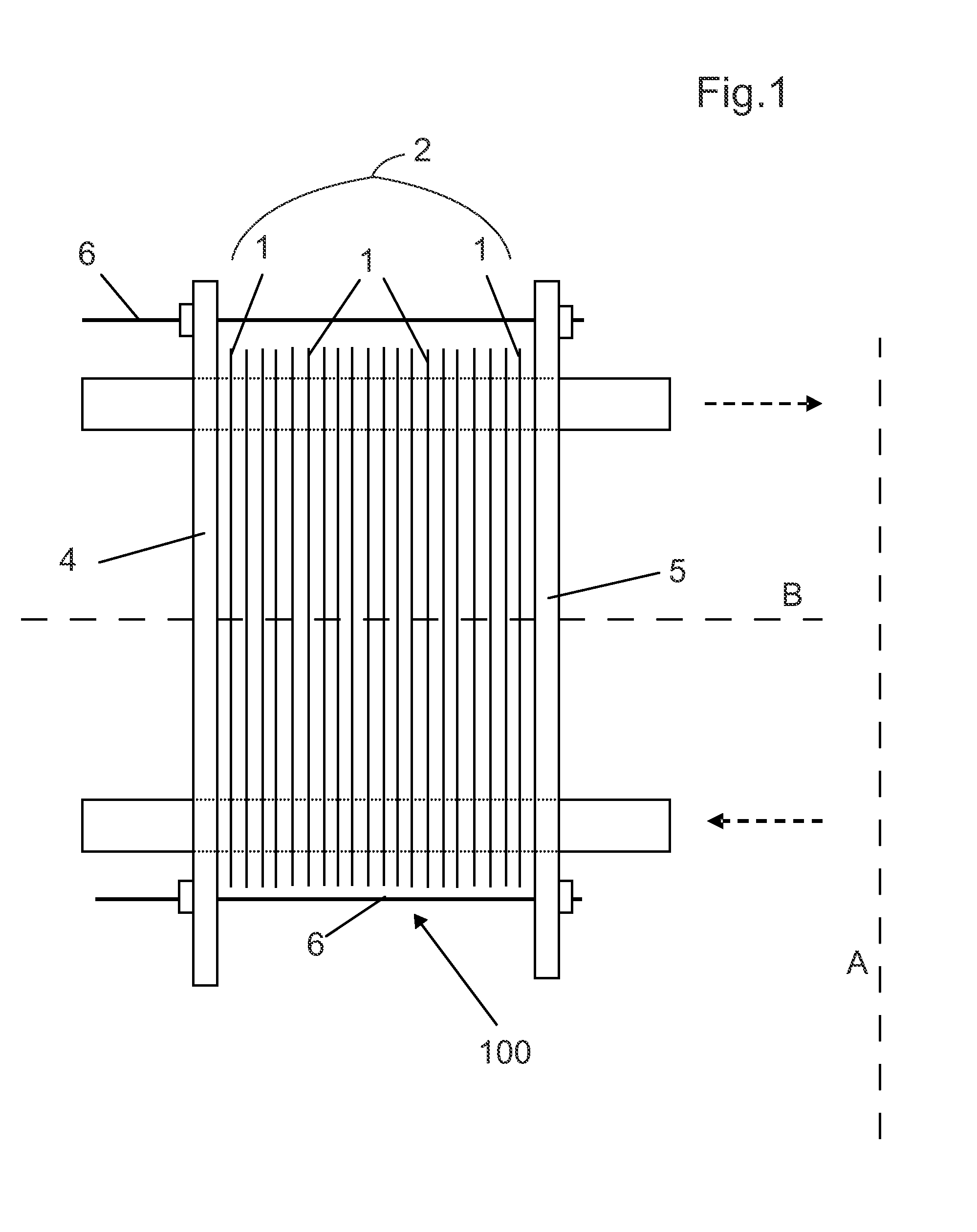

Method, system and mould-box for creating form-moulded items of edible ice

ActiveUS20060034989A1Speed up the flowEfficient use ofLighting and heating apparatusIce productionEngineeringControl unit

A method, a system, and a mould box for creating form-moulded items of edible ice from an ice mass. The method includes filling at least one mould created between a number of mould boxes with ice mass, and the introduction of cooling or heating medium into the mould boxes, where the flow of the cooling or heating medium is controlled by one or more control units in the mould boxes.

Owner:TETRA LAVAL HLDG & FINANCE SA

Plate and gasket for a plate heat exchanger

ActiveUS20110259561A1Speed up heat exchangeOptimal utilisationHeat exchanger fasteningLaminated elementsPlate heat exchangerEngineering

The invention relates to a heat exchanger plate for a plate heat exchanger, whereby the heat exchanger plate has a number of ports, distribution regions, adiabatic regions, a heat transfer region, and an edge region which extends outside the ports and the regions, whereby the heat exchanger plate includes a gasket groove extending in the edge region outside the regions and round the ports, whereby the gasket groove accommodates a gasket for sealing abutment against an adjacent heat exchanger plate in the plate heat exchanger where the gasket groove creates at least a recess of the heat transfer region along each side of the heat transfer region and that the recess enables a clip-on tab to be securely fastened to an edge region of the heat exchanger plate at the recess.

Owner:ALFA LAVAL CORP AB

Oxygenating nozzle

ActiveUS7533874B2Optimal utilisationIncrease consumptionFlow mixersUsing liquid separation agentEngineeringOxygen

Owner:MESSER IND USA INC

Cache device for coupling to a memory device and a method of operation of such a cache device

ActiveUS8200902B2Number of time blockRaise the possibilityEnergy efficient ICTEnergy efficient computingRegular patternComputer science

A cache device is provided for use in a data processing apparatus to store data values for access by an associated master device. Each data value has an associated memory location in a memory device, and the memory device is arranged as a plurality of blocks of memory locations, with each block having to be activated before any data value stored in that block can be accessed. The cache device comprises regular access detection circuitry for detecting occurrence of a sequence of accesses to data values whose associated memory locations follow a regular pattern. Upon detection of such an occurrence of a sequence of accesses by the regular access detection circuitry, an allocation policy employed by the cache to determine a selected cache line into which to store a data value is altered with the aim of increasing a likelihood that when an evicted data value output by the cache is subsequently written to the memory device, the associated memory location resides within an already activated block of memory locations. Hence, by detecting regular access patterns, and altering the allocation policy on detection of such patterns, this enables a reuse of already activated blocks within the memory device, thereby significantly improving memory utilization, thereby giving rise to both performance improvements and power consumption reductions.

Owner:ARM LTD

Flat speaker

ActiveUS20100119095A1Optimal utilisationReduce weightCosmonautic componentsDiaphragm extensionsHigh energyArchitectural engineering

The present invention provides a flat speaker, in particular in the aerospace sector, with a panel for generating acoustic signals by vibration of the same, and a vibration exciter which is connected to a panel and excites this to vibrate. Here the panel has an edge stiffening. This provides the panel with the required stiffness, particularly against hand pressures, but at the same it guarantees high energy efficiency of the flat speaker.

Owner:AIRBUS OPERATIONS GMBH