Patents

Literature

36results about How to "Easy version management" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

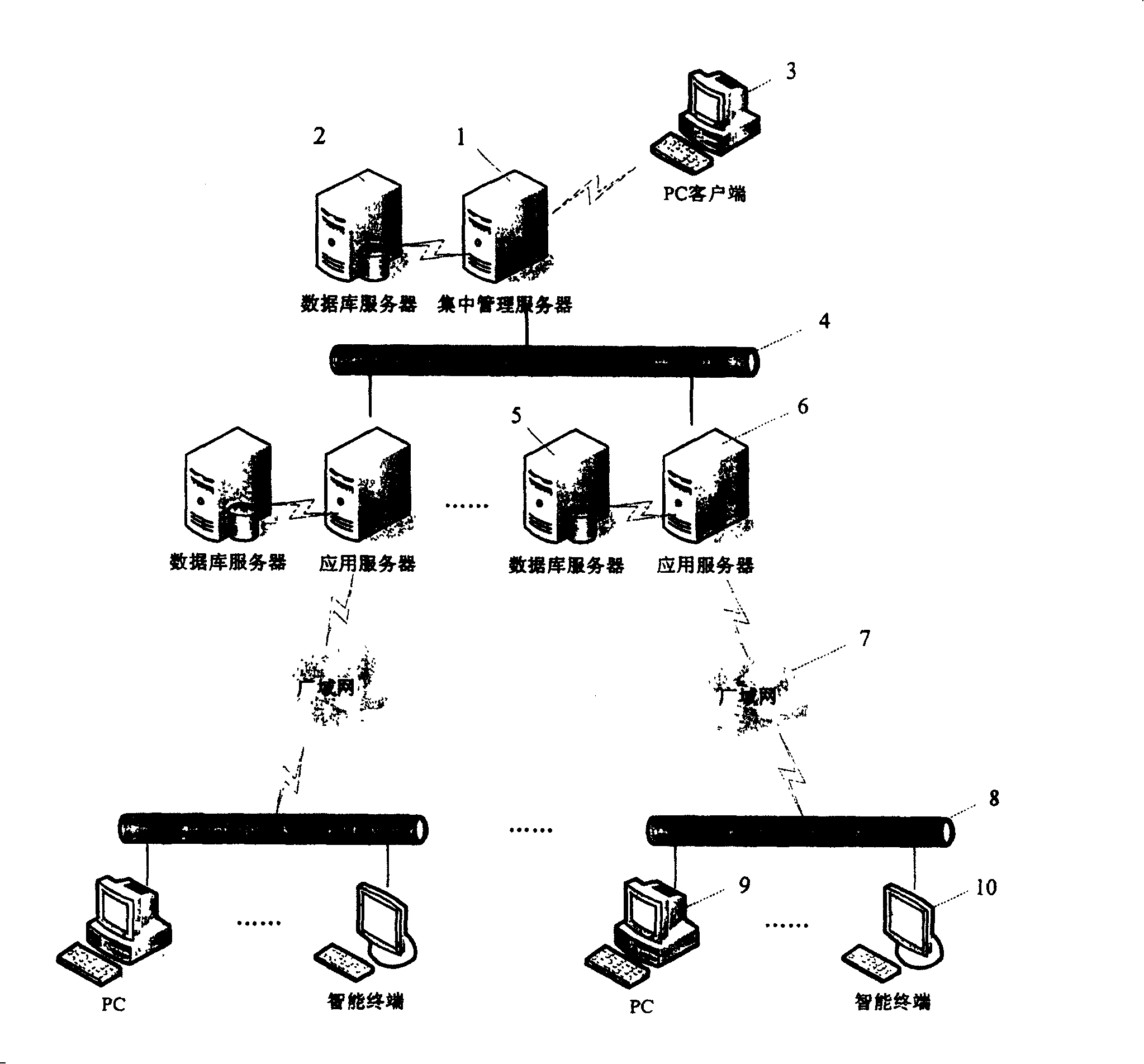

Software edition updating system in distributed service system and its method

ActiveCN1758607AImprove securityImprove reliabilityProgram loading/initiatingData switching networksApplication serverSoftware engineering

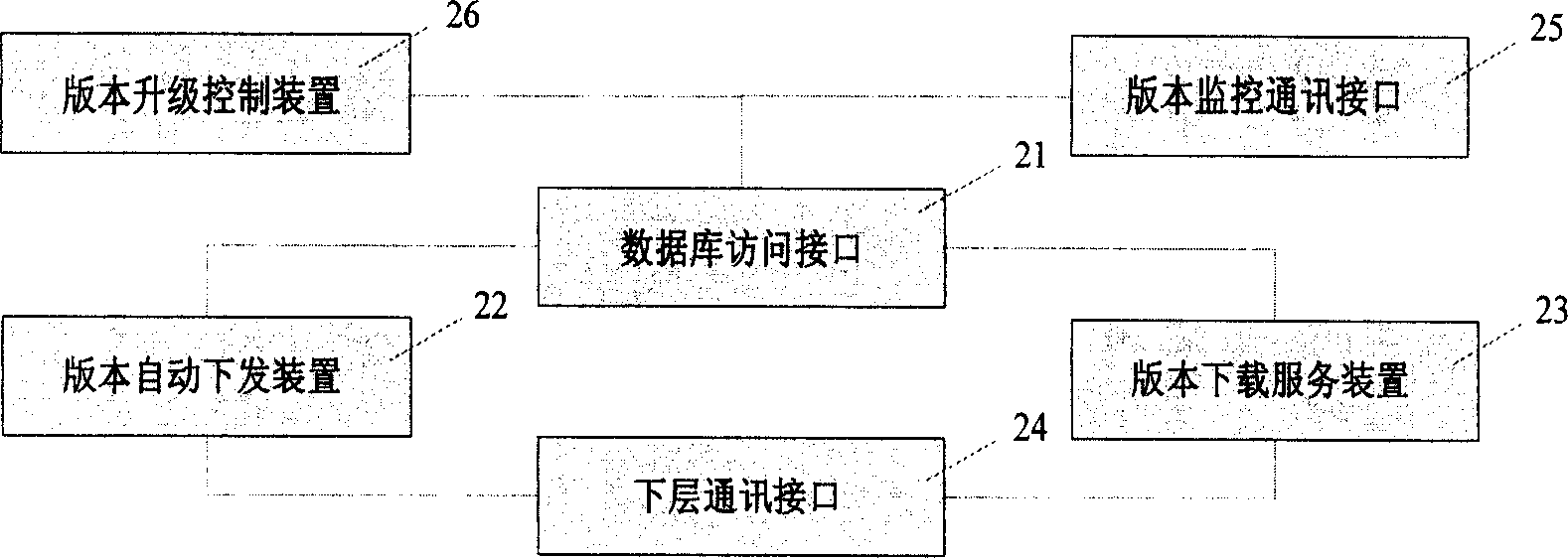

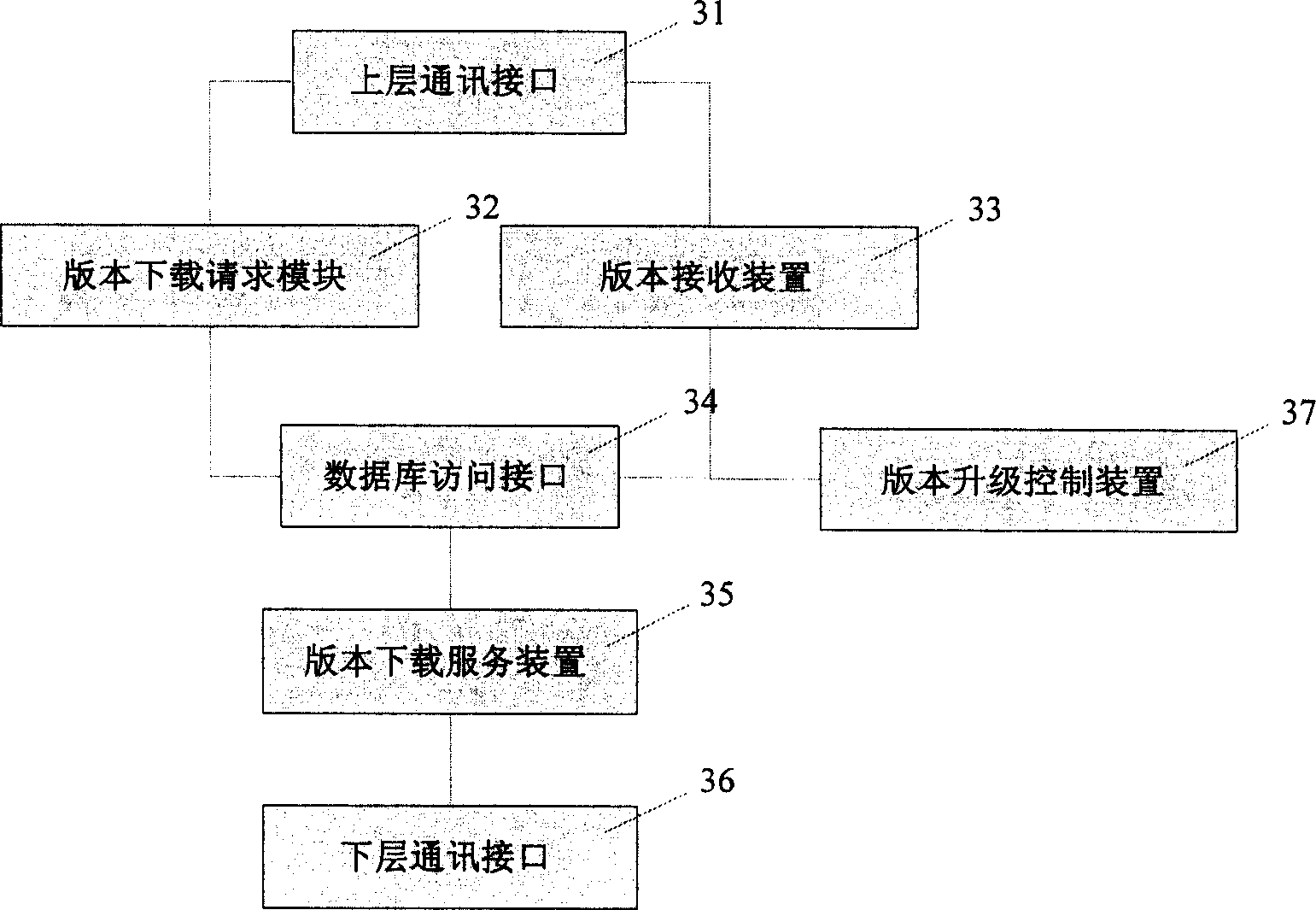

A method for upgrading software version in distributed service system includes receiving new version application software inputted from master system by centralized management server ( CMS ), updating recorded version down ¿C sending information of databank connected to CMS, down ¿C sending received new version application software to application server, updating software down ¿C sending record of databank connected to application server, installing new version application software by CMS and application server separately, providing download of new version application software for user terminal by application server and installing received new version application software by user terminal.

Owner:INDUSTRIAL AND COMMERCIAL BANK OF CHINA

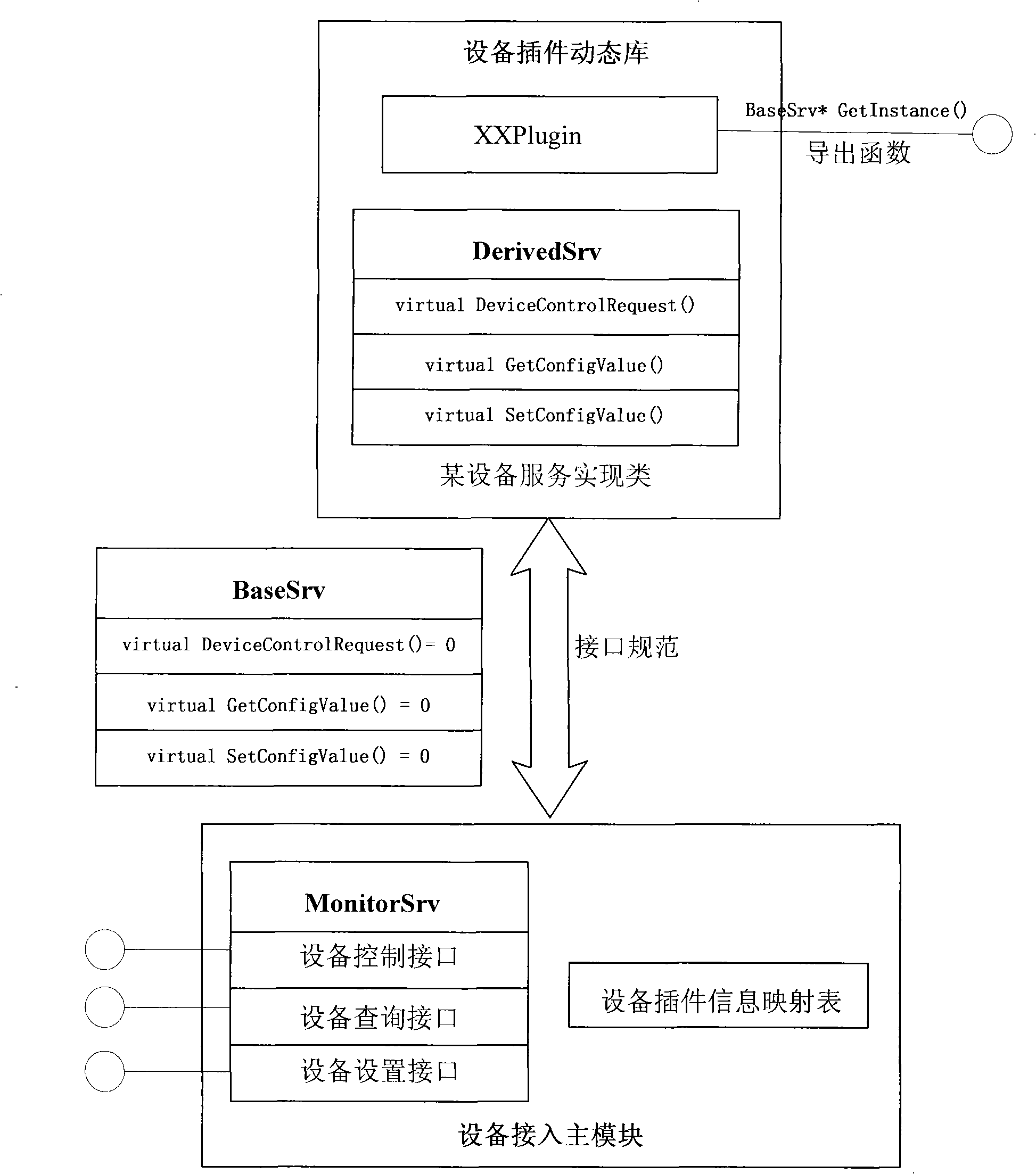

Video monitoring front end equipment access method

InactiveCN101272481AStrong scalabilityFacilitates parallel developmentClosed circuit television systemsEmbedded systemMaintainability

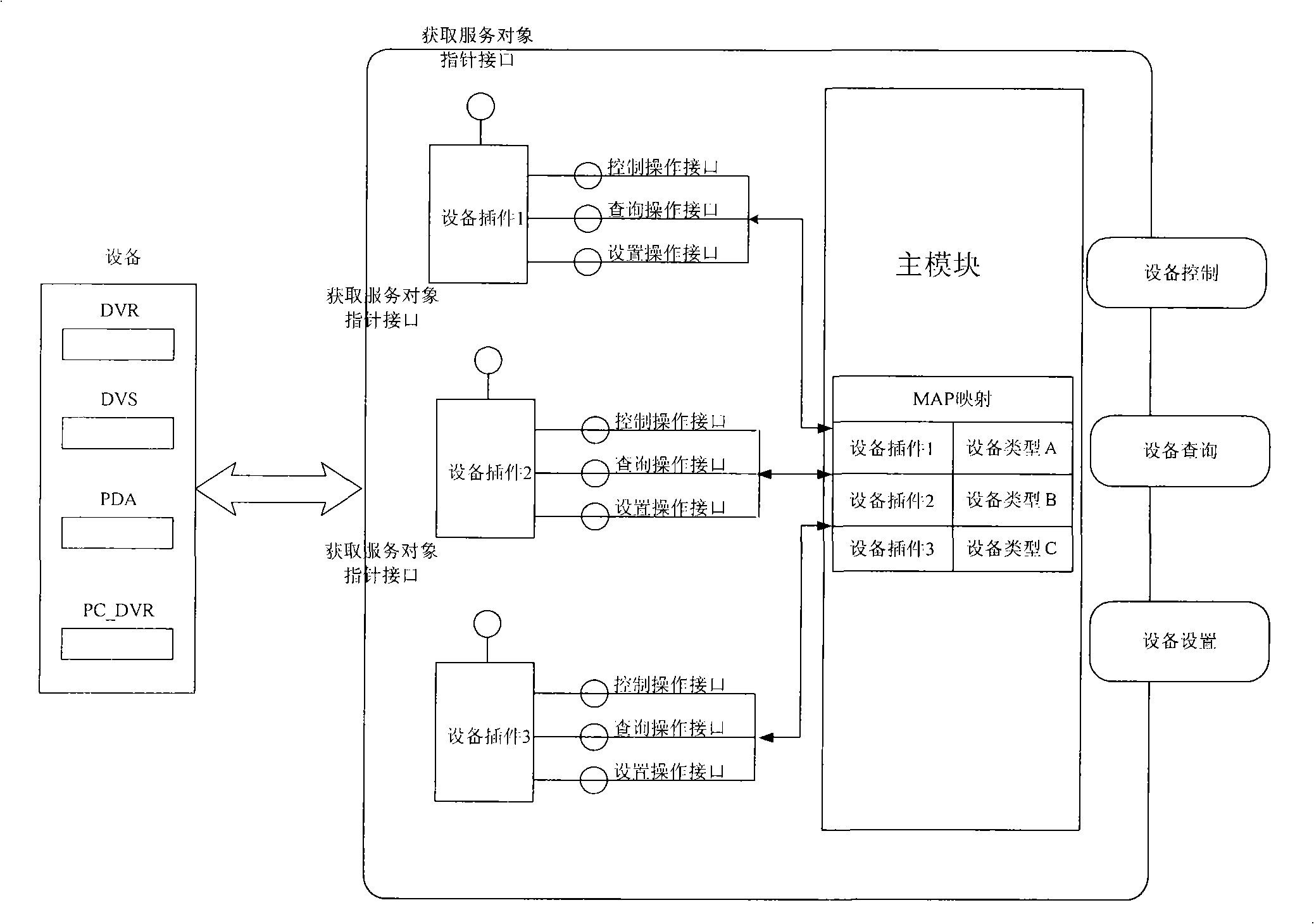

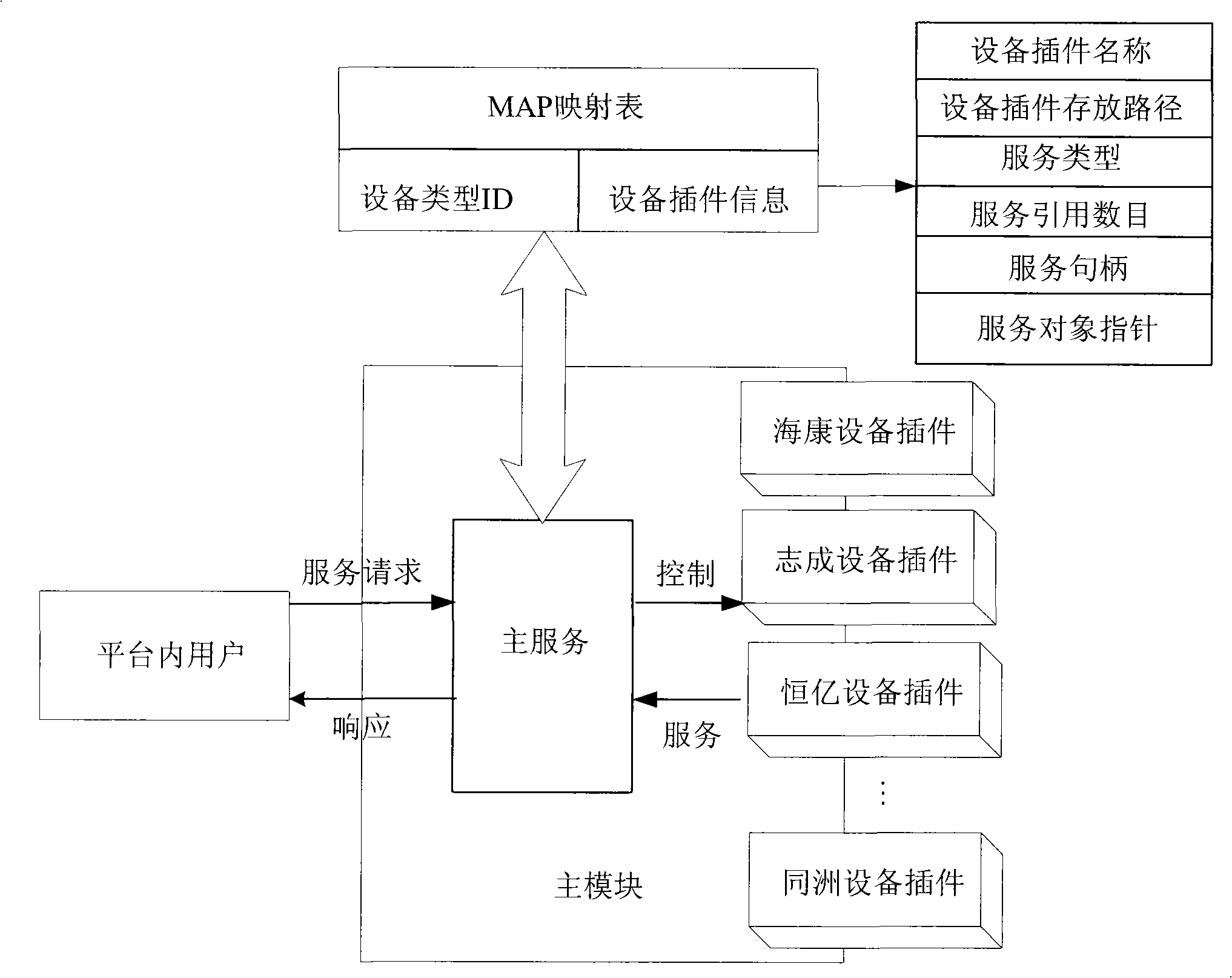

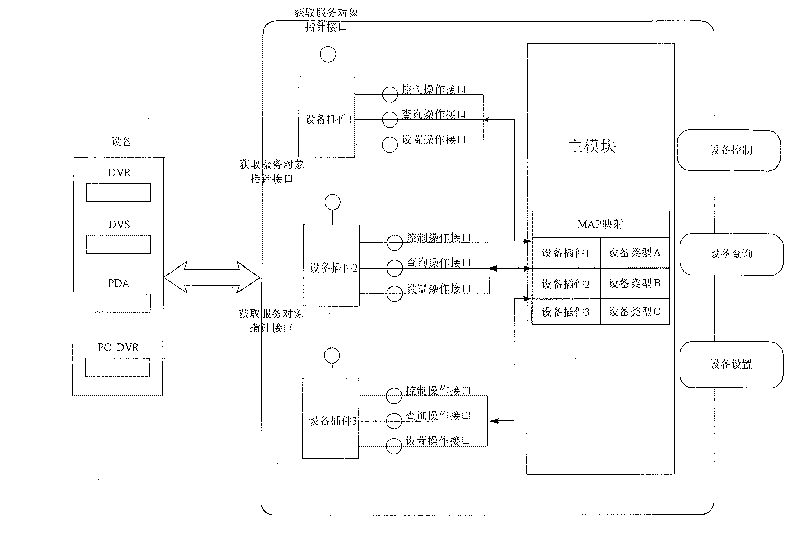

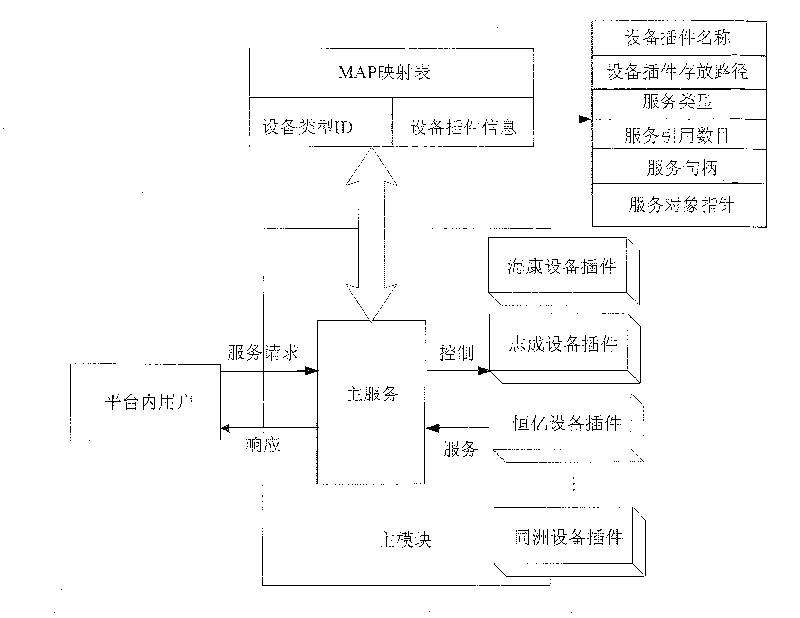

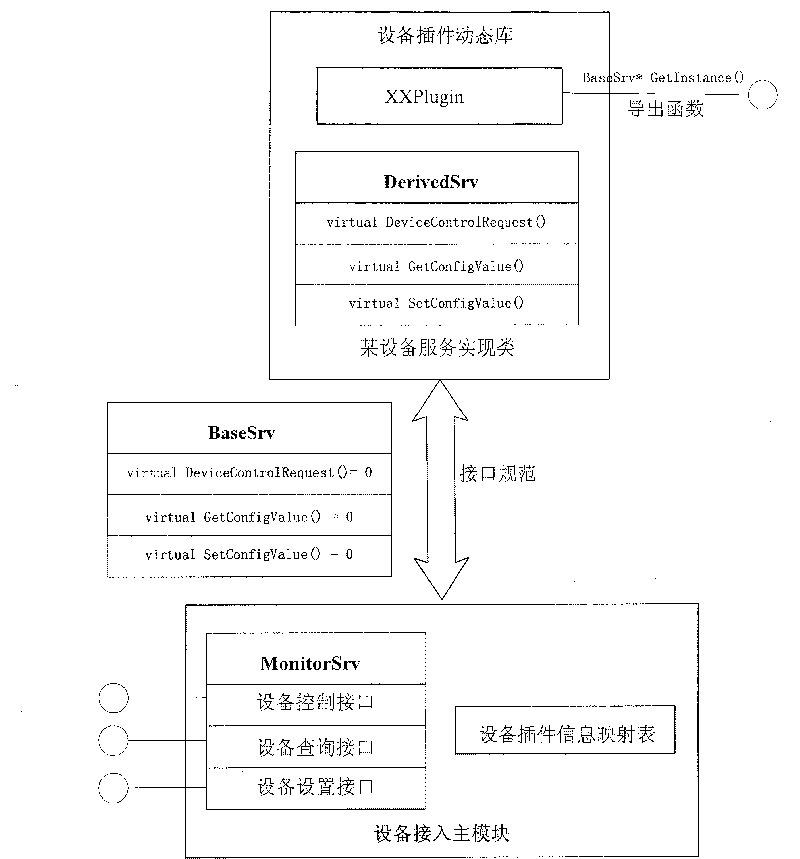

The invention relates to an access method for video monitoring front-end equipment, which is characterized in that the equipment access module of a monitoring system platform consists of two parts of a main module and a plug-in for the equipment. The main module provides a unified service interface for the inner part of the platform.. The SDK of various equipment in the monitoring system is integrated the plug-in for the equipment which is developed according to the appointed interface standard of the main module. The main module manages and controls the plug-in for the equipment and transmits the service requests of platform users to the corresponding plug-in for the equipment. And the treatment and the response of the service requests is finished by the plug-in for the equipment. In addition, the plug-in for the equipment can be dynamically loaded and unloaded to consequently finish the dynamical start and the stop control of the equipment service. The access method for the video monitoring front-end equipment has the advantage of simple and fast realization, thereby improving the scalability, the tailorability, the testability, the maintainability, the applicability and the easy use performance of the system. The technical proposal has great significance in integrating large amounts of heterogeneous video monitoring resources and establishing public video monitoring platforms with large scale.

Owner:WUHAN UNIV

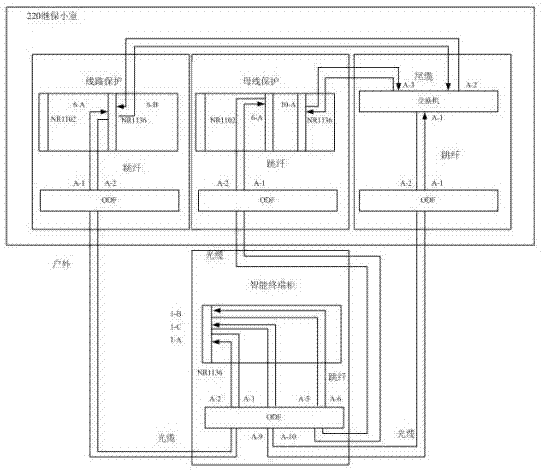

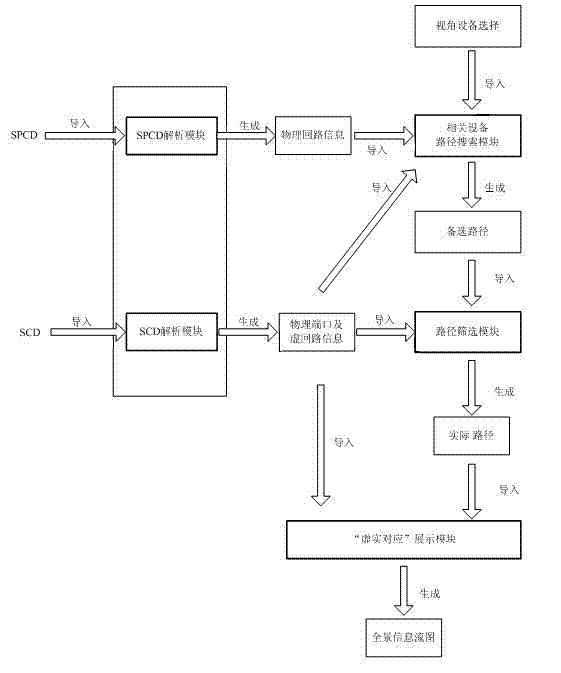

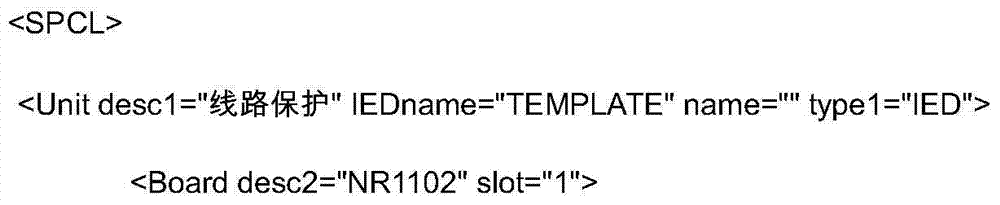

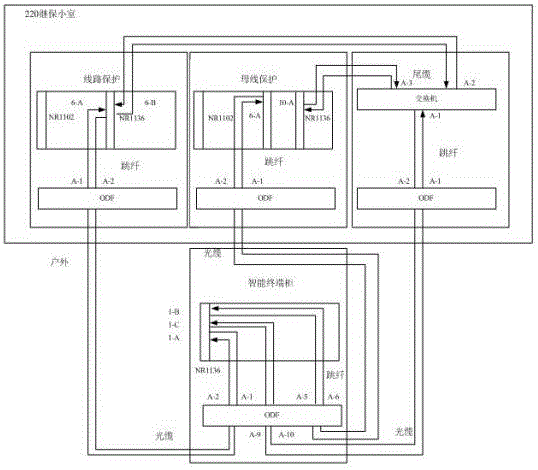

Secondary system physical loop modeling and void and actuality correspondence method of intelligent substation

ActiveCN104732021AEasy to findImprove developmentData processing applicationsSpecial data processing applicationsComputer architectureSmart substation

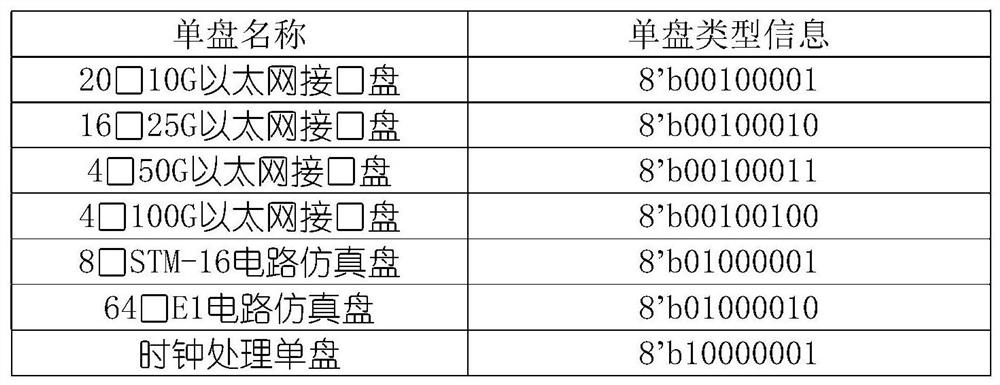

The invention discloses a secondary system physical loop modeling method of an intelligent substation. The secondary system physical loop modeling method of the intelligent substation includes the steps that firstly, a designer of an equipment manufacturer configures a physical loop IPCD file through a configuration tool, and a device board card and a physical end port in the IPCD file are described; secondly, a design unit solidifies the IPCD file into a cabinet model, then cable connection among cabinets and optical fiber connection among devices are designed, a substation physical loop SPCD description file is finished, and decoupling design of a logic loop and a physical loop is realized. According to the secondary system physical loop modeling and void and actuality correspondence method of the intelligent substation, an SCD file and an SPCD file correspond to each other in a void and actuality correspondence mode when a design graph is finished, void and actuality integration design description is also realized, design efficiency and accuracy are improved, many kinds of application software can be more easily developed and customized based on a solid loop model file, the engineering on-site debug method is enriched, and construction efficiency and convenience are improved.

Owner:STATE GRID CORP OF CHINA +5

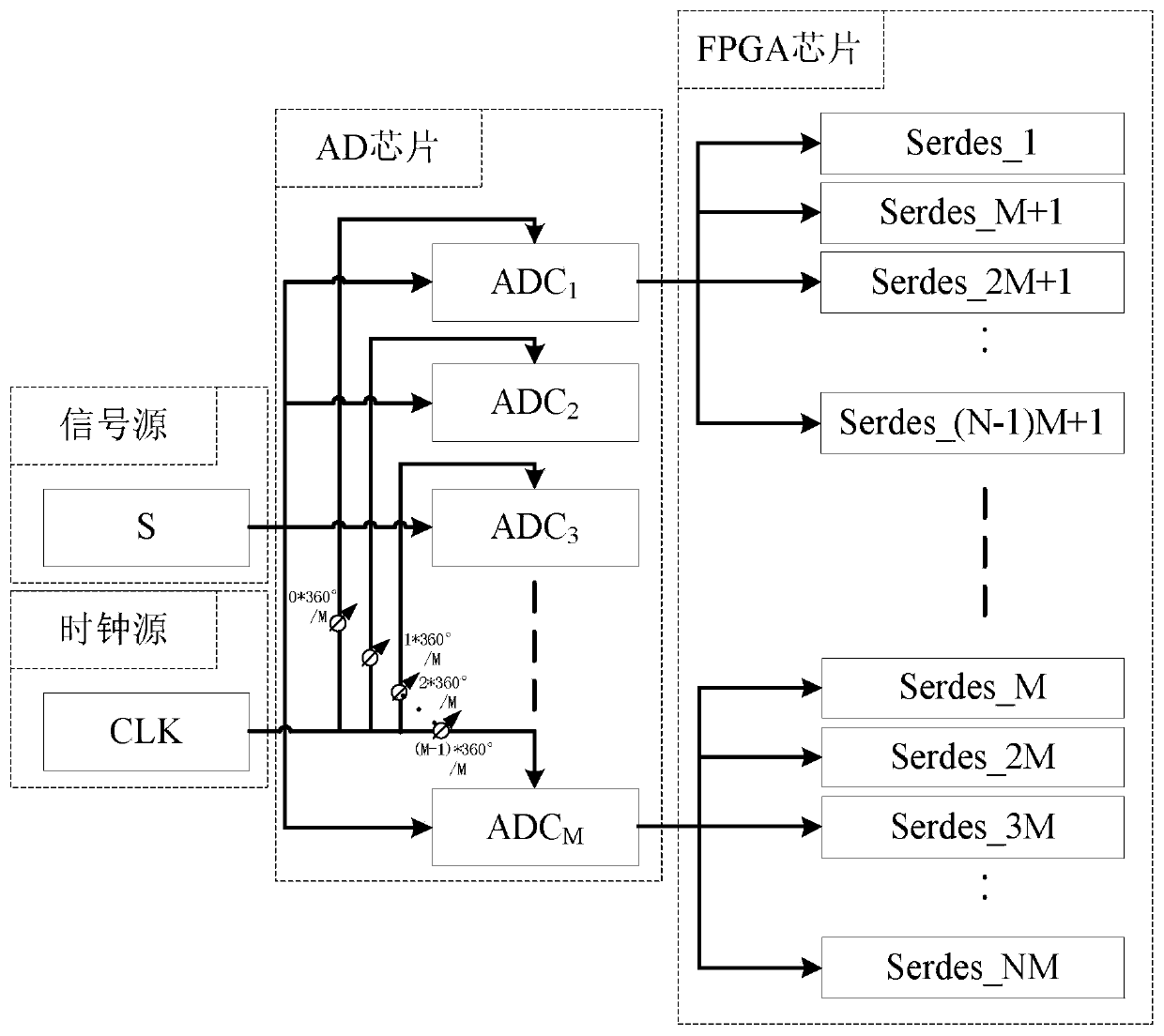

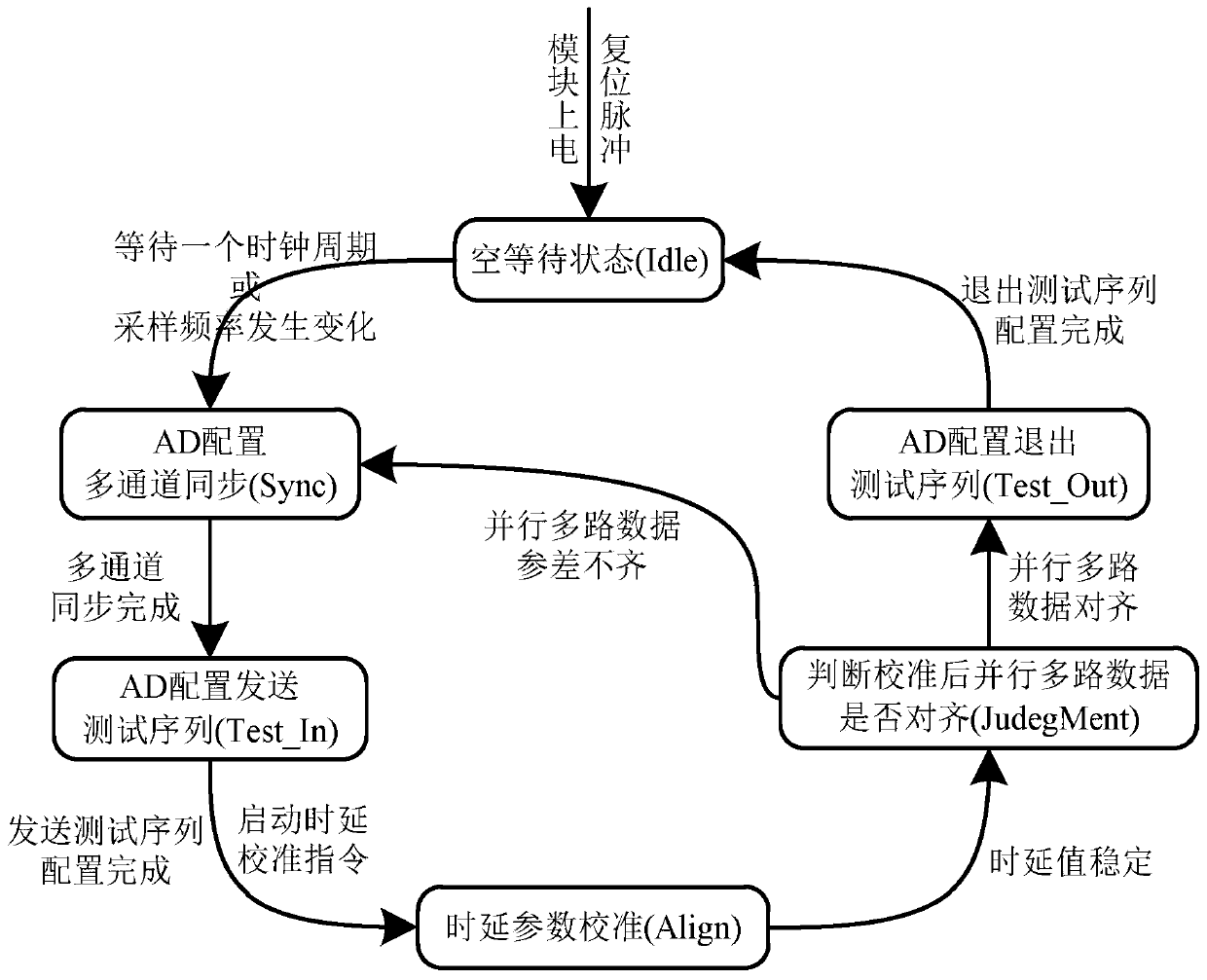

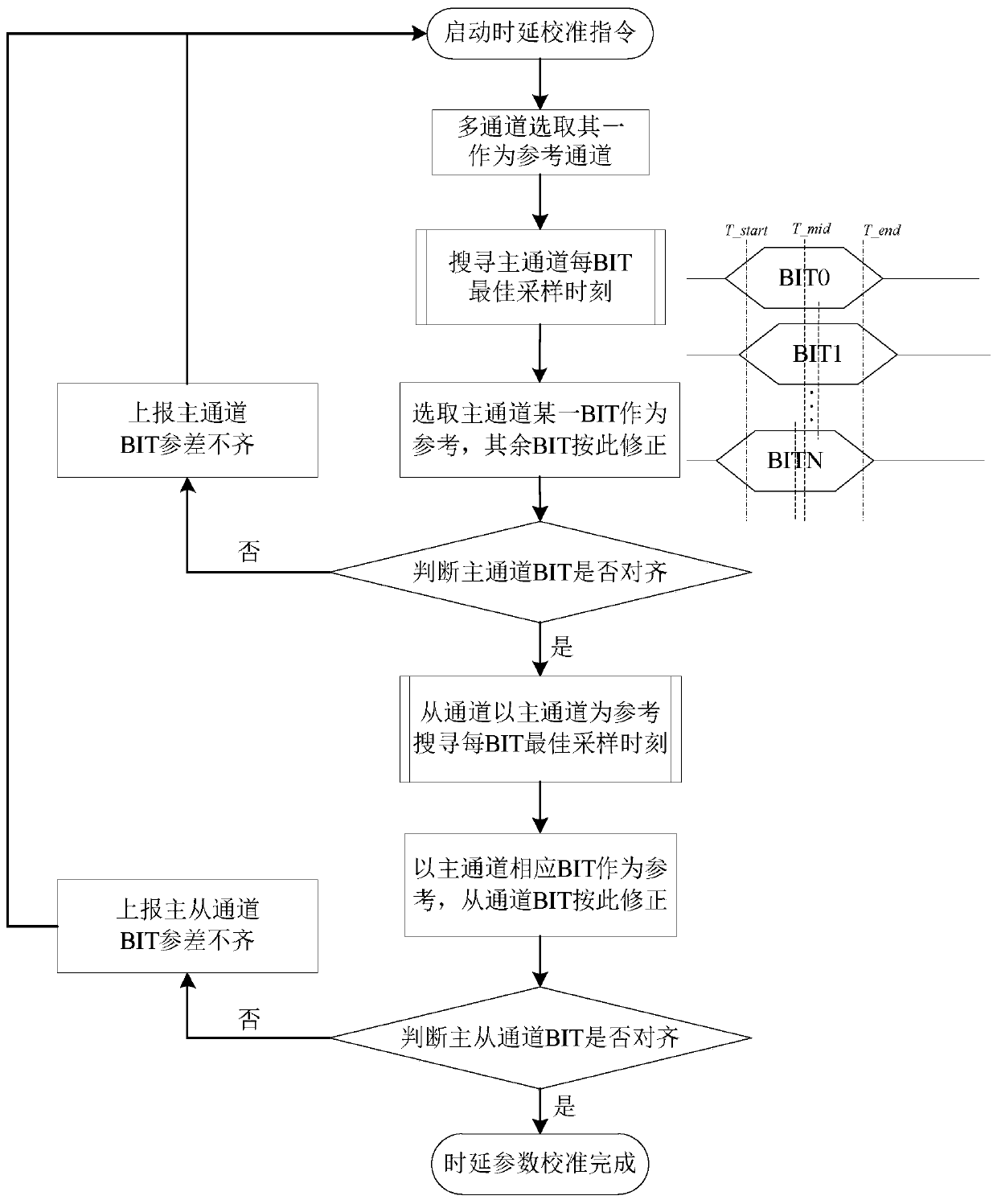

Universal calibration method for transmission path delay errors of parallel ADC sampling system

ActiveCN110798211ASimple compositionEasy to handle logicallyAnalogue-digital convertersAnalogue/digital conversion calibration/testingTime delaysEngineering

The invention provides a universal calibration method for transmission path delay errors of a parallel ADC sampling system, and aims to provide a universal method capable of adapting to sampling frequency changes and correcting multichannel data input delay. According to the technical scheme, a clock and a signal are configured into multi-channel output through an AD chip integrated with M channels, and an AD is connected with an FPGA through a serial peripheral interface to form a high-speed variable sampling rate system. The AD performs multi-channel parallel sampling on high-speed signals to realize first-stage speed reduction, and the FPGA performs serial-parallel conversion by adopting serial-parallel conversion primitives or serial-parallel conversion IP cores to realize second-stagespeed reduction. After the FPGA configures an AD to send a test sequence, a calibration instruction and a state machine are started, a time delay parameter calibration algorithm is operated, time delay parameters are dynamically placed into an FPGA input time delay control primitive, all data lines in channels and among the channels are aligned, the AD exits from the test sequence to output actual signals, and system input time delay calibration is completed.

Owner:10TH RES INST OF CETC

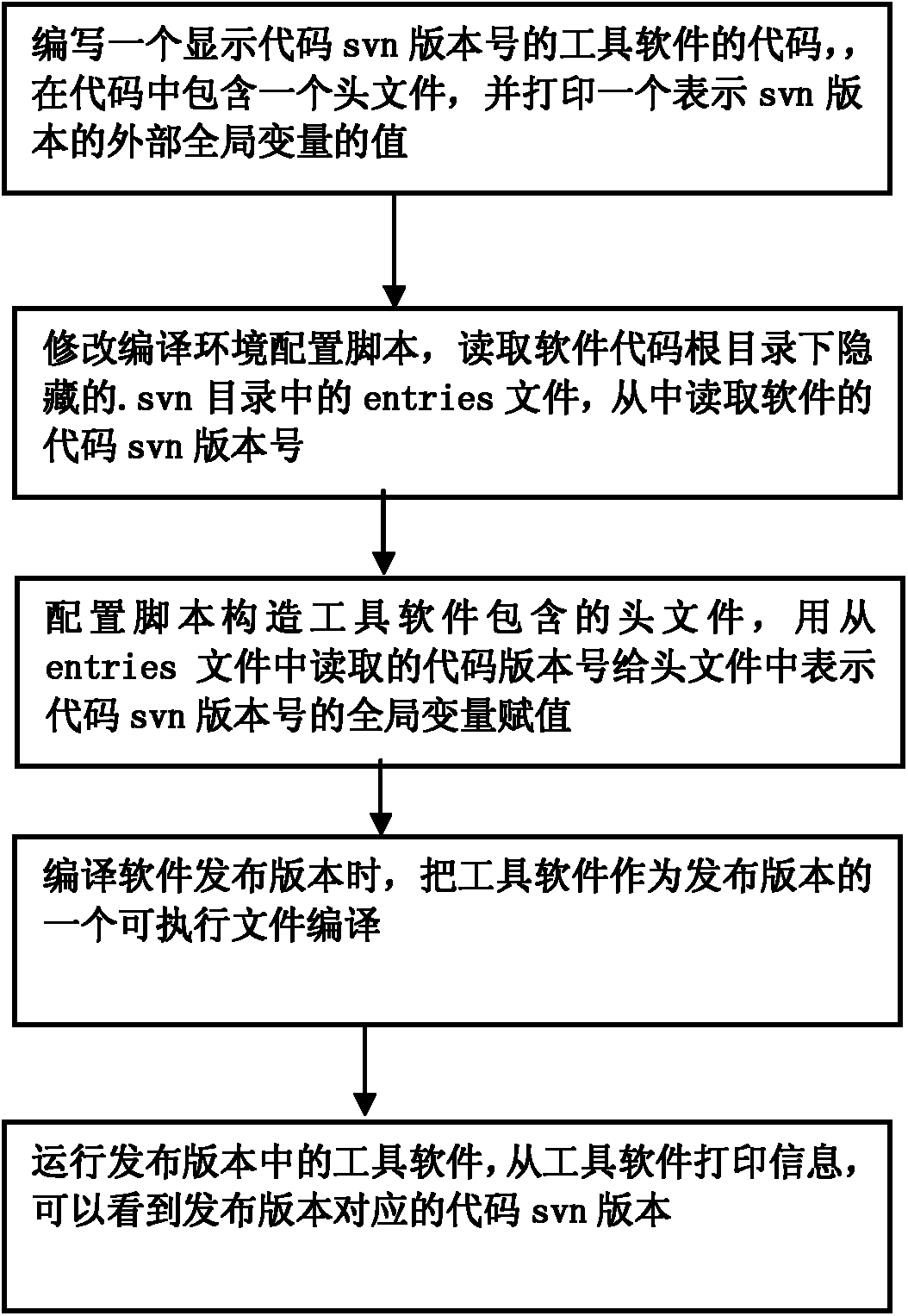

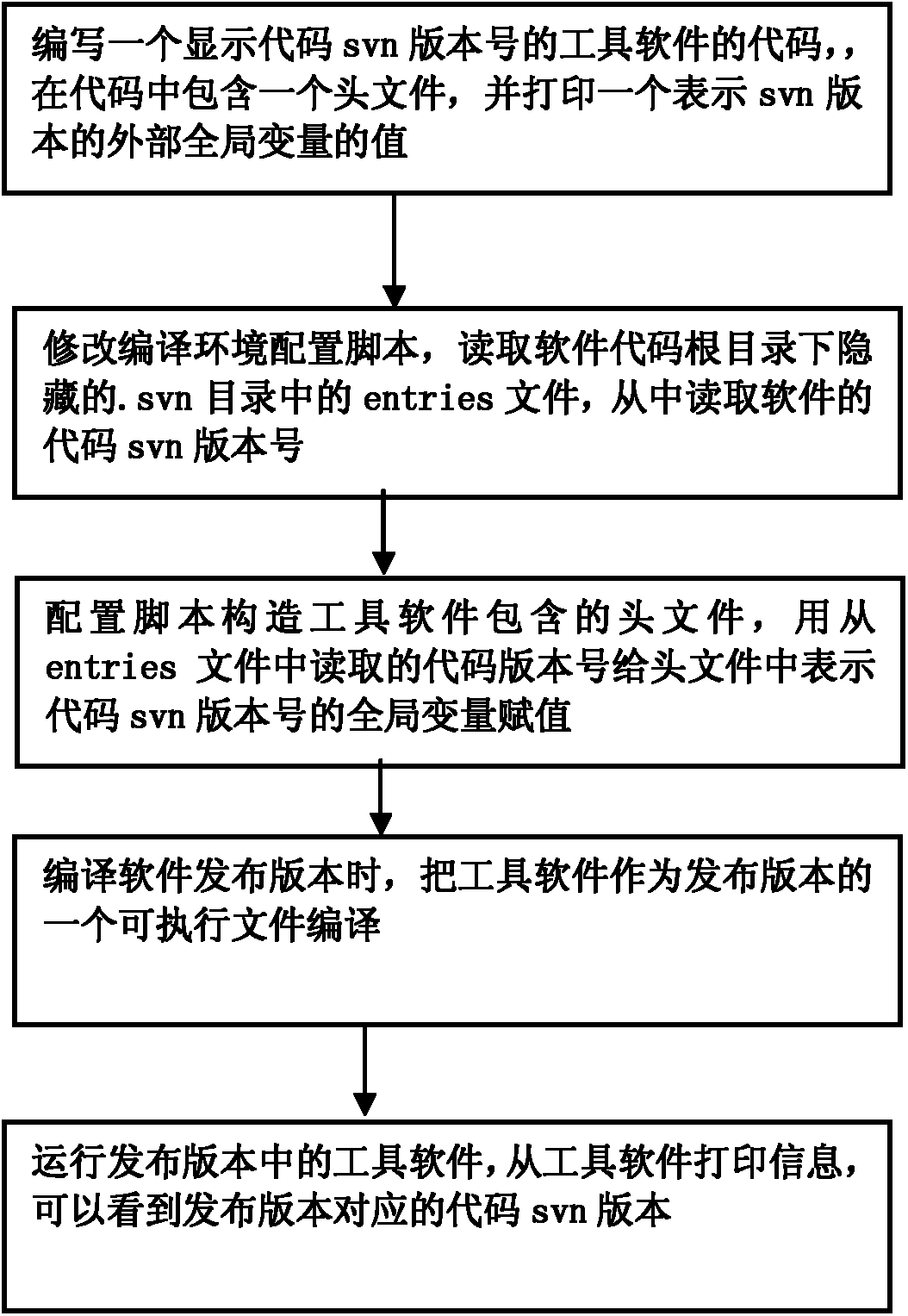

Method and system for identifying software code svn version in executable file

InactiveCN102495736AEasy version managementClear versionSpecific program execution arrangementsMemory systemsExecutableSoftware

The invention provides a method and system for identifying a software code svn version in an executable file. The system modifies a compilation process of a release vision, automatically extracts a code vision number in svn in a compilation environment configuration script and records the code vision number in the executable file so that the svn version of a code can be directly displayed through a version checking command of the executable file, thus the unification of the release vision of software and the code svn version is ensured. Compared with the prior art, the system for identifying the software code svn version in the executable file, disclosed by the invention, has the advantage of realizing the method for identifying the software code svn version in the executable file and simplifying software code version management.

Owner:DAWNING INFORMATION IND BEIJING

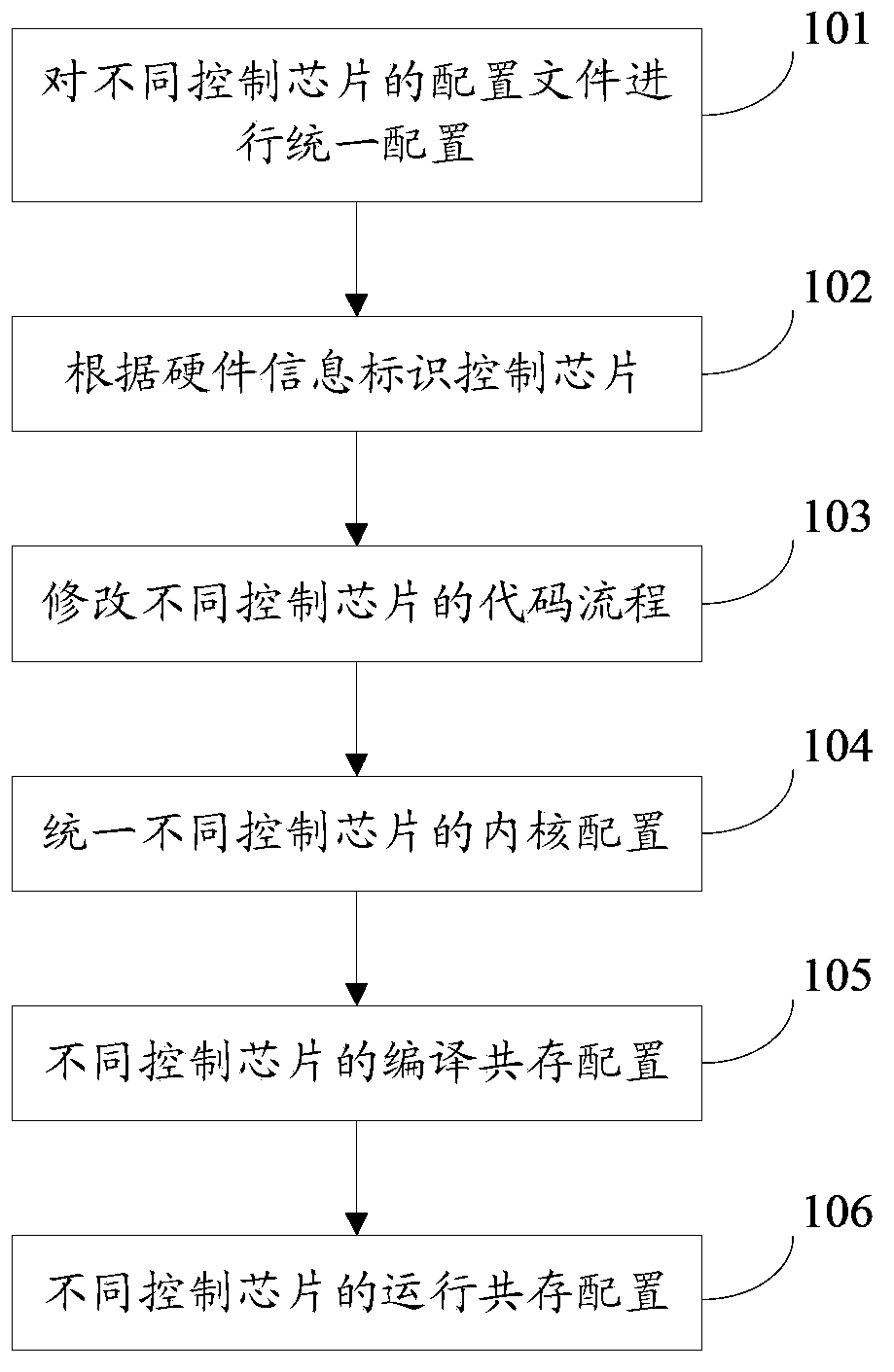

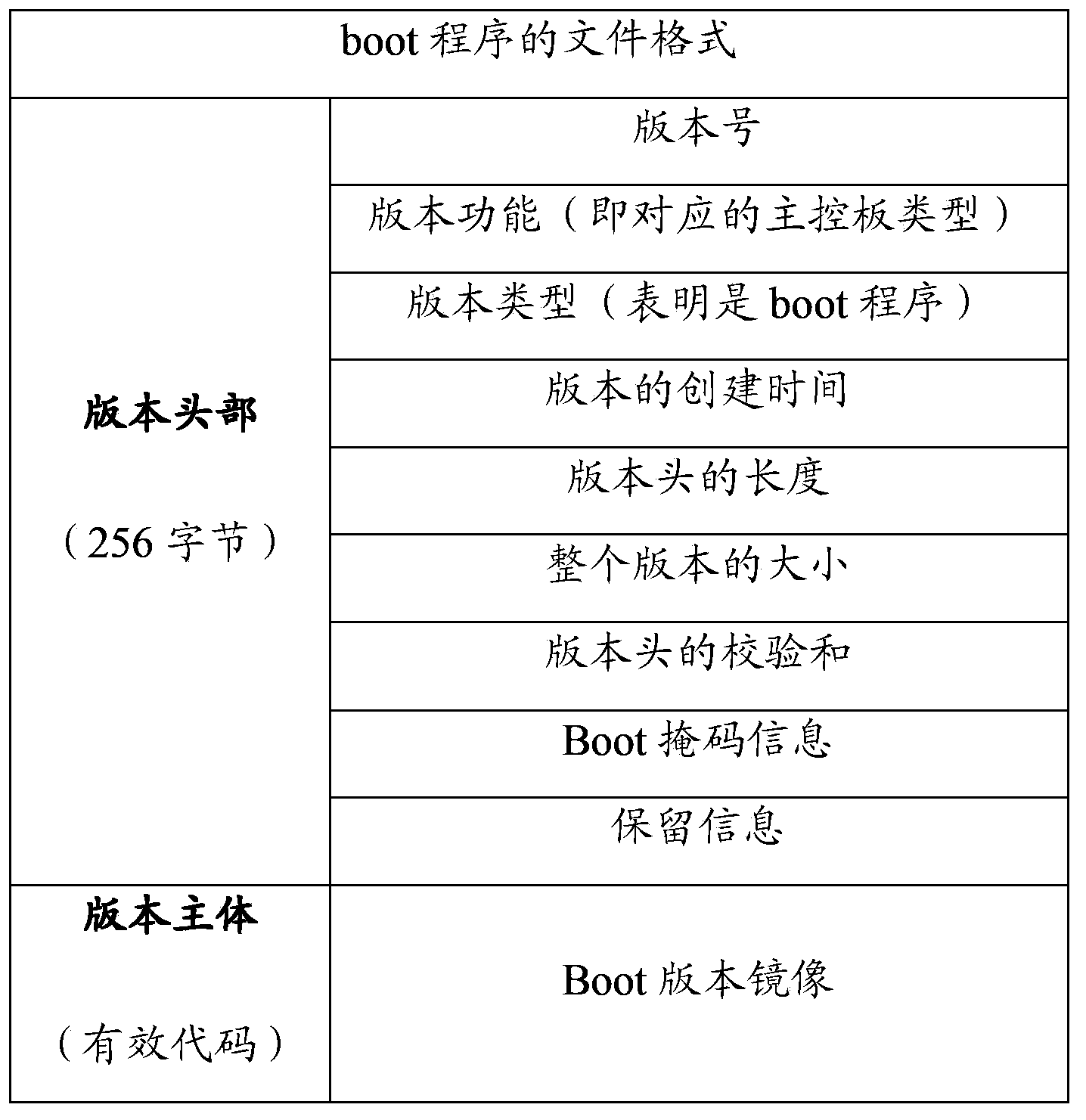

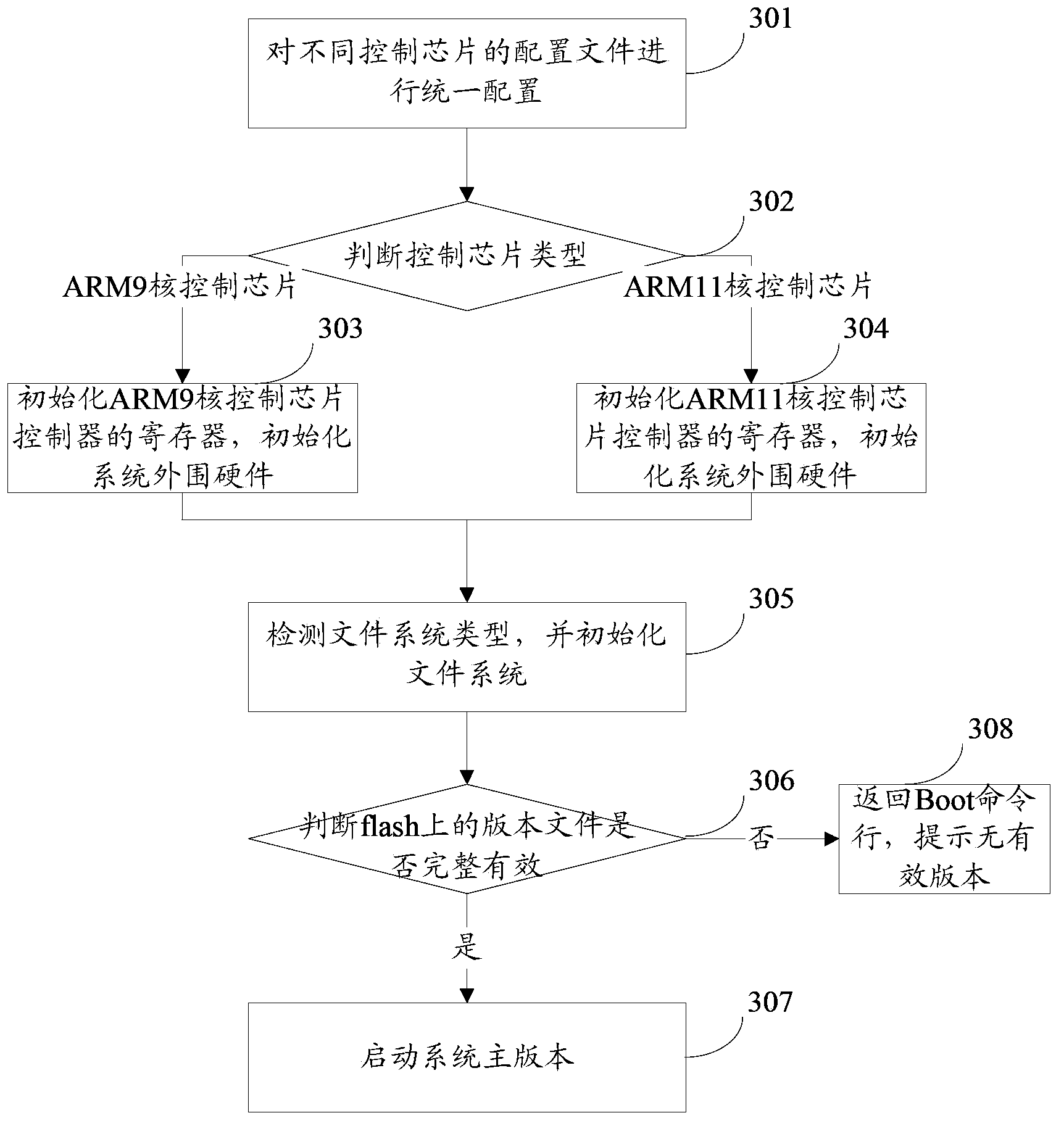

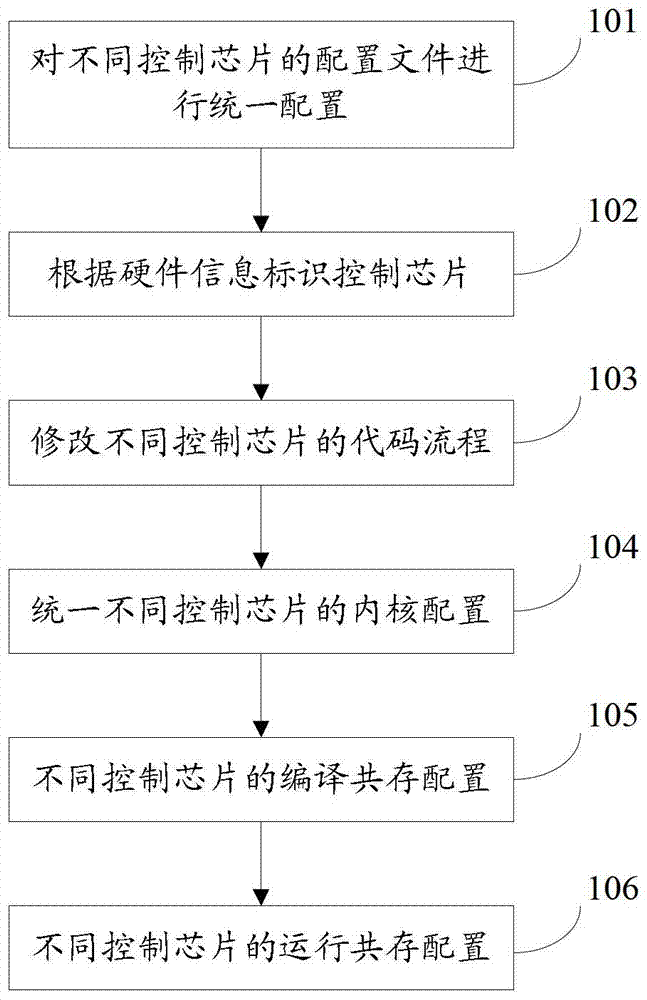

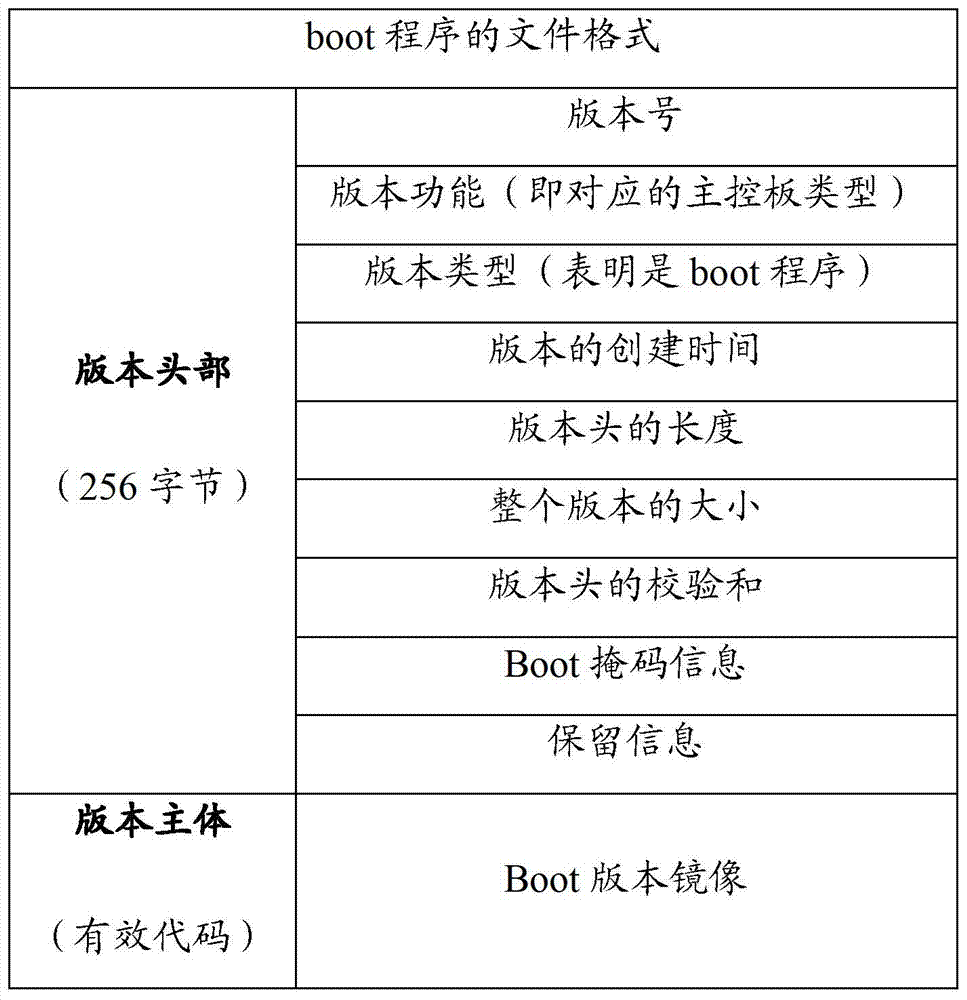

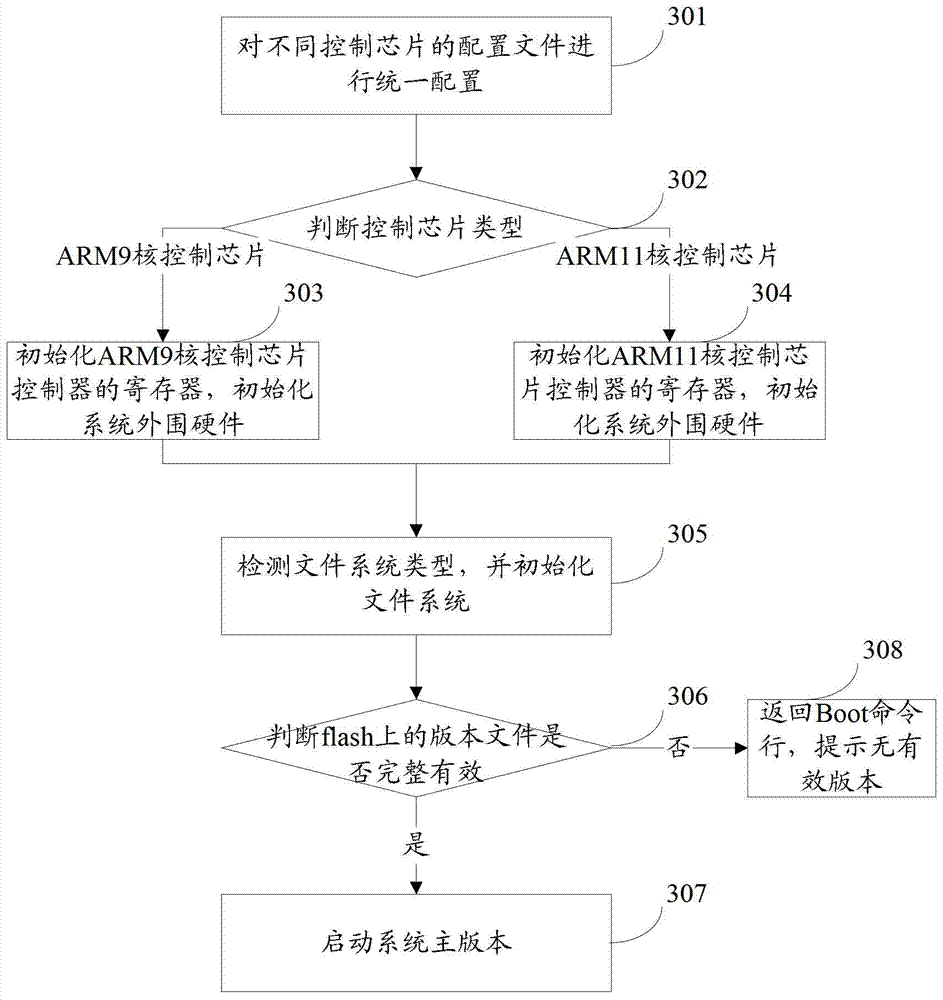

Design method for binary system unified Boot programs and kernel programs

ActiveCN103823664ABinary unification implementationIncrease costOperational speed enhancementProgram loading/initiatingComputer hardwareDesign methods

The invention discloses a design method for binary system unified Boot programs and kernel programs. The method includes: performing uniform configuration on configuration files of different control chips, marking the control chips according to hardware information, and revising code flows of the different control chips so as to complete binary system unification of the Boot programs; unifying kernel configuration of the different control chips and performing compiling coexistence configuration and running coexistence configuration of the different control chips so as to realize binary system unification of the kernel programs. By the method, a same software version can be used on two kinds or various different control chips.

Owner:ZTE CORP

Automatic monitoring method and device, terminal equipment and computer storage medium

PendingCN111026409AWork lessImprove availabilityHardware monitoringSoftware deploymentTerminal equipmentMonitoring system

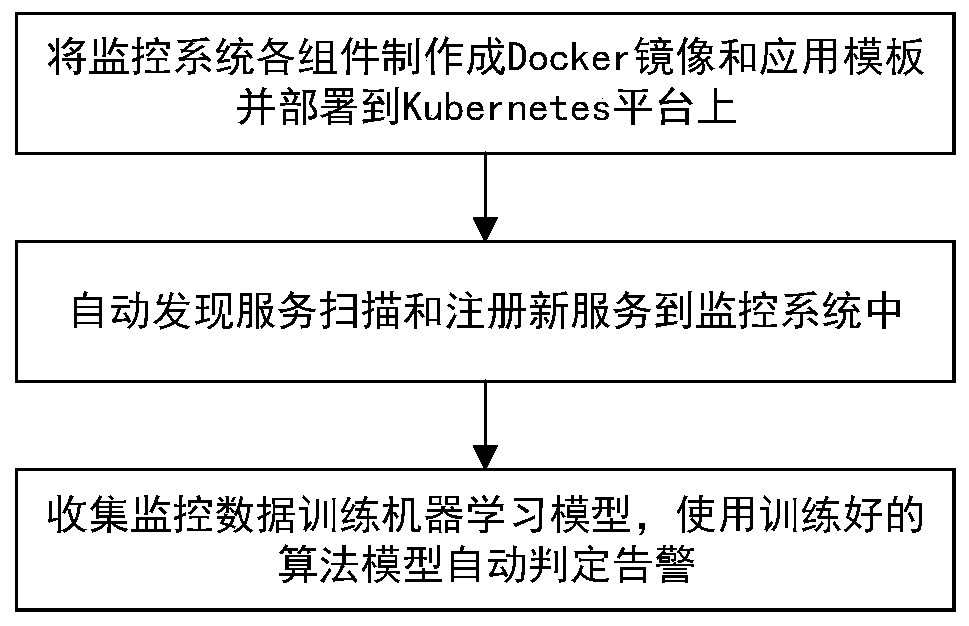

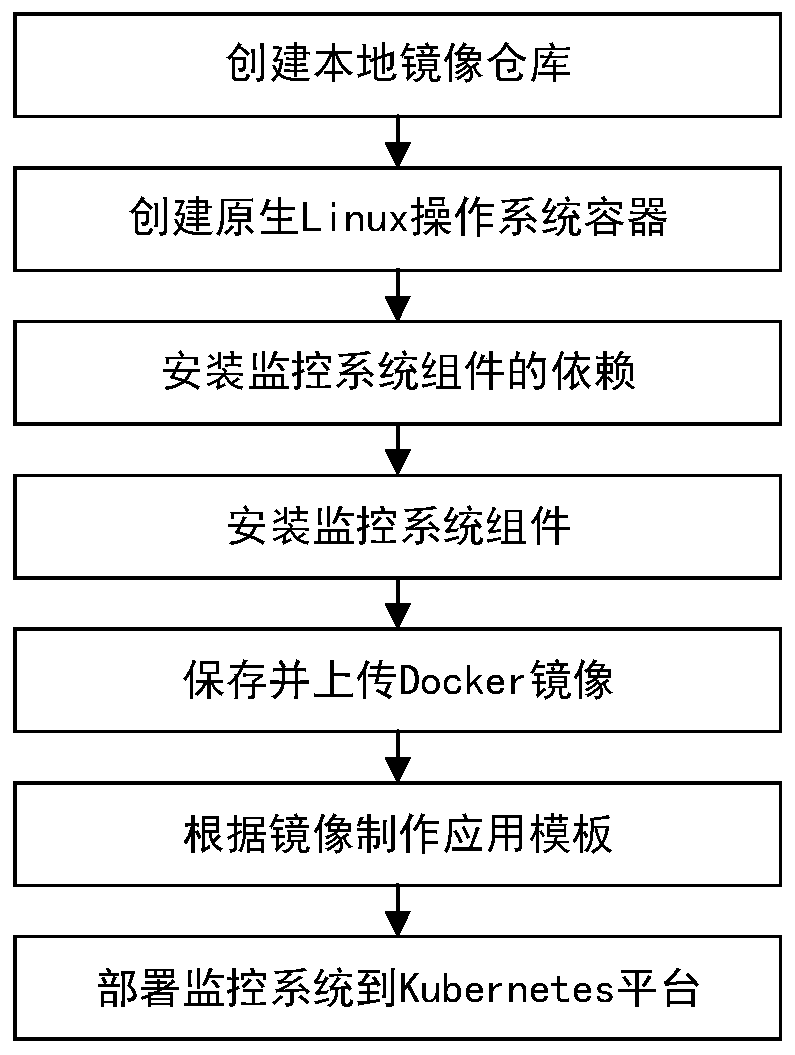

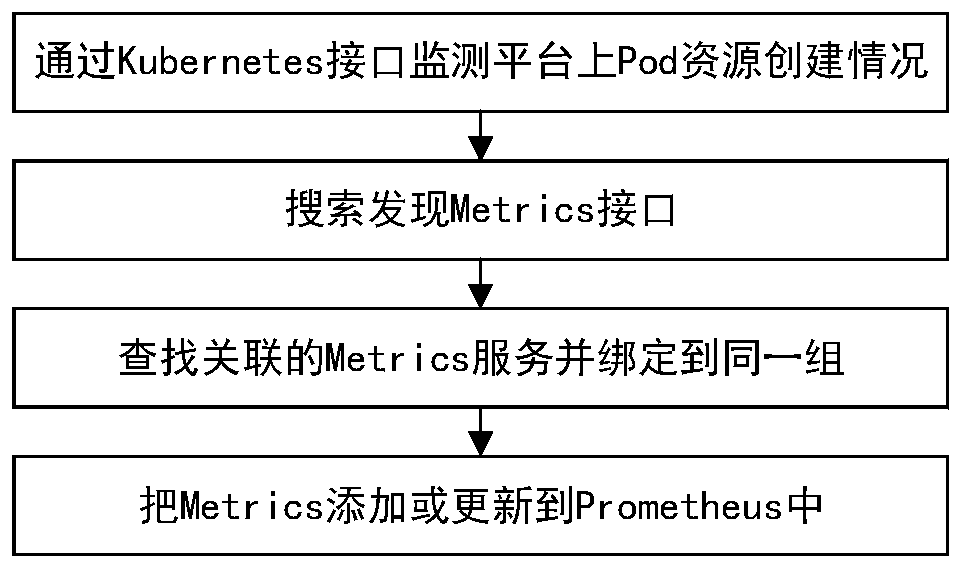

The invention discloses an automatic monitoring method and device, terminal equipment and a computer storage medium. The method comprises the following steps: making a service provided by a monitoringsystem into a Docker mirror image package and an application template, and deploying the monitoring system into a Kubernetes platform based on the Docker mirror image package and the application template; monitoring a new application deployed on the Kubernetes platform, and when the new application is provided with a metrics interface, registering the new application into Prometheus of a monitoring system so as to start a monitoring service for the new application; acquiring monitoring data acquired by Prometheus, and inputting the monitoring data into the trained machine learning model to obtain an alarm judgment result. According to the invention, cloud native and Kubernetes technologies are utilized, and a machine learning model is combined to realize automatic discovery and registration of monitoring services and automatic learning of monitoring thresholds, so that the method can adapt to environment automatic alarm; the work of operation and maintenance personnel is reduced, andthe change of application deployment is better adapted.

Owner:FENGHUO COMM SCI & TECH CO LTD

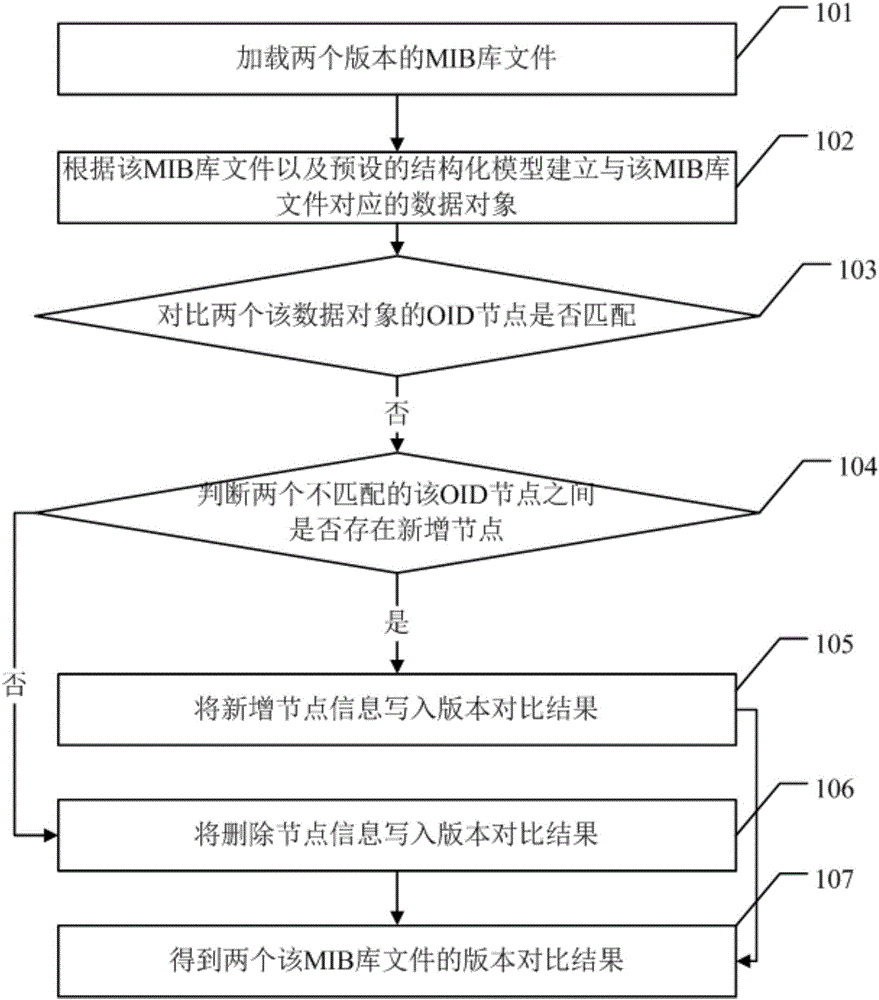

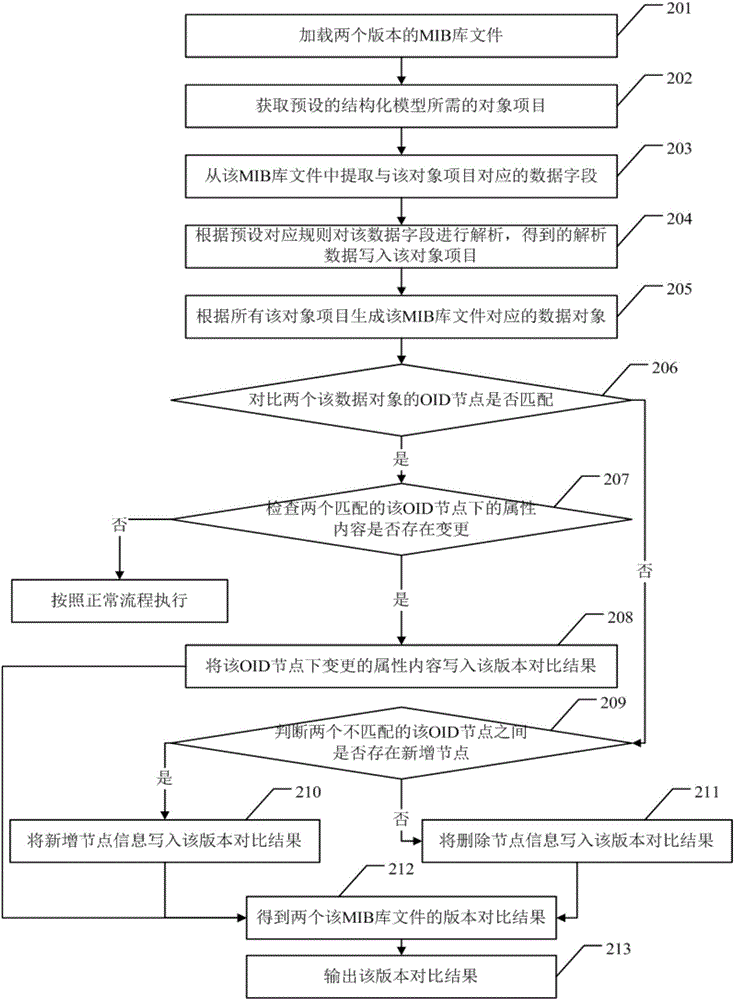

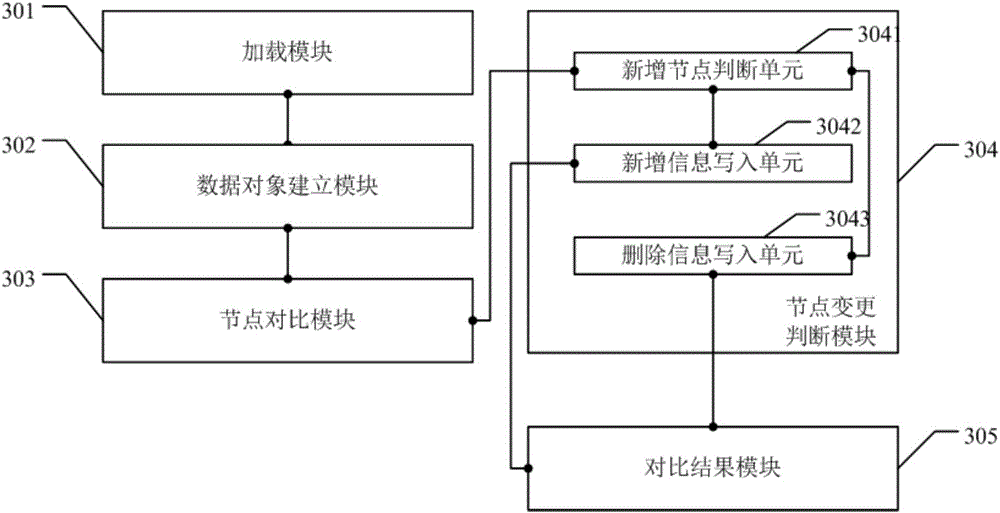

MIB (Management Information Base) version contrast method and device

ActiveCN105808748AEasy version managementEfficientSpecial data processing applicationsStructured modelManagement information base

The embodiment of the invention discloses an MIB (Management Information Base) version contrast method, which is used for solving the problems that the existing MIB library version is low in contrast efficiency and the accuracy cannot be guaranteed. The method comprises the following steps: loading MIB library files of two versions; establishing data objects corresponding to the MIB library files according to the MIB library files and a preset structural model, wherein the data objects comprise OID nodes and attribute contents under the OID nodes; contrasting whether the OID nodes of the two data objects are matched, if not, then performing node change judgment; after performing the node change judgment, obtaining a version contrast result of the two MIB library files; and the node change judgment specifically comprises: judging whether a newly added node exists between the two unmatched OID nodes, if so, then writing newly added node information into the version contrast result, and if not, then writing delete node information into the version contrast result. The embodiment of the invention further provides an MIB version contrast device.

Owner:MAYWIDE TECH

Method for developing AP middleware abiding by WOSA_XFS industry standard

InactiveCN104915197APromote rapid developmentEfficient and stable operationSpecific program execution arrangementsTechnical standardMiddleware

The invention discloses a method for developing AP middleware abiding by the WOSA_XFS industry standard and belongs to the technical field of AP middleware development. The method is characterized in that based on abidance by the WOSA_XFS industry standard, the AP middleware is quickly and stably developed, and development of the AP middleware is simplified. According to the technical scheme, the method for developing the AP middleware abiding by the WOSA_XFS industry standard includes the following steps that firstly, an IDE development tool is used for establishing an MFC ActiveX project; secondly, a corresponding file is introduced into engineering; thirdly, devices integrated into an IDevice are added; fourthly, each inheritance method is implemented; fifthly, the engineering is compiled, so that an ocx output file is acquired; sixthly, the middleware is completely developed.

Owner:浪潮(山东)电子信息有限公司

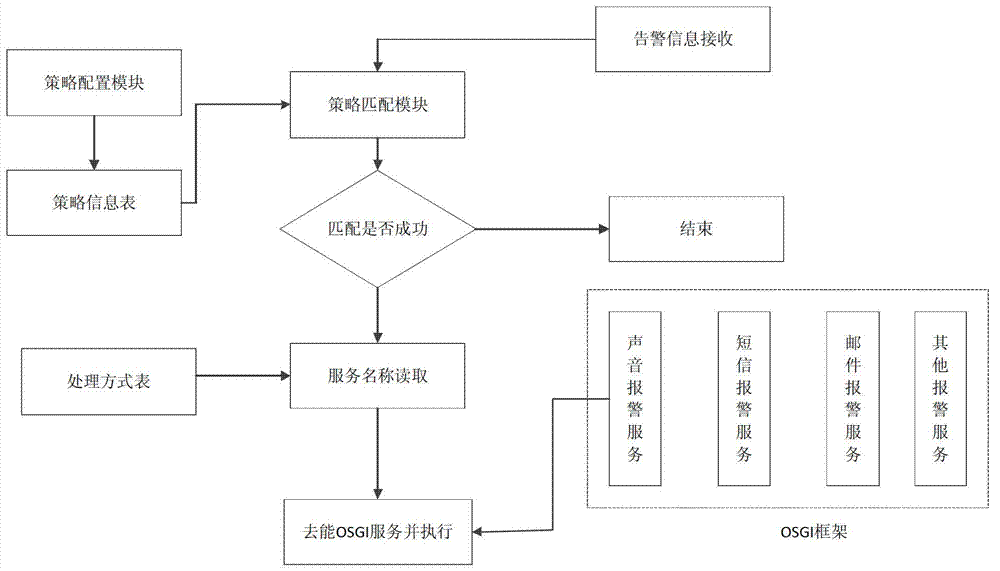

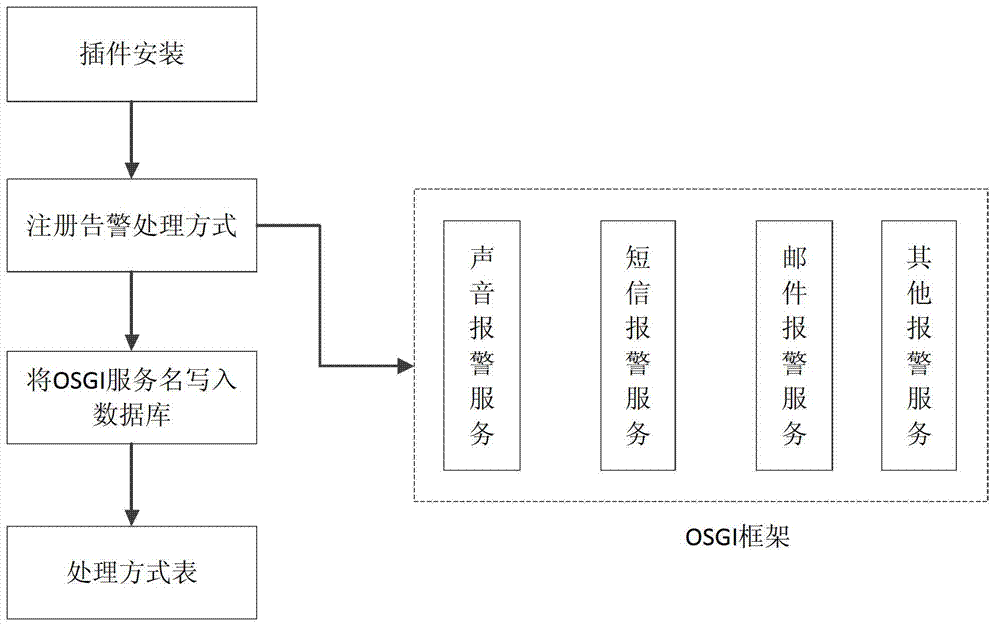

Extensible alarm emergency processing system and control method thereof

The invention discloses an extensible alarm emergency processing system and a control method thereof. The system comprises an alarm strategic management framework and an alarm emergency processing plug-in, the alarm strategic management framework is embedded into an alarm system, and the alarm emergency processing plug-in is communicated with the alarm strategic management framework by means of hot swapping to complete emergency processing of alarm information. The implementation steps include: plugging the alarm emergency processing plug-in in a computer and executing a bundle start procedure; allowing a strategy matching module to receive alarm information; allowing a strategy configuration module to search matched strategies in a strategy information table according to the alarm information; judging whether matching of the strategies in the strategy information table is successful or not; enabling an alarm emergency processing mode calling module to read corresponding alarm processing mode names in an alarm processing mode table; and obtaining OSGI (open service gateway initiative) services and executing. By means of the extensible alarm emergency processing system and the control method thereof, coupling of software products is lowered, development complexity is simplified, development efficiency is improved, software version management and maintenance are optimized, and cost is saved.

Owner:DAWNING INFORMATION IND BEIJING

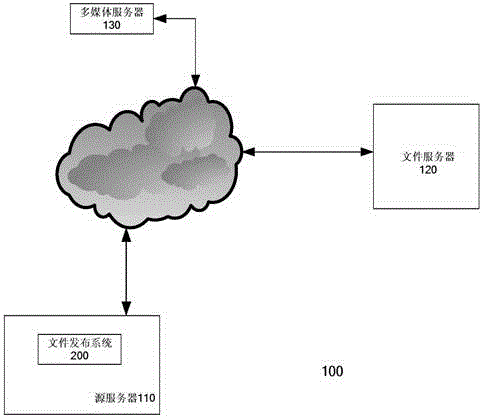

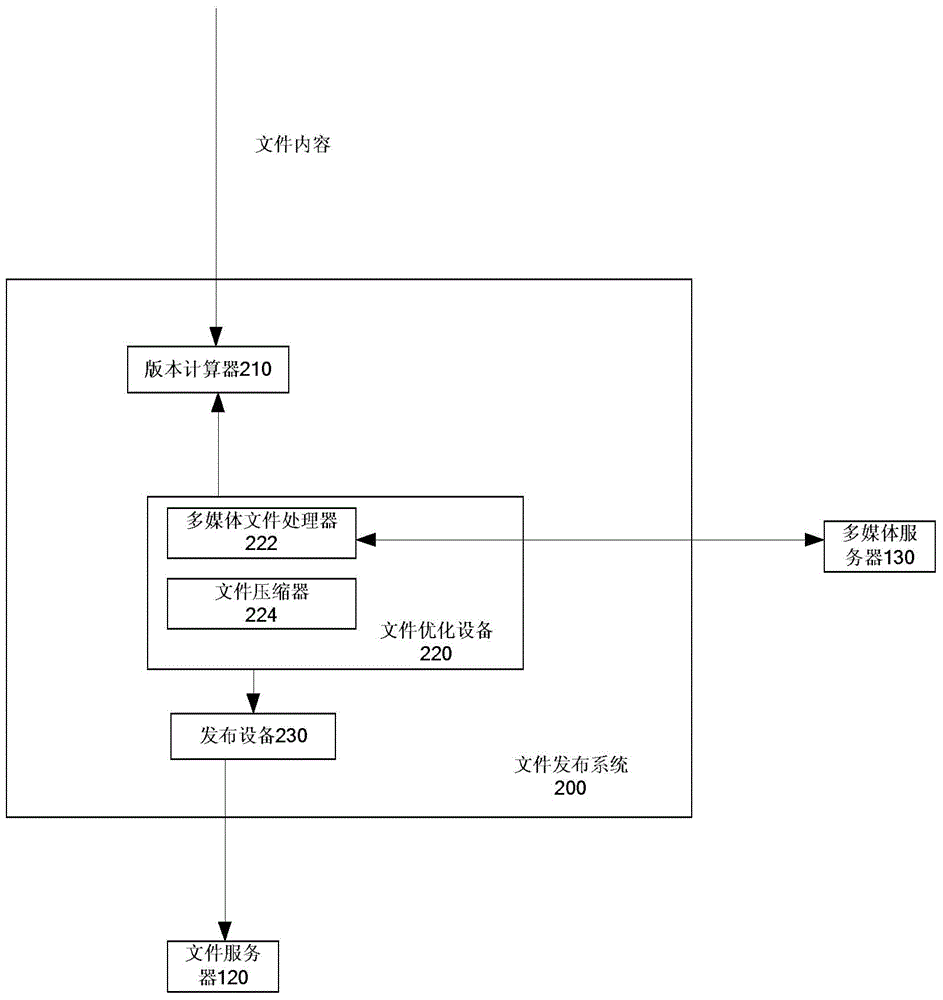

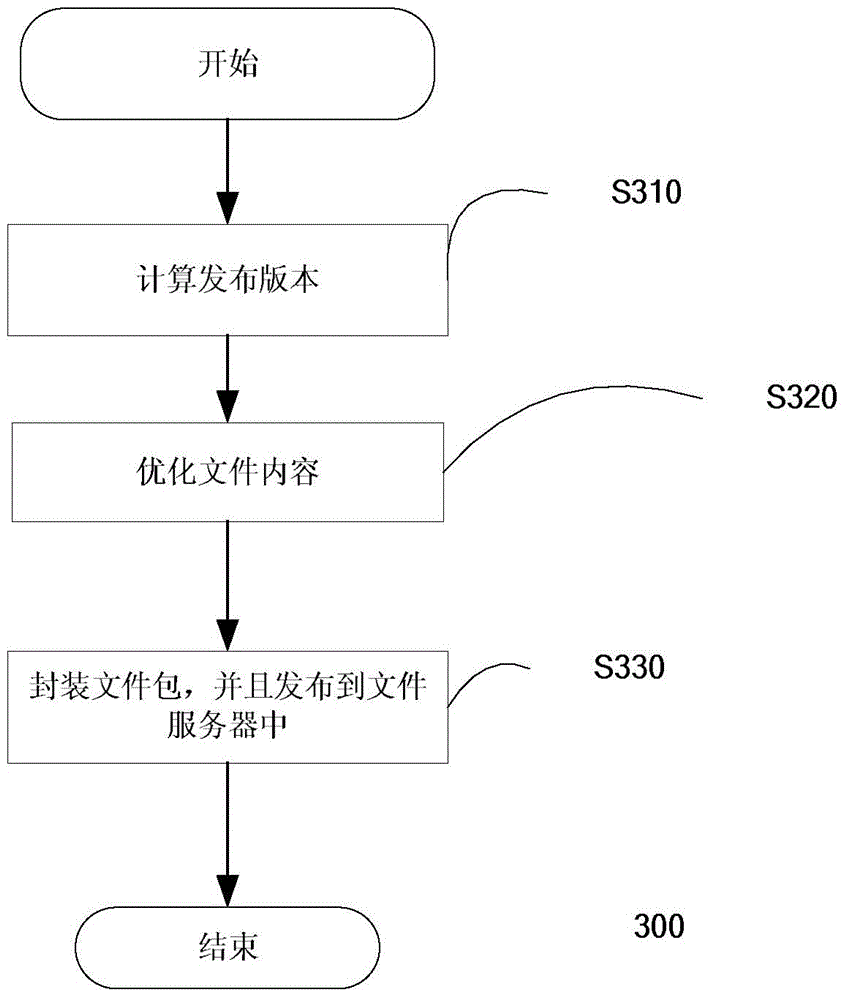

File release system, file release method and network server

ActiveCN104980465AEasy version managementEasy to manageTransmissionSpecific program execution arrangementsCalculatorNetworked system

Provided are a file release system (200), a file release method, and a network server. The file release system (200) is suitable for releasing to a file server (120) one or a plurality of files in an origin server (120), the file release system (200) comprising: a version calculator (210), suitable for calculating a release version according to the file content of the one or plurality of files; a file optimization device (220), suitable for optimizing the file content of the one or plurality of files; and a release device (230), suitable for packaging the optimized one or plurality of files into a file package and using the calculated release version to calculate a file package identifier, so as to release to the file server (120) the packaged file package carrying the file package identifier.

Owner:BEIJING QIHOO TECH CO LTD +1

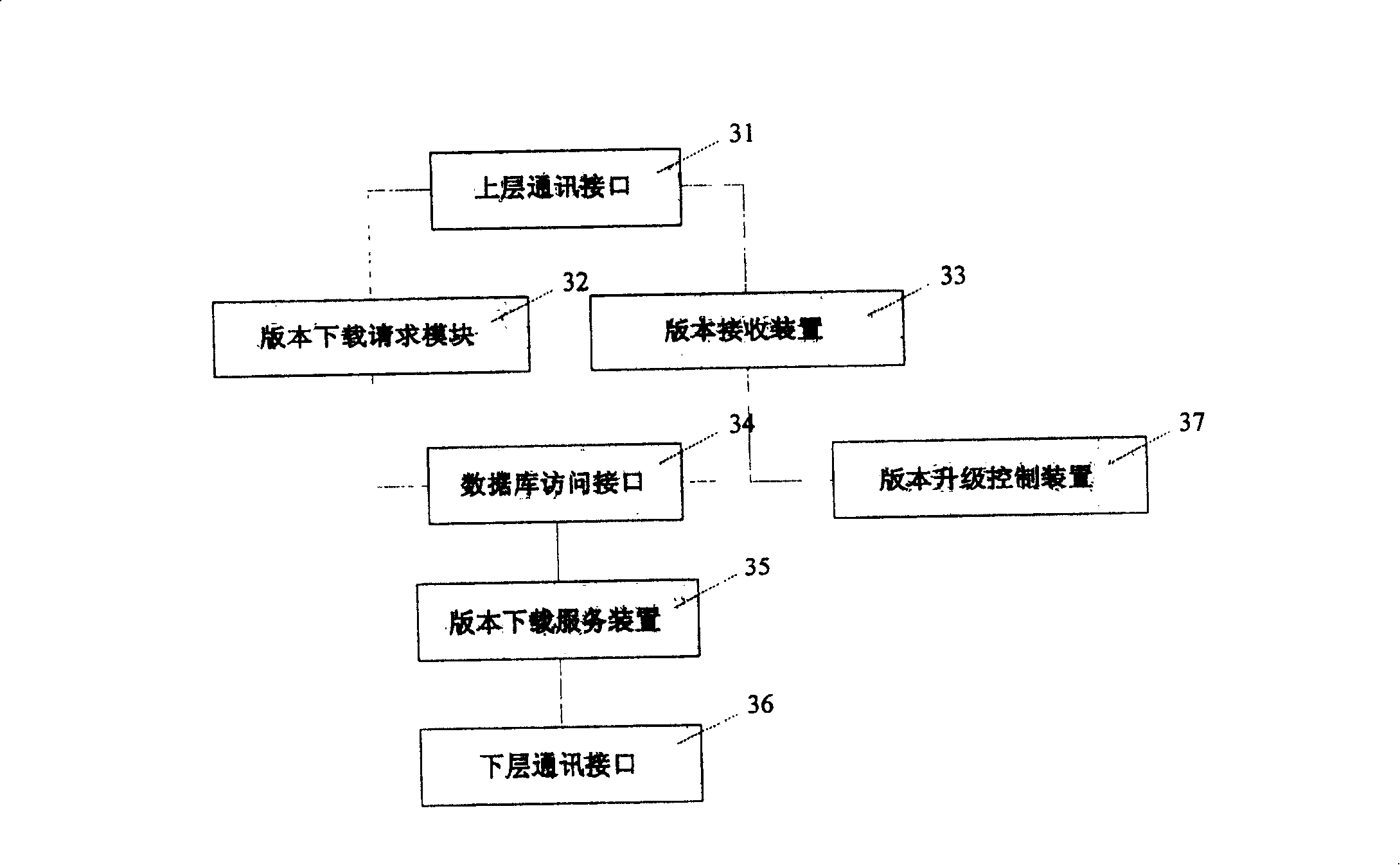

Software edition updating system in distributed service system and its method

ActiveCN100407650CCoordinated version upgradesEasy version managementProgram loading/initiatingData switching networksApplication serverSoftware engineering

A method for upgrading software version in distributed service system includes receiving new version application software inputted from master system by centralized management server ( CMS ), updating recorded version down - sending information of databank connected to CMS, down - sending received new version application software to application server, updating software down - sending record of databank connected to application server, installing new version application software by CMS and application server separately, providing download of new version application software for user terminal by application server and installing received new version application software by user terminal.

Owner:INDUSTRIAL AND COMMERCIAL BANK OF CHINA

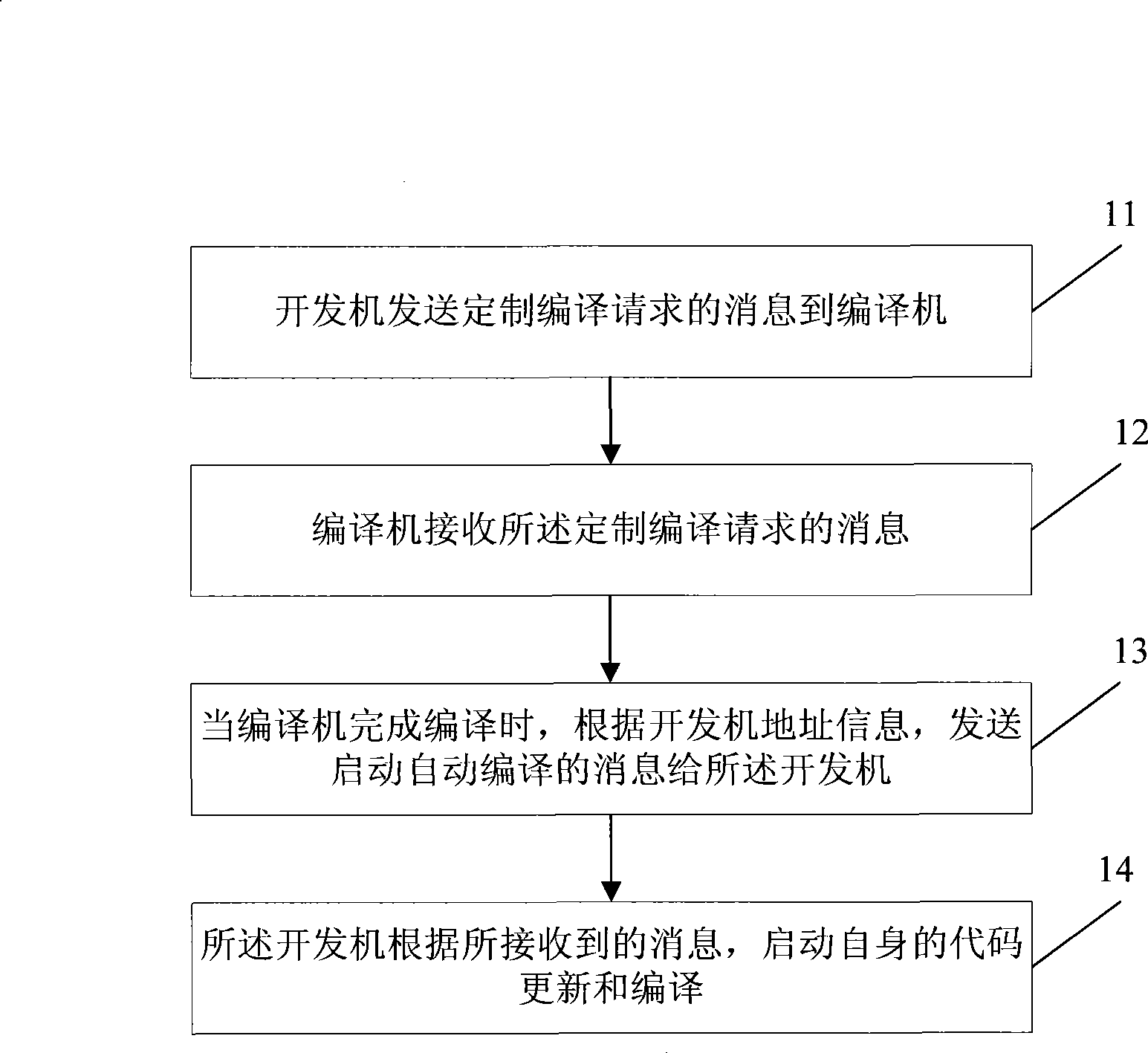

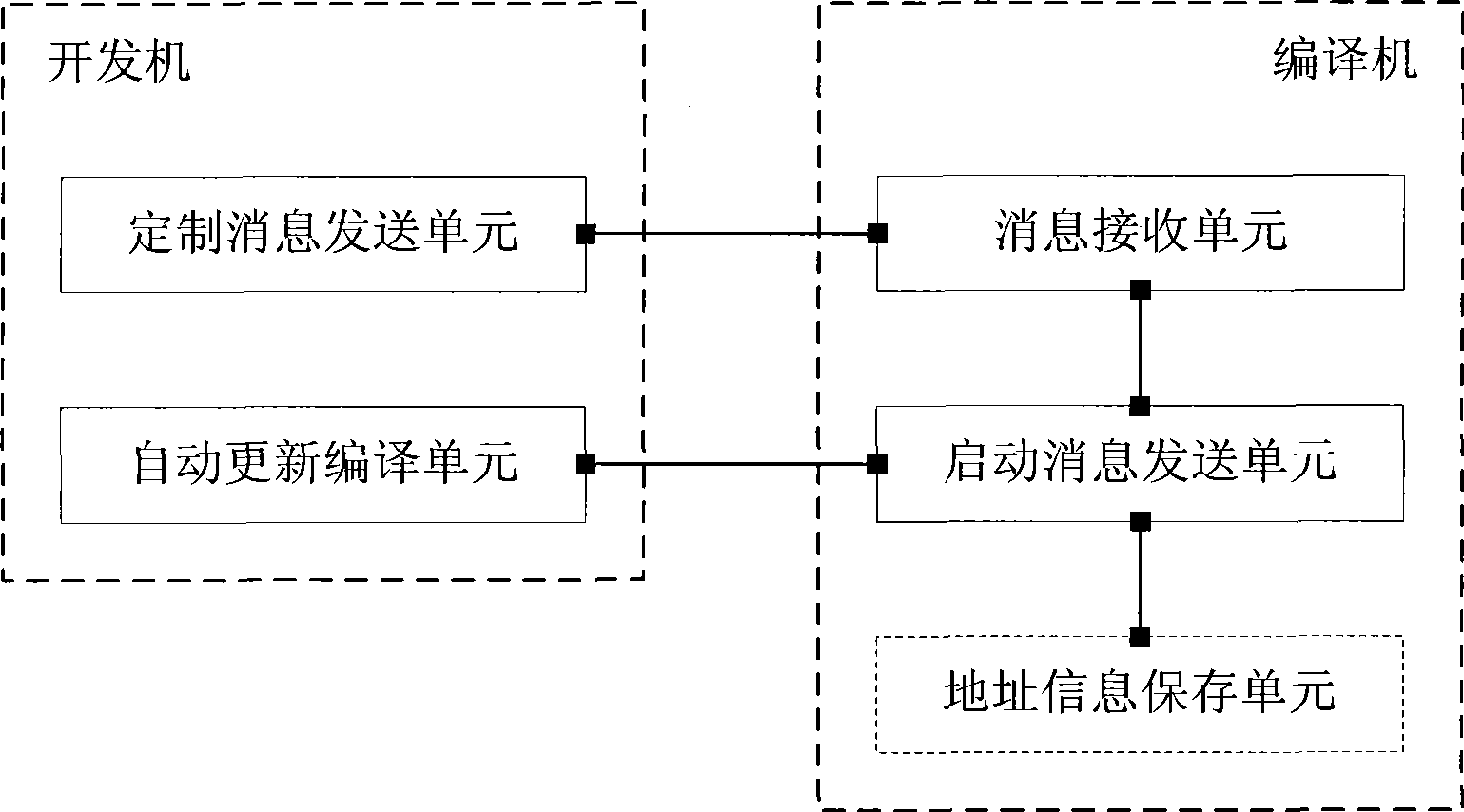

Method and apparatus for implementing automatic compilation of development machine

InactiveCN101477465AShorten the timeEasy to manageSpecific program execution arrangementsDynamic compilationSoftware development

The embodiment of the invention provides a method and a device for realizing the automatic compilation of a development kit. The method comprises the following steps: a development kit sends information about compilation customization request to a compiler; the compiler receives the information about compilation customization request; when the compilation is finished by the compiler, the information about the start of automatic compilation is sent to the development kit according to the development kit address information in the received information; the development kit starts the code update and compilation of self according to the received information. Therefore, the customizable automatic update and compilation can be realized. Furthermore, since the process can be automatically conducted at night and can not by interfered by the input of incomplete codes by other persons, the time consumed by the code update and complication conducted by a developer is greatly shortened; and the working efficiency of the software development is greatly improved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

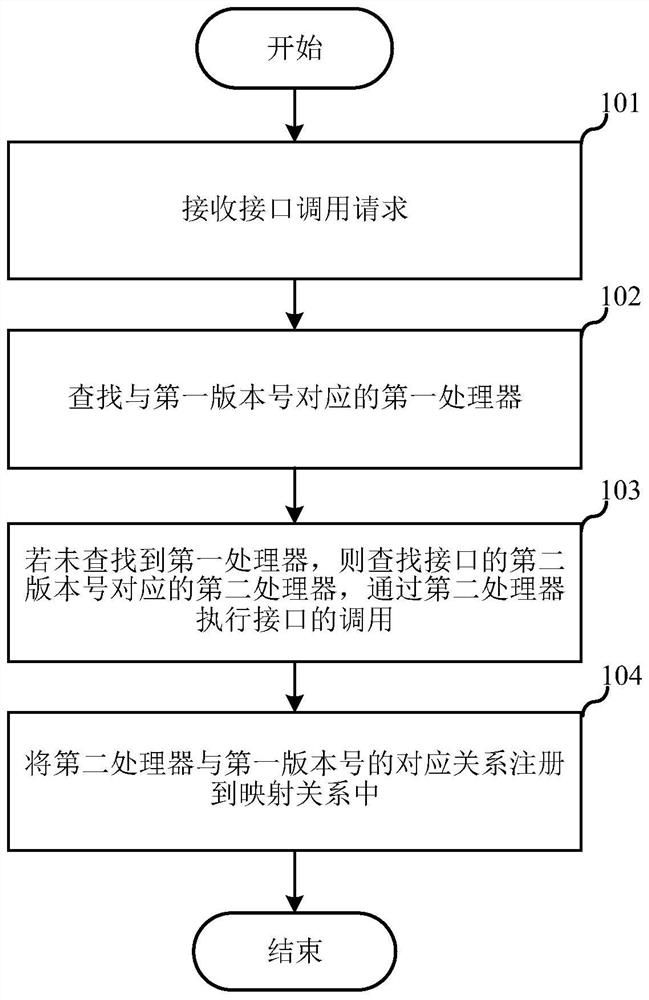

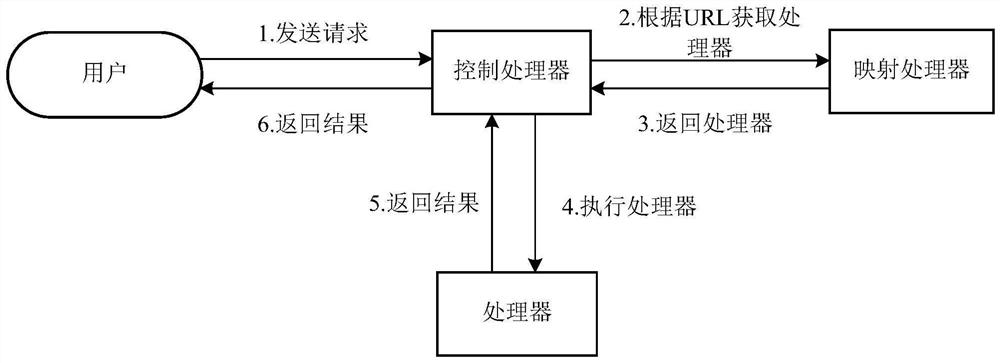

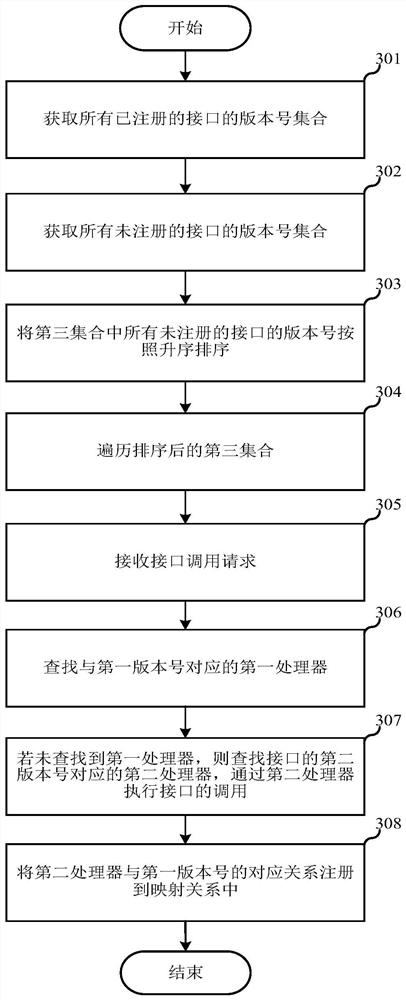

Interface calling method and device, server and computer readable storage medium

PendingCN114020319AEasy version managementSolve the problem of increasing the corresponding processorVersion controlInterprogram communicationComputer hardwareSystem development

The embodiment of the invention relates to the technical field of system development, in particular to an interface calling method and device, a server and a computer readable storage medium. The interface calling method comprises the following steps: S1, receiving an interface calling request, where the interface calling request carries a first version number of an interface requested to be called; s2, searching a first processor corresponding to the first version number; s3, if the first processor is not found, finding a second processor corresponding to a second version number of the interface, and performing calling of the interface through the second processor; s4, registering the corresponding relationship between the second processor and the first version number into a mapping relationship, wherein the mapping relationship is used for storing the corresponding relationship between the registered interface version number and the processor, wherein the second version number is the maximum version number lower than the first version number. The problem that a corresponding processor needs to be added to an interface of each version can be solved, and the versions of the interfaces can be managed more conveniently.

Owner:SHENZHEN GRANDSTREAM NETWORKS TECH

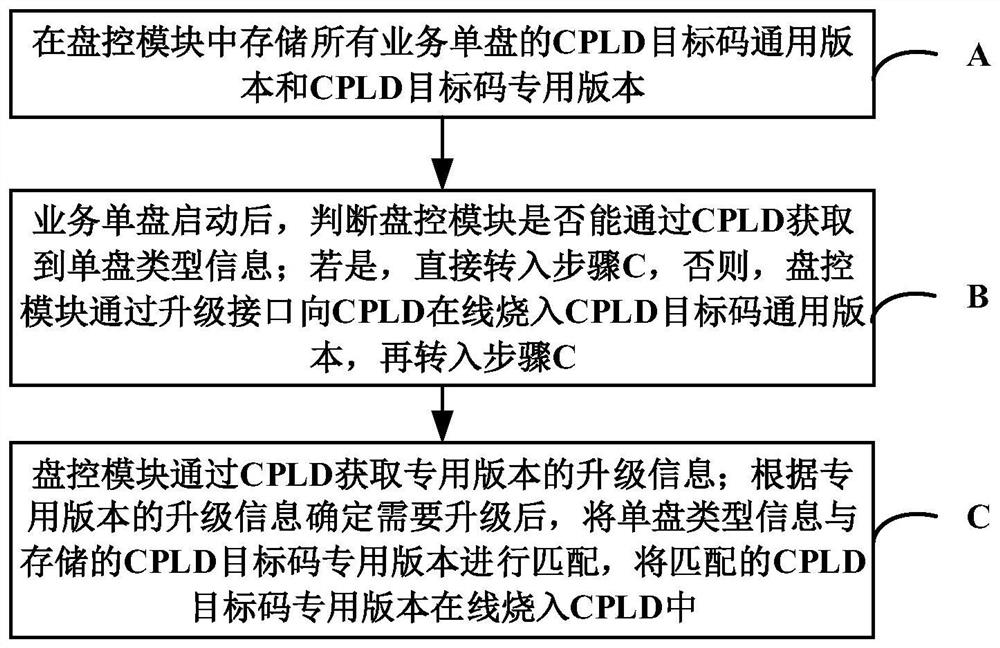

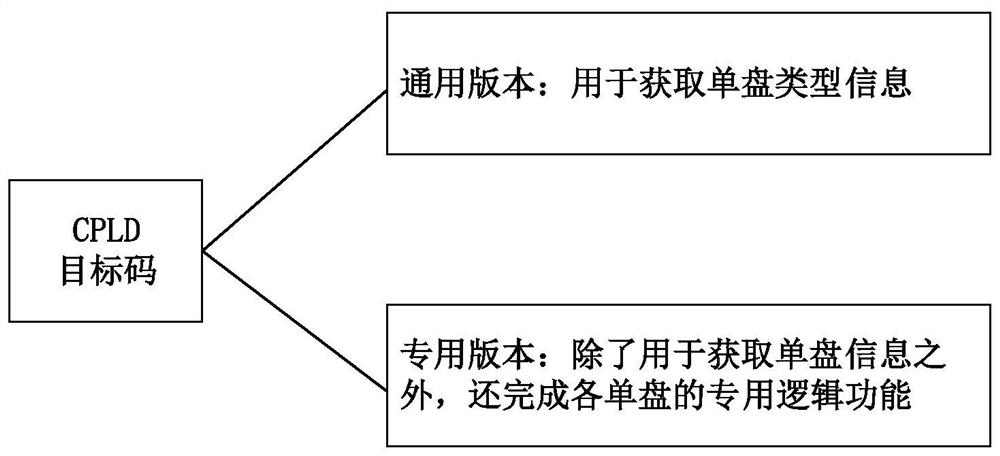

Method and device for automatically matching and upgrading CPLD of service board card

ActiveCN112052031AImprove output efficiencySave I/O resourcesVersion controlSoftware deploymentComputer hardwareEngineering

Owner:FENGHUO COMM SCI & TECH CO LTD

Video monitoring front end equipment access method

InactiveCN101272481BImprove scalabilityFacilitates parallel developmentClosed circuit television systemsVideo monitoringAccess method

The invention relates to an access method for video monitoring front-end equipment, which is characterized in that the equipment access module of a monitoring system platform consists of two parts ofa main module and a plug-in for the equipment. The main module provides a unified service interface for the inner part of the platform.. The SDK of various equipment in the monitoring system is integrated the plug-in for the equipment which is developed according to the appointed interface standard of the main module. The main module manages and controls the plug-in for the equipment and transmitsthe service requests of platform users to the corresponding plug-in for the equipment. And the treatment and the response of the service requests is finished by the plug-in for the equipment. In addition, the plug-in for the equipment can be dynamically loaded and unloaded to consequently finish the dynamical start and the stop control of the equipment service. The access method for the video monitoring front-end equipment has the advantage of simple and fast realization, thereby improving the scalability, the tailorability, the testability, the maintainability, the applicability and the easyuse performance of the system. The technical proposal has great significance in integrating large amounts of heterogeneous video monitoring resources and establishing public video monitoring platforms with large scale.

Owner:WUHAN UNIV

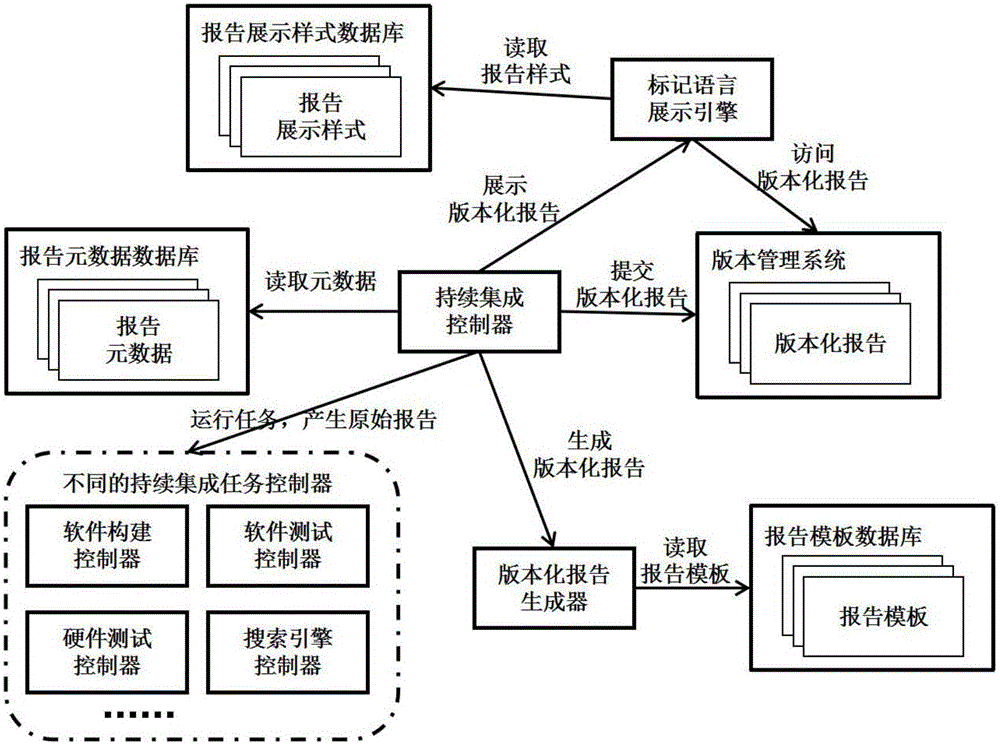

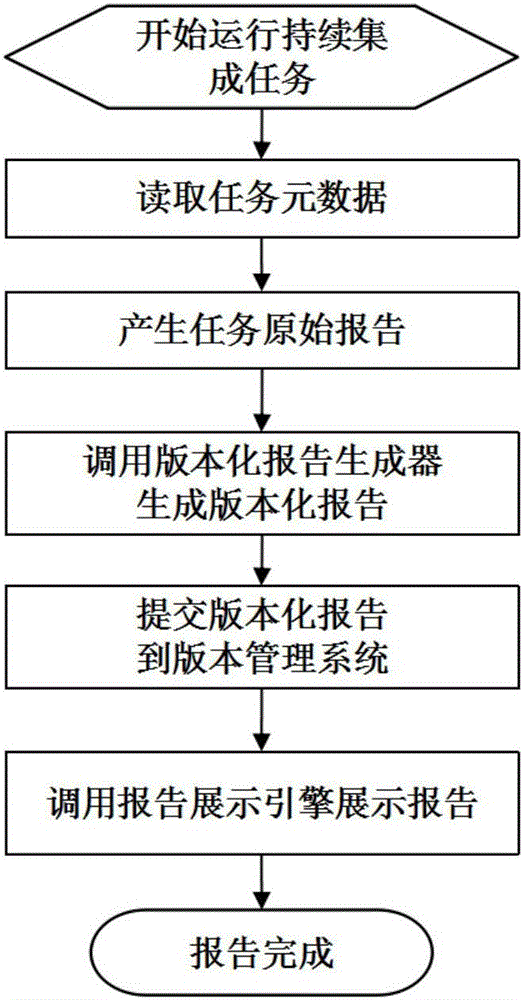

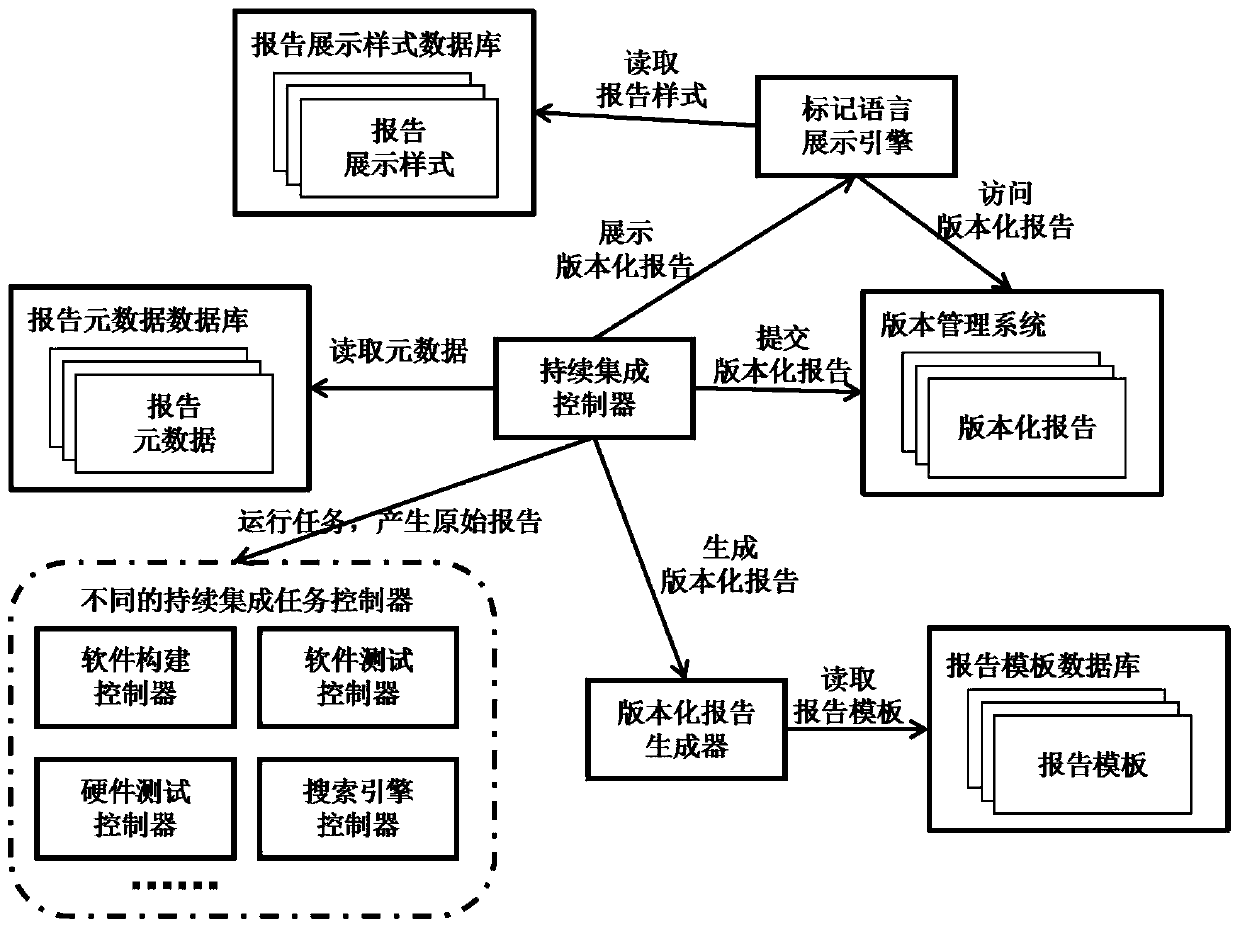

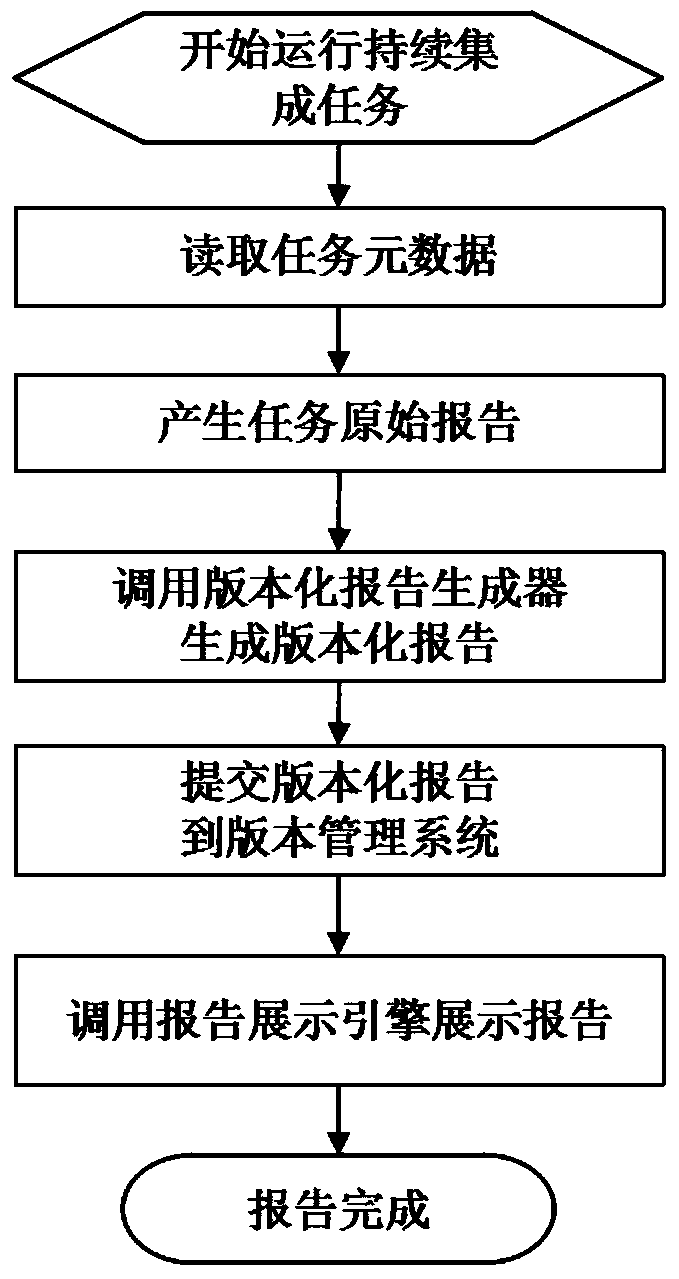

Continuous integrated report releasing system and method

InactiveCN106021303AEasy version managementEasy to browseHardware monitoringWebsite content managementContinuous integrationIntegrated controller

The invention provides a continuous integrated report releasing system and method, and belongs to the field of cloud computing. The continuous integrated report releasing system includes a report metadata database, a report display style database, a report template database, a markup language display engine, a version management system, a continuous integrated controller, and a versioning report generator. The continuous integrated report releasing method includes; S1, under the control of the continuous integrated controller, the system generates a versioning report from an original report according to metadata of the report, and displays the versioning report; and S2, the versioning report generator generates a structural report from the original report according to a report template.

Owner:BEIJING QING YUAN TECH CO LTD

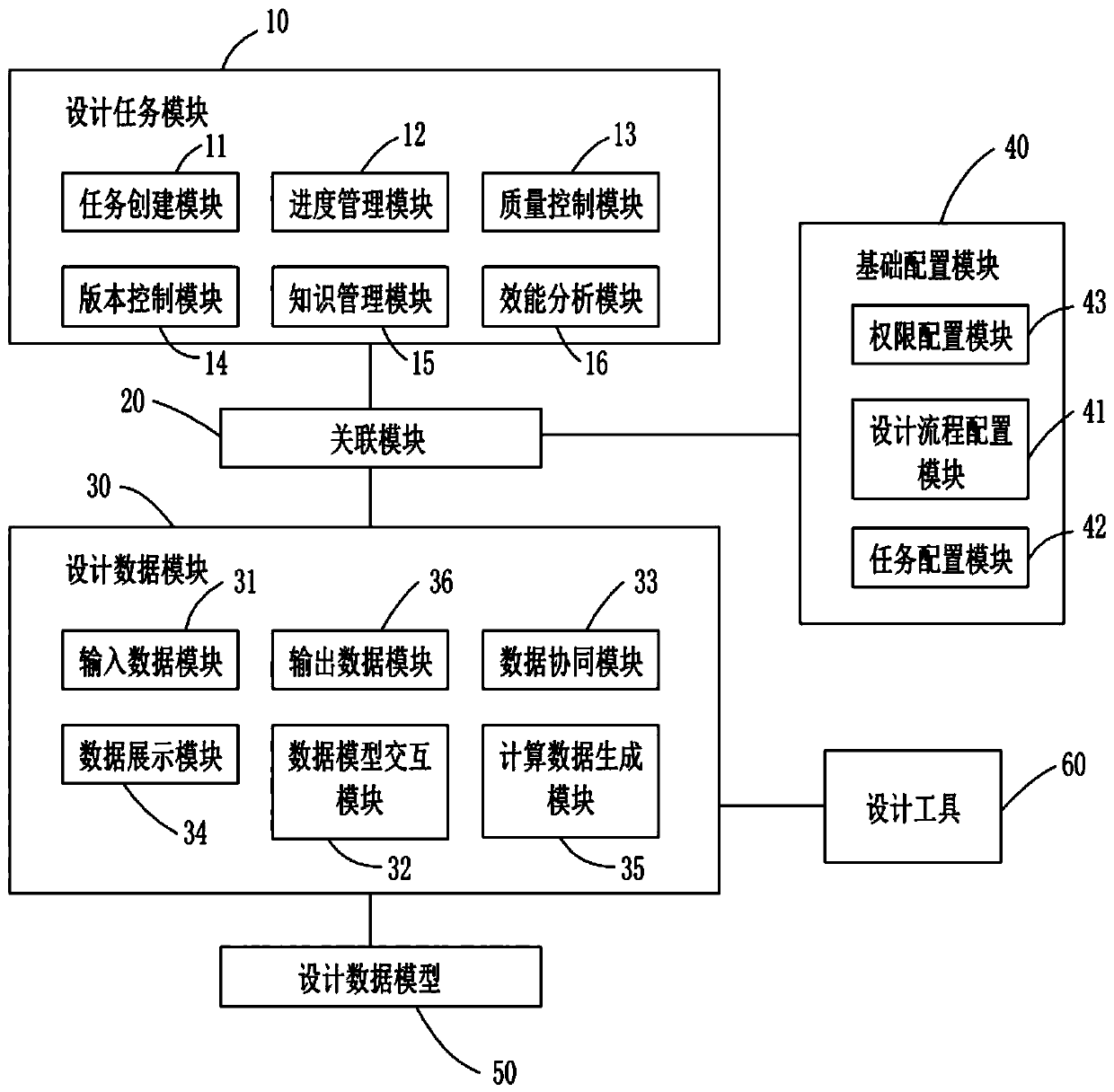

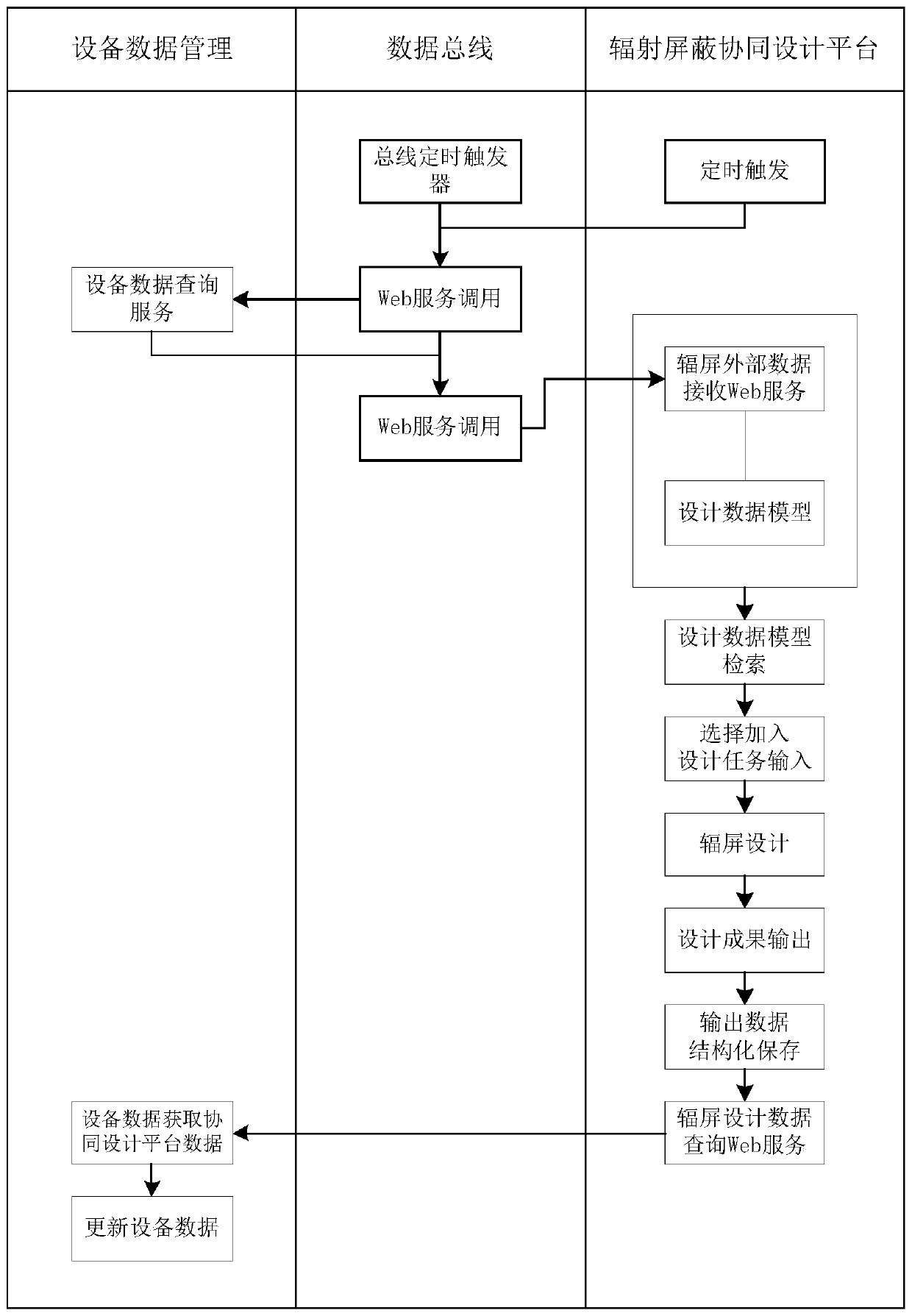

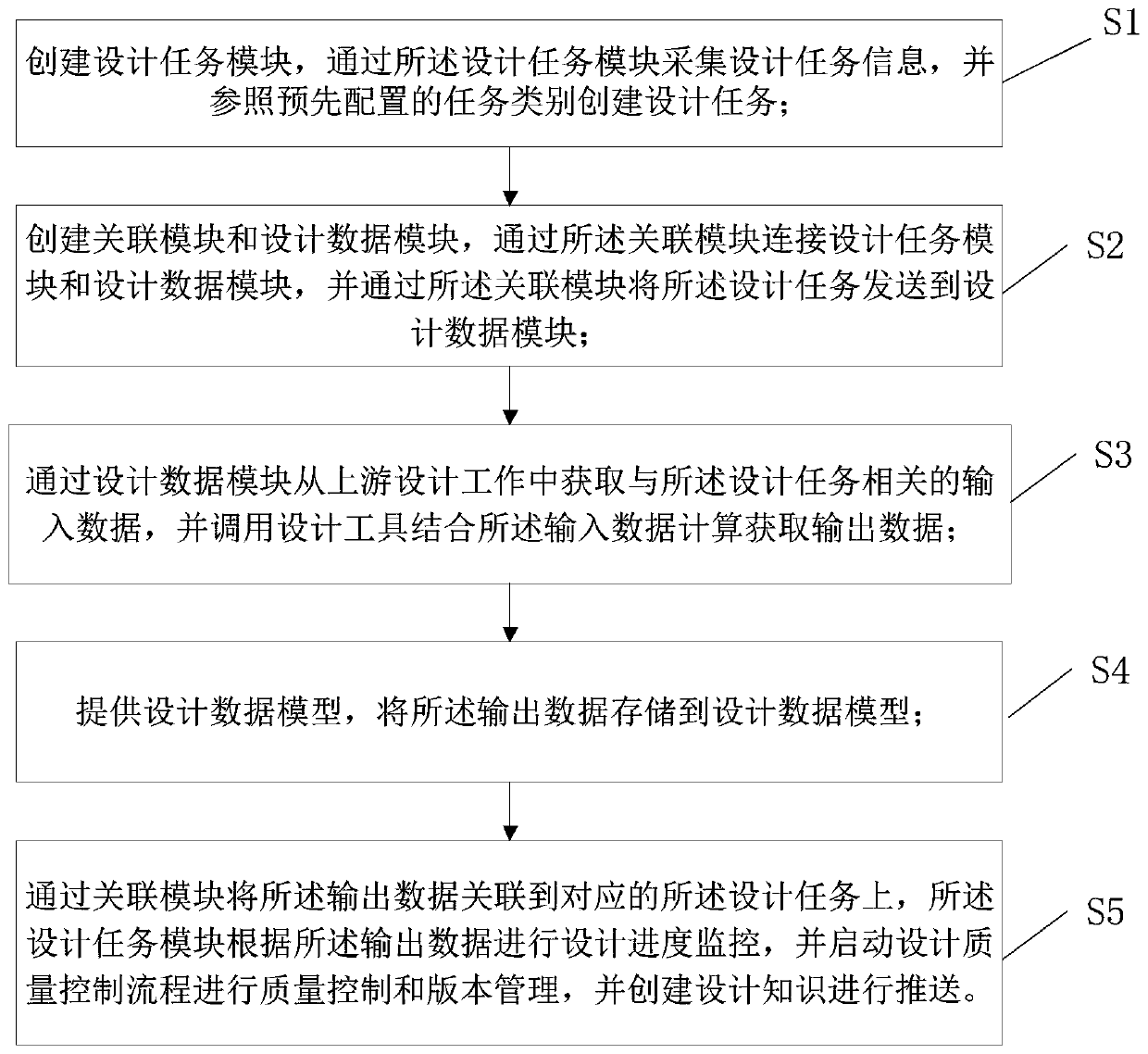

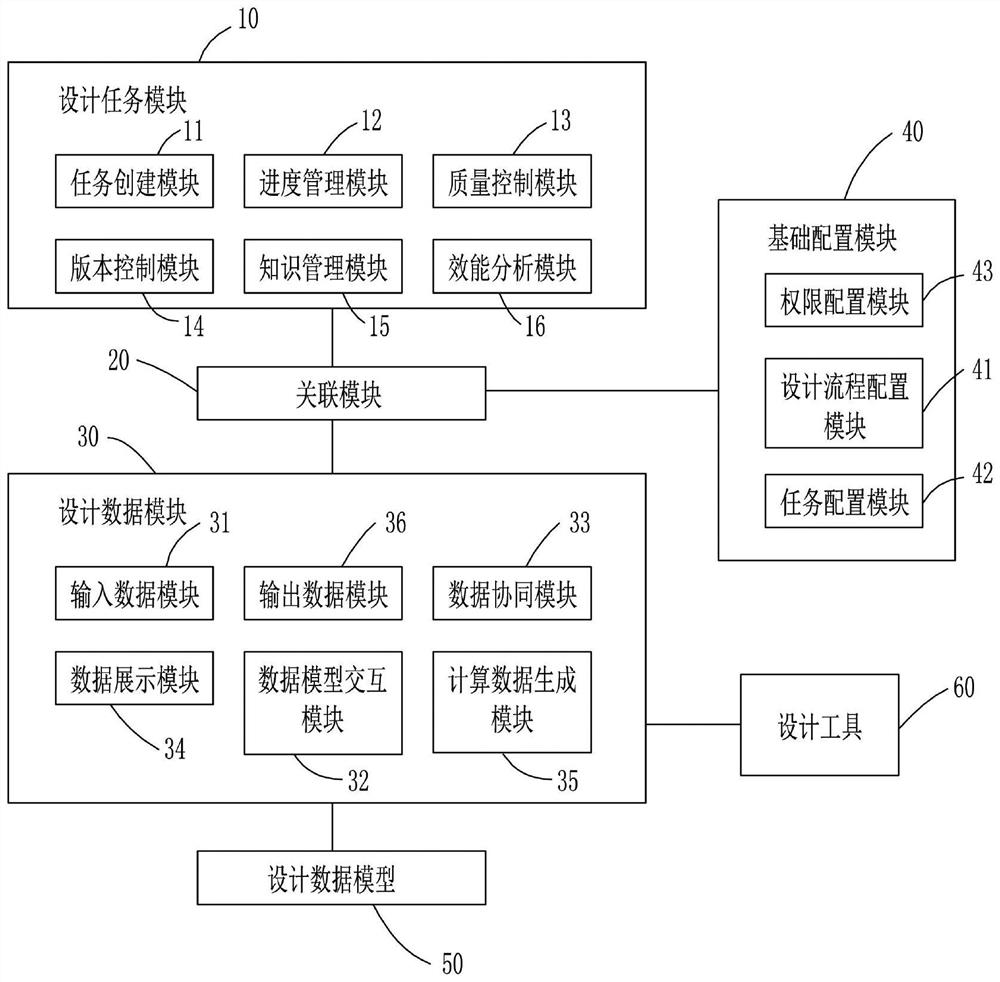

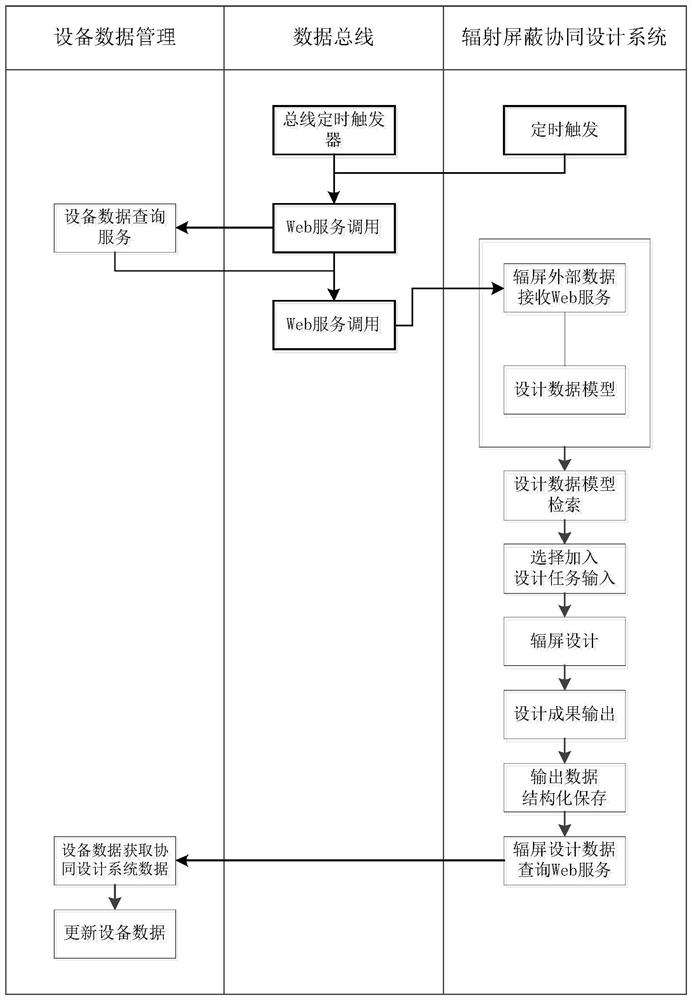

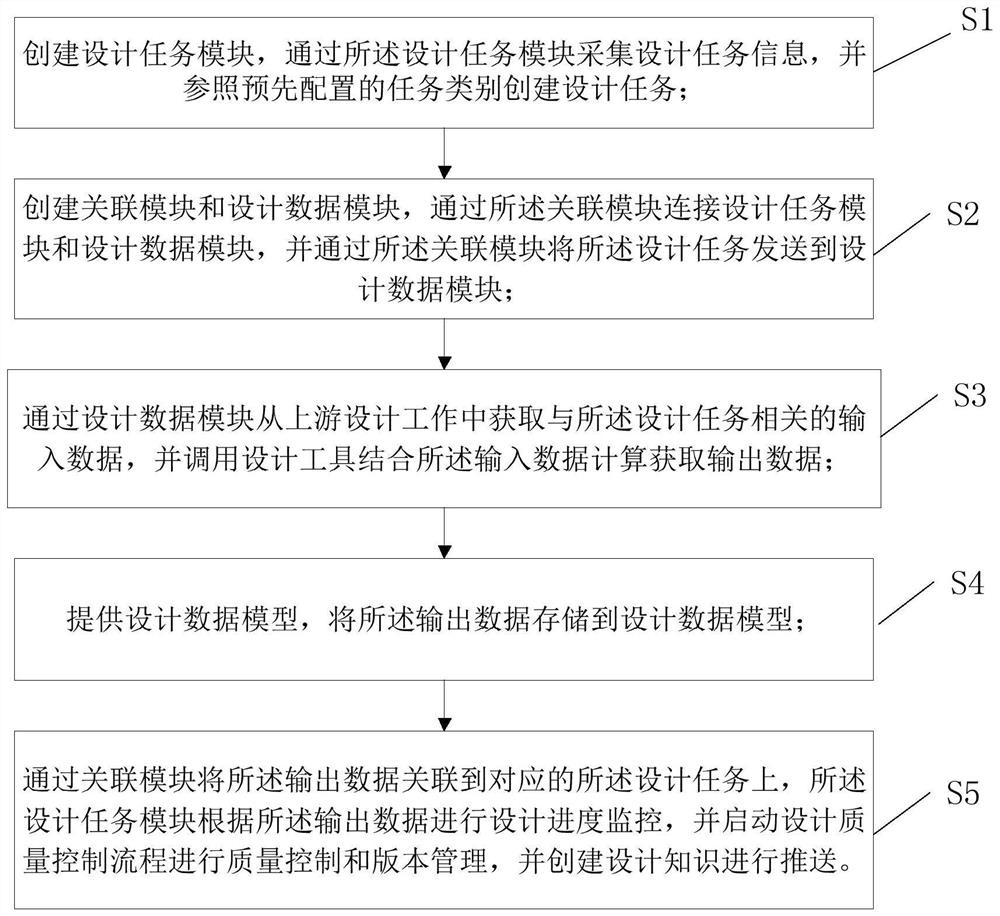

Nuclear power station radiation shielding collaborative design platform and construction method thereof

ActiveCN110210821AImplement iterationRealize traceabilityOffice automationNuclear powerQuality control

The invention provides a nuclear power station radiation shielding collaborative design platform and a construction method thereof. The nuclear power station radiation shielding collaborative design platform comprises a design task module, an association module, a design data module and a design data model, wherein the design task module is used for creating a design task, and the association module is connected with the design task module and the design data module; the design data module is used for acquiring input data from upstream design work and calling a design tool to calculate and acquire output data in combination with the input data; the design data model is used for storing output data; and the design task module is also used for monitoring the design progress according to theoutput data, starting a design quality control flow and creating design knowledge for pushing. According to the nuclear power station radiation shielding collaborative design platform and the construction method thereof, the whole design process of radiation shielding design is covered, and effective collaborative design with related majors is achieved, and the good technical effect is achieved.

Owner:中广核工程有限公司 +3

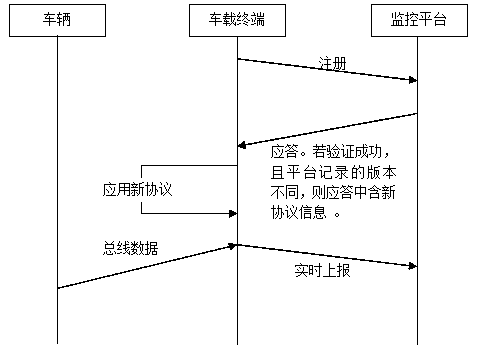

Data transmission method of electric vehicle terminal applied to remote monitoring

The invention discloses an electric vehicle-mounted terminal data transmission method applied to remote monitoring. Two kinds of communication protocols exist in a remote monitoring application of a vehicle-mounted terminal; a CAN (Controller Area Network) bus communication protocol defined by a vehicle manufacturer is followed between the vehicle-mounted terminal and a vehicle; a platform protocol is followed between the vehicle-mounted terminal and a monitoring platform; and a format of CAN bus data and a storage format of the CAN bus data in the platform protocol are redefined, so that the vehicle-mounted terminal can adapt to a new vehicle bus protocol, and a uniform protocol specification is kept between the vehicle-mounted terminal and the monitoring platform. Through adoption of the method, a vehicle-mounted terminal firmware and a monitoring platform service program do not need to be modified, the data format of the vehicle-mounted terminal is standardized, and a formatted data structure is transmitted to the terminal in order to adapt to the new bus protocol, so that the system adaptability is enhanced, and the system maintenance burden is lowered.

Owner:SHANDONG ACAD OF SCI INST OF AUTOMATION

A system and method for continuous integration report publishing

InactiveCN106021303BEasy version managementEasy to browseHardware monitoringWebsite content managementContinuous integrationIntegrated controller

The invention provides a continuous integrated report releasing system and method, and belongs to the field of cloud computing. The continuous integrated report releasing system includes a report metadata database, a report display style database, a report template database, a markup language display engine, a version management system, a continuous integrated controller, and a versioning report generator. The continuous integrated report releasing method includes; S1, under the control of the continuous integrated controller, the system generates a versioning report from an original report according to metadata of the report, and displays the versioning report; and S2, the versioning report generator generates a structural report from the original report according to a report template.

Owner:BEIJING QING YUAN TECH CO LTD

Design method of a binary-in-one boot program and kernel program

ActiveCN103823664BBinary unification implementationImprove portabilityOperational speed enhancementProgram loading/initiatingSoftware engineeringDesign methods

A setting method for binary integration of a Boot program and a kernel program is described, which includes that: unified configuration on configuration files of different control chips is performed, the control chips are identified according to hardware information, and code flows of different control chips are modified to implement the binary integration of the Boot program; and kernel configurations of different control chips are unified, and compiling coexistence configuration and running coexistence configuration on different control chips is performed to implement the binary integration of the kernel program. By the method of the disclosure, use of the same software version for two or more different control chips may be realized.

Owner:ZTE CORP

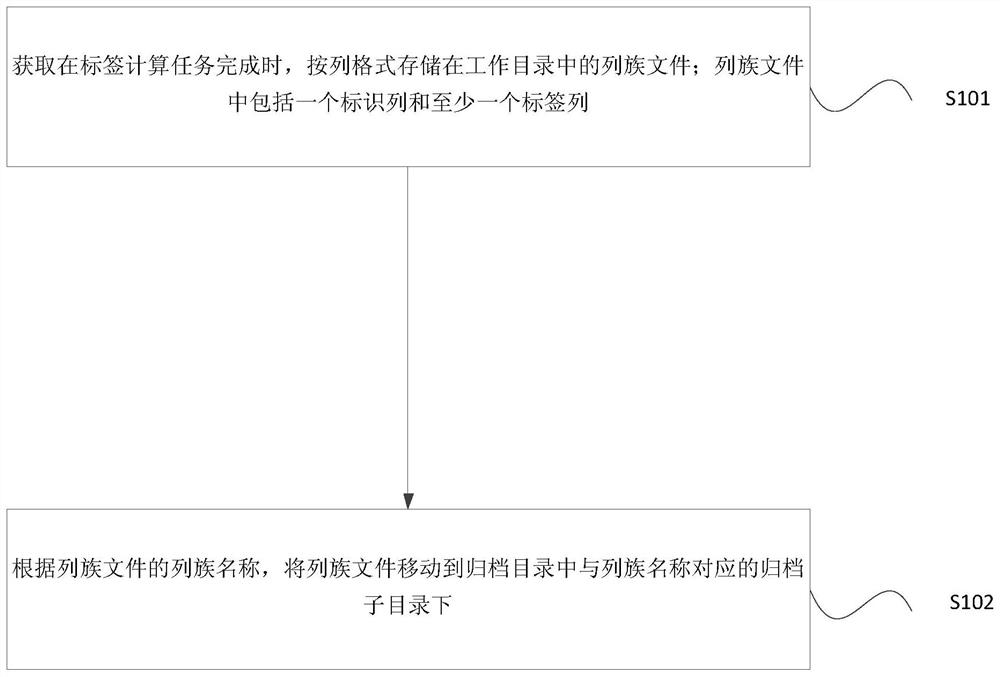

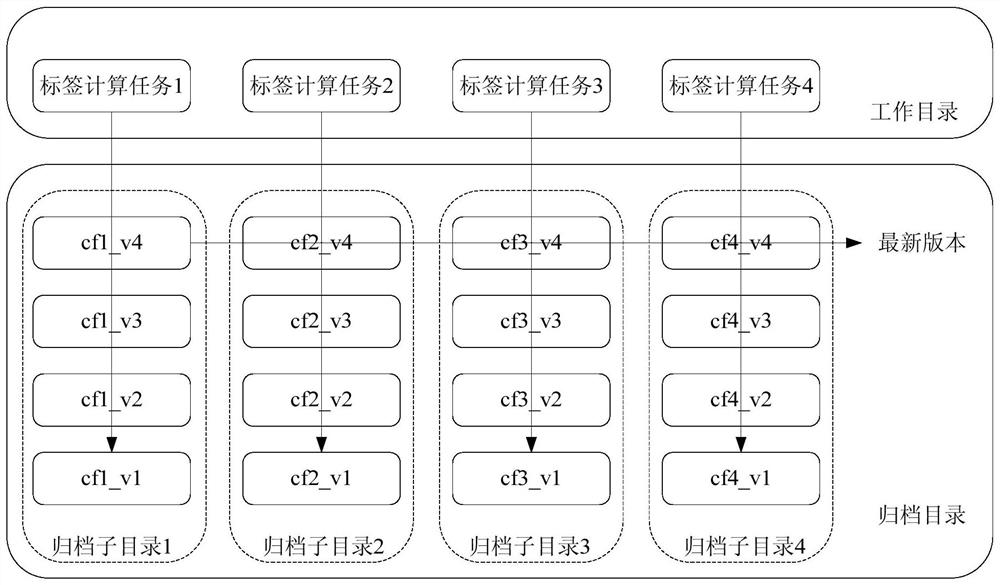

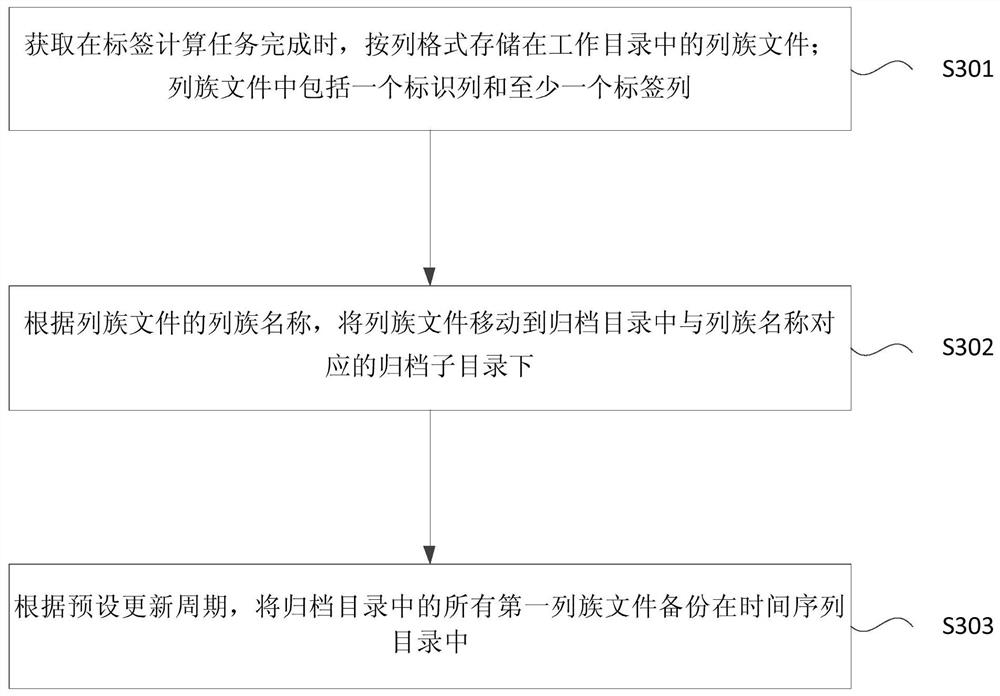

Storage method and device for labeling system data

ActiveCN107330024BReduce movementImprove batch read and write throughputDatabase distribution/replicationSpecial data processing applicationsEngineeringDirectory

Owner:HUAWEI MACHINERY

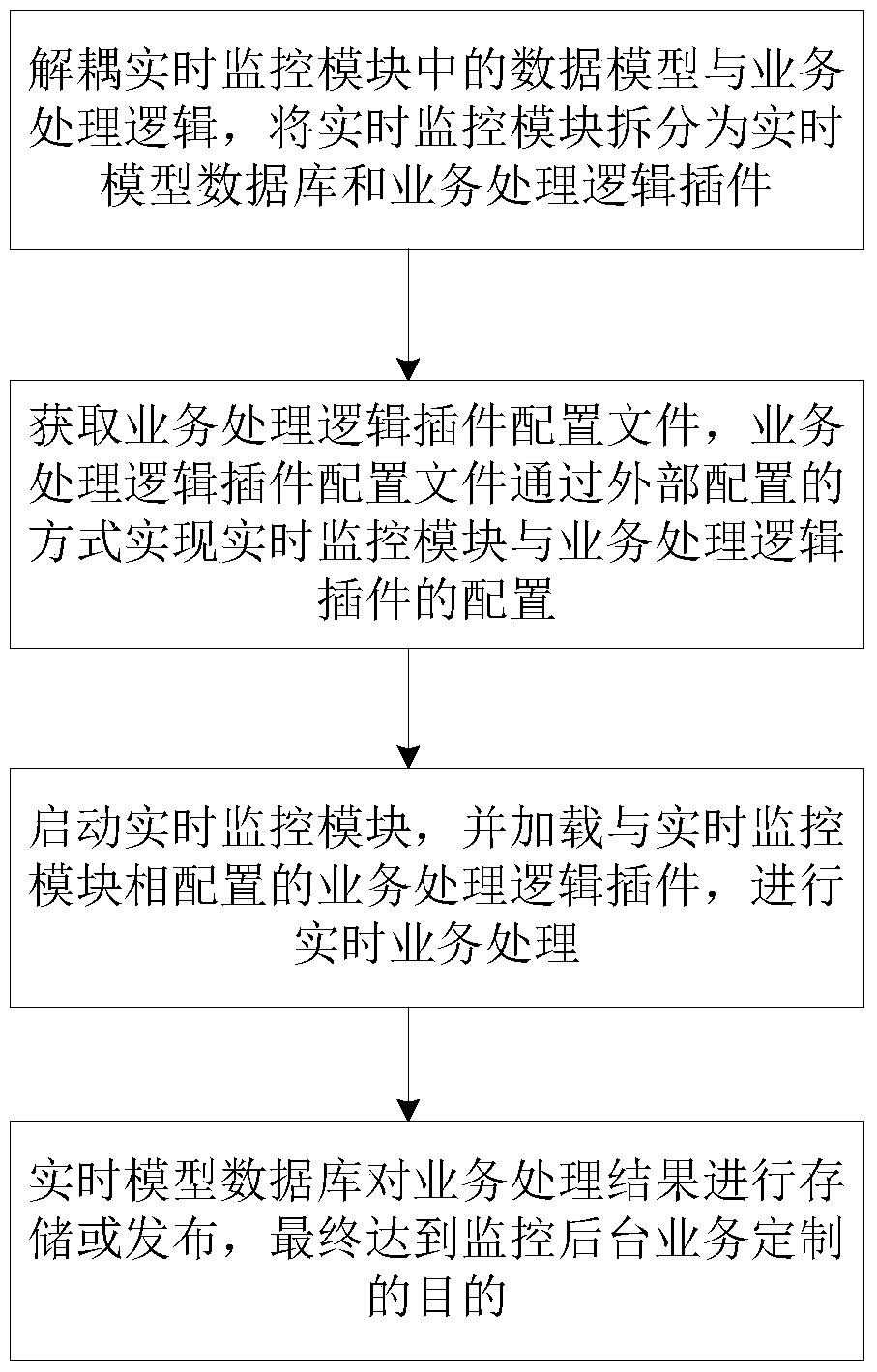

Plug-in-based monitoring background business customization method and system

ActiveCN105760272BEasy for secondary developmentSimplify workloadHardware monitoringData acquisitionData acquisition module

Owner:SHANDONG LUNENG SOFTWARE TECH

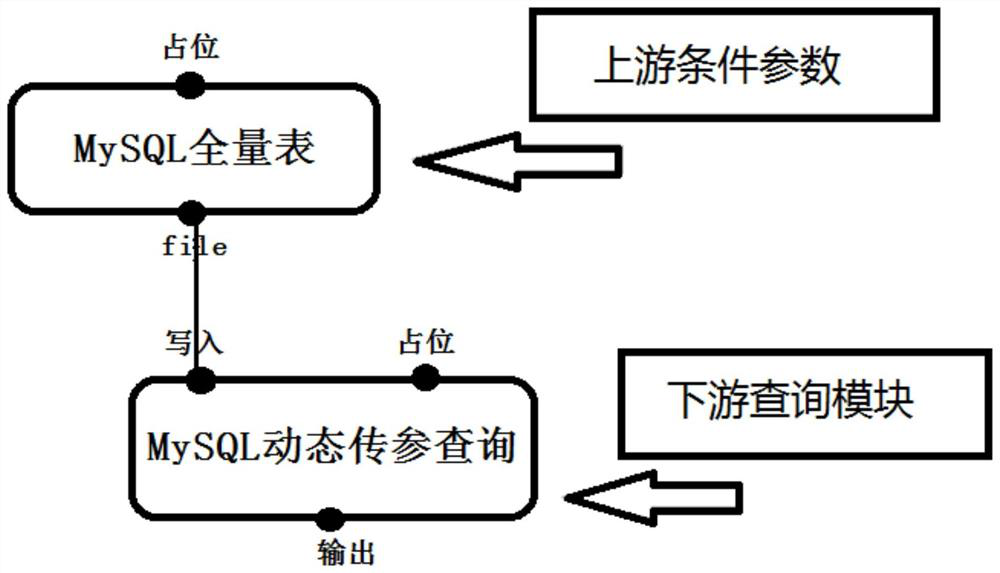

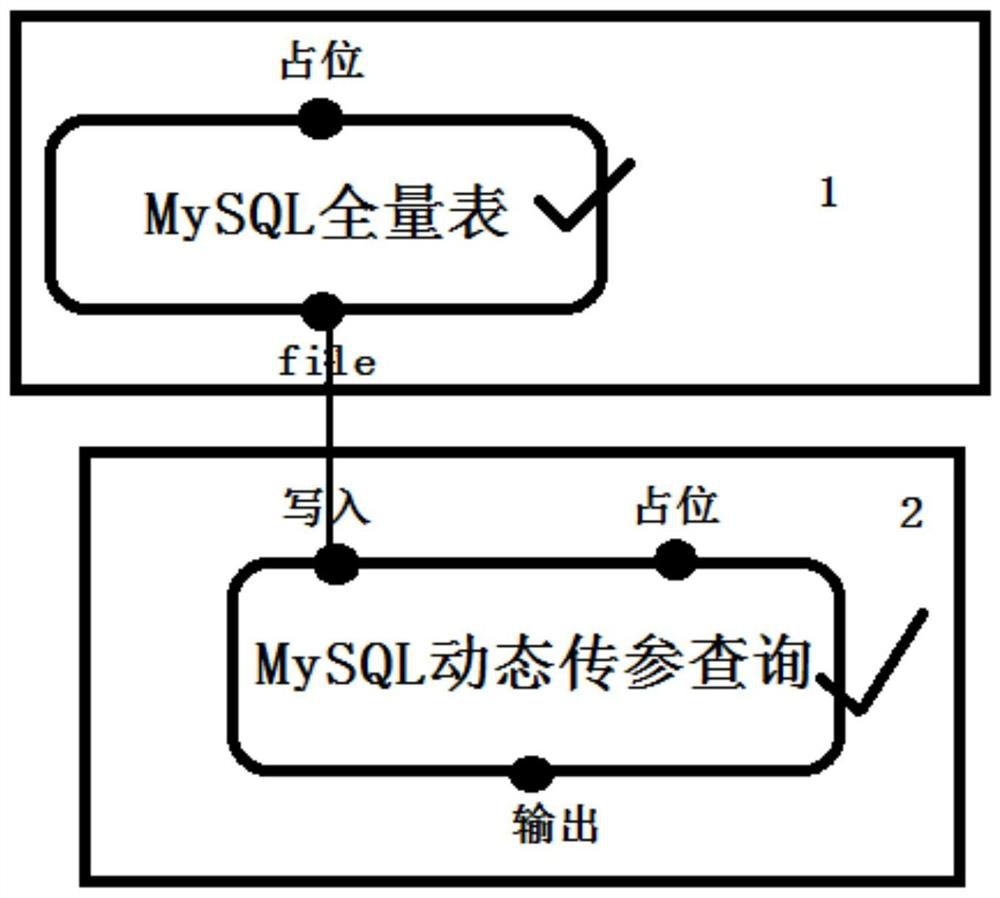

Relational database query method and device supporting dynamic parameters

PendingCN112749222AImprove work efficiencyReduce Duplicate Work ItemsDatabase management systemsSpecial data processing applicationsData queryDynamic query

The invention discloses a relational database query method and device supporting dynamic parameters. The method comprises the steps of carrying out registration on a newly-added data source, and configuring corresponding related information; carrying out dynamic query to transmit dynamic parameters wanted by a user; carrying out result query on the configured data source parameters and query statement parameters by the program; recording the query time and enabling a result to fall into the database; and storing the user query data in a fixed data address for visual preview. According to the invention, dynamic target database query is carried out by configuring query conditions for dynamic parameter pairs, service functions are modularized and parameterized, and the process is visualized, so that the functions are used in the working and production processes, the working efficiency can be greatly improved, the whole process is visualized and standardized, version management is easy, the threshold for users to use and the complexity of data processing are reduced, and dynamic data query can be completed in any environment and any database.

Owner:北京睿企信息科技有限公司 +1

Physical circuit modeling and virtual-real correspondence method for secondary system of smart substation

ActiveCN104732021BEasy to findEasy to customizeData processing applicationsSpecial data processing applicationsComputer architectureSmart substation

The invention discloses a secondary system physical loop modeling method of an intelligent substation. The secondary system physical loop modeling method of the intelligent substation includes the steps that firstly, a designer of an equipment manufacturer configures a physical loop IPCD file through a configuration tool, and a device board card and a physical end port in the IPCD file are described; secondly, a design unit solidifies the IPCD file into a cabinet model, then cable connection among cabinets and optical fiber connection among devices are designed, a substation physical loop SPCD description file is finished, and decoupling design of a logic loop and a physical loop is realized. According to the secondary system physical loop modeling and void and actuality correspondence method of the intelligent substation, an SCD file and an SPCD file correspond to each other in a void and actuality correspondence mode when a design graph is finished, void and actuality integration design description is also realized, design efficiency and accuracy are improved, many kinds of application software can be more easily developed and customized based on a solid loop model file, the engineering on-site debug method is enriched, and construction efficiency and convenience are improved.

Owner:STATE GRID CORP OF CHINA +5

A wireless upgrade system and method for gis database of locomotive cir equipment

ActiveCN107749841BReduce difficultyReduce workloadGeographical information databasesTransmissionIp addressProgram planning

Owner:BEIJING BEIJIAO XINKONG TECH

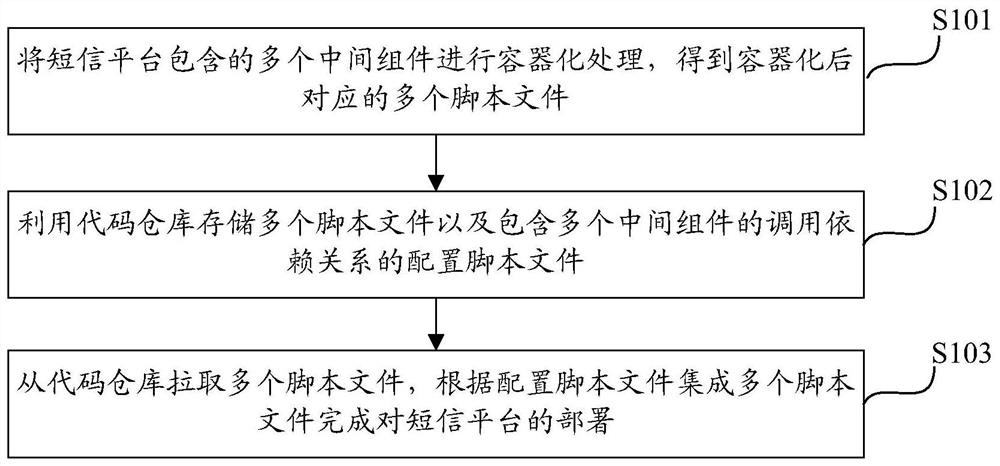

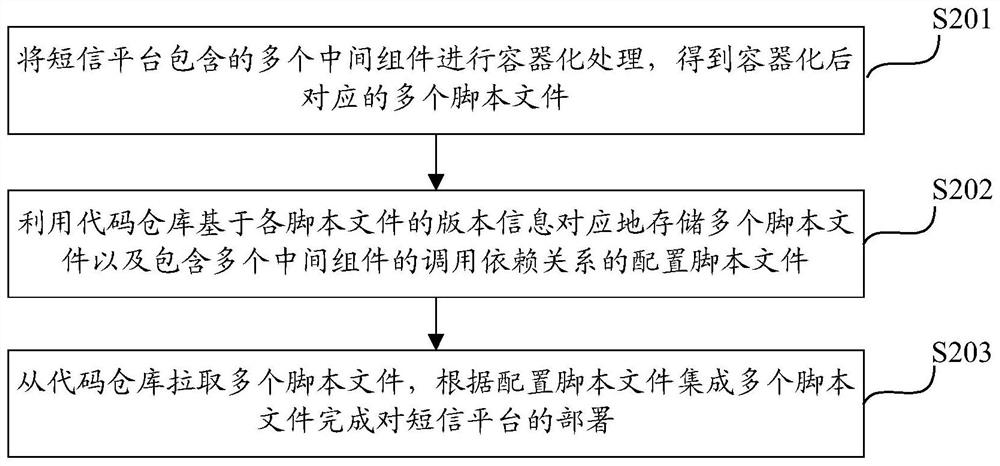

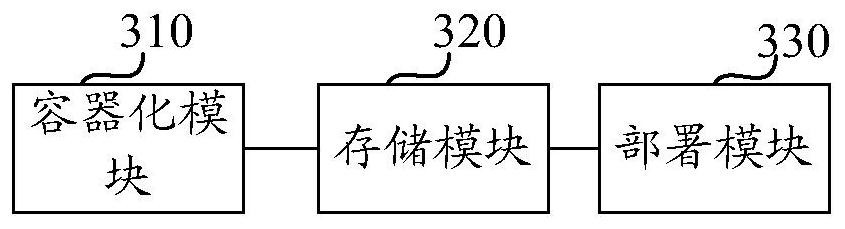

Short message platform deployment method and device, computing equipment and computer storage medium

PendingCN112015436ARapid deploymentImplement deploymentVersion controlMessaging/mailboxes/announcementsParallel computingSoftware engineering

The invention discloses a short message platform deployment method and device, computing equipment and a computer storage medium. The method comprises steps of carrying out containerization of a plurality of intermediate assemblies contained in a short message platform, and obtaining a plurality of script files corresponding to the containerized short message platform; wherein the intermediate components have a sequential calling dependency relationship; storing a plurality of script files and a configuration script file containing a calling dependency relationship of a plurality of intermediate components by utilizing a code warehouse; and pulling a plurality of script files from the code warehouse, and integrating a plurality of script files according to the configuration script file tocomplete deployment of the short message platform. According to the method, the short message platform can be quickly deployed, and integration of the short message platform is realized according to the successive calling dependency relationship of a plurality of intermediate components, so costs of time, manpower and the like required by deployment can be reduced.

Owner:BEIJING QIHOO TECH CO LTD

A nuclear power plant radiation shielding collaborative design system and its construction method

ActiveCN110210821BRealize traceabilityReduce workloadOffice automationNuclear chemistryCollaborative design

The invention provides a collaborative design system for radiation shielding of a nuclear power plant and a construction method thereof. The collaborative design system includes a design task module, an association module, a design data module and a design data model. The design task module is used to create a design task, and the association module is used to connect the design Task module and design data module; the design data module is used to obtain input data from the upstream design work, and call the design tool to calculate and obtain the output data in combination with the input data; the design data model is used to store the output data; the design task module is also used to calculate according to the output data Data is used to monitor the design progress, start the design quality control process, and create design knowledge for push. The nuclear power plant radiation shielding collaborative design system and its construction method provided by the invention cover the entire design process of radiation shielding design, realize effective collaborative design with related majors, and have good technical effects.

Owner:中广核工程有限公司 +3

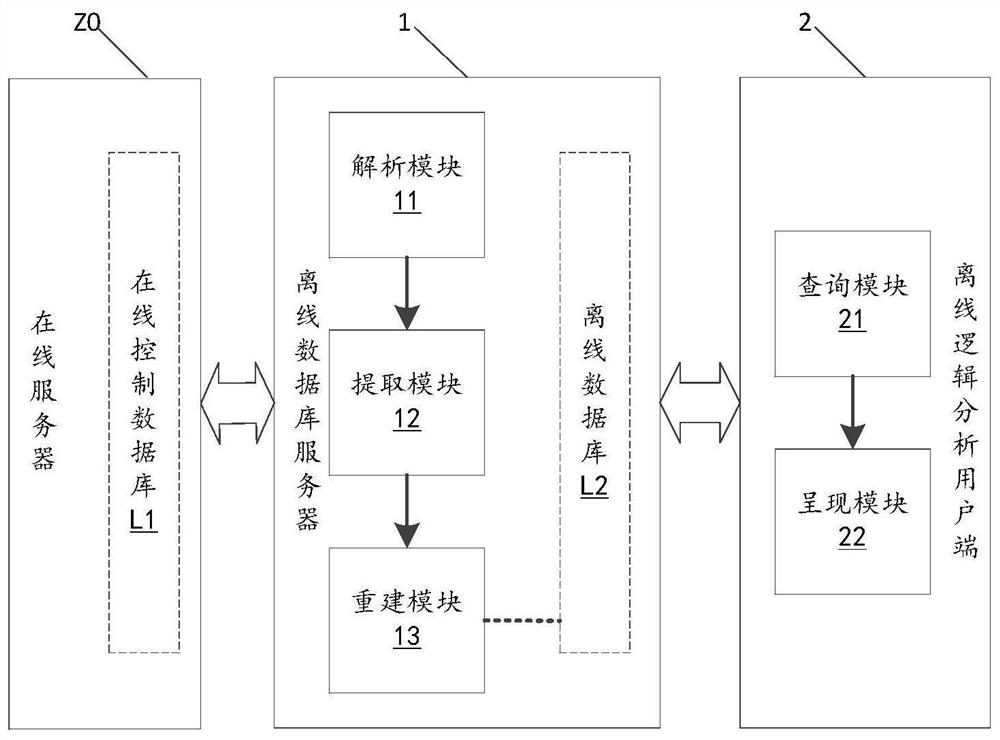

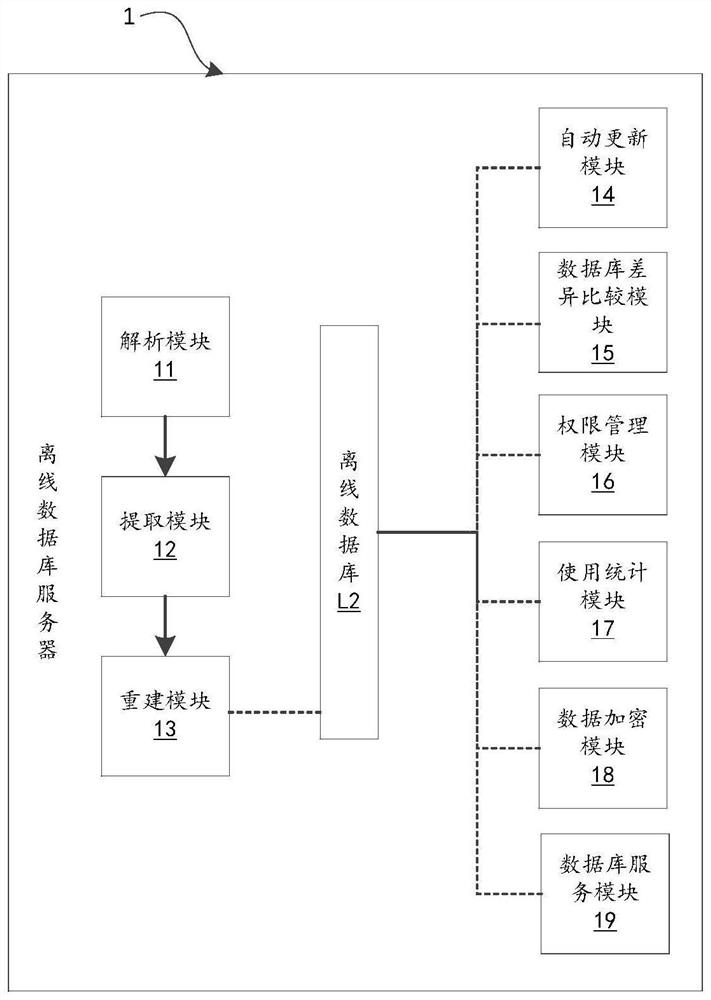

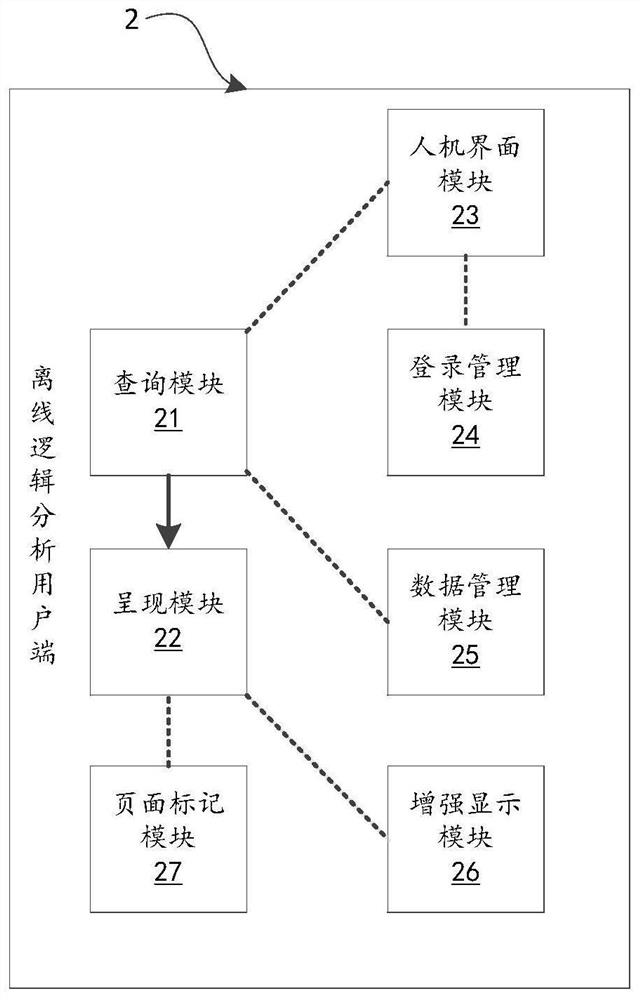

Method and system for construction, synchronization, presentation and analysis of nuclear power dcs offline database

ActiveCN110554675BGuaranteed work efficiencyAvoid human biasTotal factory controlProgramme total factory controlQuery analysisControl data

Owner:TAISHAN NUCLEAR POWER JOINT VENTURE

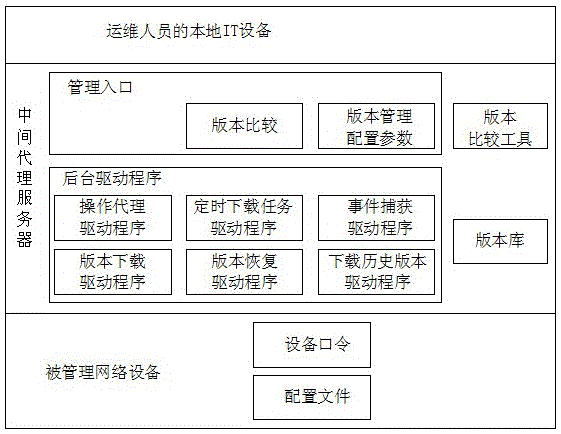

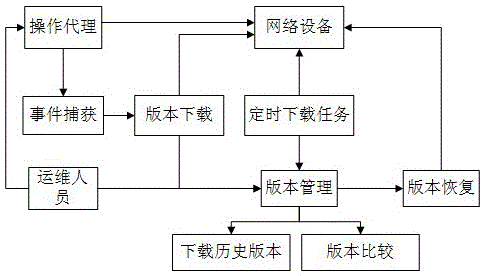

Version management system for configuration files of network devices

ActiveCN103281210BMeet actual business needsPrevent configuration lossData switching networksManagement processNetworked system

The invention discloses the version management system of the configuration file of the network device. It belongs to the field of operation and maintenance auditing technology. Its structure includes management entrance, background driver, and network devices. The management entrance is the operating entrance platform.Complete the following management: version management, version comparison, version management configuration parameters; background drivers include operating proxy drivers, regular download task drivers; network devices are IT devices in the network system; management process is: can directly host the background driver through the hosting background driver.The operating proxy driver of the program performs the version of the configuration file of the network device; or manages the version of the network device through the management of the inlet operation and uses the background driver and use the operation and maintenance protocol.The version management system of the configuration file of the web device of the present invention solves the problem of loss of configuration files caused by accidents when conducting operation and maintenance of network devices.

Owner:江苏瑞宁信创科技有限公司