Patents

Literature

481 results about "Noise attenuation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Noise Attenuation. Spectrum offers several methodologies for the attenuation of swell noise, and often combines them in an iterative sequence to reduce the effects of the noise without harming the primary energy.

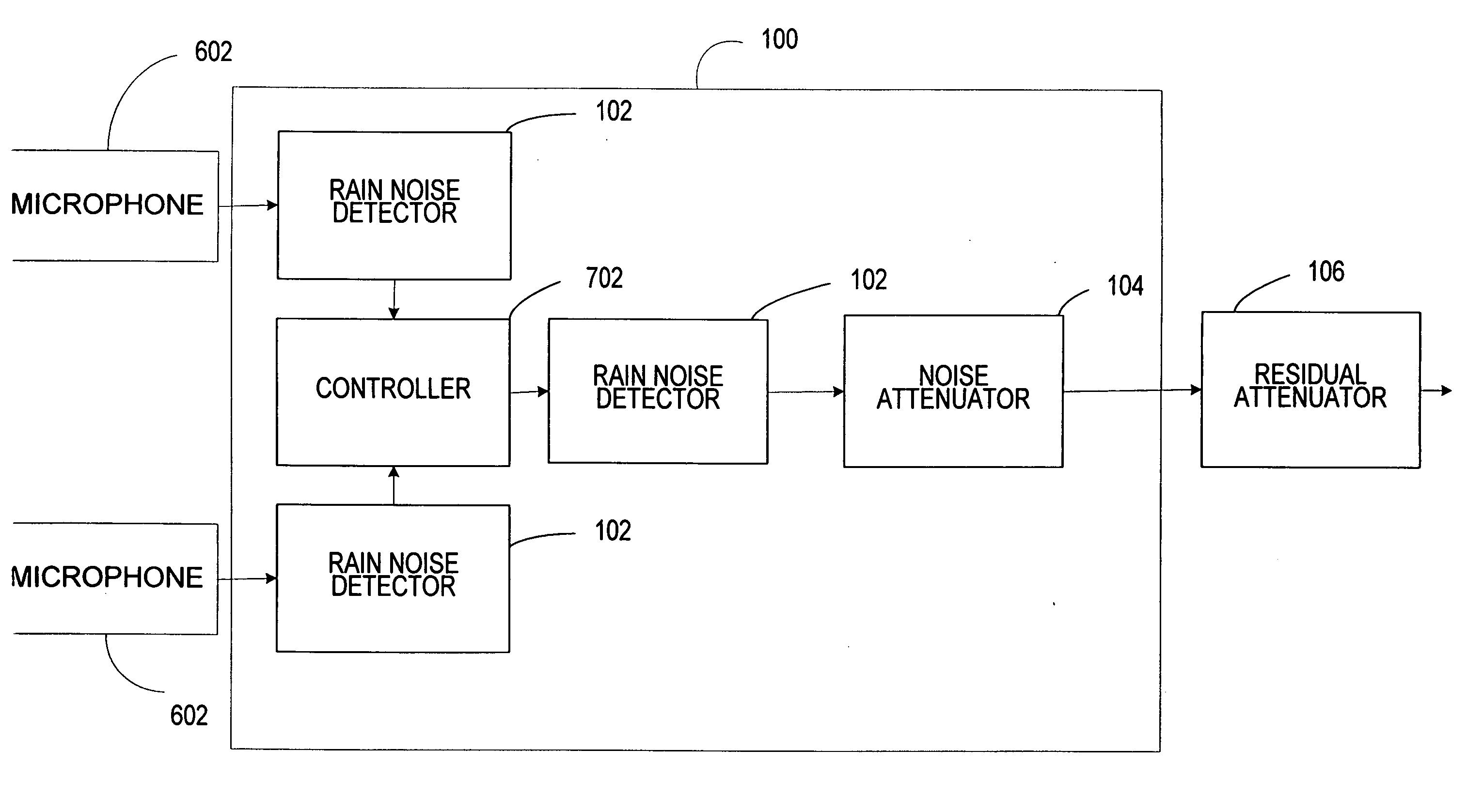

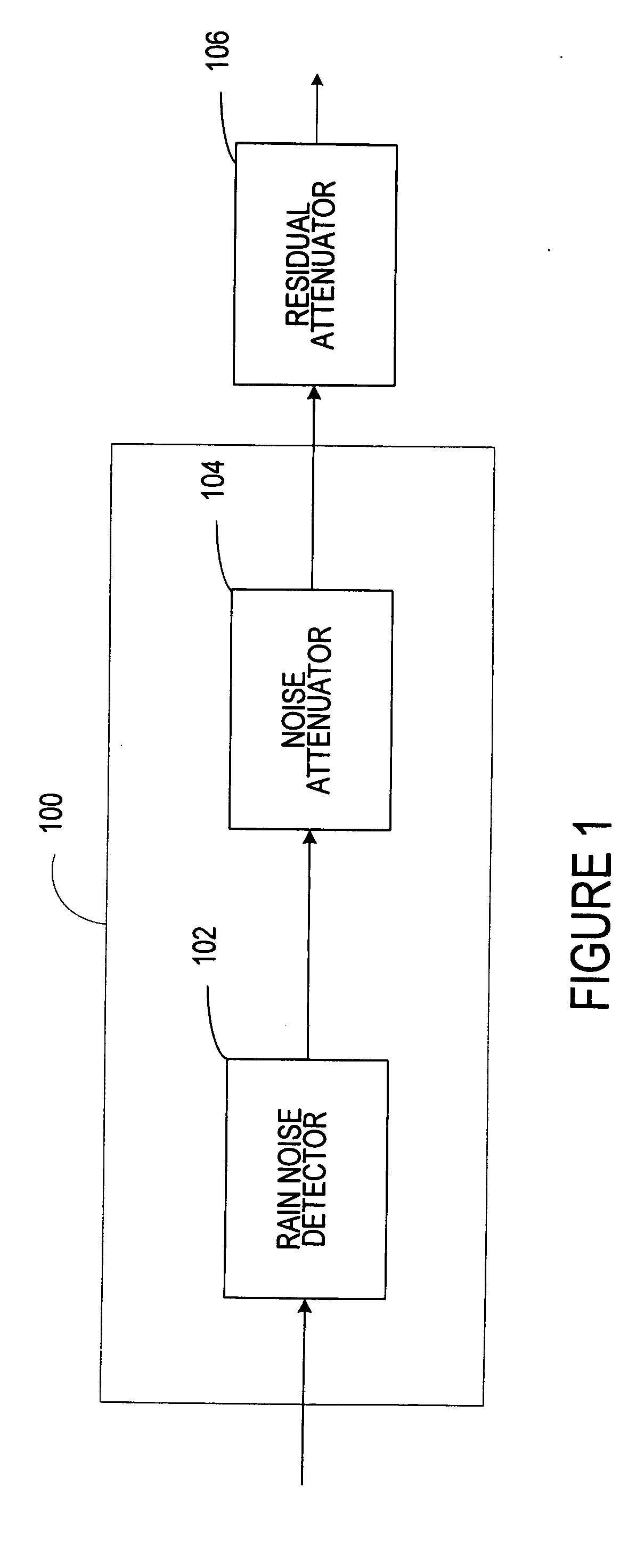

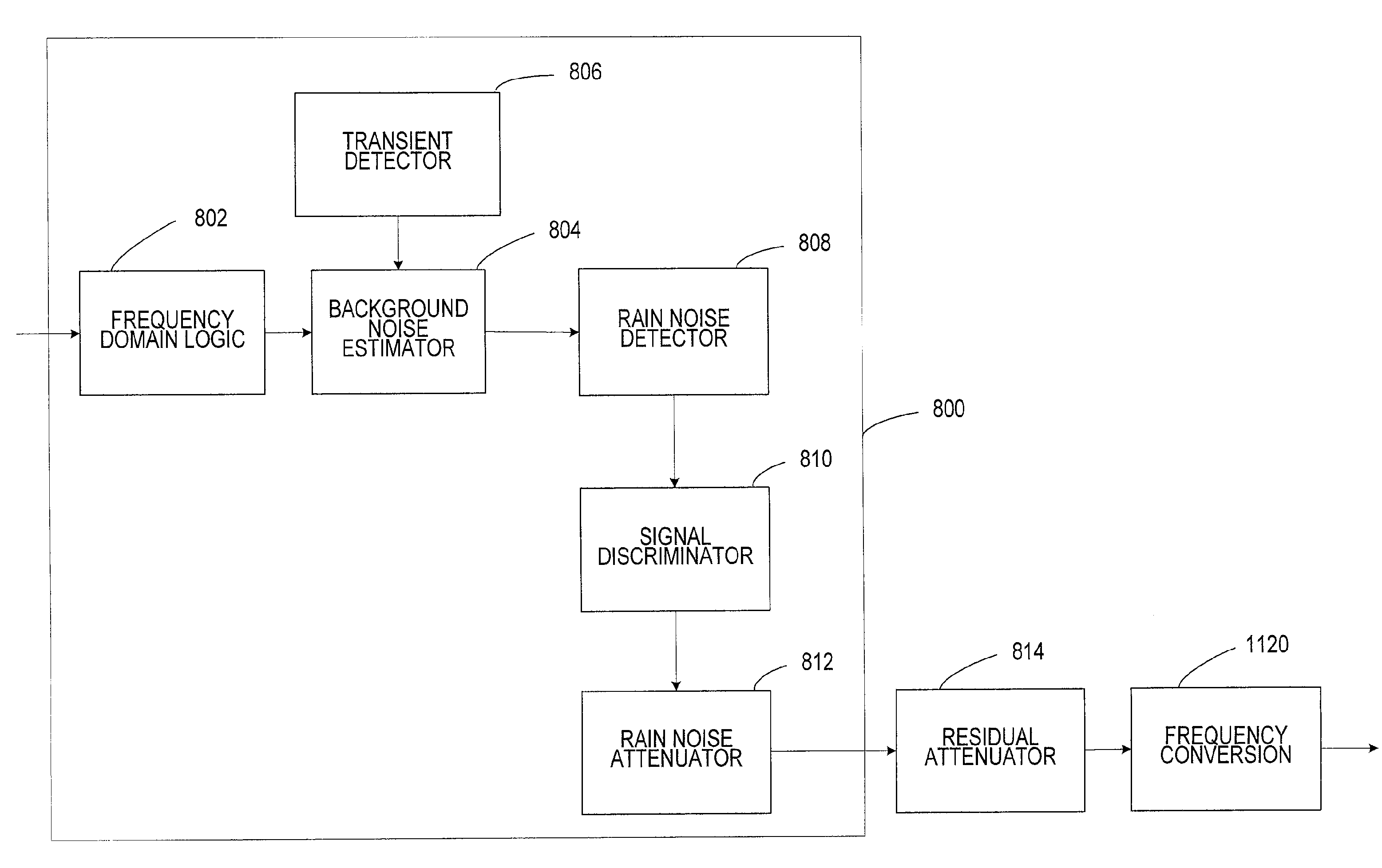

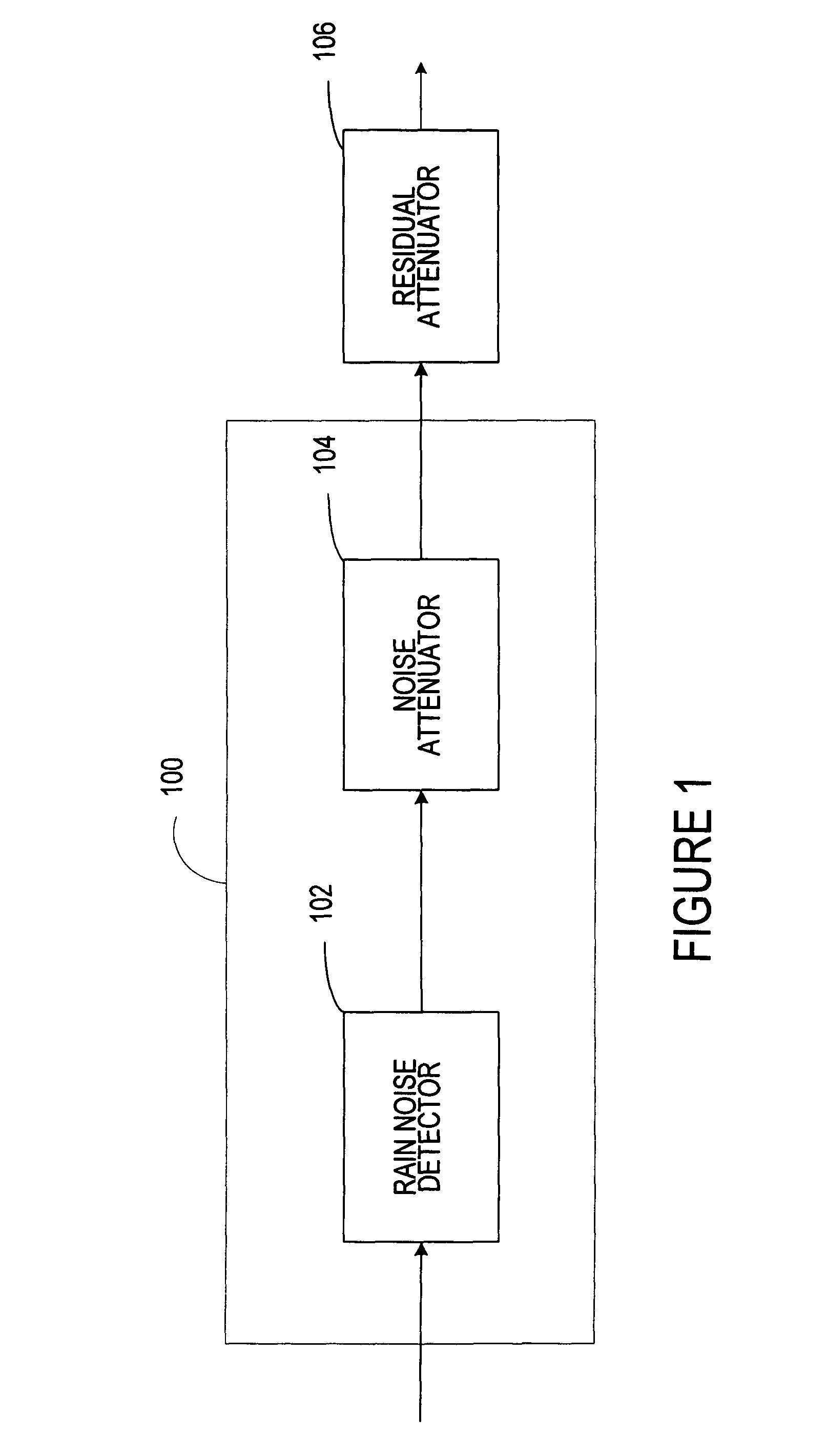

System for suppressing rain noise

ActiveUS20050114128A1Improve processing qualityReduce and dampen noiseTransducer acoustic reaction preventionSpeech recognitionComputer scienceSpeech sound

A voice enhancement logic improves the perceptual quality of a processed signal. The voice enhancement system includes a noise detector and a noise attenuator. The noise detector detects and models the noise associated with rain. The noise attenuator dampens or reduces the rain noise from a signal to improve the intelligibility of an unvoiced, a fully voiced, or a mixed voice segment.

Owner:MALIKIE INNOVATIONS LTD

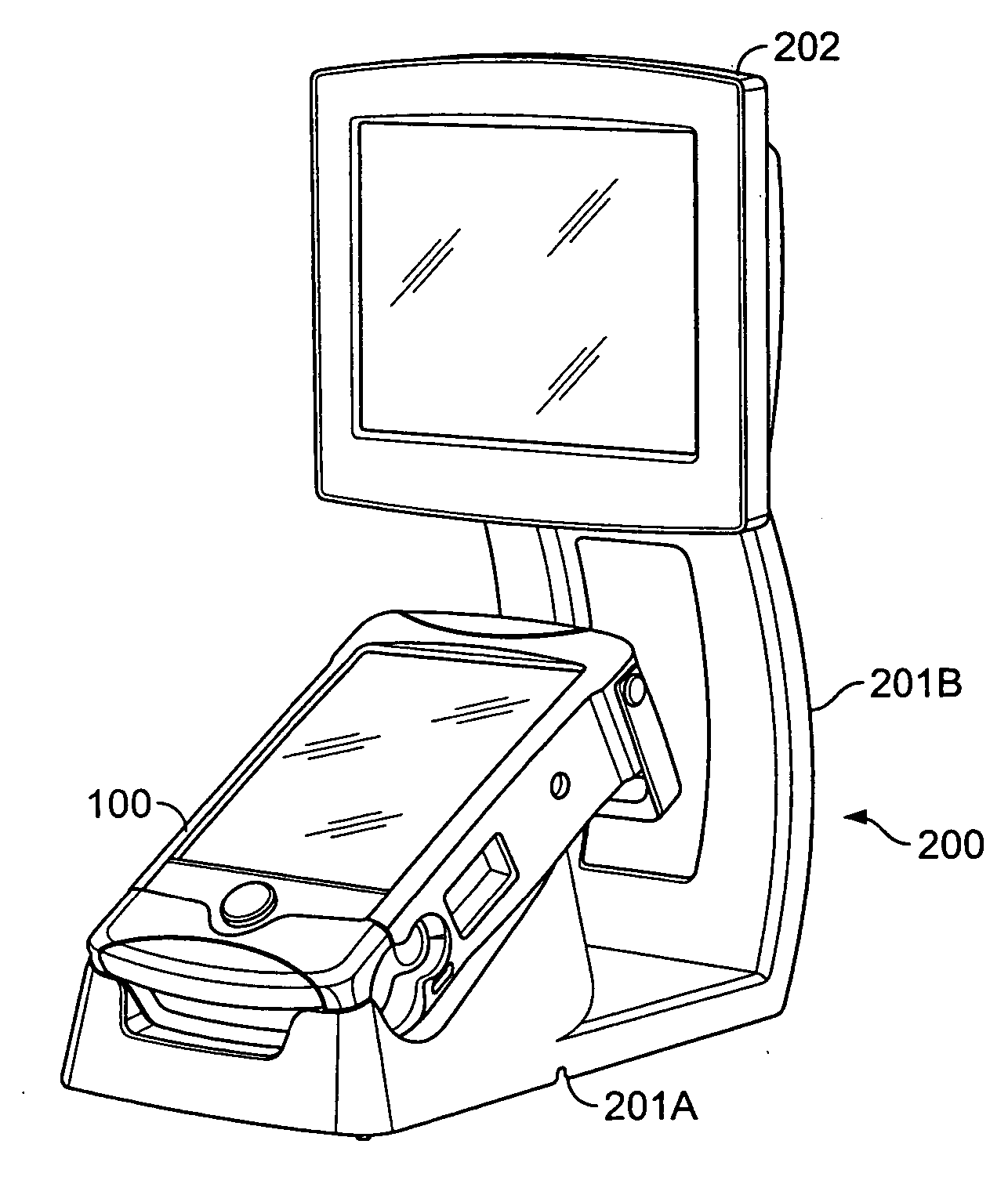

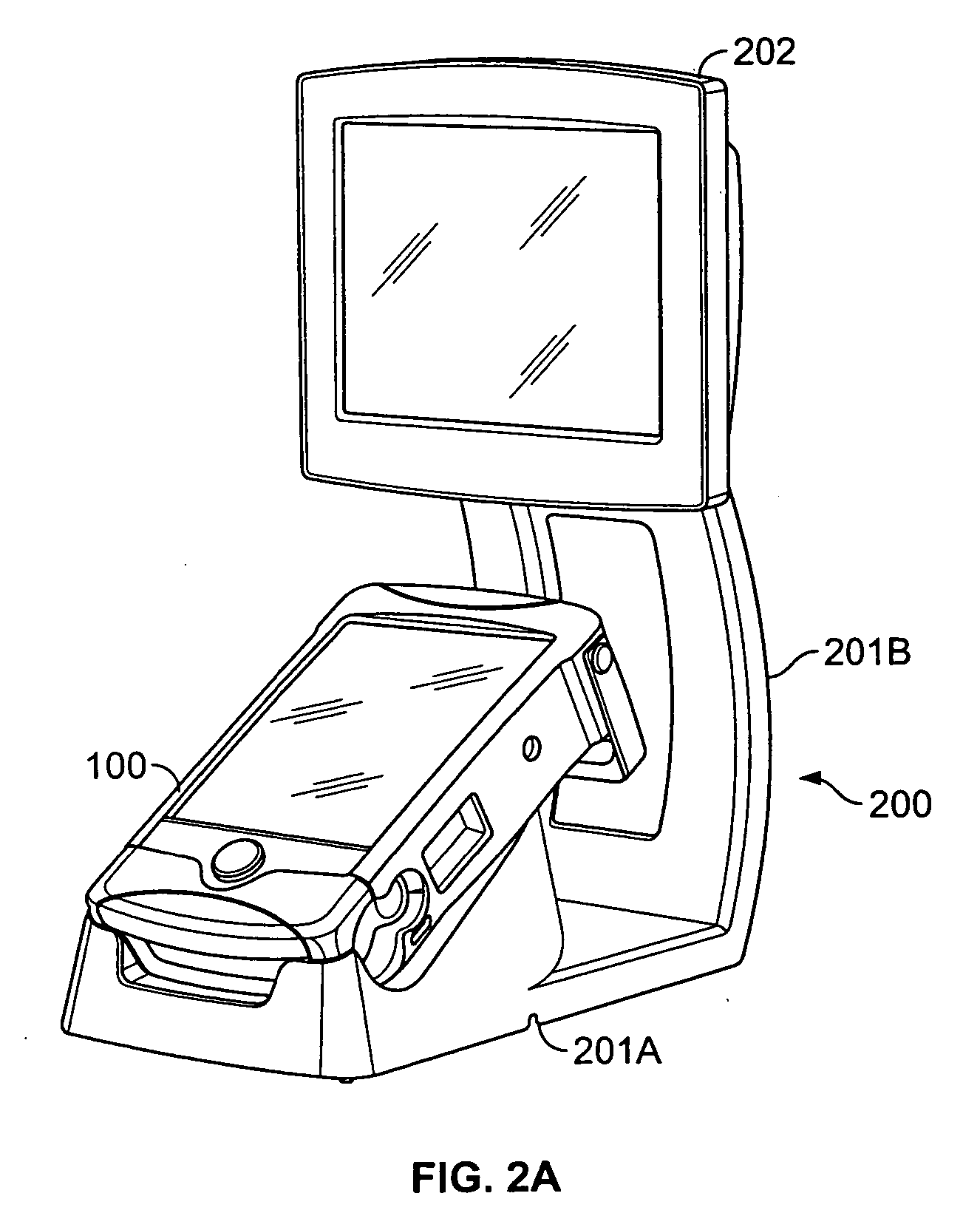

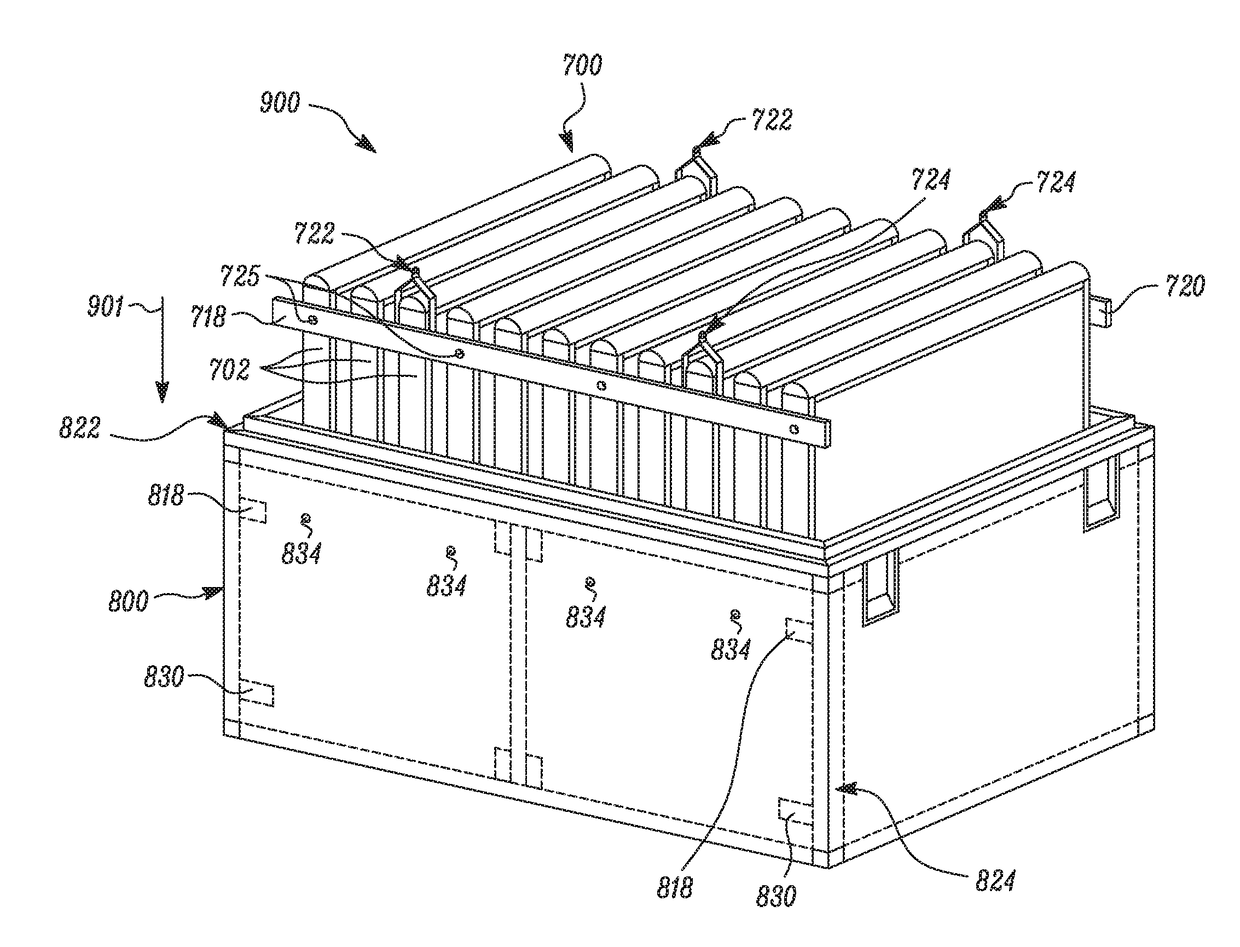

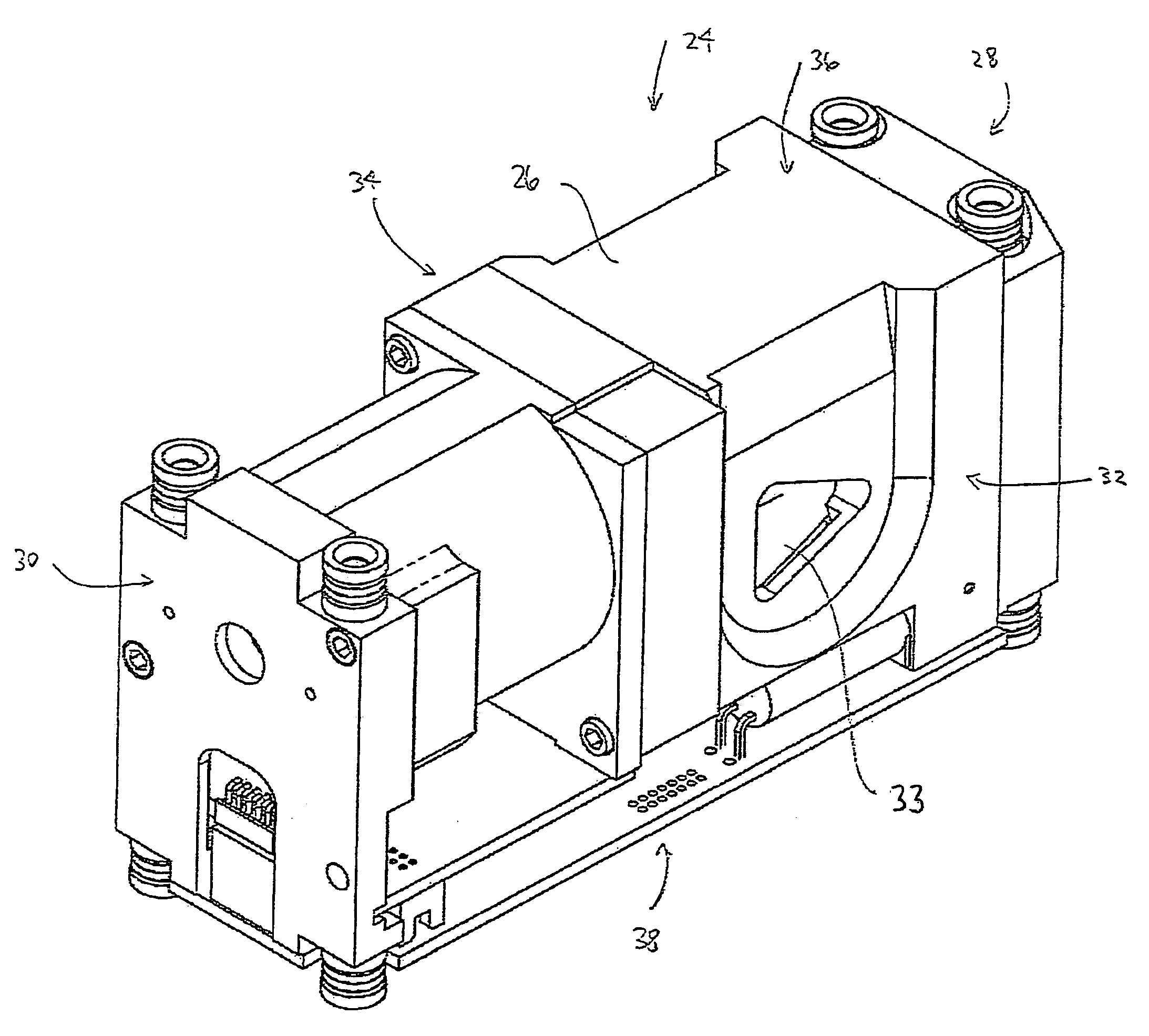

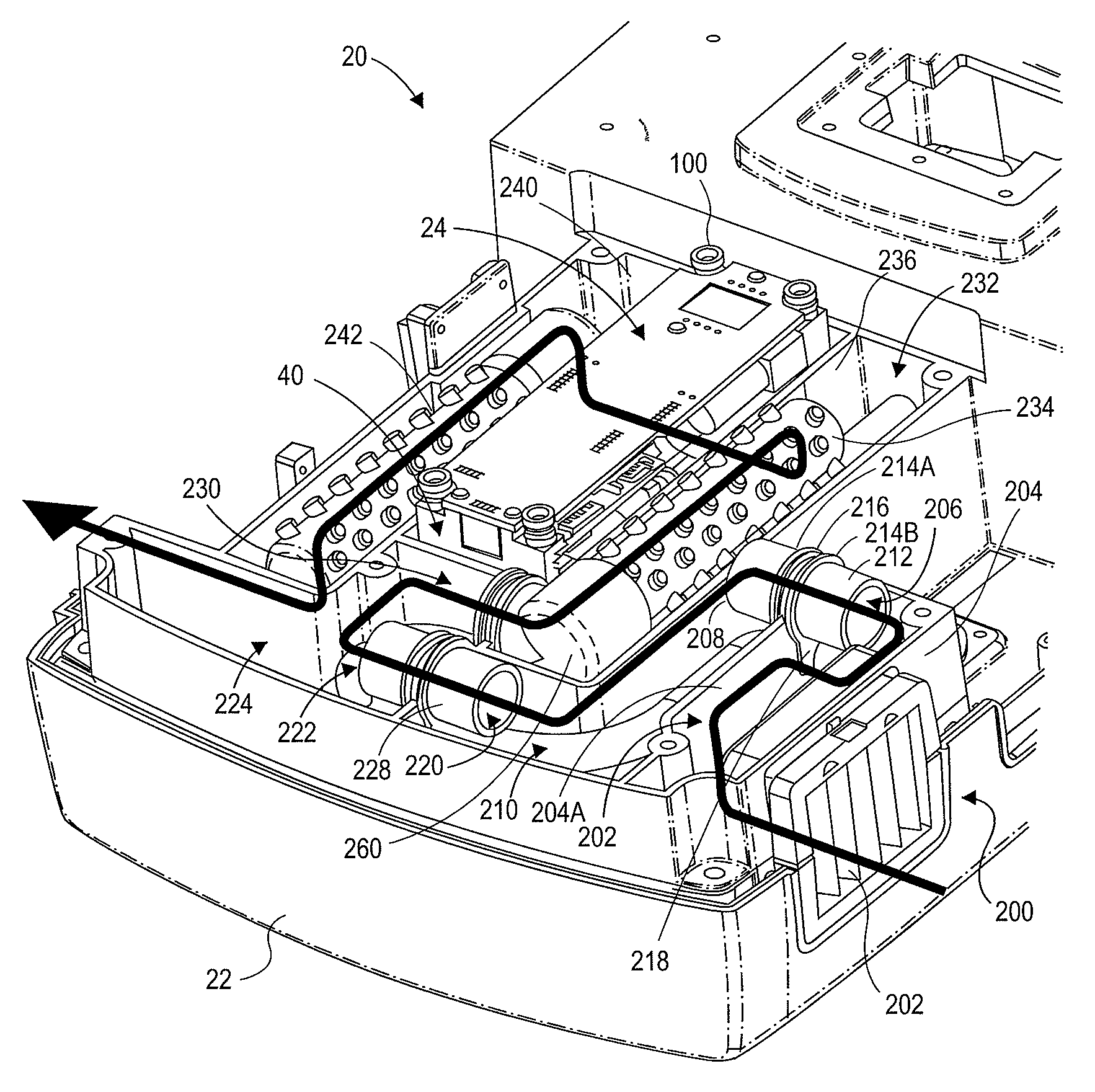

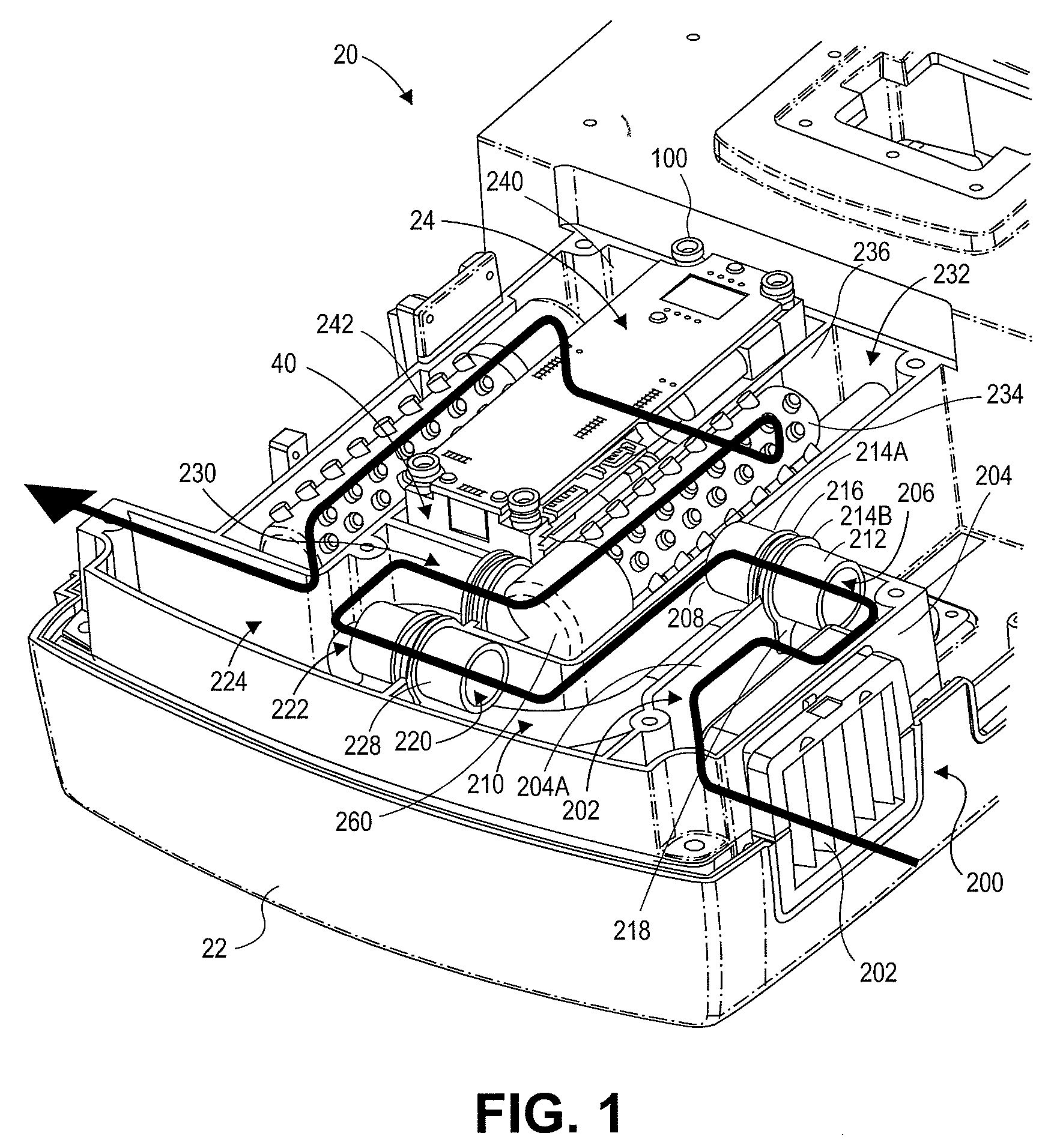

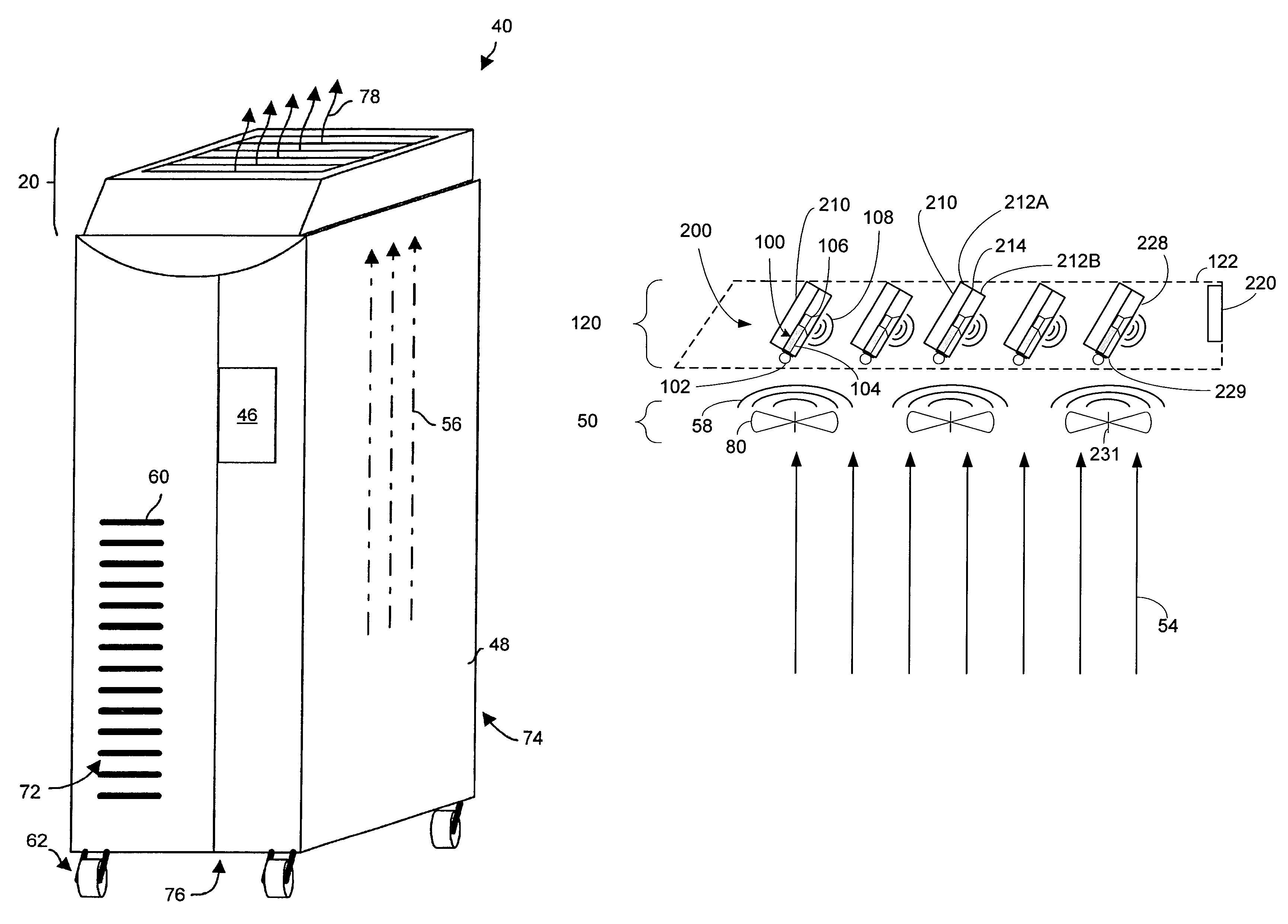

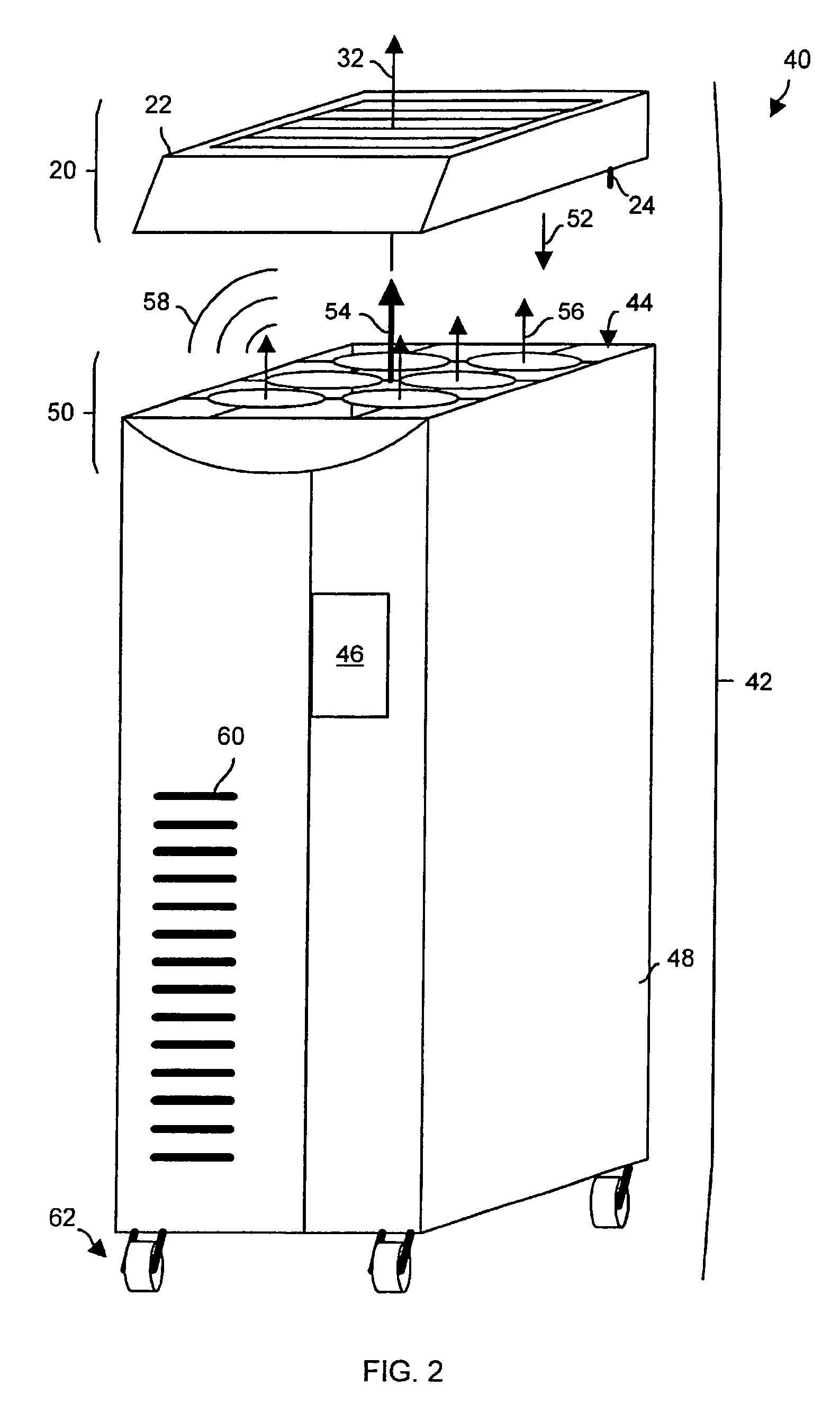

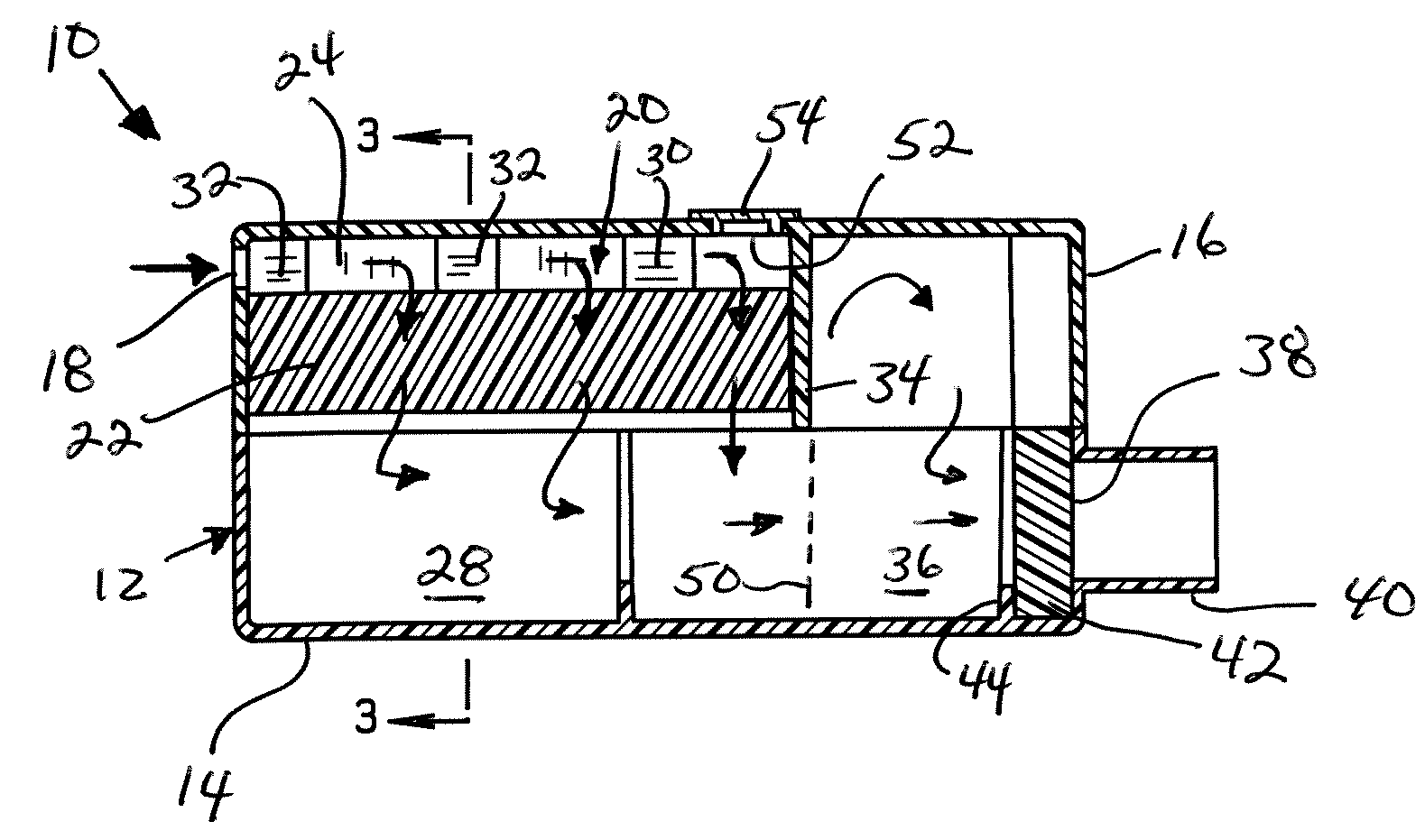

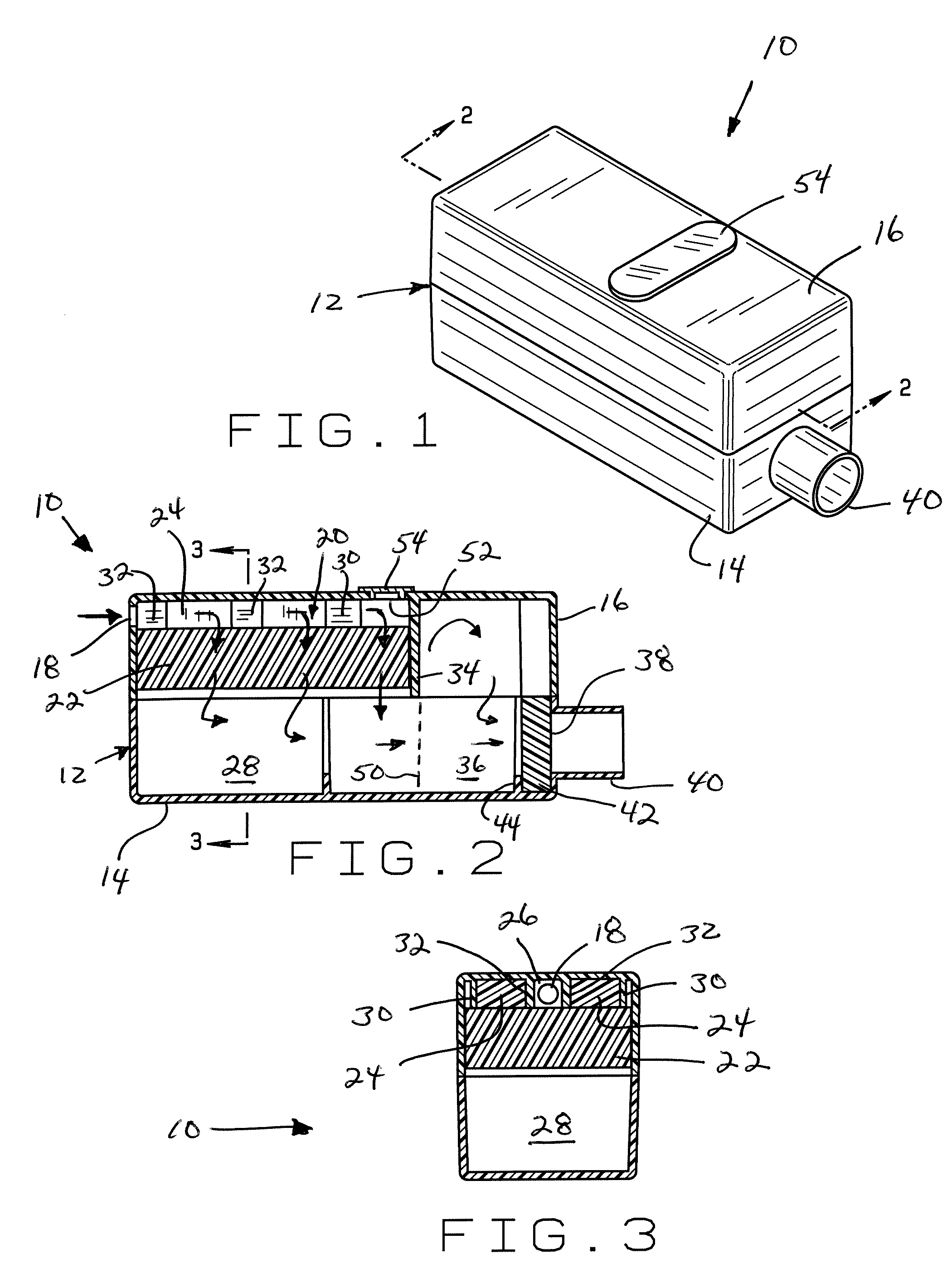

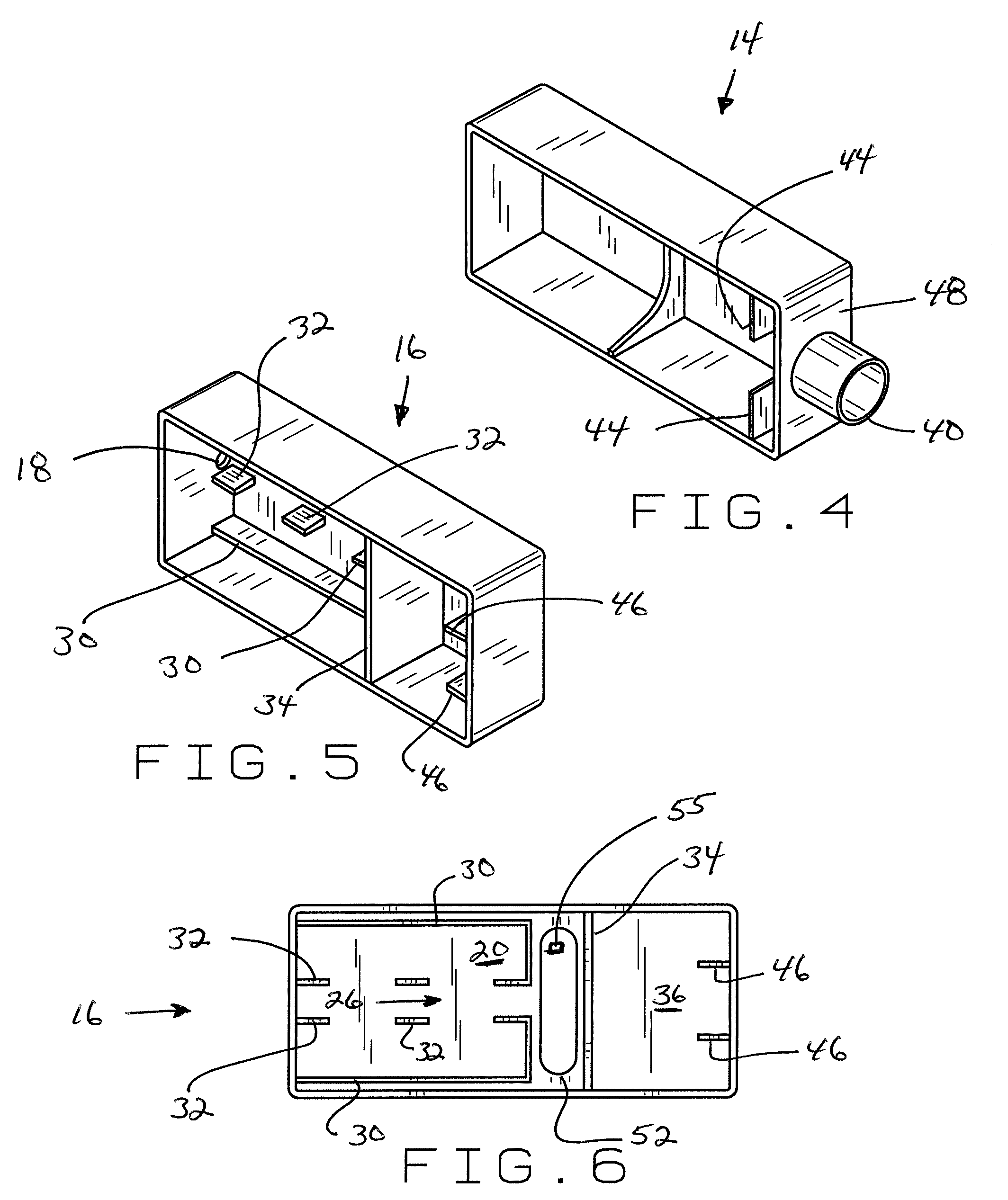

Portable ventilator system

ActiveUS20060144396A1Reduce power consumptionSmall sizeLiquid surface applicatorsPowdered material dispensingPortable ventilatorsEngineering

A portable ventilator uses a Roots-type blower as a compressor to reduce both the size and power consumption of the ventilator. Various functional aspects of the ventilator are delegated to multiple subassemblies having dedicated controllers and software that interact with a ventilator processor to provide user interface functions, exhalation control and flow control servos, and monitoring of patient status. The ventilator overcomes noise problems through the use of a noise attenuating system comprising noise reducing pressure compensating orifices on the Roots blower housing and multiple noise reducing chambers. The ventilator is configured with a highly portable form factor, and may be used as a stand-alone device or as a docked device having a docking cradle with enhanced interface and monitoring capabilities.

Owner:VYAIRE MEDICAL 203 INC

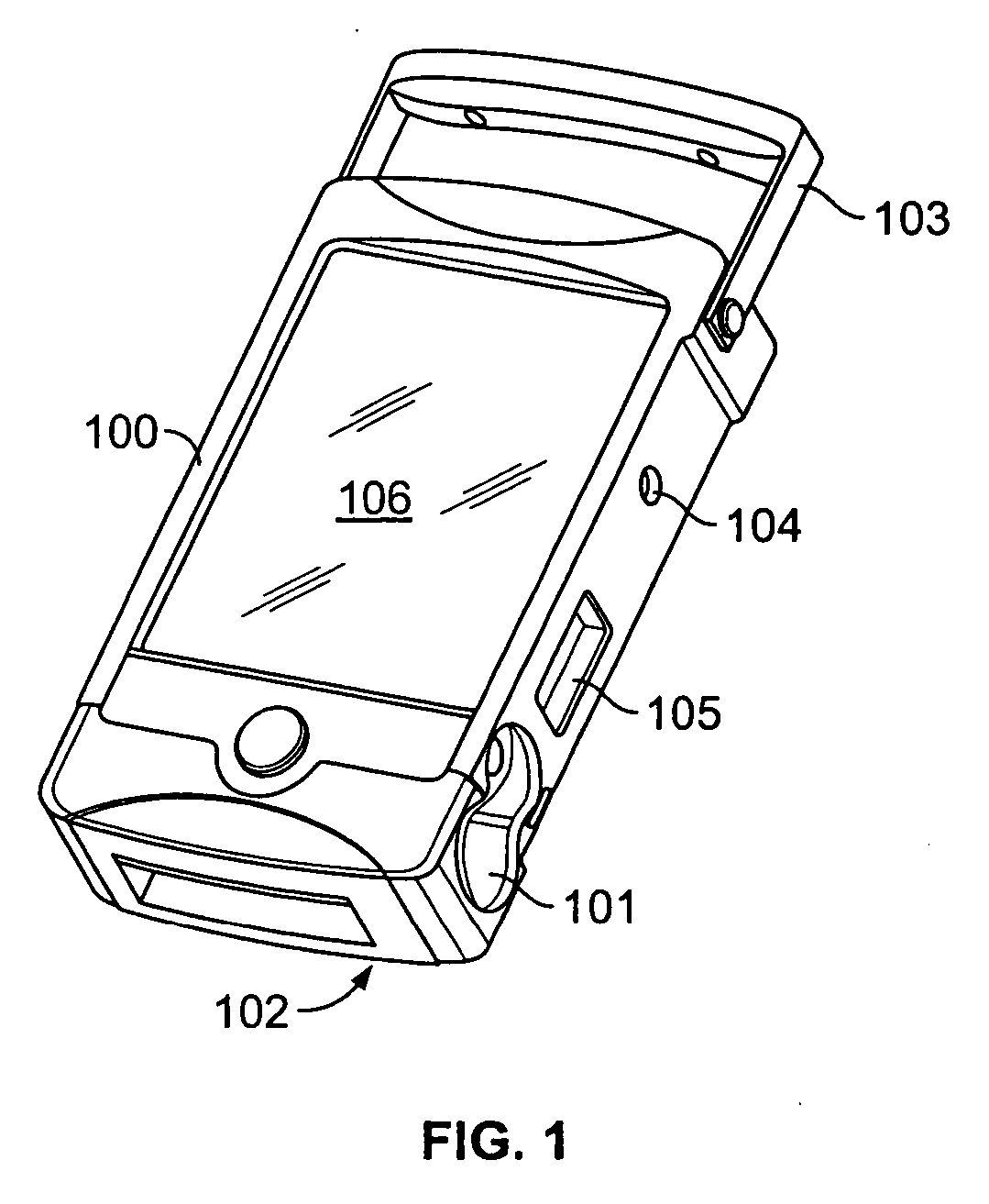

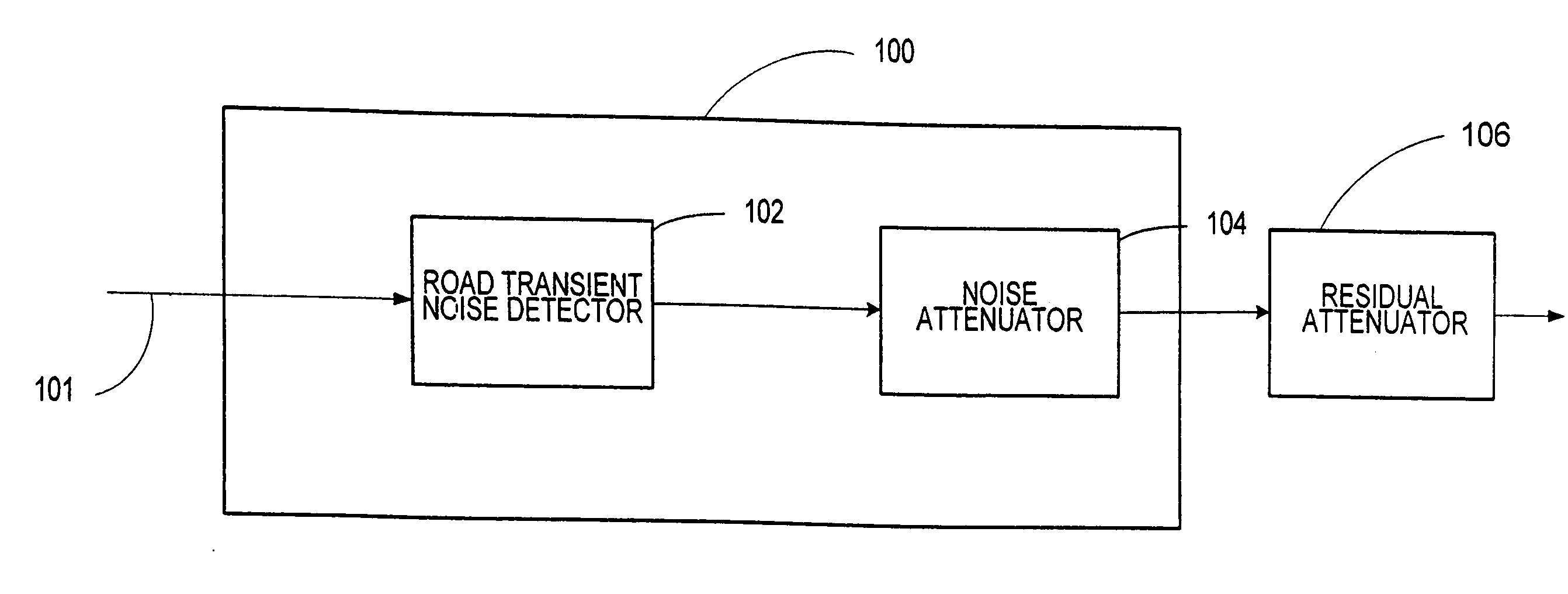

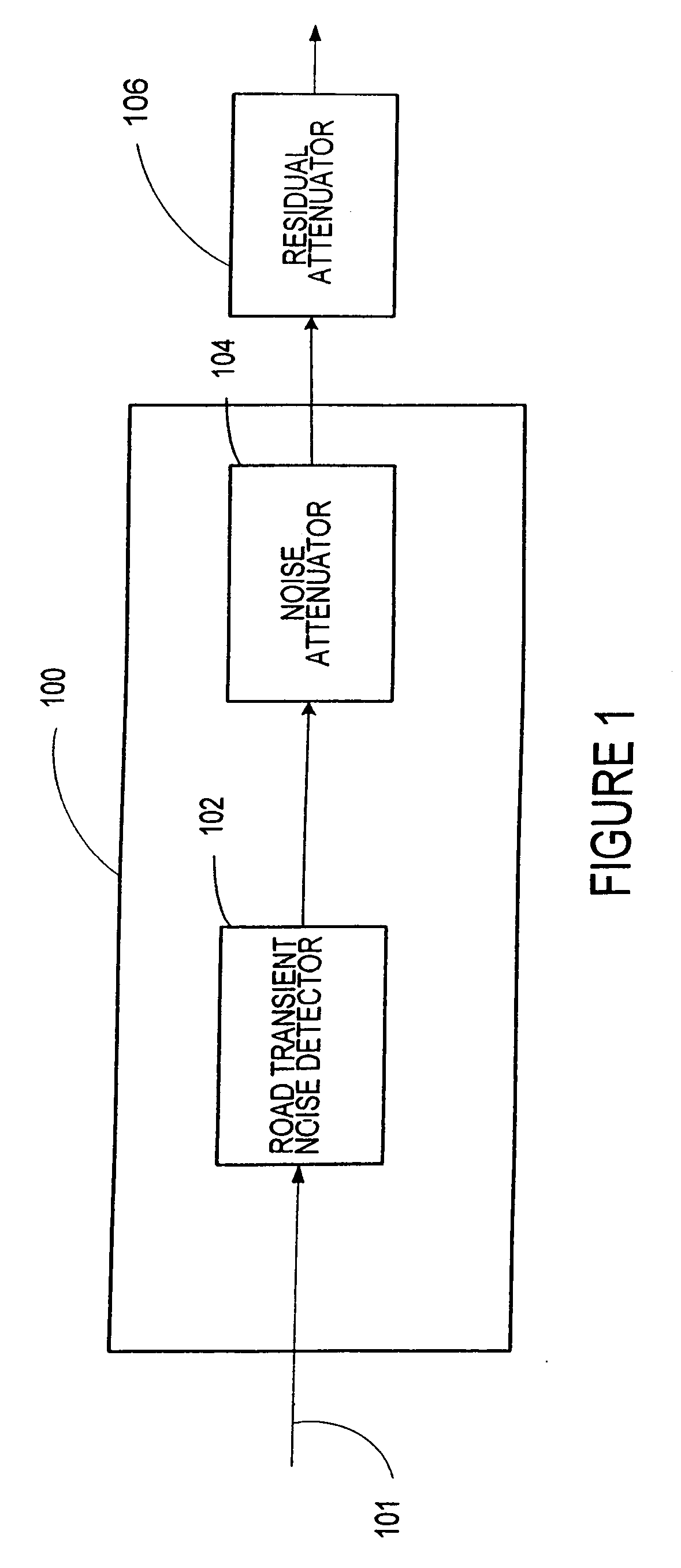

Minimization of transient noises in a voice signal

ActiveUS20060100868A1Improve processing qualityImprove reception qualityTransducer acoustic reaction preventionSpeech recognitionFrequency spectrumEngineering

A voice enhancement system is provided for improving the perceptual quality of a processed voice signal. The system improves the perceptual quality of a received voice signal by removing unwanted noise from a voice signal recorded by a microphone or from some other source. Specifically, the system removes sounds that occur within the environment of the signal source but which are unrelated to speech. The system is especially well adapted for removing transient road noises from speech signals recorded in moving vehicles. Transient road noises include common temporal and spectral characteristics that can be modeled. A transient road noise detector employs such models to detect the presence of transient road noises in a voice signal. If transient road noises are found to be present, a transient road noise attenuator is provided to remove them from the signal.

Owner:MALIKIE INNOVATIONS LTD

Baffle assembly for a duct

ActiveUS20180291781A1Continuous combustion chamberSilencing apparatusEngineeringMechanical engineering

A noise attenuation baffle assembly for a duct, is provided. The baffle assembly includes a number of baffles arranged in a spaced apart relation to one another. Each baffle includes a first side and a second side. The baffle assembly further includes a first bracket coupled to the first side of each baffle of the number of baffles. The baffle assembly further includes a second bracket coupled to the second side of each baffle of the number of baffles. The first and the second bracket are configured to be coupled to the duct.

Owner:SOLAR TURBINES

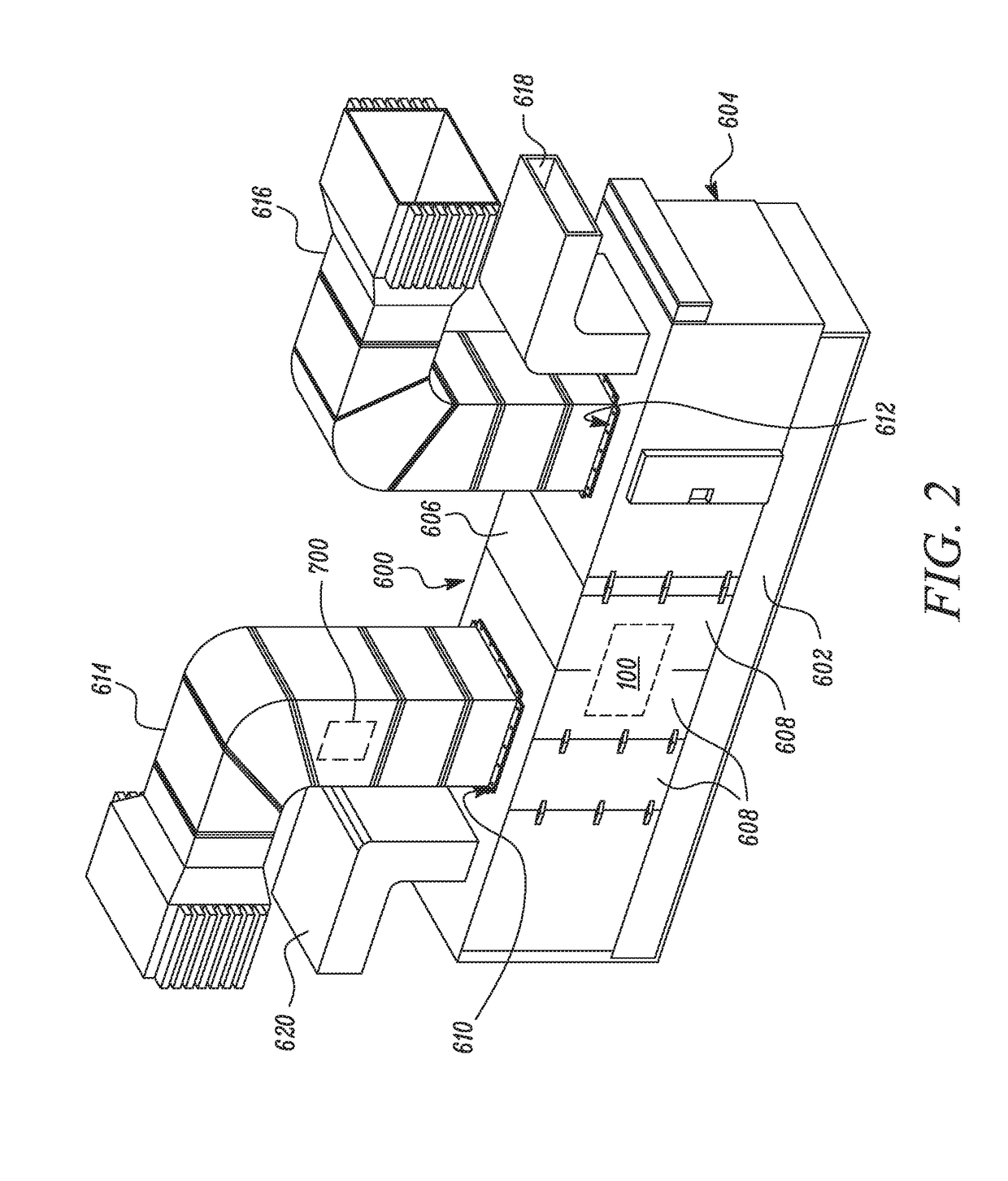

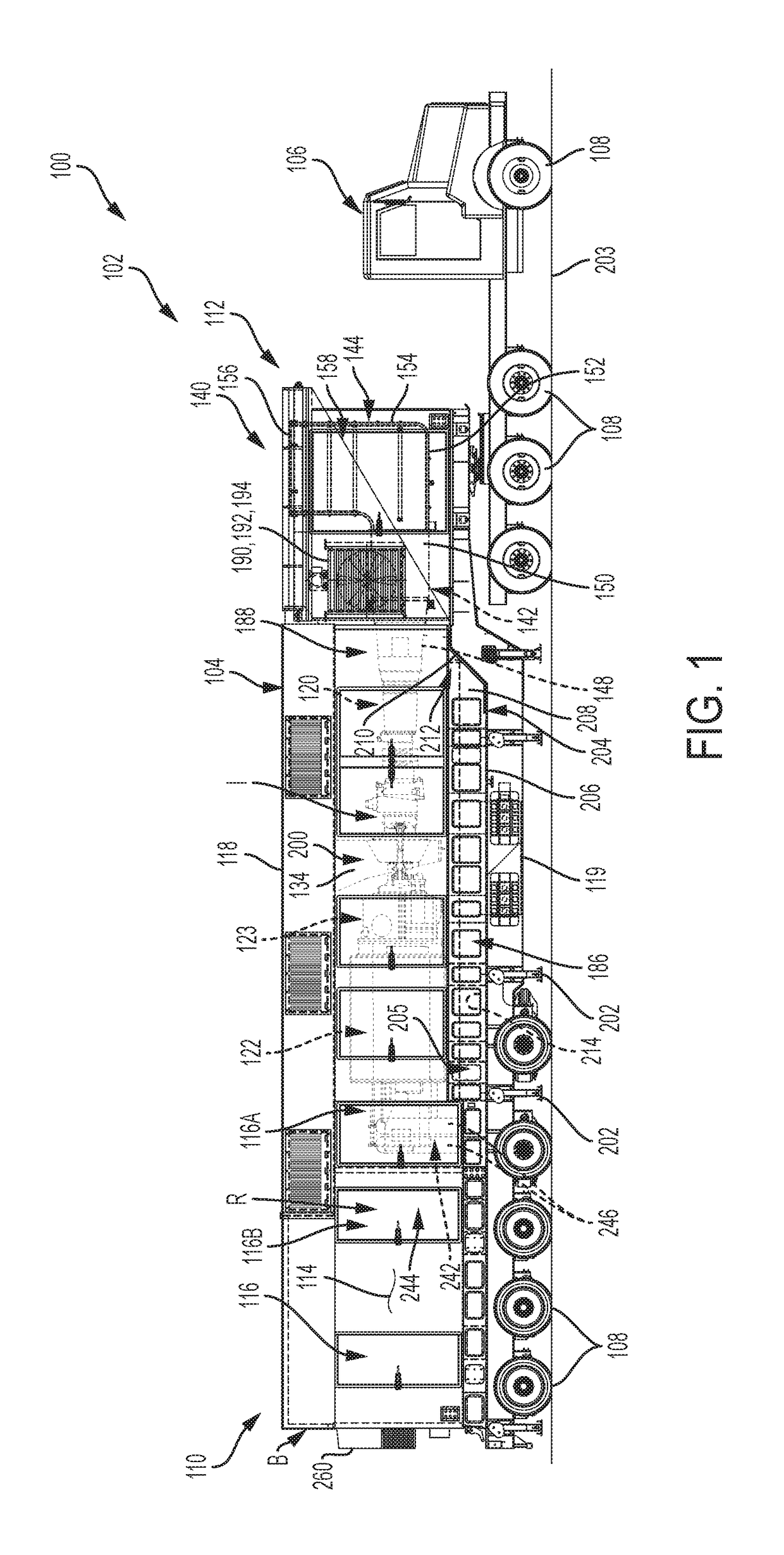

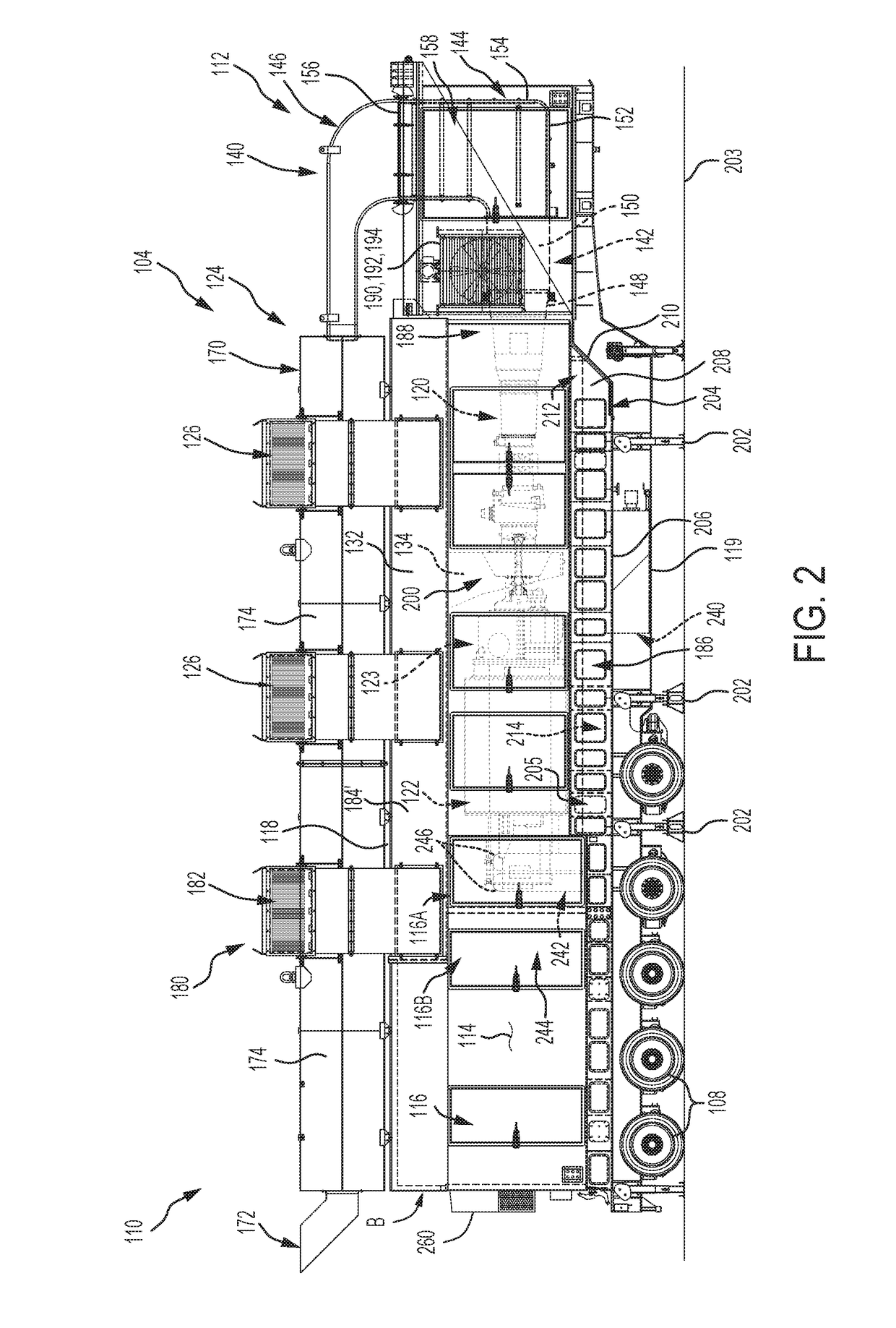

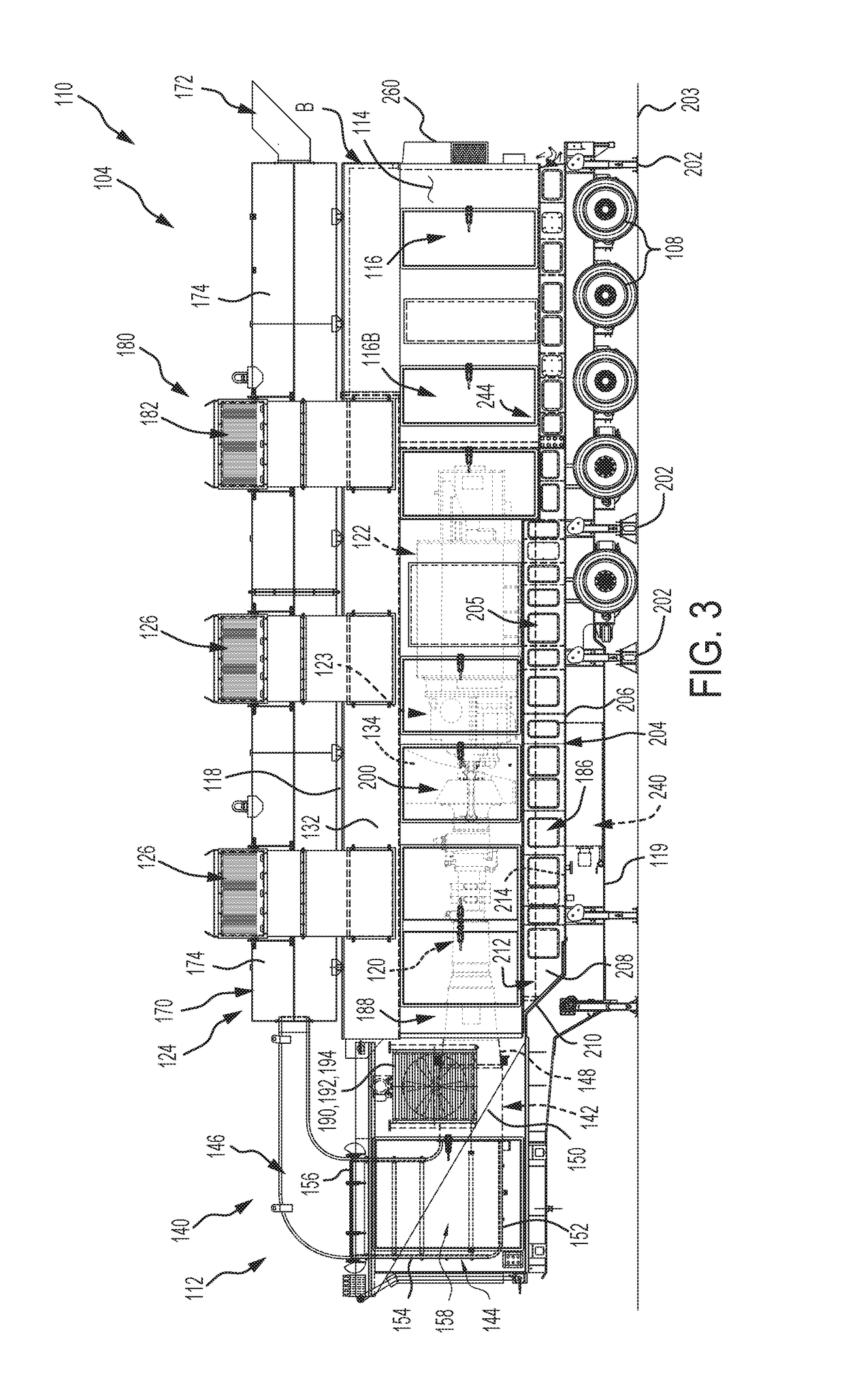

Mobile power generation system including noise attenuation

A mobile power generation system includes a trailer, a gas turbine housed inside the trailer, an electrical generator coupled to the gas turbine to generate electricity, an exhaust silencer system configured to receive exhaust has from the gas turbine, and a noise attenuation assembly coupled to and in fluid communication with the exhaust silencer system. The exhaust silencer system may be attached to a front end of the trailer and may include a diffuser system, a lower exhaust elbow silencer coupled to and in fluid communication with the diffuser system, and an upper exhaust elbow in fluid communication with the lower exhaust elbow silencer and comprising an outlet. The noise attenuation assembly includes an exhaust silencer unit mounted to a top end of the trailer. The exhaust silencer unit includes an inlet in fluid communication with the outlet of the upper exhaust elbow of the exhaust silencer system.

Owner:ON POWER INC

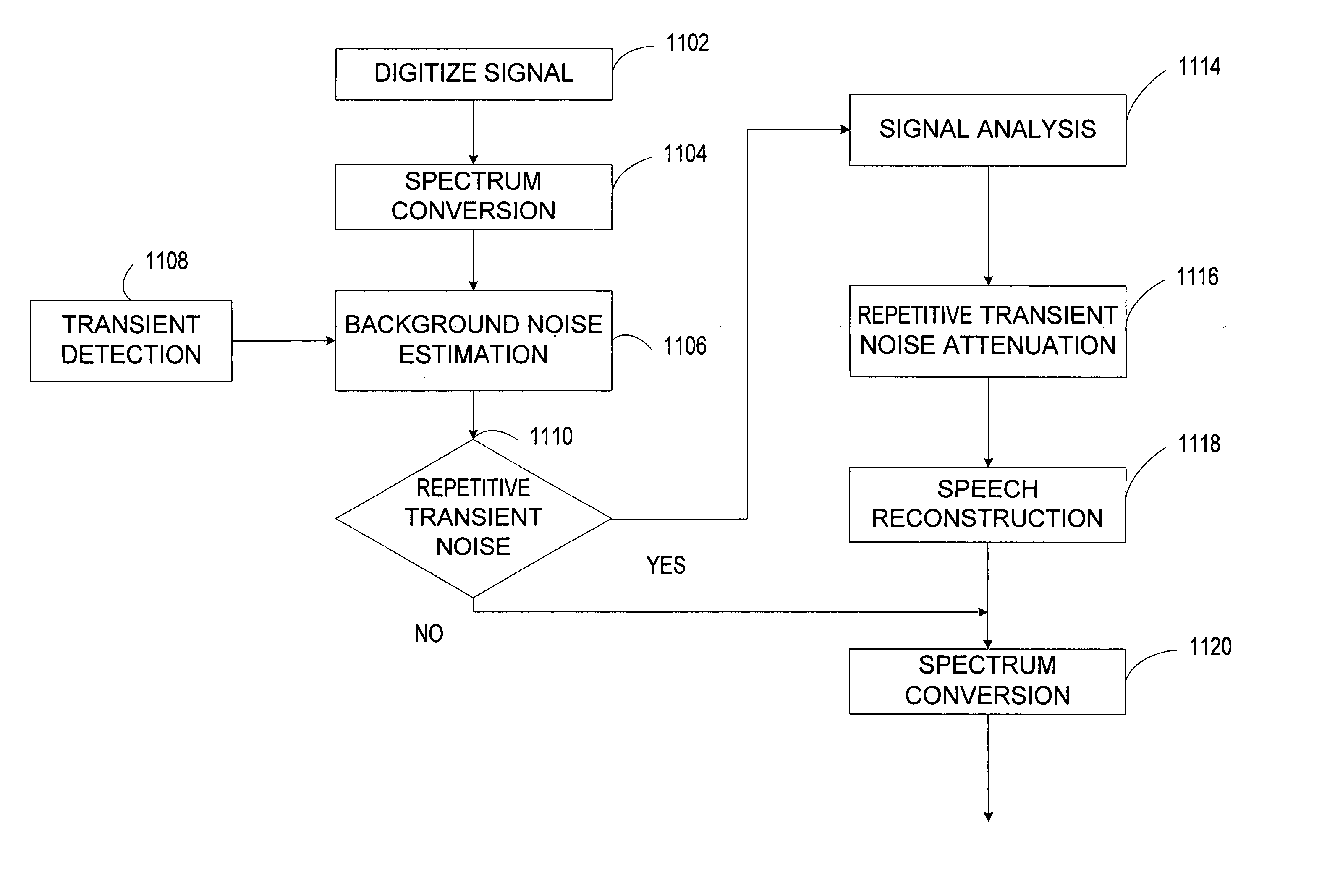

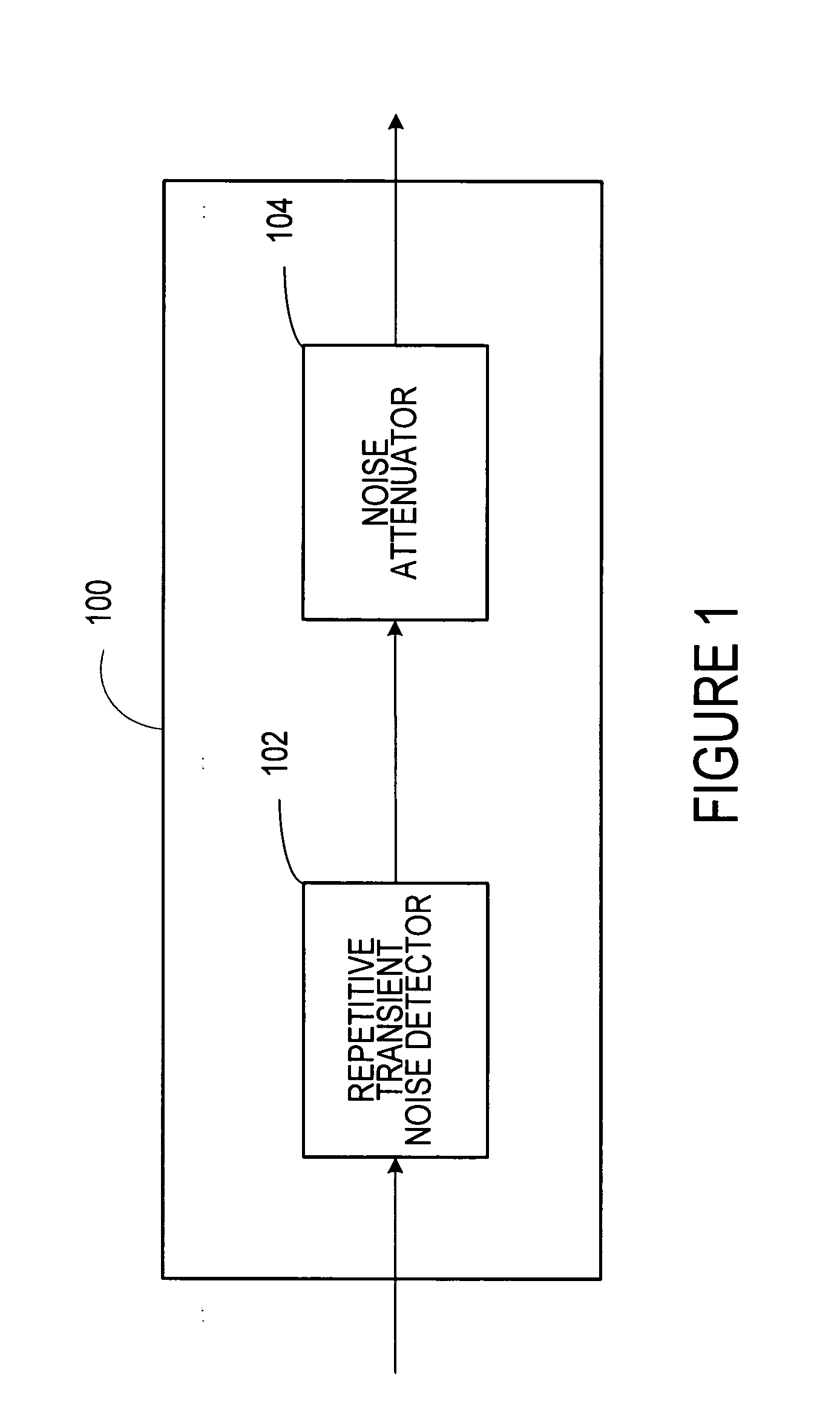

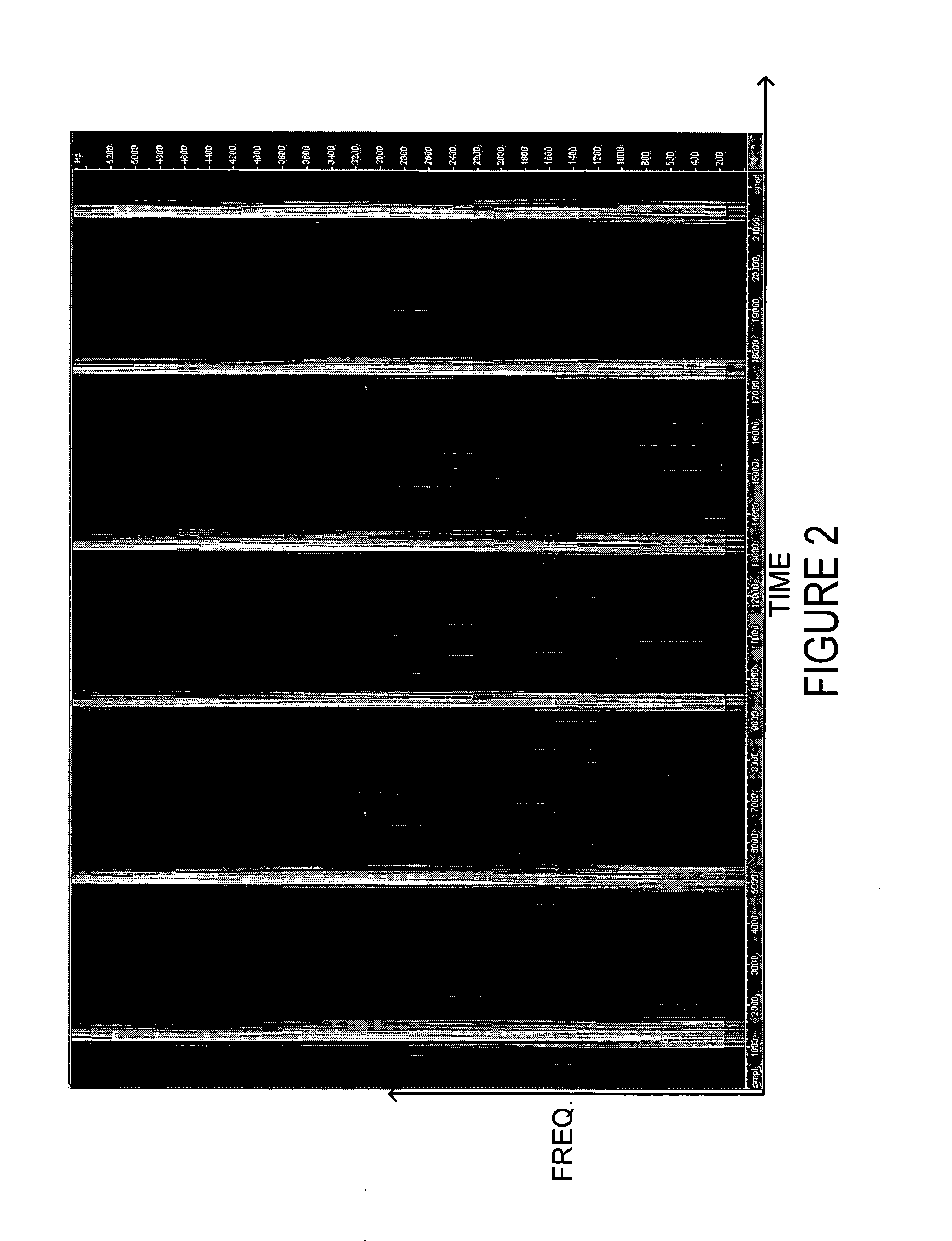

Repetitive transient noise removal

ActiveUS20060116873A1Improve voice qualityRemove and dampens repetitive transient noiseSpeech recognitionFrequency spectrumHarmonic

A system improves the perceptual quality of a speech signal by dampening undesired repetitive transient noises. The system includes a repetitive transient noise detector adapted to detect repetitive transient noise in a received signal. The received signal may include a harmonic and a noise spectrum. The system further includes a repetitive transient noise attenuator that substantially removes or dampens repetitive transient noises from the received signal. The method of dampening the repetitive transient noises includes modeling characteristics of repetitive transient noises; detecting characteristics in the received signal that correspond to the modeled characteristics of the repetitive transient noises; and substantially removing components of the repetitive transient noises from the received signal that correspond to some or all of the modeled characteristics of the repetitive transient noises.

Owner:MALIKIE INNOVATIONS LTD

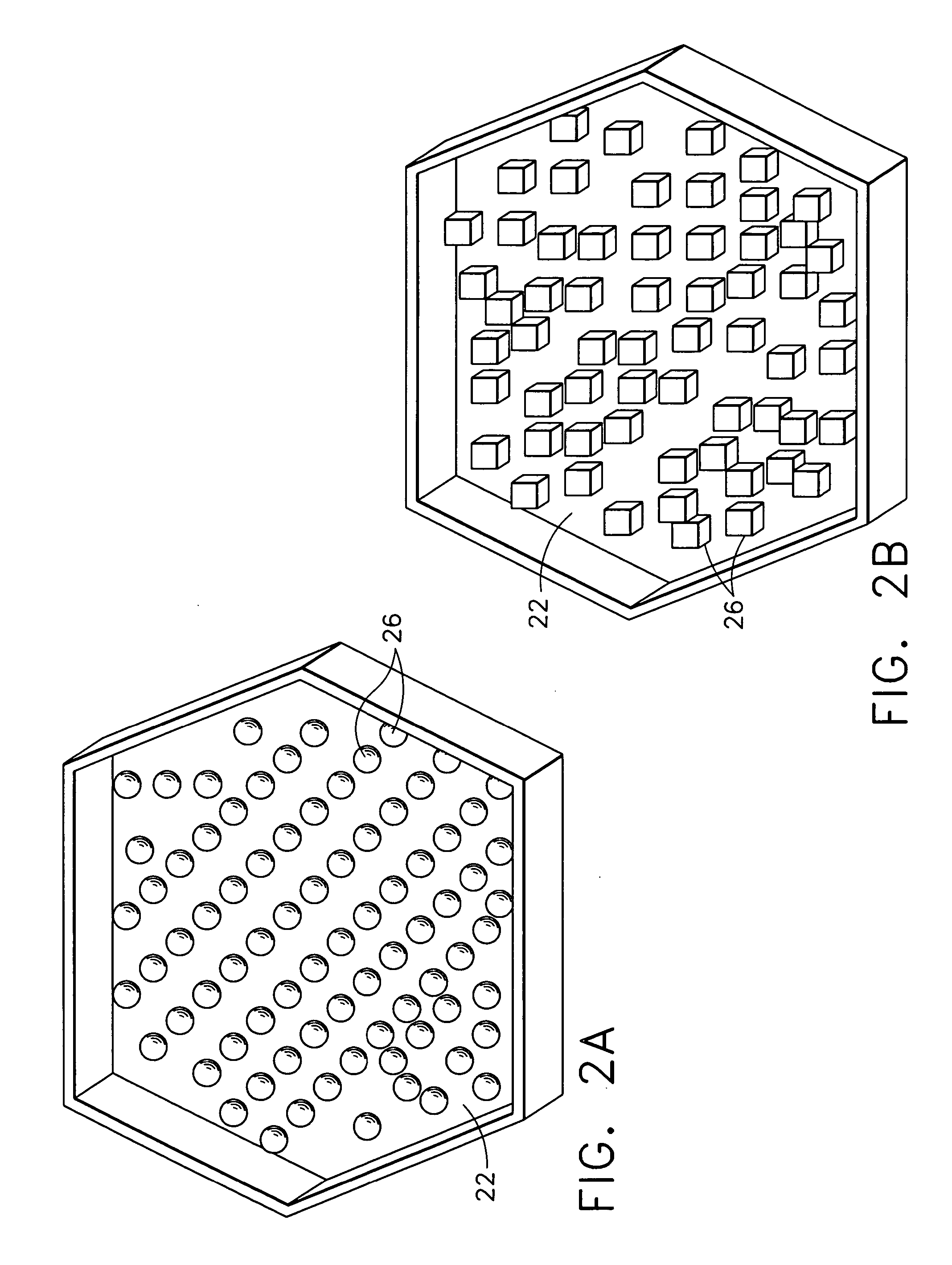

Apparatus and method for aircraft cabin noise attenuation via non-obstructive particle damping

InactiveUS20050194210A1Increase dampingIncreased durabilityLayered productsFuselage insulationFilling materialsEngineering

An apparatus for reducing noise in an aircraft cabin is disclosed. The apparatus comprises a structure portion and filler material. The structure portion further comprises an internal member having at least one cavity disposed therein. Each of the at least one cavity of the structure portion are filled with the filler material.

Owner:THE BOEING CO

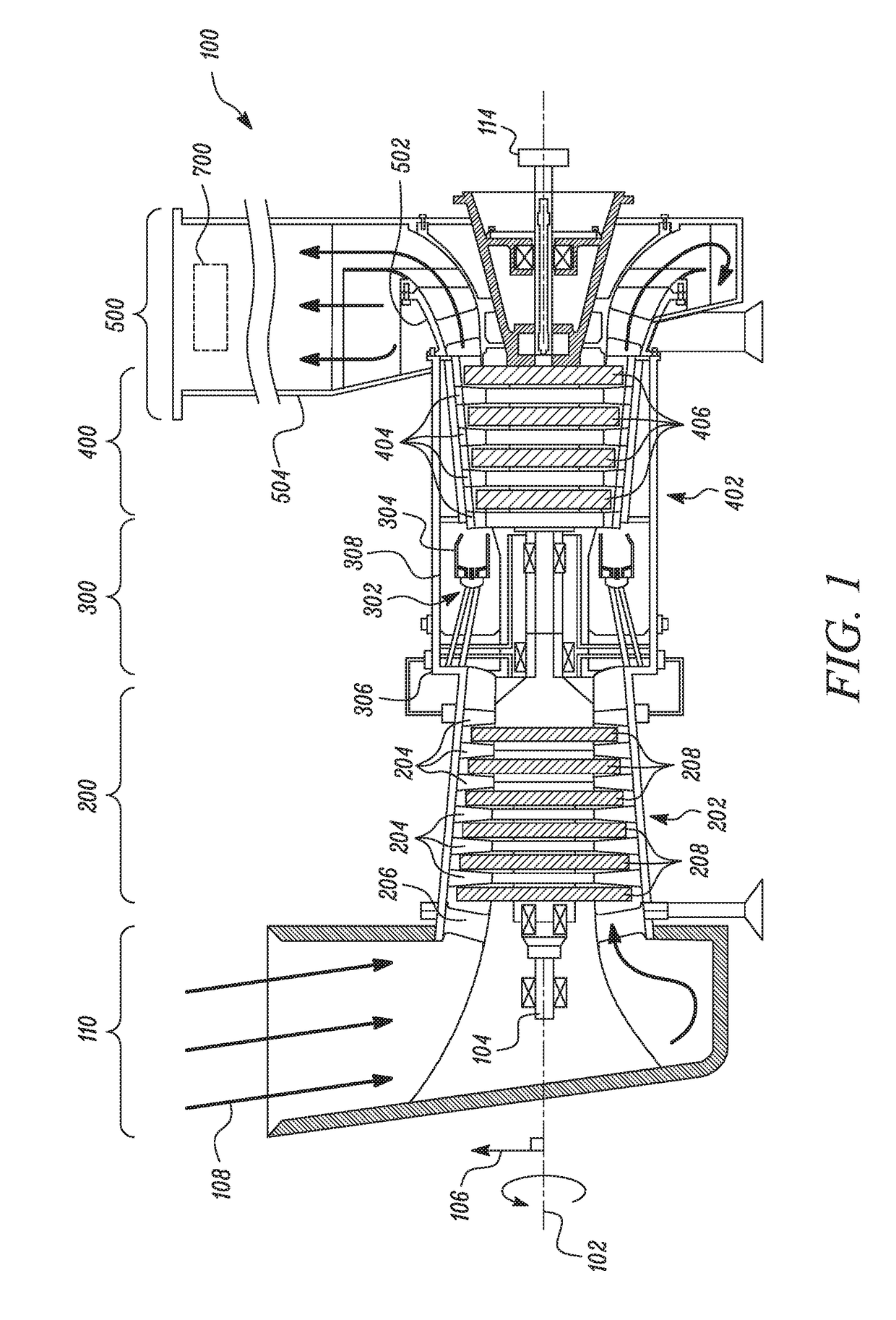

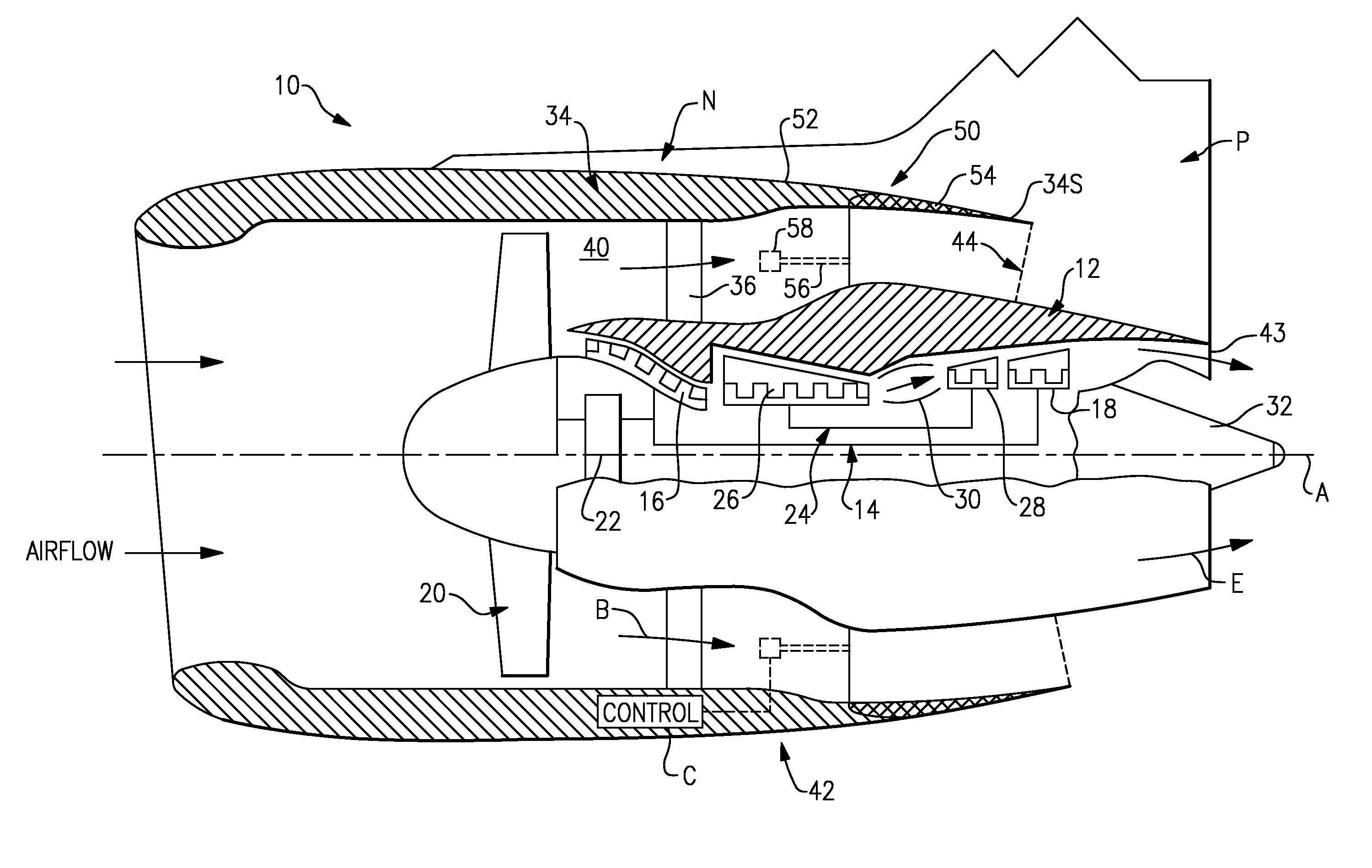

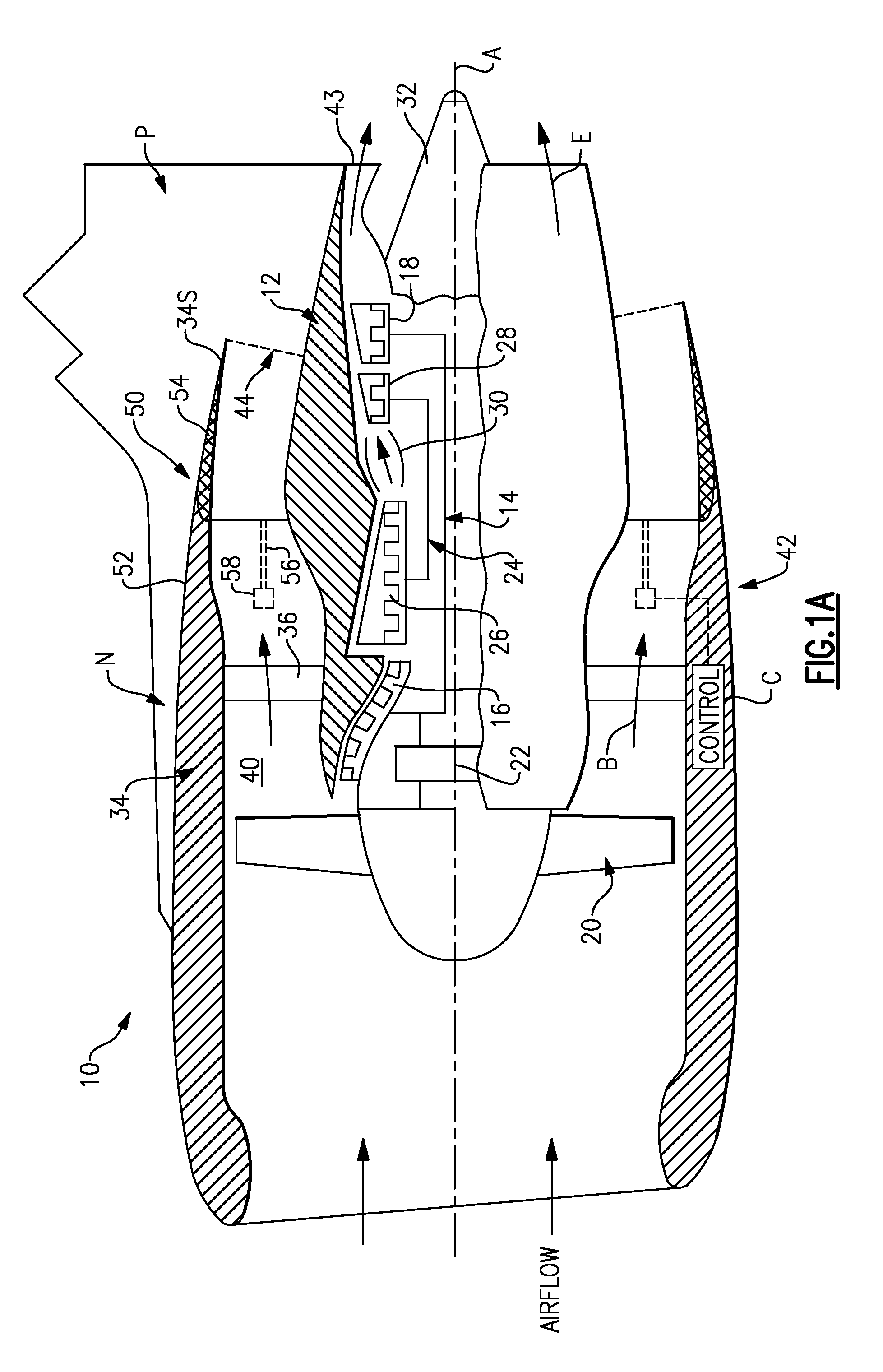

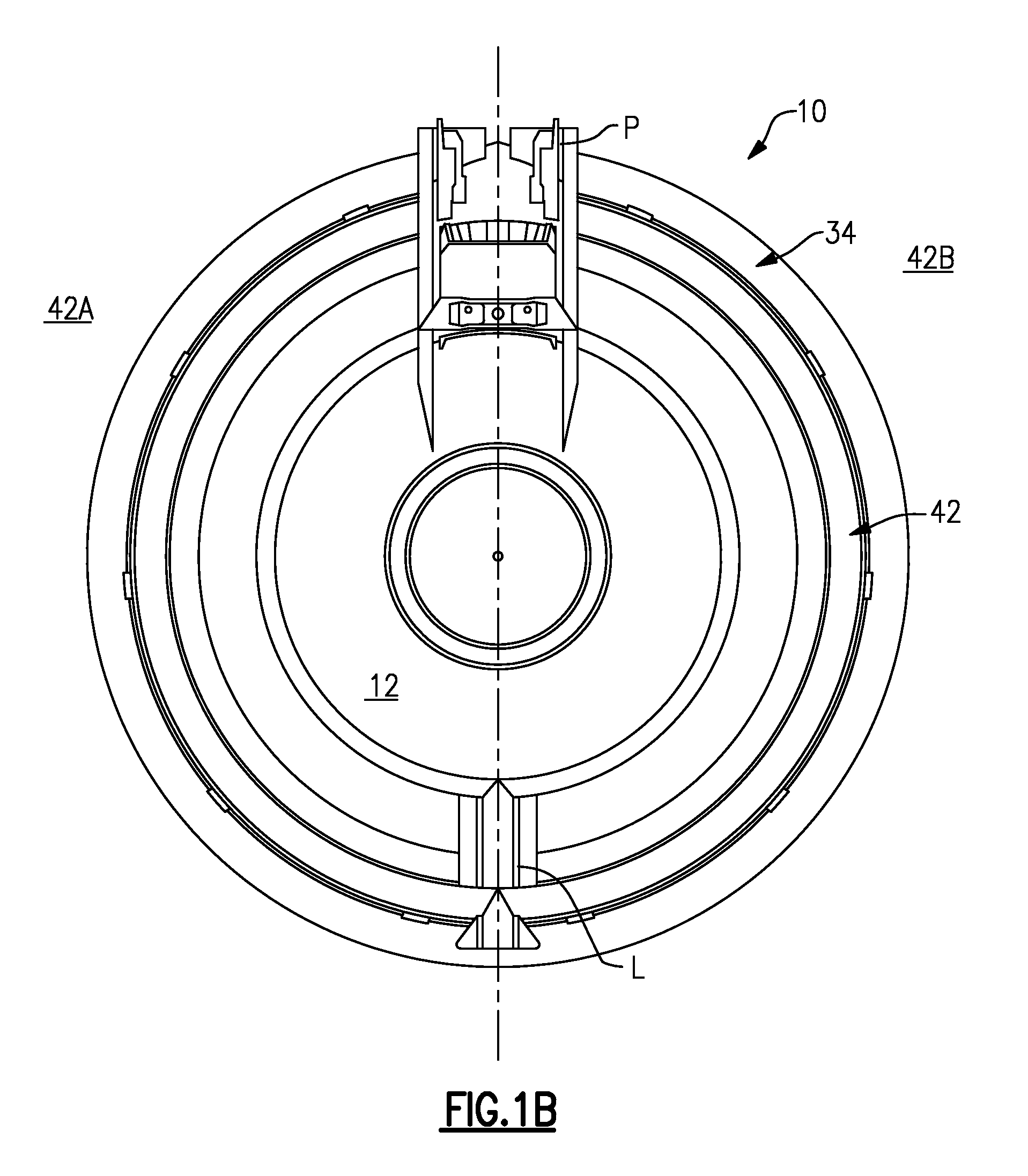

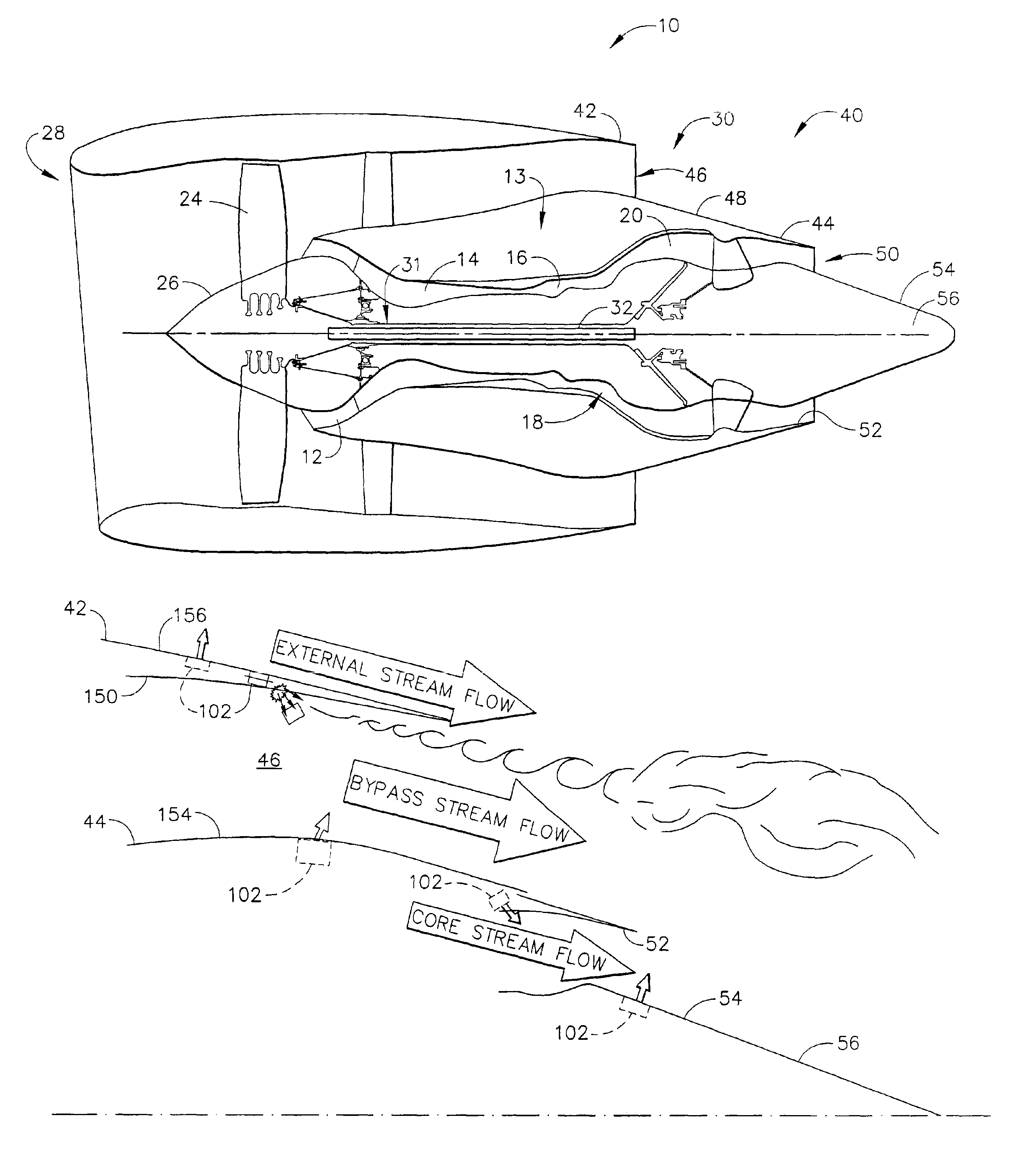

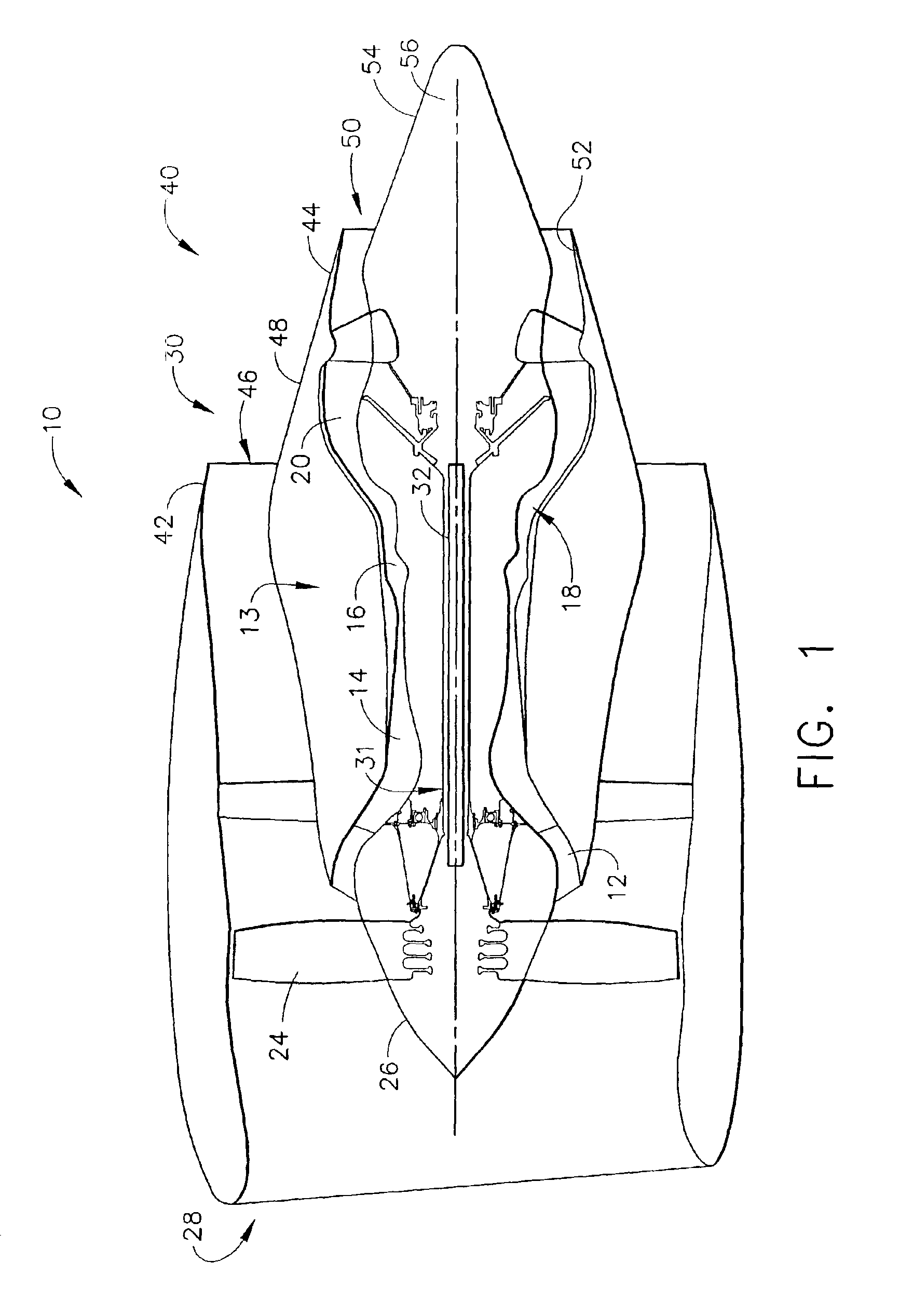

Gas turbine engine with noise attenuating variable area fan nozzle

A high-bypass gas turbine engine includes a variable area fan nozzle with an acoustic system having an acoustic impedance.

Owner:RTX CORP

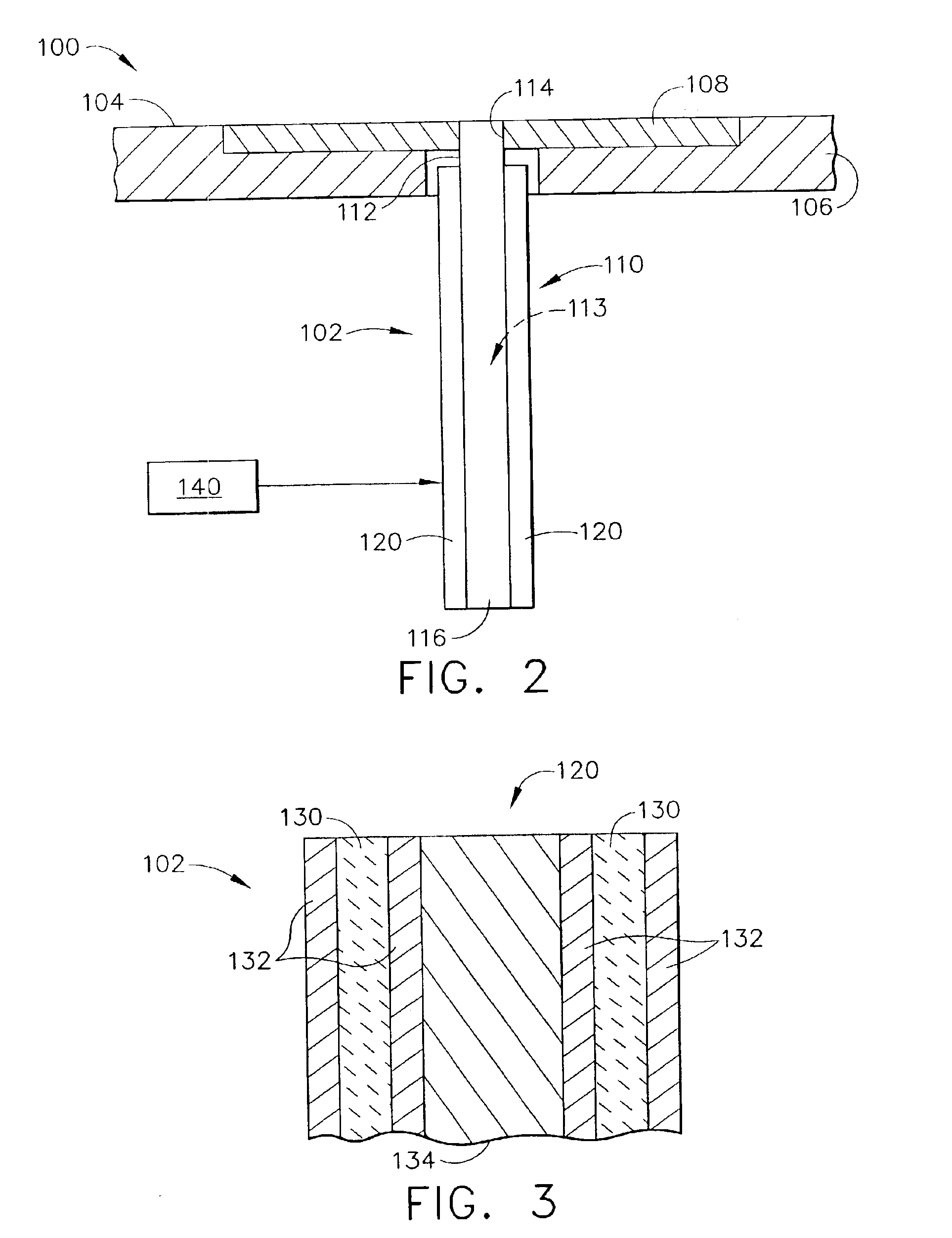

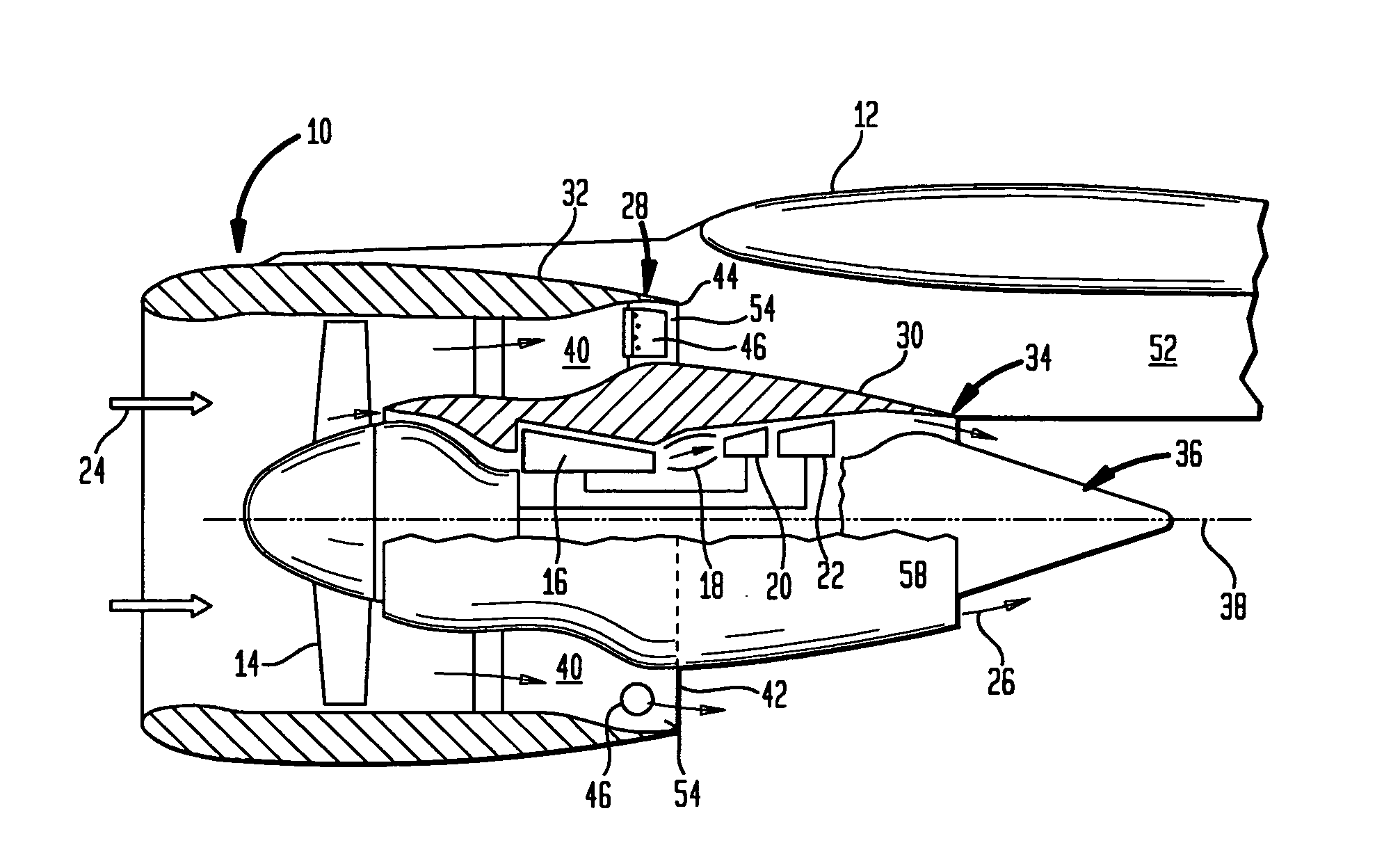

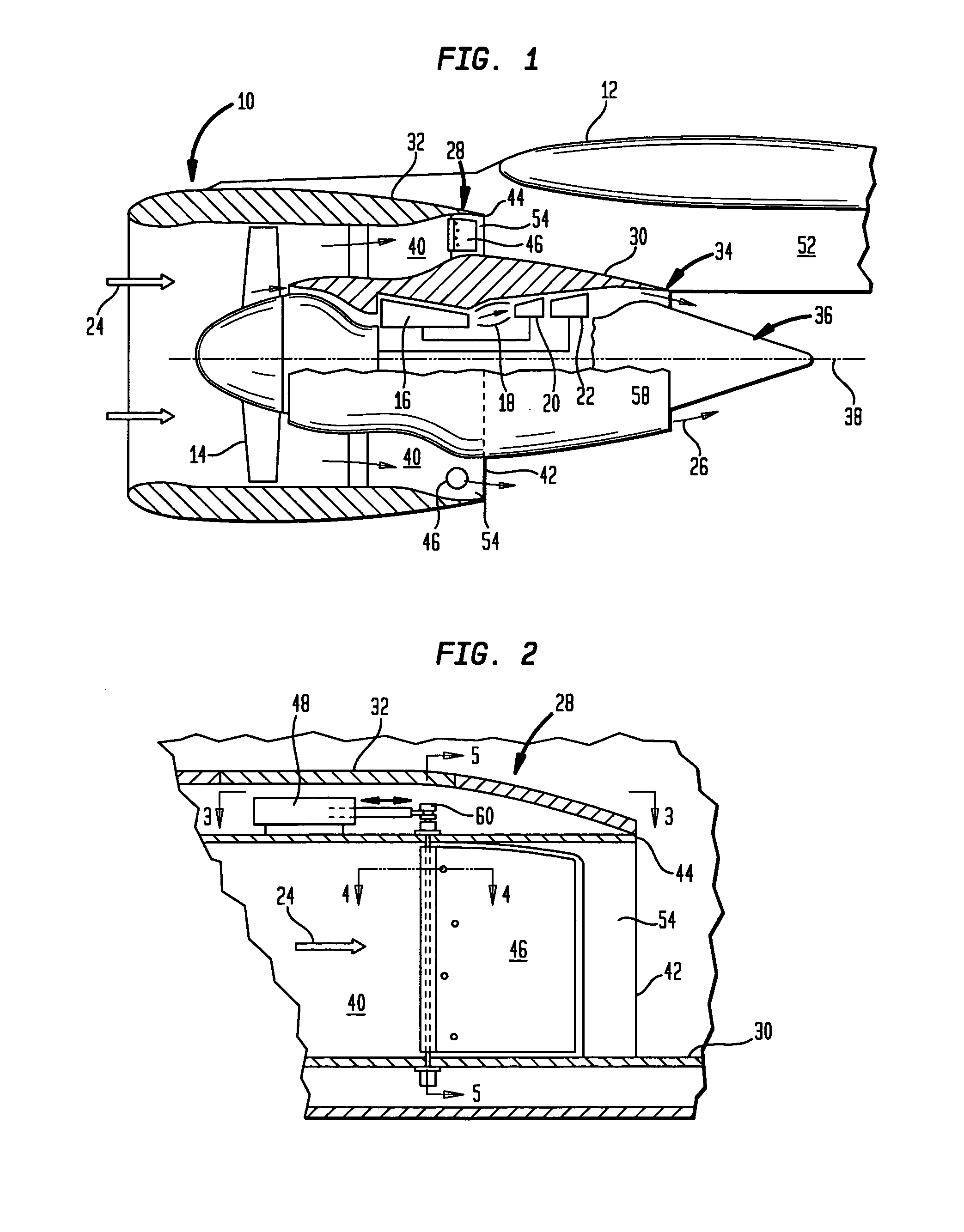

Method and apparatus for noise attenuation for gas turbine engines using at least one synthetic jet actuator for injecting air

ActiveUS7055329B2Facilitate attenuating jet noiseEasy to operatePower plant exhaust arrangementsCosmonautic vehiclesActuatorNoise suppression

A method enables a gas turbine engine to be operated. The method comprises channeling exhaust gases from a core engine through an exhaust assembly and past at least one flow boundary surface, and selectively operating a noise suppression system extending from the at least one flow boundary surface to facilitate attenuating noise generated during engine operation.

Owner:GENERAL ELECTRIC CO

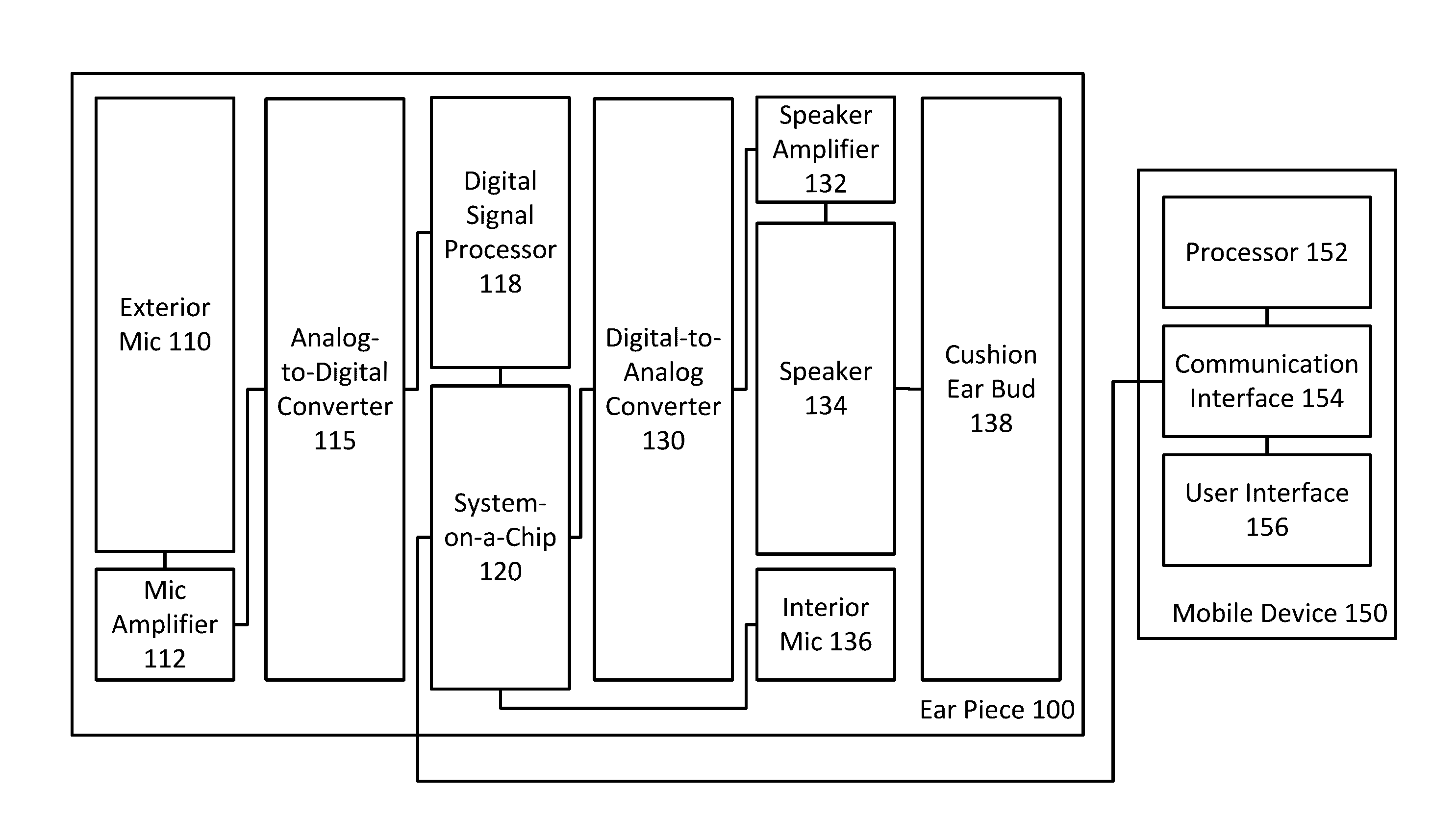

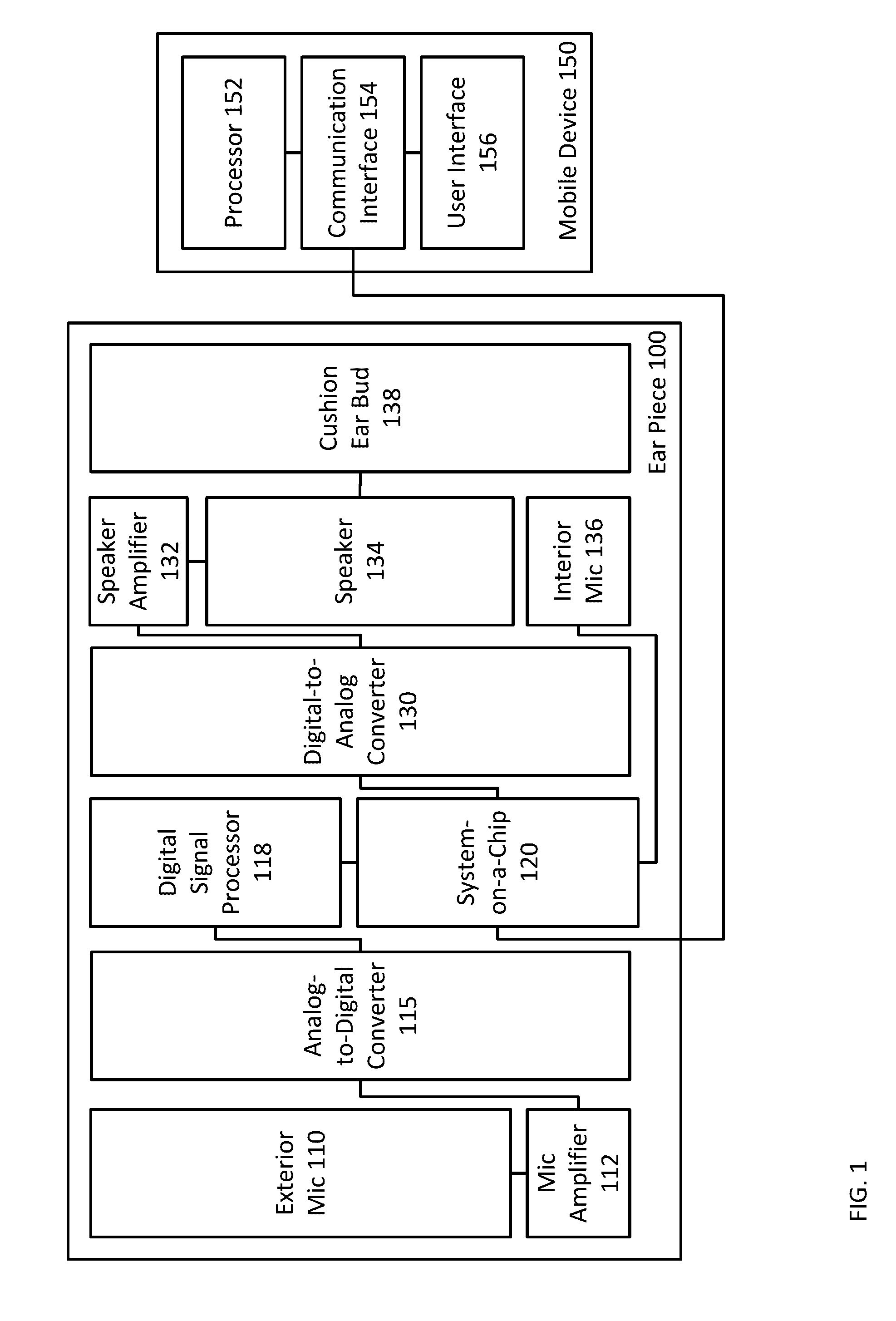

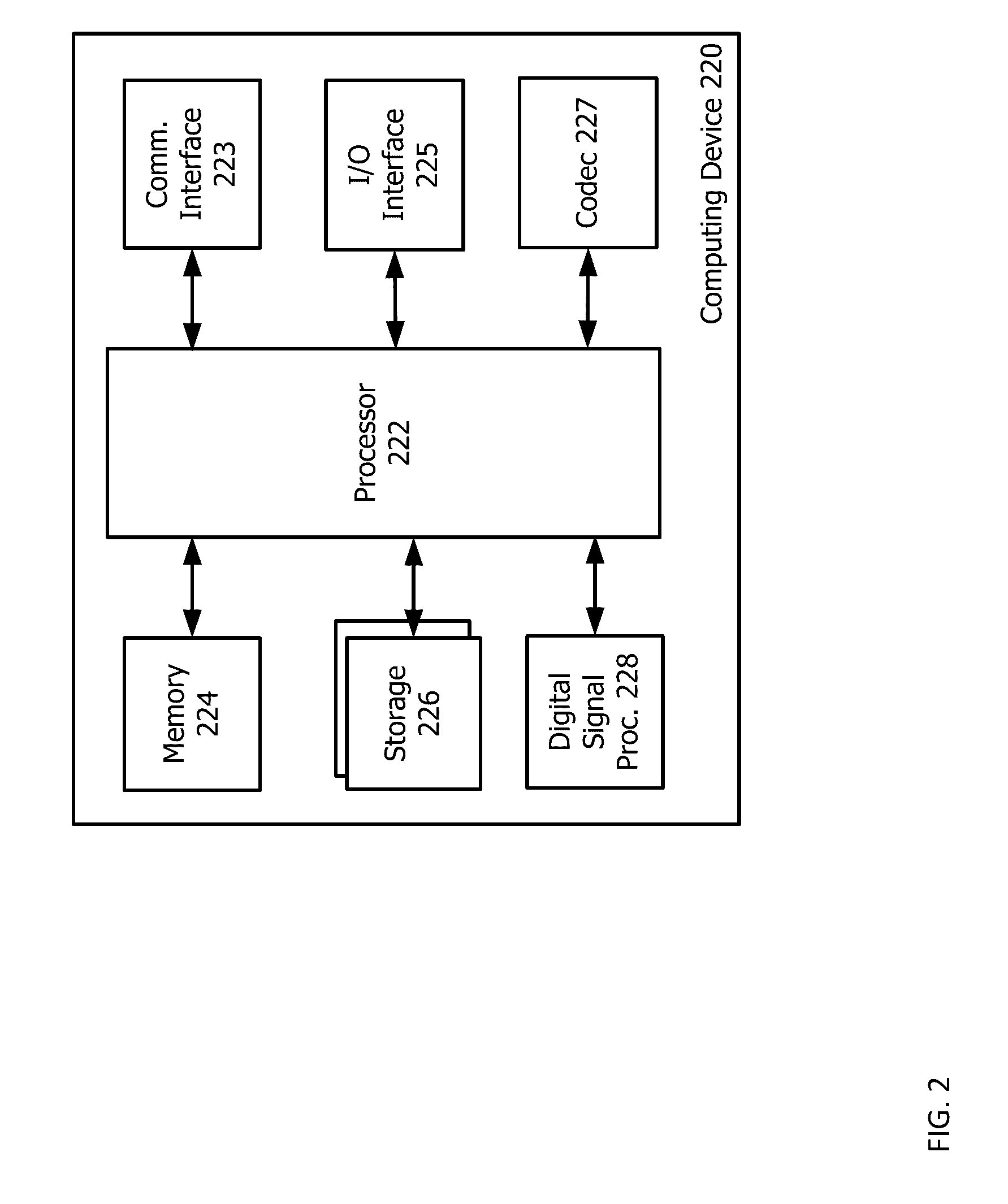

Real-time audio processing of ambient sound

An earpiece for real-time audio processing of ambient sound includes an ear bud that provides passive noise attenuation to the earpiece such that exterior ambient sound is substantially reduced within an ear of a wearer, an exterior microphone that receives ambient sound and converts the received ambient sound into analog electrical signals, and an analog-to-digital converter that converts the analog electrical signals into digital signals representative of the ambient sounds. The earpiece further includes a digital signal processor that performs a transformation operation on the digital signals according to instructions received from a mobile device, the transformation operation transforms the digital signals into modified digital signals, a digital-to-analog converter that converts the modified digital signals into modified analog electrical signals, and a speaker that outputs the modified analog electrical signals as audio waves.

Owner:DOLBY LAB LICENSING CORP

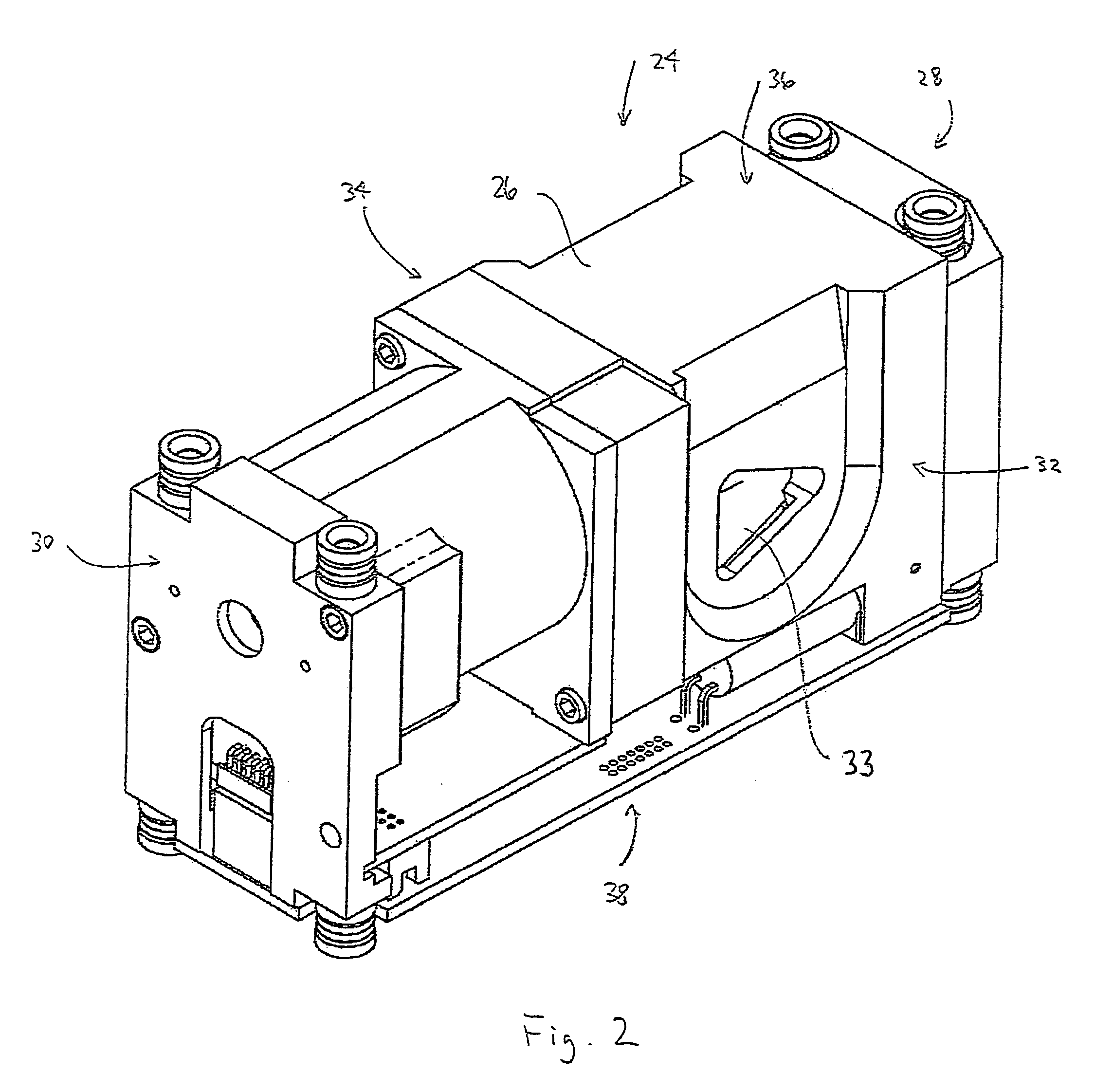

Turbofan variable fan nozzle

A turbofan exhaust nozzle includes a fan duct defined between a fan nacelle and core engine cowling. The duct includes an arcuate outlet at the trailing edge of the nacelle. A movable flap is disposed in a minor portion of the fan duct, with a remaining major portion of the fan duct having a constant flow area. The flap may be moved between stowed and deployed positions to locally decrease flow area inside the duct for noise attenuation.

Owner:JPMORGAN CHASE BANK NA

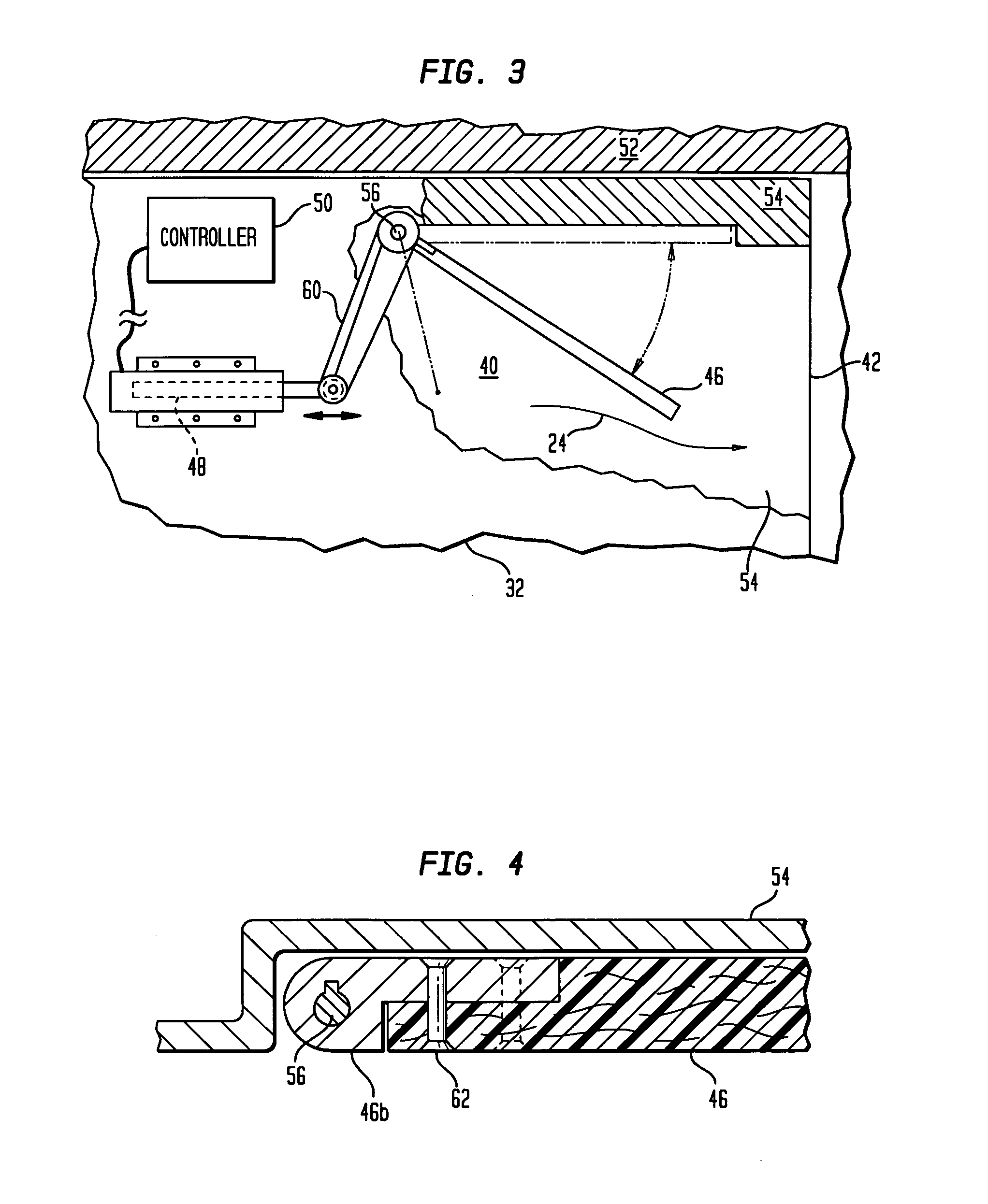

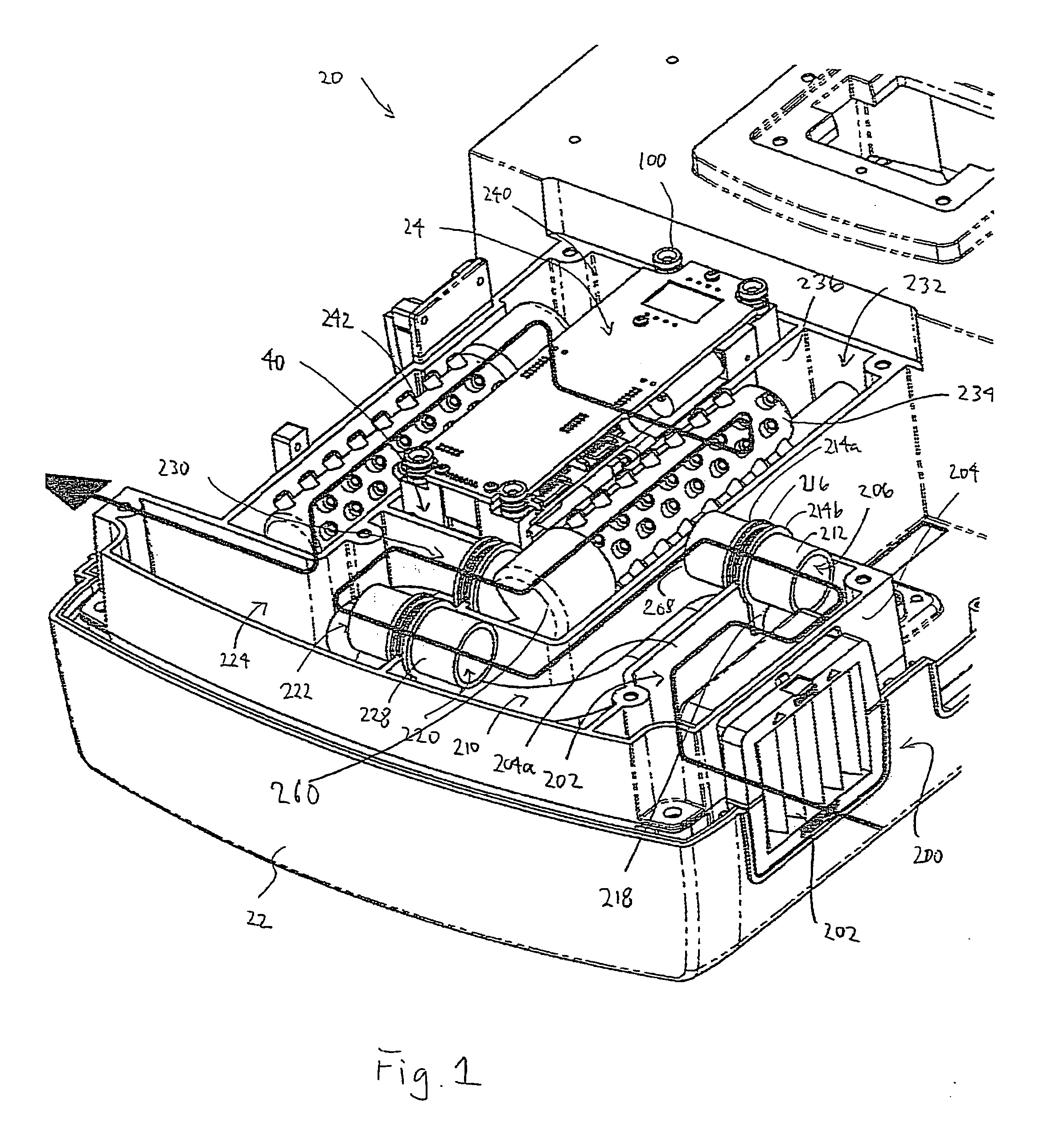

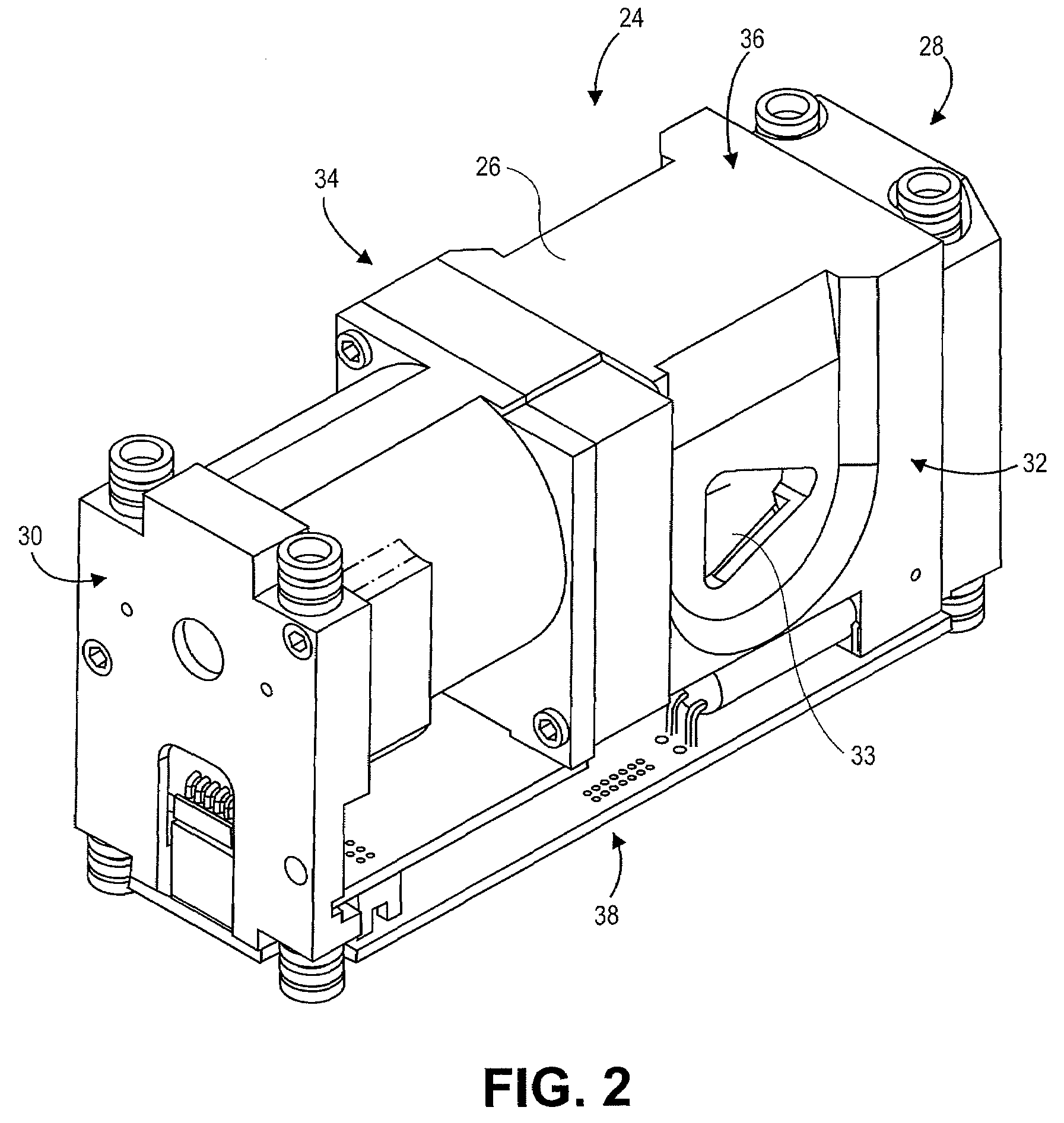

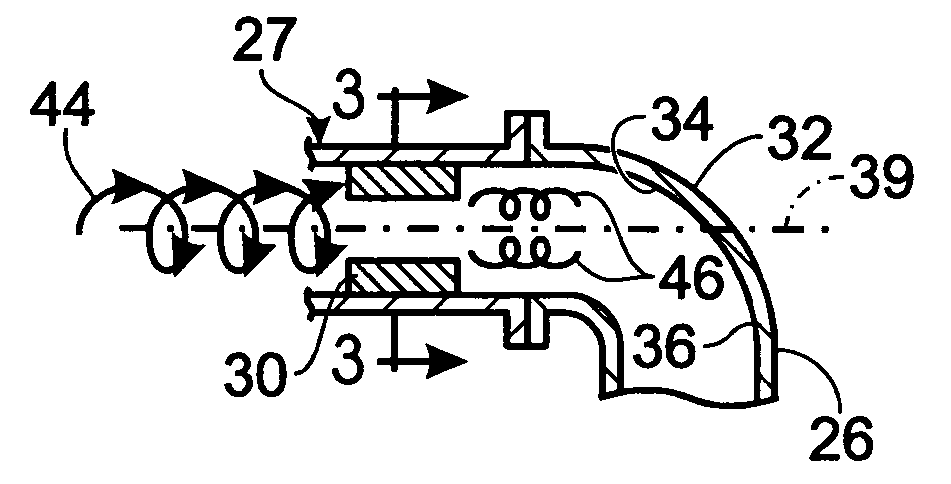

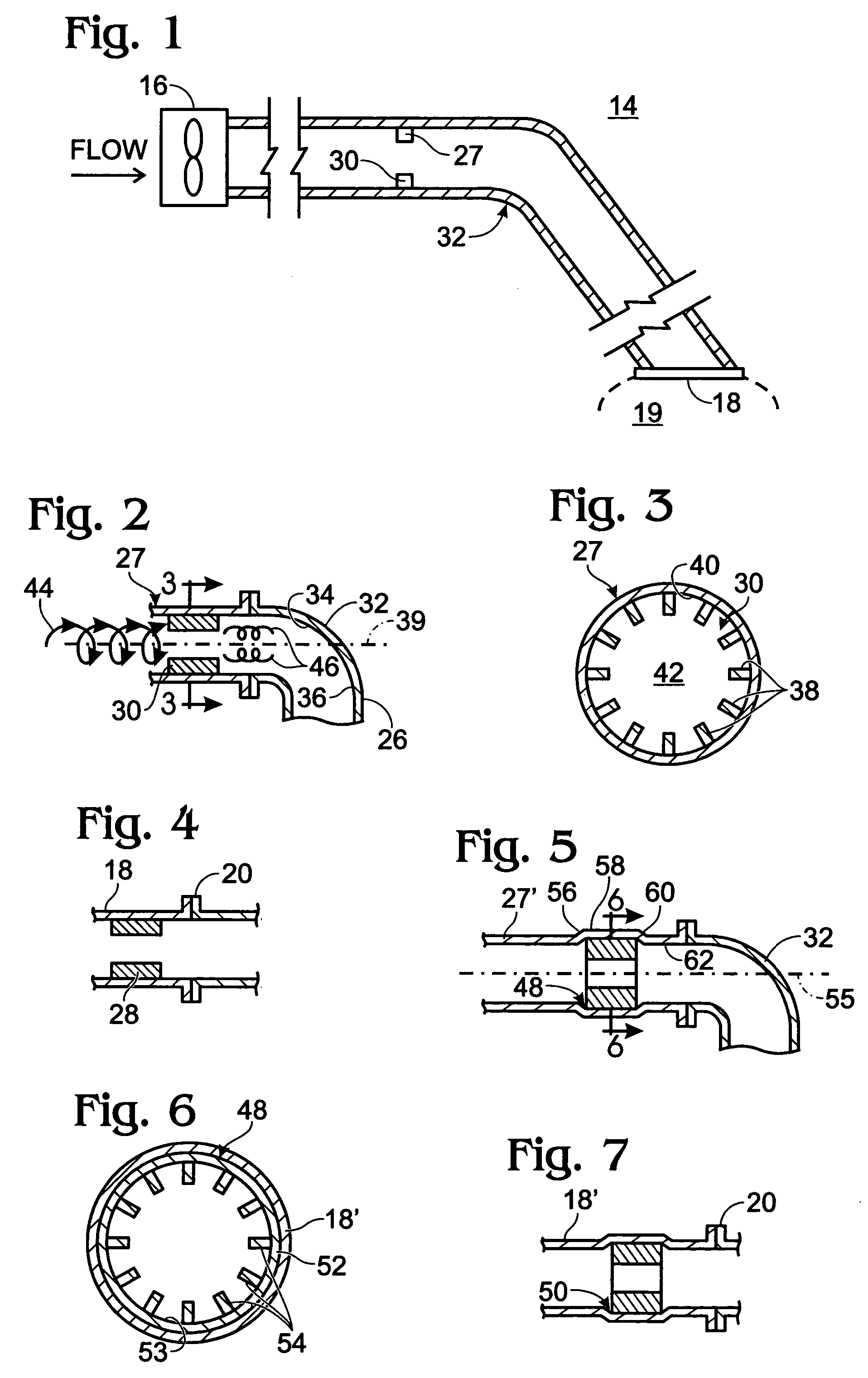

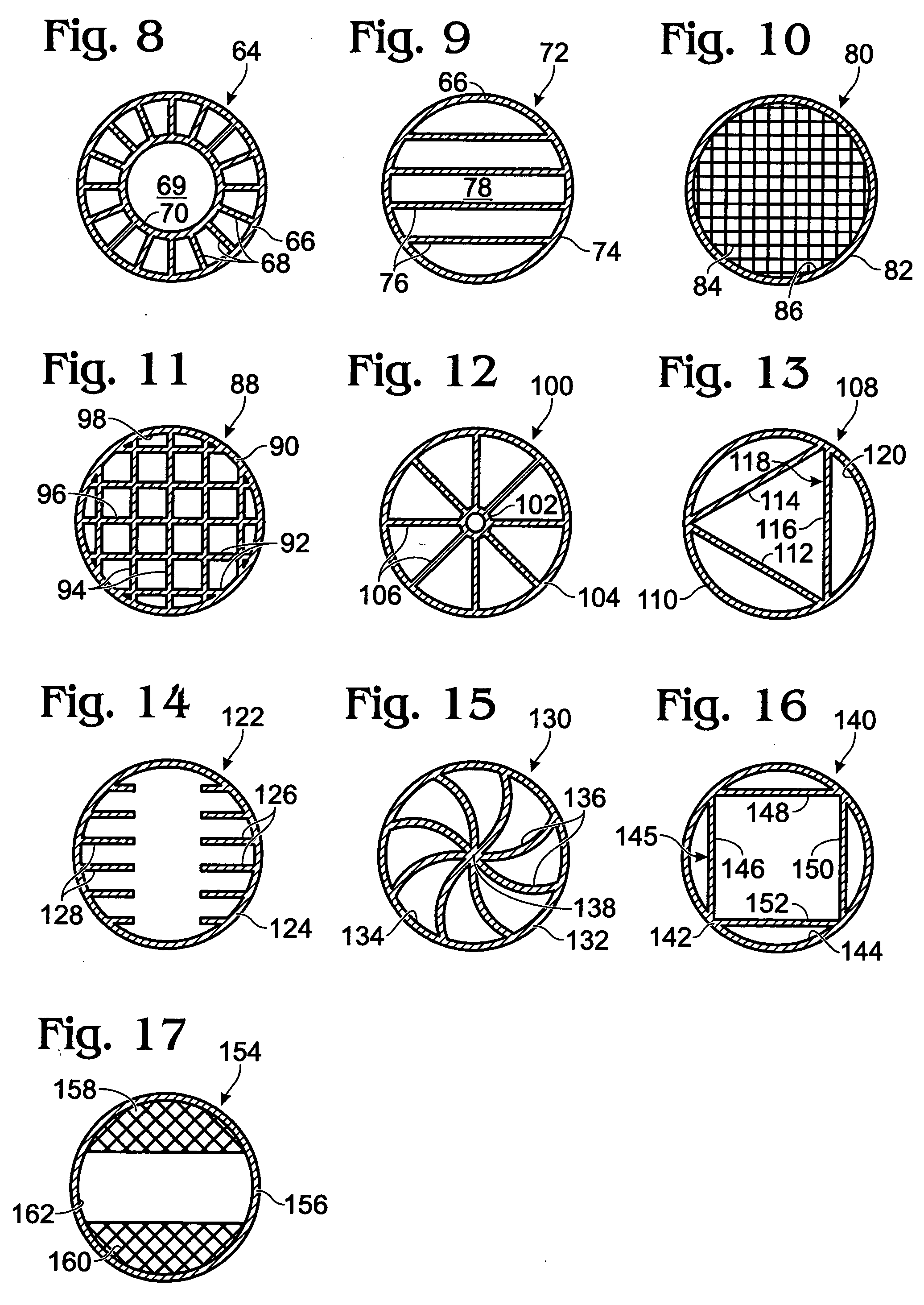

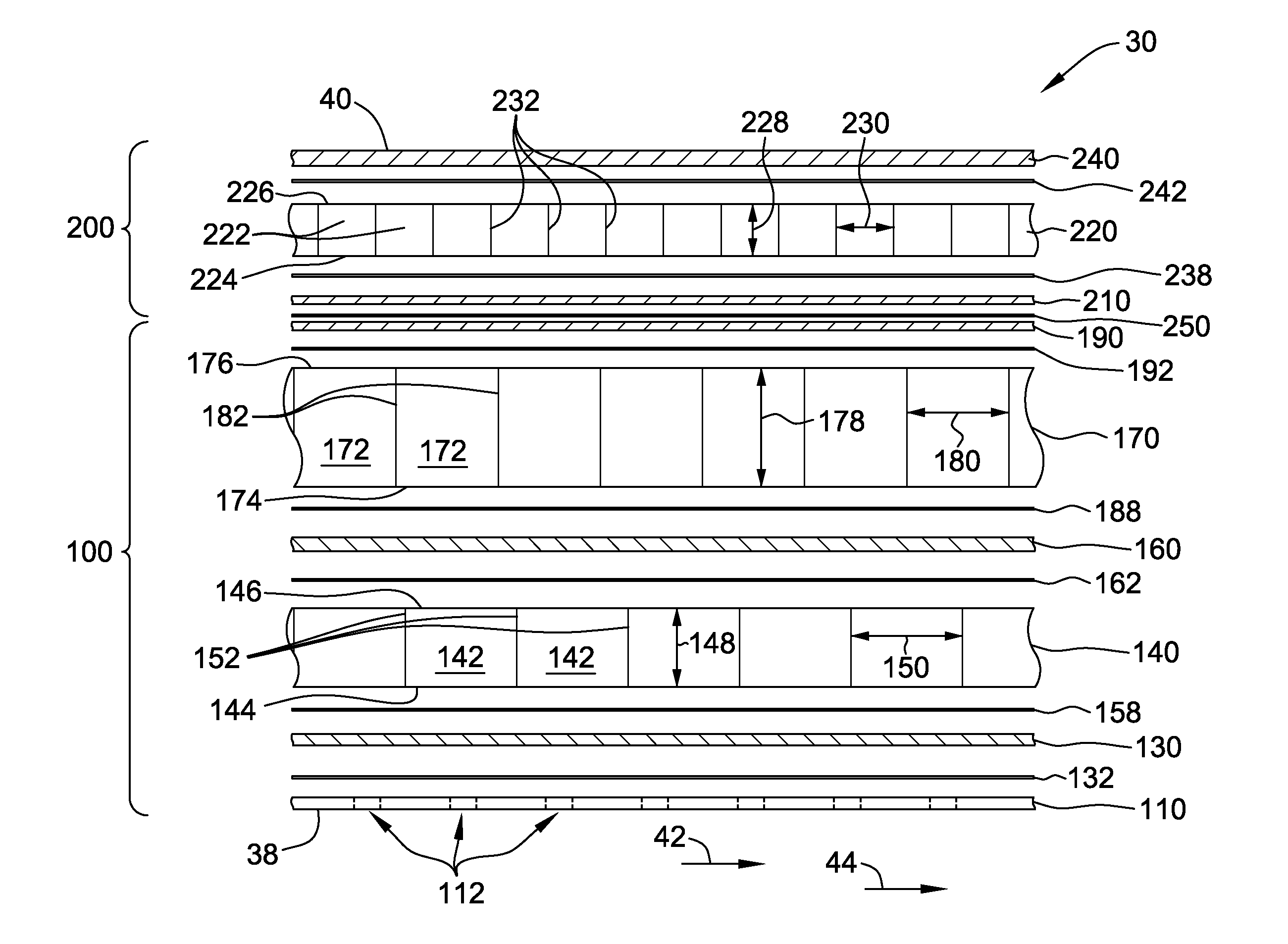

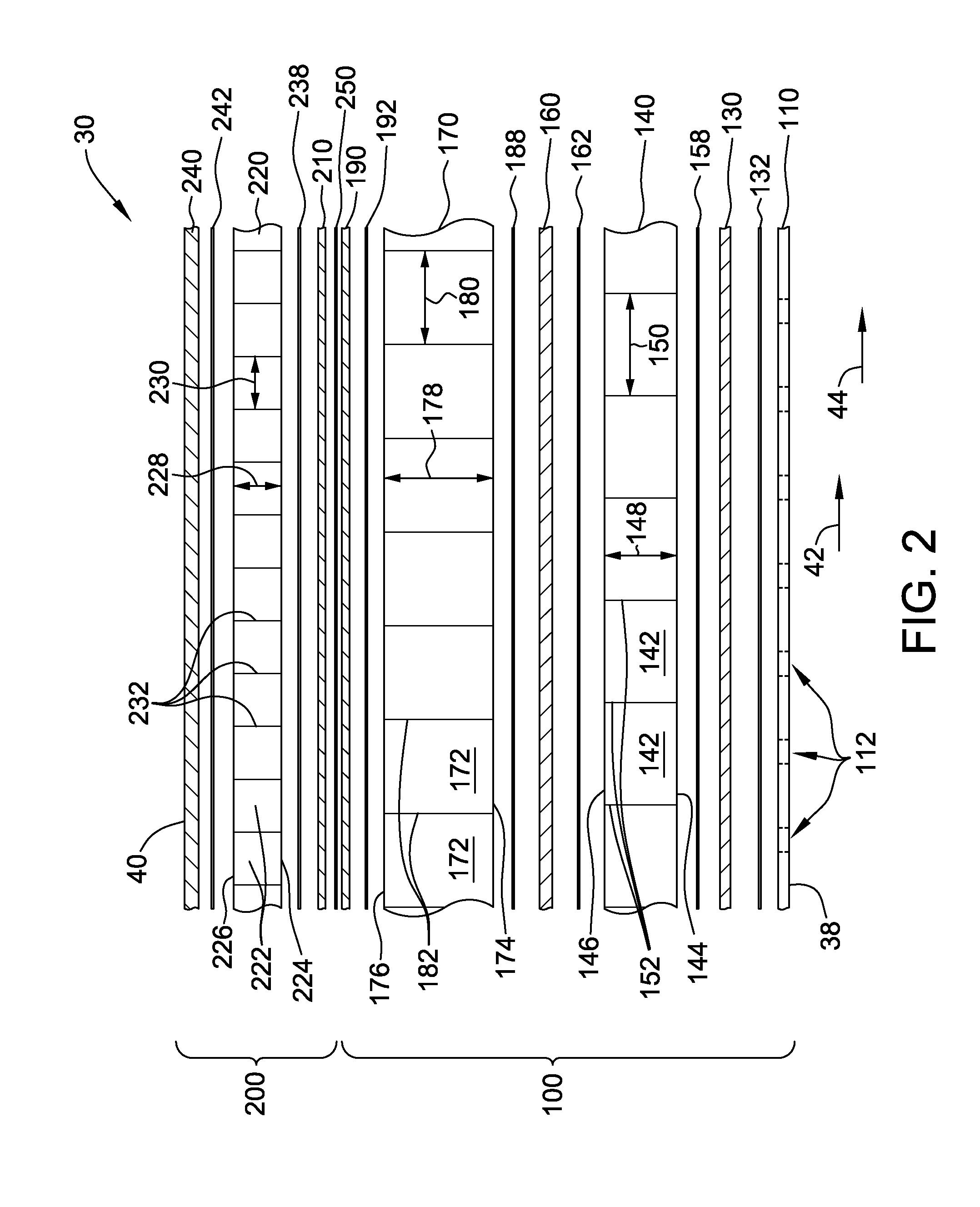

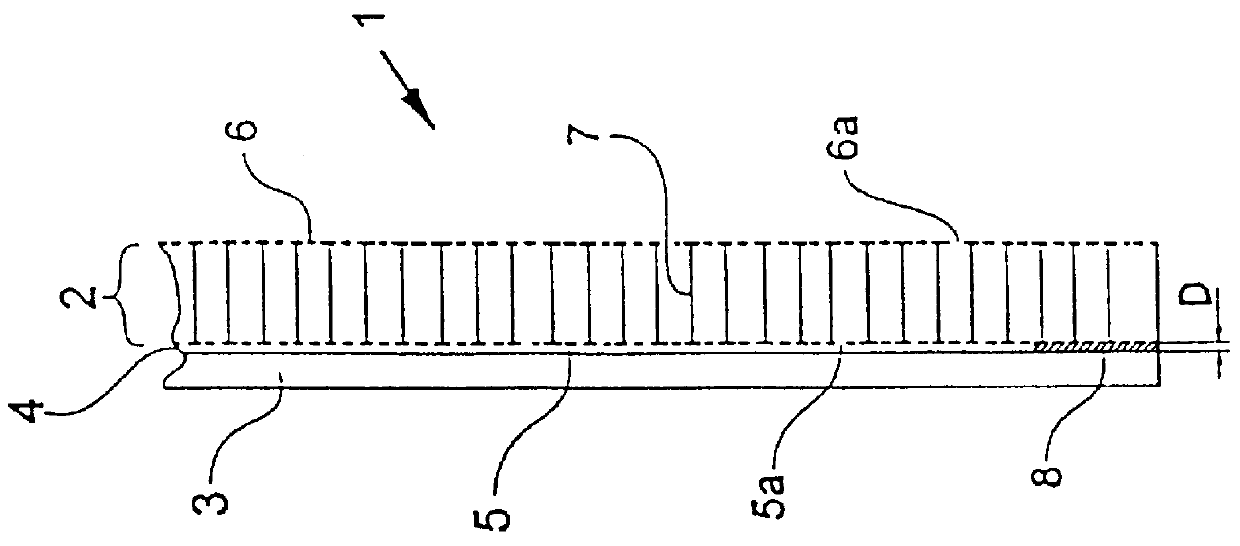

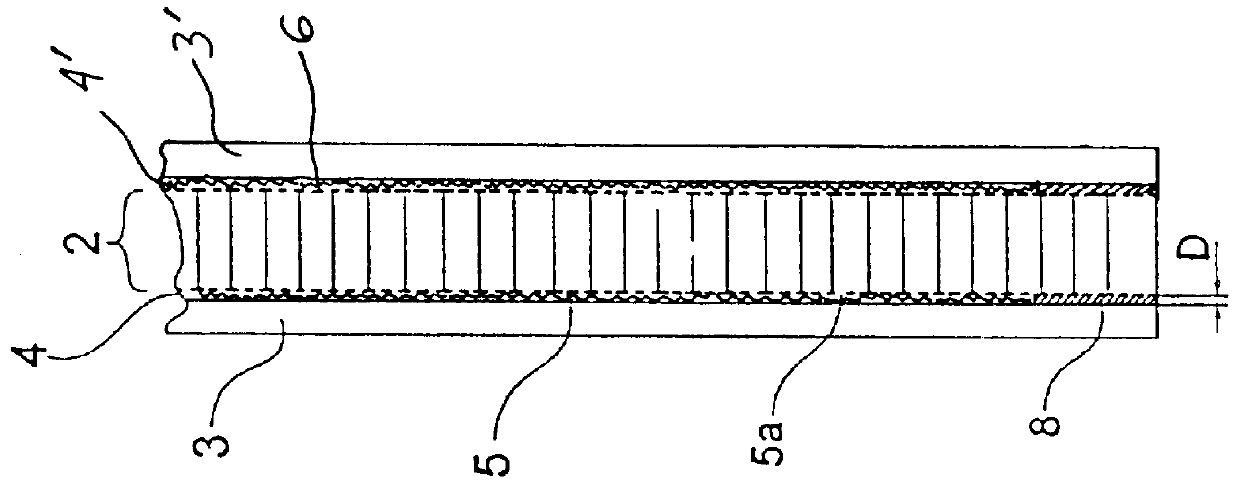

Method and apparatus for attenuating compressor noise

ActiveUS20050166921A1Reduce noiseReduce the amount of noiseRespiratorsOperating means/releasing devices for valvesPortable ventilatorsEngineering

The invention comprises a method and apparatus for reducing the noise generated by compressors, including Roots-type blowers. The invention has particular use for reducing noise generated by compressors used in mechanical ventilators, though the advantages thereof may be realized in many different applications. One embodiment of the invention comprises a noise-attenuating gas flow path for a compressor contained in a portable ventilator housing. In one embodiment, the gas flow path comprises a plurality of chambers interconnected by flow tubes. The flow path is folded so as to fit into the limited space of a portable ventilator housing. The dimensions of the chambers and the flow tubes are selected so that an impedance mismatch is created between the chambers and the flow tubes. In one embodiment of the invention, the flow path comprises one or more perforated tubes located in one or more of the chambers. The perforated tube has a port through which gas is accepted and at least one exterior tube through which gas exits. Impedance mismatches are created between the inlet chamber and the exterior tubes and between the exterior tubes and the chamber in which the perforated tube is located, which are useful in attenuating noise. One embodiment of the invention comprises a noise attenuating mounting system for a compressor. The mounting system comprises flexible mounts that cooperate to dampen vibrations generated by the compressor.

Owner:VYAIRE MEDICAL 203 INC

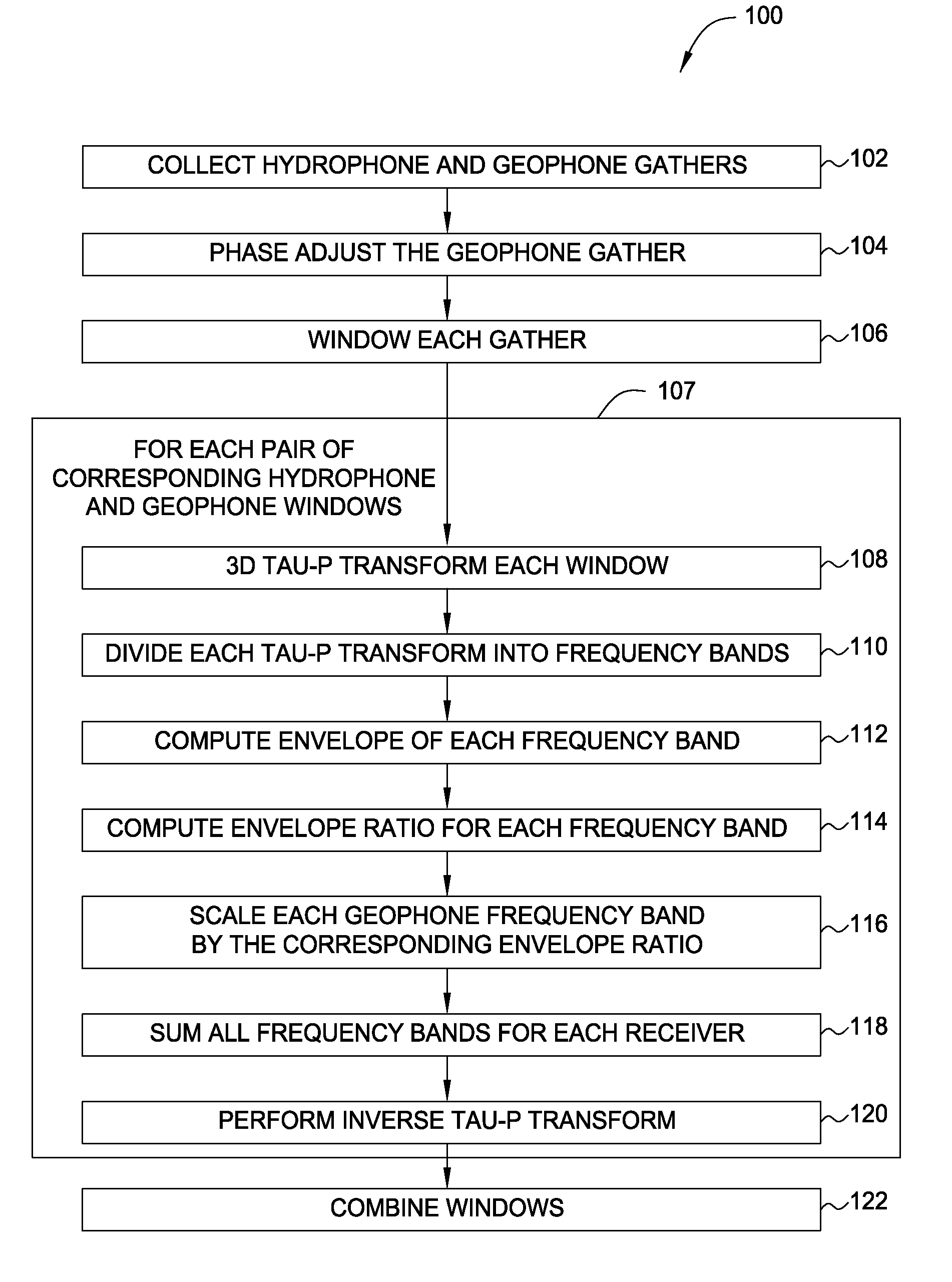

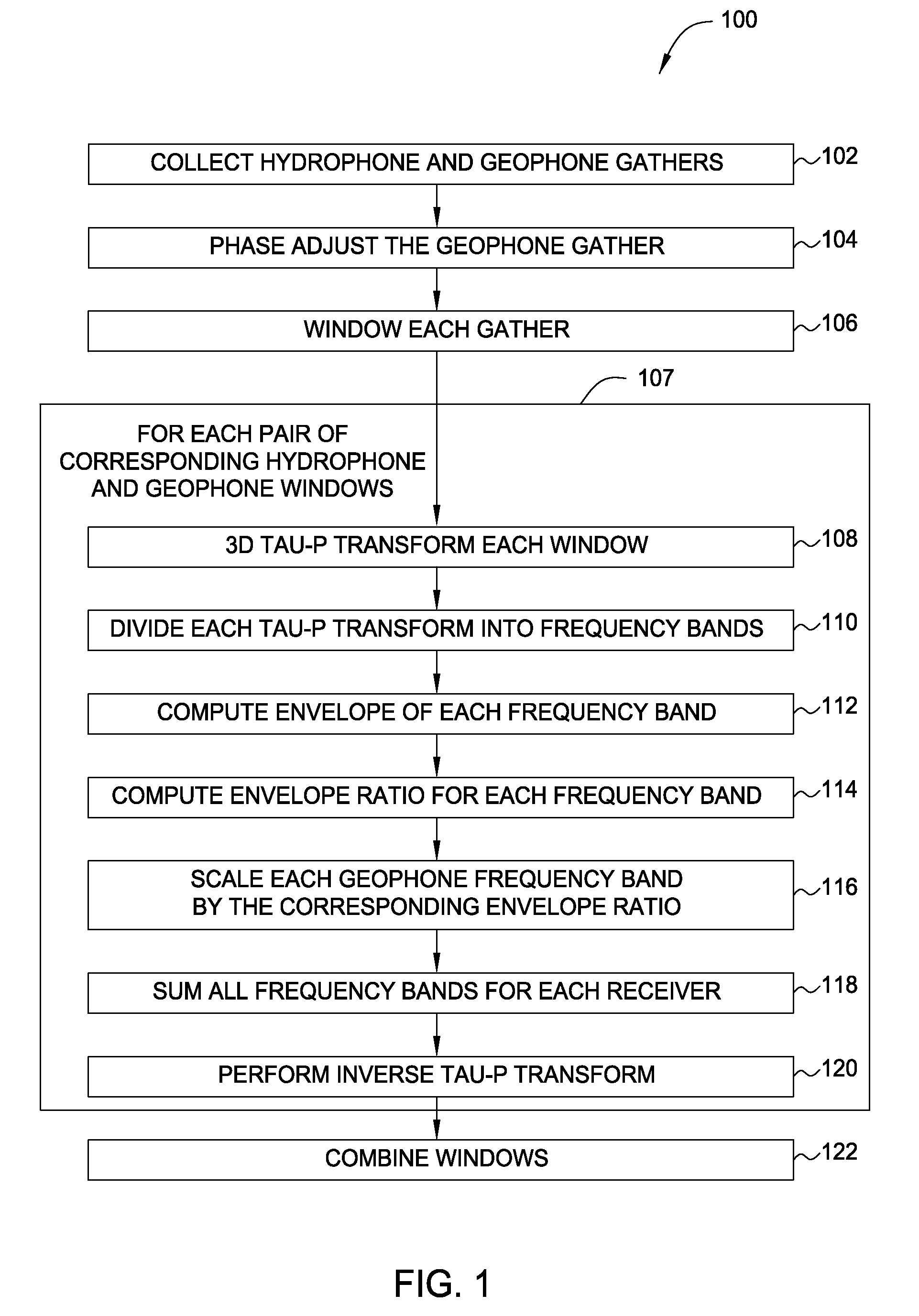

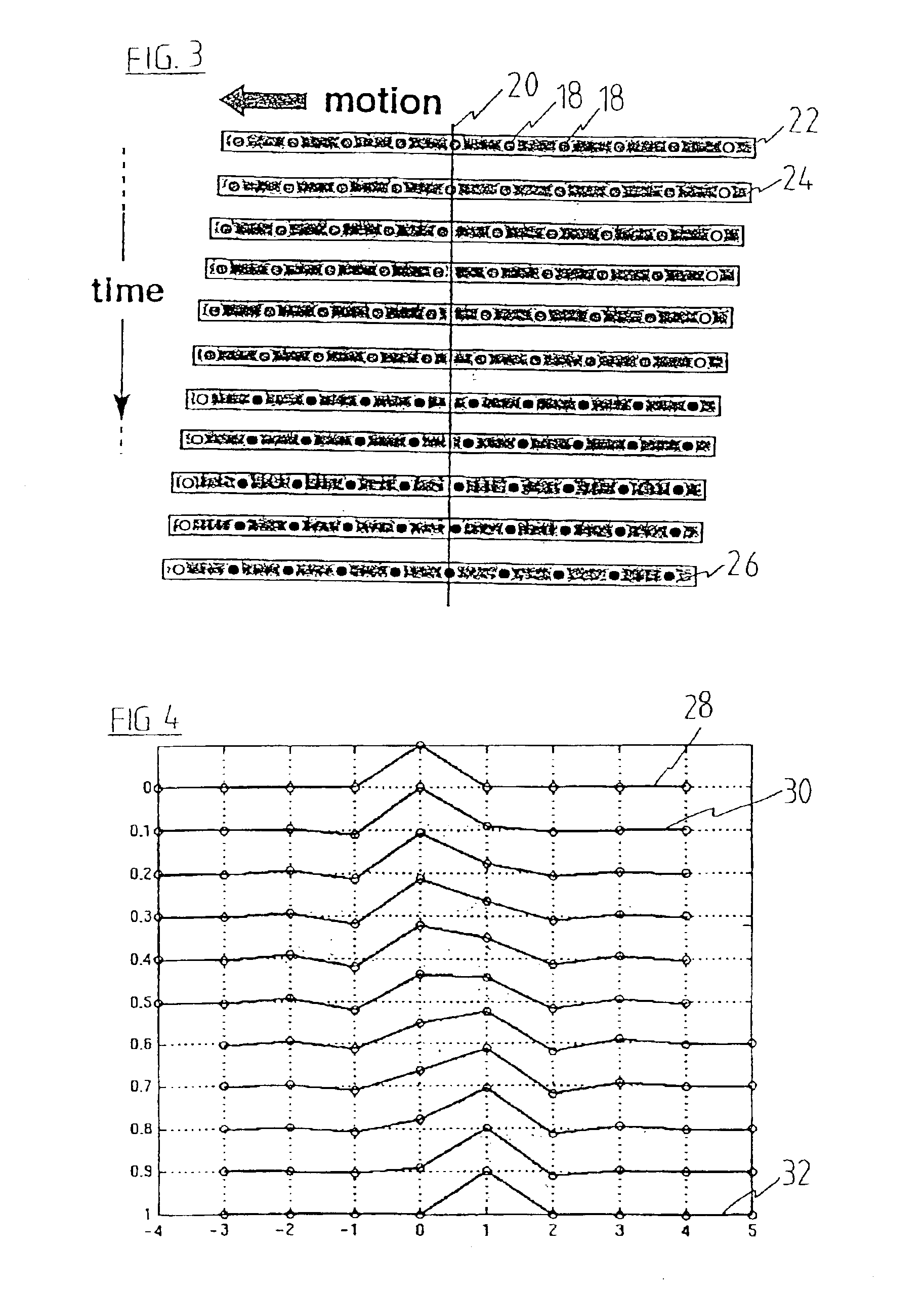

Geophone noise attenuation and wavefield separation using a multi-dimensional decomposition technique

ActiveUS20080221801A1Cancel noiseEasy to separateDigital variable/waveform displaySeismic signal processingGeophoneHydrophone

Methods and apparatus for processing dual sensor (e.g., hydrophone and vertical geophone) data that includes intrinsic removal of noise as well as enhancing the wavefield separation are provided. The methods disclosed herein are based on a decomposition of data simultaneously into dip and frequency while retaining temporal locality. The noise removed may be mainly coherent geophone noise from the vertical geophone, also known as V(z) noise.

Owner:FAIRFIELD INDUSTRIES INC

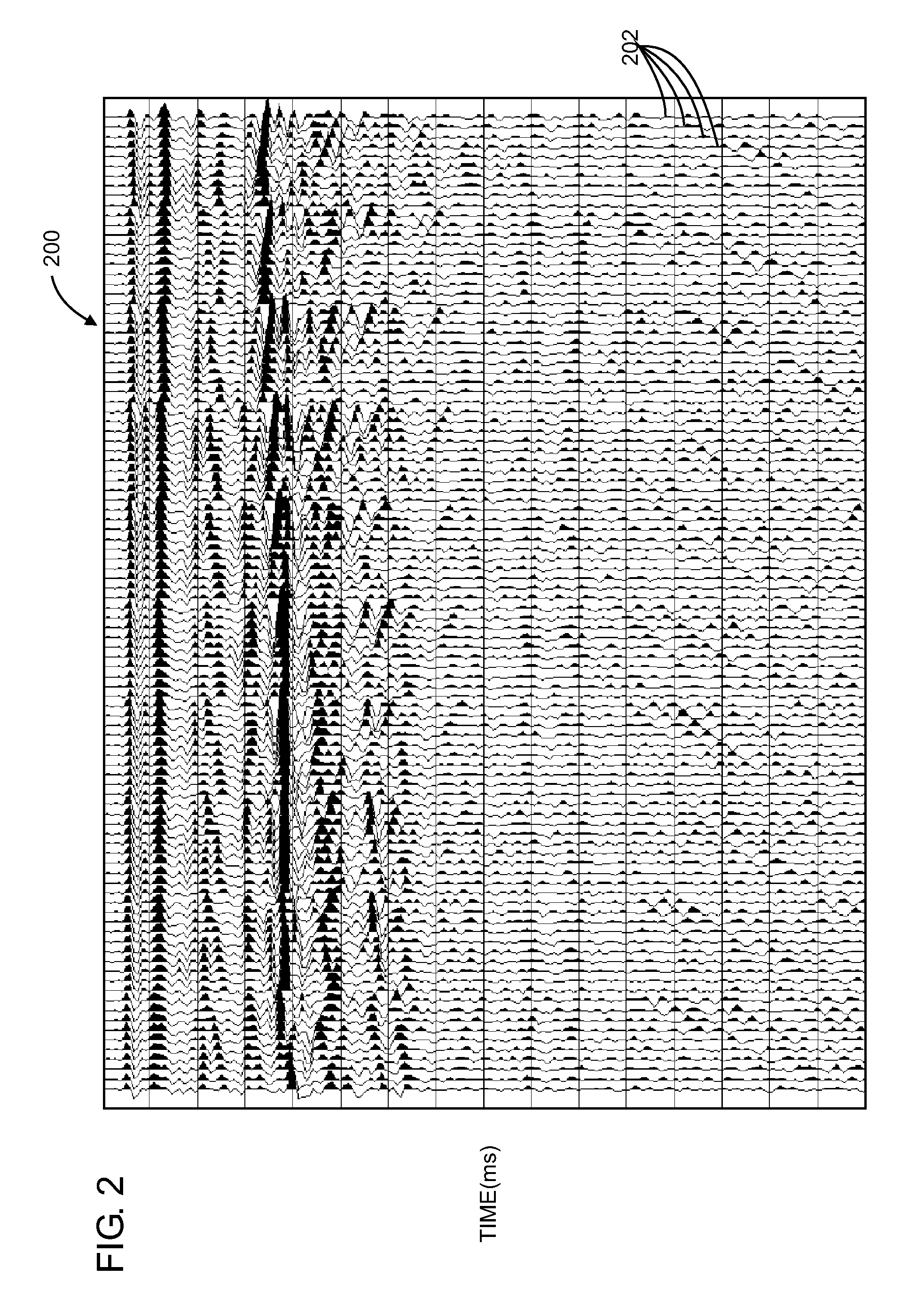

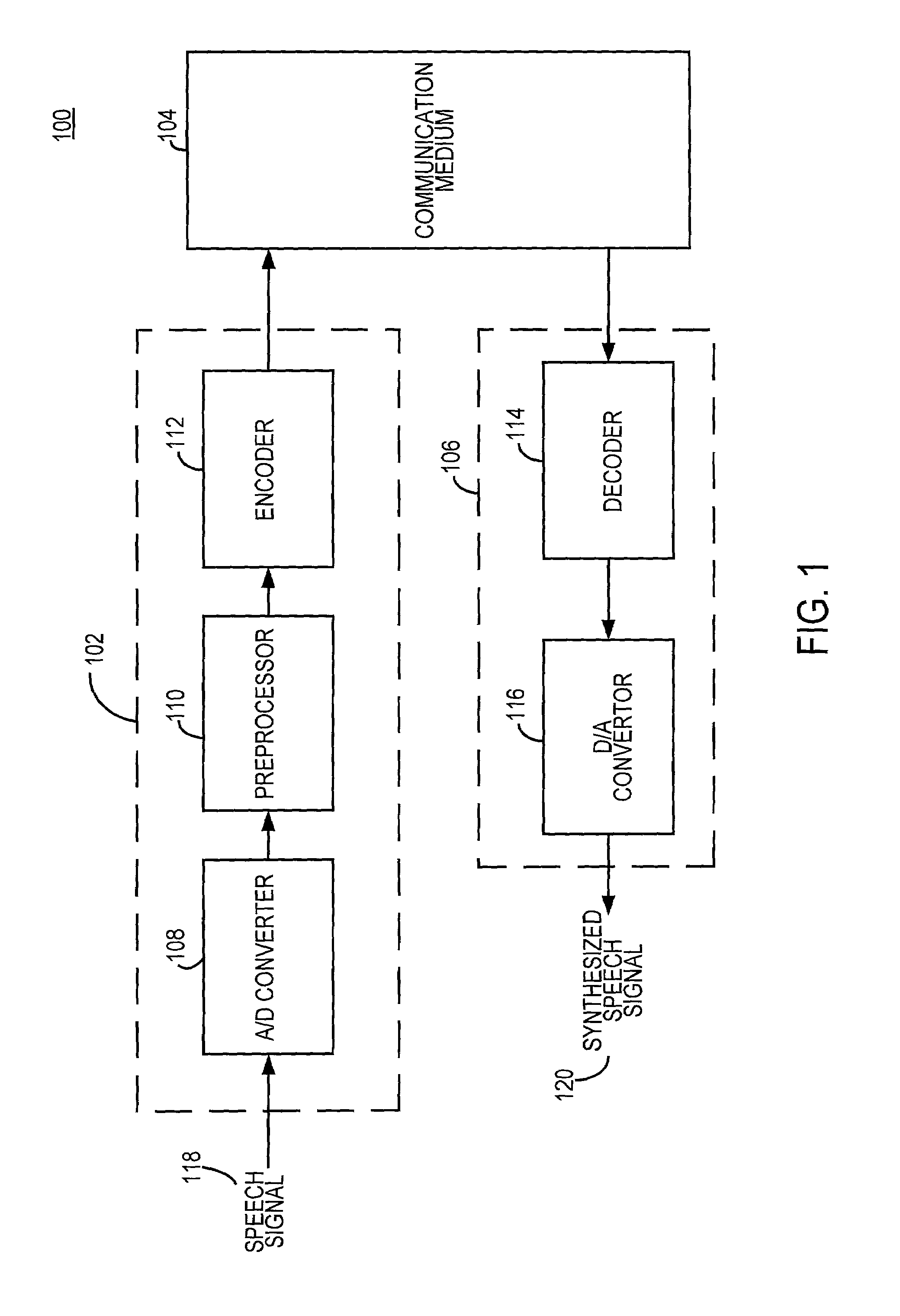

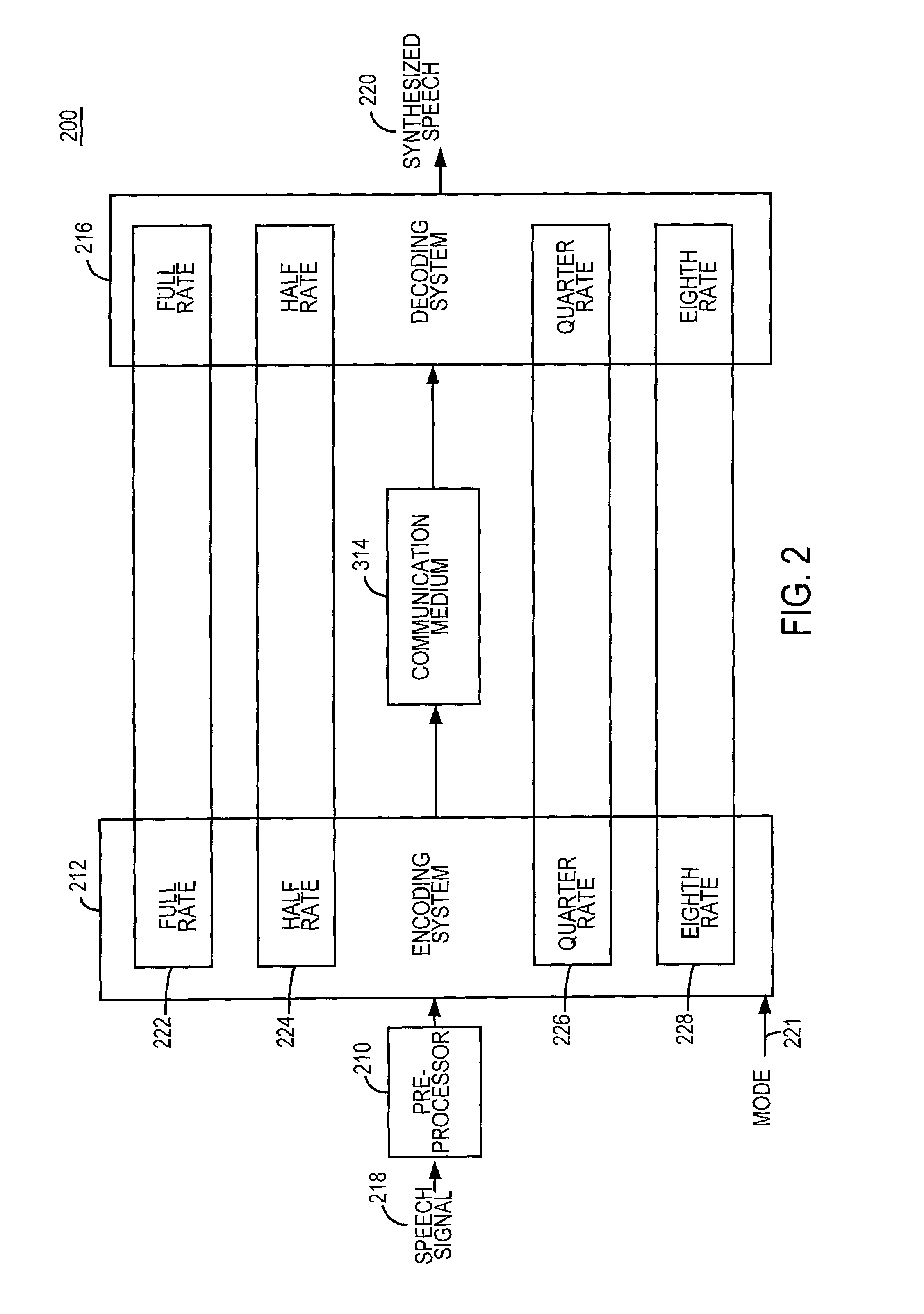

Speech coding system with time-domain noise attenuation

InactiveUS7020605B2Suppress noiseReduce background noiseSpeech analysisAnalog-to-digital converterBackground noise

A speech coding system is provided with time-domain noise attenuation. The speech coding system has an encoder operatively connected to a decoder via a communication medium. A preprocessor processes a digitized speech signal from an analog-to-digital converter. Speech coding systems are used to encode and decode a bitstream. Gains from the speech coding are adjusted by a gain factor Gf that provides time-domain background noise attenuation.

Owner:MACOM TECH SOLUTIONS HLDG INC +1

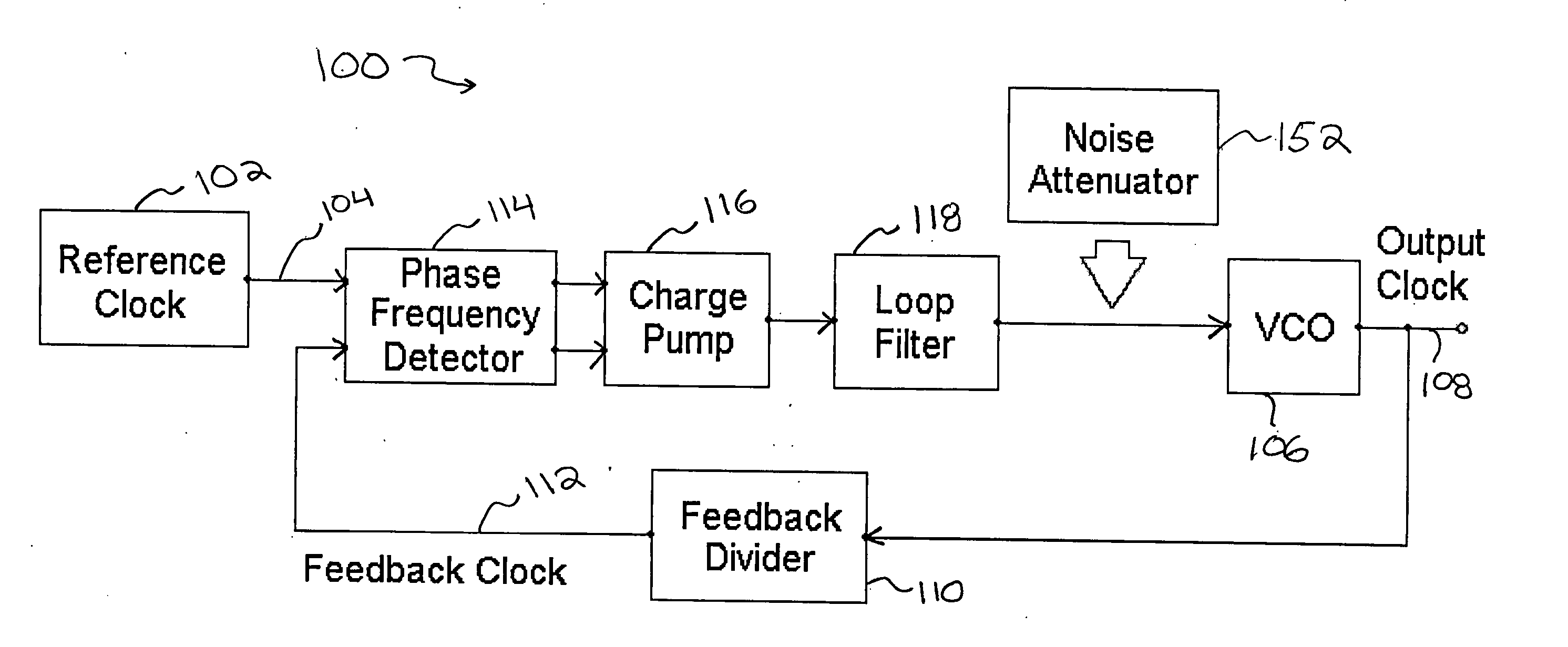

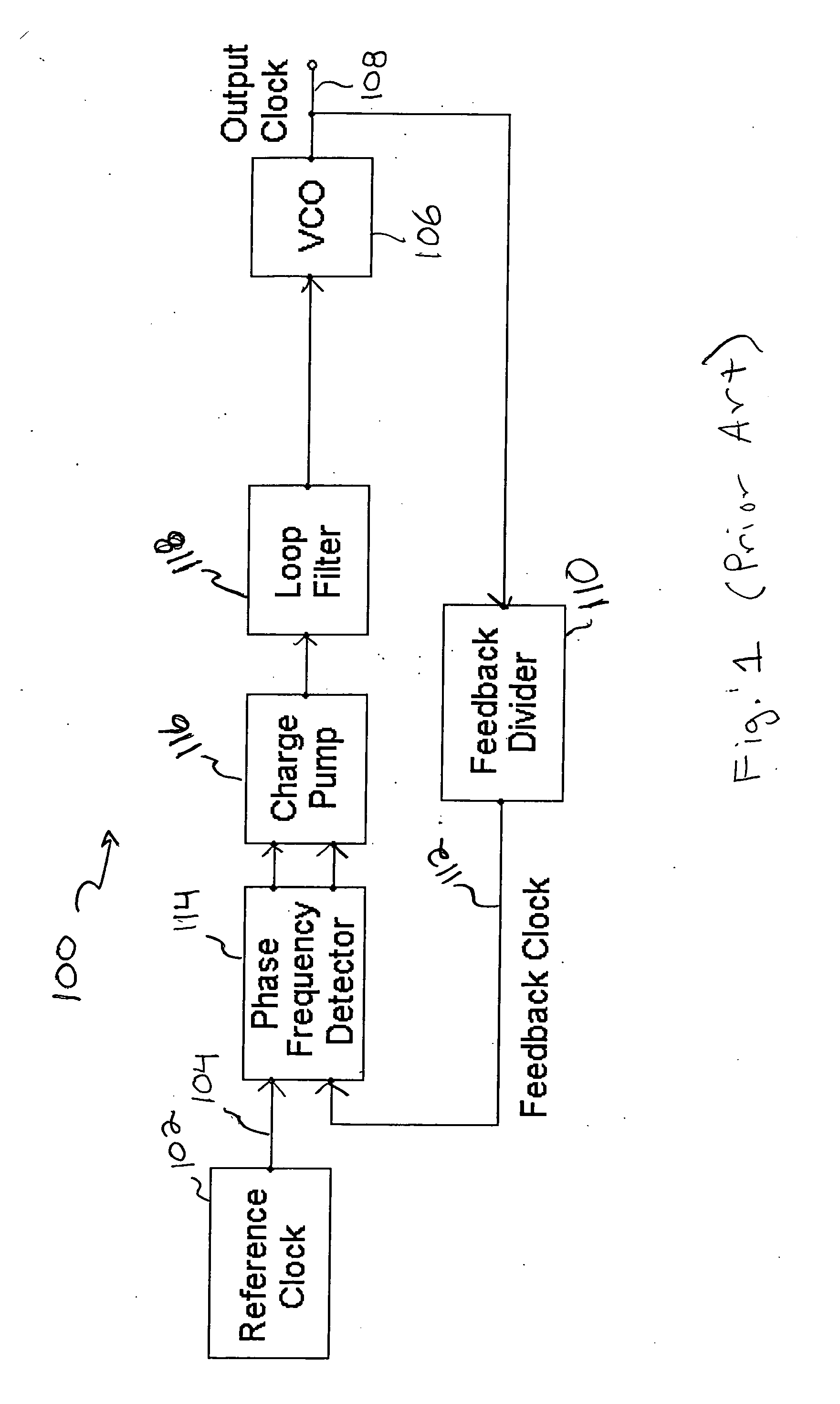

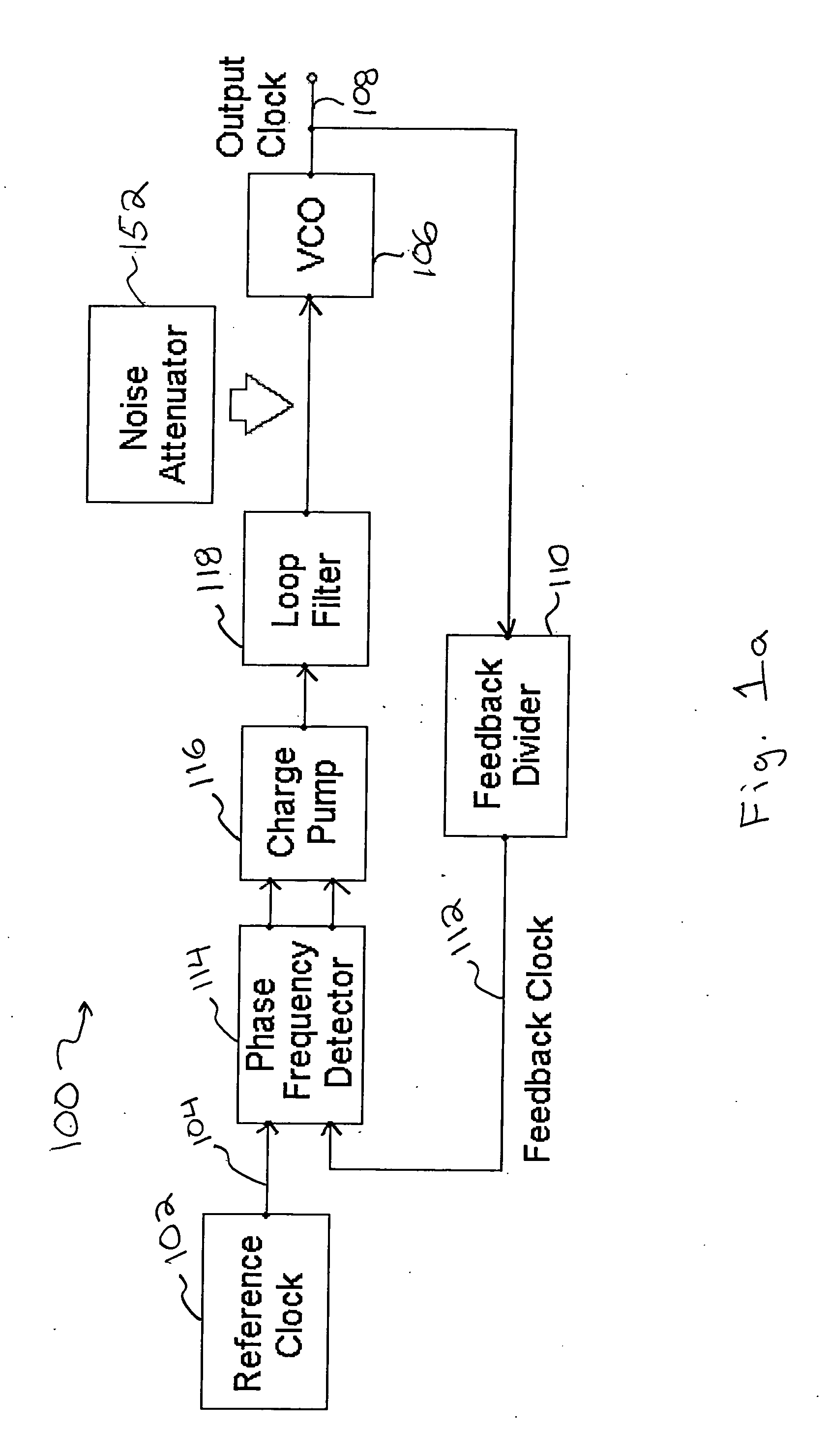

Method and apparatus to reduce the jitter in wideband PLL frequency synthesizers using noise attenuation

InactiveUS20060141963A1Reduce noise contributionReduce phase noisePulse automatic controlTransmissionMOSFETCapacitance

A noise attenuator loop filter for PLL applications that allows a full on-chip integration of the loop filter capacitors, while ensuring a low output clock phase noise (jitter) is disclosed. A voltage attenuator (A) is inserted between the loop filter (passive or active) and the controlled oscillator. The attenuator attenuates the noise coming from the loop filter. In case of a passive RC filter, the series resistor noise power is attenuated by A2 times, allowing the usage of a resistor that is A2 times larger and therefore the loop filter capacitors result A2 times smaller (easy to integrate on-chip). The relatively low value capacitor allows the usage of thick-oxide accumulation-mode MOSFET capacitors that take a reasonable low area, have a good linearity, are isolated from the substrate by the grounded N-well, and have negligible gate leakage current. Several embodiments of the noise attenuator are proposed for different practical applications: clock generation for digital circuits, frequency translation, low or high supply voltage, narrow or wide frequency range, processes with or without isolated well devices, processes with or without polysilicon resistors, and medium or high reference spurs rejection.

Owner:SILICON LAB INC

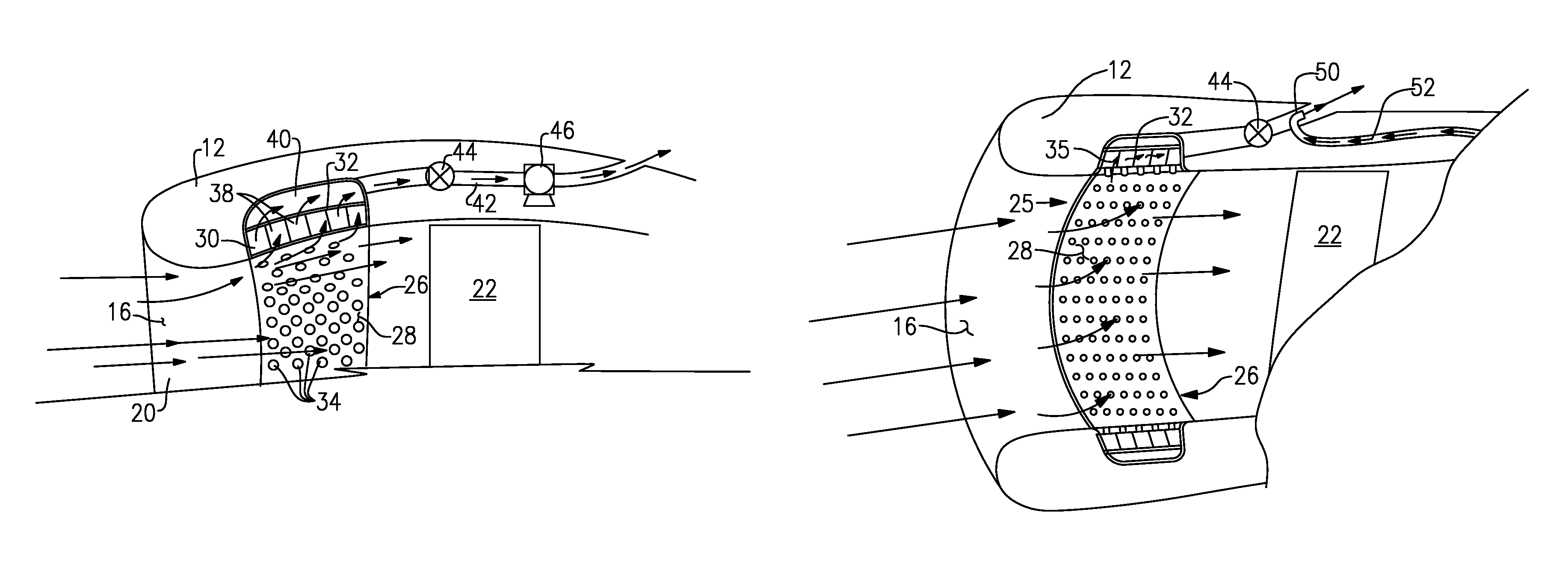

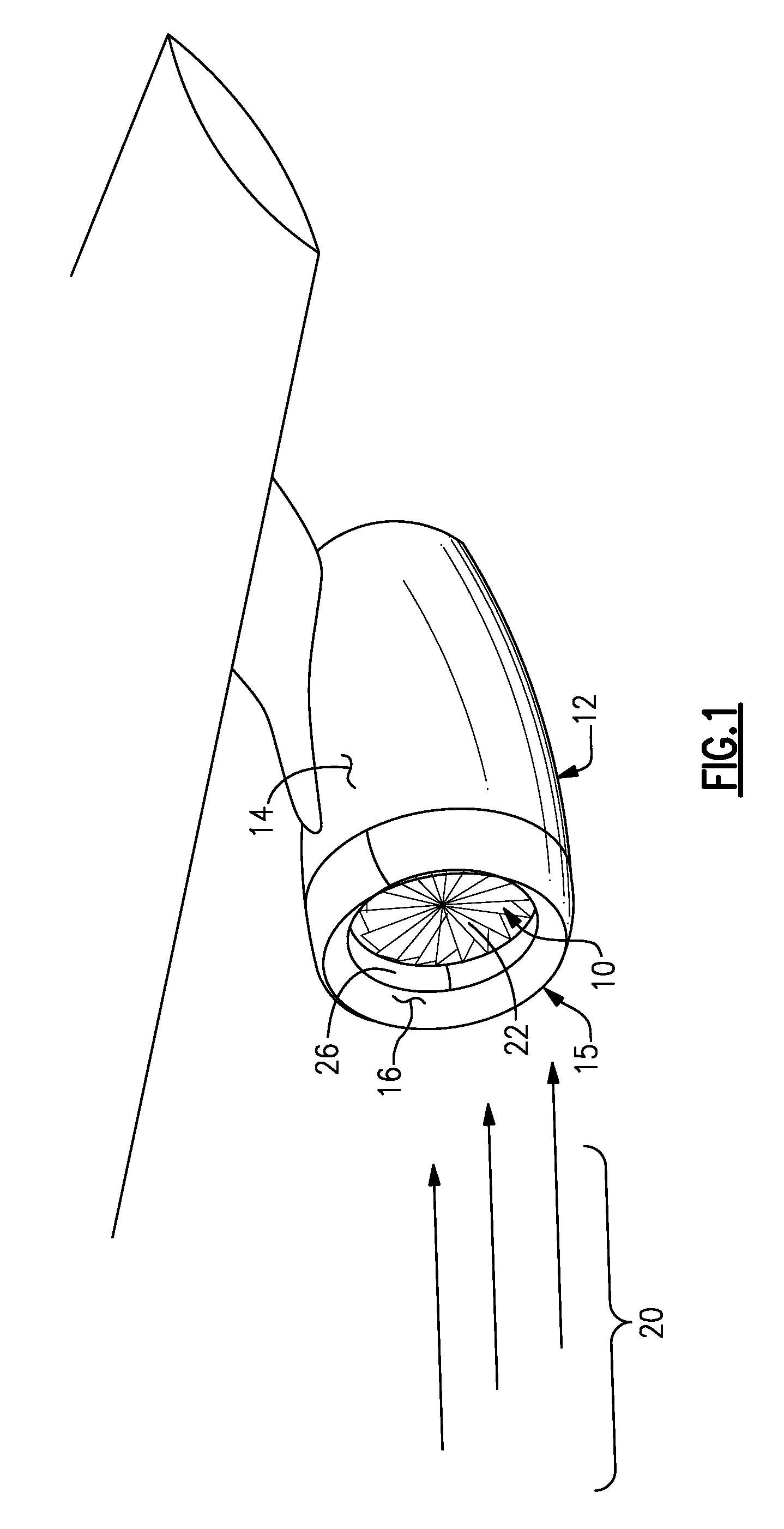

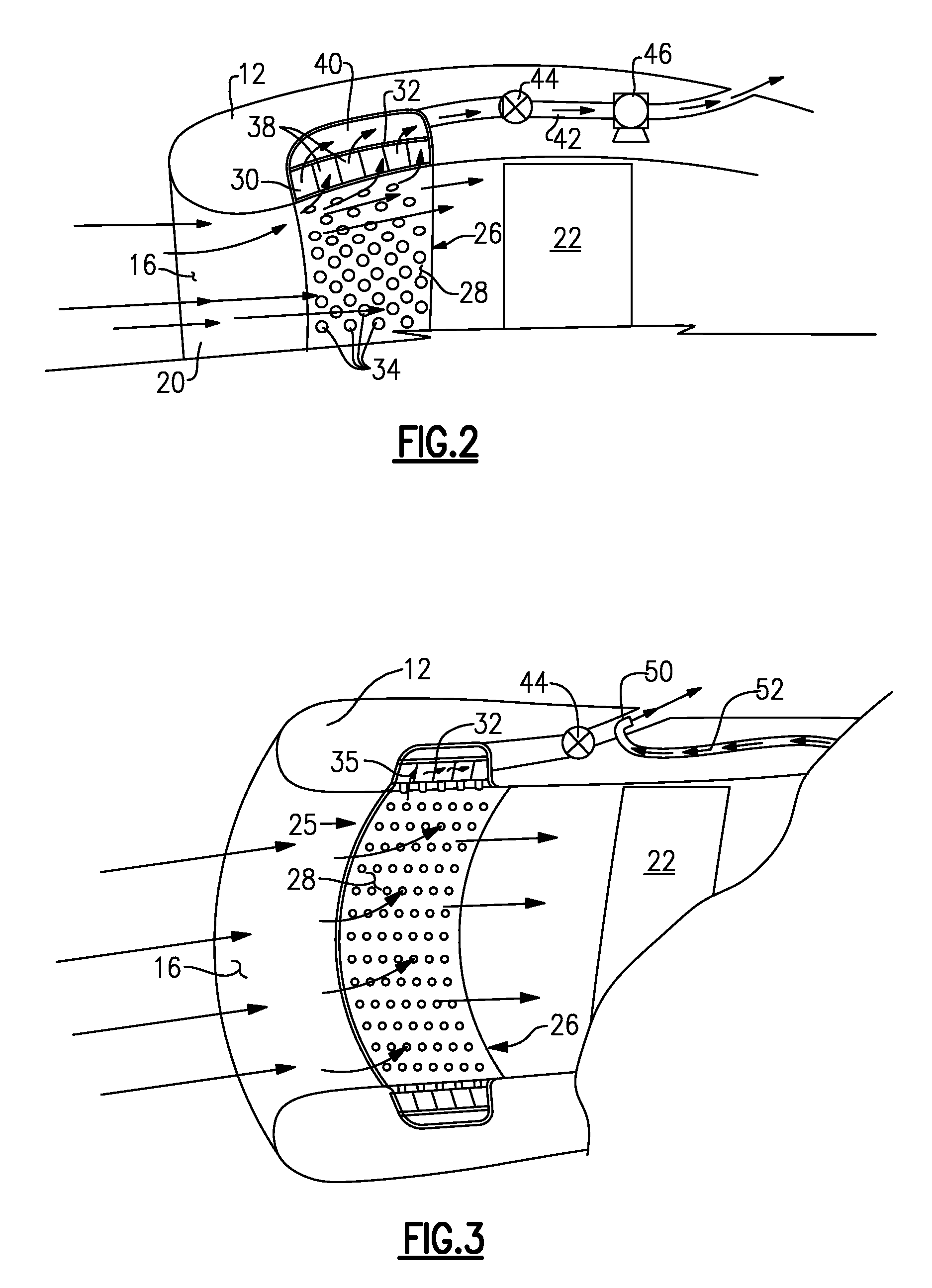

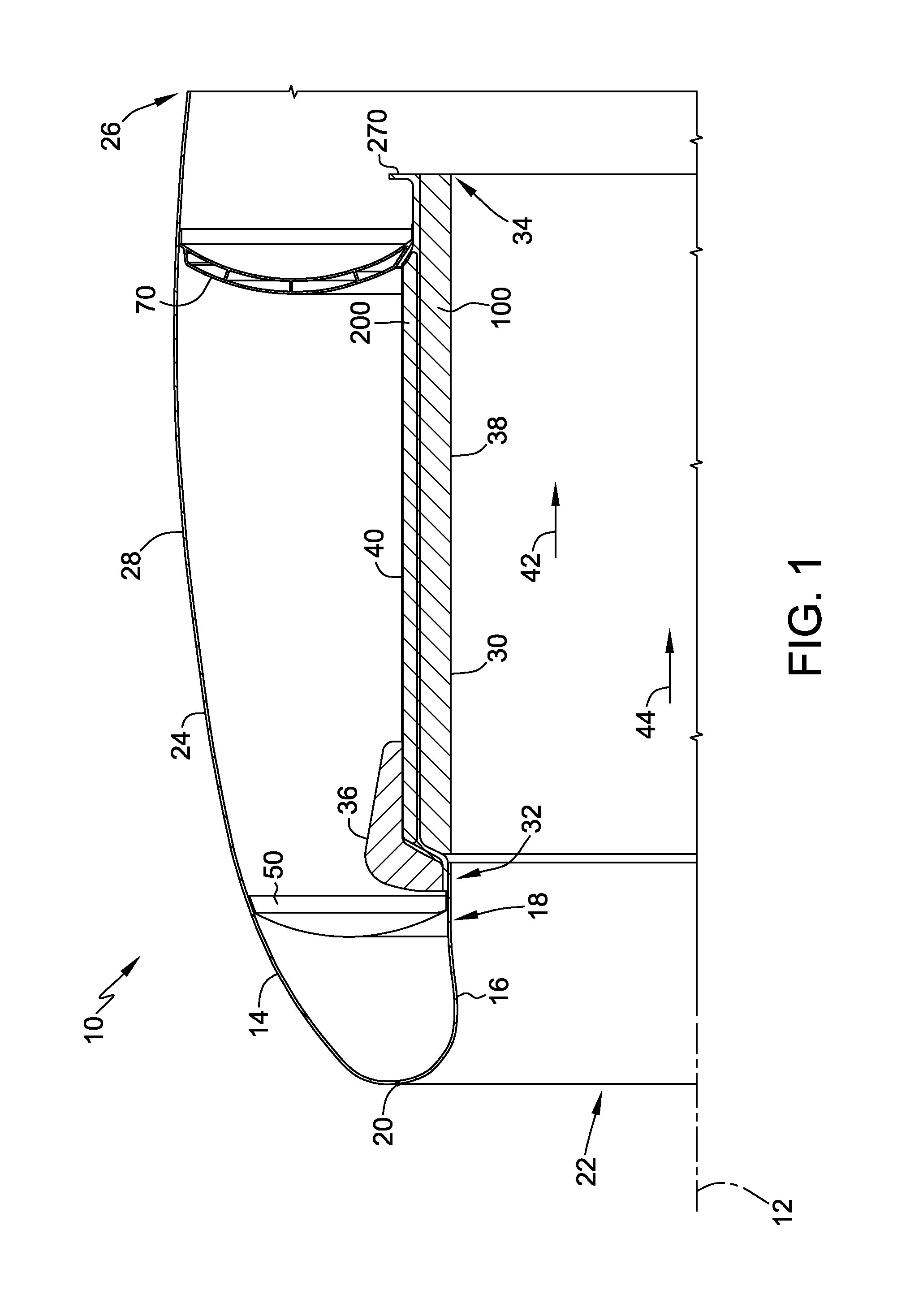

Integral suction device with acoustic panel

InactiveUS7766280B2Avoid separationLower performance requirementsEngine fuctionsWingsNacelleControl system

An inlet flow control system disposed within a nacelle includes a panel on an inner surface of that nacelle. The panel includes a noise attenuation layer that dissipates noise energy. A vacuum source generates a pressure differential across the noise attenuation layer for drawing airflow through the panel and away from an inner surface of the nacelle.

Owner:RAYTHEON TECH CORP

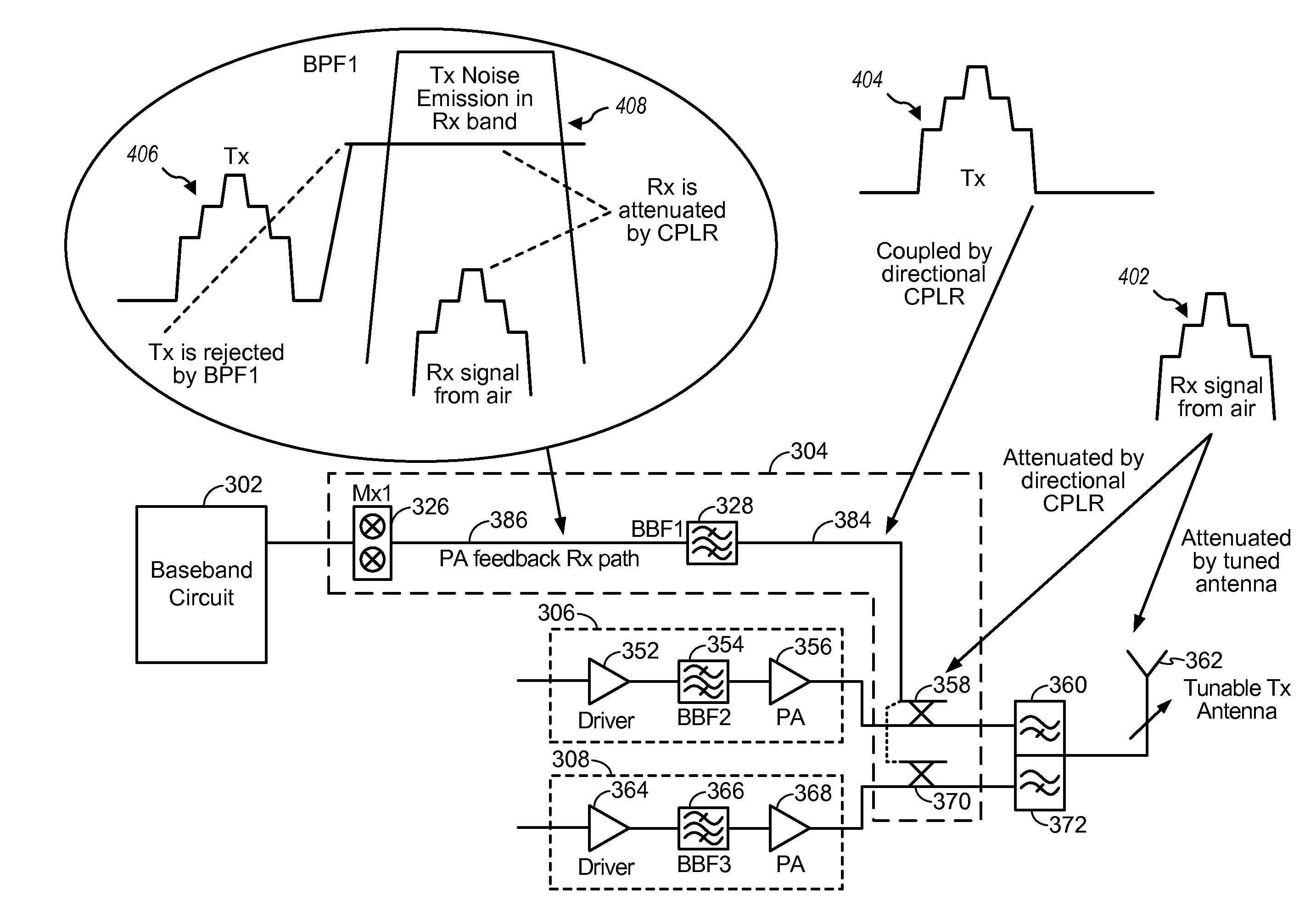

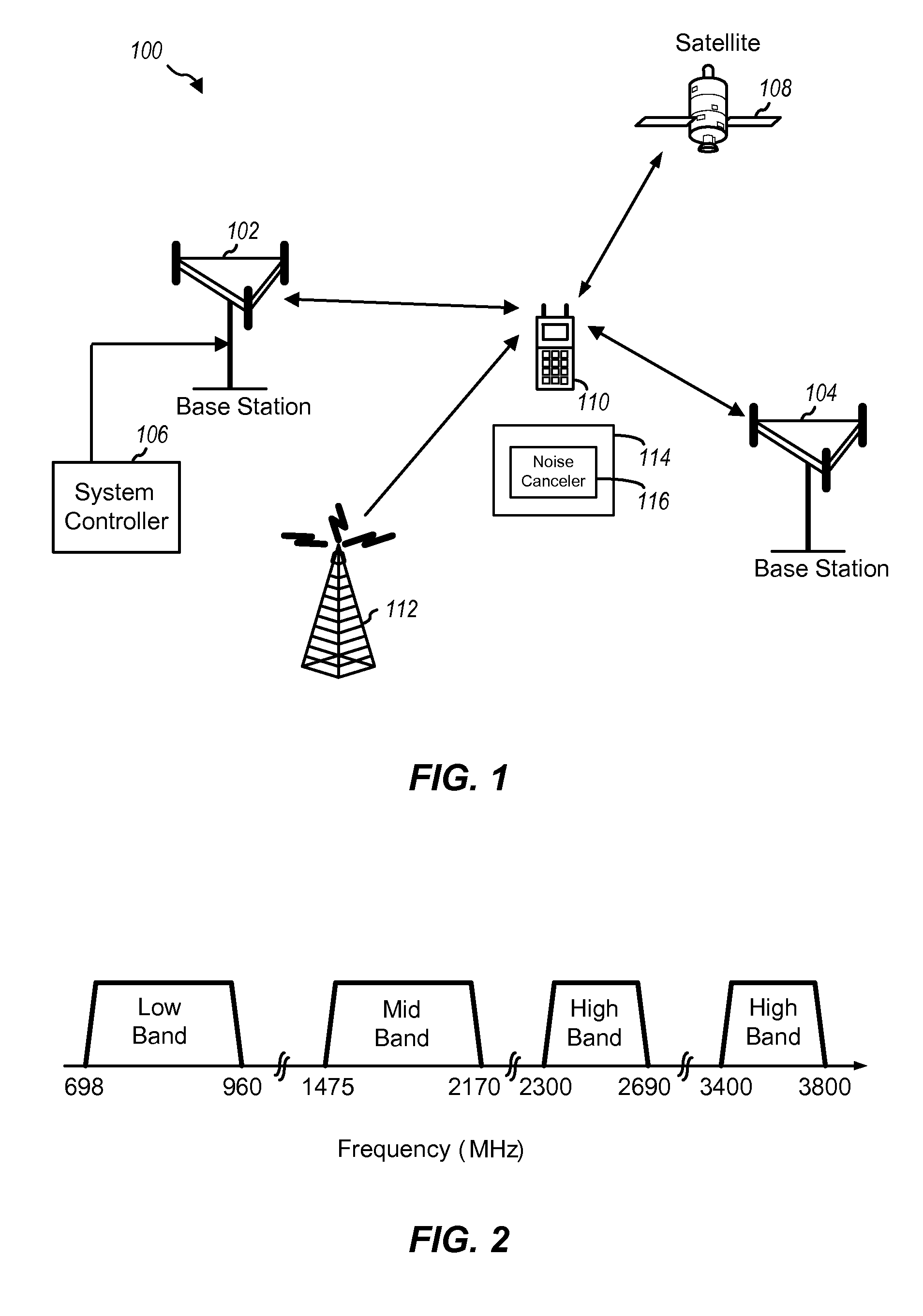

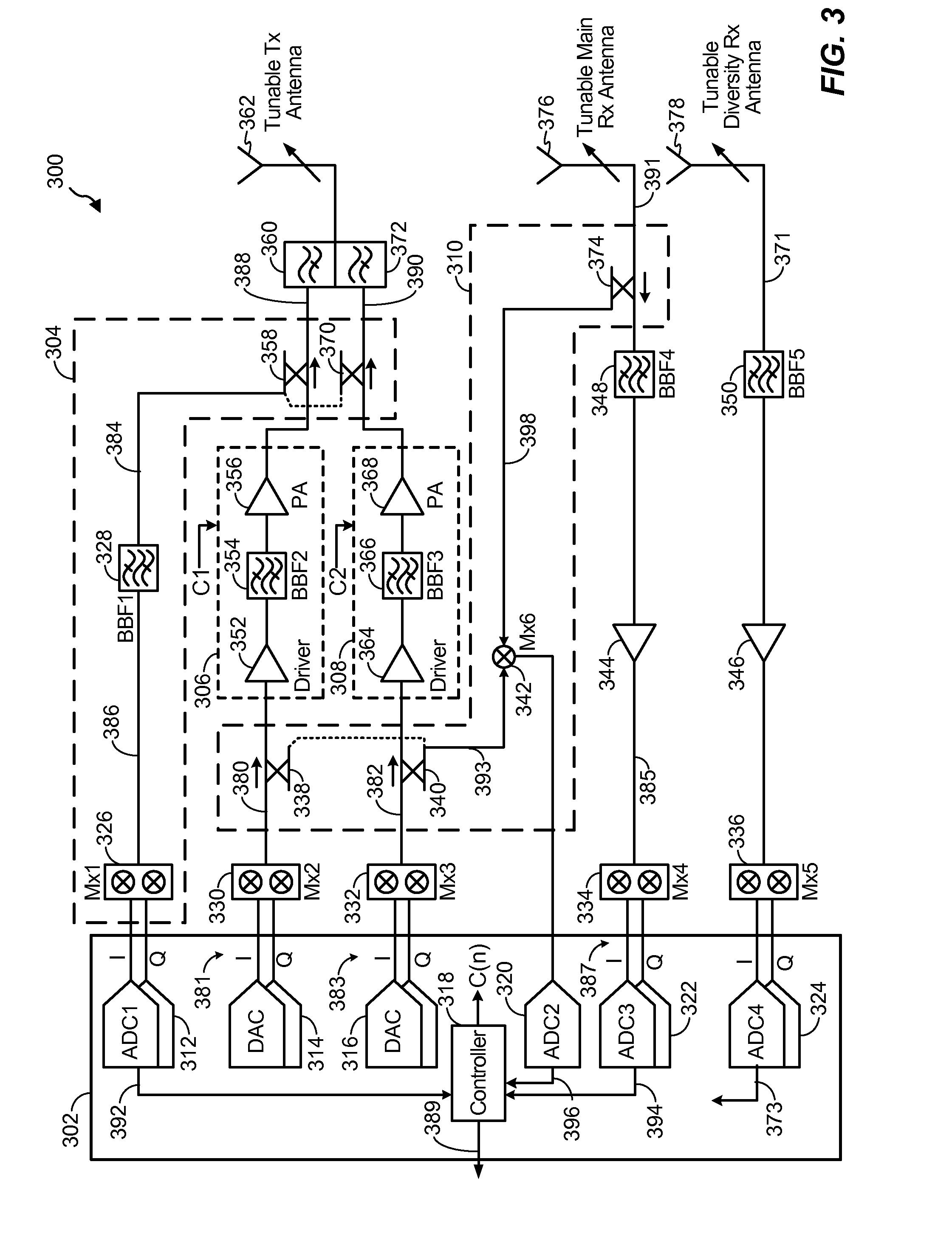

Noise canceler for use in a transceiver

A noise canceler for use in a transceiver is disclosed. In an exemplary embodiment, an apparatus includes a split amplifier to output an amplified transmit signal, the split amplifier providing a first noise attenuation factor in a receive band. The apparatus also includes a transmit antenna to transmit the amplified transmit signal, the transmit antenna being isolated from a receive antenna by an antenna isolation factor that provides a second noise attenuation factor in the receive band. The apparatus also includes a noise canceler configured to subtract a detection signal from a received signal to obtain an adjusted received signal, wherein subtraction of the detection signal provides a third noise attenuation factor in the receive band, and wherein the first, second, and third noise attenuation factors combine to provide a selected amount of noise attenuation in the receive band.

Owner:QUALCOMM INC

Method and apparatus for attenuating compressor noise

ActiveUS7527053B2Reduce noiseReduce the amount of noiseRespiratorsOperating means/releasing devices for valvesPortable ventilatorsEngineering

The invention comprises a method and apparatus for reducing the noise generated by compressors, including Roots-type blowers. The invention has particular use for reducing noise generated by compressors used in mechanical ventilators, though the advantages thereof may be realized in many different applications. One embodiment of the invention comprises a noise-attenuating gas flow path for a compressor contained in a portable ventilator housing. In one embodiment, the gas flow path comprises a plurality of chambers interconnected by flow tubes. The flow path is folded so as to fit into the limited space of a portable ventilator housing. The dimensions of the chambers and the flow tubes are selected so that an impedance mismatch is created between the chambers and the flow tubes. In one embodiment of the invention, the flow path comprises one or more perforated tubes located in one or more of the chambers. The perforated tube has a port through which gas is accepted and at least one exterior tube through which gas exits. Impedance mismatches are created between the inlet chamber and the exterior tubes and between the exterior tubes and the chamber in which the perforated tube is located, which are useful in attenuating noise. One embodiment of the invention comprises a noise attenuating mounting system for a compressor. The mounting system comprises flexible mounts that cooperate to dampen vibrations generated by the compressor.

Owner:VYAIRE MEDICAL 203 INC

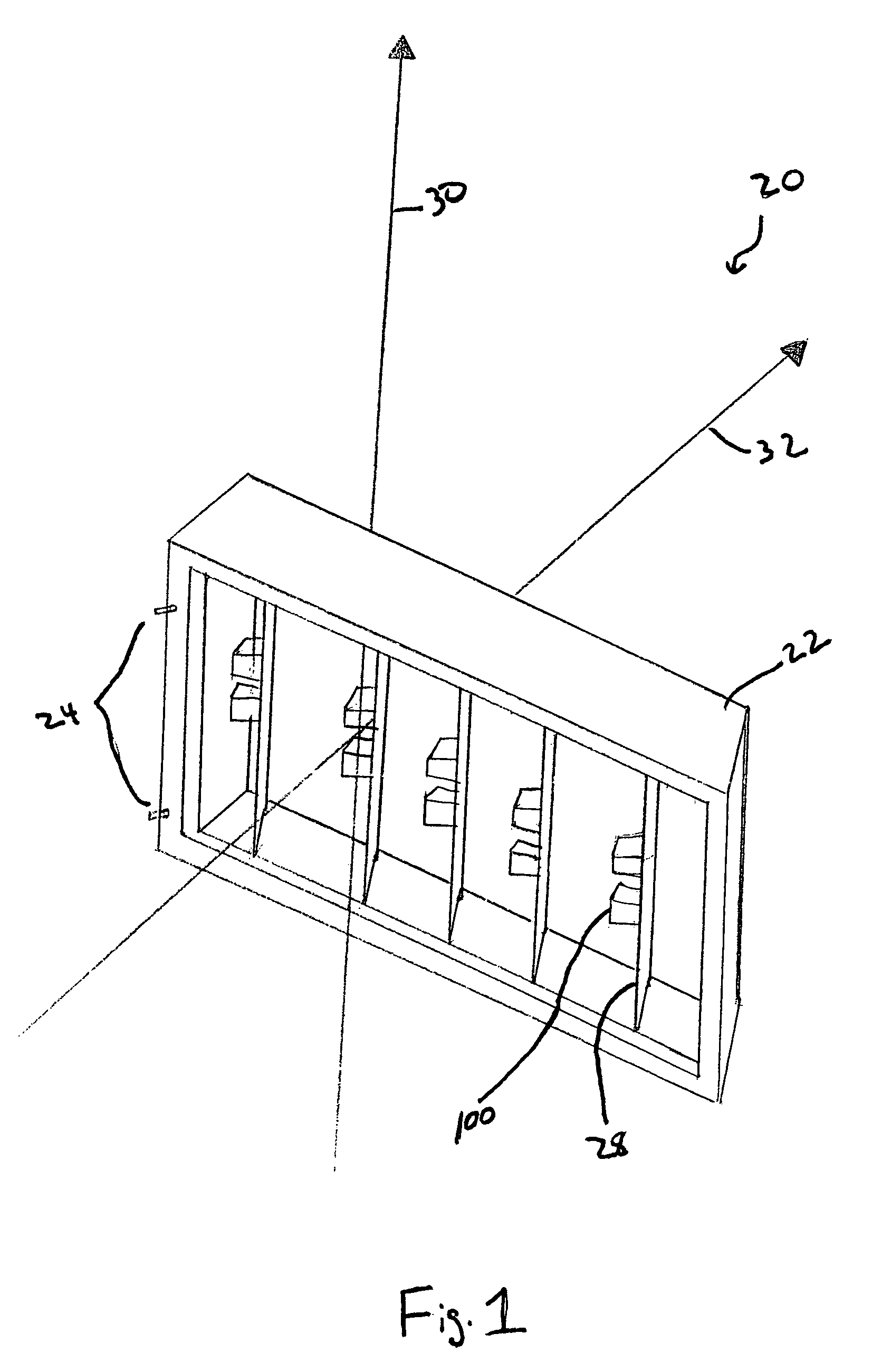

Method and system for attenuating noise from a cabinet housing computer equipment

ActiveUS7353908B1Cancel soundSubstantial and superior ear protectionEar treatmentSilencing apparatusOutput deviceEngineering

An apparatus for attenuating noise emanating from a cabinet housing noise-generating equipment includes a frame including at least one support member configured to be mountable on the cabinet, proximate the noise-generating equipment, at least one noise attenuation device mounted to each support member proximate the noise-generating equipment, the at least one noise attenuation device comprising a sound input device for receiving a noise signal output from the noise-generating equipment, a processing device for determining characteristics of the noise signal and generating a cancellation signal which is identical to the noise signal but approximately 180 degrees out-of-phase with the noise signal, and a sound output device for outputting the cancellation signal proximate the noise-generating equipment, to attenuate the noise emanating from the cabinet; and a noise absorption member mounted on each support member, the noise absorption members define surfaces that form sides of airflow channels through the apparatus.

Owner:EMC IP HLDG CO LLC

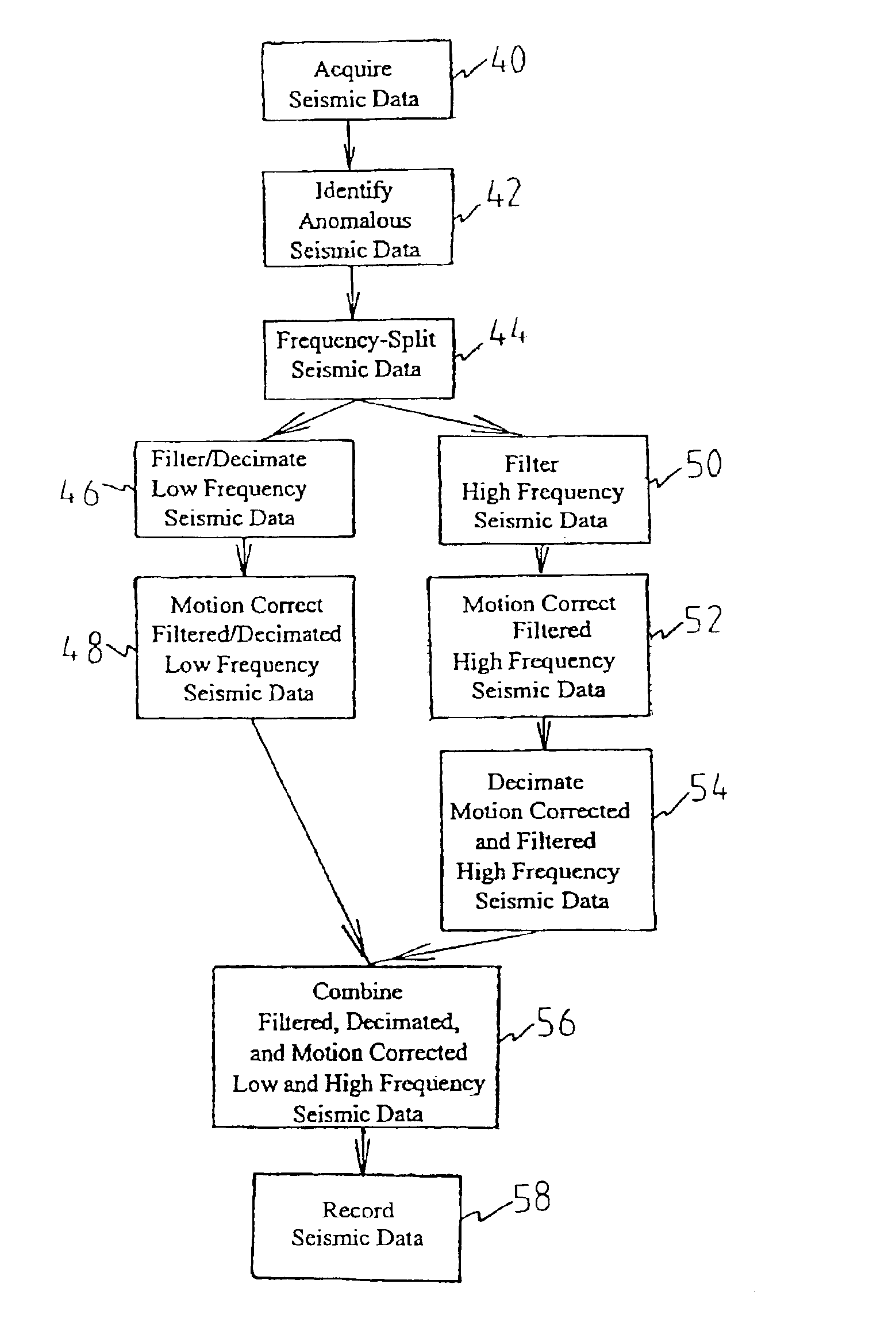

Seismic data acquisition and processing method

InactiveUS6876599B1Seismic signal processingSeismology for water-covered areasData acquisitionDigitization

A method of acquiring and processing seismic data including: acquiring digitized seismic data associated with a plurality of moving receiver points using a plurality of seismic sensors; attenuating noise in the moving receiver point based digitized seismic data using digitized seismic data associated with a plurality of nearby receiver points; transforming noise attenuated moving receiver point based digitized seismic data into stationary receiver point based digitized seismic data; and recording noise attenuated and transformed digitized seismic data associated with stationary receiver points having an average spatial separation interval at least twice the average moving receiver point spatial separation interval. This method is particularly effective at attenuating coherent low frequency noise and correcting for the receiver motion effect in marine seismic data.

Owner:REFLECTION MARINE NORGE AS

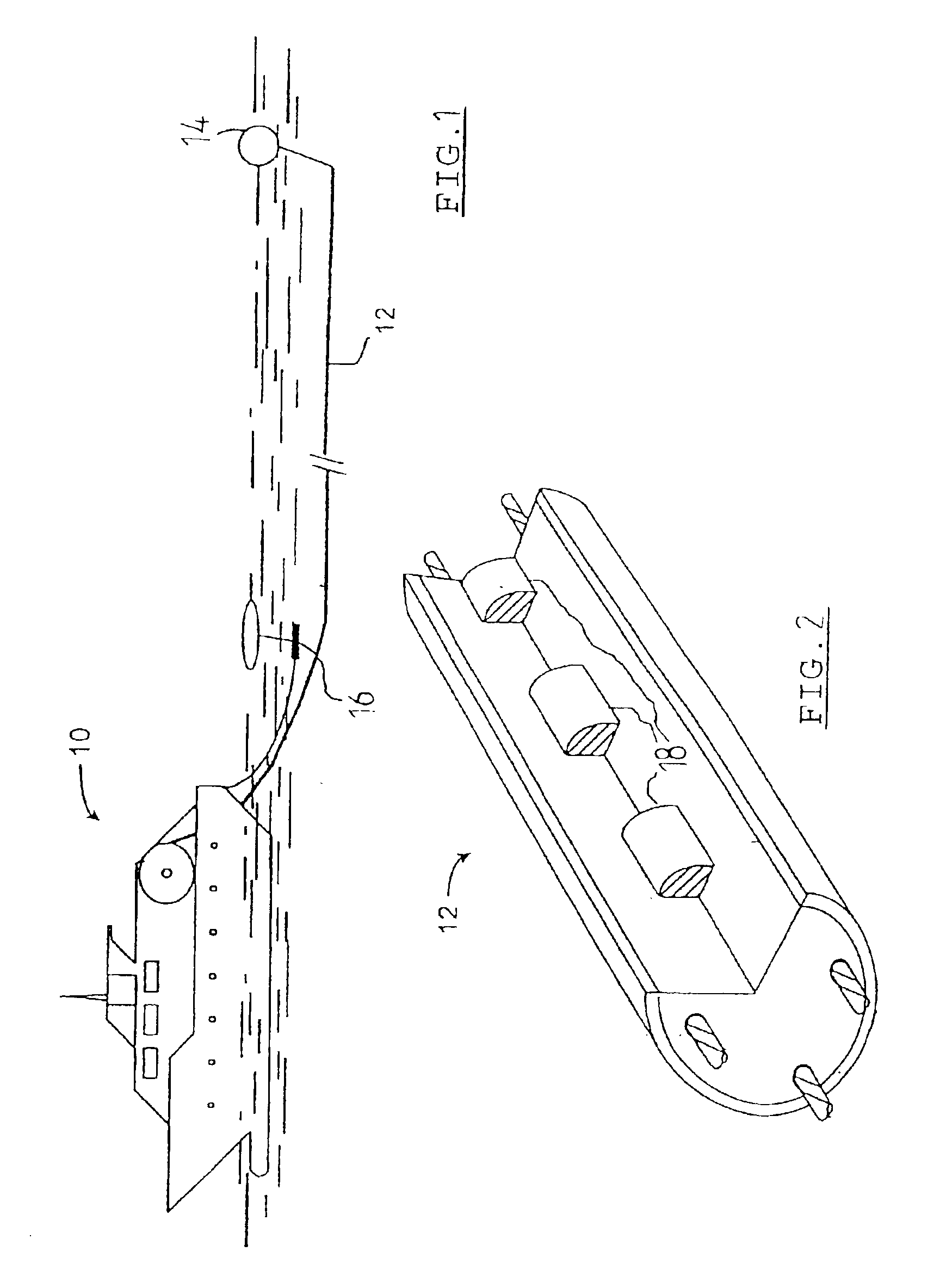

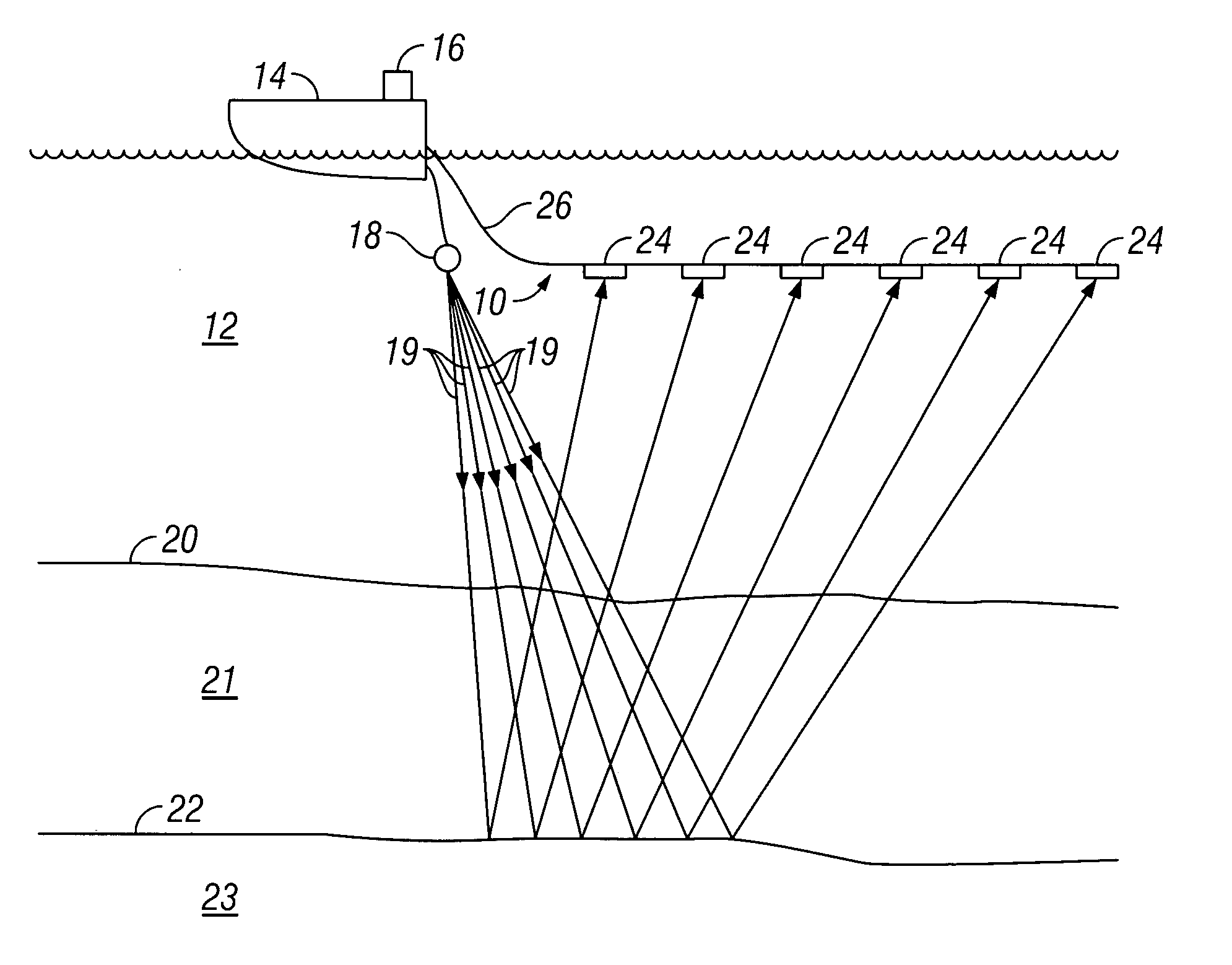

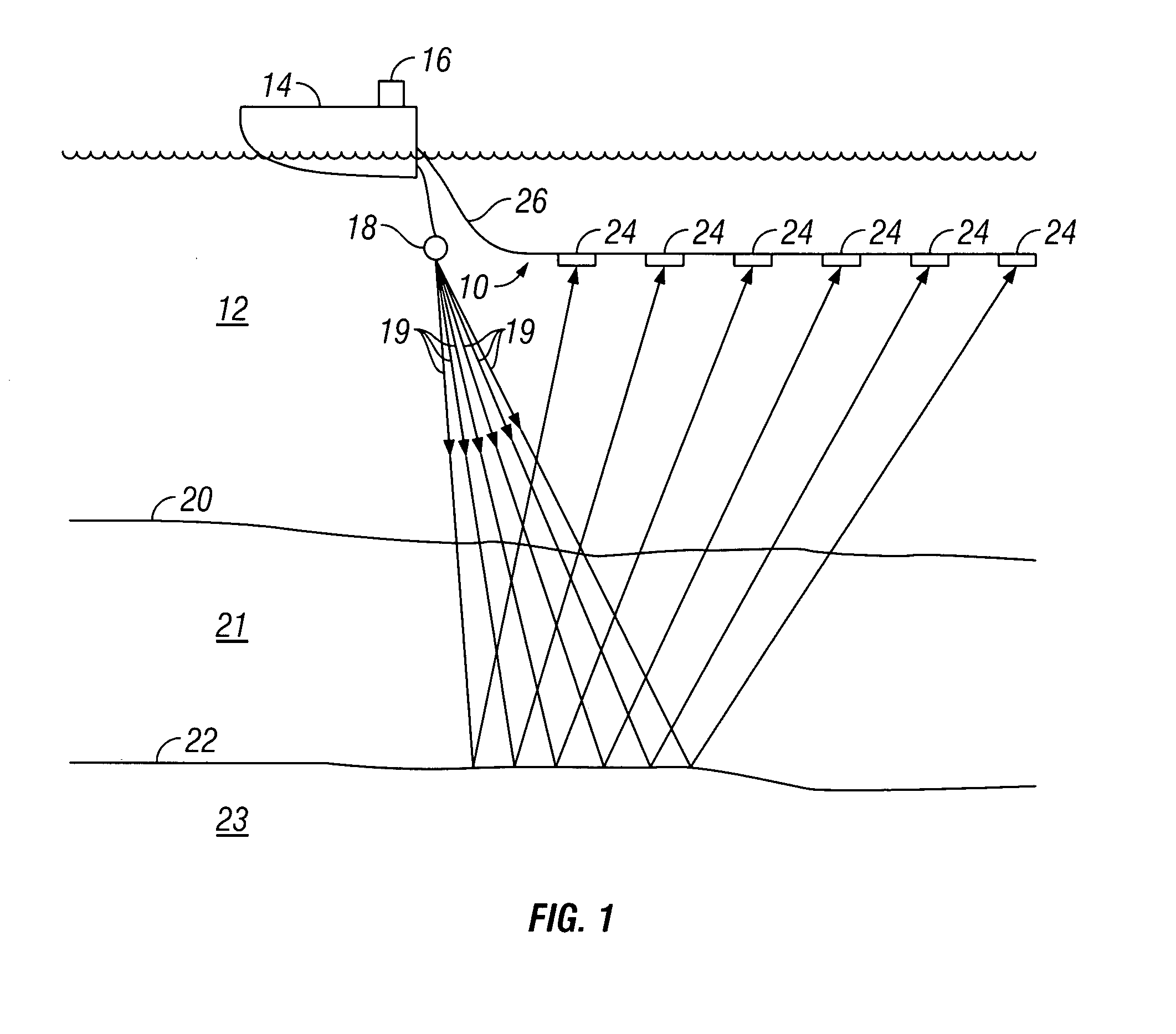

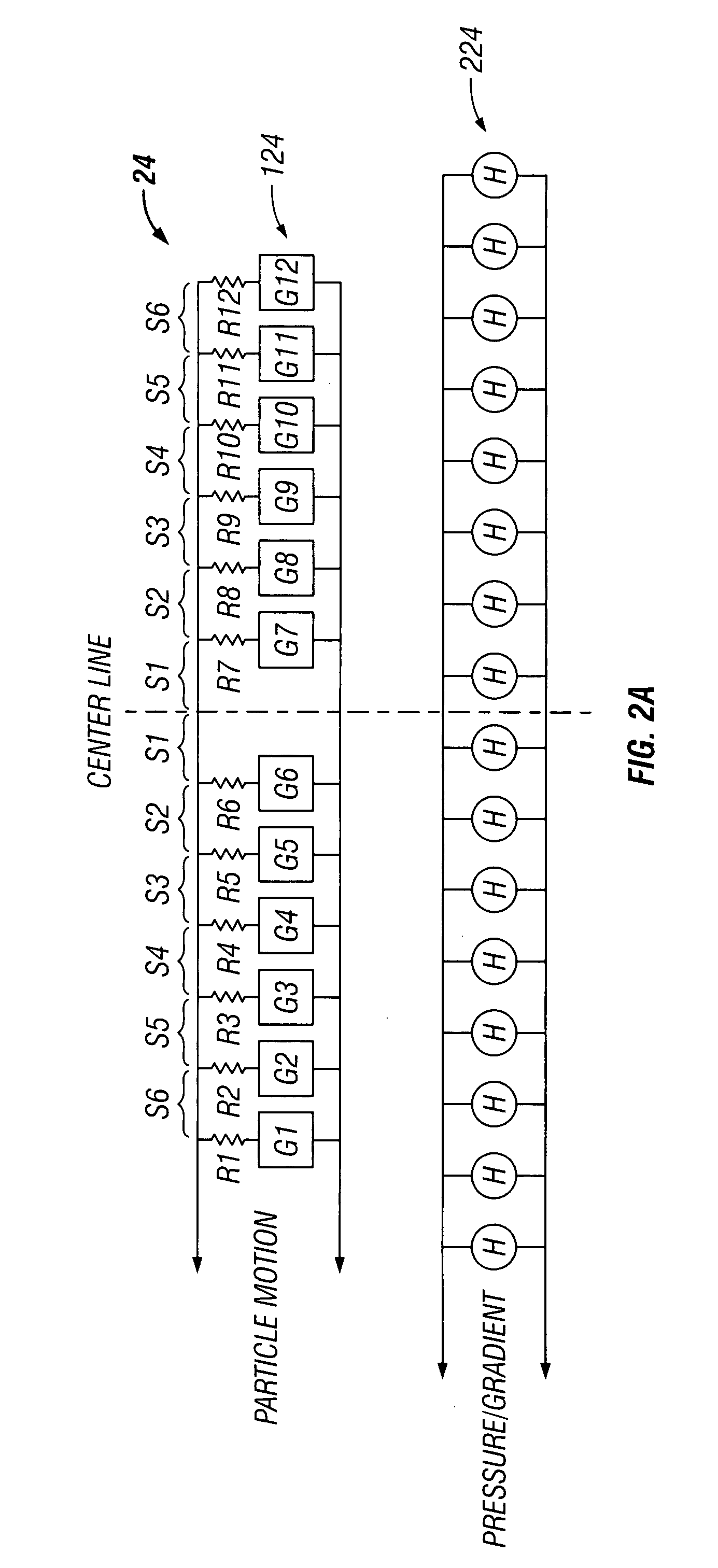

Array grouping of seismic sensors in a marine streamer for optimum noise attenuation

A marine seismic streamer includes at least one particle motion sensor array. The array includes a plurality of particle motion sensors disposed at spaced apart locations along the streamer. Outputs of the particle motion sensors are functionally coupled to form an array. A number of the particle motion sensors and a spacing between adjacent particle motion sensors are selected to attenuate noise in a selected mode of propagation and within a selected wavenumber range. The streamer includes means for weighting a signal output of each particle motion sensor in the at least one array. A signal weight applied to each sensor by the means for weighting is selected to optimize attenuation of the noise.

Owner:PGS GEOPHYSICAL AS

Noise attenuating device for a heating-ventilation-cooling system of a motor vehicle

InactiveUS20050076668A1Reduce impingementReduce flow noiseAir-treating devicesLighting and heating apparatusNoise attenuationAutomotive engineering

Owner:FORD GLOBAL TECH LLC

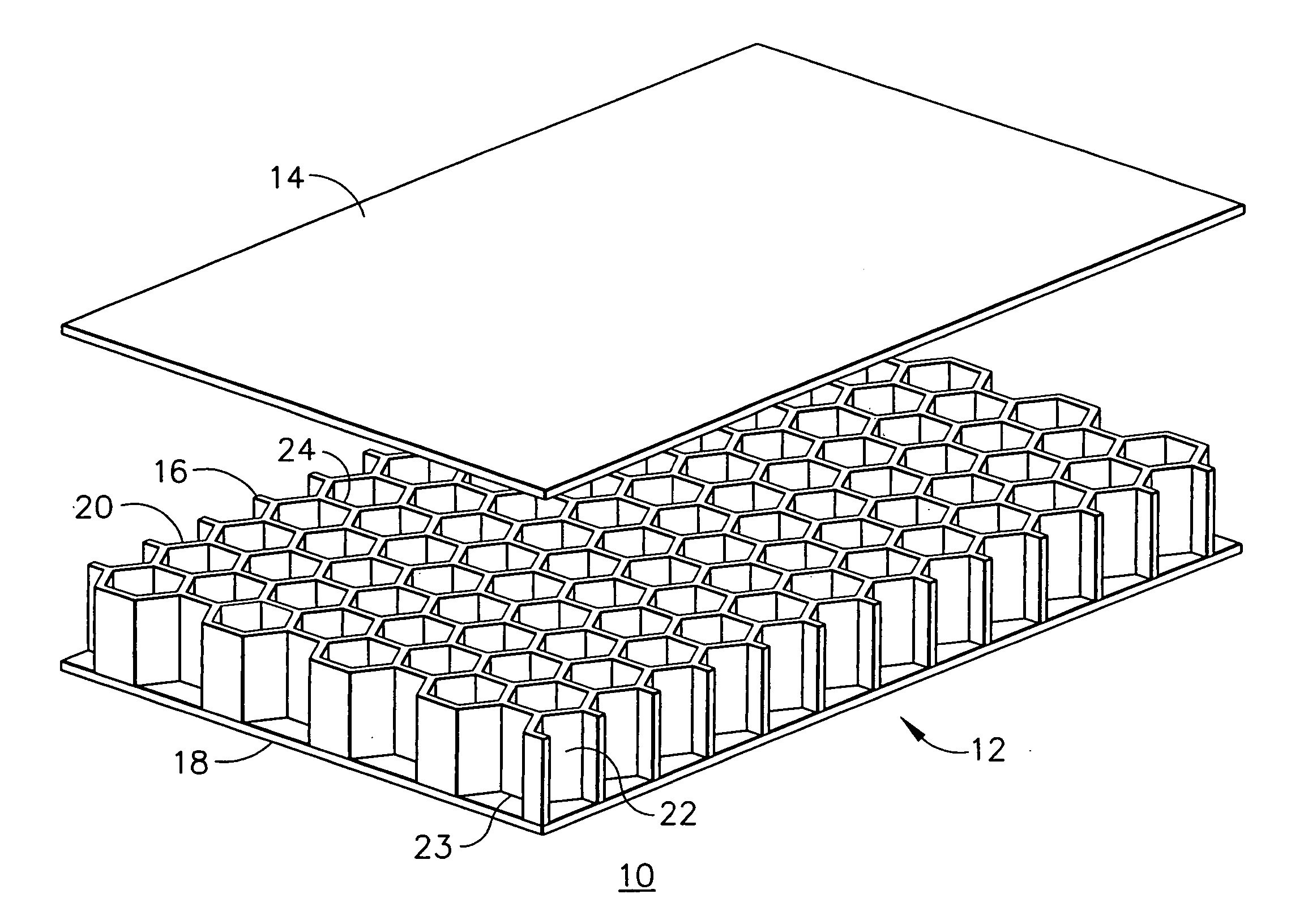

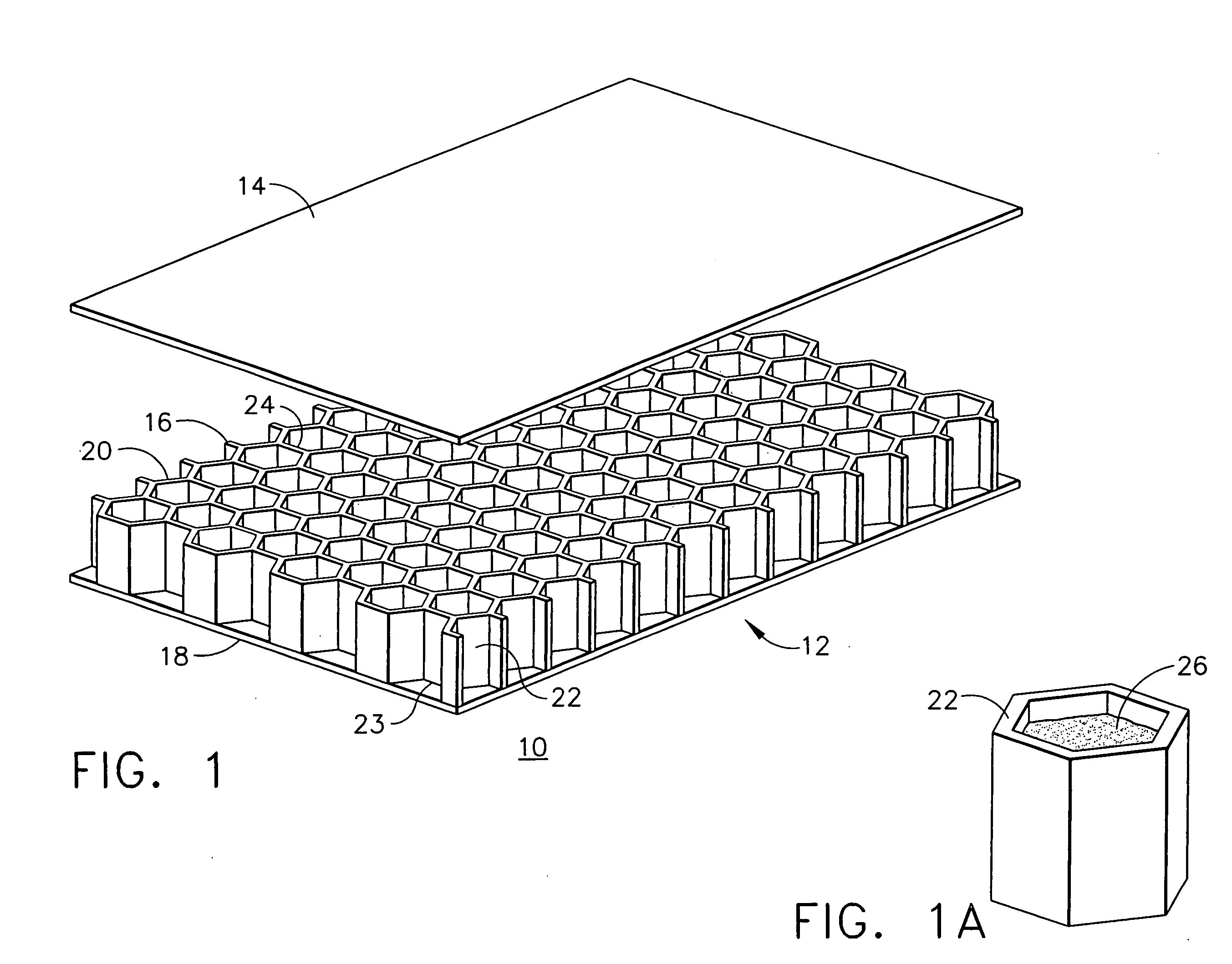

Methods and apparatus for noise attenuation in an engine nacelle

An acoustic liner includes a first core that has a plurality of first core cells defined by a corresponding plurality of first core cell walls. The first core has a first core thickness. The acoustic liner also includes a second core that has a plurality of second core cells defined by a corresponding plurality of second core cell walls. The second core has a second core thickness, and the first core thickness and the second core thickness are unequal. The acoustic liner further includes a second fabric sheet coupled between the first core and the second core. Each of the plurality of second core cell walls generally is not coplanar with any of the plurality of first core cell walls.

Owner:THE BOEING CO

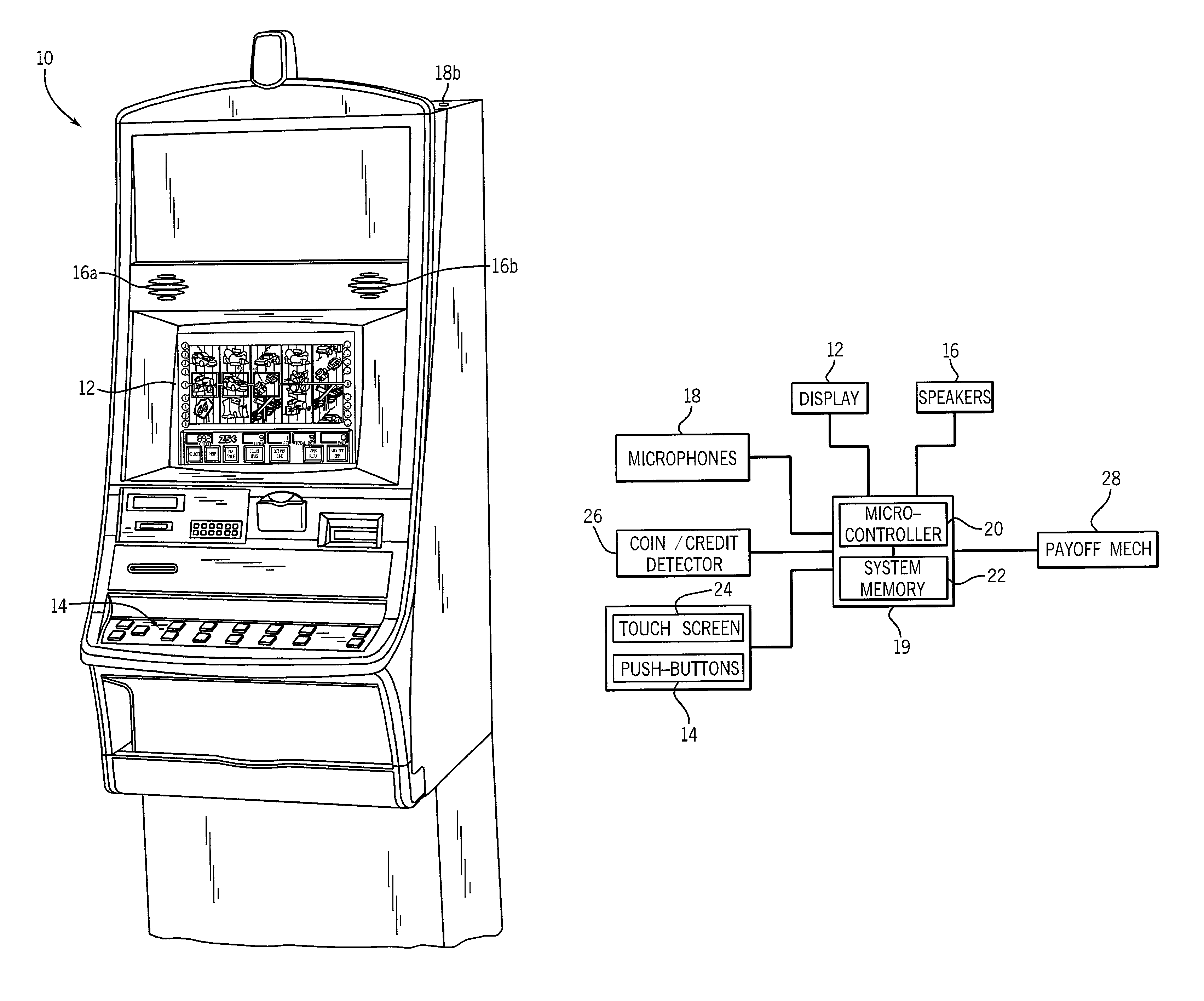

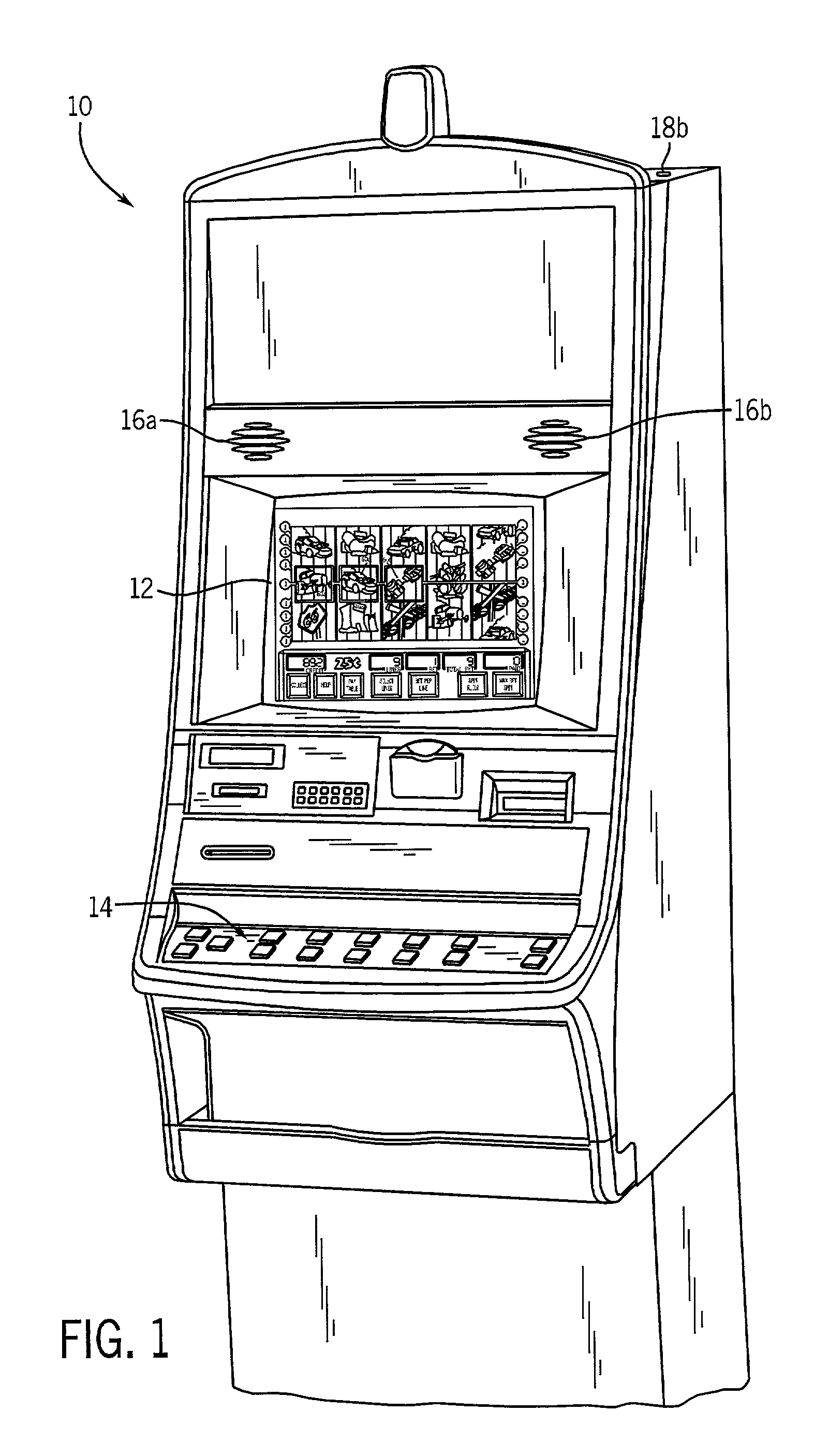

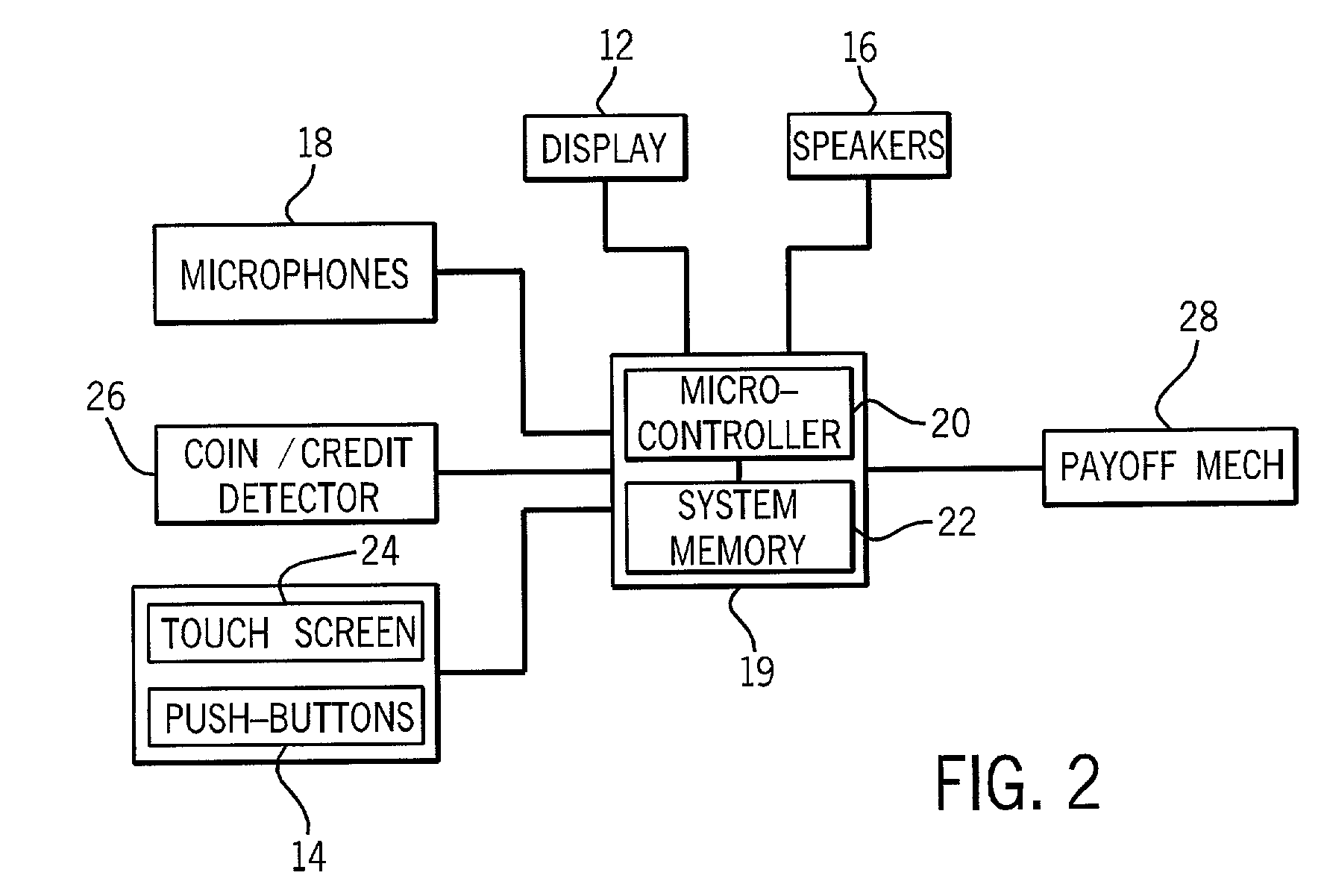

Gaming machine with ambient noise attenuation

InactiveUS7112139B2Reduce environmental noiseEar treatmentGain controlEnvironmental noiseEngineering

A gaming machine in a gaming establishment enhances its game sounds by attenuating ambient noise in the establishment. The gaming machine includes a microphone, processing circuitry, and an audio speaker. The microphone detects ambient noise and generates a noise signal from the sensed ambient noise. The processing circuitry generates an anti-noise signal from the noise signal and adds the anti-noise signal to a game sound signal generated by the gaming machine to produce an output signal. The audio speaker is driven with the output signal.

Owner:BALLY GAMING INC

Noise attenuating wall element

InactiveUS6065717AReduce the amount requiredAvoid it happening againFuselage framesConstruction materialEngineeringFuselage

A wall element has a noise attenuating characteristic and is suitable for use as an aircraft cabin interior panel element that is mounted directly on the aircraft fuselage structure. The wall element includes a rigid lightweight composite panel having a core arranged between two cover layers, and an outer layer arranged adjacent and spaced away from one of the cover layers. The core and the cover layers of the composite panel are air permeable in a direction through the thickness of the panel, while the outer layer is non-air-permeable and is relatively soft and flexible. The outer layer is connected to the composite panel preferably only along the perimeter edge thereof. The non-permeable outer layer faces the aircraft cabin space, while the permeable composite panel is mounted on the fuselage structure. With this structure, acoustic vibrations of the fuselage, to which the wall element is attached, are attenuated and do not result in substantial noise radiation from the outer layer into the cabin.

Owner:DAIMLER CHRYSLER AEROSPACE AIRBUS

Filter assembly with noise attenuation

ActiveUS7141101B2Suppress noiseReduce pressureCombination devicesAuxillary pretreatmentEngineeringAcoustic wave

A filter assembly configured for acoustic dampening for use with compressor assemblies such as oxygen concentrators including a compartmented housing member having an inlet opening, an outlet opening, a filter member, and a plurality of noise attenuating members positioned and located therewithin. The configuration of the compartmented housing member in conjunction with the positioning and location of the filter member and the noise attenuating members therewithin all contribute to absorb and dissipate any sound waves generated within the housing member due to air flow movement therethrough. This substantially reduces and minimizes noise associated with the present filter assembly.

Owner:AG IND LLC

System for suppressing rain noise

ActiveUS7949522B2Improve processing qualitySuppress noiseTransducer acoustic reaction preventionSpeech recognitionSpeech soundComputer science

A voice enhancement logic improves the perceptual quality of a processed signal. The voice enhancement system includes a noise detector and a noise attenuator. The noise detector detects and models the noise associated with rain. The noise attenuator dampens or reduces the rain noise from a signal to improve the intelligibility of an unvoiced, a fully voiced, or a mixed voice segment.

Owner:MALIKIE INNOVATIONS LTD

System and Method for Enhancing a Decoded Tonal Sound Signal

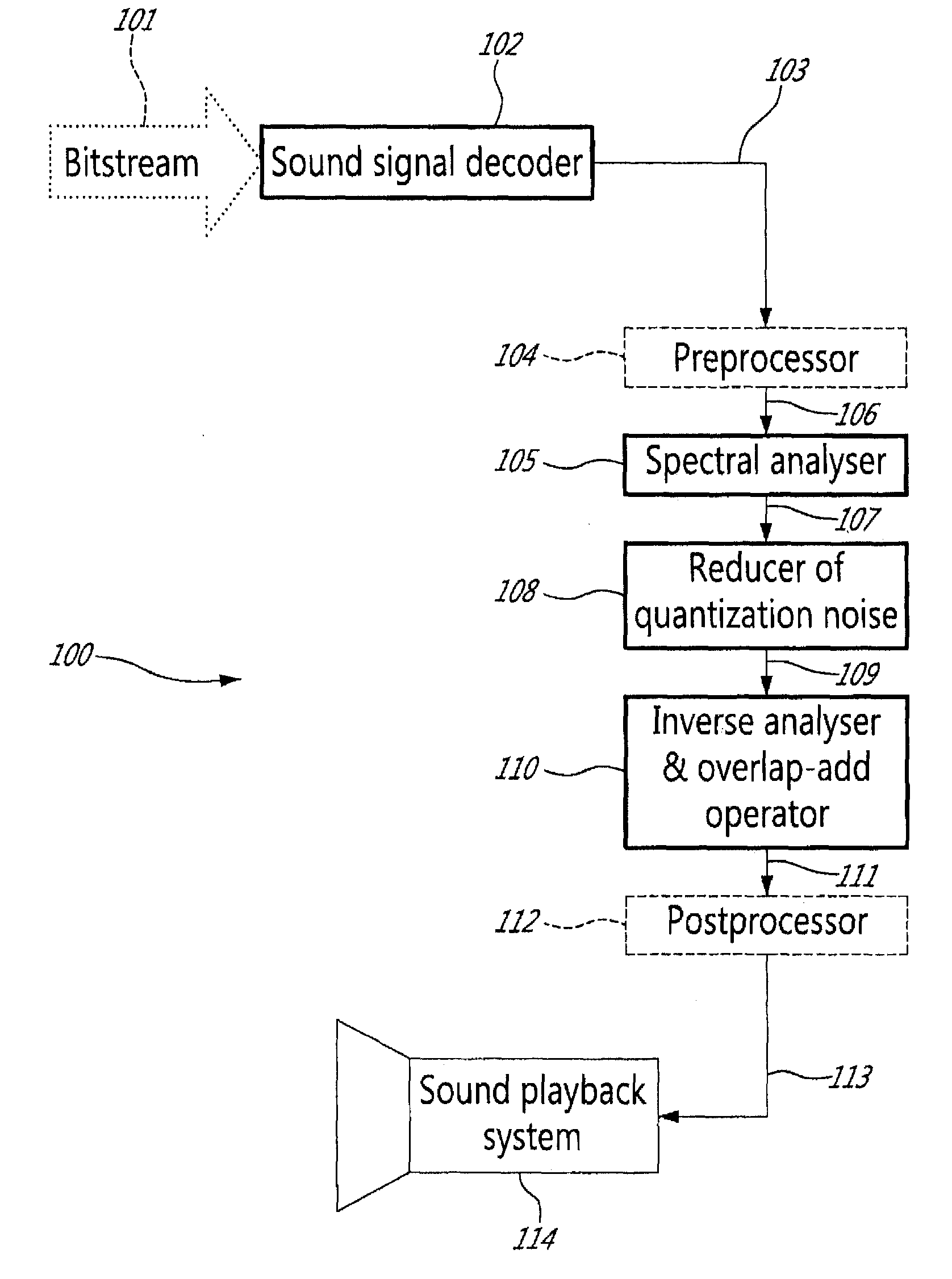

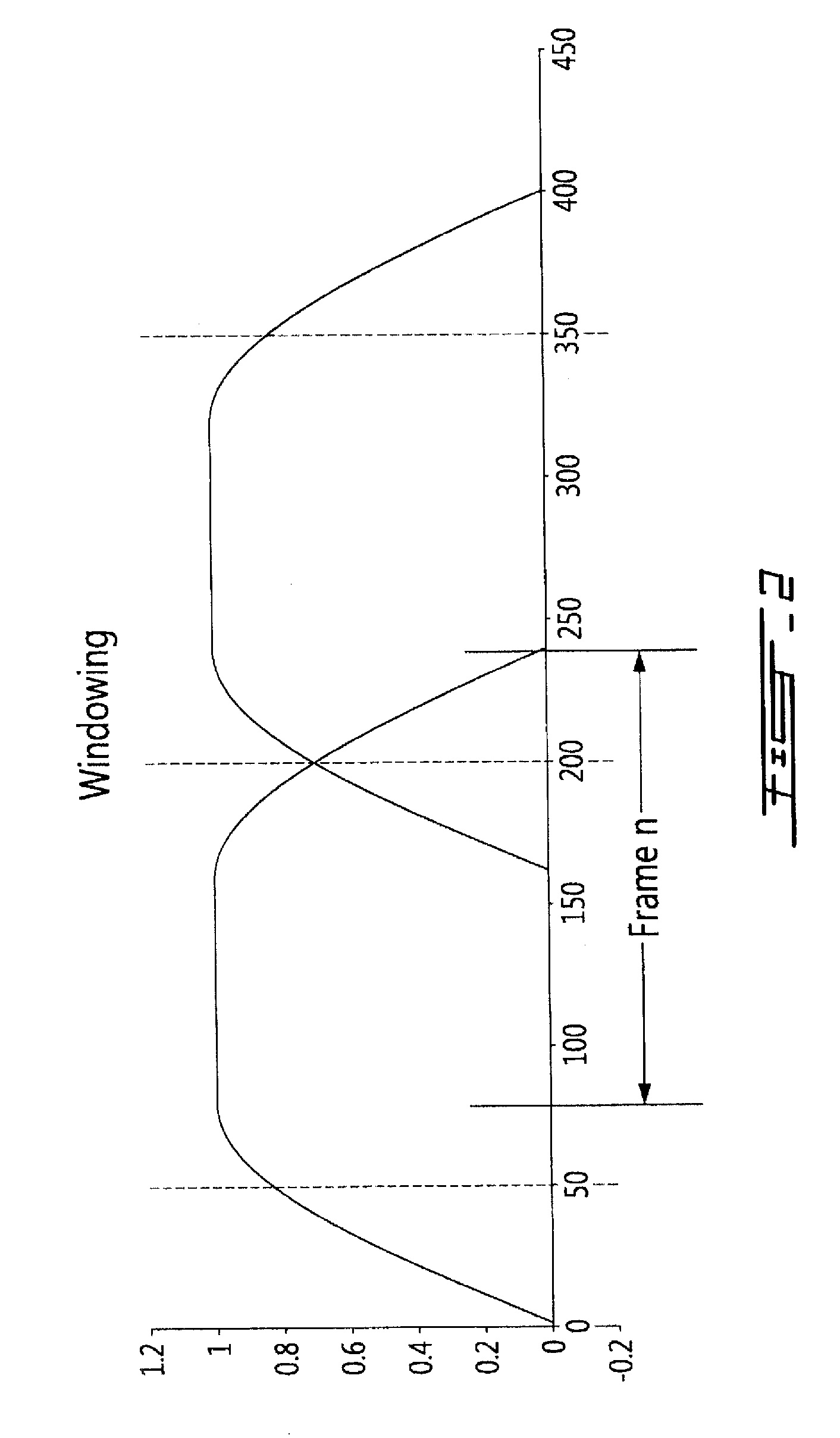

ActiveUS20110046947A1Enhanced signalReduce quantization noiseSpeech analysisTransmission noise suppressionFrequency spectrumSpectrum analyzer

A system and method for enhancing a tonal sound signal decoded by a decoder of a speech-specific codec in response to a received coded bit stream, in which a spectral analyser is responsive to the decoded tonal sound signal to produce spectral parameters representative of the decoded tonal sound signal. A quantization noise in low-energy spectral regions of the decoded tonal sound signal is reduced in response to the spectral parameters produced by the spectral analyser. The spectral analyser divides a spectrum resulting from spectral analysis into a set of critical frequency bands each comprising a number of frequency bins, and the reducer of quantization noise comprises a noise attenuator that scales the spectrum of the decoded tonal sound signal per critical frequency band, per frequency bin, or per both critical frequency band and frequency bin.

Owner:VOICEAGE EVS LLC

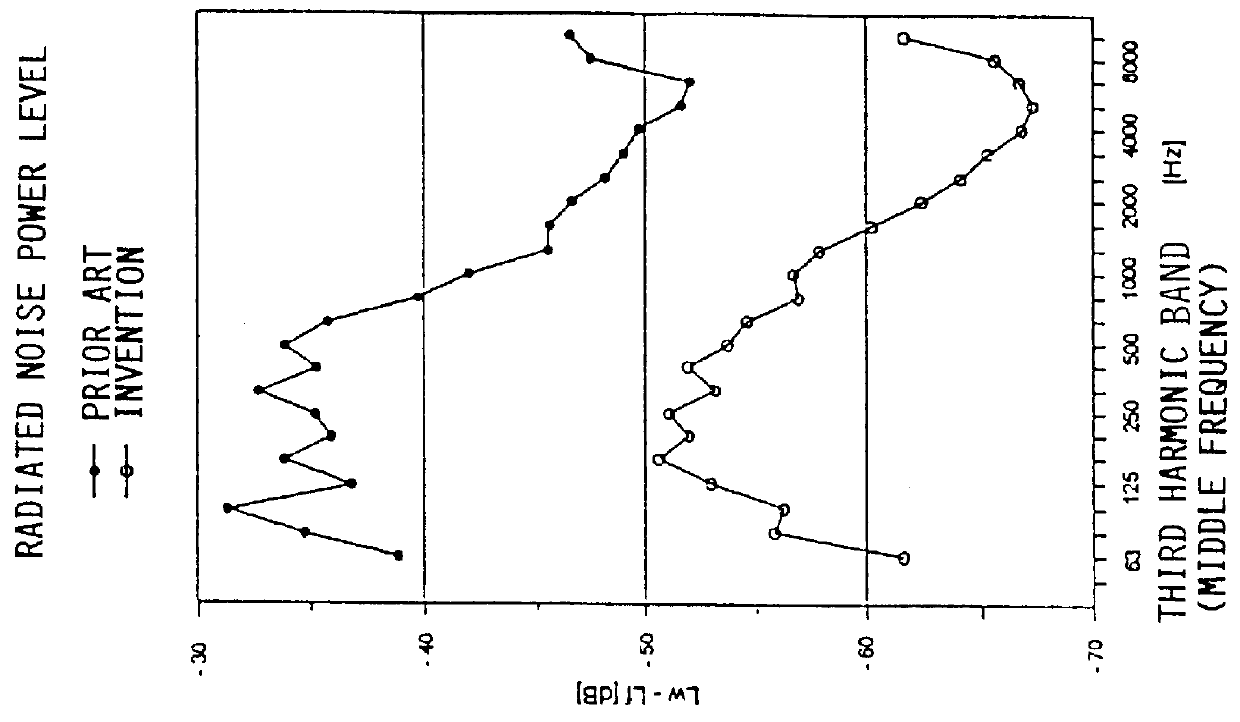

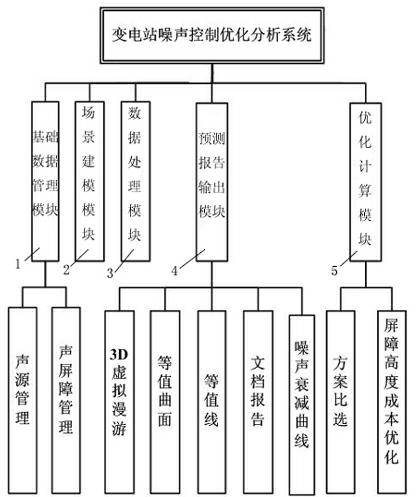

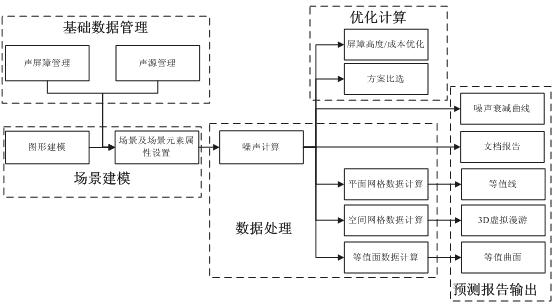

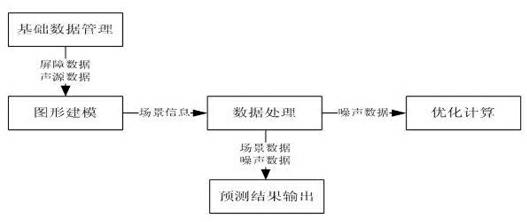

Optimized analytical method and system for noise control in transformer station

ActiveCN102194027ALow costQuick and effective design referenceSpecial data processing applicationsEnvironmental resistanceNoise control

Owner:STATE GRID CHONGQING ELECTRIC POWER CO ELECTRIC POWER RES INST +1

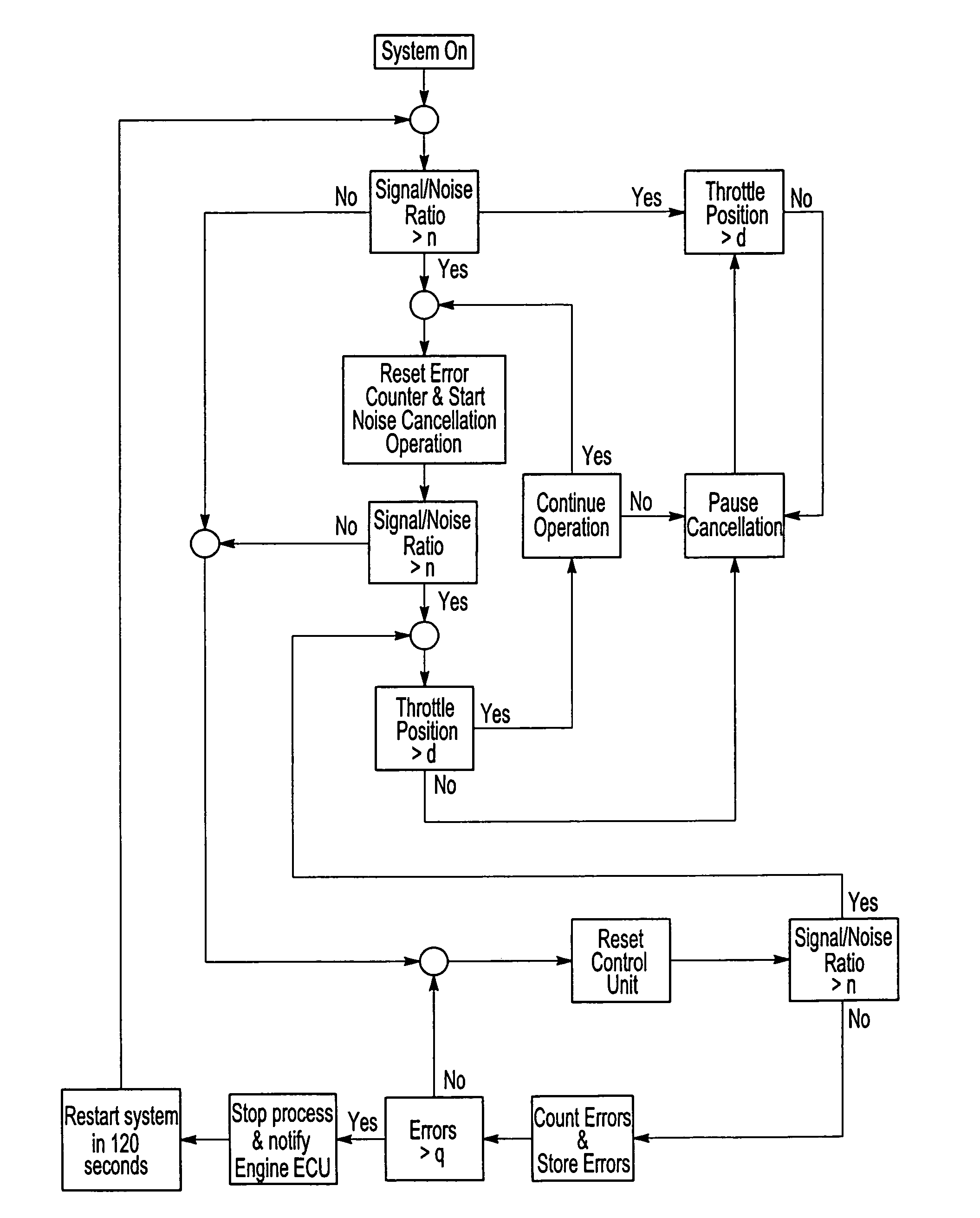

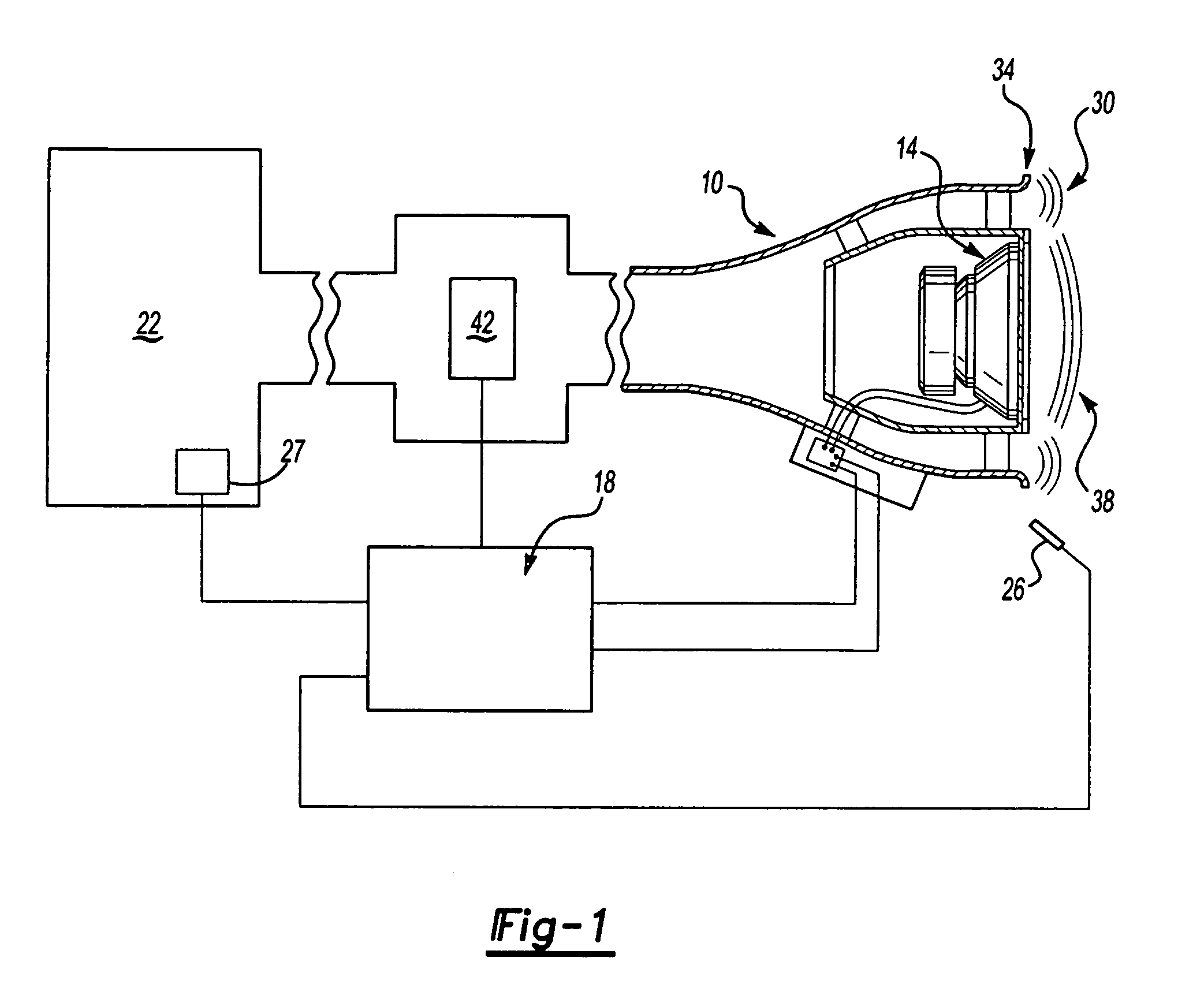

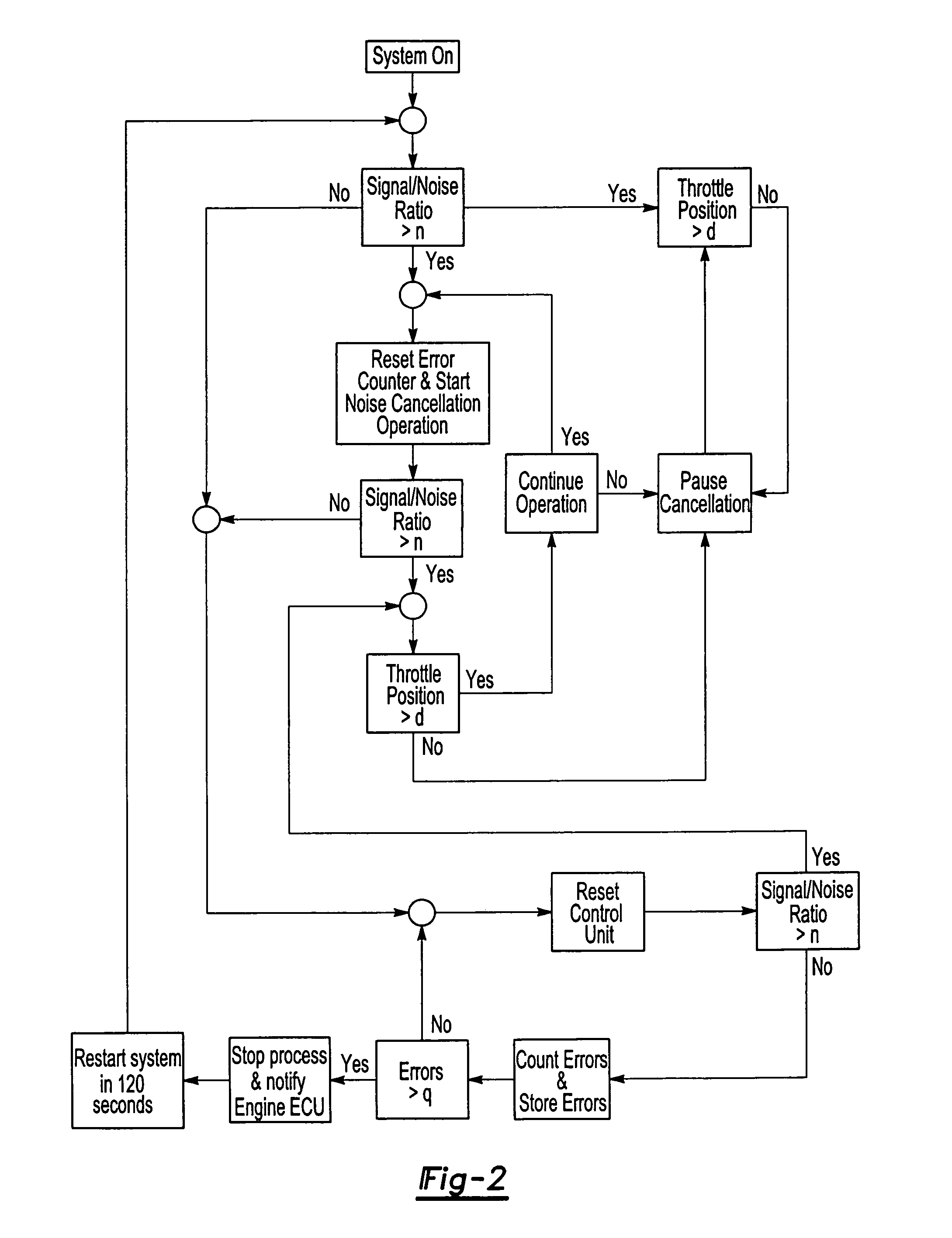

Active noise cancellation stability solution

ActiveUS7106866B2Reduce engine noiseControlling noise attenuationEar treatmentSilencing apparatusEngineeringLoudspeaker

The method of noise attenuation comprises the steps of generating a noise canceling signal, sensing for an system condition, and ceasing the generation of the noise canceling based upon the system condition. This method is embodied in a system that includes an air induction body, a speaker in proximity to the air induction body, a sensor for sensing a system condition, and a control unit with a noise cancellation feature. The control unit is in communication with both the speaker and the sensor. Based upon the sensed system condition, the control unit may disable the noise cancellation feature.

Owner:SIEMENS VDO AUTOMOTIVE CORP