Patents

Literature

150 results about "Positive data" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

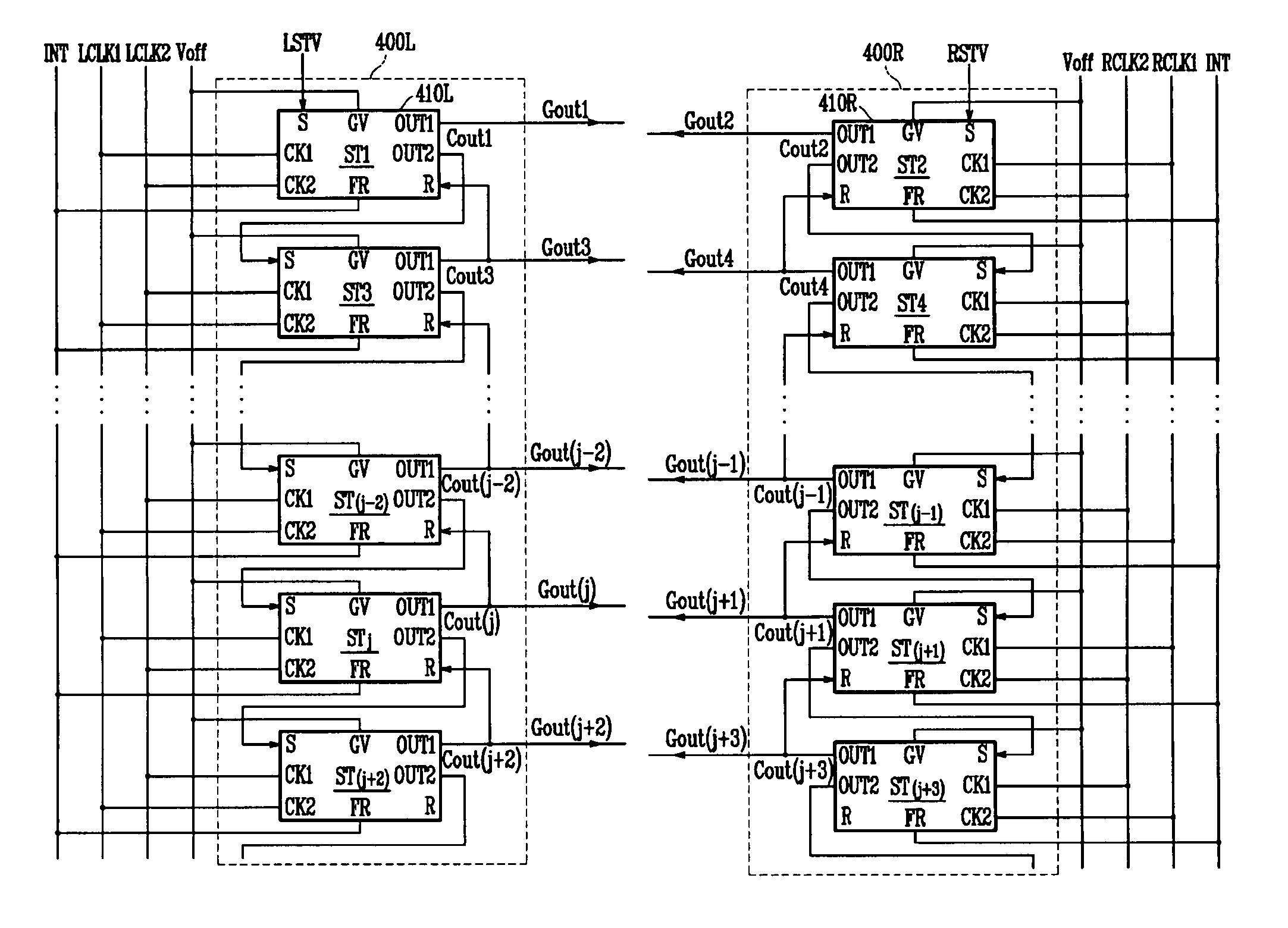

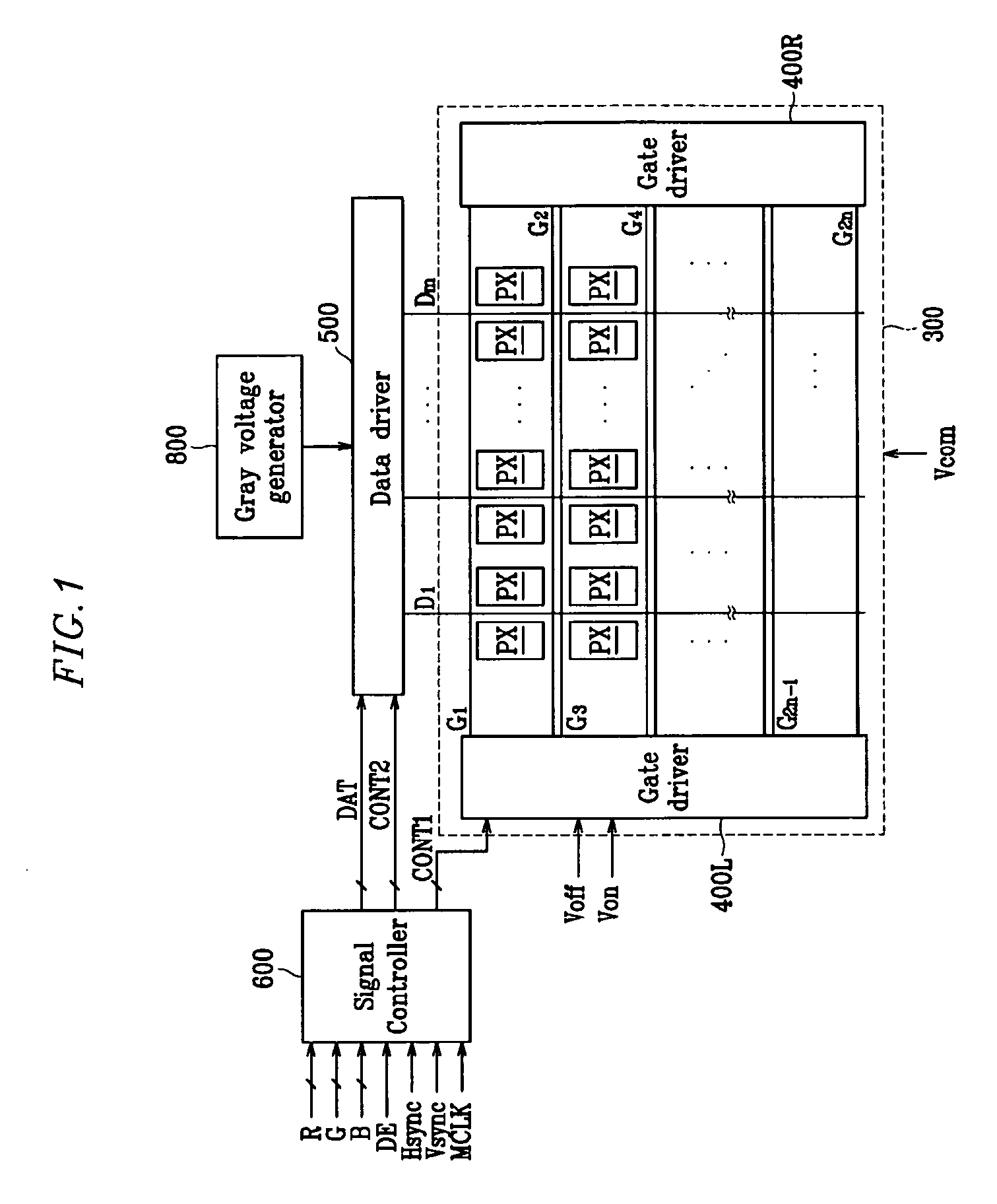

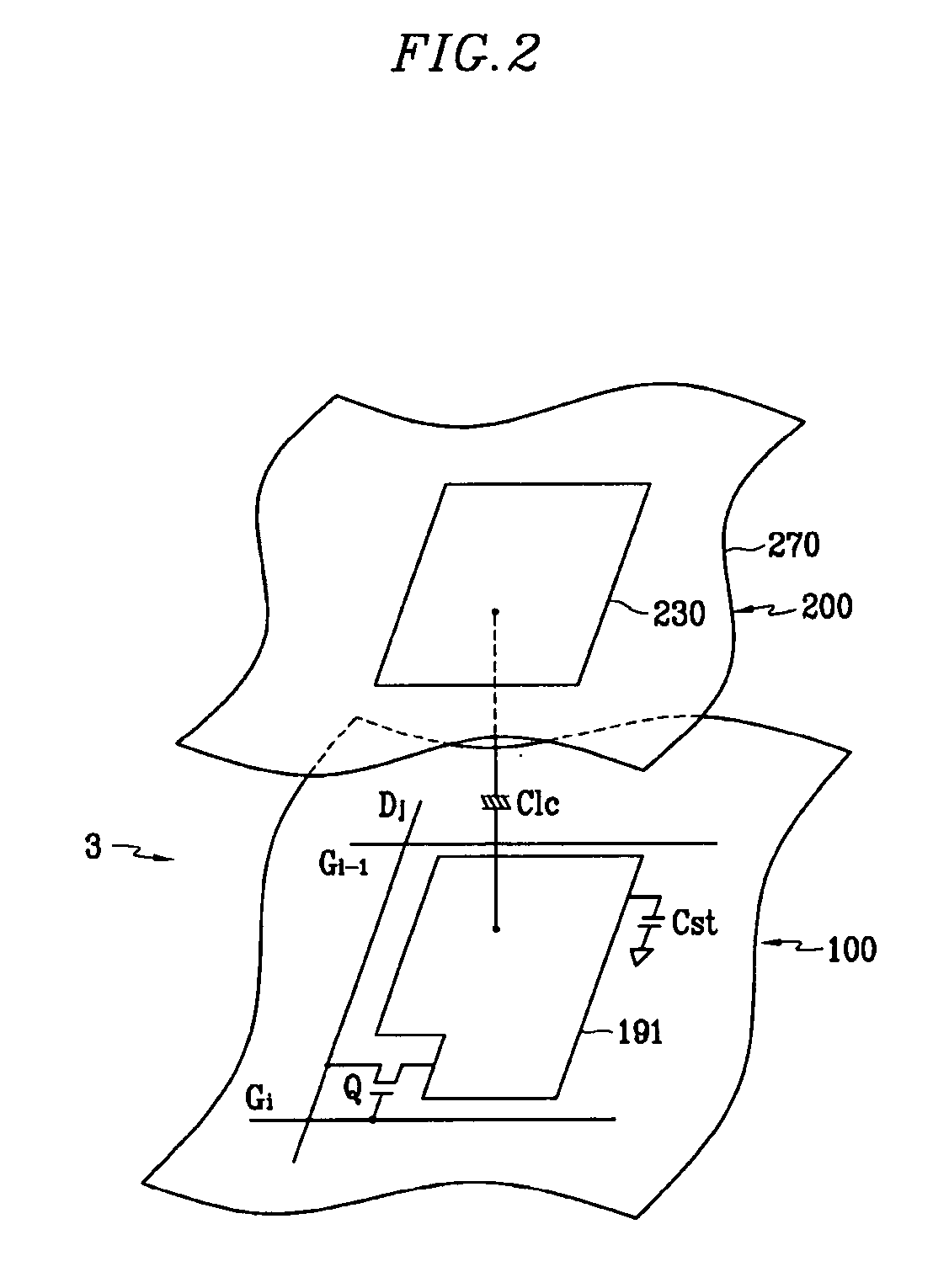

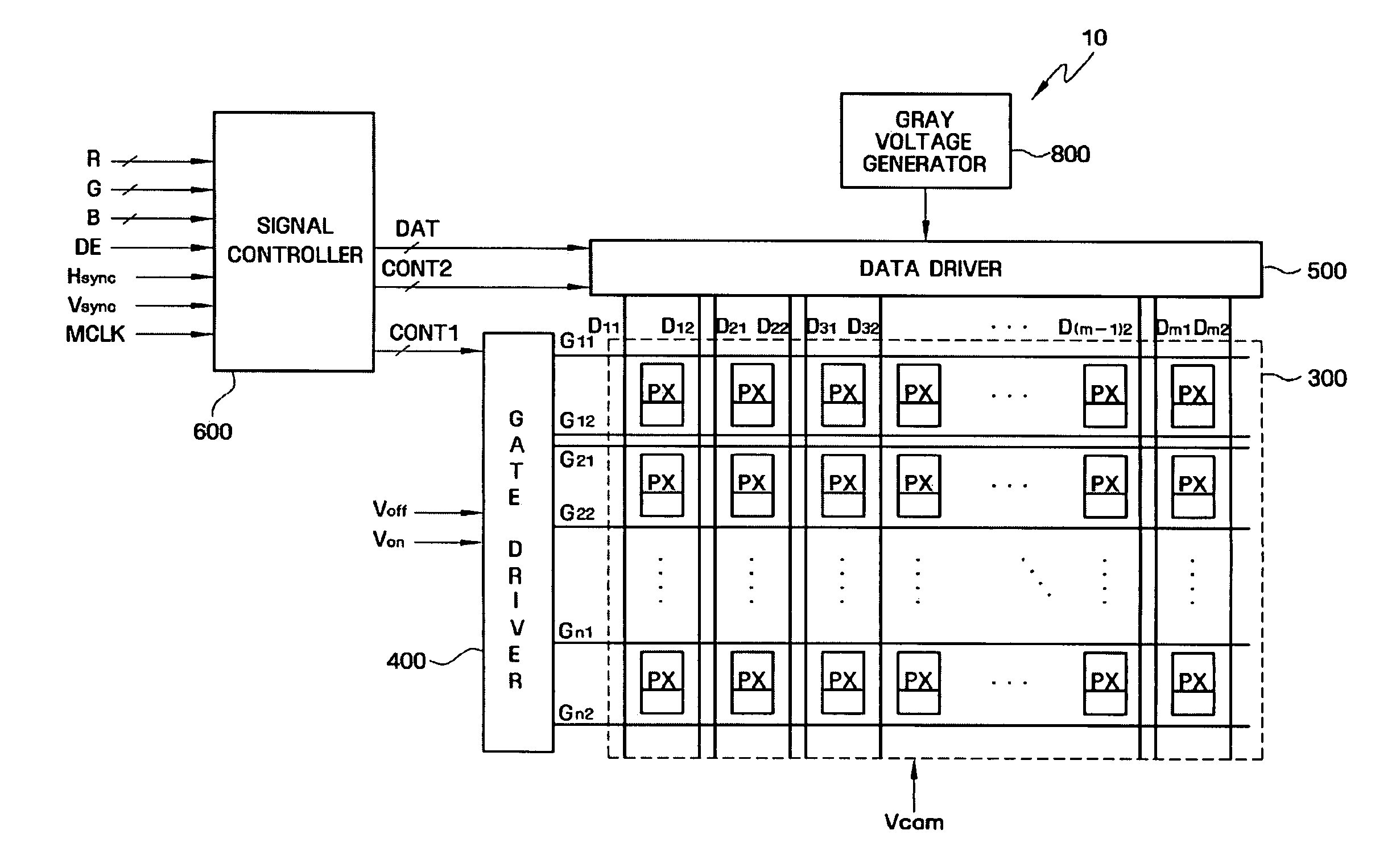

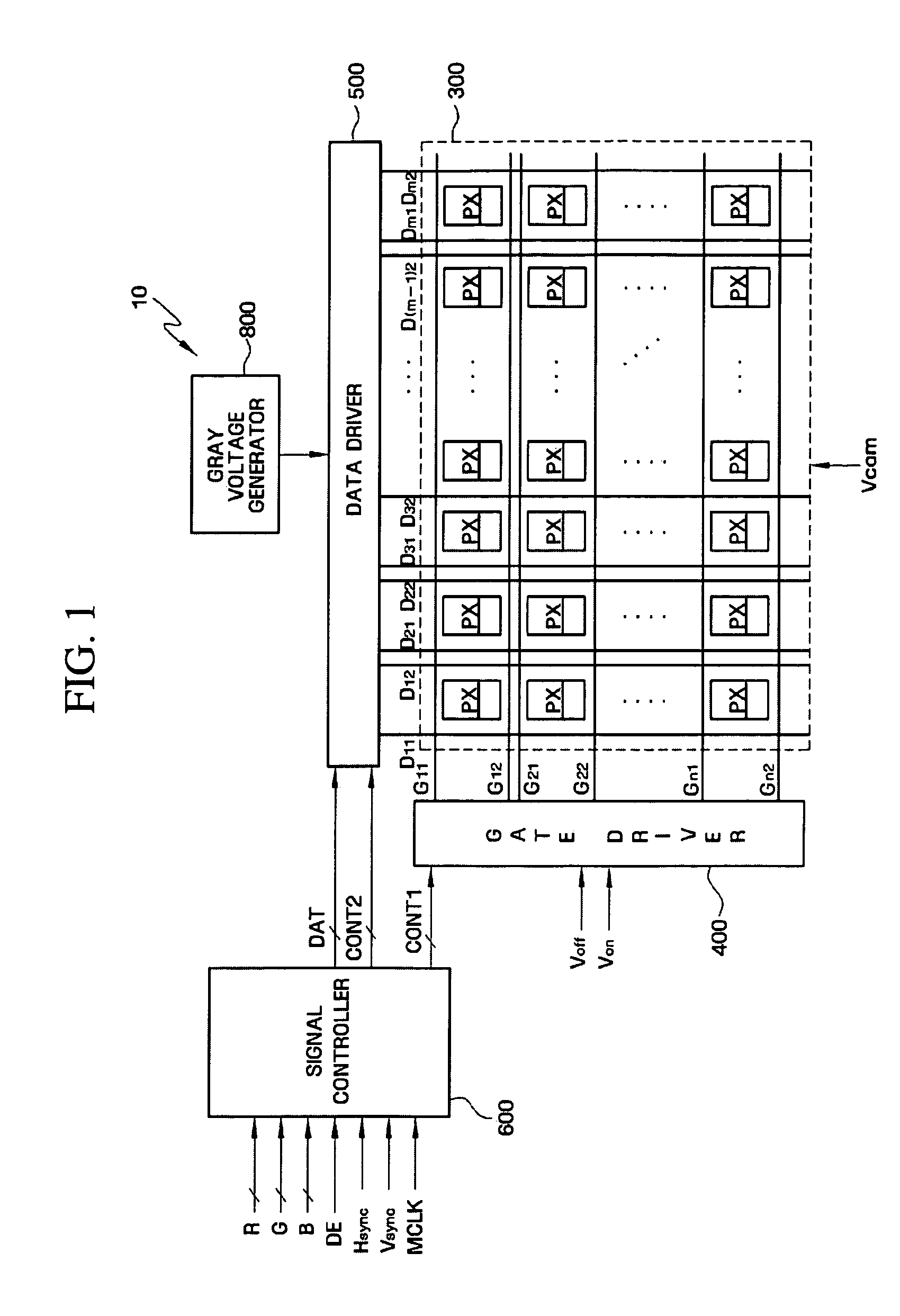

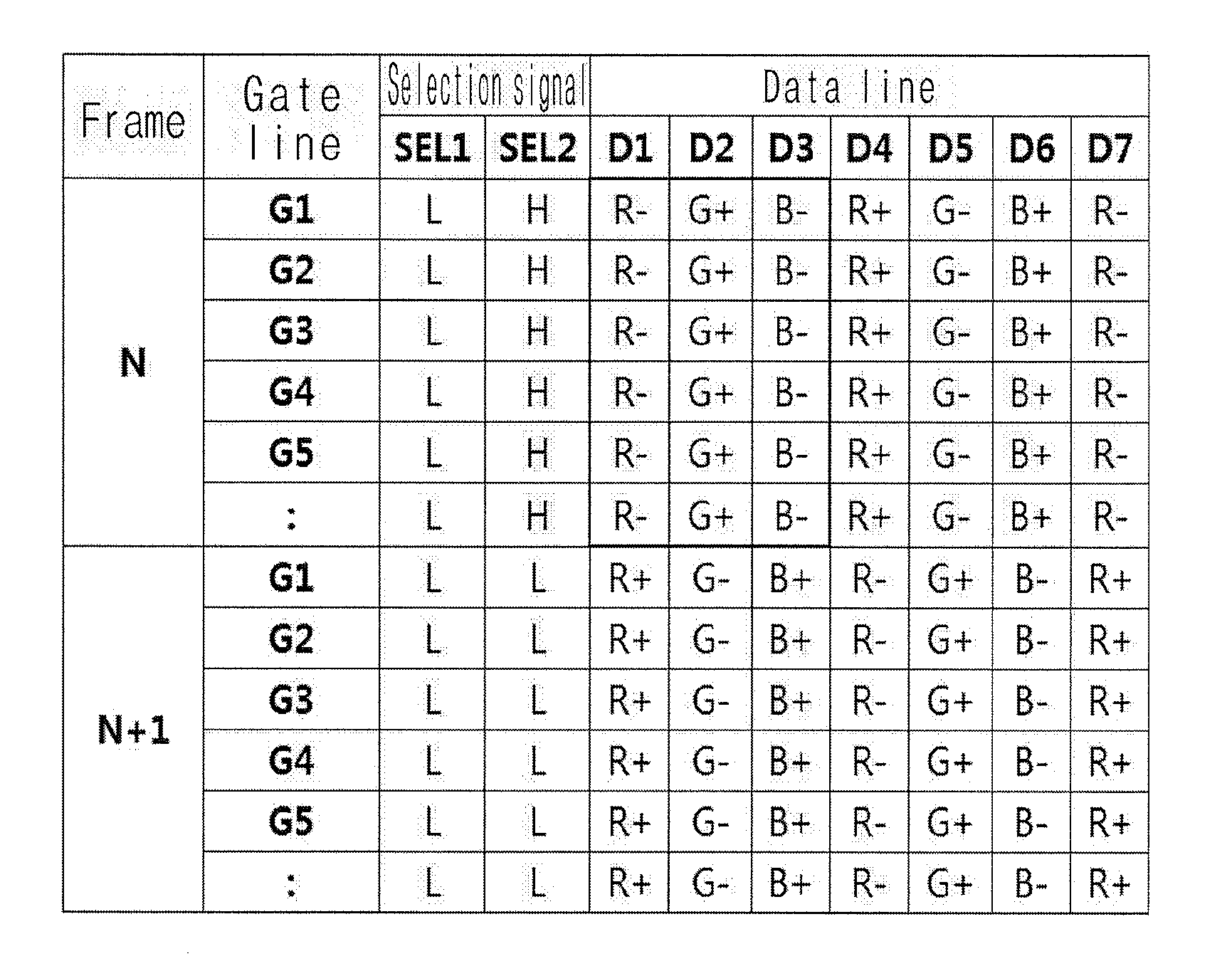

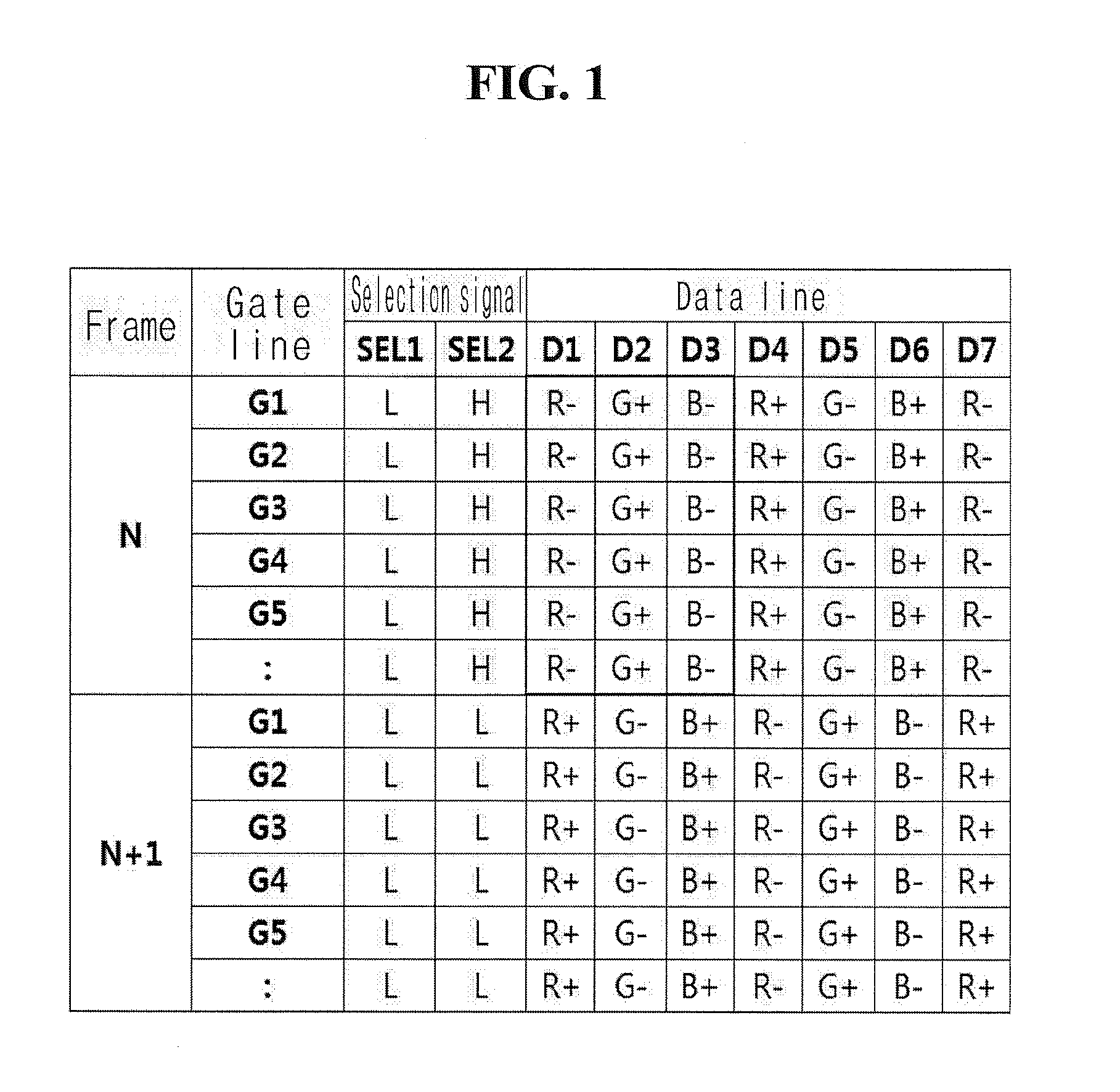

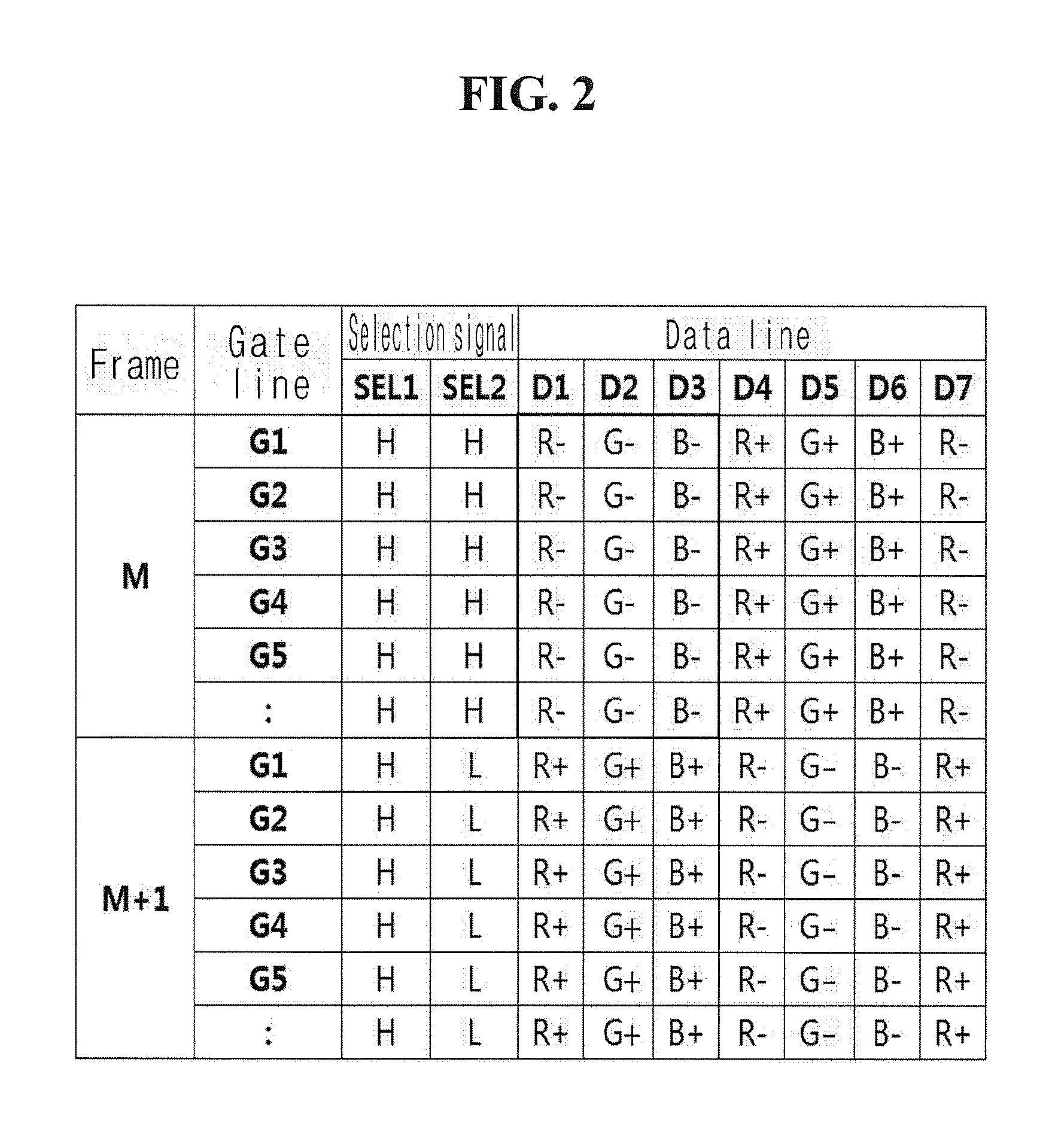

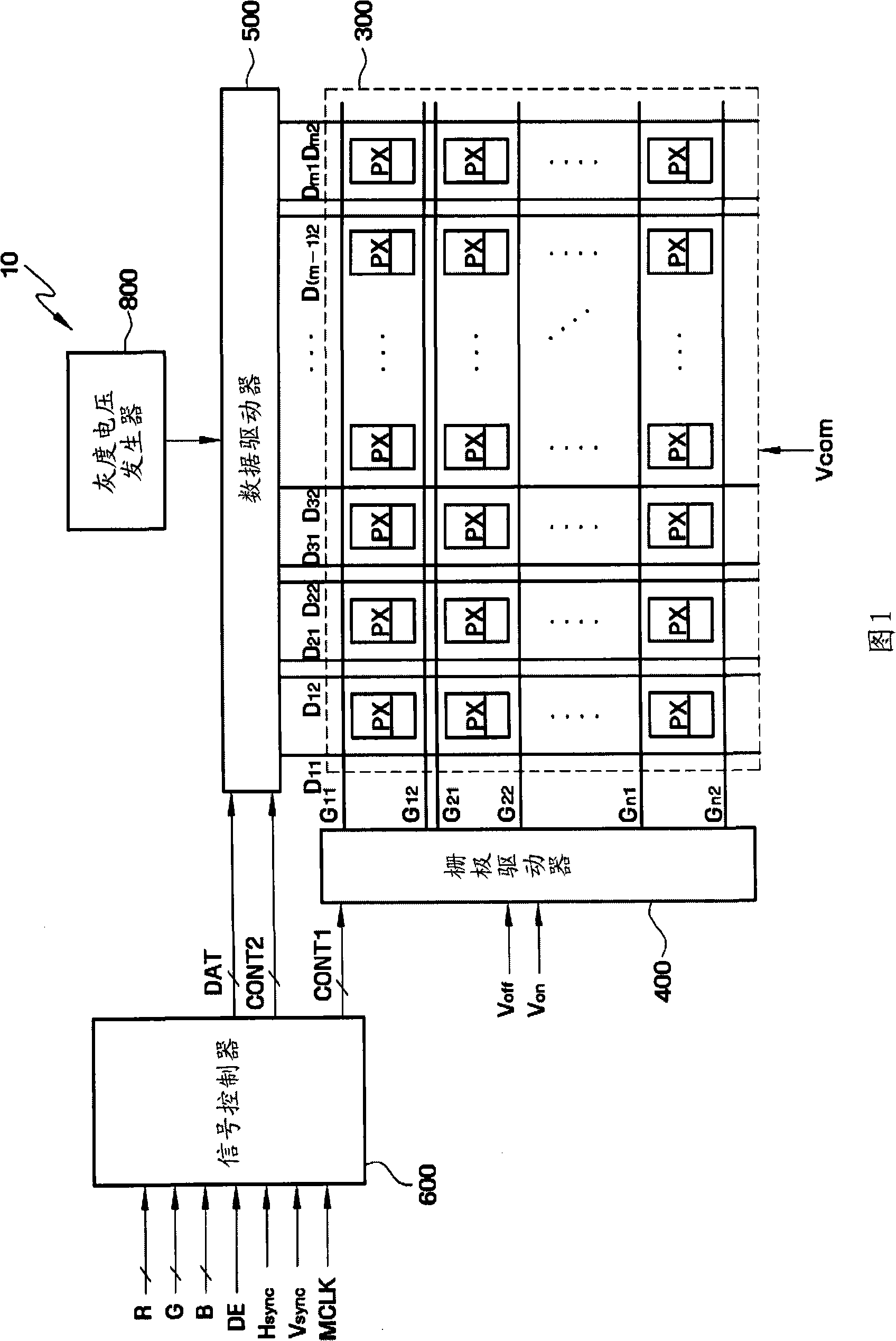

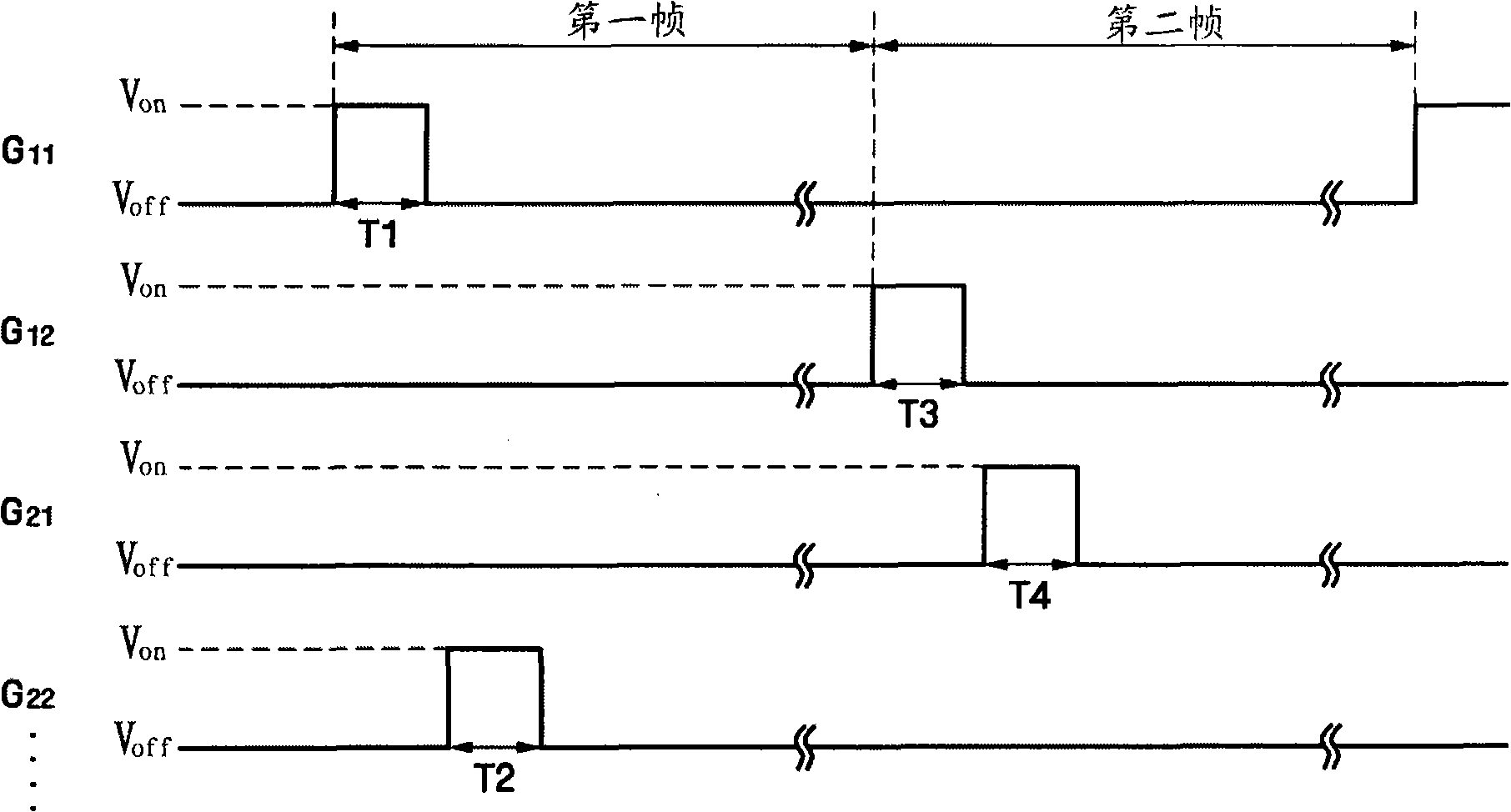

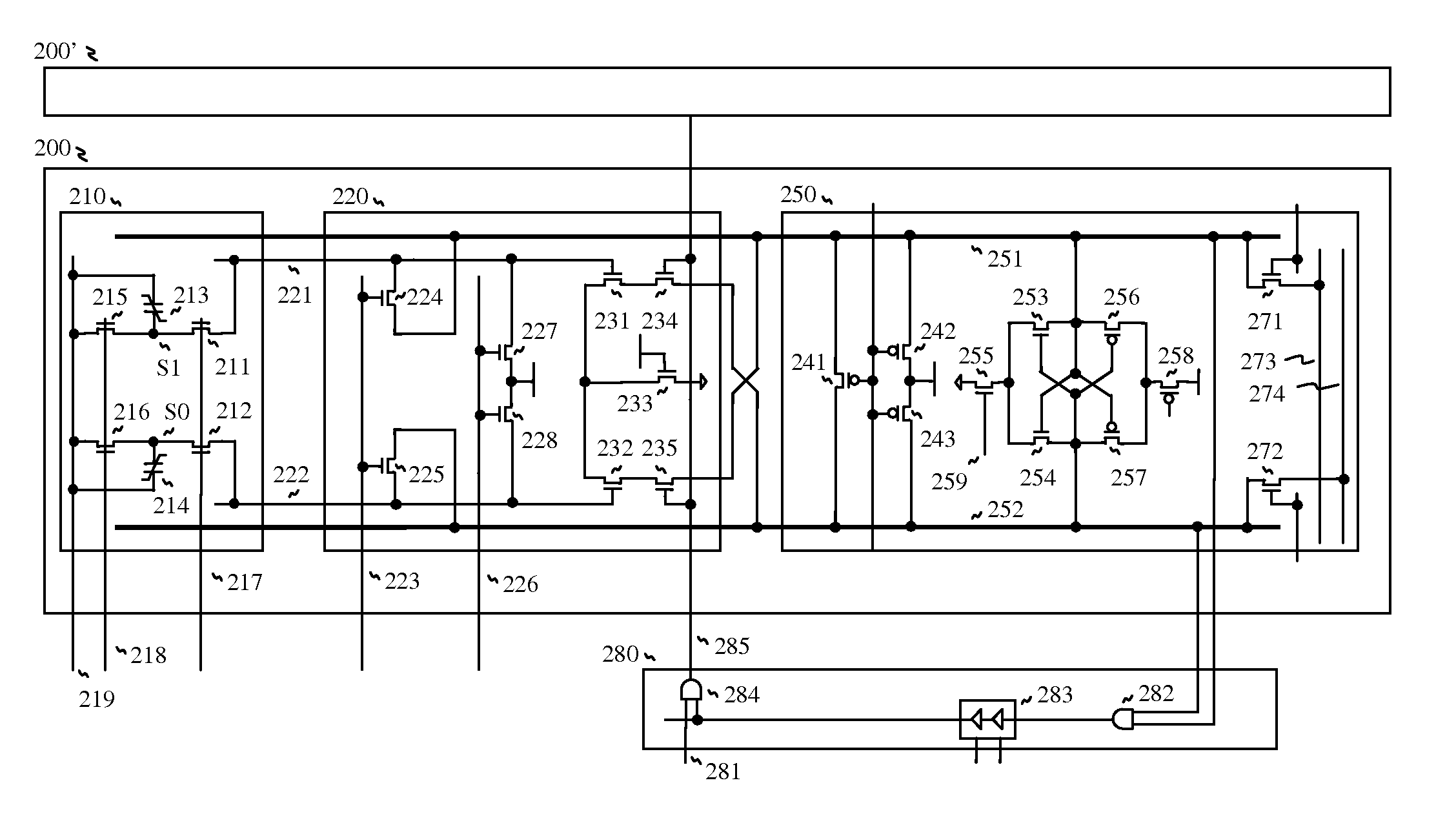

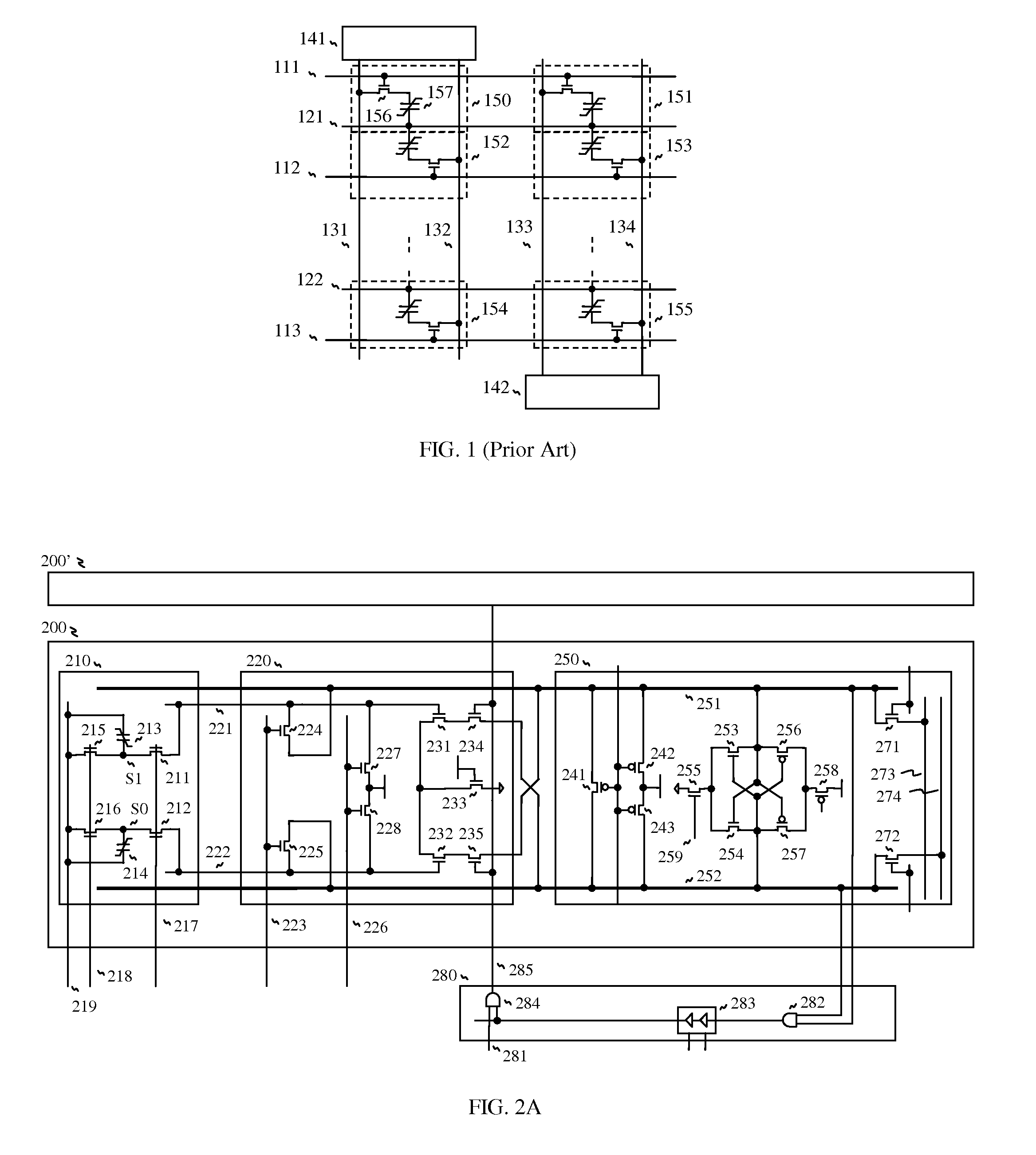

Driver for display apparatus and display apparatus including the same

InactiveUS20070052658A1Avoid flickeringAvoid stainsStatic indicating devicesDigital storagePhase differenceVoltage drop

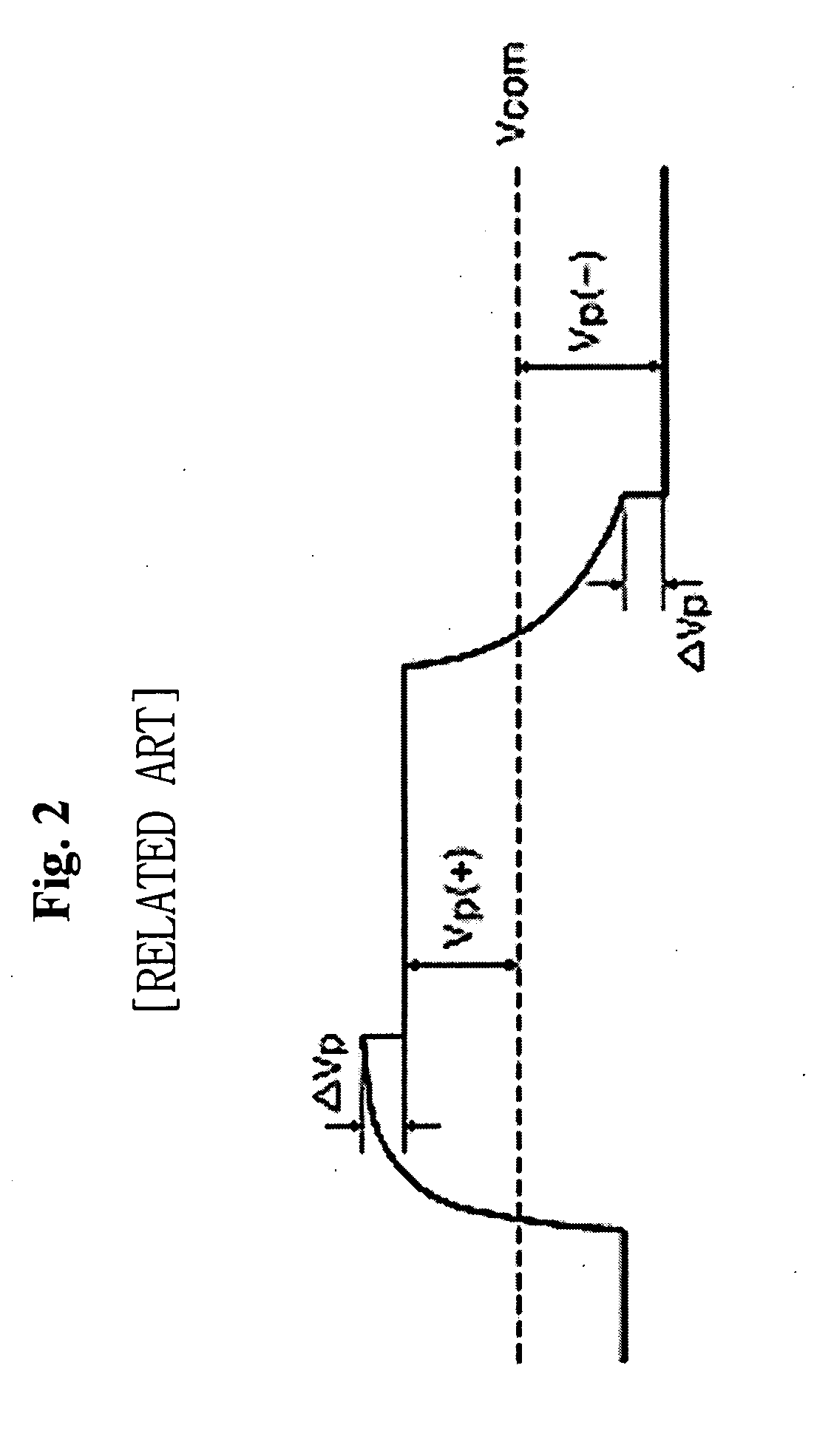

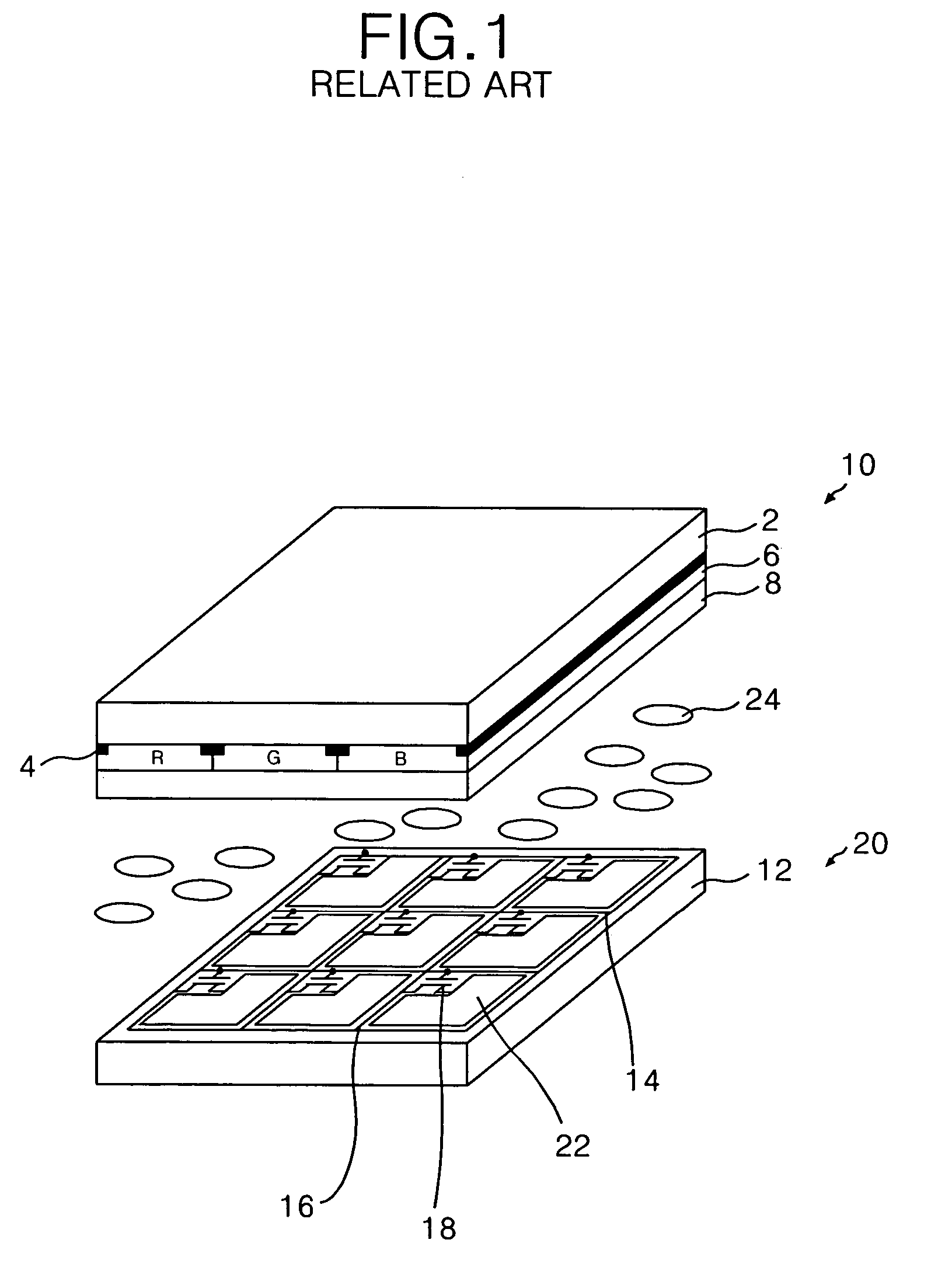

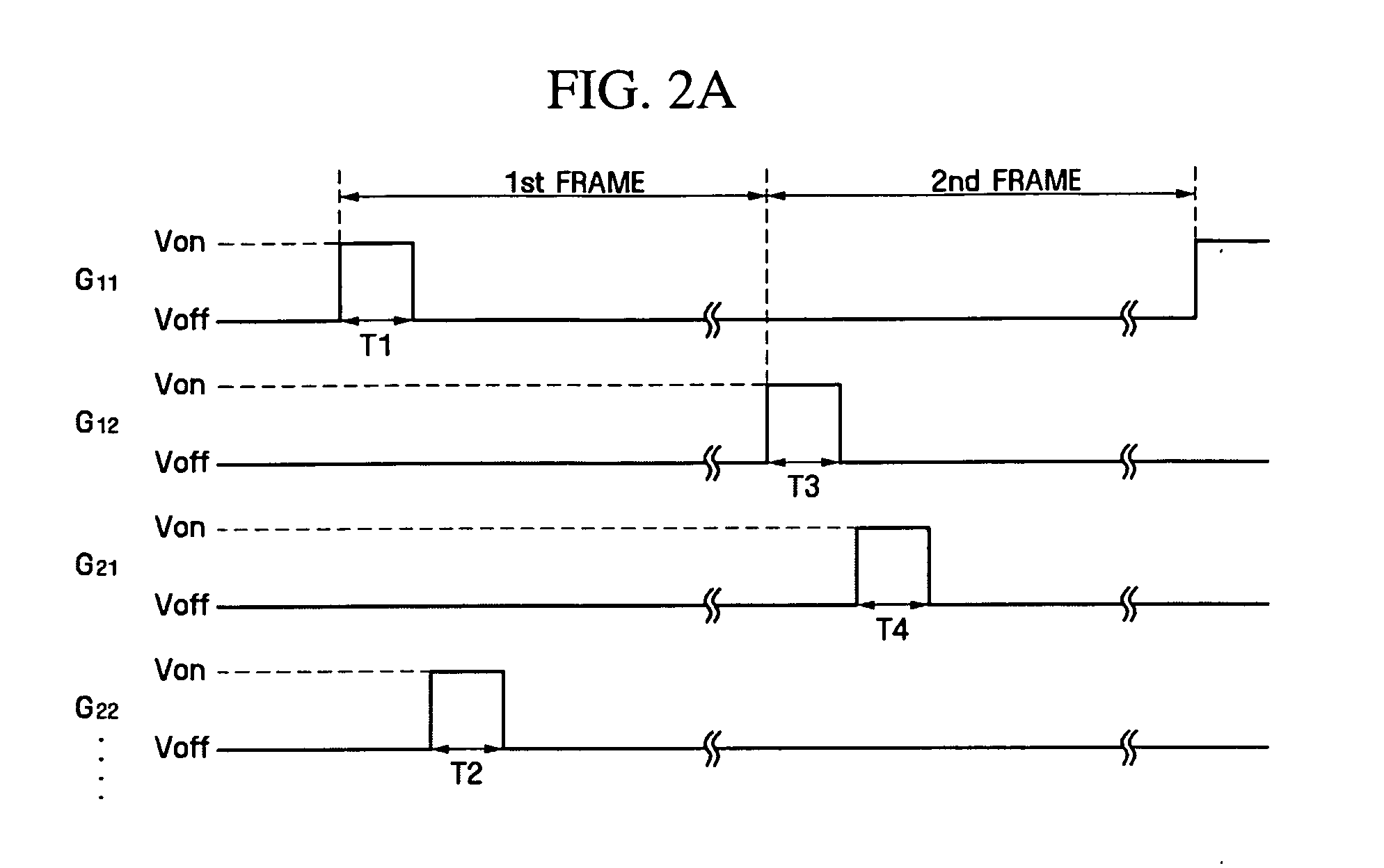

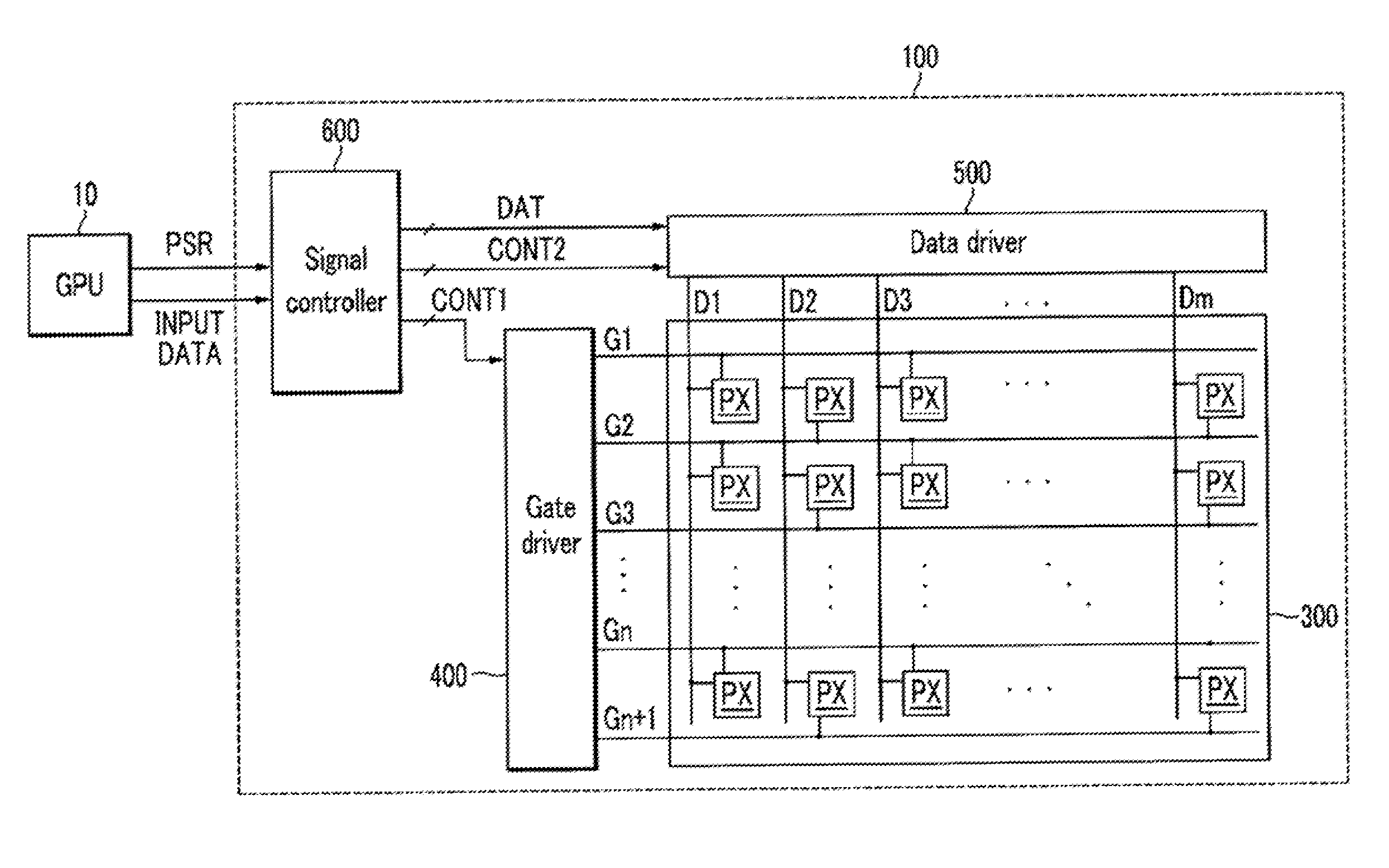

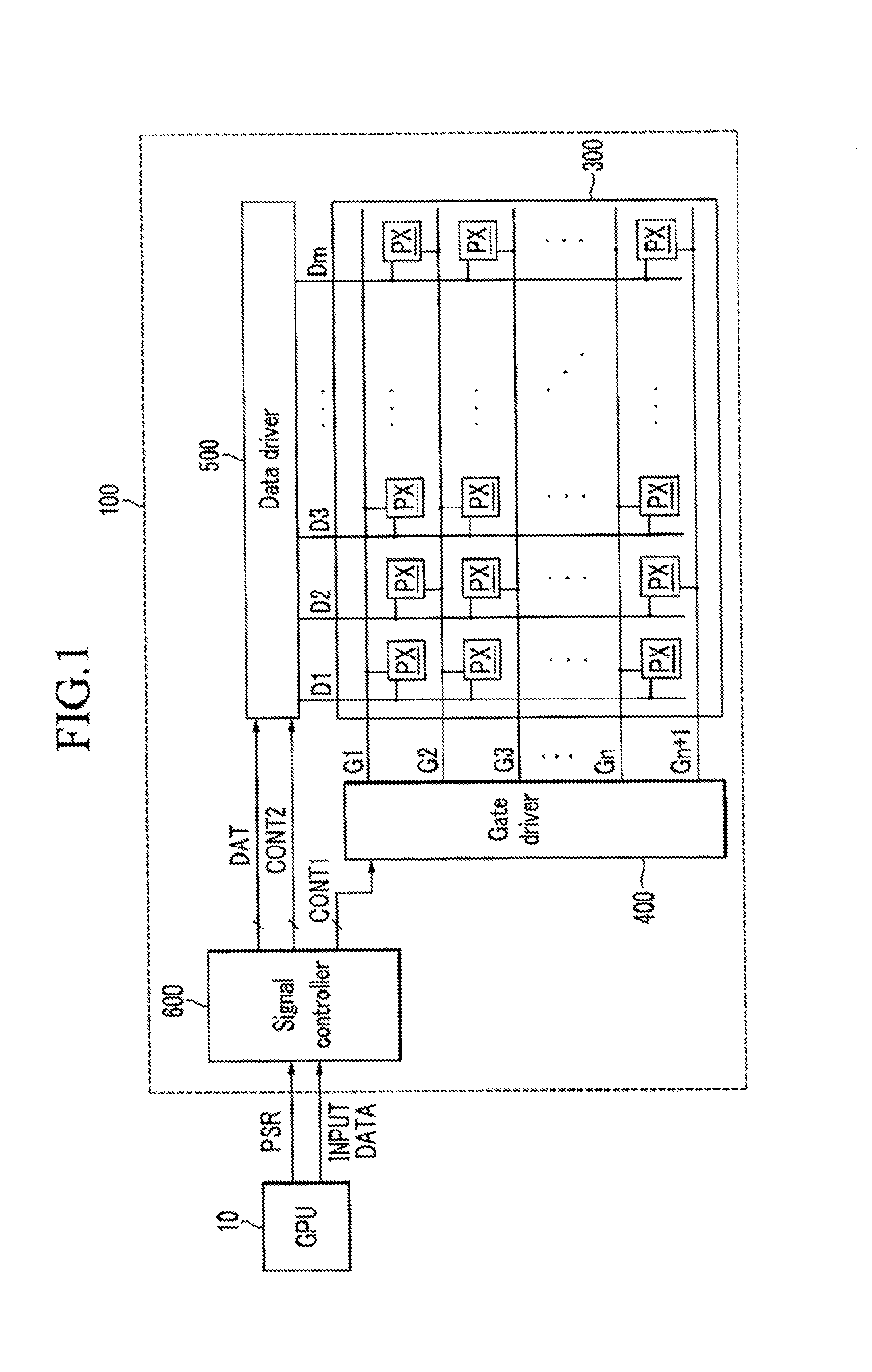

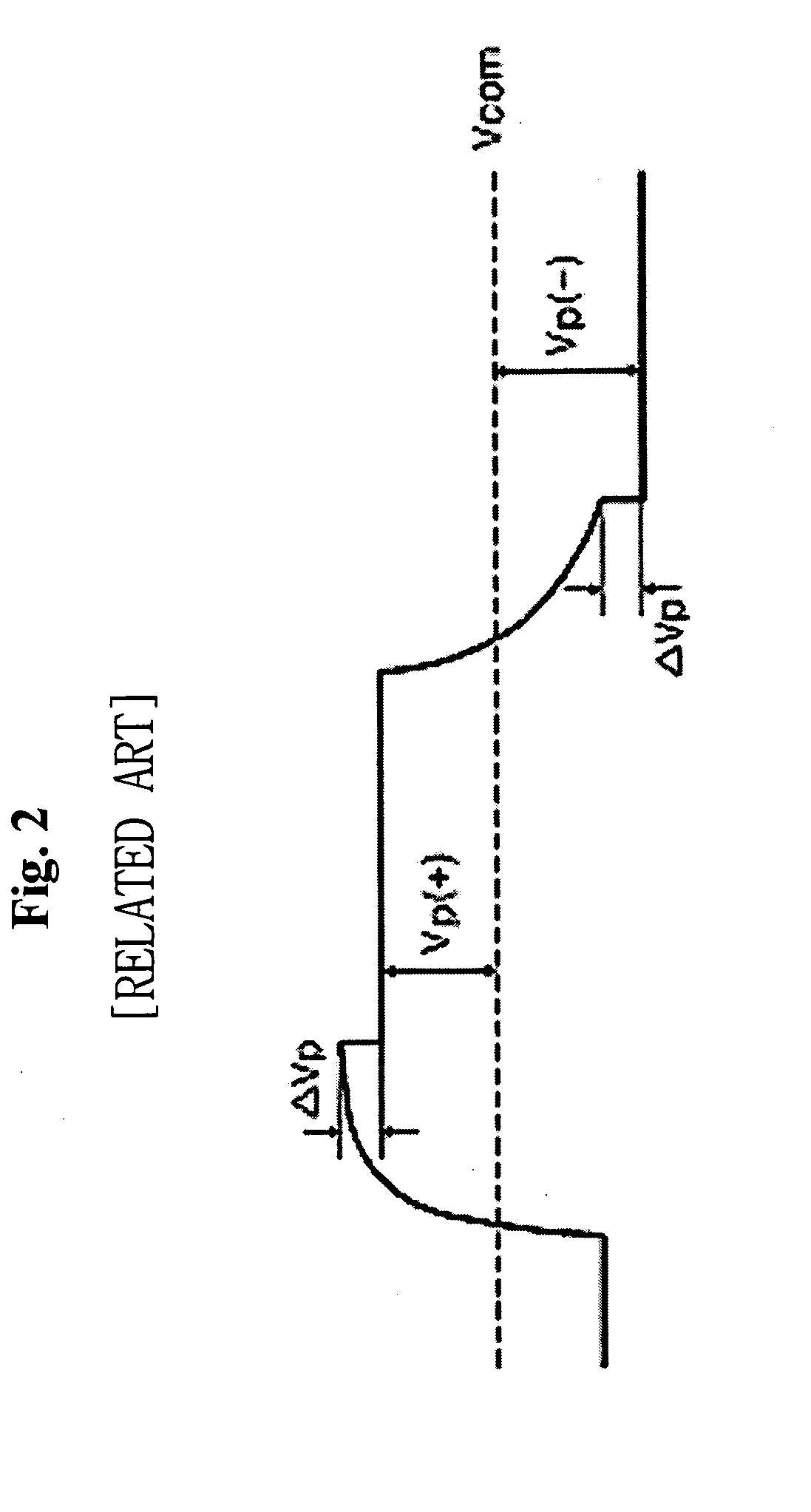

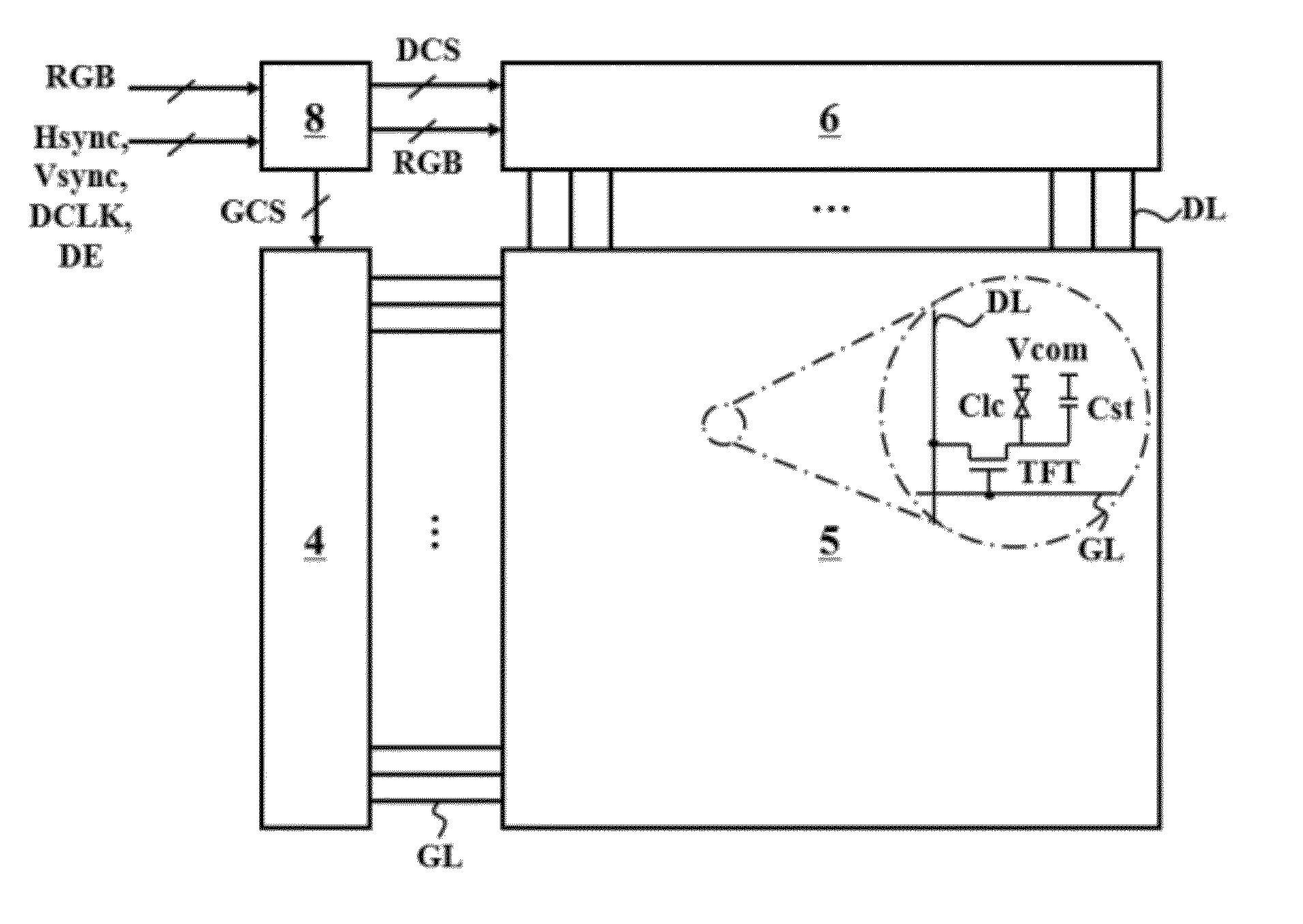

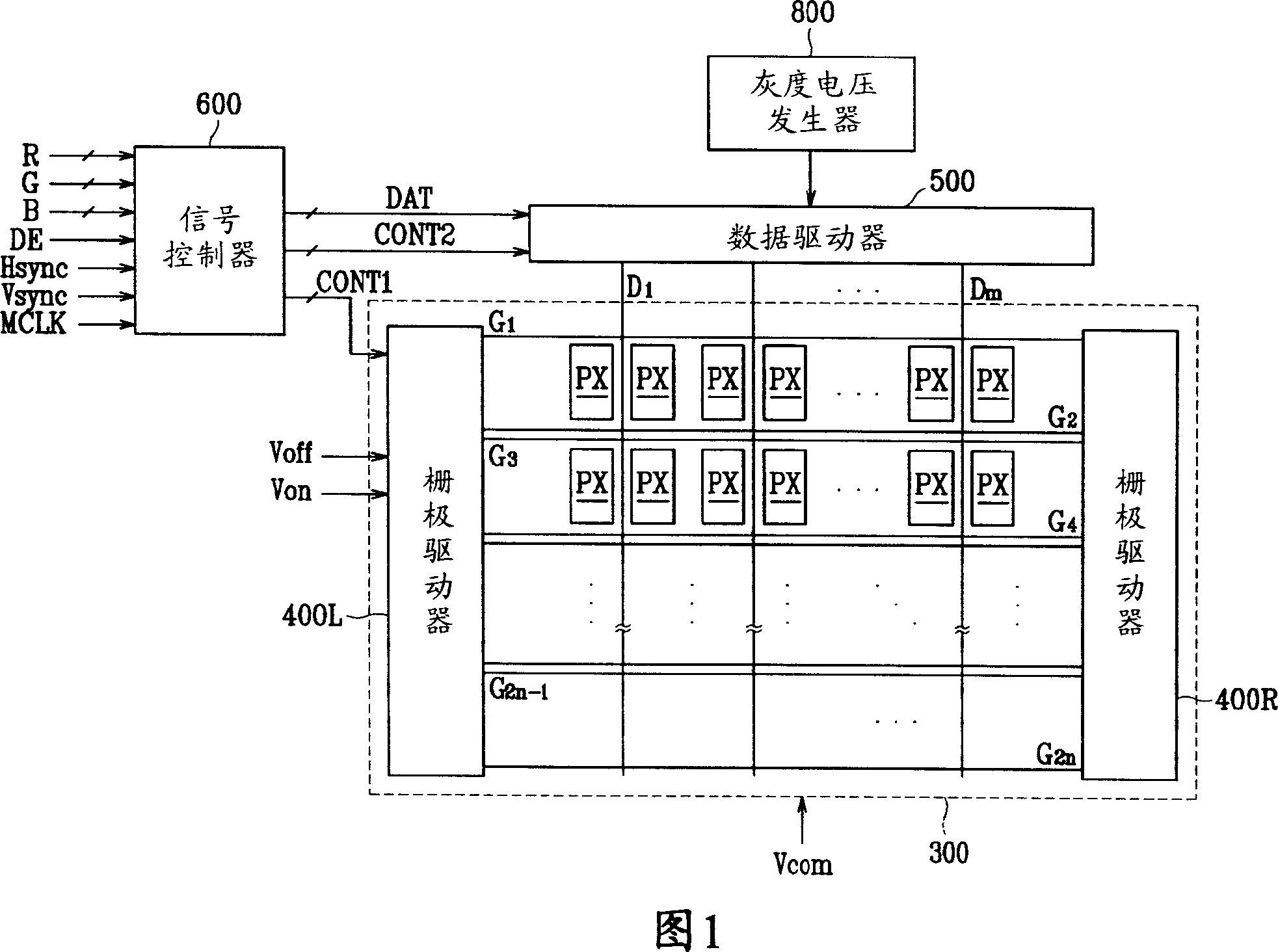

Provided is a driver for a display apparatus and a display apparatus having the same. The driver includes a plurality of gate lines that transmit gate signals, and first and second gate drivers that are respectively connected to odd-numbered and even-numbered gate lines among the plurality of gate lines and generate the gate signals based on a plurality of clock signals, wherein two adjacent clock signals among the plurality of clock signals have a phase difference equal to or greater than 180° and less than 360°. Accordingly, voltage drop caused by a kickback voltage occurs only one time by allowing two adjacent clock signals to have a predetermined time delay from each other, so that a positive data voltage is the same as a negative data voltage, thereby preventing flicker or stain.

Owner:SAMSUNG ELECTRONICS CO LTD

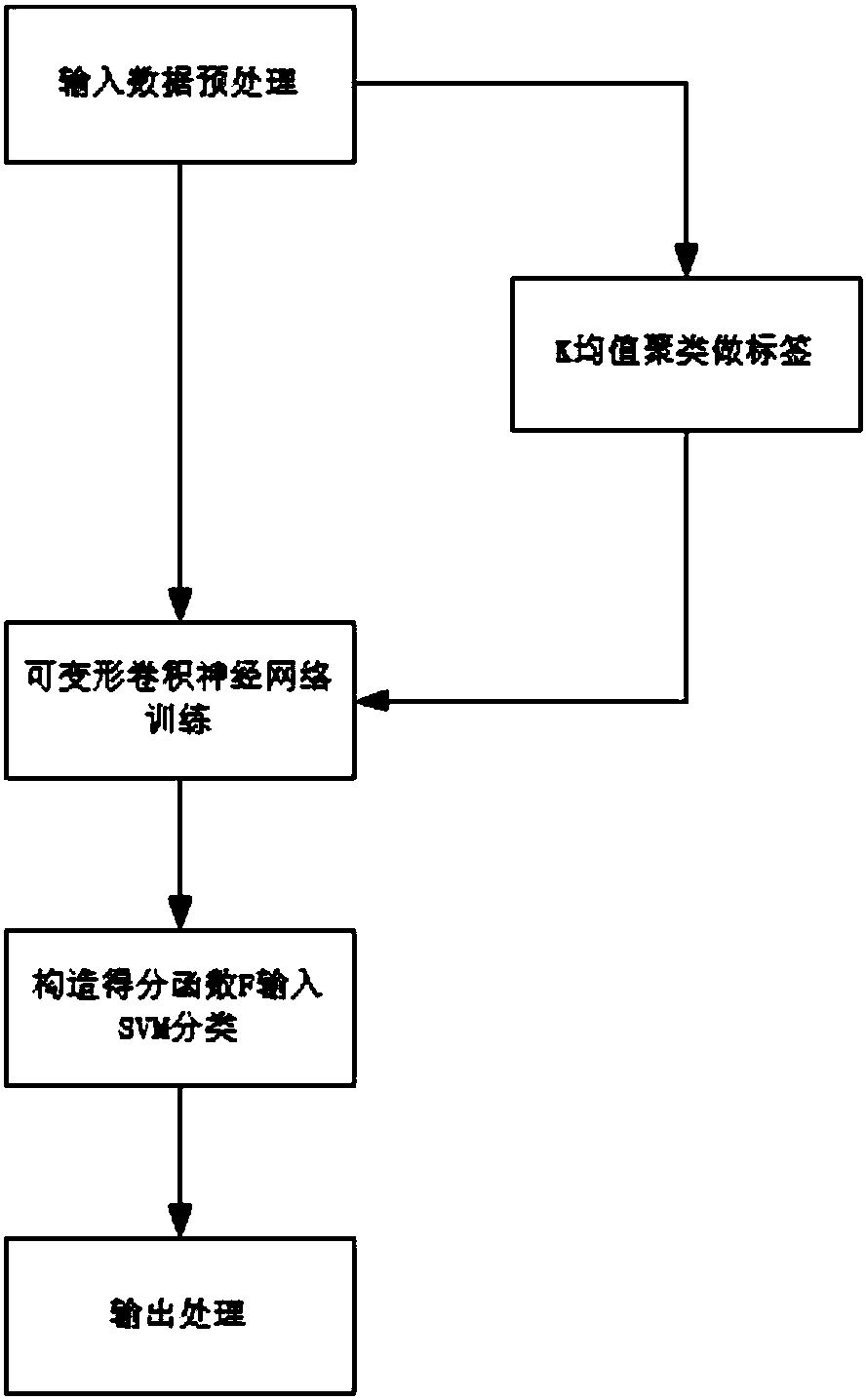

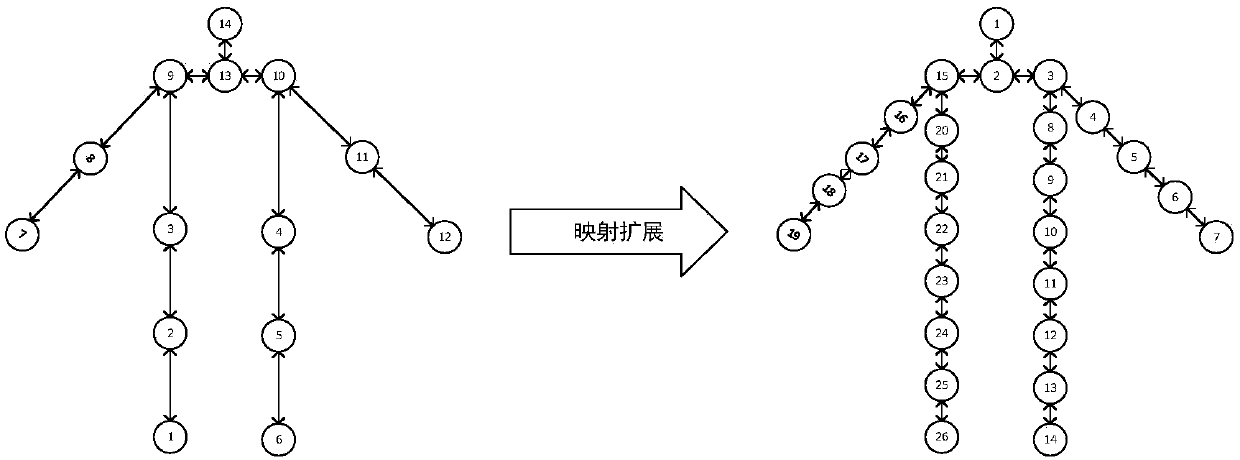

Human posture estimation method based on deformable convolutional neural network

ActiveCN107609541AImprove recognition rateEfficient extractionCharacter and pattern recognitionNeural architecturesValidation testData set

The invention relates to the technical field of depth learning and computer vision, in particular to a human posture estimation method based on a deformable convolutional neural network. The method comprises the following steps of 1, preprocessing an input dataset, wherein expanding and data set picture cutting are included; 2, performing K-means clustering on training set pictures; 3, adopting the K-means clustering result as a label, and inputting a training set into the deformable convolutional neural network to be trained; 4, constructing a score function F for training an SVM for joint classification; 5, performing outputting treatment. By reading the positive data sets, some data sets are adopted as the training set, some data sets are adopted as the validation set, negative data isread for comparison, and the negative data set is introduced for training, so that the background can be effectively filtered away to obtain interference, and the recognition rate is increased.

Owner:HARBIN UNIV OF SCI & TECH

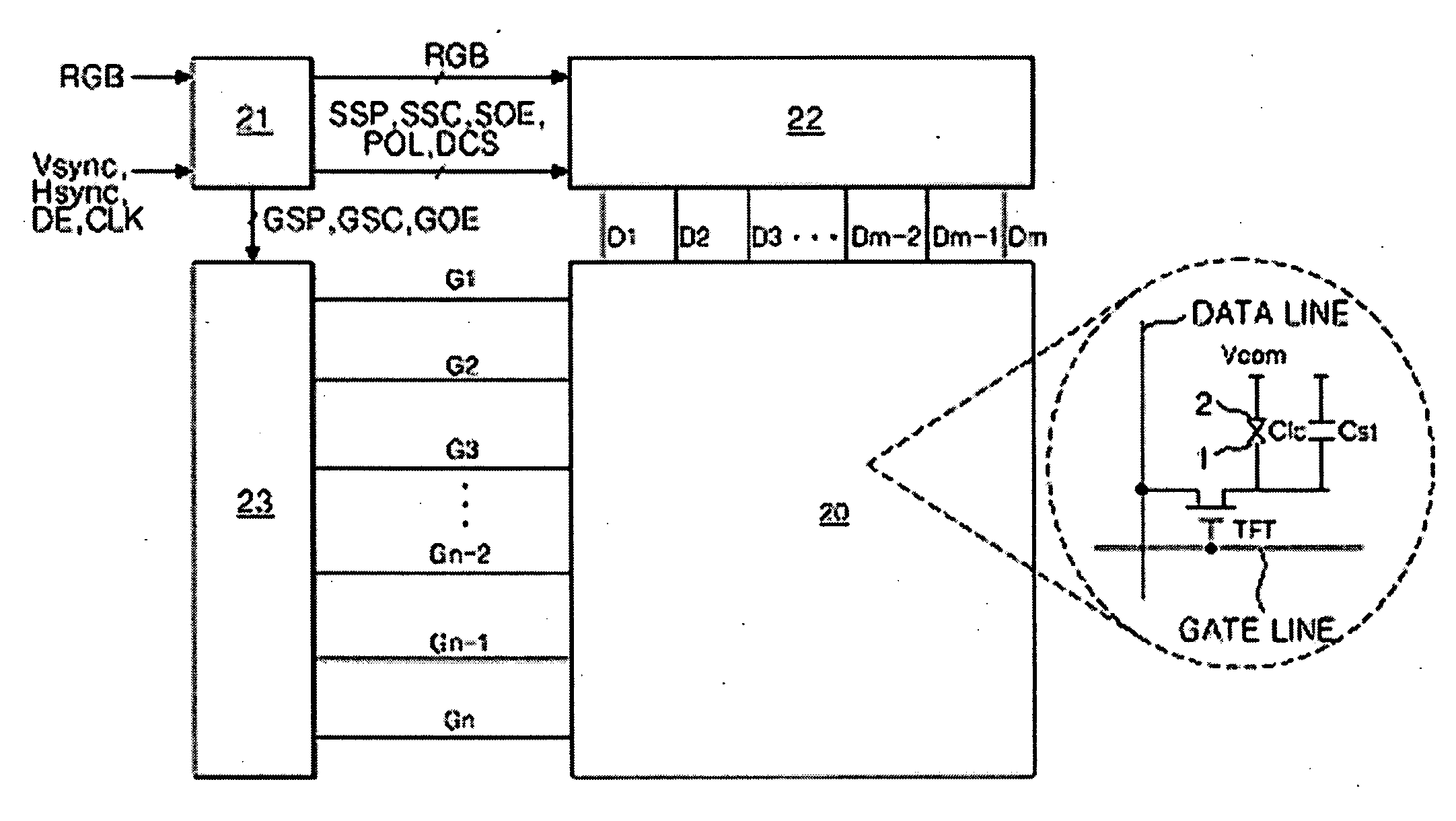

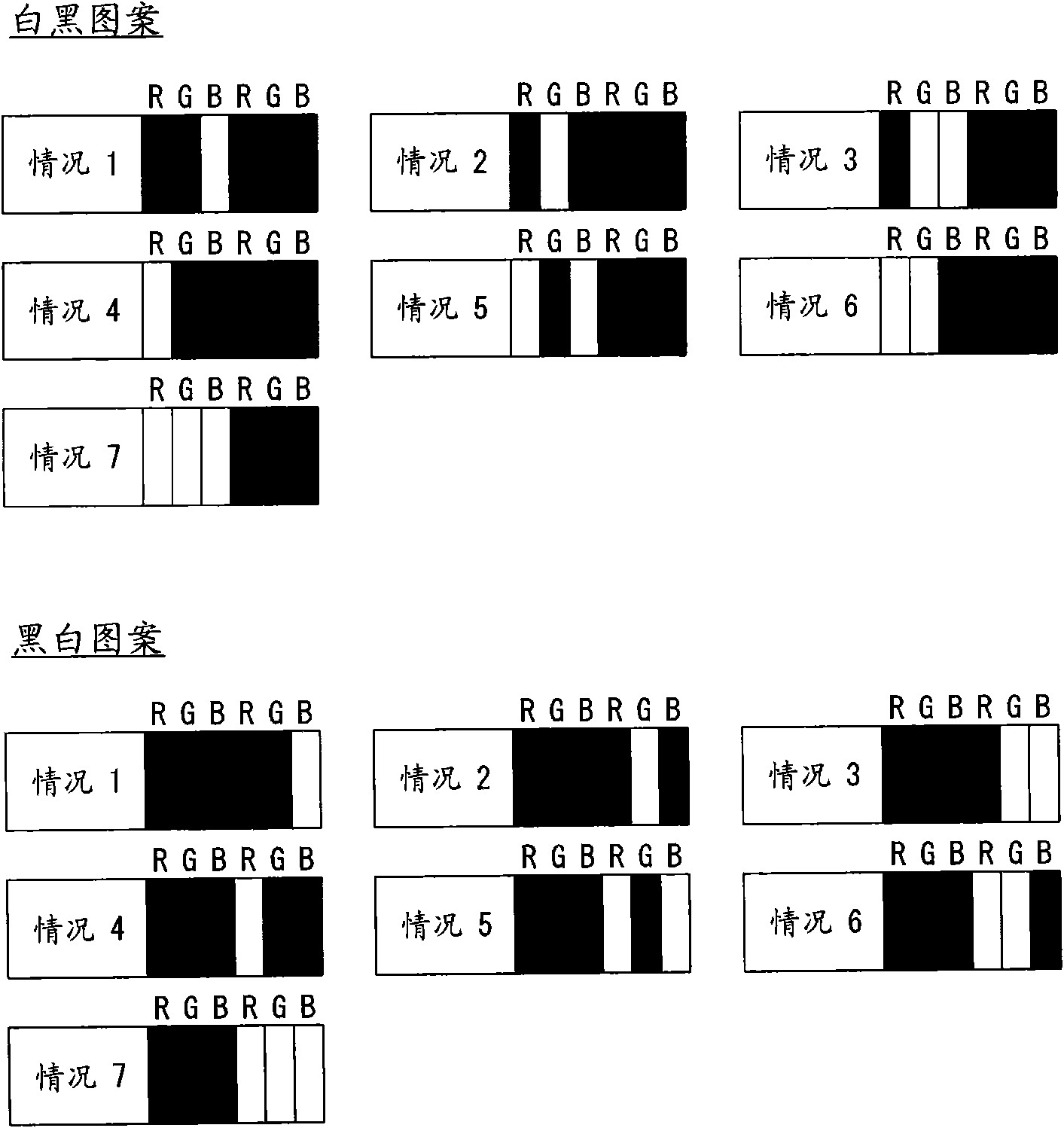

Liquid crystal display and driving method thereof

ActiveUS20090002302A1Reduce heat consumptionLow heat generationCathode-ray tube indicatorsNon-linear opticsDigital videoControl signal

A liquid crystal display includes a liquid crystal display panel having a plurality of data lines, a plurality of gate lines crossing the plurality of data lines, and a plurality of liquid crystal cells, a timing controller to determine gray levels of input digital video data and a time at which a polarity of a data voltage to be supplied to the data lines is inverted, to activate a dynamic charge share control signal to indicate a time at which the gray level of the data voltage is changed from a white gray level to a black gray level and a time at which the polarity of the data voltage is inverted, to detect weakness patterns in which the data of the white gray level and the black gray level are regularly arranged in the input digital video data, and to activate a dot inversion control signal for widening a horizontal polarity inversion period of data voltages to be supplied to the data lines when the weakness patterns are input, a data driving circuit to convert the digital video data from the timing controller into the data voltage, to convert the polarity of the data voltage, to supply any one of a common voltage and a charge share voltage between a positive data voltage and a negative data voltage to the data lines in response to the dynamic charge share control signal, and to widen the horizontal polarity inversion period of the data voltages in response to the dot inversion control signal, and a gate driving circuit to sequentially supply a scan pulse to the gate lines under the control of the timing controller.

Owner:LG DISPLAY CO LTD

Liquid crystal display panel and method of driving the same

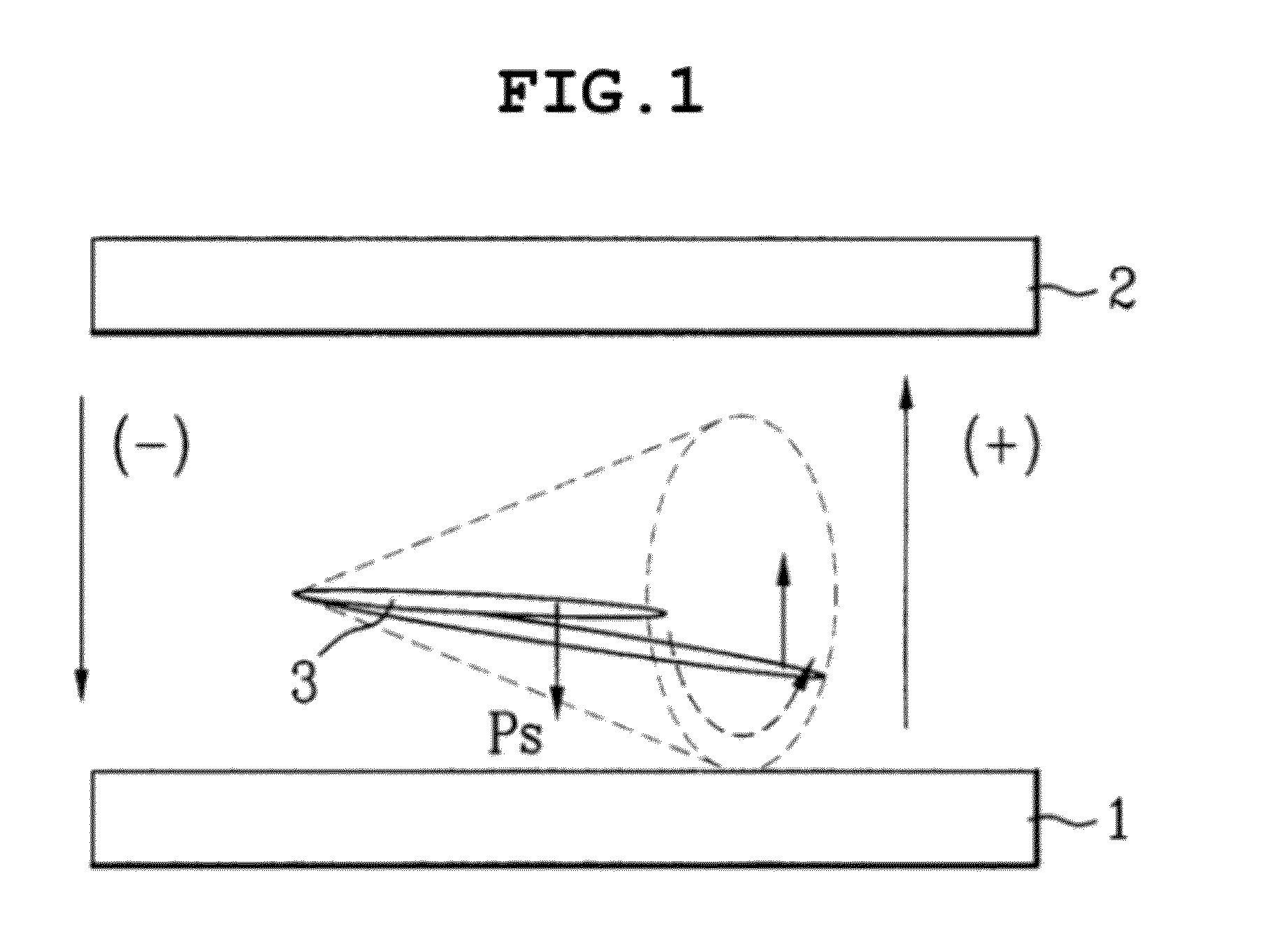

This invention relates to a three electrode liquid crystal display panel that is adaptive for AC-driving liquid crystal cells inclusive of three electrodes, and a driving method thereof. A three electrode liquid crystal display panel according to an embodiment of the present invention includes first and second pixel electrodes disposed on a first substrate with an insulating film therebetween; and a common electrode disposed in a second substrate which is bonded with the first substrate with a liquid crystal therebetween, and wherein the first pixel electrode selectively supplies a maximum voltage and a minimum voltage, the common electrode supplies a medium voltage between the maximum voltage and the minimum voltage as a reference voltage, and the second pixel electrode supplies a positive data voltage and a negative data voltage on the basis of the reference voltage in a range between the maximum voltage and the minimum voltage, thereby AC-driving the liquid crystal.

Owner:LG DISPLAY CO LTD

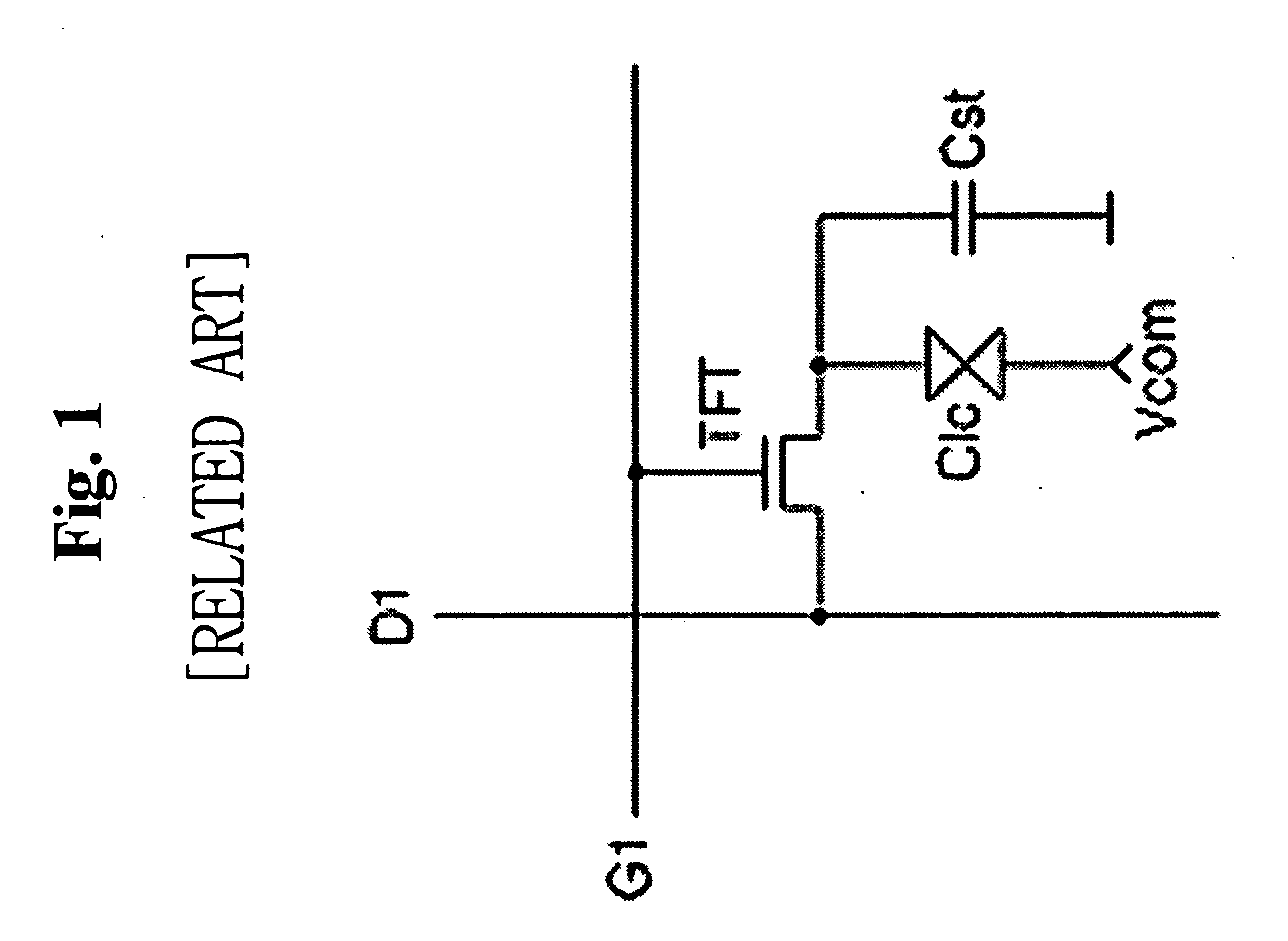

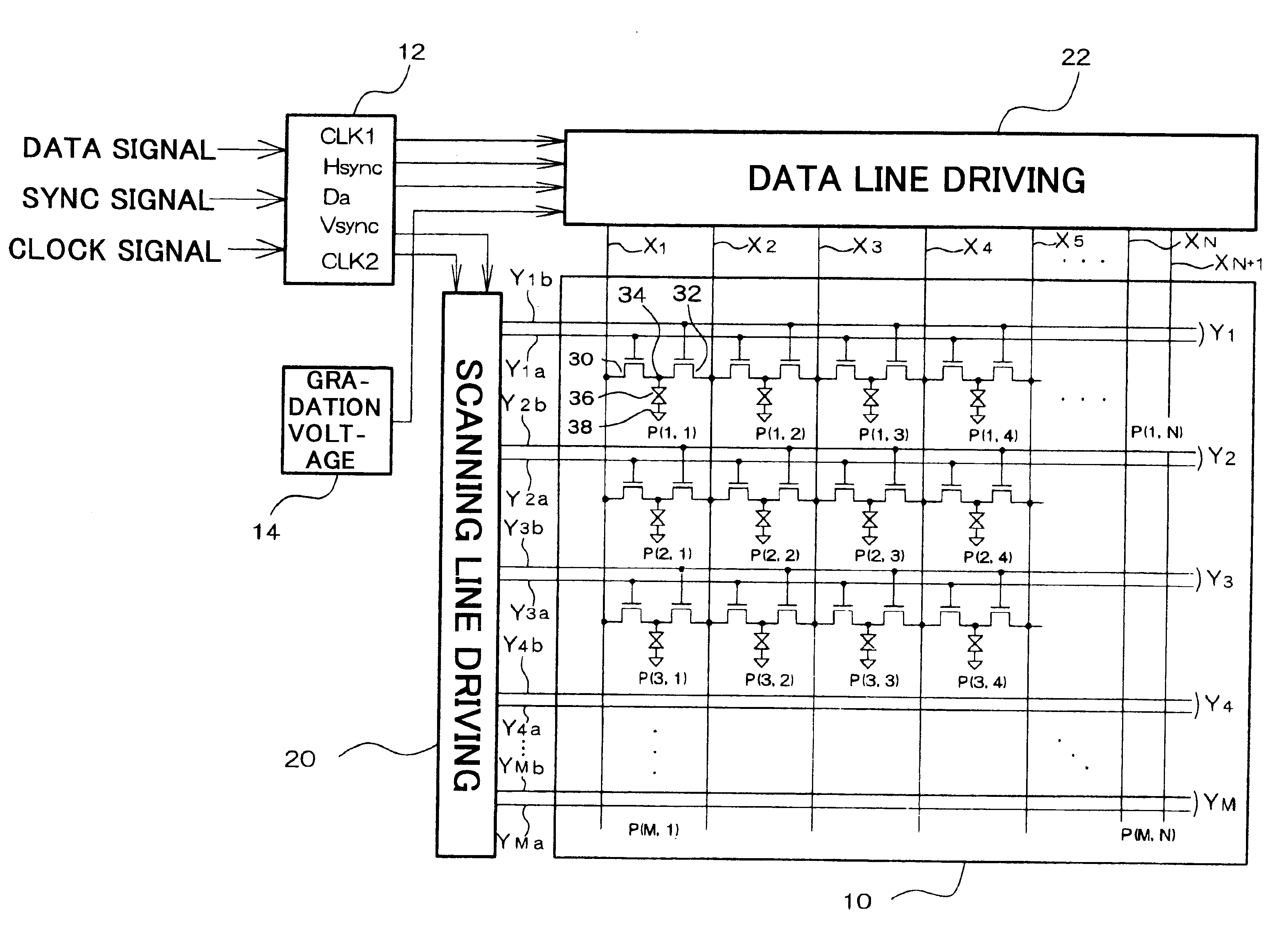

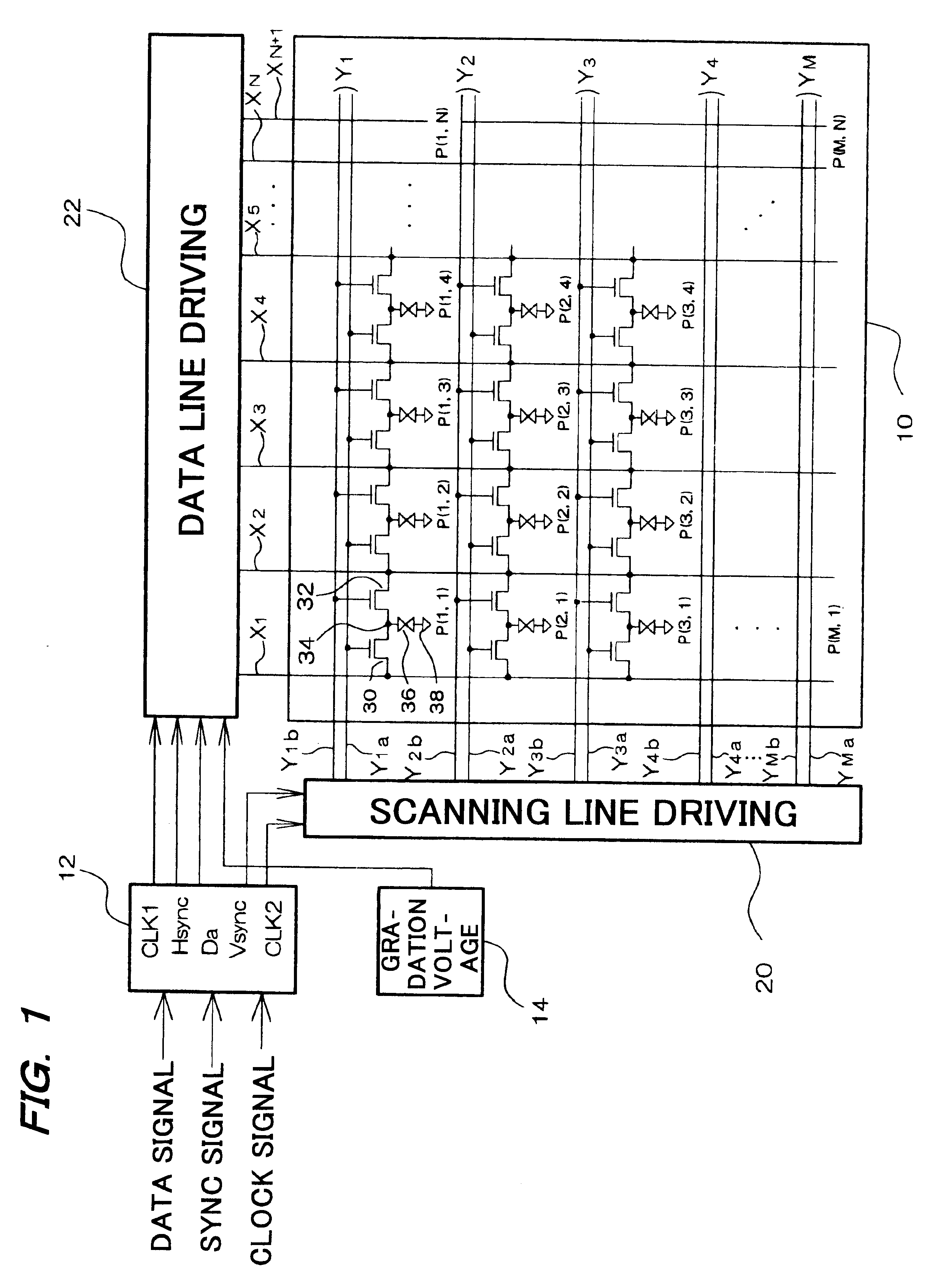

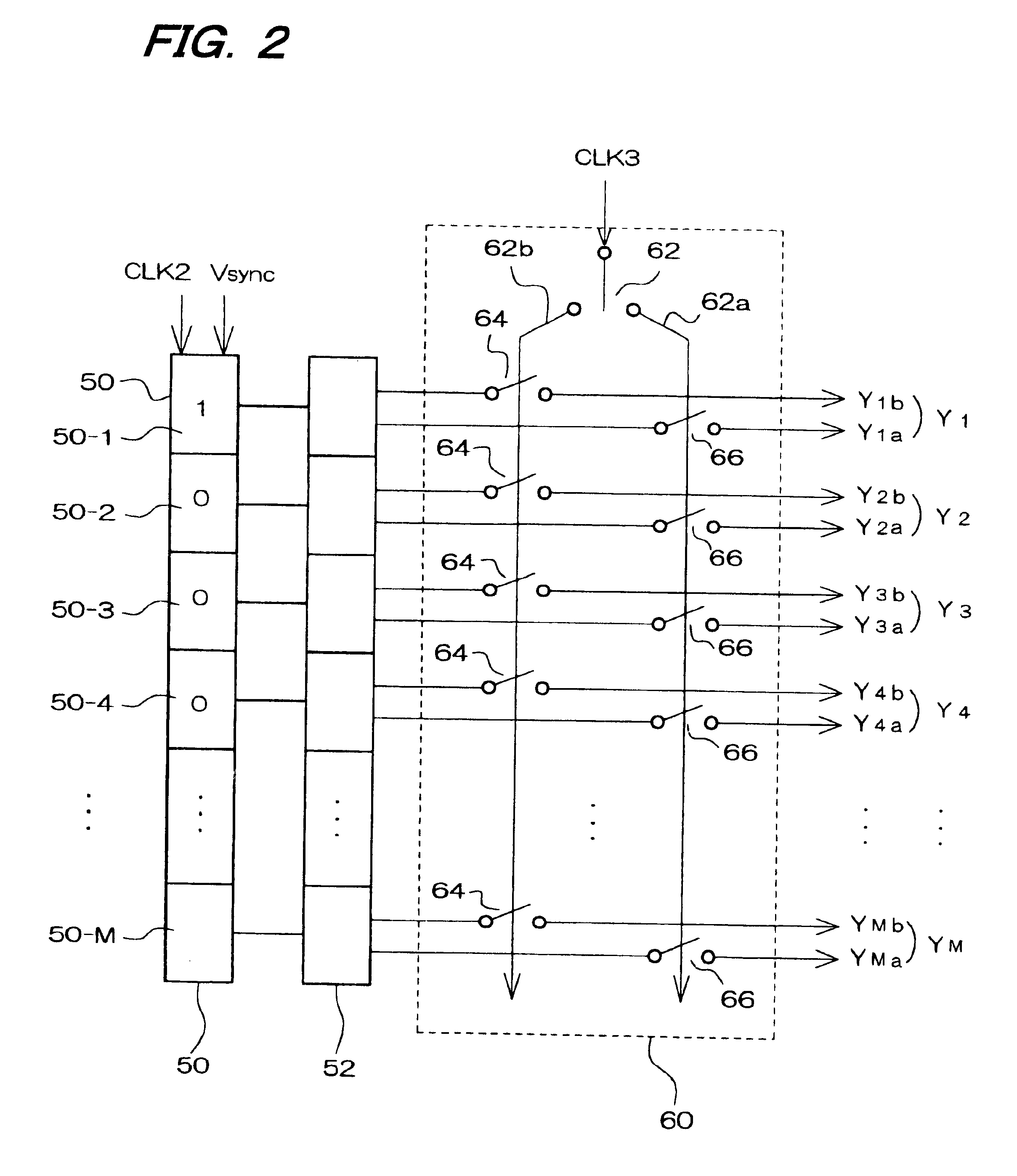

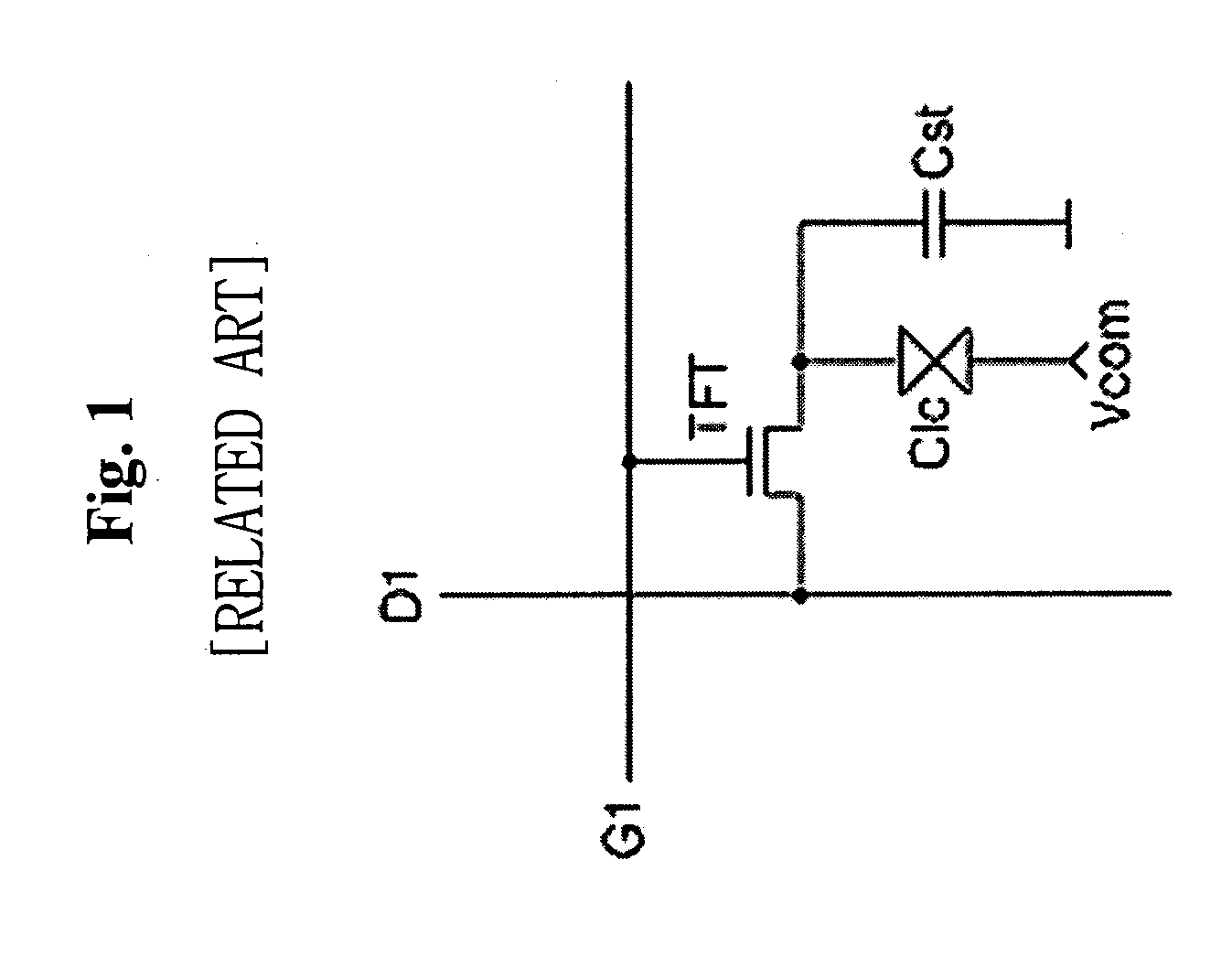

Electro-optical device, method of driving the same, and electronic apparatus using the same

InactiveUS6566643B2Reduce power consumptionFully chargedSolid-state devicesMaterial analysis by optical meansData signalPositive data

A liquid crystal panel has odd-numbered data lines Xa to which a positive data signal voltage is supplied and even-numbered data lines Xb to which a negative data signal voltage is supplied. The liquid crystal panel has MxN pixels P (m, n) that are arranged in such a manner that each pixel P(m, n) corresponds to one of the odd-numbered data lines and one of the even-numbered data lines that is adjacent to the one odd-numbered data line. The aperture portion of each pixel P (m, n) is provided with a switching element that is connected to a scanning line Ym and one of the data lines Xa, and a switching element that is connected to the scanning line Ym and one of the data lines Xb that is adjacent to the one data line Xa. In performing dot inversion driving on this liquid crystal device, a data line driving circuit supplies positive data signal voltages to the data lines Xa and negative data signal voltages to the data lines Xb. In synchronism with this operation, a scanning line driving circuit controls opening / closing of the two switching elements.

Owner:SEIKO EPSON CORP

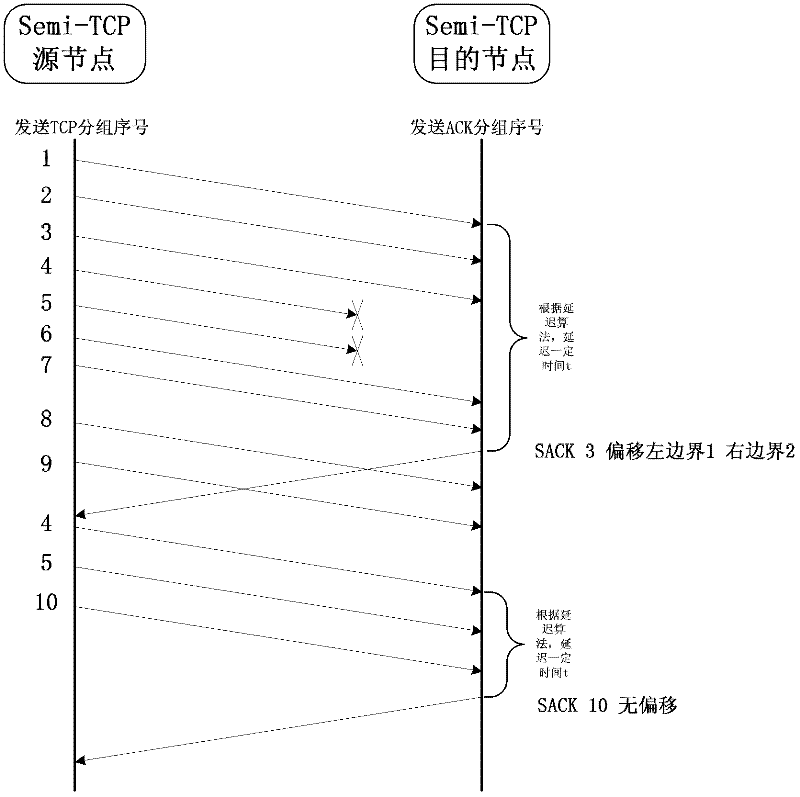

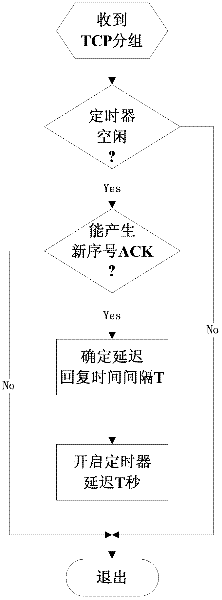

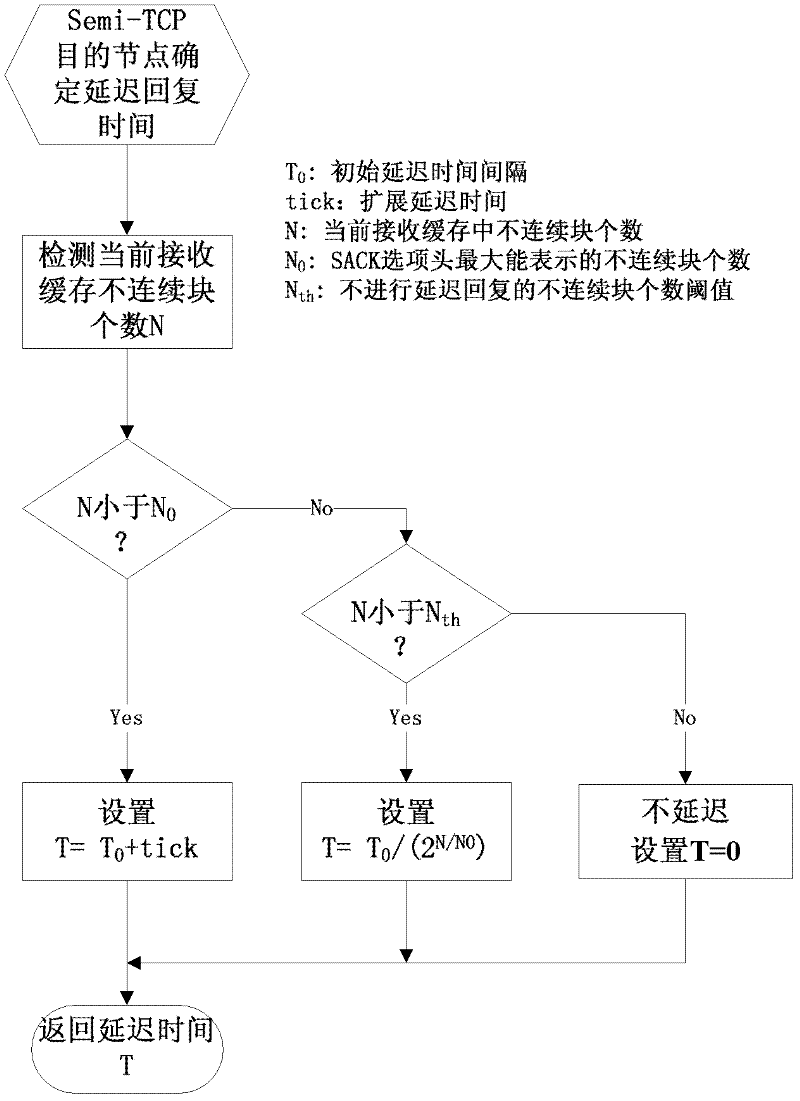

Method for adaptively determining packet delayed sending for Semi-TCP (transmission control protocol)

ActiveCN102413503APlay the role of reliability controlReduce in quantityNetwork traffic/resource managementSelf adaptivePositive data

The invention discloses a method for adaptively determining packet delayed sending for Semi-TCP (transmission control protocol). In the method, after receiving a TCP packet, a destination node using the Semi-TCP adaptively determines the time of sending an acknowledgement packet of a data packet, thus the sending quantity of the ACK (acknowledgement) packet is compressed, the sending of repeated ACK is canceled, and the competition for a wireless channel between a positive data flow and a negative data flow is reduced; and an acknowledgment state is a state described by the following parameters: continuity of packets in a receiving cache of the destination node, the maximum number of block boundaries which can be contained by a selective acknowledgement (SACK) packet head, a set time interval of sending ACK and the like. Meanwhile, in the method, the traditional SACK packet head is improved, and the sequence numbers of discontinuous TCP block boundaries are marked by a relative offset so as to improve the acknowledgment rate of the Semi-TCP source node packet and reduce the overhead resulting from the introduction of SACK.

Owner:SHANGHAI MARITIME UNIVERSITY

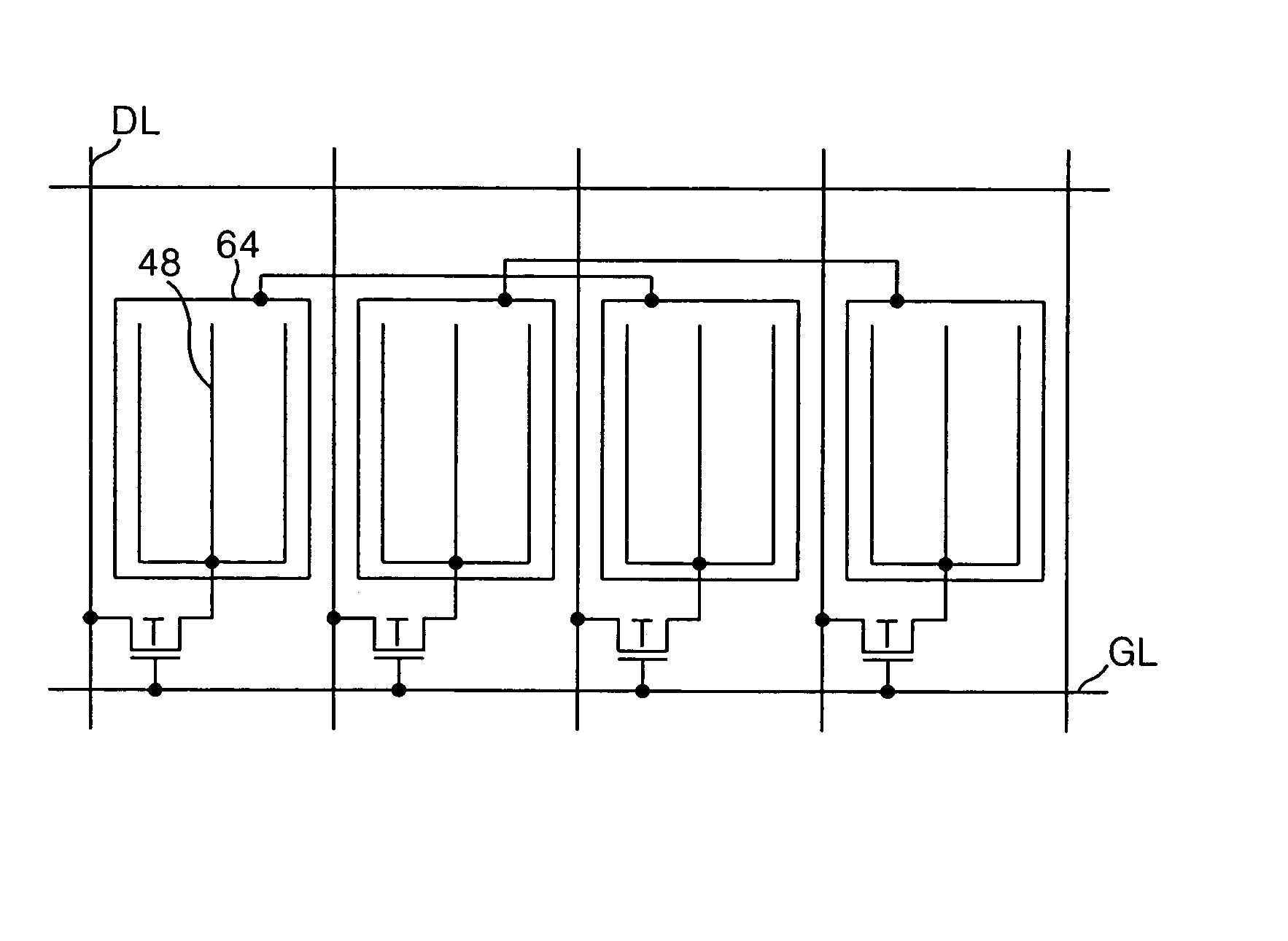

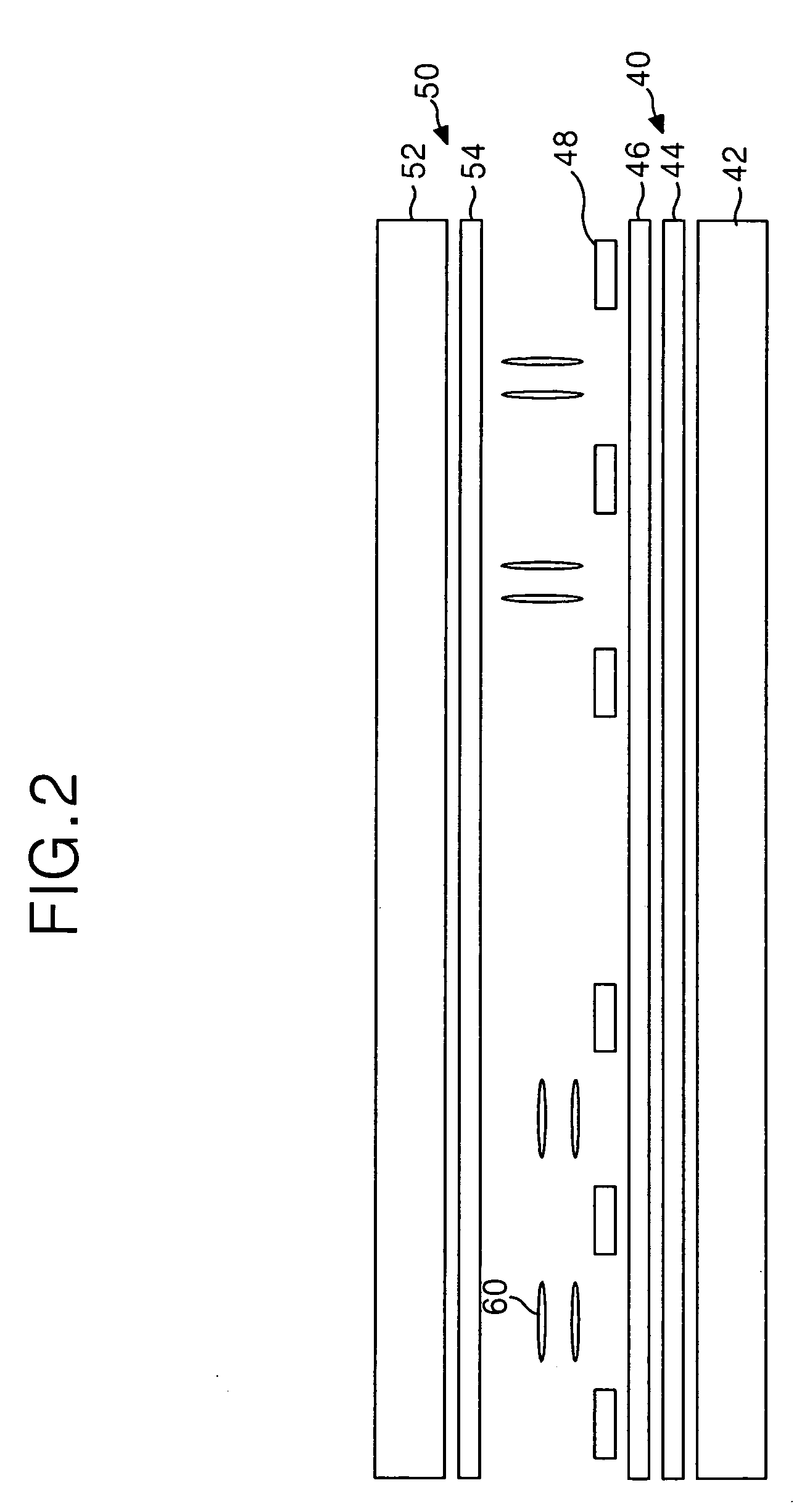

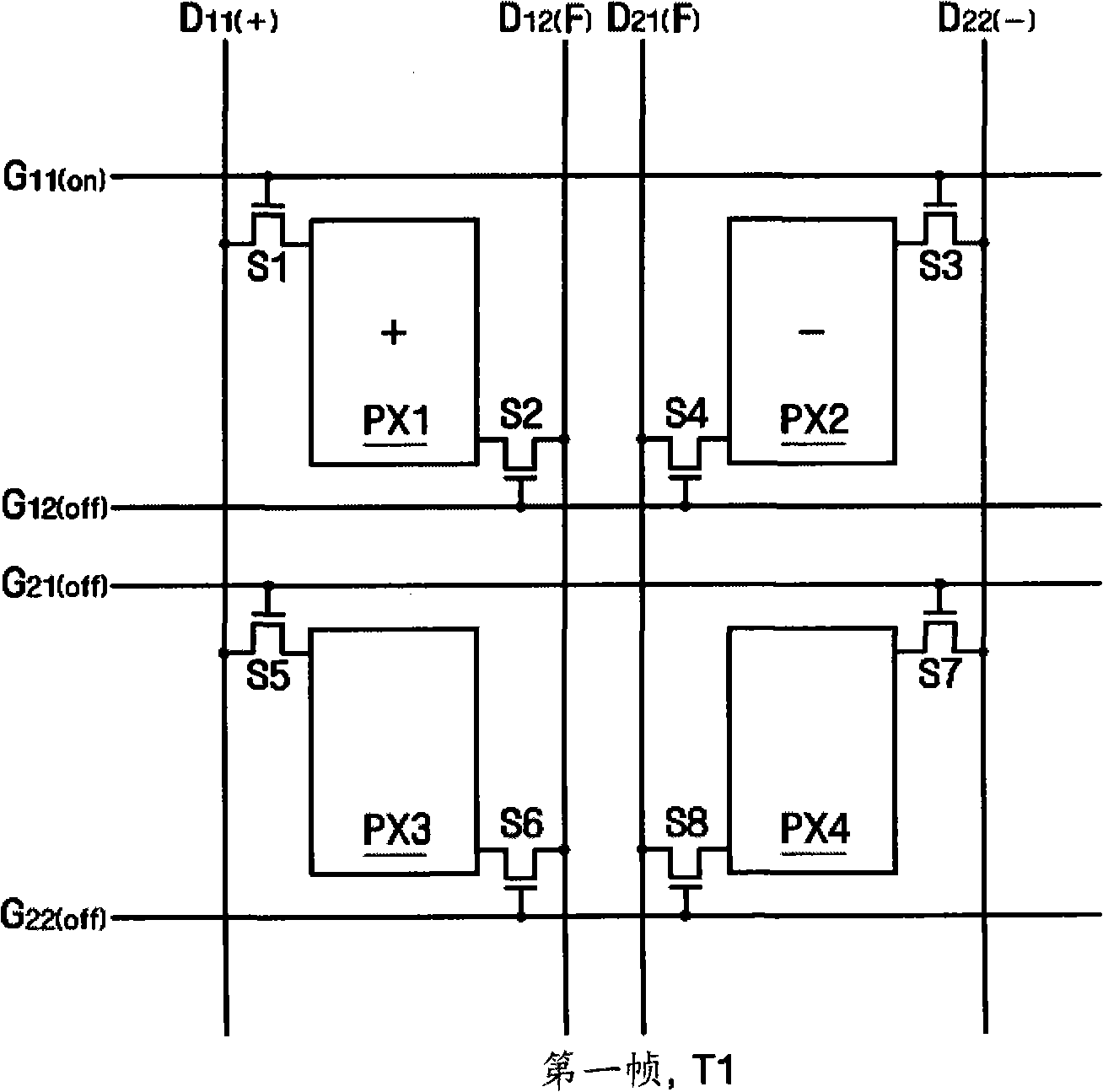

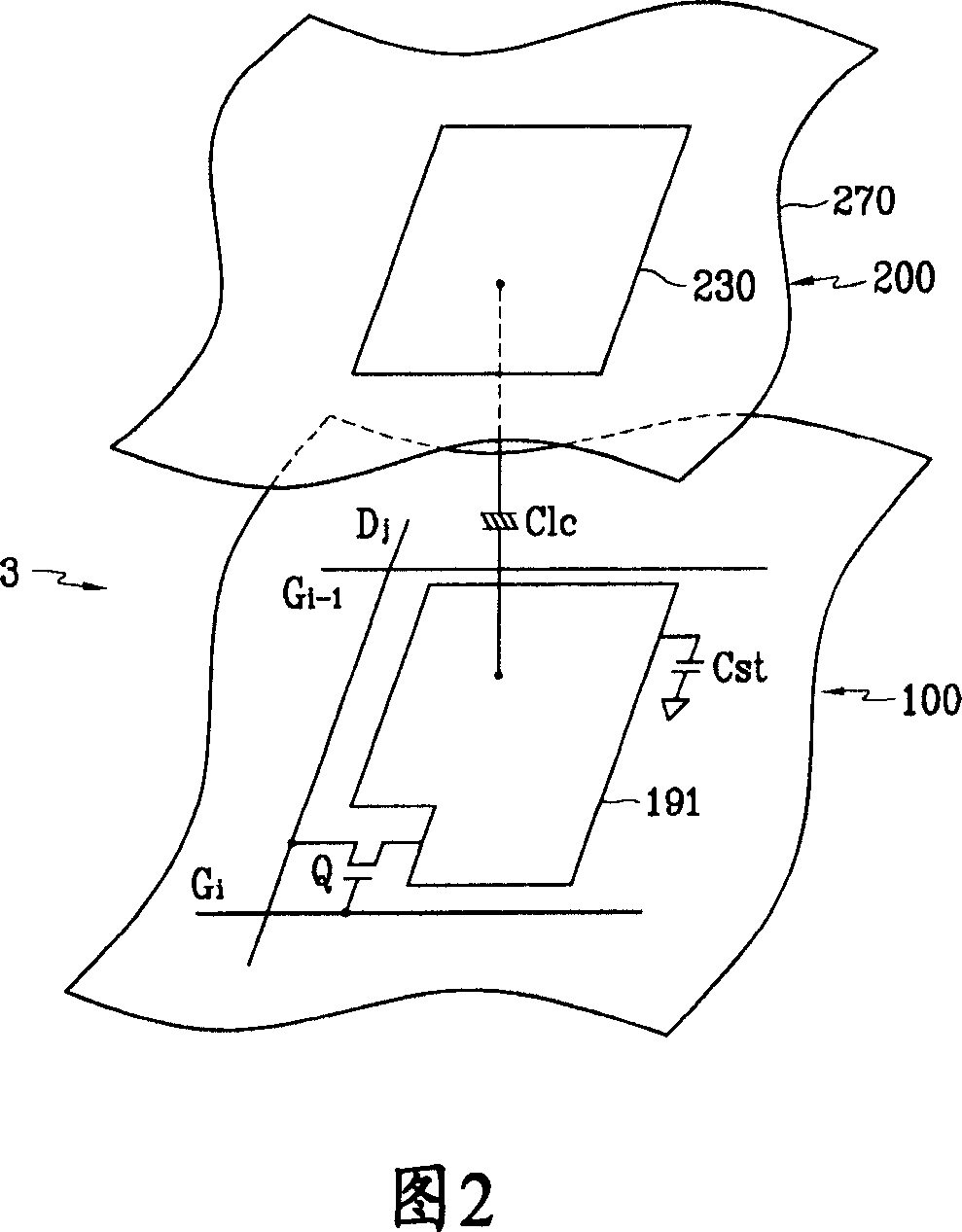

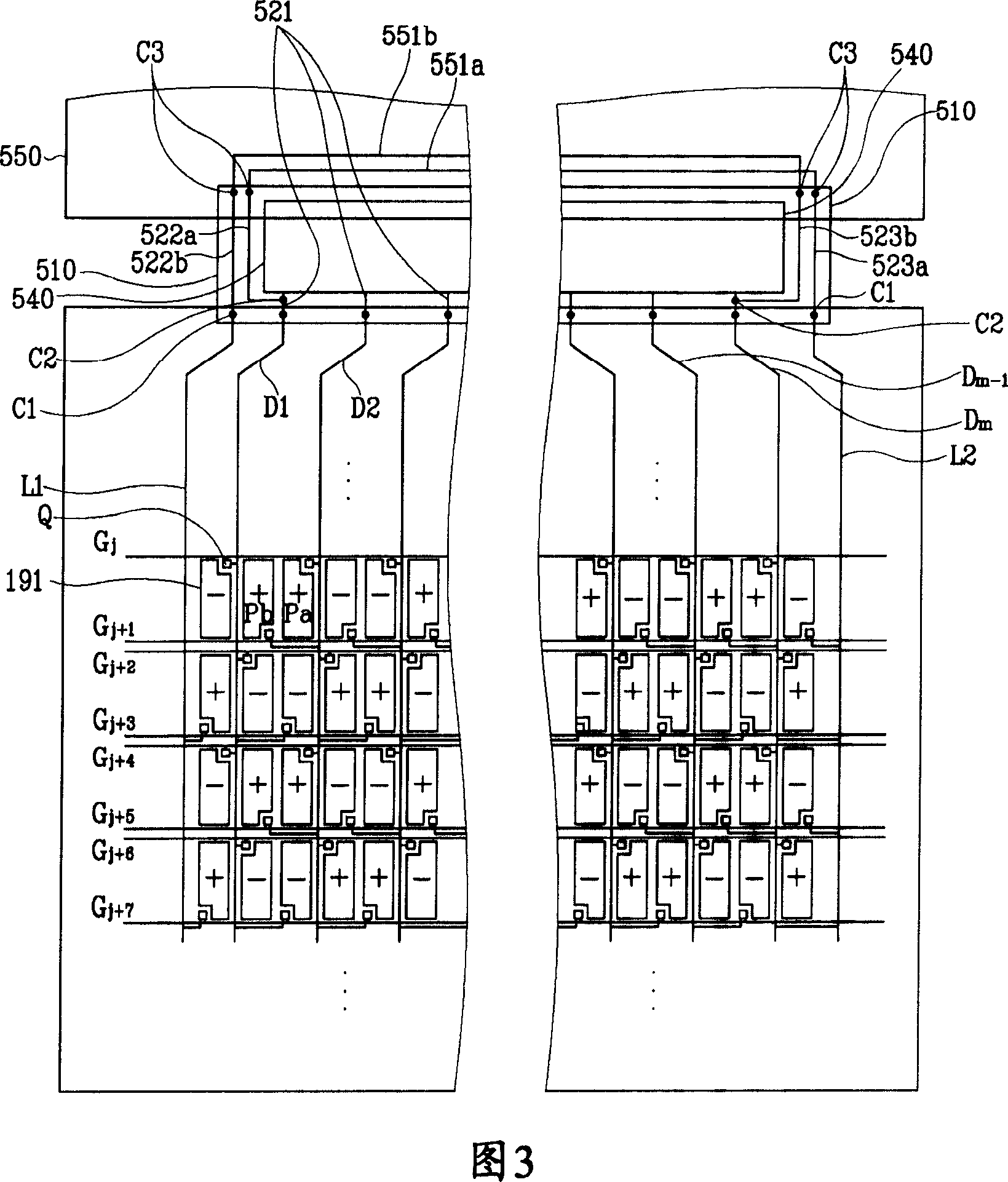

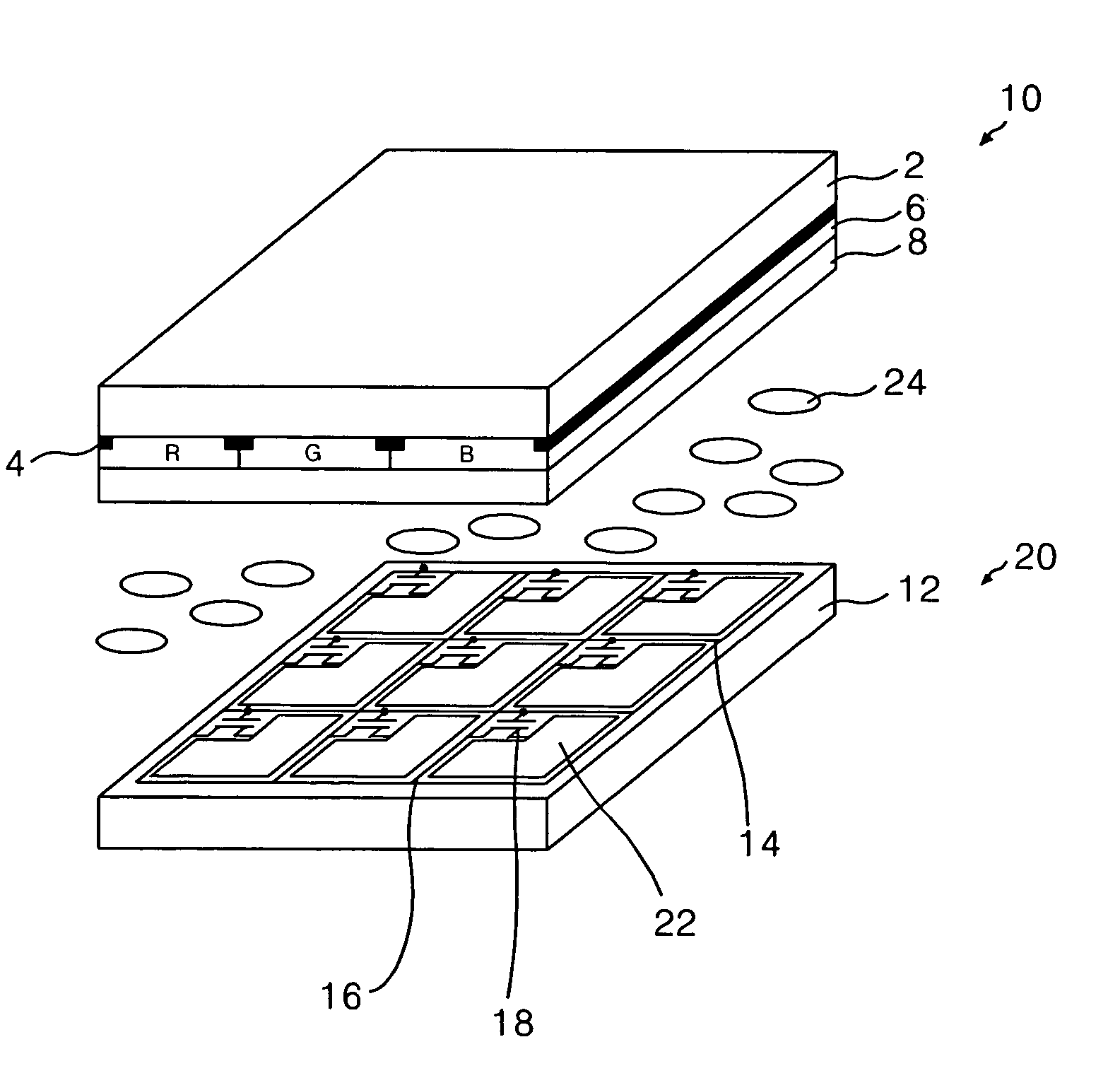

Display substrate and liquid crystal display having the same

InactiveUS20080246720A1Reduce power consumptionStatic indicating devicesNon-linear opticsLiquid-crystal displayEngineering

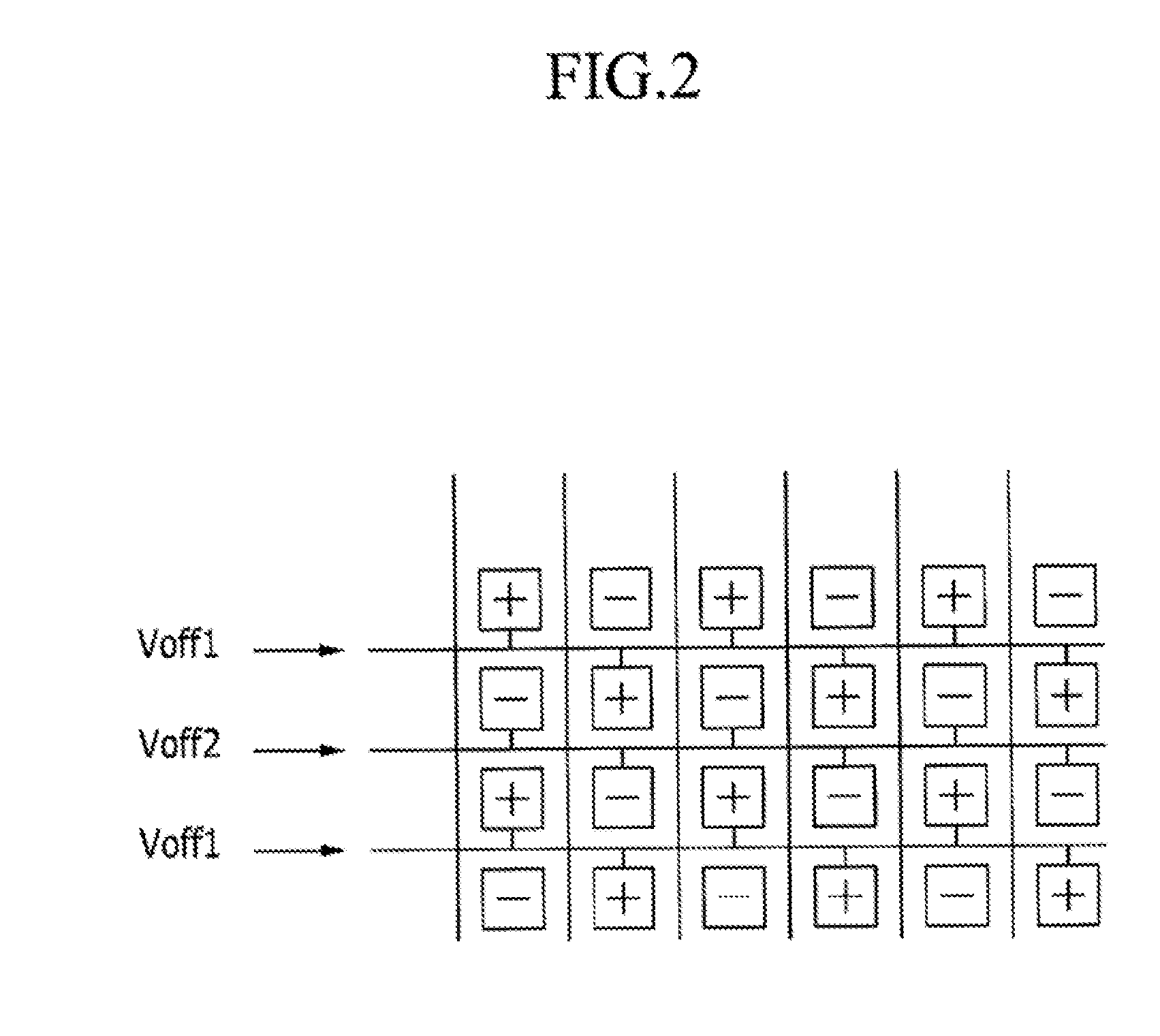

A liquid crystal display includes: a first pixel connected to first and second gate lines, a first positive data line and a first negative data line, and which is supplied with a positive data voltage from the first positive data line when enabled by a first gate-on voltage from the first gate line, and is supplied with a negative data voltage from the first negative data line when enabled by a second gate-on voltage from the second gate line; and a second pixel connected to the first and second gate lines, a second positive data line and a second negative data line, and which is supplied with a negative data voltage from the second negative data line when enabled by the first gate-on voltage and is supplied with a positive data voltage from the second positive data line when enabled by the second gate-on voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

Display device and driving method thereof

ActiveUS20140313181A1Reduce voltageCathode-ray tube indicatorsInput/output processes for data processingDisplay deviceControl theory

A controller controls the driving frequency and voltages for a display device. If image data corresponds to a moving picture, the controller drives a data driver and a gate driver at a moving picture frequency. If image data corresponds to a still image, drives the data driver and the gate driver at a still image frequency lower frequency than the moving picture frequency. When the still image is to be displayed, the signal controller also controls leakage current of a thin film transistor of a pixel based on a representative value of the image data, such that positive leakage current applied for a positive data voltage is equal to negative leakage current applied for a negative data voltage.

Owner:SAMSUNG DISPLAY CO LTD

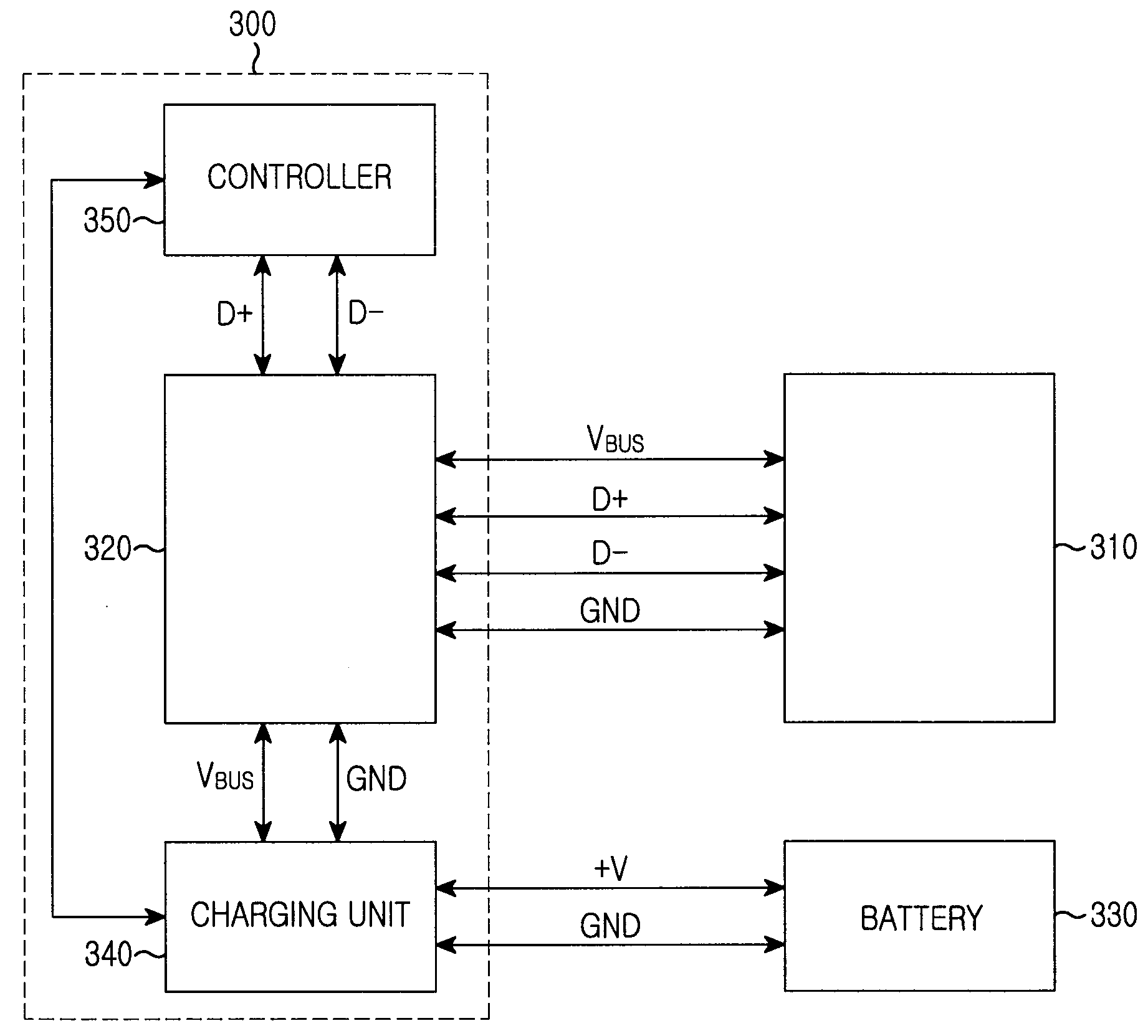

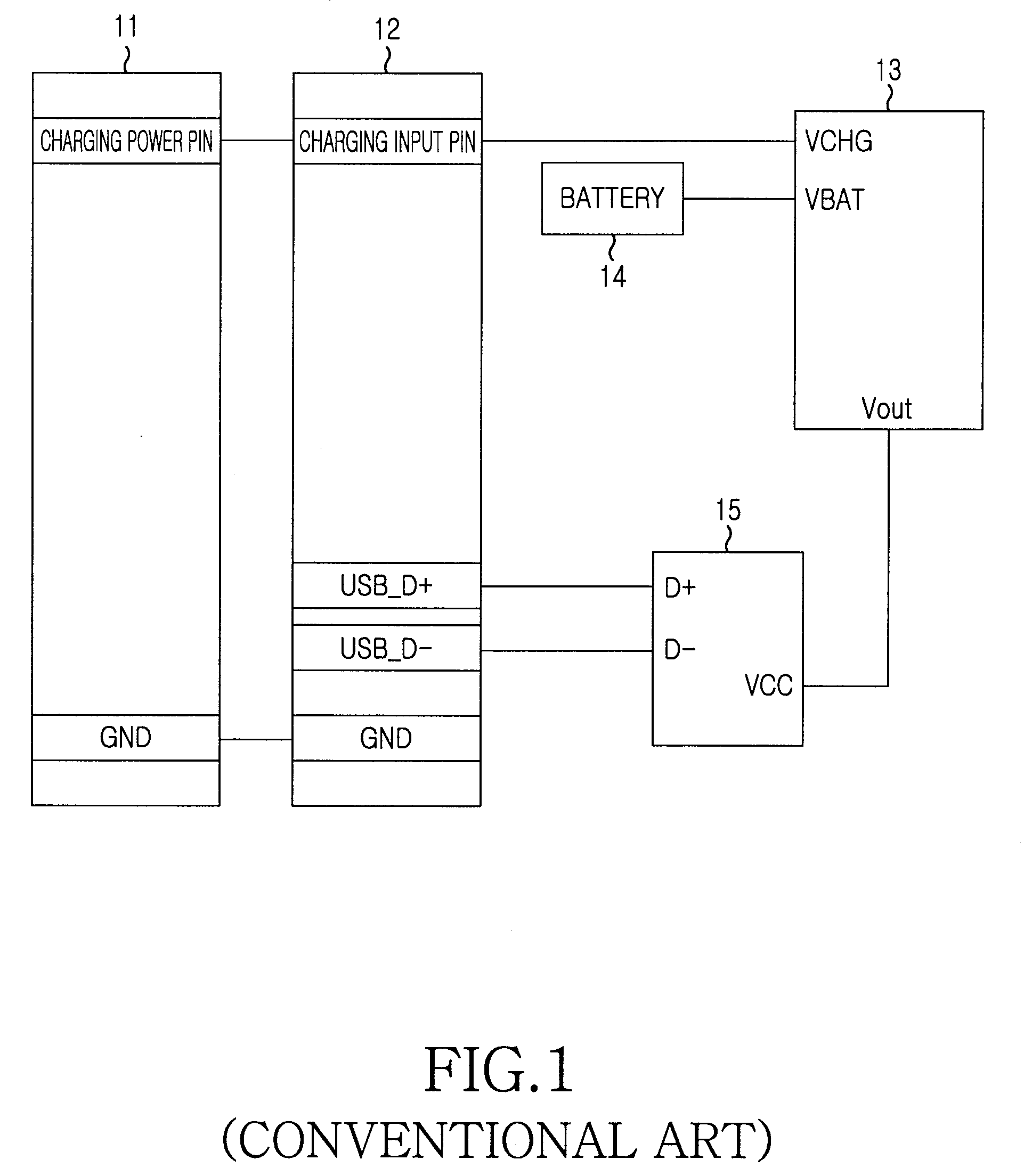

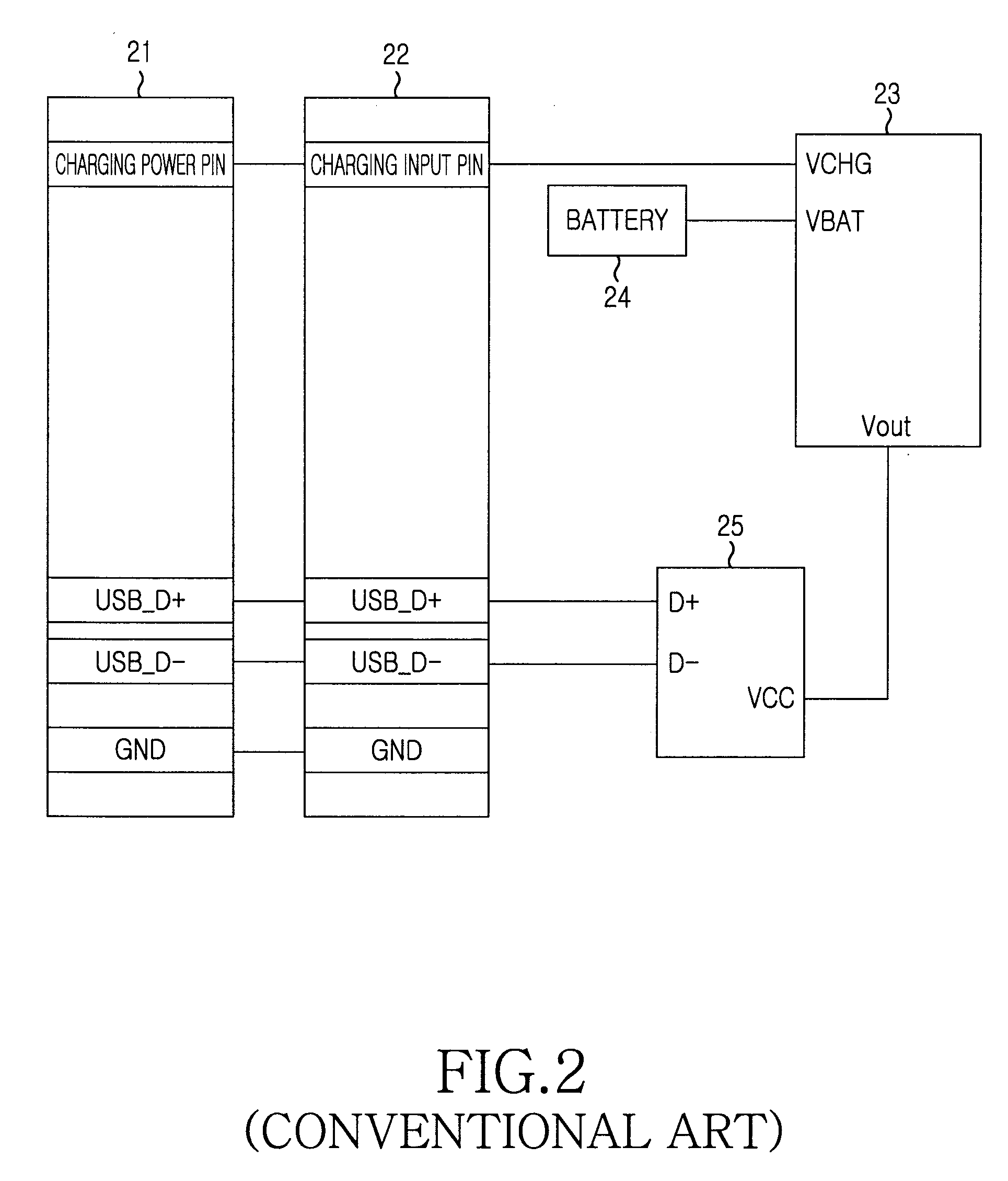

Portable communication device and method for charging through discernment of charging cable

InactiveUS20090027010A1Accurately cable connectedAccurate identificationBatteries circuit arrangementsElectric powerEngineeringPositive data

A portable communication device and method for charging through discernment of a charging cable are provided. When the portable communication device is connected to an external charging device through a connector in order to charge a power source in the portable communication device, a configuration signal is received from the external charging device through a positive data line and a negative data line of the connector, a logic characteristic value is output according to the received configuration signal, the charging cable is discerned by analyzing a current characteristic through connection with a resistance circuit according to the on / off state of a switch which operates according to the logic characteristic value, and a control operation is performed such that a battery is charged from the external charging device through the corresponding charging cable.

Owner:SAMSUNG ELECTRONICS CO LTD

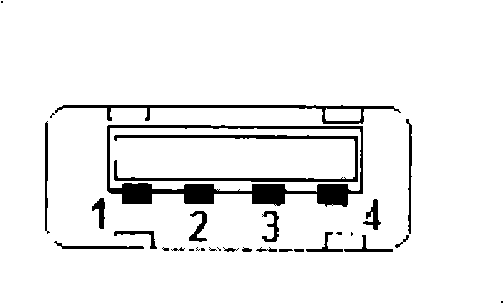

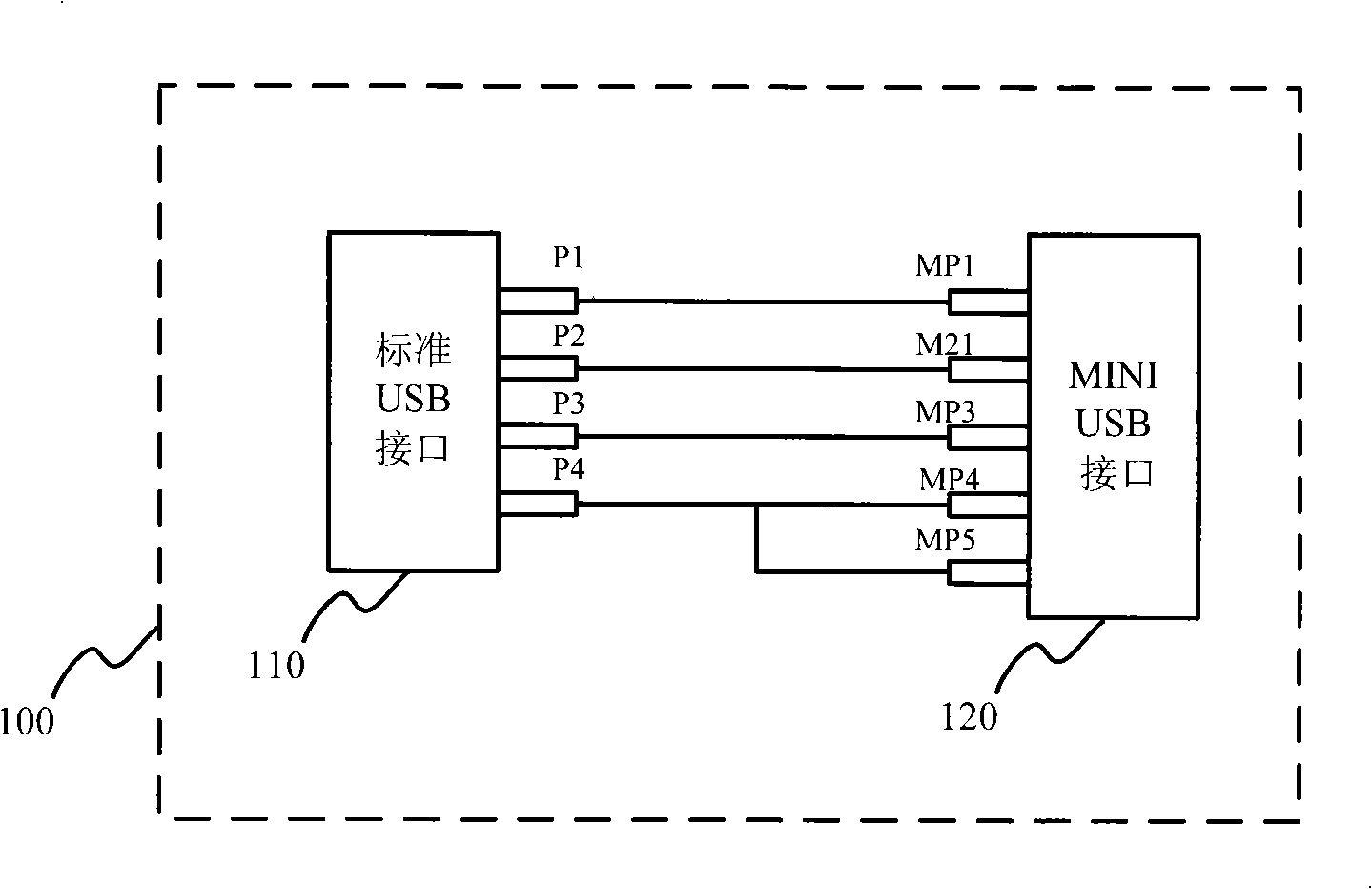

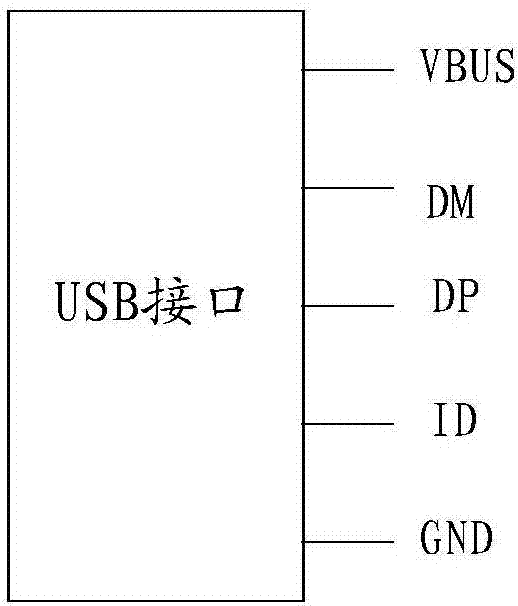

USB interface switching device

ActiveCN101281421AFirmly connectedAchieve mutual communicationCoupling device connectionsInput/output processes for data processingInterconnectionUSB

The invention provides a USB interface transfer device which realizes interconnection of a MINI USB interface and a standard USB interface. Particularly, the invention provides the USB interface transfer device, comprising a USB interface and the MINI USB interface. The USB interface is connected with the MINI USB interface via a cable. The USB interface comprises a first power pin, a first positive data line, a first negative data line and a first grounding pin. The MINI USB interface comprises a second power pin, a second positive data line, a second negative data line, a second grounding pin and a control pin. The first power pin, the first positive data line, the first negative data line and the first grounding pin of the USB interface are correspondingly connected with the second power pin, the second positive data line, the second negative data line and the second grounding pin of the MINI USB interface via the cable. The control pin is at least connected with one of the second power pin or the second grounding pin. Applying the USB interface transfer device of the invention can conveniently connect a USB device and a MINI USB device to reach the aim of intercommunicating.

Owner:GUIYANG HISENSE ELECTRONICS

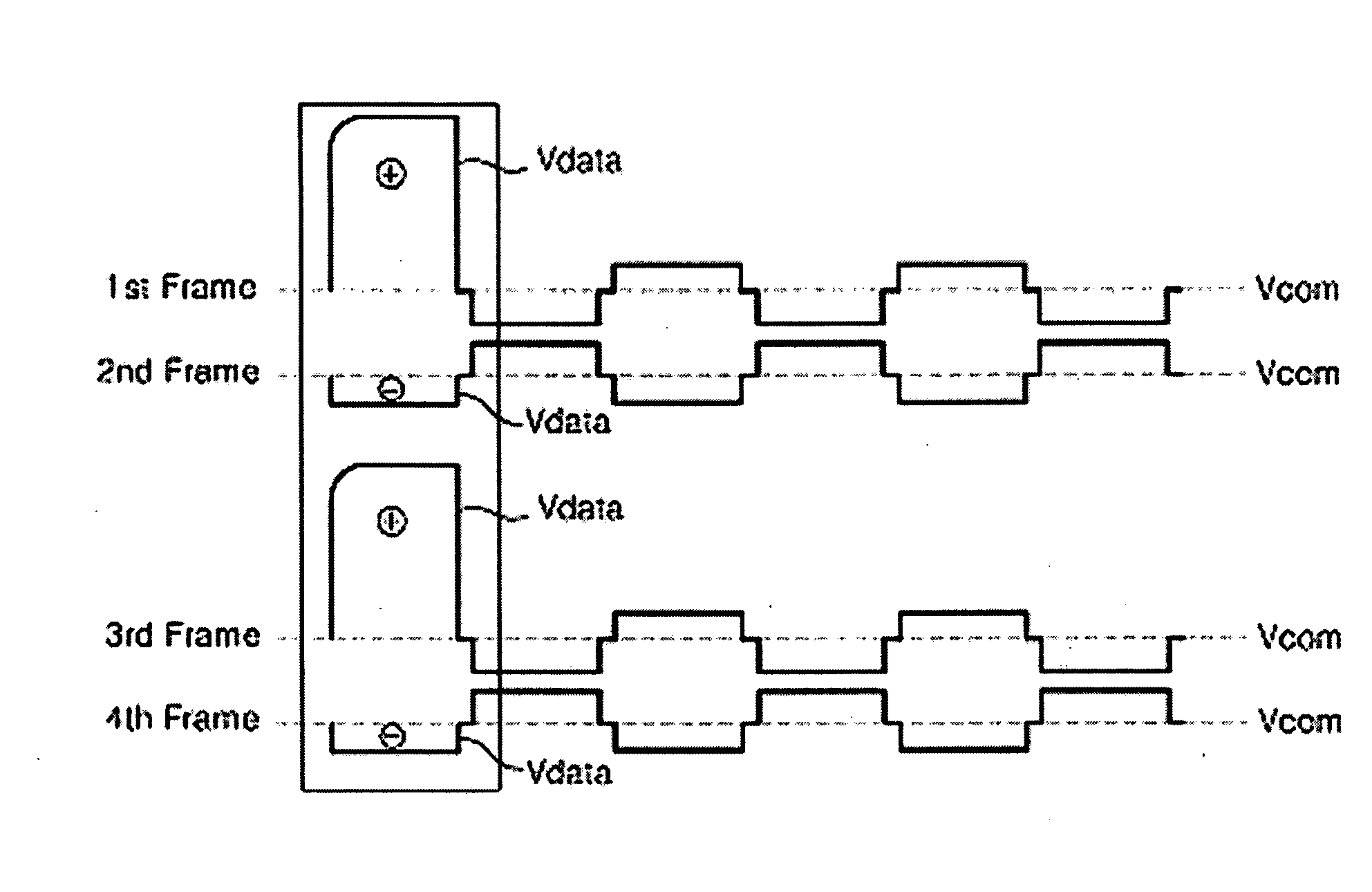

Liquid crystal display and driving method thereof

ActiveUS20090002301A1Reduce heat consumptionLow heat generationCathode-ray tube indicatorsNon-linear opticsDigital videoControl signal

A liquid crystal display includes a liquid crystal display panel having a plurality of data lines, a plurality of gate lines, and a plurality of liquid crystal cells, a timing controller to determine gray levels of input digital video data and a time at which a polarity of a data voltage to be supplied to the data lines is inverted and generate a dynamic charge share control signal to indicate a time at which the gray level of the data voltage is changed from a white gray level to a black gray level and a time at which the polarity of the data voltage is inverted, and to detect weakness patterns in which the data of the white gray level and the black gray level are regularly arranged in the input digital video data and generate a dot inversion control signal for widening a horizontal polarity inversion time of data voltages to be supplied to the data lines when the weakness patterns are input, a data driving circuit to convert the digital video data from the timing controller into the data voltage, change the polarity of the data voltage, supply any one of a common voltage and a charge share voltage between a positive data voltage and a negative data voltage to the data lines in response to the dynamic charge share control signal, and widen the horizontal polarity inversion time of the data voltages in response to the dot inversion control signal, and a gate driving circuit to sequentially supply a scan pulse to the gate lines under the control of the timing controller, wherein the liquid crystal display panel includes first and second liquid crystal cell groups whose polarity is inverted every 2 frame periods, and a polarity inversion time of the first liquid crystal cell group and a polarity inversion time of the second liquid crystal cell group overlap.

Owner:LG DISPLAY CO LTD

Liquid Crystal Display Device and Method for Driving the Same

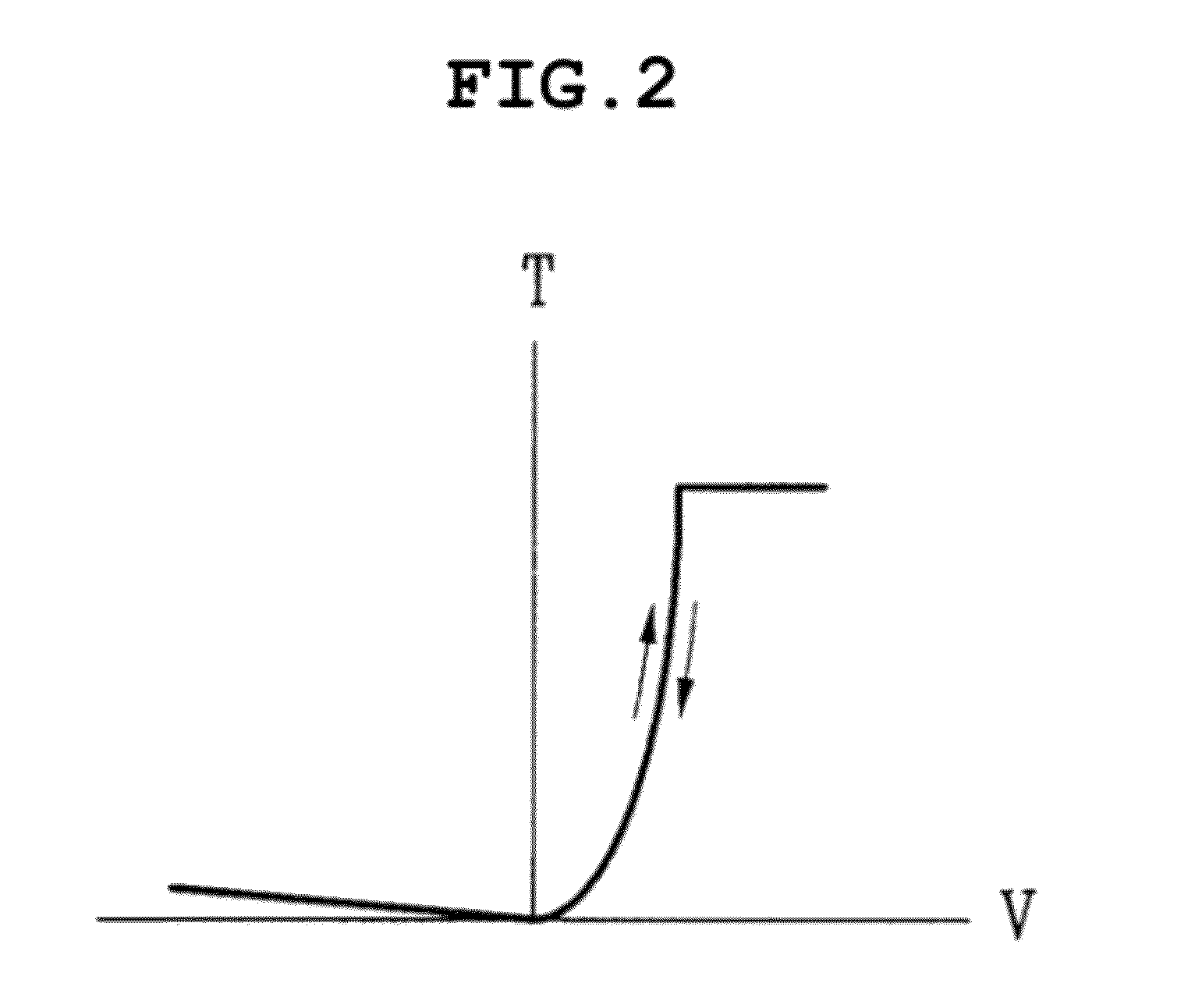

InactiveUS20120287100A1High light transmittanceIncrease brightnessCathode-ray tube indicatorsNon-linear opticsLiquid-crystal displayTransmittance

Disclosed is a liquid crystal display device increasing transmittance to improve brightness while employing ferroelectric liquid crystals in a half-V mode. The liquid crystal display device includes a liquid crystal panel including ferroelectric liquid crystals of a half-V mode, and a driving circuit driving a liquid crystal panel so that a first frame period, which the positive data voltages are supplied to the liquid crystal panel, becomes longer than a second frame period, which the negative data voltages are supplied to the liquid crystal panel.

Owner:LG DISPLAY CO LTD

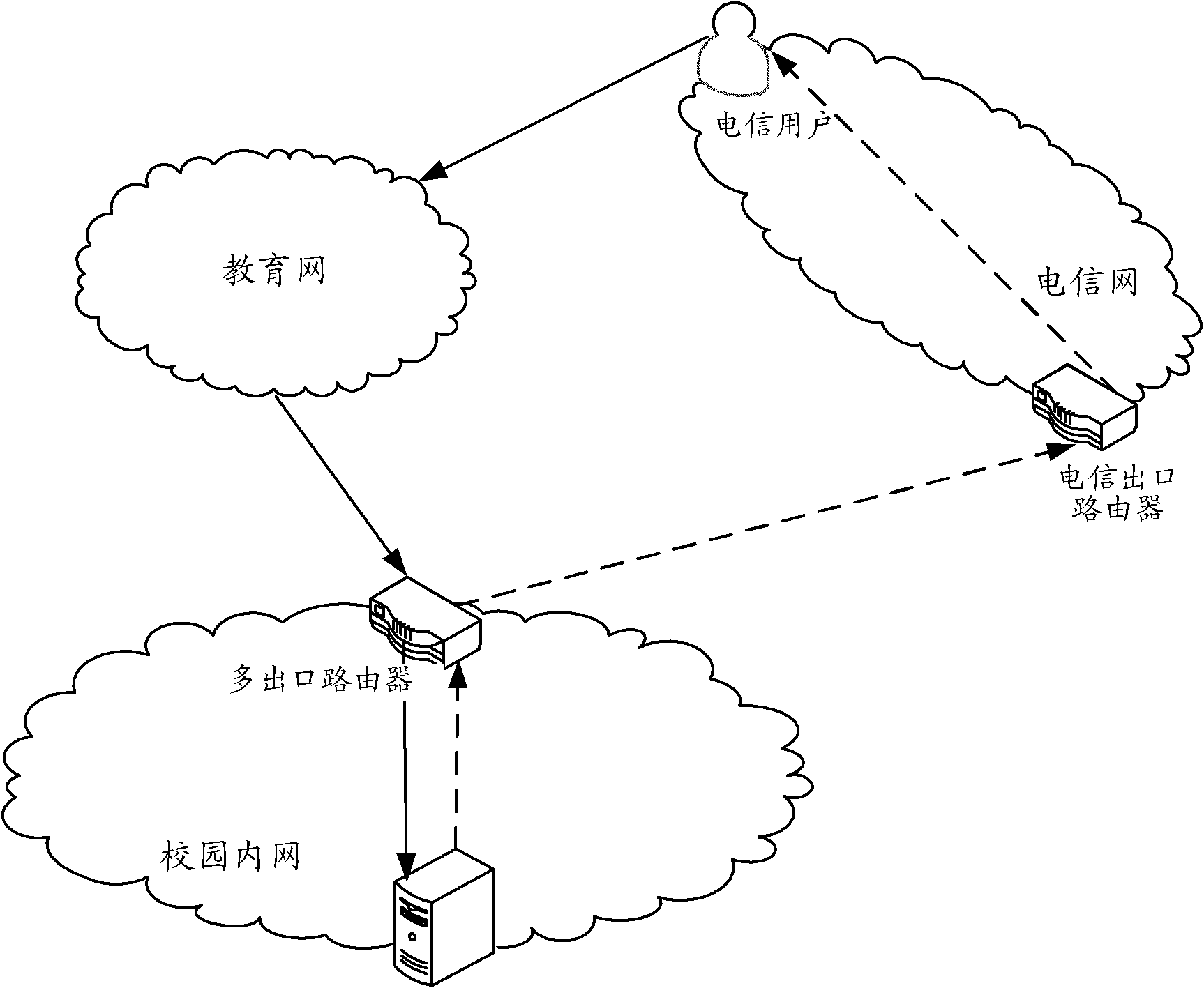

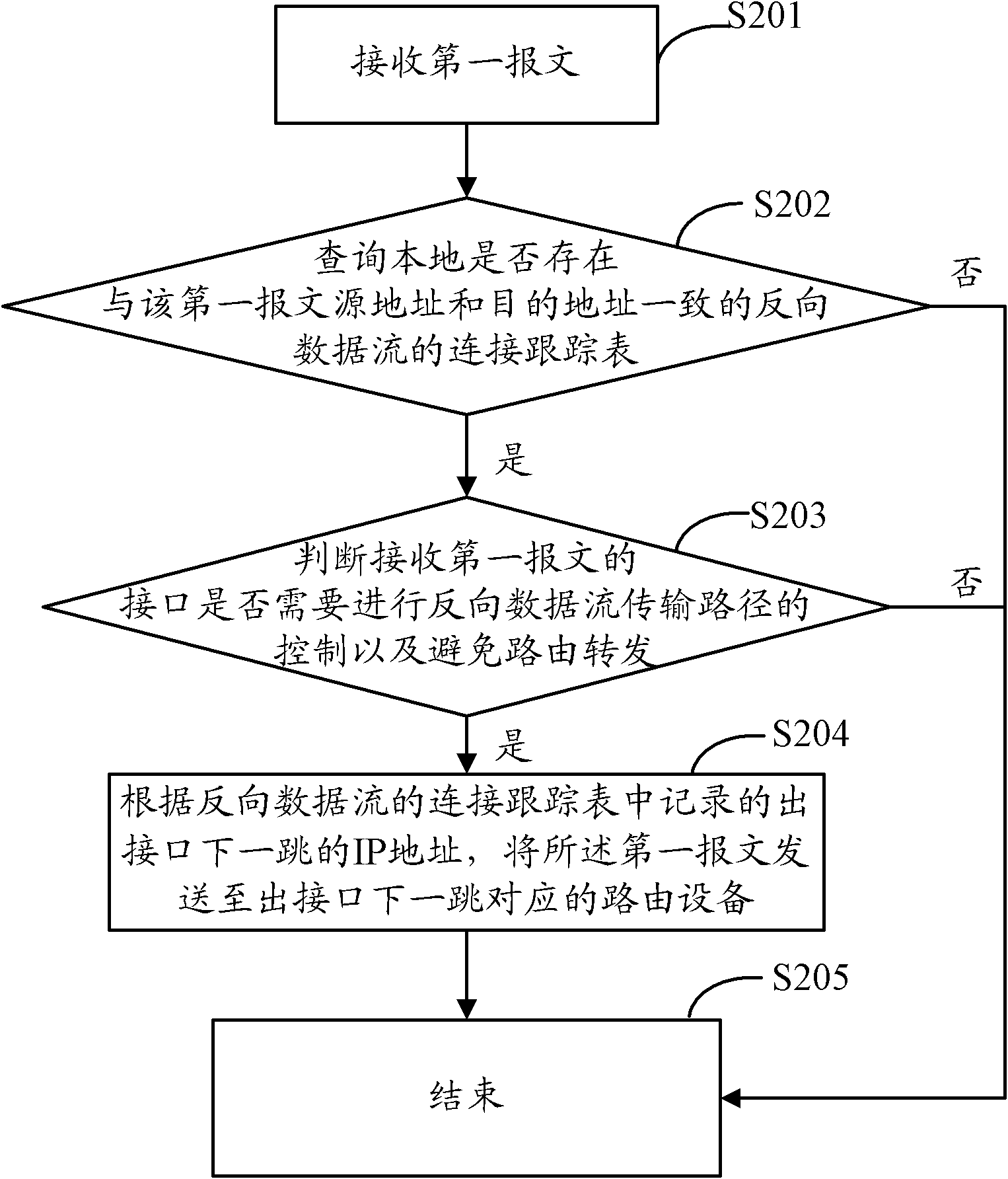

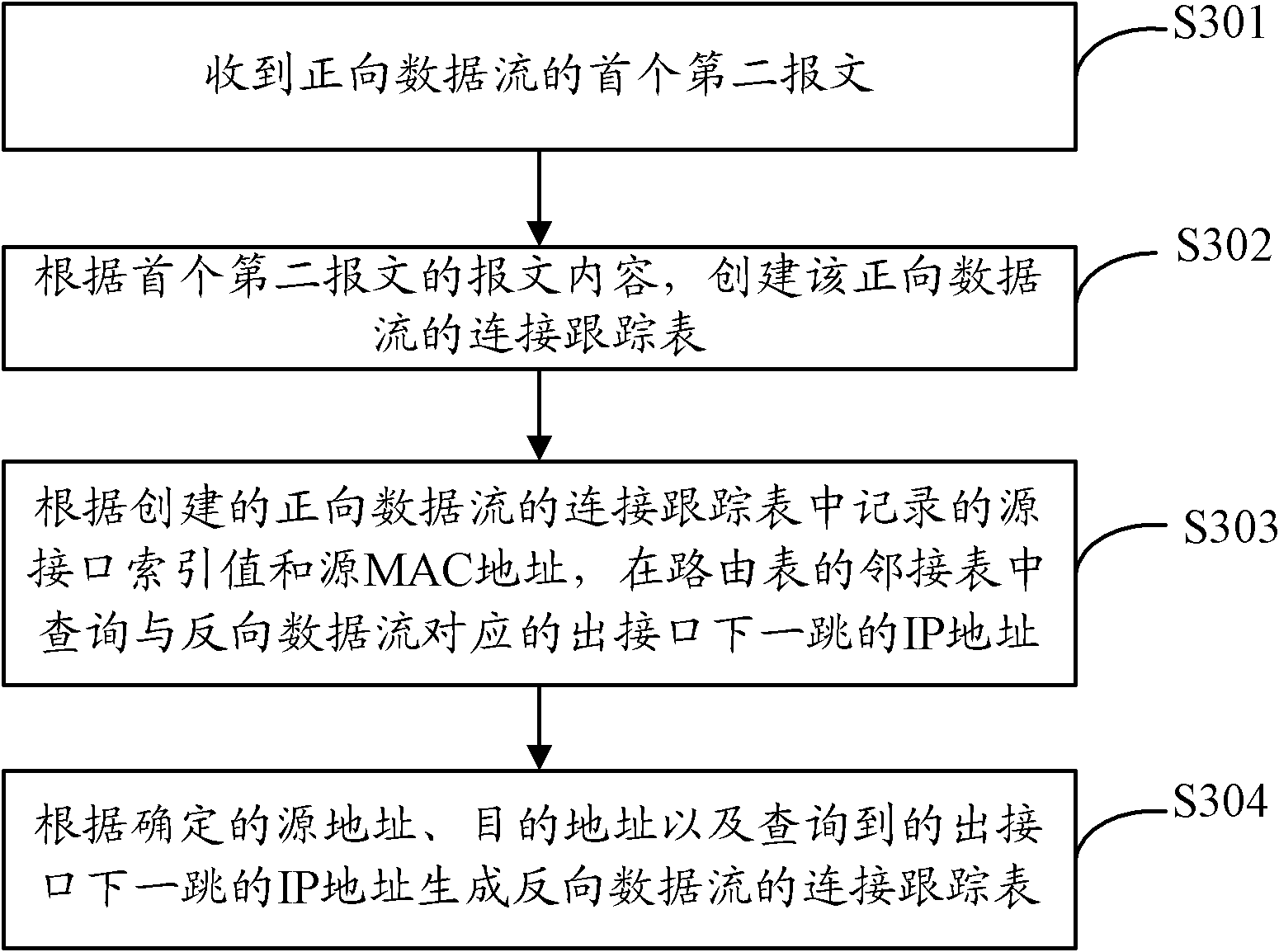

Control method for data flow transmission route, device and route equipment

The invention discloses a control method for data flow transmission route, a device and route equipment. The method comprises the steps of: aiming at the received first message, inquiring if a connection track table for reverse data flow consistent with a first message source address and a target address exists locally, if yes, judging if an interface transferring the first message is arranged asrequiring the control of the reverse data flow transmission route and avoiding transferring by using a route, and if yes, sending the first message to the route equipment corresponding to a next skipping IP address of an outlet interface according to the next skipping IP address of the outlet interface recorded in the connection track table for reverse data flow. The invention solves the problem of message lose caused by the semi-connection because of the unsymmetrical transmission routes of positive data flow and negative data flow under the condition of connecting the route equipment to different ISP.

Owner:BEIJING XINWANG RUIJIE NETWORK TECH CO LTD

Liquid crystal display

ActiveUS20120249603A1Small sizeIncrease in sizeCathode-ray tube indicatorsInput/output processes for data processingLiquid-crystal displayComputer science

A liquid crystal display includes a plurality of pixels, a plurality of data lines connected to the plurality of pixels, and a data driver connected to the plurality of data lines, where the data driver supplies data voltage to the plurality of data lines, where the data driver includes a data latch which outputs input image data in response to image data corresponding to the plurality of pixels, wherein the data latch rearranges a sequence of the image data, and a digital-to-analog converting unit which includes a positive digital-to-analog converter which generates a positive data voltage in response to the input image data, and a negative digital-to-analog converter which generates a negative data voltage in response to the input image data.

Owner:SAMSUNG DISPLAY CO LTD

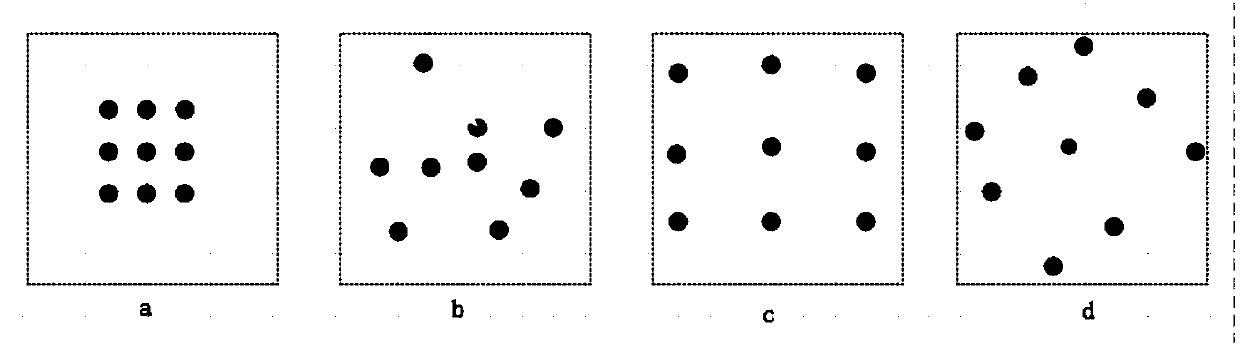

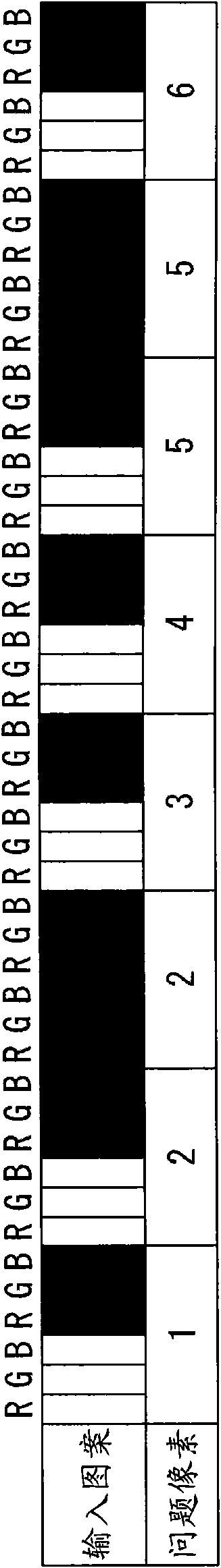

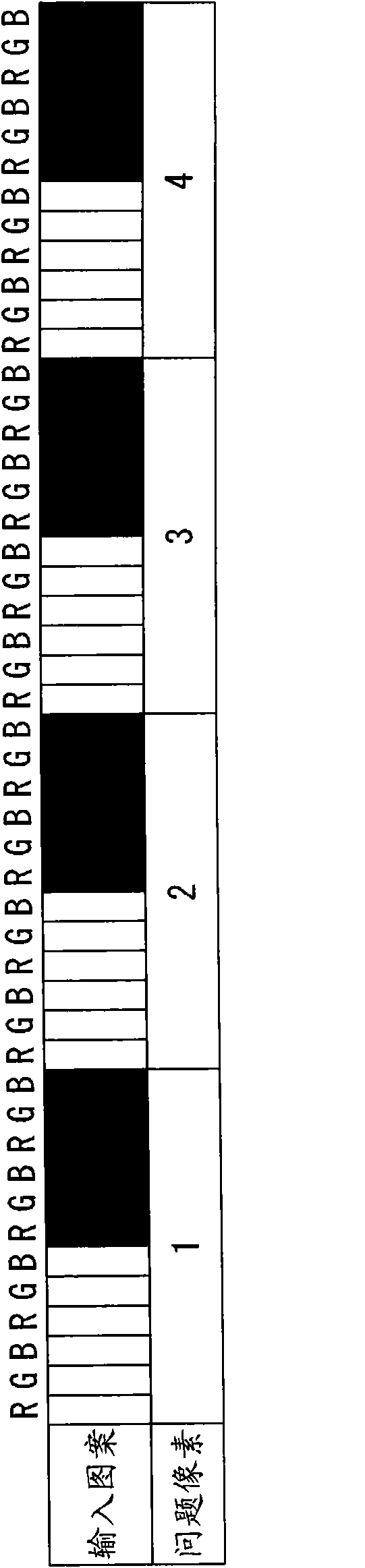

Liquid crystal display and method of controlling dot inversion thereof

ActiveCN101995694AStatic indicating devicesNon-linear opticsLiquid-crystal displayElectrical polarity

The invention discloses a liquid crystal display and a method of controlling dot inversion thereof. A liquid crystal display includes: a liquid crystal display panel including data lines and gate lines crossing each other; a timing controller that maps data of an input image to polarity patterns of 1-dot inversion and 2-dot inversion, counts the number of positive data and the number of negative data, determines whether any one of the positive data and negative data becomes dominant or not based on a difference between the counted numbers, and selects either one of the 1-dot and 2-dot inversions; a data driving circuit that converts the data of the input image into data voltages to be supplied to the data lines and inverts the polarity of the data voltages by the selected dot inversion; and a gate driving circuit that sequentially supplies gate pulses synchronized with the data voltages to the gate lines.

Owner:LG DISPLAY CO LTD

Display substrate and LCD with the same

The present invention provides a display substrate and liquid crystal display having the same. The liquid crystal display includes: a first pixel connected to first and second gate lines, a first positive data line and a first negative data line, and which is supplied with a positive data voltage from the first positive data line when enabled by a first gate-on voltage from the first gate line, and is supplied with a negative data voltage from the first negative data line when enabled by a second gate-on voltage from the second gate line; and a second pixel connected to the first and second gate lines, a second positive data line and a second negative data line, and which is supplied with a negative data voltage from the second negative data line when enabled by the first gate-on voltage and is supplied with a positive data voltage from the second positive data line when enabled by the second gate-on voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

Driver for display apparatus and display apparatus including the same

InactiveCN1928981AAvoid flickeringAvoid pollutionStatic indicating devicesDigital storageTime delaysPhase difference

Owner:SAMSUNG ELECTRONICS CO LTD

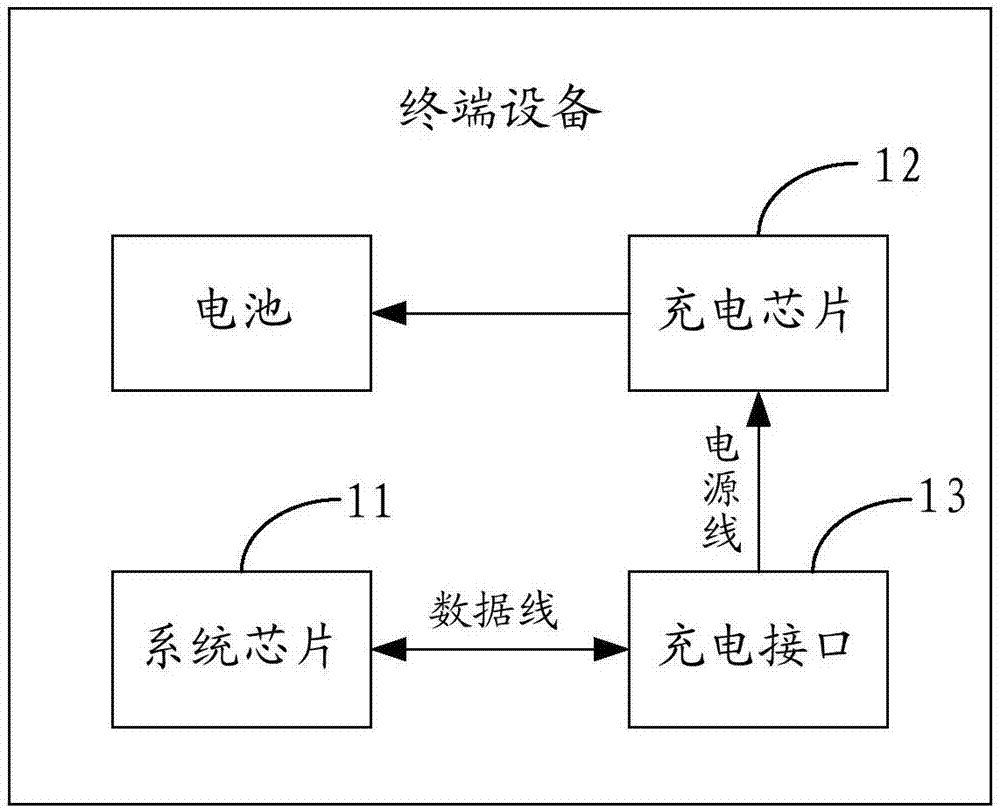

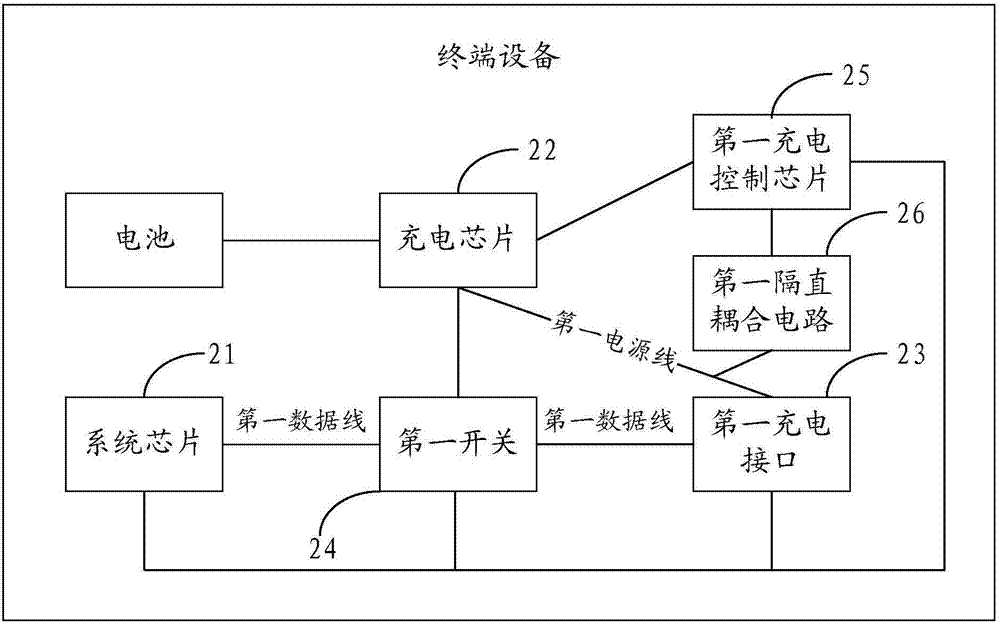

Terminal equipment, power adapter and charging control method

PendingCN107294172AReduce feverReduce voltage differenceBatteries circuit arrangementsAc-dc conversion without reversalState of artCharge current

An embodiment of the invention provides terminal equipment, a power adapter and a charging control method. The Terminal equipment provided by the embodiment of the invention comprises a system chip, a charging chip, a first charging interface, a first switch, a first charging control chip and a first blocking coupling circuit, wherein the first charging control chip can control the first switch when the terminal equipment is being charged rapidly, a positive data pin of the first charging interface is connected with a power supply pin, a negative data pin of the first charging interface is connected with a grounding pin, thus a data line and a power line in a USB transmission line are both used for charging, thereby increasing a charging current, reducing a voltage difference between an input end and an output end of the charging chip of the terminal equipment when the charging power is constant, further reducing loss of the charging chip, reducing the heating degree of the terminal equipment when in charging, improving the charging efficiency, and solving the problems of severe heating of the terminal equipment and low charging efficiency caused by great loss of the terminal equipment during the rapid charging process in the prior art to some extent.

Owner:SHENZHEN TINNO WIRELESS TECH +1

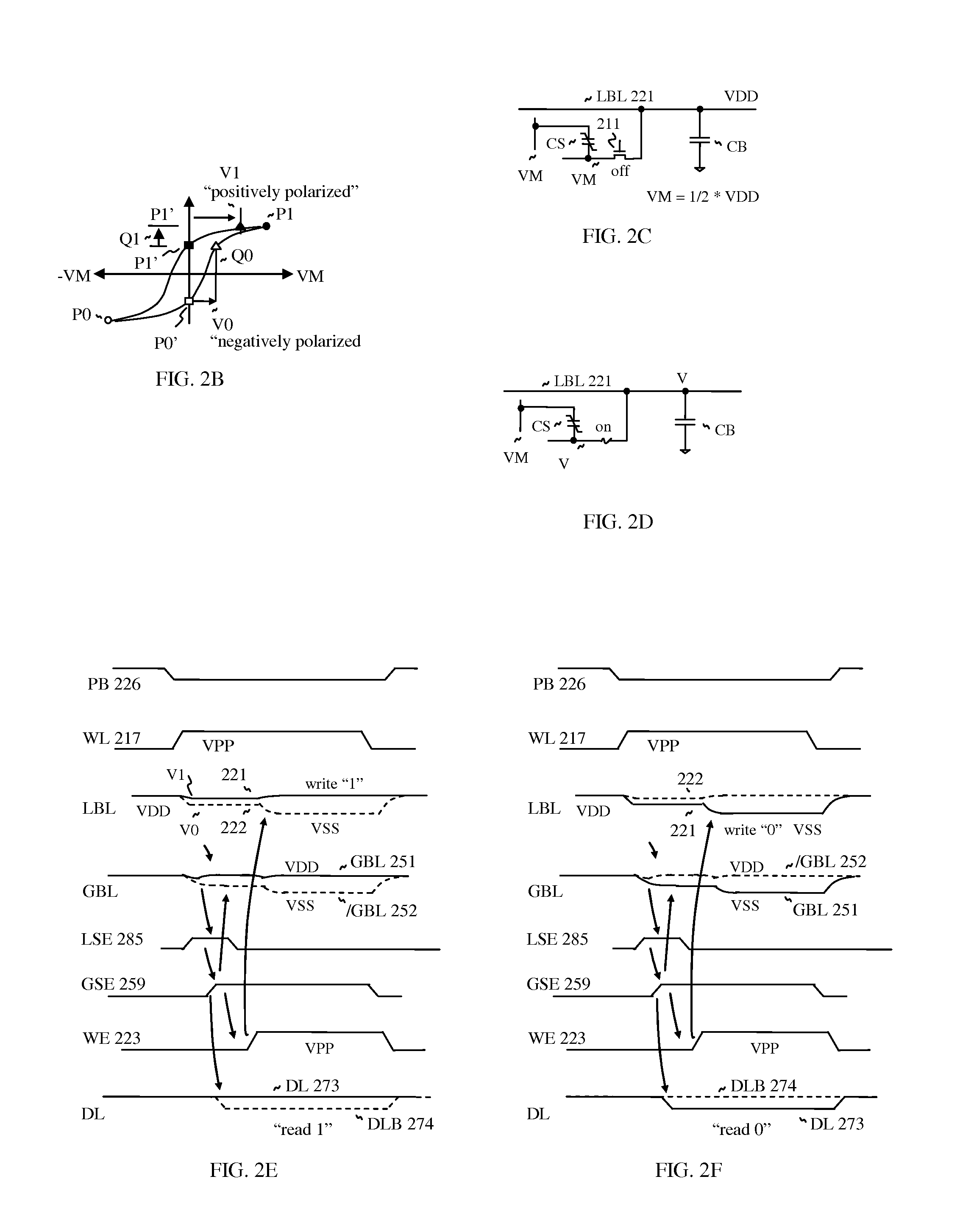

Very high speed FRAM for replacing SRAM

InactiveUS20100135062A1Improve performanceReduce parasitic capacitanceDigital storageBit lineAudio power amplifier

For replacing SRAM with very high speed FRAM, new memory architecture is realized such that plurality of FRAM cells is connected to a local bit line pair, a local sense amp is connected to the local bit line pair, a global sense amp is connected to the local sense amp through a global bit line pair, and a locking signal generator is connected to the global sense amp for generating a locking signal which disables the local sense amp after reading for quick write-back operation. With short bit line architecture, bit lines are multi-divided for reducing parasitic capacitance of the local bit line, which realizes to reduce the ferroelectric capacitor proportionally. The FRAM cell includes an access transistor pair, a ferroelectric capacitor pair for storing positive data and negative data, and a reset transistor pair for resetting storage nodes. And various circuits for implementing the memory are described.

Owner:KIM JUHAN

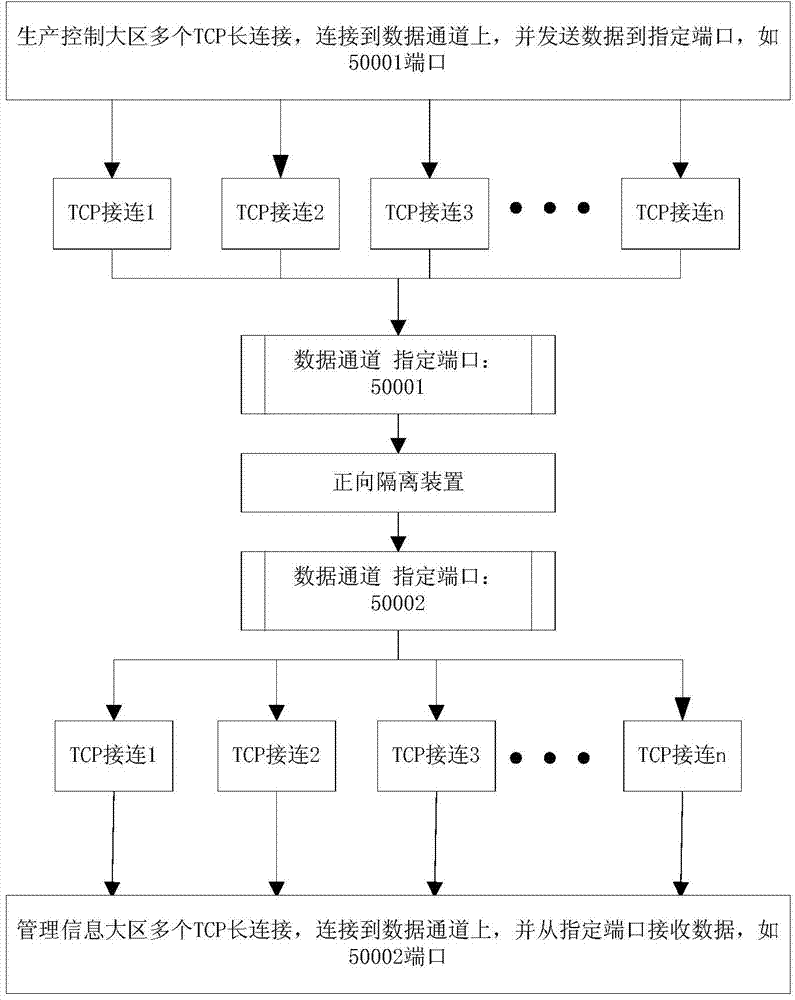

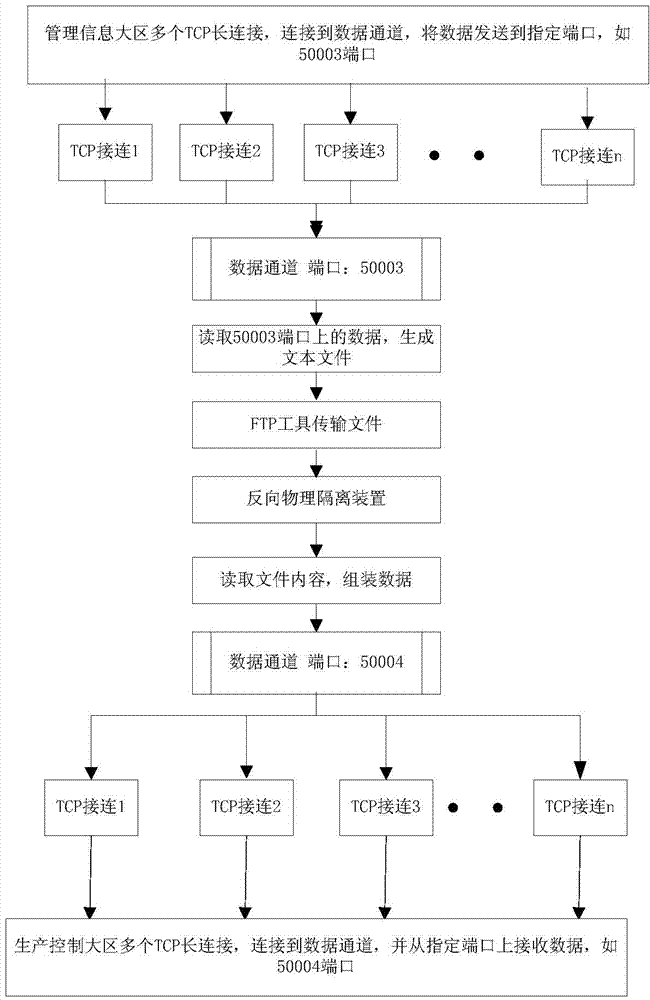

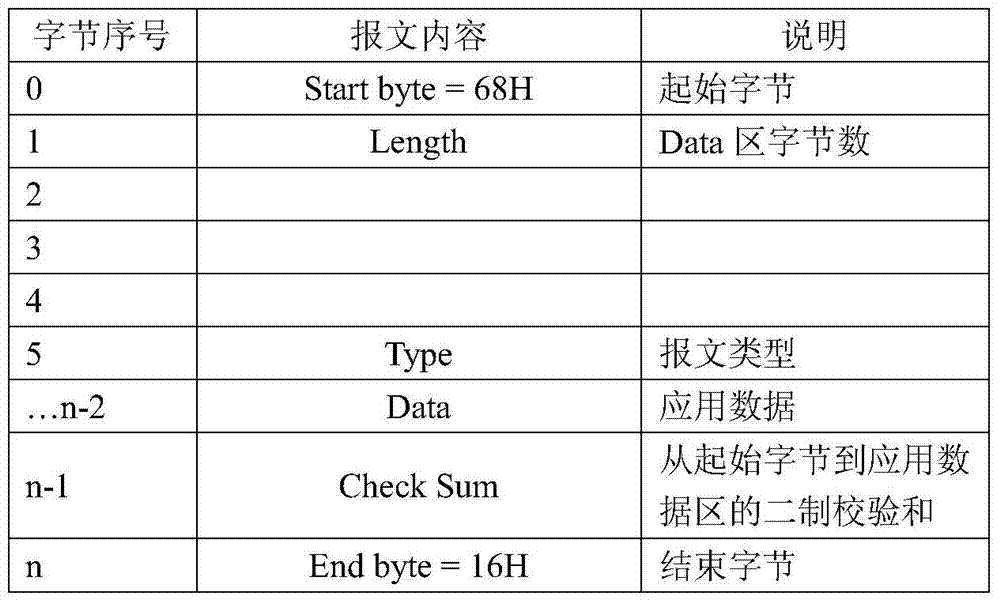

Closed-loop control system and method for positive and reverse isolators

ActiveCN104516334AAvoid difficultiesHigh precisionTransmissionTotal factory controlClosed loopLinked data

The invention discloses a closed-loop control system and method for positive and reverse isolators. The system comprises a data communication module, a message segmenting module and an engineering maintenance module; the data communication module is used for organizing service data and positive heartbeat messages of a positive data channel and service data E files and reverse heartbeat files of a reverse data channel; the message segmenting module is used for ensuring that no packet splicing occurs in the TCP (transmission control protocol) long-link data transceiving mode; the engineering maintenance module allows a maintenance engineer to only need to locate the communication problem at one end of the positive and revere isolators. The problem that device crash or data transmission channel causes cannot be quickly located when service data transmission of the positive and reverse isolators is jammed is solved, and according to the application features of a high-safety communication model, the problem that maintenance crossing two ends of the positive and reverse isolators is difficult is solved.

Owner:STATE GRID CORP OF CHINA +2

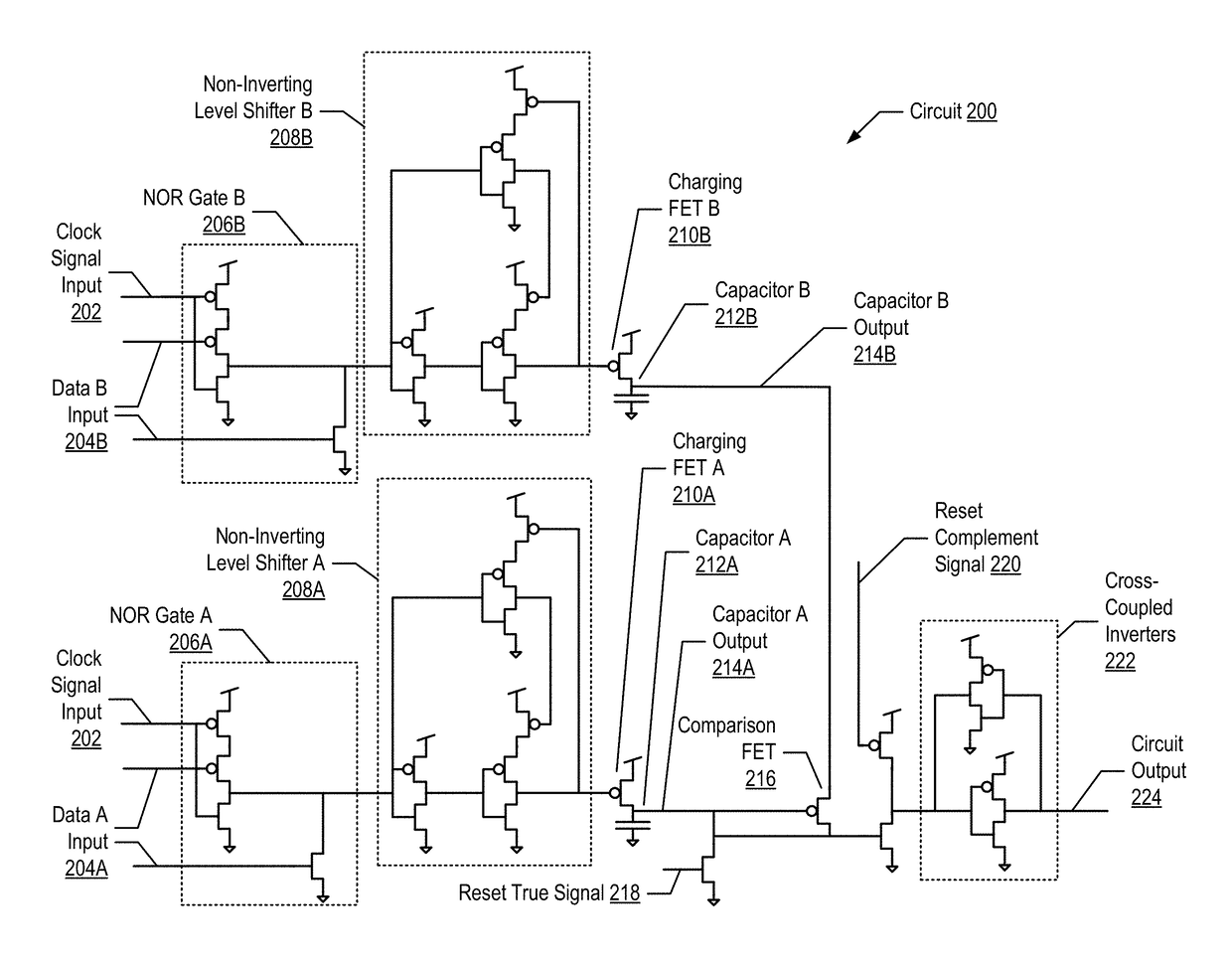

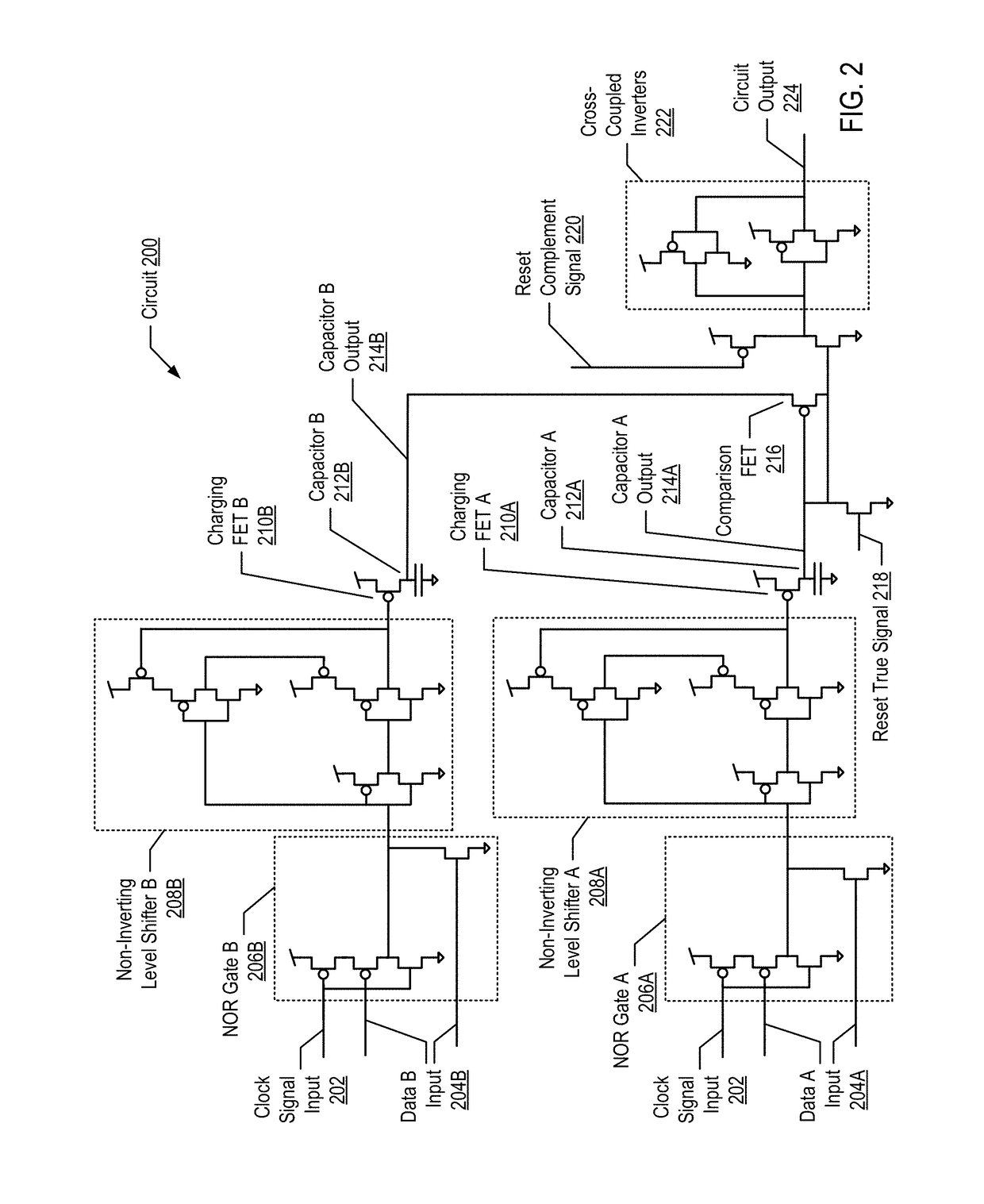

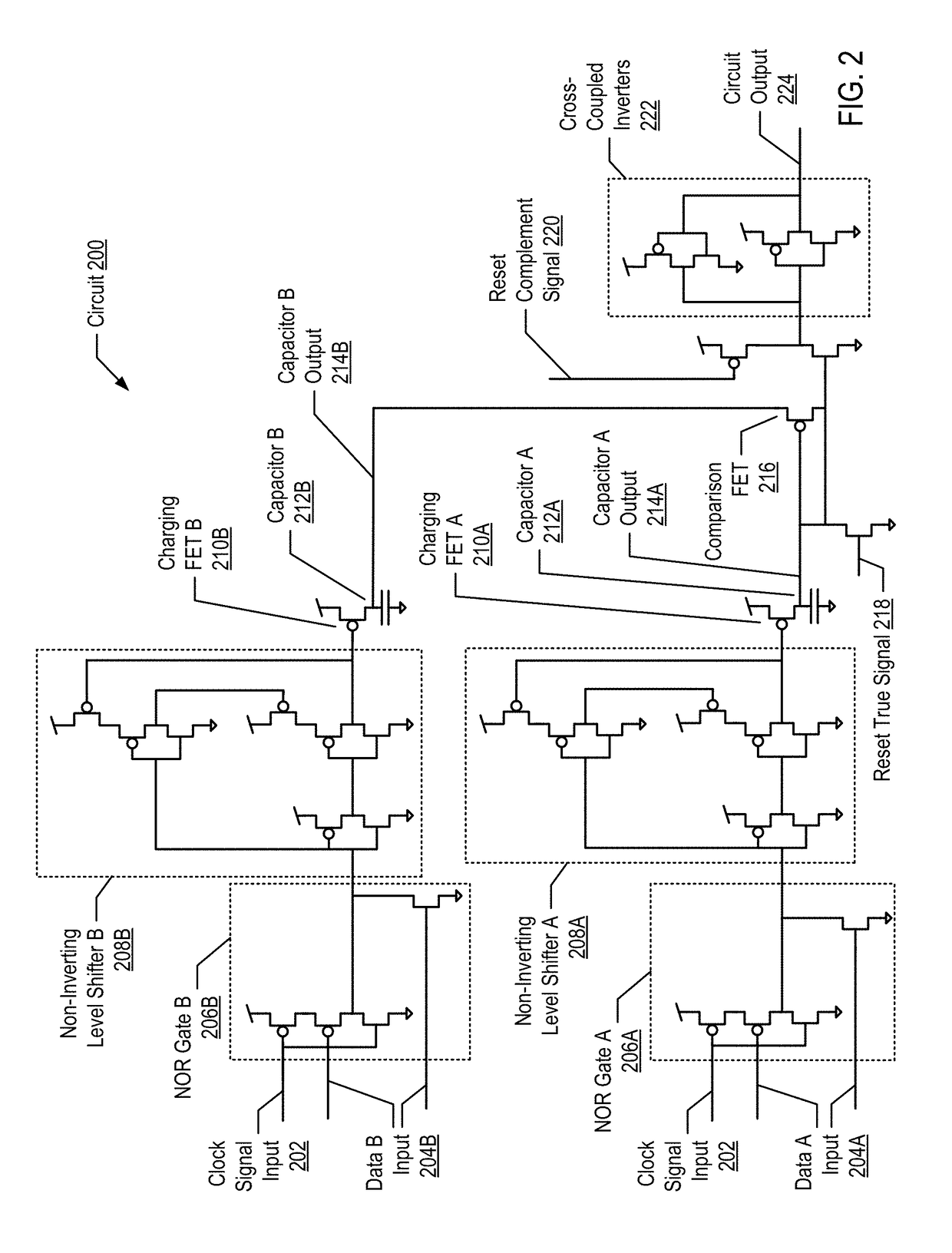

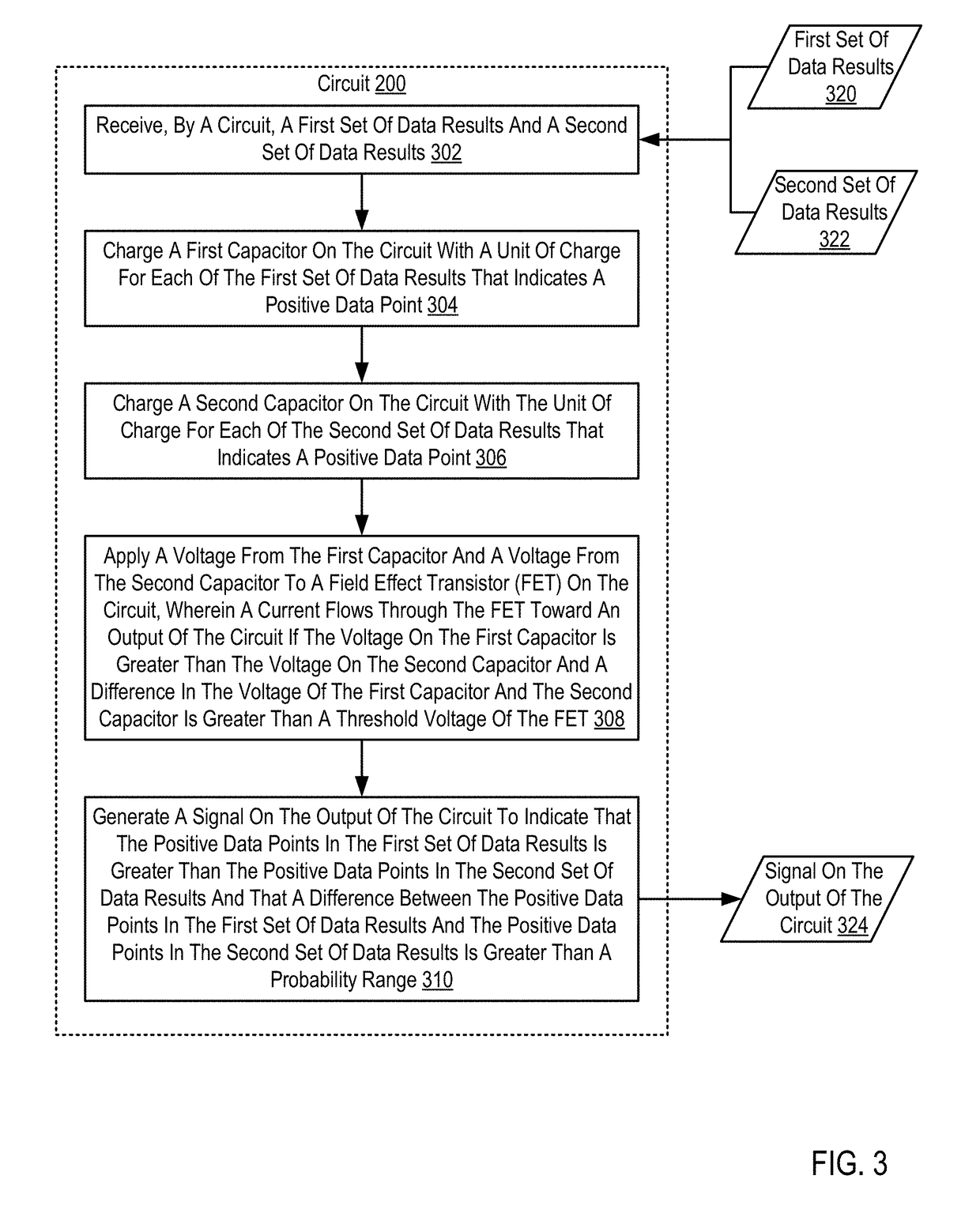

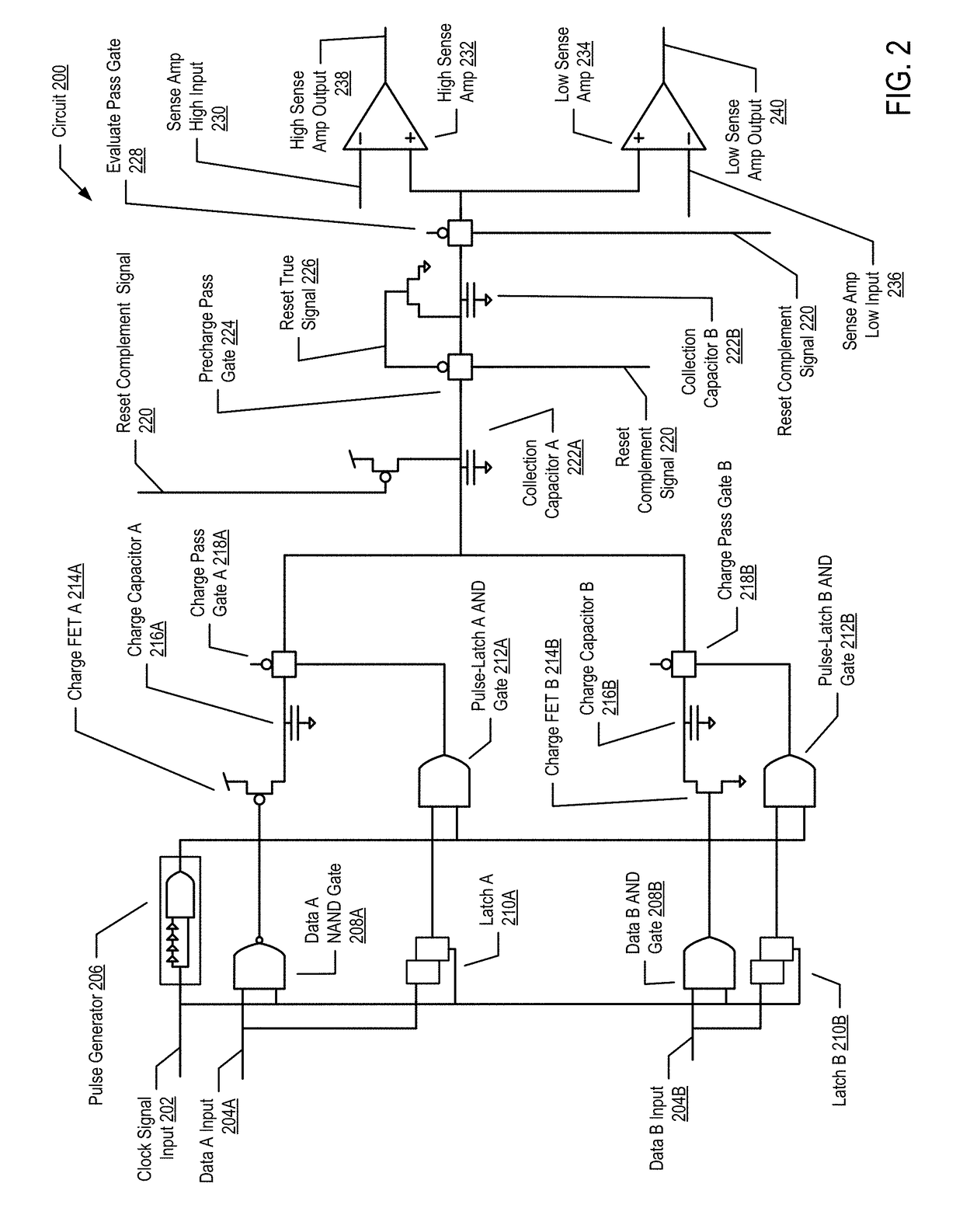

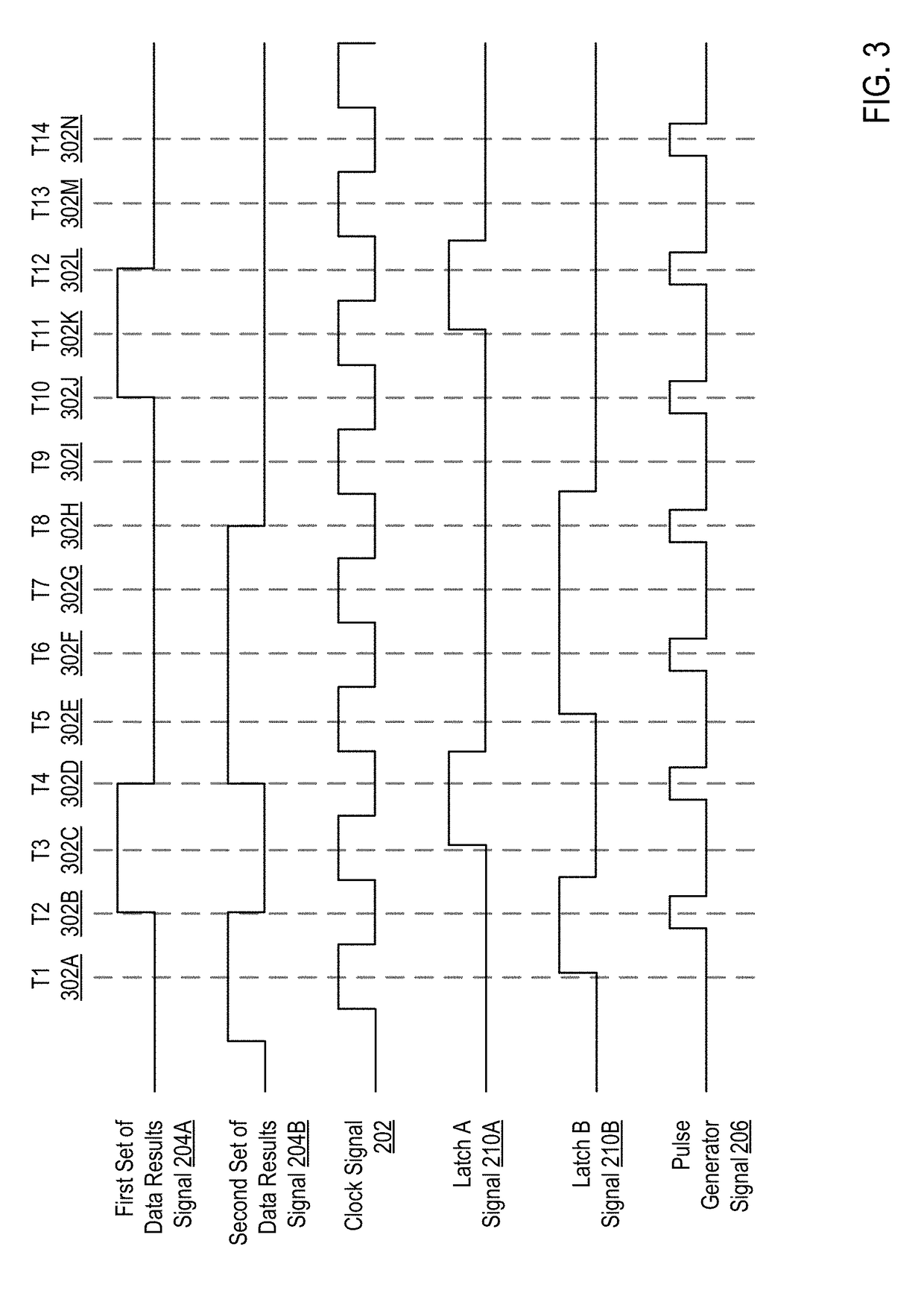

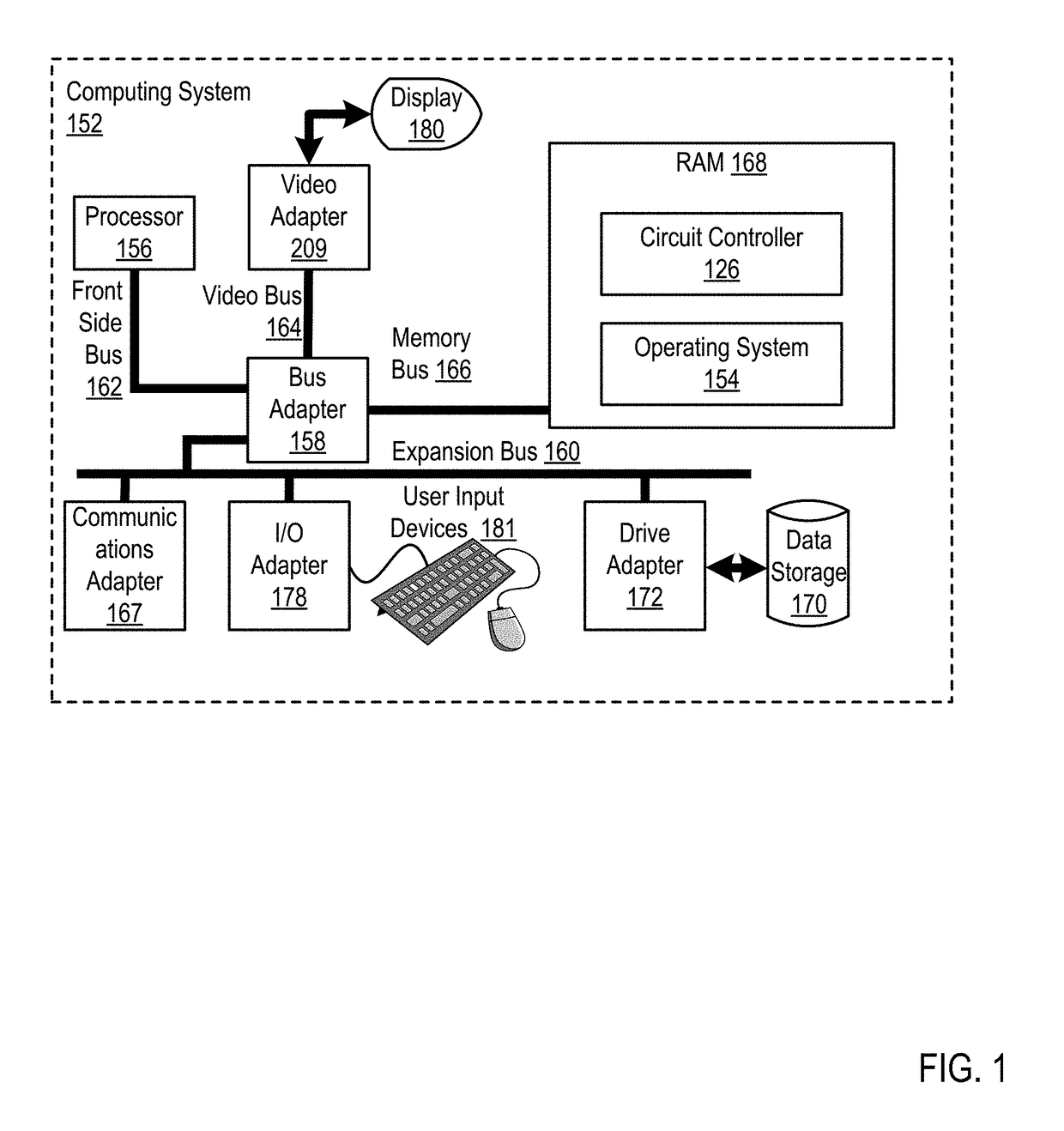

Optimizing data approximation analysis using low power circuitry

Optimizing data approximation analysis using low power circuitry including receiving a first set of data results and a second set of data results; charging a first capacitor on the circuit with a unit of charge for each of the first set of data results that indicates a positive data point; charging a second capacitor on the circuit with the unit of charge for each of the second set of data results that indicates a positive data point; applying a voltage from the first capacitor and a voltage from the second capacitor to a FET on the circuit, wherein a current flows through the FET toward an output of the circuit if the voltage on the first capacitor is greater than the voltage on the second capacitor and a difference in the voltage of the first capacitor and the second capacitor is greater than a threshold voltage of the FET.

Owner:IBM CORP

Liquid crystal display panel and method of driving the same

This invention relates to a three electrode liquid crystal display panel that is adaptive for AC-driving liquid crystal cells inclusive of three electrodes, and a driving method thereof.A three electrode liquid crystal display panel according to an embodiment of the present invention includes first and second pixel electrodes disposed on a first substrate with an insulating film therebetween; and a common electrode disposed in a second substrate which is bonded with the first substrate with a liquid crystal therebetween, and wherein the first pixel electrode selectively supplies a maximum voltage and a minimum voltage, the common electrode supplies a medium voltage between the maximum voltage and the minimum voltage as a reference voltage, and the second pixel electrode supplies a positive data voltage and a negative data voltage on the basis of the reference voltage in a range between the maximum voltage and the minimum voltage, thereby AC-driving the liquid crystal.

Owner:LG DISPLAY CO LTD

Display device

ActiveUS20140022232A1Reduce power consumptionCathode-ray tube indicatorsNon-linear opticsDisplay deviceData signal

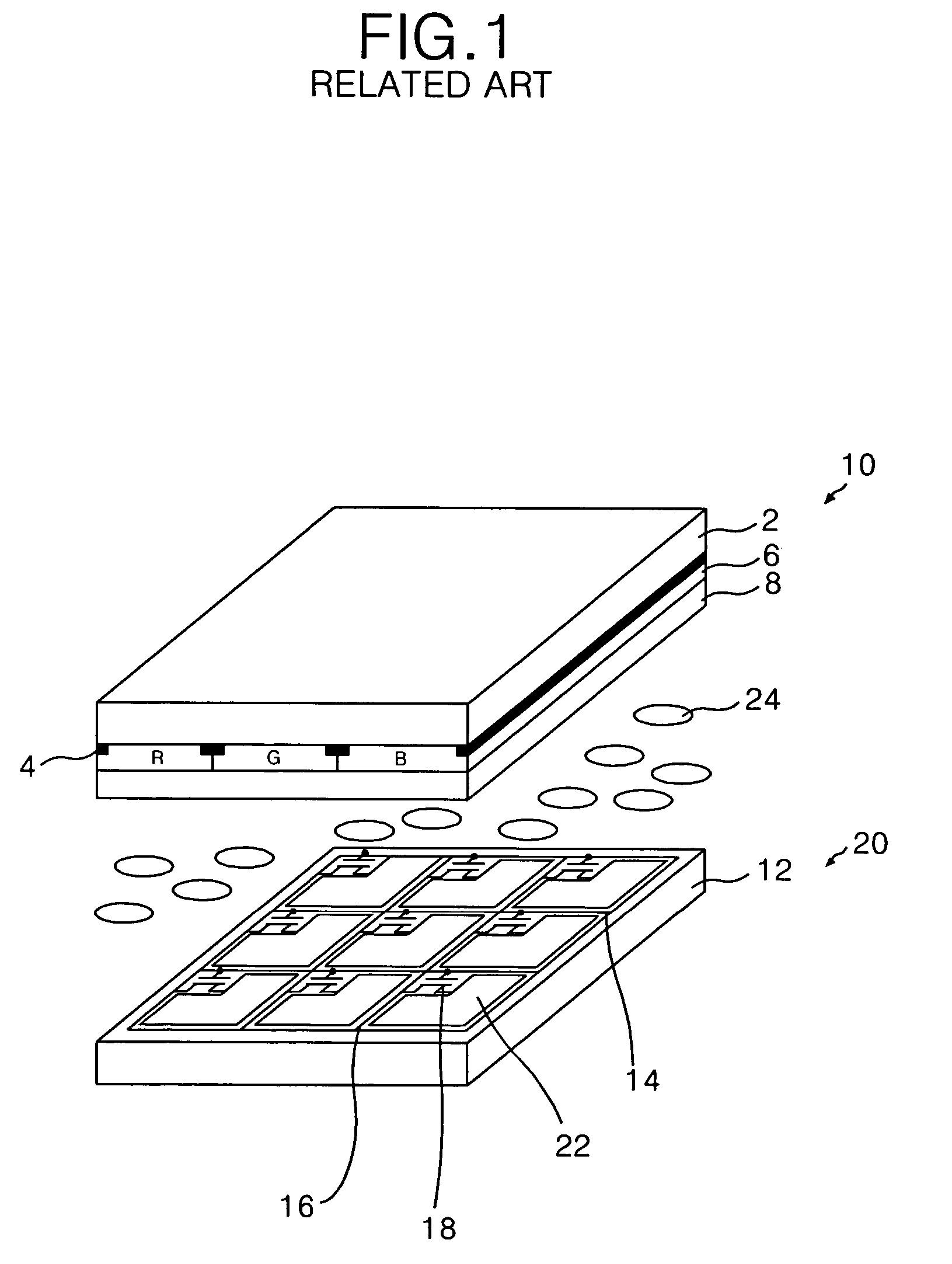

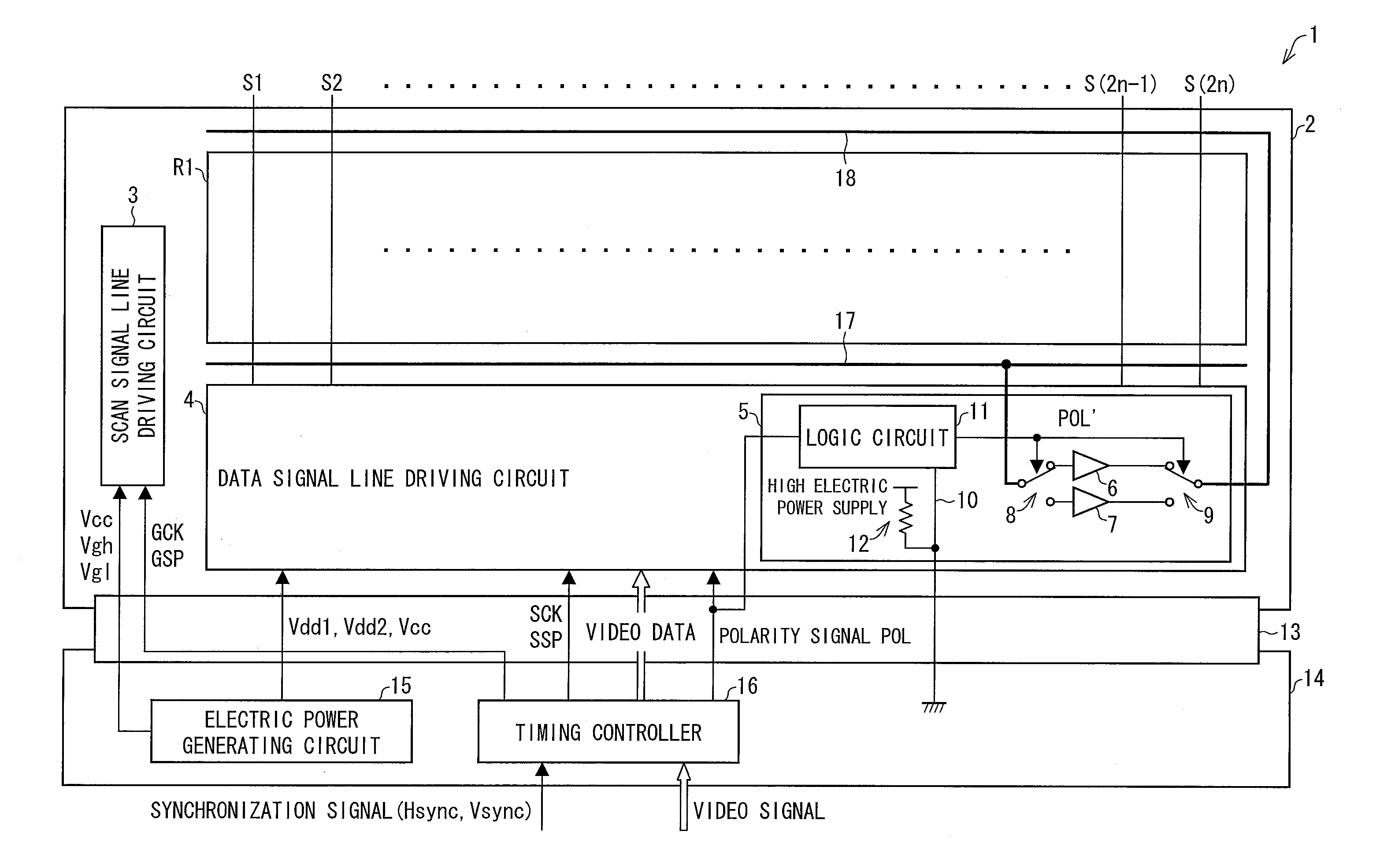

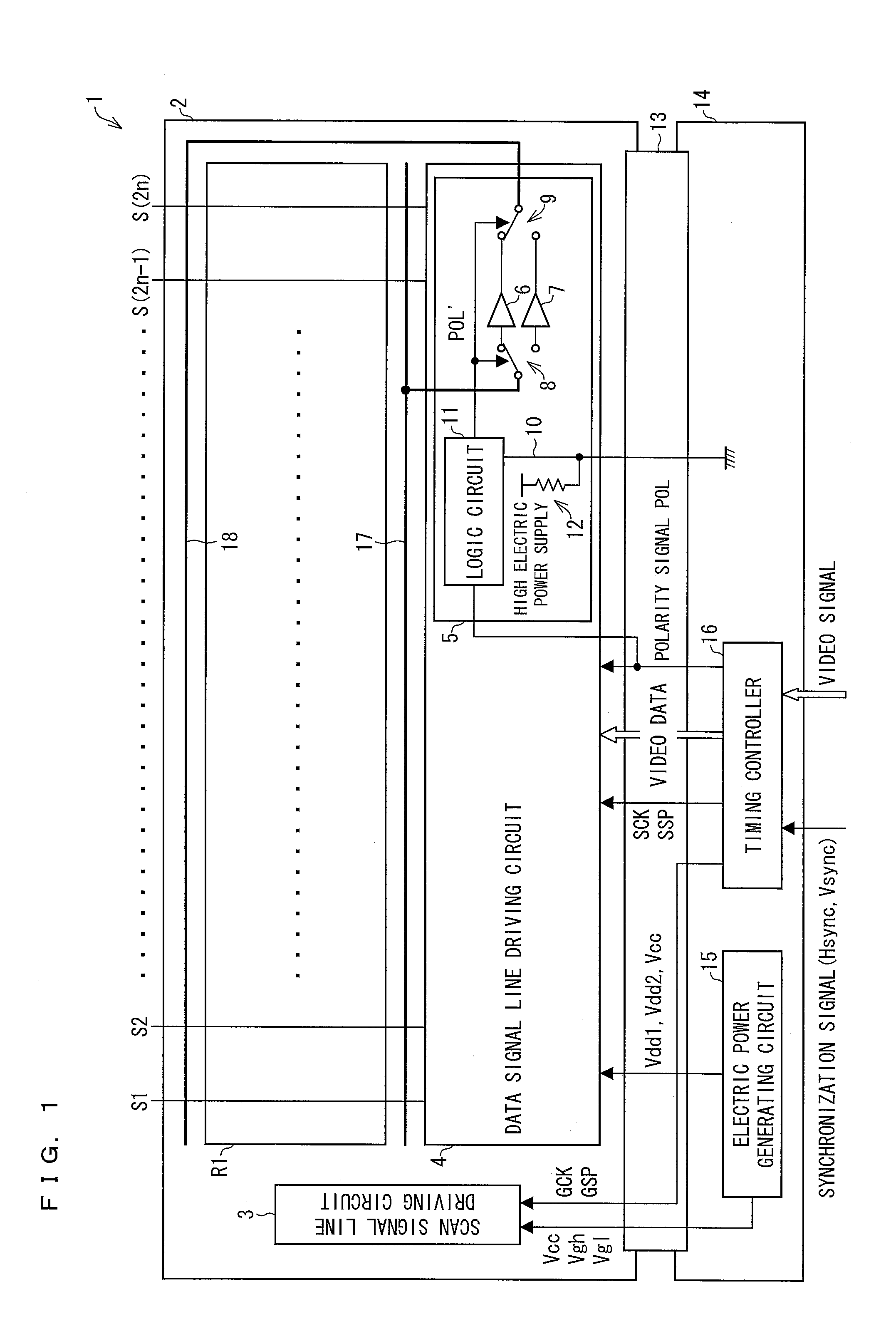

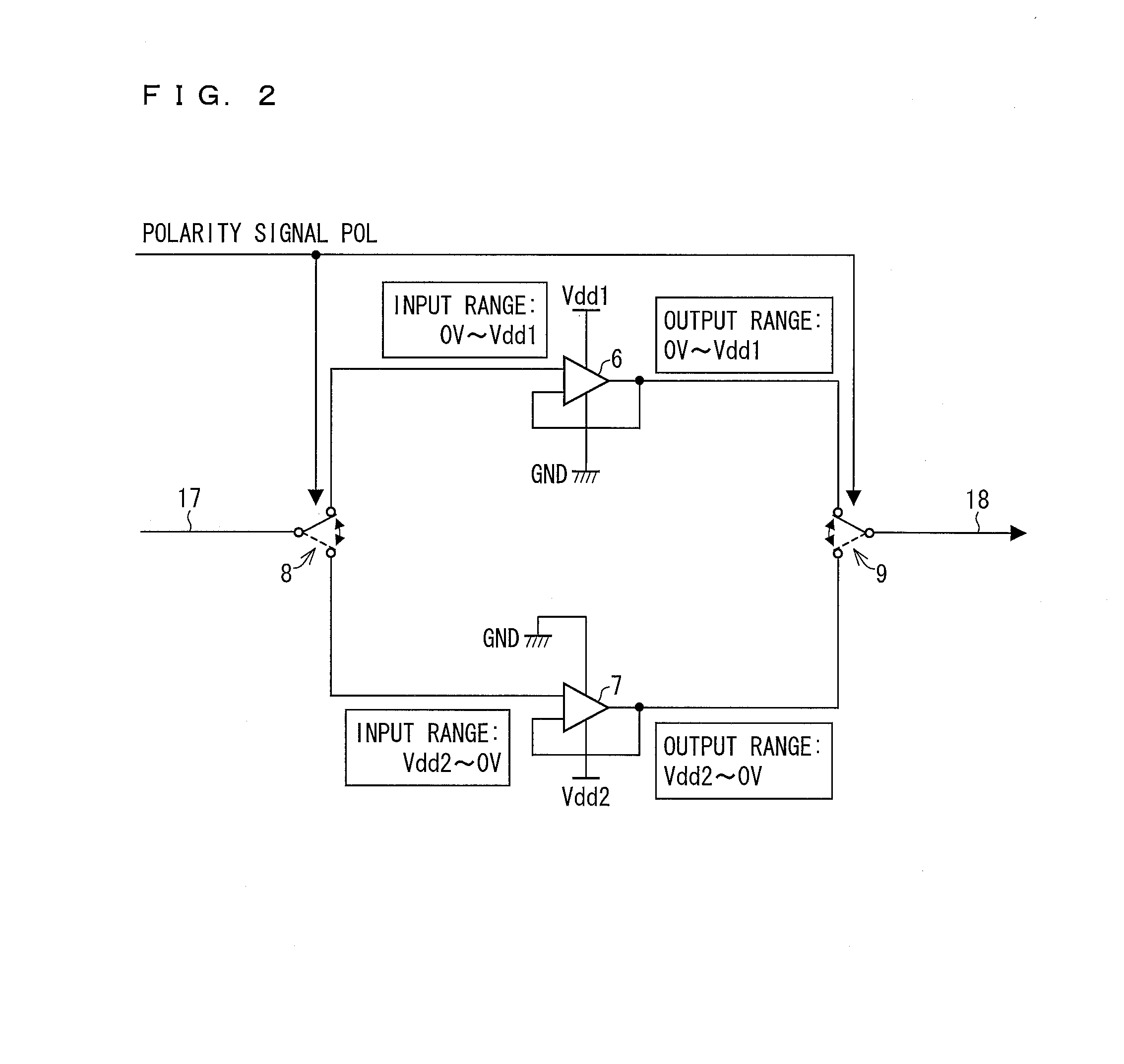

An auxiliary wire, which can be connected to each of a plurality of data signal lines (Sn), is constituted by (i) a first auxiliary wire (17) provided so as to intersect the plurality of data signal lines (Sn) on a side where end parts of the respective plurality of data signal lines (Sn) are connected to a data signal line driving circuit (4) and (ii) a second auxiliary wire (18) provided so as to intersect the plurality of data signal lines (Sn) on a side of the other end parts of the respective plurality of data signal lines (Sn). Between the first auxiliary wire (17) and the second auxiliary wire (17), there are provided (i) a positive-polarity amplifier circuit (6) for receiving a positive data signal from the data signal line driving circuit (4) and (ii) a negative-polarity amplifier circuit (7) for receiving a negative data signal from the data signal line driving circuit (4). An output signal is supplied to the second auxiliary wire (18) from the positive-polarity amplifier circuit (6) or the negative-polarity amplifier circuit (7).

Owner:SHARP KK

Optimizing data approximation analysis using low power circuitry

Optimizing data approximation analysis using low power circuitry including receiving a first set of data results and a second set of data results; charging a first capacitor on the circuit with a unit of charge for each of the first set of data results that indicates a positive data point; charging a second capacitor on the circuit with the unit of charge for each of the second set of data results that indicates a positive data point; applying a voltage from the first capacitor and a voltage from the second capacitor to a FET on the circuit, wherein a current flows through the FET toward an output of the circuit if the voltage on the first capacitor is greater than the voltage on the second capacitor and a difference in the voltage of the first capacitor and the second capacitor is greater than a threshold voltage of the FET.

Owner:INT BUSINESS MASCH CORP

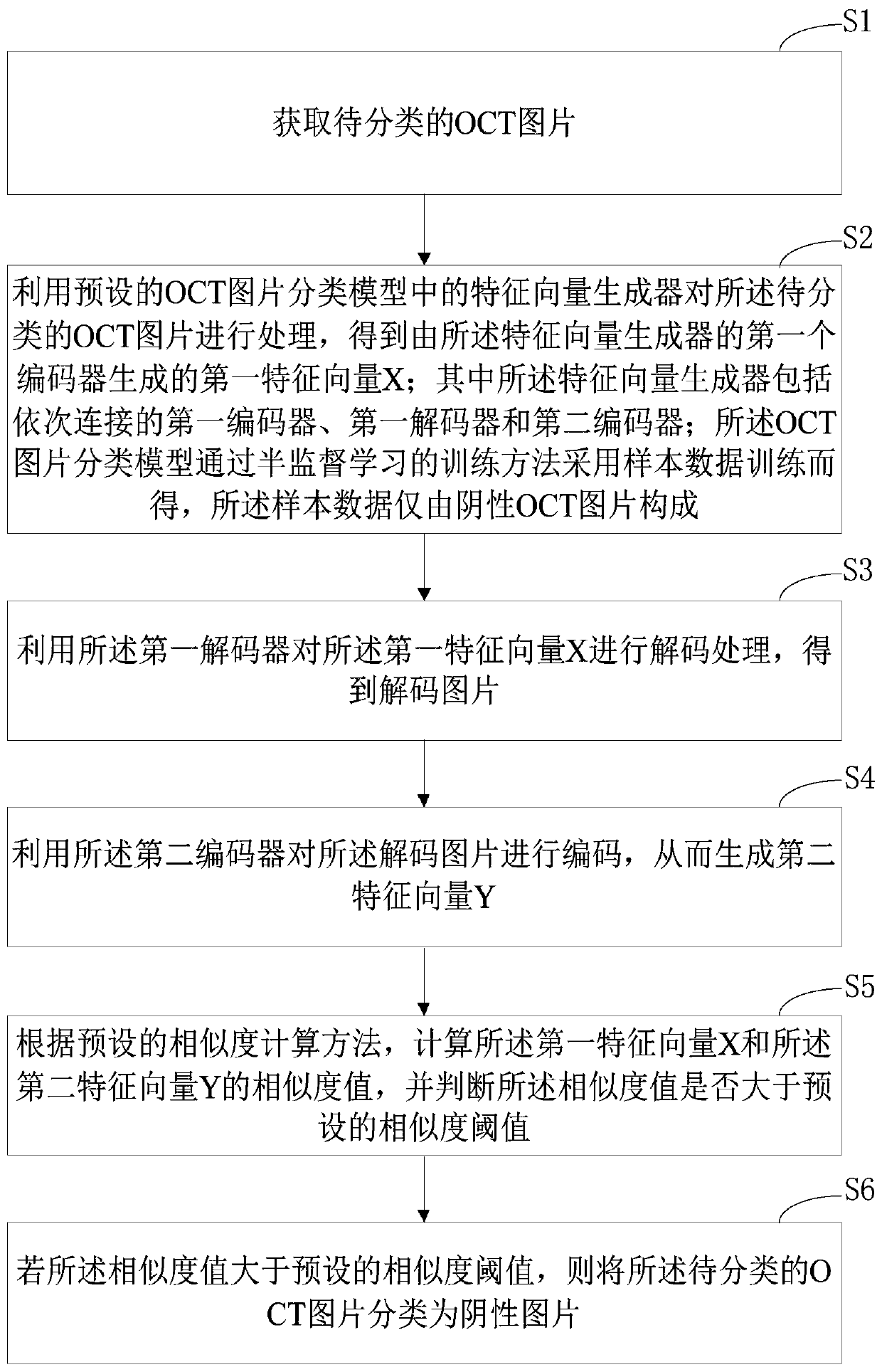

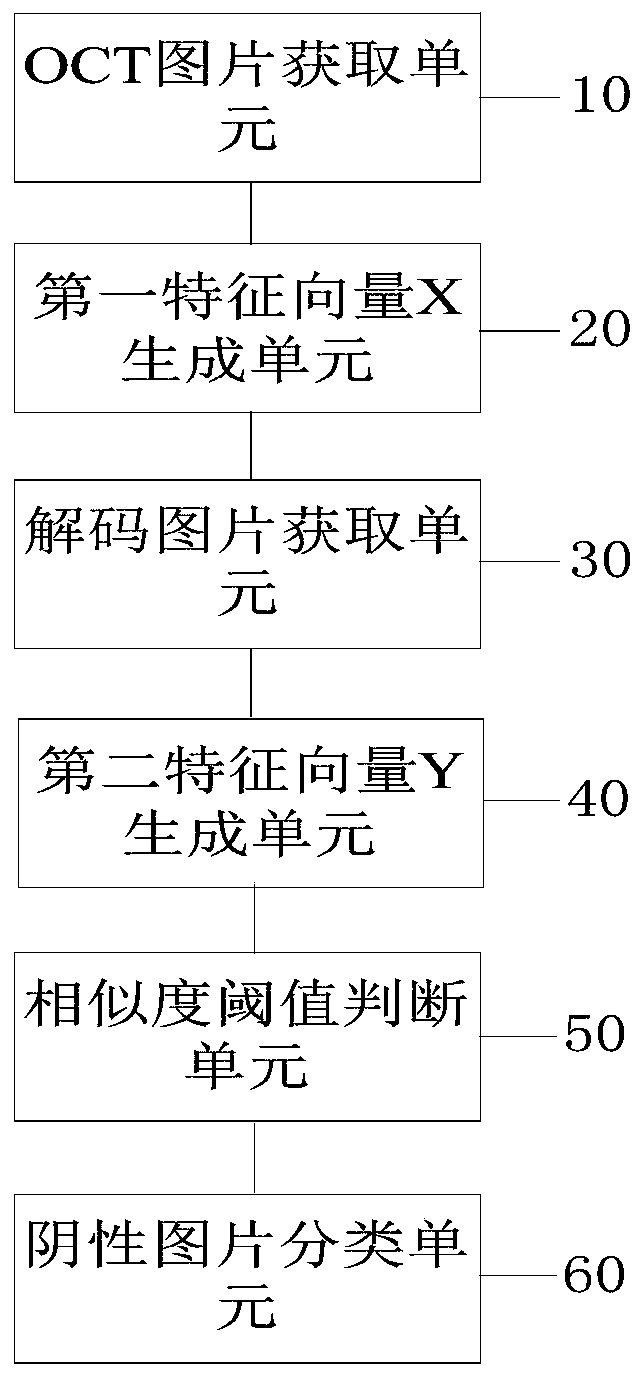

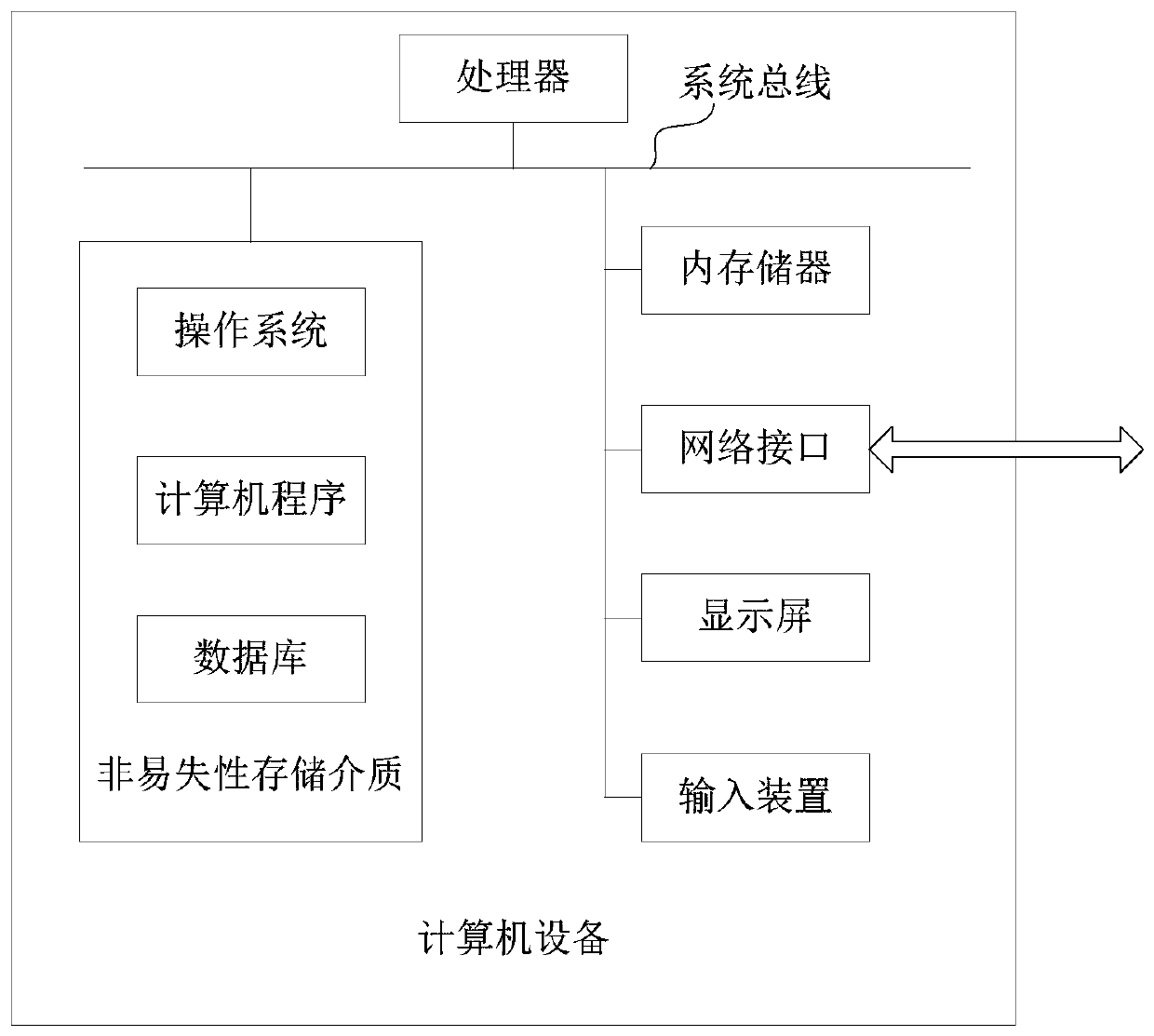

Picture classification method and device based on semi-supervised learning and computer equipment

PendingCN111008643AOvercome the defect of collecting difficultiesCharacter and pattern recognitionFeature vectorClassification methods

The invention discloses a picture classification method and device based on semi-supervised learning, computer equipment and a storage medium. The method comprises the steps that acquiring OCT pictures to be classified; processing the OCT pictures to be classified by using a feature vector generator in a preset OCT picture classification model to obtain a first feature vector X generated by a first encoder; decoding the first feature vector X by using the first decoder to obtain a decoded picture; generating a second feature vector Y by using the second encoder; calculating a similarity valueof the first feature vector X and the second feature vector Y according to a preset similarity calculation method, and judging whether the similarity value is greater than a preset similarity threshold value or not; and if the similarity value is greater than the preset similarity threshold, classifying the OCT pictures to be classified as negative pictures. Therefore, OCT picture classification is completed without positive data, and the defect that the positive data is difficult to collect is overcome.

Owner:PING AN TECH (SHENZHEN) CO LTD

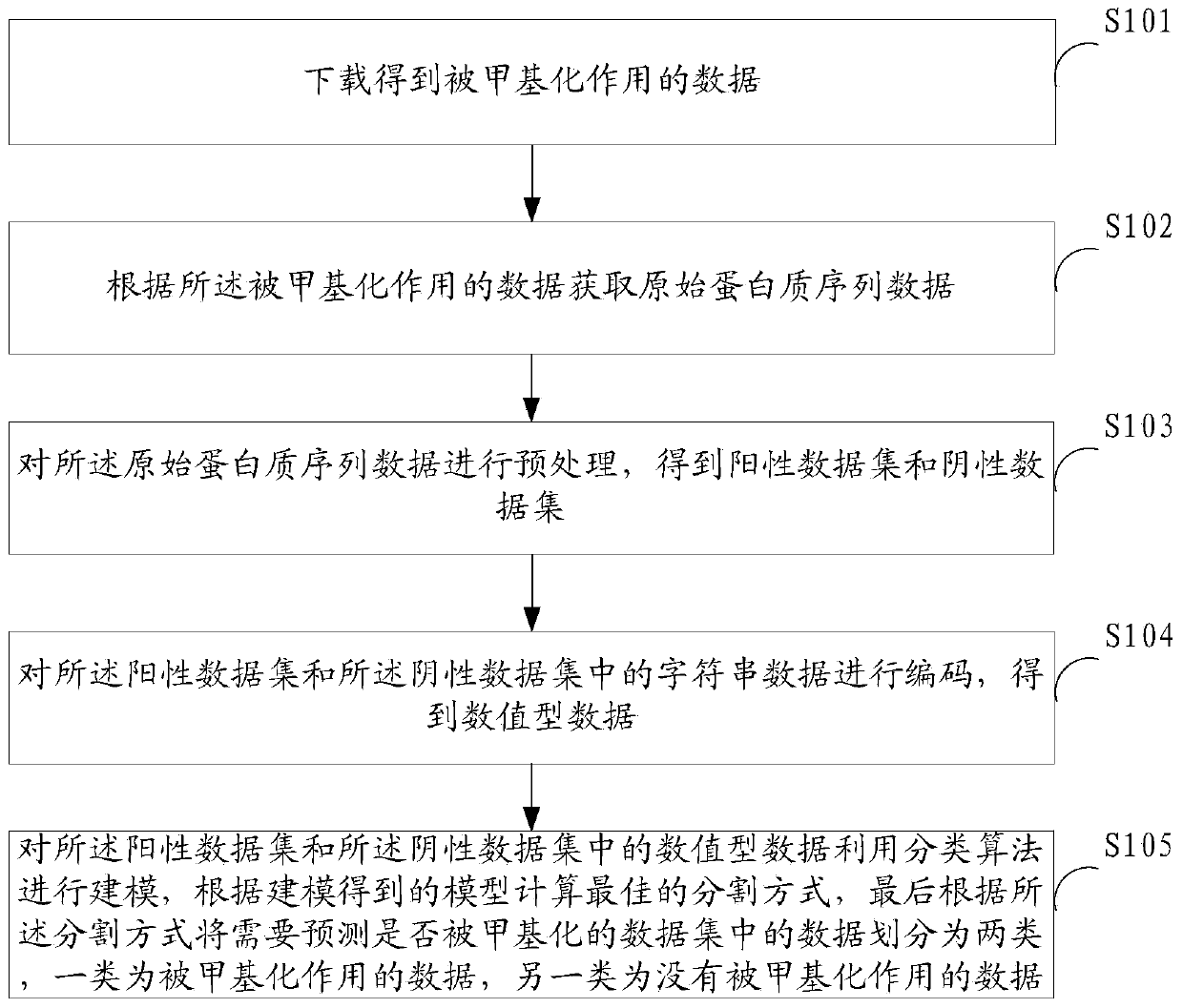

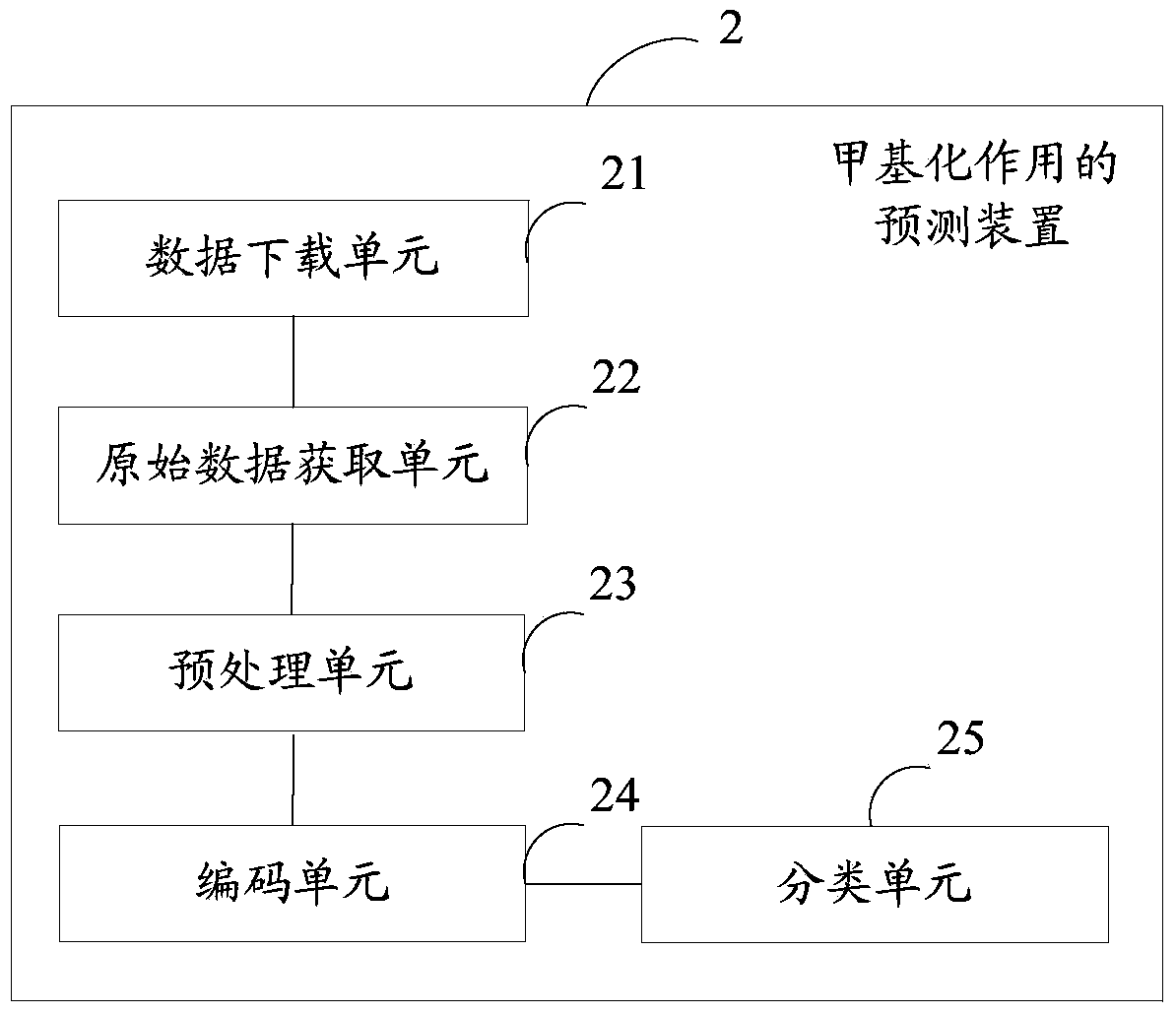

Method and device for predicting methylation

ActiveCN103559423AShorten the timeLow costSpecial data processing applicationsTime efficientData set

The invention is suitable for the technical field of biological information and provides a method and a device for predicting methylation. The method comprises the following steps of: downloading to obtain methylated data; according to the methylated data, acquiring original protein sequence data; carrying out preprocessing on the original protein sequence data to obtain a positive data set and a negative data set; carrying out encoding on character string data in the positive data set and the negative data set to obtain numeric data; carrying out modeling on the numeric data in the positive data set and the negative data set by utilizing a classification algorithm, calculating the optimal division mode according to a model obtained by modeling, and finally, according to the division mode, dividing the data which need to be predicted whether to be methylated into two categories in a centralized mode, wherein one category is the methylated data and the other category is data which are not methylated. According to the invention, personnel do not need to participate, a graph also does not need to be drawn, time can be saved and cost is low.

Owner:SHENZHEN INST OF ADVANCED TECH

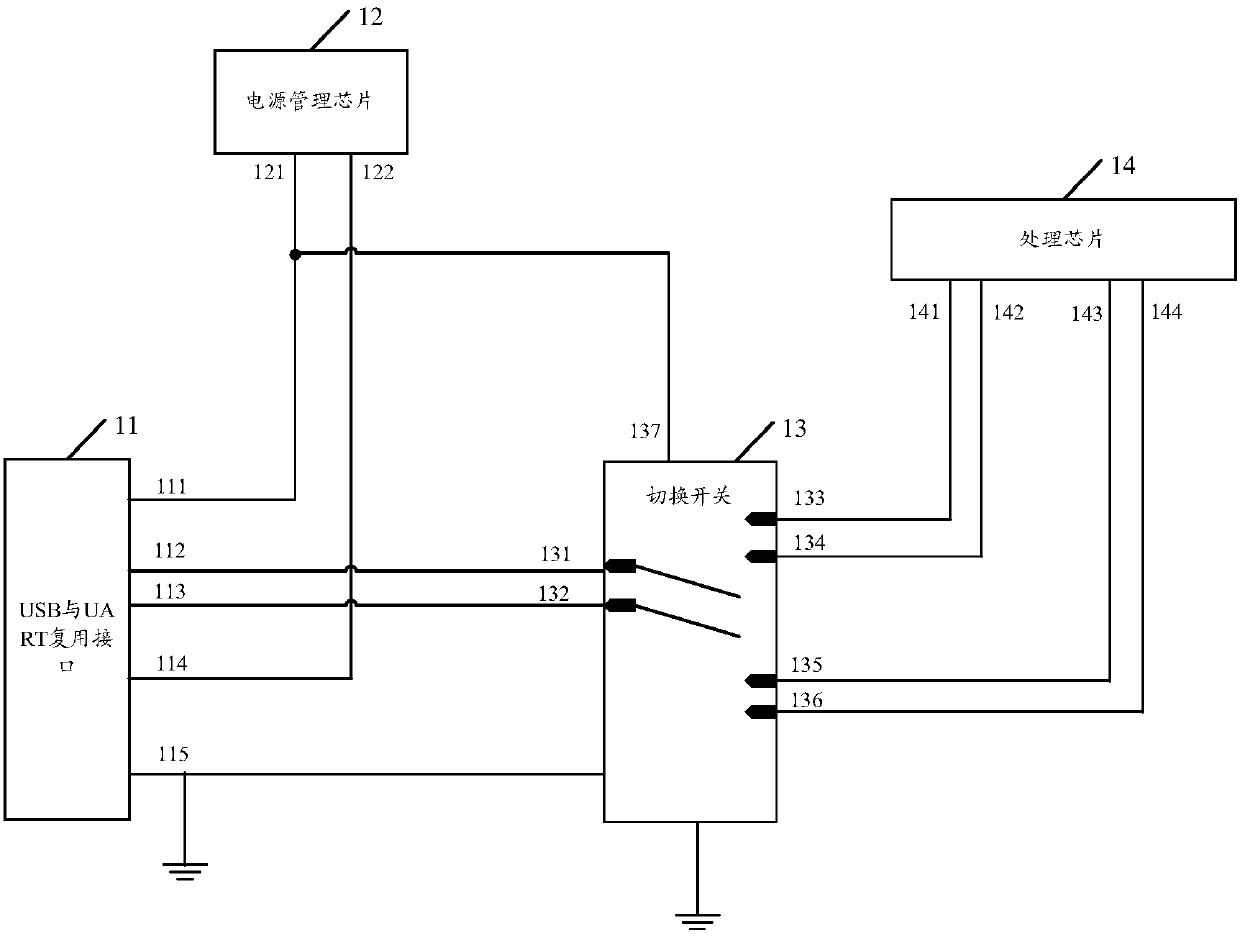

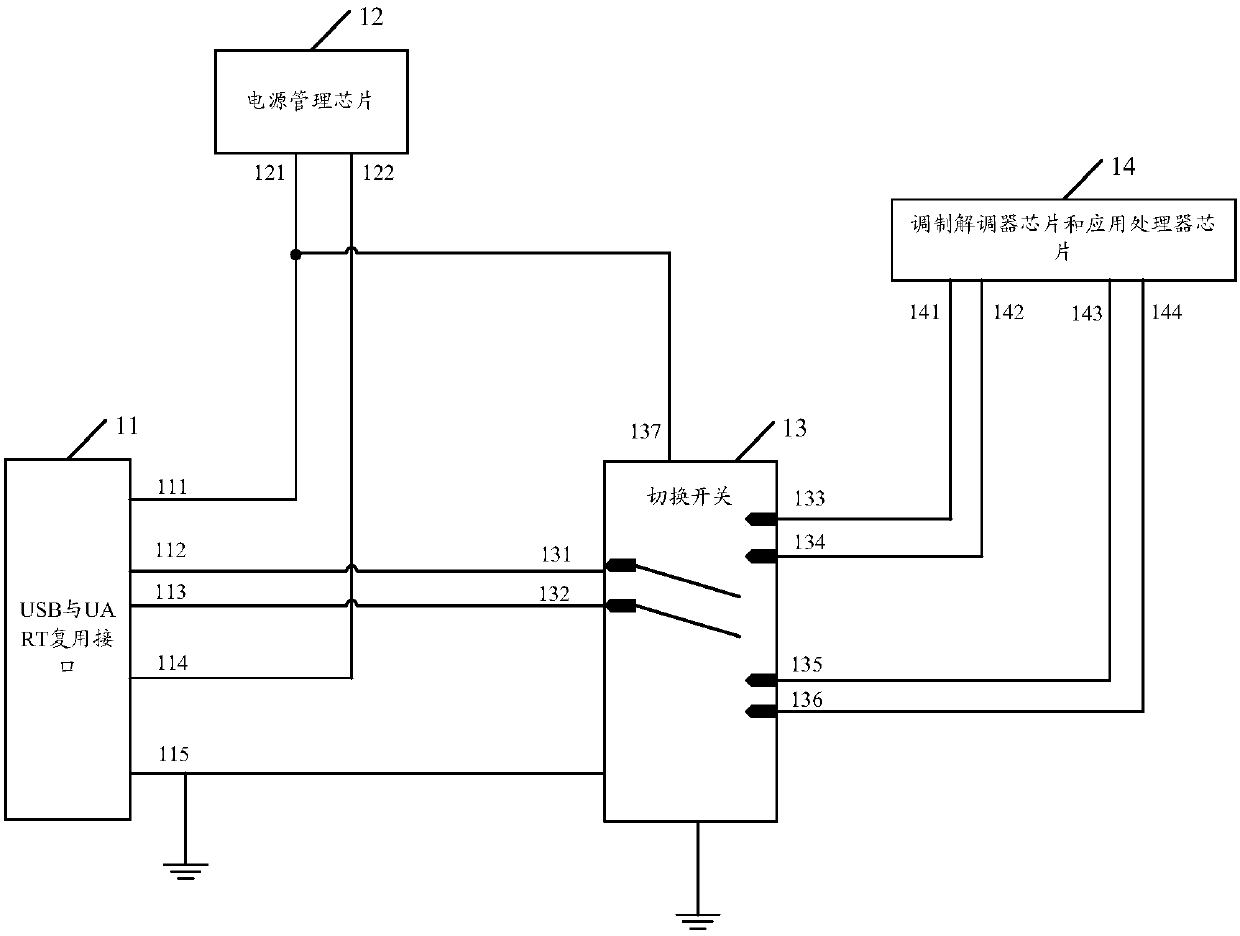

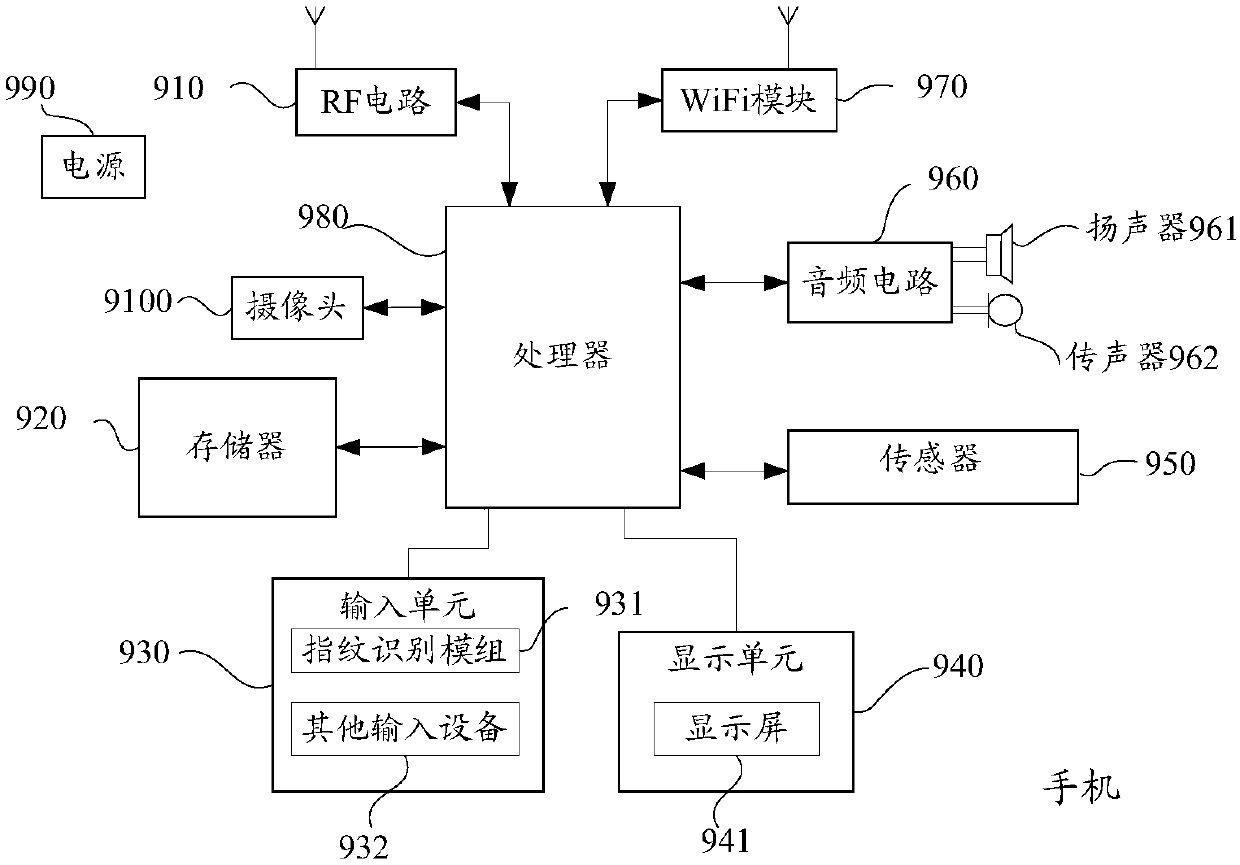

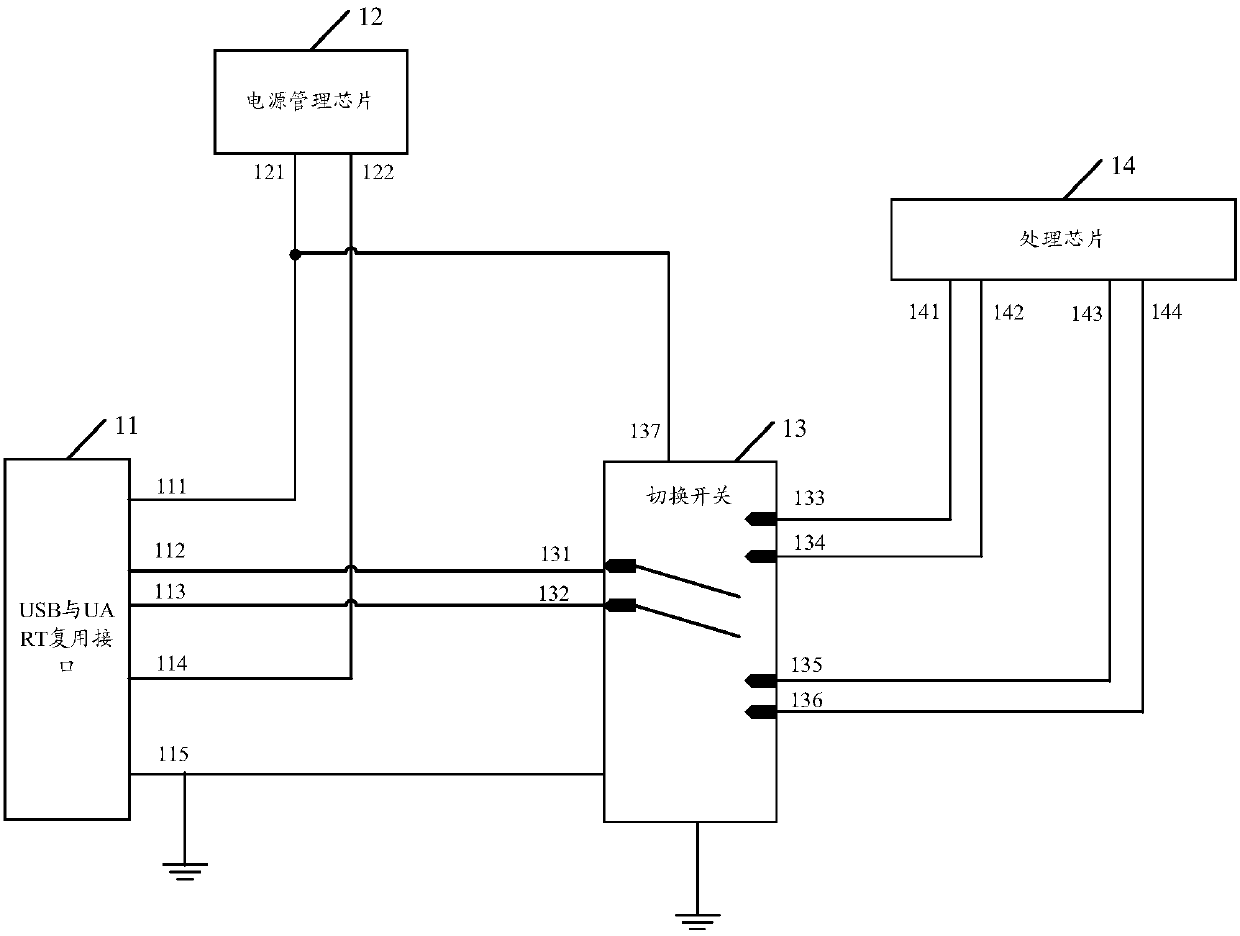

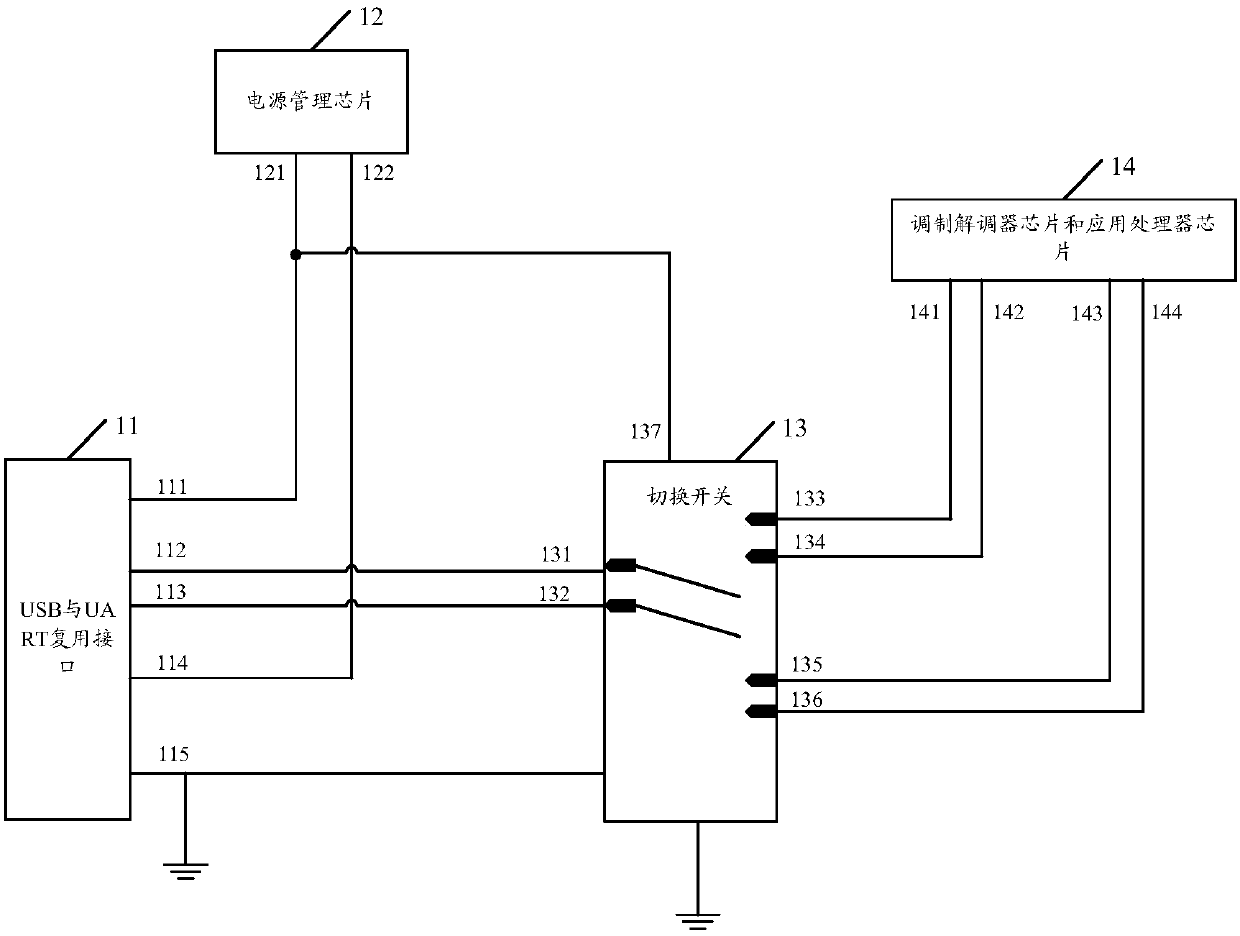

UART and USB multiplex circuit and mobile terminal

ActiveCN107635069AInitialization went wellAvoid interferenceSubstation equipmentEngineeringUniversal asynchronous receiver/transmitter

Embodiments of the invention disclose a UART and USB multiplex circuit and a mobile terminal. The UART and USB multiplex circuit comprises a universal serial bus (USB) and universal asynchronous receiver / transmitter (UART) multiplex interface, a power management chip, a selector switch and a processing chip, wherein a power output end is connected to a control end and a power line pin; a detectionend is connected to a detection pin; a positive data line pin is connected to a first selection end; a negative data line pin is connected to a second selection end; a first positive data end is connected to a UART positive connection end; a first negative data end is connected to a UART negative connection end; a second positive data end is connected to a USB positive connection end; and a second negative data end is connected to a USB negative connection end. According to the embodiments of the invention, the normal work of USB equipment can be guaranteed in a process of switching the UARTinterface to the USB interface.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

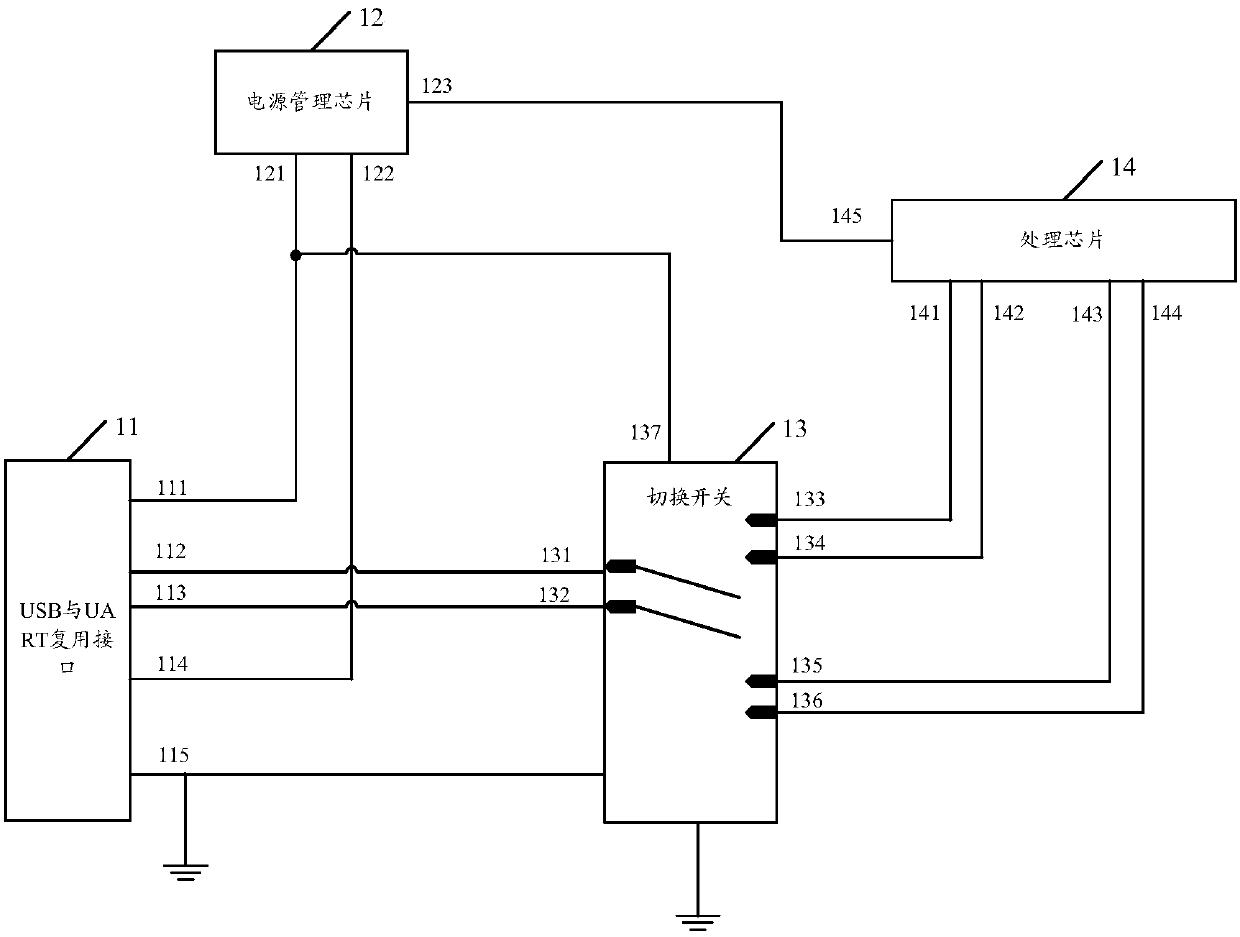

UART (Universal Asynchronous Receiver/Transmitter)-USB (Universal Serial Bus) multiplexing circuit and mobile terminal

ActiveCN107678989AInitialization went wellAvoid interferenceElectric digital data processingMultiplexingEngineering

The embodiment of the invention discloses a UART (Universal Asynchronous Receiver / Transmitter)-USB (Universal Serial Bus) multiplexing circuit and a mobile terminal. The UART-USB multiplexing circuitcomprises a USB-UART multiplexing interface, a power management integrated circuit, a changeover switch and a processing integrated circuit; a power output end is connected to a control end and a power line pin; a detection end is connected to a detection pin; a positive data line pin is connected to a first selection end; a negative data line pin is connected to a second selection end; a first positive data end is connected to a positive connection end of a UART; a first negative data end is connected to a negative connection end of the UART; a second positive data end is connected to the positive connection end of a USB; and a second negative data end is connected to the negative connection end of the USB. According to the embodiment, a USB device can be guaranteed to work normally in the process of switching an UART interface to a USB interface.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

Real time cognitive monitoring of correlations between variables

ActiveUS20180348274A1Capacitance measurementsMeasurement through mechanical displacementCapacitanceComputer science

Real time cognitive monitoring of correlations between variables including receiving, by a circuit, a first set of data results and a second set of data results, wherein each set of data results comprises binary data points; adding a unit of charge to a collection capacitor on the circuit for each of the first set of data results that indicates a positive data point; removing a unit of charge from the collection capacitor for each of the second set of data results that indicates a positive data point; and triggering a first sense amp on the circuit if the charge on the collection capacitor exceeds a high charge threshold, indicating that the positive data points in the first set of data results is greater than the positive data points in the second set of data results to a first statistical significance.

Owner:IBM CORP

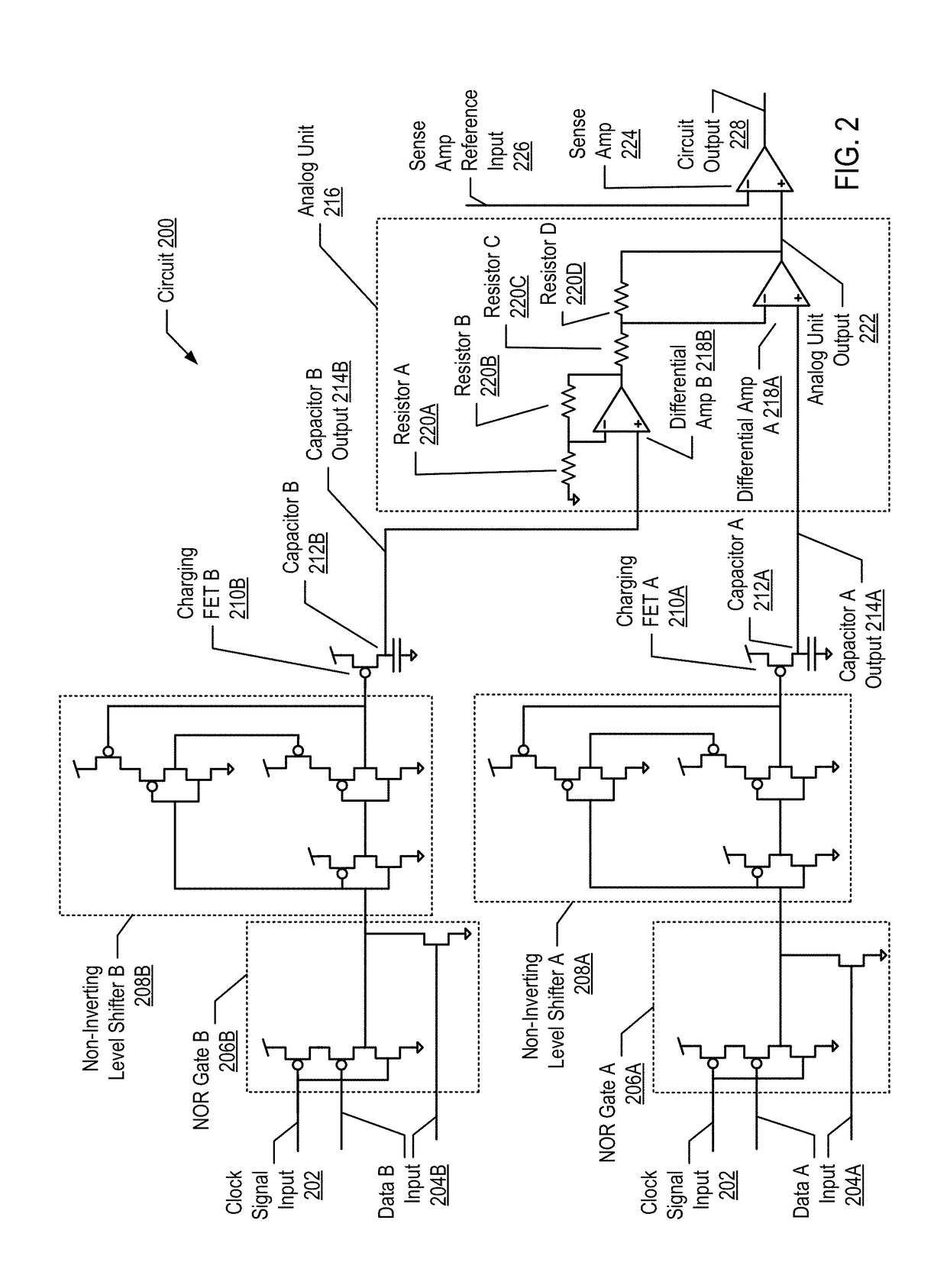

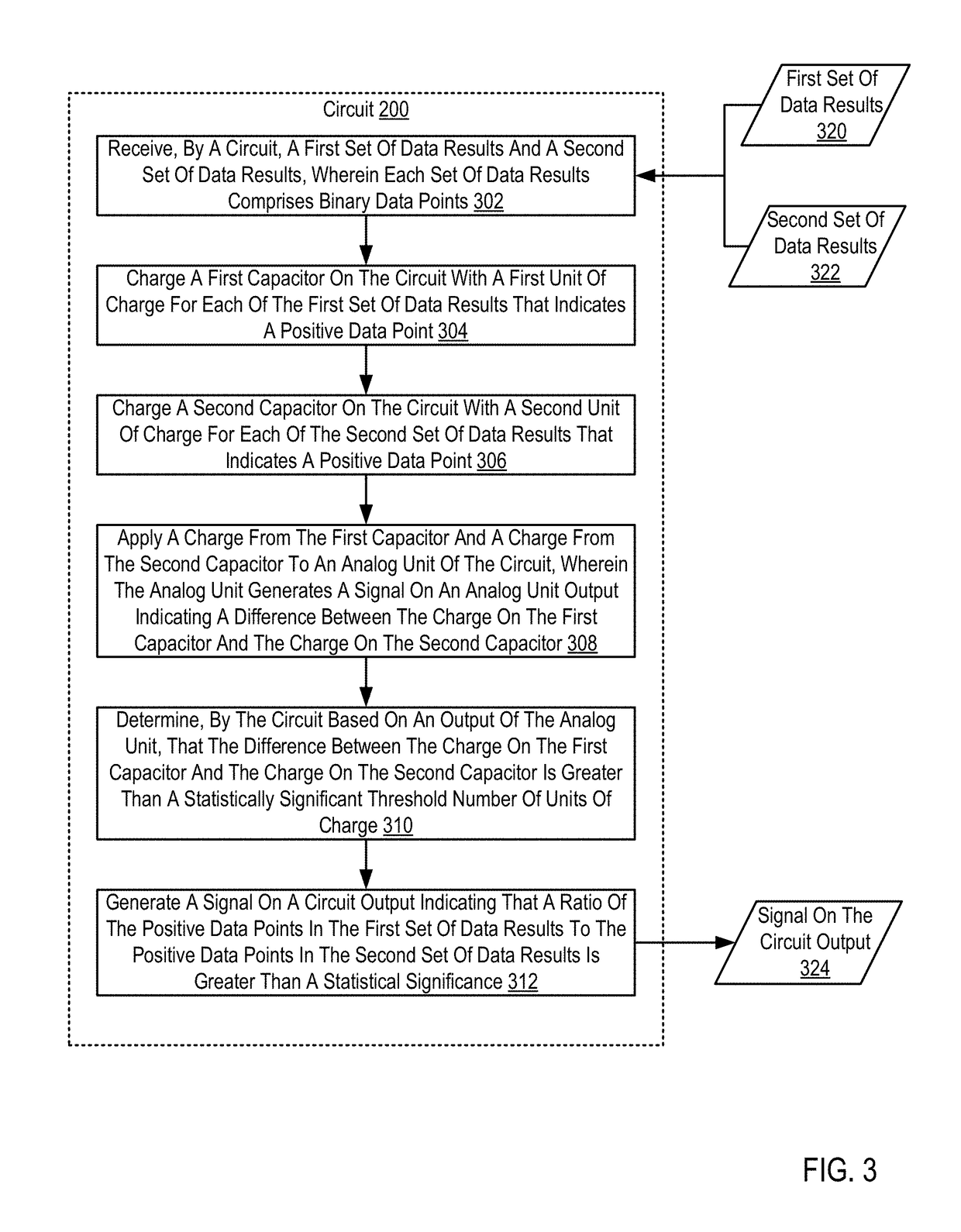

Cognitive analysis using applied analog circuits

ActiveUS20180348273A1Capacitance measurementsComputing operations for addition/subtractionCapacitanceSignal on

Cognitive analysis using applied analog circuits including receiving, by a circuit, a first set of data results and a second set of data results; charging a first capacitor on the circuit with a first unit of charge for each of the first set of data results that indicates a positive data point; charging a second capacitor on the circuit with a second unit of charge for each of the second set of data results that indicates a positive data point; applying a charge from the first capacitor and a charge from the second capacitor to an analog unit of the circuit; and generating a signal on a circuit output indicating that a ratio of the positive data points in the first set of data results to the positive data points in the second set of data results is greater than a statistical significance.

Owner:IBM CORP