Patents

Literature

50results about How to "Reduce invalid operations" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

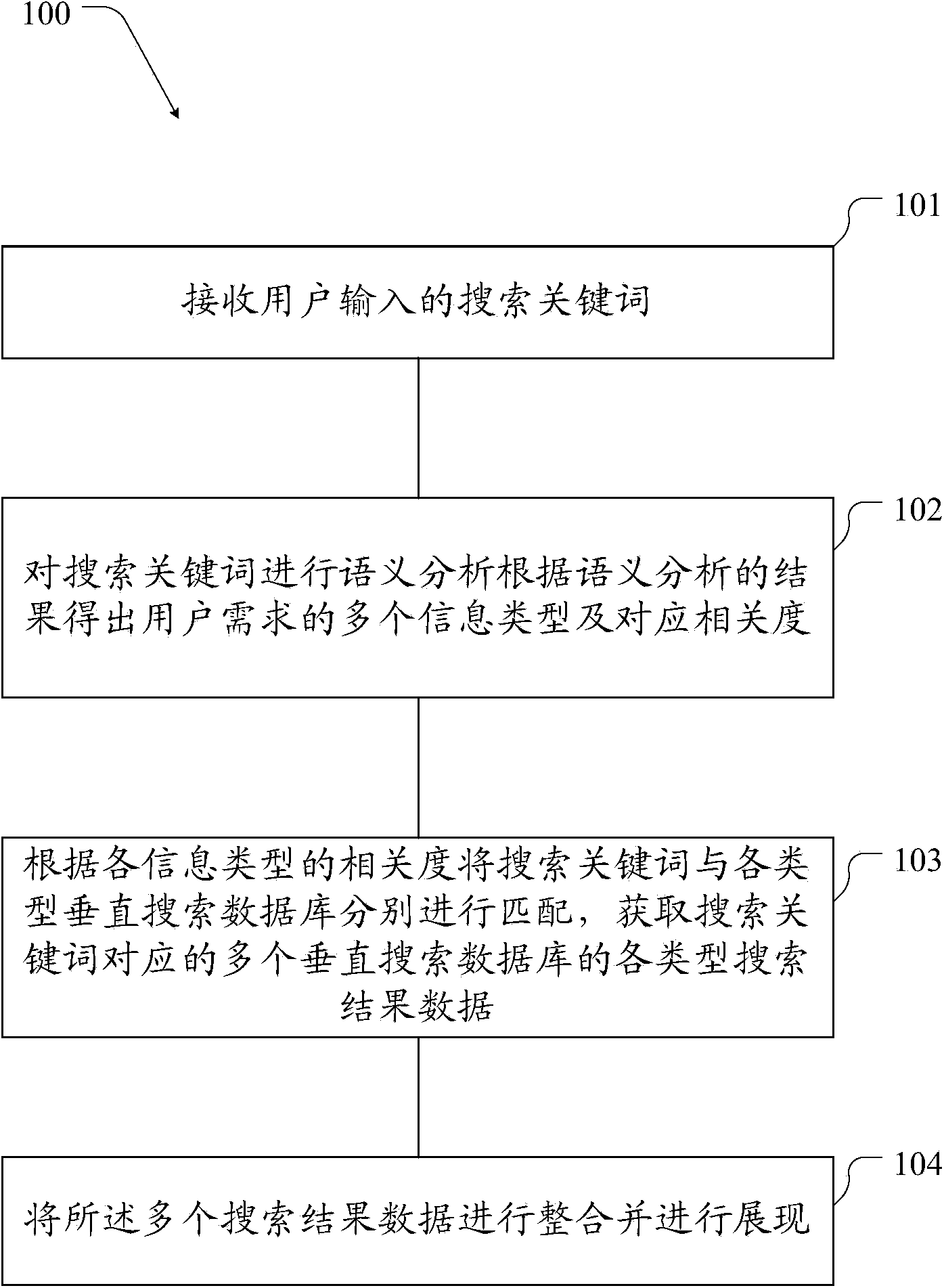

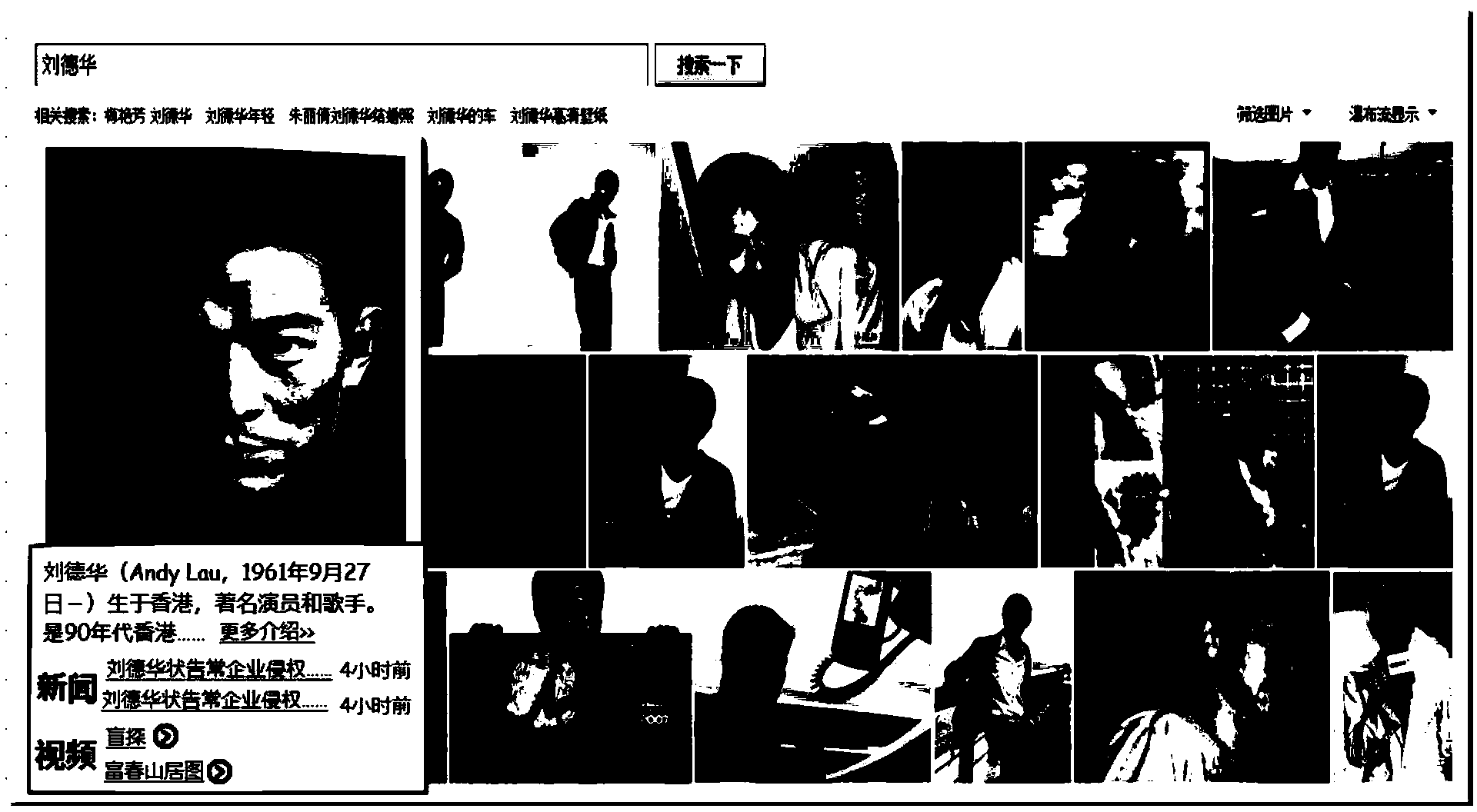

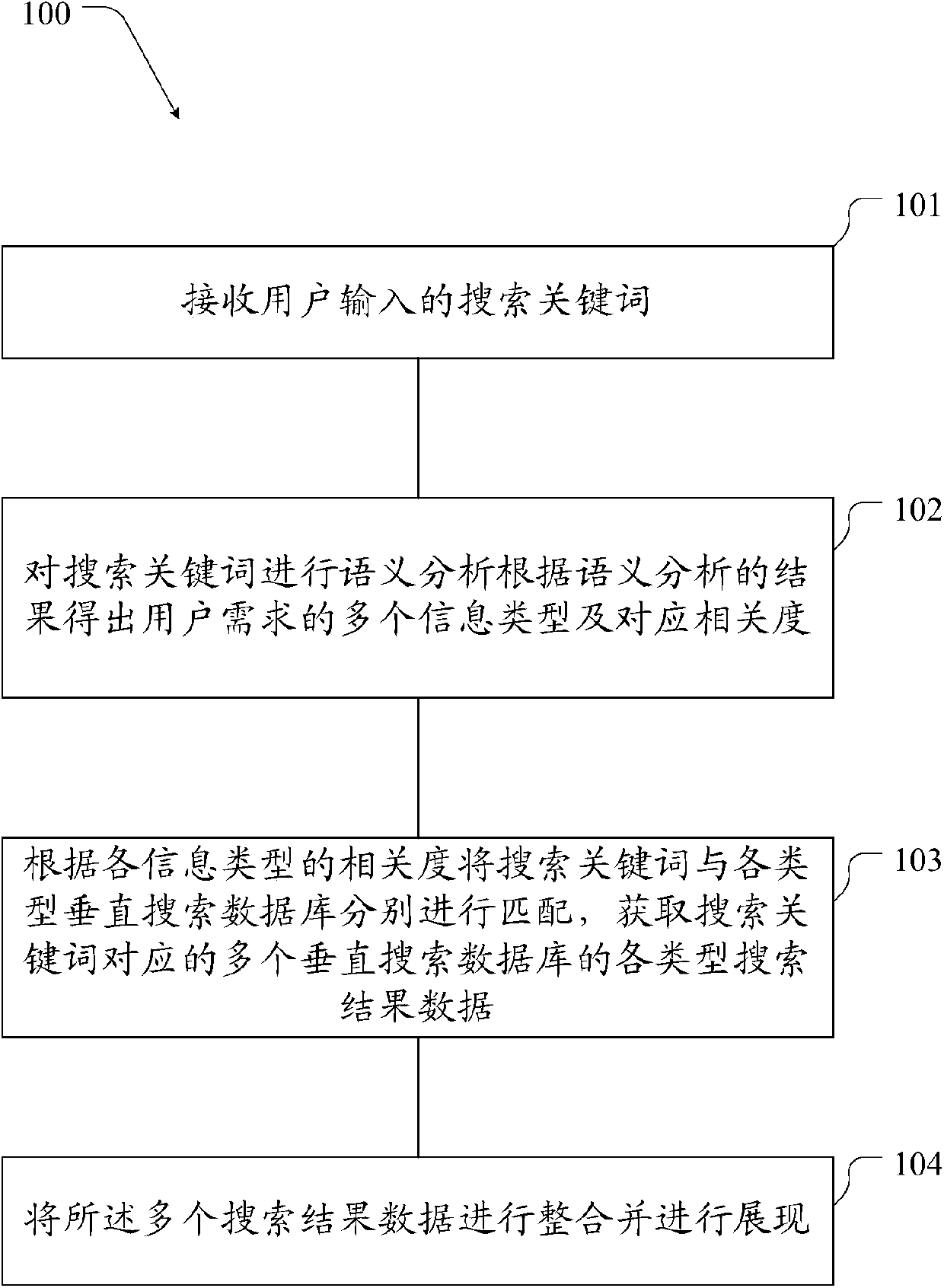

Information searching method and device

ActiveCN103514299AMeet needsReduce invalid operationsWeb data indexingSemantic analysisUser needsInformation type

The invention discloses an information searching method and device. The method comprises the steps that search keywords input by a user are received; semantic analysis is conducted on the search keywords, and a plurality of information types and corresponding relevancies required by the user are obtained according to results of the semantic analysis; the search keywords are matched with various vertical search data bases according to the relevancies of the information types, and various types of search result data of the vertical search data bases corresponding to the search keywords are obtained; the various types of search result data are integrated and shown. According to the information searching method and device, the search results which are obtained finally integrate content of a plurality of vertical channels, and comprise various possible requirements of the user. Compared with universal search, pertinence is stronger, the situation that the user can only select the current channel in vertical search is avoided, and therefore invalid operation of the user is reduced, and the requirements of the user are met more rapidly.

Owner:BEIJING QIHOO TECH CO LTD

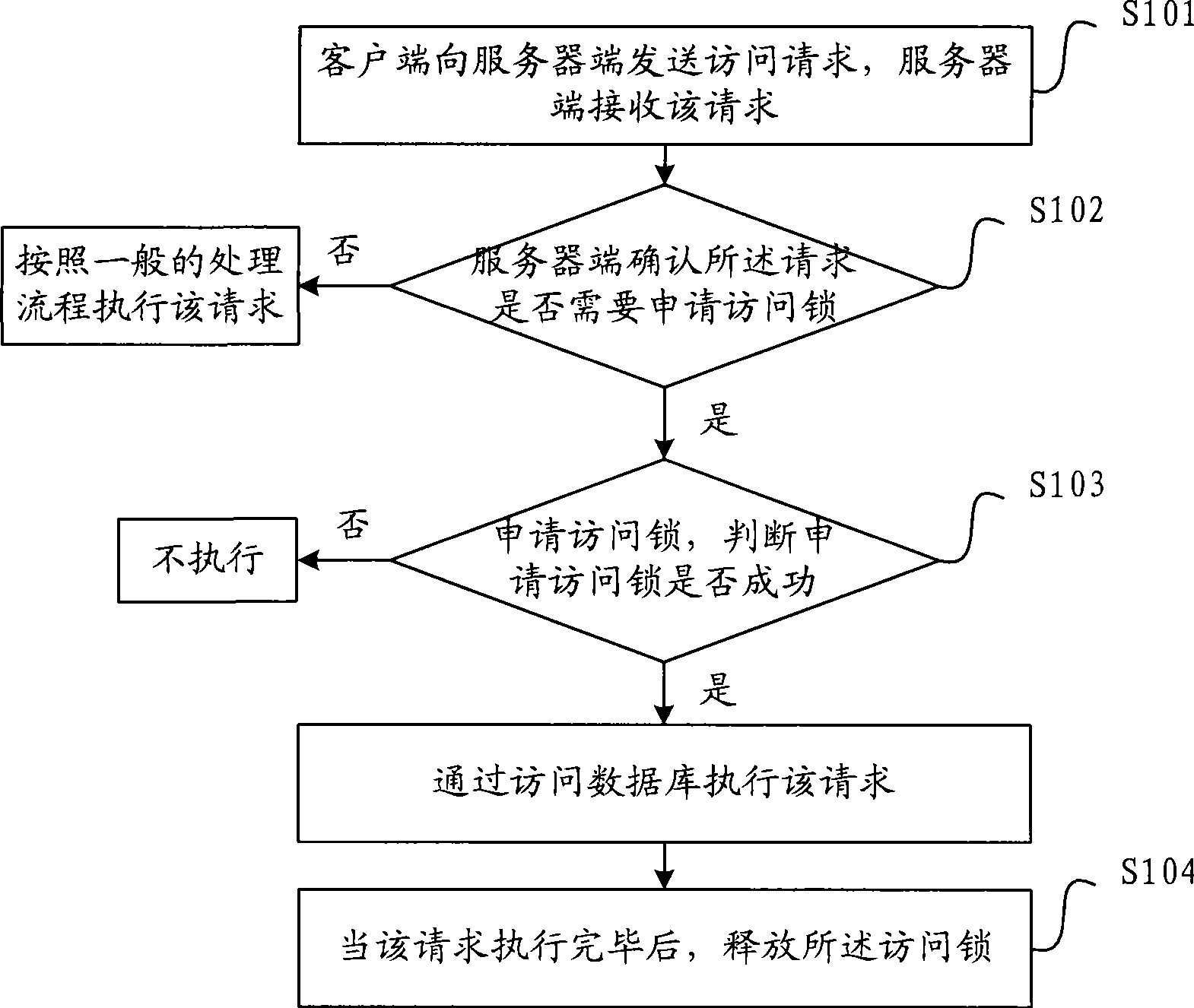

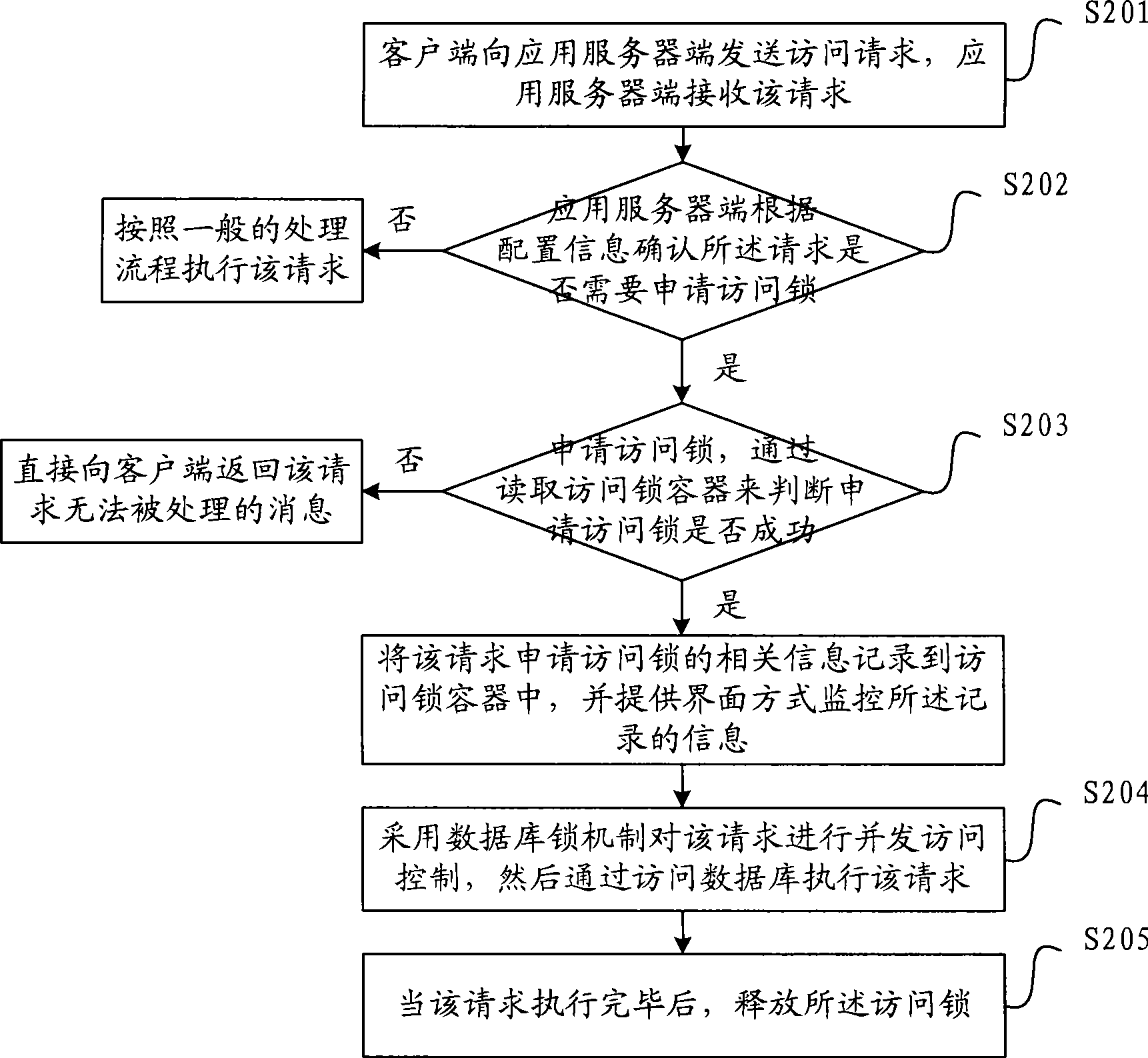

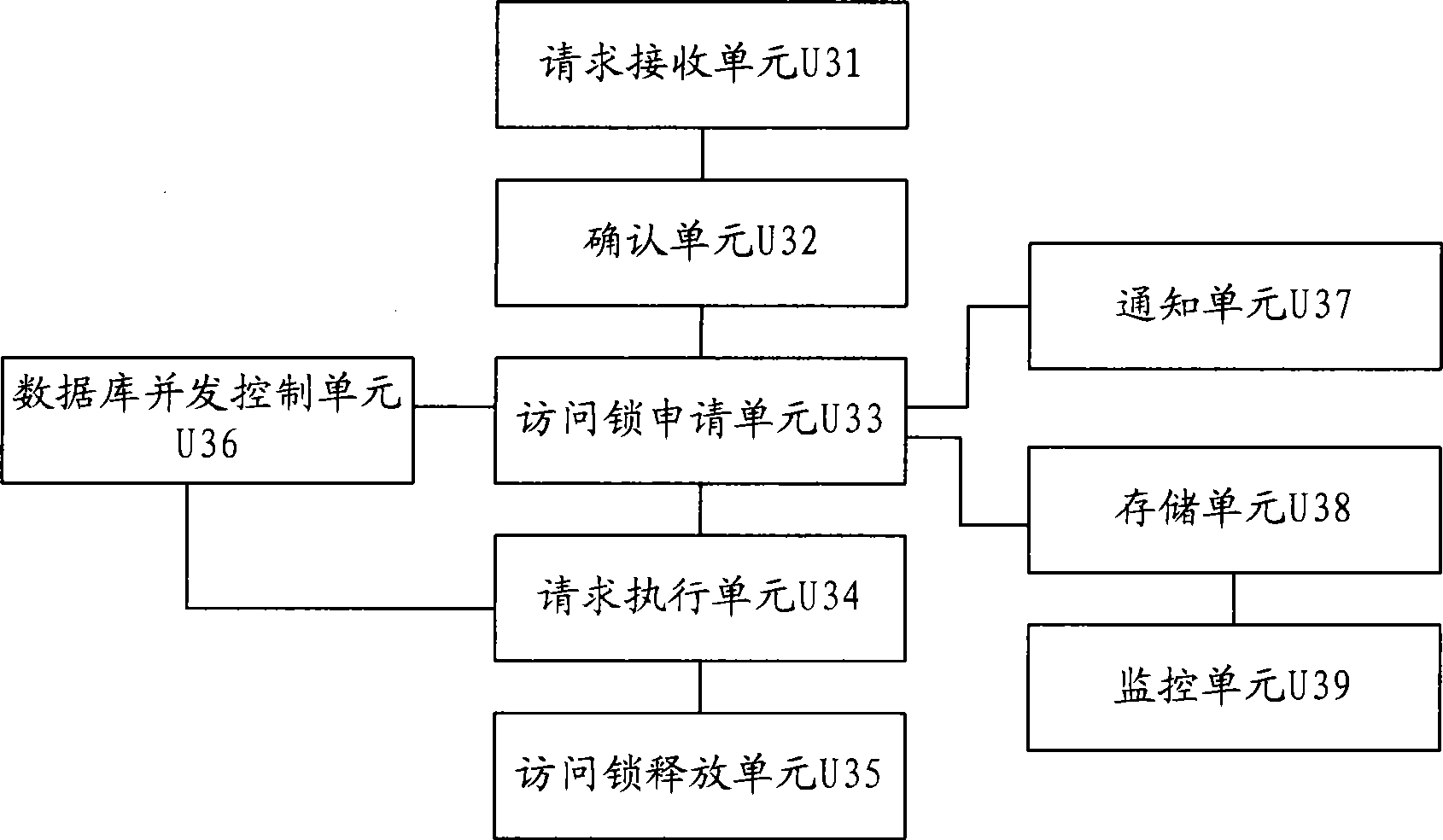

Concurrent access control method and device

ActiveCN101364230AControl concurrent accessControl modificationSpecial data processing applicationsApplication serverLocking mechanism

The invention discloses a concurrent access control method and a device which solve the problem that a database has heavier burdens and is easy to cause deadlocks in the prior database locking mechanism. The concurrent access control method comprises: a server receives an access request; confirming whether the request needs to apply for an access lock, if necessary, the access lock is visited; if the application for the access lock is approved, the request is performed via an access database; after the request is performed, the access lock is released. The concurrent access control method and the device provide a set of locking mechanisms at the application level. The locking mechanism can control the concurrent access to the server, so requests are filtered by the application server before arriving at the database, namely, the concurrent requests are filtered. Therefore, under the condition of multi-user and concurrent access, the concurrent access control method and the device can effectively control the concurrent access and modification of data, relieve the burdens of the database, and effectively reduce the abnormal situations of a database, such as deadlocks, waiting, etc.

Owner:KINGDEE SOFTWARE(CHINA) CO LTD

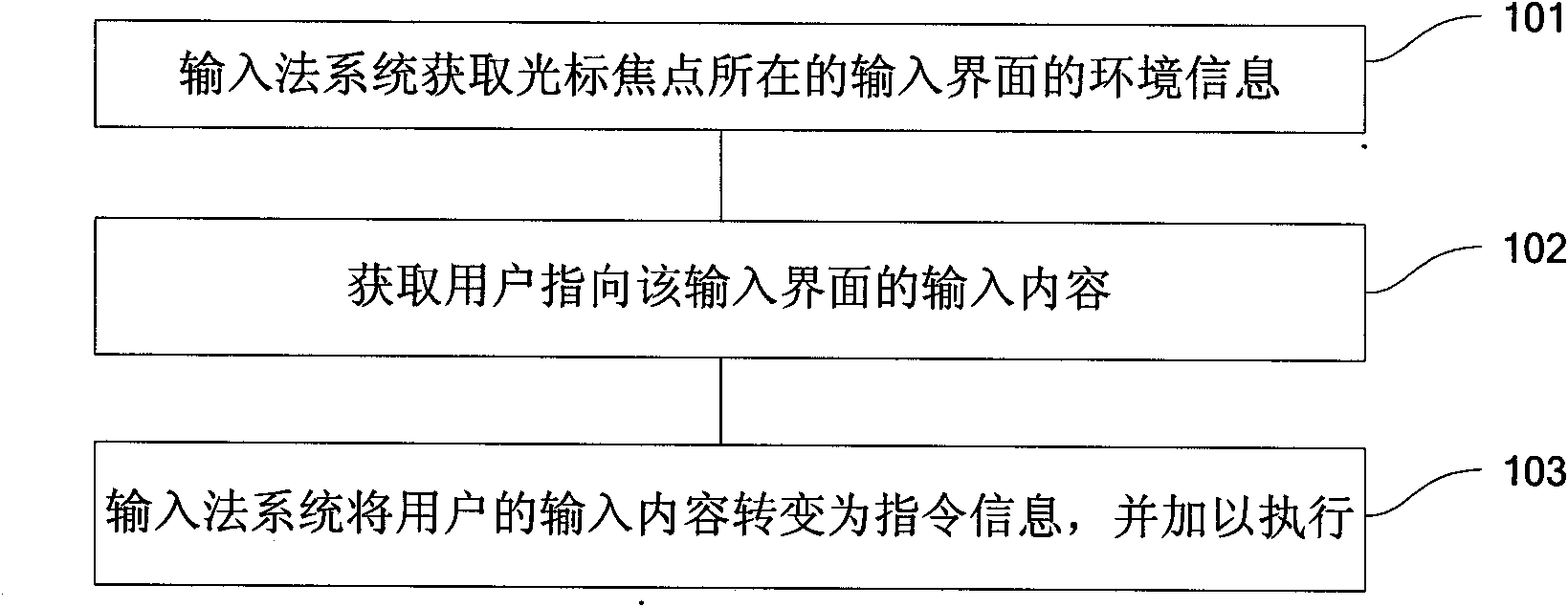

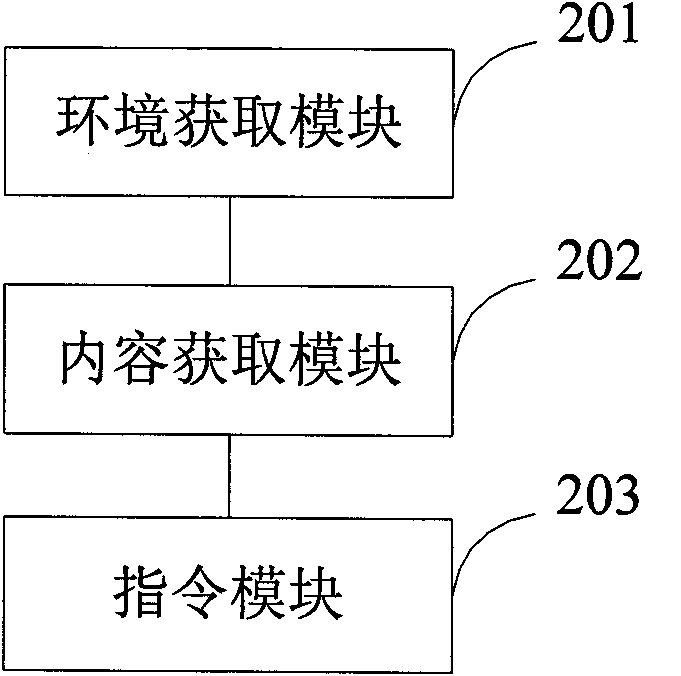

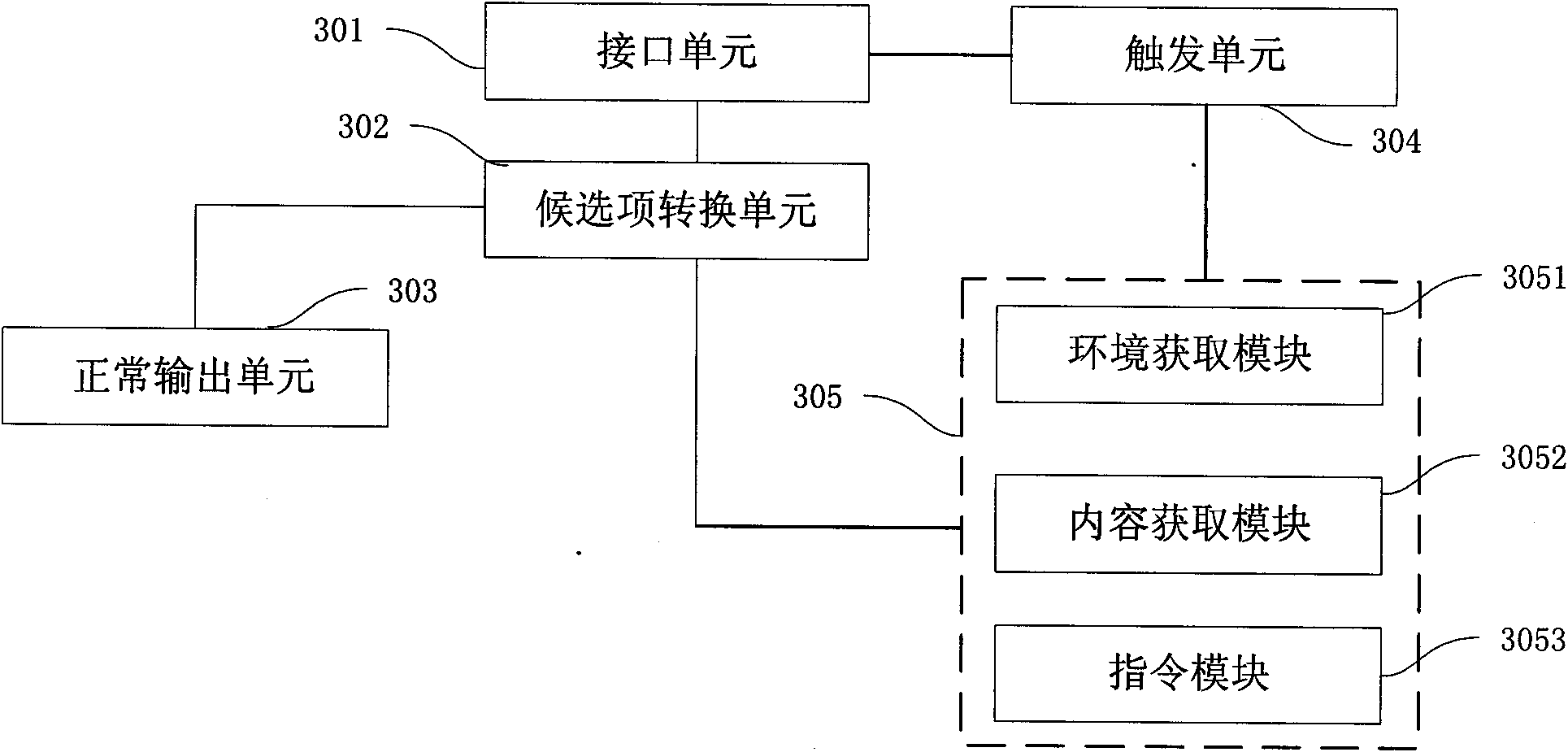

Method and device for carrying out information input and execution based on input interface

InactiveCN101882007AReduce memory loadImprove user experienceSpecific program execution arrangementsInput/output processes for data processingComputer hardwareHuman–computer interaction

The invention provides a method and a device for carrying out information input and execution based on an input interface and an input method system, wherein the method comprises the following steps that the input method system acquires the environment information of the input interface in which a cursor focus is located; the input method system acquires the input content of a user pointing the input interface; and the input method system converts the input content of the user into command information and executes the command information. When the user triggers the flow of the invention, the invention can automatically acquire the environment information of a current input box, and automatically acquires the input content of the user pointing the input interface from the input method system, and further, the input content is converted into the command information, and the command information is executed.

Owner:BEIJING SOGOU TECHNOLOGY DEVELOPMENT CO LTD

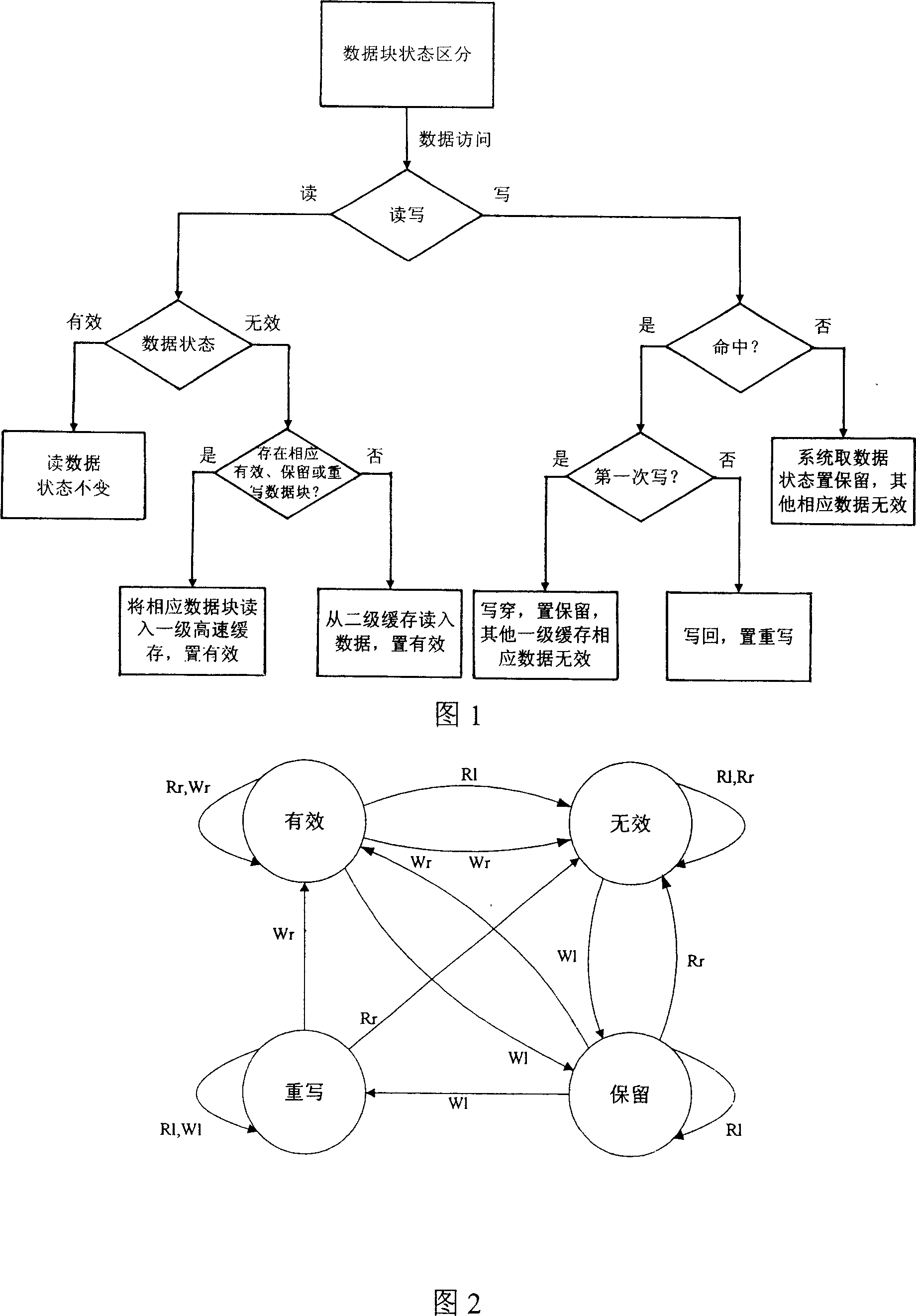

Embedded heterogeneous polynuclear cache coherence method based on bus snooping

InactiveCN101008921AReduce trafficImprove efficiencyMemory adressing/allocation/relocationMulti processorCache coherence

This invention discloses one imbed abnormal multi-nuclear buffer accordance method based on bus detection, which is based on one time strategy processor one degree high speed buffer accordance with main function to keep same data in multi-nuclear local one degree high speed buffer and sharing two degree high speed buffer multiple copy accordance. This invention is suitable for abnormal multi-nuclear system processor based on bus to combine two strategies advantages.

Owner:ZHEJIANG UNIV

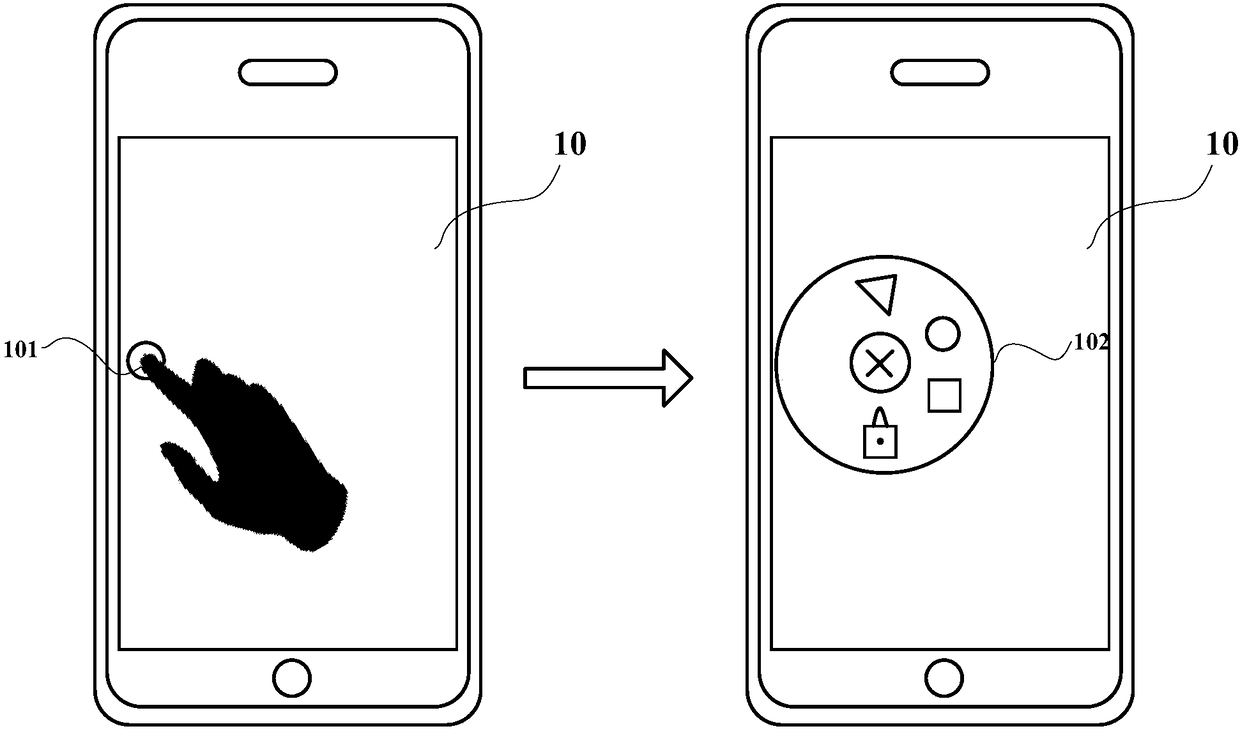

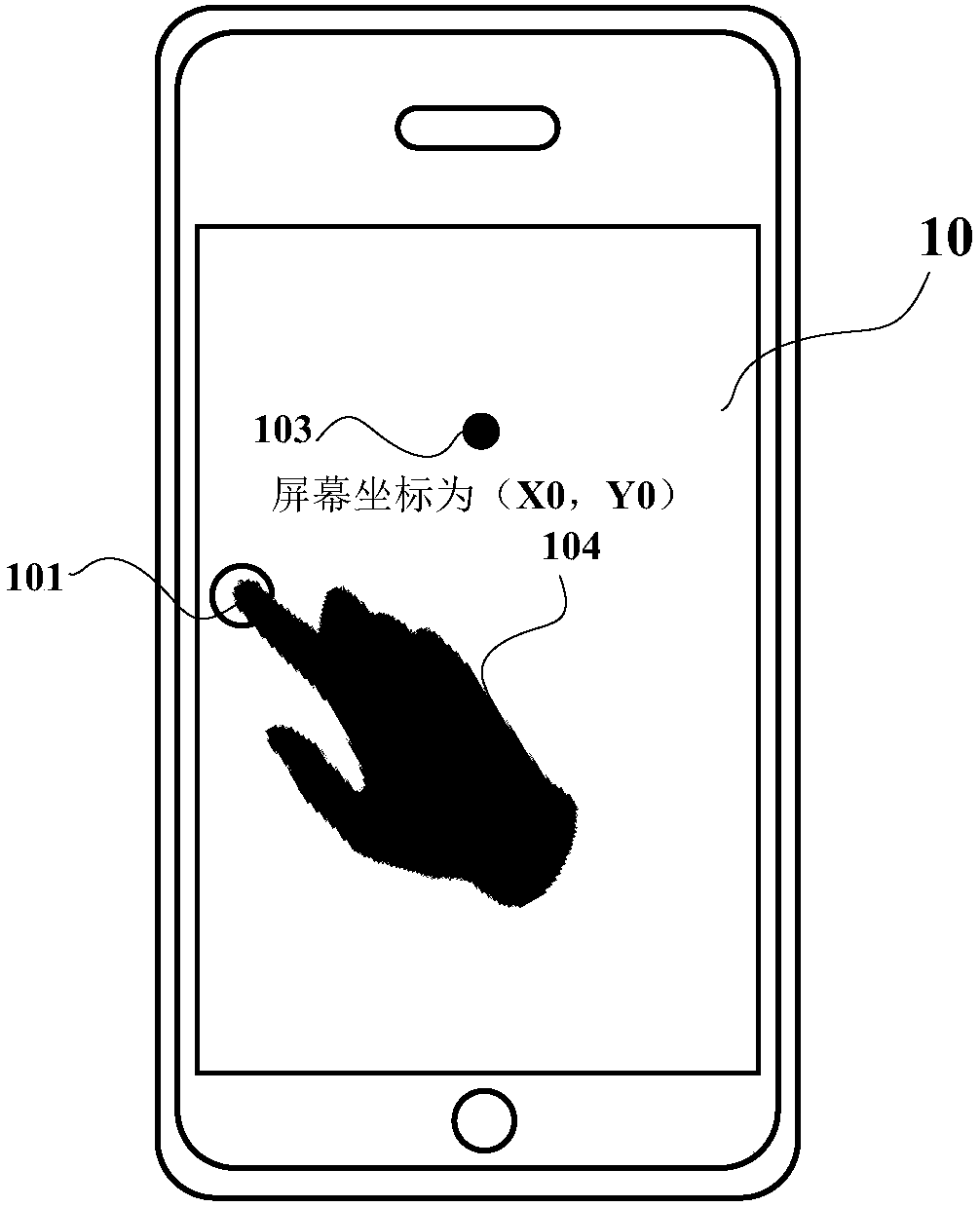

Hover button control method, terminal and computer readable storage medium

InactiveCN108279820AHigh touch efficiencyImprove user experienceInput/output processes for data processingTarget controlHuman–computer interaction

The embodiment of the invention discloses a hover button control method, a terminal and a computer readable storage medium. The method comprises the steps that the terminal receives a first touch operation of a user for a hover button on a display screen of the terminal, wherein the first touch operation is used for triggering touch on a target area corresponding to the hover button; the terminaltriggers a second touch operation for a target control in the target area, wherein the second touch operation is same as or different from the first touch operation in operation type. Accordingly, theterminal is combined with the area determined by a hover button to achieve control over the terminal display screen, the efficiency of touching the terminal can be improved, and the use experience ofthe user is improved.

Owner:SHENZHEN GIONEE COMM EQUIP

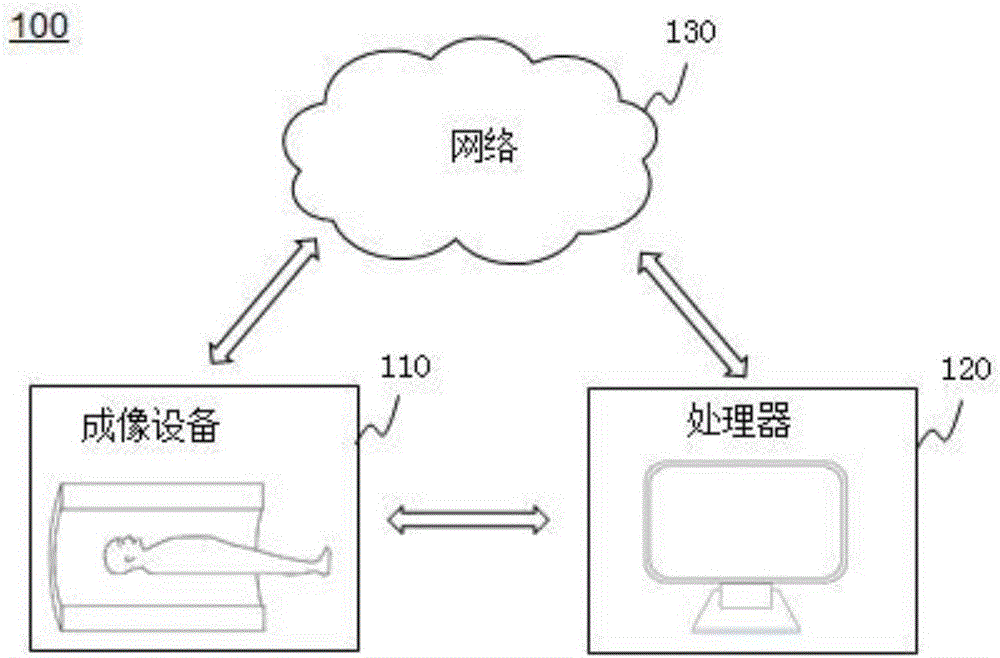

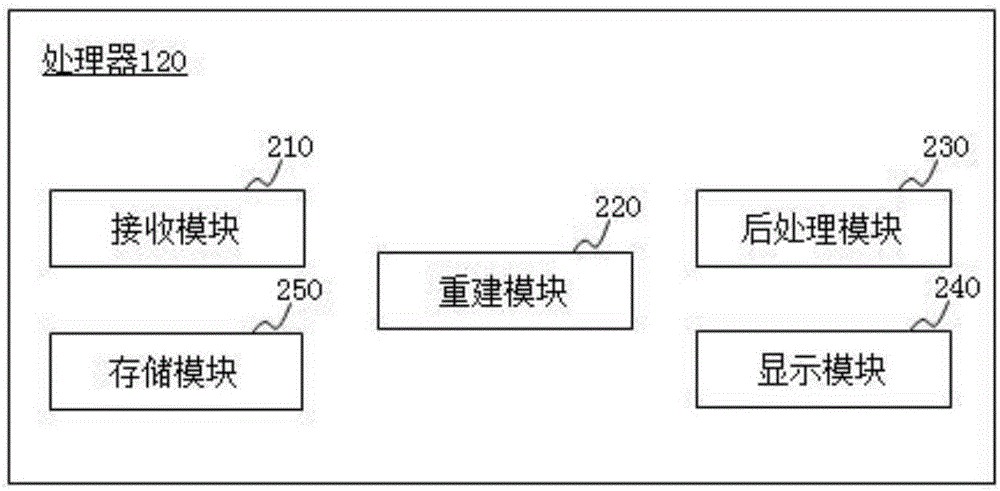

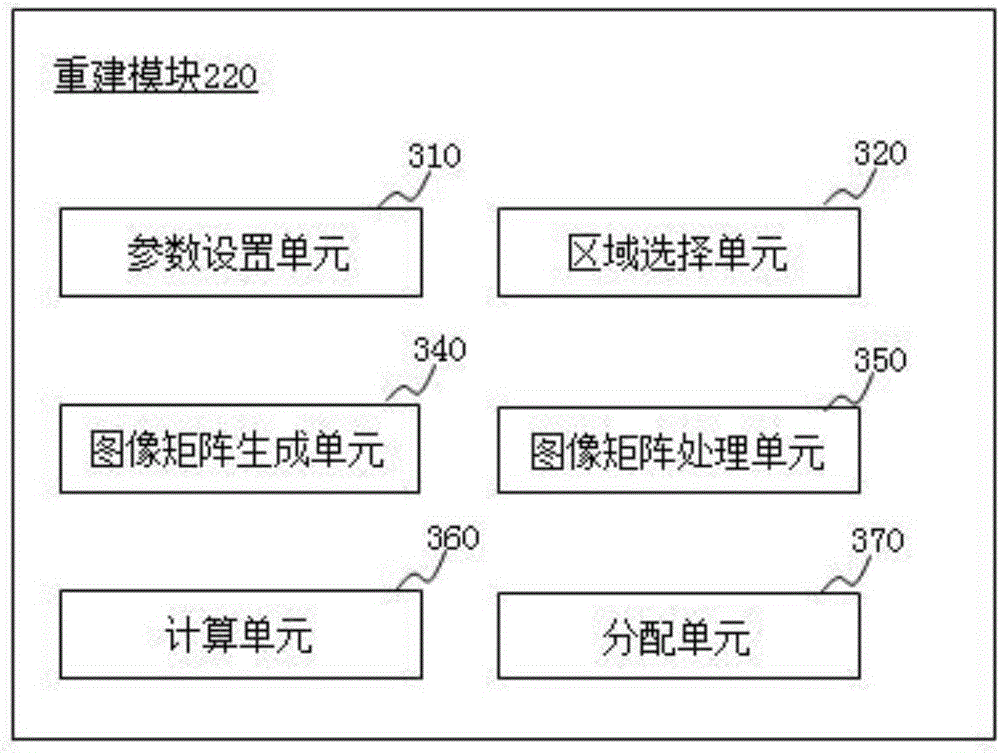

Image reconstruction method and image reconstruction system

ActiveCN106296764AReduce consumptionReduce invalid operationsReconstruction from projectionVoxelReconstruction method

The invention discloses an image reconstruction method and an image reconstruction system. The method comprises steps that an image matrix is determined, and the image matrix corresponds to a scanning zone and corresponds to voxels in a certain quantity; the image matrix is divided into multiple sub image matrixes, at least one of the multiple sub image matrixes corresponds to one sub scanning zone of the scanning zone, and the voxels are partially included; the at least one sub image matrix is transformed, and at least one transformation matrix is generated; the at least one sub image matrix is reconstructed on the basis of the transformation matrix; the image matrix can be reconstructed on the basis of the reconstructed at least one sub image matrix. Through the method and the system, internal storage loss of a high-performance calculation unit in a reconstruction process can be reduced through matrix transformation, ineffective operation is further reduced, and an operation speed is accelerated.

Owner:SHANGHAI UNITED IMAGING HEALTHCARE

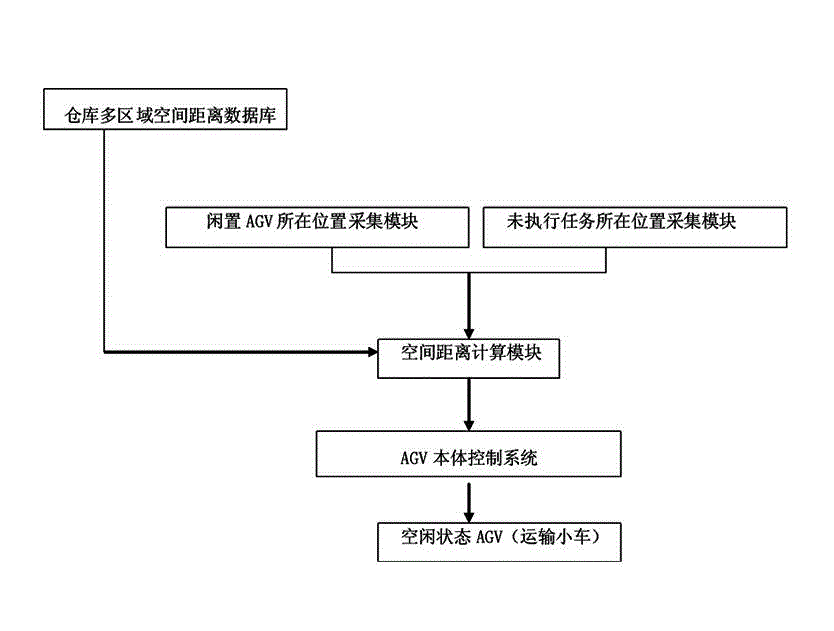

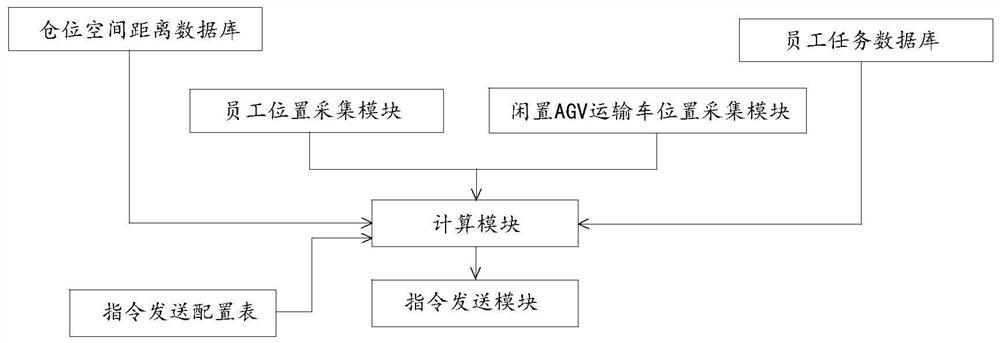

Compound circulating adjusting system of automatic guided vehicle (AVG) transfer carriage in automated logistics

InactiveCN103150640AReduce invalid operationsImprove logistics efficiencyLogisticsControl systemComputer module

The invention discloses a compound circulating adjusting system of an automatic guided vehicle (AVG) transfer carriage in automated logistics. The system comprises a computer scheduling system and an AGV body control system which controls the AVG transfer carriage. The compound circulating adjusting system is characterized in that the computer scheduling system comprises a bin multiple-area spatial distance data base, an idle AVG position collecting module, and an unexecuted task position collecting module, and further comprises a spatial distance computing module, wherein the spatial distance computing module is connected with the idle AGV position collecting module, the unexecuted task position collecting module and the AVG body control system. A close-distance execution technology is adopted in the system so that invalid operation of the AGV transfer carriage is reduced, and finally logistics efficiency is improved.

Owner:XIAMEN TOBACCO IND

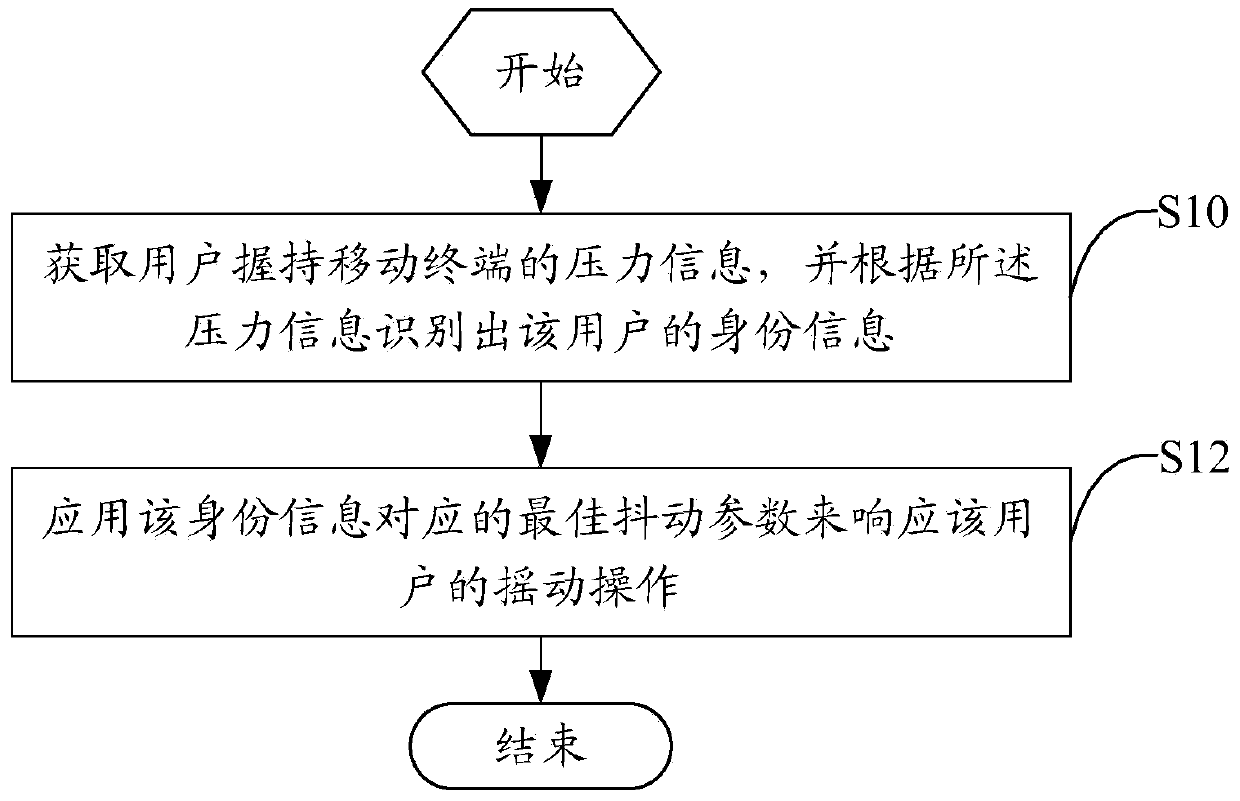

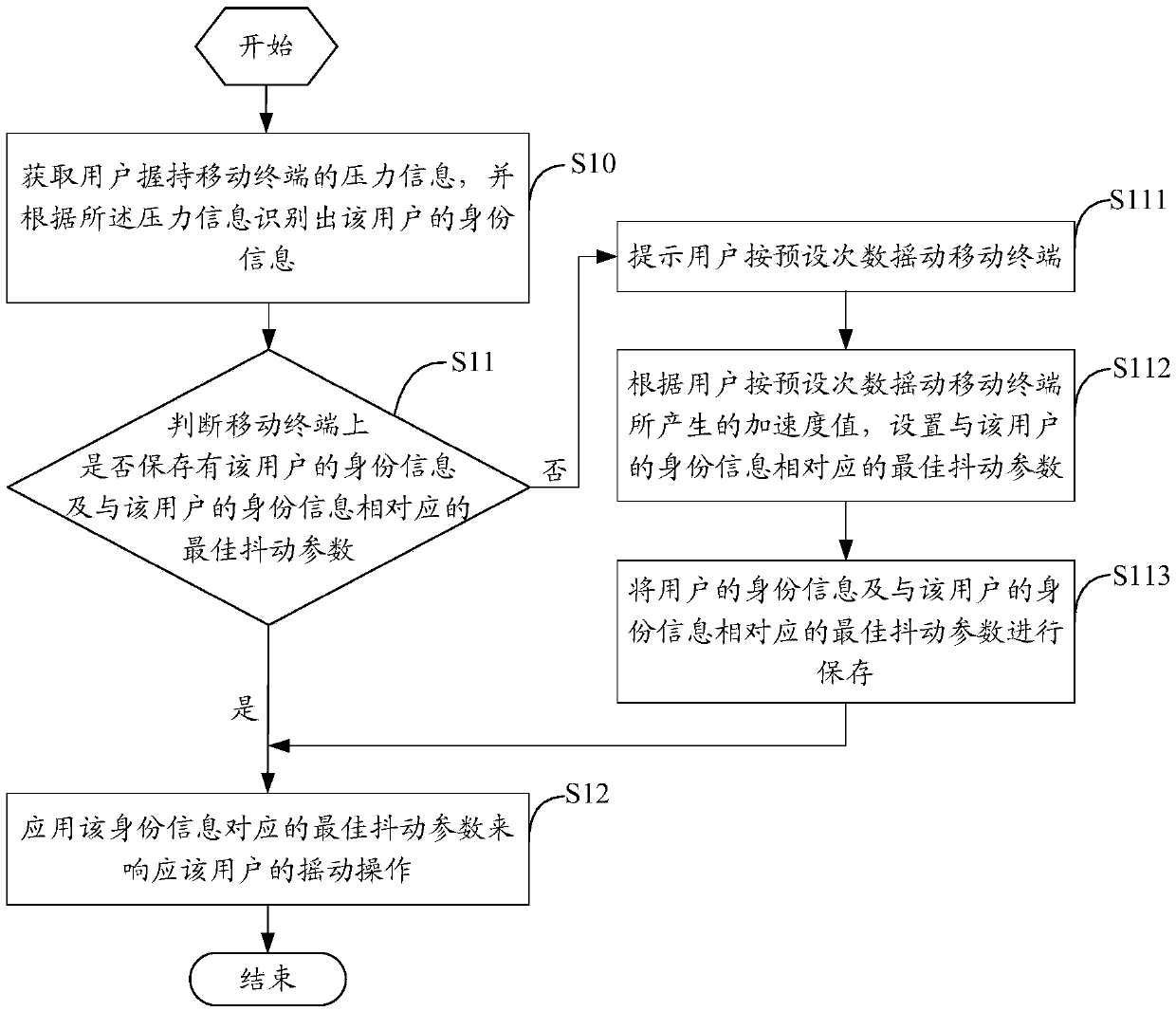

Method of mobile terminal for responding to operation according to different user identities and mobile terminal

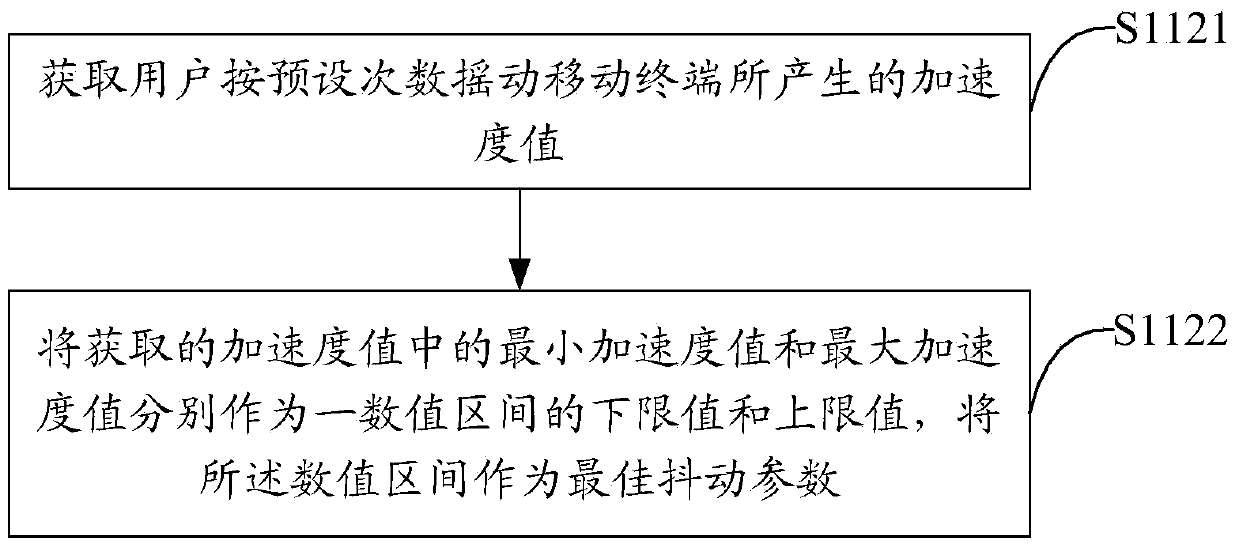

The invention discloses a method of a mobile terminal for responding to operation according to different user identities and the mobile terminal. The method of the mobile terminal for responding to the operation according to different user identities comprises the steps of (1) obtaining information of pressure of a user when the user holds the mobile terminal, and identifying identity information of the user according to the information of the pressure; (2) using an optimal shake parameter corresponding to the identity information to respond to the shake operation of the user. According to the method of the mobile terminal for responding to the operation according to different user identities, due to the fact that the acceleration value generated by the movement that the user shakes the mobile terminal is obtained according to the identified identity information of different users, reasonable optimal shake parameters are set on the mobile terminal for different users, the situation that the mobile terminal can more accurately identify follow-up shake operation of the users can be facilitated, the requirements of different users are met, the speed of the mobile terminal to respond to the shake operation of the user is greatly increased, the accuracy of the mobile terminal to respond to the shake operation of the user is greatly improved, the frequency of invalid operation, incapable of being identified by the mobile terminal, of the shake operation of the users is reduced, gravity sensing experience of the users is improved, and convenience and rapidness are provided for the users.

Owner:SHENZHEN TCL NEW-TECH CO LTD

Linear element spatial index construction method and system and retrieval method and system thereof

ActiveCN103473268AReduce areaReduce dataSpecial data processing applicationsLinear elementSpatial information systems

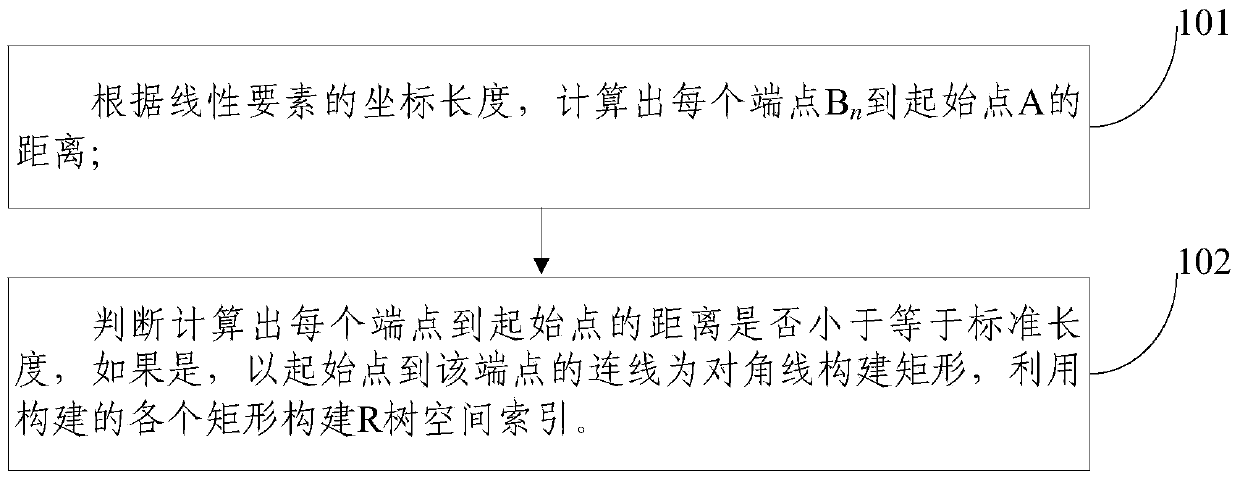

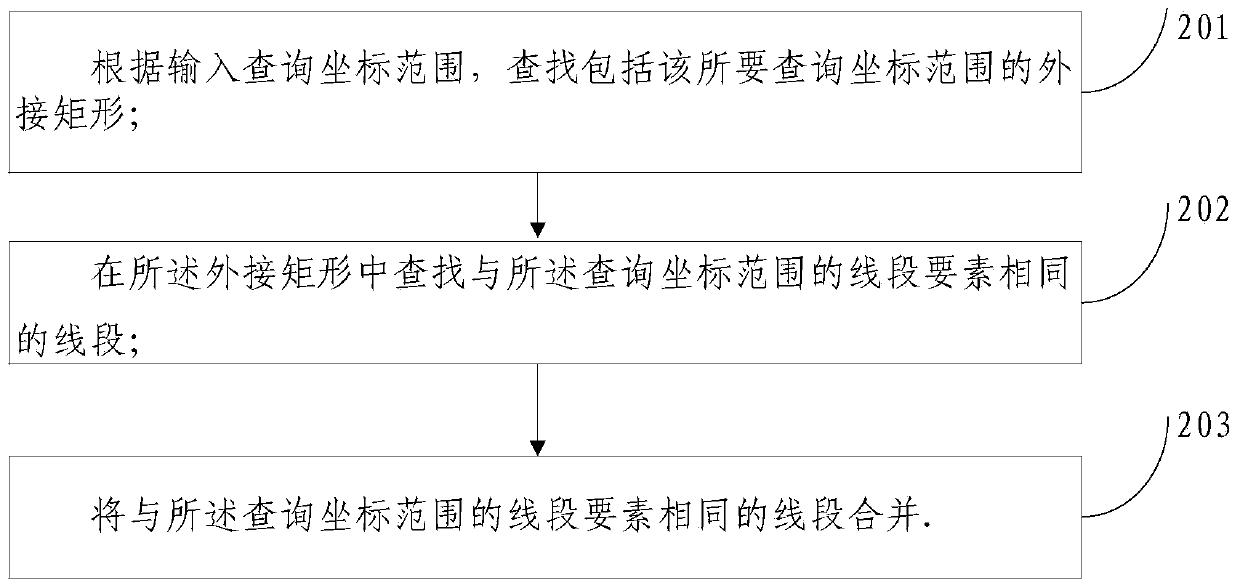

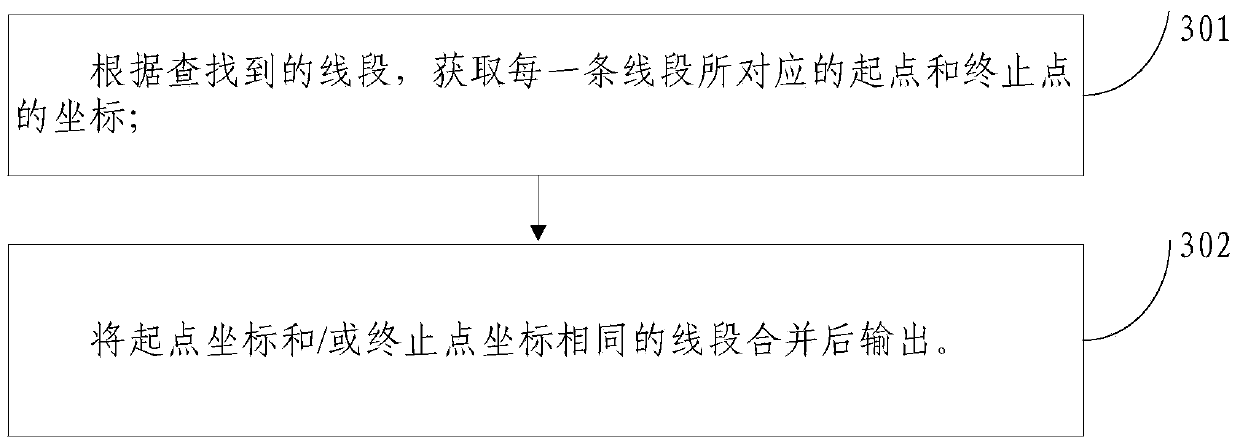

The invention discloses a linear element spatial index construction method and system and a retrieval method and a system thereof, relating to the technical field of spatial information systems. The building method comprises the following steps: calculating the distance between each end point Bn and an initial point A according to the coordinate length of a linear element; judging whether the calculated distance between each end point and the initial point is less than or equal to a standard length or not; if so, constructing a rectangle by taking a connection line from the initial point to the end point as a diagonal; and constructing an R tree spatial index by using each constructed rectangle. The invention further discloses a linear element spatial index construction system based on an R tree, a retrieval method and a retrieval system thereof. According to the technical scheme disclosed by the invention, specific to long linear elements, the area of an external rectangle is reduced, the data volume of returned data and invalid operation are reduced, and the query efficiency and accuracy are increased.

Owner:北京恒达时讯科技股份有限公司

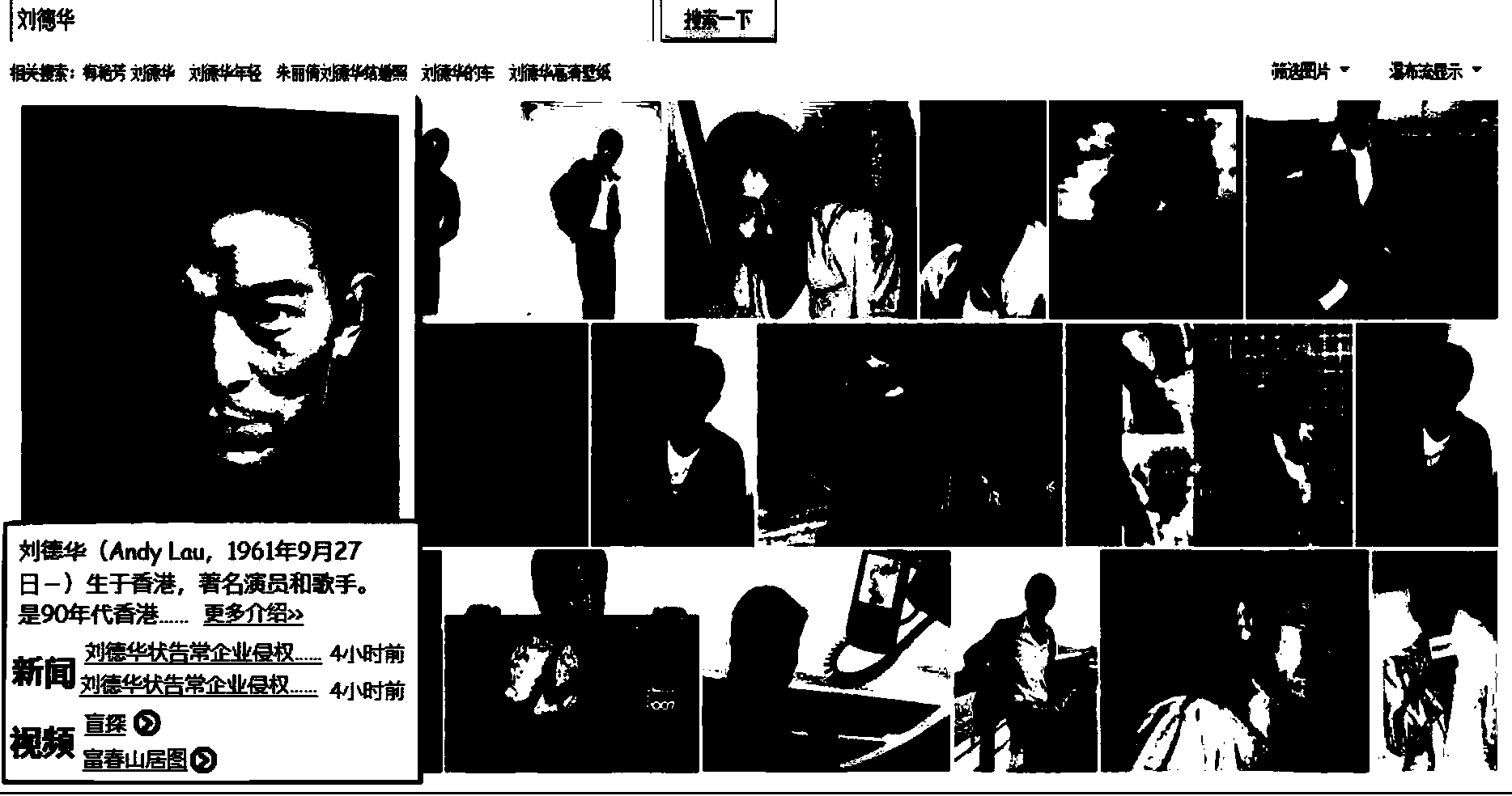

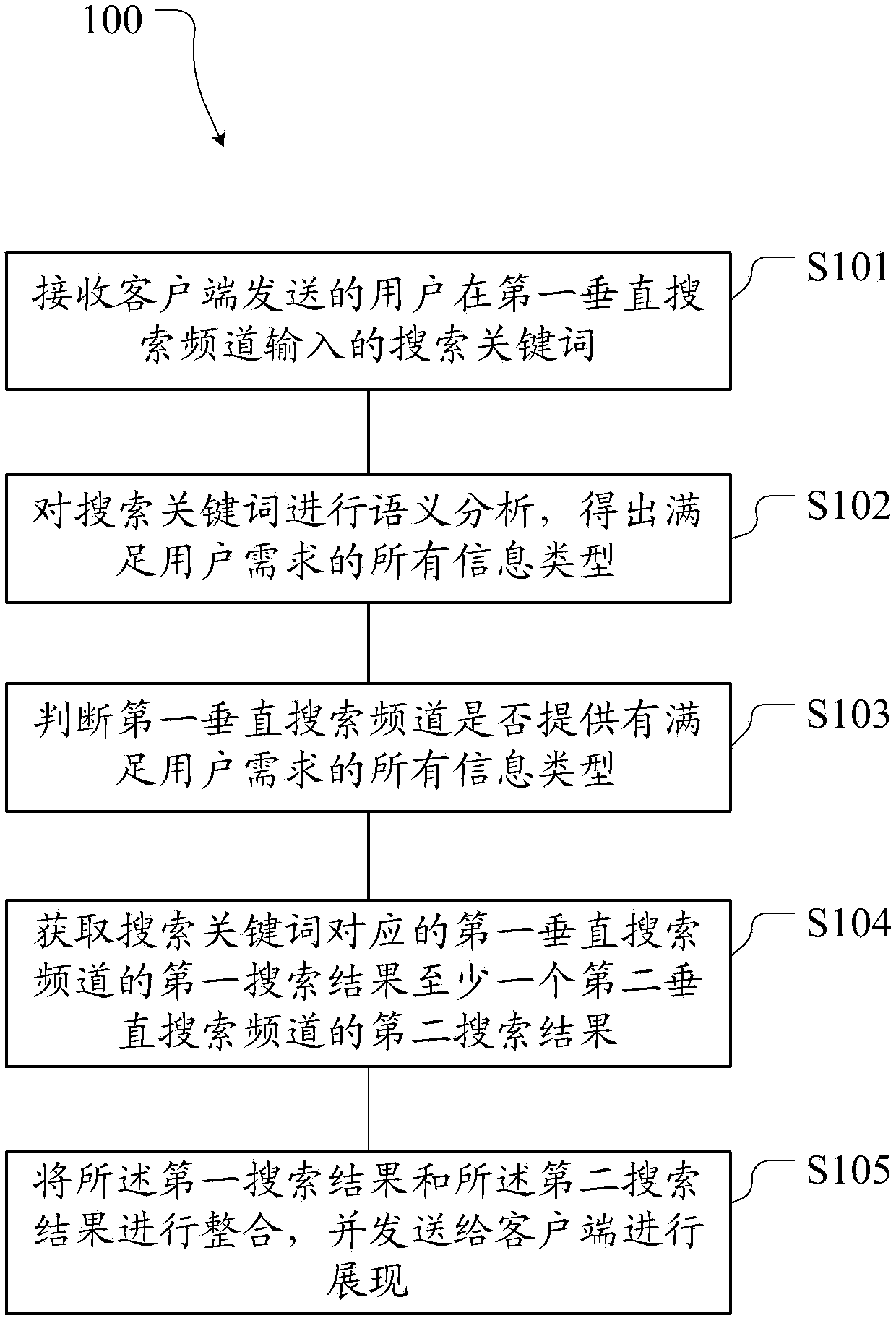

Method and device for searching for information based on vertical searching channels

InactiveCN103530385AReduce switching costsReduce invalid operationsWeb data indexingSpecial data processing applicationsInformation typeUser needs

The invention discloses a method and device for searching for information based on vertical searching channels. The method comprises the steps of receiving searching keywords which are sent by a client terminal and input by a user at the first vertical searching channel, conducting semantic analysis on the keywords, obtaining all information types meeting user requirements according to the result of the semantic analysis, judging whether the first vertical searching channel provides all the information types meeting the user requirements or not, and if the first vertical searching channel does not provide all the information types meeting the user requirements, obtaining a first searching result of the first vertical searching channel corresponding to the searching keywords and a second searching result of at least one second vertical searching channel, wherein the at least one second vertical searching channel provides the information types which meet the user requirements and are not provided by the first vertical searching channel. According to the method, the searching result obtained by the user is not limited in the current first vertical searching channel, so that the user requirements are well met, the cost for switching the channels is reduced, and the number of invalid operations by the user is reduced.

Owner:BEIJING QIHOO TECH CO LTD +1

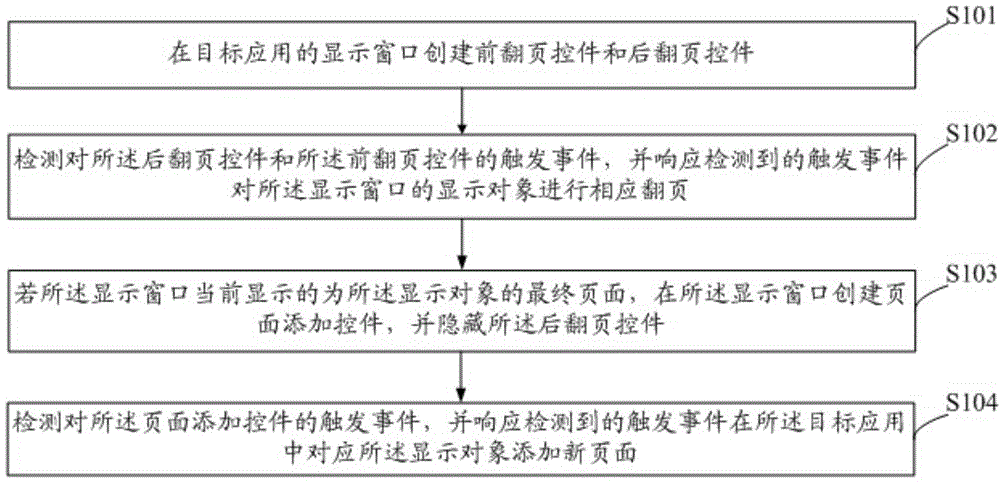

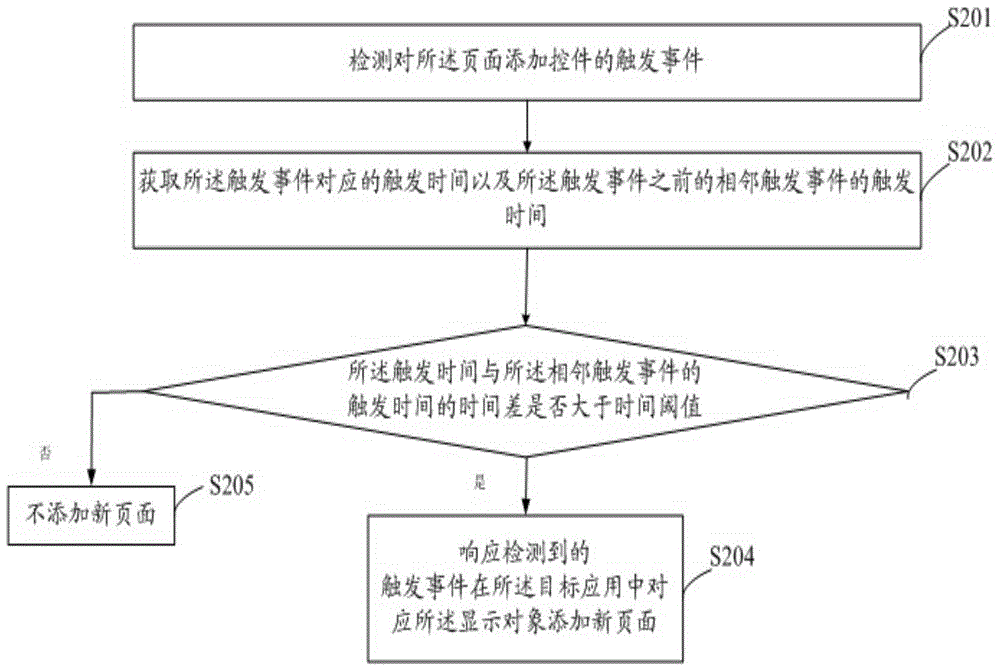

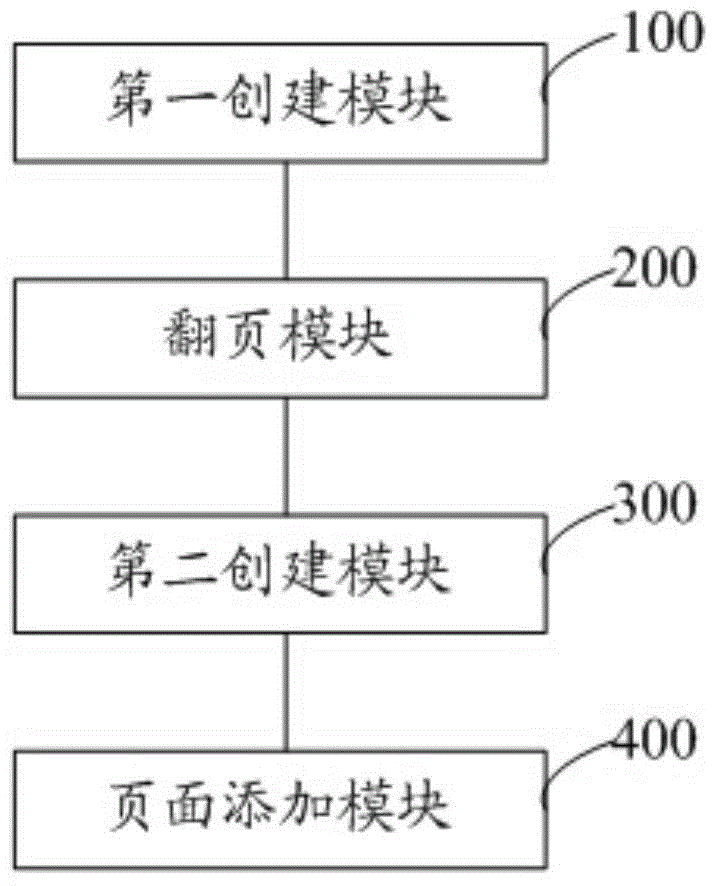

Webpage control method and system

InactiveCN104461291AReduce invalid operationsImprove operational efficiencyInput/output processes for data processingClient-side

The invention discloses a webpage control method and system. The webpage control method includes the steps that a page up control and a page down control are created on a display window of a target application; a trigger event for the page down control and the page up control is detected, and corresponding page turning operation is carried out on a display object of the display window by responding to the detected trigger event; if the webpage displayed currently on the display window is the final webpage of the display object; a webpage addition control is created on the display window, and the page down control is hidden; a trigger event of the webpage addition control is detected, and a new webpage is added by responding to the display object corresponding to the detected trigger event in the target application. The webpage control method and system can effectively avoid mistaking trigger in the page turning process, reduce invalid operation of a client side, and improve the operation efficiency of the client side.

Owner:GUANGZHOU SHIRUI ELECTRONICS

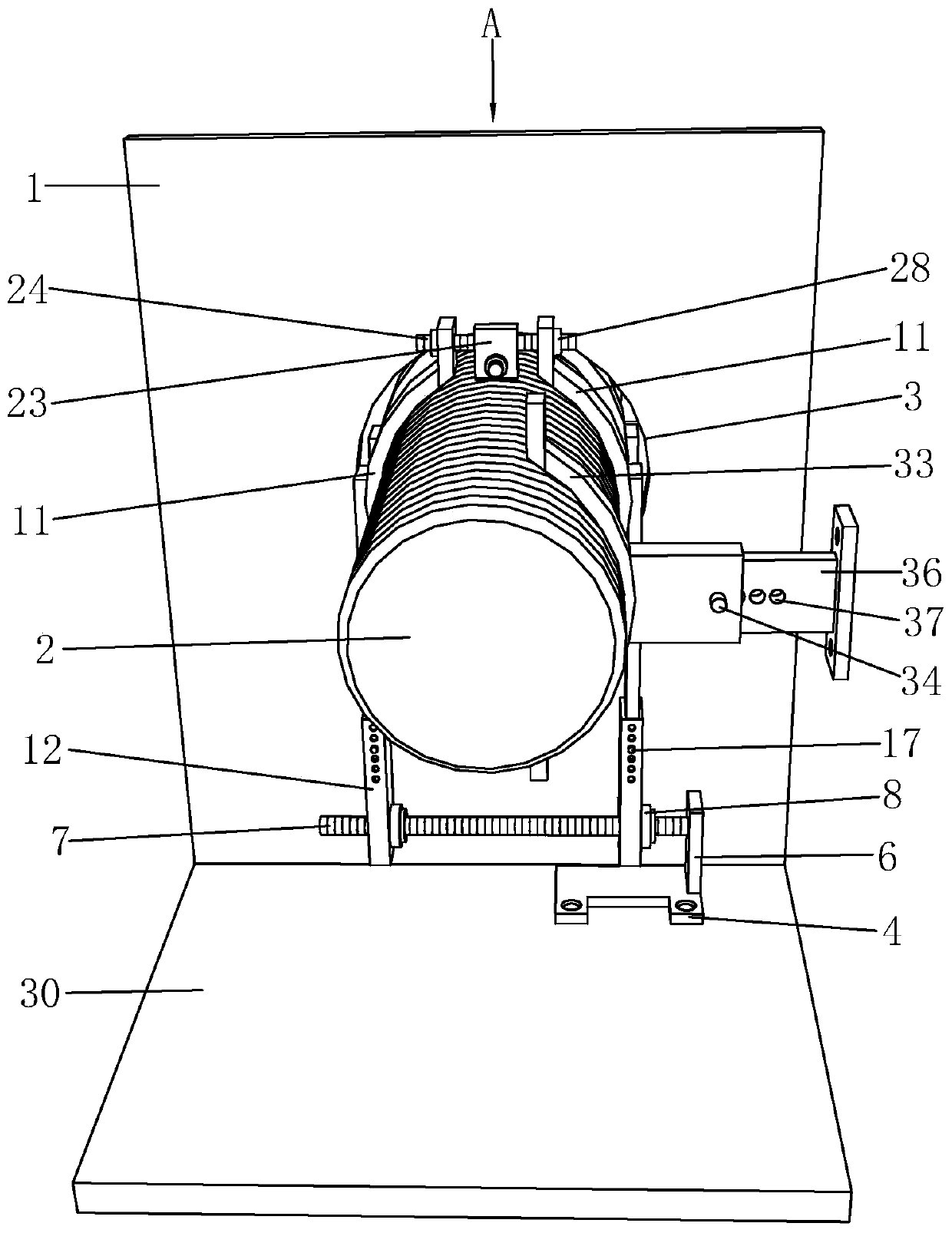

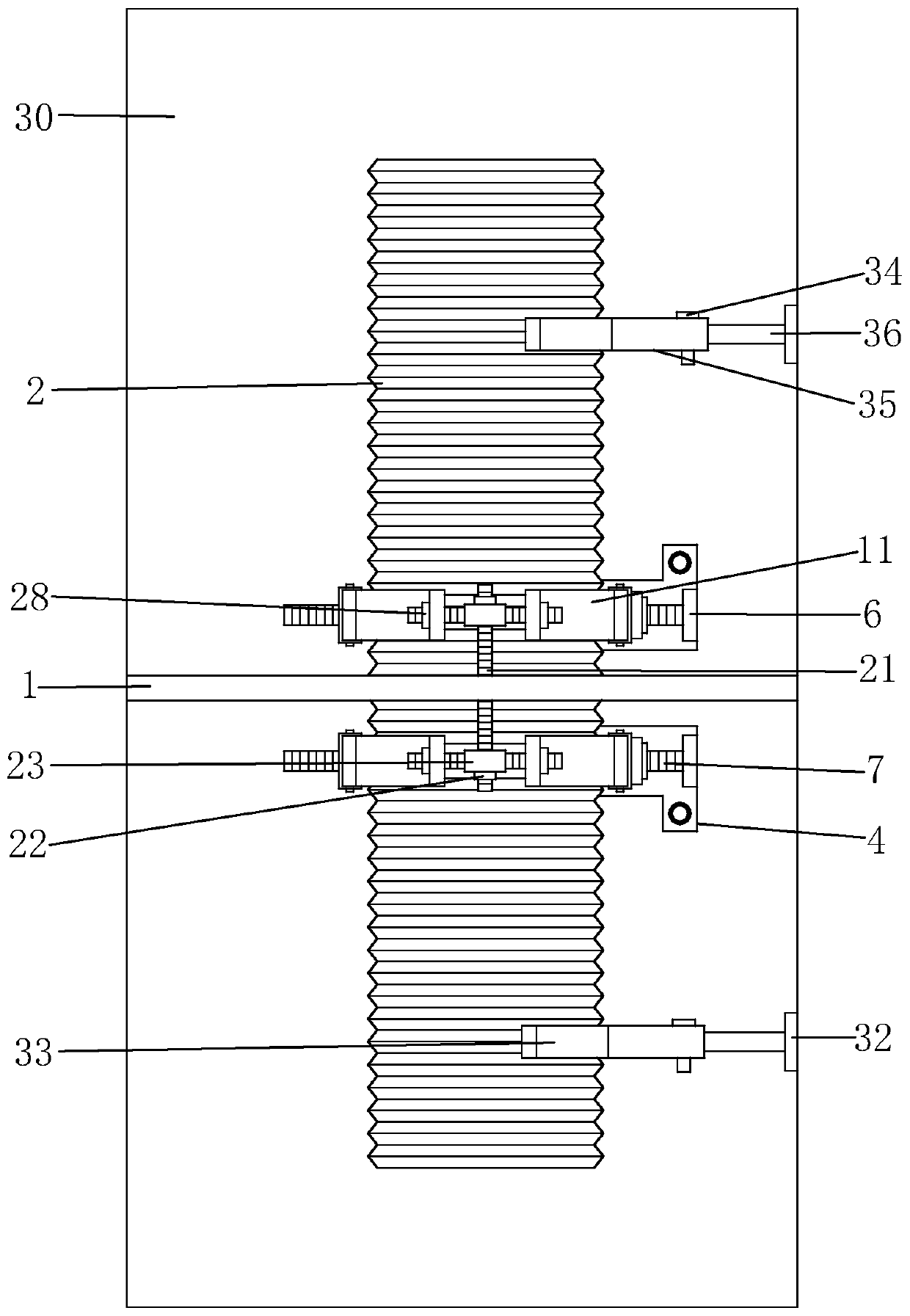

Reinforcing method and supporting assembly for integrated cooker smoke exhaust pipe

ActiveCN110748705ARealize location positioningGood contact positionPipe supportsDomestic stoves or rangesStructural engineeringCupboard

The invention discloses a reinforcing method and a supporting assembly for an integrated cooker smoke exhaust pipe. The reinforcing method includes the following steps that (a), clamping protection plates are assembled; (b), a reinforcing position is determined; (c), side clamping rods are mounted; (d), upper and lower clamping protection is carried out; and (e), left and right connection is carried out. The supporting assembly comprises a mounting plate, a supporting block is arranged on the mounting plate, a fixing screw is arranged on the supporting block, and supporting nuts and the clamping protection plates are connected to the fixing screw. The clamping protection plates comprise telescopic plates and arc-shaped protection plates, the arc-shaped protection plates are arranged on thetelescopic plates, the supporting nuts support the telescopic plates, and the side clamping rod are arranged between the arc-shaped protection plates. The reinforcing method is easy to operate, low in difficulty, wide in reinforcing range, good in reinforcing effect and easy to adjust, the reinforcing quality can be effectively guaranteed, the problem caused by the fact that the hole size of a kitchen cabinet plate is not matched with the pipe diameter of the smoke exhaust pipe is solved, and the supporting assembly is novel in structure, capable of being flexibly assembled on site, high in adaptability, good in supporting effect and reliable to use.

Owner:浙江蓝炬星电器有限公司

Staggering discharging device of adjusting box

PendingCN106044177APrecise positioningGuaranteed uptimeConveyorsControl devices for conveyorsEngineeringMechanical engineering

Owner:梁启明

Rapid correcting device for cable core

PendingCN108333464AProofreading is intuitive and accurateImprove accuracyElectrical testingMicrocomputerElectricity

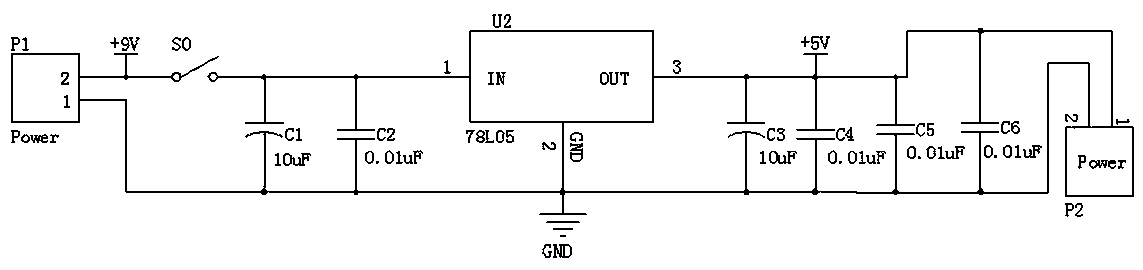

The invention discloses a rapid correcting device for a cable core. The rapid correcting device comprises a first correcting device and a second correcting device; the first correcting device and thesecond correcting device respectively comprise a microcomputer processing control unit, an electric signal sampling unit, an audio intercommunication unit, a stabilized voltage supply unit, a strip light indicating unit, a buzzer sound production unit, a first testing line and a second testing line; and the electric signal sampling unit, the audio intercommunication unit, the stabilized voltage supply unit, the strip light indicating unit, the buzzer sound production unit, the first testing line and the second testing line are all electrically connected with the microcomputer processing control unit. The rapid correcting device has the advantages that: the cable core is more intuitively and accurately corrected and is easy to judge, and the correcting accuracy of the cable core is effectively improved; the correcting workload of the cable core is reduced, the manpower, the material and the time are saved; the invalid operation in the process of correcting operation of the cable core isreduced, and the working efficiency is improved.

Owner:国网湖北省电力有限公司荆门供电公司 +1

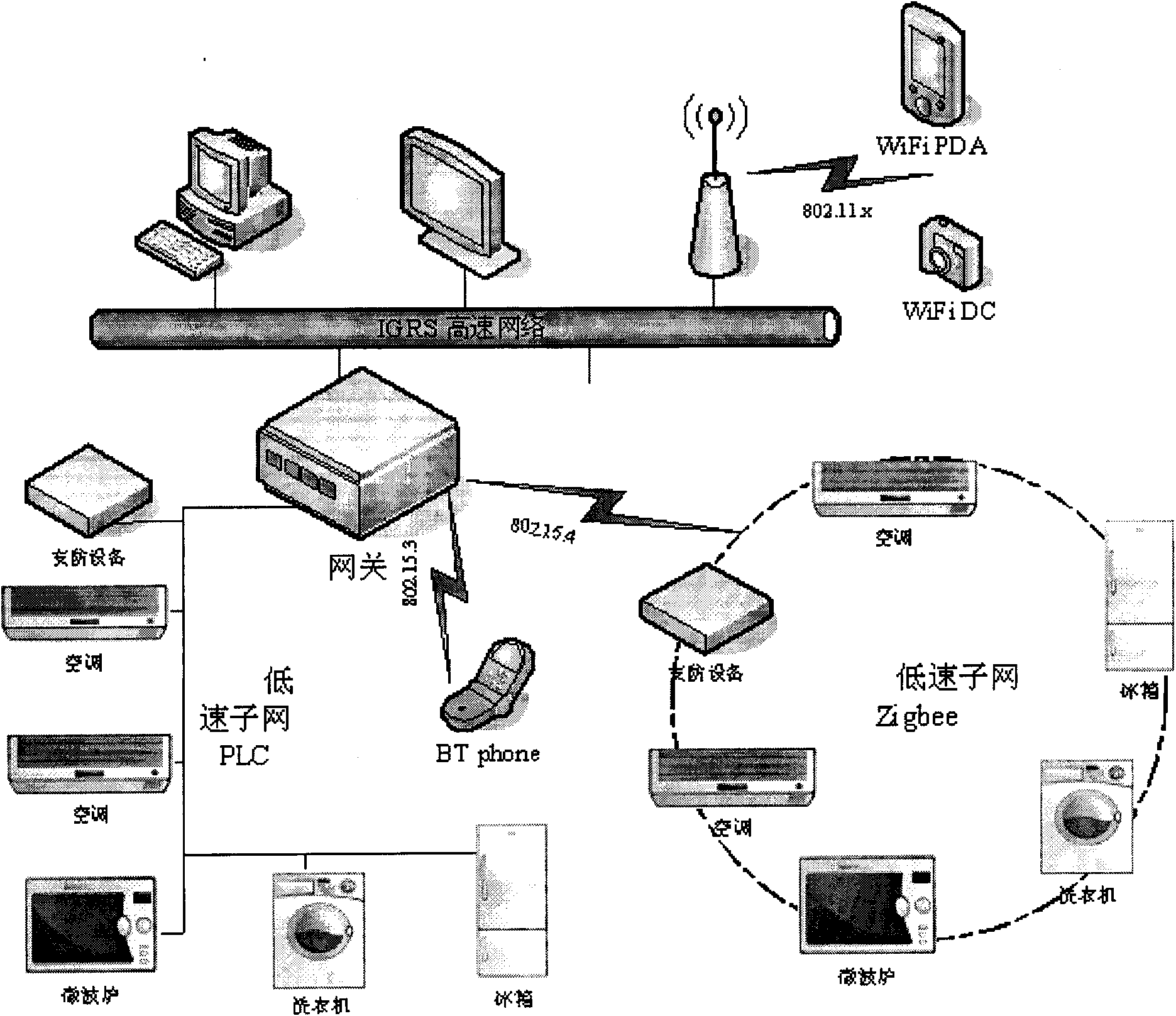

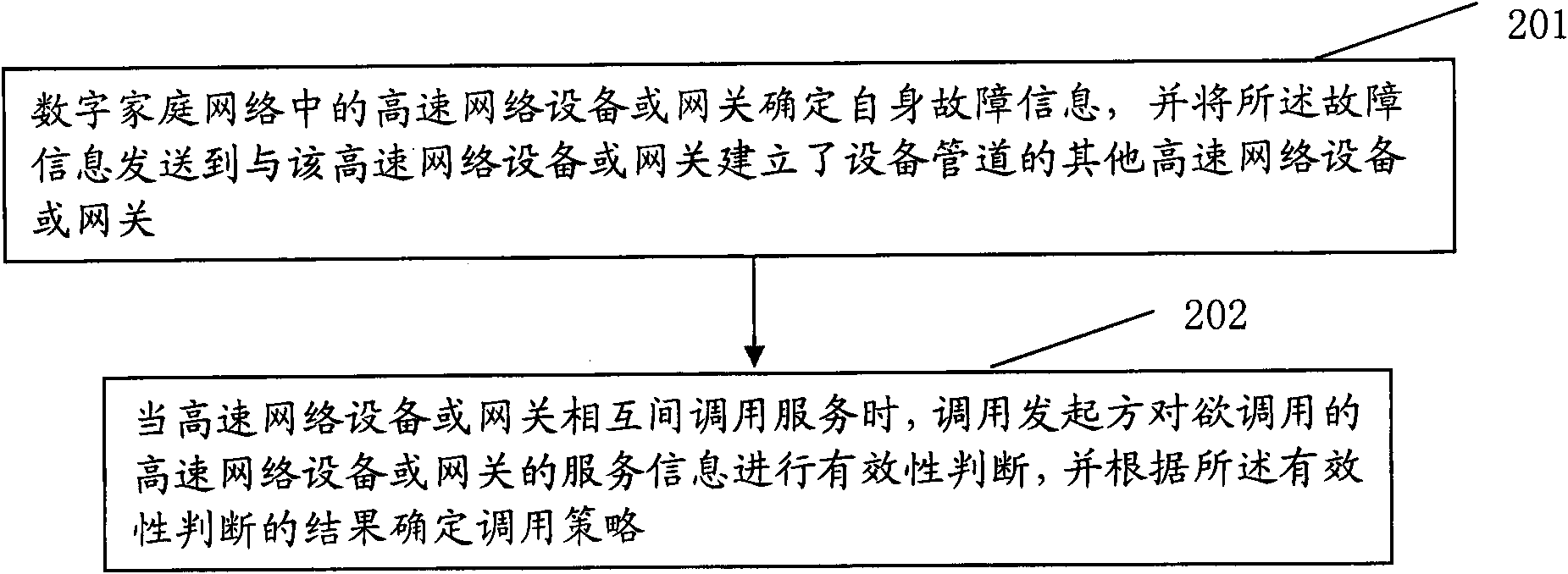

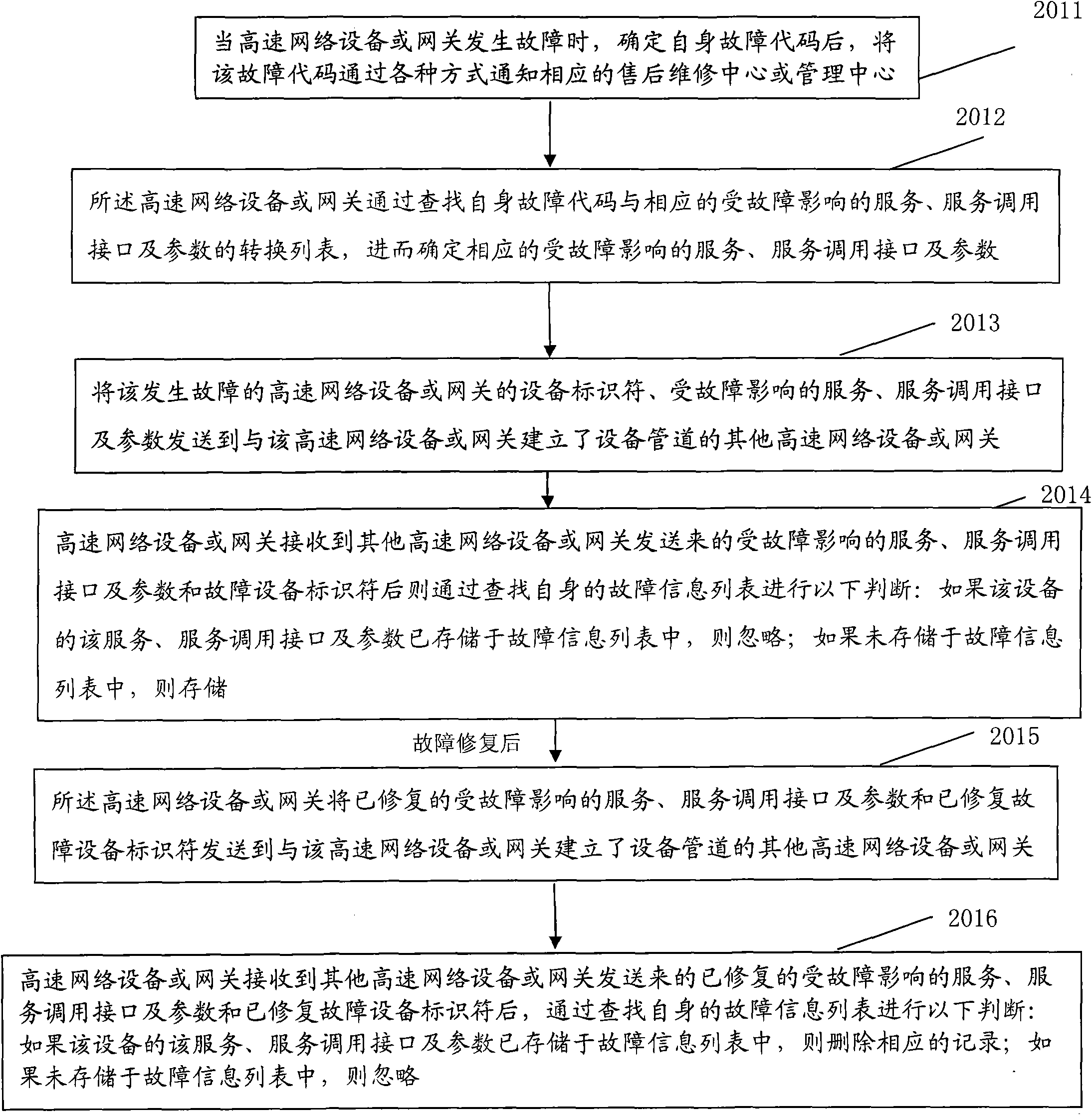

Method and system for realizing friendly interaction of digital home network equipment

ActiveCN101883031AReduce invalid operationsData switching by path configurationService informationEmbedded system

The invention discloses a method and a system for realizing friendly interaction of digital home network equipment, and relates to the technical field of digital home networks. The method and the system aim to reduce invalid operation and improve the friendliness and convenience of the home network. The method for realizing the friendly interaction of the digital home network equipment comprises the following steps of: determining fault information through high-speed network equipment or a gateway in the digital home network, and sending the fault information to other high-speed network equipment or gateways which establish equipment channels with the high-speed network equipment or the gateway; and when the high-speed network equipment or the gateways call services with each other, performing validity judgment on the service information of the to-be-called network equipment or the to-be-called gateway through a calling initiator, and determining a calling strategy according to the result of the validity judgment. The method and the system are suitable for a digital home network system with a fault self-checking mechanism.

Owner:HISENSE

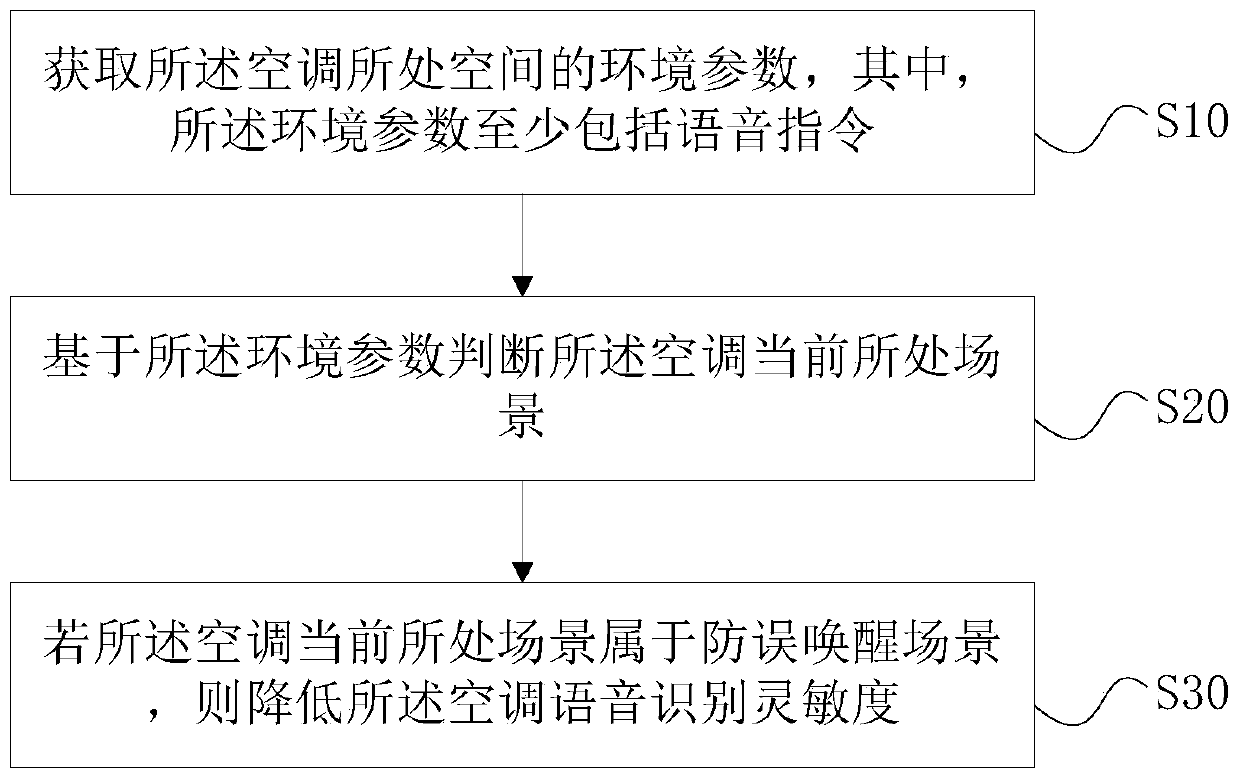

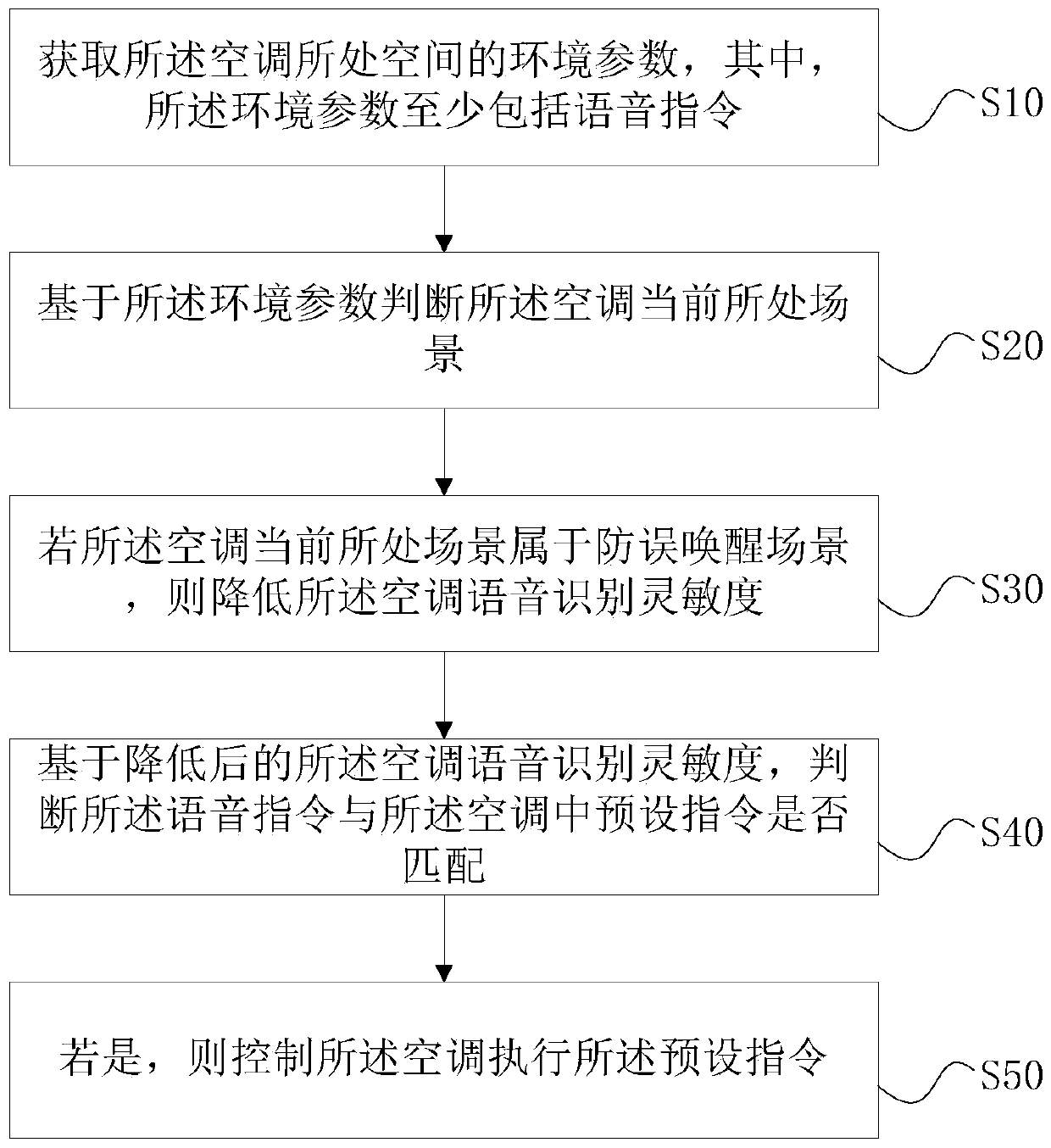

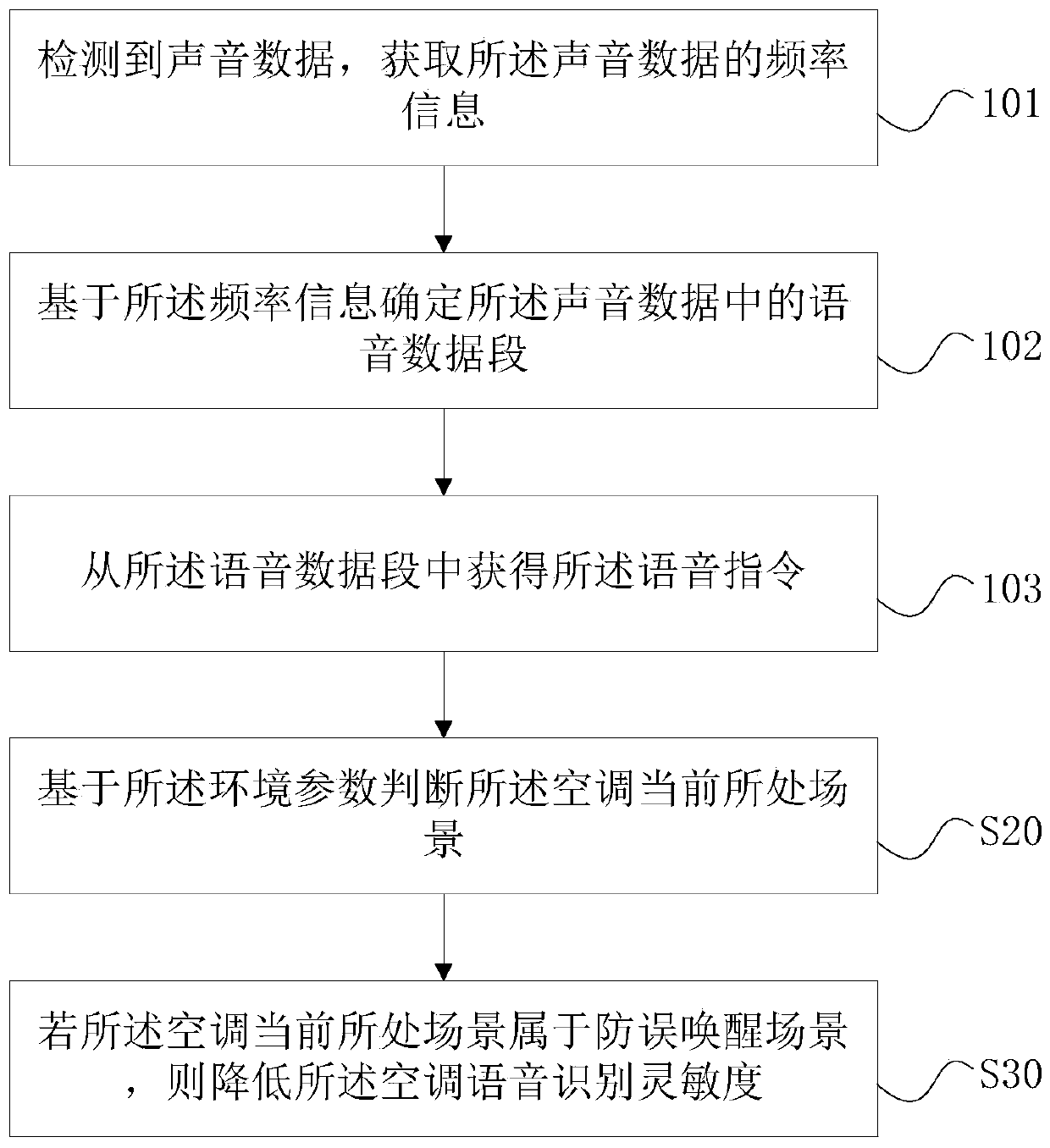

Air conditioner voice control method and device as well as air conditioner

ActiveCN110500721AReduce voice recognition sensitivityRaising Responsive Access ThresholdMechanical apparatusSpace heating and ventilation safety systemsFalse awakeningEngineering

The invention provides an air conditioner voice control method and device as well as an air conditioner. The air conditioner voice control method comprises the following steps of acquiring environmental parameters of a space where the air conditioner is located, wherein the environmental parameters at least comprise a voice command; judging a current scene of the air conditioner based on the environmental parameters; and reducing the voice recognition sensitivity of the air conditioner if the current scene of the air conditioner belongs to an anti-false awakening scene. According to the air conditioner voice control method and device as well as the air conditioner, risks of false awakening of the air conditioner can be reduced.

Owner:NINGBO AUX ELECTRIC +1

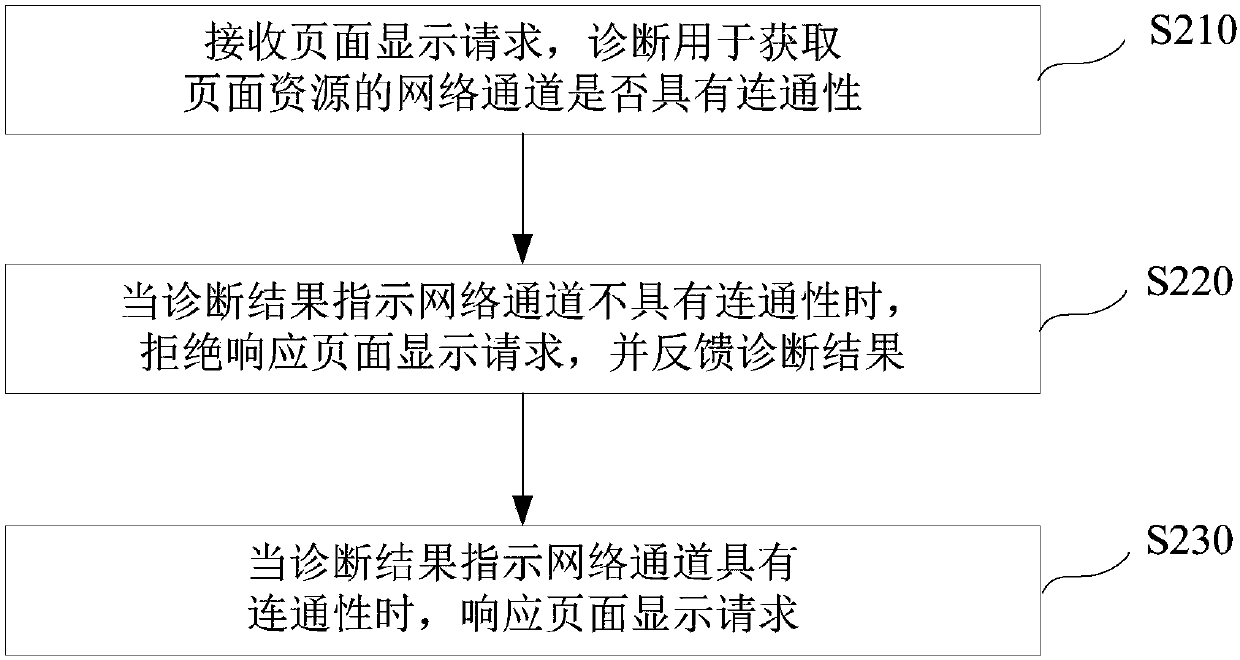

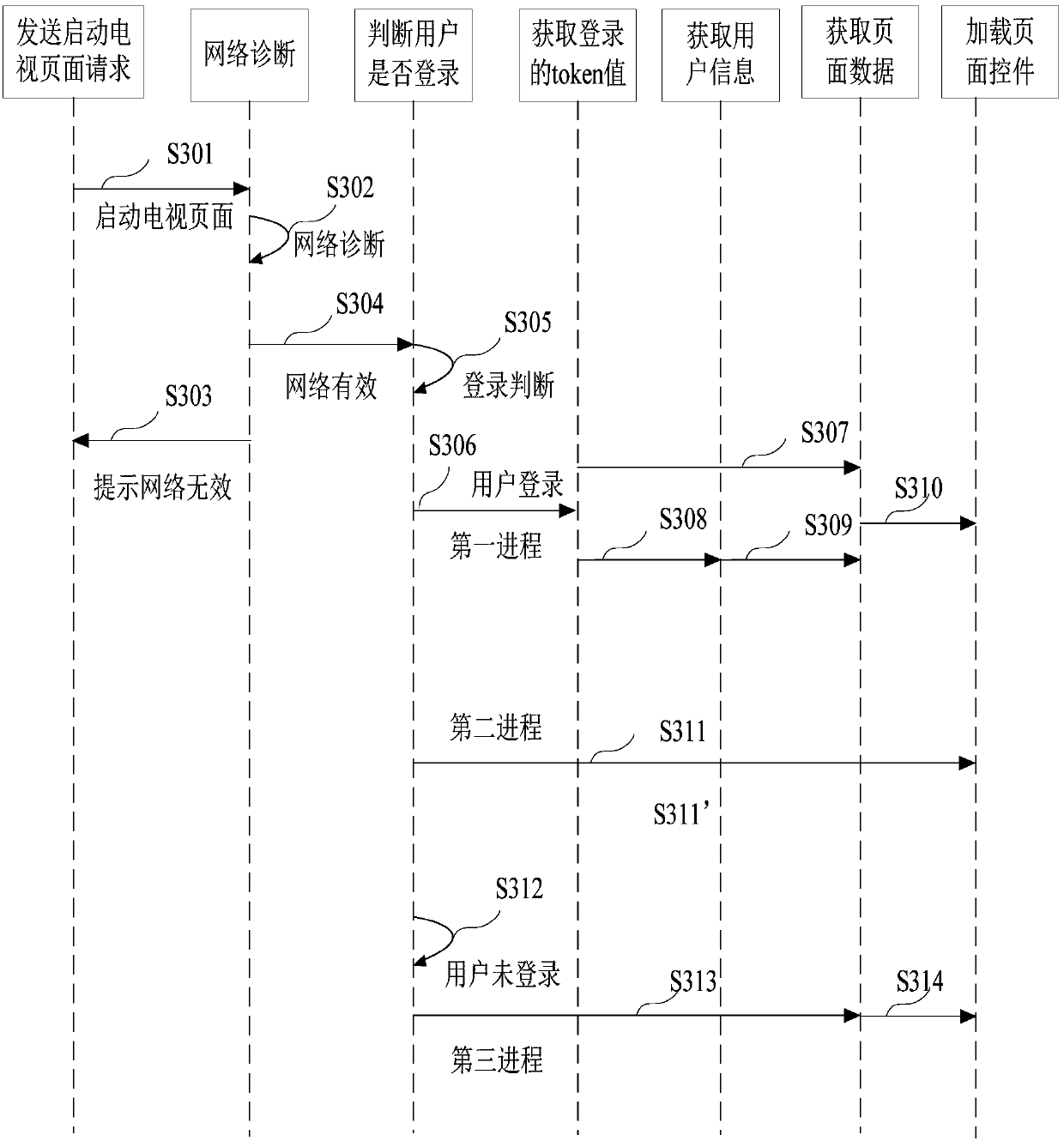

Page display method and device and storage medium

ActiveCN110166835AAvoid deformitiesReduce invalid operationsSelective content distributionData switching networksChannel useComputer engineering

The invention discloses a page display method and device and a storage medium. The method comprises: receiving a page display request, and diagnosing whether a network channel used for obtaining pageresources has connectivity or not; when the diagnosis result indicates that the network channel does not have connectivity, refusing to respond to the page display request, and feeding back the diagnosis result; and when the diagnosis result indicates that the network channel has connectivity, responding to the page display request. According to the embodiment of the invention, the problem of pagemalformation caused by carrying out a subsequent invalid loading process be avoided, invalid operation of a user and performance consumption can be reduced, and the user experience is improved.

Owner:BANMA ZHIXING NETWORK HONGKONG CO LTD

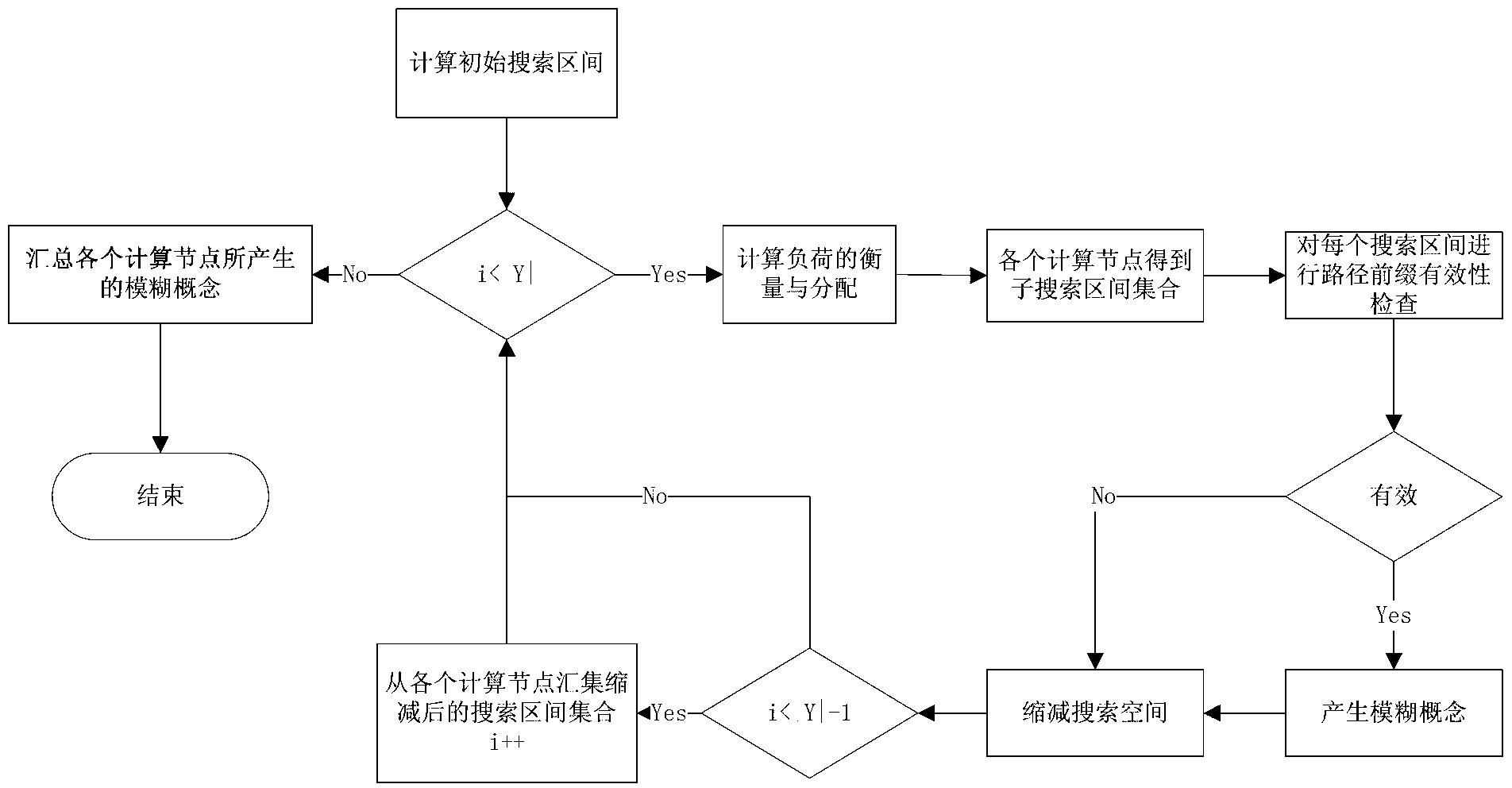

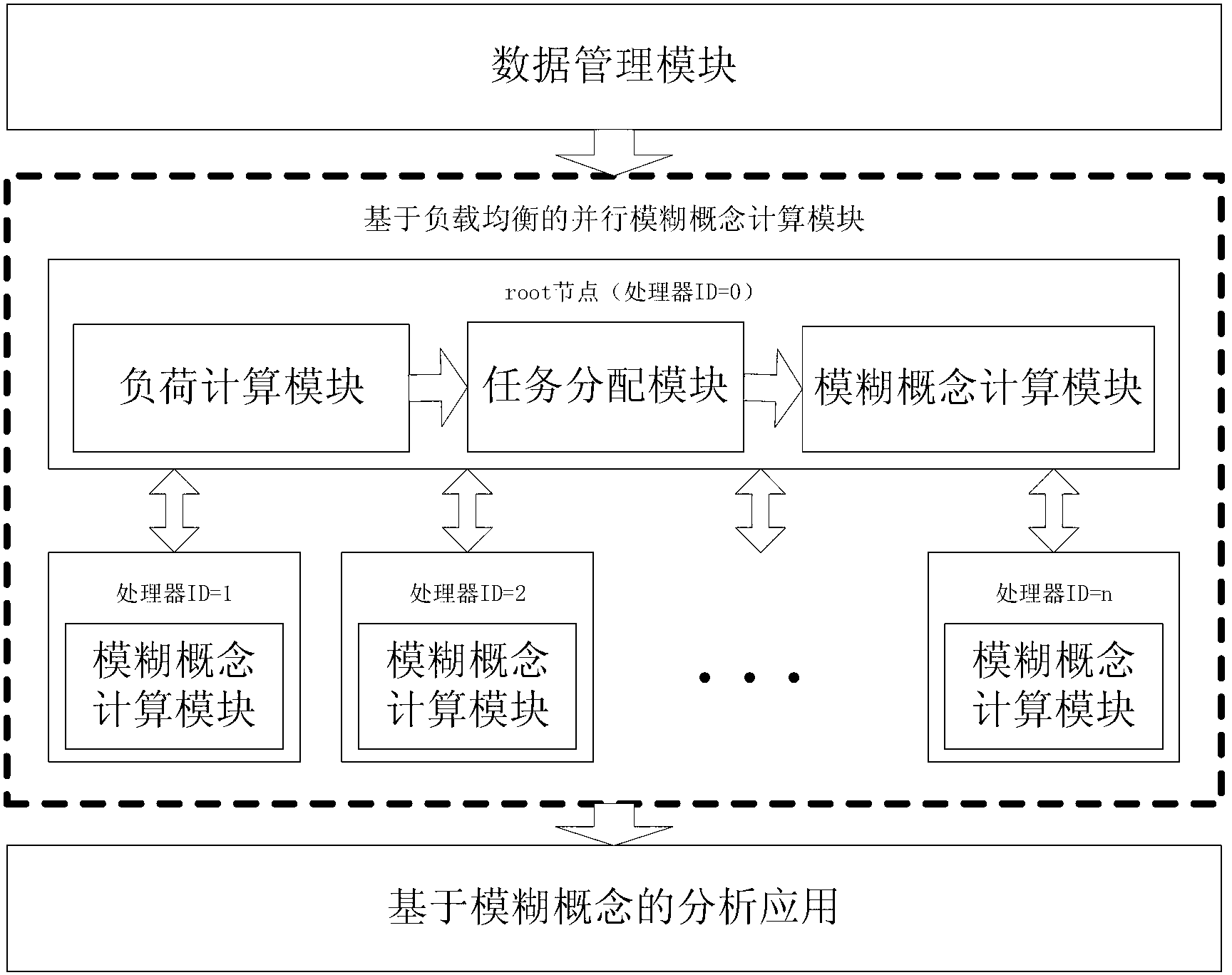

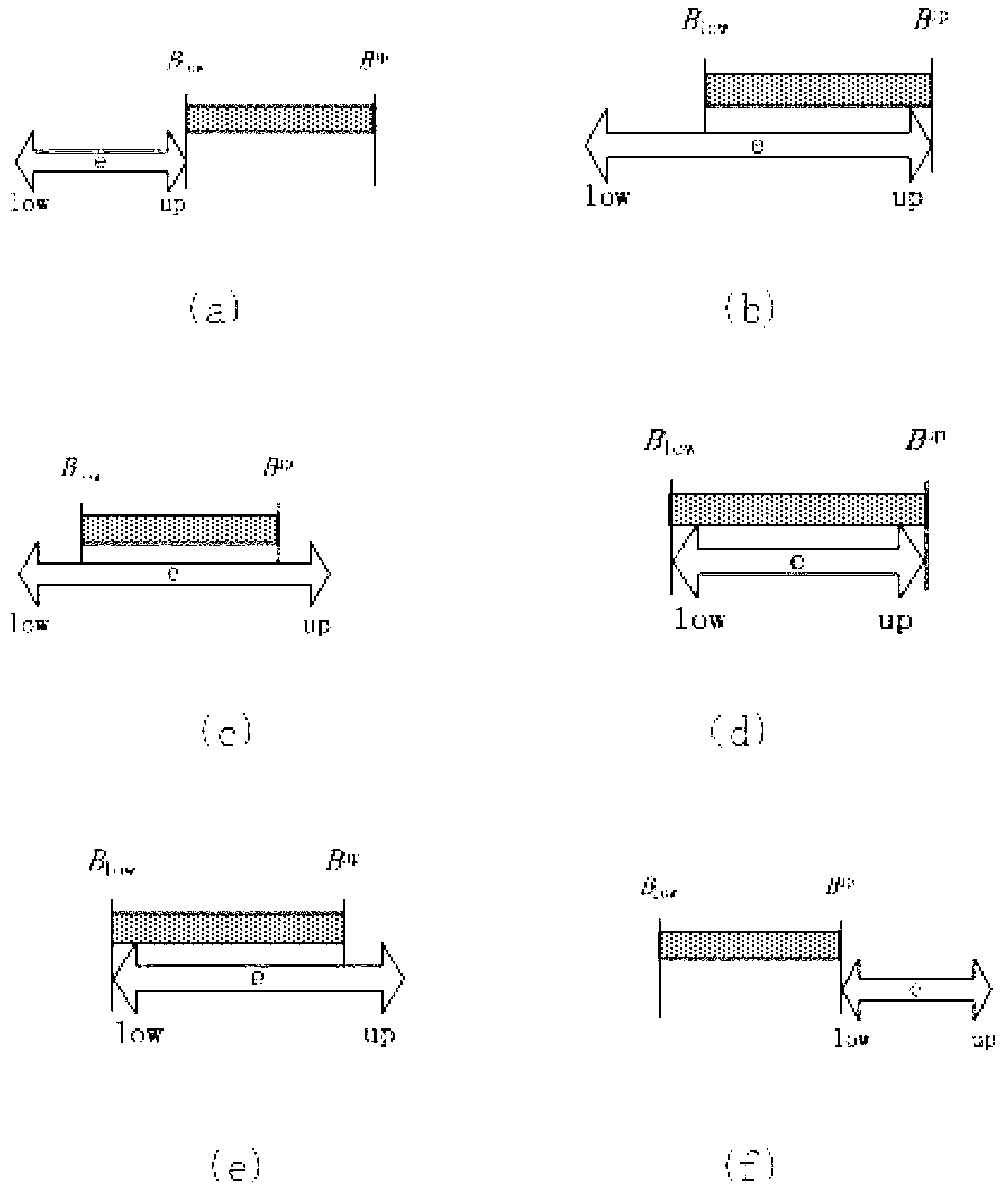

Fuzzy concept related parallel generating method based on load balancing

InactiveCN103324468AImprove good performanceReduce invalid operationsResource allocationConcurrent instruction executionData setTheoretical computer science

The invention discloses a fuzzy concept related parallel generating method based on load balancing. The fuzzy concept related parallel generating method includes the following steps: (1) generating a fuzzy formal background according to a dataset to be processed and an accuracy requirement, (2) initializing a global section set according to the fuzzy formal background, namely (a formula), (3) carrying out breadth-first traversal from top to bottom on an ||L|| complete search tree of a high order ||Y||, regarding i as the current height, (4) calculating total loads Qi under the current height i by a root node processor according to a global search section set E, a first formula and a second formula, (5) assigning a subtask range (Blow, Bup)of each node in a balanced mode according to the number D of processors which can be governed under the current parallel calculation environment, a fifth formula, a sixth formula and a seventh formula, (6) enabling each processor to obtain a partial task section set, and regarding Esub as the partial task sections. According to the fuzzy concept related parallel generating method based on load balancing, the parallel calculation technology and a load balancing calculating method are used for solving the problems that in a fuzzy concept building process, the time complexity is excessively high and consumed time is excessively long.

Owner:ZHENGZHOU UNIV

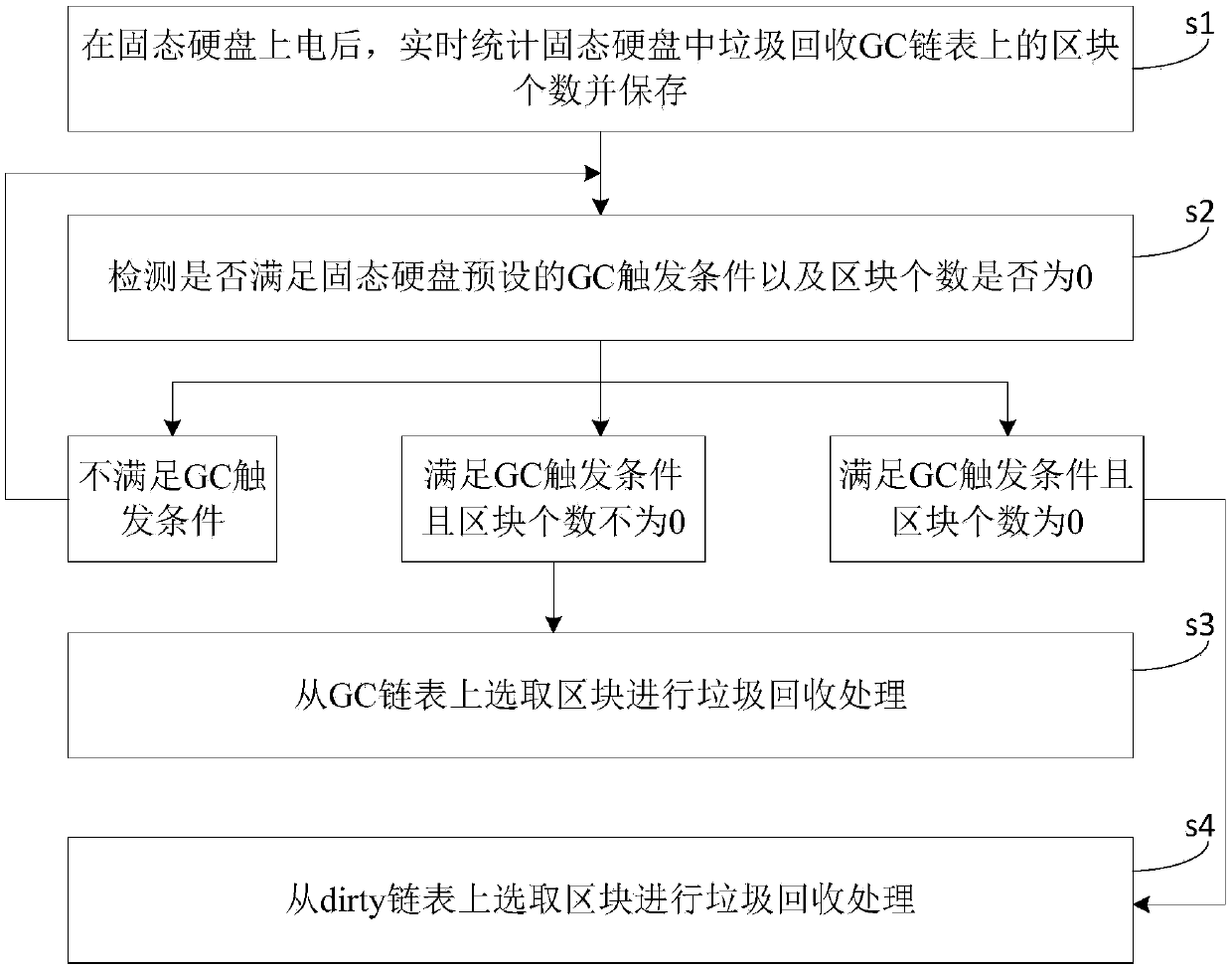

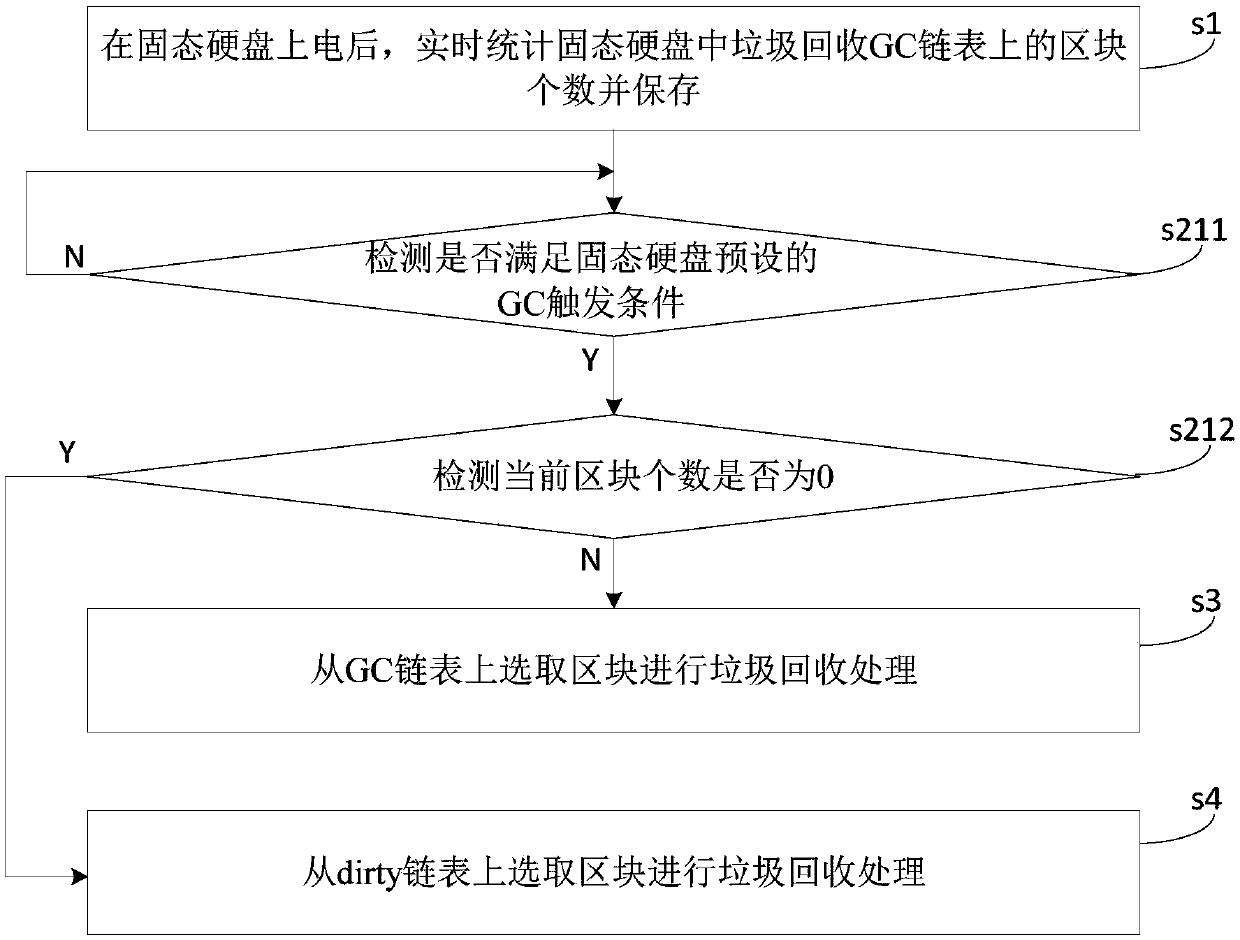

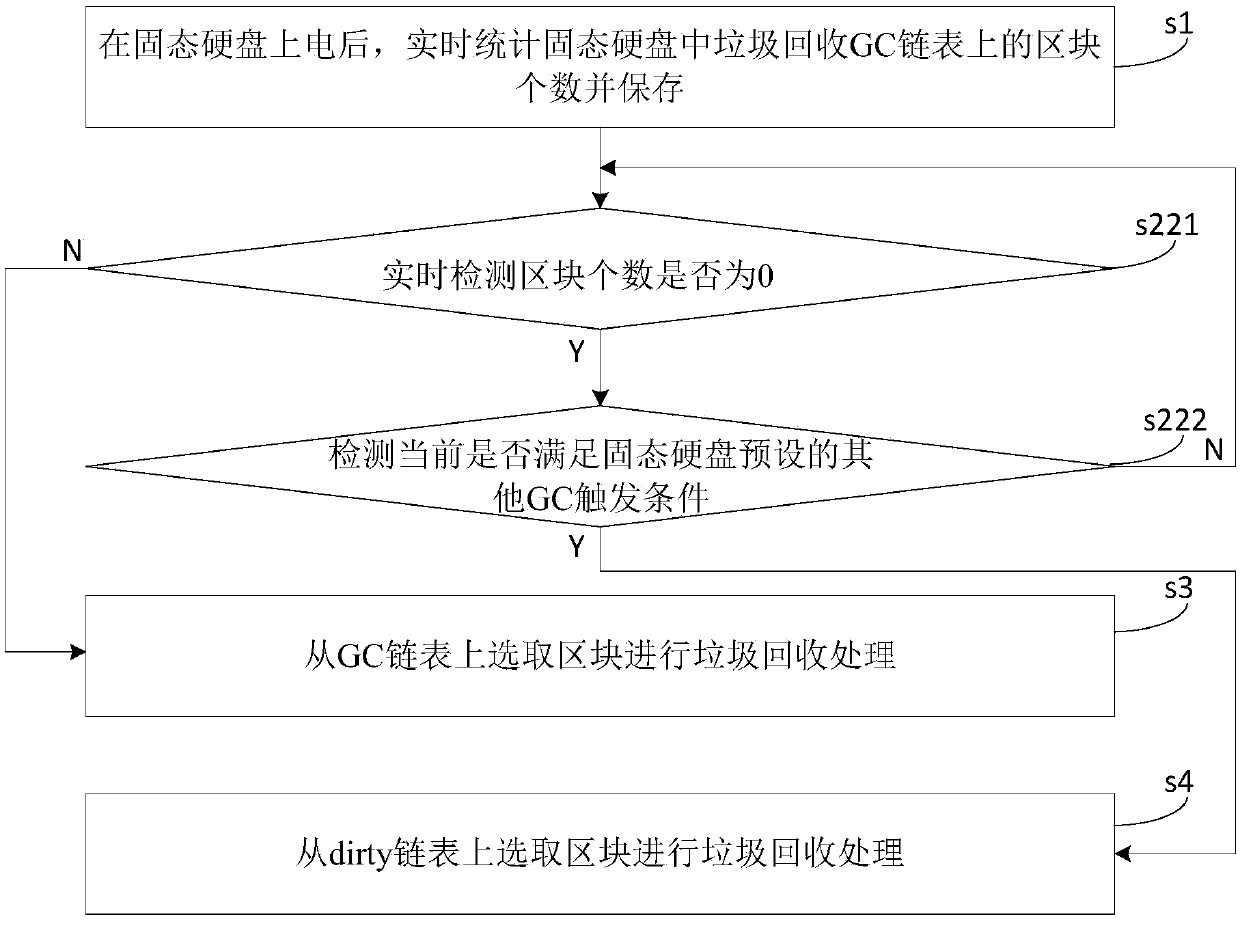

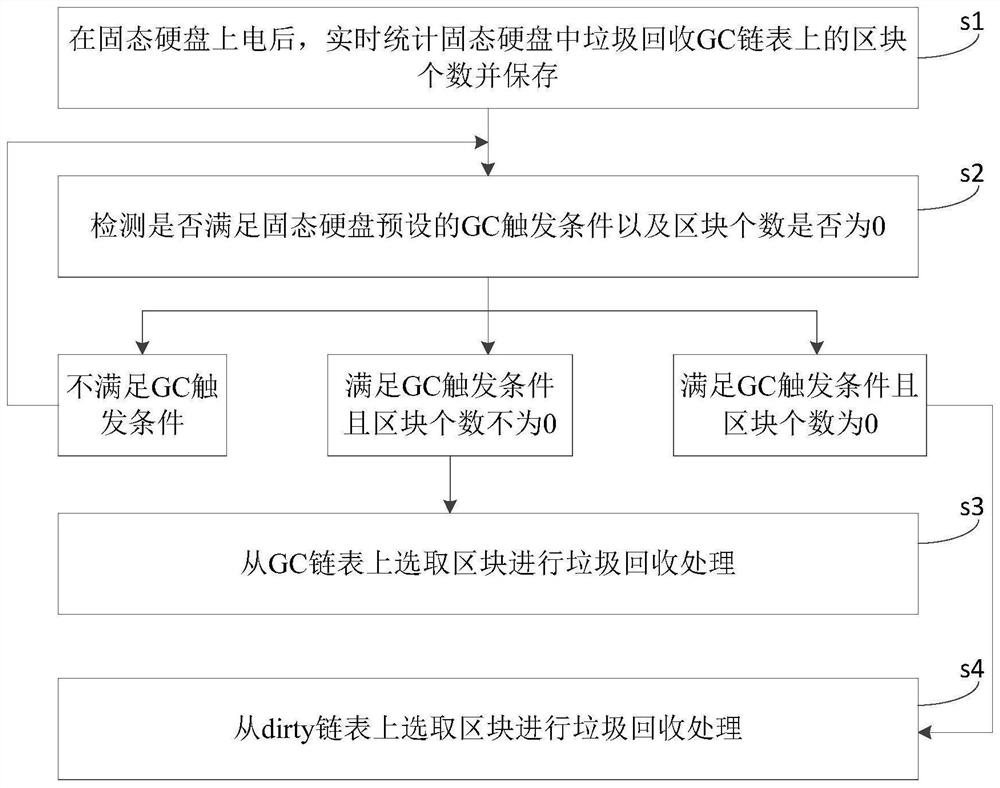

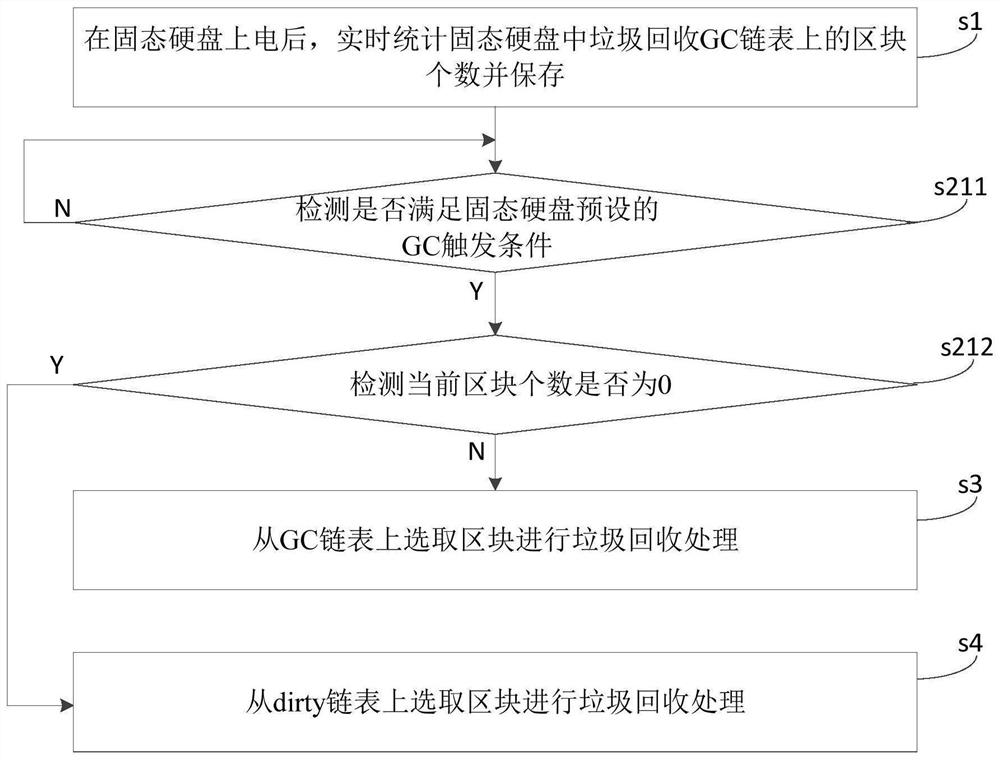

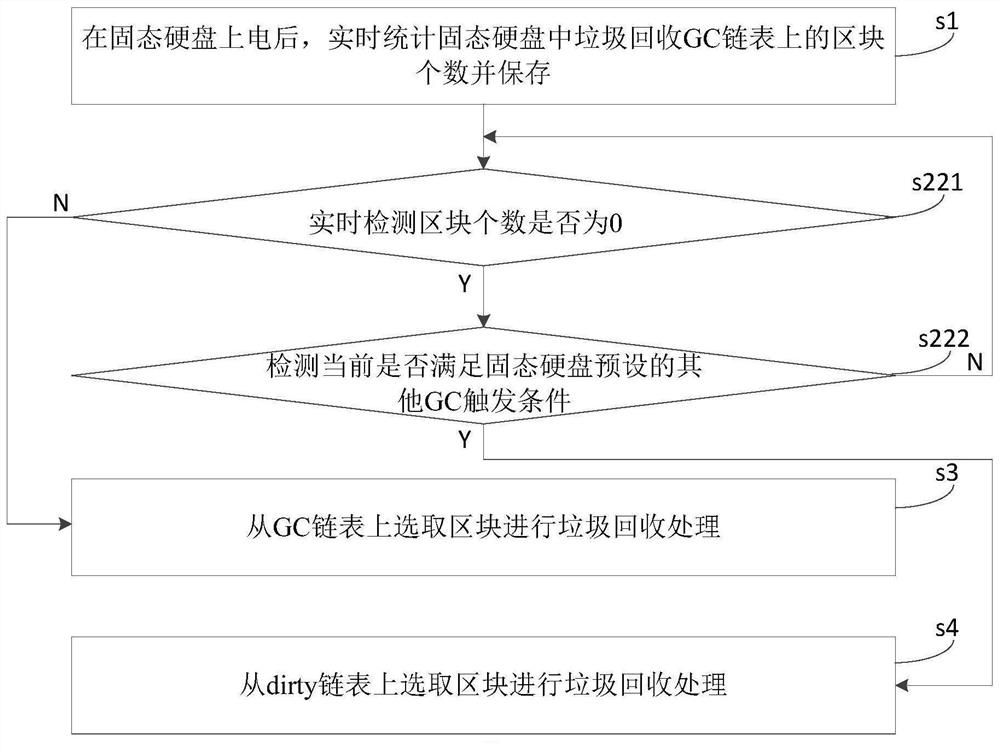

Solid state disk garbage collection management method, device and equipment

ActiveCN109597584AReduce invalid operationsImprove the efficiency of selecting SRCblockInput/output to record carriersElectricitySolid-state drive

The invention discloses a solid state disk garbage collection management method, which comprises the following steps: after a solid state disk is powered on, counting the number of blocks on a garbagecollection GC linked list in the solid state disk in real time and storing the number; Detecting whether a preset GC trigger condition of the solid state disk is met and whether the number of blocksis 0 or not, and if the GC trigger condition is met and the number of blocks is not 0, selecting the blocks from the GC linked list to carry out garbage collection processing; And if the GC trigger condition is met and the number of the blocks is 0, selecting the blocks from the dirty chain table to carry out garbage collection processing. According to the method, the existence condition of the blocks on the GC linked list can be perceived in advance, when the trigger condition is met and the number of the blocks on the GC linked list is 0, the blocks are directly obtained from the linked listoutside the GC linked list, and the garbage collection efficiency is higher; The invention further discloses a device and equipment based on the method and a computer readable storage medium.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

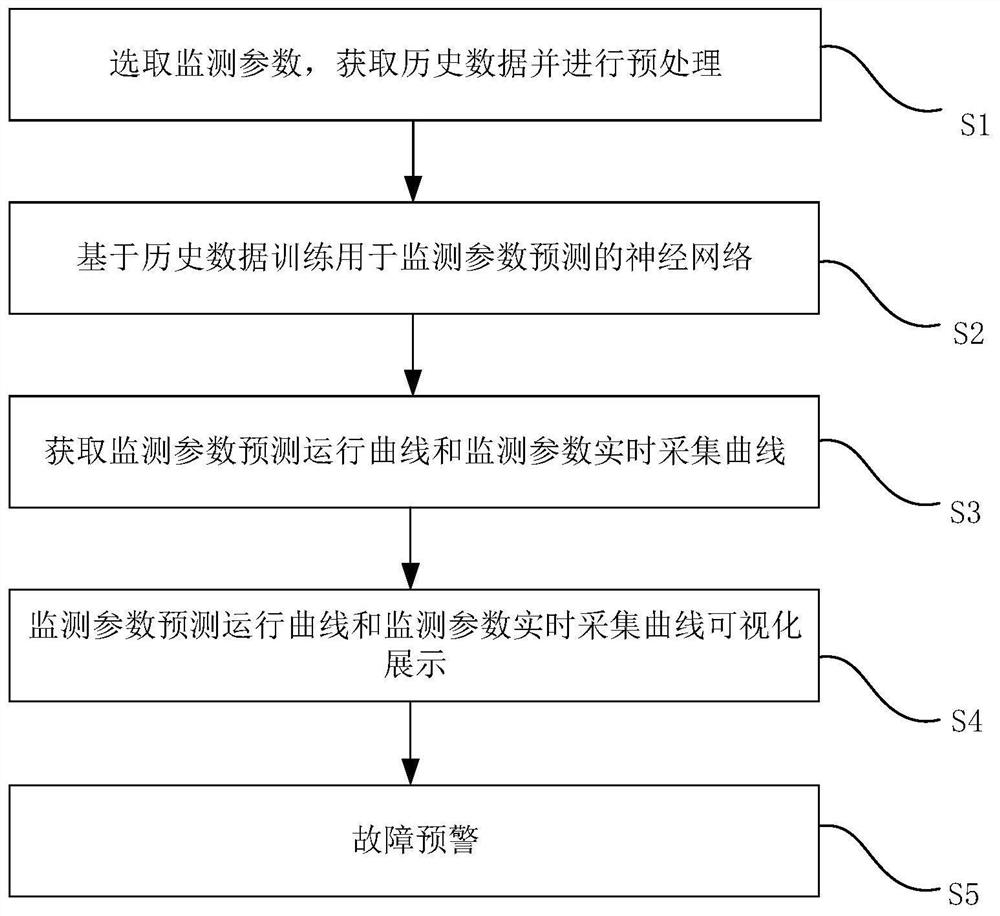

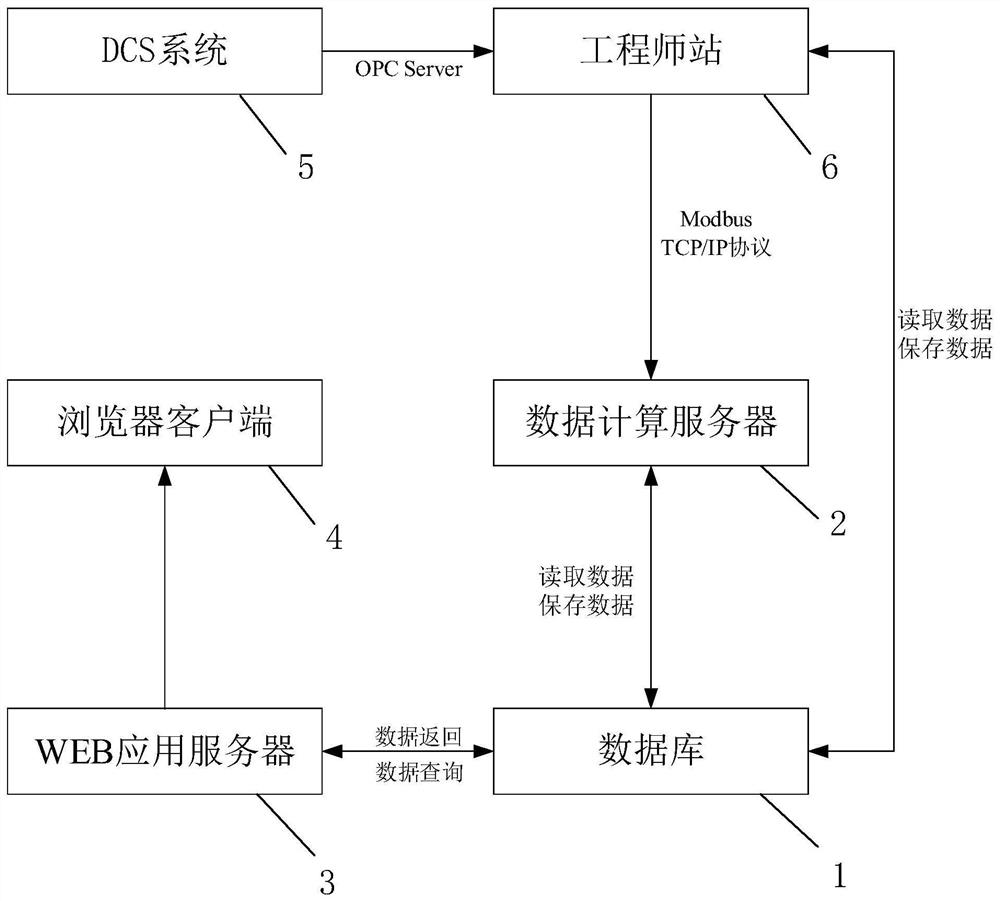

Performance monitoring and fault early warning method and system in initial operation stage of integrated energy system

PendingCN113991855ASimple methodEasy to operateEnergy industrySingle network parallel feeding arrangementsIntegrated energy systemBusiness enterprise

The invention relates to a performance monitoring and fault early warning method and system in the initial operation stage of an integrated energy system, and the method comprises the steps: S1, selecting monitoring parameters, obtaining historical data, and carrying out the preprocessing of the historical data; S2, training a neural network for monitoring parameter prediction based on historical data; S3, acquiring monitoring parameters online in real time, inputting the monitoring parameters into the neural network model to obtain a monitoring parameter prediction operation curve, and drawing a monitoring parameter real-time acquisition curve based on the monitoring parameters acquired in real time; S4, visually displaying the monitoring parameter real-time acquisition curve and the monitoring parameter prediction operation curve; S5, taking the monitoring parameter prediction operation curve as a reference, comparing the monitoring parameter prediction operation curve with data in the monitoring parameter real-time acquisition curve, and performing fault early warning when the monitoring parameter deviation exceeds a set value. Compared with the prior art, the method can find potential faults in the initial operation stage of the system, avoids fault expansion, and improves the economic benefits and working efficiency of enterprises.

Owner:SHANGHAI MUNICIPAL ELECTRIC POWER CO +1

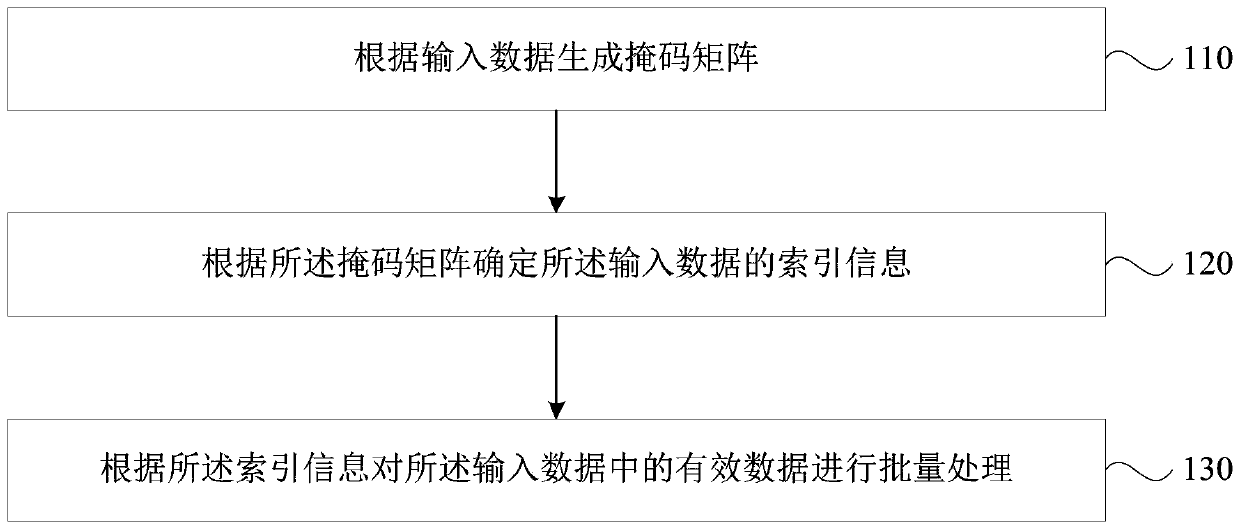

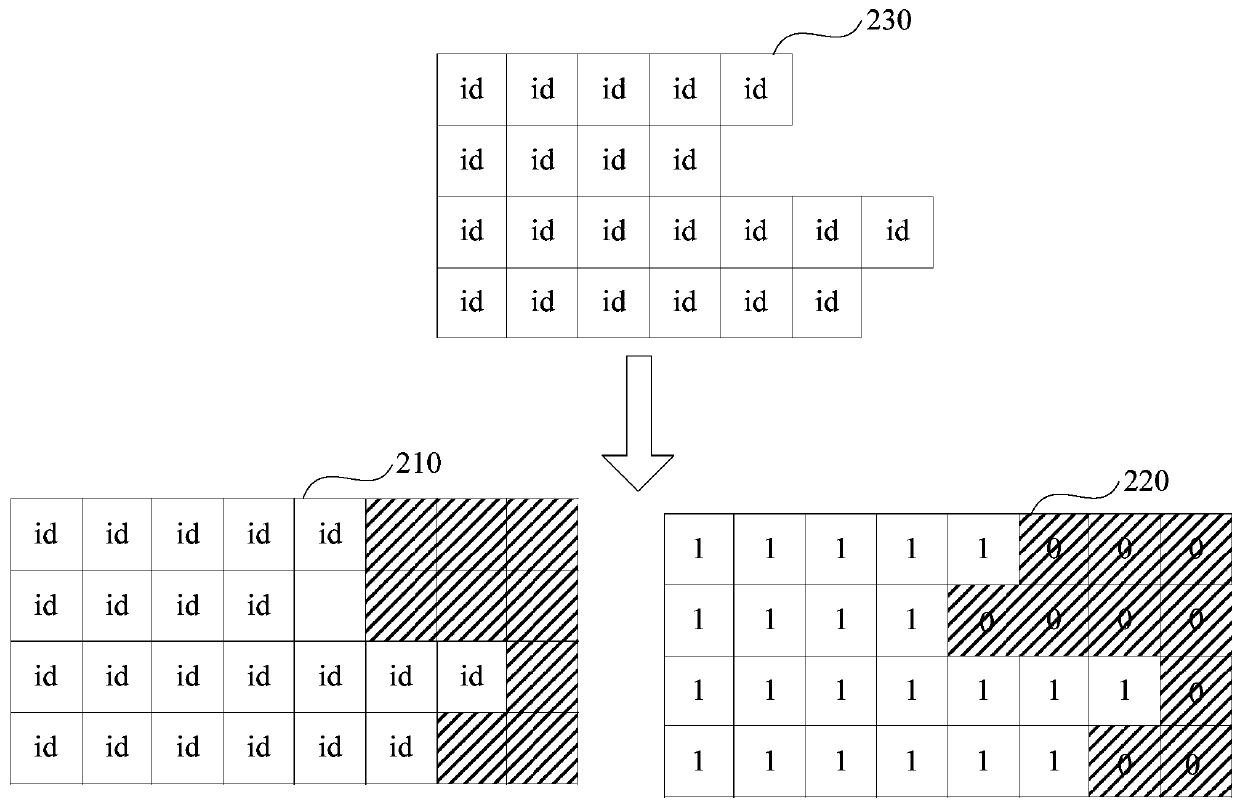

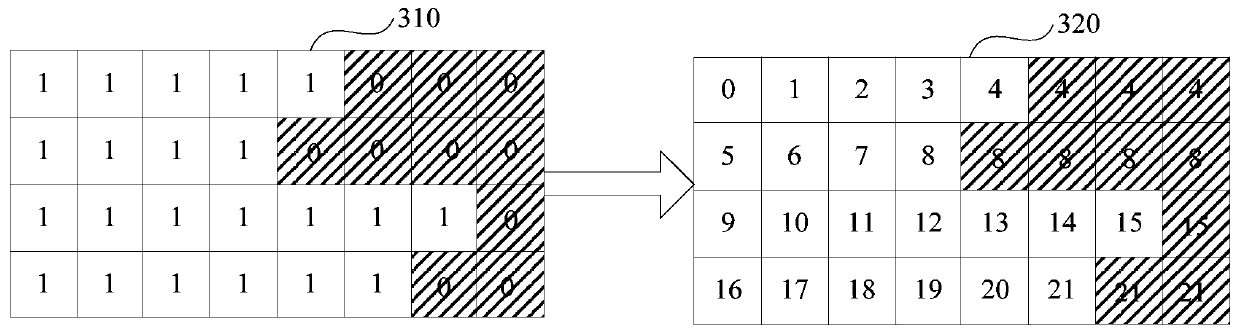

Batch processing method and device for non-fixed-length input data, terminal and storage medium

ActiveCN111382557AReduce invalid operationsIncrease computing speedText processingEnergy efficient computingData packBatch processing

The embodiment of the invention discloses a batch processing method and device for non-fixed-length input data, a terminal and a storage medium. The method comprises the steps of generating a mask matrix according to input data, and the input data comprises at least two word sequences with different lengths; determining index information of the input data according to the mask matrix; and performing batch processing on effective data in the input data according to the index information. Through the method of the embodiment of the invention, invalid operation aiming at the filling data can be reduced, and the operation speed and the processing efficiency of the deep learning model during batch processing of the non-fixed-length input data are improved.

Owner:BYTEDANCE INC +1

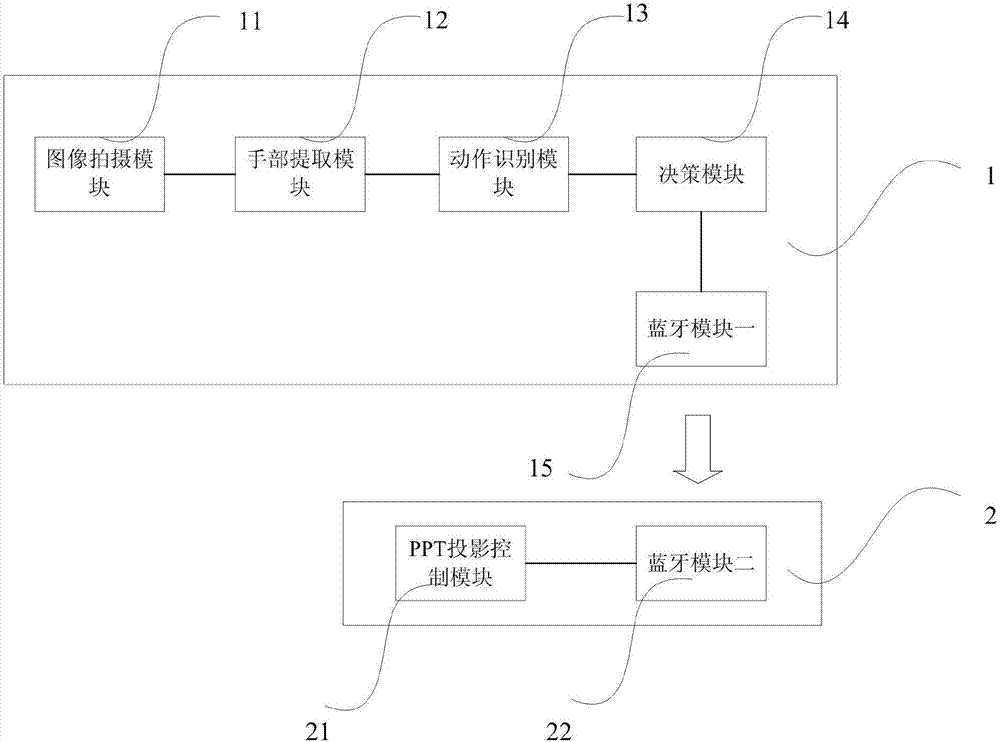

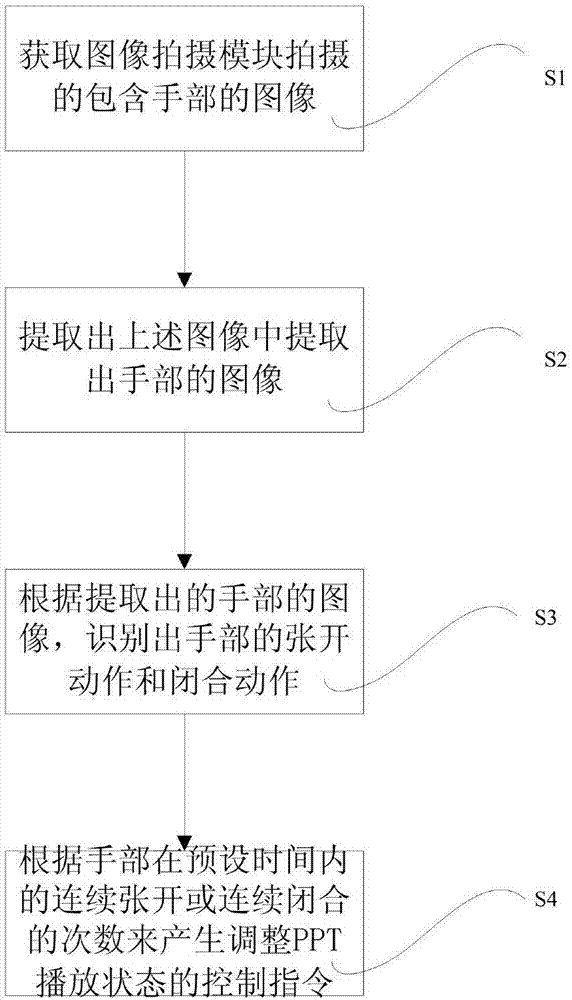

PPT playing control method and system based on gesture recognition

InactiveCN107357421ARealize remote controlReduce invalid operationsInput/output for user-computer interactionCharacter and pattern recognitionRemote controlEmbedded system

The invention discloses a PPT playing control method and system based on gesture recognition. According to the PPT playing control method and system, a control instruction for adjusting the PPT playing state is generated according to the number of times of continuous opening and the number of times of continuous closing of hands in a preset time, and an operator can remotely control a PPT conveniently and easily on the premise of not carrying any remote control device.

Owner:CHINA UNIV OF GEOSCIENCES (WUHAN)

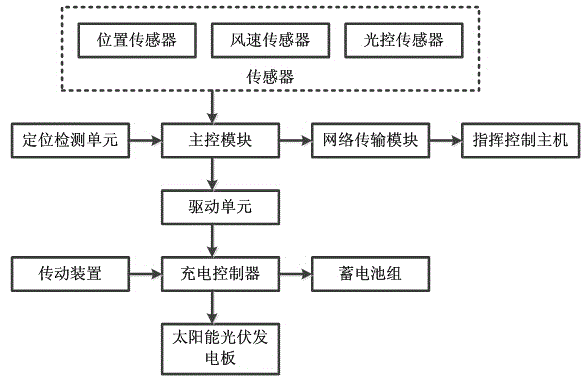

Intelligent solar energy photovoltaic generation automatic following control system

InactiveCN105676878ARealize intelligent power generationMaximum Efficiency AcquisitionControl using feedbackCells panelControl system

The present invention discloses an intelligent solar energy photovoltaic generation automatic following control system. The system comprises a sensor, a positioning detection unit, a master control module, a network transmission module, a command control host, a driving unit, a transmission device, a charging controller, a solar energy photovoltaic generation plate and a storage battery set. The sensor, the positioning detection unit, the master control module, the network transmission module, the command control host, the driving unit, the charging controller and the solar energy photovoltaic generation plate are connected in order, and the transmission device, the charging controller and the storage battery set are connected in order. The intelligent solar energy photovoltaic generation automatic following control system is reasonable in design, easy to operate and high in sensitivity, and realizes automatic tracking of sunlight through a solar panel and the maximum power output of a cell panel through adoption of the sensor technology.

Owner:TIANJIN SILVER ARROW TECH

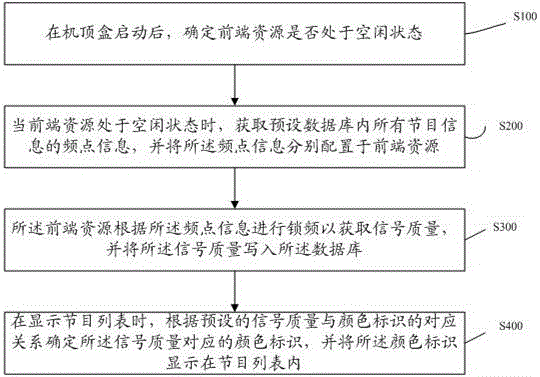

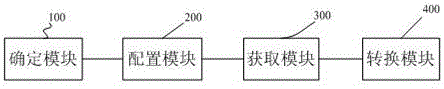

Method and system for controlling program list to display signal quality

InactiveCN106534985AReduce invalid operationsEasy to useSelective content distributionSignal qualitySoftware engineering

The invention discloses a method and system for controlling a program list to display signal quality. The method comprises the steps of after a set top box is started, determining whether front end resources are in idle states or not; when the front end resources are in the idle states, obtaining frequency point information of all program information in a preset database and configuring the frequency point information to front end resources; carrying out frequency locking by the front end resources according to the frequency point information and writing the signal quality into the database; and when the program list is displayed, determining color identifiers corresponding to the signal quality according to a preset corresponding relationship between the signal quality and the color identifiers, and displaying the color identifiers in the program list. In this way, a user can eliminate programs incapable of being played according to the signal quality, invalid operations of the user are reduced, and the usage convenience is provided for the user.

Owner:SHENZHEN SKYWORTH DIGITAL TECH CO LTD

A solid-state hard disk garbage collection management method, device and equipment

ActiveCN109597584BReduce invalid operationsImprove the efficiency of selecting SRCblockInput/output to record carriersSoftware engineeringGarbage collection

The invention discloses a solid-state hard disk garbage collection management method. If the condition and the number of blocks are 0, if the GC trigger condition is met and the number of blocks is not 0, the block is selected from the GC linked list for garbage collection processing; if the GC trigger condition is met and the number of blocks is 0, the Select blocks on the dirty list for garbage collection. The present invention can sense the existence of blocks on the GC linked list in advance, and when the trigger condition is met and the number of blocks on the GC linked list is 0, blocks are directly obtained from linked lists other than the GC linked list, and the efficiency of garbage collection is higher; The invention also discloses an apparatus, a device and a computer-readable storage medium based on the above method.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

Information search method and device

ActiveCN103514299BMeet needsReduce invalid operationsWeb data indexingSemantic analysisInformation typeUser needs

The invention discloses an information searching method and device. The method comprises the steps that search keywords input by a user are received; semantic analysis is conducted on the search keywords, and a plurality of information types and corresponding relevancies required by the user are obtained according to results of the semantic analysis; the search keywords are matched with various vertical search data bases according to the relevancies of the information types, and various types of search result data of the vertical search data bases corresponding to the search keywords are obtained; the various types of search result data are integrated and shown. According to the information searching method and device, the search results which are obtained finally integrate content of a plurality of vertical channels, and comprise various possible requirements of the user. Compared with universal search, pertinence is stronger, the situation that the user can only select the current channel in vertical search is avoided, and therefore invalid operation of the user is reduced, and the requirements of the user are met more rapidly.

Owner:BEIJING QIHOO TECH CO LTD

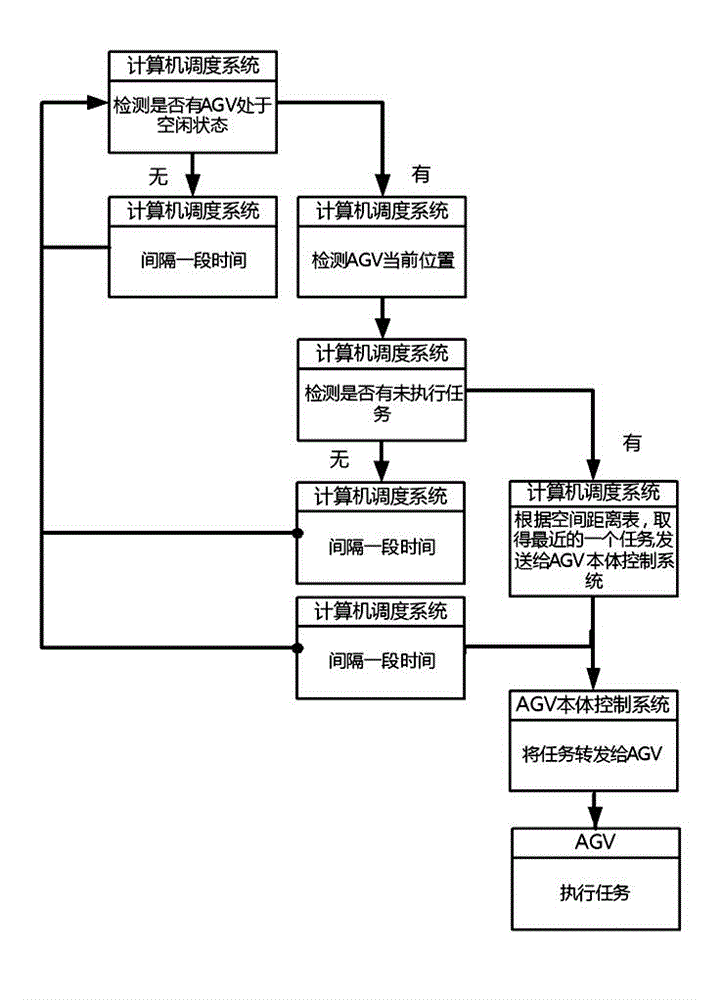

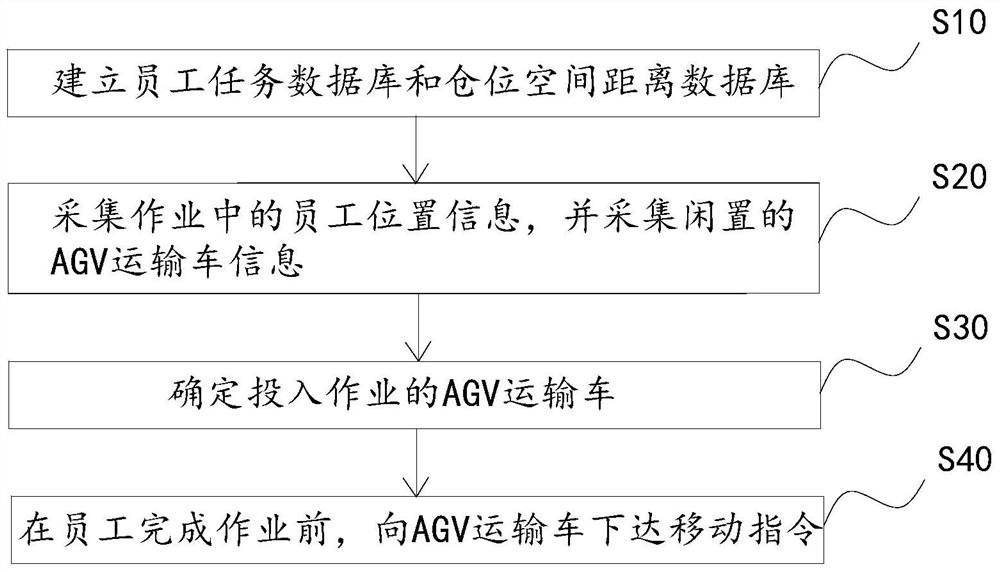

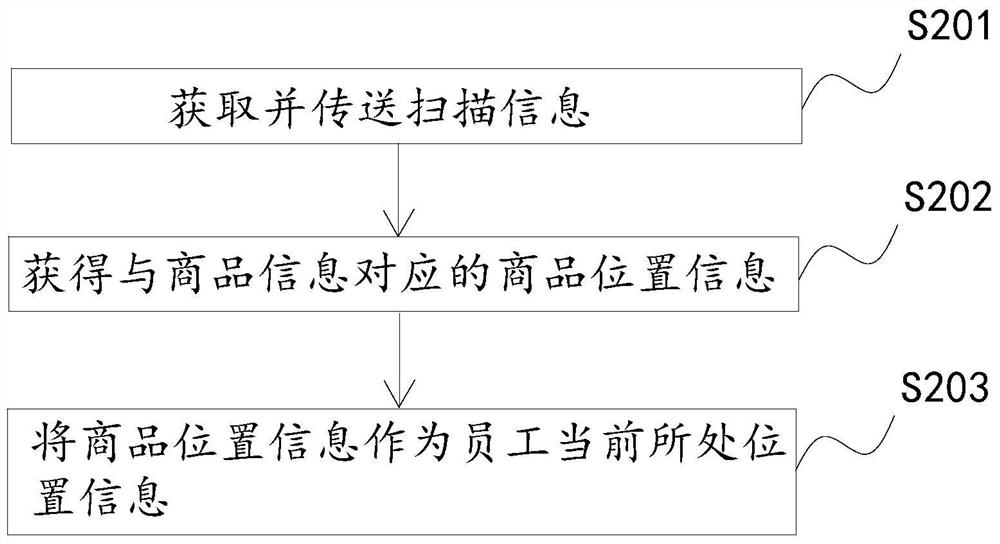

A method and system for dispatching AGV transport vehicles in automated warehousing

ActiveCN107025491BImprove operational efficiencyReduce invalid operationsForecastingResourcesOperating systemIndustrial engineering

The embodiment of the present invention discloses a dispatching method and system for AGV transport vehicles in automated warehousing, which relates to the field of warehousing and can send instructions to AGV transport vehicles in advance based on the spatial location of on-site employees, employee task completion status, AGV position and speed. , realizing the instant connection between the AGV transport vehicle and the operating staff. The method of the present invention includes: establishing an employee task database and a warehouse space distance database; collecting employee location information during operations and collecting idle AGV transport vehicle information; determining the AGV transport vehicle that is put into operation; and transporting to the AGV before the employee completes the operation. The car sends movement instructions.

Owner:JIANGSU SUNING LOGISTICS CO LTD

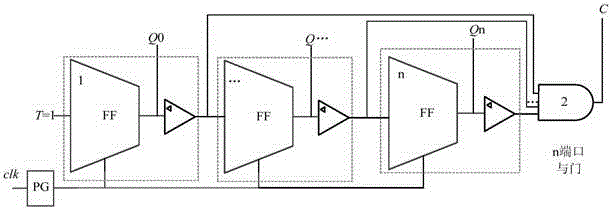

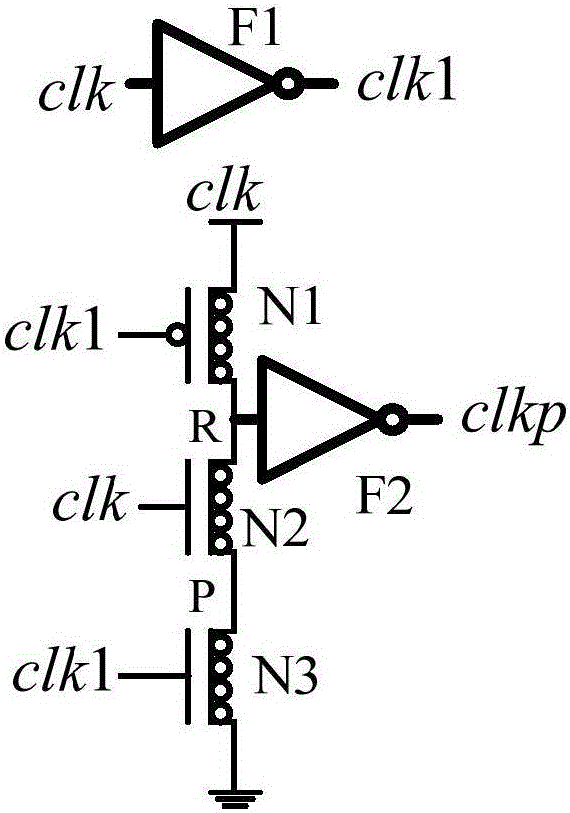

Three-valued addition counter based on CNFETs

ActiveCN106067807AReduce power consumptionLower latencyCounting chain pulse counters using semiconductor devicesTime delaysEngineering

The invention discloses a three-valued addition counter based on CNFETs. The three-valued addition counter comprises a pulse signal generator, n addition counting units, and an n input AND gate. The pulse signal generator has an input end and output end. Each addition counting unit has an input end, an output end, a clock control end, and a carry output end. The n input AND gate has n input ends and an output end. The output end of the pulse signal generator is connected with the clock control ends of the n addition counting units. The carry output ends of the n addition counting units and the n input ends of the n input AND gate are connected in one-to-one correspondence. The output end of the n input AND gate is the carry output end of the three-valued addition counter. The carry output end of the kth addition counting unit is connected with the input end of the (k+1)th addition counting unit, wherein k=1, 2, ..., n-1. The output end of the jth addition counting unit is the jth output end of the three-valued addition counter, wherein j=1, 2, ..., n. The three-valued addition counter reduces invalid operation, decreases circuit power consumption and time delay, and has a high-speed low-power-consumption characteristic.

Owner:NINGBO UNIV

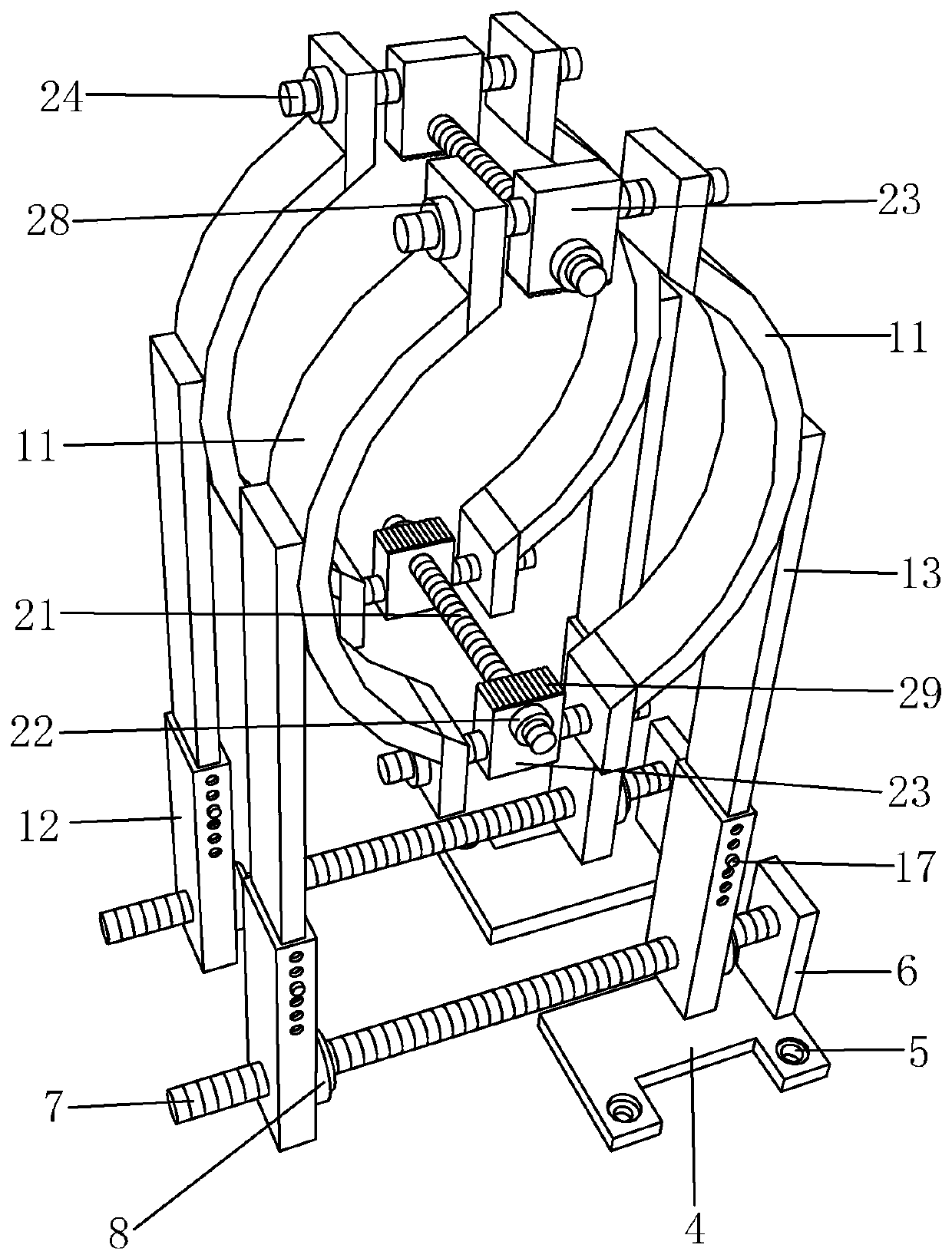

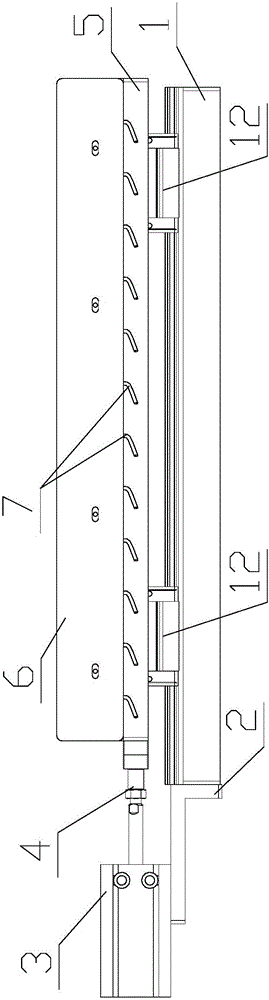

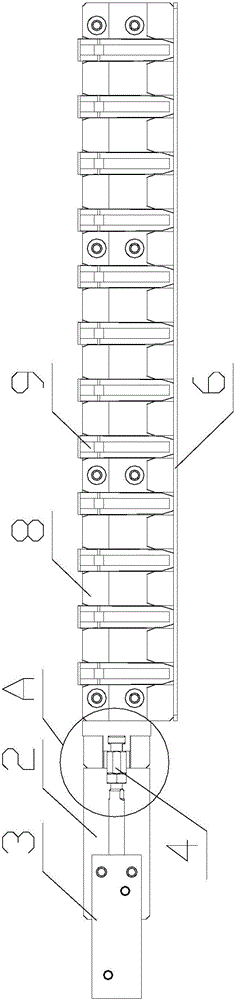

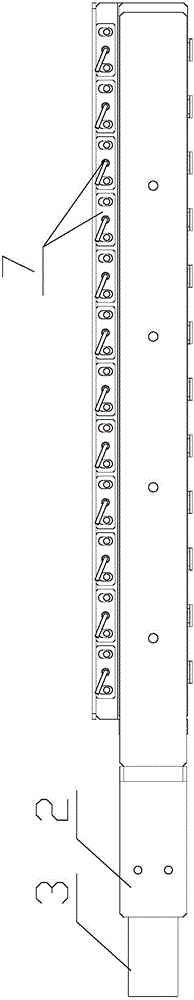

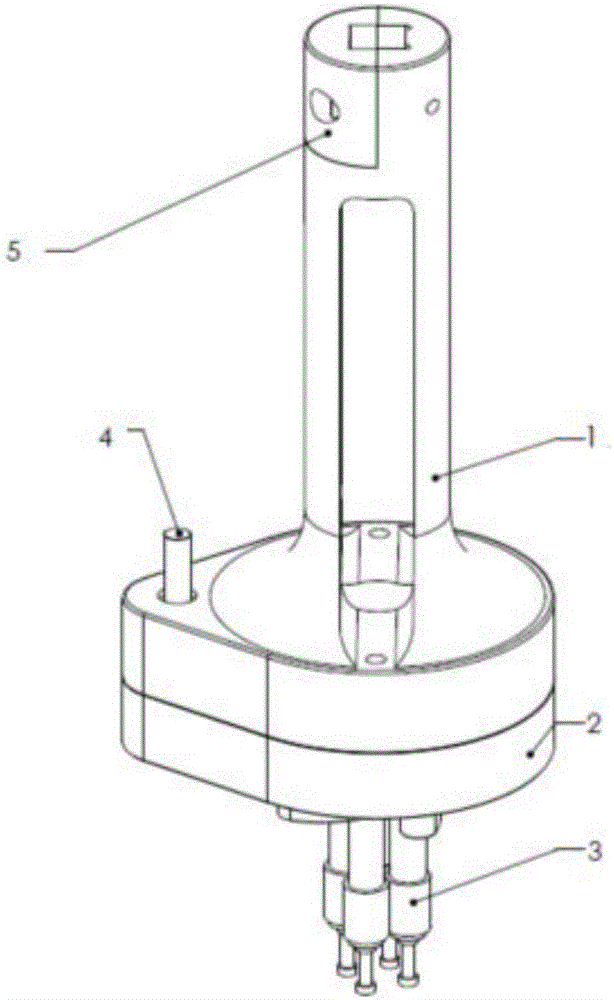

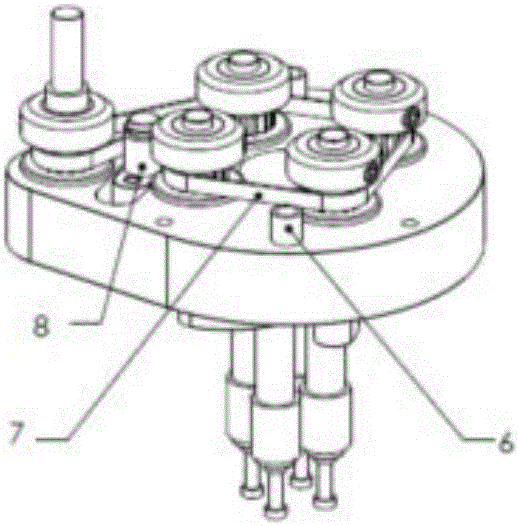

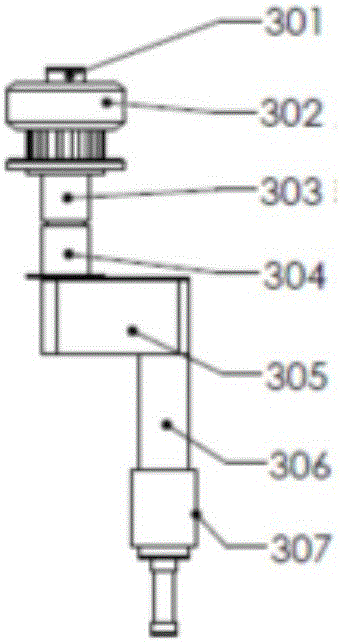

Clamper

ActiveCN106669547AReduce running locatorsReduce invalid operationsChemical/physical/physico-chemical processesFeed devicesDrive shaftHigh throughput technology

The invention discloses a clamper and relates to the field of the high throughput technology. The clamper solves the technical problem that the existing clamper cannot integrate a charging / discharging system and a clamping system. The clamper comprises an upper base which is provided with a first through hole, a lower base which is provided with a second through hole, a clamping jaw which is arranged on the lower surface of the lower base, a driving shaft which is connected to the clamping jaw and is used for driving the clamping jaw to clamp a work piece, and a burdening assembly which is used for burdening of the work piece through the first and second through holes. The charging / discharging system and the clamping system are integrated so that a running and positioning device of the experimental system is avoided, an ineffective running process of the experimental device is avoided and experimental effects are improved.

Owner:王学军

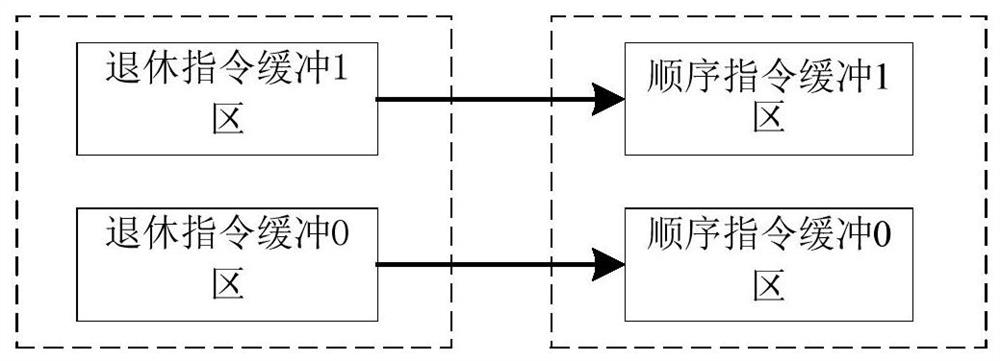

A Local Jump Instruction Fetching Circuit

ActiveCN107943518BConsecutive addressesImprove execution efficiencyConcurrent instruction executionComputer architectureEngineering

The invention belongs to the technical field of computer hardware and relates to a local jump instruction fetching circuit. The invention includes a PC update module, a sequential instruction buffer, a retirement instruction buffer and a PC stack. The PC update module is responsible for updating the PC address. The retired instruction buffer stores 16 instructions that have been executed. The sequential instruction buffer stores 8 instructions being executed and 8 instructions to be executed. The PC stack is used to save and restore the PC when functions are nested. According to the jump address of the jump instruction, the present invention can realize fast instruction forward partial jump in the retired instruction buffer and backward in the sequential instruction buffer, thereby improving the execution efficiency of the jump instruction and the update efficiency of the buffer instruction, Reduce the waiting delay of the pipeline and improve the execution efficiency of the processor.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA