Patents

Literature

57results about How to "Convenient power control" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

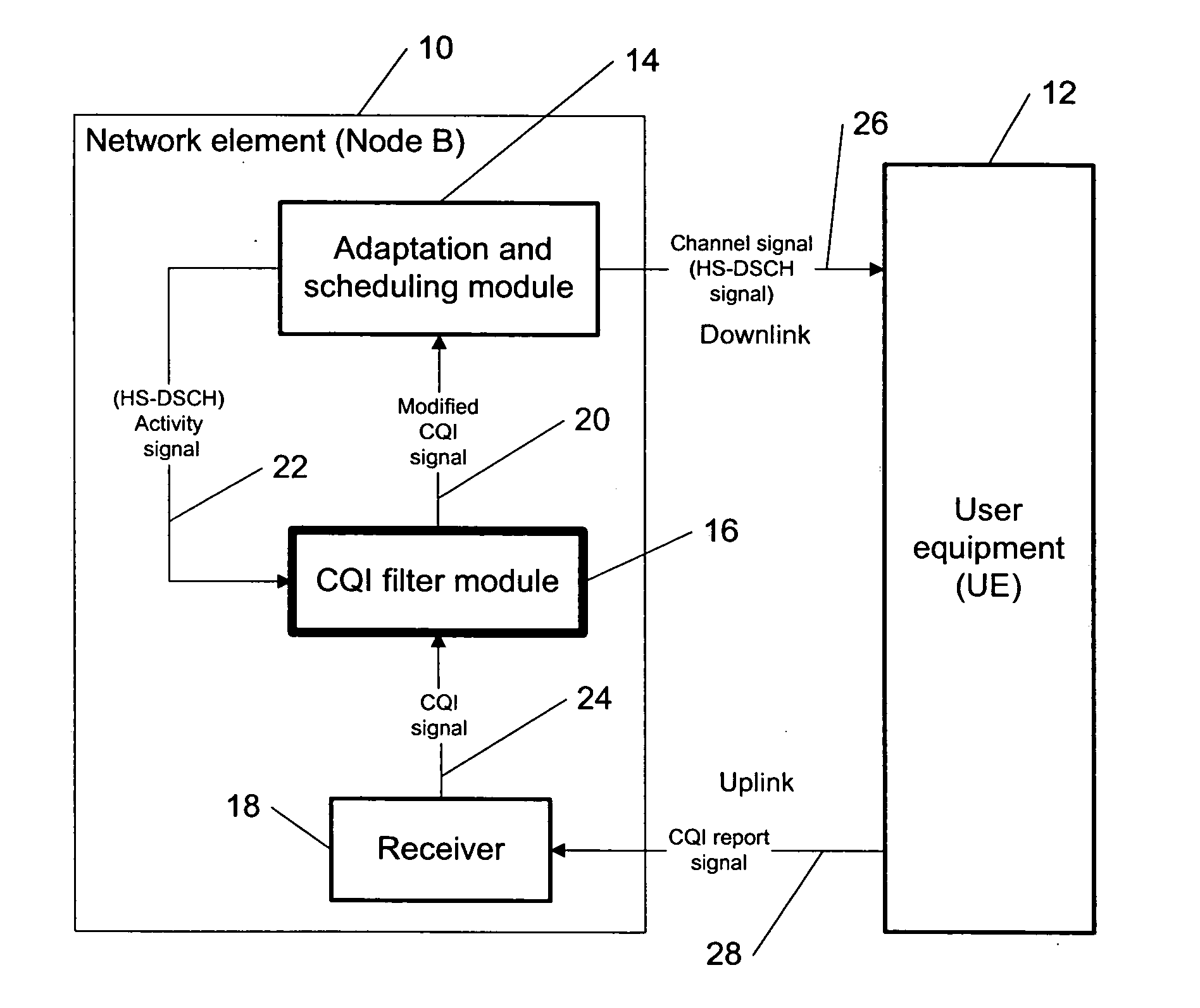

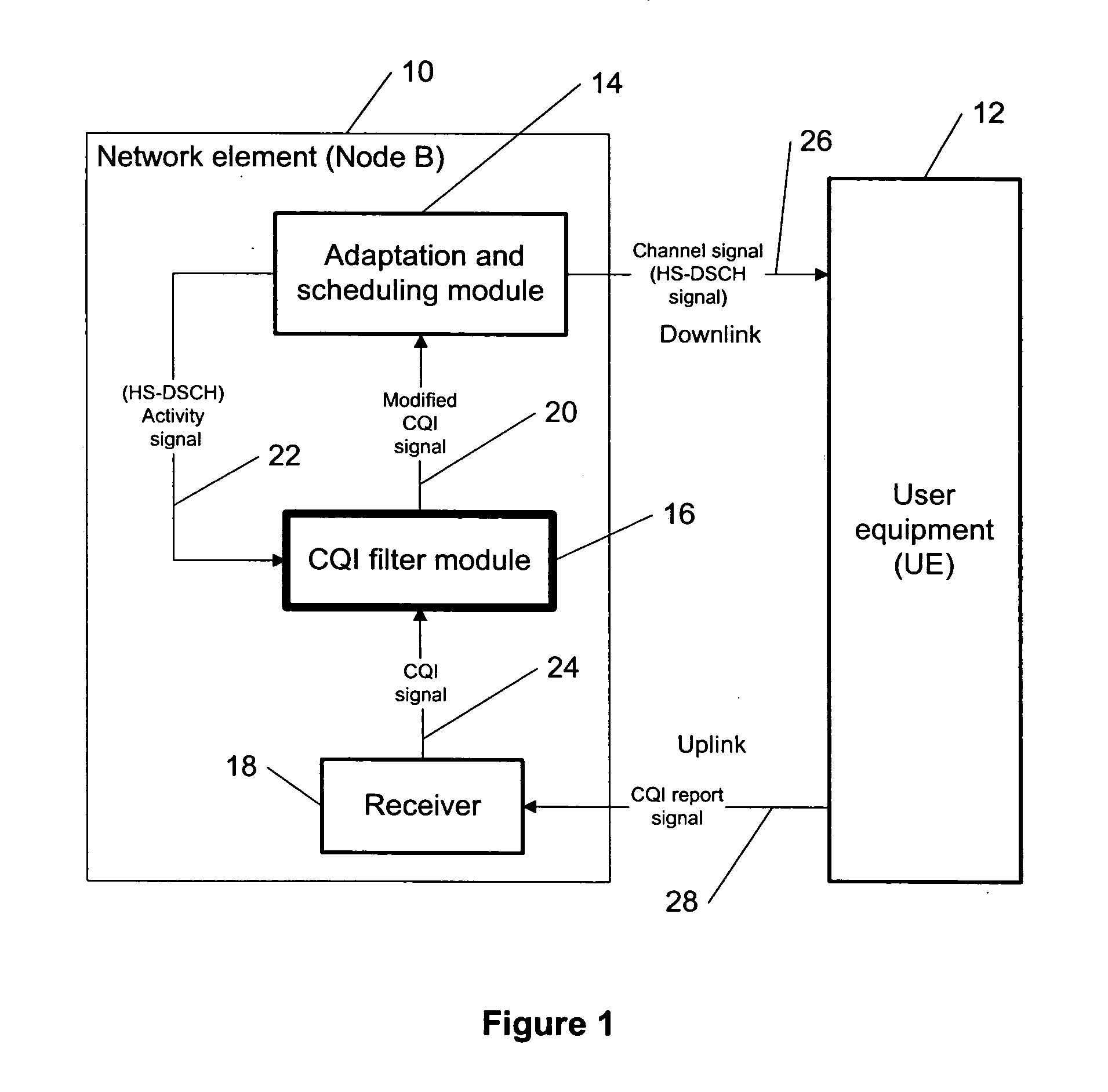

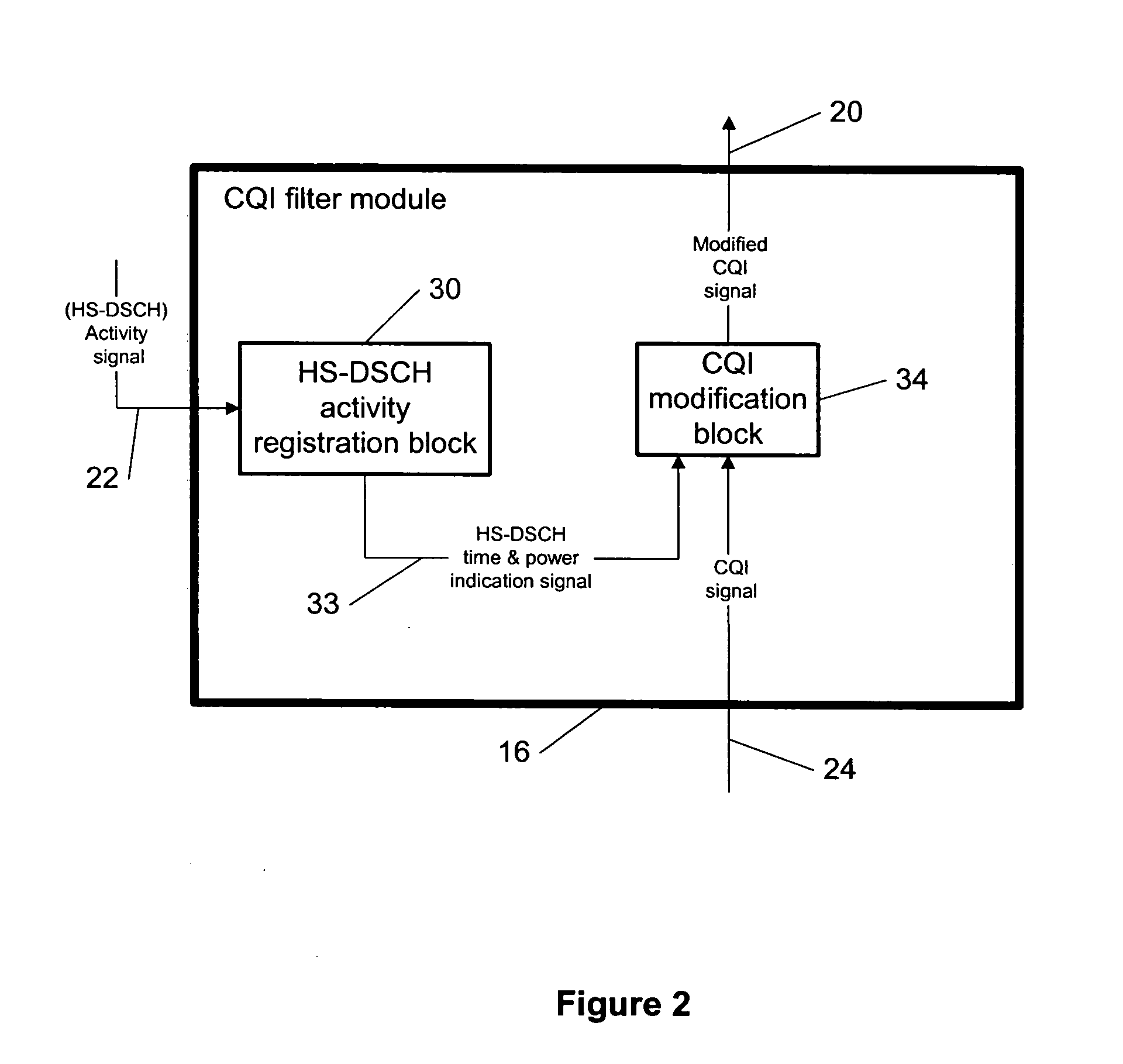

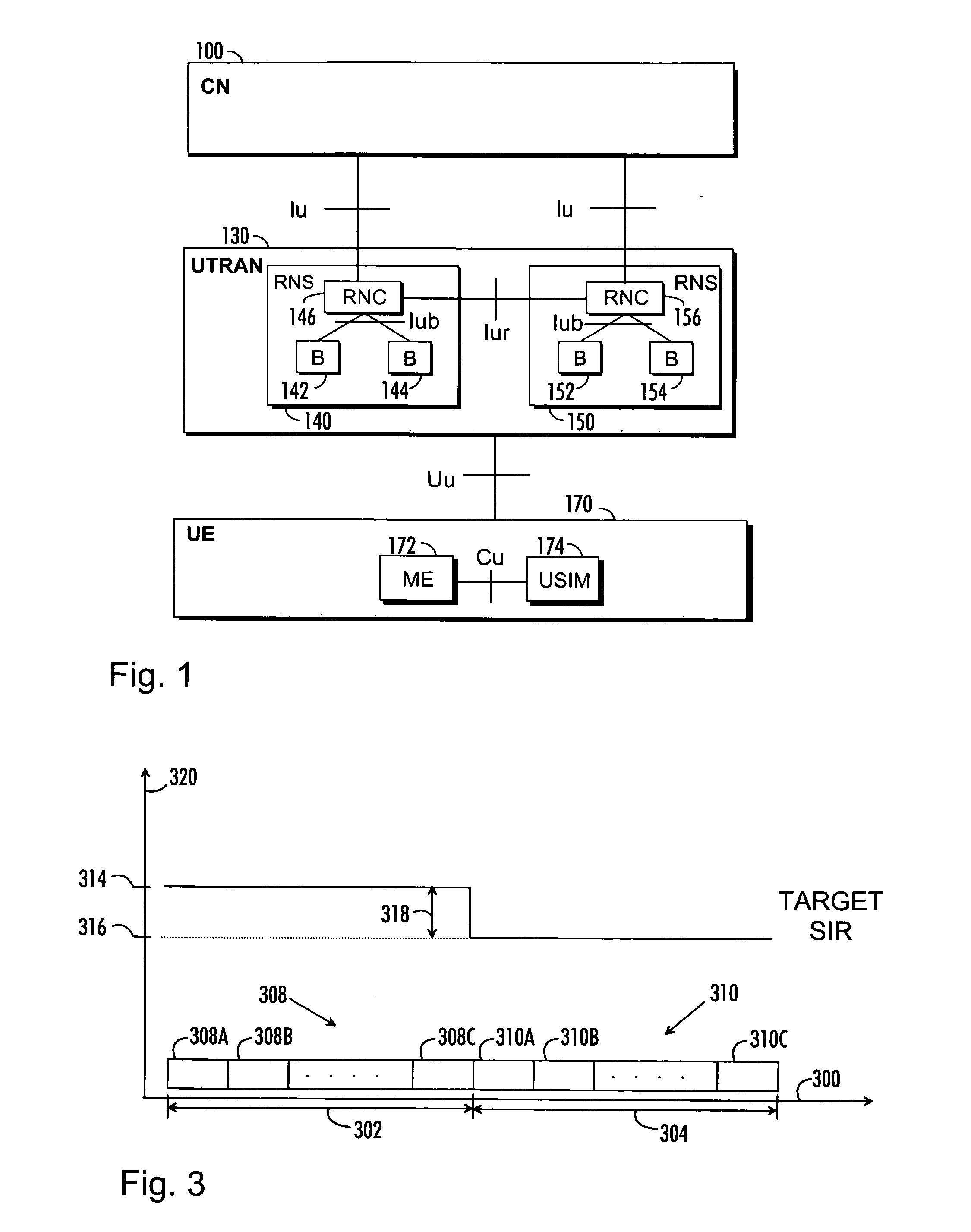

Method for improving an HS-DSCH transport format allocation

InactiveUS20060089104A1Improve accuracyIncrease benefitReceivers monitoringRadio/inductive link selection arrangementsMobile telephonyNetwork element

This invention describes a method for a new methodology for improving a high speed downlink shared channel (HS-DSCH) transport format allocation in communication systems (e.g., mobile phone networks) using, e.g., a network element such as a node B. As CQI (channel quality indicator) reports made by a user terminal) are time stamped in a sense that they correspond to a given reference period, the Node B is able to determine what time instant in the past the given CQI report corresponds to. As the Node B scheduler knows a history of HS-DSCH (high speed downlink shared channel) transmission, it is able to determine how much HS-DSCH power was transmitted during the time corresponding to the received CQI report. Based on this information, it determines the bias required to the CQI reports received at different times to improve an accuracy of the allocated HS-DSCH transport format.

Owner:NOKIA SOLUTIONS & NETWORKS OY

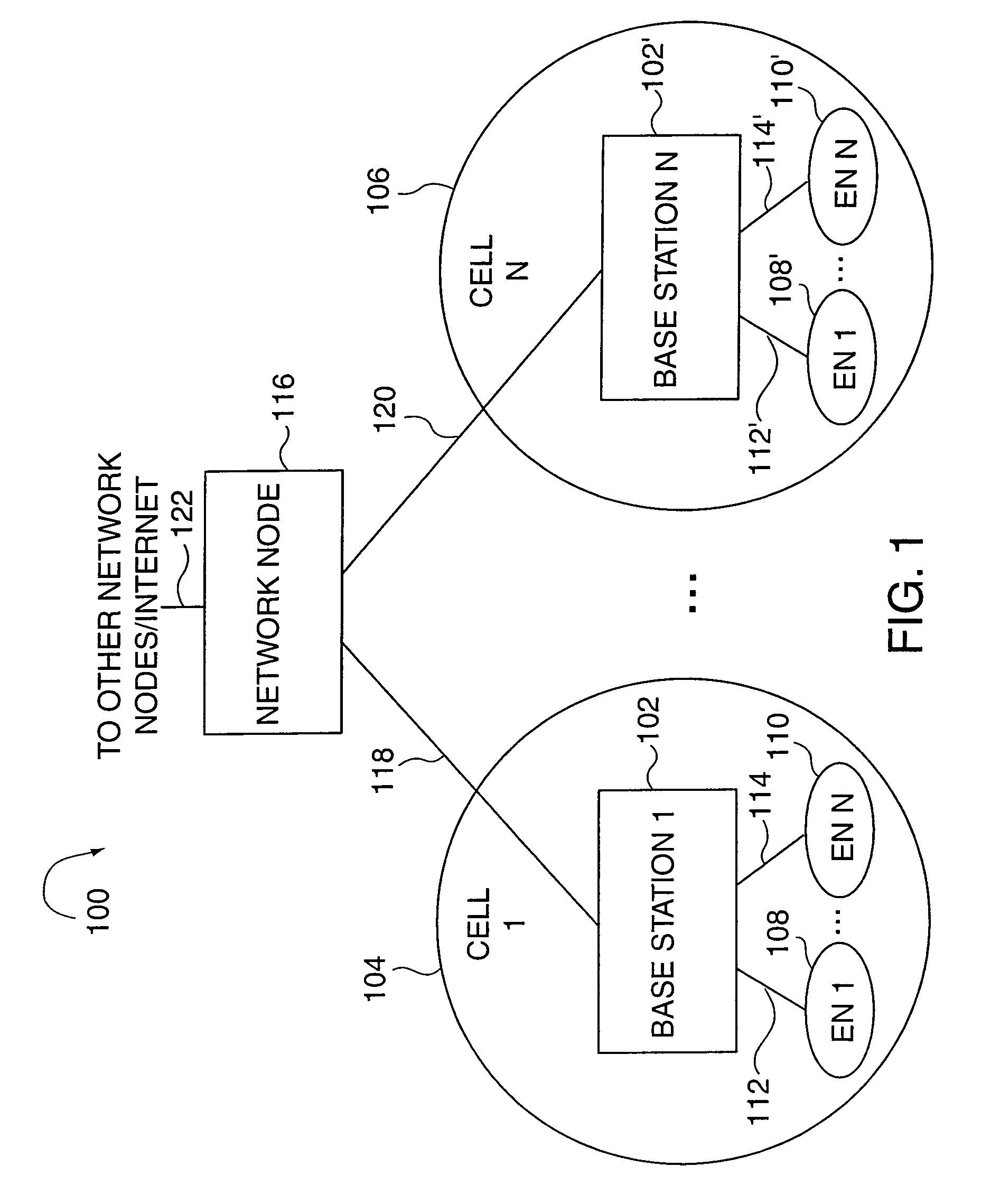

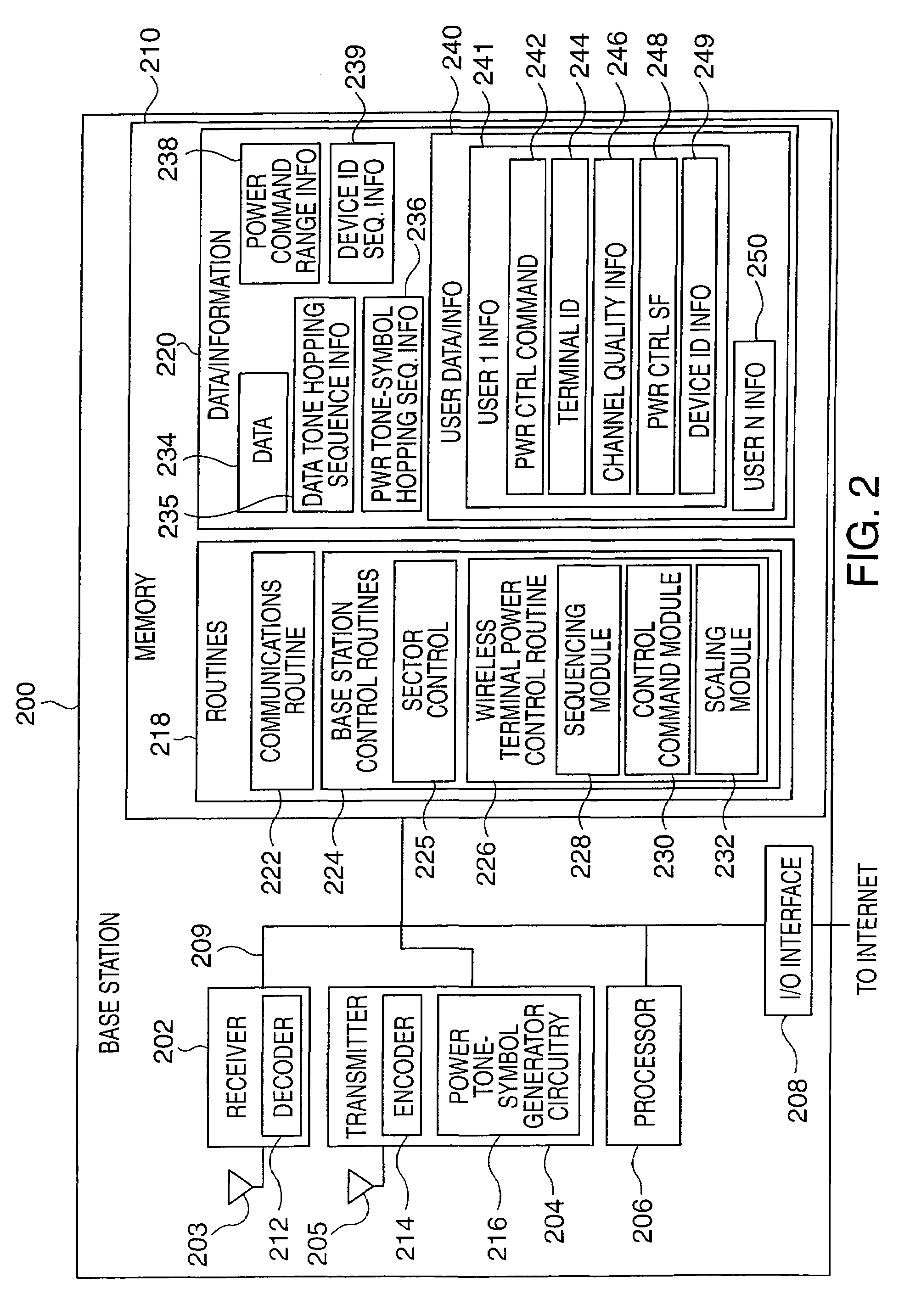

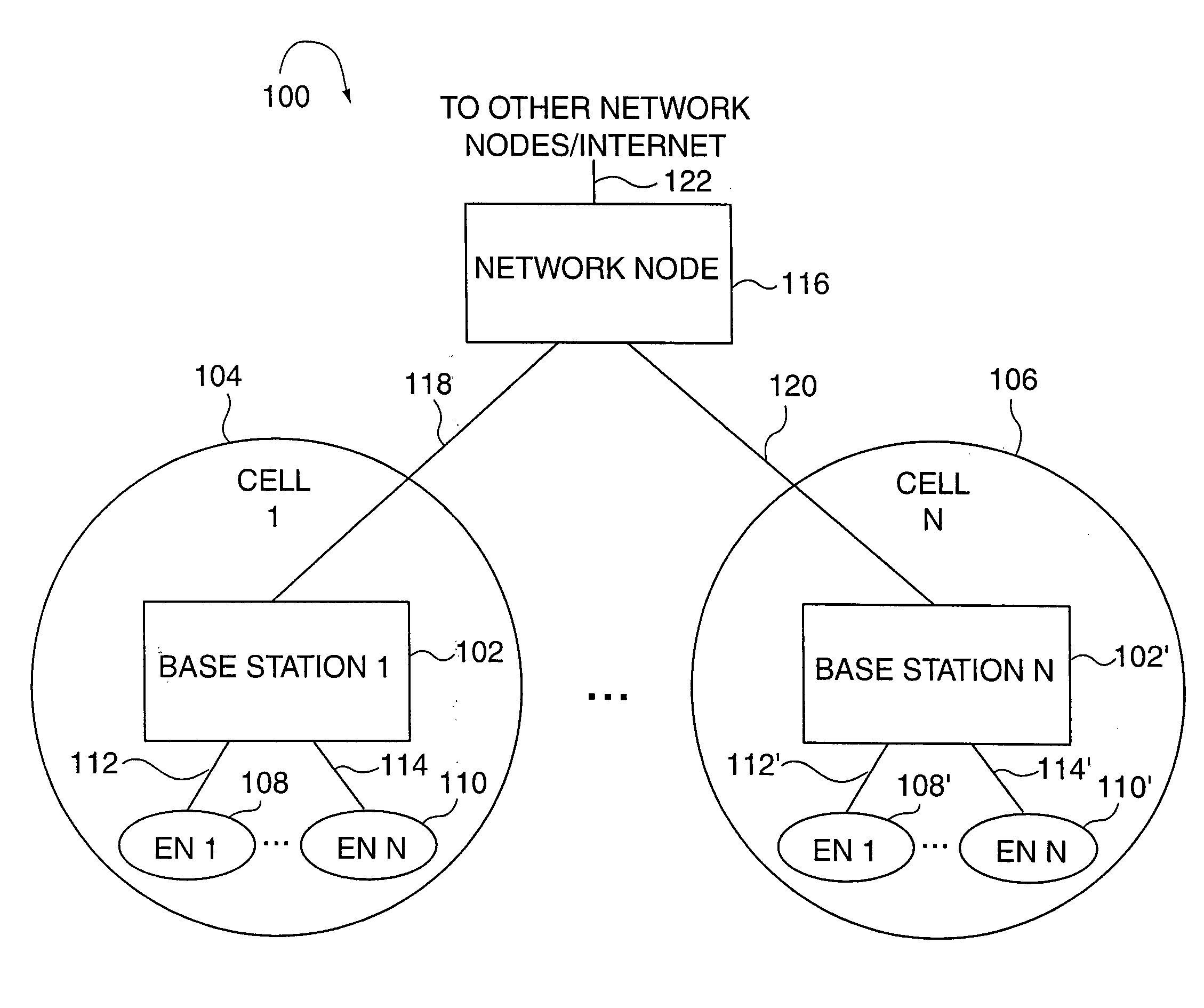

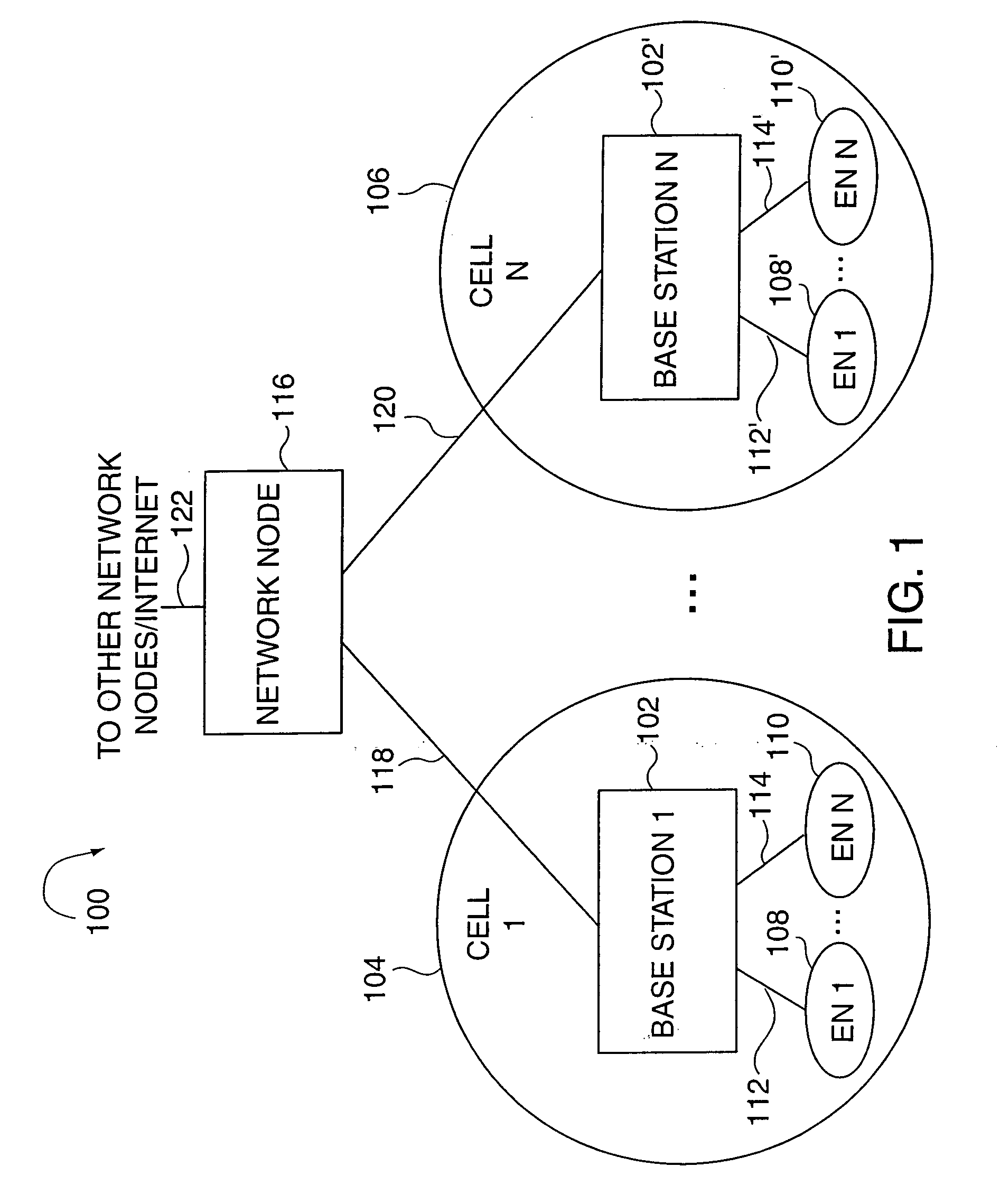

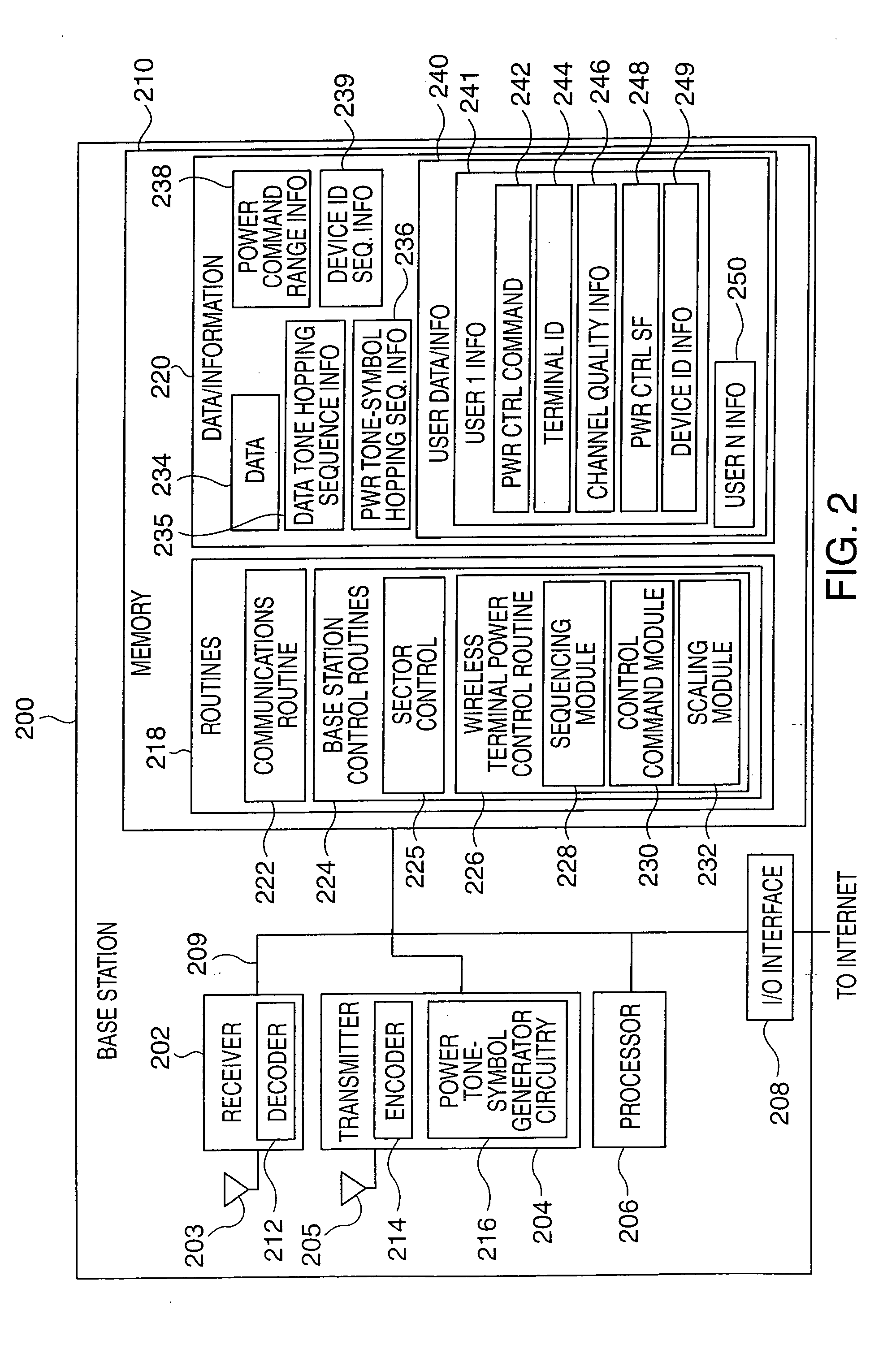

Methods and apparatus of power control in wireless communication systems

InactiveUS7420939B2Limit and overcome interferenceIncrease transmit powerEnergy efficient ICTPower managementSignal qualityCommunications system

The present invention involves apparatus and methods to perform wireless terminal transmission power control. The invention uses novel and highly efficient methods to: convey power control information, specify power control level adjustments, recognize power control information, limit interference in the power control signaling, and recognize corrupted power control signaling, thus conserving wireless terminal energy and minimizing power control signaling and associated bandwidth. Base stations send analog power control command signals, with a continuous range of control levels, to wireless terminals for transmission power adjustments. Power control signals include two components which can be used to convey information, e.g., power control commands, signal quality, device identity information. For zero power adjustment, the control component signal is not transmitted. For a non-zero adjustment, power control signals are sent using control ranges and limits, known to the base station and wireless terminal, with the scaling adjusted or synchronized based upon feedback information.

Owner:QUALCOMM INC

Methods and apparatus of power control in wireless communication systems

InactiveUS20050036441A1Limit and overcome interferenceIncrease transmit powerPower managementEnergy efficient ICTSignal qualityCommunications system

The present invention involves apparatus and methods to perform wireless terminal transmission power control. The invention uses novel and highly efficient methods to: convey power control information, specify power control level adjustments, recognize power control information, limit interference in the power control signaling, and recognize corrupted power control signaling, thus conserving wireless terminal energy and minimizing power control signaling and associated bandwidth. Base stations send analog power control command signals, with a continuous range of control levels, to wireless terminals for transmission power adjustments. Power control signals include two components which can be used to convey information, e.g., power control commands, signal quality, device identity information. For zero power adjustment, the control component signal is not transmitted. For a non-zero adjustment, power control signals are sent using control ranges and limits, known to the base station and wireless terminal, with the scaling adjusted or synchronized based upon feedback information.

Owner:QUALCOMM INC

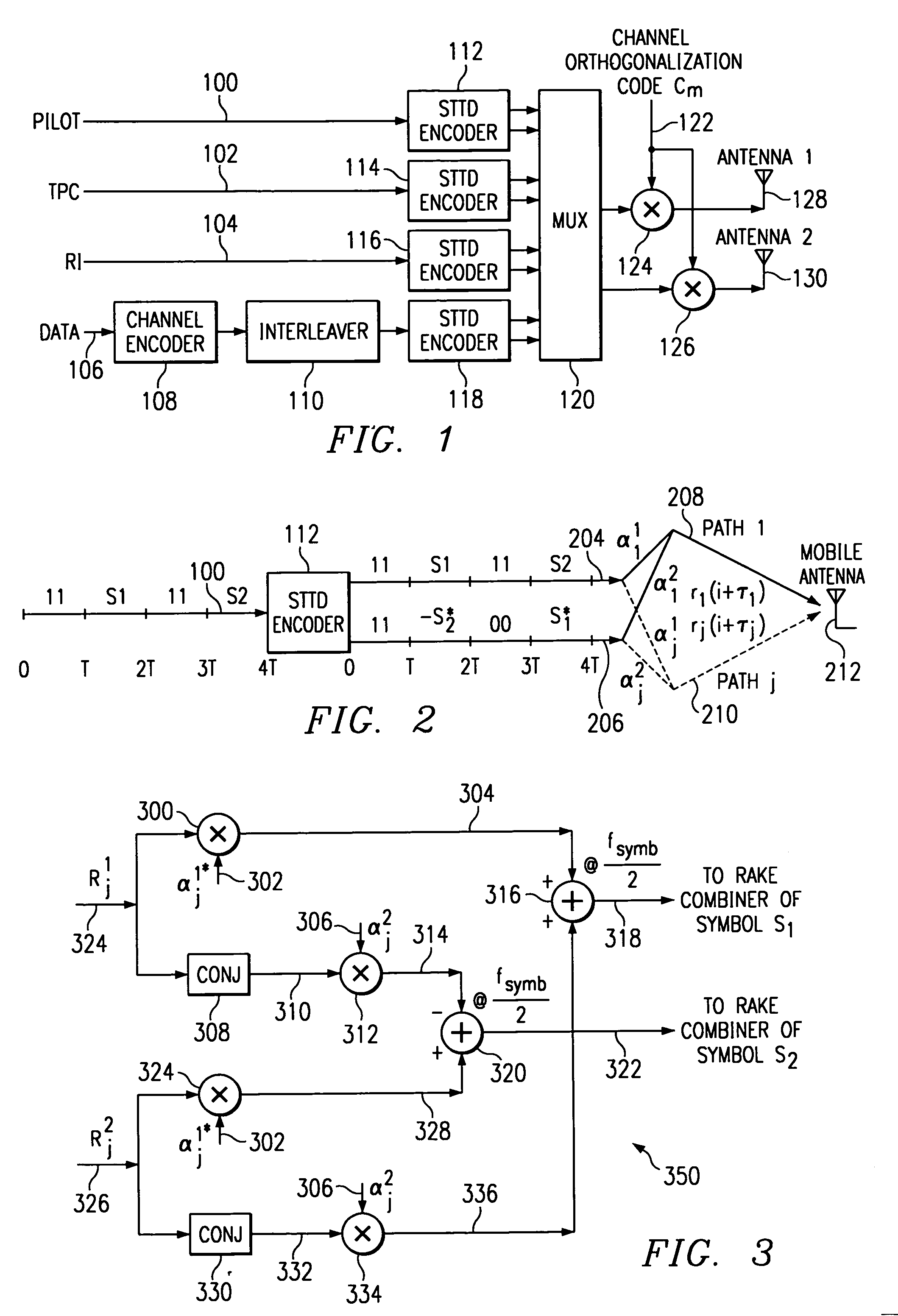

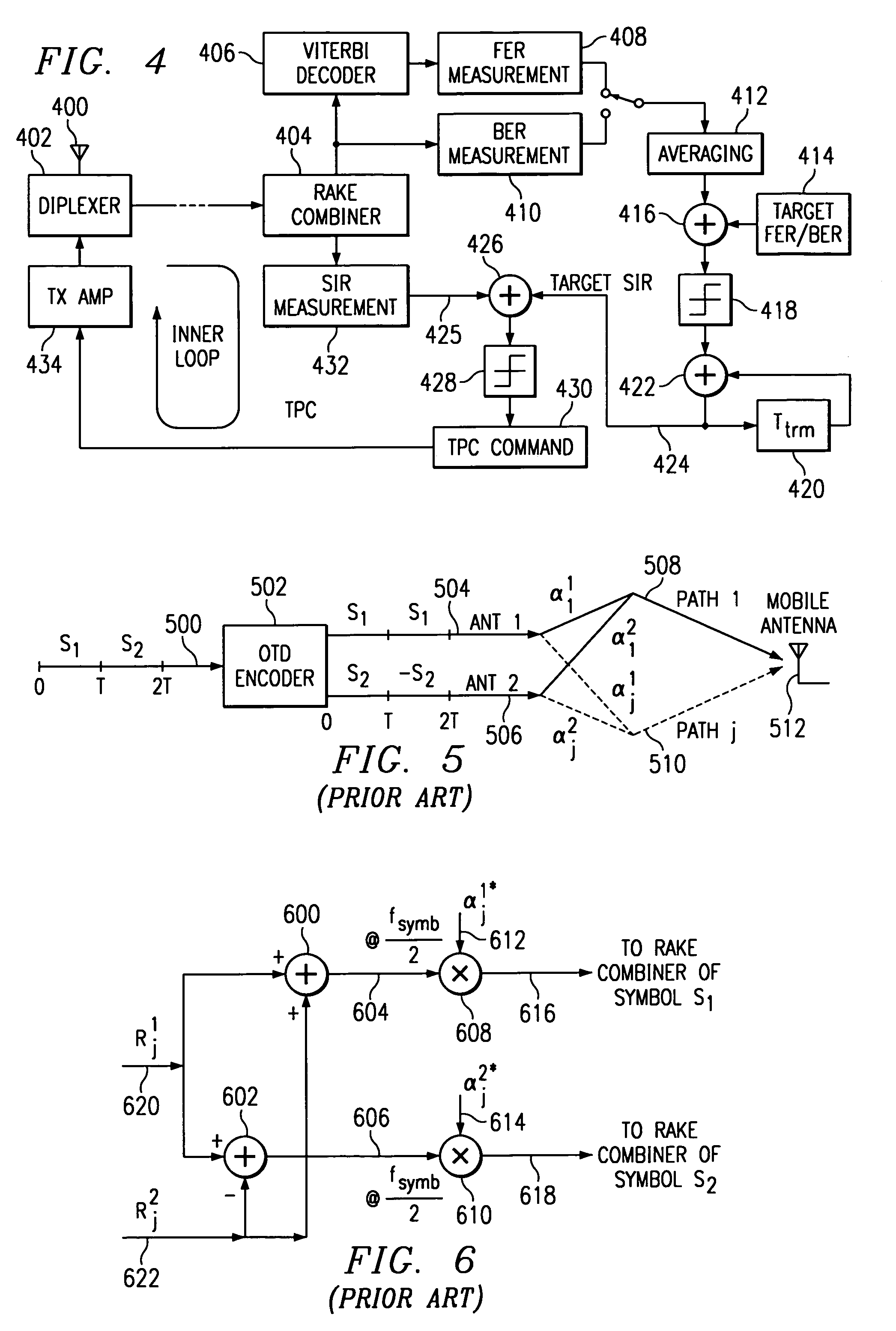

Power control with space time transmit diversity

InactiveUS6977910B1Convenient power controlPower managementTransmission control/equalisingSpace time transmit diversityControl signal

A circuit is designed with a measurement circuit (432). The measurement circuit is coupled to receive a first input signal (903) from a first antenna (128) of a transmitter and coupled to receive a second input signal (913) from a second antenna (130) of the transmitter. Each of the first and second signals is transmitted at a first time. The measurement circuit produces an output signal corresponding to a magnitude of the first and second signals. A control circuit (430) is coupled to receive the output signal and a reference signal. The control circuit is arranged to produce a control signal at a second time in response to a comparison of the output signal and the reference signal.

Owner:INTEL CORP

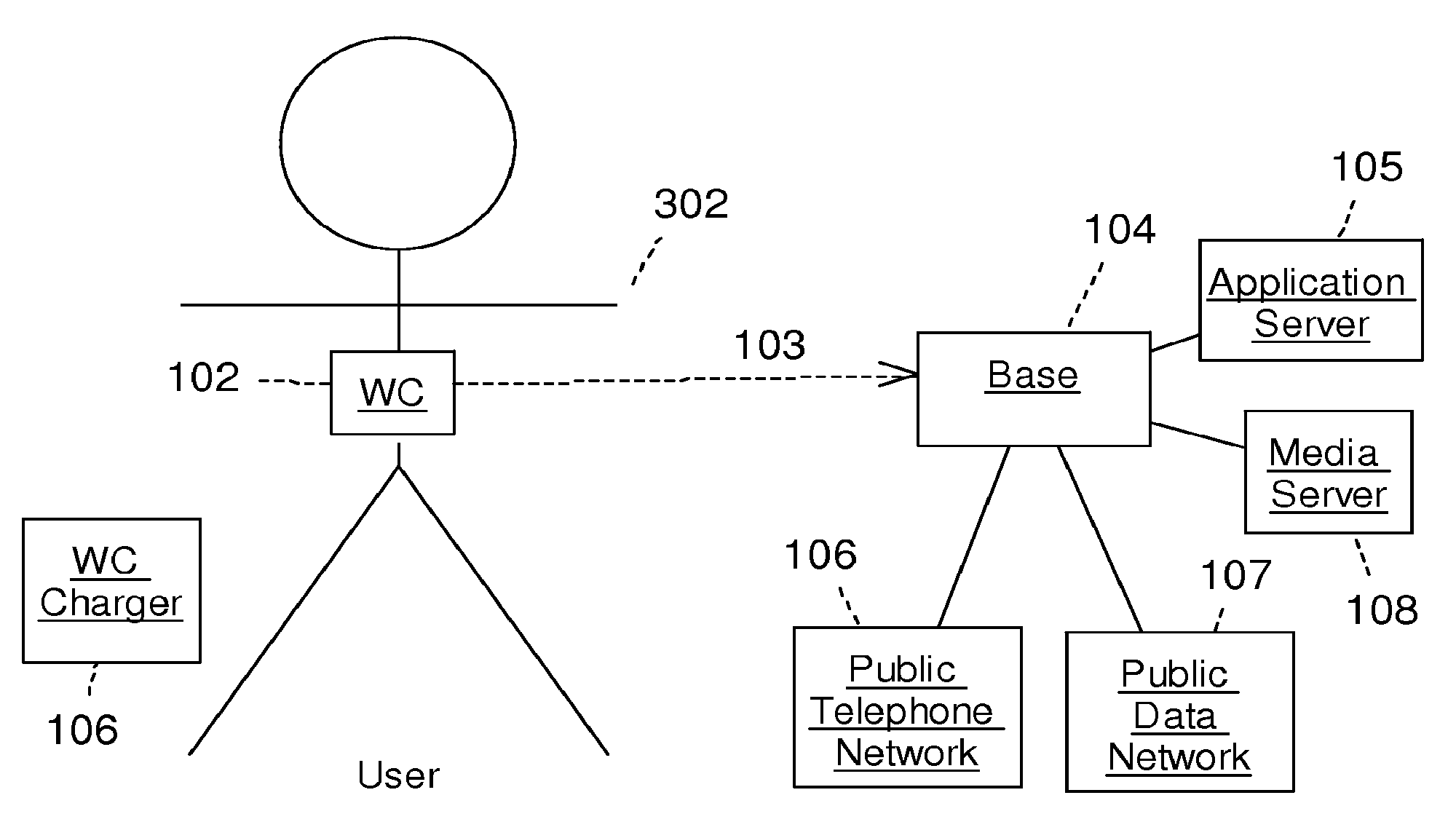

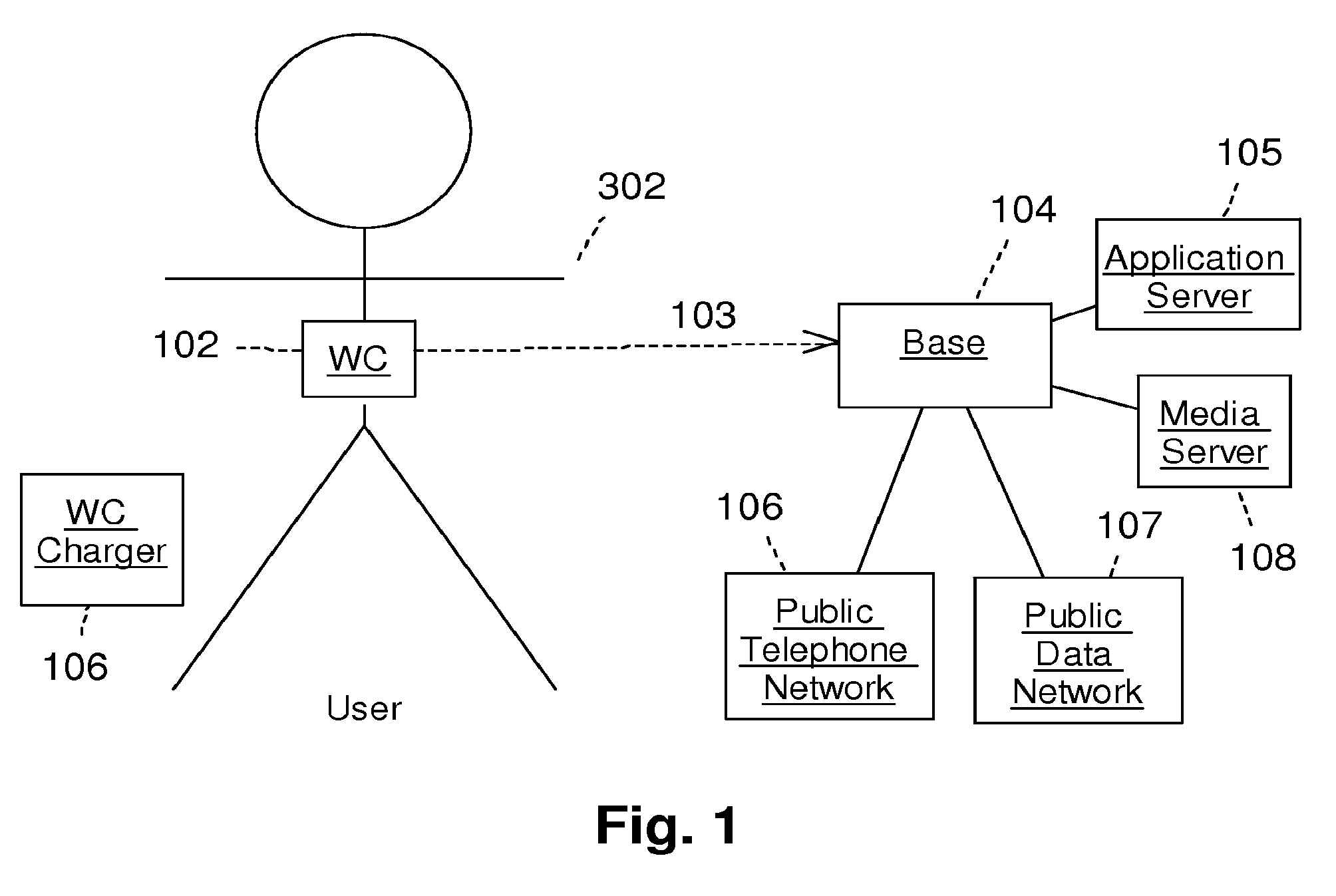

Power-optimized wireless communications device

InactiveUS20120010890A1Requires minimizationLong-term usePower managementSpeech analysisMicrocontrollerPower application

The present invention is an Always On, Hands-free, Speech Activated, Power-optimized Wireless Communications Device with associated base. The unique value of the device is that a person can use the device at any time, 24×7, with hands-free operation. People can wear it 24×7 on their body either around their neck or on their wrist or wherever it best meets their needs. Speech activation provides greater convenience for the person in using the wireless communications device, and at the same time, it allows the microcontroller greater control of power consuming resources. The wireless communications device may host simple, low power applications. In addition, applications will reside in the base, and in an application (either voice or data) server that is accessed by the wireless communications base.

Owner:KOVERZIN RAYMOND CLEMENT

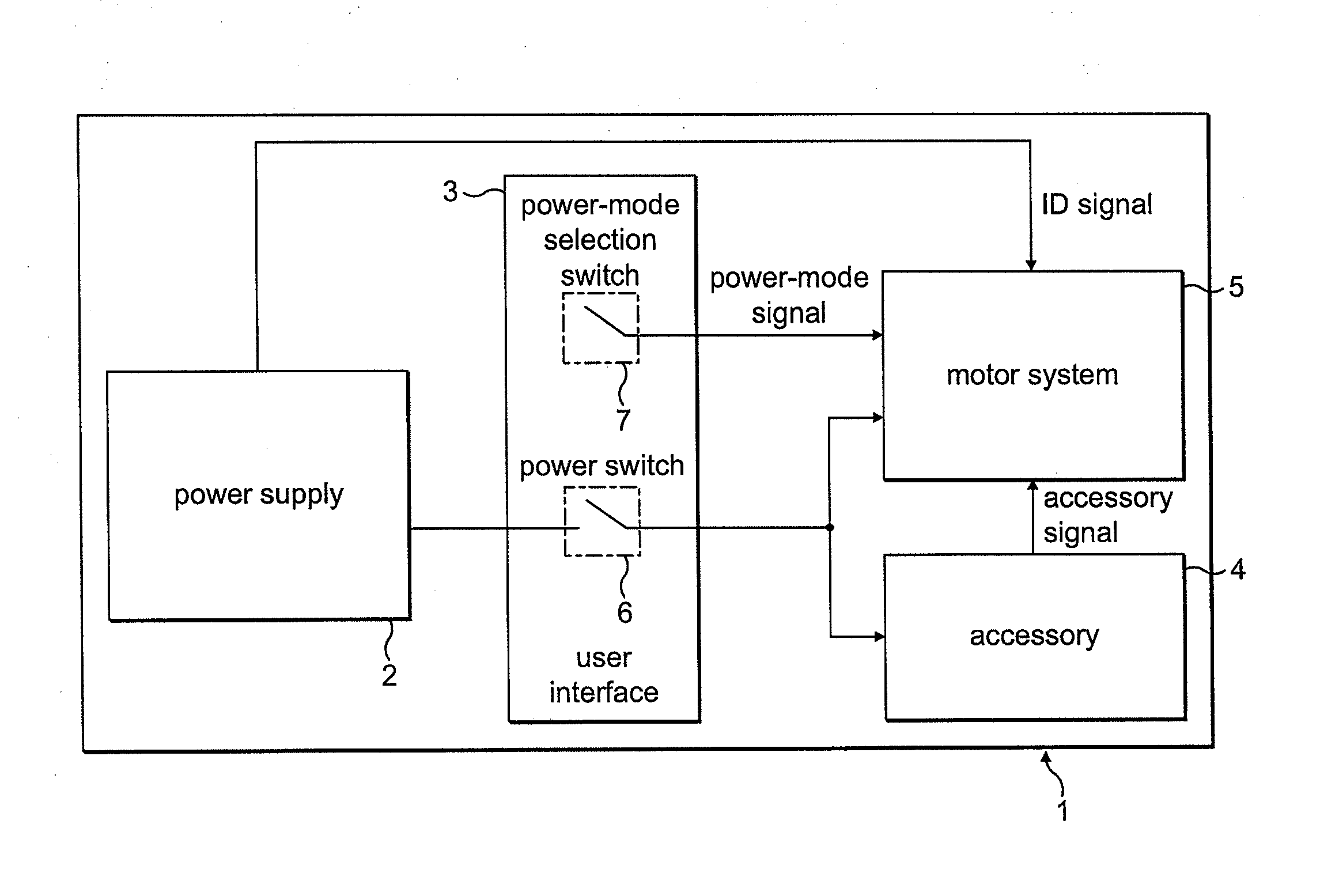

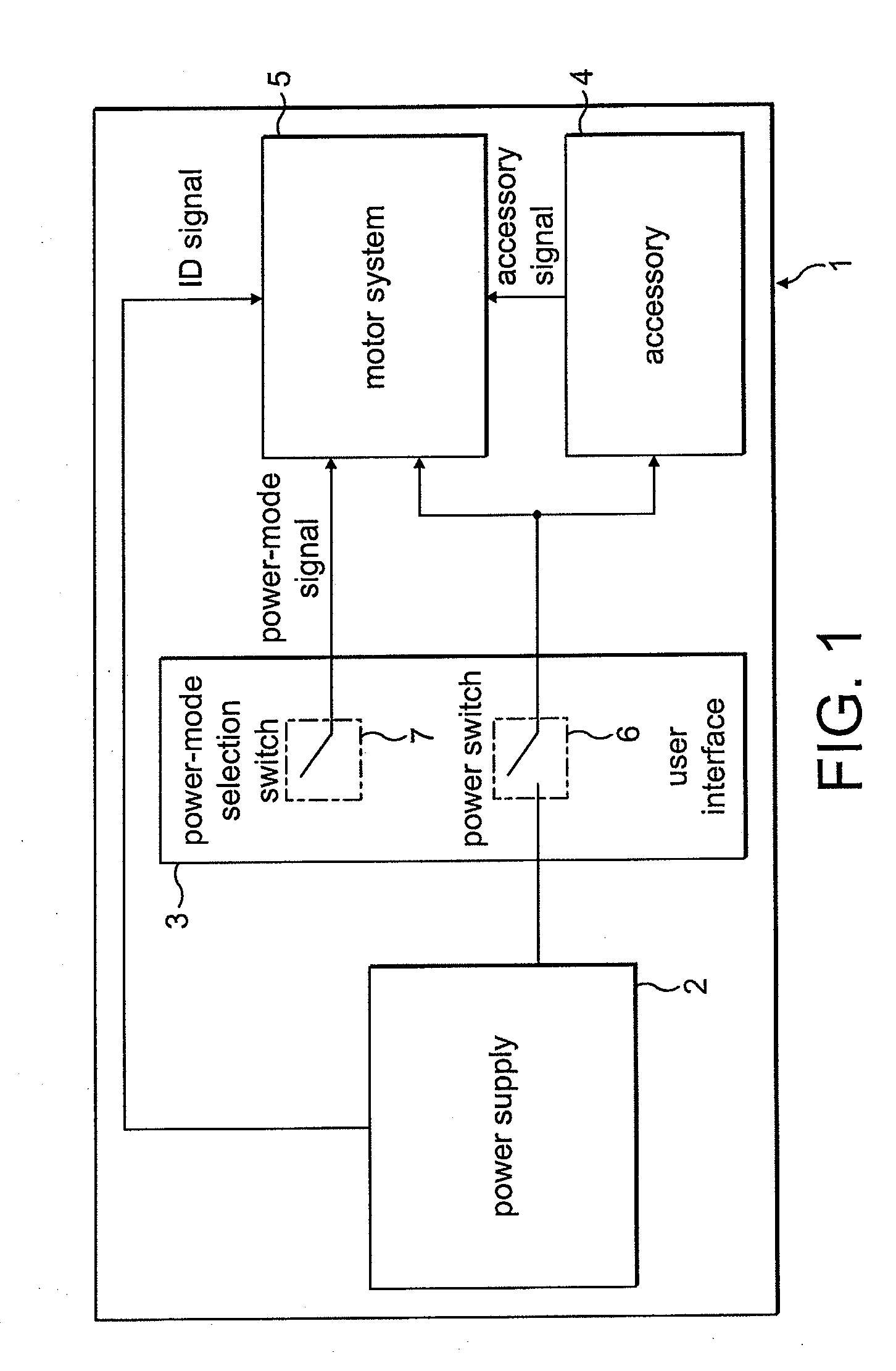

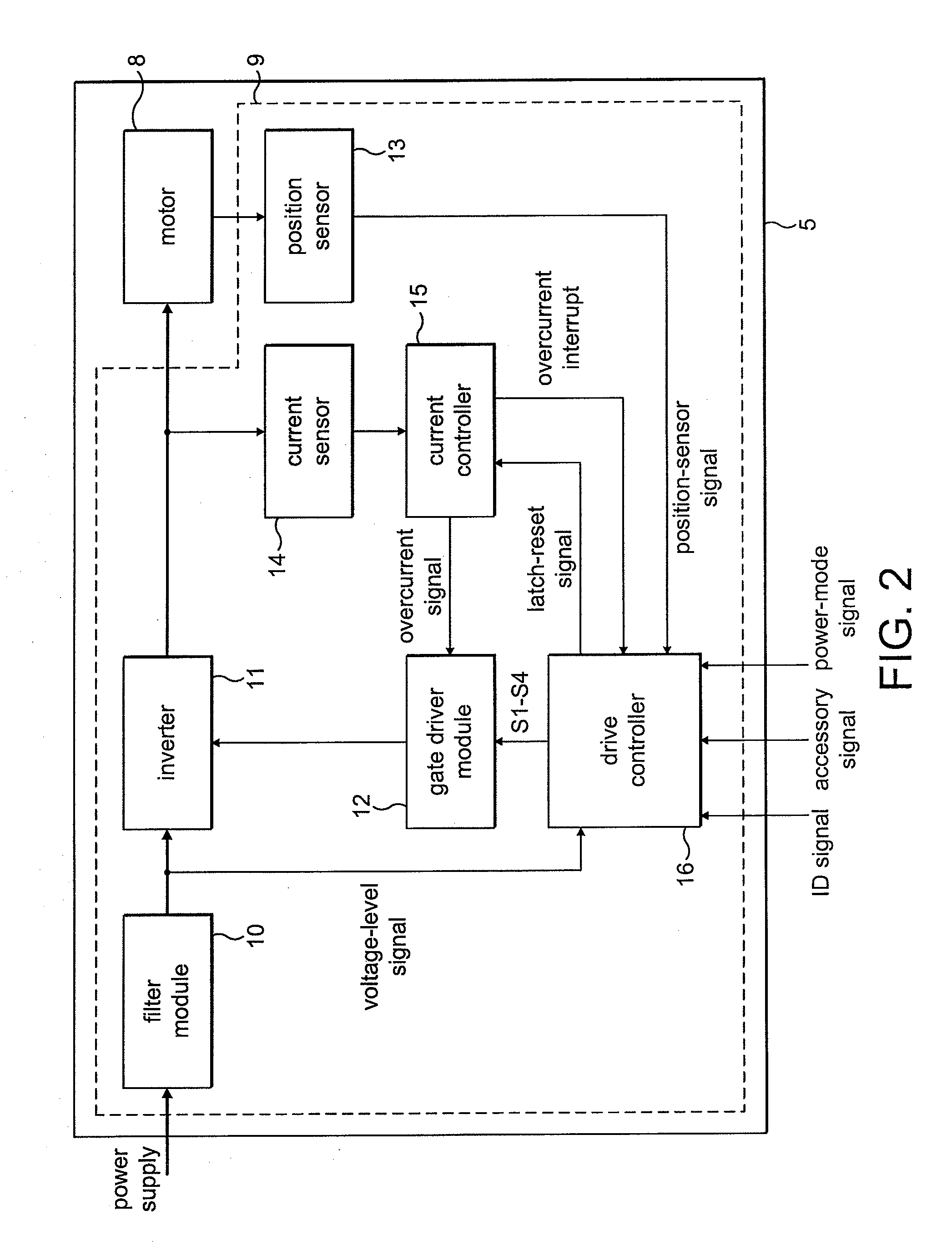

Control of an electric machine

ActiveUS20100253263A1Convenient power controlDecreasing freewheel angleMotor/generator/converter stoppersSynchronous motors startersFreewheelFree rotation

A method of controlling an electric machine that includes sequentially exciting and freewheeling a winding of the electric machine. The winding is excited by an excitation voltage and is freewheeled over a freewheel angle. The method then includes varying the freewheel angle in response to changes in the excitation voltage. Additionally, a control system for an electric machine, and a product incorporating the control system and electric machine.

Owner:DYSON TECH LTD

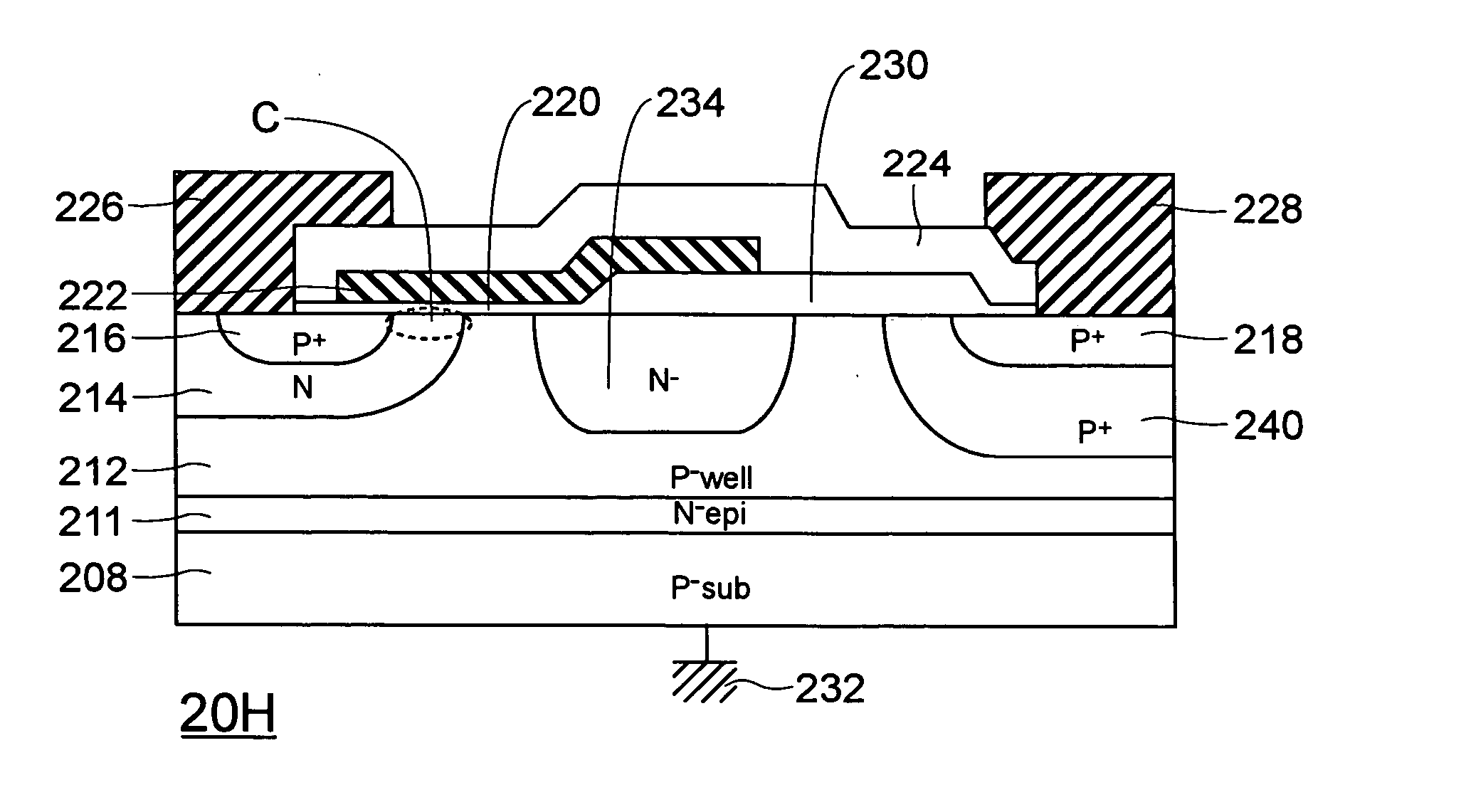

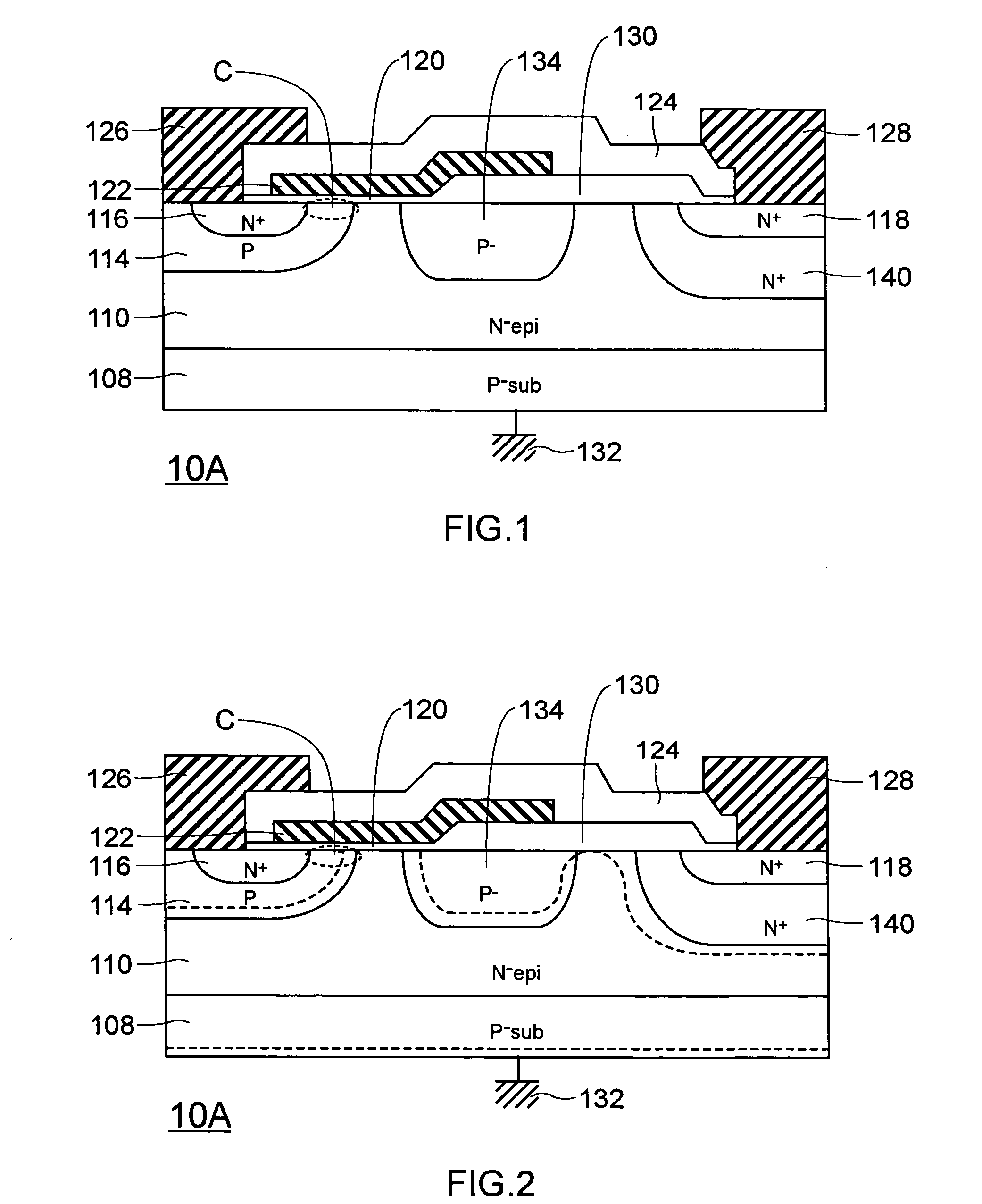

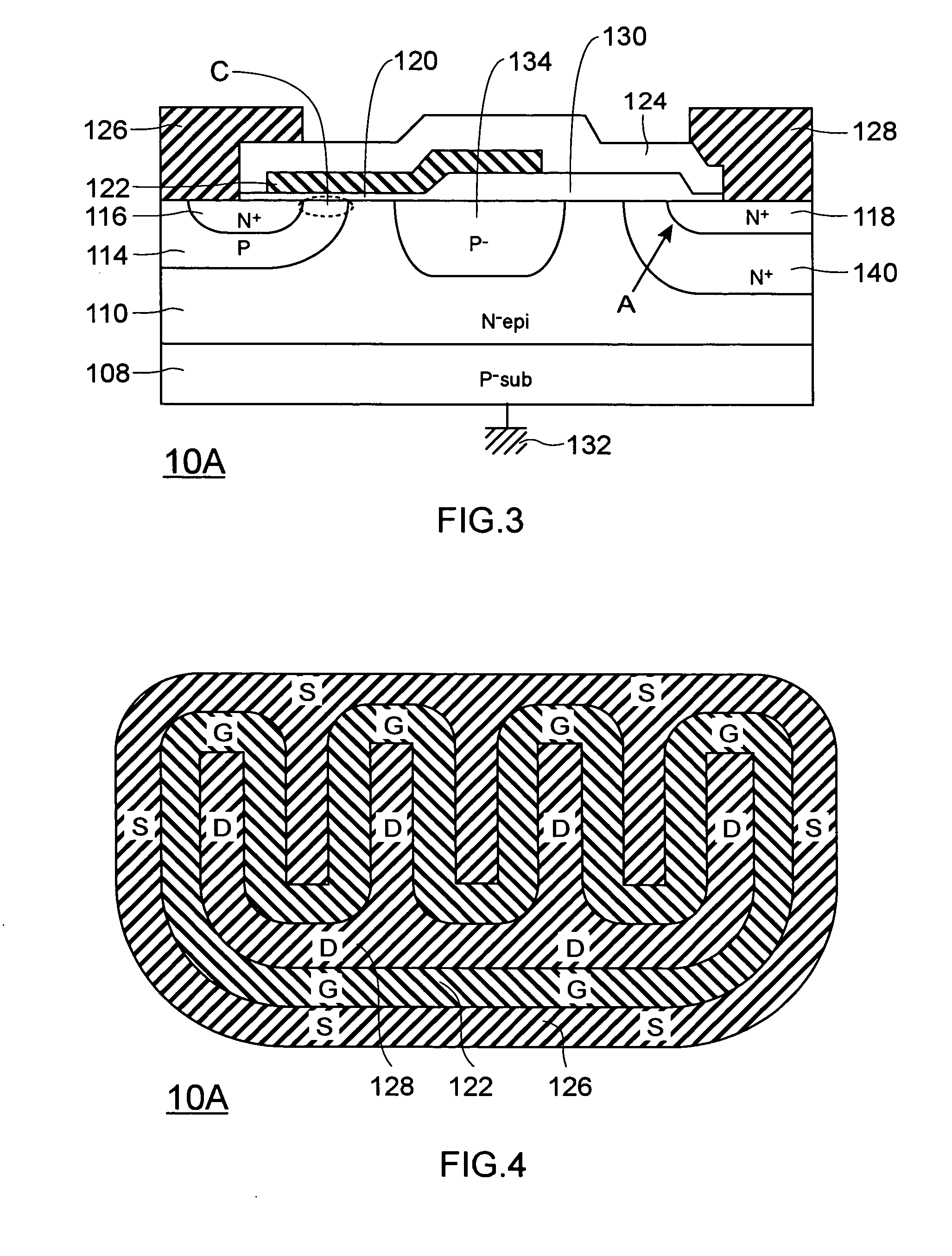

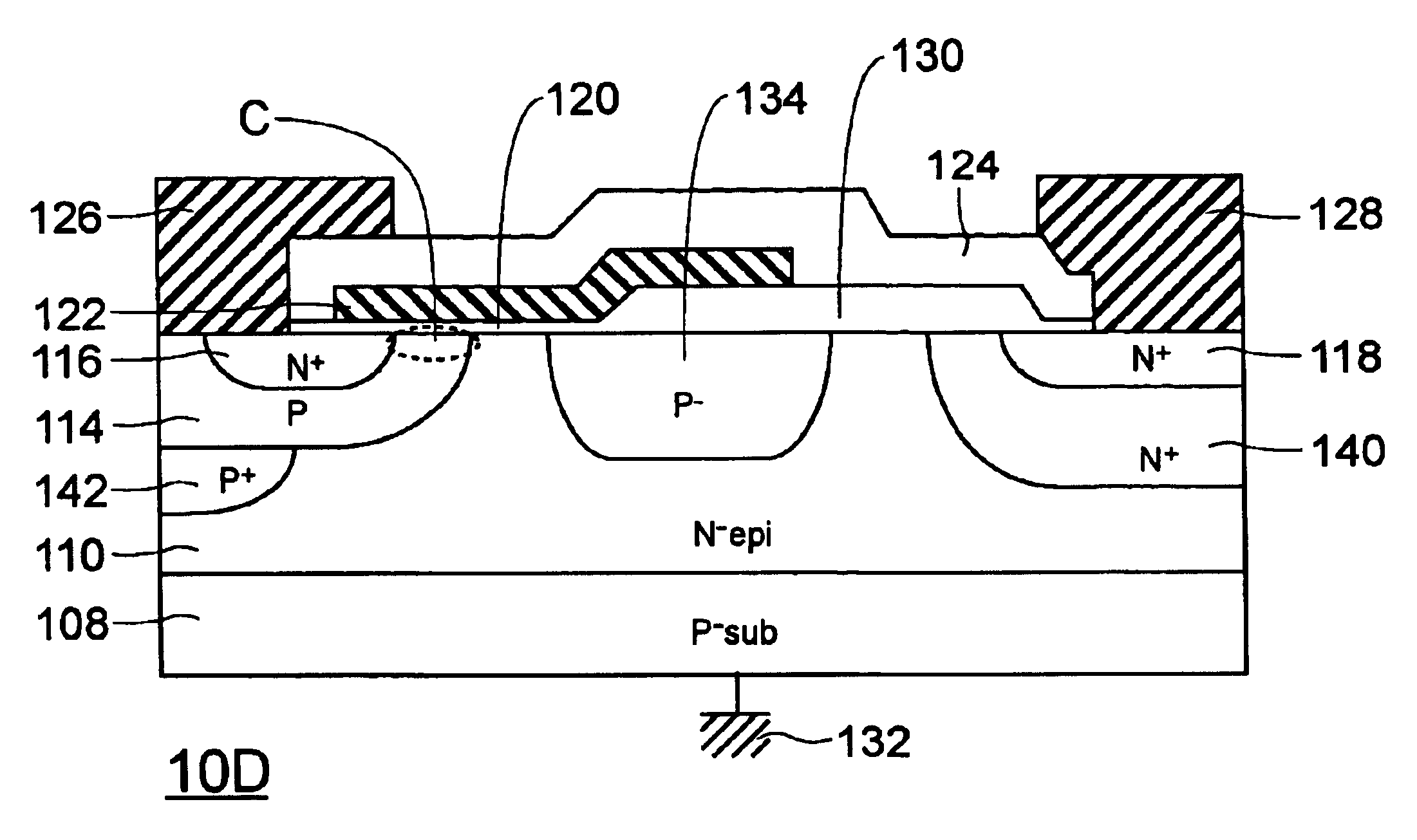

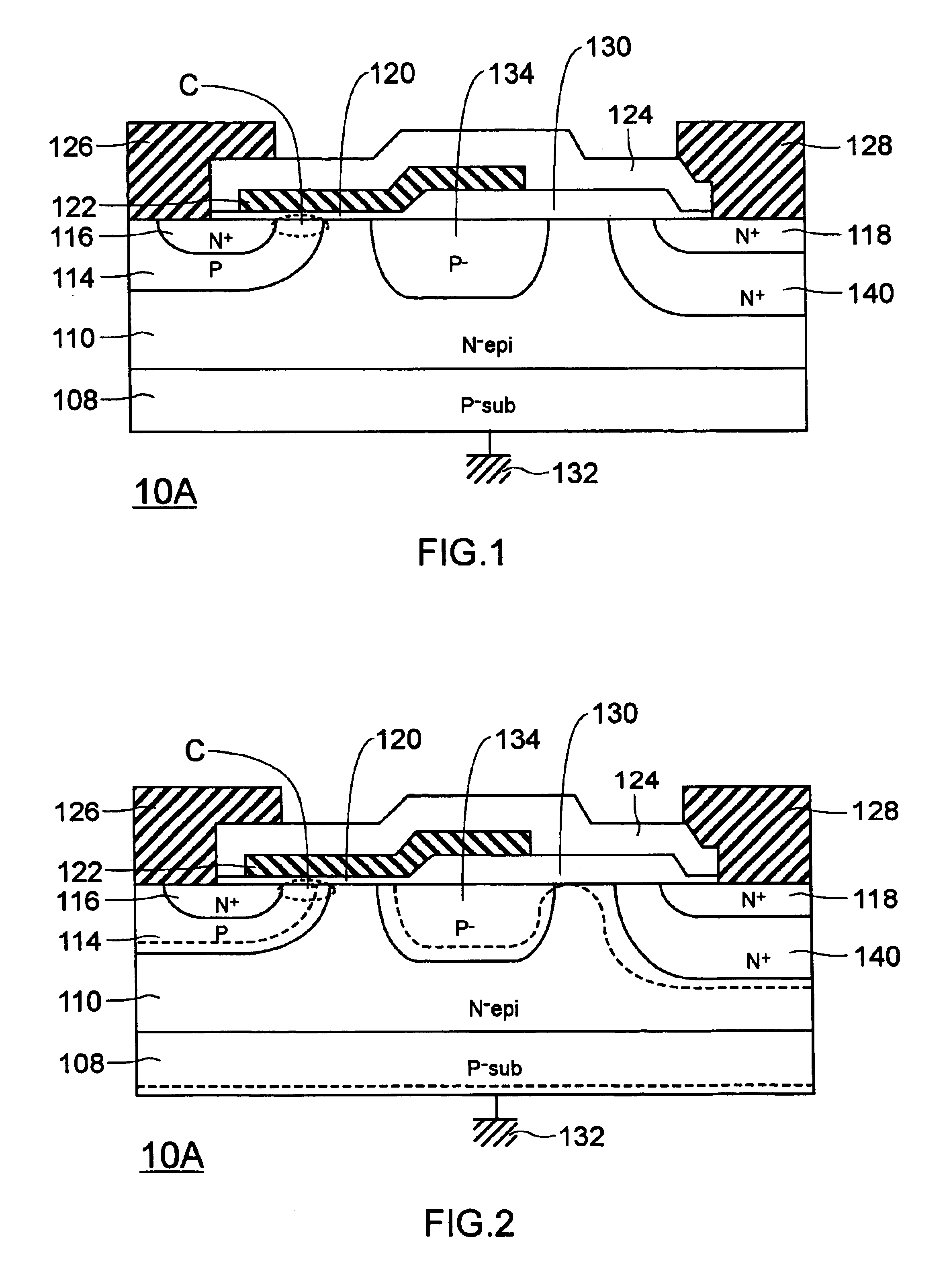

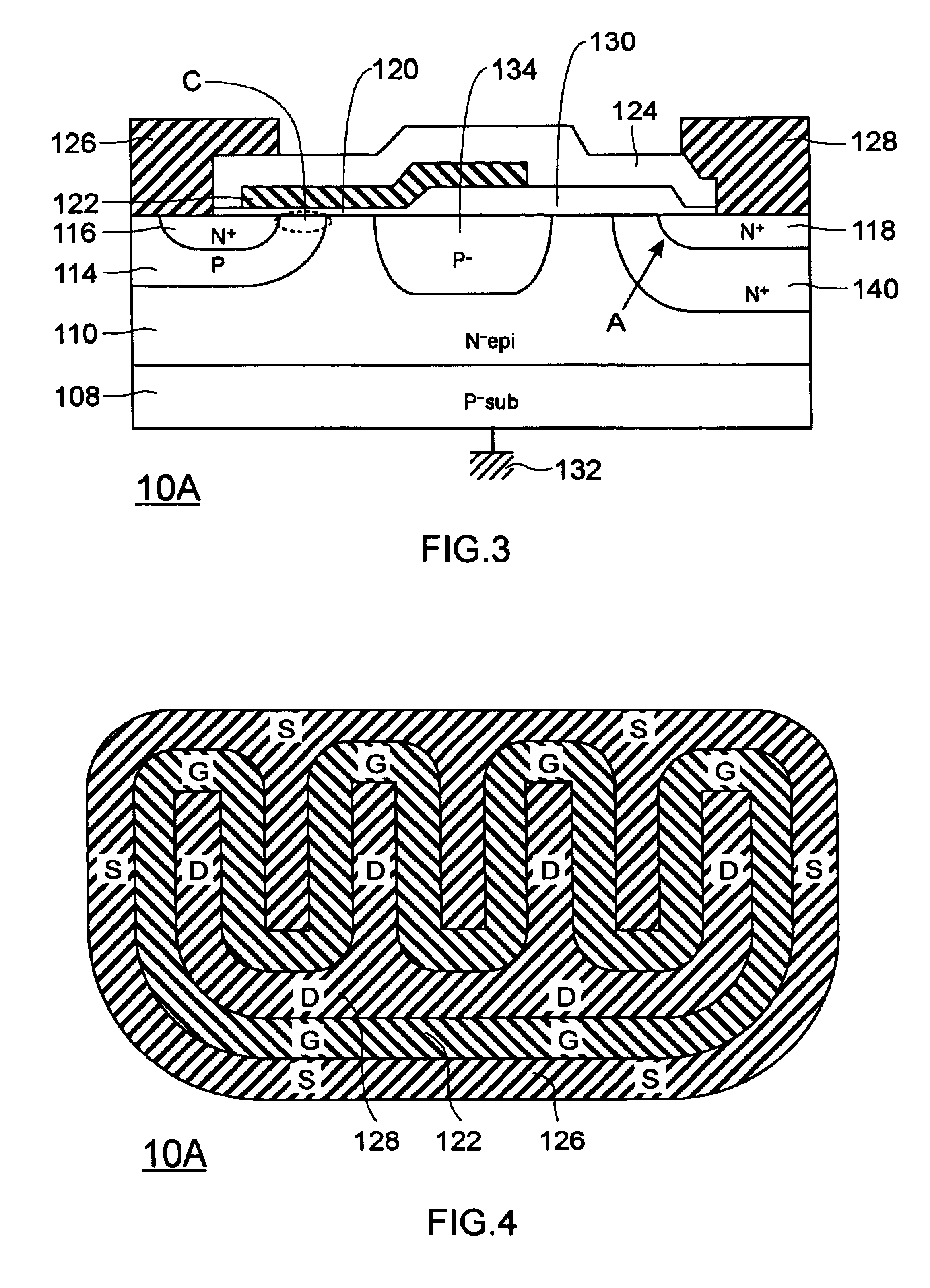

Lateral short-channel dmos, method of manufacturing the same, and semiconductor device

InactiveUS20050062125A1Lower resistanceReduce resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationDevice material

A lateral short-channel DMOS according to the present invention is a lateral short-channel DMOS in which an N−-type semiconductor region is formed, with the surface of the N−-type semiconductor region becoming almost completely depleted during reverse bias. The lateral short-channel DMOS 10A according to the present invention includes an N−-type epitaxial layer 110 that is formed in one surface of a P−-type semiconductor substrate 108, a P-type well 114 that is formed in the surface of the N−-type epitaxial layer 110 and includes a channel forming region C, an N+-type source region 116 that is formed in a surface of the P-type well 114, an N+-type drain region 118 formed in a surface of the N−-type epitaxial layer 110, and a gate electrode 122 formed via a gate insulating film 120 in at least an upper part of the channel forming region C out of a region from the N+-type source region 116 to the N+-type drain region 118. The lateral short-channel DMOS 10A according to the present invention also includes an N+-type well 140 that is formed in a surface of the N-type epitaxial layer 110 and includes a higher concentration of N-type dopant than the N−-type epitaxial layer 110 and a lower concentration of N-type dopant than the N+-type drain region 118, with the N+-type drain region 118 being formed in a surface of this N+-type well 140. As described above, according to the present invention, ON resistance is reduced while maintaining high breakdown characteristics, so that it is possible to provide a lateral short-channel DMOS with high breakdown characteristics and superior current driving characteristics.

Owner:SHINDENGEN ELECTRIC MFG CO LTD

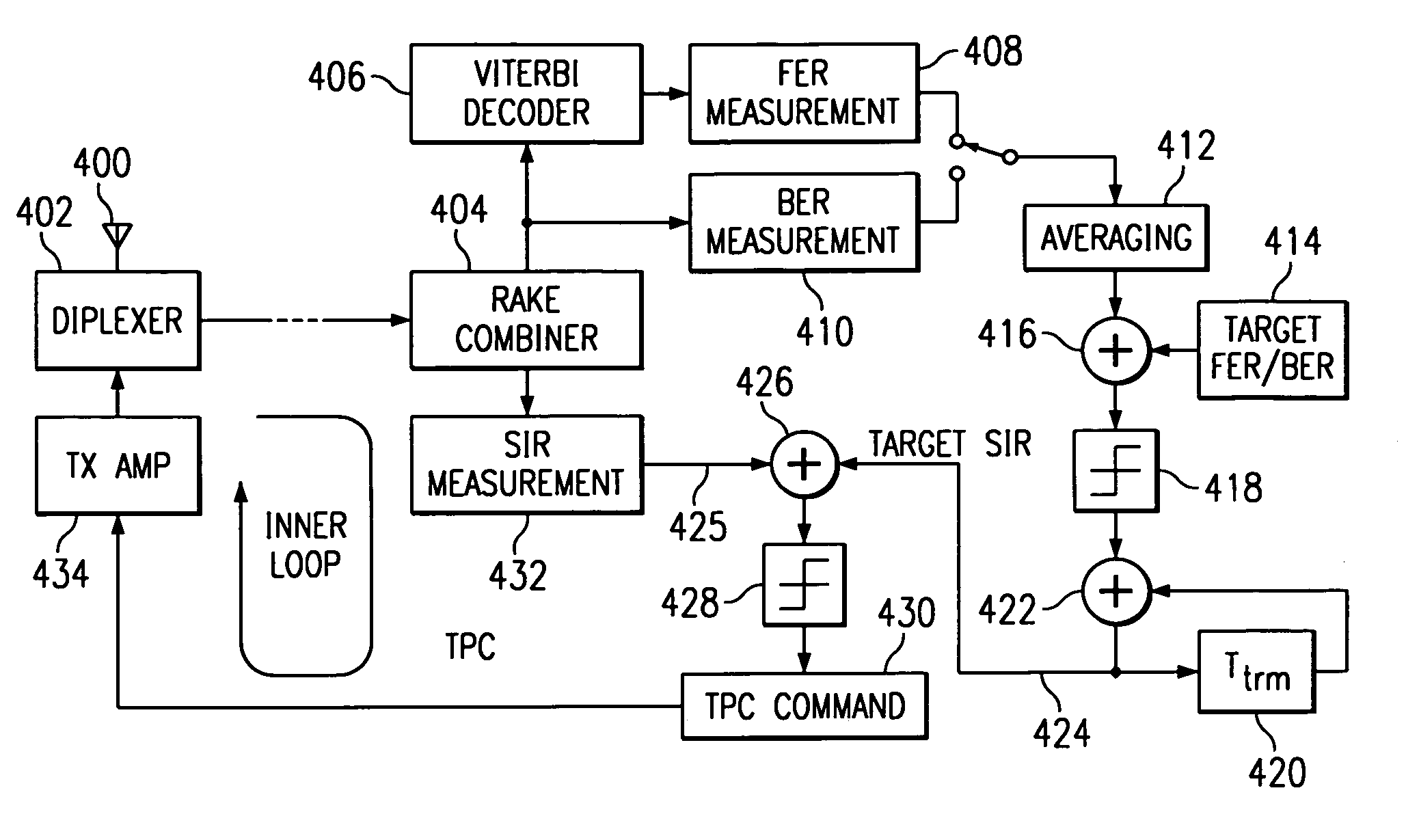

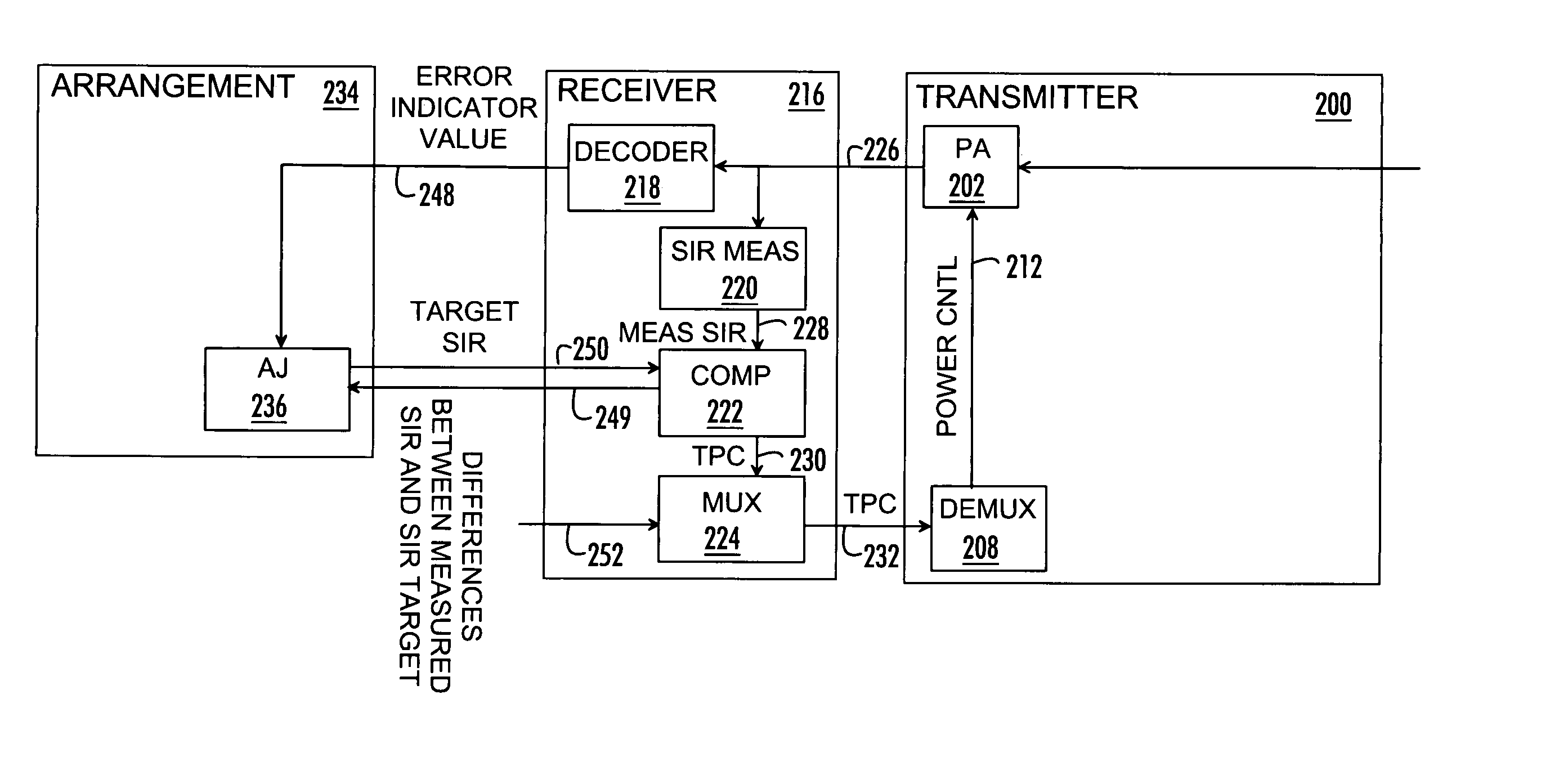

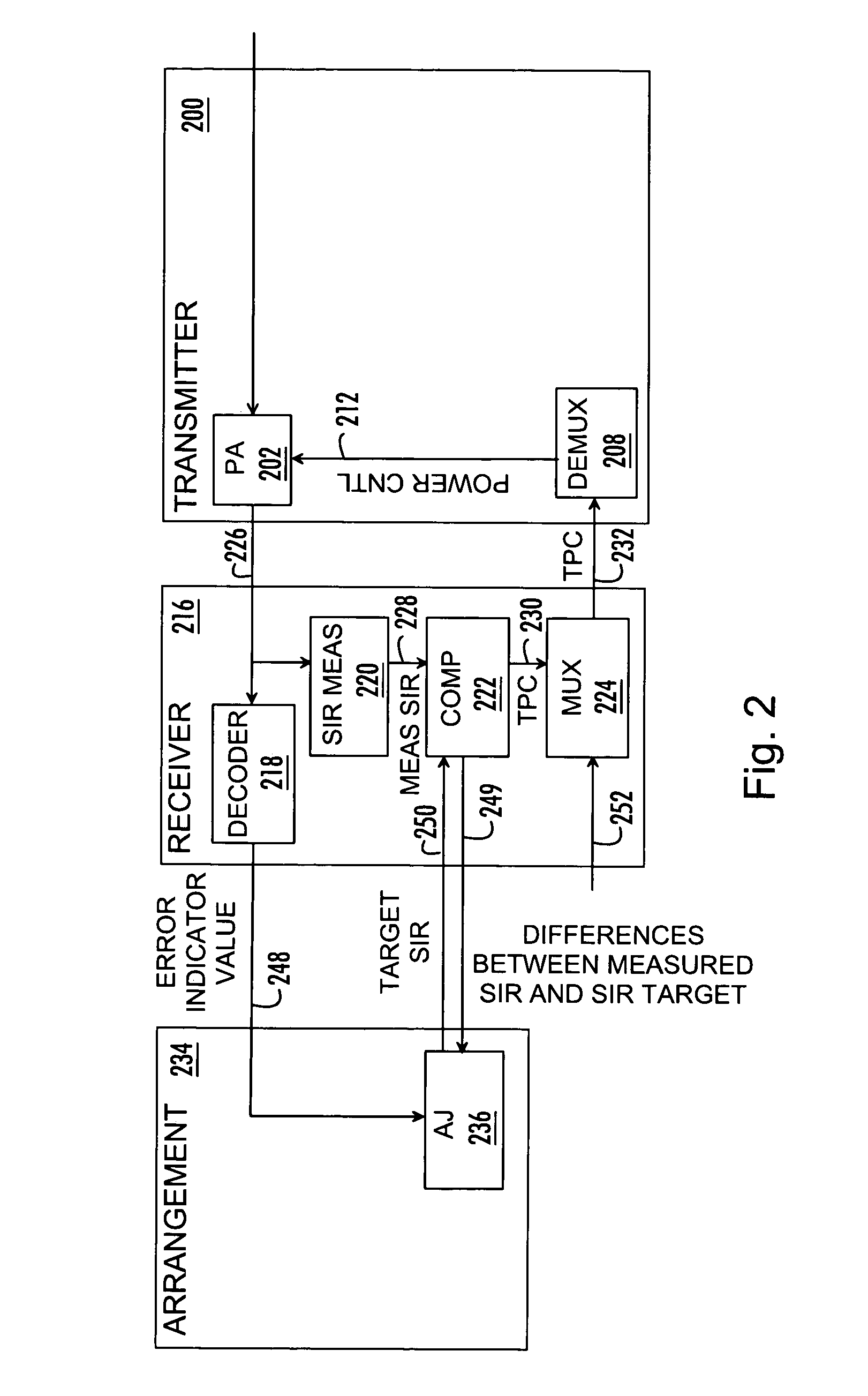

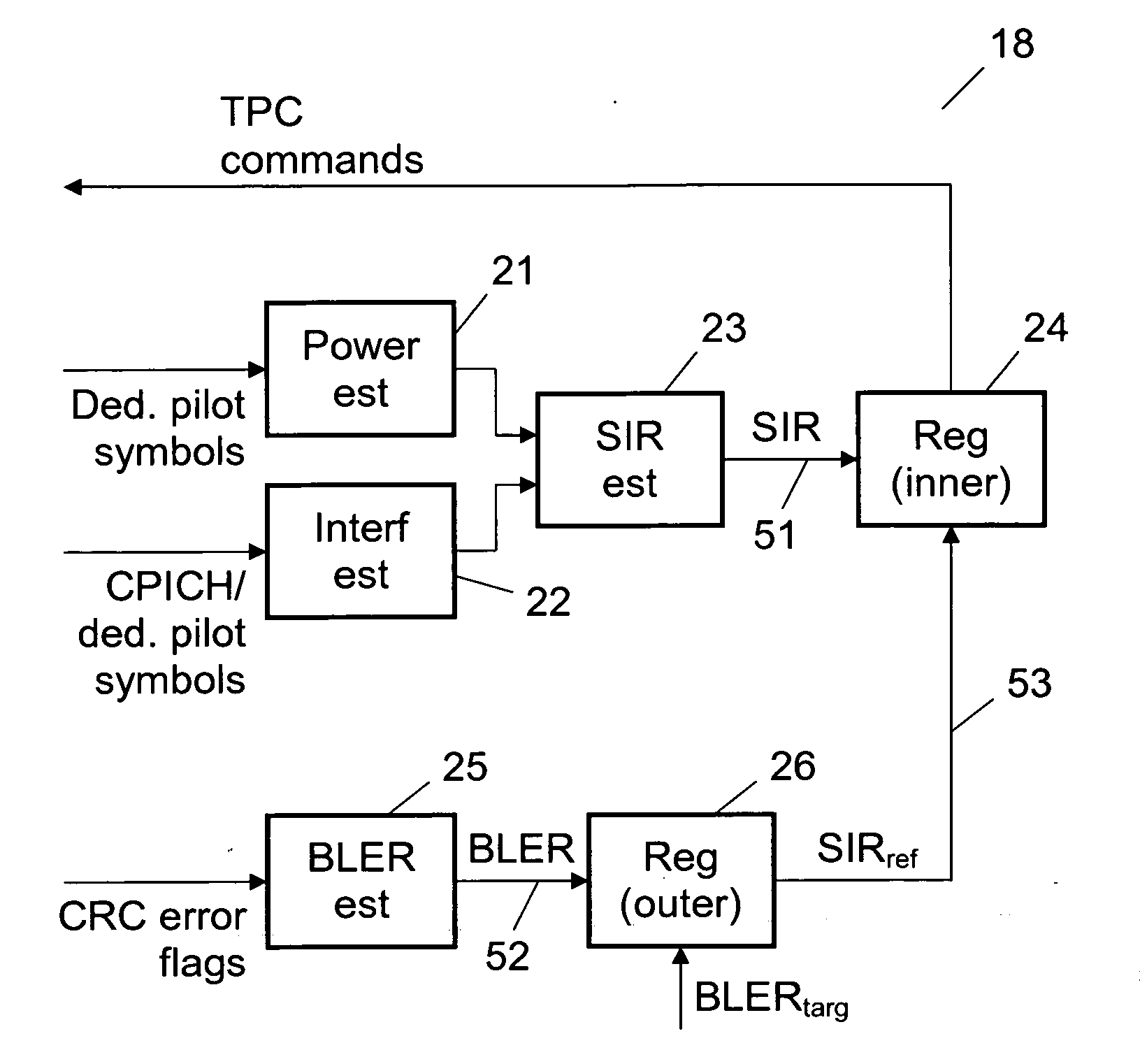

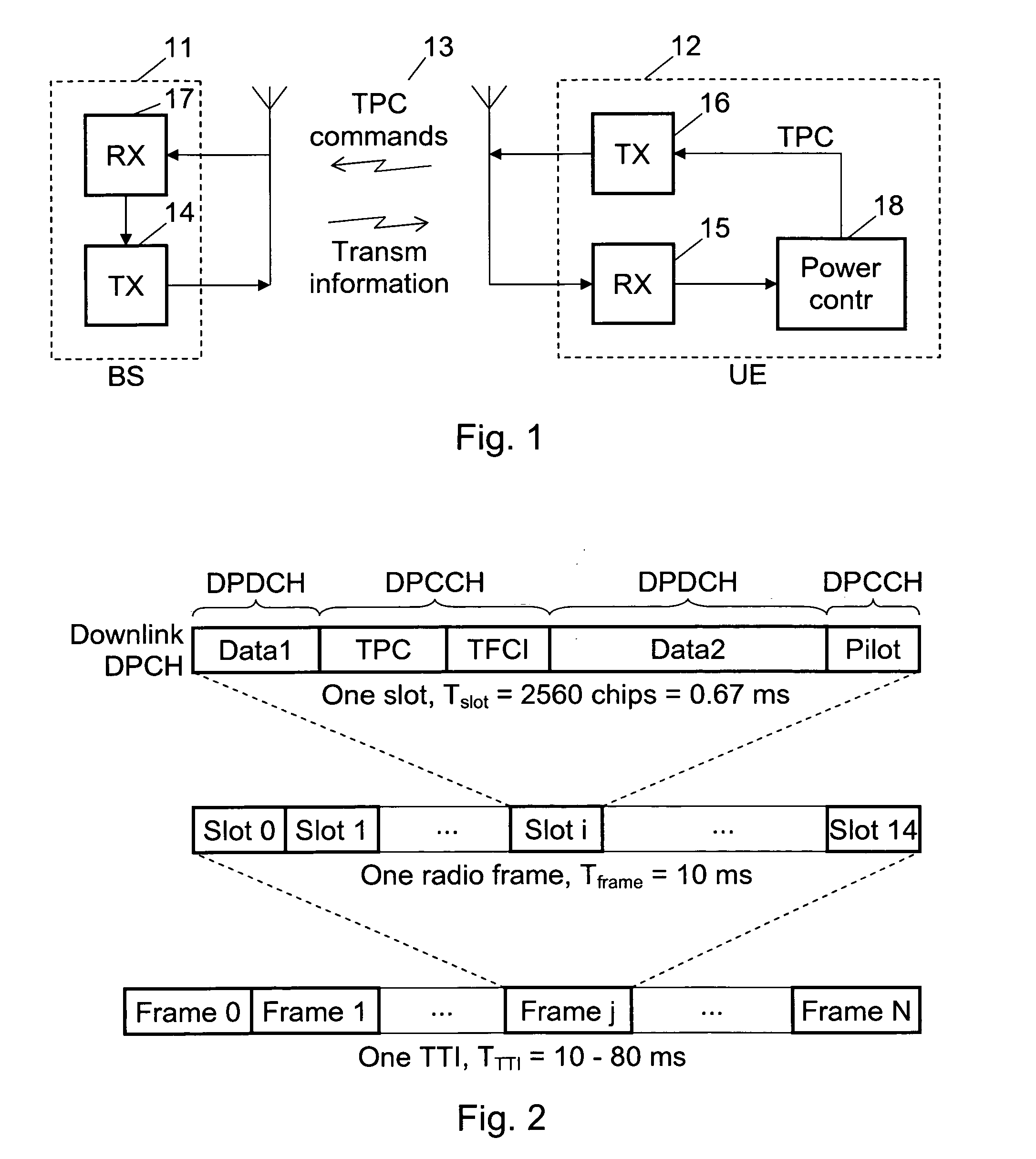

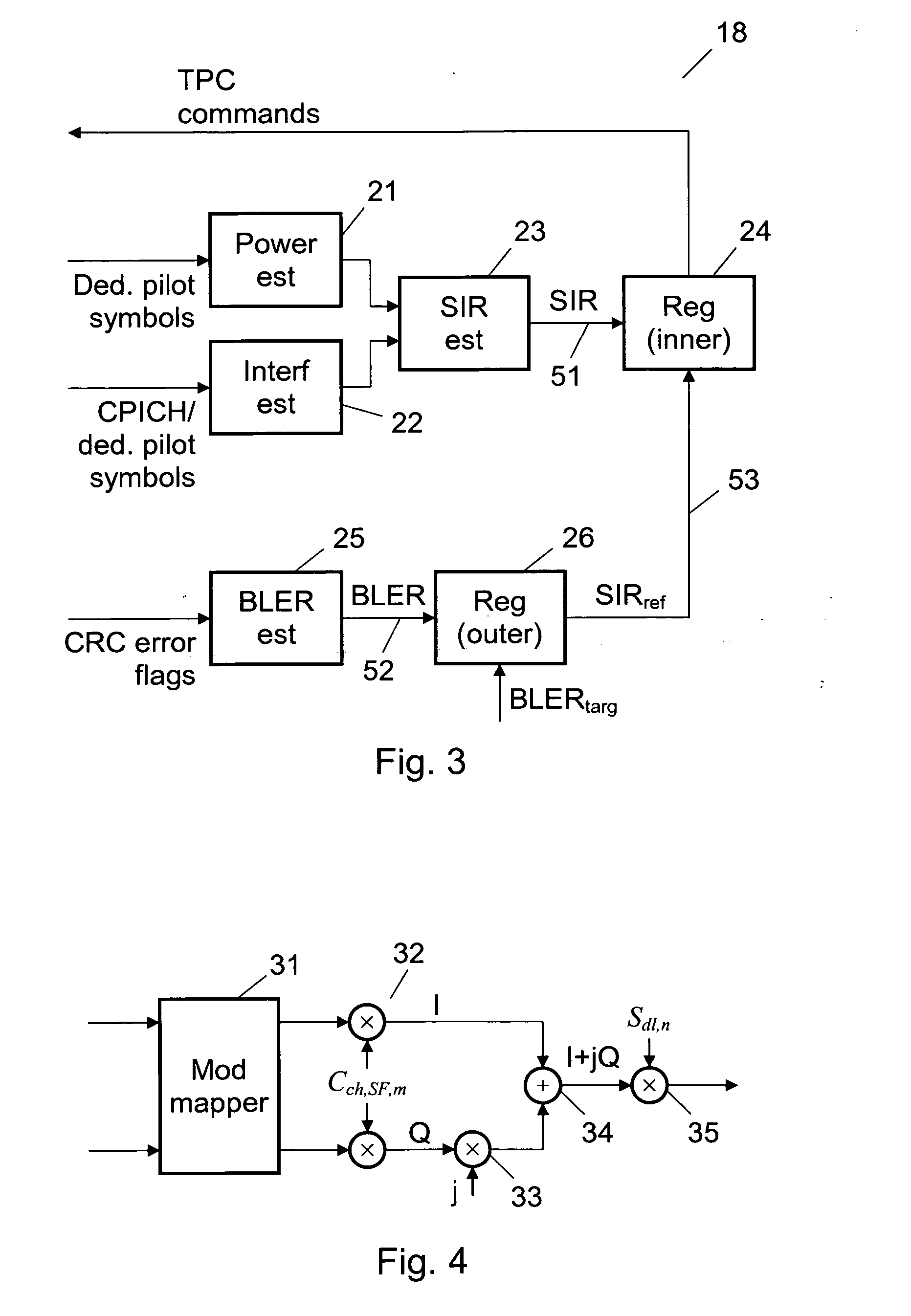

Transmit power control method and radio arrangement

InactiveUS20050143012A1Convenient power controlReduce transmit powerPower managementTransmission control/equalisingCoding blockTransmitted power

A radio and a transmit power control method in a radio system supporting a use of coding blocks in communication between a base station and user equipment is disclosed. The method comprises producing a measured SIR (signal-to-interference ratio) value and compares the measured SIR value with the target SIR value. Accordingly, the method also comprises determining the quality of the received coding blocks. The method also comprising storing samples of the differences between the measured SIR value and the target SIR value. The method also comprises adjusting the target SIR value based on the values of the samples of differences between the measured SIR value and the target SIR value and the quality of the received coding block. The method also comprises providing a transmit power control command based on the adjusted target SIR value to the user equipment.

Owner:NOKIA CORP

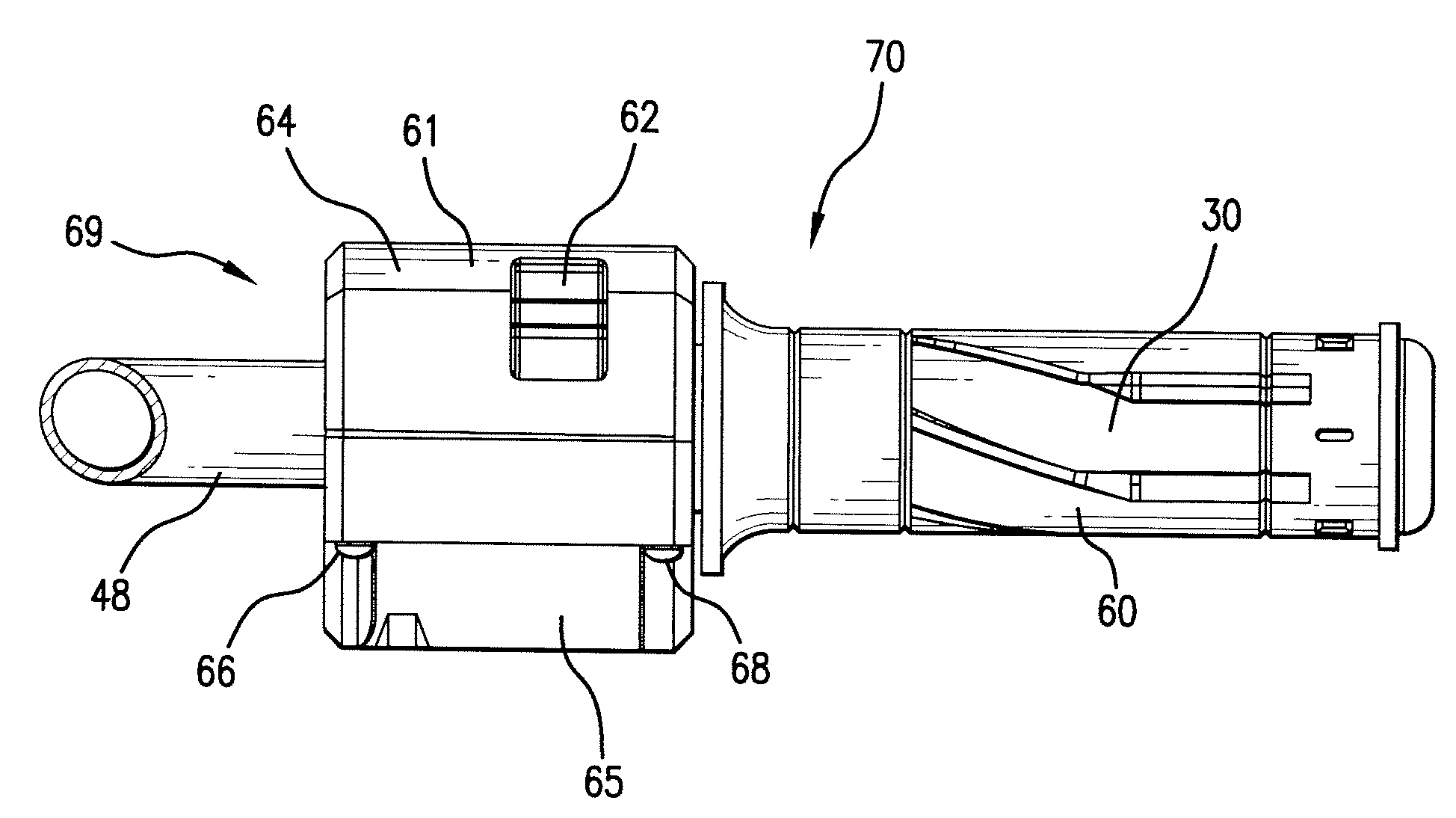

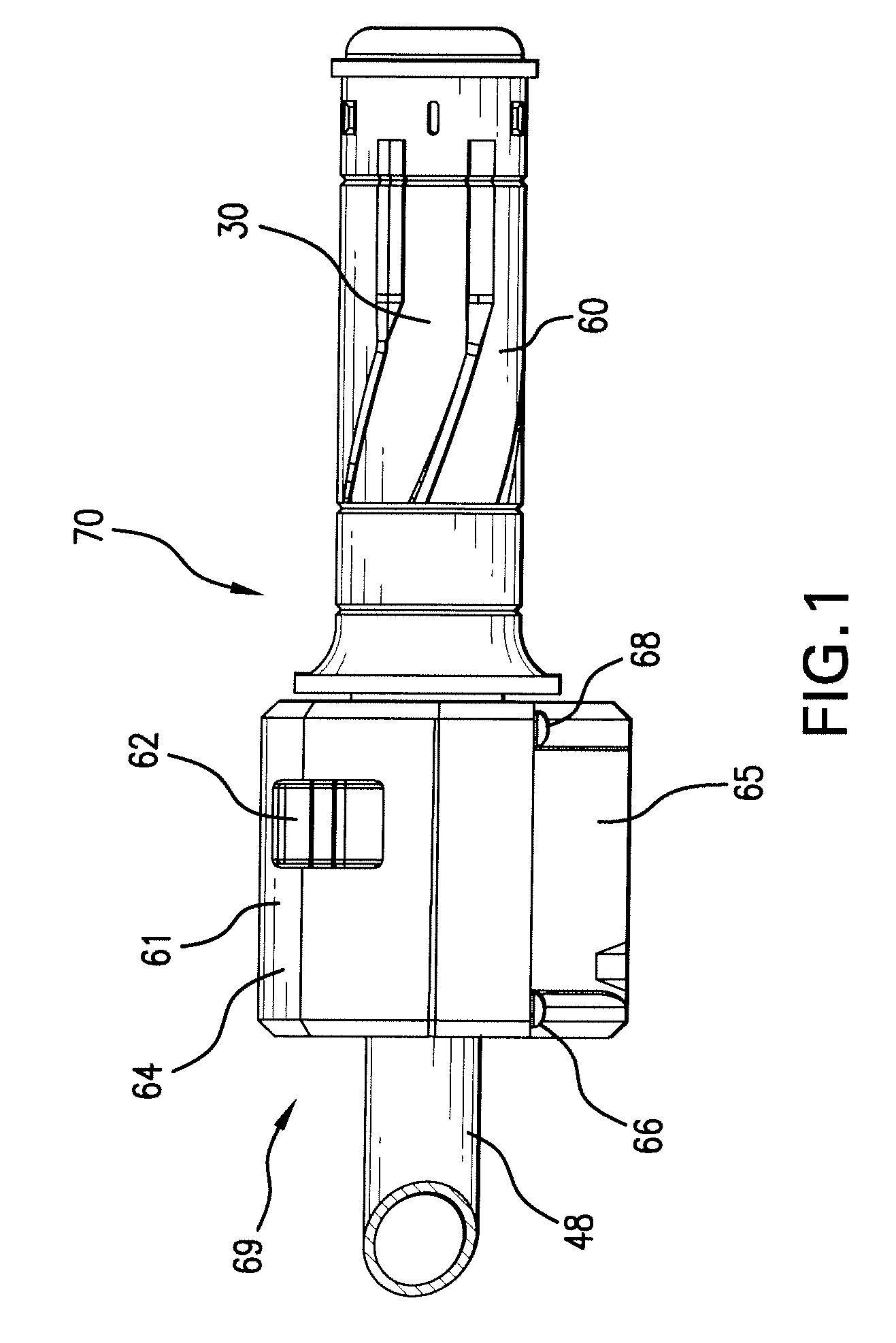

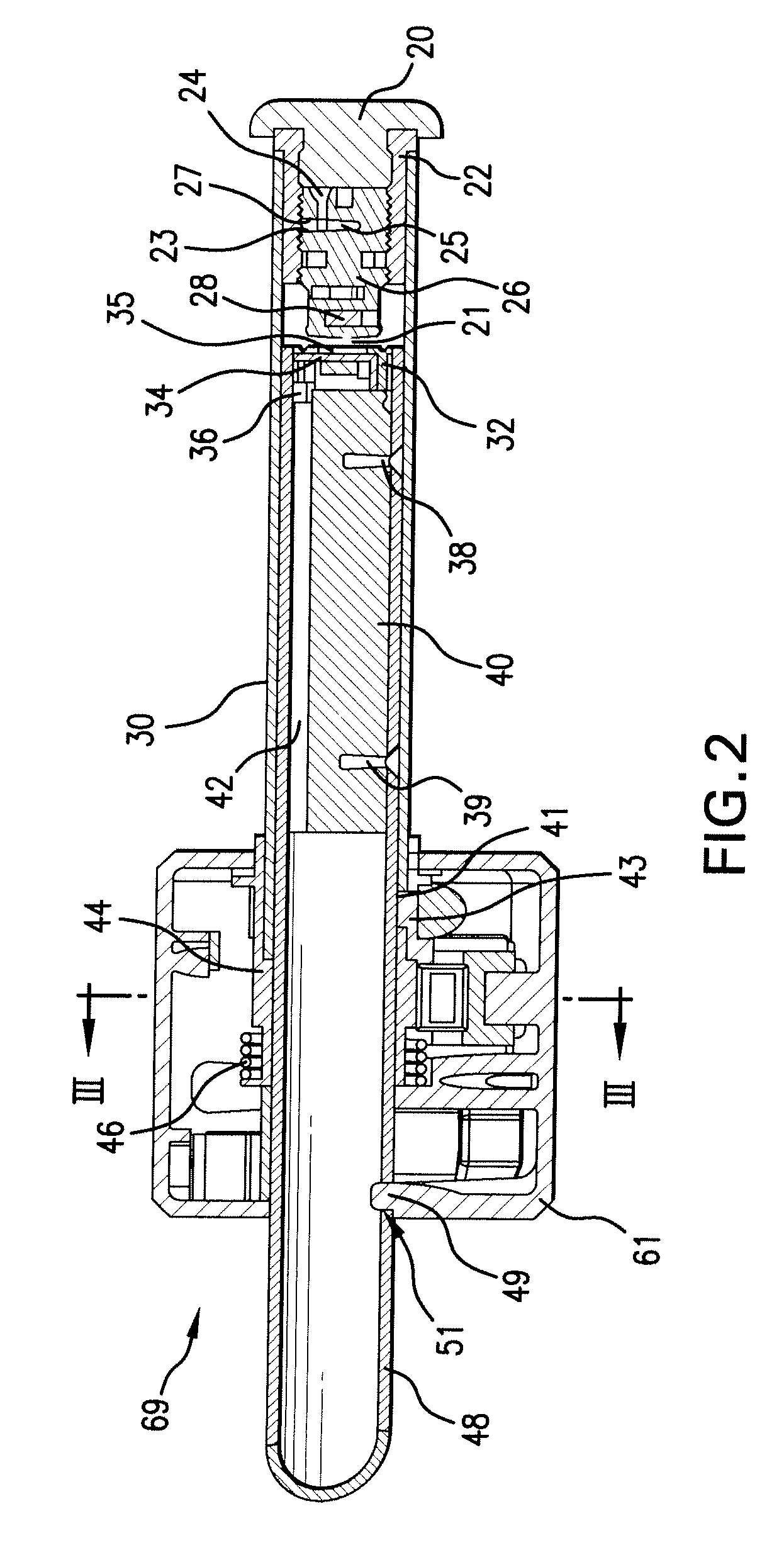

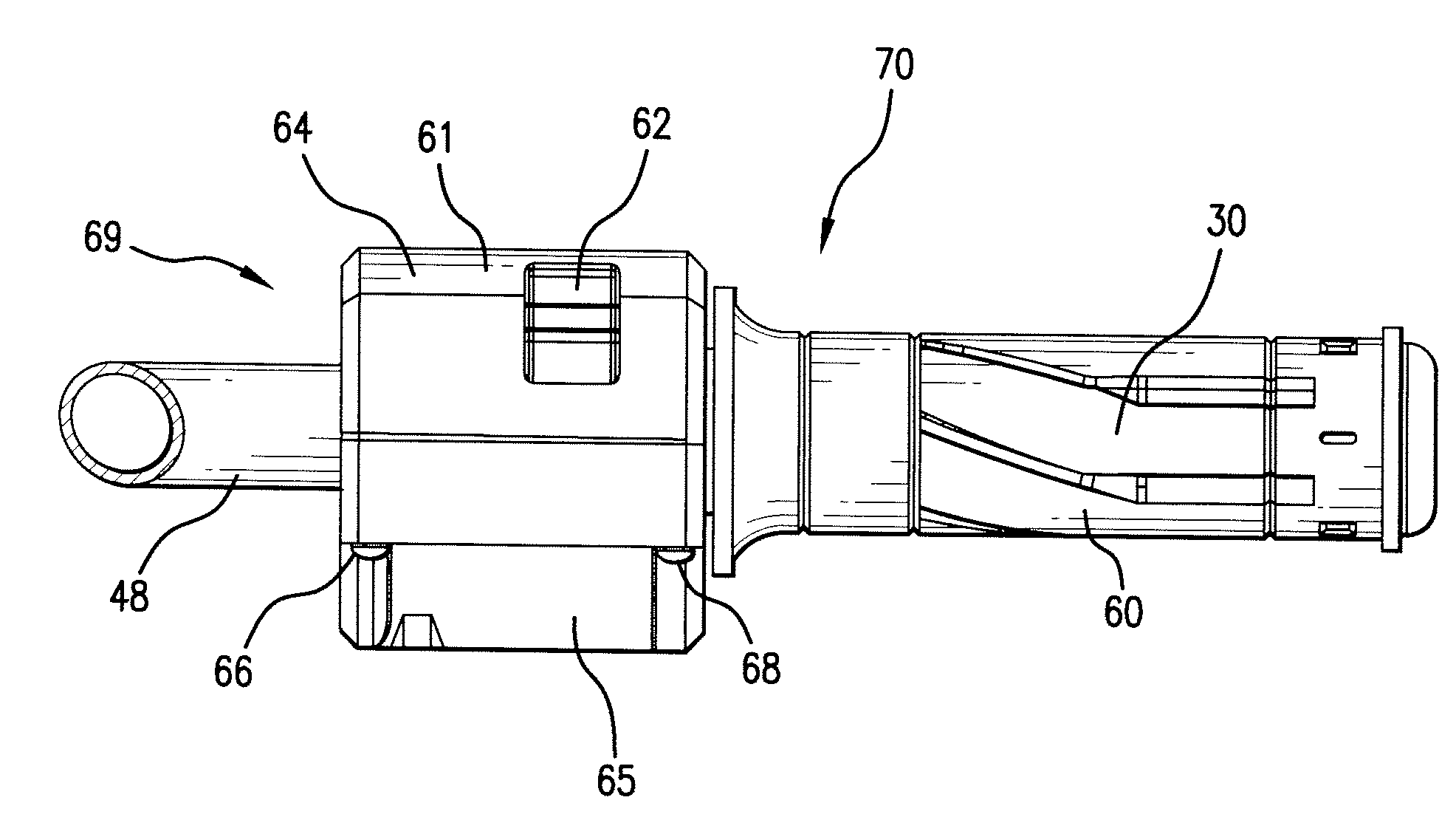

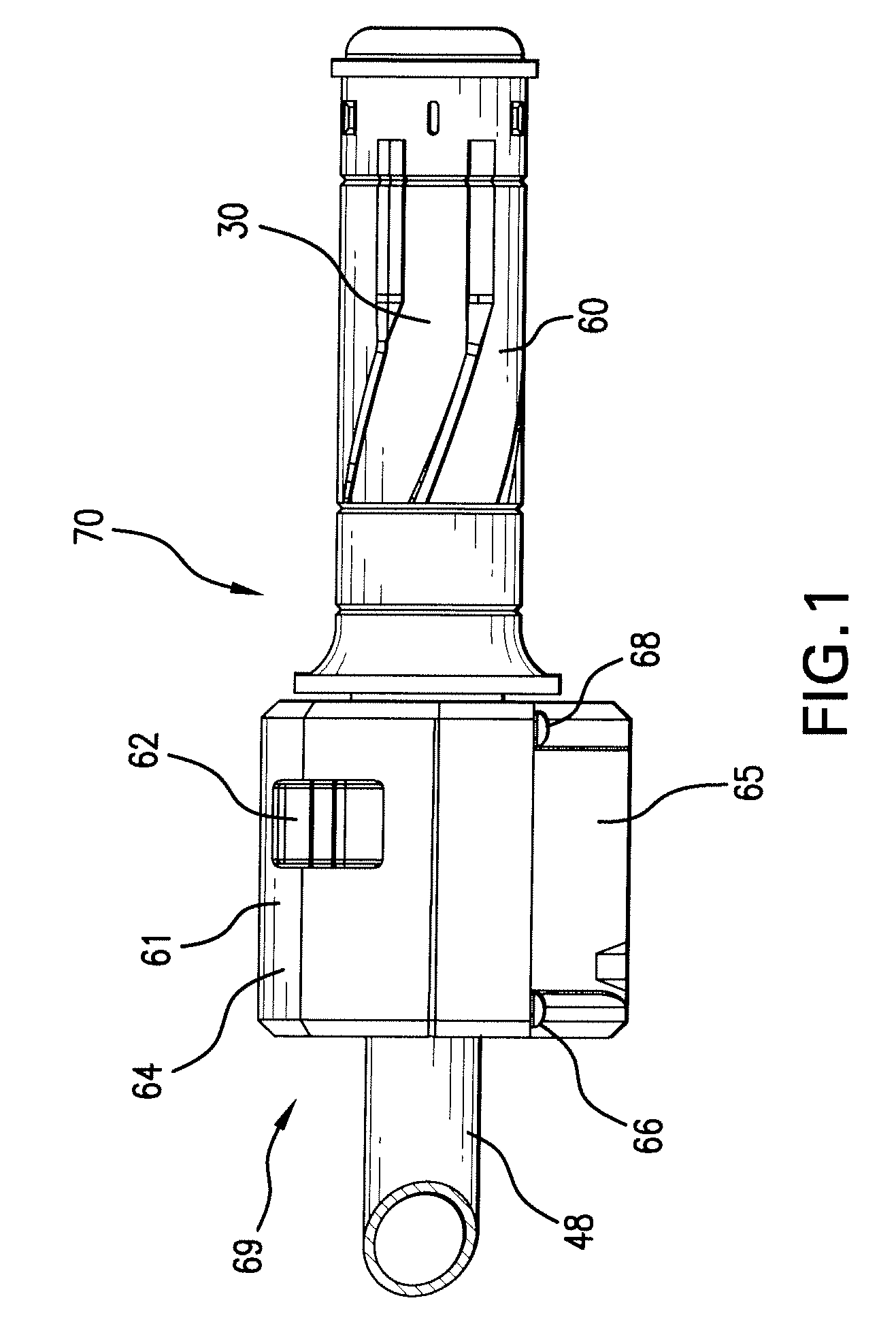

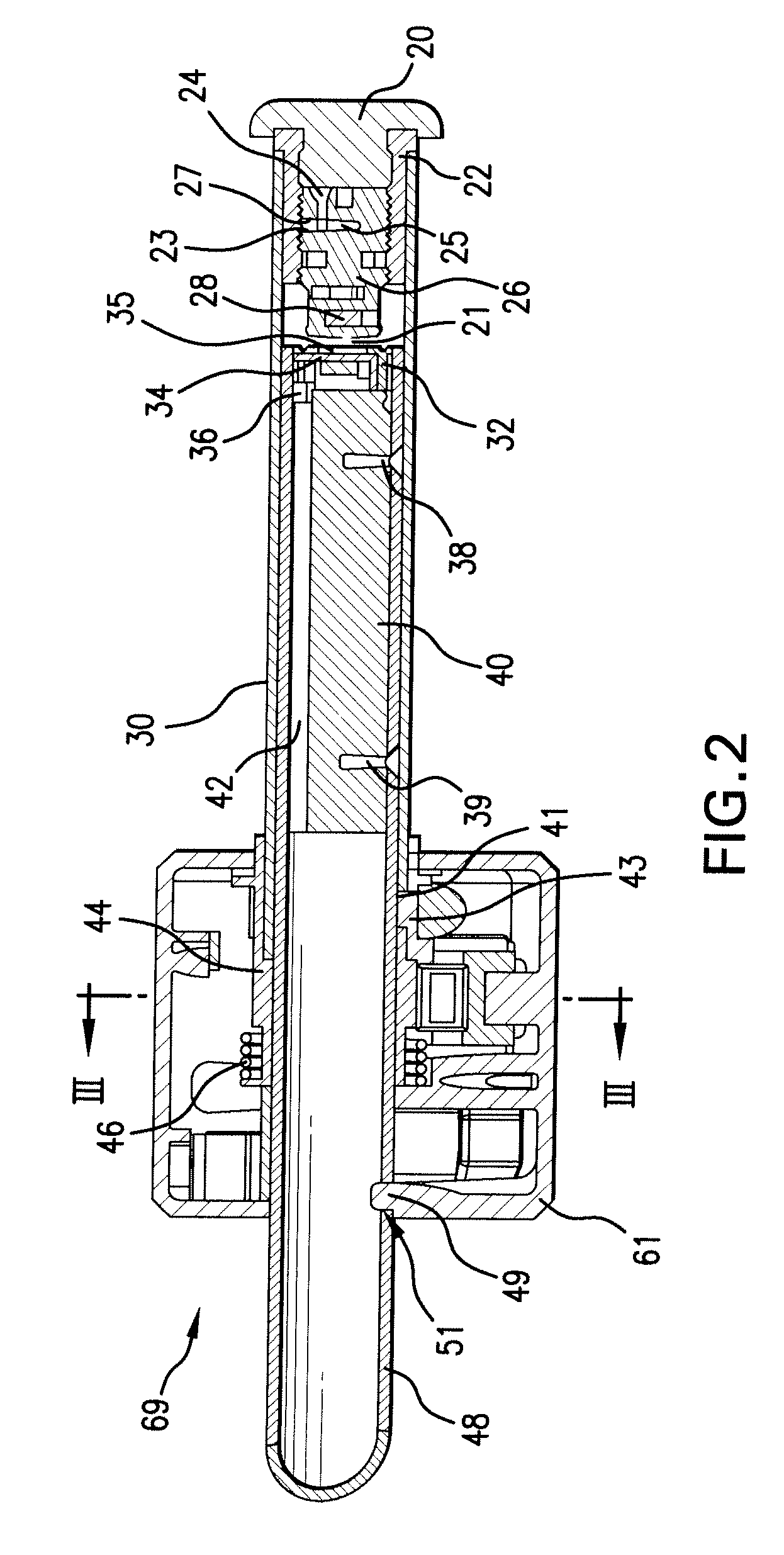

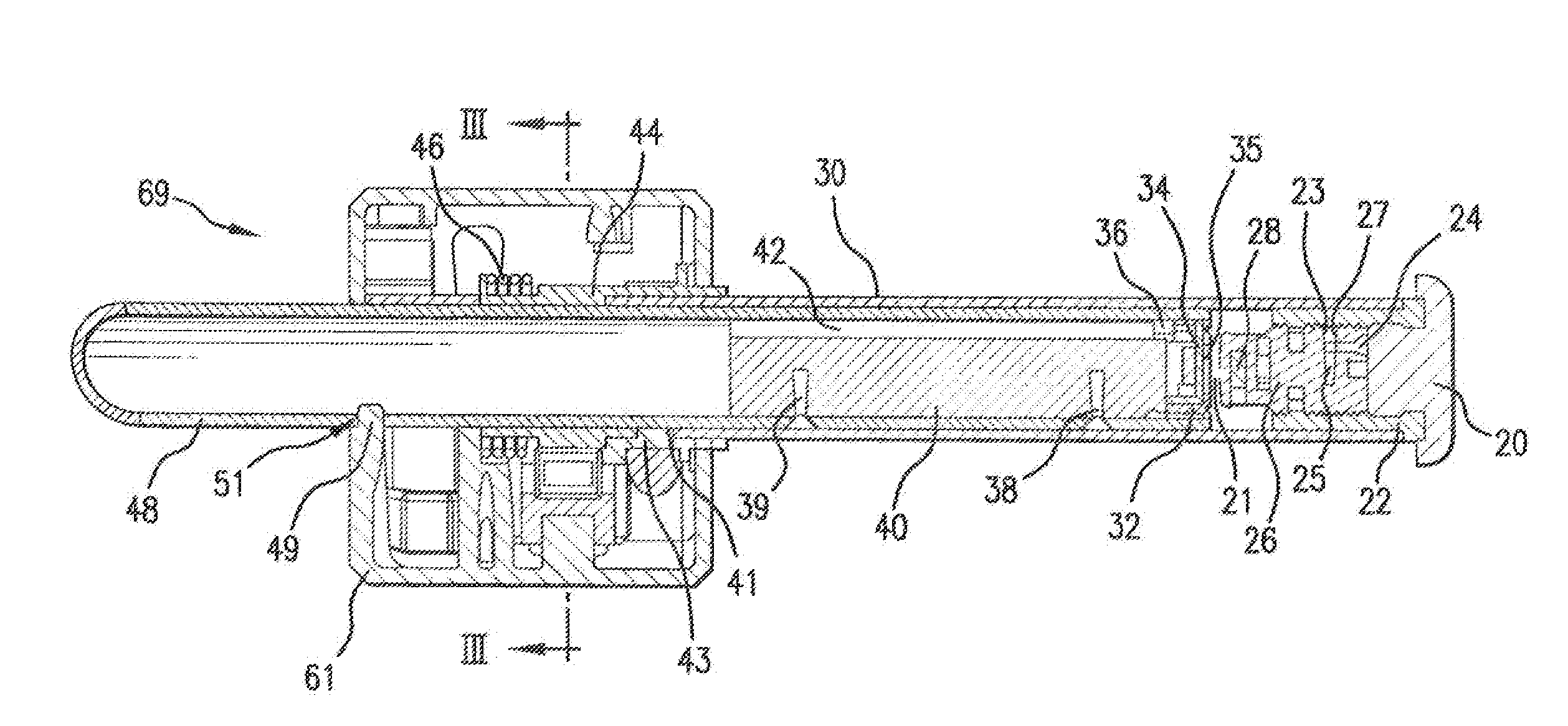

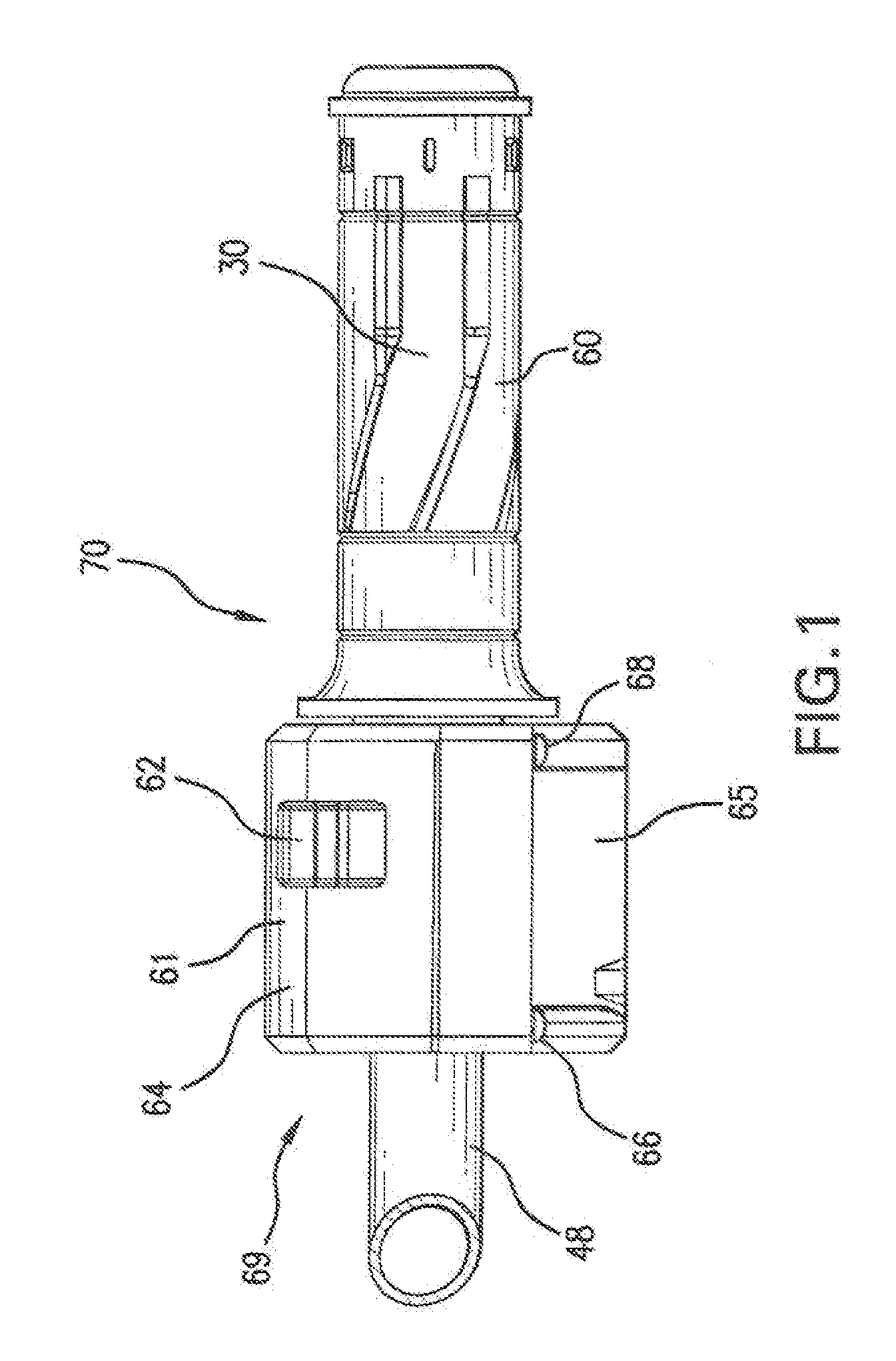

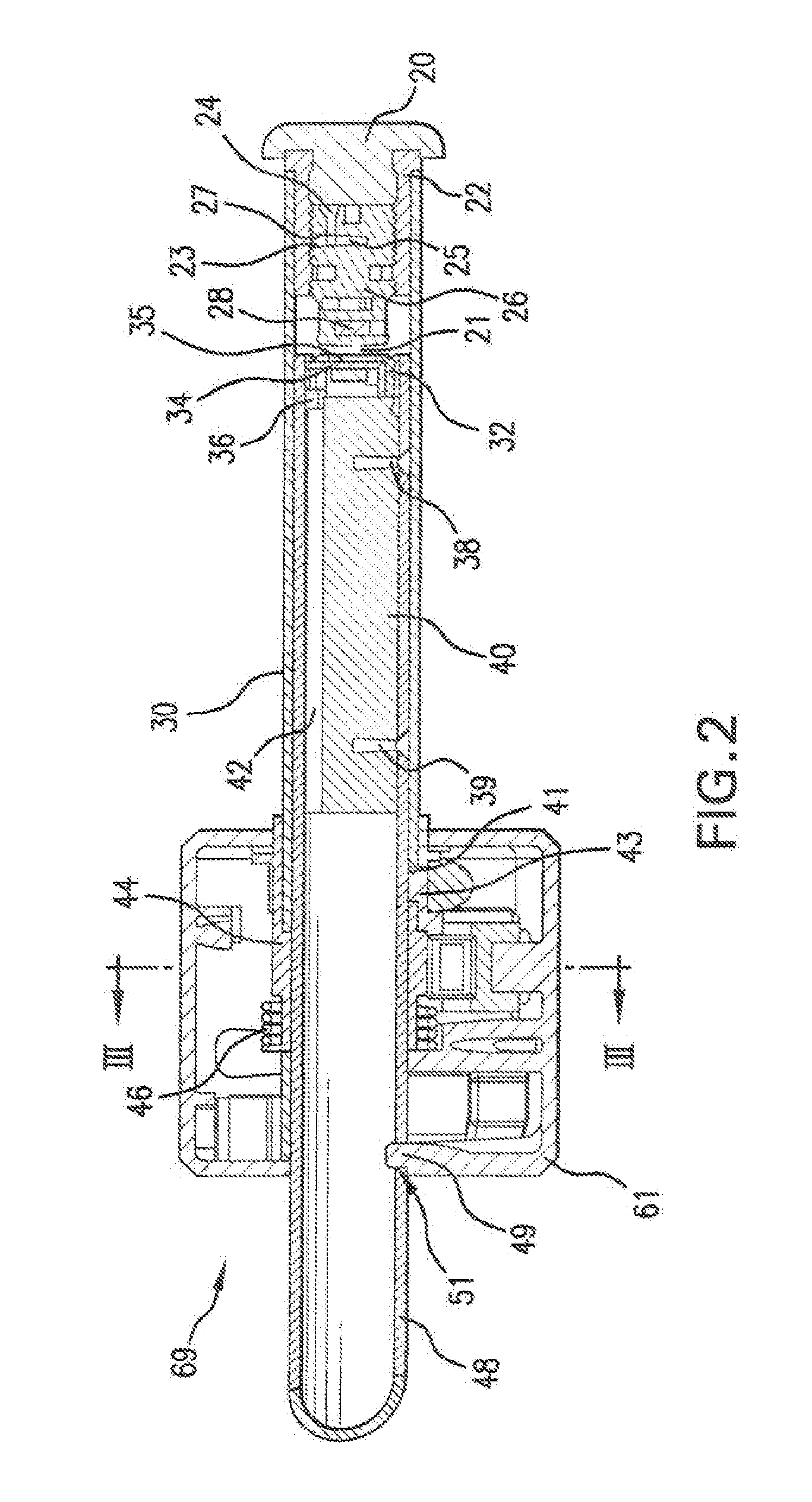

Vehicle with contactless throttle control

InactiveUS20080114523A1Convenient power controlImprove reliabilityAnalogue computers for vehiclesElectrodynamic brake systemsThrottle controlControl theory

A vehicle power control that includes a throttle mounting portion and a throttle that is movably mounted to the throttle mounting portion and configured for manipulation and operation by a rider. The power control also includes a sensor in contactless association with at least one of the throttle and throttle mounting portion. The sensor is configured for sensing a position of the throttle with respect to the mounting portion, in the contactless association, and generating a signal based on the sensed position for controlling motive power of a vehicle.

Owner:GP TECH & INNOVATION LTD

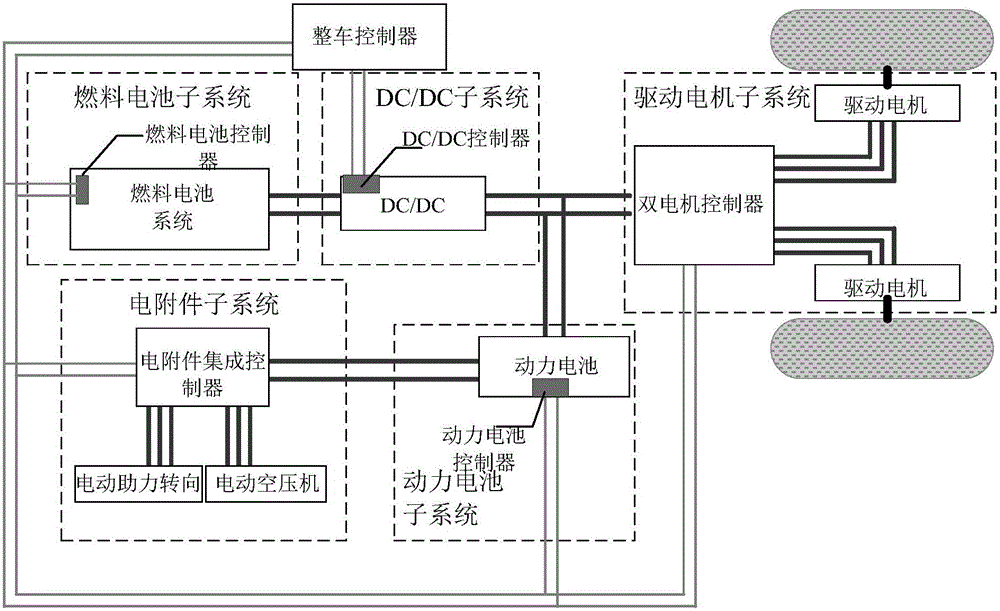

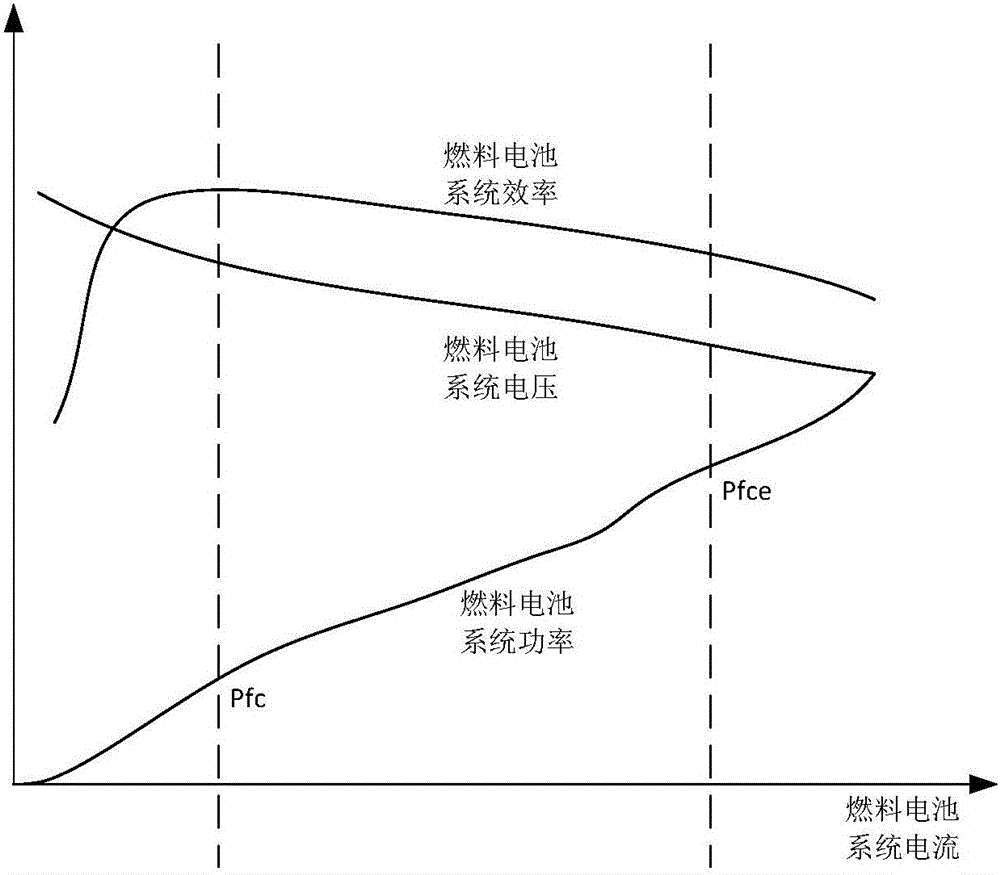

Power control method for fuel cell bus and power system of fuel cell bus

InactiveCN105835712AIncreased durabilityEasy to use for a long timeVehicular energy storageBattery/fuel cell control arrangementElectrical batteryEngineering

The invention relates to a power control method for a fuel cell bus and a power system of the fuel cell bus. The power control method comprises the steps that required power P of the bus is acquired in real time; when the required power P of the bus meets the condition that P is smaller than Pfc, a fuel cell operates at Pfc, and a (Pfc-P) part charges a power cell; when the required power P of the bus meets the condition that P is larger than or equal to Pfc and is smaller than Pfce, the fuel cell operates at Pfce, and a (Pfce-P) part charges the power cell; when the required power P of the bus meets the condition that P is larger than or equal to Pfce, the fuel cell operates at Pfce, and a (P-Pfce) part is provided by the power cell, wherein Pfc and Pfce are two set threshold values of certain output power of the fuel cell. With adoption of the control mode, the output power of the fuel cell is prevented from frequent fluctuation and continuous loading and unloading, the durability of the fuel cell can be improved, investment cost is saved, and reliable operation of the power system is guaranteed.

Owner:ZHENGZHOU YUTONG BUS CO LTD

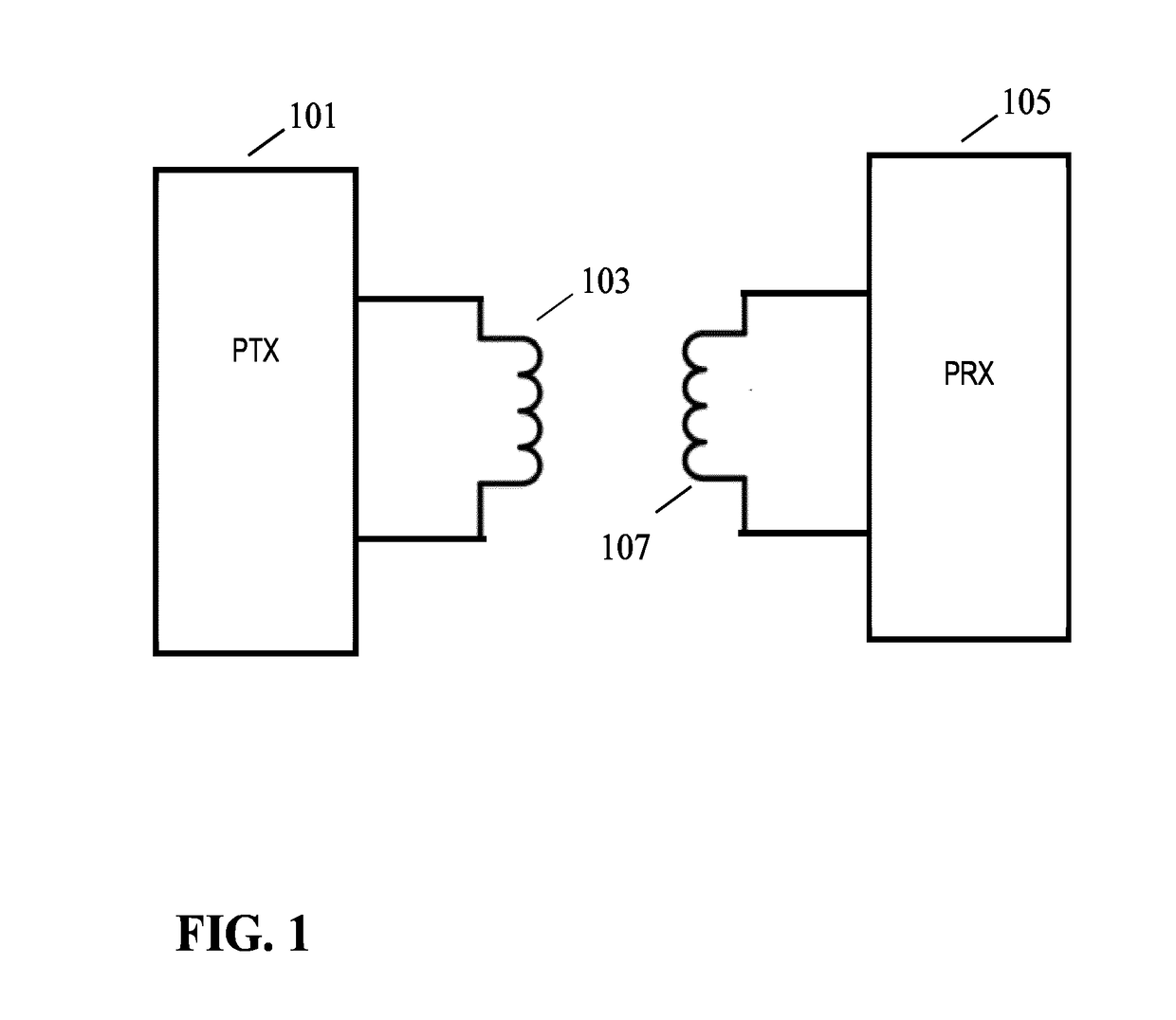

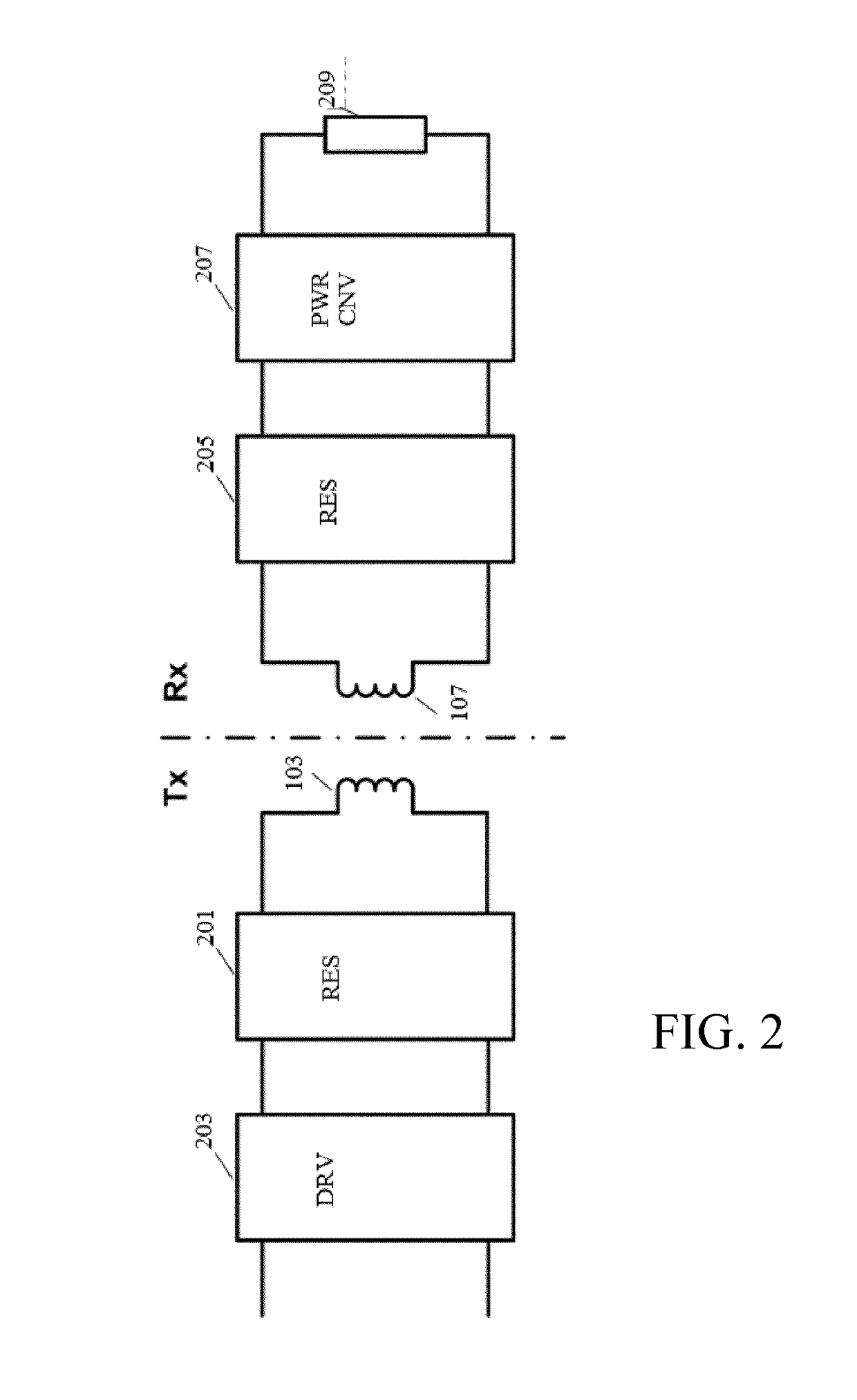

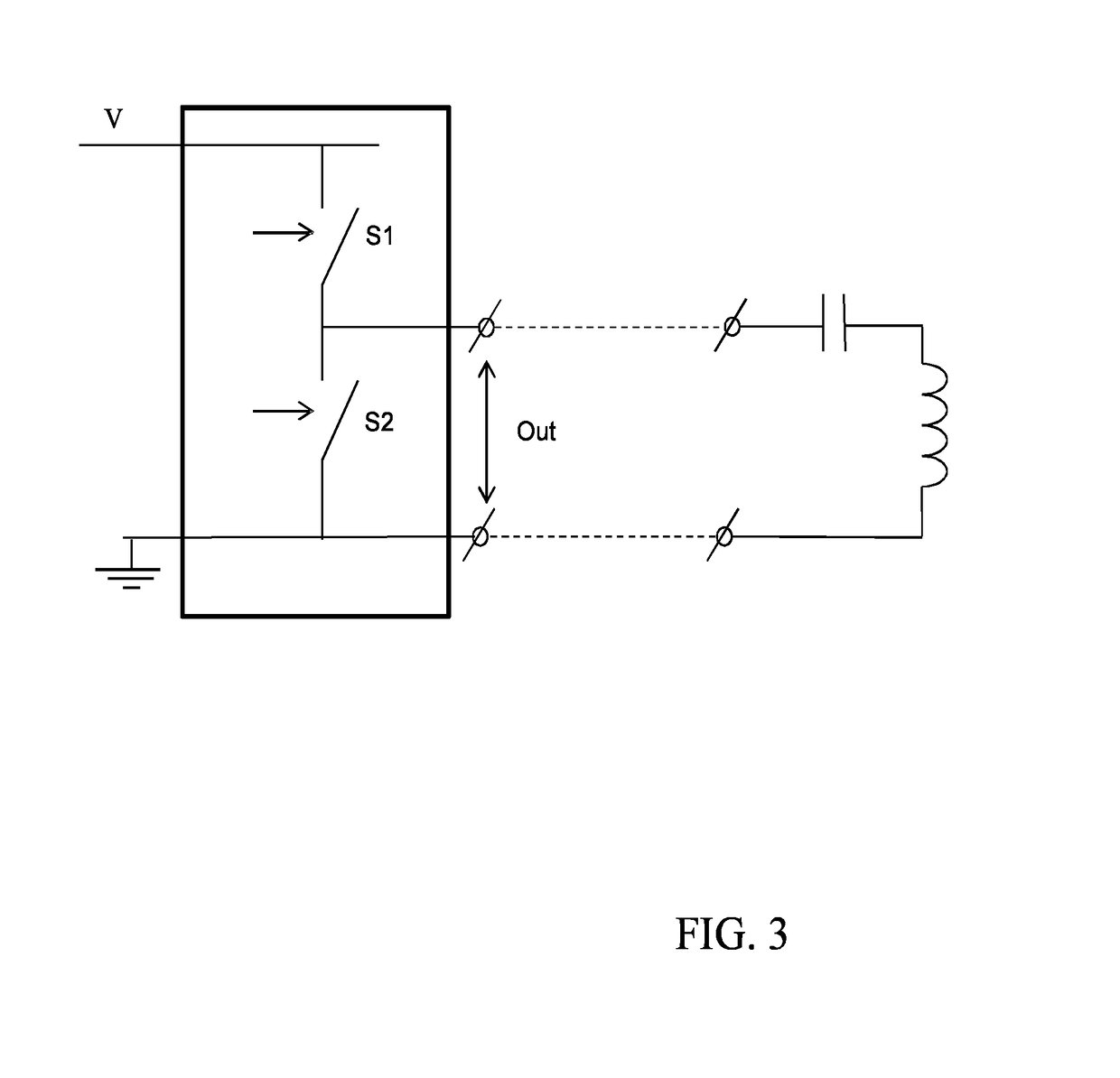

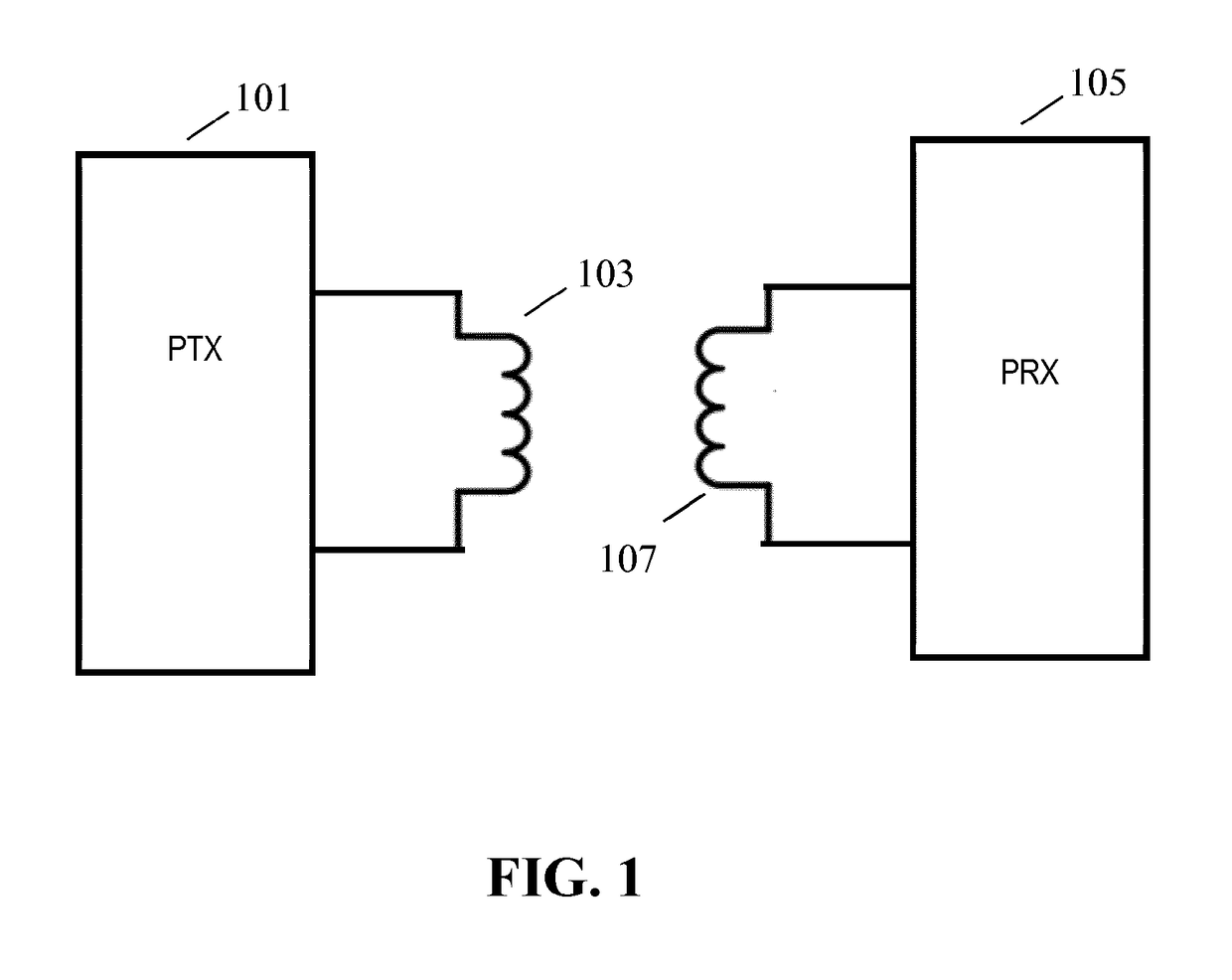

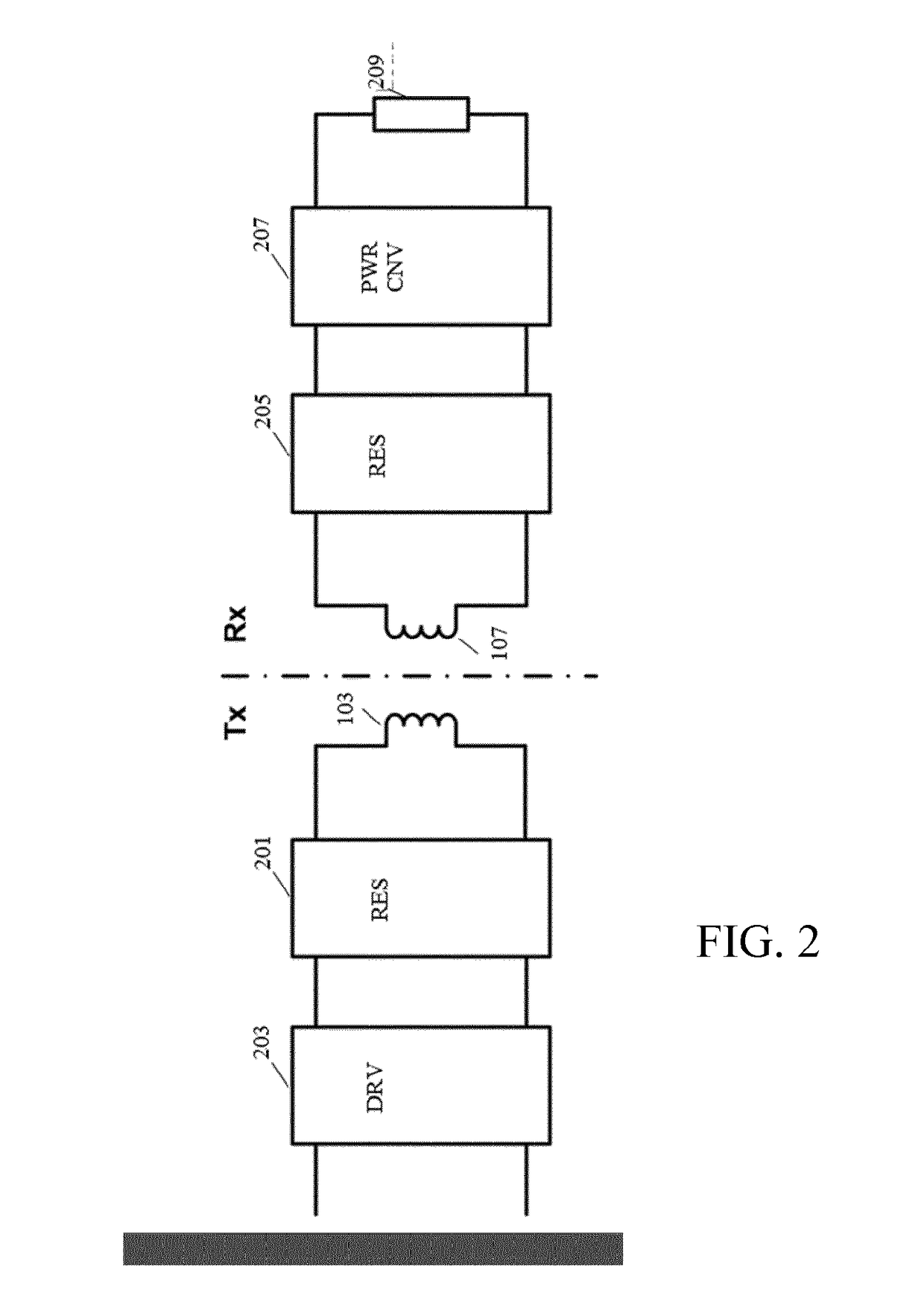

Wireless inductive power transfer

ActiveUS20190027969A1Efficient power controlEnhanced couplingBatteries circuit arrangementsTransformers/inductances coils/windings/connectionsTransmitter coilElectric power transmission

A power transmitter (101) of a wireless power transfer system comprises a resonance including a transmitter coil (103) for generating a power transfer signal for wirelessly transferring power to a power receiver (105). Further, a driver (1303) generates a drive signal for the resonance circuit (201) and a message receiver (1305) is arranged to receive messages from the power receiver (105). A power loop controller (1307) implements a power control loop by adapting the power of the drive signal in response to power control messages received from the power receiver (105). However, the regulation is subject to a constraint of at least one of a current or voltage of the resonance circuit and a power of the drive signal being below a maximum limit. Further, the power transmitter (101) comprises an adapter (1309) which adapts the maximum limit in response to a load indication indicative of a loading of the power transfer signal by the power receiver (105).

Owner:KONINKLJIJKE PHILIPS NV

Lateral short-channel DMOS, method of manufacturing the same, and semiconductor device

InactiveUS6946705B2Improve breakdown characteristicsSuperior current driving characteristicSemiconductor/solid-state device manufacturingSemiconductor devicesDopantSemiconductor

A lateral short-channel DMOS includes an N−-type epitaxial layer 110 in a P−-type semiconductor substrate 108, a P-type well 114 in the N−-type epitaxial layer 110 with a channel forming region C, an N+-type source region 116 in the P-type well 114, an N+-type drain region 118 in N−-type epitaxial layer 110, and a gate electrode 122 formed via a gate insulating film 120 in at least an upper part of the channel forming region C out of a region from the N+-type source region 116 to the N+-type drain region 118. The lateral short-channel DMOS also includes an N+-type well 140 that is formed in the N−-type epitaxial layer 110 and includes a concentration of N-type dopant higher than the N−-type epitaxial layer 110 and lower than the N+-type drain region 118, with the N+-type drain region 118 being formed in this N+-type well 140.

Owner:SHINDENGEN ELECTRIC MFG CO LTD

Vehicle with contactless throttle control

InactiveUS7762231B2Convenient power controlImprove reliabilityAnalogue computers for vehiclesElectrodynamic brake systemsThrottle controlControl theory

A vehicle power control that includes a throttle mounting portion and a throttle that is movably mounted to the throttle mounting portion and configured for manipulation and operation by a rider. The power control also includes a sensor in contactless association with at least one of the throttle and throttle mounting portion. The sensor is configured for sensing a position of the throttle with respect to the mounting portion, in the contactless association, and generating a signal based on the sensed position for controlling motive power of a vehicle.

Owner:GP TECH & INNOVATION LTD

Vehicle With Contactless Throttle Control

ActiveUS20100326760A1Improve stability and reliabilityImproved power controlAnalogue computers for vehiclesEngine controllersPower controlThrottle control

A vehicle power control that includes a throttle mounting portion and a throttle that is movably mounted to the throttle mounting portion and configured for manipulation and operation by a rider. The power control also includes a sensor in contactless association with at least one of the throttle and throttle mounting portion. The sensor is configured for sensing a position of the throttle with respect to the mounting portion, in the contactless association, and generating a signal based on the sensed position for controlling motive power of a vehicle.

Owner:GP TECH & INNOVATION LTD

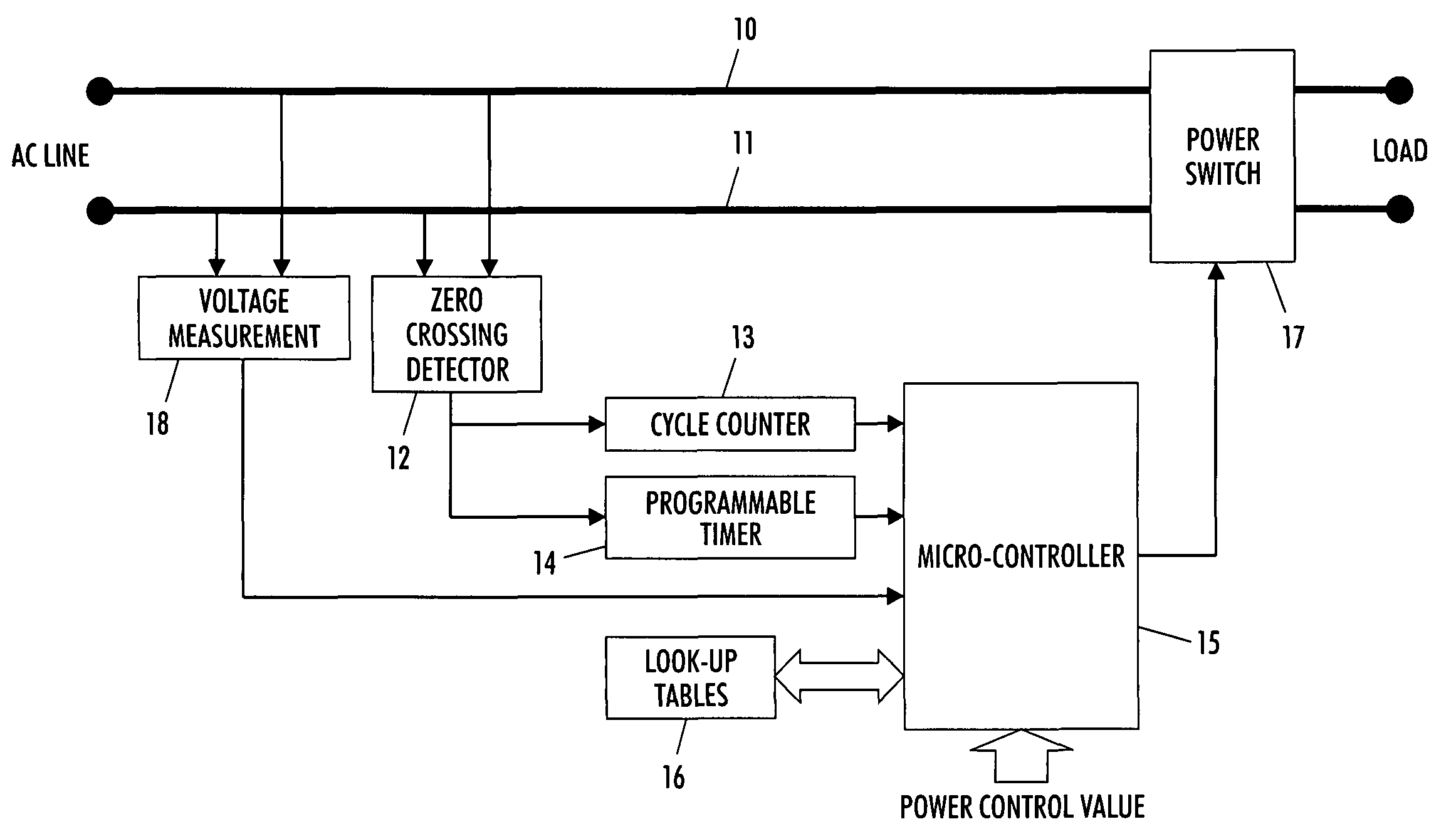

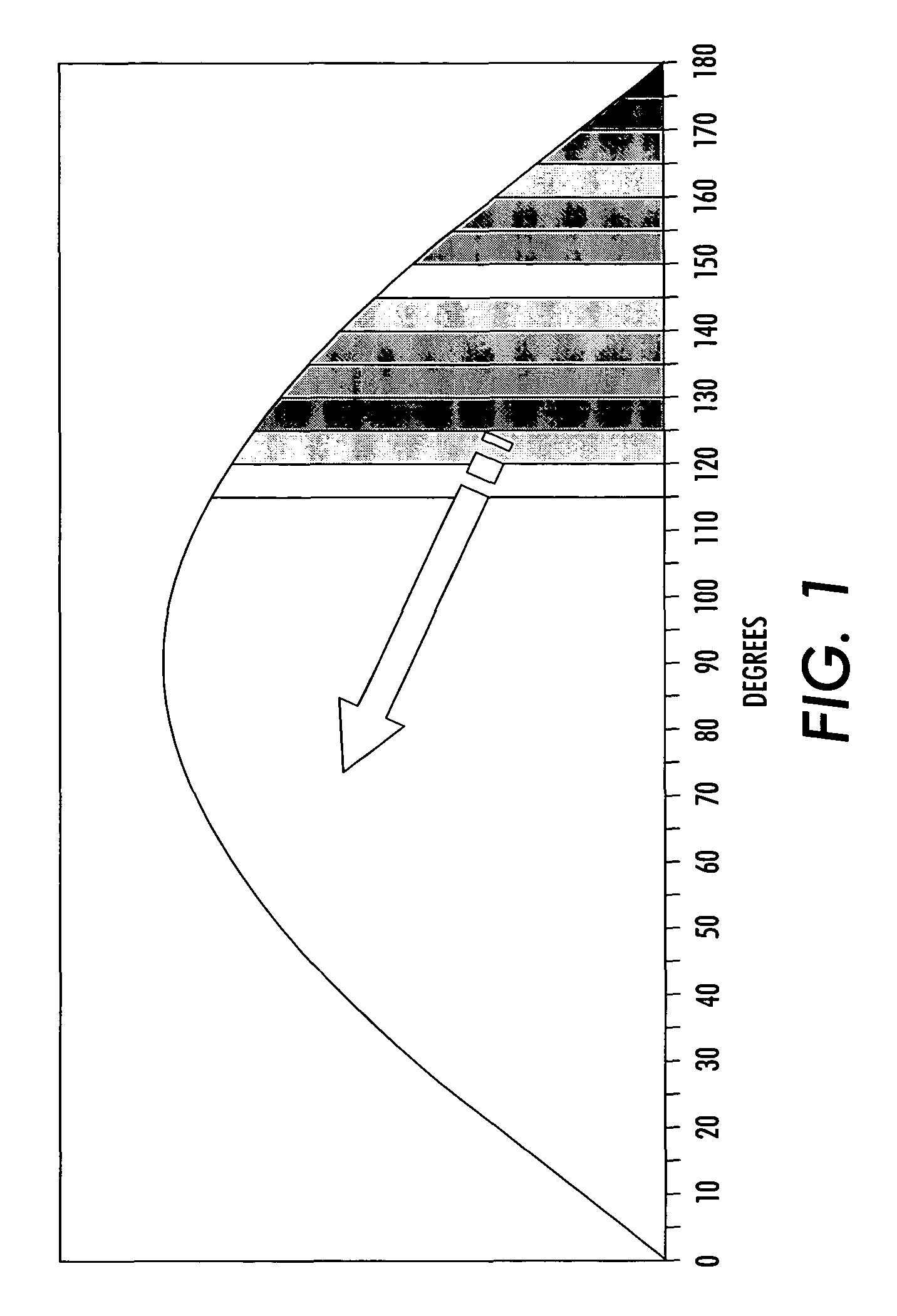

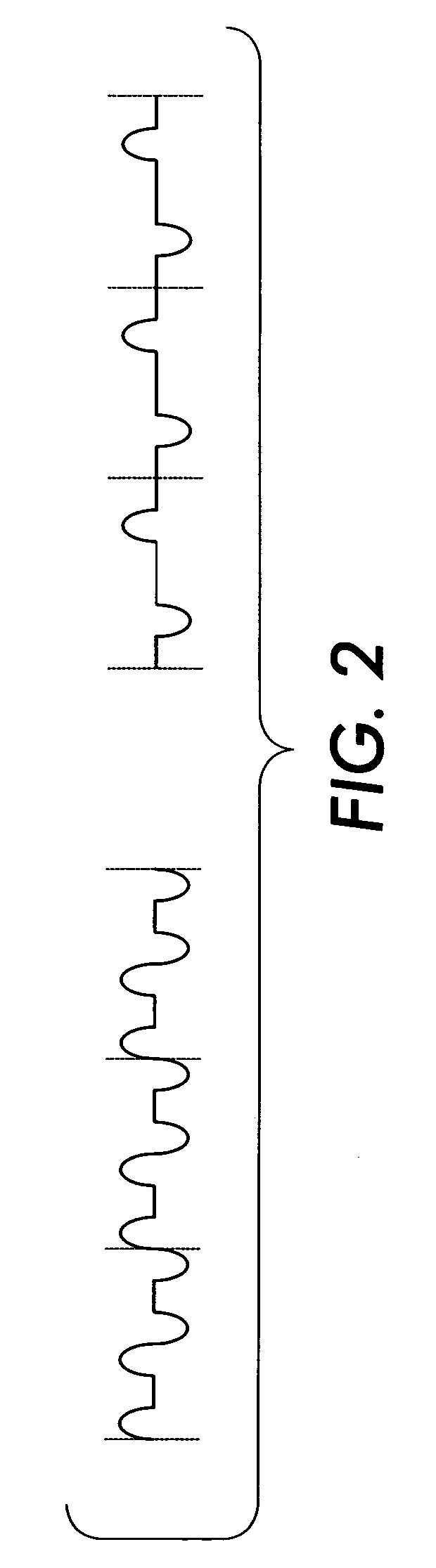

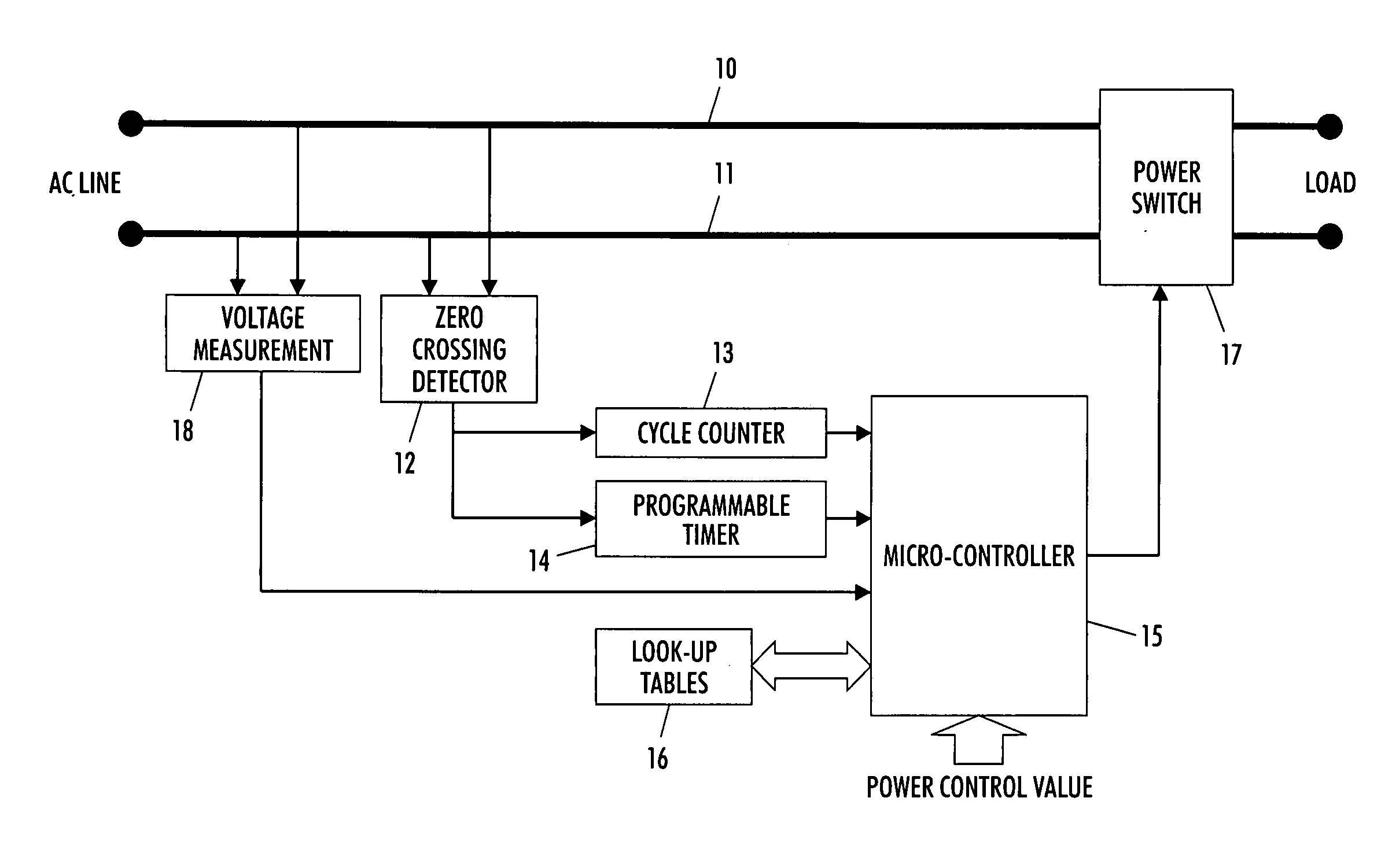

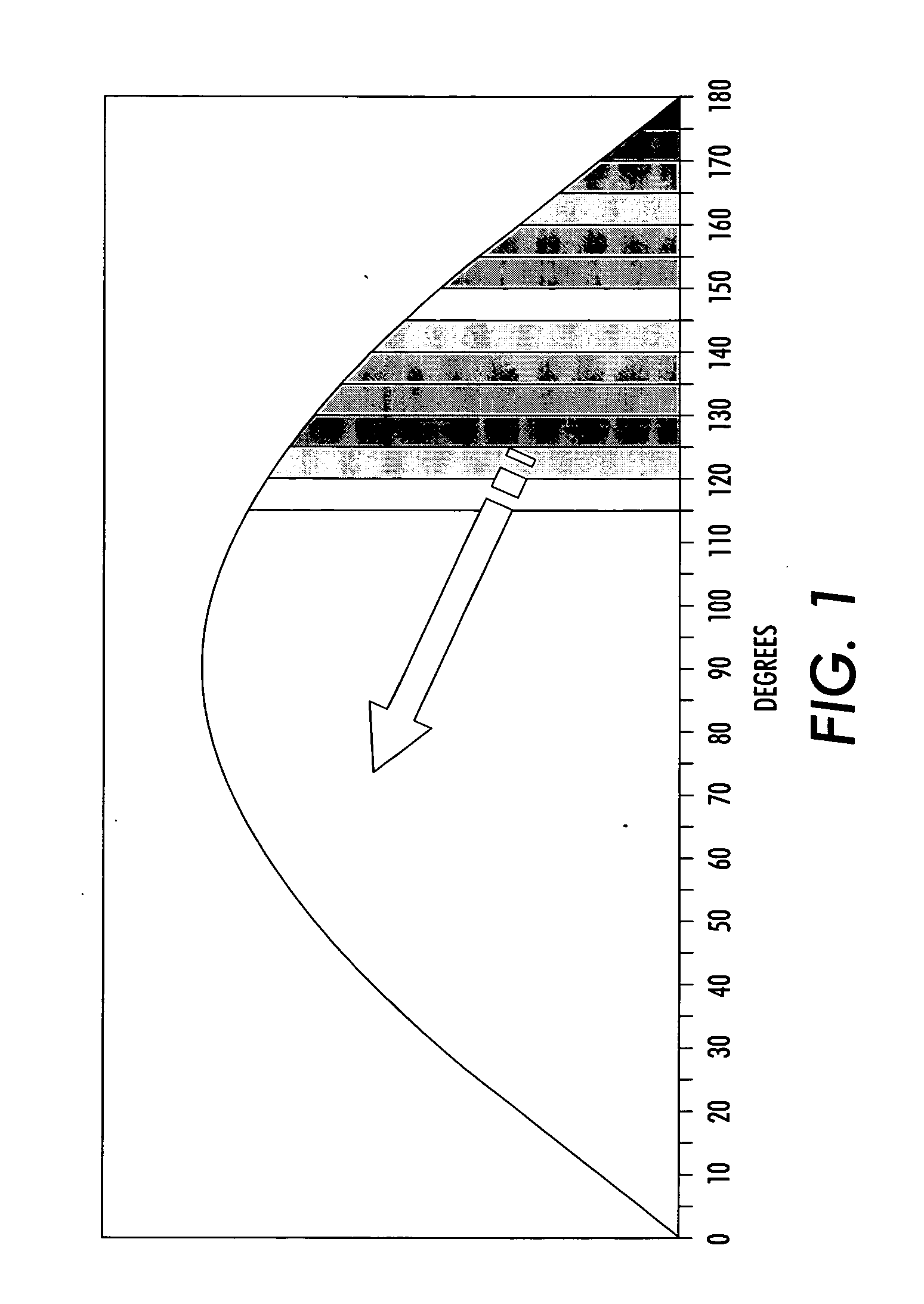

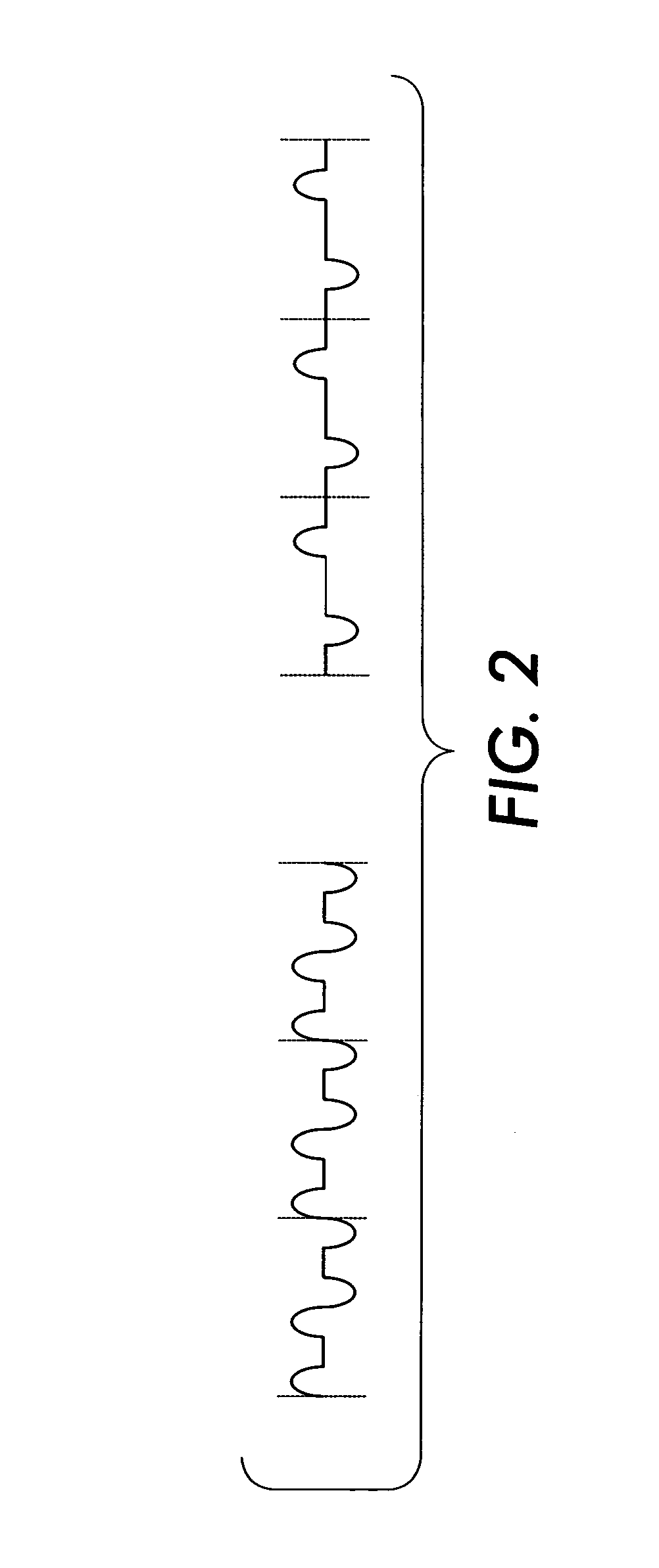

Power control using at least 540 degrees of phase

InactiveUS7893680B2Fine tuning of amountIncrease heightMultiple input and output pulse circuitsDc network circuit arrangementsHarmonicEngineering

A circuit and method for generating an electrical alternating current power signal in which the alternating current signal is dropped once at a non-zero crossing point in every 540 plus N degrees, where N is a non-negative number. This manner of controlling power to a device enables wide ranges of power control while generating acceptable levels of power line harmonics and while conforming to existing international regulations governing voltage variations.

Owner:XEROX CORP

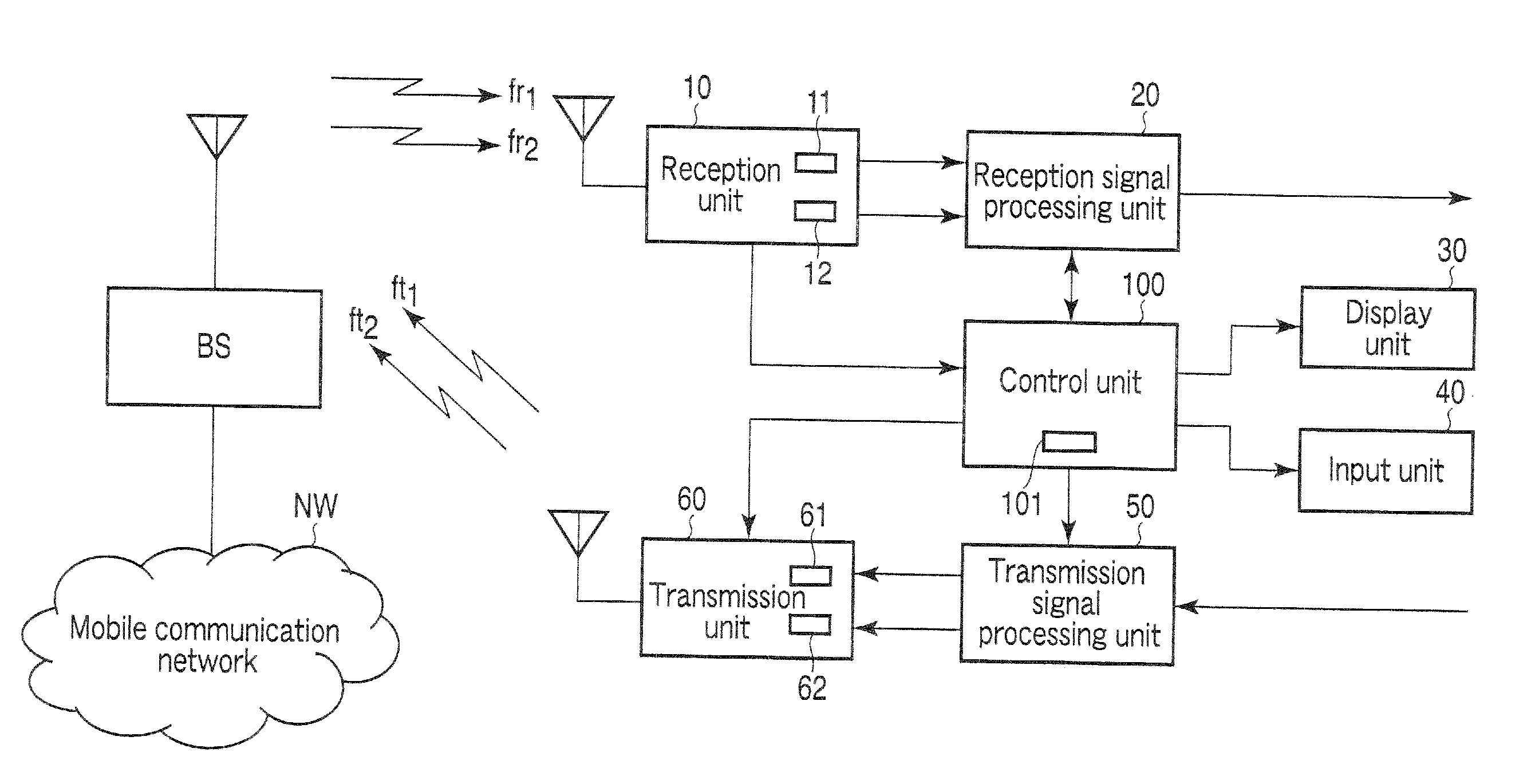

Wireless communication apparatus and wireless communication method

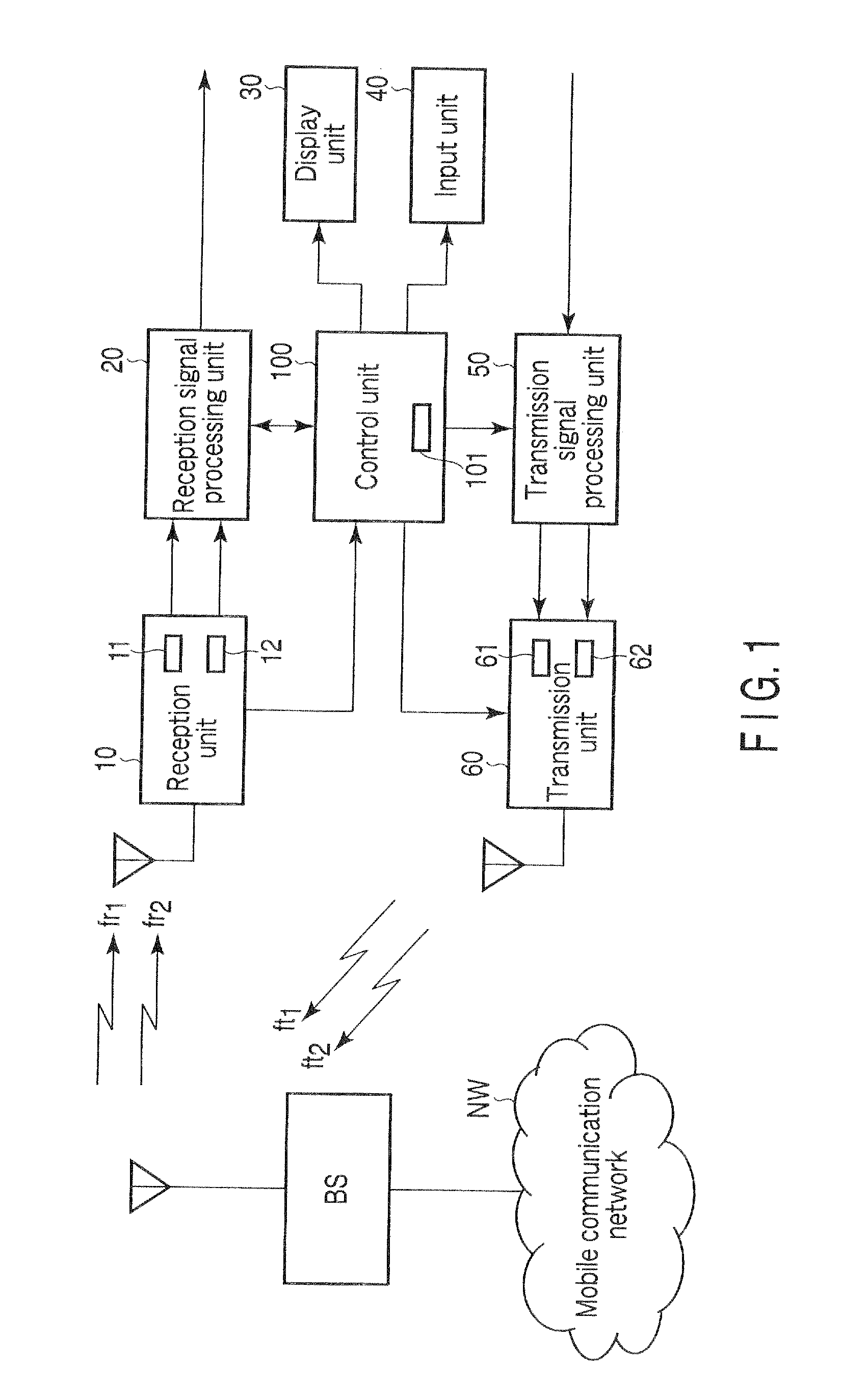

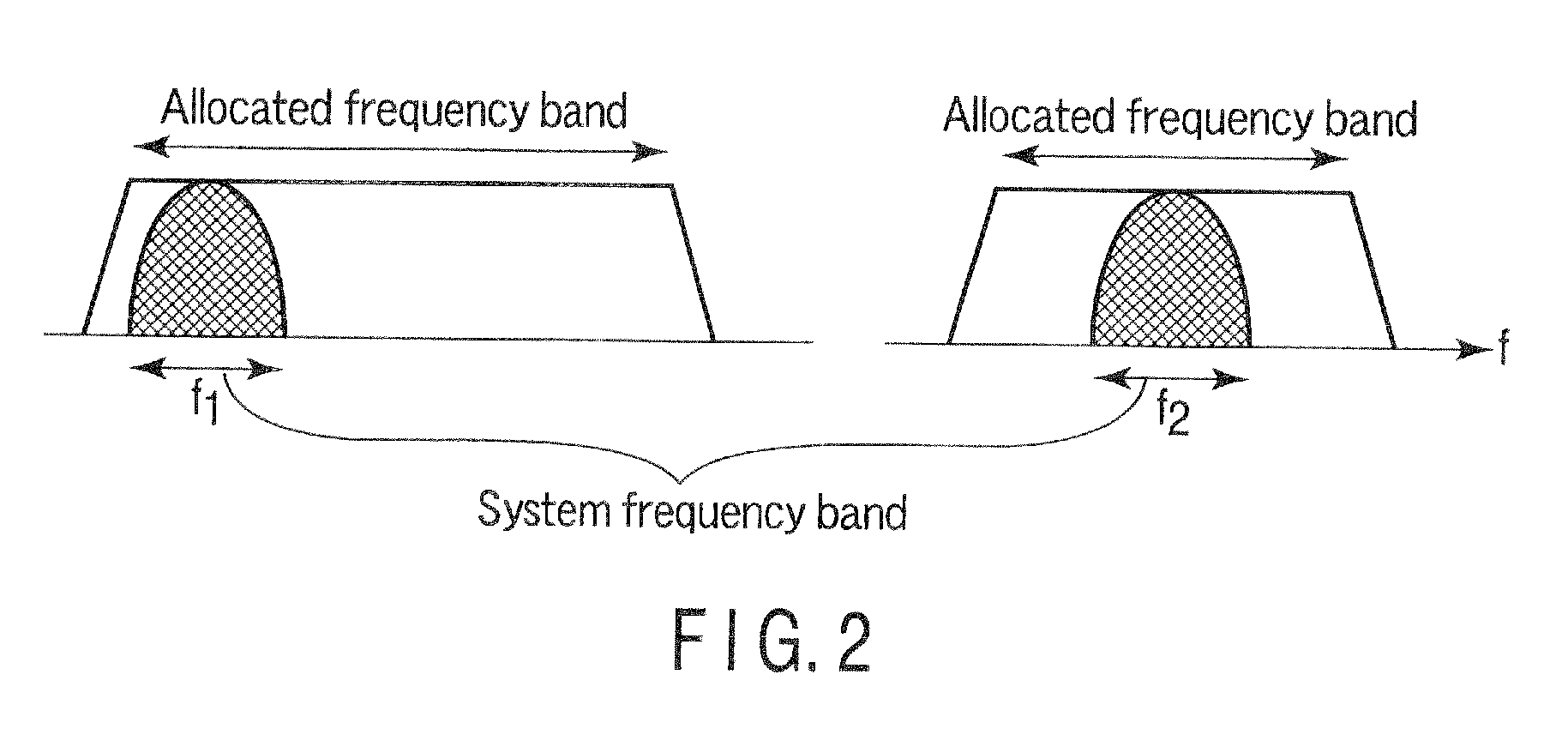

InactiveUS20100167660A1Good transmission power controlCircuit configuration does notPower managementRadio transmissionFrequency bandPower level

A reception unit measures a reception power level of a reference signal which is received from a base station apparatus BS. A reception signal processing unit acquires information indicative of a transmission power level of the reference signal. A control unit finds a path loss on the basis of the reception power level and this information. The control unit determines, on the basis of the path loss, a transmission power level of that one of two transmission frequency bands, which is closer to a frequency band with respect to which the pass loss has been measured. The control unit determines a transmission power level of the other transmission frequency band, which is farther from the frequency band with respect to which the pass loss has been measured, by correcting the transmission power level on the basis of a correction value based on a difference in frequency.

Owner:FUJITSU TOSHIBA MOBILE COMM LTD

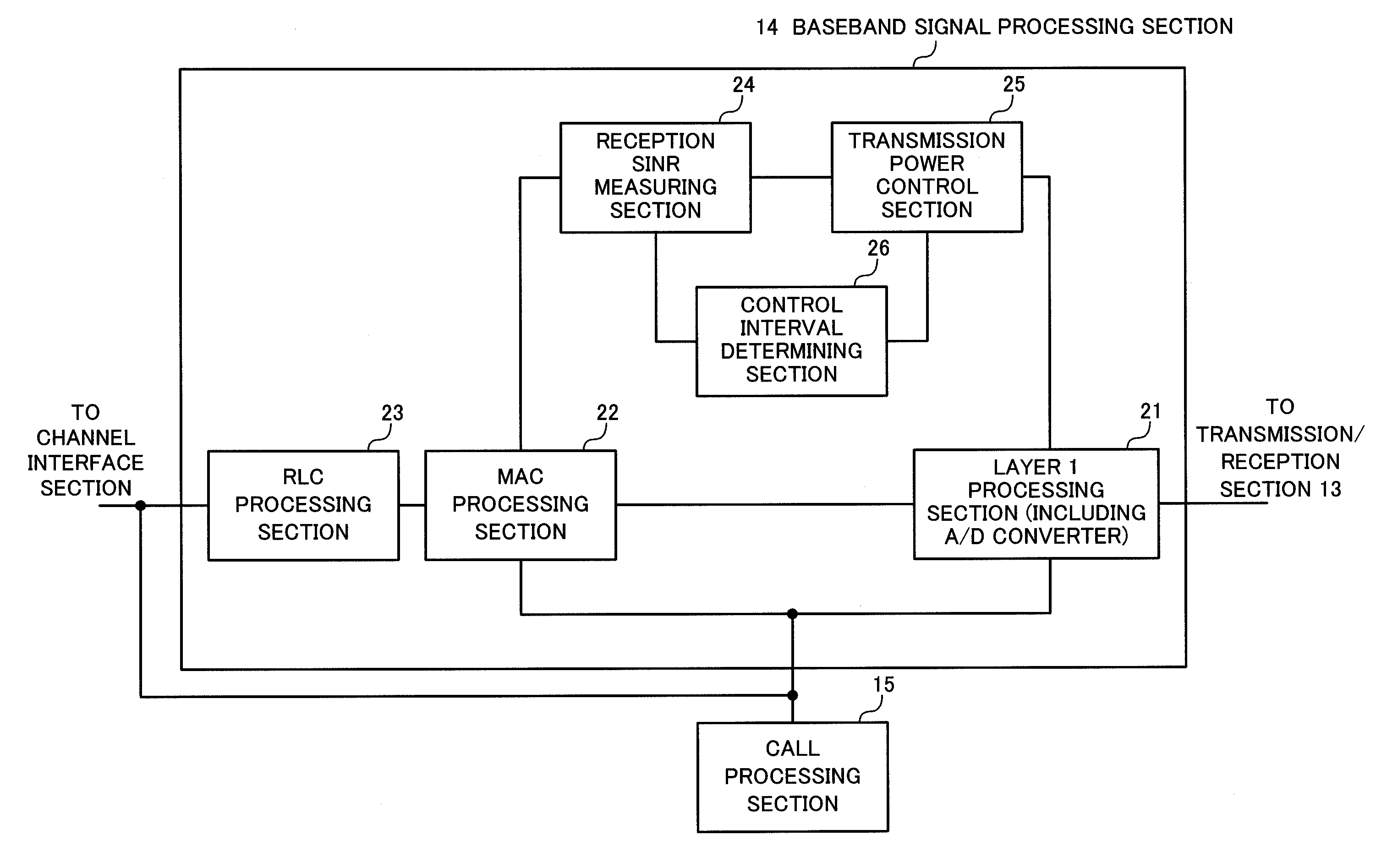

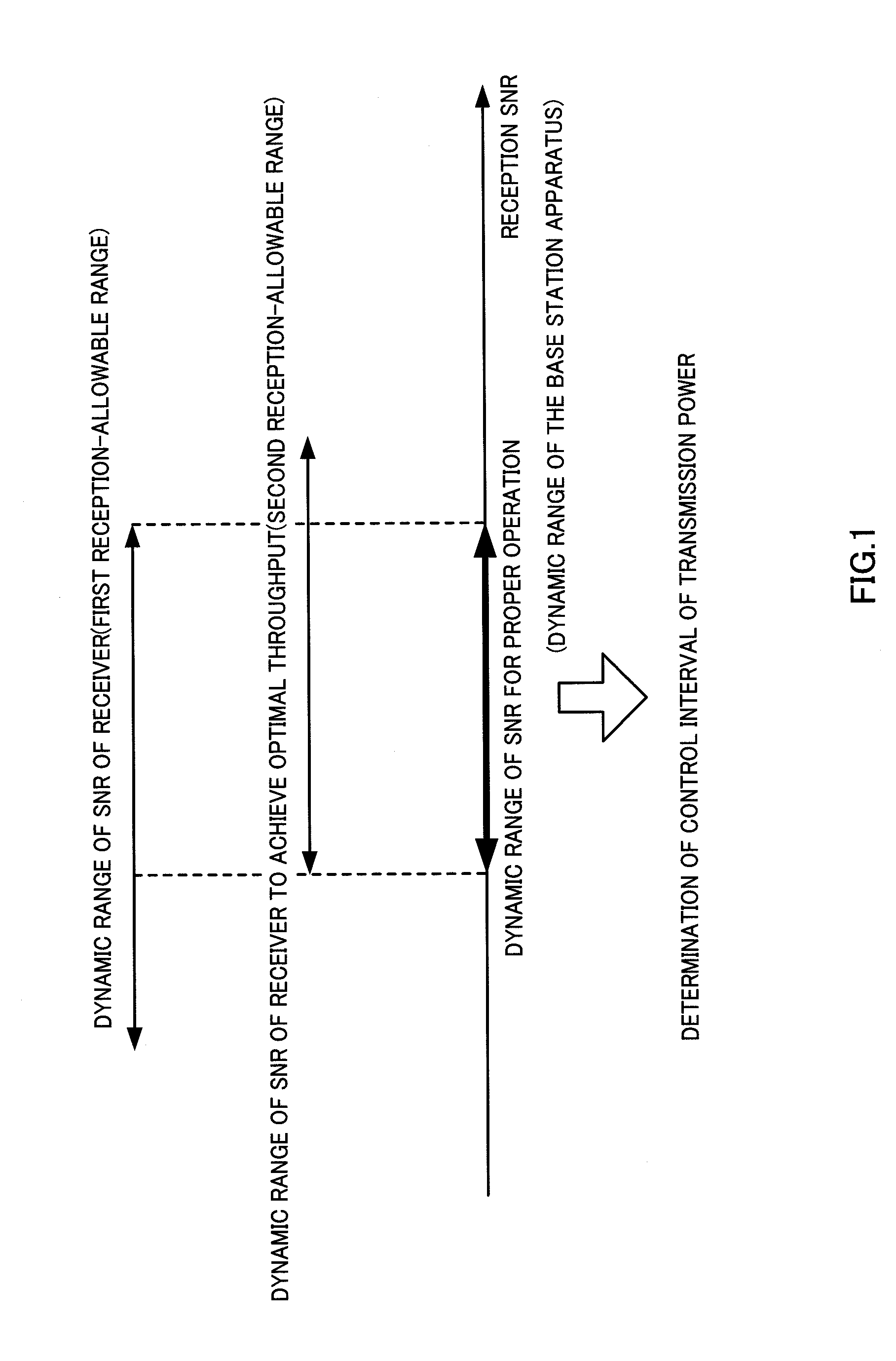

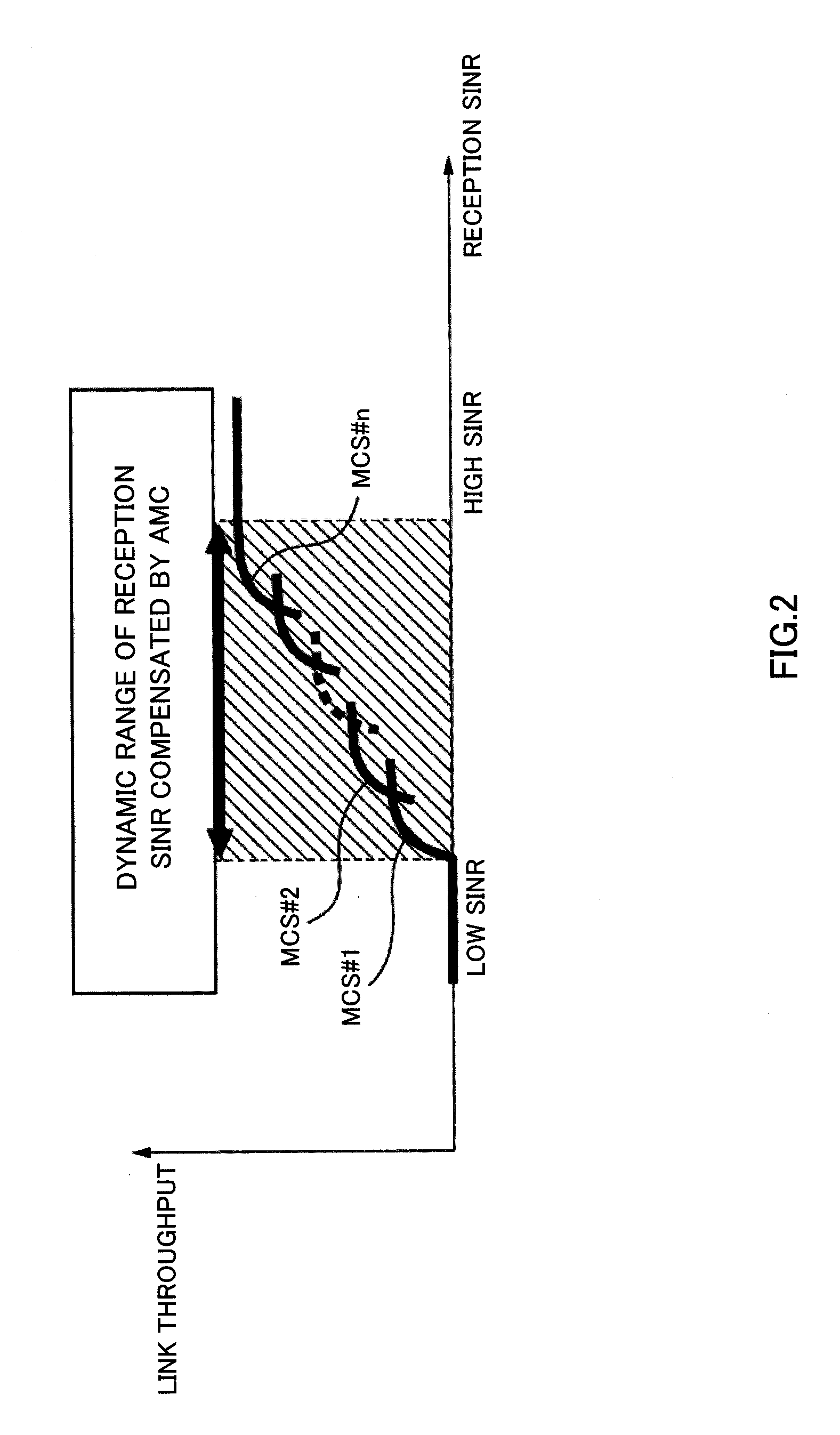

Closed-loop transmission power control method and radio base station apparatus

InactiveUS20110190026A1Convenient power controlAccurate operationPower managementRadio transmissionUplink transmissionClosed loop

To set an optimal transmission power control interval such that a base station apparatus properly receives signals from a mobile station, while exploiting fast scheduling and fast AMC, in this closed-loop transmission power control method, reception SINR and average interference level are measured in a signal received in uplink, a time period for averaging reception quality is determined corresponding to an overlapped size of a dynamic range of a base station apparatus that is a region of overlapping a first reception-allowable range depend on reception capability of the base station apparatus, with a second reception-allowable range, varying corresponding to the interference level, depend on the number of a modulation and coding scheme set, each set achieving required throughput, the reception SINR is averaged using the determined time period, and a TPC command indicative of uplink transmission power to be controlled in a terminal apparatus is generated using a difference value between the averaged reception SINR and target reception SINR, and is transmitted in downlink.

Owner:NTT DOCOMO INC

Controlling a Power Level in a Wireless Communications System with Different Scrambling Codes

ActiveUS20100039972A1Easy to solveIncrease powerPower managementTransmission systemsCommunications systemEngineering

A power level of signals transmitted in a wireless communications system under a first or a second scrambling code, is controlled in an inner power control loop, where a quality measure is repetitively estimated and control commands generated from the quality measure and a quality measure reference value, which in an outer power control loop is adjusted in dependence on a performance level calculated for signals received during a time interval. A first value is adjusted in dependence on a performance level for time intervals with all signals transmitted under the first scrambling code and used during such time intervals. A second value is adjusted in dependence on a performance level for time intervals with at least some signals transmitted under the second scrambling code and used during at least a part of such time intervals.

Owner:TELEFON AB LM ERICSSON (PUBL)

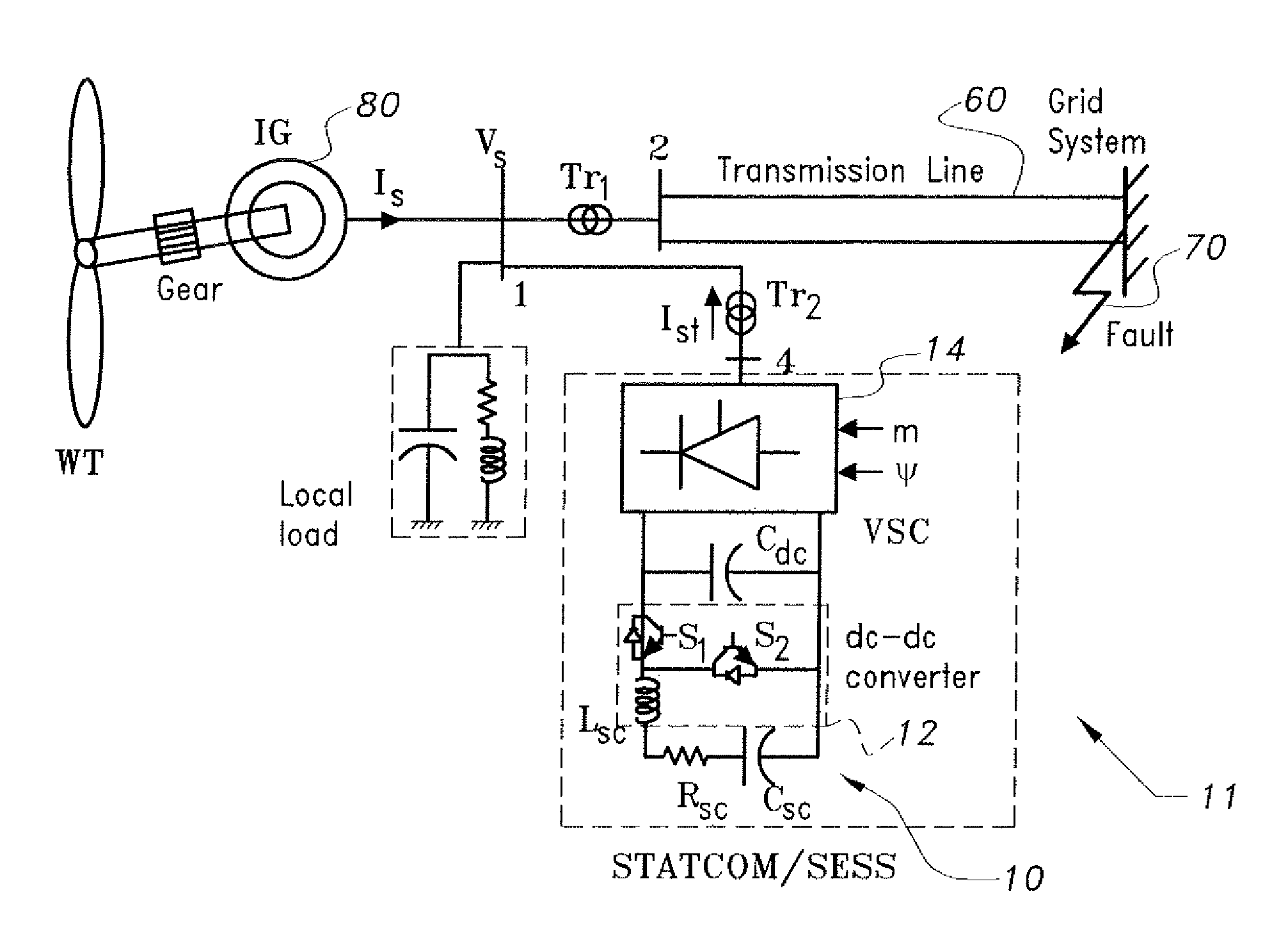

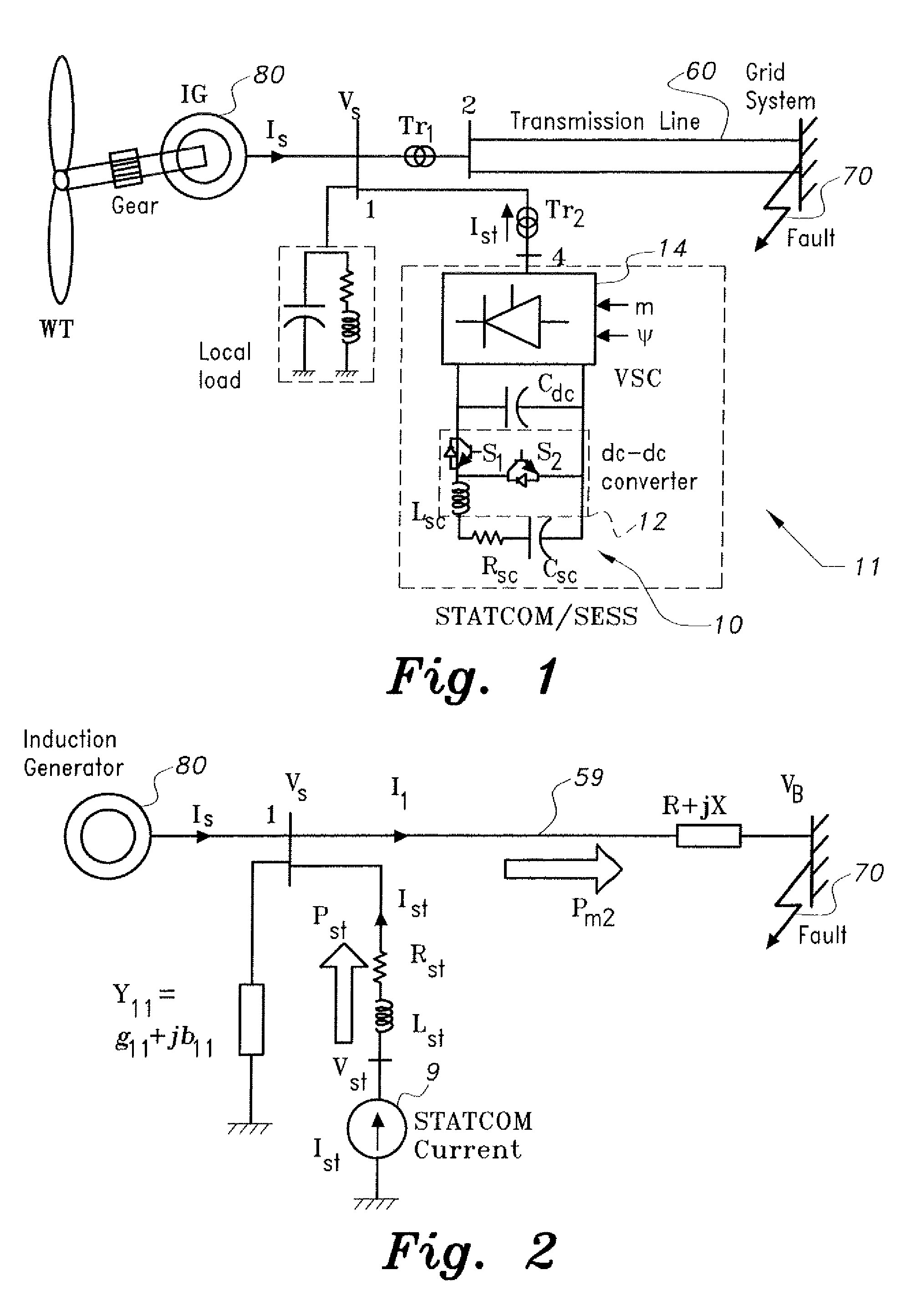

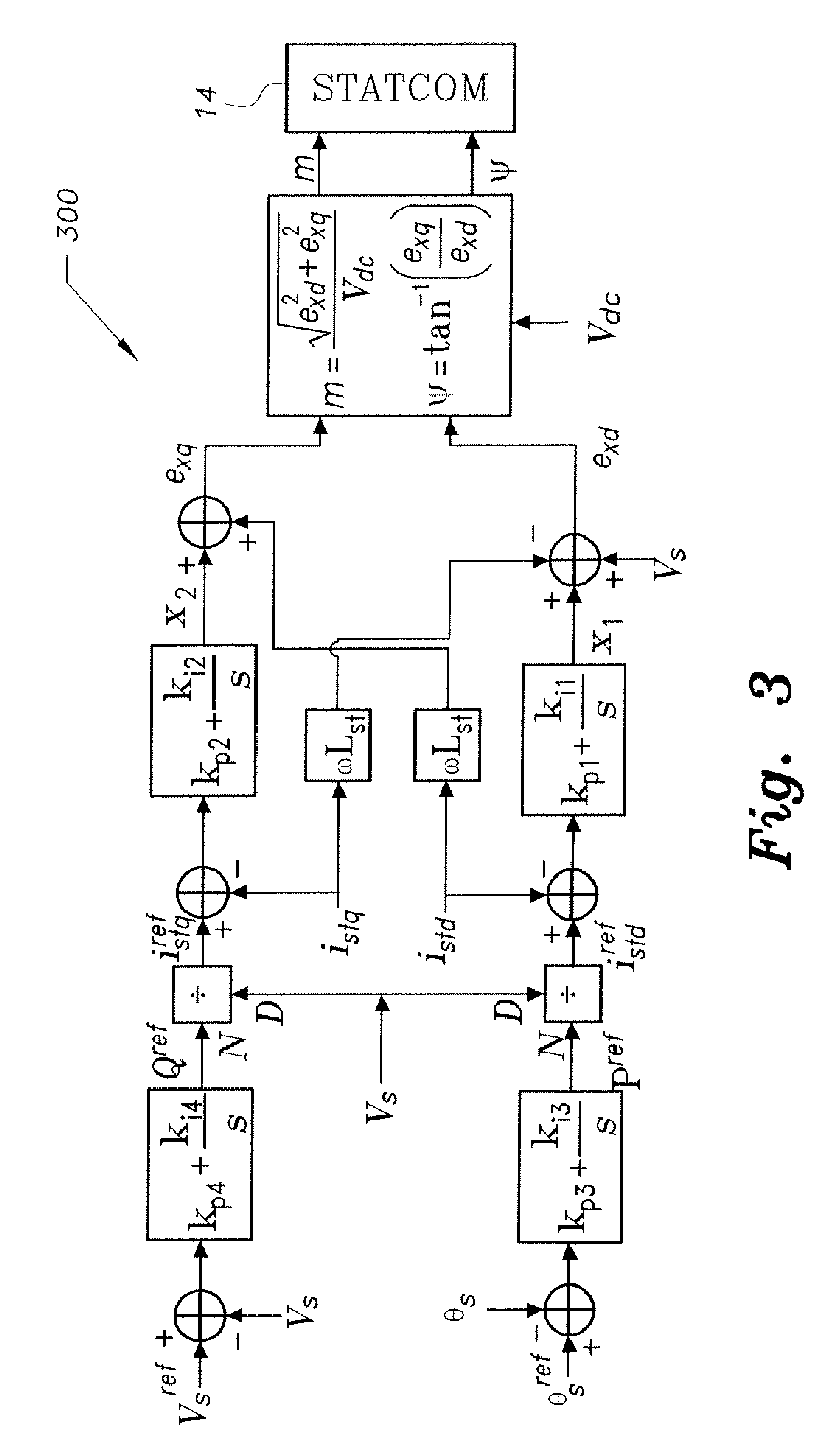

Supercapacitor-based grid fault ride-through system

InactiveUS8866340B2Improve power densityExtend the life cycleElectric signal transmission systemsFlexible AC transmissionDynamic modelsEngineering

Owner:KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS

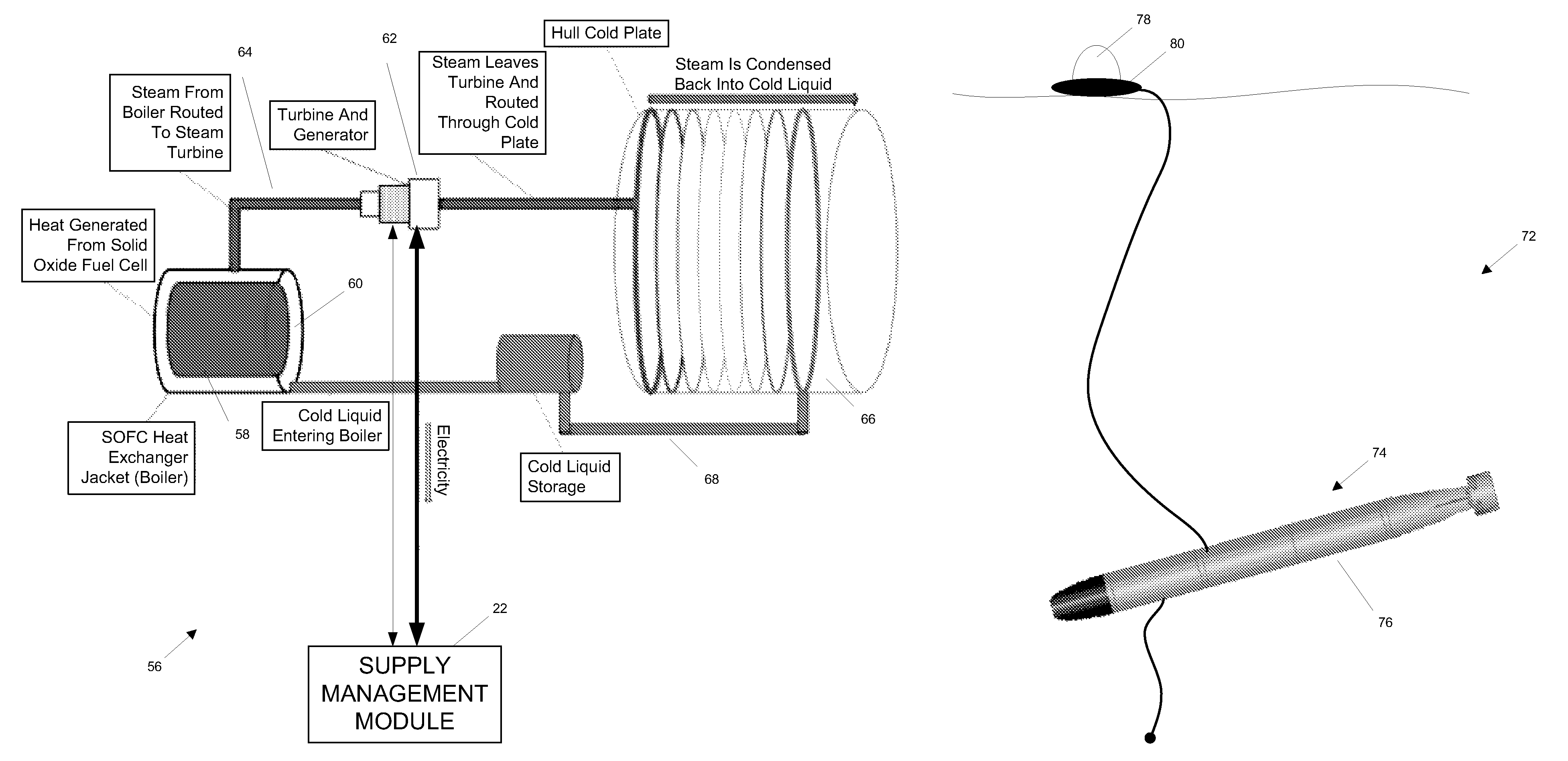

System configured to control and power a vehicle or vessel

InactiveUS8427002B2Convenient power controlImprove power efficiencySpeed controllerElectric devicesControl systemElectric power system

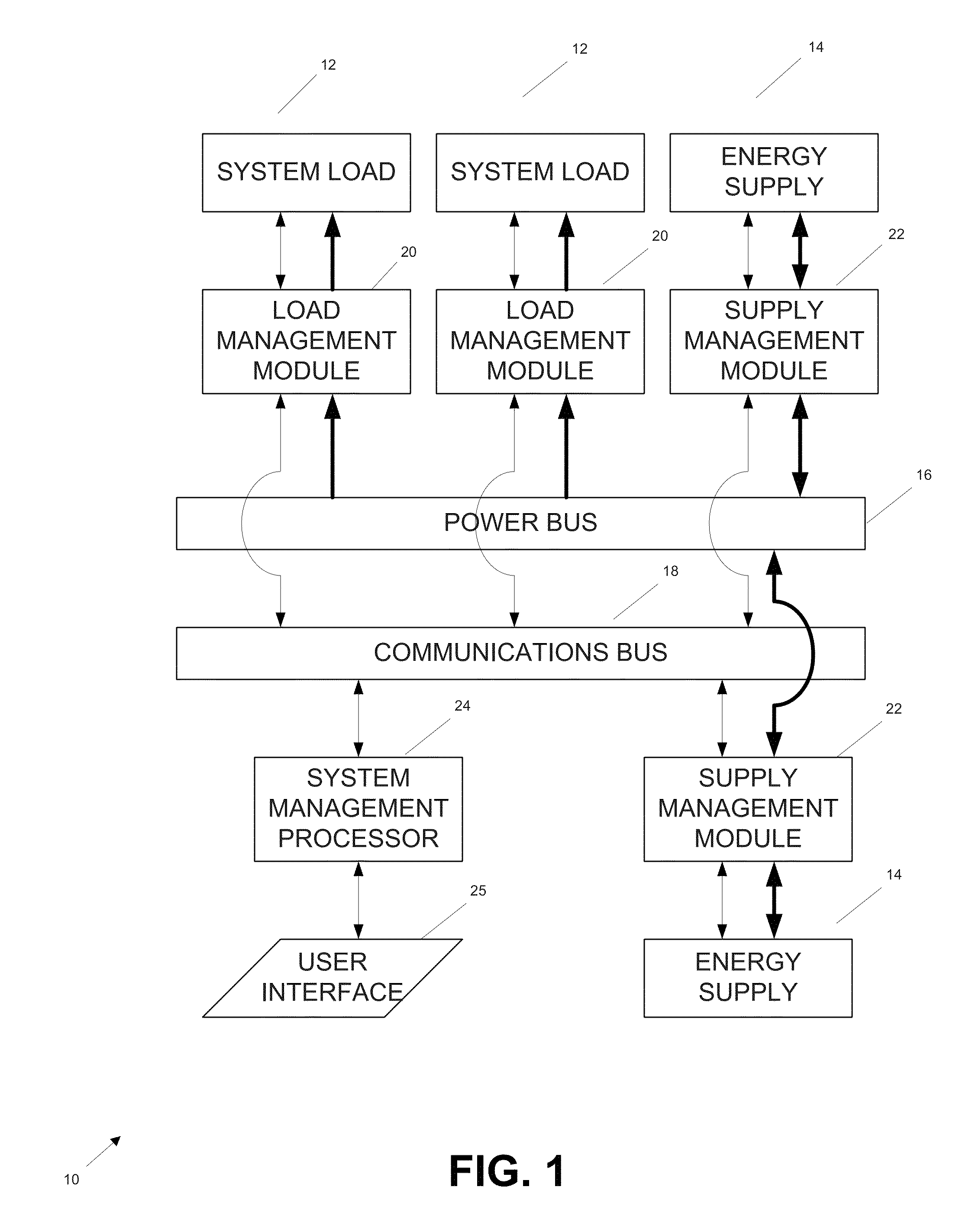

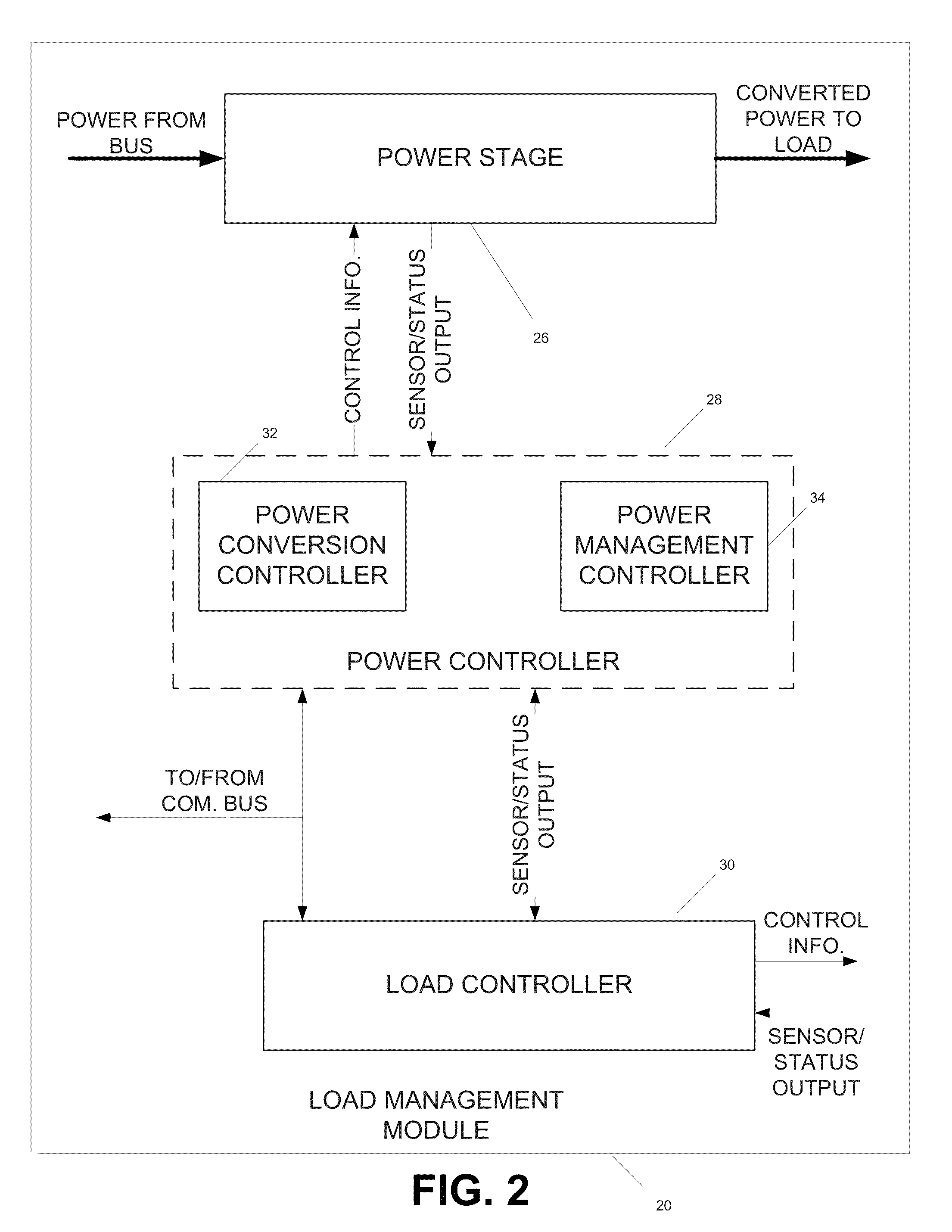

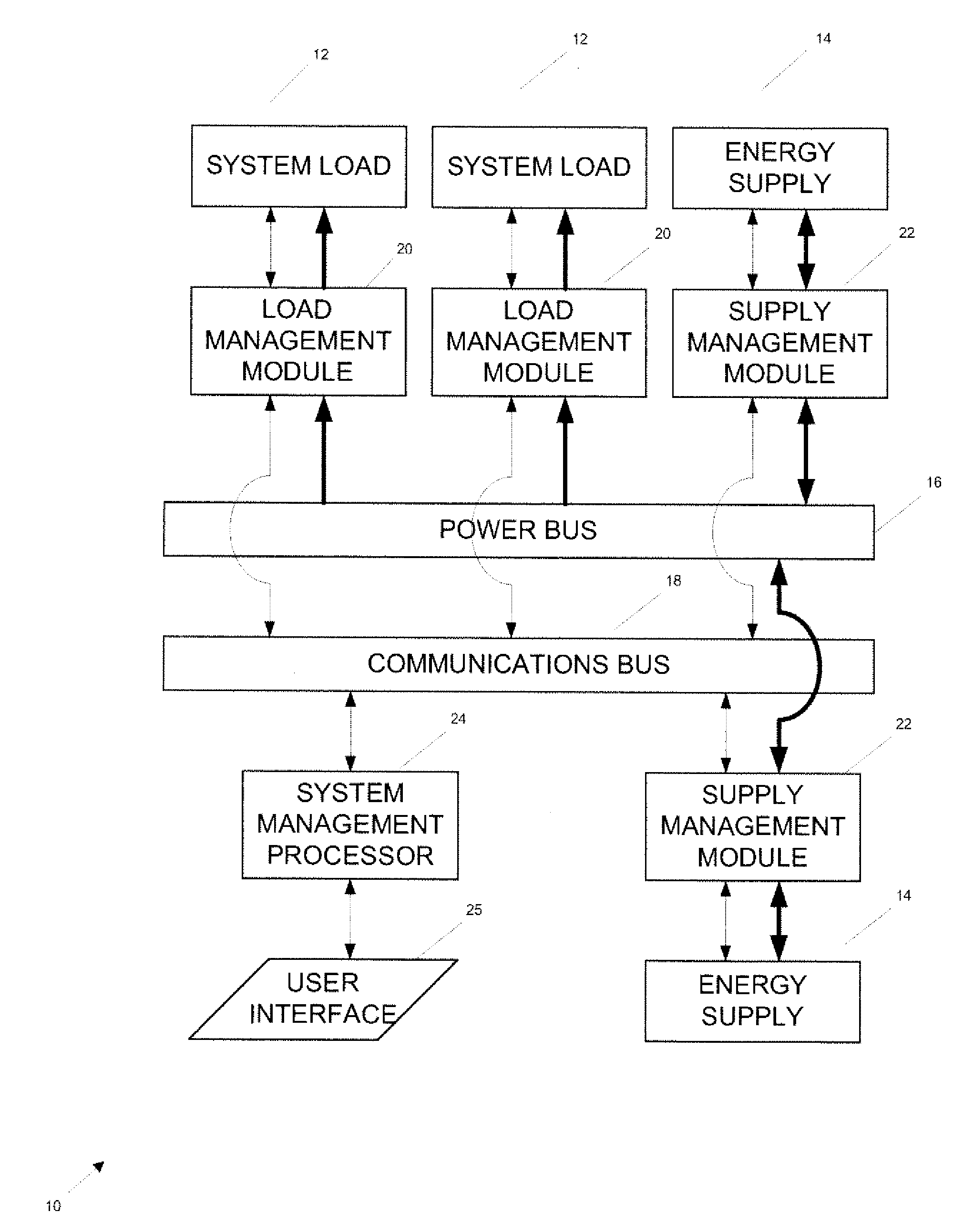

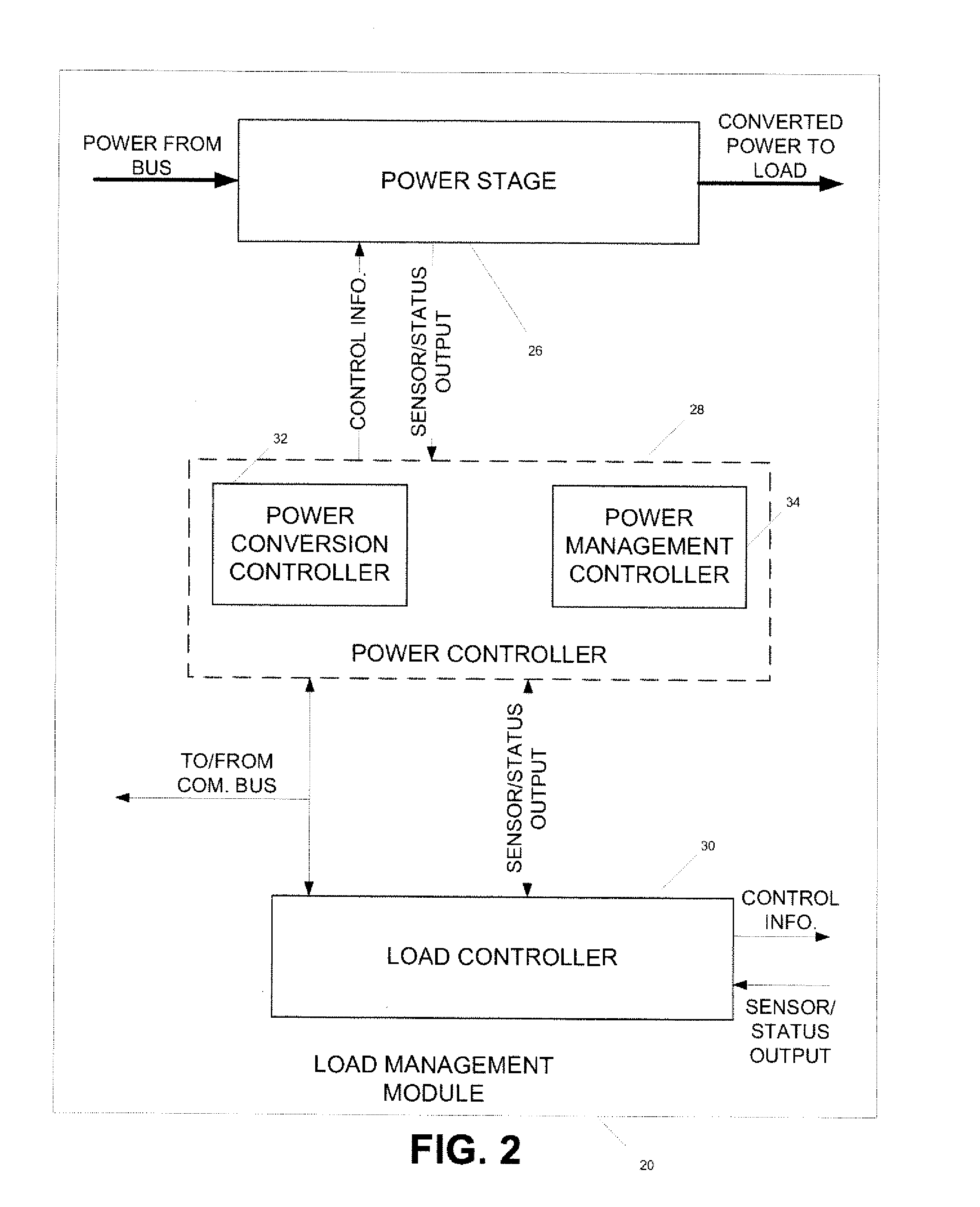

A system configured to power a vehicle or vessel. The system may include an enhanced power control system. The enhanced power control system having a distributed architecture such that power conversion and / or management is provided for individual energy supplies and / or system loads. The distributed architecture of the power control system may enhance the power efficiency of the vehicle or vessel. The distributed architecture of the power control system may enable a plurality of different energy supplies and / or system loads to be incorporated into the power system in a selectable, configurable manner. This may facilitate the addition and / or subtraction of energy supplies and / or system loads from the system to customize the vehicle or vessel for a specific use and / or mission without having to reconfigure the power control system as a whole.

Owner:INSCOPE SOLUTIONS LLC

Wireless inductive power transfer

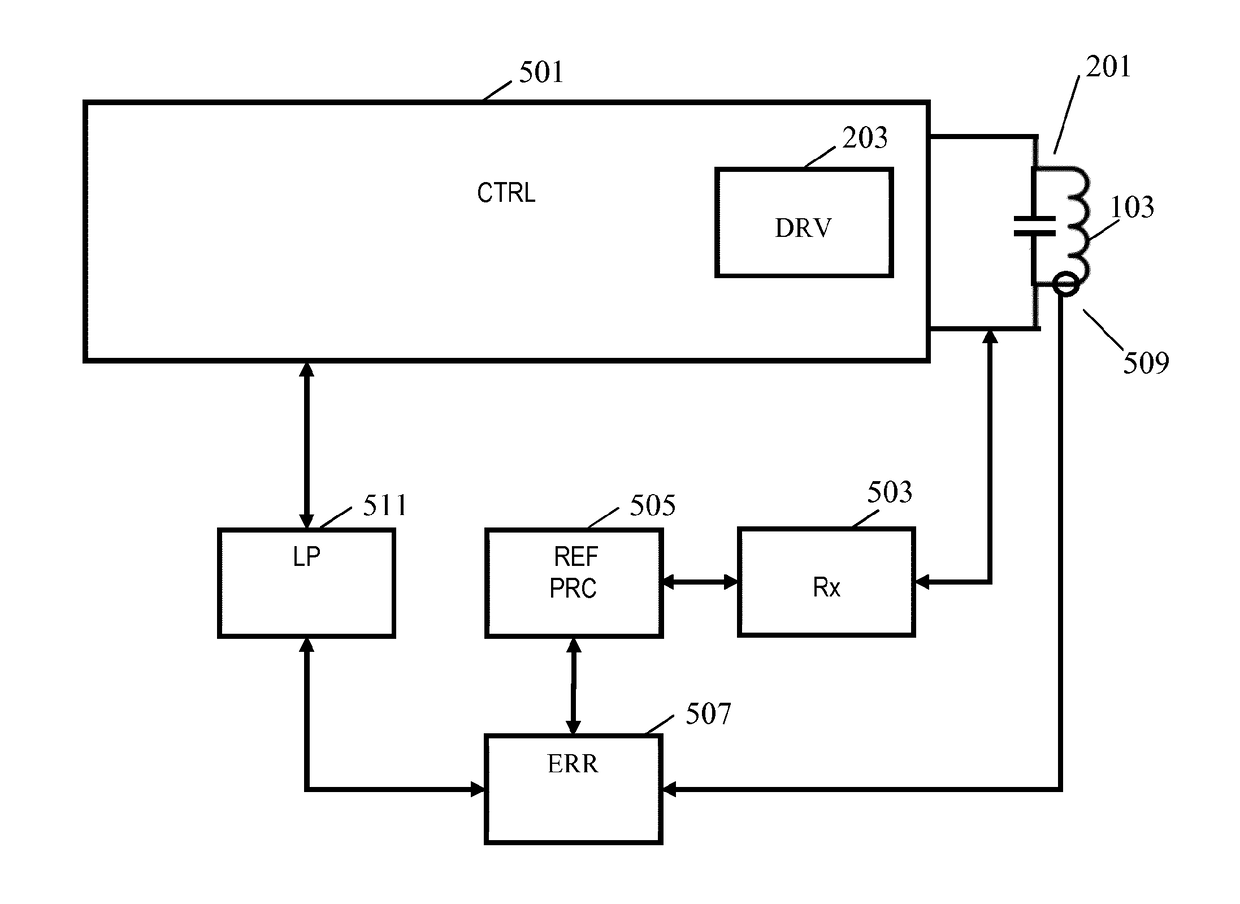

ActiveUS20180323648A1Improve performanceEasy to controlNear-field transmissionBatteries circuit arrangementsTransmitter coilResonance

A power transmitter (101) inductively transferring power to a power receiver (105) comprises a resonance circuit (201) comprising a transmitter coil (103). A driver (203) generates a drive signal for the resonance circuit (201) and a data receiver (513) receives messages load modulated onto a power transfer signal by the power receiver (105) during communication time intervals. An error unit (507) determines a coil current error and a control loop (511) controls the current through the transmitter coil (103) in response to the coil current error with the control loop (511) being active during the communication time intervals. A loop response of the control loop is attenuated for coil current errors in a reduced control range relative to coil current error indications outside the reduced control range, where the reduced control range includes a zero coil current error.

Owner:KONINKLJIJKE PHILIPS NV

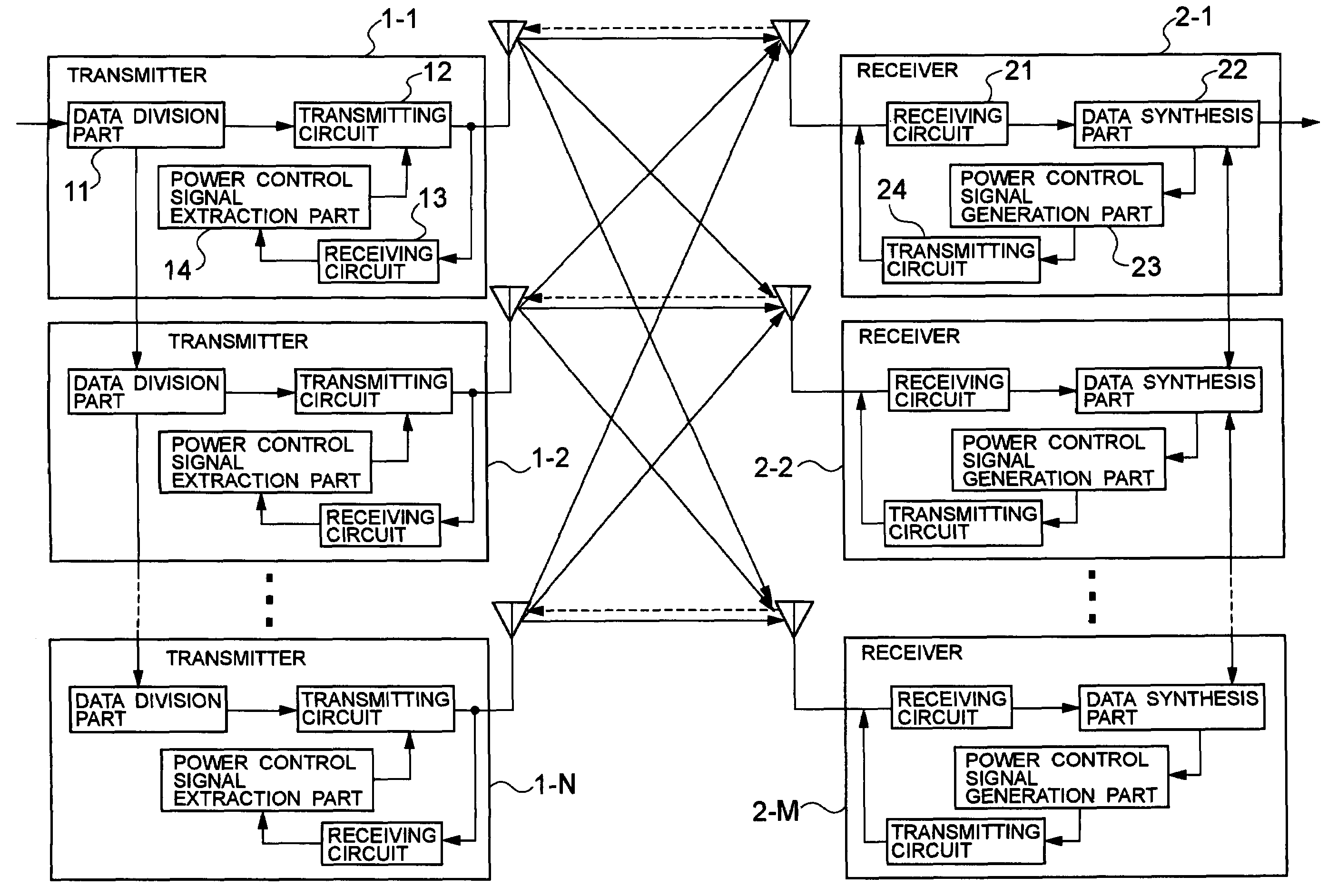

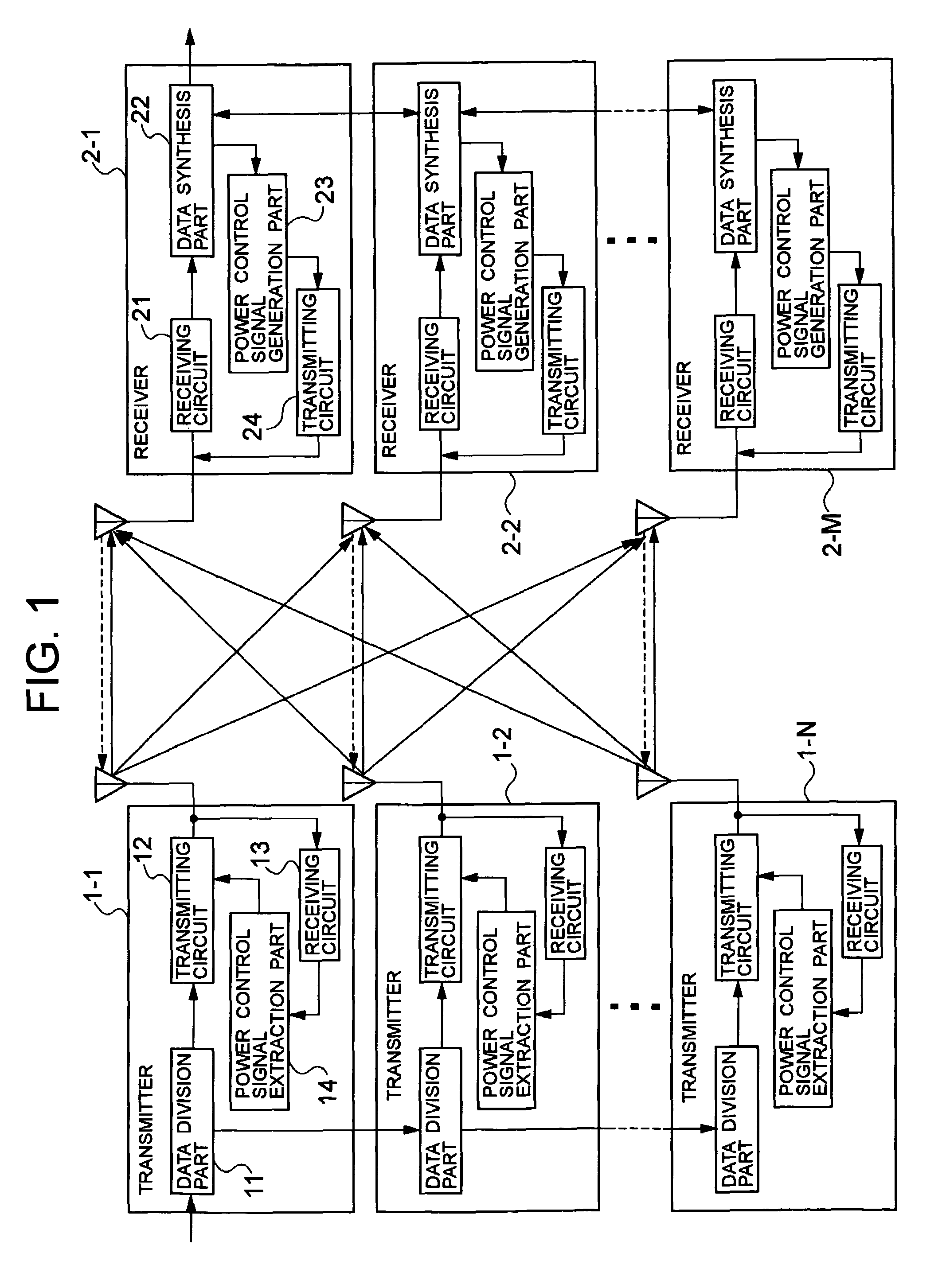

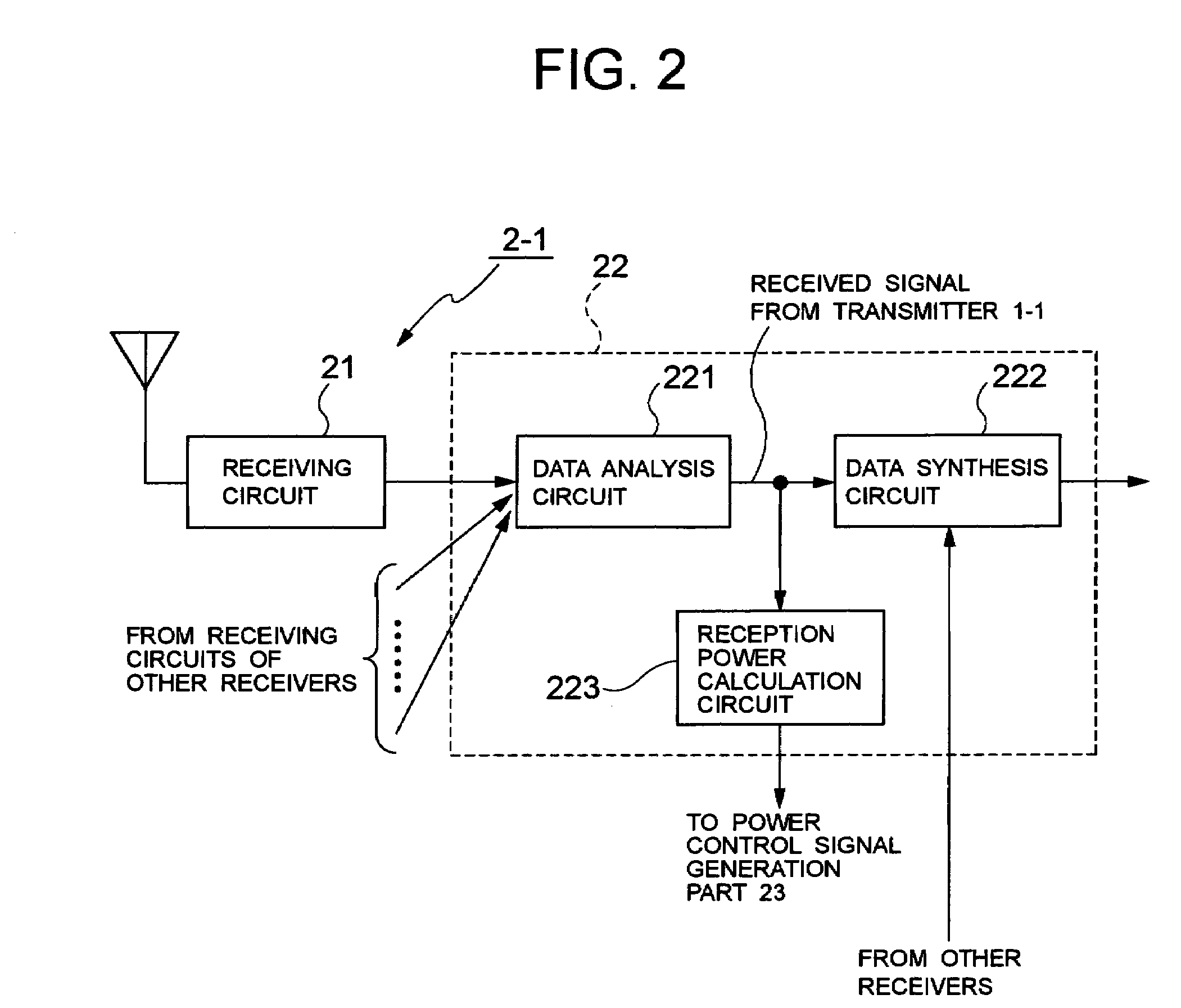

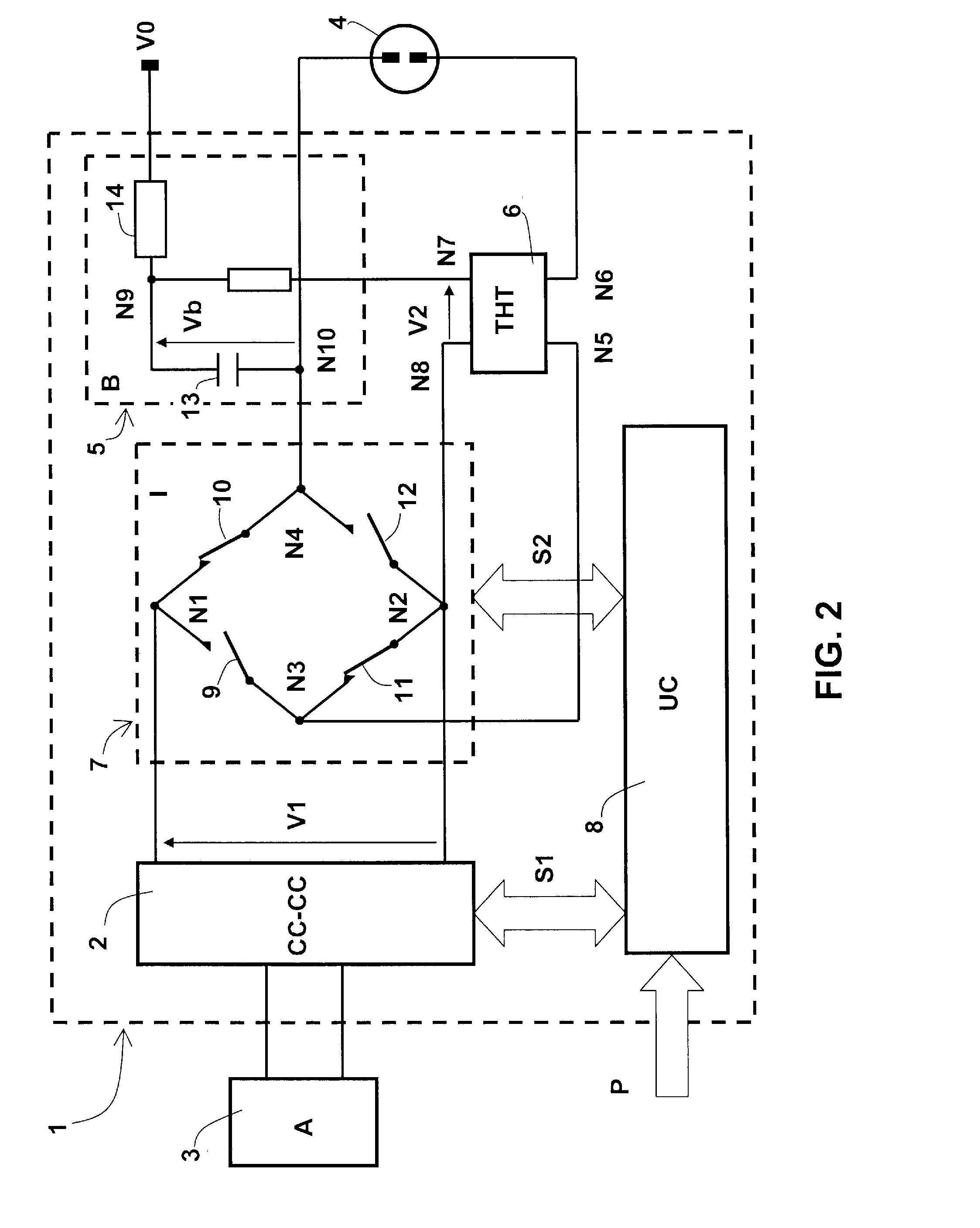

Communication system and transmitter-receiver for use therewith

ActiveUS7564911B2Convenient power controlPower managementSpatial transmit diversityCommunications systemControl signal

To achieve the optimal power control of a system in an MIMO communication method.When decoding in accordance with a receiving algorithm of the MIMO communication method in plural receivers, each receiver acquires the reception power level of a received signal from a transmitter paired with the receiver, and generates a transmitter power control signal based on a comparison result of comparing the reception power with a predetermined value. For example, if the reception power level is lower than the predetermined value, a transmitter power control signal of instructing to increase the transmitter power is generated, or otherwise, a transmitter power control signal of instructing to decrease the transmitter power is generated. The generated control signal is transmitted from the receiver to the transmitter paired with the receiver. Each transmitter controls the transmitter power in accordance with the received control signal.

Owner:NEC CORP

System configured to control and power a vehicle or vessel

InactiveUS20130229051A1Convenient power controlImprove power efficiencyElectric devicesElectrical apparatusControl systemDistributed structure

A system configured to power a vehicle or vessel. The system may include an enhanced power control system. The enhanced power control system having a distributed architecture such that power conversion and / or management is provided for individual energy supplies and / or system loads. The distributed architecture of the power control system may enhance the power efficiency of the vehicle or vessel. The distributed architecture of the power control system may enable a plurality of different energy supplies and / or system loads to be incorporated into the power system in a selectable, configurable manner. This may facilitate the addition and / or subtraction of energy supplies and / or system loads from the system to customize the vehicle or vessel for a specific use and / or mission without having to reconfigure the power control system as a whole.

Owner:INSCOPE SOLUTIONS LLC

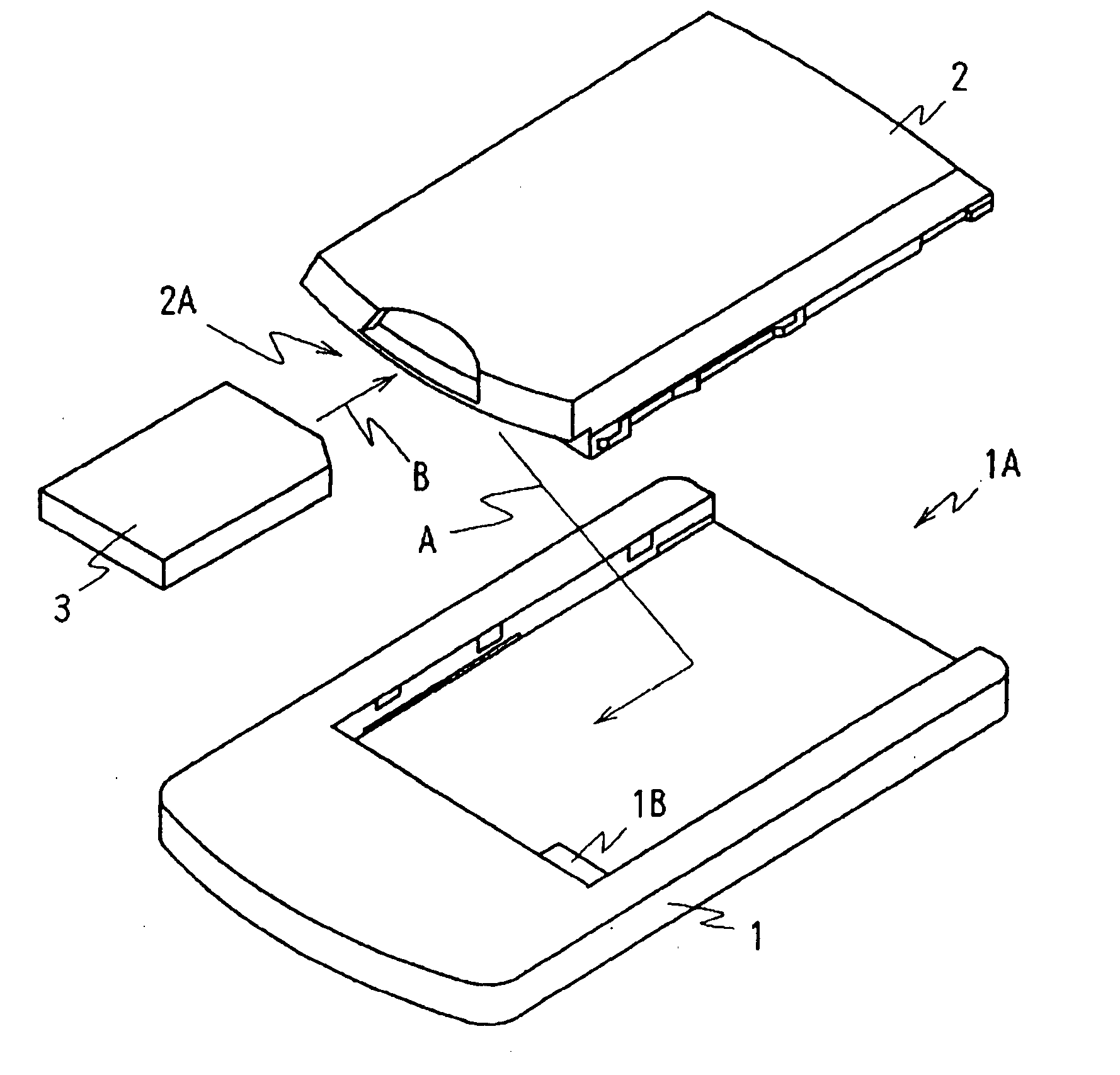

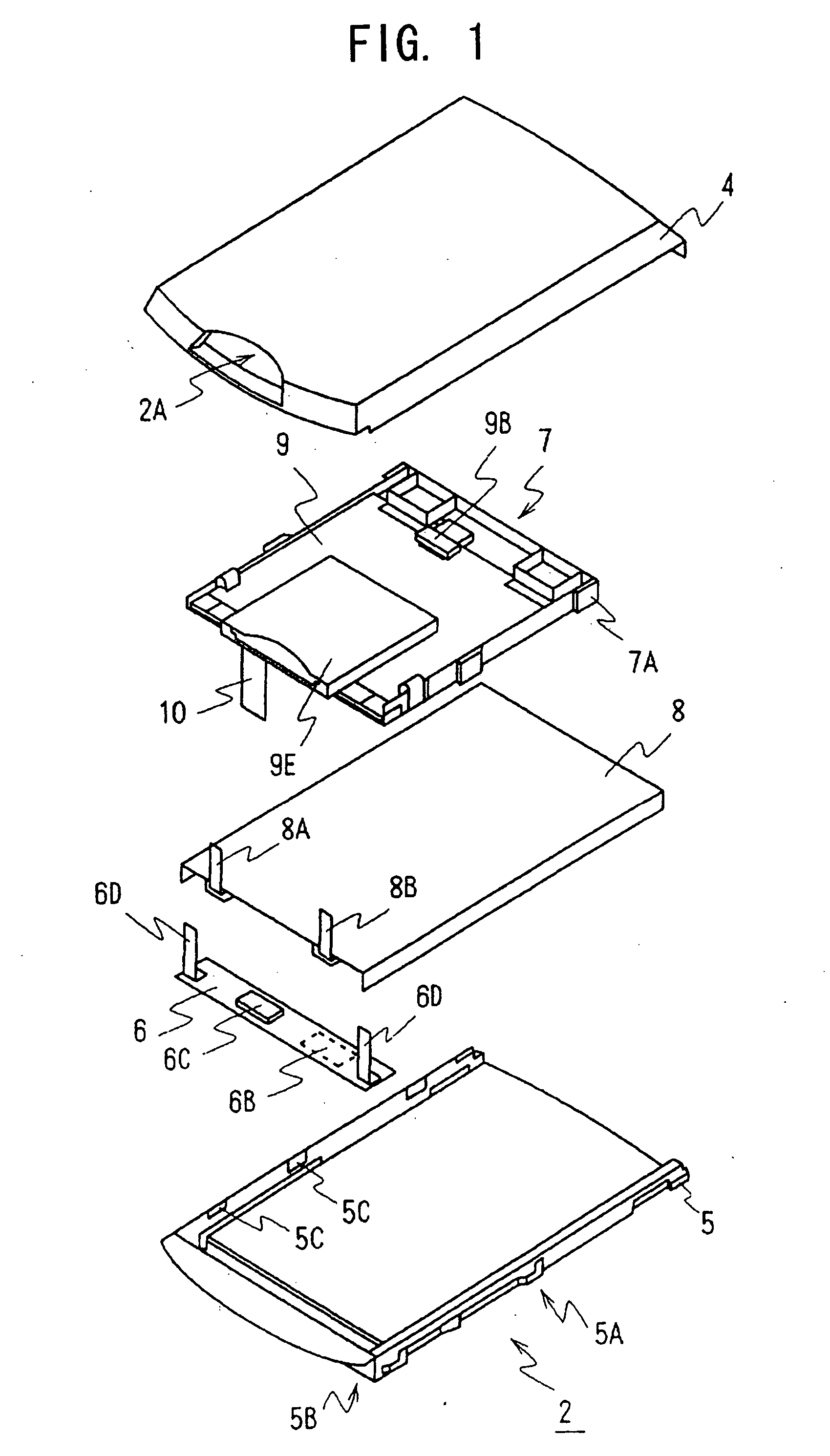

Battery pack

ActiveUS20050258804A1Enhanced couplingConvenient power controlBatteries circuit arrangementsFinal product manufactureEngineeringControl circuit

There is disclosed a battery pack, which has a plate-shaped resin-formed body to divide an internal space of the battery pack into at least two spaces in a thickness direction thereof, so that a battery is received in a first internal space, while a wiring substrate having a control circuit packaged thereon is placed in a second internal space, thereby allowing the battery pack to hold an input / output circuit or the like of a memory card securely in a limited space in the battery pack, while ensuring that a sufficient insulation is provided to the battery, when the battery pack is used for PDA'S, for instance.

Owner:MURATA MFG CO LTD

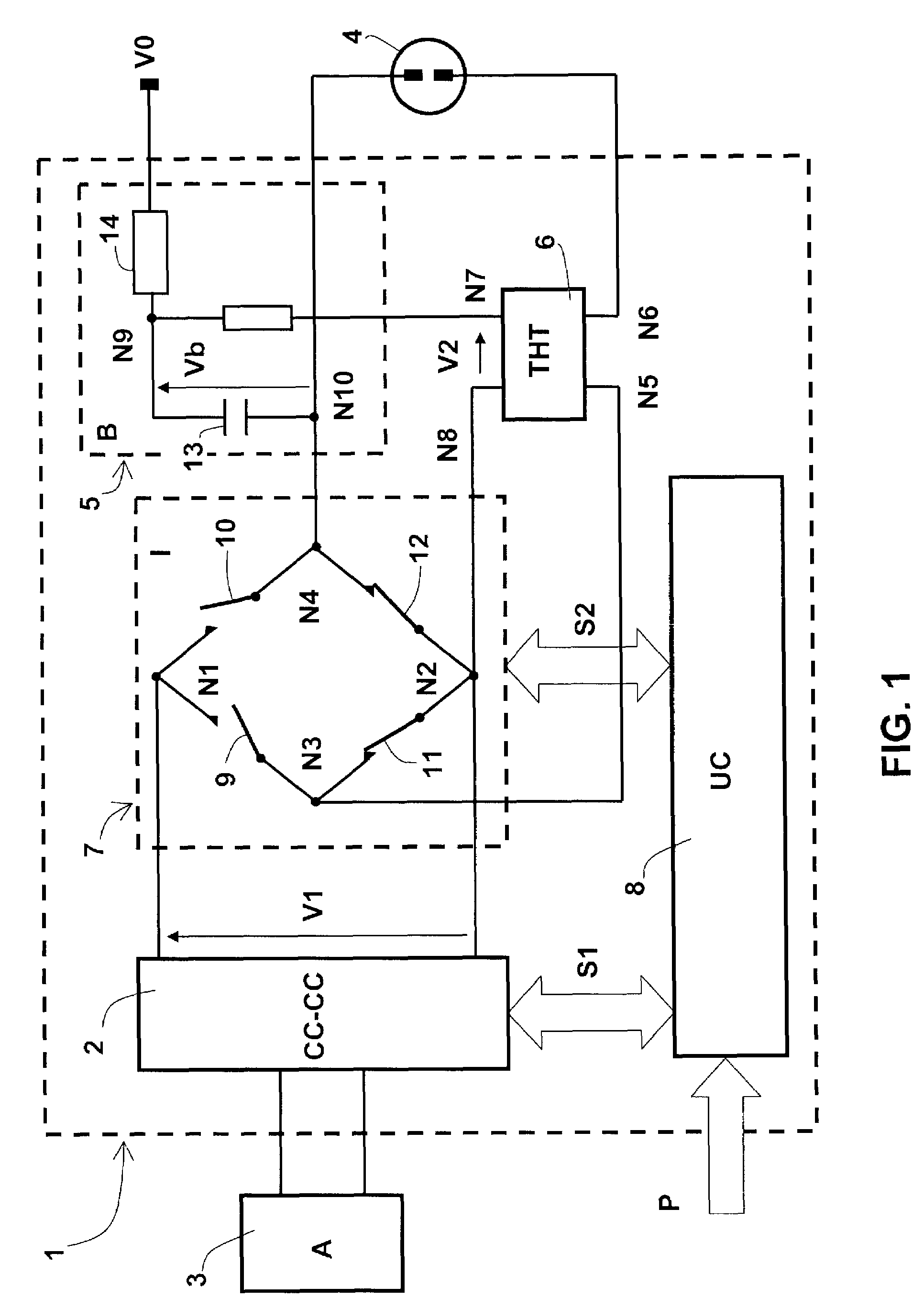

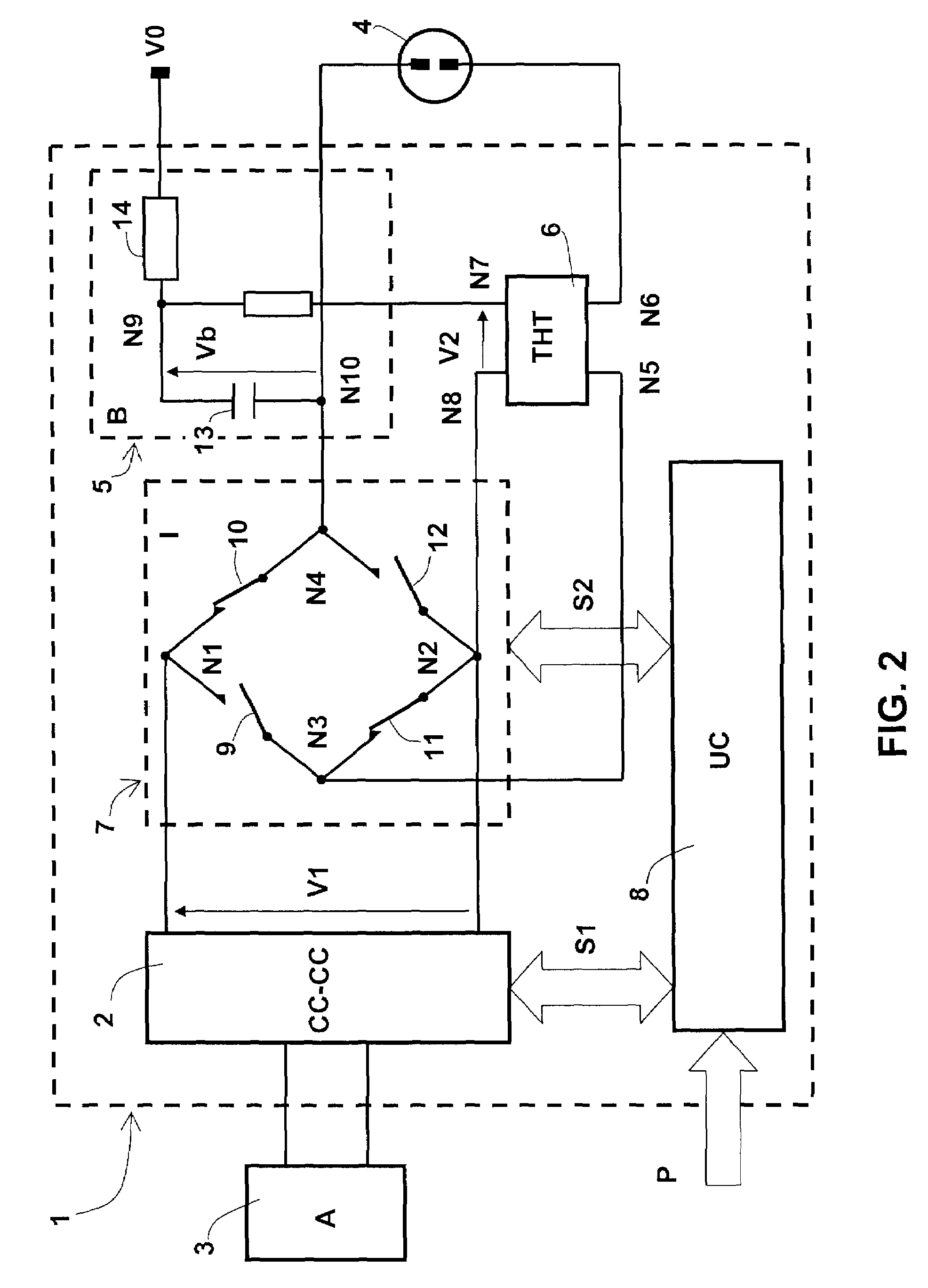

Ballast for a gas discharge lamp and a method of controlling this ballast

InactiveUS7449846B2Reduce capacitanceConvenient power controlElectrical apparatusDigital data processing detailsGas-discharge lampVoltage generator

Owner:VALEO VISION SA

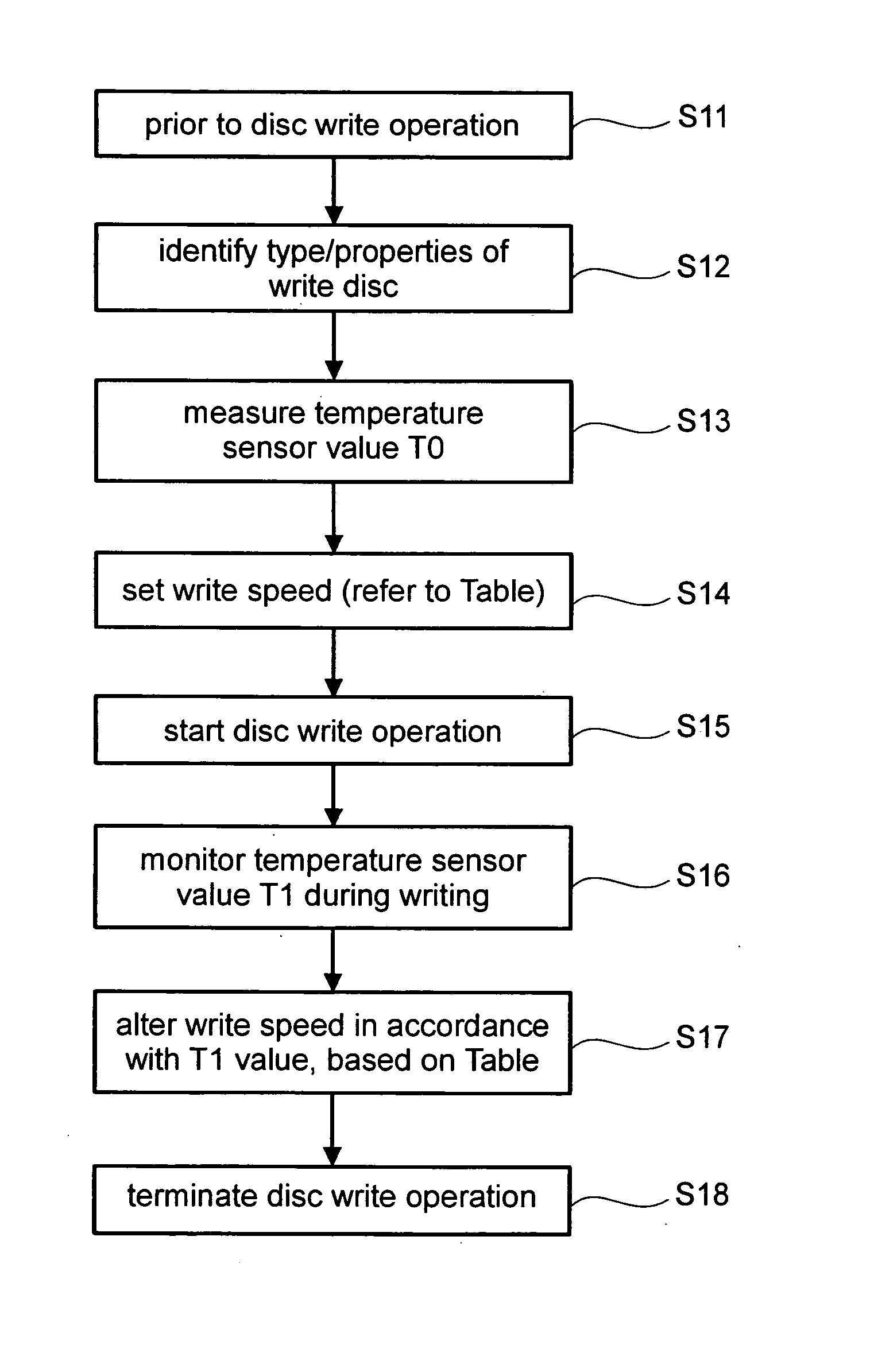

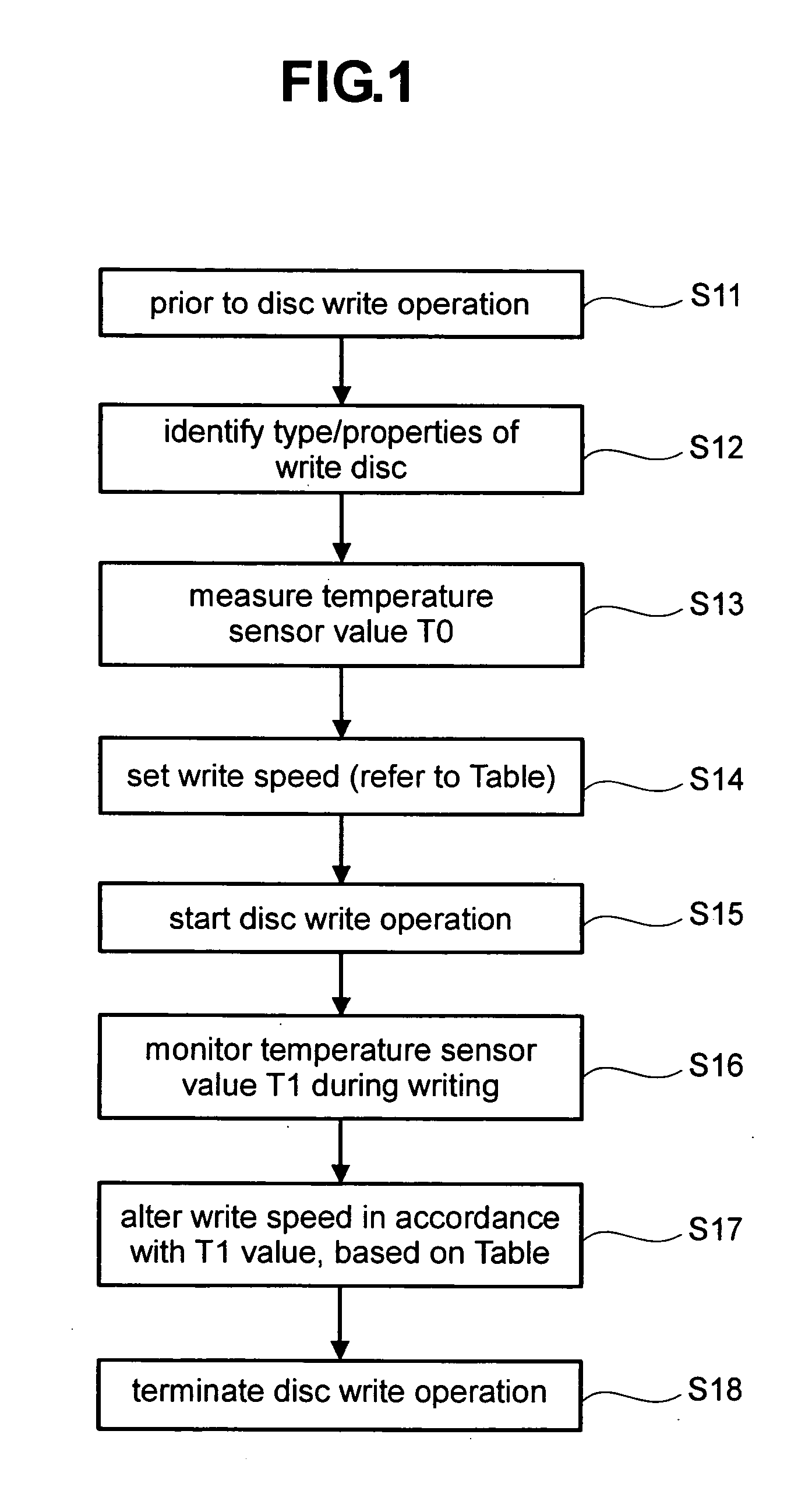

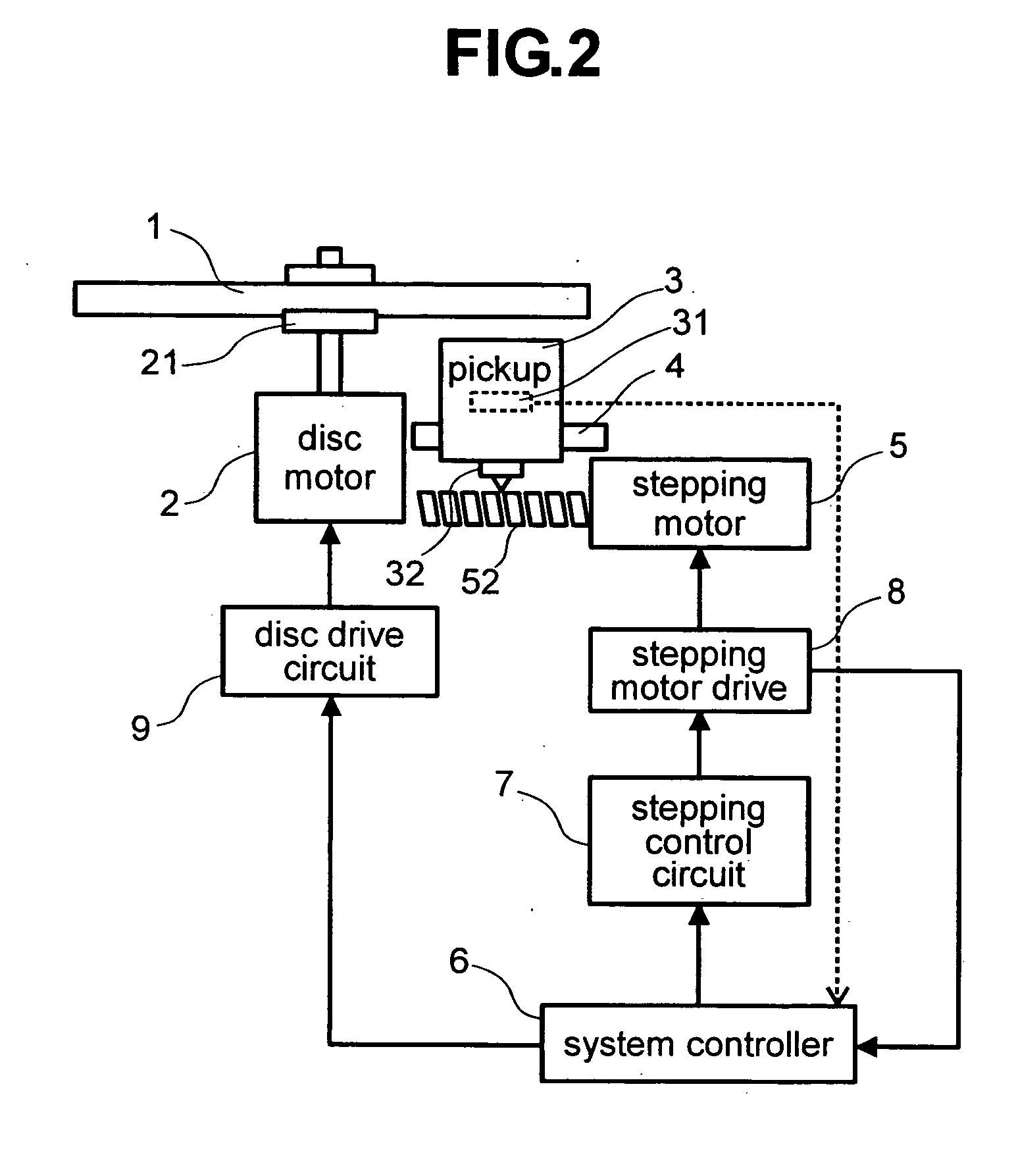

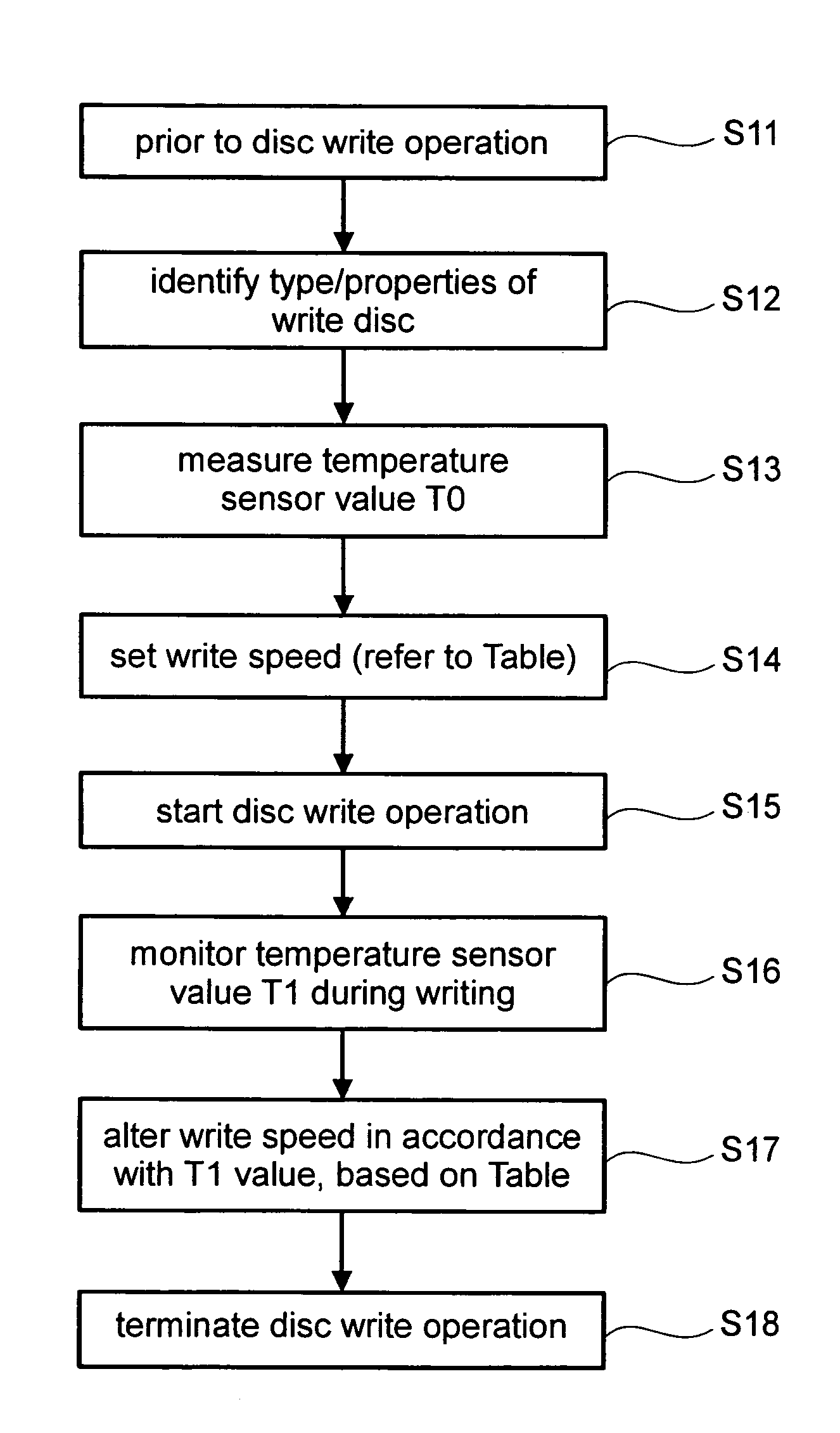

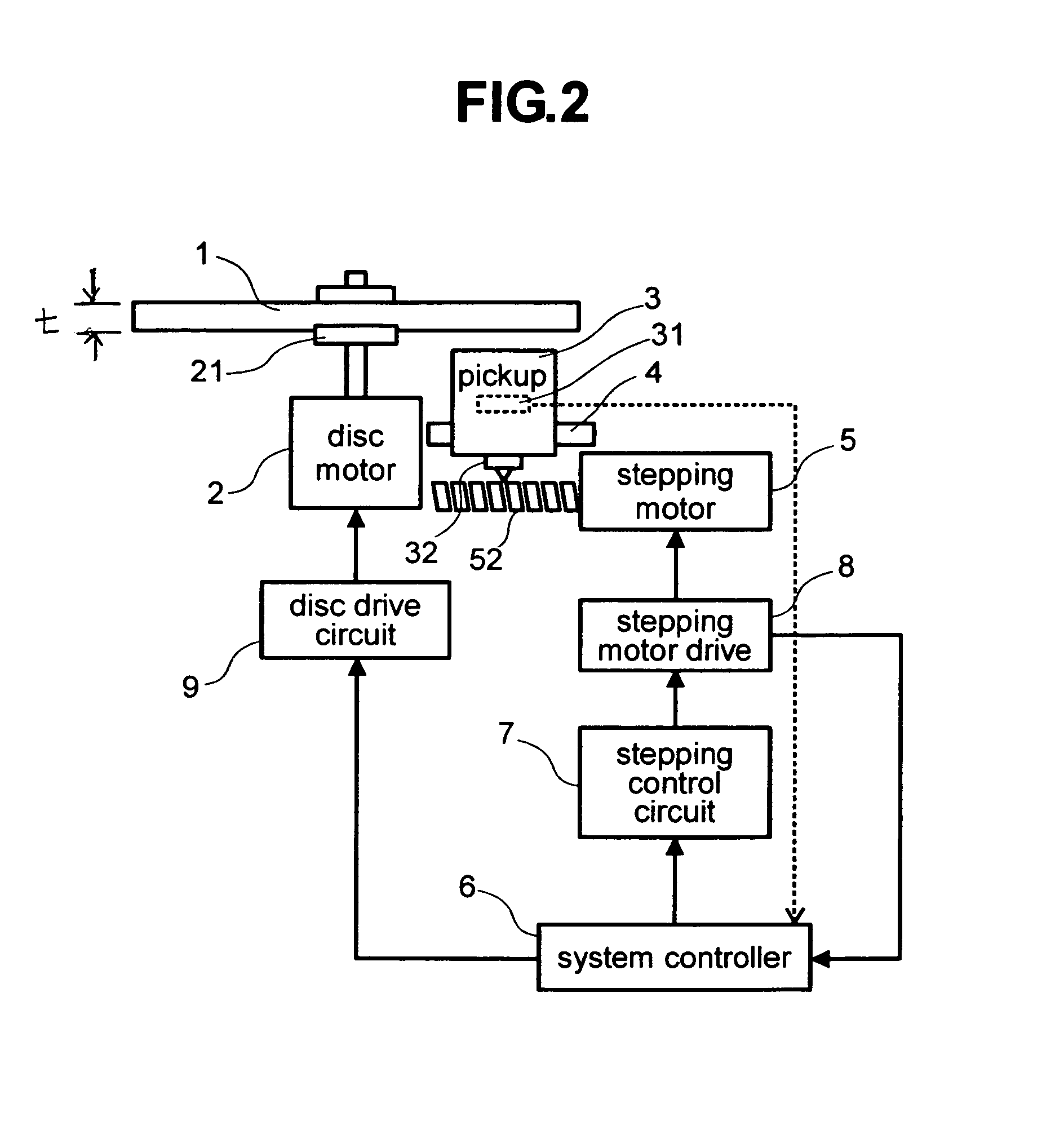

Optical disc device and data recording method for optical disc device

ActiveUS20050030859A1Improve recording qualityQuality improvementReducing temperature influence on carrierFilamentary/web record carriersDriving currentElectric machine

In an optical disc device comprising: a pickup 3 having a laser diode and generating a laser beam for recording onto an optical disc 1; a disc motor 2 that drives the rotation of an optical disc mounted thereon; a stepping motor that moves the pickup in the radial direction of the disc; and a system controller 6 that supplies drive current to the laser diode, and that controls the rotational speed of the disc motor and the position of the pickup by means of the stepping motor; the pickup has a temperature sensor 31 in its interior and system controller 6 restricts the drive current supplied to the laser diode in accordance with a detected temperature during data recording and controls the rotational speed of the disc motor, based on the detected temperature and the data recording properties of the optical disc which have been determined.

Owner:HITACHI-LG DATA STORAGE

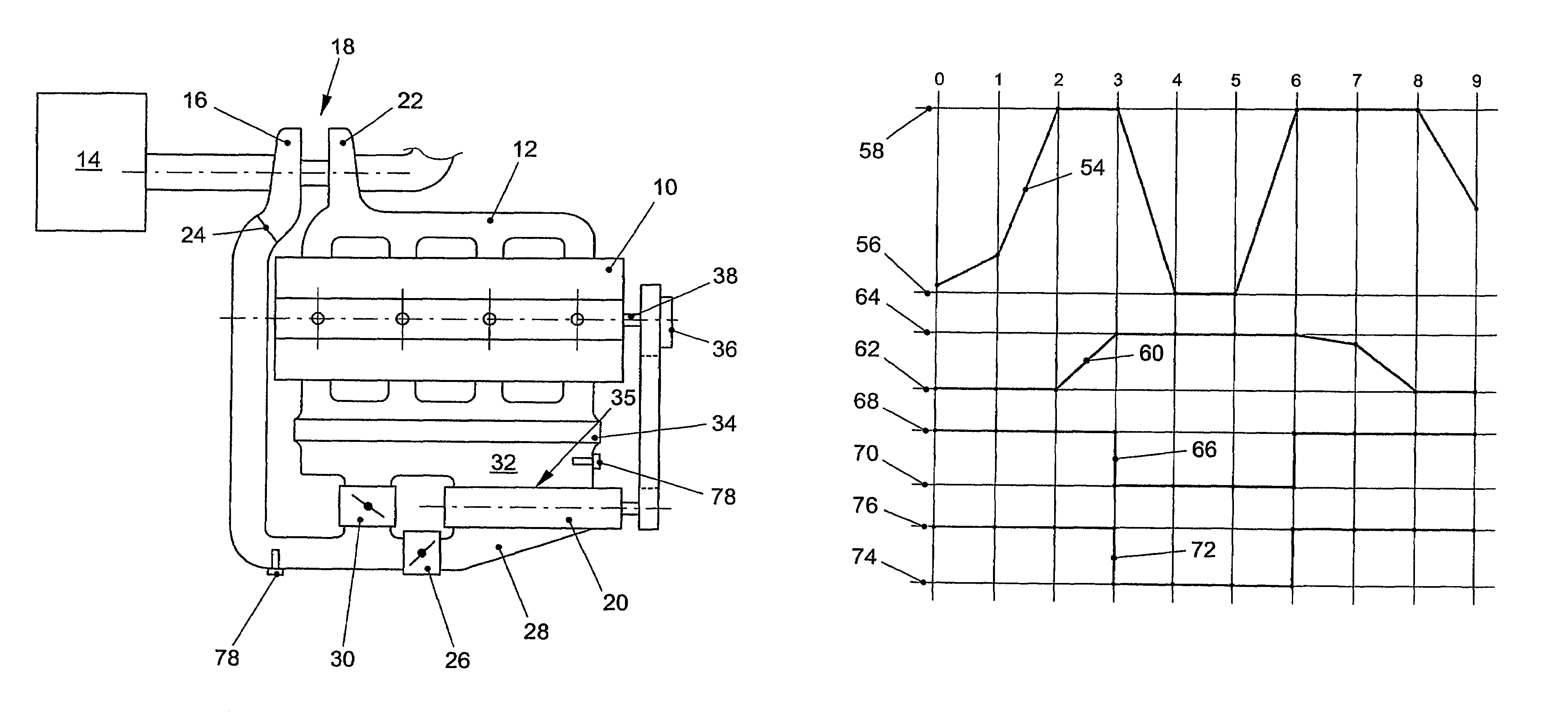

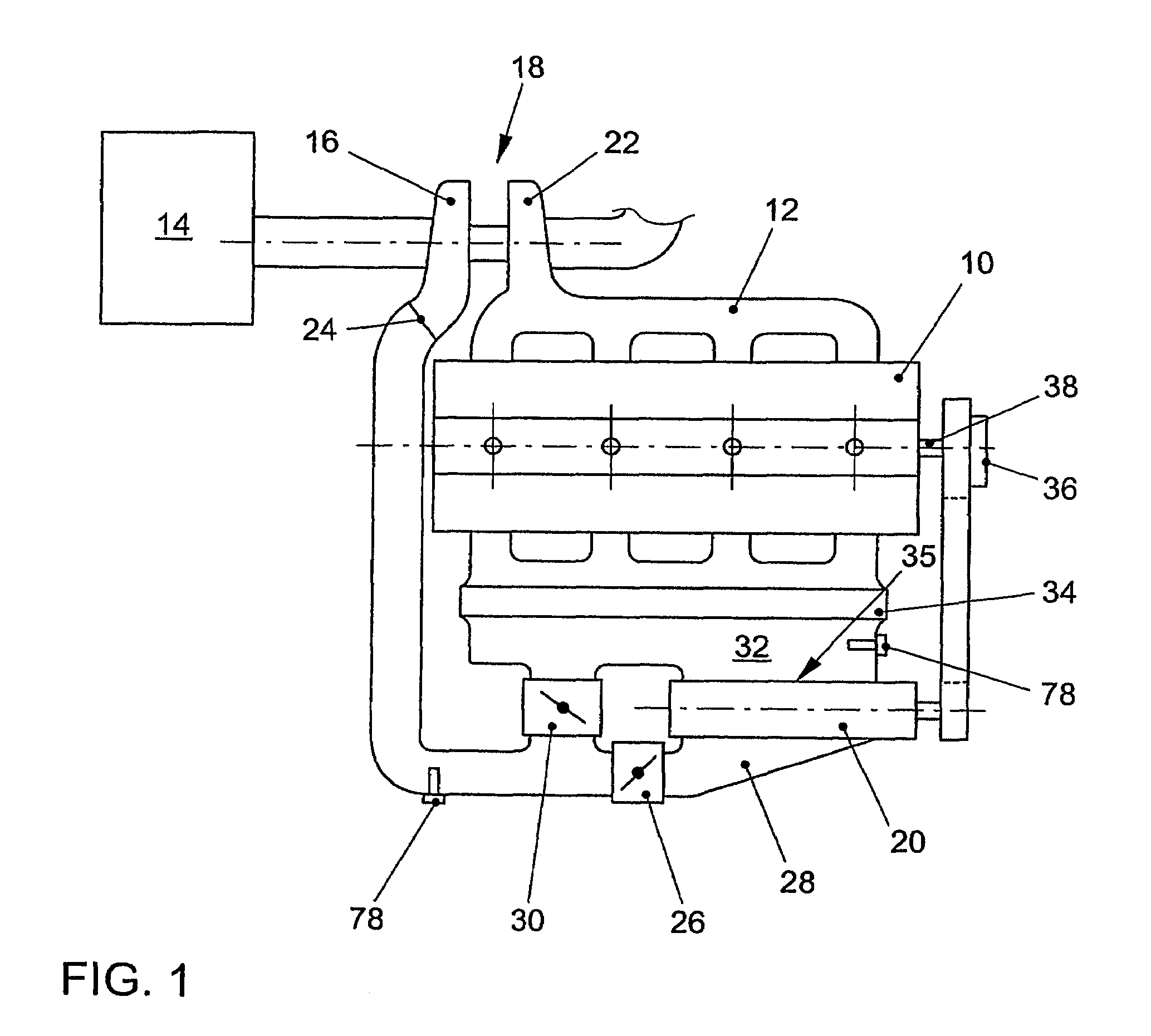

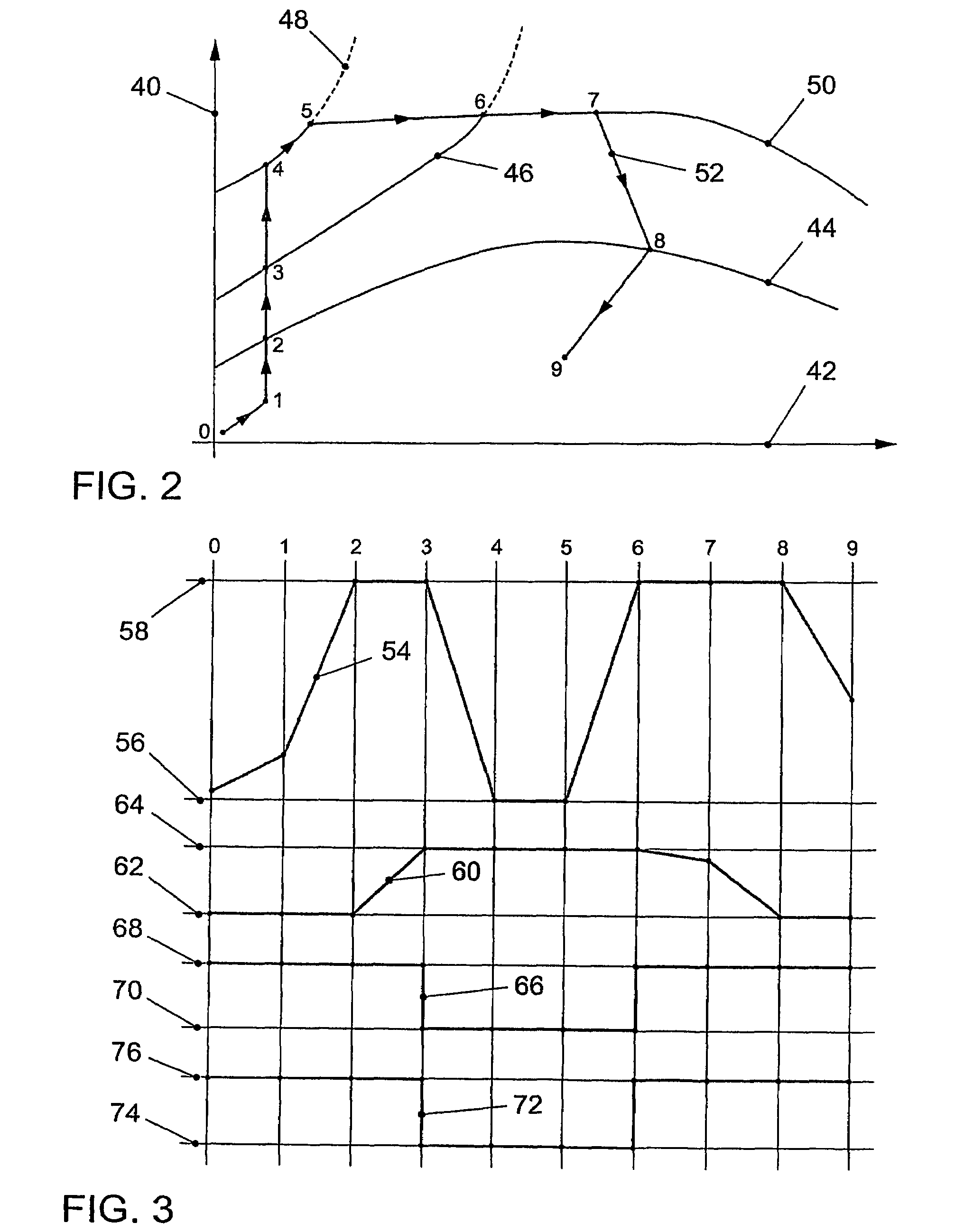

Dual-charged internal combustion engine and method for operating the same

InactiveUS7810329B2Improvement in the dynamic behaviorConvenient power controlInternal combustion piston enginesTurbochargerCoupling

The invention relates to an internal combustion engine, especially of a motor vehicle, which comprises an air path for intake air in which a mechanically driven charge unit (20), especially a compressor, which can be connected and disconnected by means of a coupling (36), an exhaust gas turbocharger (18), an intake pipe (32), connected to air inlets of a cylinder block (10) of the internal combustion engine, and a charge cooler (34) are mounted. One pressure outlet (35) of the mechanically driven charge unit (20 is directly connected to the intake pipe (32) and one pressure outlet (24) of the exhaust gas charger (18) is connected to an intake inlet (28) of the mechanically driven charge unit (20). The pressure outlet (24) of the exhaust gas charger (18) is connected to the intake inlet (28) of the mechanically driven charge unit (20) via an on-off butterfly valve (26) and upstream of said on-off butterfly valve (26) to the intake pipe (32) via a load butterfly valve (30). The charge cooler (34) is integrated into the intake pipe (32) to give an intake / charge cooler module.

Owner:VOLKSWAGEN AG

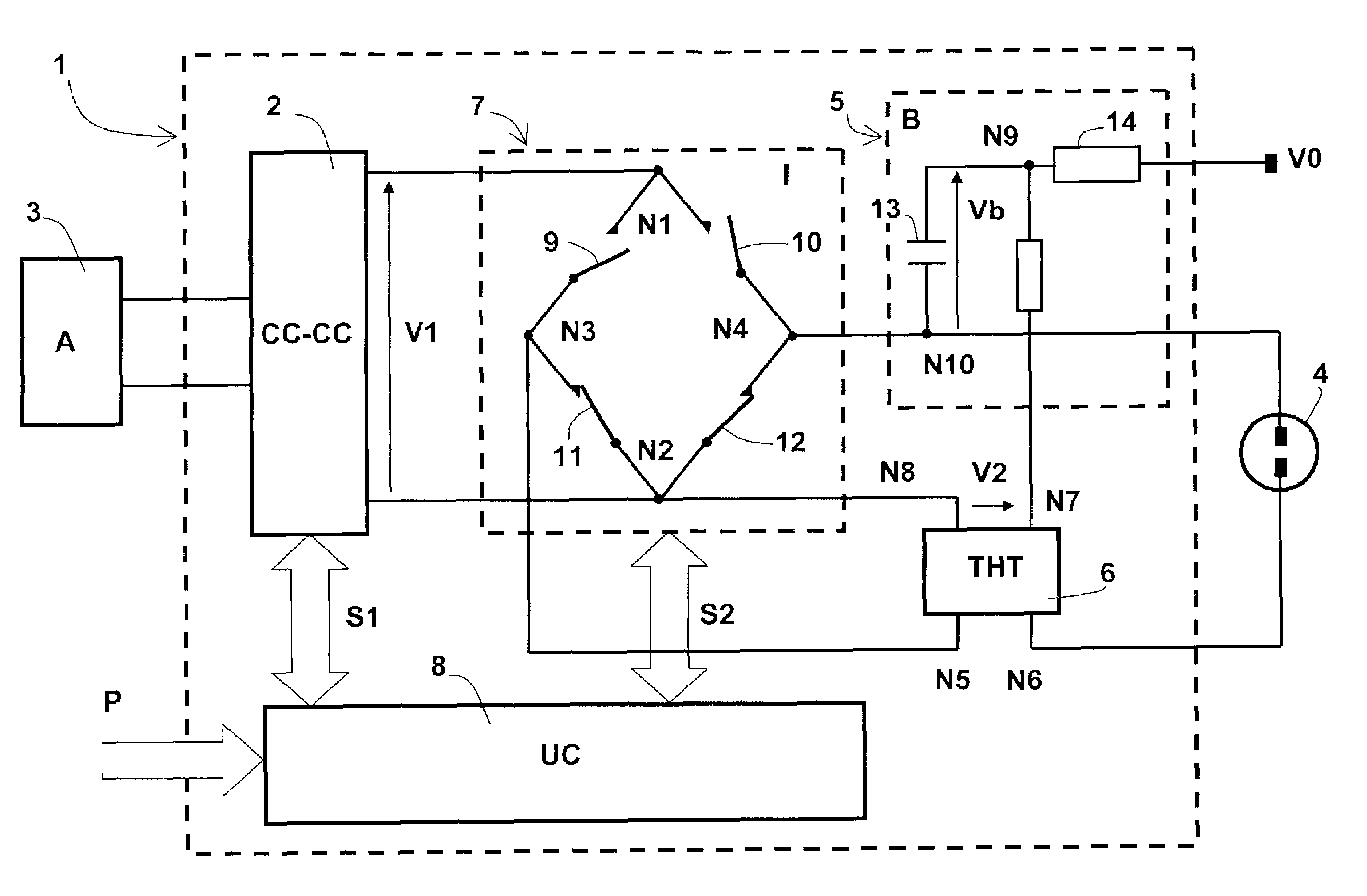

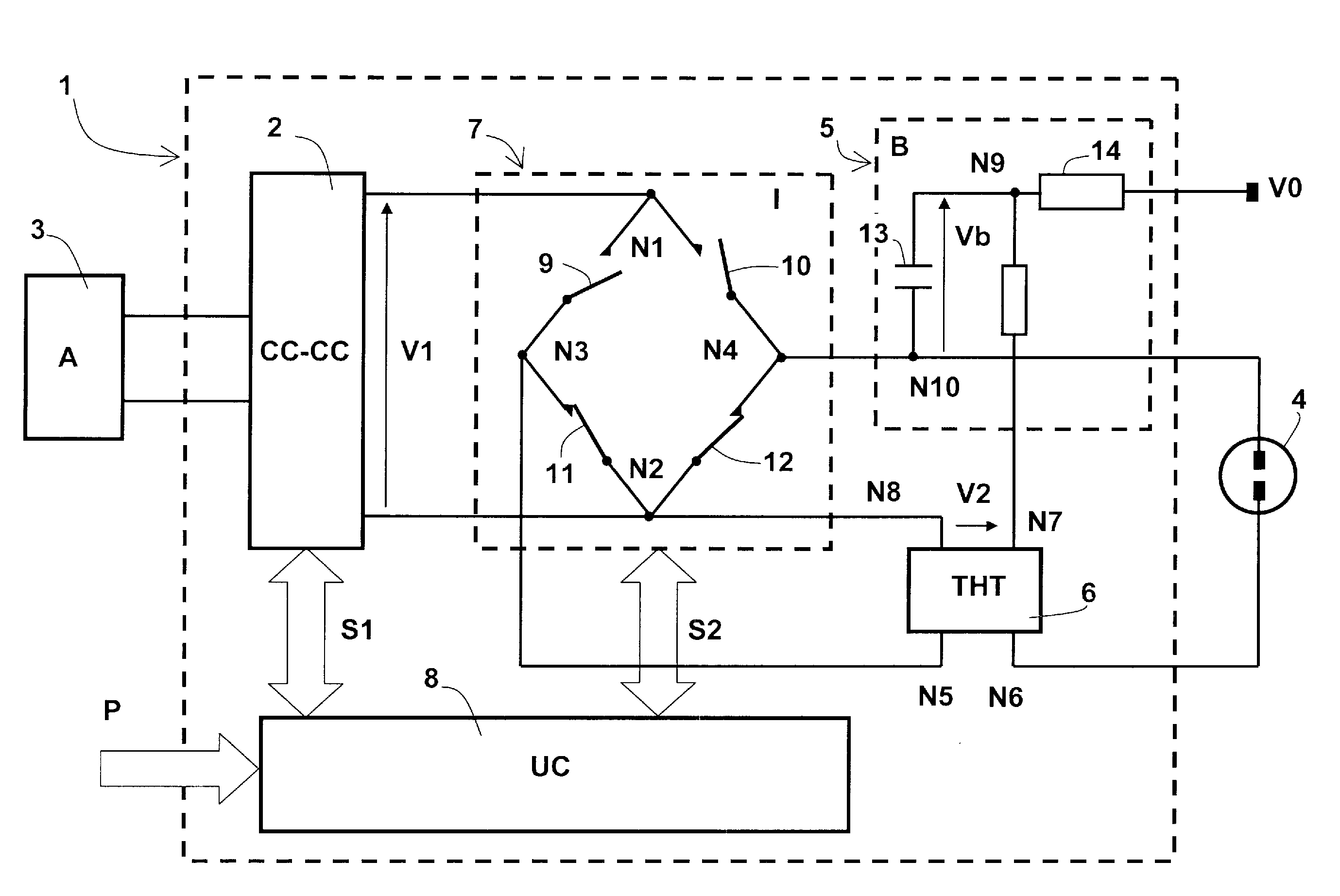

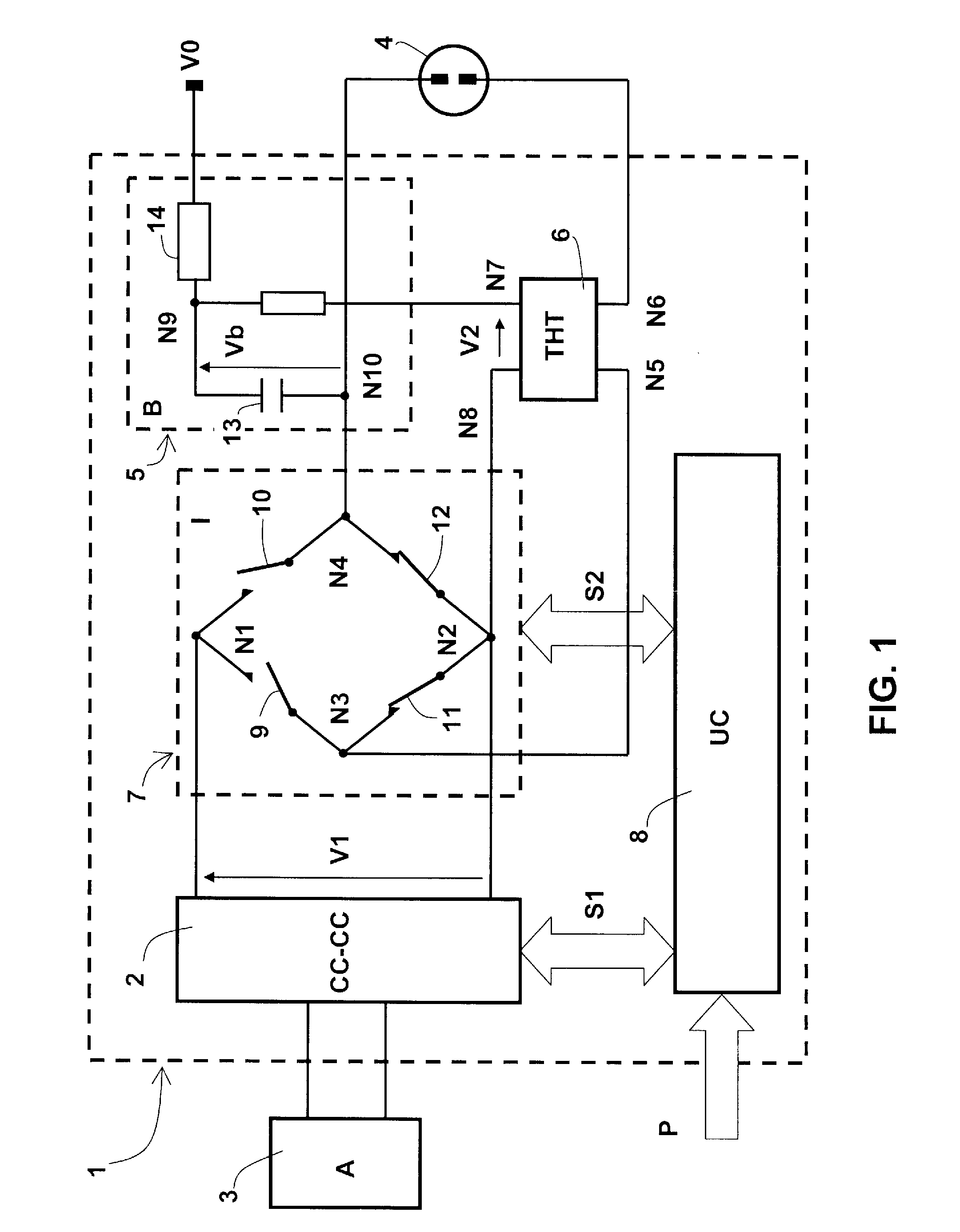

Ballast for a gas discharge lamp and a method of controlling this ballast

InactiveUS20070152602A1Increased power controlReduce capacitanceElectrical apparatusElectric light circuit arrangementDc ac converterEngineering

A ballast that comprises a DC-DC converter, a DC-AC converter, a lighting voltage generator and a control unit. A difference in voltage between input terminals of the lighting voltage generator is generated by a voltage step-up circuit of the “self-boosting” type from a DC voltage supplied by the DC-DC converter and an auxiliary voltage source V0. The ballast makes it possible to obtain a voltage level V2 that is equal to twice a first voltage level V1 increased by the auxiliary voltage V0.

Owner:VALEO VISION SA

Optical disc device for recording different types of optical discs and data recording method for optical disc device

ActiveUS7423942B2Quality improvementIncrease speedReducing temperature influence on carrierFilamentary/web record carriersDriving currentData control

In an optical disc device comprising: a pickup 3 having a laser diode and generating a laser beam for recording onto an optical disc 1; a disc motor 2 that drives the rotation of an optical disc mounted thereon; a stepping motor that moves the pickup in the radial direction of the disc; and a system controller 6 that supplies drive current to the laser diode, and that controls the rotational speed of the disc motor and the position of the pickup by means of the stepping motor; the pickup has a temperature sensor 31 in its interior and system controller 6 restricts the drive current supplied to the laser diode in accordance with a detected temperature during data recording and controls the rotational speed of the disc motor, based on the detected temperature and the data recording properties of the optical disc which have been determined.

Owner:HITACHI-LG DATA STORAGE

Power control using at least 540 degrees of phase

InactiveUS20060097758A1Minimize signal artifactConvenient power controlMultiple input and output pulse circuitsDc network circuit arrangementsHarmonicEngineering

An electrical alternating current power signal and a circuit and method for generating the same in which the alternating current signal is dropped once at a non-zero crossing point in every 540 plus N degrees, where N is a non-negative number. This manner of controlling power to a device enables wide ranges of power control while generating acceptable levels of power line harmonics and while conforming to existing international regulations governing voltage variations.

Owner:XEROX CORP