Patents

Literature

41results about How to "Quick compilation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

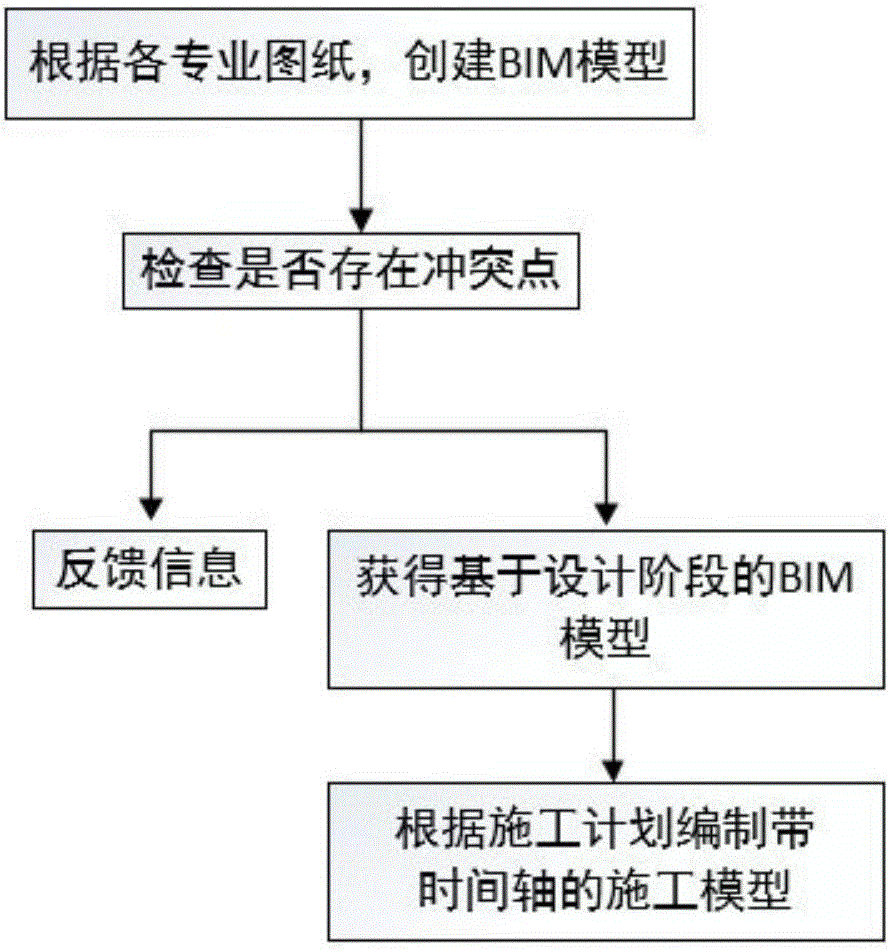

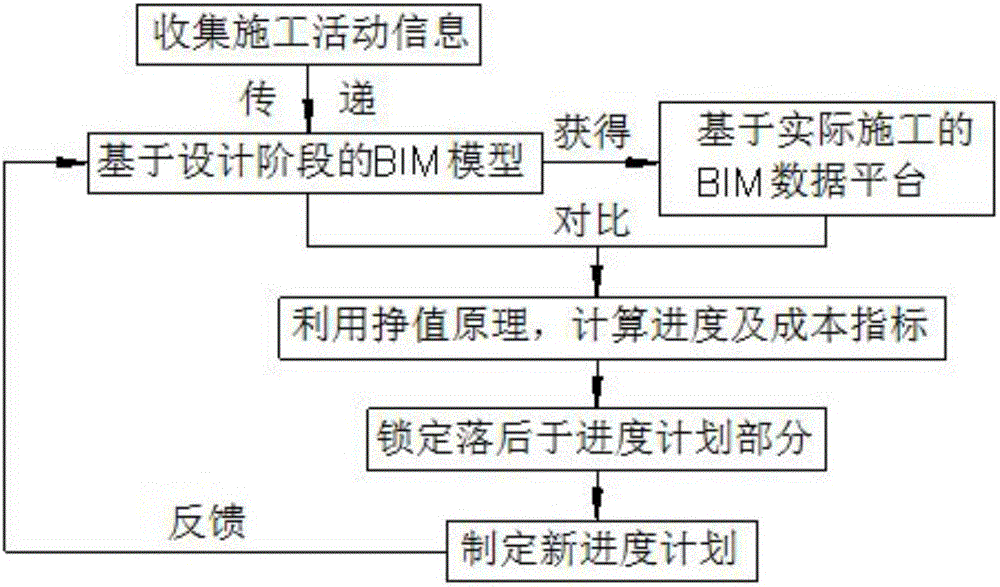

BIM project progress and cost management system based on earned value theory

InactiveCN106022587AQuick compilationFast and Accurate BudgetOffice automationResourcesProgram planningCost Controls

The invention discloses a BIM project progress and cost management system based on an earned value theory. The system comprises steps of establishing a BIM building model based on design paper and adding an environmental factor simulating a construction field; collecting construction activity information and associating the construction activity information with corresponding engineering information in the BIM building model; comparing and analyzing the engineering amount of current real complete part and the engineering amount of a planned complete part on the basis of the earned value theory and determining whether a project progress lags, and determining whether project cost exceeds planned cost by comparing generated cost with current budget amount. The BIM project progress and cost management system based on the earned value theory is used in building projects, may clear the project progress and cost control case, may feed back the project progress and cost control state in a visualized way by using the BIM building model, and has a wide application prospect.

Owner:广州络维建筑信息技术咨询有限公司

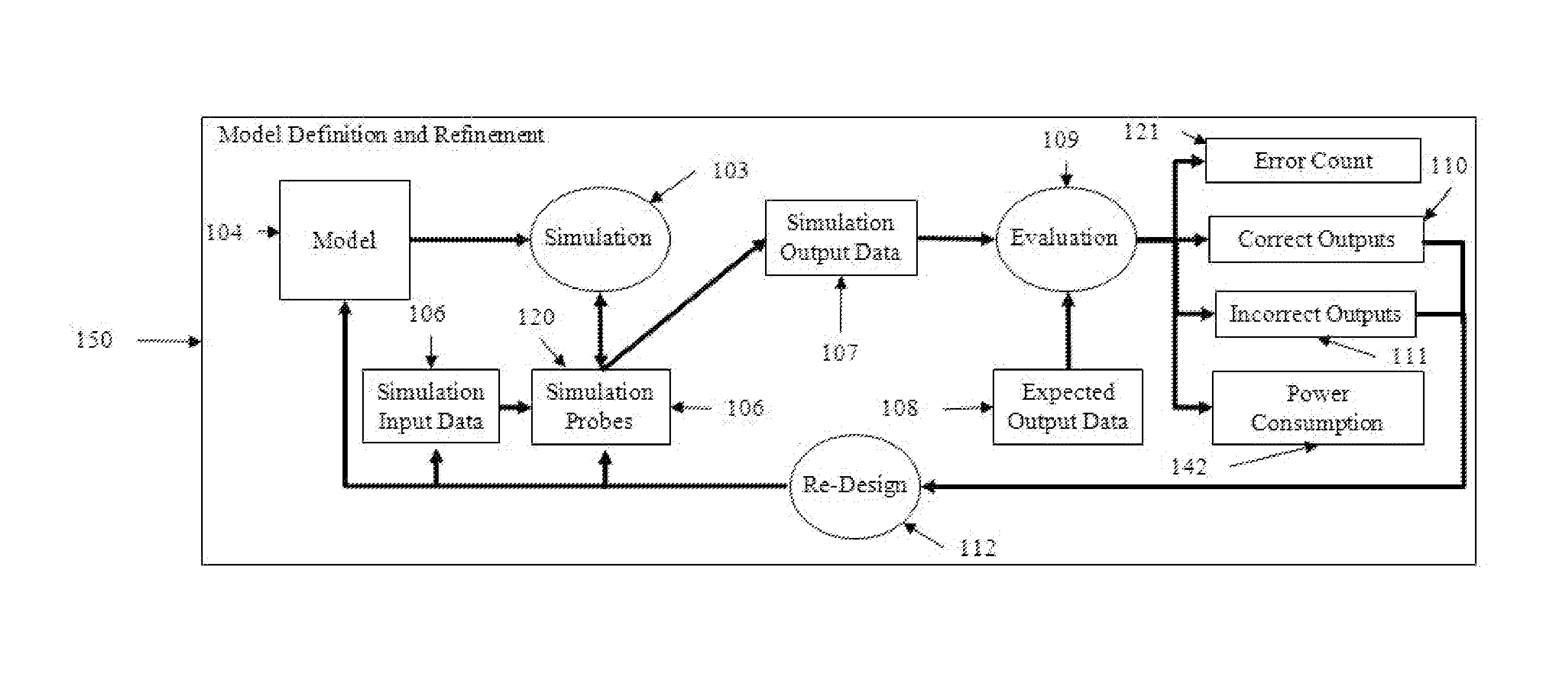

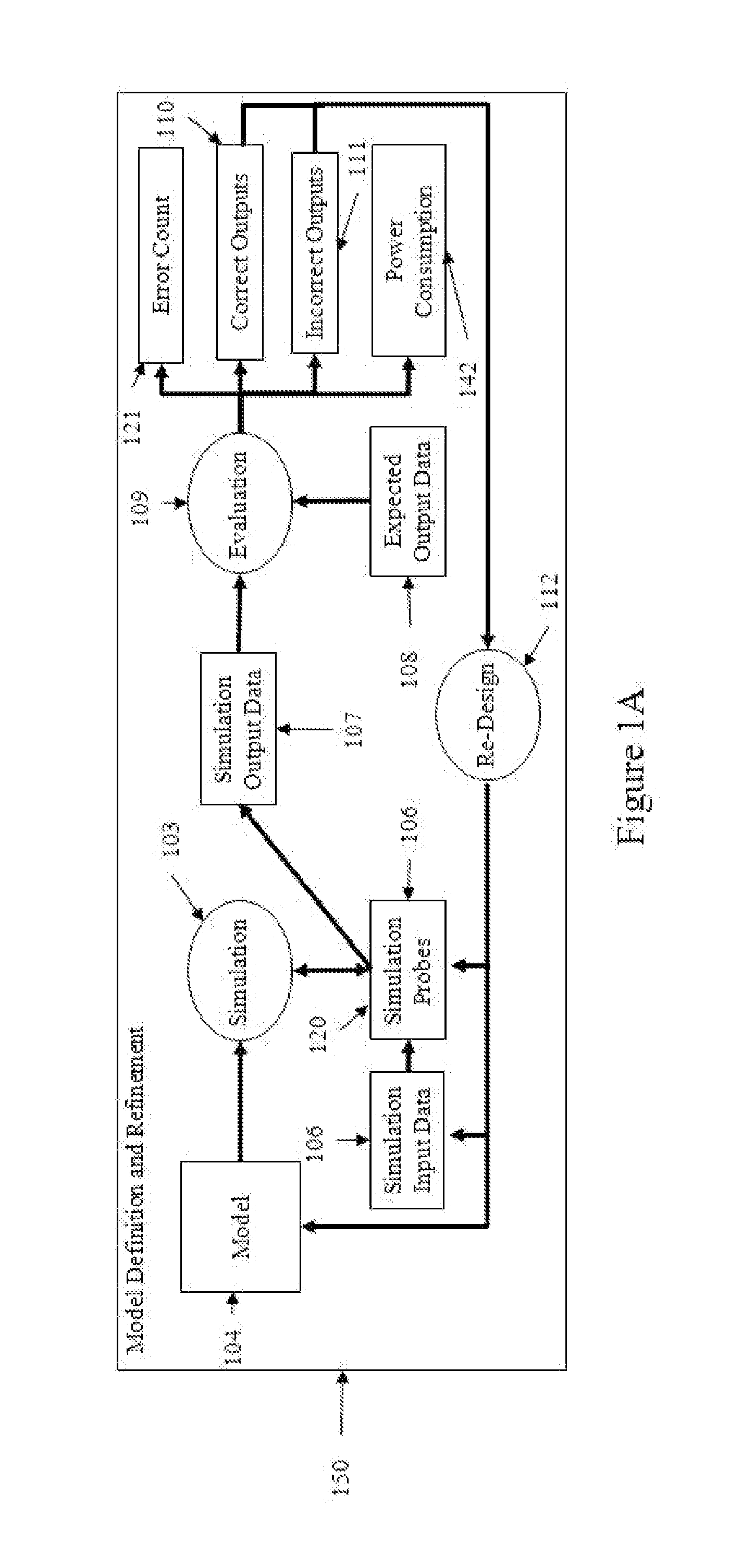

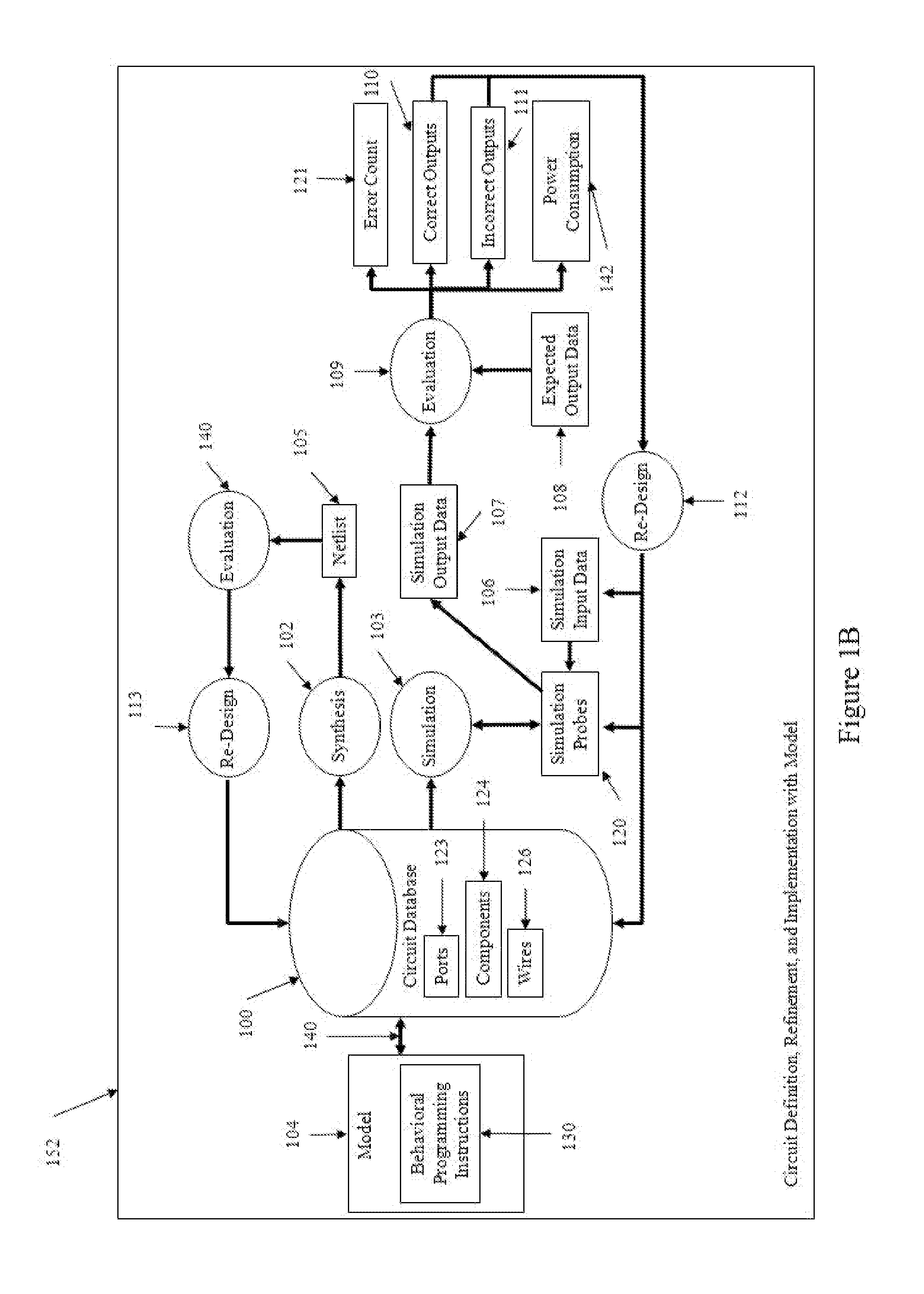

Systems and methods for circuit design, synthesis, simulation, and modeling

InactiveUS20130144589A1Quick compilationSynthesis fastCAD circuit designSpecial data processing applicationsComputer architectureProgram unit

Systems and methods for specifying, modelings simulating, and implementing a circuit design using a circuit design database comprising re-usable program elements to represent circuit design elements. The re-usable program elements may be used to build an overall circuit design description in the database. In example embodiments, the circuit design may be structured as a computer program and library to deterministically specify the circuit design elements to be used. Circuit synthesis functionality and circuit simulation functionality may be embedded as part of the re-usable program elements. Libraries may be compiled with the computer program instructions specifying the circuits to generate an executable that can be used for synthesis and simulation The combined executable code may be executed on an instruction set processor directly or through an interpreter.

Owner:LEVI DELON

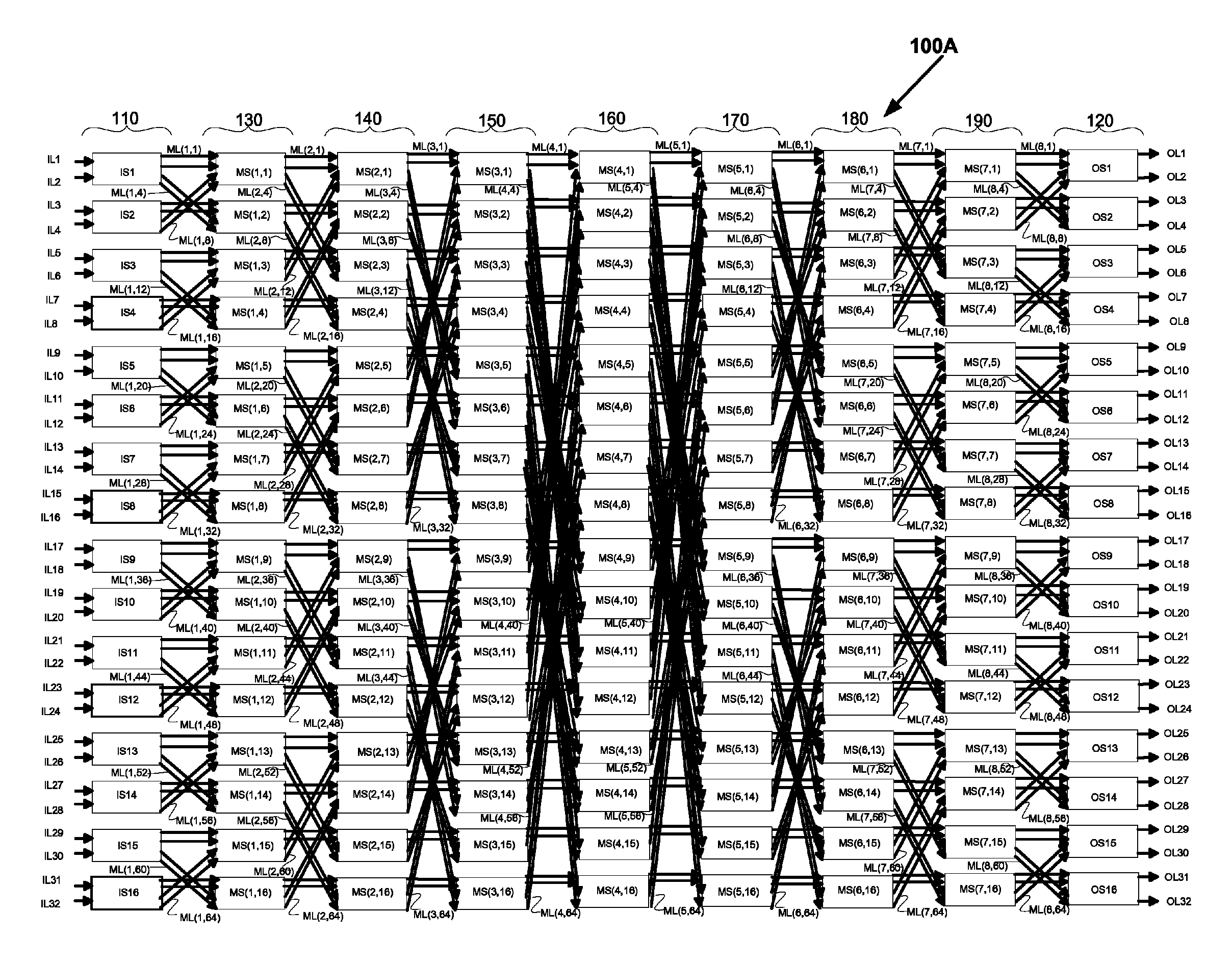

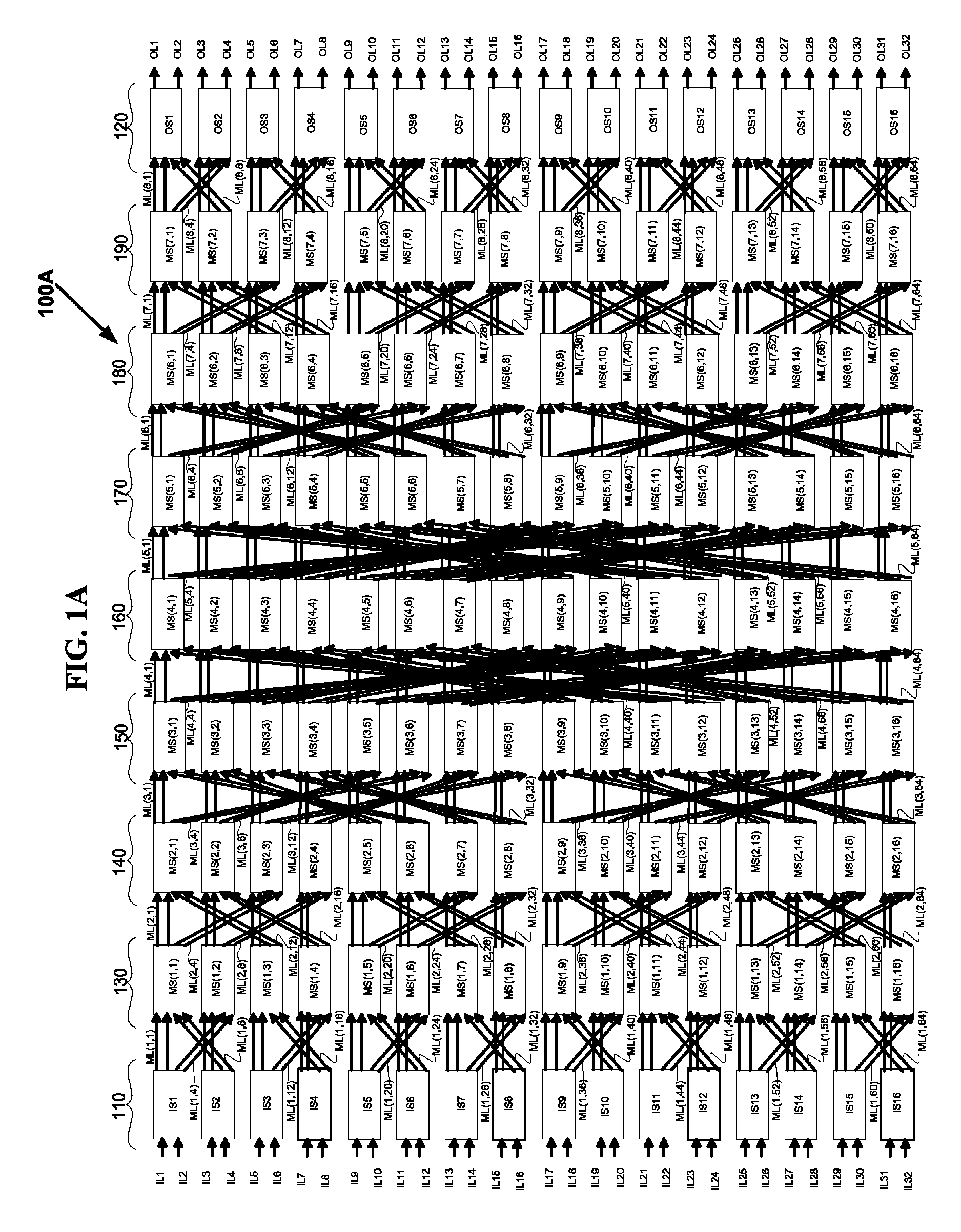

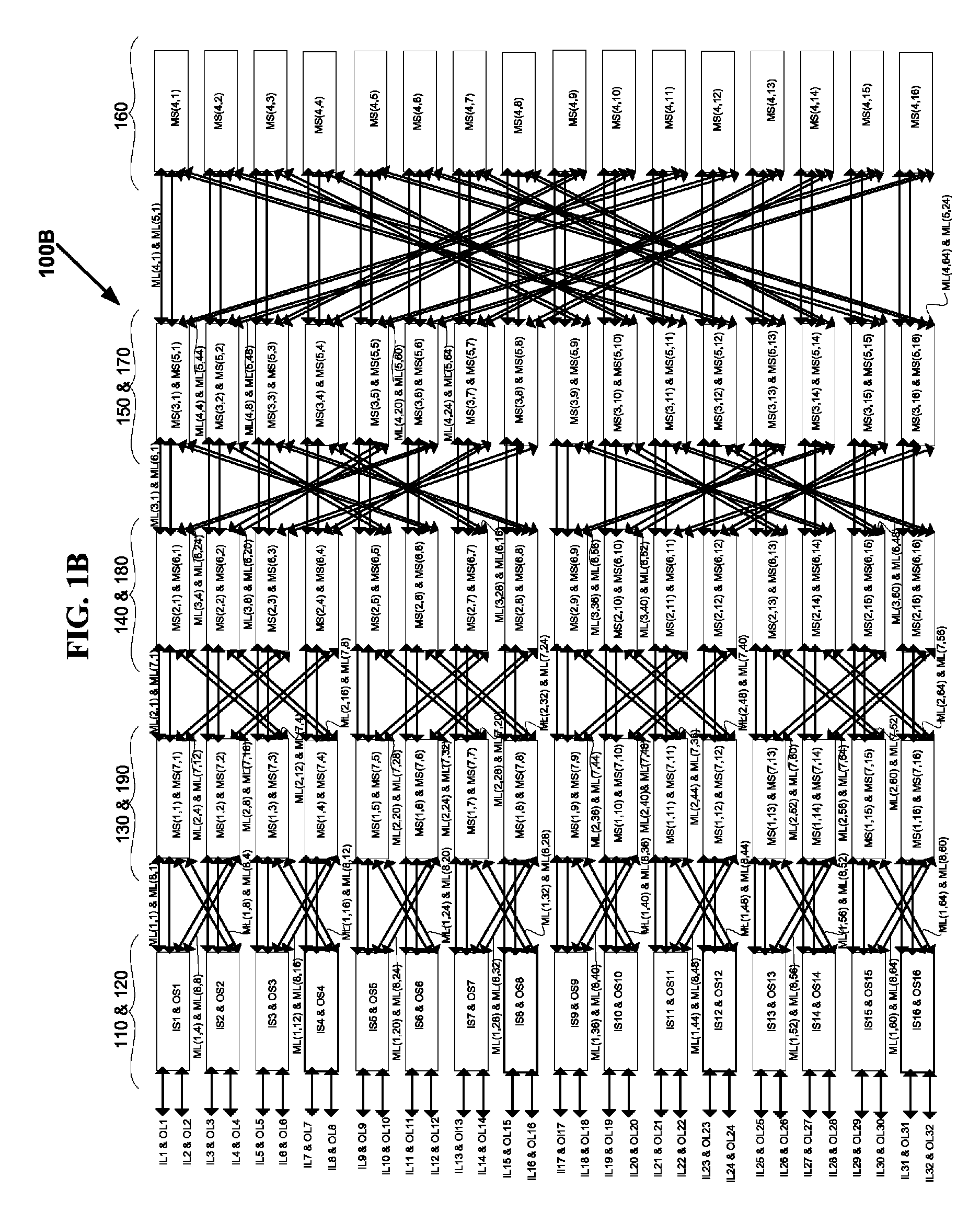

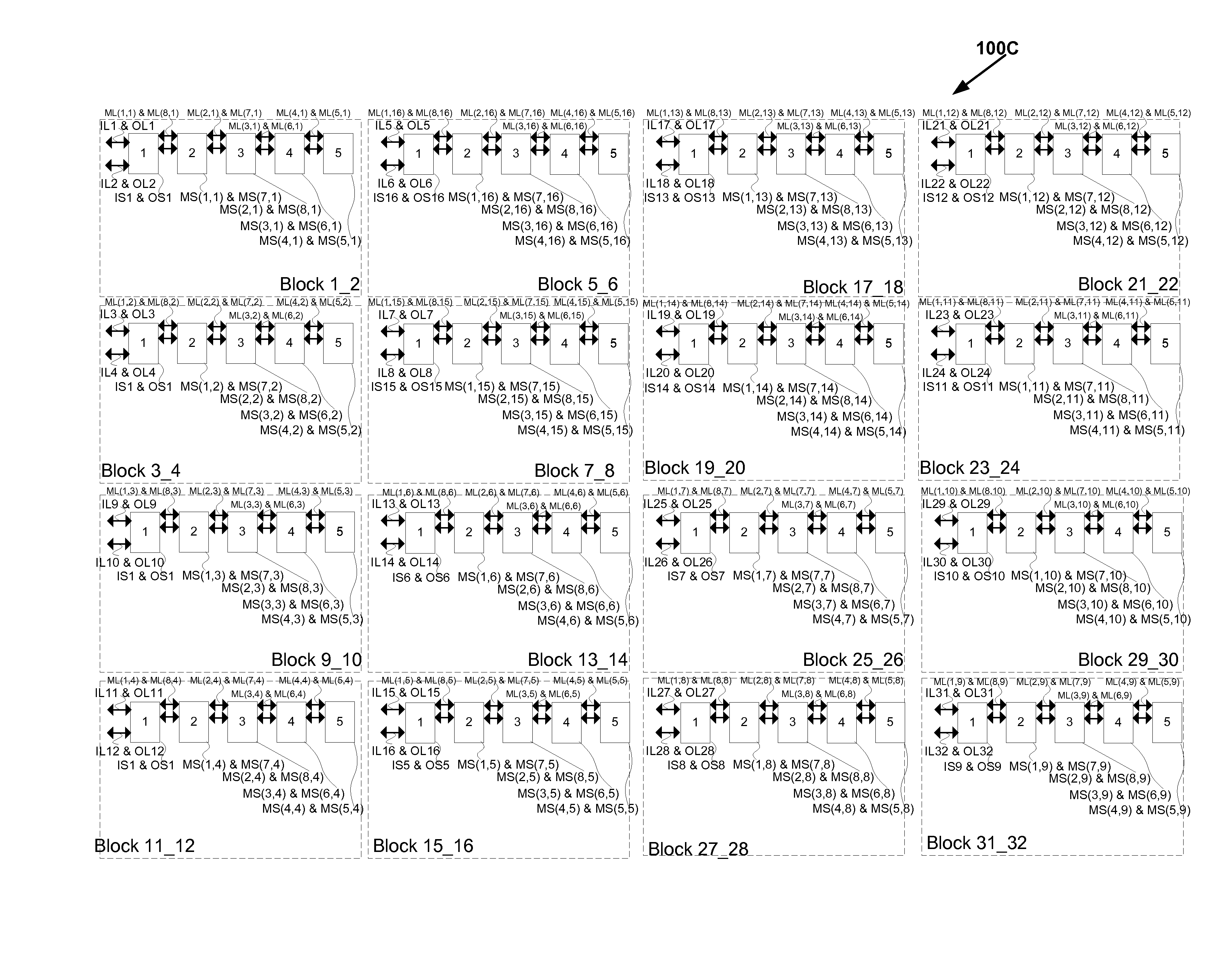

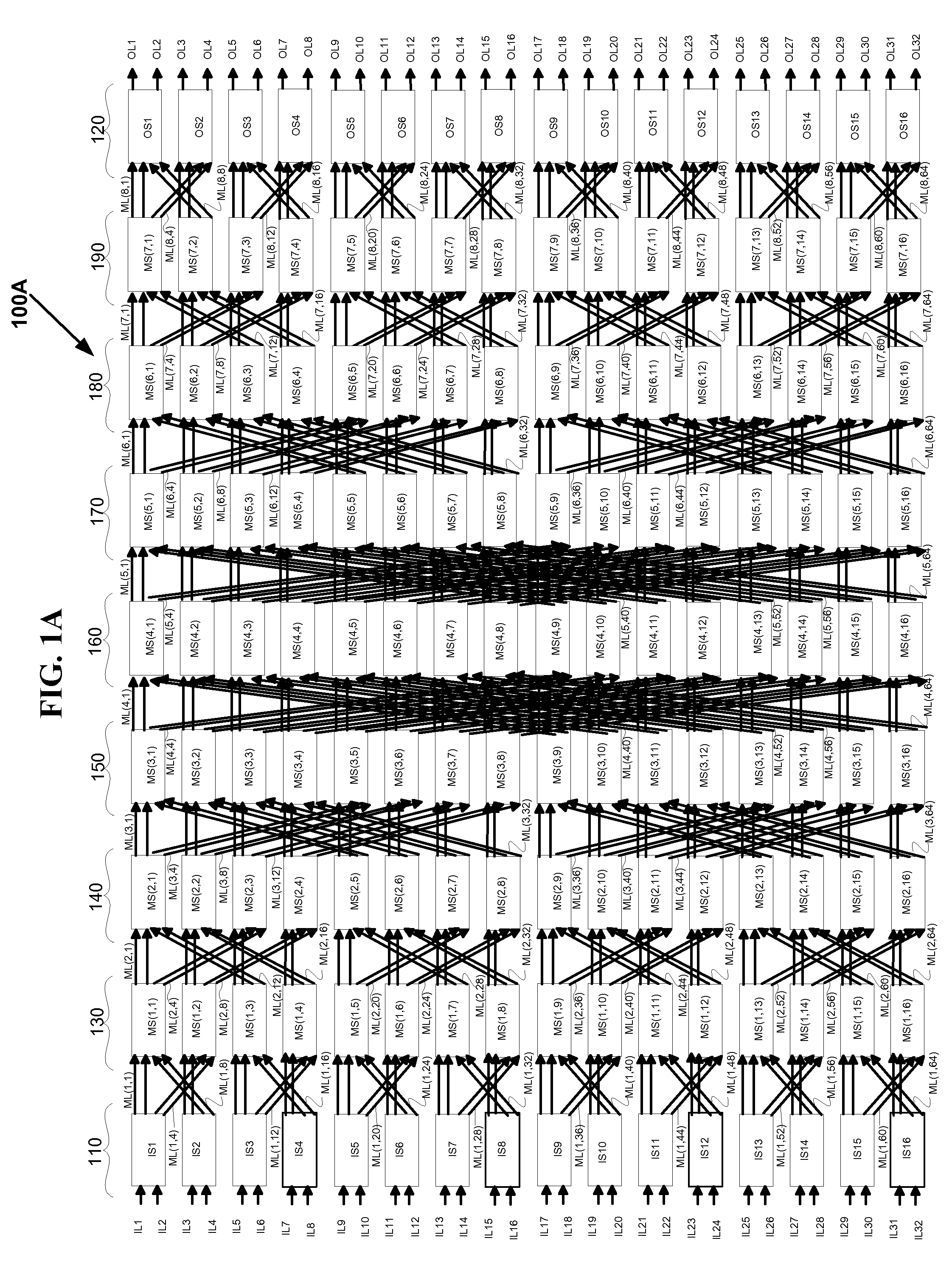

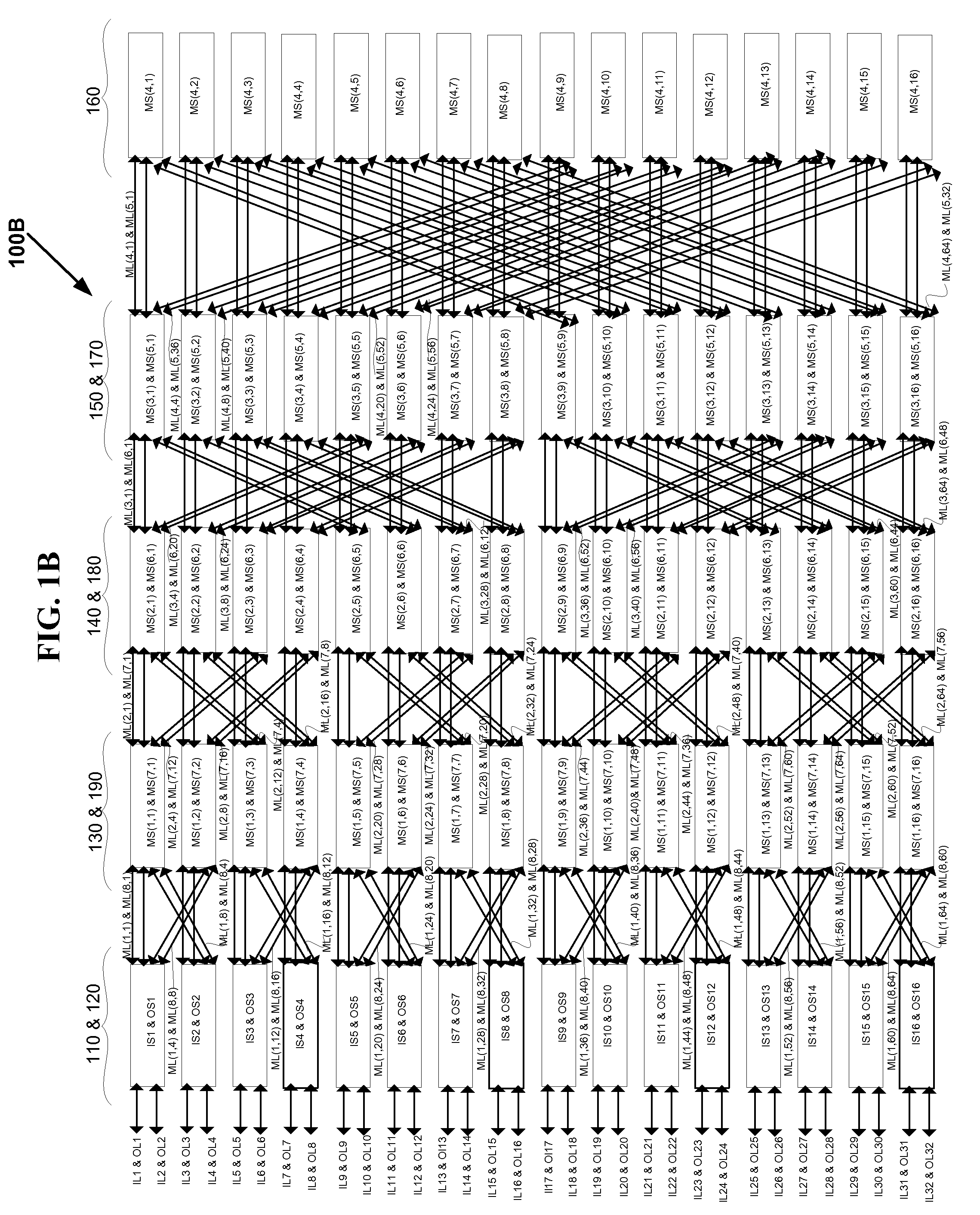

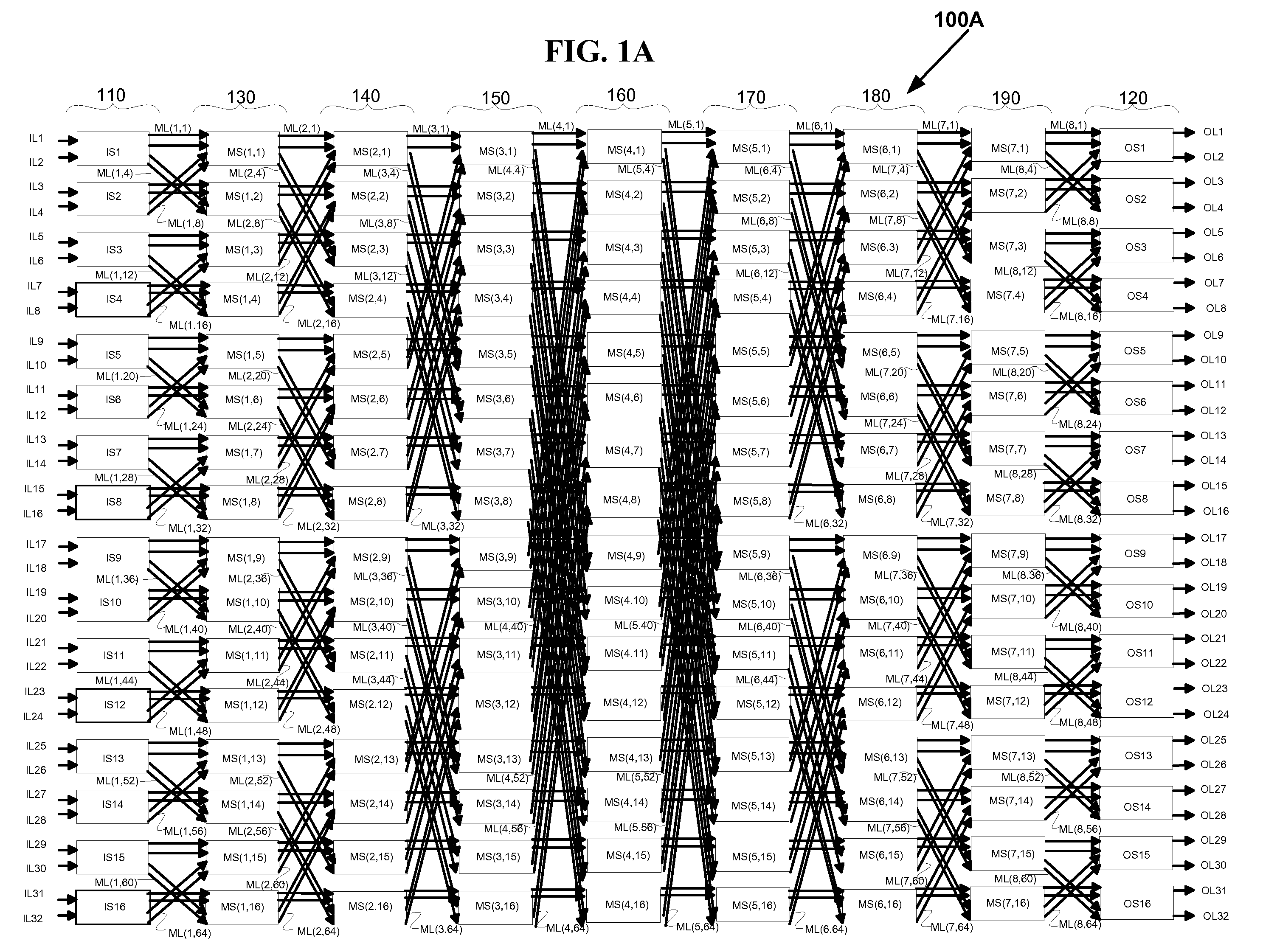

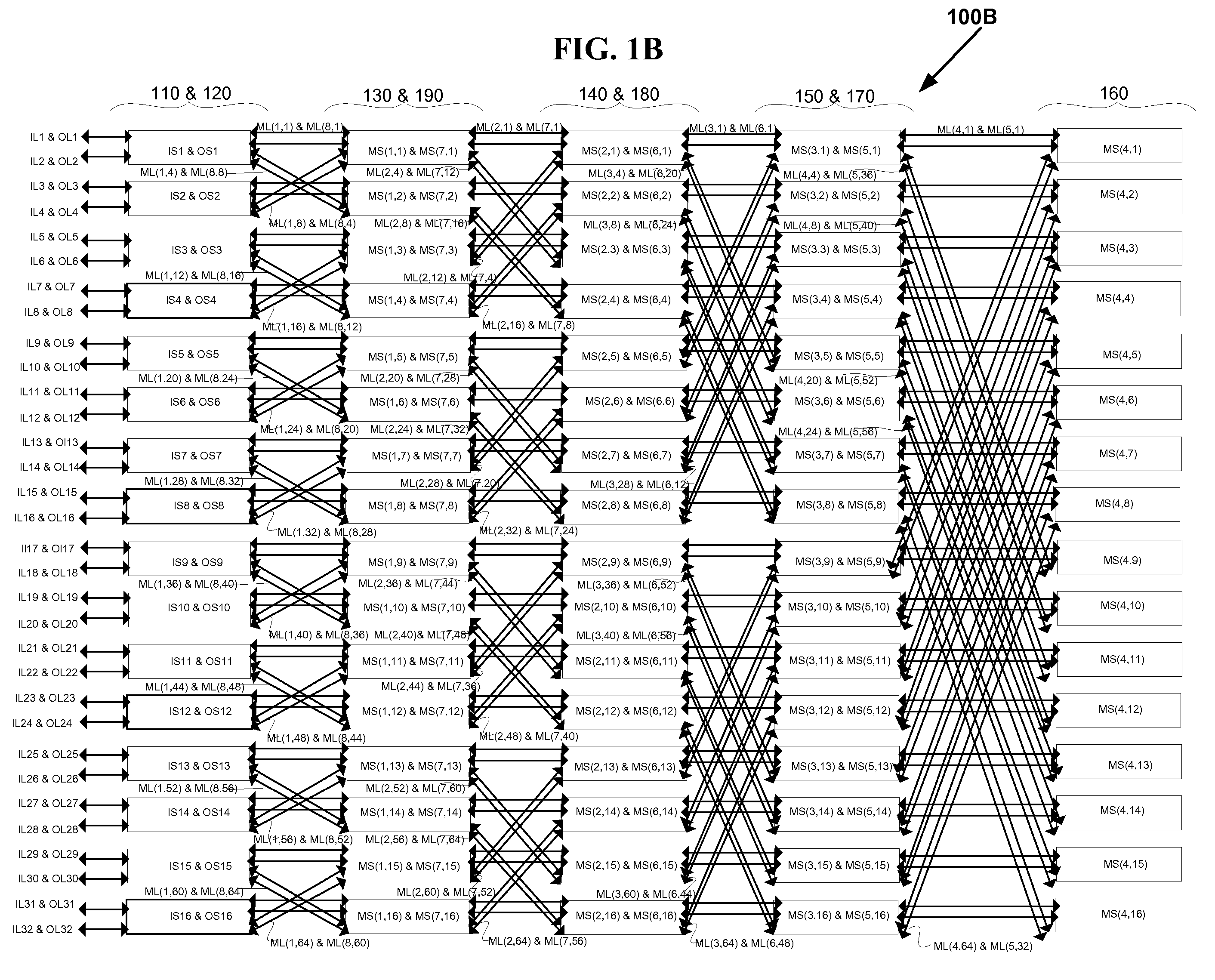

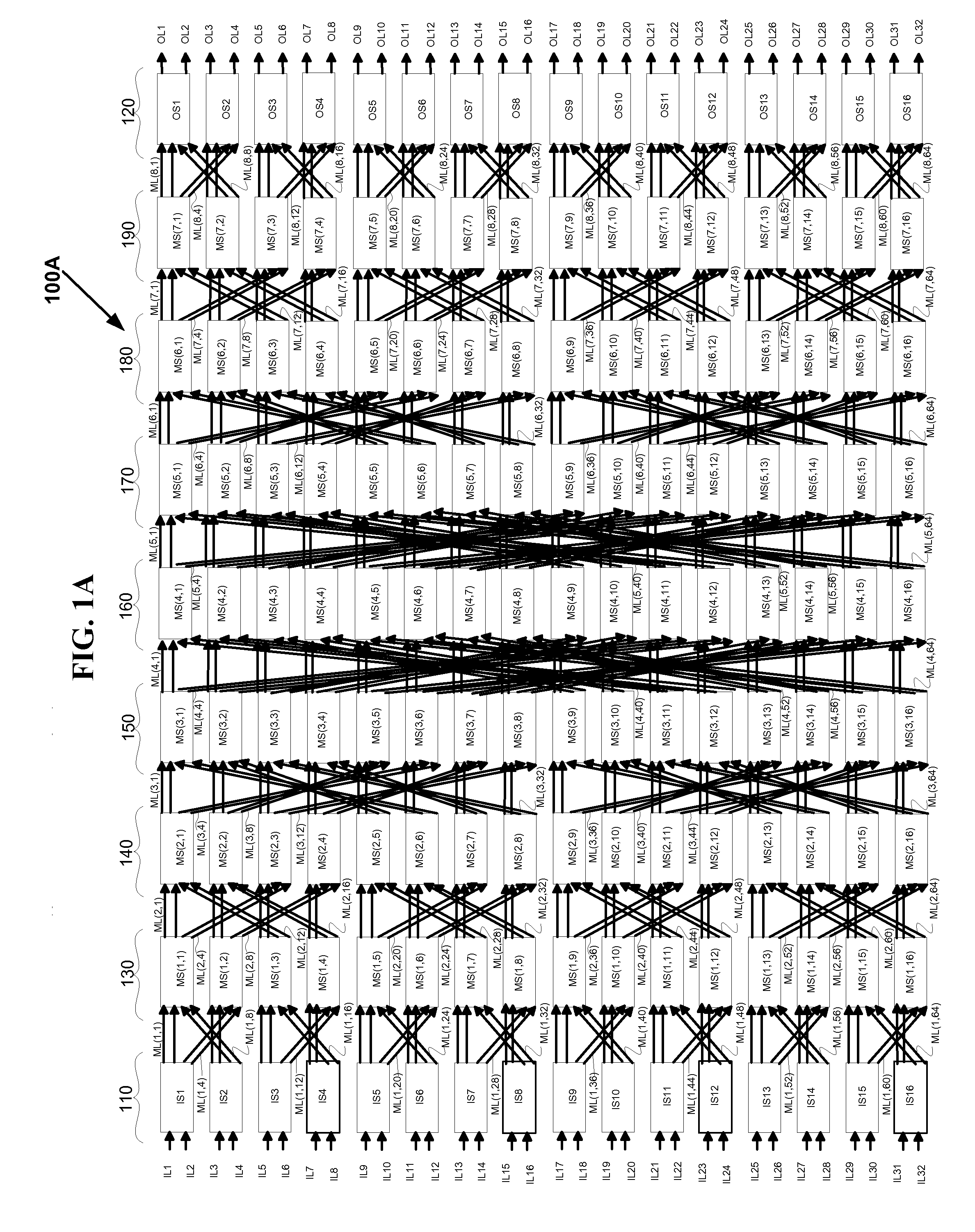

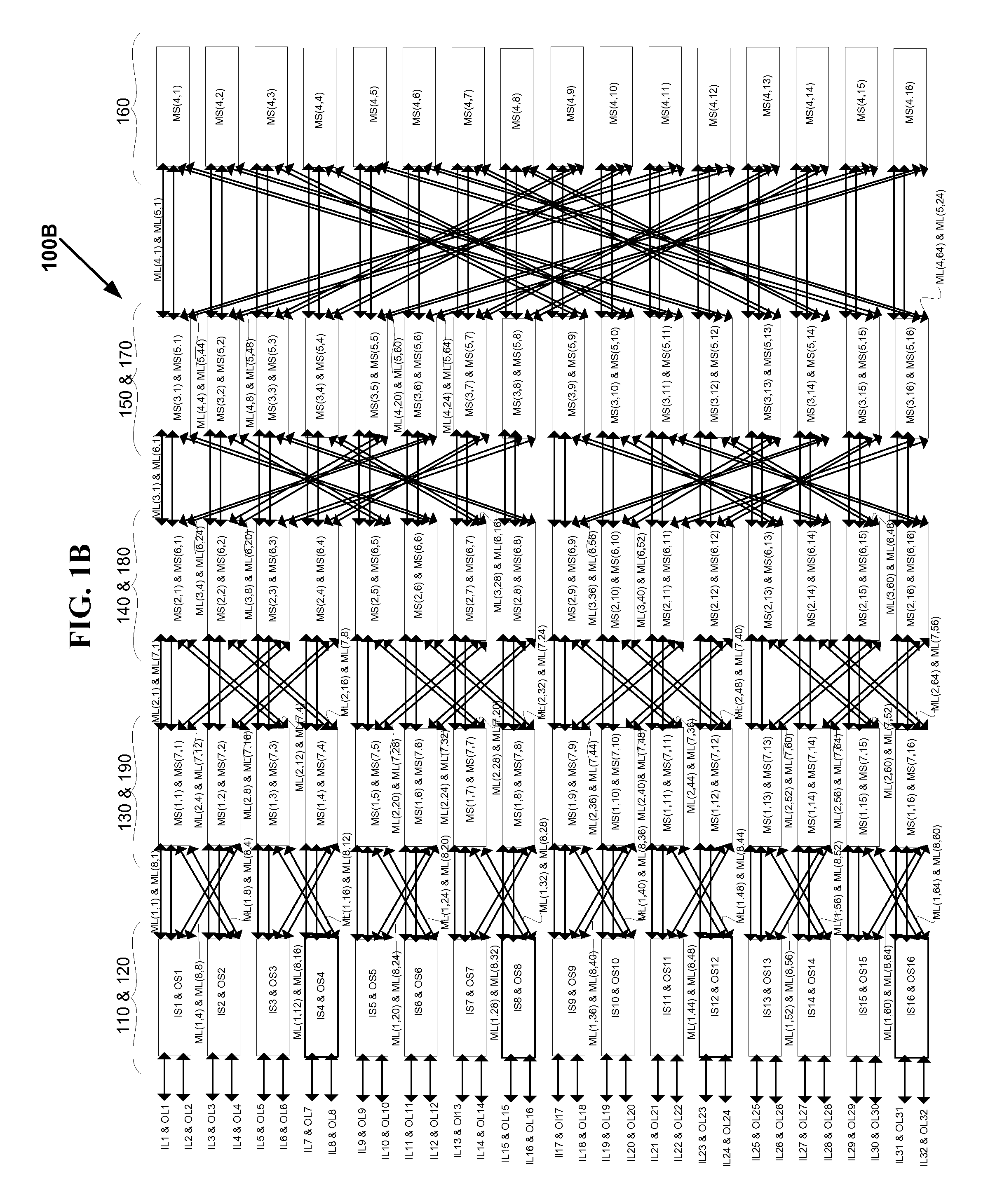

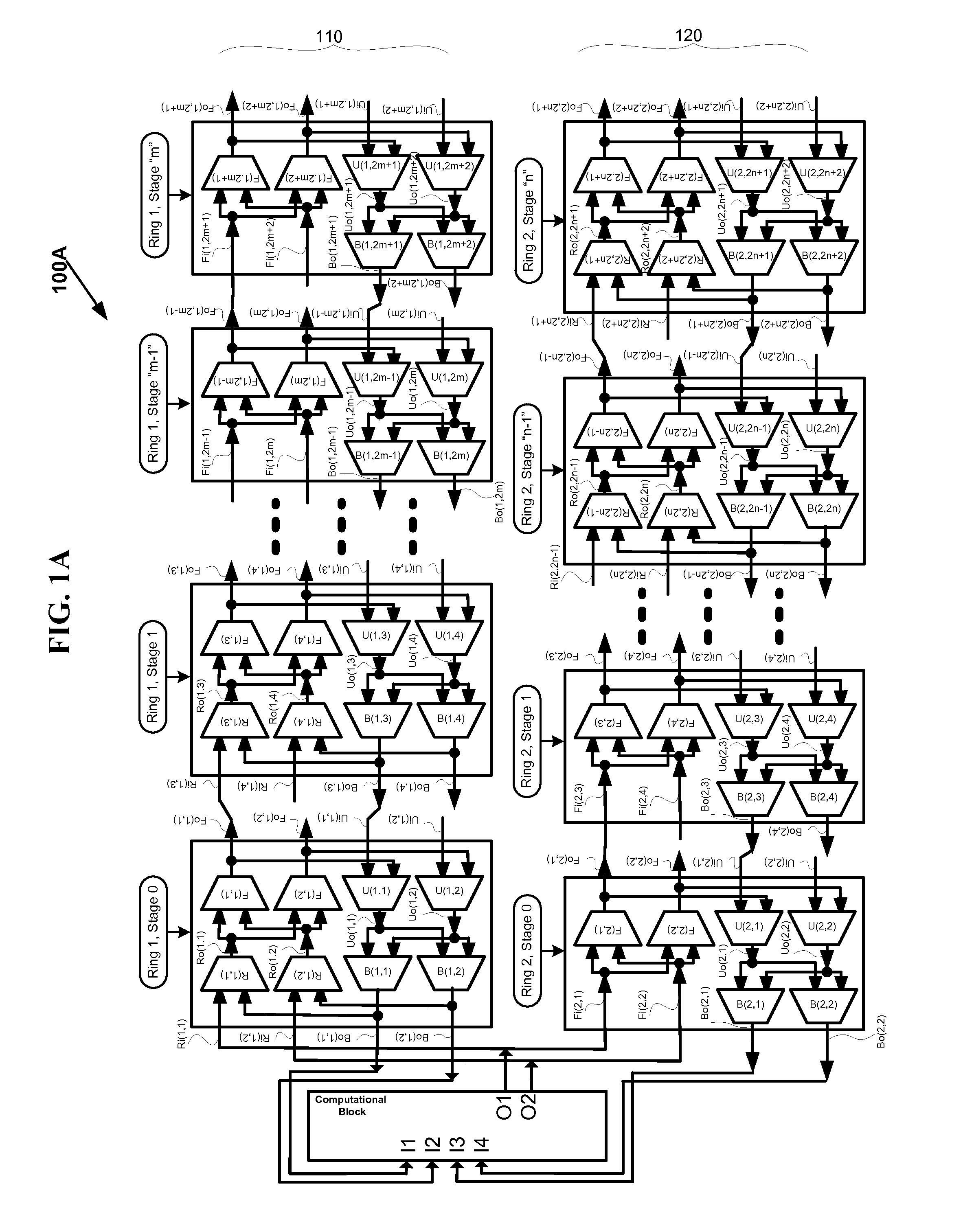

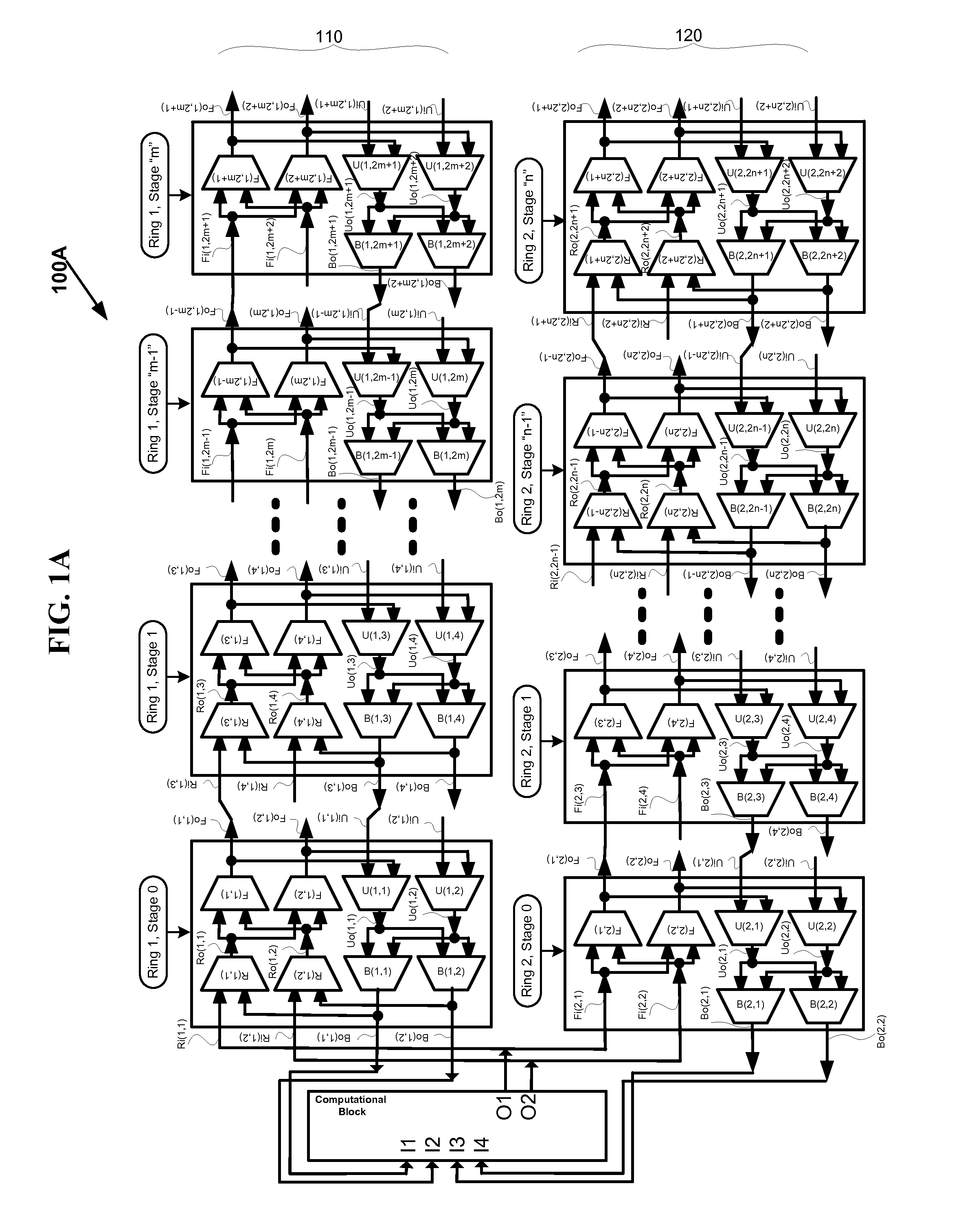

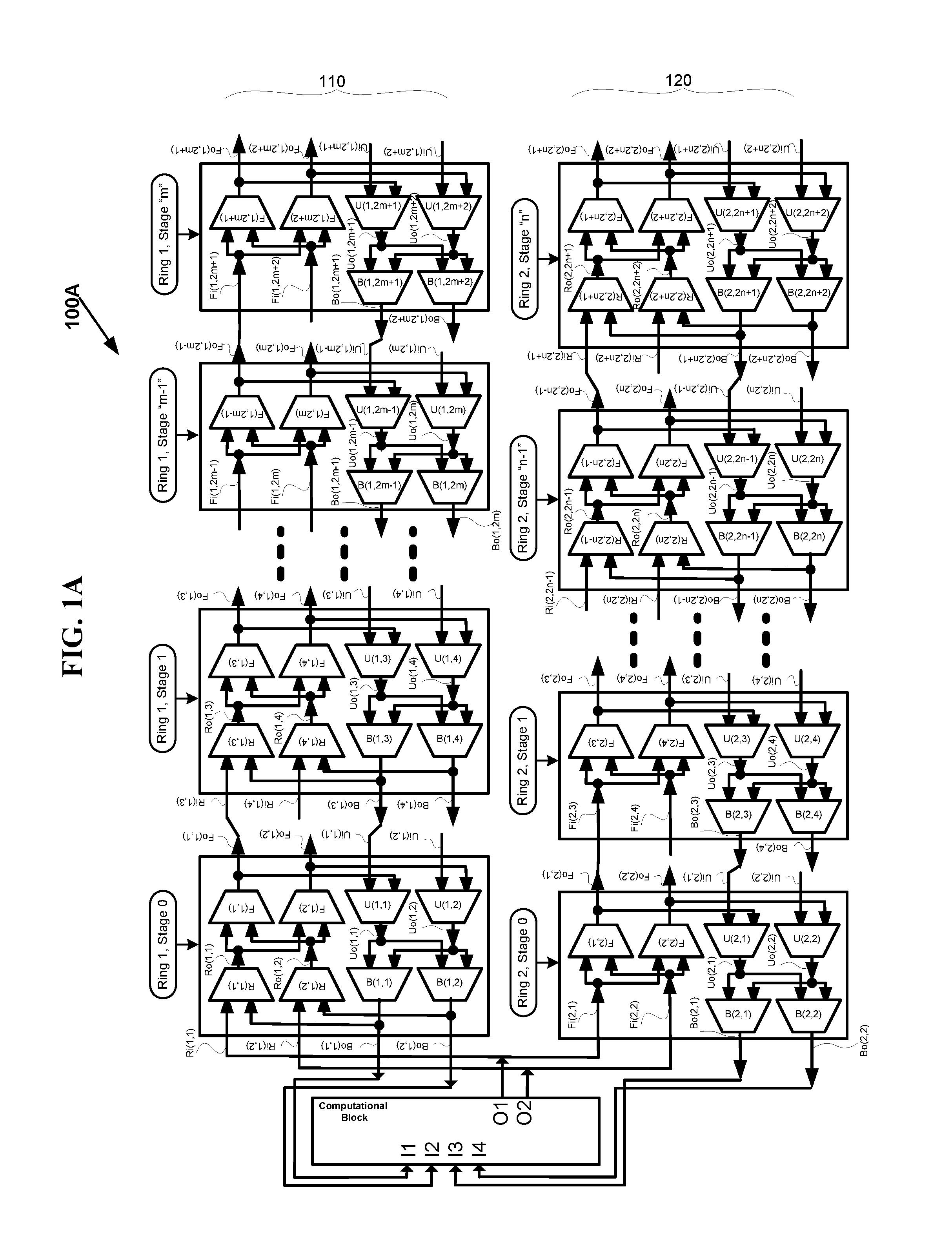

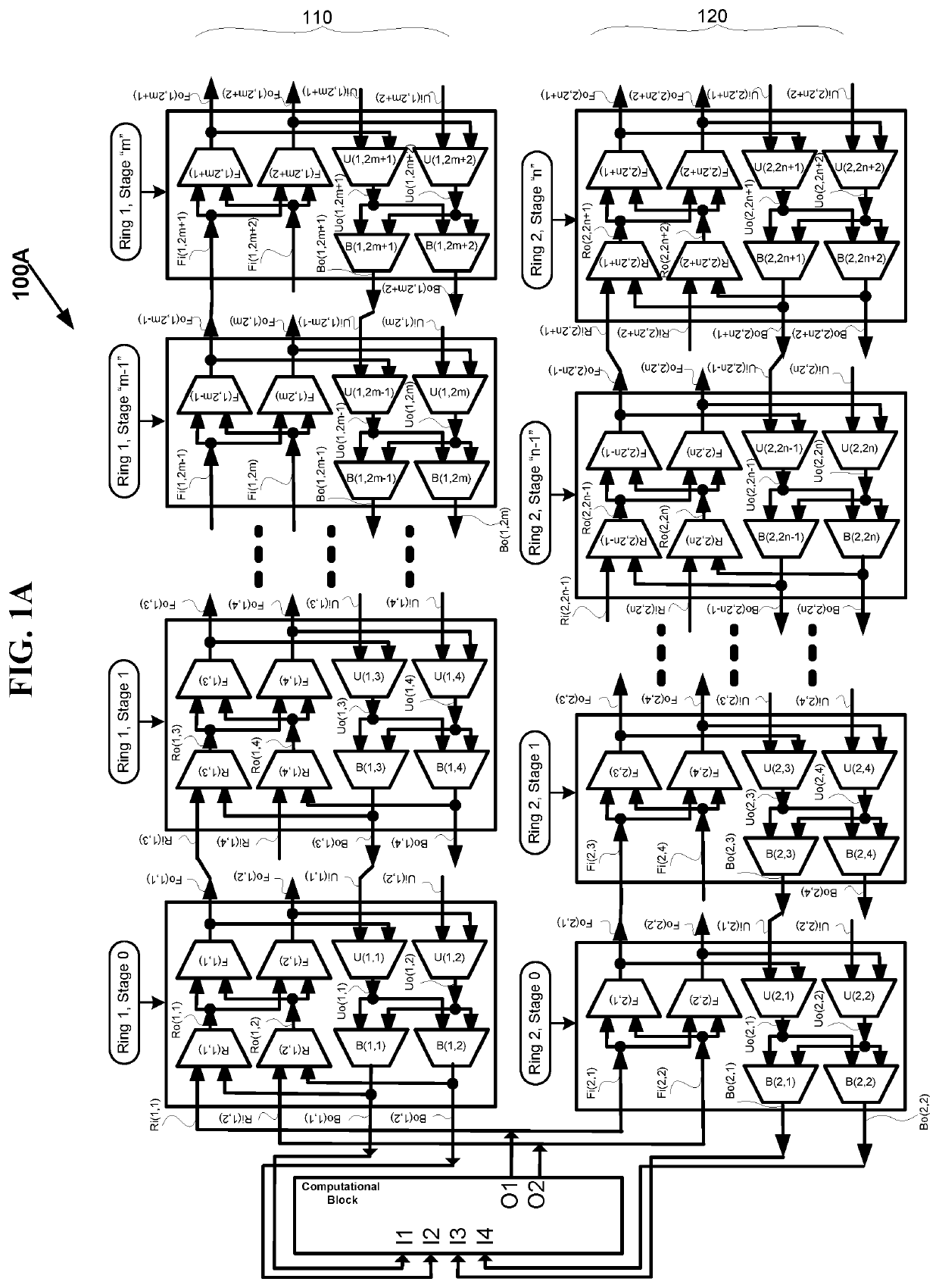

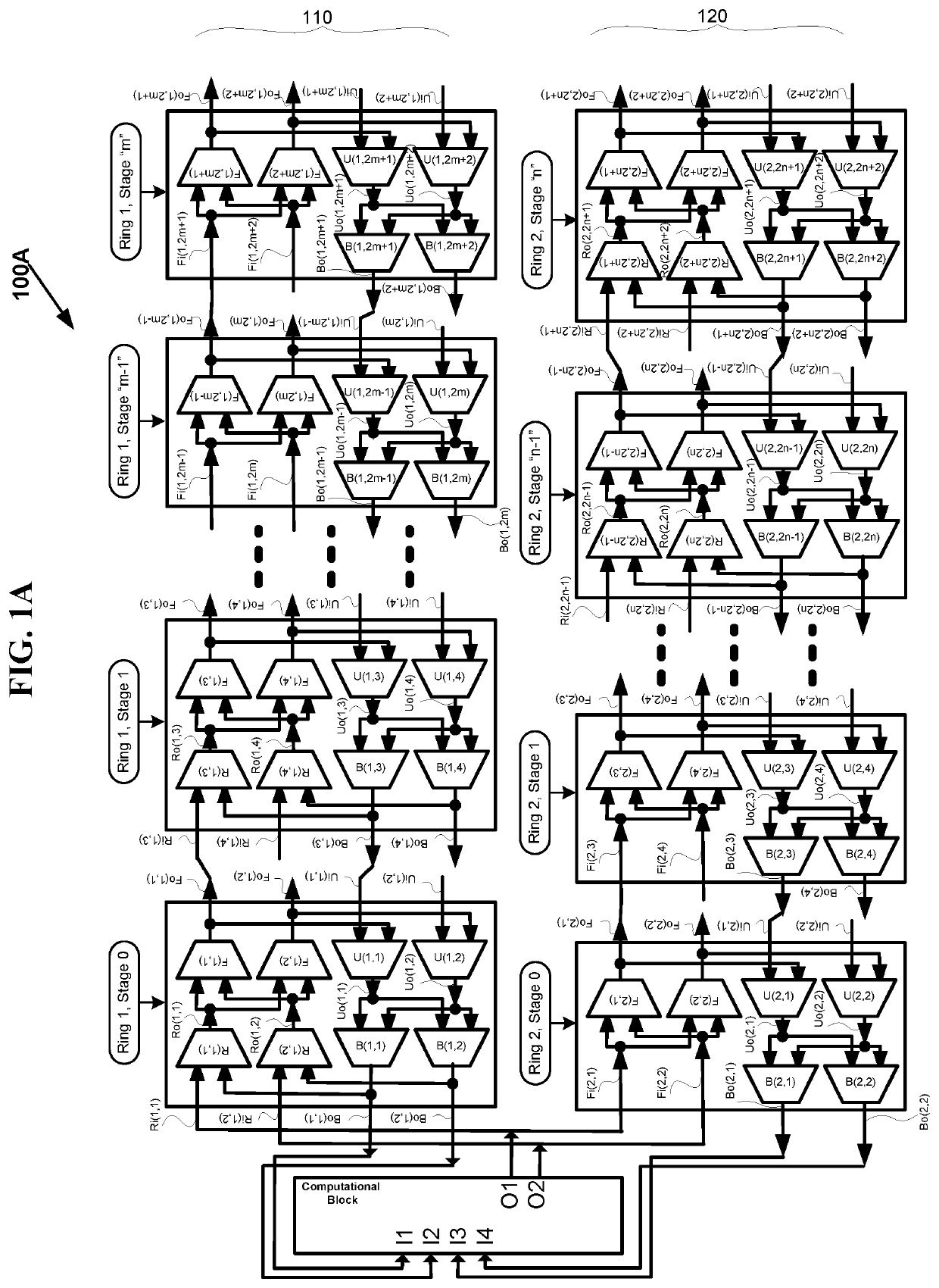

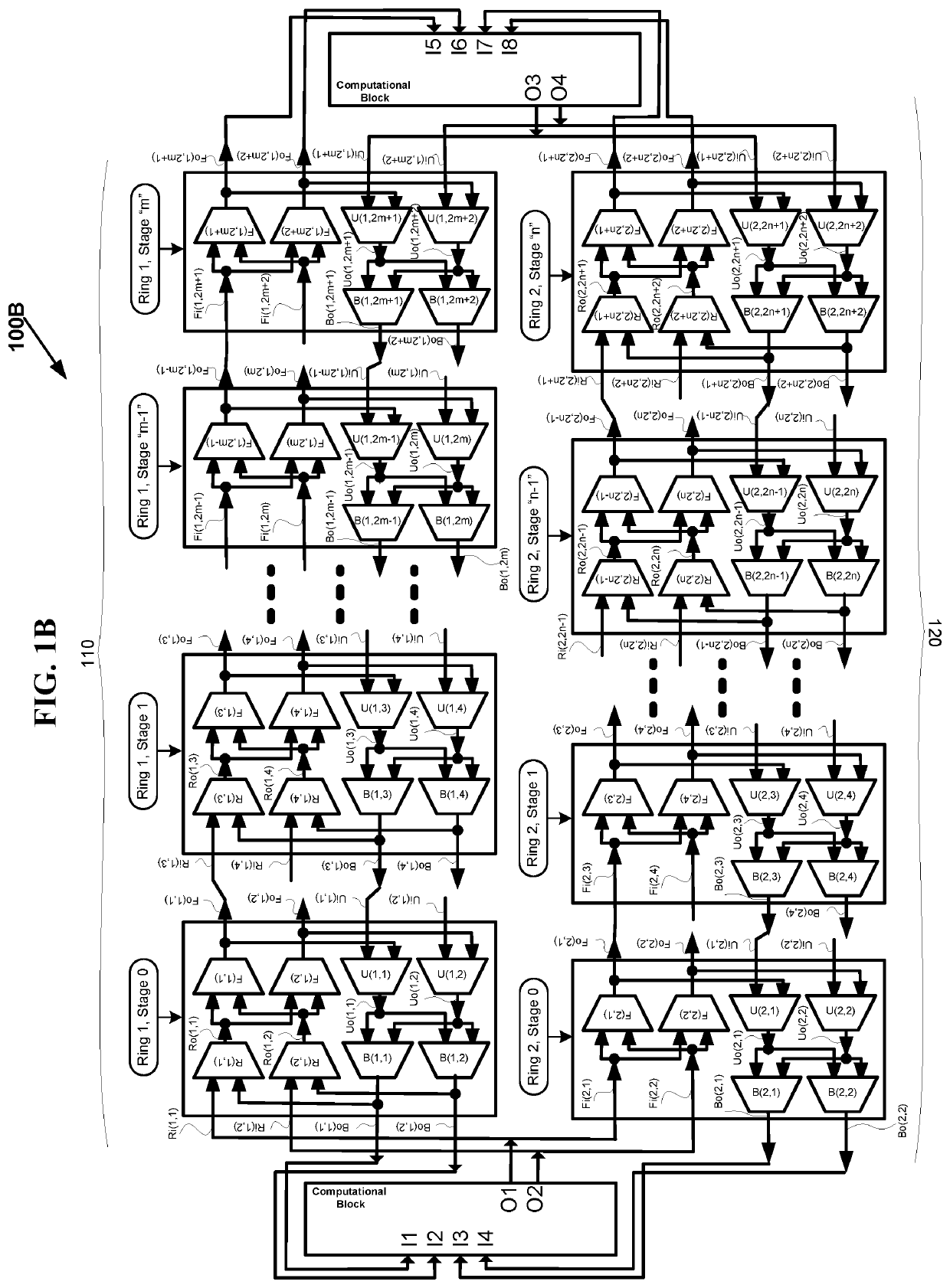

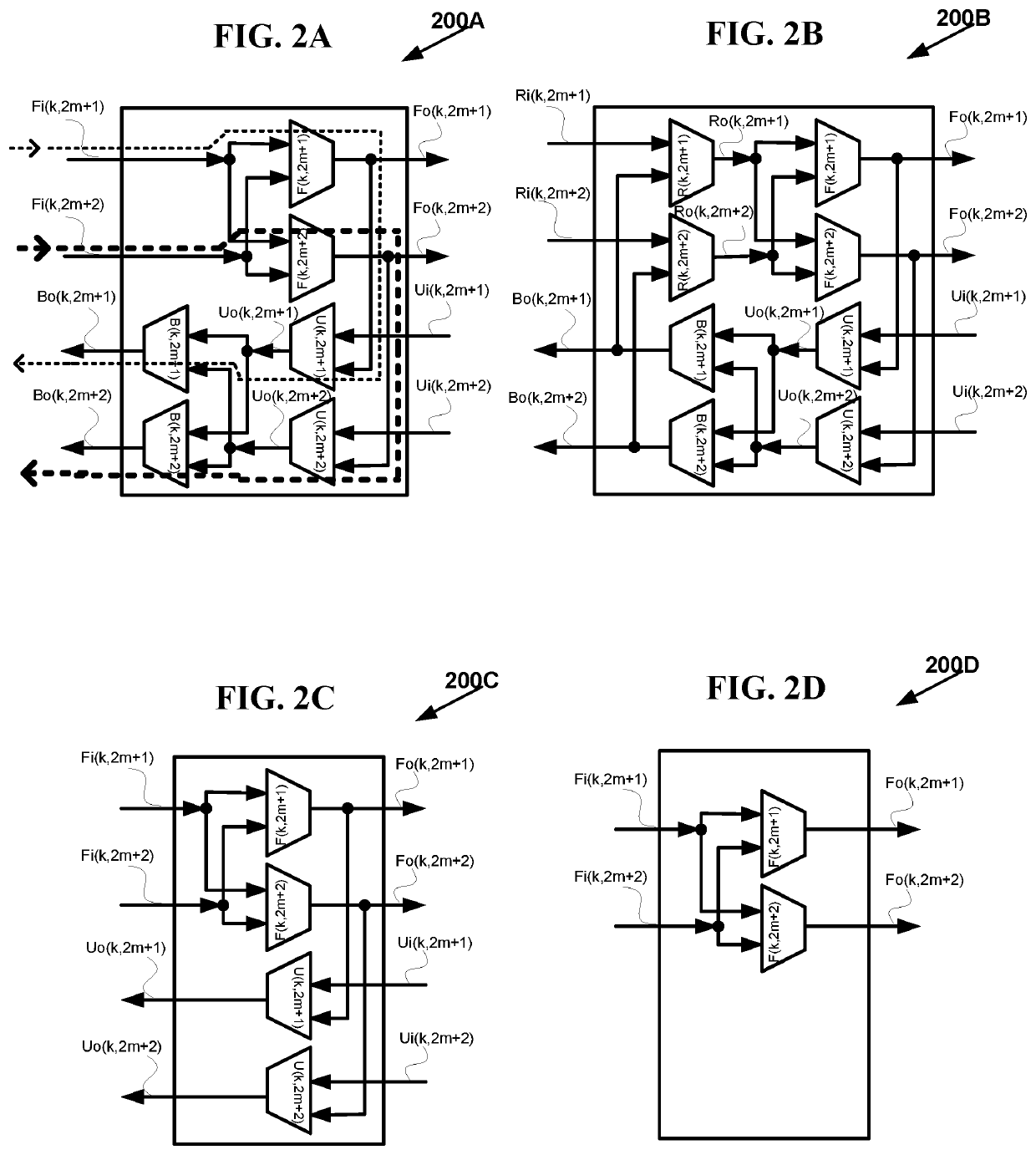

VLSI layouts of fully connected generalized and pyramid networks with locality exploitation

ActiveUS8898611B2Low pour pointReduce signal delayMultiplex system selection arrangementsGeometric CADCross-linkMulti link

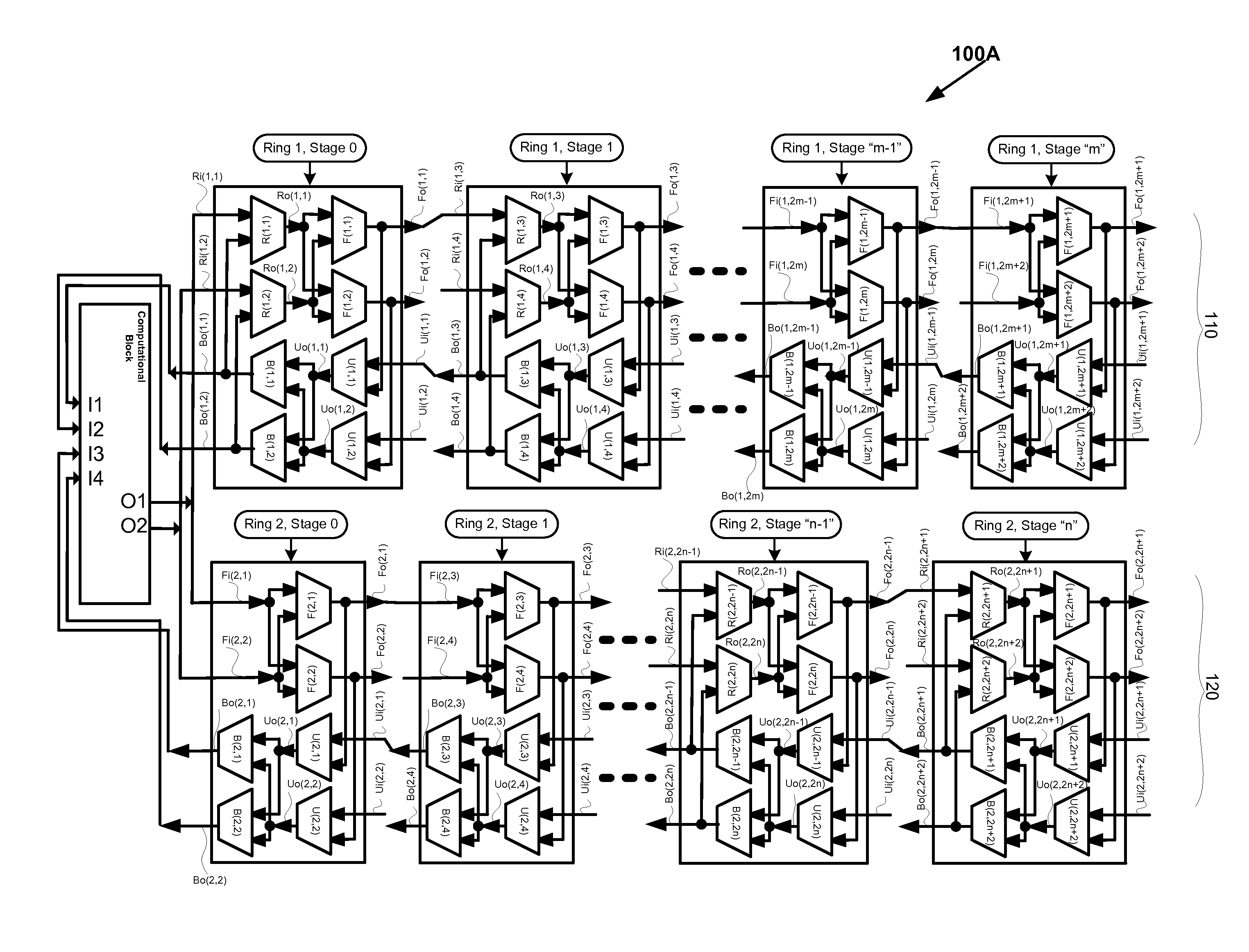

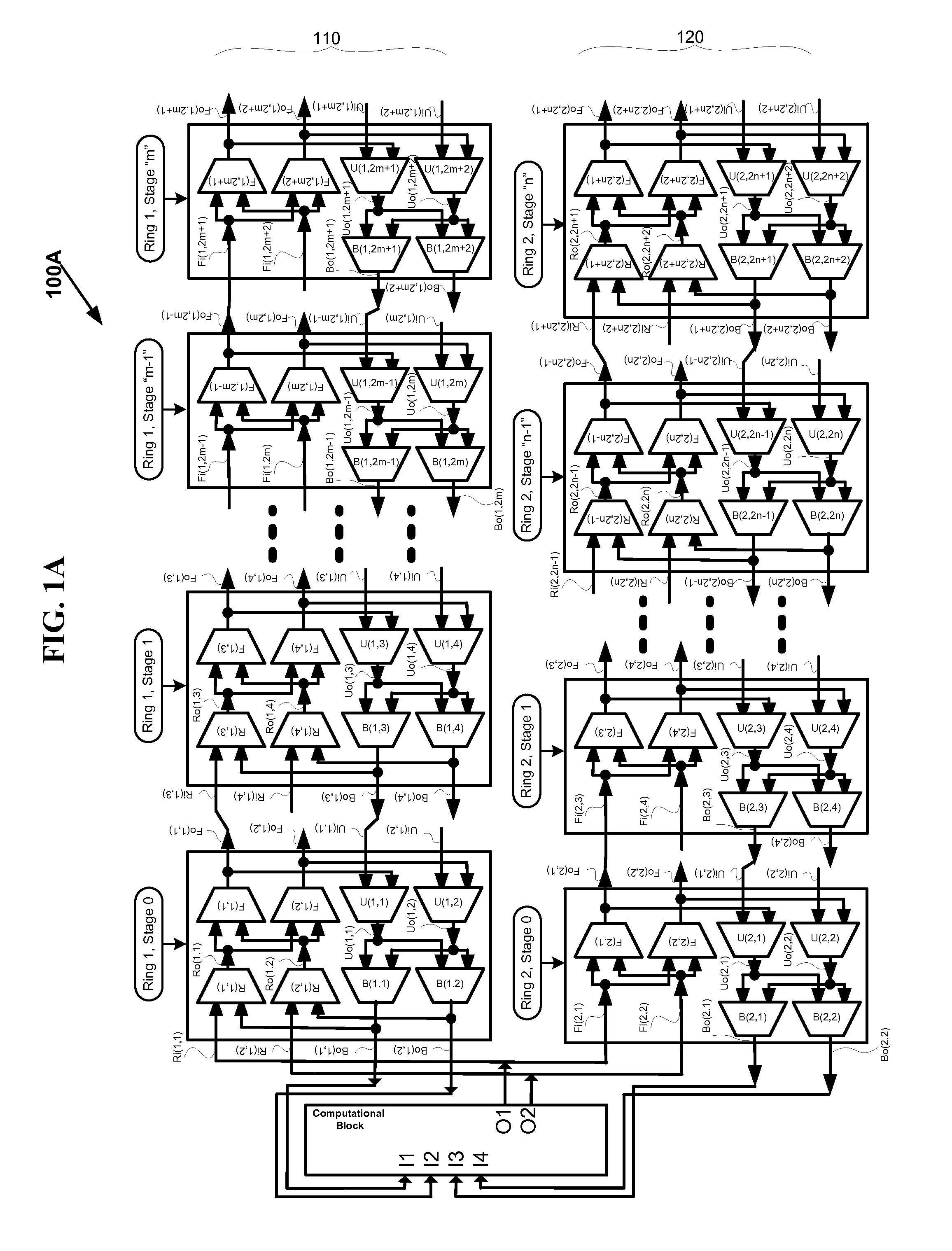

VLSI layouts of generalized multi-stage and pyramid networks for broadcast, unicast and multicast connections are presented using only horizontal and vertical links with spacial locality exploitation. The VLSI layouts employ shuffle exchange links where outlet links of cross links from switches in a stage in one sub-integrated circuit block are connected to inlet links of switches in the succeeding stage in another sub-integrated circuit block so that said cross links are either vertical links or horizontal and vice versa. Furthermore the shuffle exchange links are employed between different sub-integrated circuit blocks so that spacially nearer sub-integrated circuit blocks are connected with shorter links compared to the shuffle exchange links between spacially farther sub-integrated circuit blocks. In one embodiment the sub-integrated circuit blocks are arranged in a hypercube arrangement in a two-dimensional plane. The VLSI layouts exploit the benefits of significantly lower cross points, lower signal latency, lower power and full connectivity with significantly fast compilation.The VLSI layouts with spacial locality exploitation presented are applicable to generalized multi-stage and pyramid networks, generalized folded multi-stage and pyramid networks, generalized butterfly fat tree and pyramid networks, generalized multi-link multi-stage and pyramid networks, generalized folded multi-link multi-stage and pyramid networks, generalized multi-link butterfly fat tree and pyramid networks, generalized hypercube networks, and generalized cube connected cycles networks for speedup of s≧1. The embodiments of VLSI layouts are useful in wide target applications such as FPGAs, CPLDs, pSoCs, ASIC placement and route tools, networking applications, parallel & distributed computing, and reconfigurable computing.

Owner:KONDA TECH

VLSI layouts of fully connected generalized networks

ActiveUS8269523B2Low pour pointReduce signal delaySolid-state devicesComputer aided designCross-linkMulti link

Owner:KONDA VENKAT

VLSI layouts of fully connected generalized networks

ActiveUS20110037498A1Low pour pointReduce signal delaySolid-state devicesComputer aided designCross-linkMulti link

In accordance with the invention, VLSI layouts of generalized multi-stage networks for broadcast, unicast and multicast connections are presented using only horizontal and vertical links. The VLSI layouts employ shuffle exchange links where outlet links of cross links from switches in a stage in one sub-integrated circuit block are connected to inlet links of switches in the succeeding stage in another sub-integrated circuit block so that said cross links are either vertical links or horizontal and vice versa. In one embodiment the sub-integrated circuit blocks are arranged in a hypercube arrangement in a two-dimensional plane. The VLSI layouts exploit the benefits of significantly lower cross points, lower signal latency, lower power and full connectivity with significantly fast compilation.The VLSI layouts presented are applicable to generalized multi-stage networks V(N1, N2, d, s), generalized folded multi-stage networks Vfold(N1, N2, d, s), generalized butterfly fat tree networks Vbft(N1, N2, d, s), generalized multi-link multi-stage networks Vmlink(N1, N2, d, s), generalized folded multi-link multi-stage networks Vfold-mlink(N1, N2, d, s), generalized multi-link butterfly fat tree networks Vmlink-bft(N1, N2, d, s), and generalized hypercube networks Vhcube(N1, N2, d, s) for s=1, 2, 3 or any number in general. The embodiments of VLSI layouts are useful in wide target applications such as FPGAs, CPLDs, pSoCs, ASIC placement and route tools, networking applications, parallel & distributed computing, and reconfigurable computing.

Owner:KONDA VENKAT

VLSI layouts of fully connected generalized and pyramid networks with locality exploitation

ActiveUS9529958B2Low pour pointReduce signal delayCircuit switching systemsCAD circuit designCross-linkMulti link

VLSI layouts of generalized multi-stage and pyramid networks for broadcast, unicast and multicast connections are presented using only horizontal and vertical links with spacial locality exploitation. The VLSI layouts employ shuffle exchange links where outlet links of cross links from switches in a stage in one sub-integrated circuit block are connected to inlet links of switches in the succeeding stage in another sub-integrated circuit block so that said cross links are either vertical links or horizontal and vice versa. Furthermore the shuffle exchange links are employed between different sub-integrated circuit blocks so that spacially nearer sub-integrated circuit blocks are connected with shorter links compared to the shuffle exchange links between spacially farther sub-integrated circuit blocks. In one embodiment the sub-integrated circuit blocks are arranged in a hypercube arrangement in a two-dimensional plane. The VLSI layouts exploit the benefits of significantly lower cross points, lower signal latency, lower power and full connectivity with significantly fast compilation. The VLSI layouts with spacial locality exploitation presented are applicable to generalized multi-stage and pyramid networks, generalized folded multi-stage and pyramid networks, generalized butterfly fat tree and pyramid networks, generalized multi-link multi-stage and pyramid networks, generalized folded multi-link multi-stage and pyramid networks, generalized multi-link butterfly fat tree and pyramid networks, generalized hypercube networks, and generalized cube connected cycles networks for speedup of s≧1. The embodiments of VLSI layouts are useful in wide target applications such as FPGAs, CPLDs, pSoCs, ASIC placement and route tools, networking applications, parallel & distributed computing, and reconfigurable computing.

Owner:KONDA TECH

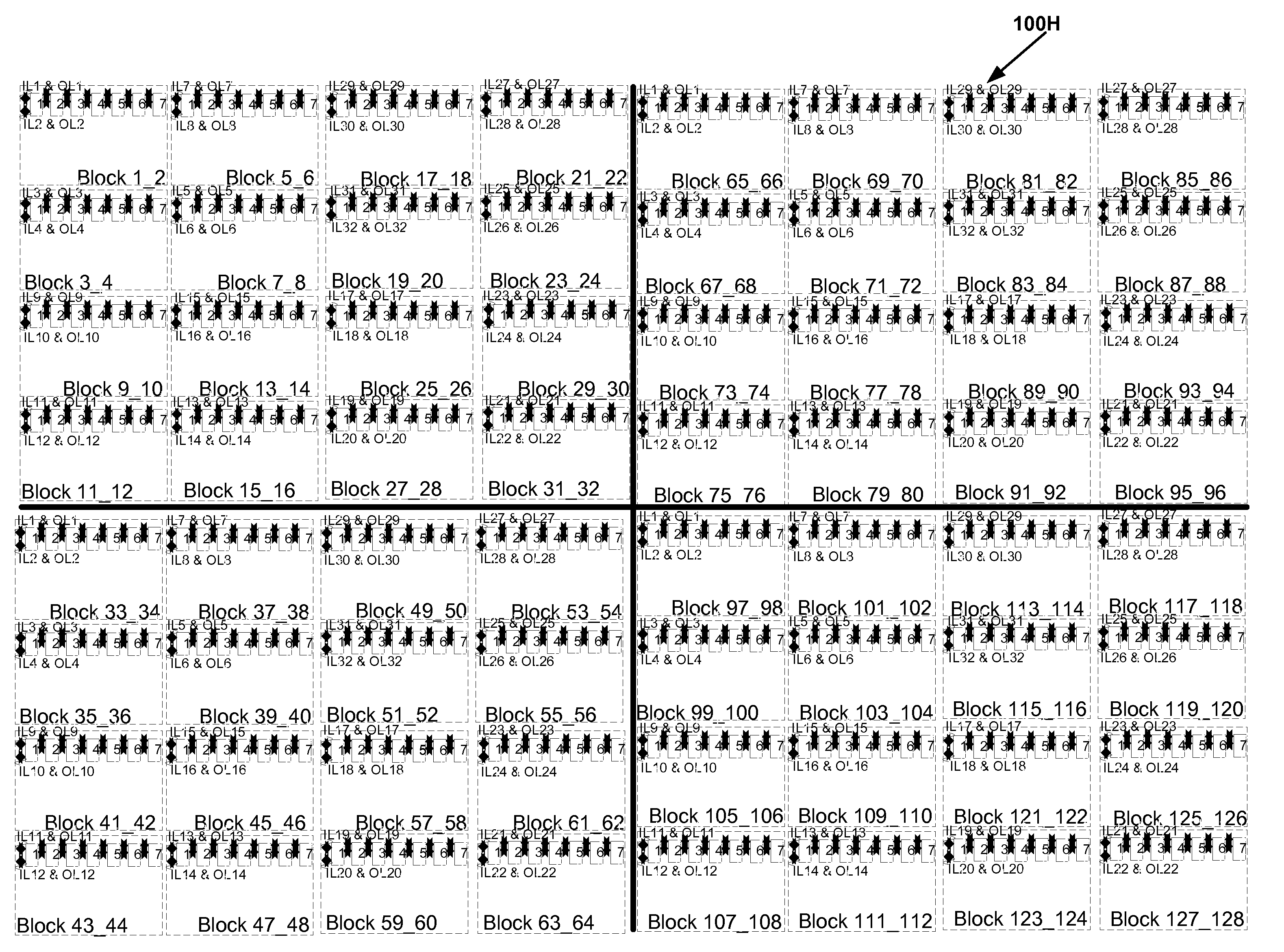

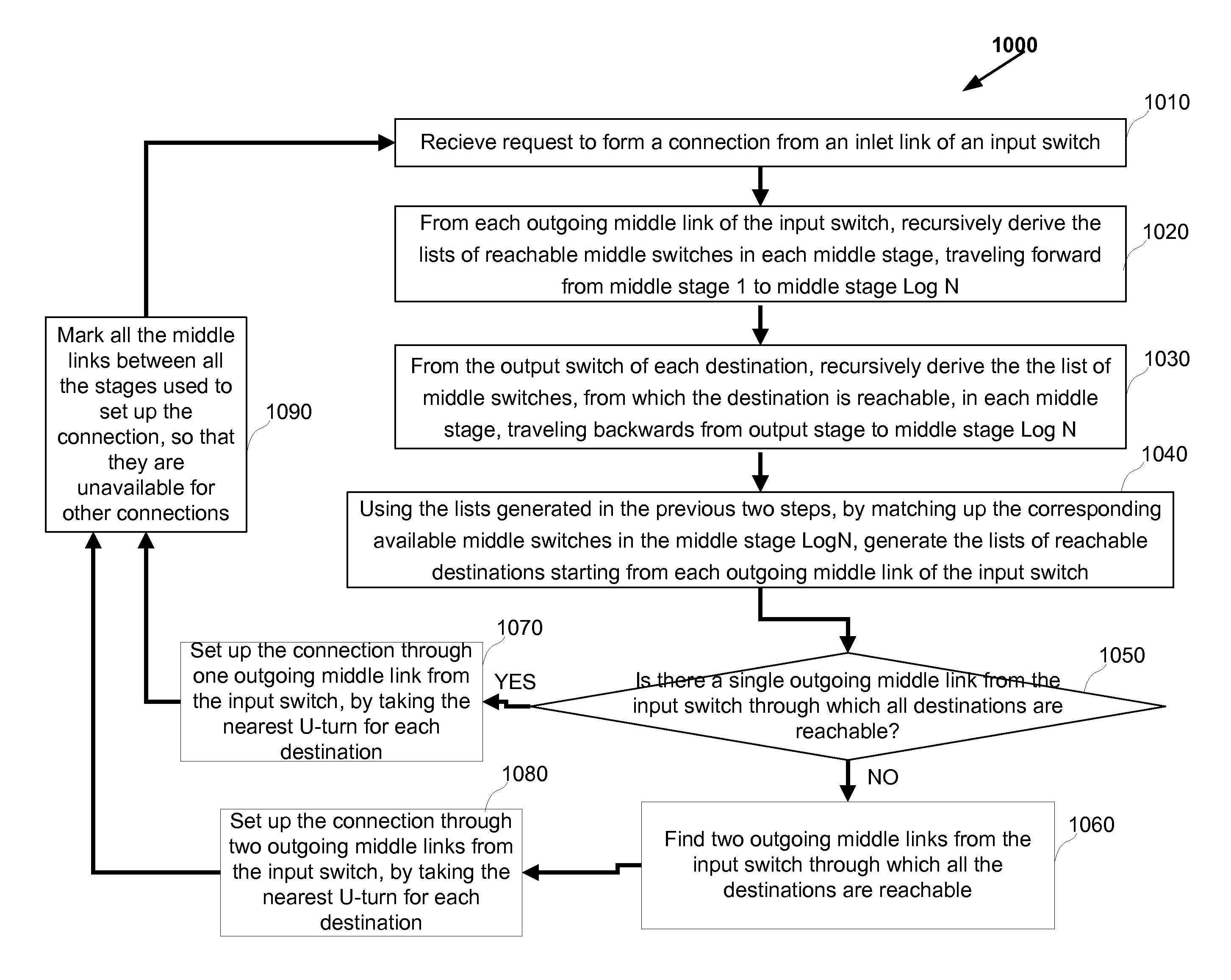

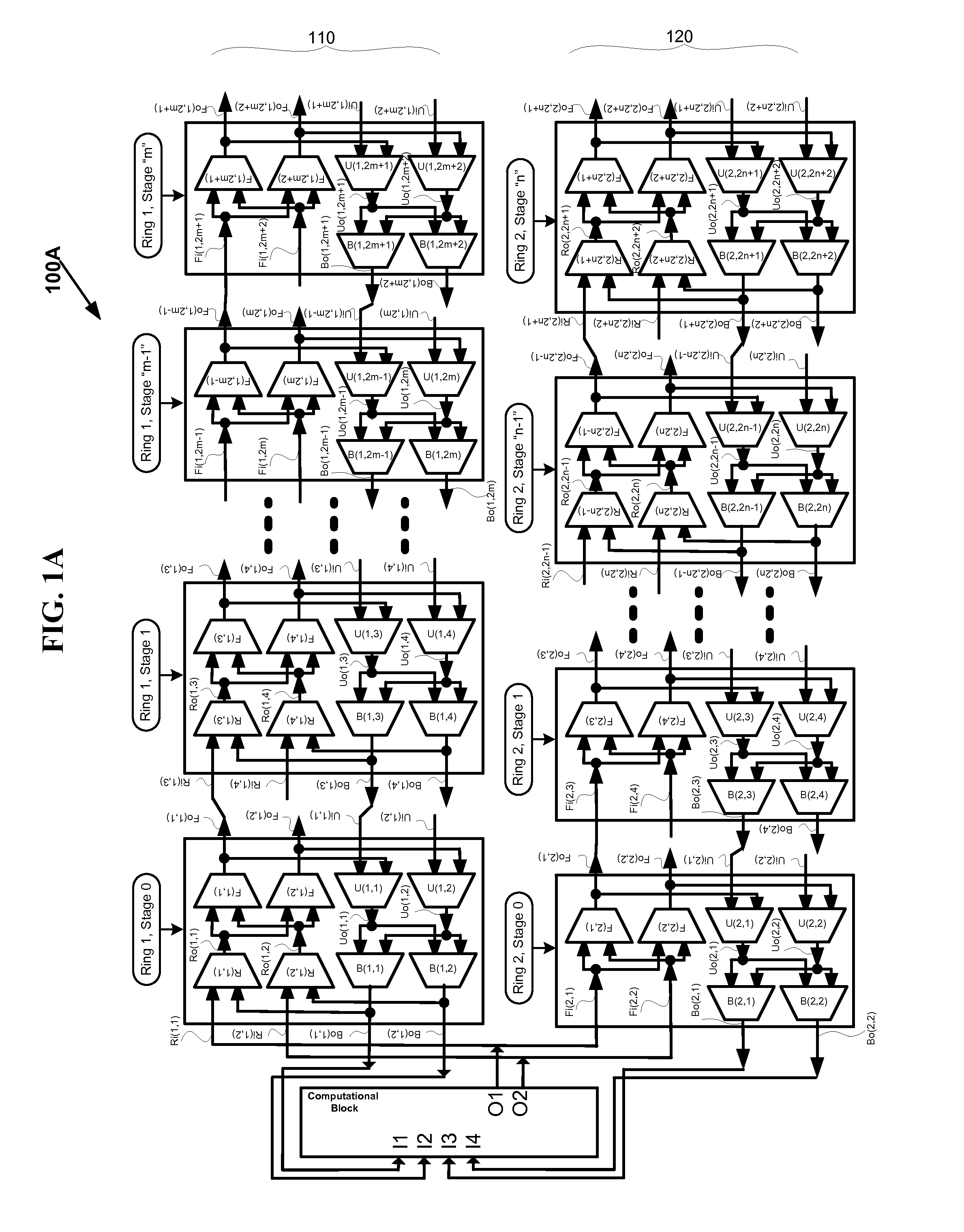

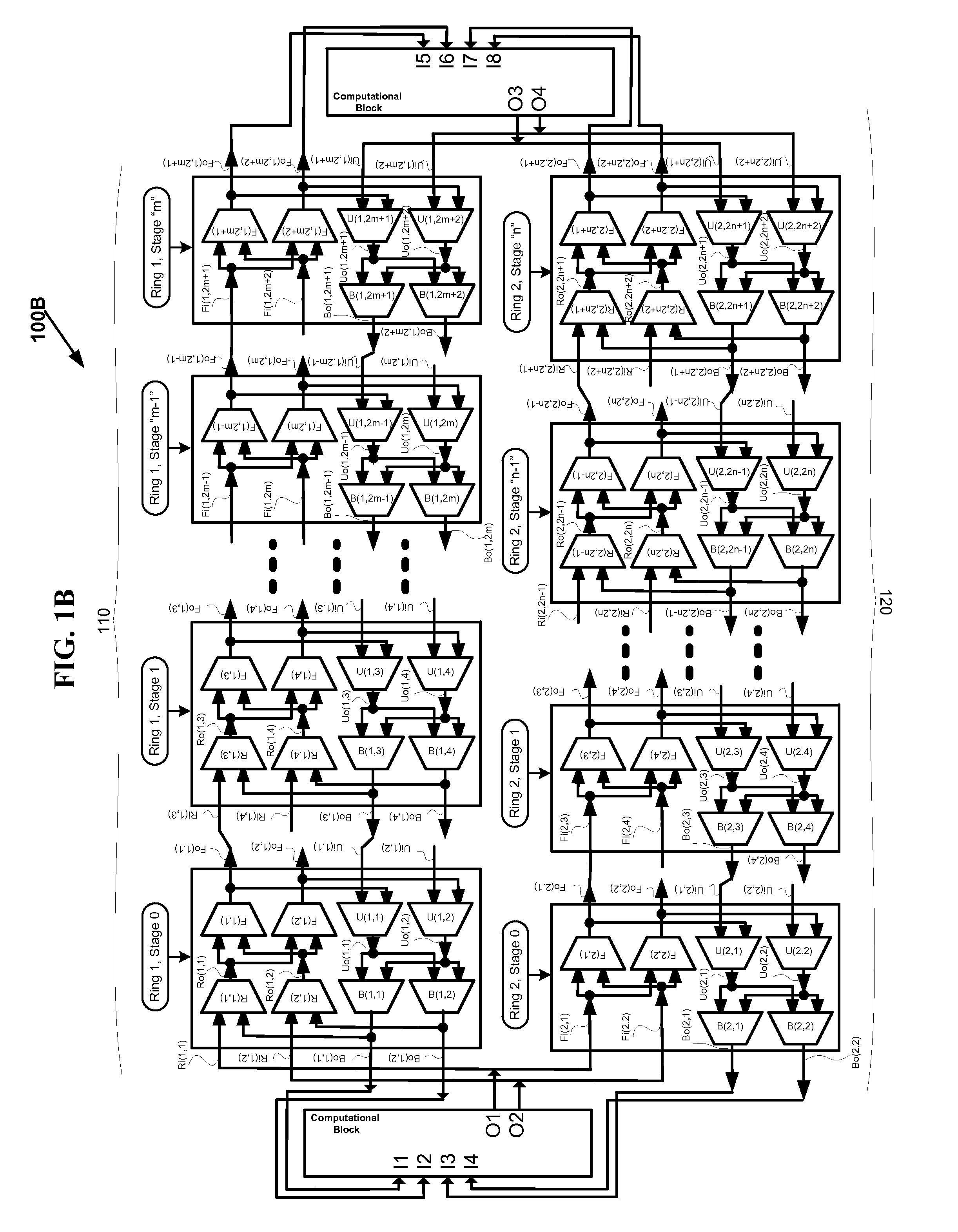

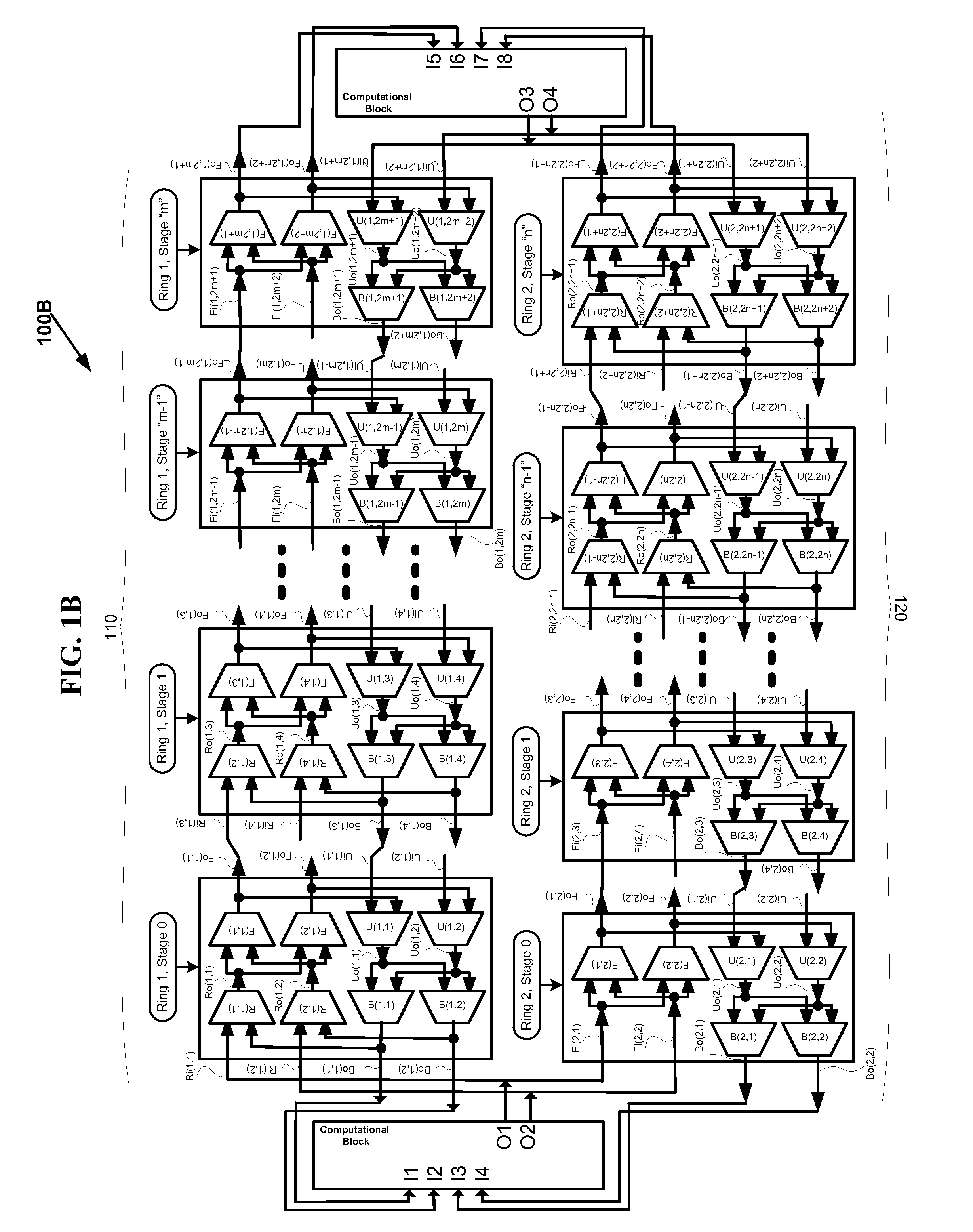

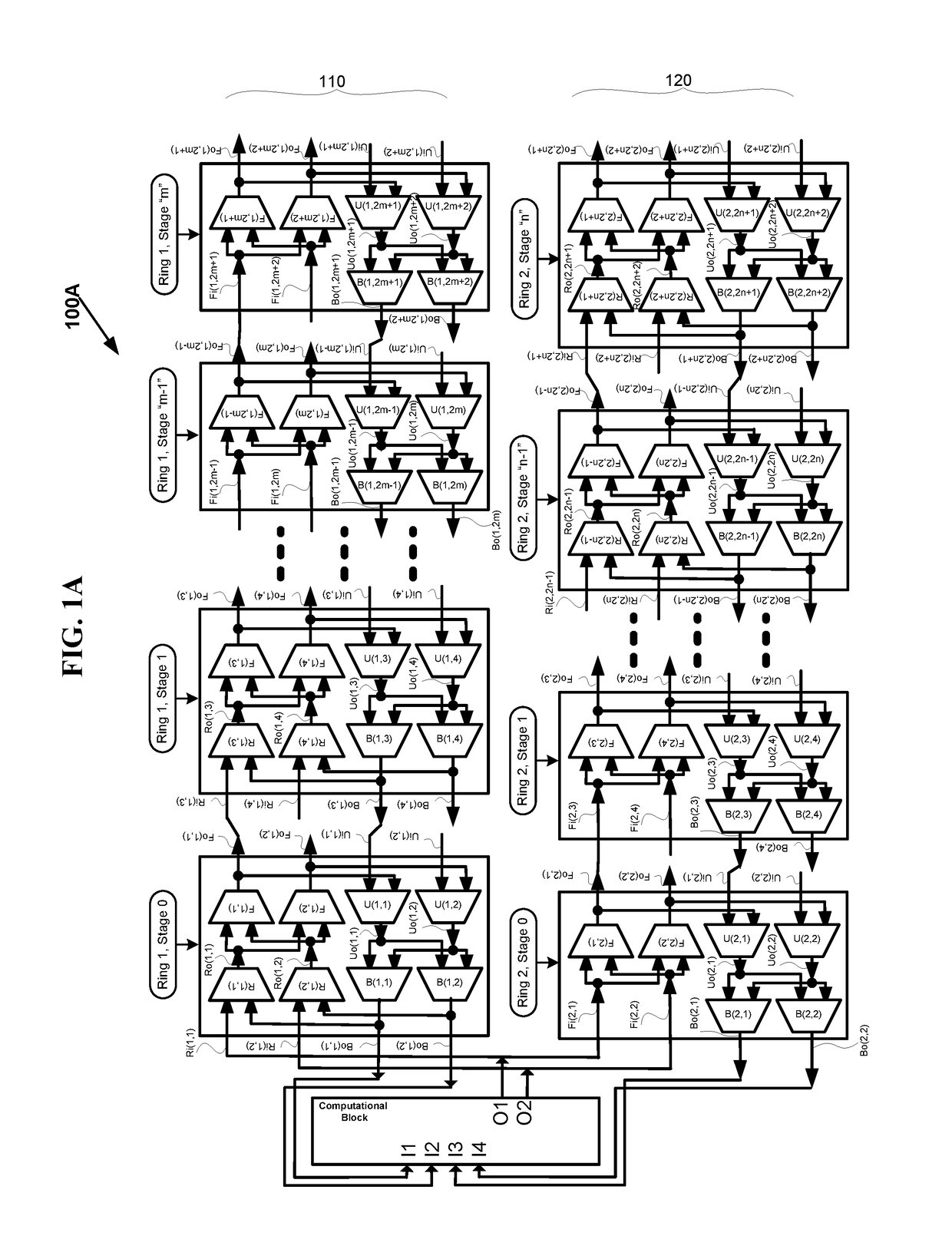

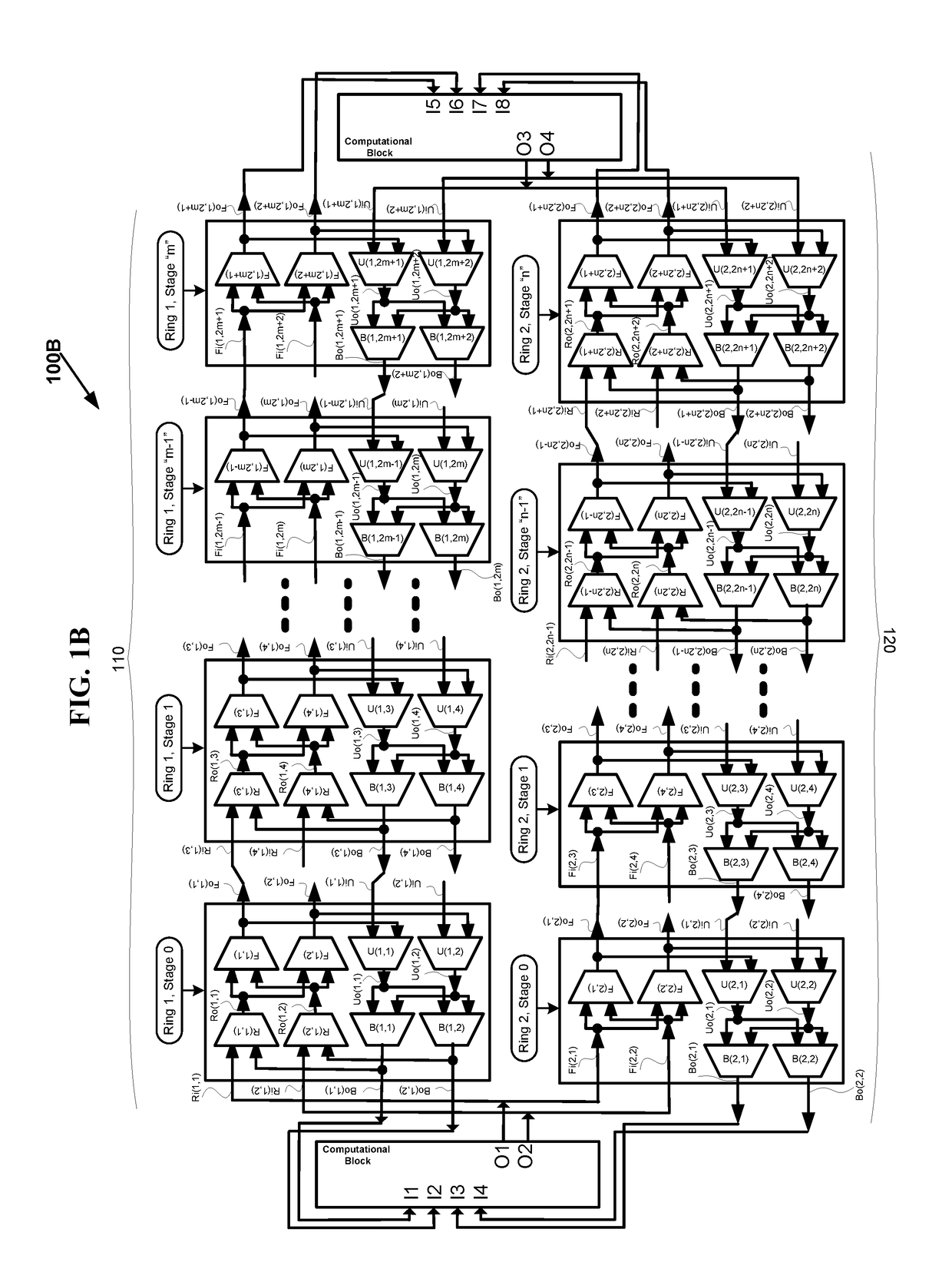

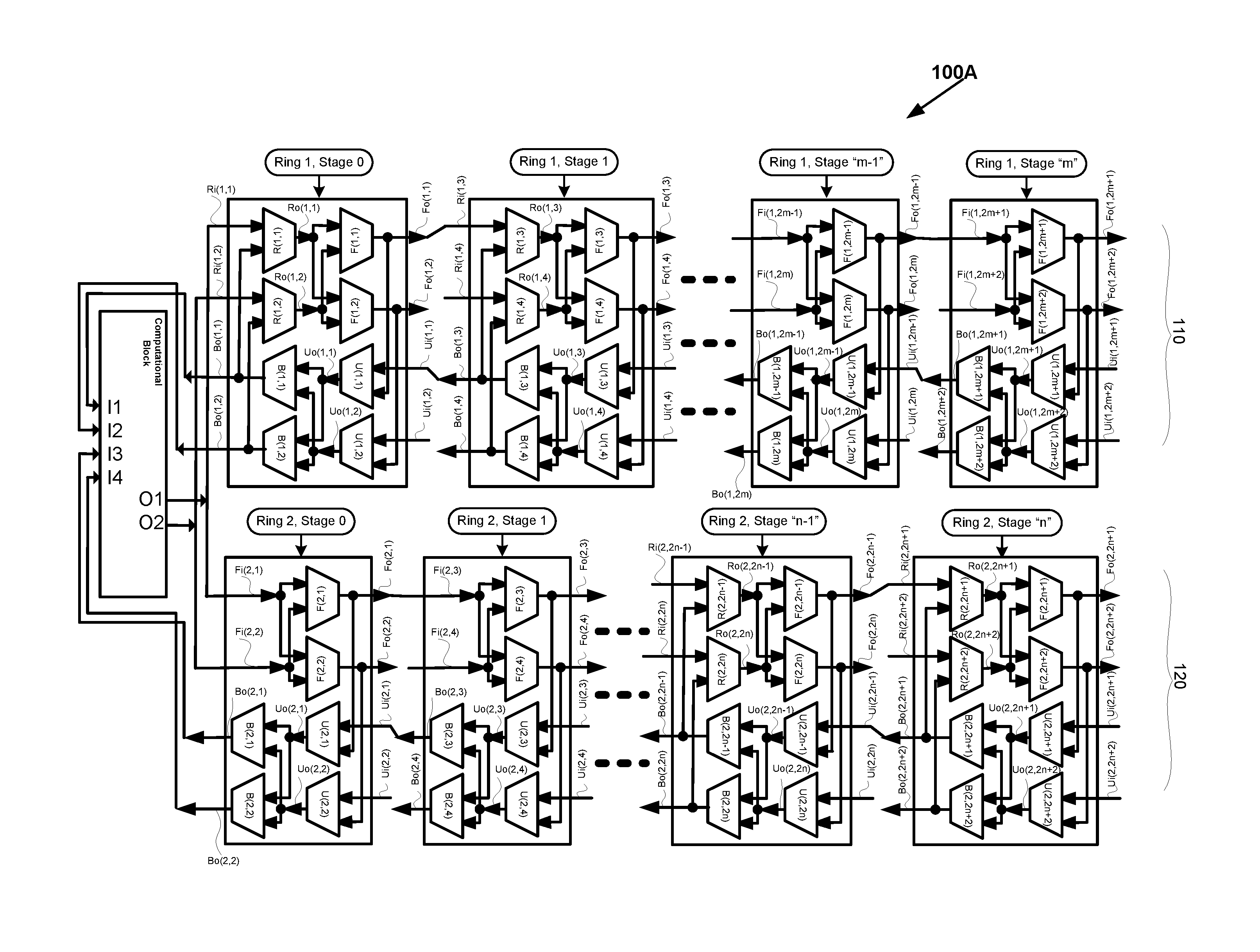

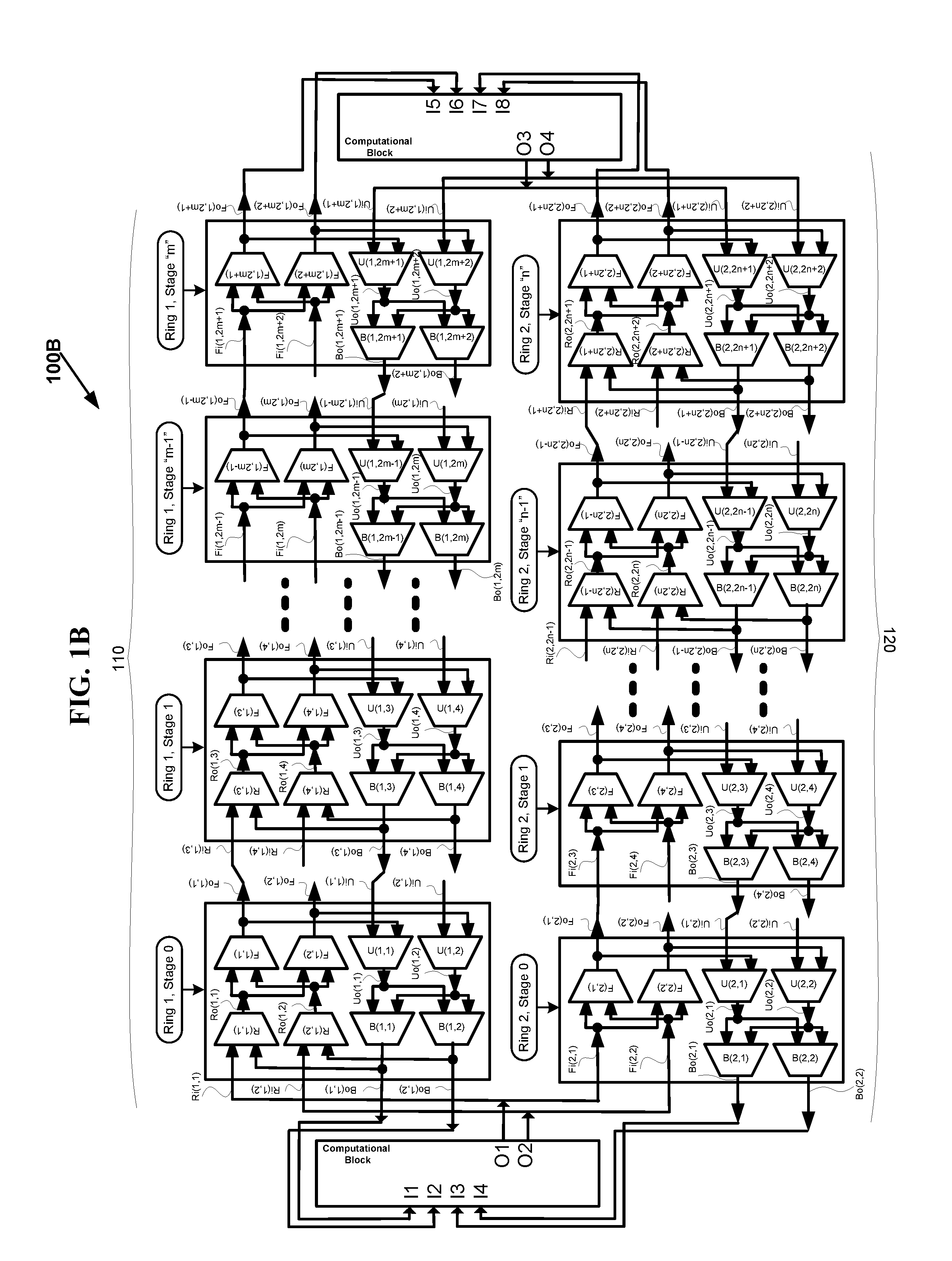

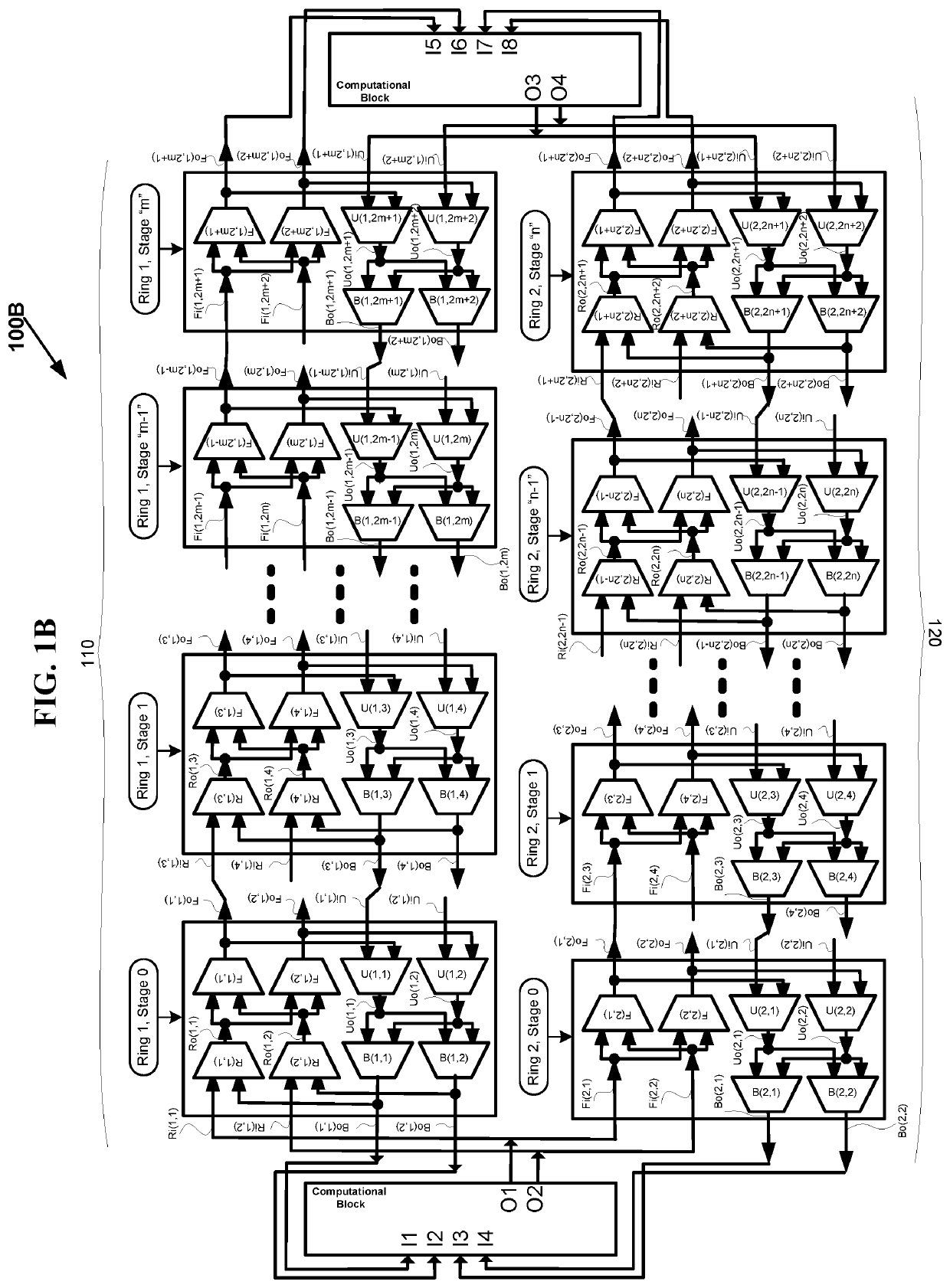

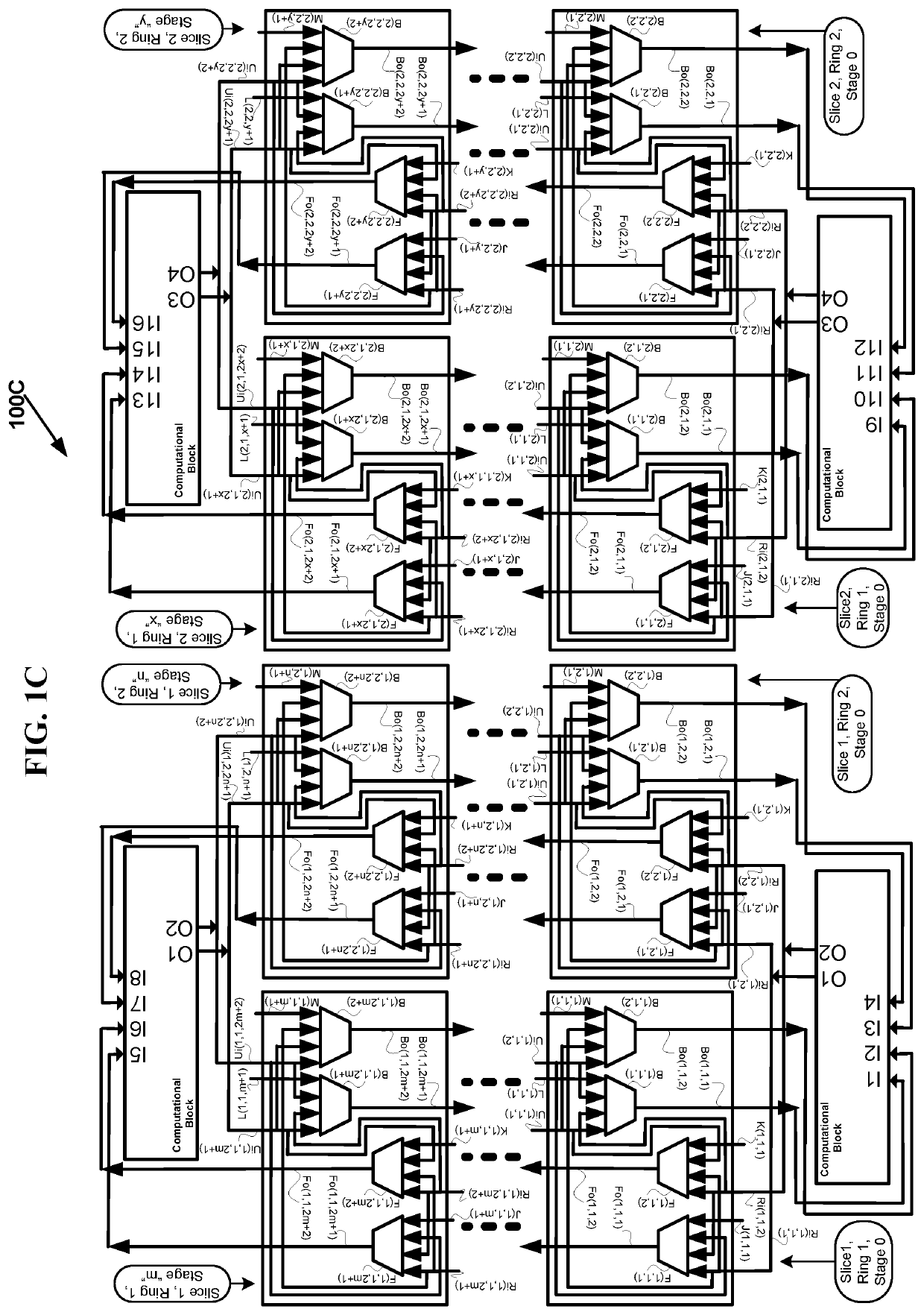

Fast scheduling and optmization of multi-stage hierarchical networks

ActiveUS20150049768A1Quick dispatchHigh routabilityData switching by path configurationCross-linkVlsi layout

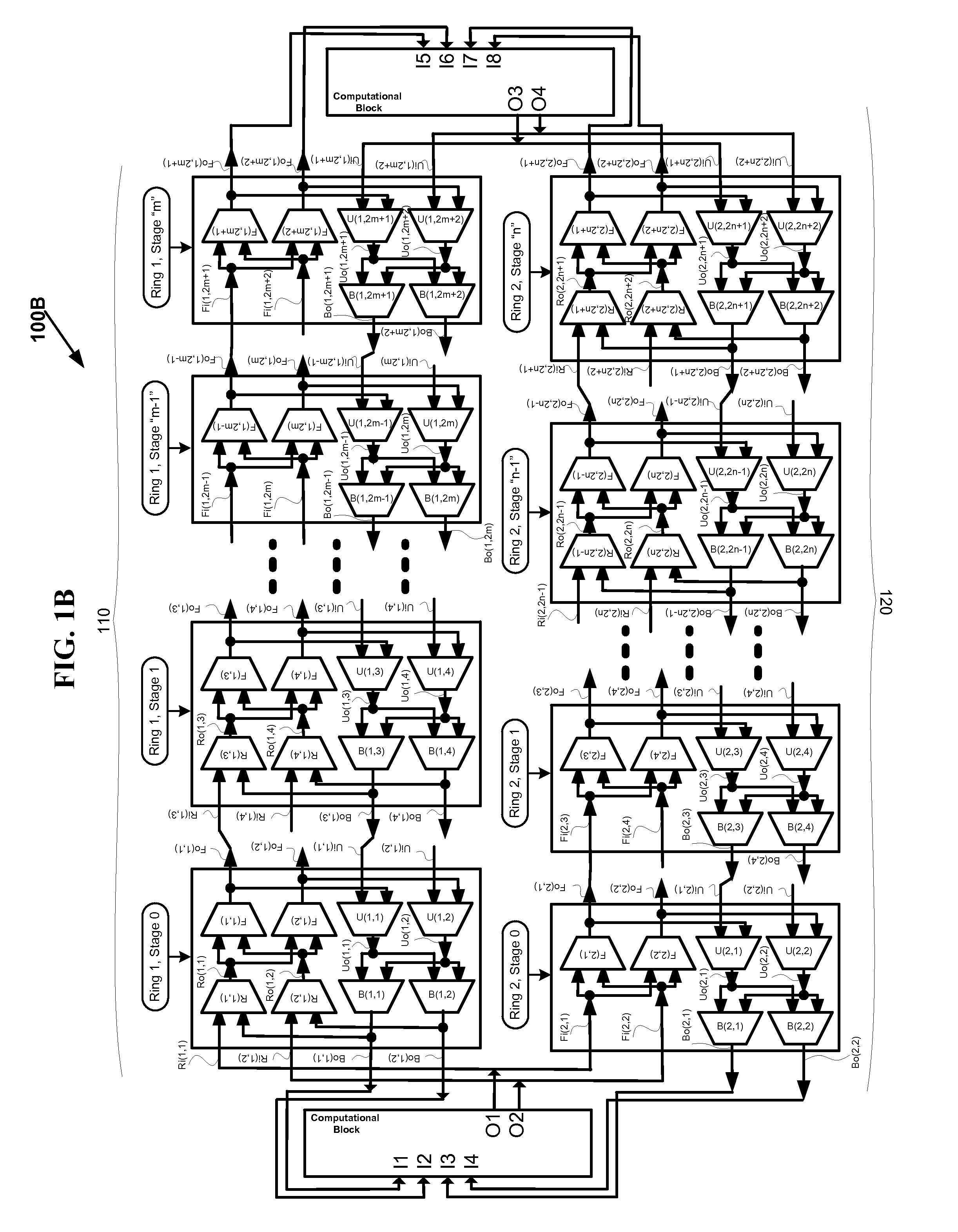

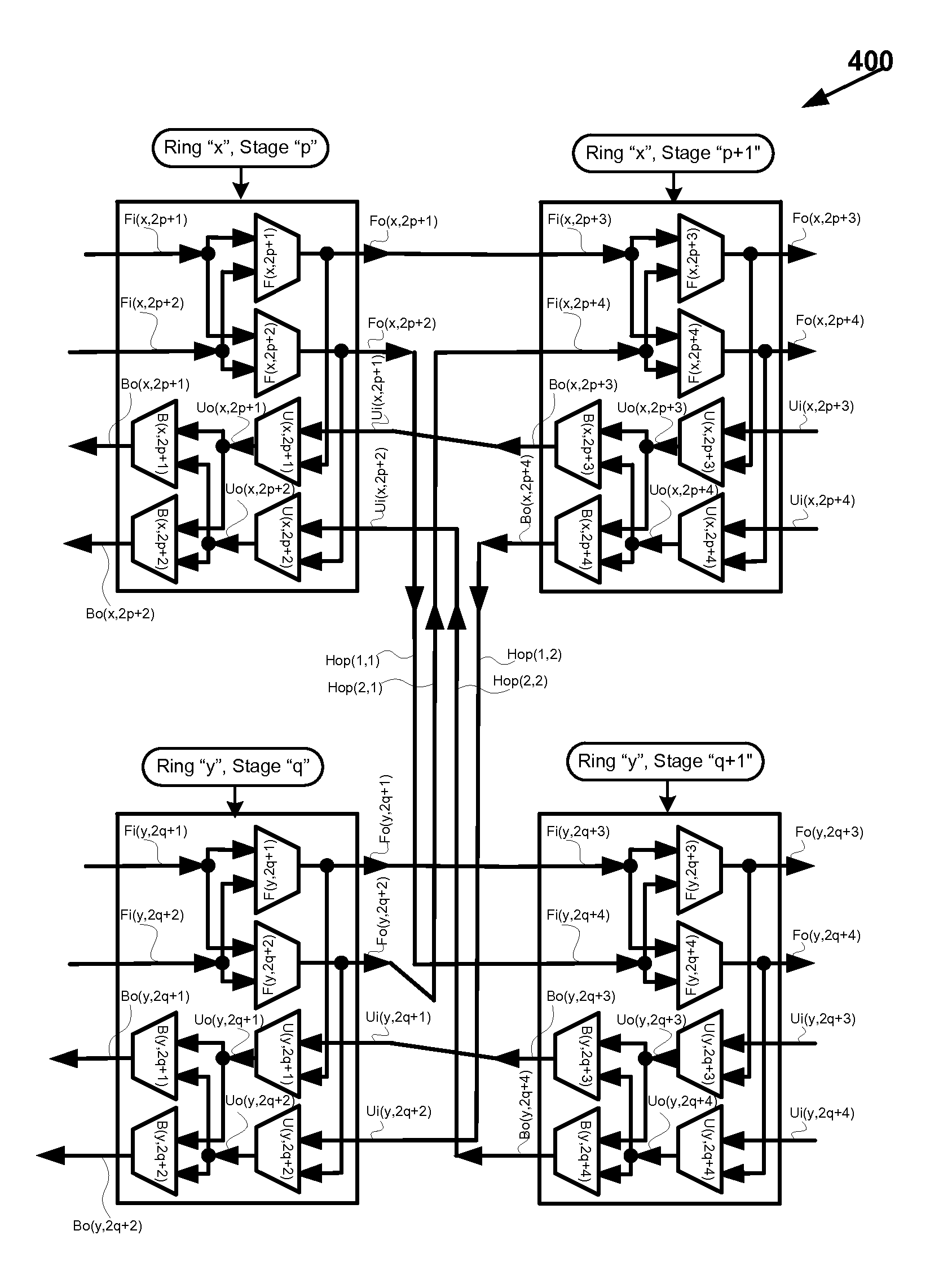

Significantly optimized multi-stage networks with scheduling methods for faster scheduling of connections, useful in wide target applications, with VLSI layouts using only horizontal and vertical links to route large scale sub-integrated circuit blocks having inlet and outlet links, and laid out in an integrated circuit device in a two-dimensional grid arrangement of blocks are presented. The optimized multi-stage networks in each block employ several slices of rings of stages of switches with inlet and outlet links of sub-integrated circuit blocks connecting to rings from either left-hand side only, or from right-hand side only, or from both left-hand side and right-hand side; and employ multi-drop links where outlet links of cross links from switches in a stage of a ring in one sub-integrated circuit block are connected to either inlet links of switches in the another stage of a ring in the same or another sub-integrated circuit block.

Owner:KONDA TECH

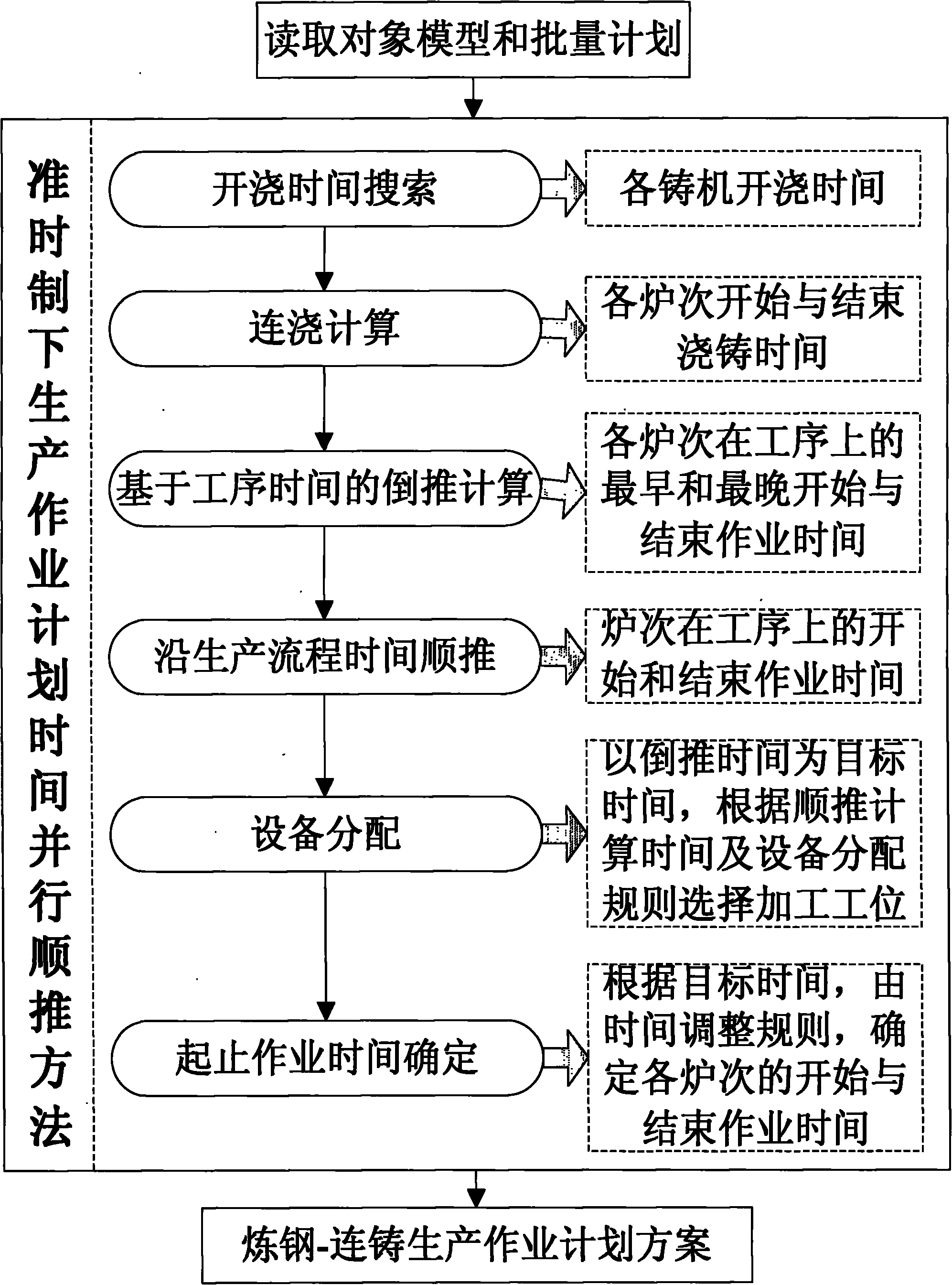

Just-in-time-based parallel forward calculation programing method for steel-making production planned time

The invention discloses a just-in-time-based parallel forward calculation programing method for steel-making production planned time. The method comprises the following steps of: on the basis that a steel-making production process flow network bottom layer object model takes a working position, a working procedure and a transport line as basic elements and the normal distribution rules of the operation time and transportation time of various steel grades are considered, regarding the pouring start time of each heat of sequential casting constraint calculation as a delivery date; taking the operation start time of each heat in the aspect of working procedure based on working procedure backward calculation as the planned reference target time; after the start and end operation time of each heat are calculated by time parallel forward calculation, distributing an appropriate processing working position for each heat by a working position selection rule; and adjusting and determining the start and end operation time on a corresponding working position of each heat by a heat operation time adjusting strategy in reference to the reference target time. An executable operation planning and dispatching scheme for realizing sequential casting production can be programmed rapidly and the method has high generality and wide applicability to the optimization of steel-making production operation planning and dispatching.

Owner:KUNMING UNIV OF SCI & TECH

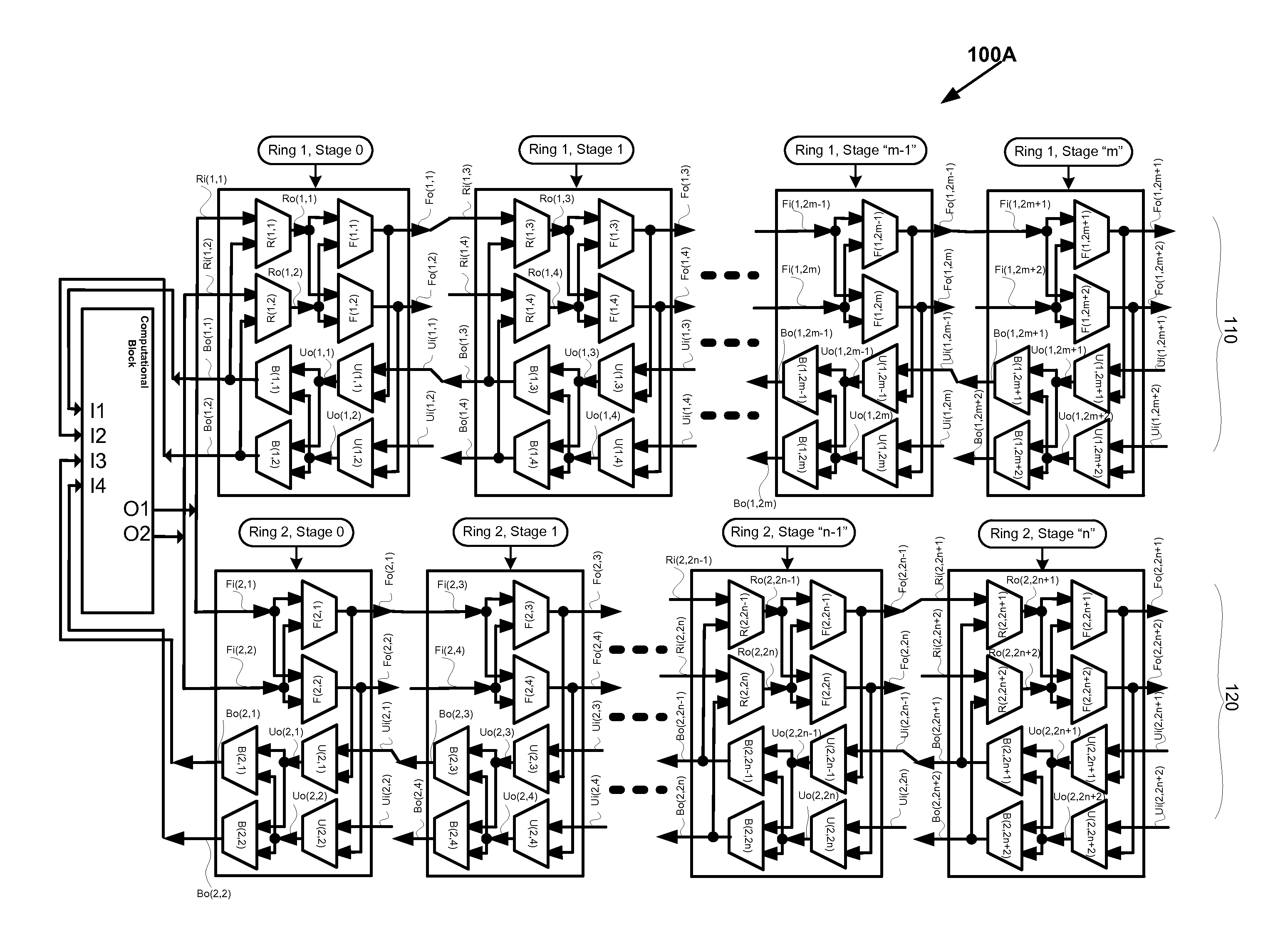

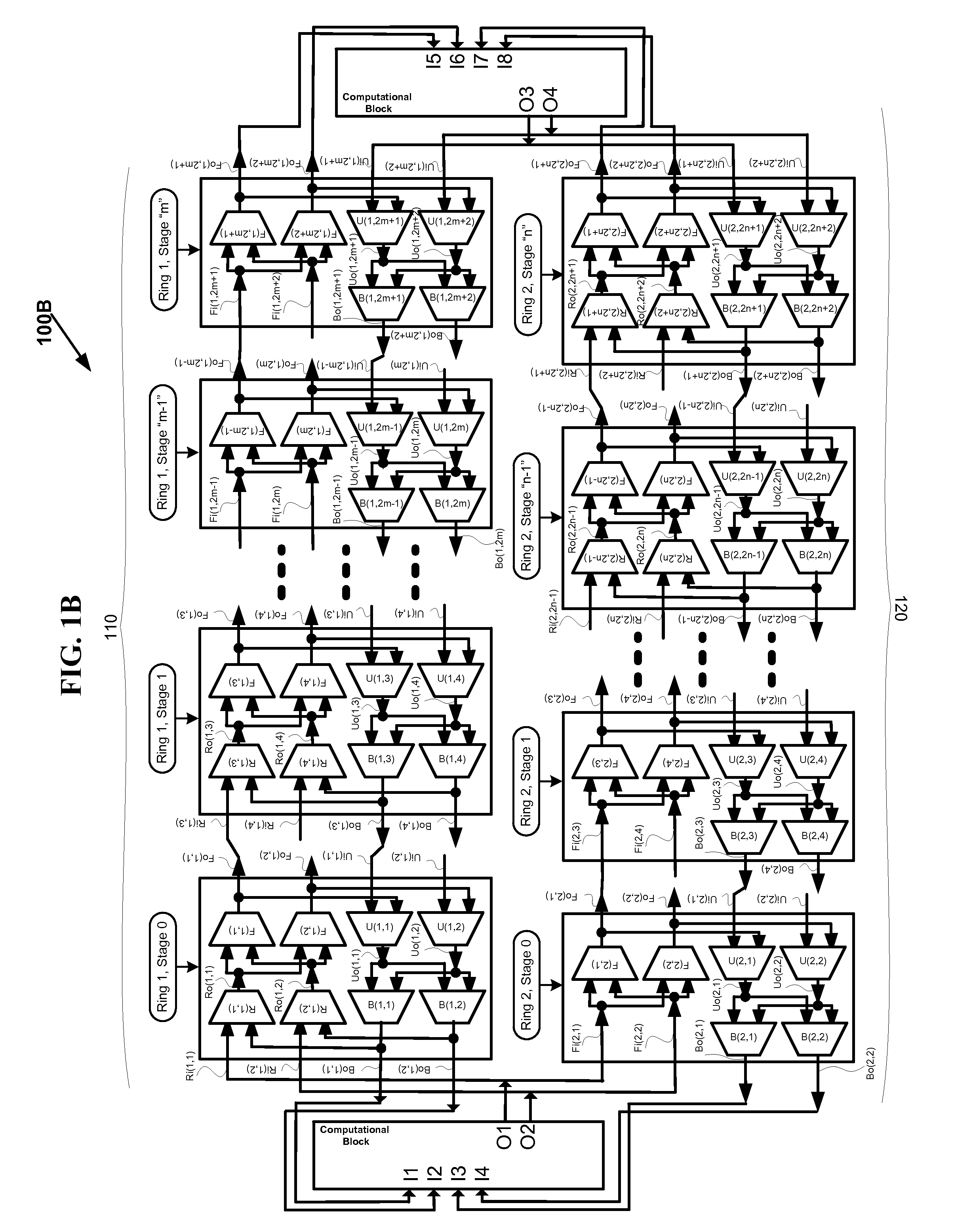

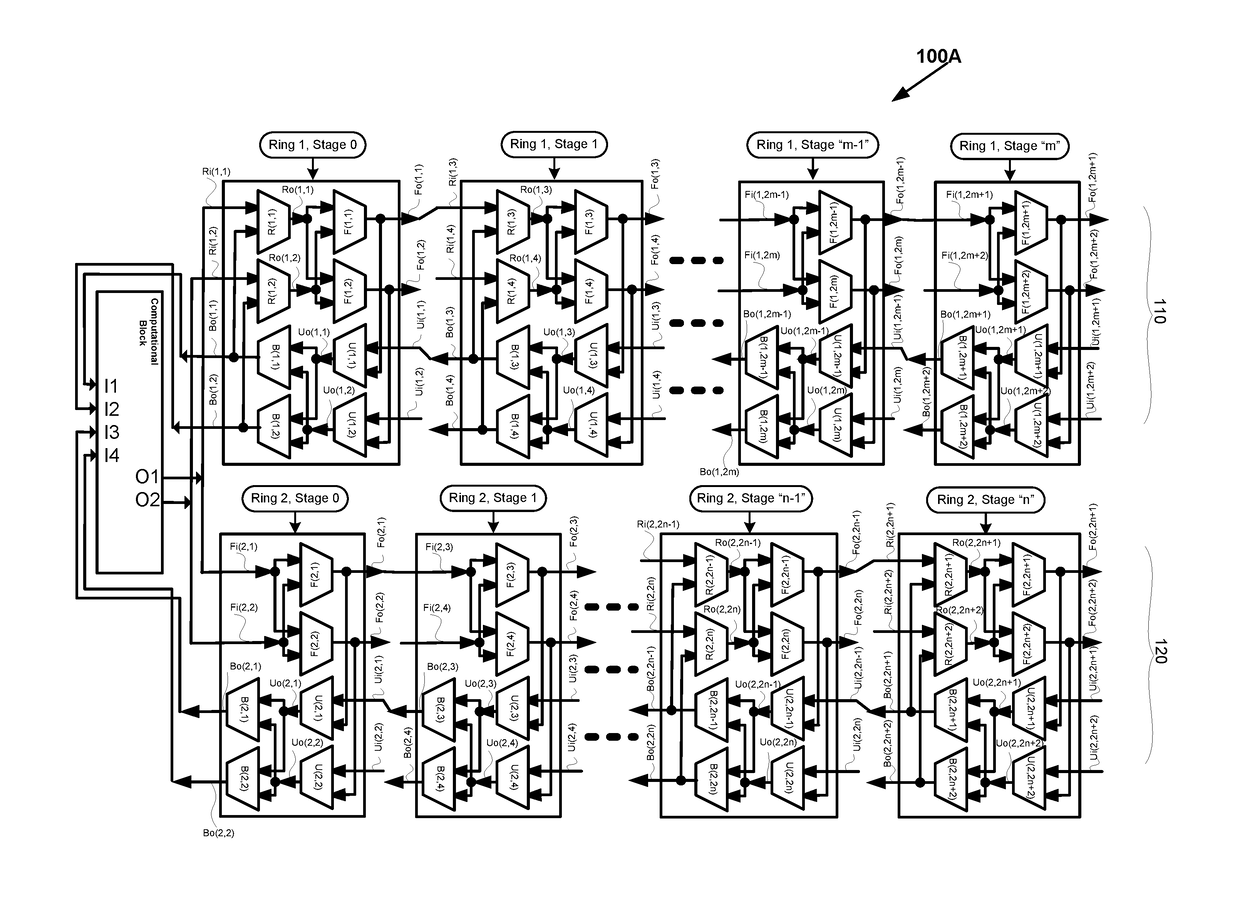

Optimization of multi-stage hierarchical networks for practical routing applications

ActiveUS20140313930A1High routabilityLow pour pointData switching by path configurationCross-linkVlsi layout

Significantly optimized multi-stage networks, useful in wide target applications, with VLSI layouts using only horizontal and vertical links to route large scale sub-integrated circuit blocks having inlet and outlet links, and laid out in an integrated circuit device in a two-dimensional grid arrangement of blocks are presented. The optimized multi-stage networks in each block employ several rings of stages of switches with inlet and outlet links of sub-integrated circuit blocks connecting to rings from either left-hand side only, or from right-hand side only, or from both left-hand side and right-hand side; and employ shuffle exchange links where outlet links of cross links from switches in a stage of a ring in one sub-integrated circuit block are connected to either inlet links of switches in the another stage of a ring in the same or another sub-integrated circuit block.

Owner:KONDA VENKAT

Fast scheduling and optmization of multi-stage hierarchical networks

Significantly optimized multi-stage networks with scheduling methods for faster scheduling of connections, useful in wide target applications, with VLSI layouts using only horizontal and vertical links to route large scale sub-integrated circuit blocks having inlet and outlet links, and laid out in an integrated circuit device in a two-dimensional grid arrangement of blocks are presented. The optimized multi-stage networks in each block employ several slices of rings of stages of switches with inlet and outlet links of sub-integrated circuit blocks connecting to rings from either left-hand side only, or from right-hand side only, or from both left-hand side and right-hand side; and employ multi-drop links where outlet links of cross links from switches in a stage of a ring in one sub-integrated circuit block are connected to either inlet links of switches in the another stage of a ring in the same or another sub-integrated circuit block.

Owner:KONDA TECH

Optimization of multi-stage hierarchical networks for practical routing applications

Significantly optimized multi-stage networks, useful in wide target applications, with VLSI layouts using only horizontal and vertical links to route large scale sub-integrated circuit blocks having inlet and outlet links, and laid out in an integrated circuit device in a two-dimensional grid arrangement of blocks are presented. The optimized multi-stage networks in each block employ several rings of stages of switches with inlet and outlet links of sub-integrated circuit blocks connecting to rings from either left-hand side only, or from right-hand side only, or from both left-hand side and right-hand side; and employ shuffle exchange links where outlet links of cross links from switches in a stage of a ring in one sub-integrated circuit block are connected to either inlet links of switches in the another stage of a ring in the same or another sub-integrated circuit block.

Owner:KONDA VENKAT

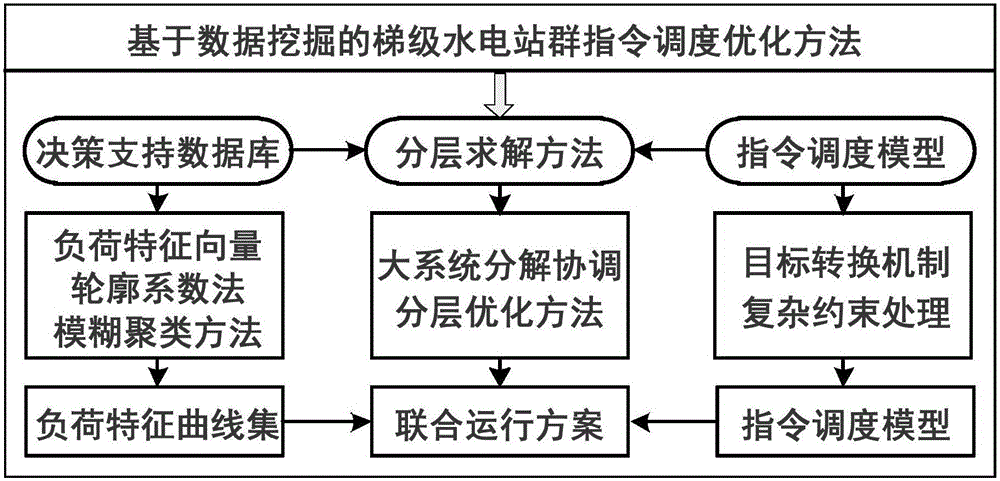

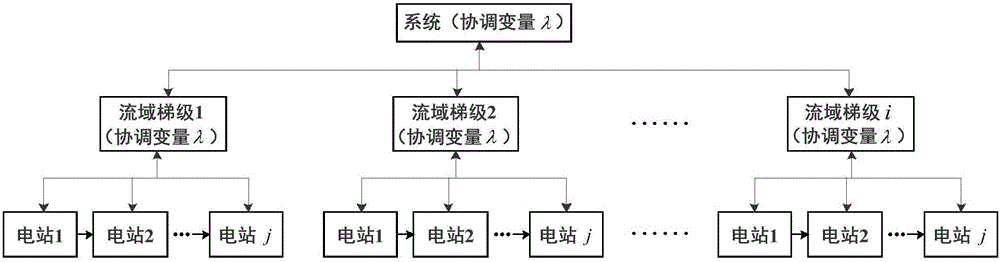

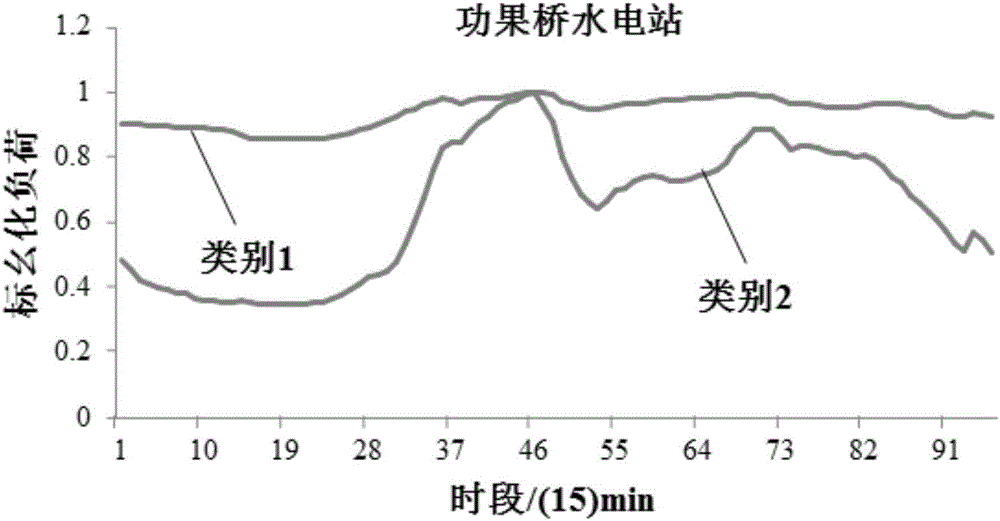

Step hydropower station group instruction scheduling optimization method based on data mining

ActiveCN105809272AImplement cluster analysisQuick compilationForecastingSystems intergating technologiesDecompositionInstruction scheduling

The invention discloses a step hydropower station group instruction scheduling optimization method based on data mining. Cluster analysis of a typical daily load curve is realized on the basis that the power generating feature of a power station itself is fully utilized, and a step hydropower station group short-term optimization scheduling scheme according to scheduling habits can be obtained by use of a layered solving method. The technical scheme provided by the invention is as follows: first of all, on the basis that the power generating feature of a hydropower station is fully analyzed and utilized, typical load curve feature research is conducted, the cluster analysis is performed by use of a data mining technology so as to form a step hydropower station decision support database, then an instruction scheduling optimization model taking a routine object function in short-term optimization scheduling and complex constraint conditions into compressive consideration is constructed, an object function conversion mechanism based on different conditions and a complex contain processing method are given, and finally, through combination with a large-system decomposition coordination idea, a step hydropower station group daily generating plan is rapidly made by use of the layered solving method. According to the invention, a step combined scheduling scheme according with scheduling demands and habits can be rapidly obtained, and the method is a feasible method for realizing practicality of a hydropower station group short-term scheduling scheme under a complex condition.

Owner:DALIAN UNIV OF TECH

Optimization of multi-stage hierarchical networks for practical routing applications

Significantly optimized multi-stage networks, useful in wide target applications, with VLSI layouts using only horizontal and vertical links to route large scale sub-integrated circuit blocks having inlet and outlet links, and laid out in an integrated circuit device in a two-dimensional grid arrangement of blocks are presented. The optimized multi-stage networks in each block employ several rings of stages of switches with inlet and outlet links of sub-integrated circuit blocks connecting to rings from either left-hand side only, or from right-hand side only, or from both left-hand side and right-hand side; and employ shuffle exchange links where outlet links of cross links from switches in a stage of a ring in one sub-integrated circuit block are connected to either inlet links of switches in the another stage of a ring in the same or another sub-integrated circuit block.

Owner:KONDA VENKAT

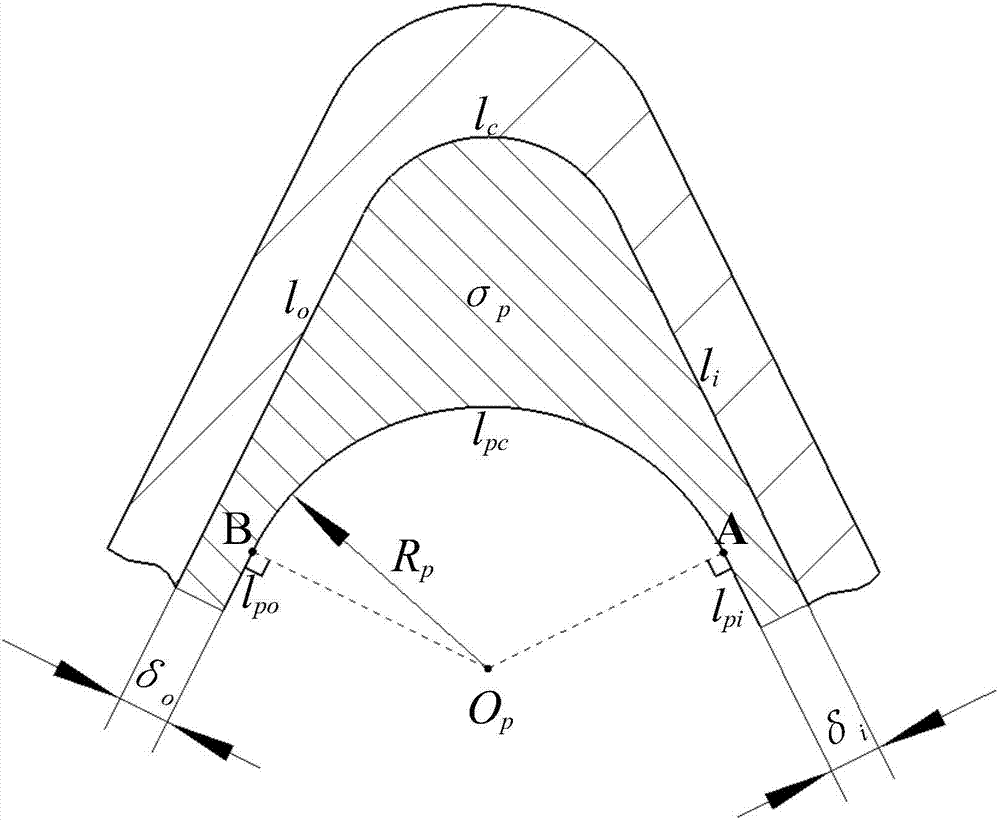

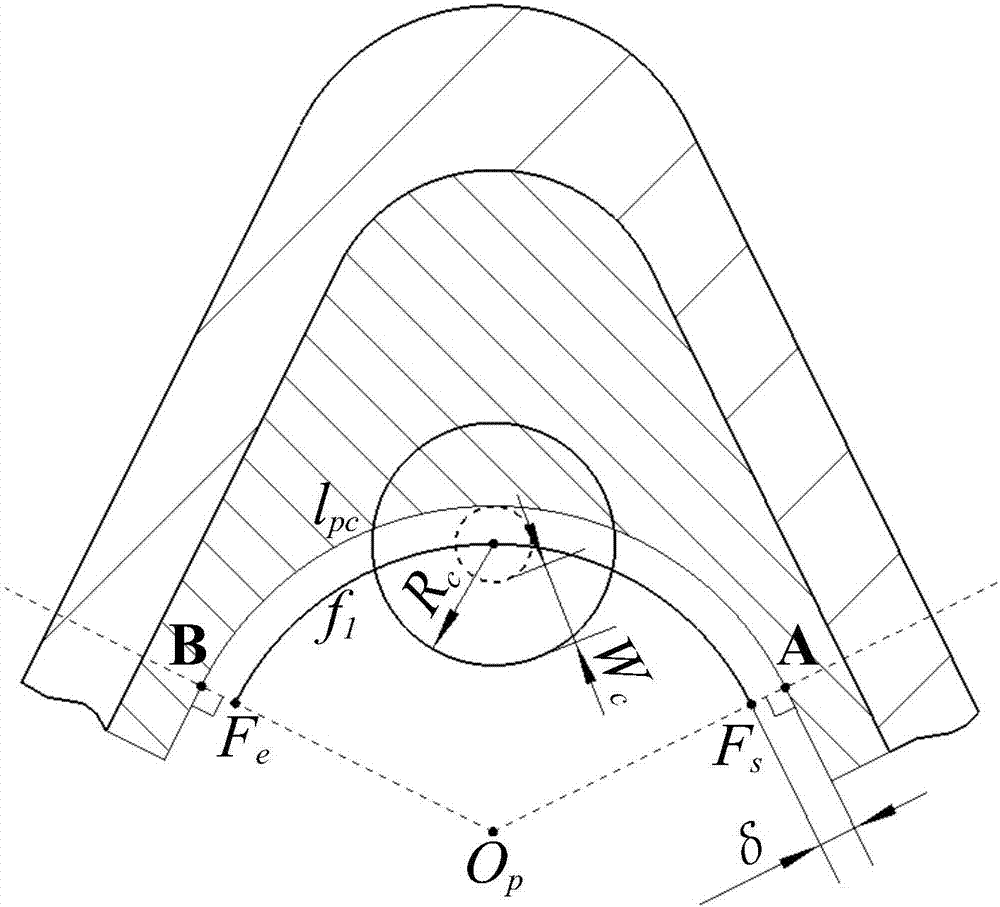

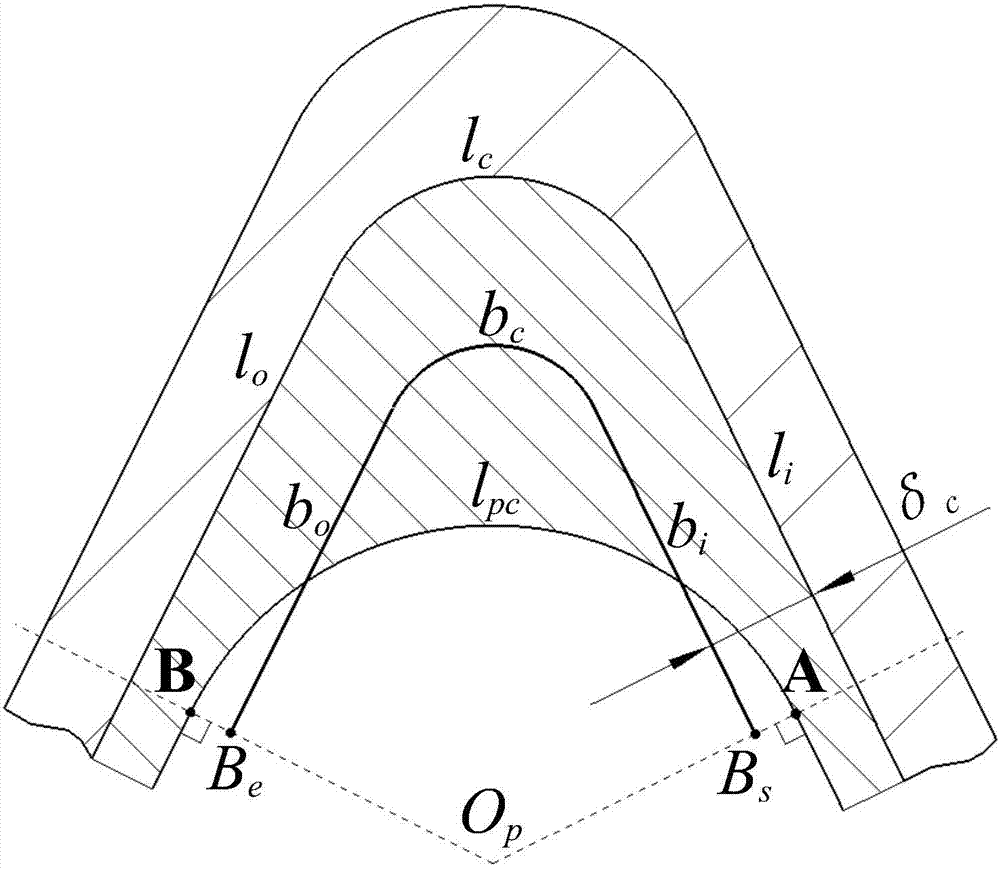

Method for constructing plunge milling points for corner plunge milling

ActiveCN107350528ASave plunge mill positionsImprove processing efficiencyMeasurement/indication equipmentsMilling equipment detailsEngineeringCorner angle

The invention provides a method for constructing plunge milling points for corner plunge milling, and belongs to the technical field of digitized manufacturing of aircraft structural parts. The method is based on the remaining area of a corner, and on the premise of ensuring the limiting cutting width of a process cutter, the processing cutting width of the cutter is adopted as a step distance, and the mode of residual retreat is adopted to carry out layered point distribution, so that the construction of the corner plunge milling points is realized. According to the method for constructing the plunge milling points for corner plunge milling, the construction of the corner plunge milling points in the structural parts can be realized, a key technology is provided for rapid numerical control programming of corner plunge milling, and rapid establishment of a numerical control program of corner plunge milling based on the remaining area is achieved; besides, great reference can be provided for programming of plunge milling with other structural features.

Owner:SHENYANG AIRCRAFT CORP

Optimization of multi-stage hierarchical networks for practical routing applications

Significantly optimized multi-stage networks, useful in wide target applications, with VLSI layouts using only horizontal and vertical links to route large scale sub-integrated circuit blocks having inlet and outlet links, and laid out in an integrated circuit device in a two-dimensional grid arrangement of blocks are presented. The optimized multi-stage networks in each block employ several rings of stages of switches with inlet and outlet links of sub-integrated circuit blocks connecting to rings from either left-hand side only, or from right-hand side only, or from both left-hand side and right-hand side; and employ shuffle exchange links where outlet links of cross links from switches in a stage of a ring in one sub-integrated circuit block are connected to either inlet links of switches in the another stage of a ring in the same or another sub-integrated circuit block.

Owner:KONDA VENKAT

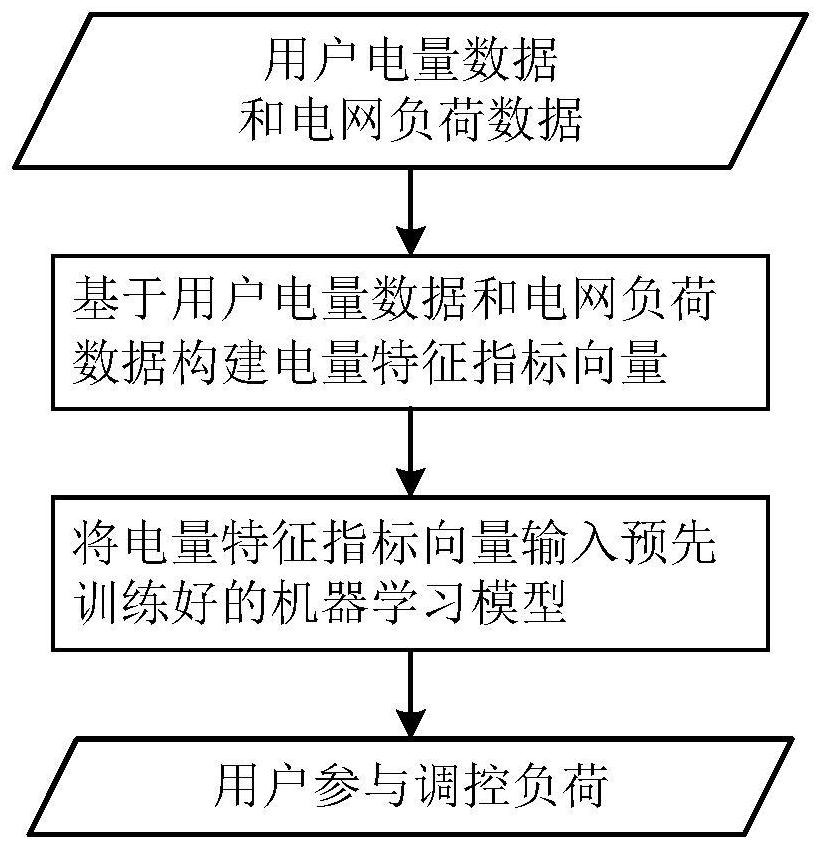

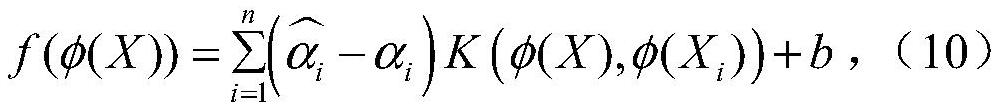

Regulable load prediction method and system for users participating in orderly power utilization

PendingCN114707817ASafe and stable operationQuick compilationResourcesMachine learningLoad forecastingControl engineering

The invention discloses an adjustable load prediction method and system for users participating in orderly power utilization, and the method comprises the steps: constructing an electric quantity characteristic index vector based on the electric quantity data of users and the load data of a power grid, comprising the following eight characteristic indexes: power utilization fluctuation ratio, power utilization peak-valley difference, peak-to-average power utilization ratio, off-peak load difference, weekly rest load difference, weekly load drop rate, maintenance load difference and maximum utilization hour rate; and inputting the electric quantity characteristic index vector into a pre-trained machine learning model to obtain a corresponding user participation regulation and control load. According to the method, deep mining can be carried out on user electric quantity characteristics through machine learning, user adjustable load prediction based on historical electric quantity data is further realized, related business personnel can rapidly compile an orderly power utilization plan, and safe and stable operation of a power grid and reliable power supply are guaranteed.

Owner:STATE GRID HUNAN ELECTRIC POWER +2

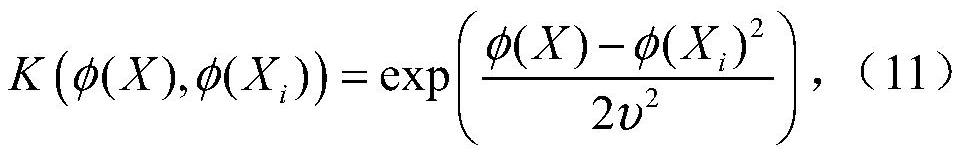

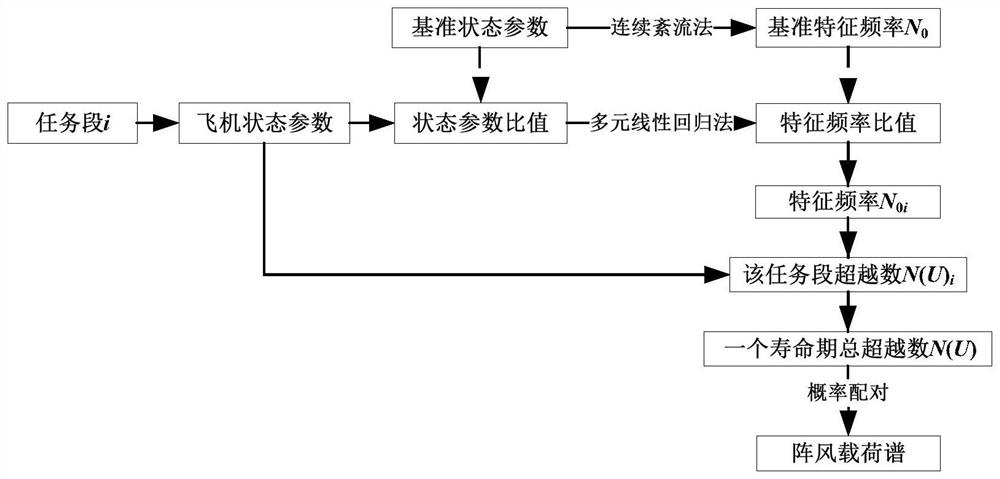

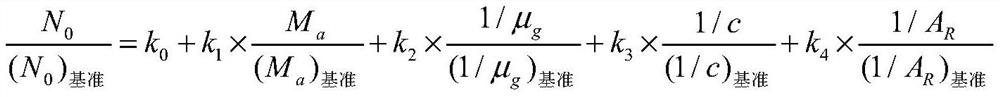

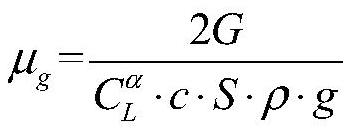

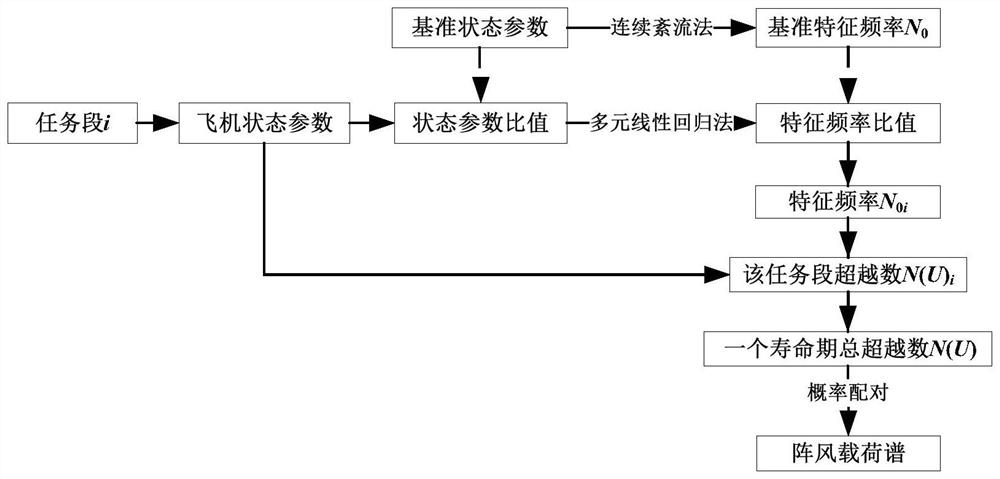

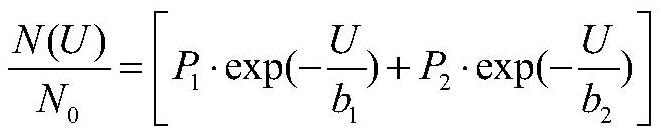

Unmanned aerial vehicle gust load spectrum quick compiling method

ActiveCN112528478AQuick compilationShorten the notation cycleSustainable transportationDesign optimisation/simulationAviationFlight vehicle

The invention belongs to the field of aircraft structure fatigue life design, and relates to an unmanned aerial vehicle gust load spectrum quick compiling method. A group of reference state parametersof the unmanned aerial vehicle are selected, continuous turbulence analysis is adopted to calculate gust response reference characteristic frequency only once, and for the flight state of any task section, a multiple linear regression method is directly adopted to obtain gust response characteristic frequency of the task section. Finally, the transcendental number of each gust speed is calculatedaccording to each task section time in one life cycle so as to finish the quick compilation of the gust load spectrum. According to the method, the multivariate regression equation of the key state parameter ratio and the gust response characteristic frequency ratio only needs to be constructed once, and quick compilation of the design load spectrum, the actual measurement load spectrum and the single-machine load spectrum can be realized, so that the compilation period is shortened; The method is simple and efficient in system, has good engineering applicability, and can be popularized to various aviation aircraft.

Owner:CHENGDU AIRCRAFT DESIGN INST OF AVIATION IND CORP OF CHINA

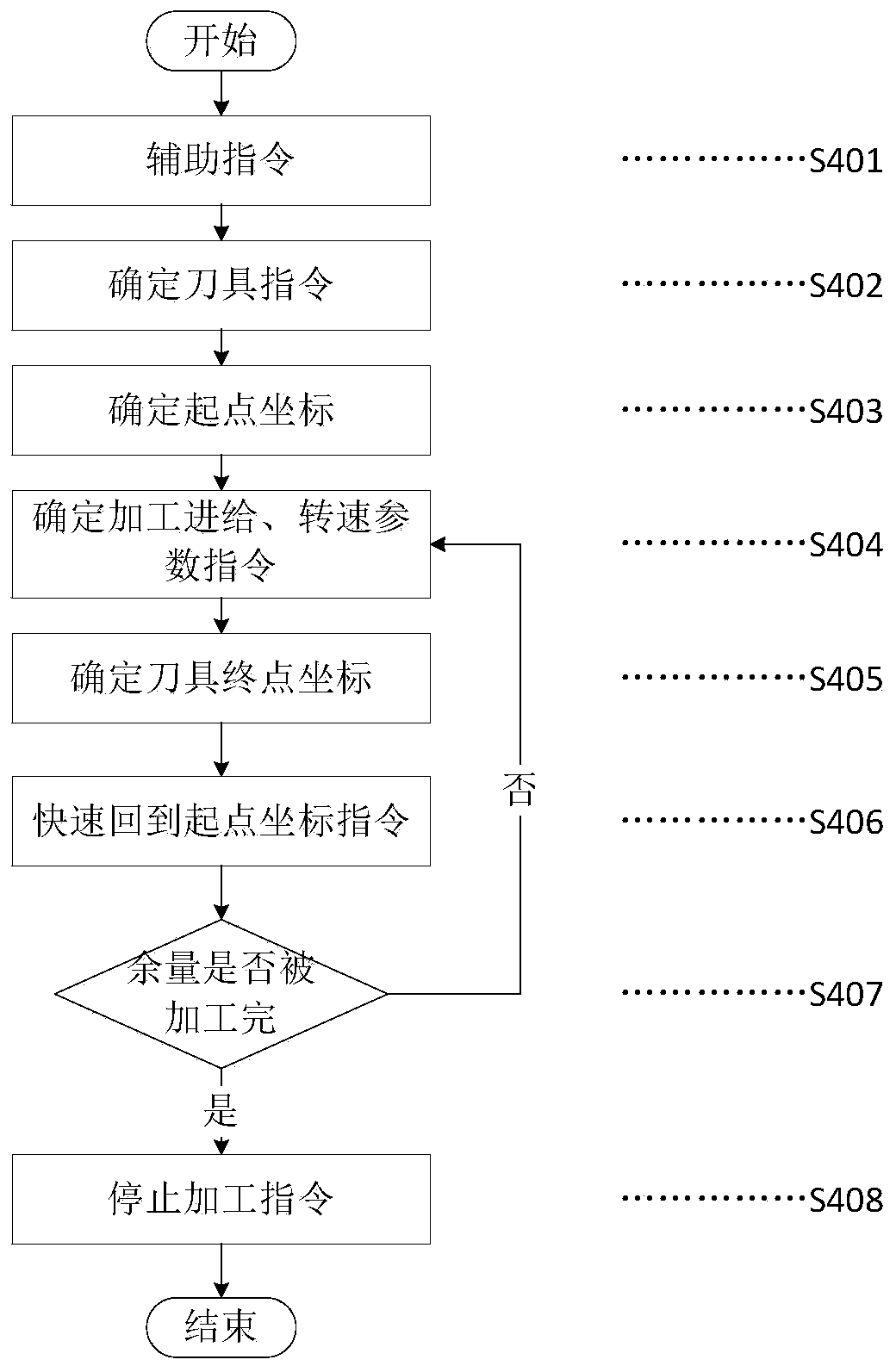

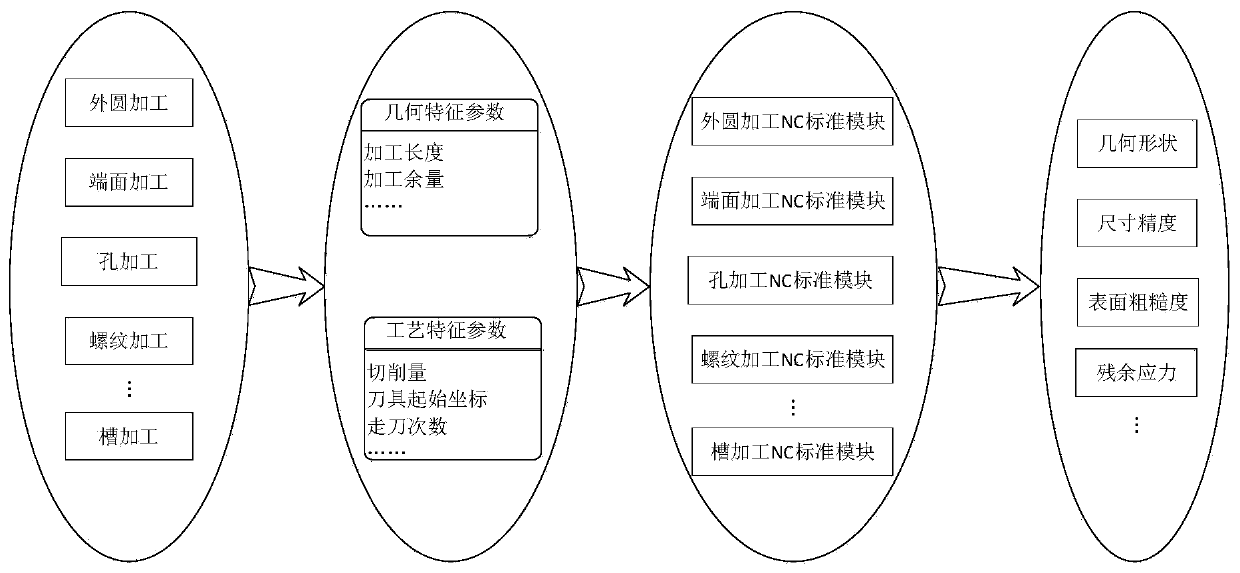

Machining process numerical control code standardized integration model and method

PendingCN111007803AQuick compilationSimple processProgramme controlComputer controlNumerical controlModularity

The invention provides a machining process numerical control code standardized integration model and method. In order to solve problems that in the machining process, the quality of machined parts isunstable because habits of different operators are different in the numerical control encoding process and the labor cost of enterprises is increased because numerical control programming needs professional technicians, the method is used for establishing an integrated model of numerical control machining codes in the numerical control machine tool machining process. Standard modular numerical control machining codes are given according to different machining processes in the machining process and used for guiding the numerical control programming personnel to quickly compile numerical controlcodes in the machining process in a standardized mode, so that the machining quality of mechanical products is guaranteed, compiling standardization of the numerical control codes is guaranteed, andthen the efficiency of the machining process is improved.

Owner:WUHAN UNIV OF TECH

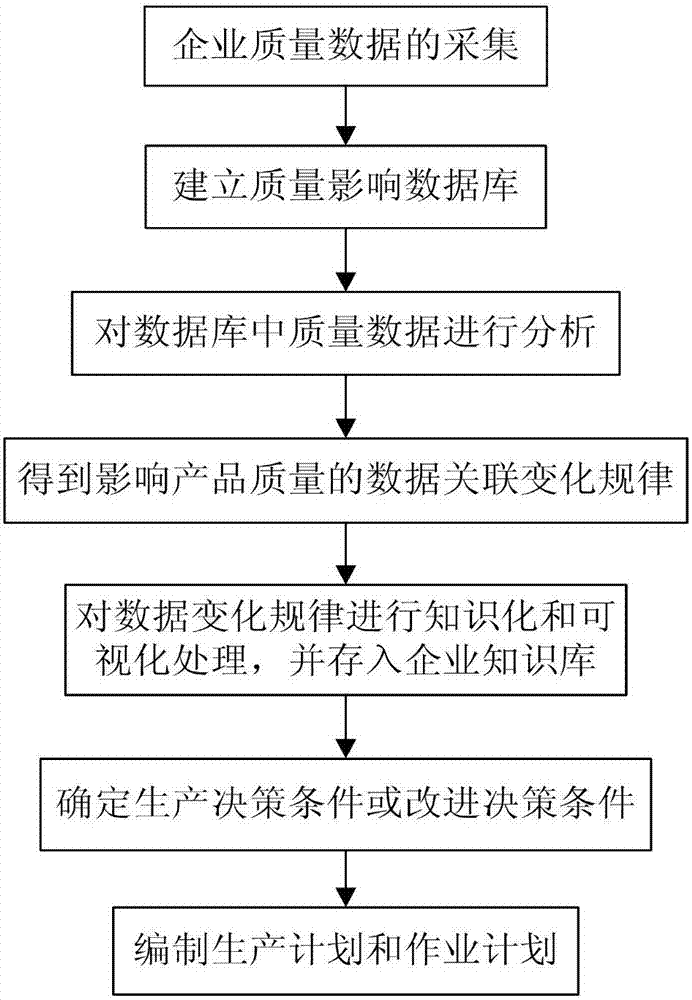

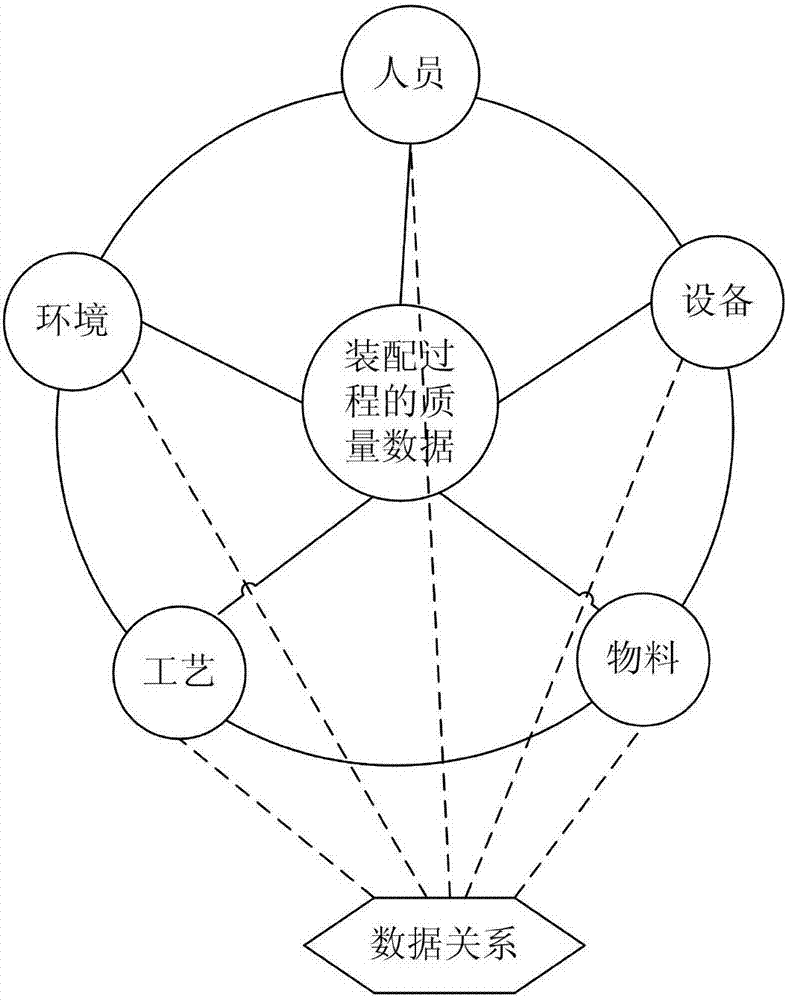

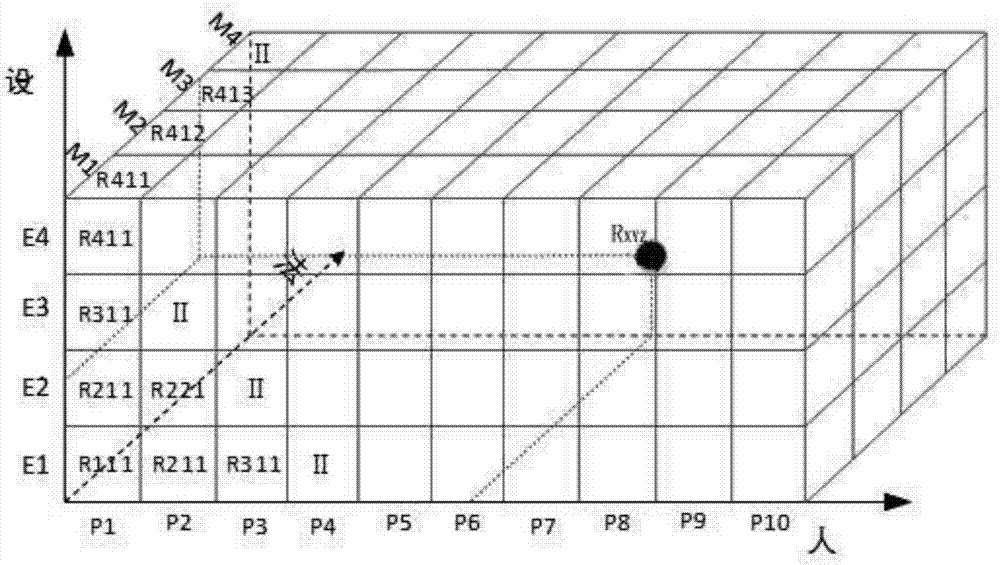

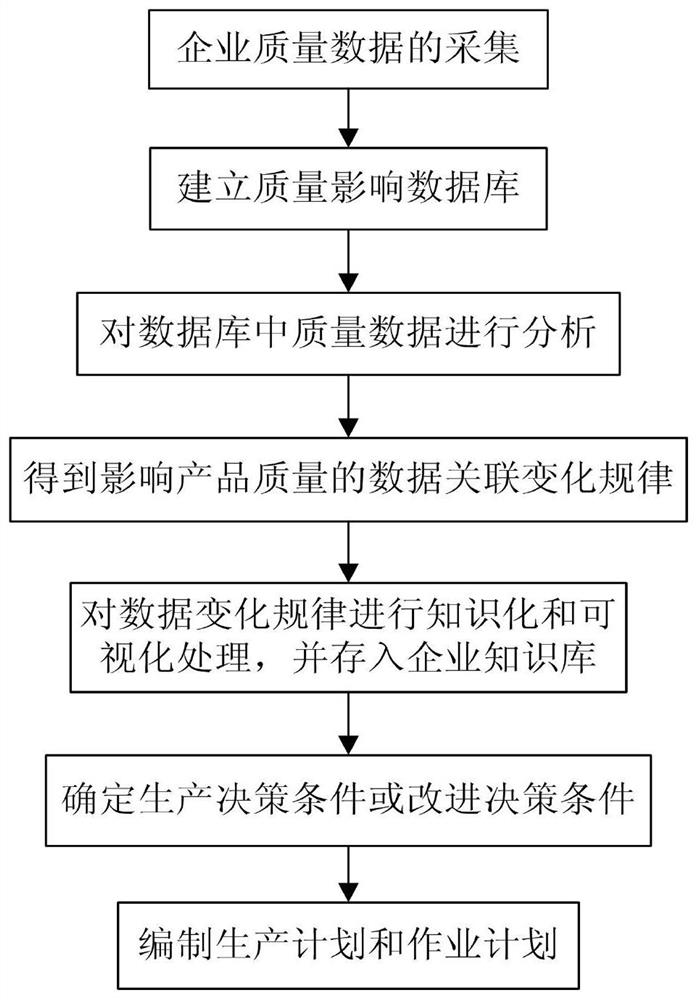

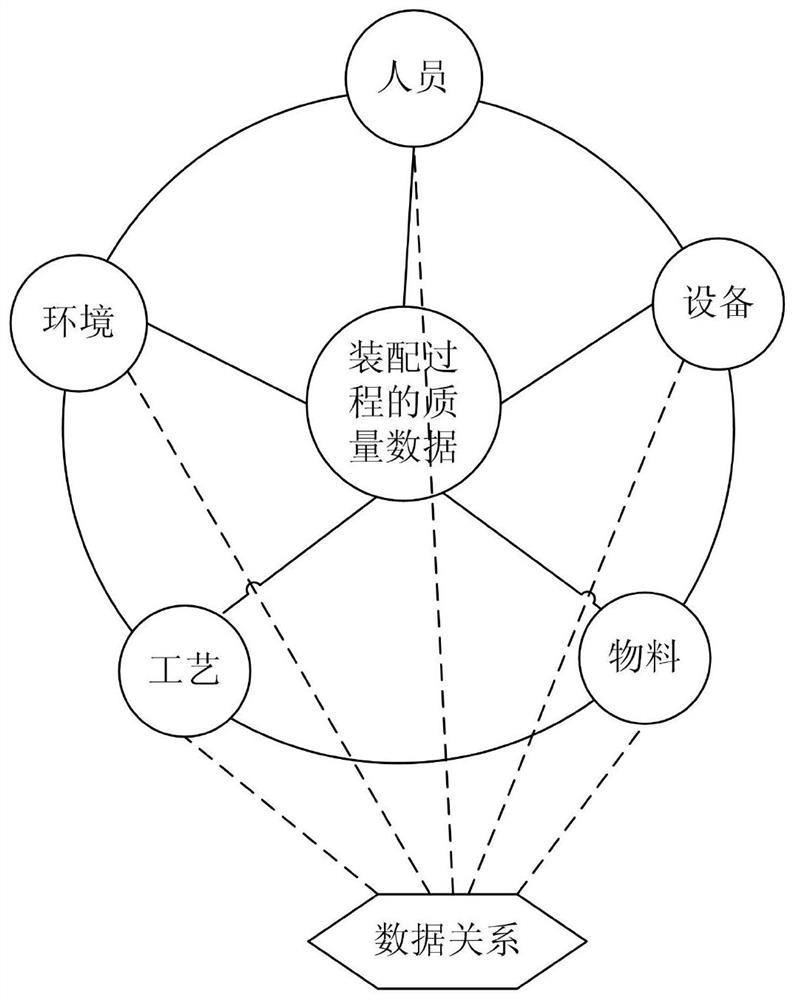

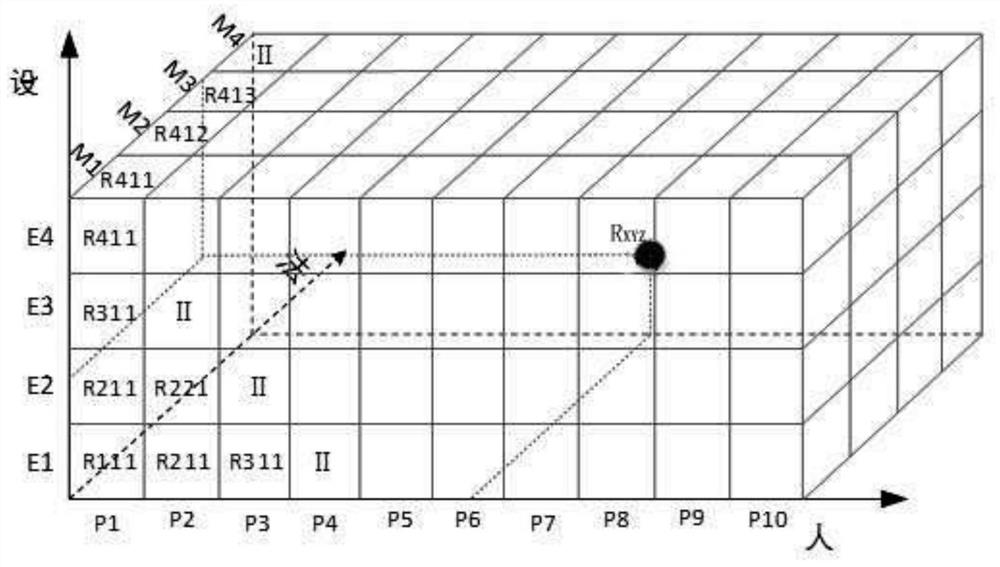

Production plan formulation method based on quality data depth analysis

ActiveCN107392385AImprove the preparation levelQuality improvementForecastingKnowledge representationProduction planningResearch Object

The invention provides a production plan formulation method based on quality data depth analysis, which relates to the technical field of intelligent manufacturing of mechanical parts. According to the production plan formulation method based on quality data depth analysis, on the basis that an enterprise has long-time and complete quality data, with data of five features of persons, machines, materials, the process and the environment as research objects, integrated analysis is carried out on the quality data influencing the product quality, an association change law between the quality data is obtained, knowledge and visualization processing are carried out, enterprise production decision conditions are obtained, and based on the production decision conditions, formulation of an enterprise production plan and an operation plan is completed. According to the production plan formulation method based on quality data depth analysis provided by the invention, quick high-efficiency and optimal production plan formulation can be realized, a convenient and intelligent tool for production plan formulation is provided for an MES system, and the mechanical part production plan formulation level is improved.

Owner:沈阳昊成智能装备有限公司

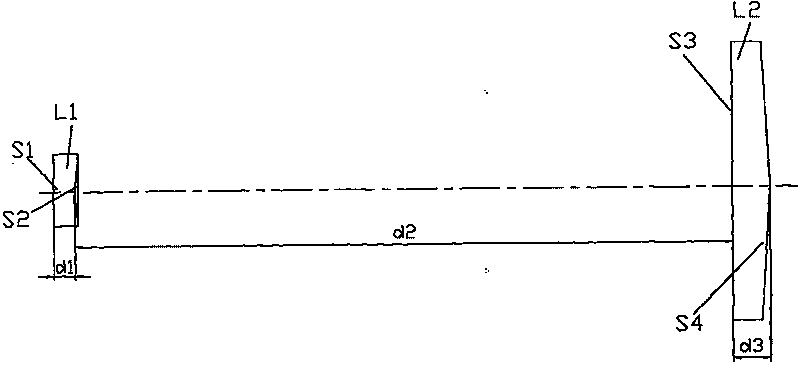

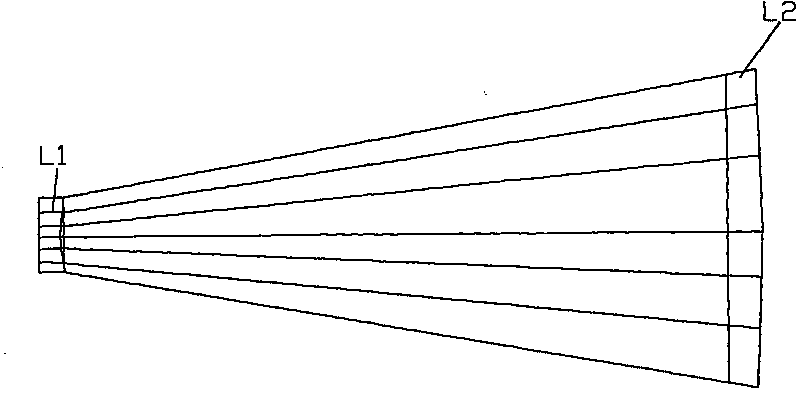

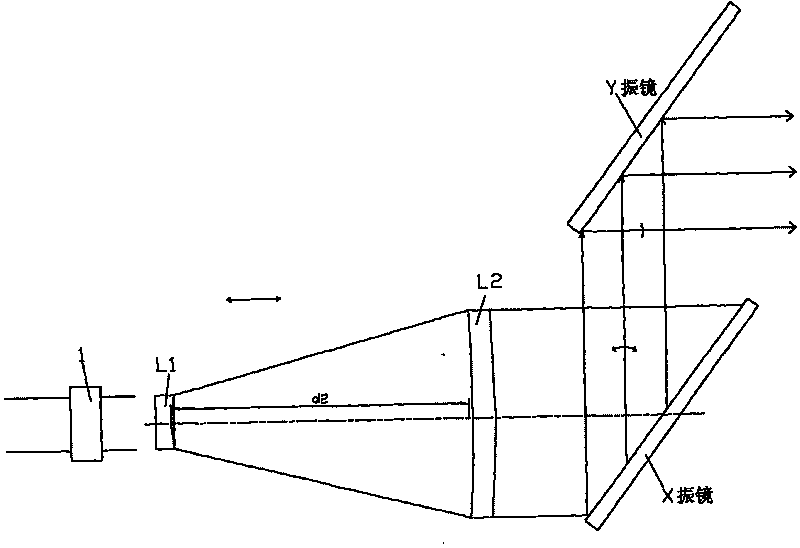

Laser beam expanding lens system

The invention provides a laser beam expanding lens system, comprising a laser, lenses and a oscillating lens, wherein, the two lenses are located at the same optical axis; the first lens is a double concave lens, and the curved surface backs the incident direction of the light; the second lens is a meniscus-type lens, and the curved surface faces the incident direction of the light; the first lens is the beam expanding lens; through arranging the meniscus-type lens and the double-concave lens, and through adjusting the distance between the lens as the precision adjustment light beam, the emitted light beam is lead to display light beam with clear light, in order to meet different needs. The laser beam expanding lens system is used as advertisement demonstration, stage demonstration and other occasions, therefore, the invention is widely used, the scanning of the laser beam expanding lens system is flexible, and patterns of various colors and designs can be rapidly weaved through the oscillating lens.

Owner:HANS LASER TECH IND GRP CO LTD

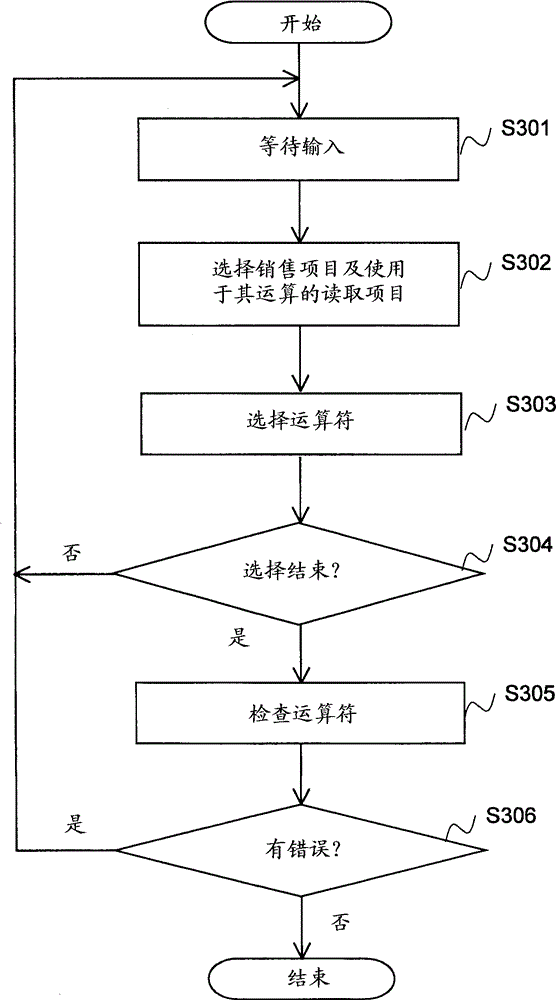

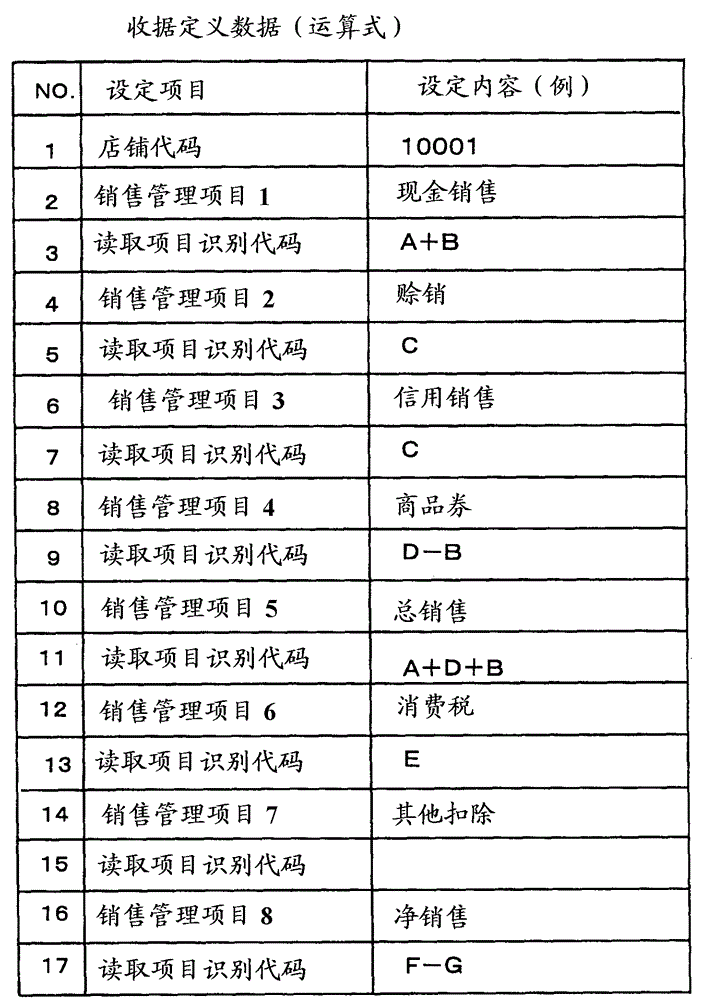

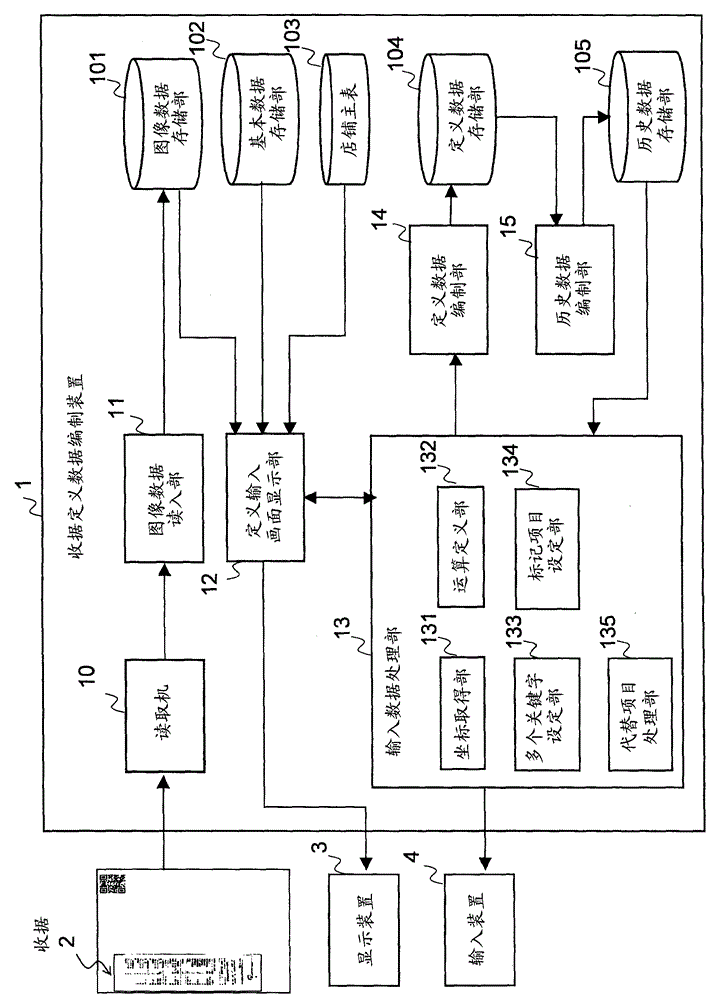

Receipt definition data compiling device

ActiveCN103150652AAvoid typosSimple input jobCharacter and pattern recognitionCommerceData storeCharacter recognition

A receipt definition data compiling device is capable of compiling necessary definition data efficiently when sales management data used for managing sales of lessees are collected through character recognition from receipts. A definition input image display part (12) displays a definition input image containing display of sales management item information and display of receipt mapping data. An input data processing part (13) inputs amount column position information corresponding to read items of the receipts and read times of mapping data and corresponding information of the read items and the sales management items from the definition input image. A definition data compiling part (14) compiles receipt definition data from the information input by the input data processing part (13) and stores the receipt definition data in a definition data storage part (104).

Owner:FUJITSU LTD

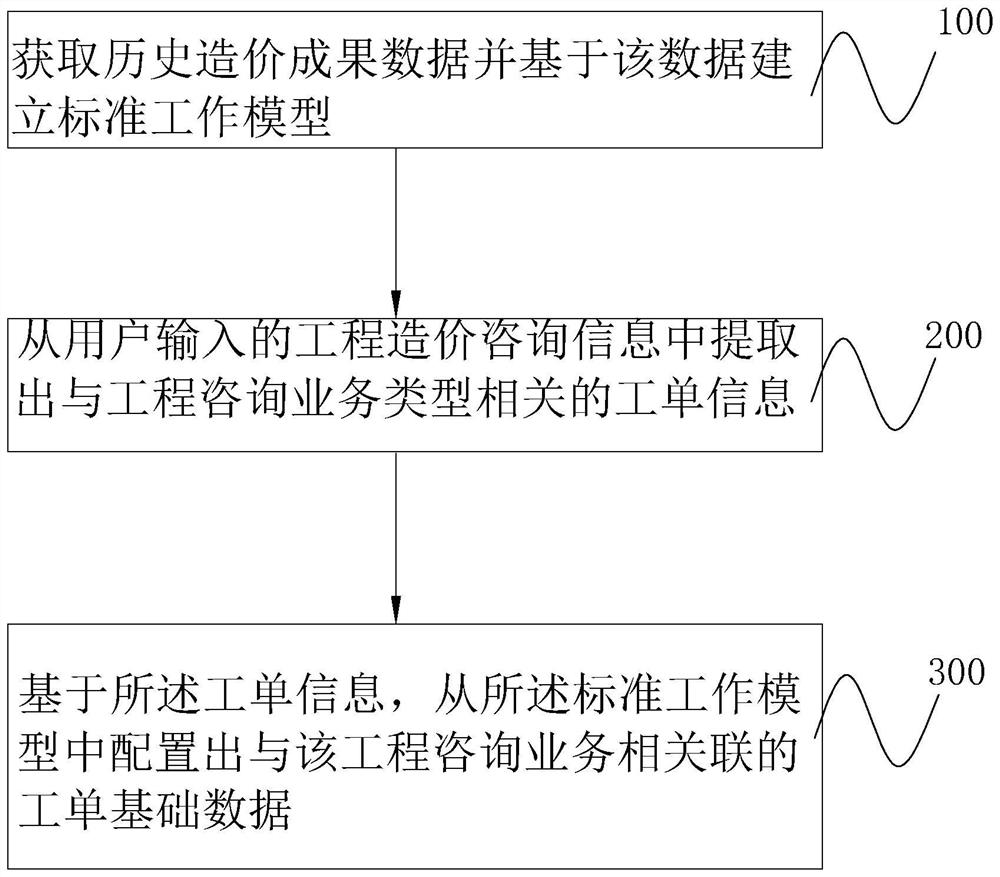

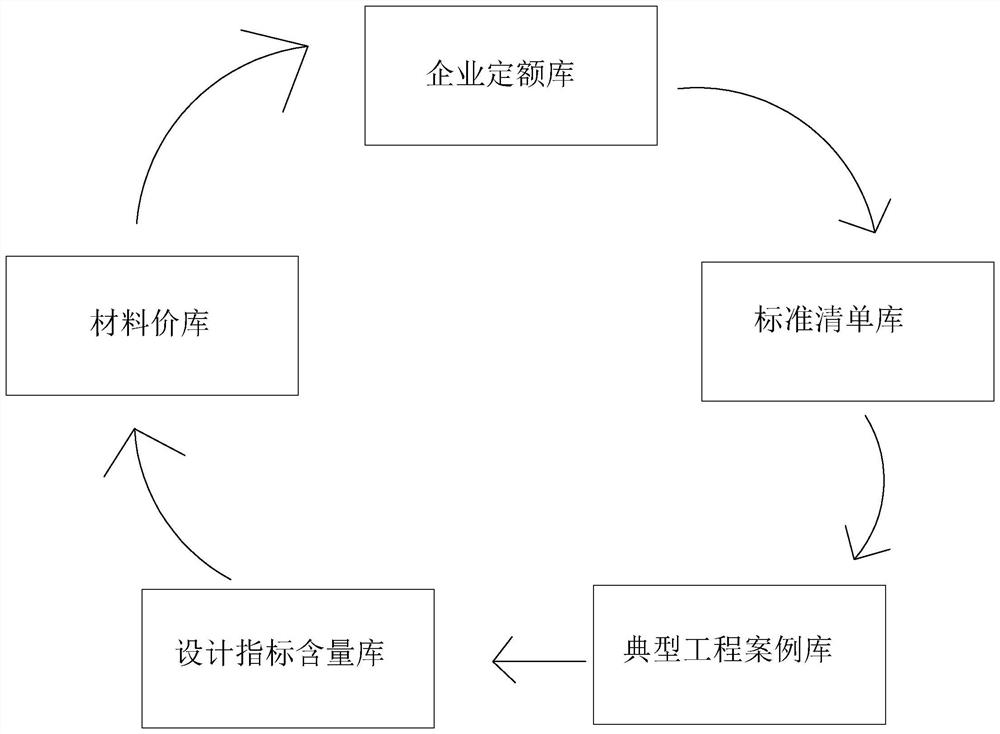

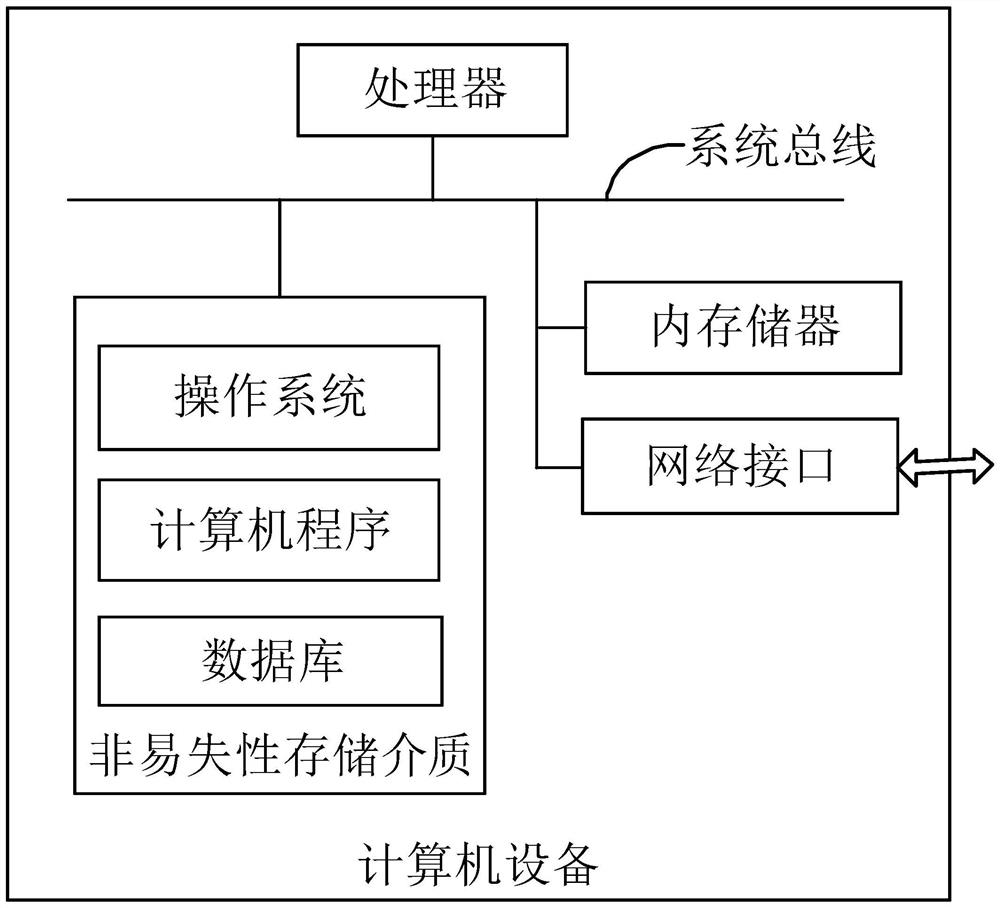

Project cost work order database automatic matching method and system

InactiveCN113886653AQuick compilationGuaranteed to workProduct appraisalOther databases indexingMatching methodsDatabase

The invention discloses a project cost work order database automatic matching method and system. The method comprises the following steps of: acquiring historical cost achievement data and establishing a standard work model based on the data; extracting character string information related to the project consultation service type from project cost consultation information input by a user; and based on the character string information, configuring work order basic data associated with the project consultation service from the standard work model, so that a worker can perform project compiling and acceptance work according to the basic data. According to the technical scheme, the work order information related to the project business type is extracted from the input of the user, the historical information related to the work order is searched from the standard work model according to the work order information to serve as the auditing reference of the project cost, the quality and efficiency of the project cost consultation service are improved, and the dependence on human experience is reduced.

Owner:广州翔实工程咨询有限公司

A Rapid Compilation Method of UAV Gust Load Spectrum

ActiveCN112528478BQuick compilationShorten the notation cycleSustainable transportationDesign optimisation/simulationAviationFlight vehicle

The invention belongs to the field of fatigue life design of aircraft structures, and relates to a rapid compiling method for a gust load spectrum of an unmanned aerial vehicle; a set of "reference state parameters" of an unmanned aerial vehicle are selected, and continuous turbulence analysis is used to calculate only one gust response "reference characteristic" For the flight state of any mission segment, the multiple linear regression method is directly used to obtain the gust response characteristic frequency of the mission segment. Finally, according to the time of various tasks in a life cycle, the surpassing number of gust speeds at all levels is calculated, and then the rapid compilation of the gust load spectrum is completed. The invention only needs to construct a multiple regression equation of the ratio of the key state parameter and the characteristic frequency of the gust response, and can realize the rapid compilation of the designed load spectrum, the measured load spectrum and the single-machine load spectrum, thereby shortening the spectrum compilation period; the method system is simple and efficient, and And it has good engineering applicability and can be extended to various types of aircraft.

Owner:CHENGDU AIRCRAFT DESIGN INST OF AVIATION IND CORP OF CHINA

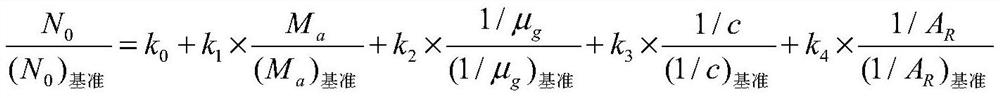

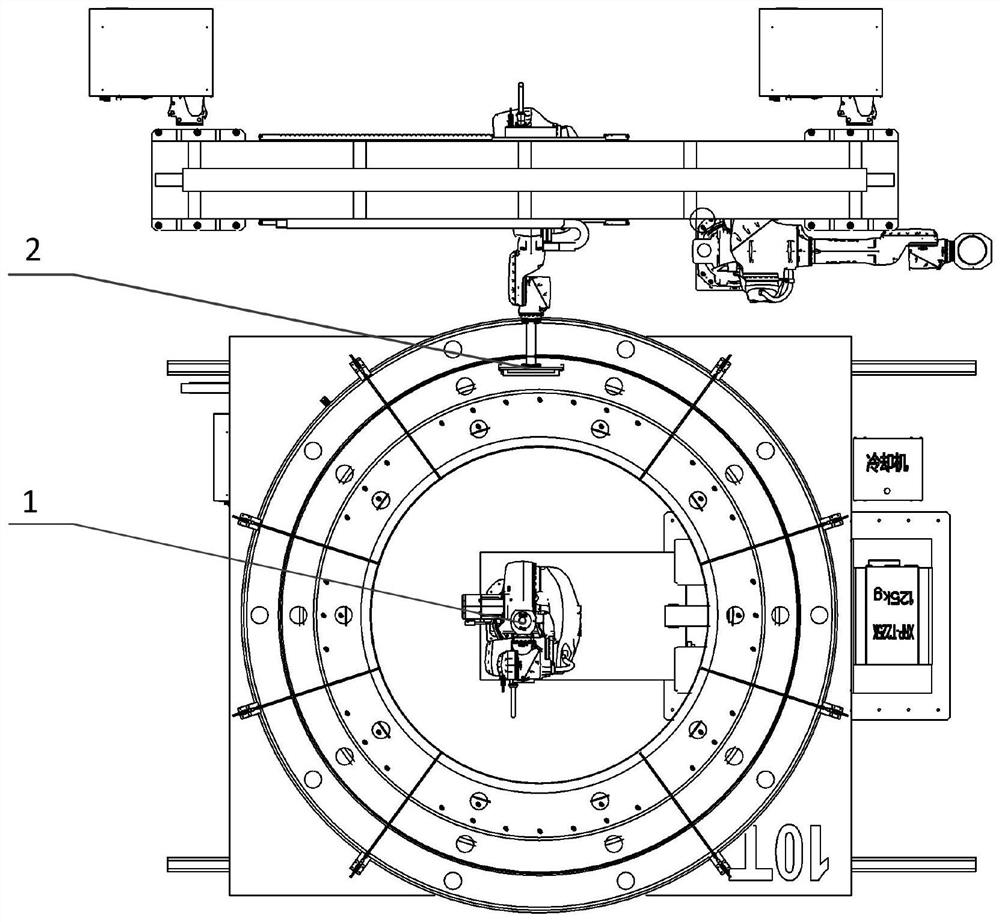

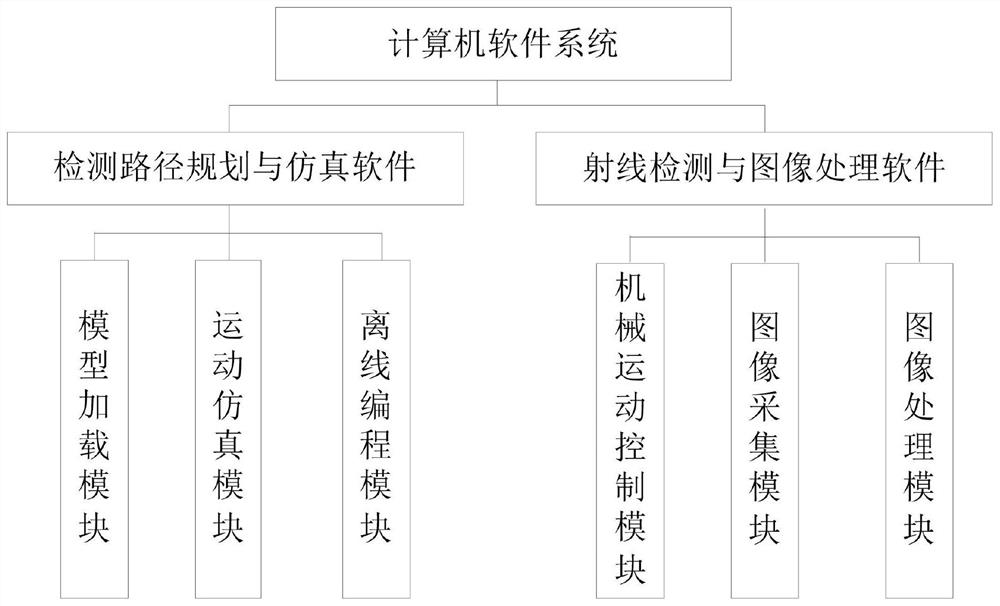

Ray digital imaging detection device based on cooperation of multiple manipulators and detection method thereof

PendingCN113866189AImprove detection efficiencyQuick compilationProgramme-controlled manipulatorMaterial analysis by transmitting radiationNuclear physicsManipulator

The invention provides a ray digital imaging detection device based on cooperation of multiple manipulators and a detection method thereof. The ray digital imaging detection device is characterized in that an X-ray machine is mounted on an X-ray machine clamping manipulator; the X-ray machine clamping manipulator is mounted on an X-ray machine clamping manipulator guide rail; the X-ray machine clamping manipulator guide rail is mounted in a pit; in the detection process, the X-ray machine clamping manipulator clamps an X-ray machine to move, so that the X-ray machine can perform transillumination on different positions of a detected workpiece; a radiation detector is mounted on the radiation detector clamping manipulator; a radiation detector clamping manipulator is mounted on the radiation detector clamping manipulator guide rail; the radiation detector clamping manipulator moves along the radiation detector clamping manipulator guide rail; and in the detection process, the radiation detector clamping manipulator clamps the radiation detector to move, so that the radiation detector synchronously moves to the other side, opposite to the workpiece, of the X-ray machine along with the X-ray machine to perform ray imaging on the detected workpiece.

Owner:SHANGHAI SPACE PRECISION MACHINERY RES INST

A Production Planning Method Based on Deep Analysis of Quality Data

ActiveCN107392385BRaise the level of preparationQuality improvementDigital data information retrievalForecastingQuality dataBusiness enterprise

Owner:沈阳昊成智能装备有限公司

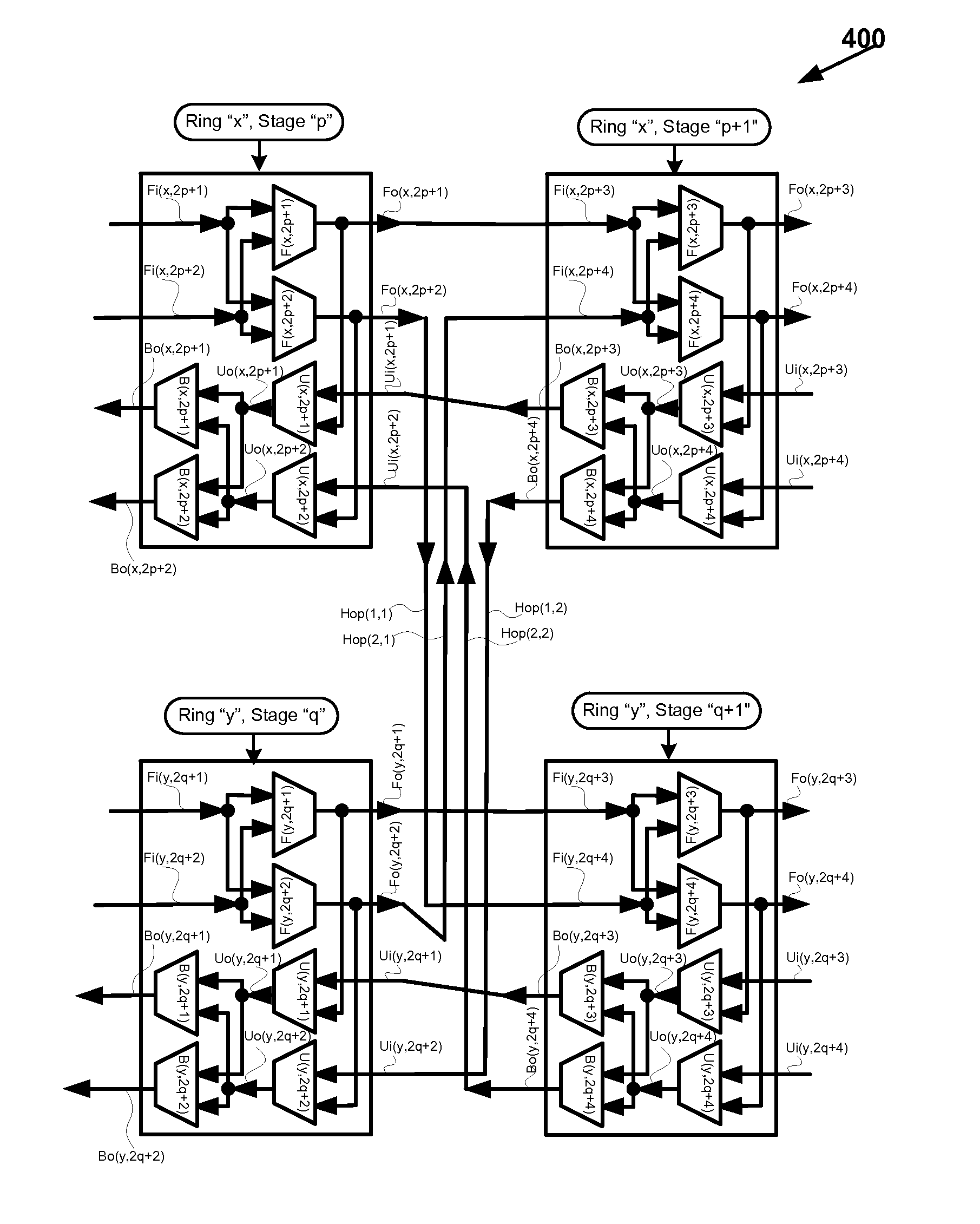

Fast scheduling and optimization of multi-stage hierarchical networks

Significantly optimized multi-stage networks including scheduling methods for faster scheduling of connections, useful in wide target applications, with VLSI layouts using only horizontal wires and vertical wires to route large scale partial multi-stage hierarchical networks having inlet and outlet links, and laid out in an integrated circuit device in a two-dimensional grid arrangement of blocks are disclosed. The optimized multi-stage networks in each block employ one or more slices of rings of stages of switches with inlet and outlet links of partial multi-stage hierarchical networks connecting to rings from either left-hand side or right-hand side; and employ hop wires or multi-drop hop wires wherein hop wires or multi-drop wires are connected from switches of stages of rings of slices of a first partial multi-stage hierarchical network to switches of stages of rings of slices of the first or a second partial multi-stage hierarchical network.

Owner:KONDA TECH

Optimization of multi-stage hierarchical networks for practical routing applications

ActiveUS11405331B1High routabilityLow pour pointData switching networksTelecommunicationsVlsi layout

Significantly optimized multi-stage networks, useful in wide target applications, with VLSI layouts using only horizontal and vertical links to route large scale sub-integrated circuit blocks having inlet and outlet links, and laid out in an integrated circuit device in a two-dimensional grid arrangement of blocks are presented. The optimized multi-stage networks in each block employ several rings of stages of switches with inlet and outlet links of sub-integrated circuit blocks connecting to rings from either left-hand side only, or from right-hand side only, or from both left-hand side and right-hand side; and employ shuffle exchange links where outlet links of cross links from switches in a stage of a ring in one sub-integrated circuit block are connected to either inlet links of switches in the another stage of a ring in the same or another sub-integrated circuit block.

Owner:KONDA TECH

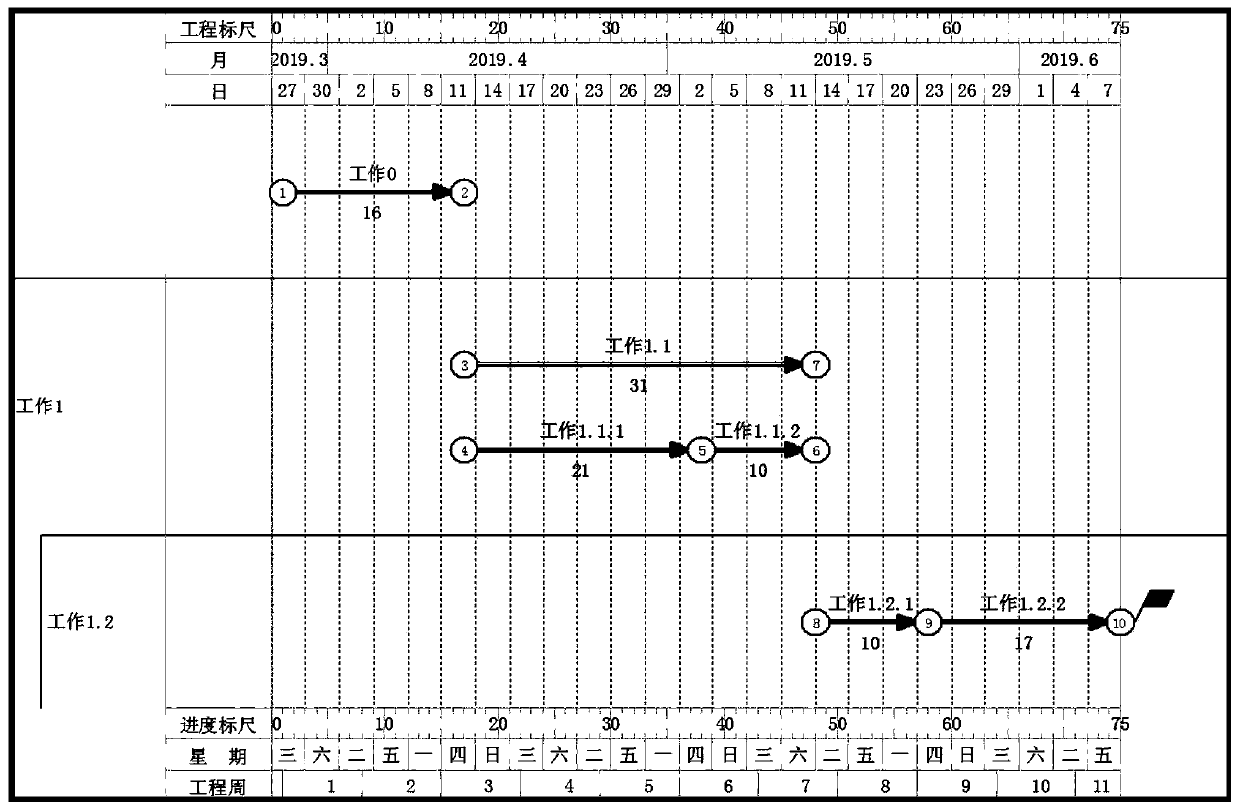

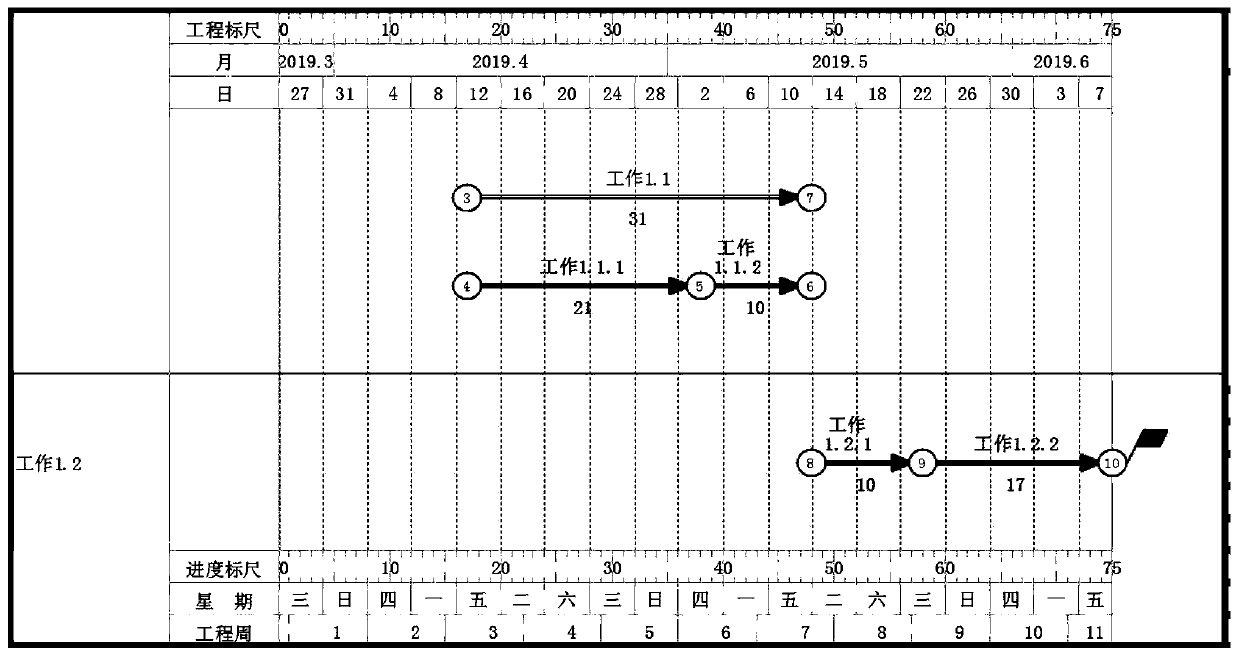

Drill-drill display control method, system and device and storage medium

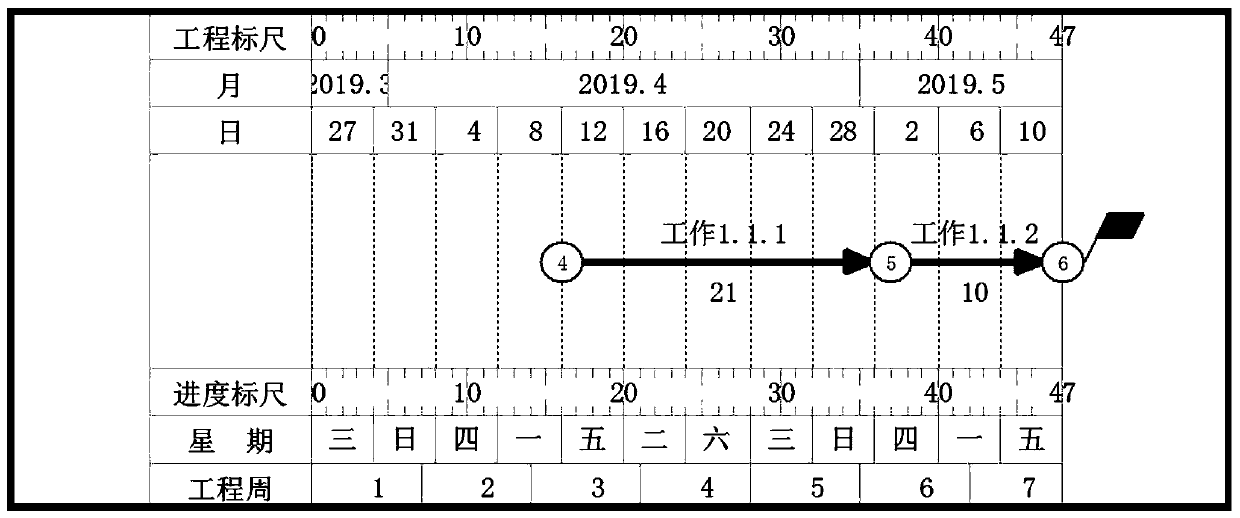

ActiveCN110377894AQuick compilationImprove reliabilityNatural language data processingOffice automationRelationship - FatherComputer science

The invention belongs to the field of project progress plan making, and particularly relates to drill-drill display control method, system and device and a storage medium. At present, multi-level display of a dual-code network plan in the market in a workshop is expressed in a partition form, and the dual-code network plan cannot enter a certain specific branch to be focused and compiled. A user is allowed to enter a work item through selection and drilling, only all child work of the work item is displayed in a double-code network diagram, child work of a father-child structure is displayed through the double-line father-child structure, the display mode is that a line part of a father work arrow line is double lines, and all child work of the father work arrow line is performed in parallel below the father work; and after checking or compiling the sub-work displayed after drilling, jumping out through drilling, and the updated highest-level dual-code network diagram including all theplanned contents is displayed. The planning efficiency is greatly improved, the planning difficulty is reduced for operators, and the operation is flexible, simple and convenient.

Owner:GLODON CO LTD

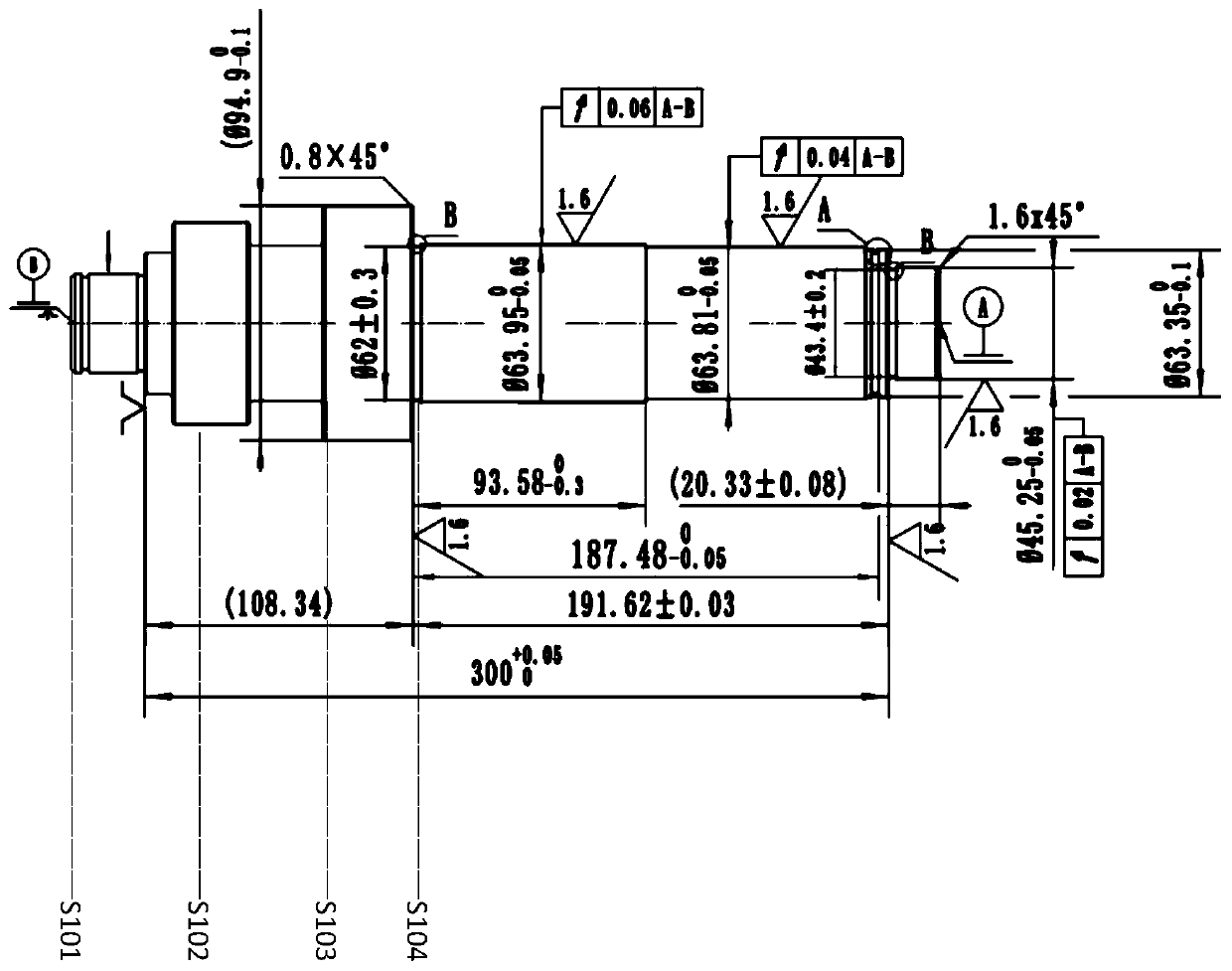

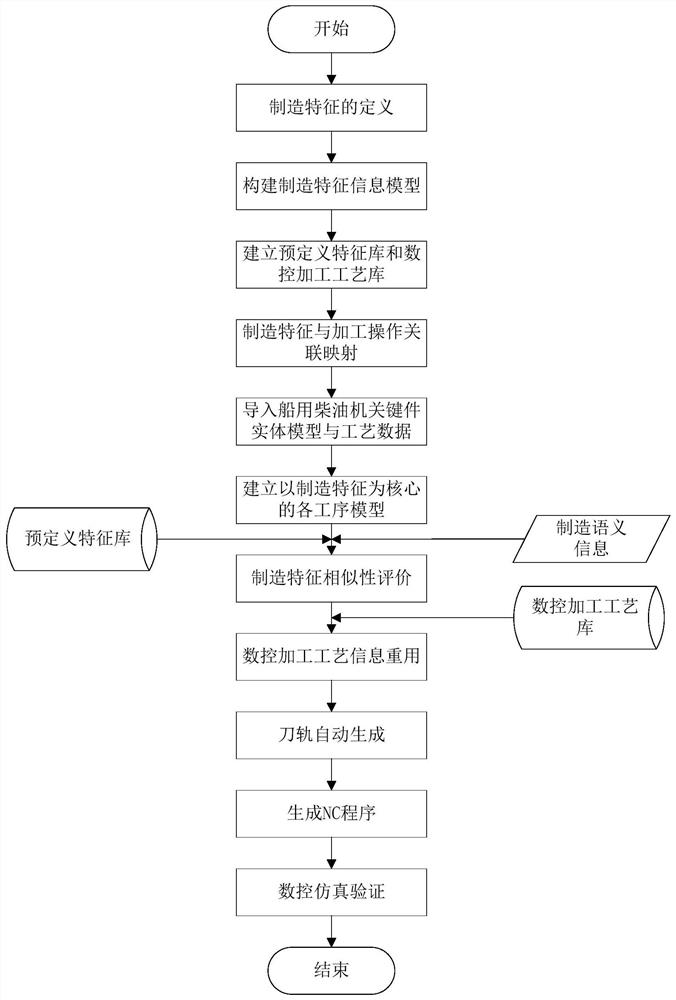

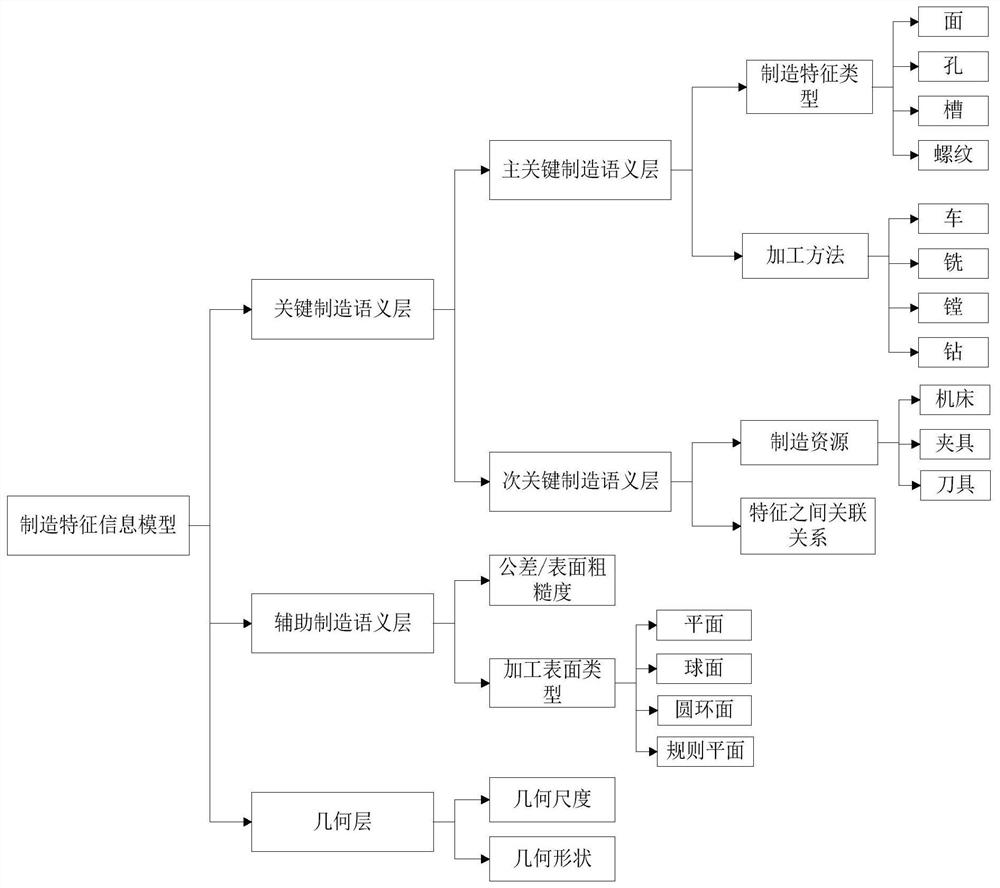

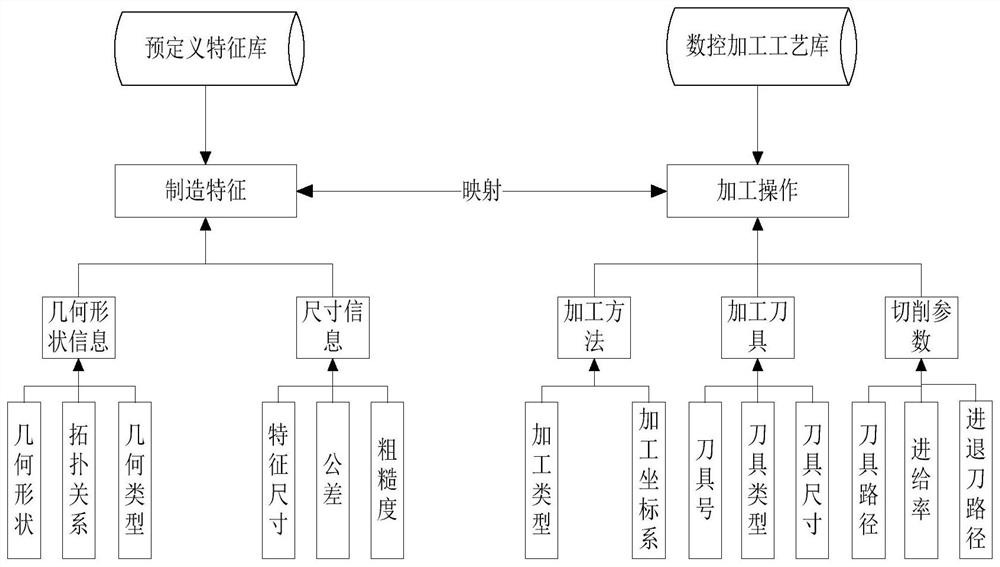

A NC programming method for key components of marine diesel engines

ActiveCN108227627BQuick compilationQuality improvementProgramme controlComputer controlNumerical controlControl engineering

The invention discloses a numerical control procedure programming method for key parts of a marine diesel engine in the fields of numerical control processing and digital manufacturing. The numericalcontrol procedure programming method comprises the following steps: firstly, defining manufacturing features of the key parts, constructing a manufacturing feature information model and creating a predefined feature library and a numerical control processing technology library; extracting processing operation information, correlating the processing operation information with the manufacturing features in the predefined feature library and then introducing an entity model and process data to form all procedure models; traversing the manufacturing features in the procedure models, identifying similar features from the predefined feature library, obtaining numerical control processing technology information corresponding to characteristics and reusing according to identified characteristics and a correlation mapping relationship between the characteristics and the processing operation information; and finally, adjusting tool path parameters by combining with the numerical control processing technology information and generating a final tool path and codes. According to the numerical control procedure programming method for the key parts of the marine diesel engine, disclosed by the invention, the manufacturing characteristics at the processing stage are identified and matched, the compilation of numerical control programs can be quickly completed and the quality and the efficiencyof numerical control programming are improved.

Owner:JIANGSU UNIV OF SCI & TECH

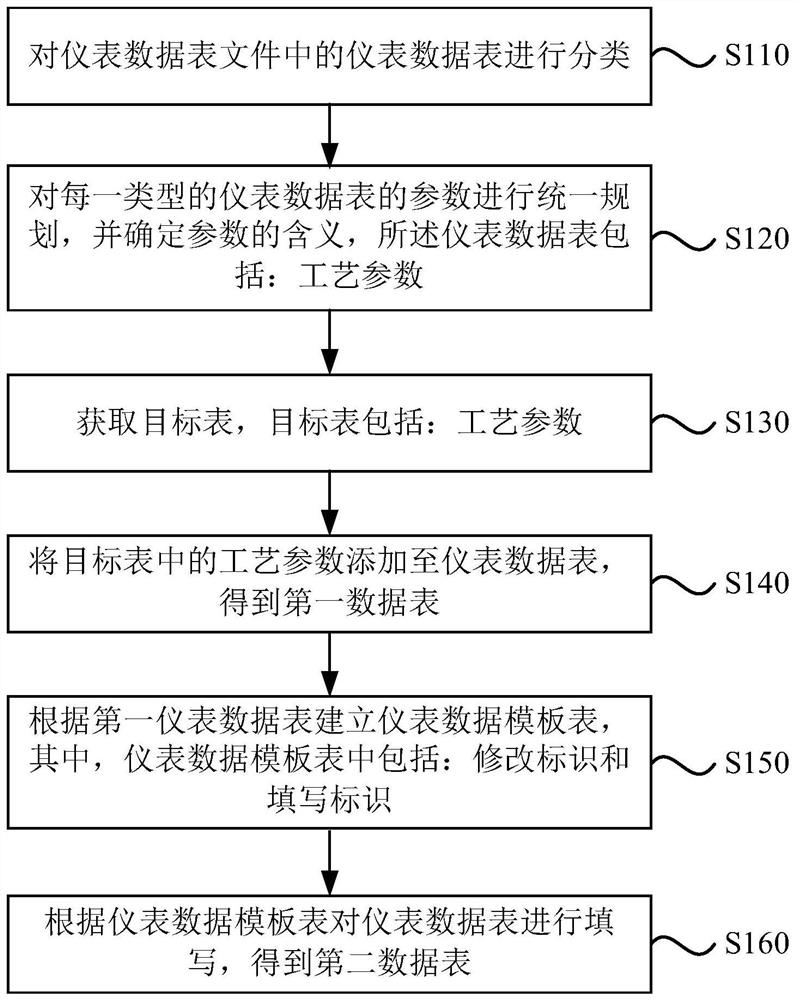

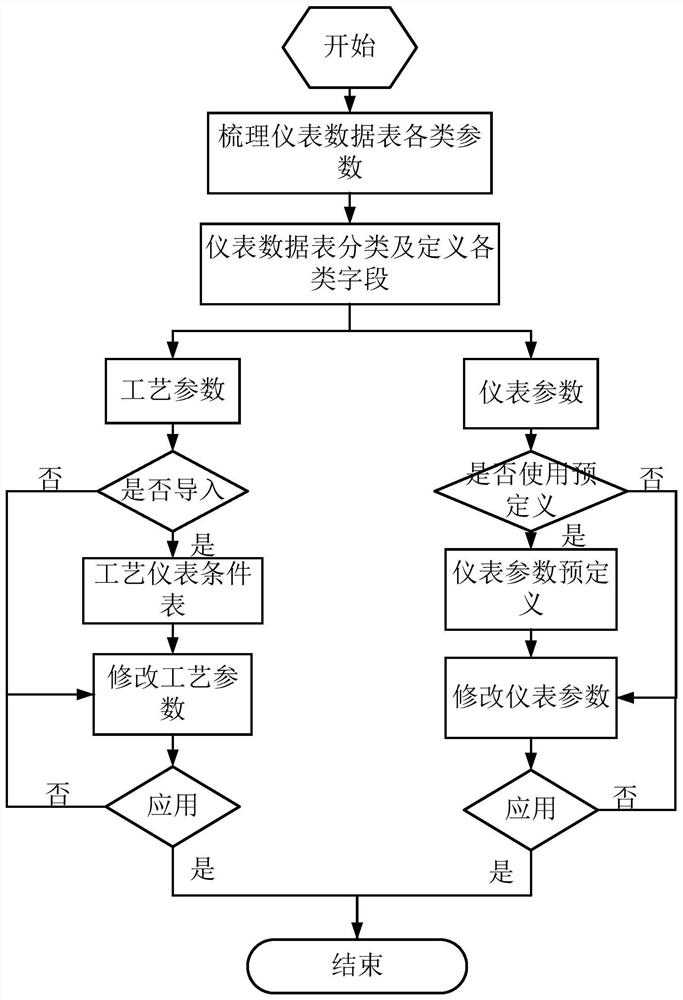

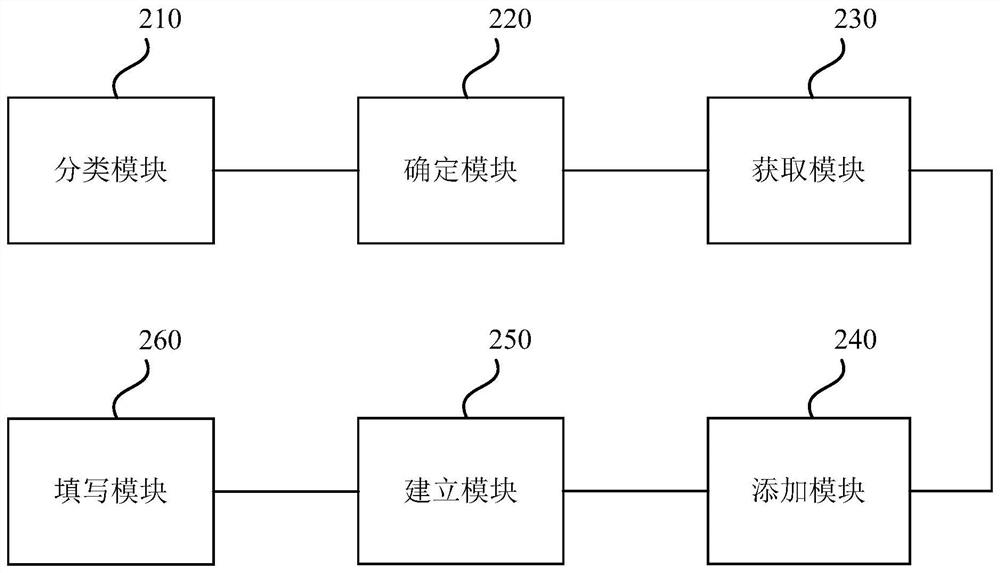

Instrument data table filling method, device and equipment and storage medium

PendingCN112287646ASolve technical problems with low preparation efficiencyThe method of preparation is reasonableText processingDatasheetEngineering

The invention discloses an instrument data table filling method, device and equipment and a storage medium. The method comprises the following steps: classifying instrument data tables in an instrument data table file; planning parameters of each type of instrument data tables in a unified mode, and determining the meanings of the parameters, wherein the instrument data tables comprise process parameters; obtaining a target table, wherein the target table comprises process parameters; adding the process parameters in the target table to the instrument data table to obtain a first data table; establishing an instrument data template table according to the first data table, wherein the instrument data template table comprises a modification identifier and a filling identifier; according to the instrument data template table, filling in the instrument data table to obtain a second data table. According to the technical scheme of the invention, the instrument data table compiling method isreasonable and efficient, and the instrument data table compiling quality and efficiency are practically improved.

Owner:CHINA NAT OFFSHORE OIL CORP +2