Patents

Literature

283results about How to "Avoid issuing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

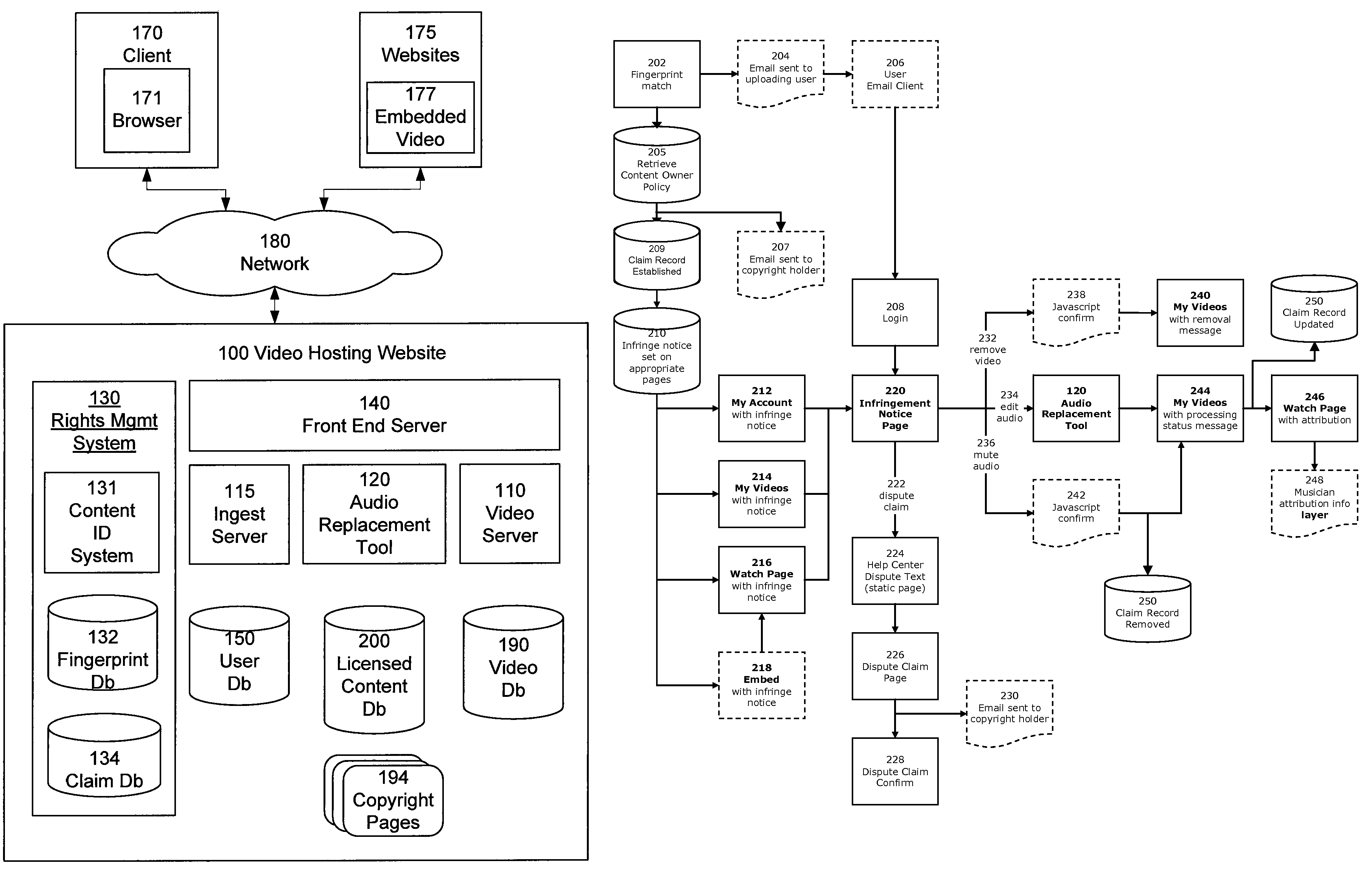

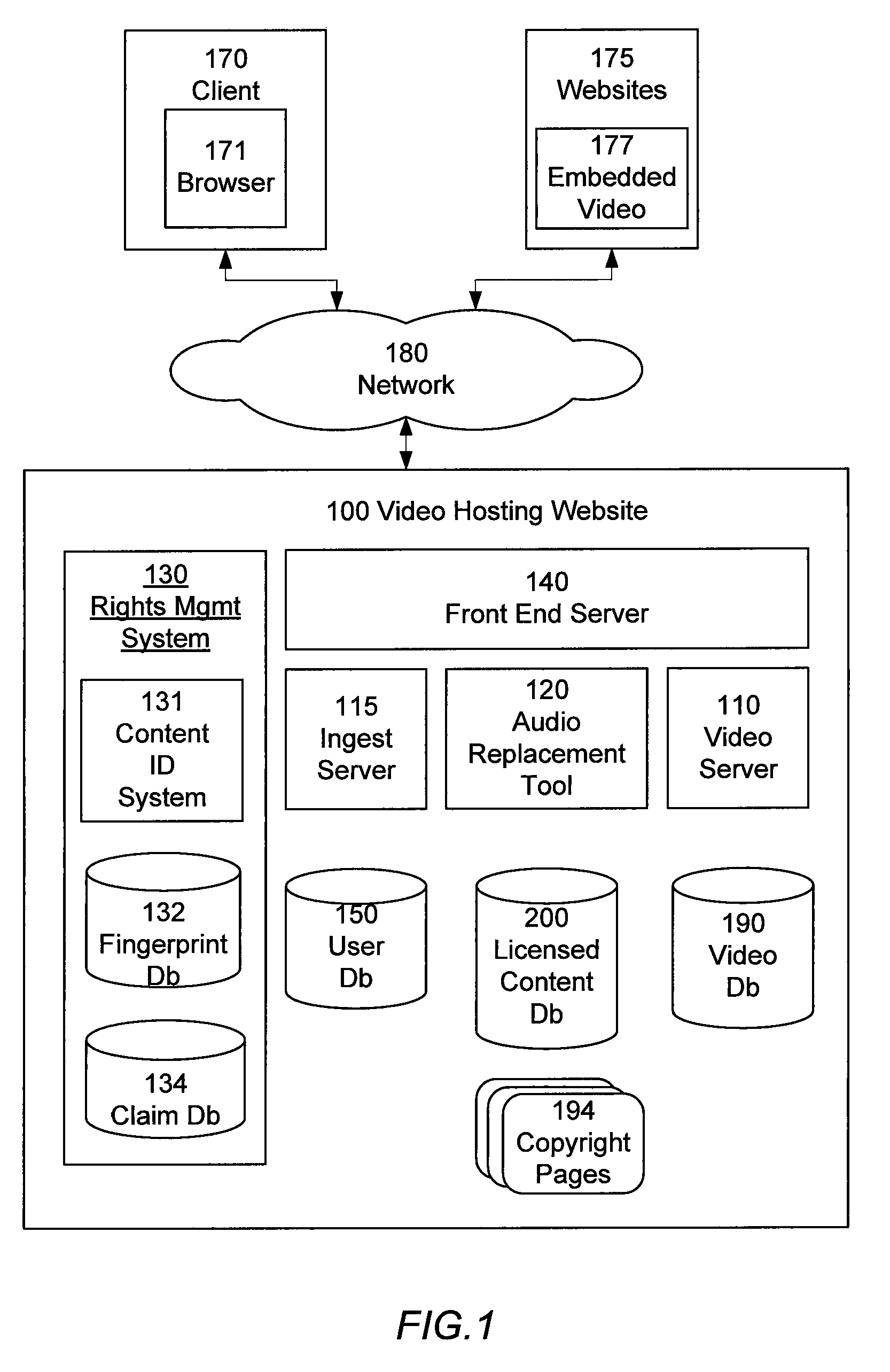

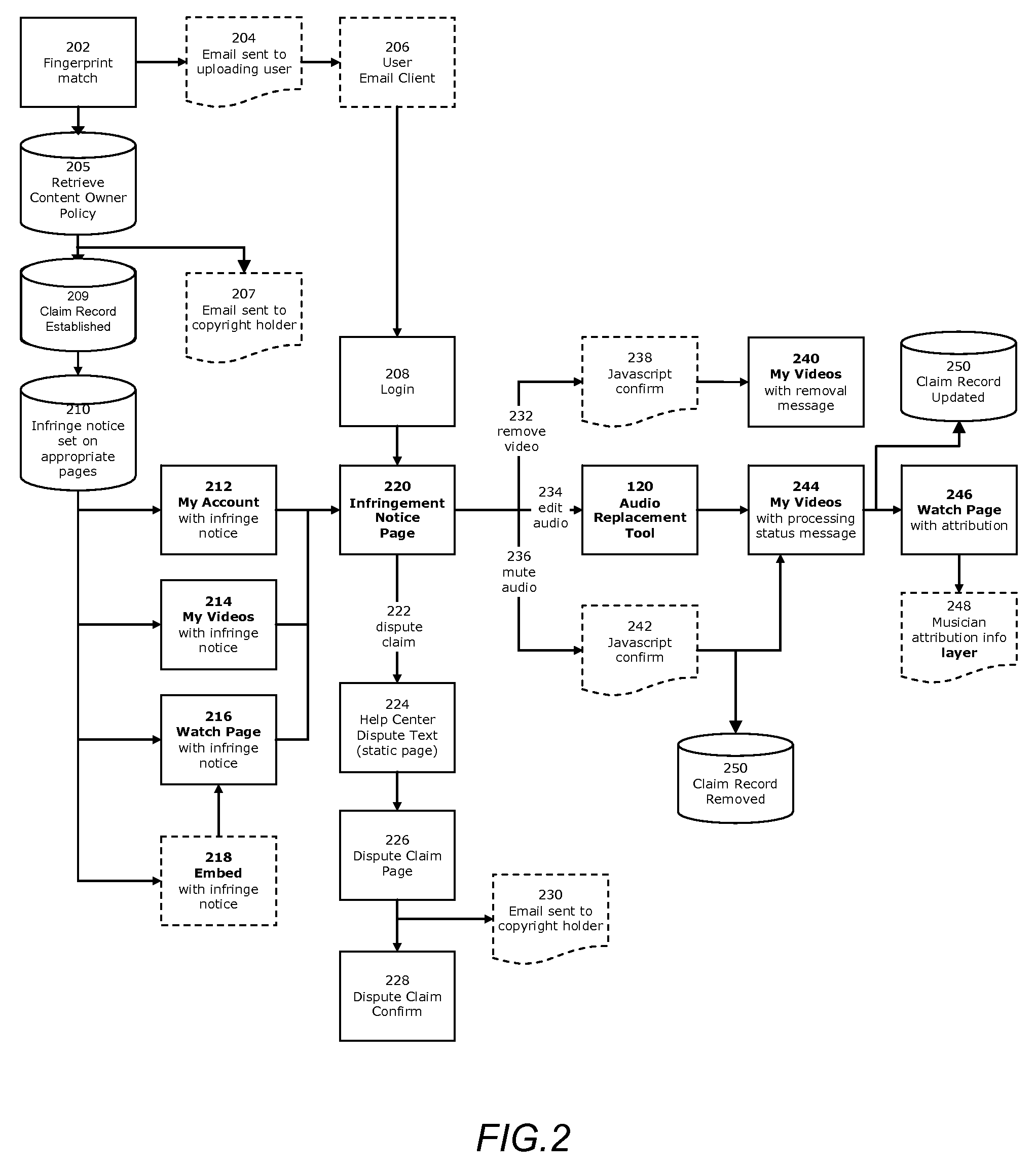

Blocking of unlicensed audio content in video files on a video hosting website

ActiveUS7707224B2Optimize allocationReduce complicationsDigital data processing detailsComputer security arrangementsClient-sideSoftware tool

A system, method and various software tools enable a video hosting website to automatically identified unlicensed audio content in video files uploaded by users, and initiate a process by which the user can replace the unlicensed content with licensed audio content. An audio replacement tool is provided that enables the user to permanently mute the original, unlicensed audio content of a video file, or select a licensed audio file from a collection of licensed audio, and insert the selected in place of the original audio. Where a video file includes unlicensed audio, the video hosting website provides access to video files to a client device, along with an indication to the client device to mute the audio during playback of the video.

Owner:GOOGLE LLC

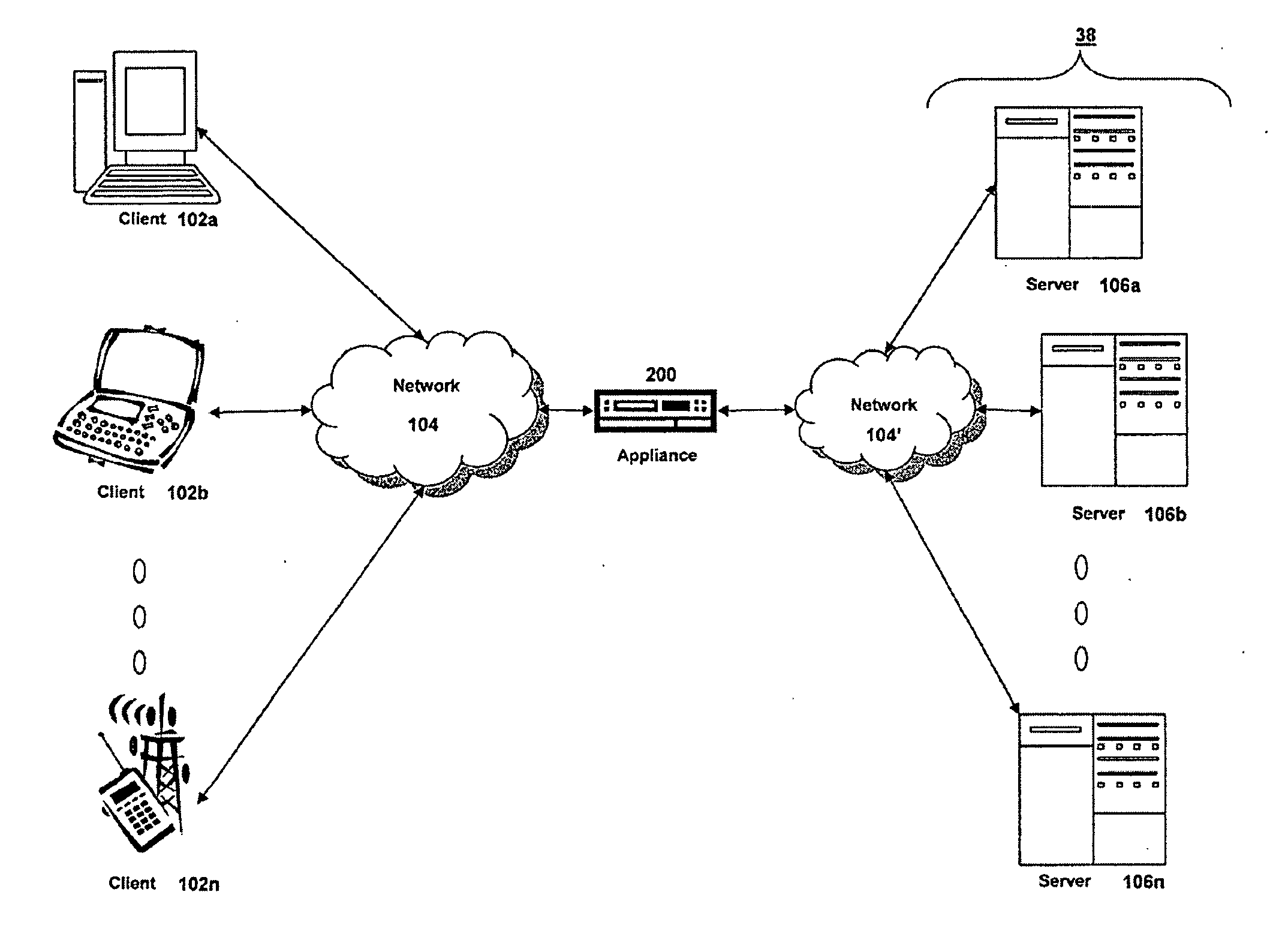

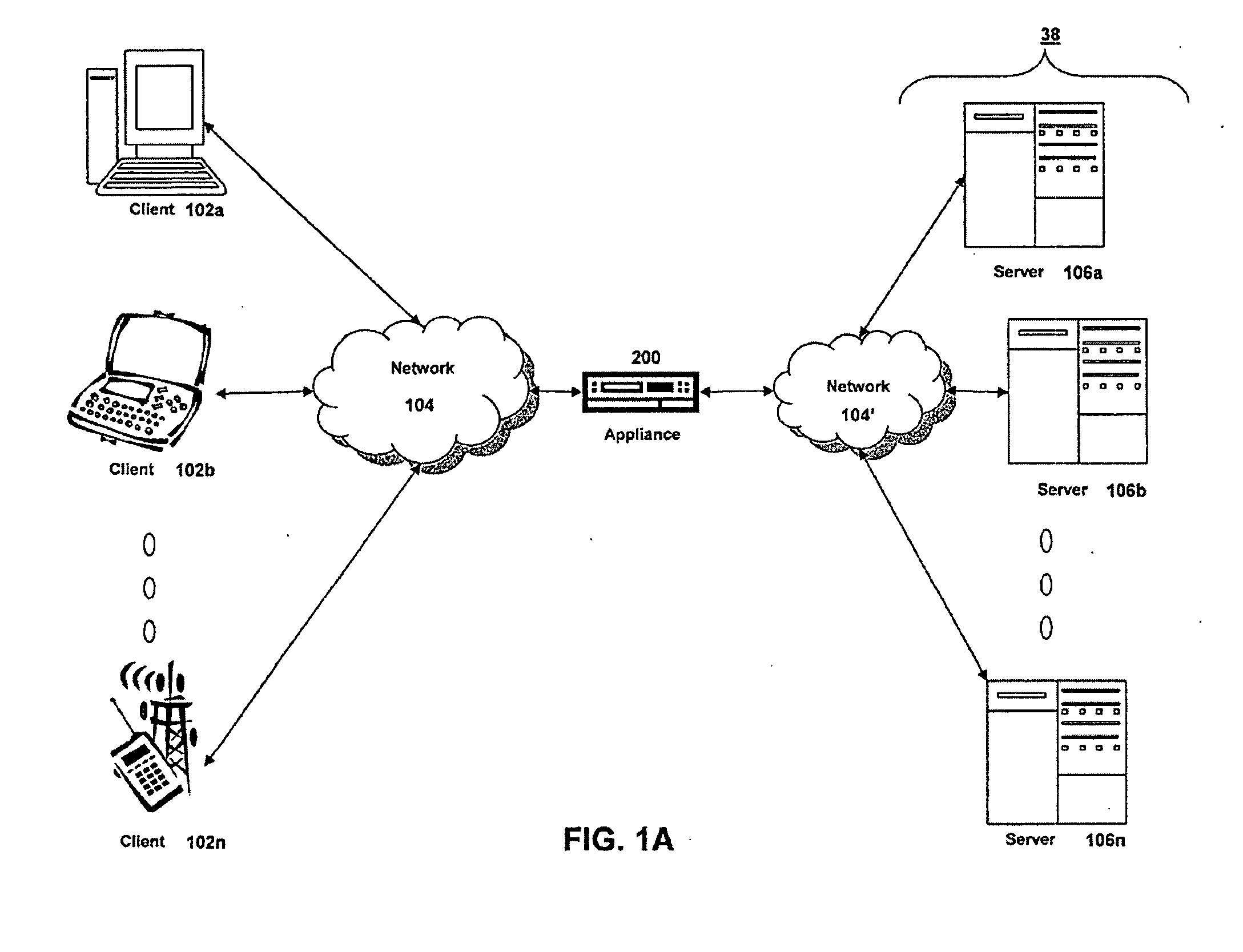

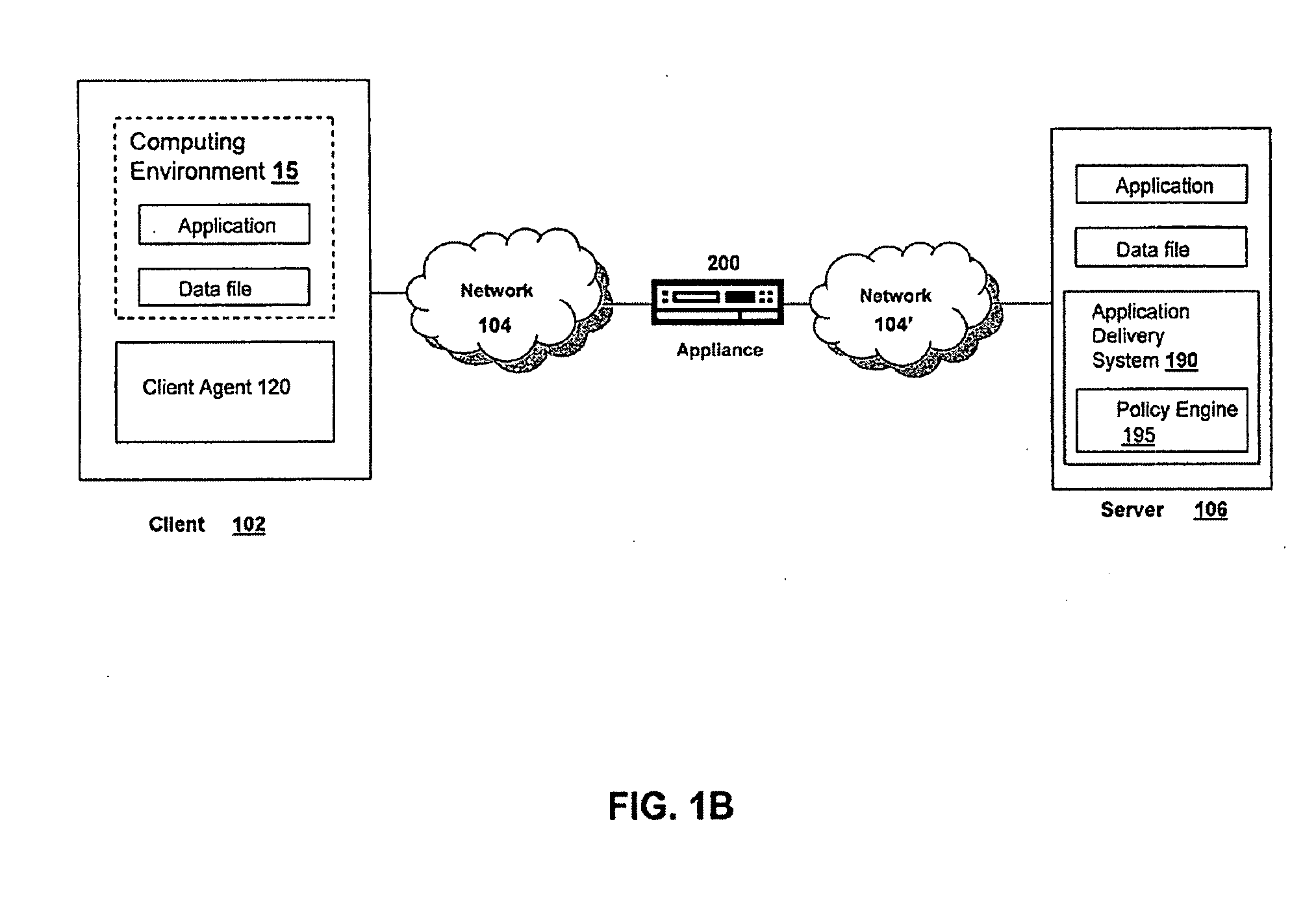

Systems and Methods of Symmetric Transport Control Protocol Compression

ActiveUS20080046616A1Reduce network latencyImprove experienceNetwork traffic/resource managementWireless network protocolsTraffic capacityData compression

A method for compressing a stream of application layer network traffic communicated over a transport layer connection of a virtual private network connection between a client and a server using an appliance. The appliance intercepts one or more transport layer packets of a stream of application network traffic communicated via a transport layer connection of a virtual private network connection between a client and a server. The appliance accumulates data from a payload of the intercepted transport layer packets, determines data accumulated for transmission should be compressed based on one or more compression trigger, and compresses the accumulated data into a self-contained compression block for transmission.

Owner:CITRIX SYST INC

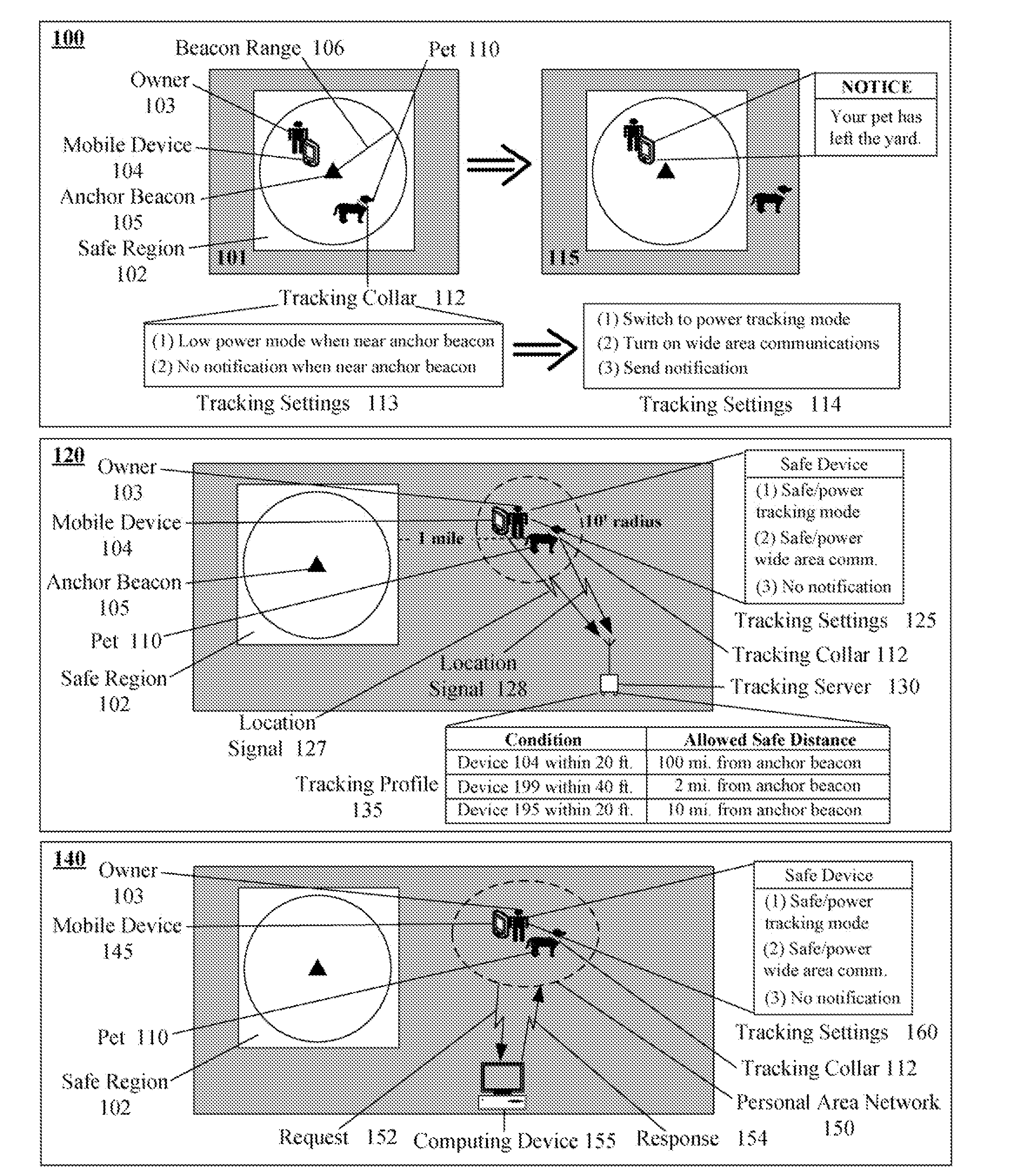

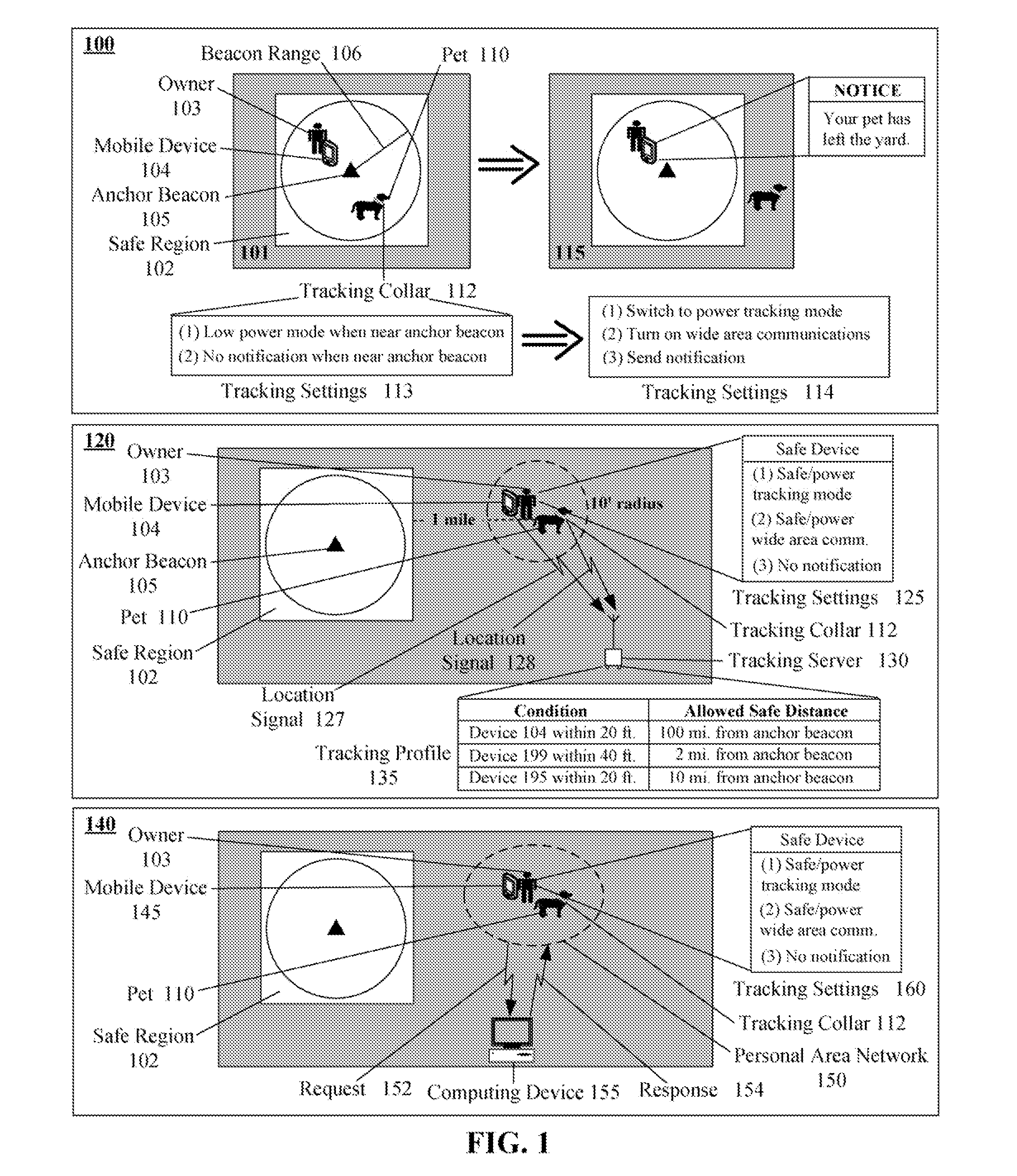

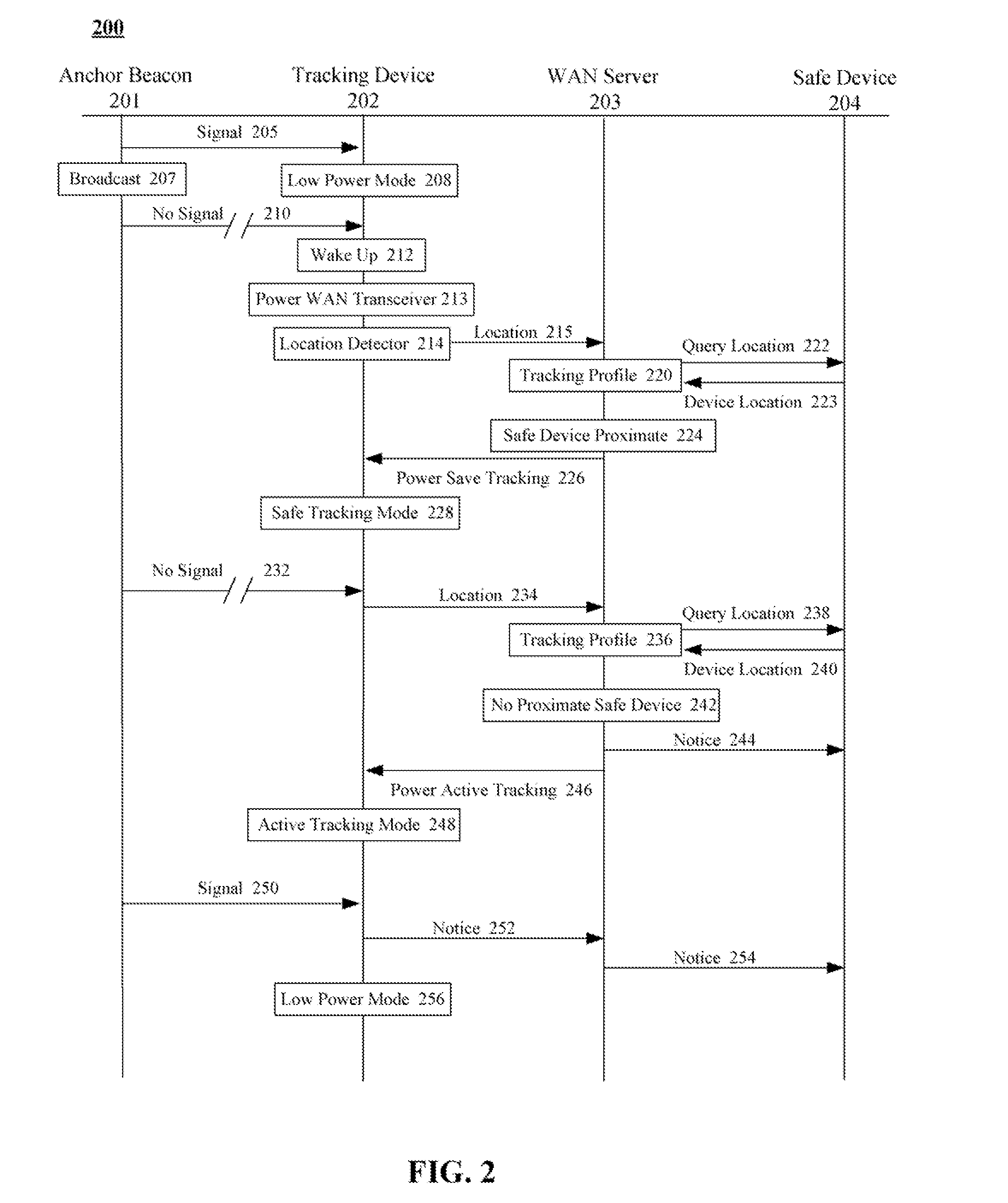

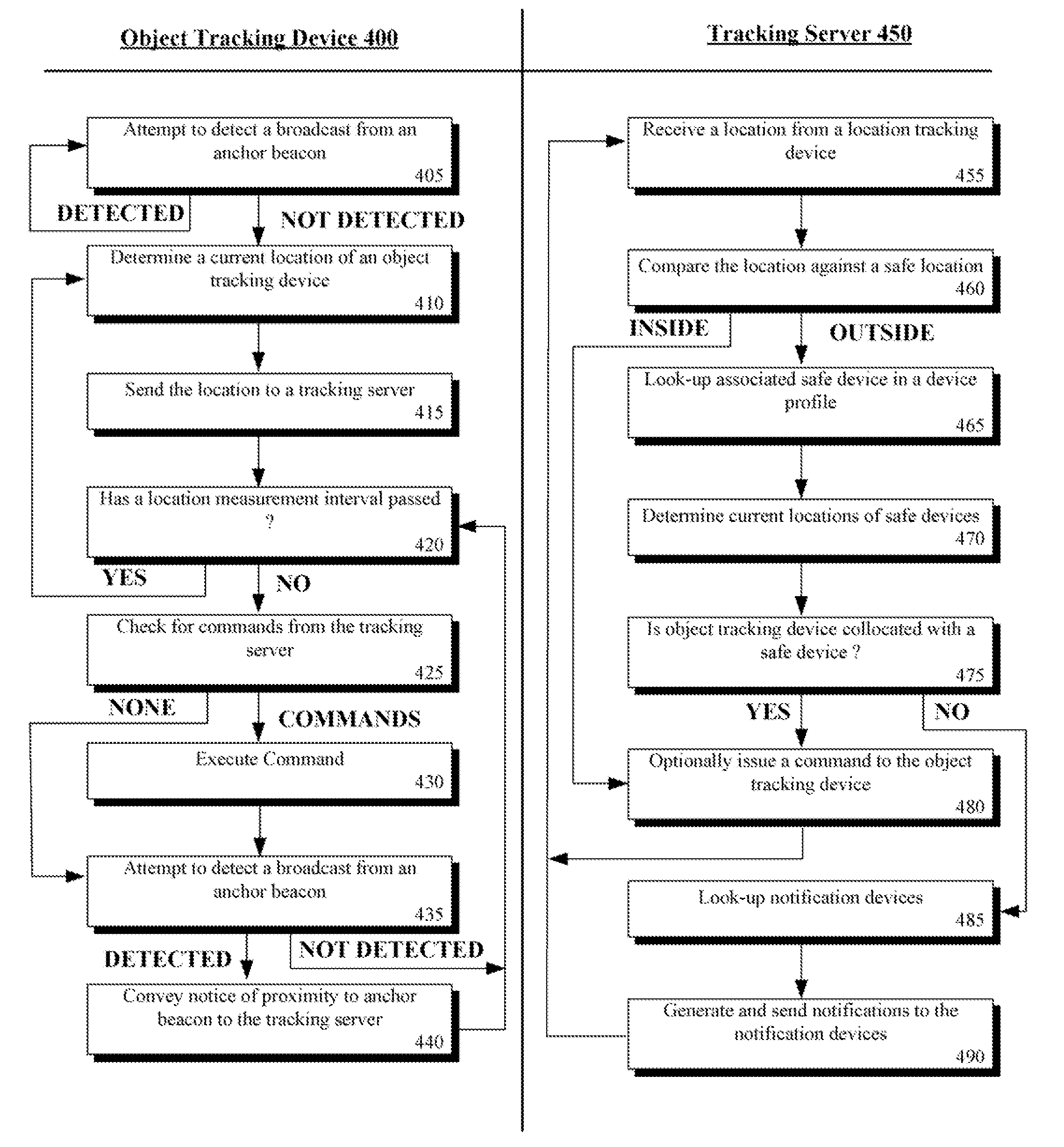

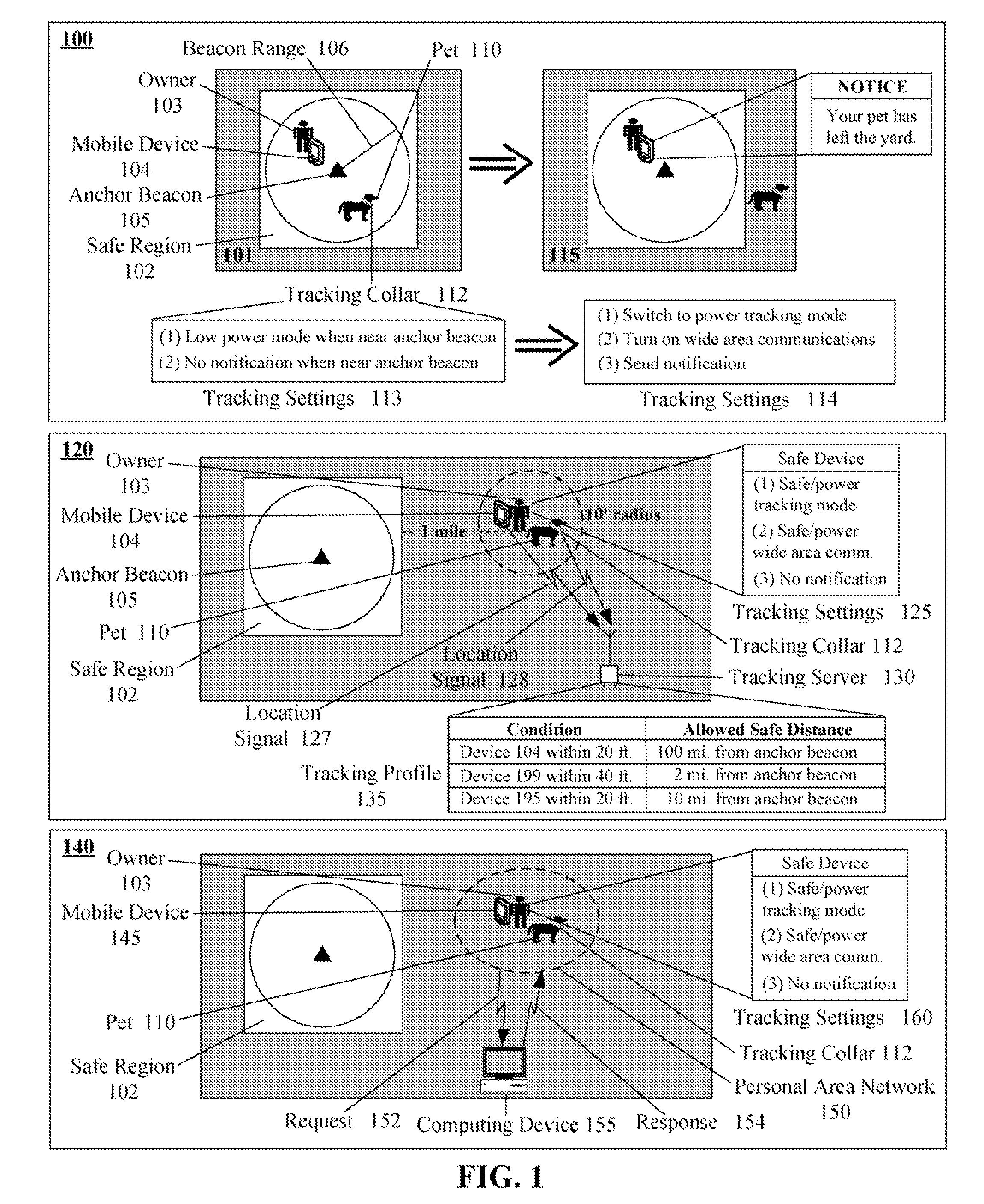

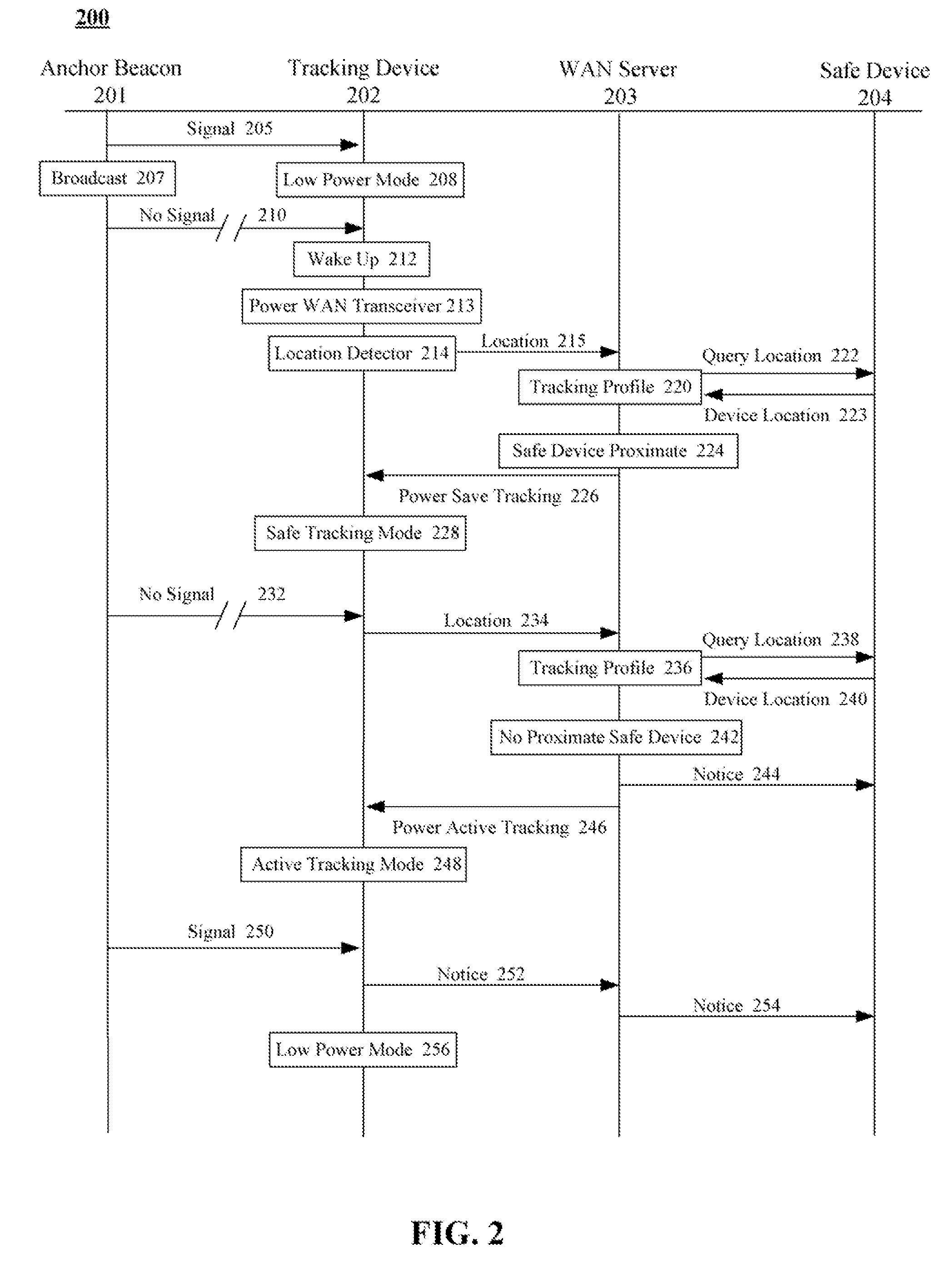

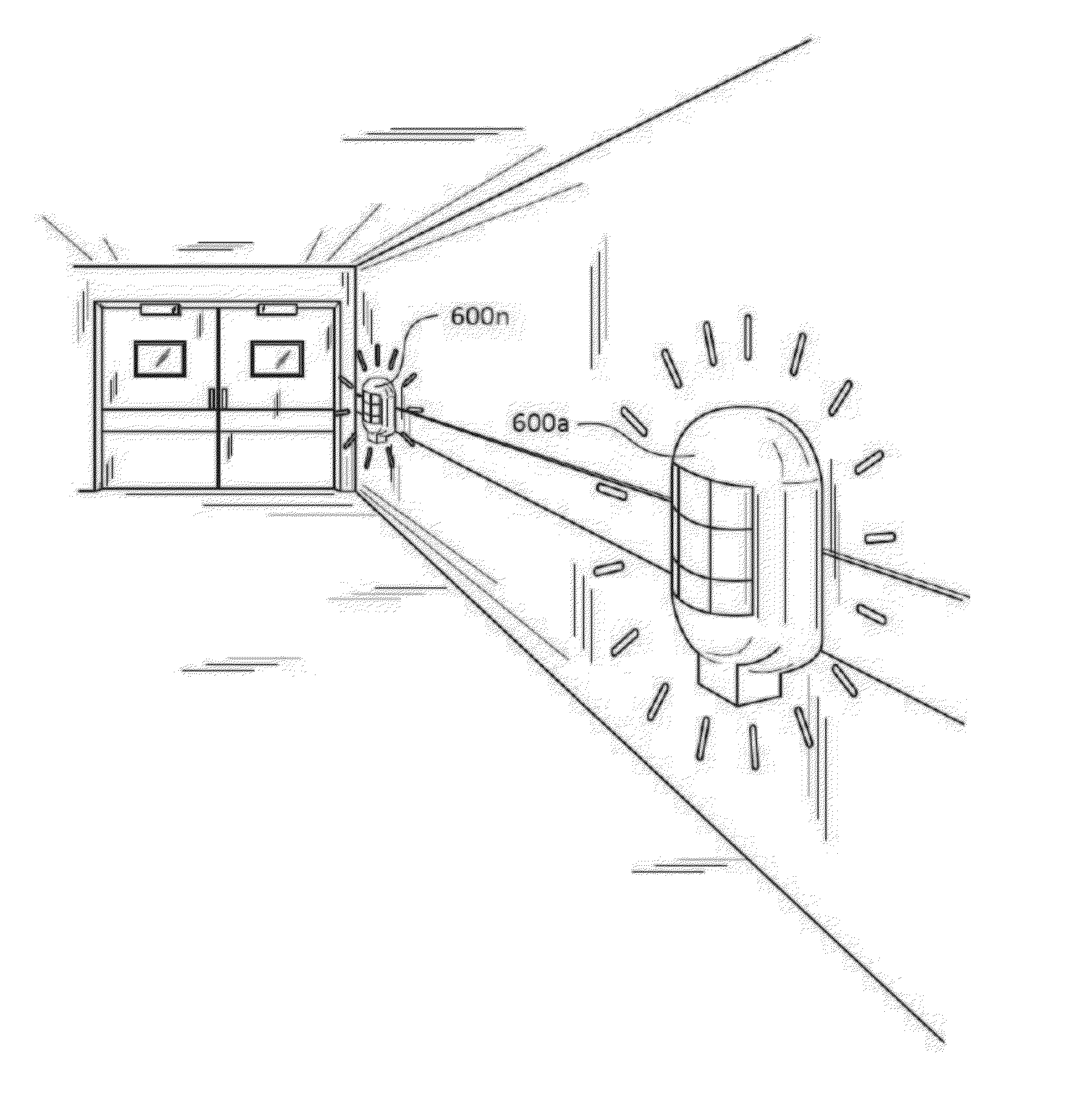

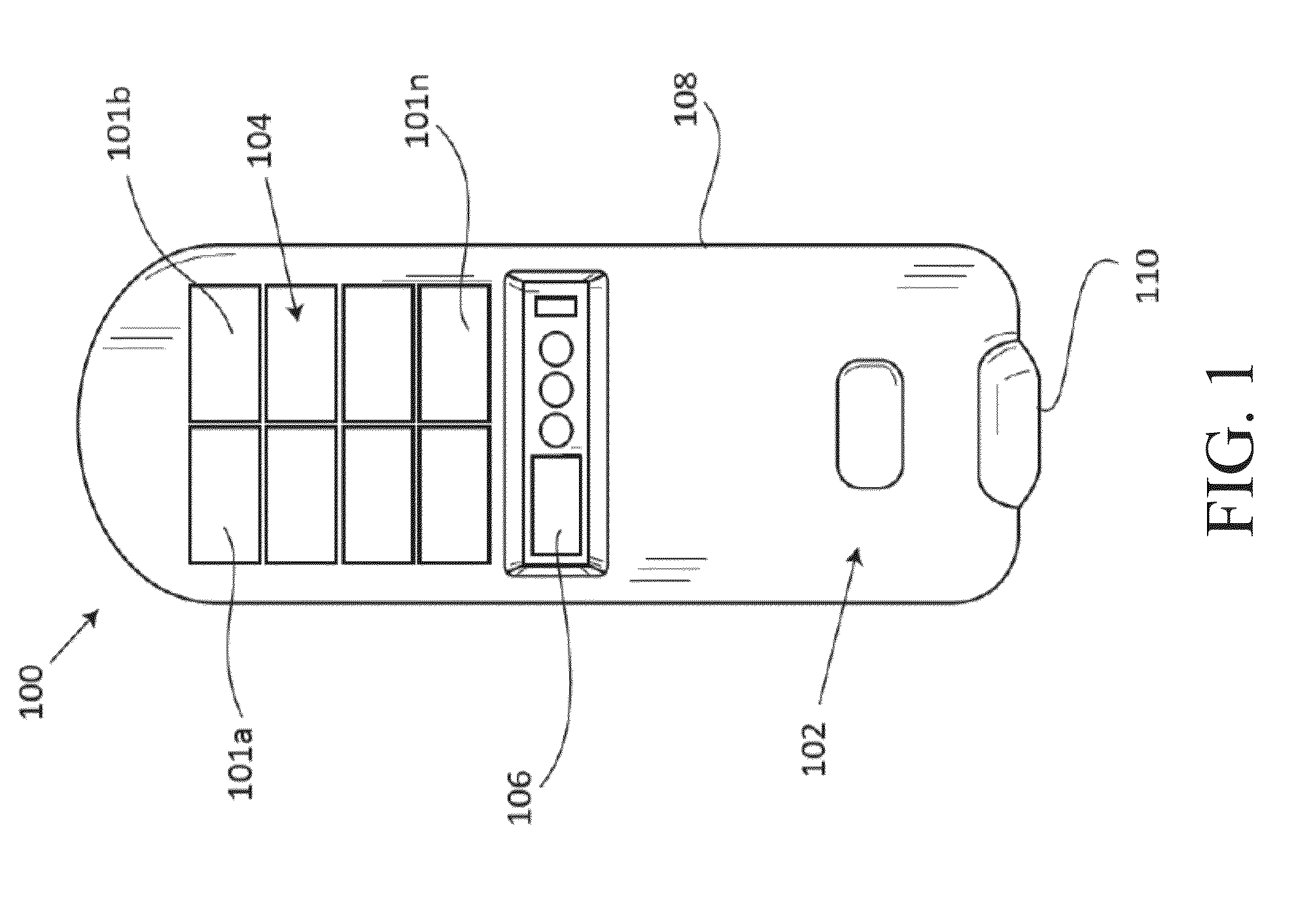

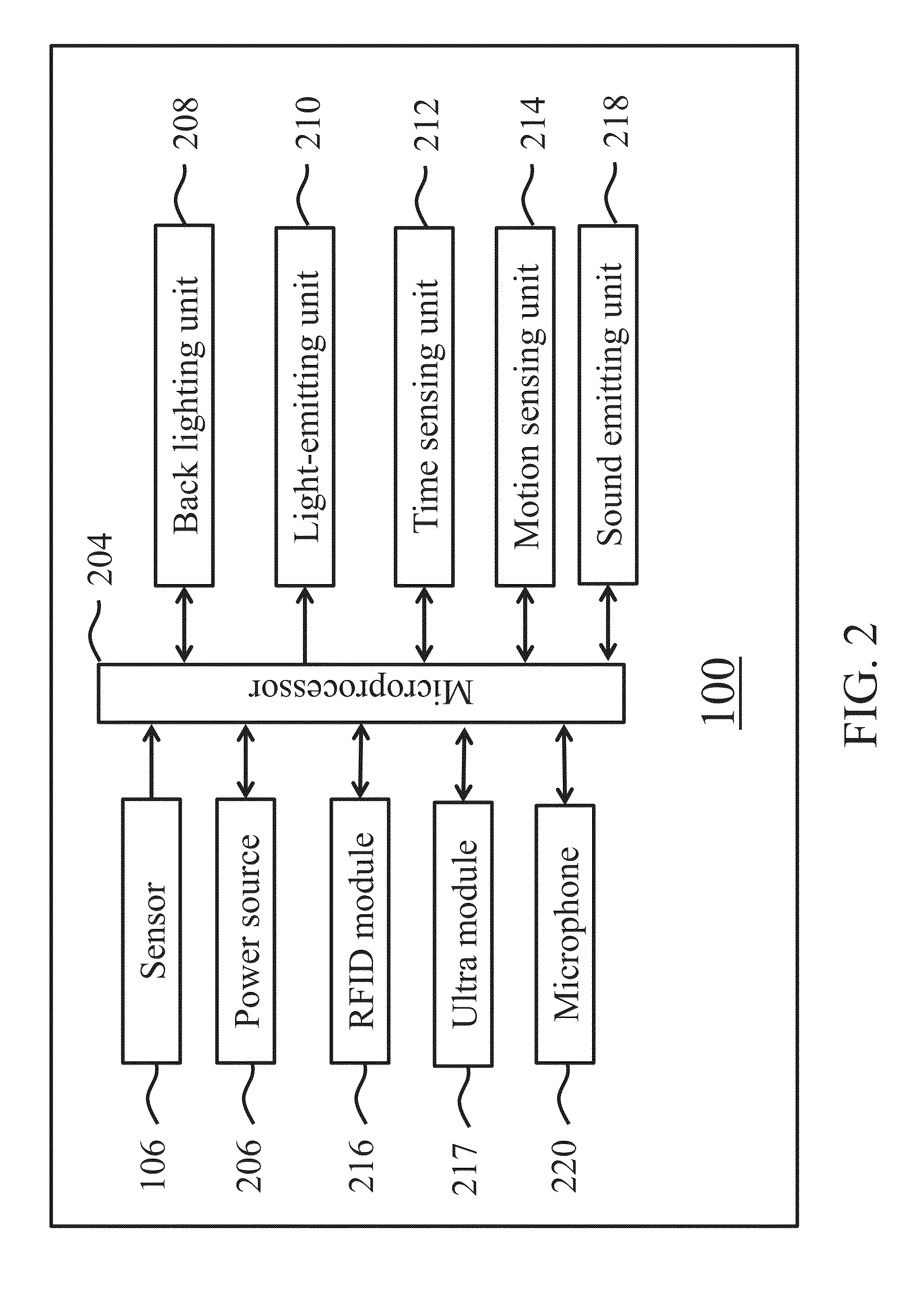

Selectively sending notifications when an object tracking device is outside a range of an anchor beacon

ActiveUS20080143516A1Avoid issuingPosition fixationRadio/inductive link selection arrangementsComputer visionBroadcasting

The present invention discloses a method of tracking objects. In the method, an anchor beacon can emit a broadcast over a range that is detectable by an object tracking device. The object tracking device can automatically detect a presence or absence of the broadcast. When the broadcast is present; the object tracking device can take no action. When the broadcast is absent, the object tracking device can determine a current location for the object tracking device and can convey an OTA communication to a tracking server. The OTA communication can indicate the absence of the broadcast and can also including the current location. The tracking server can selectively send a notification to a previously designated communication device to notify a user that the object tracking device is outside the range.

Owner:GOOGLE TECH HLDG LLC

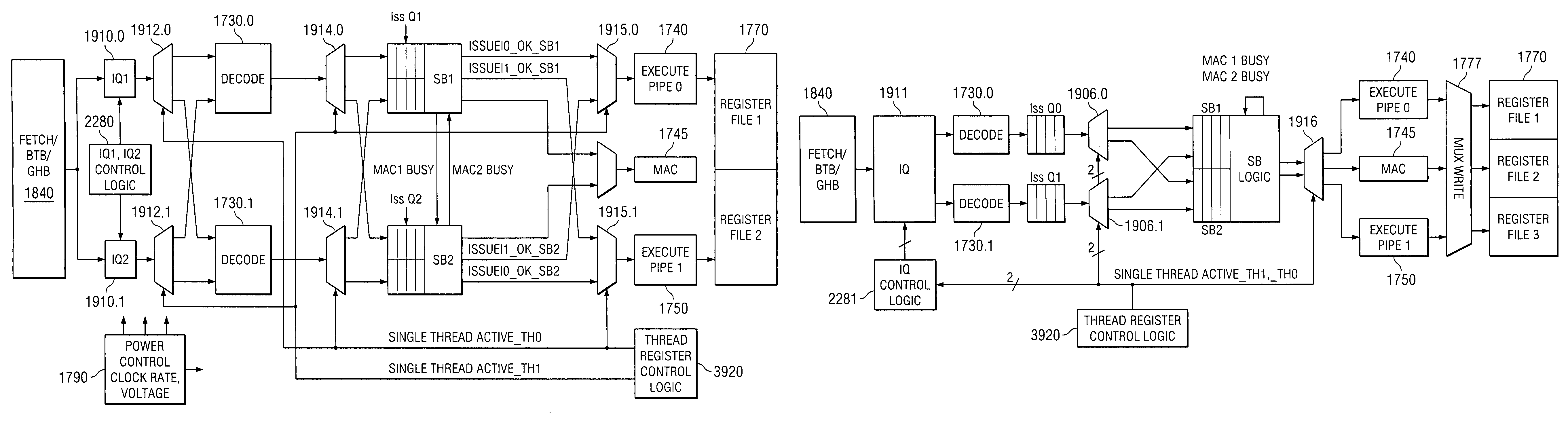

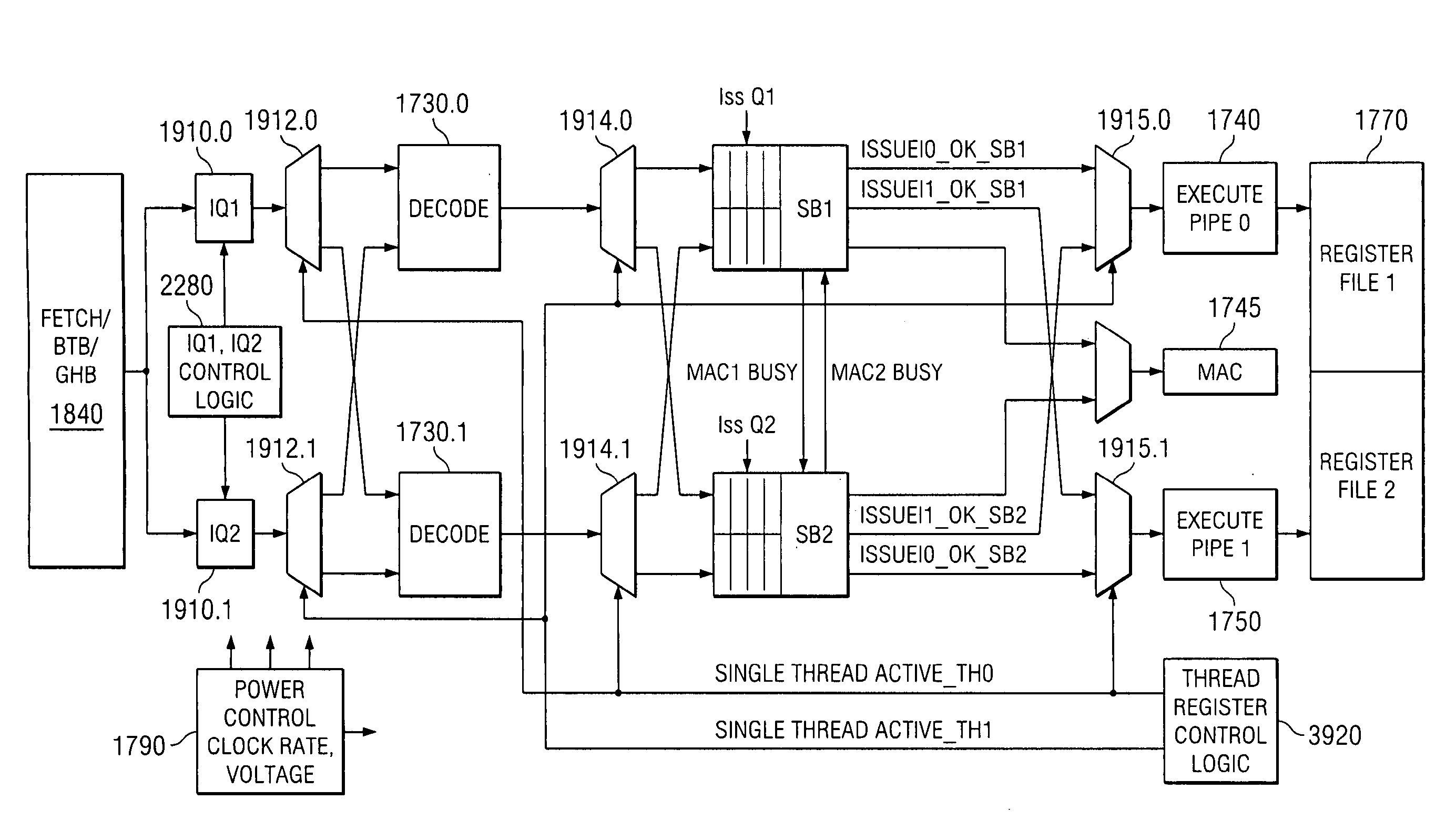

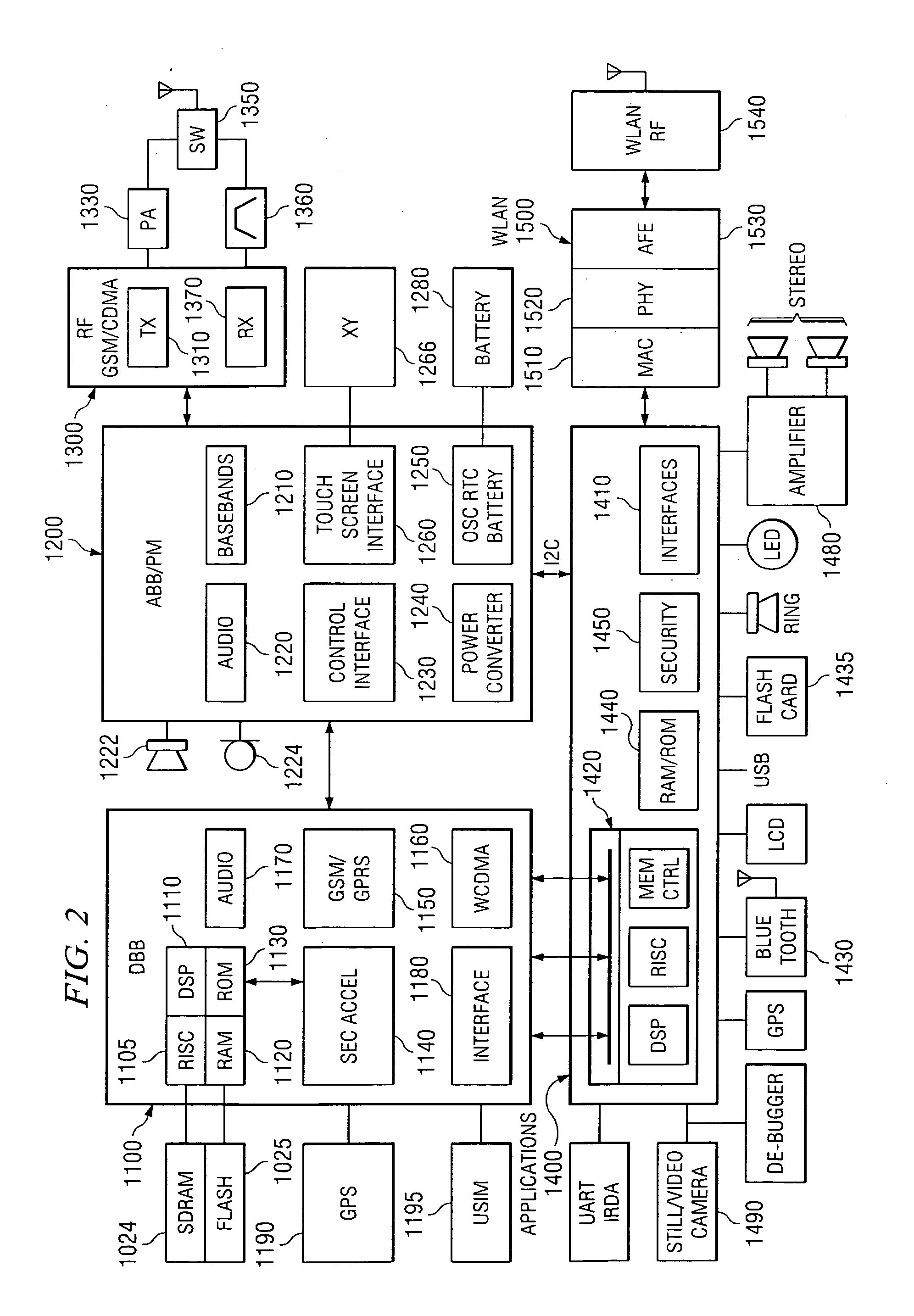

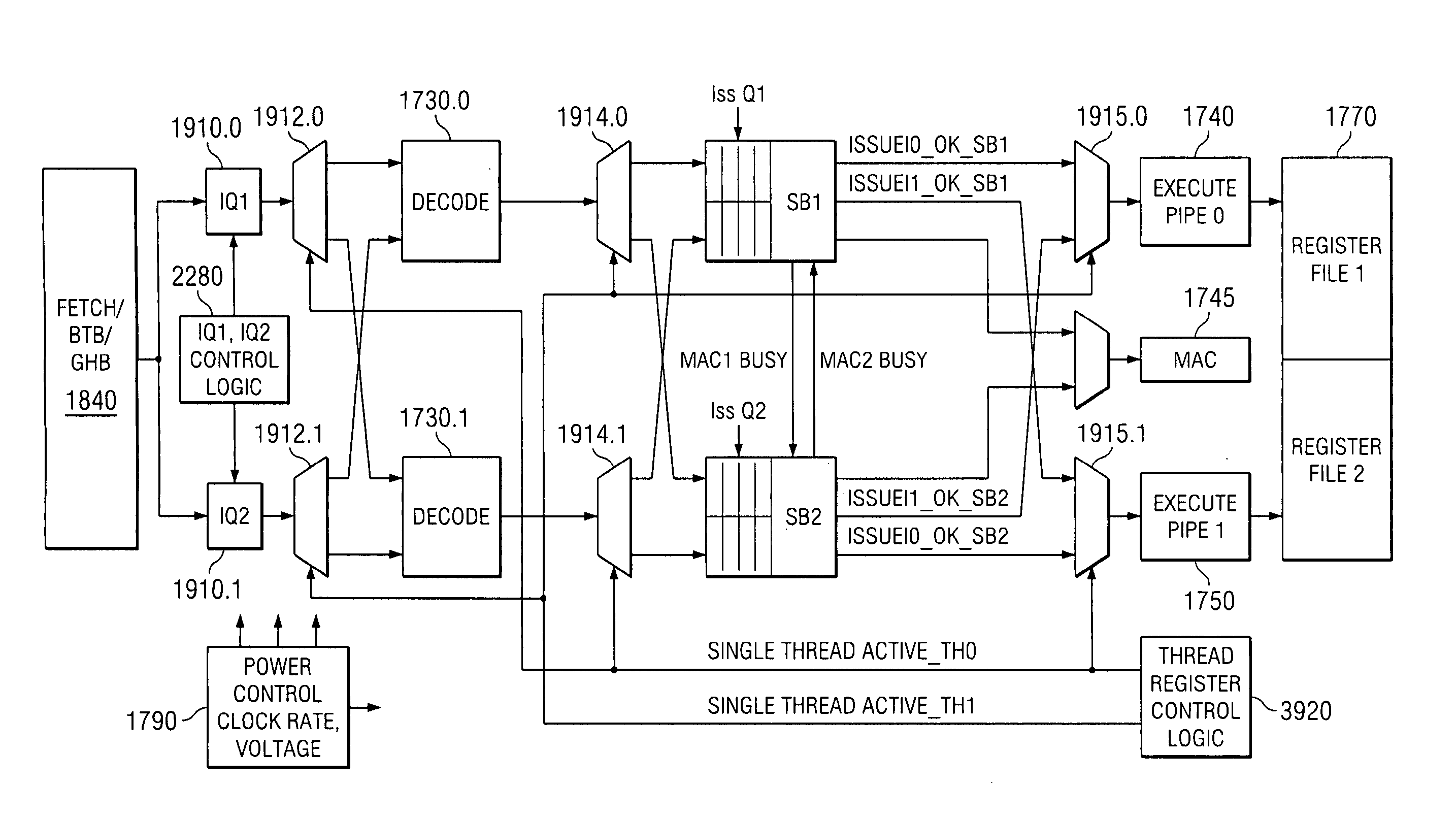

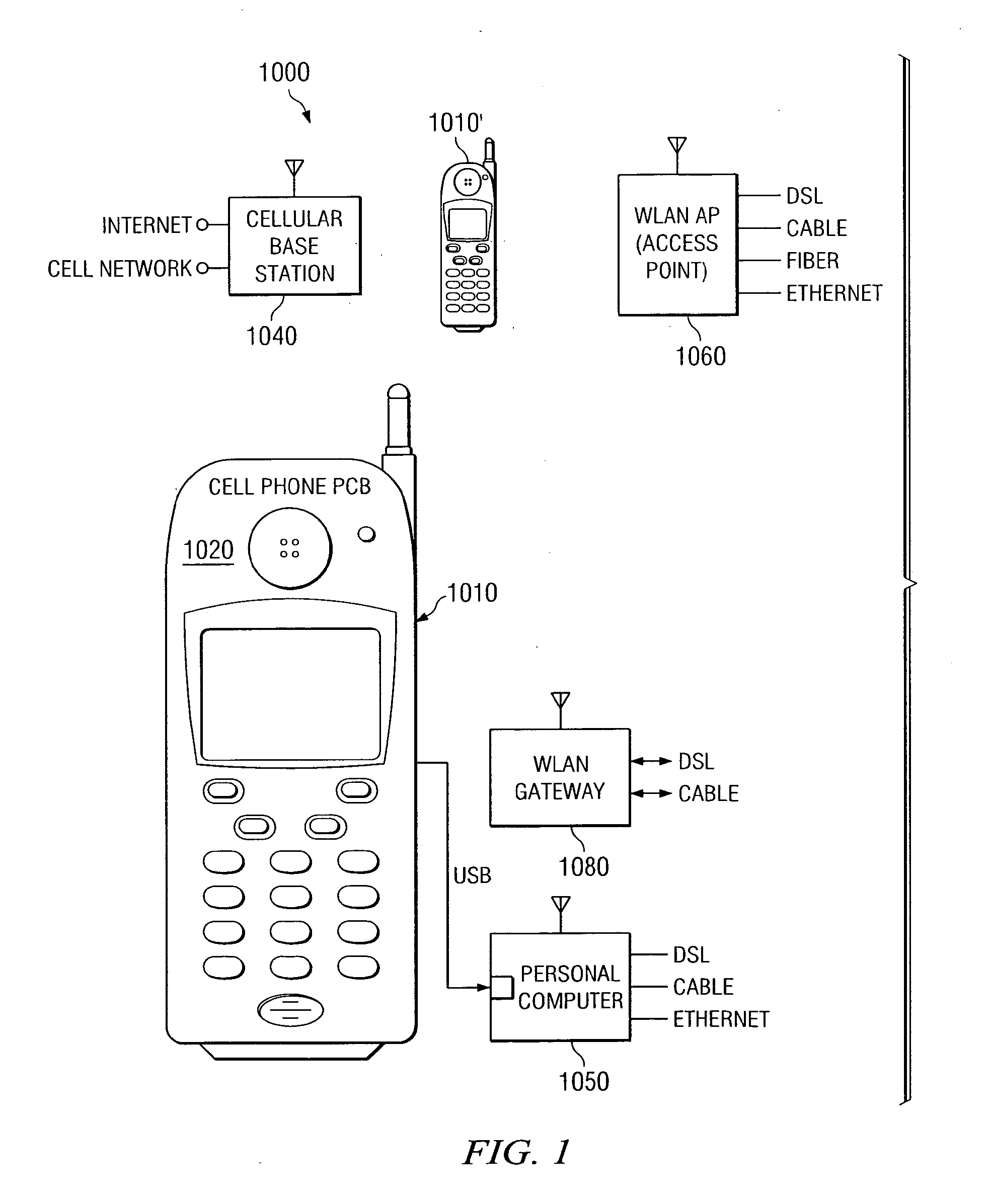

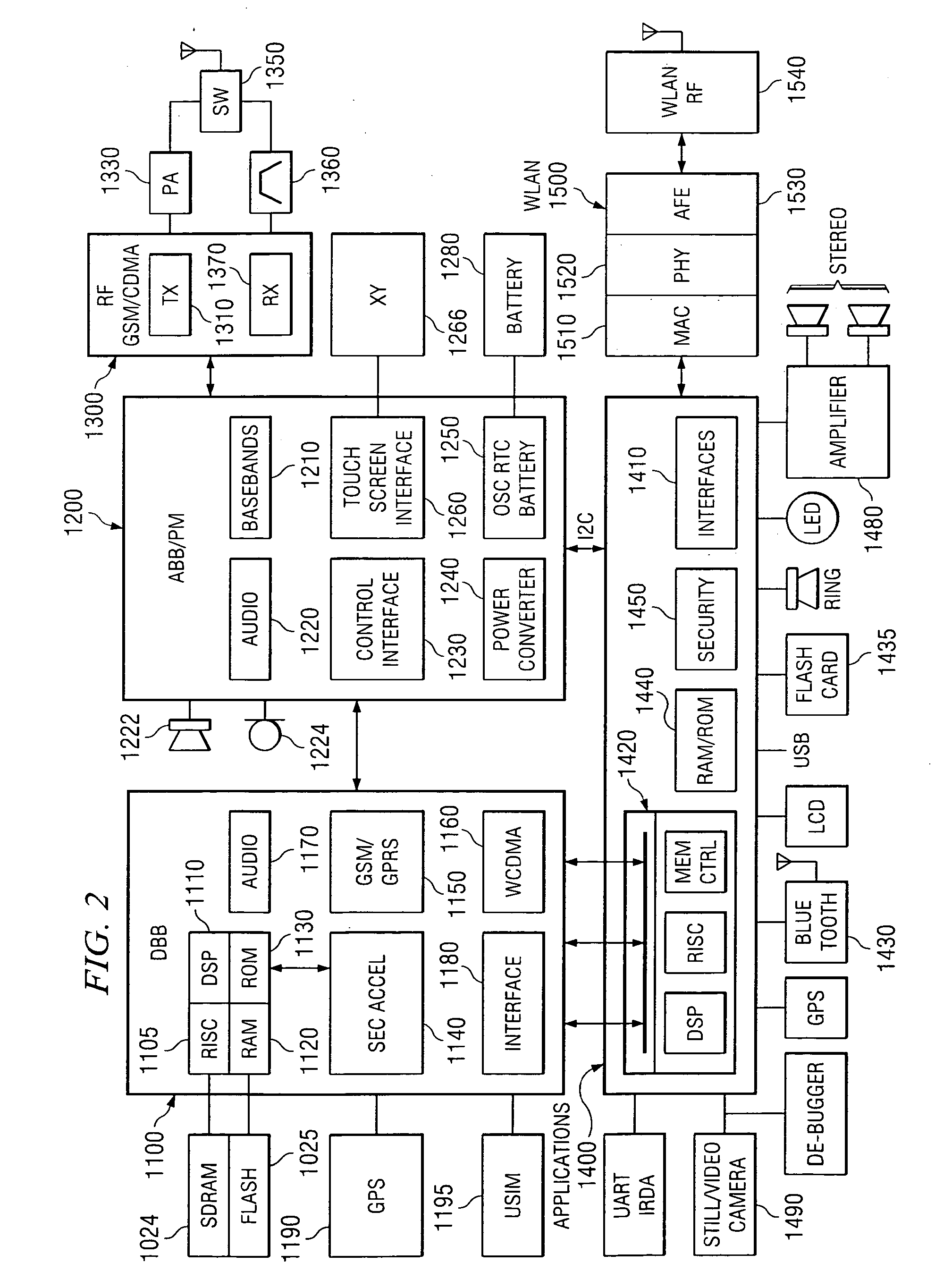

Multi-threading processors, integrated circuit devices, systems, and processes of operation and manufacture

ActiveUS7890735B2Avoid issuingDigital data processing detailsMemory systemsCouplingParallel computing

A multi-threaded microprocessor (1105) for processing instructions in threads. The microprocessor (1105) includes first and second decode pipelines (1730.0, 1730.1), first and second execute pipelines (1740, 1750), and coupling circuitry (1916) operable in a first mode to couple first and second threads from the first and second decode pipelines (1730.0, 1730.1) to the first and second execute pipelines (1740, 1750) respectively, and the coupling circuitry (1916) operable in a second mode to couple the first thread to both the first and second execute pipelines (1740, 1750). Various processes of manufacture, articles of manufacture, processes and methods of operation, circuits, devices, and systems are disclosed.

Owner:TEXAS INSTR INC

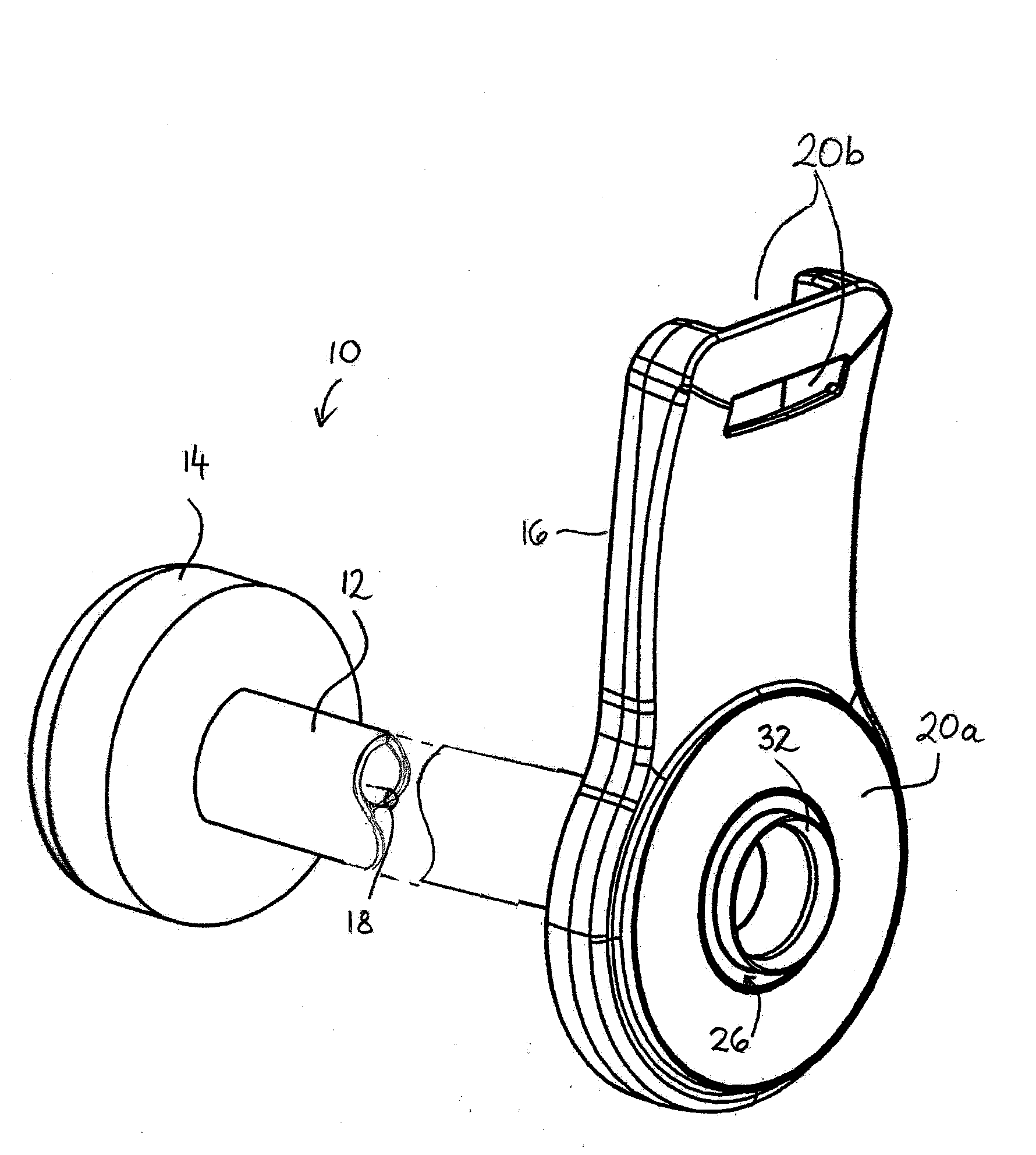

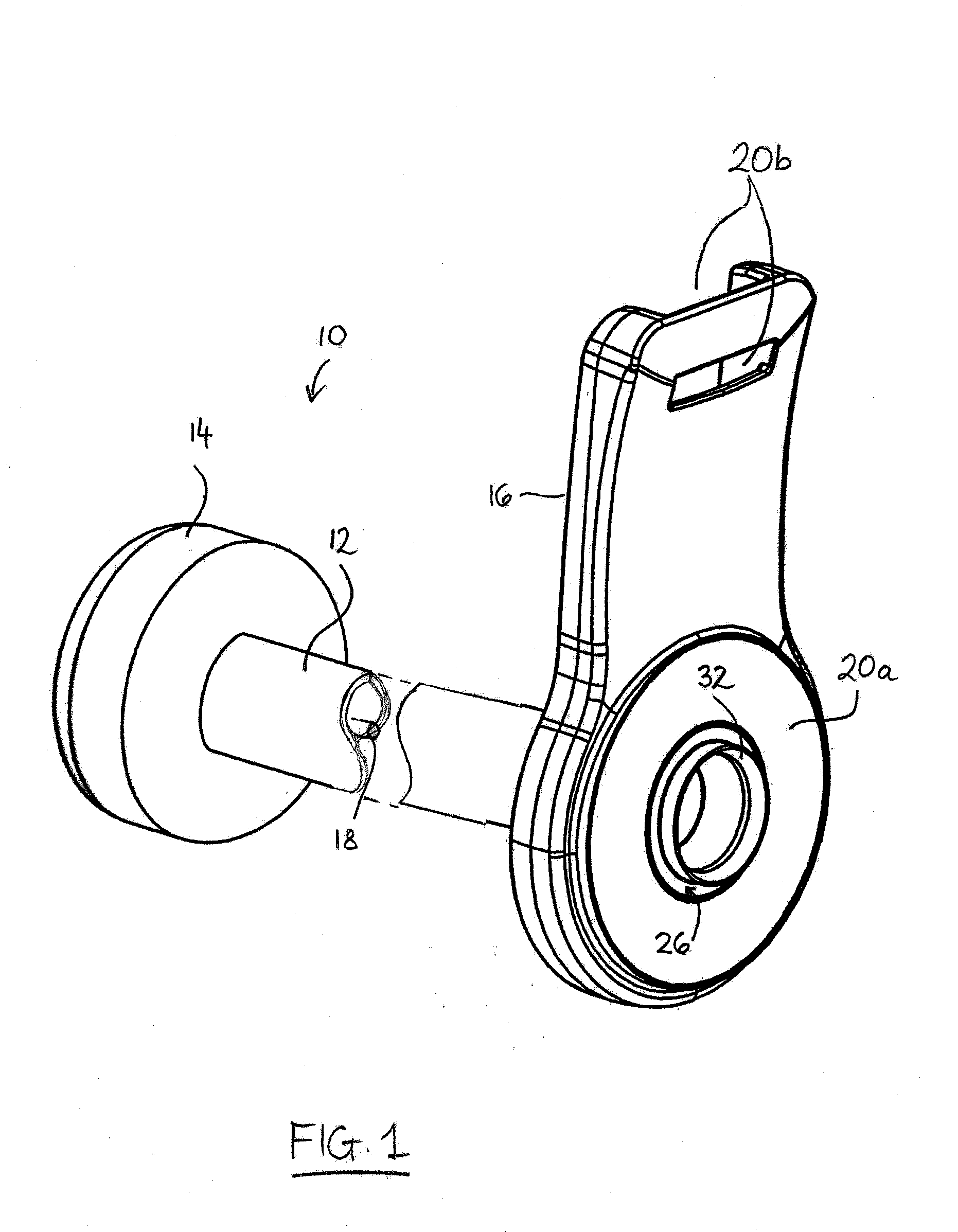

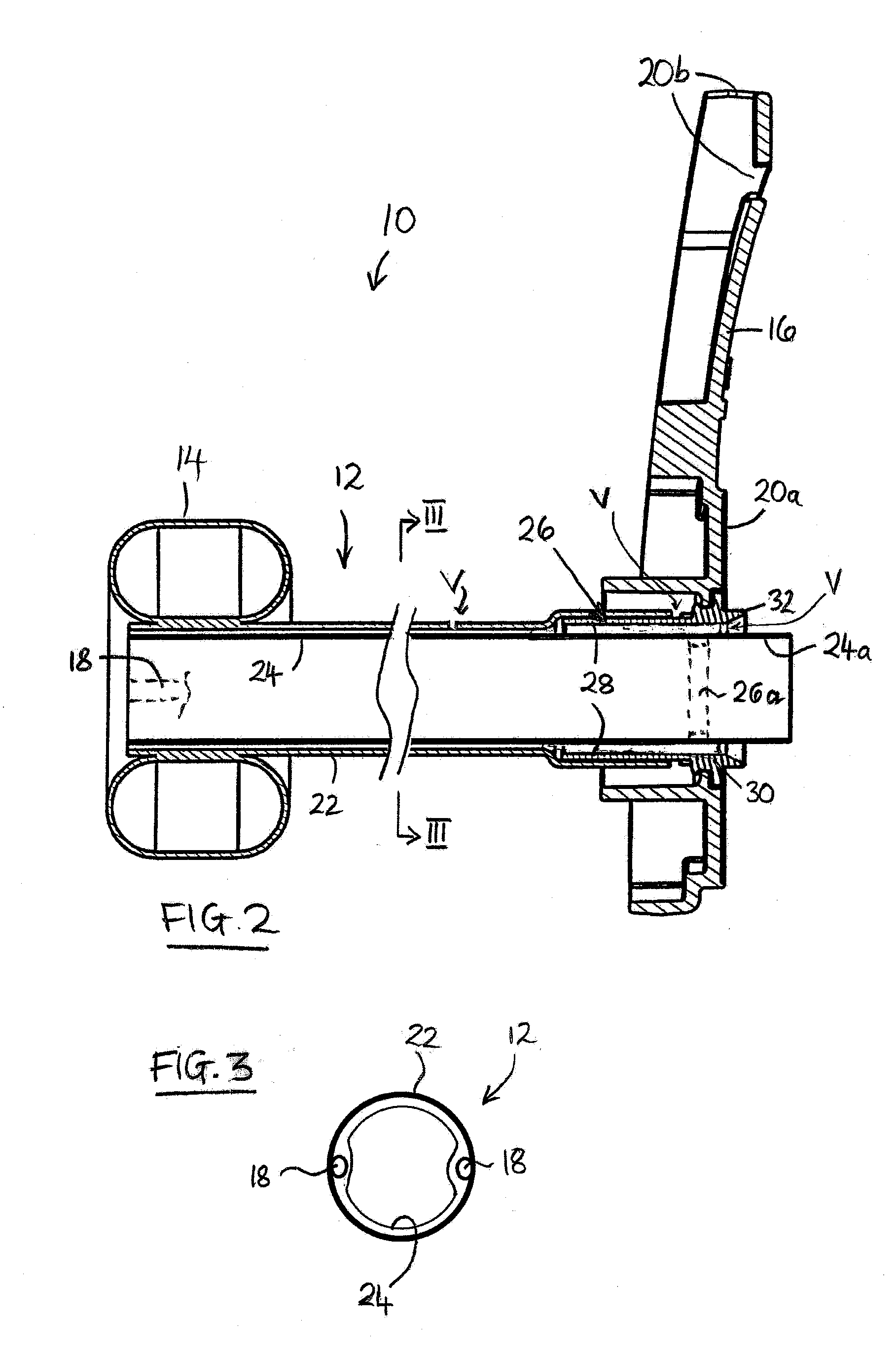

LED light for examinations and procedures

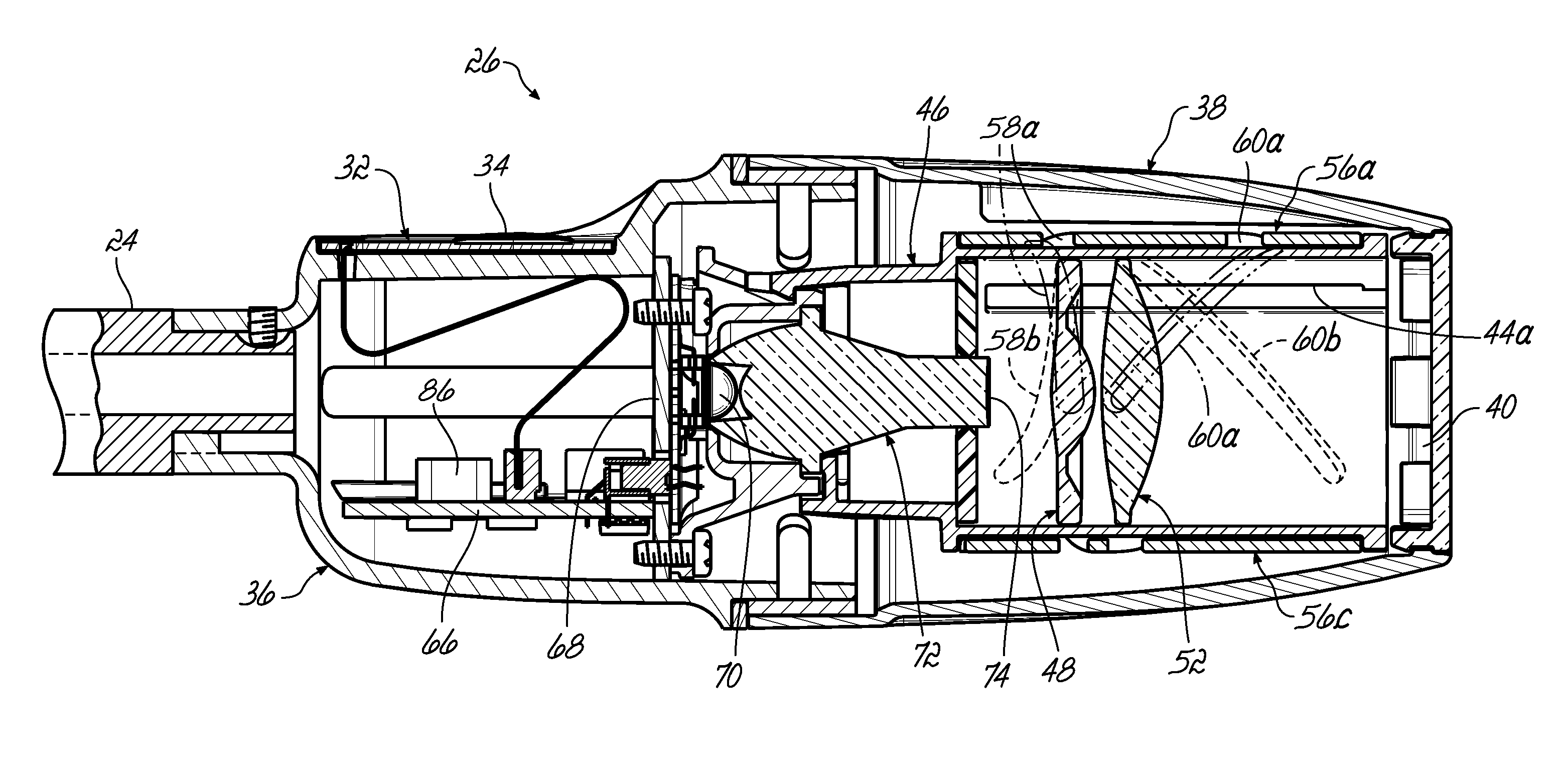

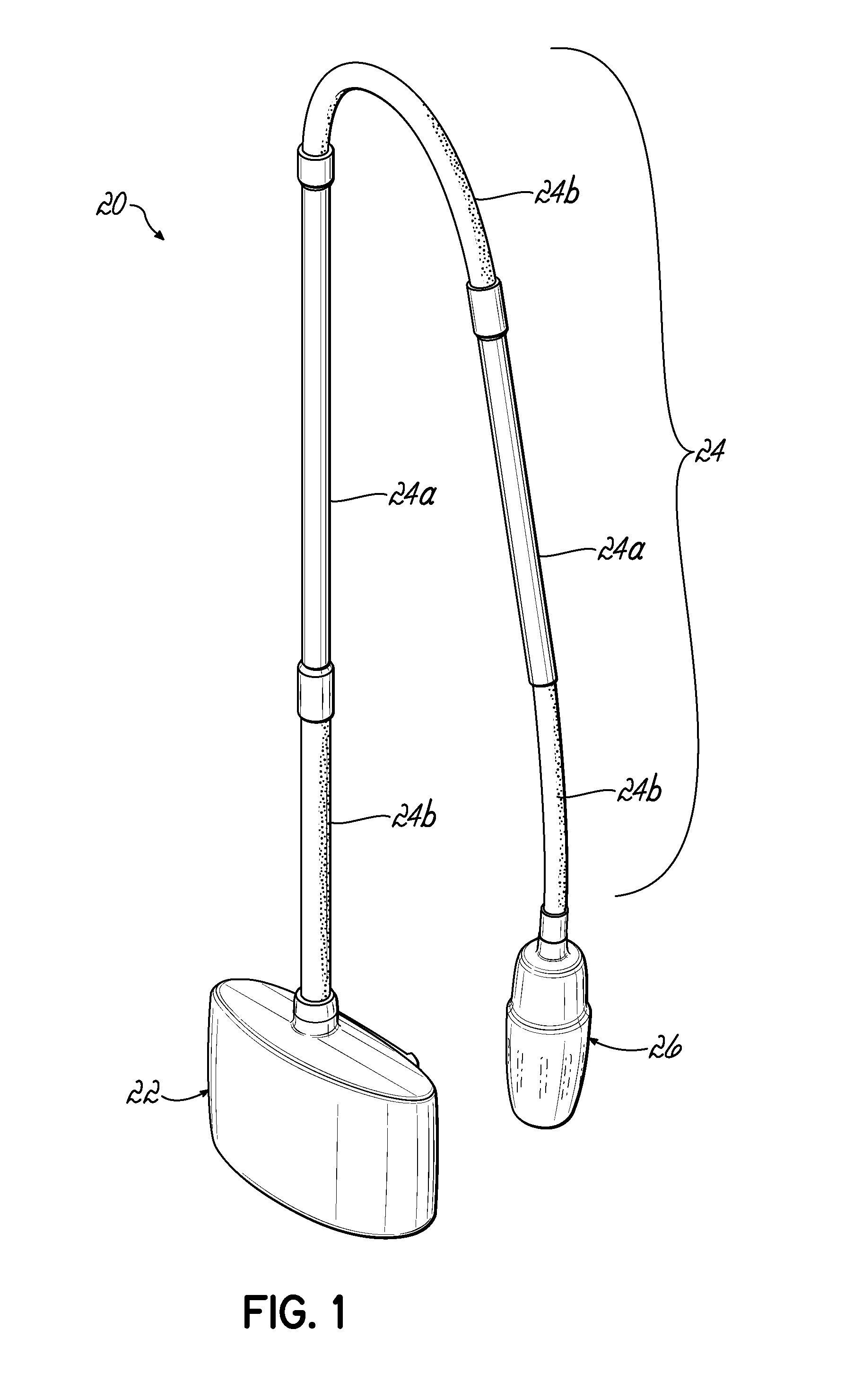

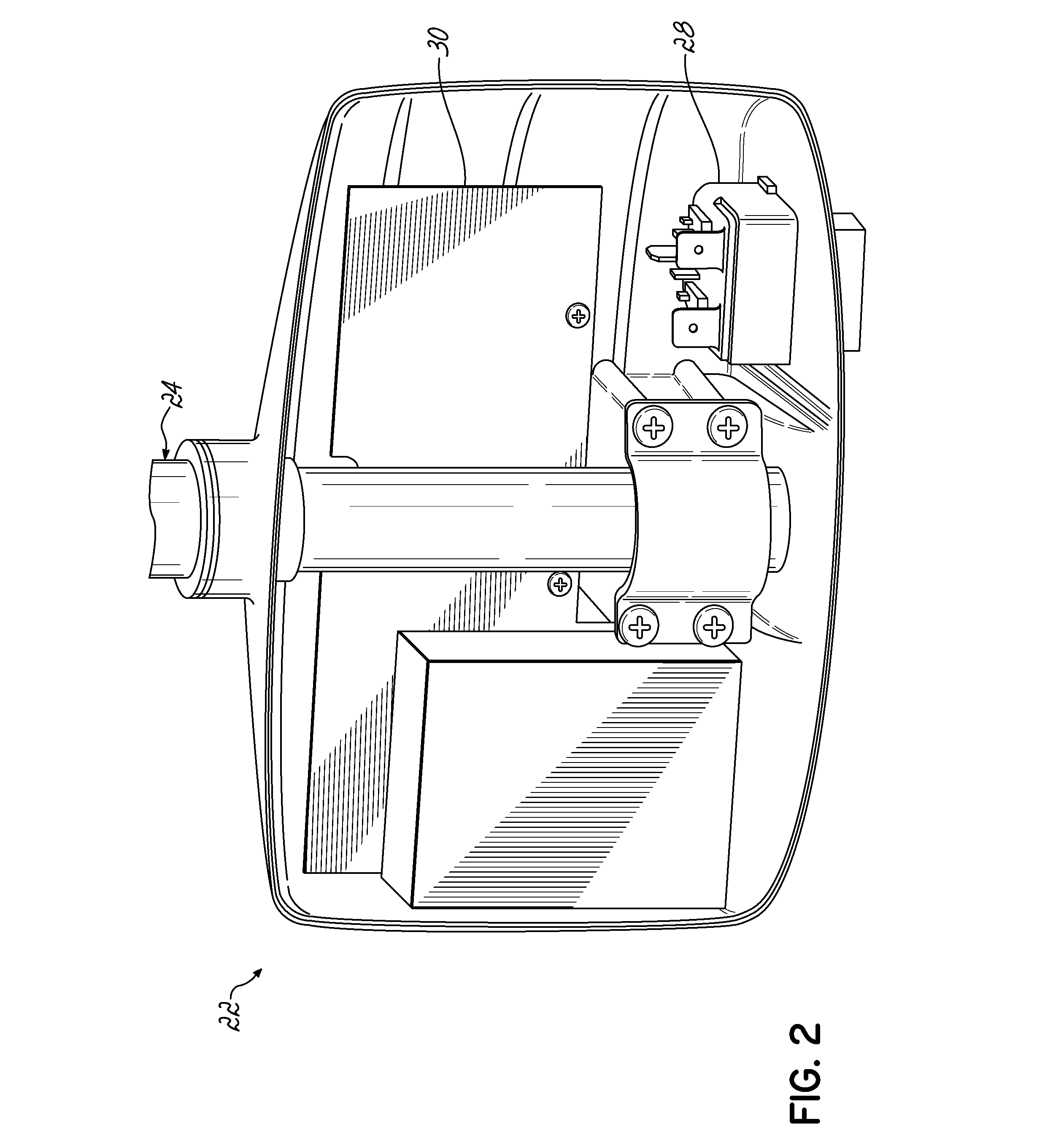

ActiveUS8872435B2Maximum accessibilityReducing floor clutterMechanical apparatusLighting support devicesDriving currentPower flow

A light is provided having a base unit, an arm extending from the base unit, and a lamp head coupled to the arm. The lamp head includes an LED configured to provide light based on an input drive current, an optical mixing element configured to collect the light produced by the LED and a zoom lens configured to adjust an output size of a spot generated by the light collected in the mixing element. A controller receives DC power from the base unit through the arm. The controller is configured to set the input drive current for the LED to control an output light density of the spot in response to an operator selected input and configured to adjust the output light density of the spot in response to a change in the size of the spot.

Owner:MIDMARK

Selectively sending notifications when an object tracking device is outside a range of an anchor beacon

A method of tracking objects uses an anchor beacon that can emit a broadcast over a range that is detectable by an object tracking device. The object tracking device can automatically detect a presence or absence of the broadcast. When the broadcast is present, the object tracking device can take no action. When the broadcast is absent, the object tracking device can determine a current location for the object tracking device and can convey an OTA communication to a tracking server. The OTA communication can indicate the absence of the broadcast and can also including the current location. The tracking server can selectively send a notification to a previously designated communication device to notify a user that the object tracking device is outside the range.

Owner:GOOGLE TECHNOLOGY HOLDINGS LLC

Multi-threading processors, integrated circuit devices, systems, and processes of operation and manufacture

ActiveUS20110099355A1Avoid issuingDigital data processing detailsDigital computer detailsCouplingParallel computing

Owner:TEXAS INSTR INC

System and method for improving hand hygiene

A hand hygiene module and method of instructing and monitoring compliance of a hand hygiene event include a sanitizer dispensing device and the steps of identifying an initiation of a use of the sanitizer dispensing device and actively sequentially providing a plurality of stimuli to a user during the use of the sanitizer dispensing device, the plurality of stimuli including at least one of an audible signaling and a visual signaling and actively sequentially instructing each of a plurality of hygiene steps.

Owner:DIAZ MARC HOWARD

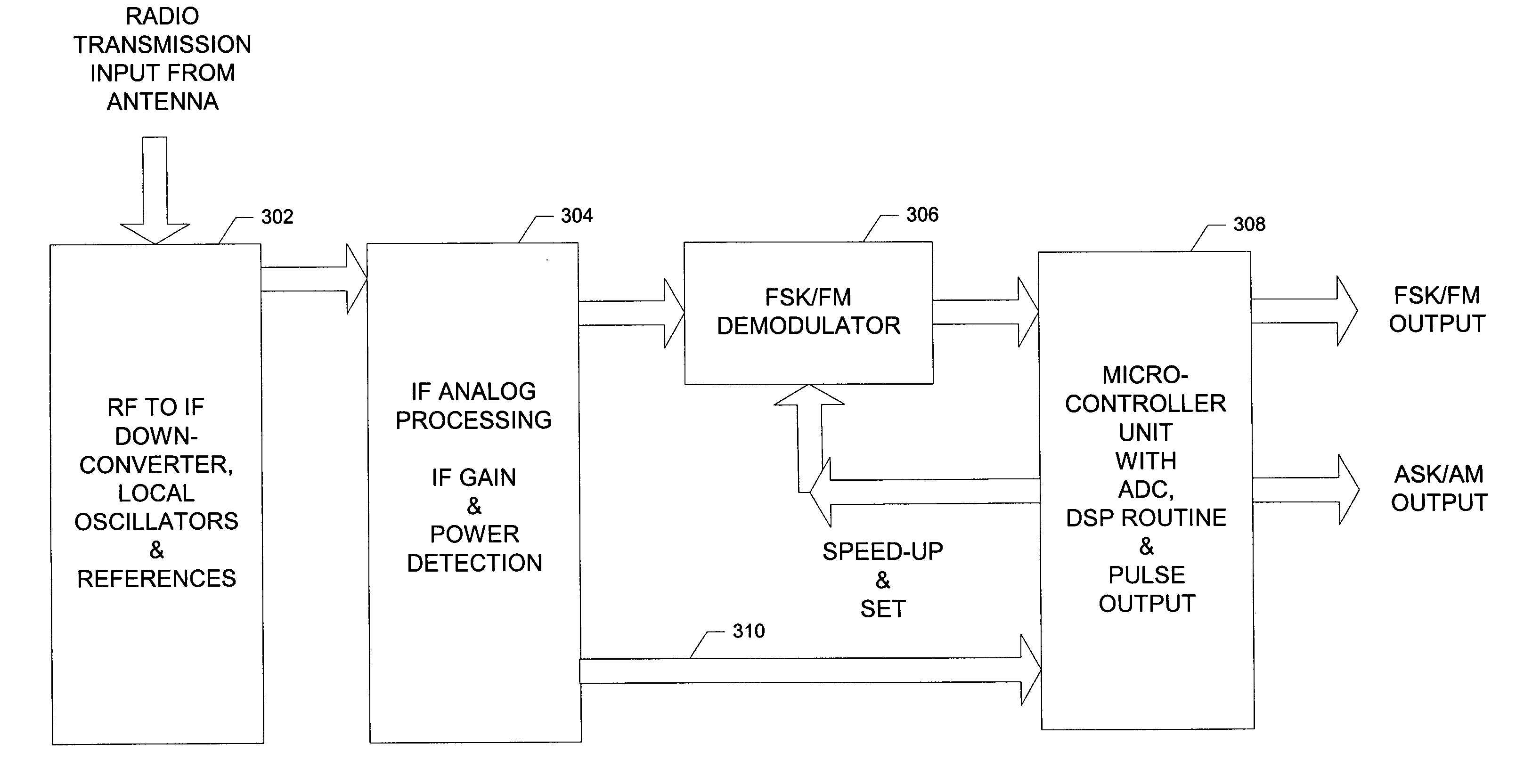

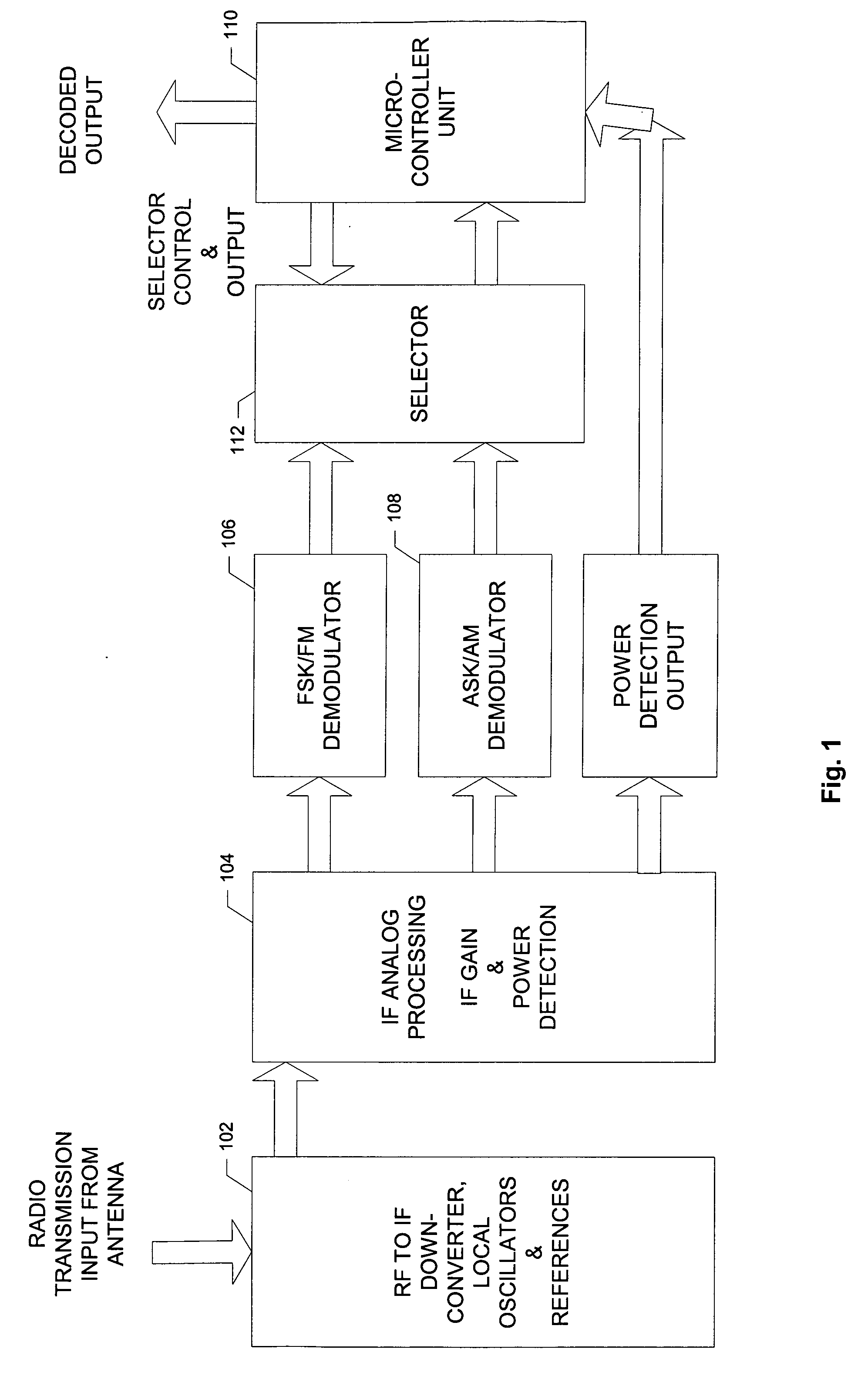

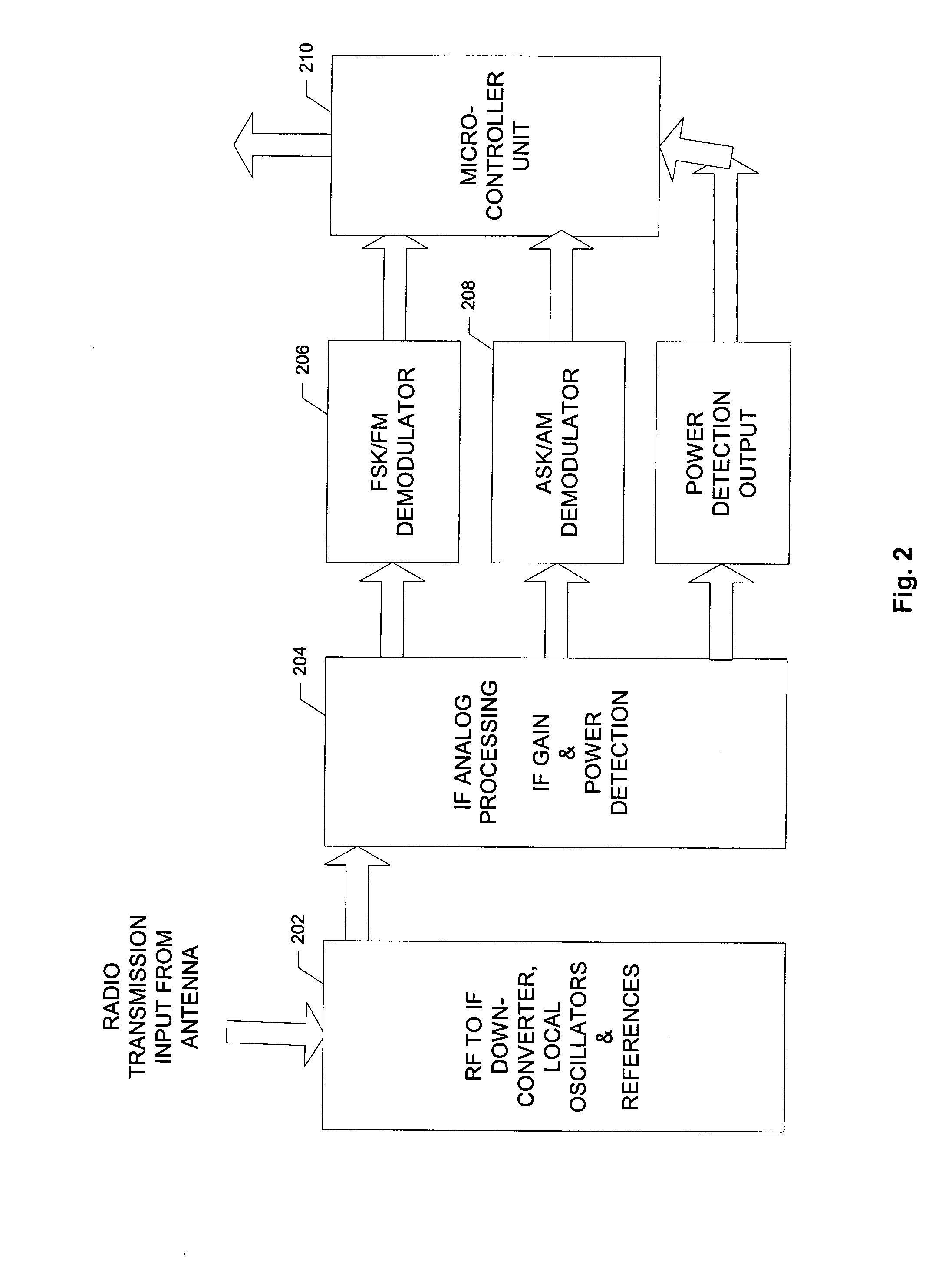

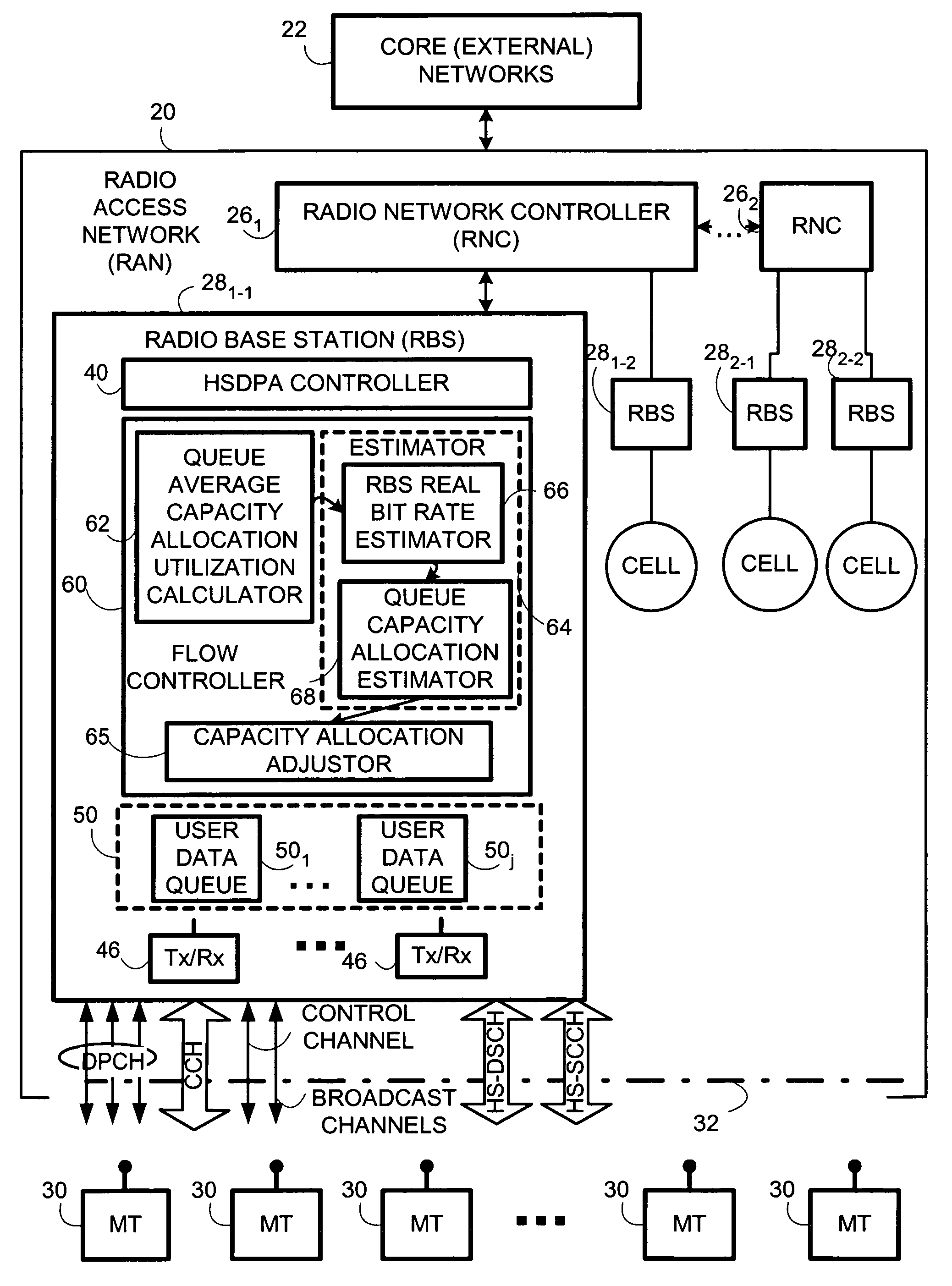

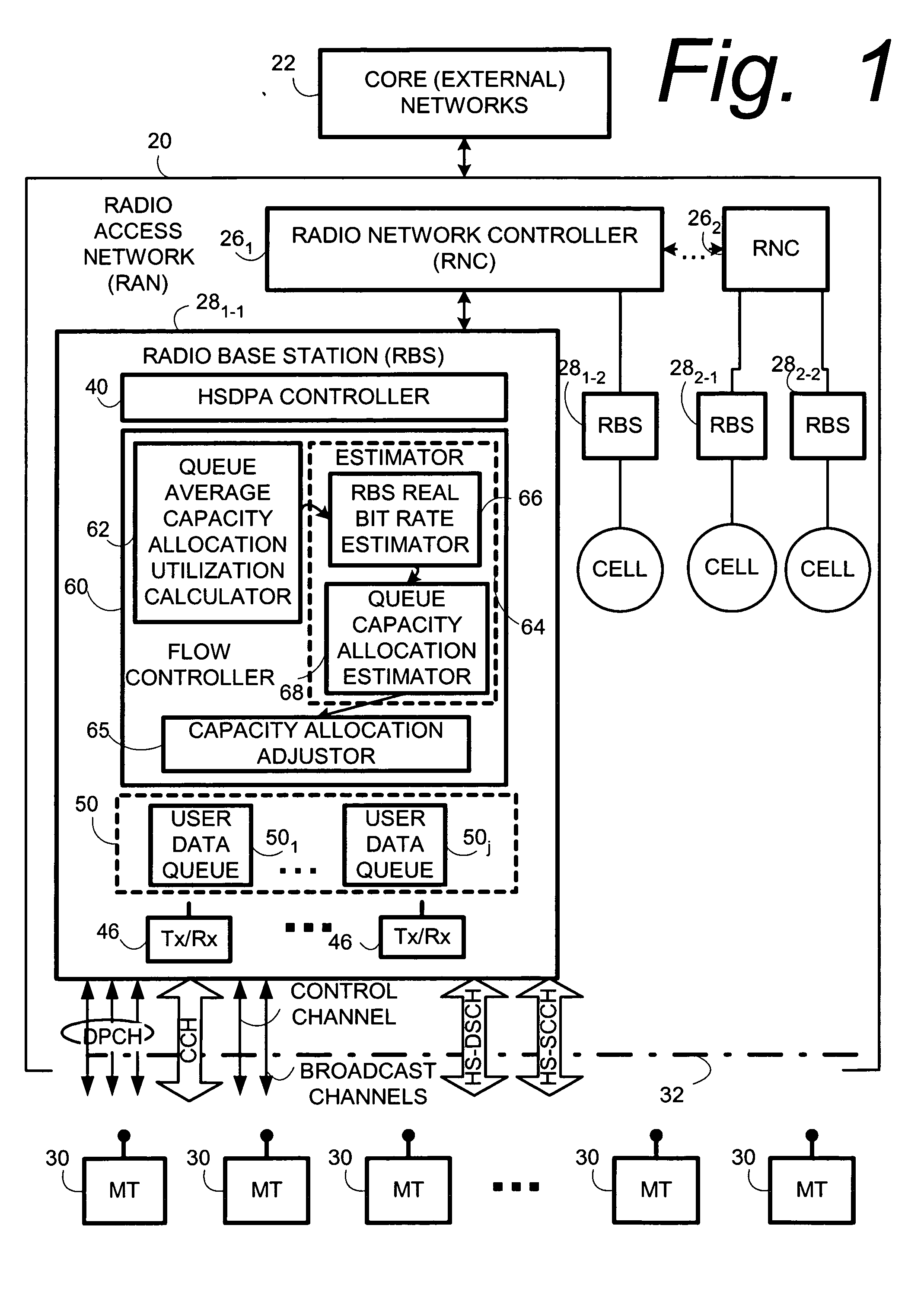

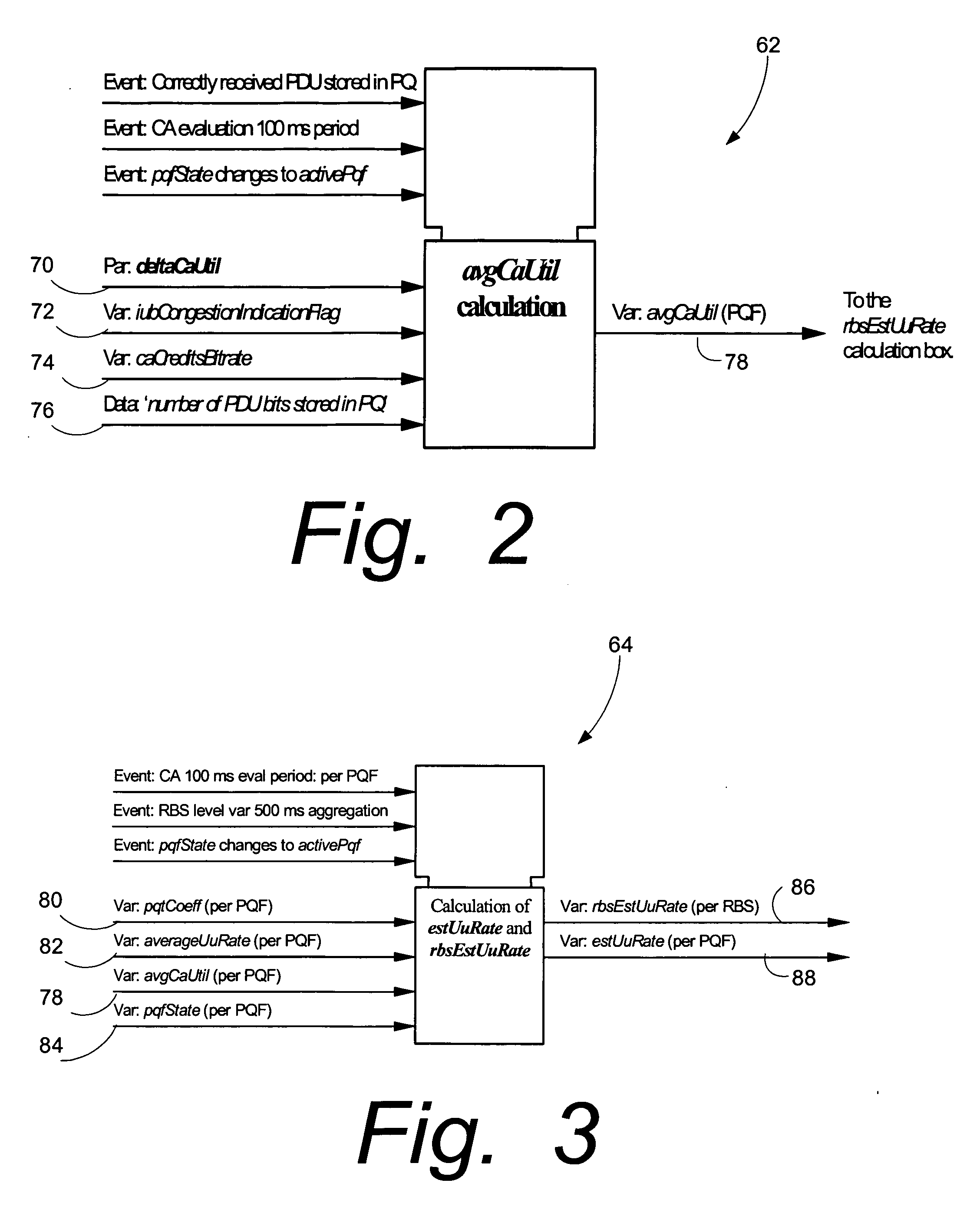

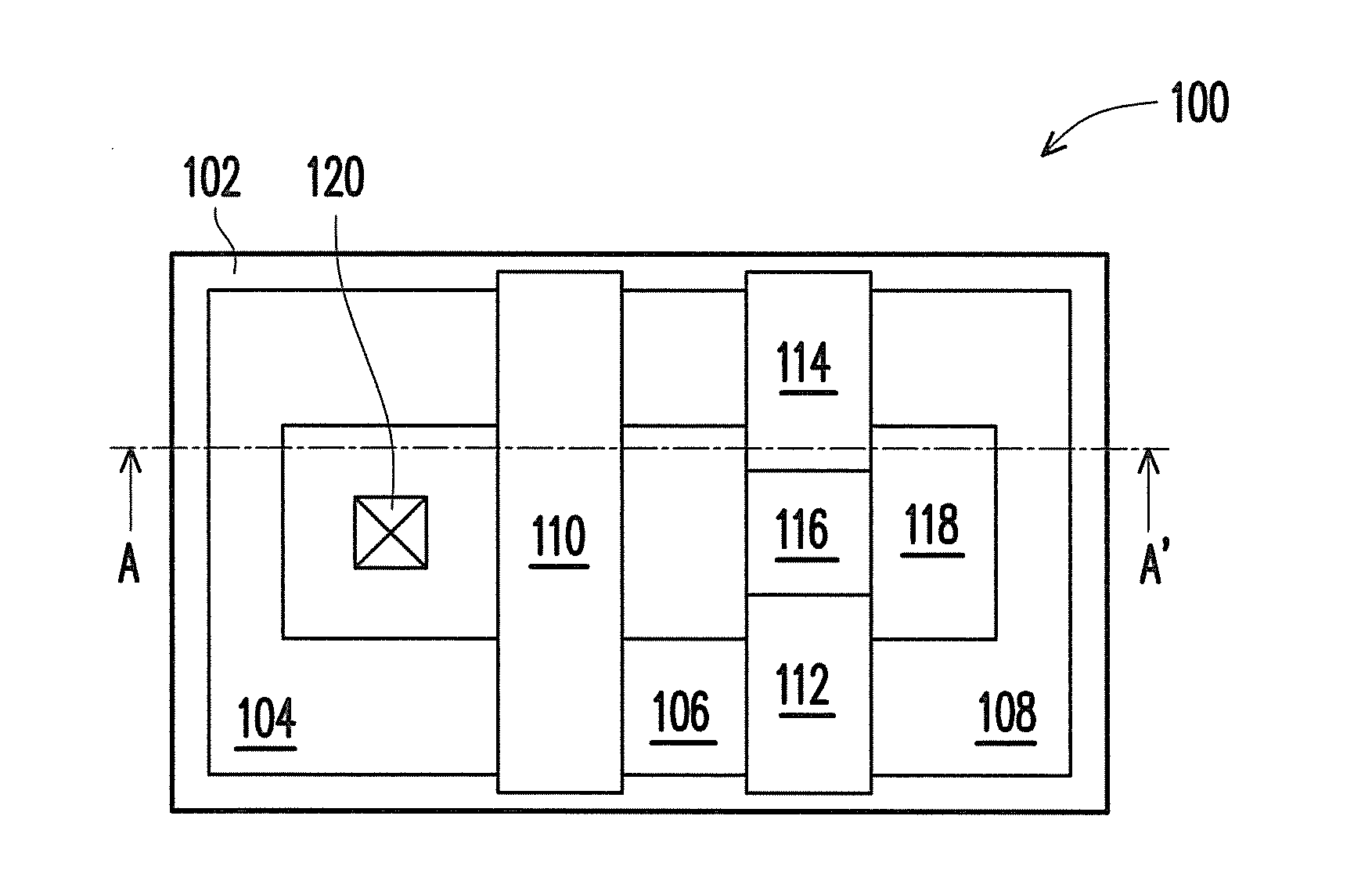

Flow control for low bitrate users on high-speed downlink

ActiveUS20070127522A1Avoid issuingNetwork traffic/resource managementTime-division multiplexTraffic volumeRadio access

Owner:TELEFON AB LM ERICSSON (PUBL)

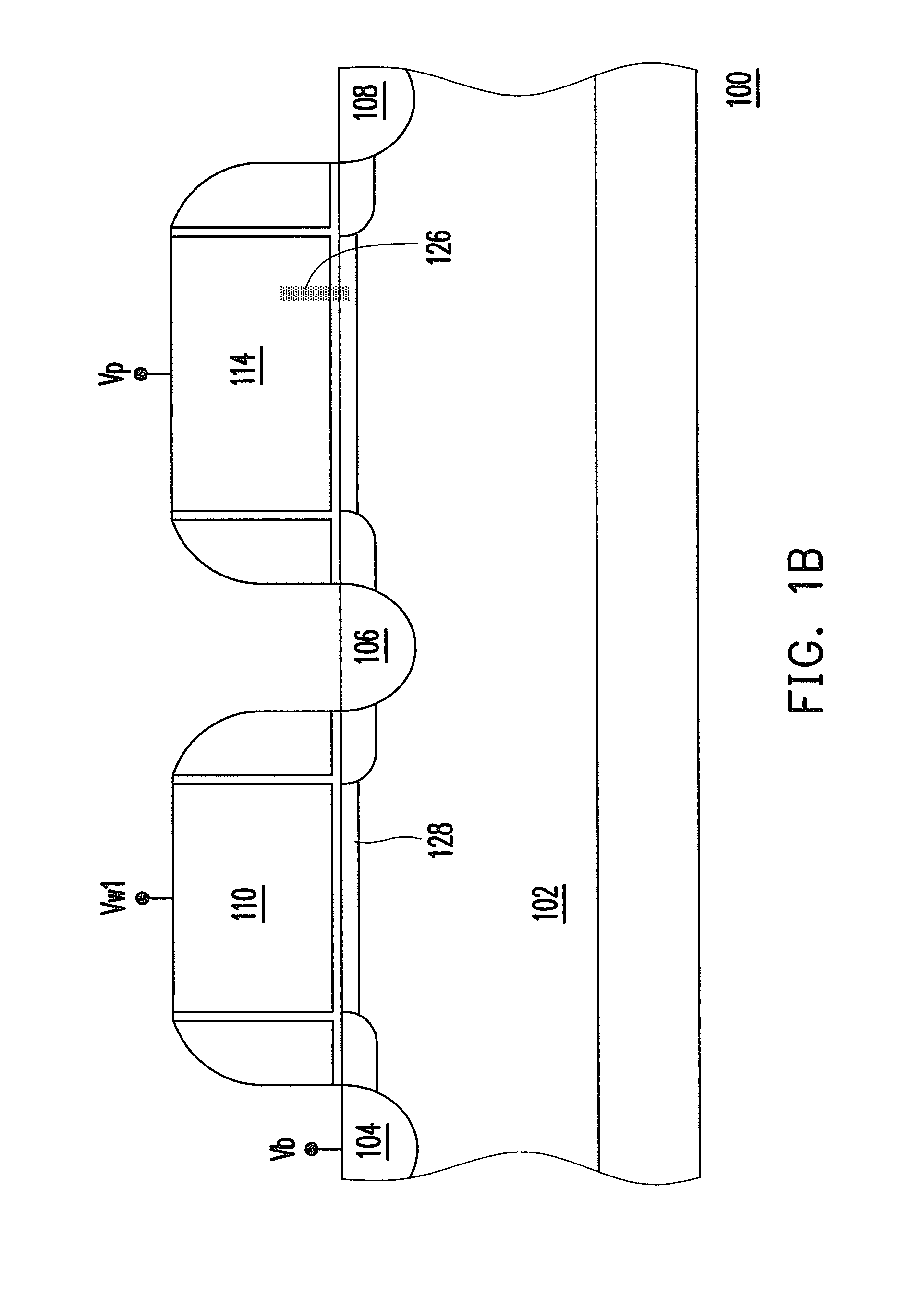

Antifuse otp memory cell with performance improvement prevention and operating method of memory

ActiveUS20140098591A1Avoid yield lossImprove performanceTransistorSemiconductor/solid-state device detailsGate dielectricAntifuse

Provided is an OTP memory cell including a first antifuse unit, a second antifuse unit, a select transistor, and a well region. The first and the second antifuse unit respectively include an antifuse layer and an antifuse gate disposed on a substrate in sequence. The select transistor includes a select gate, a gate dielectric layer, a first doped region, and a second doped region. The select gate is disposed on the substrate. The gate dielectric layer is disposed between the select gate and the substrate. The first and the second doped region are respectively disposed in the substrate at two sides of the select gate, wherein the second doped region is disposed in the substrate at the periphery of the first and the second antifuse unit. The well region is disposed in the substrate below the first and the second antifuse unit and is connected to the second doped region.

Owner:EMEMORY TECH INC

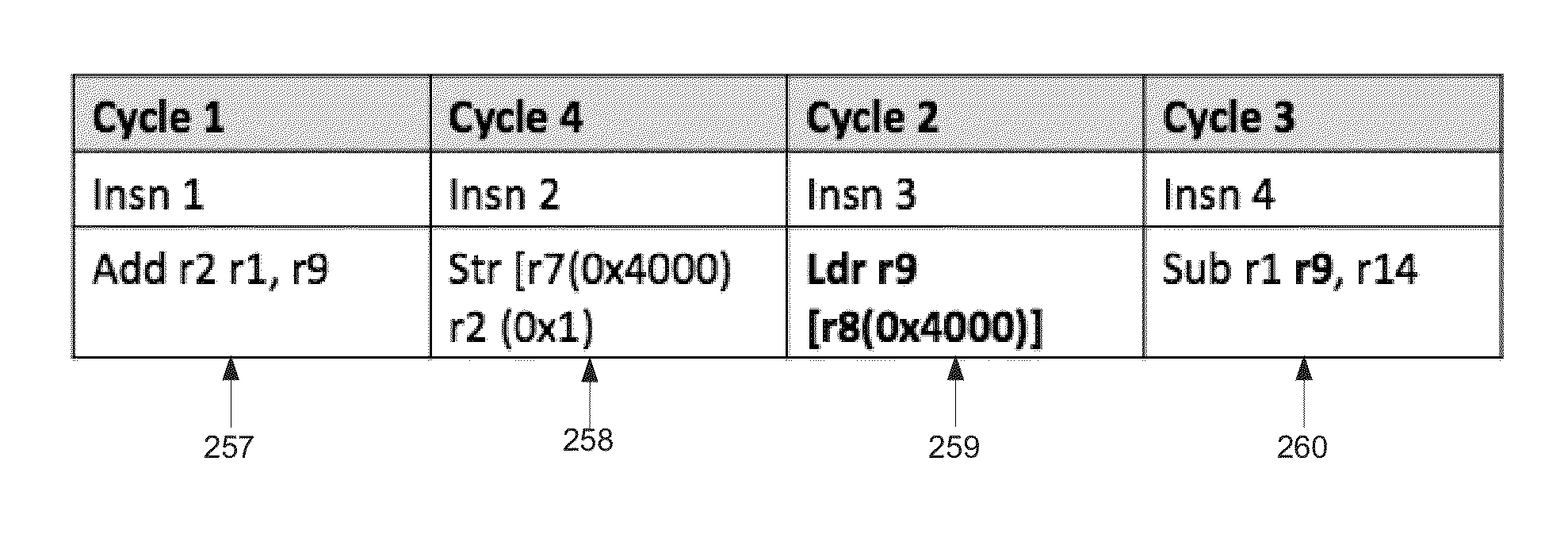

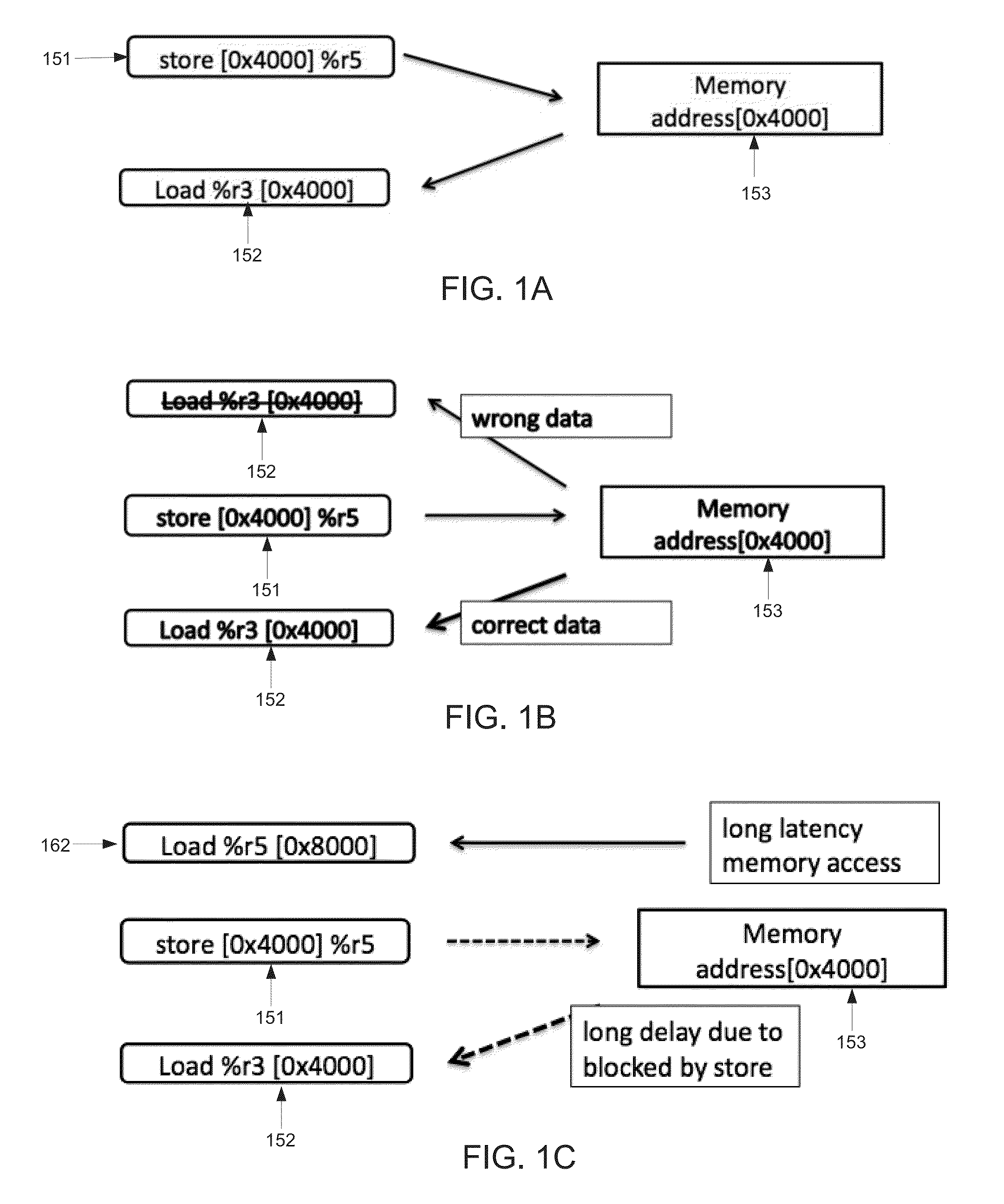

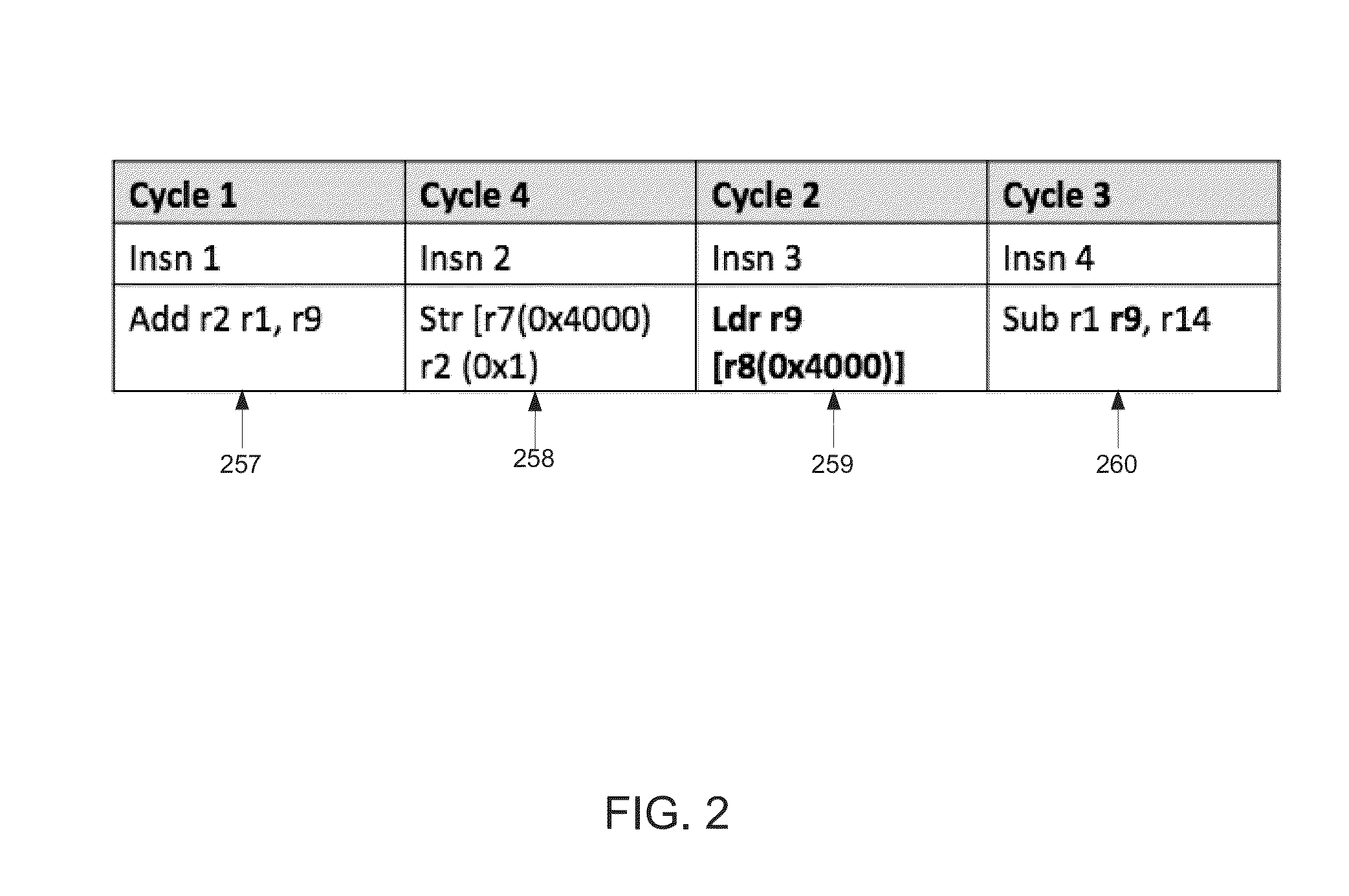

Method and apparatus for predicting forwarding of data from a store to a load

ActiveUS20140281408A1Prevent memory RAW delayLower performance requirementsDigital computer detailsMemory systemsData miningStore instruction

A method for gating a load operation based on entries of a prediction table is presented. The method comprises performing a look-up for the load operation in a prediction table to find a matching entry, wherein the matching entry corresponds to a prediction regarding a behavior of the load operation, and wherein the matching entry comprises: (a) a tag field operable to identify the matching entry; (b) a distance field operable to indicate a distance of the load operation to a prior aliasing store instruction; and (c) a confidence field operable to indicate a prediction strength generated by the prediction table. The method further comprises determining if the matching entry provides a valid prediction and, if valid, retrieving a location for the prior aliasing store instruction using the distance field. It finally comprises performing a gating operation on said load operation.

Owner:INTEL CORP

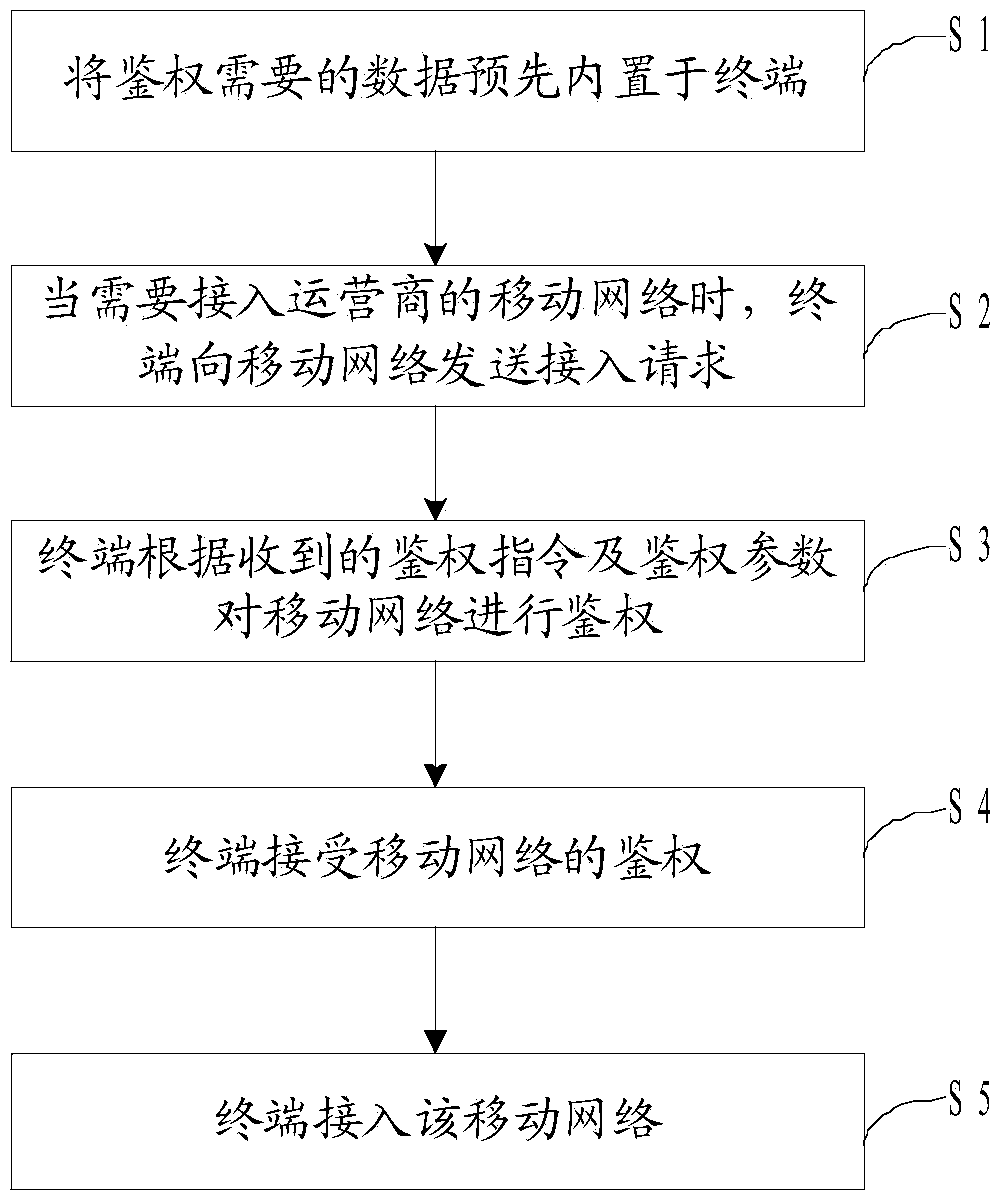

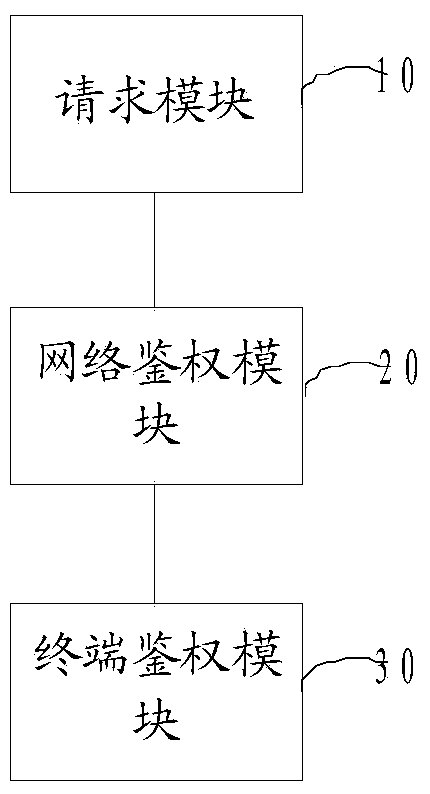

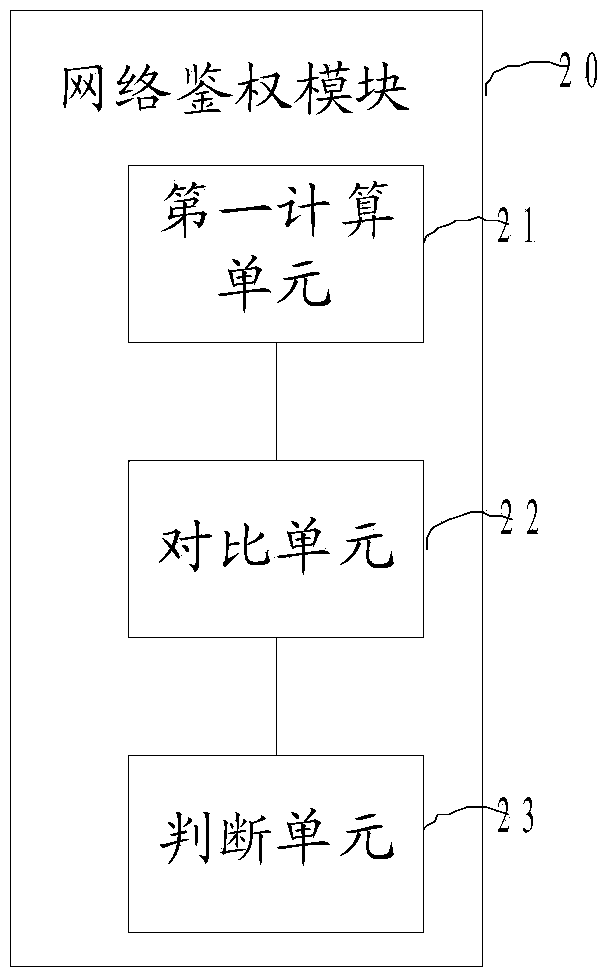

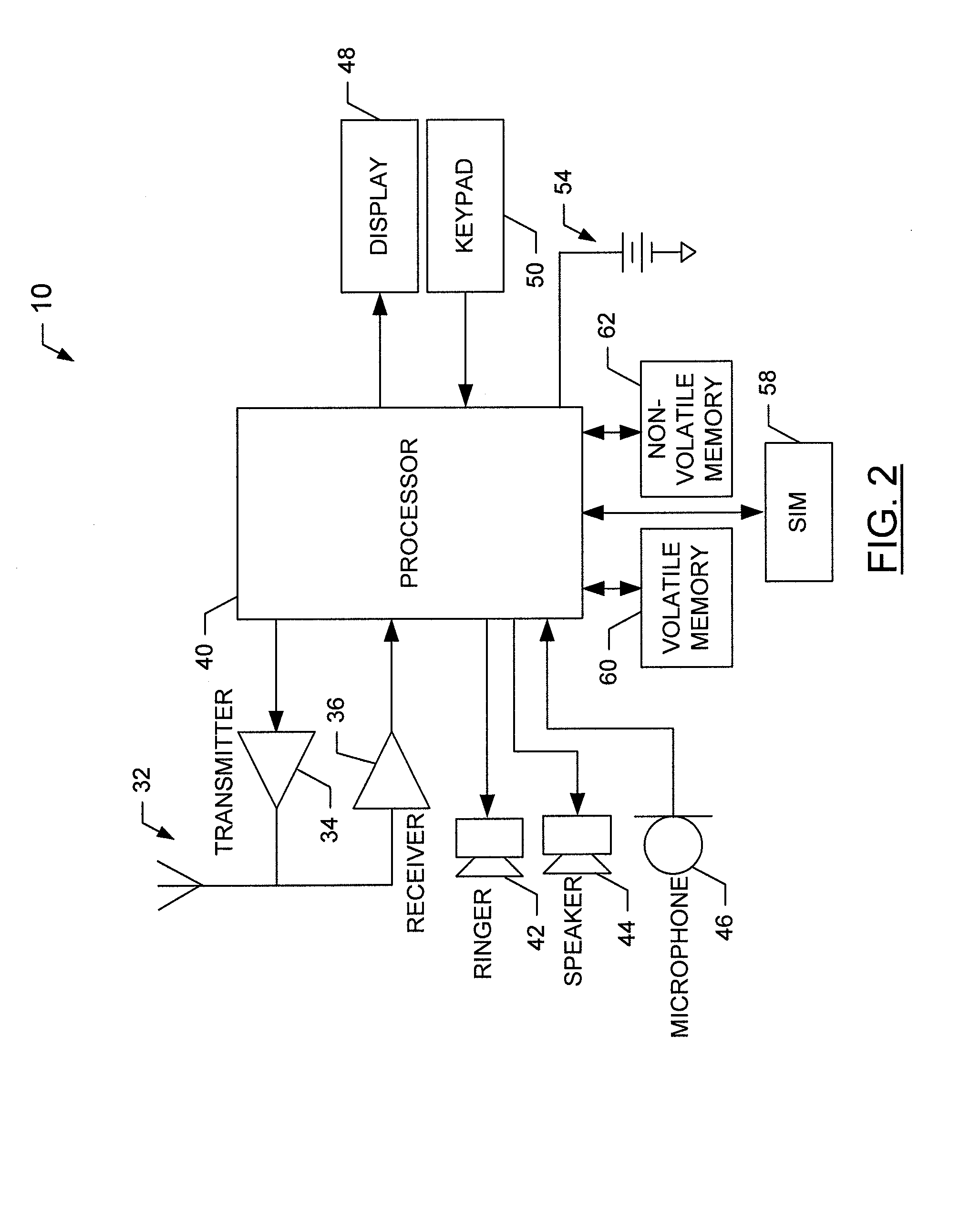

Method, device and mobile terminal of virtual SIM card

InactiveCN103415017AAvoid issuingEasy to operate on a large scaleAssess restrictionSecurity arrangementComputer terminalMobile Web

The invention relates to the field of communication, and provides a method, device and system of a virtual SIM card. The method comprises the steps that when a terminal needs to have access to a mobile network, the terminal sends access requests to the mobile network, so that the mobile network can issue authentication parameters according to the access requests; the authentication parameters comprise random numbers, authentication tokens and network authentication weight values; authentication is carried out on the mobile network according to the authentication parameters. The method, device and system of the virtual SIM card achieve the operation that an operator network can be accessed without the SIM card.

Owner:高新兴物联科技股份有限公司

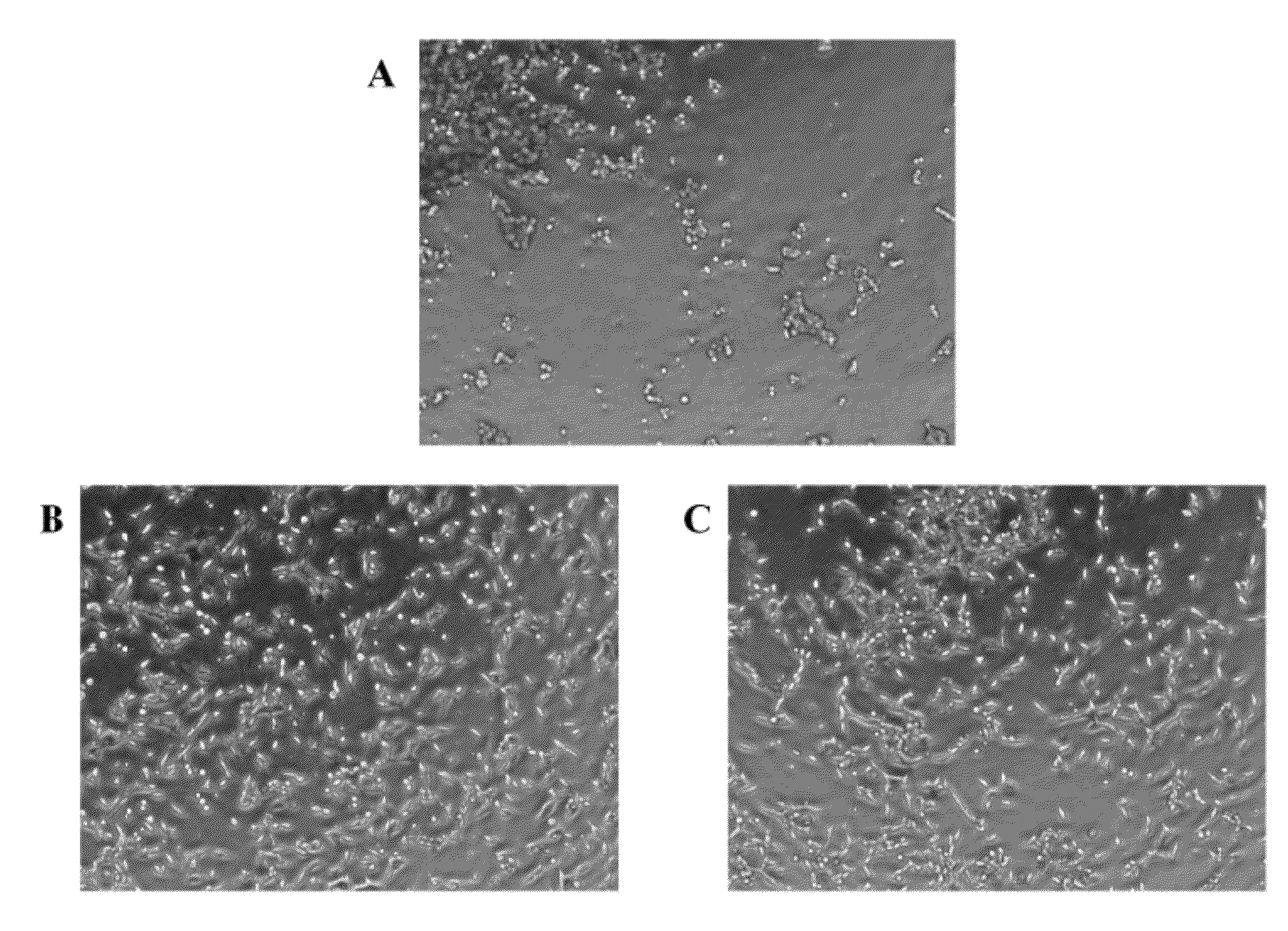

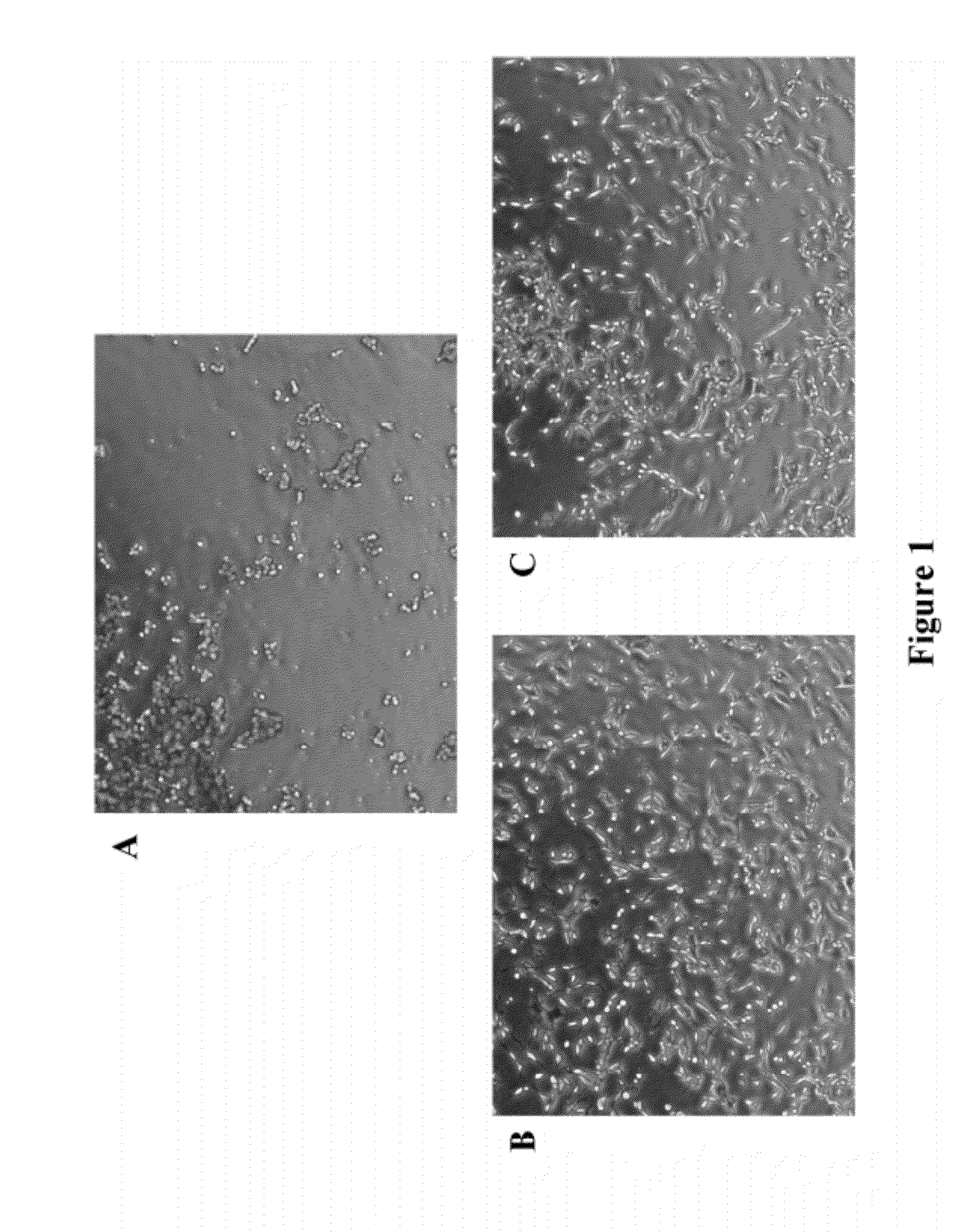

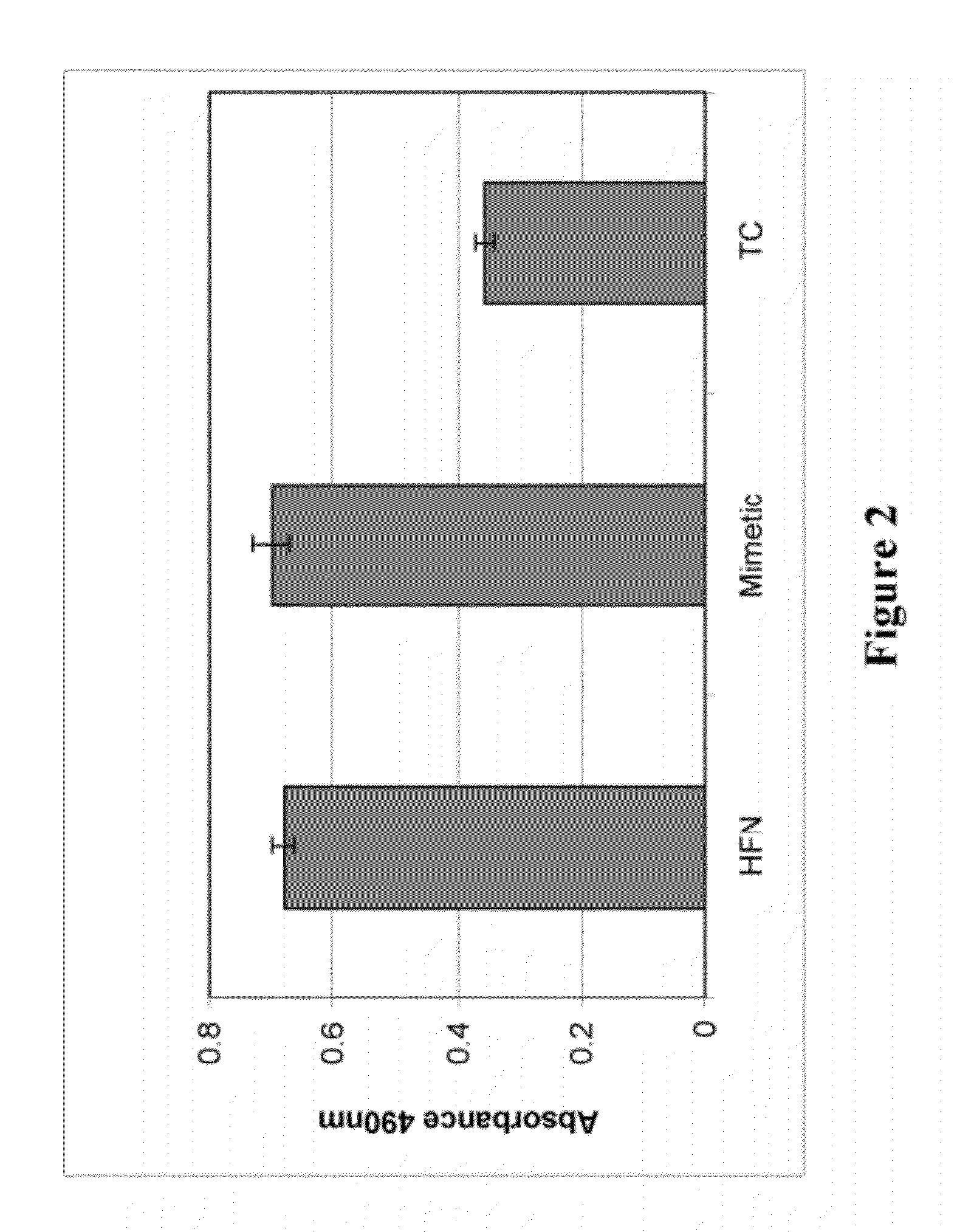

Synthetic, Defined Fibronectin Mimetic Peptides And Surfaces Modified With The Same

ActiveUS20120149871A1Avoid issuingConnective tissue peptidesPeptide/protein ingredientsFibronectinCell biology

The present invention discloses compositions for applications that mimic fibronectin coated surfaces. Advantageously, such compositions provide an animal free (xeno-free, and human-component-free), synthetic, chemically defined surface that mimics at least one of the functionalities of fibronectin.

Owner:CORNING INC

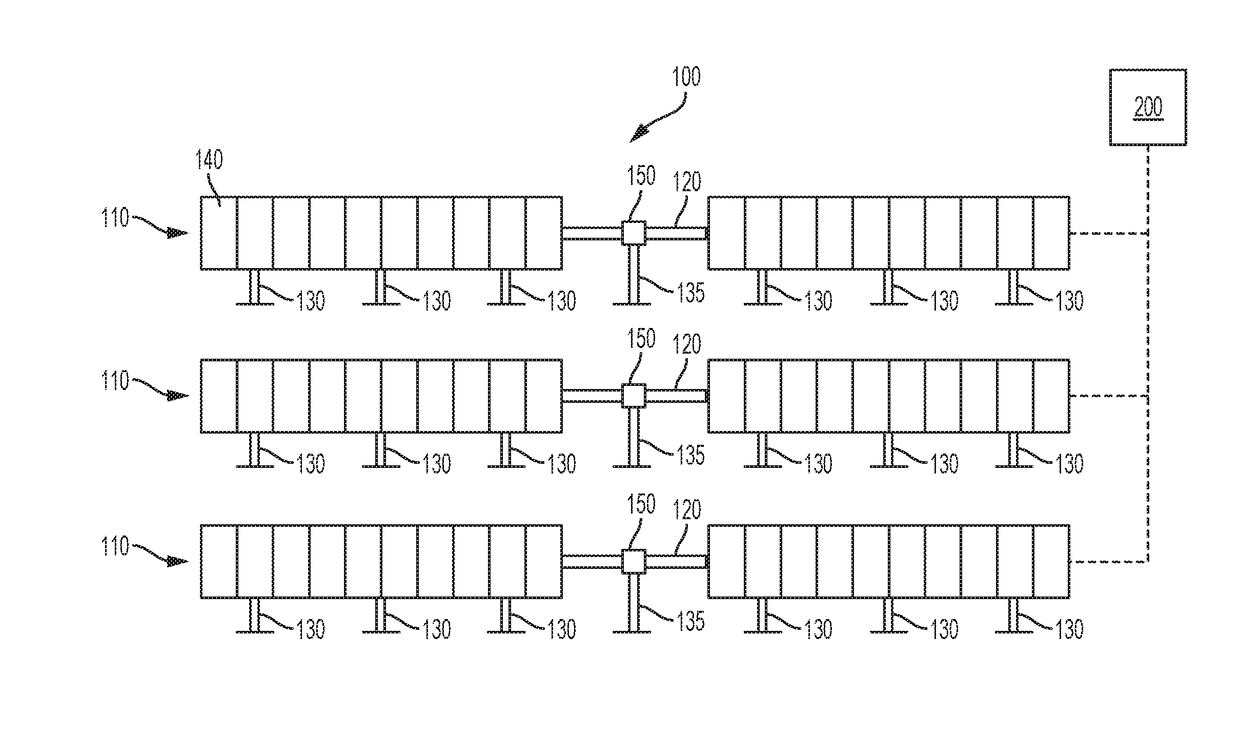

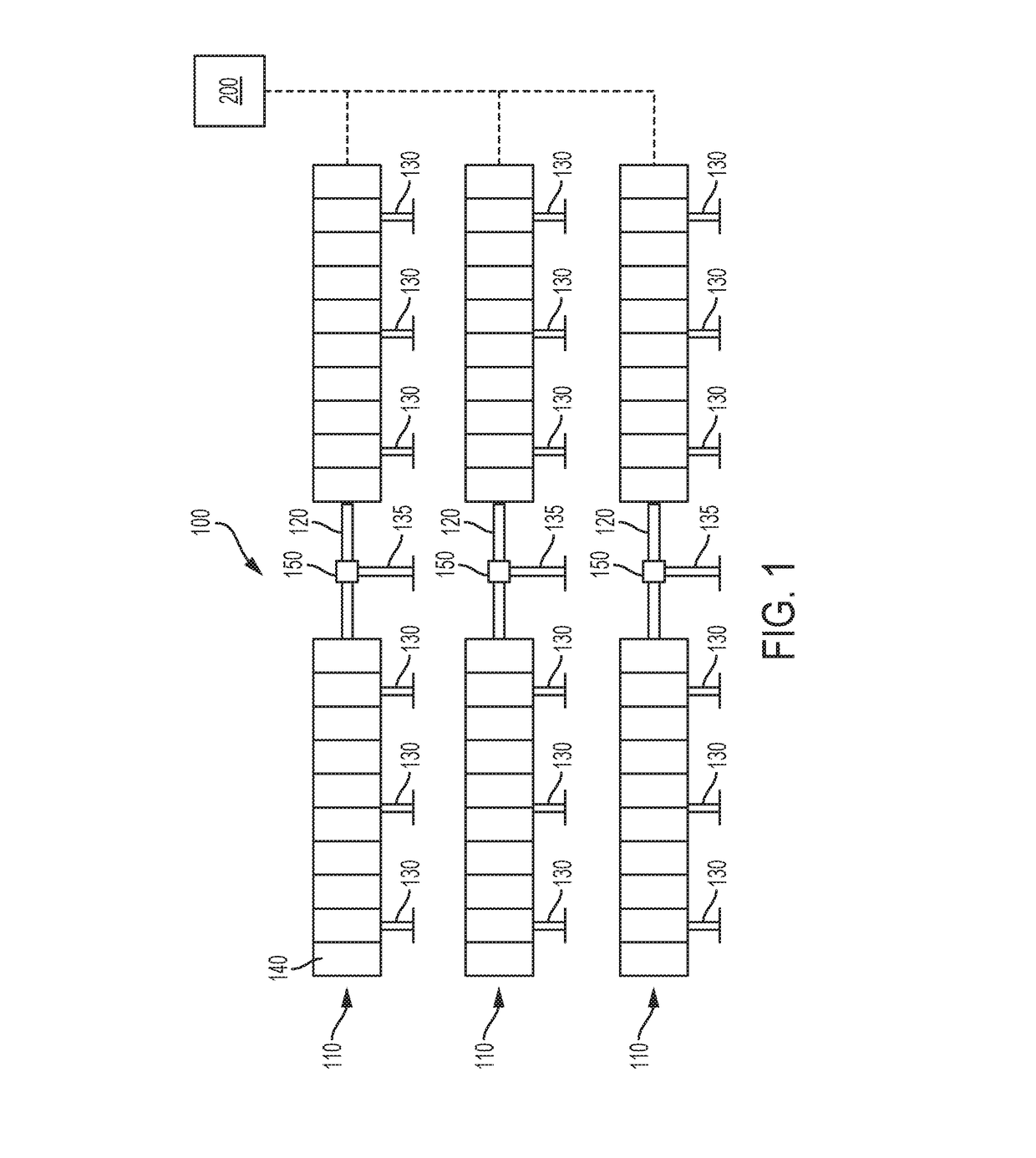

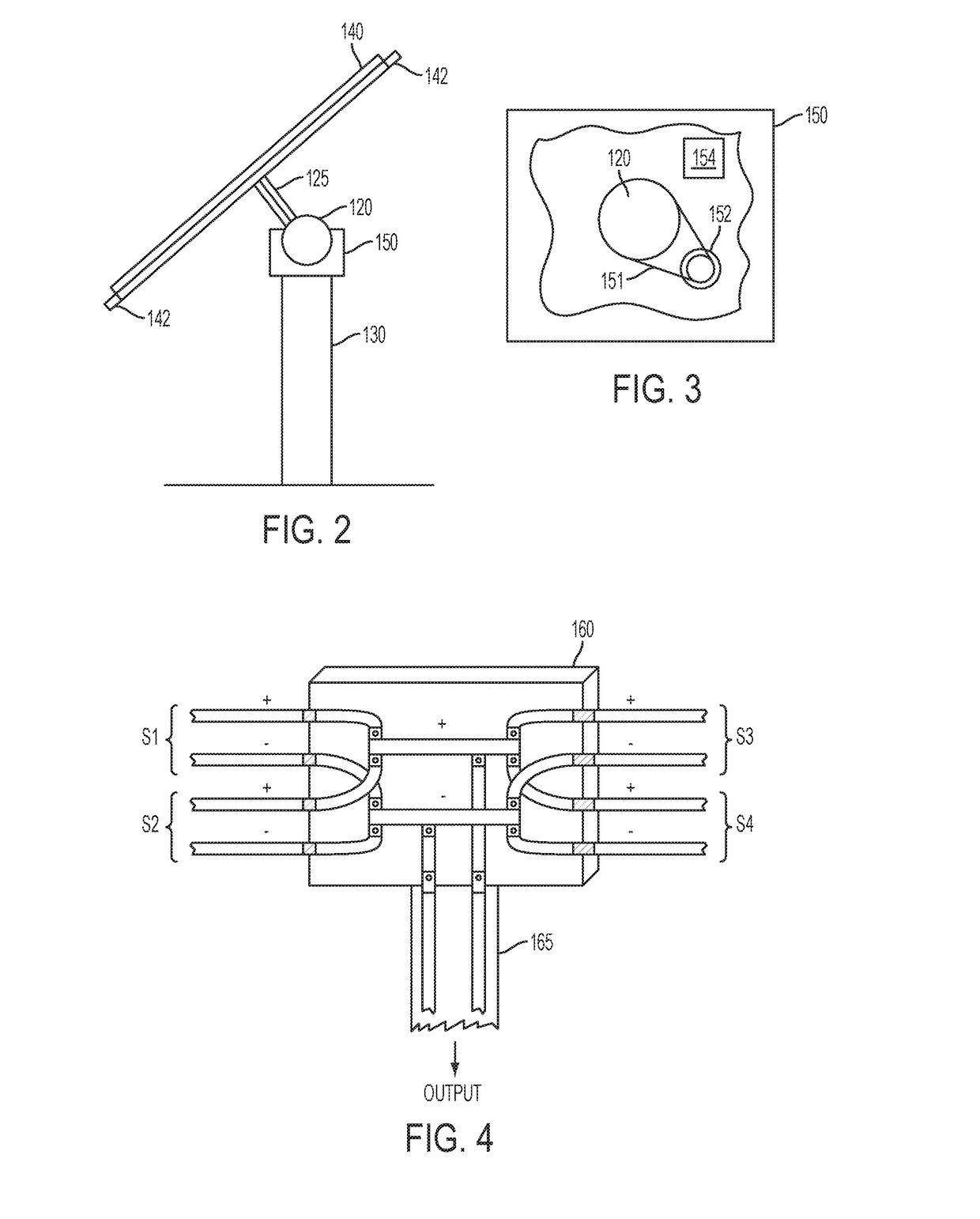

Array powered solar tracking system

InactiveUS20170093329A1Requires minimizationMinimizing amount of wiringPhotovoltaic supportsSolar heating energyElectricityComputer module

A self-powered solar tracker array system and related method, where a torque tube supporting a plurality of strings of photovoltaic (PV) modules, a DC drive motor with a motor controller circuit, and a drive assembly is capable to rotate the torque tube with torque generated by the drive motor, where the power for operating the drive motor is taken from electricity generated by the PV modules. The system can include a battery to provide a power source for rotating the torque tubes when the PV modules are not generating electricity.

Owner:SOLARCITY

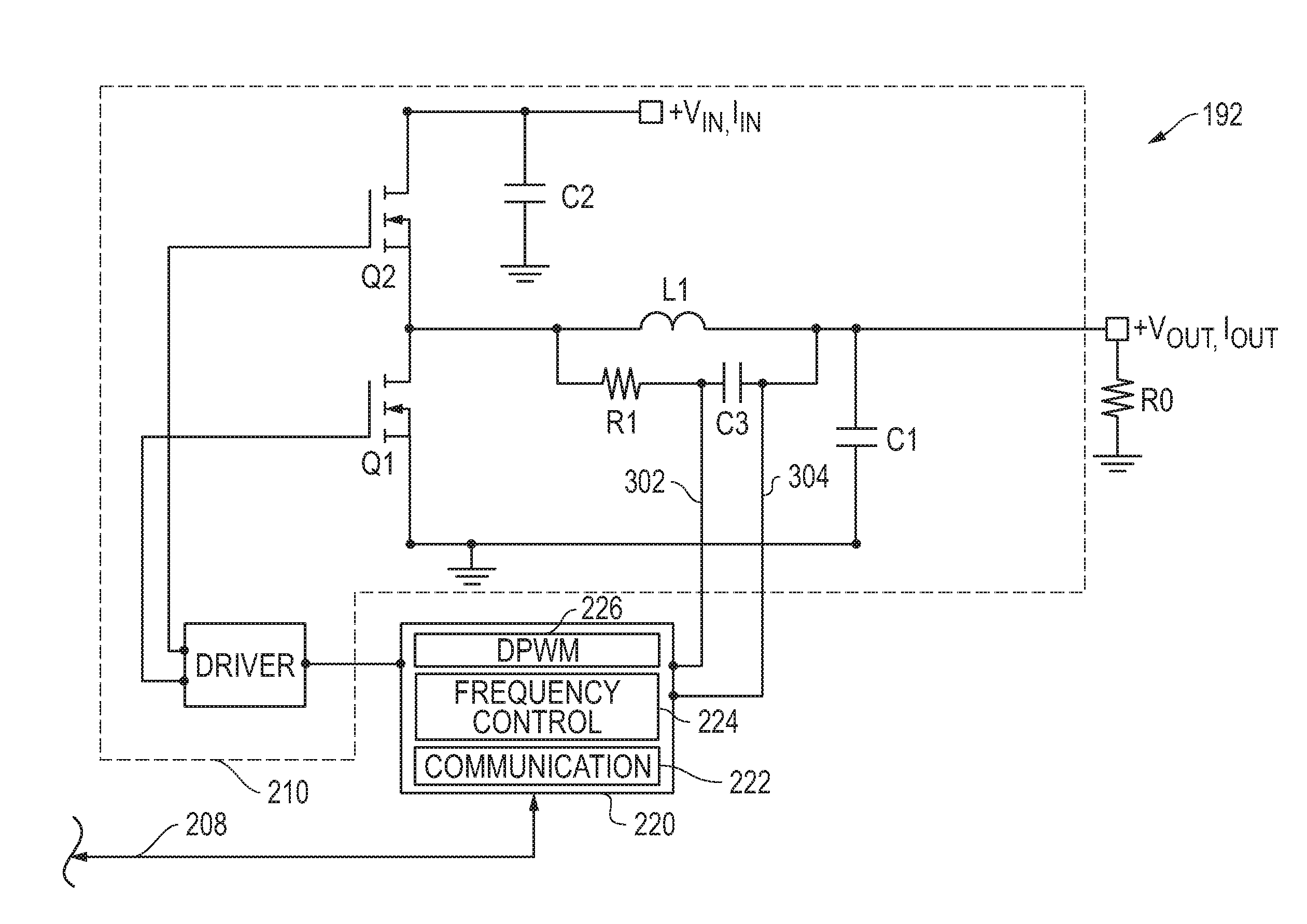

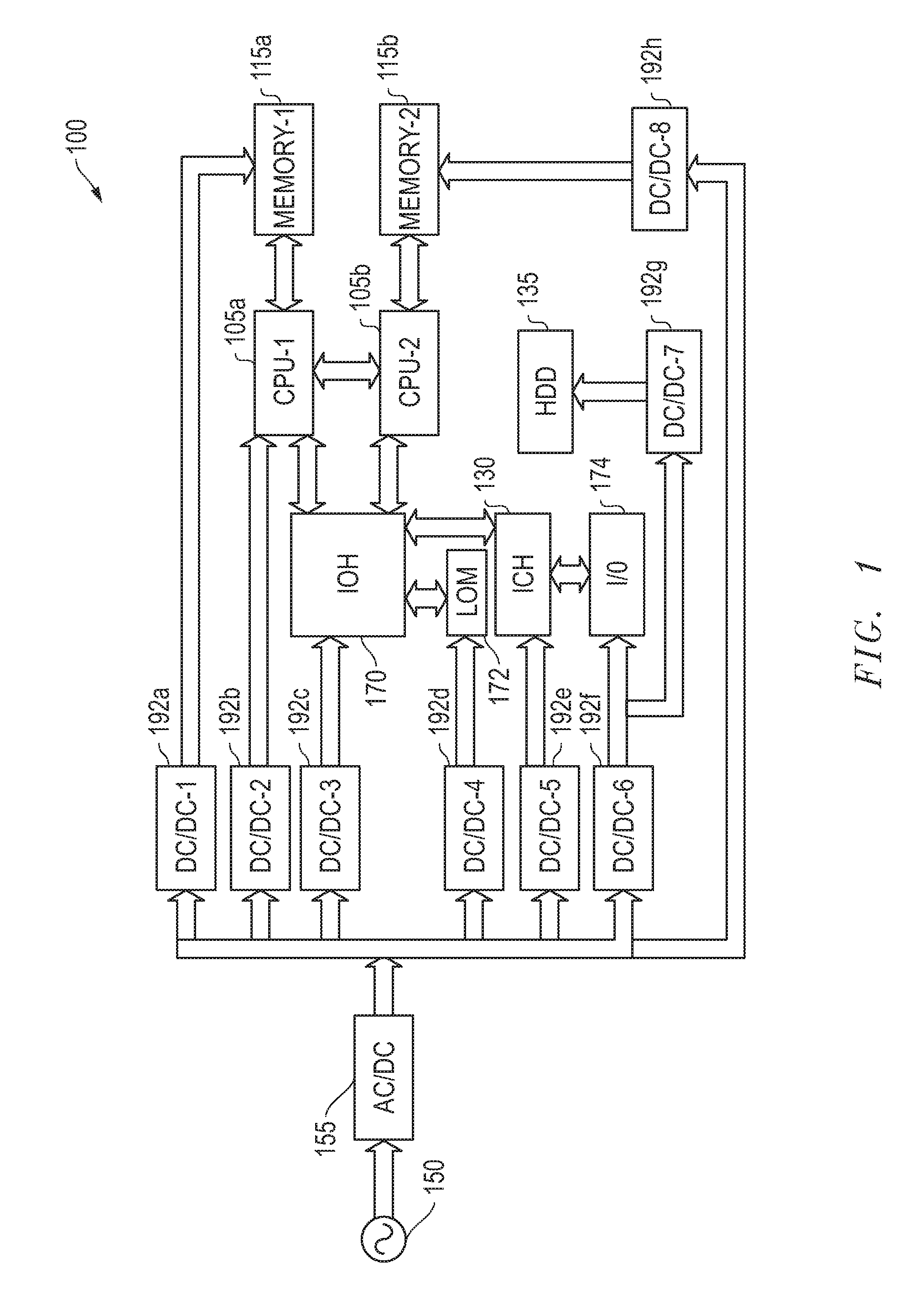

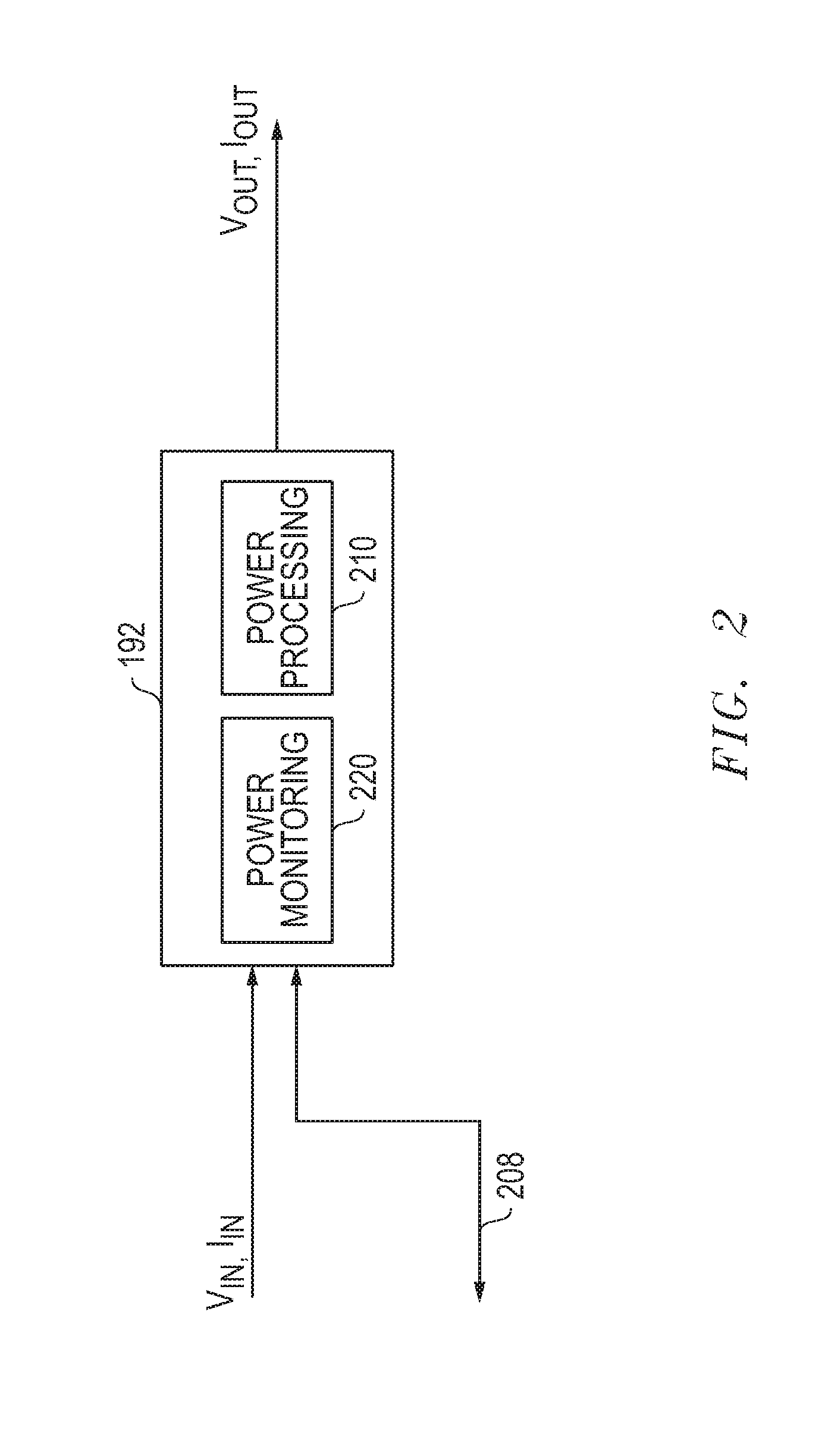

Systems and methods for dynamic management of switching frequency for voltage regulation

ActiveUS20130207630A1Reduced switching & conducting lossSaving and ease of implementationEnergy efficient ICTDigital data processing detailsInformation processingVoltage regulation

Systems and methods are provided that may be implemented to dynamically manage voltage regulator switching frequency. In one embodiment, the disclosed systems and methods may be implemented to dynamically find the optimal voltage regulator switching frequency based on the load current (IOUT) and efficiency in a switching voltage regulator device (VR), such as a voltage regulator down device (VRD) that is embedded on a system board of an information handling system.

Owner:DELL PROD LP

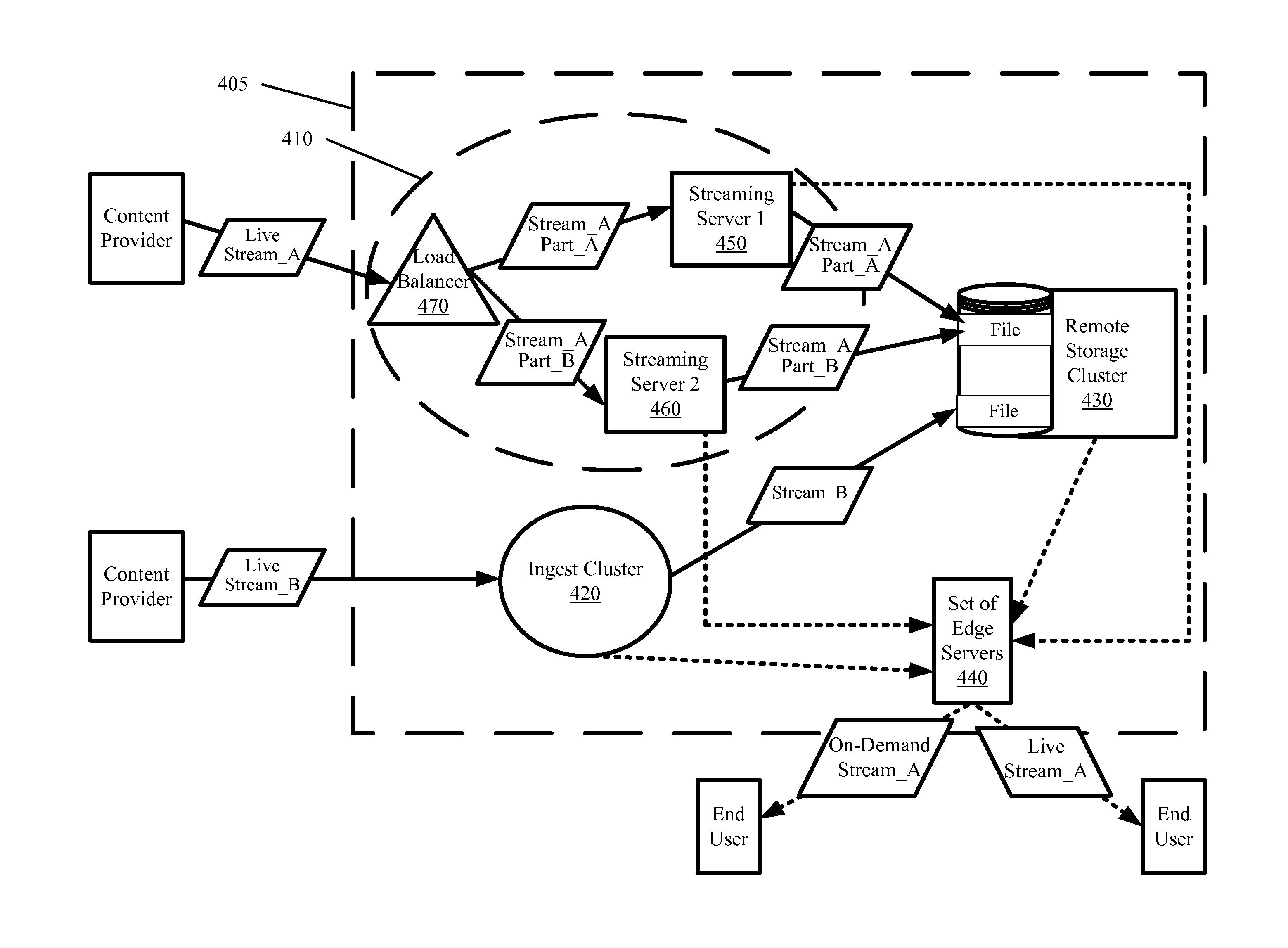

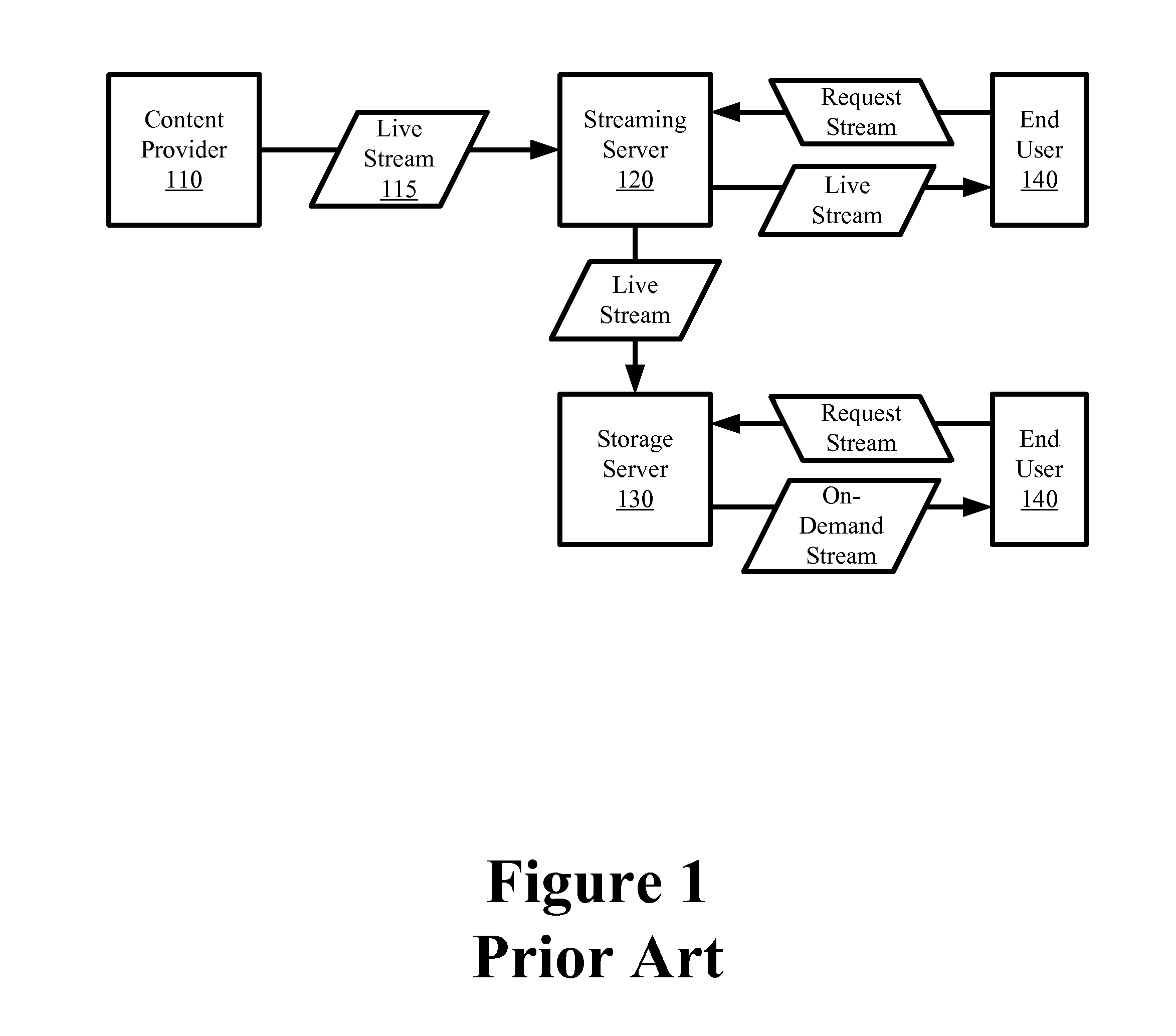

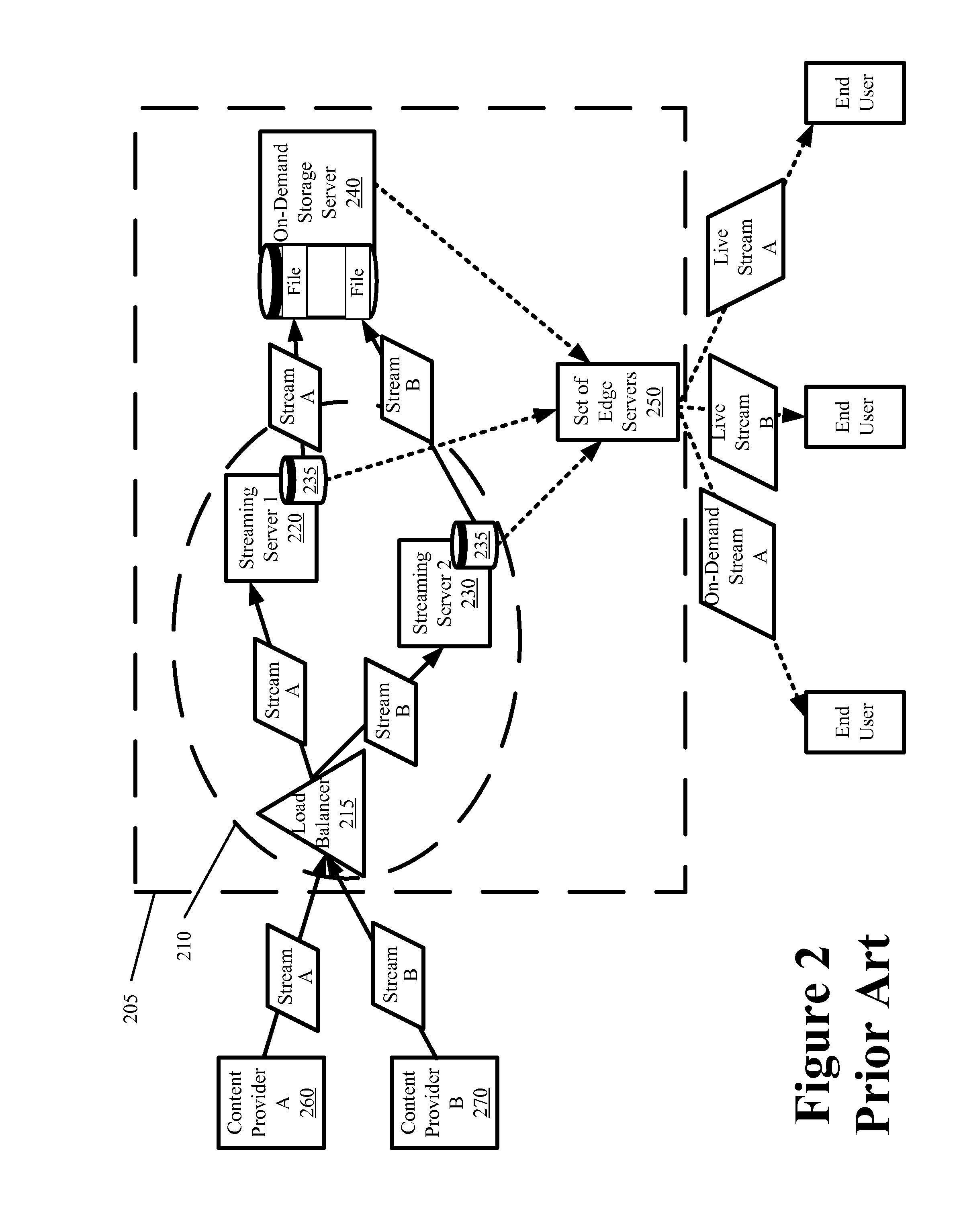

Scalable Content Streaming System with Server-Side Archiving

ActiveUS20120131146A1Avoid issuingDigital data information retrievalMultiple digital computer combinationsDistributed serversMedia server

Some embodiments provide a scalable content streaming system that performs server-side archiving. The content streaming system includes a set of streaming server clusters, a remote storage server, and a set of distributed servers. Each streaming server cluster includes at least one streaming server and a local storage server. Each streaming server of a particular cluster distributes a content stream that is uploaded to the streaming server while also recording the content stream to the local storage server of that particular cluster. The remote storage server stores files from the local storage servers that are transferred when recording to those files is complete. The set of distributed servers distribute a live stream of content from a particular streaming server when the content is being uploaded to the particular streaming server and distribute a recorded stream of the content from the remote storage server when the upload is complete.

Owner:EDGIO INC

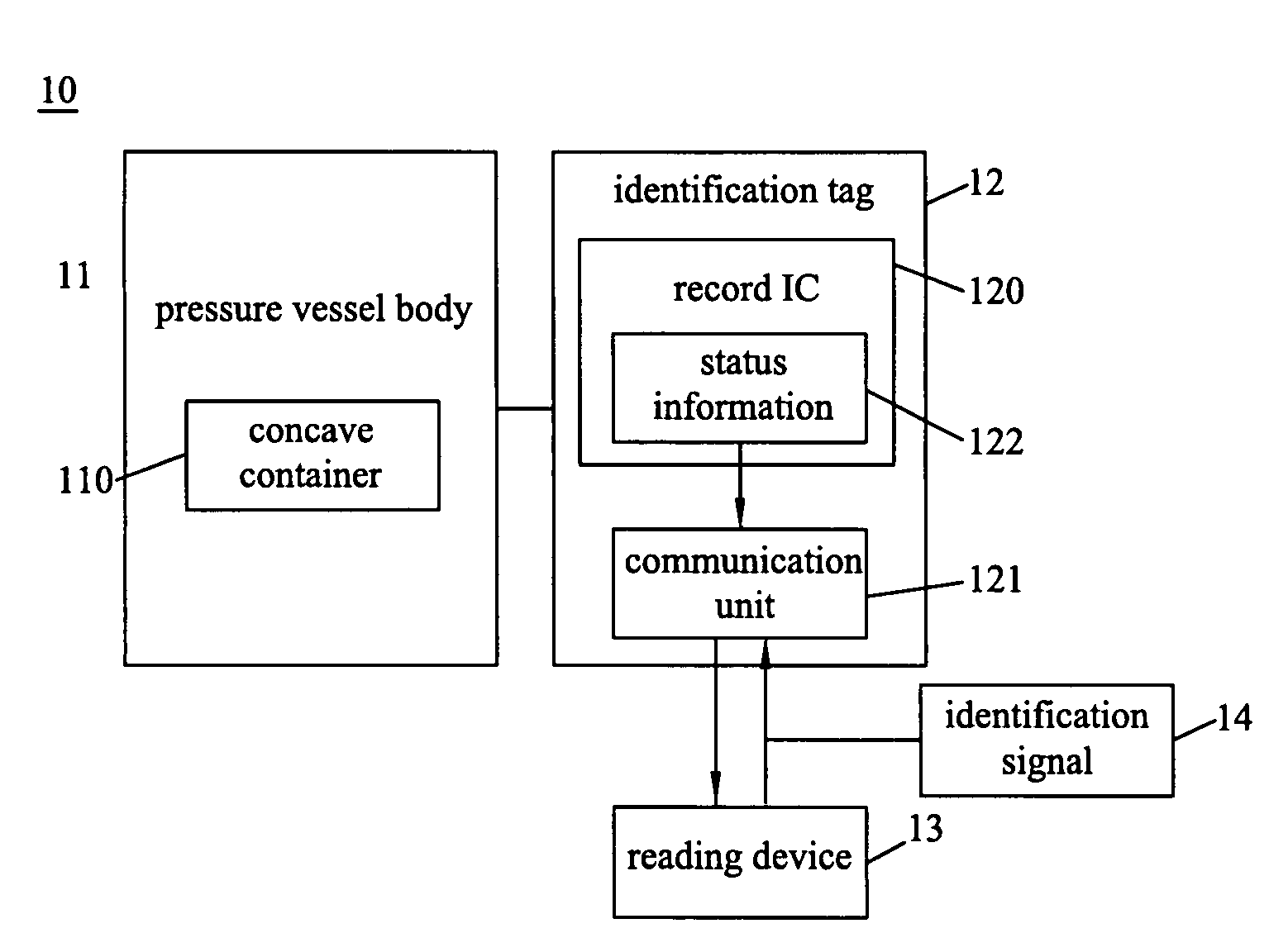

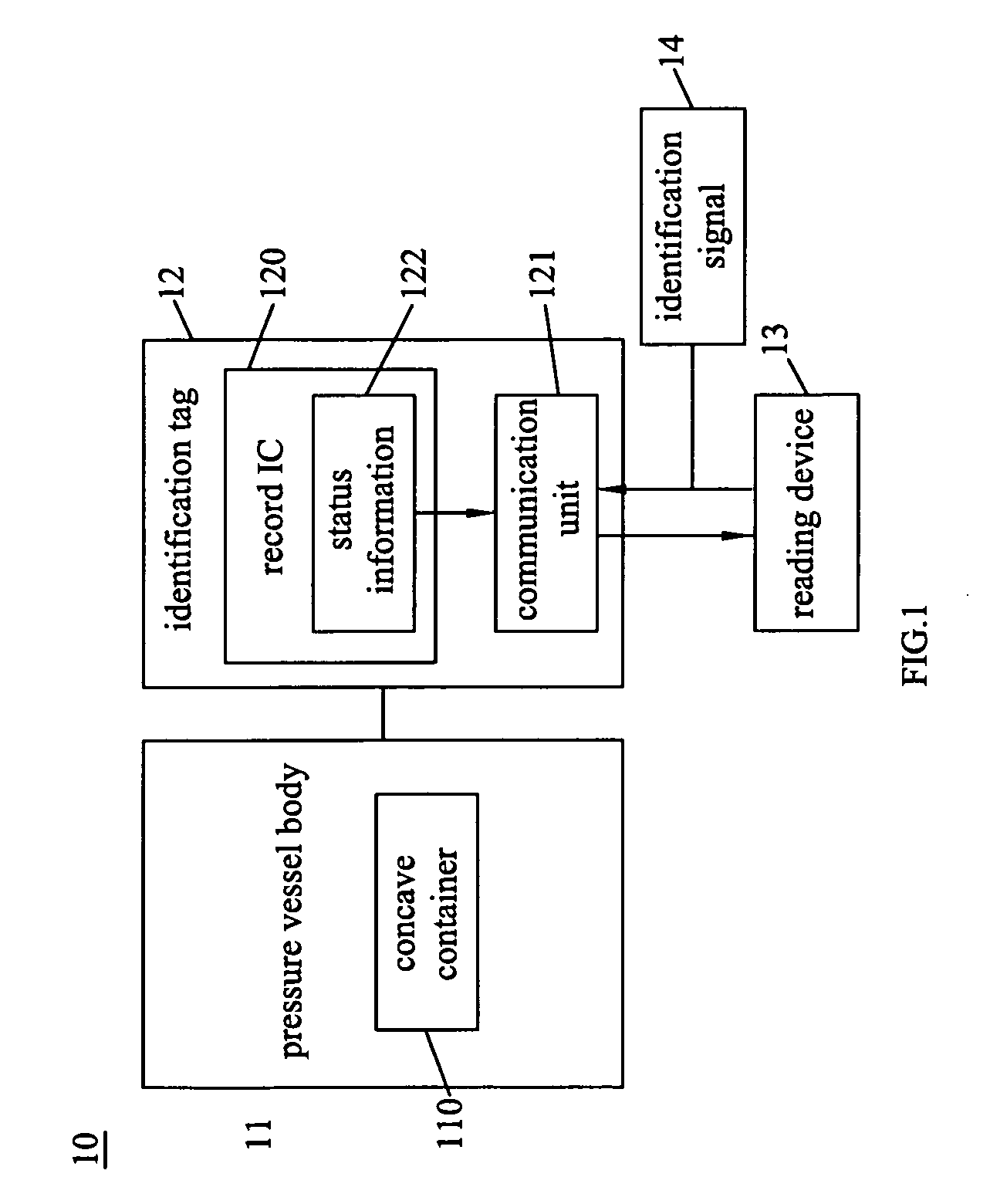

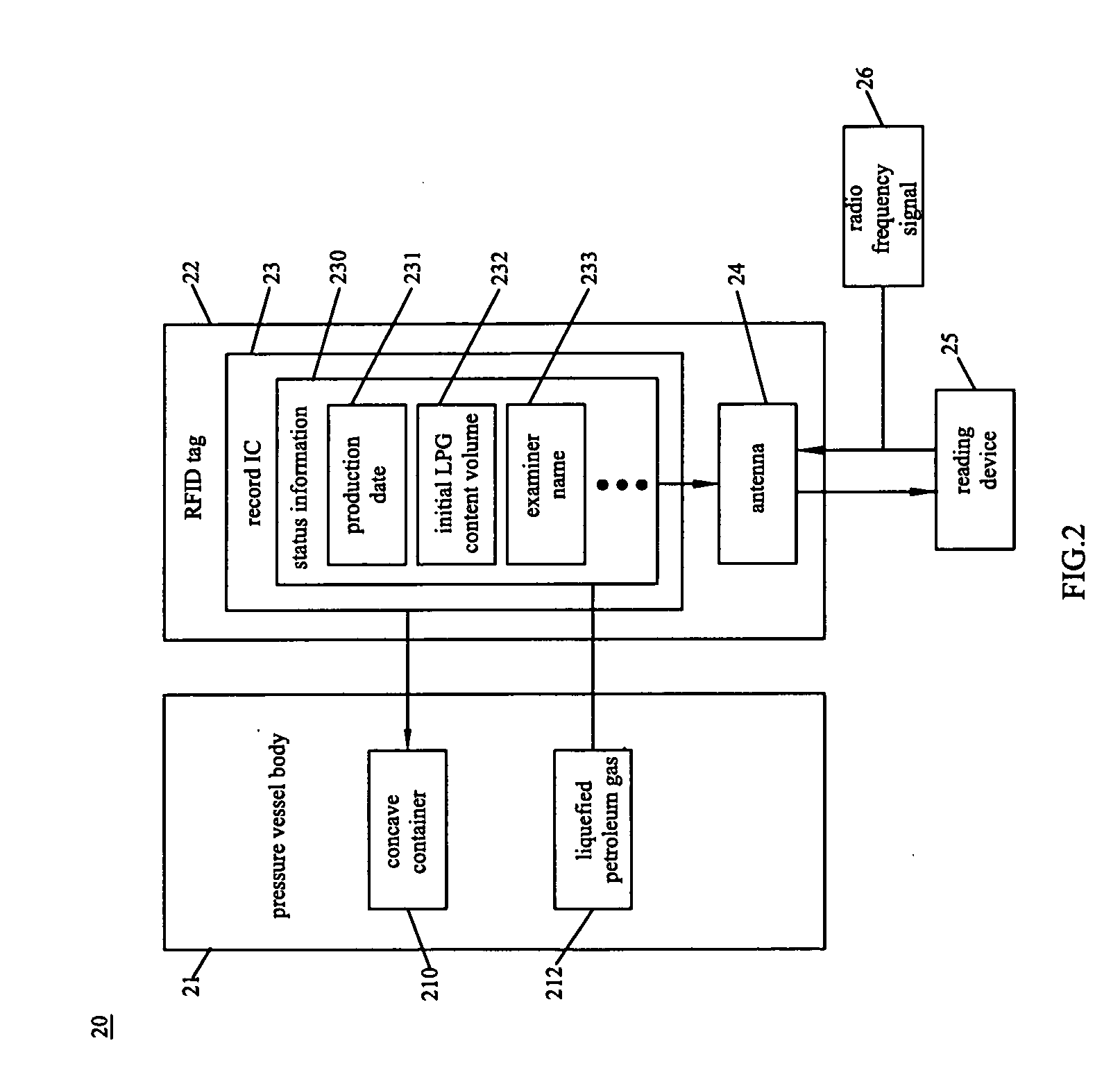

Pressure vessel apparatus with sensing identification function

InactiveUS20090140867A1Avoid issuingNot easy to replaceVessel mounting detailsVessel manufacturingCommunication unitEngineering

The present invention discloses a pressure vessel apparatus with sensing identification function, comprising a pressure vessel body and an an identification tag. The pressure vessel body has a concave container located on its surface. The identification tag is located in the concave container, comprising a record IC and a communication unit. The record IC is used for recording the status information of the pressure vessel body. When the reading device reads the identification tag, and thus provides an identification signal such that the communication unit transmits the status information to the reading device to verify whether the lifetime of the pressure vessel apparatus was expired. Moreover, a sensing unit is applied for detecting the varying status of the content in the pressure vessel body, and such information is provided to the reading device as a judging reference for content filling and the pressure reading of the pressure vessel apparatus, in order to improve the safety of the pressure vessel apparatus.

Owner:TAIWAN NAME PLATE

Silicone based tube for transporting malodoriforous matter from the

ActiveUS20080103463A1Need complex and expensiveComplex and expensive processSynthetic resin layered productsLaminationHuman bodyBiomedical engineering

A tube assembly for carrying malodoriforous matter from the human body comprises a silicone based tube having a central bore for the malodoriforous matter, and a tubular sleeve member comprising an odor barrier material, the silicone based tube and the tubular sleeve member being arranged one within the other such that the tubular sleeve member provides an odor barrier to obstruct leakage of odors from malodoriforous matter in the bore of the silicone based tube. The tube assembly is especially suitable for use in fecal or bowel management apparatus.

Owner:CONVATEC TECH INC

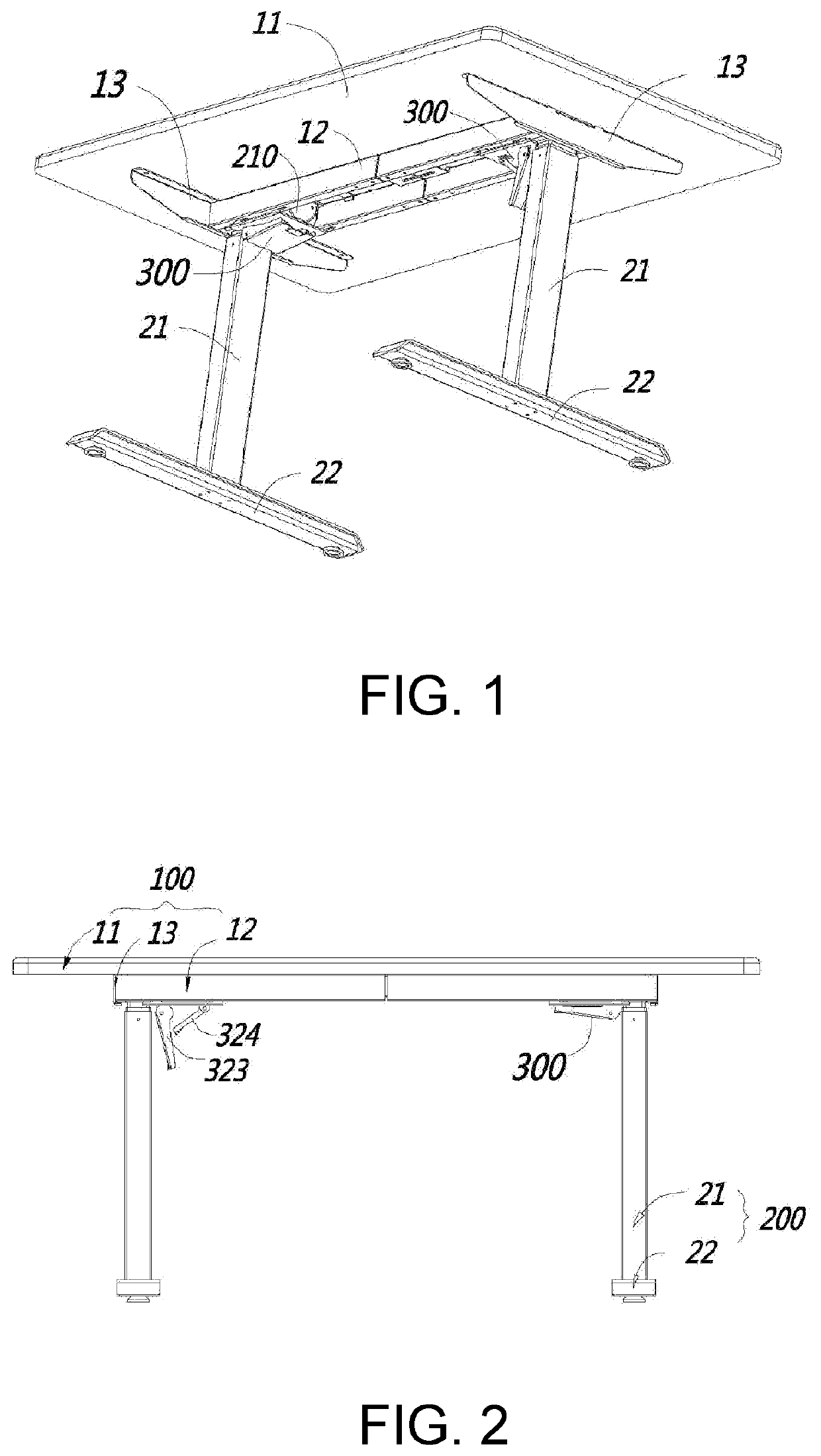

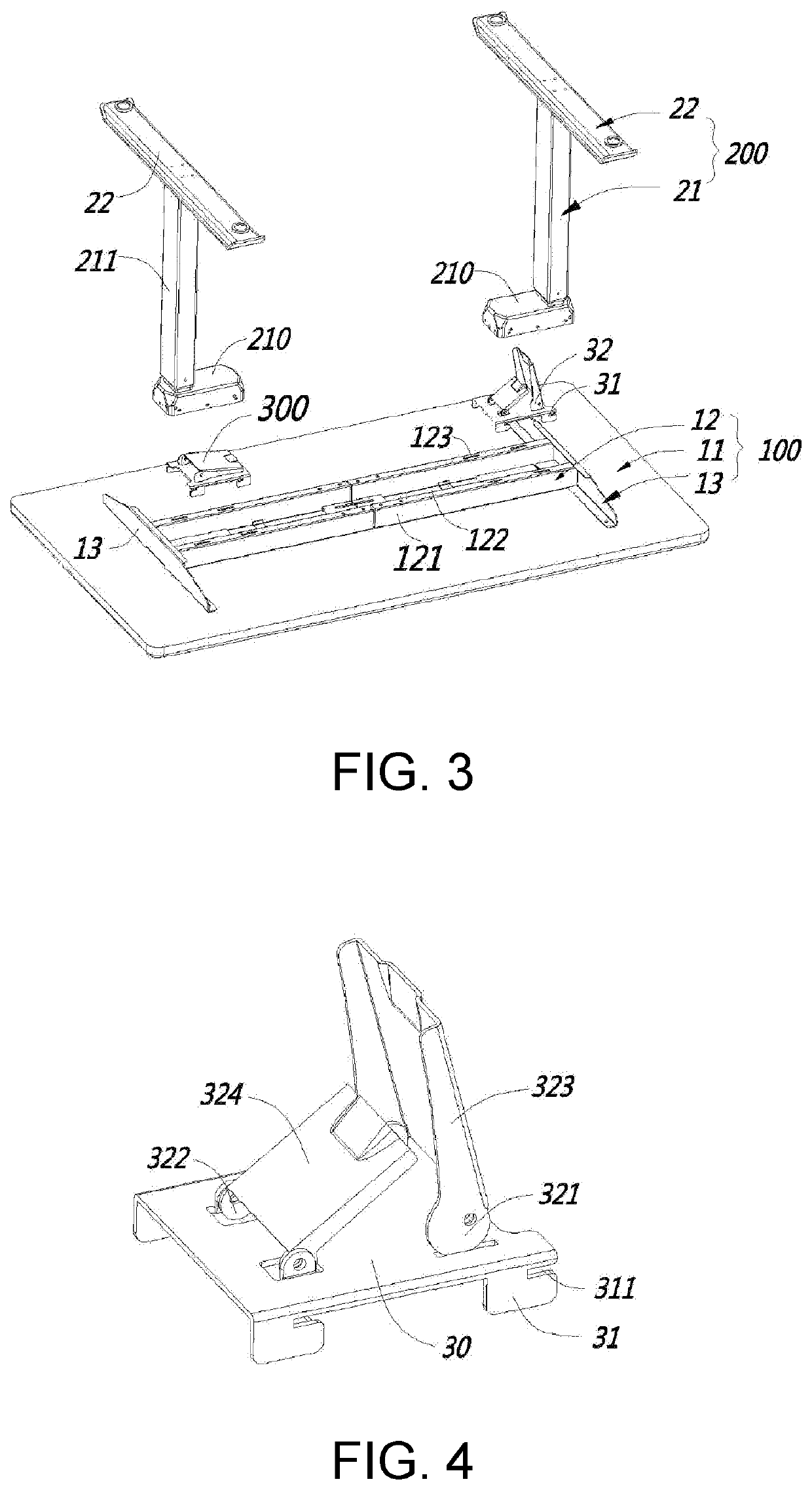

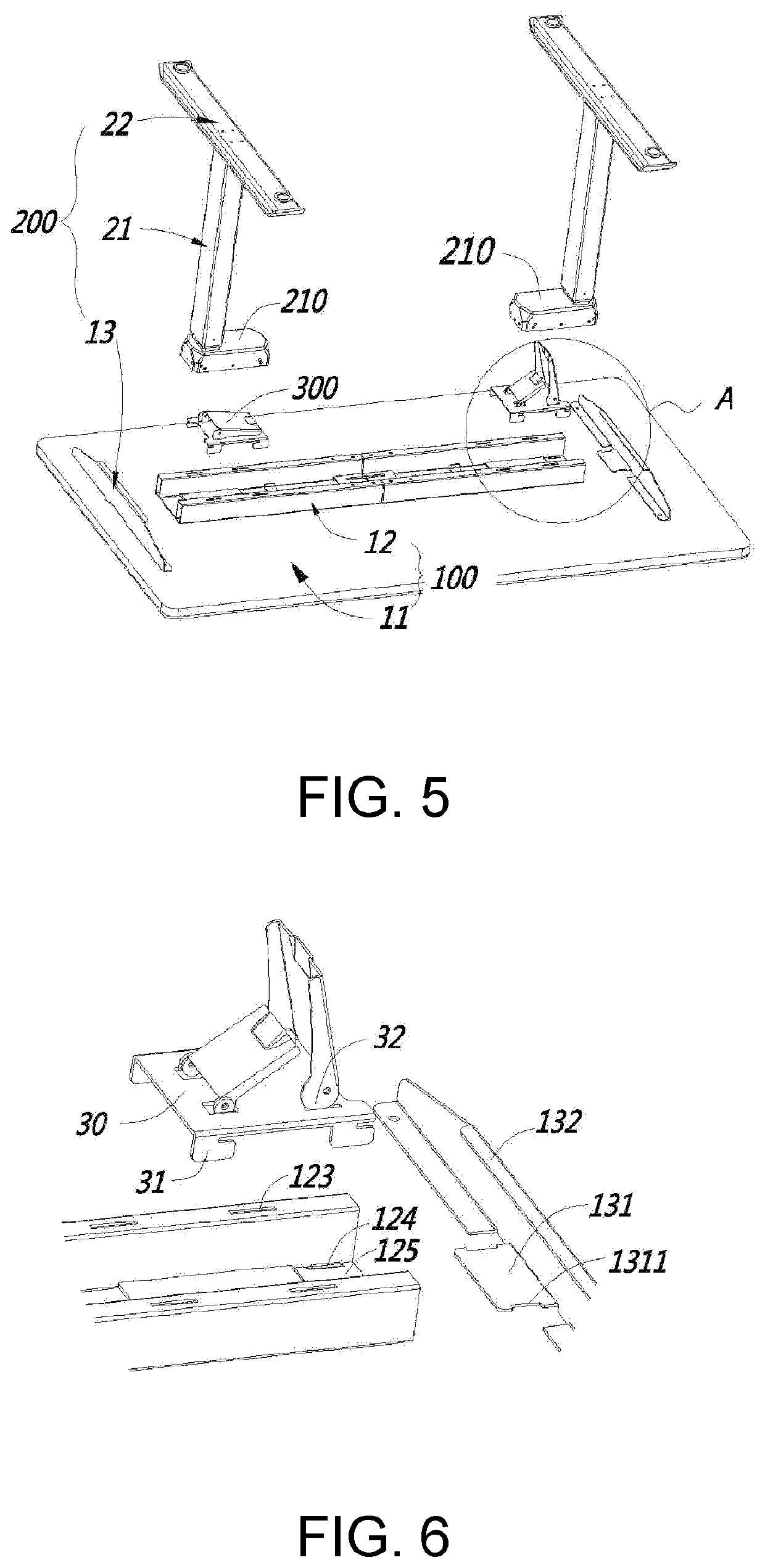

Modularized fast assembly lift desk and fast assembly method therefor

ActiveUS20200359785A1Convenient and fast wayThe process is convenient and fastOffice tablesVariable height tablesSoftware engineeringElectric machinery

A modularized fast assembly lift desk includes a preassembled module, a matched module and a clamping member. The preassembled module includes a combined body formed by connection between a desktop platform and a transverse beam. The matched module includes a lift column including a motor housing. The clamping member includes a fixed connecting end and a movable squeezing end. When a user assembles the lift desk, the fixed connecting end of the clamping member is engaged with the preassembled module. The movable squeezing end of the clamping member is pressed to generate a squeezing force between the movable squeezing end and the motor housing. The motor housing and the preassembled module are fixedly connected to implement locking between the preassembled module and the matched module.

Owner:ZHEJIANG JIECHANG LINEAR MOTION TECH

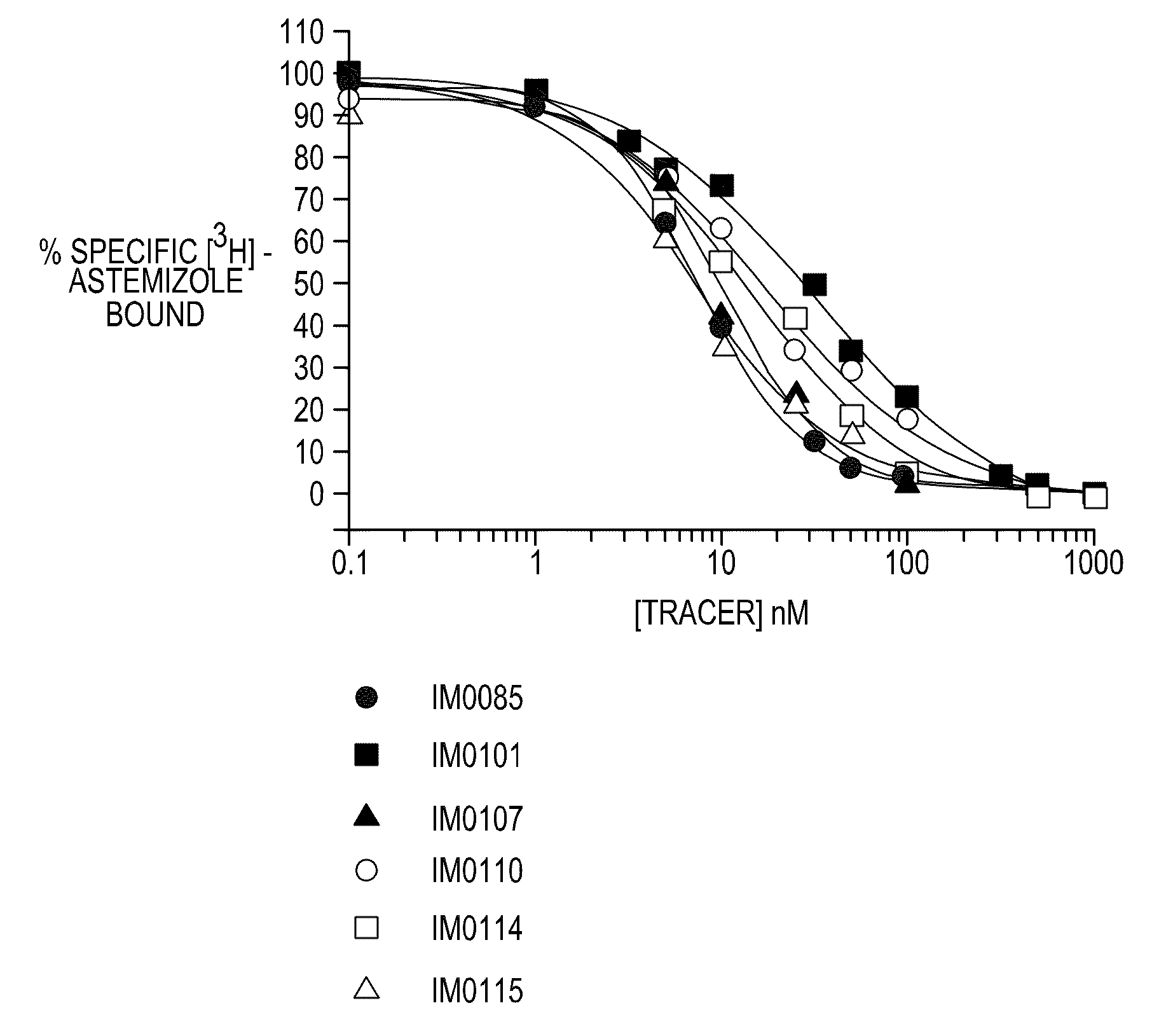

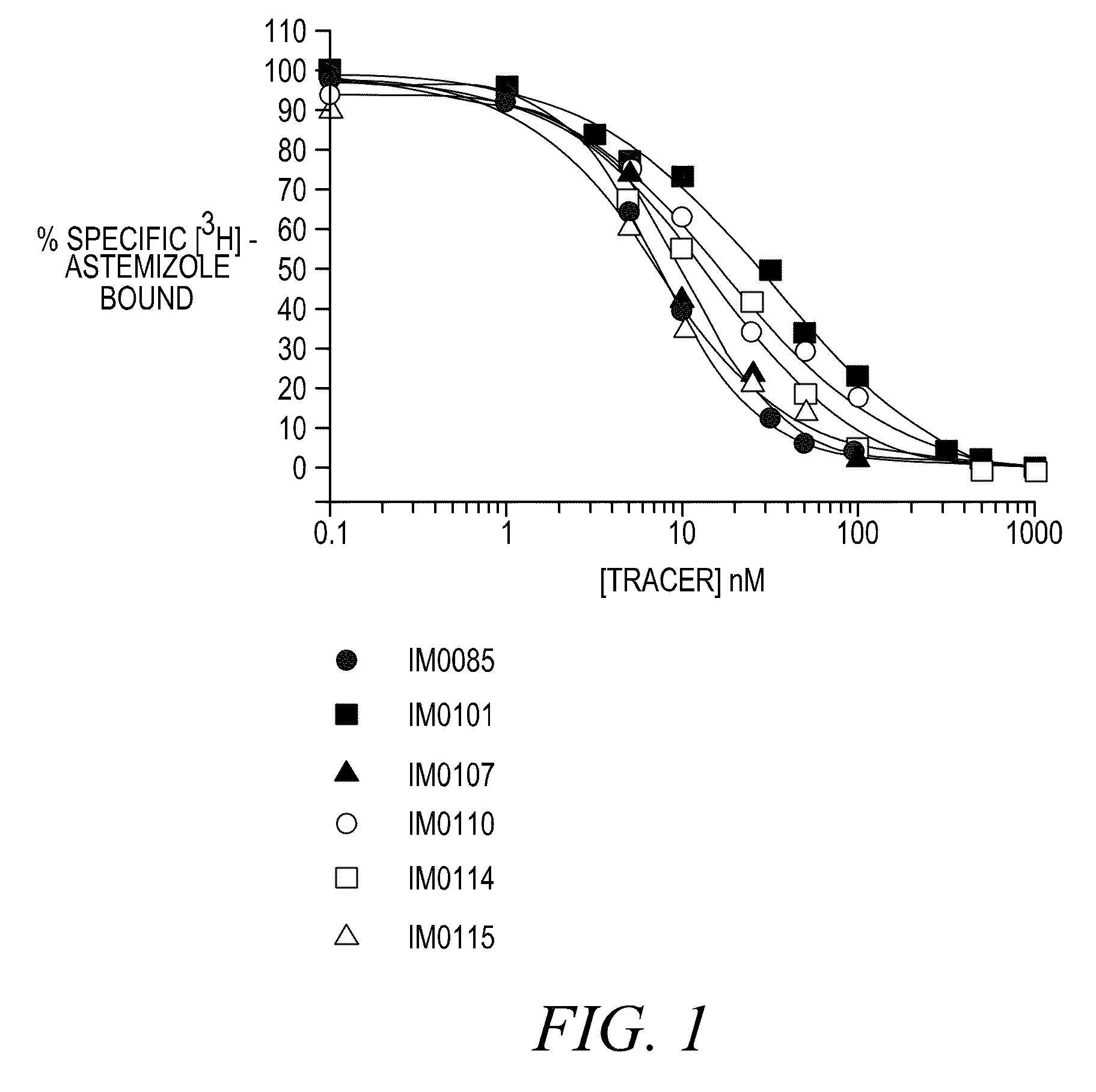

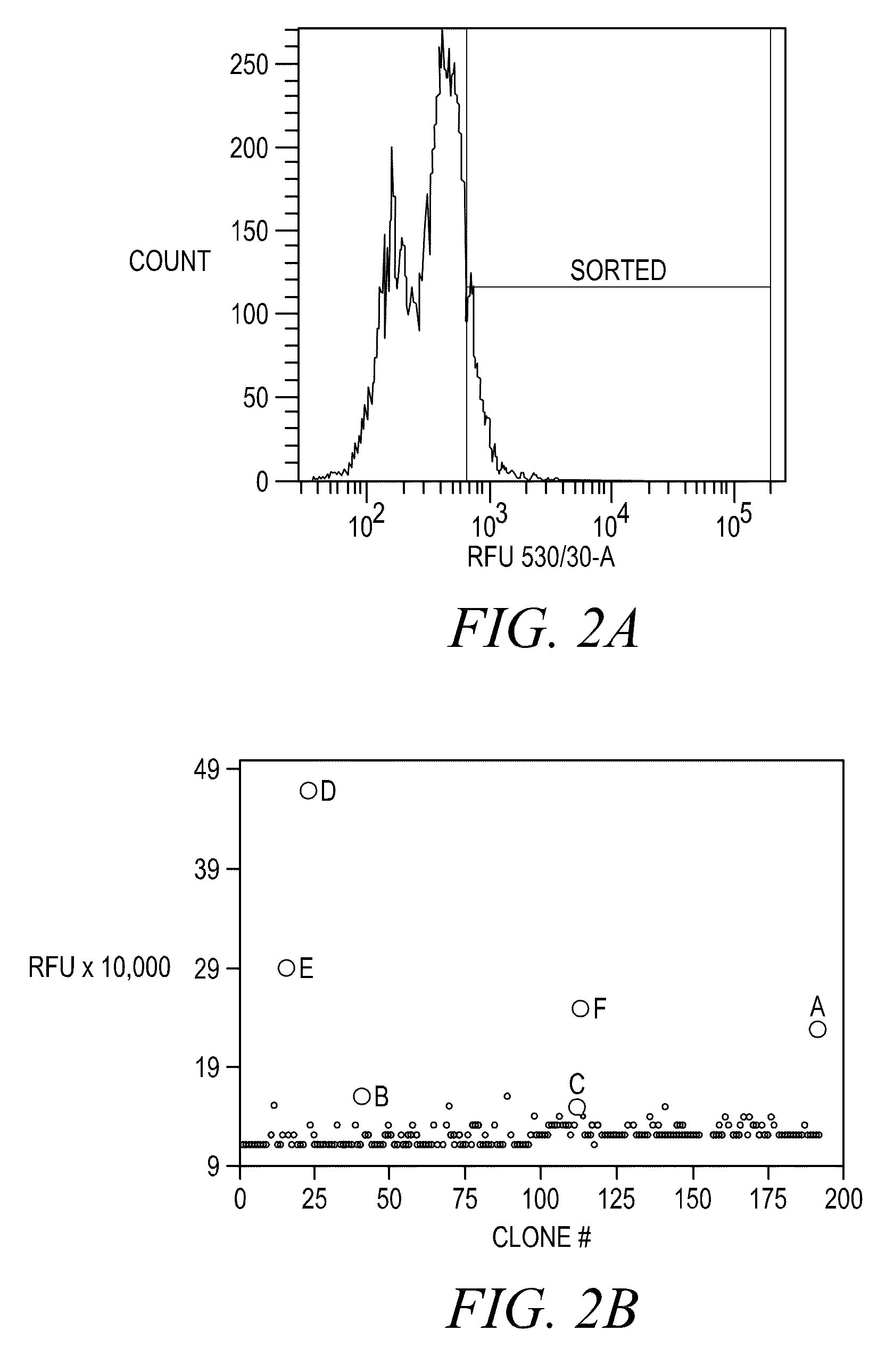

FLUORESCENCE POLARIZATION hERG ASSAY

ActiveUS20090253148A1Easy to operateAvoid issuingOrganic chemistryArtificial cell constructsHUMAN ETHER-A-GO-GO-RELATED GENECardiotoxicity

Disclosed are assays, methods, and kits for the screening of test compounds for their capability to induce cardiotoxicity in a subject. In particular, whether a test compound has the effect to prolong the Q-T interval as measured by an electrocardiogram in a human. The assays, methods, and kits disclosed herein make use of the binding interaction between novel fluorescent tracers and the hERG K+ channel, and the propensity of a test compound to influence that binding interaction.

Owner:LIFE TECH CORP

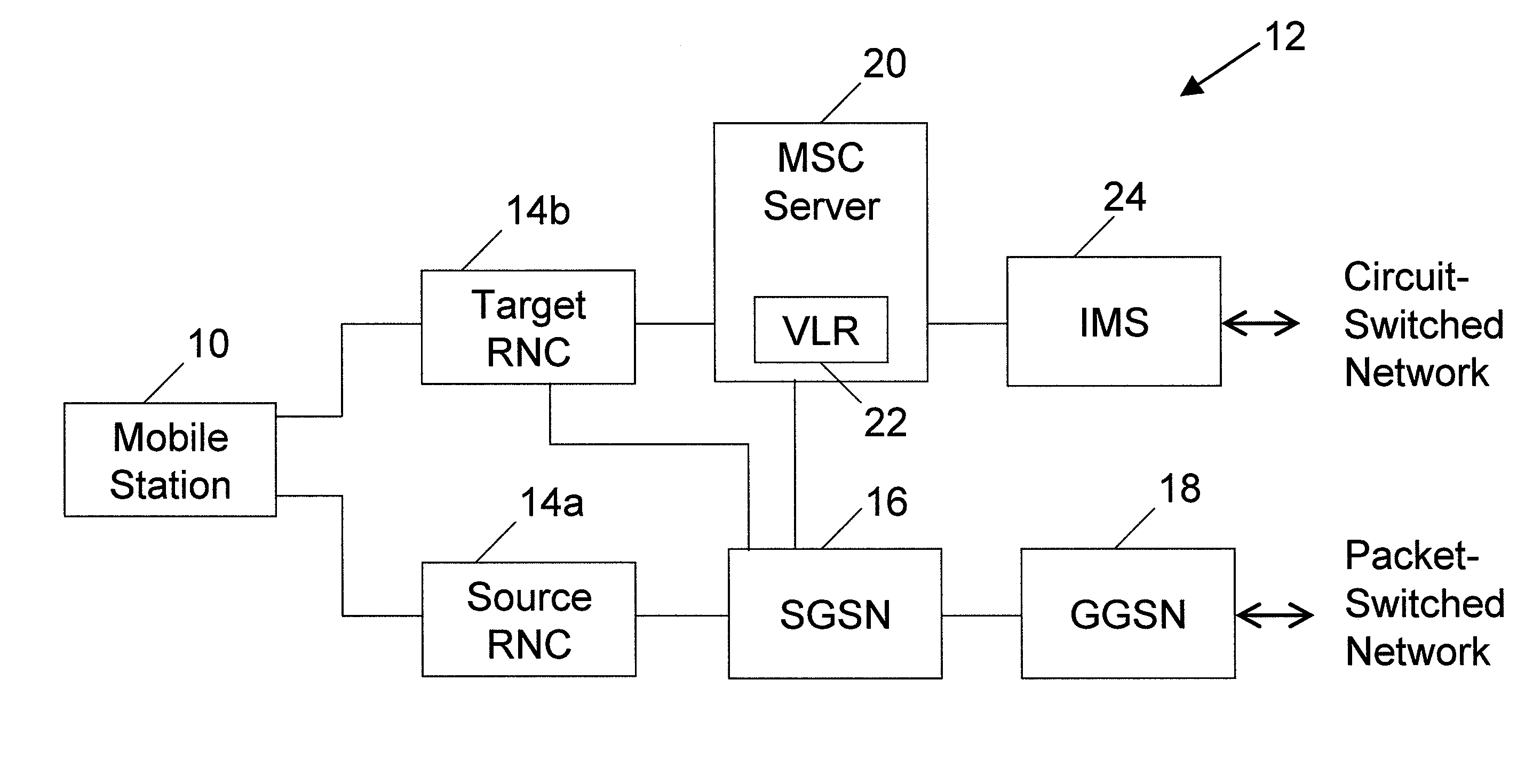

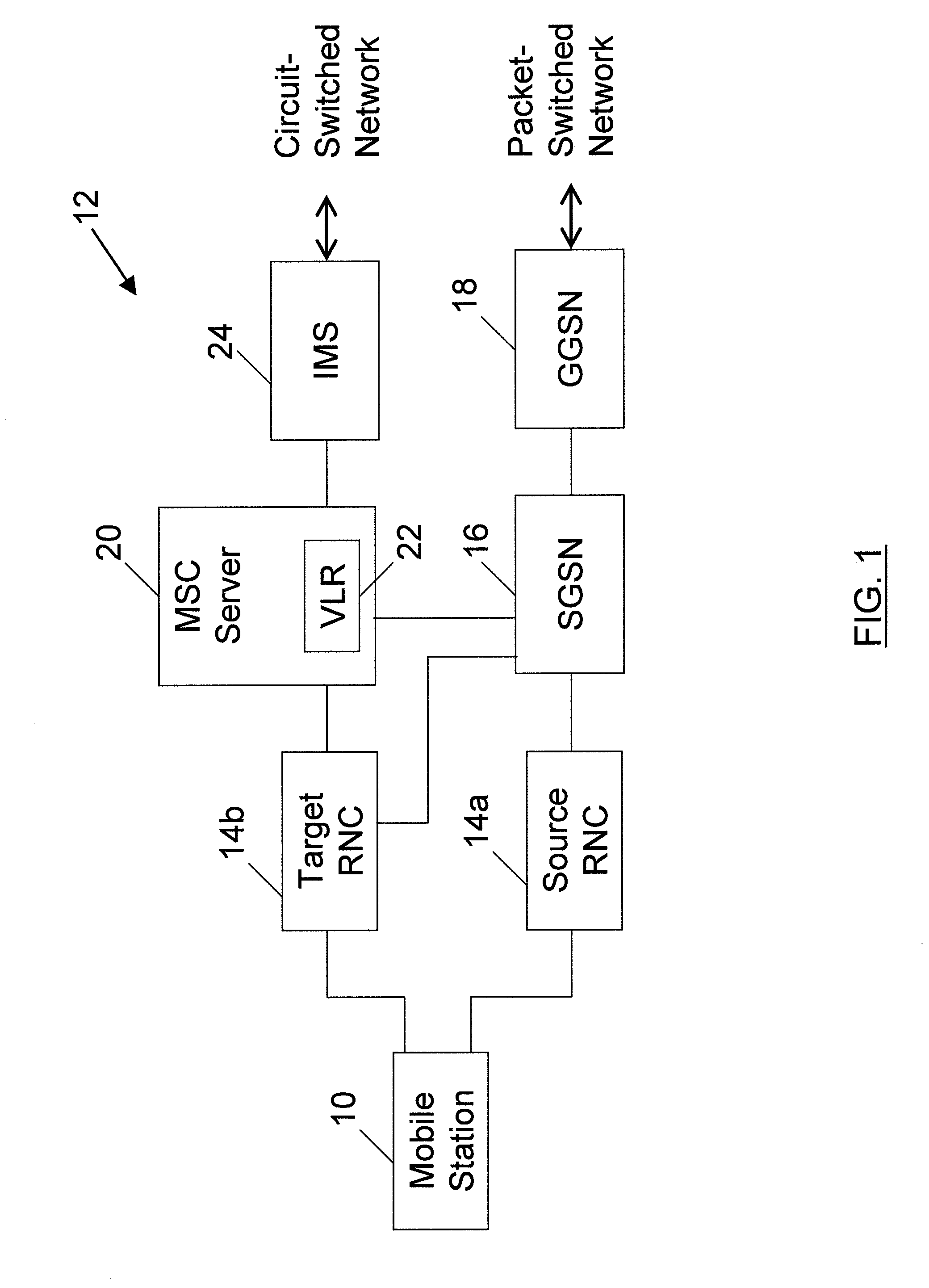

Method, Apparatus And Computer Program Product For Providing Security During Handover Between A Packet-Switched Network And A Circuit-Switched Network

ActiveUS20100220862A1Enhance security in responseImprove securityEncryption apparatus with shift registers/memoriesSecret communicationHandoverComputer science

A method, apparatus and computer program product are provided to facilitate security in response to a handover from an initial network to a subsequent network, such as a handover between a packet-switched network and a circuit-switched network. The method, apparatus and computer program product may provide at least one security key for use in the subsequent network following handover from the initial network such that communications conducted via the subsequent network, including initial communications, may be secure. In order to provide at least one security key for use in the subsequent network, at least one security key of the initial network may be identified along with a nonce in response to a determination that a handover is to be made. The at least one security key of the subsequent network may then be determined based upon the at least one security key of the initial network and the nonce.

Owner:NOKIA TECHNOLOGLES OY

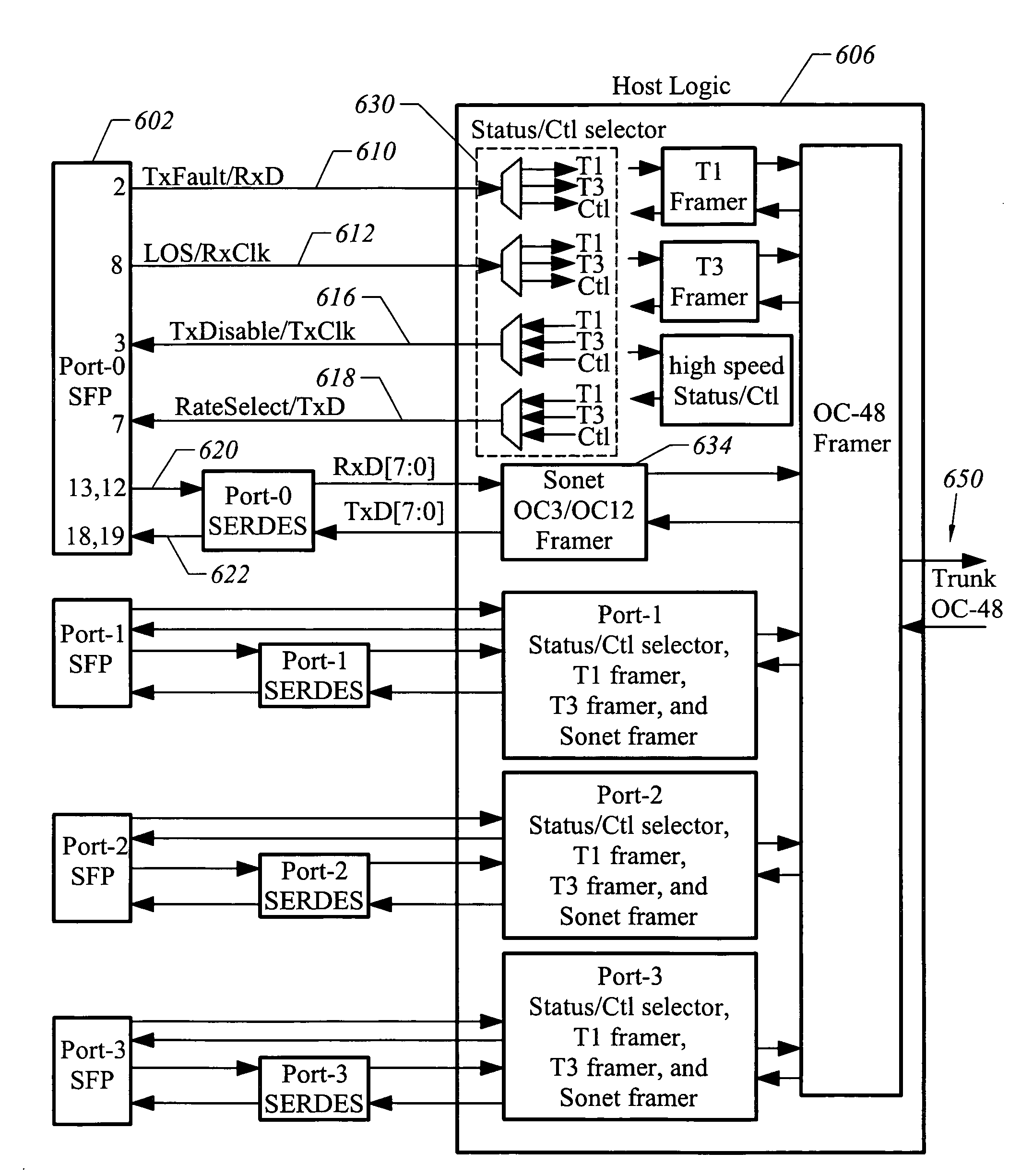

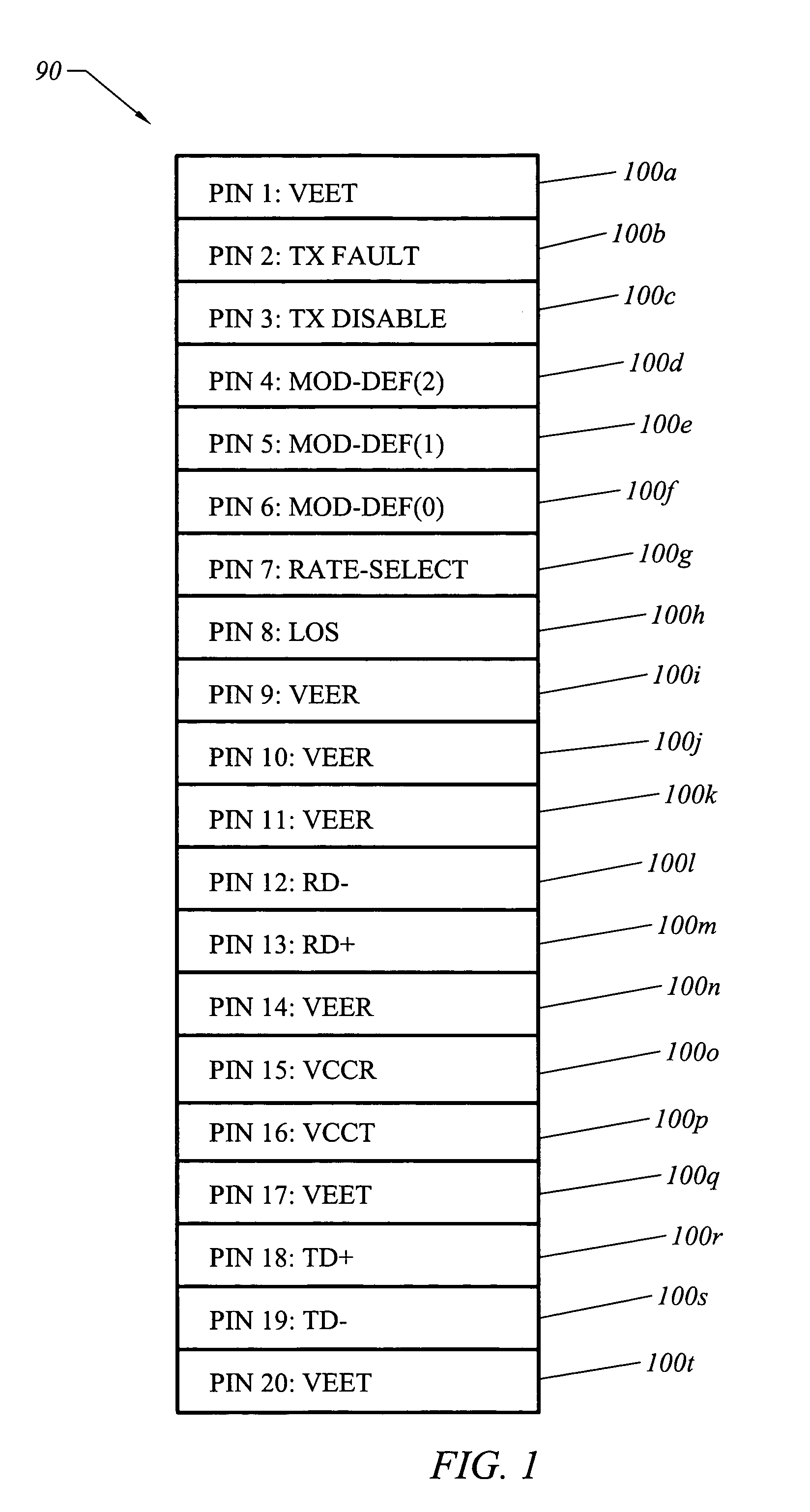

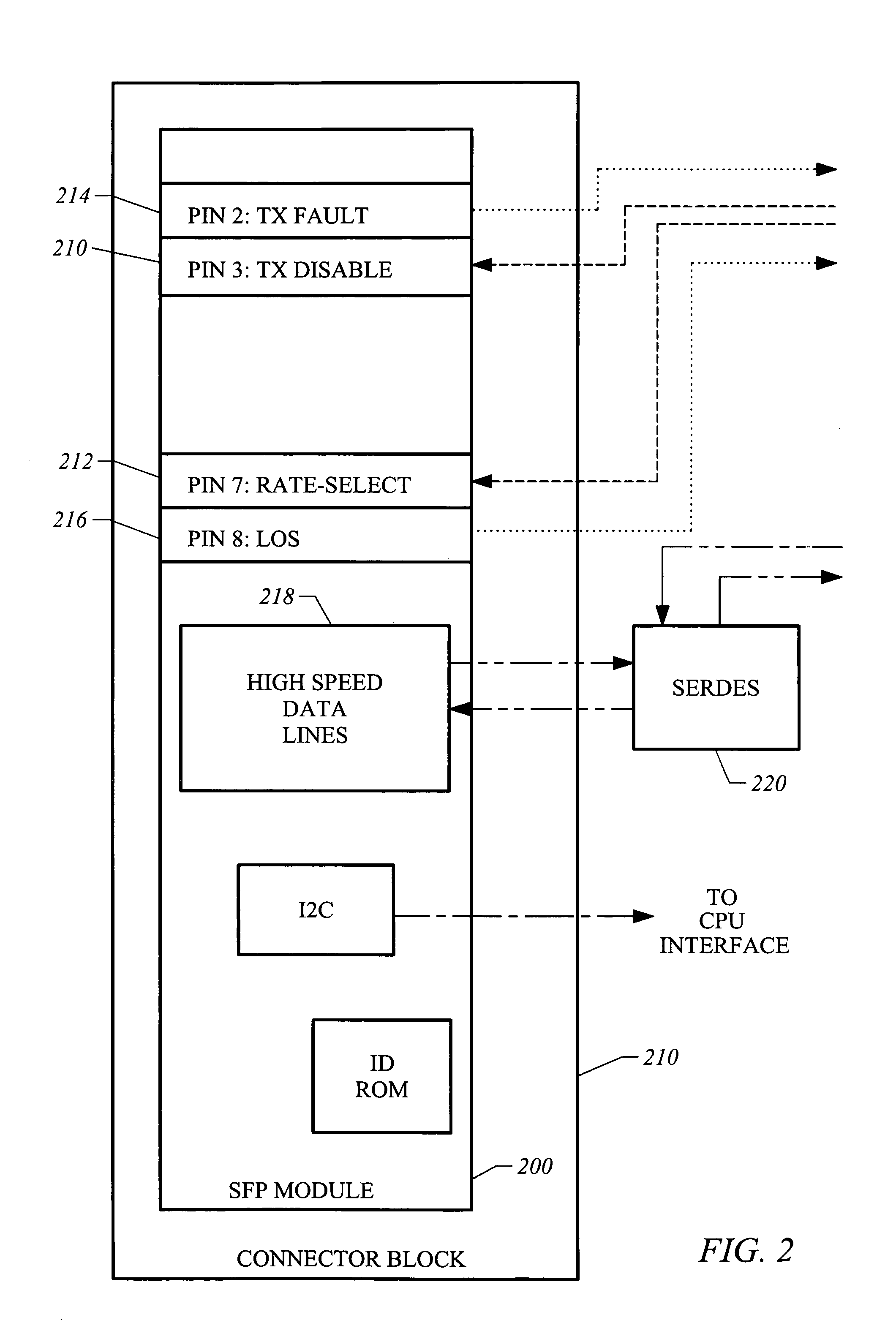

Low speed data path for SFP-MSA interface

ActiveUS7360954B1Improve practicalityIncrease data rateTime-division multiplexCoupling light guidesLow speedNetworked system

Methods and apparatus for enabling a protected circuit path to be created efficiently are disclosed. In accordance with one embodiment of the present invention, a method for creating a protected circuit path within an optical network system includes identifying a first node, a second node, and a third node. Once the nodes are identified, a pseudo link or a virtual link may be created between the second node and the third node. A first circuit path is then routed between the first node and the second node, and a second circuit path which protects that first circuit path is routed between the first node and the third node using the pseudo link.

Owner:CISCO TECH INC

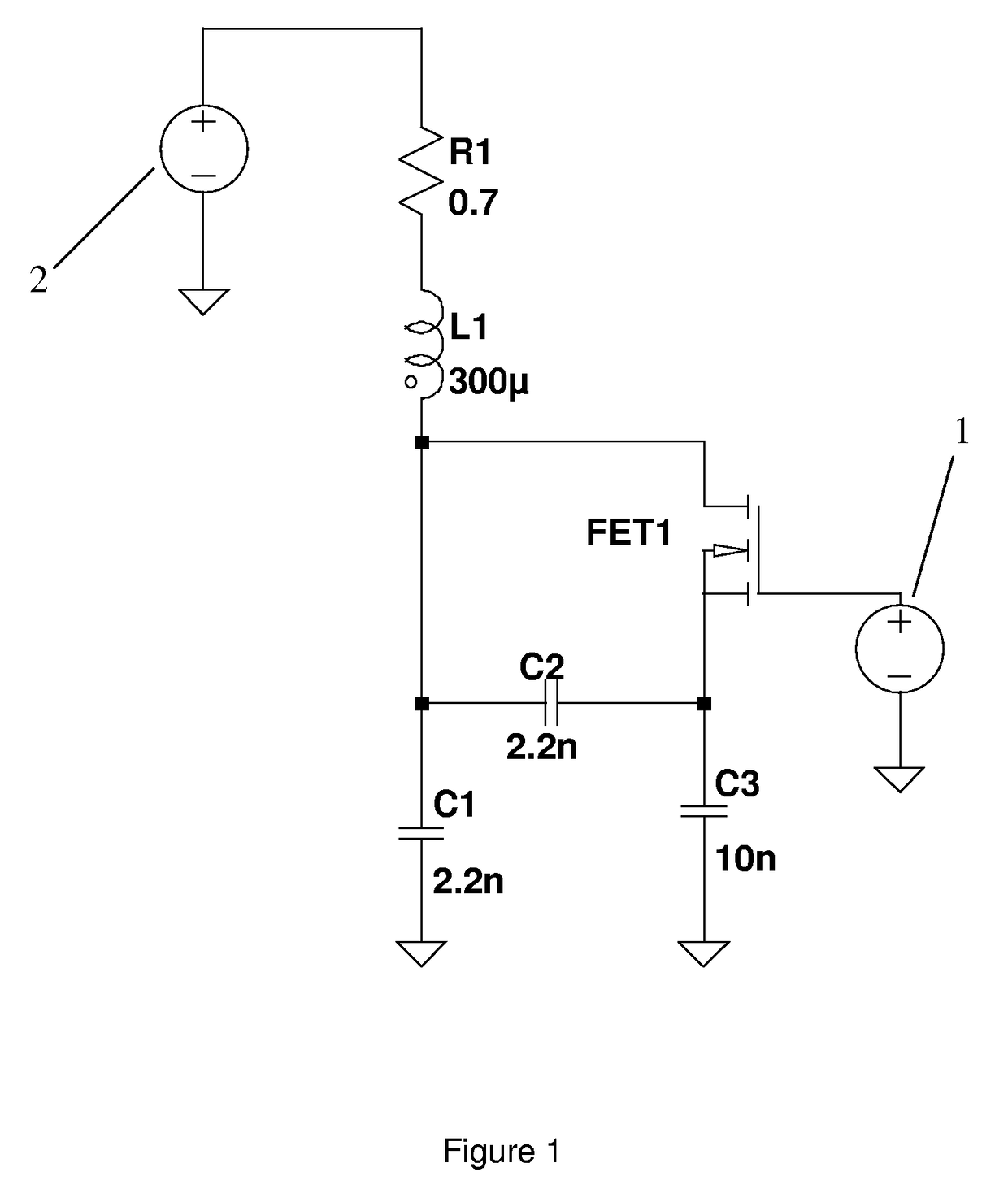

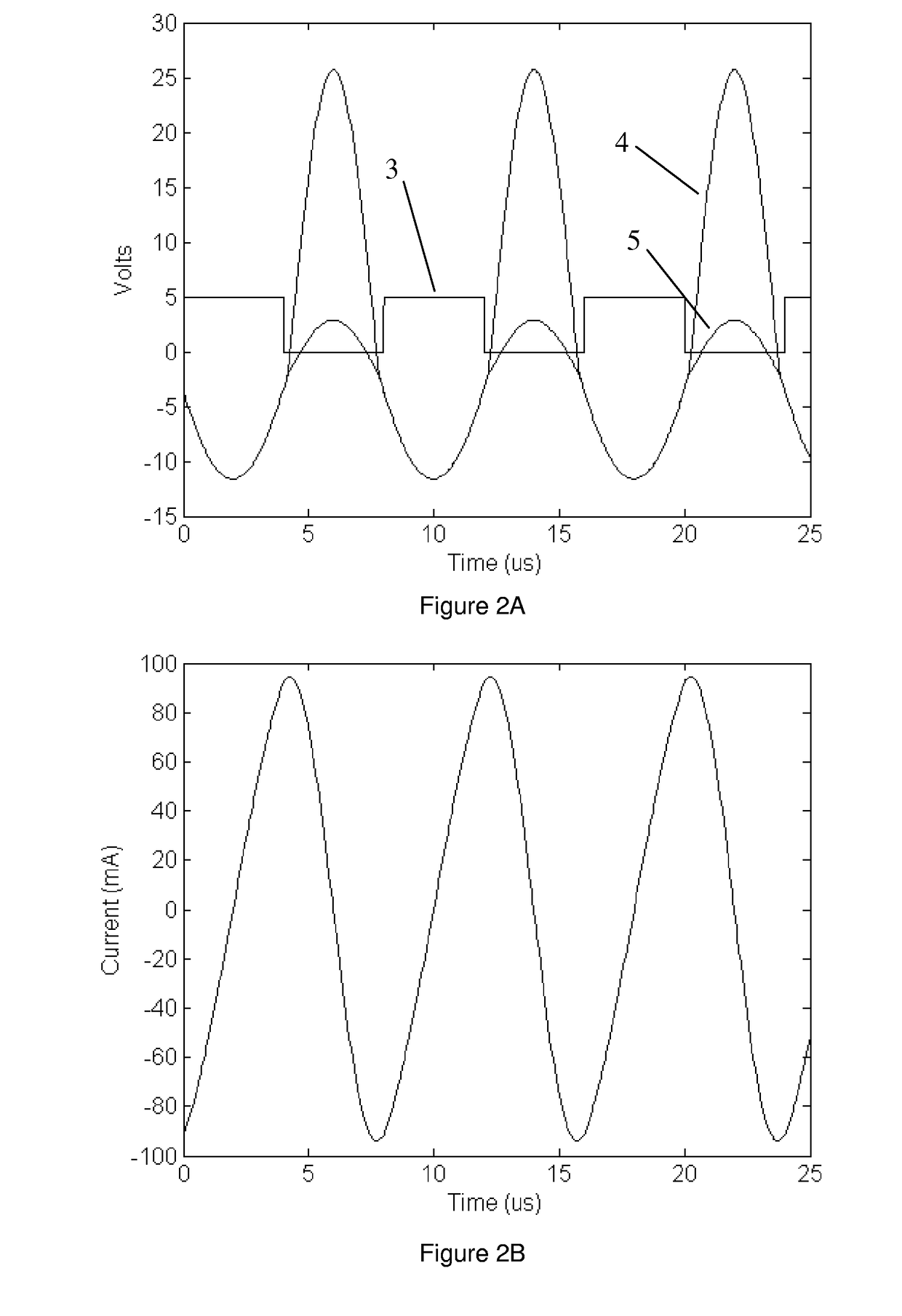

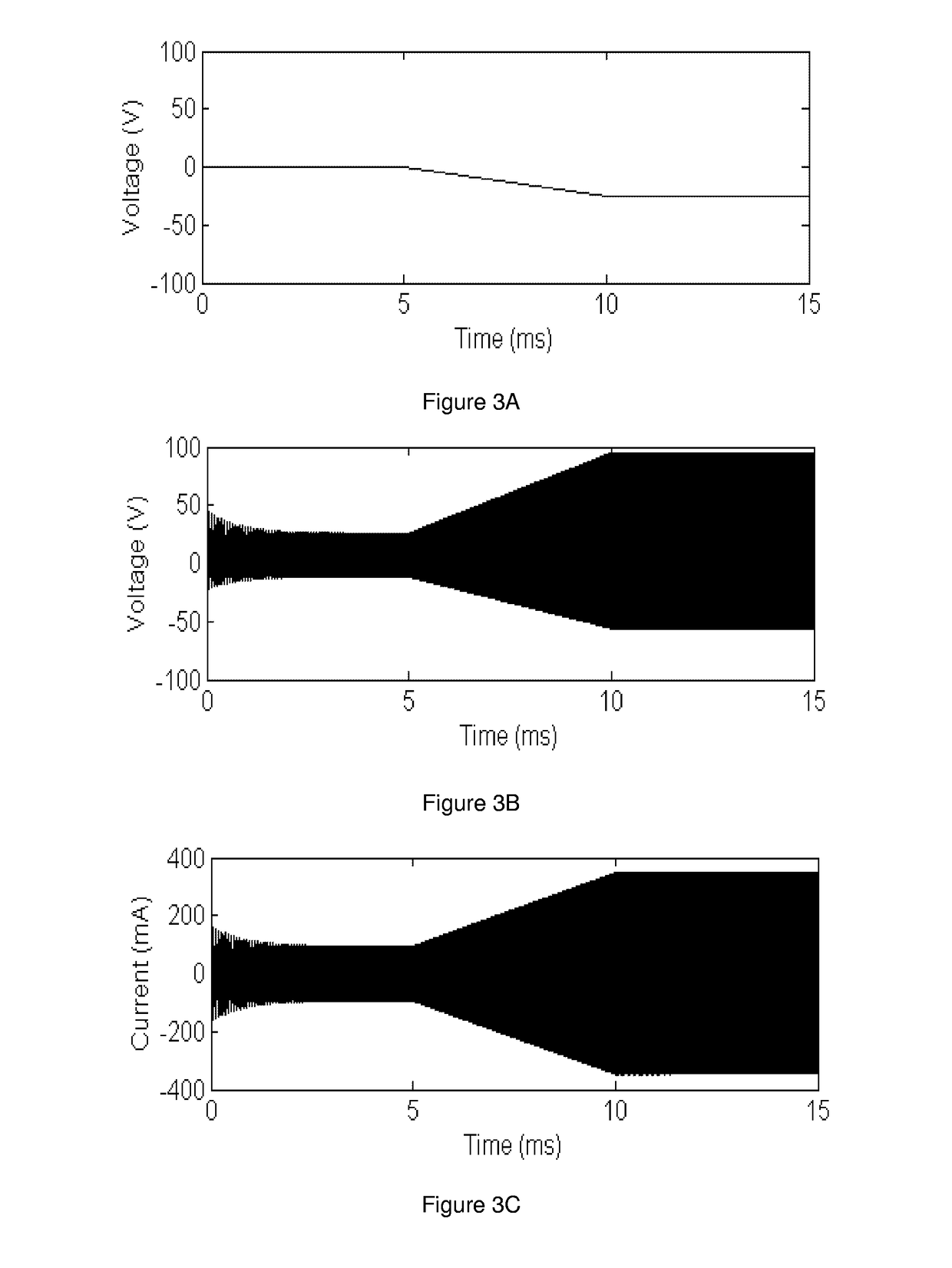

Resonant circuits

ActiveUS8471642B2Avoid damageRestrict levelGenerator stabilizationElectric pulse generatorSignal onInductor

Embodiments of the invention relate to resonant circuits; particularly but not exclusively the embodiments relate to resonant circuits in RPID (radio frequency identification) responsive to a wide frequency range. A controllable electric resonator comprising an inductor coupled to a first capacitor to form a resonant circuit, the resonator further comprising a controllable element, a second capacitor controllable coupled across said first capacitor by said controllable element, and a control device to control said controllable element such that a total effective capacitance of said first and second capacitor varies over a duty cycle of an oscillatory signal on said resonator.

Owner:SUREFLAP

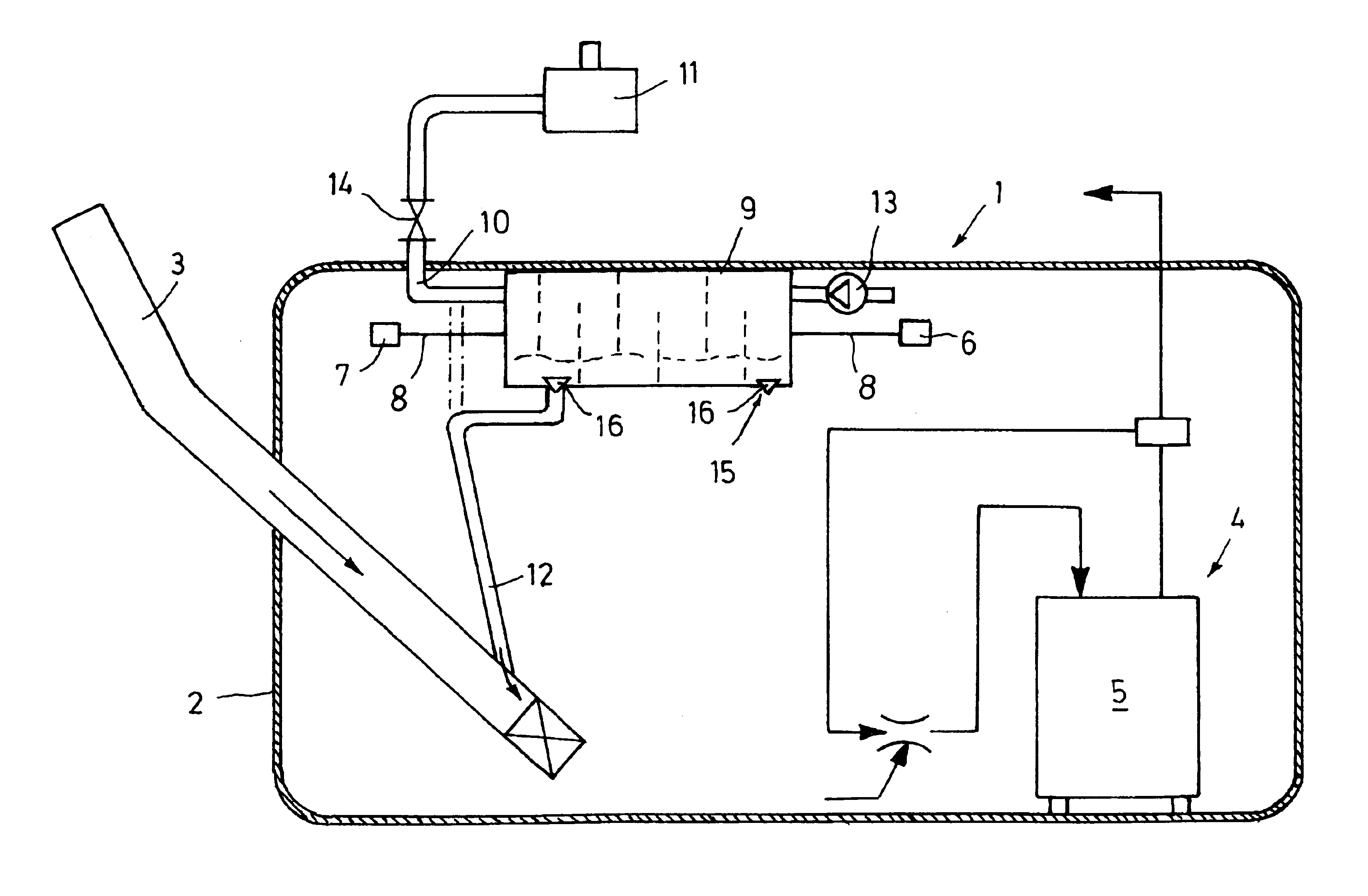

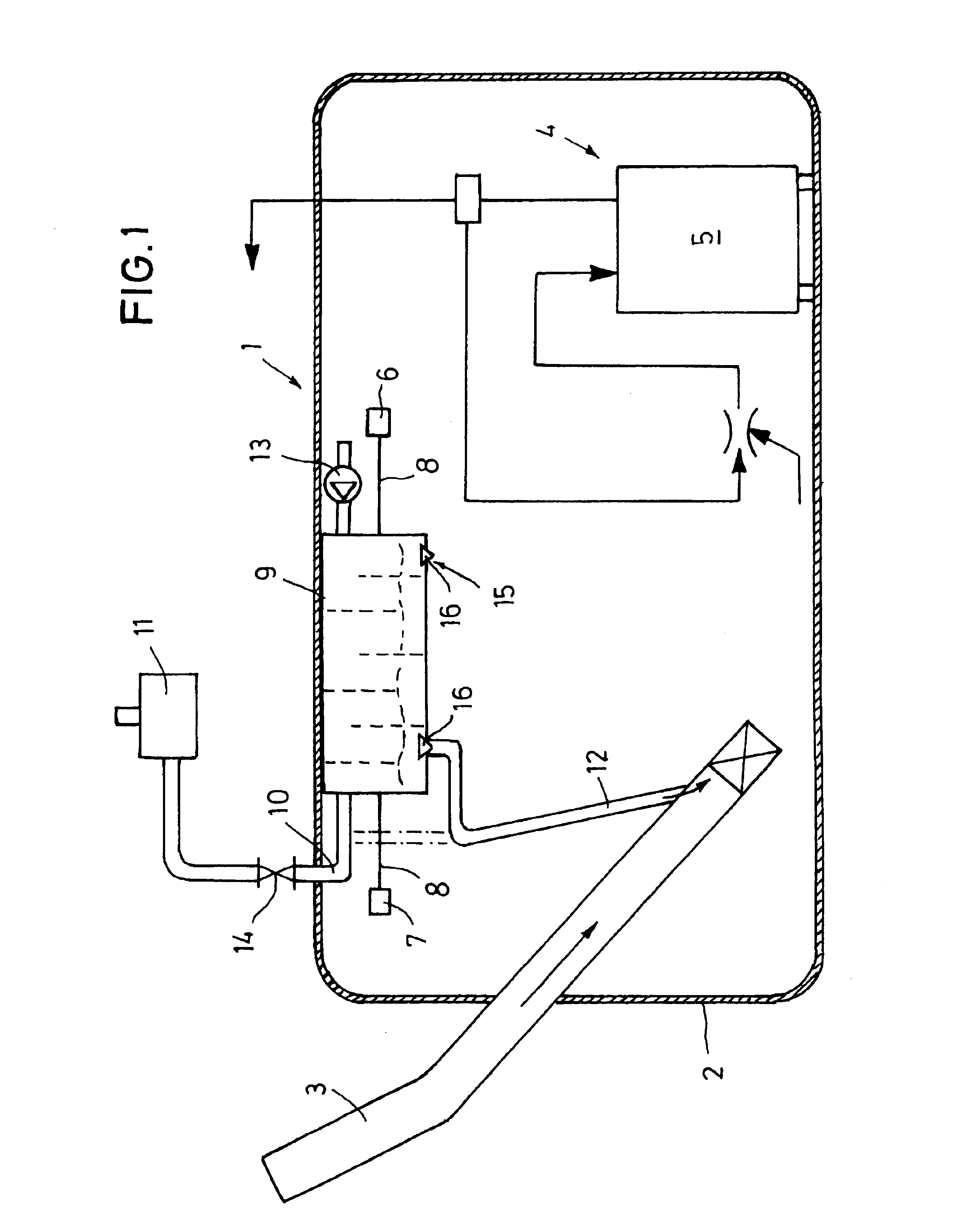

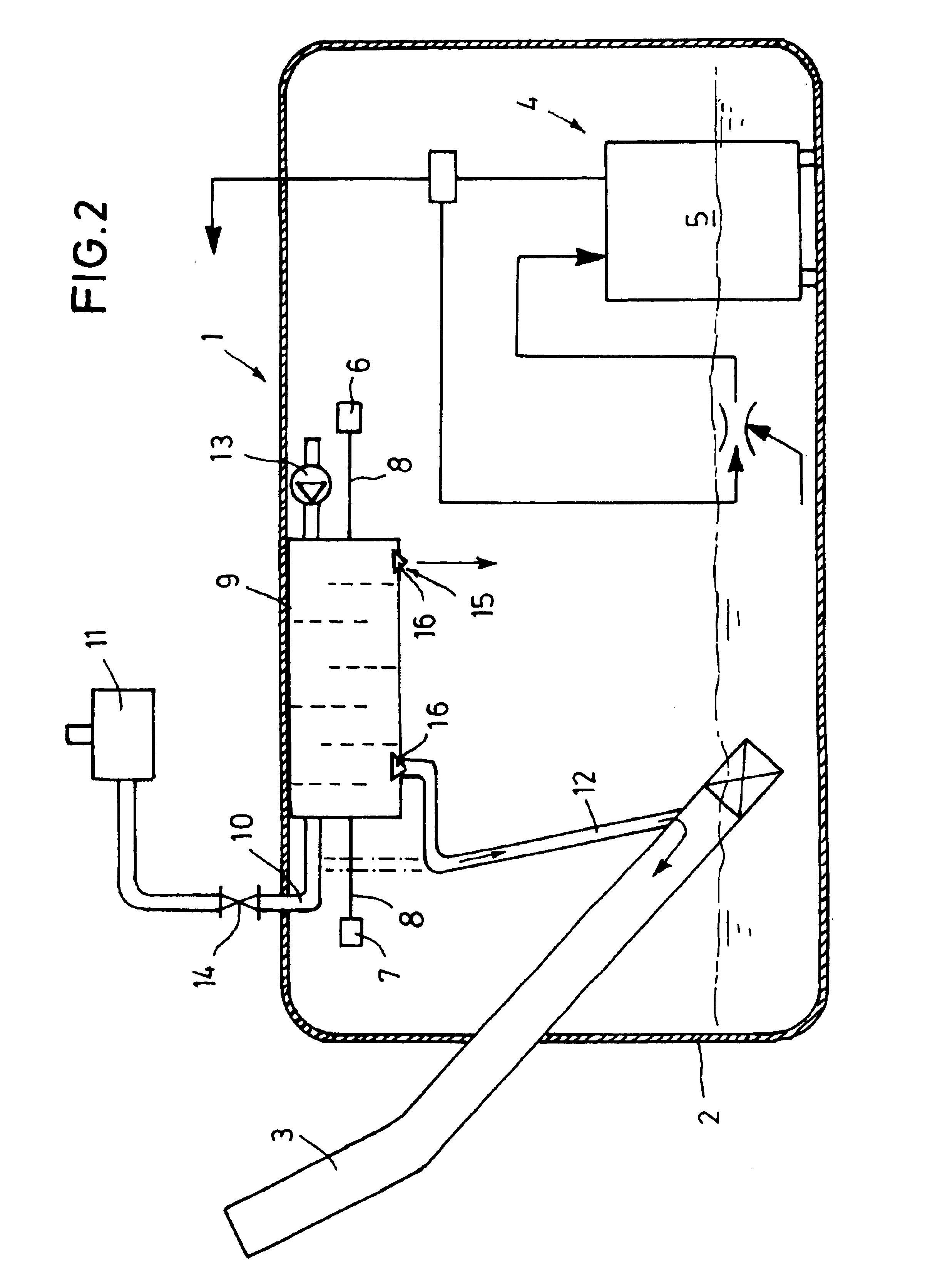

Fuel tank

InactiveUS6948523B2Reduce trafficAvoid issuingUsing liquid separation agentLarge containersMobile vehicleFuel tank

A fuel tank for a motor vehicle has means for introducing air into and venting air from the tank, and a filler pipe for filling the tank with fuel. A recirculation conduit communicates with the filler pipe. The recirculation conduit is connected to the filler pipe within the volume enclosed by the tank, approximately in the region of the outlet end of the filler pipe.

Owner:KAUTEX TEXTRON

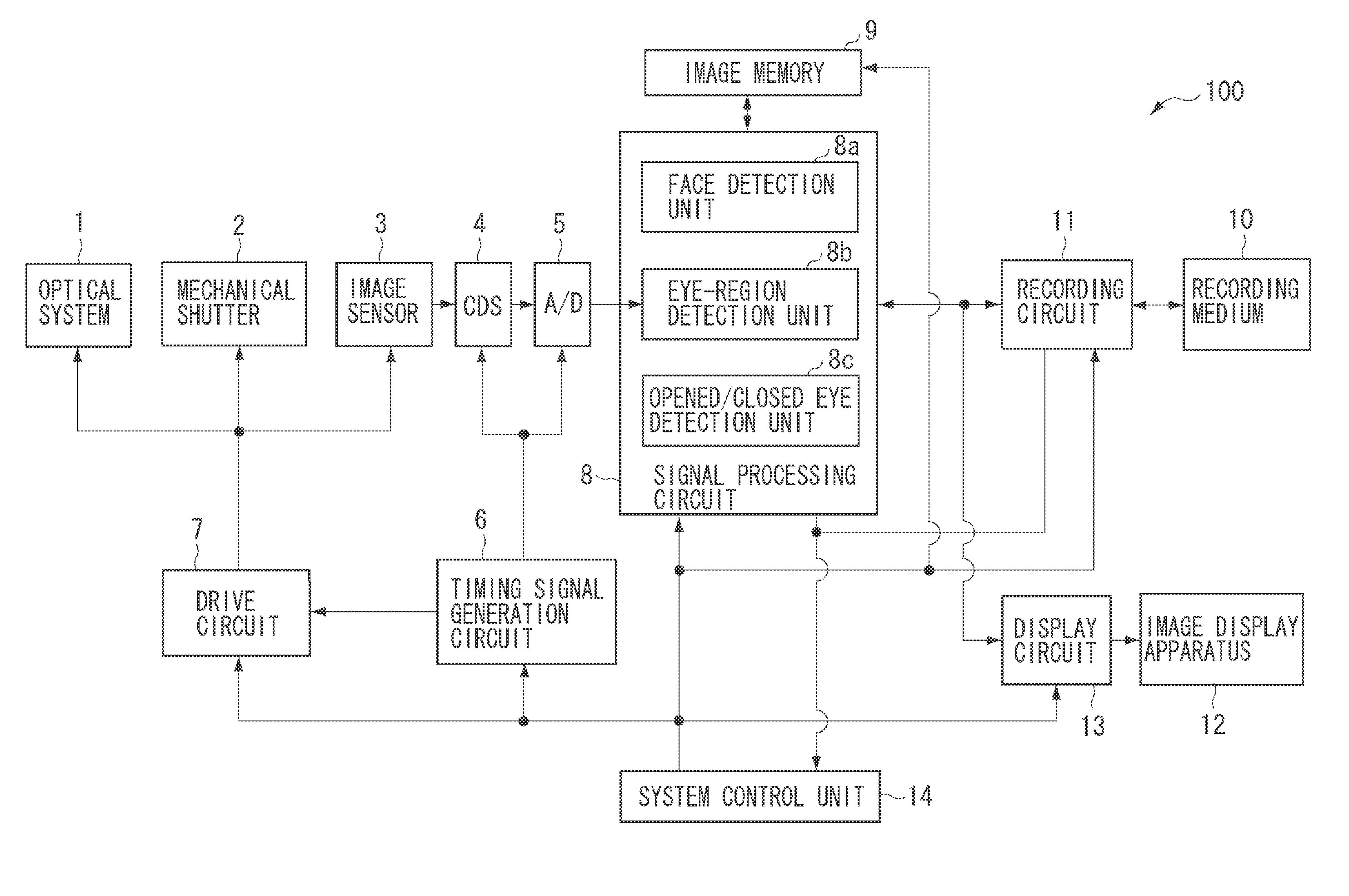

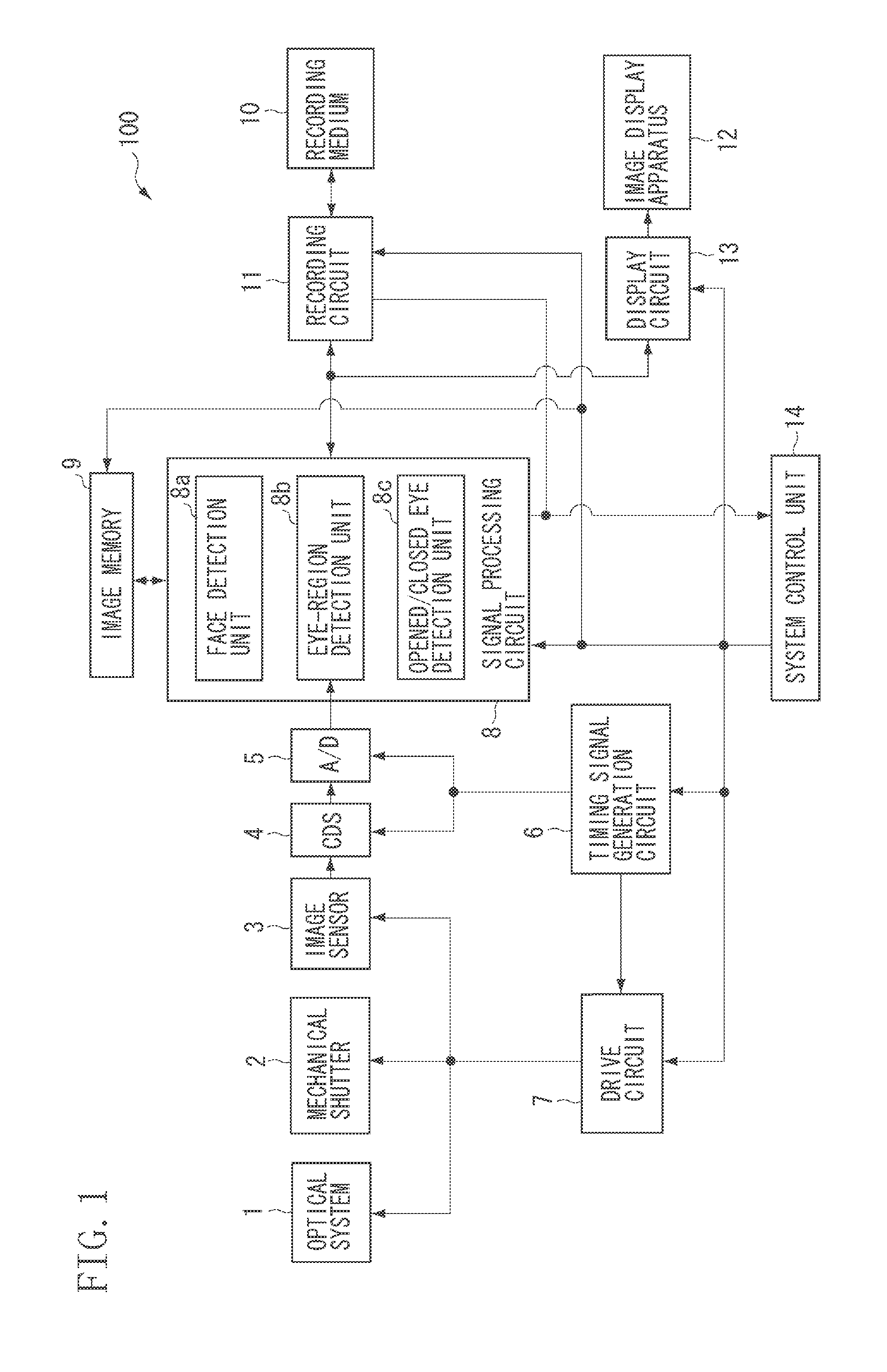

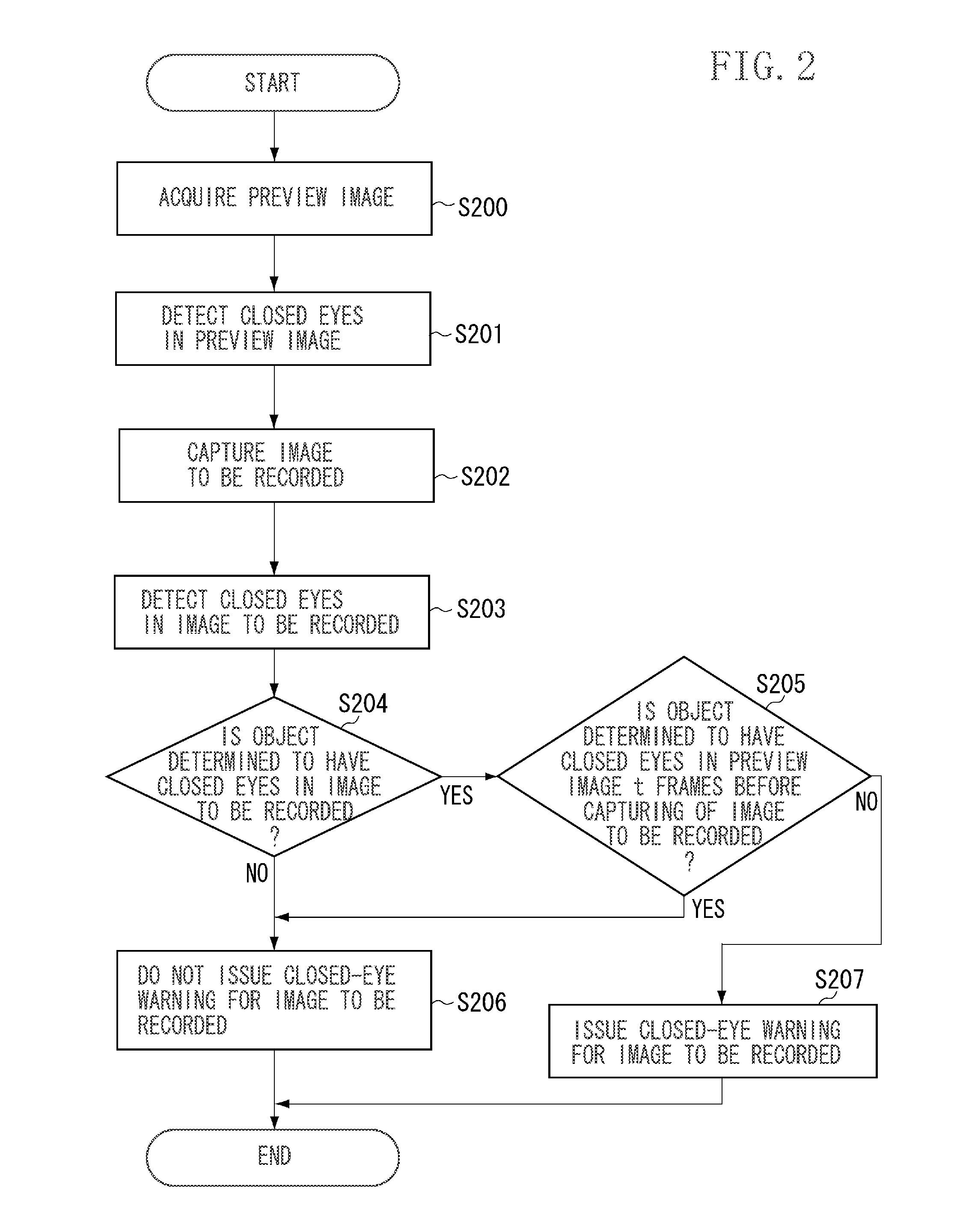

Imaging apparatus and imaging method

ActiveUS20110069194A1Avoid issuingTelevision system detailsCharacter and pattern recognitionImage captureImaging equipment

An imaging apparatus includes an imaging unit, a closed-eye detection unit configured to detect a face from an image captured by the imaging unit and to detect whether the detected face has closed eyes, and a control unit configured to determine whether to issue a warning about a captured image to be recorded according to a detection result detected by the closed-eye detection unit for the captured image to be recorded and a detection result detected by the closed-eye detection unit for a preview image captured before the image to be recorded is captured.

Owner:CANON KK

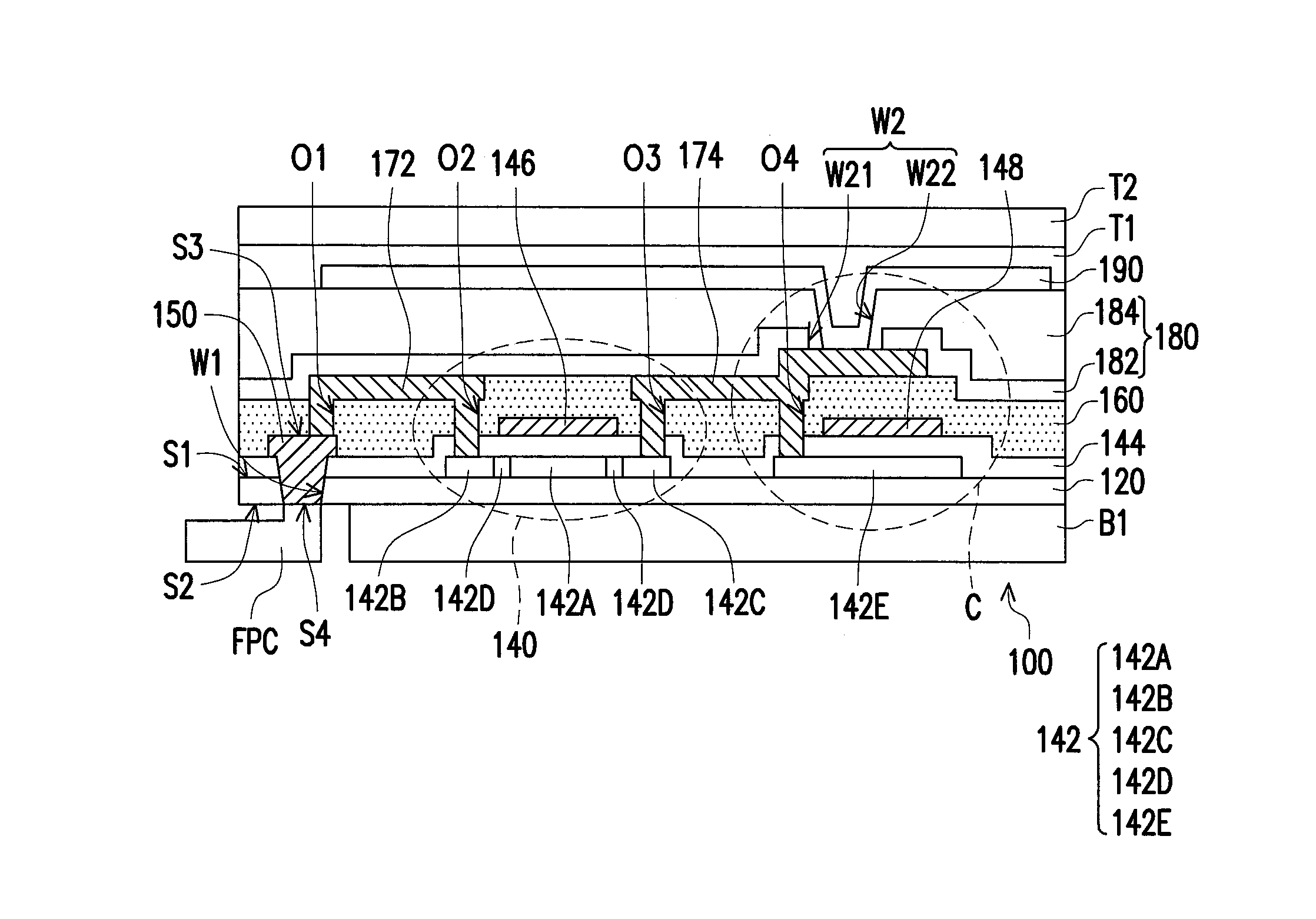

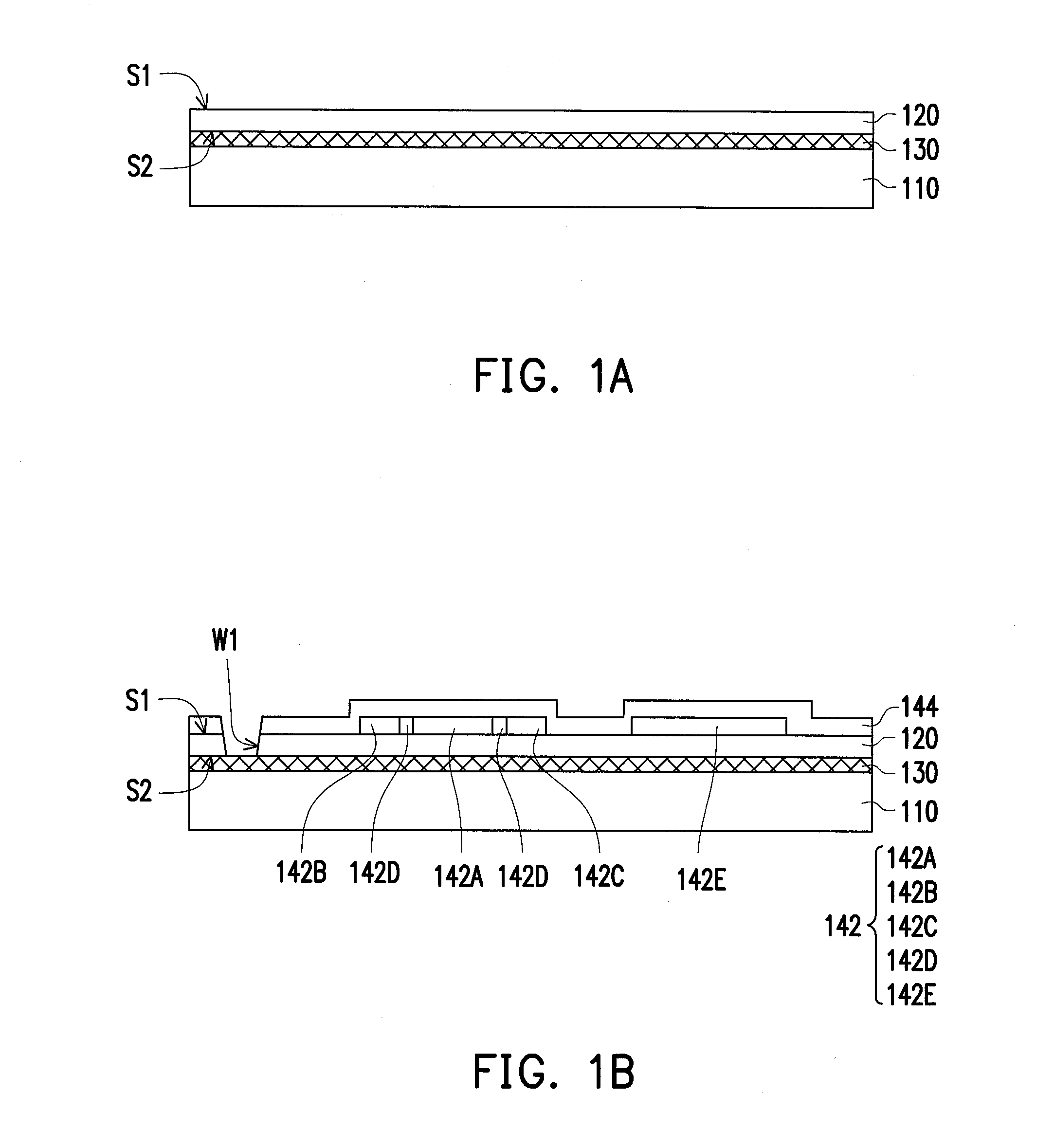

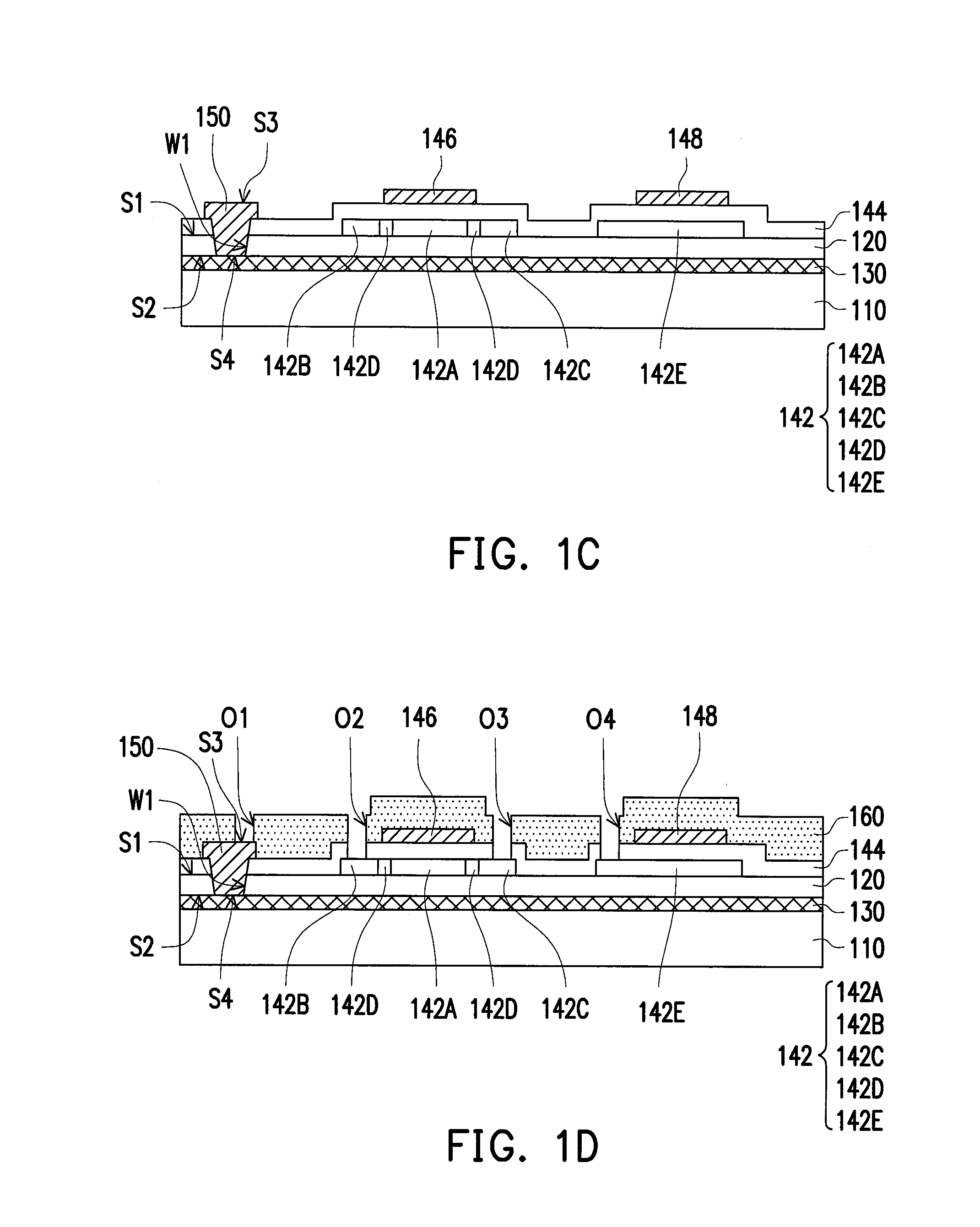

Flexible display panel and manufacturing method thereof

ActiveUS20140375916A1Improve reliabilityThe production process is simpleStatic indicating devicesSolid-state devicesActive componentDisplay device

A flexible display panel including a buffer layer, an active element, a pad, a display device and a signal transmission circuit is provided. The active element is located on the buffer layer. The pad is located in the buffer layer and is electrically connected to the active element. The display device is located on the active element and is electrically connected to the active element, in which the display device includes a pixel electrode, an opposite electrode and a display medium layer located therebetween. The active element and the signal transmission circuit are respectively located at a first surface and a second surface of the buffer layer, the second surface is opposite to the first surface, and the signal transmission circuit is electrically connected to the active element via the pad. A manufacturing method of a flexible display panel is also provided.

Owner:AU OPTRONICS CORP

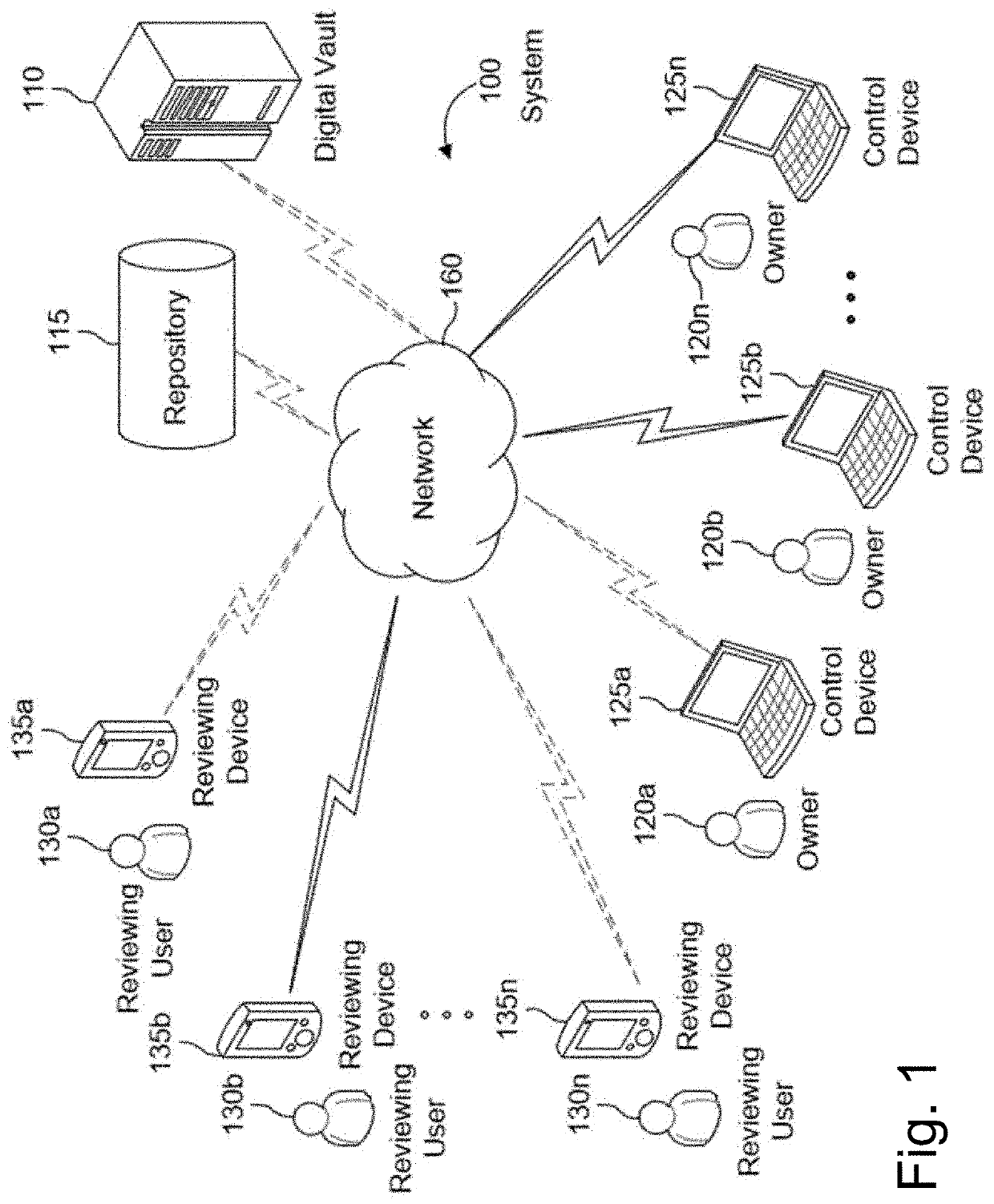

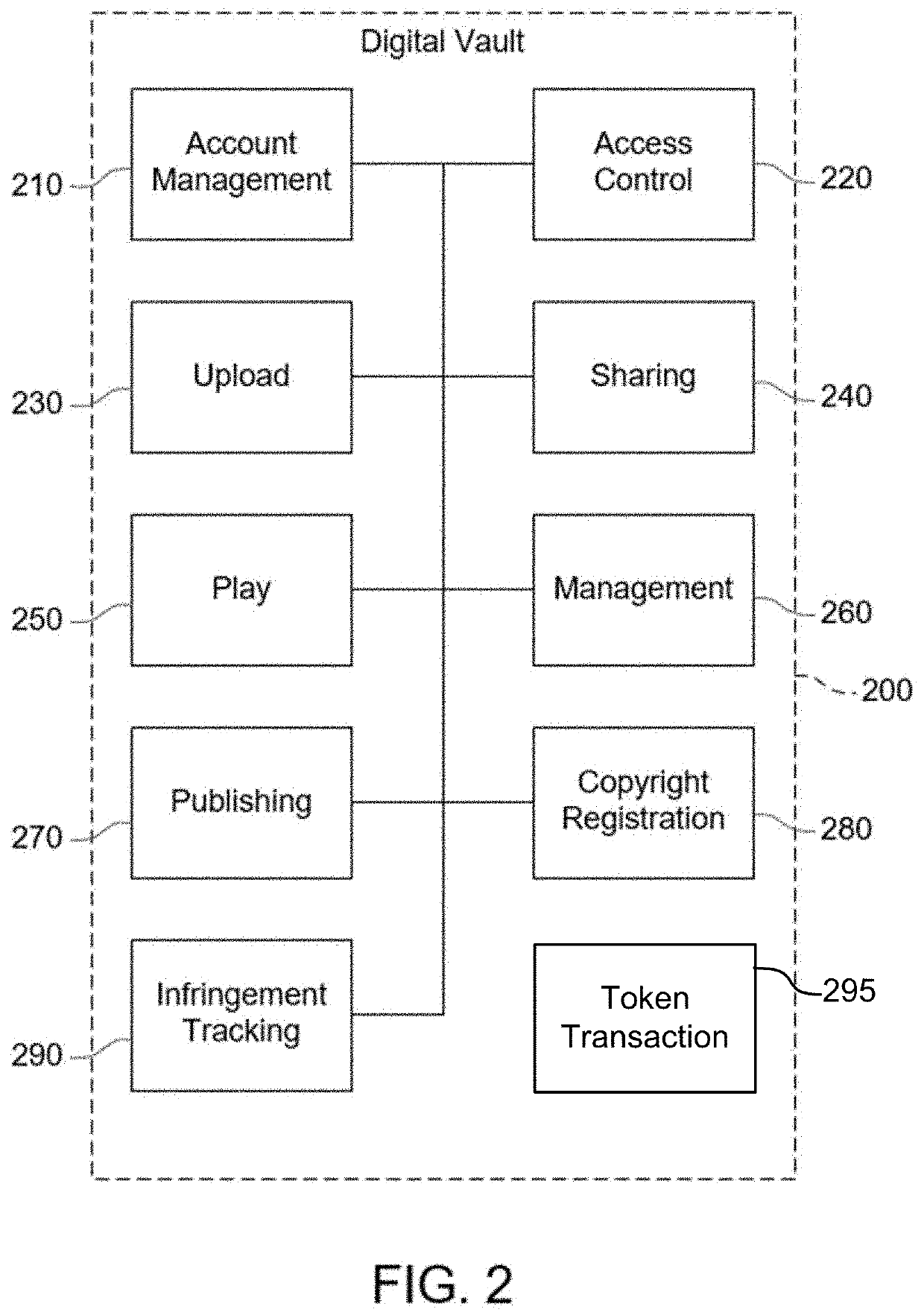

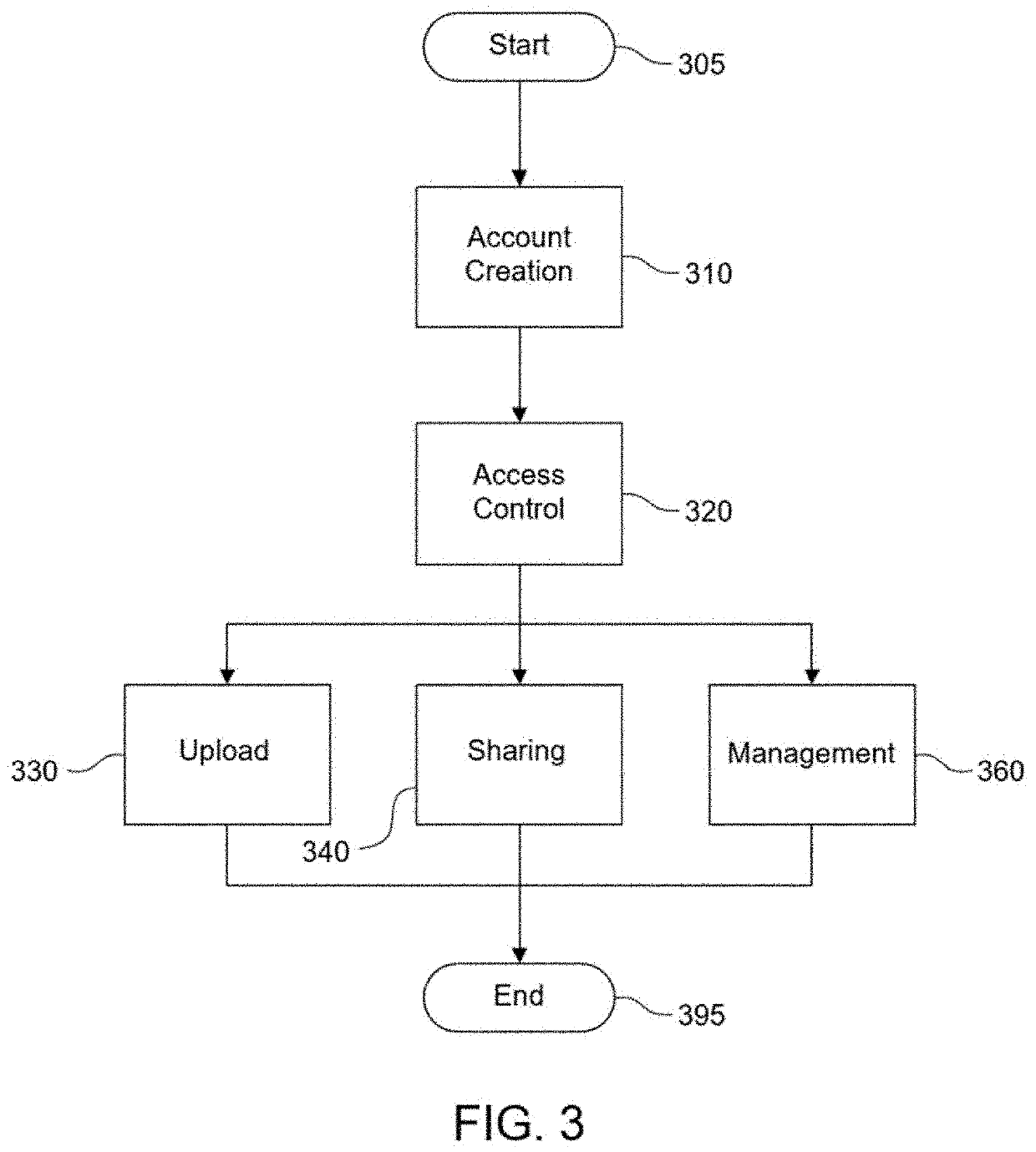

Tokenized media content management

ActiveUS20210279305A1Effective trackingAvoid issuingMetadata audio data retrievalMultimedia data indexingContent managementInternet privacy

A system and method for media content management include creating, via a digital vault, a container file comprising media content submitted by a user and content metadata; verifying, via the digital vault, a completeness of the content metadata associated with the media content in the container file; classifying, via the digital vault, the container file based on the completeness of the media content; identifying a salable content item that is to be put up for sale via a nonfungible token (NFT) transaction; determining, via the digital vault, whether other stakeholders of the salable content item hold rights in the salable content item and whether consent for the NFT transaction of any such other stakeholder is required; and the digital vault prohibiting the sale of the salable content item until consent for the sale is received from each stakeholder from whom consent is required.

Owner:TUNEGO INC

Multi-threading processors, integrated circuit devices, systems, and processes of operation and manufacture

ActiveUS20110099393A1Avoid issuingDigital data processing detailsProgram controlCouplingParallel computing

A multi-threaded microprocessor (1105) for processing instructions in threads. The microprocessor (1105) includes first and second decode pipelines (1730.0, 1730.1), first and second execute pipelines (1740, 1750), and coupling circuitry (1916) operable in a first mode to couple first and second threads from the first and second decode pipelines (1730.0, 1730.1) to the first and second execute pipelines (1740, 1750) respectively, and the coupling circuitry (1916) operable in a second mode to couple the first thread to both the first and second execute pipelines (1740, 1750). Various processes of manufacture, articles of manufacture, processes and methods of operation, circuits, devices, and systems are disclosed.

Owner:TEXAS INSTR INC

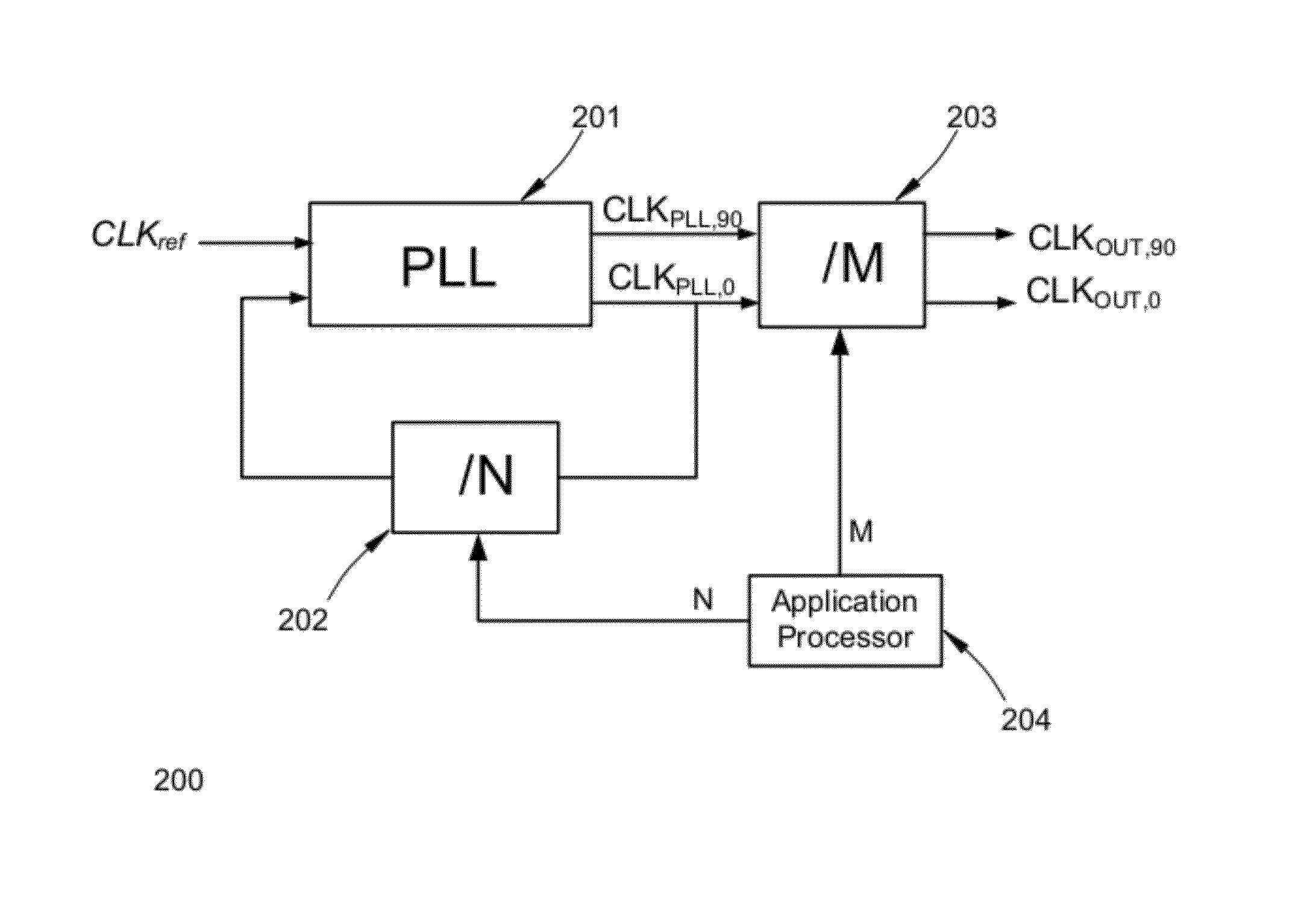

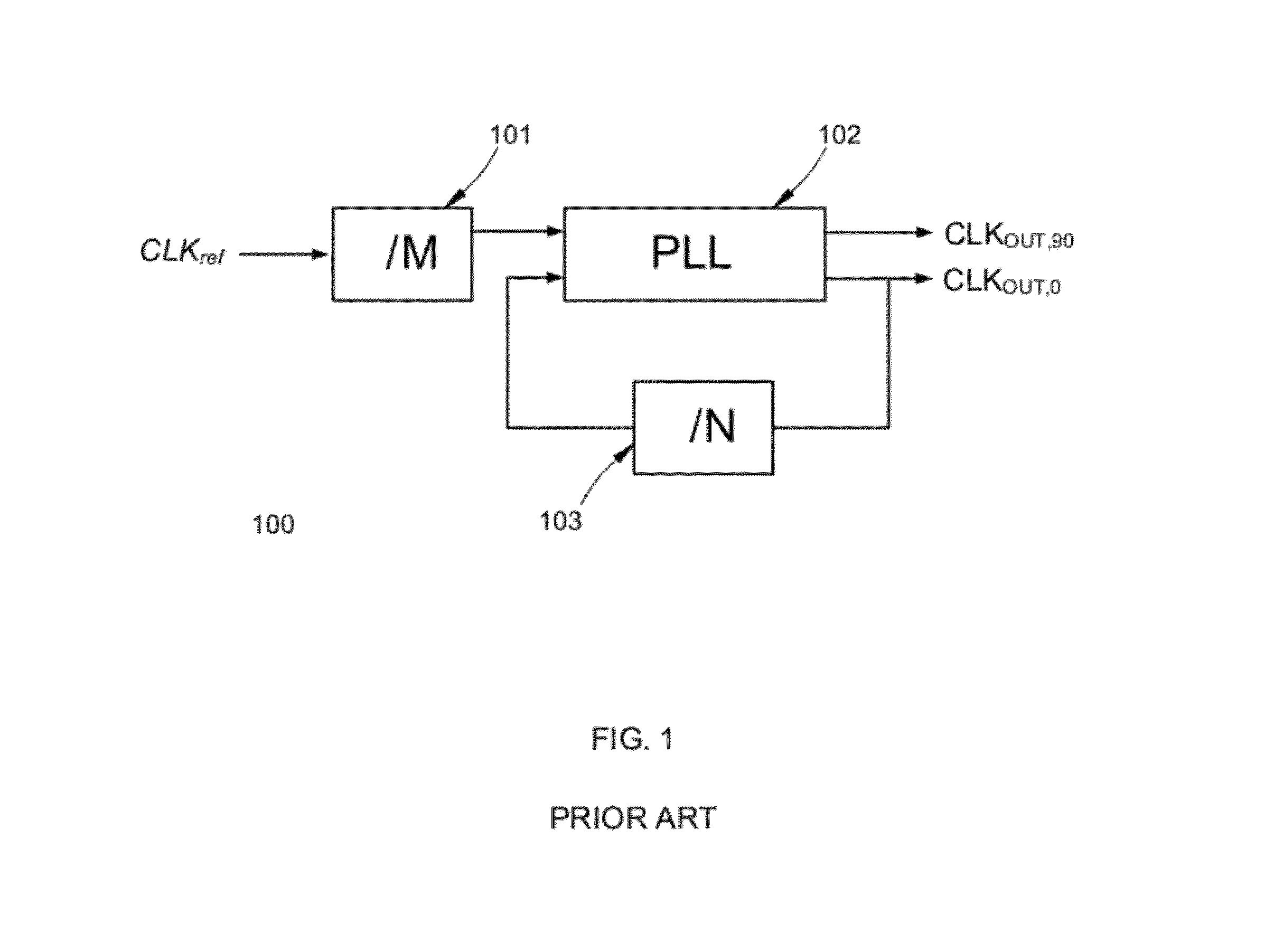

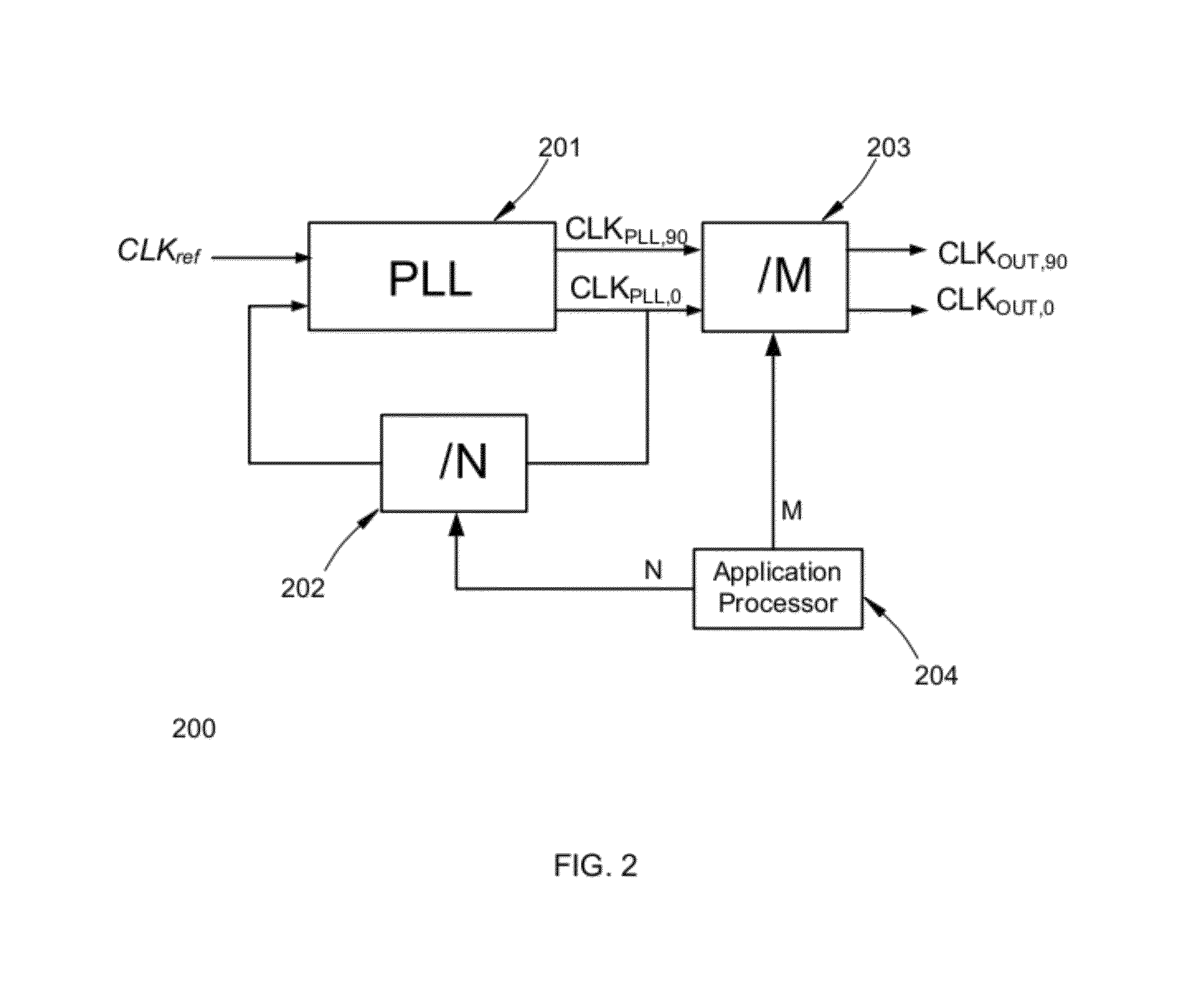

Programmable frequency synthesizer with I/Q outputs

ActiveUS8368436B1Efficient designCost effectivePulse automatic controlEqualisersLow inputFrequency synthesis

Various embodiments of the present invention relate to systems, devices and method of frequency synthesis that generate in-phase and quadrature-phase clock signals at a programmable frequency. The generated frequency, which can range from a fraction to multiples of the input reference frequency, is generated by dividers following a phase-locked loop, thus avoiding the use of a low input reference frequency as well as frequency doubling.

Owner:MAXIM INTEGRATED PROD INC