Patents

Literature

51results about How to "Avoid refresh" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

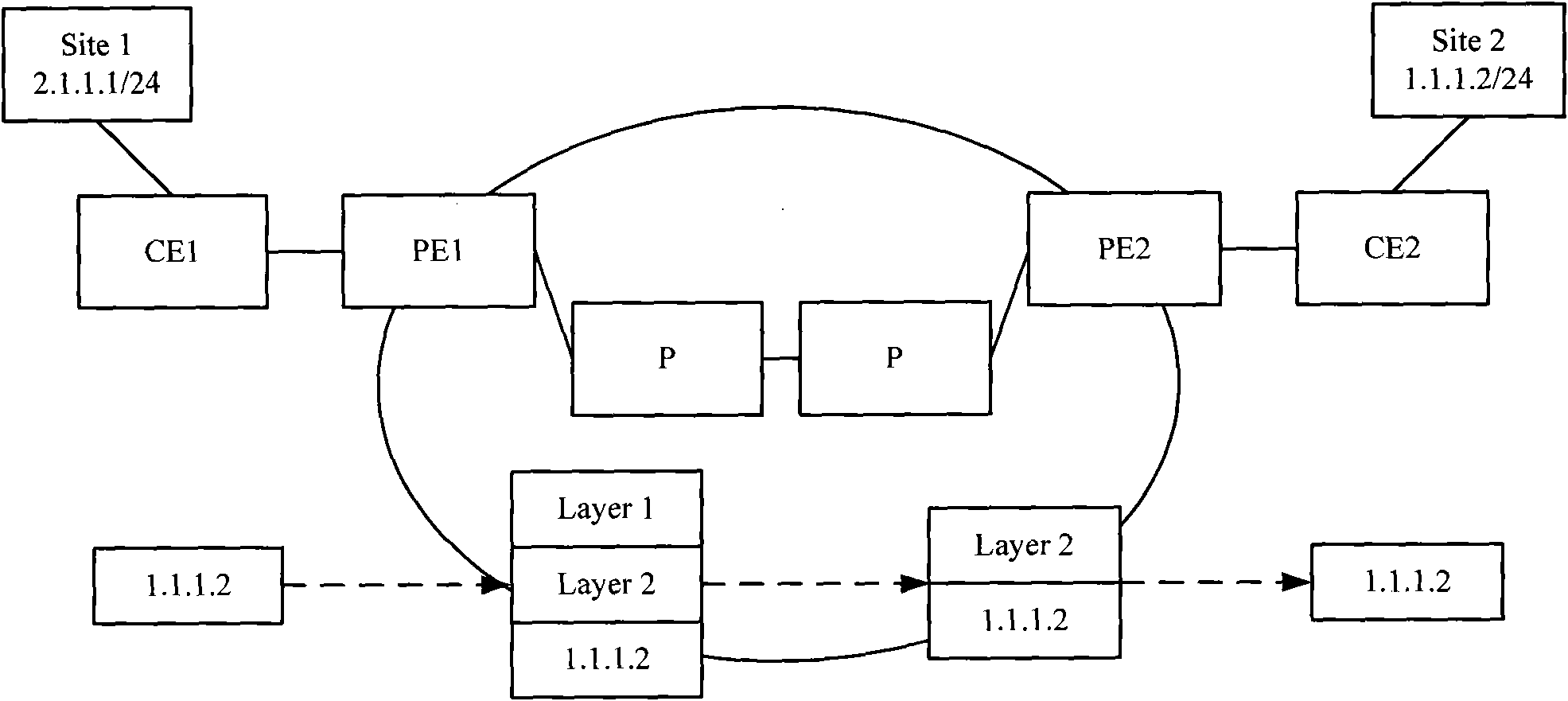

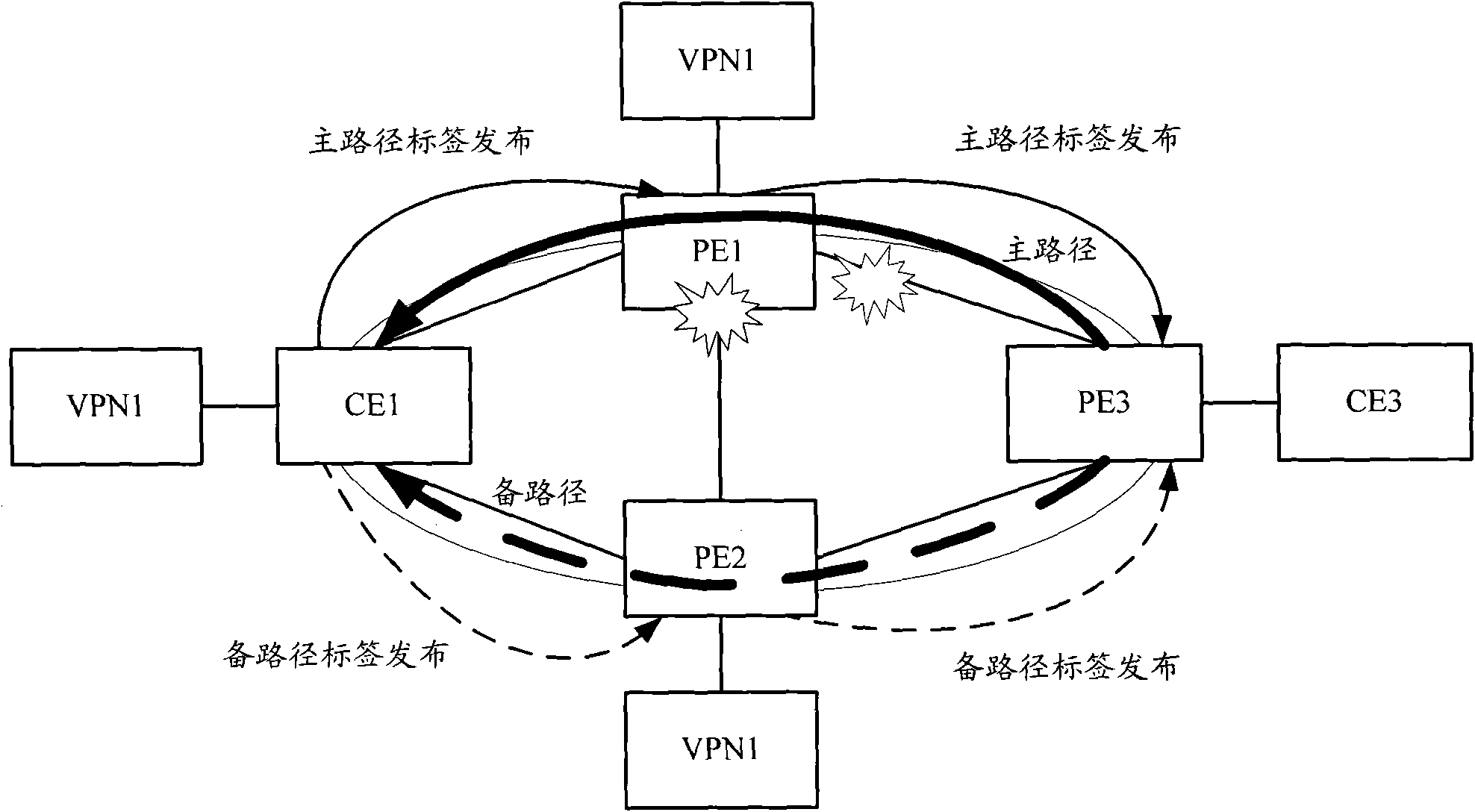

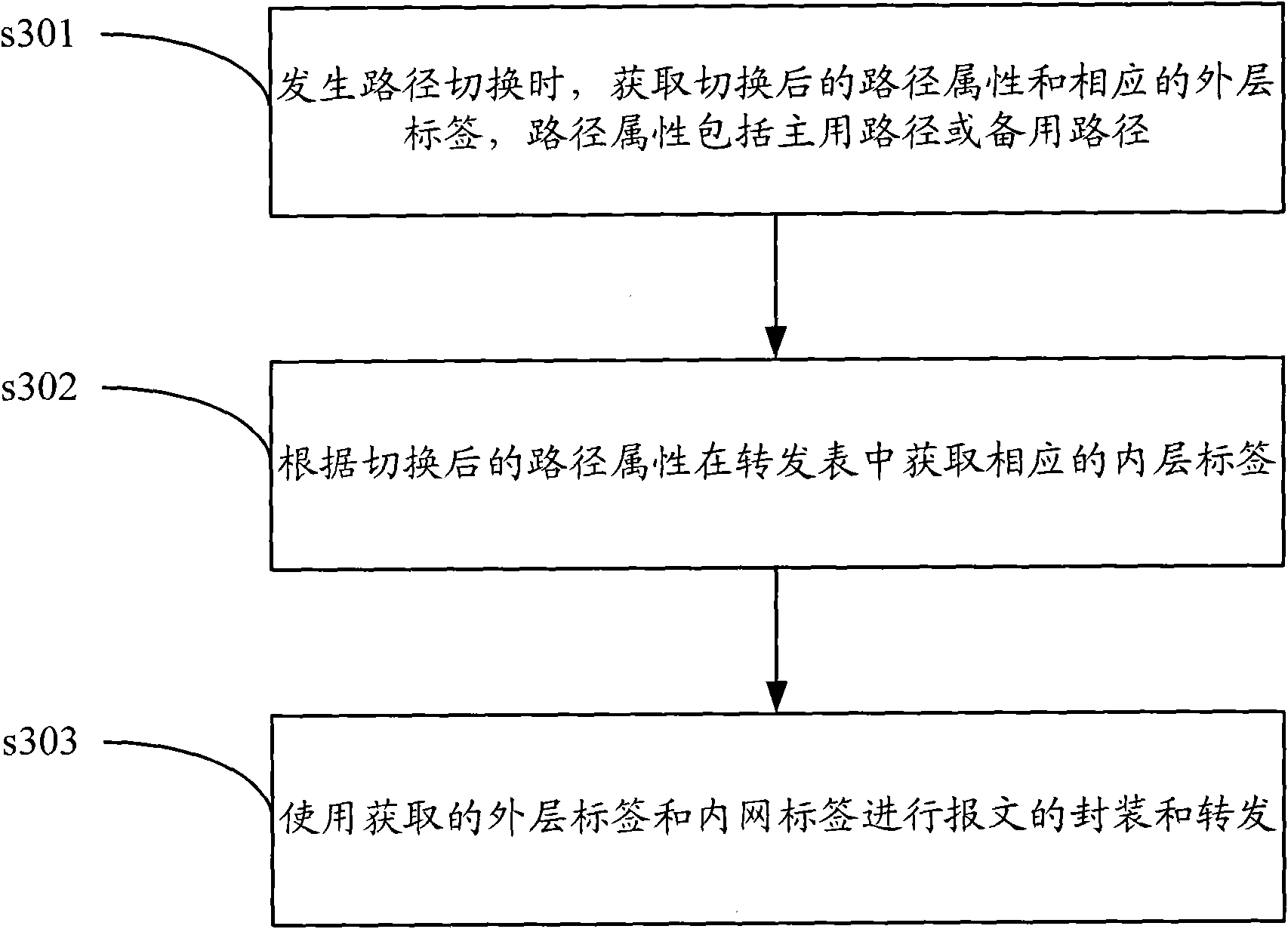

Protection switching method and equipment thereof

ActiveCN101667970AFast switching speedAvoid refreshNetworks interconnectionPath switchingCall routing

The invention discloses a protection switching method and equipment thereof. The method is used for PE in MPLS L3VPN, the PE is provided with a primary path and a standby path about a called route, and a forwarding table of the PE is previously memorized with a primary inner layer mark corresponding to the primary path and a standby inner layer mark corresponding to the standby path. The method comprises the steps of: when occurring path switching, obtaining the switched path attribute and a corresponding outer layer mark, wherein the path attribute comprises the primary path or the standby path; obtaining the corresponding inner layer mark according to the switched path attribute in the forwarding table; and enveloping and transmitting a report with the obtained outer layer mark and the inner network mark. The invention realizes the fast switching of the inner layer mark and an outer network mark of the path when switching the primary path with the standby path.

Owner:NEW H3C TECH CO LTD

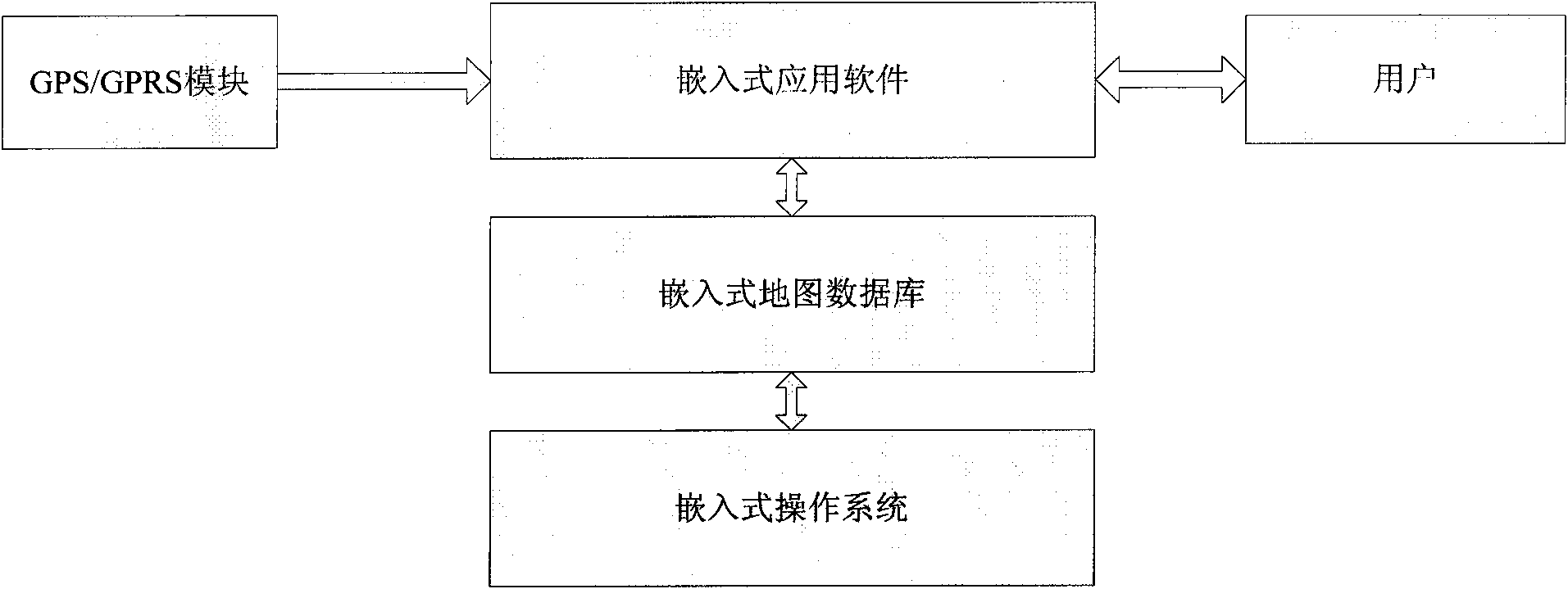

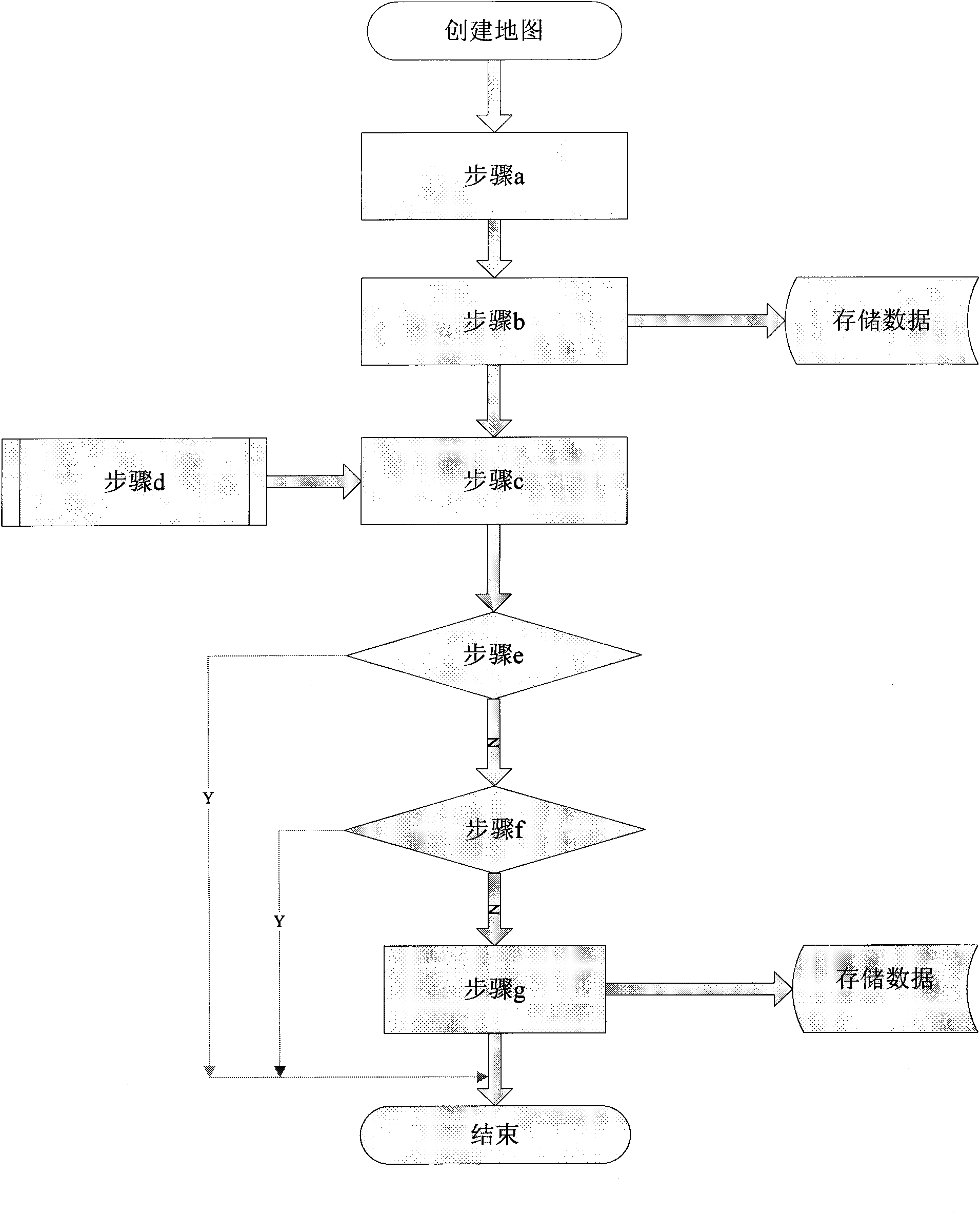

Method for updating embedded mobile electronic map data base in real time

InactiveCN101556165AAvoid refreshImplement incremental updatesInstruments for road network navigationMobile navigationLongitude

The invention relates to a method for updating an embedded mobile electronic map data base in real time, wherein map elements in the electronic map data base is firstly coded, and the IDs of the map elements are determined; the data of the relationship among the map elements is stored into the corresponding memory area of a map information storing device according to the IDs of the map elements; one item or a plurality of items of data of the relationship among the map elements can be extracted from the memory area of the map data, and the IDs of the map elements and the update state thereof are be obtained; data is acquired from a GPS / GPRS module and then is converted into geographic data compatible with the map data base, and whether the current travelling route belongs to certain map element is judged according to the coordinate figures of longitude and latitude; whether the map elements requires addition or modification is hinted according to the judged result; or by setting the travelling time threshold value, the map elements are automatically added when being more than the threshold value; finally, the updated data and the update state are stored into the map information memory area, thus electronic map data of a mobile navigation device can be stored and updated.

Owner:NOAH SOLUTION SUZHOU

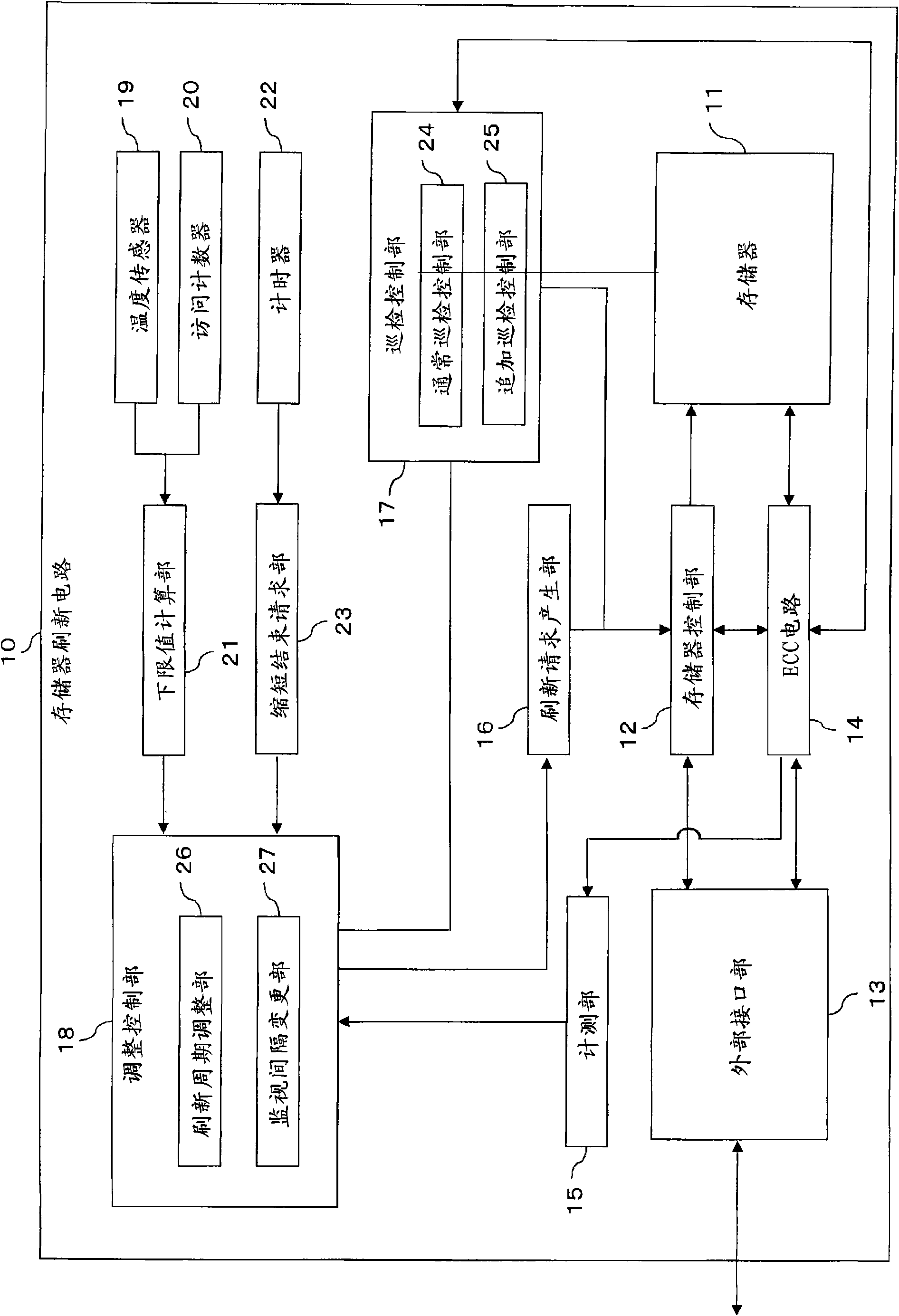

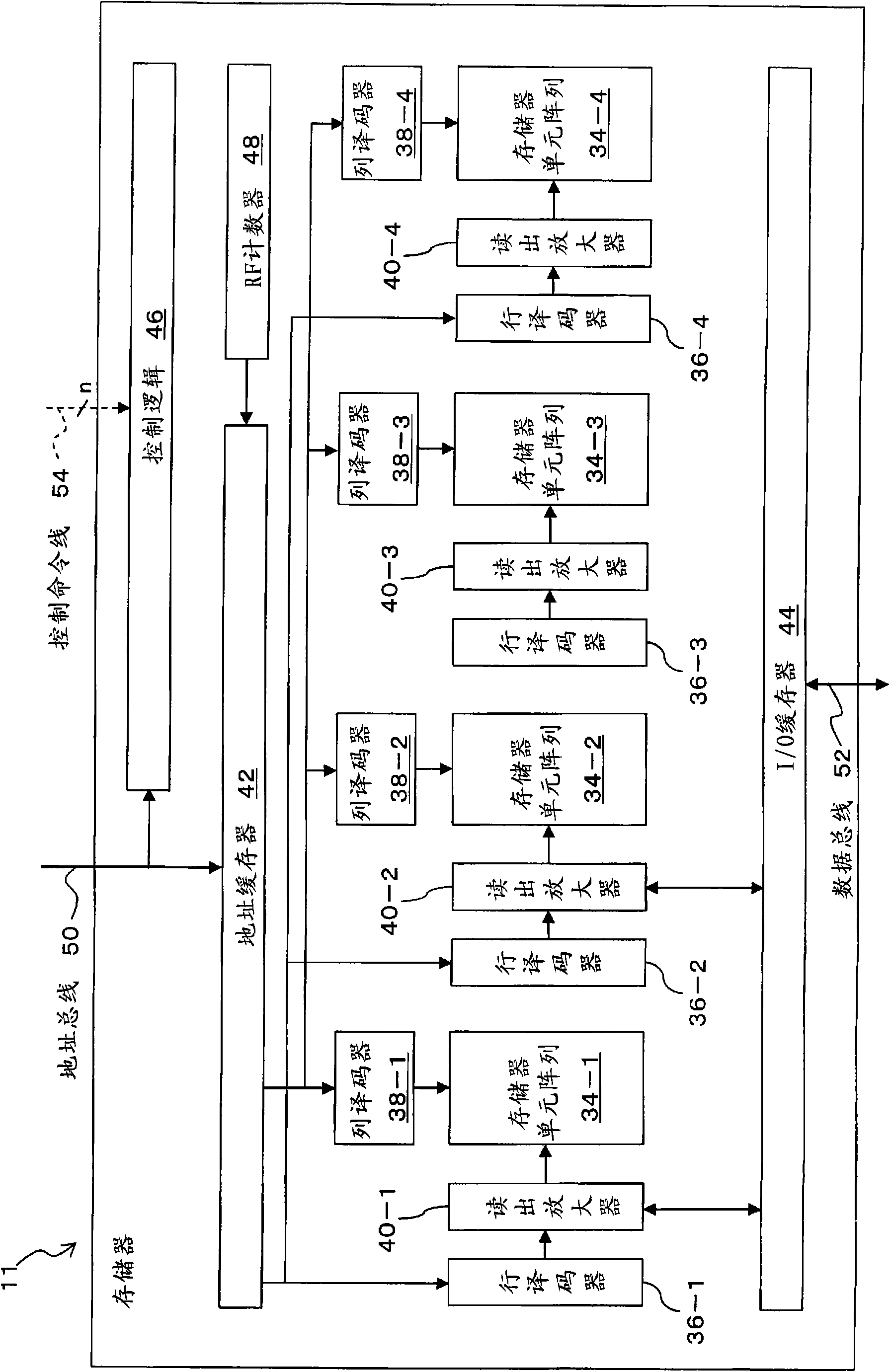

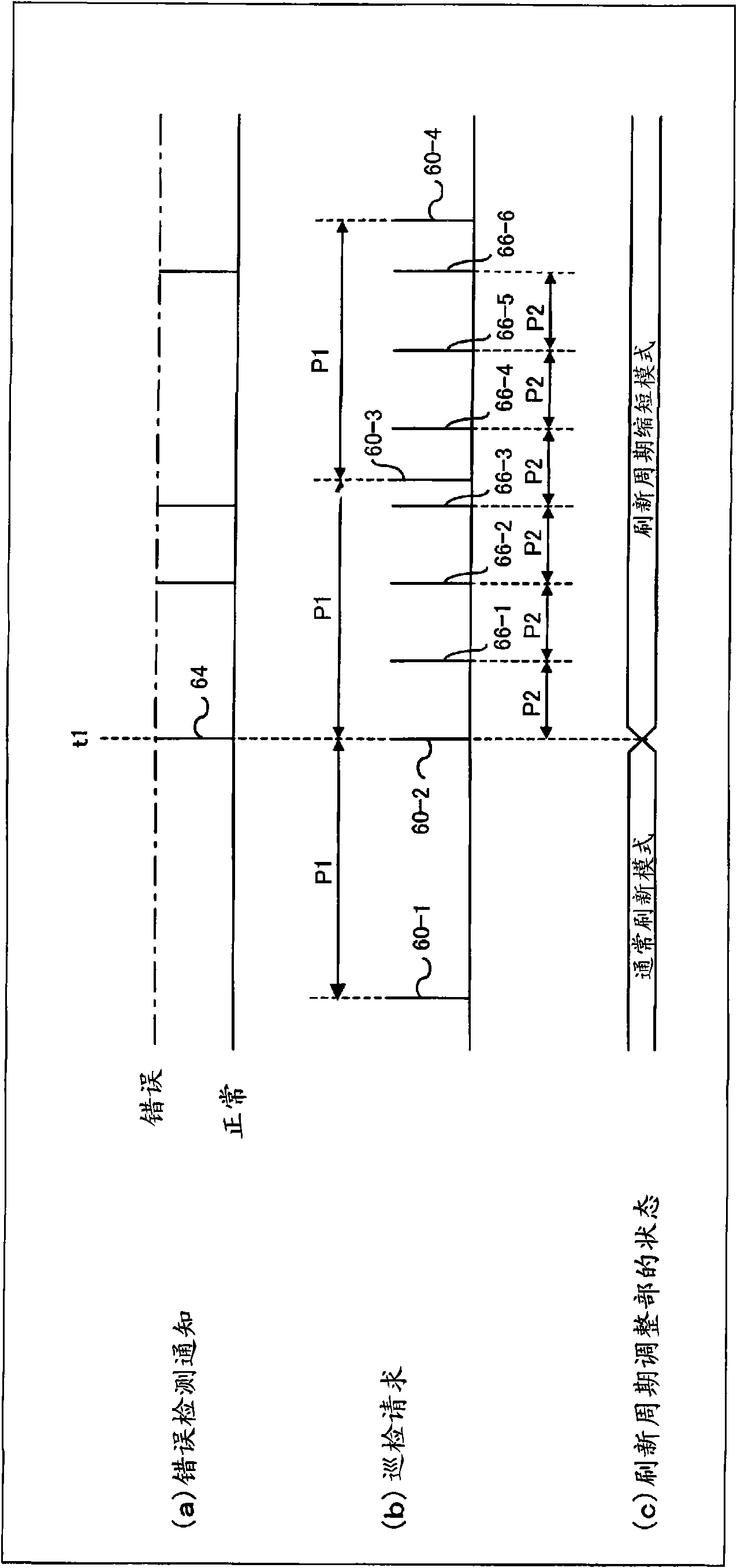

Memory refresh device and memory refresh method

InactiveCN101796497AImprove responsivenessShorten the refresh cycleMemory loss protectionError detection/correctionComputer hardwareRefresh cycle

A memory refresh device comprises an ordinary patrol control unit (24) for controlling an ordinary patrol operation in which a memory (11) is patrolled, an additional patrol control unit (25) for, when an error of the memory (11) is detected in the ordinary patrol operation, controlling an additional patrol operation in which an error generating portion in the memory (11) is patrolled, a measuring unit (15) for, when an error is detected in the additional patrol operation, measuring information on the error in the error generating portion as error frequency, and a refresh period adjusting unit (26) for adjusting a refresh period according to the error frequency measured by the measuring unit (15). Thus, the optimization of the refresh period is efficiently performed according to the state of the generation of the error in the memory.

Owner:FUJITSU LTD

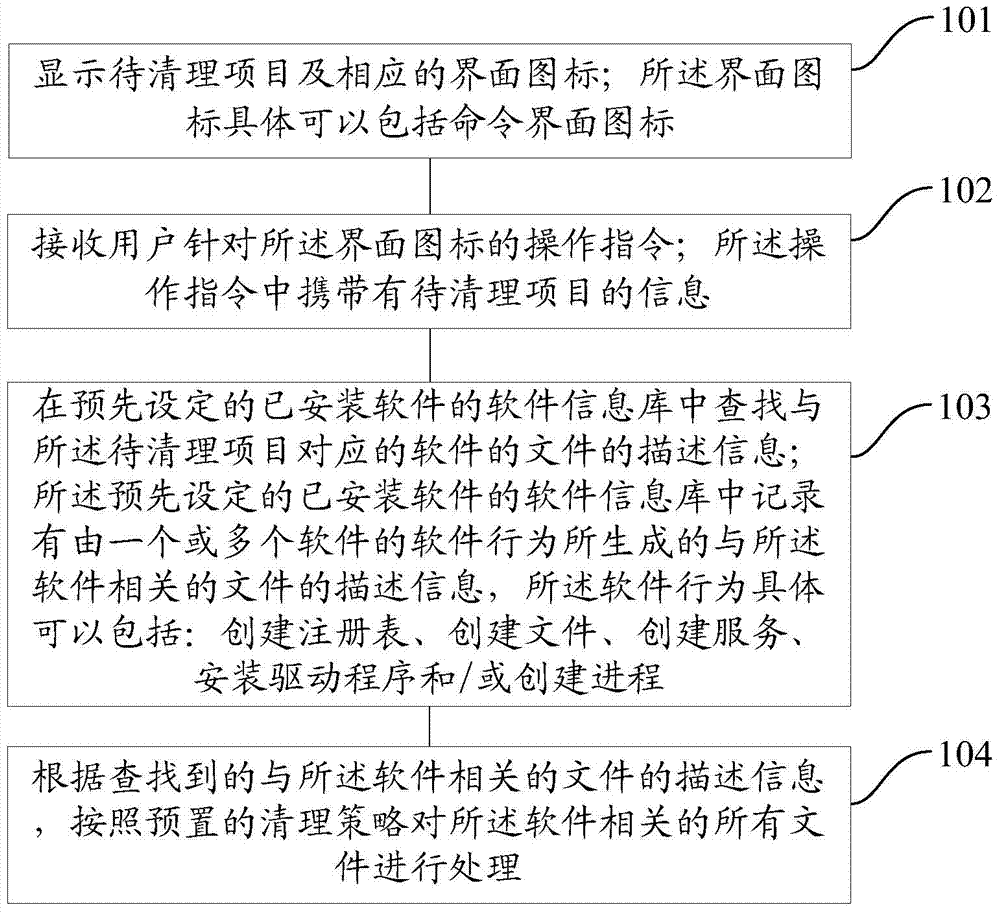

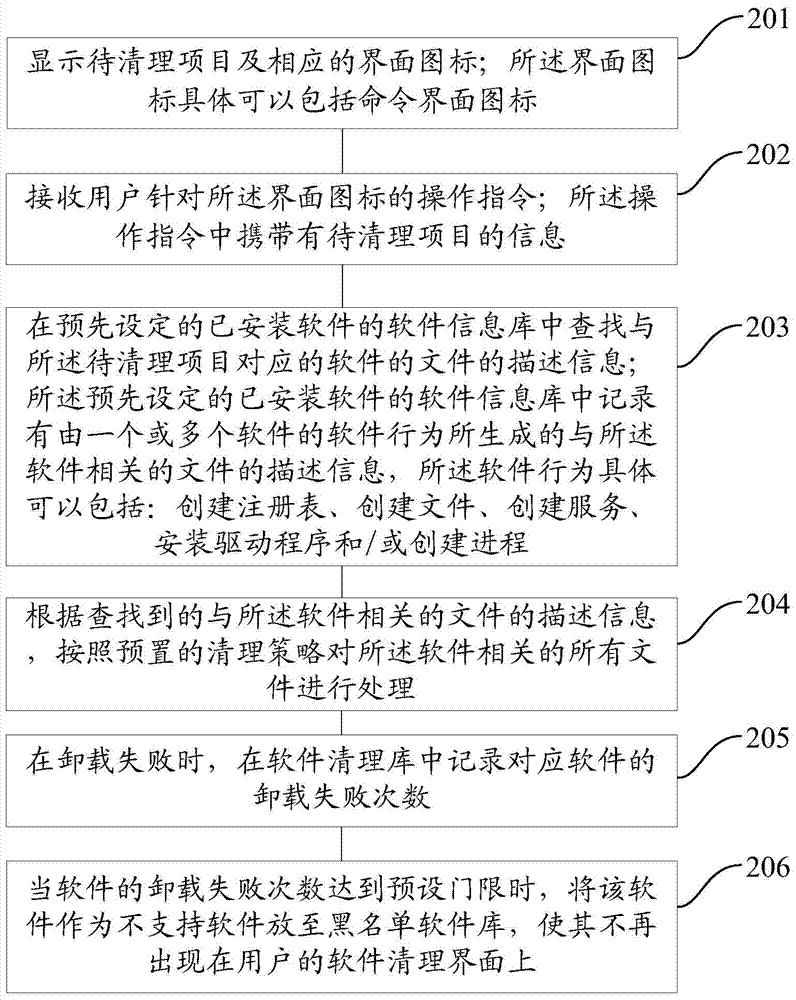

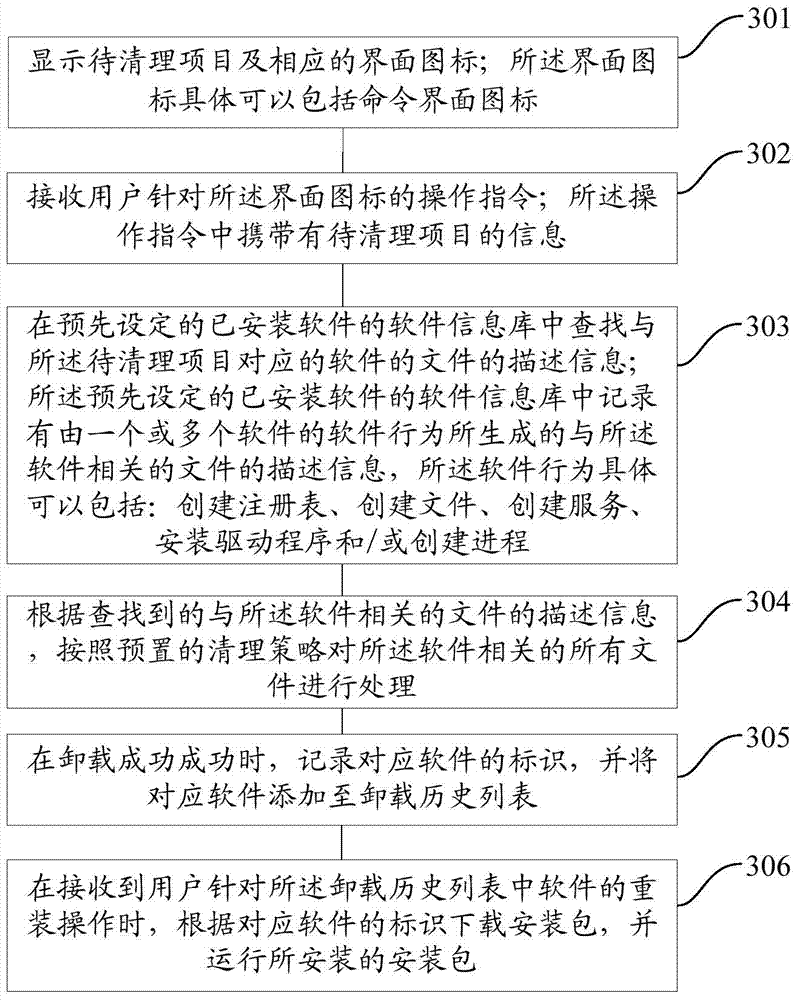

Software clearing method and software clearing device

ActiveCN103927198ARealize automatic uninstallationRealize one-click cleaningProgram loading/initiatingInformation repositorySoftware engineering

An embodiment of the invention discloses a software clearing method and a software clearing device. The software clearing method specifically includes: displaying to-be-cleared items and corresponding interface icons, wherein the interface icons include commanded interface icons; receiving operating commands aiming at the interface icons, wherein the operating commands carry information of the to-be-cleared items; finding description information of files of software corresponding to the to-be-cleared items in a software information library of the preset installed software; when the interface icons are the commanded interface icons, processing all the software related files according to preset clearing strategies and the found description information of the software related files. Refreshing and focus grabbing of a current screen used by a user in software uninstallation can be effectively avoided, convenience in software uninstallation can be improved for the user, and current operation of the user can be ensured to operate normally.

Owner:BEIJING QIHOO TECH CO LTD

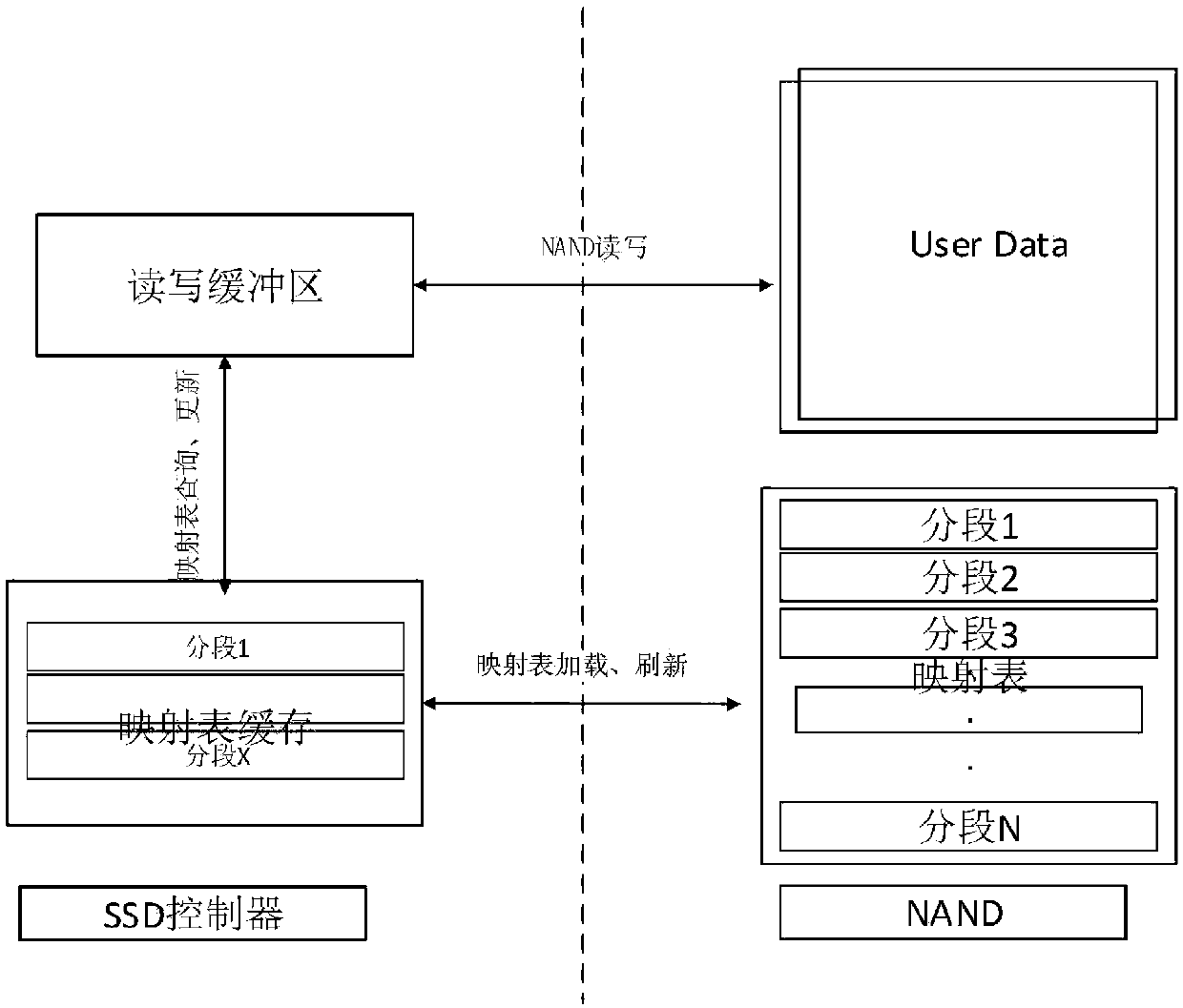

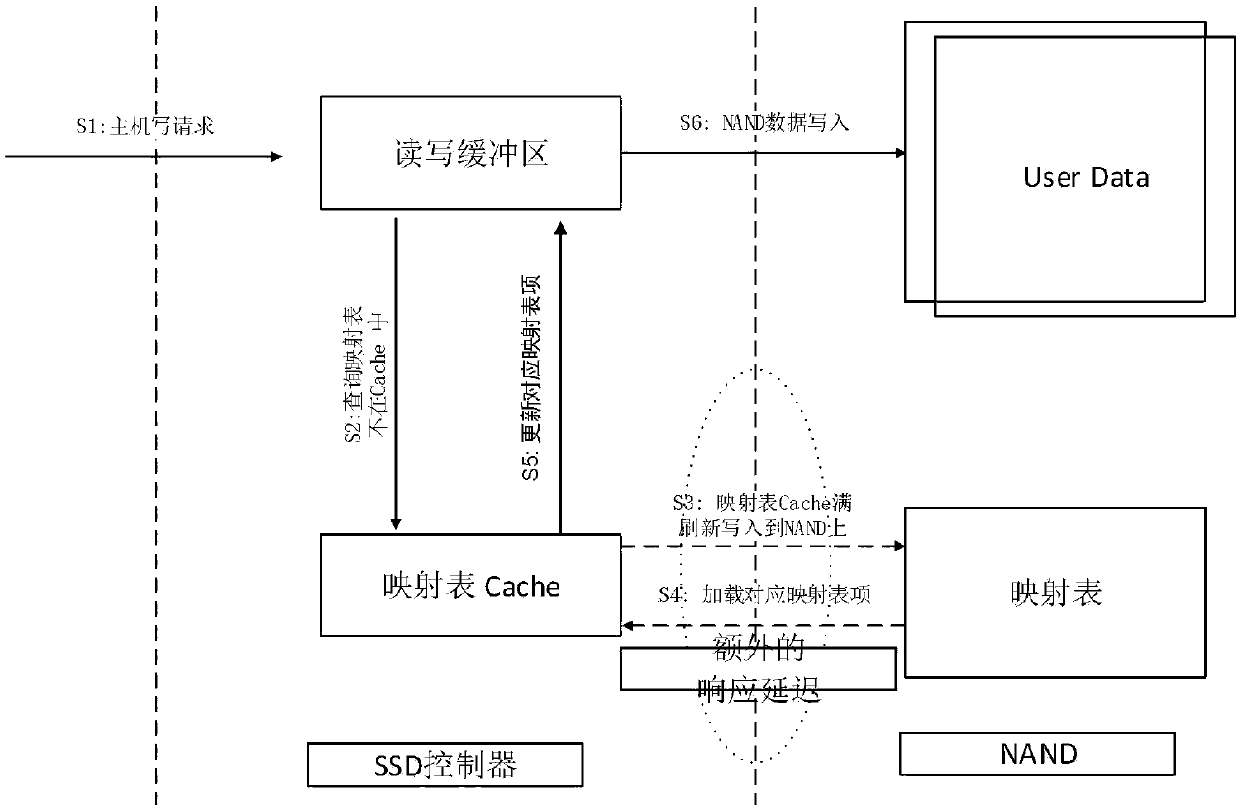

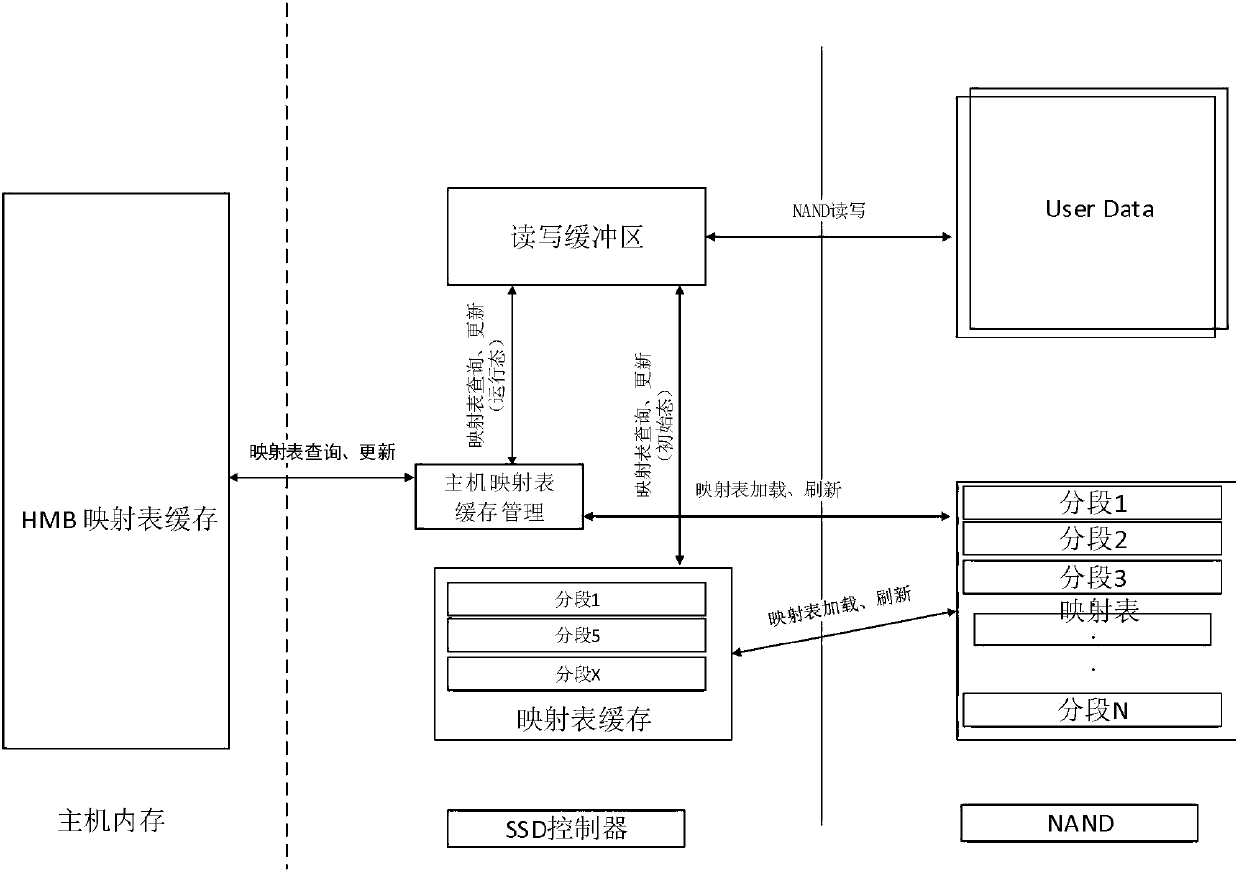

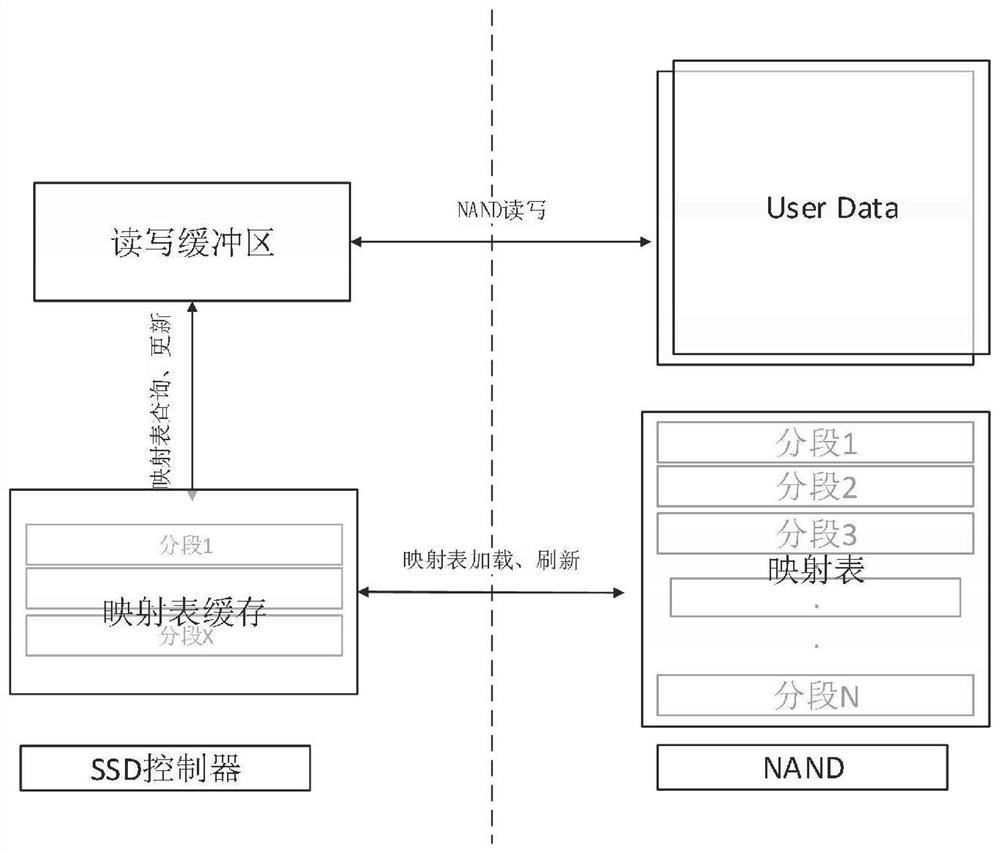

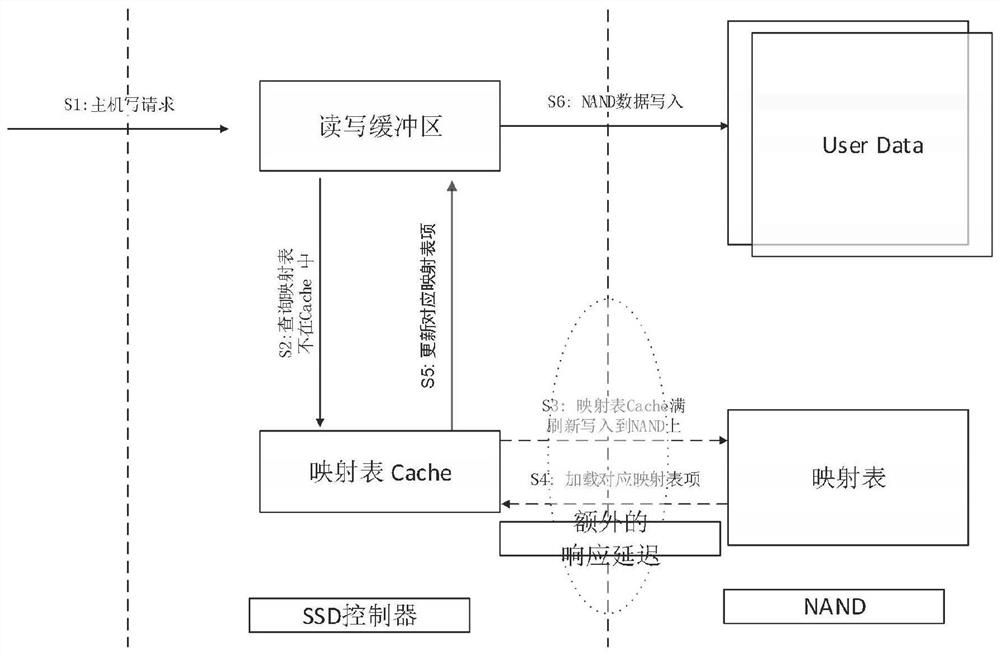

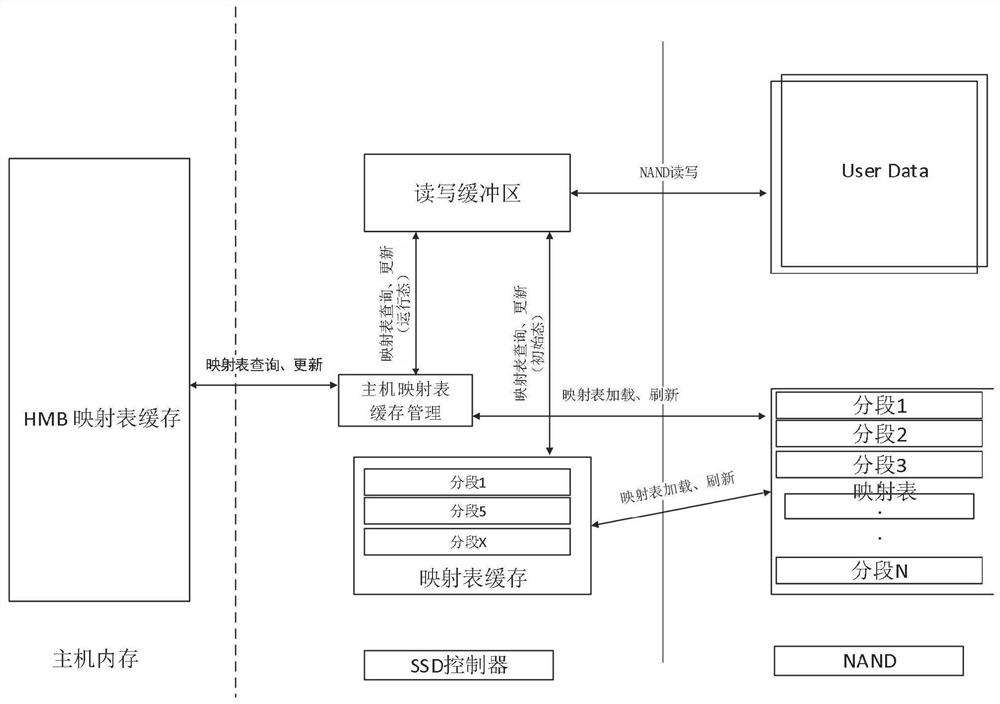

Method for improving performance of SSD (Solid State Disk), and SSD

ActiveCN108021511AAvoid loadAvoid refreshMemory adressing/allocation/relocationHost memorySolid-state

The invention discloses a method for improving the performance of an SSD (Solid State Disk), and the SSD. The method is characterized in that one memory space is applied and distributed to a host sidefrom the SSD to serve as a mapping table buffer region, a mapping table is stored in the mapping table buffer region, and the mapping table item data of the mapping table buffer region is accessed through a high-speed interface. By aiming the problem of low performance caused in that the mapping table of a Dramless SSD is limited and a host randomly reads and writes to frequently trigger internalmapping table replace, on the basis of the HMB (Host Memory Buffer) strategy of an NVMe (Non-Volatile Memory express) SSD, the Memory of the host side is applied to serve as mapping table buffer, a situation that the mapping table is frequently loaded and refreshed is avoided, and therefore, a purpose that performance for operating the SSD is improved is realized.

Owner:SHENZHEN YILIAN INFORMATION SYST CO LTD

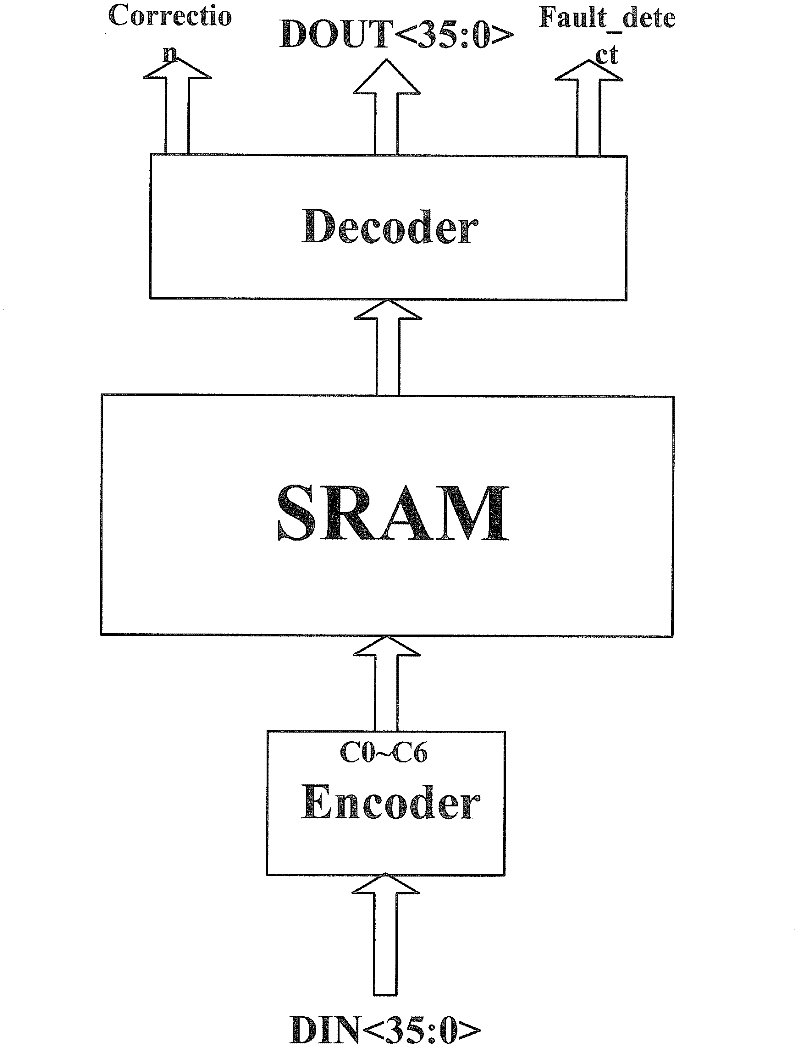

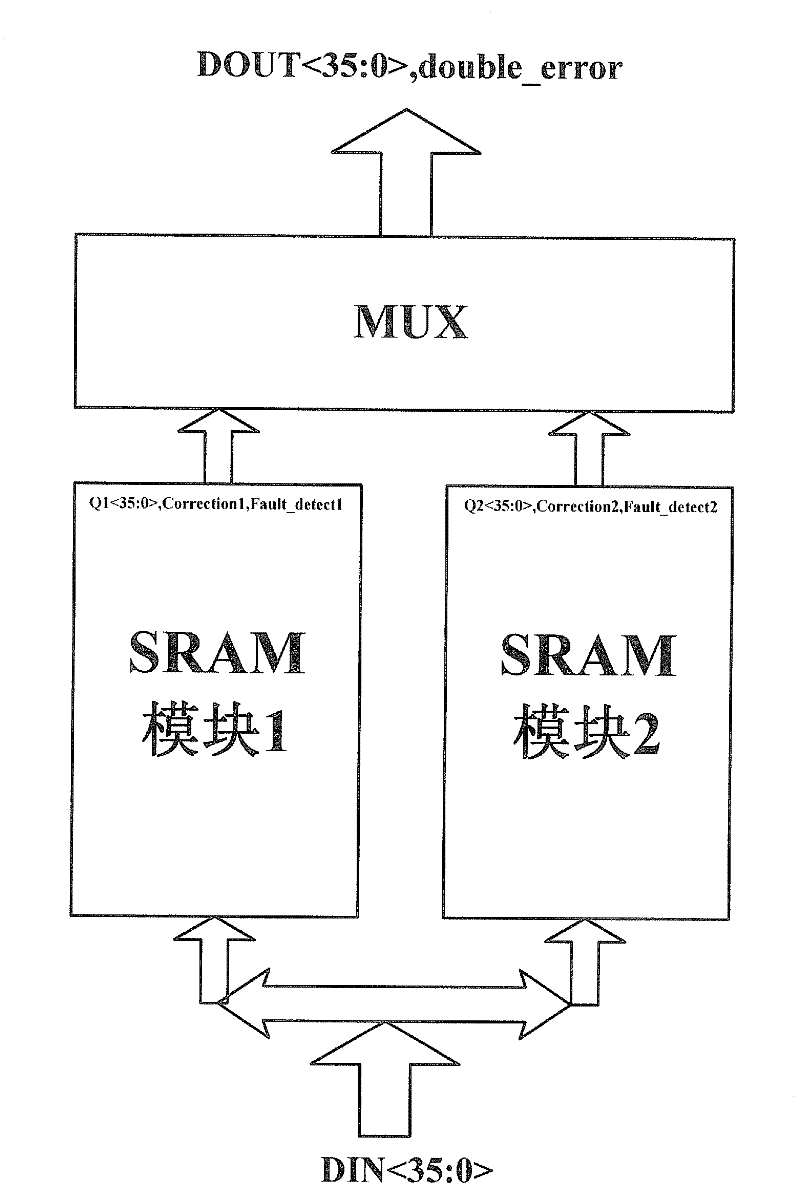

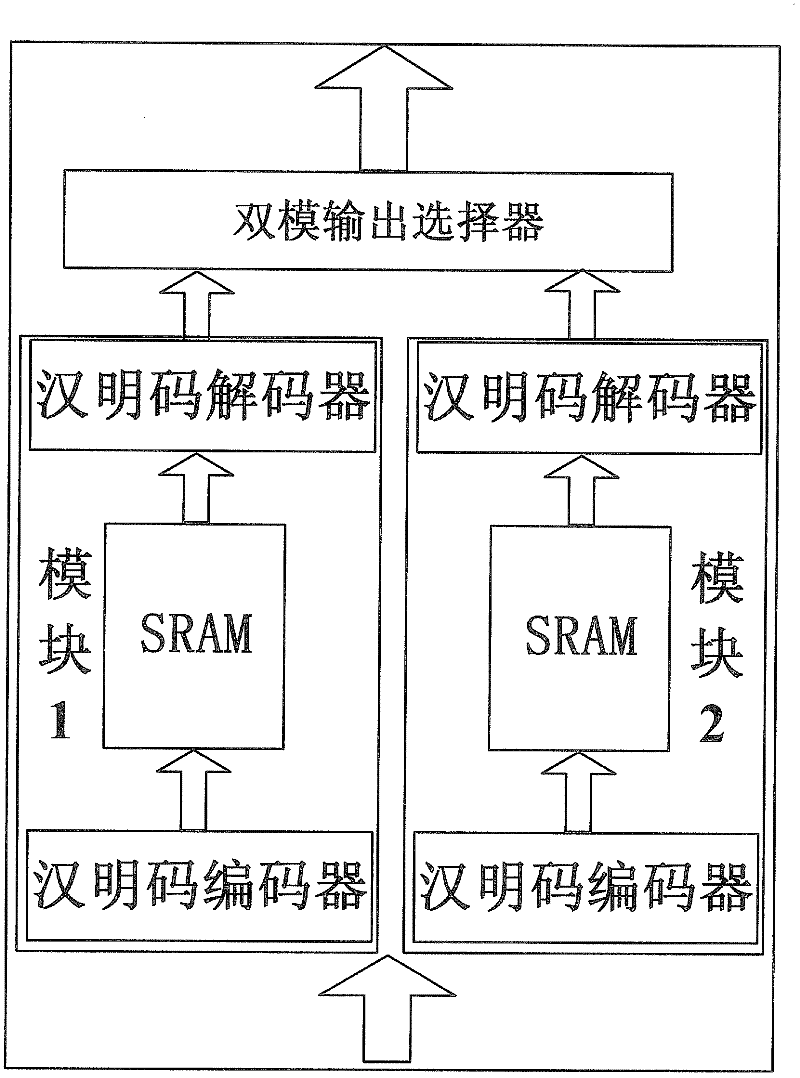

Hamming code based method for carrying out fault tolerance on static RAM multiple bit upset

The invention discloses a Hamming code based method for carrying out fault tolerance on static RAM (random-access memory) multiple bit upset. The method comprises the following steps: carrying out coding and decoding on the static RAM by employing Hamming code; employing two identical static RAMs with Hamming code coding and decoding to realize parallel input and output; and connecting a dual mode output selection circuit on output terminals of the two static RAMs. The invention has certain tolerance on SRAM multiple bit upset caused by high energy particles; and as no refresh or update is required, a system speed is increased substantially.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

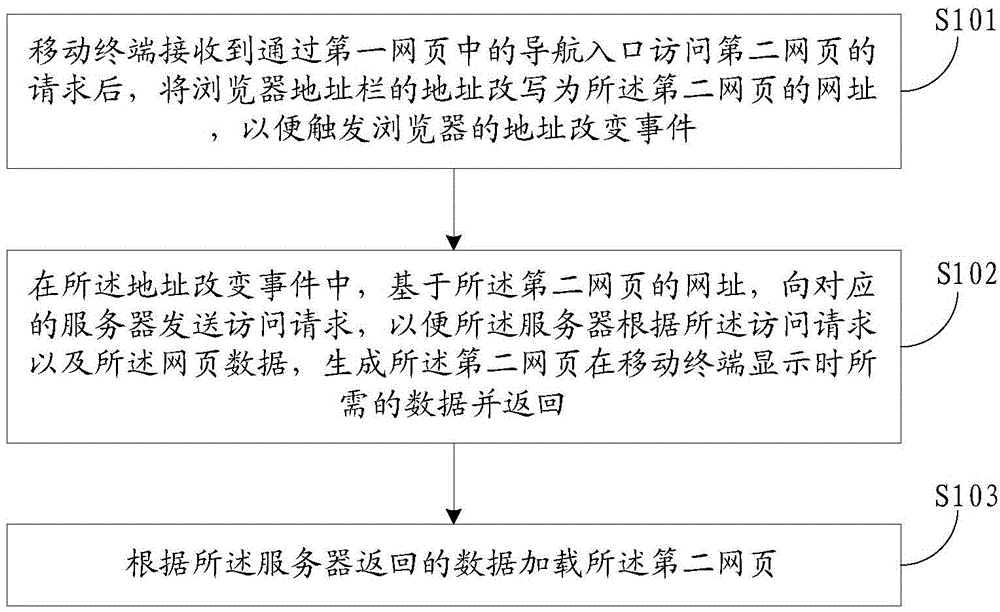

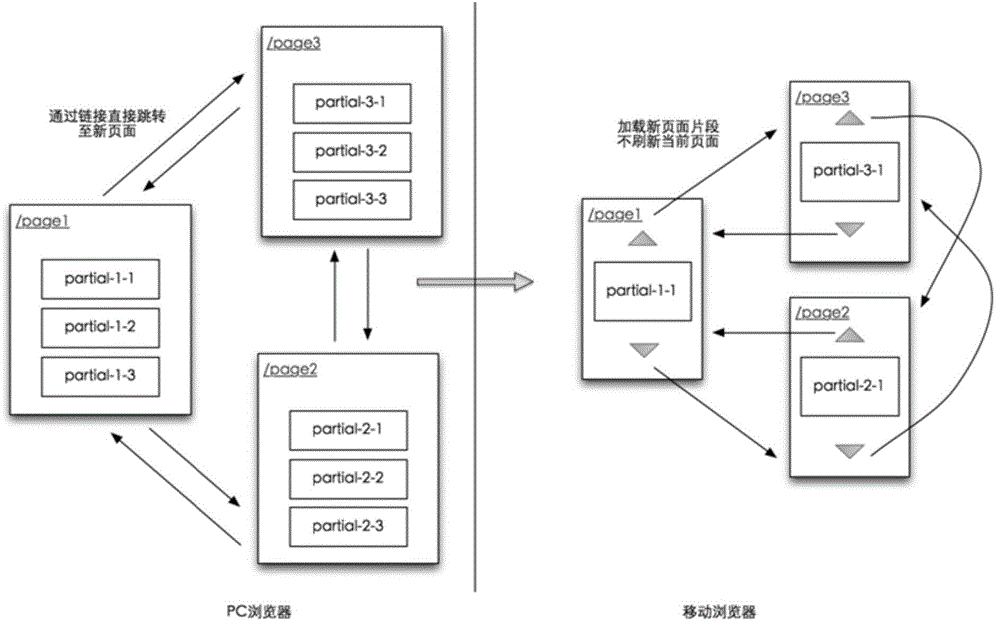

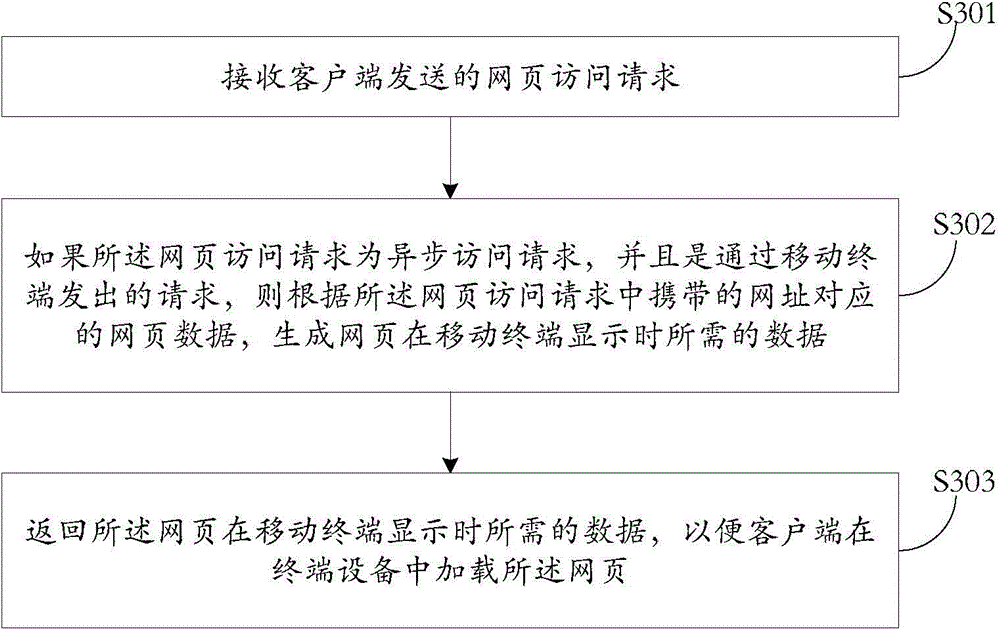

Webpage loading and webpage data providing method and device of mobile terminal

ActiveCN104423991ALow costAvoid refreshProgram loading/initiatingTransmissionAddress barComputer terminal

The invention discloses a webpage loading and webpage data providing method and device of a mobile terminal. In the method, when the mobile terminal is used to visit a webpage, the address of the webpage is identical with the address of the webpage visited by a non-mobile terminal, and the address corresponds to the same set of webpage data at a server end. The method includes: after the mobile terminal receives a request for visiting a second webpage through the navigation entry of a first webpage, the address of a browser address bar is rewritten into the address of second webpage so as to trigger the browser address changing event; in the address changing event, a visiting request is transmitted to the corresponding server according to the address of the second webpage so as to allow the server to generate the data required by the second webpage for displaying on the mobile terminal according to the visiting request and the webpage data and return the data; loading the second webpage according to the data returned by the server. By the method, cost in mobilization processes can be reduced.

Owner:ALIBABA GRP HLDG LTD

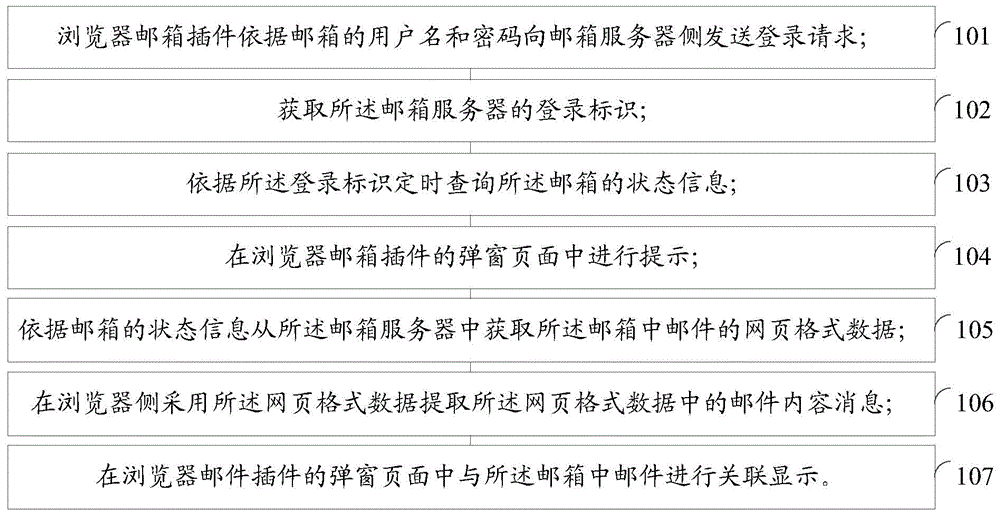

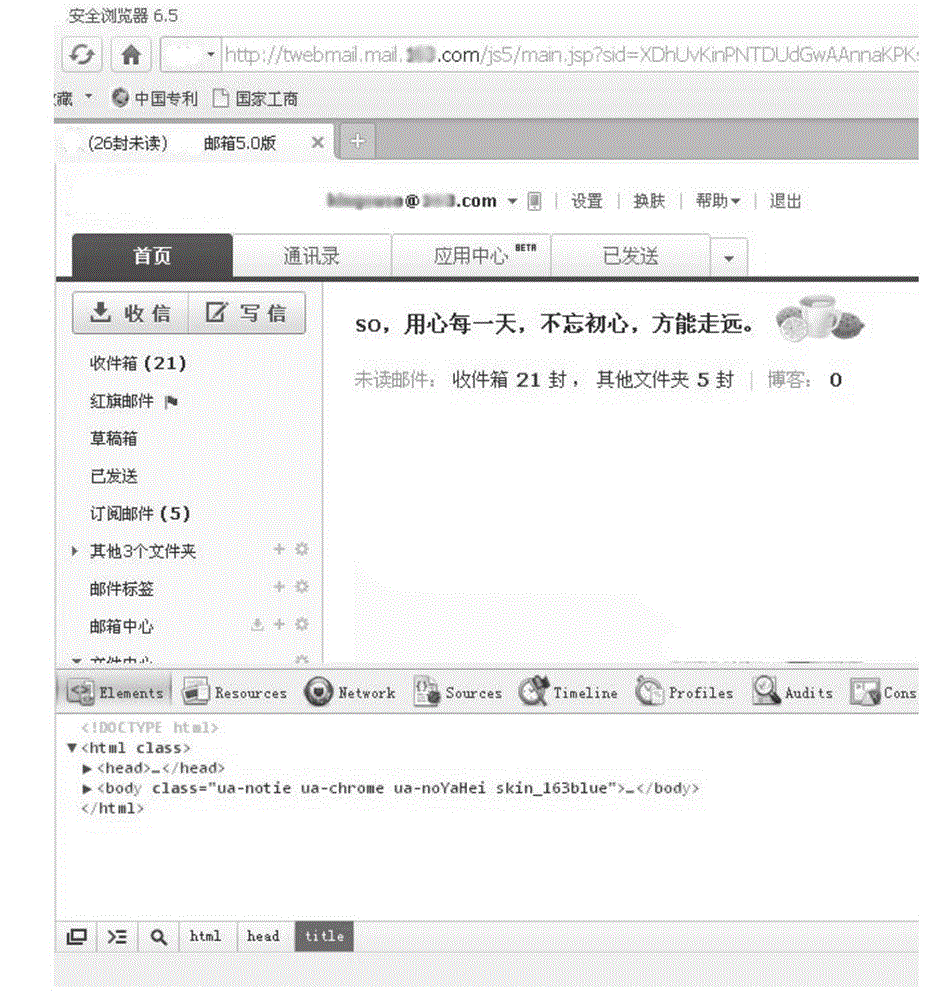

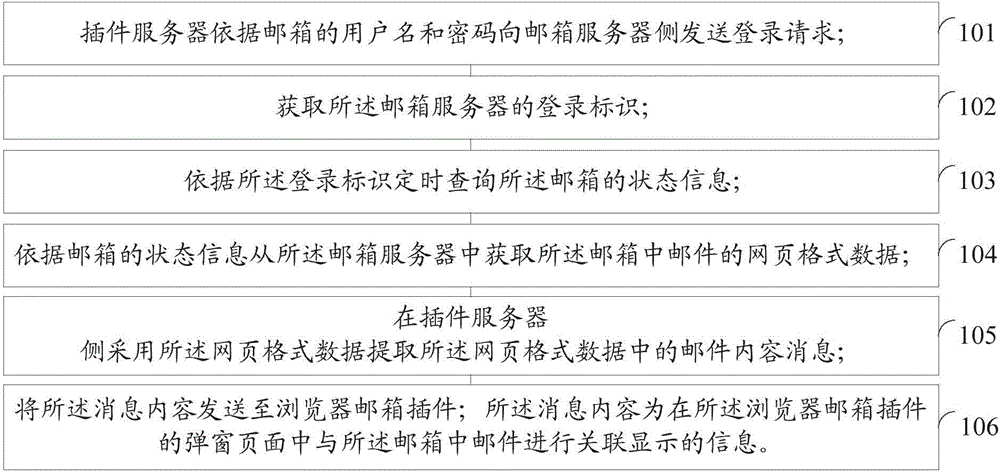

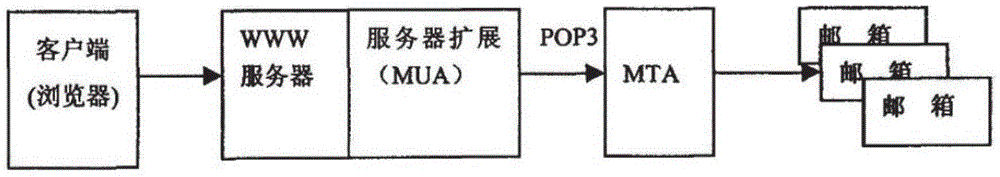

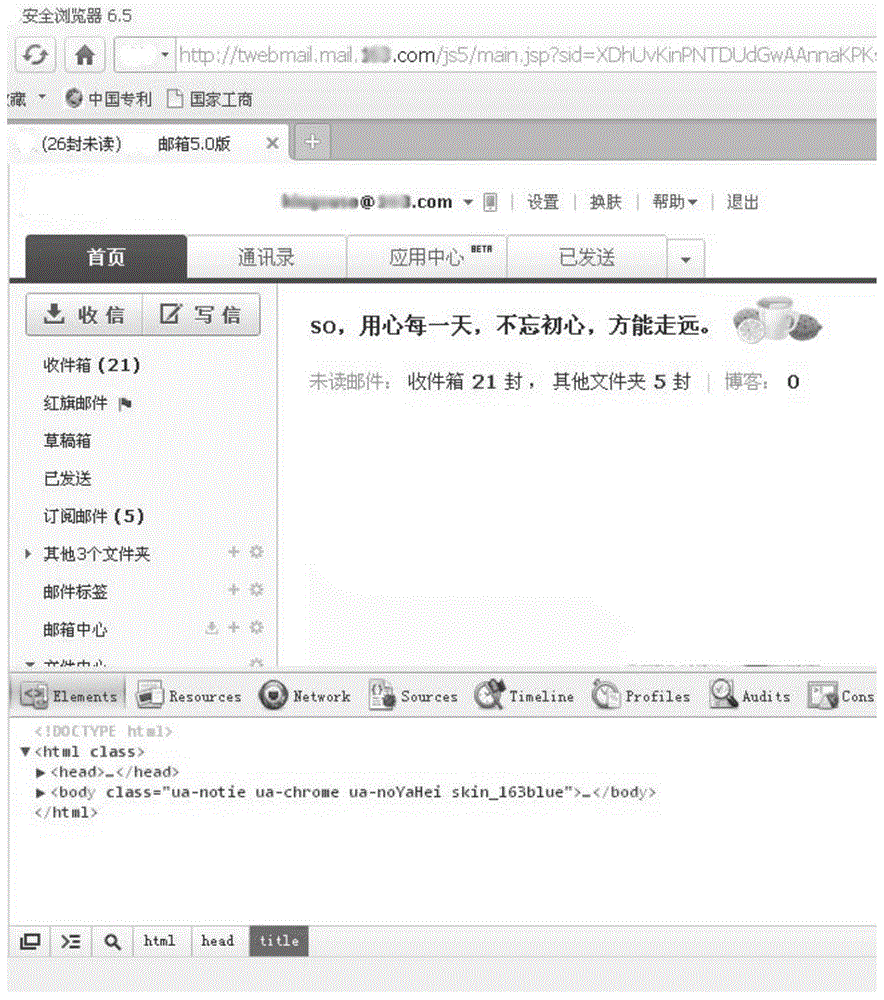

Mail content loading method and apparatus, and browser

InactiveCN103606074AImprove management efficiencyAvoid refreshOffice automationData switching networksPasswordManagement efficiency

The invention discloses a mail content loading method and apparatus, and a browser. The method comprises: a browser mail box plug-in, according to the user name and password of a mail box, sending a registration request to a mail box server side, and obtaining the registration identification of a mail box server; according to the registration identification, regularly checking the state information of the mail box, and performing prompting in the popup window page of the browser mail box plug-in; according to the state information of the mail box, obtaining the webpage format data of a mail in the mail box from the mail box server; and extracting the mail content messages of the webpage format data by use of the webpage format data at a browser side, and displaying the messages in the popup window page of the browser mail box plug-in in association with the mail in the mail box. By using the method, the apparatus and the browser, the mail contents of multiple mail boxes can be simultaneously loaded, the problem that a user has to afresh multiple mail box pages actively is avoided, the operation is convenient and fast, and the mail box management efficiency is substantially improved.

Owner:BEIJING QIHOO TECH CO LTD +1

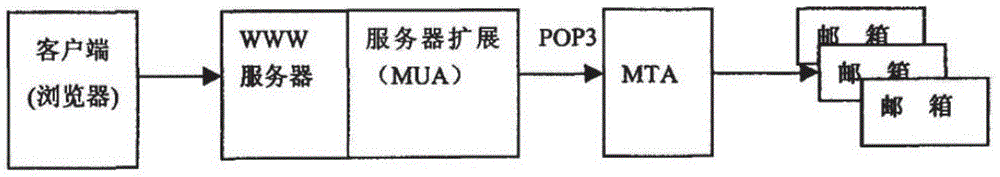

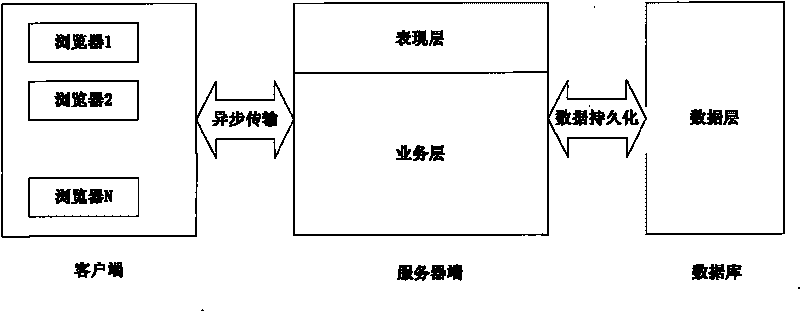

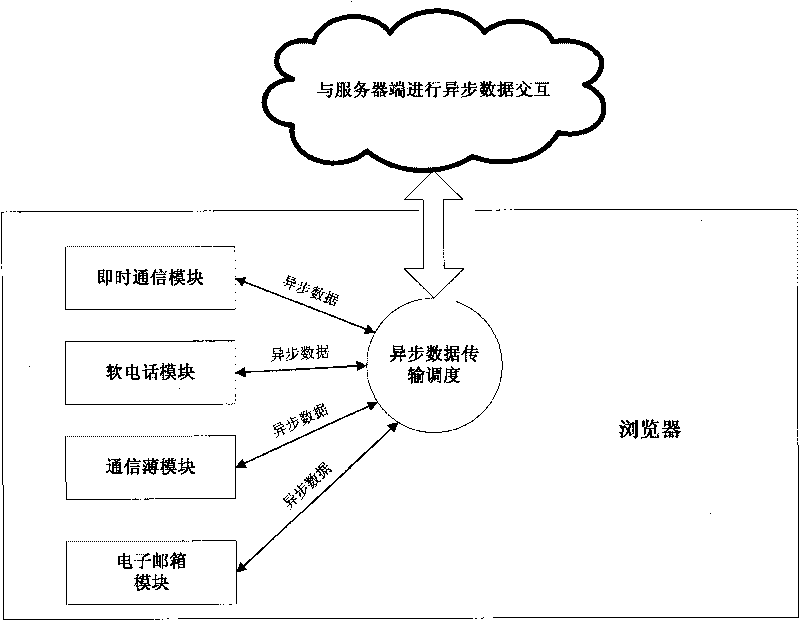

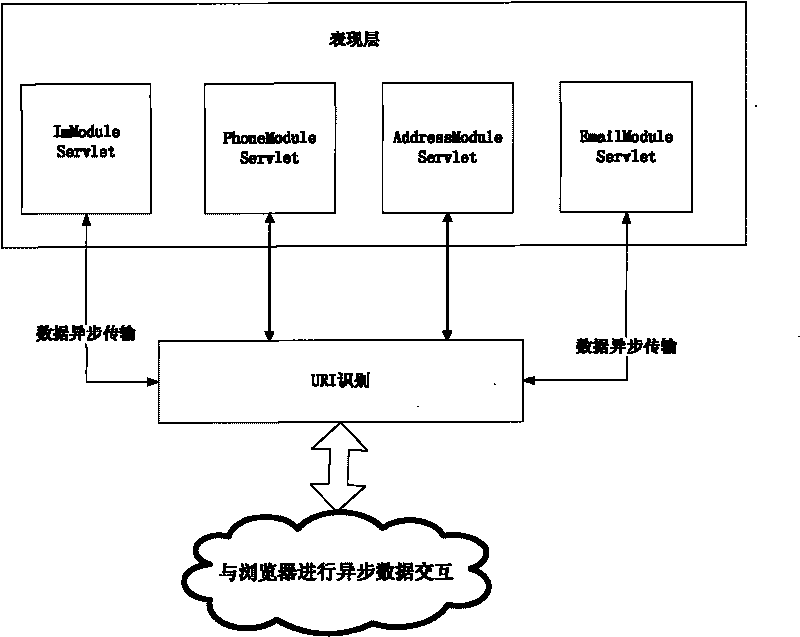

Convergence communication system based on Ajax and J2EE and data transmission method thereof

The invention provides a convergence communication system based on Ajax and J2EE and a data transmission method thereof, relating to the field of convergence communication. The convergence communication system comprises a presentation layer, a service layer, a data layer and a client layer, wherein the client layer is arranged at a client side, the presentation layer and the service layer are arranged at a server side, and the data layer is arranged in a database; the client layer consists of browsers, and each browser exchanges data with the presentation layer at the server side by using an asynchronous transfer method in an Ajax technology. The invention discloses a novel method based on data transmission between the client layer and the presentation layer in the system and proposes an asynchronous request scheduling function for processing a corresponding asynchronous request according to the priority of the module, thereby getting rid of the traditional C / S structure and the B / S structure applied to the traditional Web; in addition, a server / browser mode is adopted to facilitate deploy and be safer.

Owner:SOUTHEAST UNIV

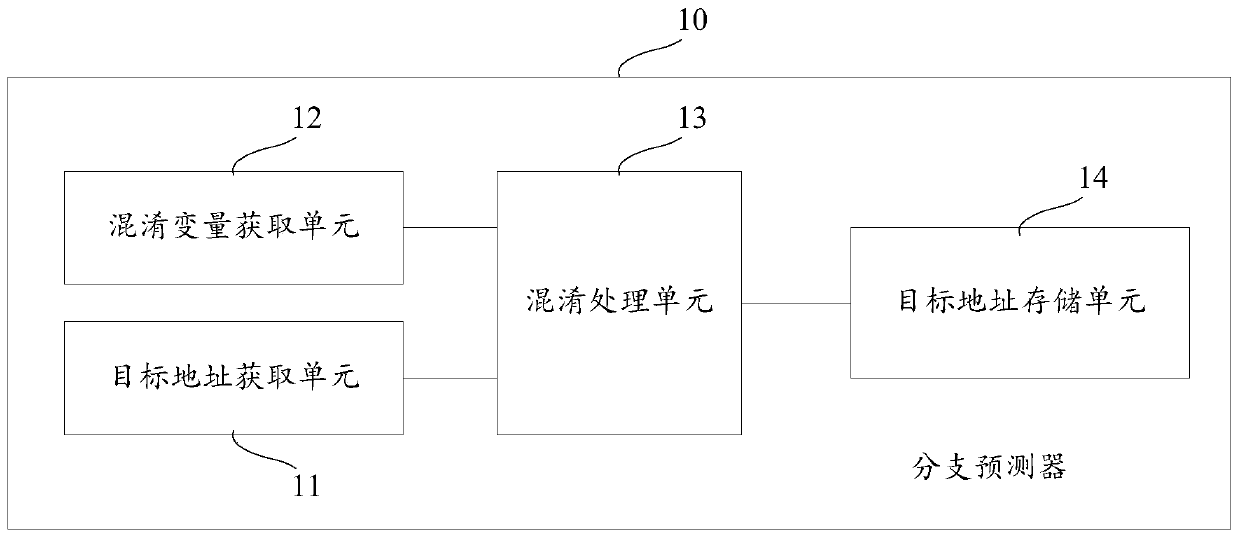

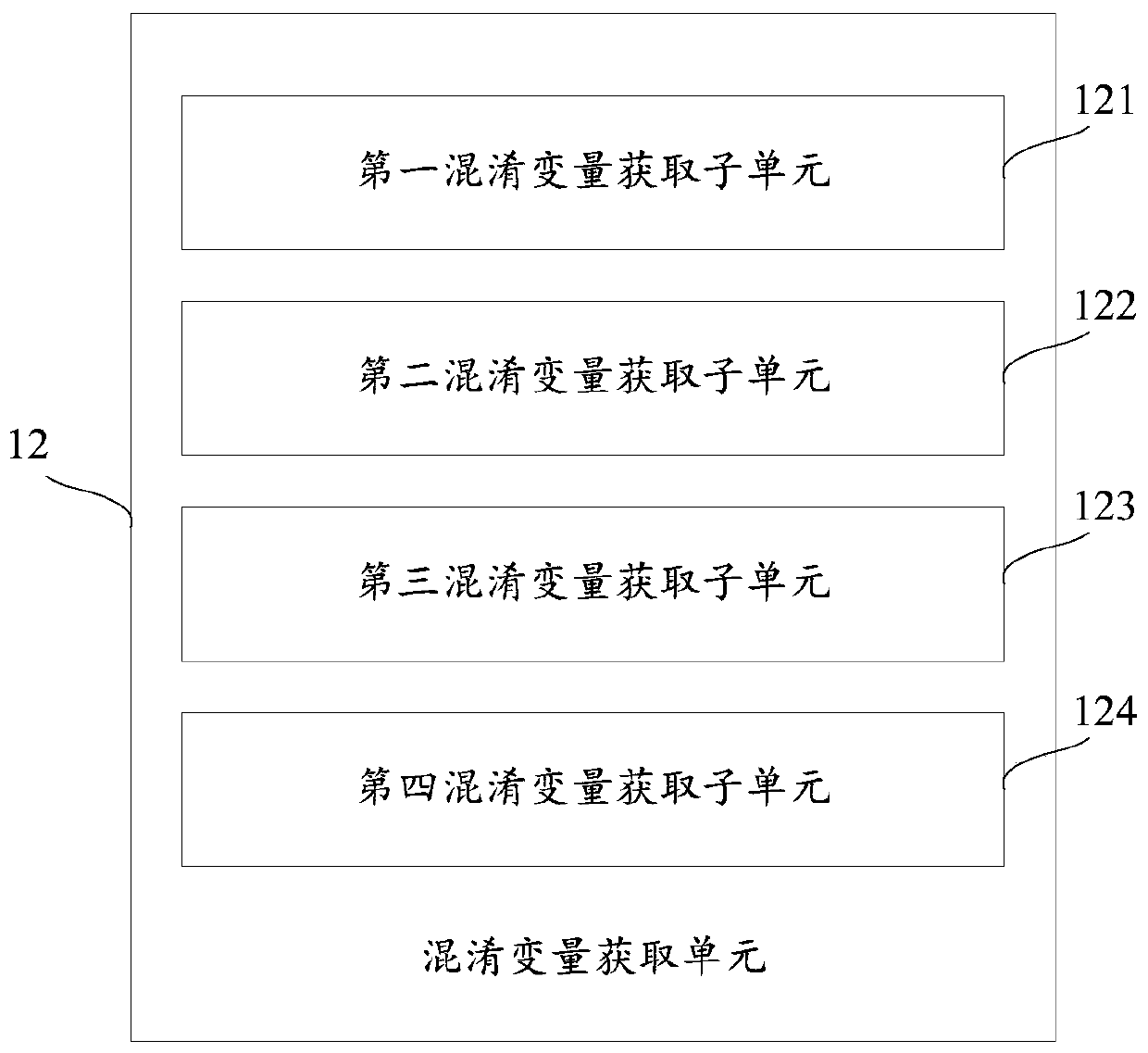

Processor, branch predictor, data processing method of branch predictor and branch prediction method

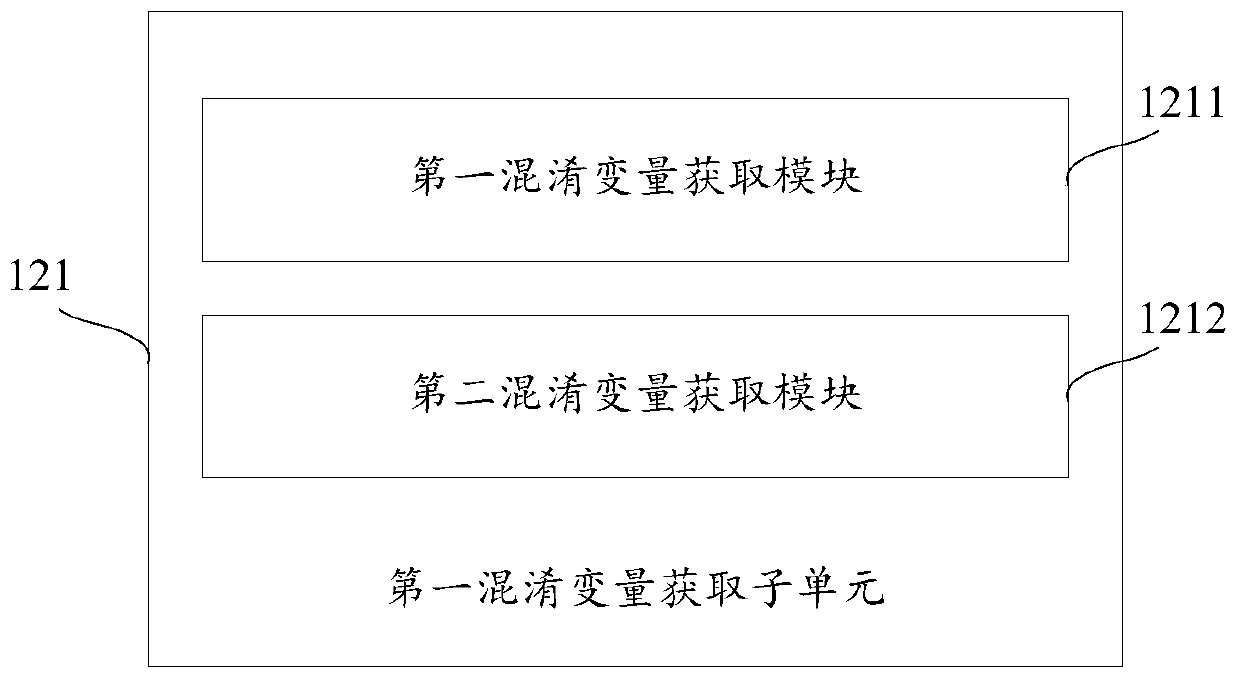

ActiveCN110347432AImprove securityIncrease diversityConcurrent instruction executionProgram/content distribution protectionObfuscationTheoretical computer science

The invention discloses a processor, a branch predictor, a branch prediction data processing method thereof and a branch prediction method, and the branch predictor comprises a target address obtaining unit which is suitable for obtaining a prediction target address of a branch instruction; a confusion variable acquisition unit suitable for acquiring feature information generated by adopting a preset rule, wherien the feature information comprises at least one of random feature information and non-random feature information; an obfuscation processing unit suitable for performing obfuscation processing on the predicted target address acquired by the target address acquisition unit and the feature information acquired by the obfuscation variable acquisition unit to generate an obfuscation value of the predicted target address; and a target address storage unit suitable for storing the confusion value of the predicted target address. By adopting the scheme, the security of the processor can be improved.

Owner:HYGON INFORMATION TECH CO LTD

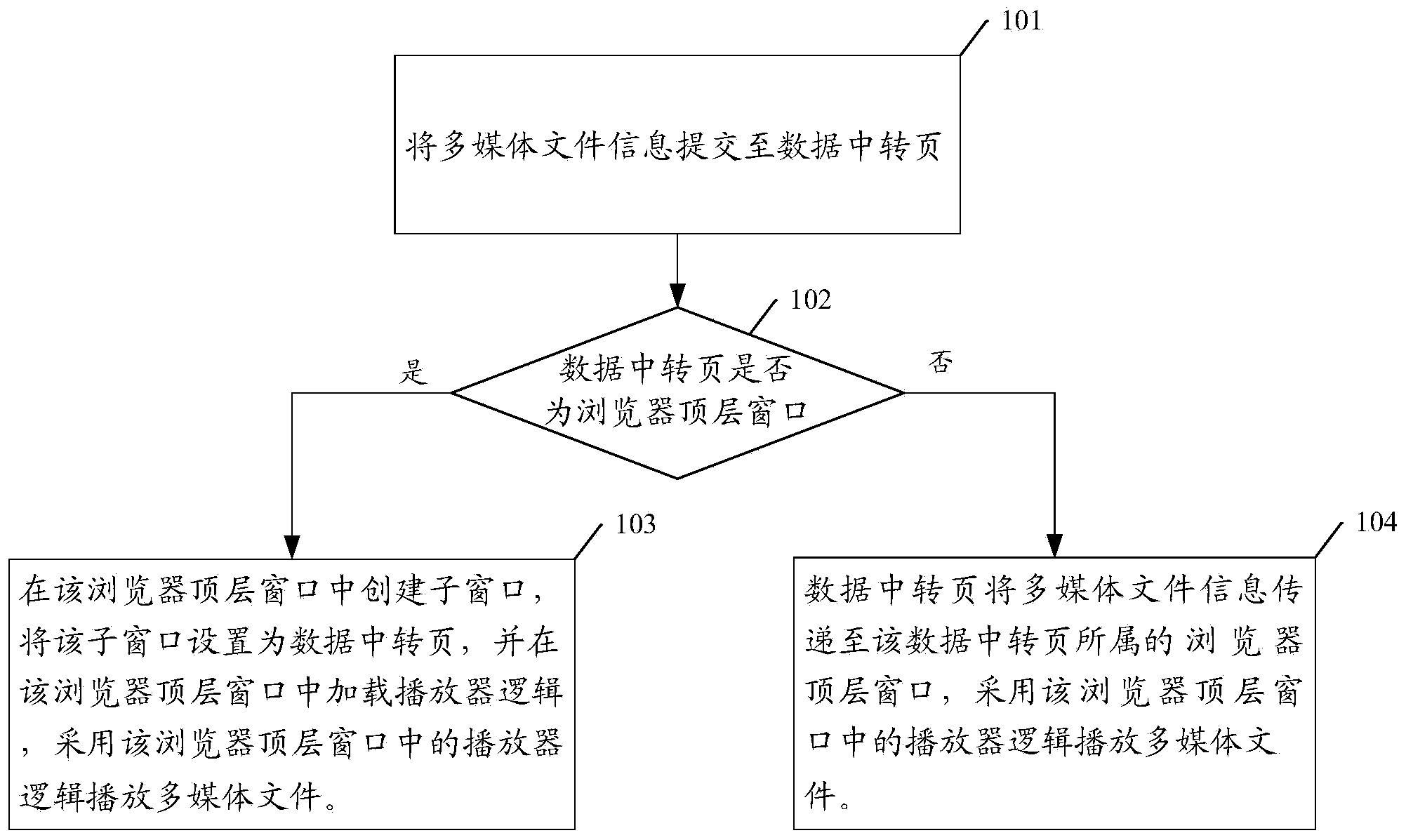

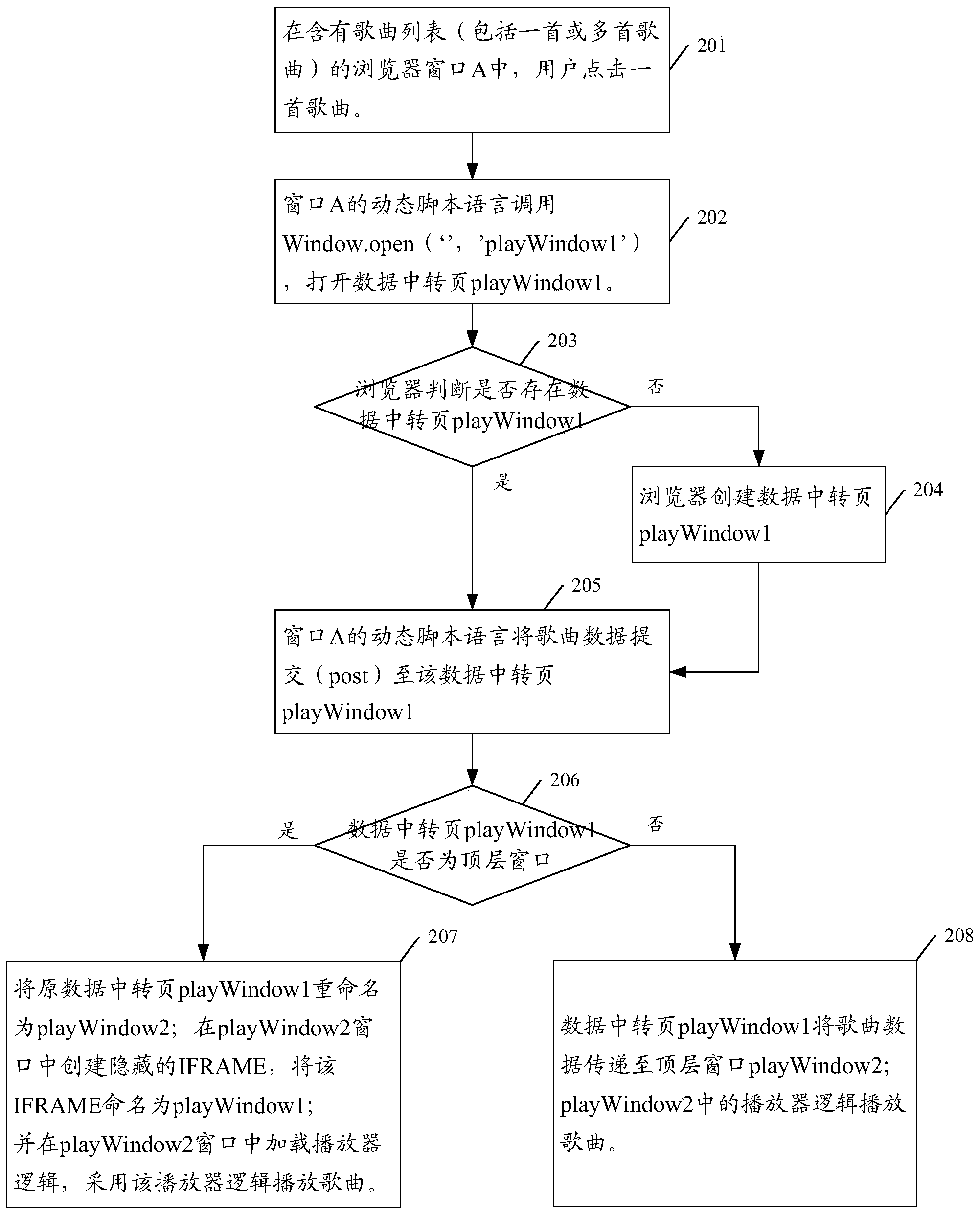

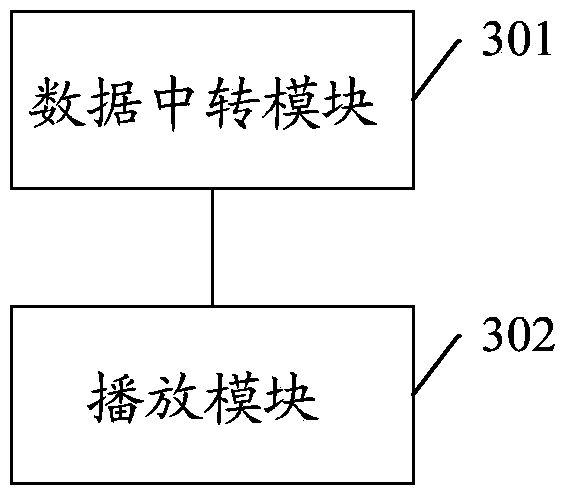

Method and device for playing webpage multimedia file

ActiveCN104090820AImprove experienceAvoid refreshProgram initiation/switchingExecution for user interfacesWeb browserWeb page

The invention provides a method and a device for playing a webpage multimedia file. The method comprises the following steps: submitting multimedia file information to a data transfer page; judging whether the data transfer page is a browser top window or not, creating a sub window in the browser top window if the data transfer page is the browser top window, setting the sub window as the data transfer page, loading a player logic in the browser top window and playing the multimedia file by adopting the player logic in the browser top window; otherwise, transferring the multimedia file information to the browser top window of the data transfer page through the data transfer page and playing the multimedia file by adopting the player logic in the browser top window. The method and the device have the benefit that the effect that a new multimedia file can be played without refreshing a webpage player window when playing requests from other webpage browser windows are received can be realized.

Owner:TENCENT TECH (SHENZHEN) CO LTD

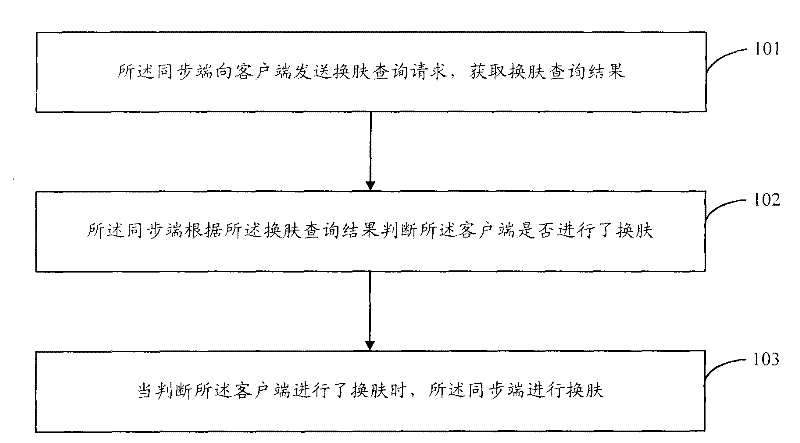

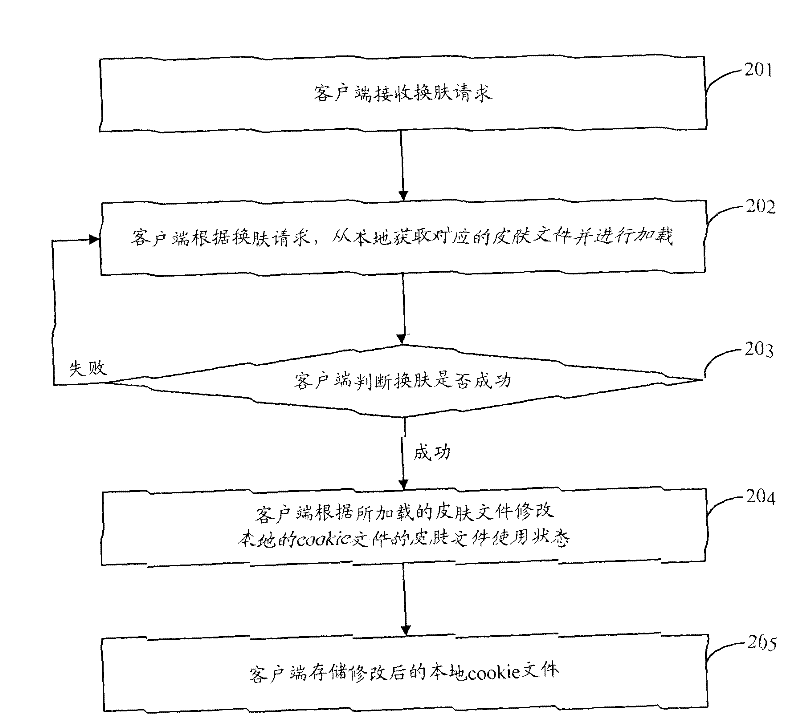

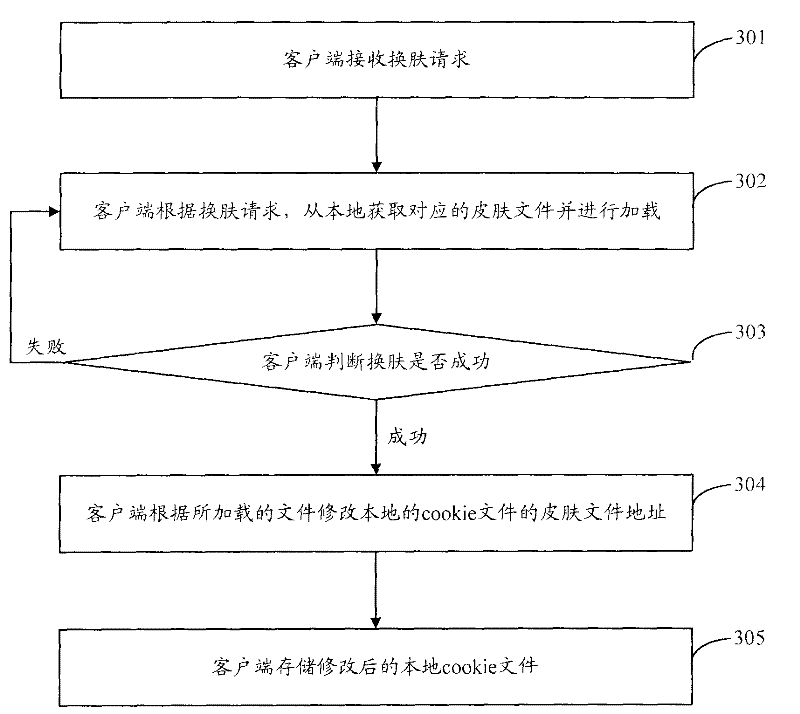

Skin changing method, system and device

ActiveCN102163197AImprove experienceAvoid refreshSpecial data processing applicationsClient-sideWeb page

The embodiment of the invention discloses a skin changing method, a skin changing system and a skin changing device, which are applied to a system which comprises a client and a synchronous end. The method comprises the following steps that: the synchronous end transmits a skin changing inquiring request to the client to acquire a skin changing inquiring result; the synchronous end judges whether the client changes skin or not according to the skin changing inquiring result; and the synchronous end changes the skin when judging that the client changes the skin. The synchronous end comprises an inquiring module for transmitting the skin changing inquiring request to the client to acquire the skin changing inquiring result, a judging module for judging whether the client changes the skin or not according to the skin changing inquiring result which is acquired by the inquiring module, and a skin changing module for changing the skin when the judging module judges that the client changes the skin. By the method, the system and the device, the skin changing can be synchronously performed on the client and a webpage, and user experience is improved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

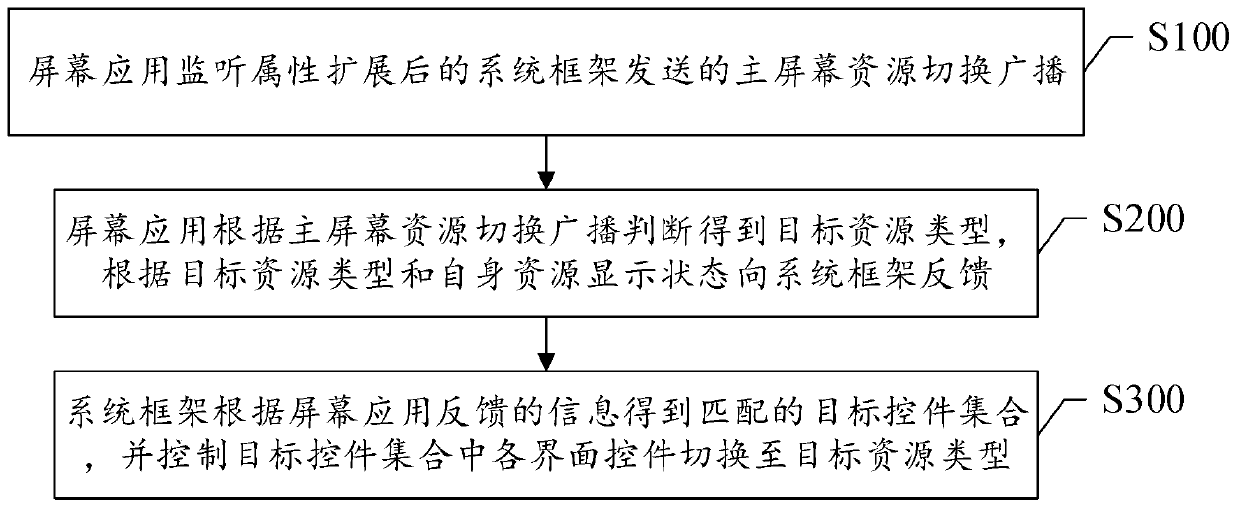

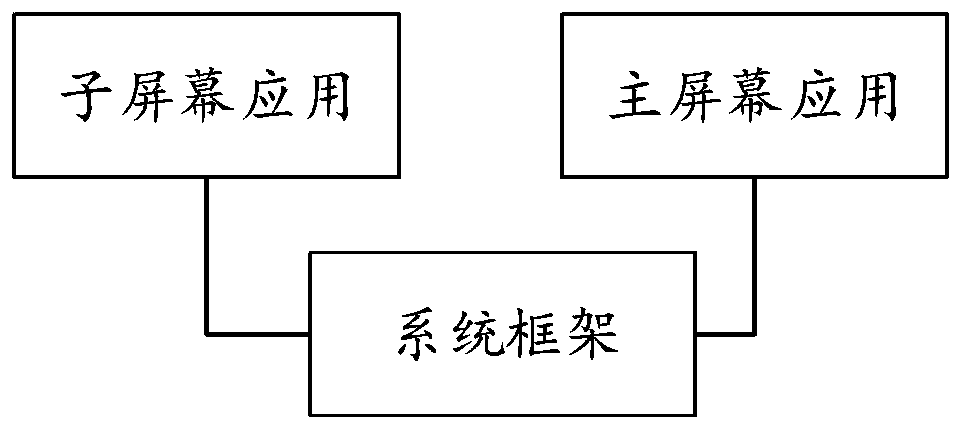

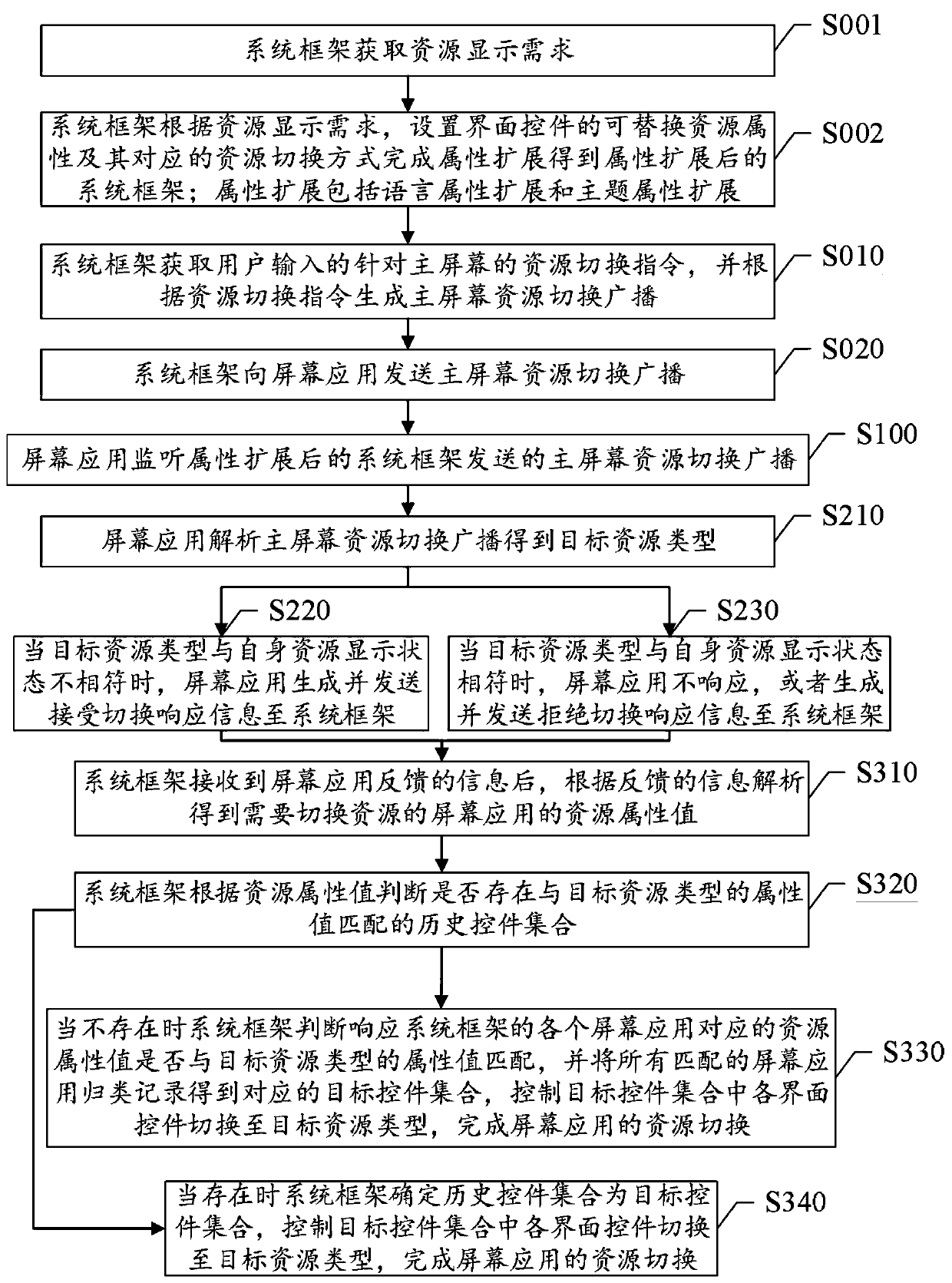

Resource switching control method and system, terminal equipment and storage medium

PendingCN110737487AImprove switching efficiencyAvoid refreshProgram initiation/switchingProgram loading/initiatingHandoff controlTarget control

The invention provides a resource switching control method and system, terminal equipment and a storage medium. The resource switching control method comprises the steps that a screen application monitors a home screen resource switching broadcast sent by a system framework after attribute expansion; the screen application judges and obtains a target resource type according to the main screen resource switching broadcast, and feeds back to the system framework according to the target resource type and a self resource display state; and the system framework obtains a matched target control setaccording to the information fed back by the screen application, and controls each interface control in the target control set to be switched to the target resource type to complete resource switchingof the screen application. According to the resource switching control method, the control is prevented from being refreshed, and the resource switching efficiency and the user experience are improved.

Owner:ARCHERMIND TECH NANJING

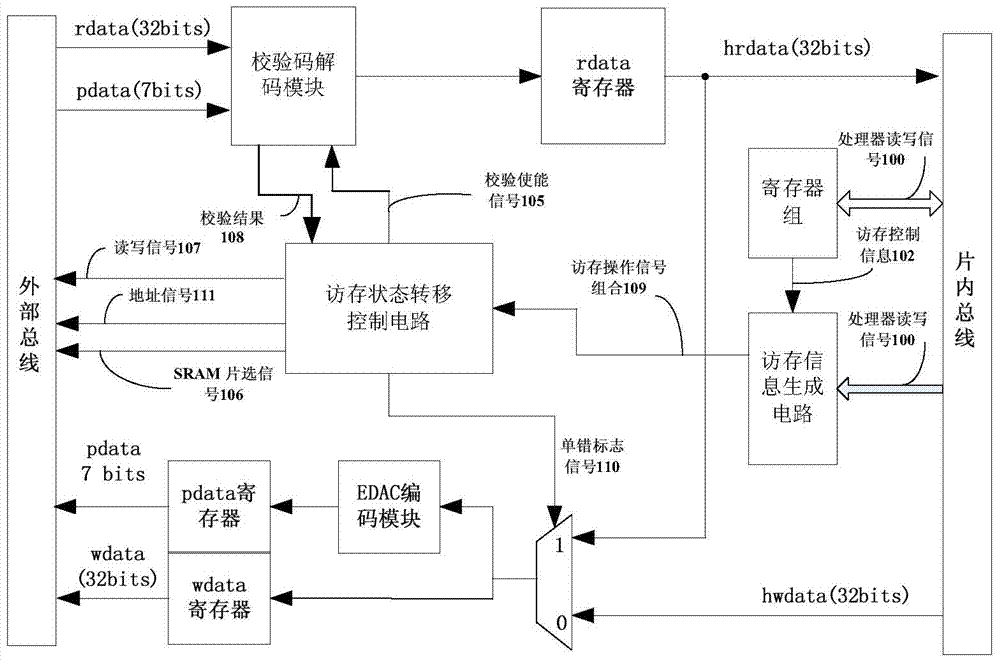

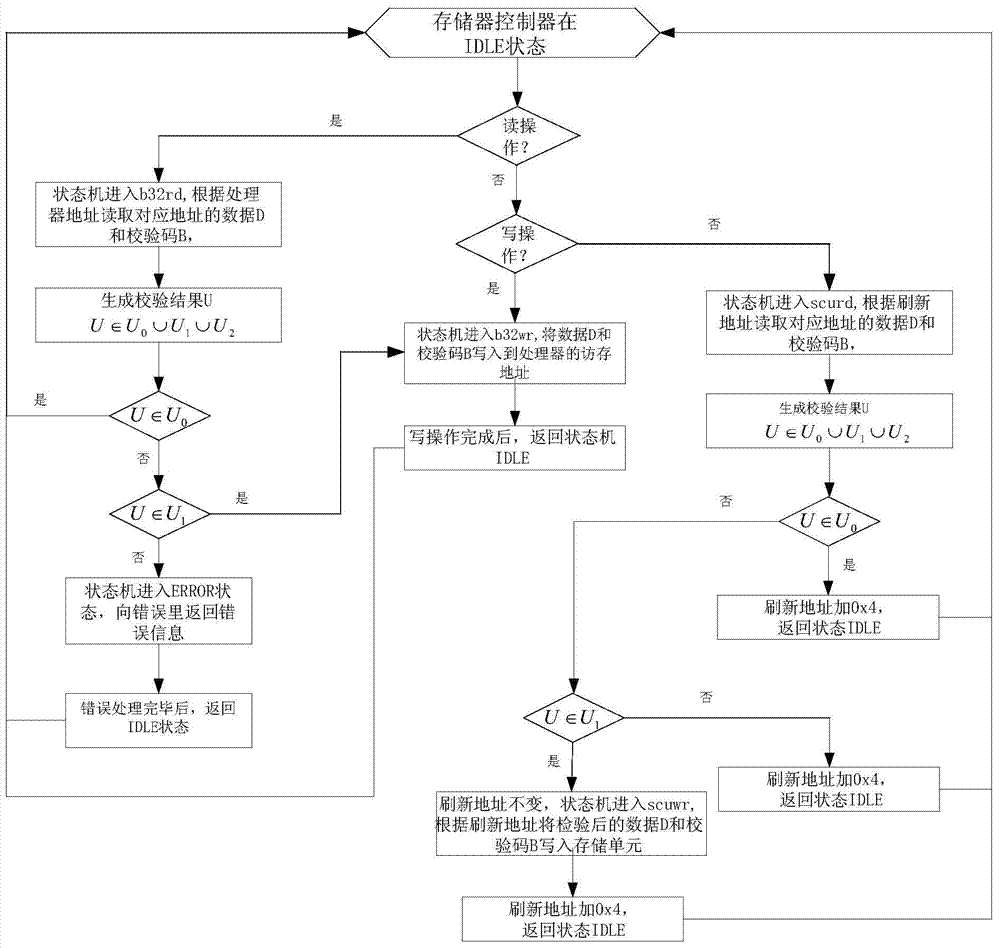

SRAM (static random access memory)-oriented anti-SEU (single-event upset) error accumulation controller and method

The invention discloses an SRAM (static random access memory)-oriented anti-SEU (single-event upset) error accumulation controller and method. The controller comprises a register group, a memory access information generation circuit, a memory access state transfer control circuit, a check code decoding module, an rdata register, a multiplexer, an EDAC (error detection and correction) encoding module, a pdata register and a wdata register. When a processor performs other operations other than access of a main memory, a memory controller of the processor autonomously performs traversal read, check and write-back operations on all storage units, the traversal refresh operation takes a most basic SRAM storage unit as a unit; when the refresh operation of one storage unit is completed, the refresh address is progressively increased, a state machine is controlled to be back to an idle state, and whether the processor has memory access operation or not is detected again. According to the controller and the method, disclosed by the invention, idle time of a system is fully utilized, and SEU error accumulation of the SRAM storage units can be avoided on the basis of not affecting the performance of the processor.

Owner:NO 771 INST OF NO 9 RES INST CHINA AEROSPACE SCI & TECH

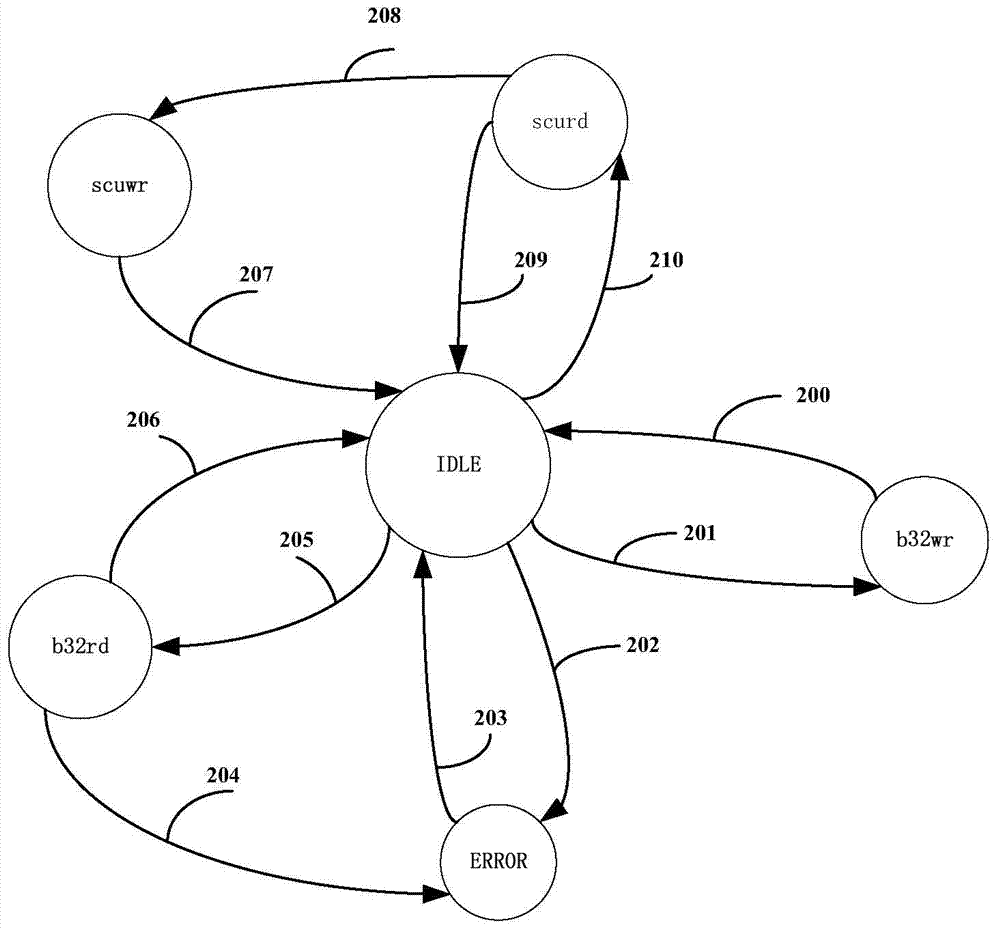

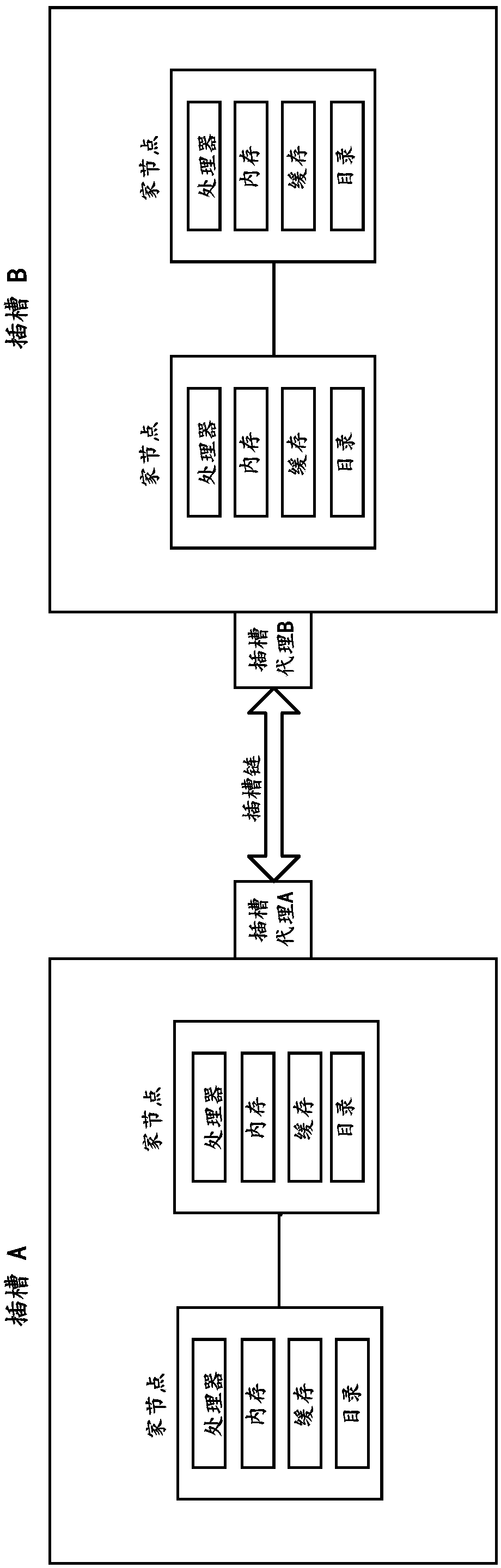

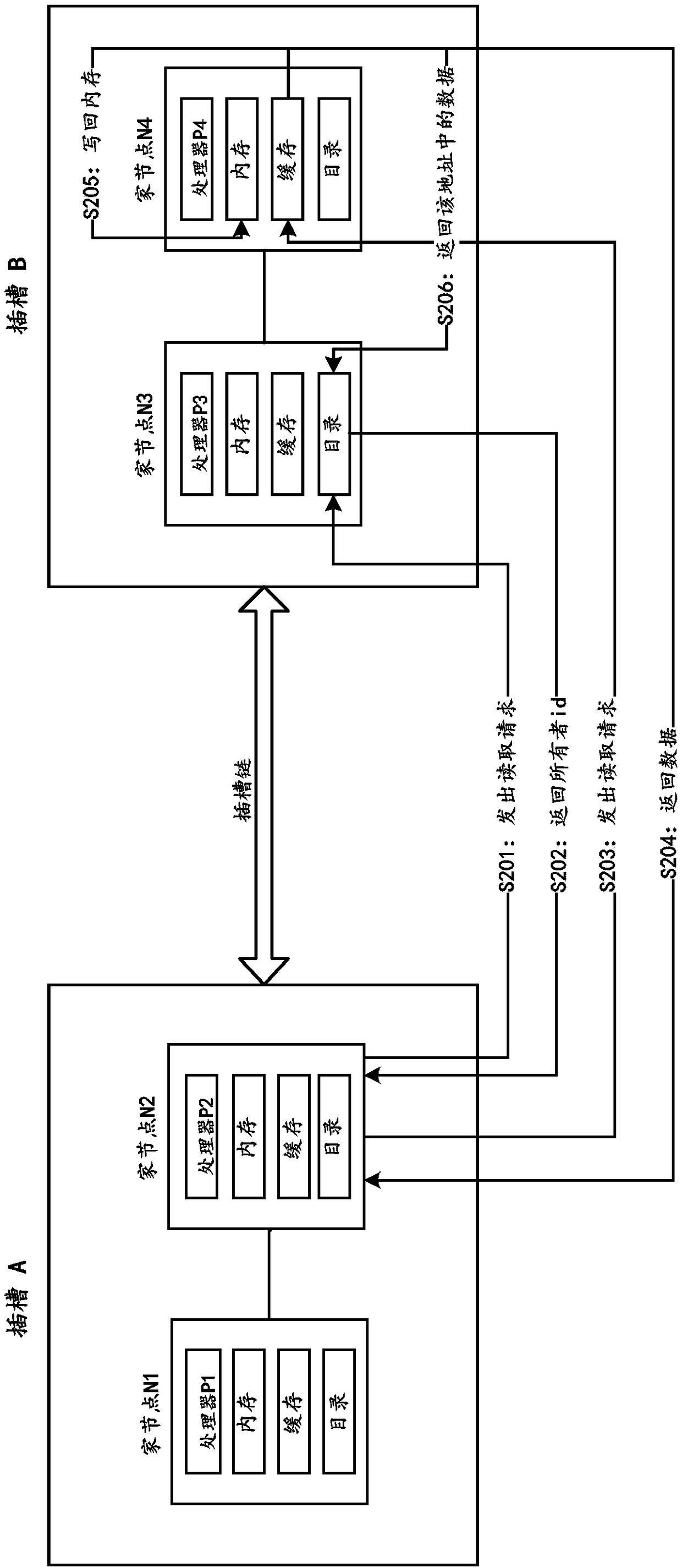

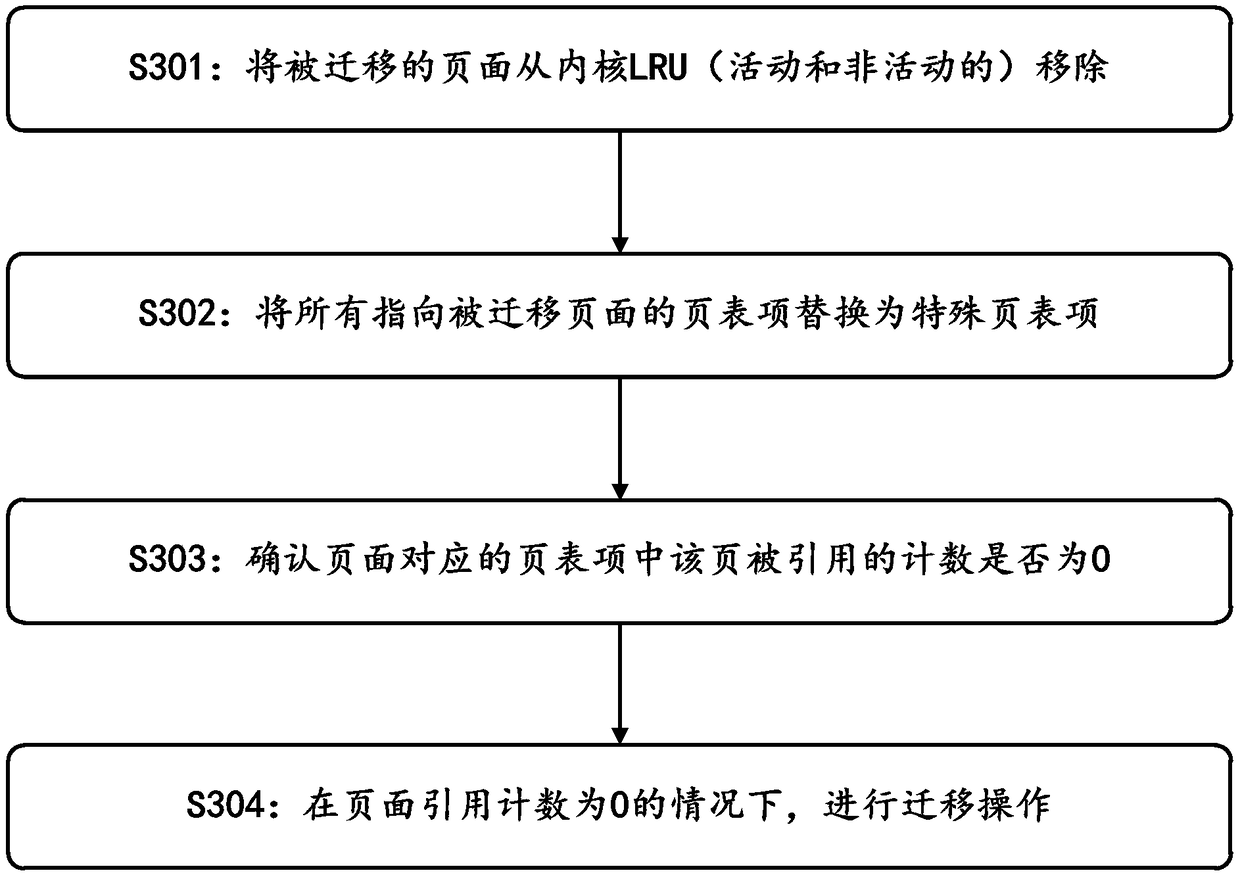

Method and apparatus for data migration or exchange between slots and multiprocessor system

ActiveCN109117416AReduce bandwidth usageLower latencyMultiple digital computer combinationsDirty dataData migration

The present disclosure provides a method and apparatus for data migration or exchange between slots and a multiprocessor system. Wherein the data migration method between slots includes locking read and write operations to data in one or more source cache line addresses of the source slots, and refreshing the source cache line addresses so that dirty data in the source cache line addresses is written back to the source memory of the source slots; after migrating the data from the source memory of the source slot to the destination memory of the destination slot, a destination address translation layer and a source address translation layer are provided at a destination slot agent and a source slot home node, respectively, respectively, the destination address translation layer and the source address translation layer translating a request to access a source cache line address into a request to access a destination cache line. The destination address translation layer and the source address translation layer translate a request to access a source cache line address into a request to access a destination cache line.

Owner:贵州华芯半导体技术有限公司

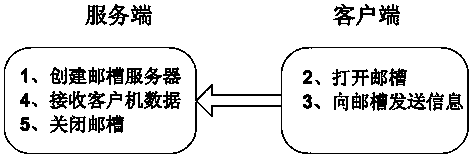

Mail content loading method and apparatus

ActiveCN103607342AImprove management efficiencyAvoid refreshData switching networksPasswordManagement efficiency

The invention discloses a mail content loading method and apparatus. The method comprises: a plug-in server, according to the user name and password of a mail box, sending a registration request to a mail box server side, and obtaining the registration identification of a mail box server; according to the registration identification, regularly checking the state information of the mail box; according to the state information of the mail box, obtaining the webpage format data of a mail in the mail box from the mail box server; and extracting the mail content messages of the webpage format data by use of the webpage format data at the plug-in server side; and sending message contents to a browser mail box plug-in, wherein the message contents are information displayed in the popup window page of the browser mail box plug-in in association with the mail in the mail box. By using the method and the apparatus, the mail contents of multiple mail boxes can be simultaneously loaded, the problem that a user has to afresh multiple mail box pages actively is avoided, the operation is convenient and fast, and the mail box management efficiency is substantially improved.

Owner:BEIJING QIHOO TECH CO LTD +1

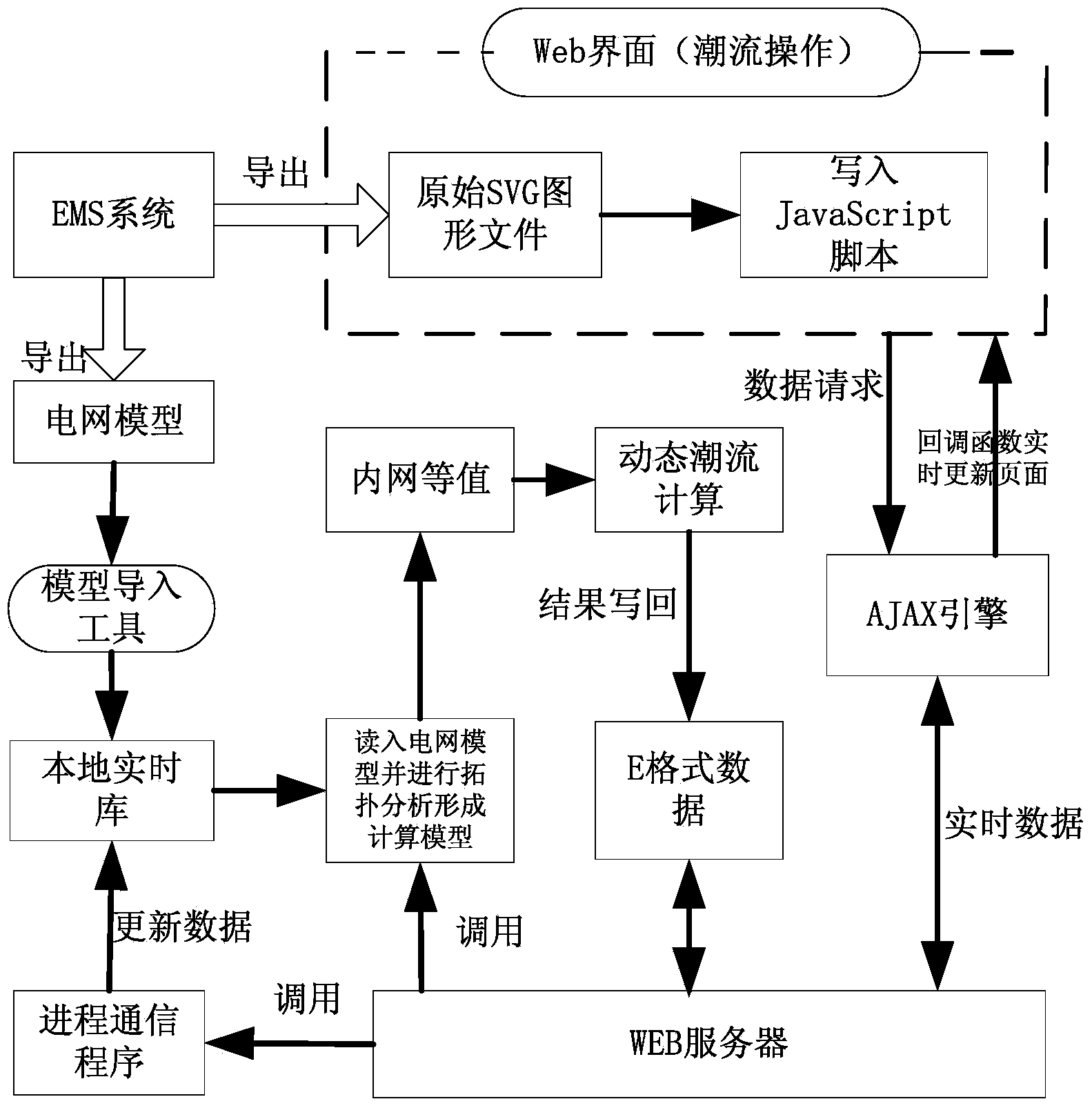

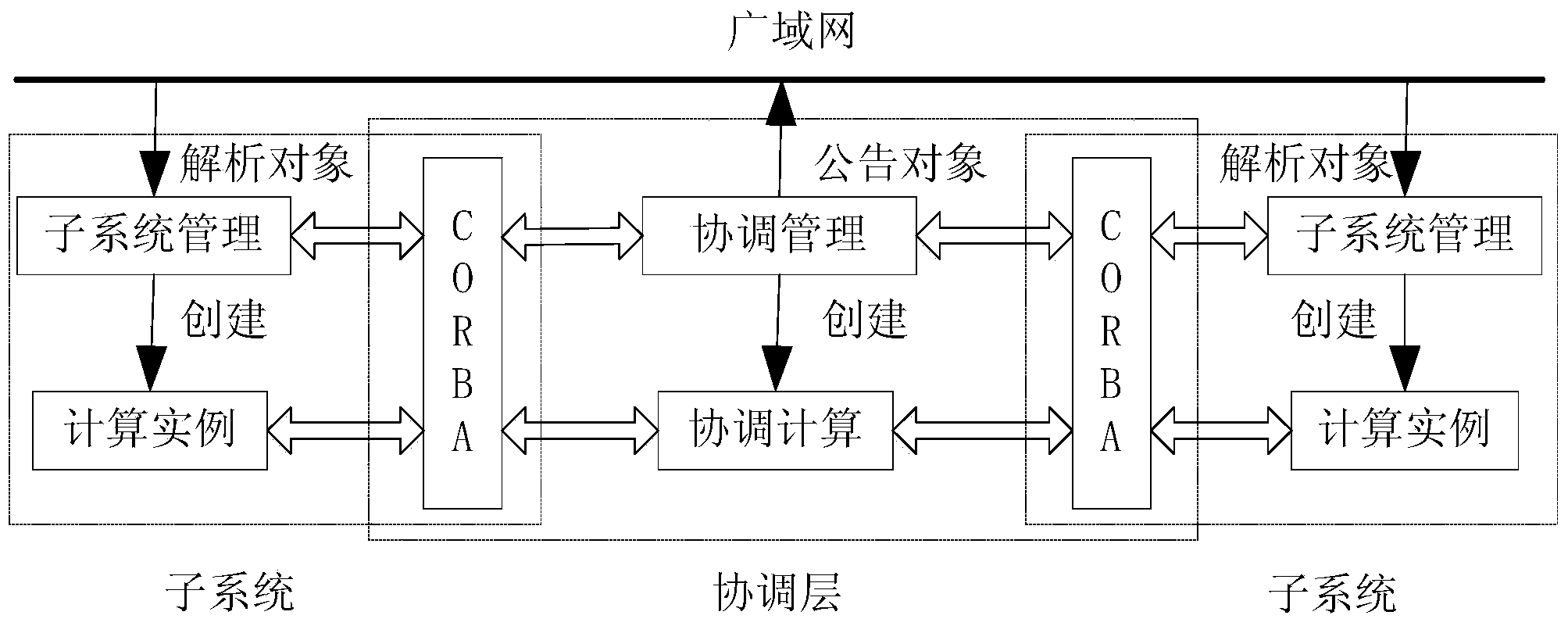

Construction method of distributed tide computing system graphics platform based on WEB-SVG

InactiveCN103530736ARealize flicker-free refresh displayGuaranteed independenceResourcesDecompositionElectric power system

The invention discloses a construction method of a distributed tide computing system graphics platform based on WEB-SVG (Scalable Vector Graphics), and belongs to the technical field of electric system energy management. The method comprises the steps that a distributed computing model is established; a power grid model is led into a local hierarchic database; an original SVG data file in an EMS (Engine Management System) is led out; an SVG file with interactivity is generated; a local real-time database model is updated in real time; graphics and model integration is realized; an Apache server is deployed as a control center of a whole WEB release system; communication is realized between subsystems and a coordination layer by a common object request broker architecture (CORBA) port by adopting a decomposition coordination mode; a distributed tide computing main program is developed; and a system management part and a computing part are mutually independent. The method achieves display of complex graphics and refreshing of real-time data, and is applied to distributed tide computing first; a practical graphics platform construction method is provided for a distributed computing system; and a foundation is laid for popularization and application of the distributed computing system.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

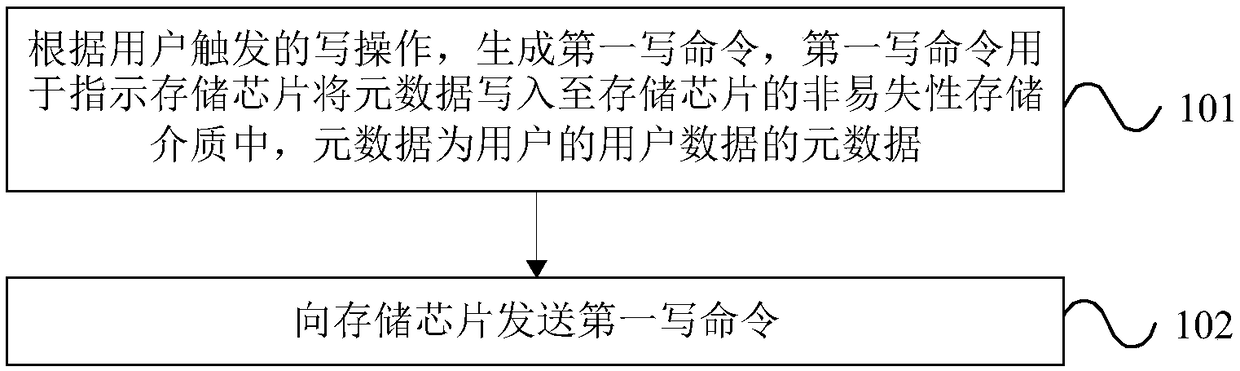

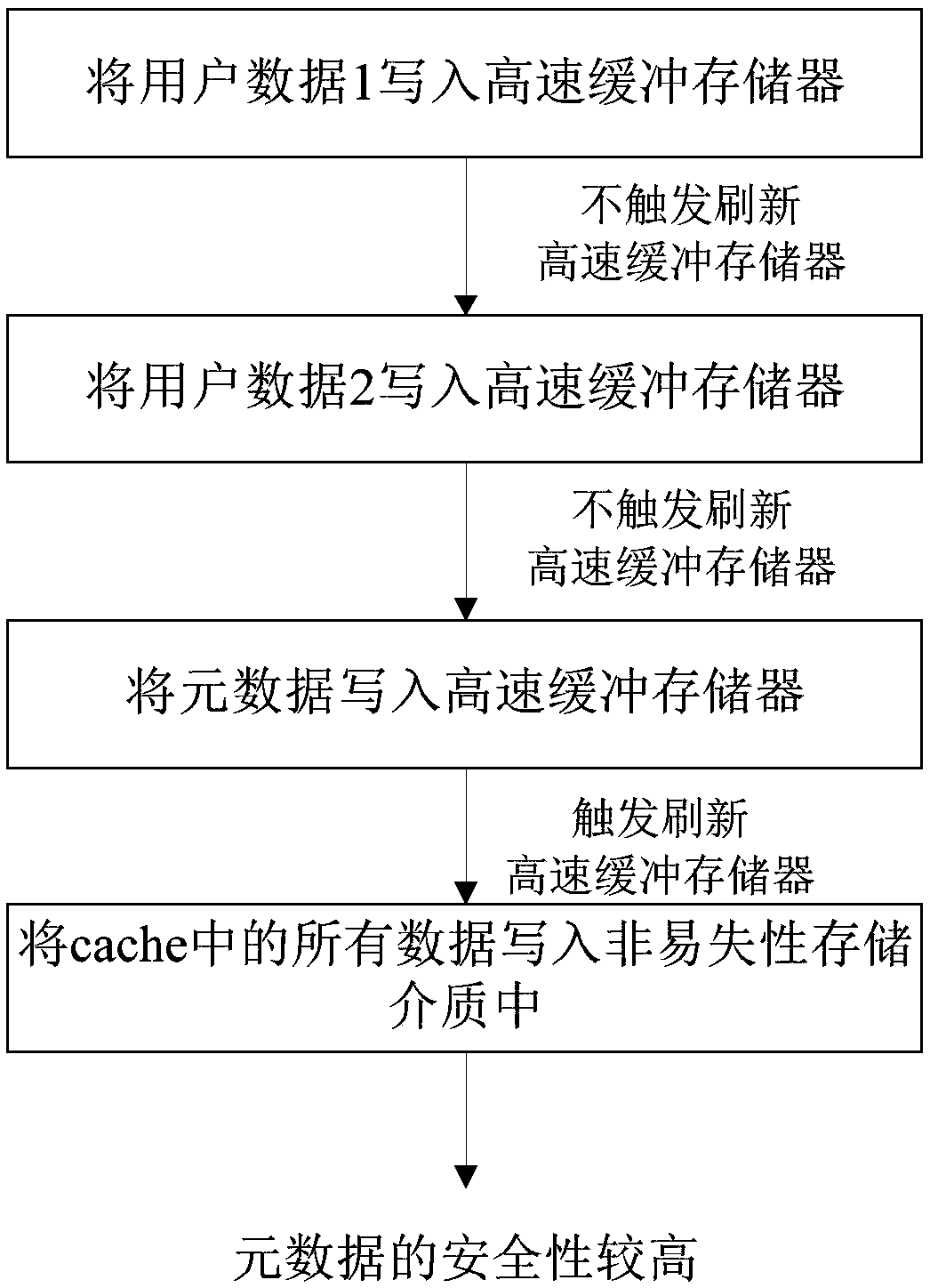

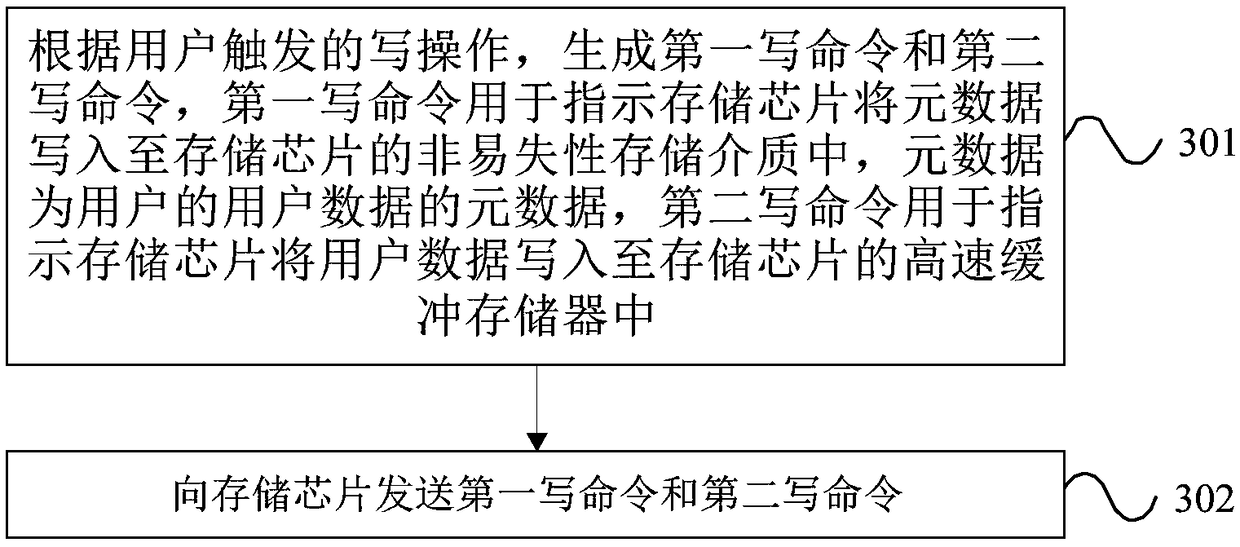

Data writing method, apparatus, apparatus, and storage medium

ActiveCN109471596AImprove securityImprove I/O performanceInput/output to record carriersMemory systemsMemory chipComputer hardware

The present disclosure relates to a data writing method, apparatus, apparatus, and storage medium. The method includes generating a first write command for instructing a memory chip to write metadatainto a non-volatile storage medium of the memory chip, the metadata being metadata of user data of the user, according to a user-triggered write operation; Sending the first write command to the memory chip. The present disclosure improves the security of metadata and avoids frequent cache refreshes, thereby improving the I / O performance of the file system.

Owner:BEIJING XIAOMI MOBILE SOFTWARE CO LTD

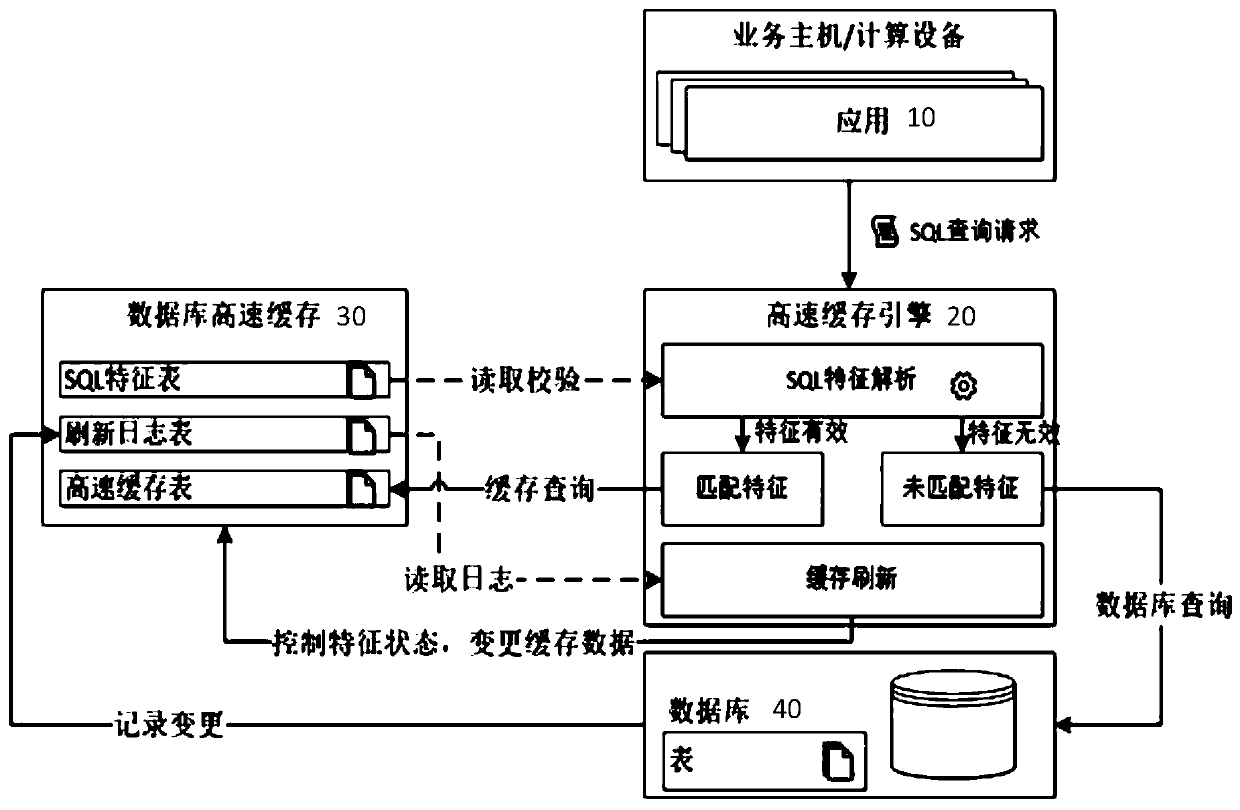

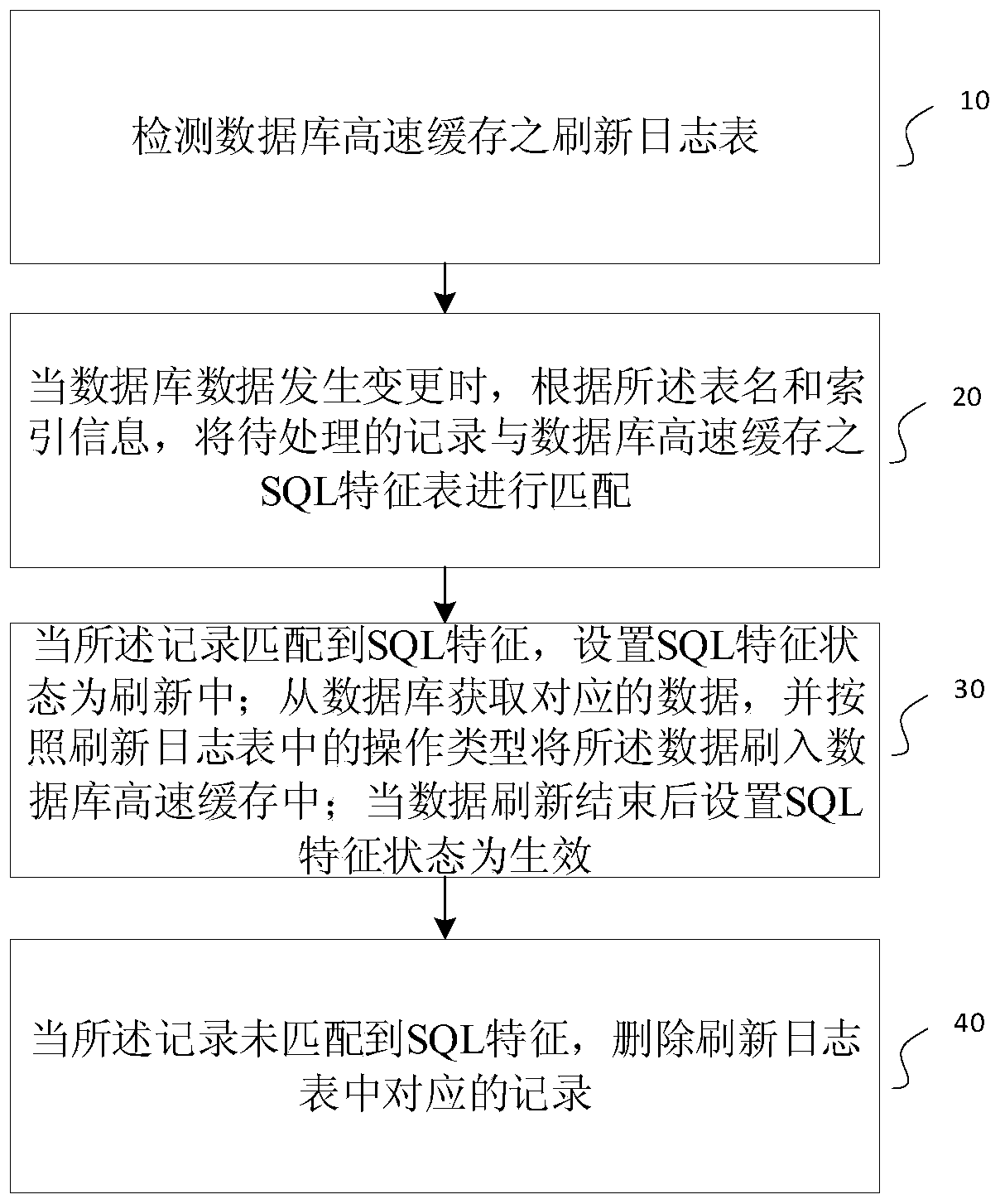

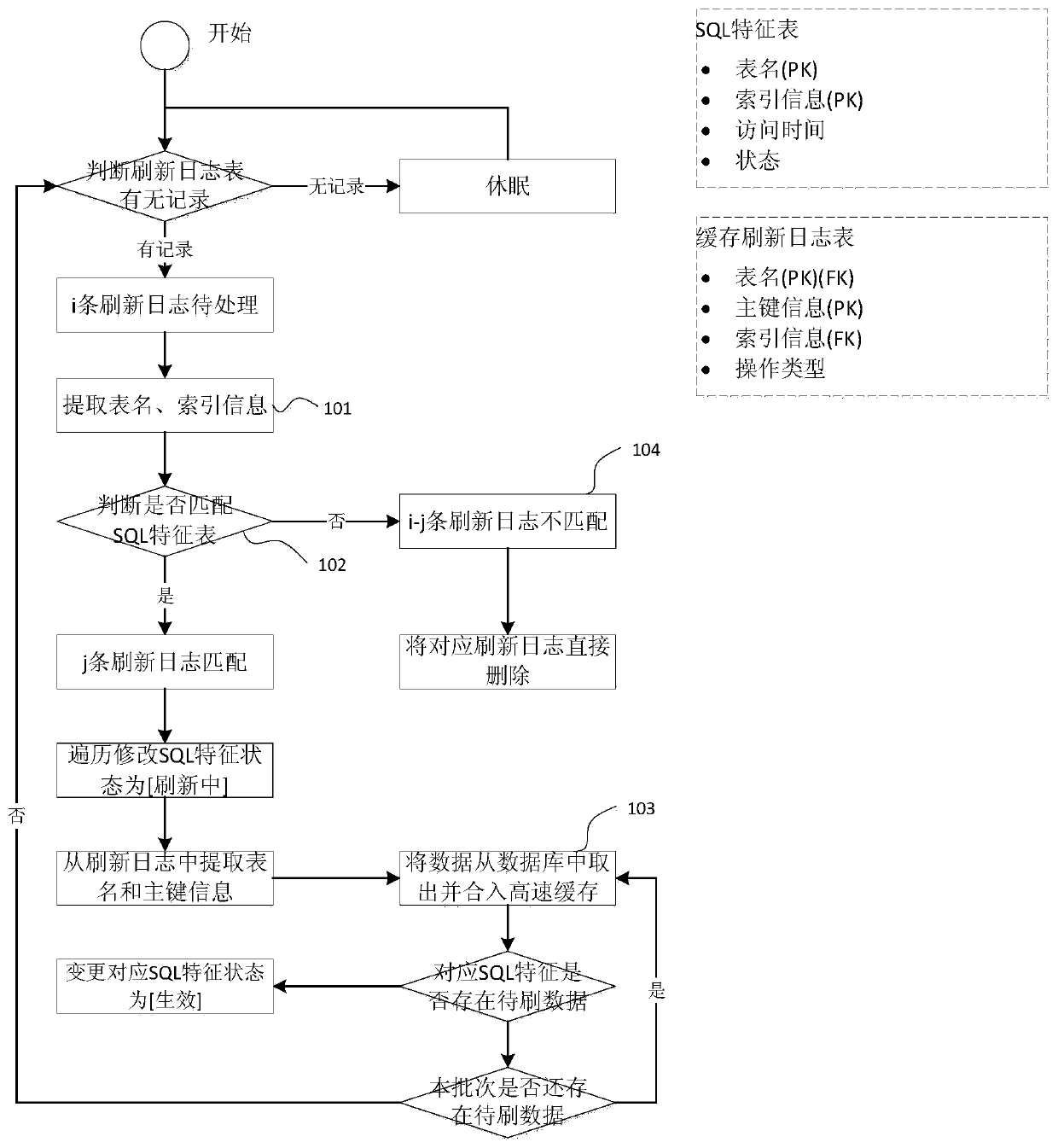

Cache asynchronous refreshing method and system and computer readable storage medium

ActiveCN111414392AImprove the performance of asynchronous refreshSolve the problem of not being able to access in the cacheDigital data information retrievalSpecial data processing applicationsTable (database)High availability

A cache asynchronous refreshing method comprises the following steps: detecting a refreshing log table of a database cache; when the database data is changed, according to the table name and the indexinformation, matching a record to be processed with an SQL feature table of the database cache, wherein the SQL feature table at least comprises SQL feature information used for maintaining a serviceapplication; when the record is matched with the SQL feature, setting the SQL feature state corresponding to the record to be in refresh; obtaining corresponding data from a database according to thetable name and primary key information in the refreshing log table, and brushing the data into the database cache; after data refreshing is finished, setting the SQL feature state corresponding to the record to be valid, and then deleting the corresponding record in the refreshing log table; and when the record is not matched with the SQL feature, deleting the corresponding record in the refreshing log table. The method has the high availability and high performance, and avoids a large amount of redundant data which is not accessed by the application in the cache.

Owner:WHALE CLOUD TECH CO LTD

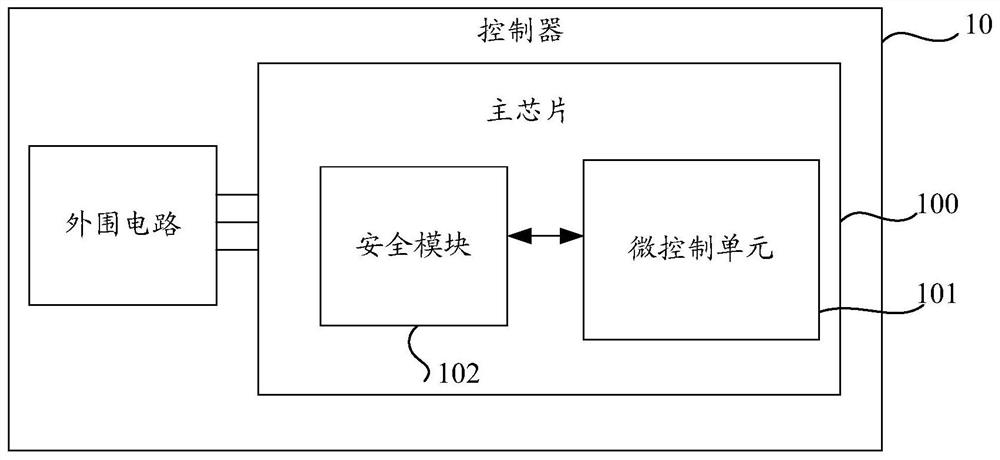

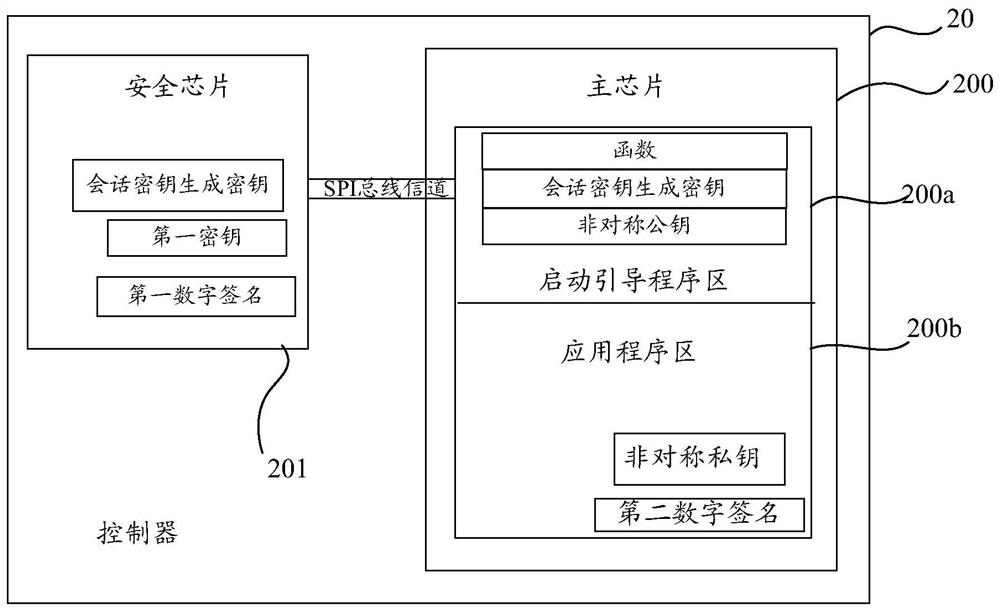

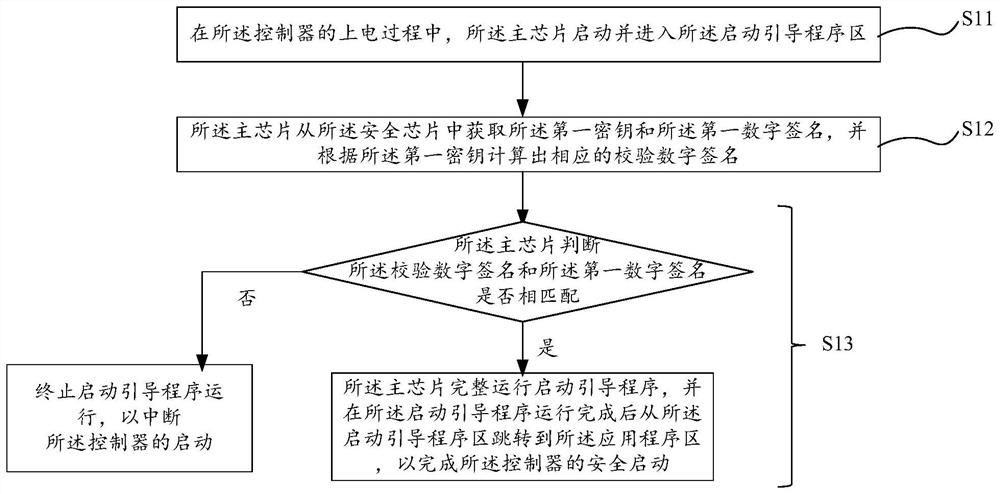

Safety protection method of controller, main chip of controller and controller

PendingCN112711761ASolve the problem of high cost of secure boot functionSolve problems with high performance requirementsDigital data protectionPlatform integrity maintainanceDigital signatureEmbedded system

The invention provides a safety protection method of a controller, a main chip of the controller and the controller, the controller comprises the main chip and a safety chip arranged outside the main chip, the main chip comprises a starting bootstrap program area and an application program area; and in the power-on process of the controller, the main chip starts and enters the starting bootstrap program area, a corresponding secret key and a digital signature can be obtained from the security chip, a corresponding verification digital signature is calculated according to the secret key; and when the verification digital signature is matched with the corresponding digital signature, the main chip completely runs a starting bootstrap program, the main chip skips to the application program area after running of the starting bootstrap program is completed, then safe starting of the controller is completed, and the problems that in an existing safe starting scheme of the controller, the cost of the safe starting function is high, and the safe starting function of the controller is difficult to achieve when the performance of a main chip is reduced can be effectively solved.

Owner:UNITED AUTOMOTIVE ELECTRONICS SYST

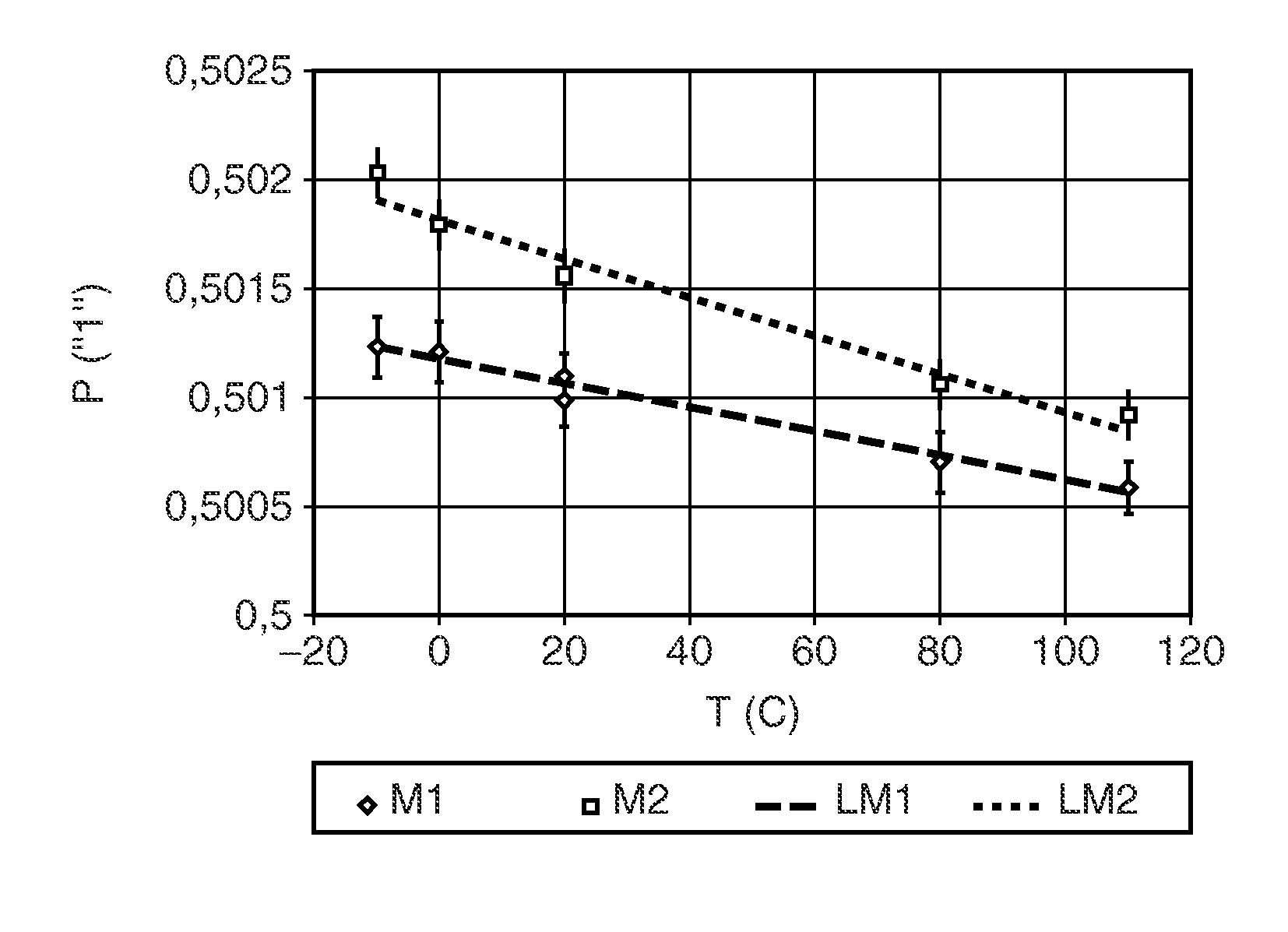

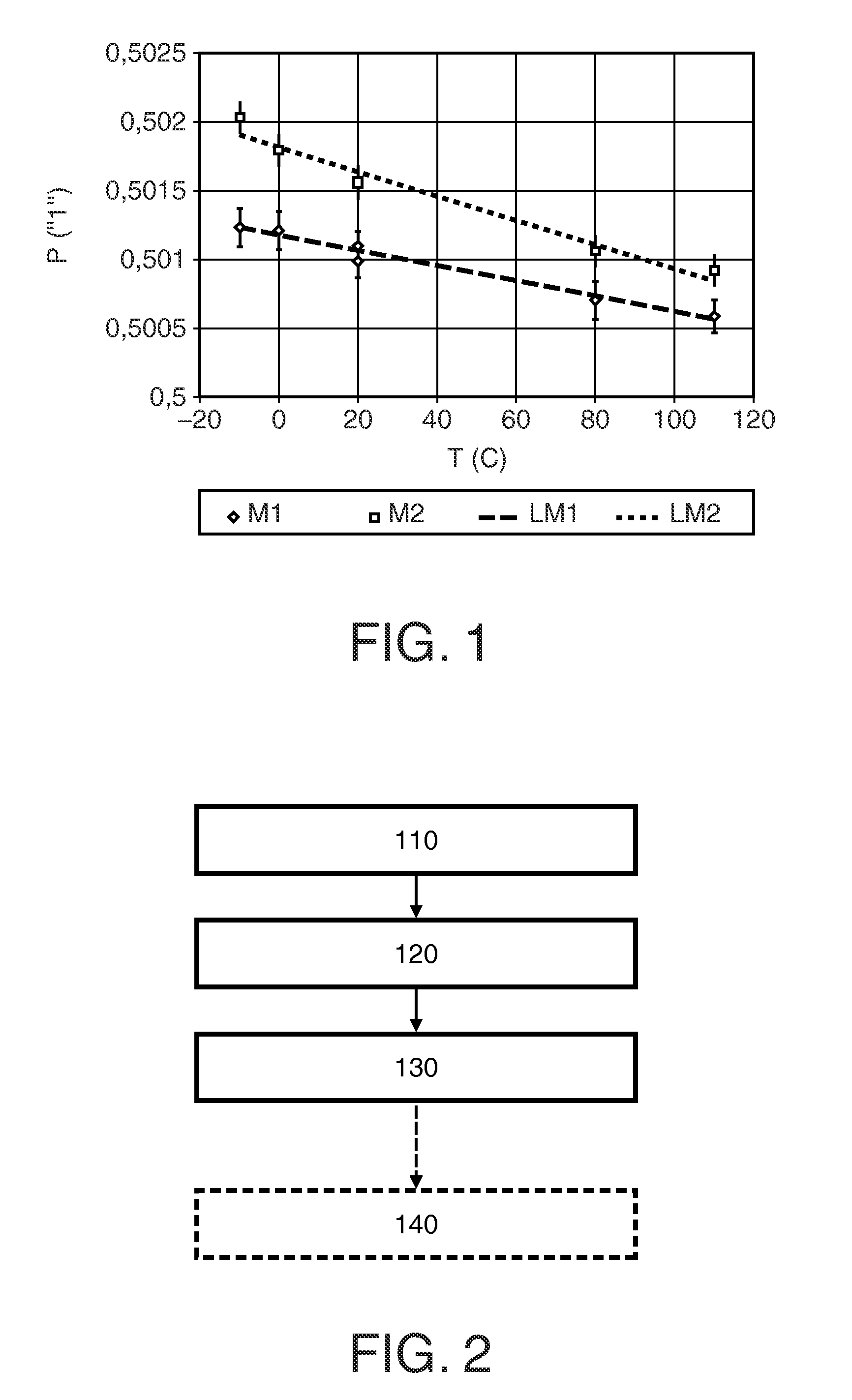

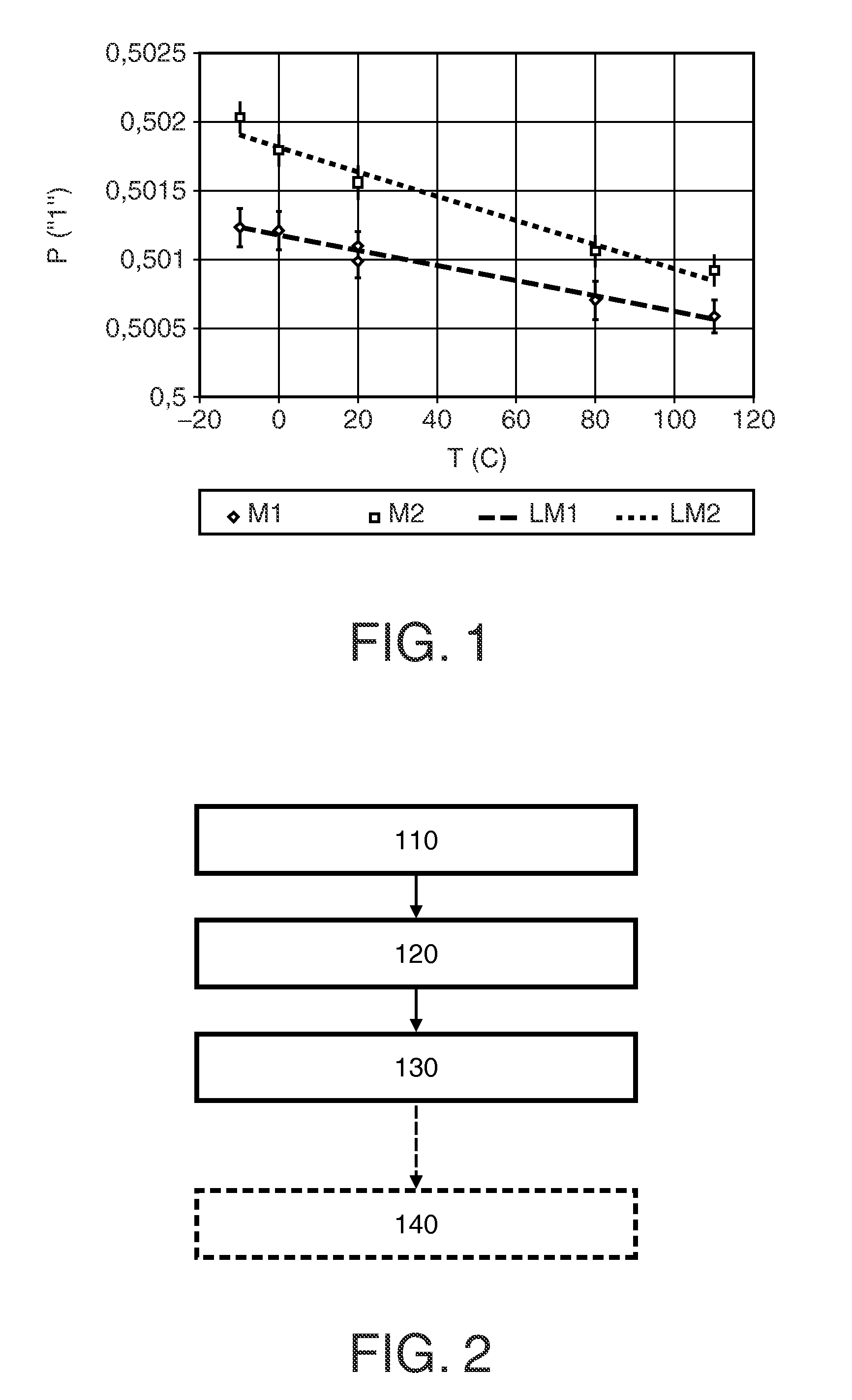

Estimating temperature of memory elements

ActiveUS8768645B2Easy to processAccurately determineThermometer detailsThermometers using material expansion/contactionParallel computingSmart card

Owner:NXP BV

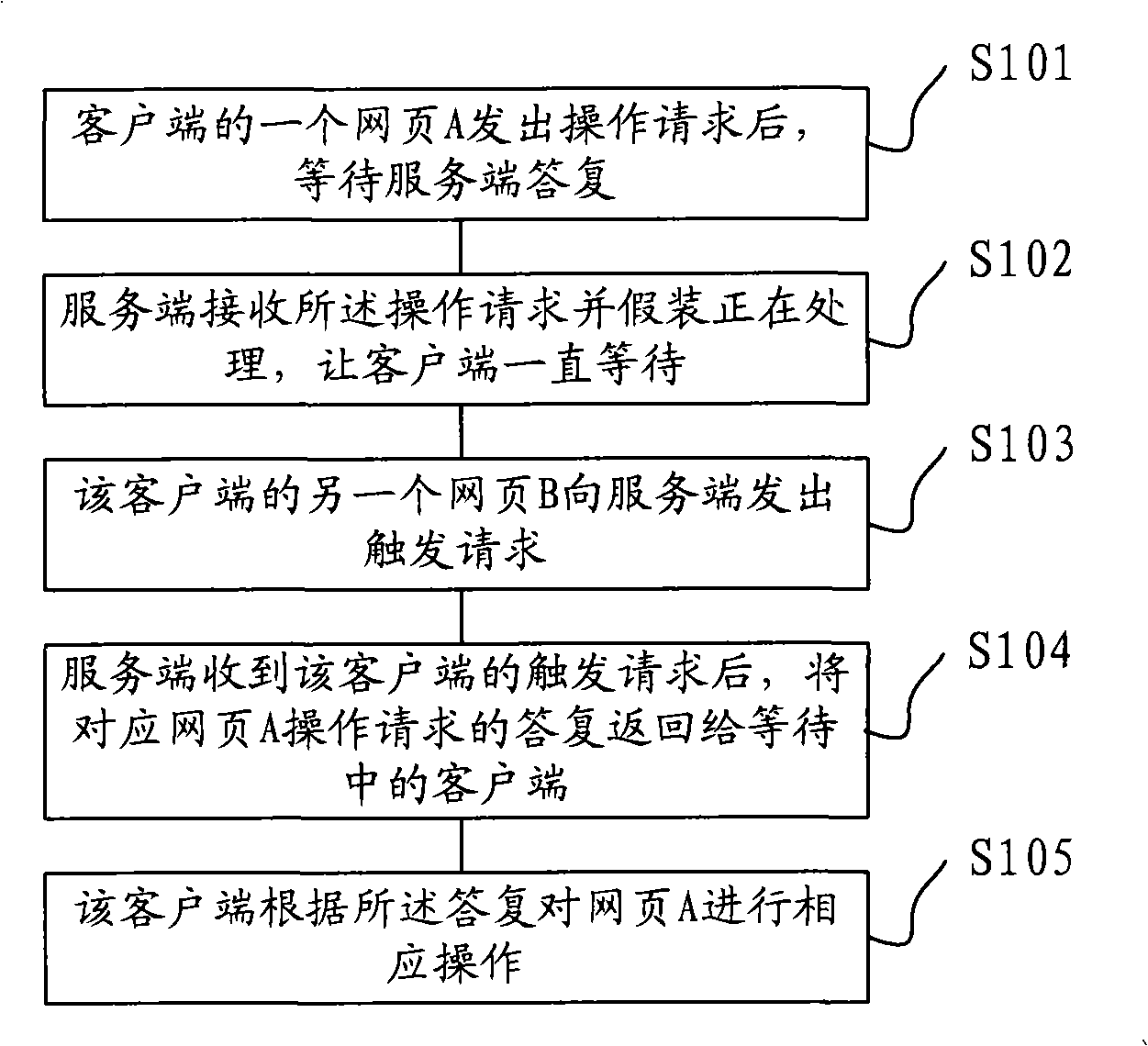

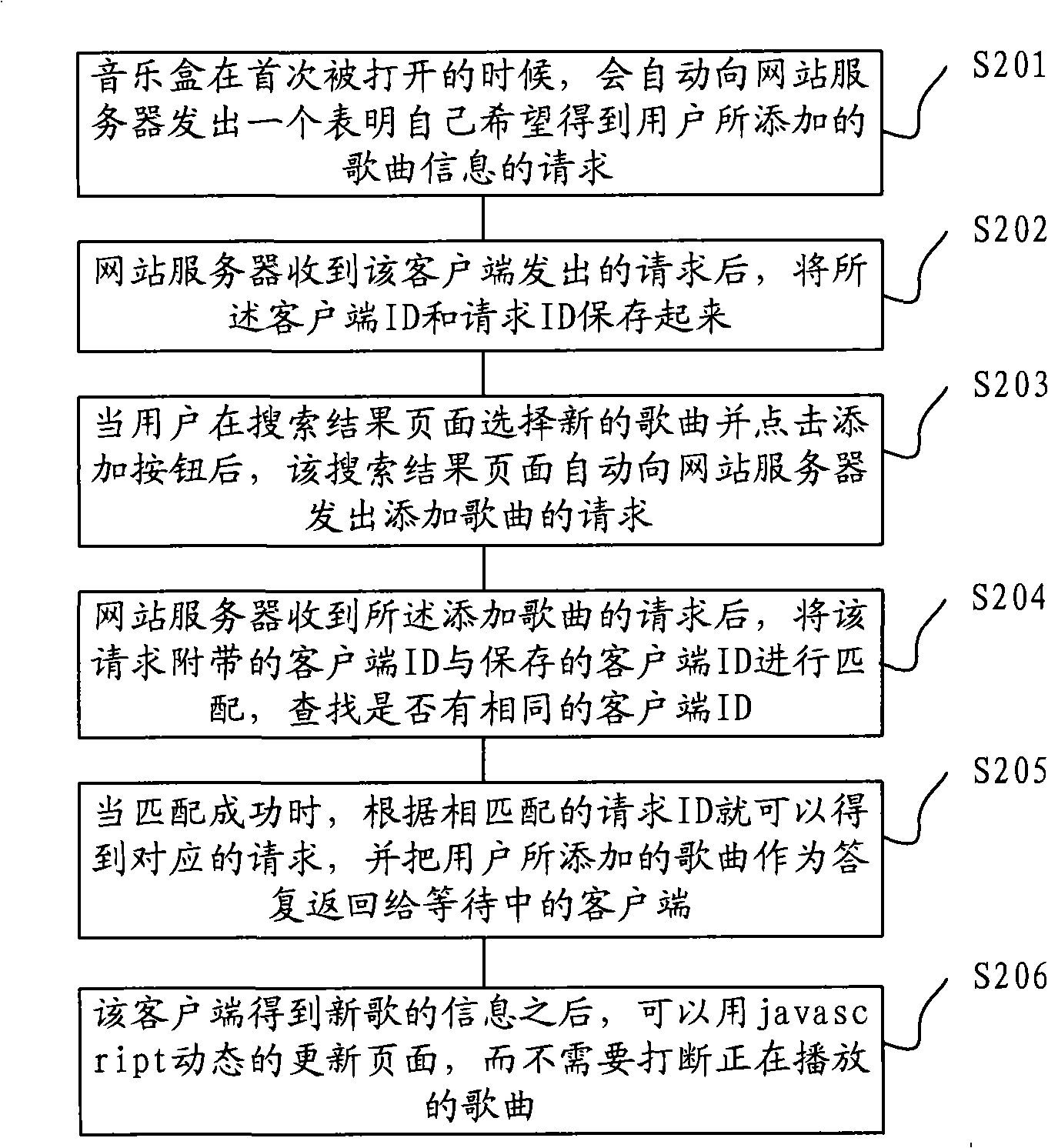

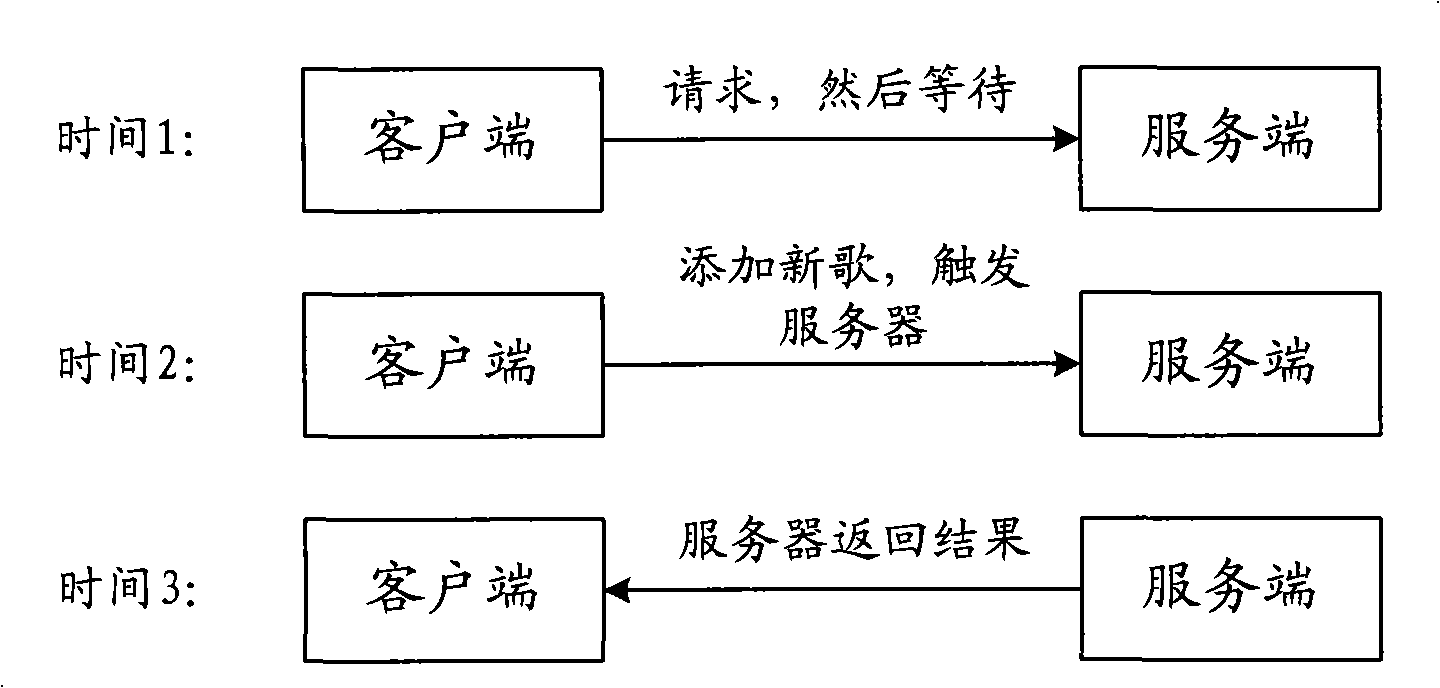

Method, system for communication among webpage, and application in music searching

ActiveCN101291273ASave resourcesAvoid refreshData switching by path configurationStore-and-forward switching systemsClient-sideWeb page

The invention discloses a method and a system for communication between web pages and application of the method and the system in music search. The invention is to solve the problems of interruption of play of the current page, bandwidth waste and untimely response of the prior means adopted of refreshing the pages or polling a server. The method comprises the following steps that: a web page A of a client sends out an operation request and then waits for reply of the server; when the server receives a trigger request sent out by another web page B of the client, the reply of the operation request of the corresponding web page A is returned to the client; and the client performs corresponding operation on the web page A according to the reply. As for the client, the method does not need polling the server and only needs connection for once, thereby the bandwidth and server resources are greatly saved. Simultaneously, when the server obtains another trigger request, the server can reply to the client, thereby the real-time communication ability is guaranteed to the maximum degree and simultaneously refreshing of the pages is avoided. Moreover, the method and the system are also suitable for communication between two unrelated web pages.

Owner:网易有道信息技术(北京)有限公司

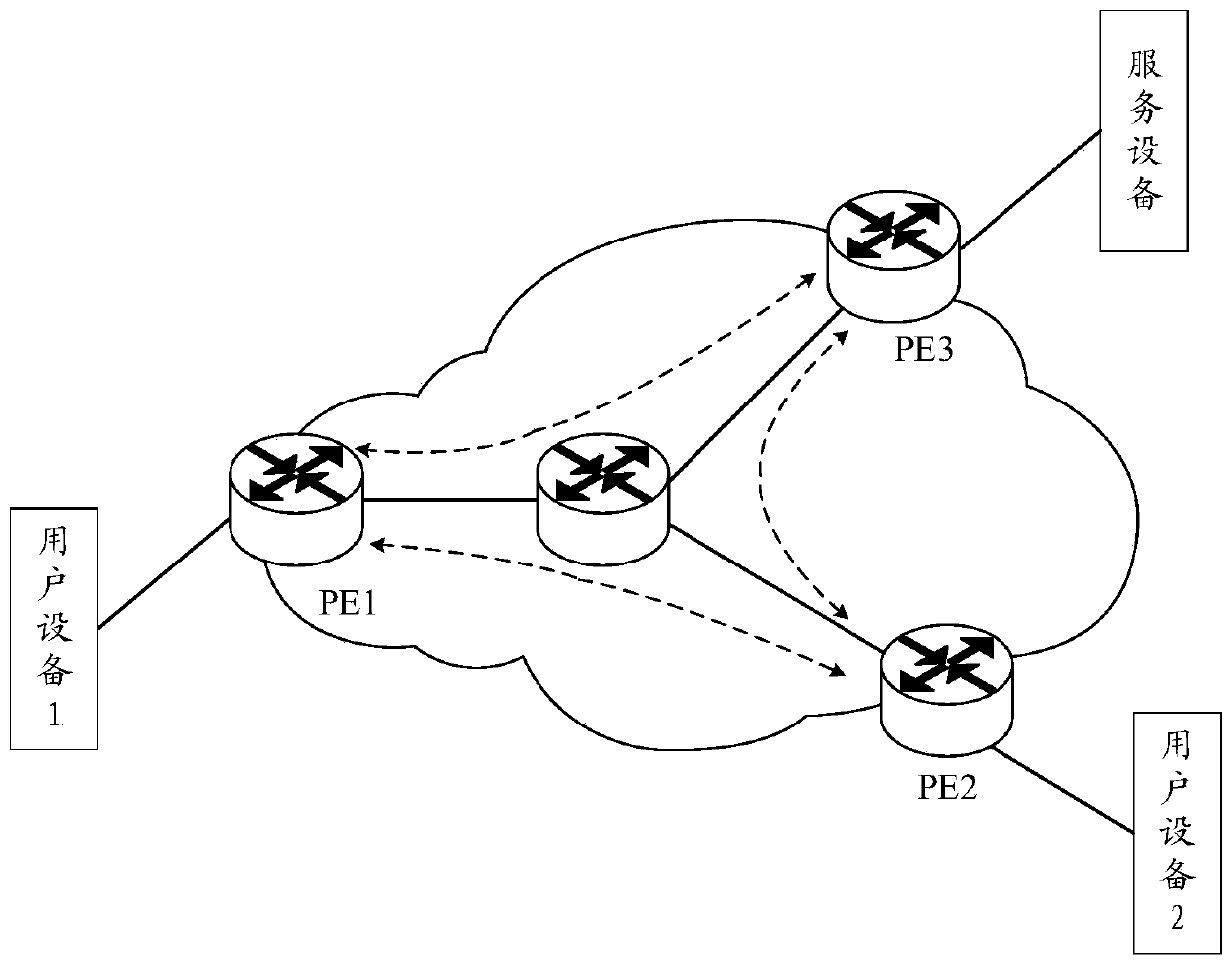

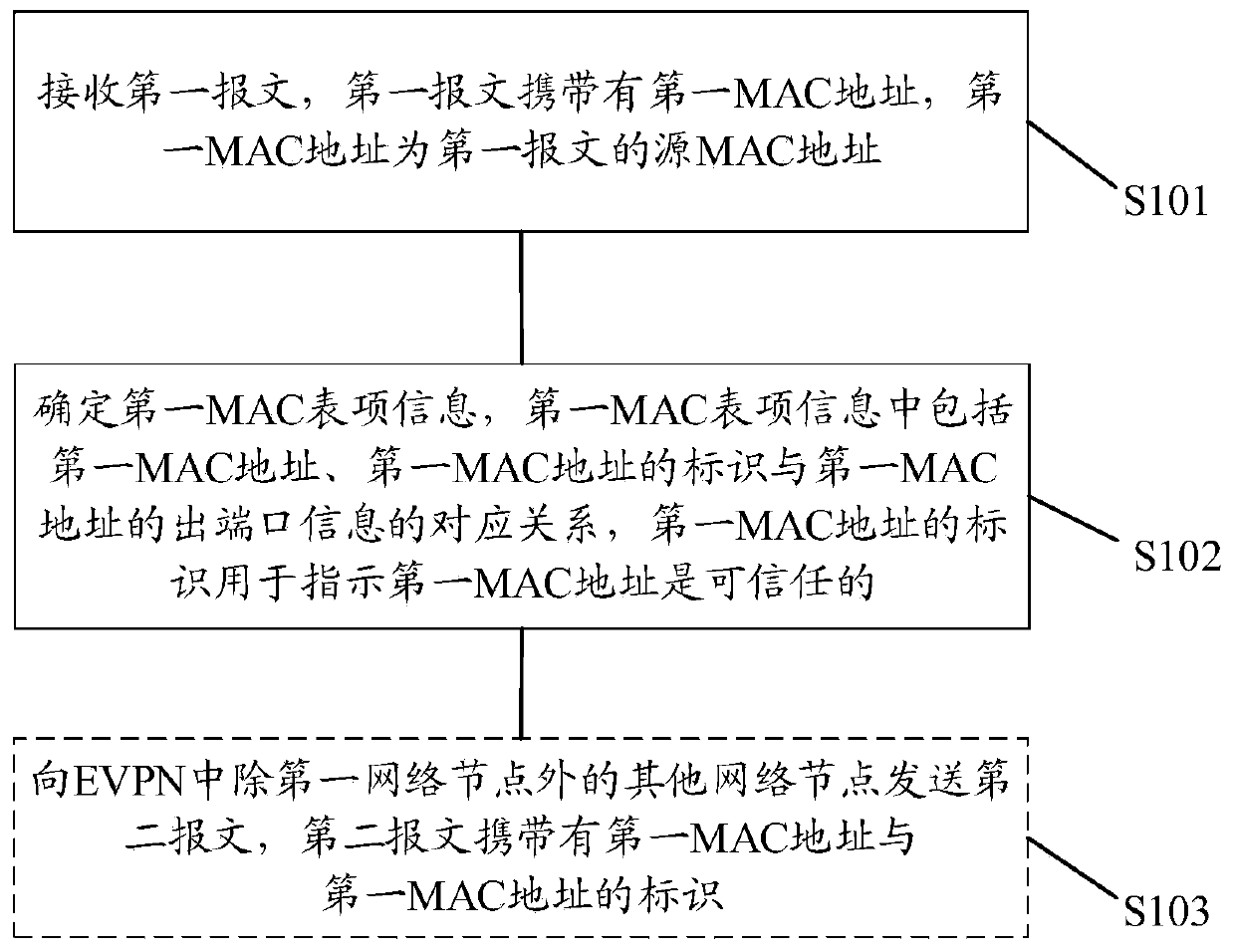

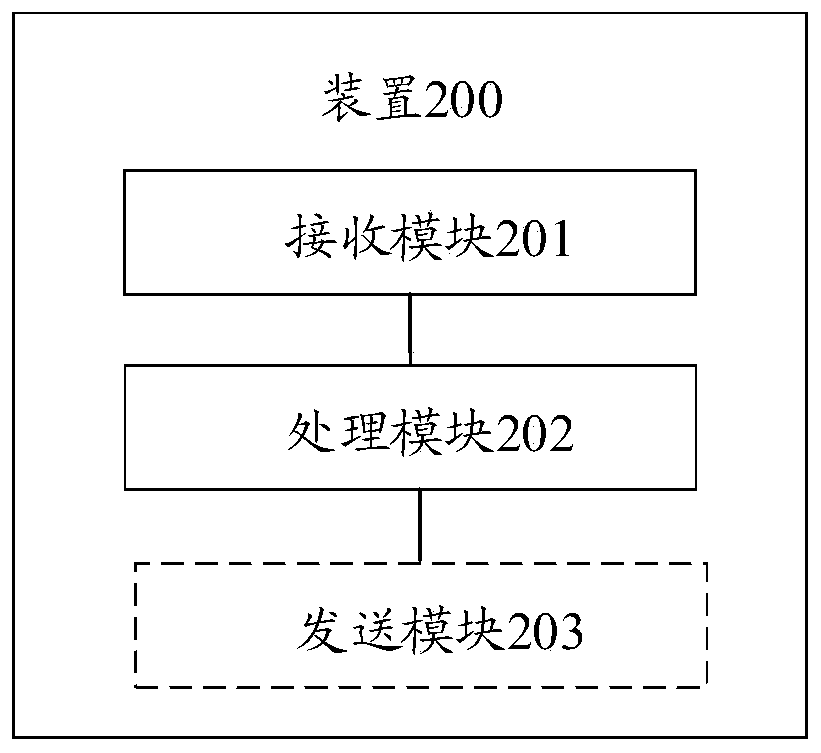

Method and device for preventing network attack

ActiveCN111526108AReduce riskAvoid refreshData switching networksMedia access controlInternet privacy

The invention provides a method for preventing a network attack, which comprises the following steps: a first network node in an Ethernet virtual private network (EVPN) receives a first message, the first message carries a first media access control (MAC) address, and the first MAC address is a source MAC address of the first message; and first MAC table entry information is determined, the firstMAC table entry information comprising a first MAC address and a corresponding relationship between an identifier of the first MAC address and egress port information of the first MAC address, and theidentifier of the first MAC address being used for indicating that an egress port corresponding to the first MAC address is a trusted port. According to the method, the risk that the EVPN is in a paralyzed state due to the fact that an attacker attacks the EVPN can be reduced.

Owner:HUAWEI TECH CO LTD

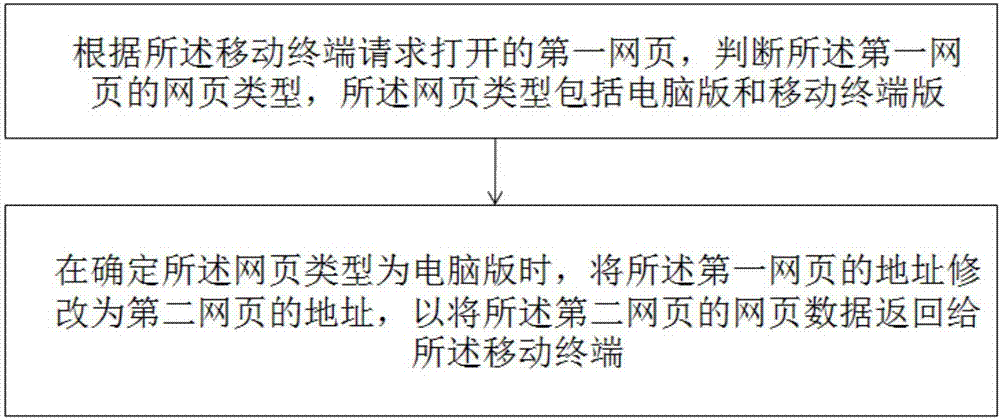

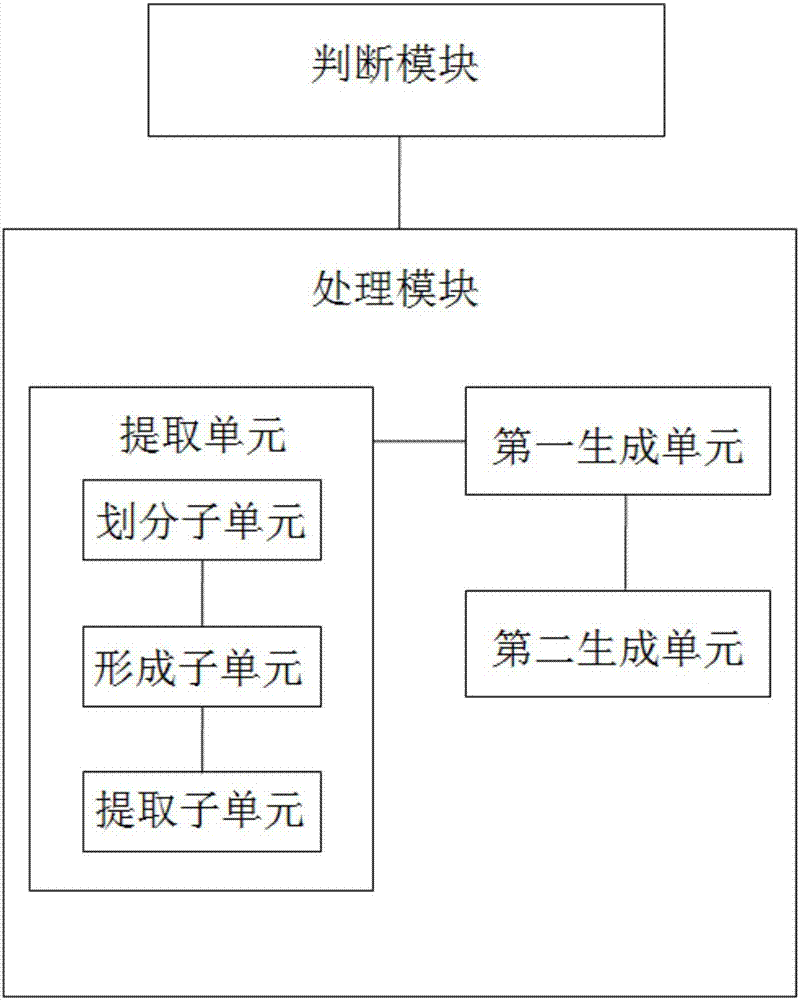

Method and device for loading web pages at mobile terminal

InactiveCN107577825AAvoid refreshIncrease jump speedSpecial data processing applicationsData formatWeb page

The invention provides a method for loading web pages at a mobile terminal. The method includes the steps: judging the web page type of a first web page according to the first web page requested to beopened by the mobile terminal; modifying the address of the first web page into the address of a second web page and returning web page data of the second web page to the mobile terminal when determining that the web page type is in a computer version. The web page type comprises the computer version and a mobile terminal version. The web page data of the second web page are compatible with thoseof the mobile terminal version, and the web page data format of the second web page is as same as that of the mobile terminal version. The web pages of a non-mobile terminal can be browsed on the mobile terminal, and generated web page data are only cached for a short time and can be deleted when a user does not need to browse the data, so that the cost of the mobile process can be saved. The twoweb pages can be accessed by the same URL (uniform resource locator).

Owner:林楚莲

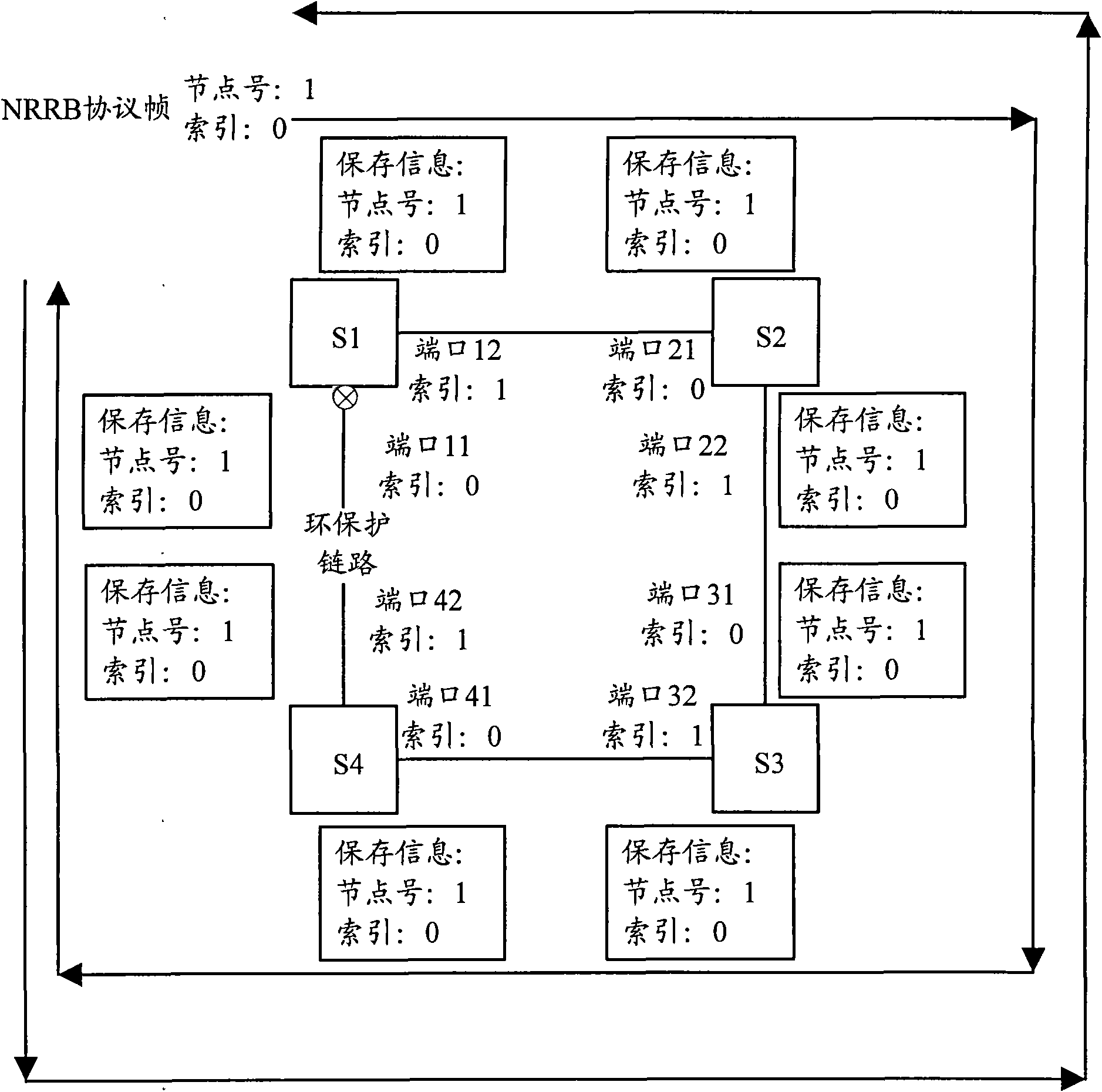

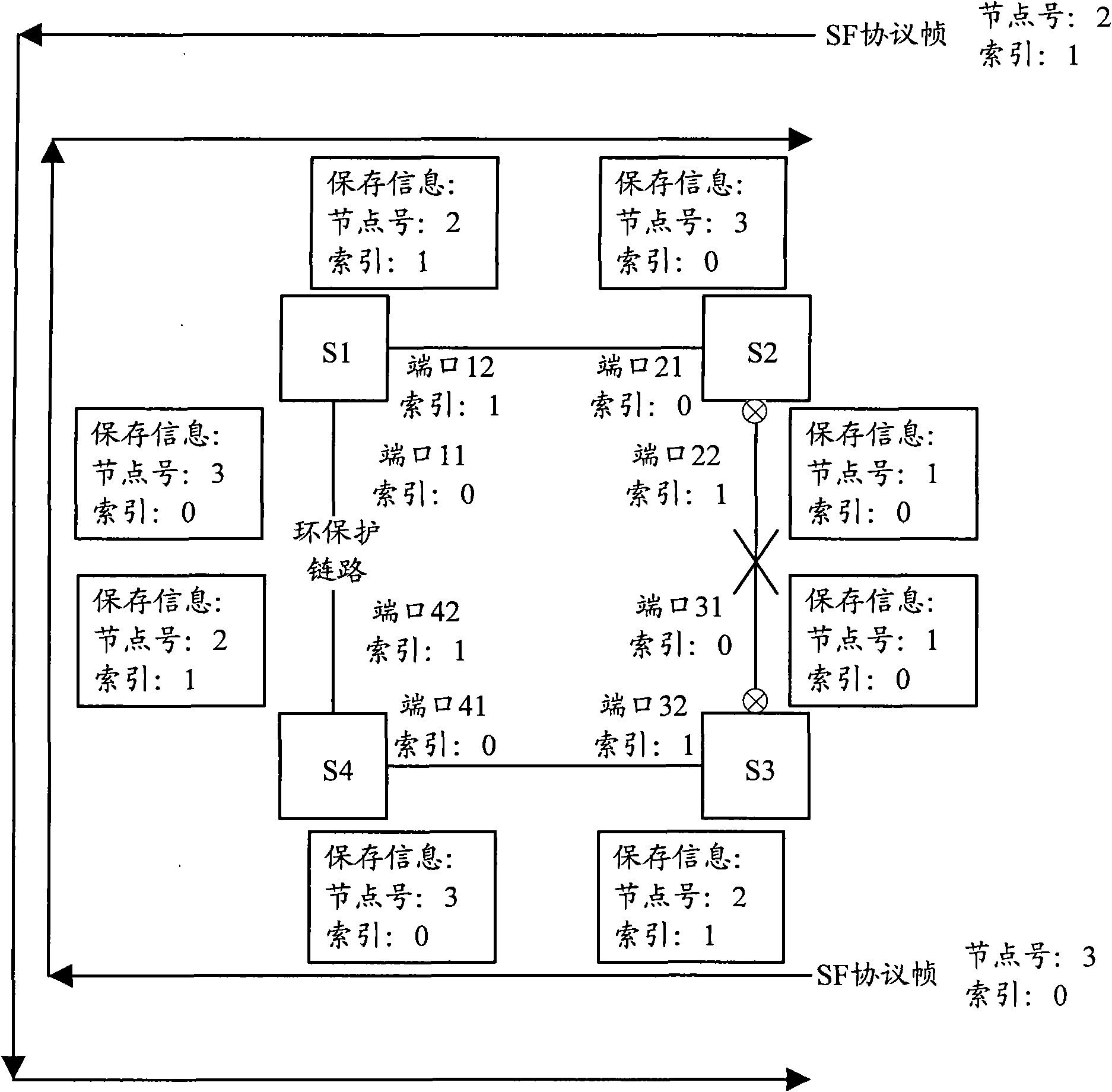

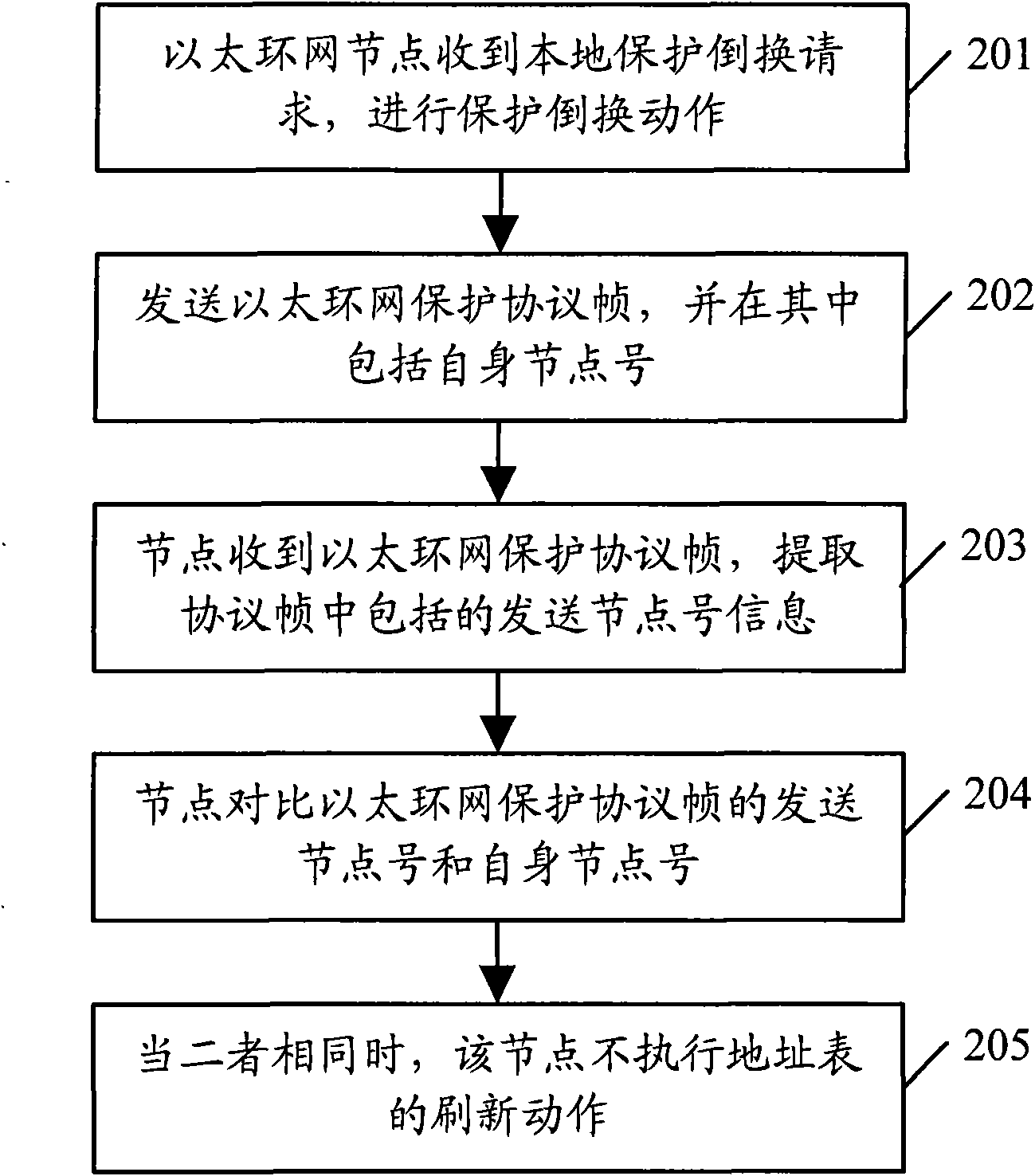

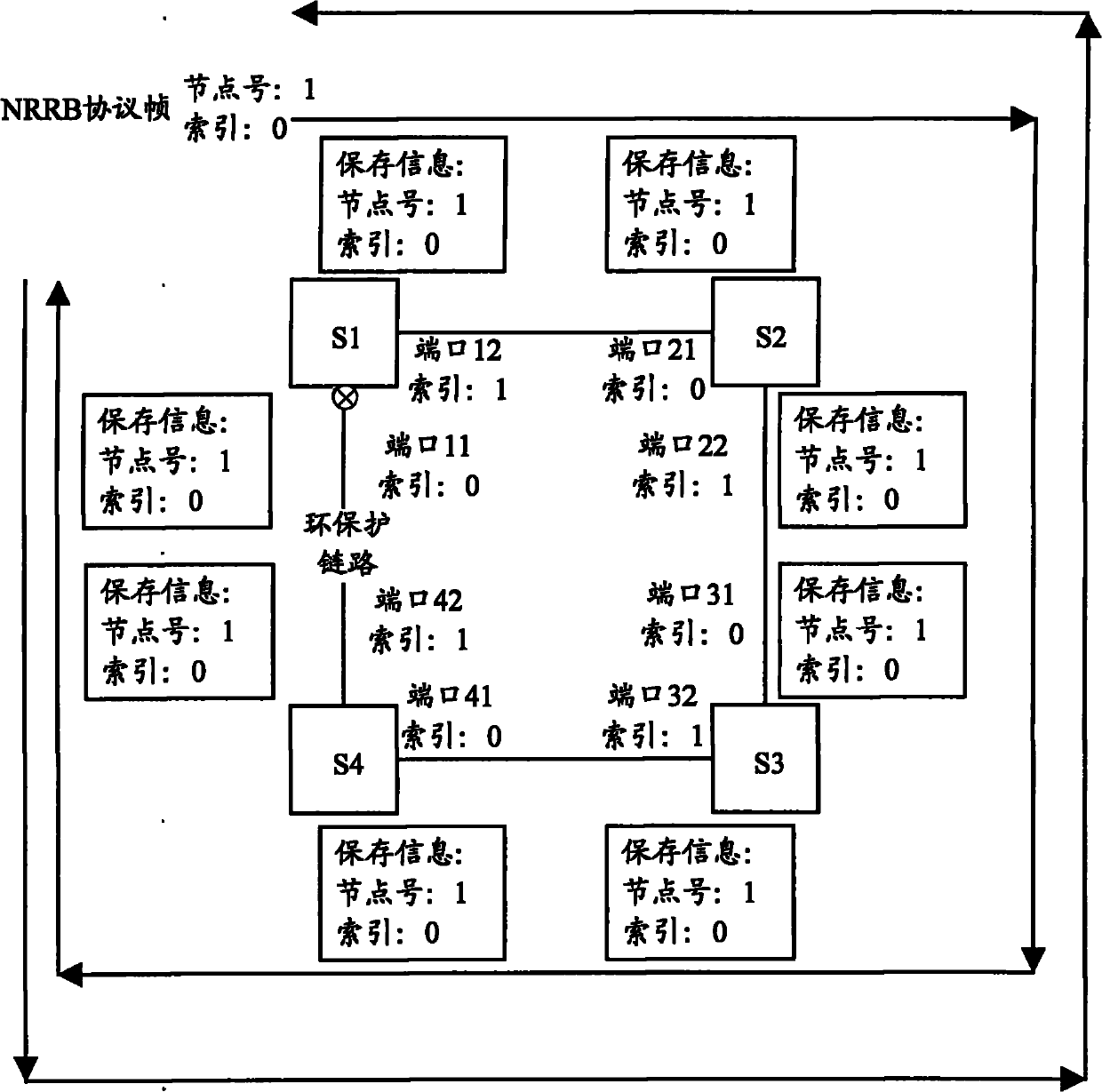

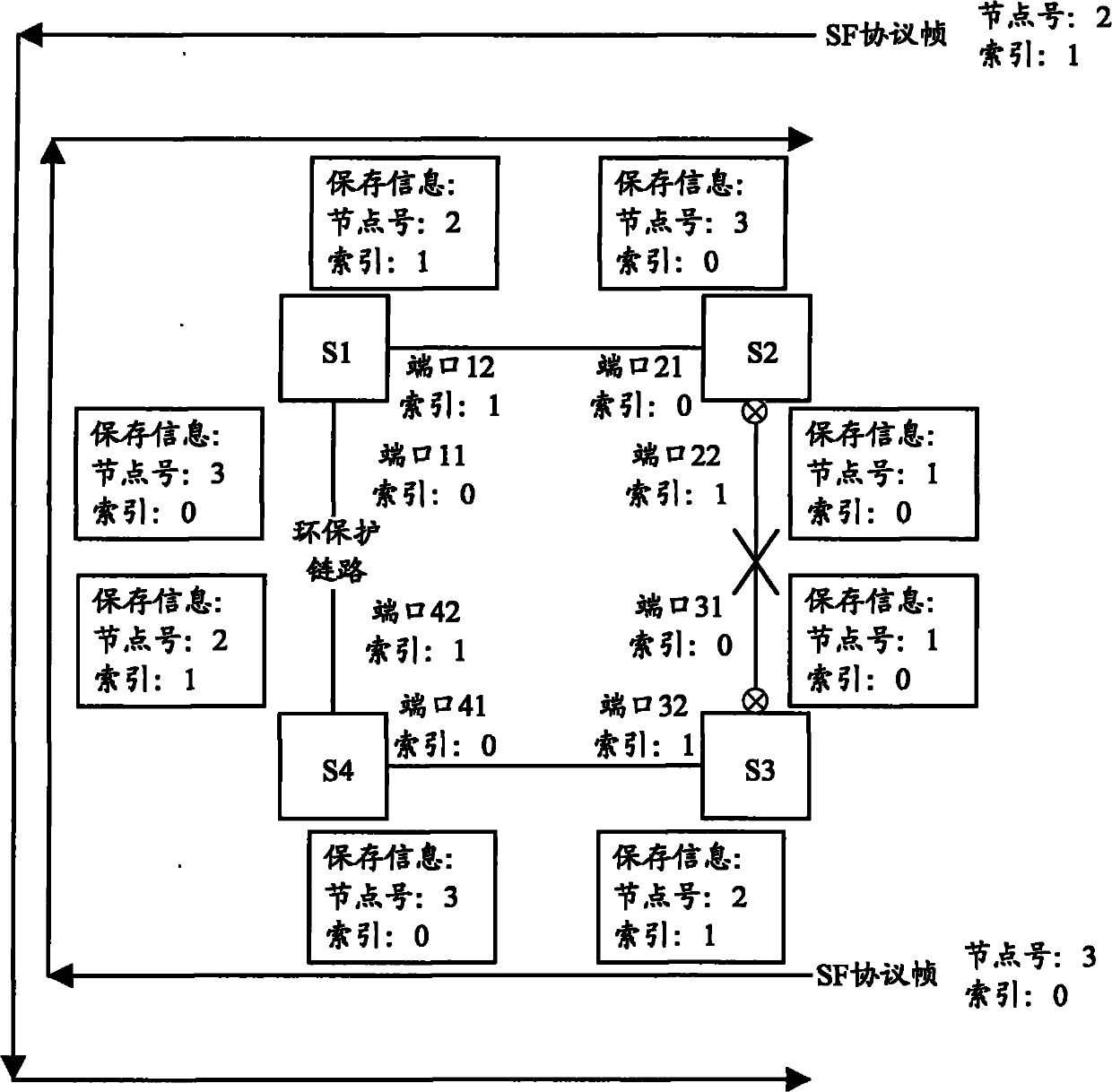

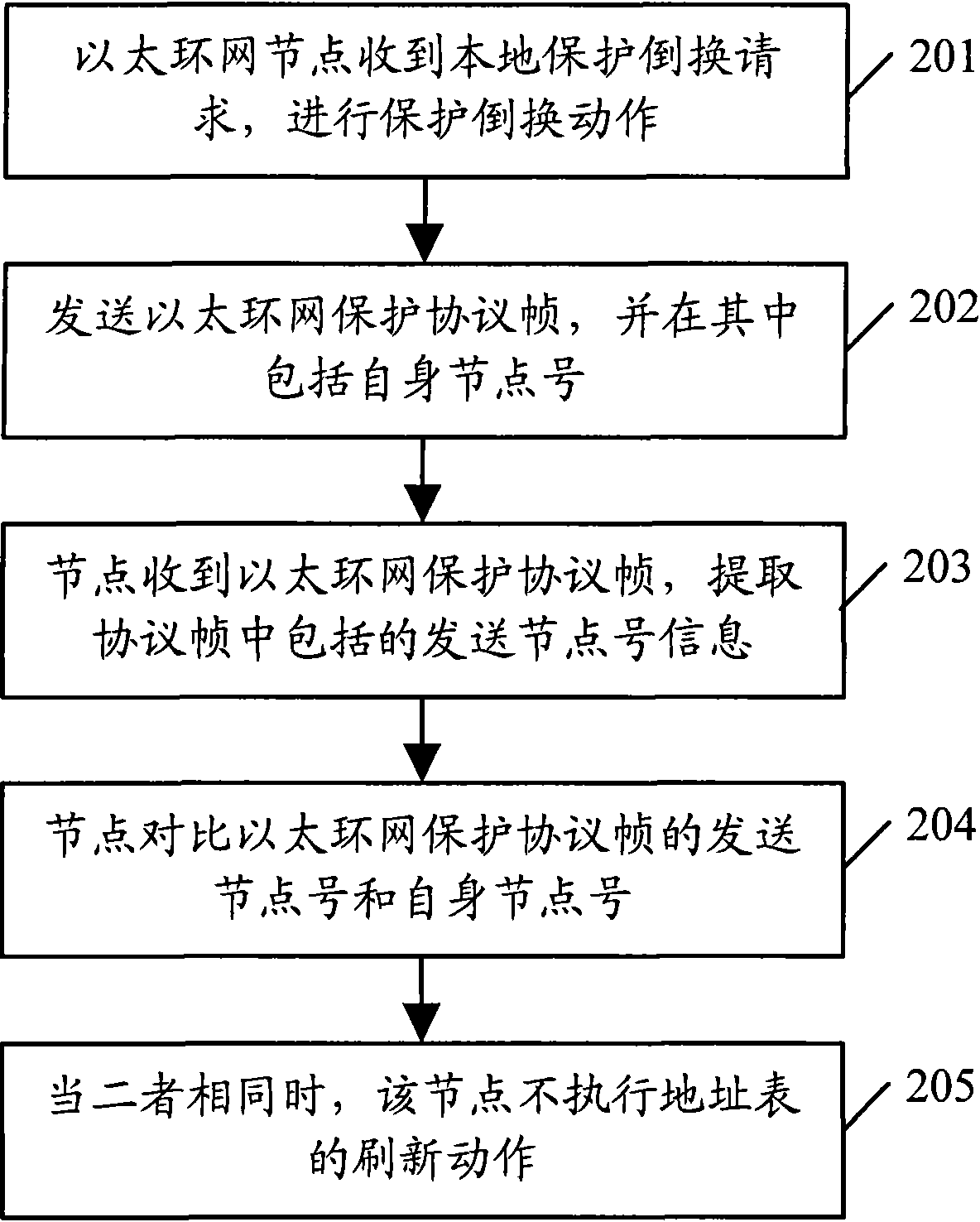

Method and system for preventing address table from being refreshed repeatedly in protection of Ethernet ring

ActiveCN102035711AAvoid refreshDuplicate Refresh PreventionData switching networksEthernetEmbedded system

The invention discloses a method for preventing an address table from being refreshed repeatedly in protection of an Ethernet ring, comprising: an Ethernet ring protocol frame is sent by an Ethernet ring node, and self node information is packed in the Ethernet ring protocol frame; the Ethernet ring node receives the Ethernet ring protocol frame and matches node information packed in the Ethernet ring protocol frame with the self node information; and when the matching is successful, the Ethernet ring node does not update the address table. The invention also discloses a system for preventing the address table from being refreshed repeatedly in protection of the Ethernet ring. In the system, a matching unit is used for matching the node information packed in the Ethernet ring protocol frame with the self node information; and when the matching is successful, the Ethernet ring node does not update the address table. By adopting the method and the system, the problem of repeated refreshing of the address table in protection of the Ethernet ring under the condition of a local protection switching request is solved.

Owner:ZTE CORP

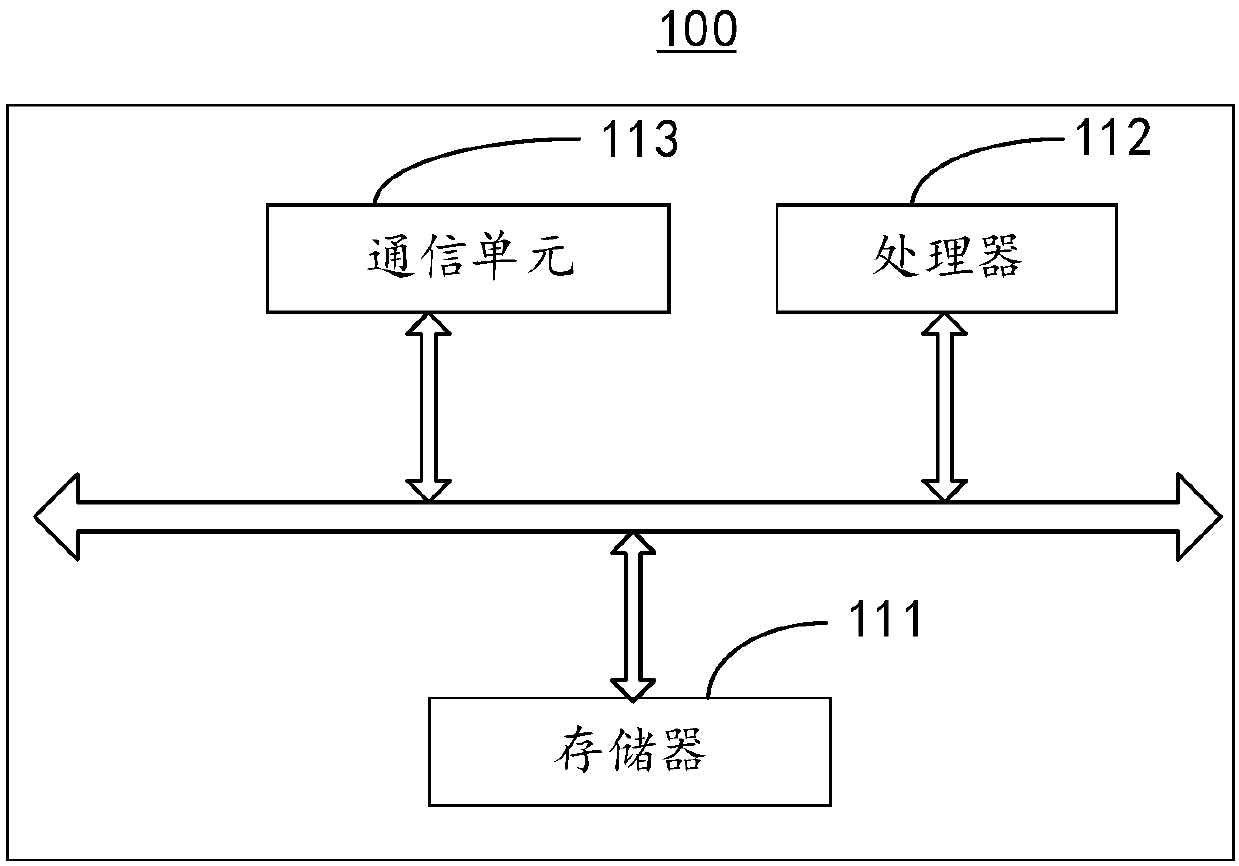

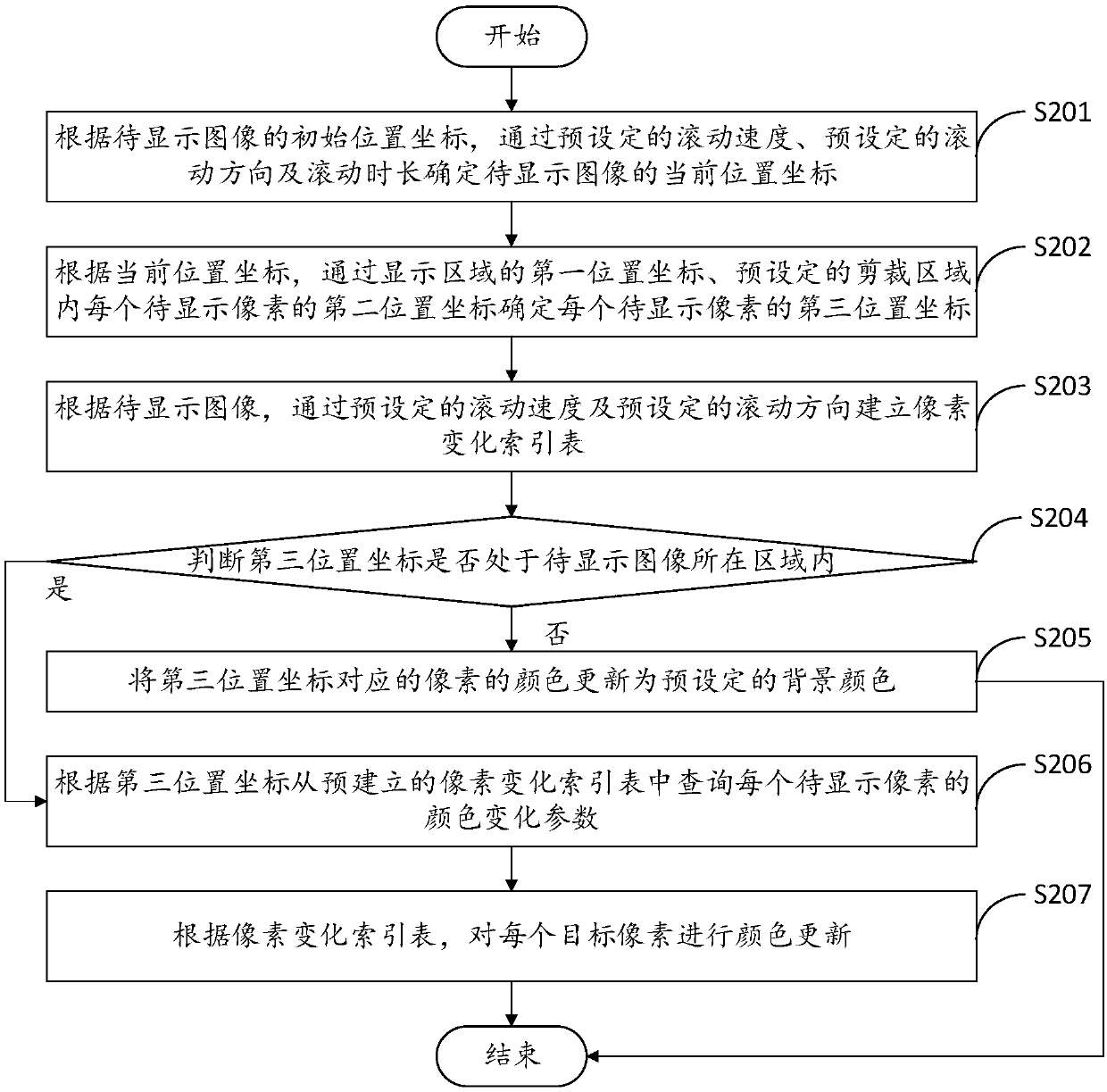

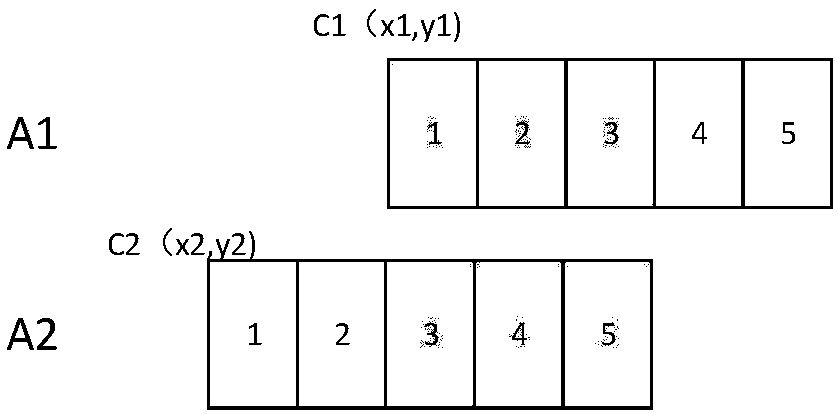

Image scroll display method and device

ActiveCN111352598AAvoid refreshReduce occupancyDigital output to display devicePhysicsComputer graphics (images)

The embodiment of the invention provides an image rolling display method and device, and relates to the technical field of image display. According to the method and the device, a third position coordinate of each to-be-displayed pixel is determined, then a color change parameter of each to-be-displayed pixel is inquired from a pre-established pixel change index table according to the third position coordinate, and finally color updating is carried out on each target pixel according to the pixel change index table. According to the index table of pixels, a judgment is made as to whether each to-be-displayed pixel has color change or not according to the third position coordinate of each to-be-displayed pixel; and if the color change exists, the color of each to-be-displayed pixel is updated according to the pixel change index table, that is, only the color of the pixel of which the color can be changed is updated, so that refreshing of all pixels in a display area is avoided, the occupancy rate of system resources is reduced, and the refreshing efficiency is improved.

Owner:ZHEJIANG UNIVIEW TECH

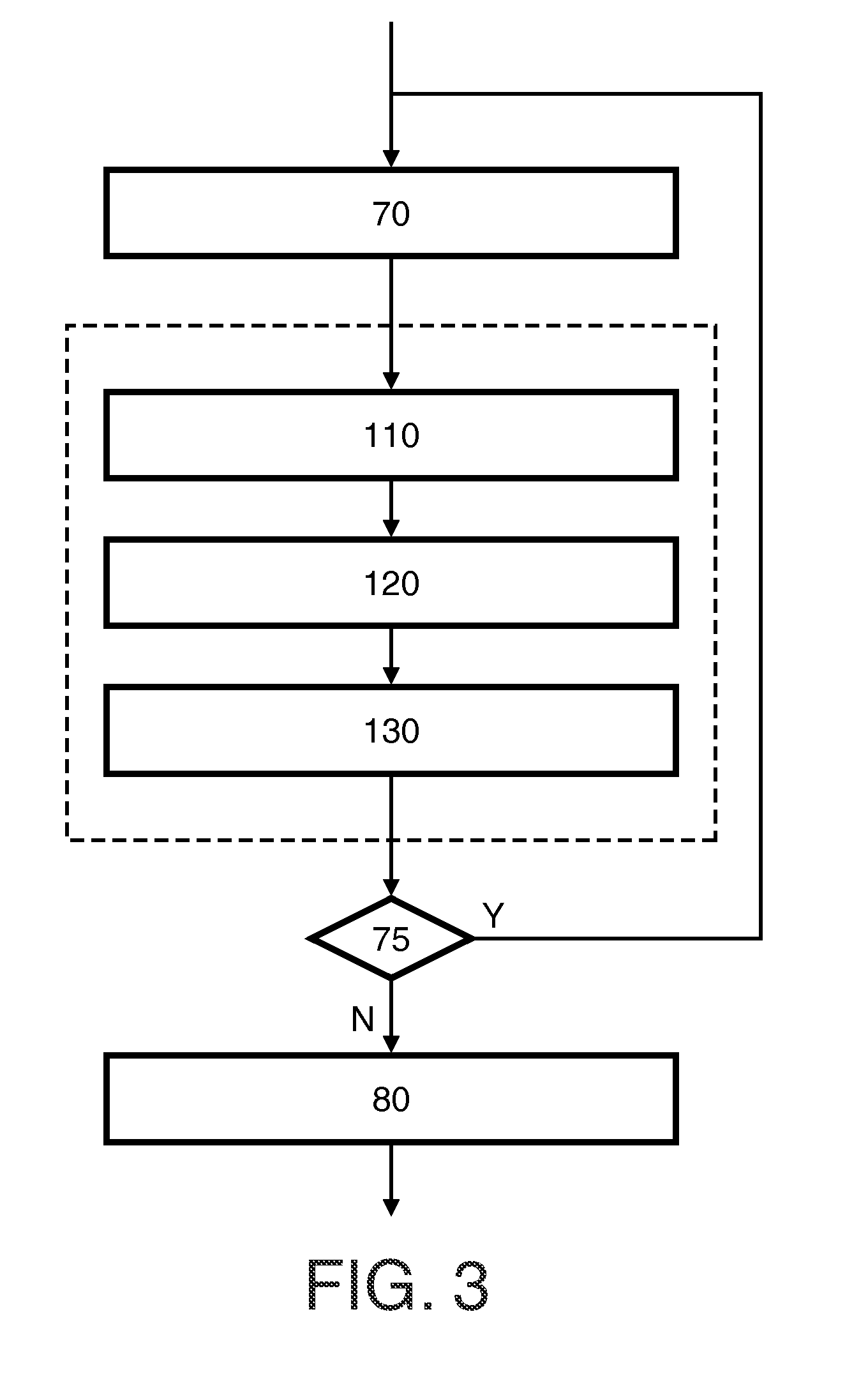

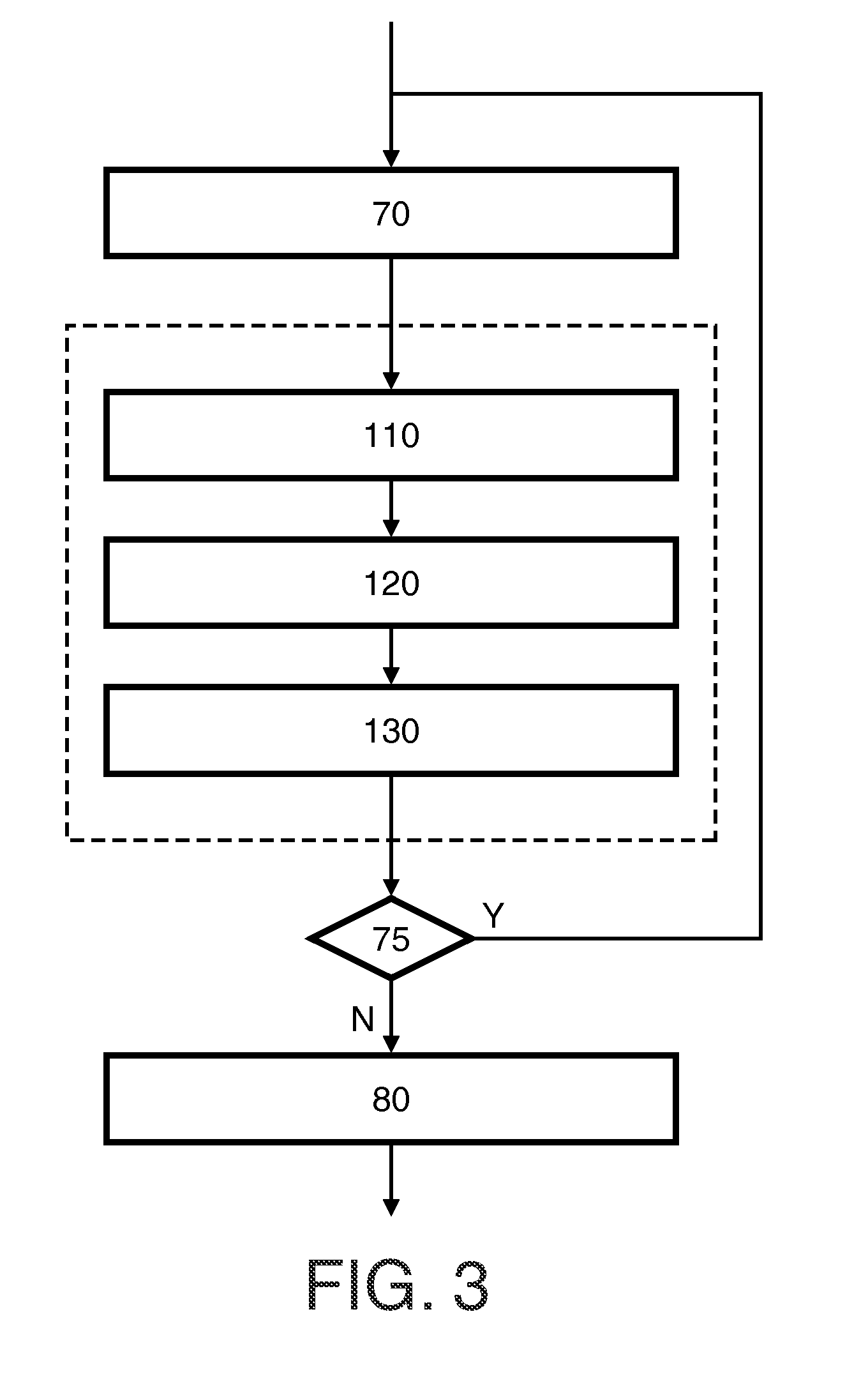

Estimating temperature of memory elements

ActiveUS20100292949A1Accurate temperatureAccurately determineThermometer detailsThermometers using material expansion/contactionParallel computingSmart card

The invention relates to a method for determining a temperature (T) of a plurality of memory elements (10) having a temperature-dependent probability (P) of assuming a particular bit value, the method comprising: triggering (110) the plurality of memory elements (10) to assume the particular bit value; reading out (120) the contents of the plurality of memory elements (10) to obtain read data (D), and processing (130) the read data (D) for determining a value (Vact) indicative of the temperature (T). The invention also relates to a program product comprising instructions for causing a processor to perform the method. Such computer program is advantageously used in a smartcard, which then does not need any structural modification at all. The invention further relates to a system for determining a temperature (T) of a plurality of memory elements (10). Such system is advantageously implemented in an integrated circuit, wherein the plurality of memory elements (10) forms part of an integrated memory. The invention provides that temperature (T) can be determined without the need for a separate temperature sensor. The only real requirement is the presence of a plurality of memory elements (10) having a temperature-dependent probability (P) of assuming particular bit value.

Owner:NXP BV

A method for improving ssd performance and ssd

ActiveCN108021511BAvoid loadAvoid refreshMemory adressing/allocation/relocationComputer hardwareComputer architecture

The invention discloses a method for improving the performance of an SSD and an SSD, which is characterized in that the SSD applies to a host for allocating a memory space as a mapping table buffer area, stores the mapping table in the mapping table buffer area, and accesses the mapping table buffer area through a high-speed interface The mapping table entry data. In view of the limitation of the mapping table of Dramless SSD, the random reading and writing of the host will frequently trigger the replacement of the internal mapping table, resulting in the problem of extremely low performance. The HMB strategy of the present invention based on NVMe SSD can be used as a mapping table cache by applying for memory on the host side , so as to avoid frequent loading and refreshing of the mapping table, thereby achieving the purpose of improving the operating performance of the SSD.

Owner:SHENZHEN YILIAN INFORMATION SYST CO LTD

Method and system for preventing address table from being refreshed repeatedly in protection of Ethernet ring

ActiveCN102035711BAvoid refreshDuplicate Refresh PreventionData switching networksRing protectionEthernet

Owner:ZTE CORP

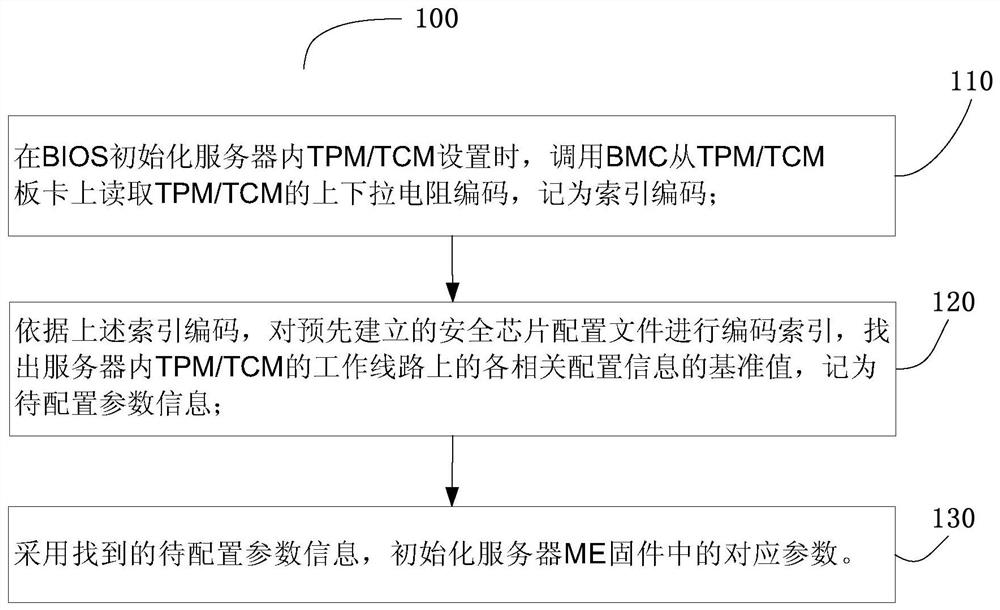

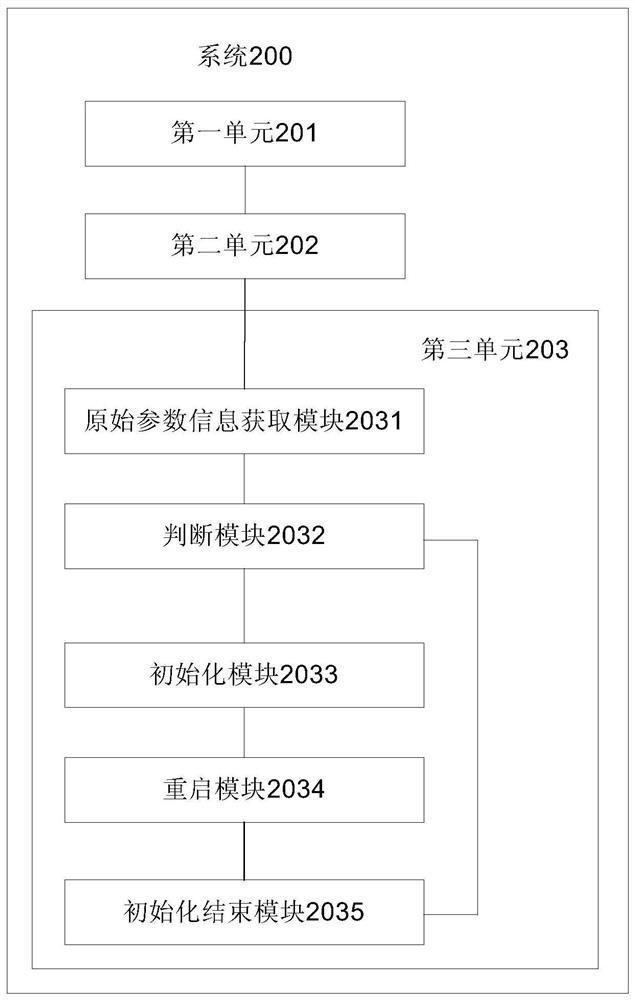

Tpm and tcm general server chip initialization method, system, bios and storage medium

The present invention provides a TPM and TCM universal server chip initialization method, system, BIOS and storage medium, all including: when TPM / TCM is set in the BIOS initialization server, call BMC to read TPM / TCM from TPM / TCM board card Pull-up and pull-down resistor codes are recorded as index codes; according to the above index codes, the pre-established security chip configuration files are coded and indexed to find out the reference values of the relevant configuration information on the working line of the TPM / TCM in the server, which are recorded as pending Configure parameter information; use the found parameter information to be configured to initialize the corresponding parameters in the server ME firmware. The invention is used to increase the convenience of TPM / TCM chip configuration in the initialization server.

Owner:SUZHOU METABRAIN INTELLIGENT TECH CO LTD