Patents

Literature

41results about How to "Implement signaling" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

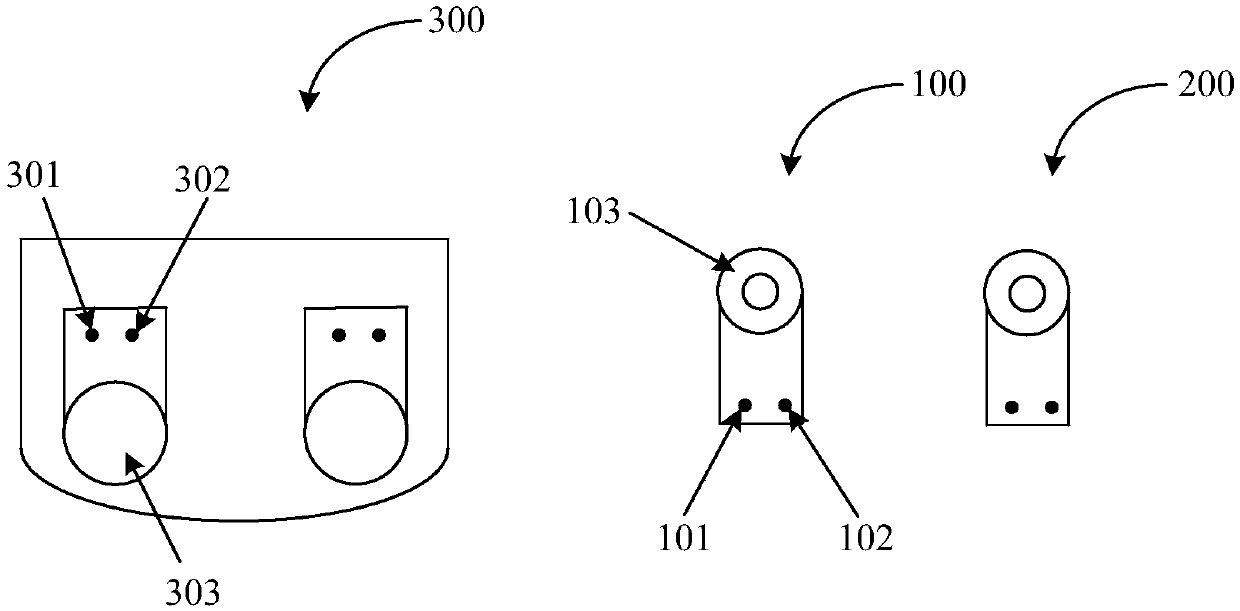

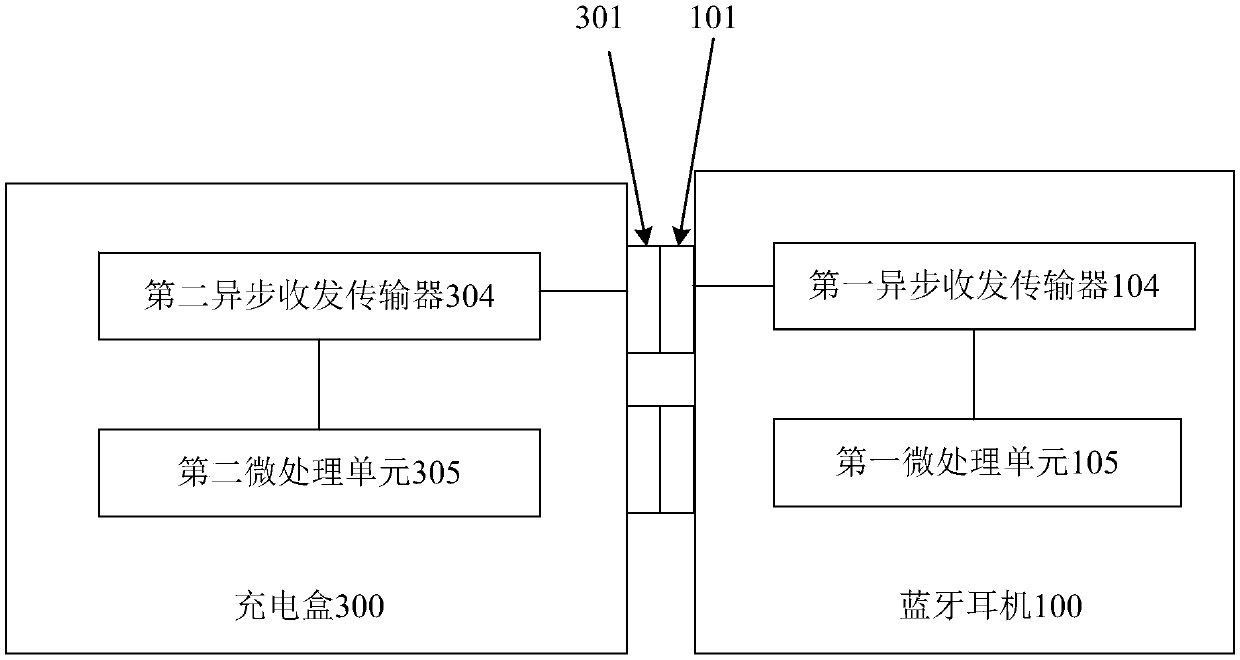

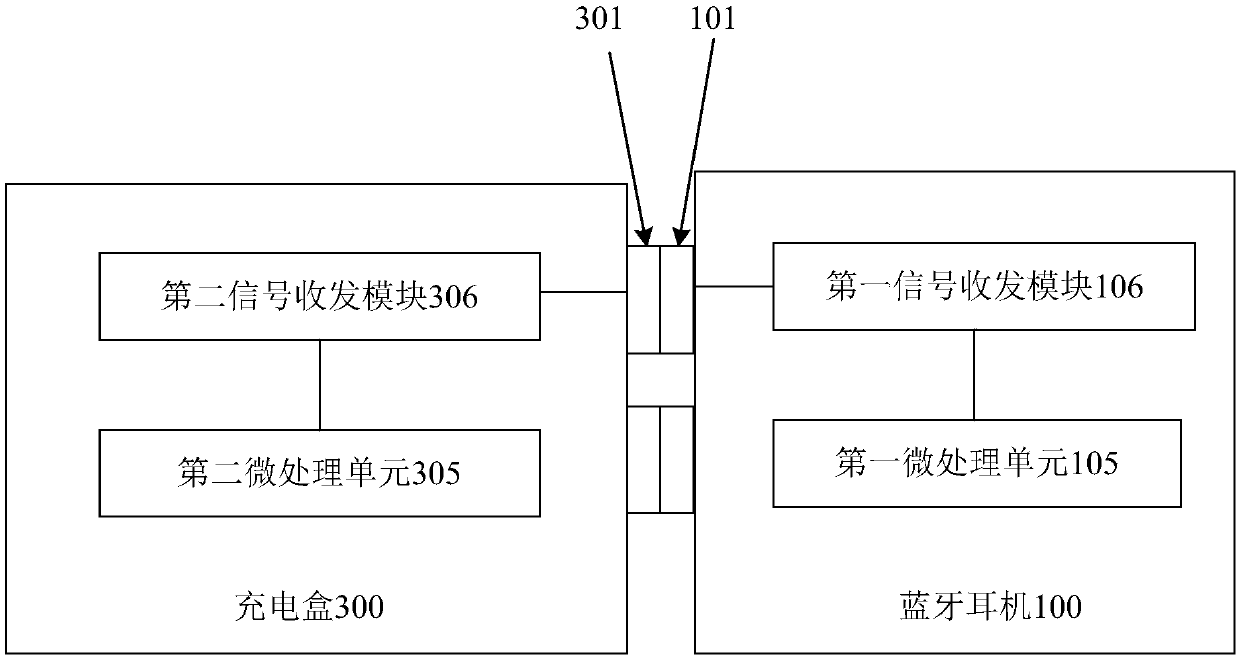

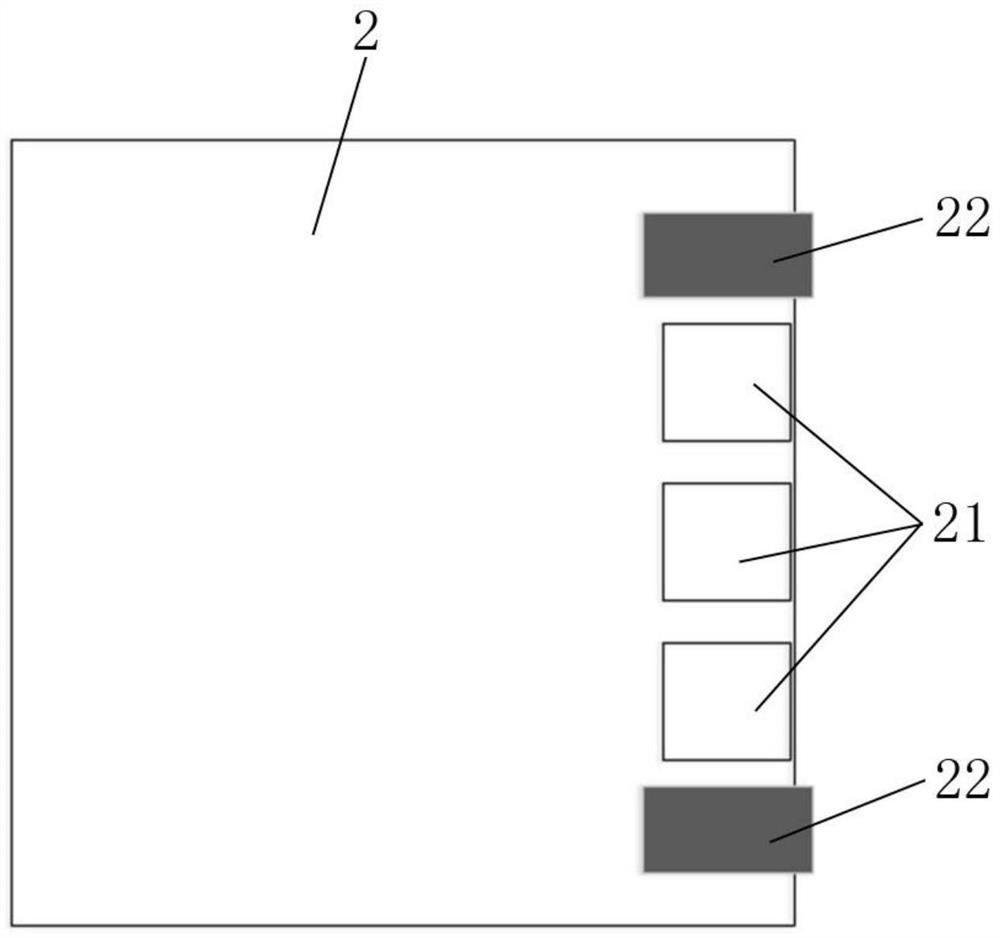

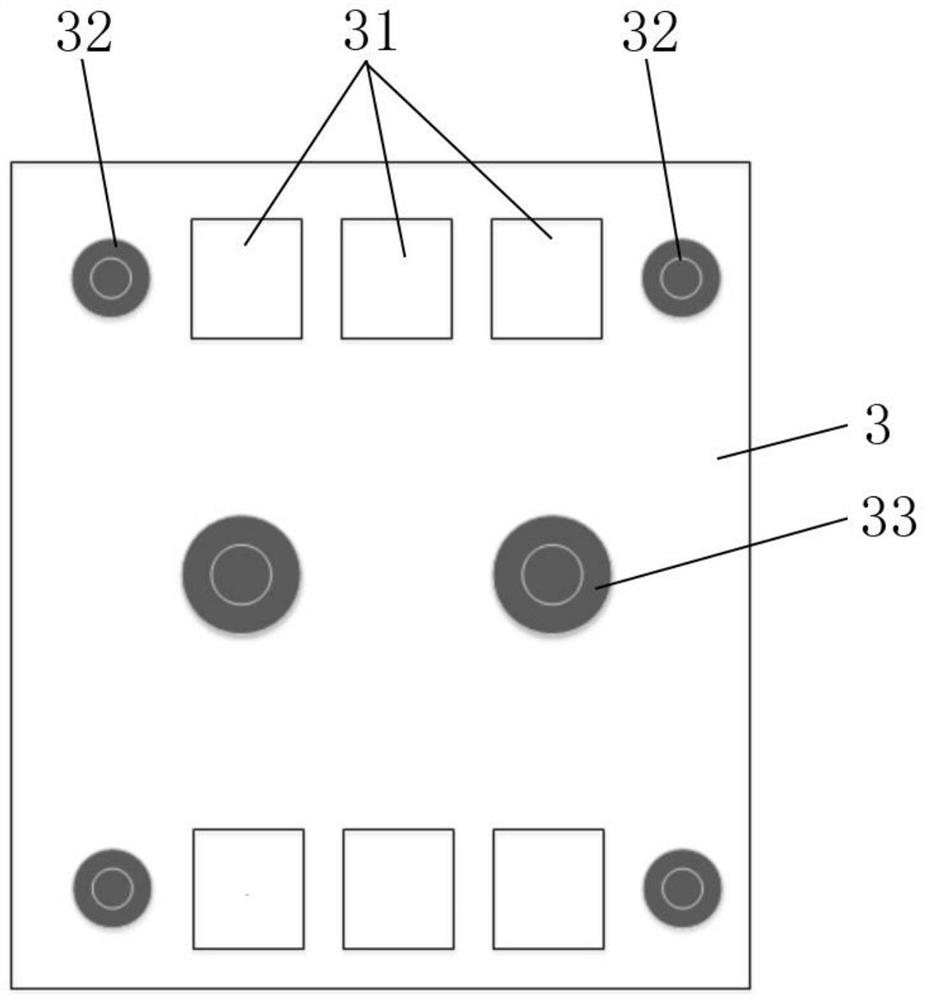

Bluetooth earphone charging box system and Bluetooth earphone test system

InactiveCN109547884AImplement signalingImprove experienceHeadphones for stereophonic communicationNetwork topologiesEngineeringBluetooth

The invention provides a Bluetooth earphone charging box system. The system includes Bluetooth earphones and a charging box. The Bluetooth earphone are provided with first GND contact points and firstVCHG contact points. The charging box is provided with second GND contact points and second VCHG contact points. When the Bluetooth earphones are placed in the charging box, the first VCHG contact points are in contact with the second VCHG contact points, the charging box charges the Bluetooth earphones through the first VCHG contact points and the second VCHG contact points in mutual contact, and the charging box and the Bluetooth earphones reuse the first VCHG contact points and the second VCHG contact points in mutual contact for communication. The system can realize communication of the left and right earphones and the charging box to improve user experience, and improves reliability of earphone test and program upgrading processes after earphone assembly completion.

Owner:BESTECHNIC SHANGHAI CO LTD

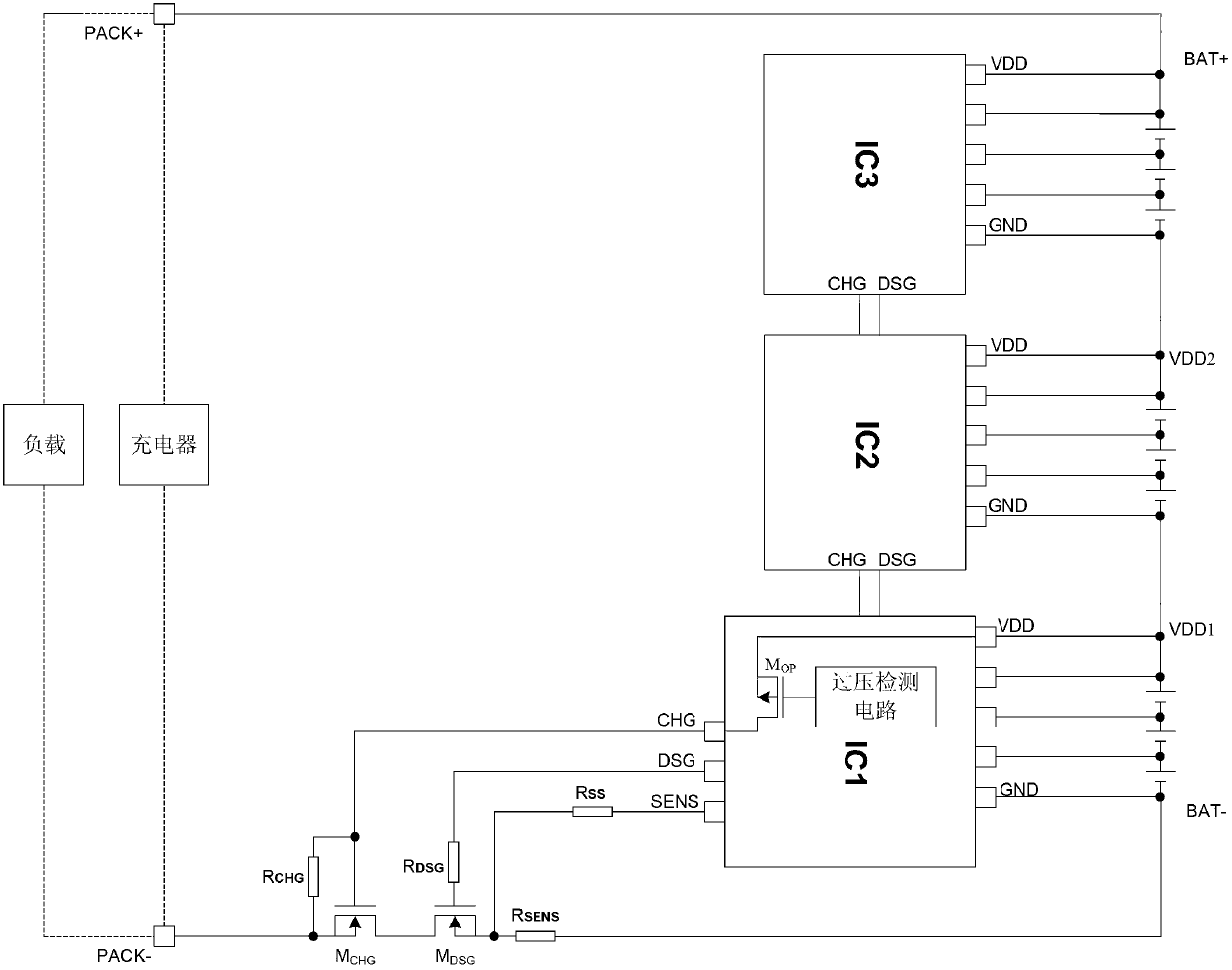

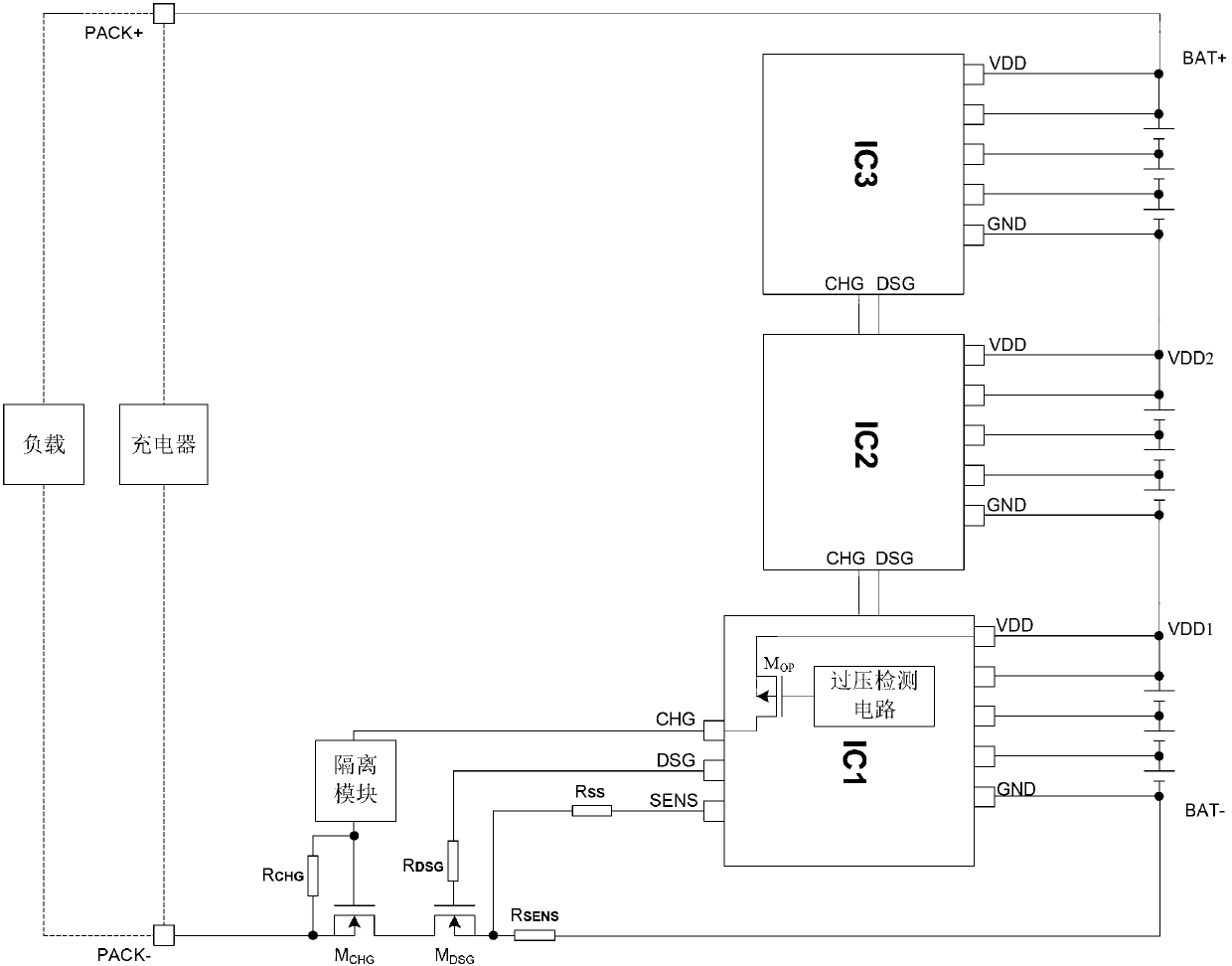

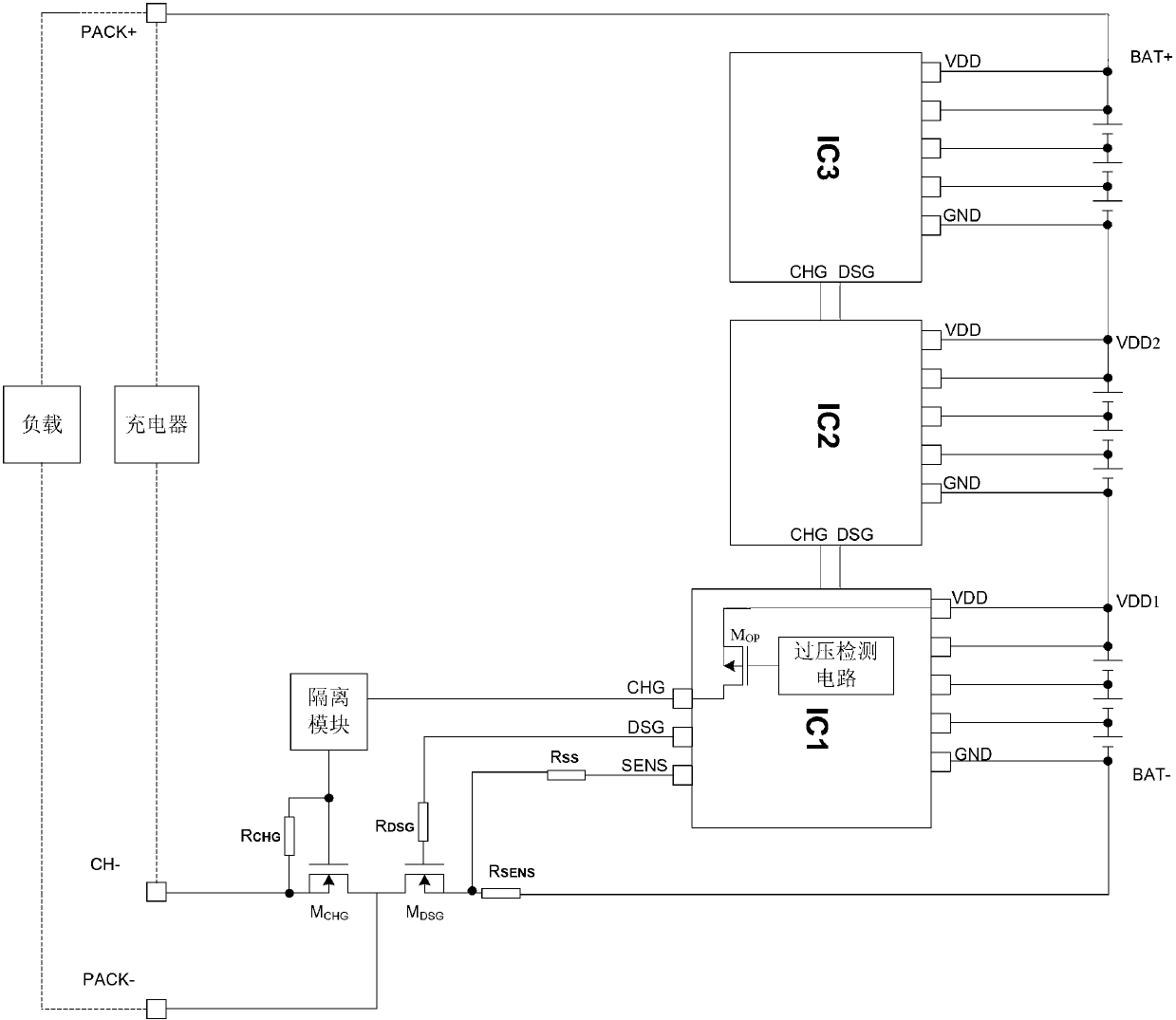

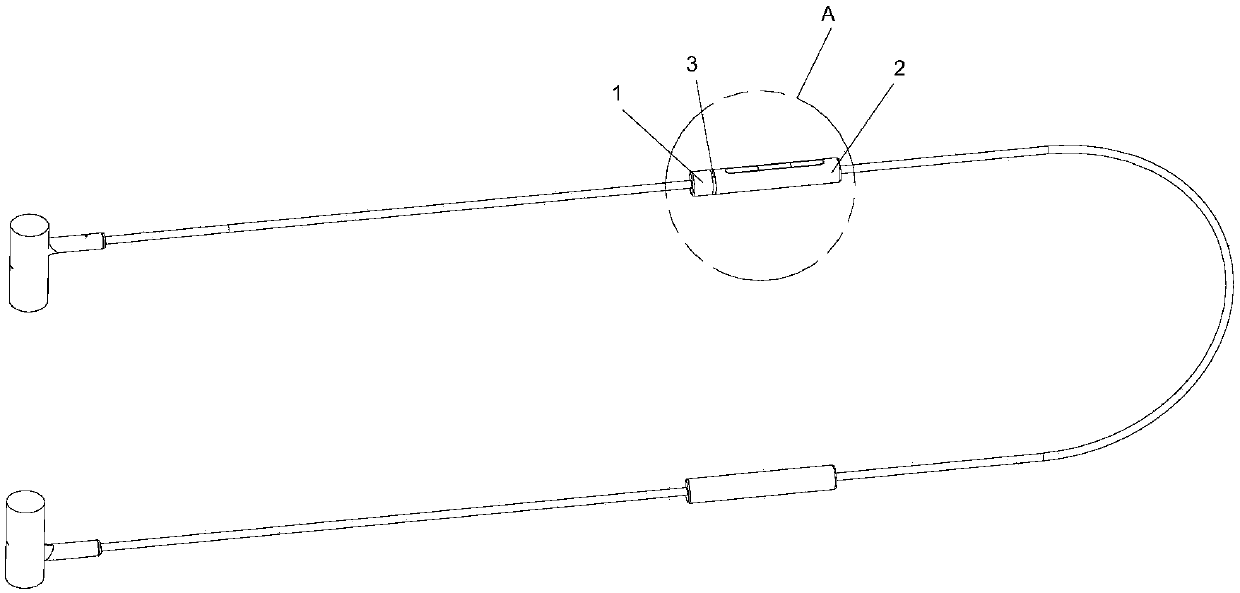

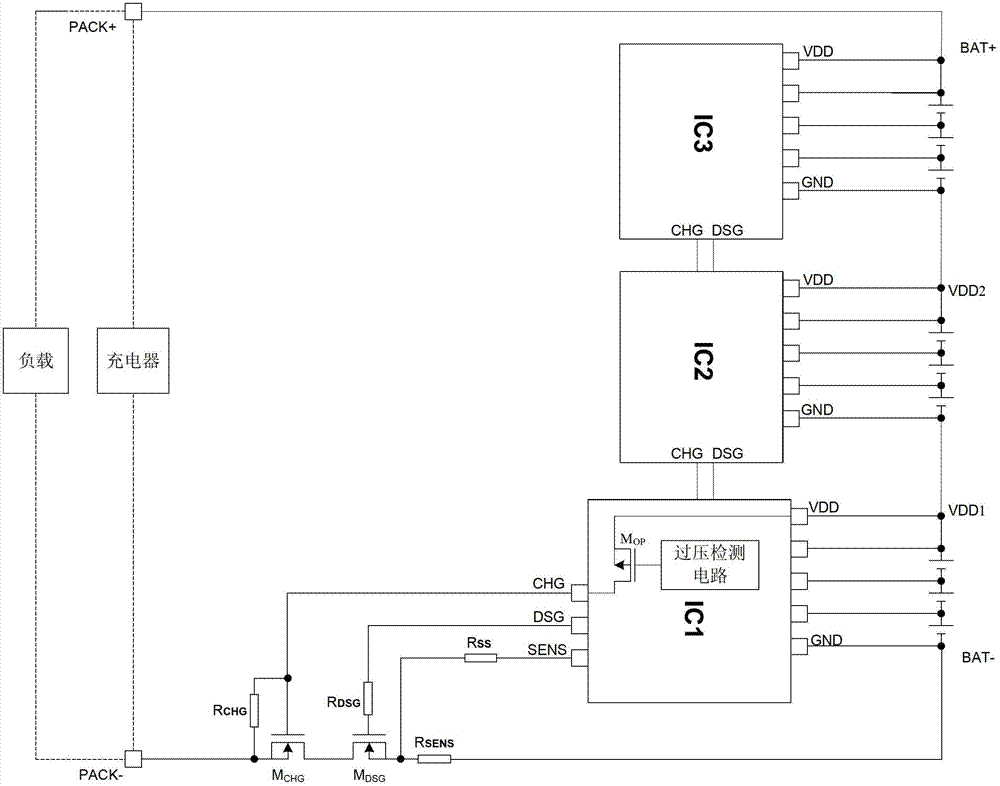

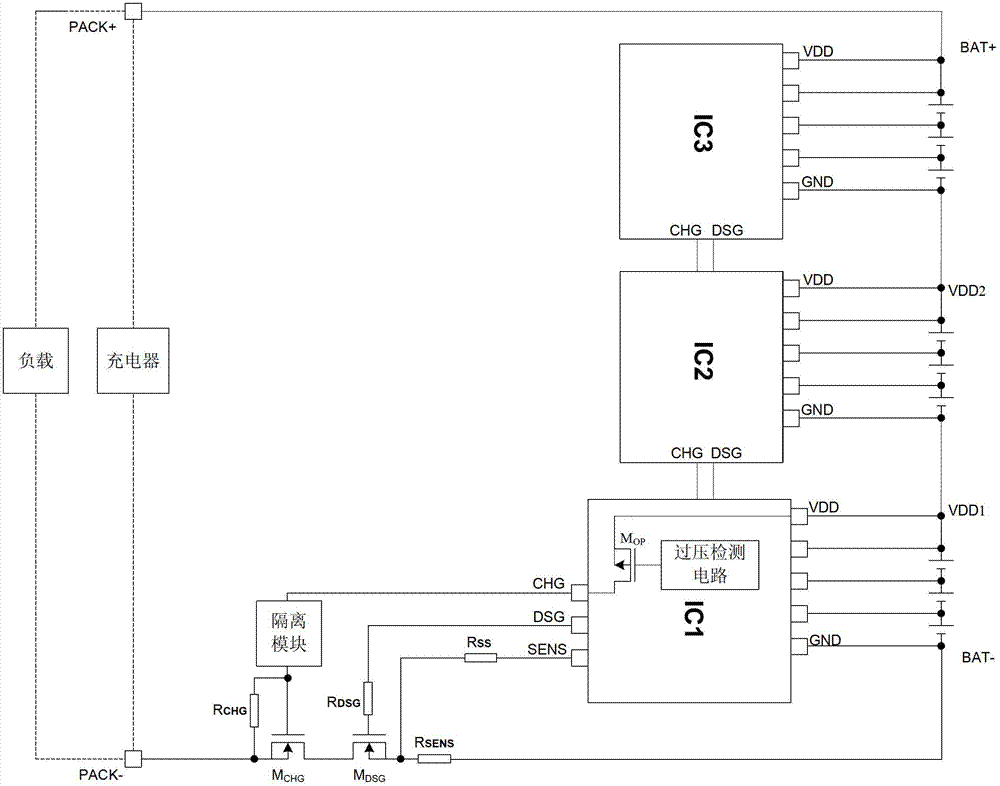

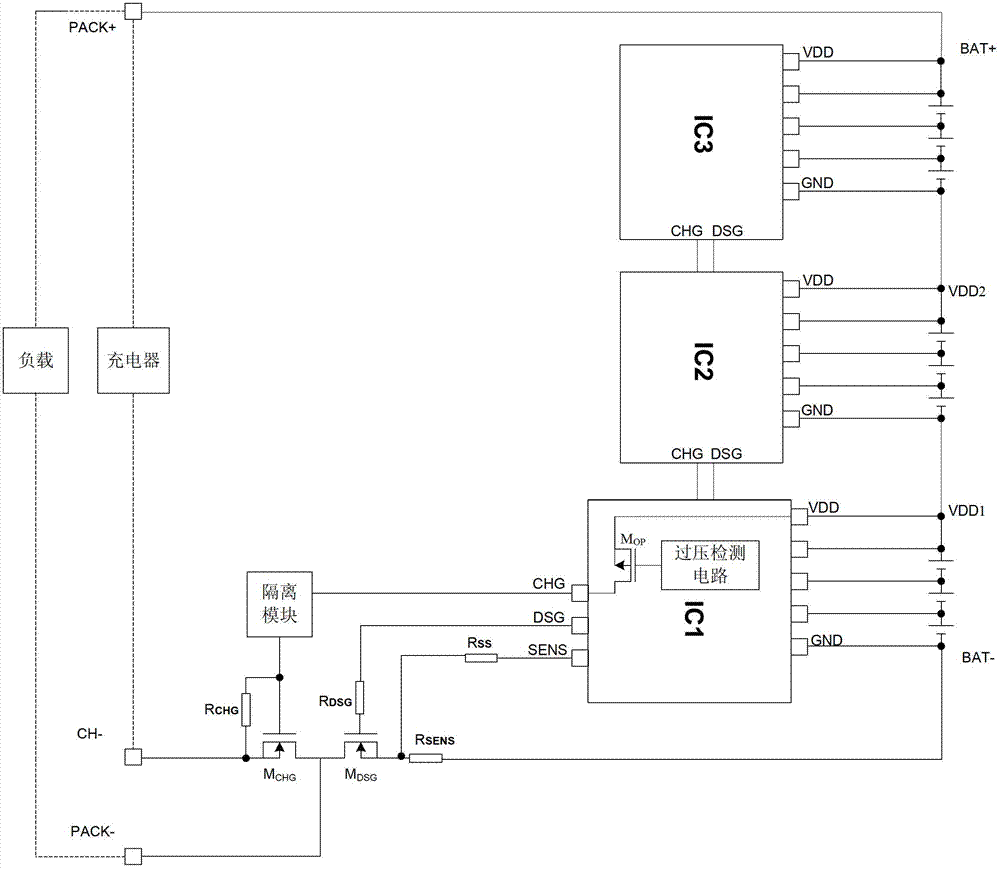

Charger detection device for battery protection cascade system

ActiveCN103217605AEnsure safetyImplement signalingBatteries circuit arrangementsElectrical testingOvervoltageControl signal

The invention provides a charger detection device for a battery protection cascade system. The charger detection device comprises N battery protection chips which are in one-to-one correspondence connection with N battery strings, wherein the first battery protection chip is a master chip and the rest battery protection chips are cascade chips; the N battery strings are connected in series, and respectively comprise M batteries, and N and M are natural numbers more than or equal to 2; each battery protection chip comprises a grounding end, a power end, a master and slave chip select signal end and a charger detection port; a connecting point of the power end of the Nth battery protection chip and the positive terminal of the Nth battery string is extracted to form the positive end of a battery pack, a connecting point of the grounding end of the master chip and the negative terminal of the first battery string is extracted to form the negative end of the battery pack, and a charger is connected between the positive end and the negative end; and the charger detection port of the master chip is connected to the negative end of the battery pack through a port resistor, the voltage of the battery pack is detected, and the connecting state of the charger is judged. The charger detection device can safely and reliably detect the connecting state of the charger, transmit an overvoltage hysteresis control signal to the cascade chips, and improve the safety of an application system.

Owner:SINO WEALTH ELECTRONICS

Antenna of handset, and built-in antenna type handset

InactiveCN1917281AEasy to installMeet functional requirementsAntenna supports/mountingsRadiating elements structural formsRadio frequencyFeed line

Characters of the antenna are that the antenna consists of metal layer of keyset of handset. The metal layer includes groove, grounding device, and feed line. The invention also discloses a handset with built-in antenna. The handset includes print circuit board, and metal layer of keyset. Being as antenna, the metal layer is in use for receiving and transmitting wireless signal. The metal layer includes groove in order to satisfy requirement of antenna size from frequency band. Being setup on the metal layer, the feed line unit connected to RF sect of print circuit board is in use for receiving and transmitting radio frequency. The grounding device setup on metal layer is connected to ground of the print circuit board.

Owner:HAIER GRP CORP +1

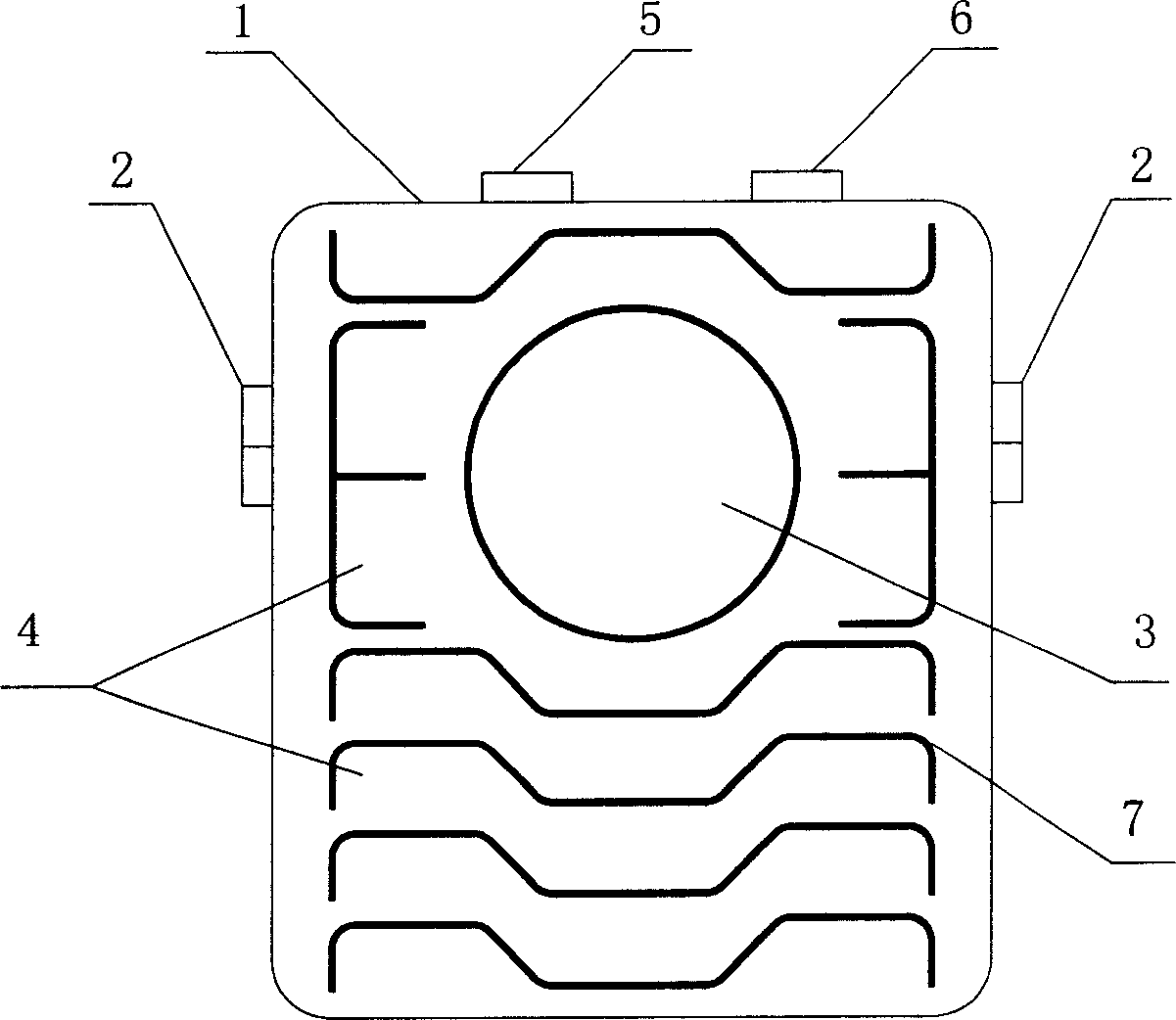

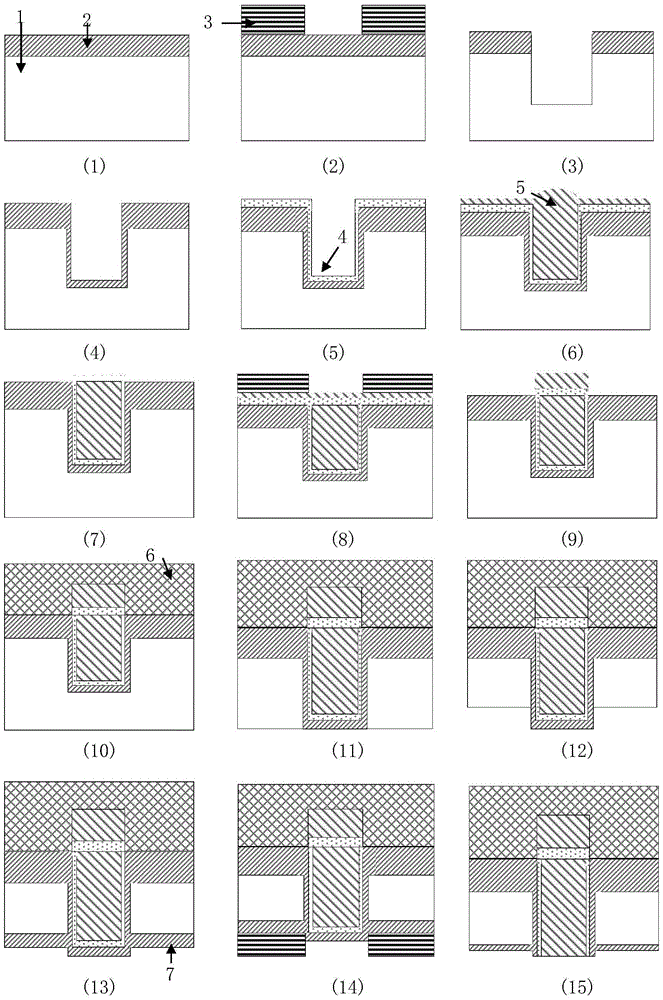

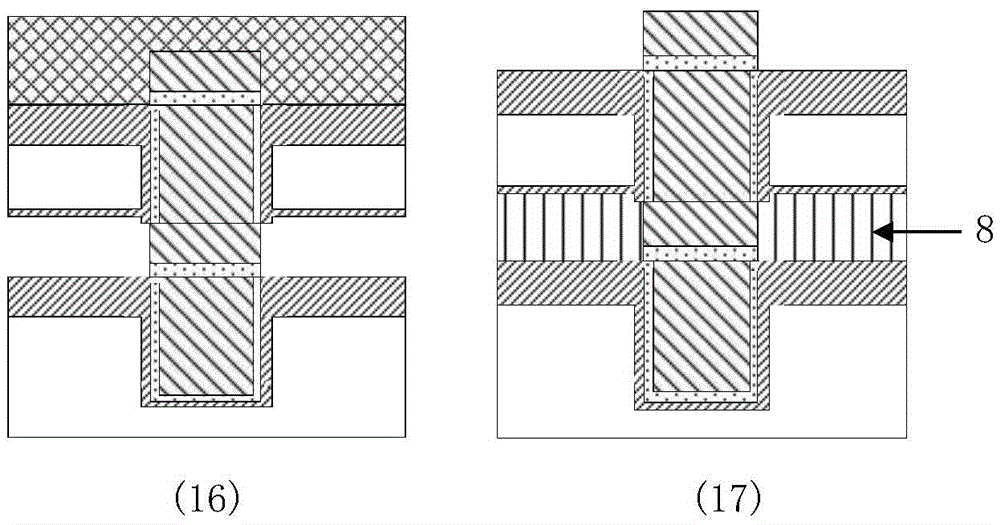

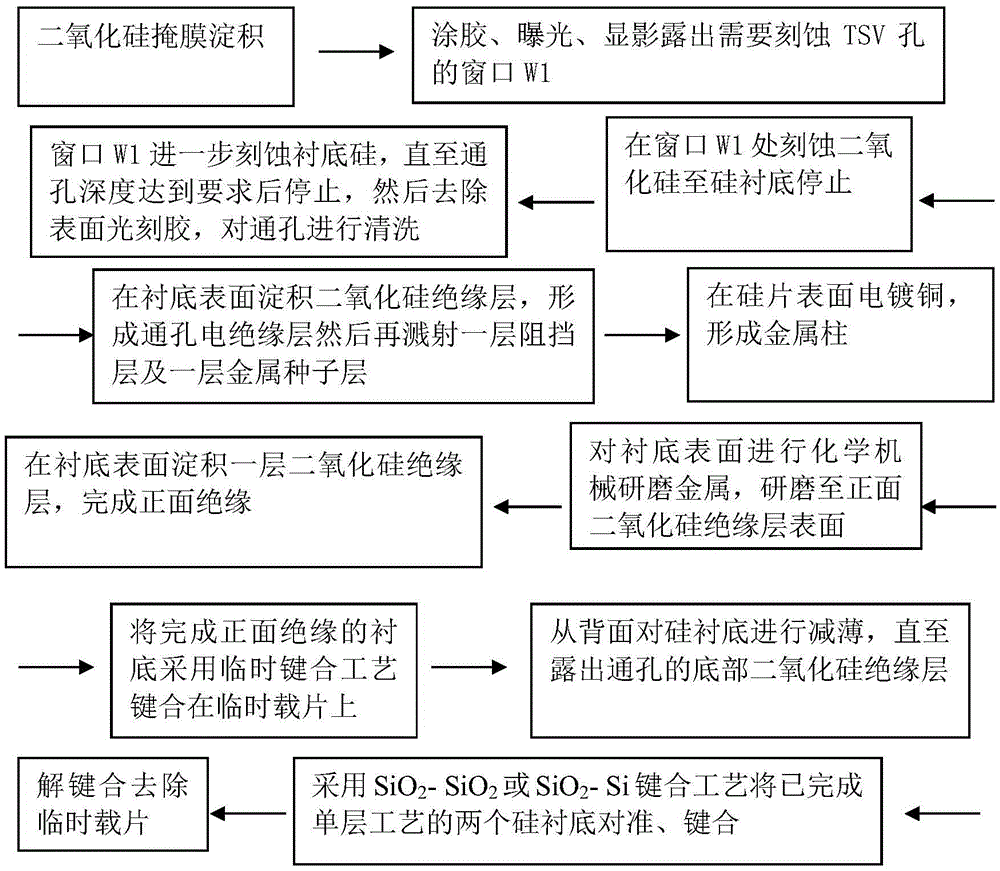

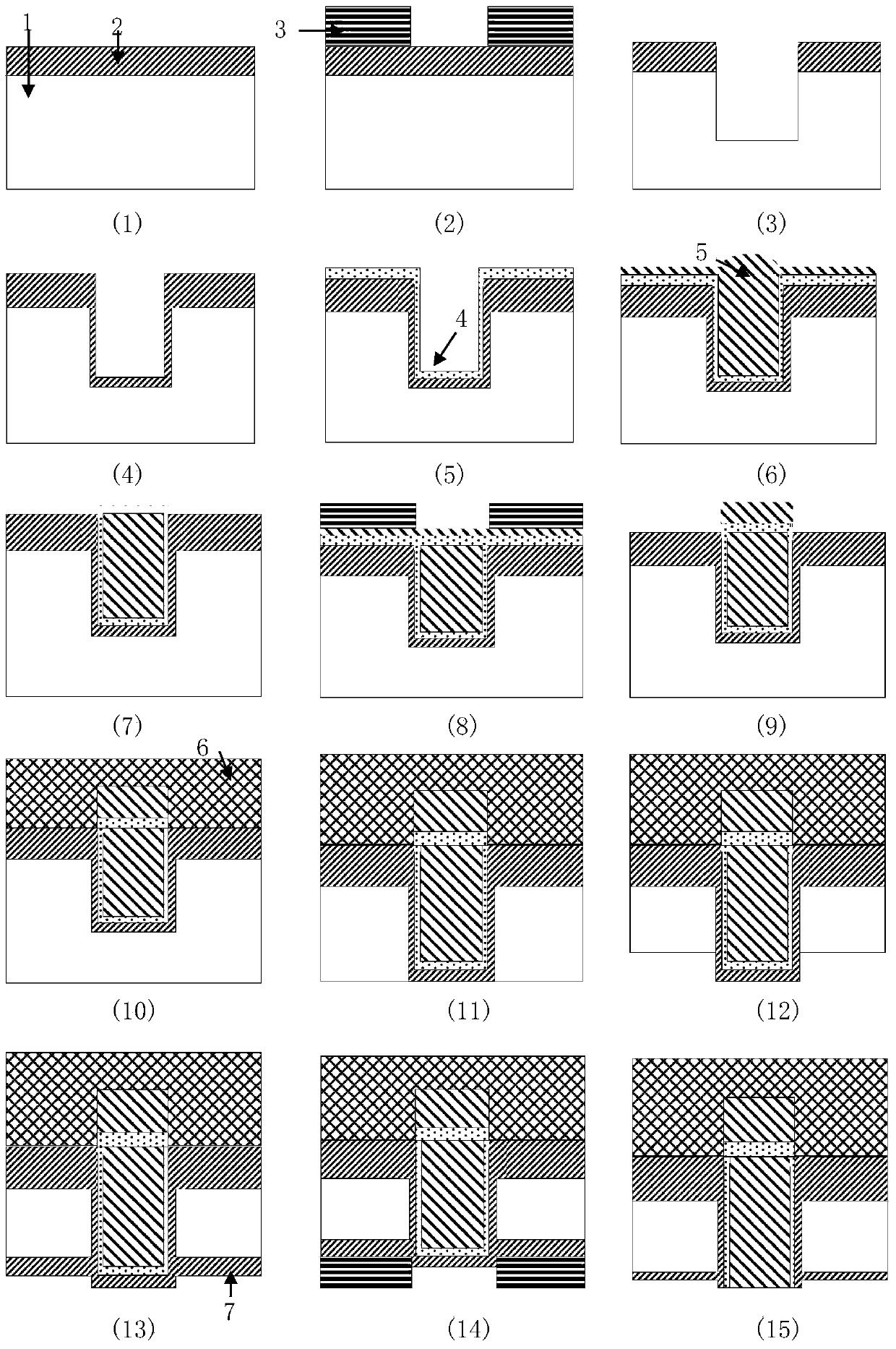

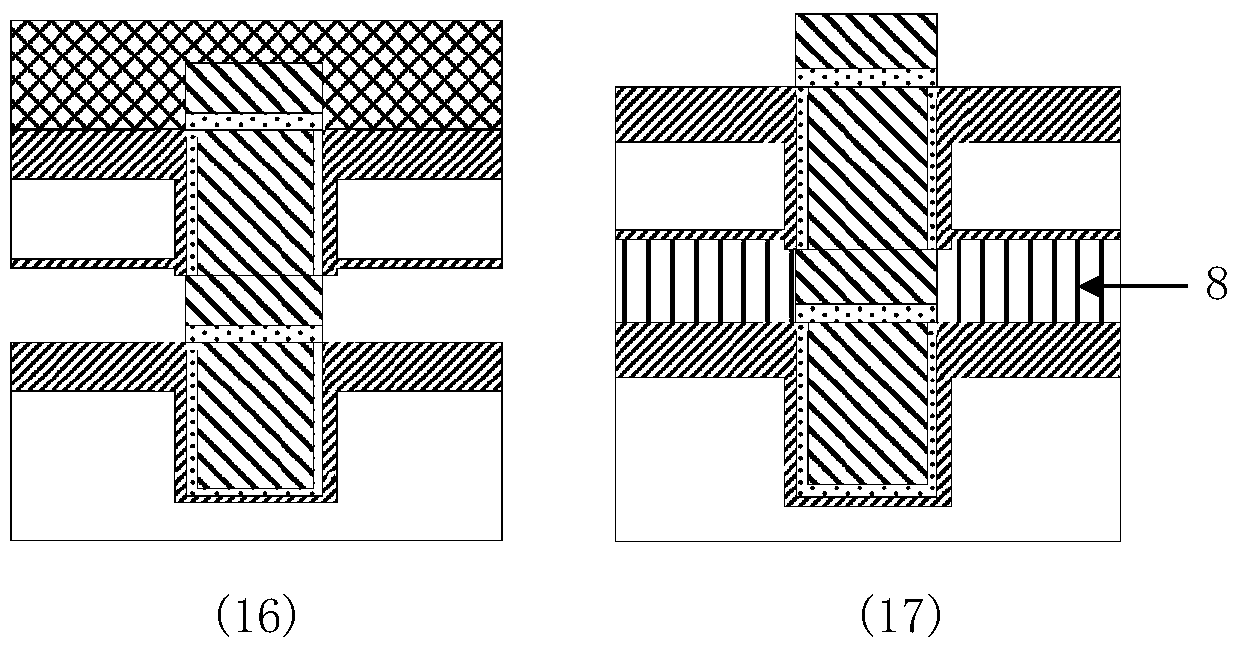

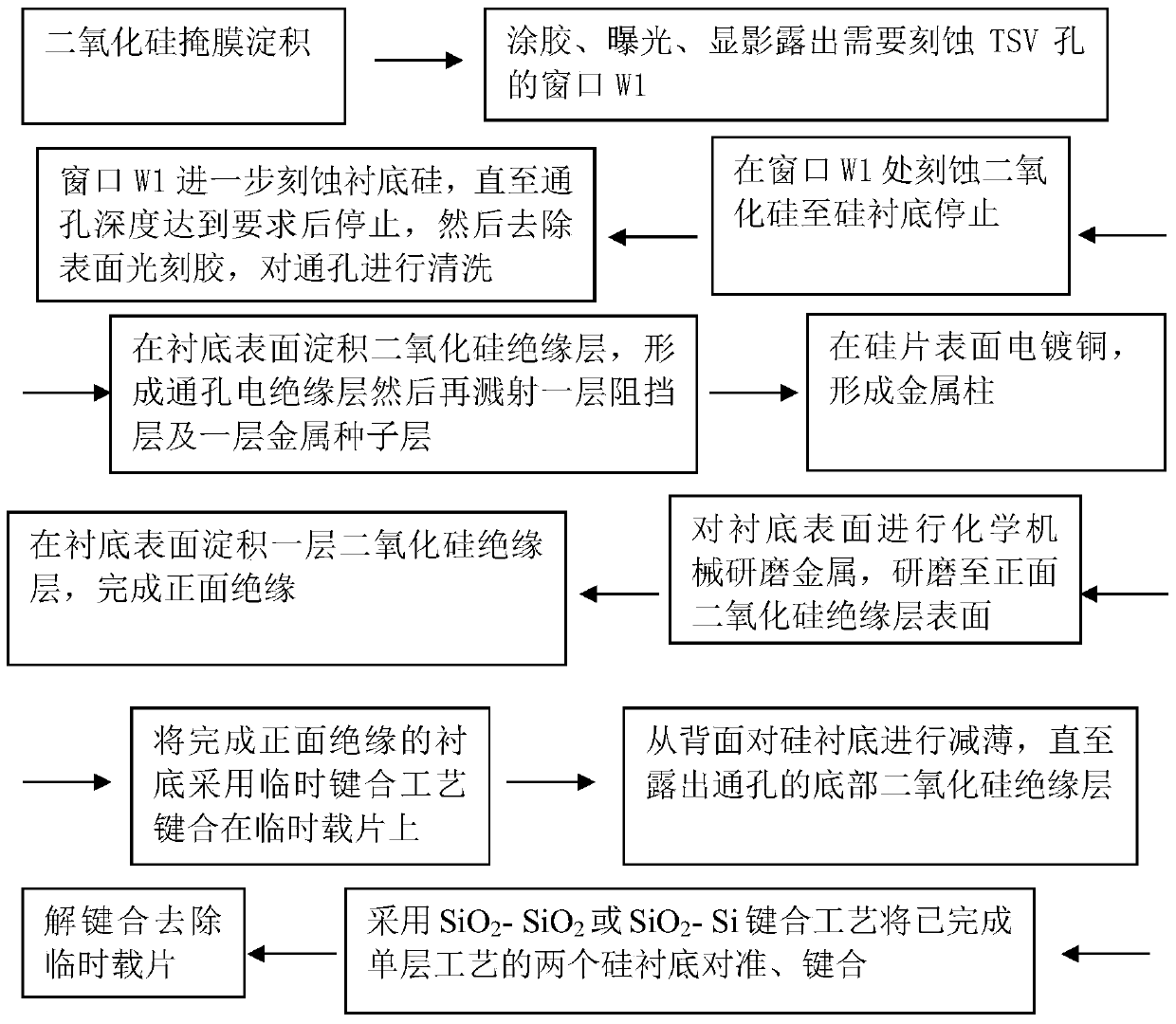

Method for manufacturing three-dimensional capacitively coupled interconnection structure based on through-silicon capacitor

ActiveCN105470225AReduce performanceLower yieldSemiconductor/solid-state device detailsSolid-state devicesCapacitanceInsulation layer

The invention discloses a method for manufacturing a three-dimensional capacitively coupled interconnection structure based on a through-silicon capacitor. The method comprises: forming two silicon substrates same in structure by machining, and bonding the back surface of one silicon substrate to the other silicon substrate in an alignment manner; forming the three-dimensional capacitively coupled interconnection structure based on the through-silicon capacitor; coaxially arranging copper columns at the upper part and the lower part of the interconnection structure; enabling the top of the copper column at the lower part to be in contact with a silicon dioxide insulation layer on the back surface of the silicon substrate at the upper part; and taking the copper column at the upper part and the copper column at the lower part as an upper electrode plate and a lower electrode plate of the capacitance respectively, taking an insulation layer between the copper column at the upper part and the copper column at the lower part as an inter-capacitance medium, and forming a through-silicon capacitor structure. Compared with a conventional TSV process, the method has the characteristics that the technological processes of making metal convex points on the front surface of a wafer, thinning the back surface to expose copper, performing insulation treatment, making micro-convex points and the like in a TSV structure making process are removed, the technological processes are remarkably reduced, the yield is increased, and required process devices are correspondingly reduced.

Owner:XI AN JIAOTONG UNIV

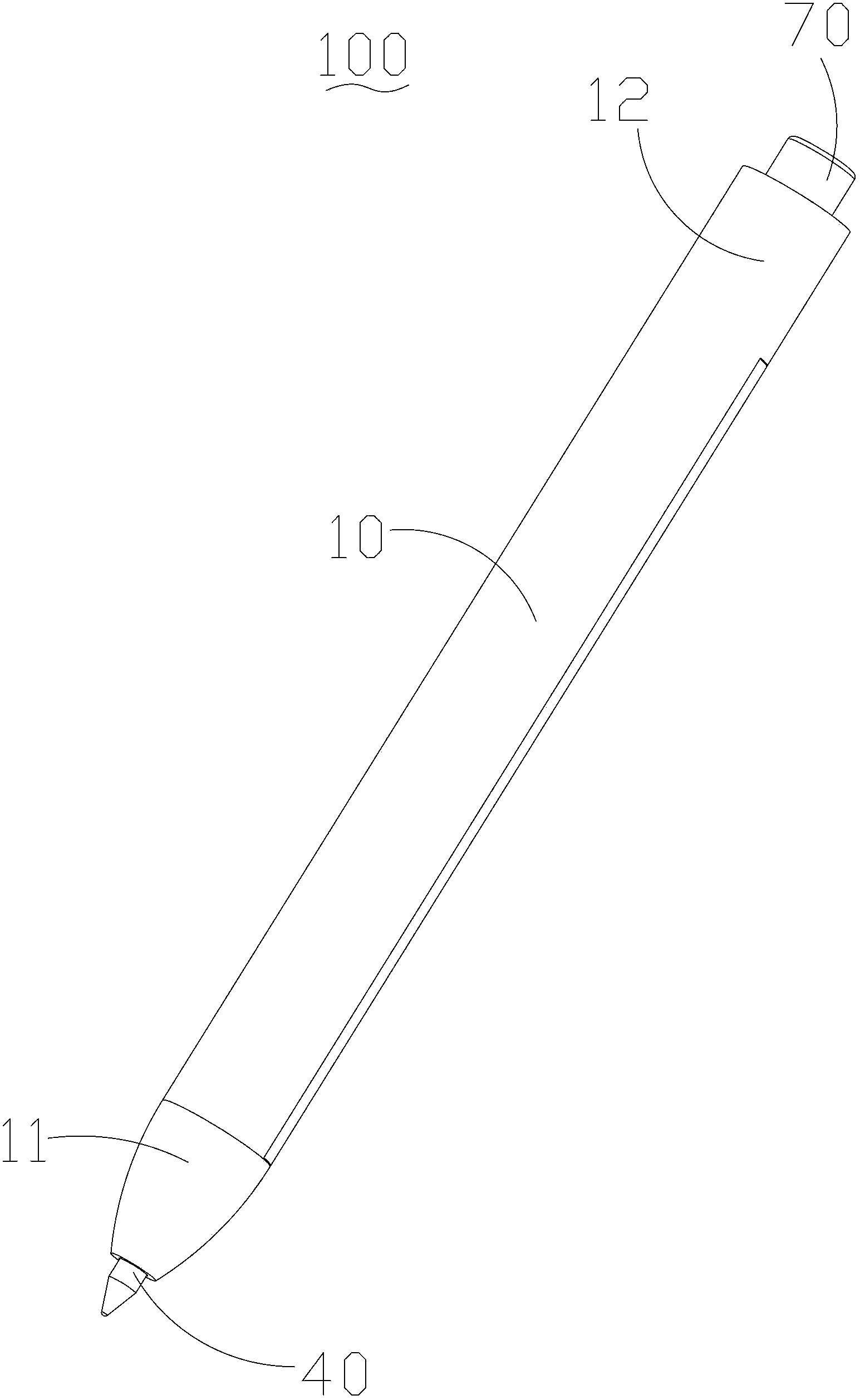

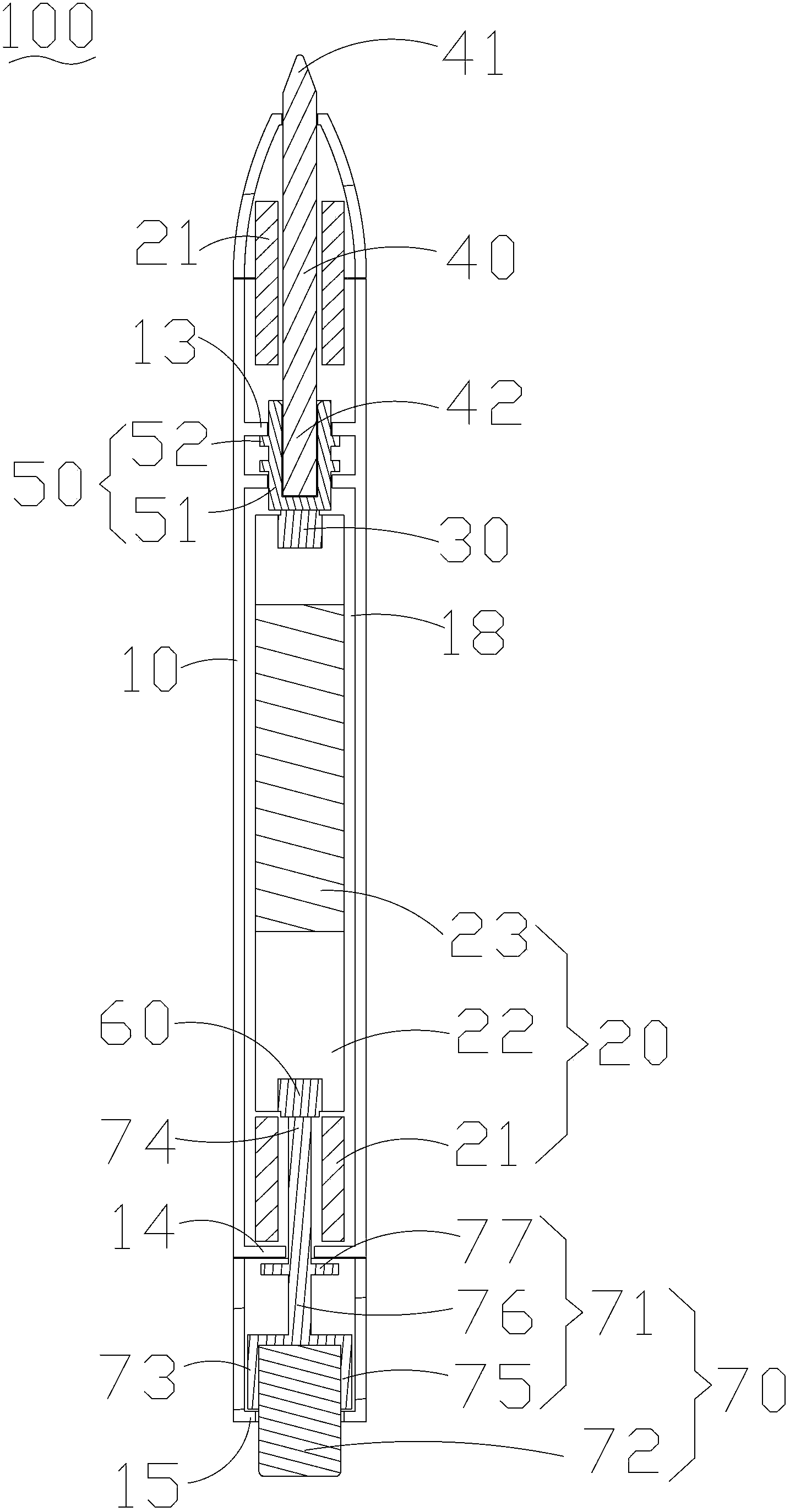

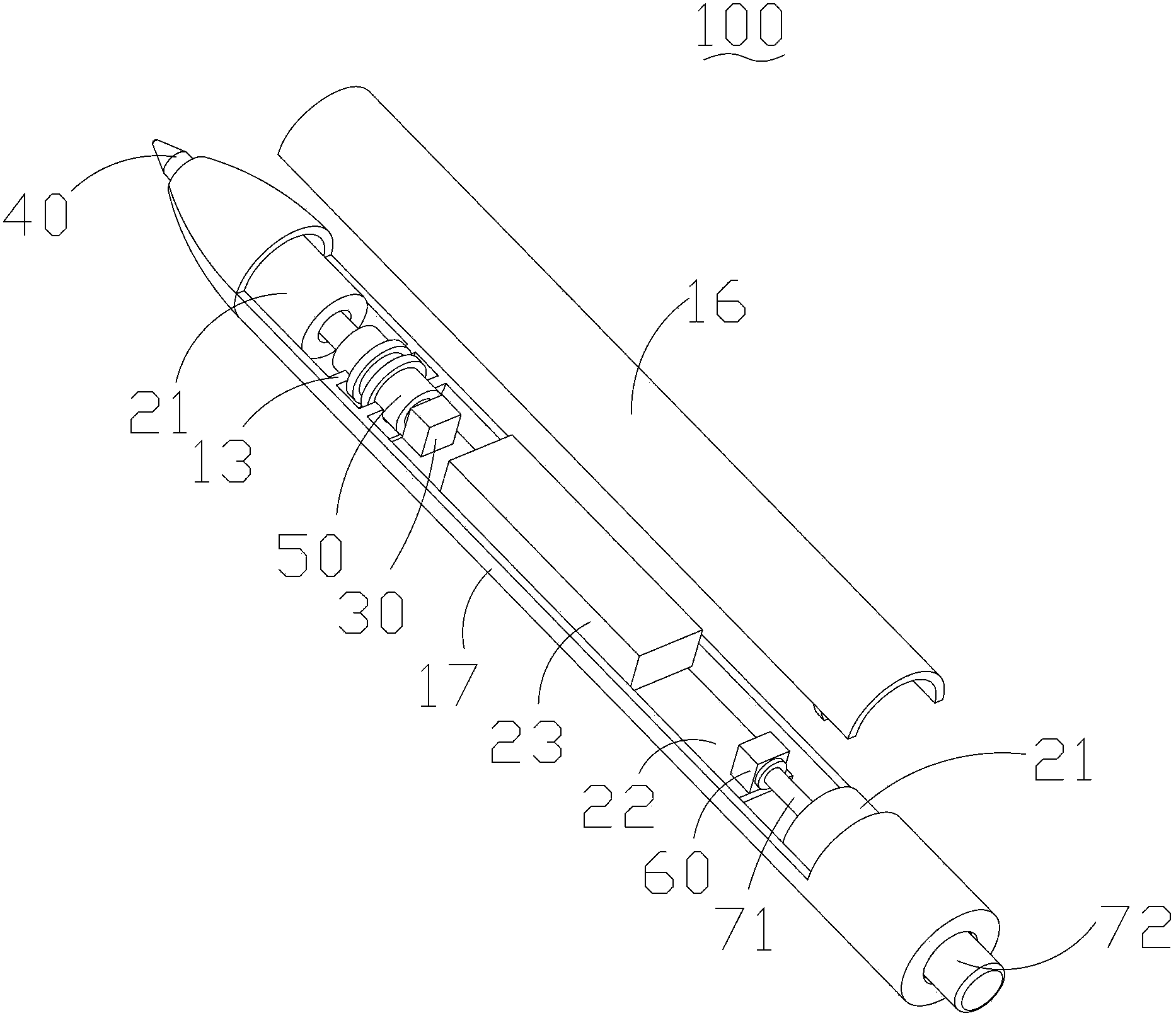

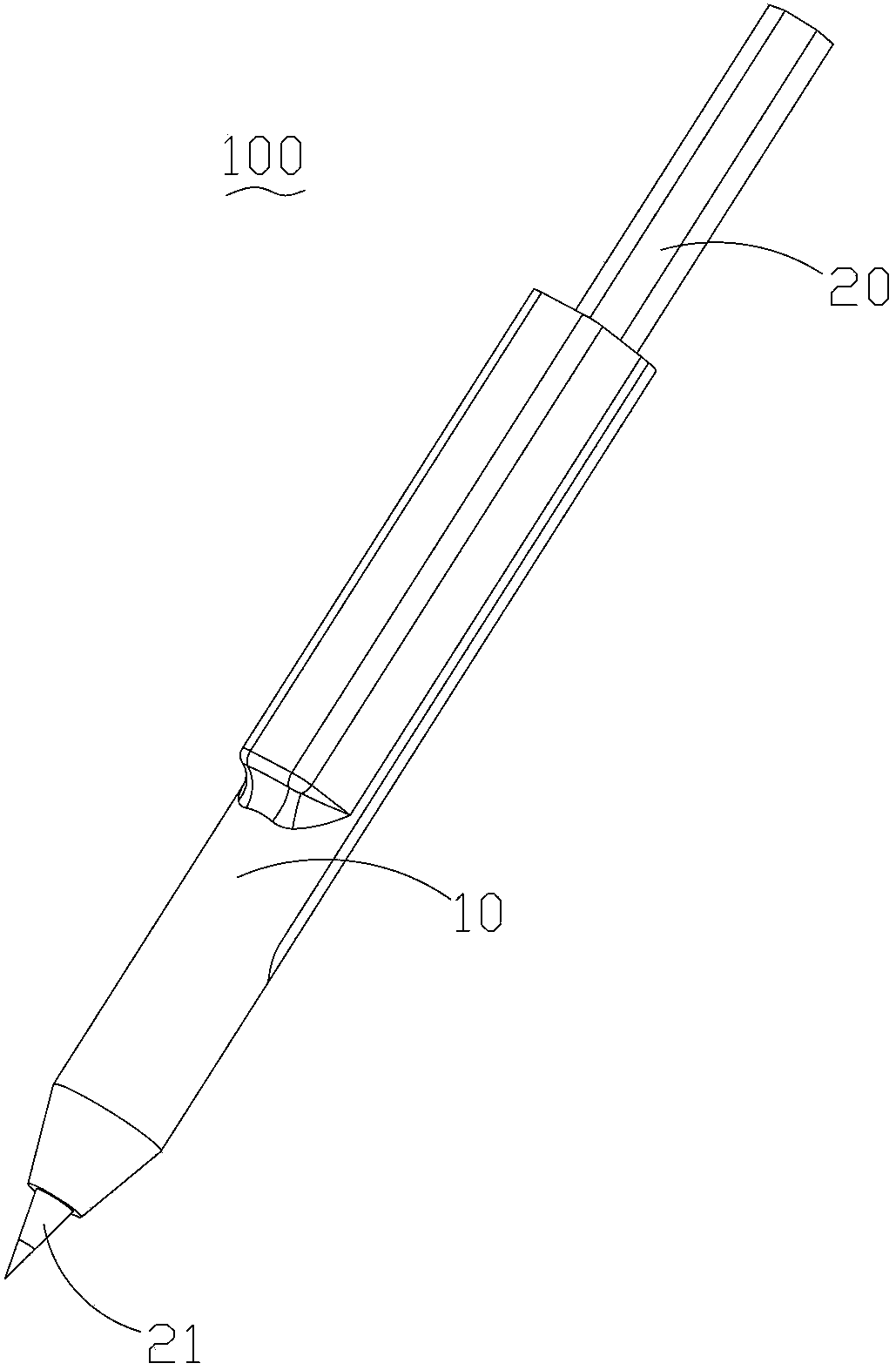

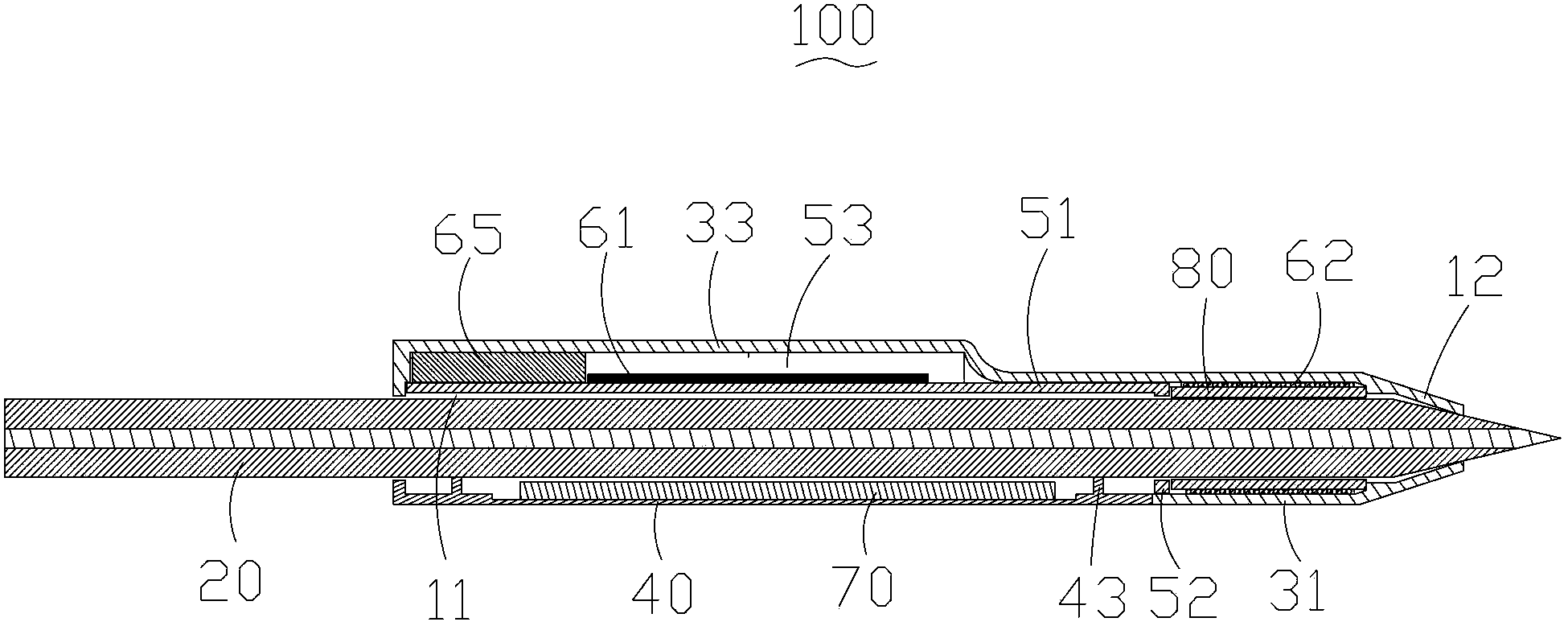

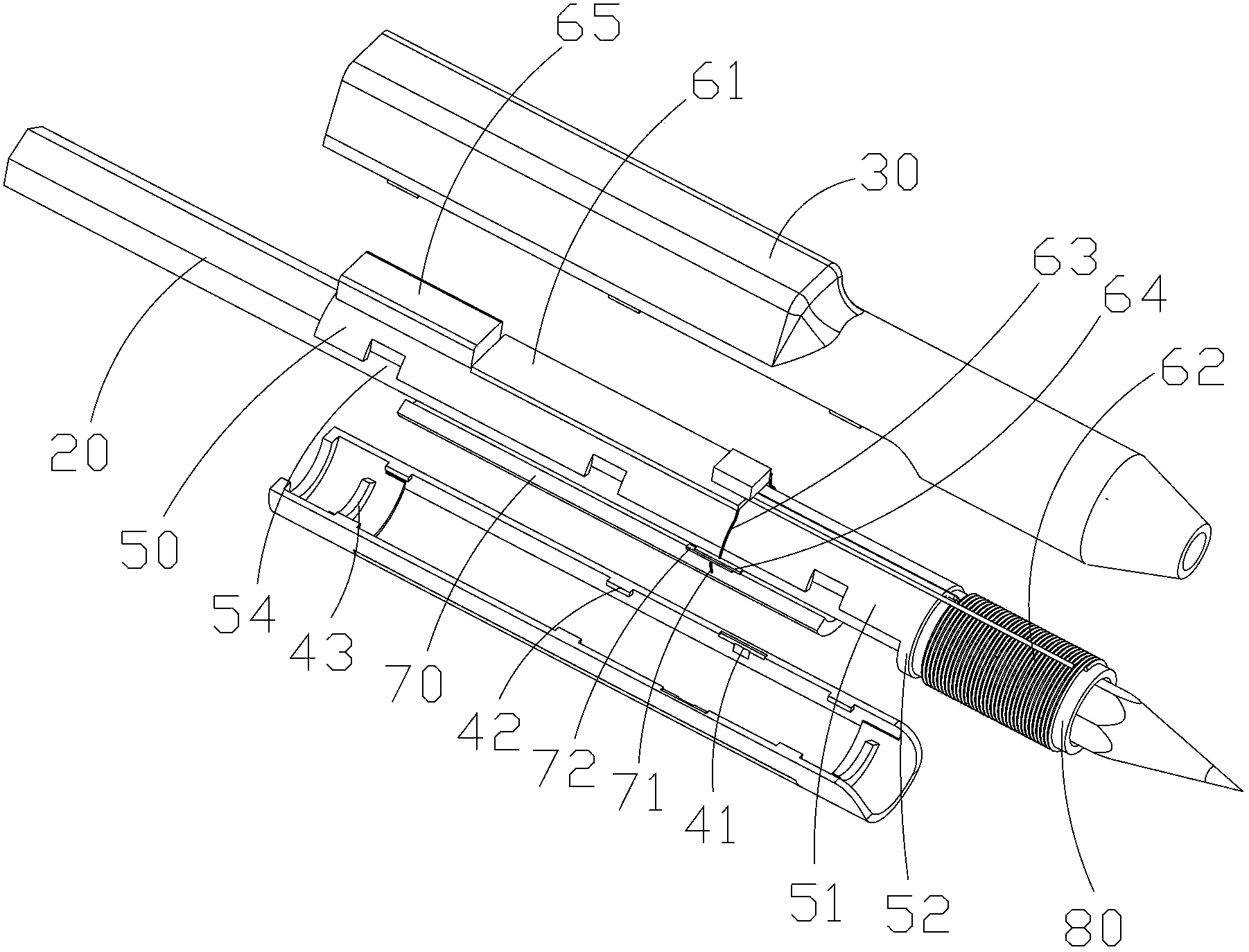

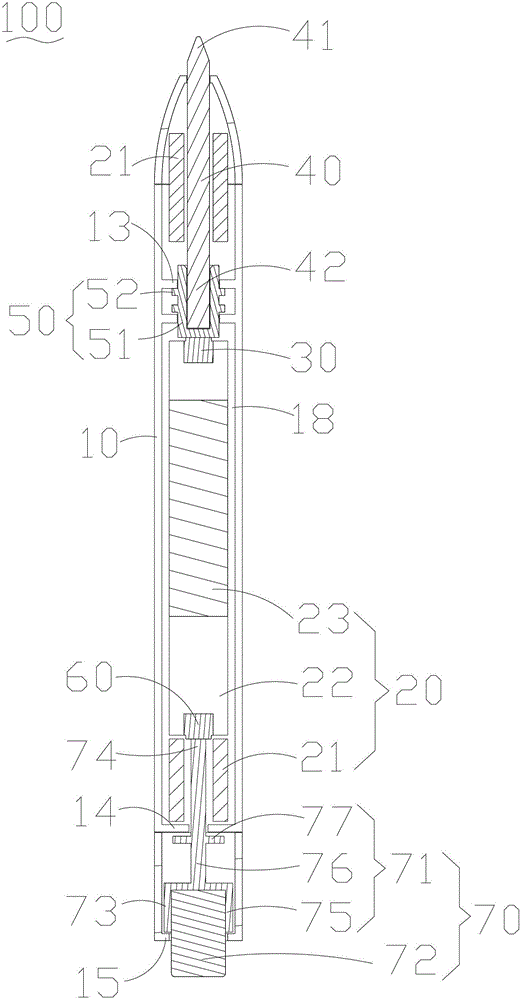

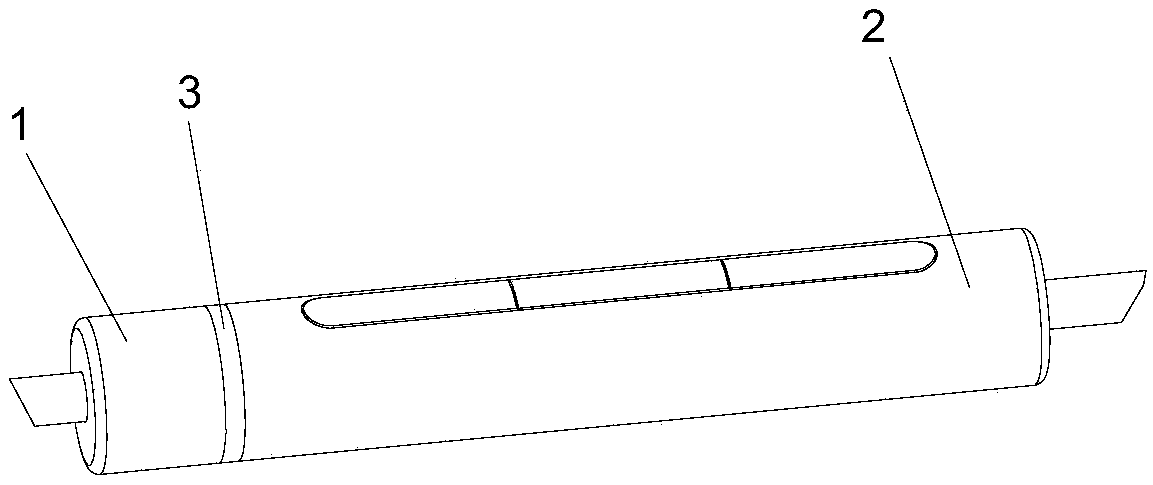

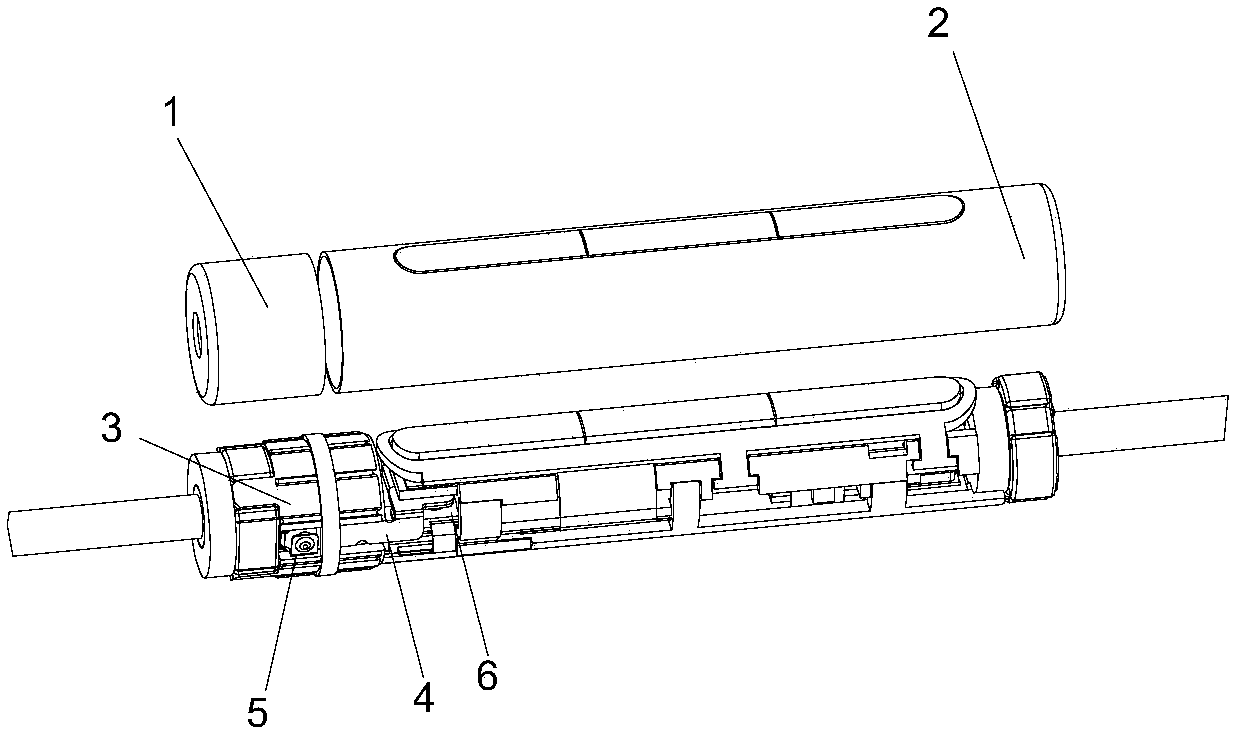

Point-reading pen

The invention provides a point-reading pen. The point-reading pen comprises: a penholder; a resonance circuit disposed inside the penholder; a trigger member disposed inside the penholder; and a pen core which is arranged on a nib portion of the penholder and is used for making the trigger member to move to trigger the resonance circuit. The pen core is provided with a writing nib and a fixed end portion, wherein the writing nib allows handwriting to be kept and can be clicked, and the fixed end portion is opposite to the writing nib. When a user clicks the writing nib, the trigger member is instantly triggered, and when the user is using the writing nib for writing, the trigger member is triggered continuously. The point-reading pen further comprises an elastic fixing member clamped inside the penholder. The fixed end portion of the pen core is detachably embedded inside the elastic fixing member in an elastic manner. When the writing nib of the pen core is pressed, the elastic fixing member deforms elastically to allow pressure to be acted on the trigger member. The point-reading pen can be clicked, can be used for writing, has the pen core that is replaceable, and enables signal transmission to be realized between writing movement and a point-reading machine.

Owner:GUANGDONG XIAOTIANCAI TECH CO LTD

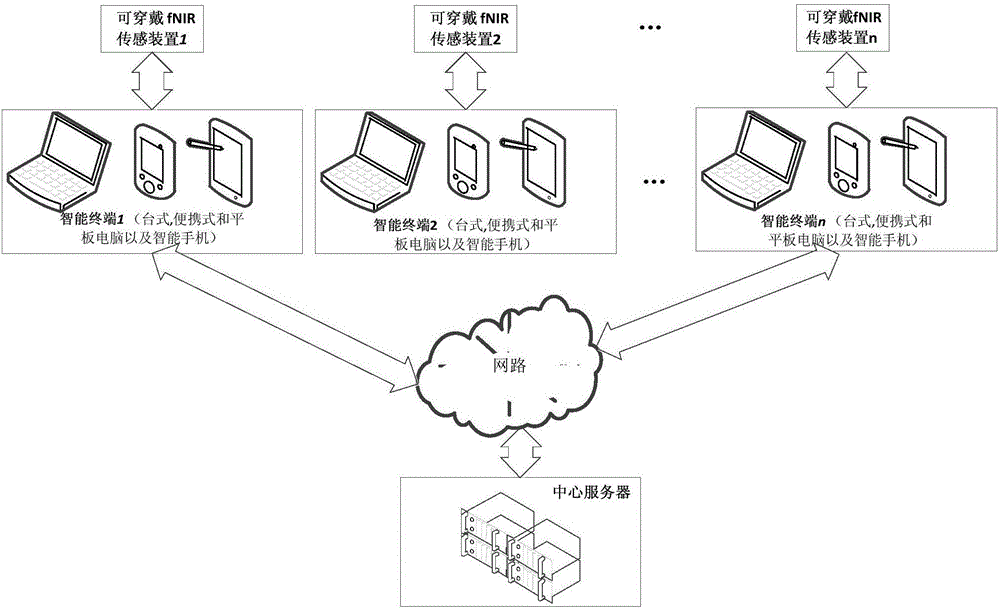

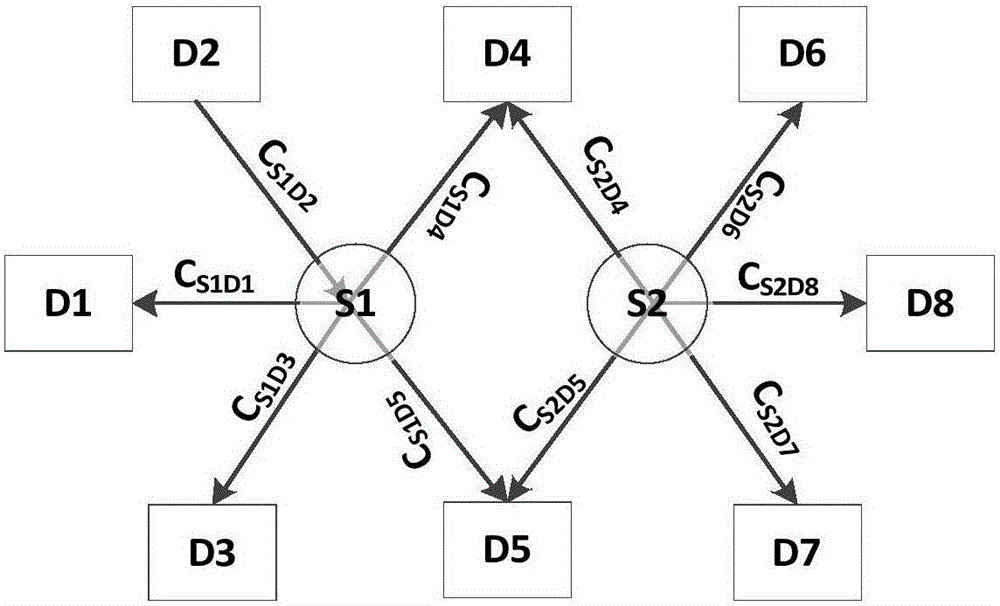

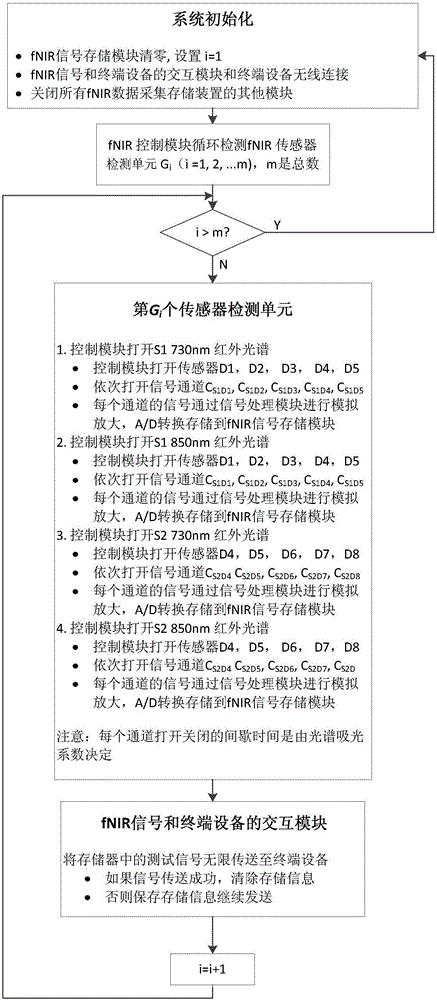

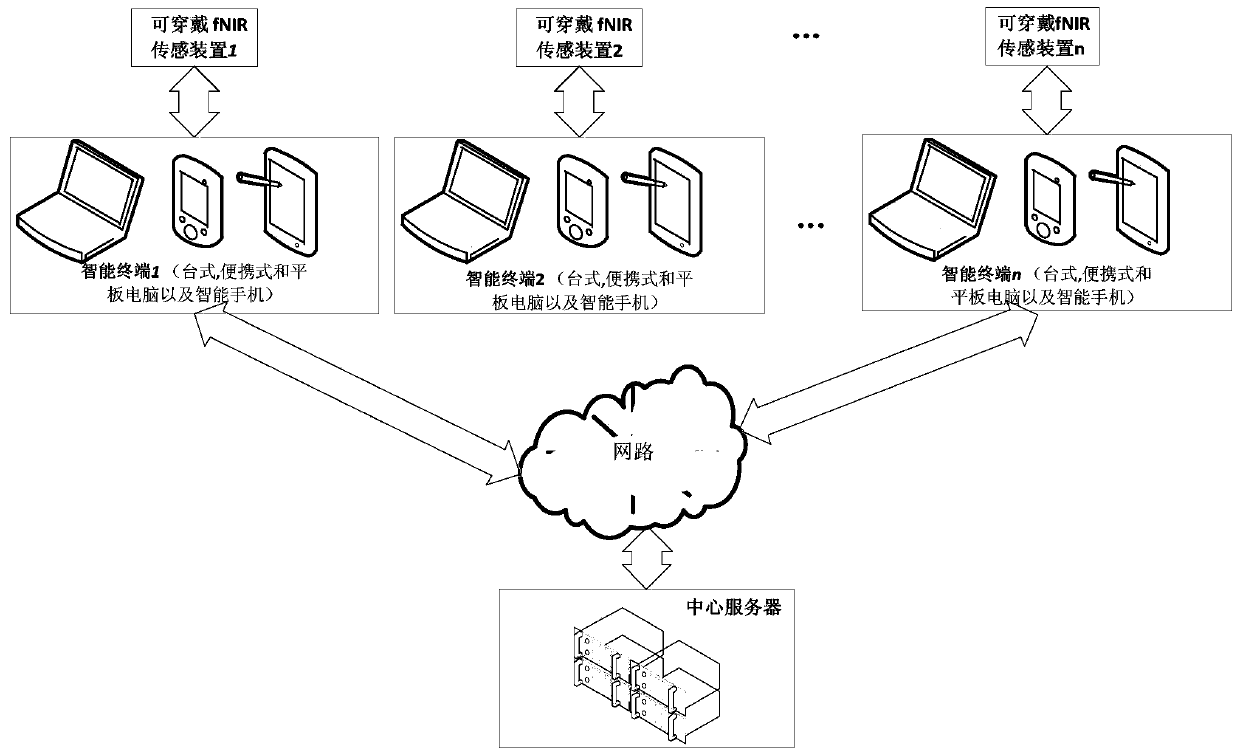

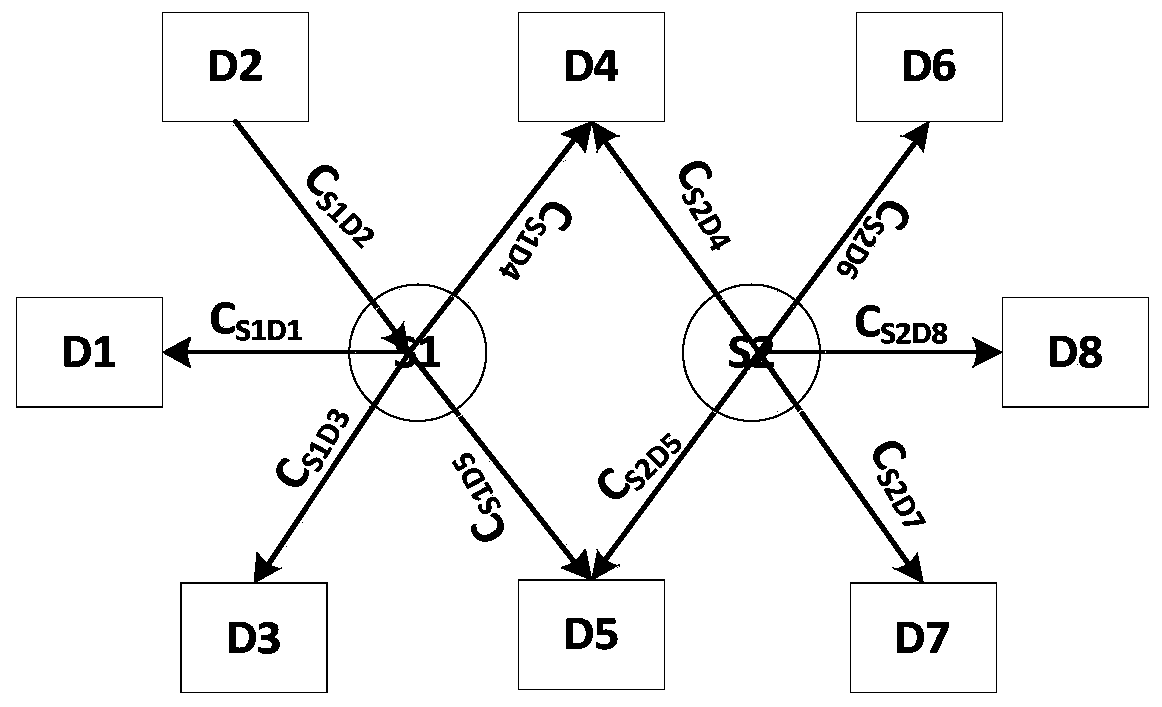

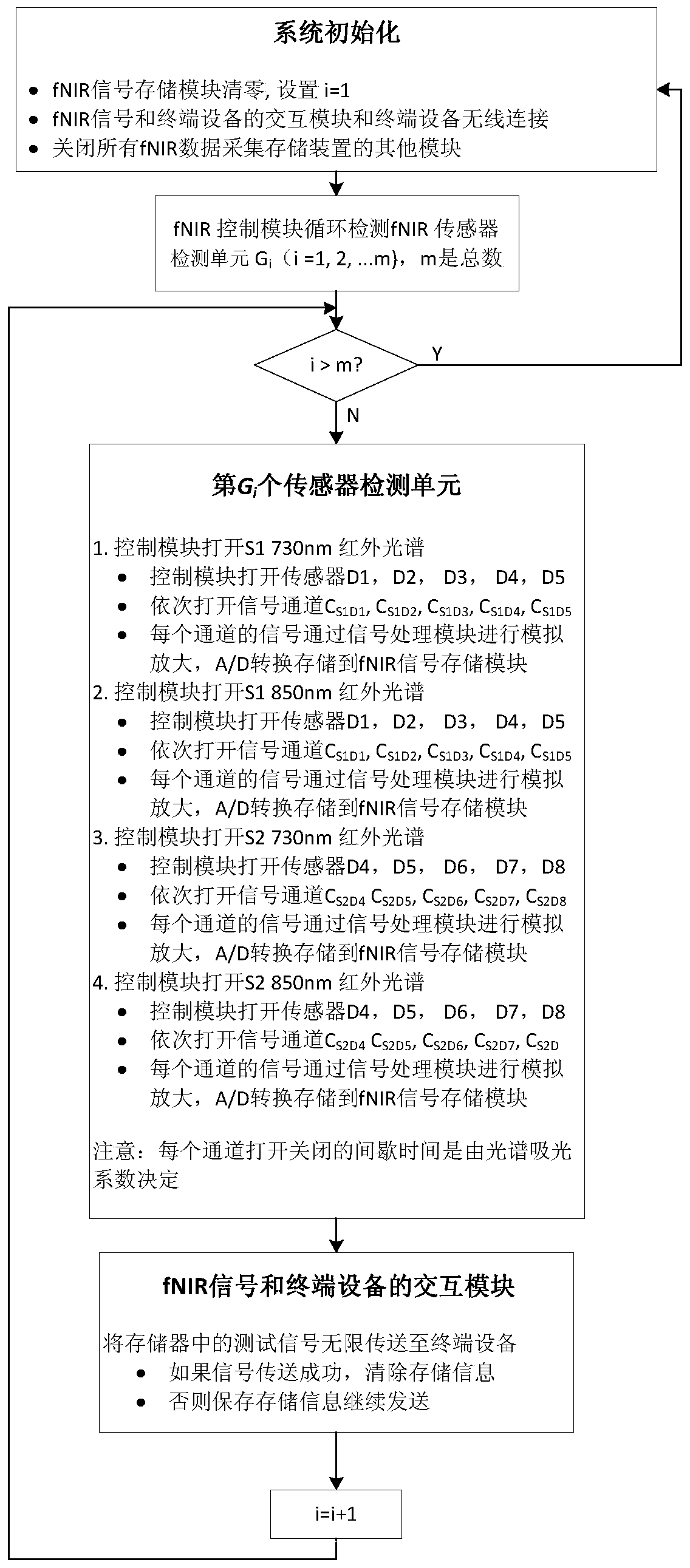

System and method for concentration detection and training based on functional near infrared spectrum technologies

InactiveCN106805985ARegulatory intelligenceSensitive Accurate Response MappingSensorsPsychotechnic devicesSignal onTerminal equipment

The invention discloses a system and method for concentration detection and training based on functional near infrared spectrum technologies. The system comprises a wearable fNIR sensing device and an intelligent terminal; a fNIR control module in the wearable fNIR sensing device controls switching-on, switching-off and spectral wavelength of a signal emission source in a fNIR signal emission module, switching-on and switching-off of a sensor in a fNIR signal collection module as well as opening and closing of signal channels, and near infrared spectrum signals on each signal channel under different spectrum lengths are collected cyclically and transmitted to the intelligent terminal; and the terminal equipment uses a built-in concentration analysis module to transform the near infrared spectrum signals into hemoglobin content information in real time and then quantify the information into a concentration index.

Owner:魏伟

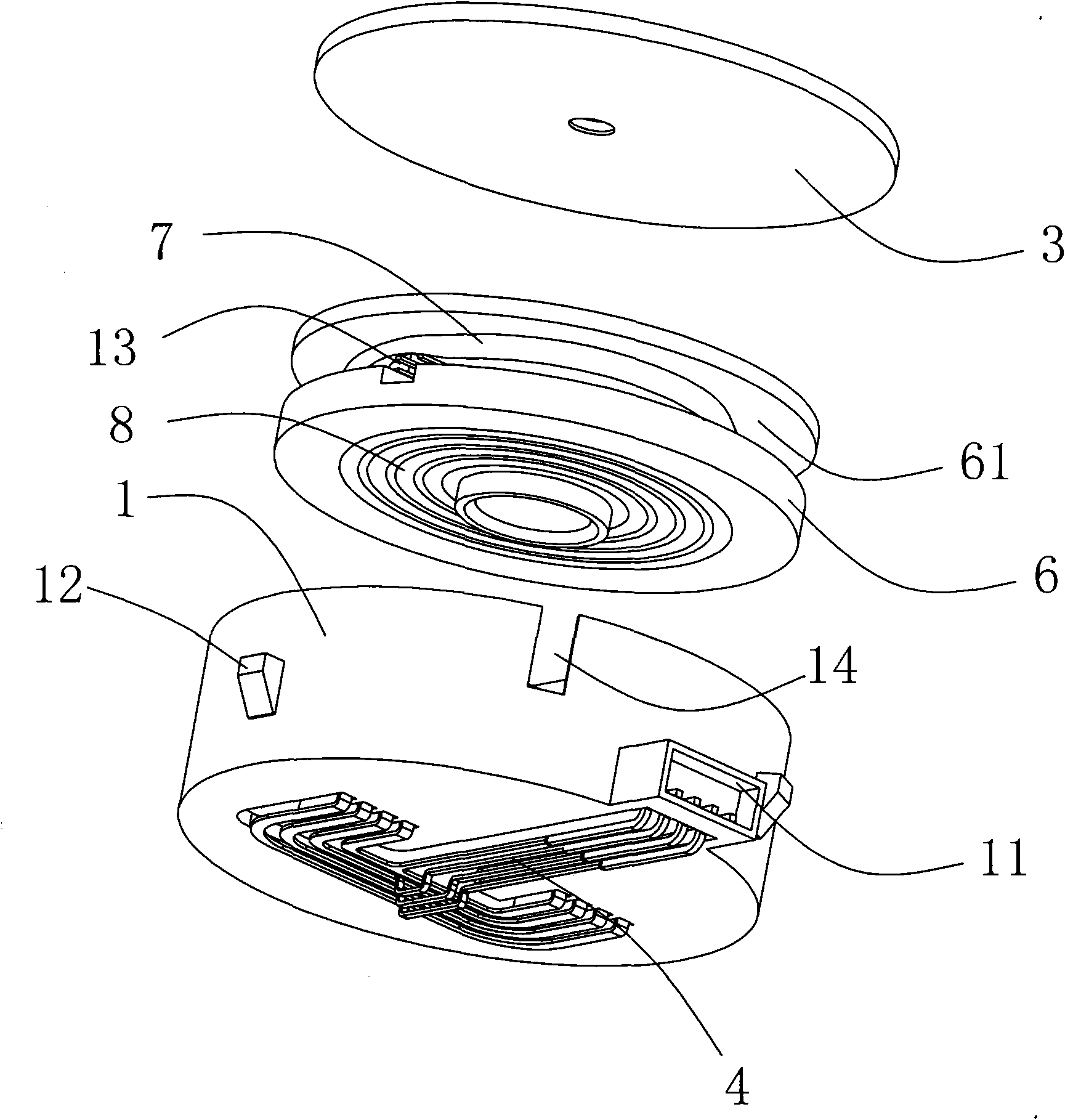

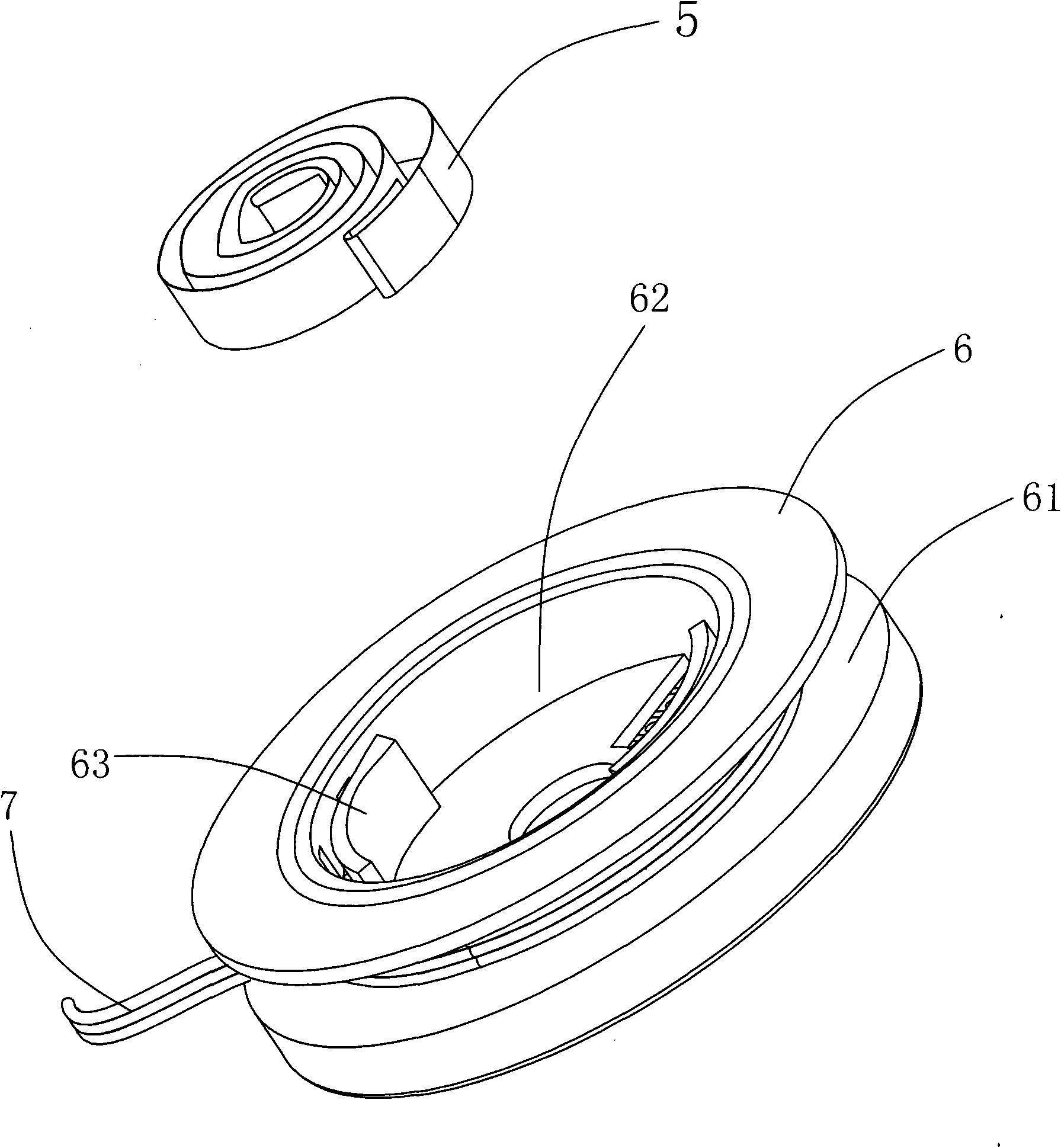

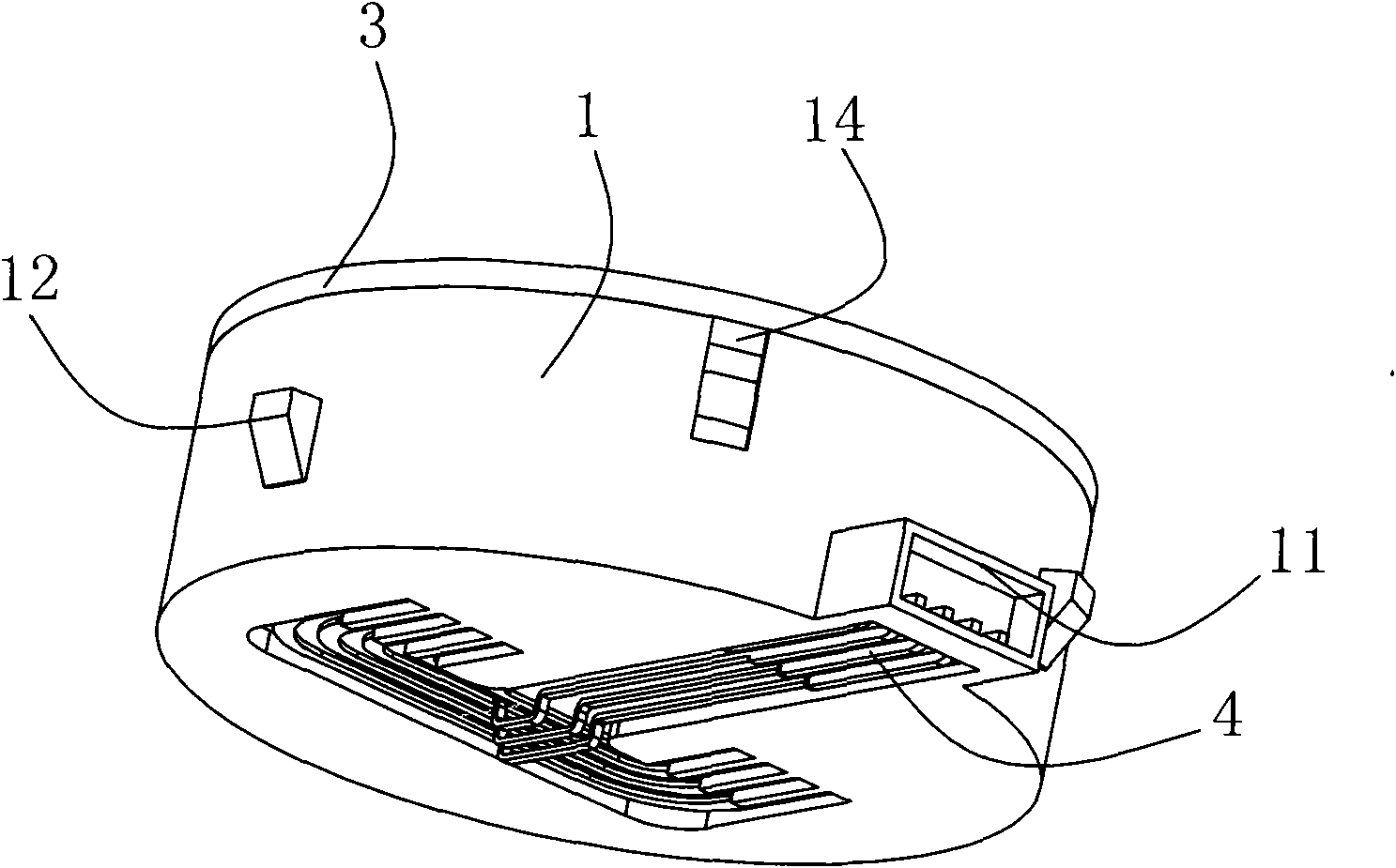

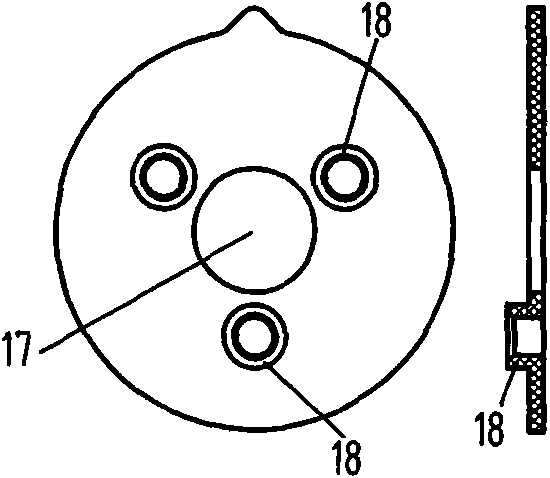

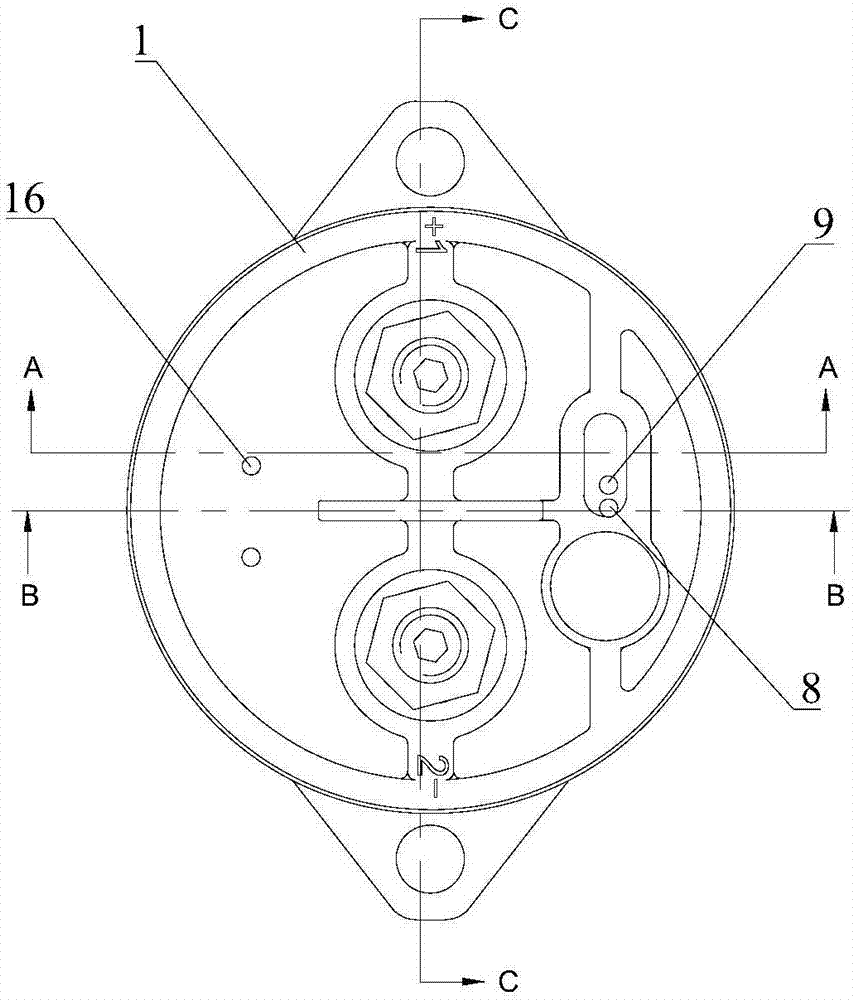

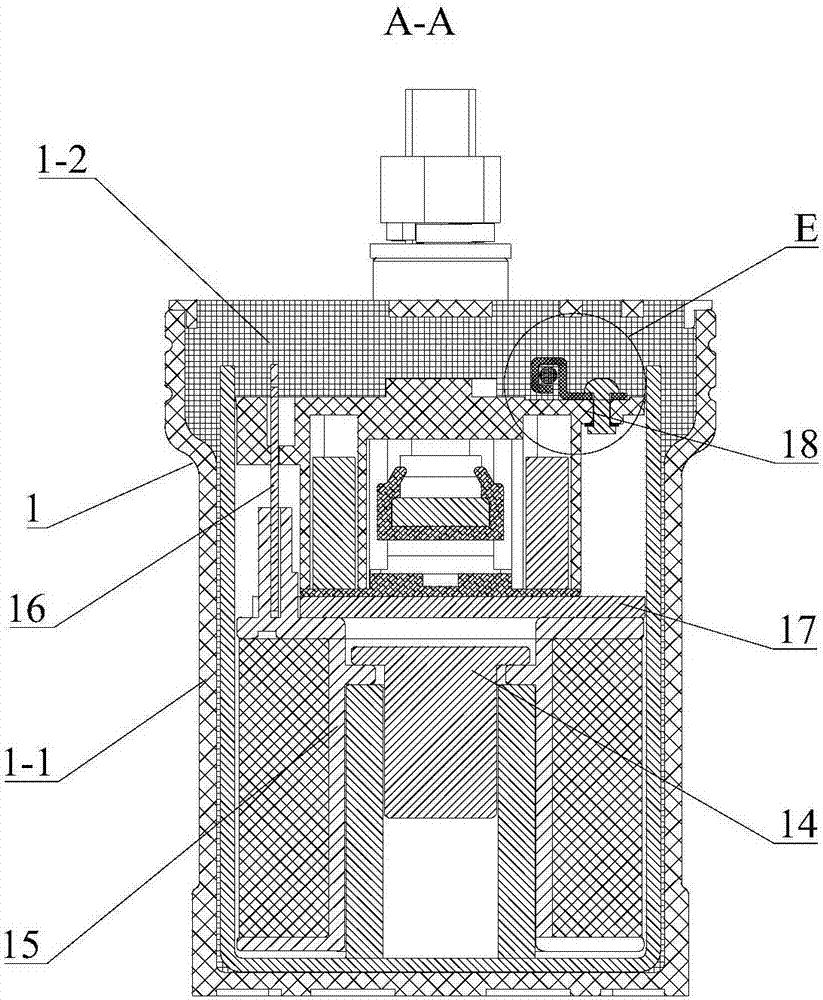

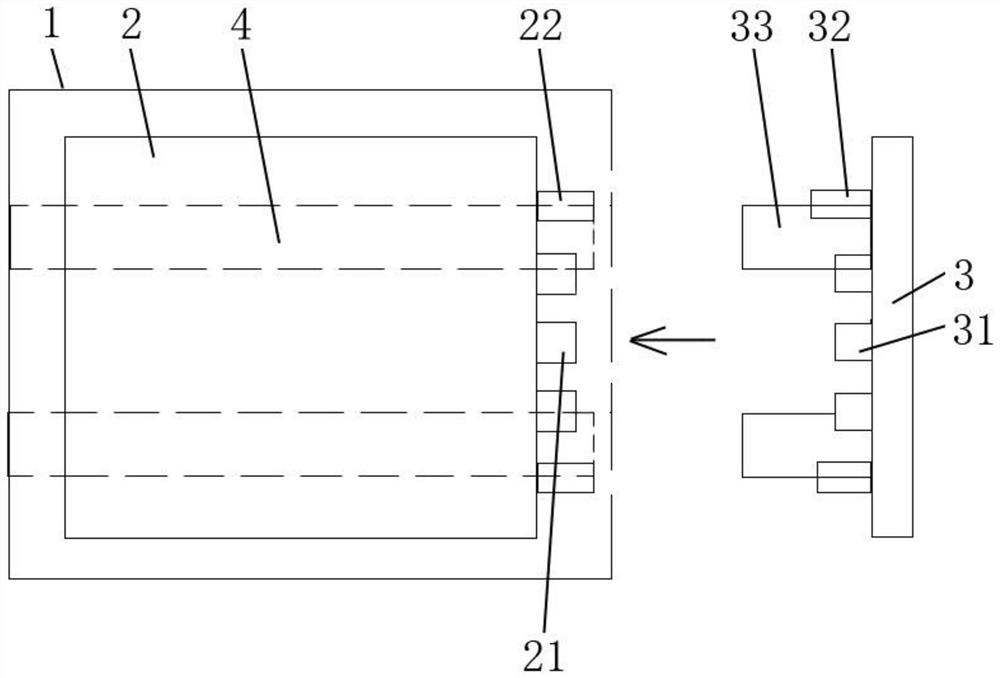

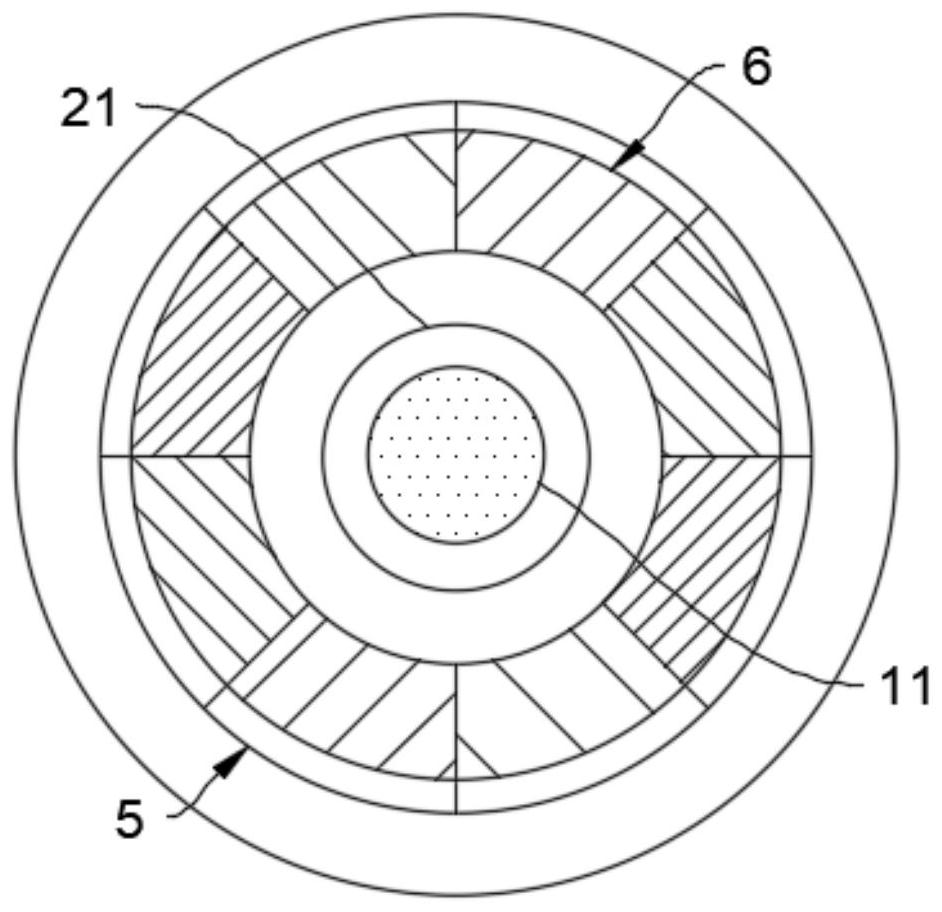

Signal adapter

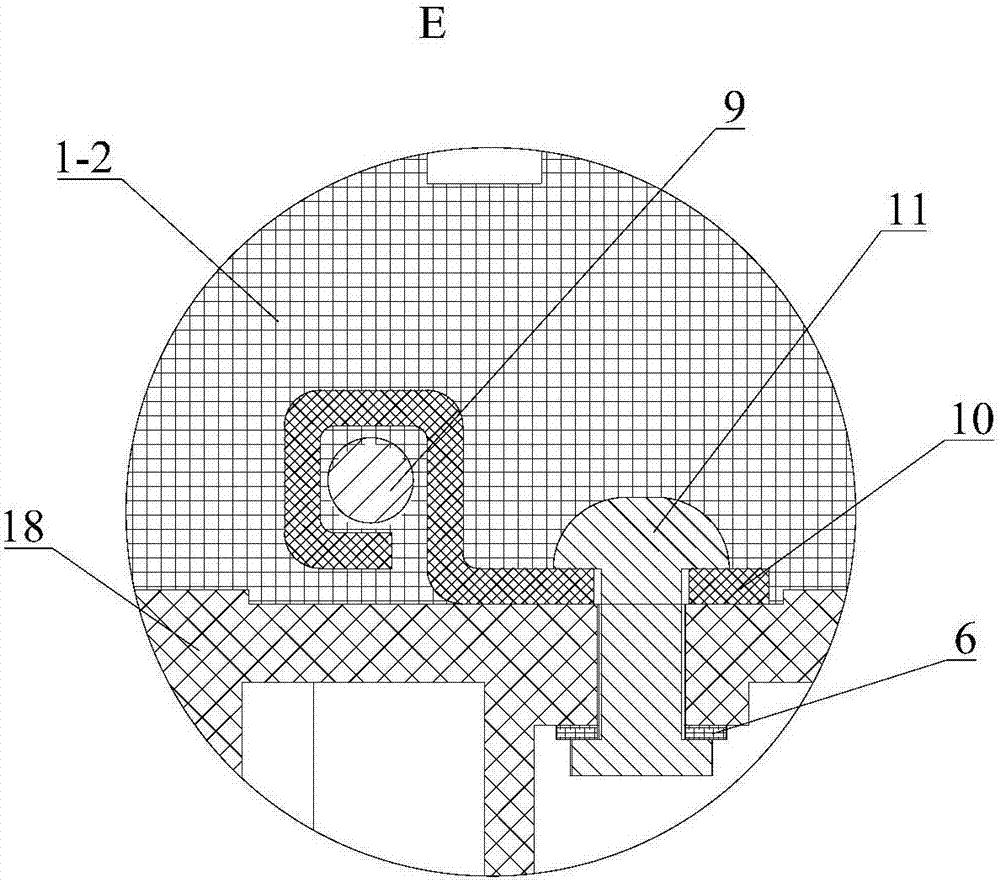

InactiveCN101615743ASimple structureSmall footprintRotary current collectorFlexible lead accommodationContactorStator

The invention relates to a signal adapter, which consists of a stator and an inner rotor formed by a base arranged in the stator, and an upper cover. The rotor realizes rotation by adopting the elastic force of a coil spring arranged in the rotor and fixed on the stator, and drives a signal transmission line wound on the outer edge of a rotating wheel to recover so as to achieve the function of automatically recovering the signal transmission line. Because a plane combining the bottom of the stator and the bottom of the rotor is provided with a first signal contactor and a second signal contactor capable of transmitting signals between the stator and the rotor, and by the first signal contactor, the second signal contactor, and the signal transmission line, signals in remote distance can be transmitted to the stator, and the signals of the stator can be transmitted remote distance to meet the requirement of people on signal remote transmission. Compared with the prior art, the signal adapter has the characteristics of simple structure and small occupied space, and is suitable for the requirement of large and small space.

Owner:吴茂庭

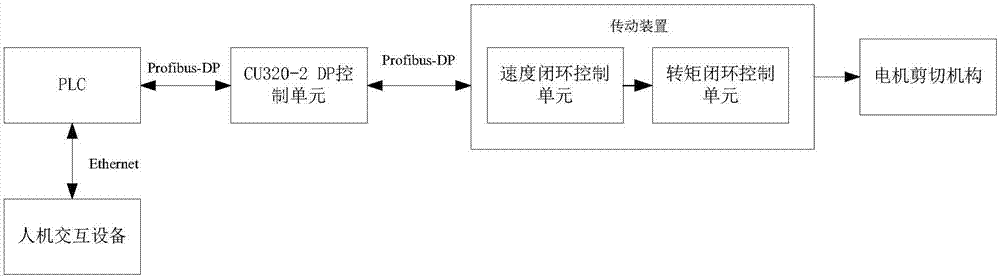

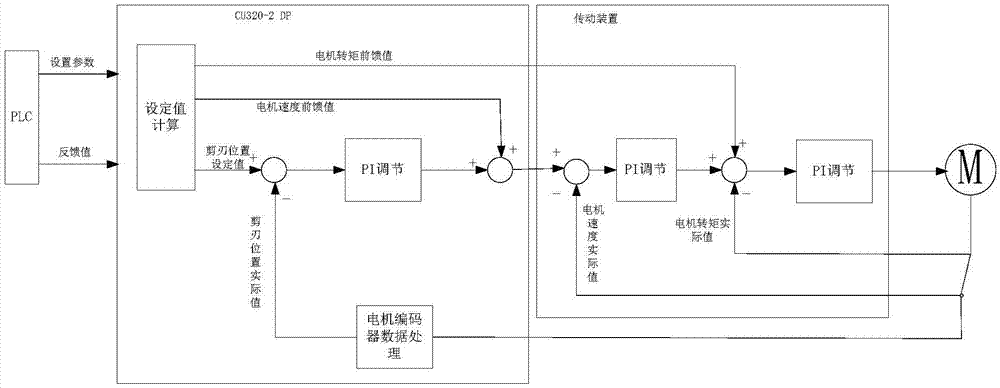

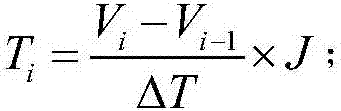

Flying shear controlling system and method

PendingCN107570786AAchieve smooth motionImprove performanceRoll mill control devicesStock shearing machinesMotor speedLoop control

The invention discloses a flying shear controlling system and method. The flying shear controlling system comprises a PLC and a CU320-2DP controlling unit which serves as a position closed loop controlling unit; the PLC is connected with the CU320-2DP controlling unit; the CU320-2DP controlling unit is connected with a transmission device, and the PLC generates a shear blade target position value,a shear blade maximum speed value and a shear blade maximum acceleration value; the CU320-2DP controlling unit calculates a shear blade position setting value, a motor speed setting value and a motortorque feedforward value and conducts position closed-loop controlling according to the shear blade position setting value and a shear blade position actual value, and the motor speed setting value is obtained by adding a motor speed compensation value and a motor speed feedforward value and is sent to the transmission device for speed closed-loop controlling; and the motor torque feedforward value is sent to the transmission device for torque closed-loop controlling. According to the flying shear controlling system and method, the CU320-2DP controlling unit is used as a controlling core, andthe flying shear controlling system and method have the beneficial effects of being low in cost, wide in applicability and high in performance.

Owner:YANGCHUN NEW STEEL CO LTD

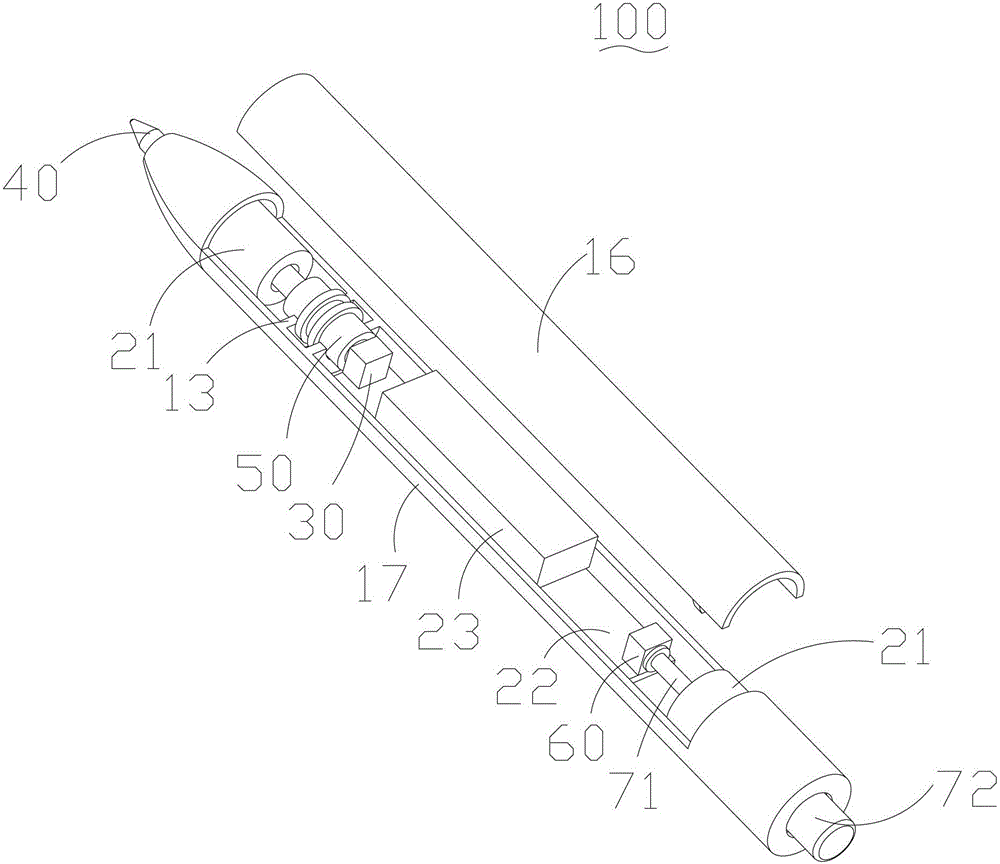

Touch and talk pen and pen cap thereof

ActiveCN103631398AGet the most out of writingImplement signalingWriting implementsInput/output processes for data processingEngineeringResonance signal

The invention provides a pen cap of a touch and talk pen. The pen cap of the touch and talk pen is used for accommodating and positioning a writing pen holder which is used in daily life. The pen cap comprises an upper cover and a lower cover which is made of soft materials, the lower cover slides in the axial direction of the pen cap to be buckled to the upper cover, and an accommodating cavity for the pen holder to be inserted into is formed by the lower cover and the upper cover jointly. The pen cap further comprises a positioning sleeve, a resonance circuit and a trigger device, wherein the positioning sleeve is arranged in the accommodating cavity and is used for clamping the pen holder together with the lower cover when the upper cover and the lower cover are buckled to prevent the pen holder from being disengaged from the pen cap during wiring or clicking, the resonance circuit is arranged in the accommodating cavity, the trigger device is arranged in the lower cover, the trigger device is triggered by the deformation of the lower cover, and then the resonance circuit is triggered. When the pen holder is used for writing or clicking, the lower cover is held with a hand, the trigger device is triggered by the deformation of the lower cover, then the resonance circuit is triggered, resonance signals are generated by the resonance circuit, and then signal transmission is conducted between the pen cap and a touch and talk machine.

Owner:GUANGDONG XIAOTIANCAI TECH CO LTD

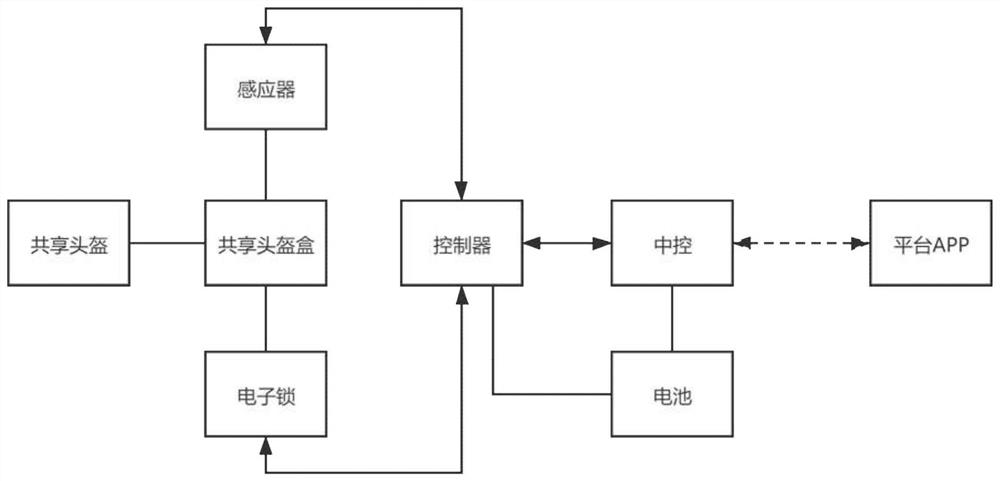

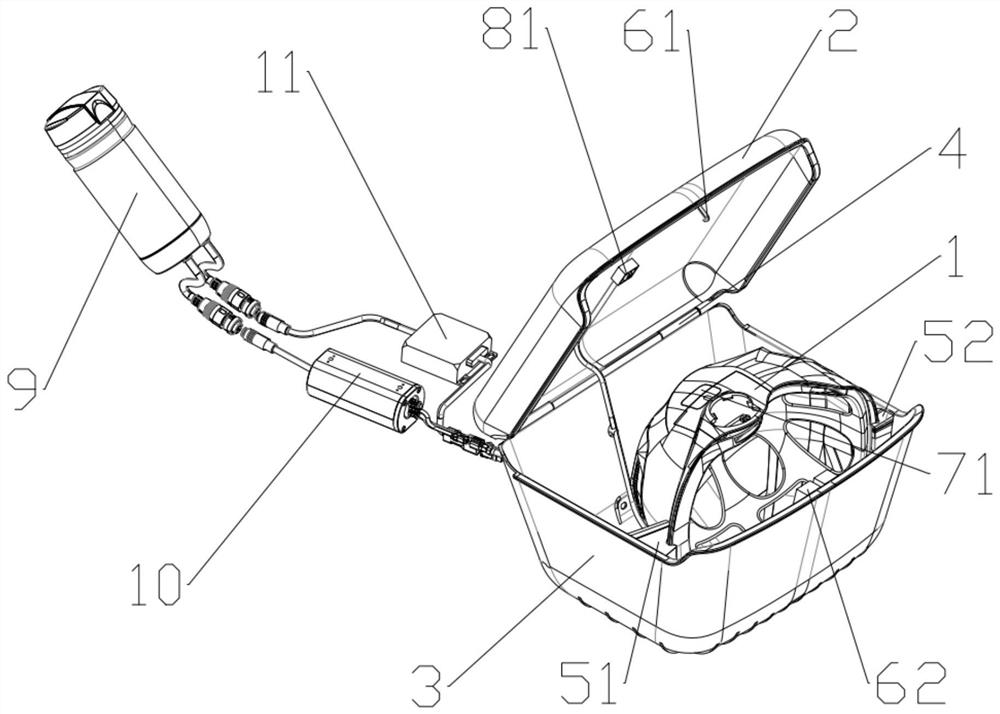

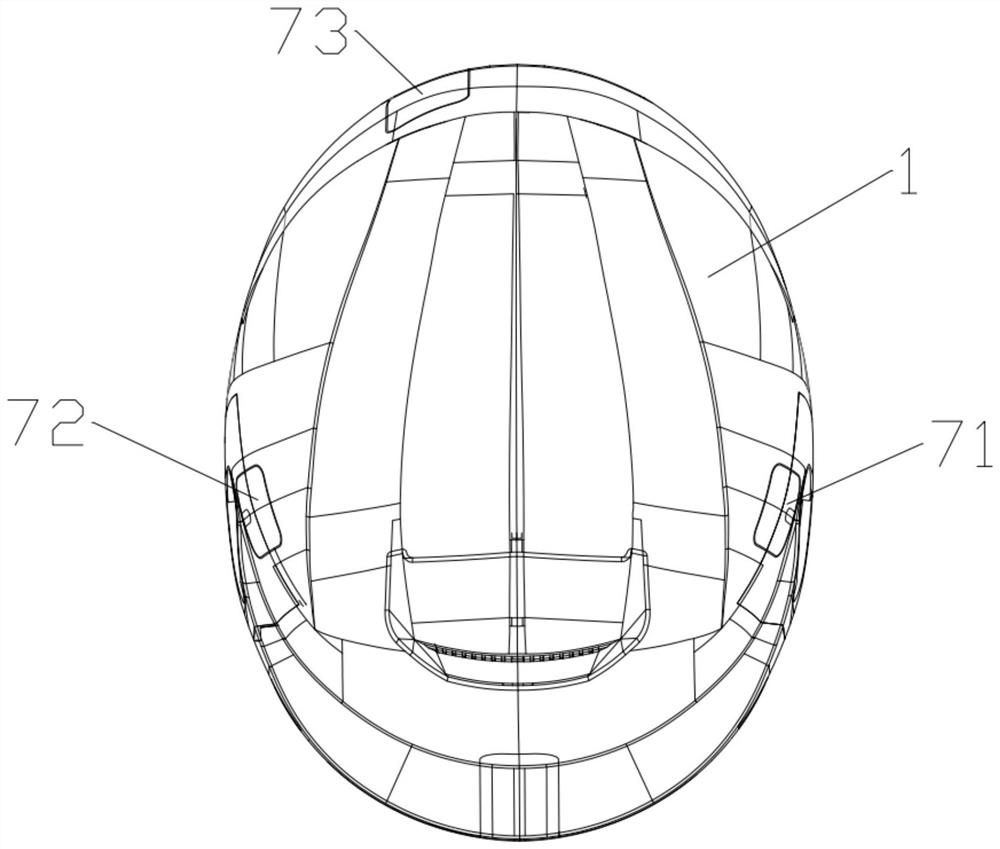

Helmet sharing system and using method thereof

InactiveCN112002071AImplement signalingShorten the timeApparatus for meter-controlled dispensingIndividual entry/exit registersComputer hardwareElectrical battery

The invention discloses a helmet sharing system and a using method thereof. The helmet sharing system comprises a shared helmet, a shared helmet box, a sensor, an electronic lock, a battery, a controller, a central controller and a platform APP, wherein the shared helmet box is used for accommodating the shared helmet; the sensor is arranged in the shared helmet box, is electrically connected withthe controller, and is used for detecting the taking and placing of helmets; the electronic lock is arranged on the shared helmet box, is electrically connected with the controller and is used for opening and closing the shared helmet box to achieve taking and returning of helmets; the controller is electrically connected with the central controller and used for transmitting signals to the central controller, the sensor and the electronic lock; and the central controller is used for transmitting and receiving signals to and from the platform APP, and transmitting signals with the controller.The helmet sharing system and the using method thereof provided by the invention can greatly improve the borrowing and returning efficiency of the shared helmet and the returning success rate and safety.

Owner:永祺(中国)车业股份有限公司

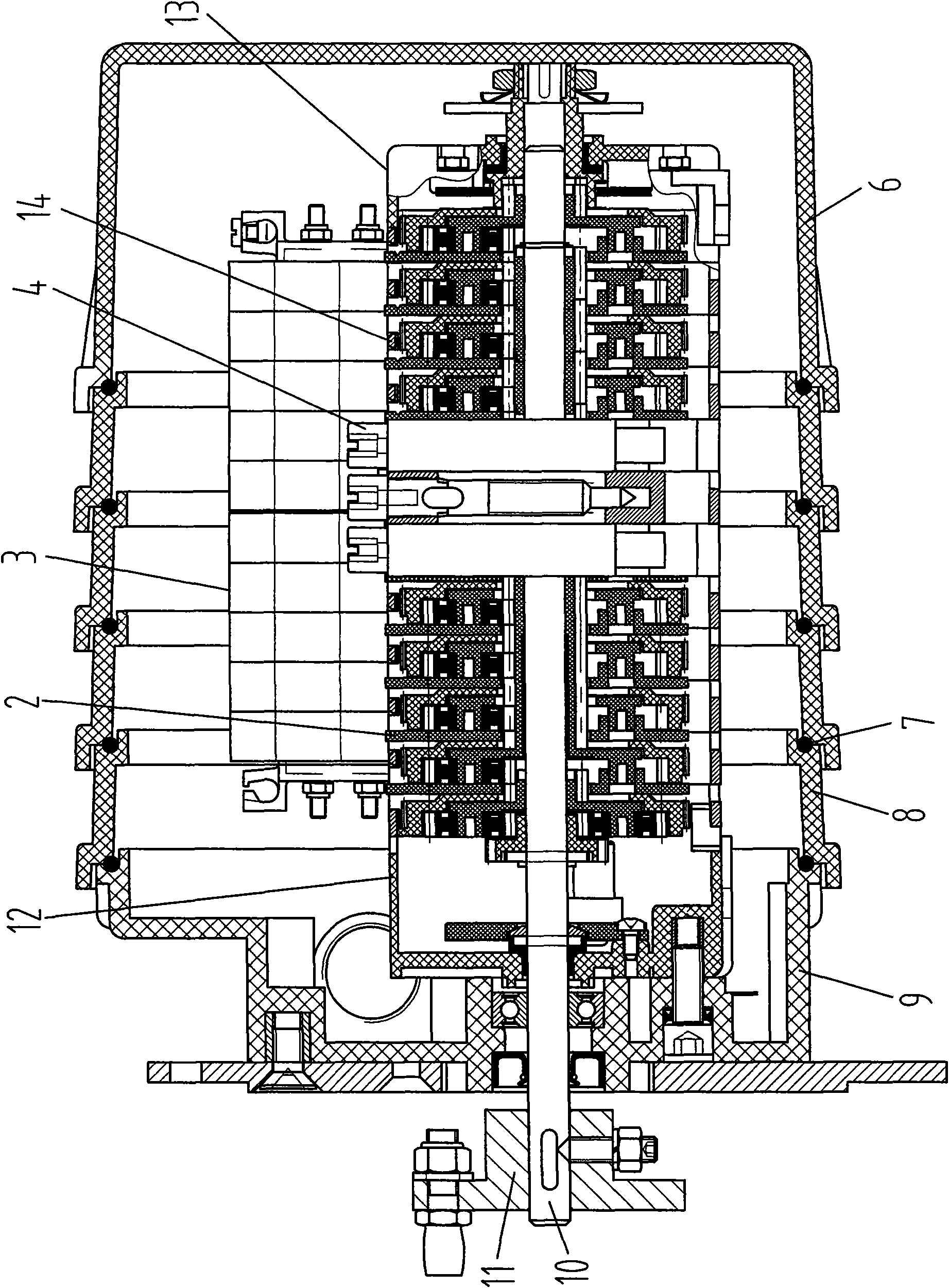

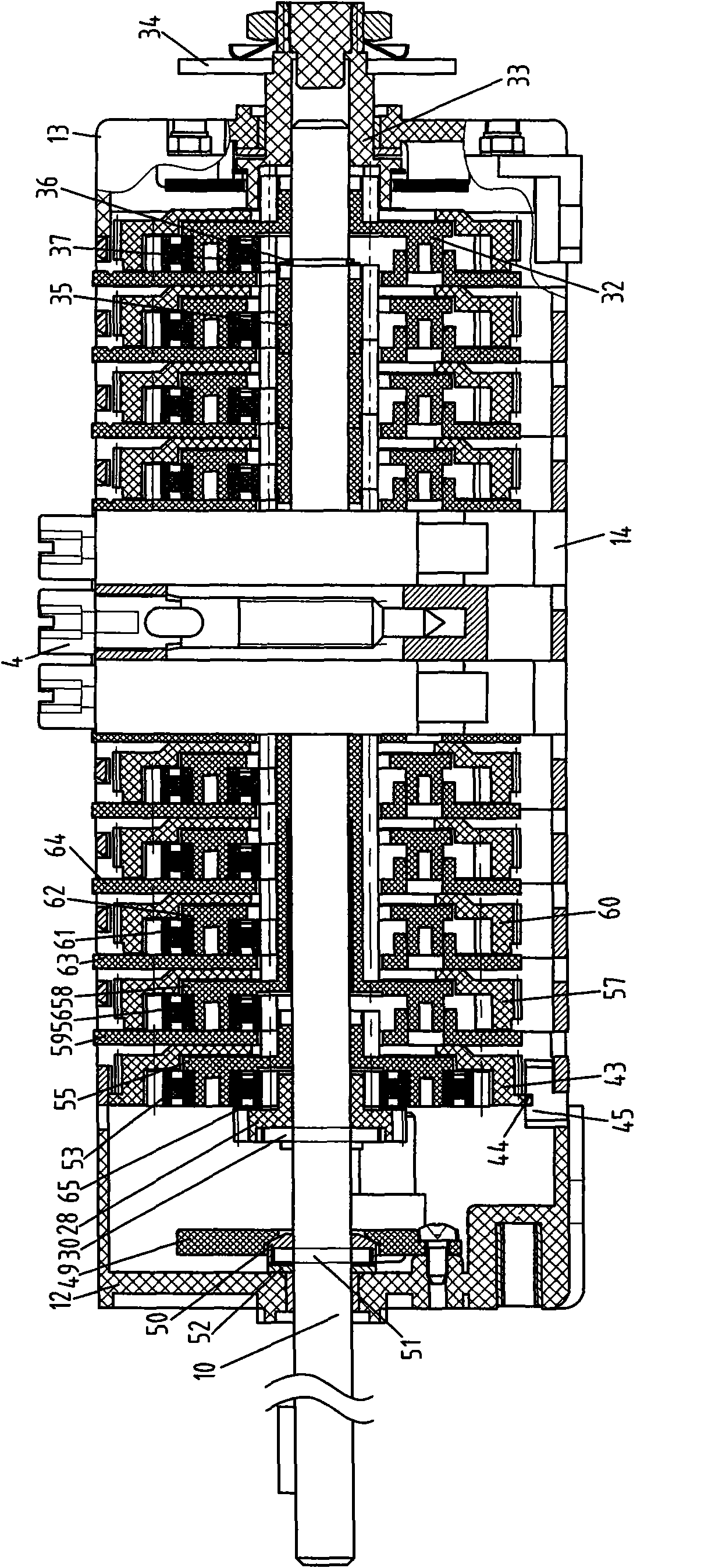

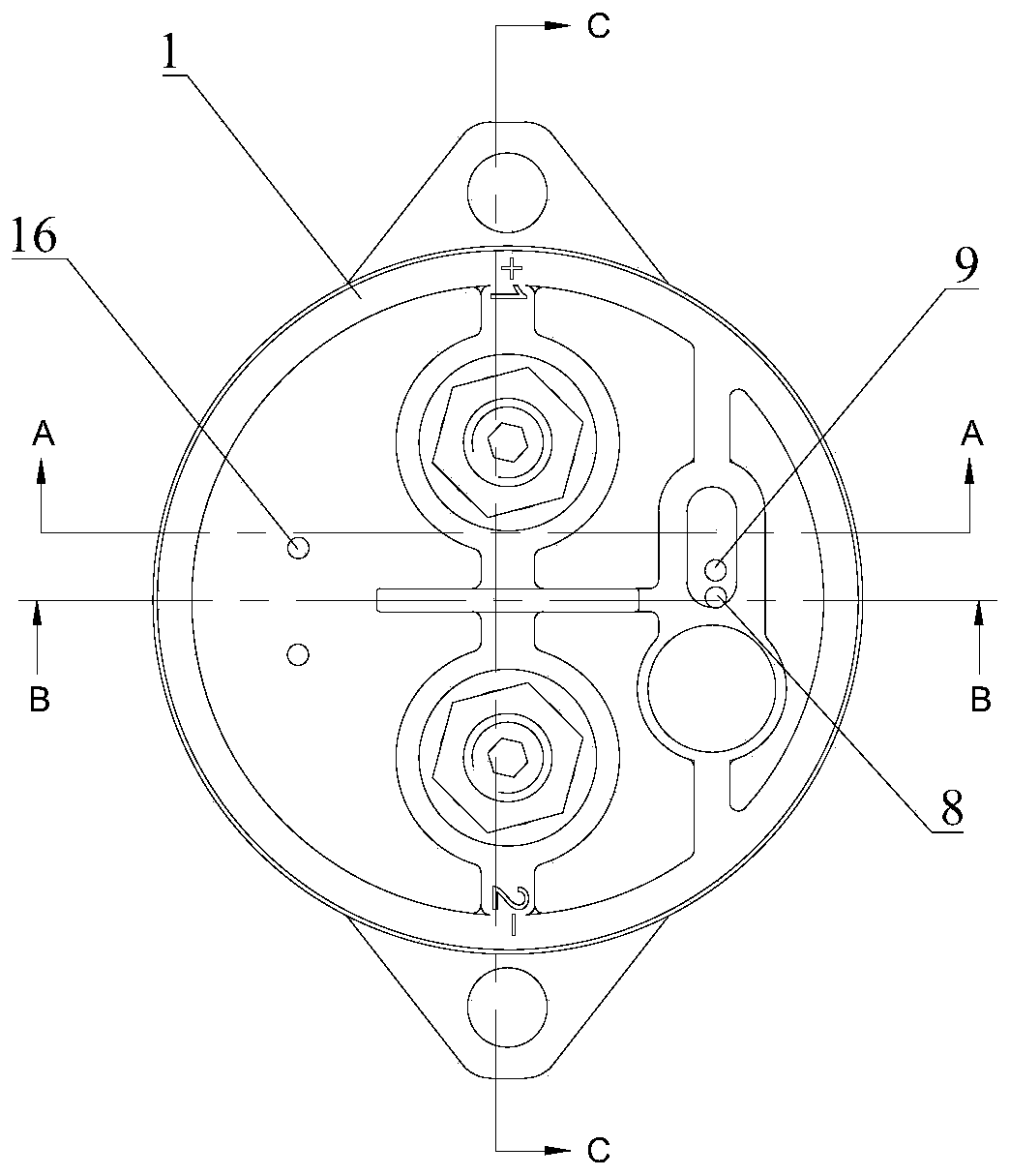

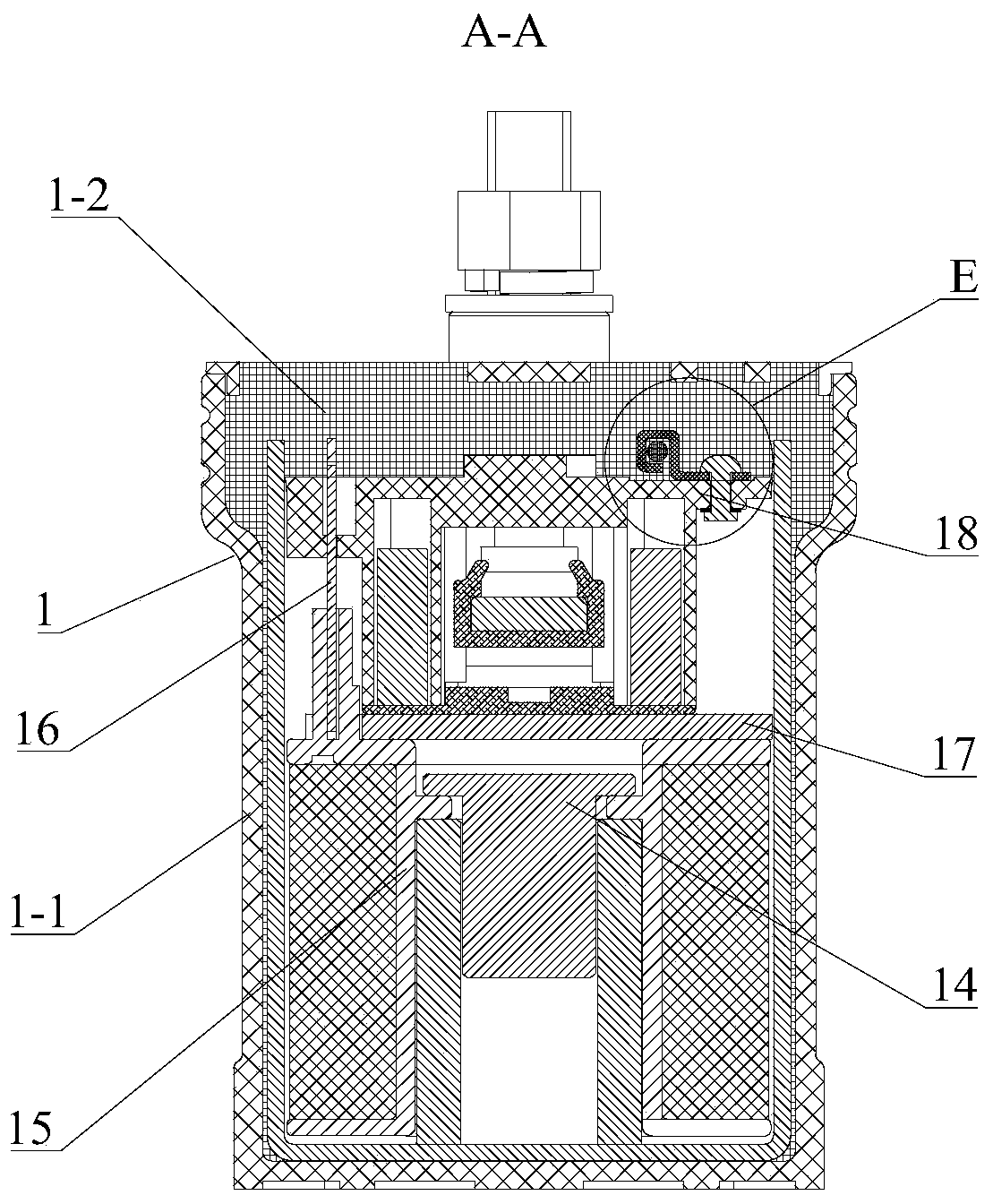

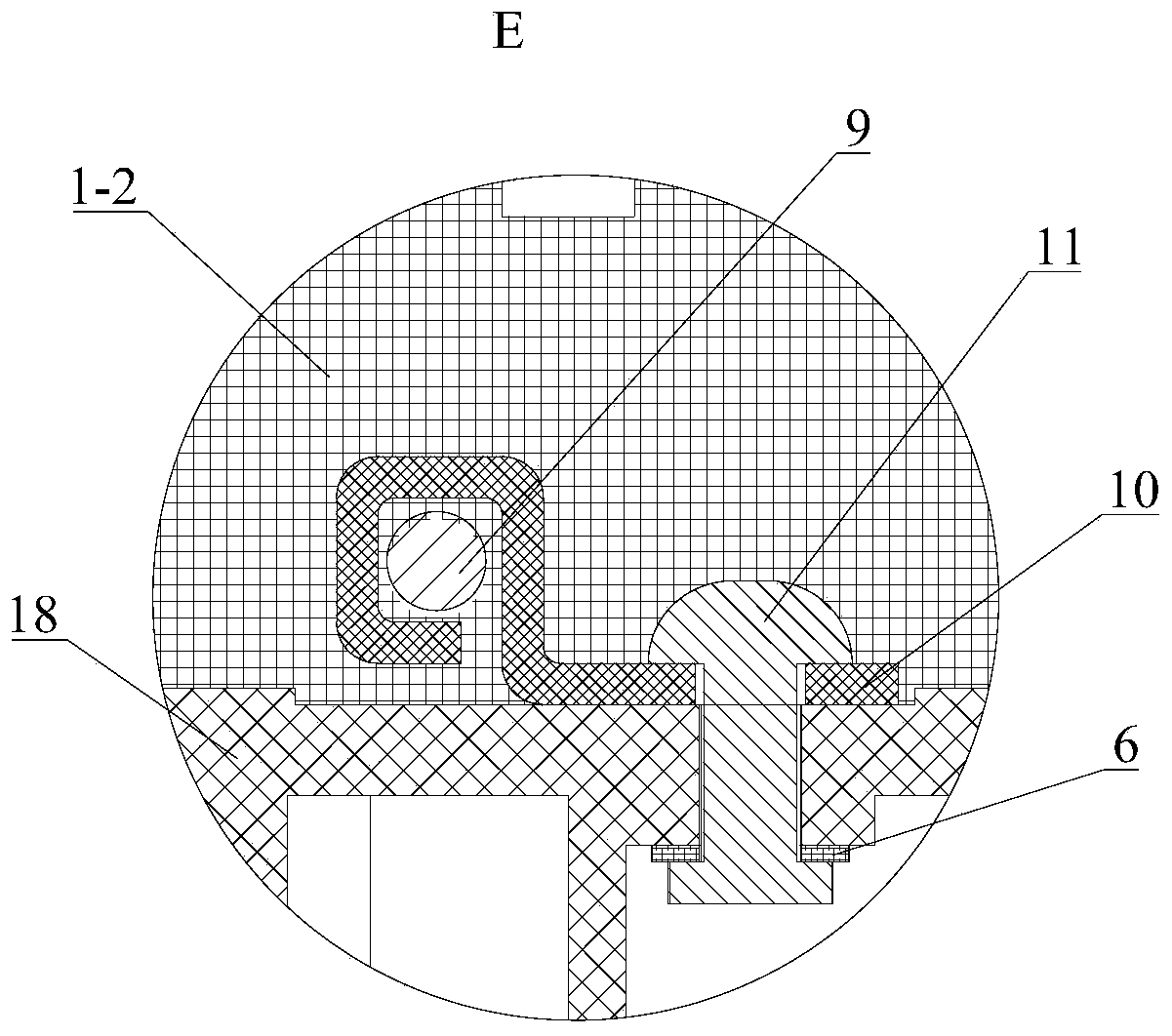

Cam limit switch

ActiveCN101604581AImplement signalingSolve the problem of single transmission ratioContact driving mechanismsDrive wheelRemote control

The invention relates to a cam limit switch, which comprises a shell, a driving wheel component arranged in the shell, a worm wheel adjusting component and a contact switch component, and is characterized in that the driving wheel component comprises a first drive-ratio gear component, a second drive-ratio gear component and a third drive-ratio gear component which use driving shafts, driving wheels, planet gears and rotating cams as structural units; the worm wheel adjusting component comprises a worm, a worm wheel, a planet gear meshed with the worm wheel and a rotating cam driven by the planet gear; and the rotating cam of the driving wheel component and an inching switch of the switch component are in movable contact to connect or disconnect an electrified circuit. The cam limit switch solves the problem that the prior cam limit switch has single drive ratio. The cams drive respective inching switch to perform signal transmission, can perform remote control of high-voltage electrical equipment, and are safe and reliable. The cam limit switch also adjusts the positions of the cams conveniently and is simple to maintain.

Owner:NINGBO WEILONG PORT MASCH CO LTD +1

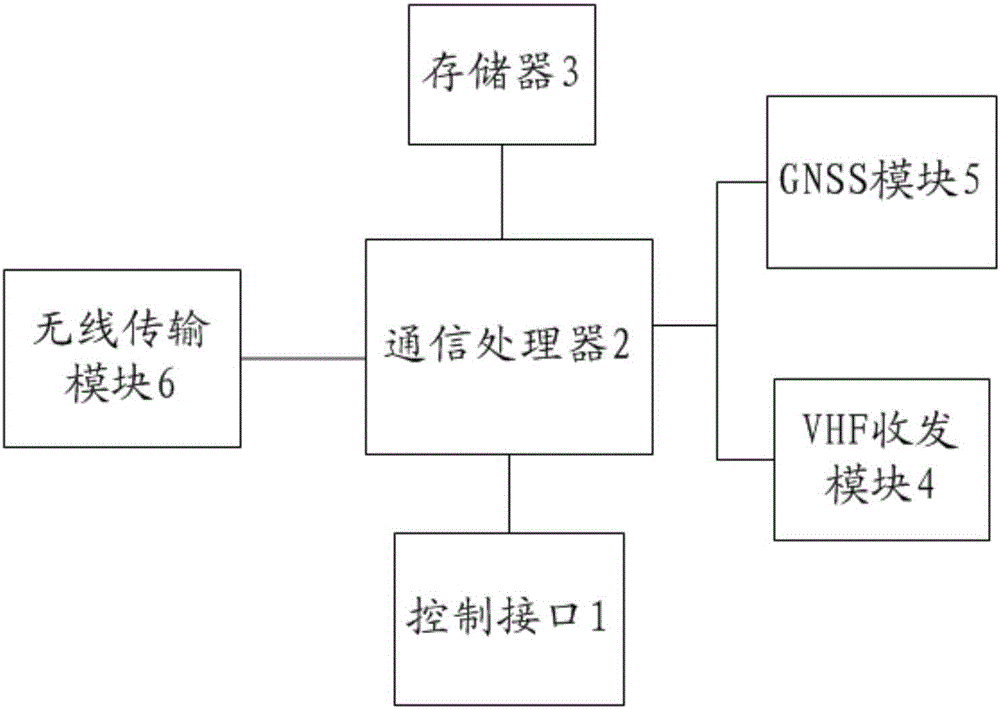

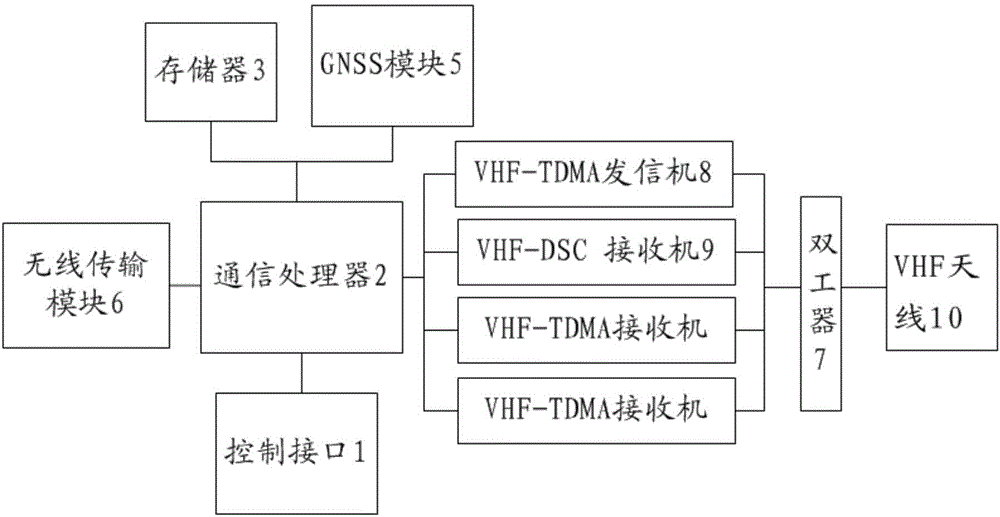

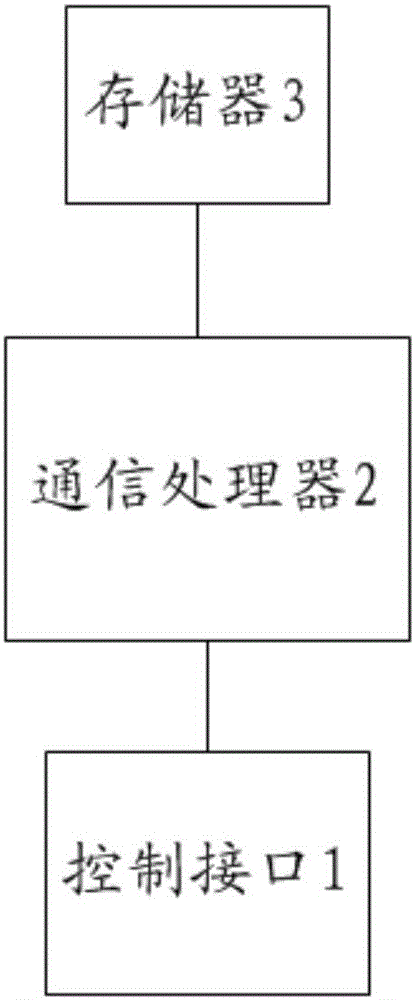

Wireless AIS base station

PendingCN106658764AEasy transferImplement signalingSatellite radio beaconingWireless communicationTransceiverWireless transmission

The invention provides a wireless AIS base station, relating to the technical field of ship communication. The wireless AIS base station comprises a communication processing system, an AIS system and a wireless transmission module; wherein the communication processing system comprises a control interface, a communication processor and a memory, which are connected in sequence, wherein the control interface is connected with a control device used for parameter setting and system debugging; the AIS system comprises a VHF transceiver module and a GNSS module, wherein the GNSS module and the VHF transceiver module are respectively connected with the communication processor; and the wireless transmission module is connected with the communication processor. The invention provides a wireless AIS base station, according to the invention, the wireless AIS base station receives and dispatches the VHF signals of other ships through the VHF transceiver module; and the VHF signals of other ships are performed encoding process by the communication processor to convert into AIS data which can be transfered by the wireless transmission module, so as to transmit to the corresponding center station equipment and realize the overall signal transmission and control.

Owner:广州嘉航通信科技有限公司

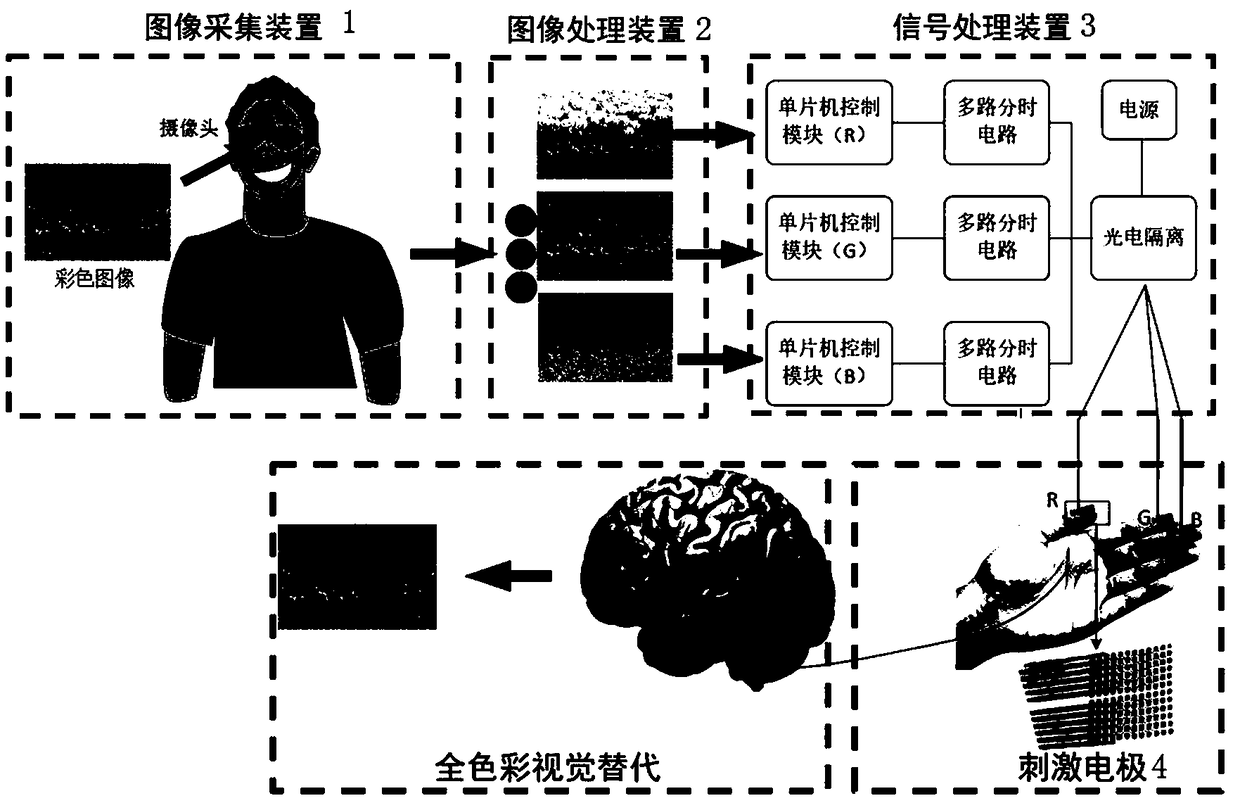

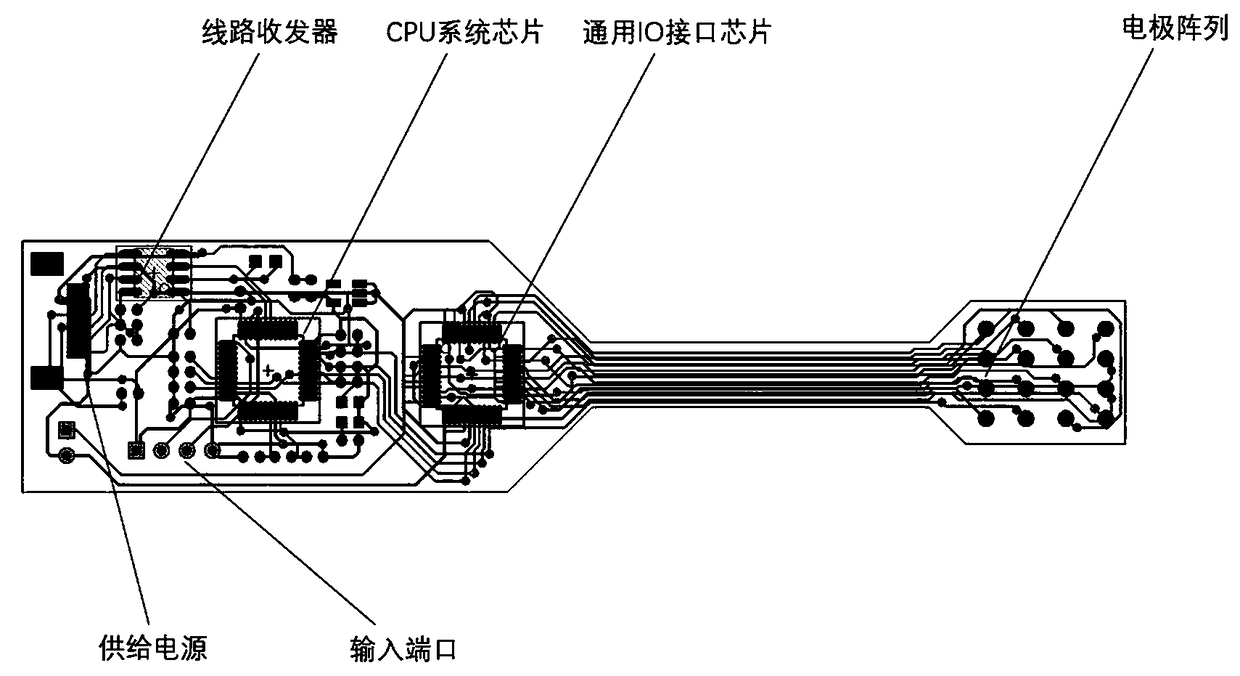

Electro-tactile based full-color visual substitution device

InactiveCN108831528AFast deliveryFast transmissionImage analysisMechanical/radiation/invasive therapiesPattern recognitionTouch Perception

The invention provides an electro-tactile based full-color visual substitution device which comprises an image collector, an image processor, a signal processor and stimulation electrodes; the stimulation electrodes make contact with different positions of the sensitive skin of the human body; the image collector is connected with the image processor via a data interface; the image processor is connected with the signal processor; the image collector collects image or video data via a camera and transmits the collected data to the image processor; the image processor encodes the collected datainto three types of potential information representing RGB color information according to RGB color codes, and sends the encoded potential information into the signal processor; the signal processorconverts the three types of encoded potential information into three types of electric stimulation signals that can be identified by the human skin, and the electric stimulation signals are output tothe human skin via the stimulation electrodes. Thus, the device of the invention can provide a full-color visual substitution scheme based on electro-tactile.

Owner:FUZHOU UNIV

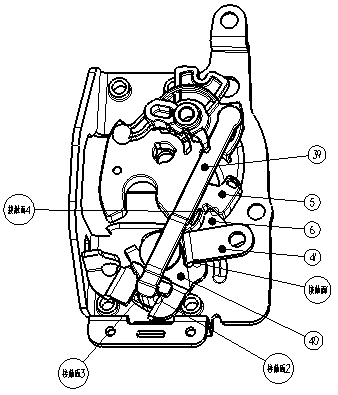

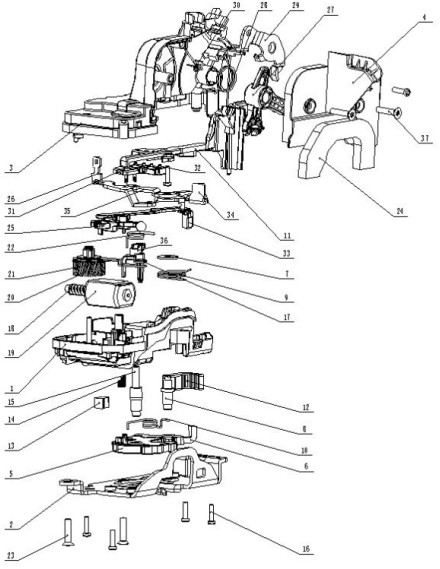

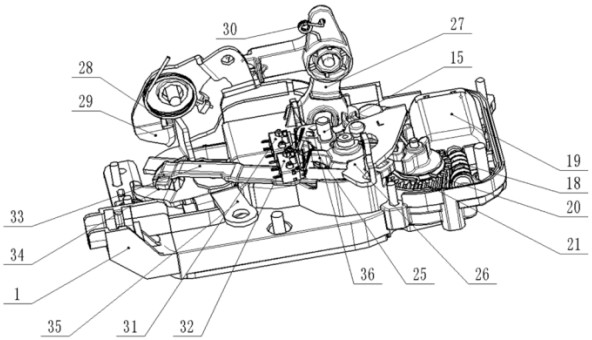

17 B multi-functional door lock assembly

PendingCN110670983ADustproof and waterproofImplement signalingNoise-prevention/anti-rattling lockingPower transmission/actuator featuresRatchetGear wheel

The invention discloses a 17 B multi-functional door lock assembly. The door lock assembly comprises a lock body, an opening rocker arm, an outer opening rocker arm, an inner opening rocker arm, a locking push rod, an outer locking rocker arm, a locking linkage block, an inner locking rocker arm and an inner locking linkage arm, and further comprises a motor, a worm, and a gear division assembly;functions of inner opening, outer opening and locking are achieved through mutual meshing effect of ratchets and pawls; the door lock assembly further comprises a ratchet signal rocker arm and a microswitch, and the signal transmission of vehicle door state information can be realized; and the microswitch in contact with the locking linkage block can realize the transmission of vehicle door lock locking and unlocking state signals so as to realize a central control function of a left door lock and a right door lock. According to the door lock assembly, the vehicle door lock is of an integratedstructure, and has the advantages of having a double-pull function, being compact in structure, good in dustproof and waterproof performance, high in transmission efficiency, better in control performance and the like.

Owner:HAOYUE AUTOMOBILE SAFETY SYSTEM TECHNOLOGY LIMITED BY SHARE LTD

Reading pen

ActiveCN103632577BAchieve replacementImplement signalingInput/output processes for data processingHandwritingEngineering

Owner:GUANGDONG XIAOTIANCAI TECH CO LTD

Concentration detection and training system and method based on functional near-infrared spectroscopy

InactiveCN106805985BRegulatory intelligenceSensitive Accurate Response MappingSensorsPsychotechnic devicesSignal onTerminal equipment

The invention discloses a system and method for concentration detection and training based on functional near infrared spectrum technologies. The system comprises a wearable fNIR sensing device and an intelligent terminal; a fNIR control module in the wearable fNIR sensing device controls switching-on, switching-off and spectral wavelength of a signal emission source in a fNIR signal emission module, switching-on and switching-off of a sensor in a fNIR signal collection module as well as opening and closing of signal channels, and near infrared spectrum signals on each signal channel under different spectrum lengths are collected cyclically and transmitted to the intelligent terminal; and the terminal equipment uses a built-in concentration analysis module to transform the near infrared spectrum signals into hemoglobin content information in real time and then quantify the information into a concentration index.

Owner:魏伟

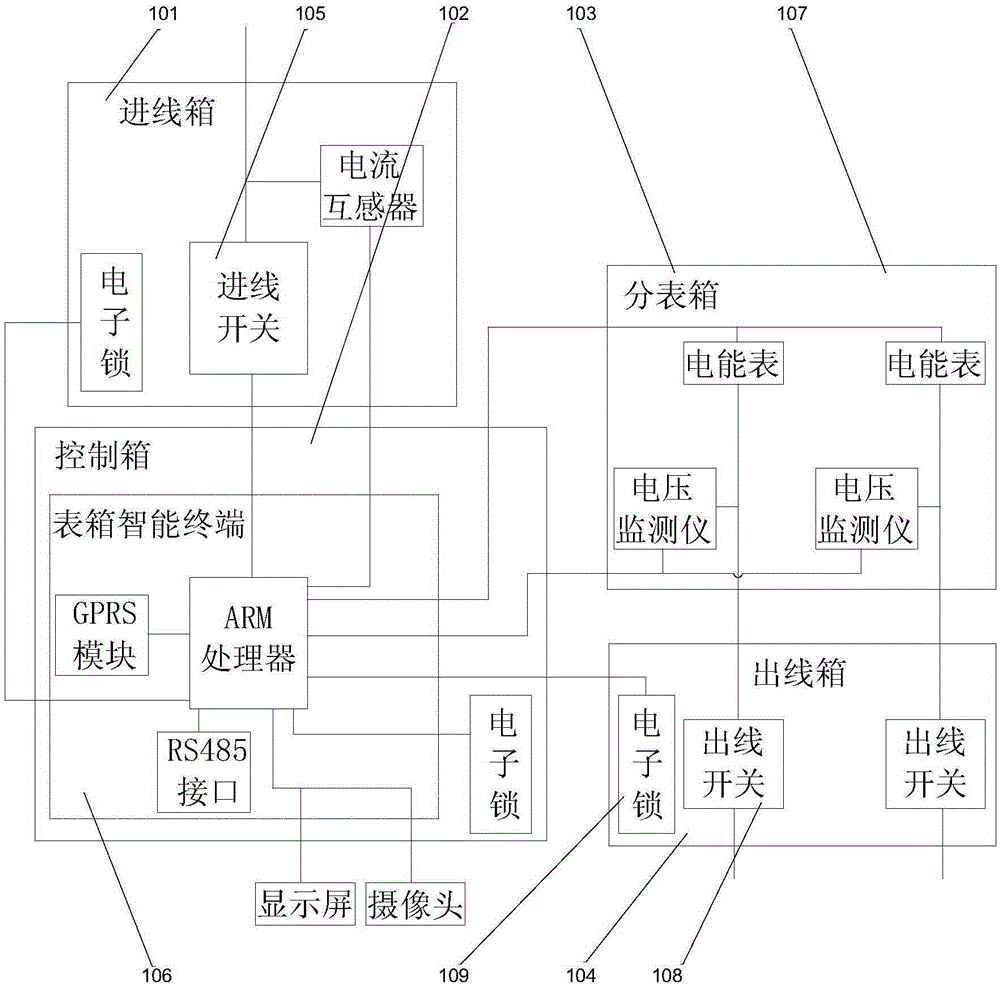

Intelligent electric meter box

InactiveCN106645838AEasy to checkPrevent Electricity StealingTime integral measurementElectric energyEngineering

The invention discloses an intelligent electric meter box, including a wire inlet box, a control box, a submeter box and a wire outlet box. A wire inlet switch is arranged in the wire inlet box, a meter box intelligent terminal connected with the wire inlet switch is arranged in the control box, a plurality of electric energy meters connected with the meter box intelligent terminal and the wire inlet switch separately are arranged in the submeter box, and wire outlet switches connected with the electric energy meters separately are arranged in the wire outlet box; voltage monitors are arranged between the wire outlet switches and the electric energy meters respectively, the voltage monitors are connected with the meter box intelligent terminal through lines, the wire inlet box, the control box, the submeter box and the wire outlet box are provided with box doors and electronic locks used for closing the box doors separately, and the electronic locks are connected with the meter box intelligent terminal through lines. The intelligent electric meter box provided by the invention can realize electric meter intelligent monitoring, realizes a function of positioning overhaul personnel, and realizes intelligent control of opening and closing of the box doors.

Owner:杭州宽辰科技有限公司

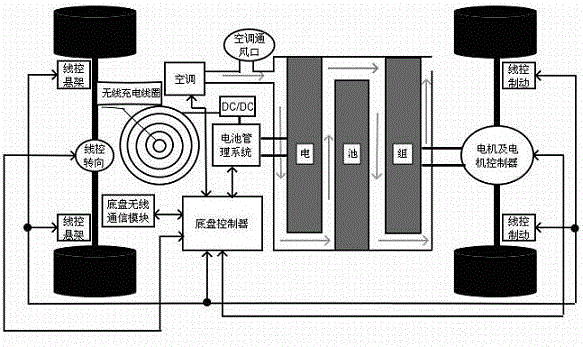

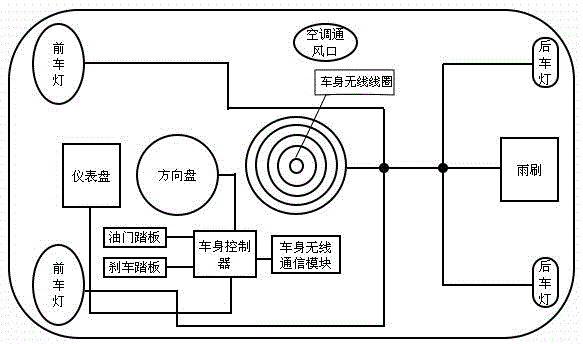

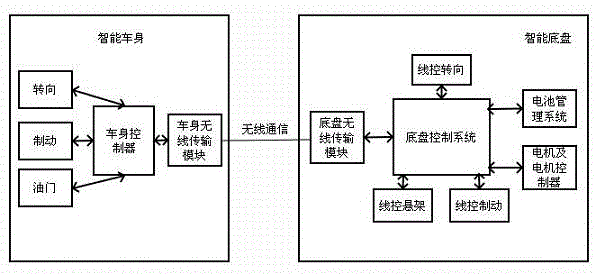

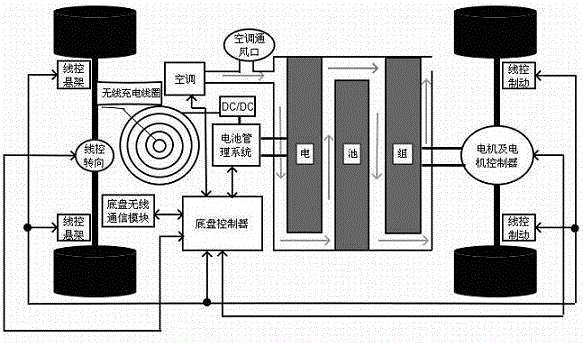

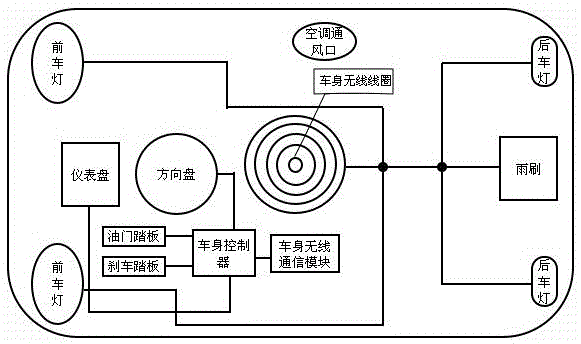

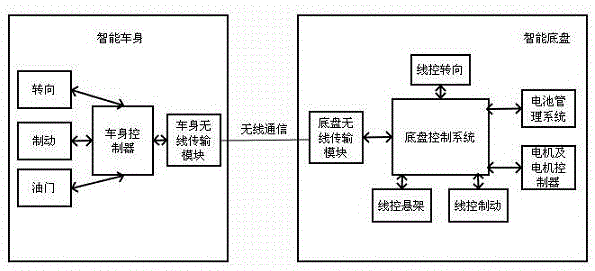

Novel electric car intelligent car body and intelligent chassis designing method

ActiveCN104608718AImplement signalingReduce electrical connectionsElectric/fluid circuitControl signalControl system

Provided is a novel electric car intelligent car body and intelligent chassis designing method. An intelligent chassis, an intelligent car body and a control system are included. Energy is transmitted between the car body and the chassis through a wireless charging technology. Control signals are transmitted through a wireless communication technology. The car body and the chassis are not electrically connected. The car body and the chassis are only connected through a fixing mechanical connecting point. A whole car air conditioning system is placed in the chassis and is communicated with the car body only through a circulating air way. Independent design of the car body and the chassis is completely achieved, and designing of an electric car is free and flexible.

Owner:南京塔孚汽车科技有限公司

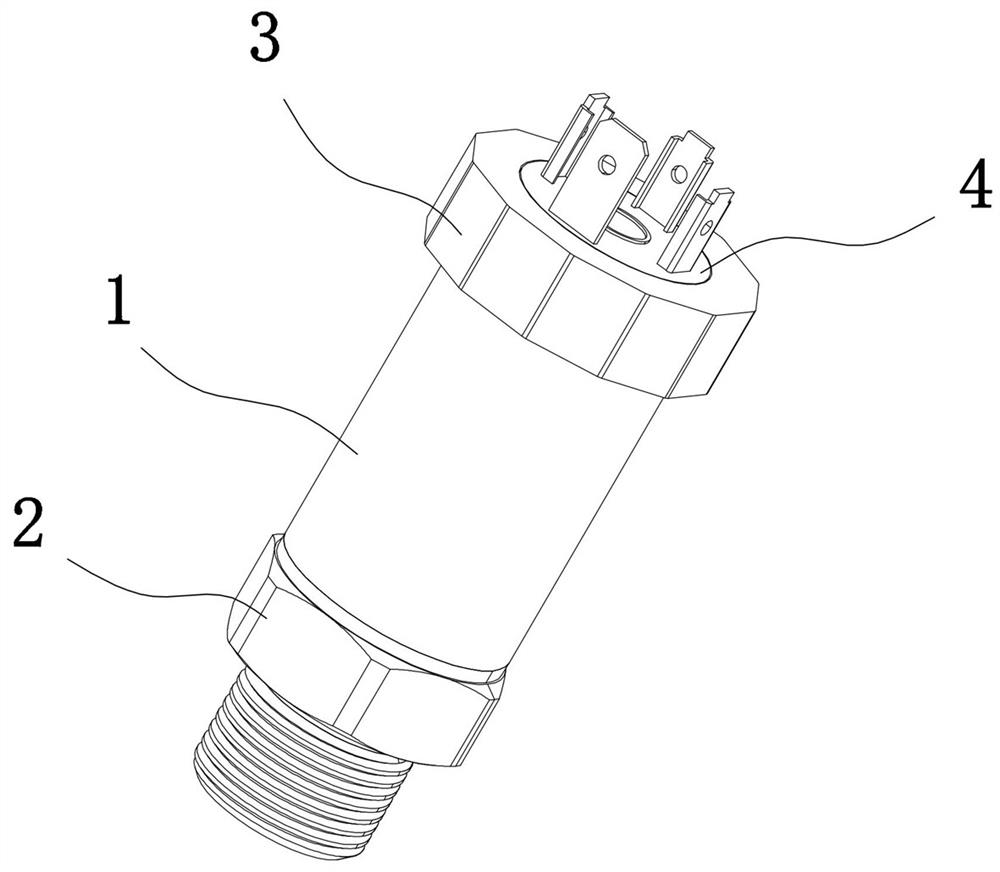

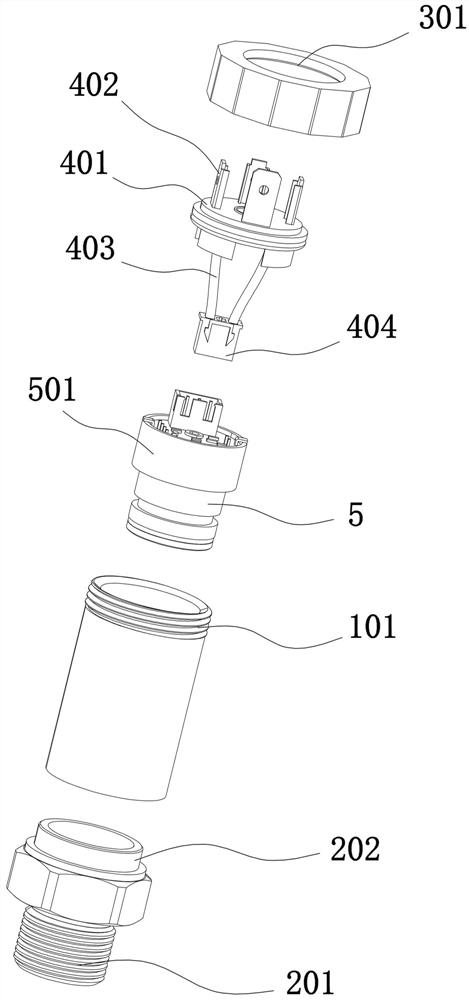

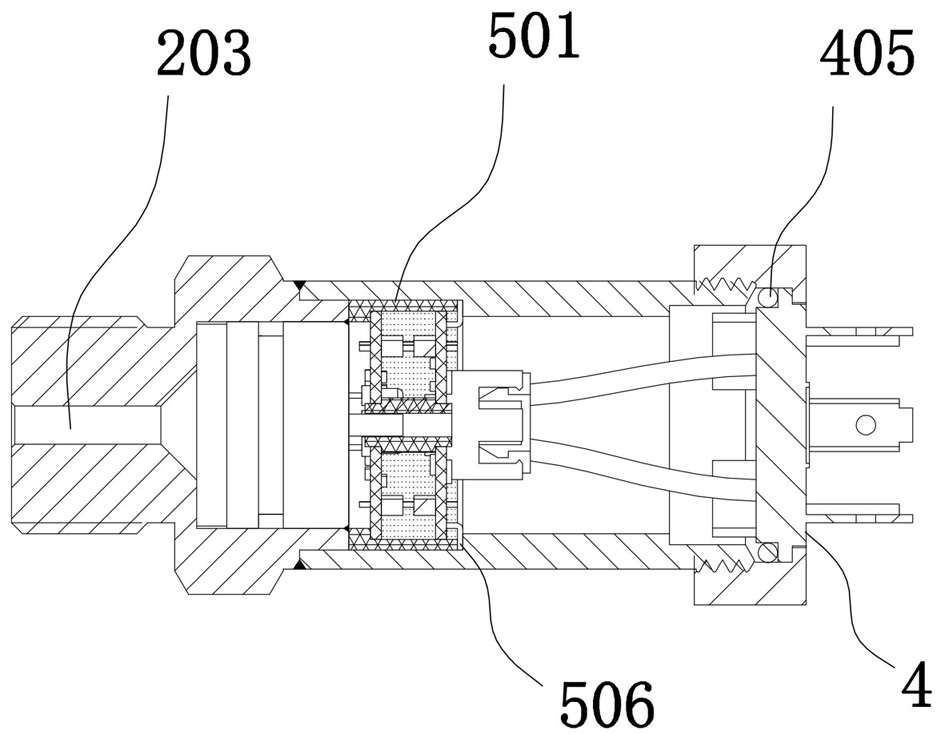

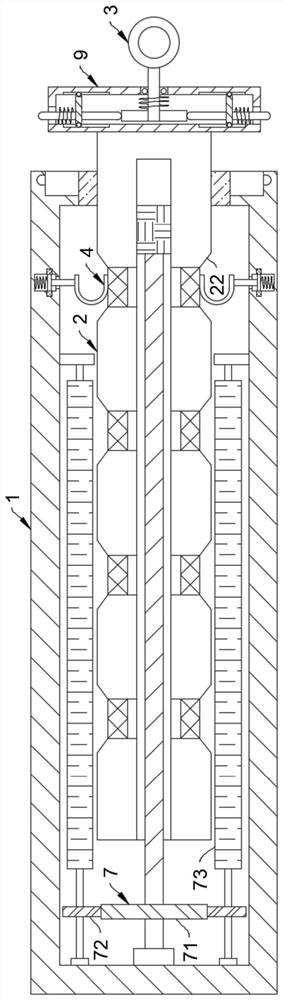

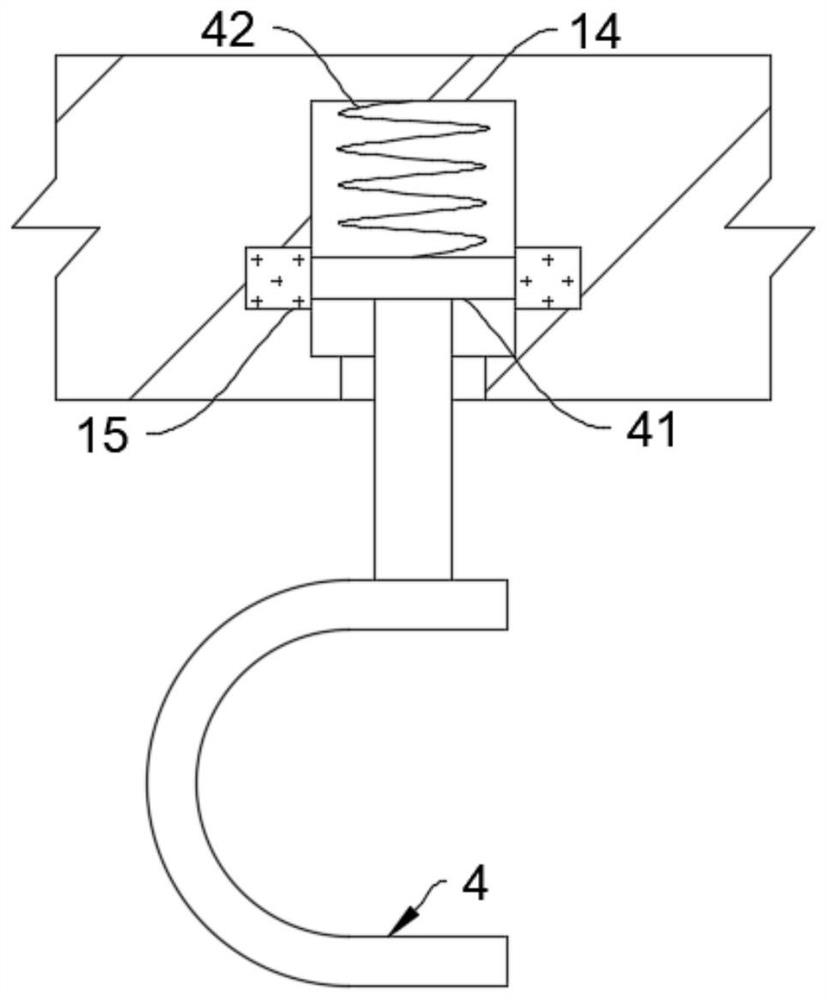

Double-plug pressure transmitter capable of being quickly assembled

ActiveCN113447191APlay a closed roleFirmly connectedFluid pressure measurementScrew threadTransmitter

The invention relates to a double-plug pressure transmitter capable of being quickly assembled. External threads are machined on the outer side wall of the upper end of a shell; a connector with threads is machined on the lower end face of the pressure inlet head. A clamping head is machined on the upper end face of the pressure inlet head. A pressure inlet hole is formed in the middle of the lower bottom surface of the pressure inlet head in a penetrating manner; an internal thread is machined on the inner side wall of the tensioning block; a connecting kit comprises an end plate; outer plugs are mounted on the upper end surfaces of the end plates at intervals; wires are symmetrically mounted on the lower end surface of the end plate; the outer plug is connected with the lead; inner plugs are mounted at the lower ends of the wires; a sealing ring is mounted on the outer side wall of the end plate in a sleeving manner; the upper end of a transmitter core body is provided with a sheath. A first amplification plate and a second amplification plate are mounted in the sheath; the double-plug pressure transmitter capable of being rapidly assembled is firm in plug connection, not prone to falling off, convenient to connect and easy to operate.

Owner:NANJING WOTIAN TECH

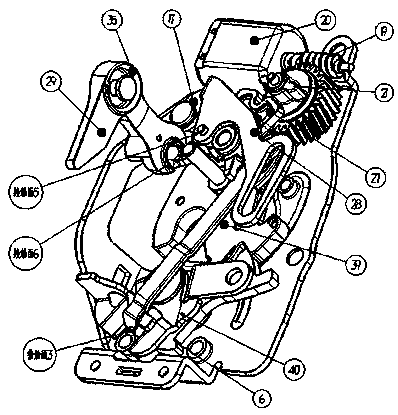

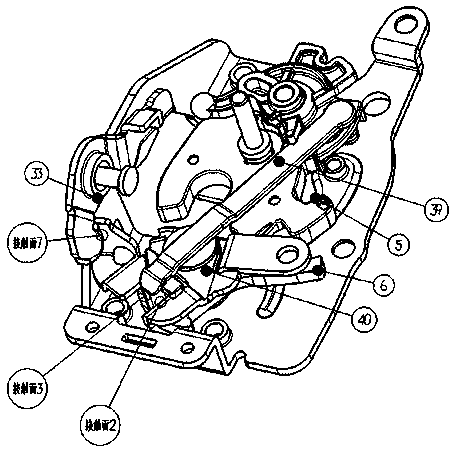

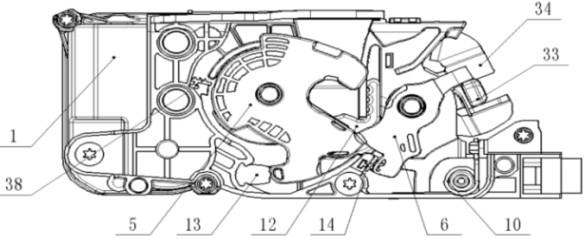

Integrated automobile door lock

PendingCN114482725AEasy to returnImplement signalingNoise-prevention/anti-rattling lockingPower transmission/actuator featuresRatchetGear wheel

The integrated automobile door lock comprises a lock body, a cover plate, a shell cover and a dustproof cover, the cover plate and the shell cover are arranged at the top and the bottom of the lock body respectively, and the dustproof cover is fixedly connected with one side of the lock body; a ratchet shaft and a pawl shaft are rotatably inserted in the lock body, a pawl shaft riveting gasket corresponding to the pawl shaft is arranged on the inner wall of the lock body, a ratchet fixedly sleeves the bottom of the ratchet shaft, a ratchet shock pad rotatably sleeves the outer portion of the ratchet shaft, and a pawl fixedly sleeves the bottom of the pawl shaft. The top of the pawl shaft is sleeved with an outward opening return spring, and the bottom of the pawl shaft is sleeved with a pawl return spring. A motor, a worm and a gear subassembly are arranged in the lock body, the output end of the motor is fixedly connected with the worm, and the output end of the worm is meshed with the input end of the gear subassembly. The automobile door lock is of an integrated structure, the structure is compact, dust and water are prevented, and the automobile door lock has the advantages of being high in transmission efficiency and better in control performance.

Owner:江苏皓月汽车科技有限公司

Drive-by-wire structure and Bluetooth headset

The invention discloses a drive-by-wire structure comprising a first metal shell, a second shell, a flexible circuit board and a circuit board, wherein the first metal shell is used as an antenna radiator; a first accommodating cavity and a second accommodating cavity are respectively formed in the first metal shell and the second shell; an insulating frame is arranged in the first accommodating cavity, and the insulating frame isolates the first metal shell from the second shell; the circuit board is arranged in the second accommodating cavity; and the flexible circuit board is electrically connected with the first metal shell and the circuit board. The drive-by-wire structure can connect a metal antenna with the circuit board within a limited space and achieve signal transfer.

Owner:GOERTEK INC

Charger detection device for battery protection cascade system

ActiveCN103217605BEnsure safetyImplement signalingBatteries circuit arrangementsElectrical testingOvervoltageElectrical battery

Owner:SINO WEALTH ELECTRONICS

Signal transmission device

ActiveCN107146720AImplement signalingAvoid misjudgmentContact electric connectionEngineeringFusion welding

The invention discloses a signal transmission device including an airtight housing, a push rod, a touch bridge, a support piece, a wiring post, an auxiliary contact board, an auxiliary contact and two signal lines. The push rod is arranged in the housing. The contact bridge sleeves the upper part of the push rod. The support rod is in rigid connection with the contact bridge. The wiring post is arranged above the contact bridge. The auxiliary contact point is fixed above the support piece. The auxiliary contact board is arranged between the auxiliary contact point and the support piece and the end of the auxiliary contact board adjacent to the auxiliary contact point is suspended and the other end of the auxiliary contact board is fixed in the housing. One signa line is connected to the auxiliary contact point while the other signal line is connected to the auxiliary contact board. The sum of the distance from the support board to the auxiliary contact board and the distance from the auxiliary contact board to the auxiliary contact point is smaller than the distance from the contact bridge to the wiring post. By adopting the signal transmission device, error judgment caused by main contact fusion welding can be prevented effectively.

Owner:NO 13 ELECTRICAL APPLIANCES +1

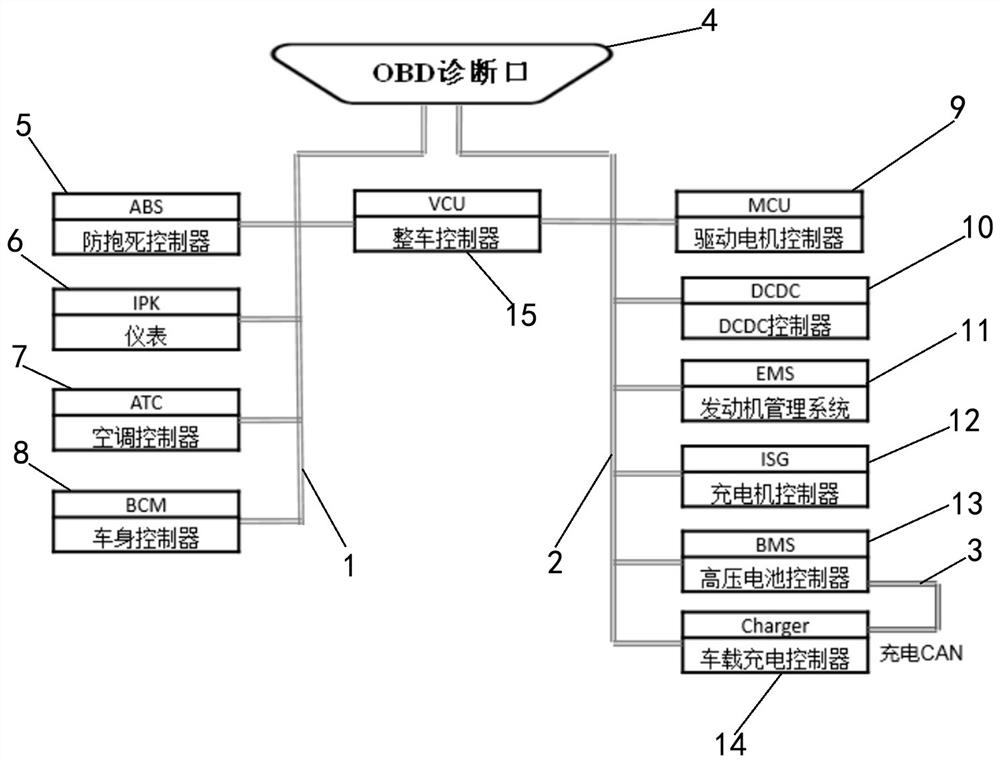

Extended-range vehicle network topology device with slow charging function

PendingCN112193086AImprove stabilityImplement signalingHybrid vehiclesCharging stationsIn vehicleElectric machinery

The invention provides an extended-range vehicle network topology device with a slow charging function. The device comprises a whole vehicle CAN bus, a power system CAN bus and a charging CAN bus, thewhole vehicle CAN bus and the power system CAN bus are connected to an OBD diagnosis port and are connected through a gateway of a whole vehicle controller, the whole vehicle CAN bus is connected with an anti-lock controller, an instrument, an air conditioner controller and a vehicle body controller, the power system CAN bus is connected with a driving motor controller, a DC / DC controller, an engine management system, a charger controller, a high-voltage battery controller and a vehicle-mounted charging controller, and the high-voltage battery controller is connected with the vehicle-mountedcharging controller through the charging CAN bus. According to the invention, except that the whole vehicle controller needs to have the capability of multiple network communication protocols, other controllers related to the power system only need to adopt one communication protocol, so that the network communication requirement of extended range can be realized on multiple whole vehicle platforms, and the development cost of the controllers related to the power system is reduced.

Owner:上海伊控动力系统有限公司

A new type of electric vehicle intelligent body and intelligent chassis

ActiveCN104608718BImplement signalingReduce electrical connectionsElectric/fluid circuitControl signalControl system

Provided is a novel electric car intelligent car body and intelligent chassis designing method. An intelligent chassis, an intelligent car body and a control system are included. Energy is transmitted between the car body and the chassis through a wireless charging technology. Control signals are transmitted through a wireless communication technology. The car body and the chassis are not electrically connected. The car body and the chassis are only connected through a fixing mechanical connecting point. A whole car air conditioning system is placed in the chassis and is communicated with the car body only through a circulating air way. Independent design of the car body and the chassis is completely achieved, and designing of an electric car is free and flexible.

Owner:南京塔孚汽车科技有限公司

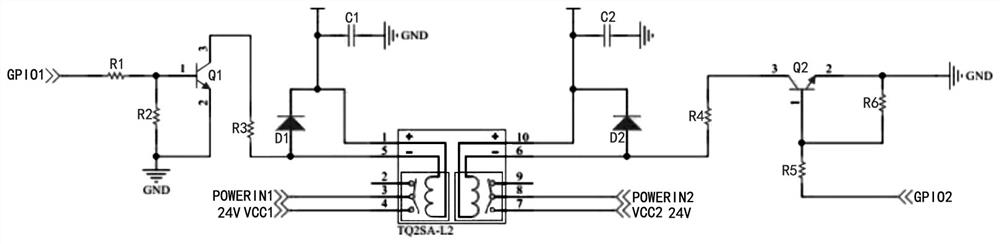

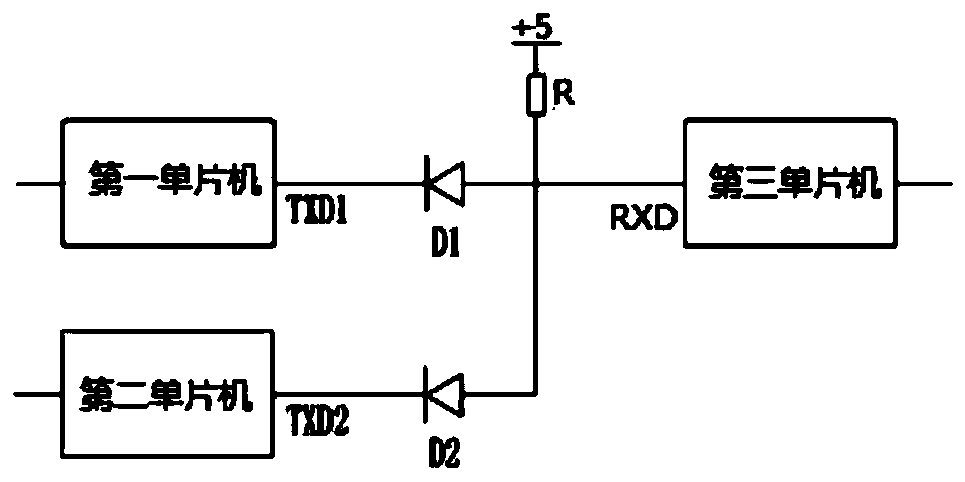

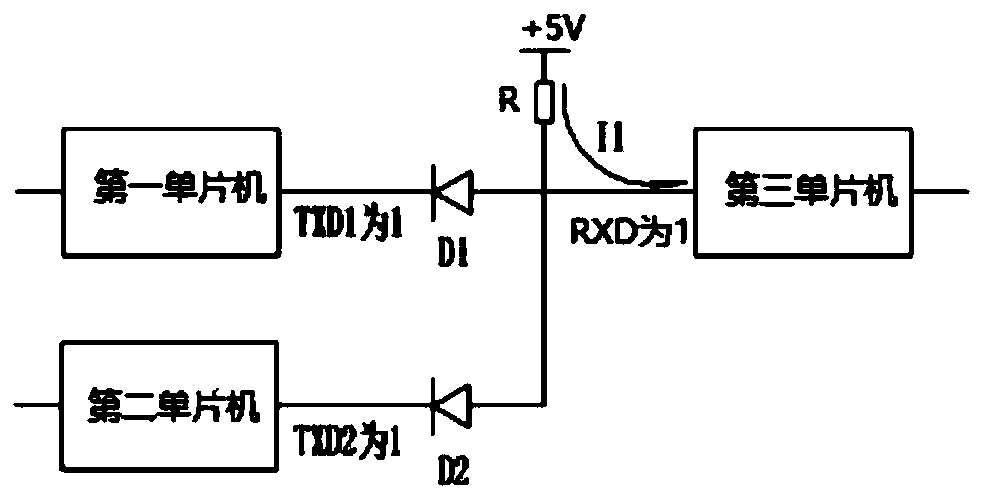

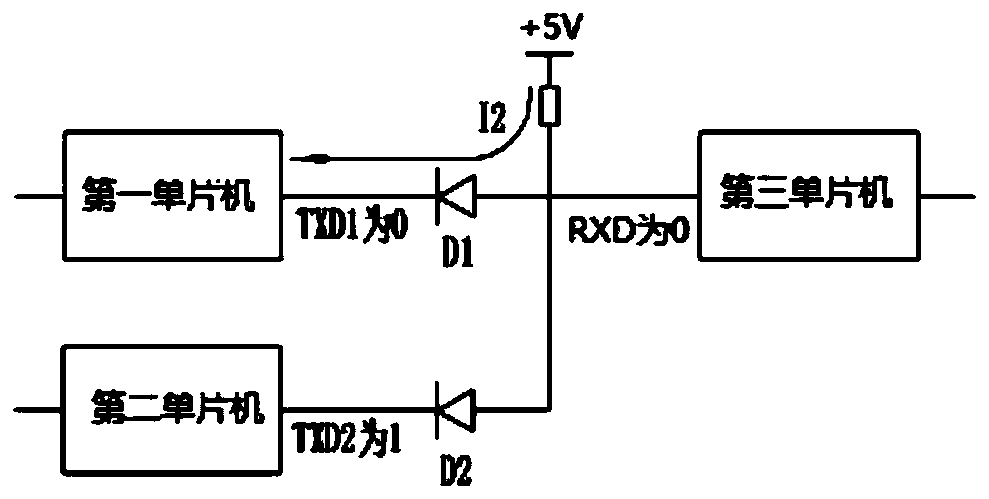

Multi-serial-port parallel transmission circuit based on diodes

PendingCN111338260ASolve the problem of parallel sendingImplement signalingProgramme controlComputer controlHemt circuitsEngineering

The invention provides a diode-based multi-serial-port parallel transmission circuit. The circuit specifically comprises a diode D1, a diode D2, a single chip microcomputer and a pull-up resistor R; the positive electrode of the diode D1 is connected with the positive electrode of the diode D2, and is connected to a + 5V power supply through the pull-up resistor R; the number of the single-chip microcomputers is multiple. The negative electrode of the diode D1 and the negative electrode of the diode D2 are connected to communication pins of different single-chip microcomputers. The beneficialeffects of the invention are that the circuit employs the design of two diodes and one resistor, solves a problem of TTL level serial port parallel transmission, achieves the signal transmission of two or more single-chip microcomputers to one single-chip microcomputer, is low in cost, and is easy to achieve.

Owner:CHINA UNIV OF GEOSCIENCES (WUHAN)

Fabrication method of three-dimensional capacitively coupled interconnect structure based on through-silicon capacitor

ActiveCN105470225BImplement signalingReduce performanceSemiconductor/solid-state device detailsSolid-state devicesDielectricCapacitance

The invention discloses a method for fabricating a three-dimensional capacitive coupling interconnection structure based on through-silicon capacitors, which comprises the following steps: forming two silicon substrates with the same structure, and aligning the back of one silicon substrate and bonding it to another silicon substrate form a three-dimensional capacitive coupling interconnect structure based on through-silicon capacitors; in the interconnect structure, the upper copper pillar and the lower copper pillar are coaxially arranged; the top of the lower copper pillar contacts the silicon dioxide insulation on the back of the upper silicon substrate The upper copper column and the lower copper column serve as the upper and lower plates of the capacitor respectively, and the insulating layer between the upper copper column and the lower copper column serves as the medium between the capacitors, forming a through-silicon capacitor structure. Compared with the conventional TSV process, the present invention omits the fabrication of metal bumps on the front side of the wafer, thinning and exposed copper on the back, insulation, and fabrication of micro-bumps in the fabrication process of the TSV structure, the fabrication process is obviously shortened, and the yield is improved , the required process equipment is reduced accordingly.

Owner:XI AN JIAOTONG UNIV

a signaling device

ActiveCN107146720BImplement signalingAvoid misjudgmentContact electric connectionEngineeringFusion welding

The invention discloses a signal transmission device including an airtight housing, a push rod, a touch bridge, a support piece, a wiring post, an auxiliary contact board, an auxiliary contact and two signal lines. The push rod is arranged in the housing. The contact bridge sleeves the upper part of the push rod. The support rod is in rigid connection with the contact bridge. The wiring post is arranged above the contact bridge. The auxiliary contact point is fixed above the support piece. The auxiliary contact board is arranged between the auxiliary contact point and the support piece and the end of the auxiliary contact board adjacent to the auxiliary contact point is suspended and the other end of the auxiliary contact board is fixed in the housing. One signa line is connected to the auxiliary contact point while the other signal line is connected to the auxiliary contact board. The sum of the distance from the support board to the auxiliary contact board and the distance from the auxiliary contact board to the auxiliary contact point is smaller than the distance from the contact bridge to the wiring post. By adopting the signal transmission device, error judgment caused by main contact fusion welding can be prevented effectively.

Owner:NO 13 ELECTRICAL APPLIANCES +1

Server and board card anti-collision butt joint structure thereof

PendingCN113703534ARealize dockingImplement signalingDigital processing power distributionEngineeringMechanical engineering

The invention discloses a board card anti-collision butt joint structure. The structure comprises a fixed board card installed in a case; the movable board card is matched and butted with the fixed board card; and the pre-positioning guide rail is connected to the inner wall of the case and extends outwards along the butt joint direction of the fixed board card and the movable board card. The fixed board card is provided with a first connector and a fixed guide rail. The movable board card is provided with a second connector which is in butt joint with the first connector, a movable guide pin which slides in cooperation with the fixed guide rail, and a positioning guide column which slides in cooperation with the pre-positioning guide rail. The length of the positioning guide column is larger than that of the movable guide pin. Therefore, the pre-positioning of the movable board card is realized after the positioning guide column and the pre-positioning guide rail are in plug-in fit, the movable guide pin and the fixed guide rail are automatically matched in the subsequent operation process, and the first connector and the second connector are butted, so that the guide pin can be prevented from colliding with the connector to cause damage on the basis of realizing accurate butting of the board card. The invention also discloses a server, which has the above beneficial effects.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

Sliding type portable radio device

InactiveCN113141188AImprove contact effectEasy to storeCleaning using toolsTransmissionWorking environmentEngineering

The invention belongs to the technical field of radio devices, and particularly relates to a sliding type portable radio device which comprises a first conductor and a second conductor, the first conductor and the second conductor are in sliding connection, and the first conductor and the second conductor are movably connected through a locking assembly. One end, close to the locking assembly, of the first conductor is provided with a connecting terminal, the connecting terminal is connected with the first conductor in a sliding mode, the second conductor is electrically connected with the connecting terminal through connecting blocks, and the adjacent connecting blocks are arranged in a matched mode. By arranging the sliding type radio device, storage and carrying work of the device in use are effectively and conveniently achieved, the use flexibility of the device is improved. Meanwhile, a cleaning assembly for automatic maintenance is arranged on a radio connecting block, the contact performance of terminal connection is improved, the service life of the device is prolonged, and multiple sets of standby connecting blocks are arranged, so that the service life of the device is prolonged. The universality of signal transmission and reception of the device in different working environments is realized, and the functionality of the device is increased.

Owner:许鹏