Patents

Literature

30results about How to "Resolve uneven diffusion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

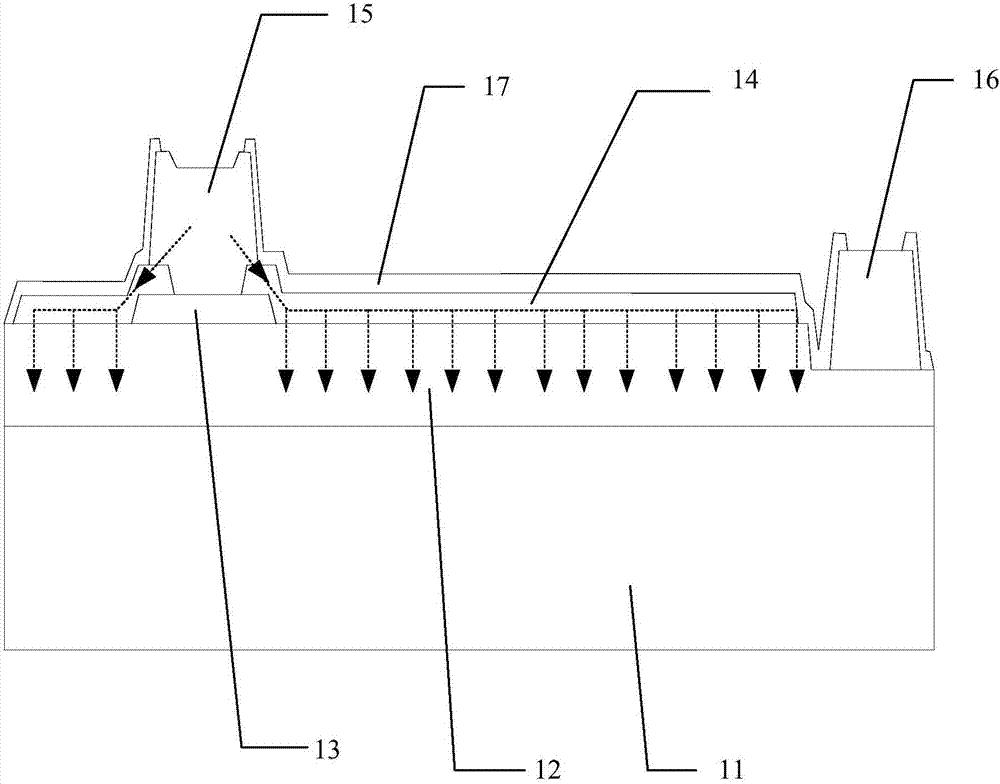

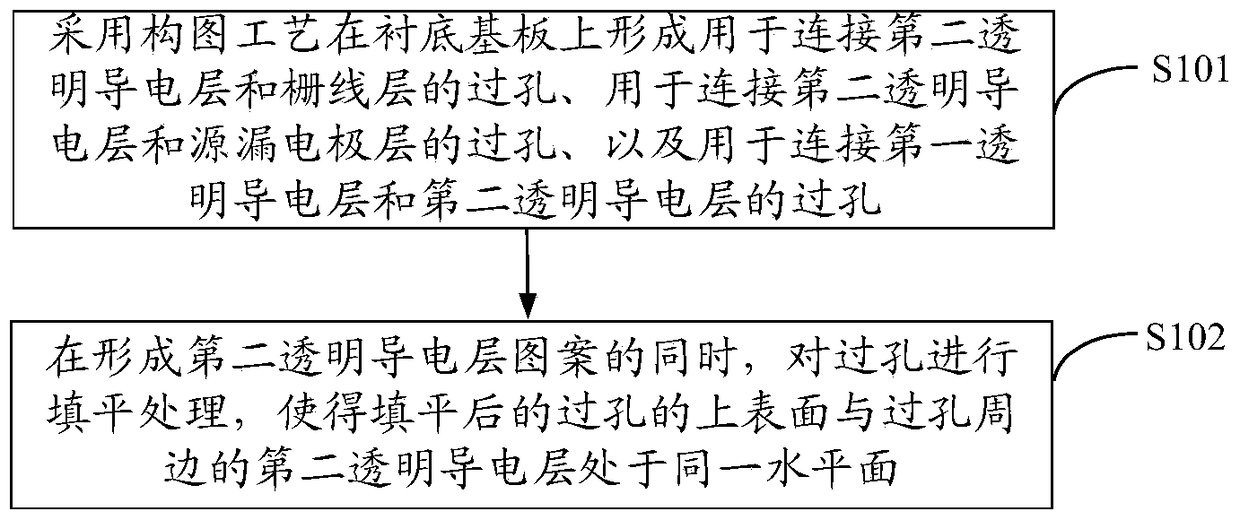

Array substrate and making method thereof, display panel and display device

ActiveCN105304649AResolve uneven diffusionReduce dropSolid-state devicesSemiconductor/solid-state device manufacturingDiffusionDisplay device

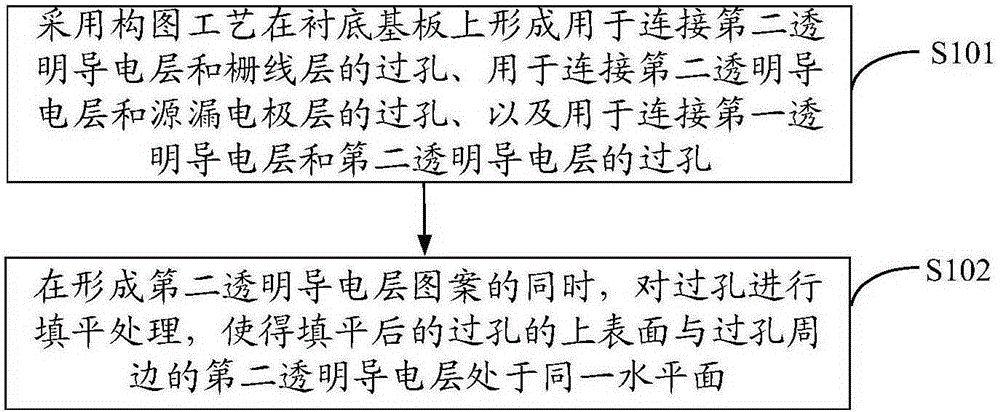

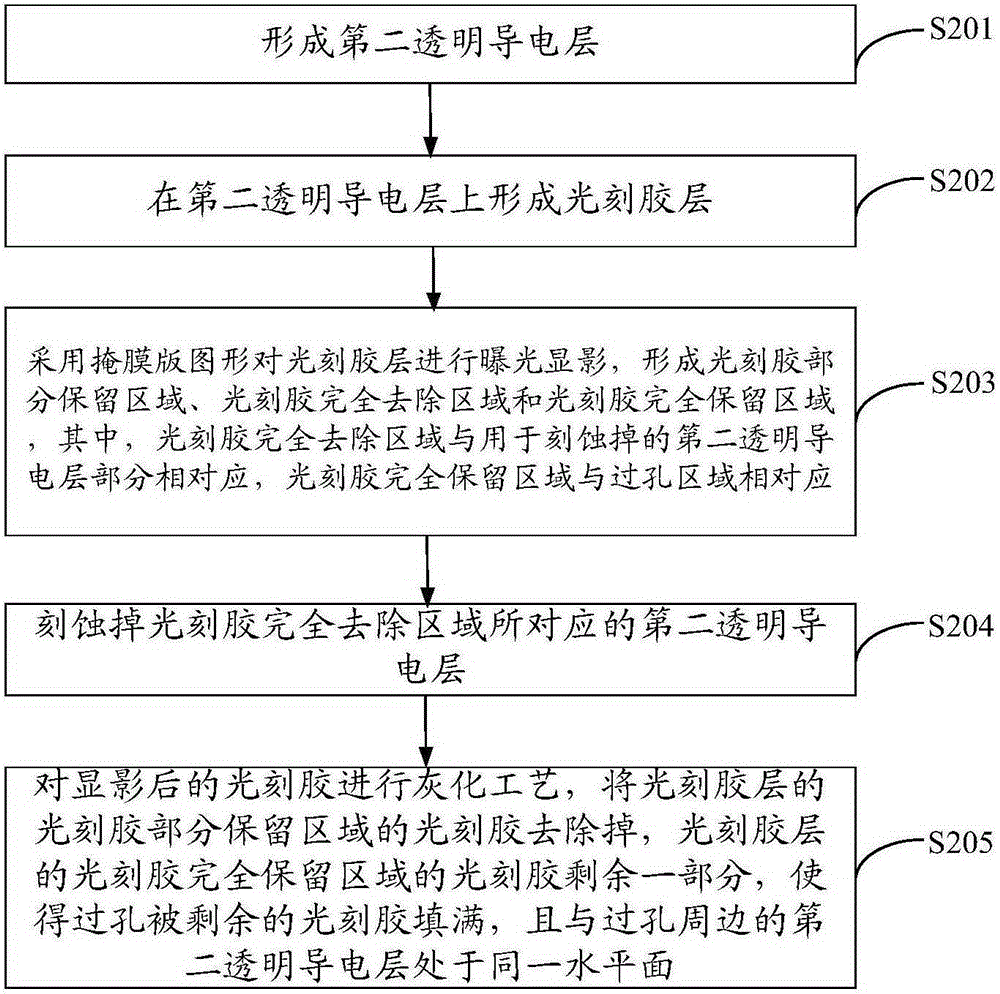

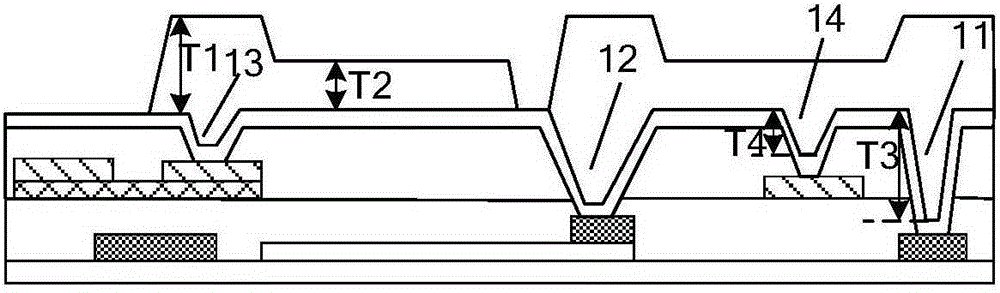

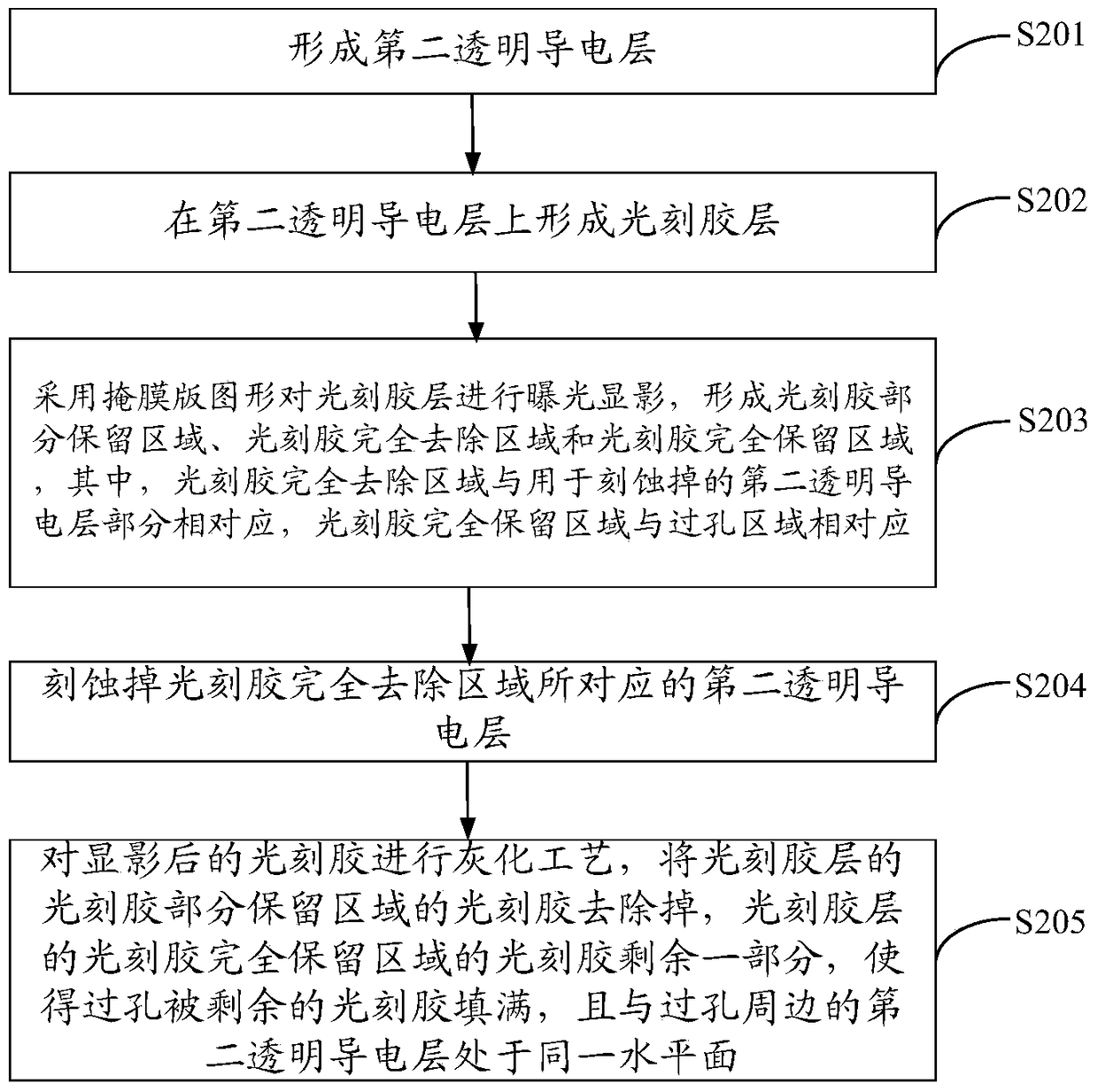

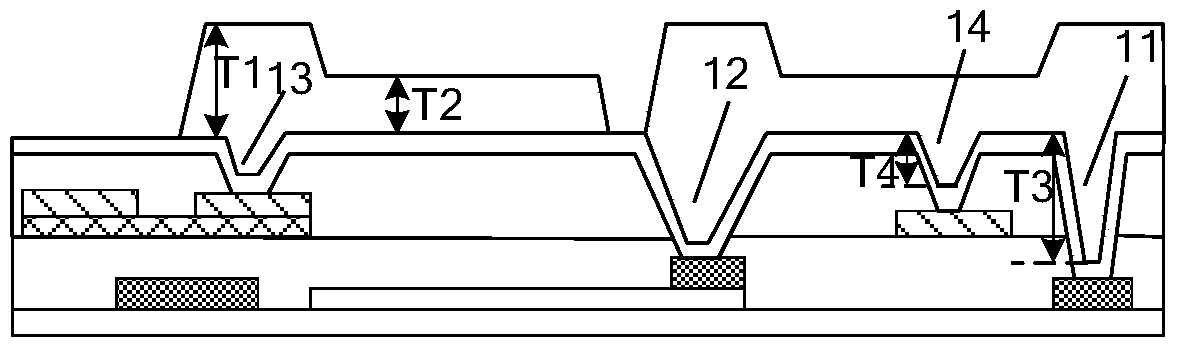

The invention discloses an array substrate and a making method thereof, a display panel and a display device in order to reduce the height difference between the transparent conductive layer on the upper surface of a via hole and the transparent conductive layer around the via hole in an array substrate, solve the problem that diffusion of polyimide film PI in the alignment layer is uneven and improve the display quality. The making method of the array substrate is characterized by comprising the following steps: using a composition process to a form a via hole used for connecting a second transparent conductive layer and a gate line layer, a via hole used for connecting the second transparent conductive layer and a source and drain electrode layer and a via hole used for connecting a first transparent conductive layer and the second transparent conductive layer; and while the pattern of the second transparent conductive layer is formed, filling and leveling up the via holes to make the second transparent conductive layer on the upper surfaces of the via holes and the second transparent conductive layer around the via holes in the same horizontal plane.

Owner:BOE TECH GRP CO LTD +1

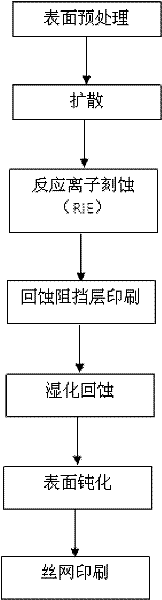

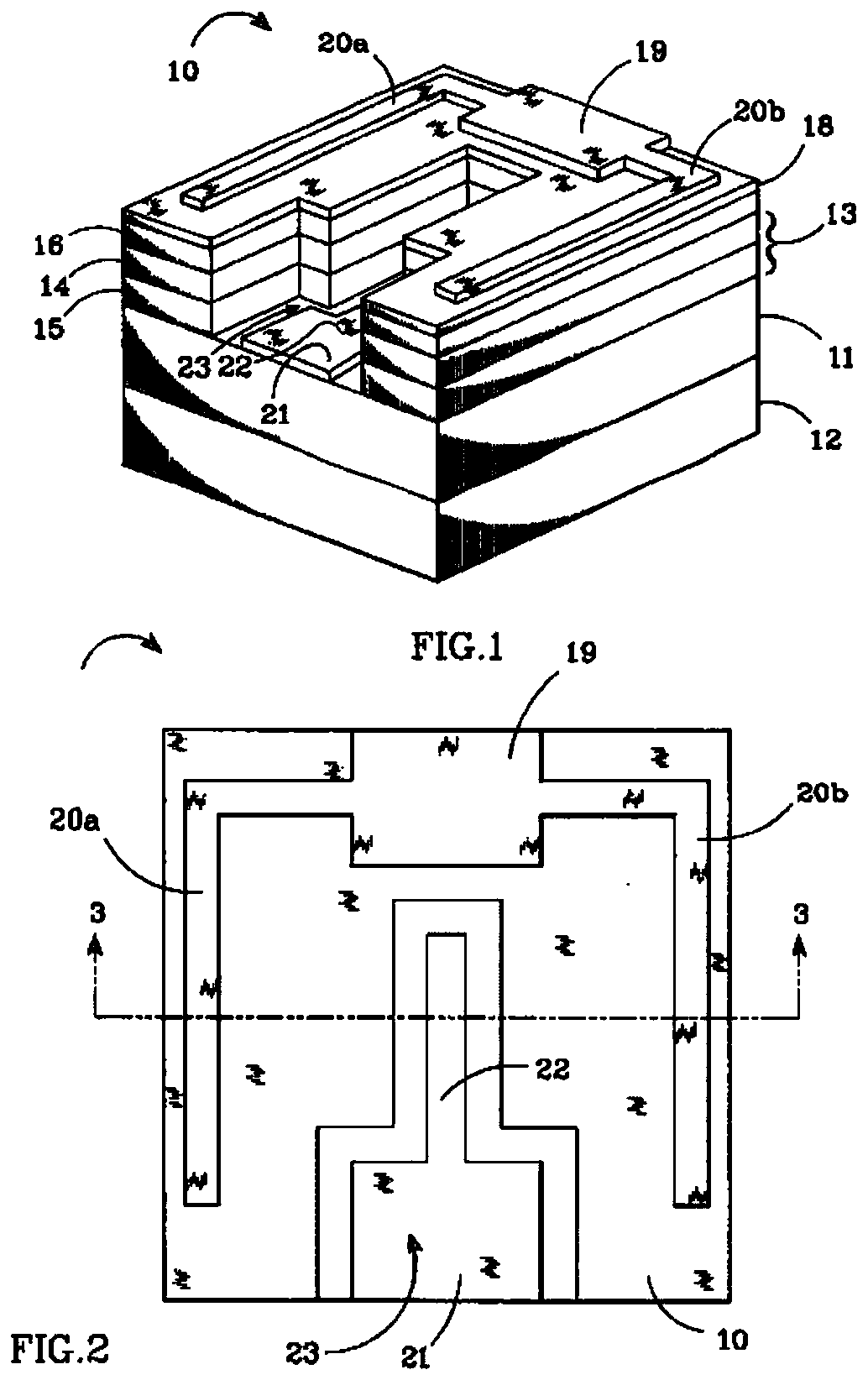

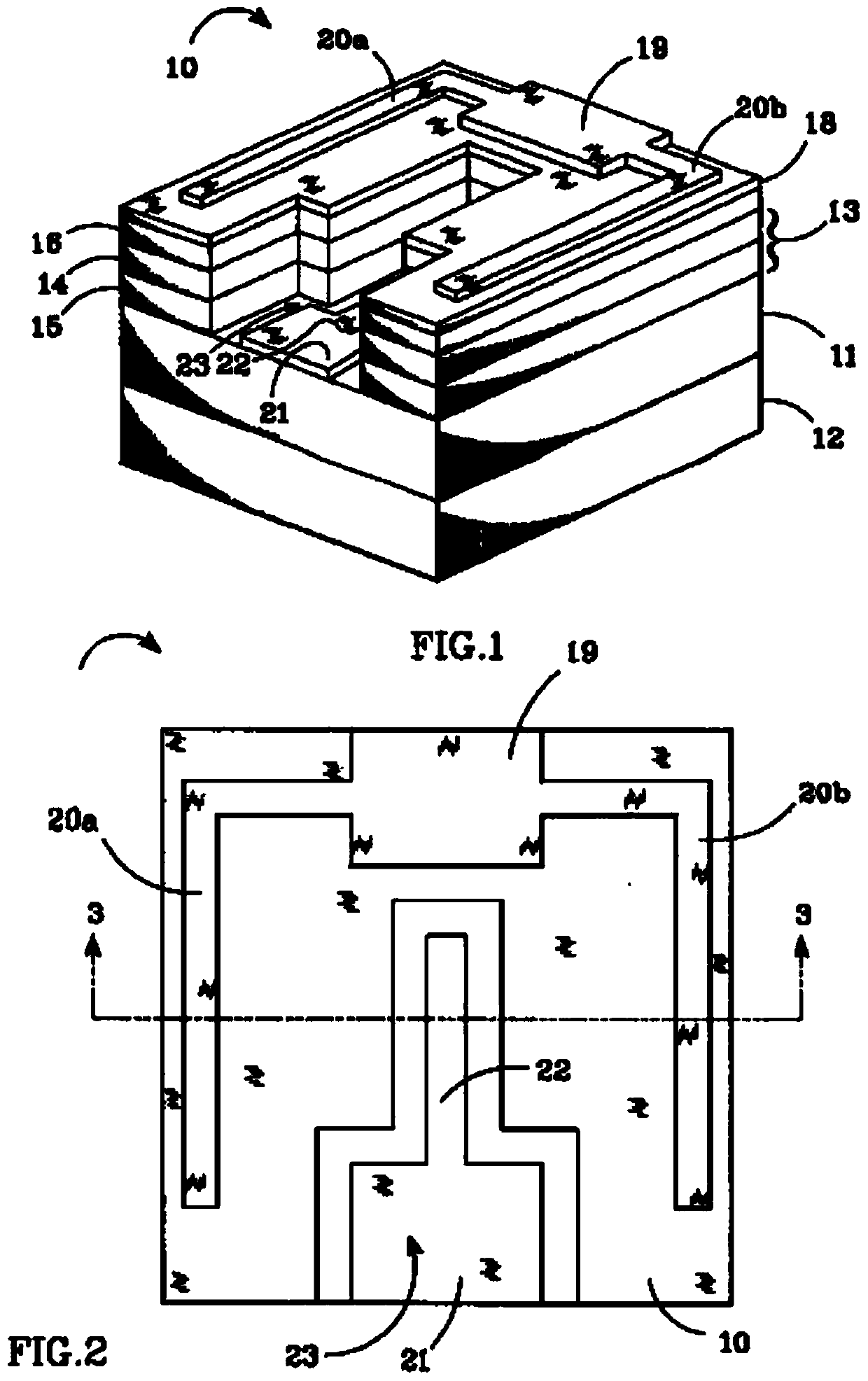

Selective emitter electrode solar battery manufacturing process combined with reactive ion etching (RIE)

InactiveCN102315317AResolve uneven diffusionImprove shortwave responseFinal product manufactureSemiconductor devicesOptoelectronicsSolar battery

The invention relates to the solar battery manufacturing method field, especially relates to a selective emitter electrode solar battery manufacturing process combined with a reactive ion etching (RIE). The method comprises the following steps that: after a surface is pretreated, a silicon chip diffuses so as to form a diffusion layer; a tiny suede is formed on a surface of the silicon chip through etching the reactive ion on the diffusion layer; a barrier layer is printed; a heavily doped region and a low doped region is formed after etching back through a local wet method; finally, an electrode is printed in the heavily doped region; sintering is performed and preparation of a cell sheet is completed. By using the technology provided in the invention, a problem of non-uniform diffusion caused by the RIE can be solved. Simultaneously, a diffusion selectivity emitter electrode technology is combined so as to raise short wave response, further increase light absorption and obtain high photoelectric conversion efficiency.

Owner:TRINA SOLAR CO LTD

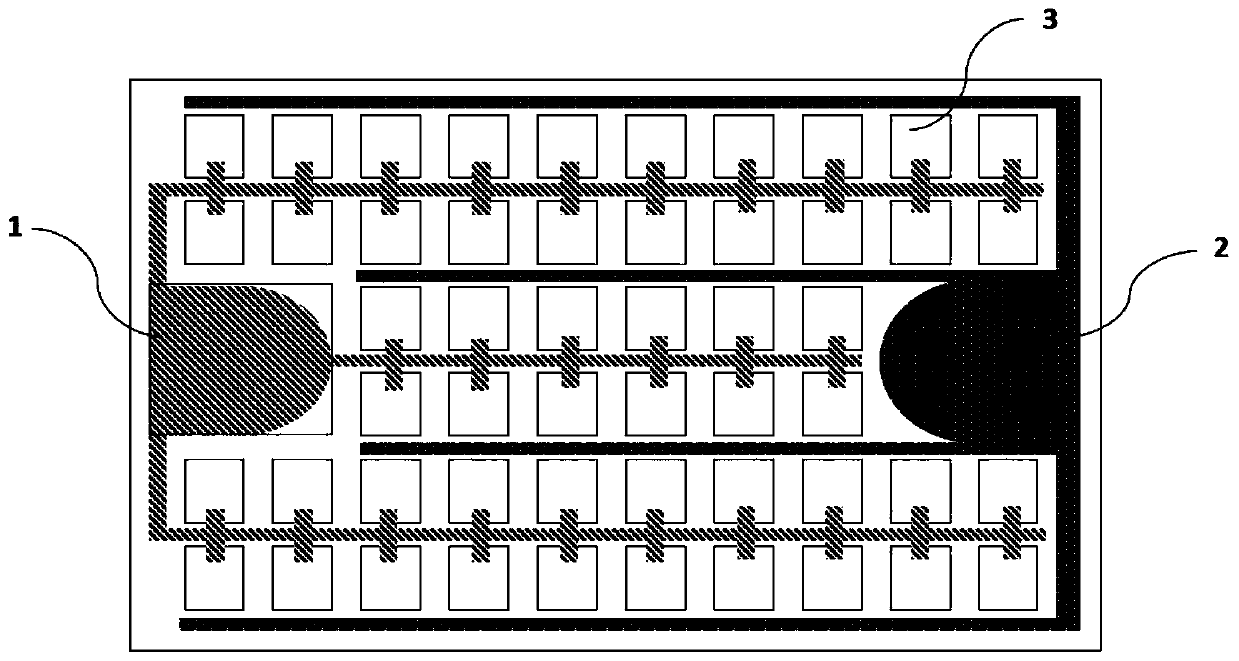

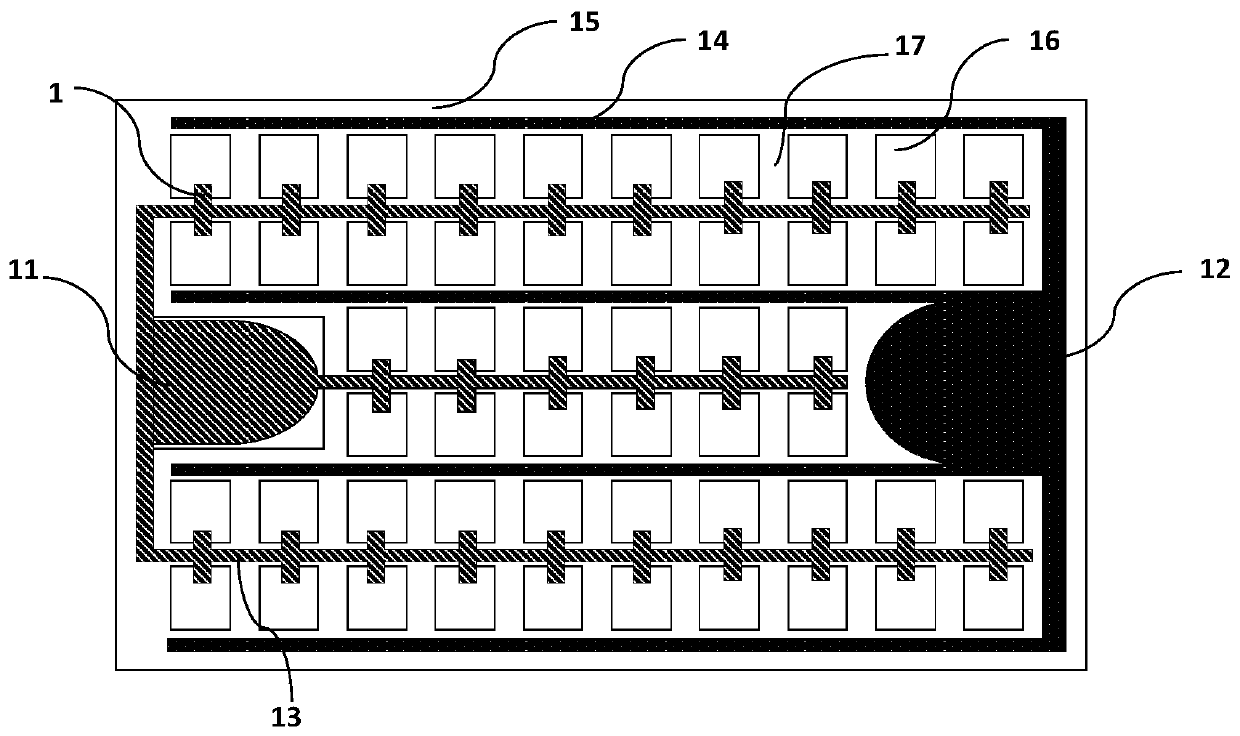

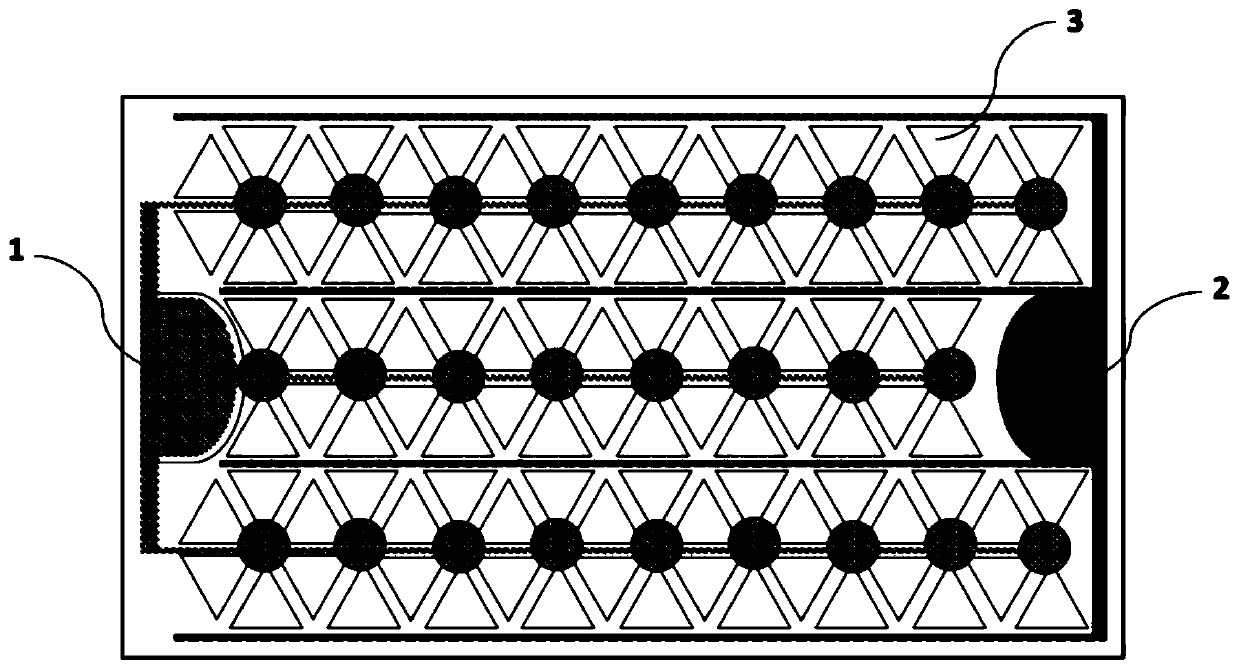

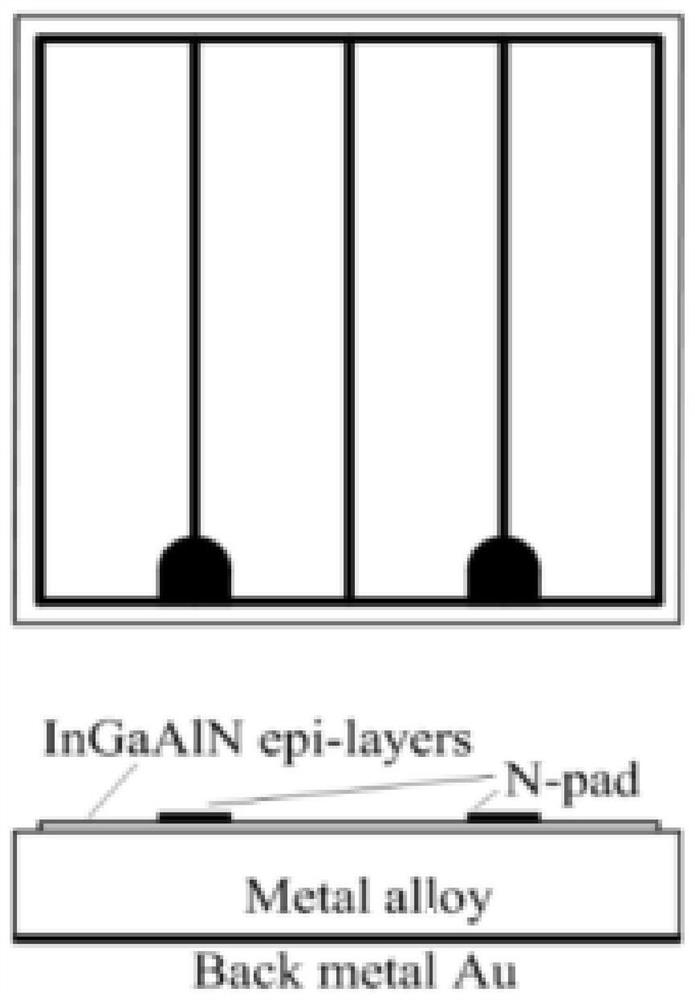

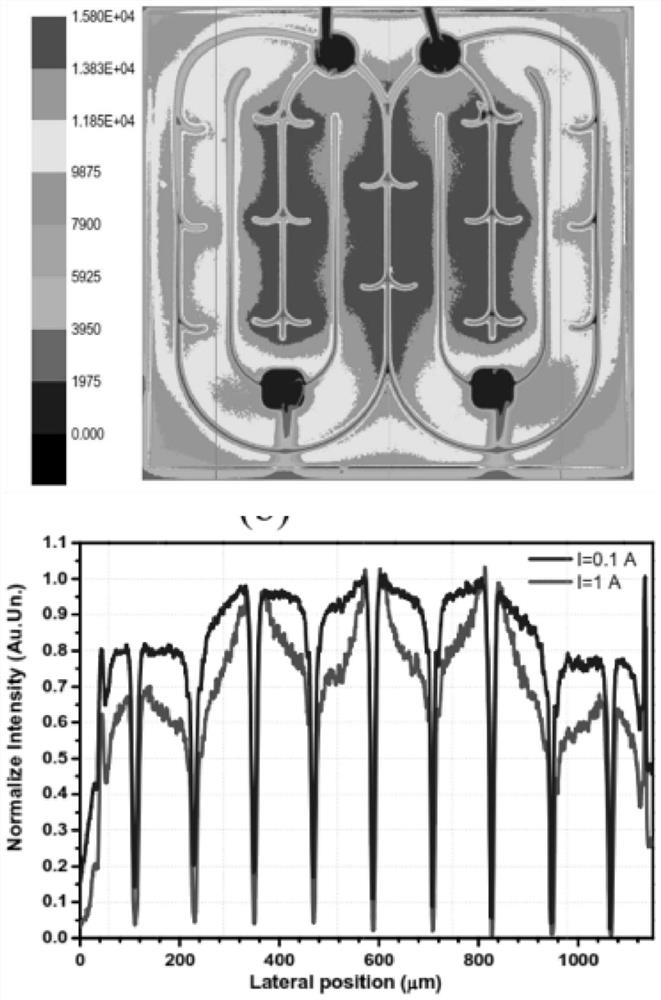

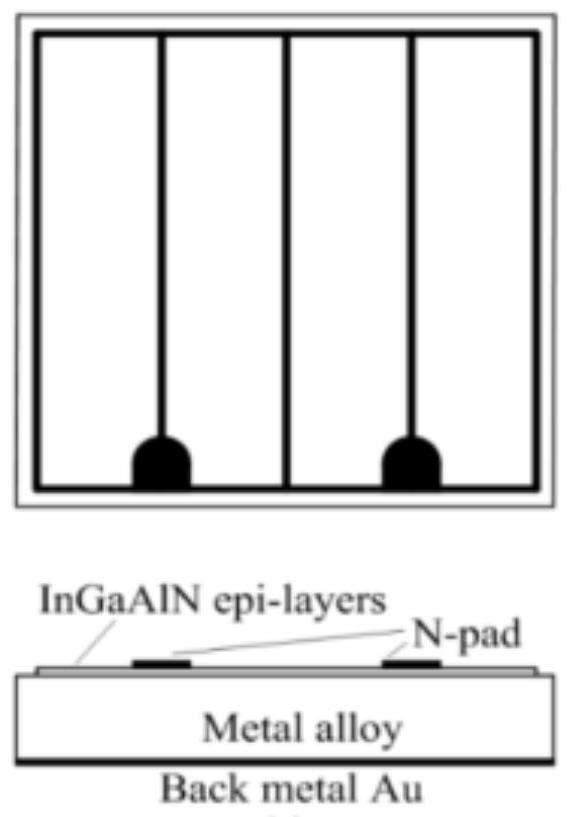

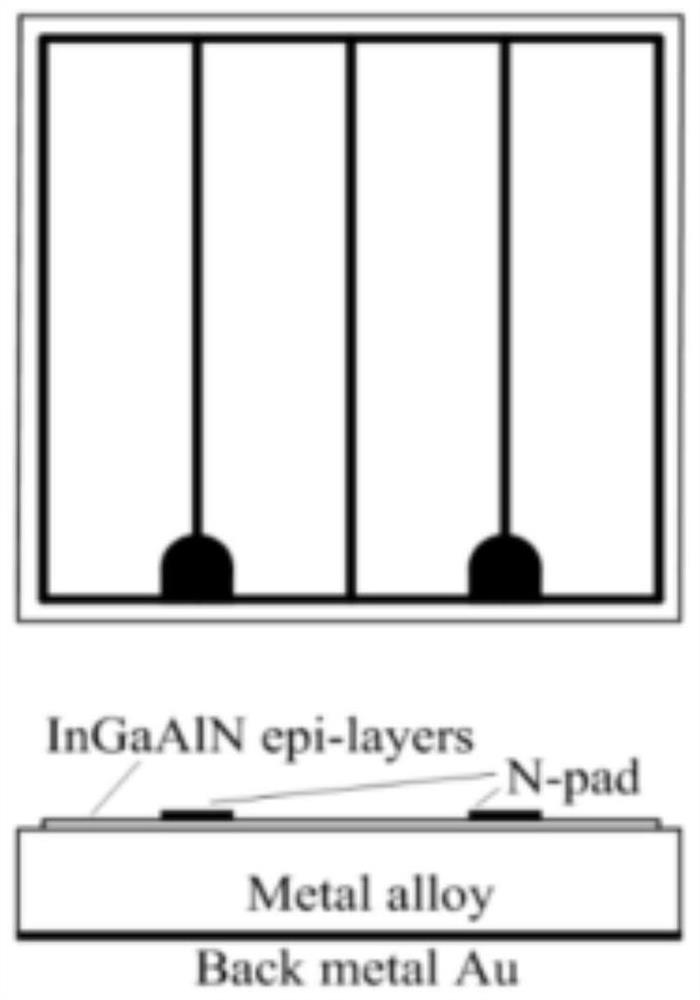

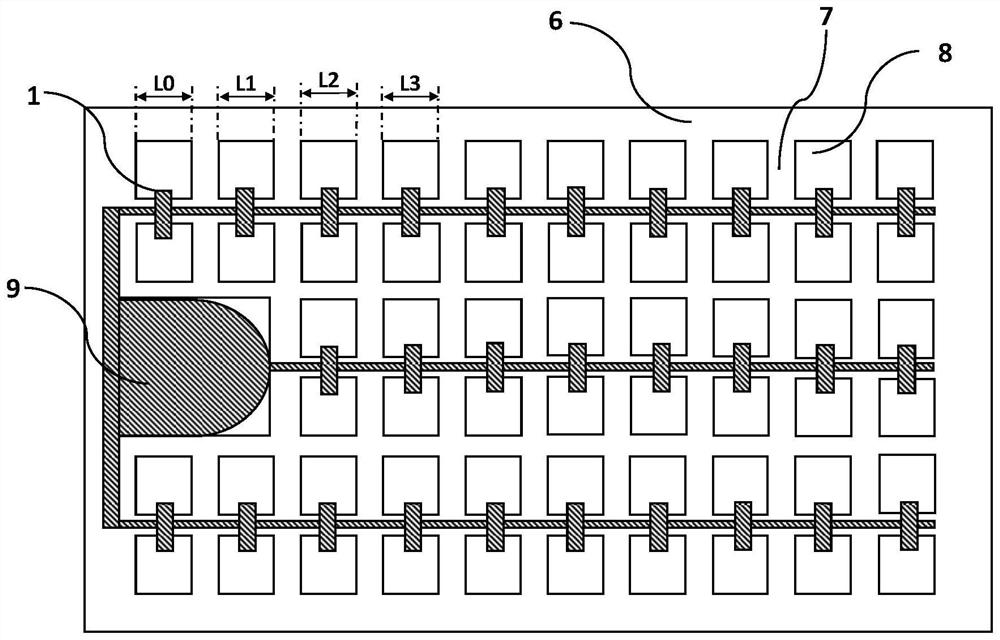

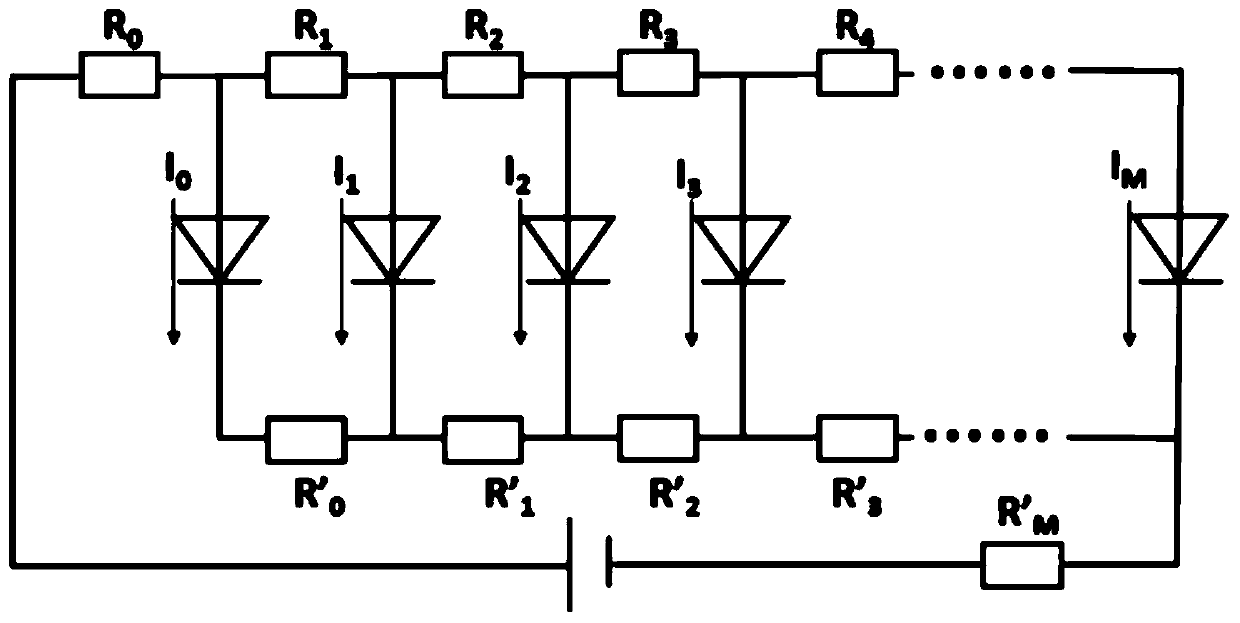

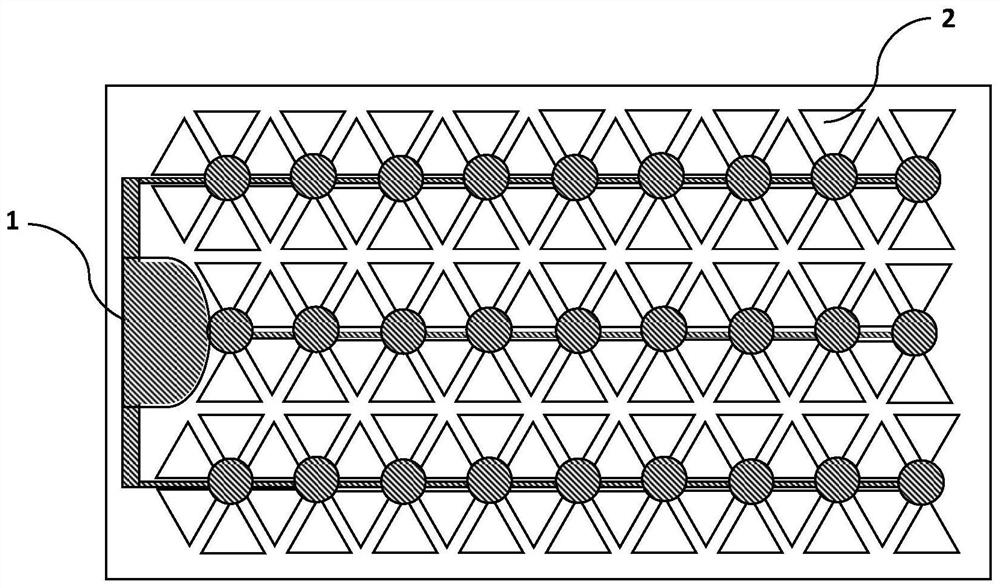

Front-mounted integrated unit light-emitting diode

PendingCN109817781ASmall sizeResolve uneven diffusionSemiconductor devicesSemiconductor materialsEngineering

The invention relates to the field of semiconductor materials and device processes, in particular to a semiconductor photoelectric device. The invention provides a front-mounted integrated unit light-emitting diode, which comprises a first conductive type electrode, a second conductive type electrode and a diode mesa structure positioned between the first conductive type electrode and the second conductive type electrode. The diode mesa structure comprises a plurality of diode units, and the plurality of diode units are arranged in a geometrical shape. The technical problem that in the prior art, a diode structure is greatly limited in three important parameters of lumen efficiency, lumen density output and lumen cost is solved, lumen output of a unit area chip is improved, and lumen costis reduced.

Owner:纳微朗科技(深圳)有限公司

Low-pressure variable-temperature diffusion method of nanometer textured polycrystalline silicon solar cell

InactiveCN104091857AResolve uneven diffusionSpread evenlyFinal product manufactureSemiconductor/solid-state device manufacturingDiffusion methodsSolar cell

The invention discloses a low-pressure variable-temperature diffusion method of a nanometer textured polycrystalline silicon solar cell, and relates to the technical field of solar cells. The low-pressure variable-temperature diffusion method comprises the steps of cleaning of silicon wafers, vacuumizing, temperature rising, power on, cooling and wafer discharging. The pressure of diffusion gas keeps 0.001-0.8 Pa, the diffusion temperature range is from 600 to 950 degrees, the silicon wafers used are p-type silicon wafers and n type silicon wafers. Low-pressure diffusion and variable-temperature diffusion are combined, the problem of uneven diffusion of the nanometer textured silicon wafers is resolved, molecular movement of a diffusion source is accelerated under a low-pressure condition, an impurity source in a diffusion cavity is distributed evenly, the partial concentration difference on the surfaces of the silicon wafers is small, and an even diffusion environment is created. Meanwhile, inside a nanometer textured structure, the diffusion length of a gas source is large, the response time is short, and it is represented that similar diffusion source atmosphere exists within a certain period of time.

Owner:EOPLLY NEW ENERGY TECH

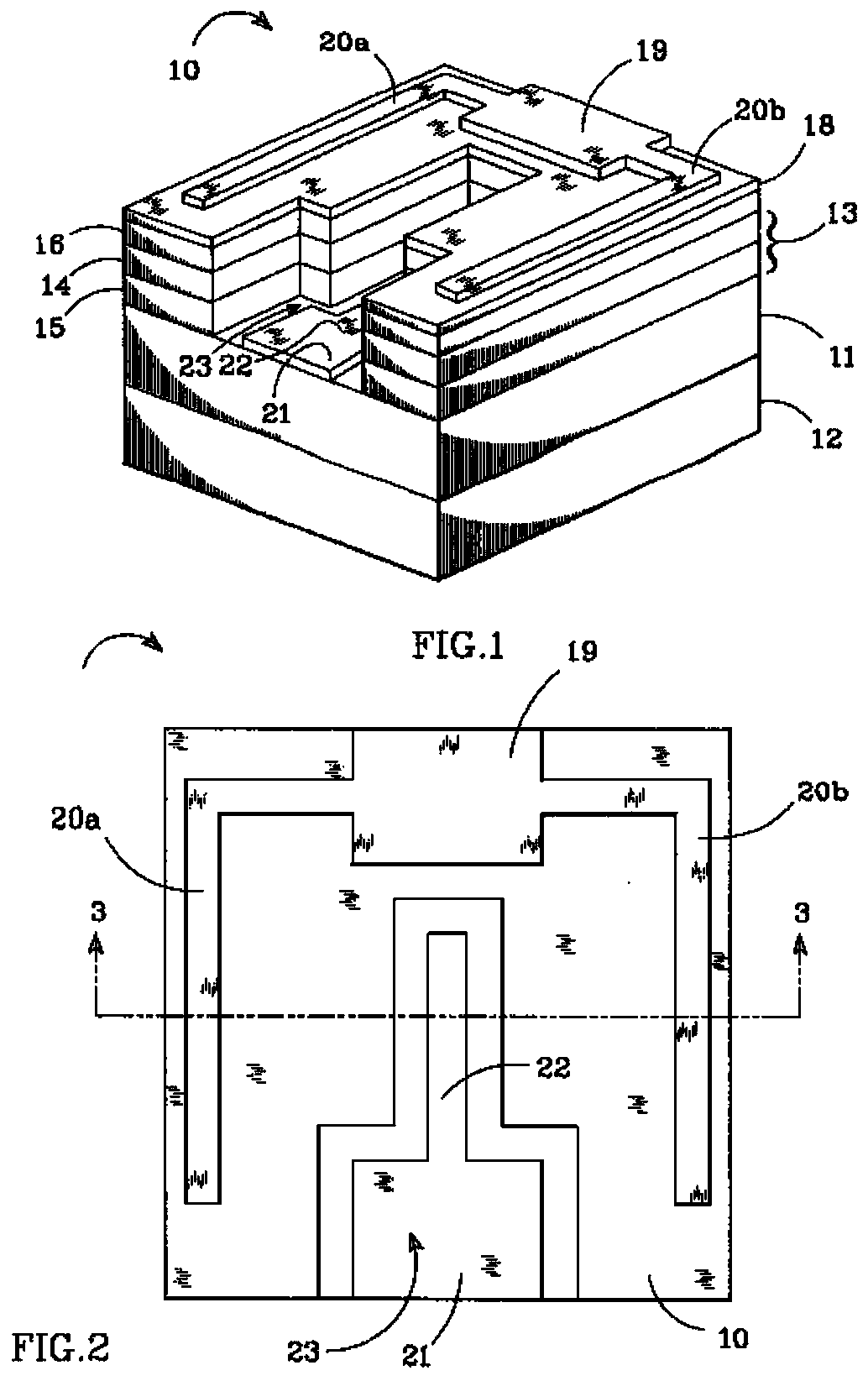

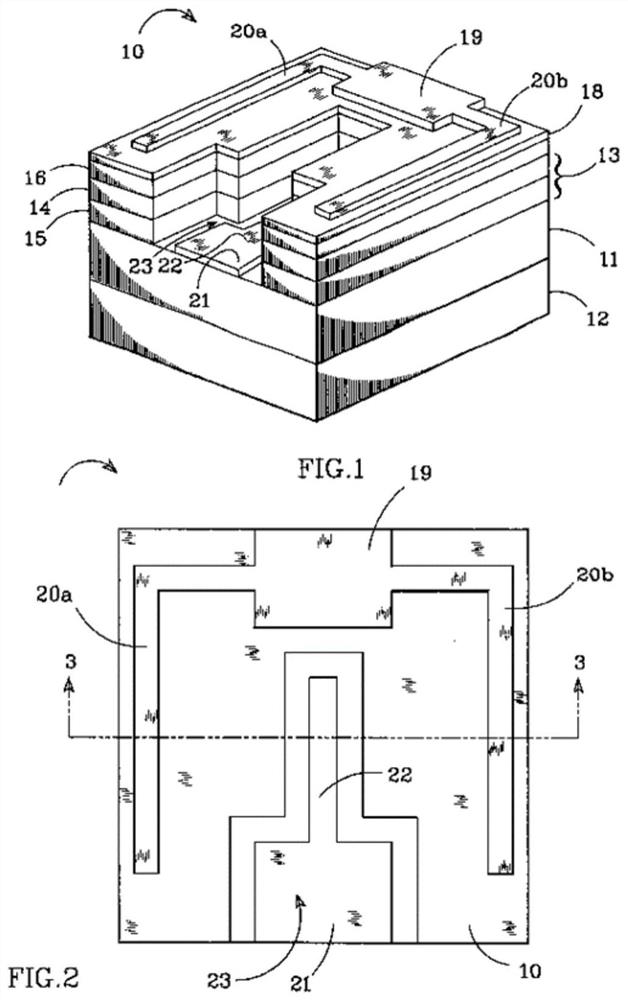

TFT substrate

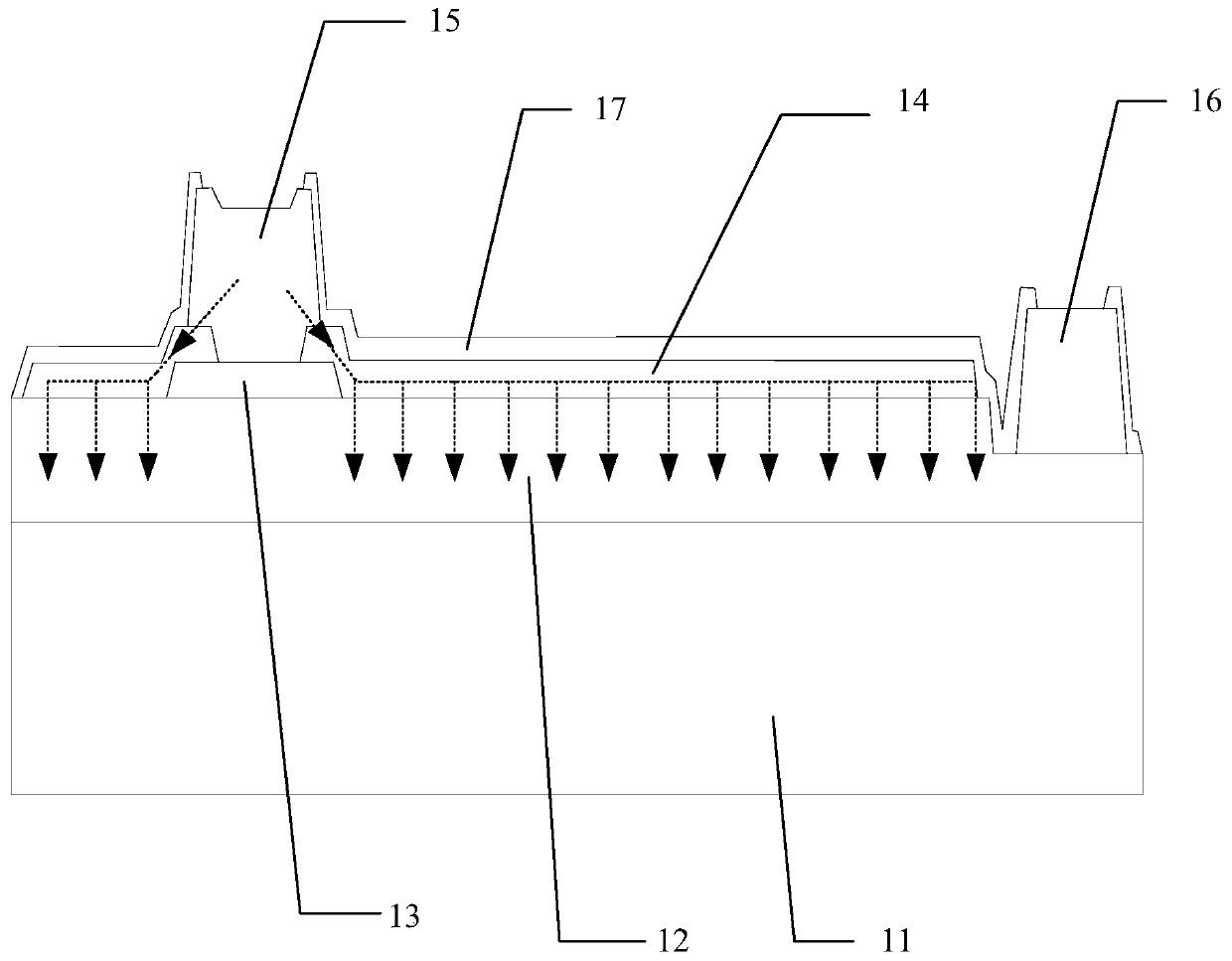

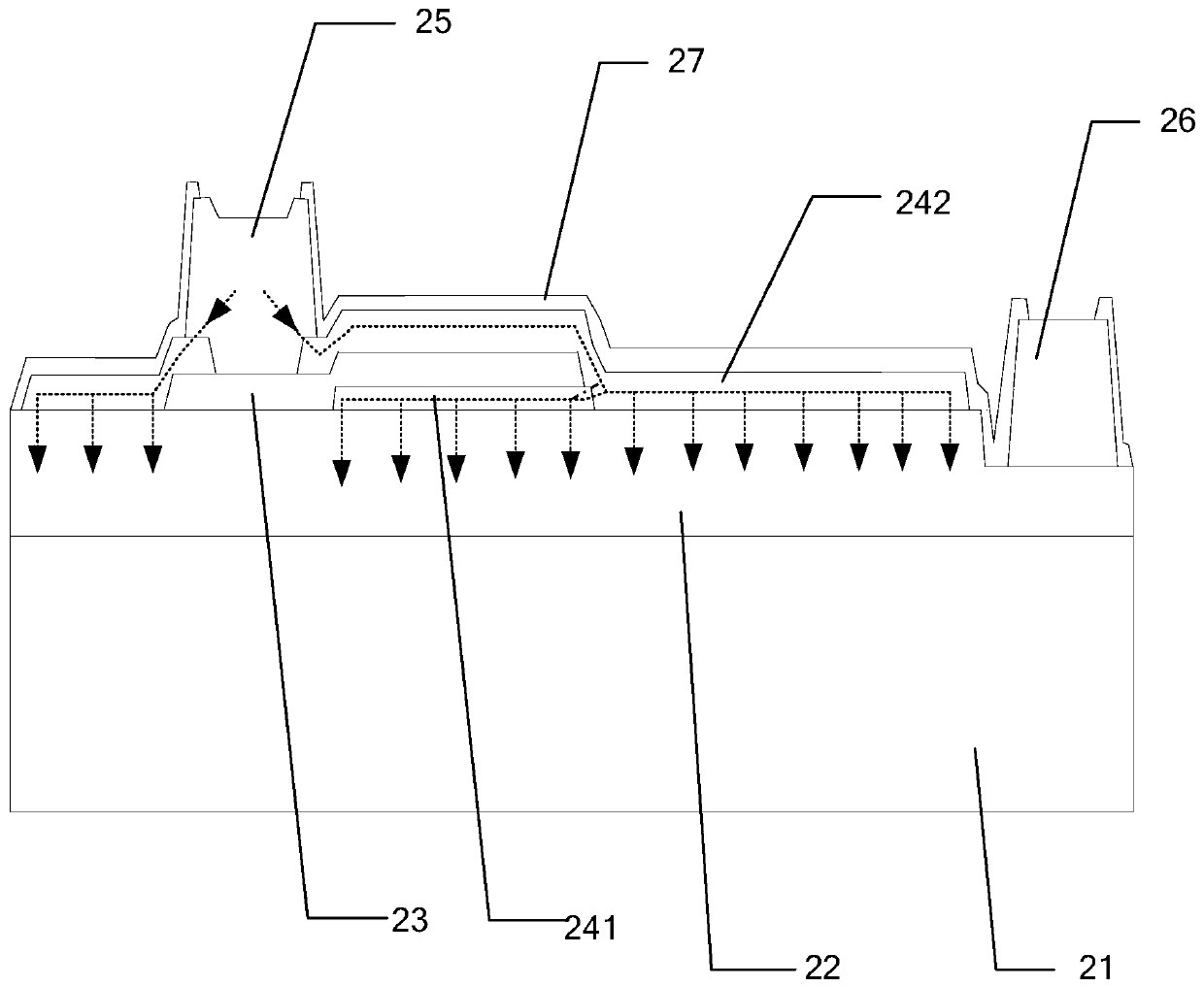

InactiveCN109240005AAvoid accumulation aroundAvoiding the PImura problemSolid-state devicesNon-linear opticsComputational physicsPolyimide

The invention discloses a TFT substrate. The TFT substrate comprises a substrate layer, a thin-film transistor, a color resistance layer, a via hole and a pixel electrode; the via hole penetrates thecolor resistance layer so that the pixel electrode and the thin-film transistor are conducted; the color resistance layer is characterized in that a bulge is formed thereon, the bulge is arranged at one side of the via hole; when coating PI solution (polyimide solution) on the color resistance layer, the bulge can obstruct the surface tension of the PI solution, so that the PI solution can flatlyflow in and fill the via hole. The TFT substrate disclosed by the invention has the advantages that a bulge structure is arranged beside the via hole so as to guide the PI solution to flow in the viahole, the condition that the PI solution is stacked around the via hole due to the problem of the own surface tension, and then the PI mura problem is effectively avoided.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

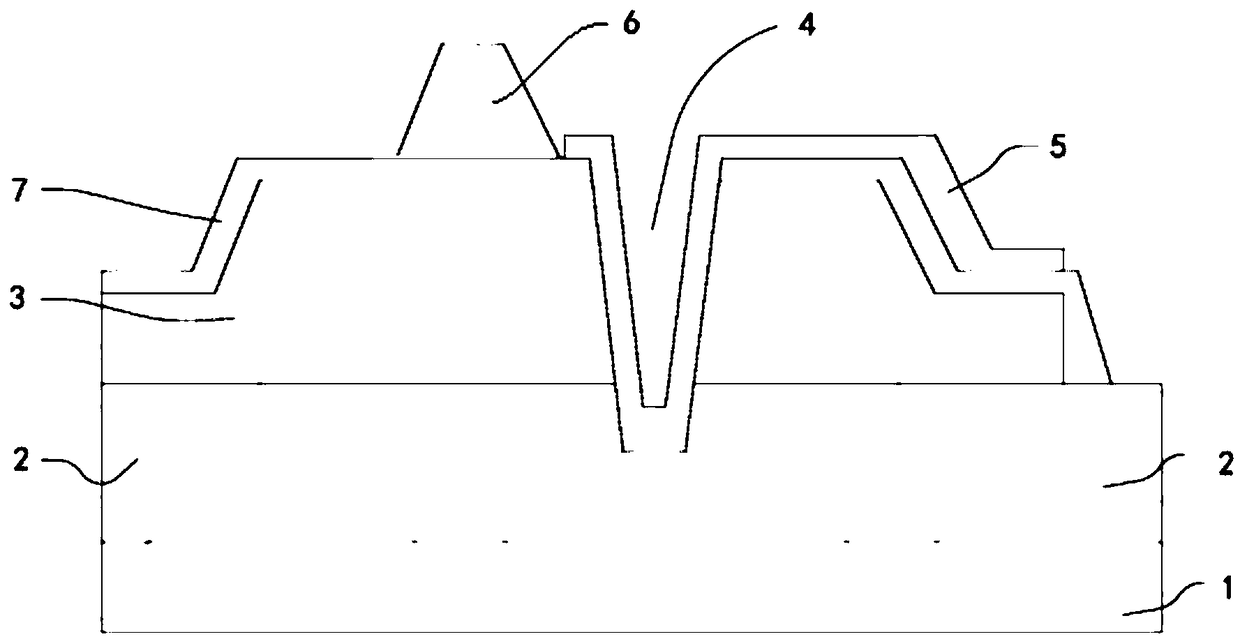

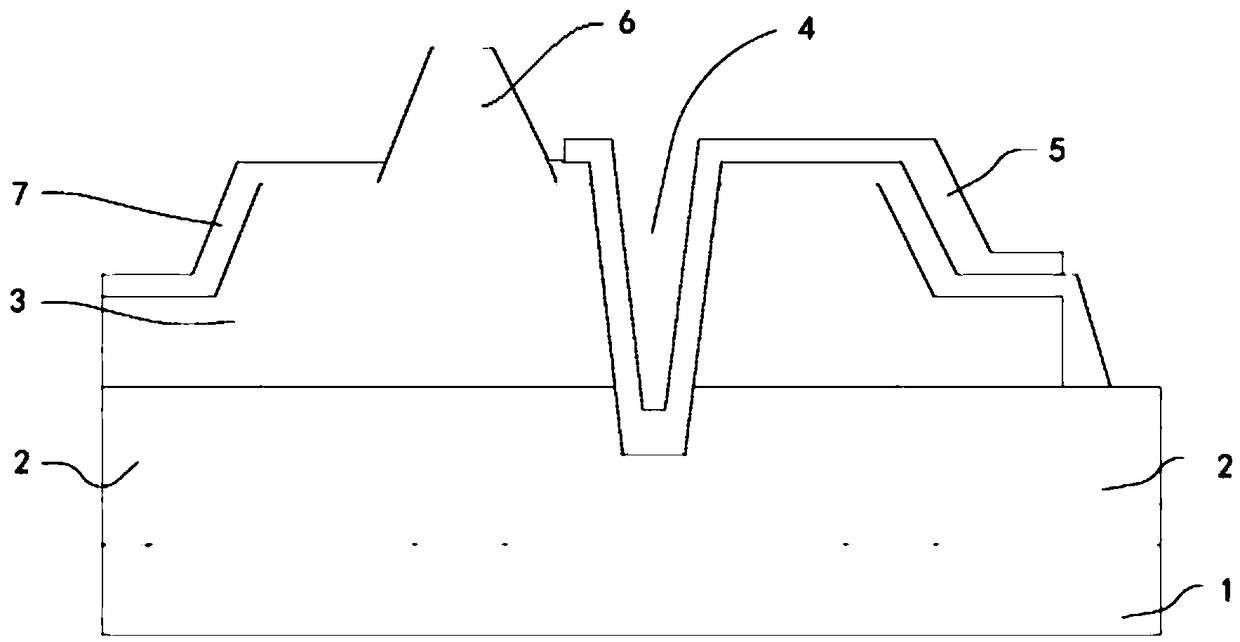

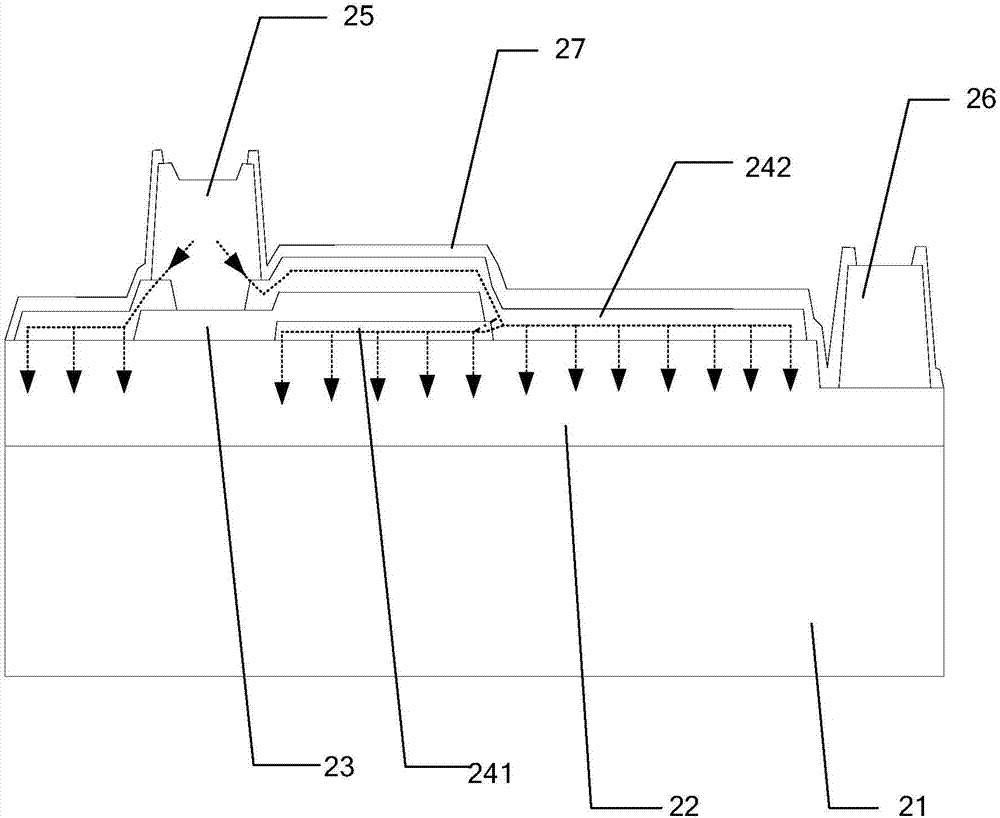

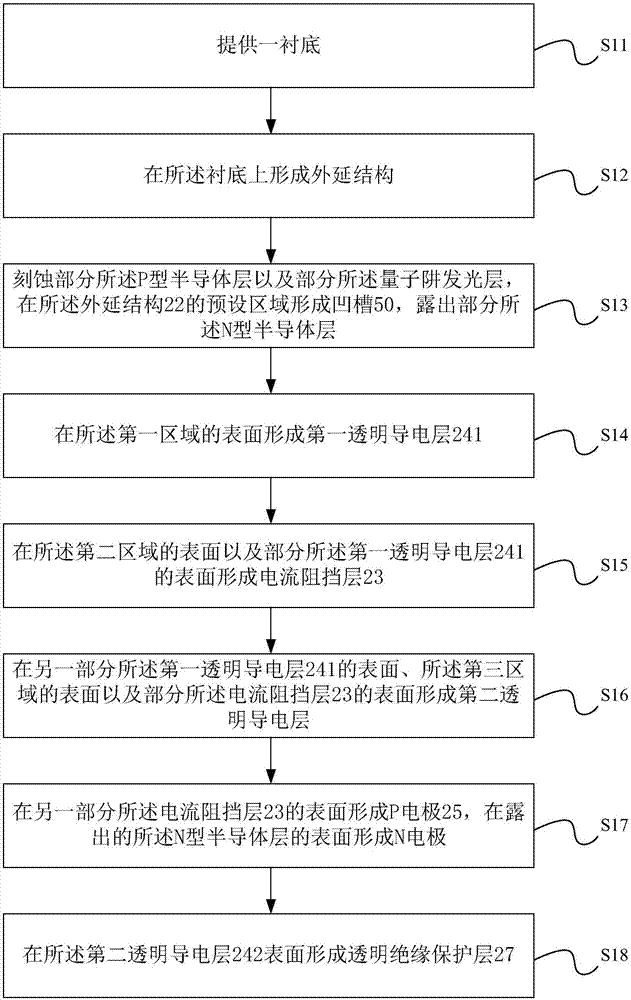

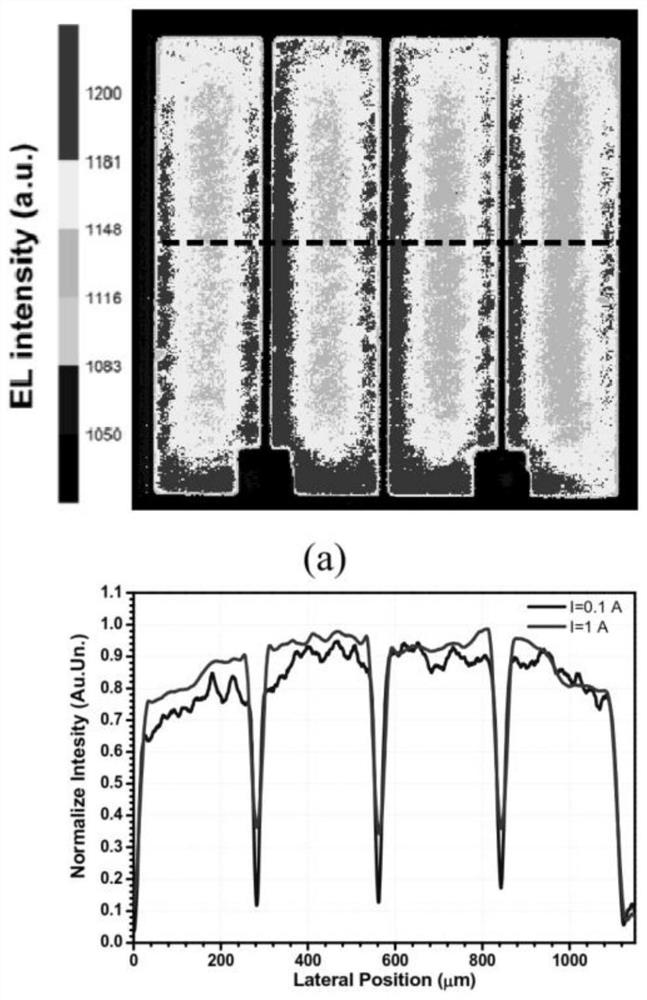

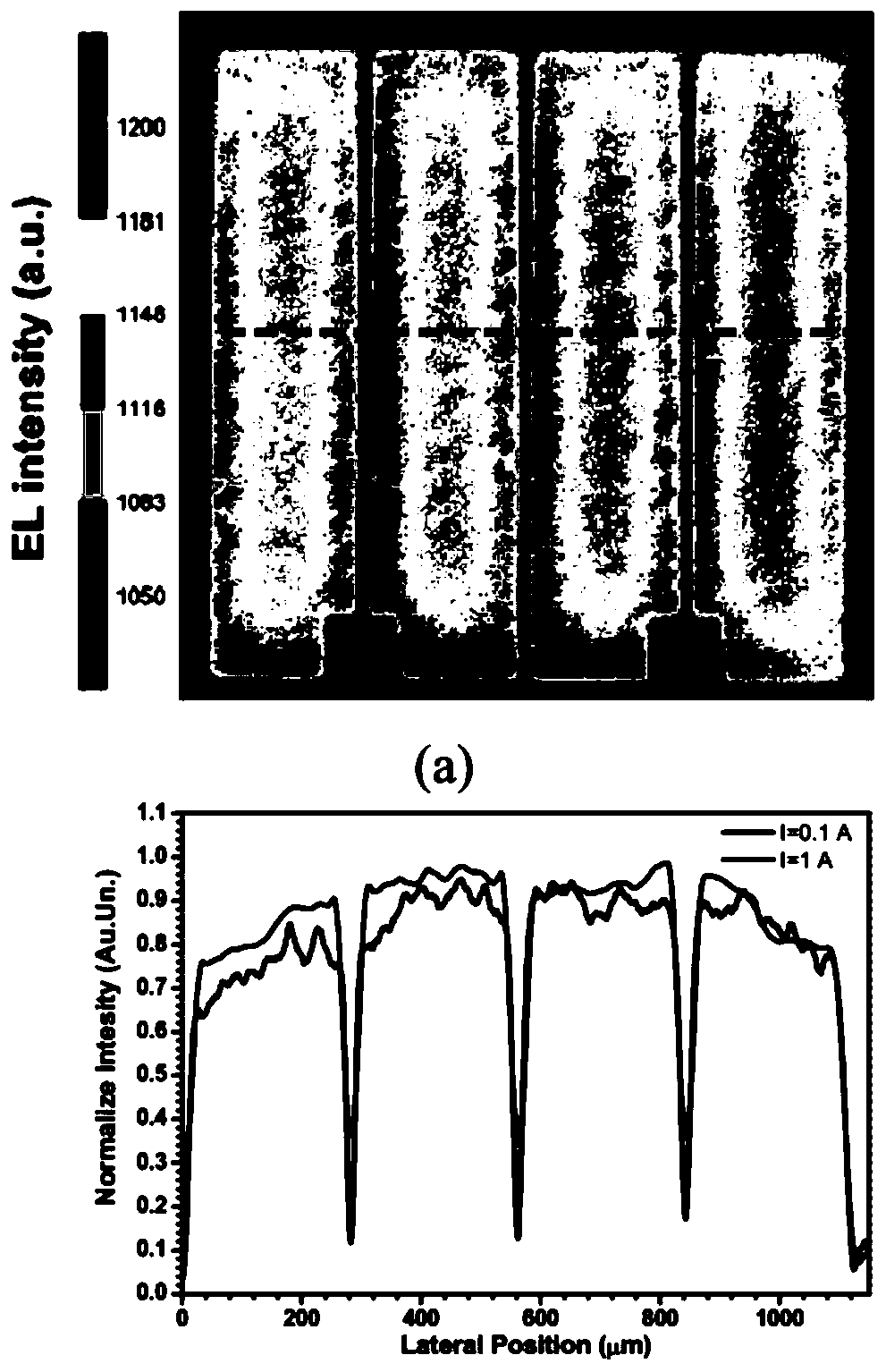

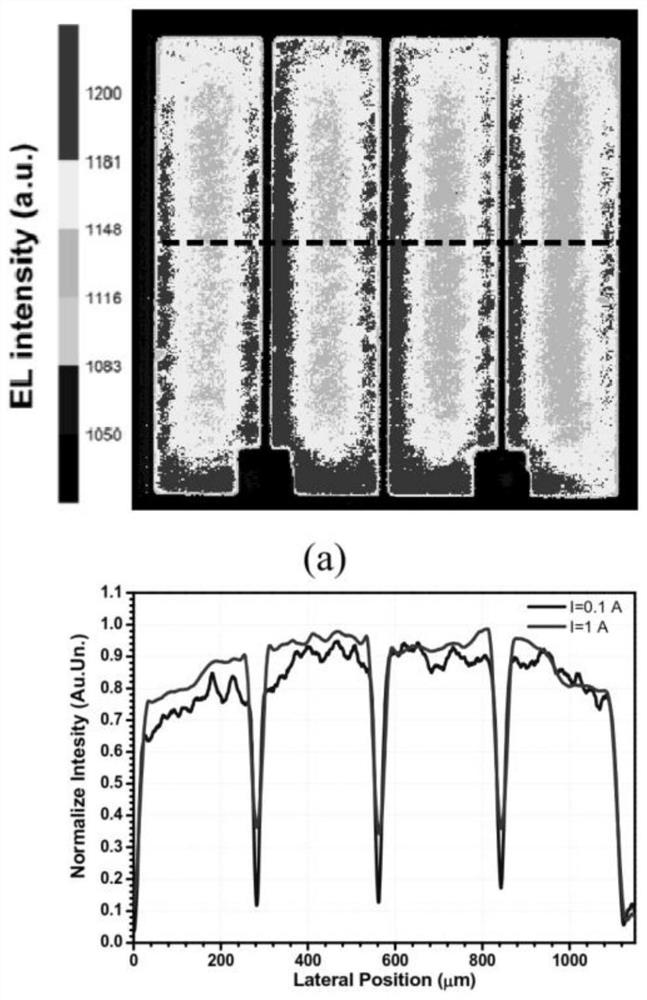

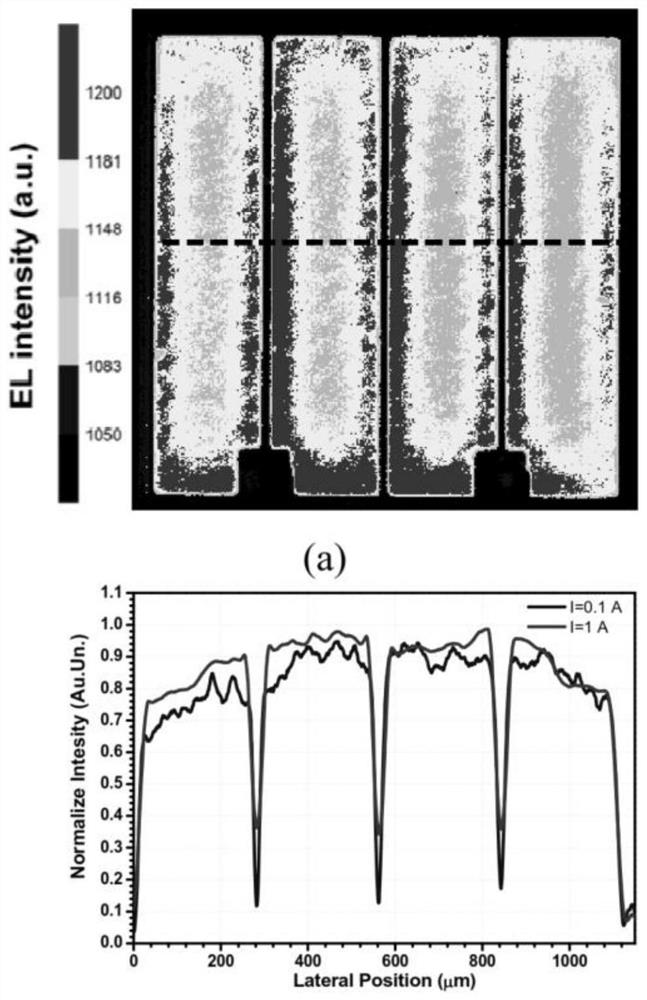

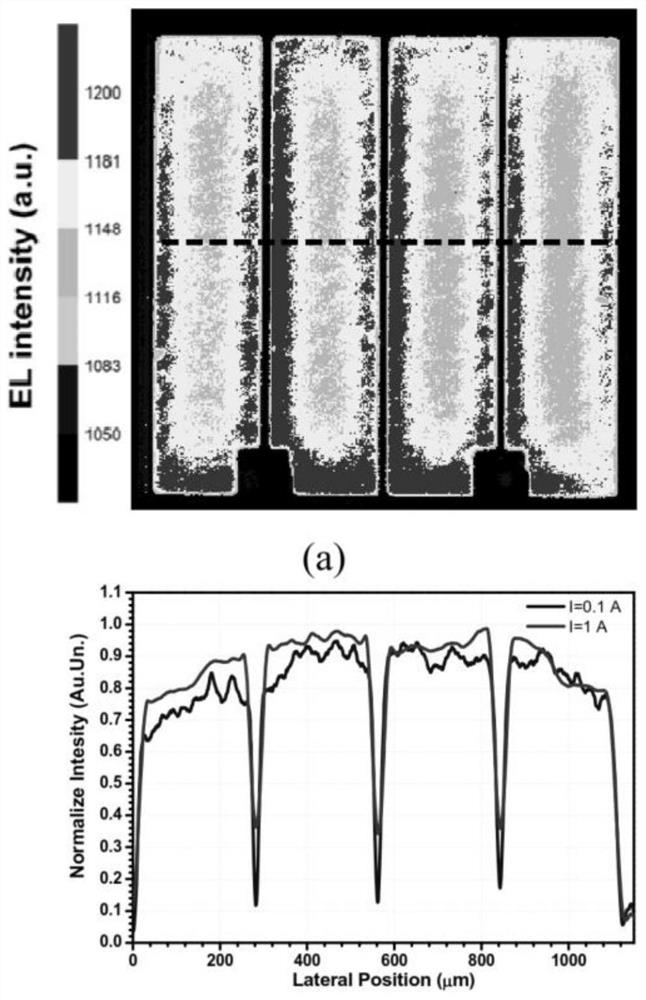

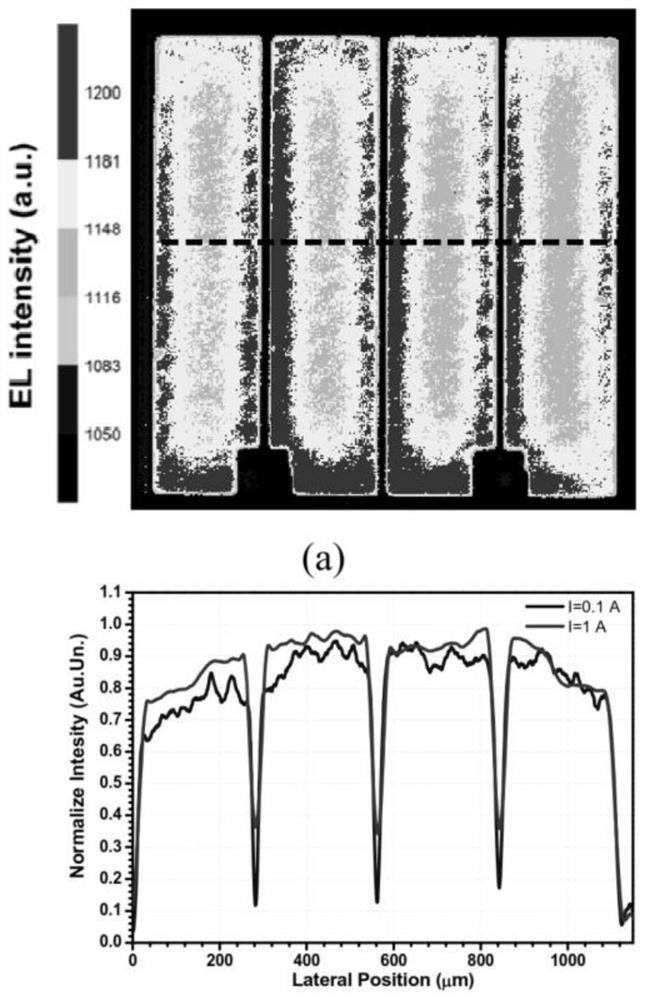

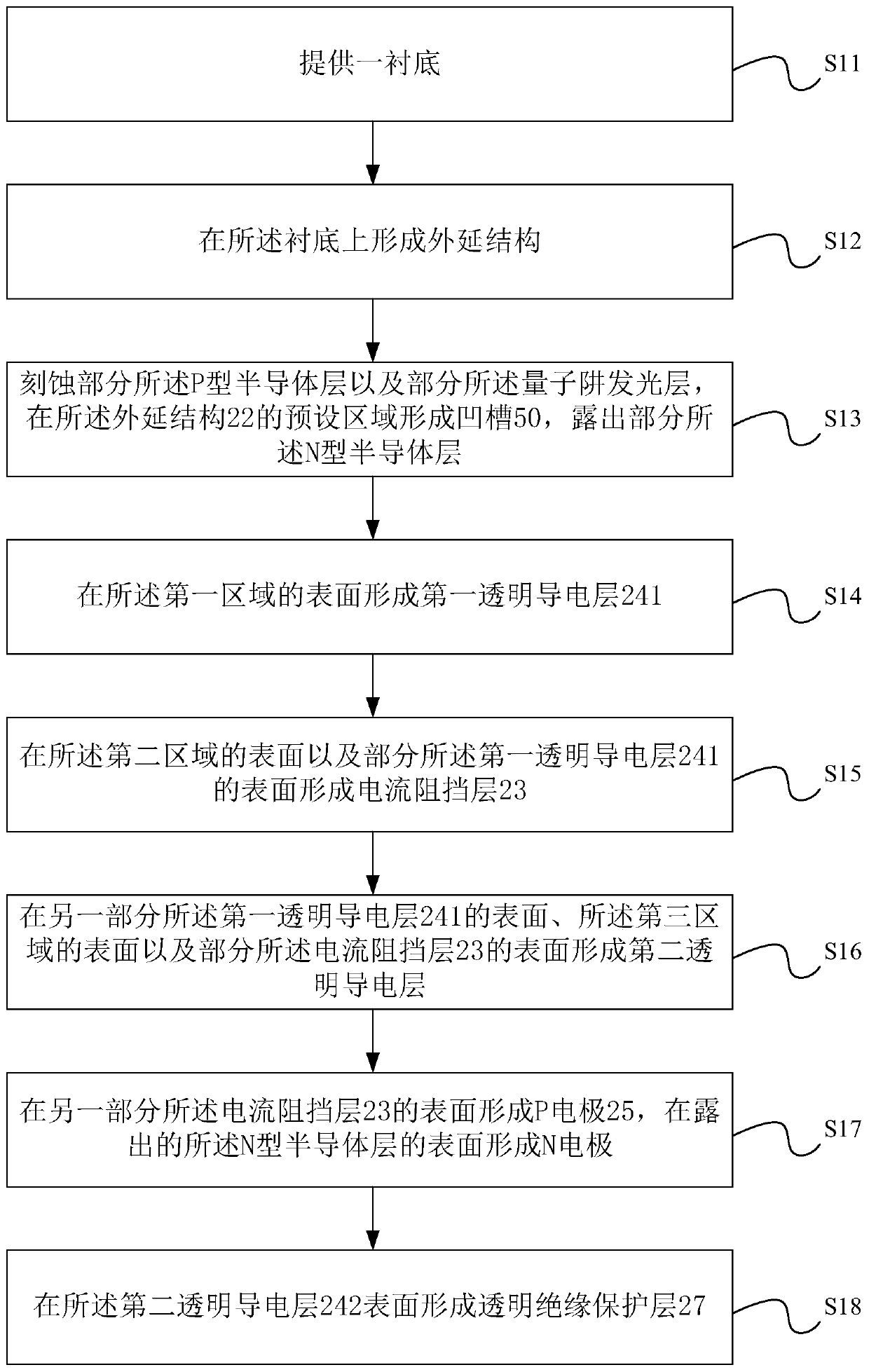

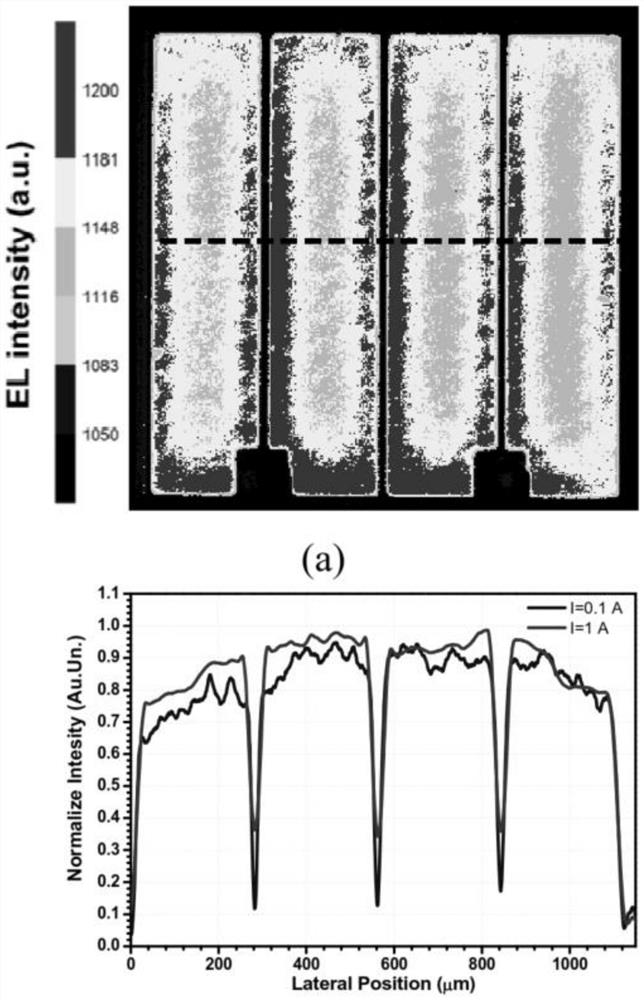

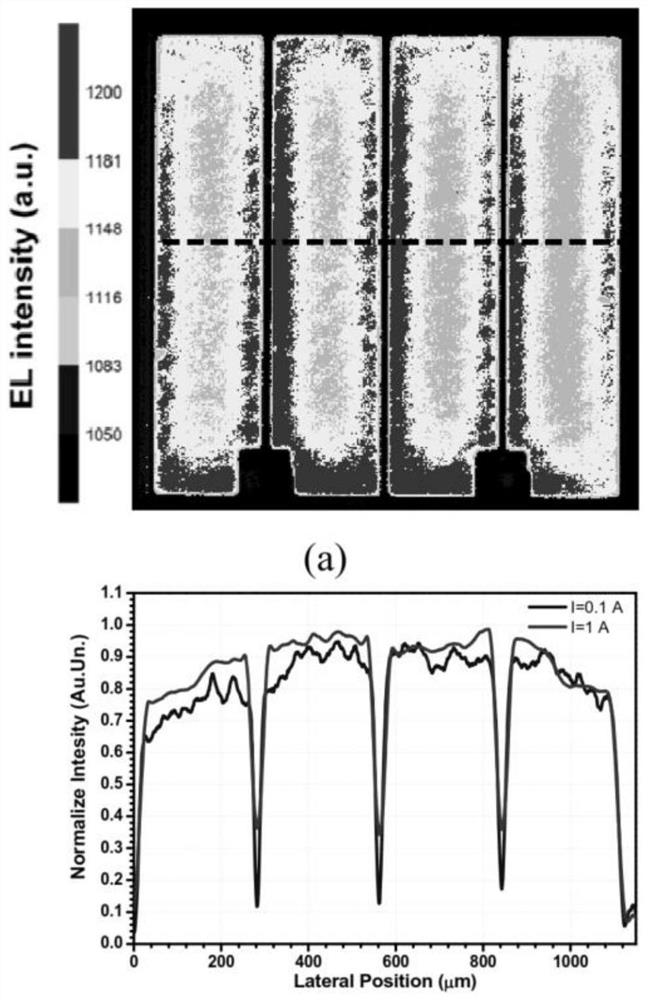

LED chip and manufacturing method thereof

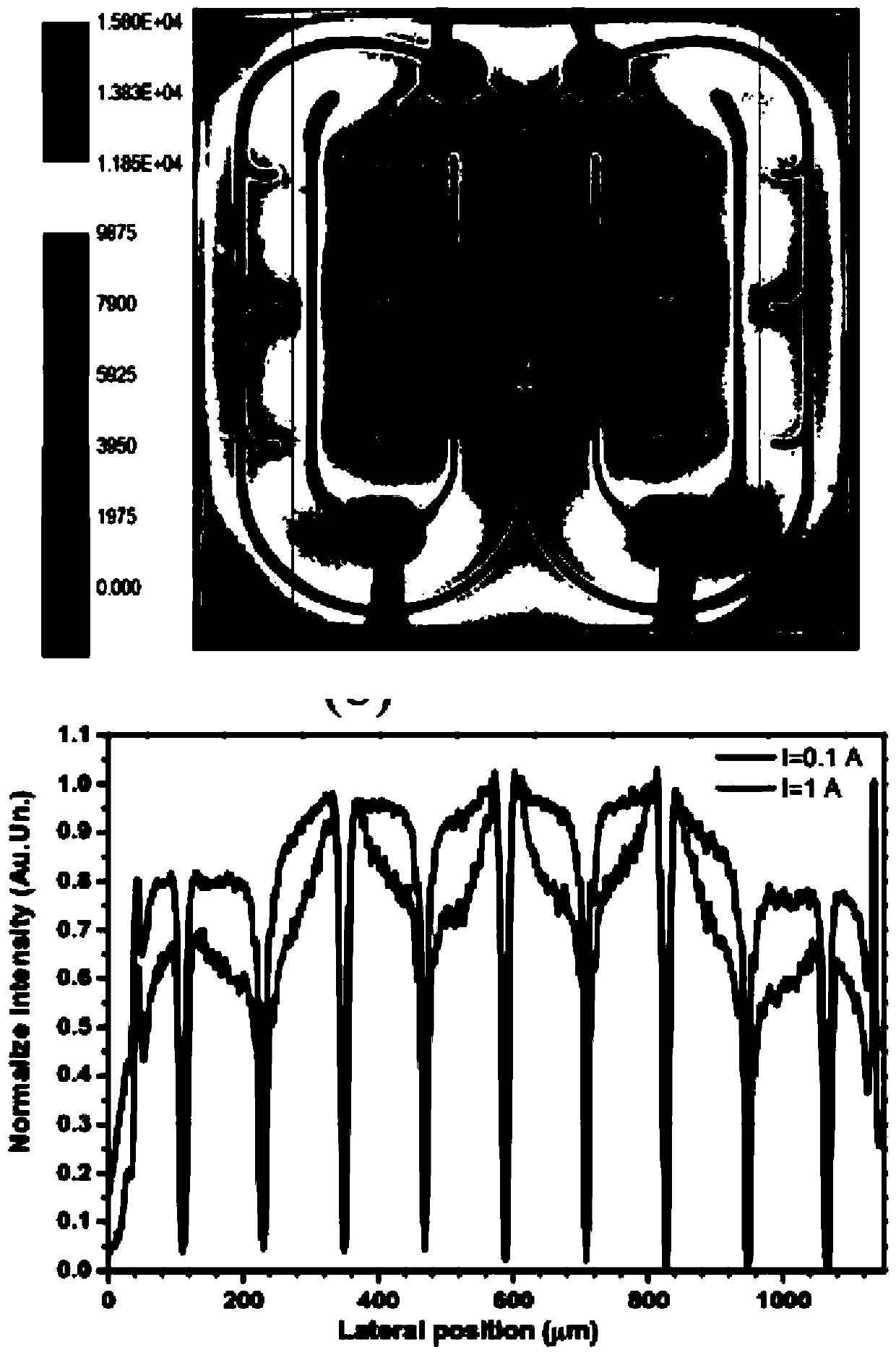

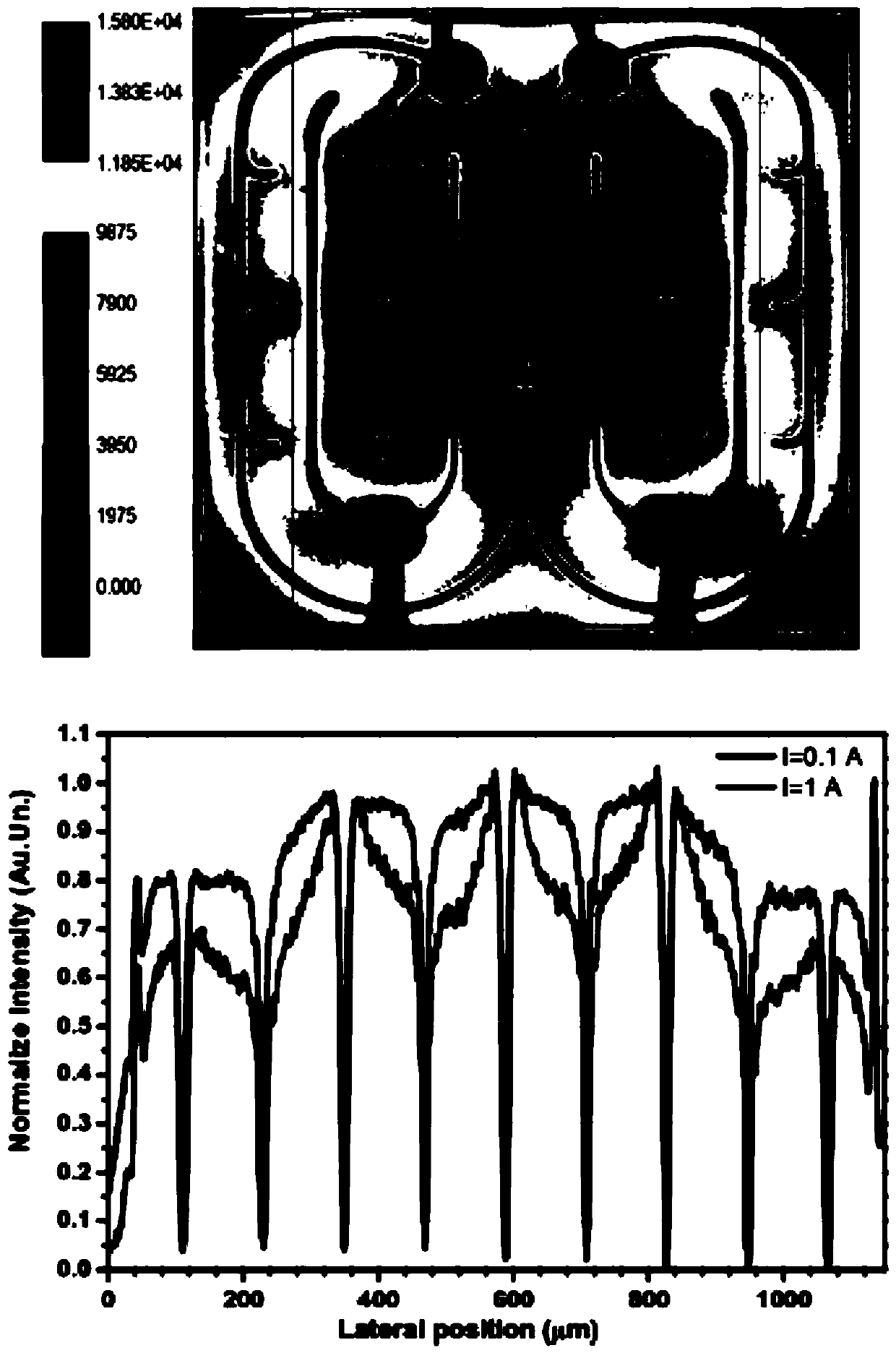

ActiveCN107275446AImprove uniformitySpread evenlySemiconductor devicesQuantum wellLight-emitting diode

The invention discloses an LED chip and a manufacturing method thereof. The LED chip includes a substrate, an epitaxial structure, a first transparent conductive layer, a current blocking layer, a second transparent conductive layer, a P electrode, and an N electrode. The epitaxial structure, which is arranged on the substrate, includes an N-type semiconductor layer, a quantum well light emitting layer and a P-type semiconductor layer arranged in sequence. The epitaxial structure has a groove in a preset region, and the groove is used to expose part of the N-type semiconductor layer. The P-type semiconductor layer has a first region, a second region and a third region. The first transparent conductive layer covers the first region. The current blocking layer covers the second region and one part of the first transparent conductive layer. The second transparent conductive layer covers the other part of the first transparent conductive layer, the third region and one part of the current blocking layer. The P electrode covers the other part of the current blocking layer. The N electrode is arranged in the groove and electrically connected with the N-type semiconductor layer. Through the technical scheme, the problem that the current in an LED chip diffuses unevenly is solved. The light emission uniformity of the LED chip is improved.

Owner:XIAMEN CHANGELIGHT CO LTD

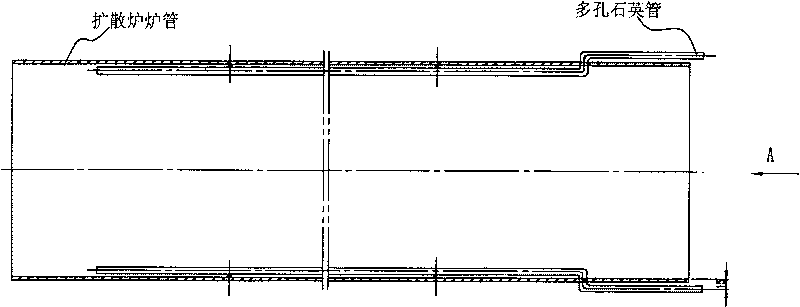

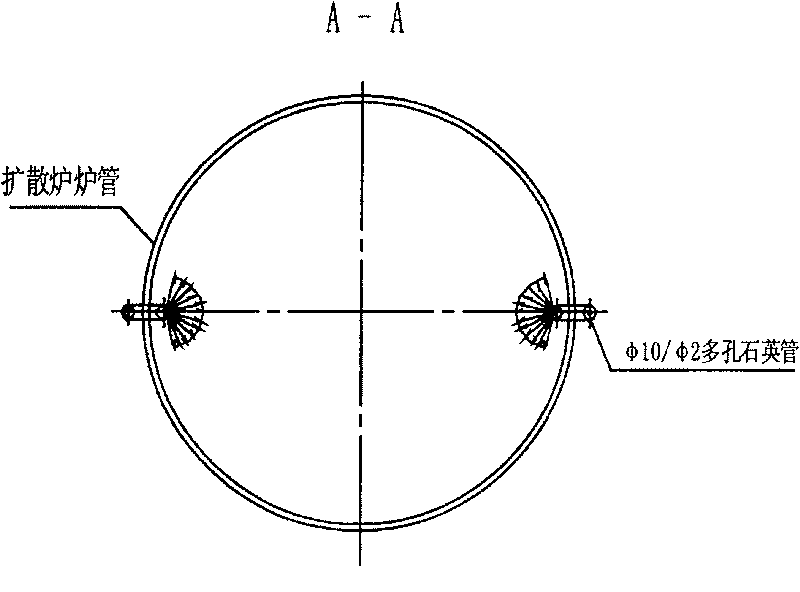

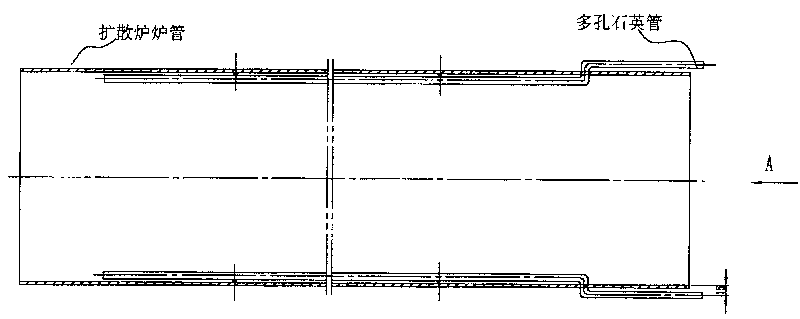

Semi-conductor silicon chip liquid stage source diffusion furnace

InactiveCN101136325AResolve uneven diffusionEliminate the effects ofSemiconductor/solid-state device manufacturingSilicon chipOpen structure

This invention discloses a diffusion furnace of semiconductor silicon plate liquid source including: a diffusion tube and quartz tubes for spraying the source, in which, the diffusion furnace tube is in a structure of two ends open, 2-10 source-spraying quartz tubes are installed on the internal wall of the tube with the diameter of pha2-pha 10mm, capillary holes in uniform aperture are distributed on the wall of the tube and the exit end of the tube is connected with the source bottle of the liquid state diffusion source.

Owner:SHANGHAI AEROSPACE AUTOMOBILE ELECTROMECHANICAL CO LTD +1

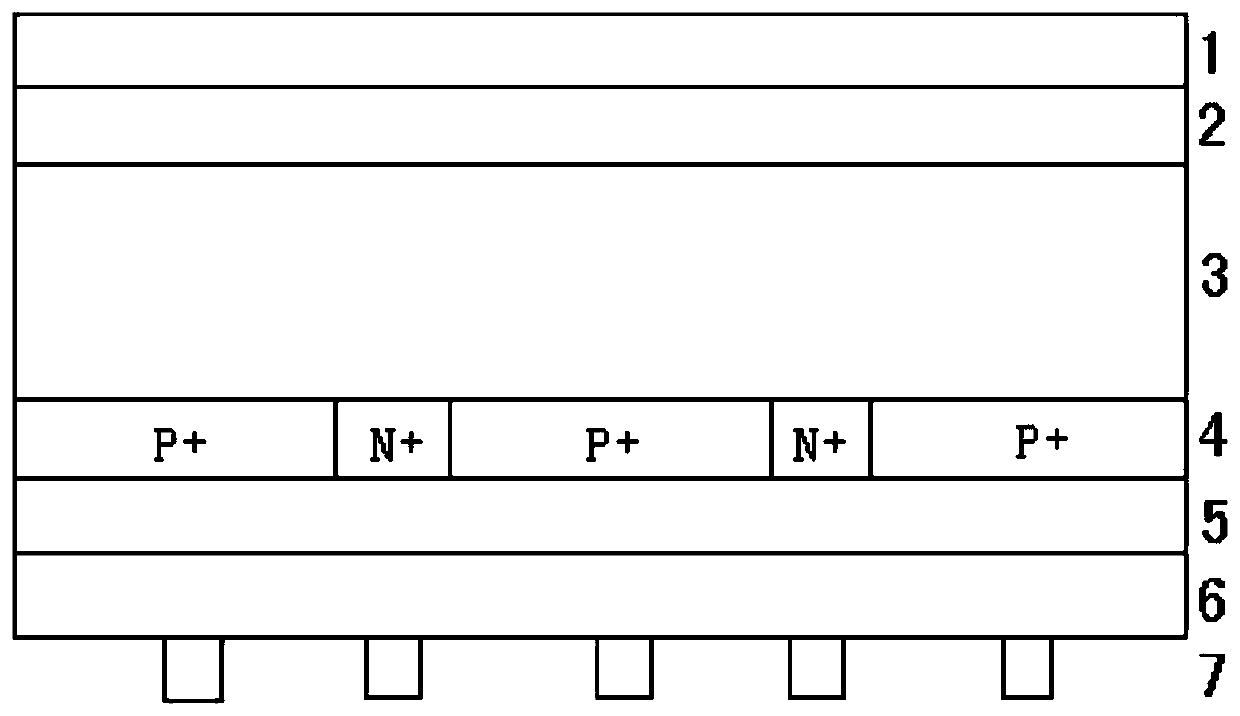

Interdigital PN-junction battery structure of IBC battery and fabrication method of interdigital PN-junction battery structure

PendingCN110600561AResolve uneven diffusionReduce manufacturing costFinal product manufactureSemiconductor/solid-state device manufacturingPicosecond laserAmorphous silicon

The invention discloses an interdigital PN-junction battery structure of an IBC battery and a fabrication method of the interdigital PN-junction battery structure. The battery structure sequentially comprises a silicon nitride anti-reflection film layer, a first silicon nitride thin film layer, an N-type single-crystal wafer substrate, an interdigital P region and N region layer, a second siliconnitride thin film layer and a Al2O3 thin film layer. The fabrication method comprises the steps of doping a back surface of the N-type single-crystal wafer substrate by a mode of printing and picoseconds laser doping, and performing phosphorus doping on a region which is not printed; growing a silicon nitride thin film by a mode of oxidization; depositing an intrinsic amorphous silicon layer; depositing the silicon nitride anti-reflection thin film; depositing the Al2O3 thin film; and opening a hole, and printing aluminum paste on the back surface to form a metal electrode. By the battery structure and the preparation method, the manufacturing process is reduced, and the manufacturing cost of the IBC battery is reduced; and moreover, the fabrication of high-quality PN on the back surface of the IBC battery can be achieved, and great output of an internal current of the IBC battery is achieved.

Owner:YELLOW RIVER PHOTOVOLTAIC IND TECH CO LTD +2

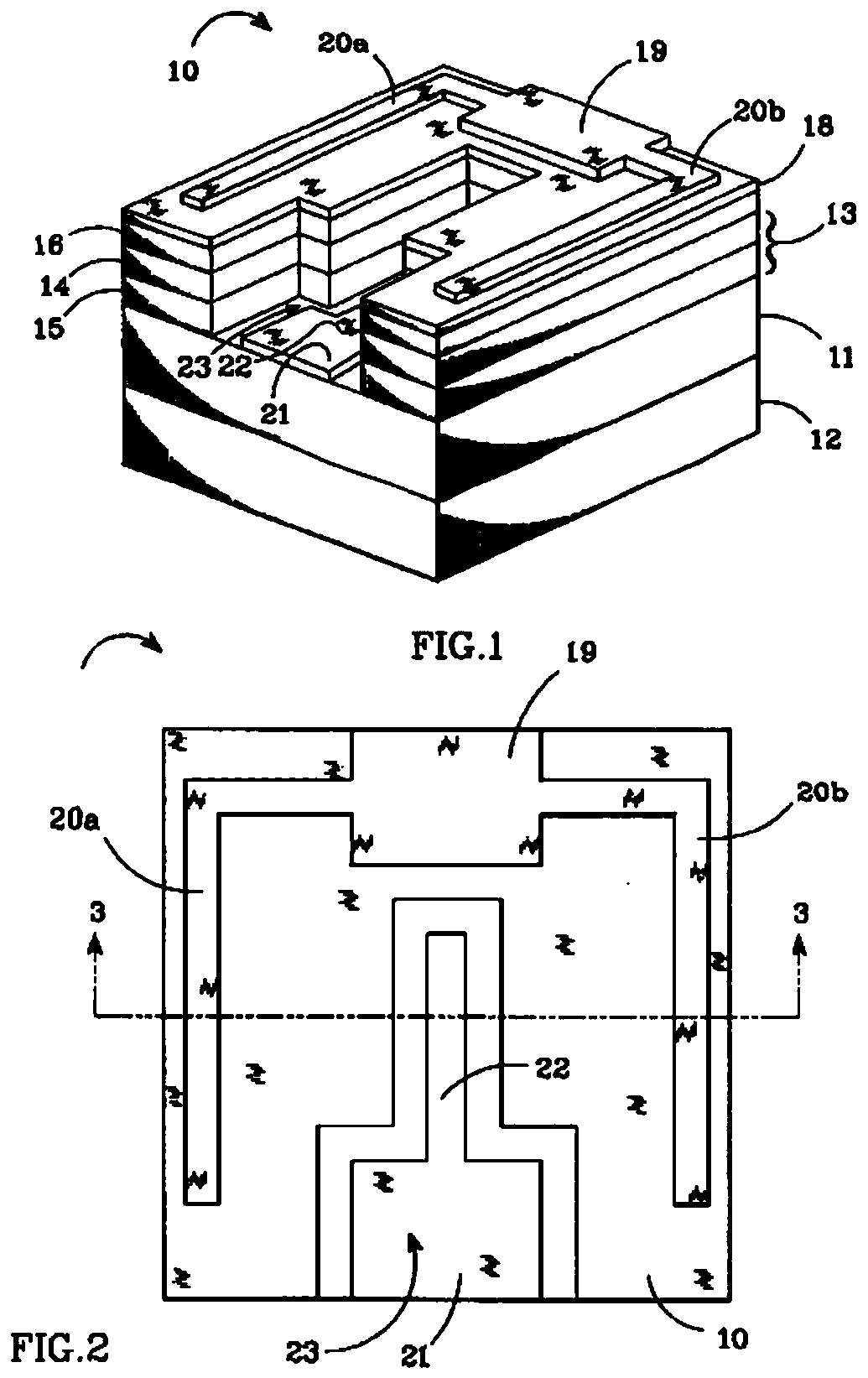

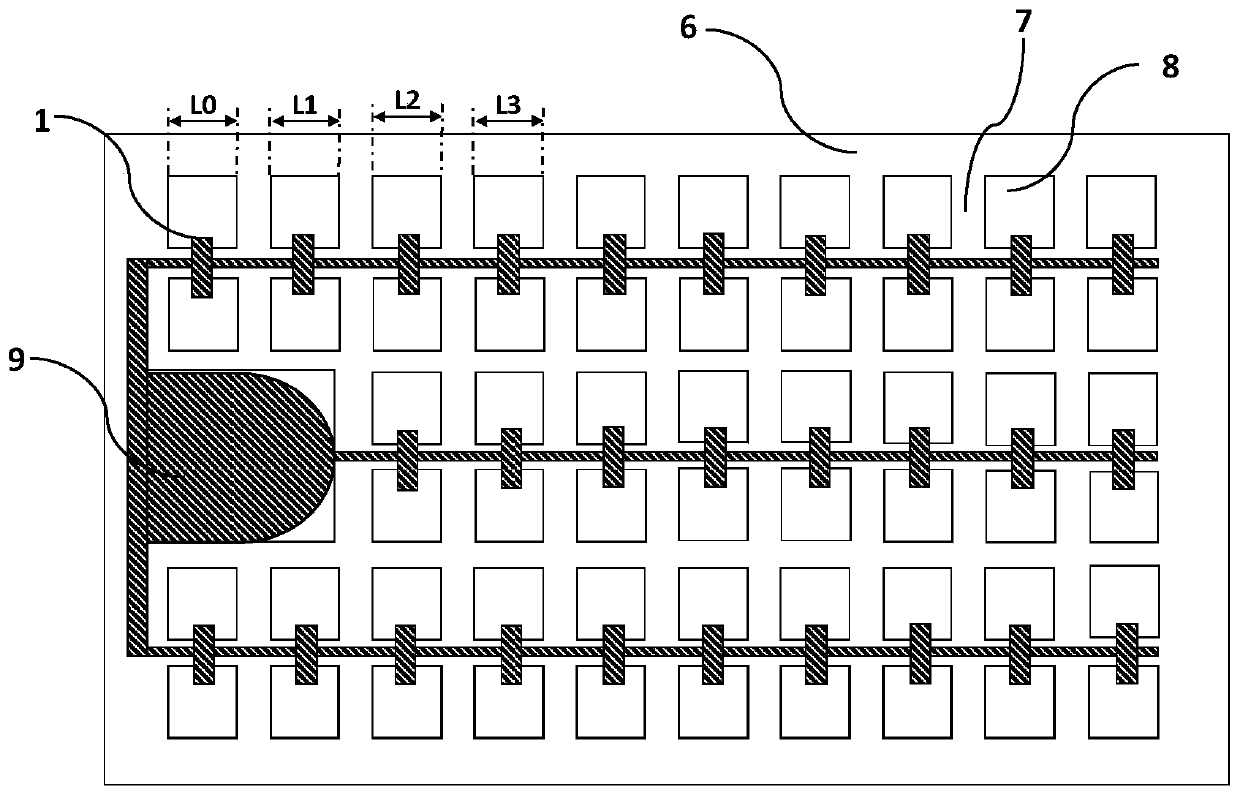

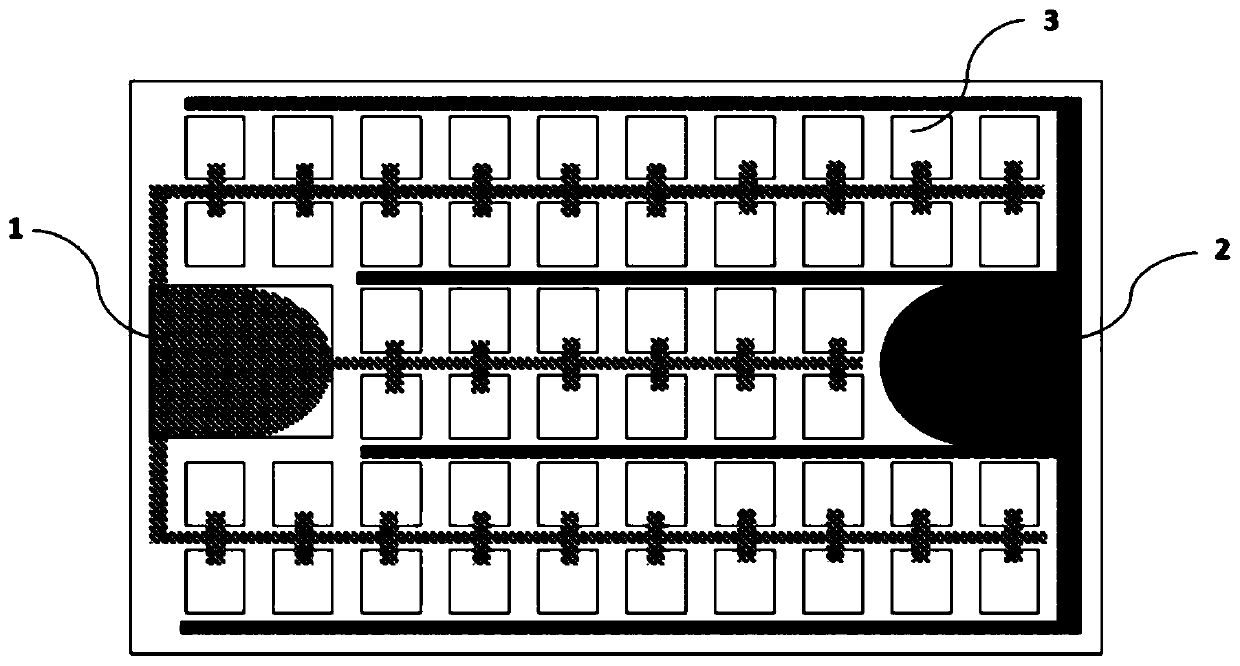

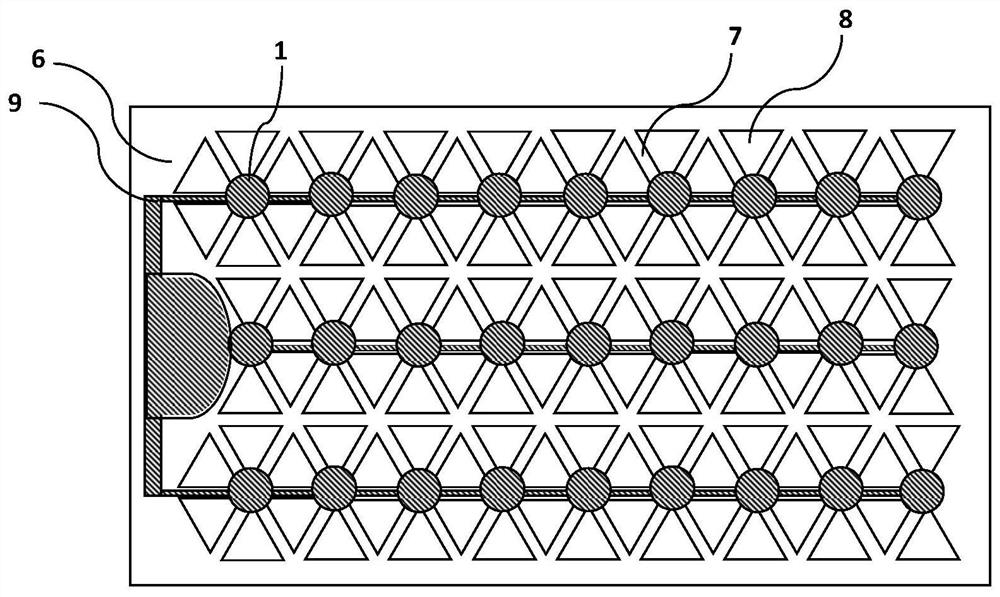

Positively-mounted integrated unit diode chip

ActiveCN109920782AImprove photoelectric conversion efficiencyImprove light extraction efficiencySolid-state devicesSemiconductor devicesPhysicsConduction type

This invention relates to the field of semiconductor materials and device processes, and in particular to semiconductor photoelectric devices. The invention provides a positively-mounted integrated unit diode chip, comprising a first conduction type electrode, a second conduction type electrode, and a diode mesa structure located between the first conduction type electrode and the second conduction type electrode, the diode mesa structure comprises n diode units, the n diode units are arranged in a geometric shape, and the width of the electrode width and the area of the mesa structure are determined according to the current. By adoption of the positively-mounted integrated unit diode chip provided by the invention, the technical problem that the diode structure has great limitation on three important parameters, that is, lumen efficiency, lumen density output and lumen cost in the prior art is solved, the lumen output of the unit diode chip in a unit area is improved, and the lumen cost is reduced.

Owner:SHENZHEN INST OF WIDE BANDGAP SEMICON

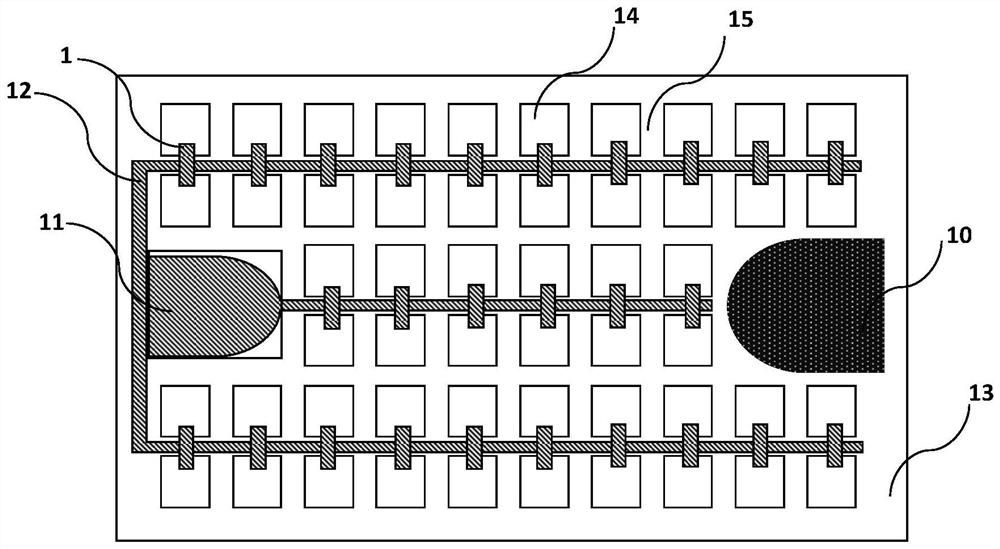

Normally-equipped integrated unit diode chip

ActiveCN110931610AWeak light absorptionImprove light extraction efficiencySolid-state devicesSemiconductor devicesDielectric layerMaterials science

The invention provides a normally-equipped integrated unit diode chip. The normally-equipped integrated unit diode chip comprises a first conductive type electrode, a second conductive type electrodeand a diode mesa structure, wherein the diode mesa structure comprises n diode units. Wherein n is greater than or equal to 2, and the first conductive type layers, the quantum well active regions, the second conductive type layers and the transparent electrodes of the n diode units are sequentially stacked to form a step structure. The second conductive type electrode partially covers one side, far away from the second conductive type layer, of the transparent electrode; and the insulating dielectric layer covers the first conductive type layer exposed out of the step structure, extends to the position between the second conductive type layer and the transparent electrode along the side wall of the step structure and partially covers the second conductive type layer to serve as a currentblocking layer between the second conductive type electrode and the second conductive type layer. According to the normally-equipped integrated unit diode chip, the lumen output of the unit area unitdiode chip is improved, and the lumen cost is reduced.

Owner:纳微朗科技(深圳)有限公司

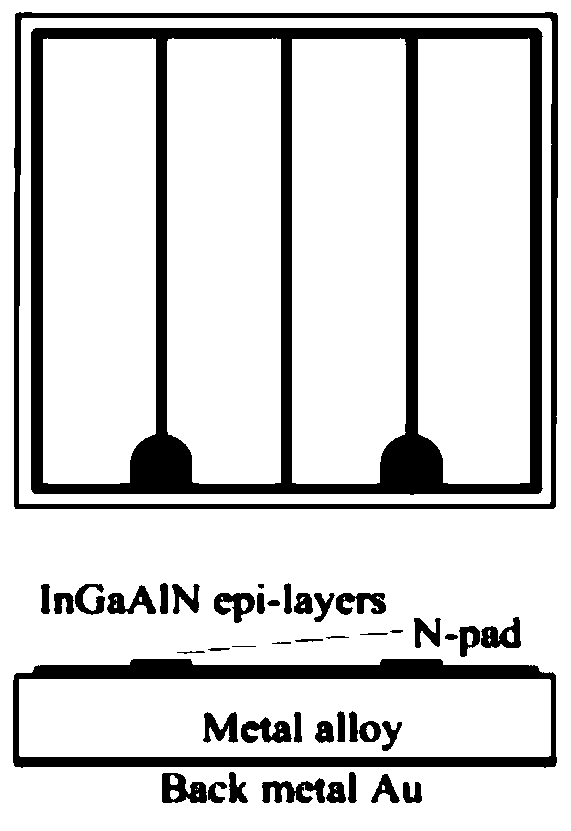

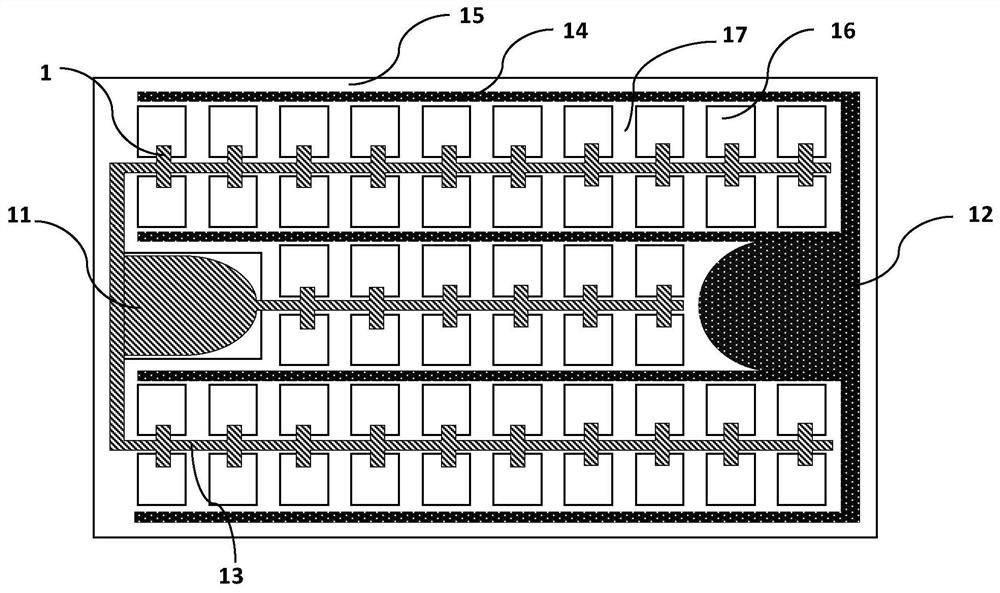

Vertical structure LED chip with novel electrode wire arrangement

PendingCN111900182AReduce layoutImprove diffusion abilitySolid-state devicesSemiconductor devicesOhmic contactElectric current flow

The invention provides a vertical structure LED chip with novel electrode wire arrangement. The vertical structure LED chip comprises a first conductive type electrode, a second conductive type electrode and a diode mesa structure located on the first conductive type electrode. The second conductive type electrode comprises a second conductive type electrode wire and a second conductive type bonding pad; the diode mesa structure comprises n diode units and a trench structure, and n is greater than or equal to 2; and the second conductive type electrode wire is in ohmic contact with the tops ofthe n diode units, and partially or completely extends from the front end surfaces to the rear end surfaces of the n diode units. The arrangement of the electrode wires between the units is reduced,the current diffusion effect is enhanced while the lightemitting area is increased, the technical problem that in the prior art, a diode structure is greatly limited in three important parameters including lumen efficiency, lumen density output and lumen cost is solved, lumen output of a unit area chip is improved, and lumen cost is reduced.

Owner:纳微朗科技(深圳)有限公司

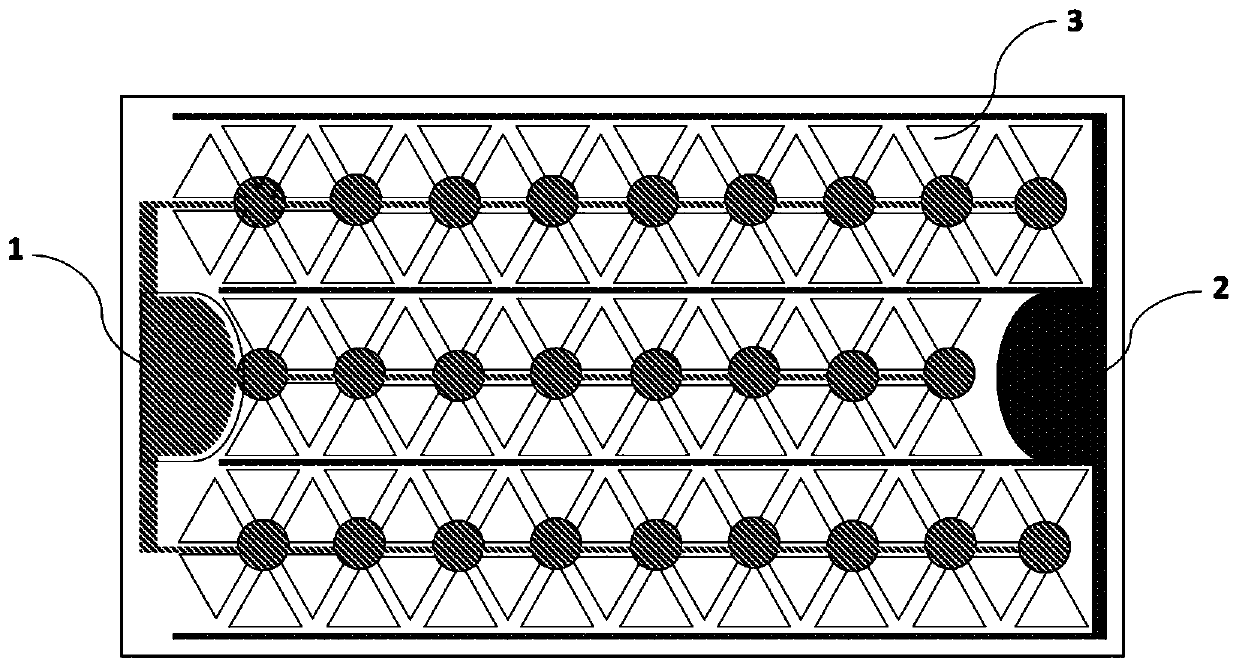

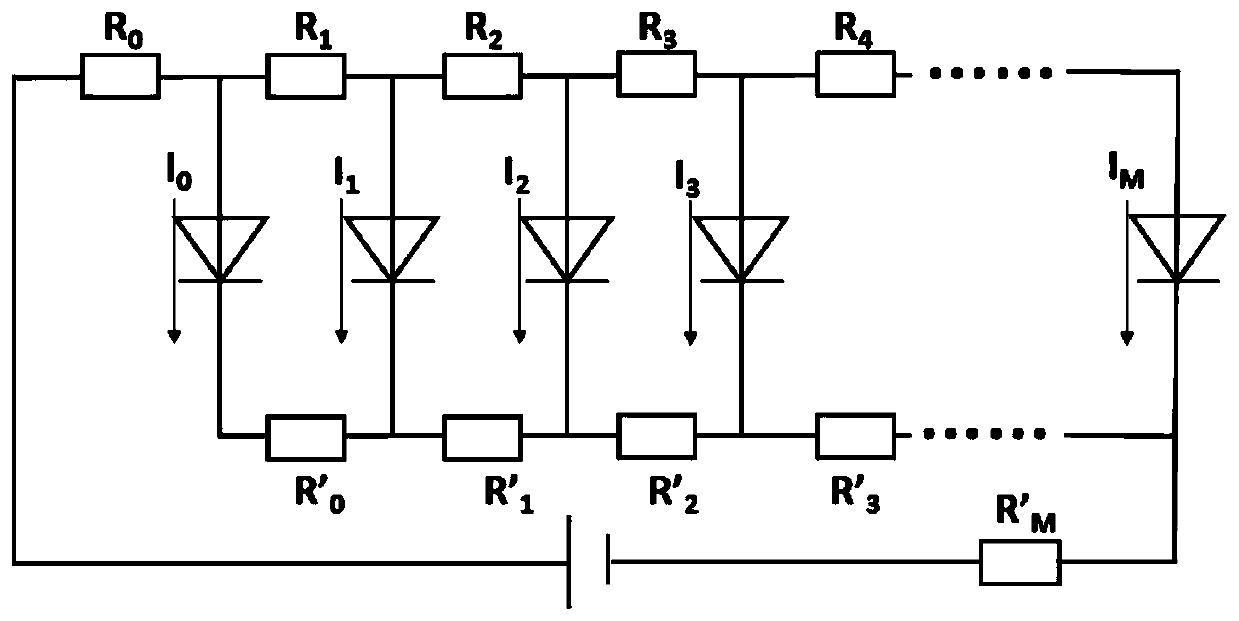

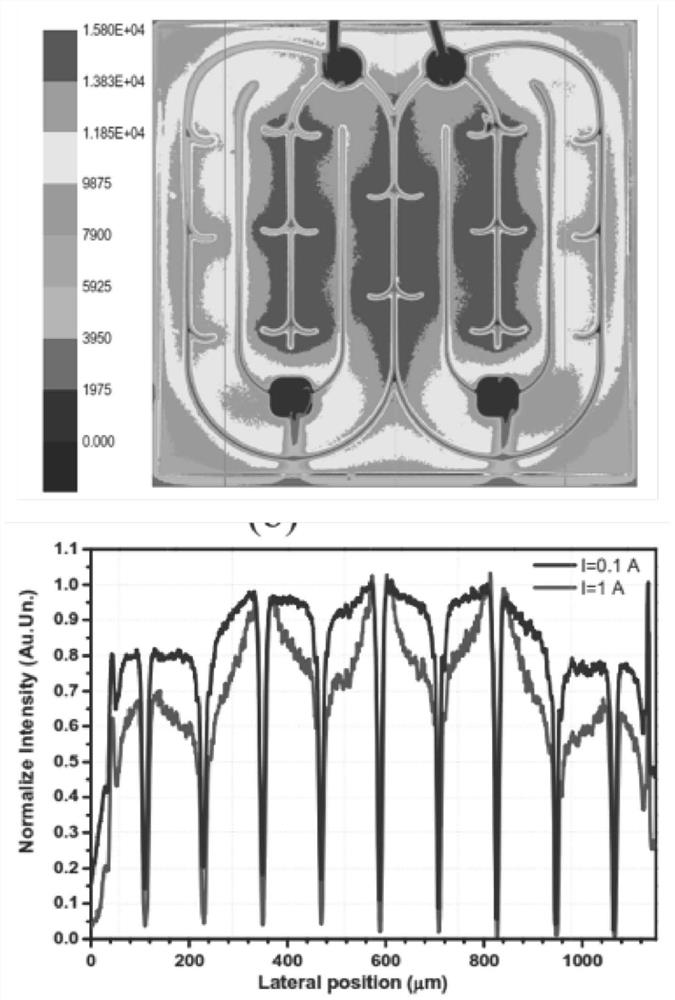

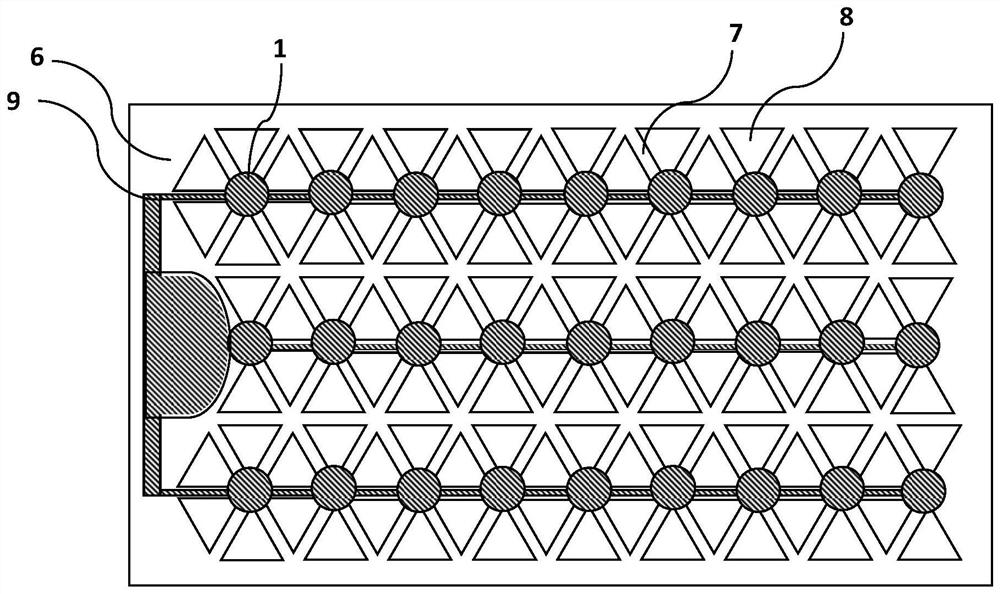

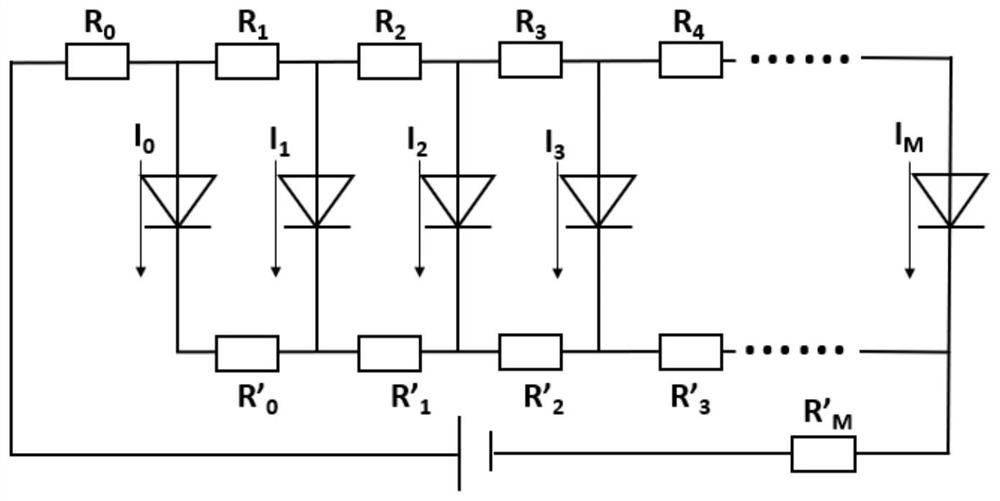

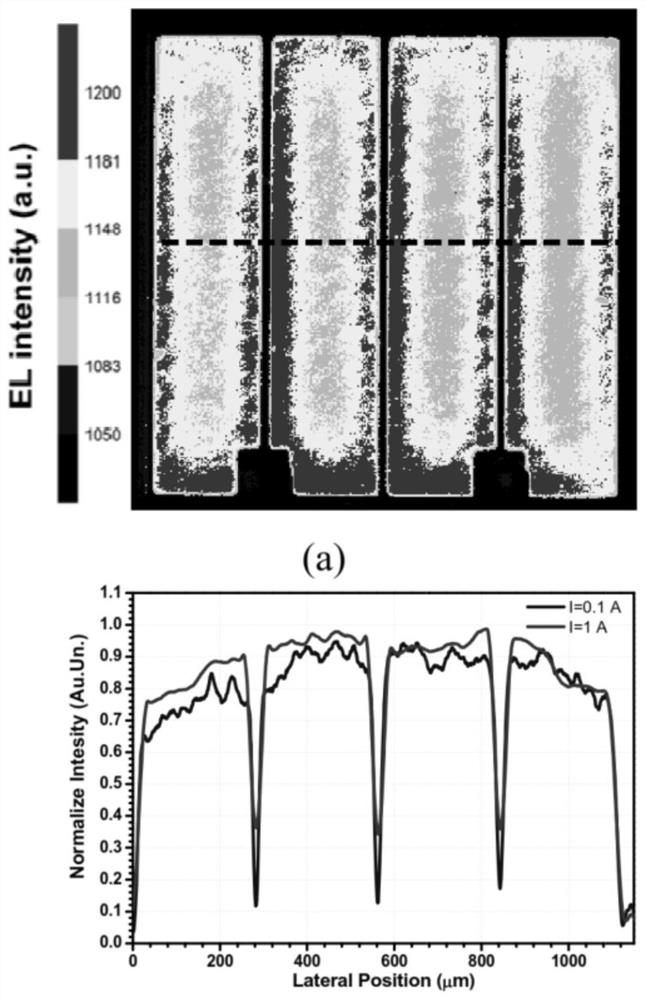

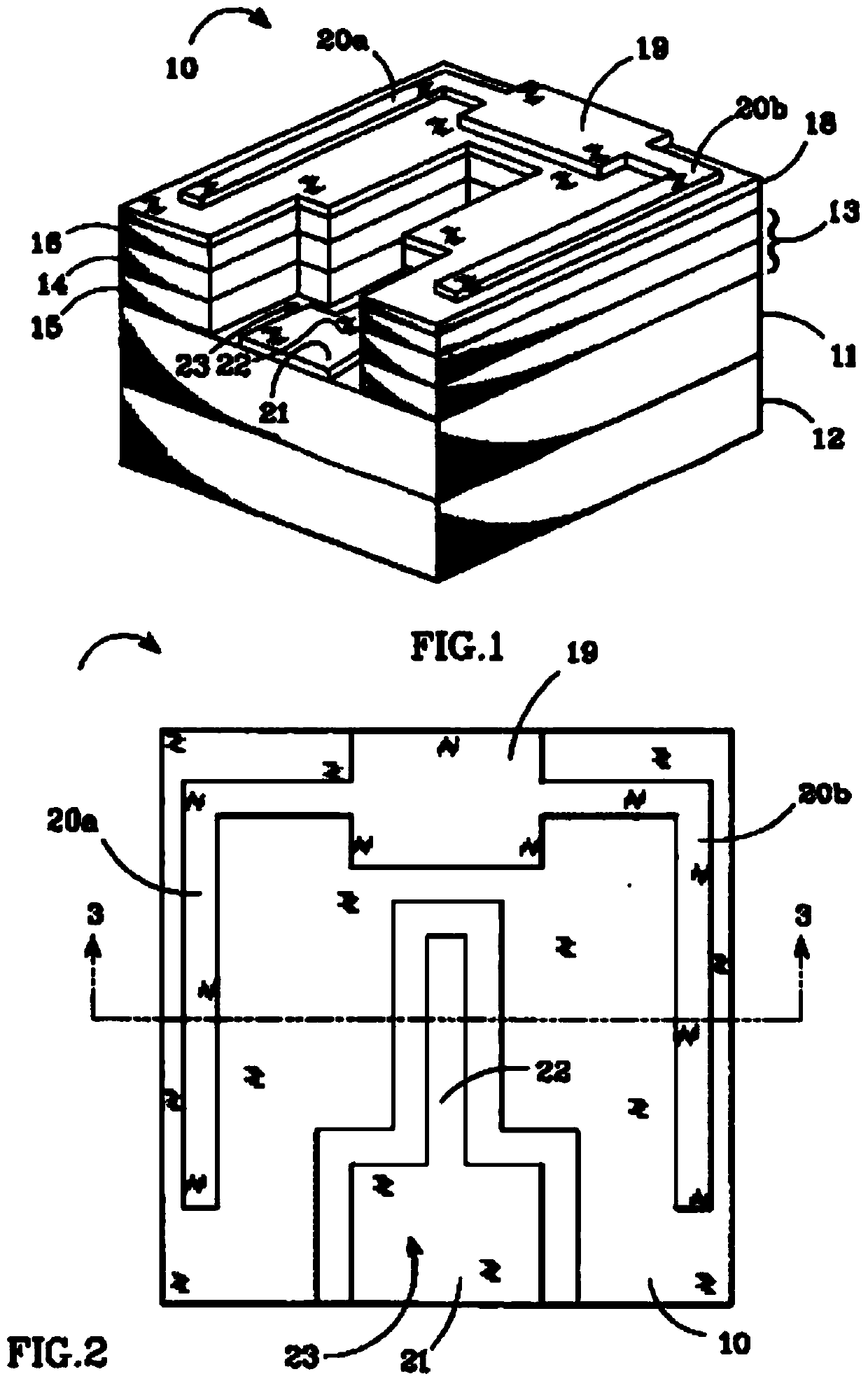

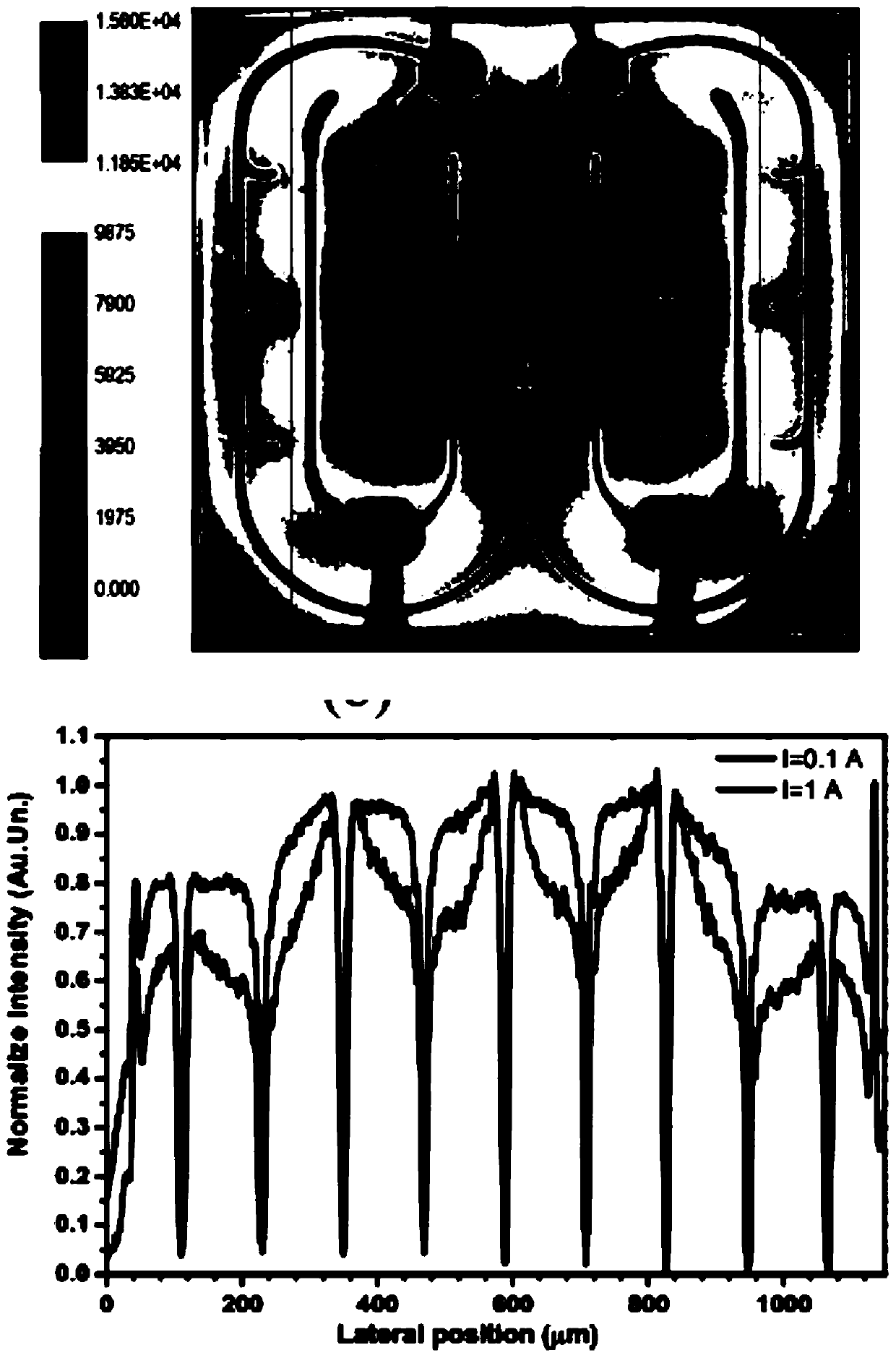

Diode chip of integrated unit

ActiveCN110797370AResolve uneven diffusionIncrease lumen outputSolid-state devicesSemiconductor devicesHeat distributionLight source

The invention provides a diode chip of an integrated unit. The diode chip includes a diode mesa structure, including a plurality of diode units. The width of the diode units in the y-axis direction gradually decreases from the middle to both sides of the integrated unit diode chip in the y-axis direction, wherein the y-axis direction is the width direction of the integrated unit diode chip. Through the design of the uneven mesa structure, ultra-uniform current distribution, heat distribution, wavelength distribution and a high-quality LED light source with narrow half-height are obtained; thetechnical problem that a diode structure in the prior art has great limitations on three important parameters of lumen efficiency, lumen density output and lumen cost is solved; lumen output per unitarea of the chip is improved; and lumen cost is reduced.

Owner:SOUTH UNIVERSITY OF SCIENCE AND TECHNOLOGY OF CHINA

Pretreatment refining method for broad width silk fabric

ActiveCN109056310AResolve uneven diffusionSolve the temperature differenceBiochemical treatment with enzymes/microorganismsGrip property fibresMetallurgyThermal water

The invention discloses a pretreatment refining method for a broad width silk fabric and belongs to the technical field of silk product pretreatment. The pretreatment refining method is characterizedby comprising the following treatment steps of charging water in a dyeing groove on a vehicle, performing heating to 58-63 DEG C, performing running for 2 passes, and draining off water; after preheating a large shaft, adding hot water with the temperature being 96-99 DEG C in the dyeing groove, and adding a refining additive; sealing a cover, performing running for 4 passes, and draining off thewater; performing washing for 3 passes with the hot water at the temperature of 96-99 DEG C, and then pouring the shaft with cold water; adding water in the dyeing groove, adding baking soda and desizing powder ZS-20 to prepare a refined solution, performing crystal form refining, performing running for 5-6 passes, and performing 4 cycles of back vehicles; and performing washing for 2 passes withthe hot water at the temperature of 96-99 DEG C, and then pouring the shaft with the cold water. The invention provides the pretreatment refining method aiming to the broad width silk fabric and mainly solves the defects of hard hand feeling of a head and a tail and different hand feelings at the left part and the right part of degumming of a silk fabric on a jig dyeing machine.

Owner:ZIBO DARANFANG SILK GRP

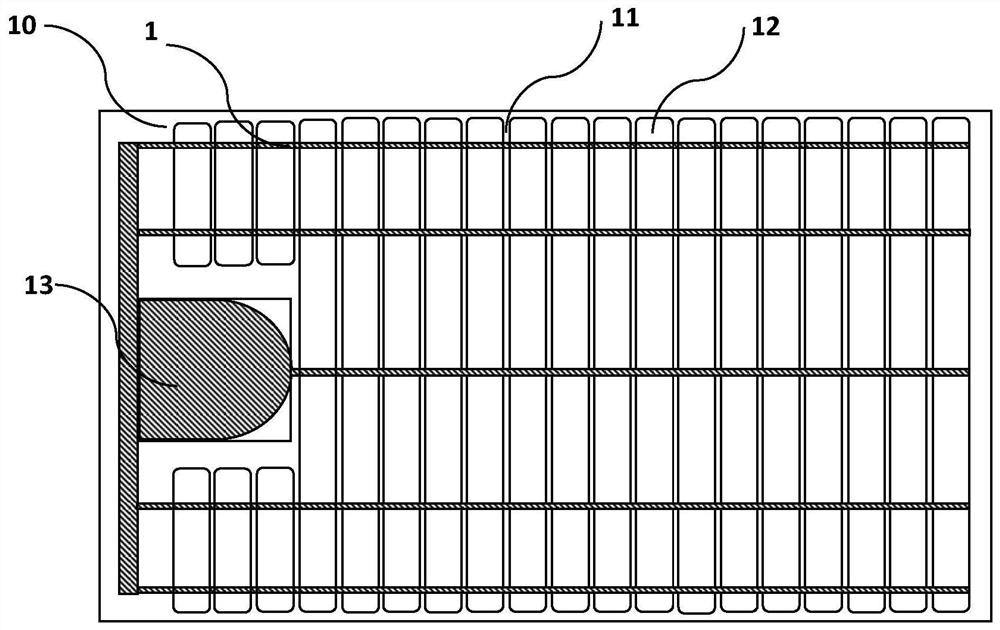

Vertical integrated unit diode chip

ActiveCN111933768AIncrease lumen outputResolve uneven diffusionSolid-state devicesSemiconductor devicesMaterials sciencePhysics

Owner:纳微朗科技(深圳)有限公司

Environment-friendly diffusion source for solar cell

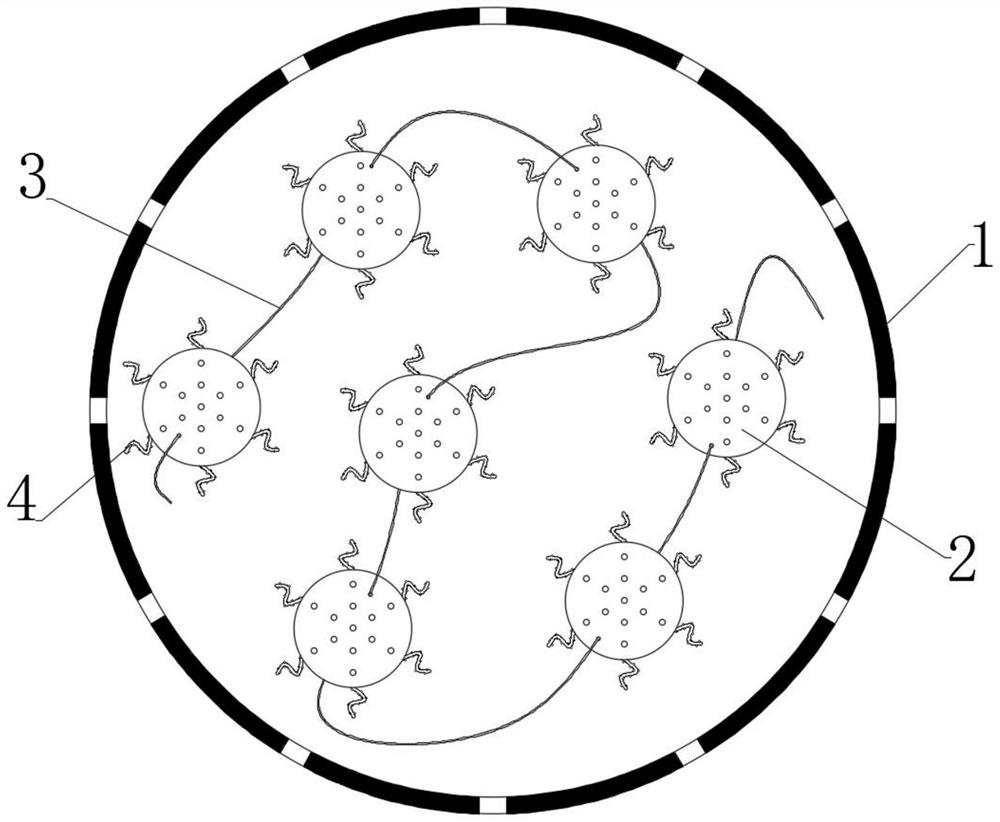

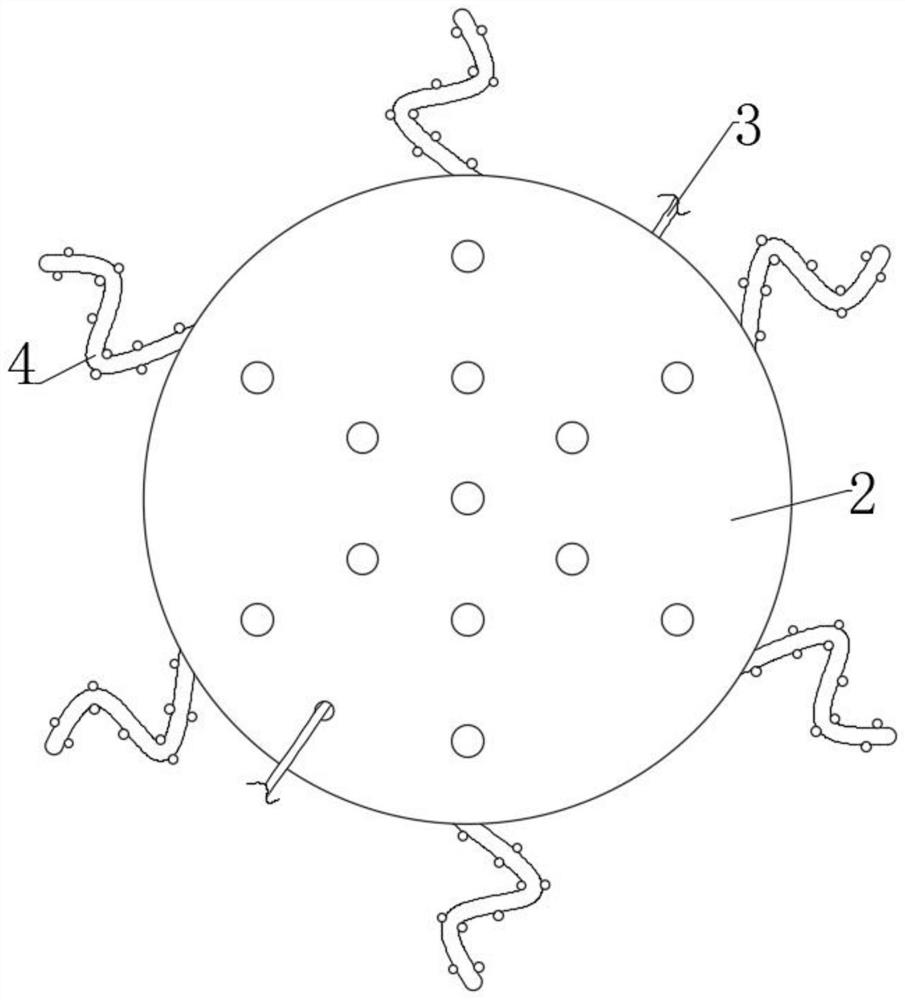

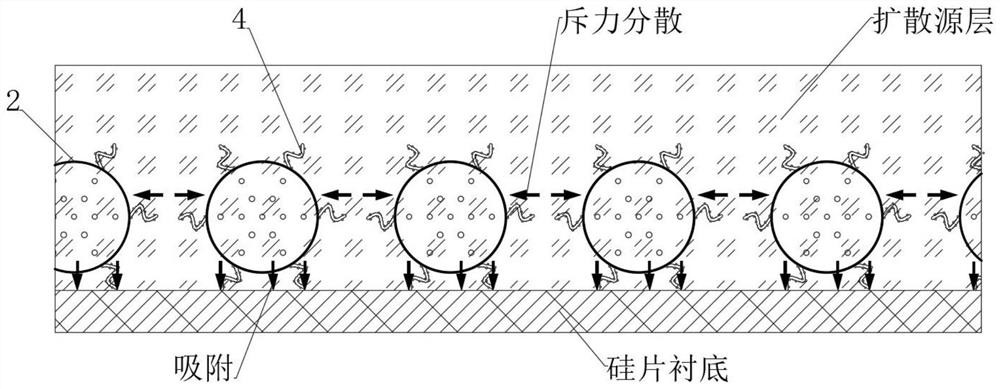

PendingCN114068315AResolve uneven diffusionReduce problemsMaterial nanotechnologyFinal product manufactureSilicon oxideSolar battery

The invention discloses an environment-friendly diffusion source for a solar cell and belongs to the field of semiconductors. The environment-friendly diffusion source for the solar cell comprises a solvent, a silicon oxide nanosphere precursor source, an impurity source and an additive, wherein the solvent is absolute ethyl alcohol or isopropyl alcohol, the silicon oxide nanosphere precursor source is any one of methyltriethoxysilane, methyltrimethoxysilane and n-silane ethyl ester, the impurity source is a diffusion boron source or a diffusion phosphorus source, and the additive is any one of ammonia water, ammonia gas and liquid ammonia; a problem of uneven diffusion on the silicon wafer substrate can be effectively solved through the environment-friendly diffusion source, the occurrence of diffusion defective products is reduced, efficiency of the solar cell is improved, and the silicon oxide nanospheres can help to improve doping uniformity of the diffusion layer.

Owner:南京欣之禾安全技术有限公司

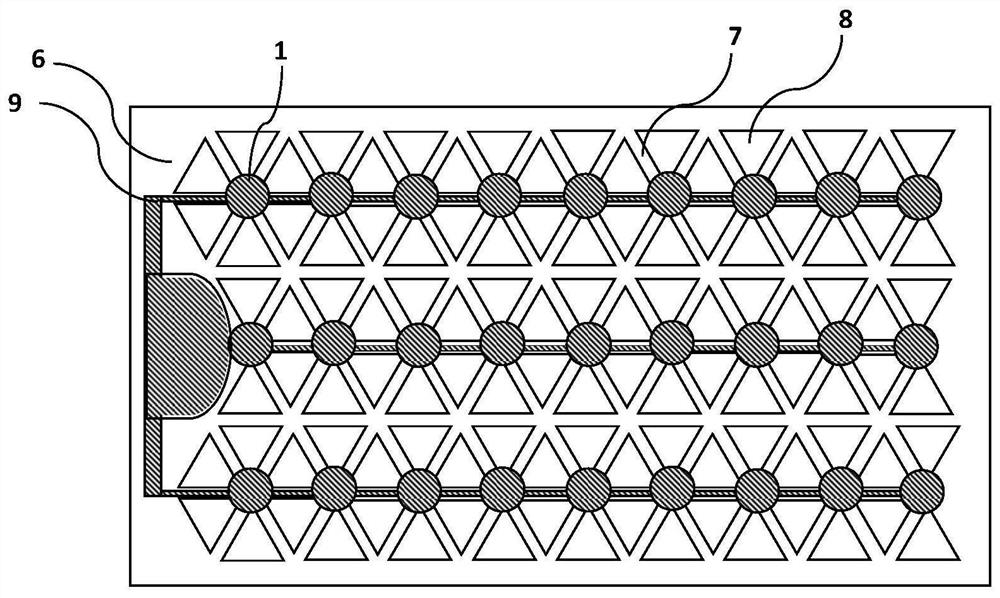

Normally-equipped integrated unit light emitting diode

ActiveCN111048639ASmall sizeResolve uneven diffusionSemiconductor devicesSemiconductor materialsLight-emitting diode

The invention relates to the field of semiconductor materials and device processes, and especially relates to a semiconductor photoelectric device. The invention provides a normally-equipped integrated unit light emitting diode. The light emitting diode comprises a plurality of diode units, a first conductive type electrode and a second conductive type electrode, wherein the first conductive typeelectrode and the second conductive type electrode are arranged among the diode units, and the first conductive type electrode and the second conductive type electrode are overlapped in a spacing areaamong the diode units. A technical problem that a diode structure in the prior art is greatly limited in three important parameters of luminous efficiency, lumen density output and lumen cost is solved, lumen output of a unit area chip is improved, and lumen cost is reduced.

Owner:纳微朗科技(深圳)有限公司

Normally-equipped integrated unit diode chip

ActiveCN111916539AWeak light absorptionImprove light extraction efficiencySolid-state devicesSemiconductor devicesQuantum wellEngineering

The invention provides a normally-equipped integrated unit diode chip. The normally-equipped integrated unit diode chip comprises a first conductive type electrode, a second conductive type electrodeand a diode mesa structure located between the first conductive type electrode and the second conductive type electrode. The diode mesa structure comprises n diode units, wherein n is greater than orequal to 2. Each of the n diode units comprises a quantum well active region located on the first conductive type layer, a second conductive type layer located on the quantum well active region, an insulating dielectric layer located on the first conductive type layer and partially covering the second conductive type layer, and a transparent electrode located on the second conductive type layer and partially covering the insulating dielectric layer, wherein the second conductive type electrode is located on the insulating dielectric layer and partially covers the transparent electrode. According to the invention, the problem that the thickness of the transparent electrode limits the transverse diffusion of the current and the light extraction efficiency of the LED in the prior art is solved, the lumen output of the unit area unit diode chip is improved, and the lumen cost is reduced.

Owner:纳微朗科技(深圳)有限公司

Vertical integrated unit diode chip

PendingCN111863853AIncrease lumen outputResolve uneven diffusionSolid-state devicesSemiconductor devicesQuantum wellEngineering

The invention provides a vertical integrated unit light emitting diode. The vertical integrated unit light emitting diode comprises a first conductive type electrode, a second conductive type electrode and a diode mesa structure located on the first conductive type electrode. Wherein the diode mesa structure comprises n diode units and a trench structure, and n is greater than or equal to 2; the trench structure is located between the diode units. The diode mesa structure further comprises a first conductive type layer, a second conductive type layer with the thickness of h1 and a quantum wellactive region located on the first conductive type layer, wherein the thickness of the quantum well active region is h2, and the trench depth L is greater than h1 and less than or equal to (h1+h2). The area of the diode mesa structure is determined according to the current diffusion length. The technical problem that a diode structure in the prior art is greatly limited in three important parameters, namely, the lumen efficiency, the lumen density output and the lumen cost, is solved, the lumen output of a unit area chip is improved, and the lumen cost is reduced.

Owner:纳微朗科技(深圳)有限公司

A Formally Mounted Integrated Unit Diode Chip

ActiveCN109920782BIncrease lumen outputResolve uneven diffusionSolid-state devicesSemiconductor devicesSemiconductor materialsMaterials science

The invention relates to the field of semiconductor materials and device technology, in particular to semiconductor optoelectronic devices. The invention provides a positively mounted integrated unit diode chip, a first conductivity type electrode, a second conductivity type electrode, and a diode mesa structure located between the first conductivity type electrode and the second conductivity type electrode, the diode mesa structure It includes n diode units, the n diode units are arranged in a geometric shape, and the electrode width and the area of the mesa structure are determined according to the current. The invention solves the technical problem of the diode structure in the prior art that has great limitations in three important parameters: lumen efficiency, lumen density output, and lumen cost, improves the lumen output of unit diode chips per unit area, and reduces the lumen cost .

Owner:NARVELLUX TECH (SHENZHEN) CO LTD

Vertical integrated unit diode chip

InactiveCN111864021AIncrease lumen outputResolve uneven diffusionSolid-state devicesSemiconductor devicesQuantum wellEngineering

The invention provides a vertical integrated unit light-emitting diode. The vertical integrated unit light-emitting diode comprises a first conductive type electrode, a second conductive type electrode and a diode mesa structure located on the first conductive type electrode, wherein the diode mesa structure comprises n diode units and a trench structure, and n is greater than or equal to 2; the trench structures are located between the diode units; the area of the diode mesa structure is determined according to the current diffusion length. The diode mesa structure also comprises a first conductive type layer, a second conductive type layer, a quantum well active region positioned on the first conductive type layer, wherein the thickness of the first conductive type layer is L1, the thickness of the second conductive type layer is L2, the thickness of the quantum well active region is L3, the trench depth L is greater than (L2+L3) and less than or equal to (L1+L2+L3), and the area ofthe diode mesa structure is determined according to the current diffusion length. According to the invention, the technical problem that a diode structure in the prior art is greatly limited in threeimportant parameters, namely, the lumen efficiency, the lumen density output and the lumen cost, is solved, the lumen output of a unit area chip is improved, and the lumen cost is reduced.

Owner:SHENZHEN INST OF WIDE BANDGAP SEMICON

An integrated unit diode chip

ActiveCN110797370BResolve uneven diffusionIncrease lumen outputSolid-state devicesSemiconductor devicesCurrent distributionEngineering

The invention provides an integrated unit diode chip, which includes a diode mesa structure, and the diode mesa structure includes a plurality of diode units, wherein the width of the diode unit along the y-axis direction gradually decreases from the middle of the integrated unit diode chip to both sides in the y-axis direction. , wherein the y-axis direction is the width direction of the integrated unit diode chip. The invention obtains ultra-uniform current distribution, heat distribution, wavelength distribution, and narrow half-height high-quality LED light source through the design of the uneven mesa structure, and solves the problem of the diode structure existing in the prior art in terms of lumen efficiency, lumen density output, The technical problem of great limitations on the three important parameters of lumen cost improves the lumen output of the chip per unit area and reduces the lumen cost.

Owner:NARVELLUX TECH (SHENZHEN) CO LTD

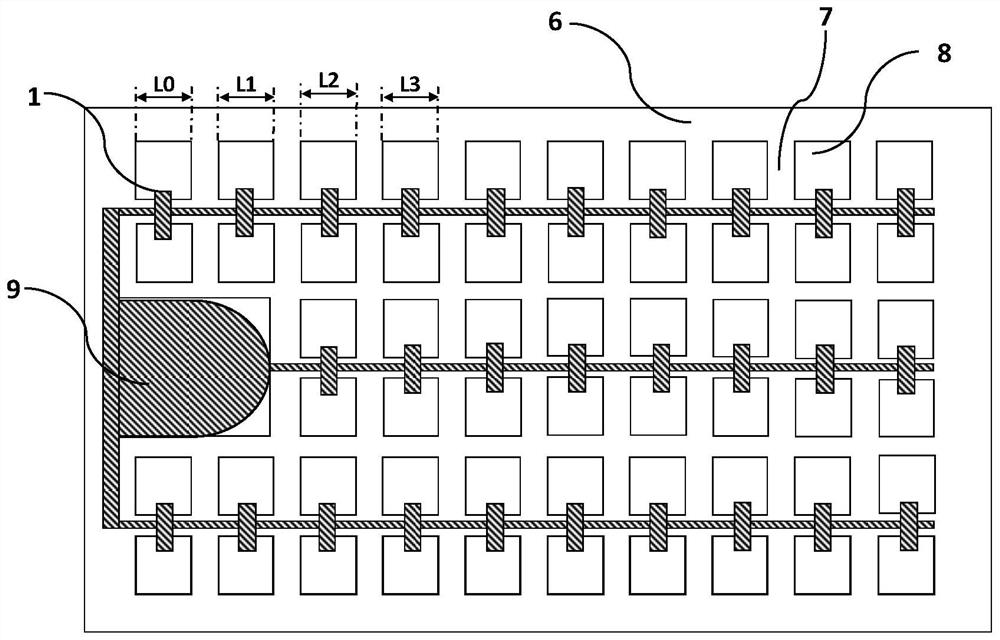

Integrated unit diode chip capable of uniformly emitting light

ActiveCN111900183AUniform current distributionHigh photoelectric conversion efficiency/lumen efficiencySolid-state devicesSemiconductor devicesCurrent distributionEngineering

The invention provides an integrated unit diode chip capable of uniformly emitting light, which comprises a first conductive type electrode, a second conductive type electrode and a diode mesa structure located on the first conductive type electrode, wherein the diode mesa structure comprises n diode units, and the n diode units are different in length in the x-axis direction or different in widthin the y-axis direction. The planar position function of the n diode units relative to the mesa structure is linear or nonlinear. The area of the mesa structure is determined according to the currentdiffusion length, and n is greater than or equal to 2. A non-uniform mesa structure design is adopted, a high-quality LED light source with super-uniform current distribution, thermal distribution, wavelength distribution and narrow half-height can be obtained, the technical problem that a diode structure in the prior art has great limitations on three important parameters of luminous efficiency,luminous density output and luminous cost is solved, luminous output of a unit area chip is improved, and the luminous cost is reduced.

Owner:纳微朗科技(深圳)有限公司

Normally-equipped integrated unit diode chip

ActiveCN111048494AIncrease lumen outputResolve uneven diffusionSolid-state devicesSemiconductor devicesSemiconductor materialsEngineering

The invention relates to the field of semiconductor materials and device processes, and especially relates to a semiconductor photoelectric device. The invention provides a normally-equipped integrated unit diode chip. The chip comprises a plurality of diode units, N-type electrode line type electrode wires and P-type electrode line type electrode wires, wherein areas of the diode units are gradually reduced from one side where the P-type electrode line type electrode wires are gathered to the other side. A technical problem that a diode structure in the prior art has great limitations in three important parameters of luminous efficiency, lumen density output and lumen cost is solved, the lumen output of a unit area unit diode chip is improved, and the lumen cost is reduced.

Owner:纳微朗科技(深圳)有限公司

Semi-conductor silicon chip liquid stage source diffusion furnace

InactiveCN101136325BResolve uneven diffusionEliminate the effects ofSemiconductor/solid-state device manufacturingLiquid stateEngineering

This invention discloses a diffusion furnace of semiconductor silicon plate liquid source including: a diffusion tube and quartz tubes for spraying the source, in which, the diffusion furnace tube isin a structure of two ends open, 2-10 source-spraying quartz tubes are installed on the internal wall of the tube with the diameter of pha2-pha 10mm, capillary holes in uniform aperture are distributed on the wall of the tube and the exit end of the tube is connected with the source bottle of the liquid state diffusion source.

Owner:SHANGHAI AEROSPACE AUTOMOBILE ELECTROMECHANICAL CO LTD +1

A pretreatment and scouring method for wide-width silk fabrics

ActiveCN109056310BGuaranteed StrengthKeep aliveBiochemical treatment with enzymes/microorganismsGrip property fibresProcess engineeringThermal water

The invention discloses a pretreatment and scouring method for wide-width real silk fabrics, which belongs to the technical field of pretreatment of real silk products. It is characterized in that the processing steps are as follows: heat the car on the water in the dyeing tank to 58°C~63°C, run 2 times, and let off the water; after preheating the main axis, add hot water at 96°C~99°C in the dyeing tank, add Scouring aid; cover and run 4 times, let off the water; wash 3 times in hot water at 96°C~99°C, then pour the shaft in cold water; add water to the dyeing tank, add baking soda and desizing powder ZS-20 to make Obtain the refining solution to refine the crystal form, run 5~6 times and press Enter 4 times; wash 2 times in hot water at 96°C~99°C, and then pour the shaft with cold water. The present invention proposes a pretreatment and refining method for wide-width real silk fabrics, which mainly solves the problems of hard hand feeling at the head and tail and different hand feelings at the left and right sides when the real silk is degummed on a jigger.

Owner:ZIBO DARANFANG SILK GRP

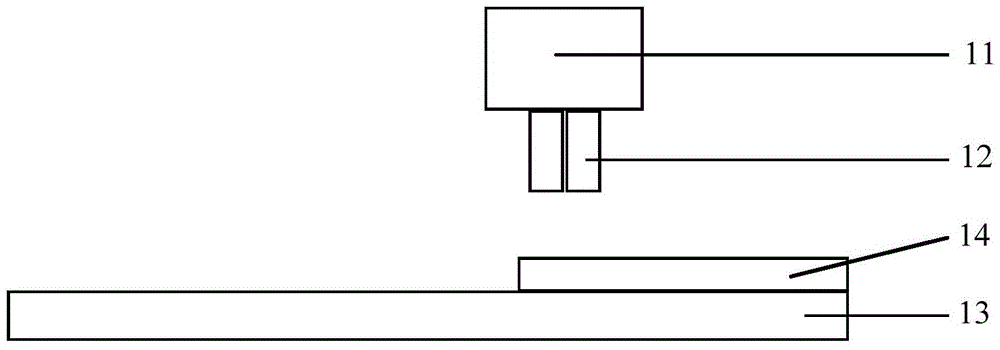

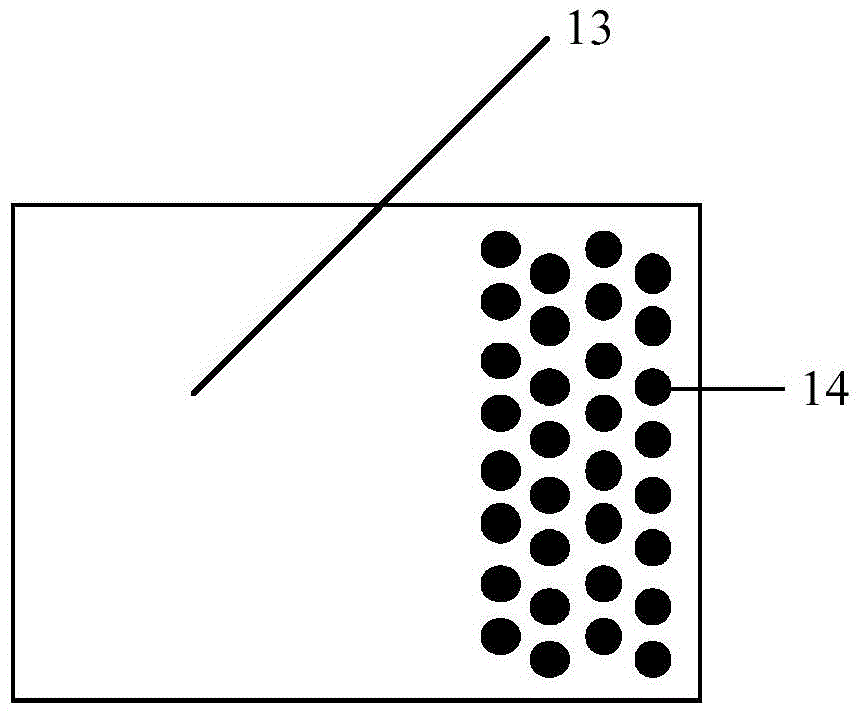

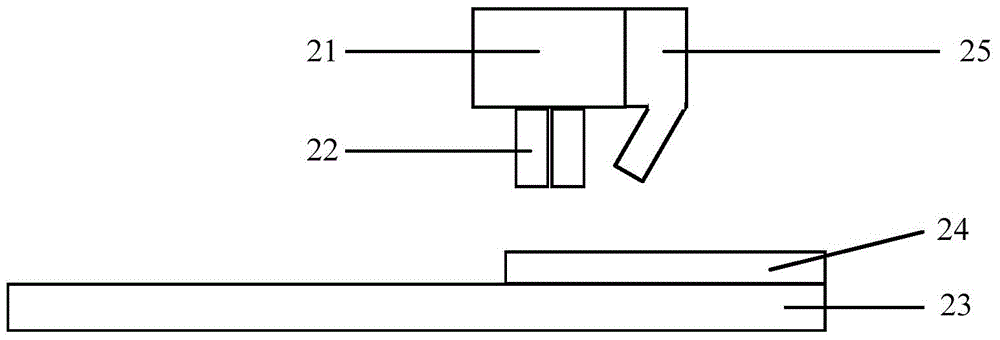

Inkjet printing device and method for coating alignment film

InactiveCN103552377BFacilitated DiffusionResolve uneven diffusionPrintingEngineeringElectrical and Electronics engineering

The invention relates to an ink jet printing device and a method for spreading an alignment layer. The ink jet printing device comprises a machine frame and an ink jet head fixed to the machine frame, and further comprises an air knife located at the back of the ink jet head and fixed to the machine frame. By the adoption of the ink jet printing device and the method for spreading the alignment layer, diffusion of the alignment layer can be quickened, and the problem that the alignment layer is uneven in diffusion is solved.

Owner:BOE TECH GRP CO LTD +1

Array substrate and manufacturing method thereof, display panel, display device

ActiveCN105304649BResolve uneven diffusionReduce dropSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

The invention discloses an array substrate and a manufacturing method thereof, a display panel and a display device, which are used to reduce the gap between the upper surface of the via hole in the array substrate and the transparent conductive layer around the via hole, so as to solve the problem of alignment layer polyimide The problem of uneven diffusion of thin film PI can improve the display quality. The manufacturing method of the array substrate is characterized in that the method comprises: forming a via hole for connecting the second transparent conductive layer and the gate line layer on the base substrate by using a patterning process, and forming a via hole for connecting the second transparent conductive layer and the The via hole of the source-drain electrode layer and the via hole used to connect the first transparent conductive layer and the second transparent conductive layer; while forming the pattern of the second transparent conductive layer, the via hole is filled and leveled, so that the filled The upper surface of the flattened via hole is at the same level as the second transparent conductive layer around the via hole.

Owner:BOE TECH GRP CO LTD +1

A kind of LED chip and its manufacturing method

ActiveCN107275446BImprove uniformitySpread evenlySemiconductor devicesQuantum wellElectrical connection

The invention discloses an LED chip and a manufacturing method thereof. The LED chip comprises: a substrate; an epitaxial structure arranged on the substrate, and the epitaxial structure includes an N-type semiconductor layer, a quantum well light-emitting layer and a P-type semiconductor layer arranged in sequence. The predetermined region of the epitaxial structure has a groove, and the groove is used to expose part of the N-type semiconductor layer; the P-type semiconductor layer has a first region, a second region and a third region; a first transparent conductive layer covering the first region; A current blocking layer covering the second region and part of the first transparent conductive layer; a second transparent conductive layer covering another part of the first transparent conductive layer, the third region and part of the current blocking layer; a P electrode covering another part of the current blocking layer; An N electrode arranged in the groove and electrically connected to the N-type semiconductor layer. The technical scheme of the invention solves the problem of uneven current diffusion in the LED chip, and improves the uniformity of light emission of the LED chip.

Owner:XIAMEN CHANGELIGHT CO LTD

A vertically integrated unit diode chip

ActiveCN110060996BIncrease lumen outputResolve uneven diffusionSolid-state devicesSemiconductor devicesEngineeringLight-emitting diode

The present invention provides a vertically integrated unit light emitting diode, comprising: a first conductivity type electrode, a second conductivity type electrode, and a diode mesa structure located between the first conductivity type electrode and the second conductivity type electrode, the diode The mesa structure includes a plurality of diode units arranged in a geometric shape. The invention solves the technical problem that the diode structure in the prior art has great limitations on the three important parameters of lumen efficiency, lumen density output and lumen cost, improves the lumen output of the chip per unit area, and reduces the lumen cost.

Owner:纳微朗科技(深圳)有限公司

Vertical integrated unit diode chip

PendingCN111863802AIncrease lumen outputResolve uneven diffusionSolid-state devicesSemiconductor devicesQuantum wellLight-emitting diode

The invention provides a vertical integrated unit light-emitting diode, which comprises a first conductive type electrode, a second conductive type electrode and a diode mesa structure located on thefirst conductive type electrode, wherein the diode mesa structure comprises n diode units and a trench structure, and n is greater than or equal to 2; the trench structure is located between the diodeunits. The diode mesa structure further comprises a first conductive type layer, a second conductive type layer and a quantum well active region located on the first conductive type layer, wherein the depth of the trench structure is less than or equal to the thickness of the second conductive type layer, and the area of the mesa structure is determined according to the current diffusion length.The technical problem that a diode structure in the prior art is greatly limited in three important parameters, namely, the lumen efficiency, the lumen density output and the lumen cost, is solved, the lumen output of a unit area chip is improved, and the lumen cost is reduced.

Owner:纳微朗科技(深圳)有限公司