Patents

Literature

72 results about "Pipeline (software)" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In software engineering, a pipeline consists of a chain of processing elements (processes, threads, coroutines, functions, etc.), arranged so that the output of each element is the input of the next; the name is by analogy to a physical pipeline. Usually some amount of buffering is provided between consecutive elements. The information that flows in these pipelines is often a stream of records, bytes, or bits, and the elements of a pipeline may be called filters; this is also called the pipes and filters design pattern. Connecting elements into a pipeline is analogous to function composition.

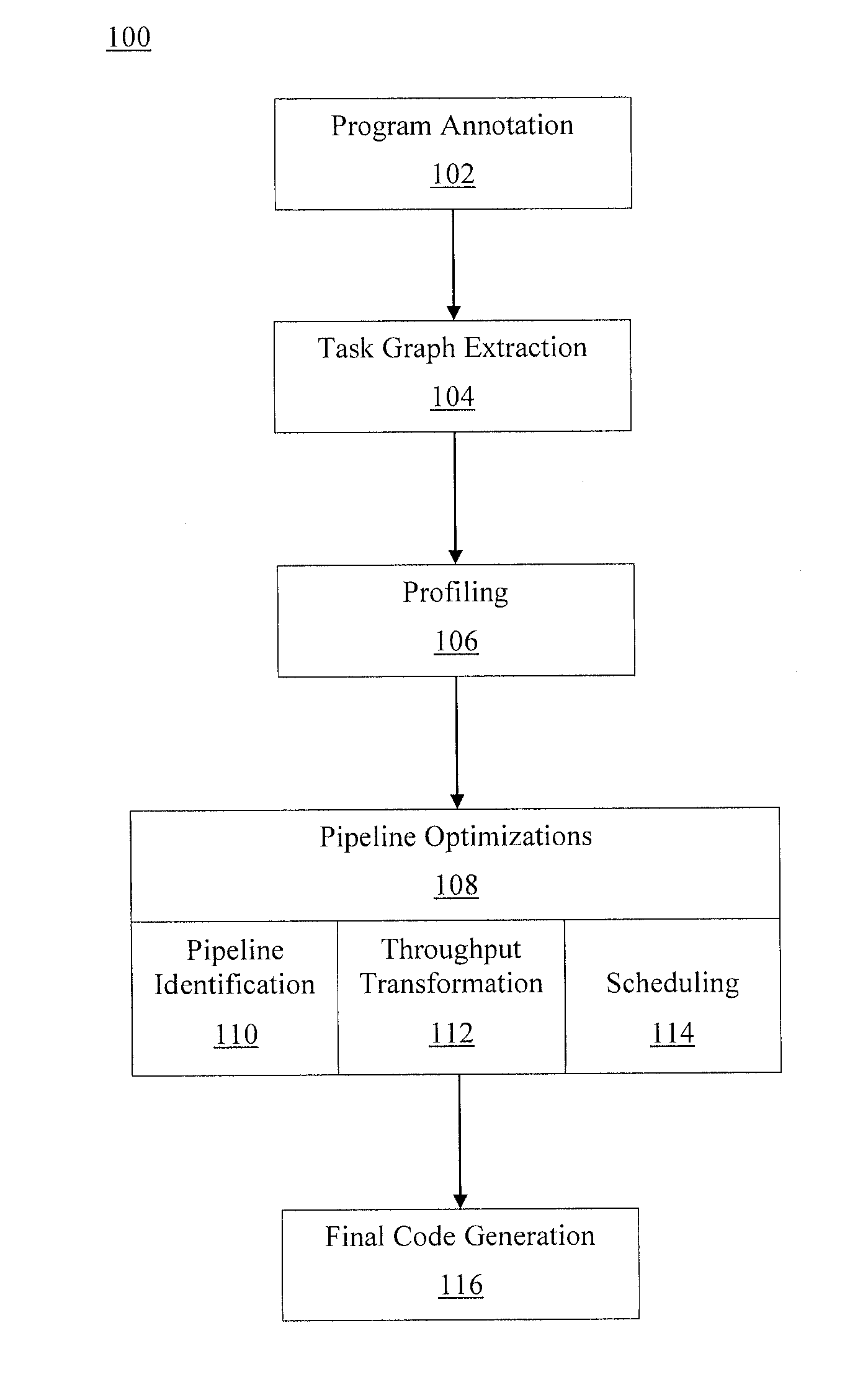

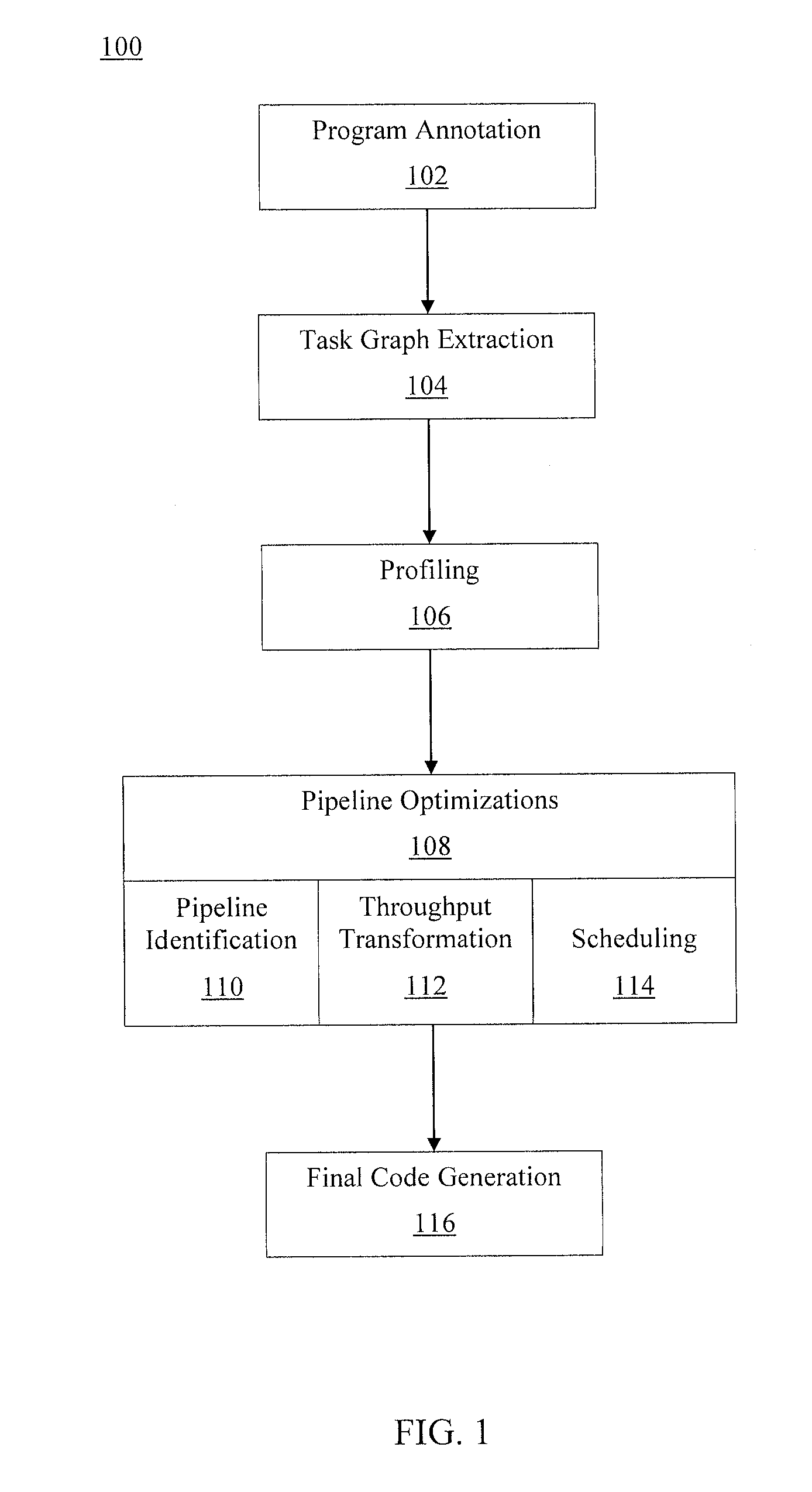

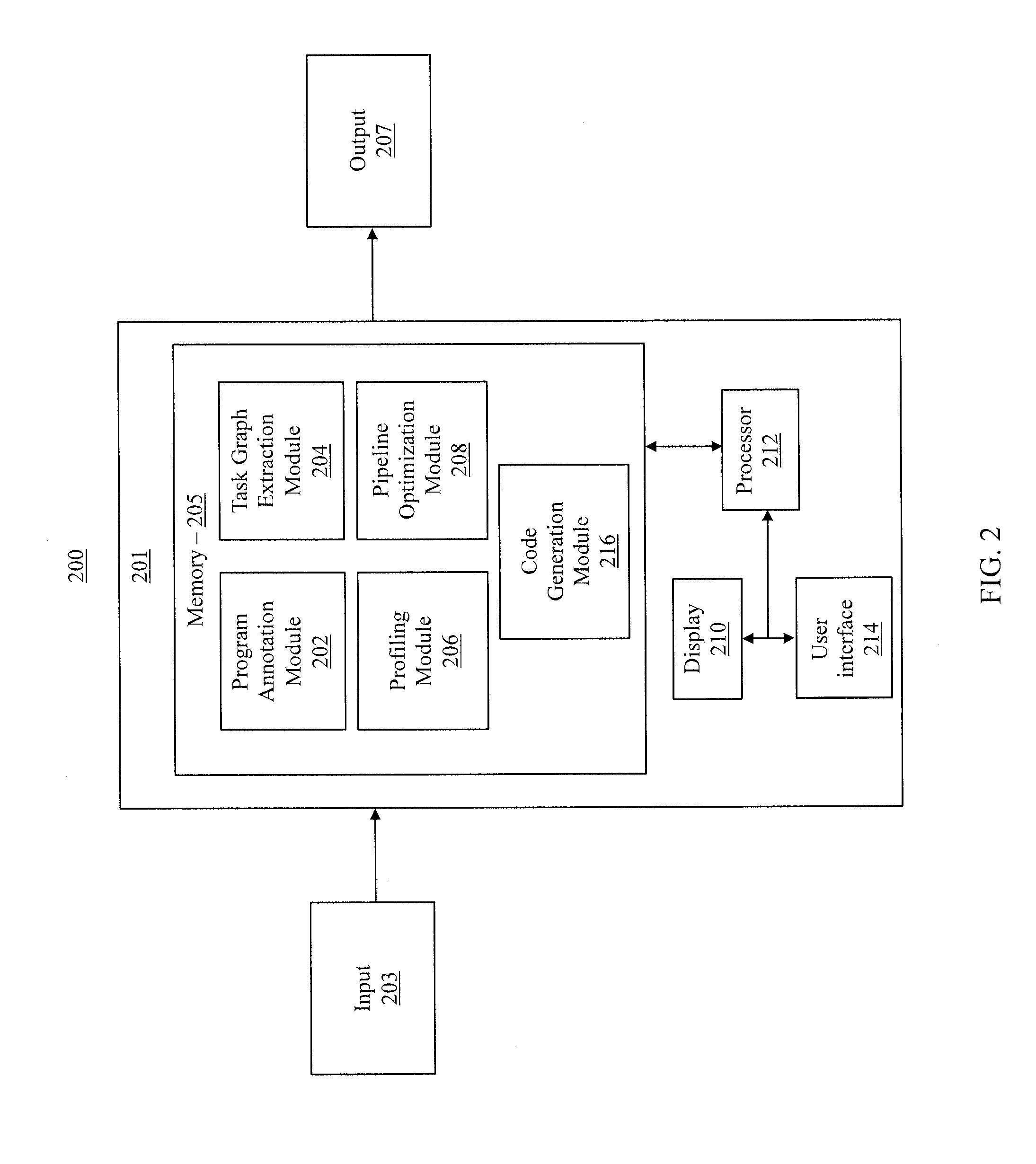

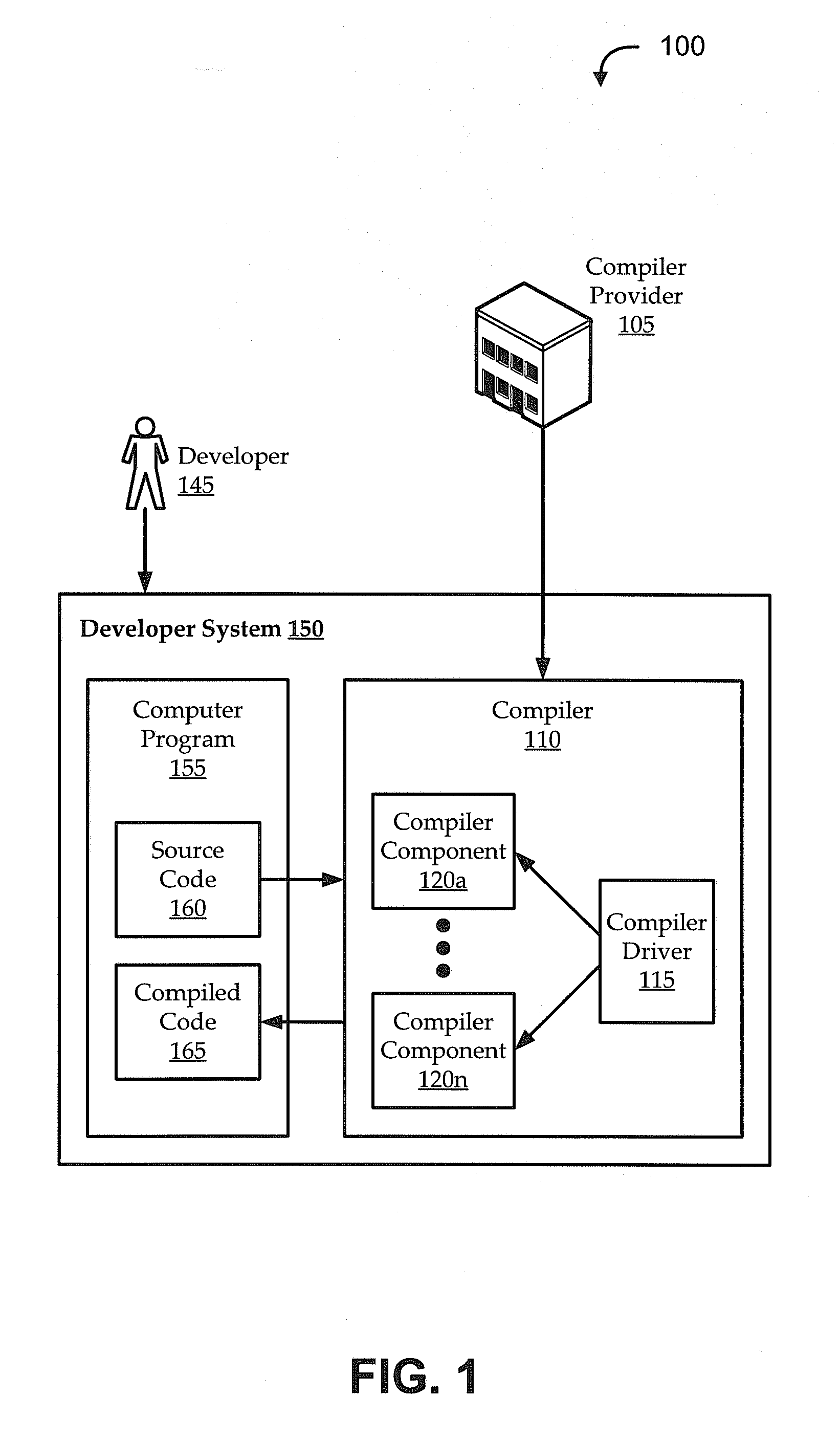

Automatic pipelining framework for heterogeneous parallel computing systems

ActiveUS20130298130A1Program initiation/switchingSoftware engineeringComputer architectureConcurrent computation

Systems and methods for automatic generation of software pipelines for heterogeneous parallel systems (AHP) include pipelining a program with one or more tasks on a parallel computing platform with one or more processing units and partitioning the program into pipeline stages, wherein each pipeline stage contains one or more tasks. The one or more tasks in the pipeline stages are scheduled onto the one or more processing units, and execution times of the one or more tasks in the pipeline stages are estimated. The above steps are repeated until a specified termination criterion is reached.

Owner:NEC CORP

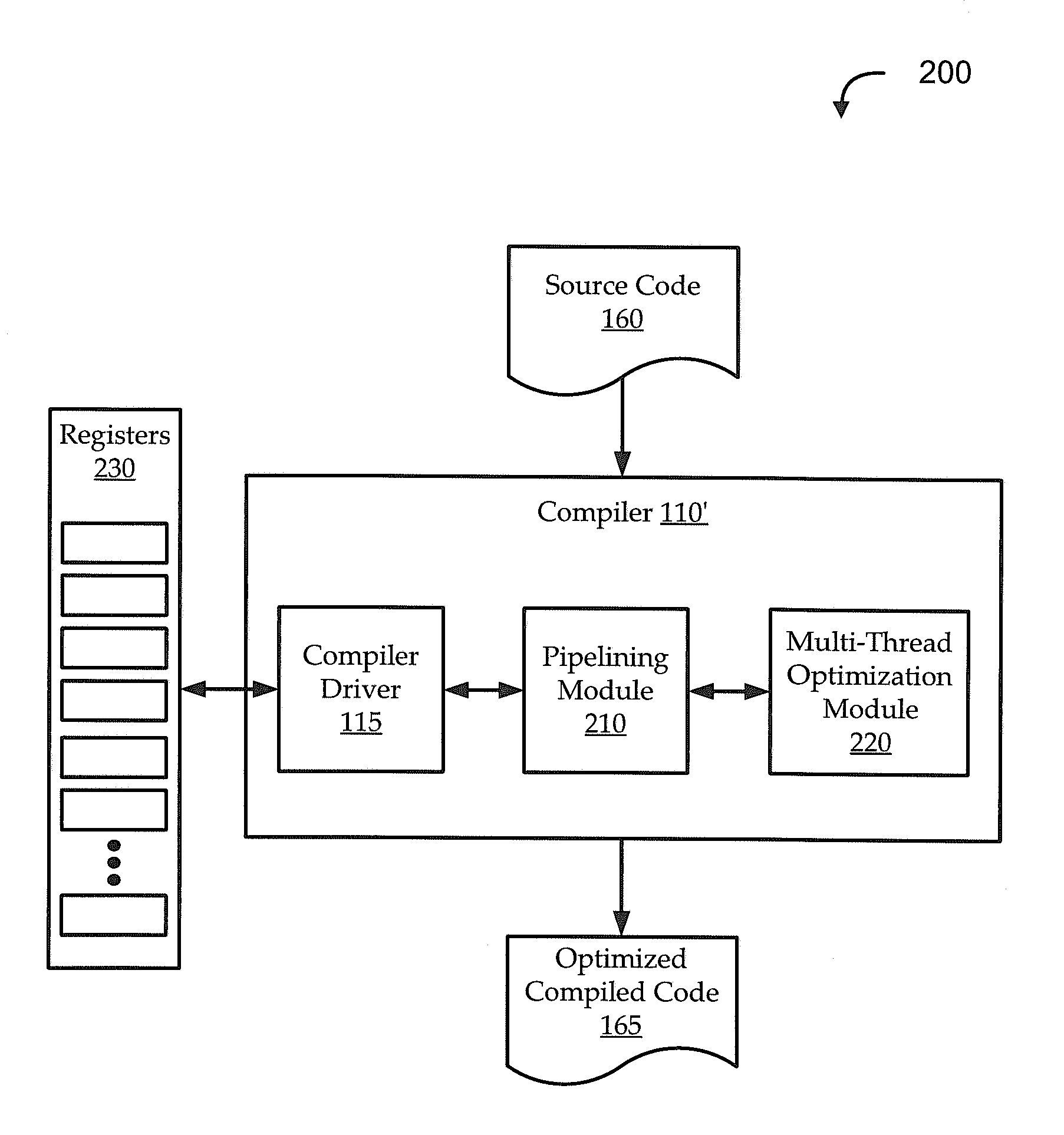

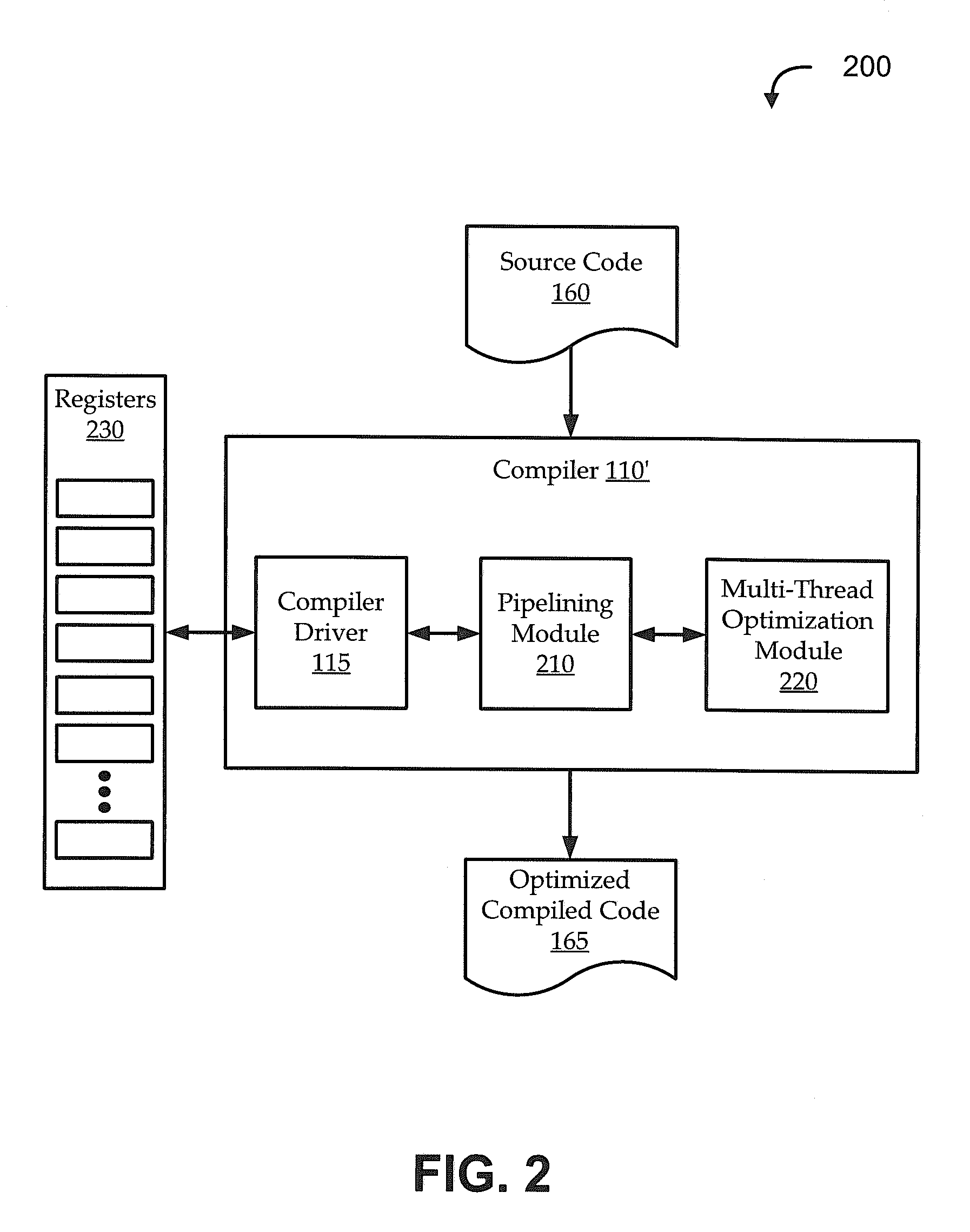

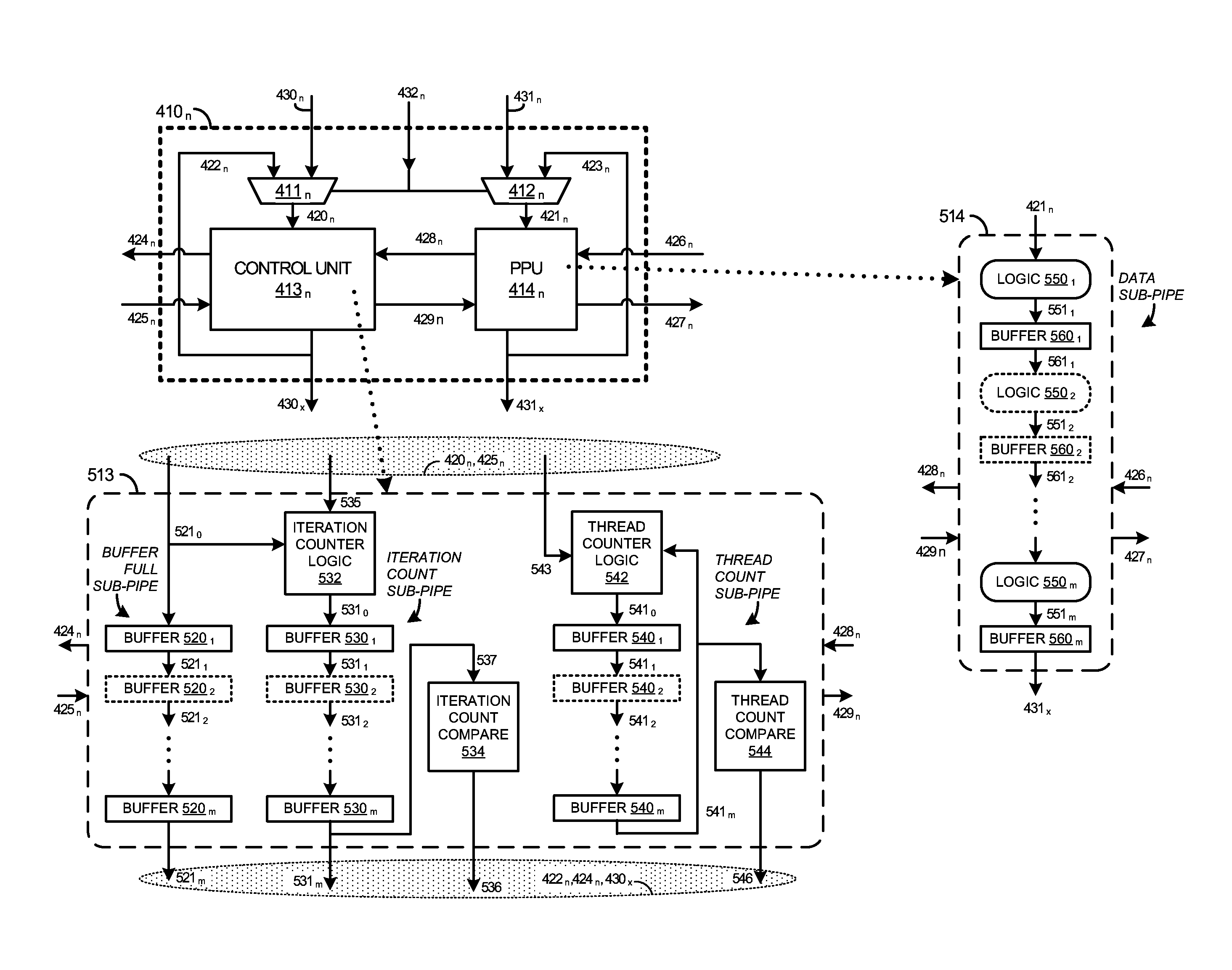

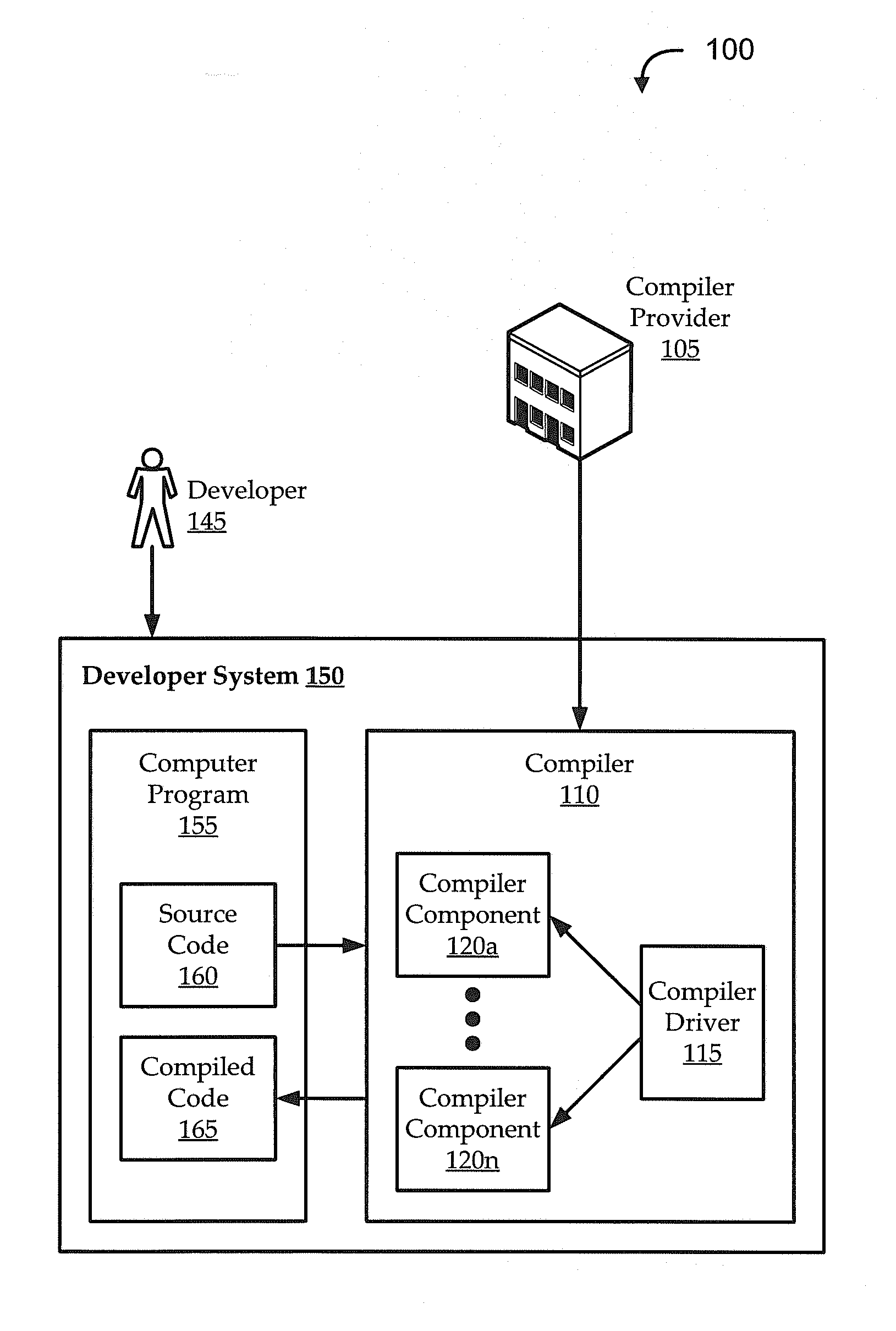

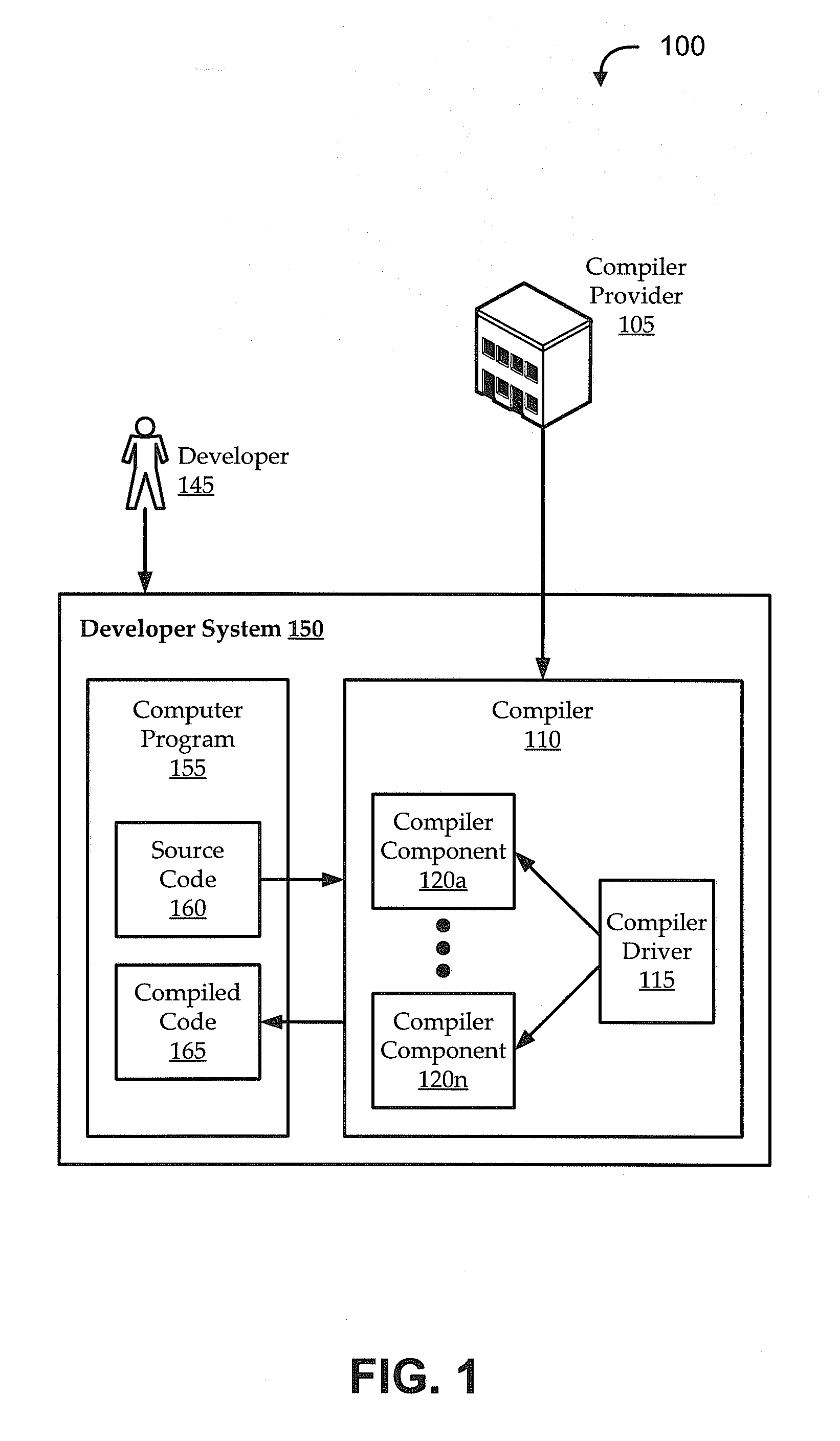

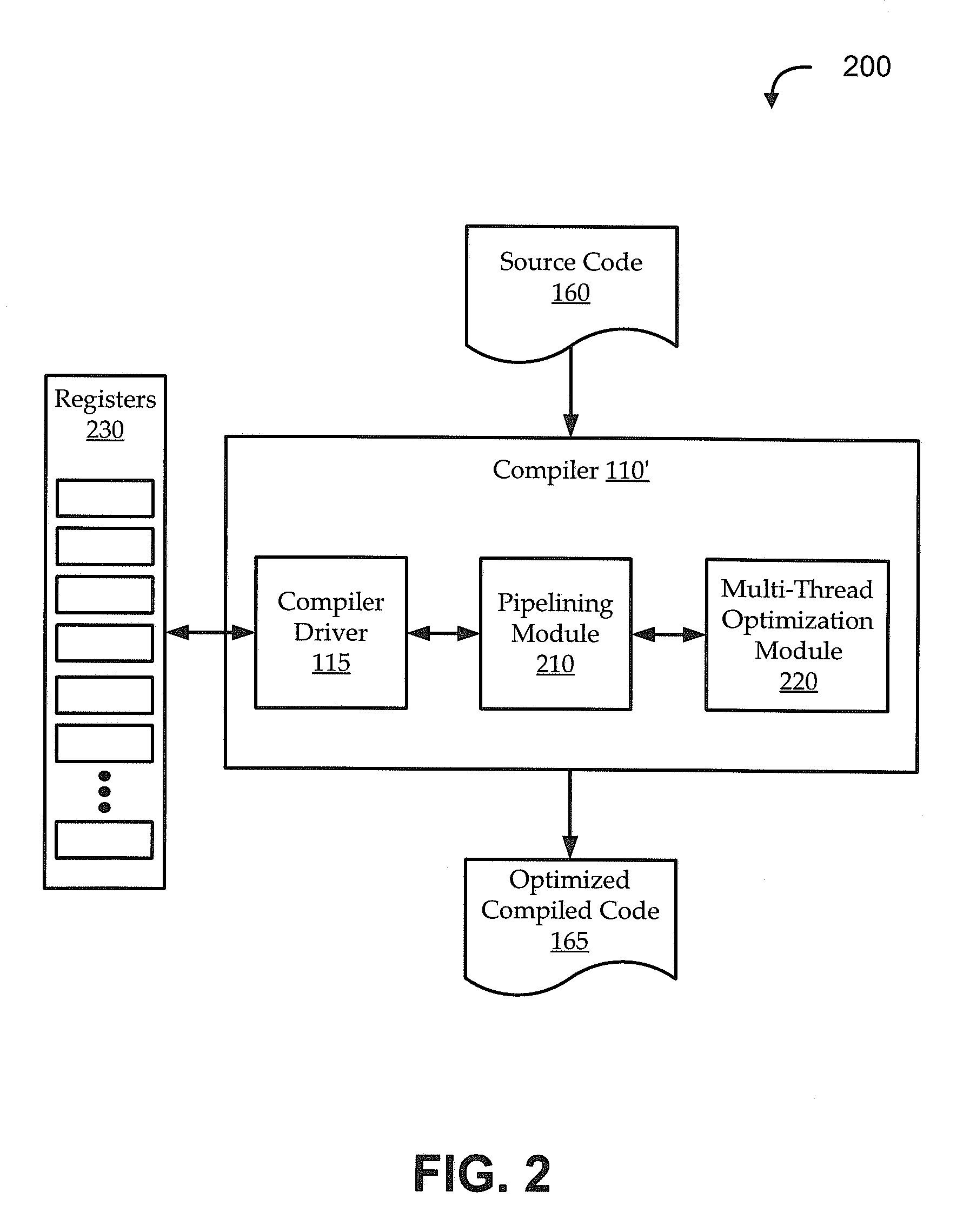

Throughput-aware software pipelining for highly multi-threaded systems

ActiveUS20130111453A1Reducing scalarityReducing latency settingSoftware engineeringProgram controlResource utilizationProcessor register

Embodiments of the invention provide systems and methods for throughput-aware software pipelining in compilers to produce optimal code for single-thread and multi-thread execution on multi-threaded systems. A loop is identified within source code as a candidate for software pipelining. An attempt is made to generate pipelined code (e.g., generate an instruction schedule and a set of register assignments) for the loop in satisfaction of throughput-aware pipelining criteria, like maximum register count, minimum trip count, target core pipeline resource utilization, maximum code size, etc. If the attempt fails to generate code in satisfaction of the criteria, embodiments adjust one or more settings (e.g., by reducing scalarity or latency settings being used to generate the instruction schedule). Additional attempts are made to generate pipelined code in satisfaction of the criteria by iteratively adjusting the settings, regenerating the code using the adjusted settings, and recalculating whether the code satisfies the criteria.

Owner:ORACLE INT CORP

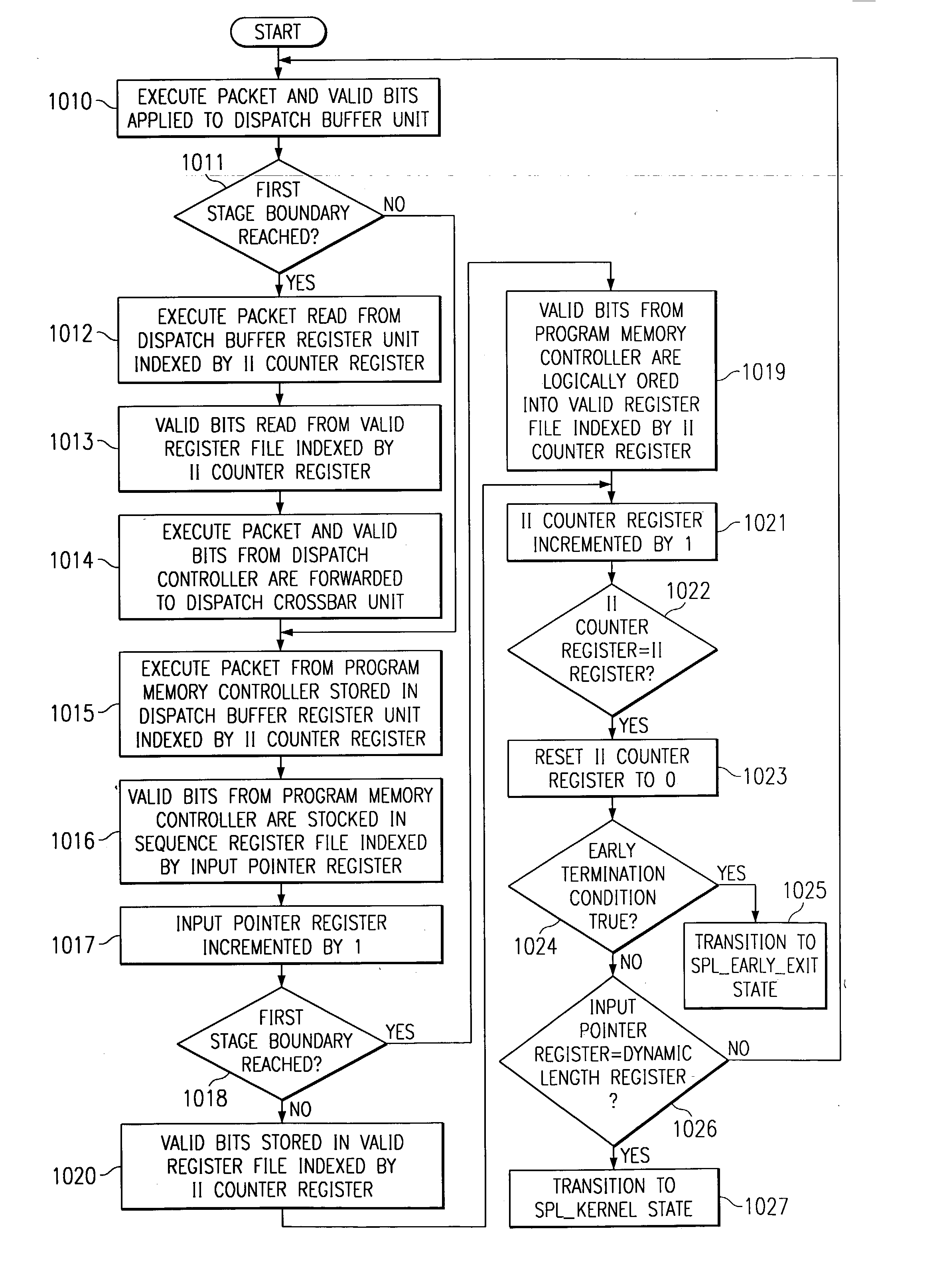

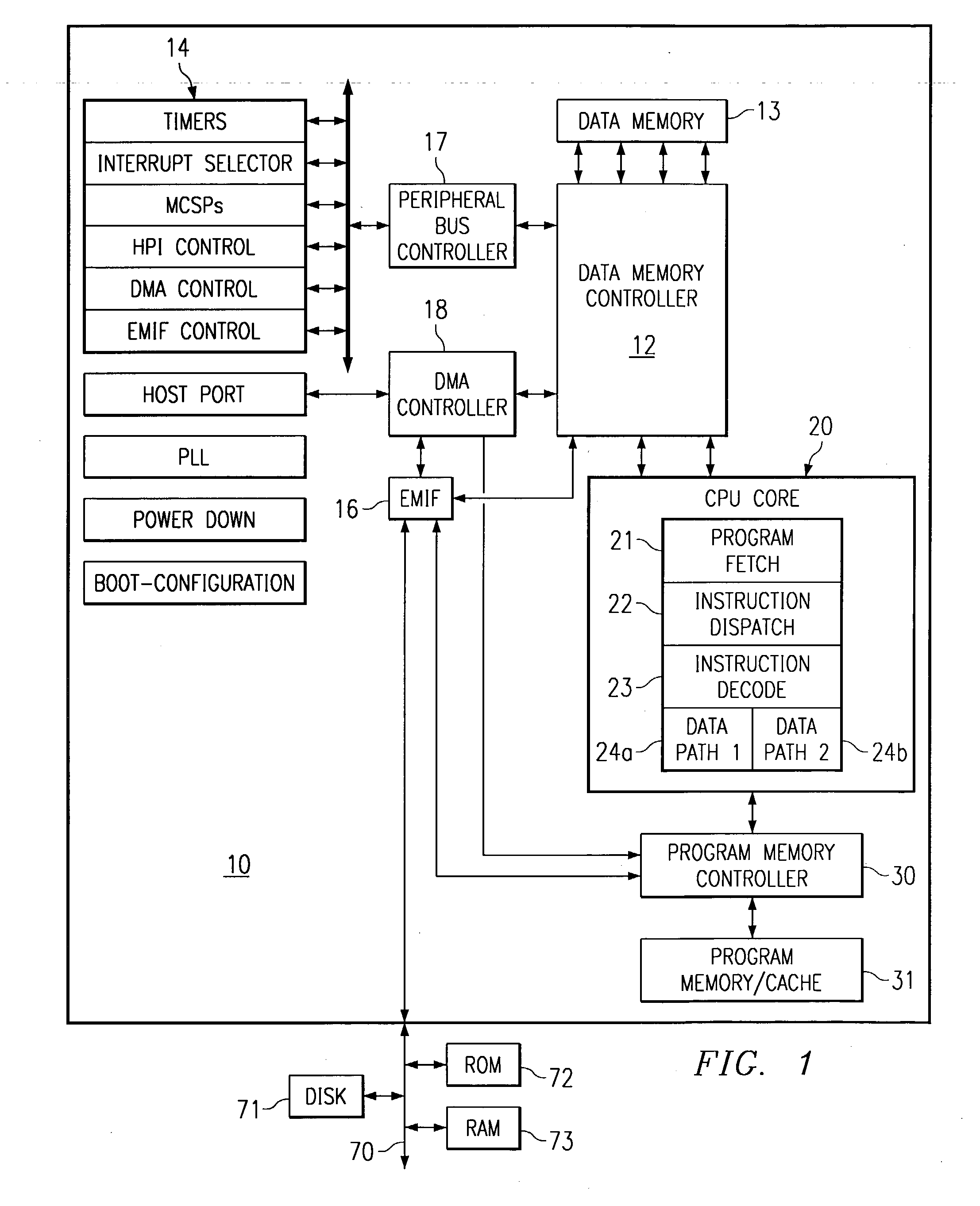

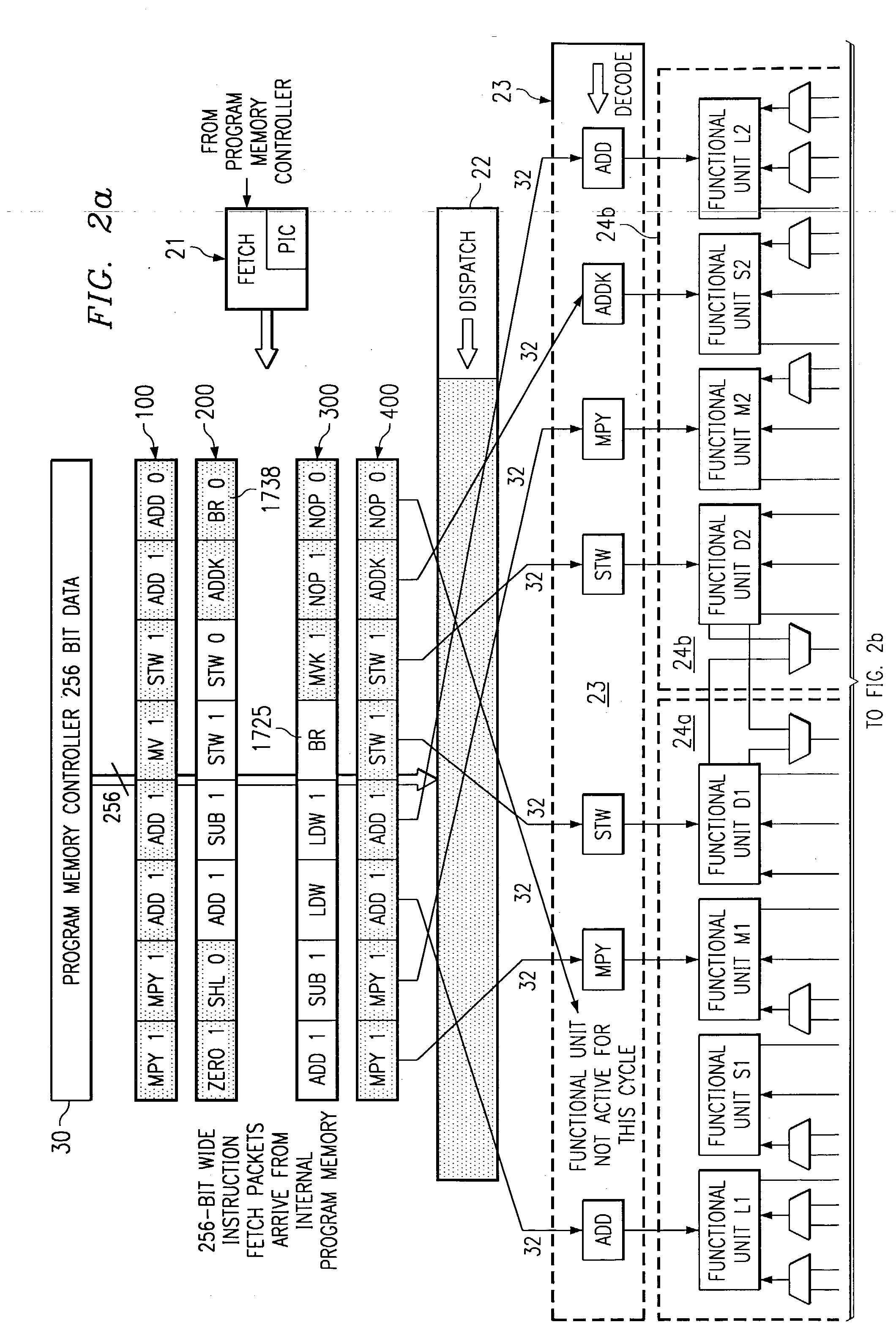

Apparatus and method for improved execution of a software pipeline loop procedure in a digital signal processor

InactiveUS20030154469A1General purpose stored program computerNext instruction address formationDigital signal processingParallel computing

A program memory controller unit includes apparatus for the execution of a software pipeline procedure in response to a predetermined instruction. The apparatus provides a prolog state, a kernel state, and an epilog state for the execution of the software pipeline procedure. In addition, in response to a predetermined condition, the software pipeline loop procedure can be terminated early. Apparatus is provided whereby a second software pipeline loop procedure can be initiated prior to the completion of a first software pipeline procedure. Two additional instructions are provided for addressing problems resulting from hardware pipeline delays and for more efficient program execution.

Owner:TEXAS INSTR INC

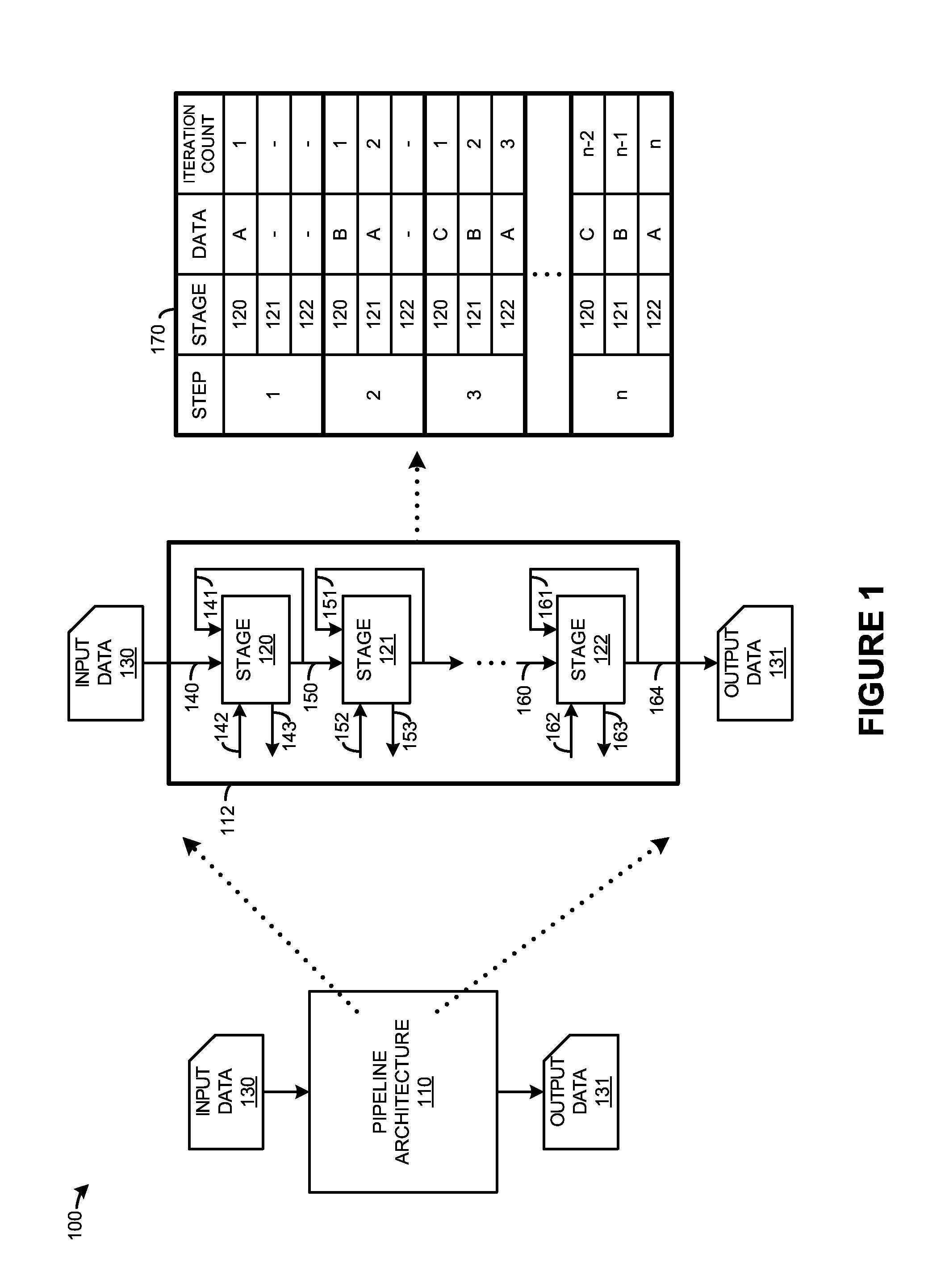

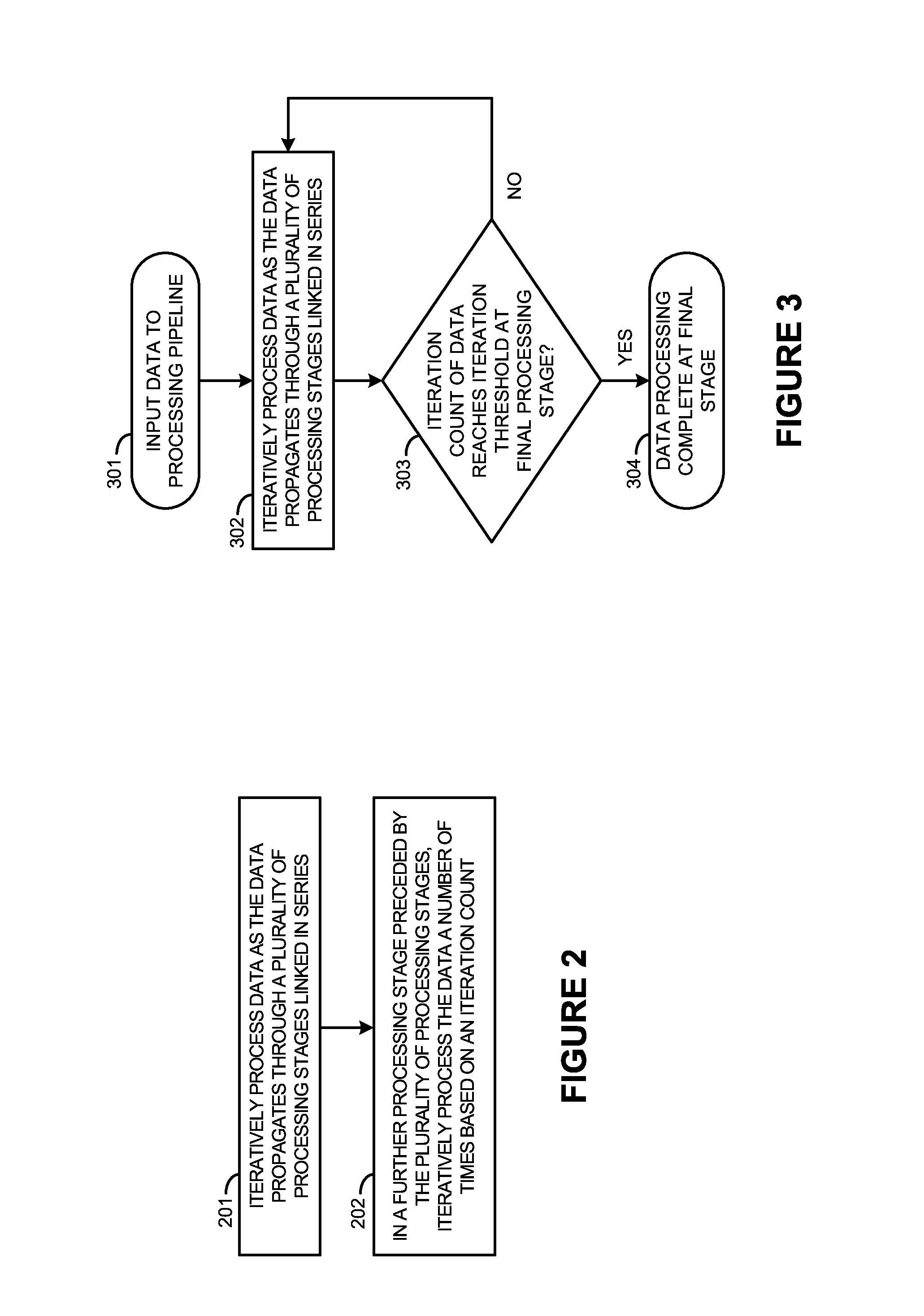

Dynamically controlled pipeline processing

ActiveUS20130212352A1Systolic arraysConcurrent instruction executionComputer hardwareComputer architecture

Systems, apparatuses, methods, and software for processing data in pipeline architectures are provided herein. In one example, a pipeline architecture is presented. The pipeline architecture includes a plurality of processing stages, linked in series, that iteratively process data as the data propagates through the plurality of processing stages. The pipeline architecture includes at least one other processing stage linked in series with and preceded by the plurality of processing stages and configured to iteratively process the data a number of times based at least on an iteration count comprising how many times the data was iteratively processed as the data propagated through the plurality of processing stages.

Owner:ANDERSON WILLIAM ERIK

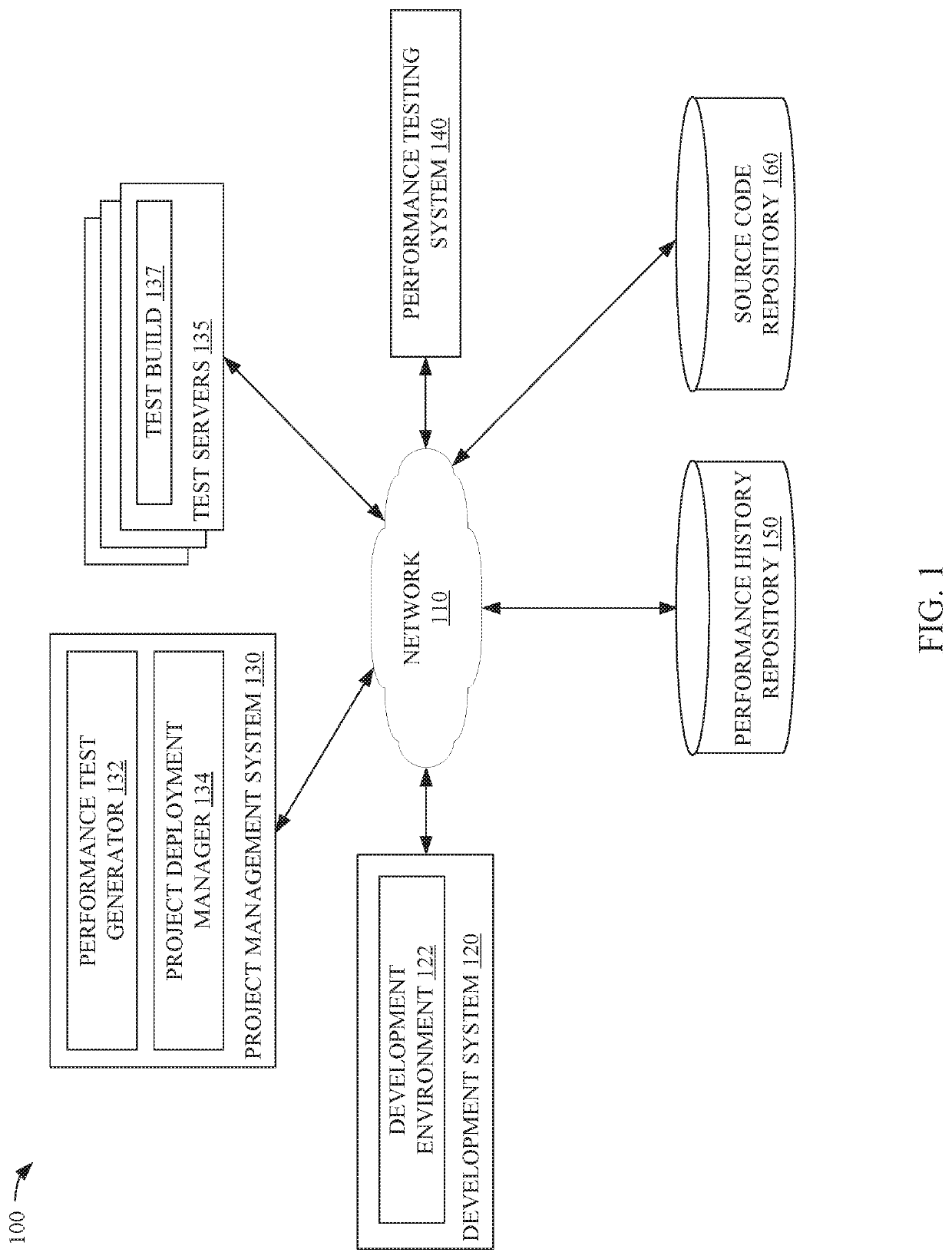

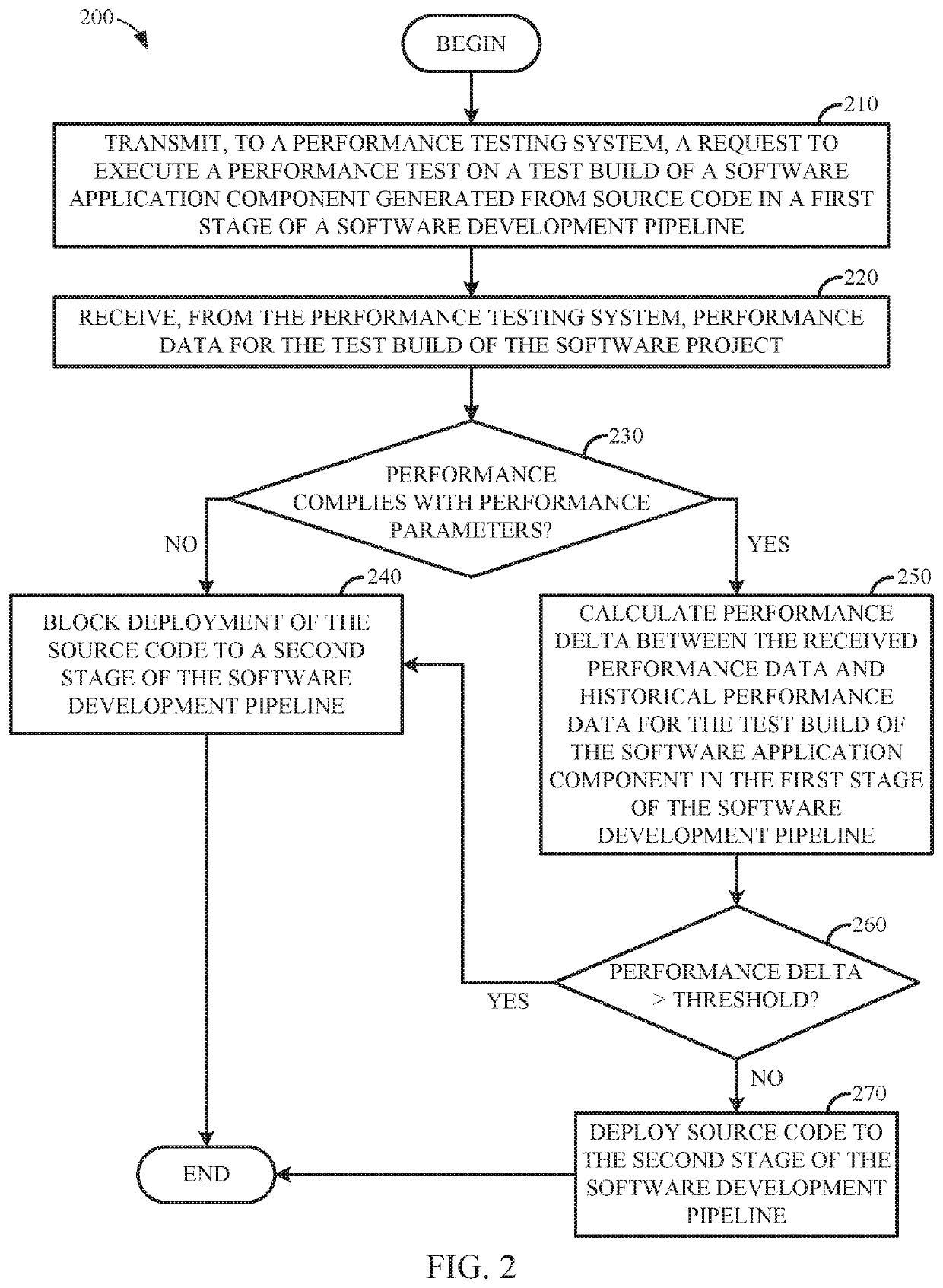

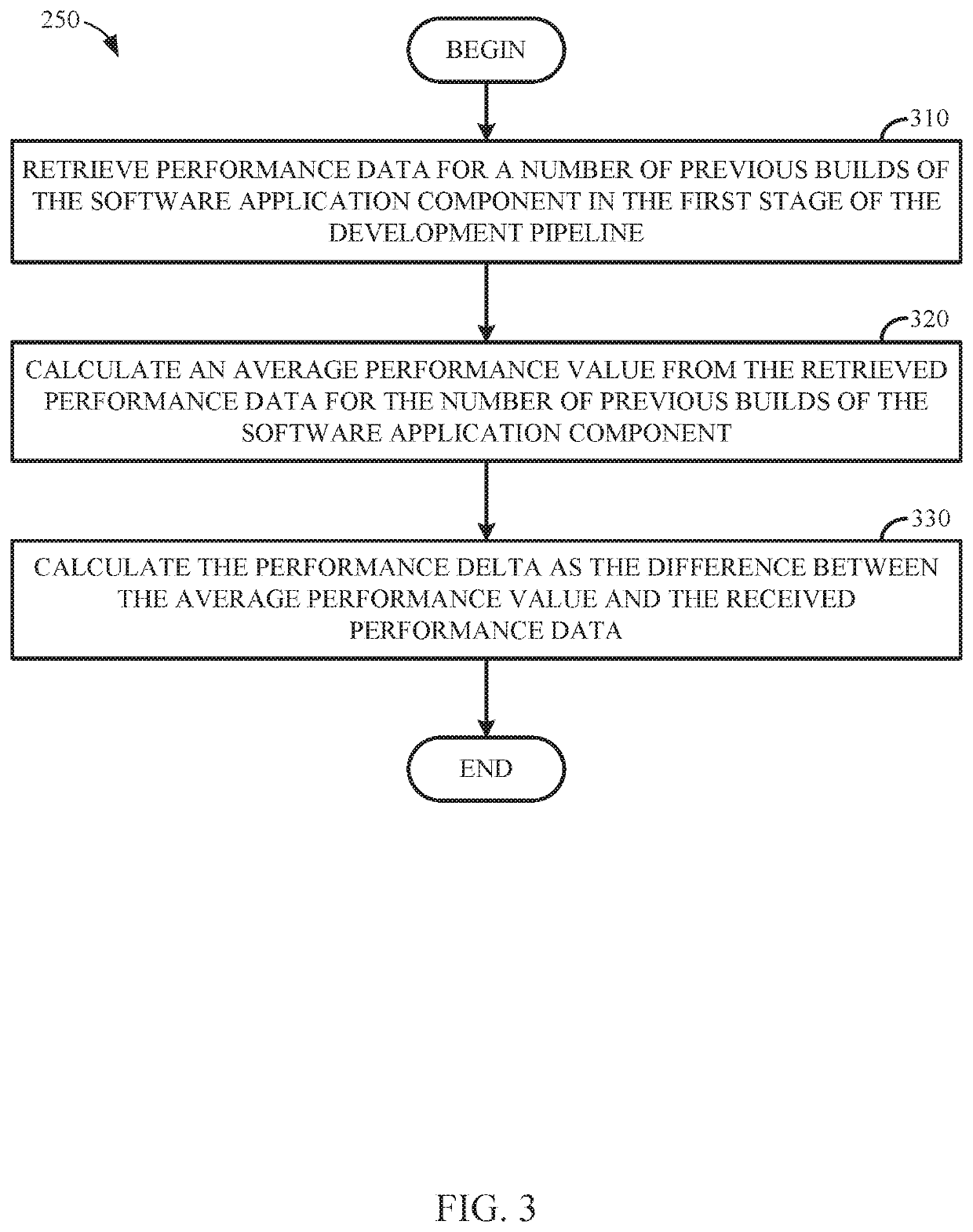

Method and system for managing deployment of software application components based on software performance data

ActiveUS10613970B1Software testing/debuggingSoftware metricsSoftware developmentDeployment environment

Certain aspects of the present disclosure provide techniques for managing the deployment of software applications based on application performance data. Embodiments include transmitting, to a performance testing system, information identifying a test build of a software application component in a first deployment environment in a software development pipeline to test. Performance information for the test build of the software application component is received from the performance testing system. The received performance information for the test build of the software application component is compared to one or more of predetermined performance parameters or historical performance data for the software application component. Based on the comparing, the system takes one or more actions to manage deployment of the test build of the software application component to a second deployment environment in the software development pipeline.

Owner:INTUIT INC

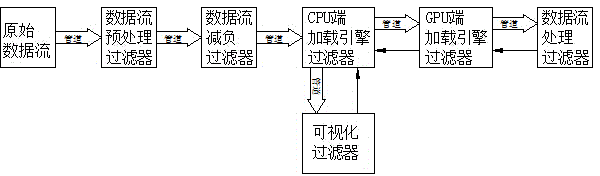

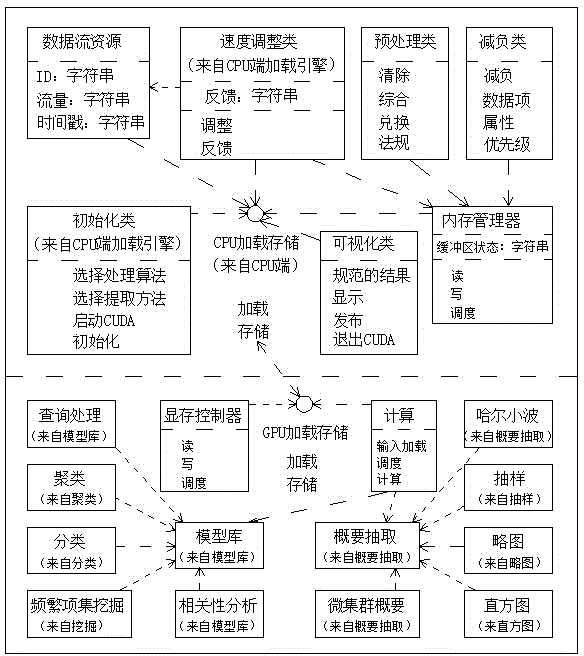

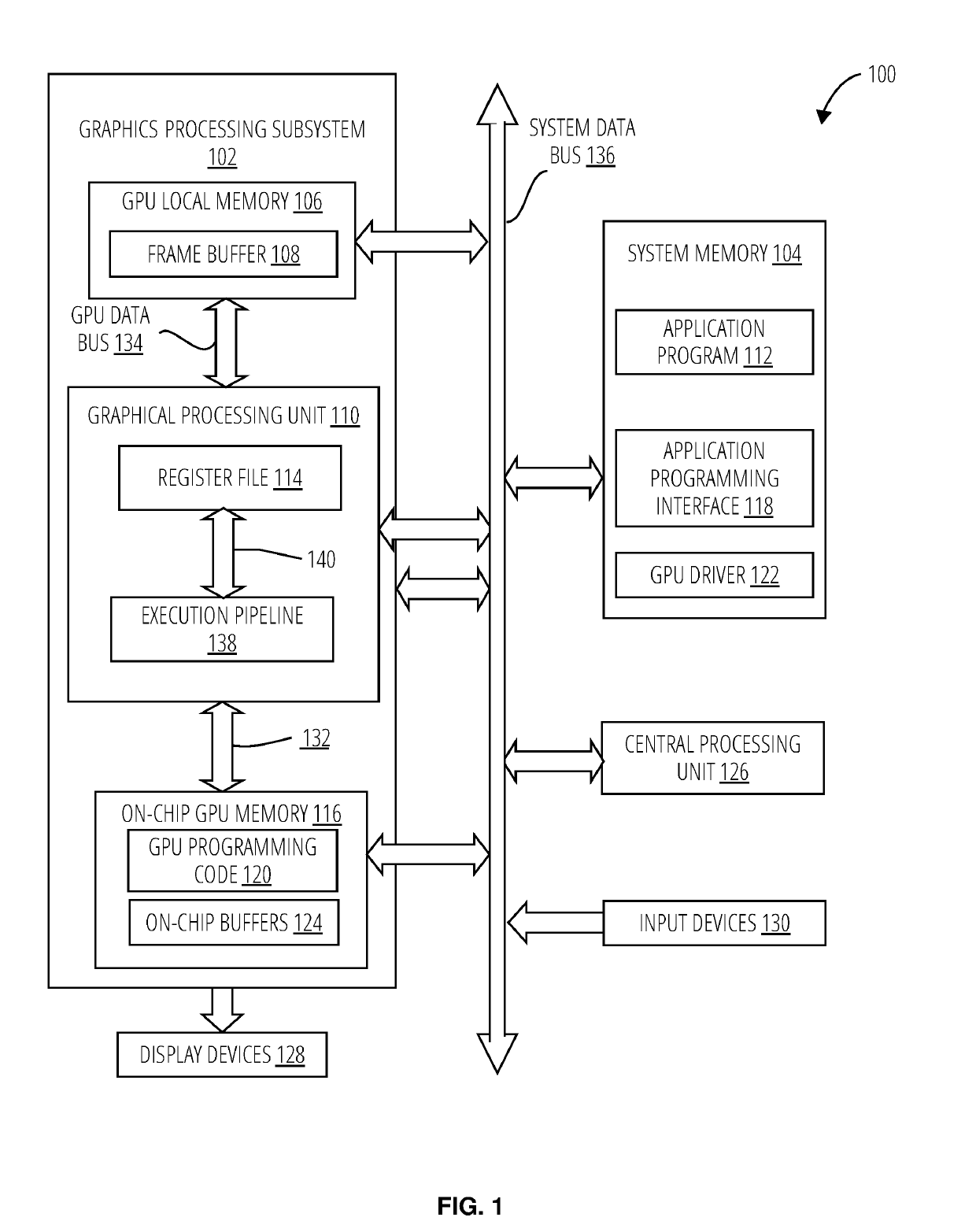

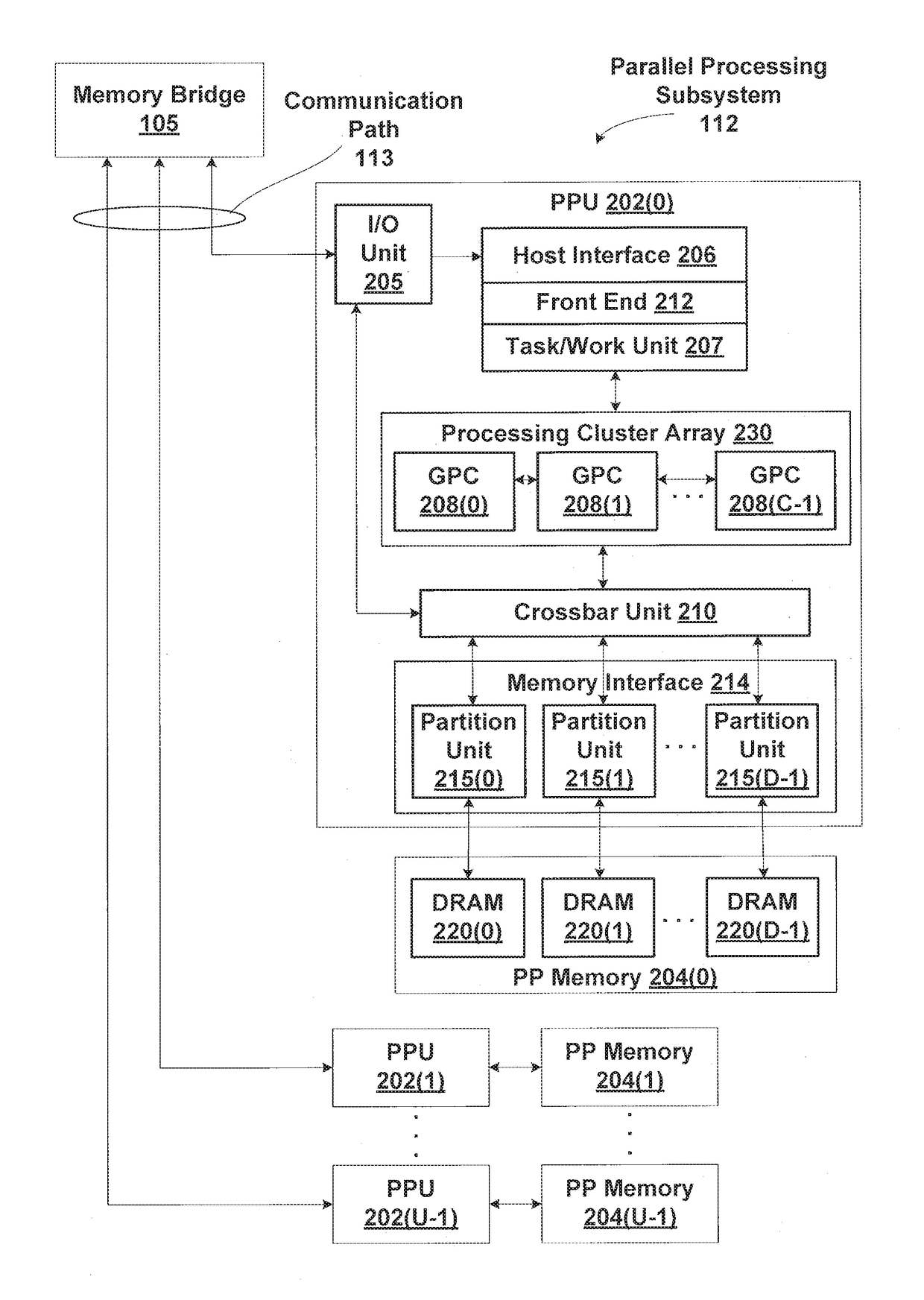

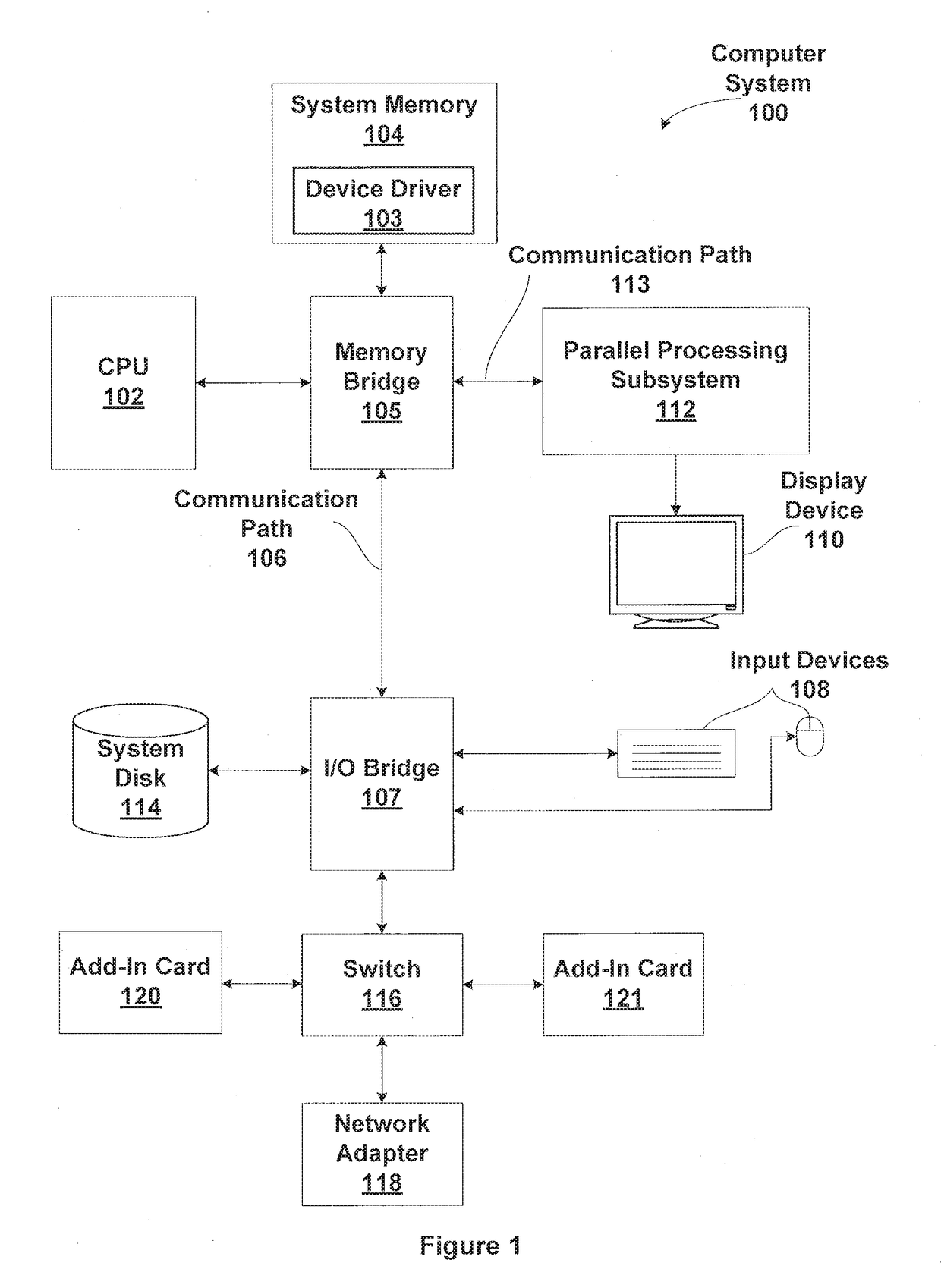

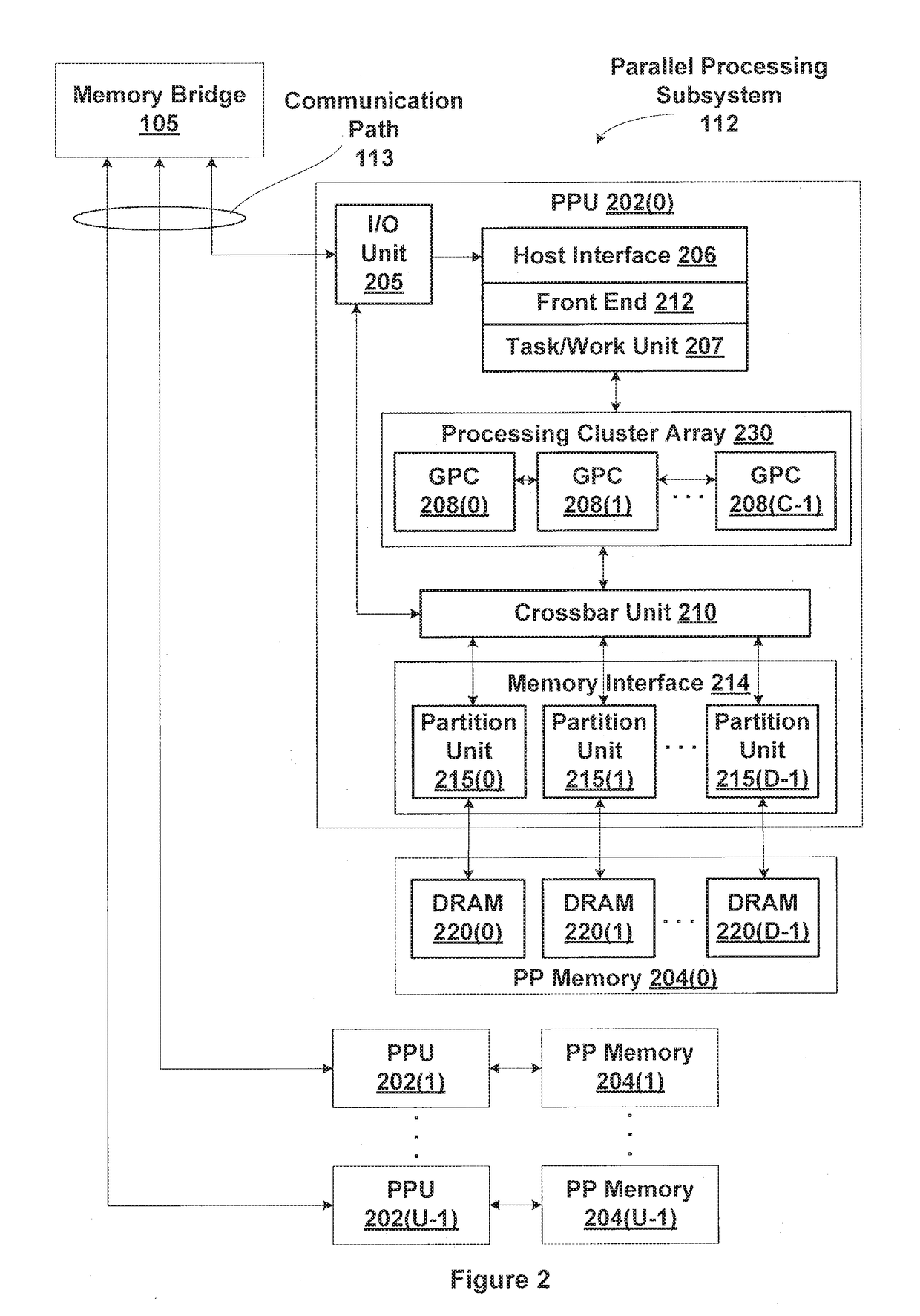

GPU (graphics processing unit) based software system architecture and UML (unified modeling language) and ADL (architecture description language) combined describing method

InactiveCN104615437AReasonably constructedFast data processingSpecific program execution arrangementsArchitecture description languageComputer architecture

The invention discloses a GPU (graphics processing unit) based software system architecture and a UML (unified modeling language) and ADL (architecture description language) combined describing method and belongs to the technical field of software system architectures. The GPU based software system architecture is characterized in that a pipeline and filter mode is applied to modeling, filters include a data stream preprocessing filter, a data stream relief filter, a CPU (central processing unit) loading engine filter, a GPU loading engine filter, a data stream processing filter and a visual filter, original data streams sequentially pass the data stream preprocessing filter, the data stream relief filter, the CPU loading engine filter, the GPU loading engine filter and the data stream processing filter through a pipeline, the data stream processing filter transmits data results to the GPU loading engine filter and the CPU loading engine filter in succession, and the CPU loading engine inputs the data results into the visual filter. UML and ADL are used together, advantages of the UML and the ADL are combined, and the GPU based software system architecture is better established.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

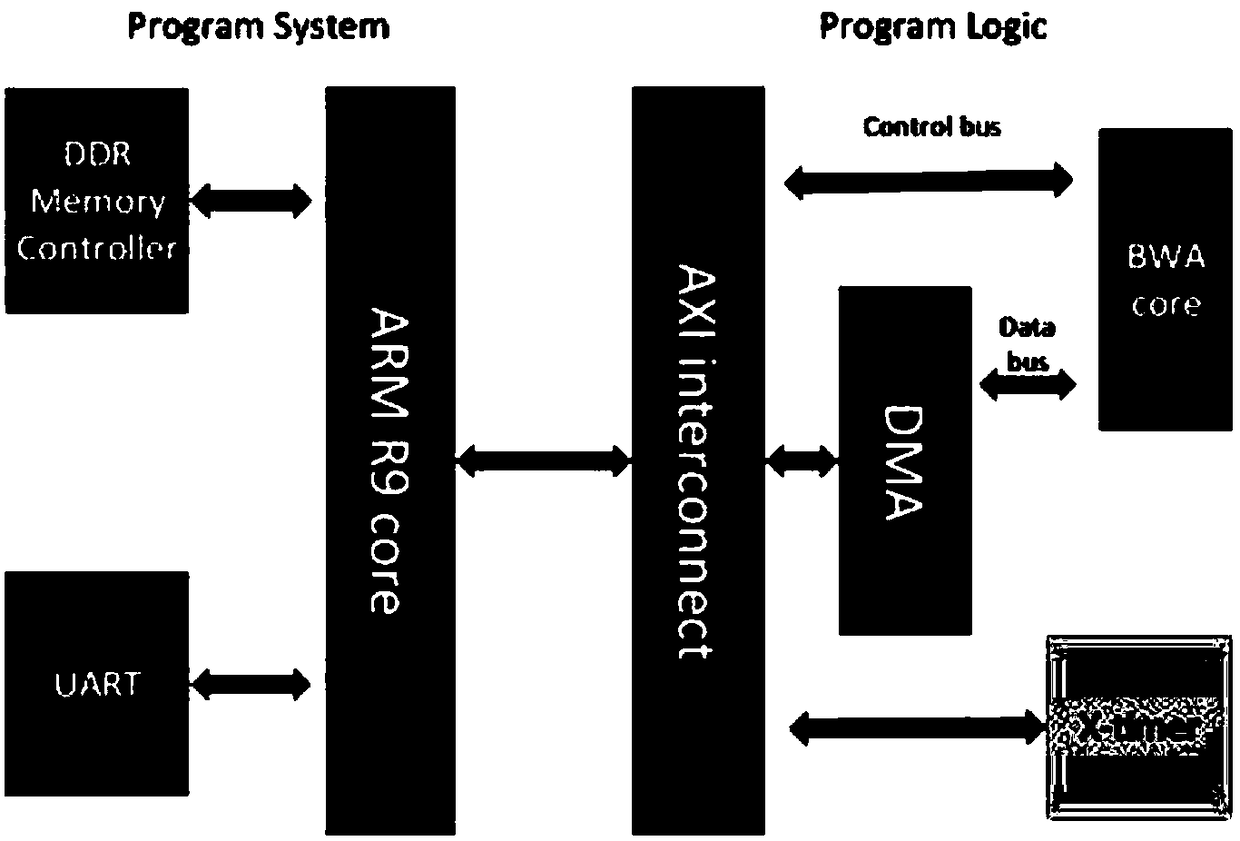

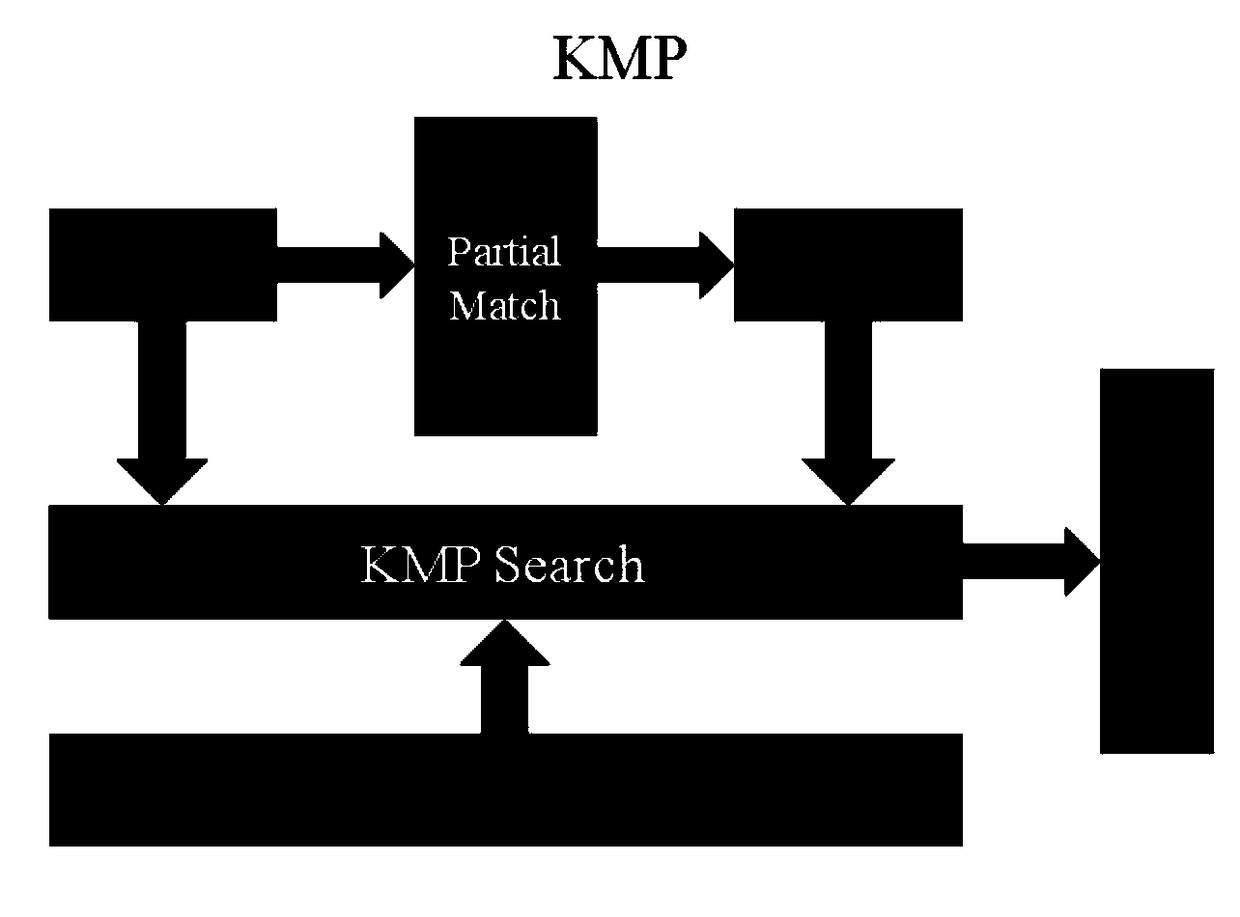

FPGA-based acceleration platform and design method for gene sequencing string matching algorithm

PendingCN108595917AImprove performanceHybridisationSpecial data processing applicationsGeneral purposeProgram logic

The invention discloses an FPGA-based acceleration platform and a design method for a gene sequencing string matching algorithm. The acceleration platform includes a PS (Program System) end and a PL (Program Logic) end, and the PS end includes a general-purpose processor and a DRAM to complete the software-side code operation and control of a hardware part, the PL end contains a plurality of IP cores that can be solidified according to requirements to achieve corresponding tasks. First, the general-purpose processor writes string data into the DRAM, and then the FPGA reads the string data fromthe DRAM and starts calculation, and the calculation result is written into the DRAM, and finally the general-purpose processor reads the matching result from the DRAM. The accelerator of the invention deploys multiple independent IP cores for calculation on the FPGA and the IP cores run in a pipeline mode, so that programmers without hardware knowledge can easily obtain good performance by usingexisting FPGA resources.

Owner:SUZHOU INST FOR ADVANCED STUDY USTC

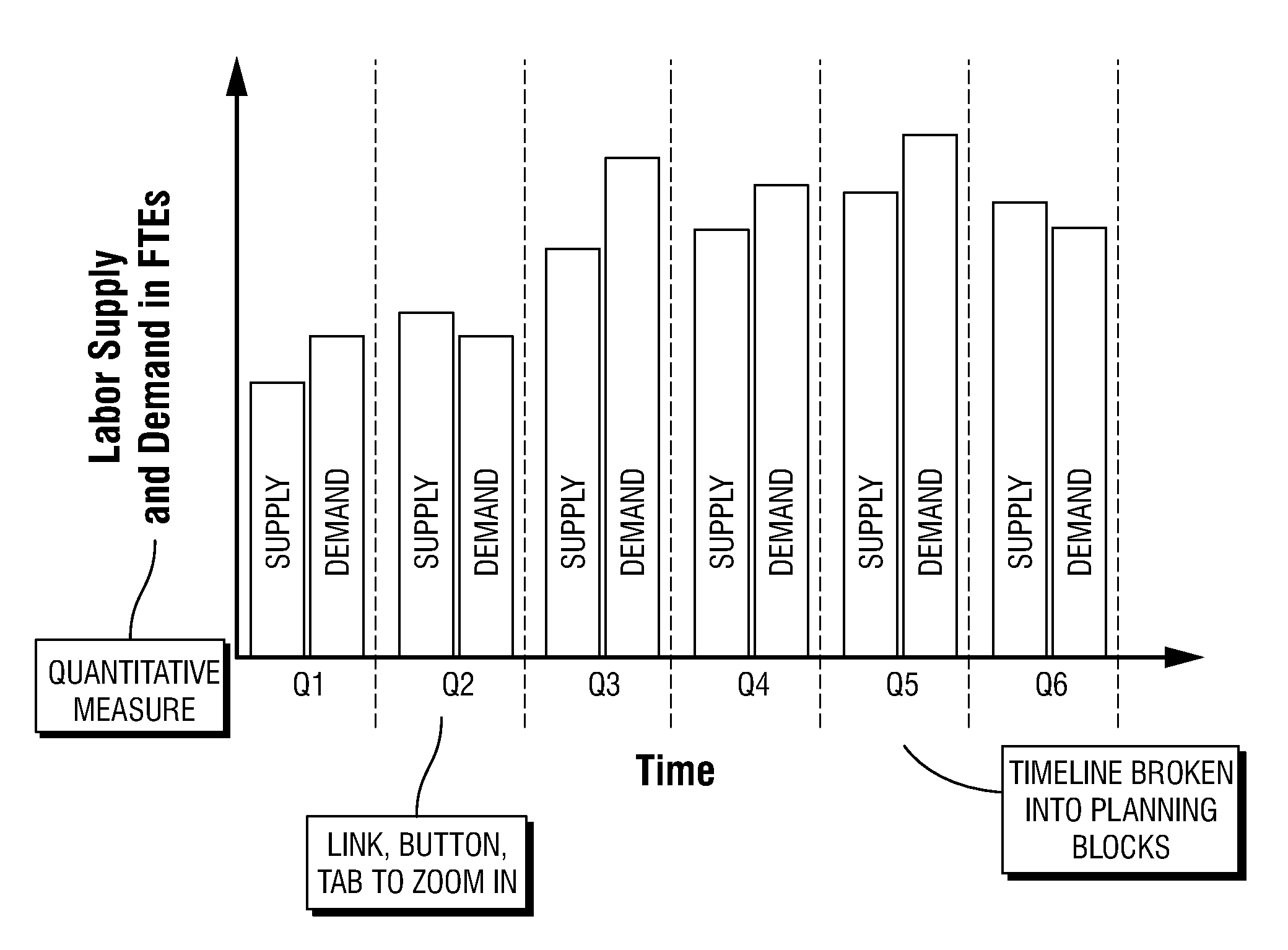

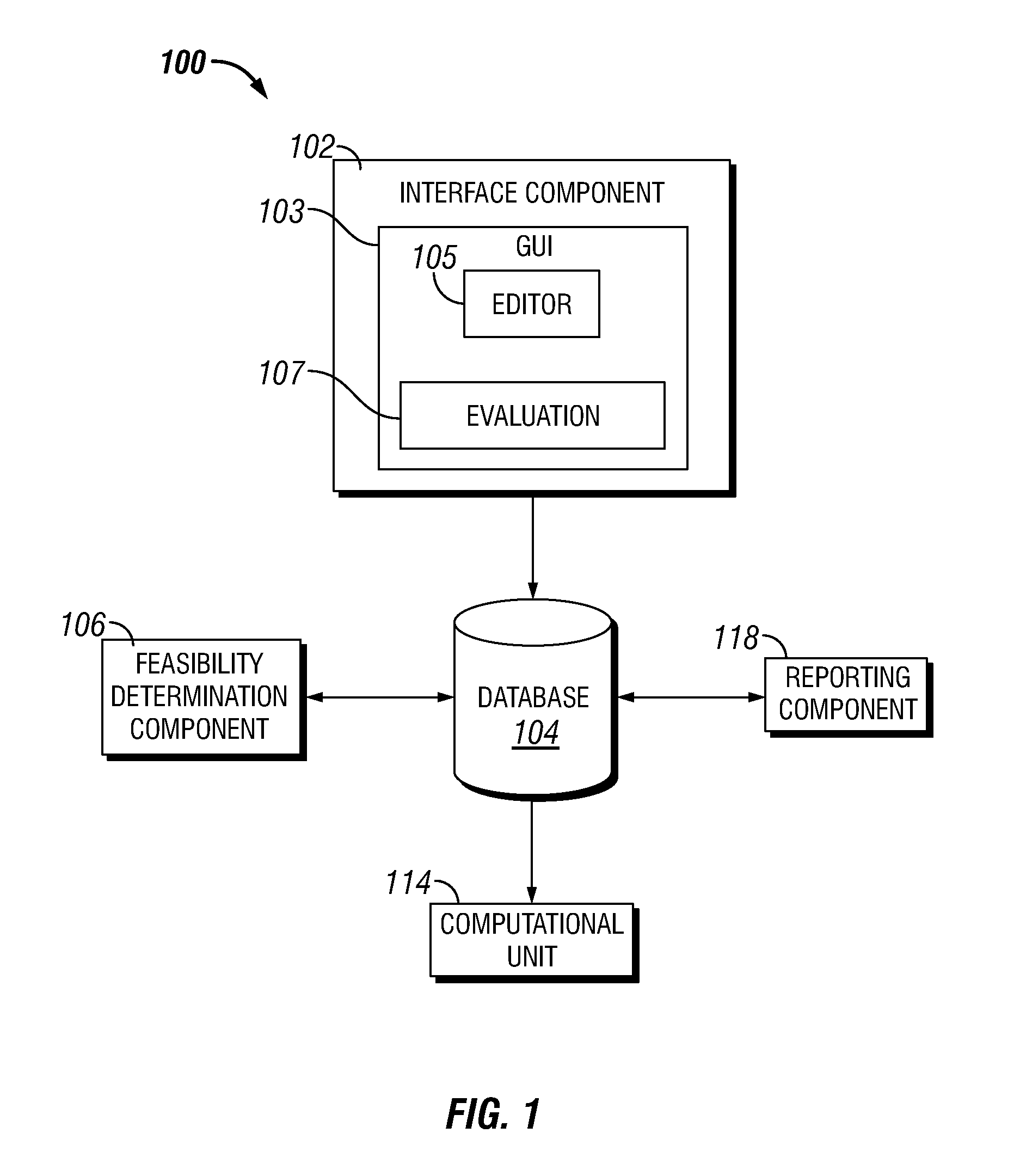

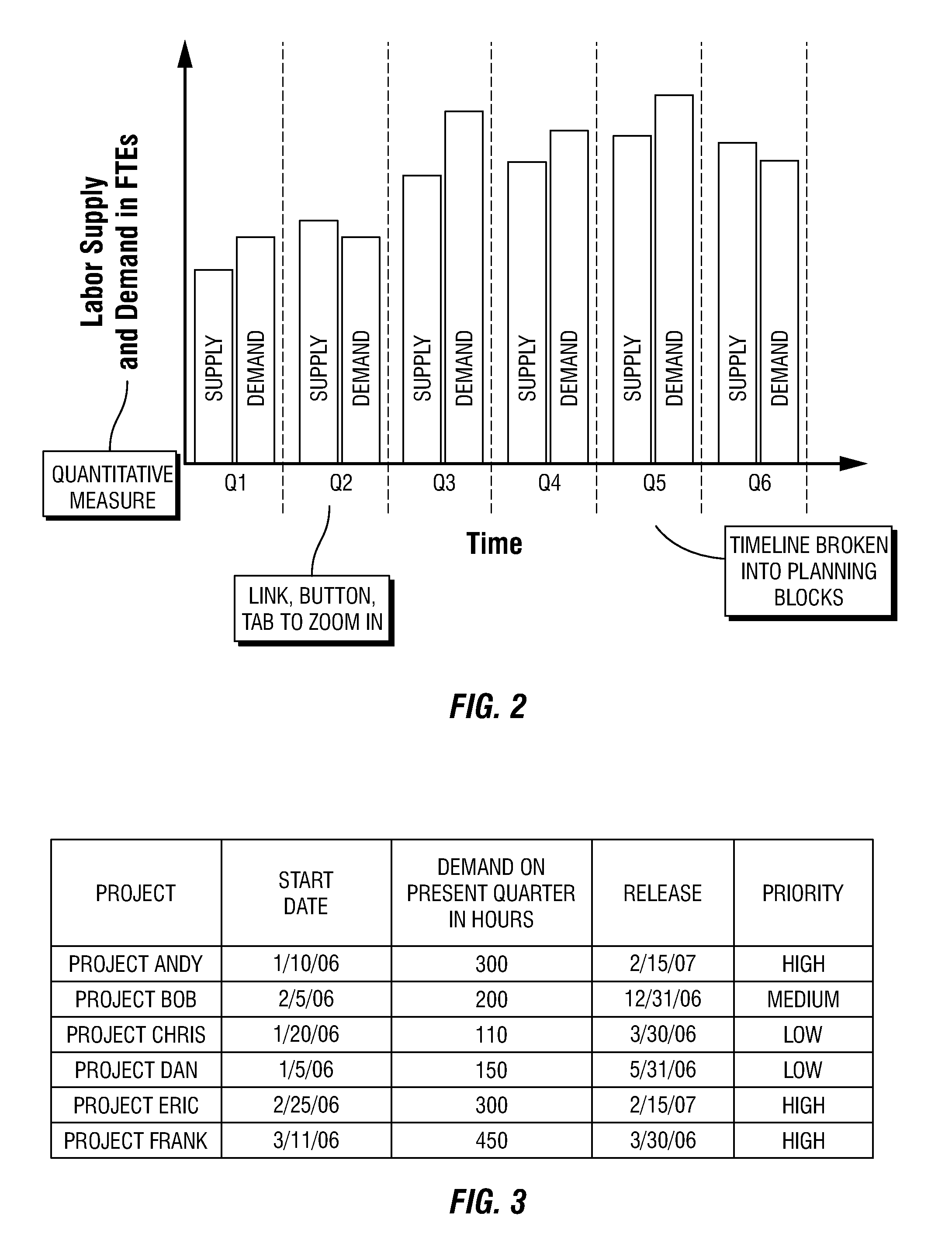

Hardware/software and vendor labor integration in pipeline management

As provided, a method of integration of hardware, software and vendor labor in software development pipeline management that comprises providing, for each of multiple projects in a software project pipeline, a set of inputs that includes 1) timing, 2) demand inputs, 3) supply inputs. The method further comprises aggregating the inputs. The method further comprises identifying one or more constraints in the software development pipeline when the demand inputs and the supply inputs are not in balance with the input timing.

Owner:SPRINT CORPORATION

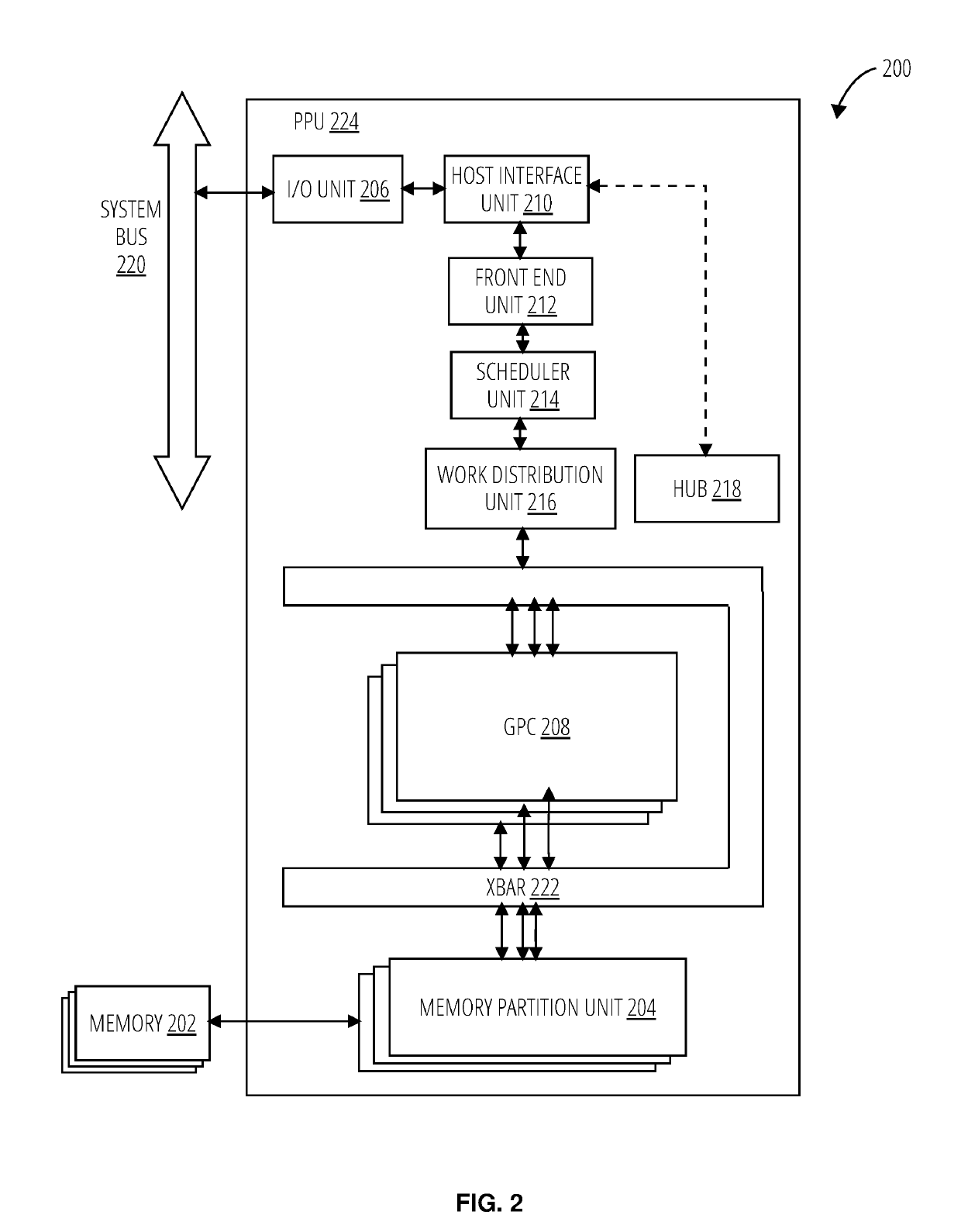

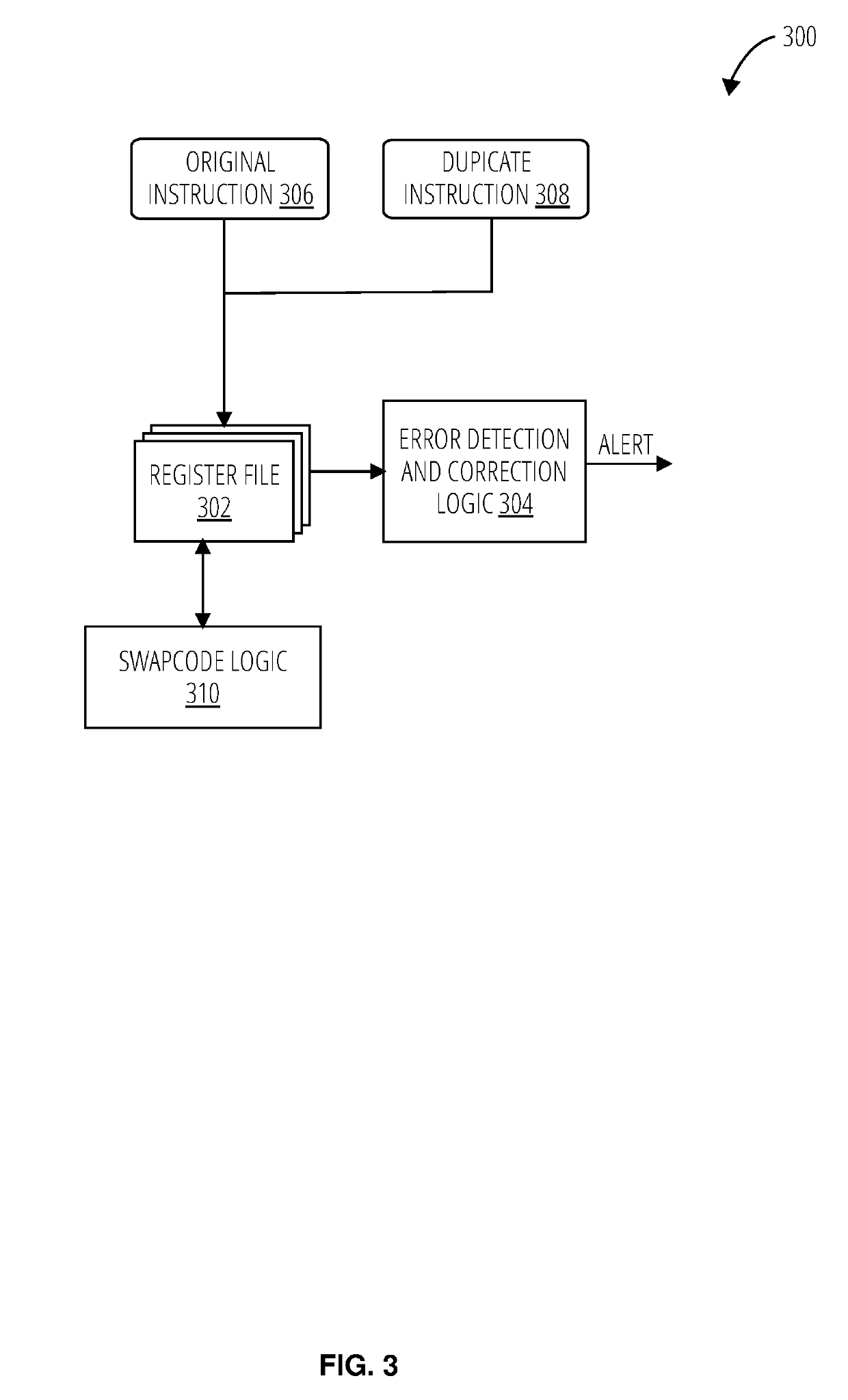

System and methods for hardware-software cooperative pipeline error detection

ActiveUS20190102242A1Reduce source of inefficiencyAvoid overheadRegister arrangementsConcurrent instruction executionEmbedded systemFalse detection

A family of software-hardware cooperative mechanisms to accelerate intra-thread duplication leverage the register file error detection hardware to implicitly check the data from duplicate instructions, avoiding the overheads of instruction checking and enforcing low-latency error detection with strict error containment guarantees.

Owner:NVIDIA CORP

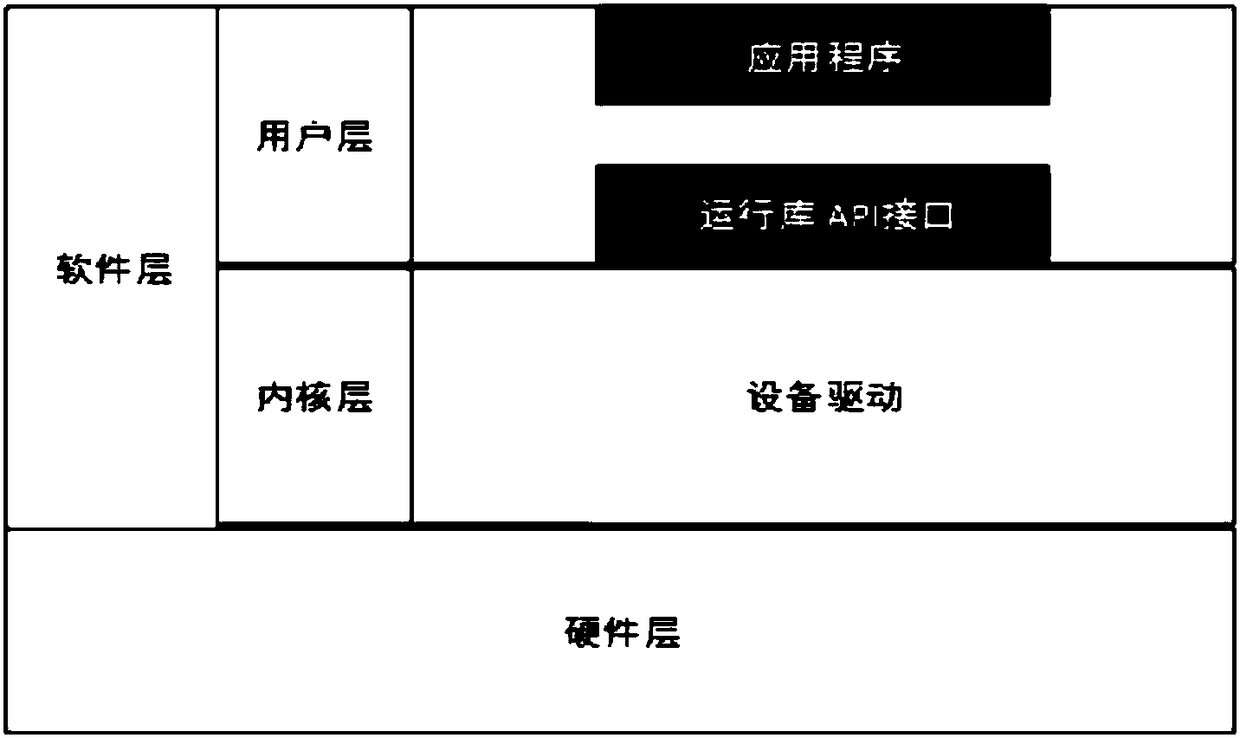

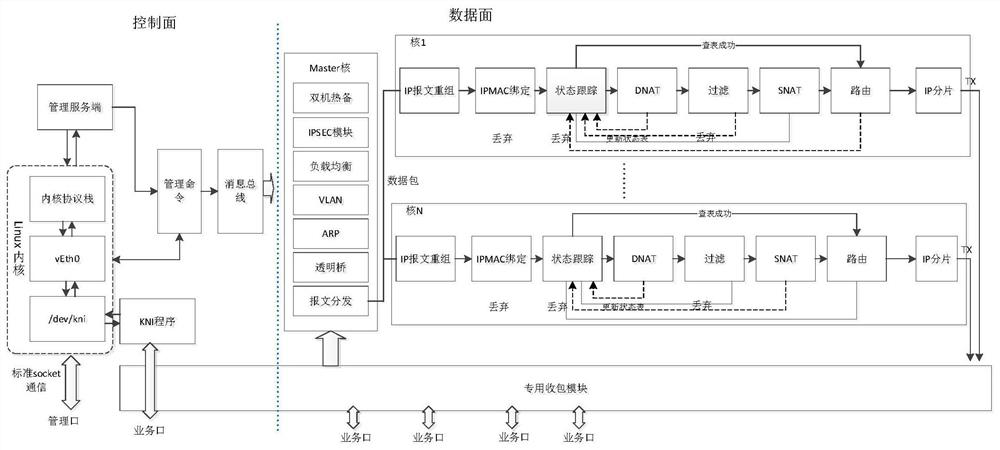

Firewall system of user mode pipeline architecture

ActiveCN111614631ASolve processing inefficienciesReduce downtimeResource allocationInterprogram communicationData packSoftware architecture

The invention discloses a firewall system of a user mode pipeline architecture. A control plane is responsible for management and control functions of the system and redirects a message sent from a management port to a kernel protocol stack; a data plane is responsible for main service functions, works in a user mode and can bypass a complex Linux kernel protocol stack to directly obtain messagesfrom a network card. The data plane decomposes firewall function software into a plurality of function modules, each function module is bound to an independent CPU core, one CPU core serves as a maincore and is responsible for receiving messages, data packet receiving and sending are achieved in a polling mode, and an assembly line framework is formed. The firewall system belongs to a software architecture which bypasses a system kernel and is suitable for a firewall function, a network card driver is usually realized in the kernel, the firewall system is realized again in a user mode, the system directly acquires a message from the network card, and the problem of low processing efficiency caused by a traditional firewall Linux kernel is effectively solved.

Owner:江苏深网科技有限公司

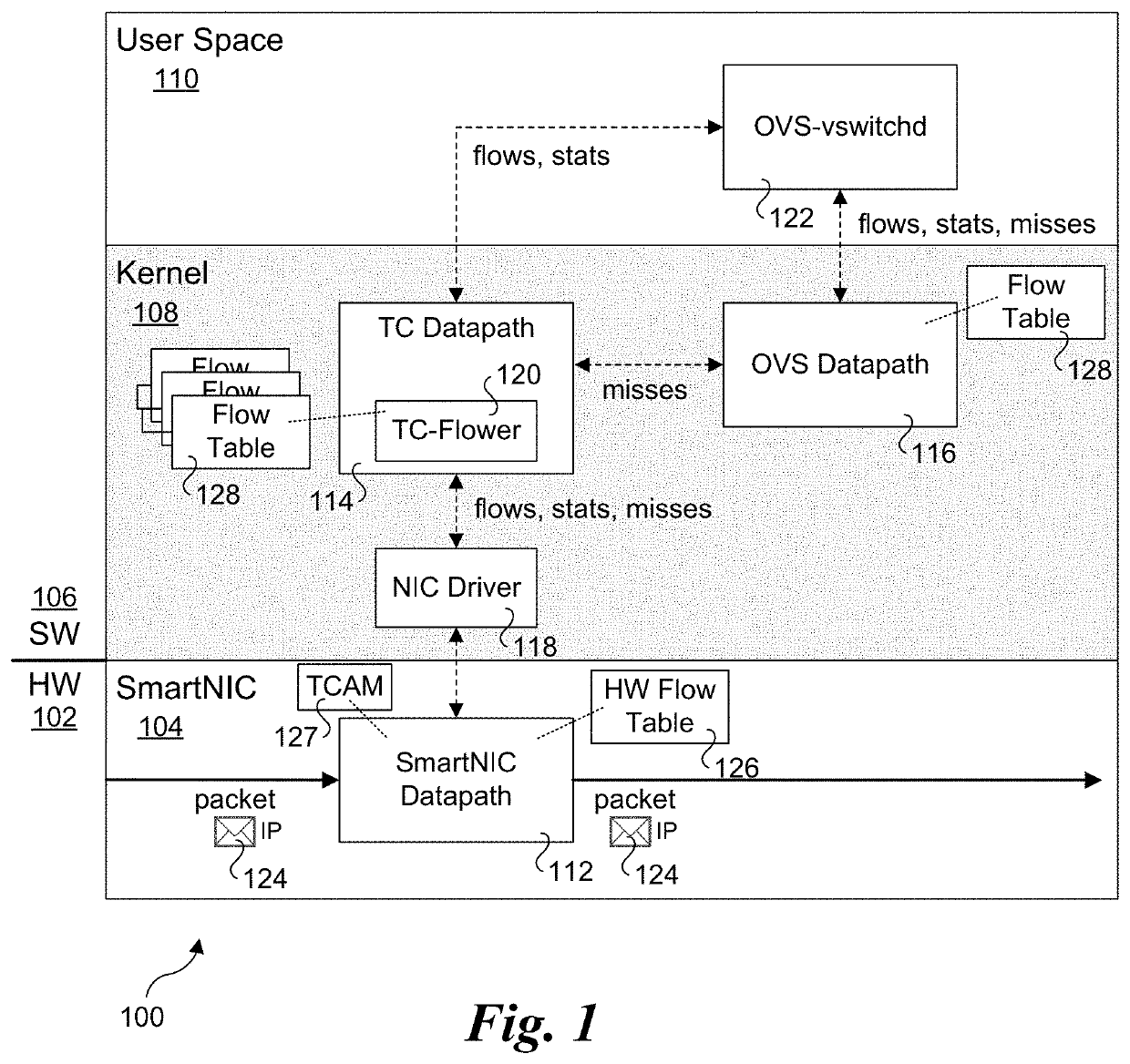

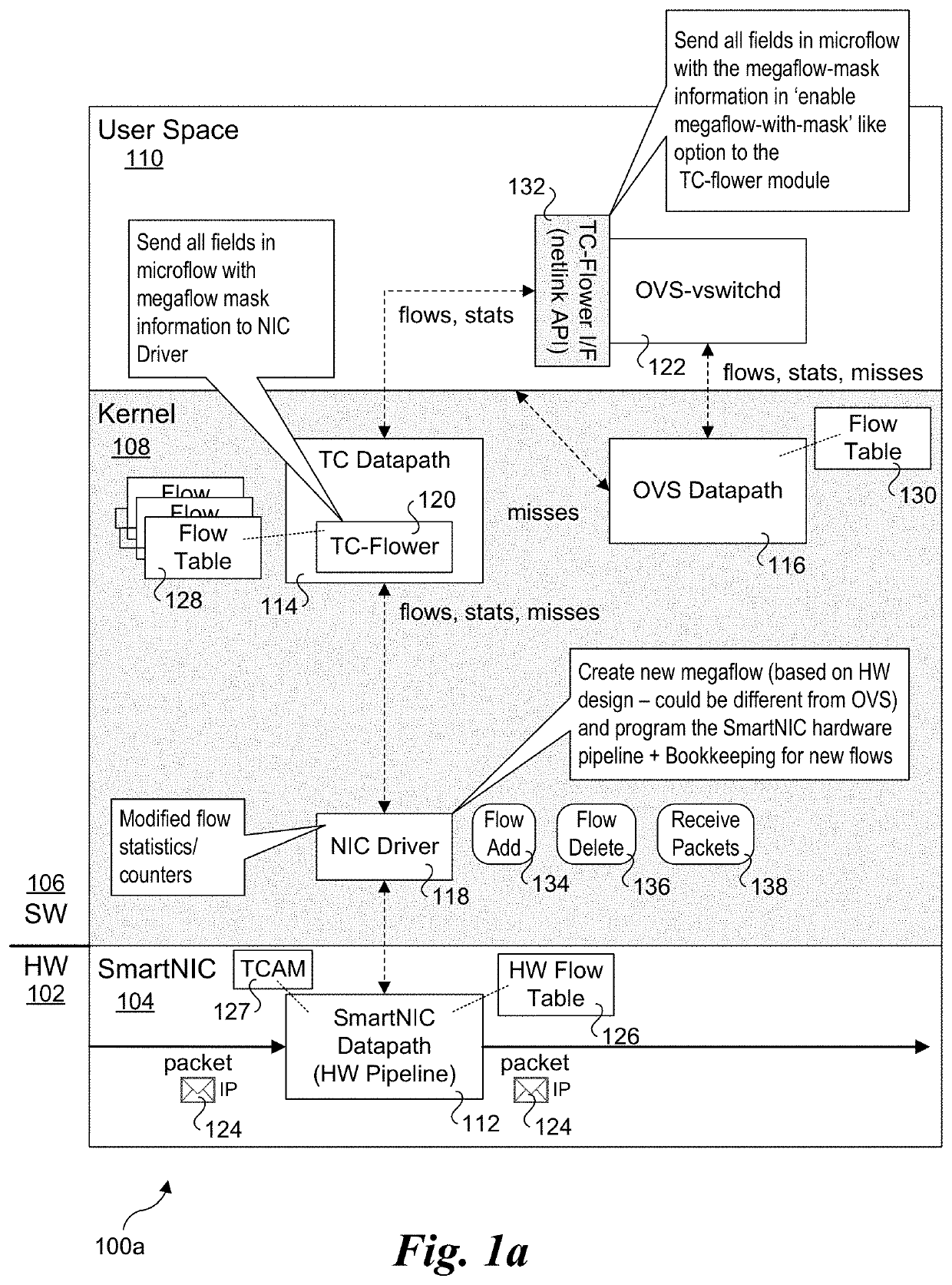

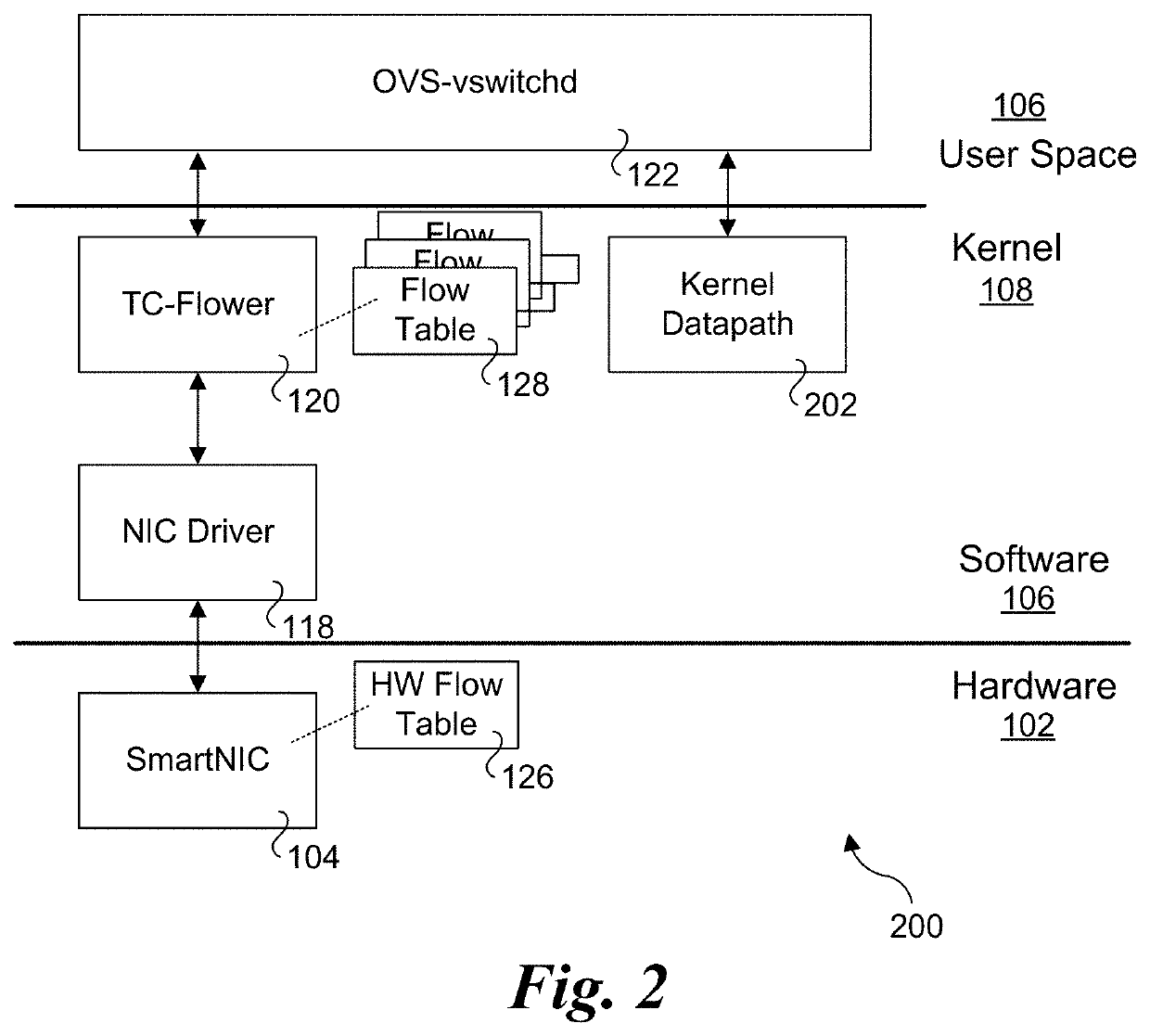

Extension of openvswitch megaflow offloads to hardware to address hardware pipeline limitations

Methods and apparatus for extending OpenvSwitch (OVS) megaflow offloads to hardware to address hardware pipeline limitations. Under a method implemented on a compute platform including a Network Interface Controller (NIC) having one or more ports and running software including OVS software and a Linux operating system having a kernel including a TC-flower module and a NIC driver a new megaflow is created with a mask in the OVS software employing a subset of microflow fields for a packet. The microflow fields and the megaflow mask is sent to the NIC driver. A new megaflow is implemented in the NIC driver employing a subset of the microflow fields and the NIC driver creates a new hardware flow on the NIC employing a packet match scheme using all the microflow fields. The NIC also programs a NIC hardware pipeline with the new hardware flow using a match scheme that may depend on the available hardware resources, such as the size of a TCAM.

Owner:INTEL CORP

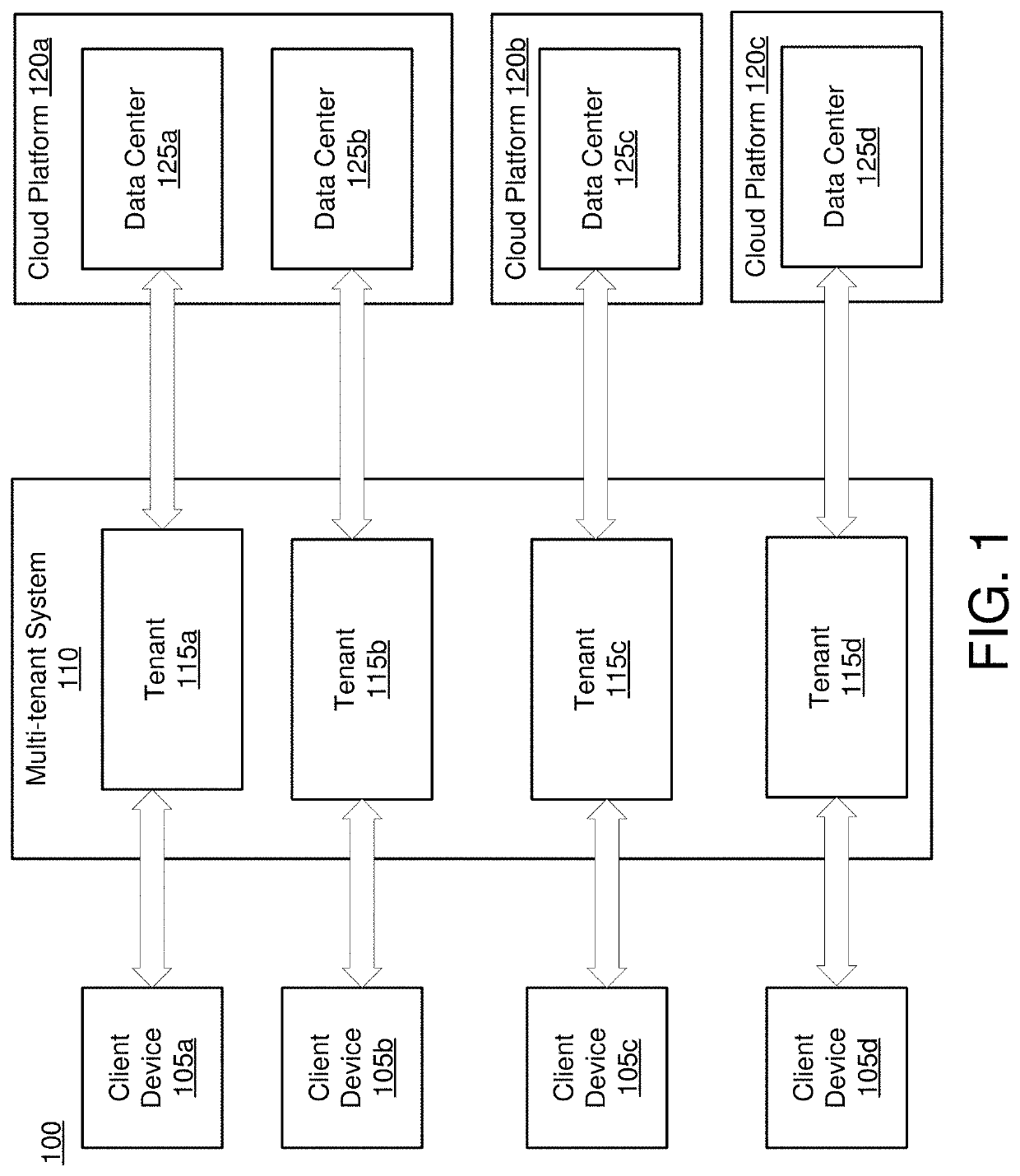

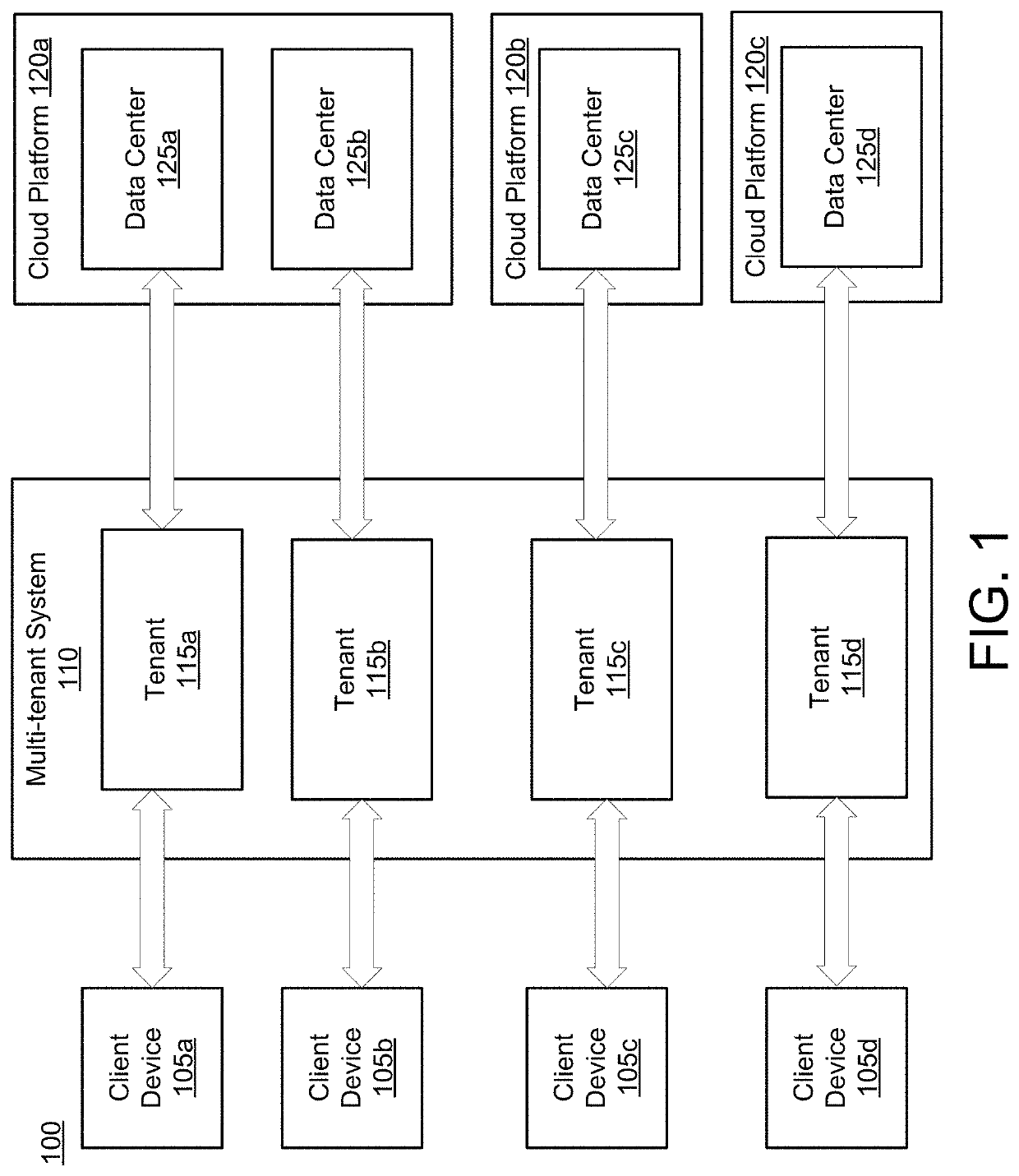

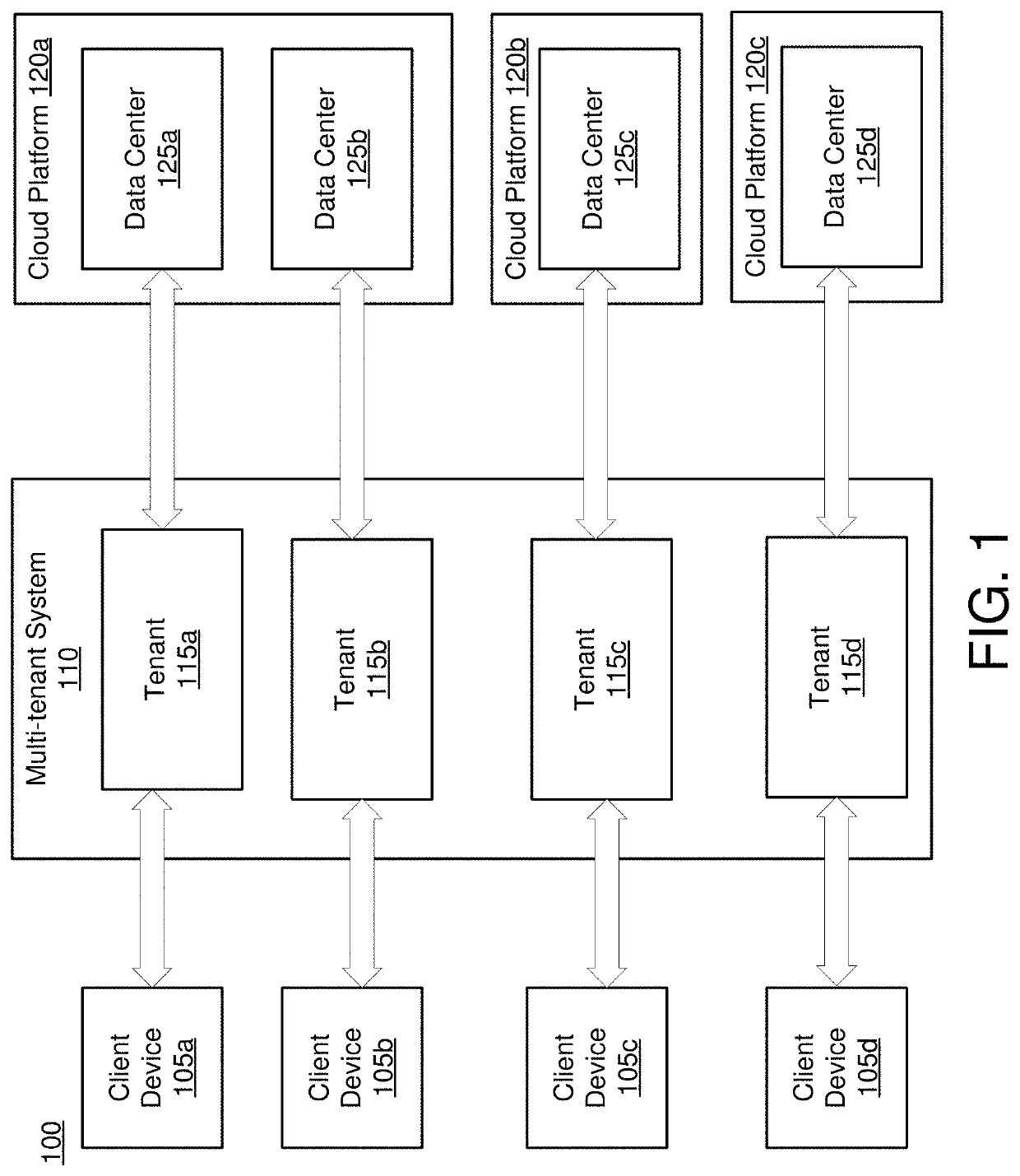

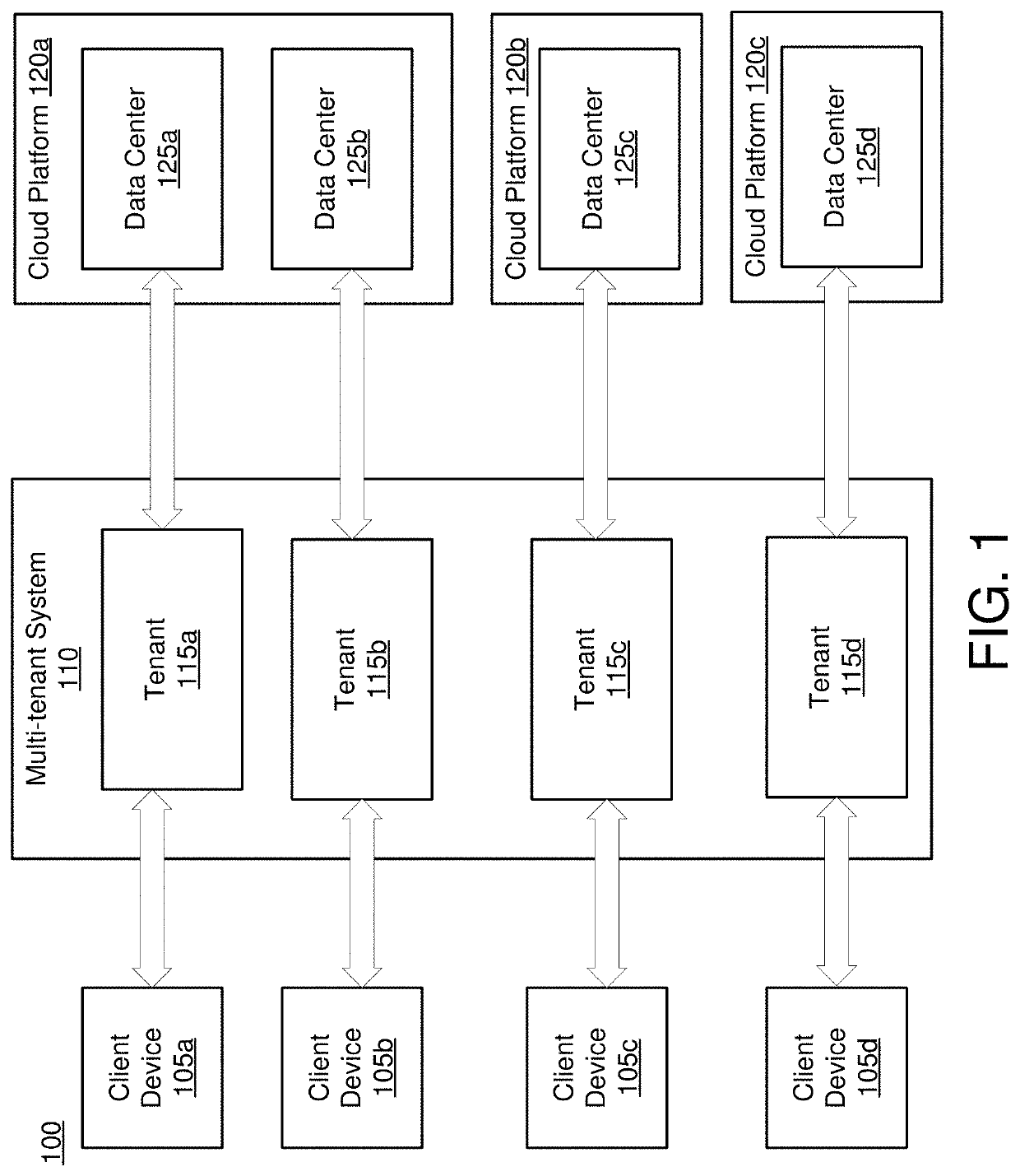

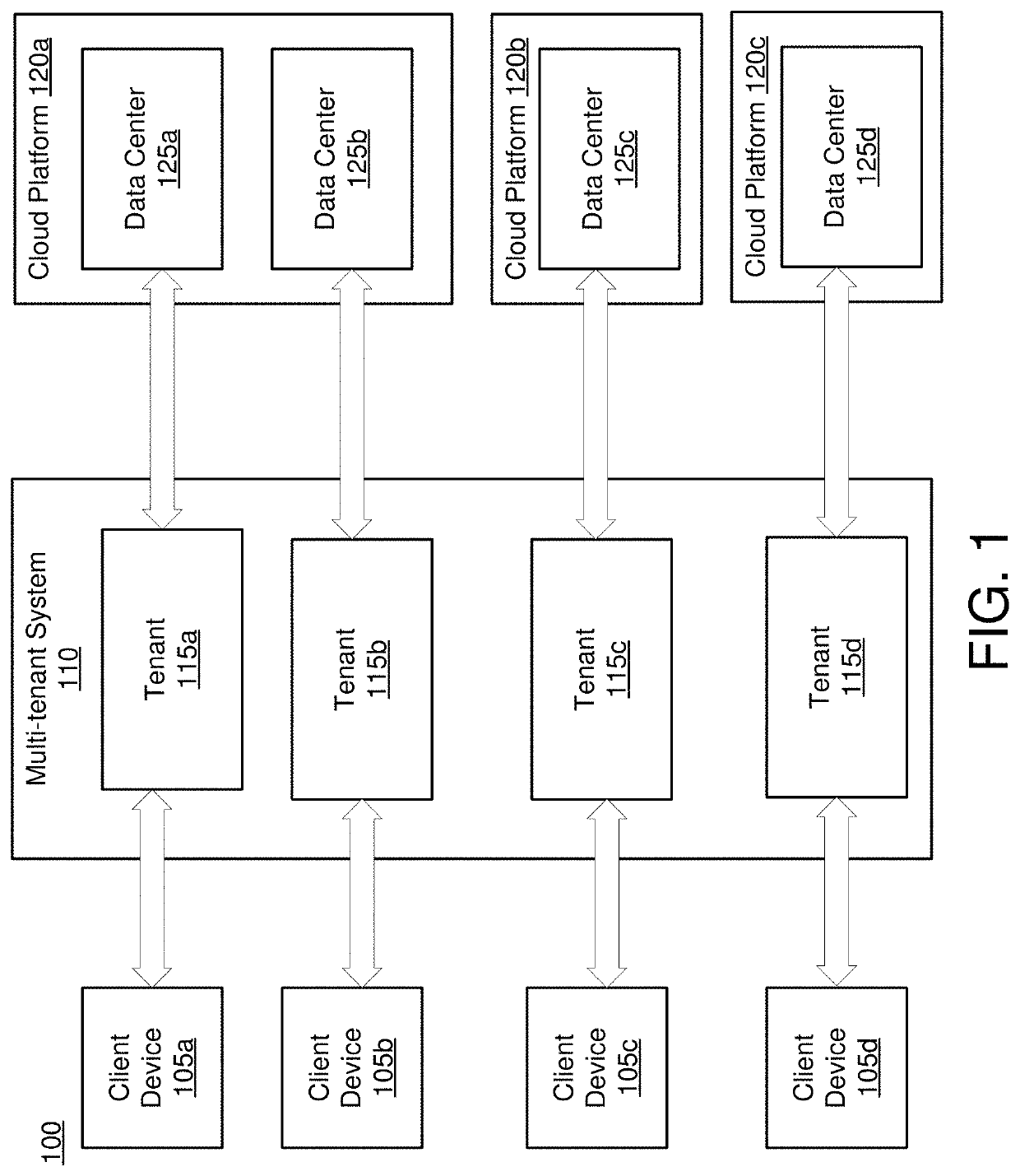

Versioning of pipeline templates for continuous delivery of services on datacenters configured in cloud platforms

Computing systems, for example, multi-tenant systems deploy software artifacts in data centers created in a cloud platform using a cloud platform infrastructure language that is cloud platform independent. The system receives pipeline templates including templating expressions that can be substituted with values for generating pipelines. A pipeline can be executed to perform a set of actions associated with continuous delivery of a software artifact. The system stores sets of partially hydrated pipeline templates. The partially hydrated pipeline templates can be compiled into executable pipelines associated with services configured on a datacenter of a cloud platform. The system stores different versions of pipeline templates as deployment packages. The system stores version pointers that identify specific deployment packages that are selected when a software release is deployed. The version pointers allow the deployment package to be updated in case of roll back or for deploying more recent changes.

Owner:SALESFORCE COM INC

Software-assisted instruction level execution preemption

ActiveUS20170249152A1Quantity minimizationQuickly preemptedConcurrent instruction executionProgram saving/restoringComputer architectureEngineering

One embodiment of the present invention sets forth a technique for instruction level execution preemption. Preempting at the instruction level does not require any draining of the processing pipeline. No new instructions are issued and the context state is unloaded from the processing pipeline. Any in-flight instructions that follow the preemption command in the processing pipeline are captured and stored in a processing task buffer to be reissued when the preempted program is resumed. The processing task buffer is designated as a high priority task to ensure the preempted instructions are reissued before any new instructions for the preempted context when execution of the preempted context is restored.

Owner:NVIDIA CORP

Data conversion method based on pipeline three-dimensional model

ActiveCN112487589AImprove consistencyResolve inconsistenciesGeometric CADDesign optimisation/simulationSoftware engineeringWorkload

The invention discloses a data conversion method based on a pipeline three-dimensional model, the combination of SPOOLGEN and multiple software becomes a mainstream working mode at present, but the combination of SPOOLGEN and E3D has the defects that ISO drawings output by SPOOLGEN are inconsistent, the workload is increased for designers to check drawers, the design and construction efficiency isreduced, and the design cost is increased. According to the method, two-dimensional projection is carried out on a pipeline three-dimensional model in E3D software, Excel tables are used for countinginformation of all elements in two-dimensional projection, three-dimensional models of all the elements are established through SolidWorks according to table data, the three-dimensional models of allthe elements are modified, the pipeline three-dimensional model and the elbow three-dimensional model established by SolidWorks are enabled to be consistent with the corresponding pipeline three-dimensional model and elbow three-dimensional model in the SPOOLGEN, the splicing of each three-dimensional model element is completed at the SPOOLGEN, the corresponding valve model is replaced at a specified position, finally a standard ISO graph is output in the SPOOLGEN, and therefore the three-dimensional model in the E3D software obtains a SPOOLGEN standard ISO graph format.

Owner:BOMESC OFFSHORE ENG CO LTD

Retry strategies for handling failures during continuous delivery of software artifacts in a cloud platform

ActiveUS11356508B1Multiple digital computer combinationsTransmissionSoftware engineeringSystem maintenance

Computing systems, for example, multi-tenant systems deploy software artifacts in data centers created in a cloud platform using a cloud platform infrastructure language that is cloud platform independent. The system generates pipelines for deploying software artifacts in data center entities configured in a cloud platform. The system allows partial execution of pipelines such that the pipeline can be executed again to complete execution of the remaining stages. The system maintains state of the pipeline execution and checks the state to determine whether a stage should be executed during subsequent executions. The system allows a failed stage to be retried multiple times based on a retry strategy. A retry strategy may depend on the data center entity in a hierarchy of data venter entities of a data center.

Owner:SALESFORCE COM INC

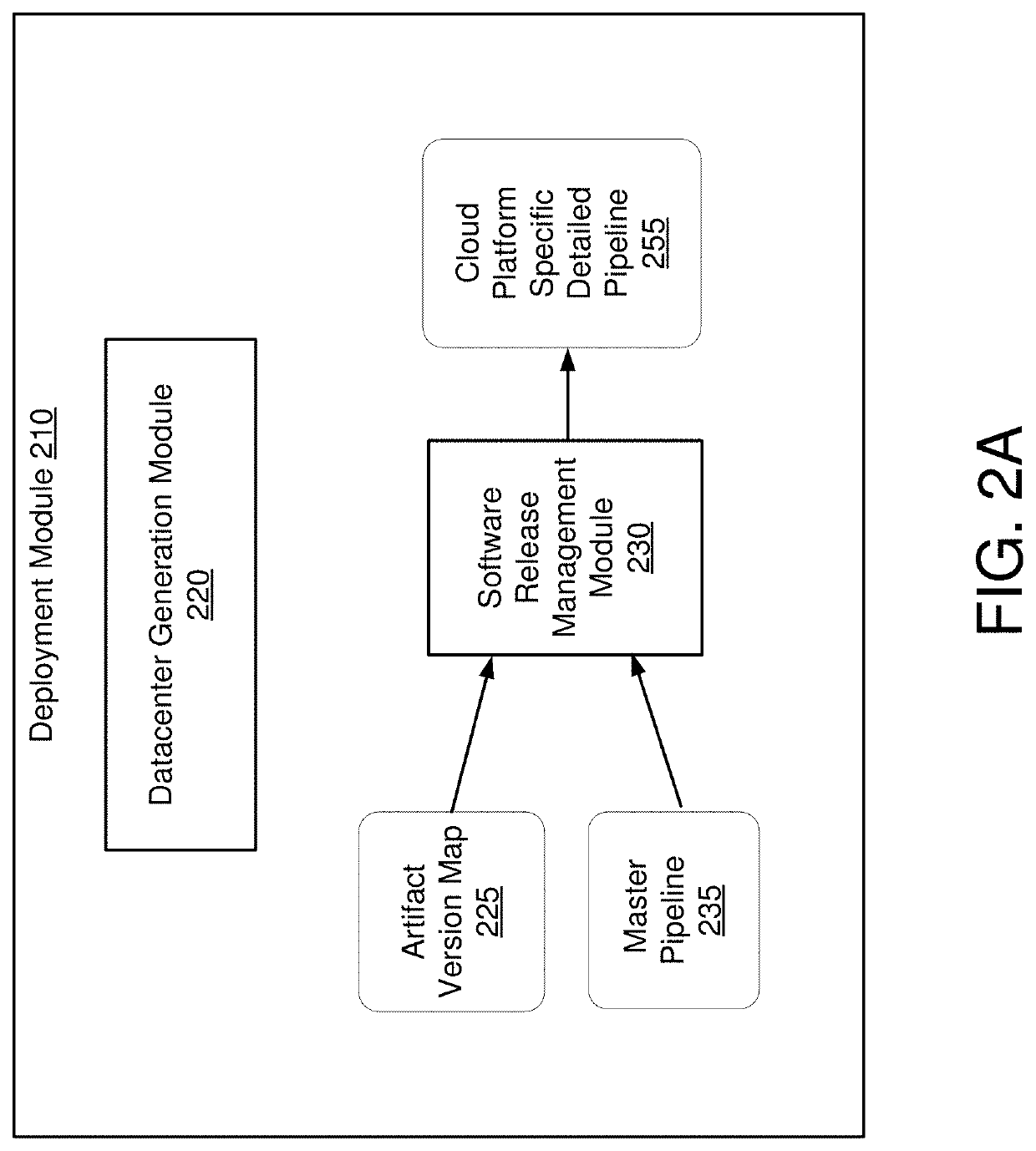

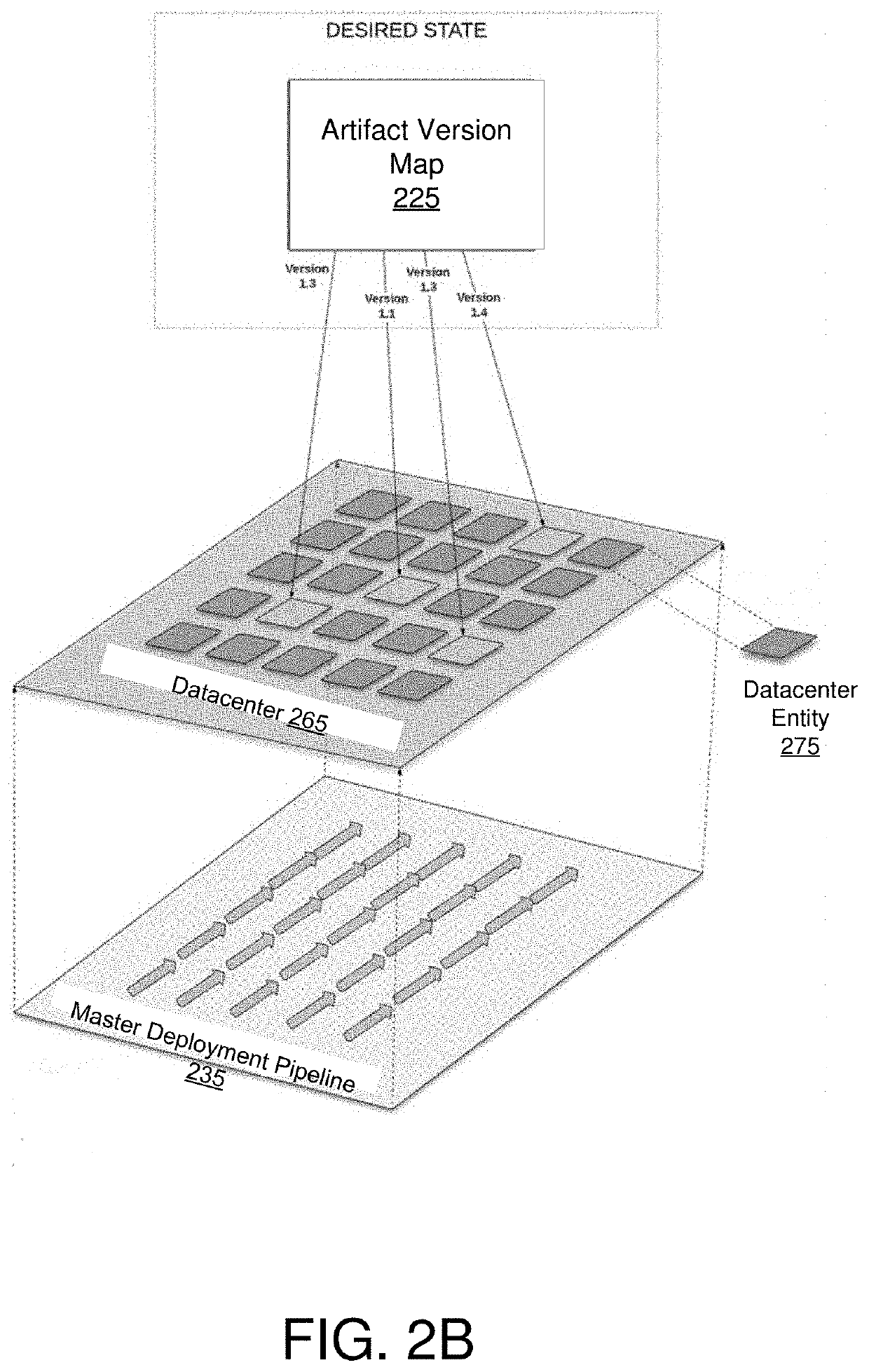

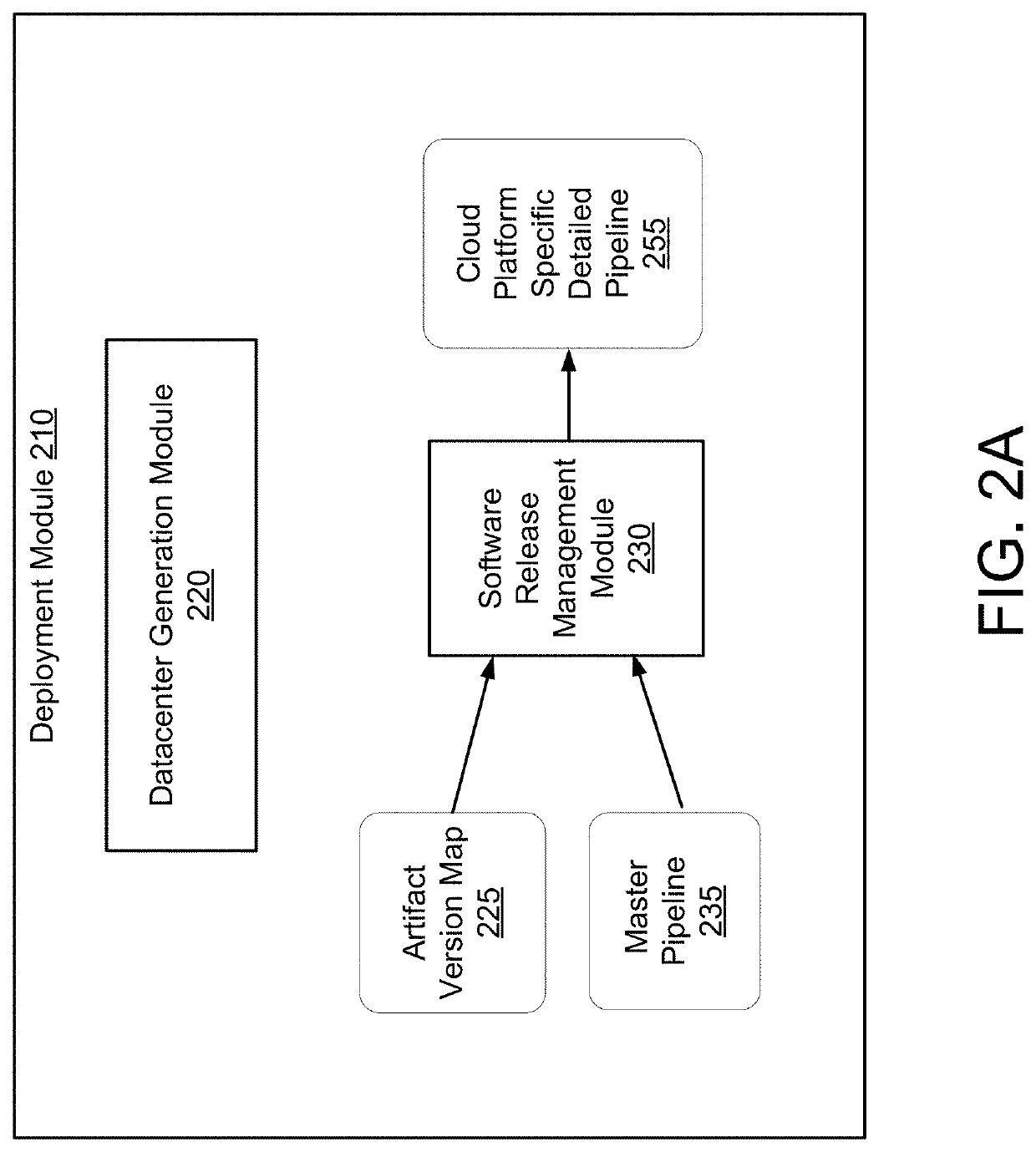

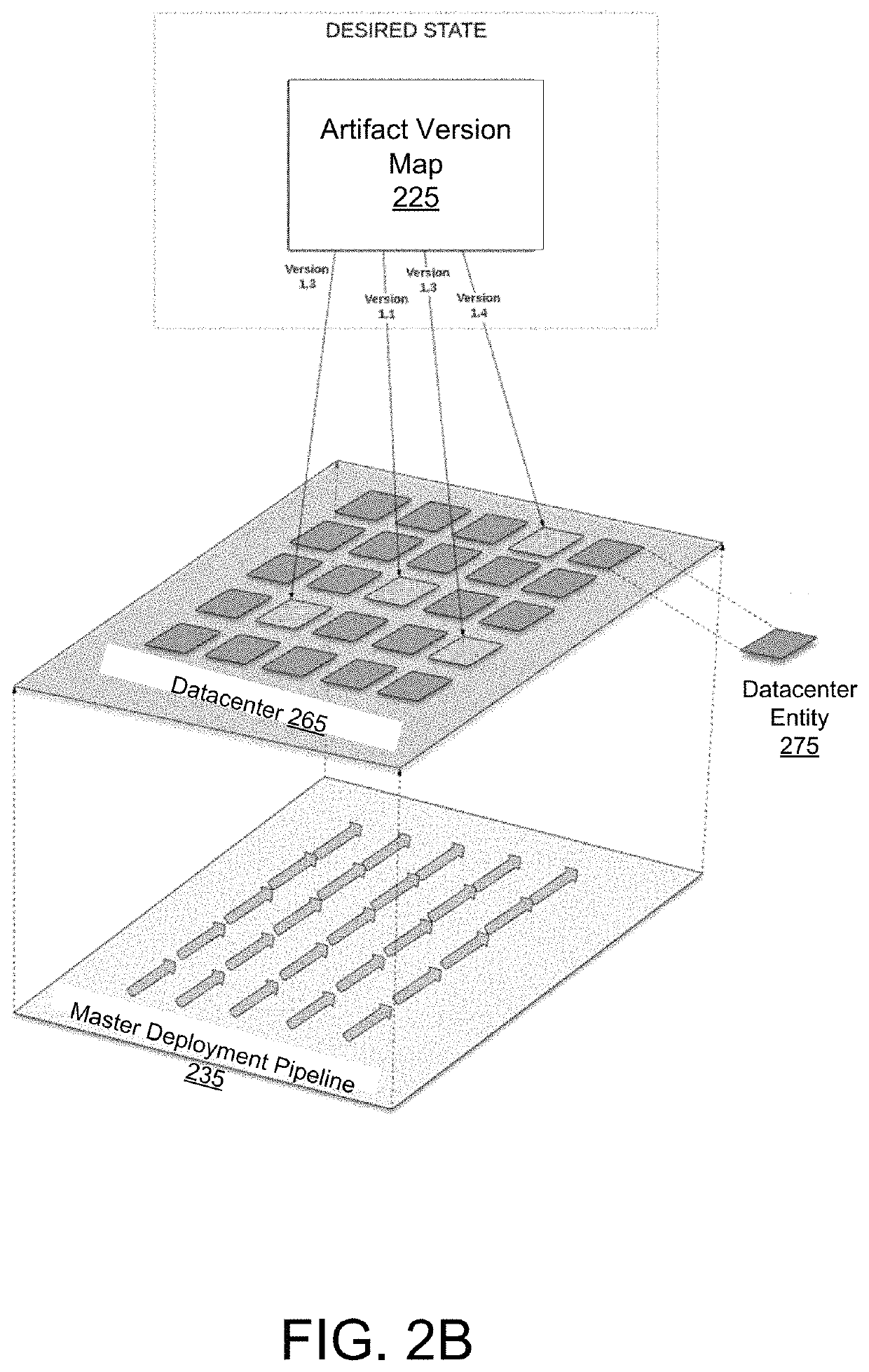

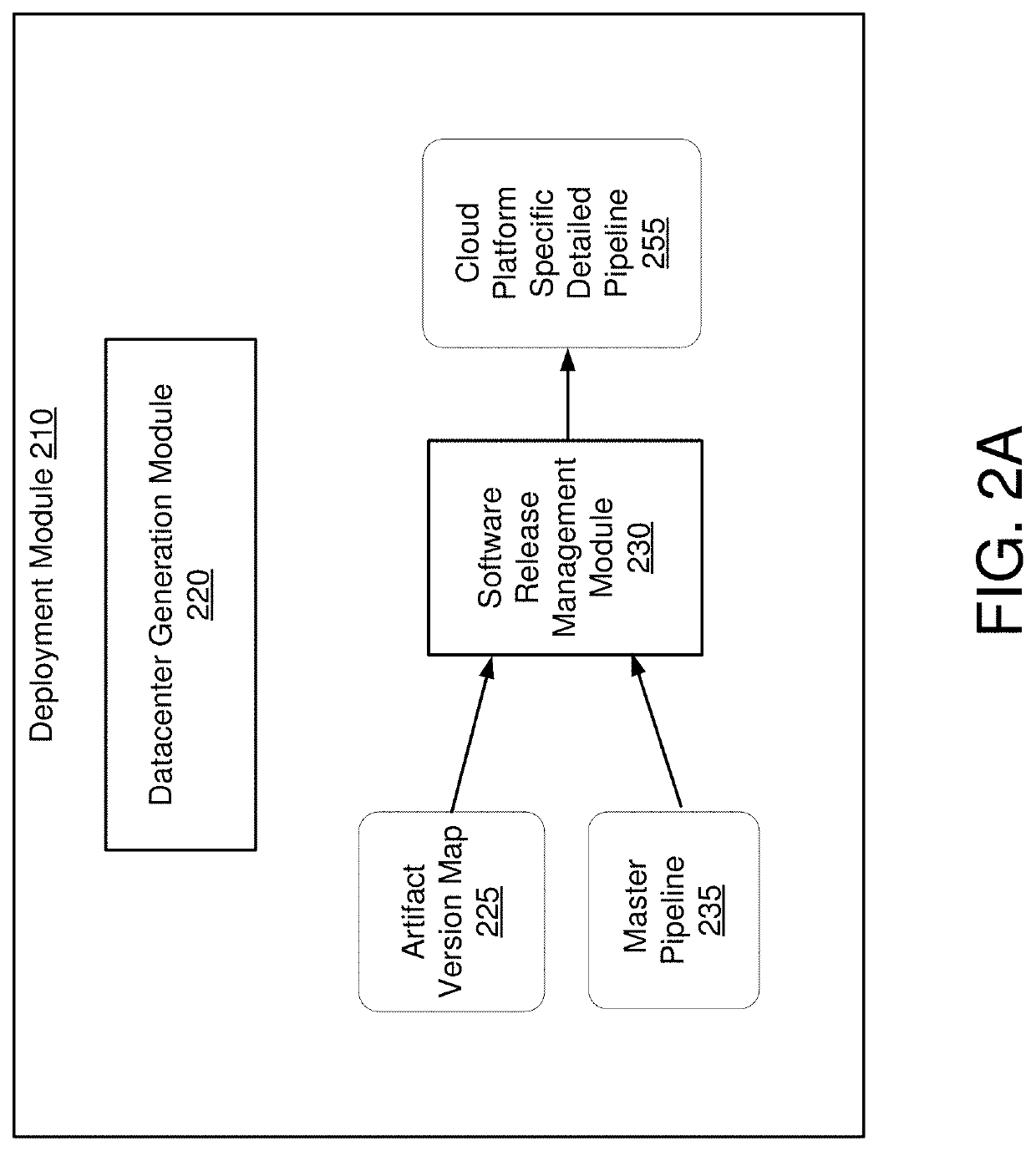

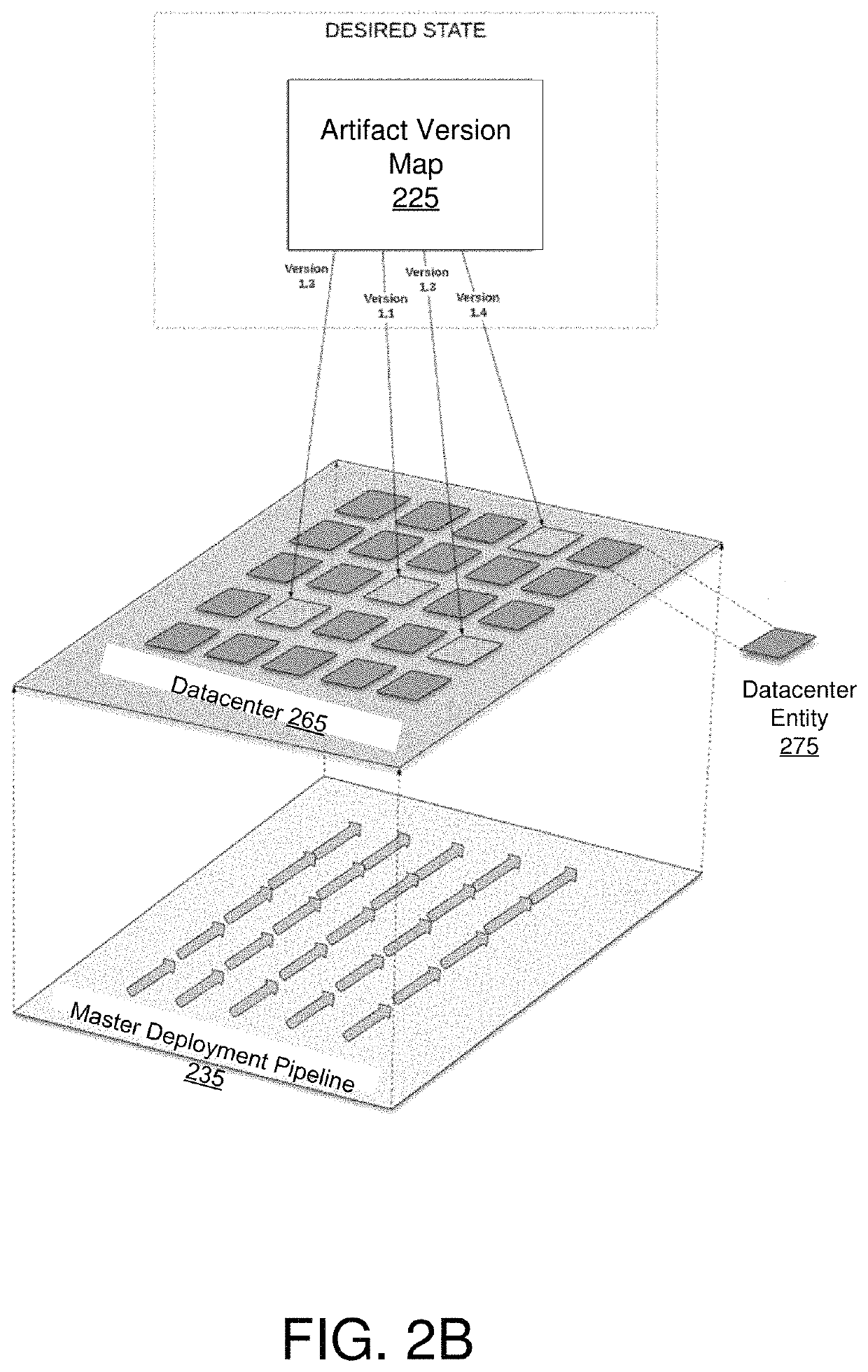

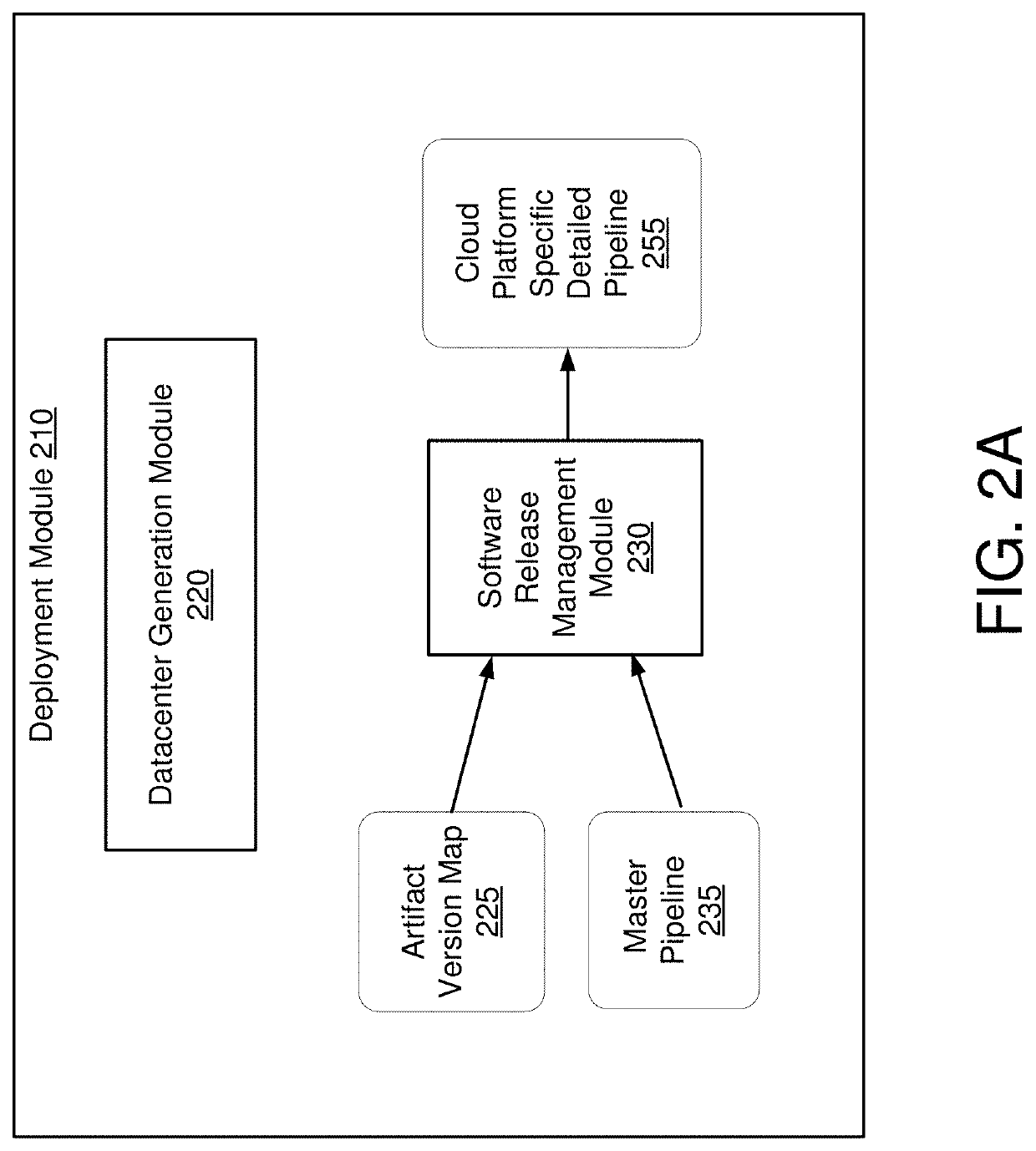

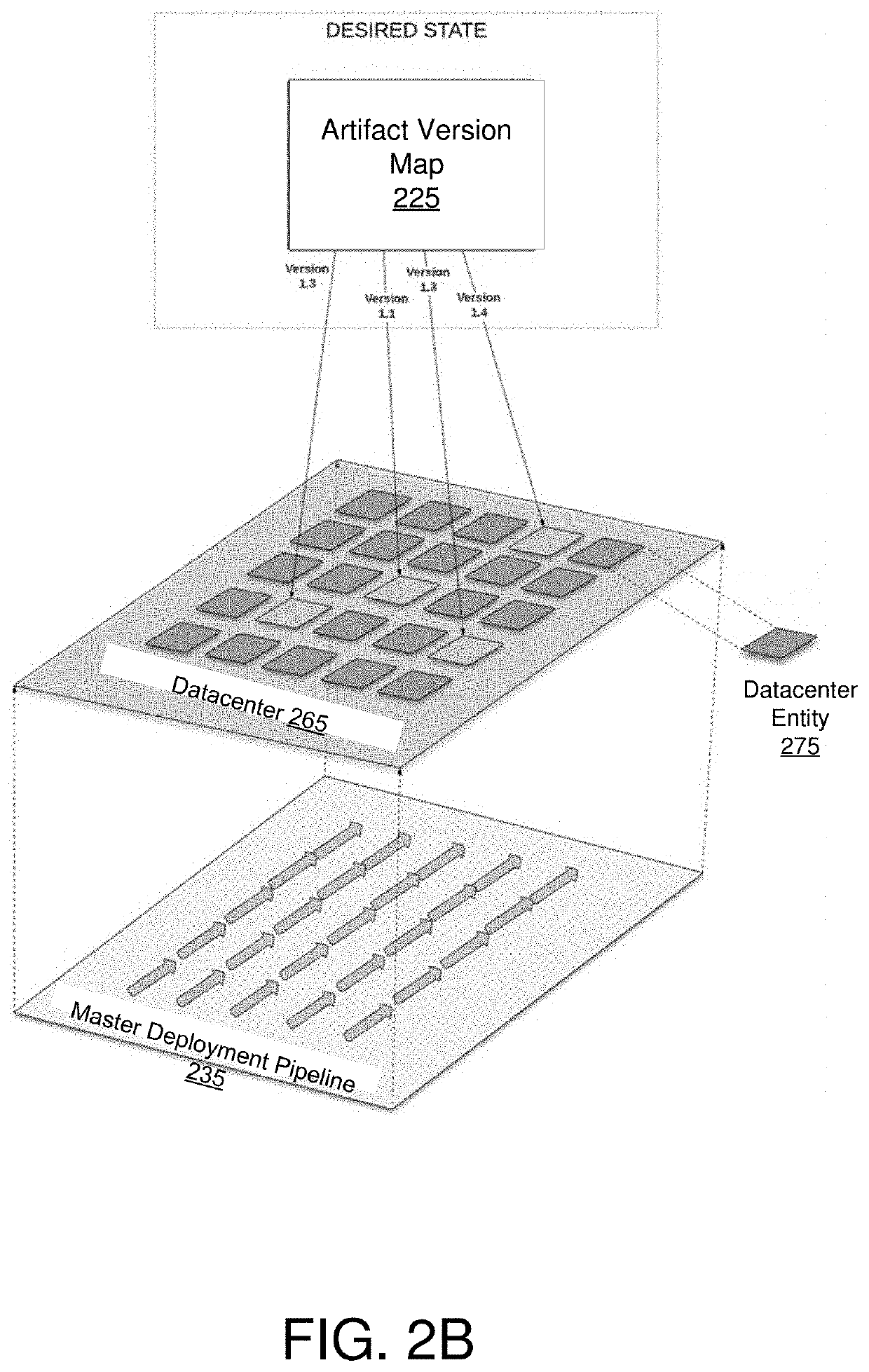

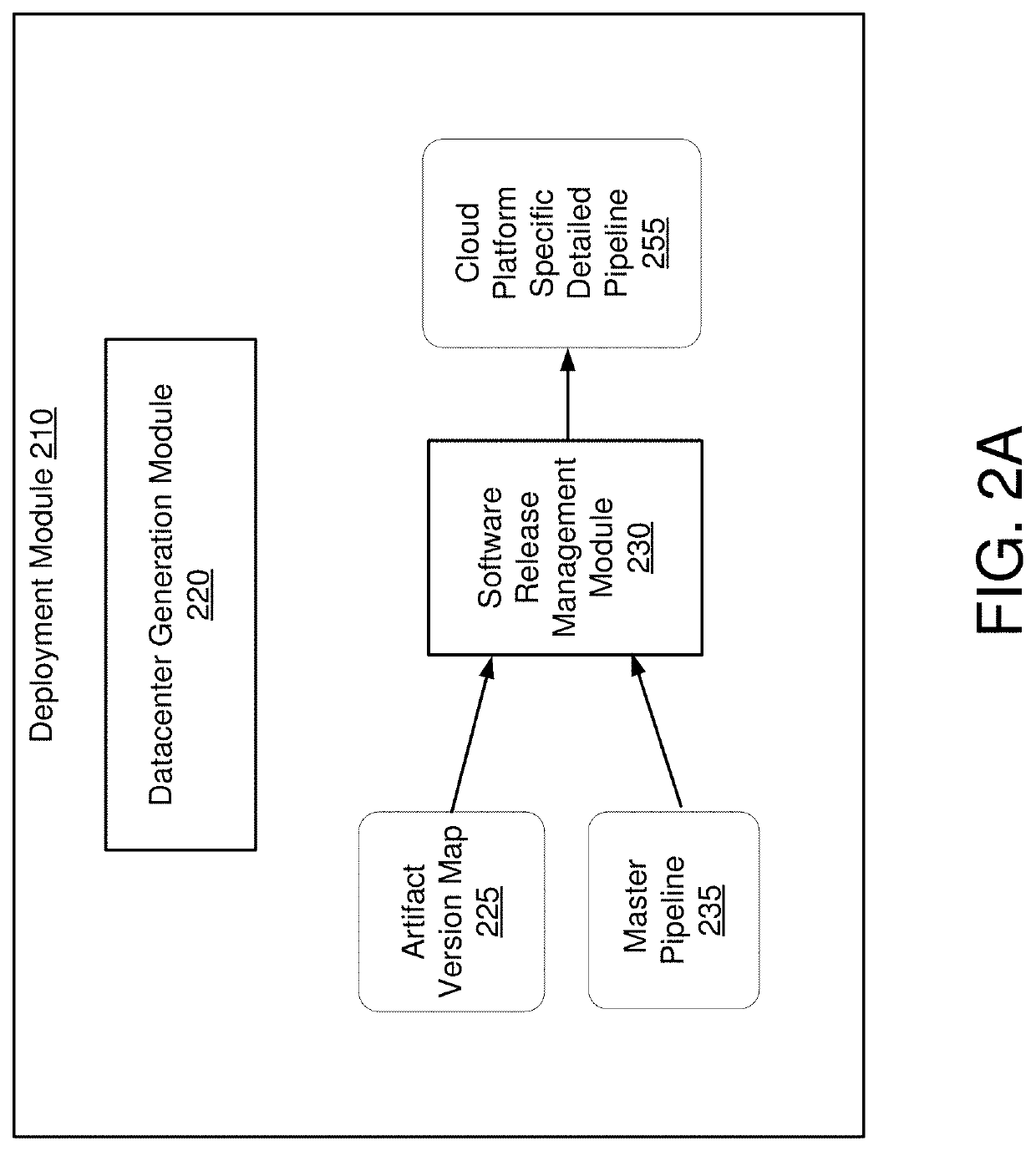

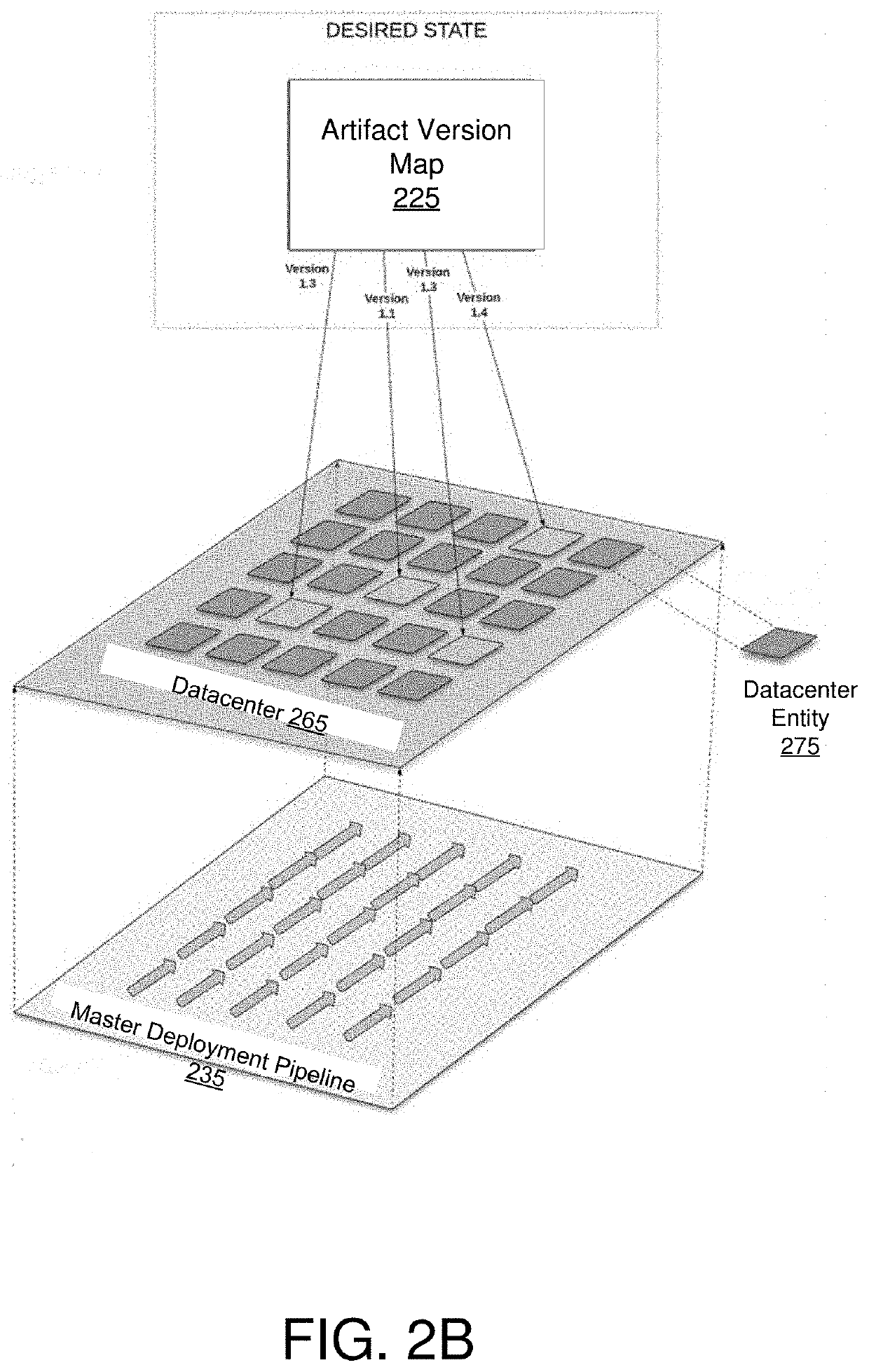

Software release orchestration for continuous delivery of features in a cloud platform based data center

ActiveUS11392361B2Version controlProgram loading/initiatingOrchestration (computing)Distributed computing

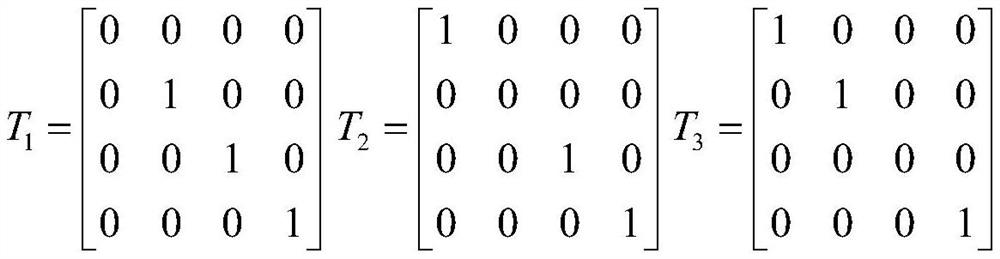

A system deploys software artifacts in data centers created in a cloud platform using a cloud platform infrastructure language that is cloud platform independent. The system receives an artifact version map that identifies versions of software artifacts for datacenter entities of the datacenter and a cloud platform independent master pipeline that includes instructions for performing operations related to services on the datacenter, including deploying software artifacts, provisioning computing resources. The system compiles the cloud platform independent master pipeline in conjunction with the artifact version map to generate cloud platform specific detailed pipeline that deploys the appropriate versions of deployment artifacts on the datacenter entities in accordance with the artifact version map. The system sends the cloud platform specific detailed pipeline to a target cloud platform for execution.

Owner:SALESFORCE COM INC

Automatic CI/CD assembly line method based on Jenkins

PendingCN112130956AHighly integratedRealize the creationSoftware testing/debuggingSoftware simulation/interpretation/emulationSoftware developmentPipeline (software)

The invention belongs to the technical field of software development, and discloses an automatic CI / CD assembly line method based on Jenkins, which enables a CI / CD assembly line to be fully automaticand high in integration degree through integrated docking of a self-developed DevOps platform and the Jenkins. Through integration of Jenkins, SonarQube, Harbor, Kubernetes and the like, Jenkins, Kubernetes and the like become transparent, all links are completed automatically, the program unification degree is high, the communication efficiency of all posts is improved, and the probability of problems caused by manual intervention of all the links is reduced. In addition, the operation of each link of the Jenkins Pipeline directly adopts the Jenkins to automatically call the Kubernetes to achieve the creation, the destruction and the dynamic expansion and contraction of the container, and host resources are not additionally occupied.

Owner:CHINA UNITECHS

Throughput-aware software pipelining for highly multi-threaded systems

Owner:ORACLE INT CORP

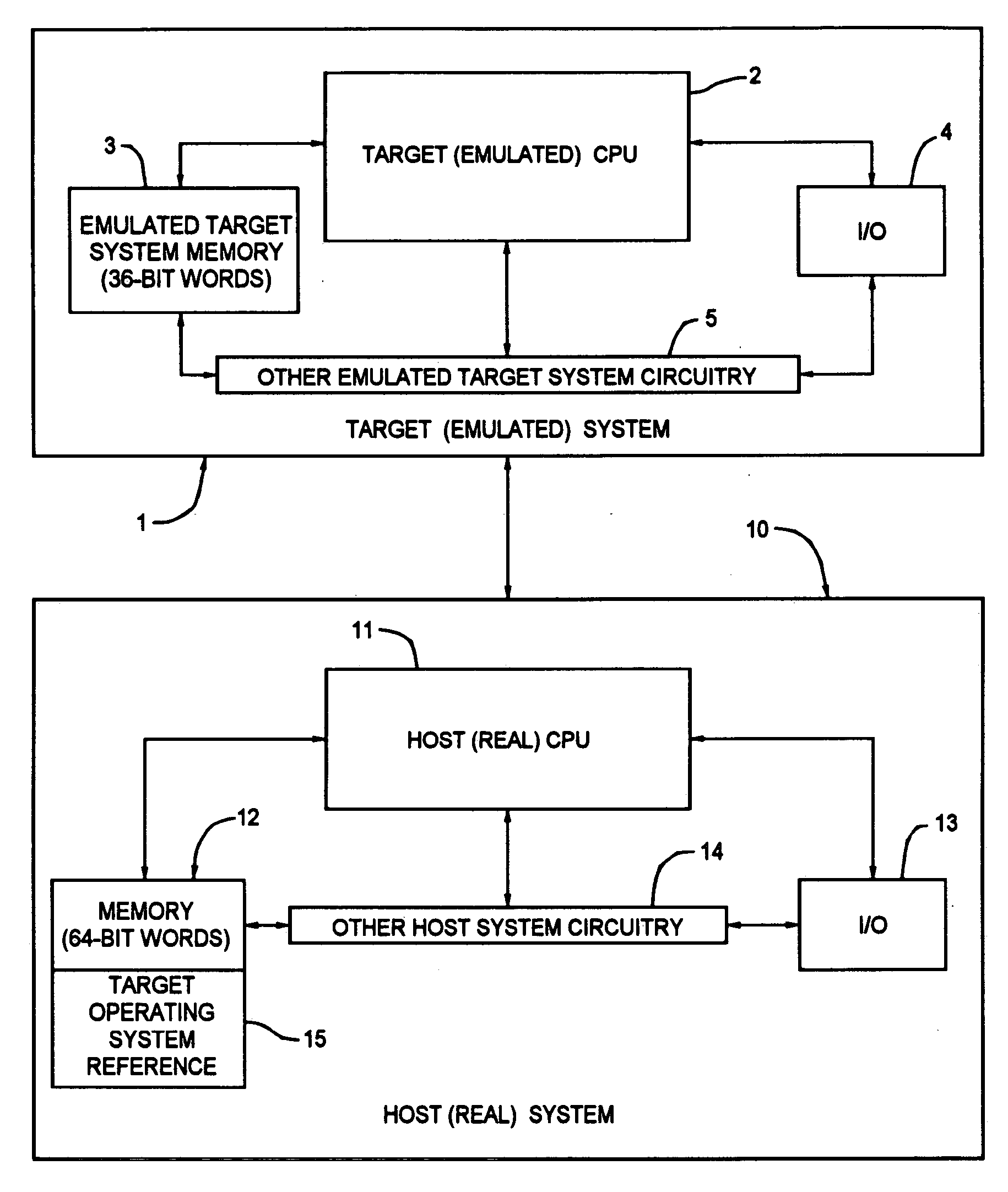

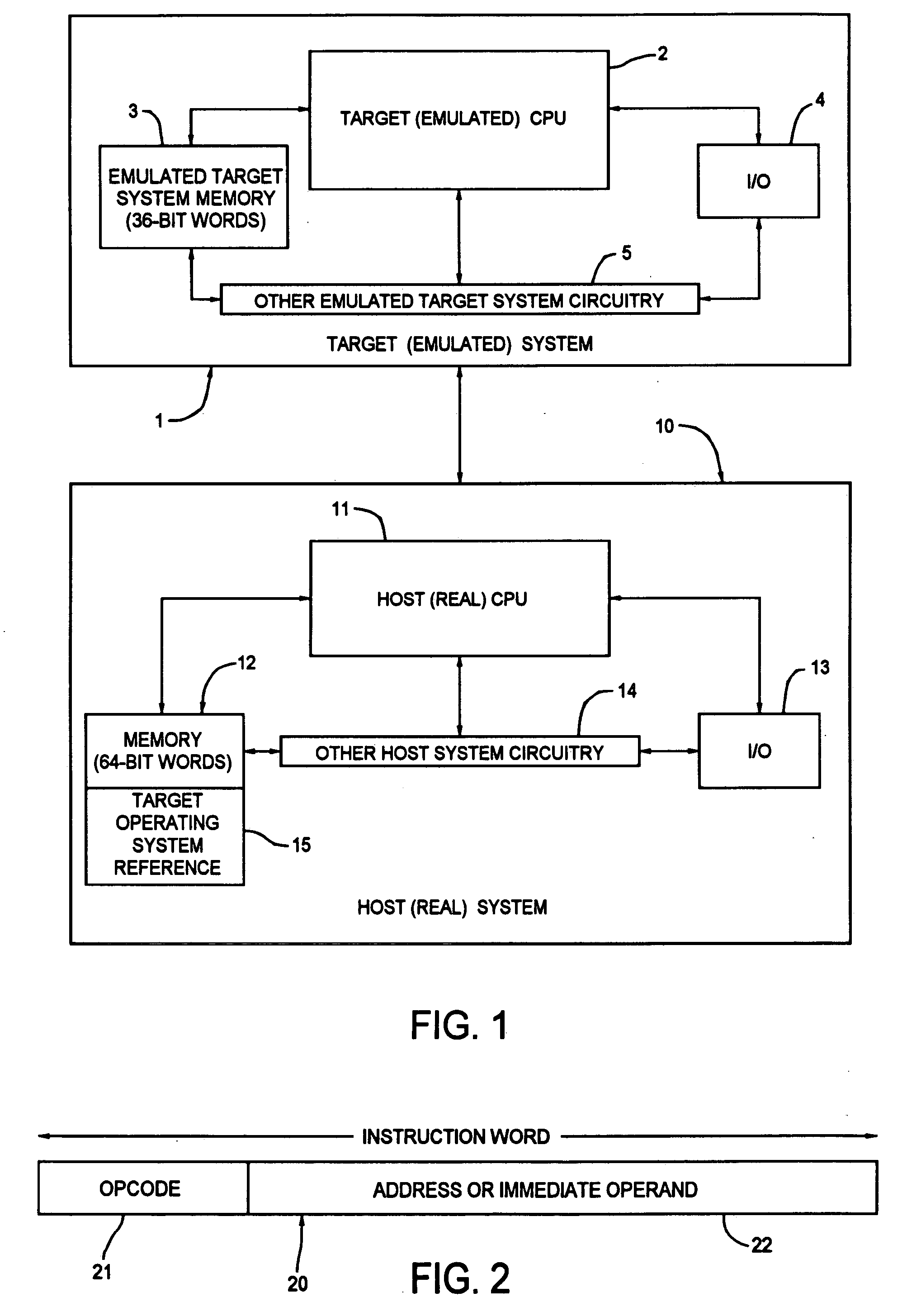

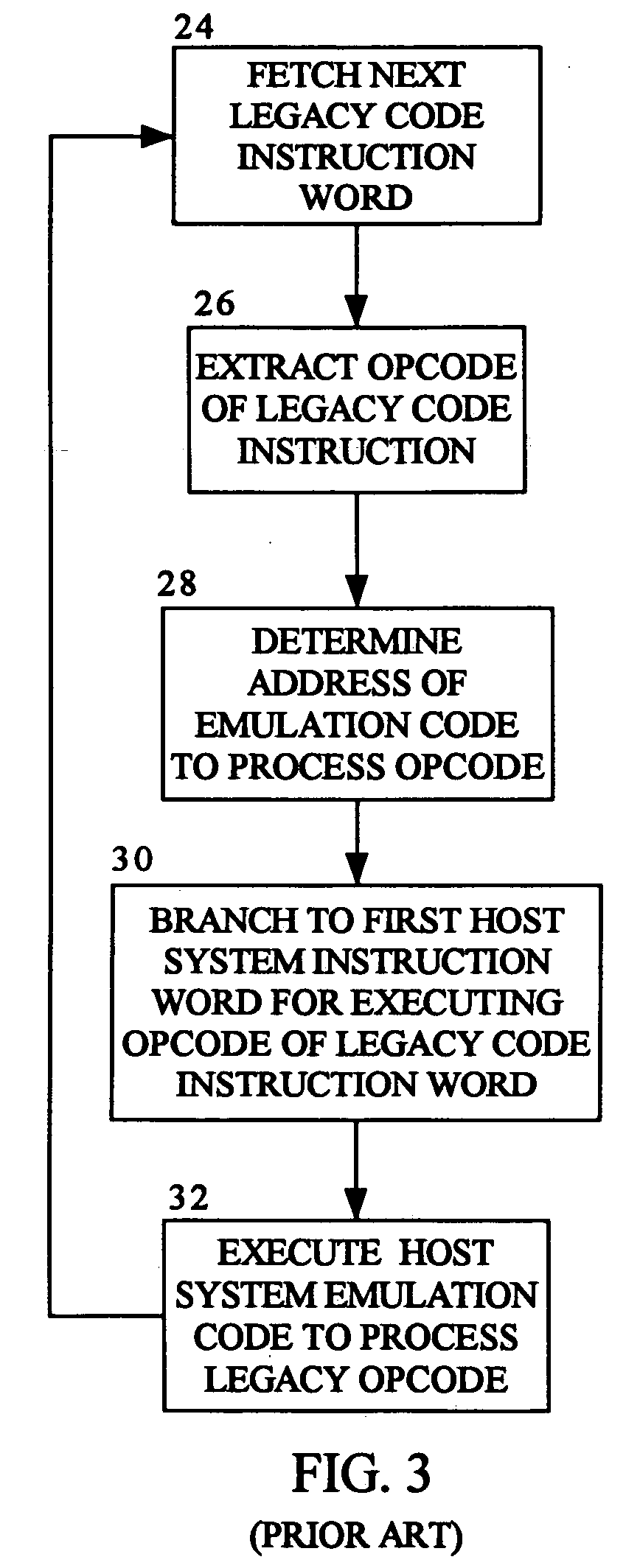

Lookahead instruction fetch processing for improved emulated instruction performance

InactiveUS20070010987A1Improve software performanceMinimizes pipeline breakSoftware simulation/interpretation/emulationMemory systemsParallel computingExecution unit

In order to avoid hardware pipeline breaks and also to enhance performance when emulating a target system in a host system employing a central processing unit including a plurality of execution units, three major pieces of processing that are required for handling every emulated instruction are overlapped. This overlap includes: 1) the instruction fetch of the emulated instruction by the emulation software, 2) the branching of the emulation code based upon the opcode of the emulated instruction to be executed and 3) the actual execution processing for each emulated instruction. The branching of the emulation code, depending upon the opcode of each instruction, utilizes special instructions configured to minimize pipeline breaks on the host system hardware and thus to minimize the effective minimum host system processing time for the simplest emulated instructions.

Owner:BULL HN INFORMATION SYST INC

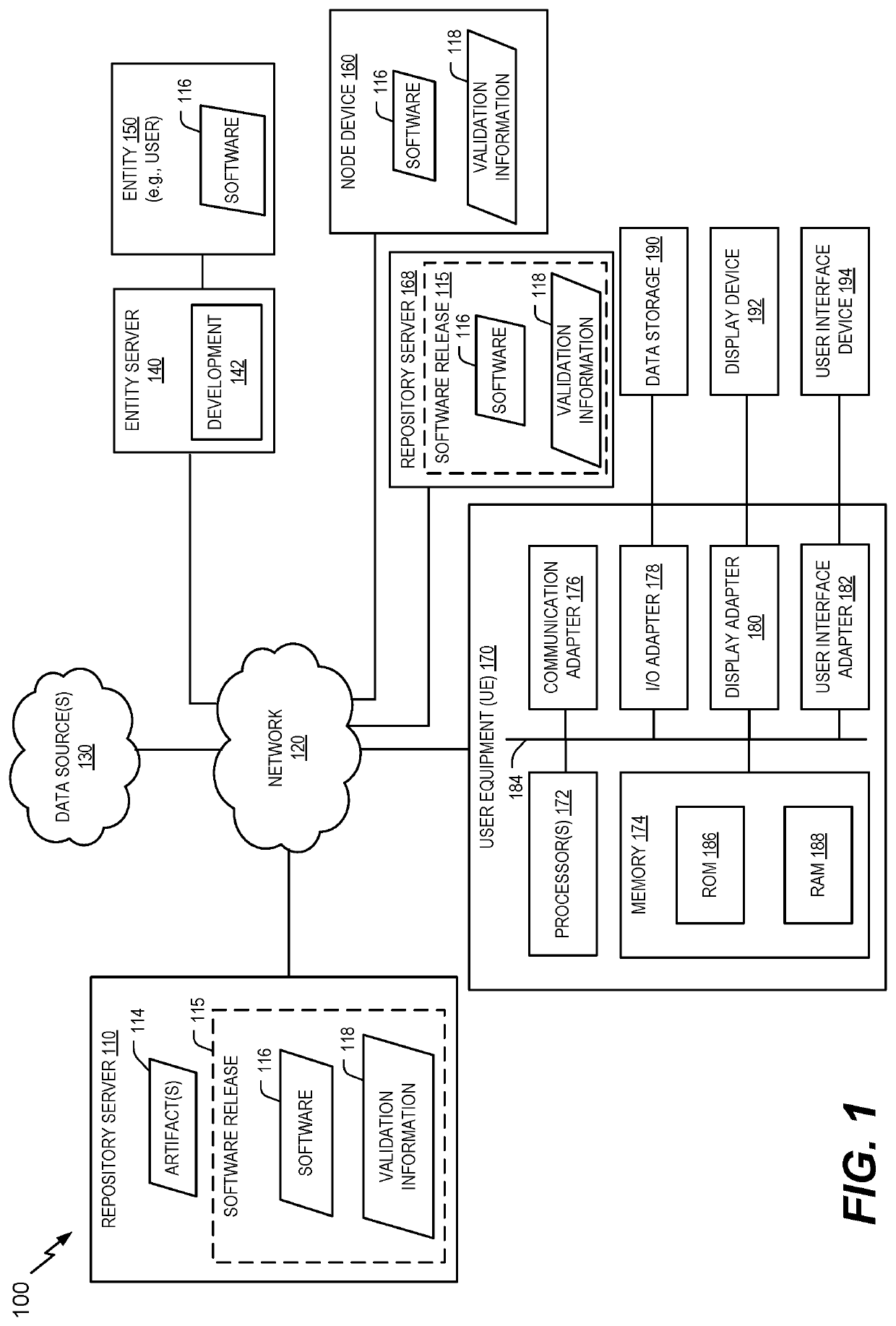

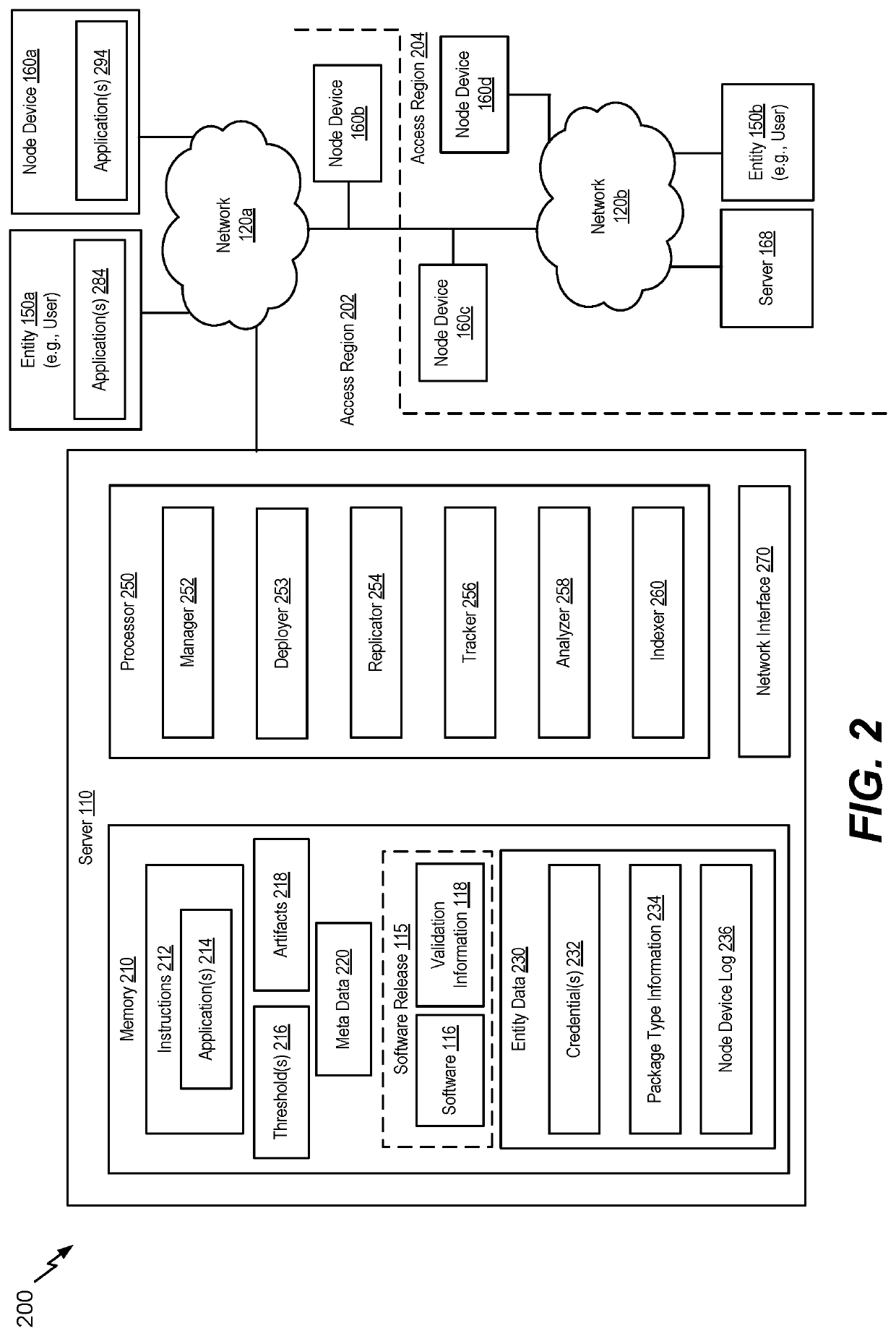

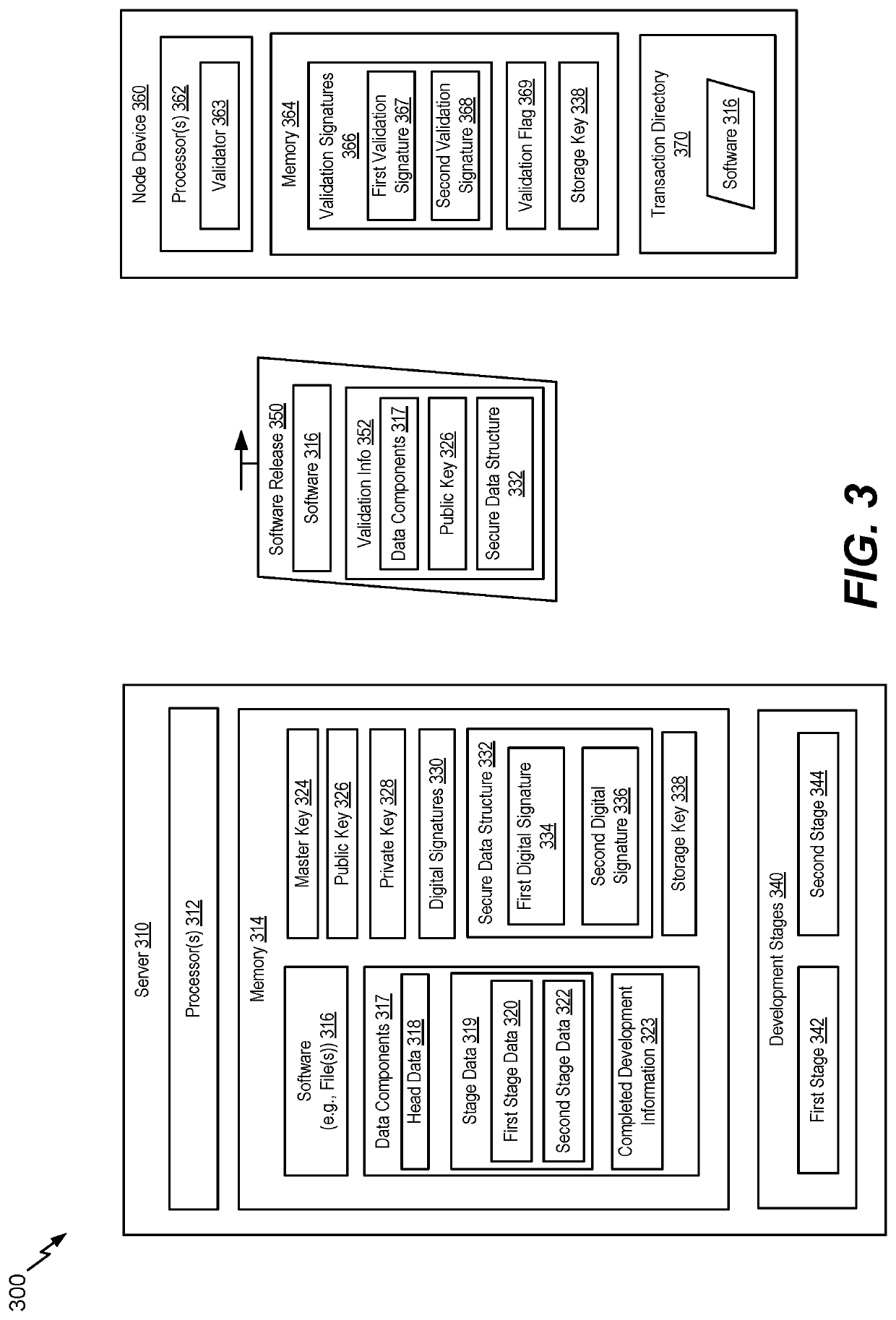

Software pipeline and release validation

PendingUS20220164452A1Small sizeImprove securityEncryption apparatus with shift registers/memoriesVersion controlDigital signatureSoftware engineering

The present disclosure provides systems, methods, and computer readable storage devices for validating that a software release has successfully completed multiple development stages of a development process without alteration. To illustrate, as software (e.g., one or more files or artifacts) completes at least a portion of a development process including the development stages, data components are generated. Digital signatures are generated based on the data components and a private key, and the digital signatures are stored in a secure data structure, such as a blockchain or a tree structure. Upon receipt of the data components (e.g., as validation data of a software release) by a node device, the node device generates validation signatures based on the data components and a public key and compares the validation signatures to the digital signatures stored in the secure data structure to validate the software before processing the software.

Owner:JFROG LTD

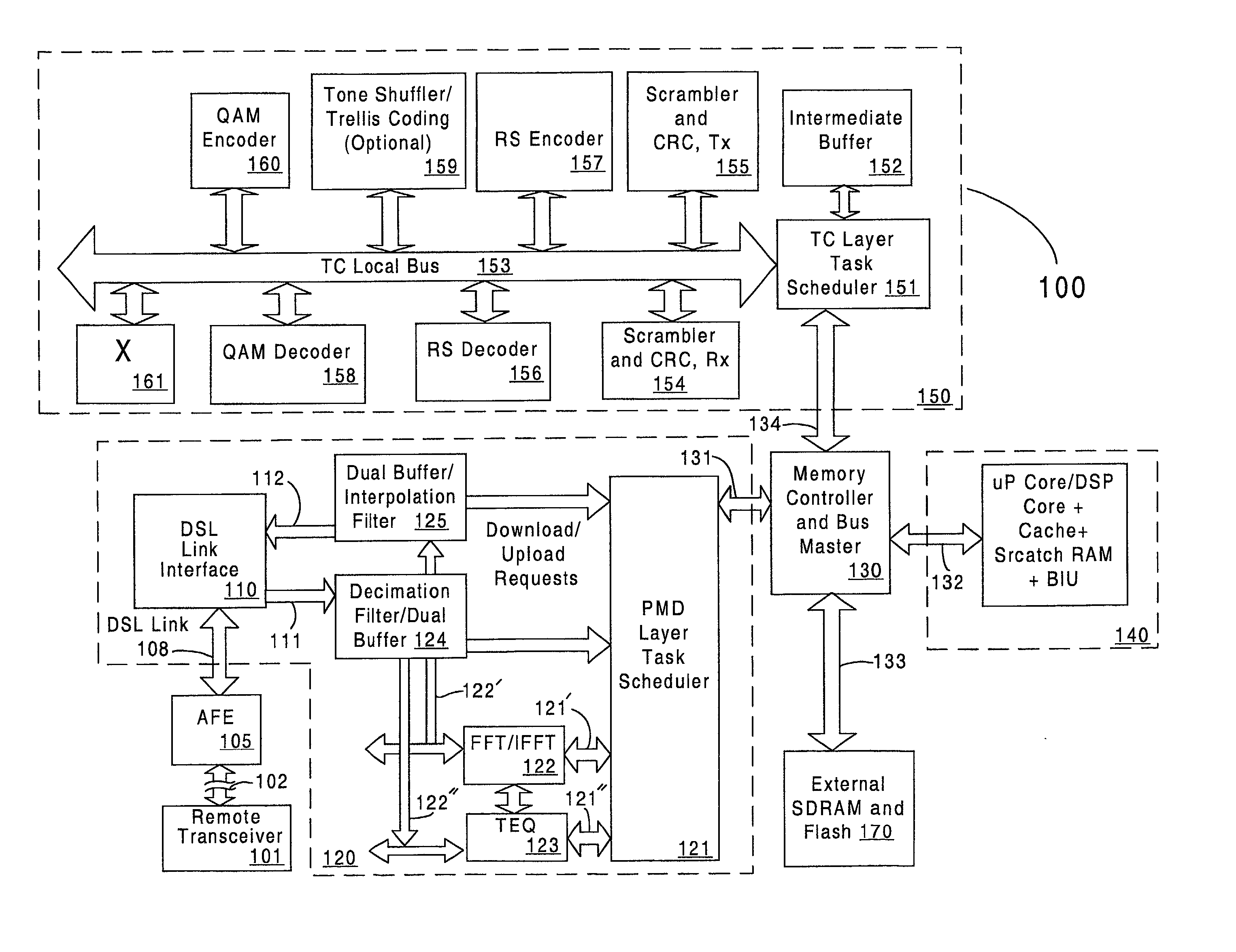

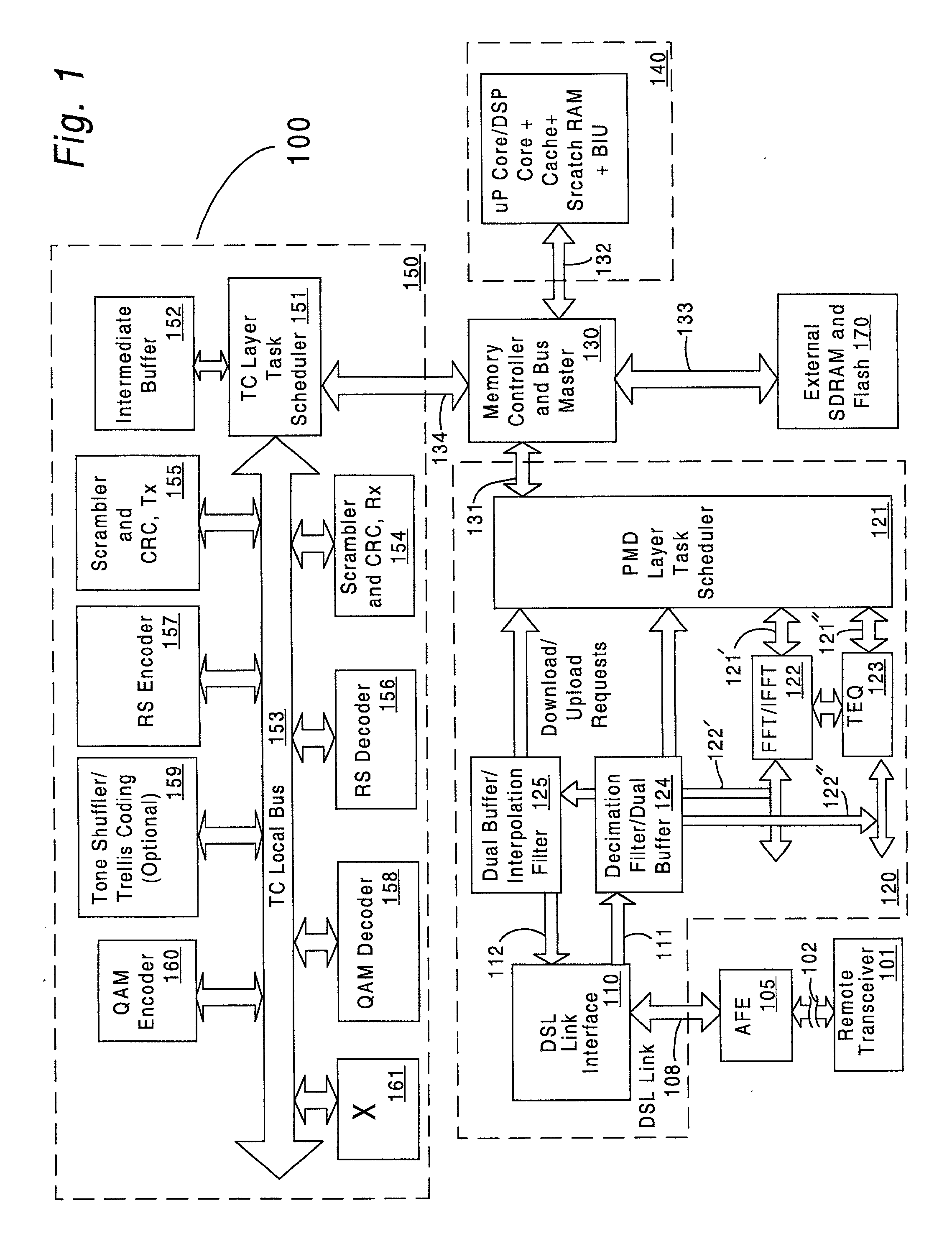

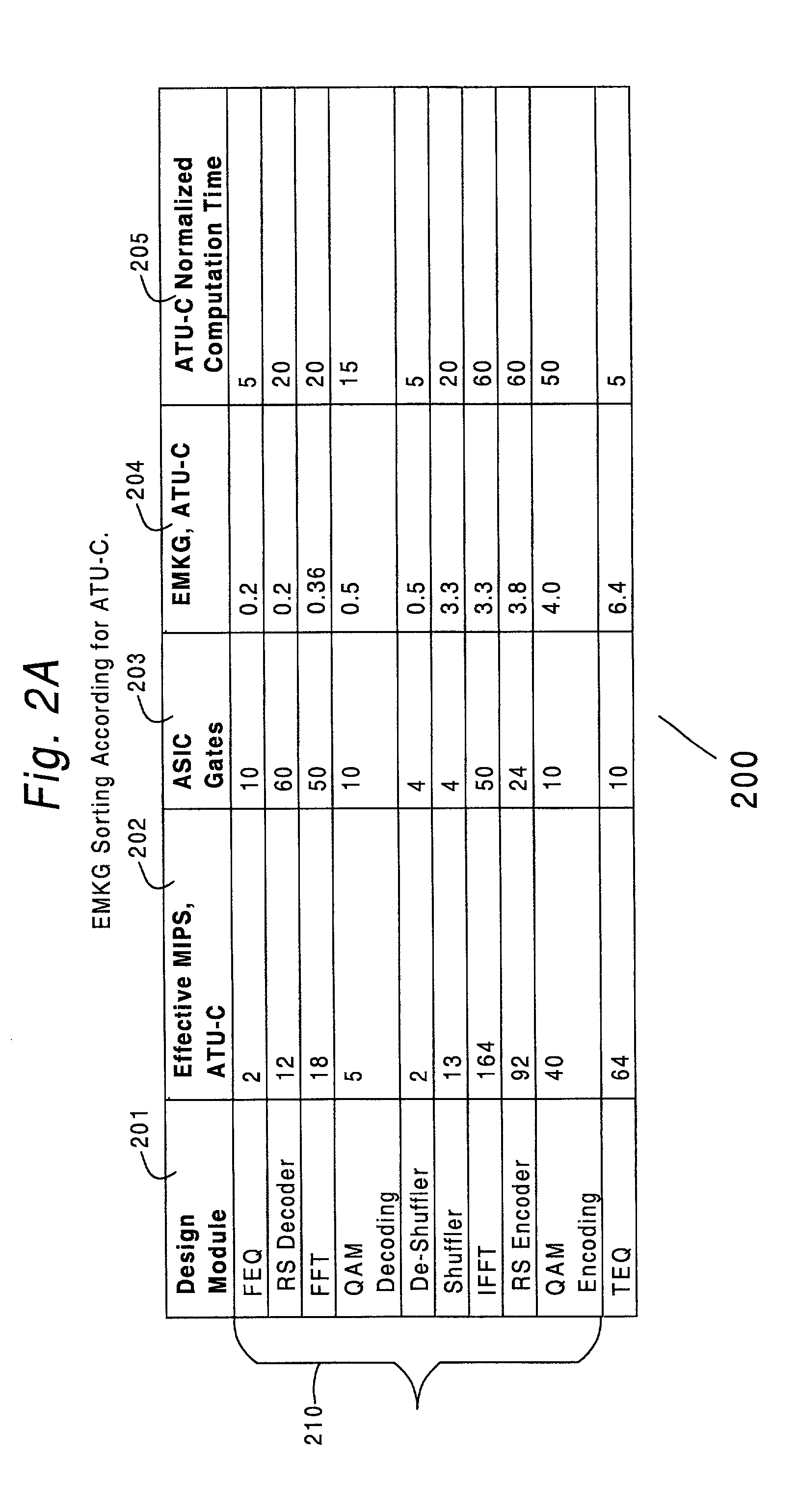

Data object architecture and method for xDSL ASIC processor

A structure for a data object is disclosed with a field and format structure optimized for use by a set of pipeline stages that are interconnected logically through a common pipeline memory. The data object includes both a first portion containing data relating to one or more of a plurality of parameters associated with the control and / or the configuration of one or more processing circuitry blocks, and a second portion containing data associated with computations performed by the processing circuitry blocks. Other portions contain both general and specific types of operational control information used by the processing circuitry blocks. The data object acts as a form of common data exchange mechanism between disparate types of pipeline stages, including in hybrid (mixed) software-hardware pipelines. The control data in the data object can be used by a first pipeline stage to affect or adaptively change operational functioning of downstream pipeline stages.

Owner:REALTEK SEMICON CORP

Optimized compilation of pipelines for continuous delivery of services on datacenters configured in cloud platforms

Computing systems, for example, multi-tenant systems deploy software artifacts in datacenters created in a cloud platform using a cloud platform infrastructure language that is cloud platform independent. A system receives pipeline templates including templating expressions that are substituted with values for generating pipelines. A pipeline is executed to perform a set of actions associated with continuous delivery of a software artifact. The system stores sets of partially hydrated pipeline templates. The partially hydrated pipeline templates are compiled into executable pipelines associated with services configured on a datacenter of the cloud platform. The system stores different versions of pipeline templates as deployment packages. The system stores version pointers that identify specific deployment packages that are selected when a software release is deployed. The version pointers allow the specific deployment packages to be updated in case of roll back or for deploying more recent changes.

Owner:SALESFORCE COM INC

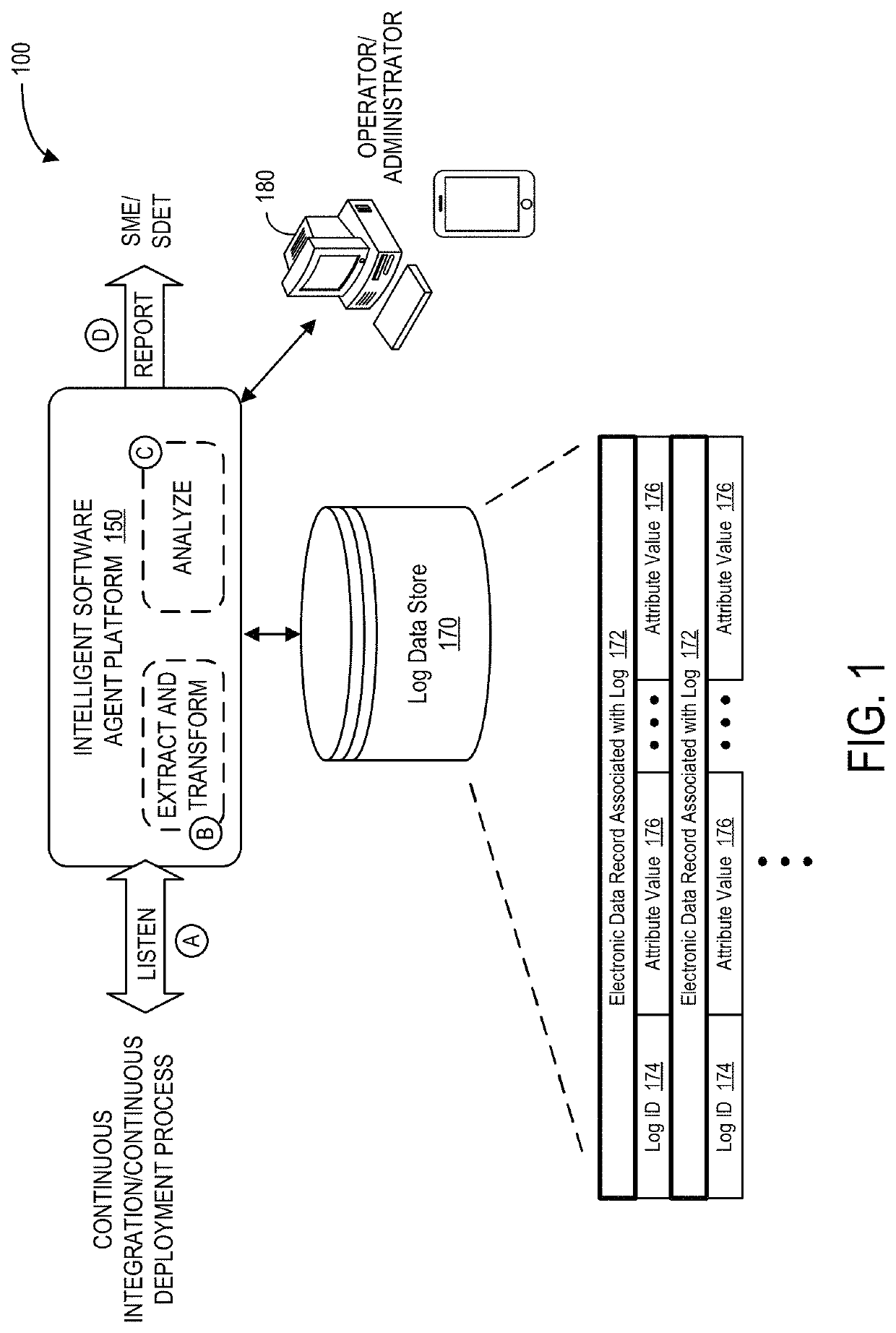

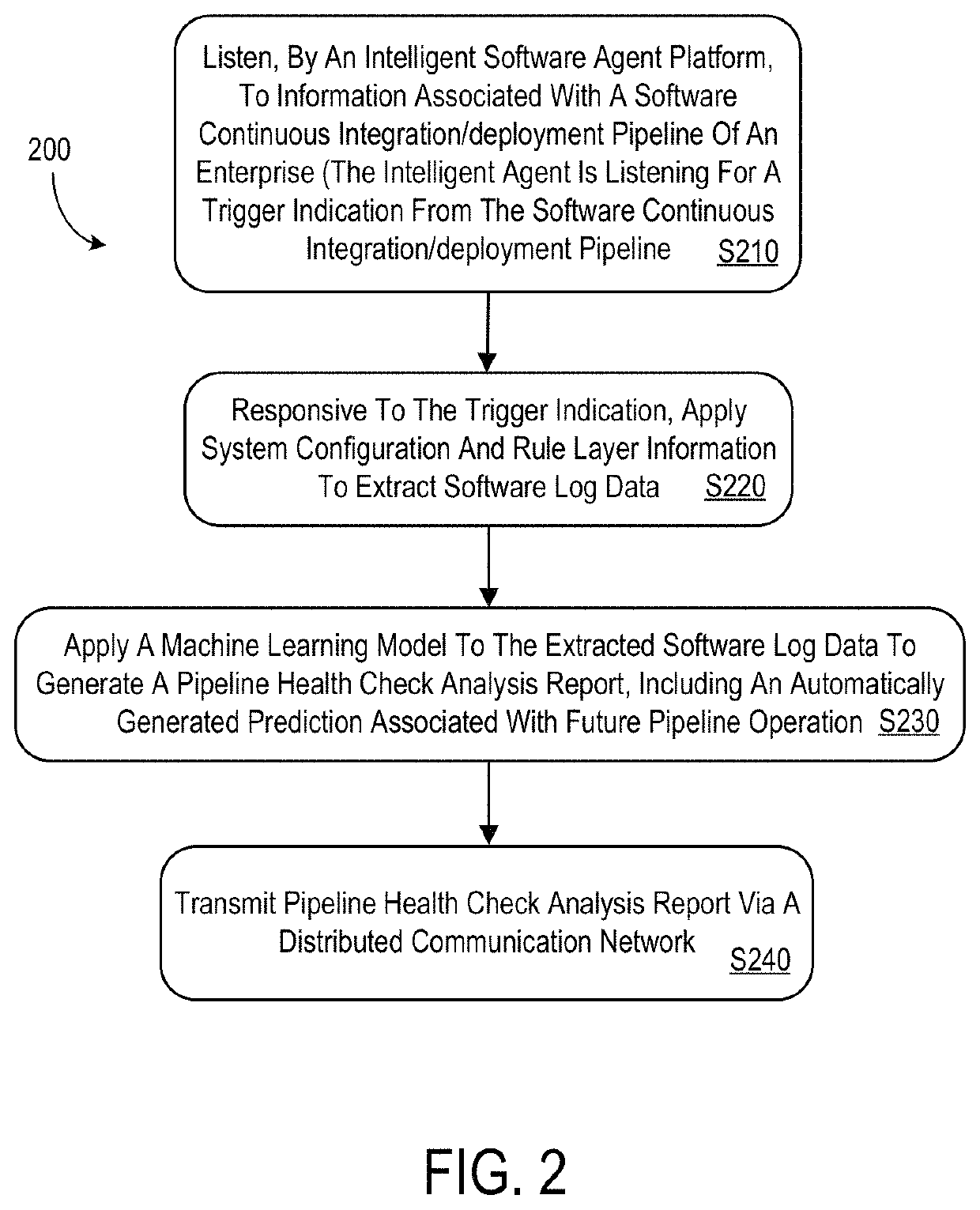

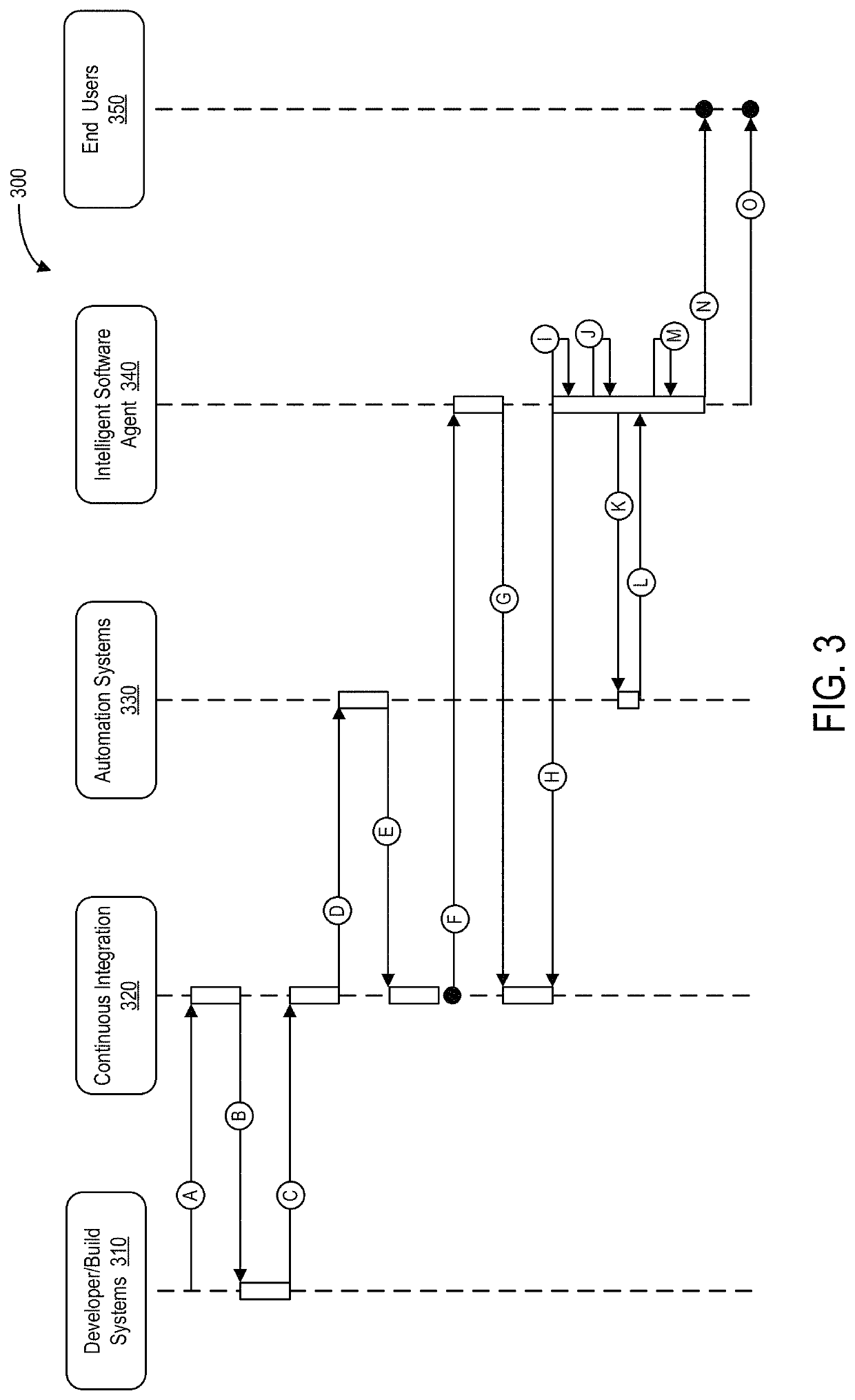

Intelligent software agent to facilitate software development and operations

ActiveUS10963242B2Facilitate software development and operationPromote disseminationInterprogram communicationHardware monitoringContinuous integrationBusiness enterprise

Some embodiments may facilitate software development and operations for an enterprise. A communication input port may receive information associated with a software continuous integration / deployment pipeline of the enterprise. An intelligent software agent platform, coupled to the communication input port, may listen for a trigger indication from the software continuous integration / deployment pipeline. Responsive to the trigger indication, the intelligent software agent platform may apply system configuration and rule layer information to extract software log data and apply a machine learning model to the extracted software log data to generate a pipeline health check analysis report. The pipeline health check analysis report may include, for example, an automatically generated prediction associated with future operation of the software continuous integration / deployment pipeline. The intelligent software agent platform may then facilitate transmission of the pipeline health check analysis report via a communication output port and a distributed communication network.

Owner:HARTFORD FIRE INSURANCE

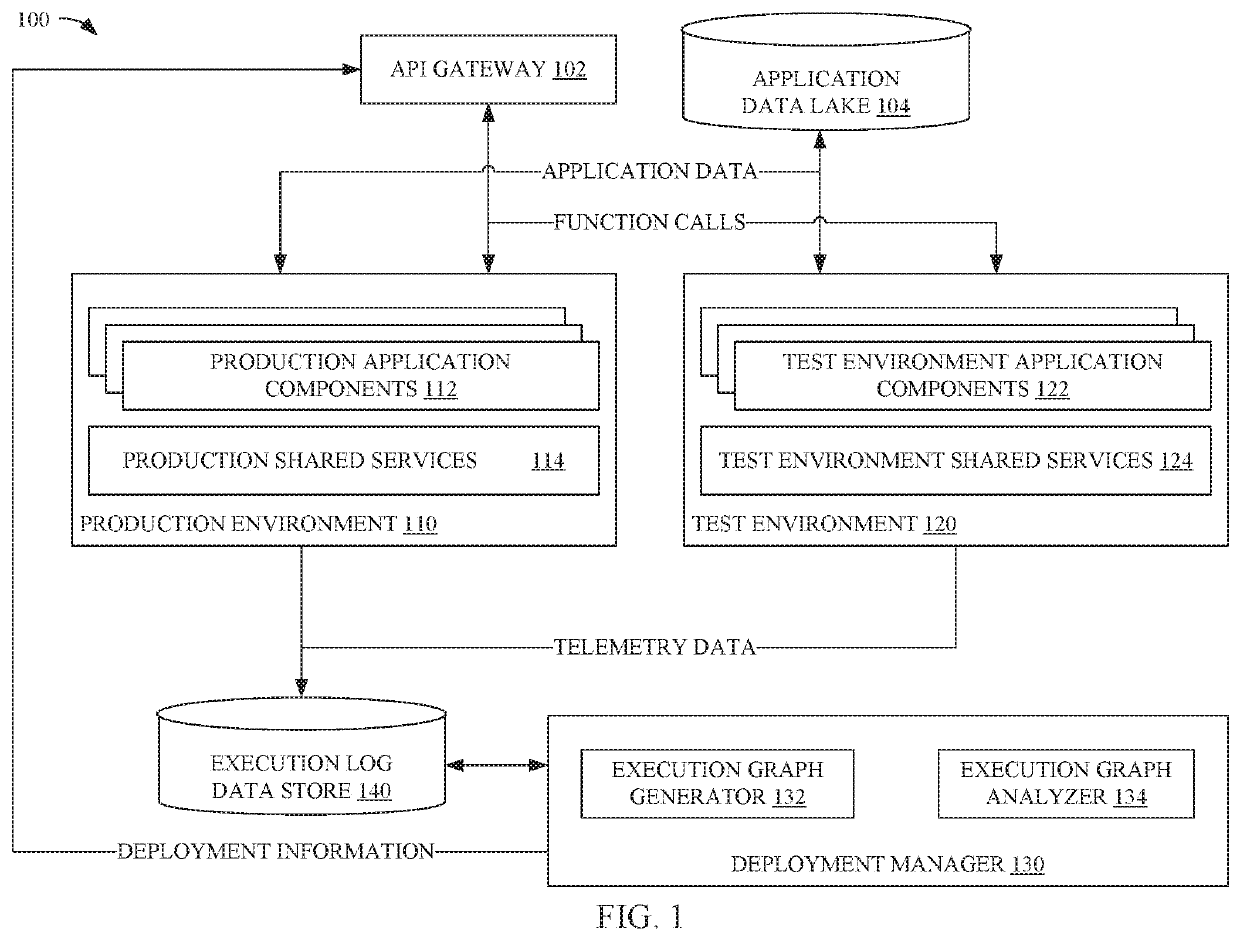

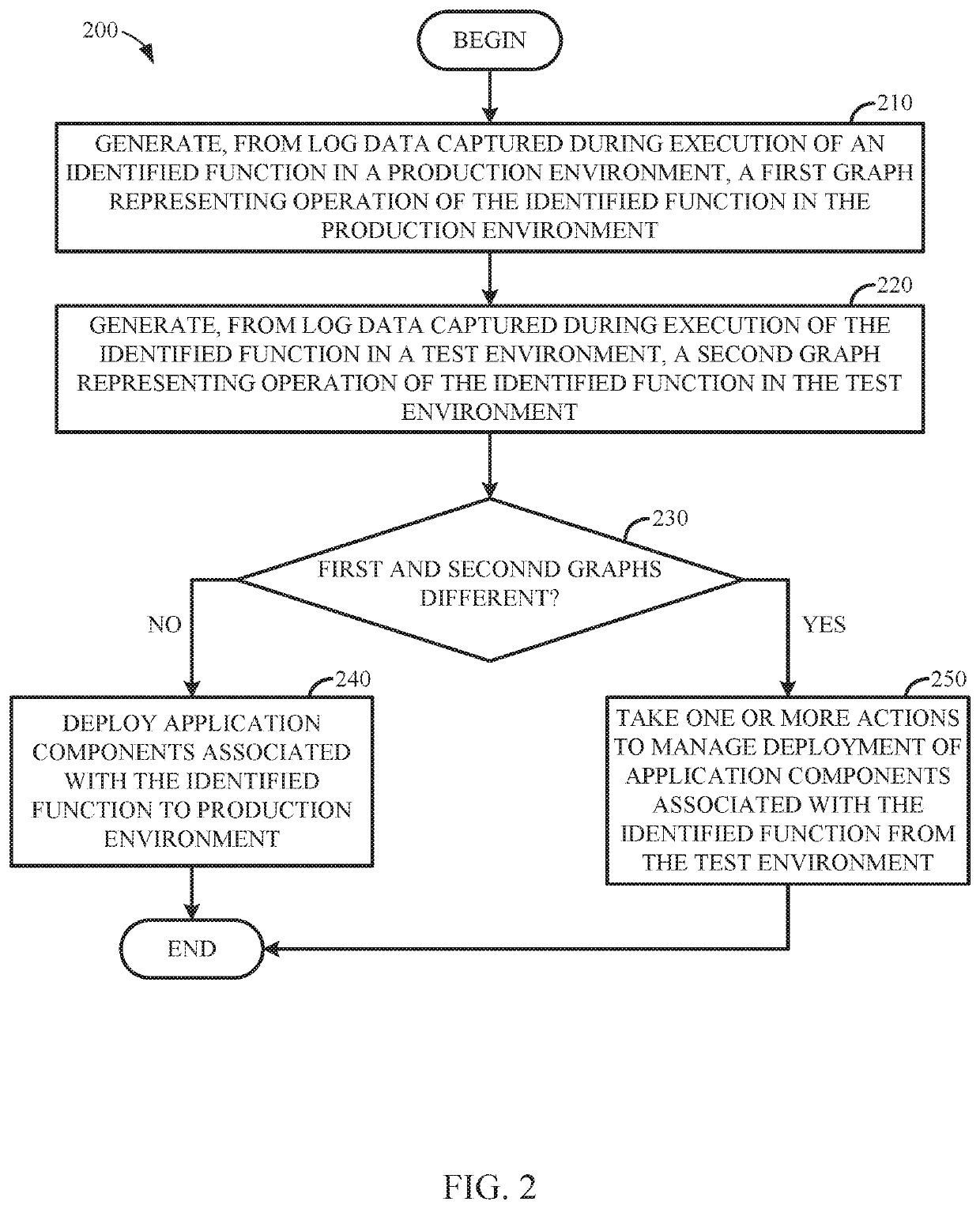

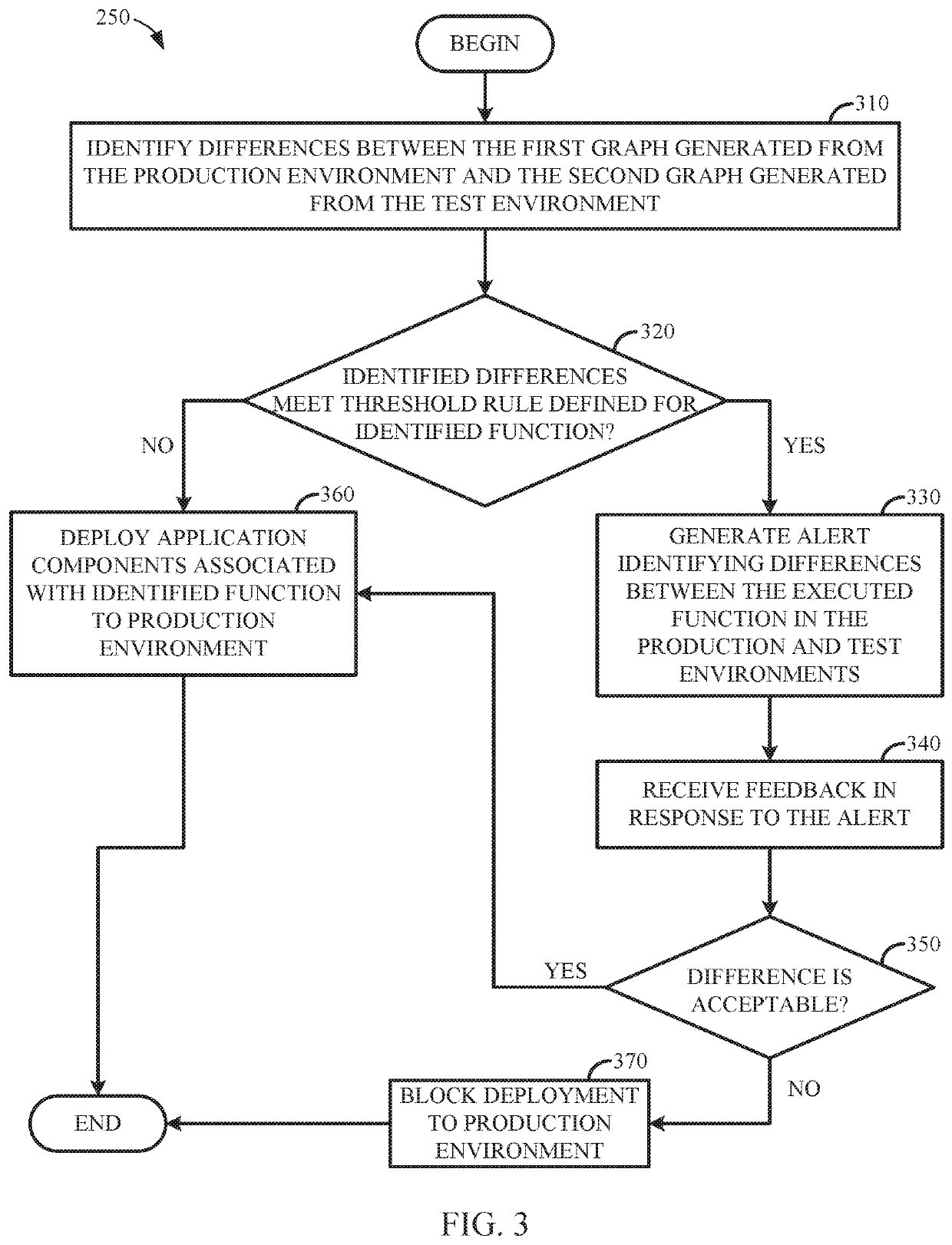

Method and system for managing deployment of software application components in a continuous development pipeline

Certain aspects of the present disclosure provide techniques for managing deployment of application components in a continuous development pipeline based on a comparison of execution graphs generated from execution of functions in production and test environments of the continuous development pipeline. Embodiments include generating a first graph representation of a function from log data captured during execution of the function in a production environment and a second graph representation of the function from log data captured during execution of the function in a test environment. Differences between the first and second graph representations are identified, and based on the identified differences, a system takes one or more actions to manage deployment of software application components implementing the function from the test environment to the production environment.

Owner:INTUIT INC

Optimized compilation of pipelines for continuous delivery of services on datacenters configured in cloud platforms

ActiveUS20220236975A1Error detection/correctionVersion controlOperational systemSoftware engineering

Computing systems, for example, multi-tenant systems deploy software artifacts in data centers created in a cloud platform using a cloud platform infrastructure language that is cloud platform independent. The system receives pipeline templates including templating expressions that can be substituted with values for generating pipelines. A pipeline can be executed to perform a set of actions associated with continuous delivery of a software artifact. The system stores sets of partially hydrated pipeline templates. The partially hydrated pipeline templates can be compiled into executable pipelines associated with services configured on a datacenter of a cloud platform. The system stores different versions of pipeline templates as deployment packages. The system stores version pointers that identify specific deployment packages that are selected when a software release is deployed. The version pointers allow the deployment package to be updated in case of roll back or for deploying more recent changes.

Owner:SALESFORCE COM INC

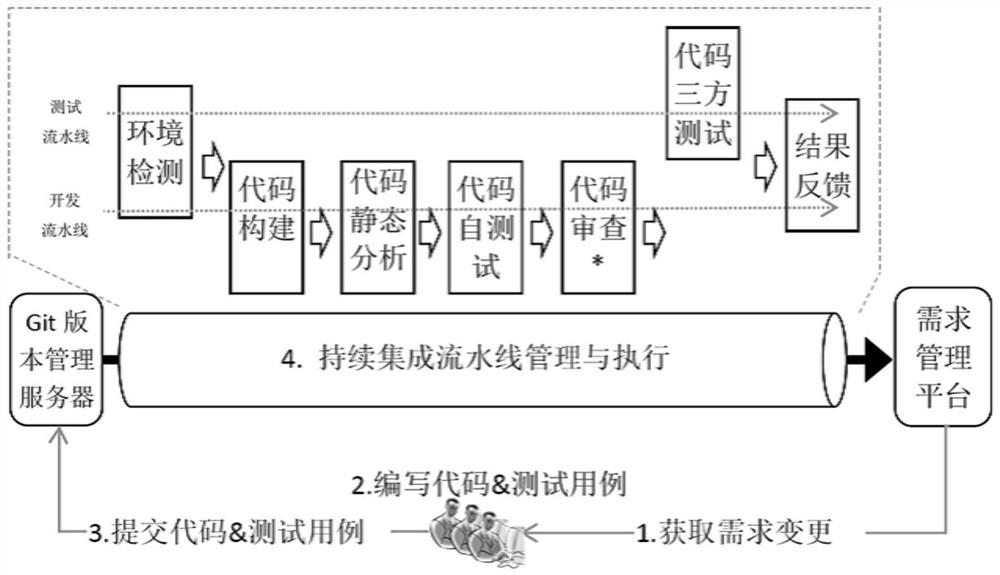

Continuous integration method for embedded high-safety software

InactiveCN112527380AStrengthen correctness managementVersion controlSoftware testing/debuggingThird partyContinuous integration

The invention relates to a continuous integration method for embedded high-safety software, which is characterized in that the design of a continuous integration assembly line considering the development efficiency and safety of the embedded software comprises a development assembly line and a test assembly line, the development assembly line is executed by developers and comprises environment detection, code construction and code static analysis, and the test assembly line comprises a test assembly line and a test assembly line. The code self-test and result feedback assembly line is executedby a third-party tester and comprises environment detection, code three-party test and result feedback, and a manual link of code review is included between the development assembly line and the testassembly line. Through reasonable continuous integration pipeline design, high efficiency and safety of embedded software research and development are considered, a code static analysis link is introduced before test intervention, so that the problem of tool exposure is solved as soon as possible, and safety is reflected in strengthening correctness management of a research and development environment; and omnibearing code quality assurance measures are taken.

Owner:CHENGDU AIRCRAFT DESIGN INST OF AVIATION IND CORP OF CHINA

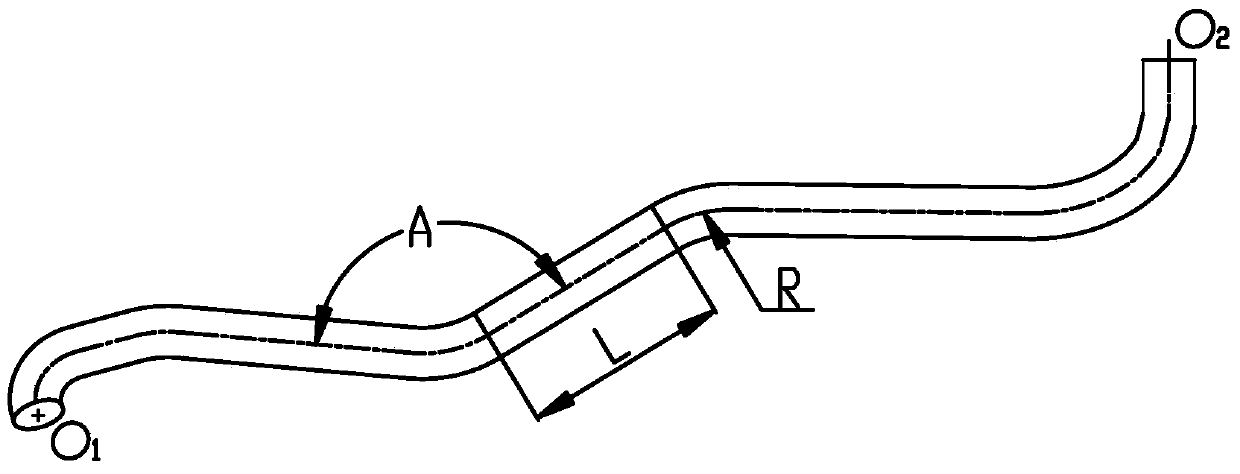

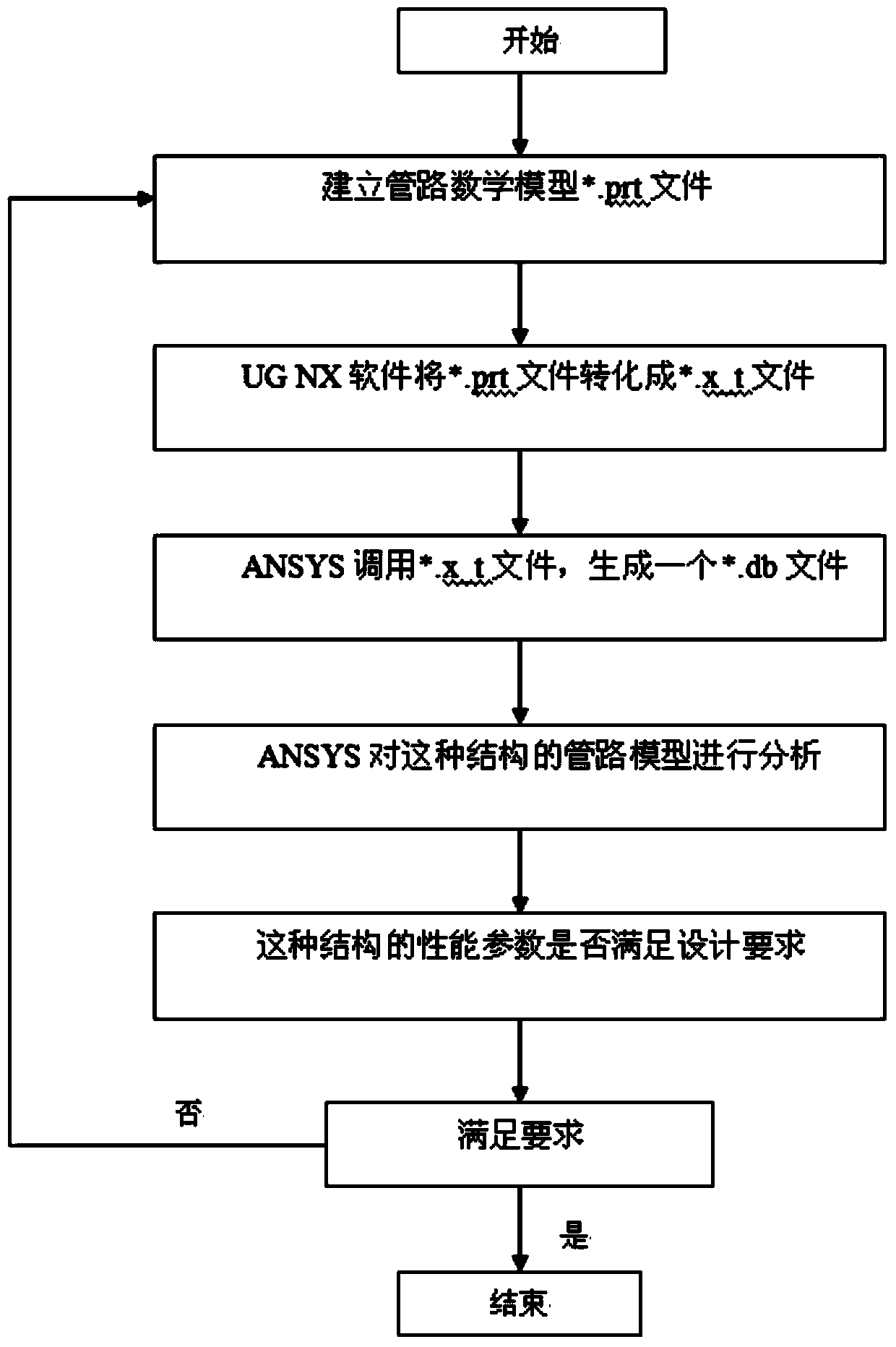

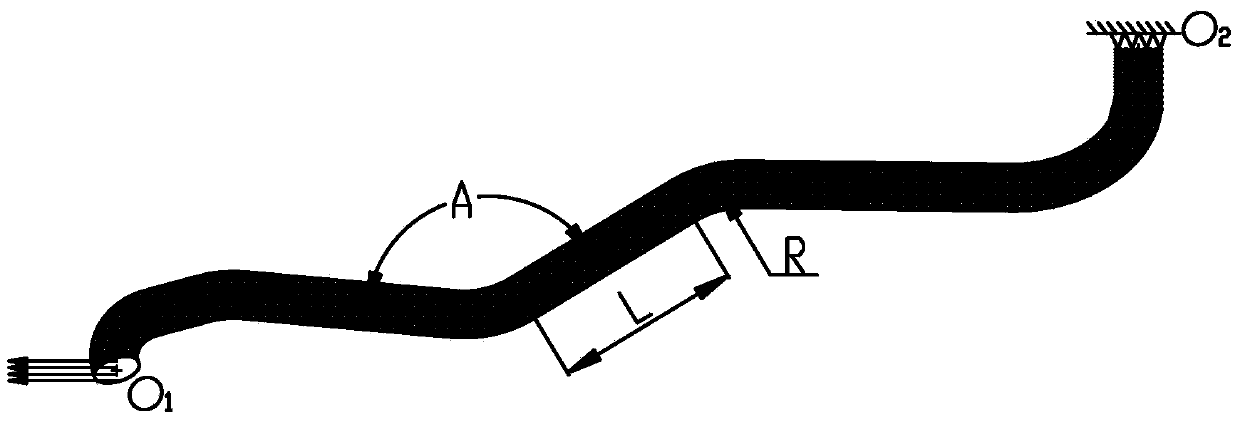

Thermal compensation design method for high-temperature air pipeline

ActiveCN103440381ASolution to short lifeImprove rationalitySpecial data processing applicationsIndustrial engineeringHigh heat

Provided is a thermal compensation design method for a high-temperature air pipeline. The thermal compensation design method includes the steps of using UG NX commercial software under a mechanical pipeline layout module to build a pipeline geometric model containing seven types of mathematical variables, carrying out pre-processing through finite element analysis software ANSYS, material parameters are given according to GH536, wherein an elasticity modulus E is equal to 187 GPa, and poisson ratio mu is equal to 0.3, utilizing boundary conditions and imposed displacement boundary conditions and temperature field load, calculating and obtaining the stress conditions of the pipeline, adjusting pipeline layout paths, carrying out calculation again according to the second content to the fourth content, and obtaining a new calculation result, that is, the maximum stress value is smaller than yield limit of materials, and yield strength reserve factor is larger than 1.5, and therefore the design requirements are met. The thermal compensation design method has the advantages of improving design reasonability and ensuring that the high-temperature air pipeline meets the requirements of engines for long service life and high reliability.

Owner:AECC SHENYANG ENGINE RES INST

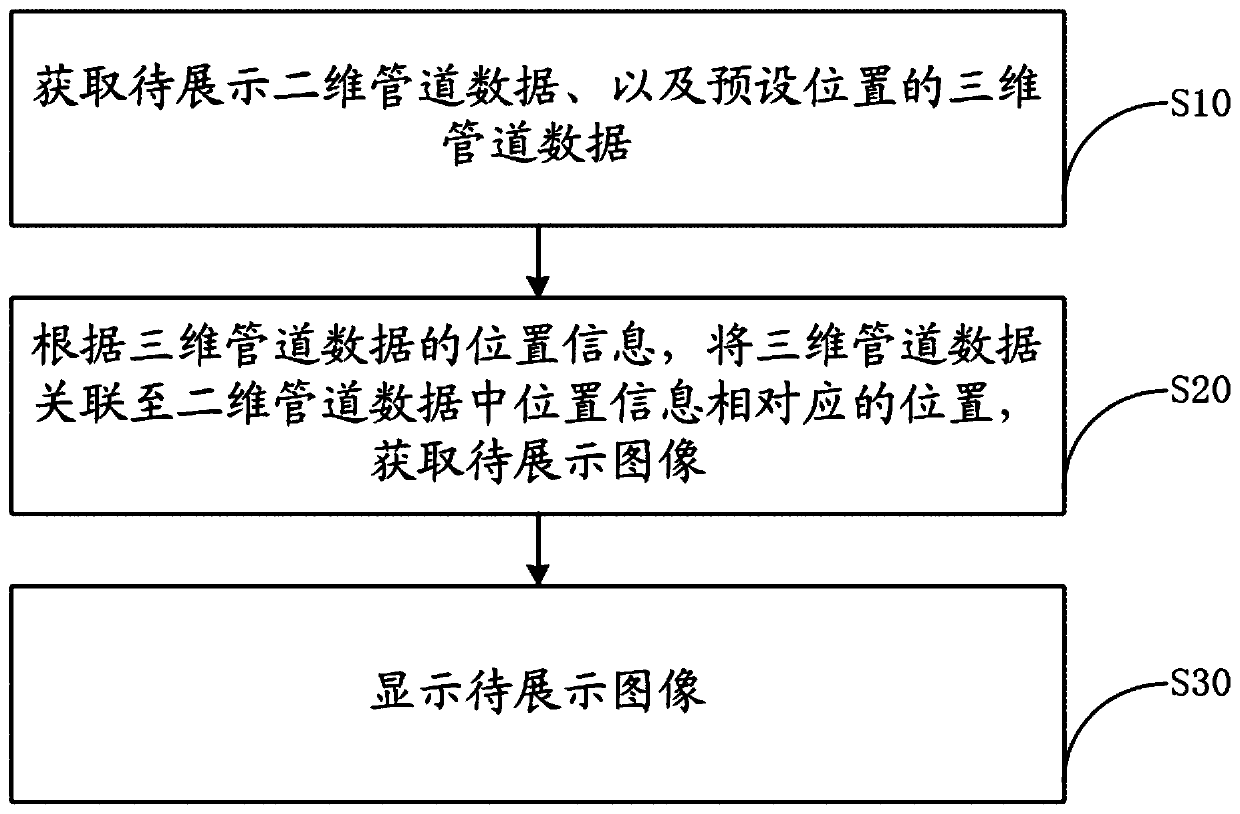

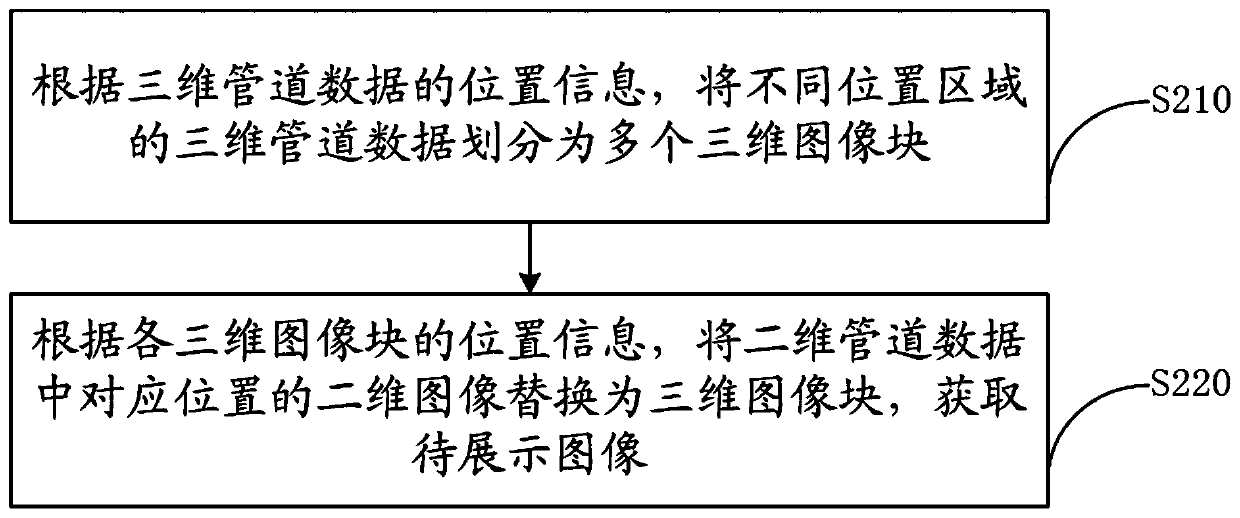

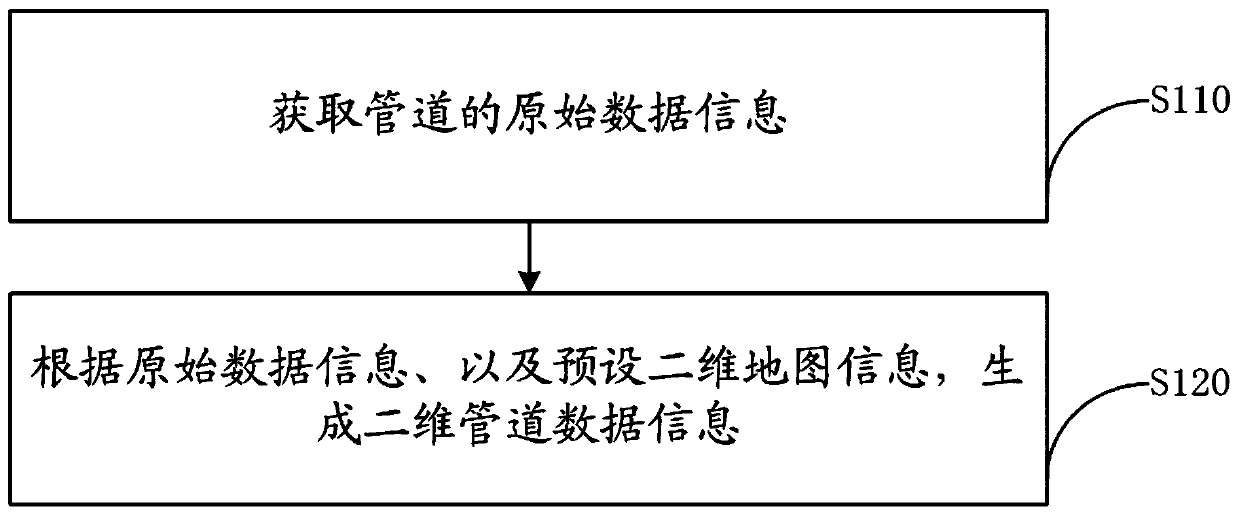

Pipeline engineering display method, device and equipment and storage medium

PendingCN111402400AImplement the display methodReduce maintenance costsGeometric image transformation3D modellingComputer hardwareComputer graphics (images)

The invention provides a pipeline engineering display method, device and equipment and a storage medium, and belongs to the technical field of software platforms. The method comprises the steps: obtaining to-be-displayed two-dimensional pipeline data and three-dimensional pipeline data of a preset position; according to the position information of the three-dimensional pipeline data, associating the three-dimensional pipeline data to a position corresponding to the position information in the two-dimensional pipeline data, and obtaining a to-be-displayed image; displaying an image to be displayed. According to the invention, various data information of the pipeline can be displayed more comprehensively and visually.

Owner:AERIAL PHOTOGRAMMETRY & REMOTE SENSING CO LTD

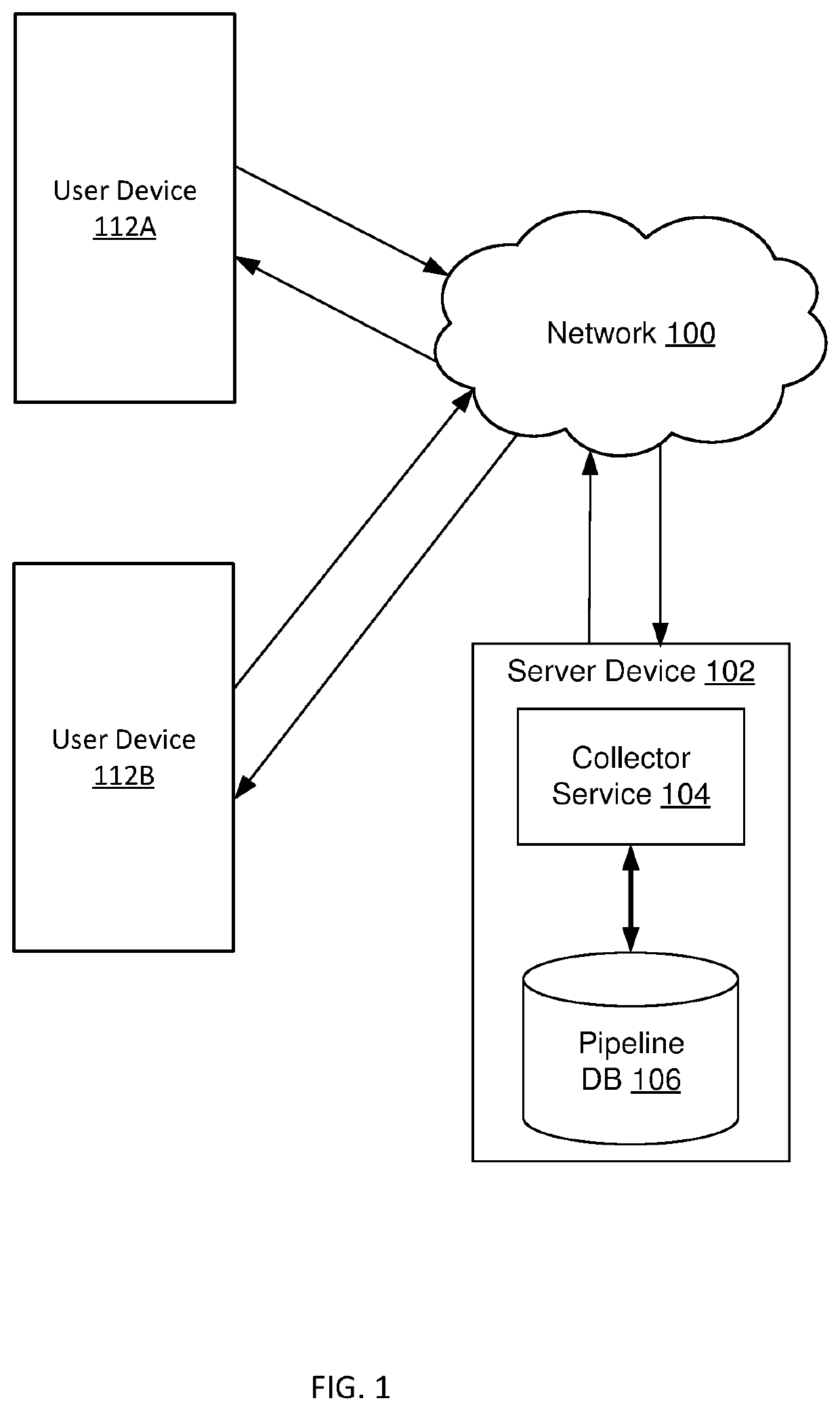

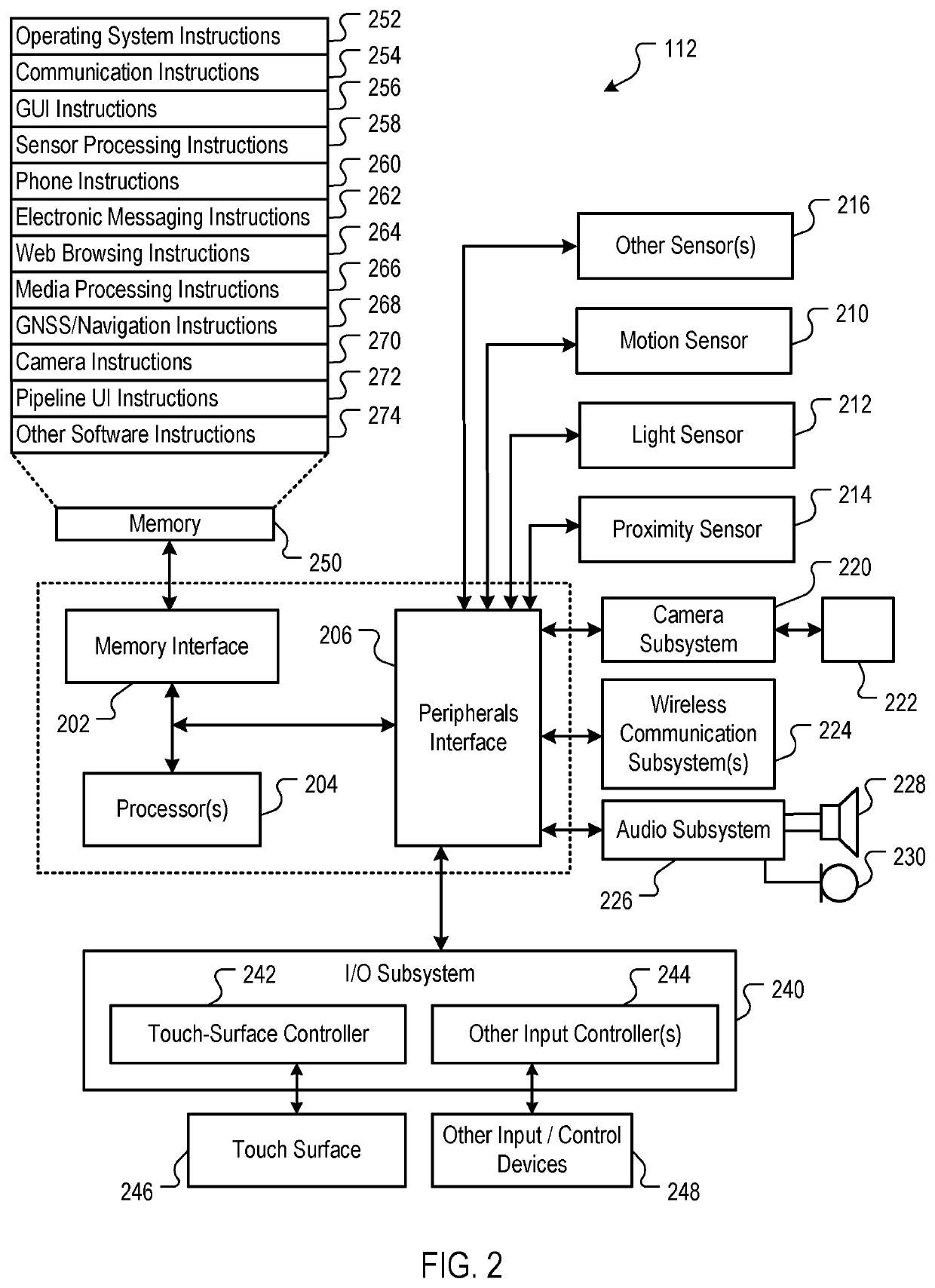

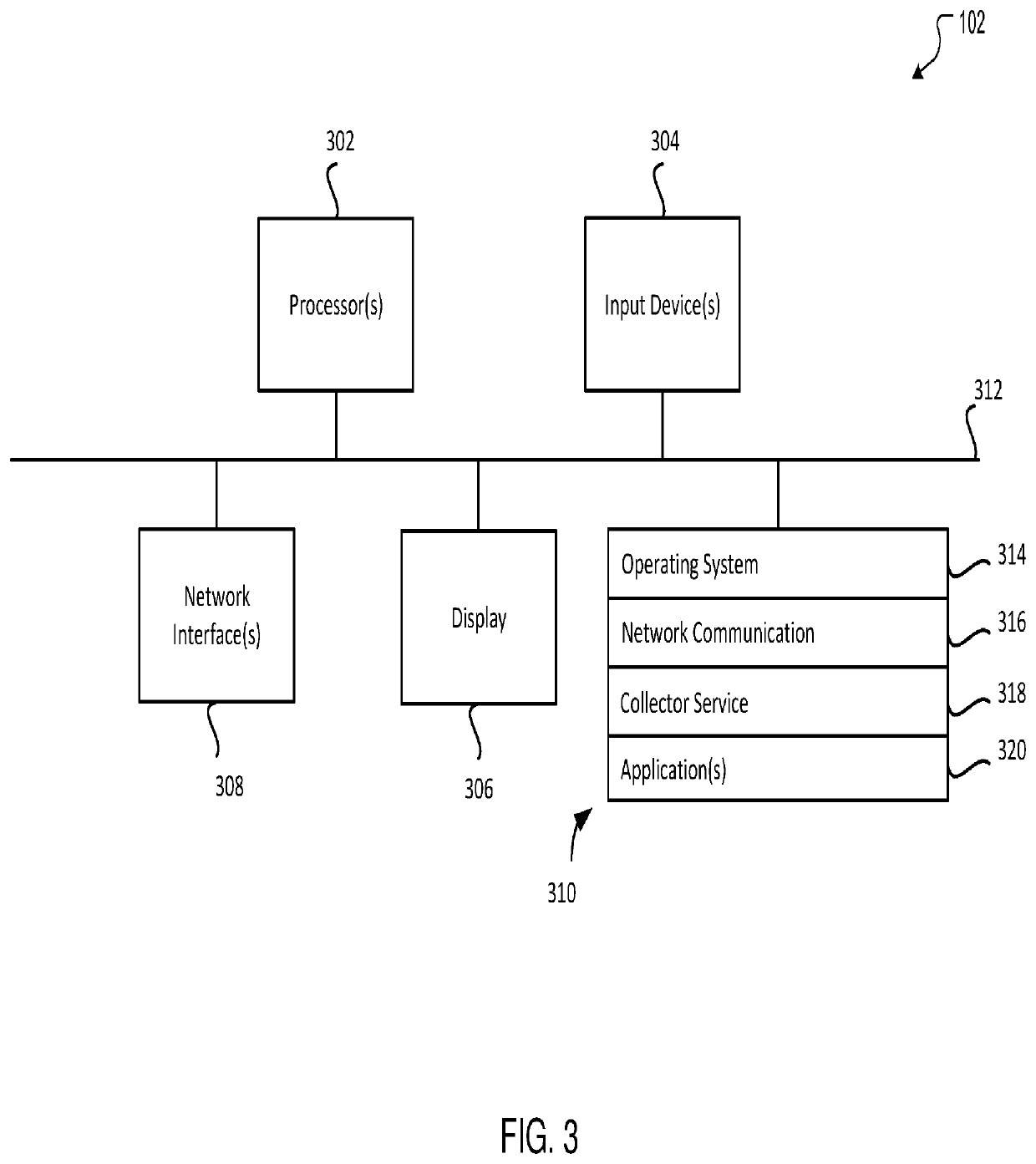

Code quality evaluation and user interfaces

A processor may generate a UI. The processor may instantiate a plurality of collectors. Each collector may be configured to collect data in real time from a separate one of a plurality of data sources. Each data source may include a different type of data relating to at least one of a plurality of software delivery pipeline tasks. The processor may separately and continuously collect data from each of the plurality of data sources using the plurality of collectors. The processor may separately and continuously analyze the stored data from each of the plurality of data sources to generate a plurality of code quality metrics for the plurality of software delivery pipeline tasks. The processor may continuously report the plurality of code quality metrics through the UI.

Owner:CAPITAL ONE SERVICES

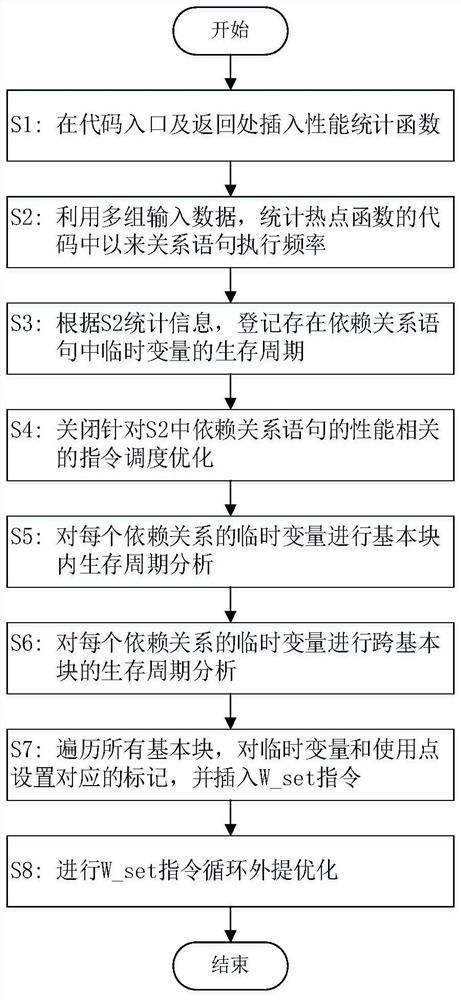

Low-power-consumption register allocation compiling optimization method

ActiveCN112445481AReduce development costsLow power potentialEnergy efficient computingCode compilationRegister allocationScheduling instructions

The invention discloses a low-power-consumption register allocation compiling optimization method. The method comprises the following steps: S1, analyzing a hotspot function and a cycle segment of a program; s2, counting the execution frequency of the dependency statement in the hotspot code segment; s3, registering a life cycle of a temporary variable in the statement with the dependency relationship; s4, closing instruction scheduling optimization related to the performance of the dependency statement to prevent instruction scheduling performed due to consideration of pipeline performance; s5, performing life cycle analysis in the basic block on the temporary variable of each dependency relationship; s6, carrying out cross-basic-block life cycle analysis on the temporary variable of eachdependency relationship; s7, traversing all the basic blocks, and tracking definition and use points (defineuse) of the temporary variables marked as low-power-consumption optimization; and S8, performing Wset instruction loop extraction optimization. According to the invention, the system operation power consumption is optimized to a certain extent, the software and hardware development cost islow, the method for reducing the power consumption is simple and direct, and the low-power-consumption potential of the register is mined to the maximum extent on the premise of considering the performance.

Owner:JIANGNAN INST OF COMPUTING TECH