Patents

Literature

53results about How to "Depth is minimized" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

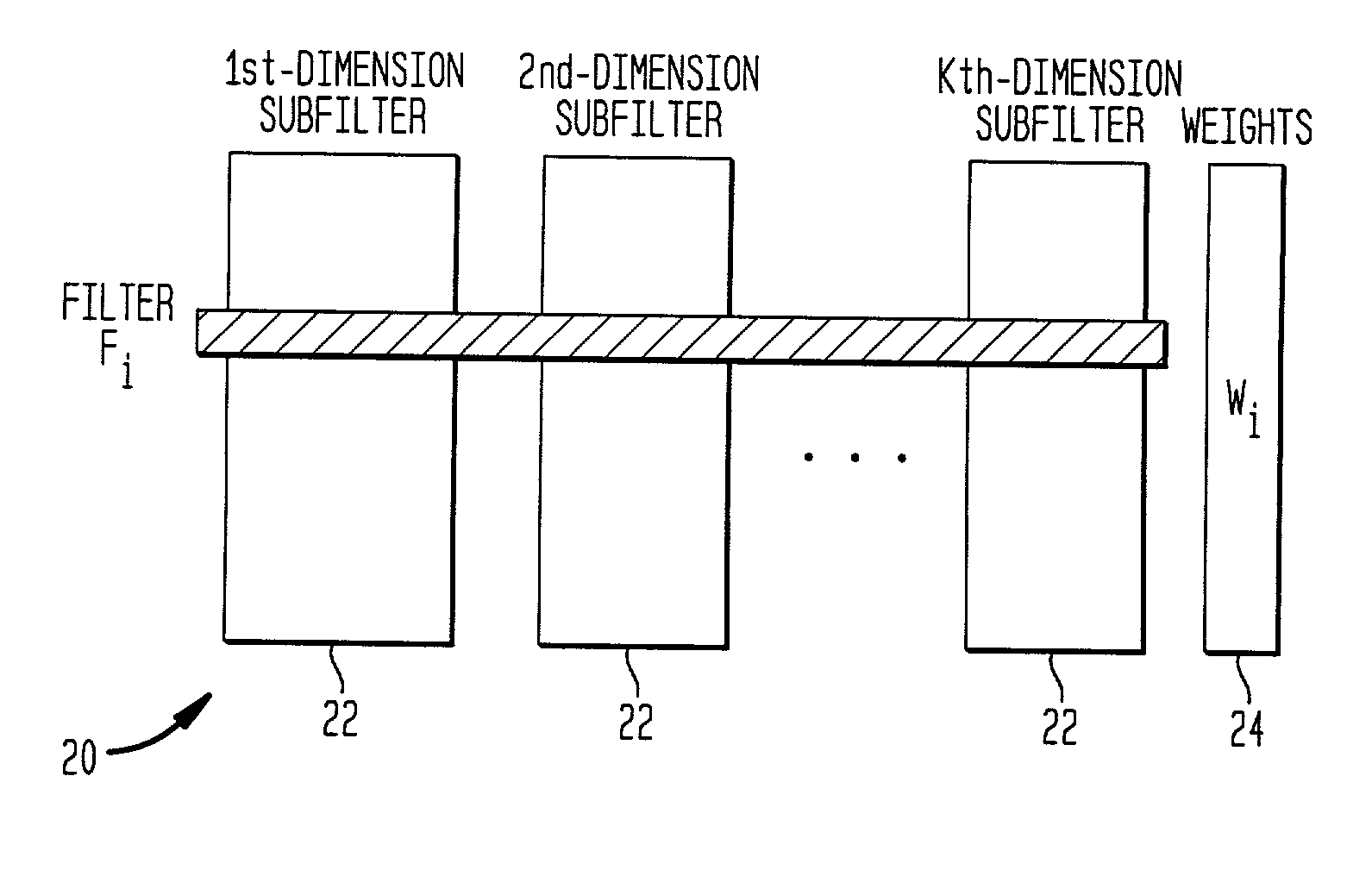

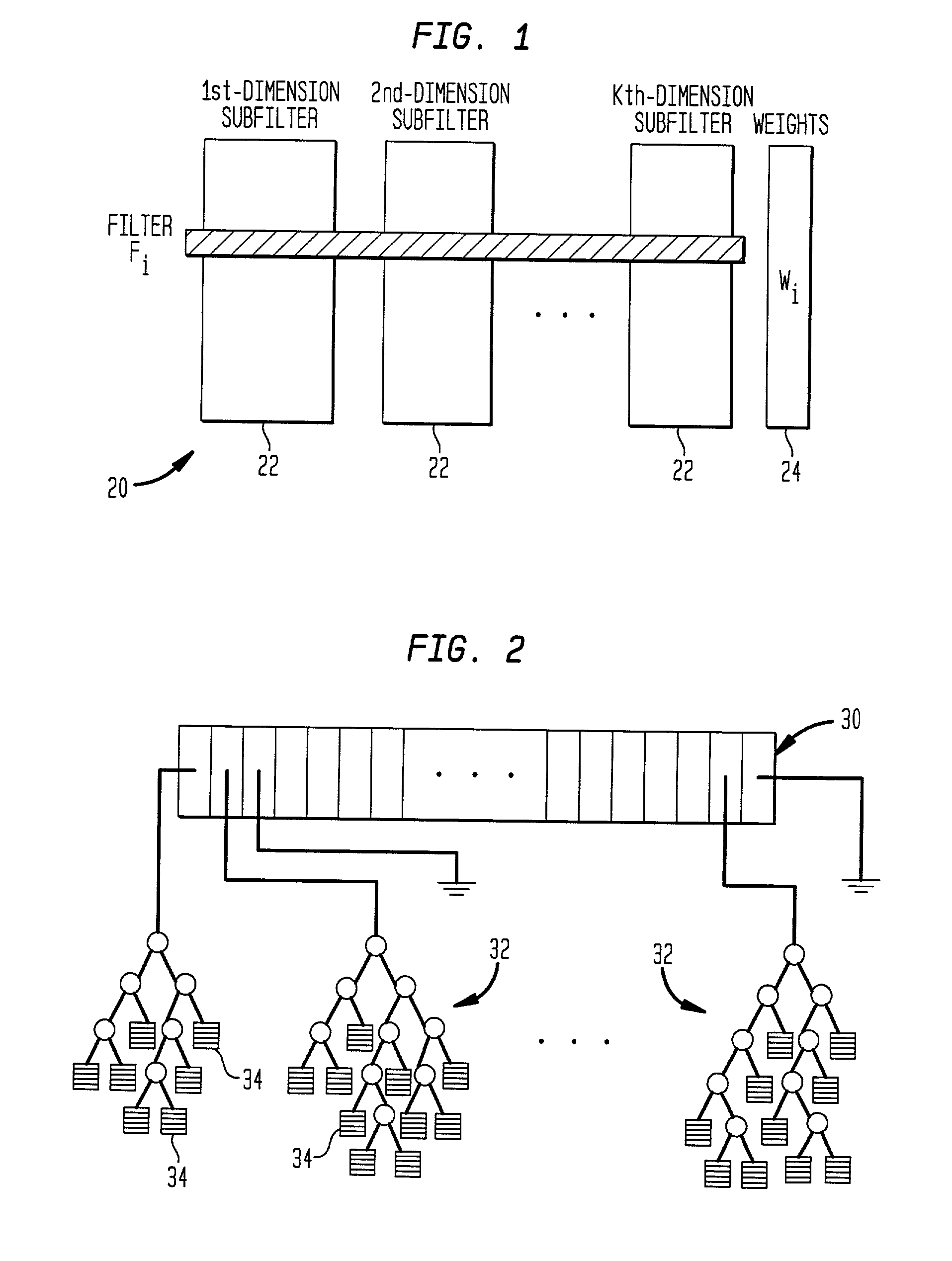

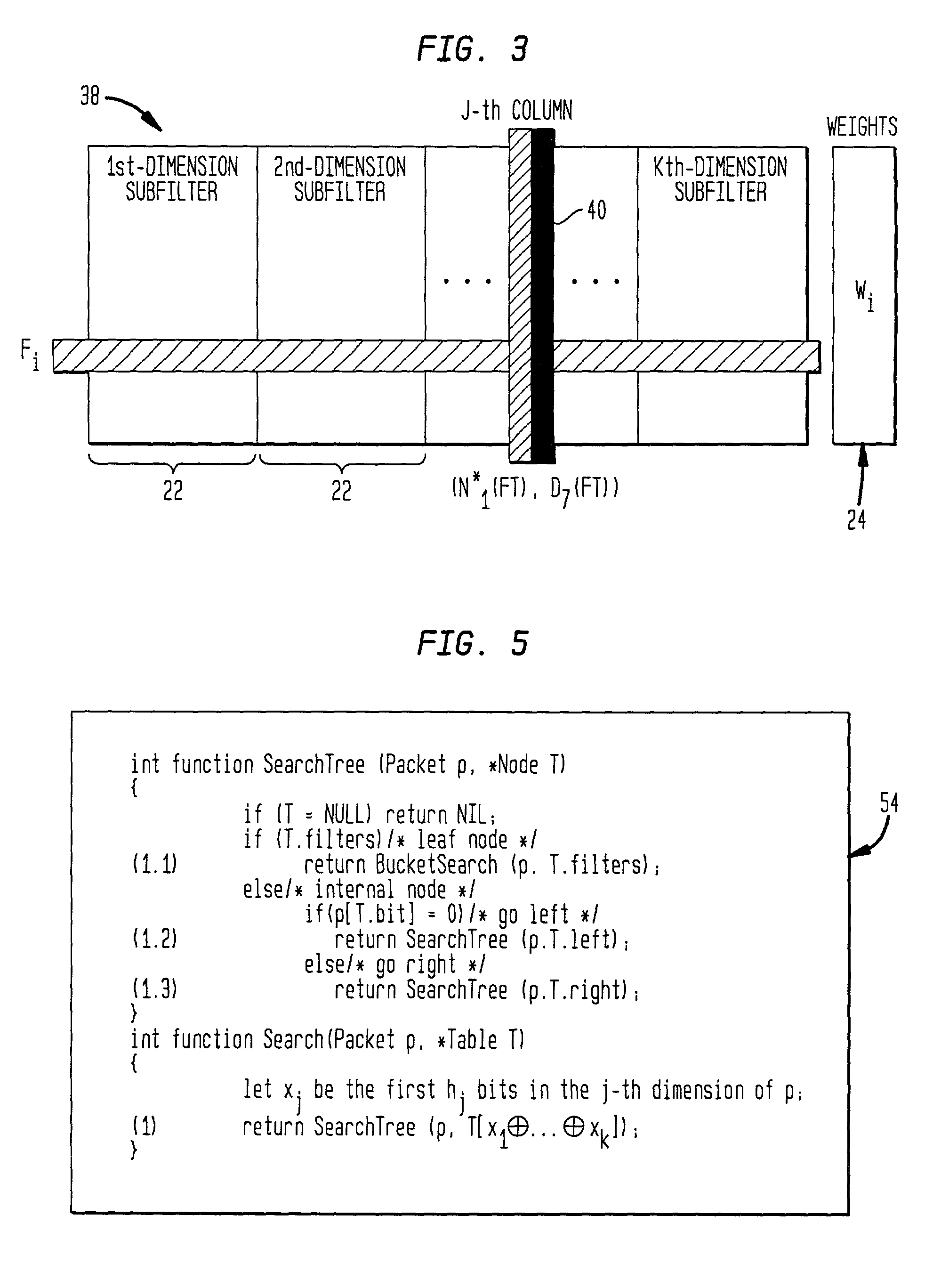

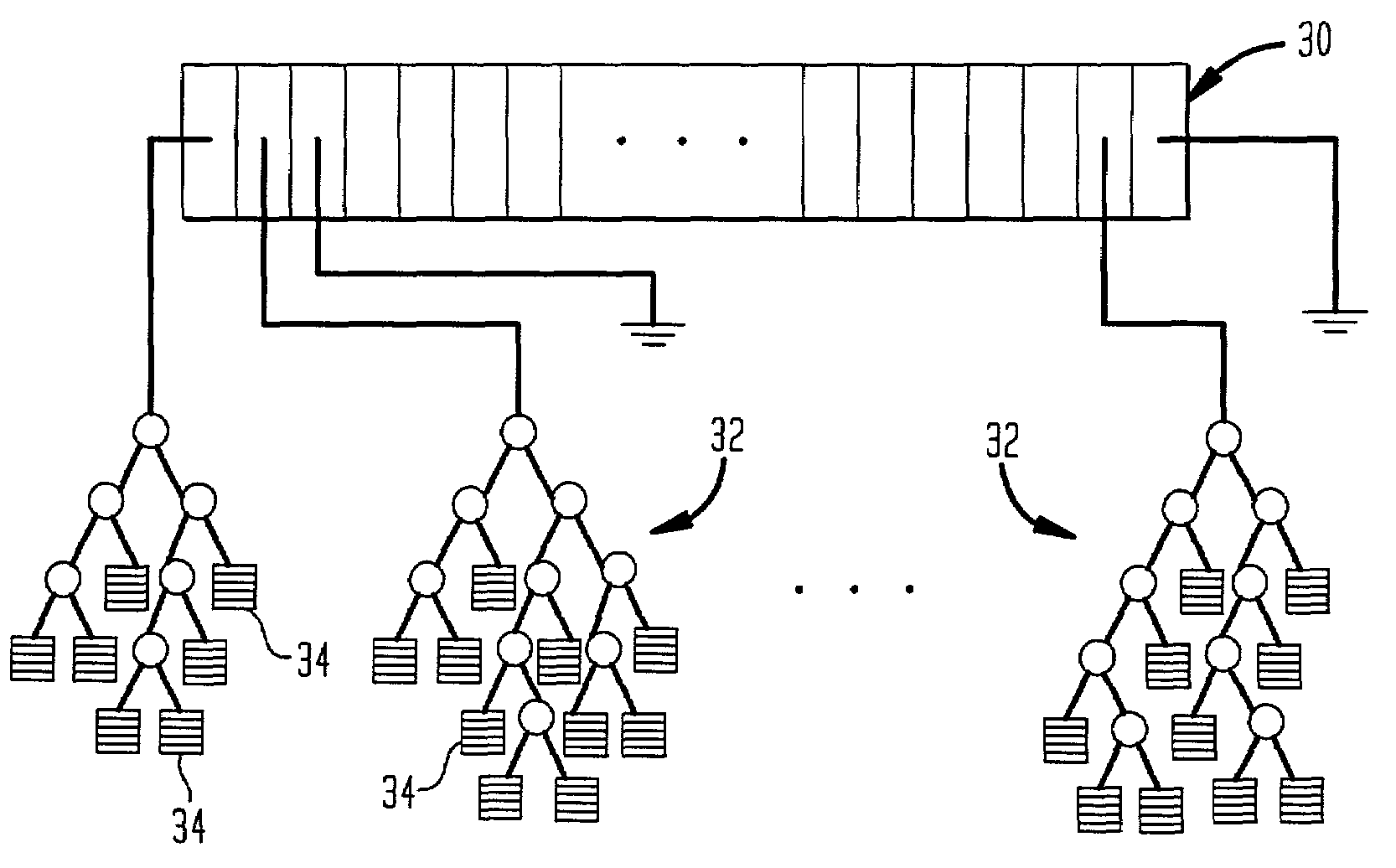

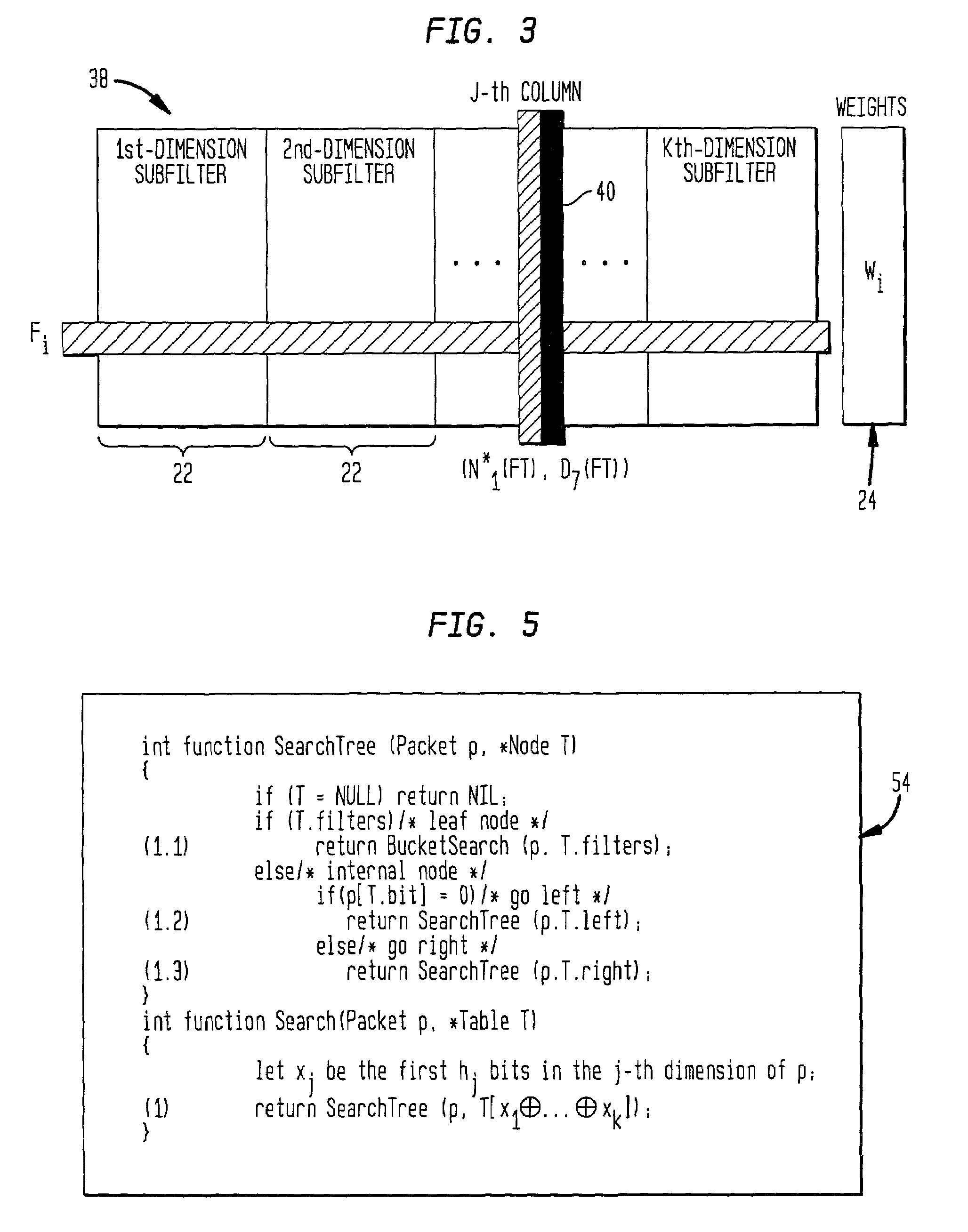

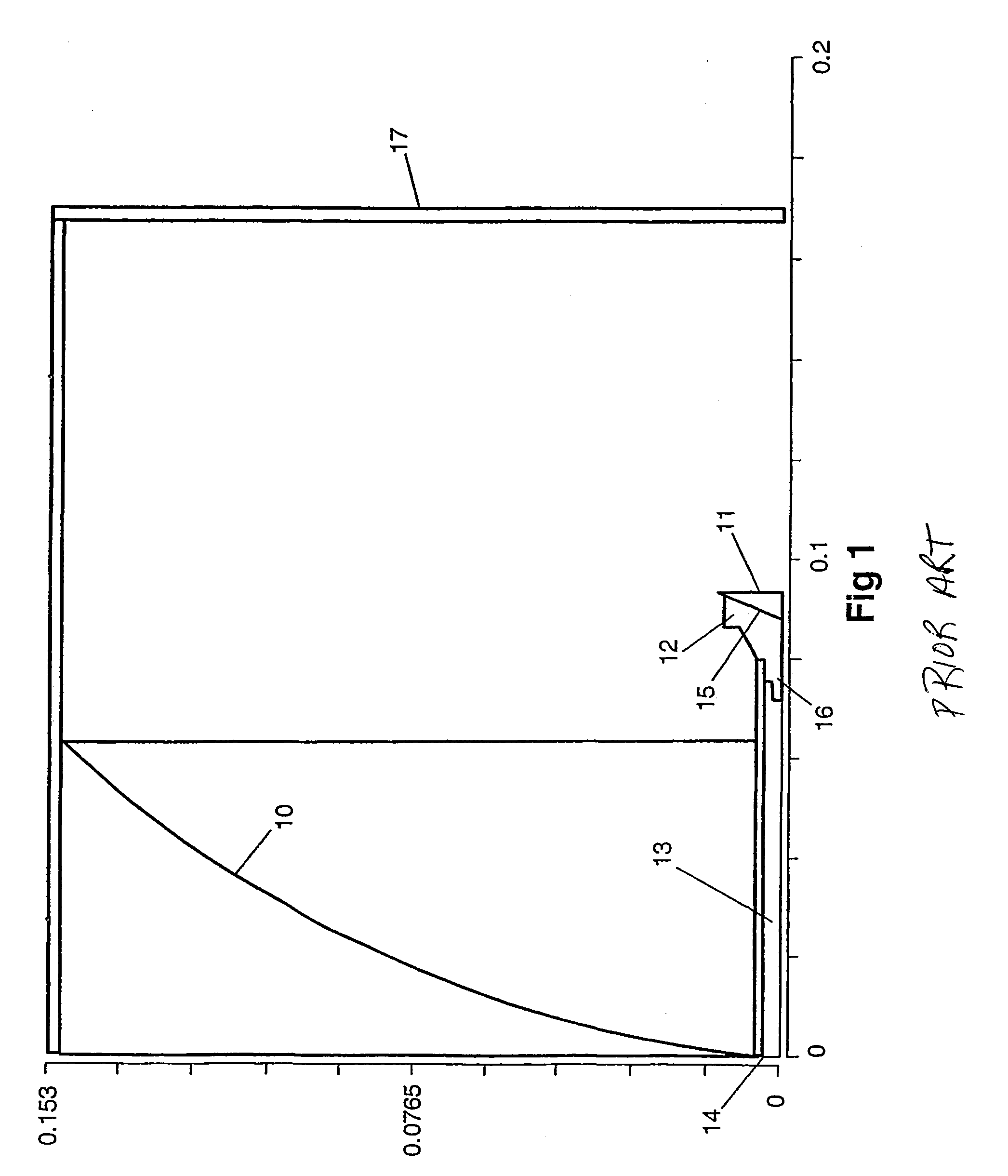

Modular packet classification

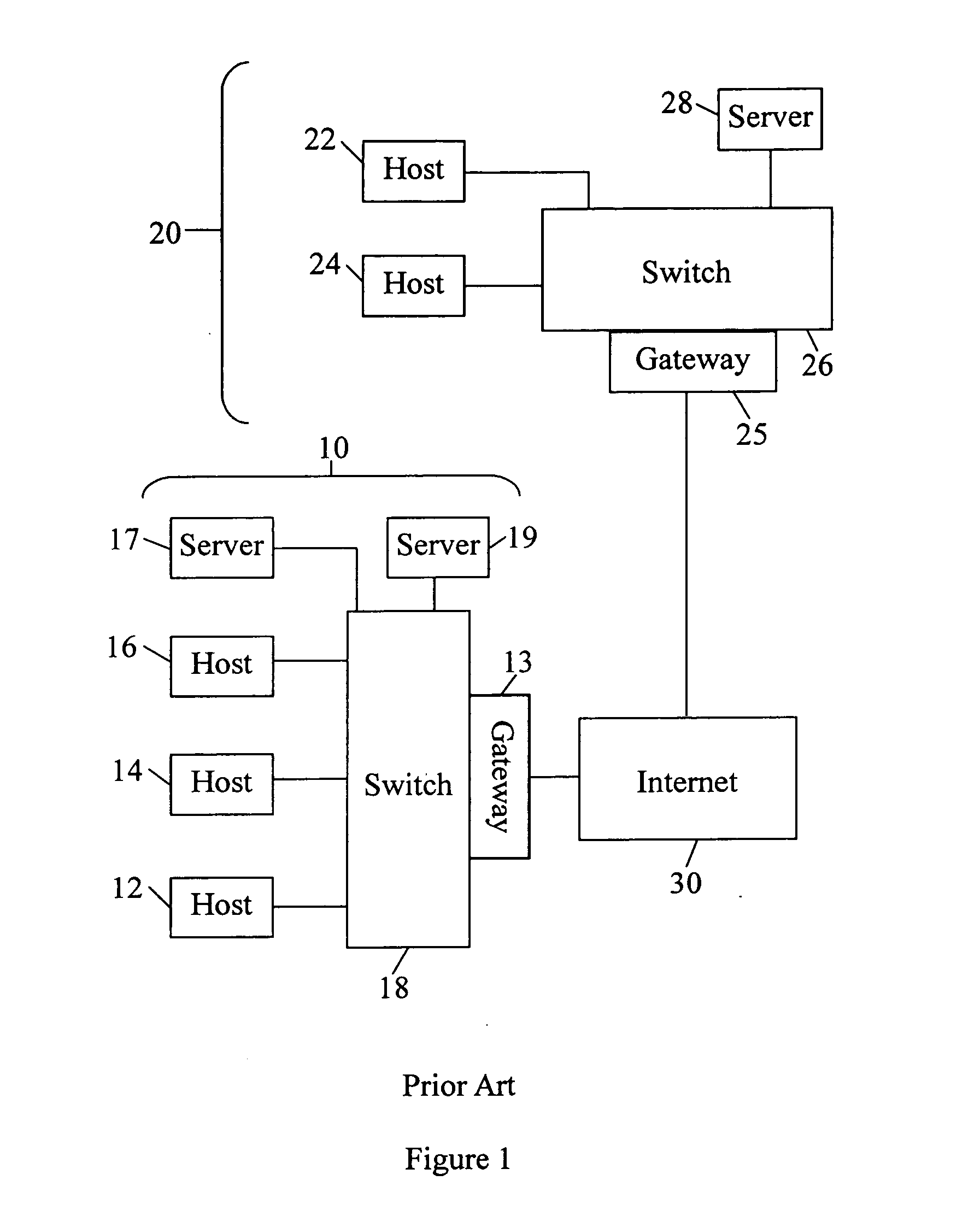

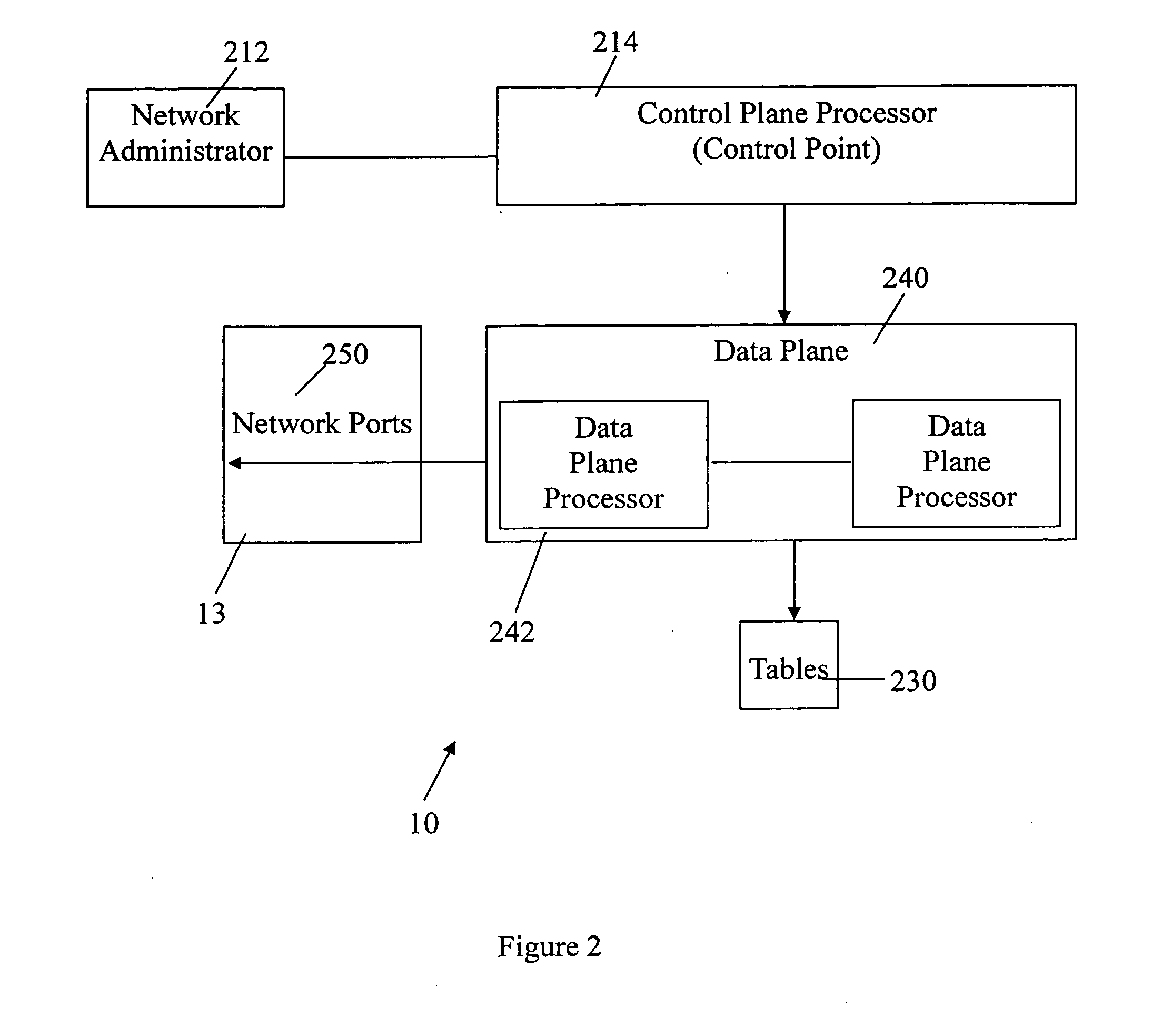

InactiveUS20020023089A1Avoid explosionDepth is minimizedDigital data processing detailsData switching by path configurationQos quality of serviceData pack

The novel method and system for classifying packets through the use of filters combines heuristic tree search with the use of filter buckets. This provides high performance and reasonable storage requirement, even when applied to large number of filters (from 4K to 1 million). In addition, the novel method can adapt to the input packet distribution by taking into account the relative filter usage. The capability of employing a large number of filters in a packet classifciation system is useful in providing value-added services, such as security, quality of service (QoS), load balancing, and traffic accounting.

Owner:LUCENT TECH INC

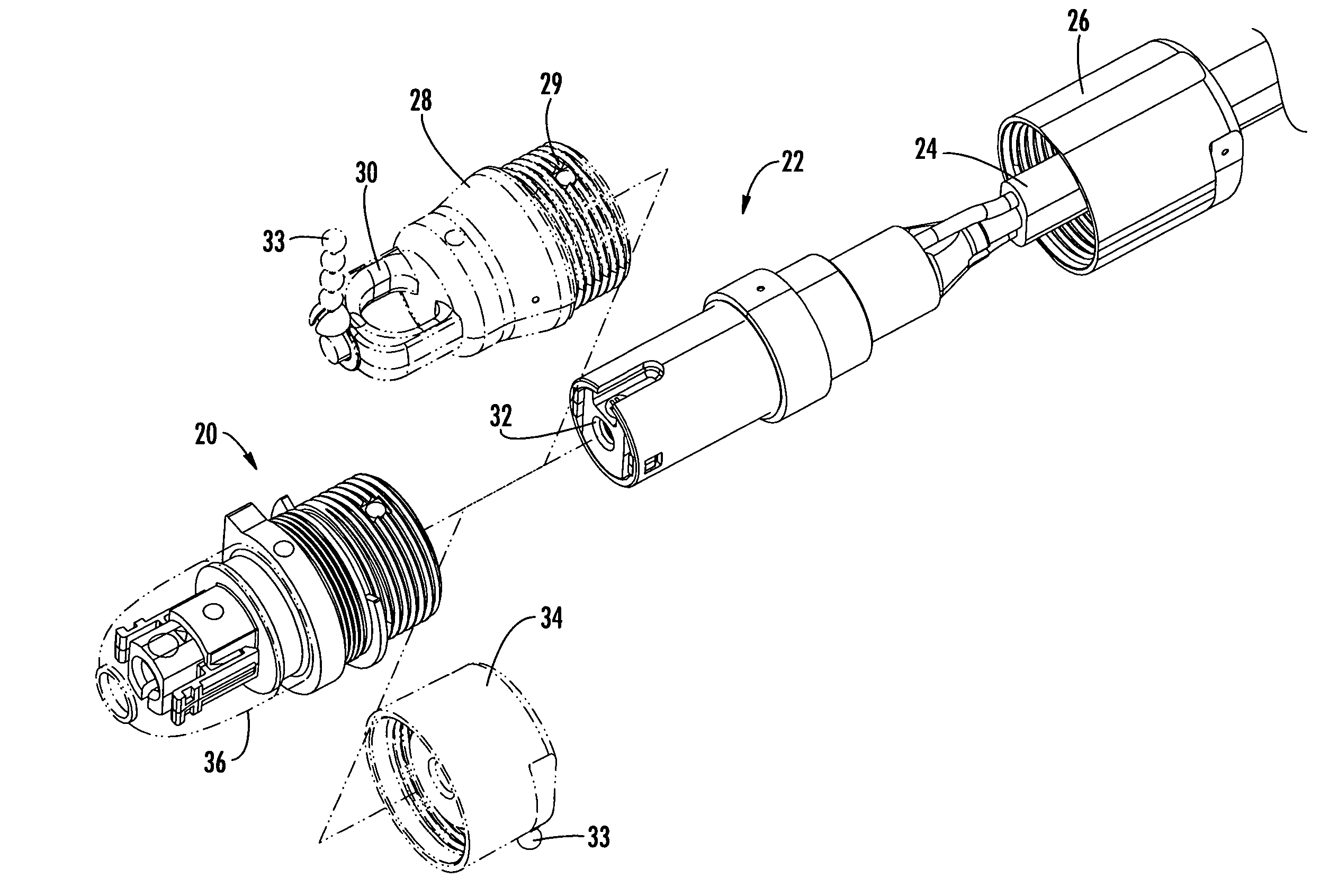

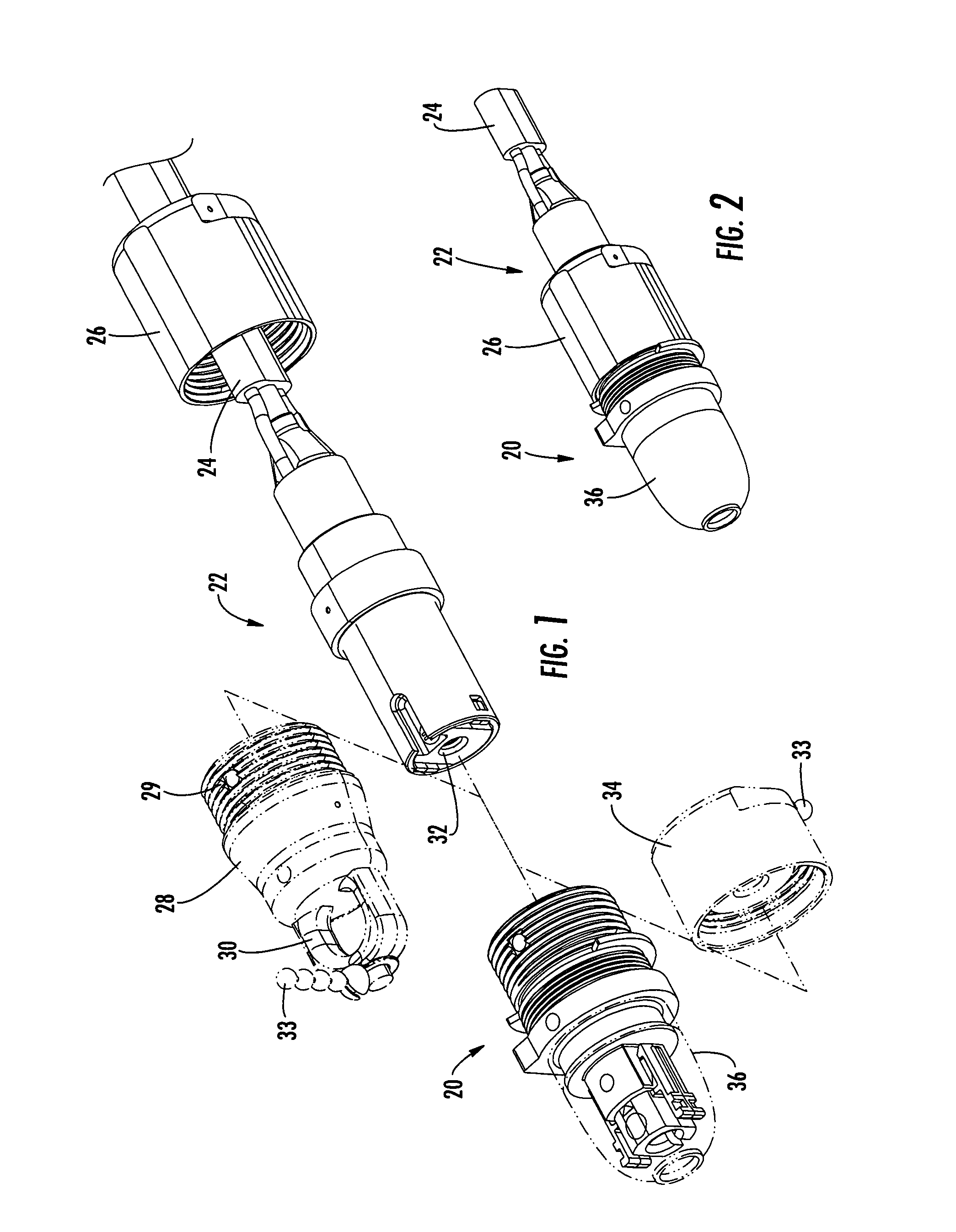

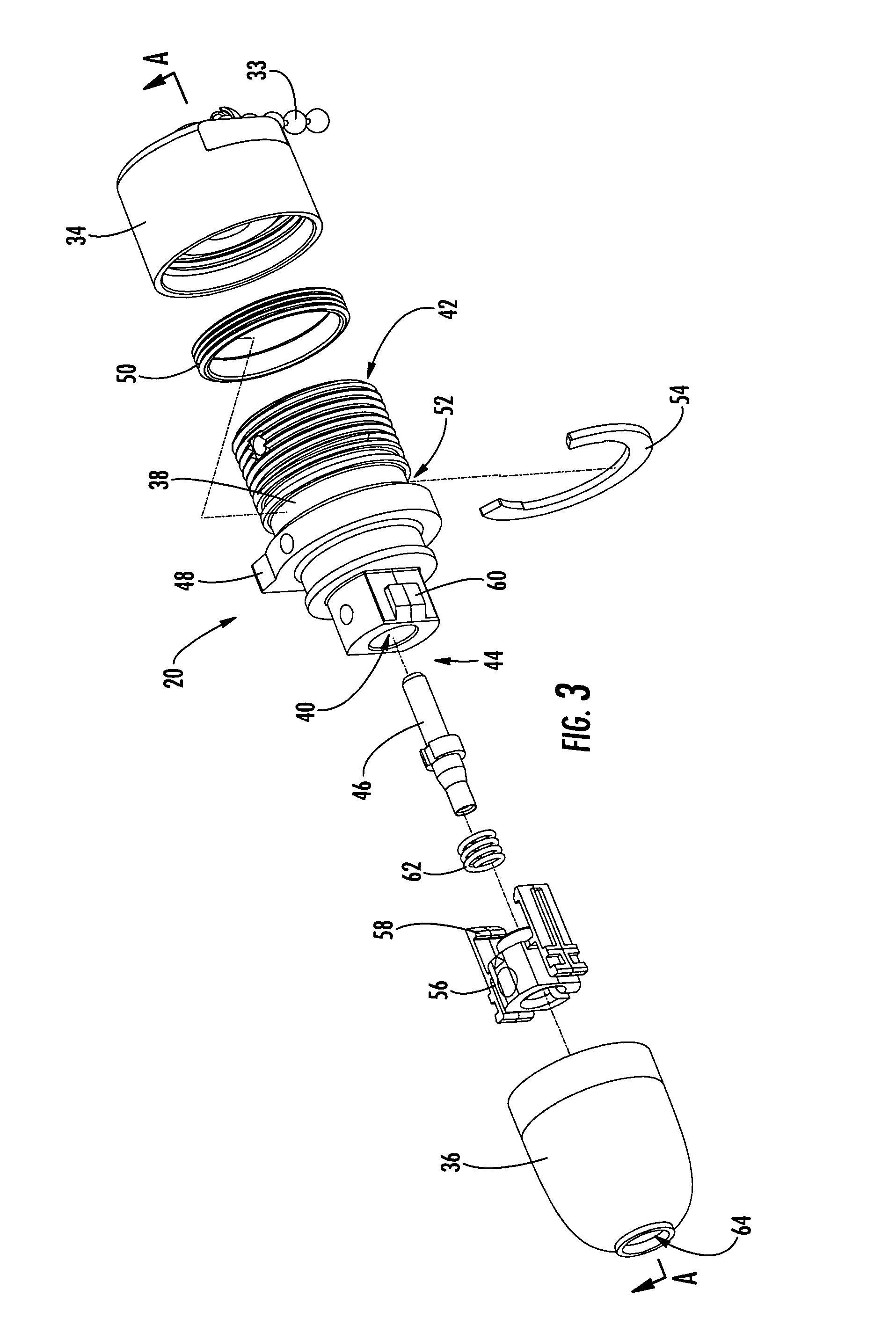

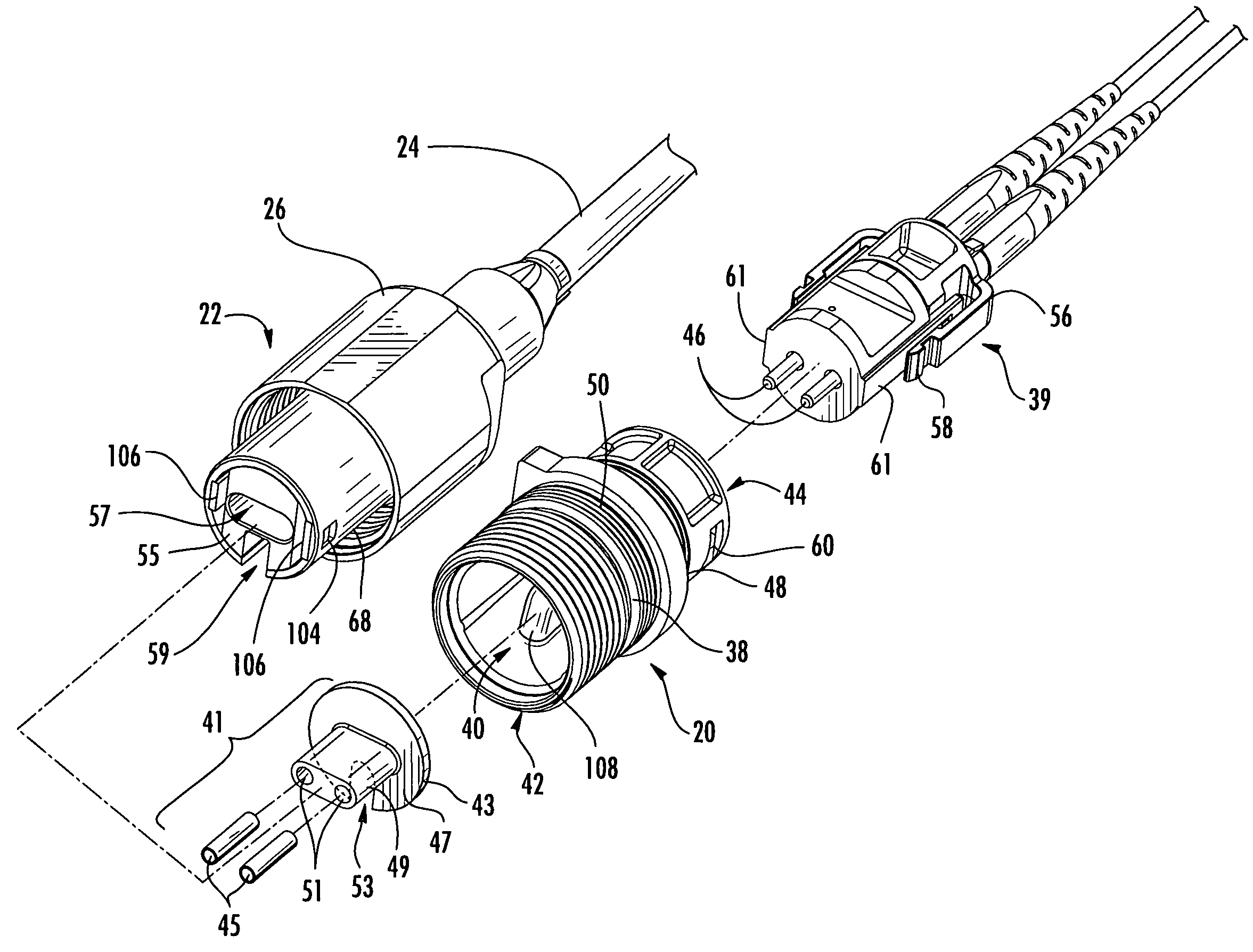

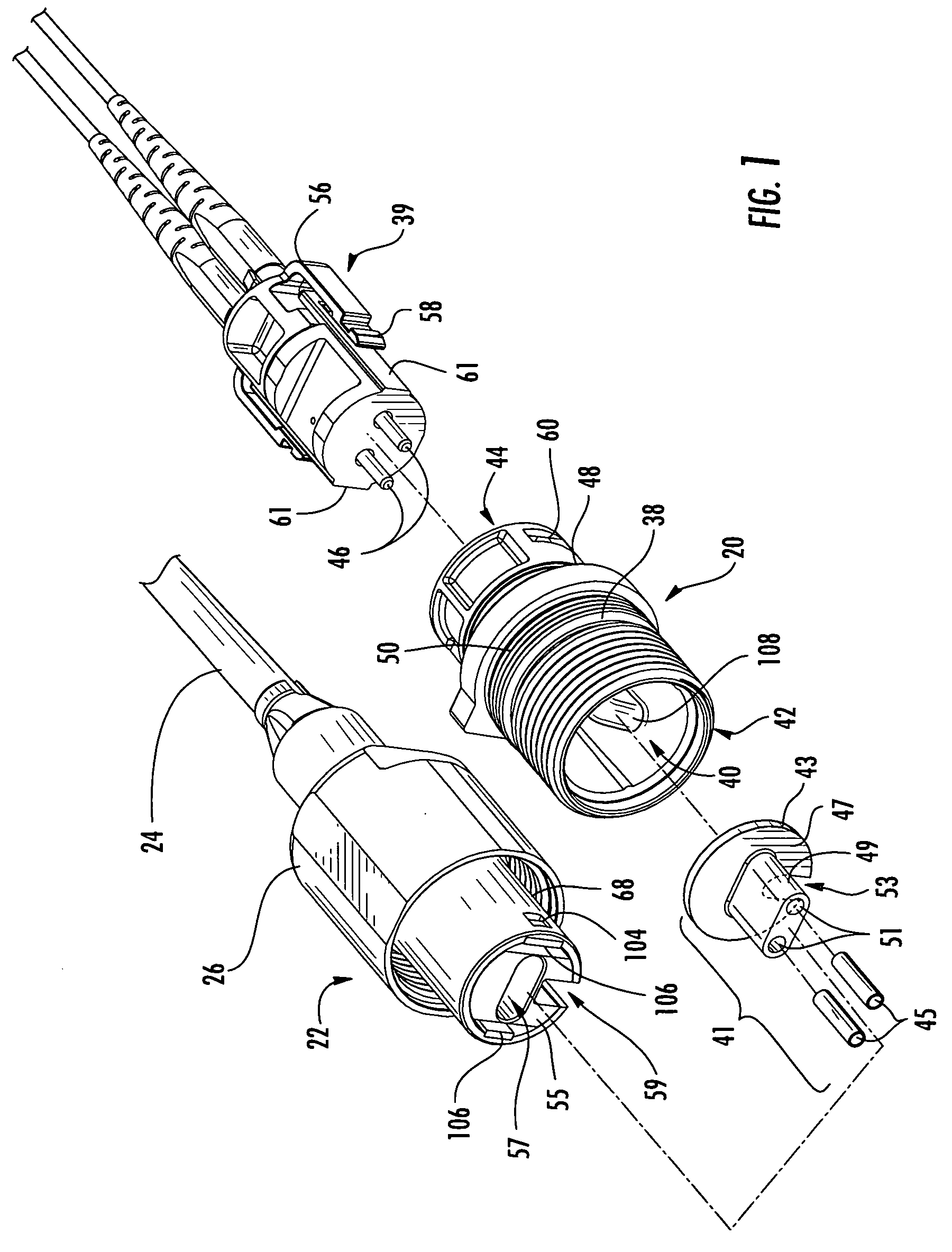

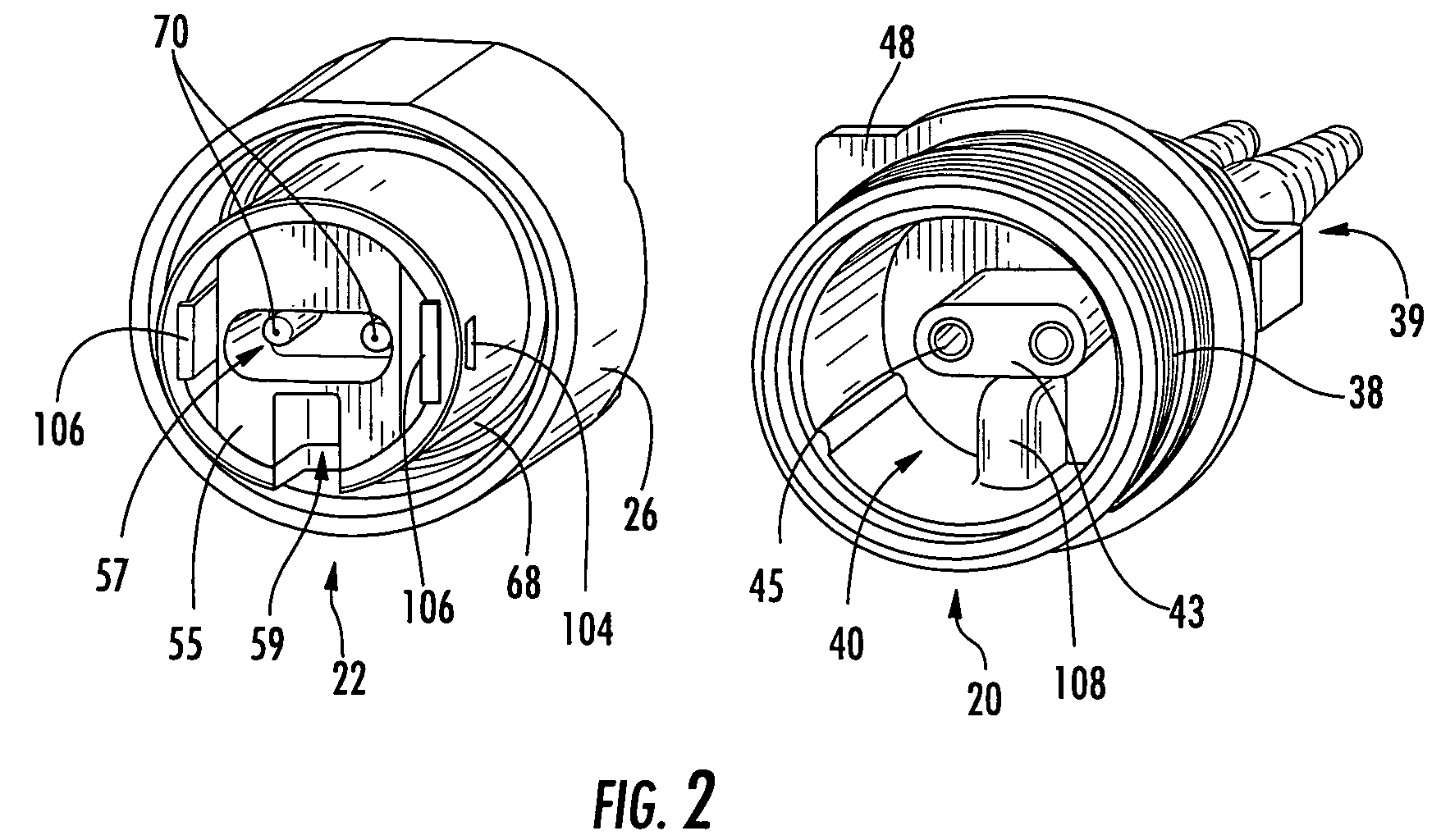

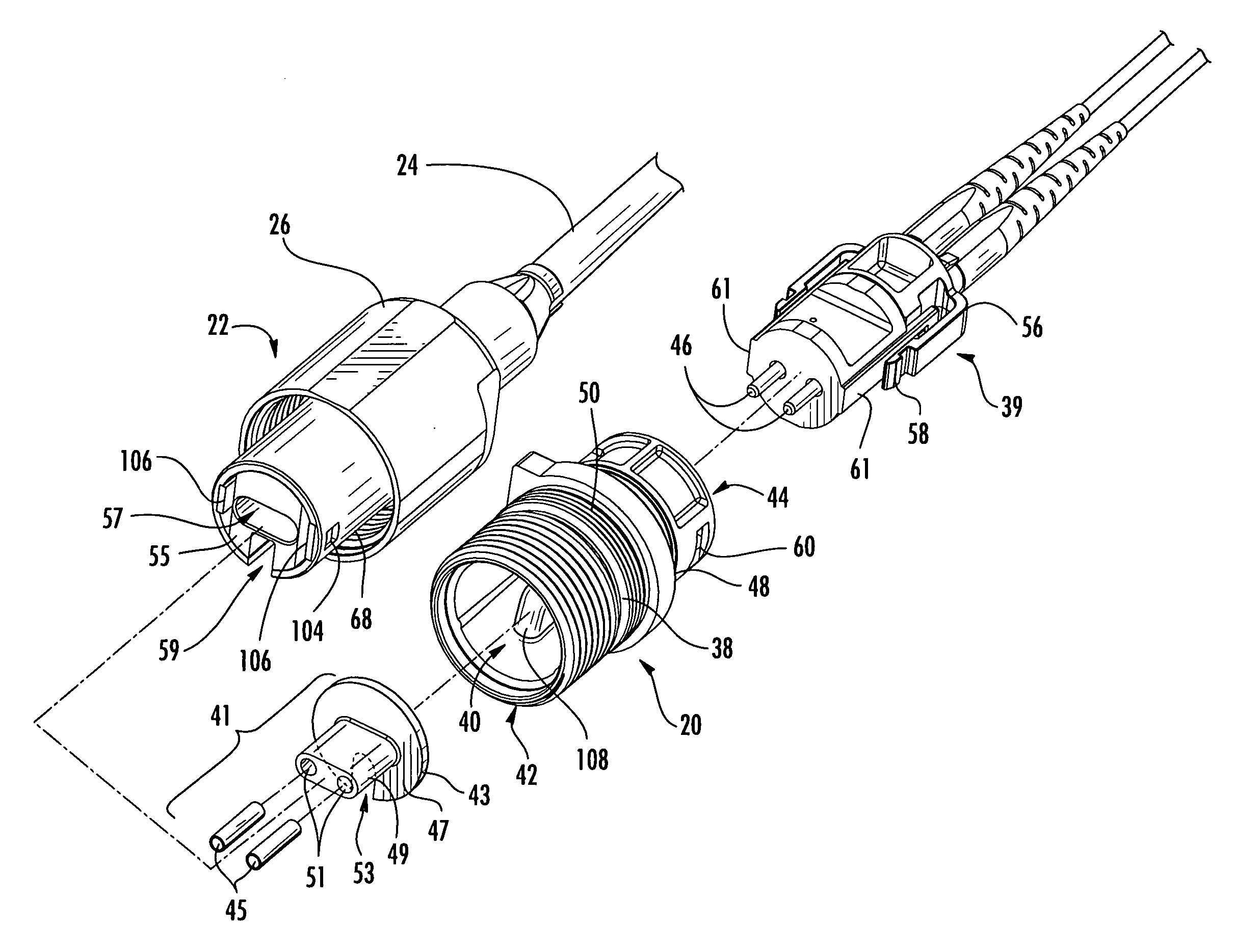

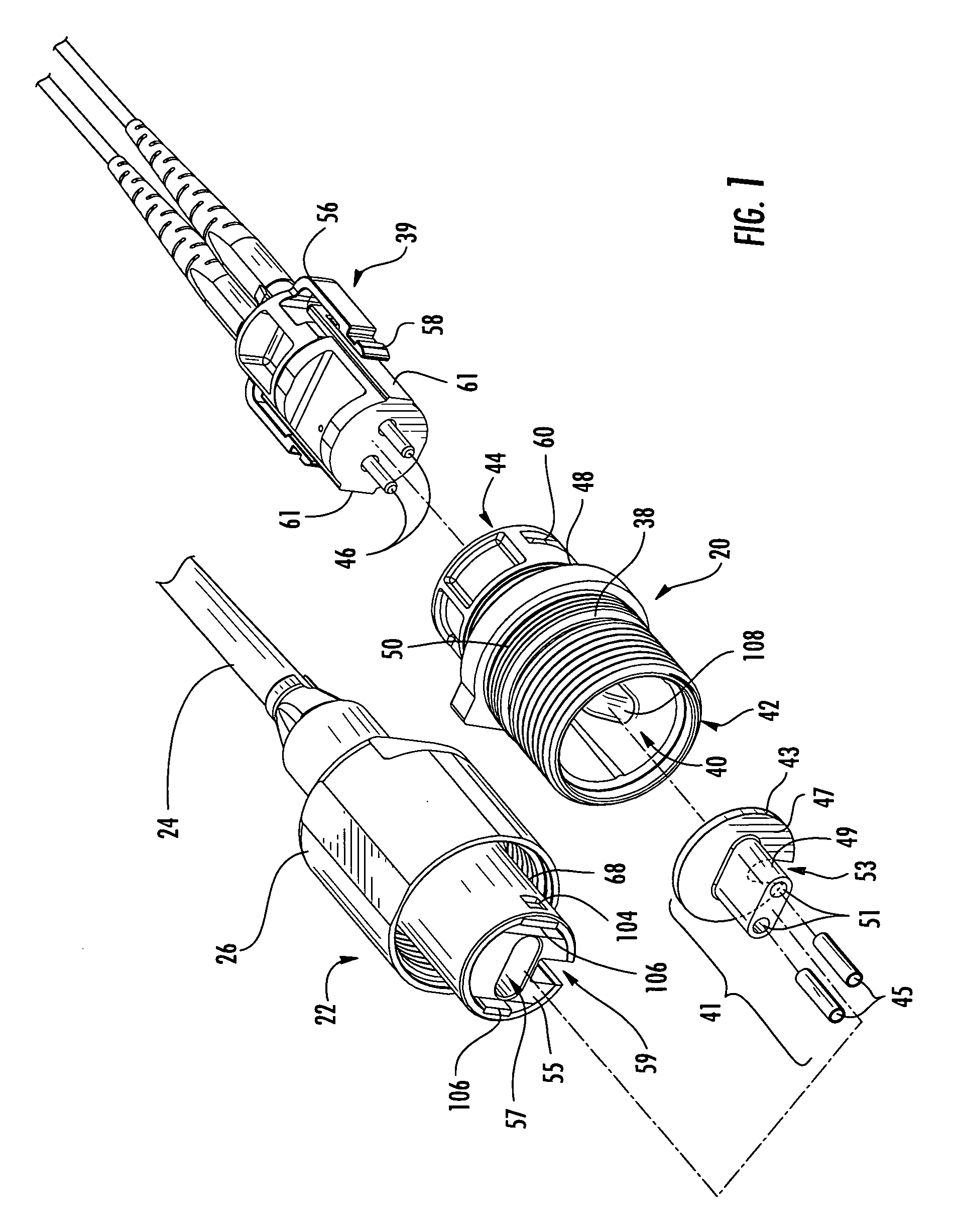

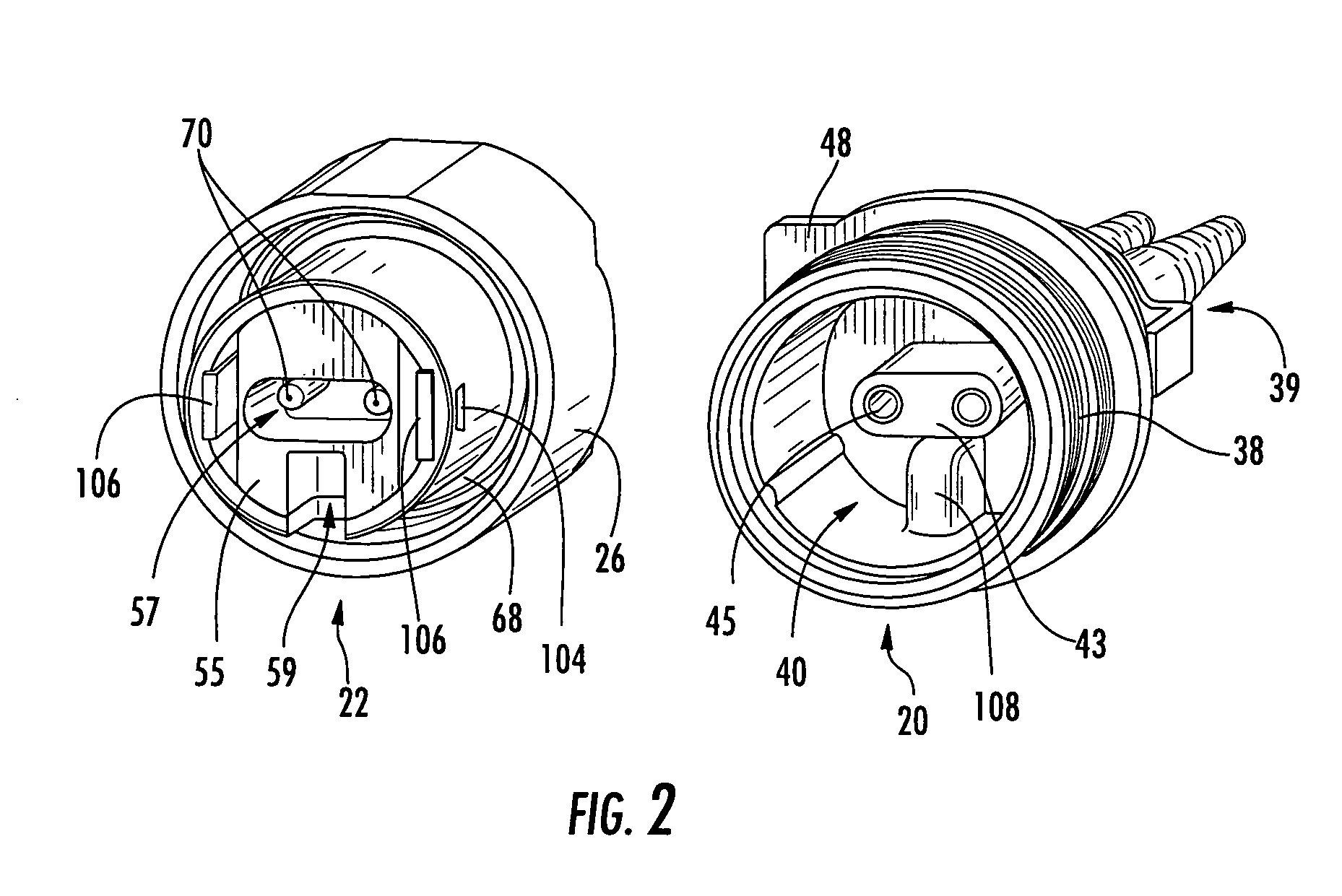

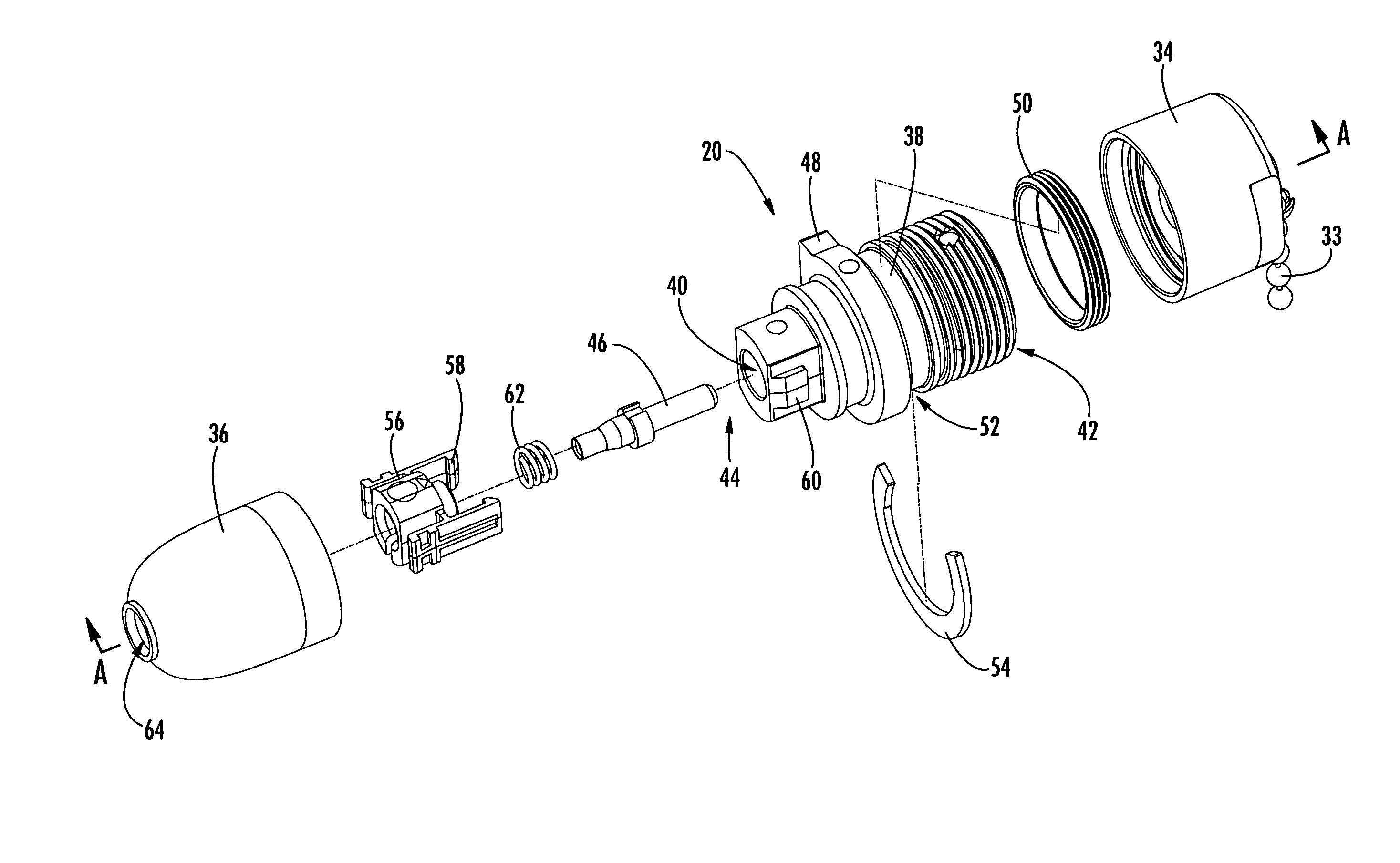

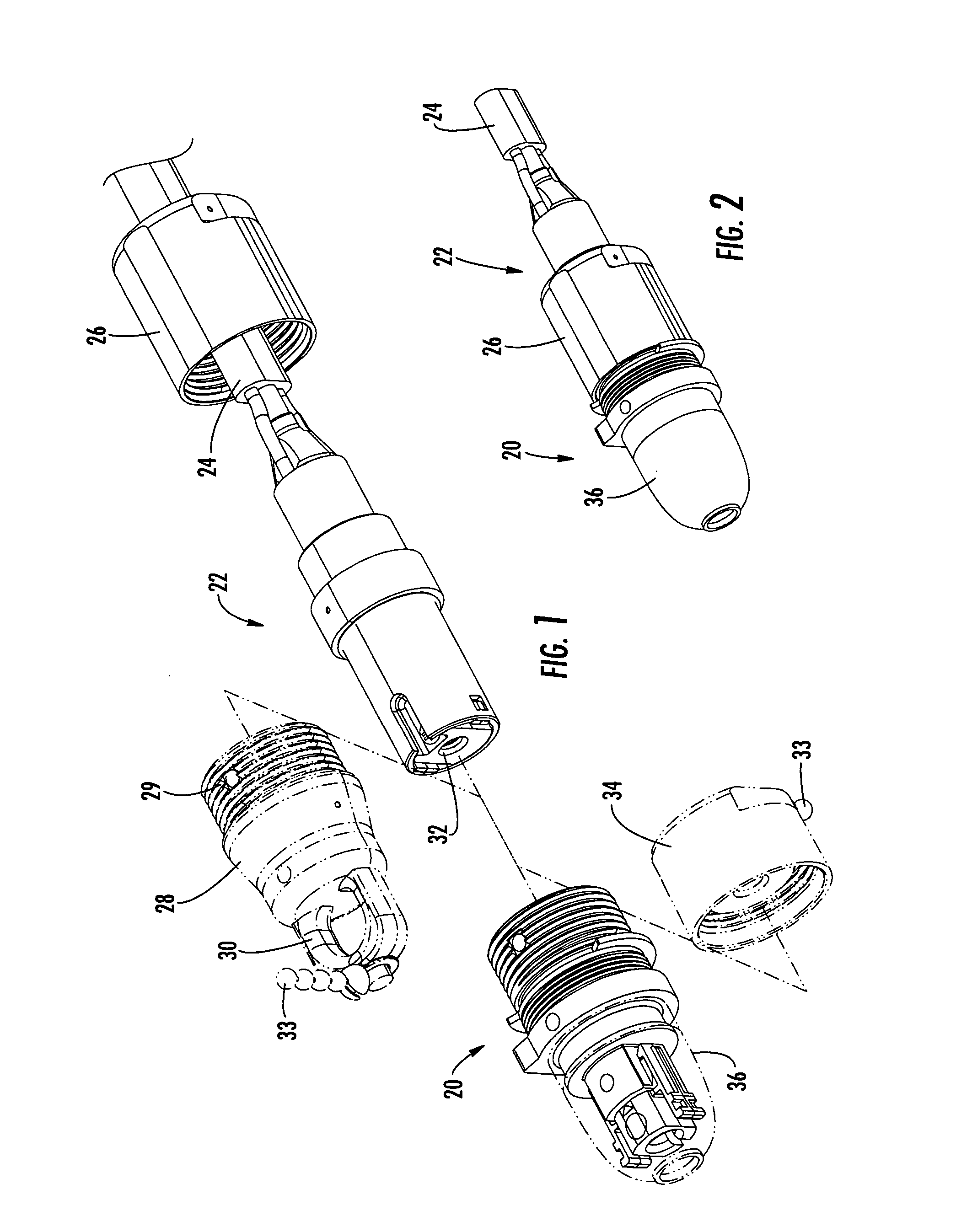

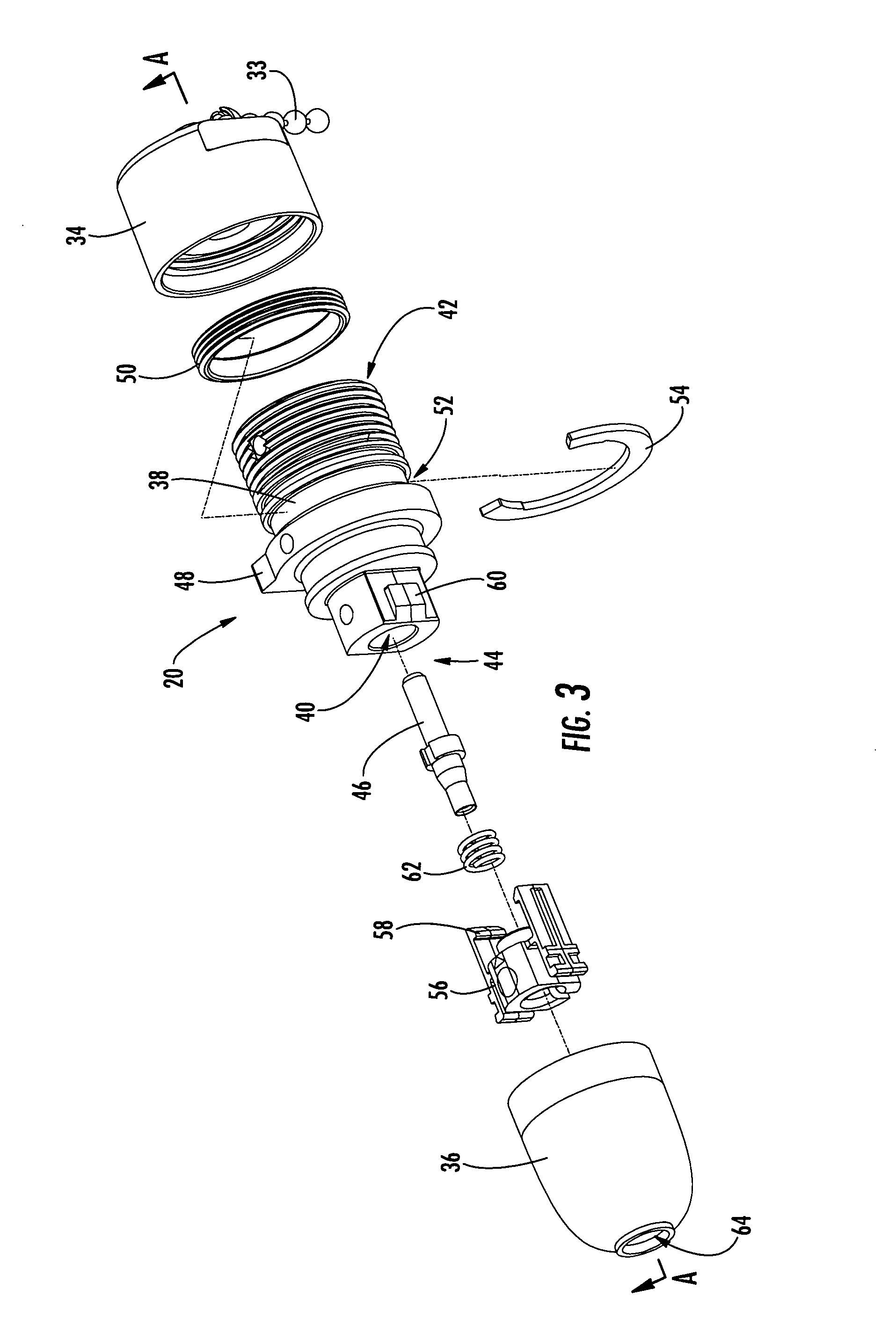

Fiber optic receptacle and plug assemblies with alignment and keying features

A fiber optic receptacle and plug assembly comprising a fiber optic receptacle adapted to be mounted within a connector port of a network connection terminal and a fiber optic plug mounted upon an end of a fiber optic cable, wherein the fiber optic receptacle and the fiber optic plug comprise complimentary alignment and keying features that allow the fiber optic receptacle to receive only a fiber optic plug of like ferrule configuration. The fiber optic plug comprises an alignment sleeve operable for receiving and optically connecting at least one plug ferrule and at least one receptacle ferrule. The receptacle is suitable for use in enclosures requiring a minimal receptacle penetration depth, wherein the fiber optic receptacle comprises a shoulder that is secured against an inner wall of the enclosure to provide strain relief against cable pulling forces of up to about 600 lbs.

Owner:CORNING OPTICAL COMM LLC

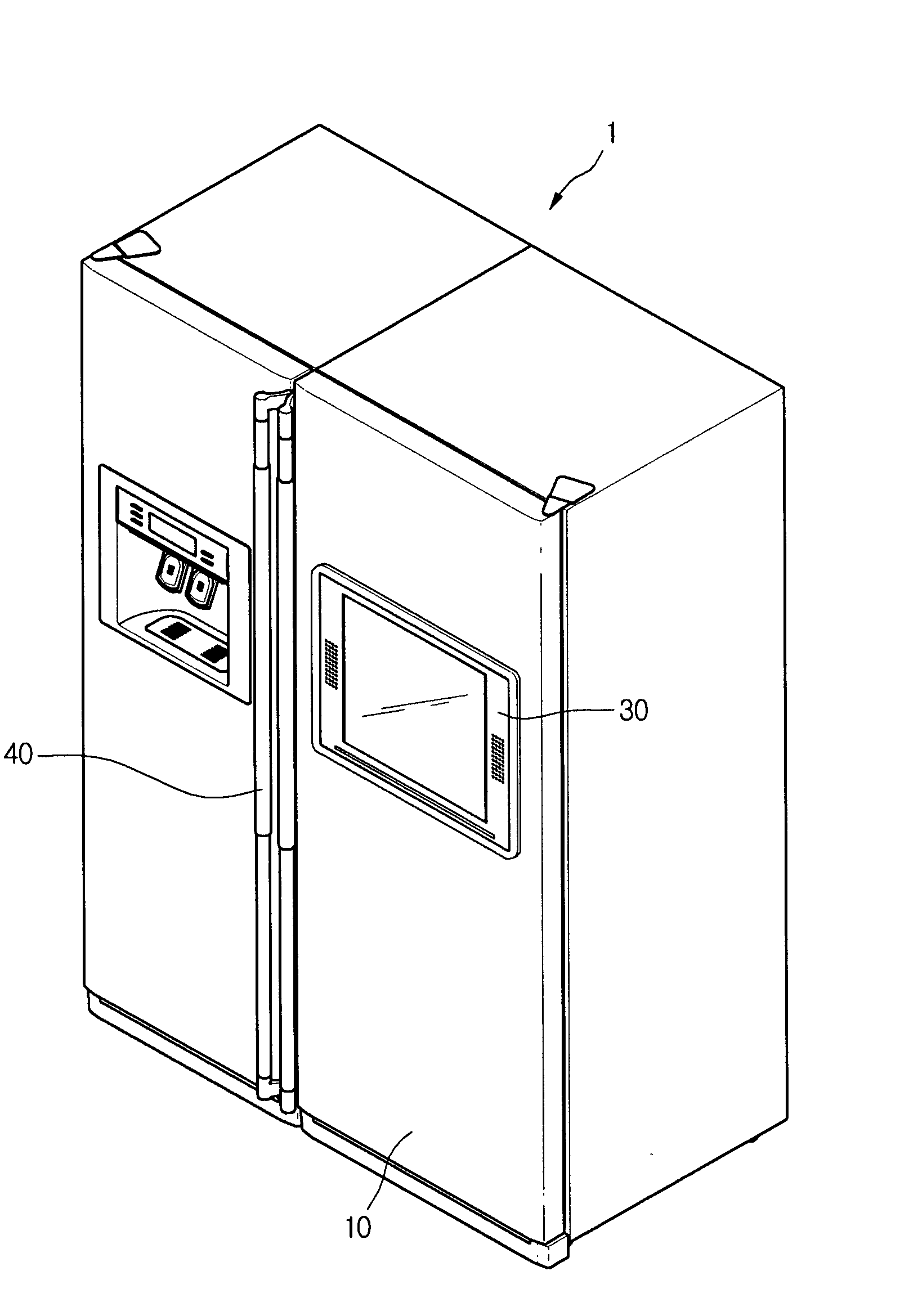

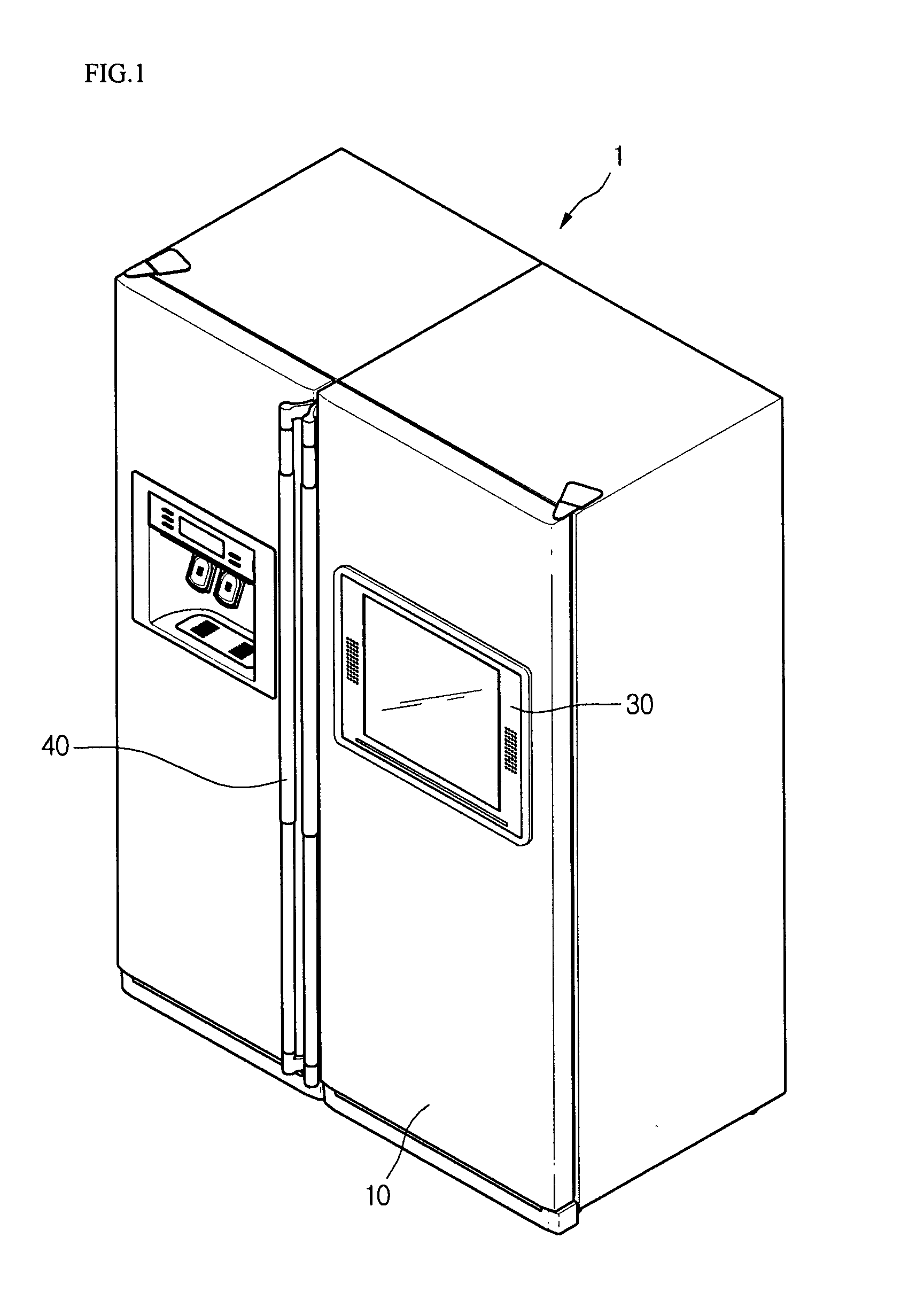

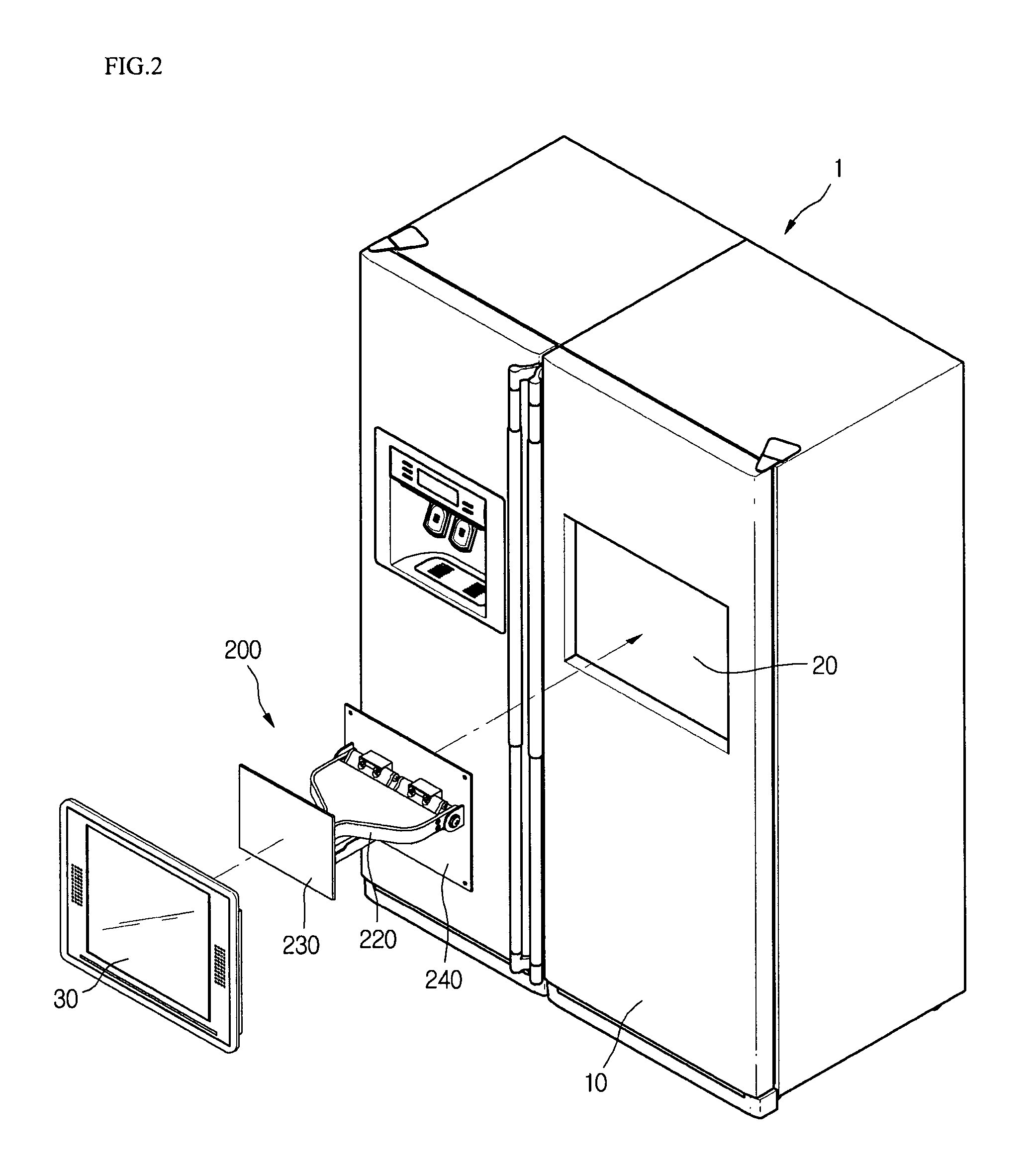

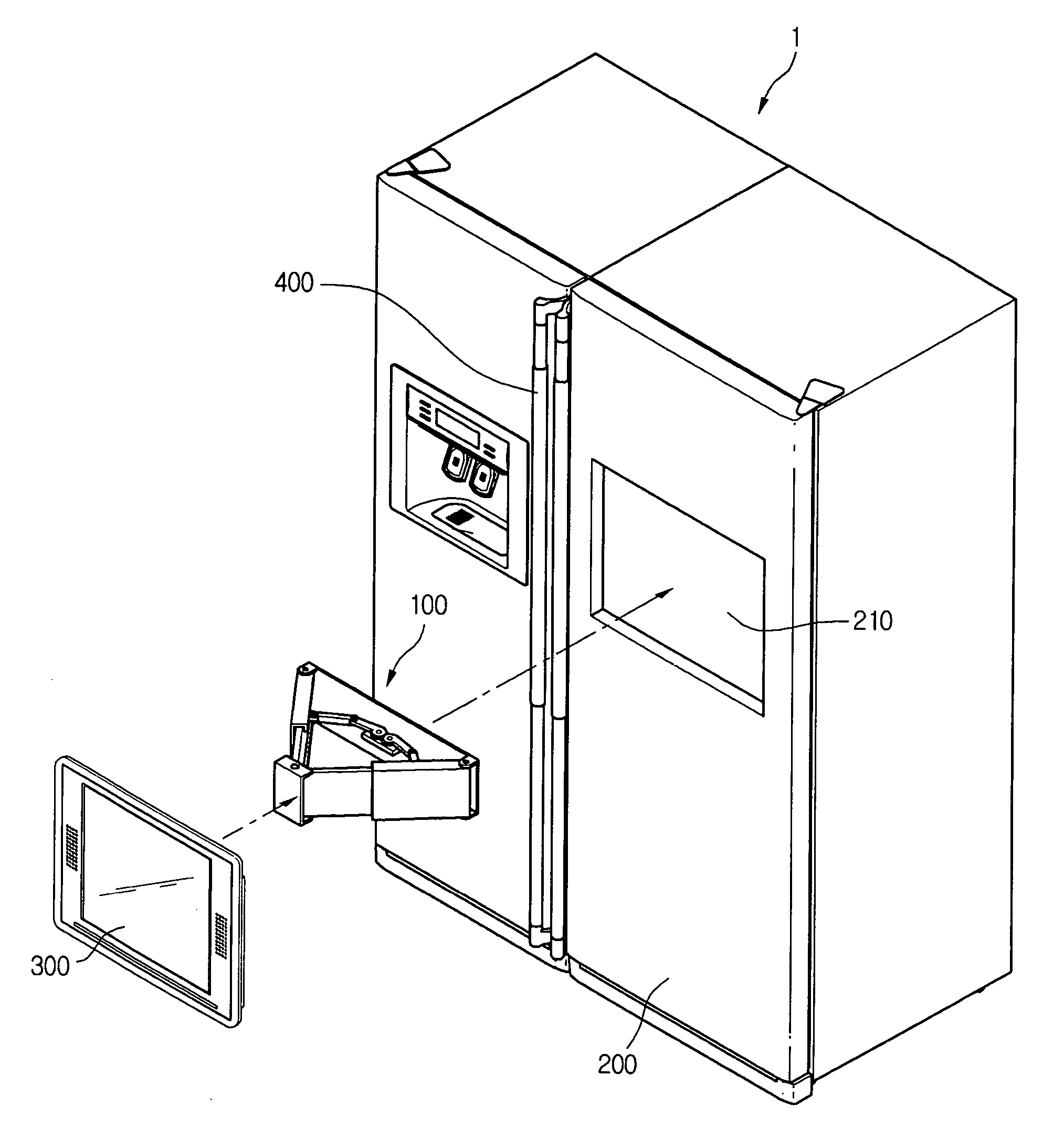

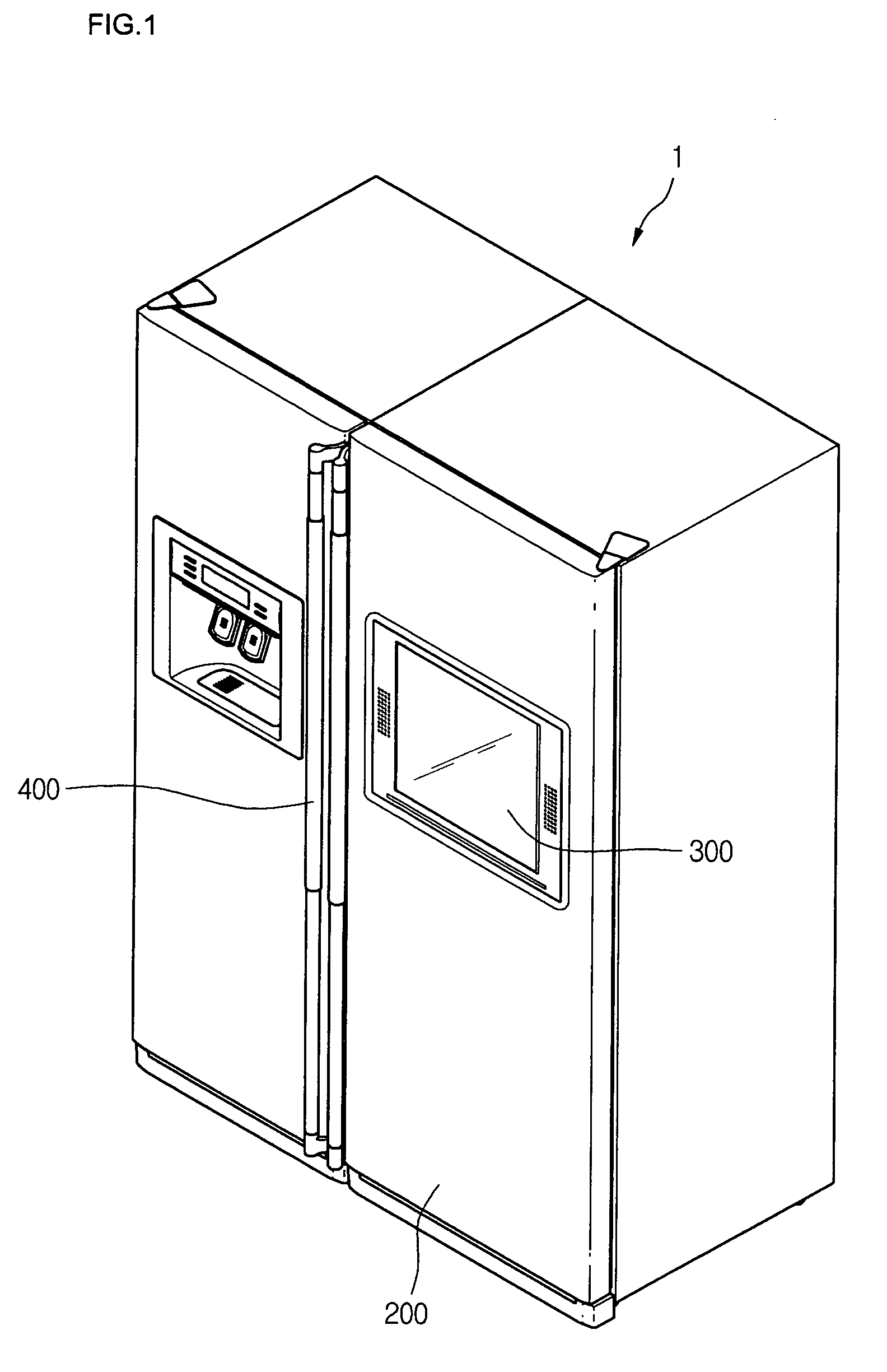

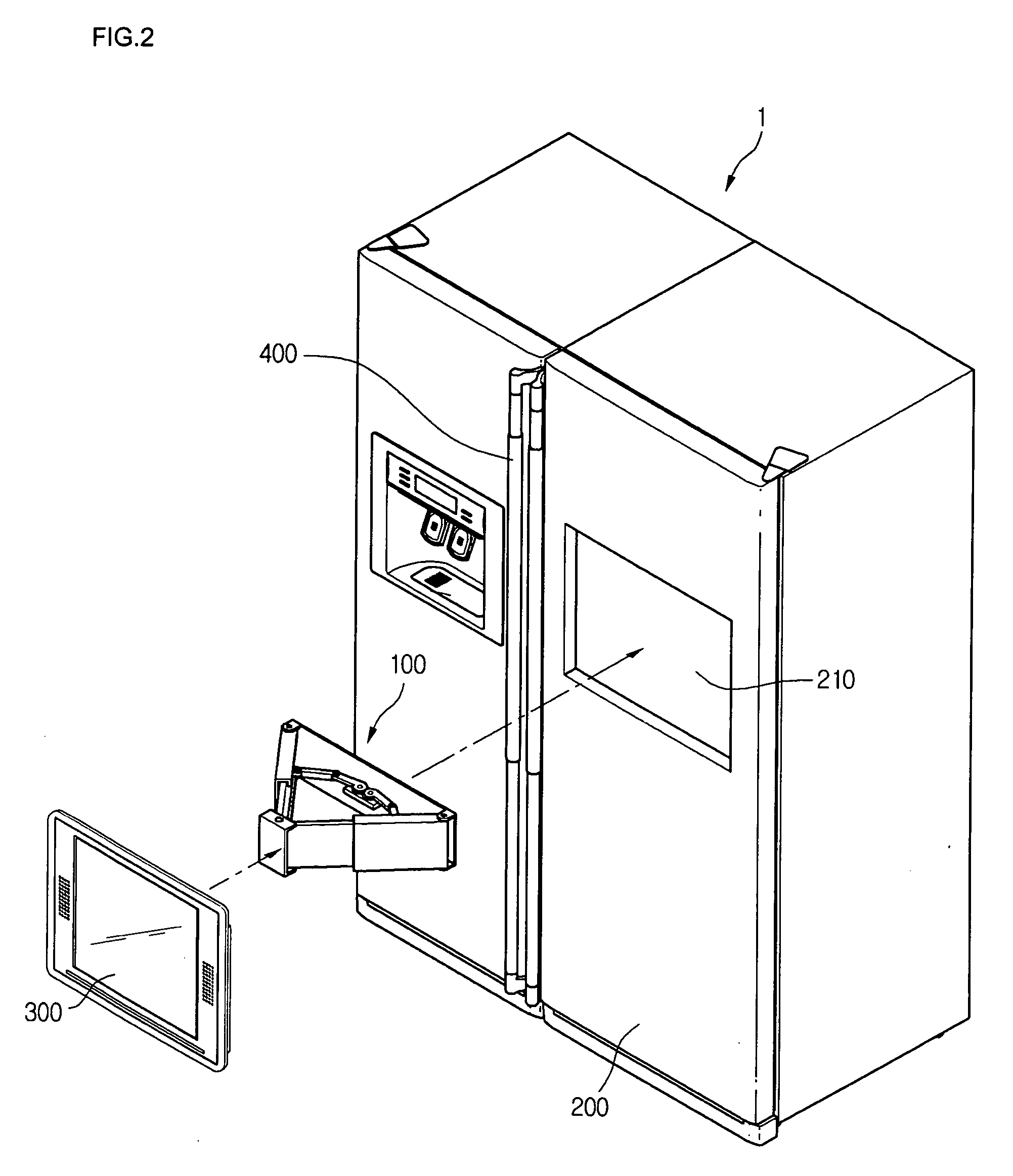

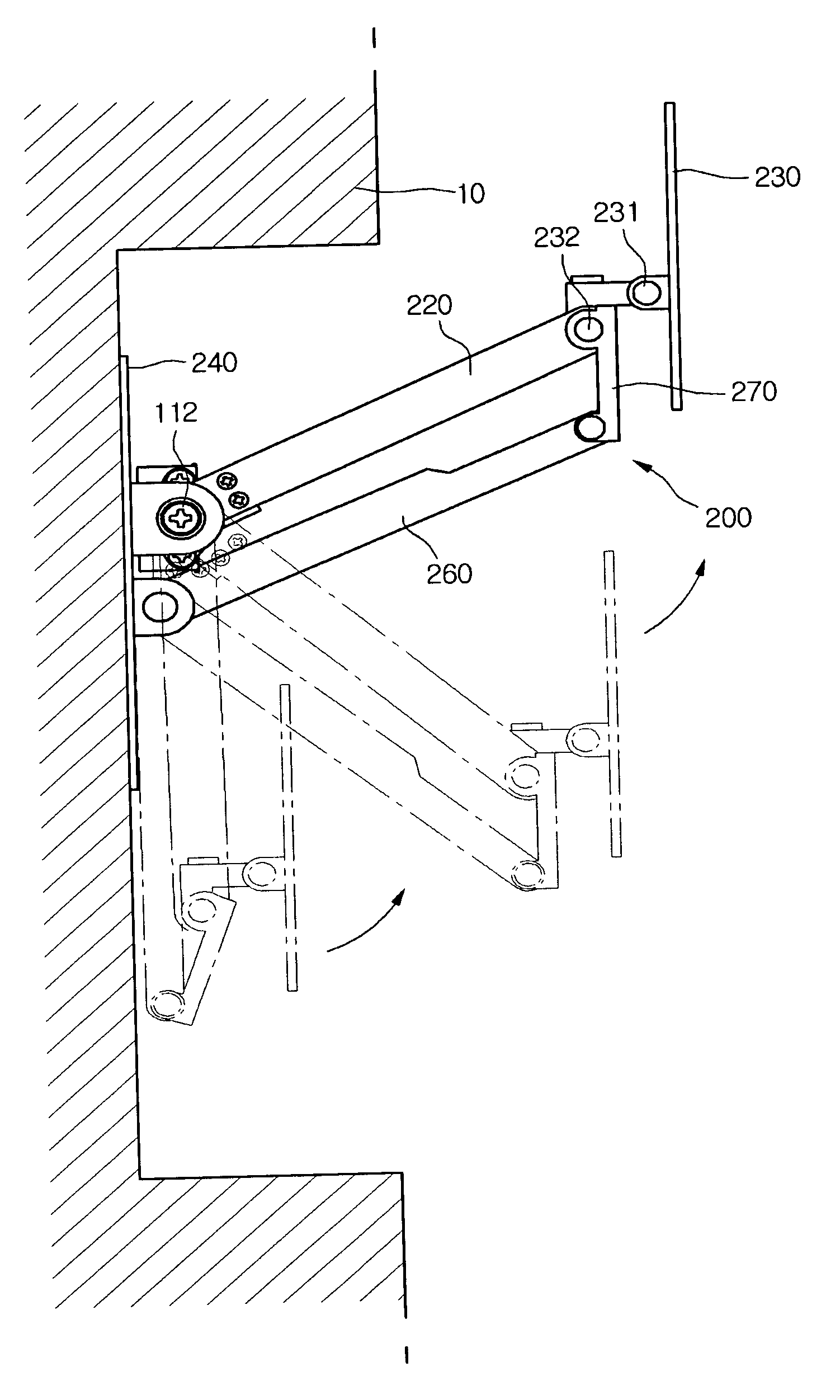

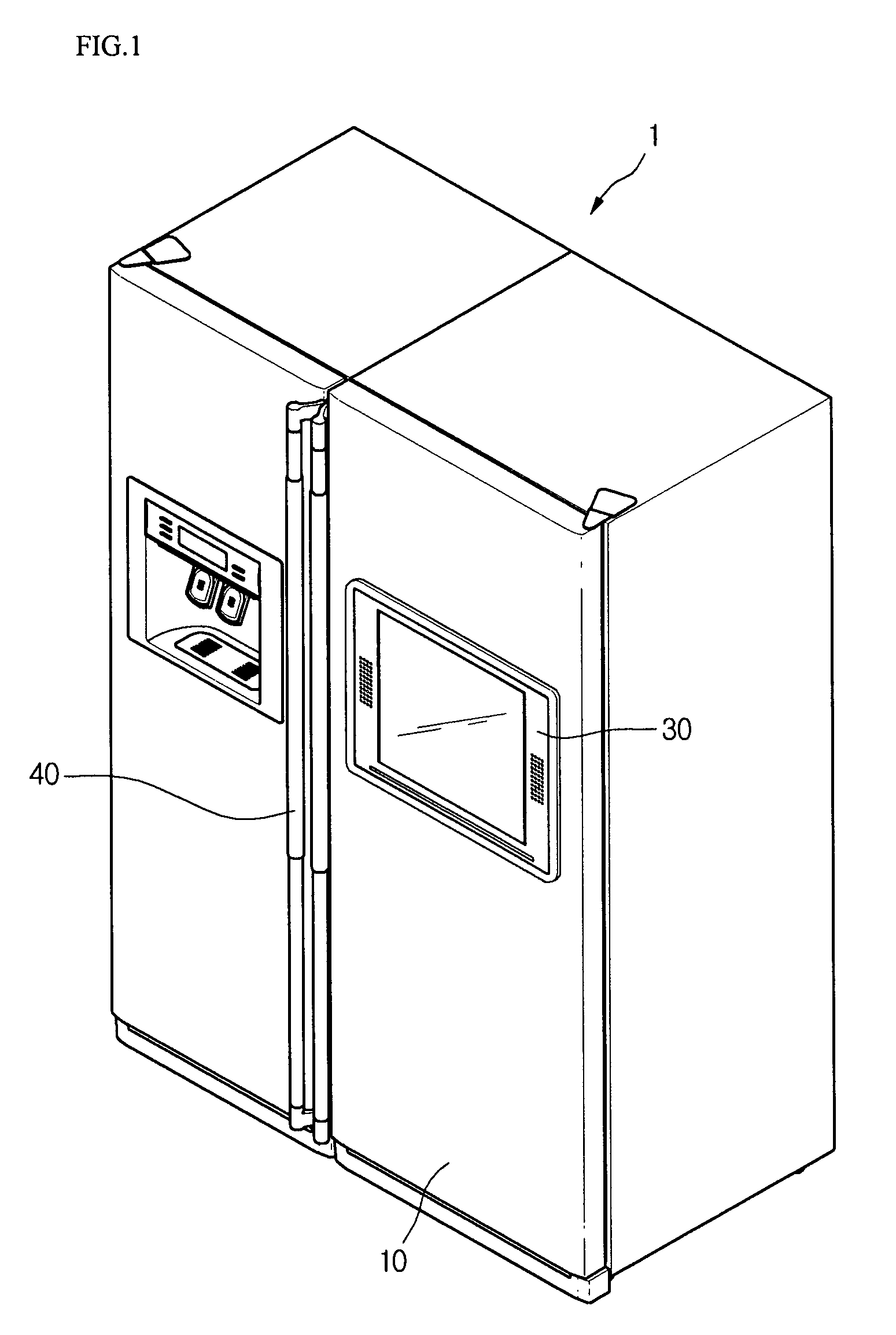

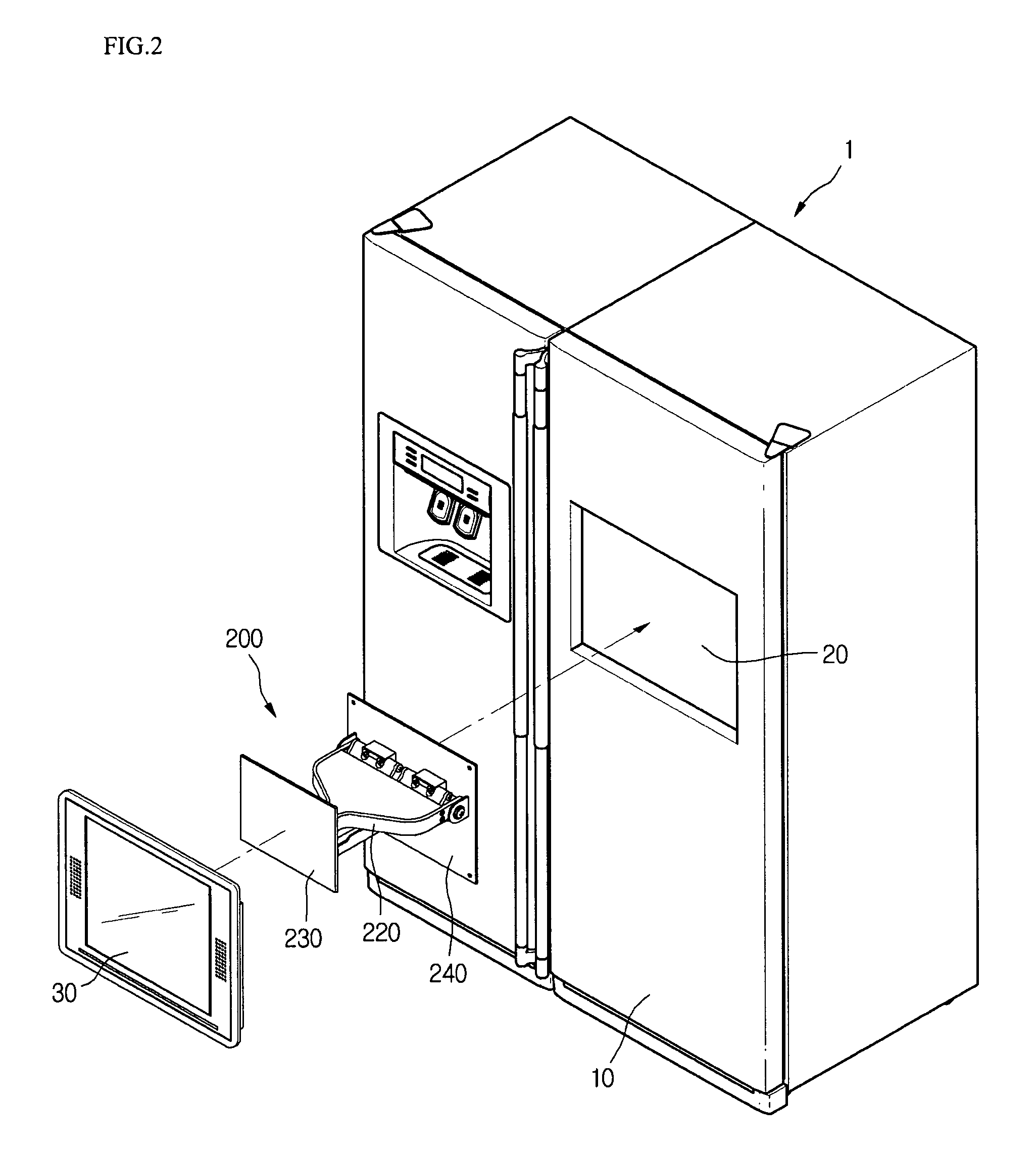

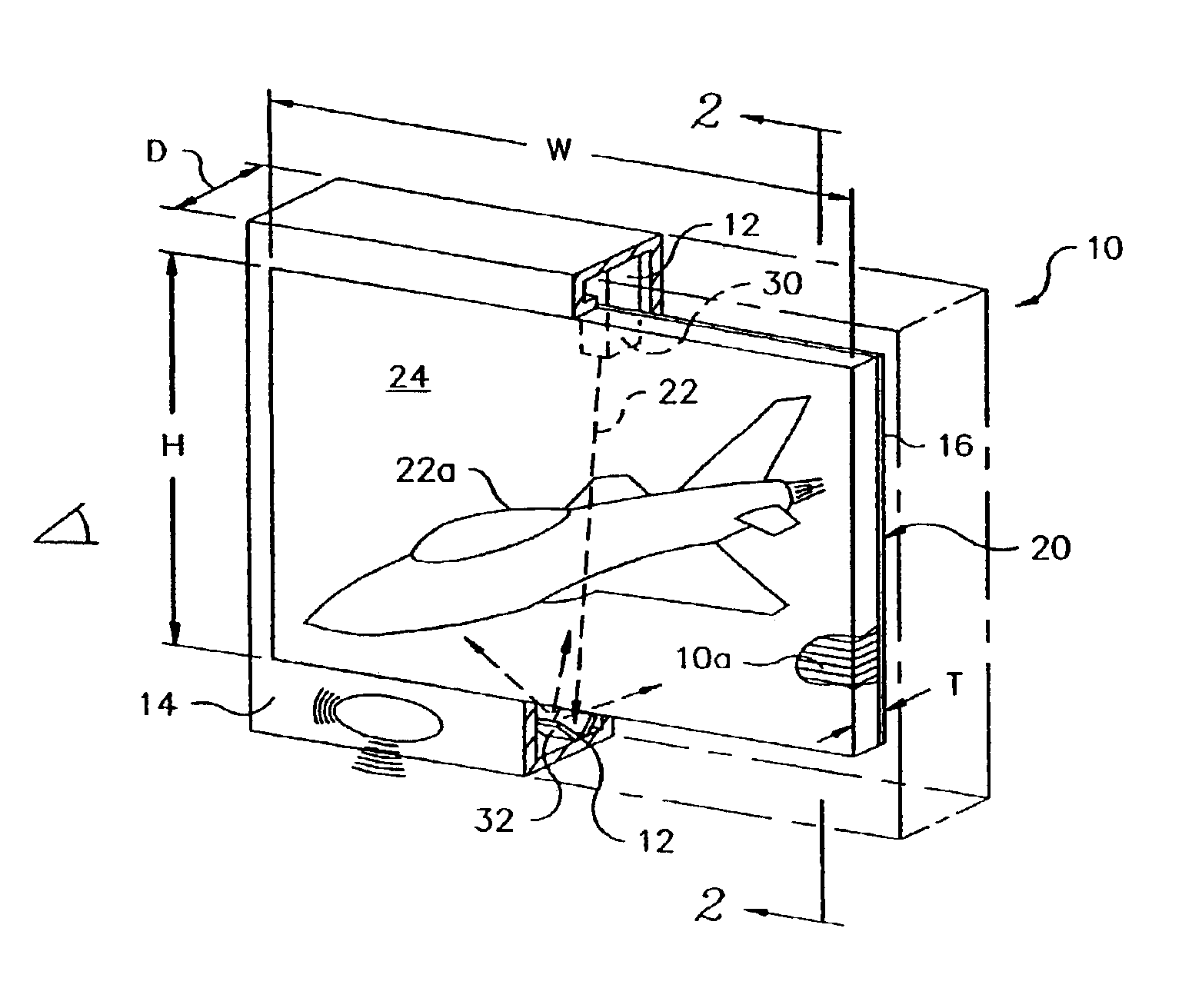

Refrigerator and display device guiding apparatus of the same

InactiveUS20060118694A1Depth is minimizedReduced insulation performancePicture framesDoors/windowsDisplay deviceEngineering

A display device guiding apparatus includes a receiving portion in which a display device can be received and a guide unit provided between the display device and the receiving portion. The guide unit includes a hinge assembly for pivoting the display at a predetermined angle, an arm assembly having first and second ends respectively connected to the hinge assembly and the receiving portion, and a pivot control unit providing a pivotal force of the arm assembly with respect to the receiving portion.

Owner:LG ELECTRONICS INC

Fiber optic receptacle and plug assembly including alignment sleeve insert

A fiber optic receptacle and plug assembly includes a fiber optic receptacle adapted to be mounted within a connector port of a network connection terminal and a fiber optic plug mounted upon an end of a fiber optic cable, wherein the fiber optic receptacle and the fiber optic plug comprise complimentary alignment and keying features that allow the fiber optic receptacle to receive only a fiber optic plug of like ferrule configuration. The fiber optic receptacle includes an alignment sleeve insert operable for receiving and optically connecting at least one receptacle ferrule and at least one opposing plug ferrule. The receptacle is suitable for use in enclosures requiring a minimal receptacle penetration depth, wherein the fiber optic receptacle comprises a shoulder that is secured against an inner wall of the enclosure to provide strain relief against cable-pulling forces of up to about 600 lbs.

Owner:CORNING OPTICAL COMM LLC

Fiber optic receptacle and plug assembly including alignment sleeve insert

A fiber optic receptacle and plug assembly includes a fiber optic receptacle adapted to be mounted within a connector port of a network connection terminal and a fiber optic plug mounted upon an end of a fiber optic cable, wherein the fiber optic receptacle and the fiber optic plug comprise complimentary alignment and keying features that allow the fiber optic receptacle to receive only a fiber optic plug of like ferrule configuration. The fiber optic receptacle includes an alignment sleeve insert operable for receiving and optically connecting at least one receptacle ferrule and at least one opposing plug ferrule. The receptacle is suitable for use in enclosures requiring a minimal receptacle penetration depth, wherein the fiber optic receptacle comprises a shoulder that is secured against an inner wall of the enclosure to provide strain relief against cable-pulling forces of up to about 600 lbs.

Owner:CORNING OPTICAL COMM LLC

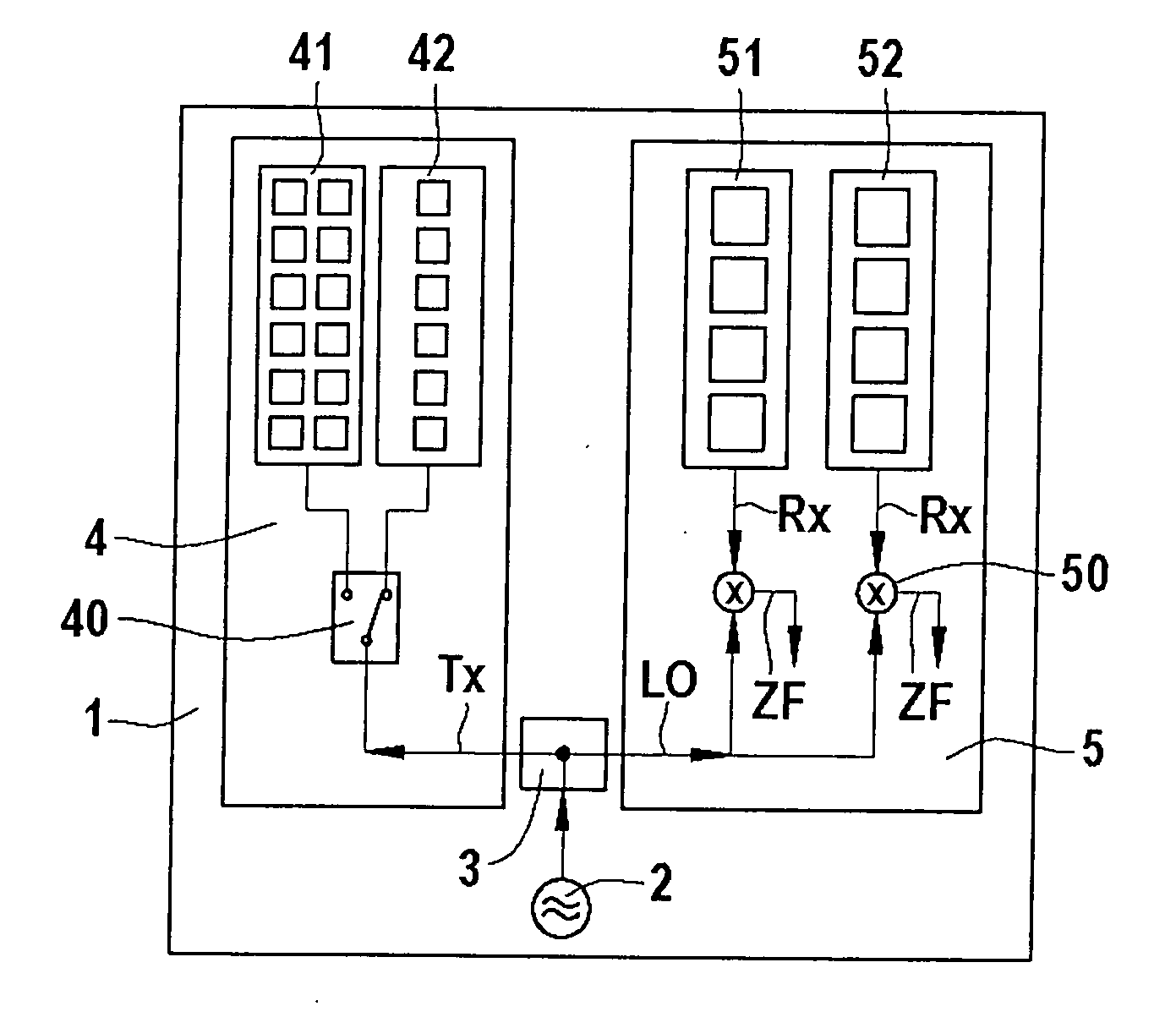

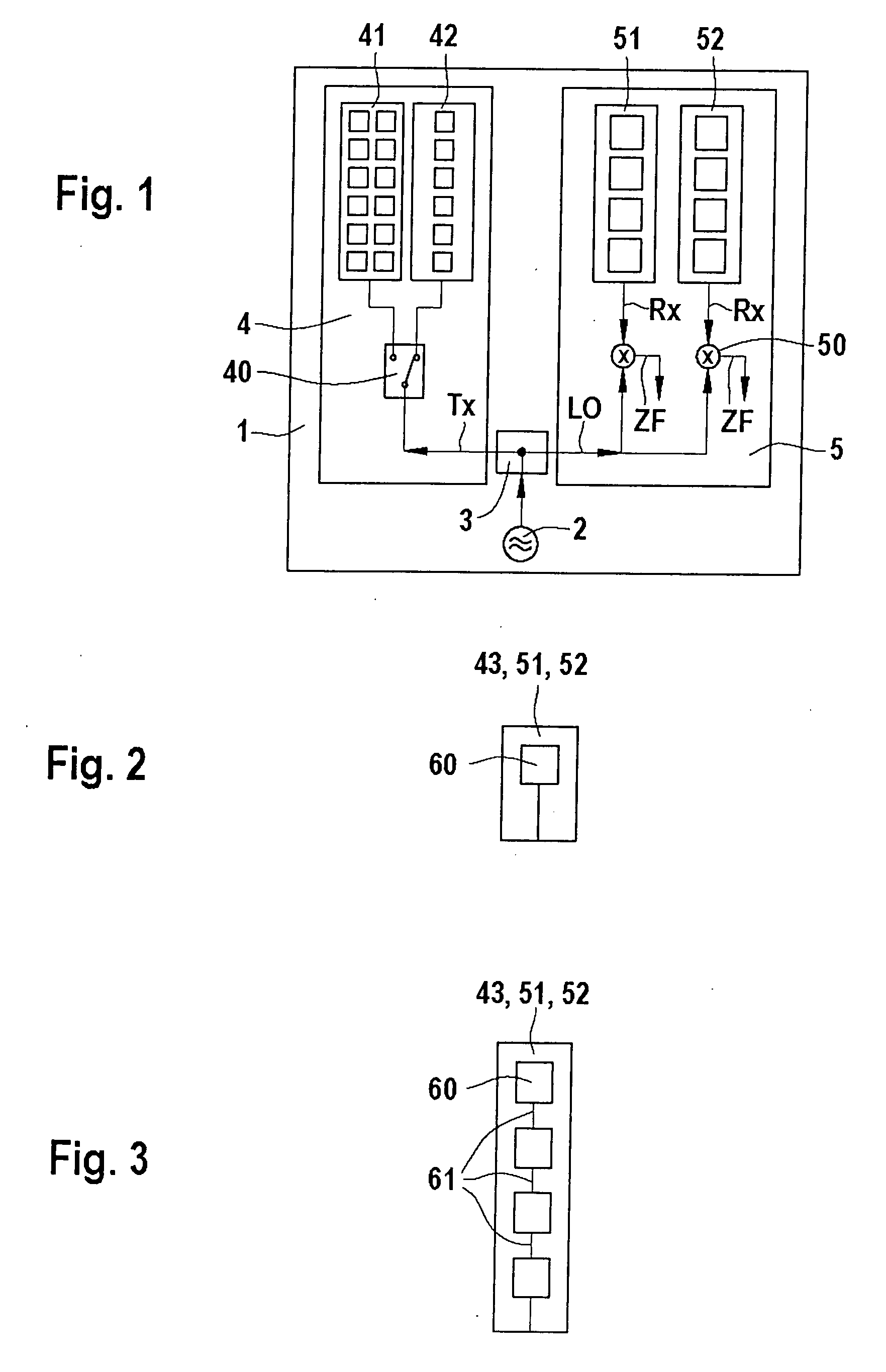

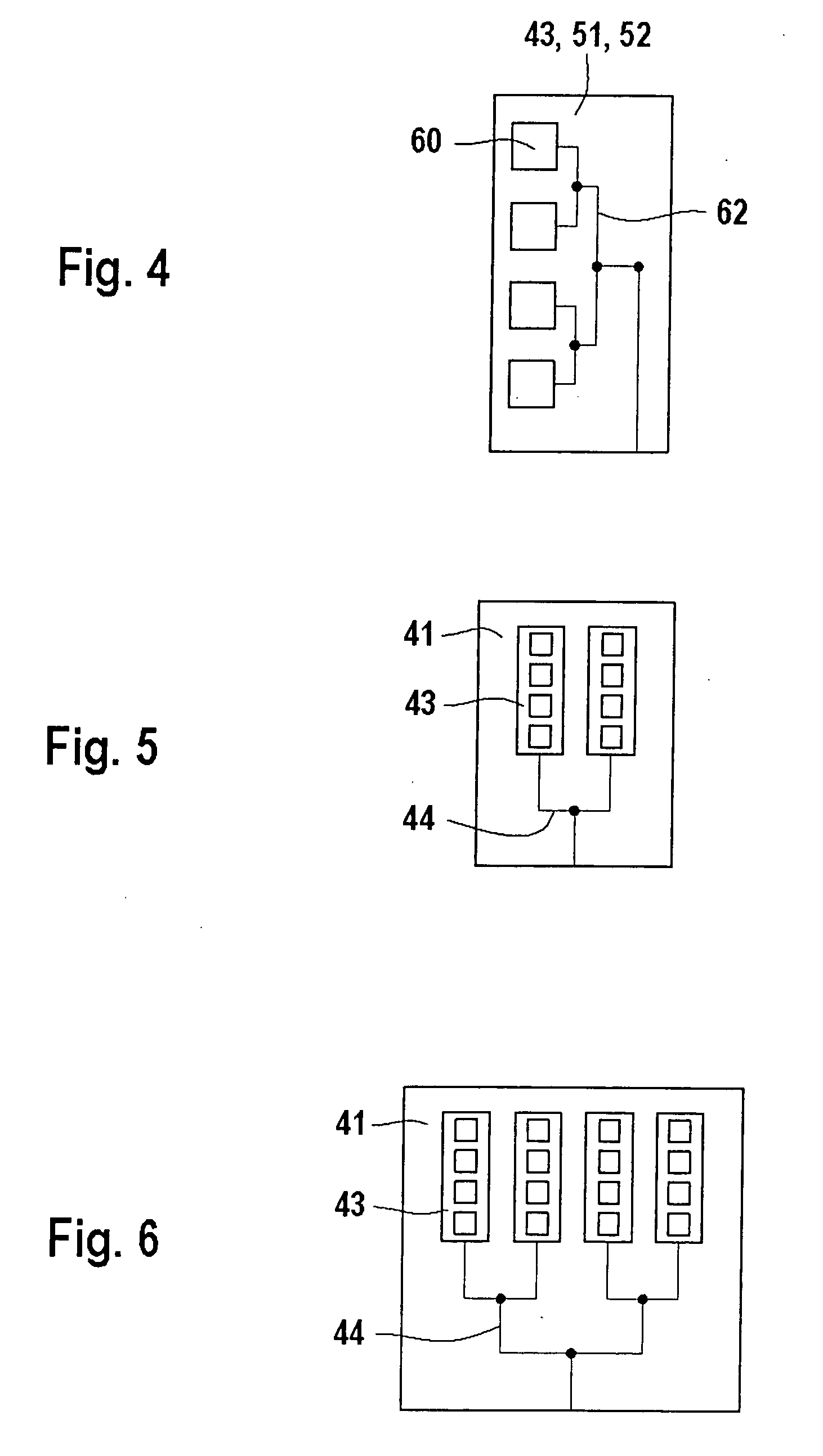

Radar System

InactiveUS20080258964A1Excellent angular separationReliable sensingAntennasRadio wave reradiation/reflectionRadar systemsDigitization

In a radar system, a switcher is provided for switching over between at least two different directional characteristics, in particular for different distance ranges, of at least two transmitting antennas. On the receiving side, a combined evaluation of the digitized signals of at least two receiving antennas is performed, in the manner of a correlation of the receiving antenna signals.

Owner:ROBERT BOSCH GMBH

Modular packet classification

InactiveUS7039641B2Avoid explosionDepth is minimizedDigital data processing detailsData switching by path configurationQuality of serviceTraffic capacity

Owner:LUCENT TECH INC

Refrigerator and guide apparatus for display of refrigerator

InactiveUS20060021360A1Easy to operateIncreased durabilityStands/trestlesRefrigeration safety arrangementDisplay deviceEngineering

Owner:LG ELECTRONICS INC

Fiber optic receptacle and plug assemblies with alignment and keying features

ActiveUS20060045430A1Readily mateSmooth connectionCoupling light guidesStrain reliefPenetration depth

A fiber optic receptacle and plug assembly comprising a fiber optic receptacle adapted to be mounted within a connector port of a network connection terminal and a fiber optic plug mounted upon an end of a fiber optic cable, wherein the fiber optic receptacle and the fiber optic plug comprise complimentary alignment and keying features that allow the fiber optic receptacle to receive only a fiber optic plug of like ferrule configuration. The fiber optic plug comprises an alignment sleeve operable for receiving and optically connecting at least one plug ferrule and at least one receptacle ferrule. The receptacle is suitable for use in enclosures requiring a minimal receptacle penetration depth, wherein the fiber optic receptacle comprises a shoulder that is secured against an inner wall of the enclosure to provide strain relief against cable pulling forces of up to about 600 lbs.

Owner:CORNING OPTICAL COMM LLC

Refrigerator and display device guiding apparatus of the same

InactiveUS7546745B2Depth is minimizedReduced insulation performancePicture framesDoors/windowsDisplay deviceEngineering

A display device guiding apparatus includes a receiving portion in which a display device can be received and a guide unit provided between the display device and the receiving portion. The guide unit includes a hinge assembly for pivoting the display at a predetermined angle, an arm assembly having first and second ends respectively connected to the hinge assembly and the receiving portion, and a pivot control unit providing a pivotal force of the arm assembly with respect to the receiving portion.

Owner:LG ELECTRONICS INC

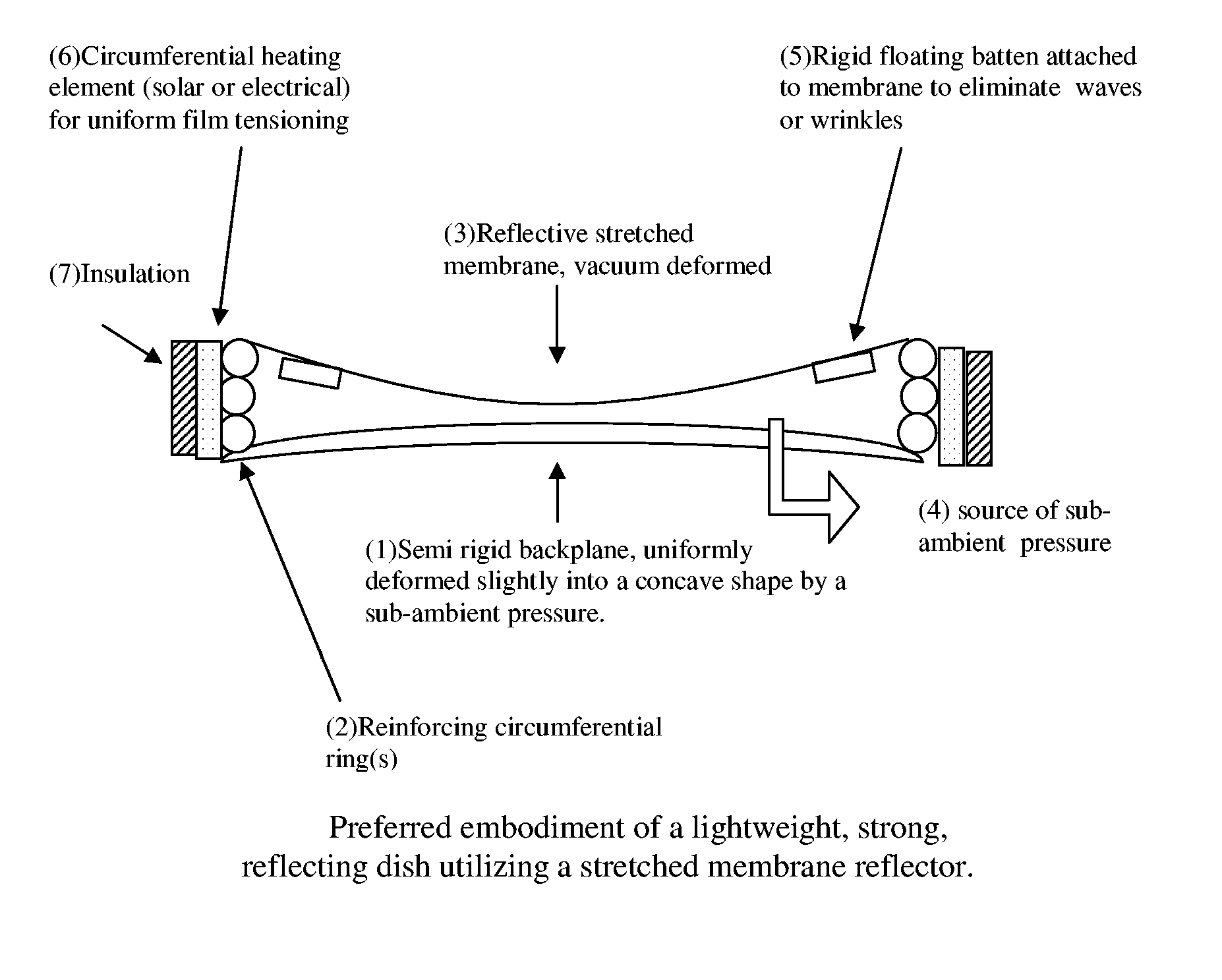

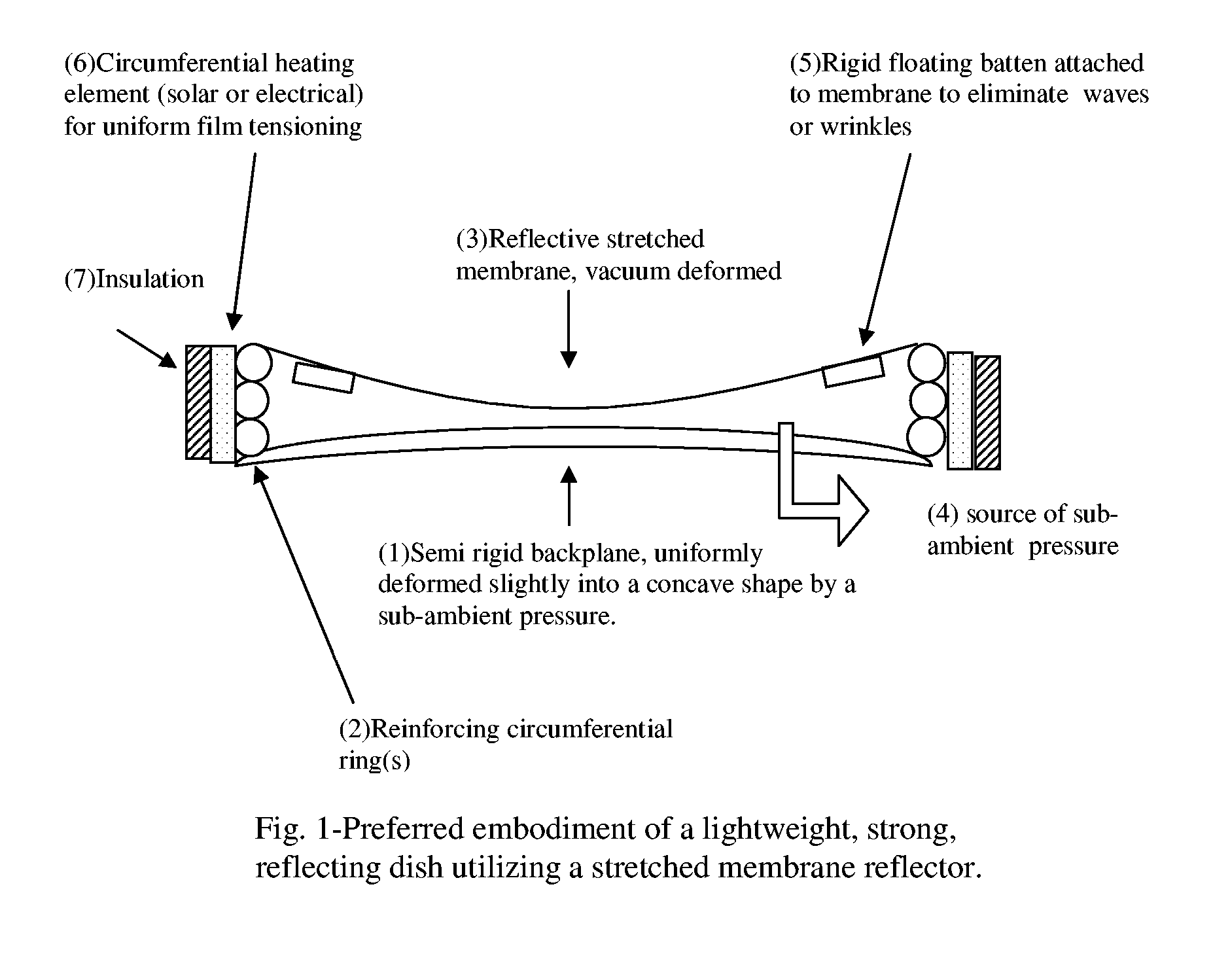

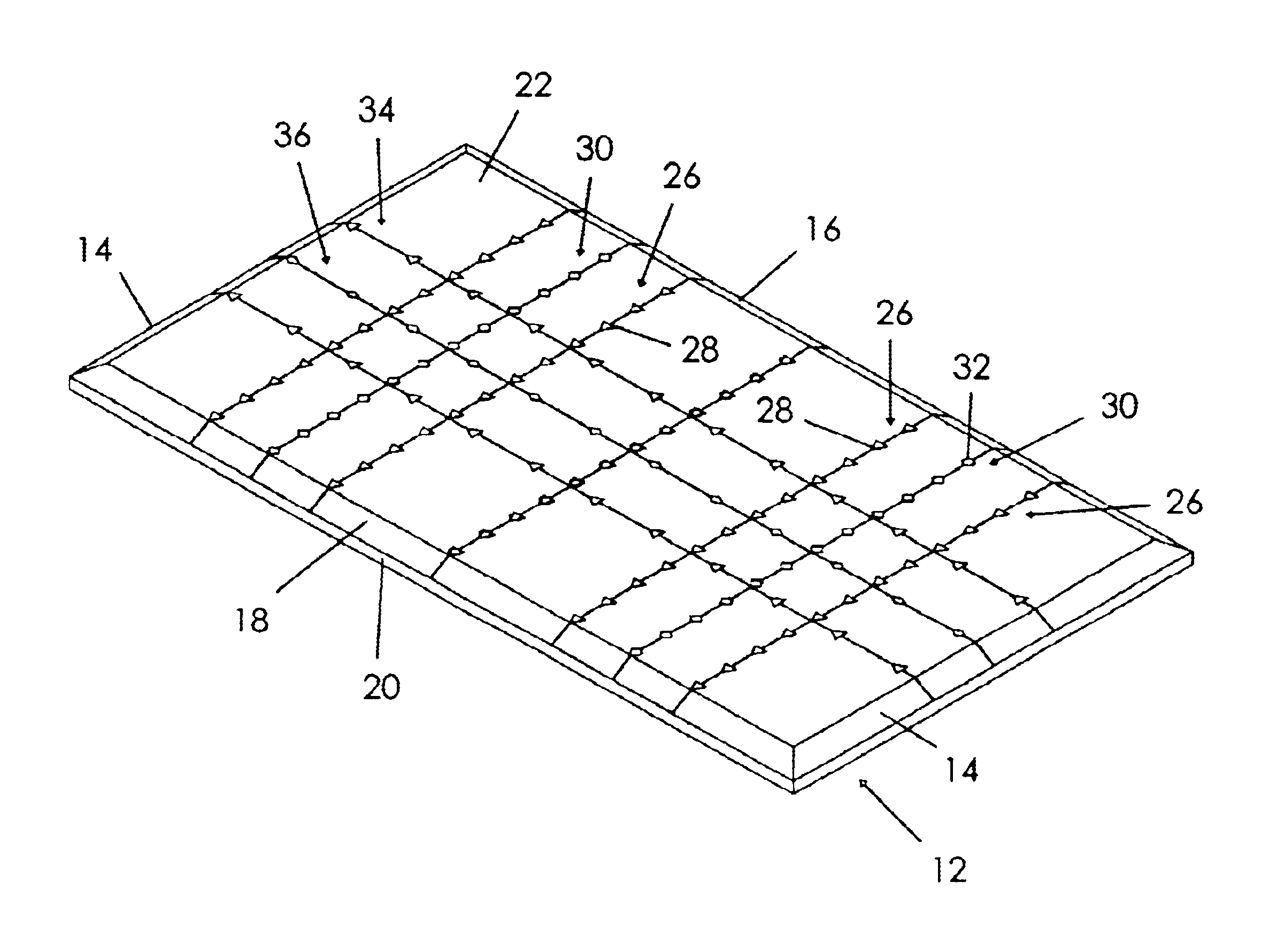

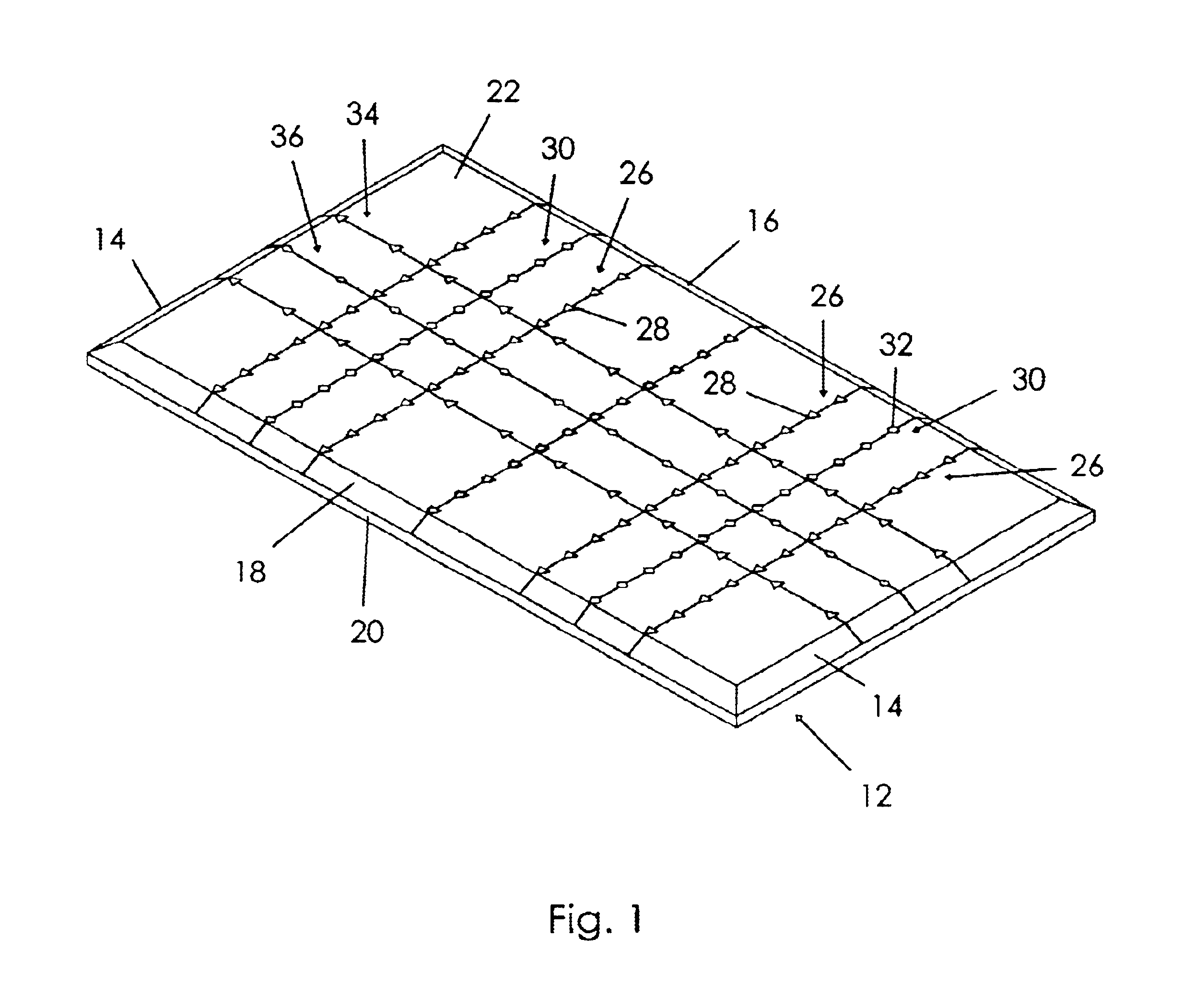

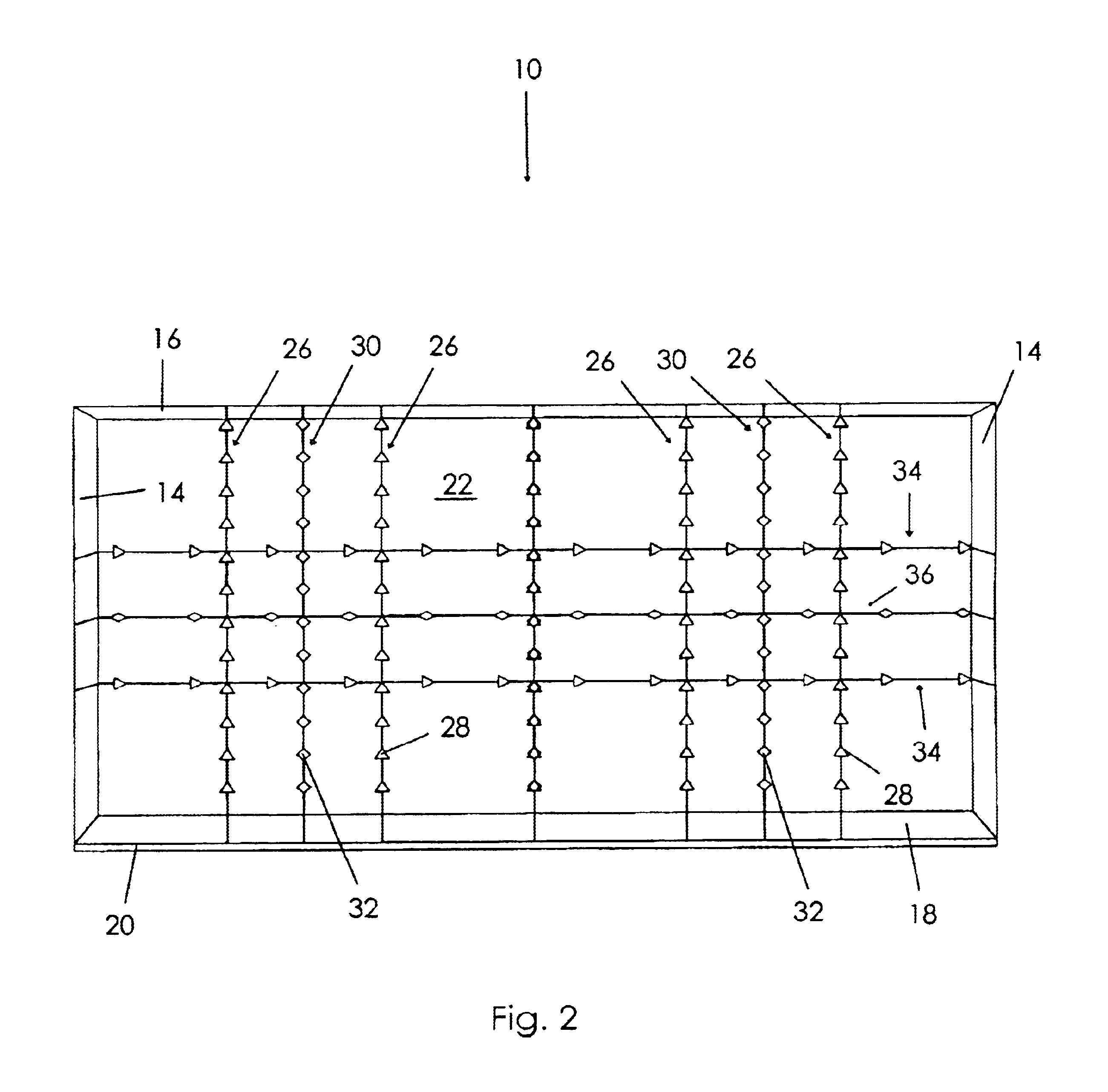

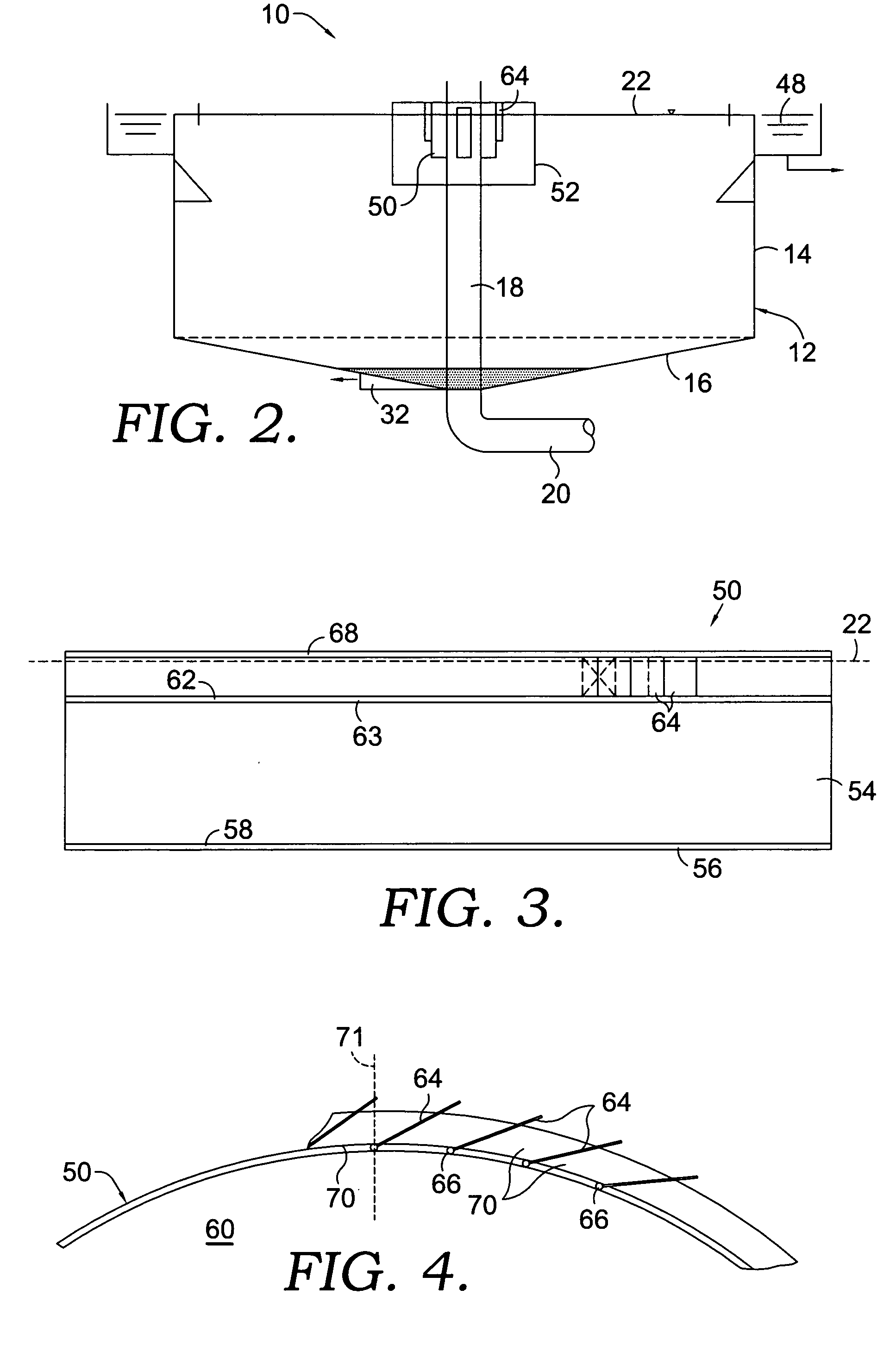

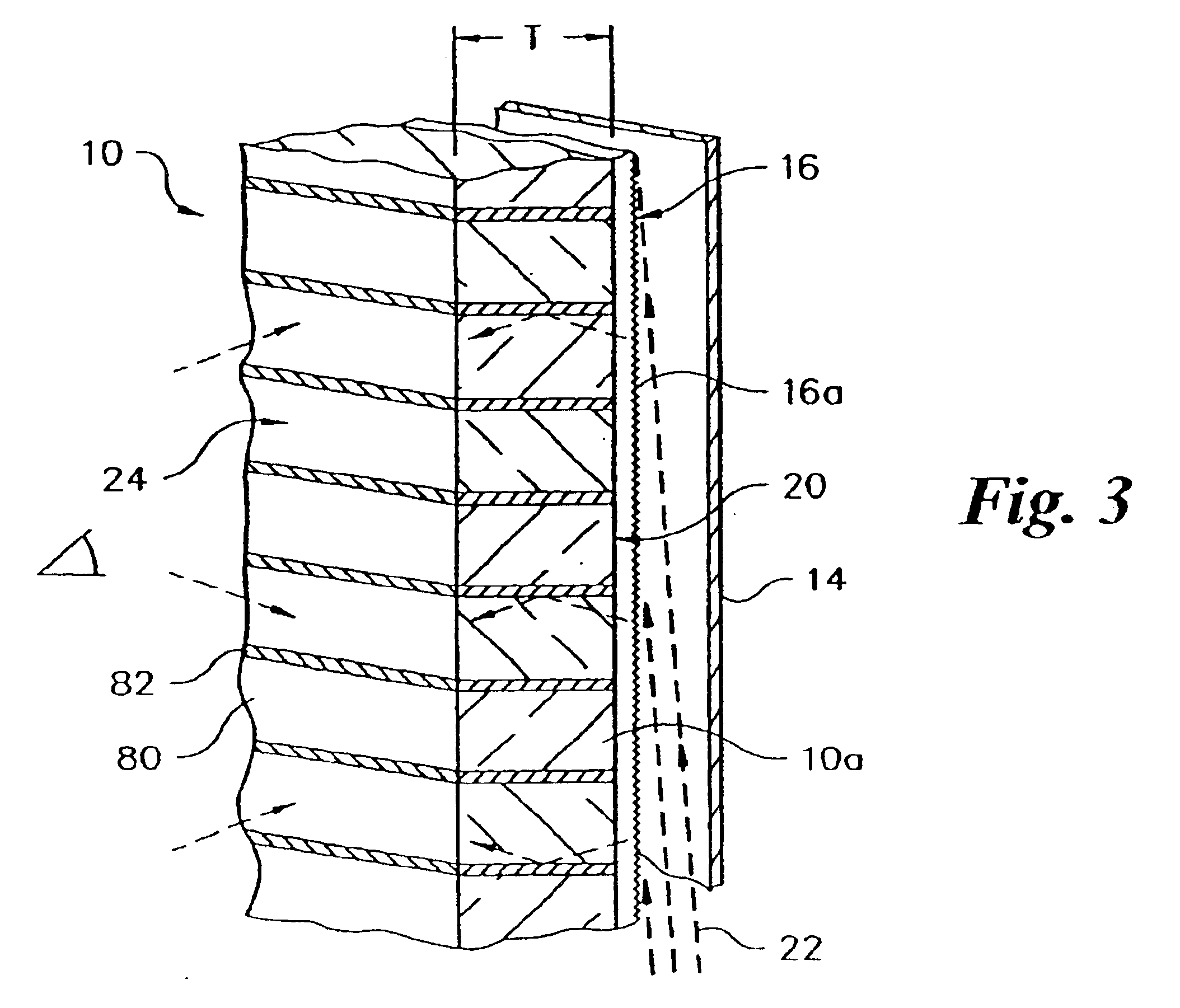

Stretched membrane device

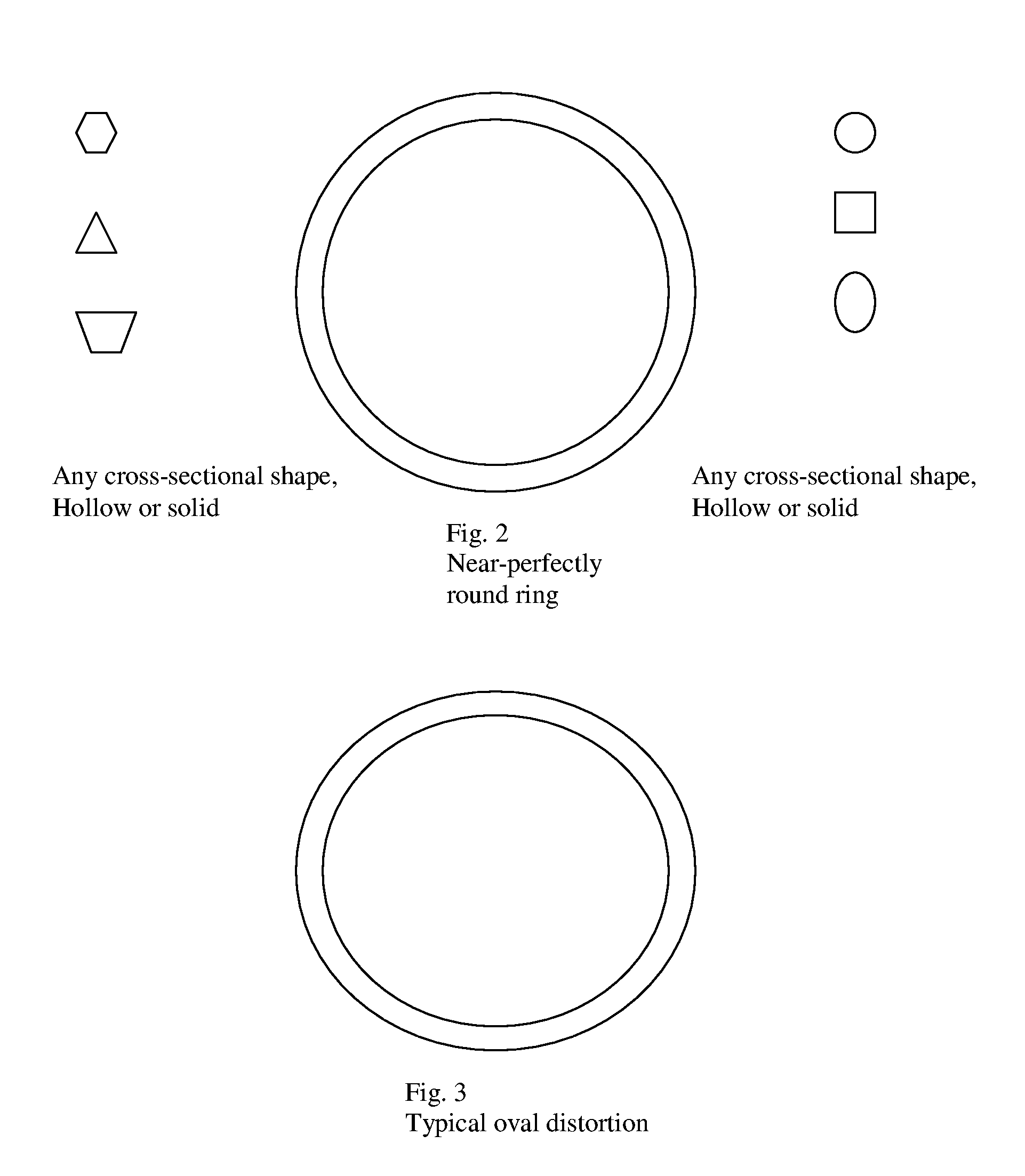

InactiveUS7374301B1Depth is minimizedStrong and more rigidMirrorsMountingsMembrane stretchWrinkle skin

An improved device for reflecting, radiating, or receiving electromagnetic radiation, acoustic waves, or other energy forms through the use of a membrane stretched across a lightweight, round, frame structure. A near perfectly round and flat semi-rigid backplane surface (1) and a near perfectly round ring or stack of rings (2) are mutually reinforced, forming a raised circumferential planar surface, and a cavity within. A membrane (3) is attached to the top of the rings, forming one wall of a sealed chamber. A source of sub-ambient pressure (4) is applied to the chamber, causing a primary uniform deformation in the membrane for the purpose of manipulating electromagnetic radiation, acoustic waves, or other energy. The backplane surface also deforms uniformly, increasing the strength of the structure. A flat, rigid floating batten (5) prevents waves or wrinkles from forming in the membrane material. A circumferential heating element (6) and insulation (7) provides tensioning of the membrane by slightly controlling the circumference of the device.

Owner:SIMMERS DOUGLAS EVAN

Vehicle bed and cross rail attachment

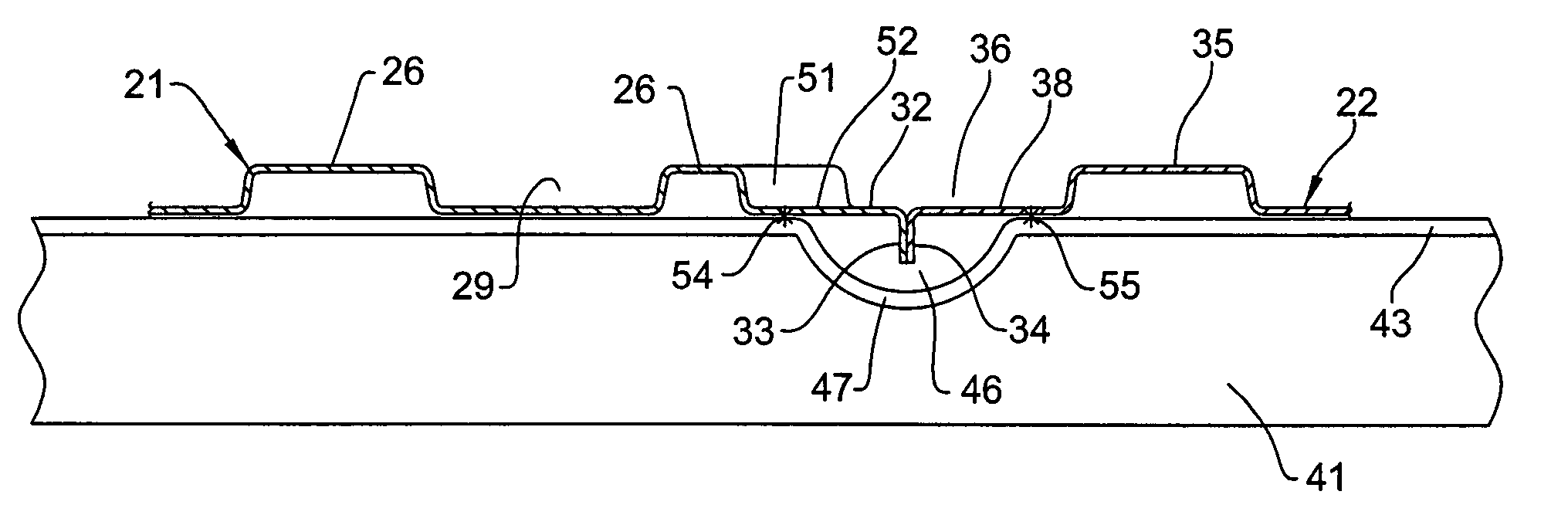

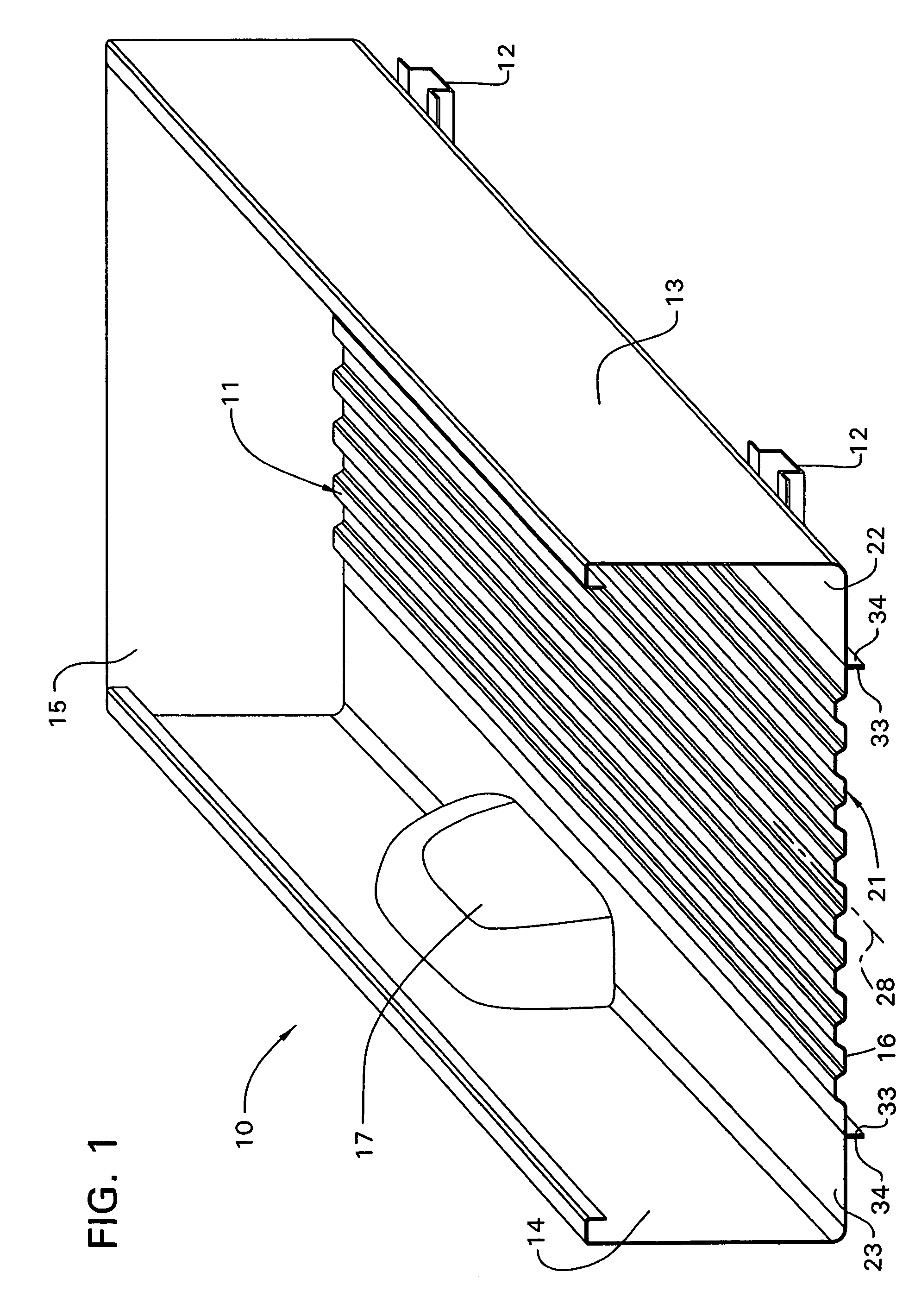

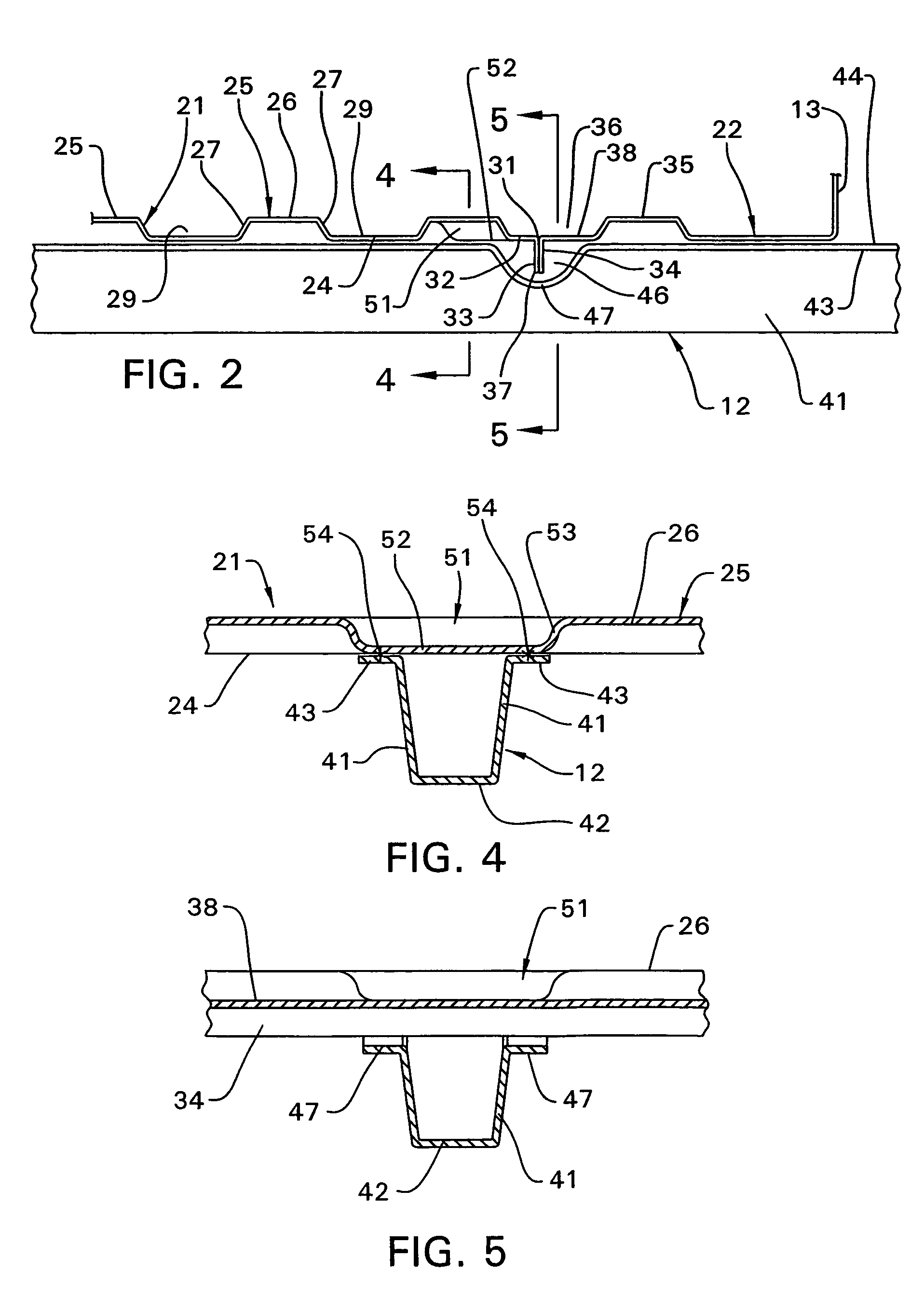

InactiveUS7152911B1Depth is minimizedMinimizes of depressionVehicle seatsSuperstructure subunitsThin metalCantilever

A bed arrangement for a vehicle including a horizontally large floor member defined by a thin metal sheet having a plurality of raised stiffening ribs extending lengthwise thereof. The floor member has a cantilevered edge flange extending along a lengthwise side edge thereof, which edge flange protrudes downwardly below a bottom surface of the floor member. A hat-shaped cross rail is disposed transversely under said floor member, and has a pair of top flanges which supportingly engages the bottom surface of the floor member. The cross rail, where it crosses the edge flange, has a depression formed therein to provide clearance for the edge flange. The top flanges having flange sections which are deformed downwardly to define the profile of the depression while maintaining the continuity of the top flanges as they extend lengthwise of the cross rail.

Owner:NOBLE ADVANCED TECH

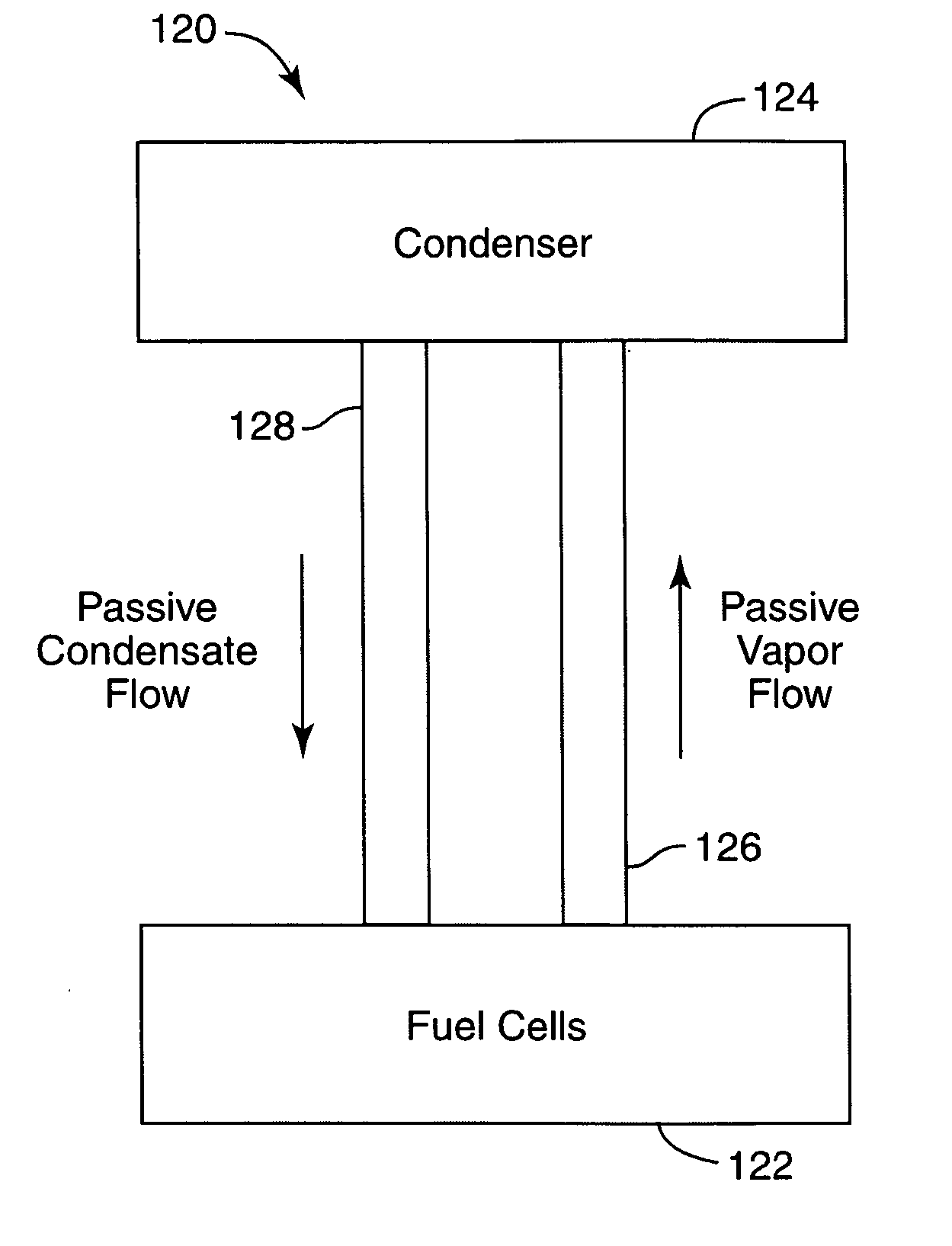

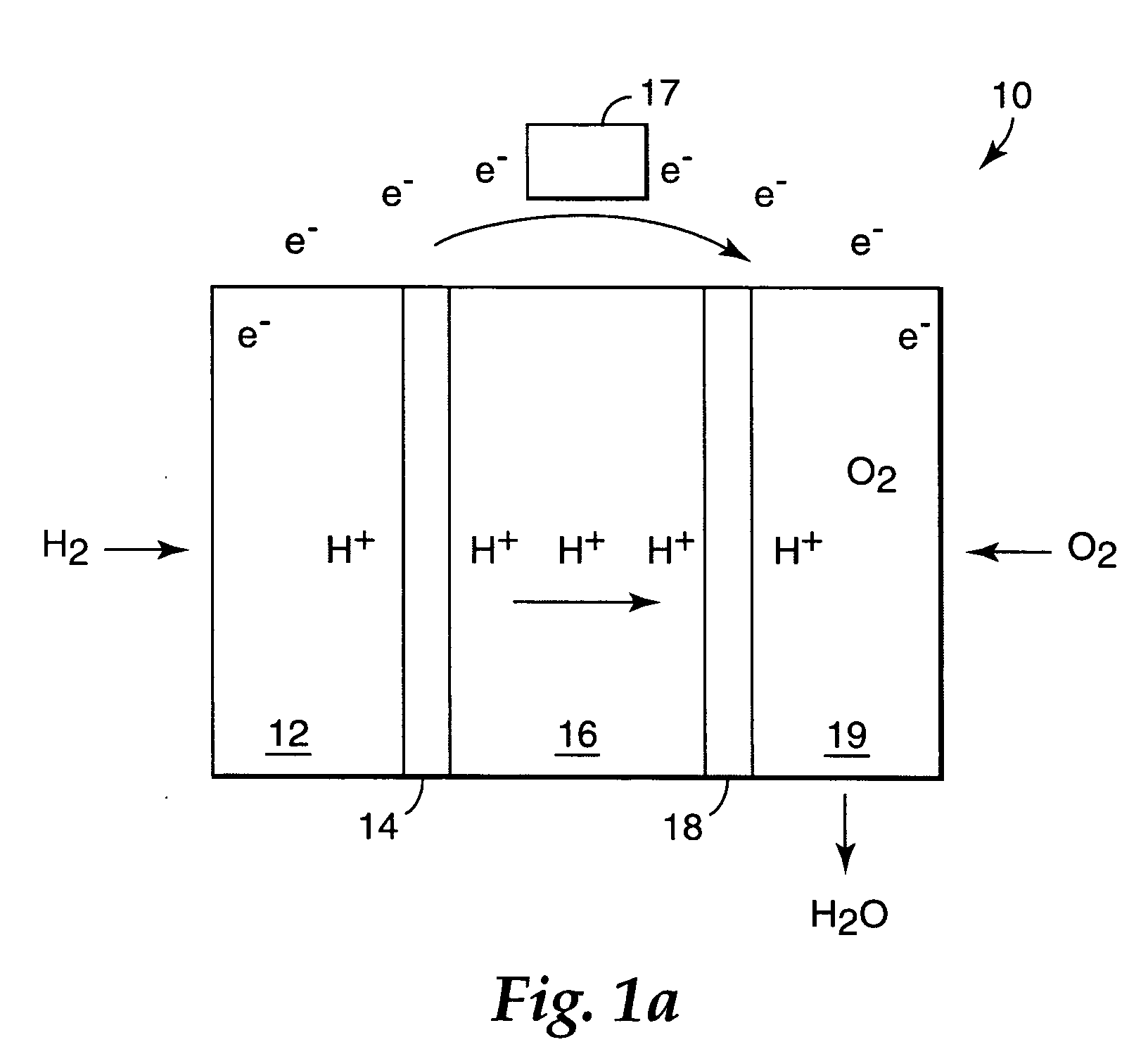

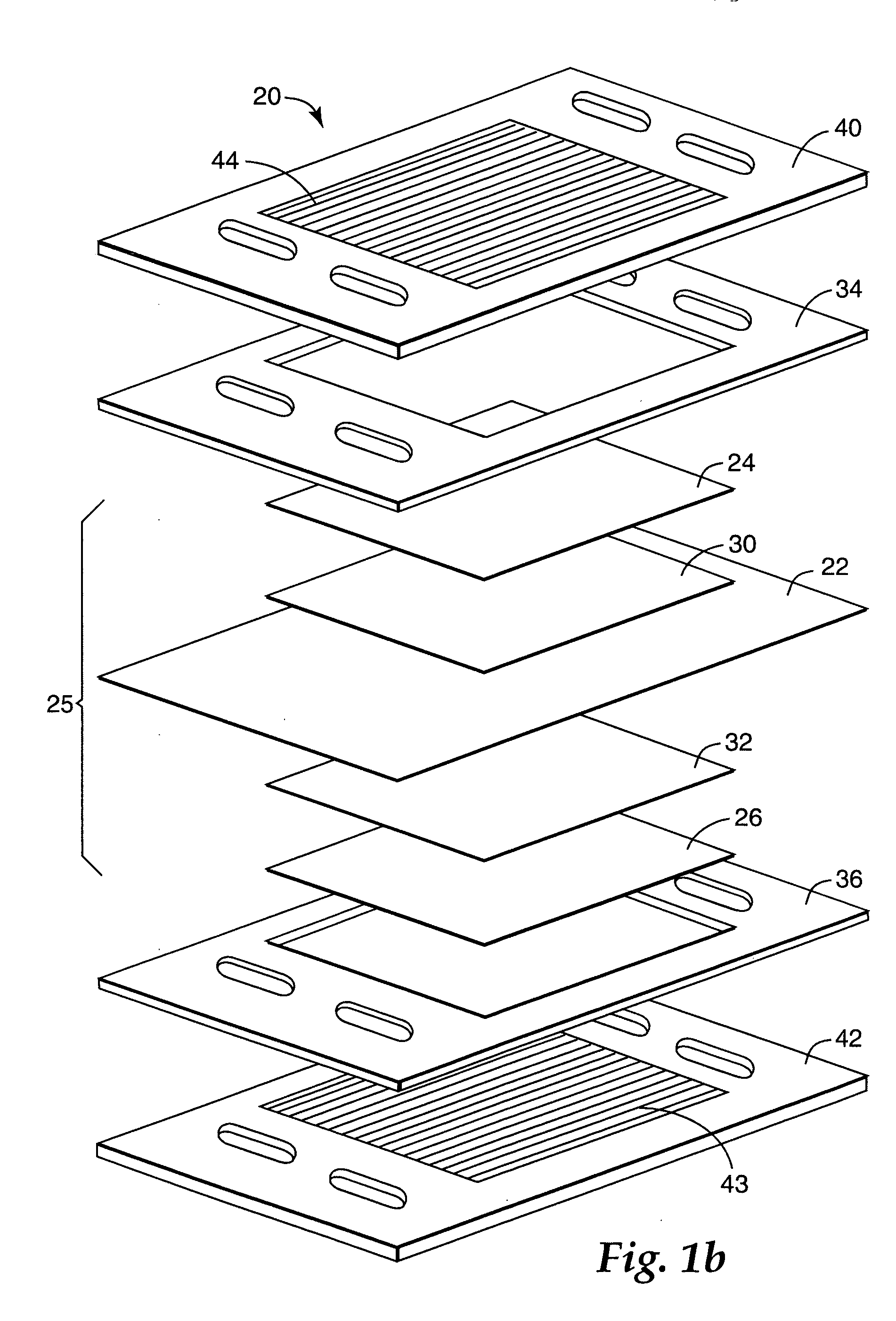

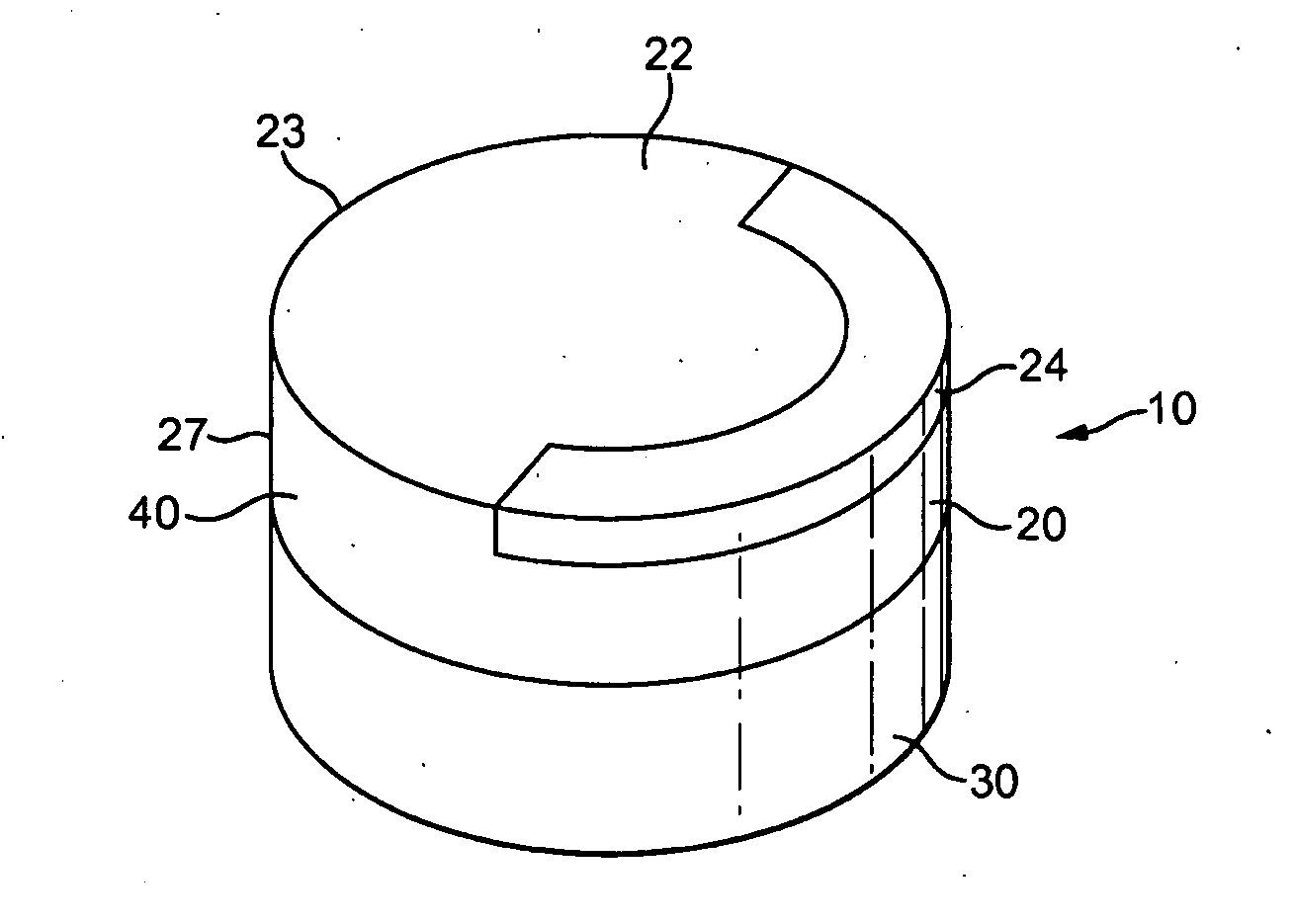

Passive dual-phase cooling for fuel cell assemblies

InactiveUS20060088746A1Improved temperature uniformityReduce cool plate thicknessMaterial nanotechnologyFuel cells groupingChannel widthHeat transfer fluid

A cooling apparatus for a fuel cell assembly includes a heat transfer fluid and at least one fluid flow field plate configured to facilitate essentially passive, two-phase cooling for an membrane electrode assembly (MEA) as the MEA is subject to changes in heat flux to the heat transfer fluid from about 0 W / cm2 to about 1.5 W / cm2. The flow field plate includes fluid flow channels that have a channel depth, a channel spacing, a channel length, and a channel width, which are dimensioned to promote nucleated boiling of the heat transfer fluid below a critical heat flux and to prevent dryout as the heat transfer fluid passes along the length of the channels. The channels may include coatings and / or features, such as microporous or nanostructured coatings, that extend the critical heat flux and preclude dryout at the distal sections of the fluid flow channels.

Owner:3M INNOVATIVE PROPERTIES CO

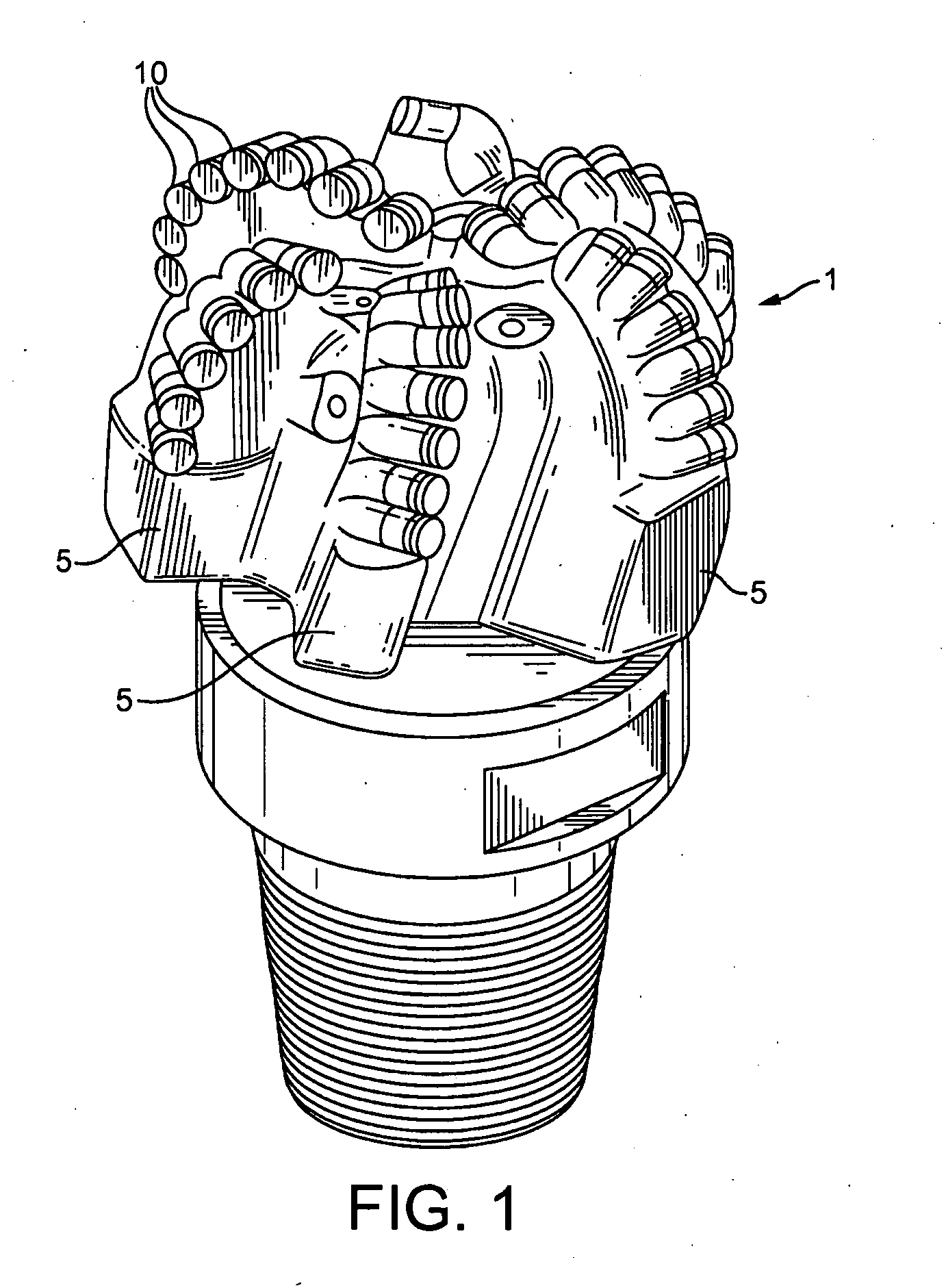

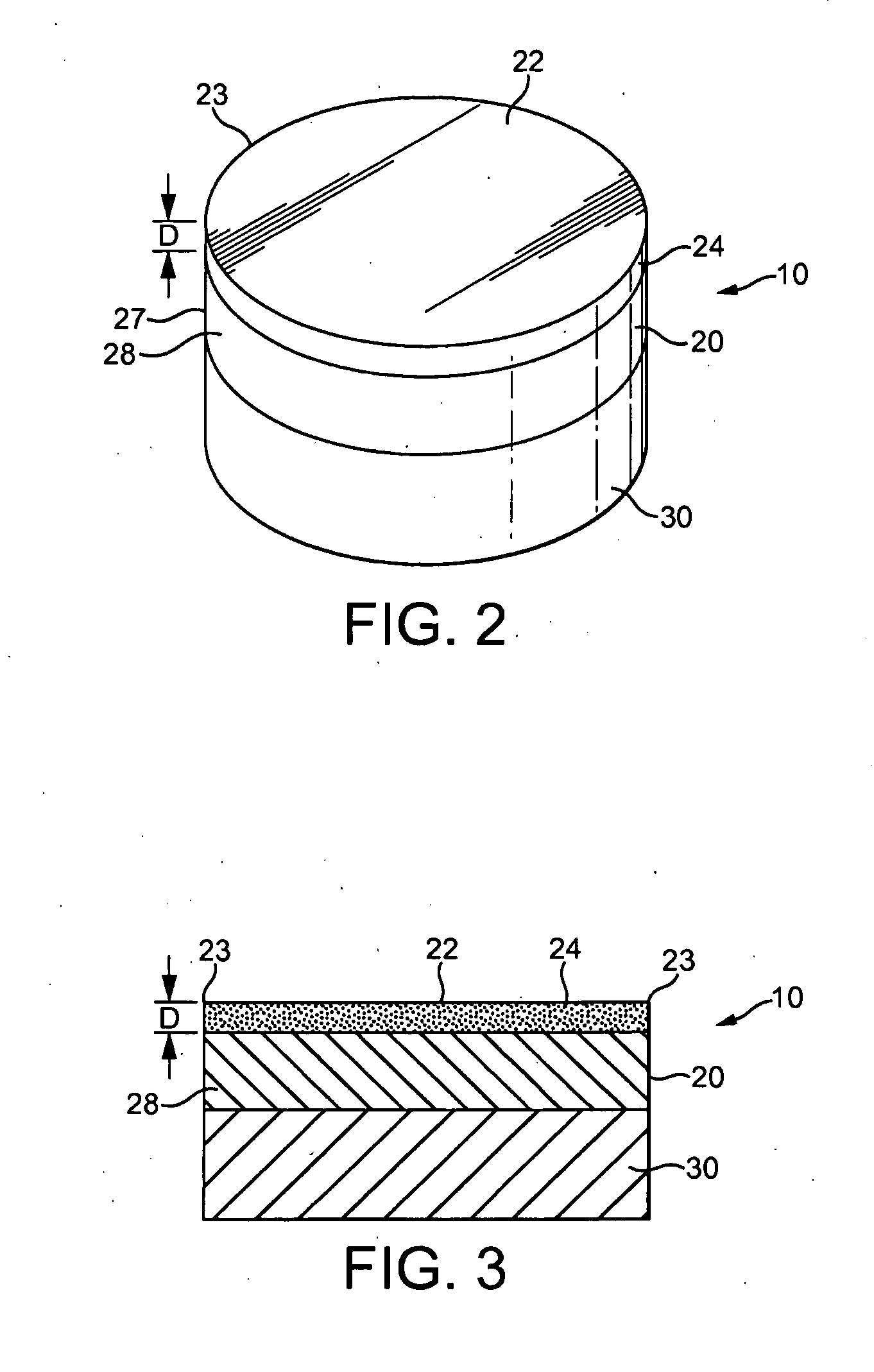

Selectively Leached Cutter

InactiveUS20140166371A1Reduce depthDepth is minimizedDrill bitsConstructionsPolycrystalline diamondDrill bit

A method of manufacturing a polycrystalline diamond (PCD) cutting element used as drill bit cutting elements (10) is disclosed. The method comprises leaching a PCD body formed from diamond particles (202) using a binder-catalyzing material so as to remove substantially all of the binder-catalyzing material from portions of a cutting surface of the PCD body. A portion (24) of the cutting surface is identified as a cutting area which, in use of the cutting element to cut material, is heated by the cutting action of the cutting element. Leaching of the PCD body includes performing a relatively deep leach in the portion of the cutting surface identified as the cutting area and performing a relatively shallow leach in at least the portion (26) of the cutting surface surrounding the identified cutting area.

Owner:HALLIBURTON ENERGY SERVICES INC

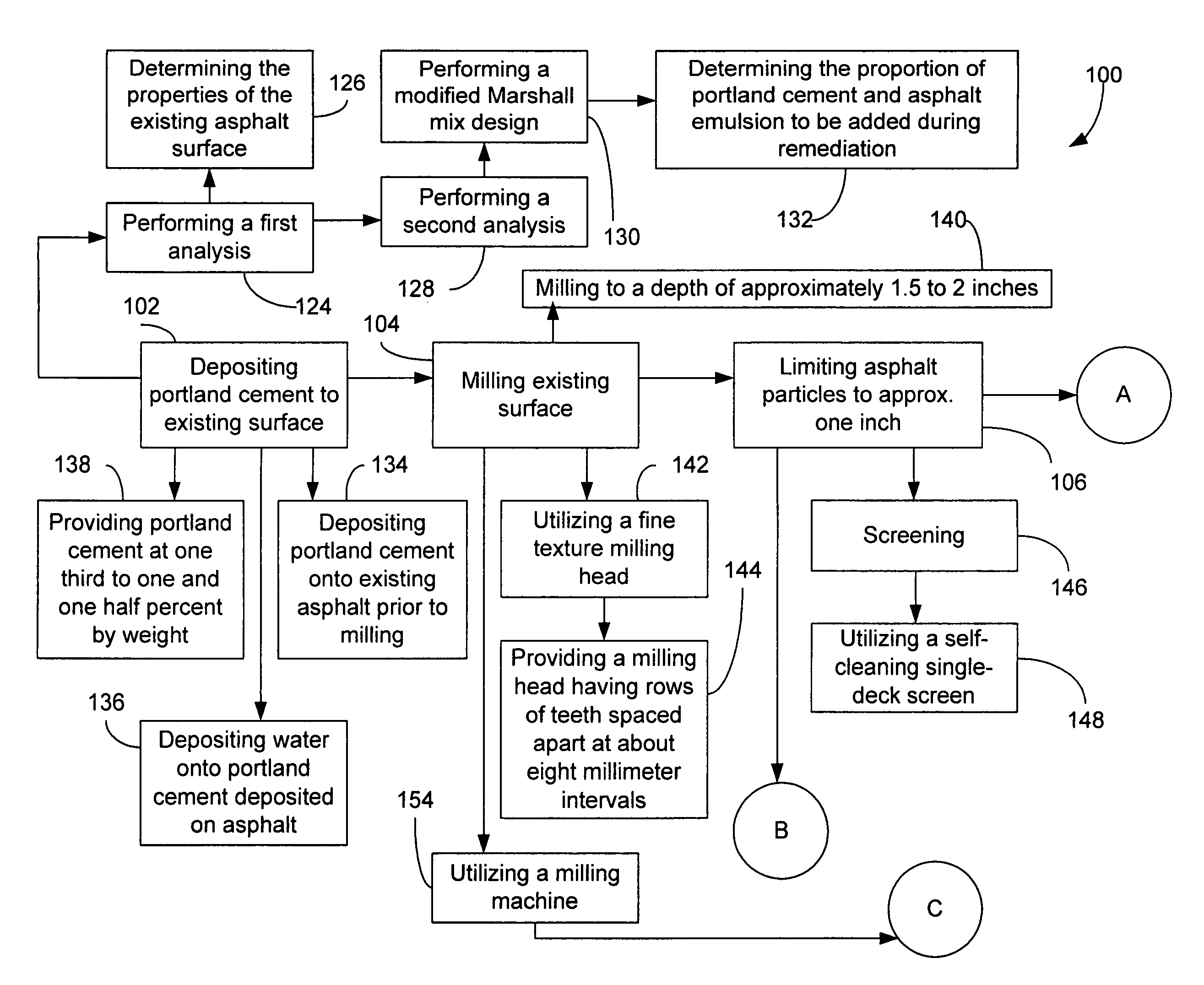

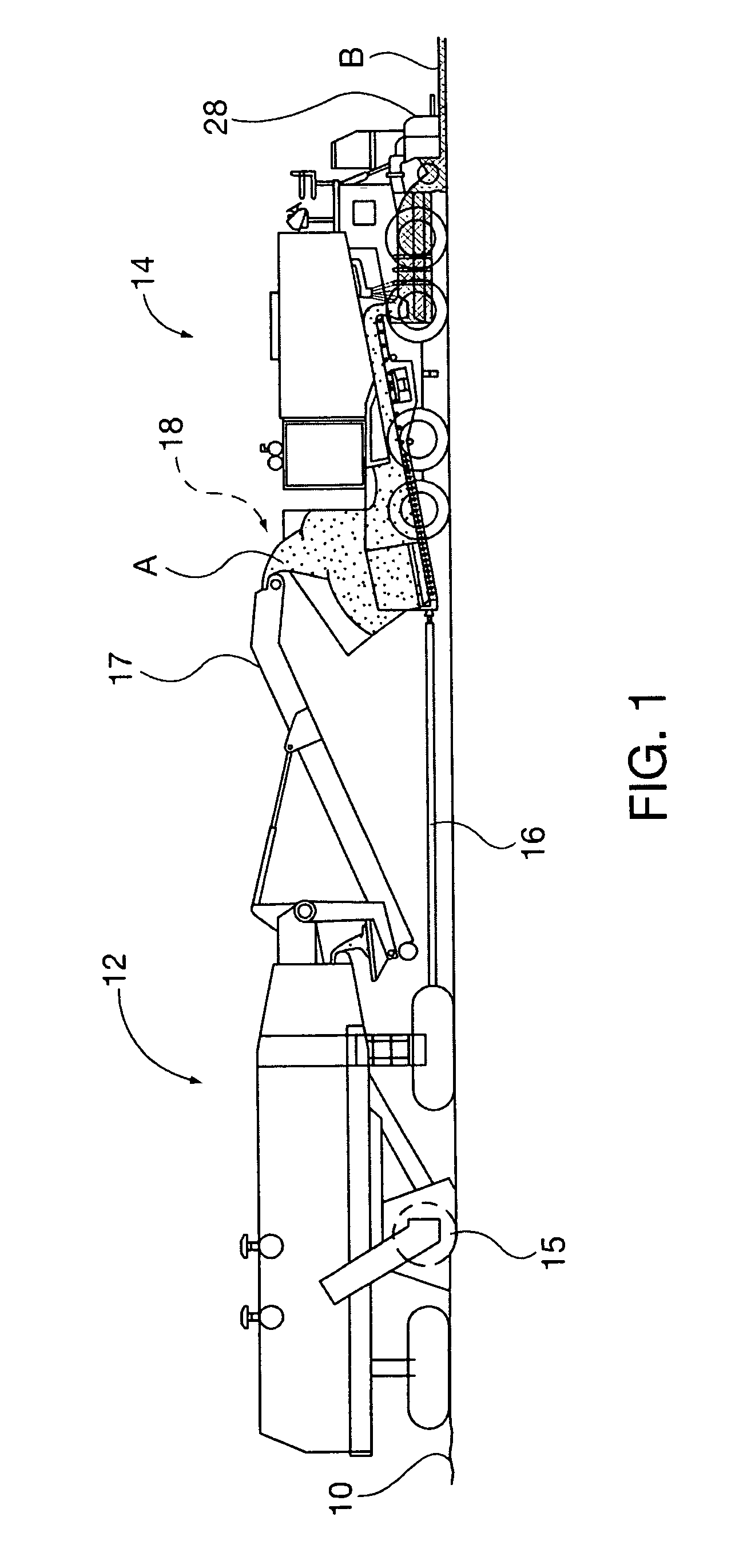

Pavement rehabilitation using cold in-place asphalt pavement recycling

ActiveUS8083434B1Less-thickEffective and easy compactionIn situ pavingsRoads maintainenceEmulsionPortland cement

A method of cold in-place recycling of asphalt to remediate distressed roads. Asphalt particles obtained by milling the existing asphalt are limited by screening to a maximum size of about one inch length. Asphalt particle size may be established by limiting tooth spacing of the road milling equipment milling head to about 5 / 16 inch or 8 millimeter spacing intervals. A predetermined proportion of portland cement, water, and asphalt emulsion are added to generated asphalt particles. Portland cement may be deposited onto the existing asphalt prior to milling. The resulting combination is mixed to generate a recycled mix, which may then be discharged onto the road being remediated and further processed, such as by screeding, compacting, and sealing.

Owner:GORMAN BROS

Construction material with multiple stud position indicia

InactiveUS6880299B2Depth is minimizedMinimize bulging or raised seamsConstruction materialDecorative surface effectsButt jointEngineering

A construction material includes a panel having opposed side walls and upper and lower walls extending longitudinally between the side walls. The panel includes front and rear surfaces. A first sheet of paper is adhered to a front surface of the panel. A first set of indicia arranged in linear relation are imprinted upon the sheet, respective lines being spaced a first predetermined distance apart. A second set of indicia arranged in linear relation are imprinted on the sheet and spaced a second predetermined distance apart. The first and second predetermined distances are different and correspond to different wall support constructions. The first and second sets of indicia also include different shape and color indicia. The side, upper, and lower walls are sloped from the front surface toward the rear surface to form respective butt joints.

Owner:MARTIN THOMAS E

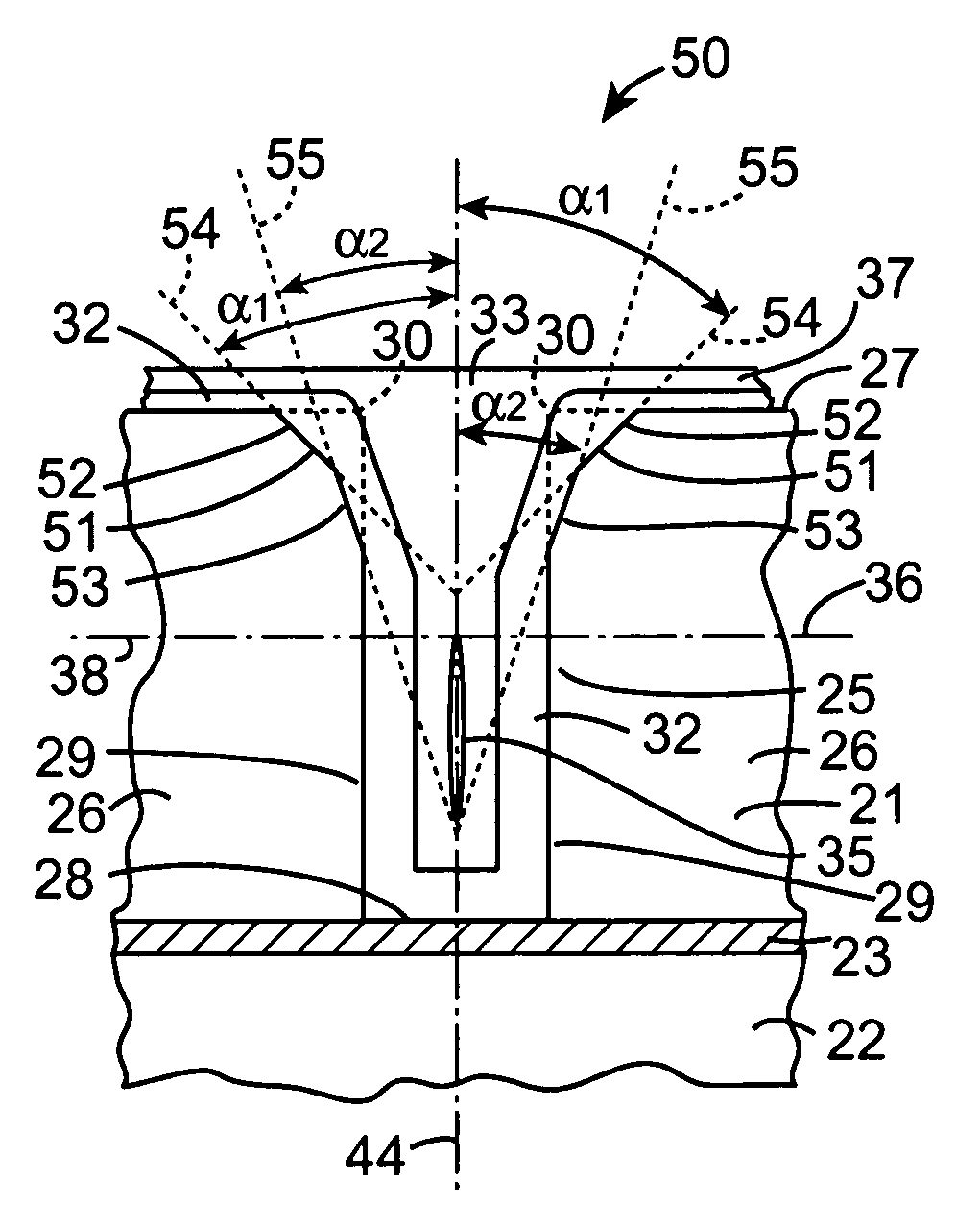

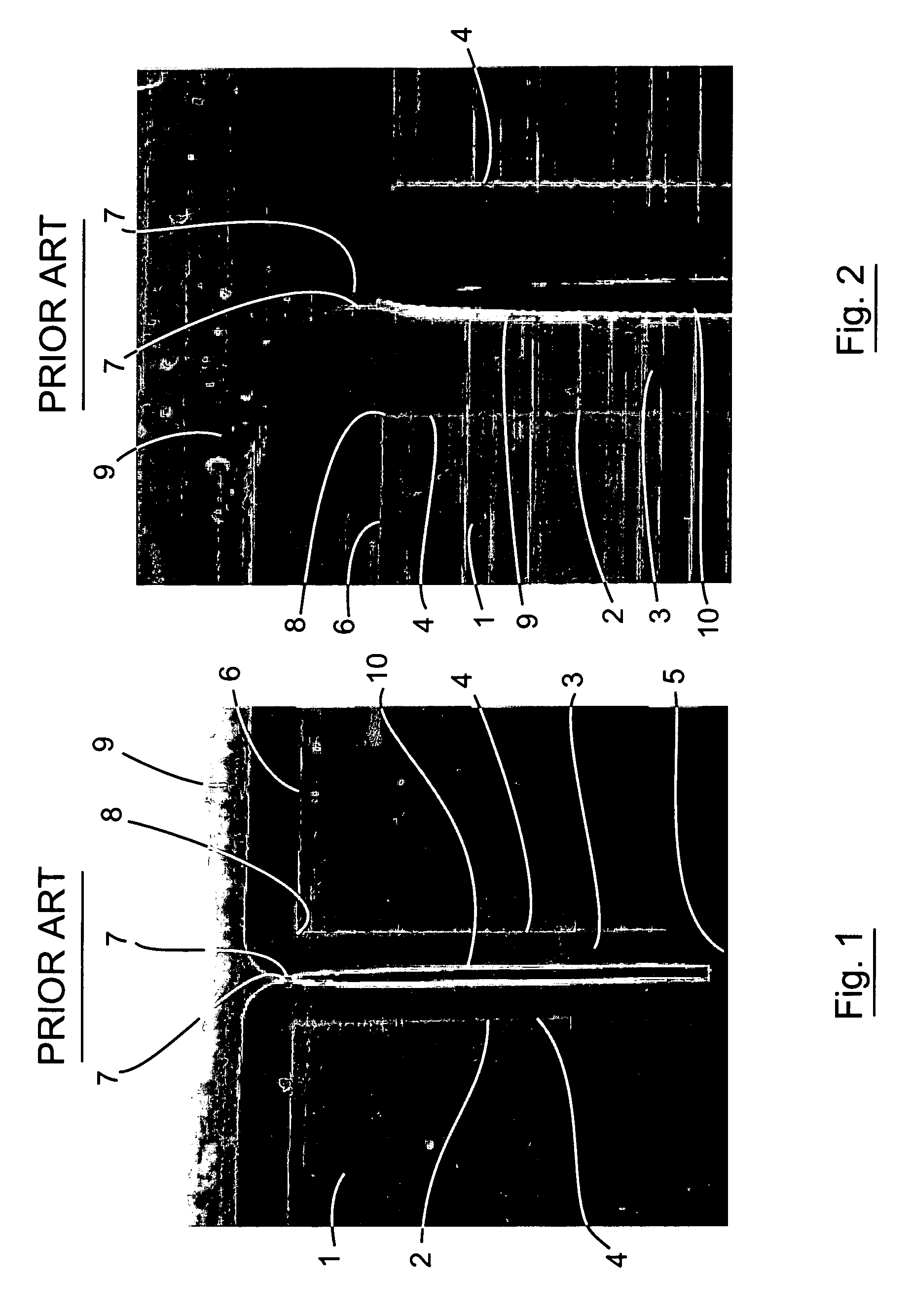

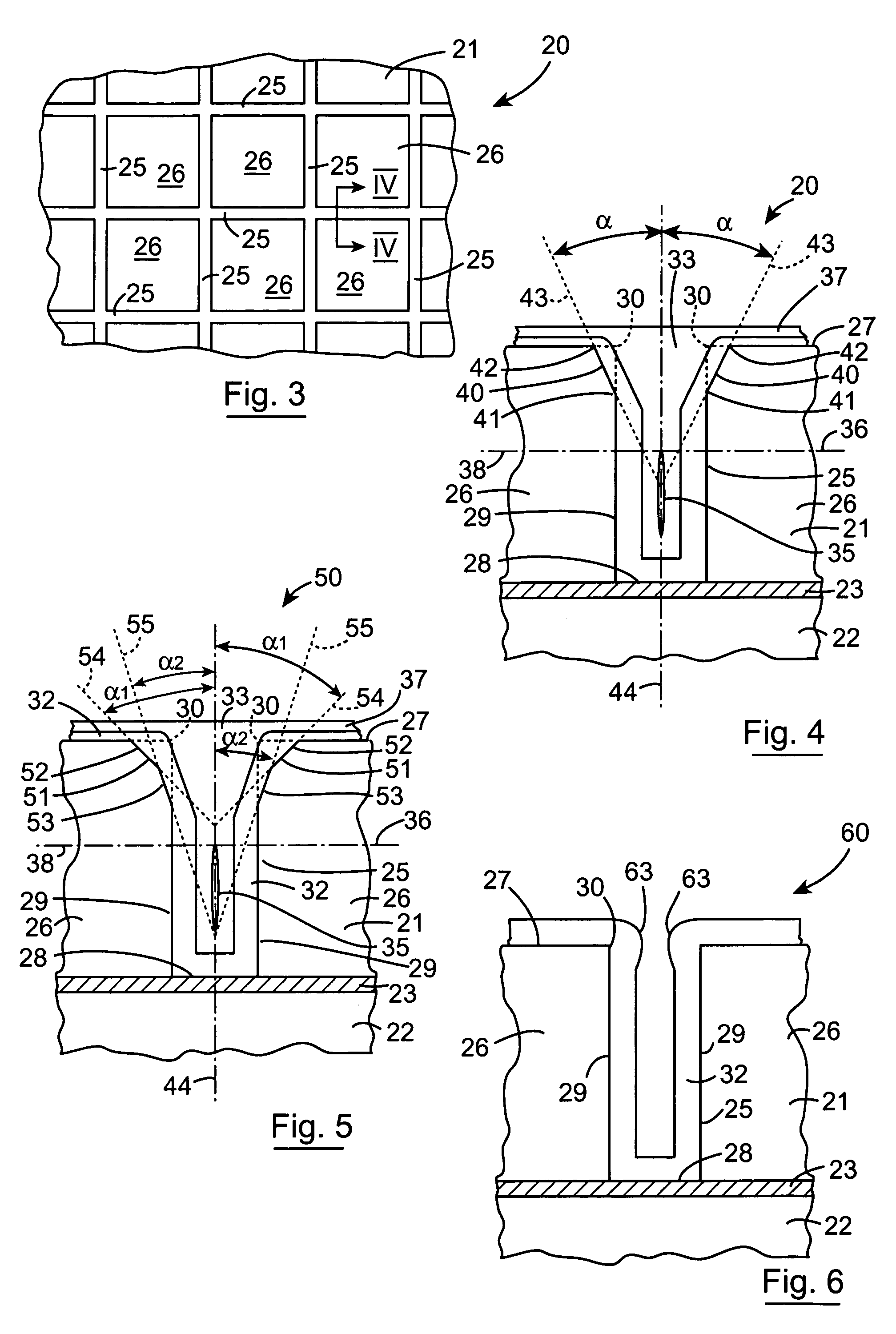

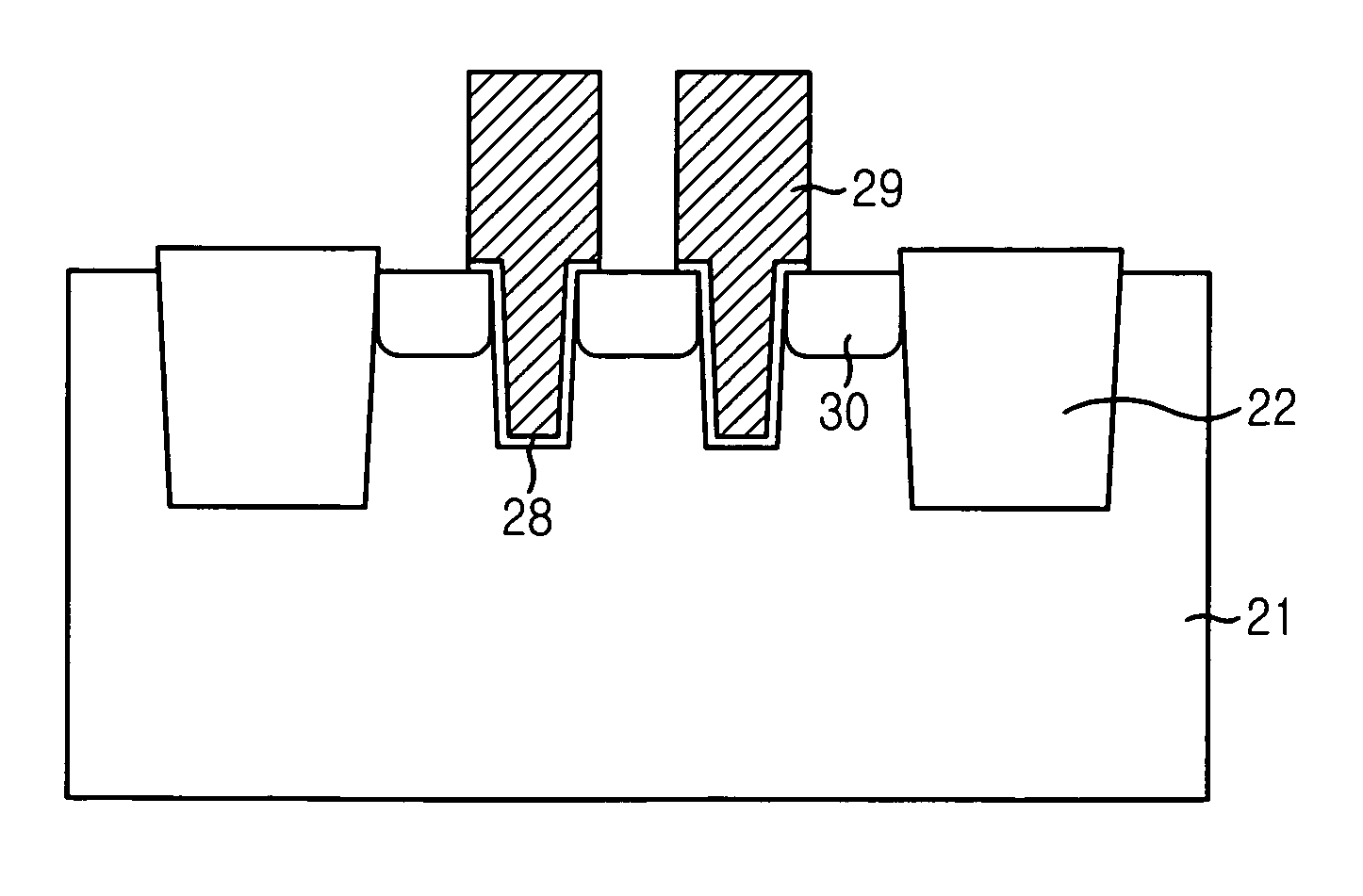

Method for forming a filled trench in a semiconductor layer of a semiconductor substrate, and a semiconductor substrate with a semiconductor layer having a filled trench therein

InactiveUS7122416B2Depth is minimizedMinimize formationSemiconductor/solid-state device manufacturingSemiconductor devicesFilling materialsSemiconductor

A method for forming an isolation filled trench (25) in a silicon layer (21) of an SOI structure (20). The trench (25) is relieved adjacent its open mouth (30) in order to displace the commencement of bridging of the trench (25) with the filling material, to a level (36) well below a first surface (27) of the silicon layer (21) for in turn displacing voids (35) from the open mouth (30) into the trench (25) below the level (36). The trench may be relieved by forming tapered portions (40) in the side wells (29) adjacent the open mouth (30), and / or by relieving one or more lining layers (32) in the trench (25) adjacent the open mouth (30) to form tapered portion (52) and (53). Instead of relieving the trench (25) by tapering the side walls (29) relieving recesses may be formed into the first surface (27) of the silicon layer (21) adjacent the open mouth (30). By relieving the trench (25) or one or more of the lining layers (32) adjacent the open mouth (30) the commencement of bridging of the trench with the filling material is displaced downwardly to a level (36), which displaces voids formed in the trench below the level (36). By sufficiently relieving the trench (25) and / or lining layers (32) adjacent the open mouth to a sufficient depth the formation of voids in the trench may be completely avoided.

Owner:ANALOG DEVICES INC

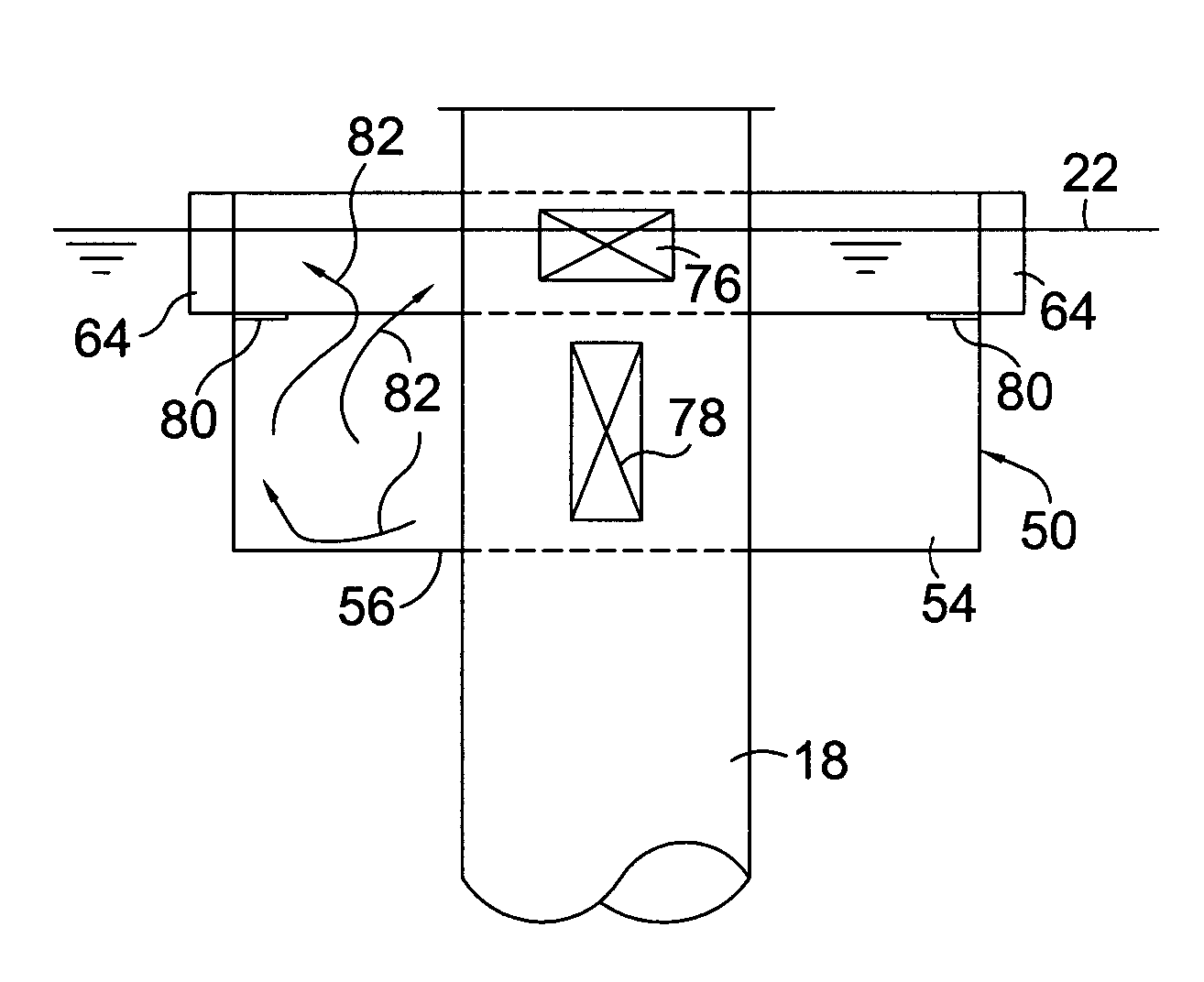

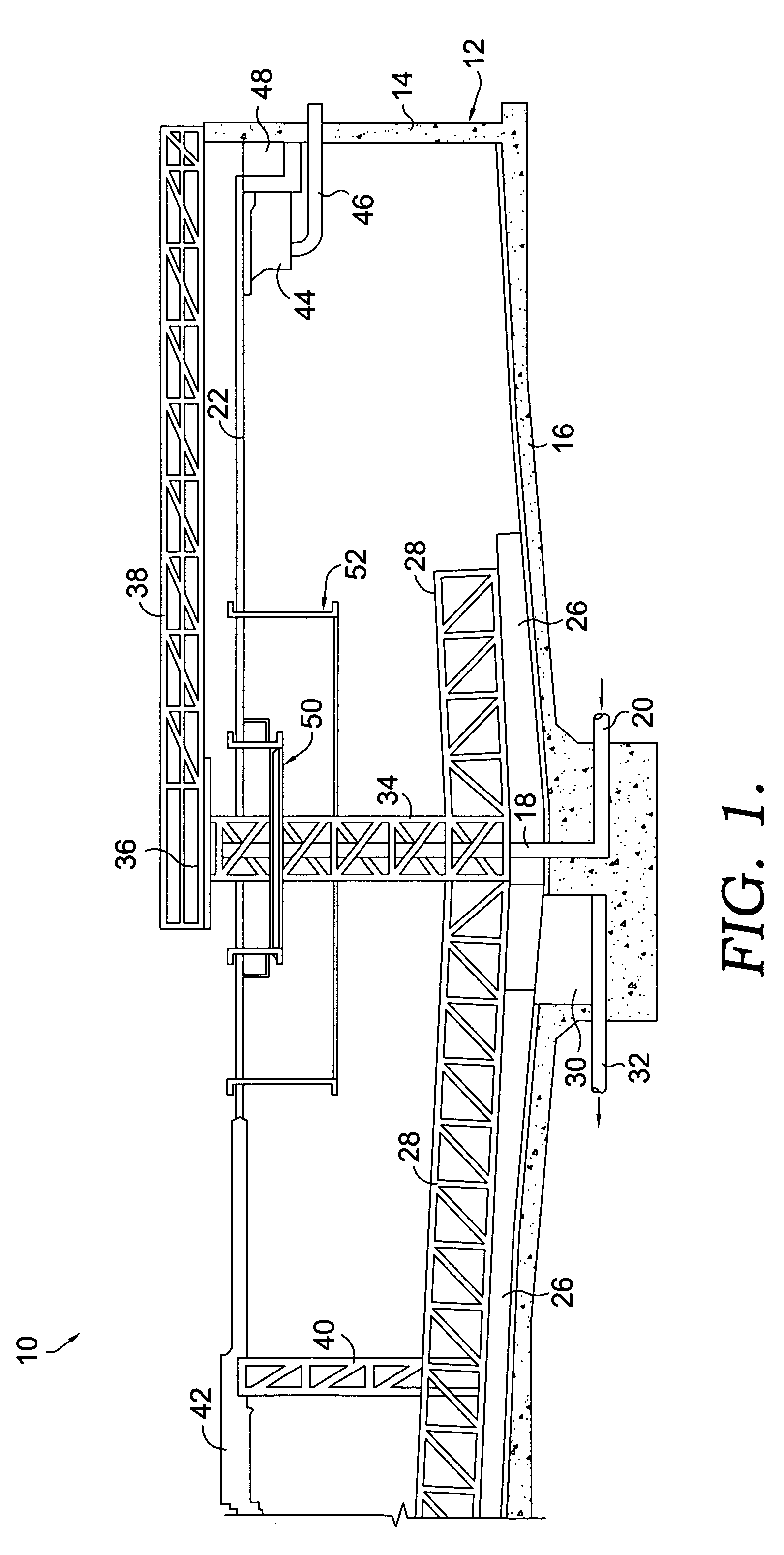

Inlet structure for clarifiers

ActiveUS20050252868A1Simple structureImprove efficiencySettling tanks feed/dischargeWater/sewage treatmentEngineeringClarifier

A clarifier is provided with an improved inlet structure which receives influent from influent column ports and discharges the influent uniformly around the entire circumference of the inlet structure. The influent column ports may be baffled. Angled guide vanes on the inlet structure reduce the flow energy and effect a tangential flow into a feedwell in the basin. The feedwell may be conical to further reduce the velocities and create an outward flow to counteract inward flows in the basin.

Owner:ORRIS E ALBERTSON LEGACY LLC

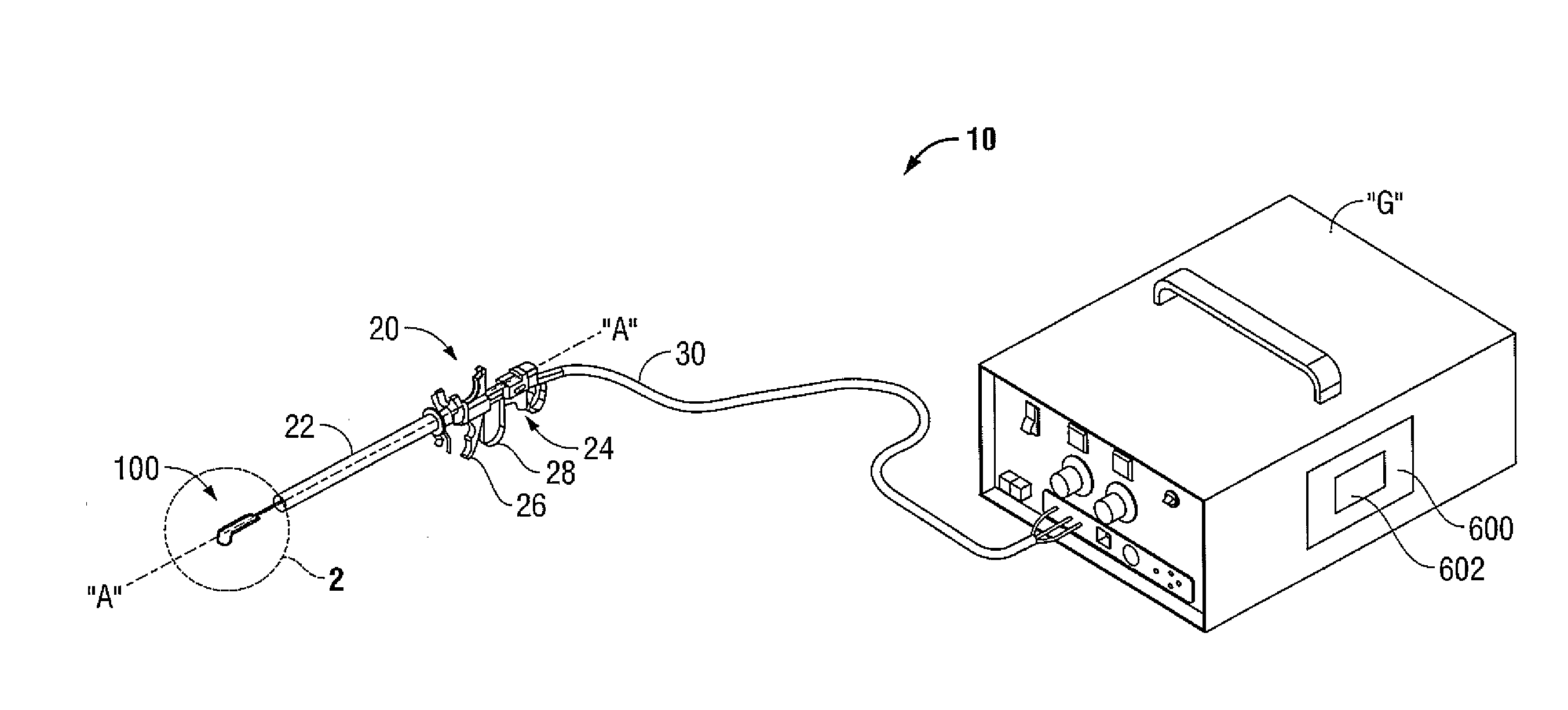

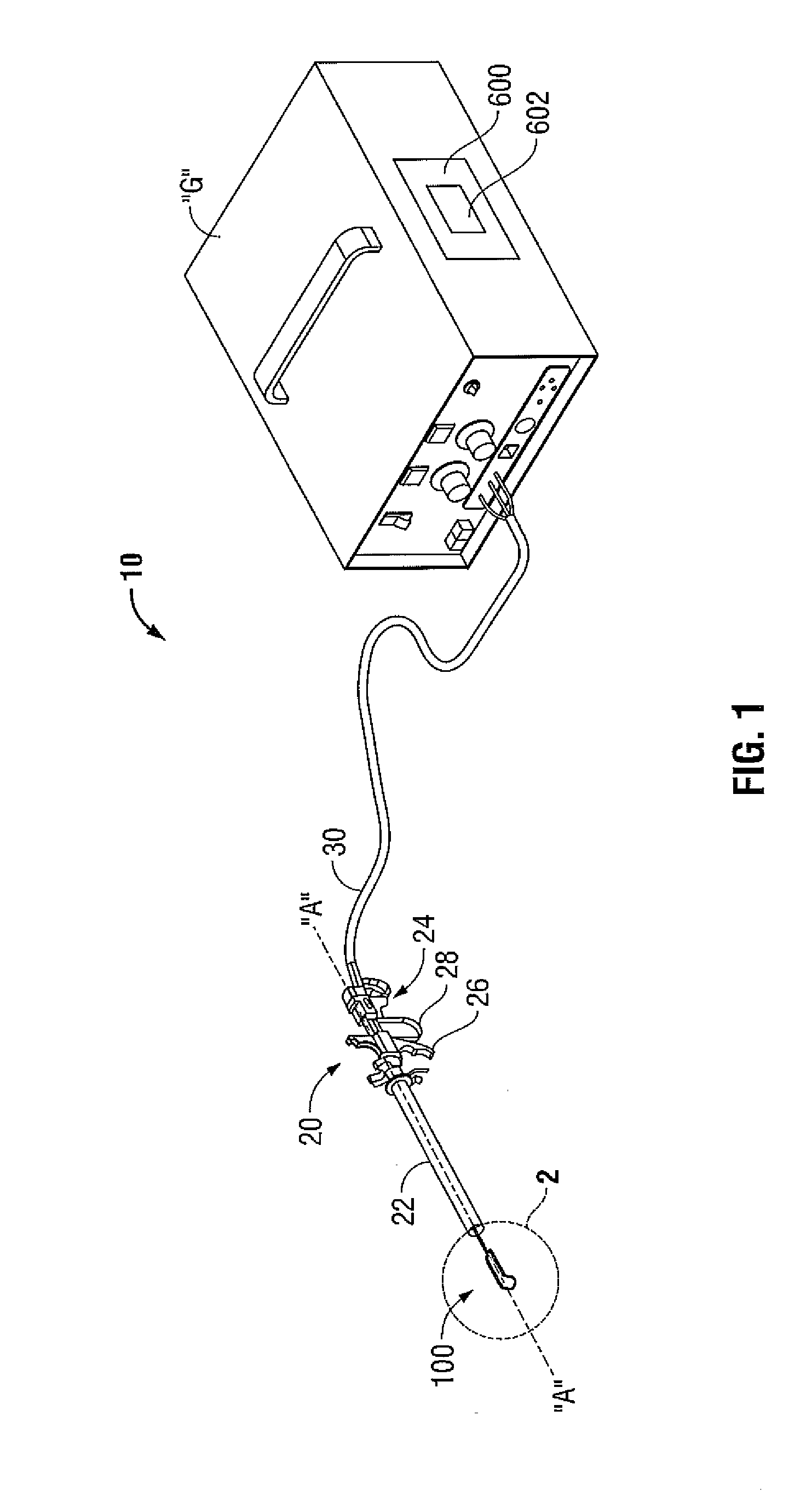

Electrosurgical electrodes

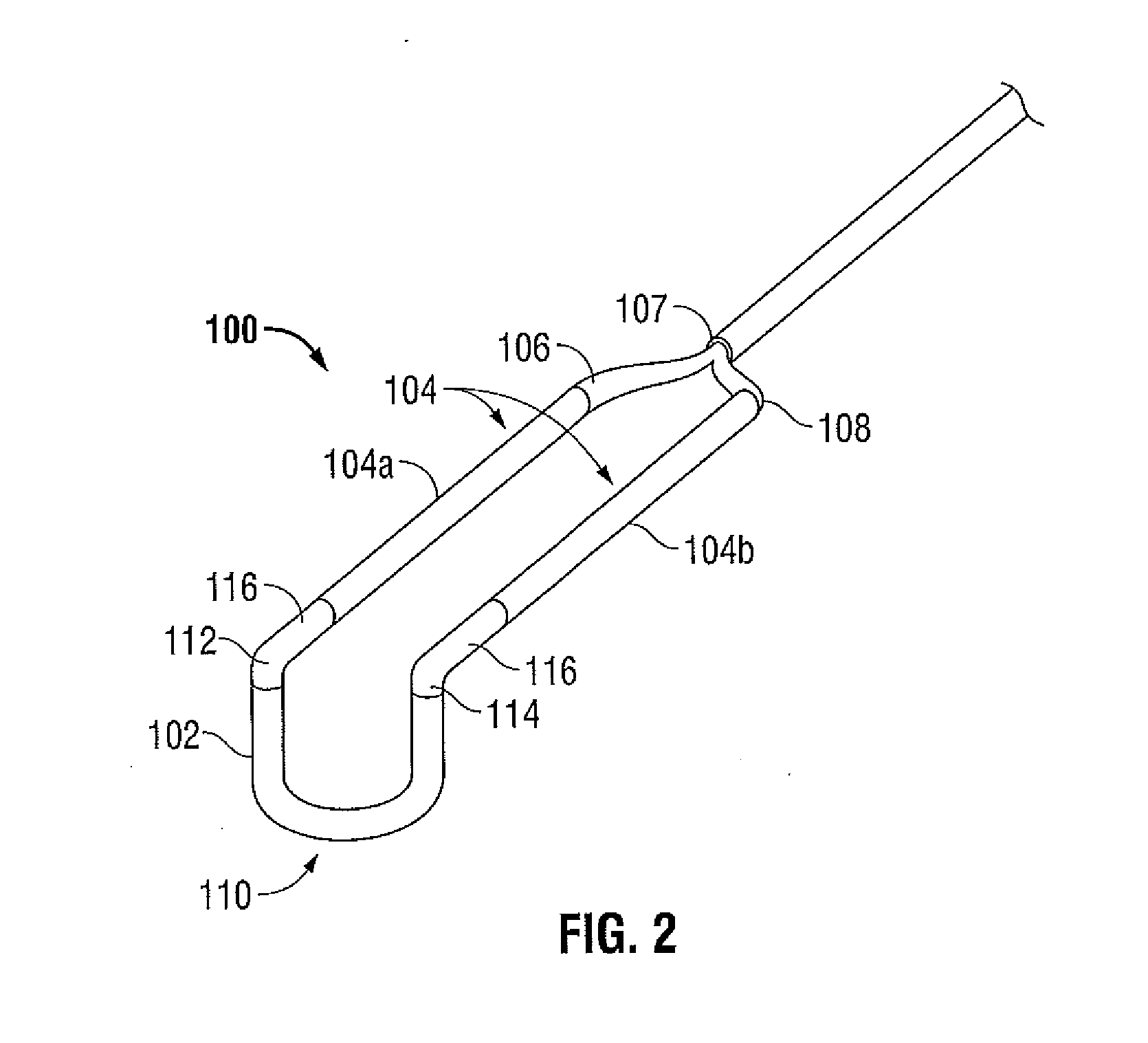

InactiveUS20140236143A1Avoid flowMinimizing overall energy requiredSurgical instruments for heatingSurgical forcepsBiomedical engineeringEnergy source

An electrode assembly is provided. The electrode assembly includes a proximal end that is adapted to connect to an electrosurgical instrument including a housing defining a longitudinal axis therethrough and an electrosurgical energy source. A distal end includes a cutting electrode having a loop configuration configured to cut tissue. The distal end includes a return electrode operably disposed adjacent the cutting electrode. A dielectric shield is operably disposed between the cutting electrode and return electrode. The dielectric shield extending distally past the cutting electrode to hinder current flow to the return electrode when the dielectric shield, cutting electrode and return electrode are submersed in a conductive solution and the cutting electrode is energized, thereby concentrating current density at the cutting electrode.

Owner:TYCO HEALTHCARE GRP LP

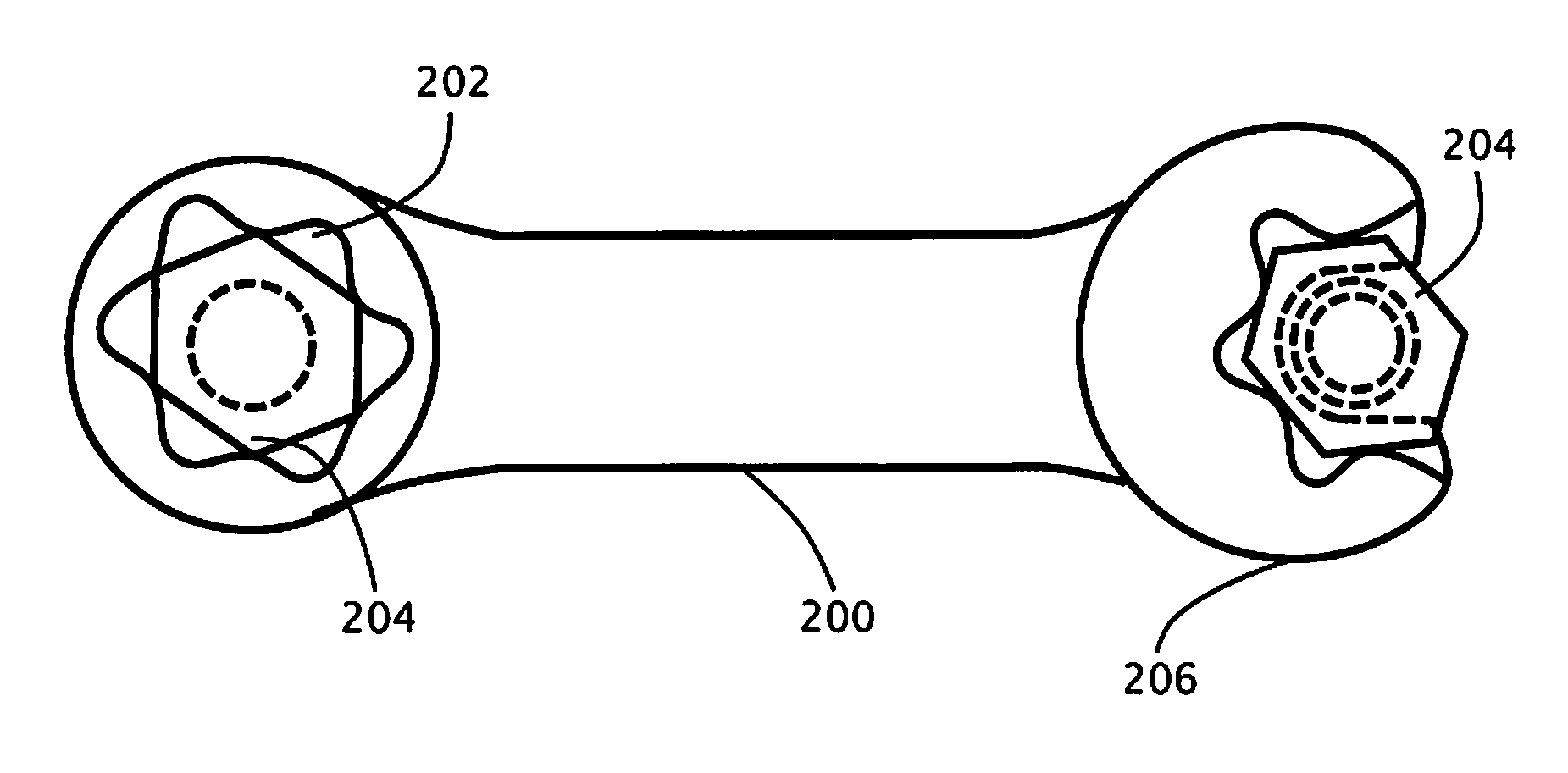

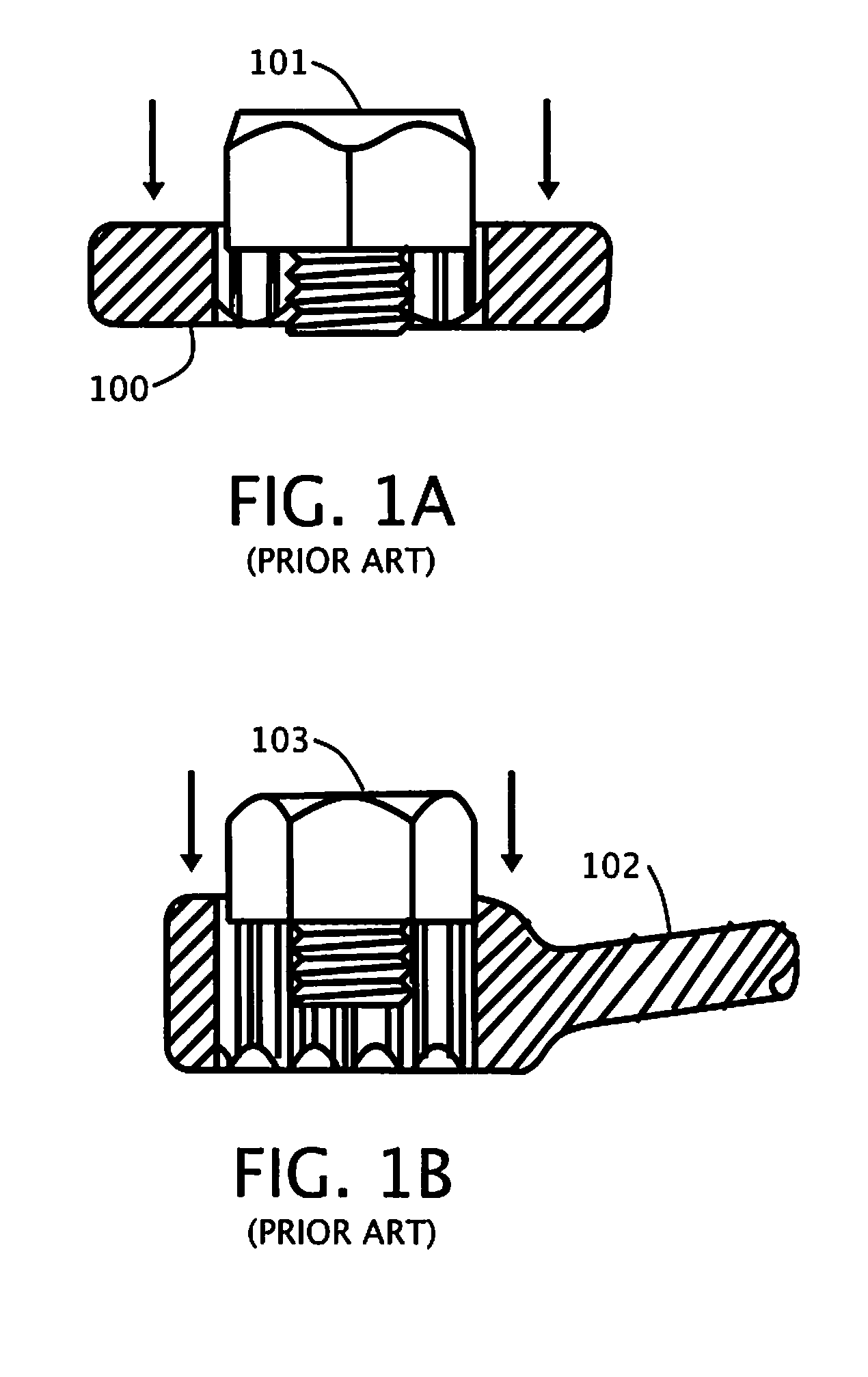

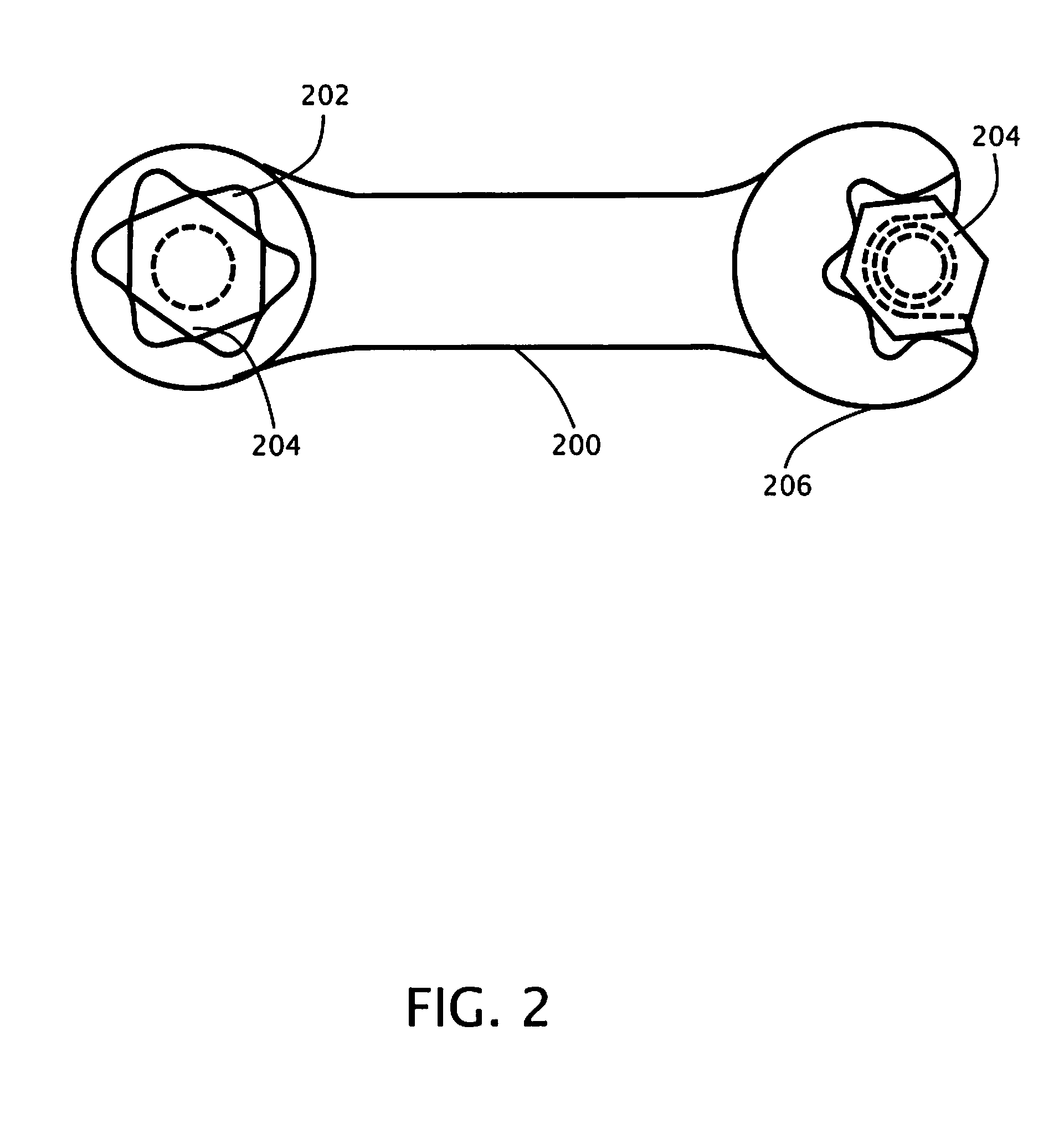

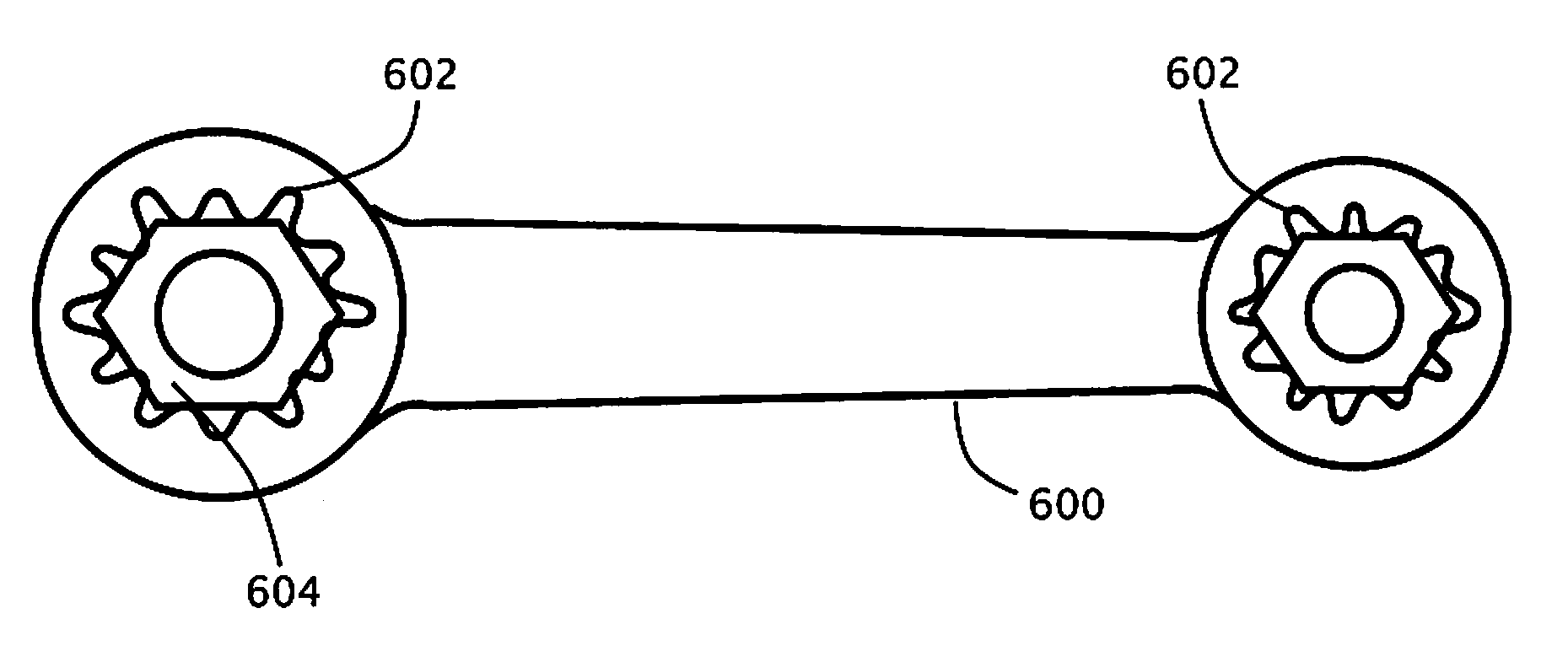

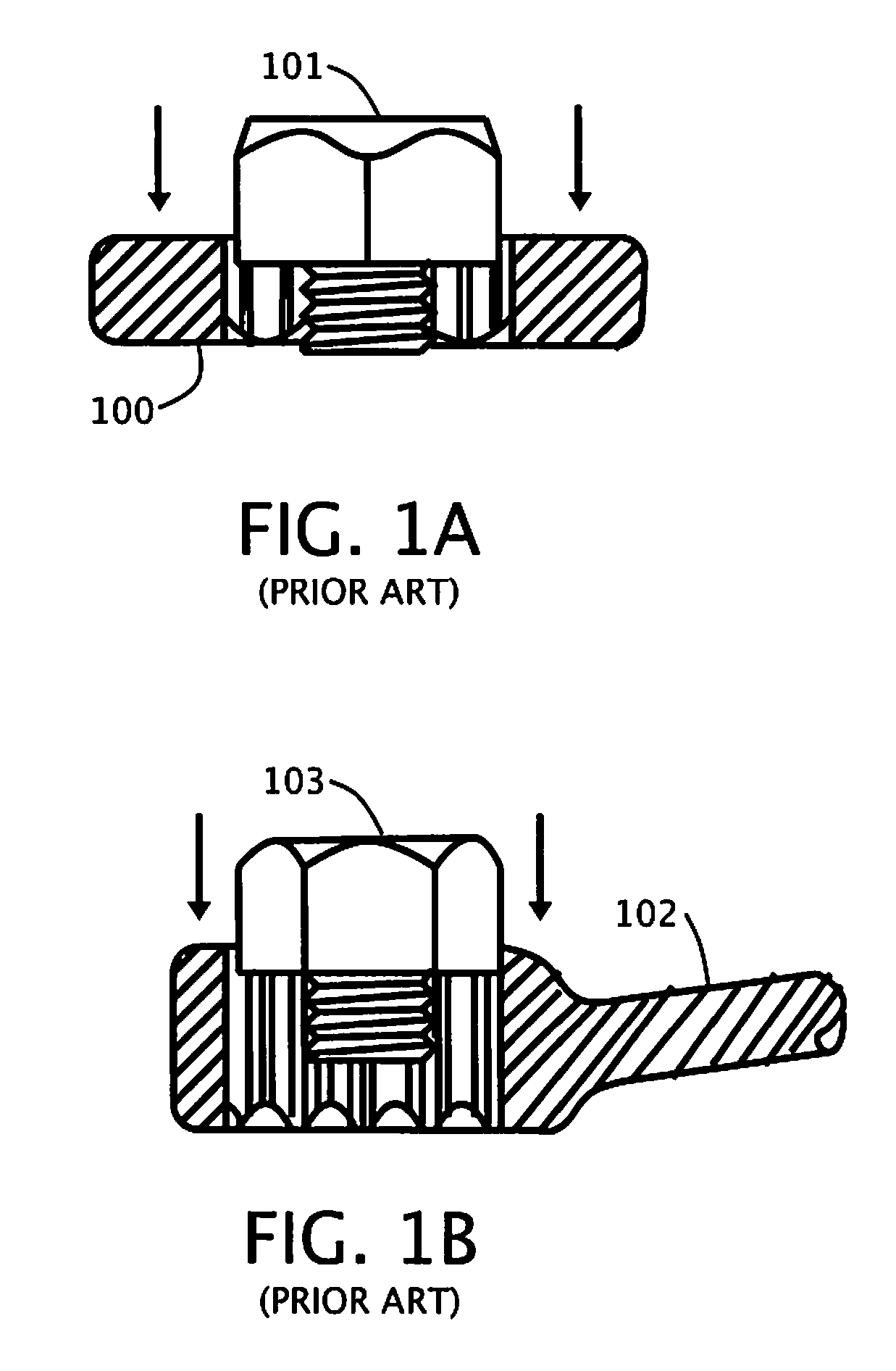

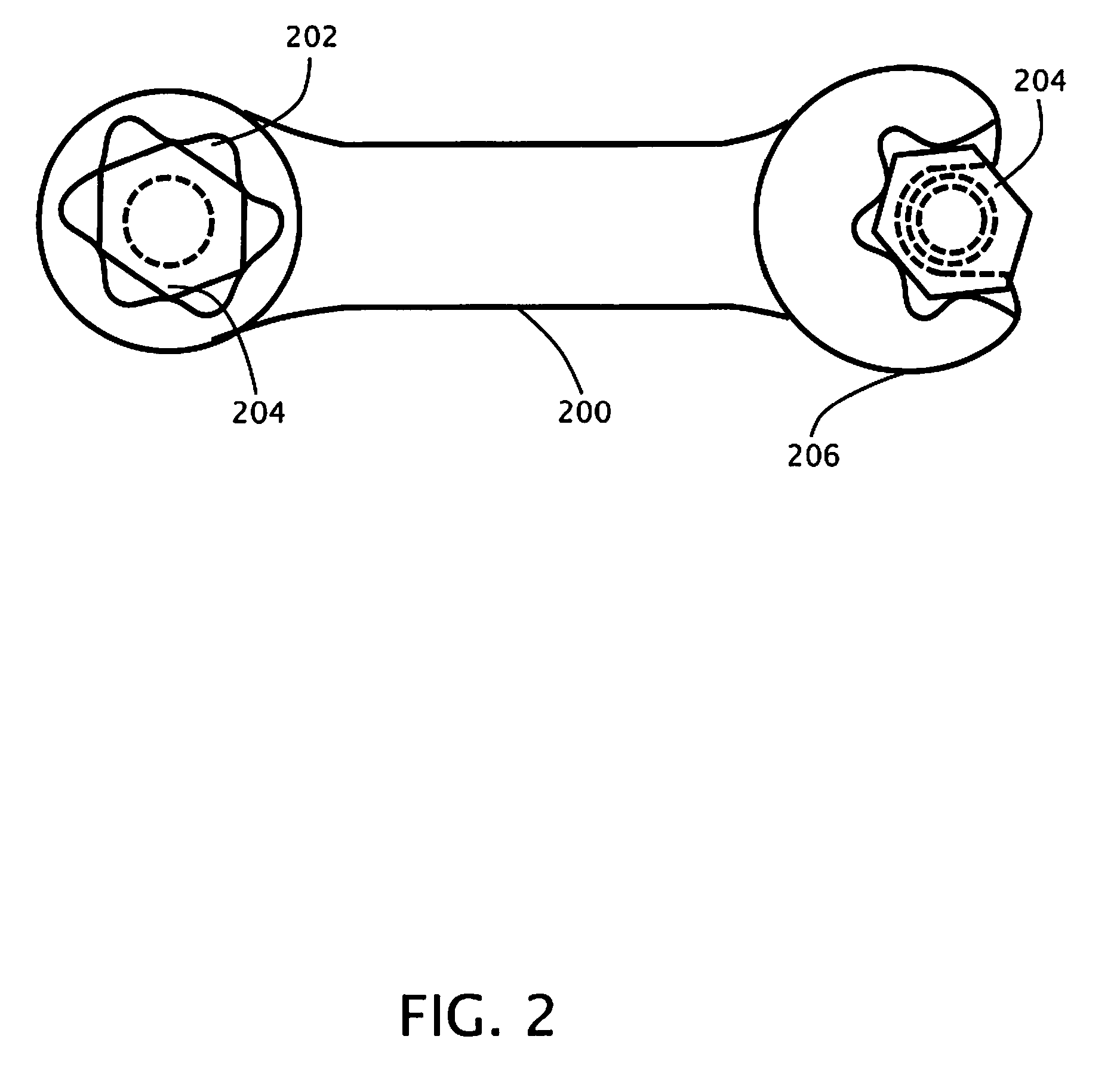

Single piece rotary wrenching tool

A rotary wrenching tool used on polygonal nuts, bolts and screws is disclosed. More particularly, the wrenching tool is a single piece rotary wrenching tool with a uniform interior having no moving parts and consisting of six or twelve inwardly projecting lobes of the same size that enable the wrench or socket to exert pressure on the flats of hexagonal objects away from the corners. This invention further relates to a duplex wrench operable on hexagonal fasteners measured by the metric, inch, or both systems. Within a defined range in one wrench, each wrench secures hexagonal objects measured by both inch and metric systems.

Owner:EDISON NATION

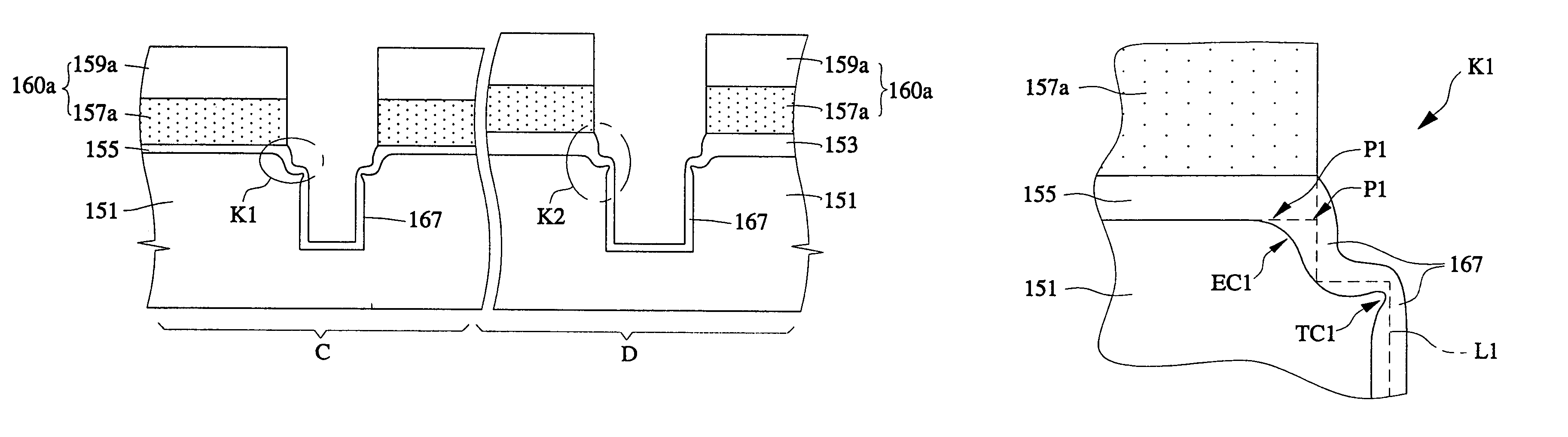

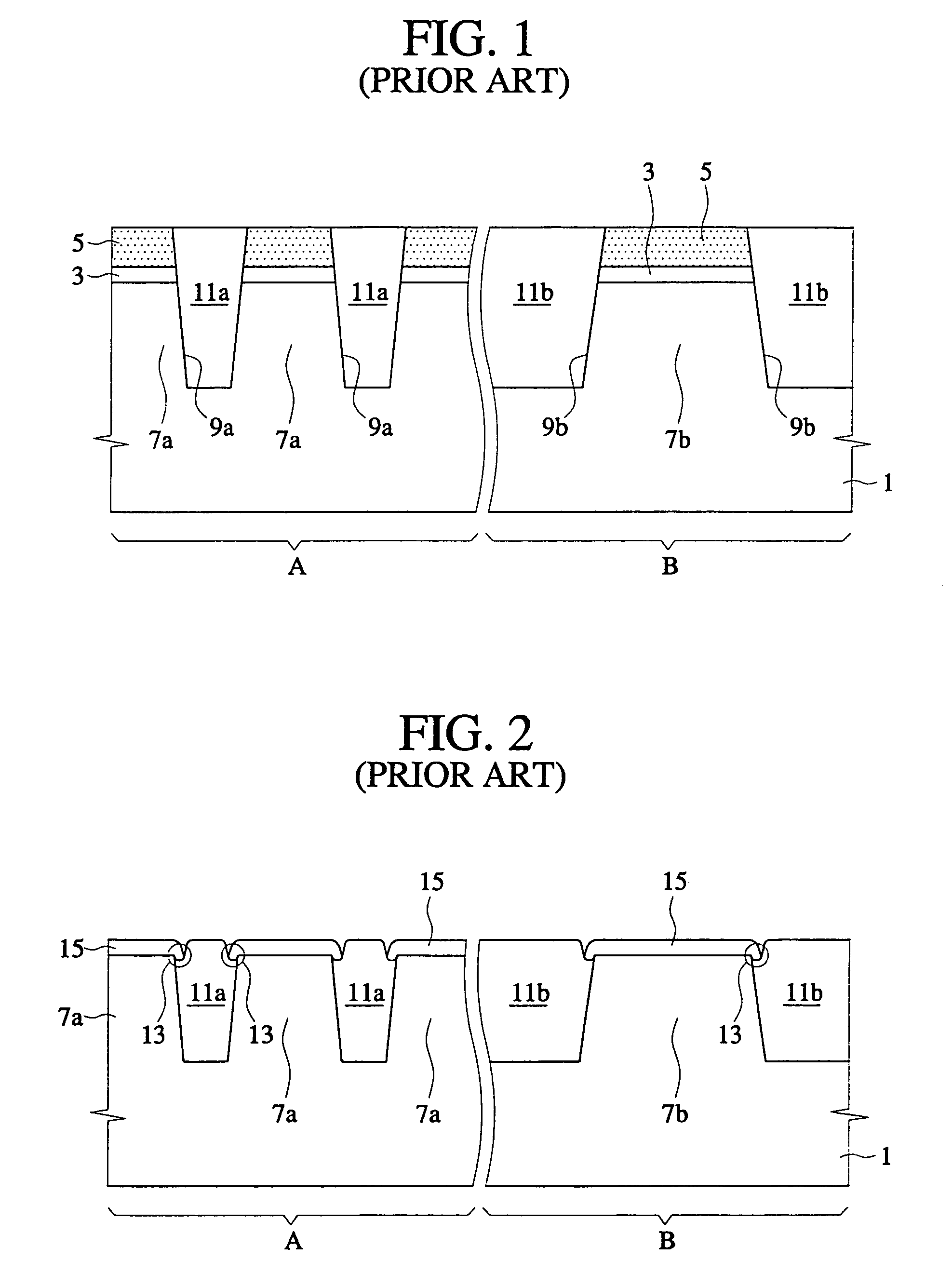

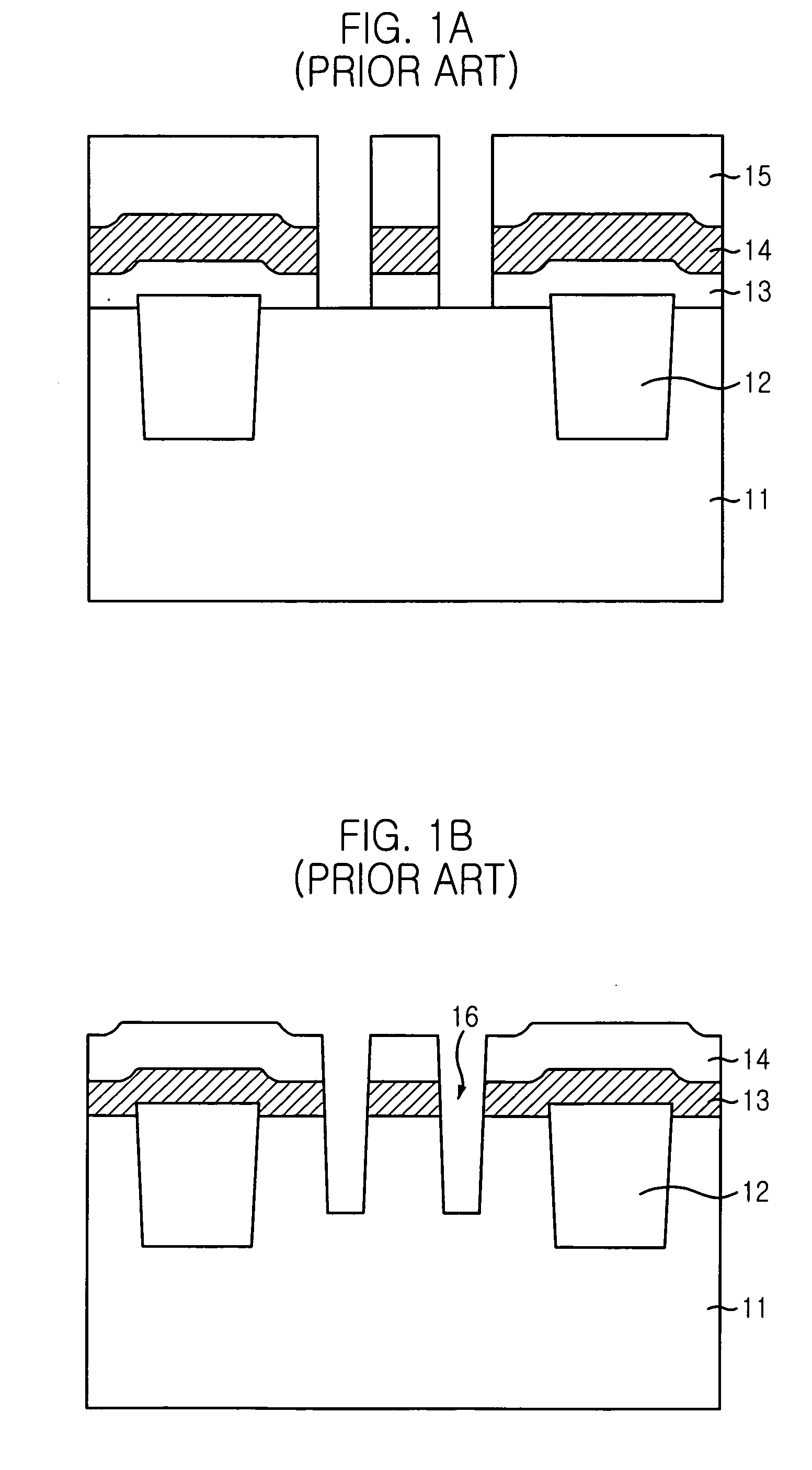

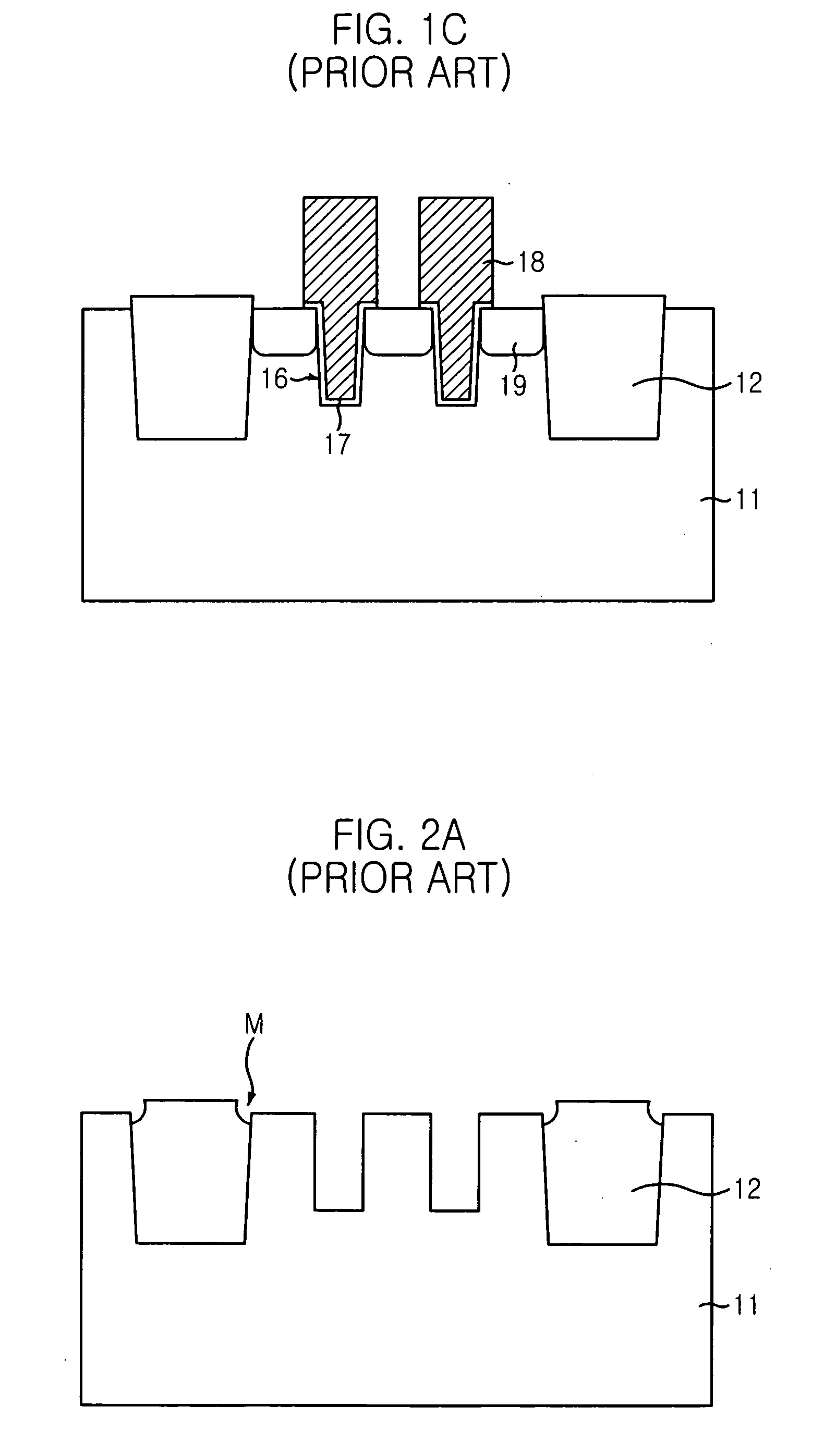

Methods of fabricating a semiconductor device having multi-gate insulation layers and semiconductor devices fabricated thereby

ActiveUS7508048B2Preventing regionDepth is minimizedTransistorSolid-state devicesEdge regionHigh pressure

Methods of fabricating a semiconductor device having multi-gate insulation layers and semiconductor devices fabricated thereby are provided. The method includes forming a pad insulation layer and an initial high voltage gate insulation layer on a first region and a second region of a semiconductor substrate respectively. The initial high voltage gate insulation layer is formed to be thicker than the pad insulation layer. A first isolation layer that penetrates the pad insulation layer and is buried in the semiconductor substrate is formed to define a first active region in the first region, and a second isolation layer that penetrates the initial high voltage gate insulation layer and is buried in the semiconductor substrate is formed to define a second active region in the second region. The pad insulation layer is then removed to expose the first active region. A low voltage gate insulation layer is formed on the exposed first active region. Accordingly, it can minimize a depth of recessed regions (dent regions) to be formed at edge regions of the first isolation layer during removal of the pad insulation layer, and it can prevent dent regions from being formed at edge regions of the second isolation layer.

Owner:SAMSUNG ELECTRONICS CO LTD

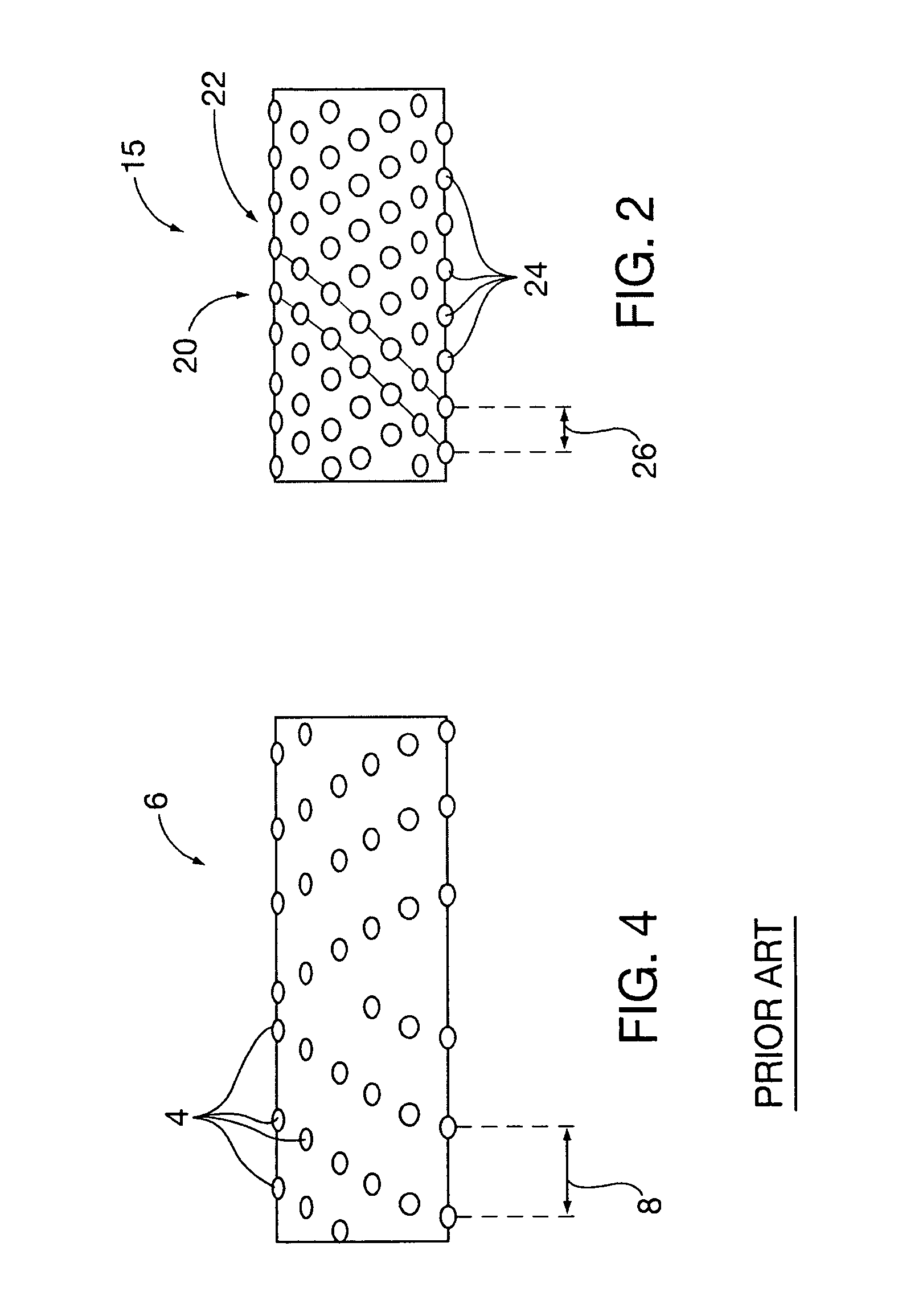

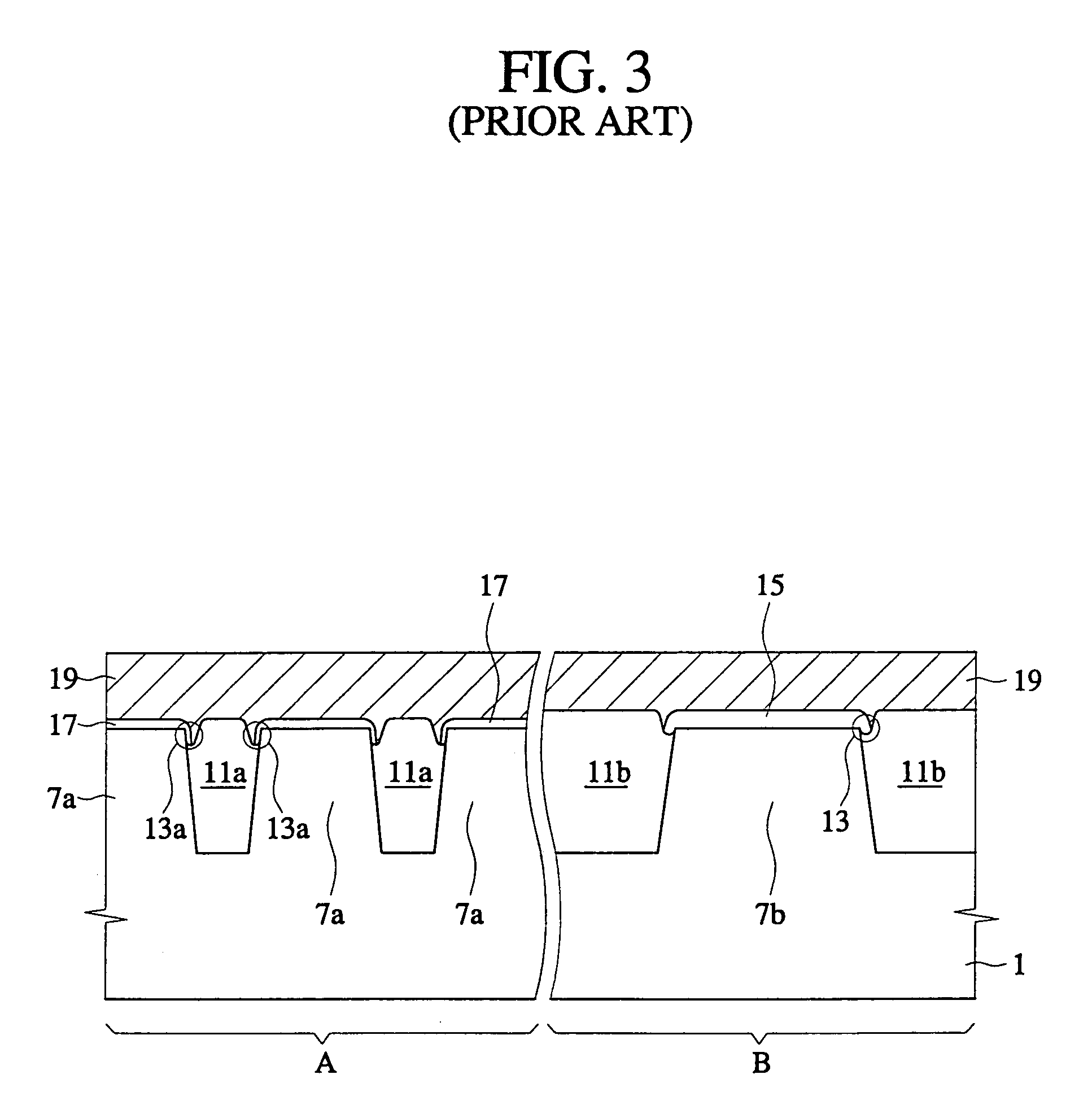

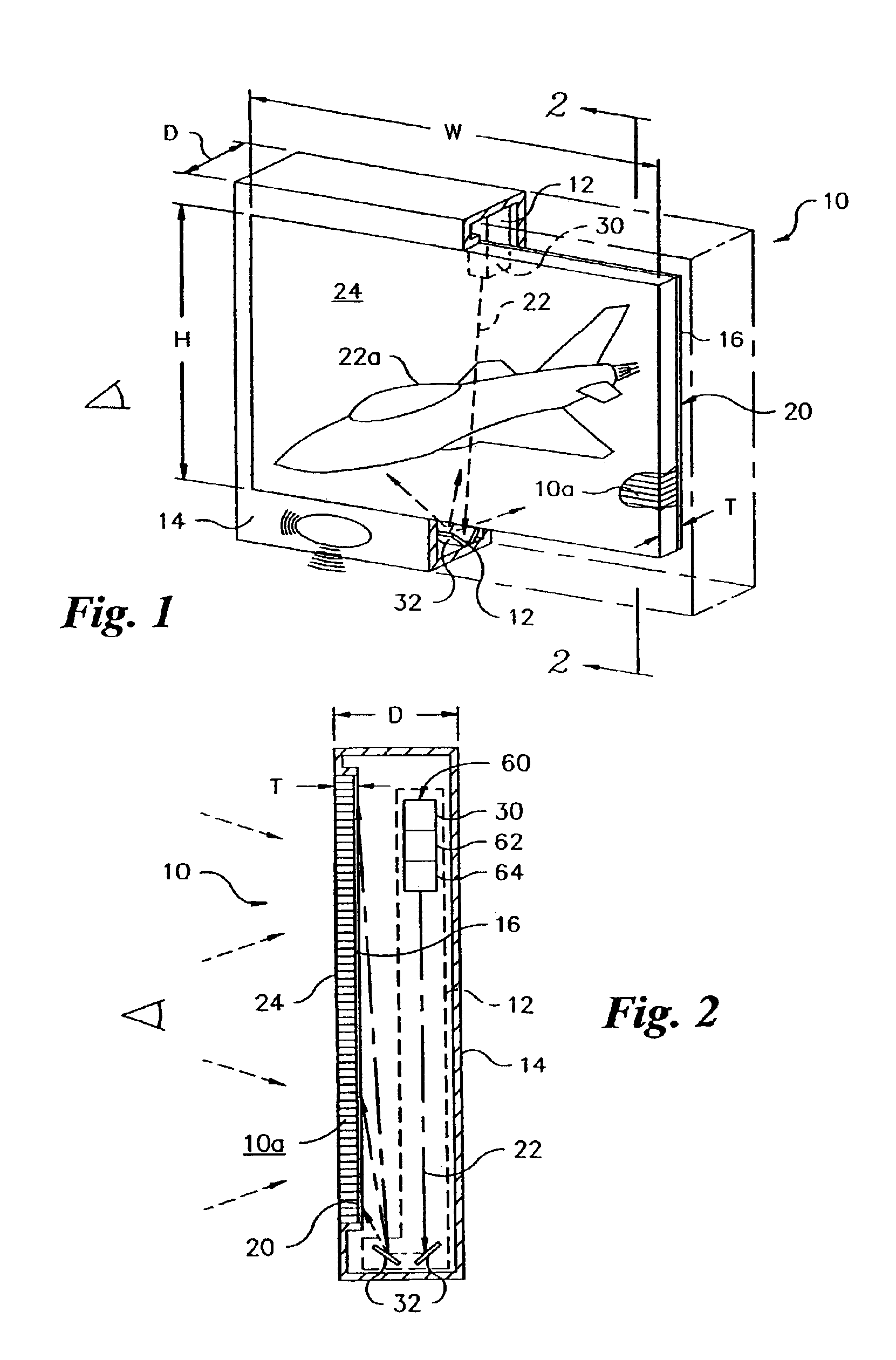

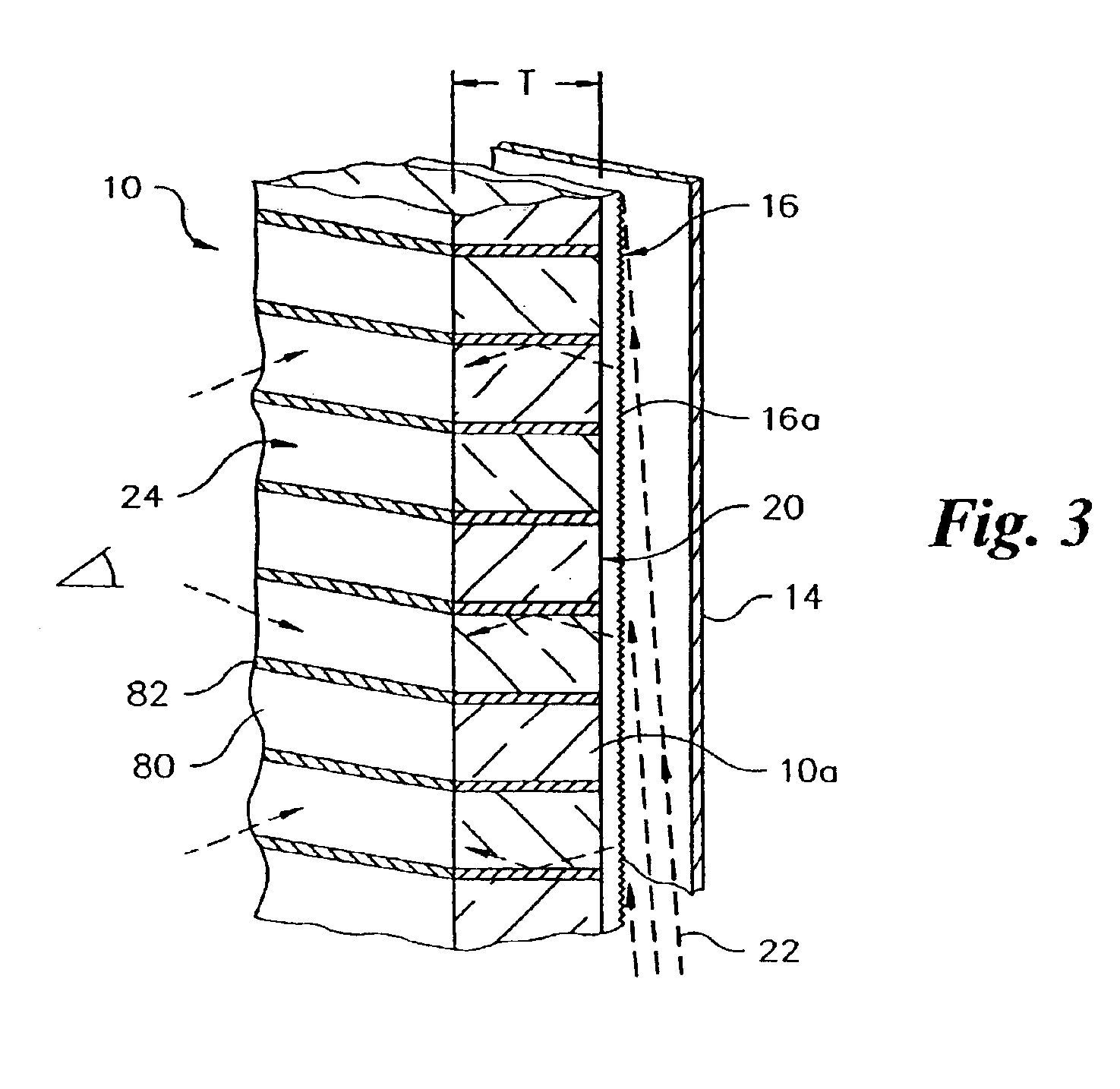

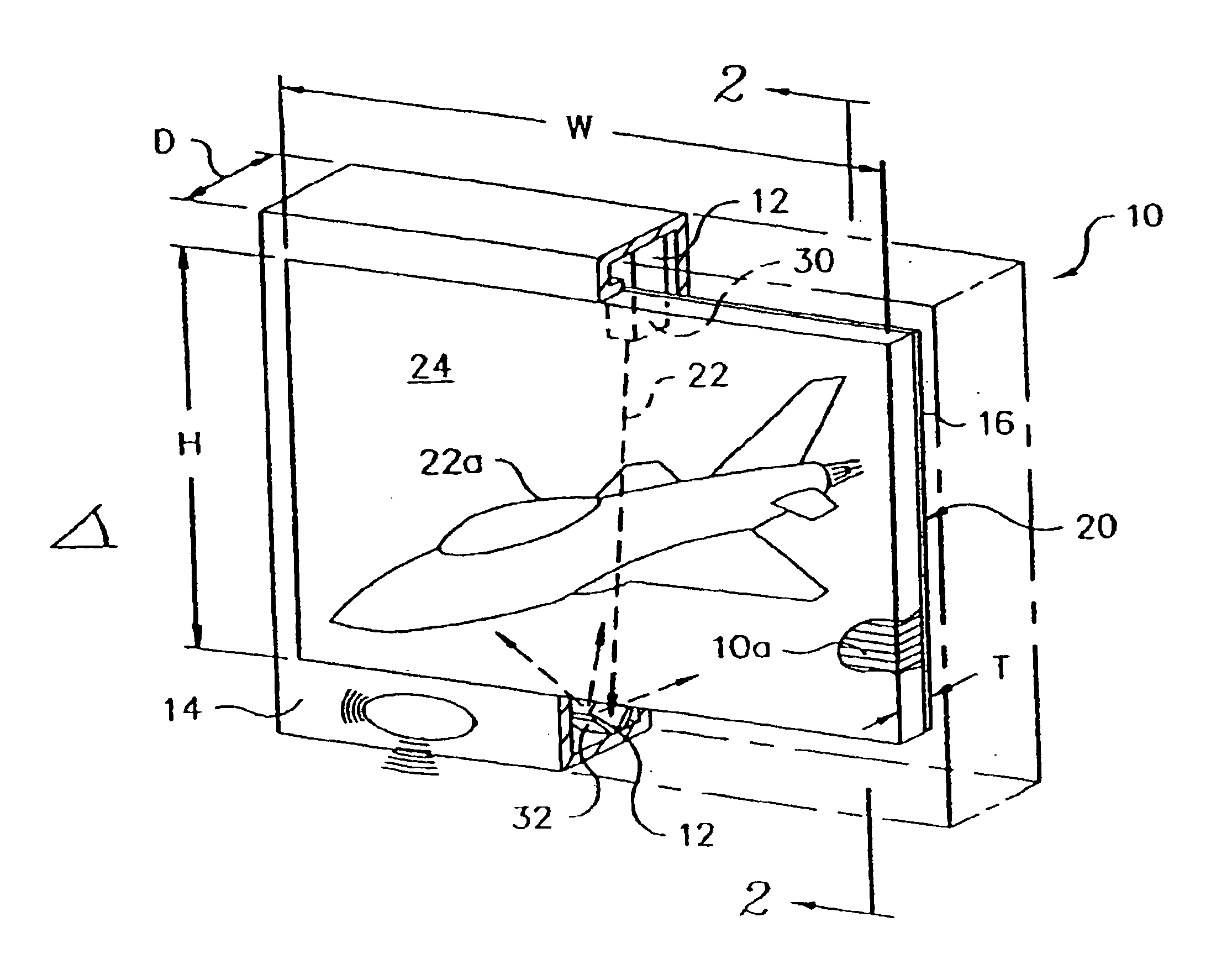

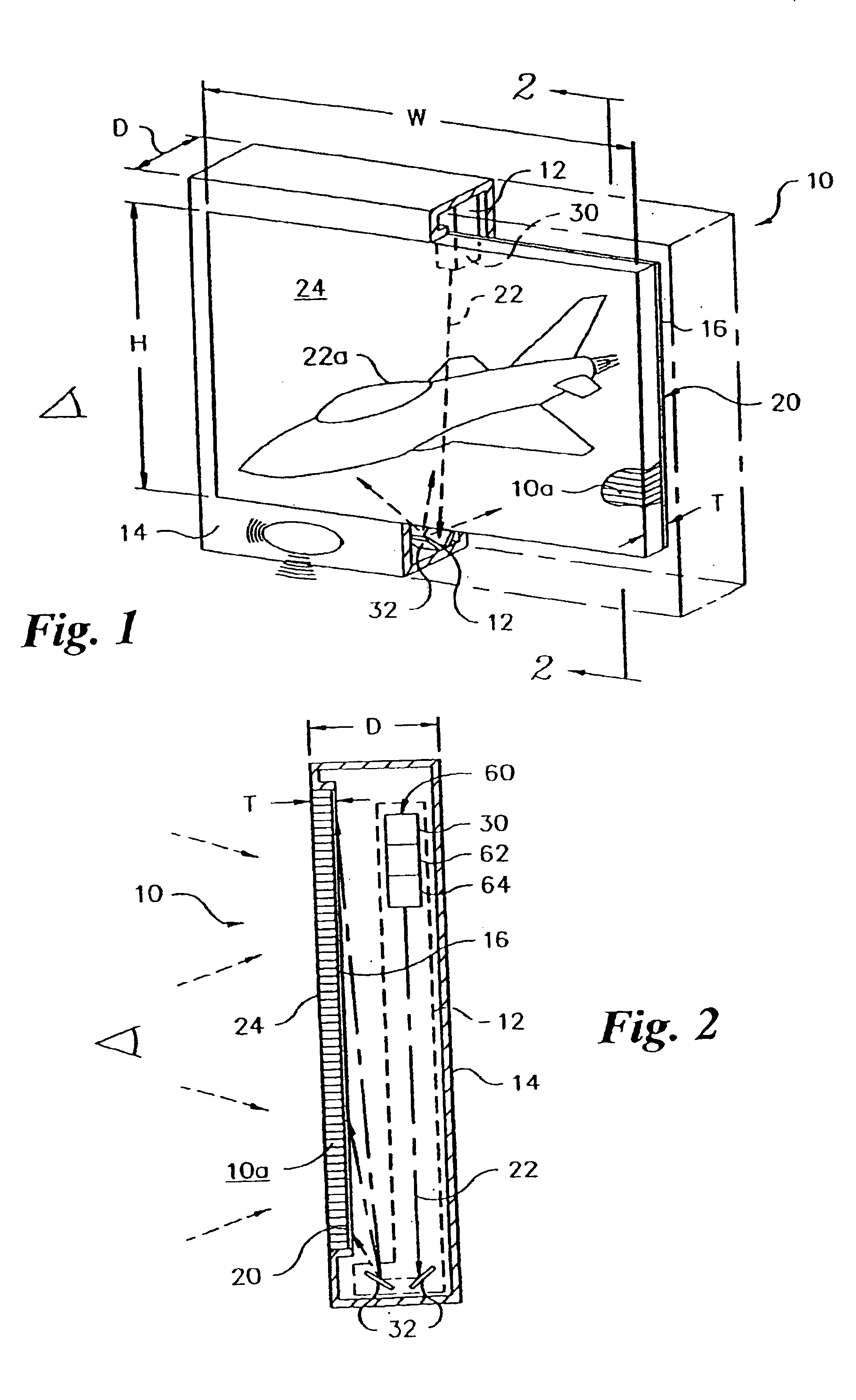

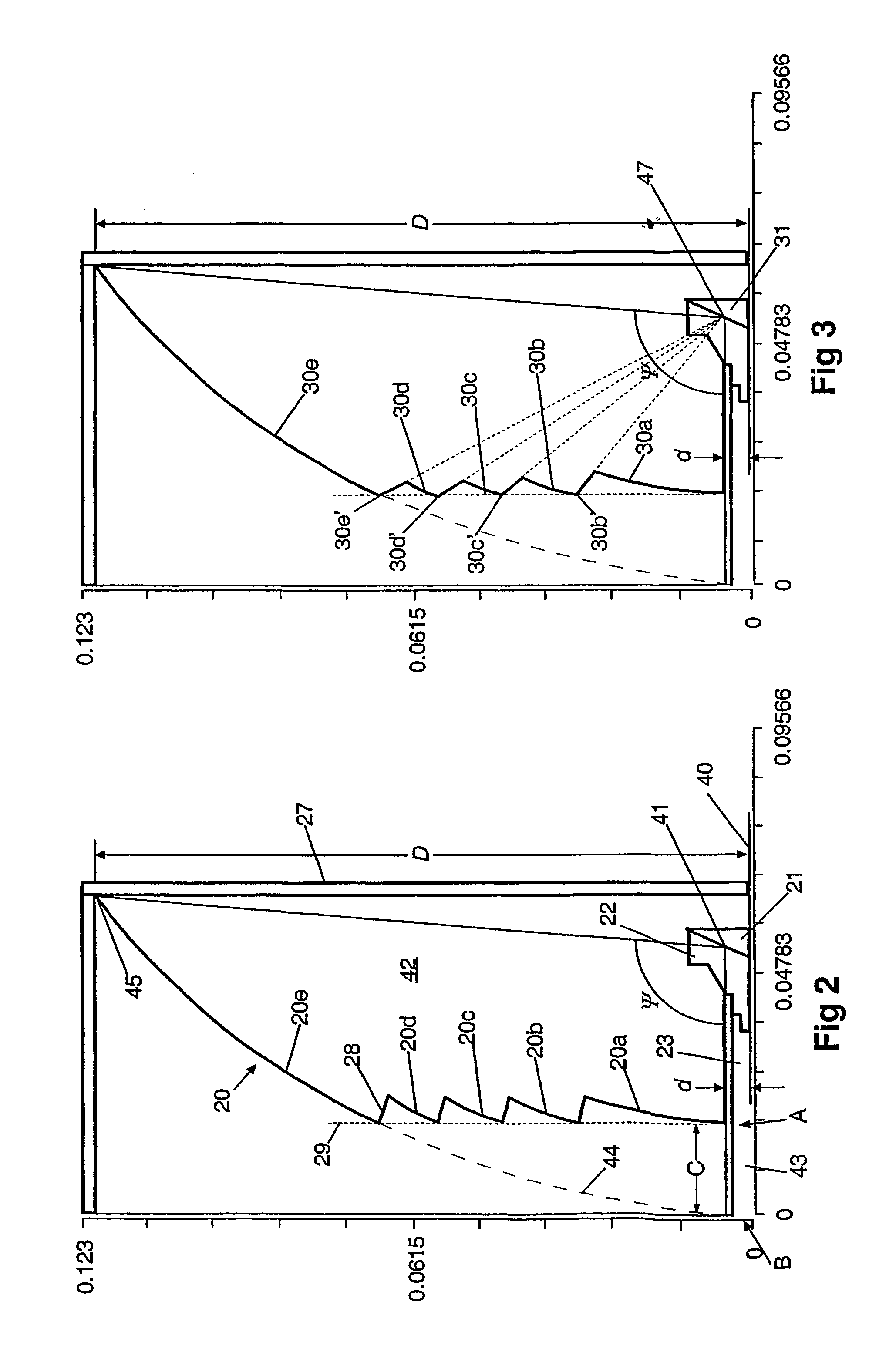

Ultrathin optical panel and a method of making an ultrathin optical panel

InactiveUS6895151B2Increase contrastDepth is minimizedTelevision system detailsProjectorsEpoxyAdhesive

Owner:BROOKHAVEN SCI ASSOCS

Ultrathin optical panel and a method of making an ultrathin optical panel

InactiveUS6856753B2Increase contrastDepth is minimizedTelevision system detailsProjectorsEpoxyAdhesive

An ultrathin optical panel, and a method of producing an ultrathin optical panel, are disclosed, including stacking a plurality of glass sheets, which sheets may be coated with a transparent cladding substance or may be uncoated, fastening together the plurality of stacked coated glass sheets using an epoxy or ultraviolet adhesive, applying uniform pressure to the stack, curing the stack, sawing the stack to form an inlet face on a side of the stack and an outlet face on an opposed side of the stack, bonding a coupler to the inlet face of the stack, and fastening the stack, having the coupler bonded thereto, within a rectangular housing having an open front which is aligned with the outlet face, the rectangular housing having therein a light generator which is optically aligned with the coupler. The light generator is preferably placed parallel to and proximate with the inlet face, thereby allowing for a reduction in the depth of the housing.

Owner:BROOKHAVEN SCI ASSOCS

Method for fabricating semiconductor device with recessed channel region

InactiveUS20050250284A1Depth be minimizeDepth is minimizedSolid-state devicesDomestic plumbingOxideSemiconductor

Disclosed is a method for fabricating a semiconductor device with a plurality of recessed channel regions. This method includes the steps of: forming a plurality of device isolation layers in a substrate; forming a hard mask nitride layer, a hard mask oxide layer and a hard mask polysilicon layer on the device isolation and the substrate, thereby obtaining a hard mask pattern; forming a plurality of trenches in the predetermined regions of the substrate with use of the hard mask pattern to expose a plurality of recessed channel regions; selectively removing the hard mask pattern; and forming a plurality of gate structures in the plurality of trenches.

Owner:SK HYNIX INC

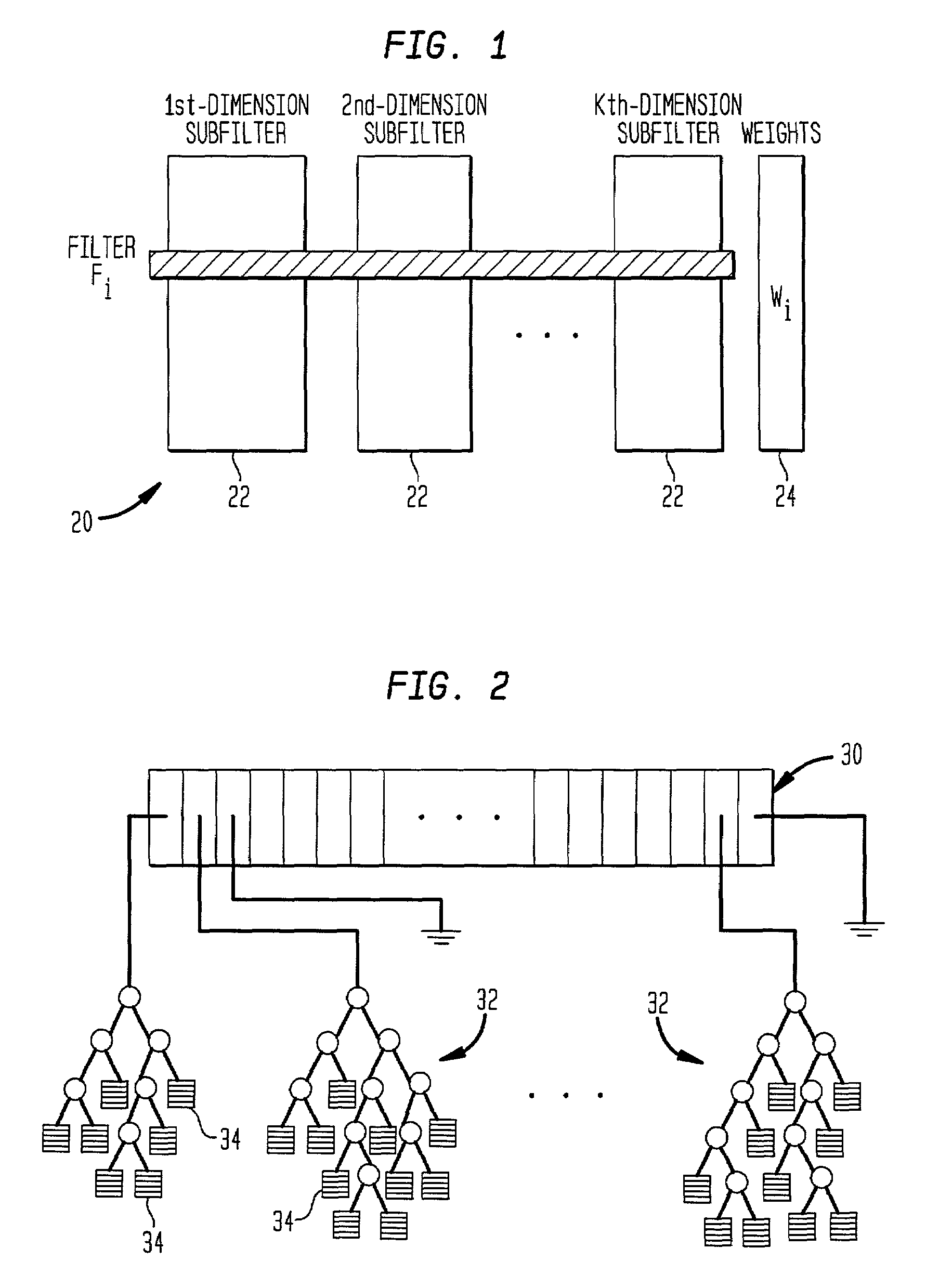

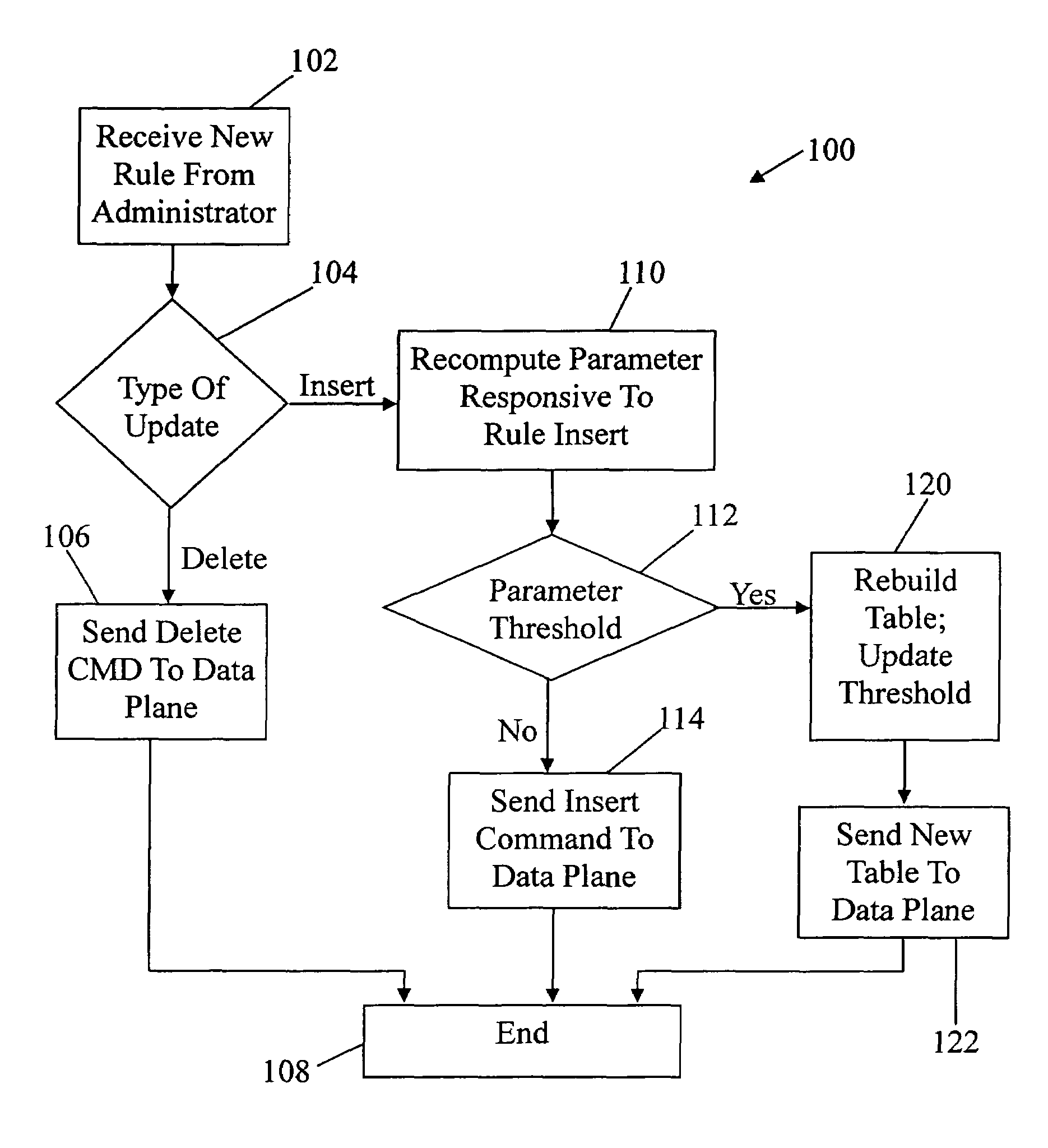

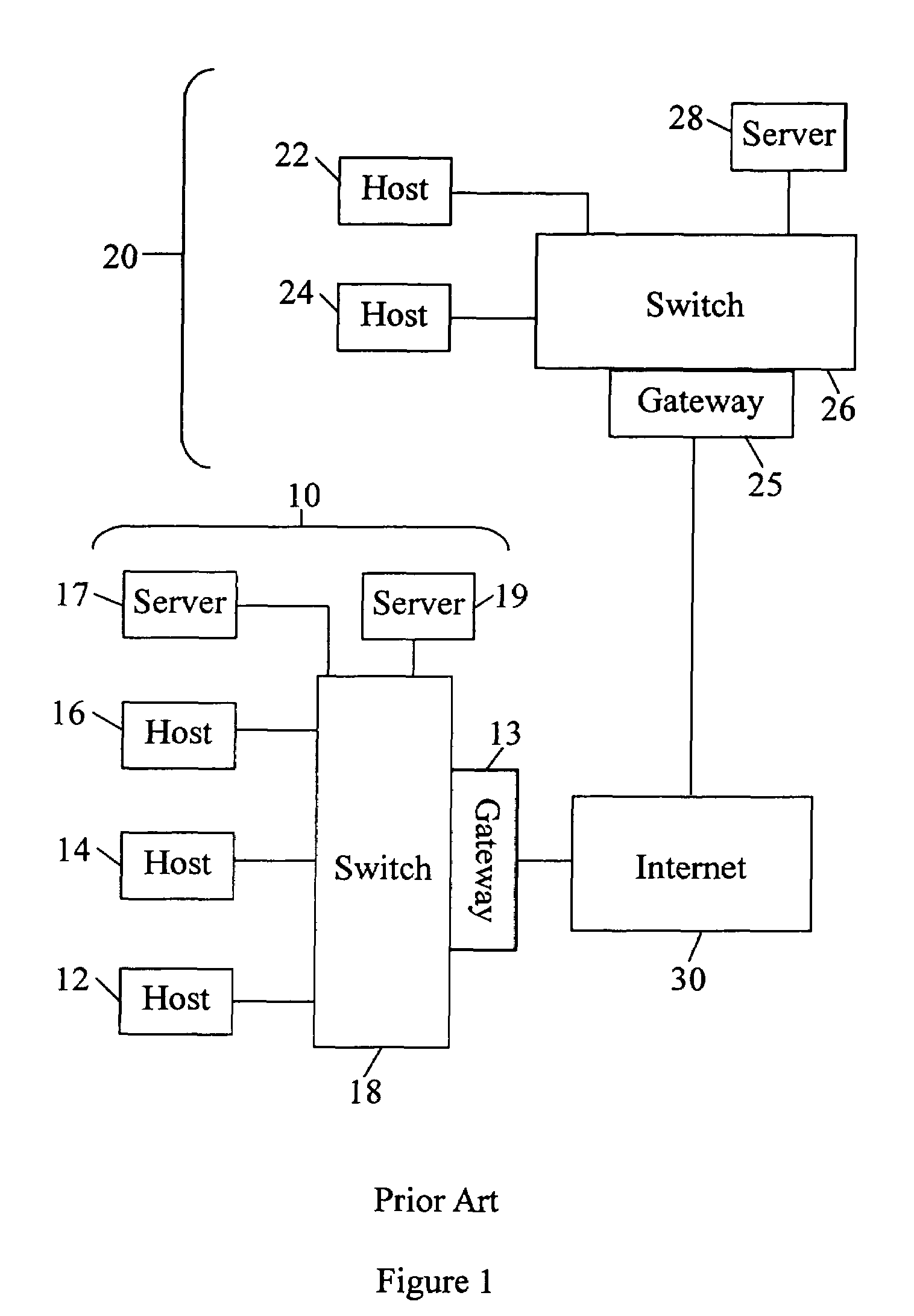

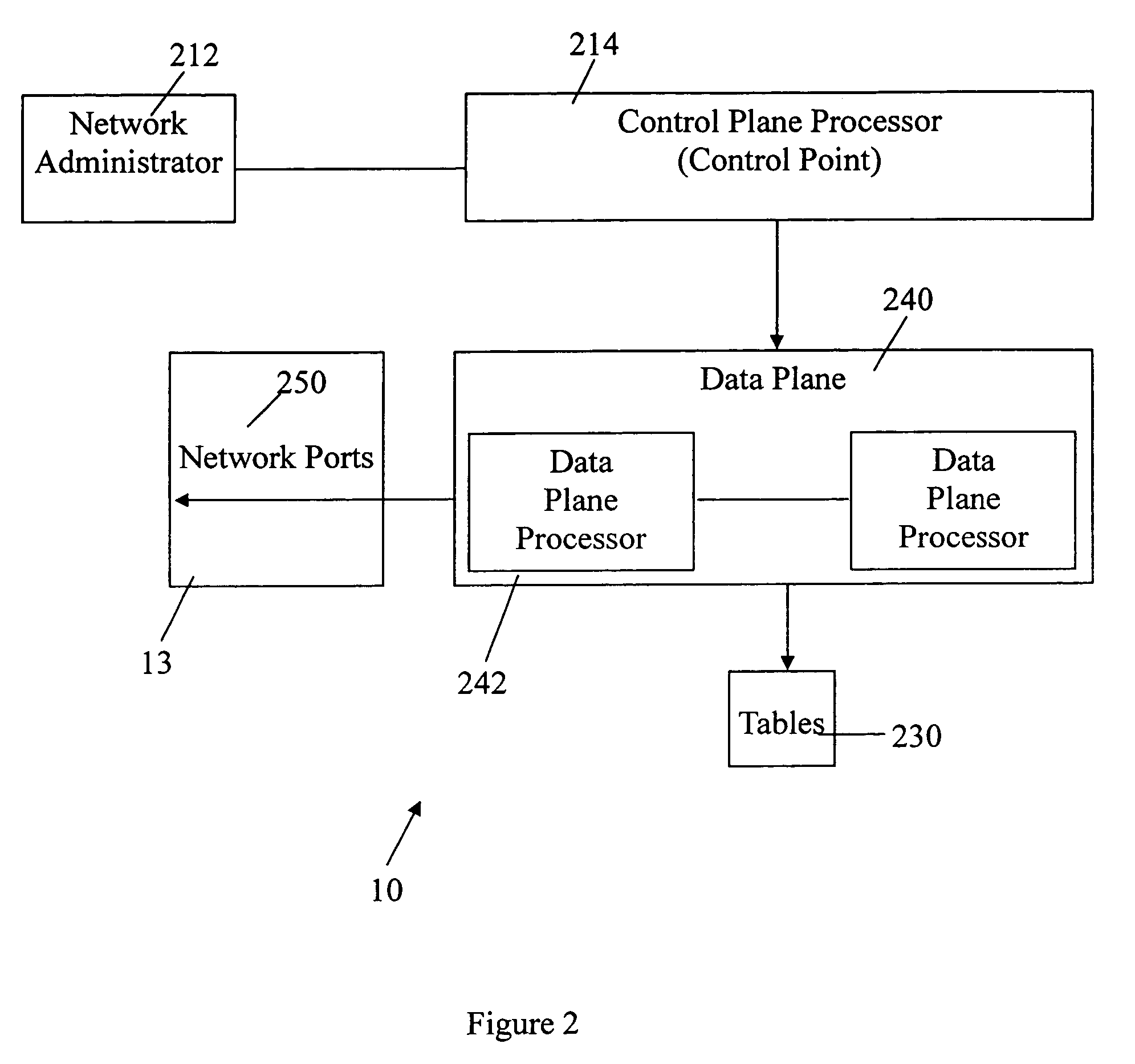

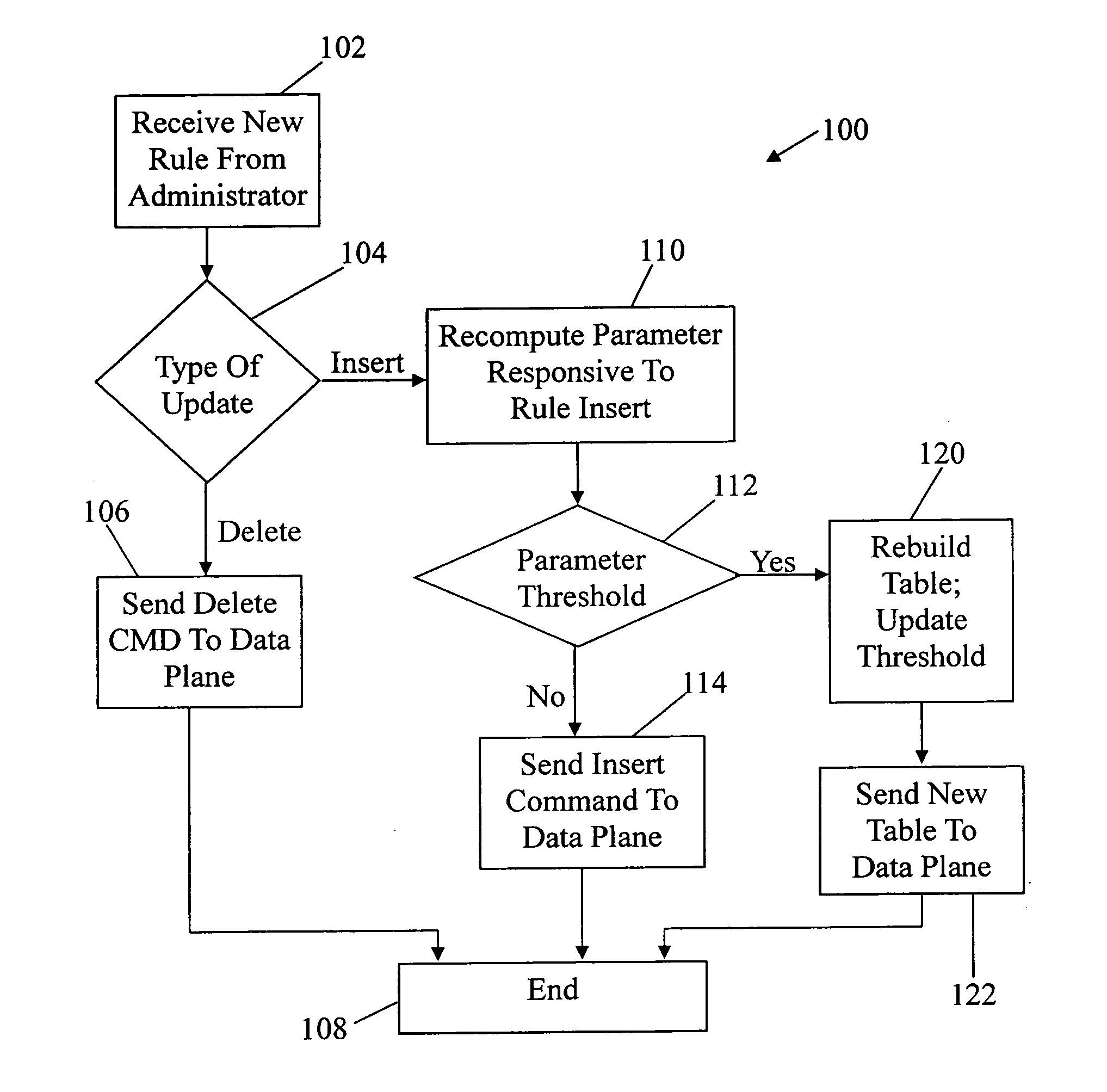

Multi-field classification dynamic rule updates

InactiveUS7478426B2Depth is minimizedMinimize timeMultiple digital computer combinationsProgram controlTotal countAlgorithm

Owner:INT BUSINESS MASCH CORP

Single piece rotary wrenching tool

A rotary wrenching tool used on polygonal nuts, bolts and screws is disclosed. More particularly, the wrenching tool is a single piece rotary wrenching tool with a uniform interior having no moving parts and consisting of six or twelve inwardly projecting lobes of the same size that enable the wrench or socket to exert pressure on the flats of hexagonal objects away from the corners. This invention further relates to a duplex wrench operable on hexagonal fasteners measured by the metric, inch, or both systems. Within a defined range in one wrench, each wrench secures hexagonal objects measured by both inch and metric systems.

Owner:HART HERBERT G

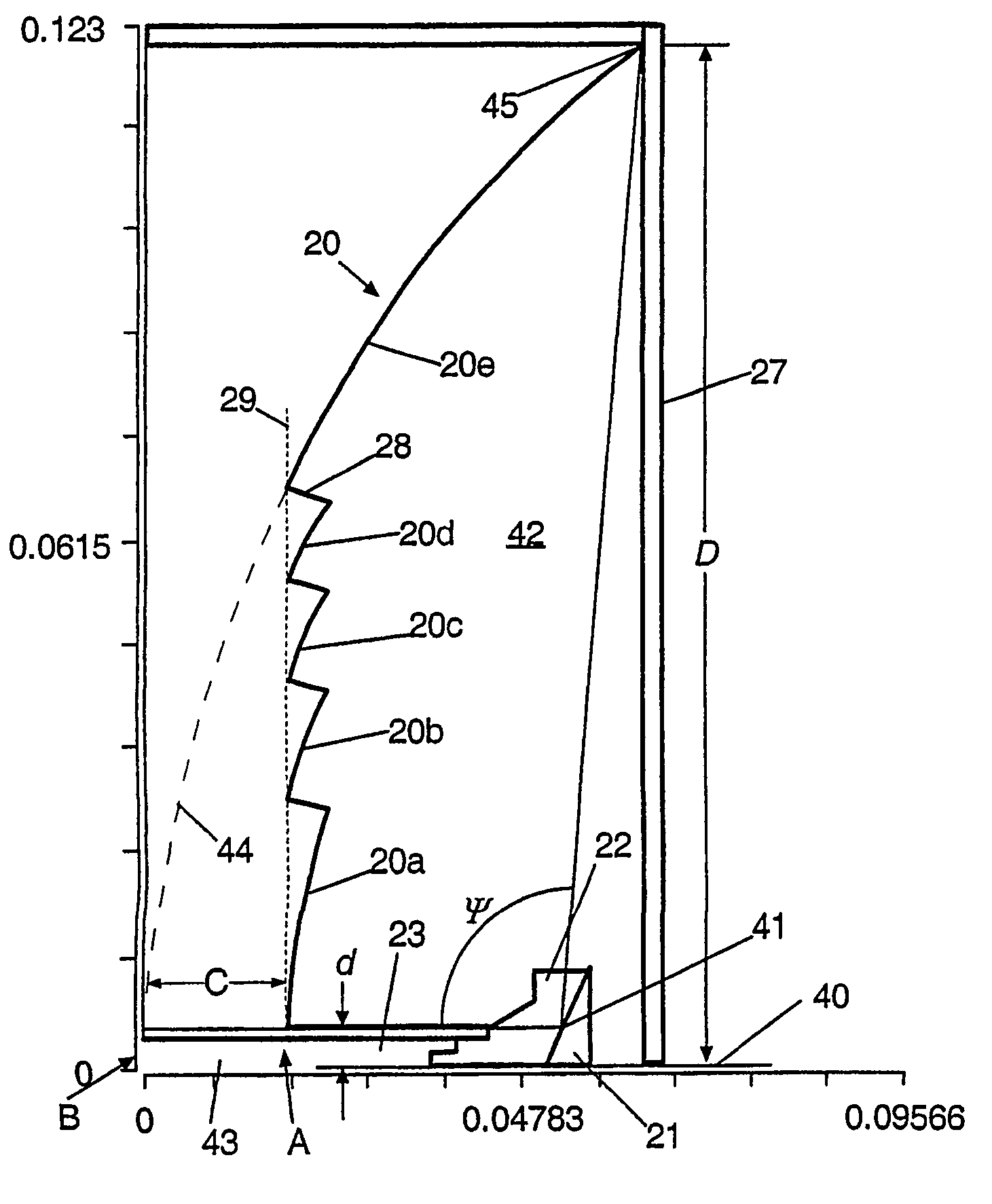

Parabolic reflector and antenna incorporating same

A parabolic reflector for an antenna has a plurality of concentric annular sections arranged in series from a first annular section nearest a central axis of the reflector to a last annular section defining an outer perimeter of the reflector. Each section has a parabolic reflecting surface between inner and outer perimeters. The sections are configured such that the focal point associated with at least the last section lies inside an internal volume of the reflector and are arranged with respect to each other along the central axis, such that an overall depth of the reflector is substantially minimized. The inner perimeters of all the sections are preferably arranged to lie substantially on a plane which is perpendicular to the central axis. The outer perimeter of each section except the last section is preferably connected with the inner perimeter of the succeeding section by means of an annular strip. The strips may either each have an angle of inclination to the reflector central axis of between 0° and 3° or they may lie on respective cones running from the respective inner perimeters of the respective sections to which they are joined, to the furthest located focal point or ring.

Owner:TELEFON AB LM ERICSSON (PUBL)

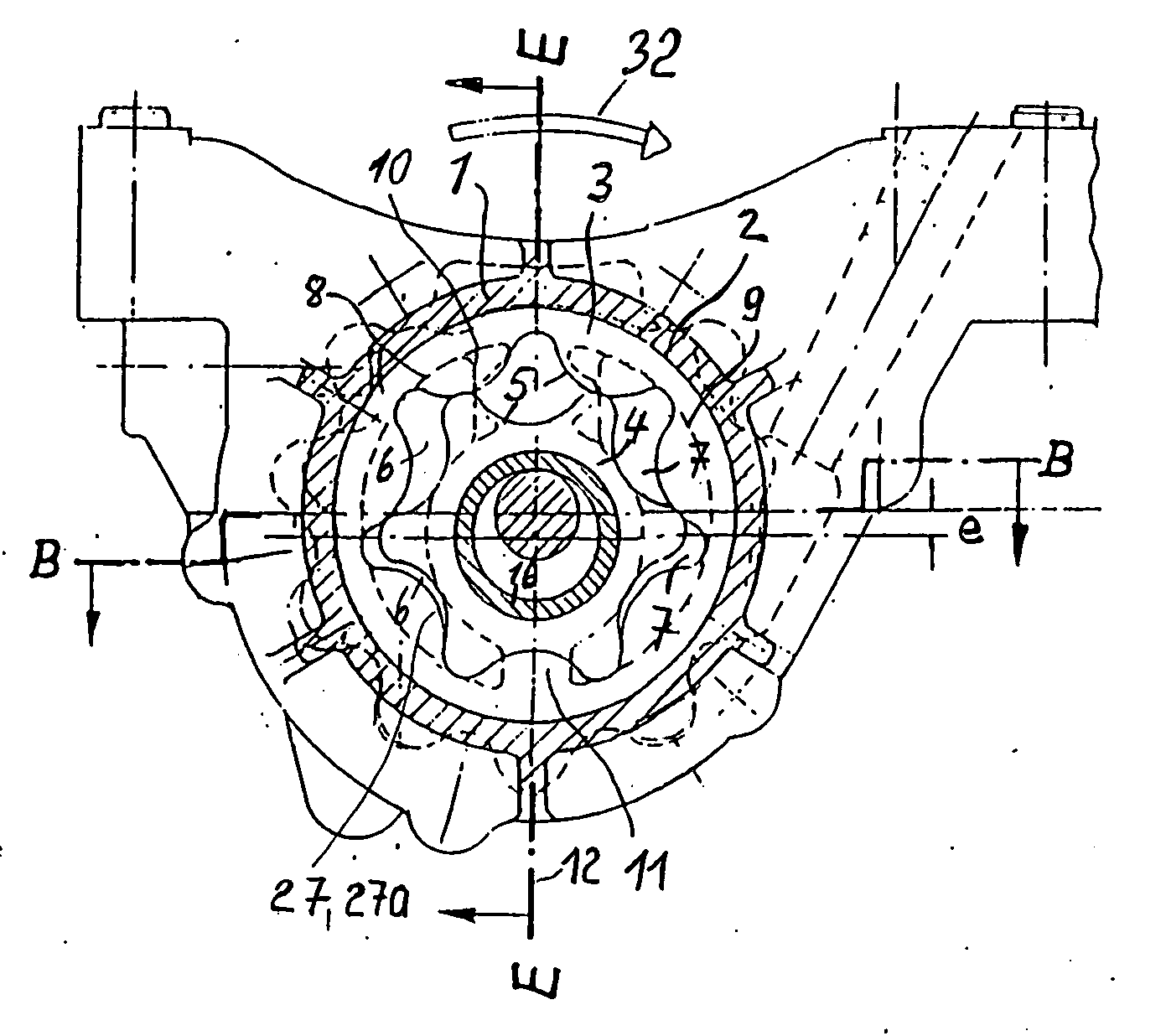

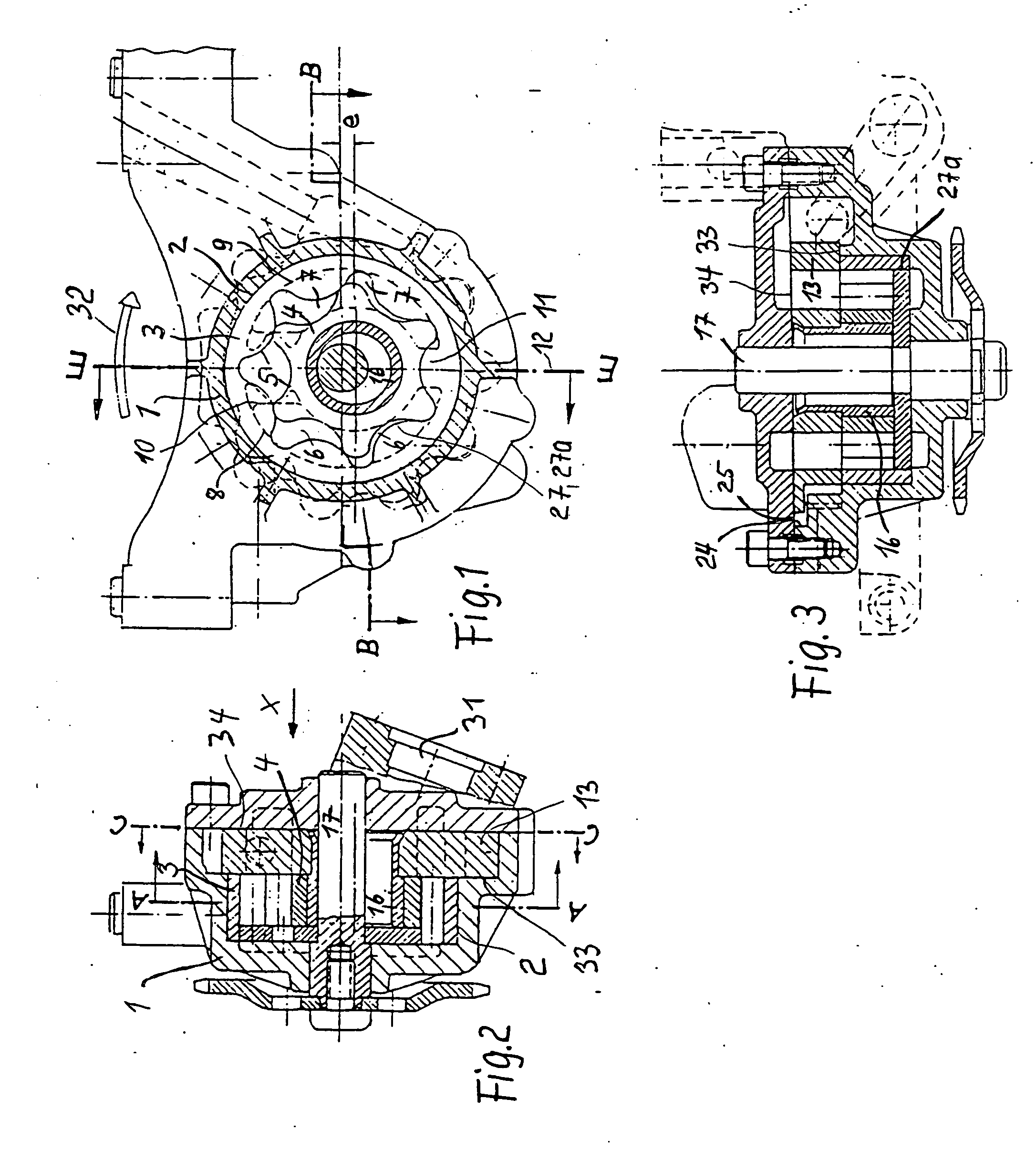

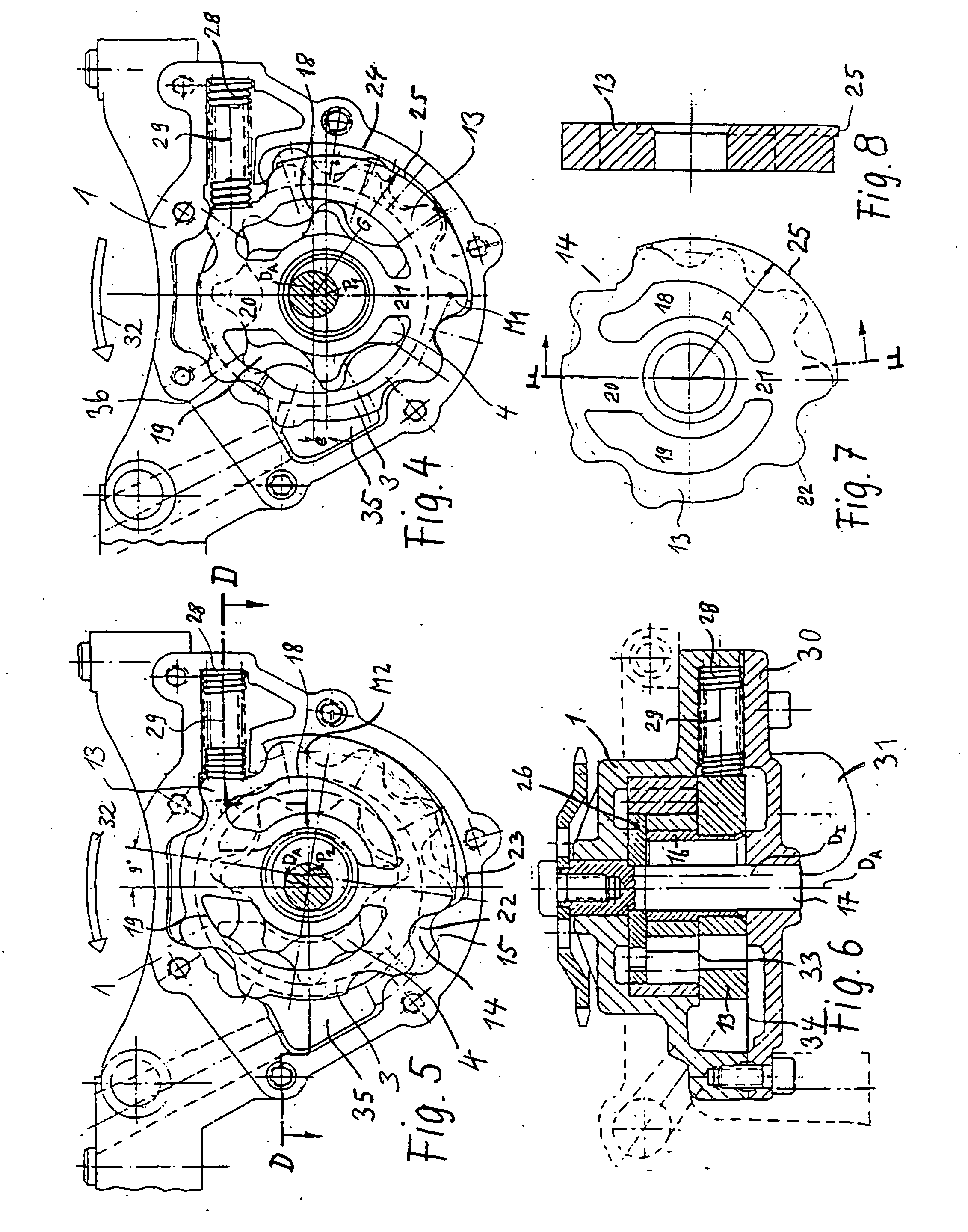

Displacement pump with variable volume flow

InactiveUS20050214149A1Reduced design spaceGreat suctionValve arrangementsEngine of arcuate-engagement typeRotational axisHigh pressure

A displacement pump with variable volume flow having a casing; a chamber with an inlet opening on a low pressure side and an outlet opening on a high pressure side for a fluid; an internal rotor capable of rotation about a rotational axis (DI); a ring having a central ring axis (DA) surrounding the internal rotor and forming together with the ring, at least one delivery cell in which fluid is delivered from a low pressure side to a high pressure side of the pump; and an adjusting device which, during an adjusting movement, rolls off on the casing without slipping is provided. The internal rotor is fixed to the adjusting device and rotatble about the rotational axis (DI), and the position of the rotational axis (DI) relative to the central ring axis (DA) of the ring is adjusted by the adjusting movement of the adjusting device.

Owner:HARLE HERMONN +1

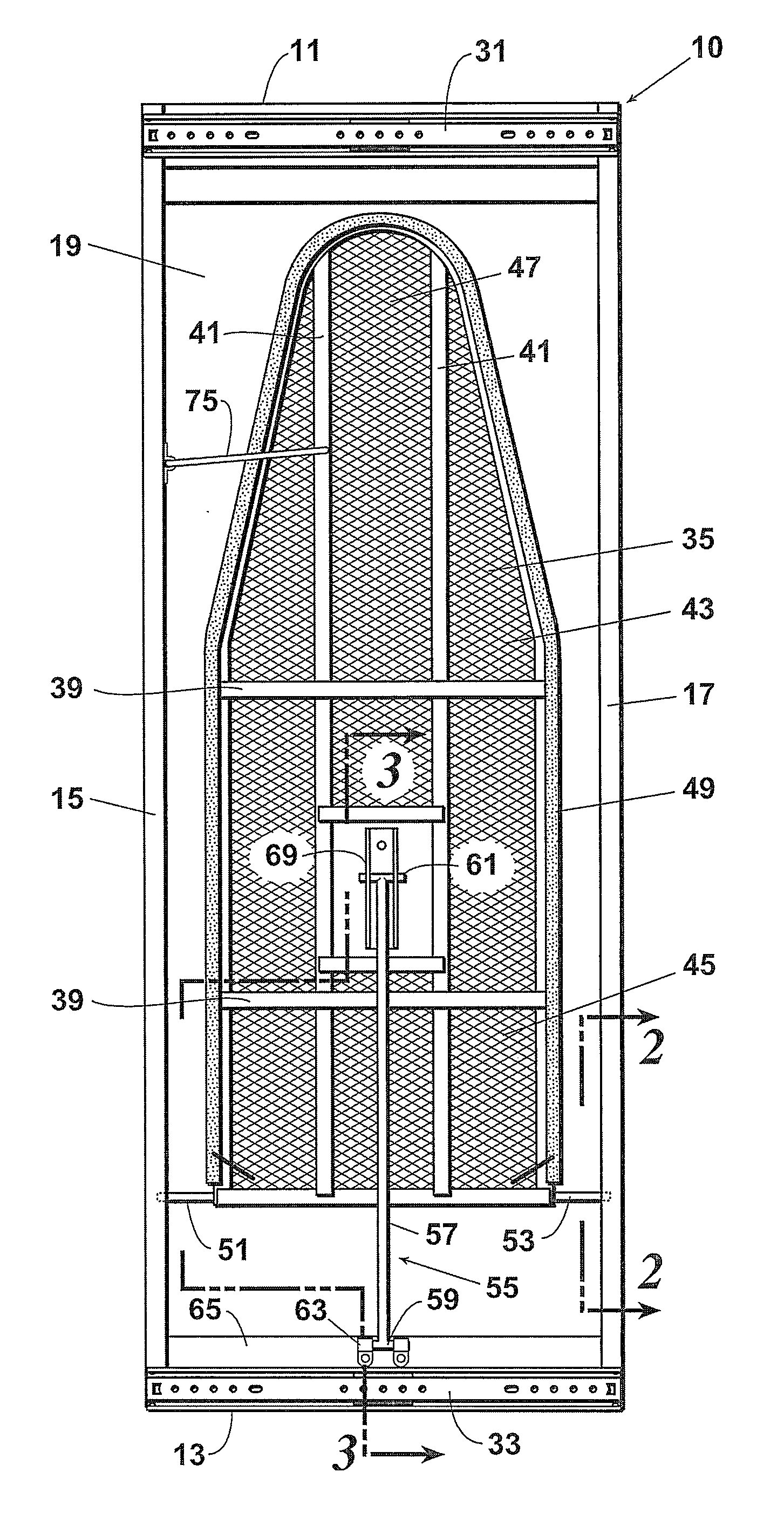

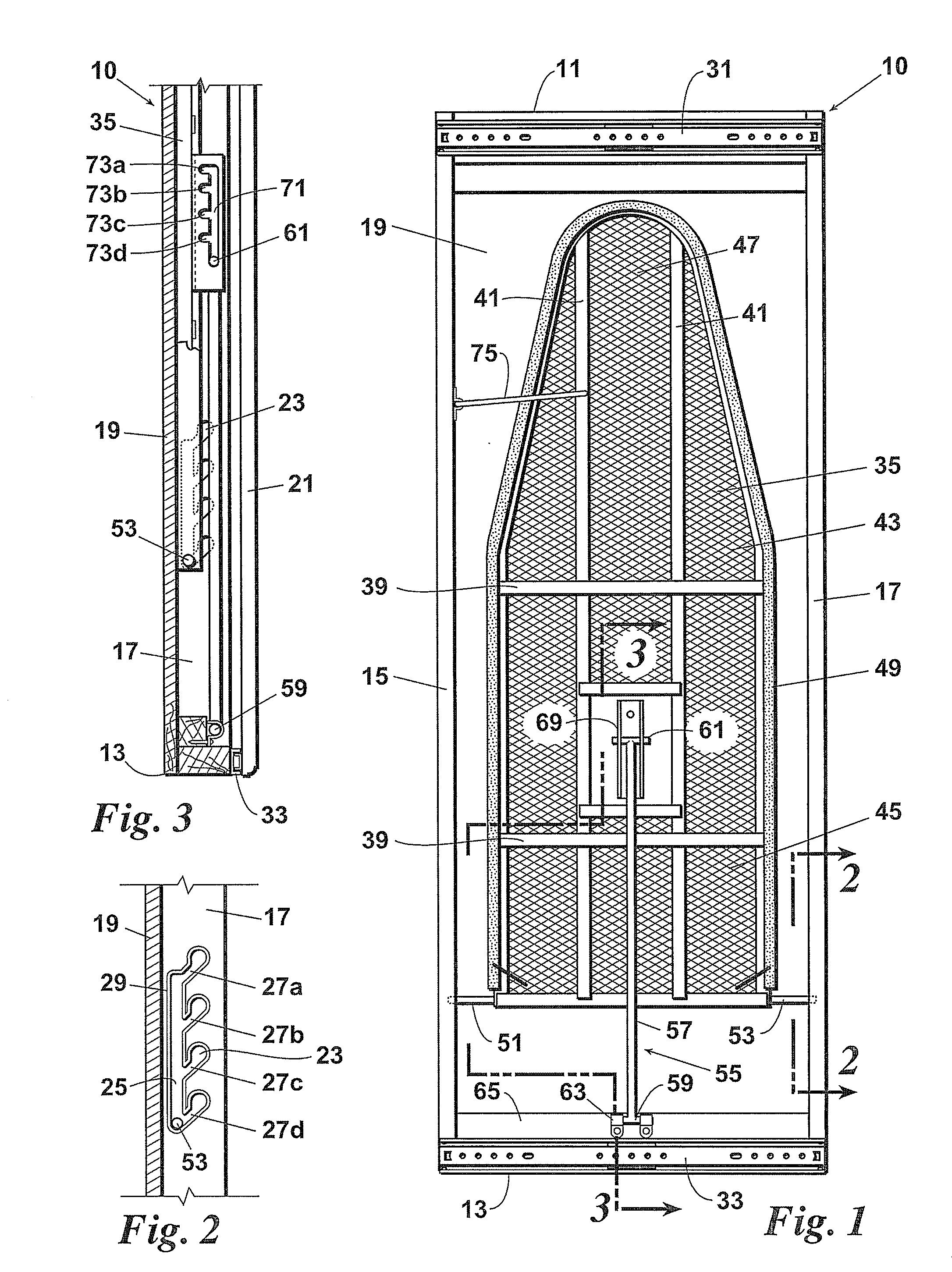

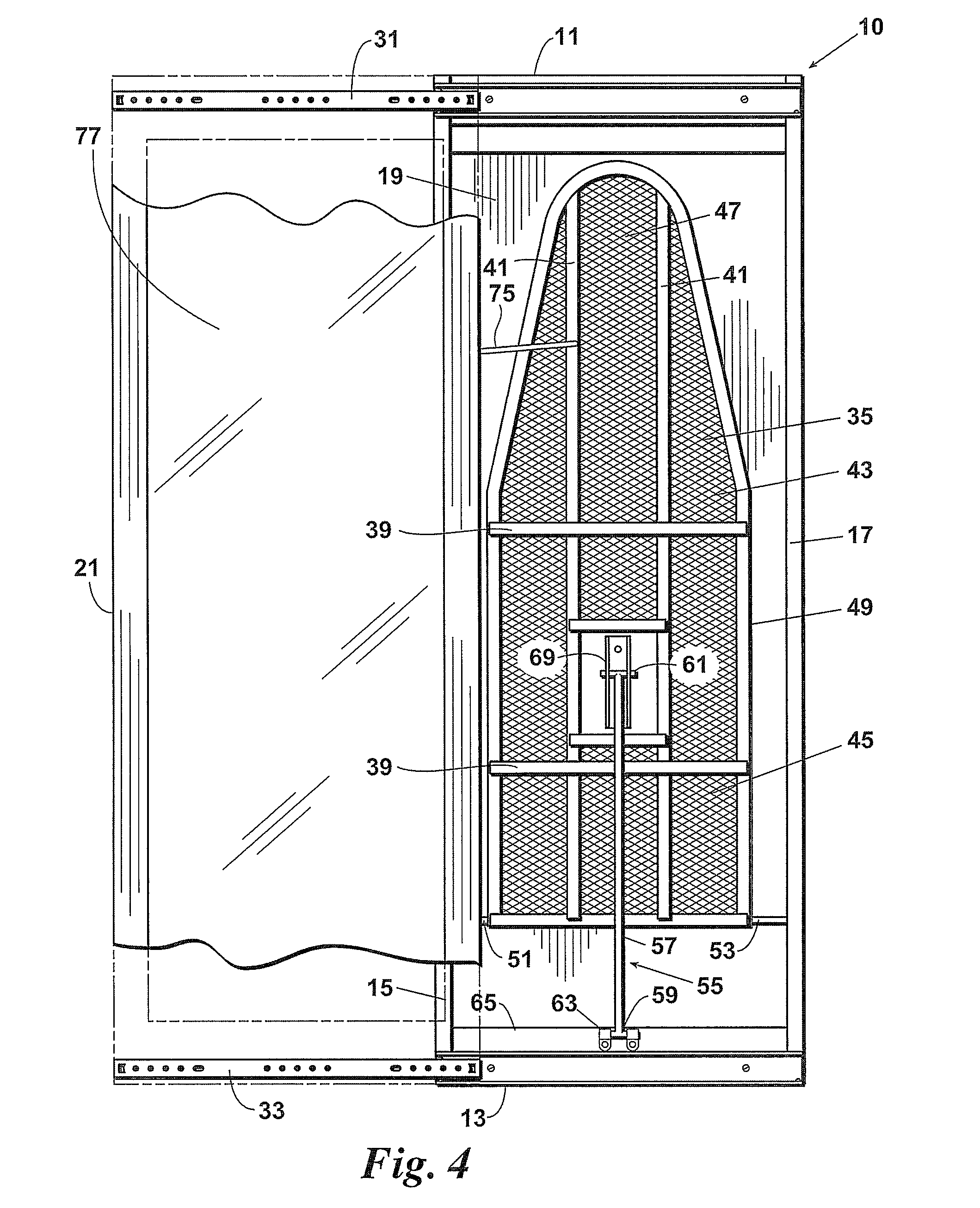

Wall Mounted Ironing Board Cabinet

InactiveUS20130154459A1Possible total numberDepth is minimizedIroning boardsCabinetsSurface levelEngineering

A wall mounted ironing board cabinet has a door on two-way sliders enabling cabinet “opened-to-the-right,”“closed” and “opened-to-the-left” conditions. The sliding door and ironing board hardware afford a cabinet which maximizes the number of possible locations of the cabinet in a room, minimizes the depth of the protrusion of the closed cabinet into the room and renders the door outer surface adaptable to uses unrelated to the storage and support of an ironing board. The ironing board hardware also allows user selection of the ironing board surface level from multiple available intervals.

Owner:C&A INT L L C

Multi-field classification dynamic rule updates

InactiveUS20060020600A1Depth is minimizedMinimize timeMultiple digital computer combinationsProgram controlTotal countAlgorithm

The present invention relates to a method and computer system device for applying a plurality of rules to data packets within a network computer system. A filter rule decision tree is updated by adding or deleting a rule. If deleting a filter rule then the decision tree is provided to a network data plane processor with an incremental delete of the filter rule. If adding a filter rule then either providing an incremental insertion of the filter rule to the decision tree or rebuilding the first decision tree into a second decision tree responsive to comparing a parameter to a threshold. In one embodiment the parameter and thresholds relate to depth values of the tree filter rule chained branches. In another the parameter and thresholds relate to a total count of rule additions since a building of the relevant tree.

Owner:IBM CORP