Patents

Literature

60results about How to "Many change" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

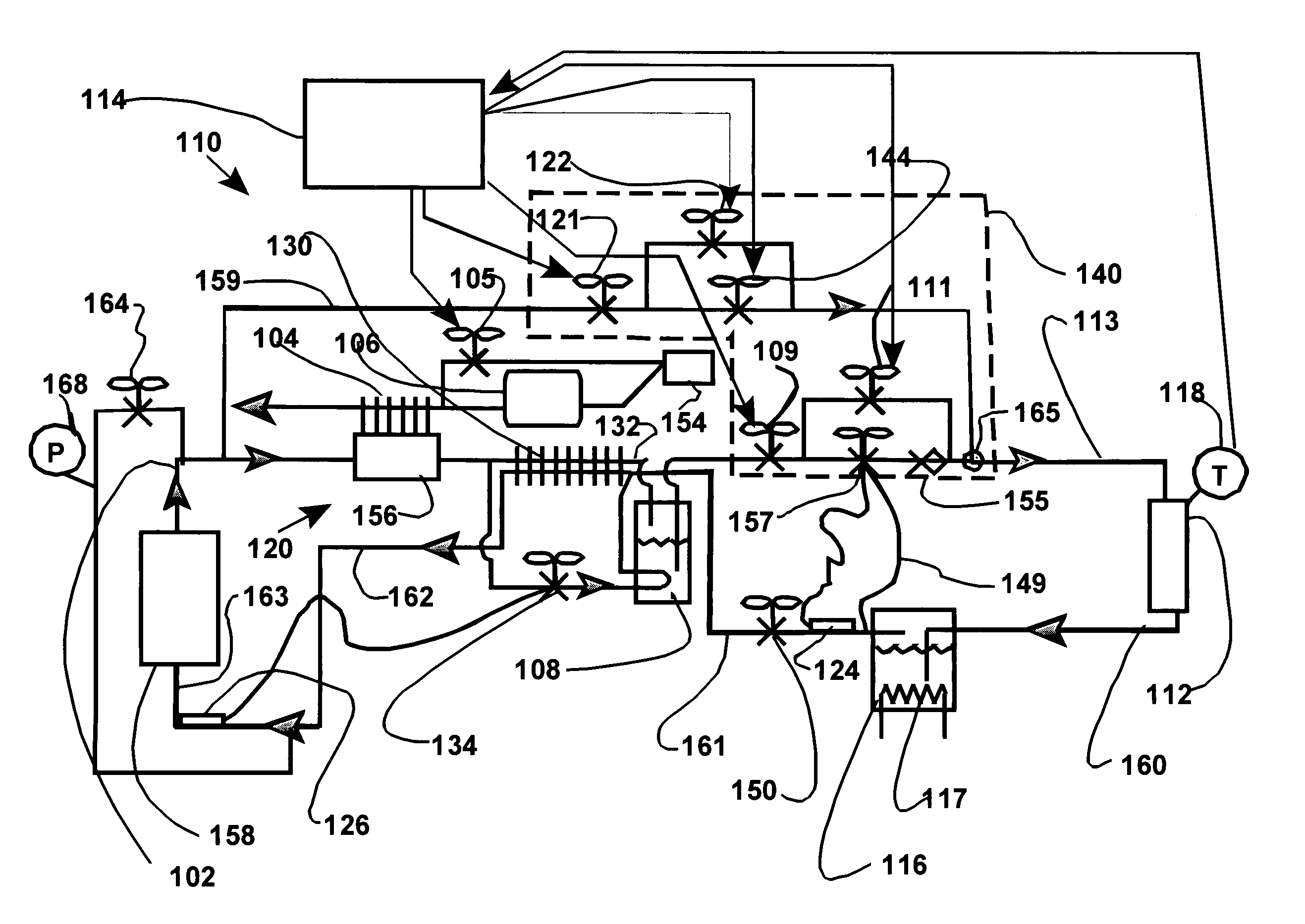

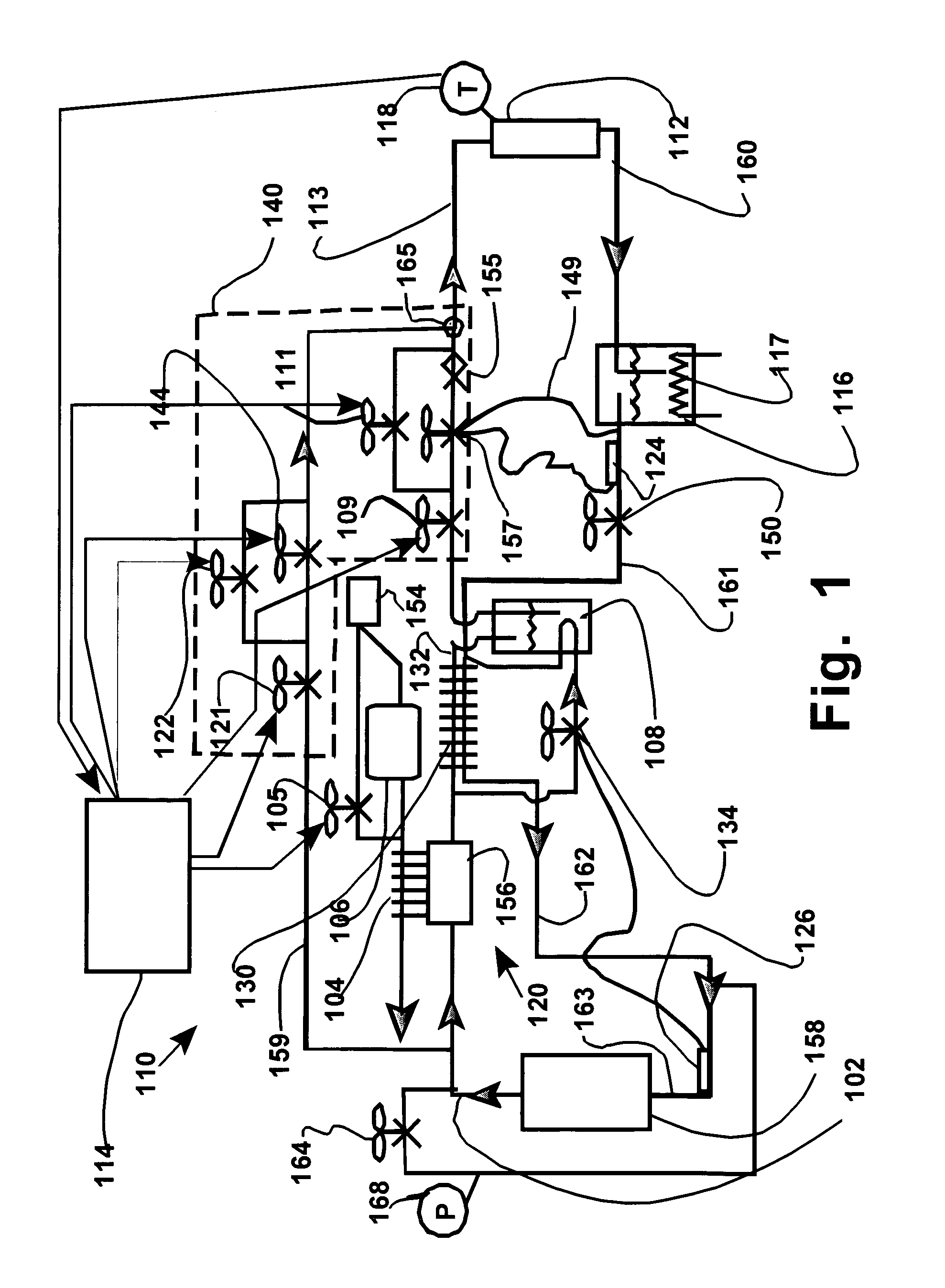

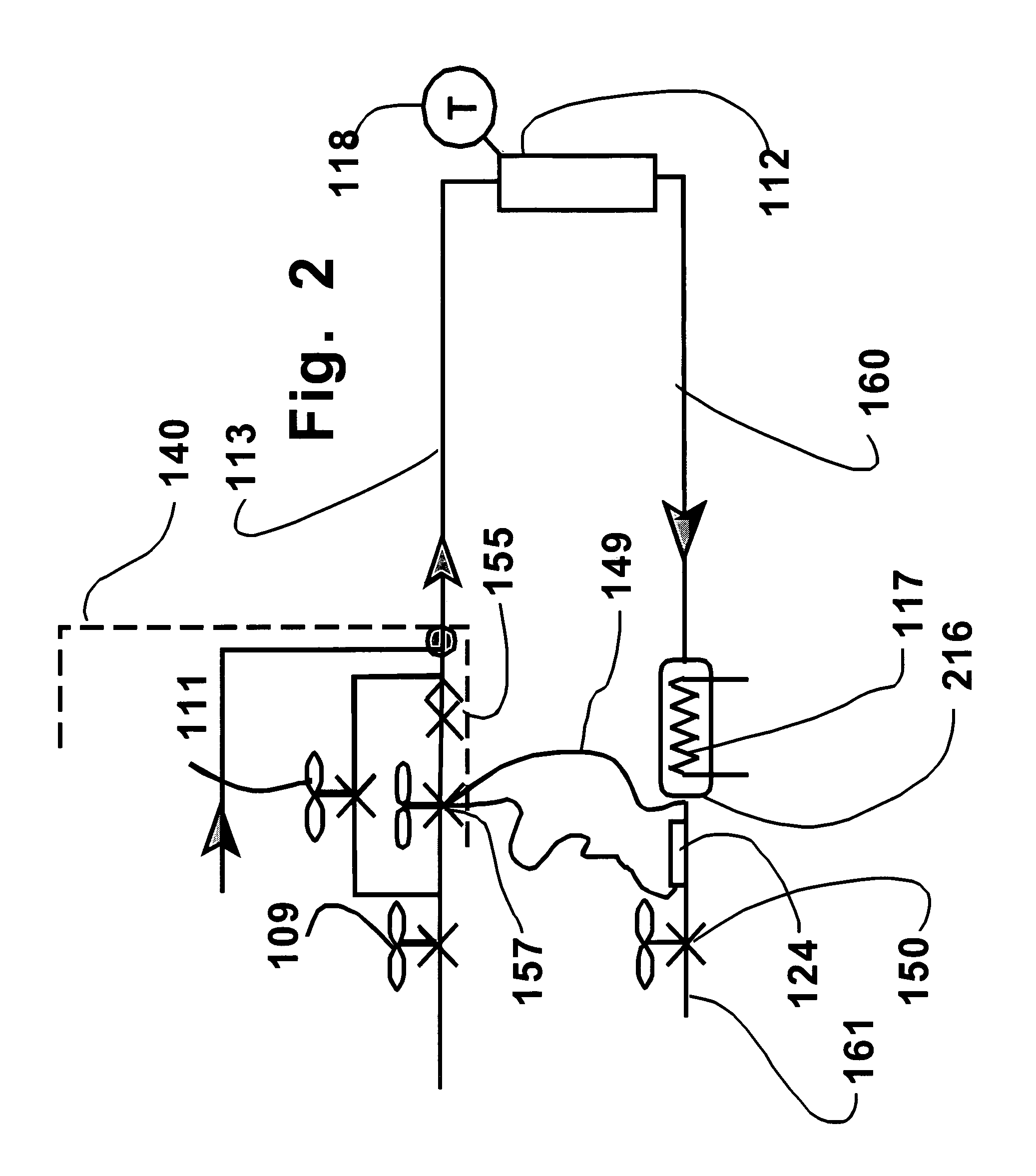

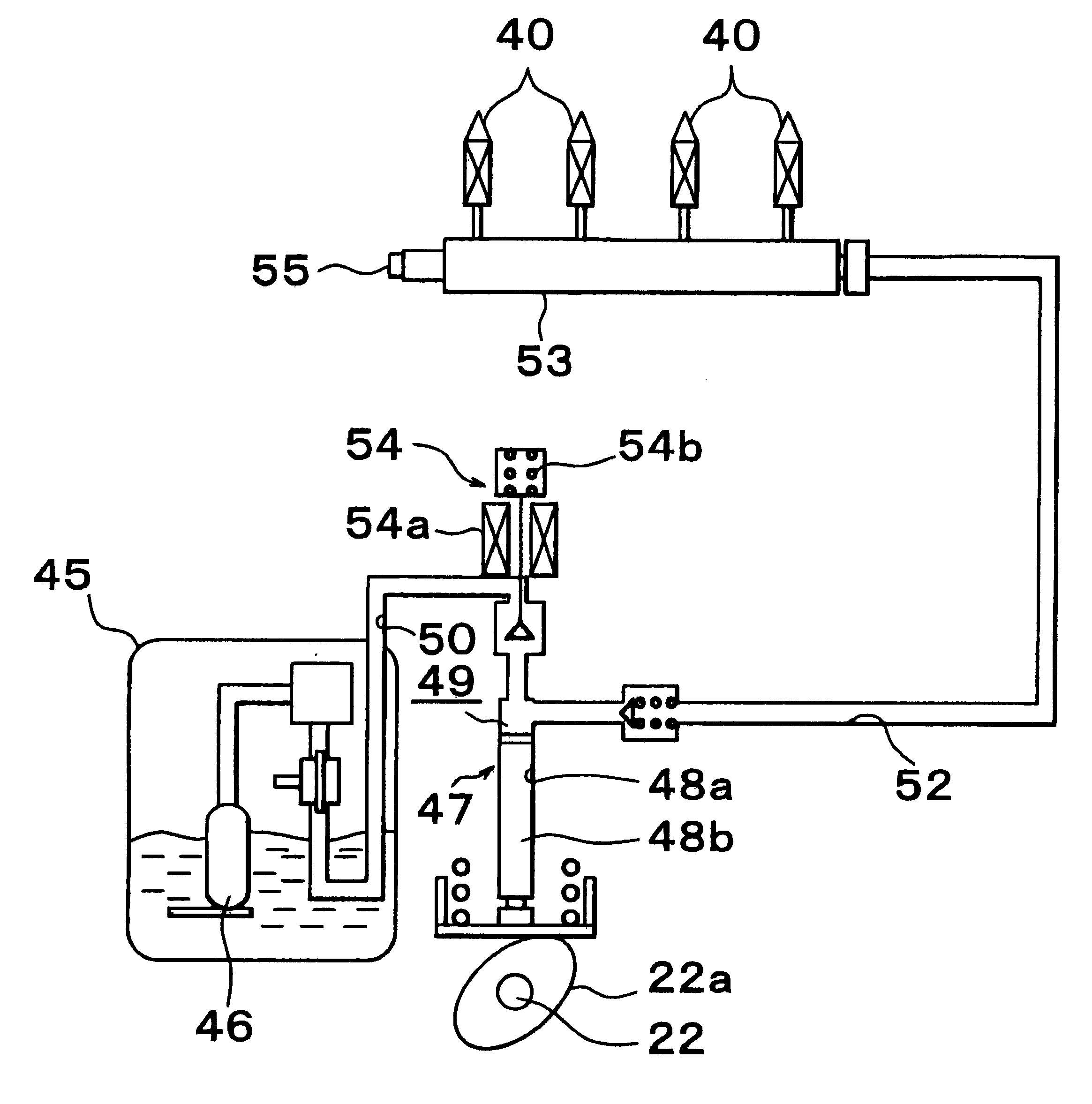

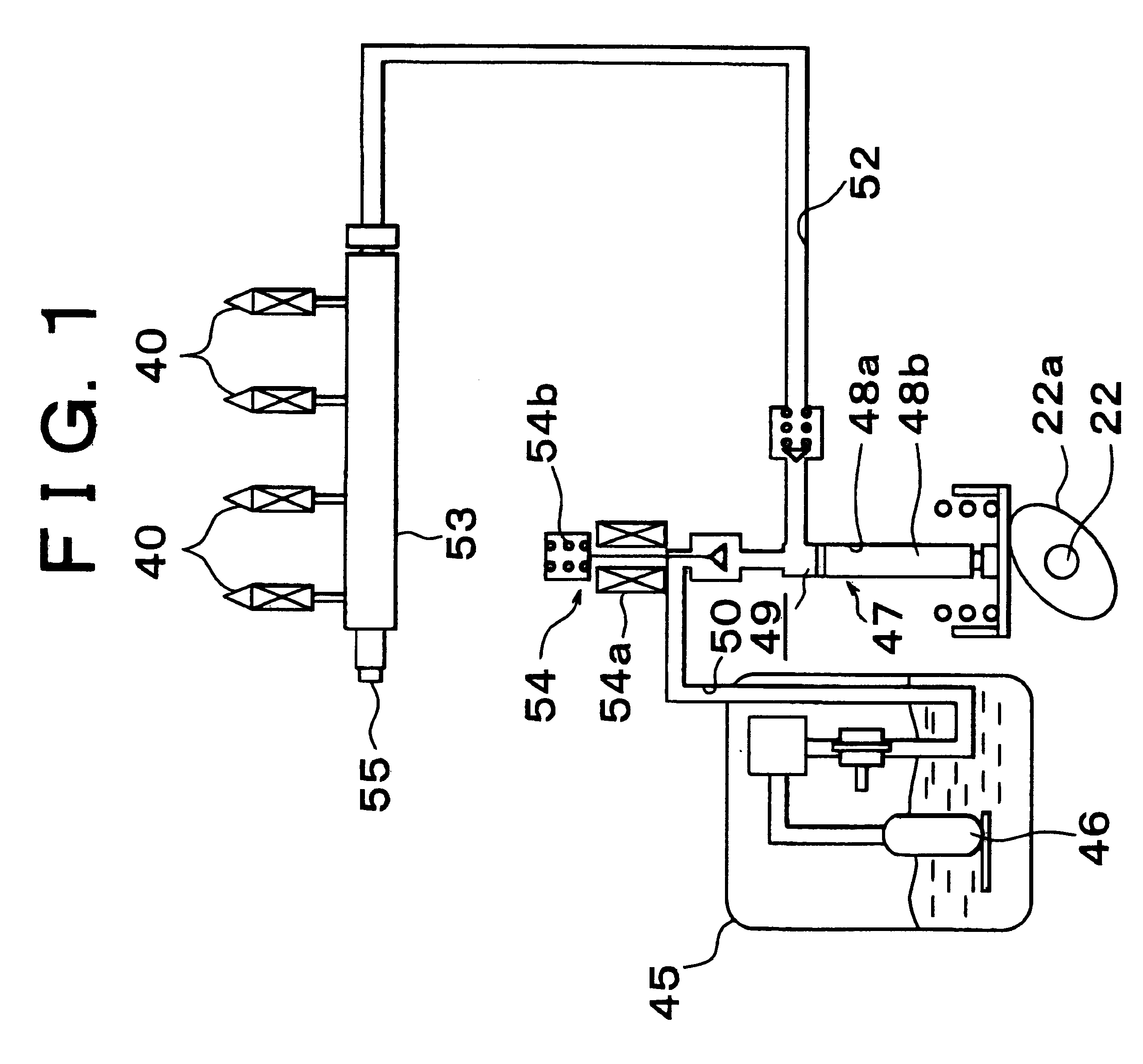

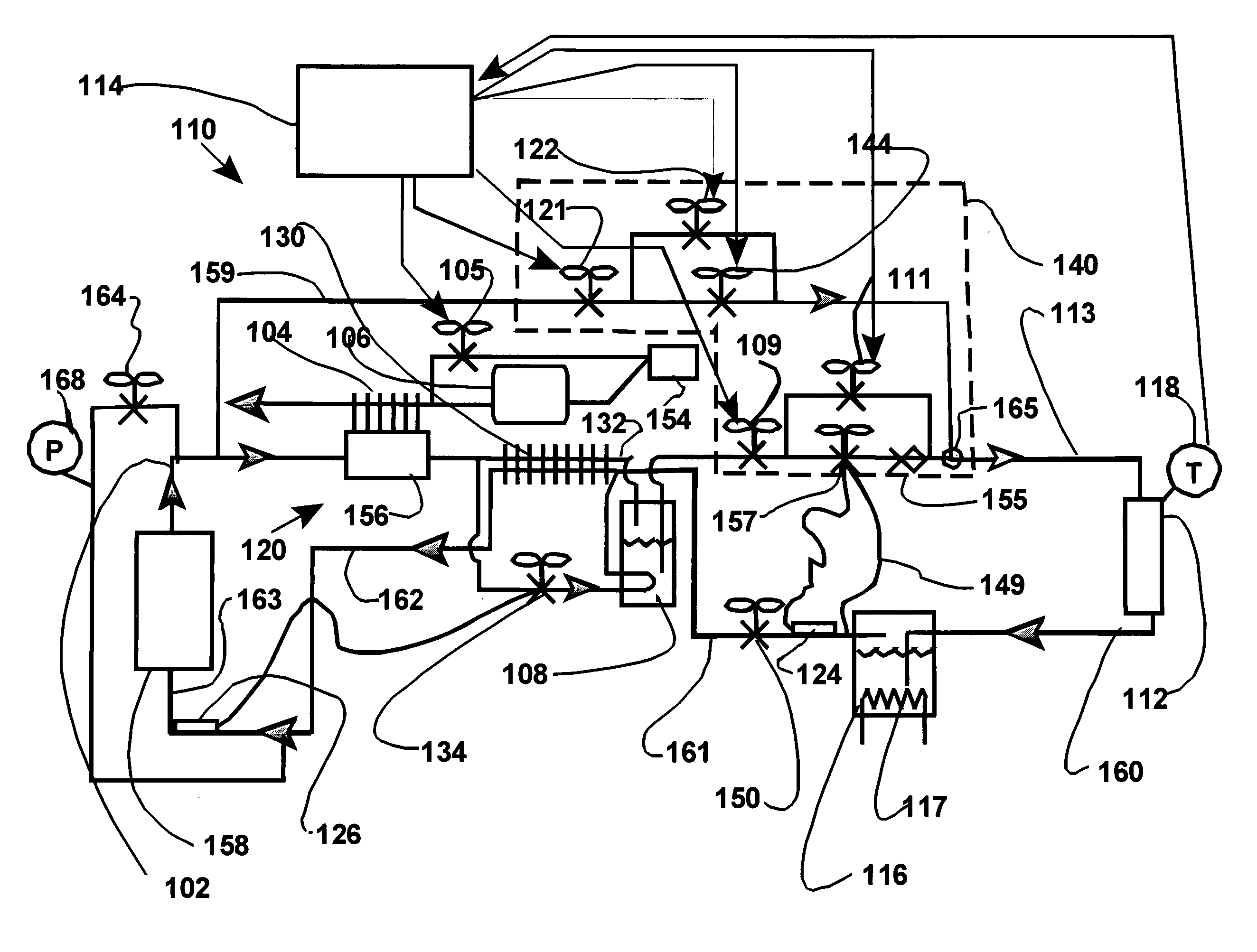

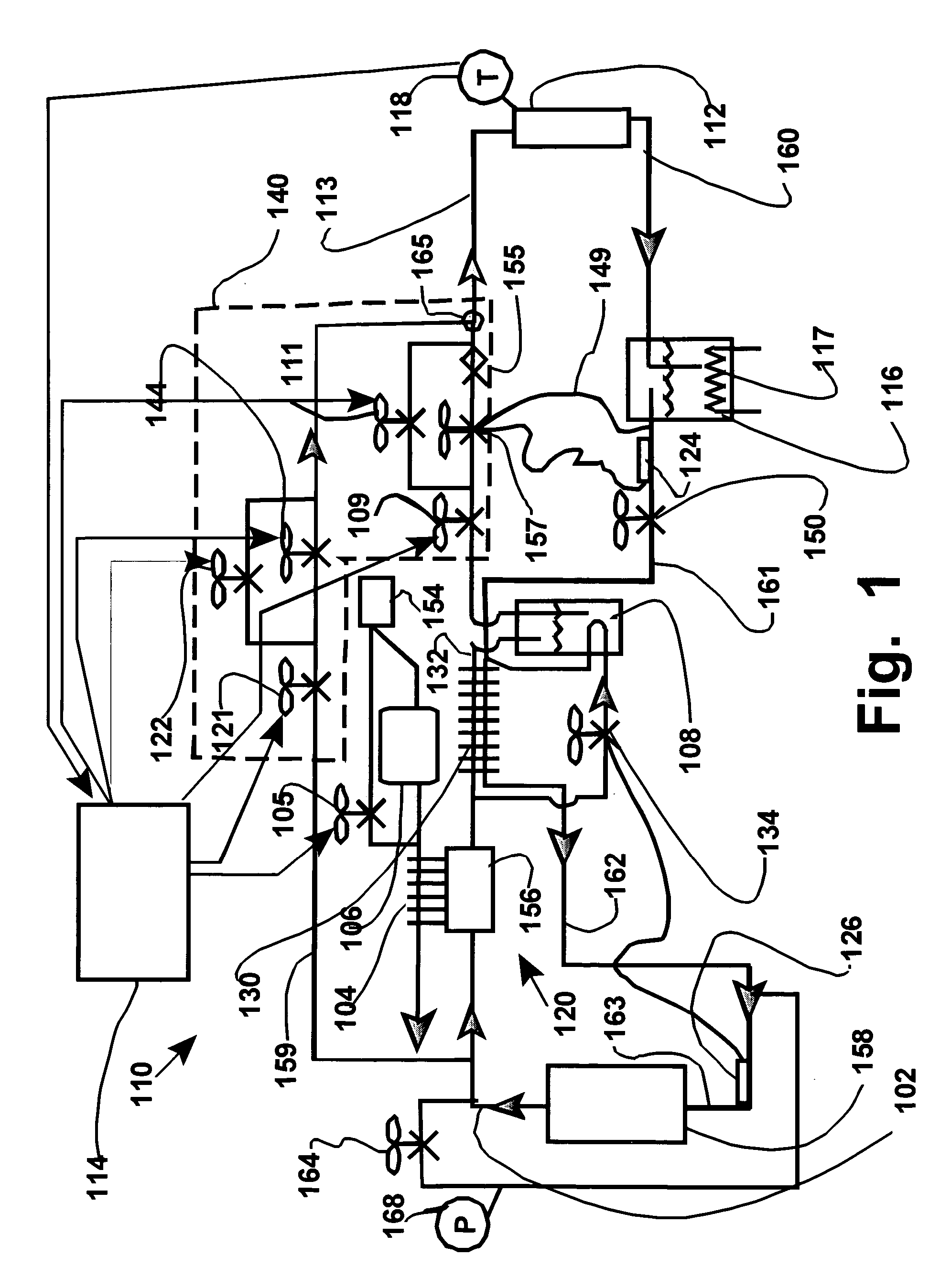

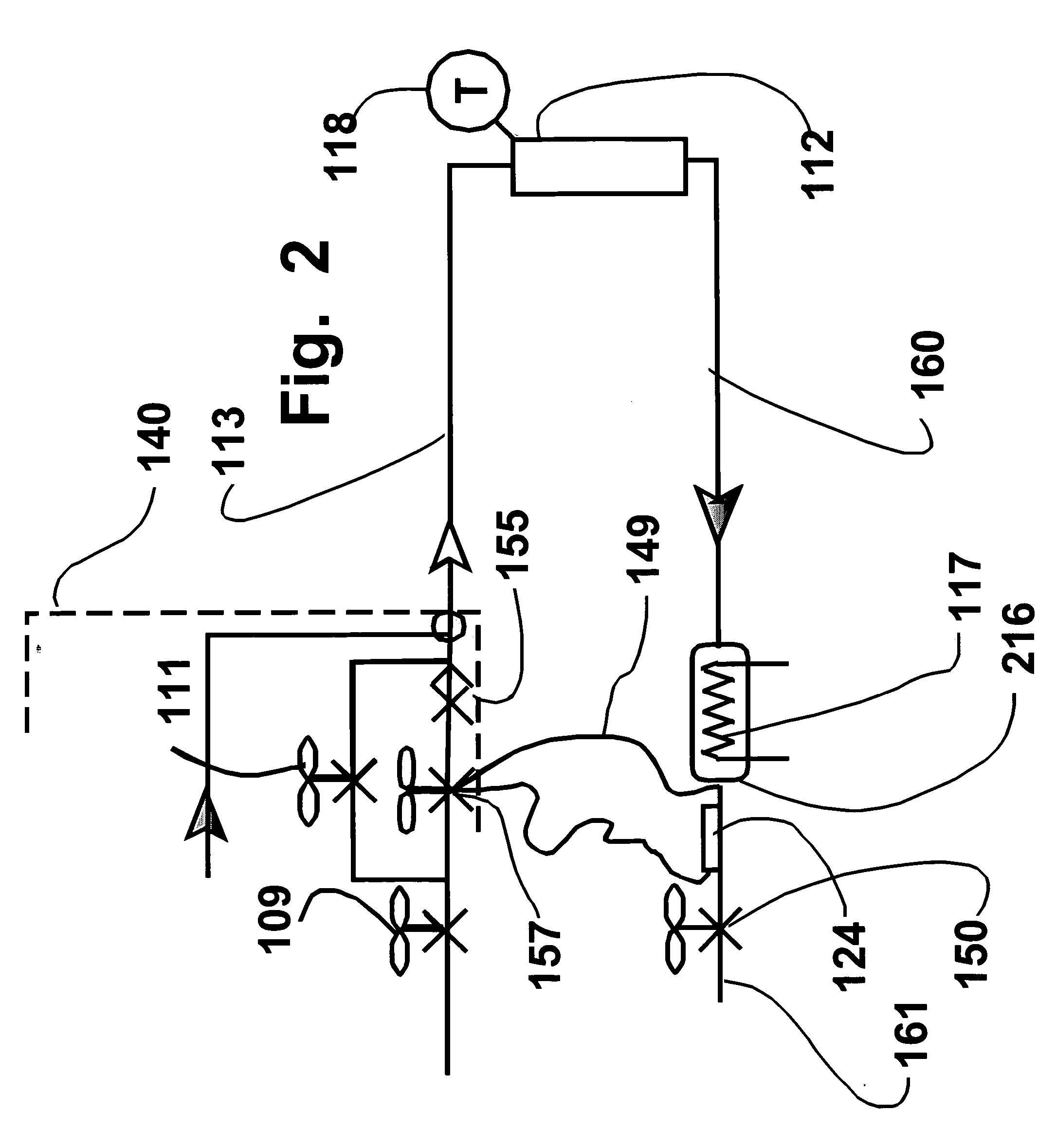

Thermal control system and method

ActiveUS7178353B2High speed responseHigh thermal efficiencyMechanical apparatusHeat pumpsProduct gasProcess engineering

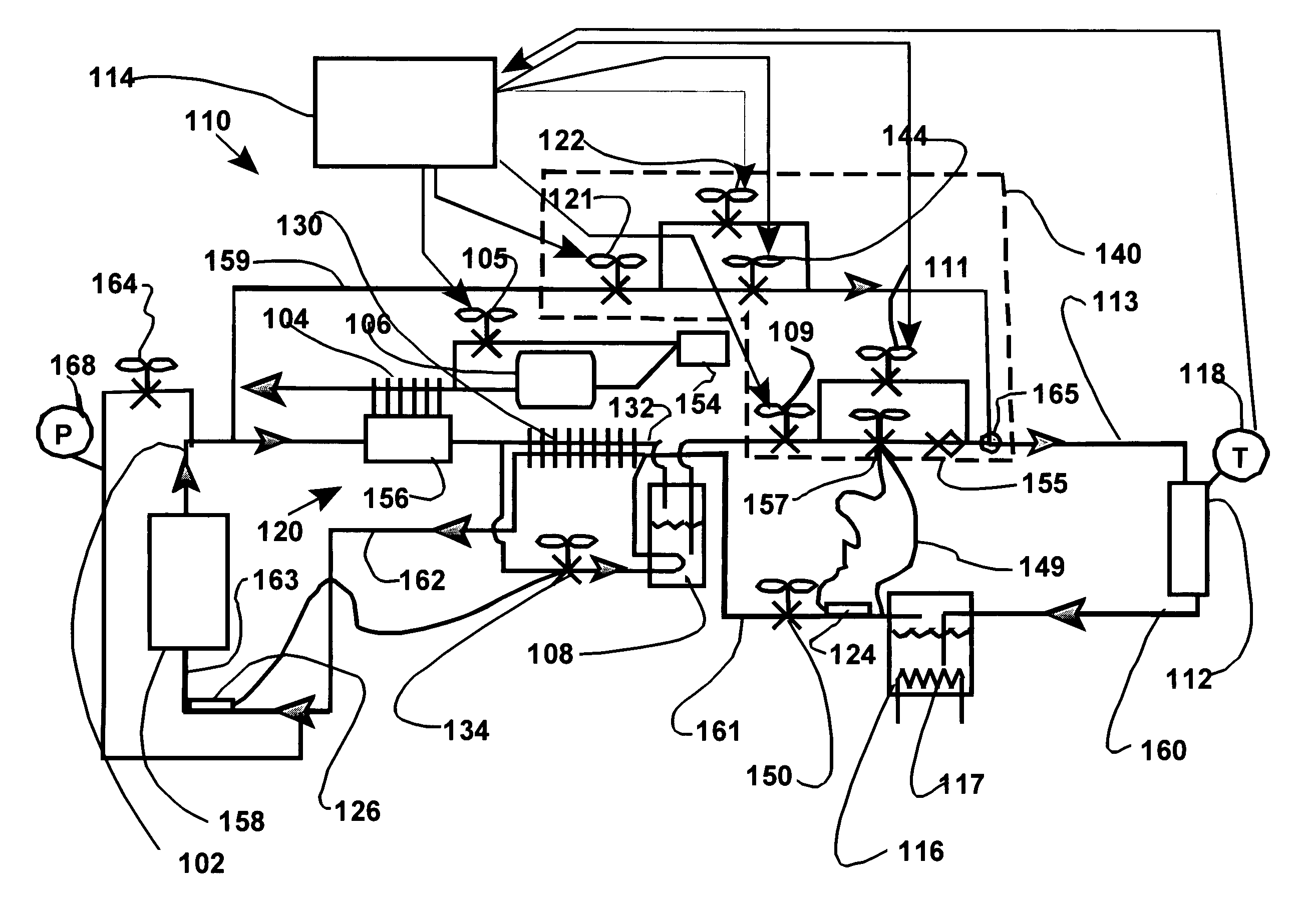

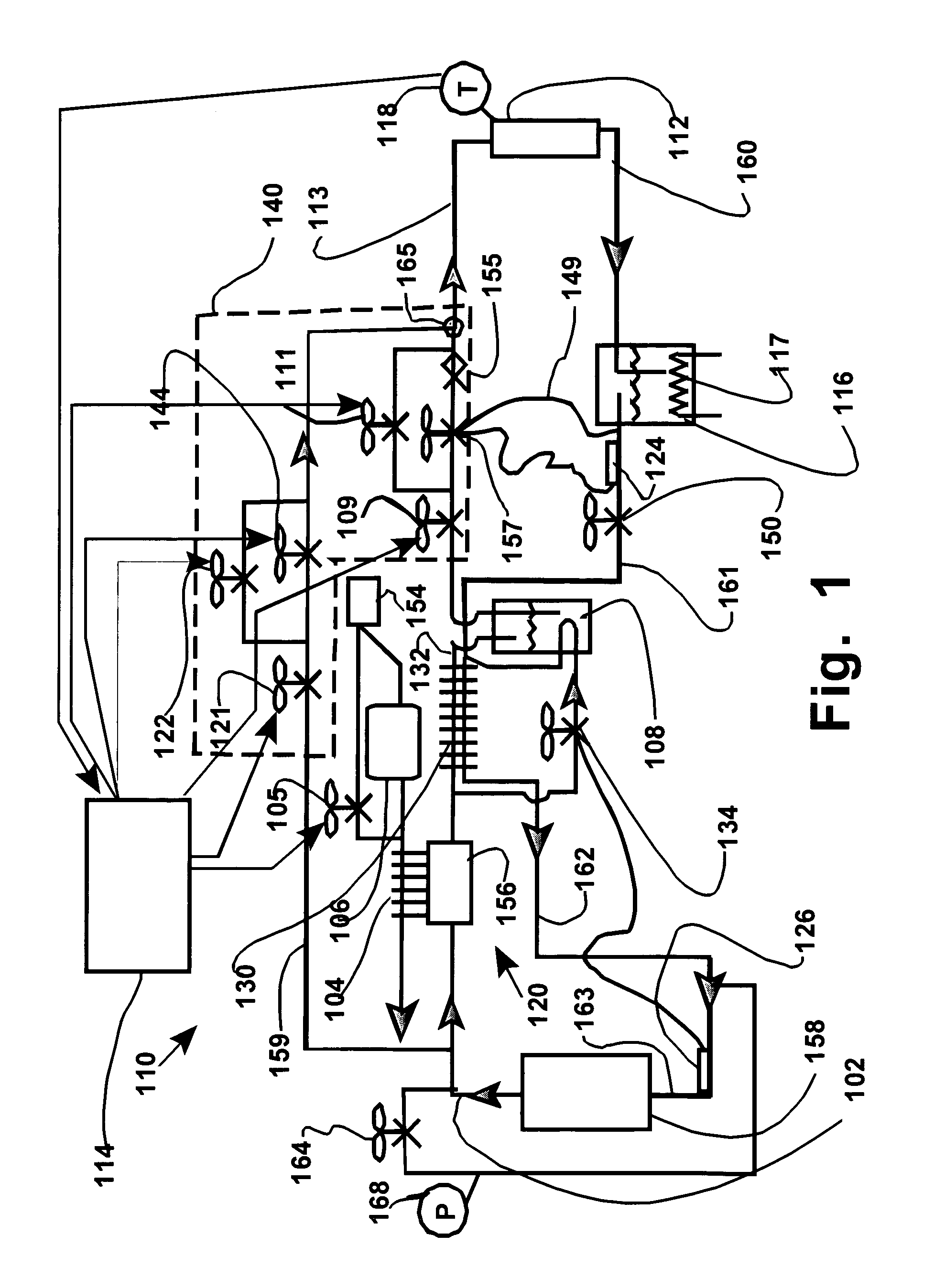

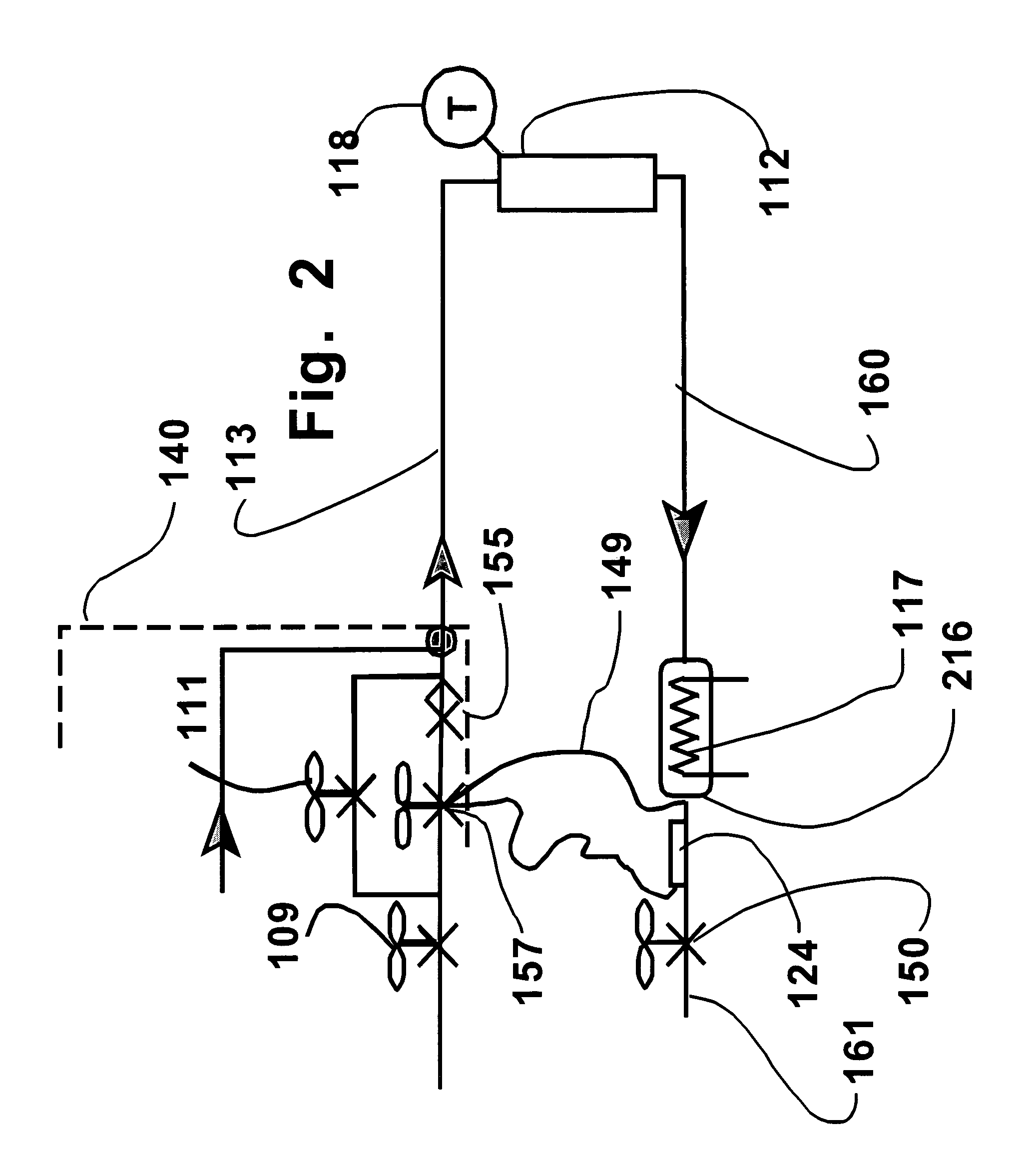

A system and method for controlling the temperature of a process tool uses the vaporizable characteristic of a refrigerant that is provided in direct heat exchange relation with the process tool. Pressurized refrigerant is provided as both condensed liquid and in gaseous state. The condensed liquid is expanded to a vaporous mix, and the gaseous refrigerant is added to reach a target temperature determined by its pressure. Temperature corrections can thus be made very rapidly by gas pressure adjustments. The process tool and the operating parameters will usually require that the returning refrigerant be conditioned and processed for compatibility with the compressor and other units, so that cycling can be continuous regardless of thermal demands and changes.

Owner:BE AEROSPACE INCORPORATED

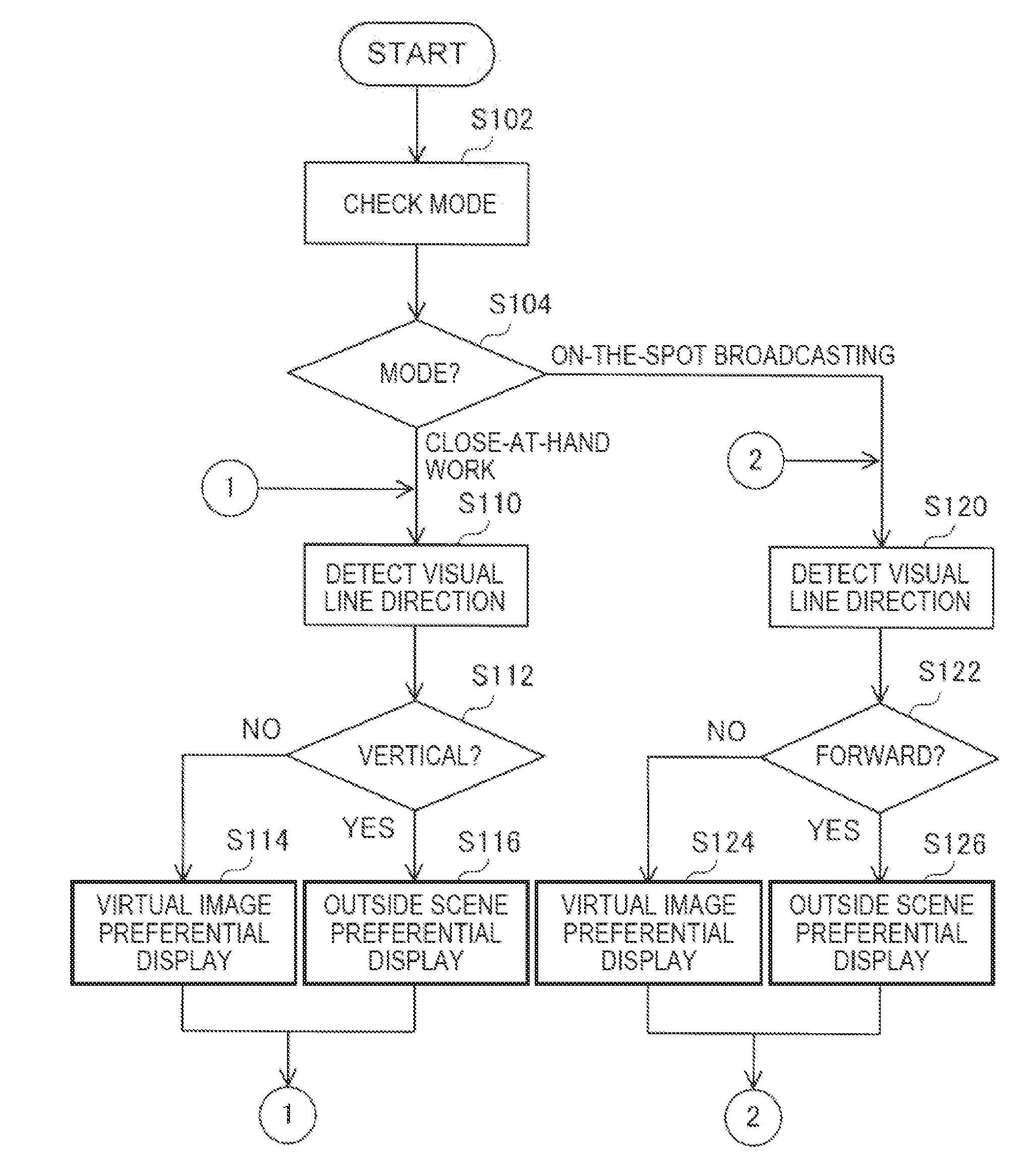

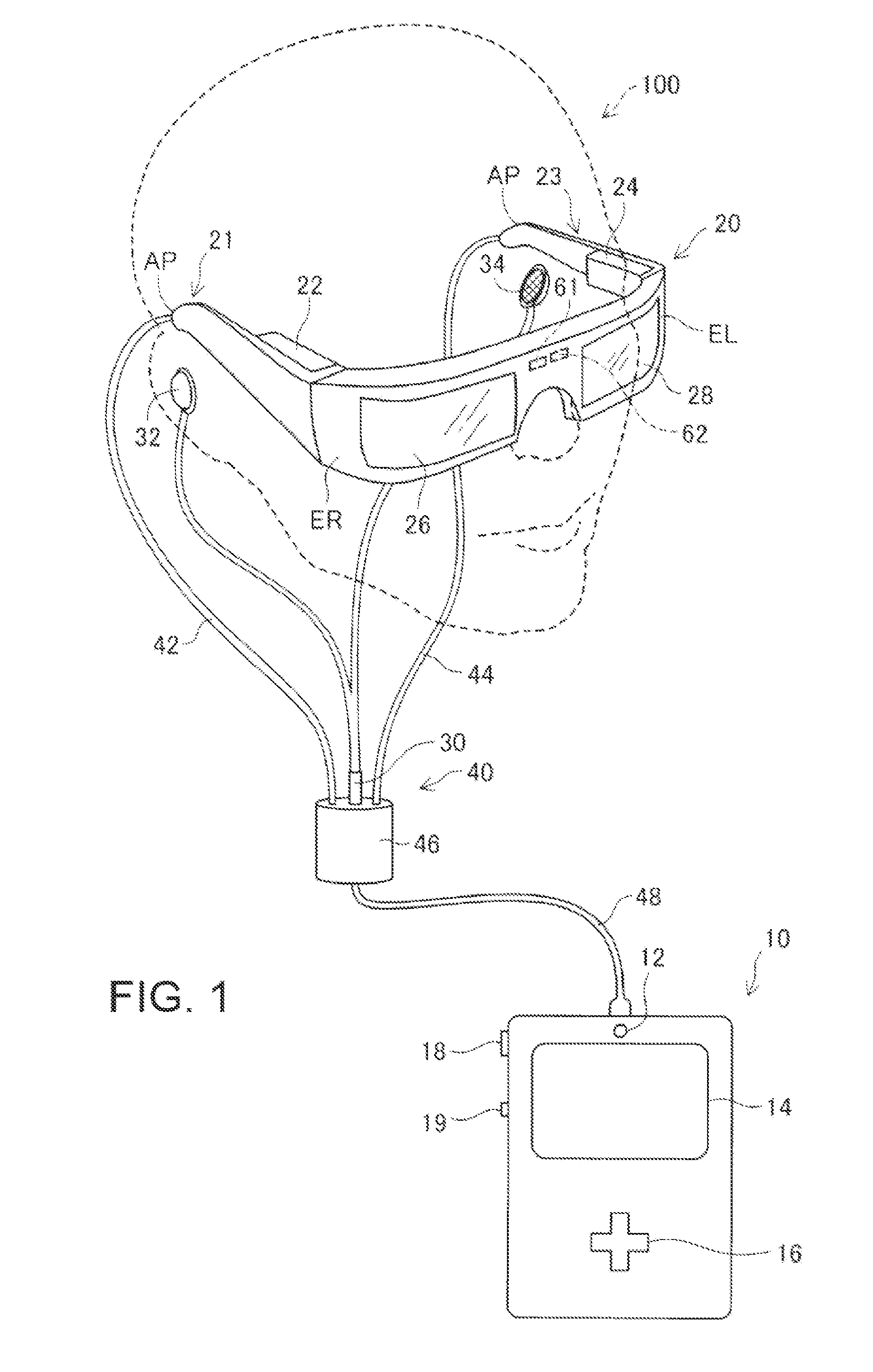

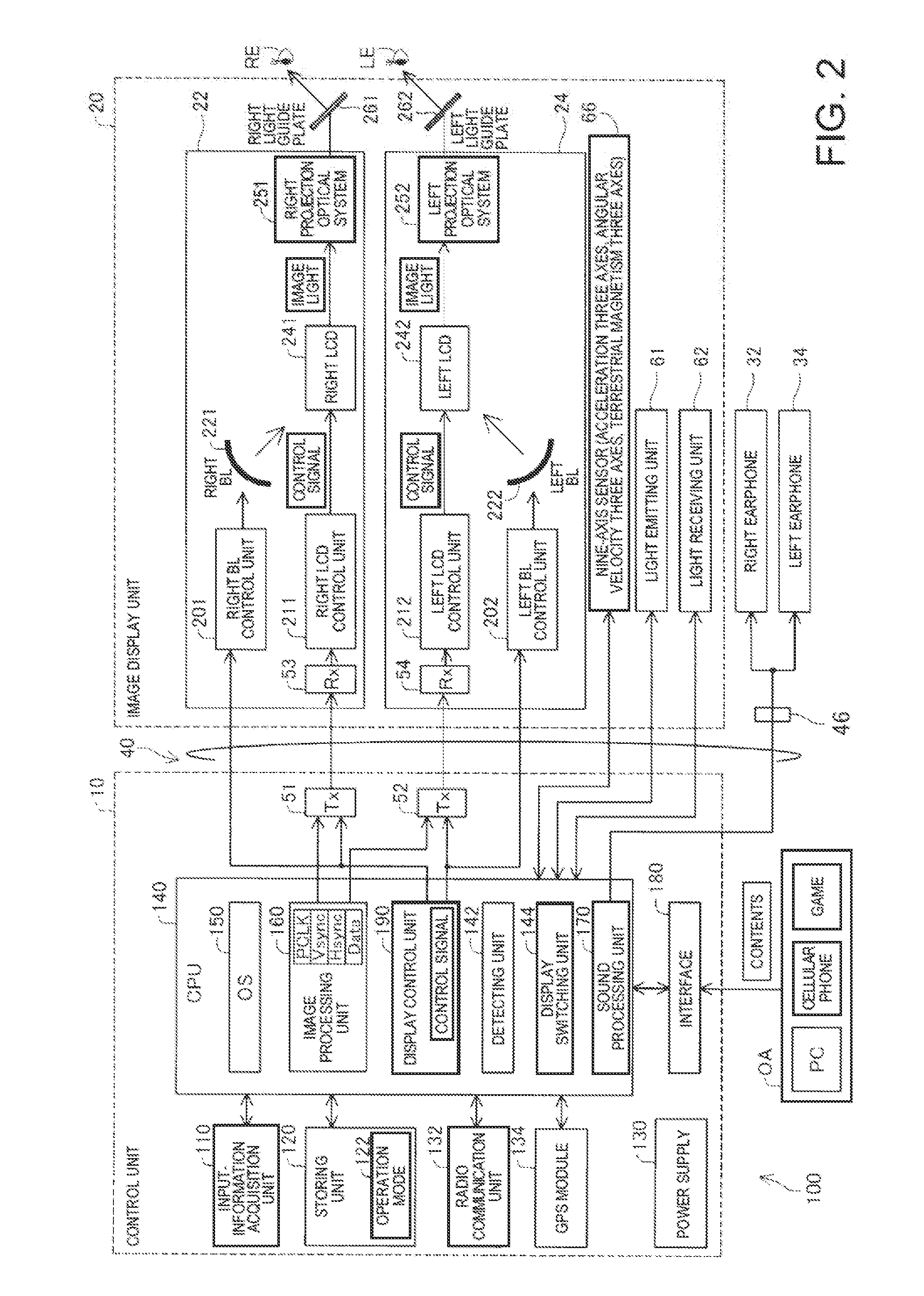

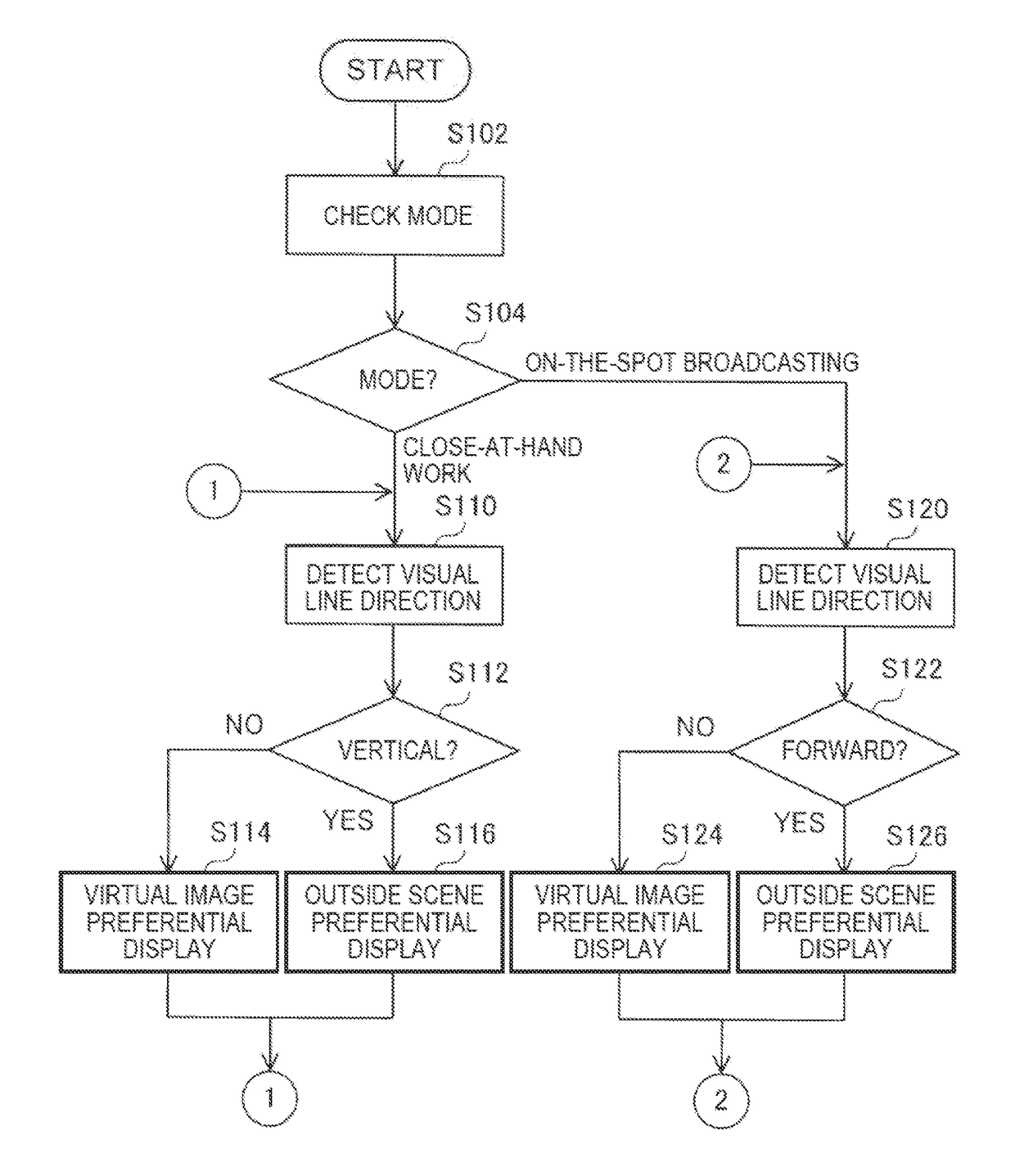

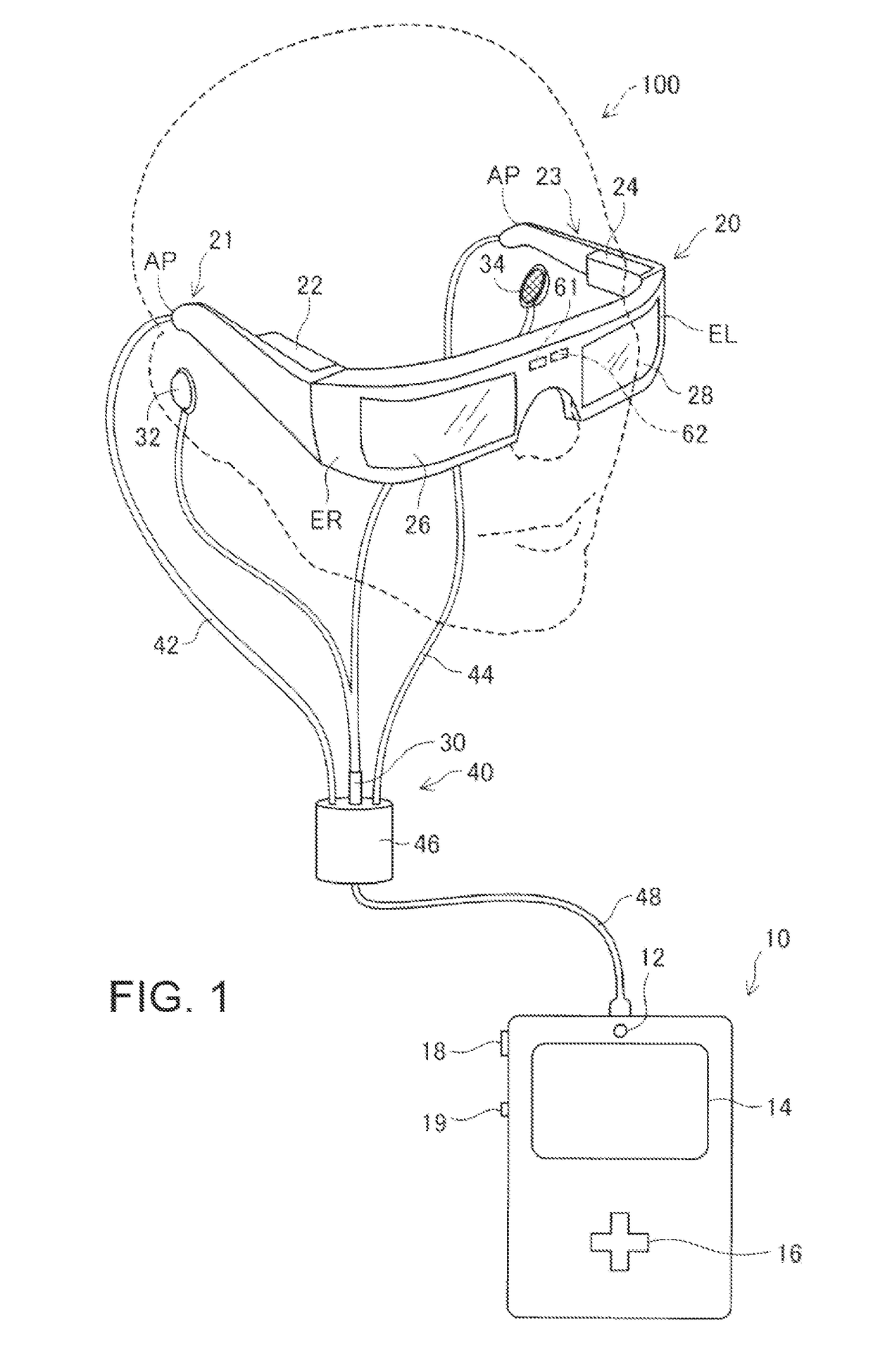

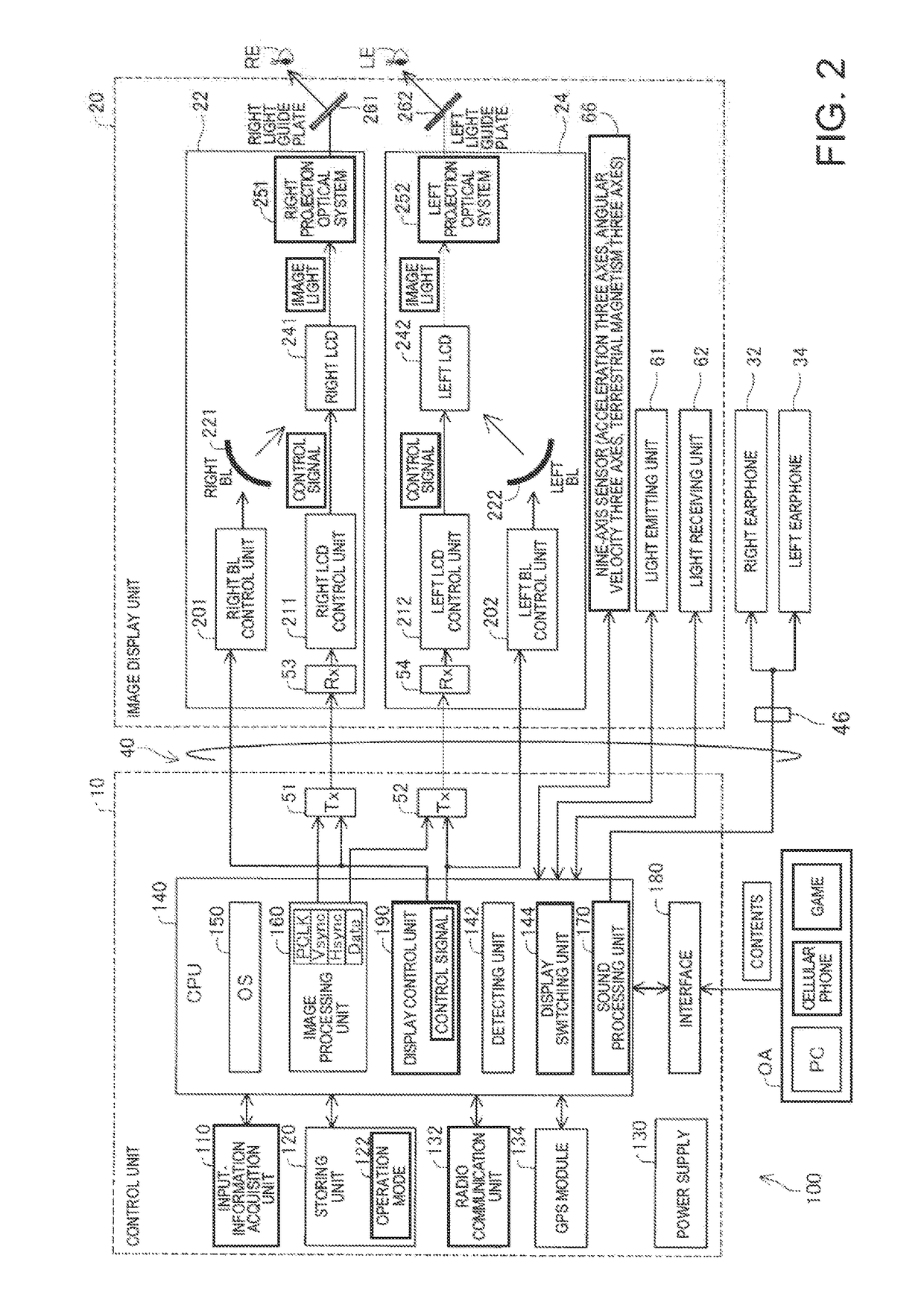

Head-mounted display device and control method for head-mounted display device

ActiveUS20140285403A1Increase awarenessImprove ease of useCathode-ray tube indicatorsInput/output processes for data processingDisplay deviceVirtual image

A head-mounted display device that enables a user to visually recognize a virtual image and an outside scene includes an image display unit configured to cause the user to visually recognize the virtual image, a detecting unit configured to detect a visual line direction of the user, and a display switching unit configured to switch, according to the detected visual line direction, display of the virtual image by the image display unit between outside scene preferential display for preferentially displaying the outside scene and virtual image preferential display for preferentially displaying the virtual image.

Owner:SEIKO EPSON CORP

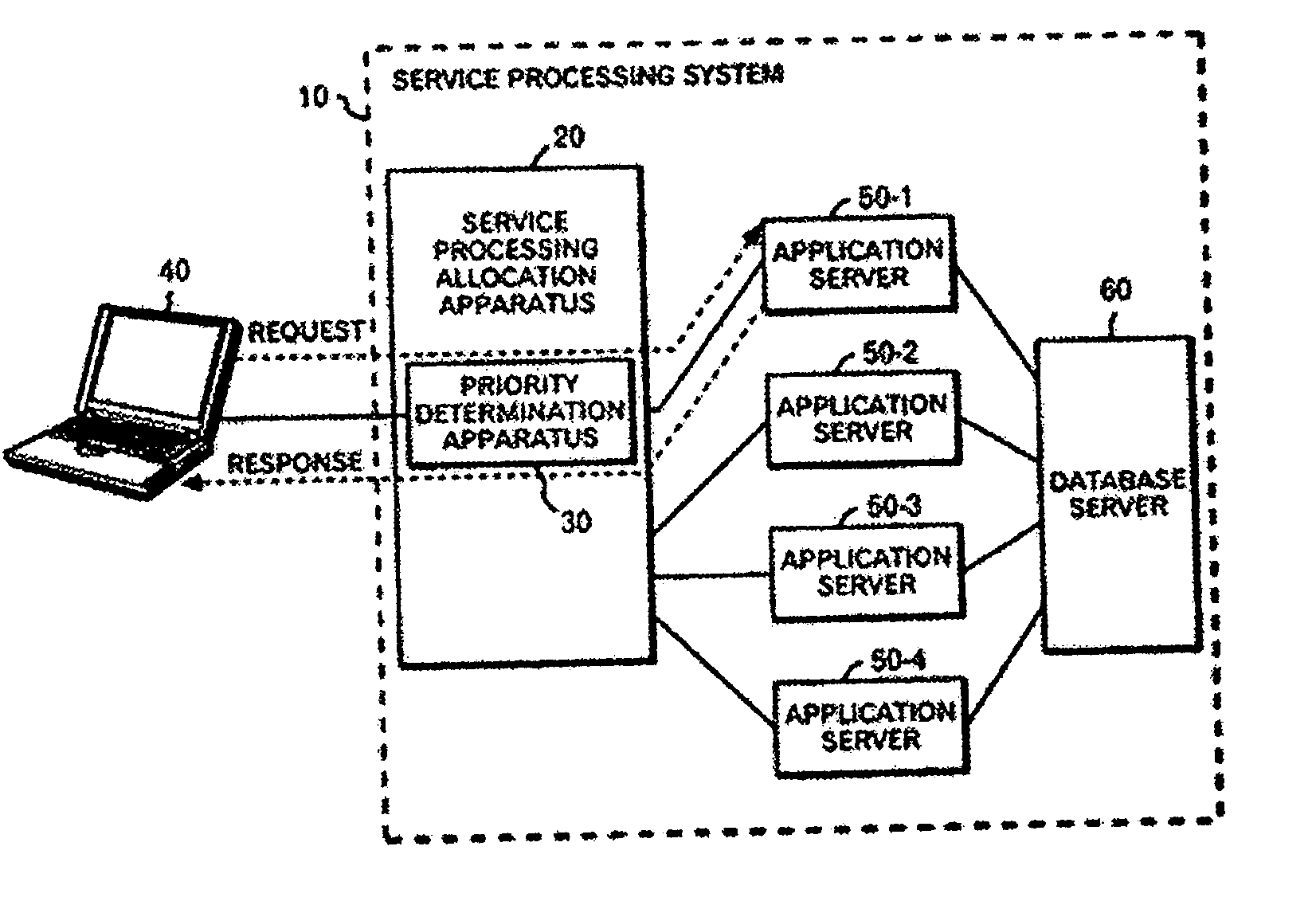

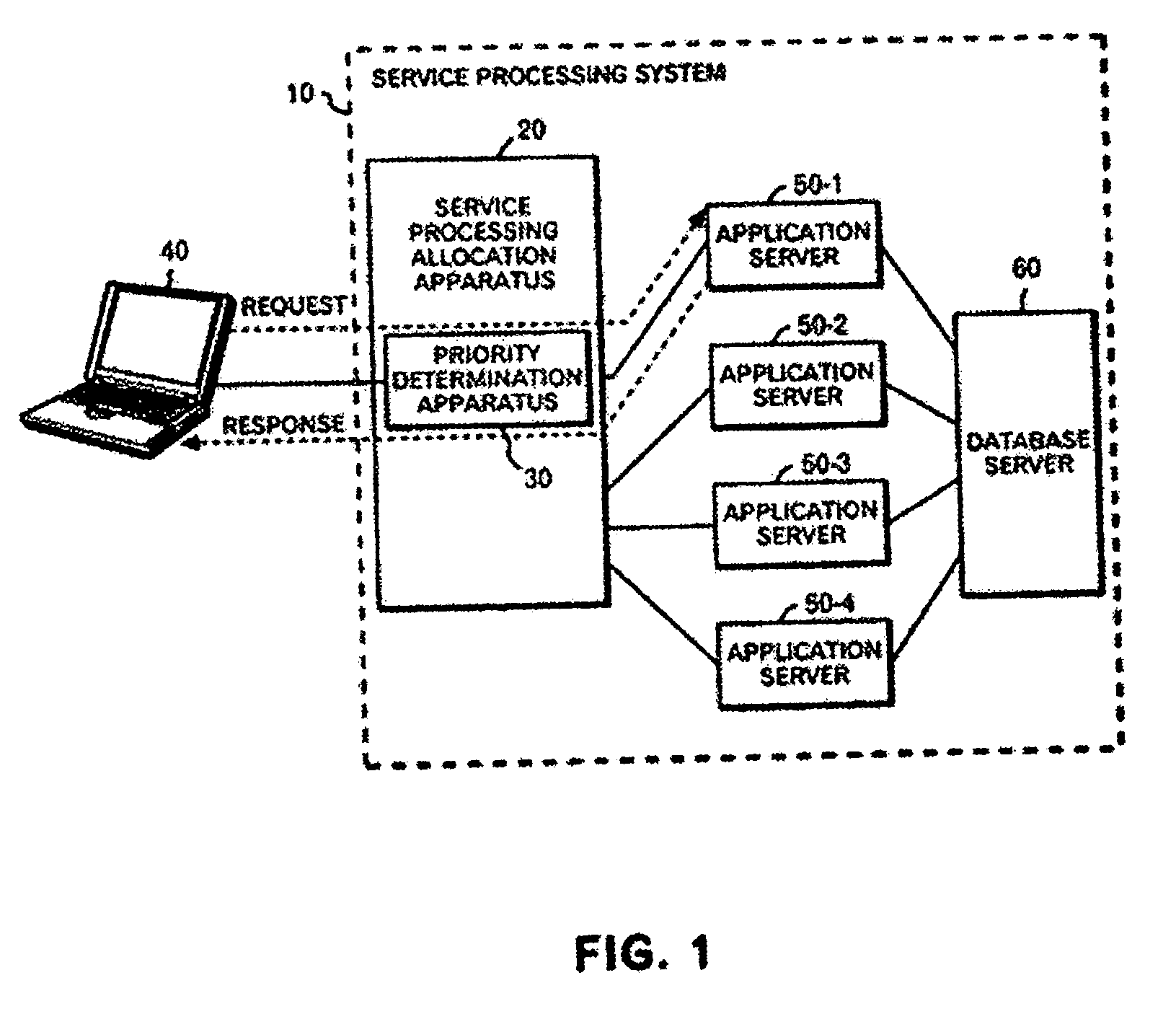

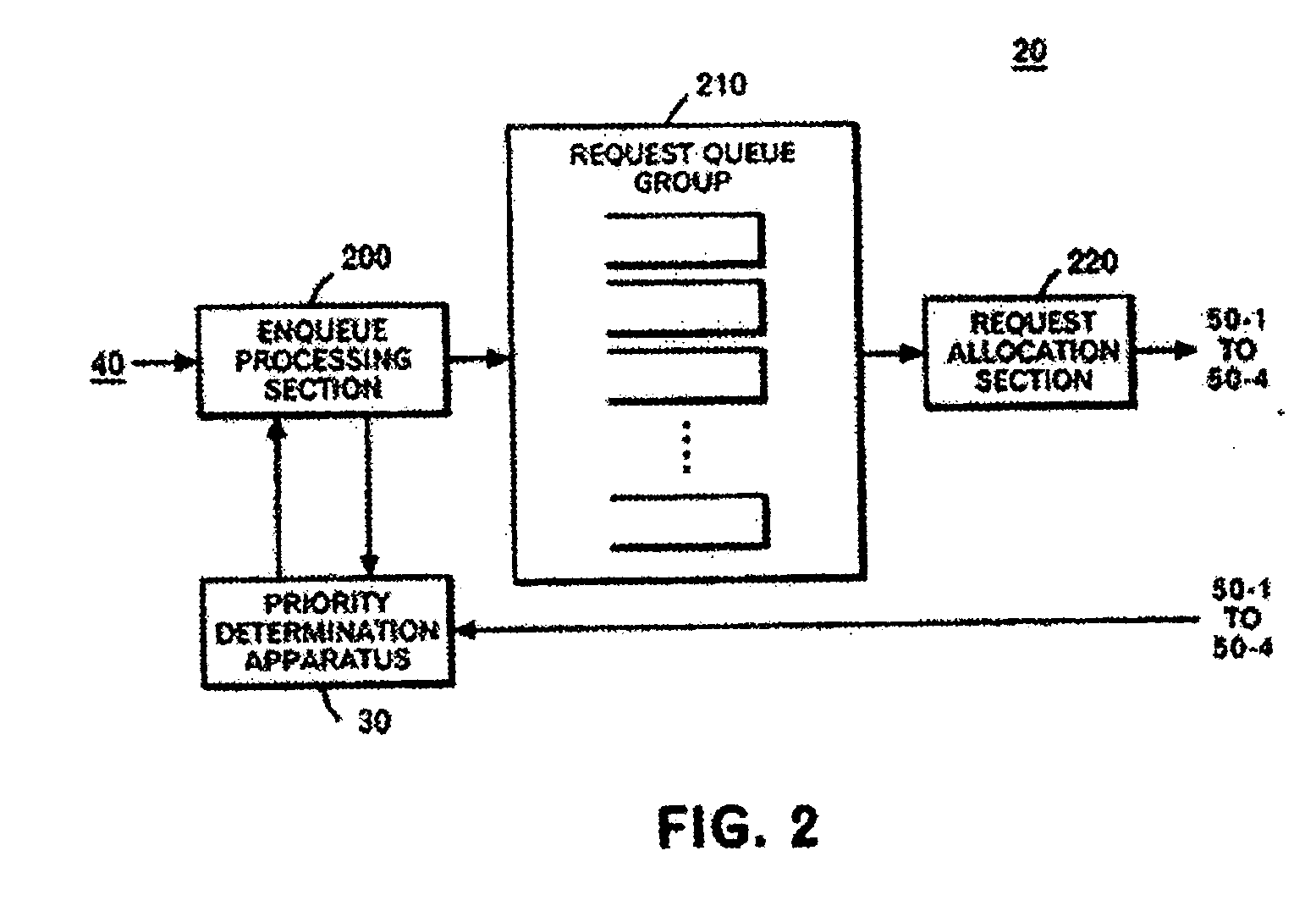

Priority Determination Apparatus, Service Processing Allocation Apparatus, Control Method and Program

A service priority is changed to allow an application server more flexibly to cope with diversified sales promotion strategies in electronic commerce. The priority of a service is determined by a service request history recording section for each user, a section for identifying the user who requested a service in response to receiving a request for the service made to the application server, and a section for determining a priority to be used in processing the service requested by the user.

Owner:IBM CORP

Thermal control system and method

ActiveUS20050183432A1High thermal efficiencyQuick adjustmentMechanical apparatusHeat pumpsRefrigerantProcess engineering

A system and method for controlling the temperature of a process tool uses the vaporizable characteristic of a refrigerant that is provided in direct heat exchange relation with the process tool. Pressurized refrigerant is provided as both condensed liquid and in gaseous state. The condensed liquid is expanded to a vaporous mix, and the gaseous refrigerant is added to reach a target temperature determined by its pressure. Temperature corrections can thus be made very rapidly by gas pressure adjustments. The process tool and the operating parameters will usually require that the returning refrigerant be conditioned and processed for compatibility with the compressor and other units, so that cycling can be continuous regardless of thermal demands and changes.

Owner:BE AEROSPACE INCORPORATED

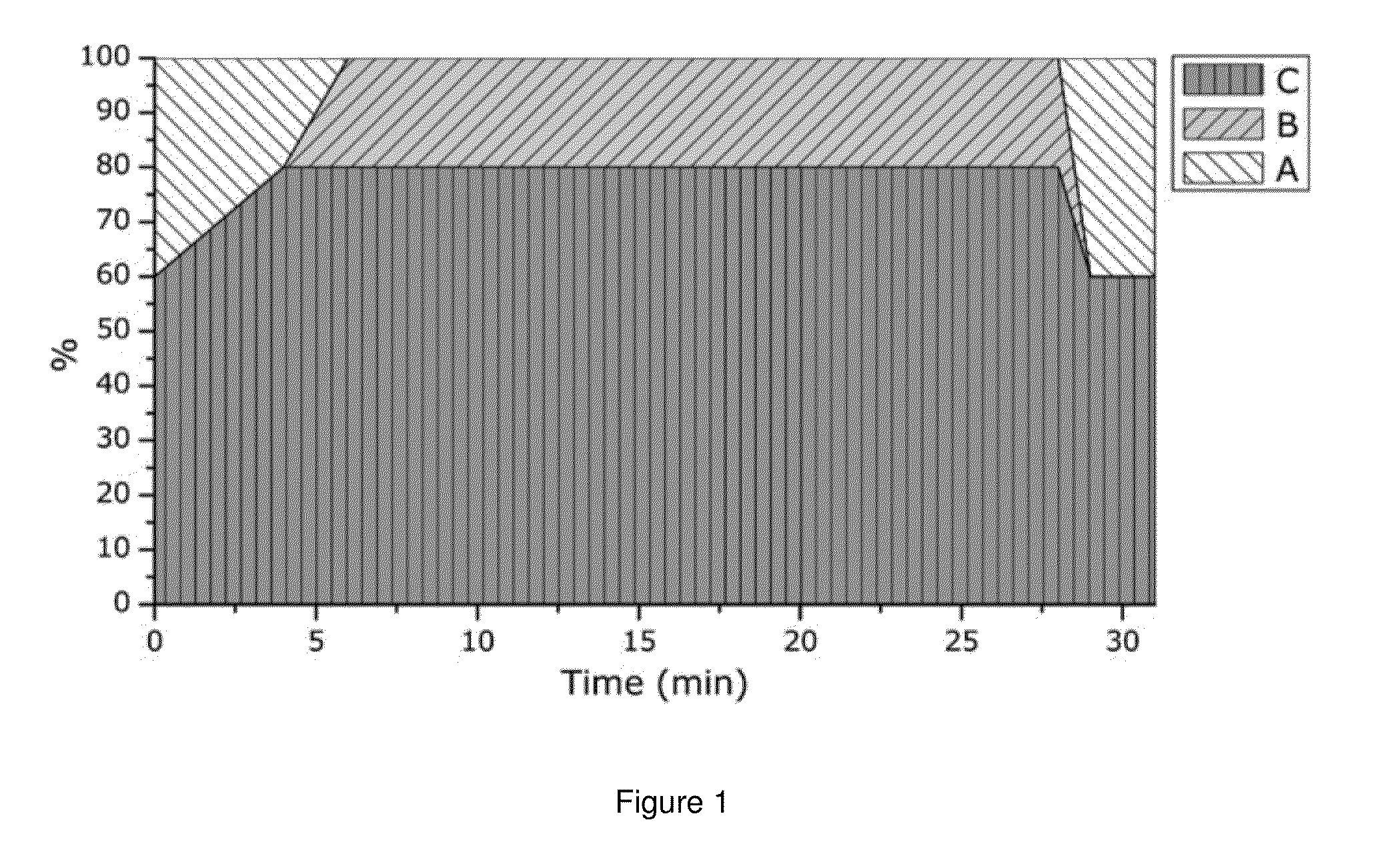

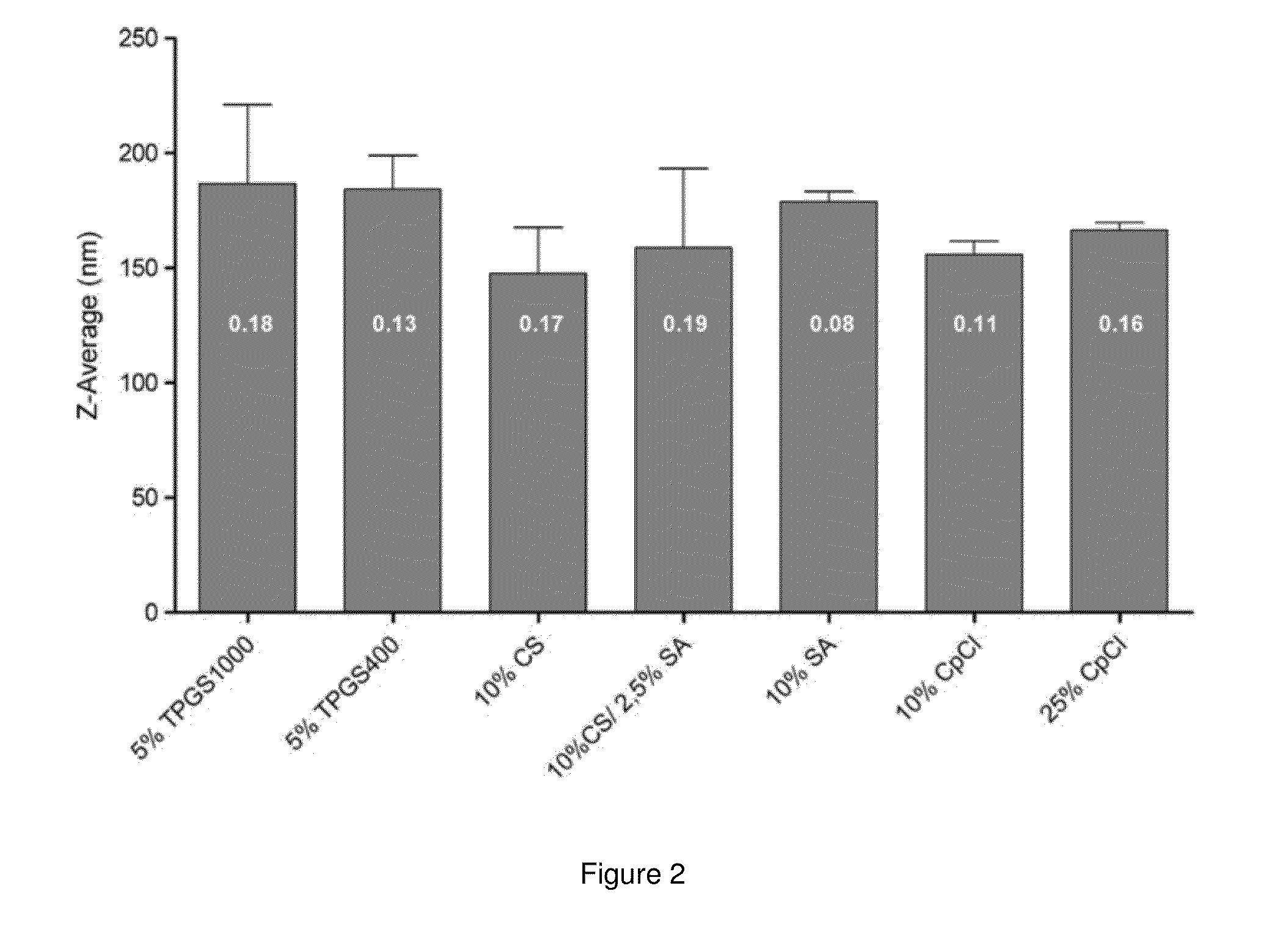

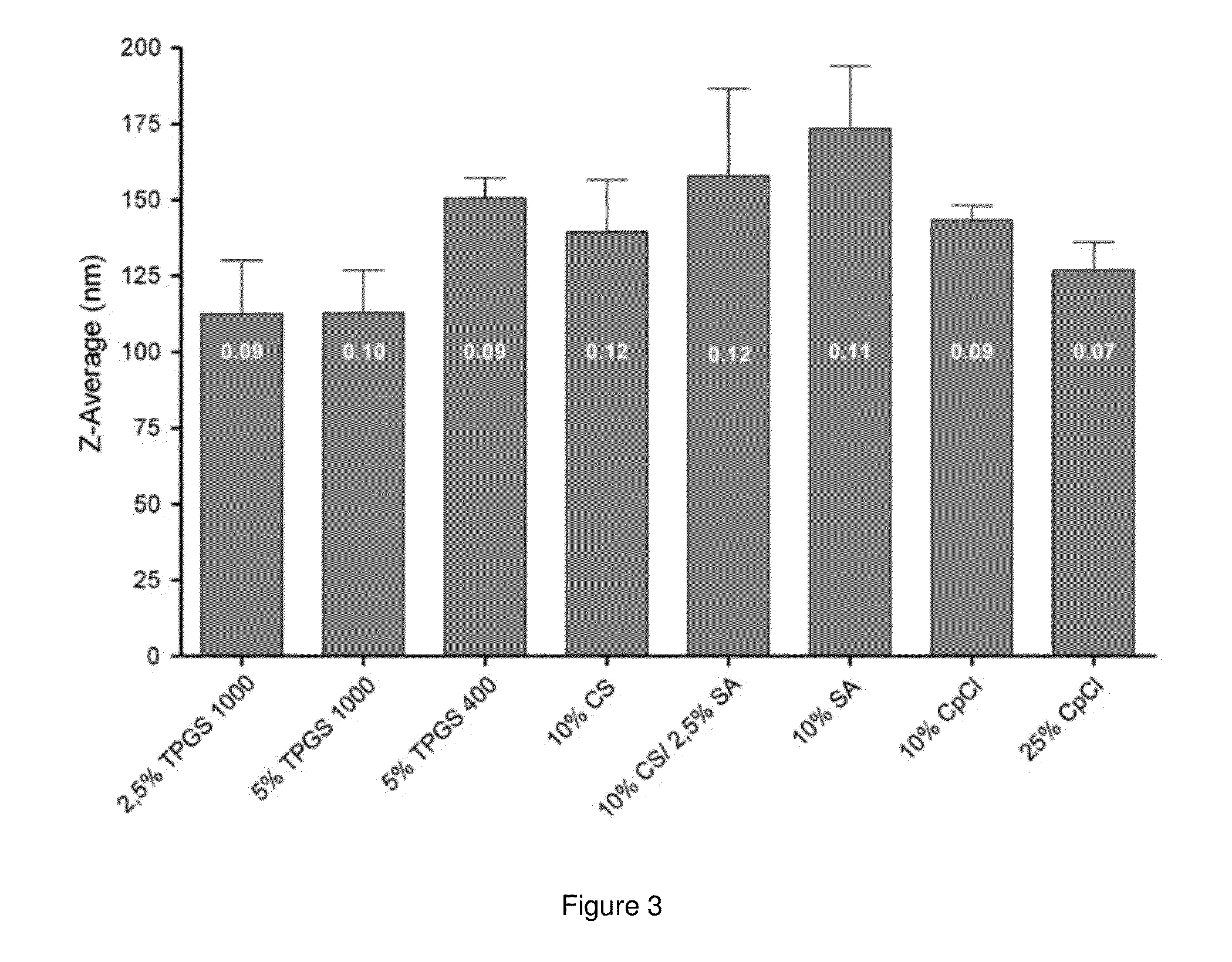

Liposomes containing permeation enhancers for oral drug delivery

InactiveUS20130251783A1Improve permeabilityQuality improvementPharmaceutical non-active ingredientsLiposomal deliveryDiseaseLiposome

The present invention relates to liposomal compositions and their application for delivery of pharmaceuticals for the treatment of disease.

Owner:UNIVERSITY OF HEIDELBERG +1

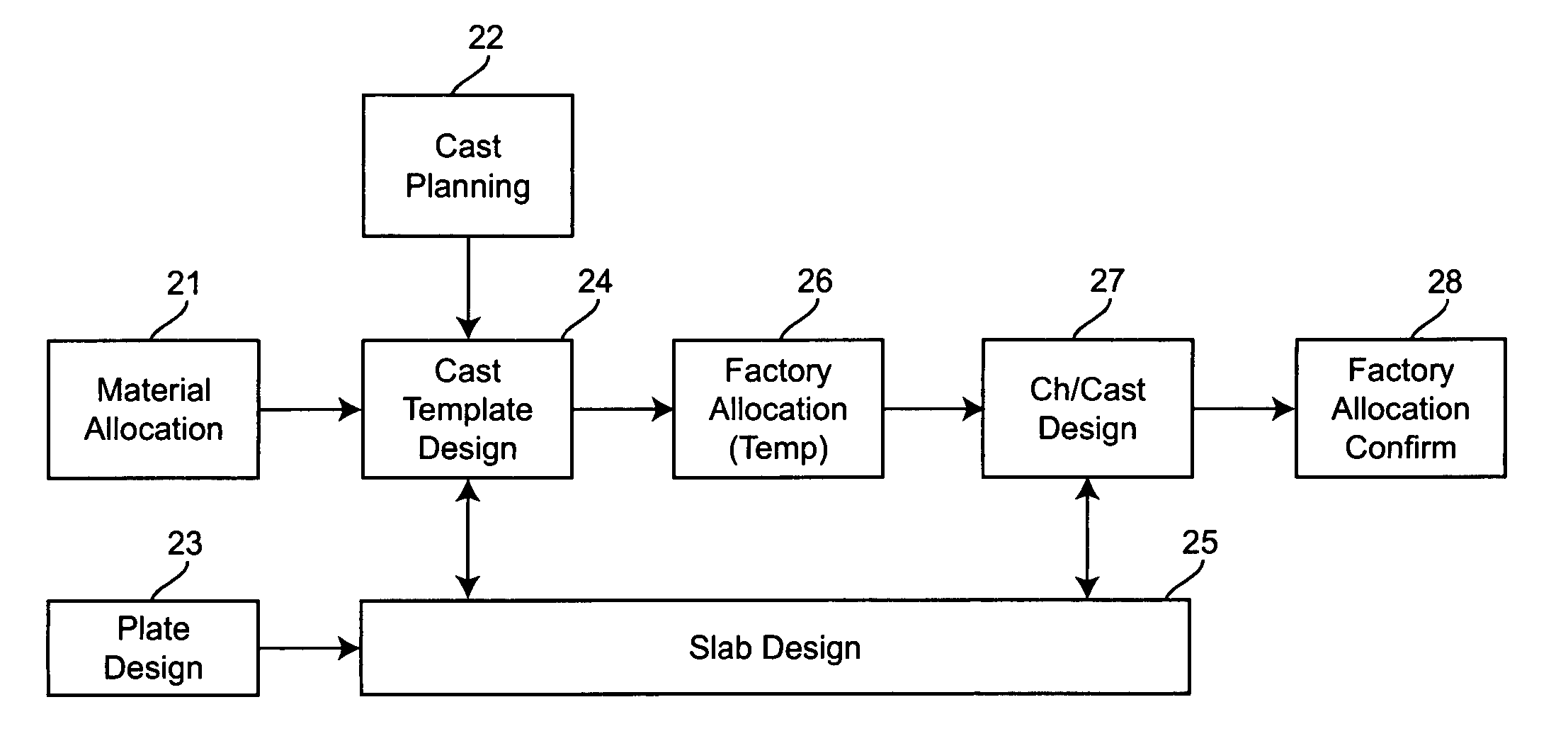

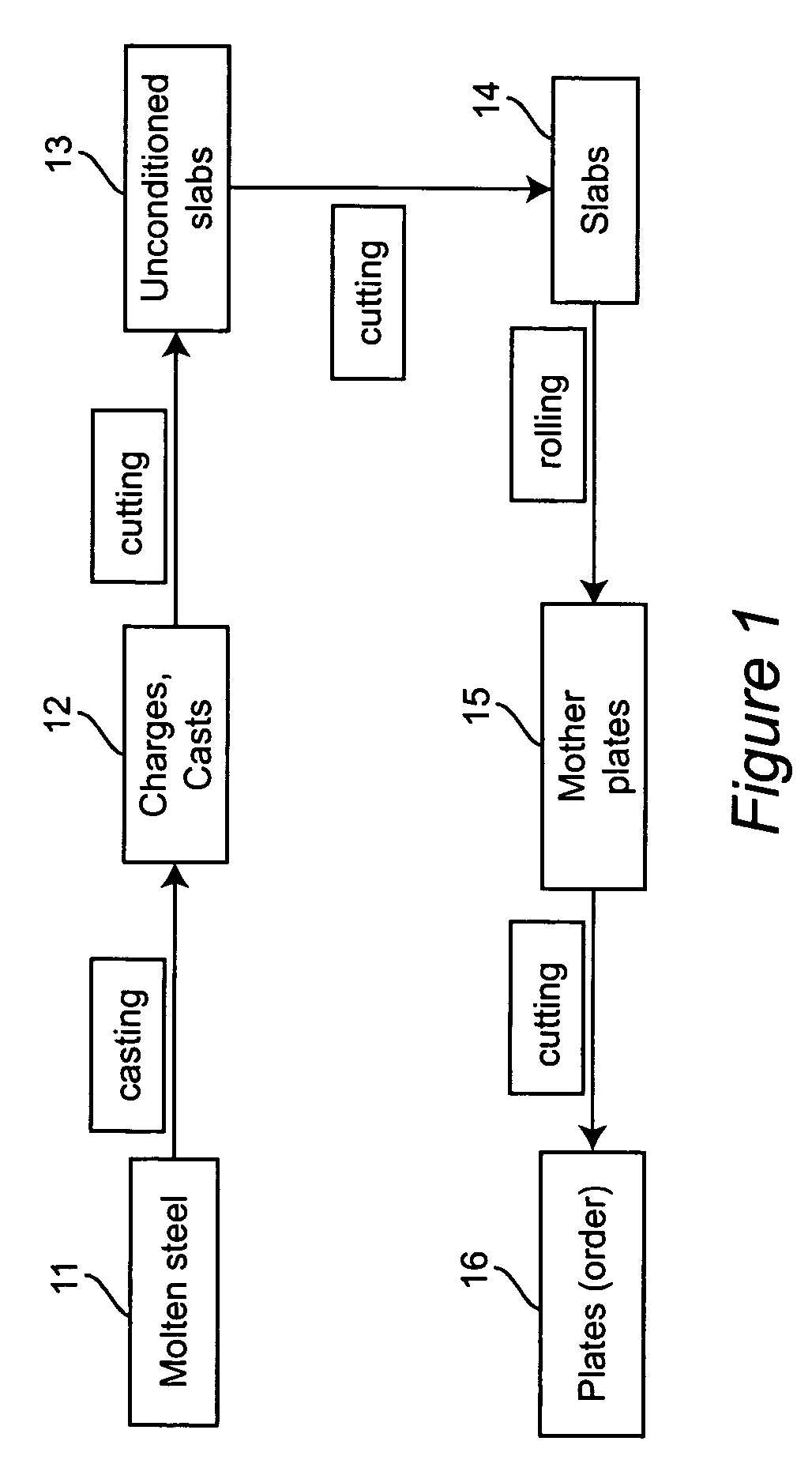

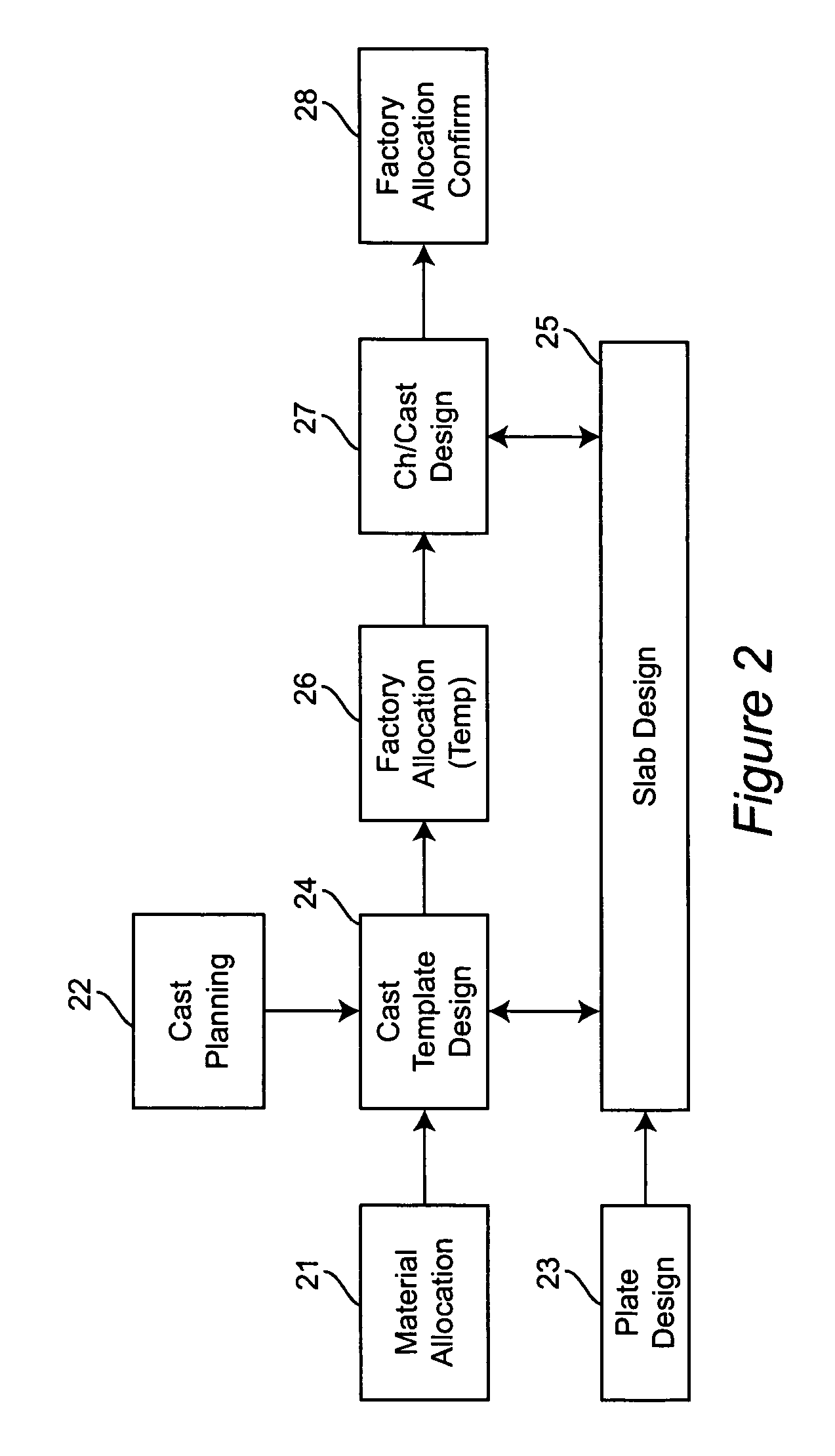

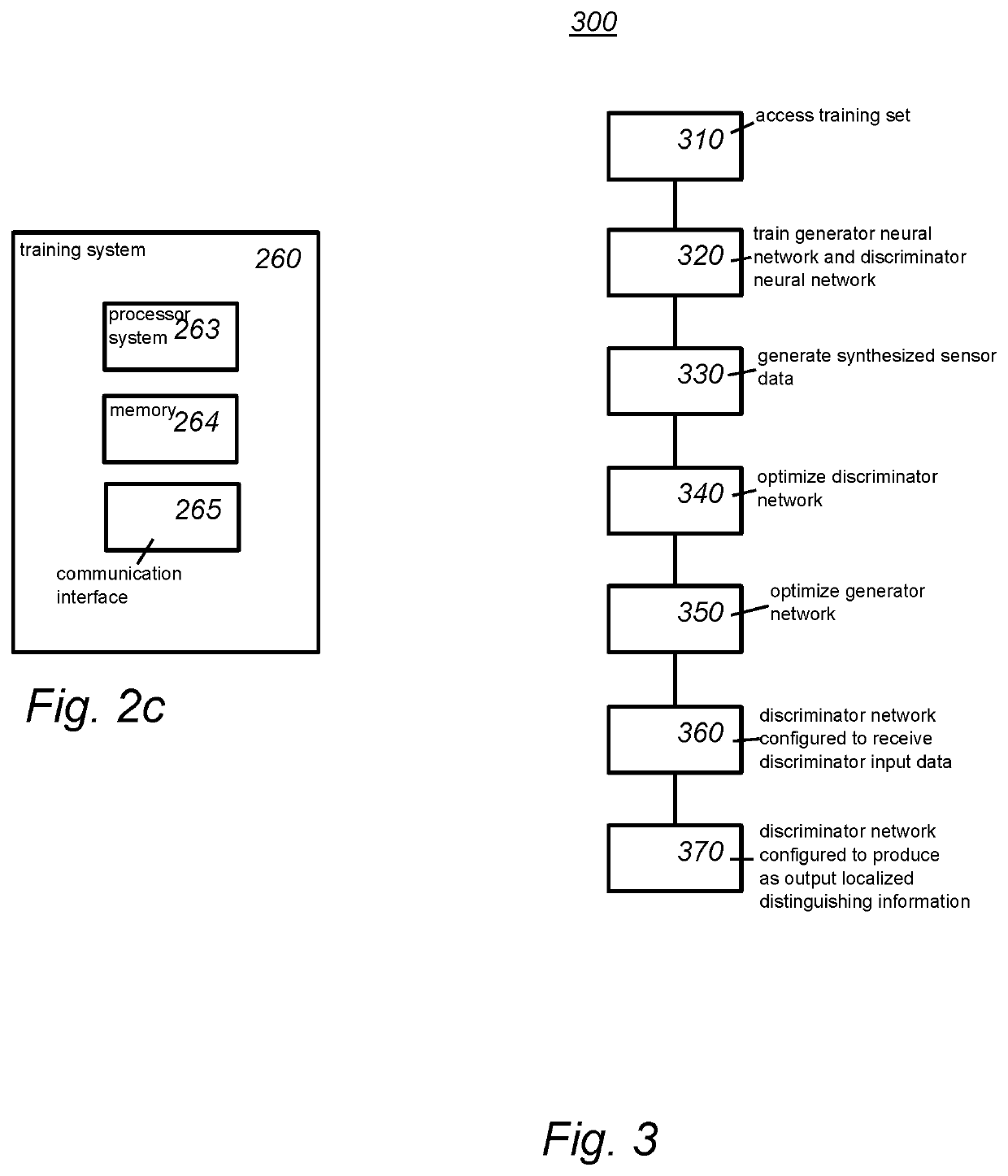

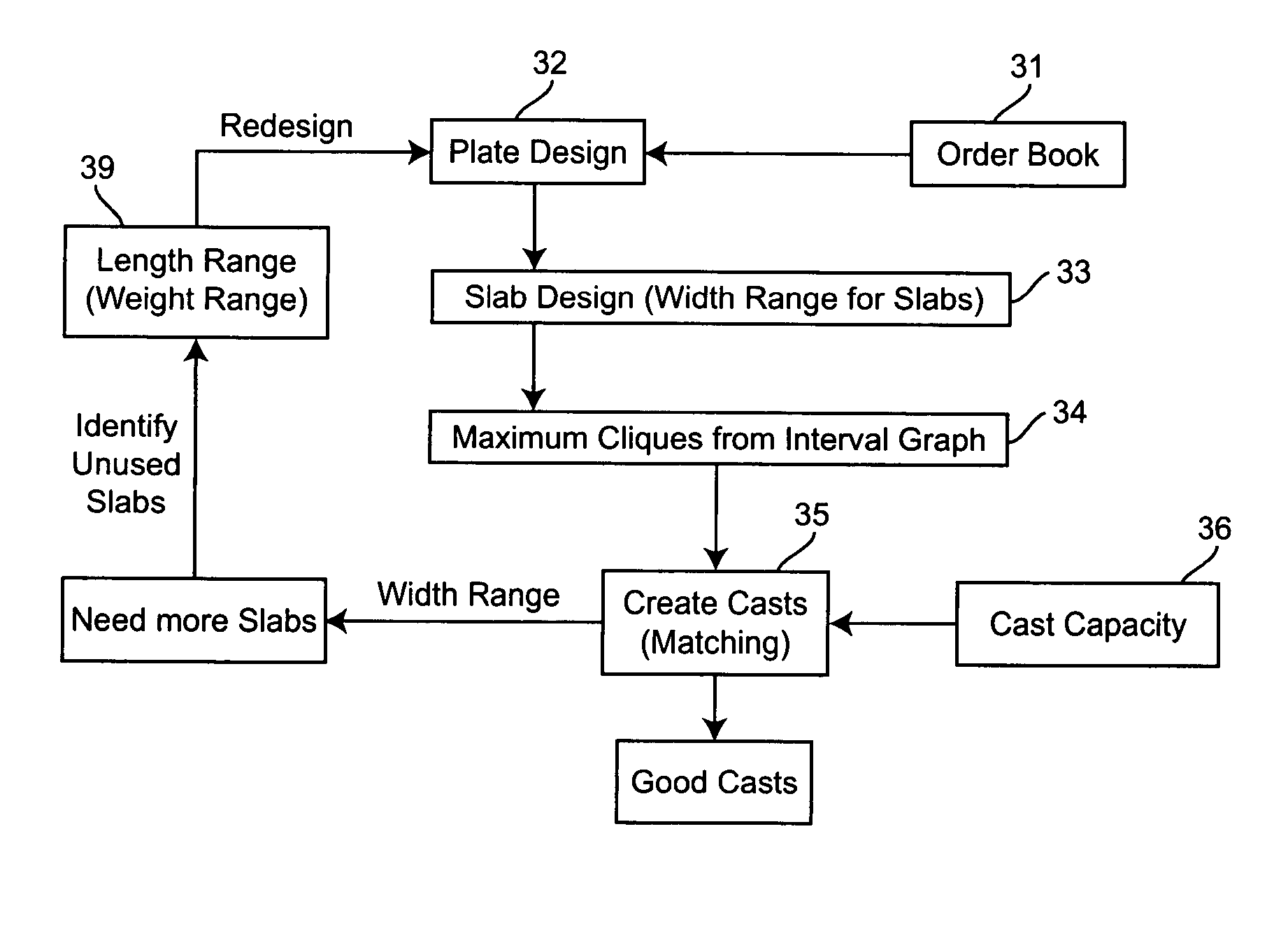

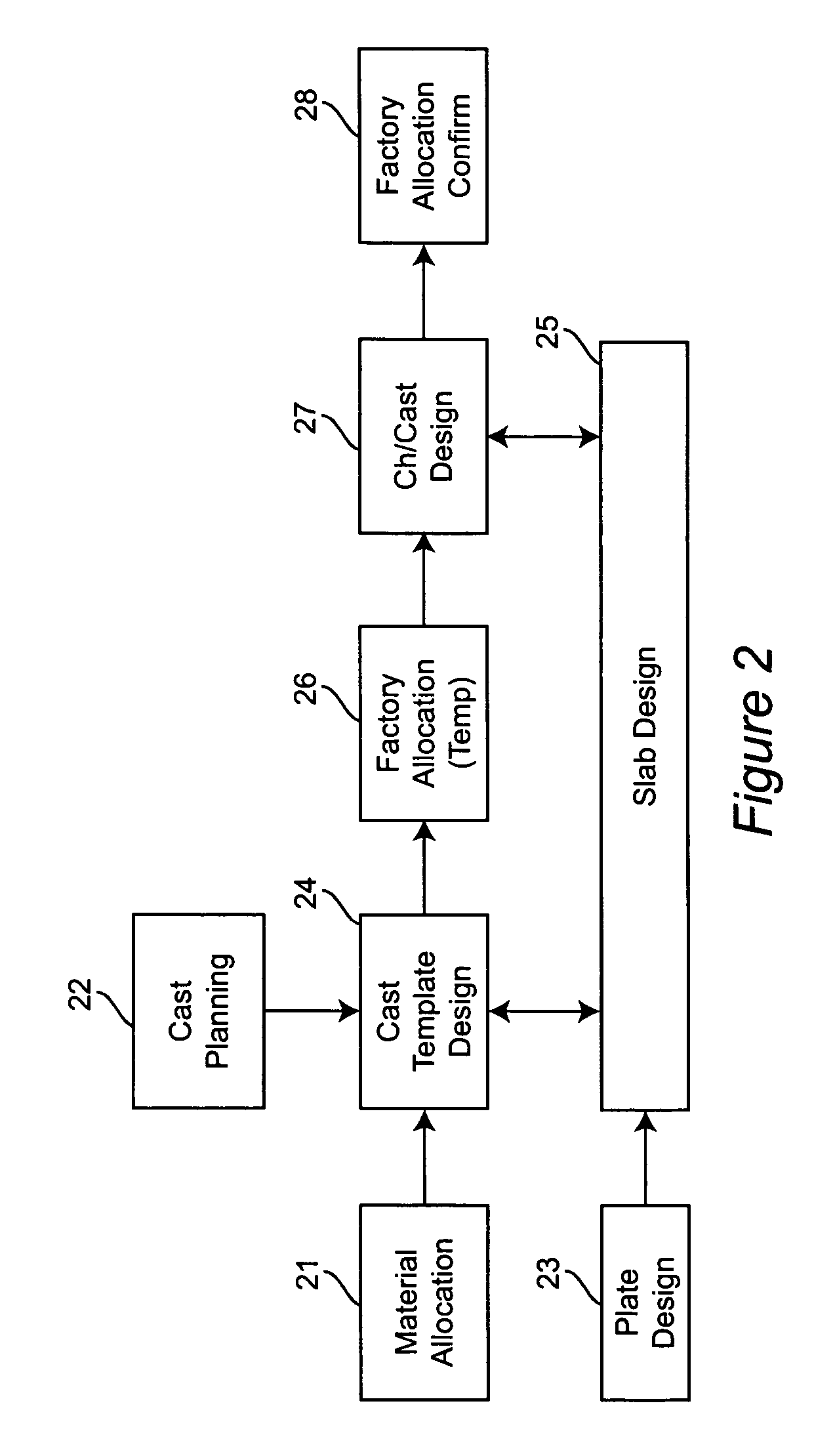

Method for production design and operations scheduling for plate design in the steel industry

ActiveUS20060100727A1Reduce wasteEasy to solveProgramme controlComputation using non-denominational number representationOrder formMaterial distribution

An automated method optimally designs plates to satisfy an order book at a steel plant so as to maximize the yield of the plates designed while using capacity fully to reduce the production of surplus slabs or plates, and satisfy order deadlines. Our method consists of four main components: (1) mother plate design, (2) slab design, (3) cast design, and (4) material allocation. A column generation framework for mother plate design is used where the problem is decomposed into a master problem and a subproblem. The master problem is used to evaluate packing patterns that should be used to fulfill the order book and the subproblem generates potential one-dimensional and two-dimensional feasible packing patterns as candidates to be evaluated by the master problem. The solution to the master problem produces a list of mother plates that need to be produced. These mother plates are transformed into candidate slabs, which are represented via an interval graph. The maximal cliques in the interval graph—maximal subsets of slabs which can be grouped together to form casts—are enumerated to generate candidate casts, from which redesign information is sent to the plate / slab design processes. The cast design process is integrated with the plate design / slab design processes in the sense that information is passed from the plate / slab design processes to the cast design process and vice versa. Finally, our method has a material allocation component to assign order plates to inventory mother-plates and slabs.

Owner:GOOGLE LLC

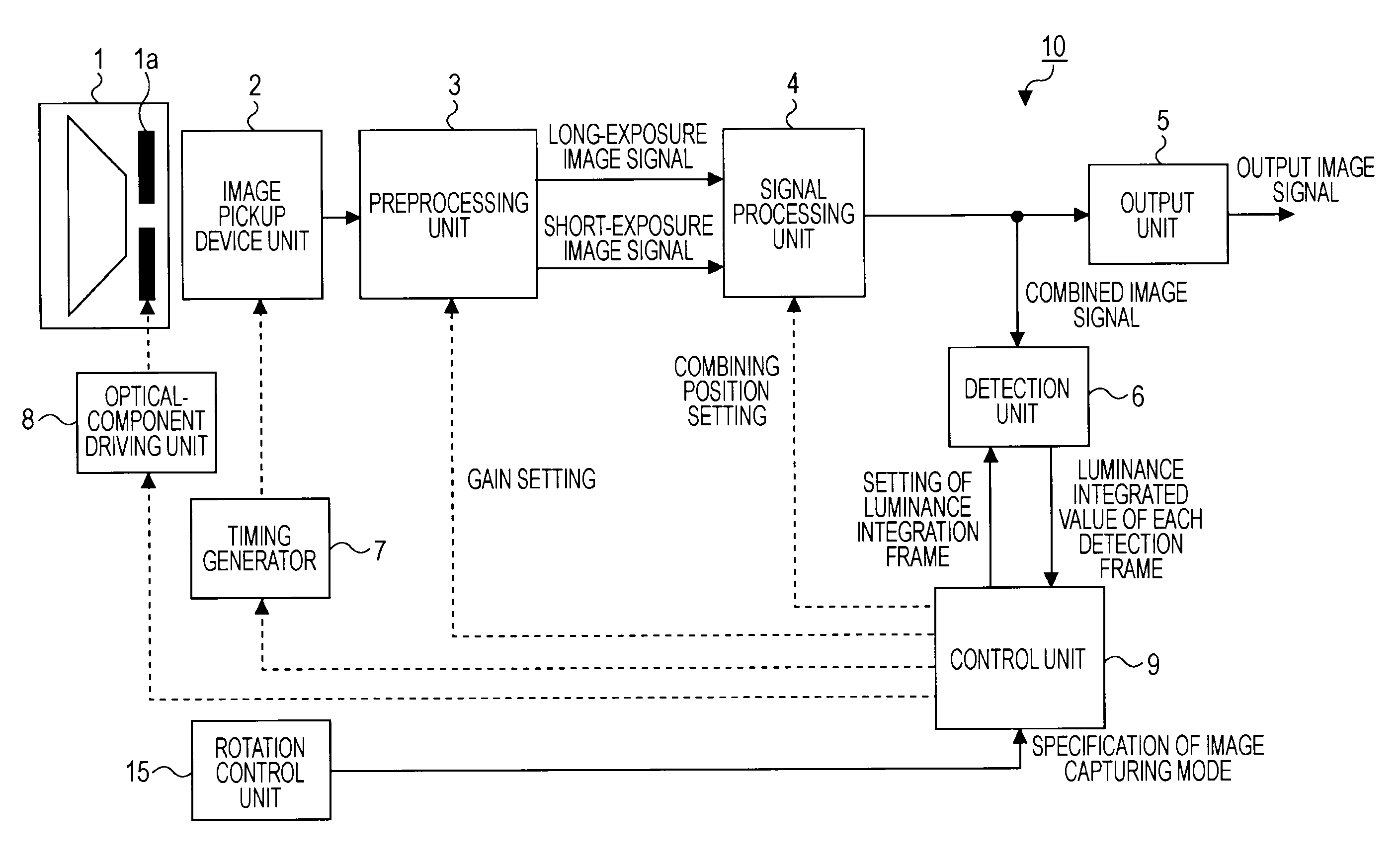

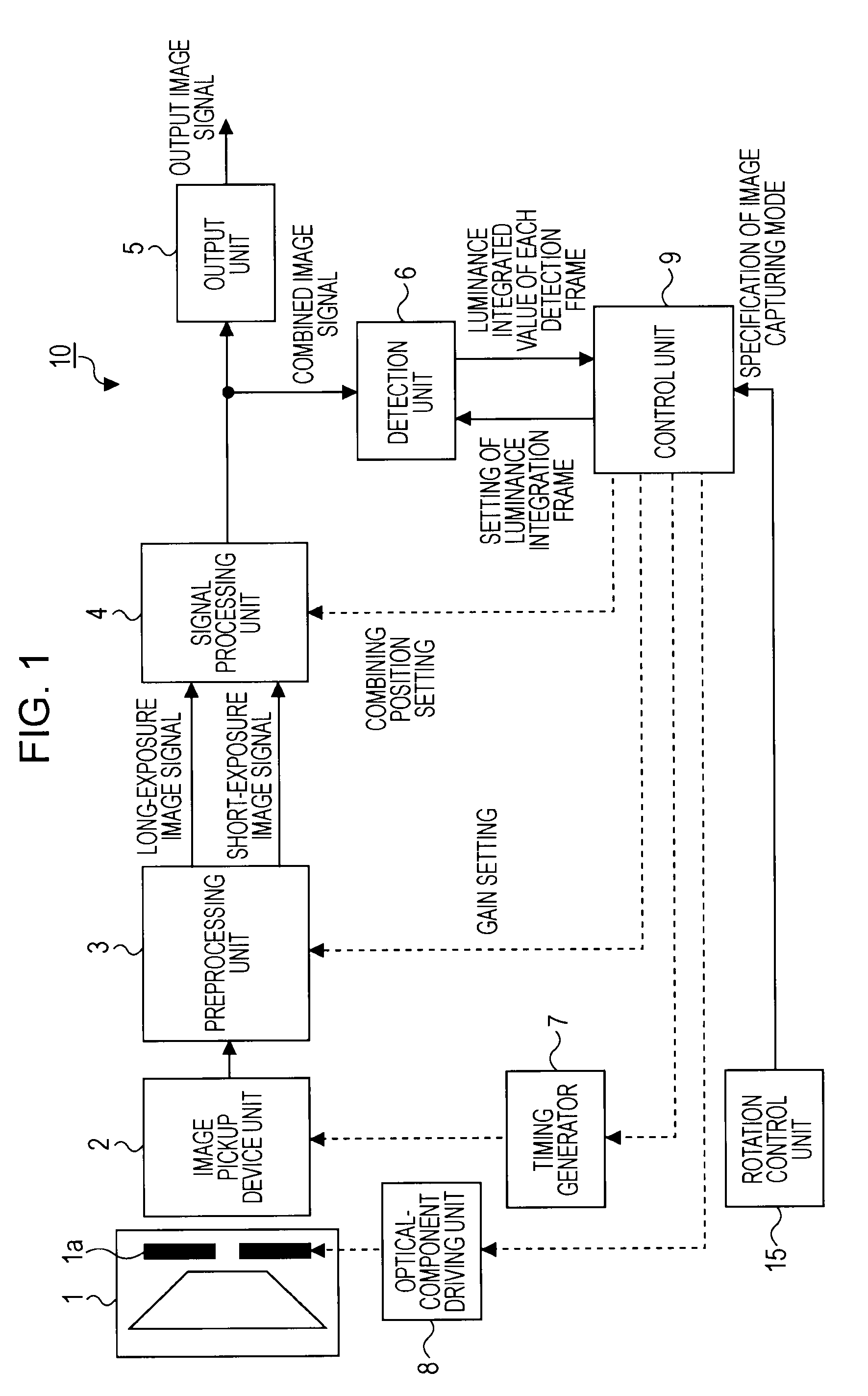

Image pickup apparatus, image pickup method, and program therefor

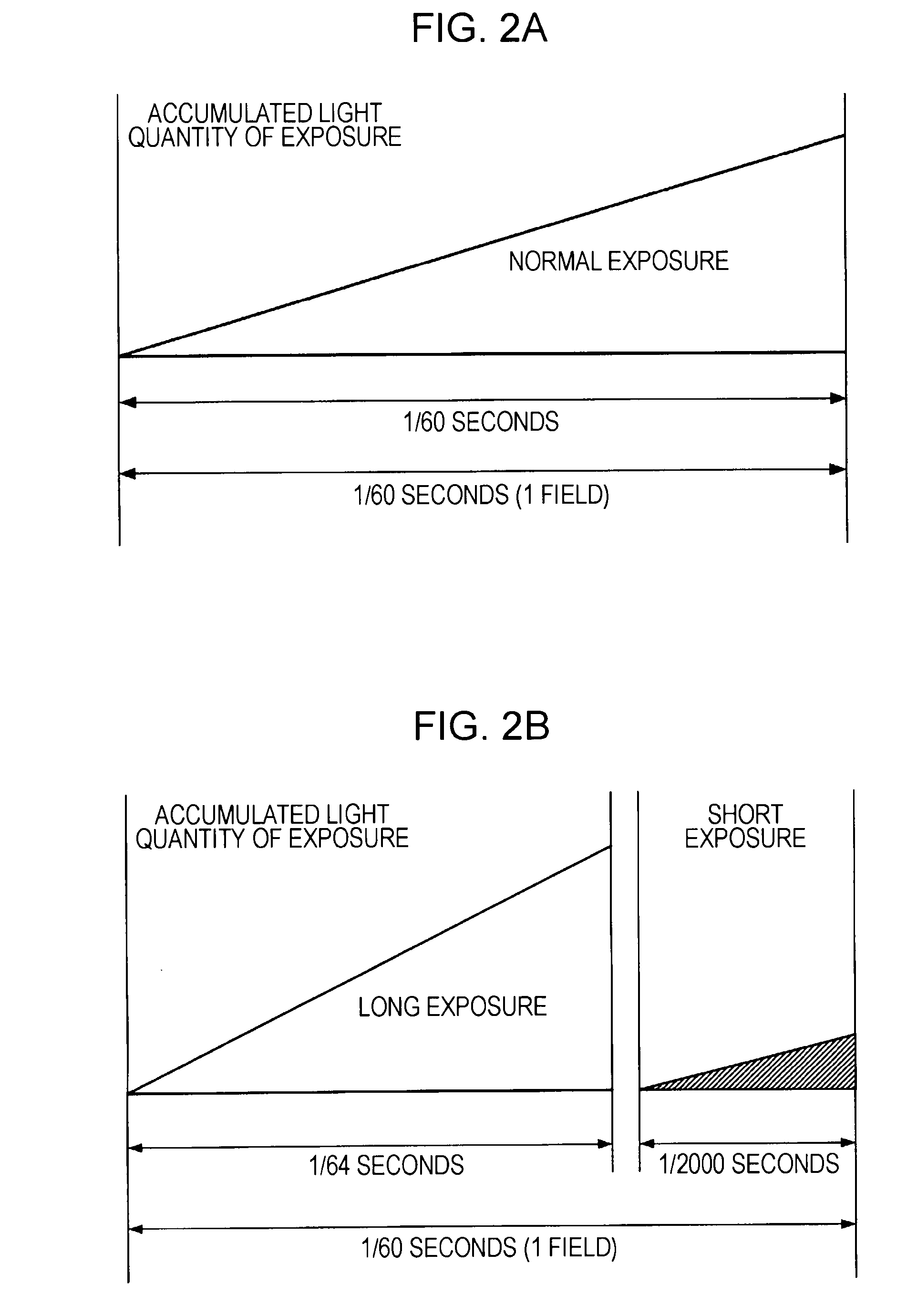

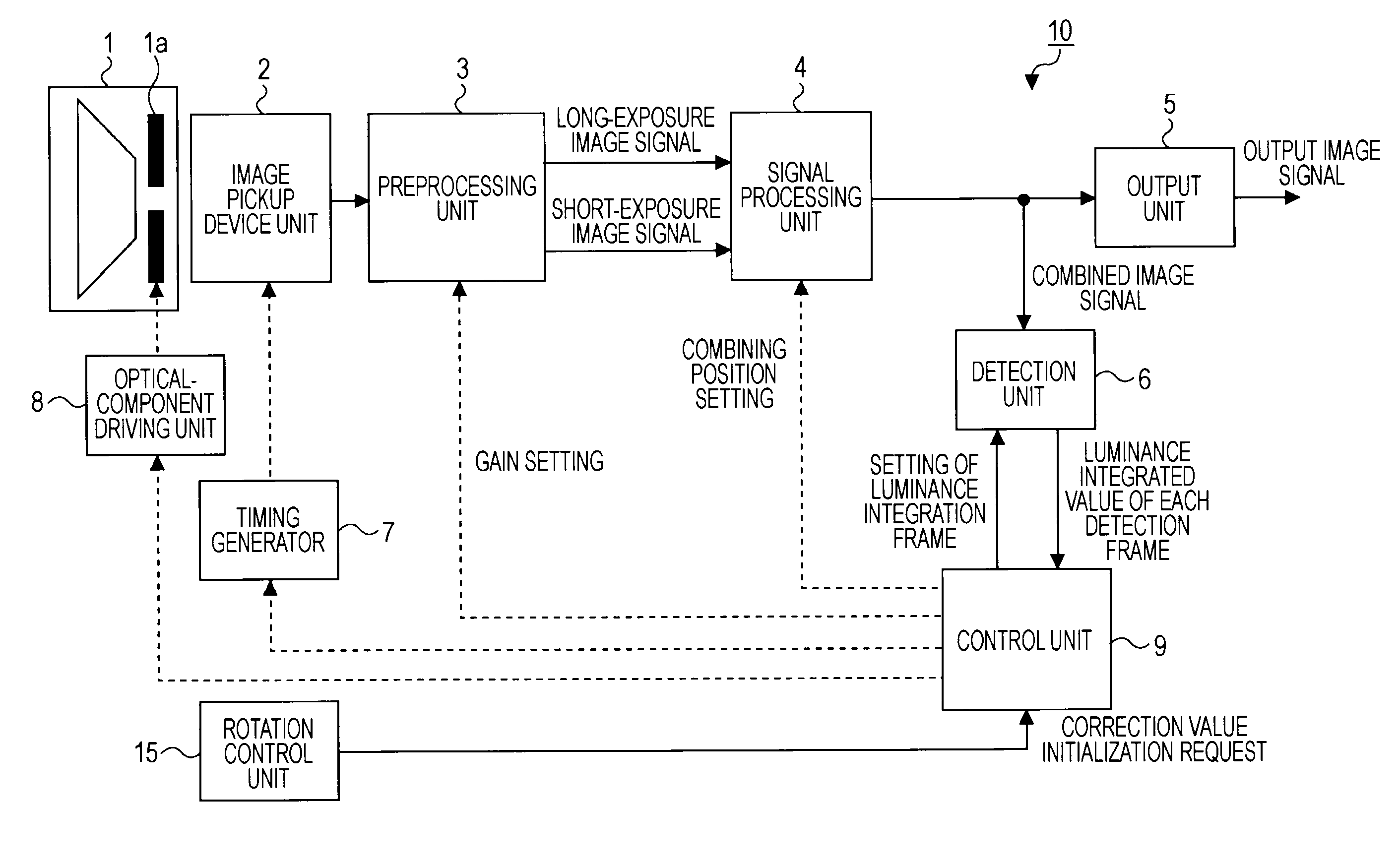

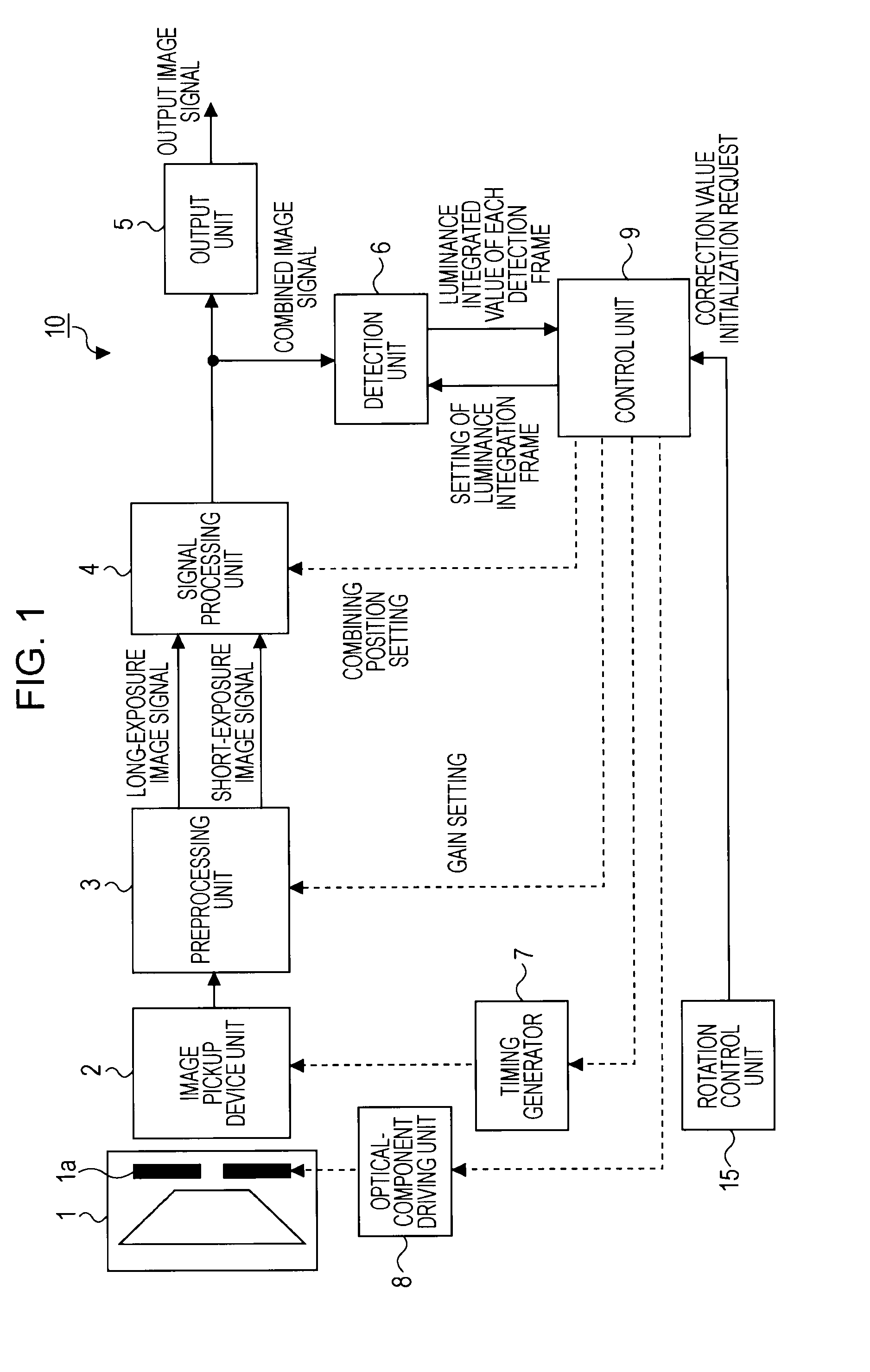

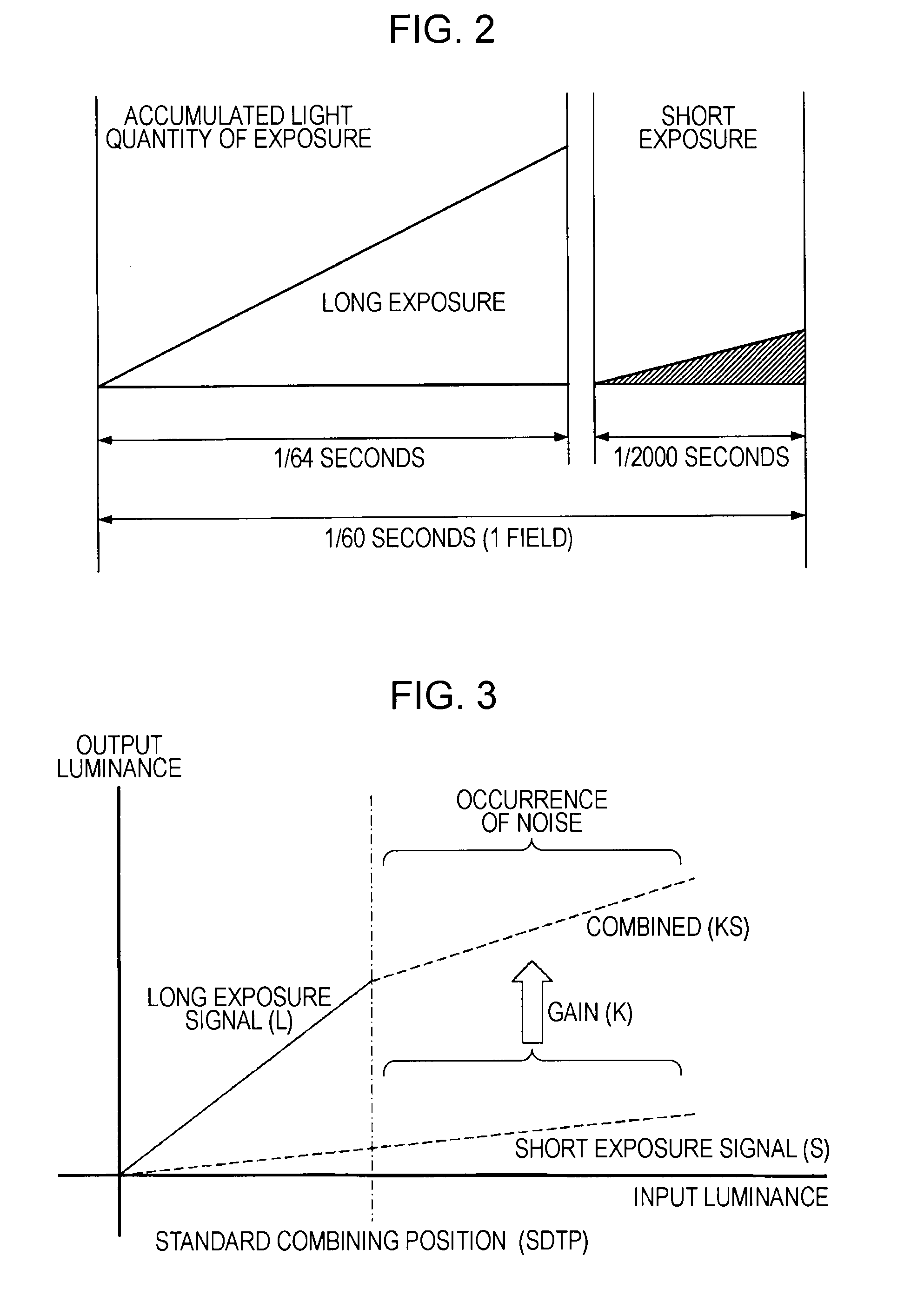

InactiveUS20090086061A1Good effectKeep for a long timeTelevision system detailsColor television detailsComputer scienceMode selection

An image pickup apparatus includes an image pickup unit selectively performing an image capturing operation in a normal image capturing mode where an exposure image signal is output in a unit period and a combined image capturing mode where long- and short-exposure image signals are output in the unit period; a signal processing unit generating a combined image signal with a dynamic range wider than that of the long-exposure image signal or the short-exposure image signal by combining the long-exposure image signal and the short-exposure image signal; a detection unit generating a luminance integrated value of the combined image signal; and a control unit performing exposure correction control using the luminance integrated value. The control unit initializes a correction value used in the exposure correction control when the mode is switched from the normal image capturing mode to the combined image capturing mode.

Owner:SONY CORP

Image pickup apparatus, image pickup method, and program therefor

InactiveUS20090086085A1Good effectKeep for a long timeTelevision system detailsImage enhancementImage signalComputer science

An image pickup apparatus includes an image pickup unit configured to output a long-exposure image signal with a relatively long exposure time and a short-exposure image signal with a relatively short exposure time; a signal processing unit configured to generate a combined image signal with a relatively wide dynamic range at least wider than that of the long-exposure image signal or that of the short-exposure image signal by combining the long-exposure image signal and the short-exposure image signal; a detection unit configured to generate a luminance integrated value of the combined image signal; and a control unit configured to perform exposure correction control using the luminance integrated value. The control unit initializes a correction value for use in the exposure correction control during a scene change.

Owner:SONY CORP

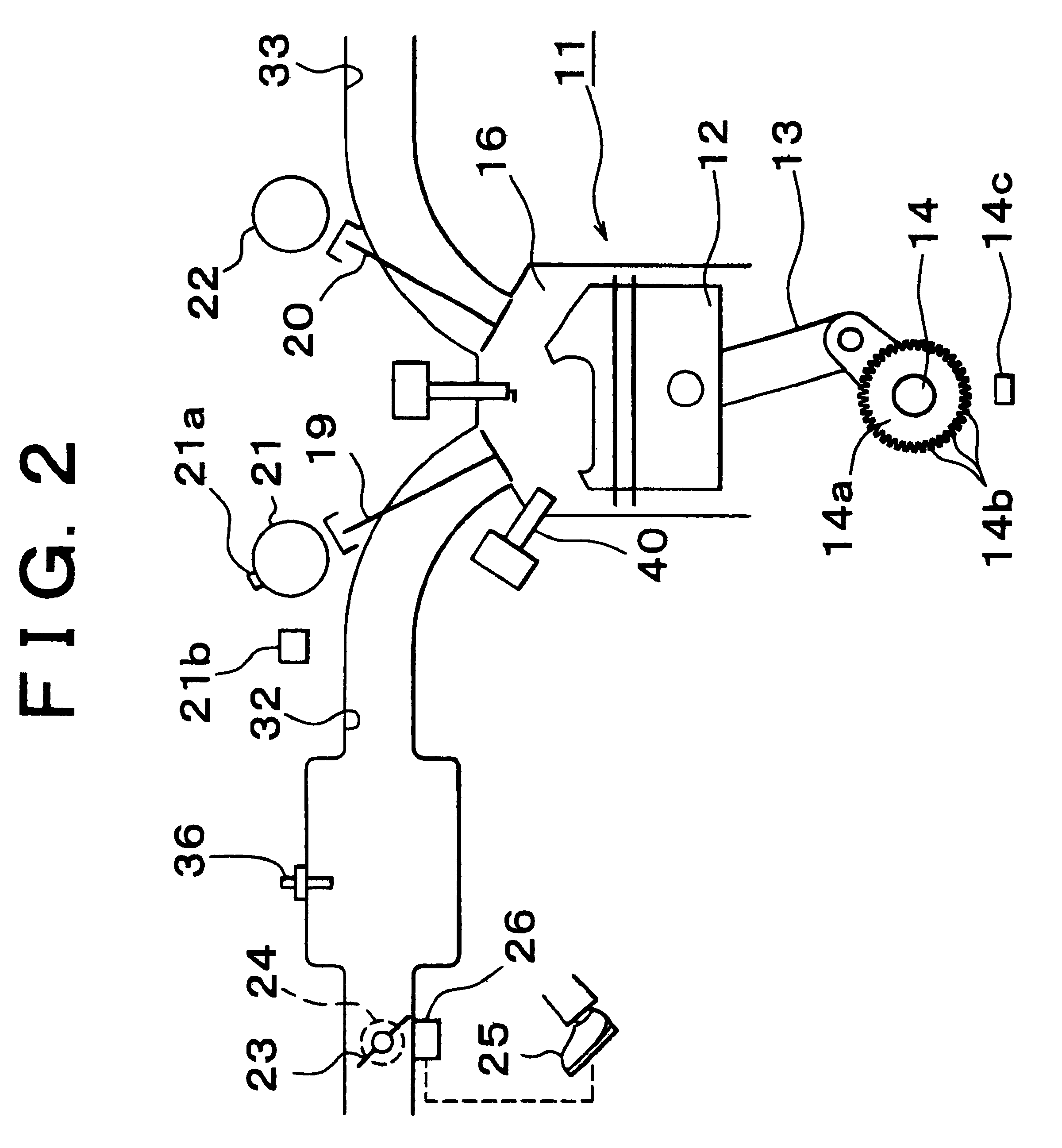

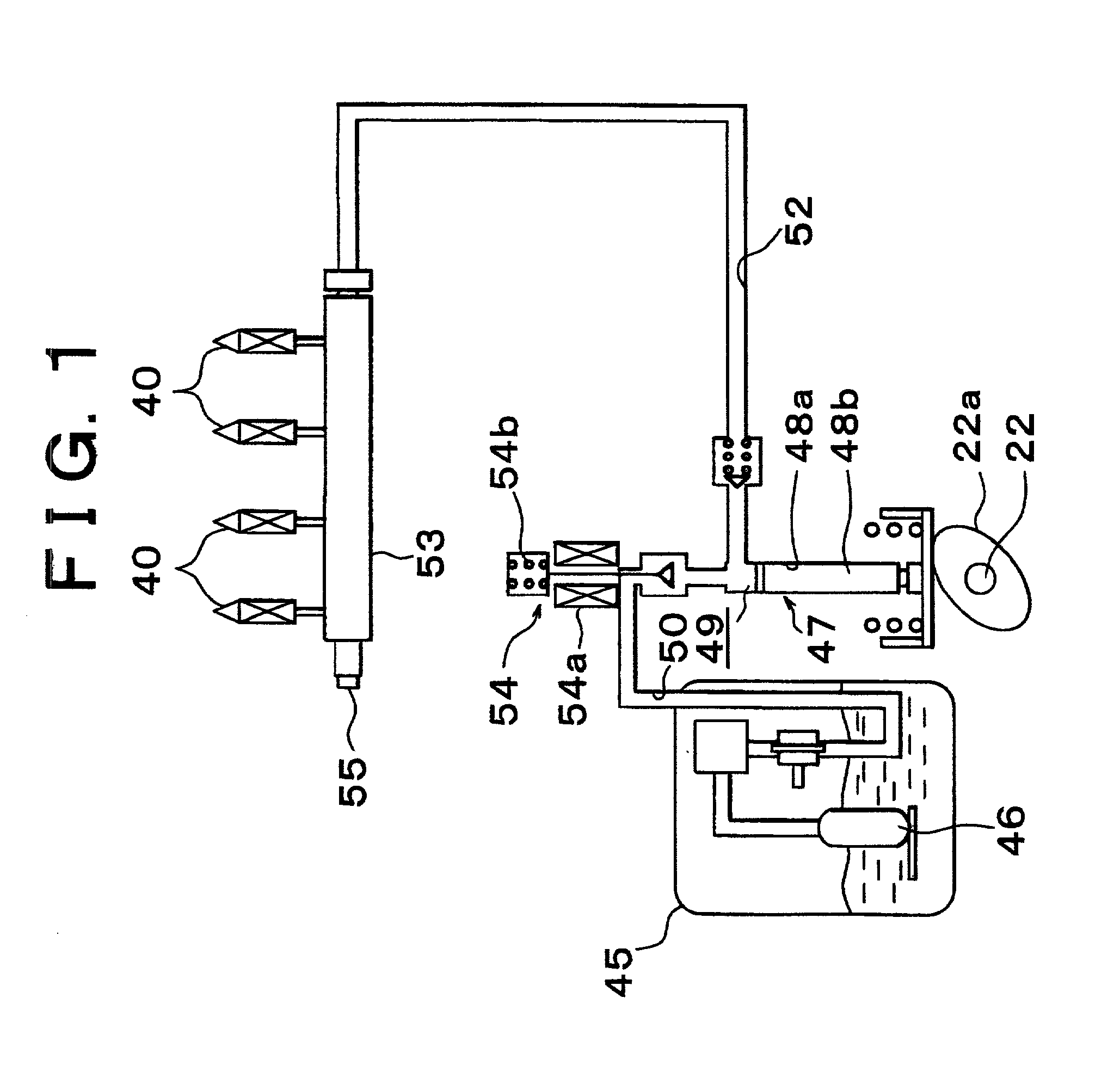

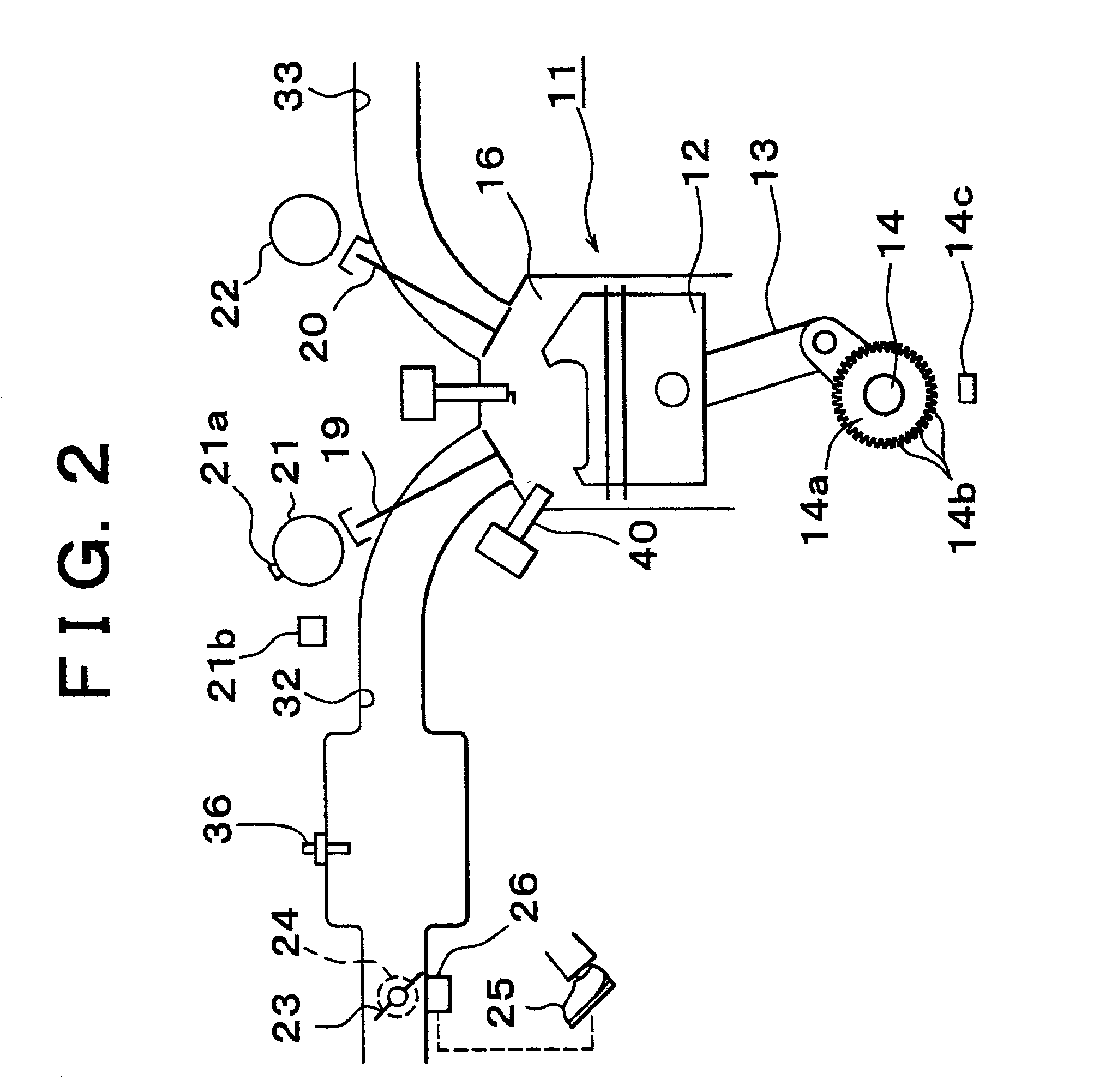

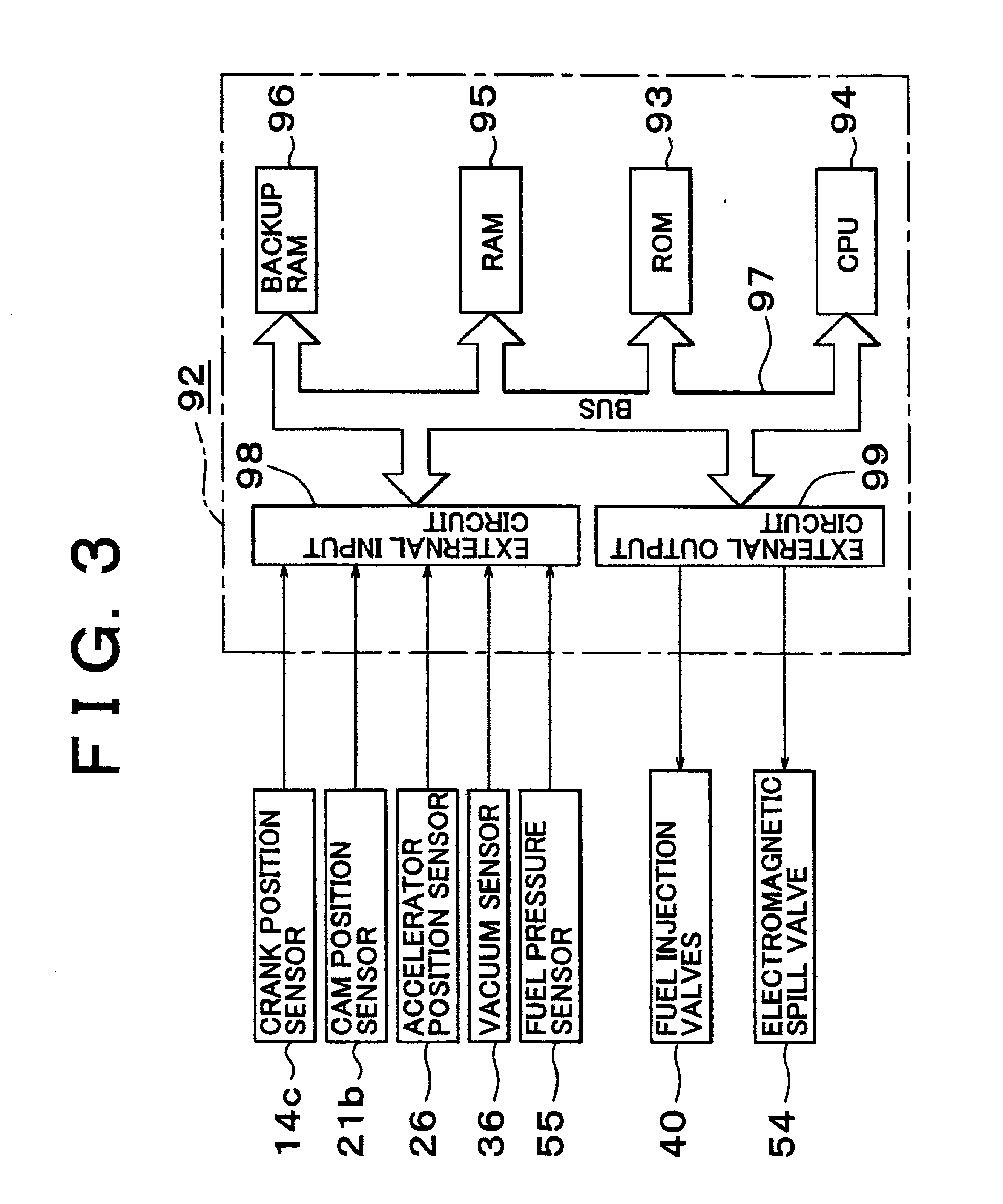

Fuel pressure control apparatus of internal combustion engine

InactiveUS6450147B2Suppress or avoid so-called "ovReduce the amount of fuelElectrical controlLow-pressure fuel injectionExternal combustion engineInternal combustion engine

Owner:TOYOTA JIDOSHA KK

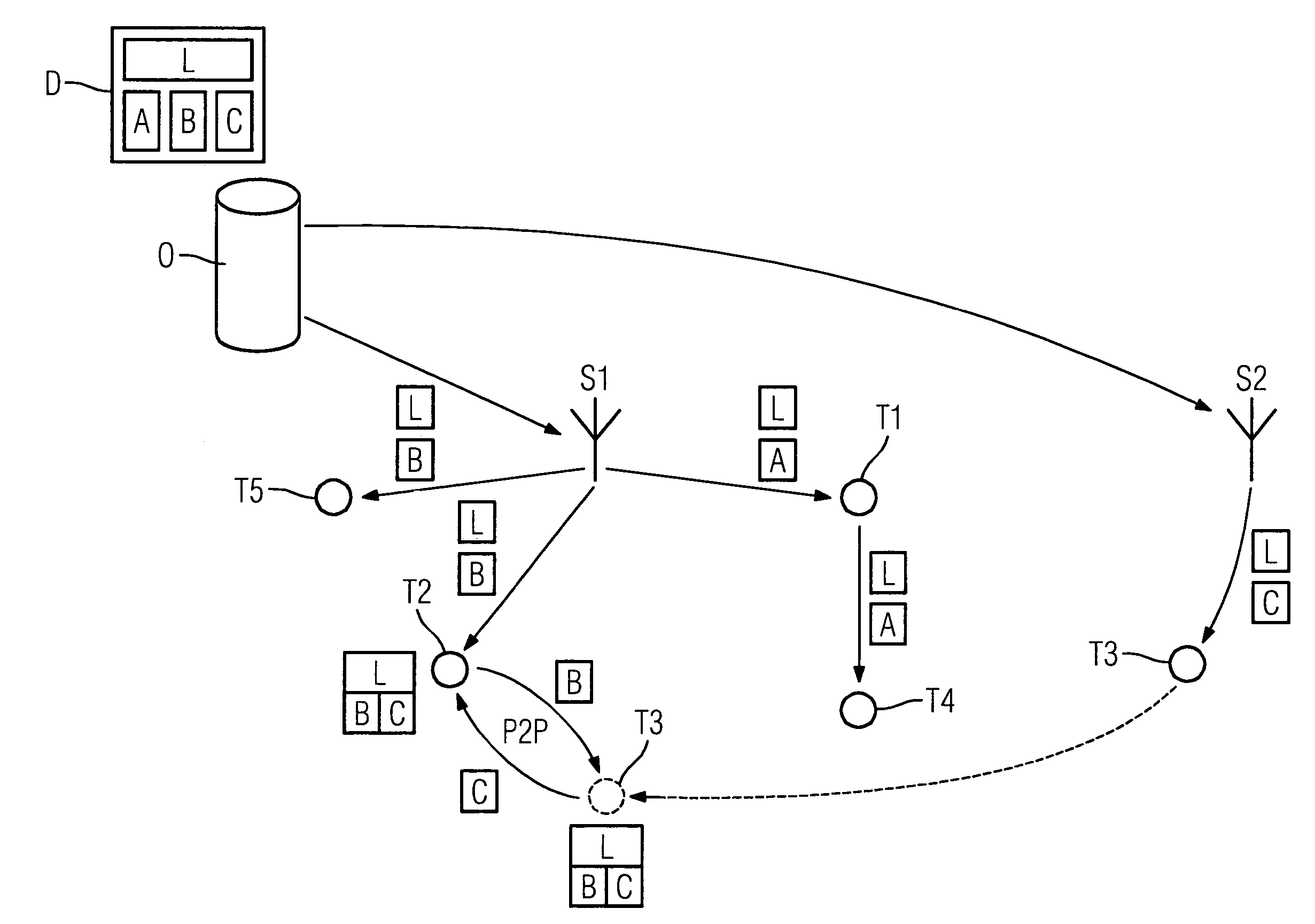

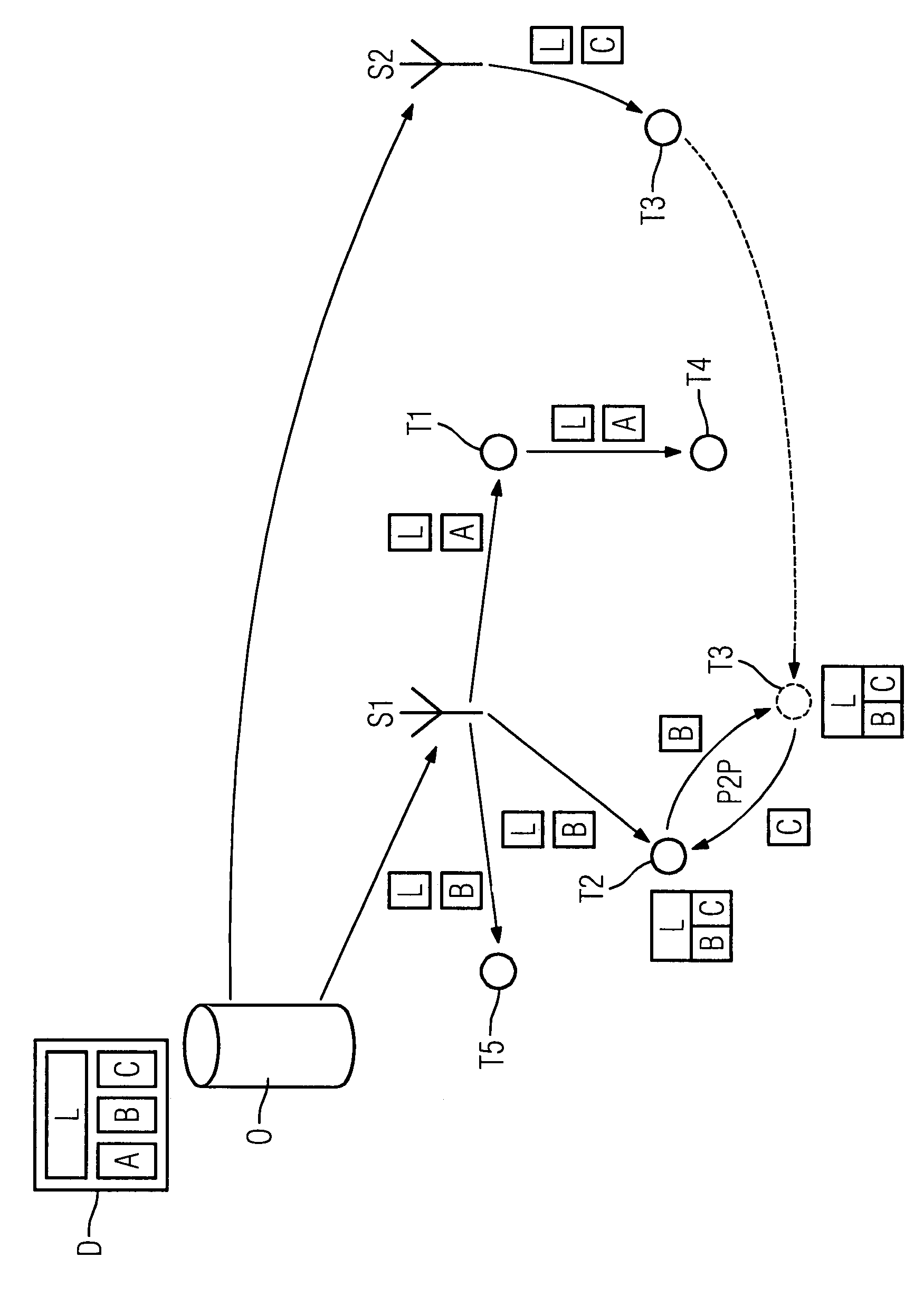

Method for distribution of software and configuration data and corresponding data network

ActiveUS8291115B2Many changeSave bandwidthNetwork topologiesMultiple digital computer combinationsSoftwareTheoretical computer science

In one aspect, software or configuration data that is to be distributed is subdivided into data blocks and a list created based on the data blocks created. Users receive the list and a portion of the data blocks. The users form ad hoc networks or P2P connections among themselves. The connections allow the data blocks to be exchanged randomly.

Owner:UNIFY GMBH & CO KG

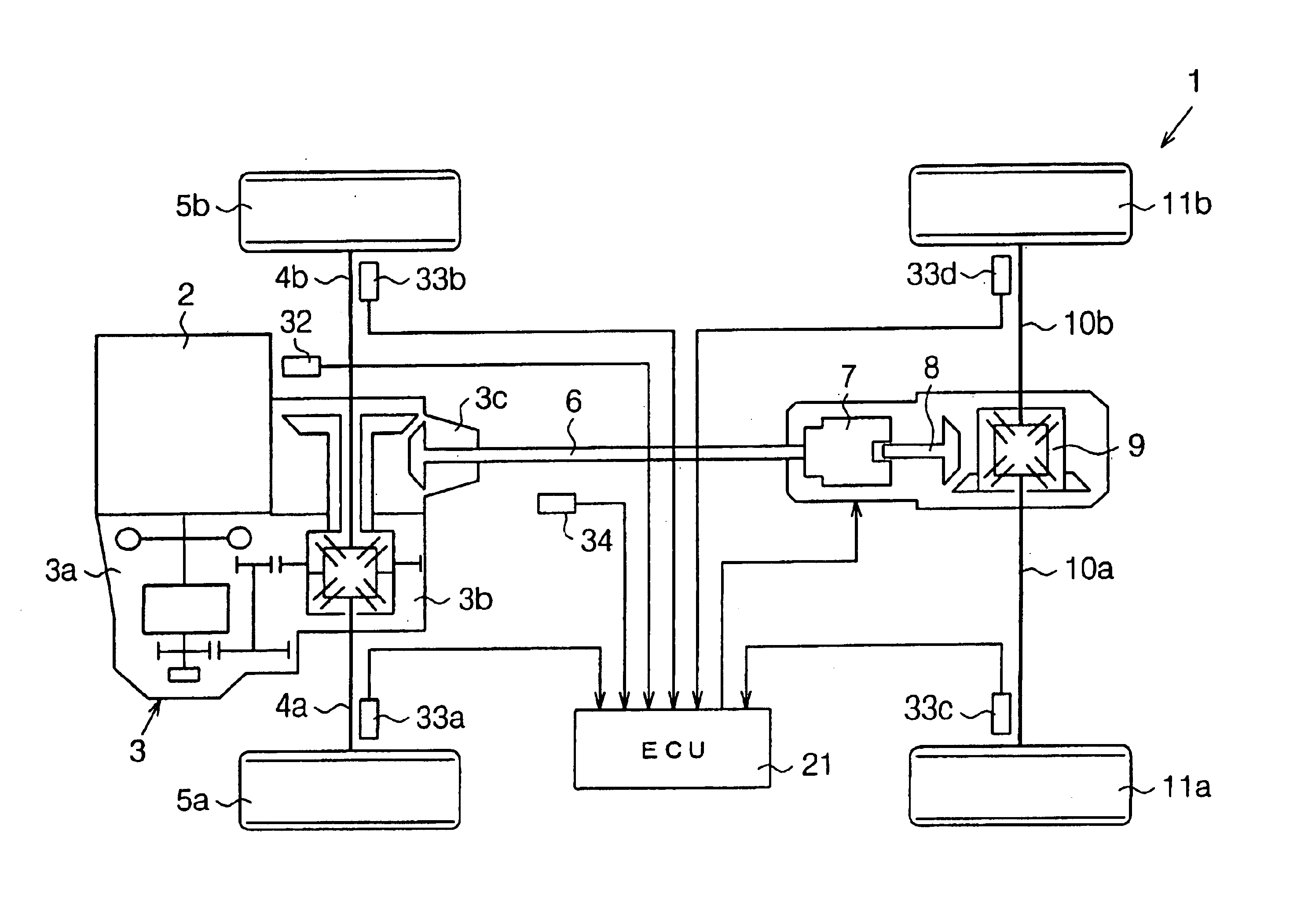

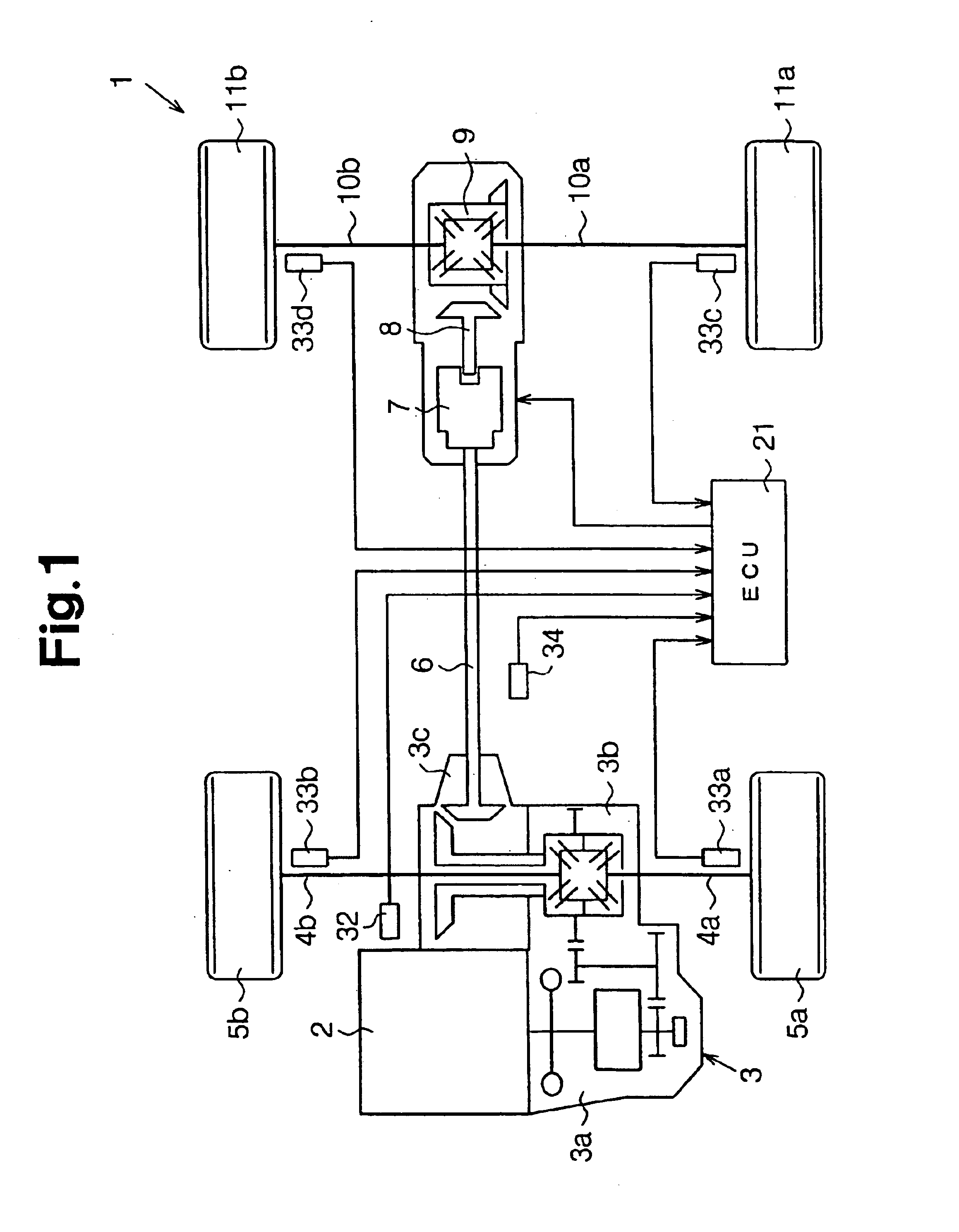

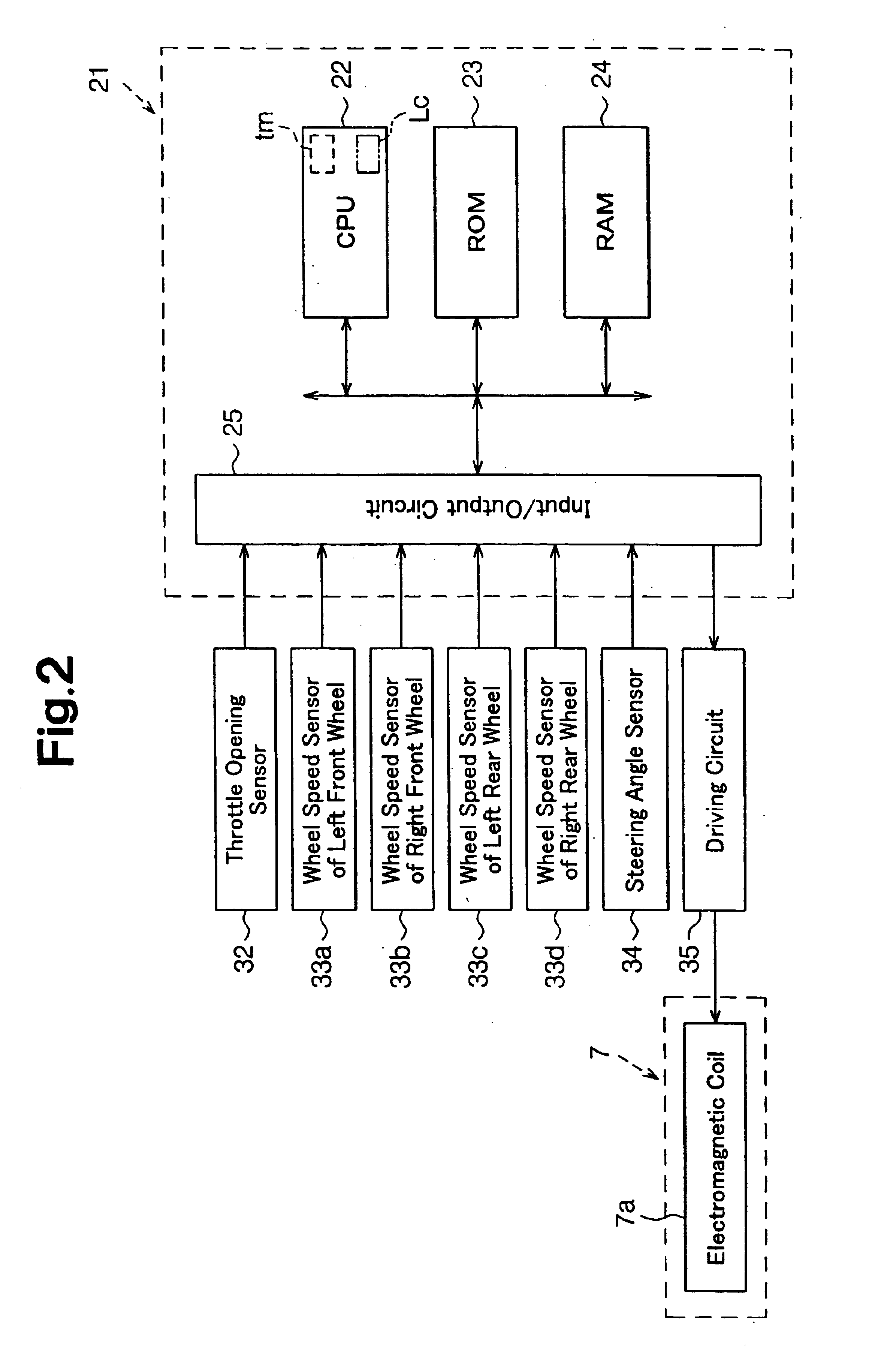

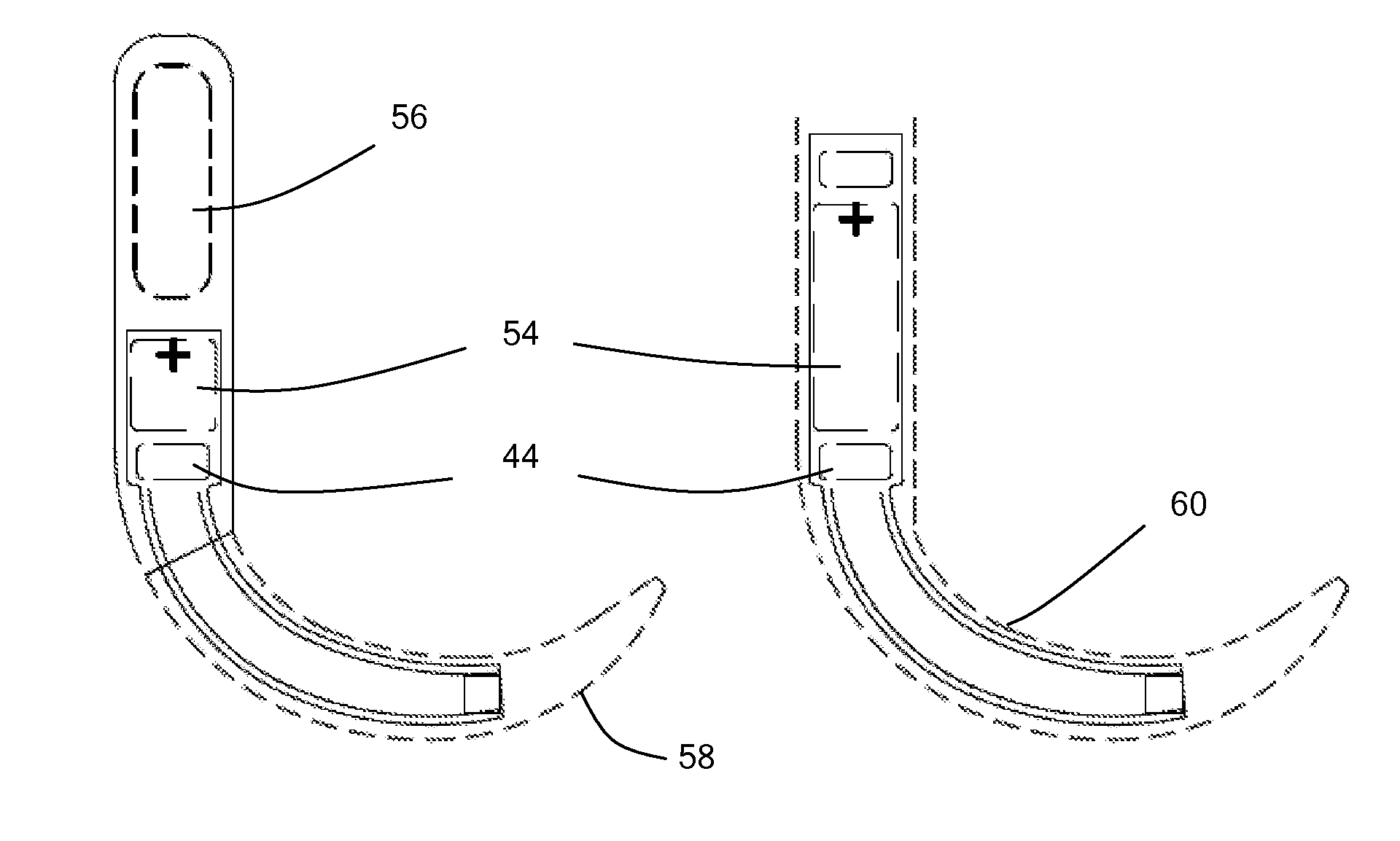

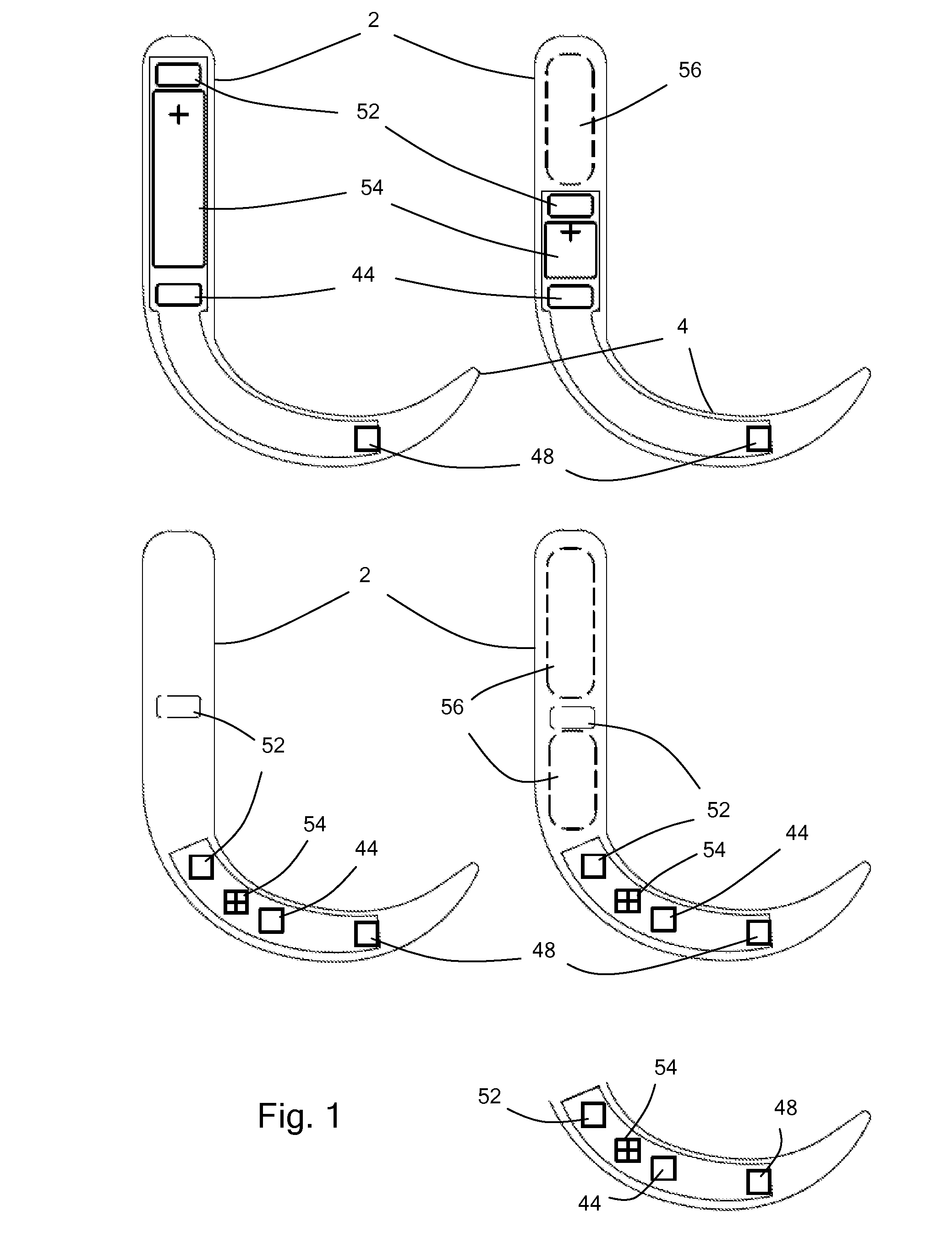

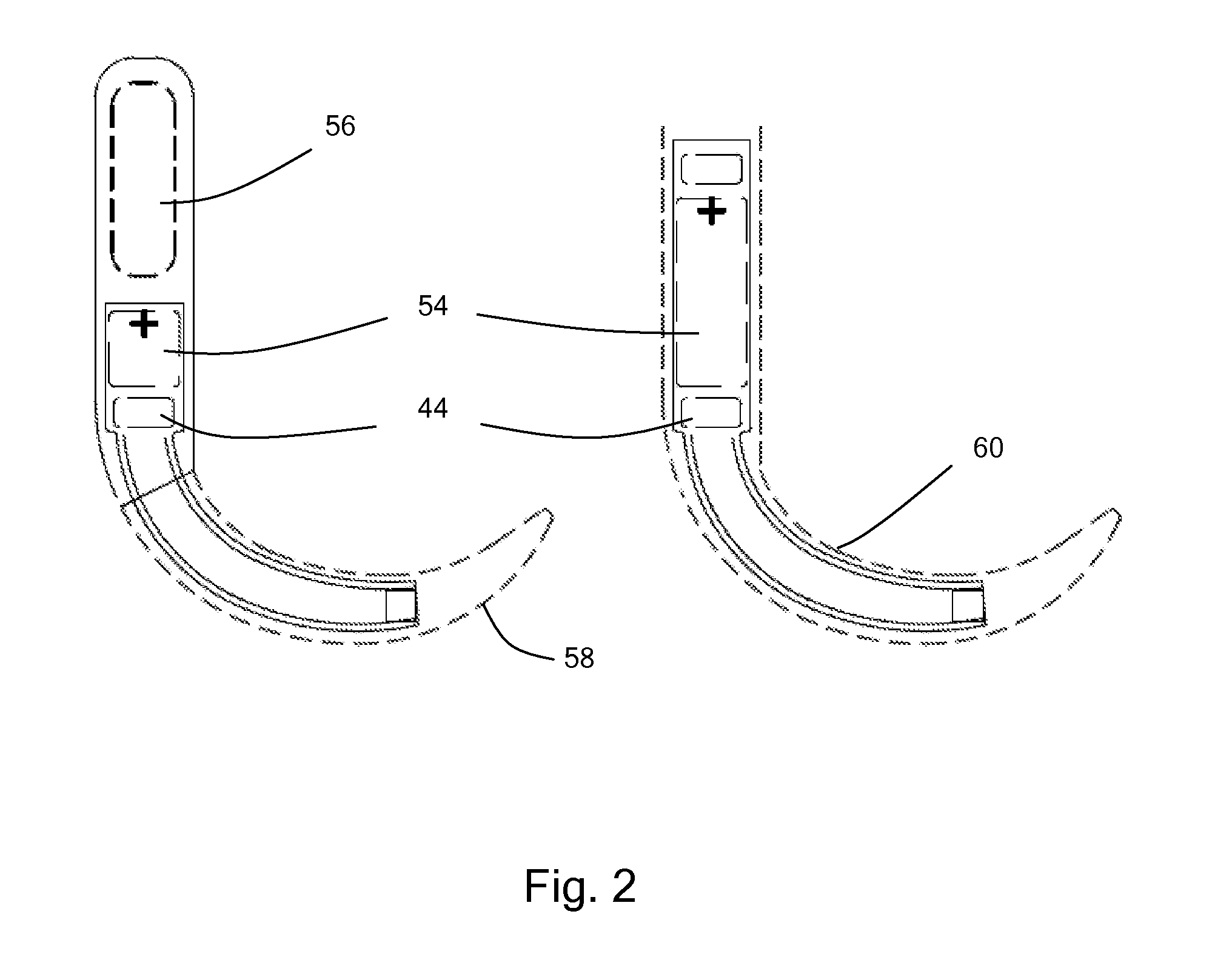

Driving force distribution control device and driving force distribution method for four-wheel drive vehicle

An ECU, which functions as a driving force distribution control apparatus for a four-wheel drive vehicle, includes a CPU. The CPU controls a coupling for changing torque distribution of front and rear wheels. The CPU determines either of first and second torque distribution modes based on detection signals of a throttle opening sensor and steering angle sensor, which are operating parameters. In the second torque distribution mode, torque is distributed to the front and rear wheels more equally than in the first torque distribution mode. The CPU sets a duration for the second torque distribution mode when the second torque distribution mode is selected. Until the duration elapses, regardless of the operating parameters, the CPU continues the control of the coupling in the second torque distribution mode.

Owner:JAPAN SCI & TECH CORP +1

Electrical device power management

ActiveUS20130066153A1Many changeConfidenceBronchoscopesLaryngoscopesEmergency procedureElectrical battery

An electrical device includes a memory storing a value indicative the remaining available rated capacity of one or more batteries. The stored value is changed in use to reflect reducing capacity. The initial stored value is chosen so that there is a very high (e.g. >99.9%) confidence that the one or more batteries will provide at least the capacity indicated by the initial stored value. This reduces the chance of failure during emergency procedures. The one or more batteries may be integral to the electrical device. An override facility is provided.

Owner:COVIDIEN AG

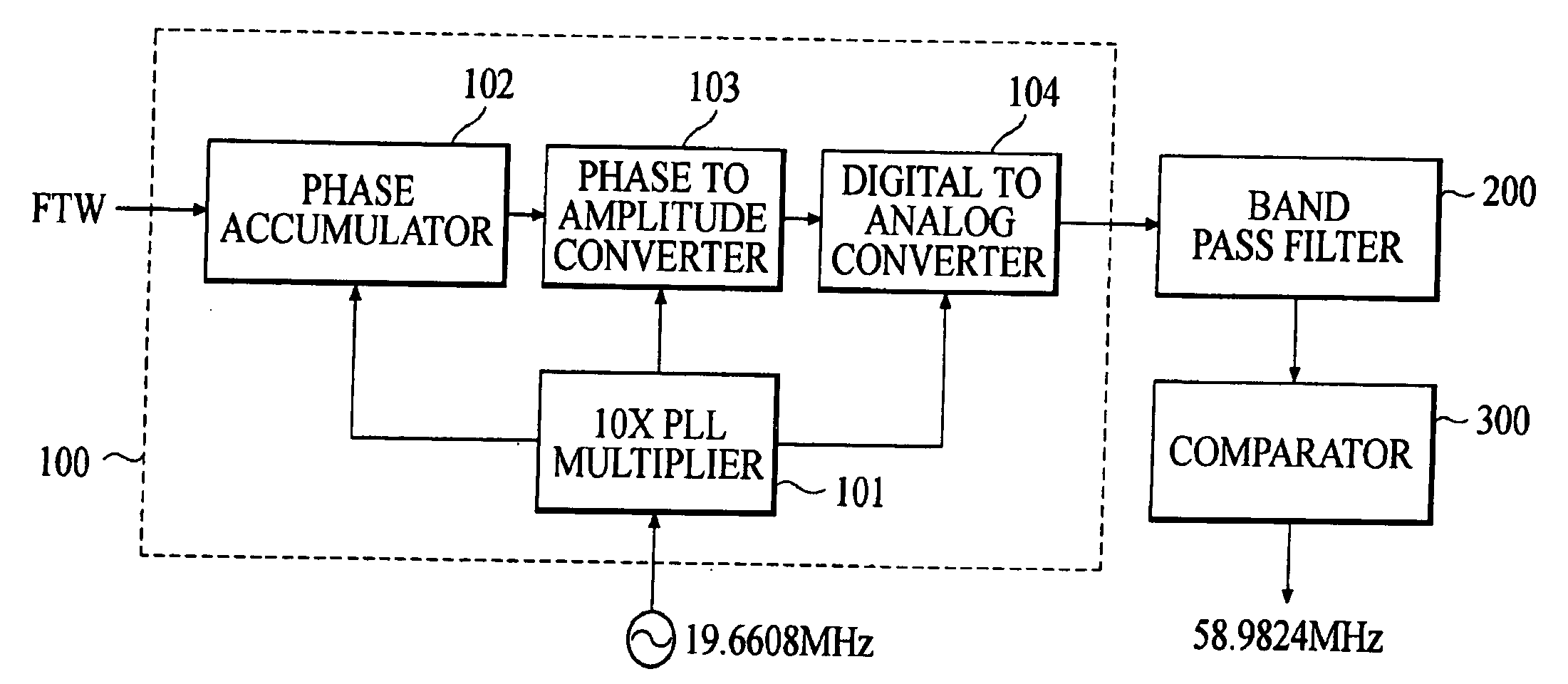

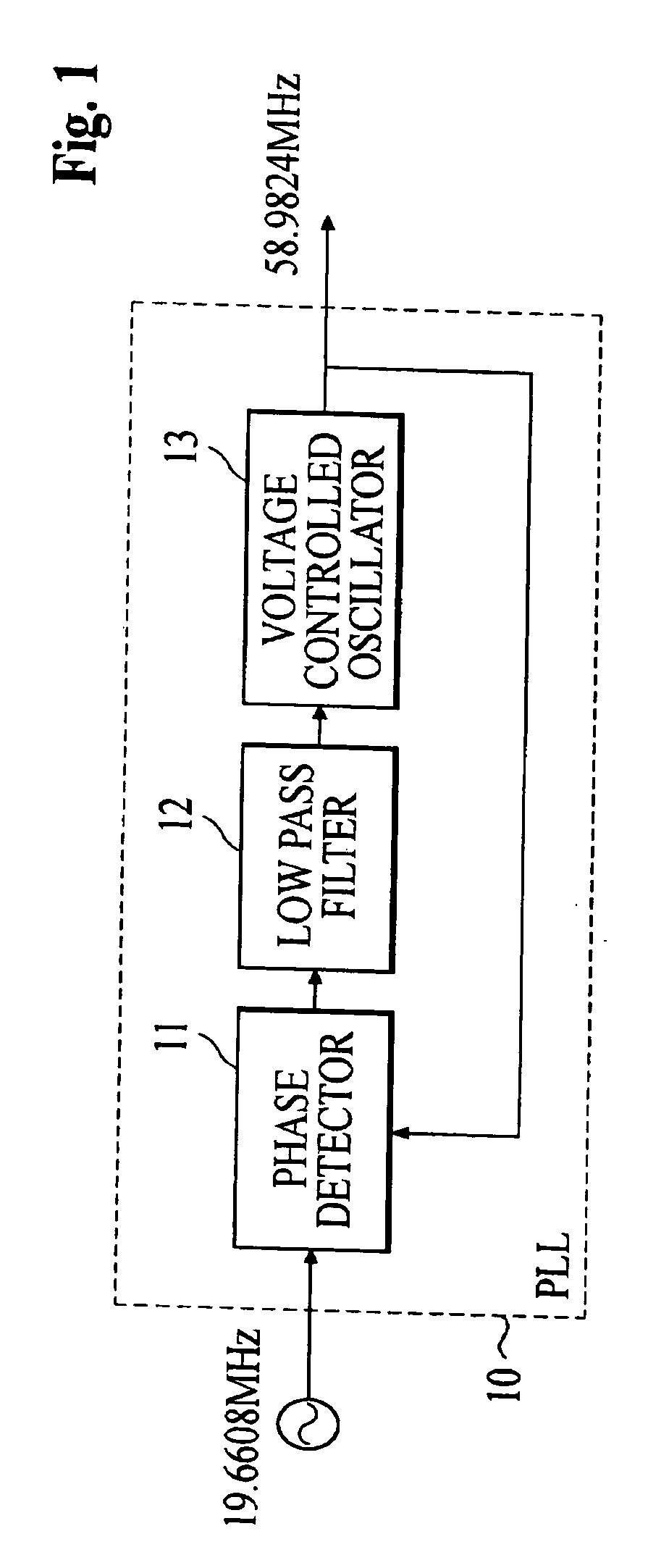

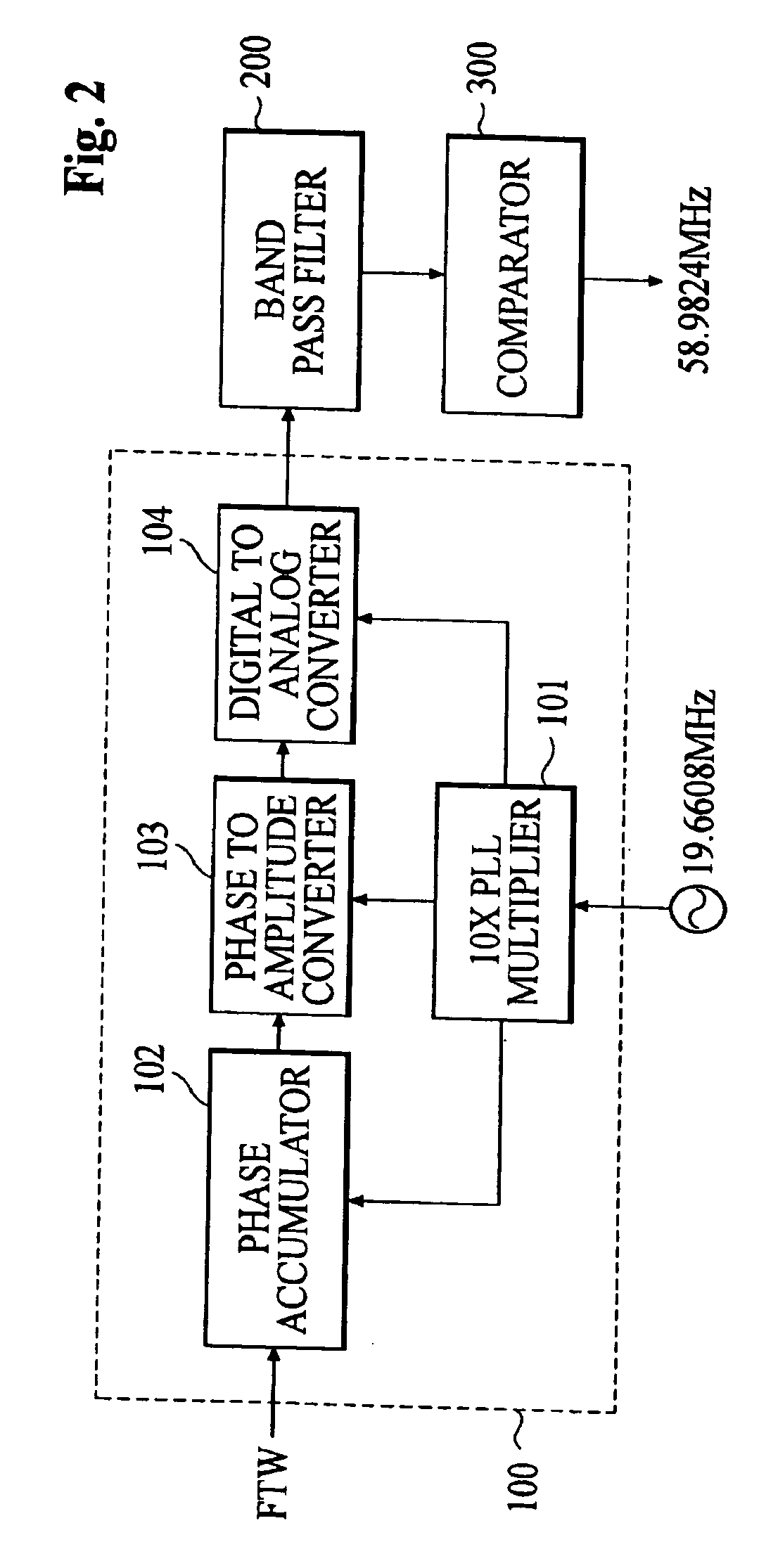

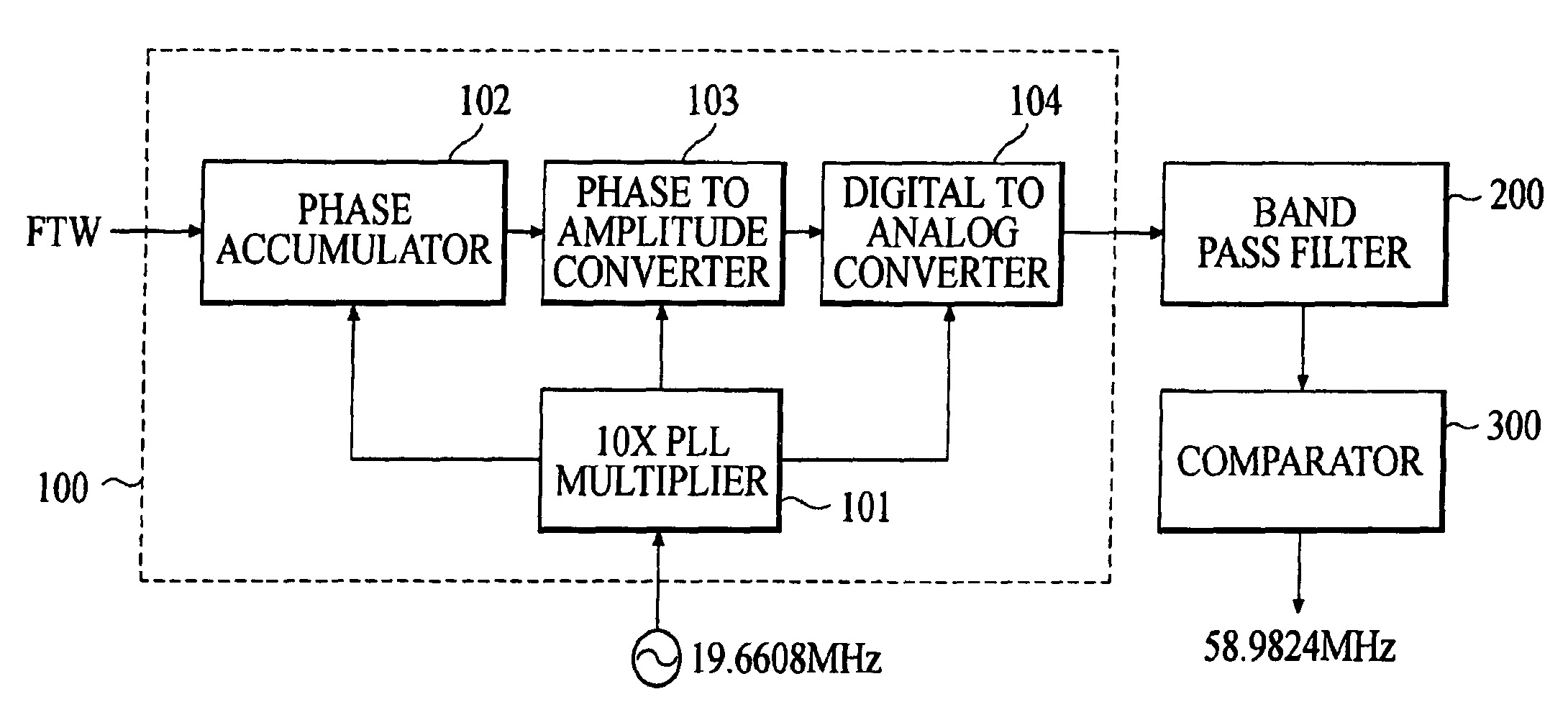

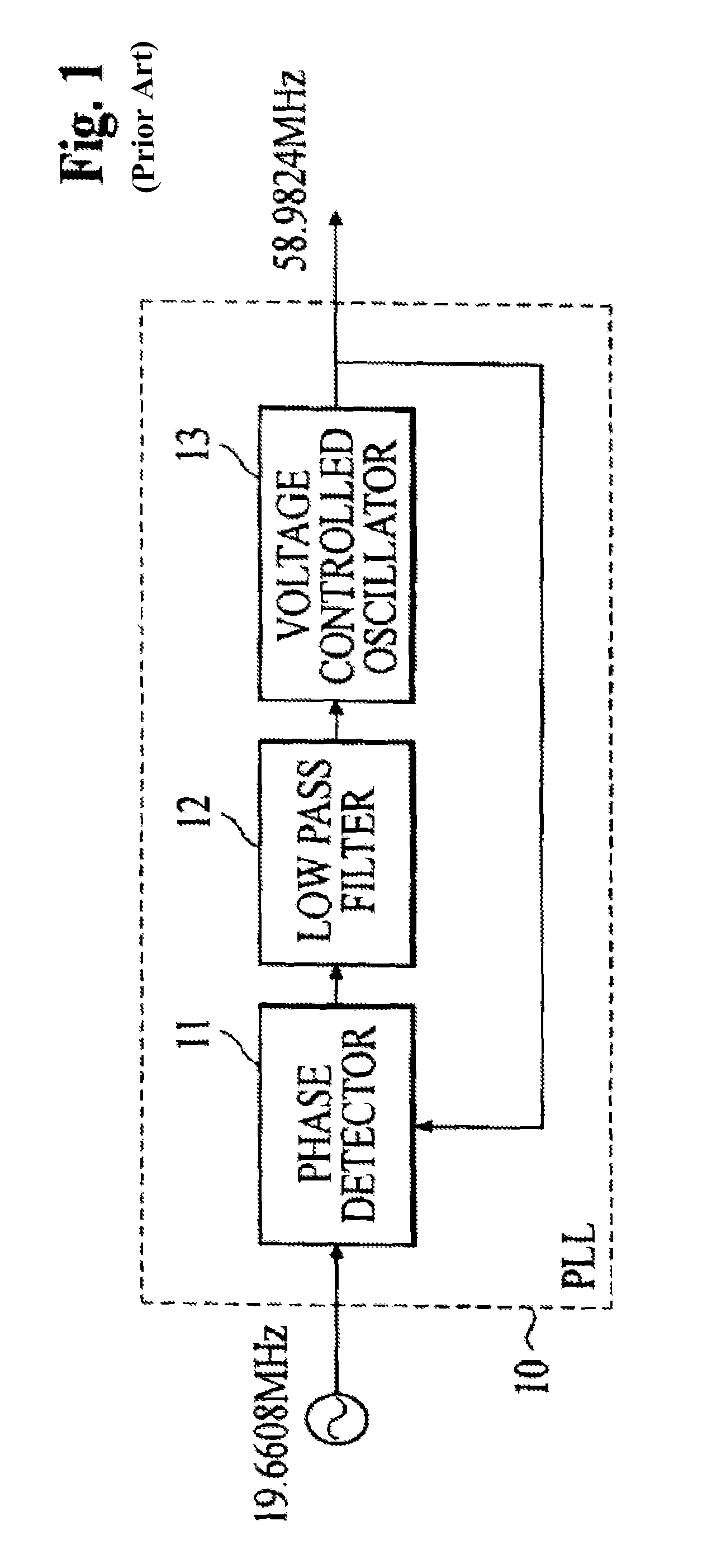

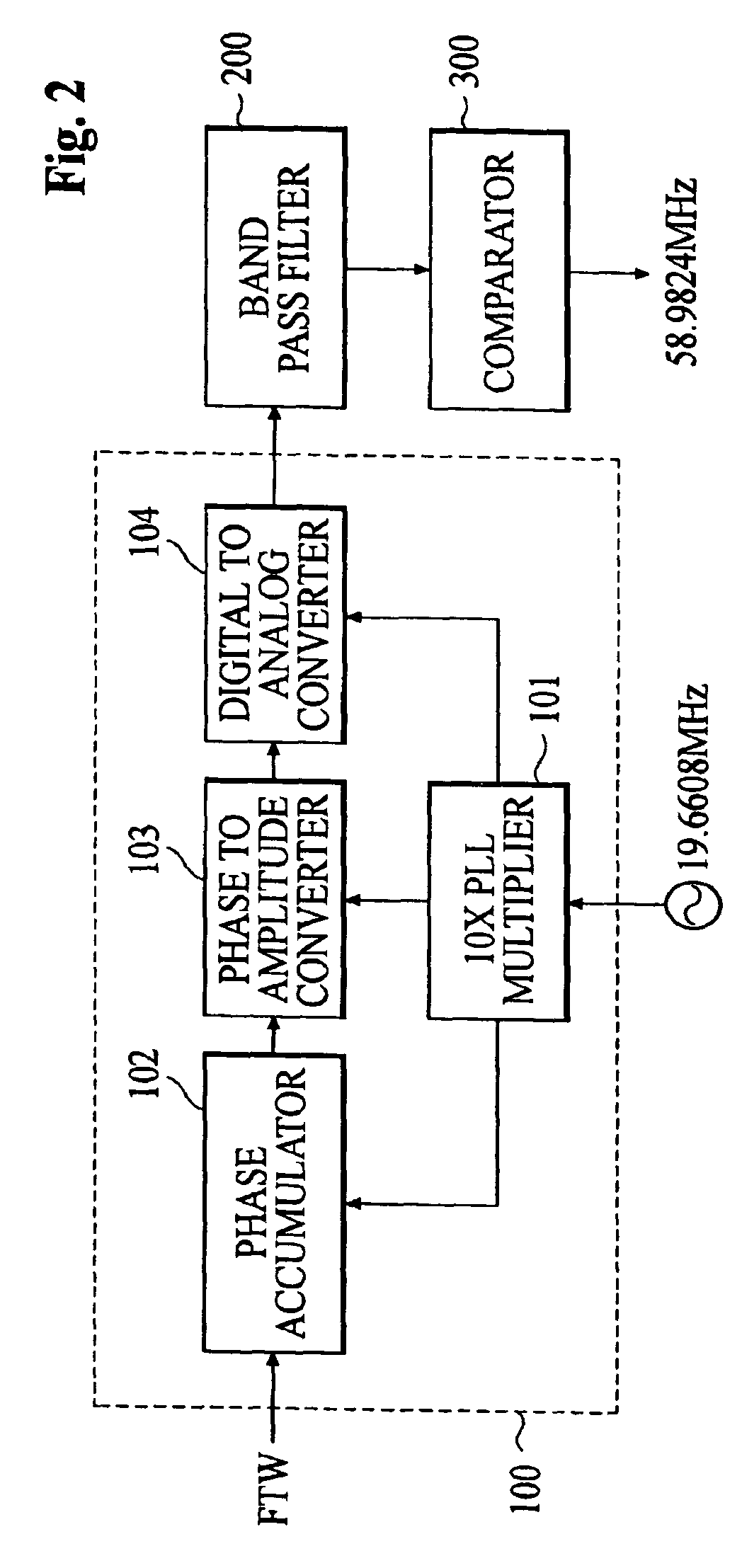

Apparatus for generating clock pulses using a direct digital synthesizer

InactiveUS20070164793A1Many changeFlexible changePulse automatic controlOscillations generatorsPhase noisePhase locked loop circuit

The present invention relates to an apparatus for generating clock pulses using a Direct Digital Synthesizer (DDS). The present invention seeks to solve the problems of the conventional clock generator using a Phase Locked Loop (PLL) circuit where the output clock frequency cannot be varied and the output clock signal is degraded because of jitter and phase noise. The claimed apparatus comprises a phase accumulator, a phase-to-magnitude converter, a Digital-to-Analog (DA) converter, a band pass filter, and a comparator, which are serially connected. A 10× PLL multiplier provides a 196.608MHz clock signal to the phase accumulator, the phase-magnitude converter and the digital analog converter, respectively. The phase accumulator also receives a Frequency Tuning Word (FTW) and using this FTW and the 196.608MHz clock, outputs a desired specific frequency value. This frequency value is processed through the phase-magnitude converter, the digital analog converter, a band pass filter and a comparator in order to become a square wave of a desired frequency with a low jitter.

Owner:TRANSPACIFIC SONIC

Thermal control system and method

ActiveUS20070169491A1High speed responseHigh thermal efficiencyMechanical apparatusHeat pumpsProduct gasProcess engineering

A system and method for controlling the temperature of a process tool uses the vaporizable characteristic of a refrigerant that is provided in direct heat exchange relation with the process tool. Pressurized refrigerant is provided as both condensed liquid and in gaseous state. The condensed liquid is expanded to a vaporous mix, and the gaseous refrigerant is added to reach a target temperature determined by its pressure. Temperature corrections can thus be made very rapidly by gas pressure adjustments. The process tool and the operating parameters will usually require that the returning refrigerant be conditioned and processed for compatibility with the compressor and other units, so that cycling can be continuous regardless of thermal demands and changes.

Owner:BE AEROSPACE INCORPORATED

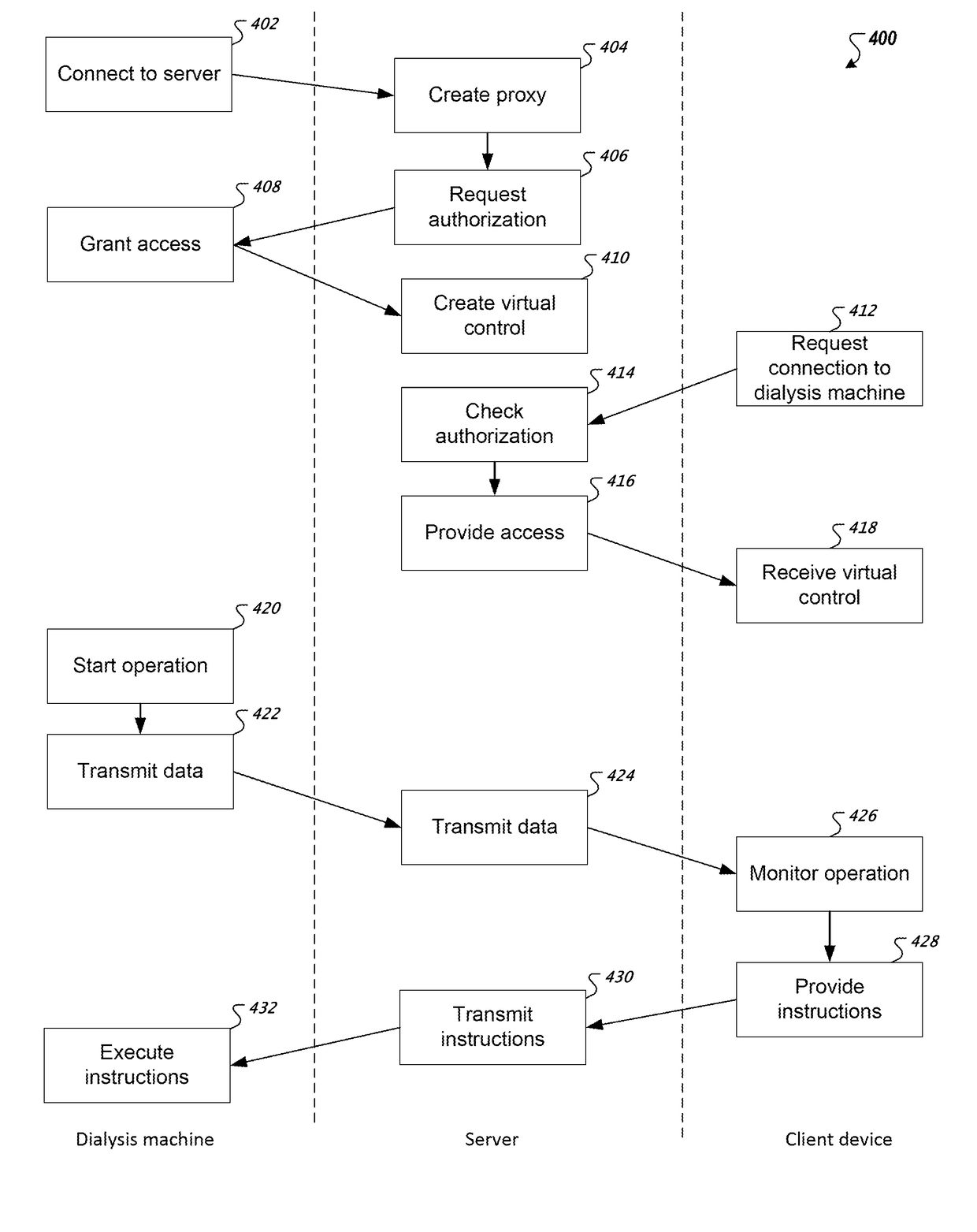

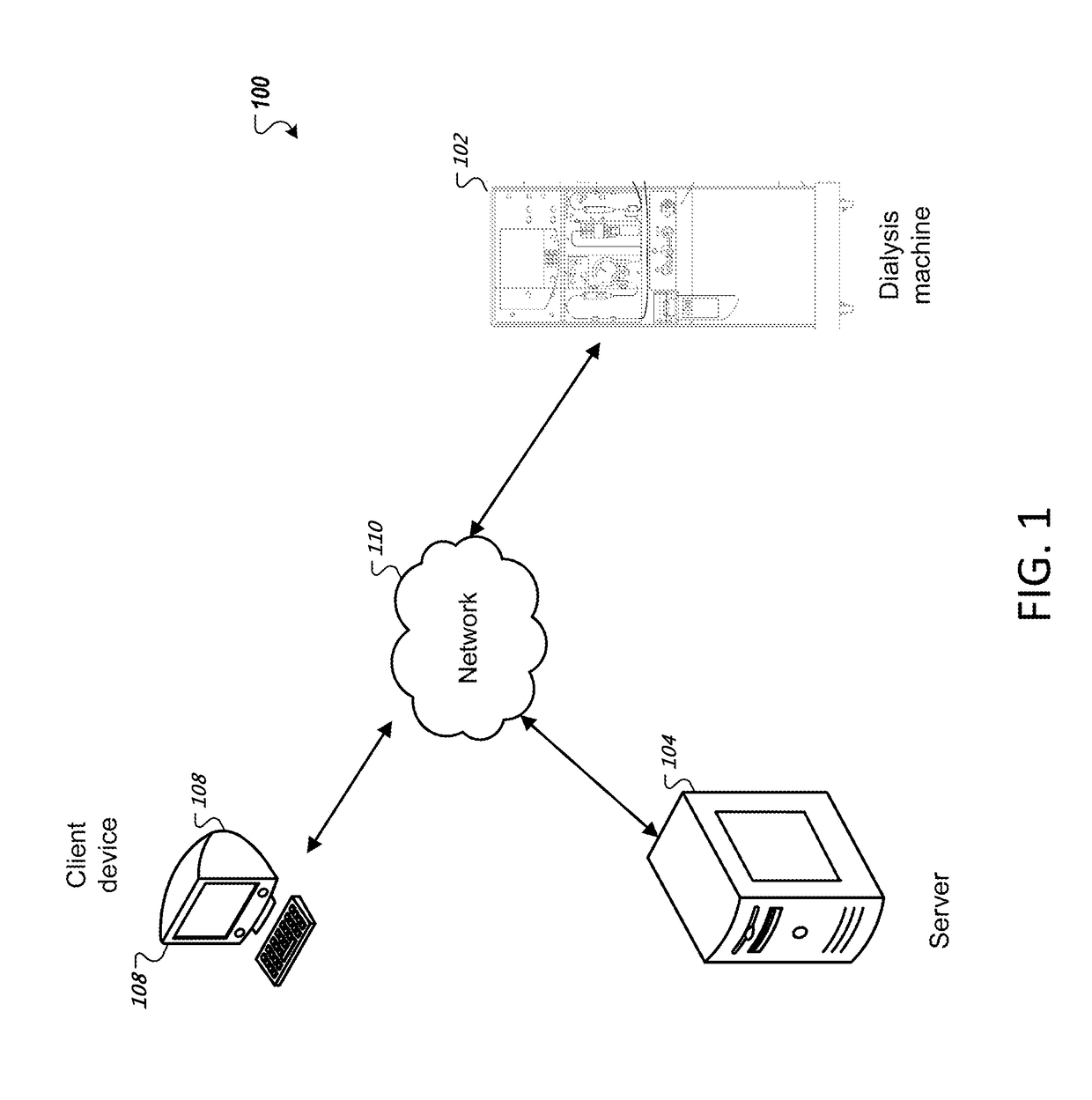

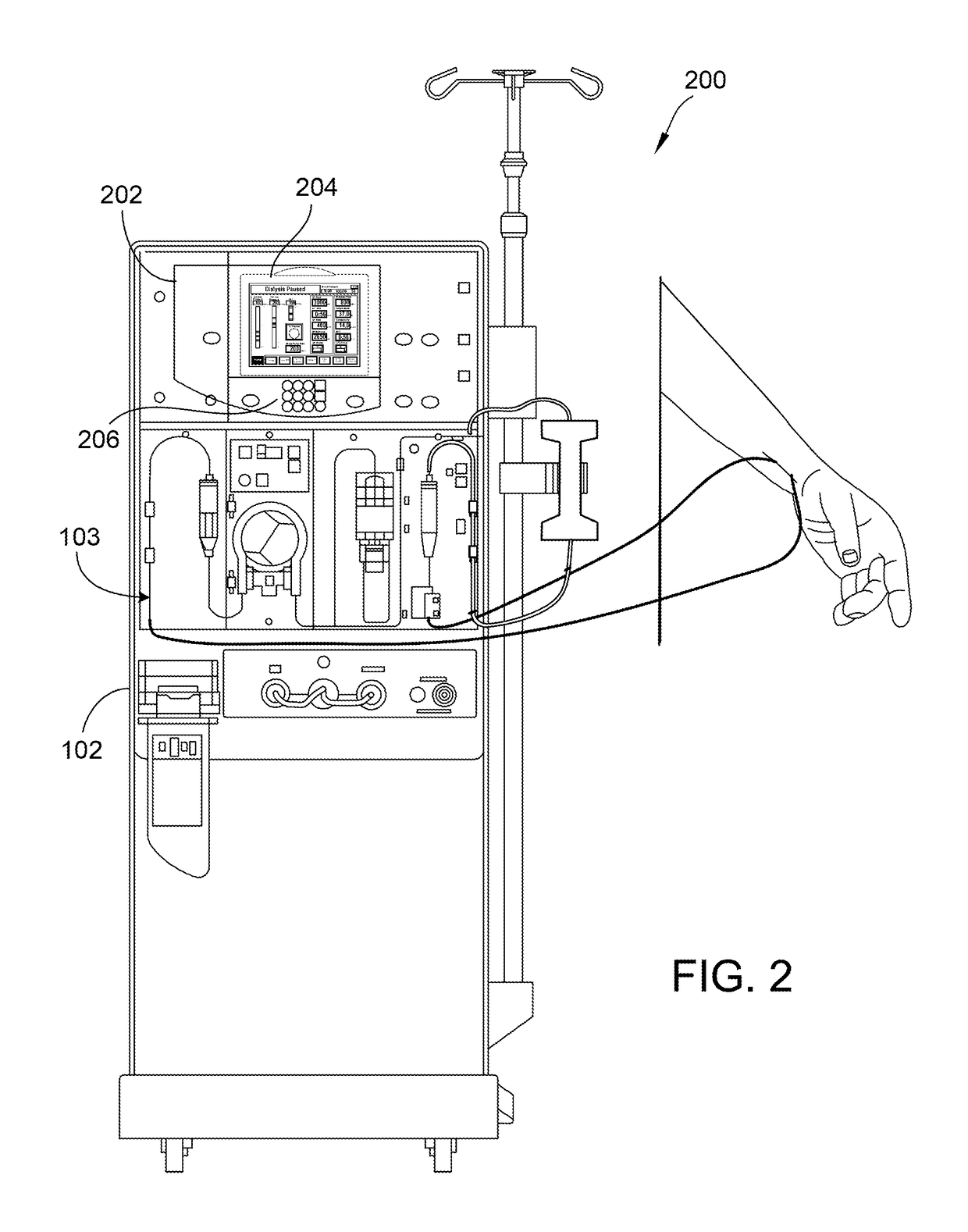

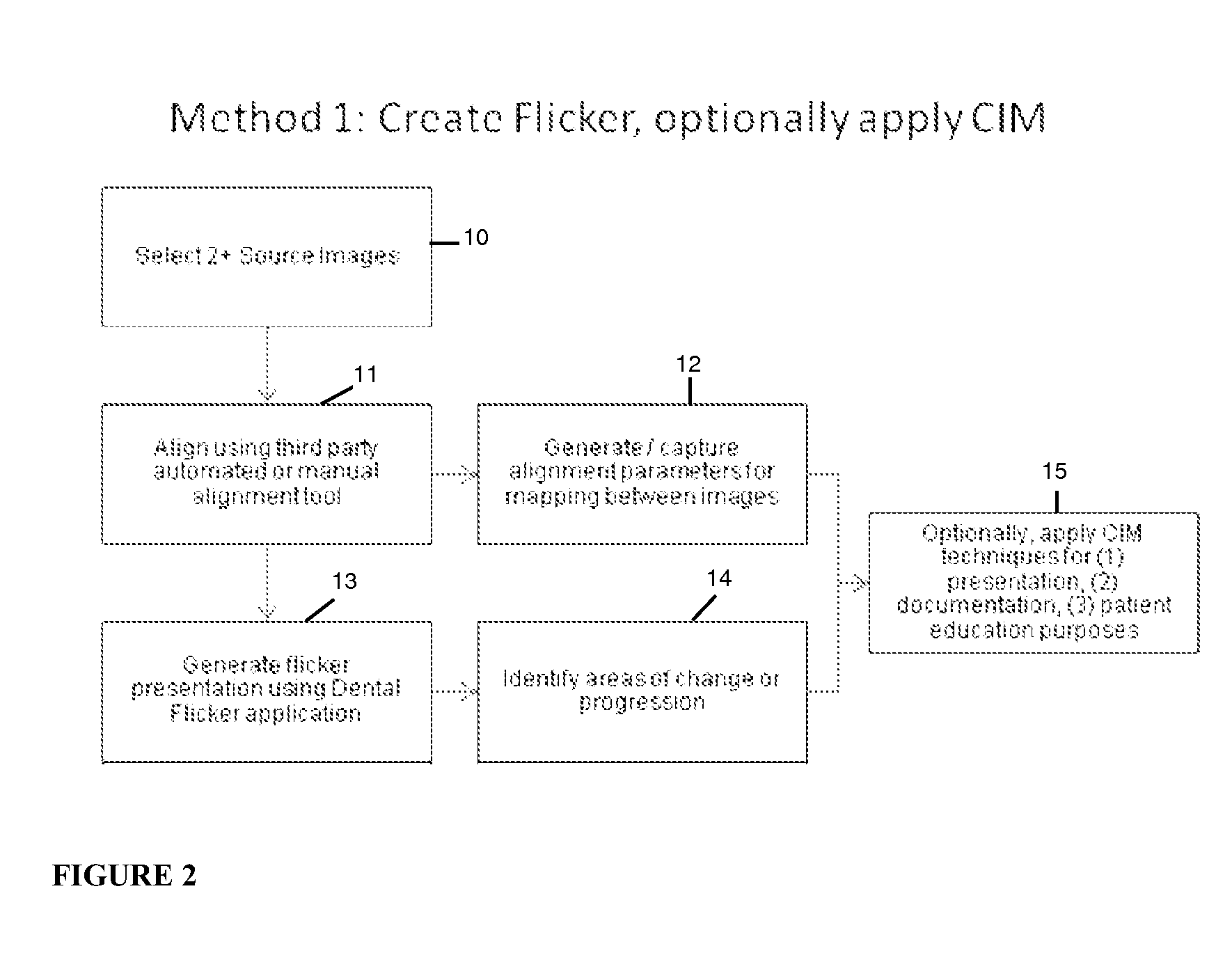

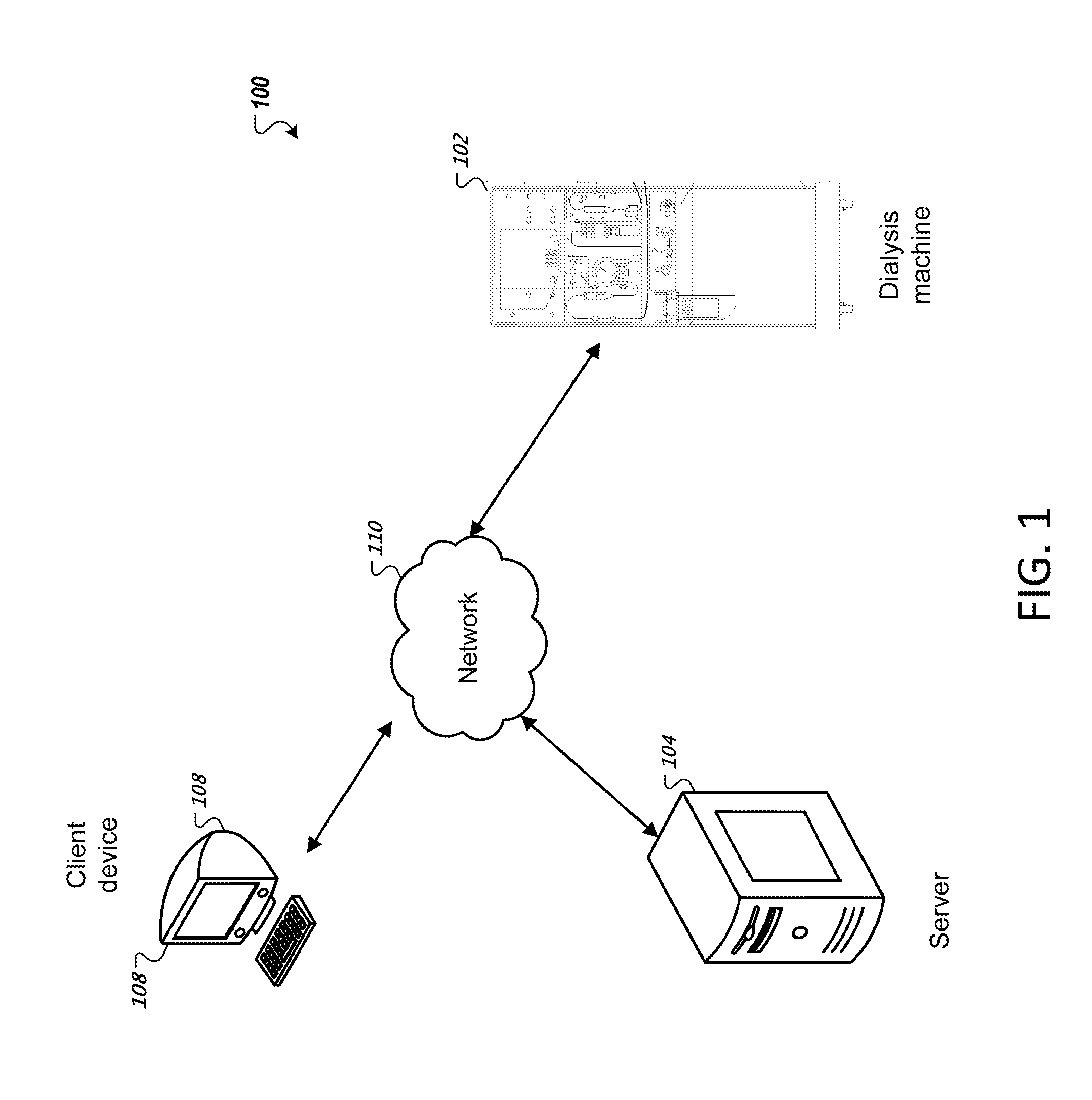

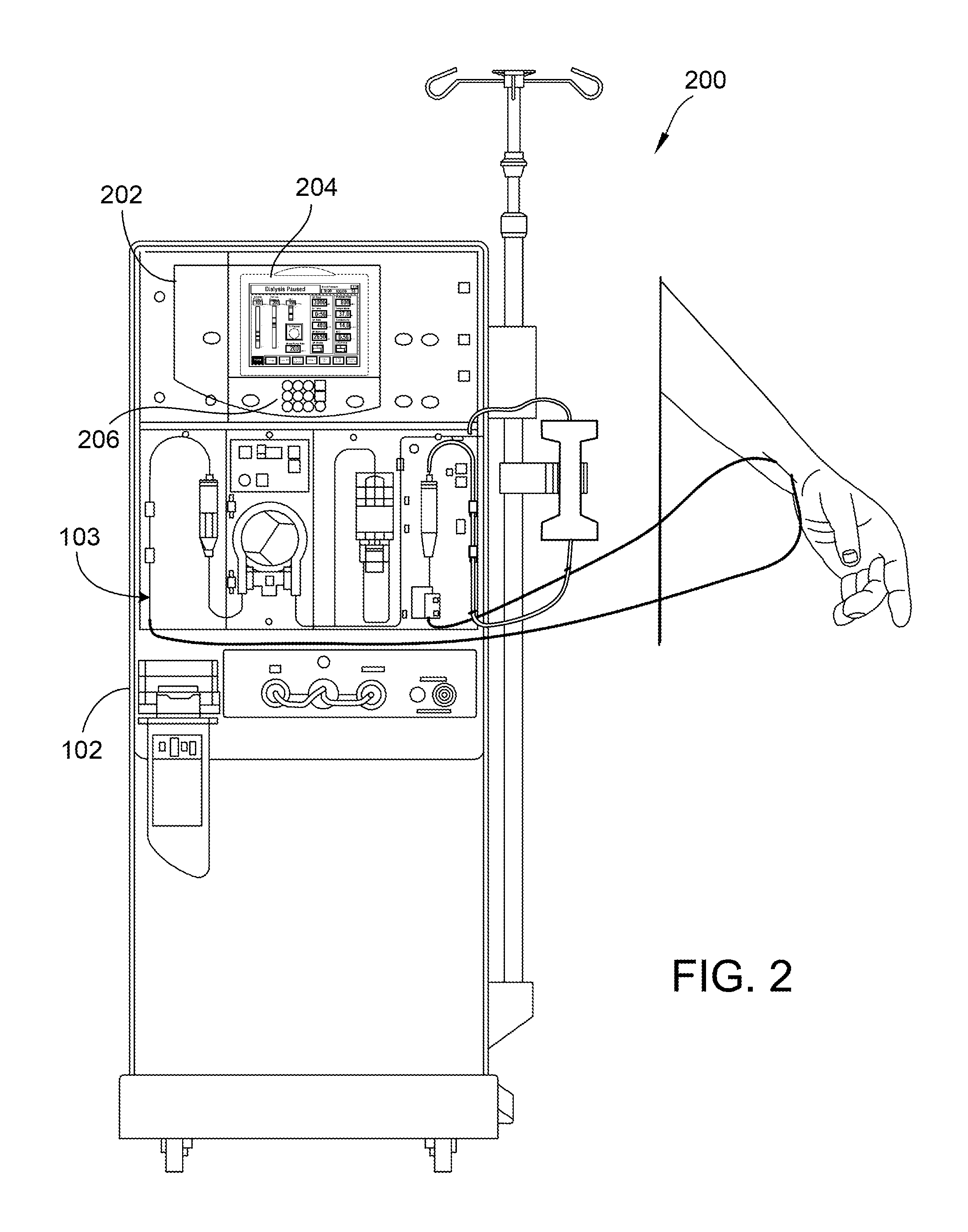

Remote control of dialysis machines

ActiveUS9635111B2Easy to controlEasy to monitorMechanical/radiation/invasive therapiesDrug and medicationsRemote controlNetwork connection

This disclosure relates to remote control of dialysis machines. In certain aspects, a method includes receiving a request for a network connection from a dialysis machine and establishing the network connection with the dialysis machine. The method also includes receiving, from a client device, a request to access the dialysis machine, authorizing the client device to access the dialysis machine, receiving, from the dialysis machine, information pertaining to an operation of the dialysis machine, and providing, to the client device, the received information.

Owner:FRESENIUS MEDICAL CARE HLDG INC

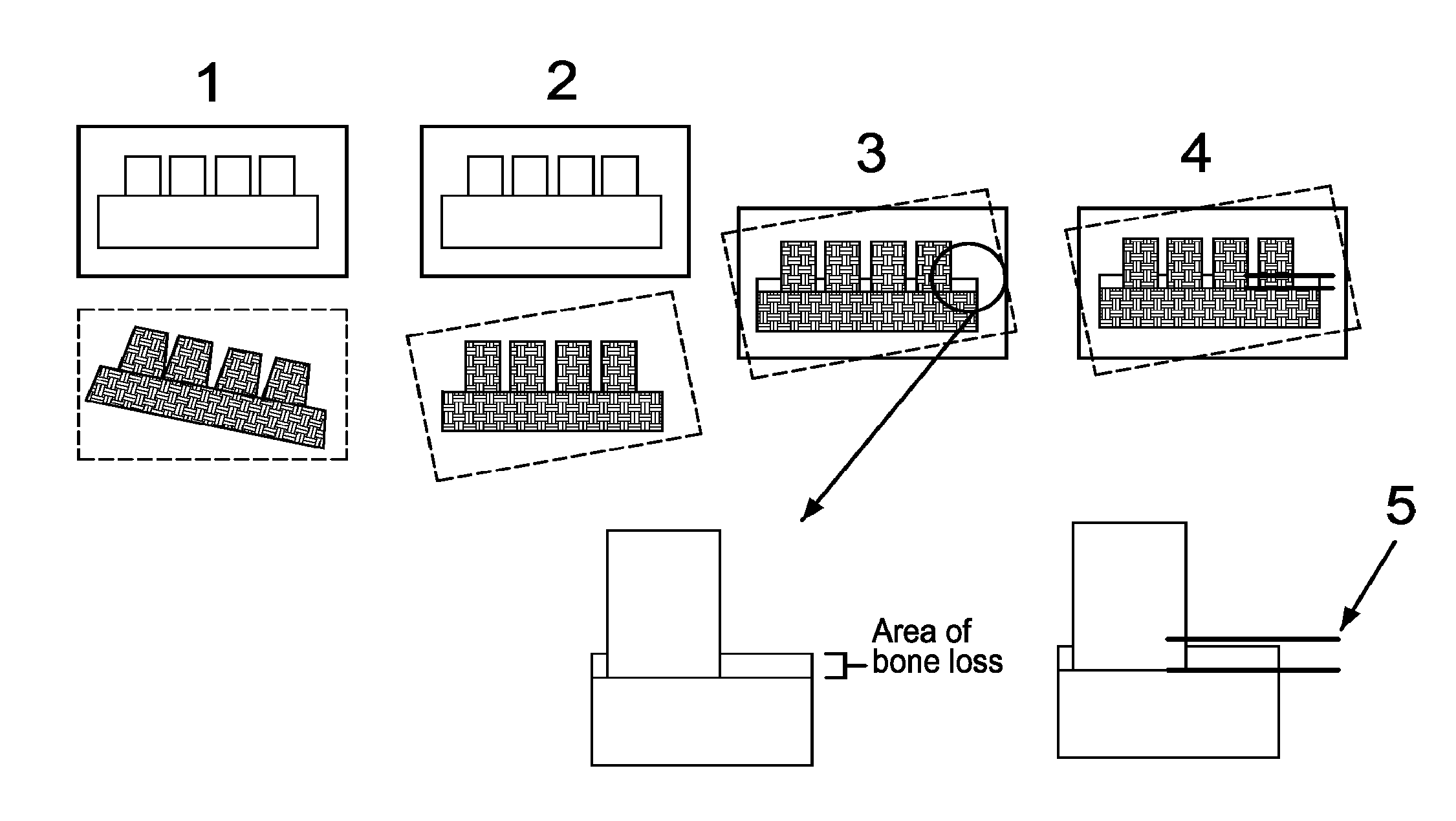

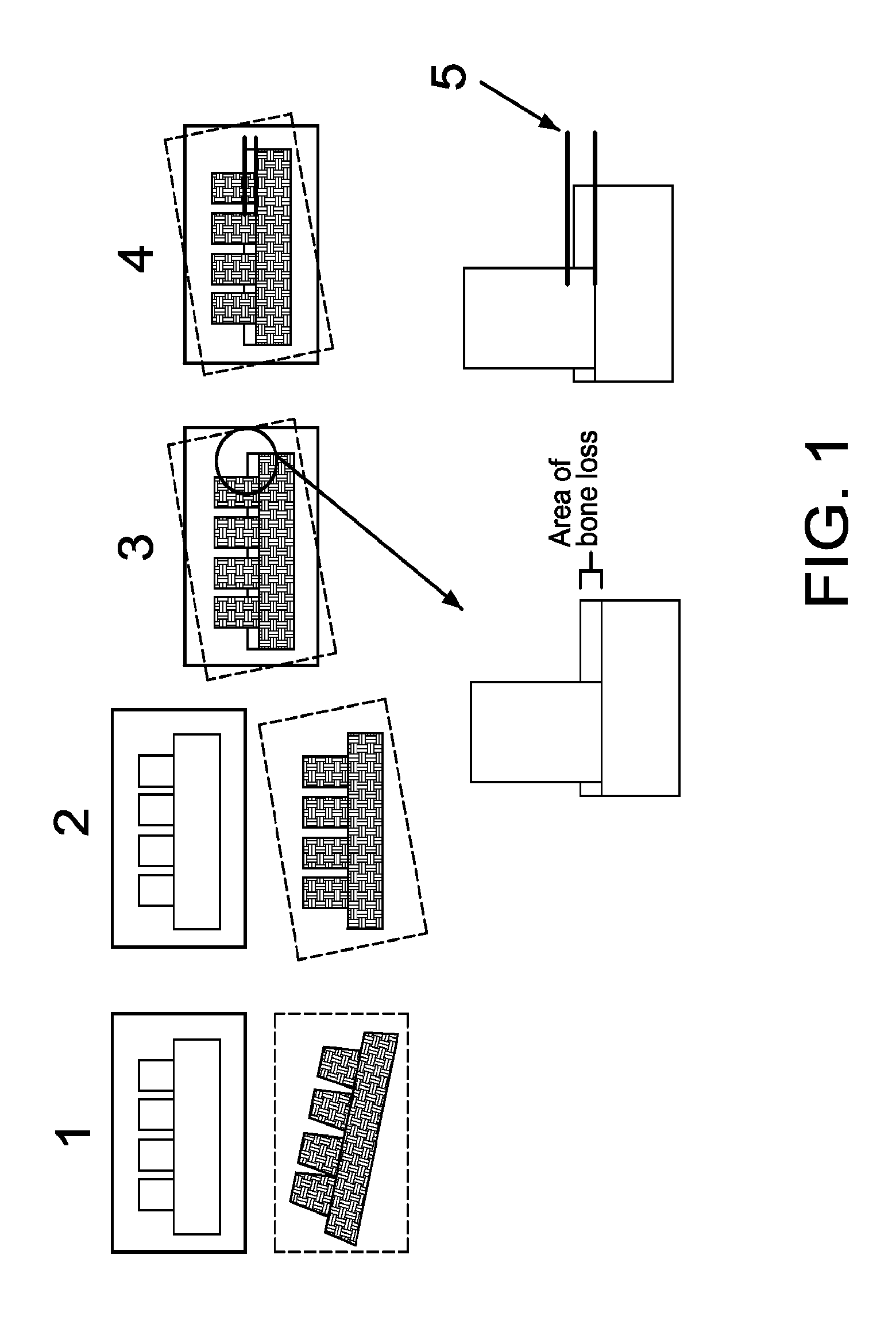

System and method for detecting and tracking change in dental x-rays and dental images

A system and method for detecting and / or rendering easily visible changes in dental images over time so as to identify bone loss, tooth movement, and other forms of change that uses dental images with similar perspectives but taken at different points in time and adjusts one or both of the dental images so as to compensate for differences in perspective, size, and rotation to thereby register the digital images to each other.

Owner:EYEIC

Remote control of dialysis machines

ActiveUS20160021191A1Easy to controlEasy to monitorMechanical/radiation/invasive therapiesDrug and medicationsRemote controlNetwork connection

This disclosure relates to remote control of dialysis machines. In certain aspects, a method includes receiving a request for a network connection from a dialysis machine and establishing the network connection with the dialysis machine. The method also includes receiving, from a client device, a request to access the dialysis machine, authorizing the client device to access the dialysis machine, receiving, from the dialysis machine, information pertaining to an operation of the dialysis machine, and providing, to the client device, the received information.

Owner:FRESENIUS MEDICAL CARE HLDG INC

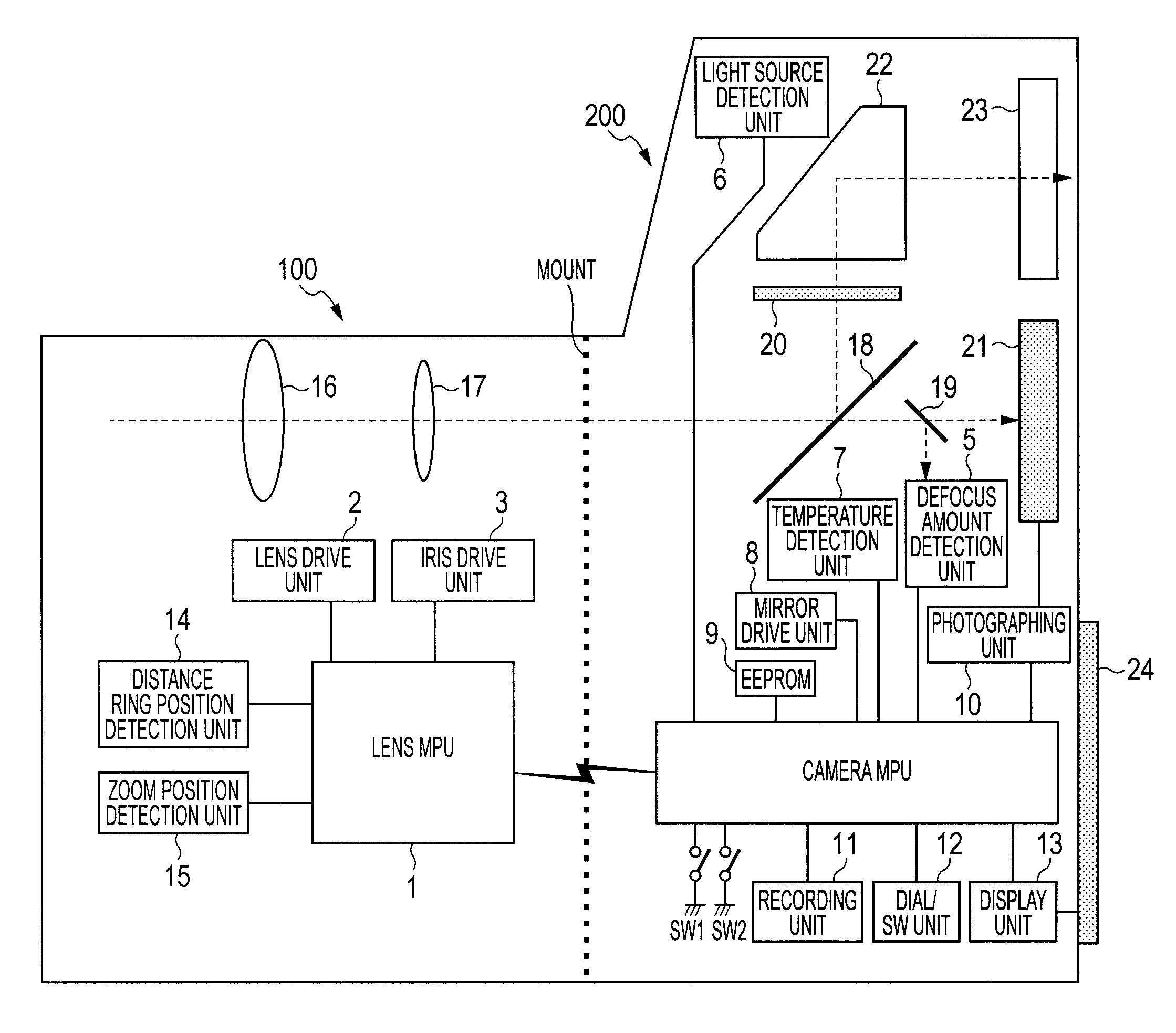

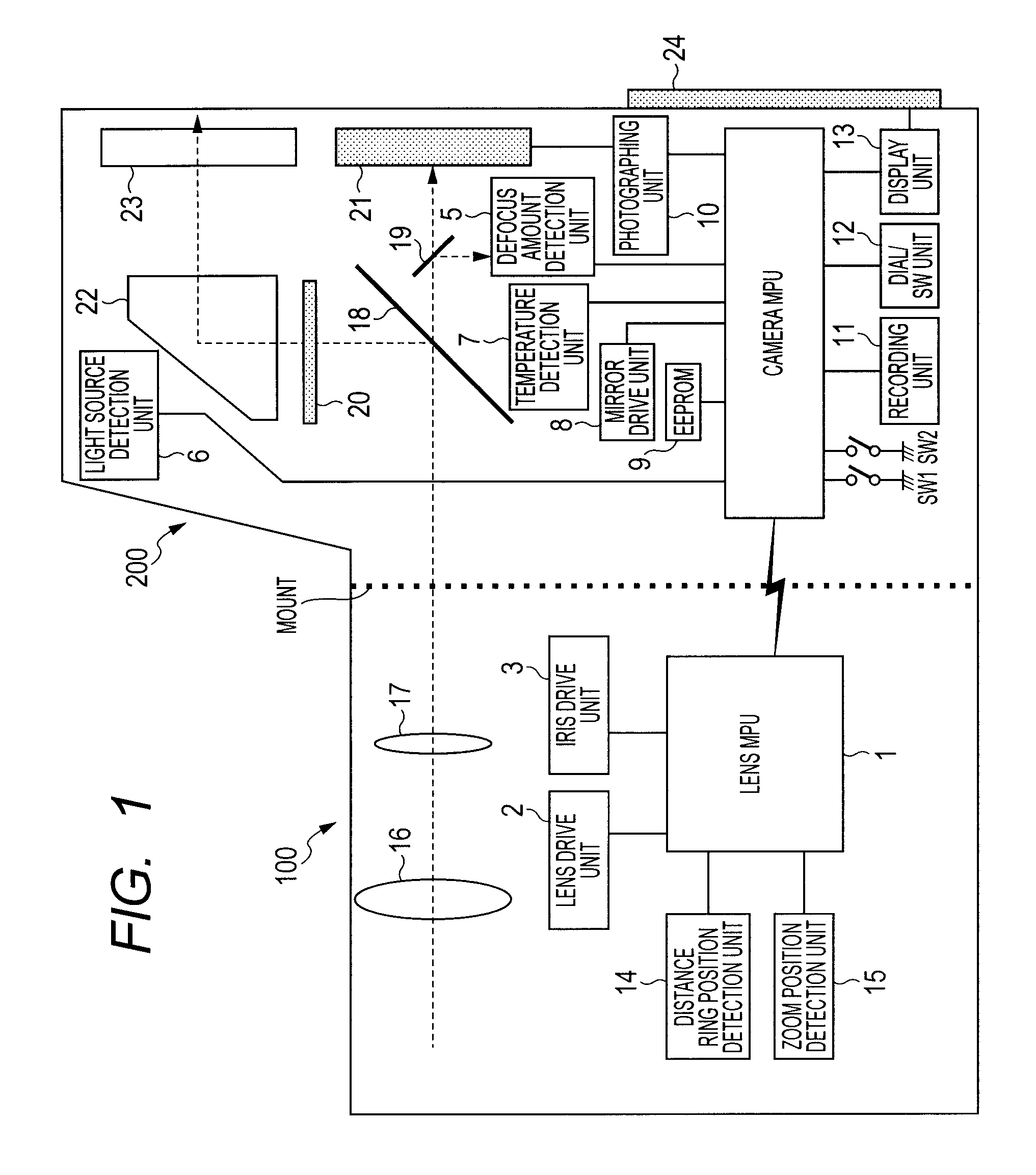

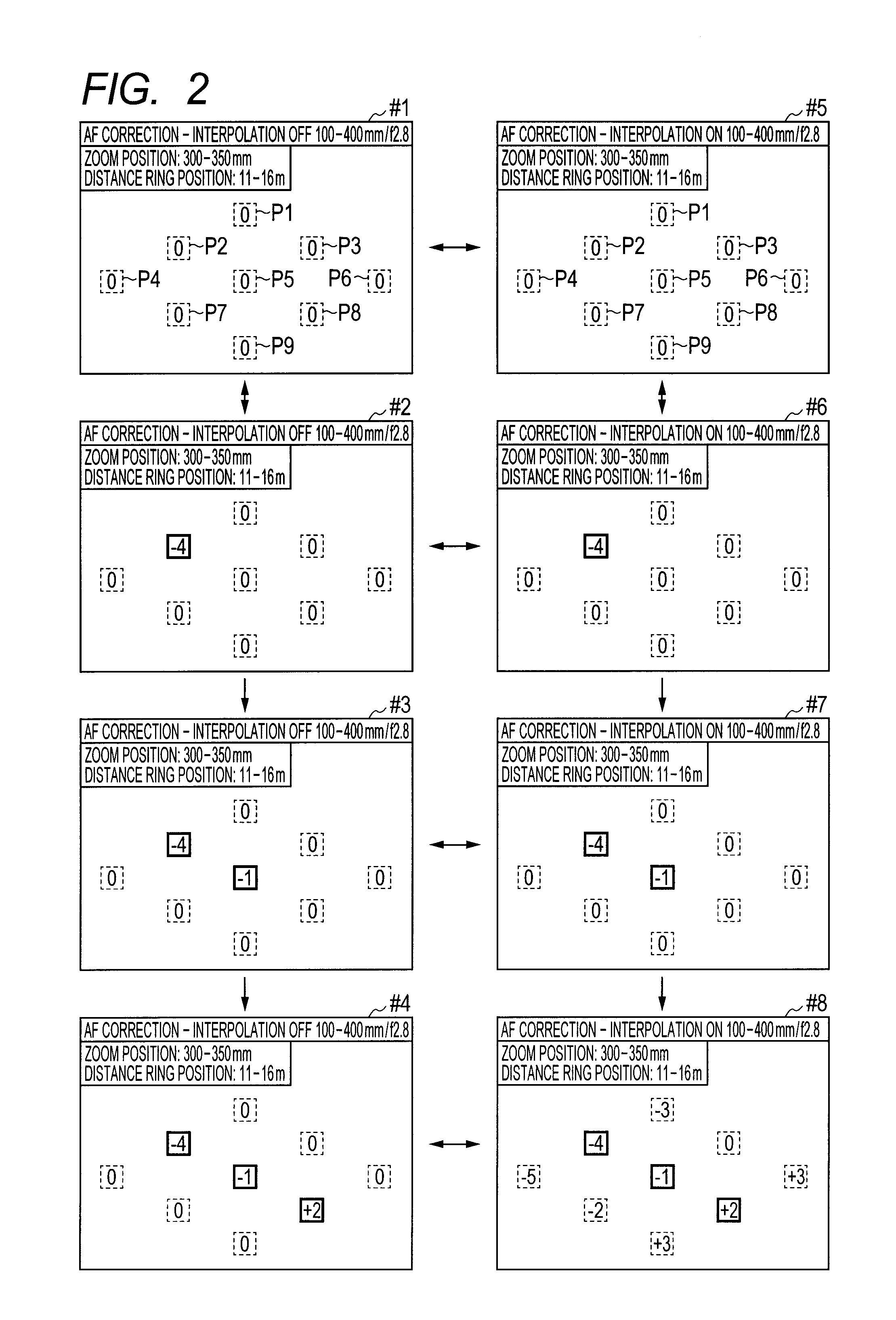

Auto focus adjustment apparatus and image pickup apparatus

ActiveUS20110095166A1Accurately changeMany changeMaterial analysis by optical meansMountingsComputer scienceFocus area

An auto focus adjustment apparatus includes: a correction unit which corrects a defocus amount detected by a defocus amount detection unit, correspondingly to a focus area selected from a plurality of focus areas; a storage unit which stores a correction value to be used by the correction unit at a time of correcting the defocus amount; and a correction value changing unit configured to change the correction value, wherein the correction value changing unit is arranged to be capable of changing the correction value for a plurality of selected focus areas and at a plurality of zoom positions.

Owner:CANON KK

Fuel pressure control apparatus of internal combustion engine

InactiveUS20010023684A1Suppress or avoid so-called "ovReduce the amount requiredElectrical controlLow-pressure fuel injectionExternal combustion engineInternal combustion engine

A fuel pressure control apparatus and method controls a pressure of fuel that is delivered from a fuel pump to a fuel pipe in an internal combustion engine of a vehicle. A controller of the fuel pressure control apparatus calculates a controlled variable based on at least an integral term that is updated in accordance with a difference between an actual fuel pressure in the fuel pipe and a target value thereof; and controls an amount of the fuel delivered from the fuel pump in a feedback manner, using the controlled variable, so that the actual fuel pressure approaches the target value. During the control of the fuel pressure, the controller inhibits updating of the integral term to a value that results in an increase in the amount of the fuel delivered from the fuel pump, when the amount of the fuel delivered is approximate to or equal to a maximum value thereof.

Owner:TOYOTA JIDOSHA KK

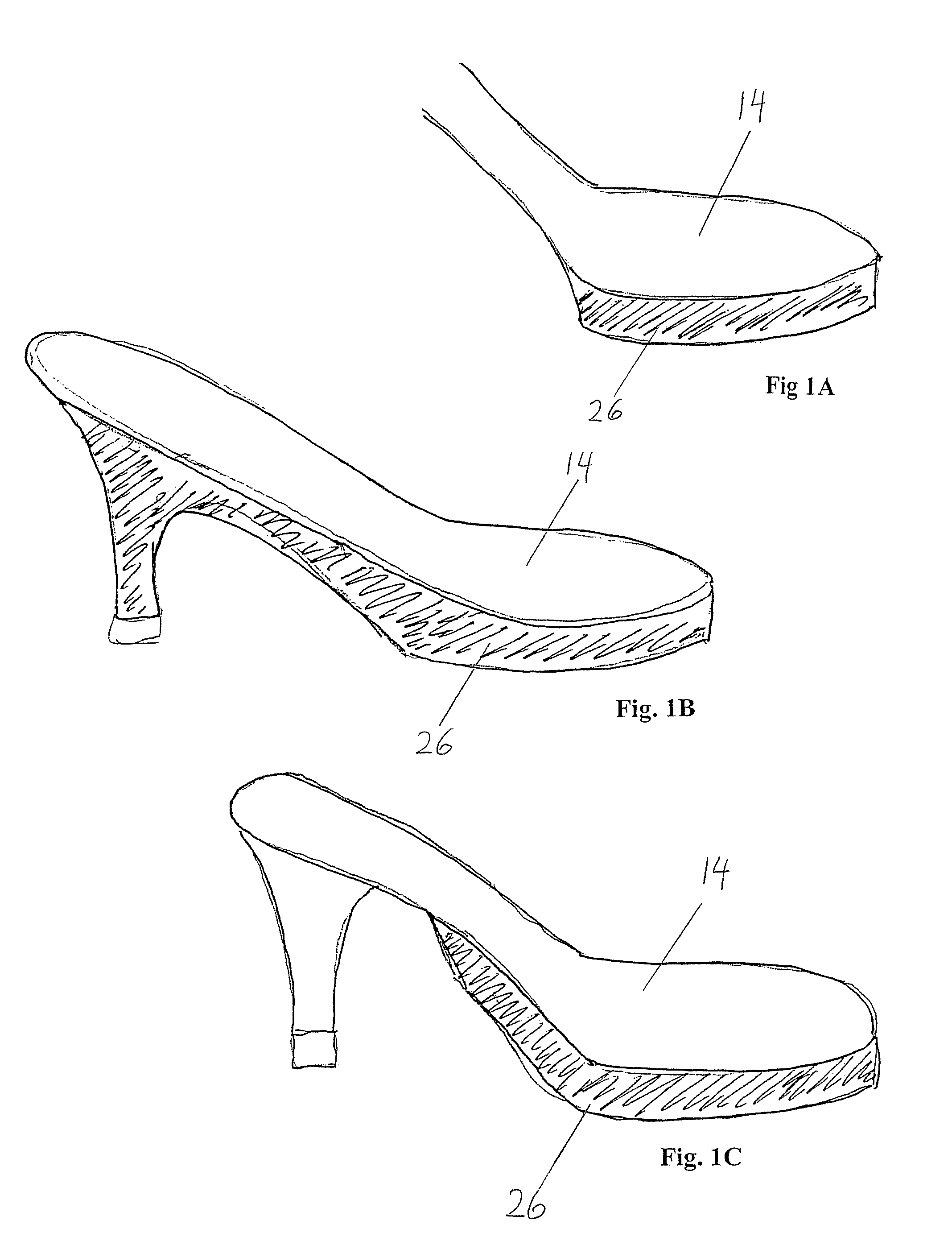

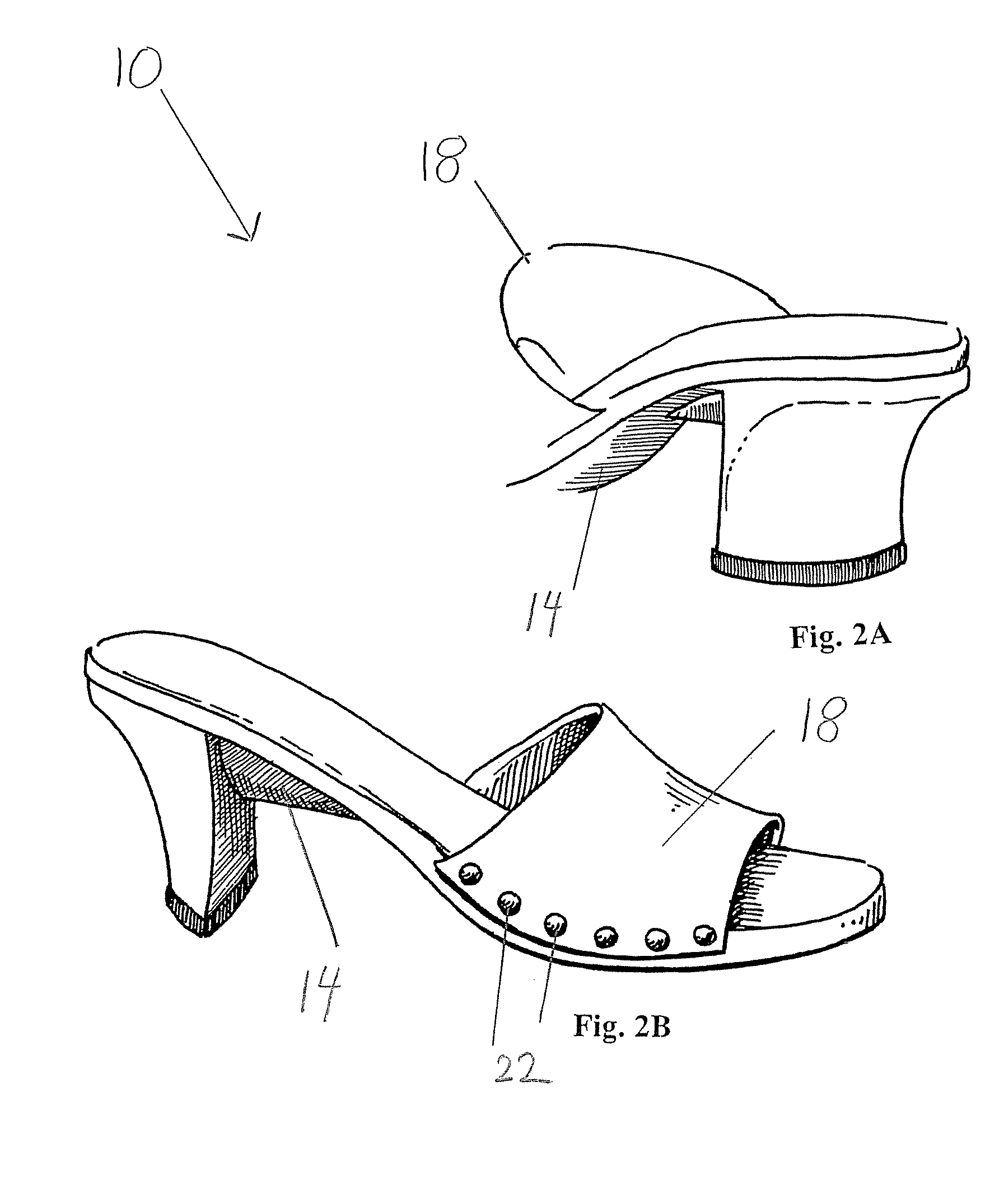

Method and apparatus for fashion adaptable footwear

Owner:ROSY CHEEKS

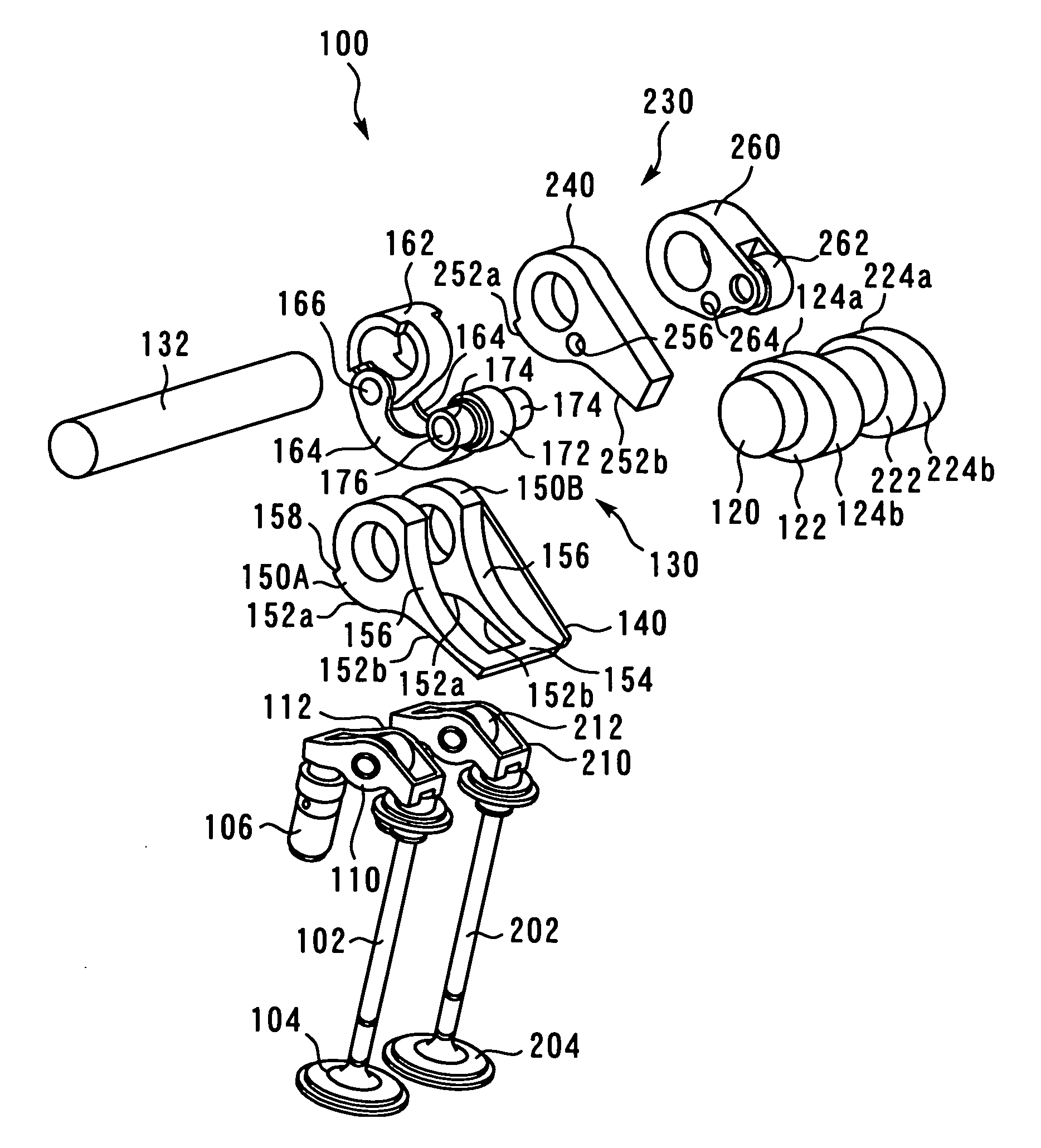

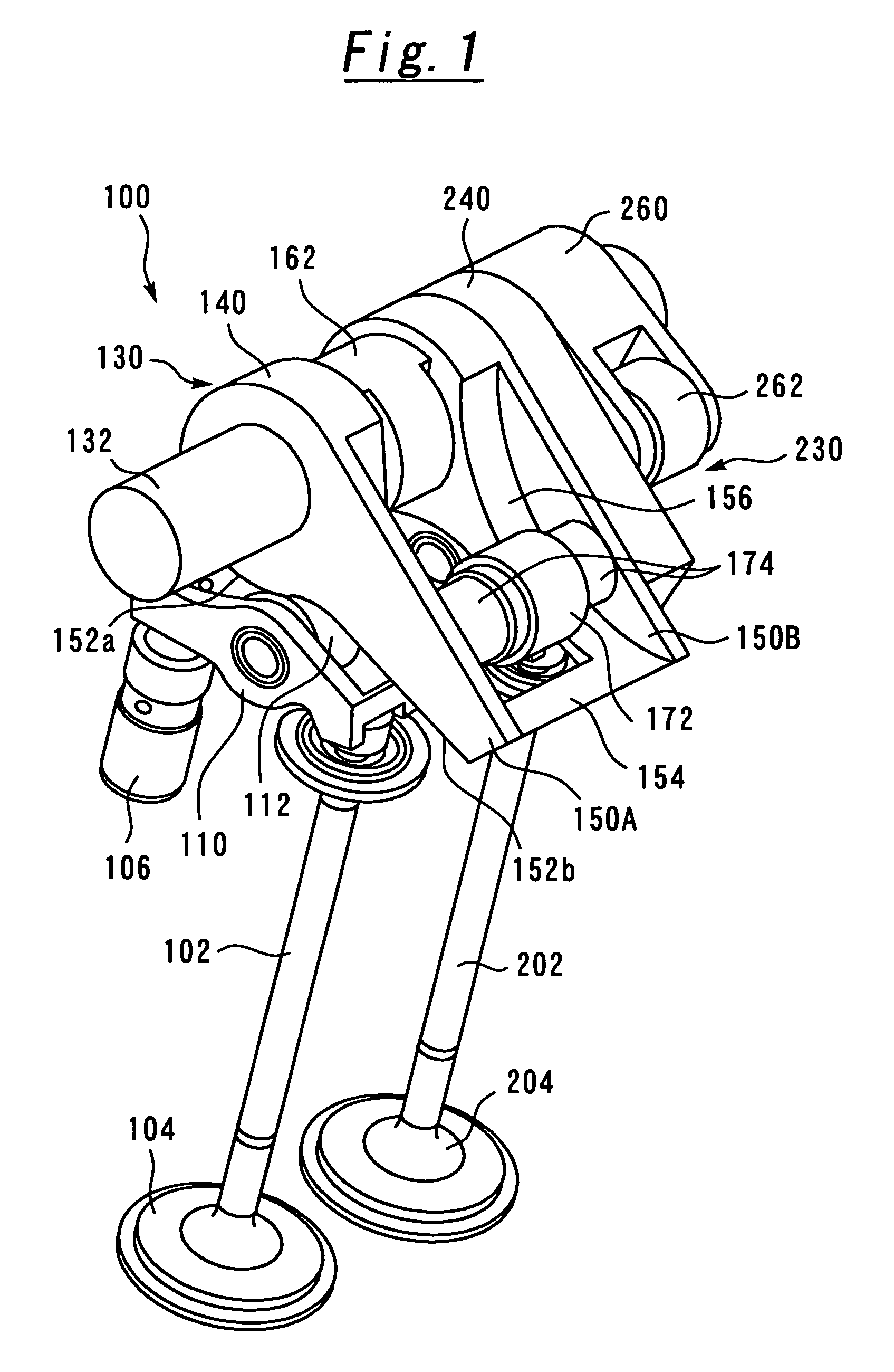

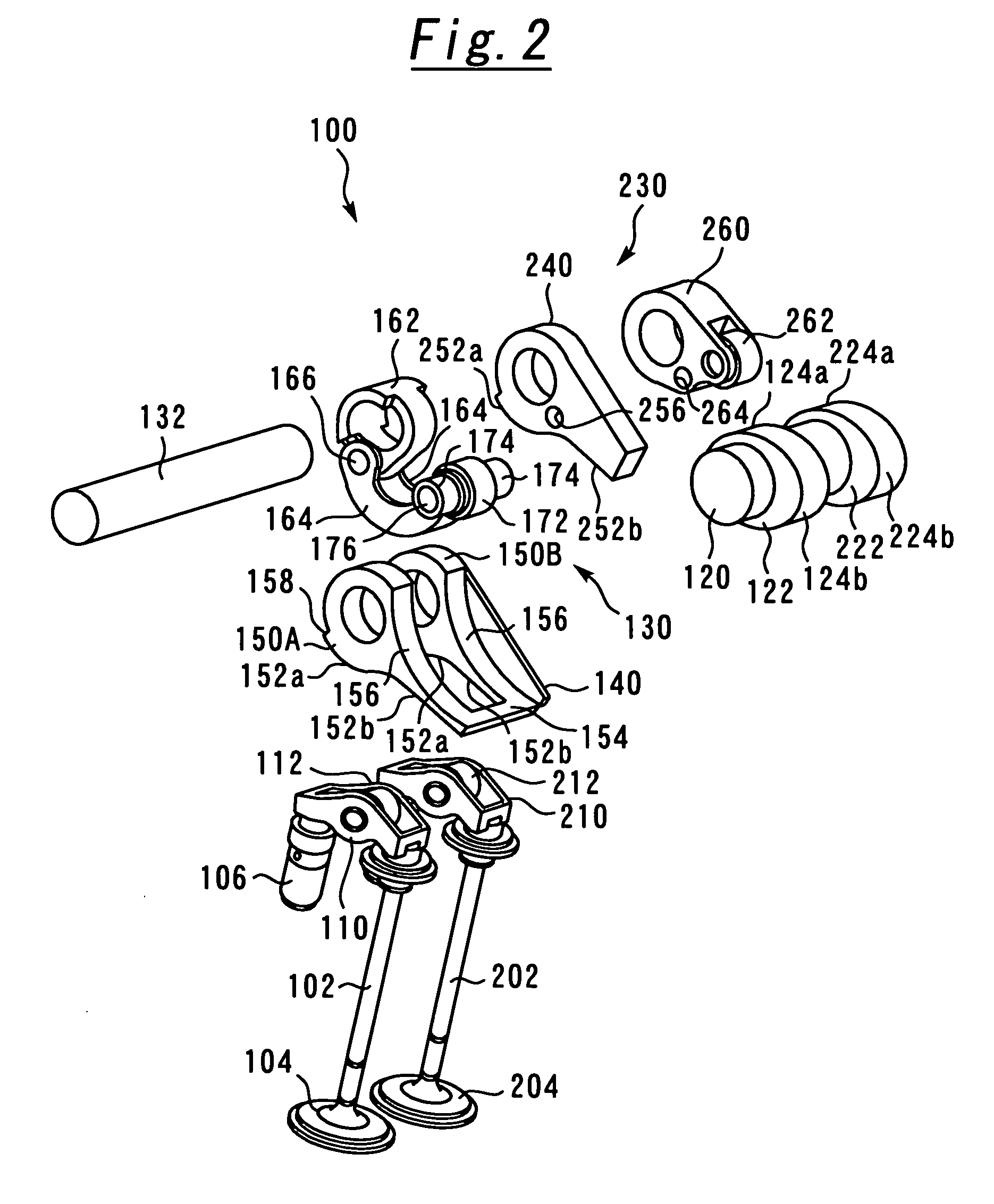

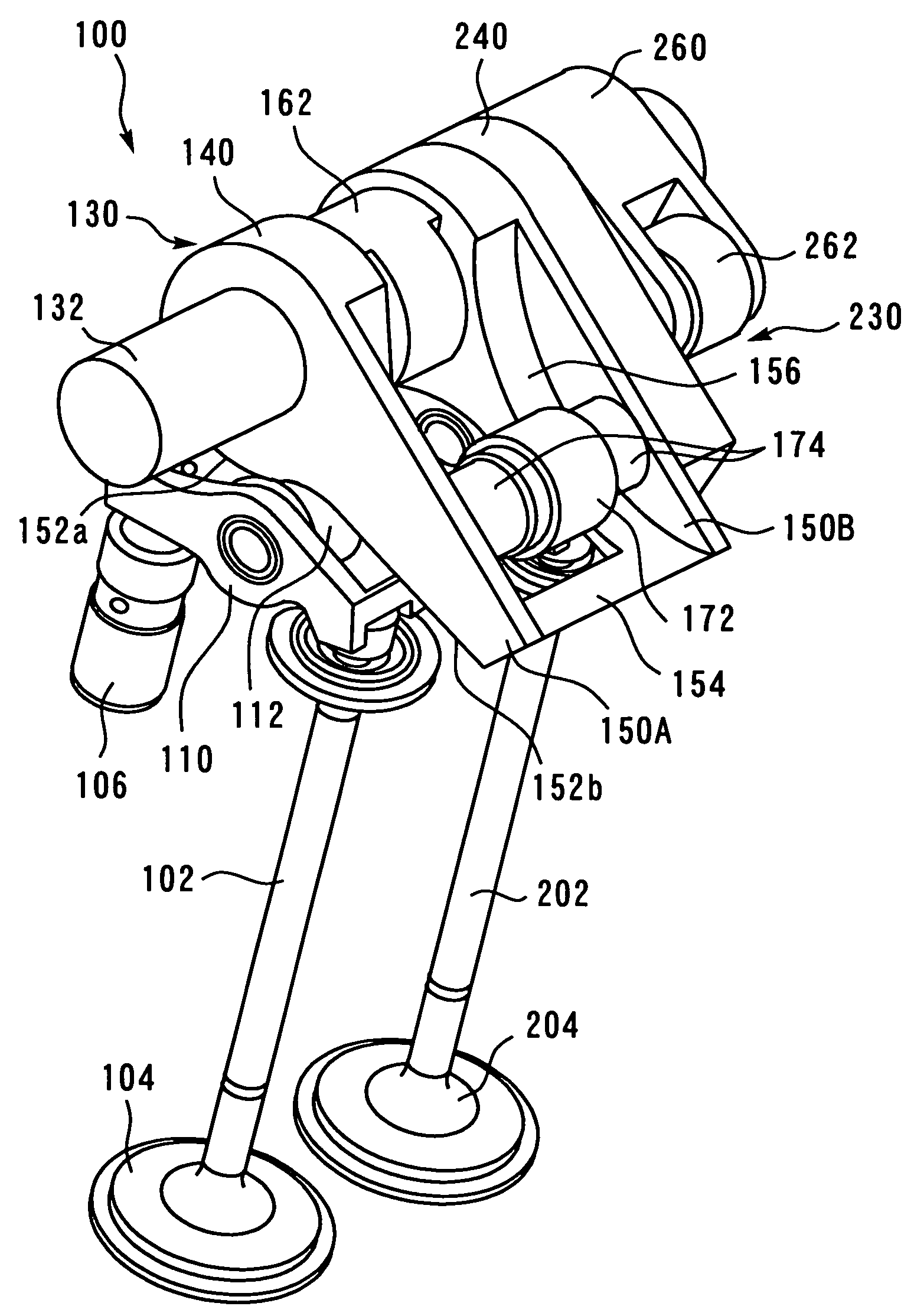

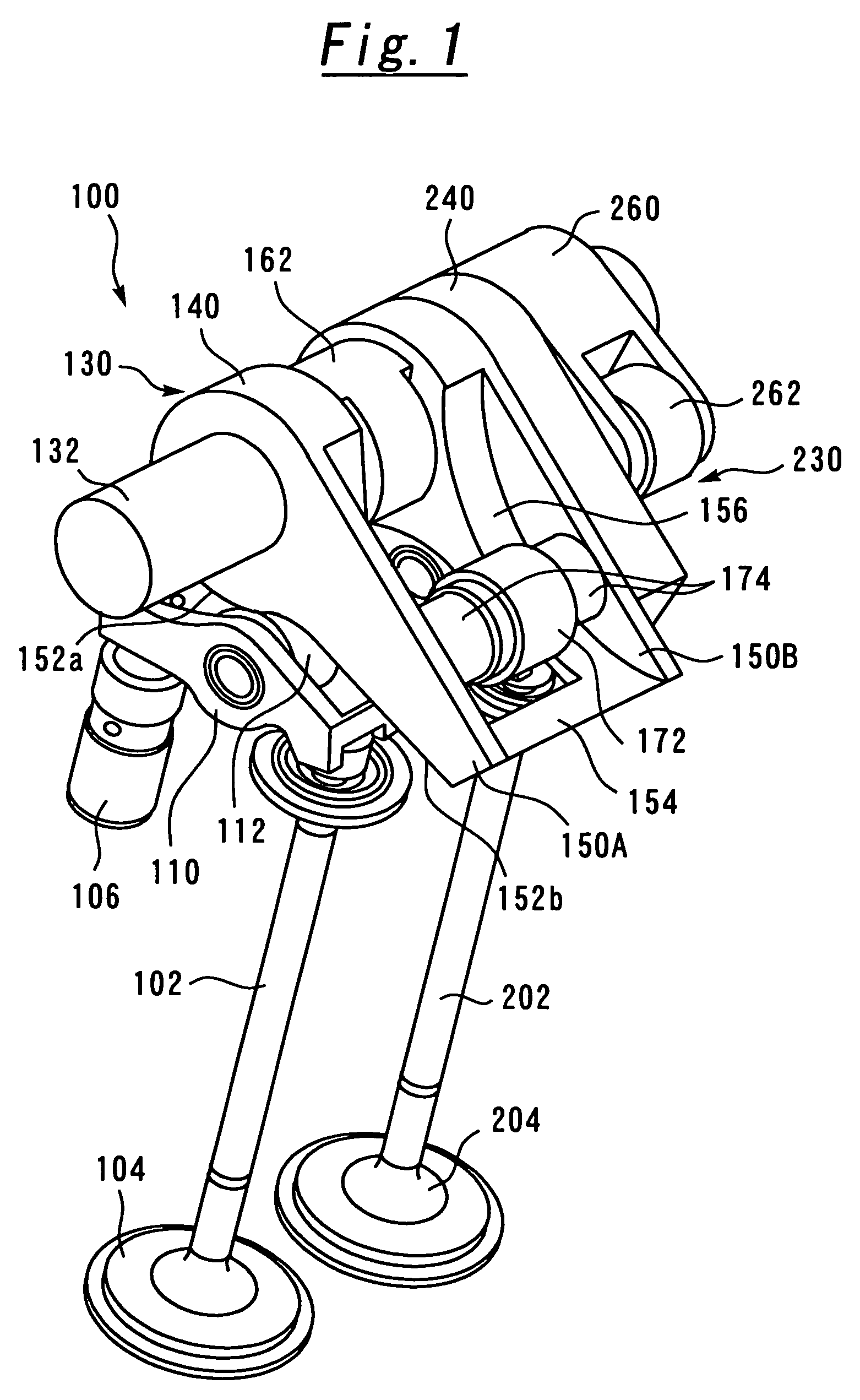

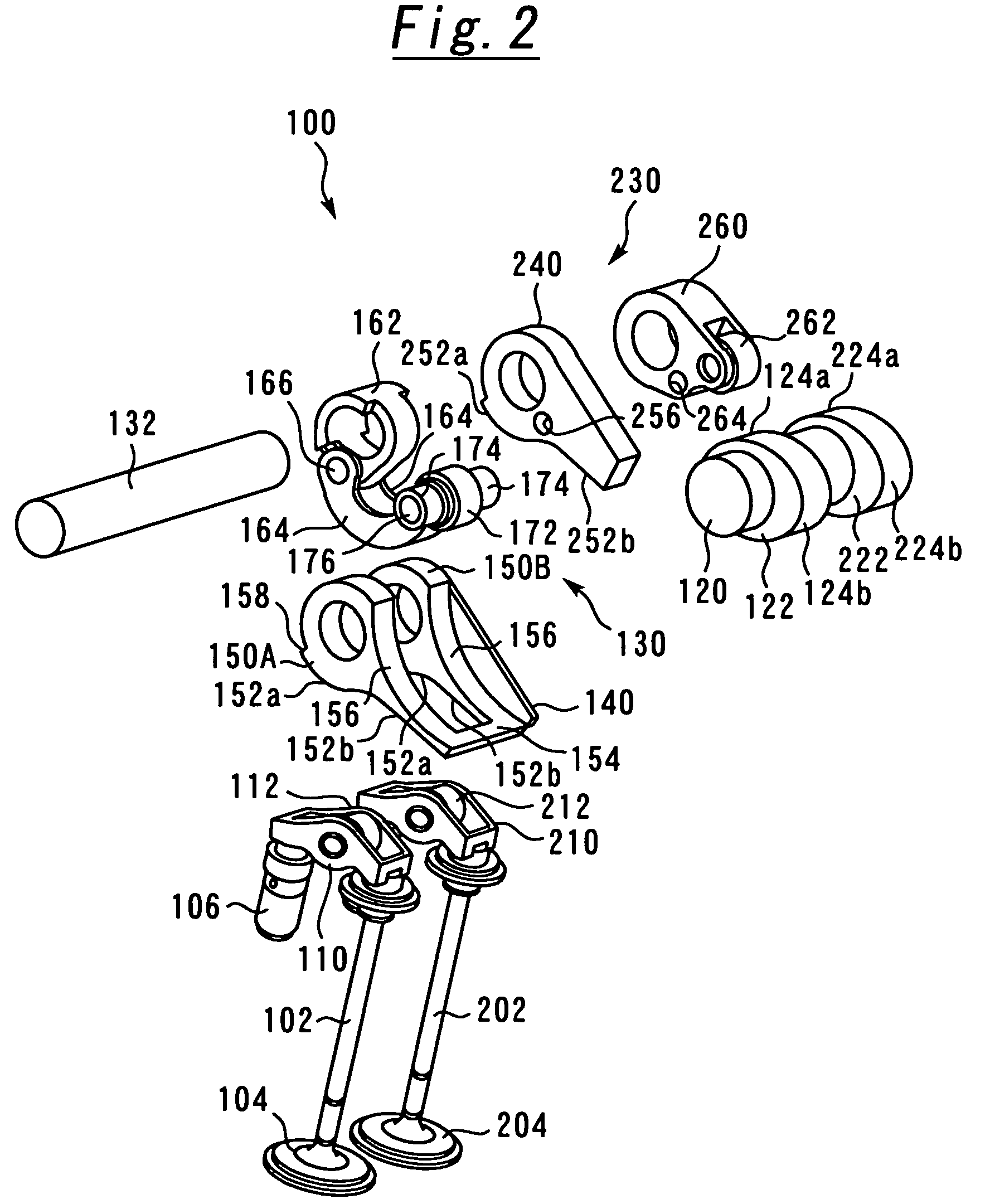

Variable valve operating device

A variable valve operating device is provided that allows an ideal valve timing-lift characteristic to be realized by associating a change in a valve timing with a change in a valve lift amount. A rotation motion of a drive cam is transmitted to a slide surface of a swing member via an intermediate member. Positions of the intermediate member on the slide surface are varied in association with the rotation of a control shaft by an interlock mechanism. The slide surface is formed to be curved toward the drive cam so that the distance from the center of a camshaft increases toward the farthest point from the swing center of the swing member within the area which the intermediate member contacts from the nearest point from the swing center of the swing member within the area which the intermediate member contacts.

Owner:TOYOTA JIDOSHA KK

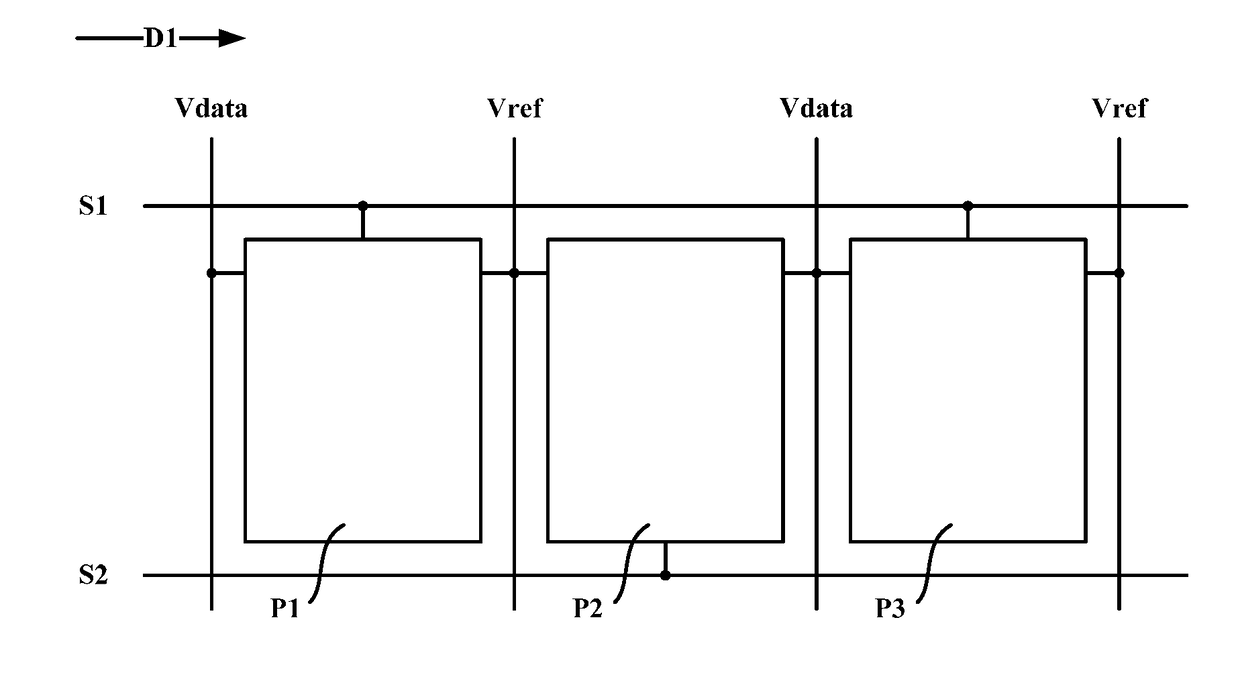

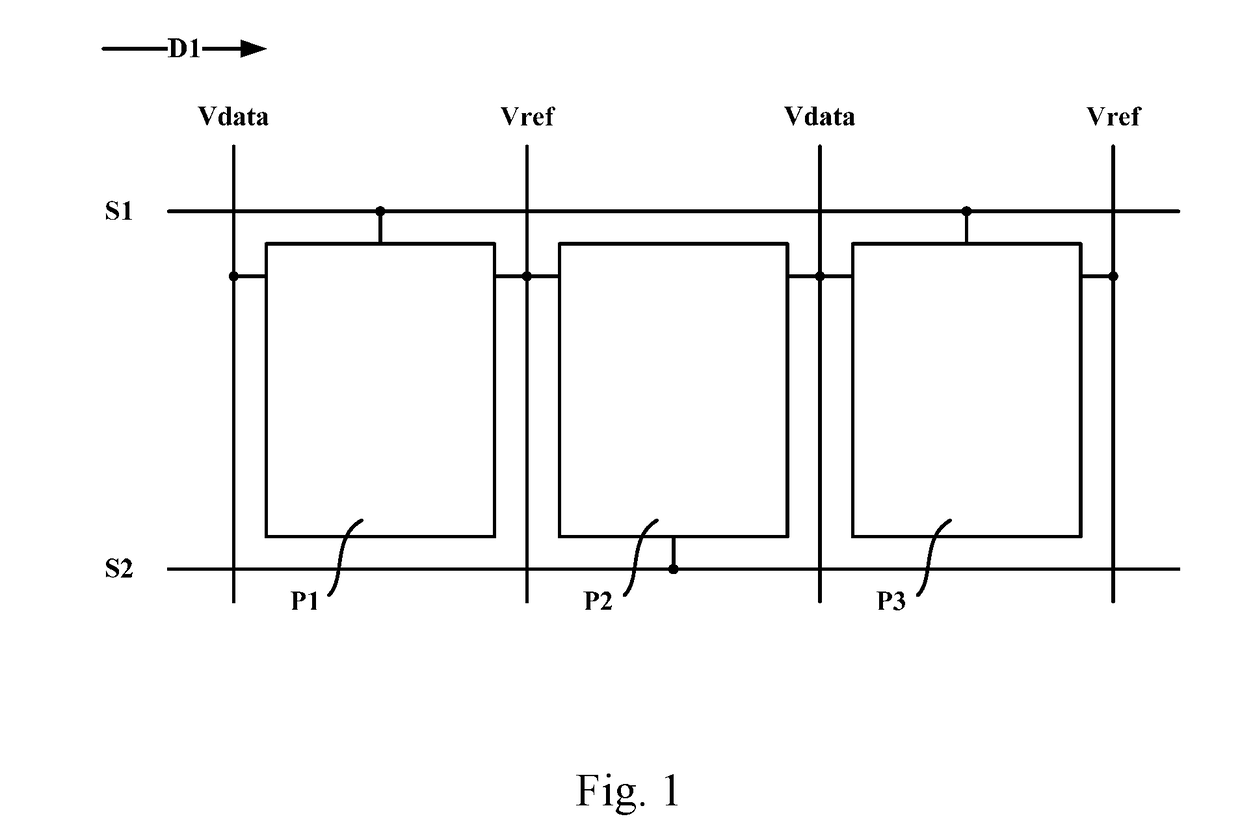

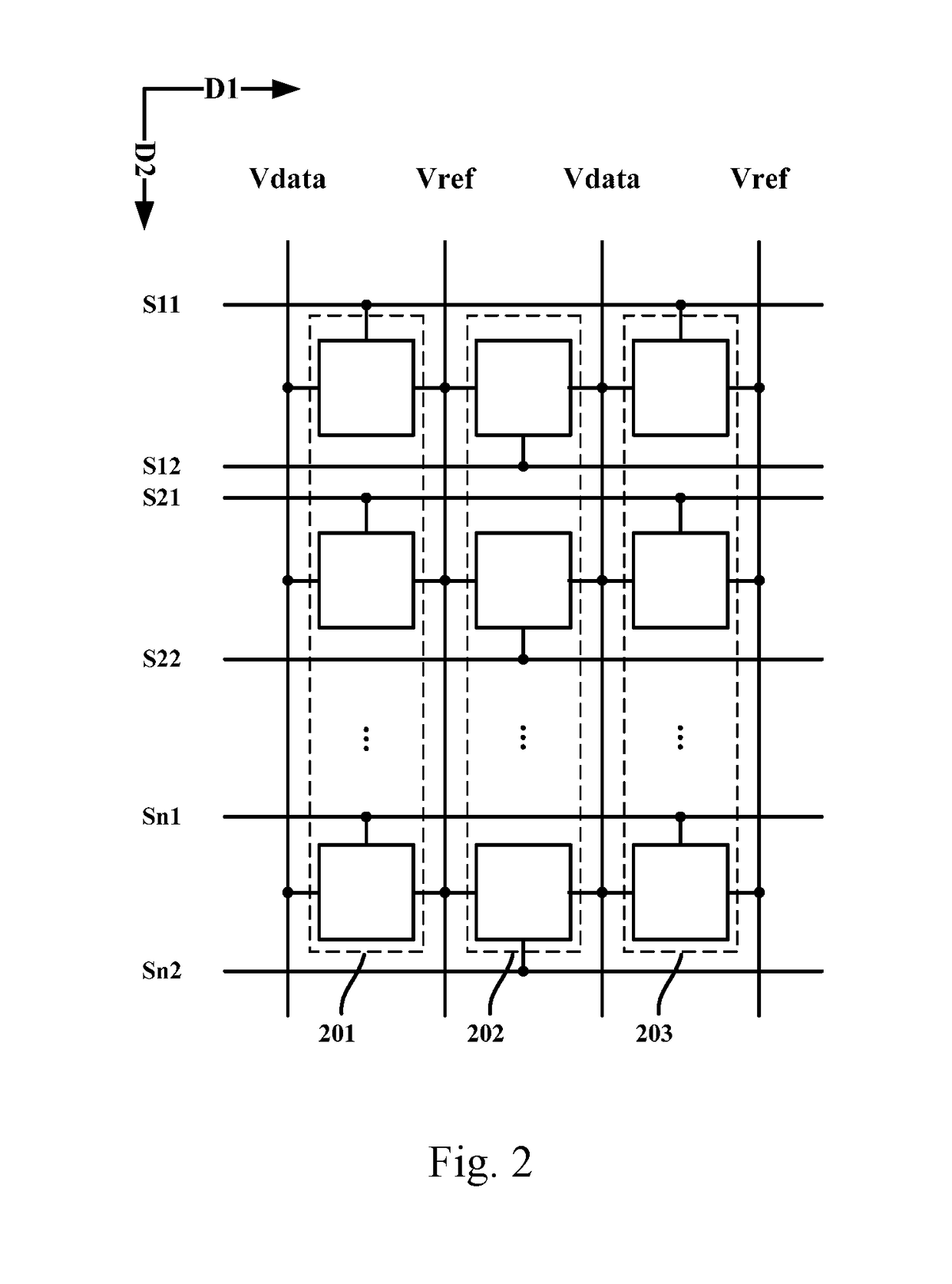

Organic Light-Emitting Display Panel And Driving Method Thereof, And Organic Light-Emitting Display Device

ActiveUS20170301286A1Reduce loadReduce power consumptionCathode-ray tube indicatorsVoltage referencePixel array

The present disclosure discloses an organic light-emitting display panel and a driving method thereof, and an organic light-emitting display device. The organic light-emitting display panel comprises a pixel array, a plurality of pixel driving circuits, a plurality of reference voltage signal lines and a plurality of data voltage signal lines. The plurality of pixel driving circuits include a first, second and third pixel driving circuits, the first pixel driving circuit and the second pixel driving circuit are adjacent to each other in a row direction of the pixel array, and the second pixel driving circuit and the third pixel driving circuit are adjacent to each other in the row direction of the pixel array. The first pixel driving circuit and the second pixel driving circuit share one reference voltage signal line, and the second pixel driving circuit and the third pixel driving circuit share one data voltage signal line.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

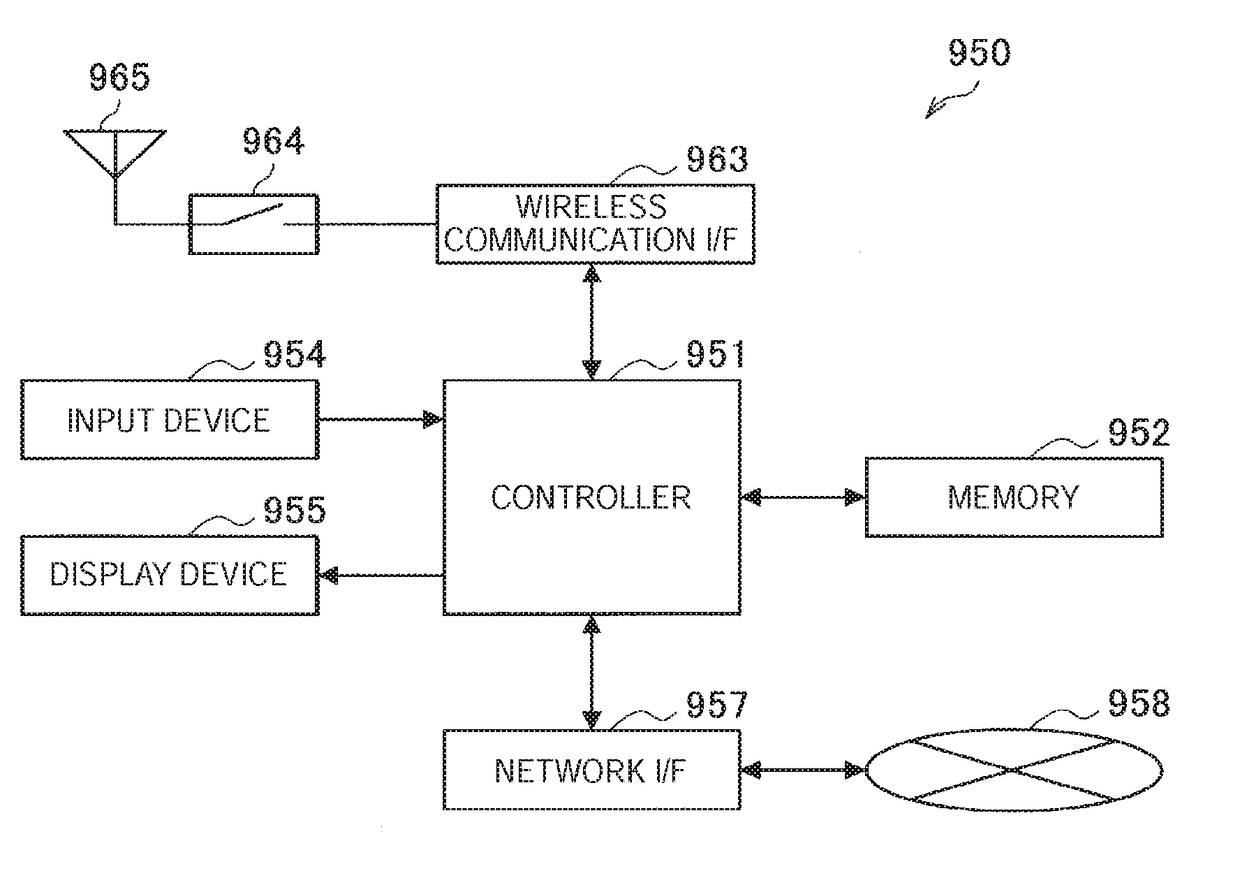

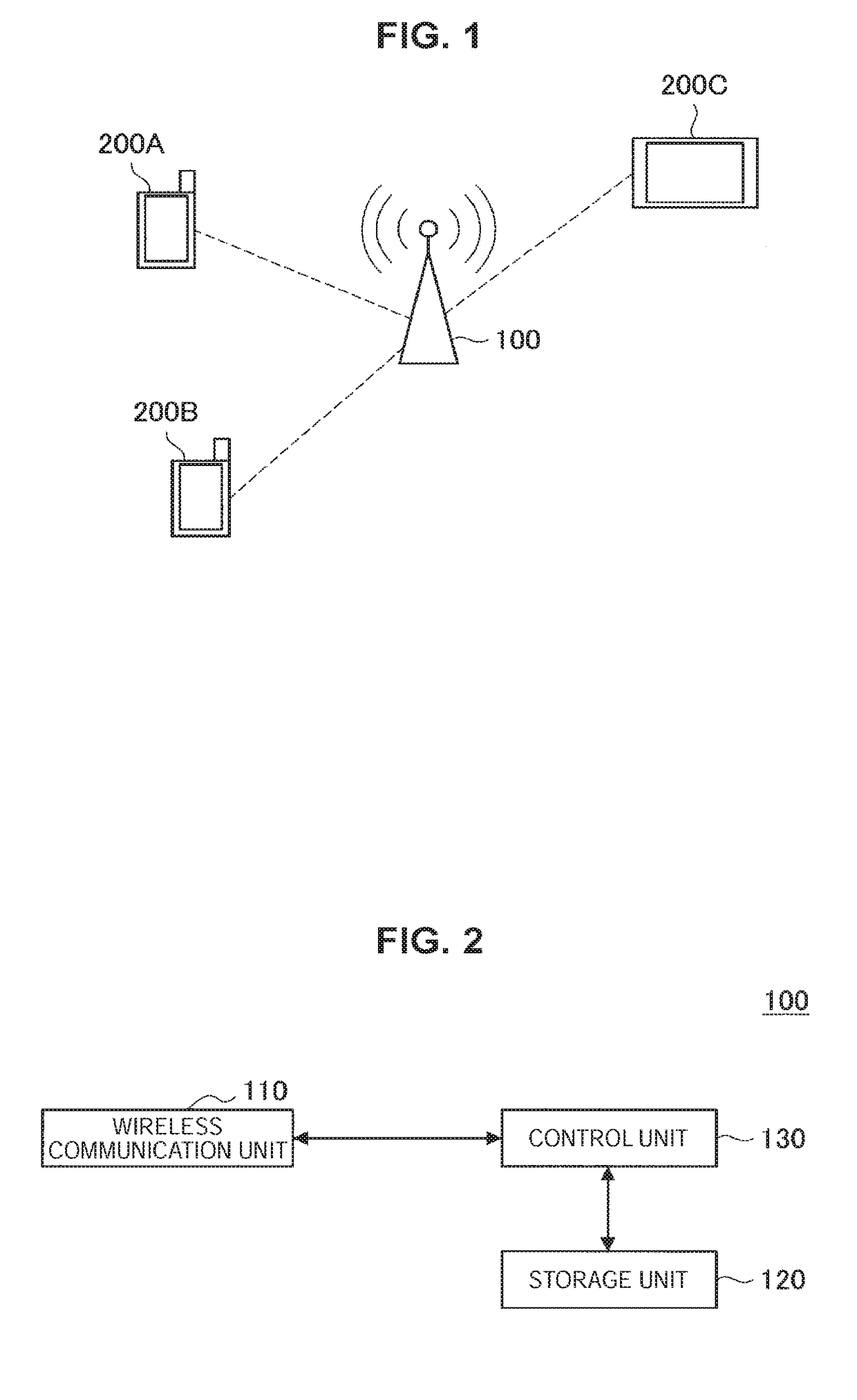

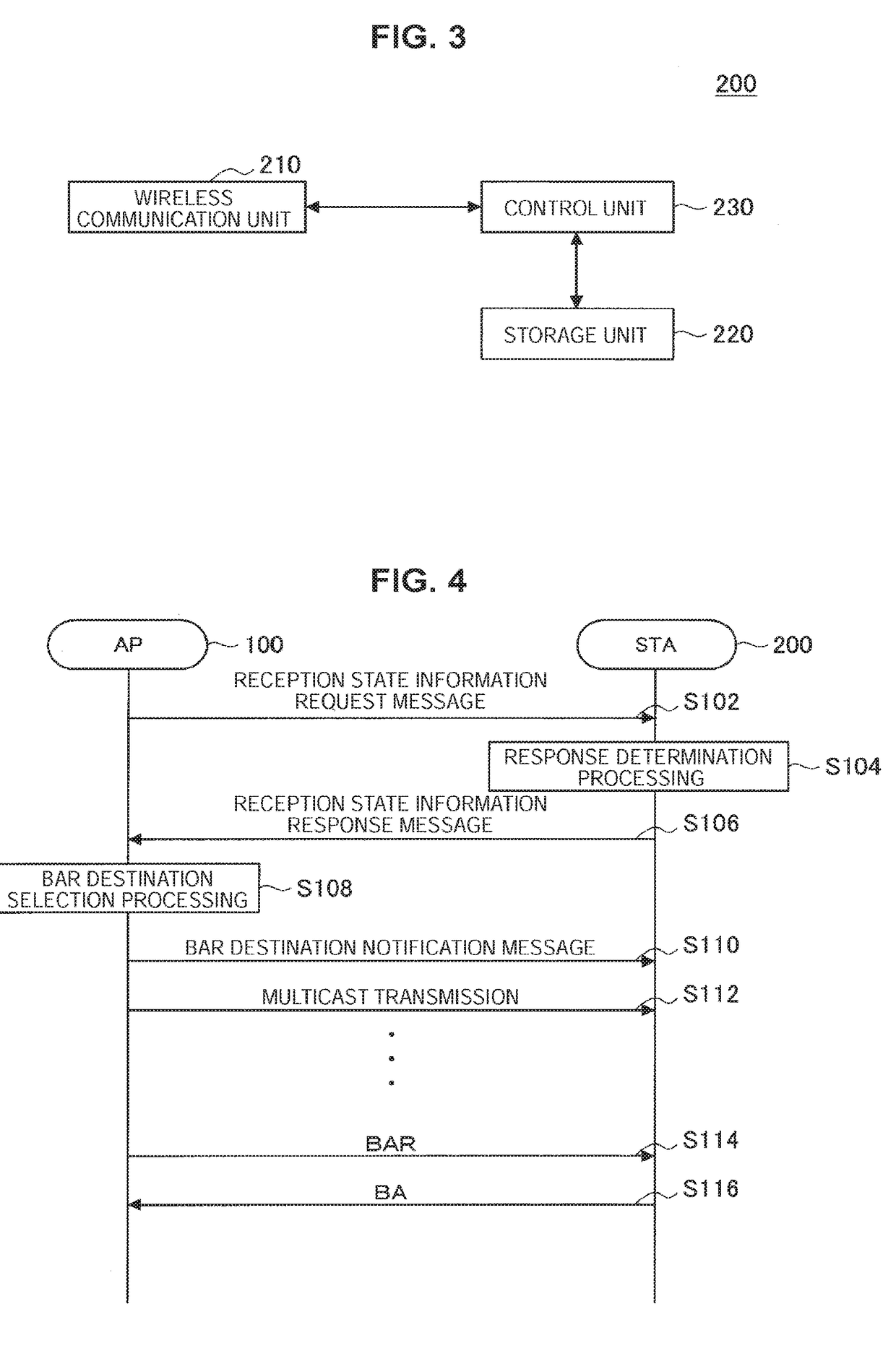

Wireless communication device, method of wireless communication, and program

ActiveUS20170366362A1Flexible changeMany changeSpecial service provision for substationNetwork traffic/resource managementCommunication interfaceTelecommunications

A wireless communication device and associated method more flexibly changes a destination of an acknowledgement request. The wireless communication device includes a wireless communication interface to communicate wirelessly with another wireless communication device, and a controller to control the wireless communication interface to transmit, to the other wireless communication device, a first message that requests change in a destination of an acknowledgement request frame relating to multicast transmission by the other wireless communication device.

Owner:SONY CORP

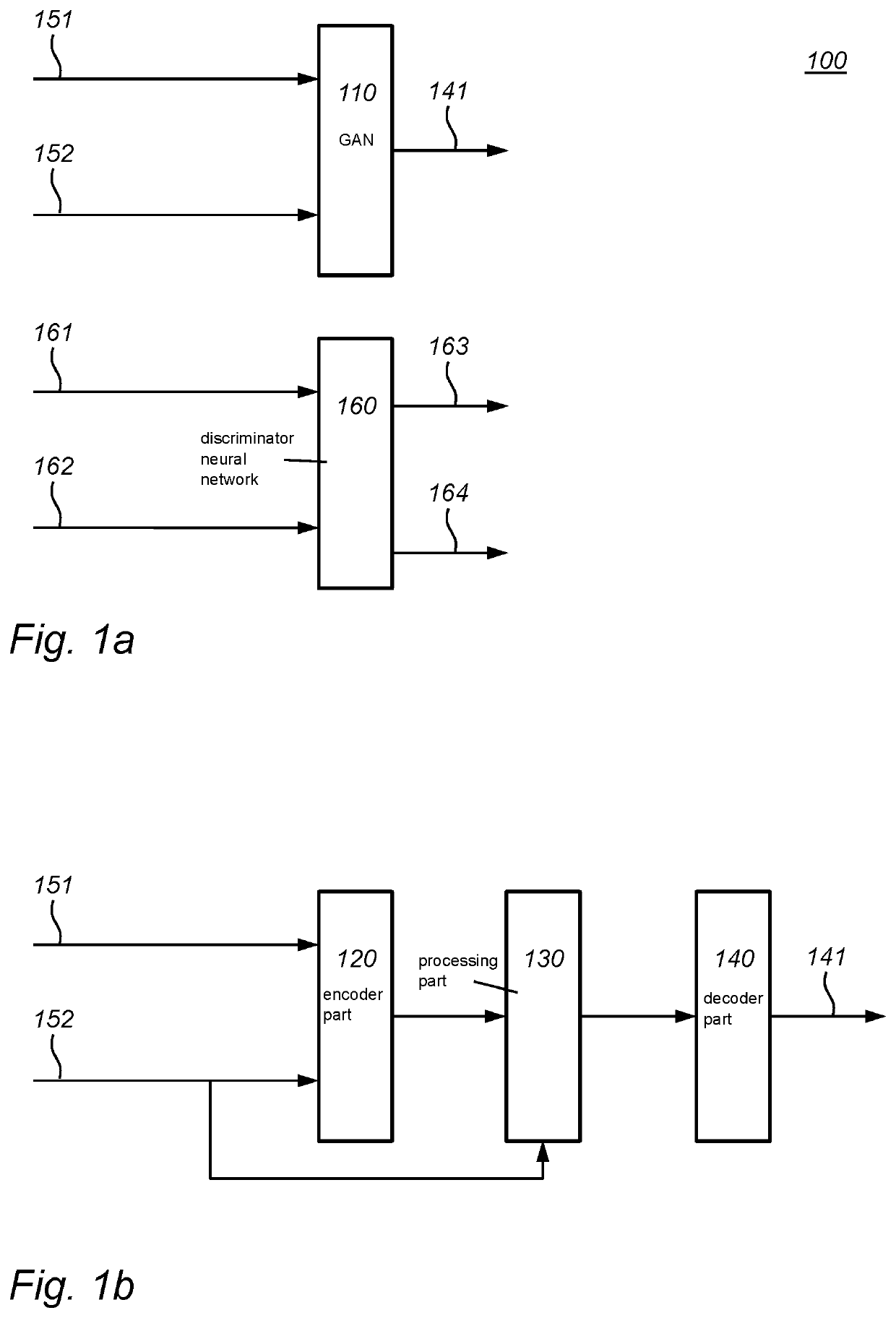

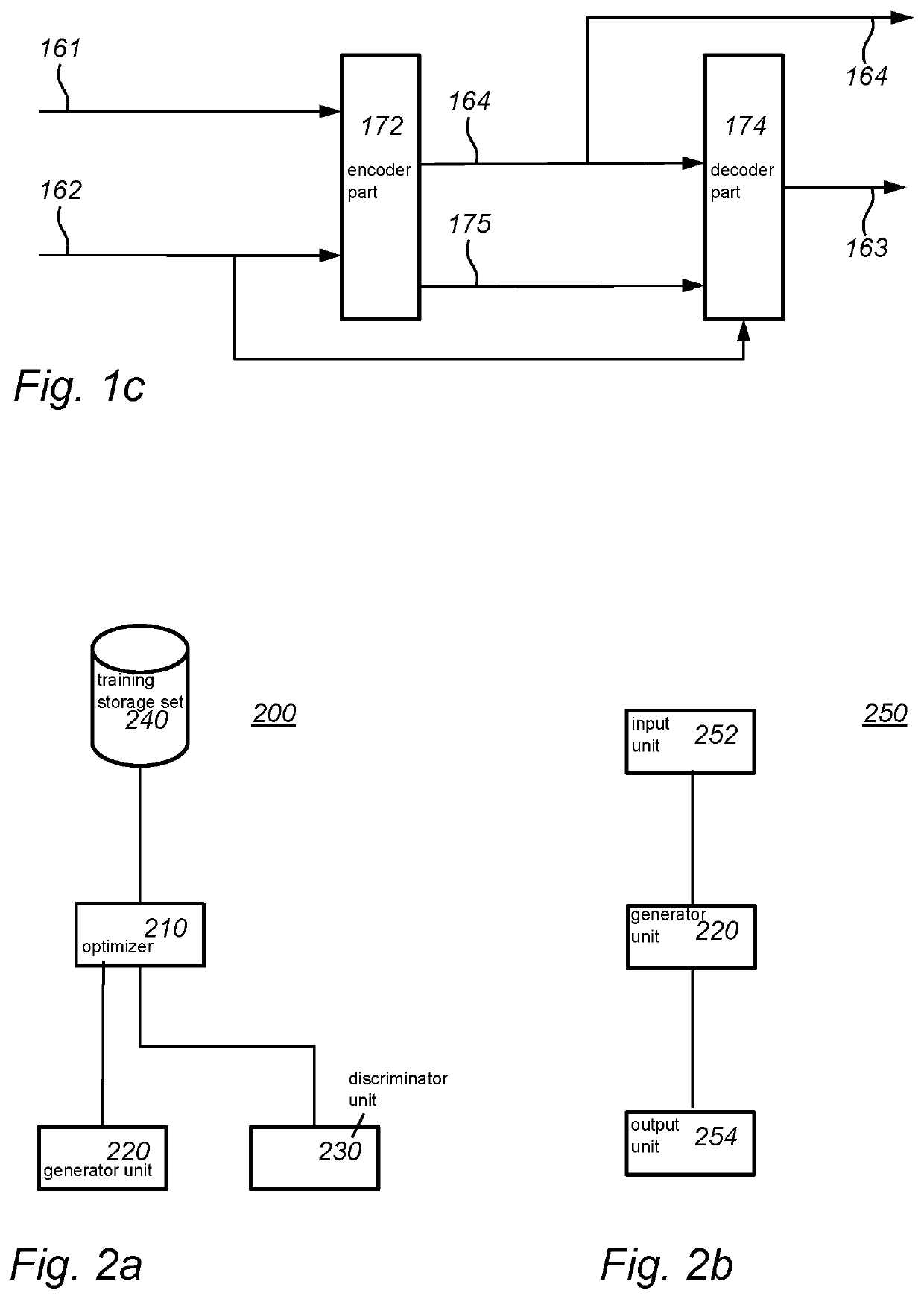

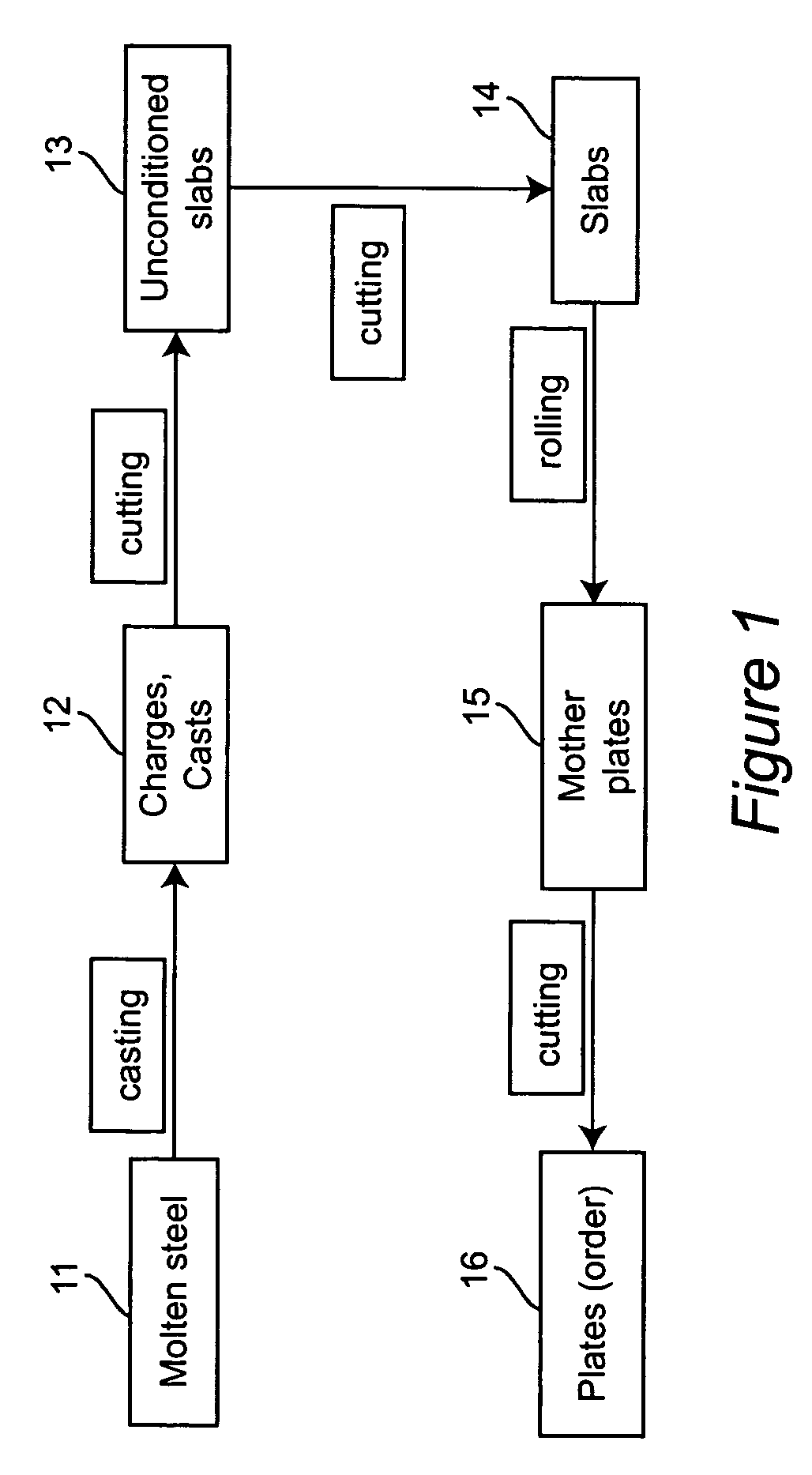

Training a generator neural network using a discriminator with localized distinguishing information

PendingUS20210237767A1Slow down trainingQuality improvementCharacter and pattern recognitionNeural architecturesData miningNeural network nn

A training method for training a generator neural network configured to generate synthesized sensor data. A discriminator network is configured to receive discriminator input data comprising synthesized sensor data and / or measured sensor data, and to produce as output localized distinguishing information, the localized distinguishing information indicating for a plurality of sub-sets of the discriminator input data if the sub-set corresponds to measured sensor data or to synthesized sensor data.

Owner:ROBERT BOSCH GMBH

Method for production design and operations scheduling for plate design in the steel industry

ActiveUS7277768B2Reduce wasteAdvantageously producedProgramme controlComputation using non-denominational number representationOrder formEngineering

Owner:GOOGLE LLC

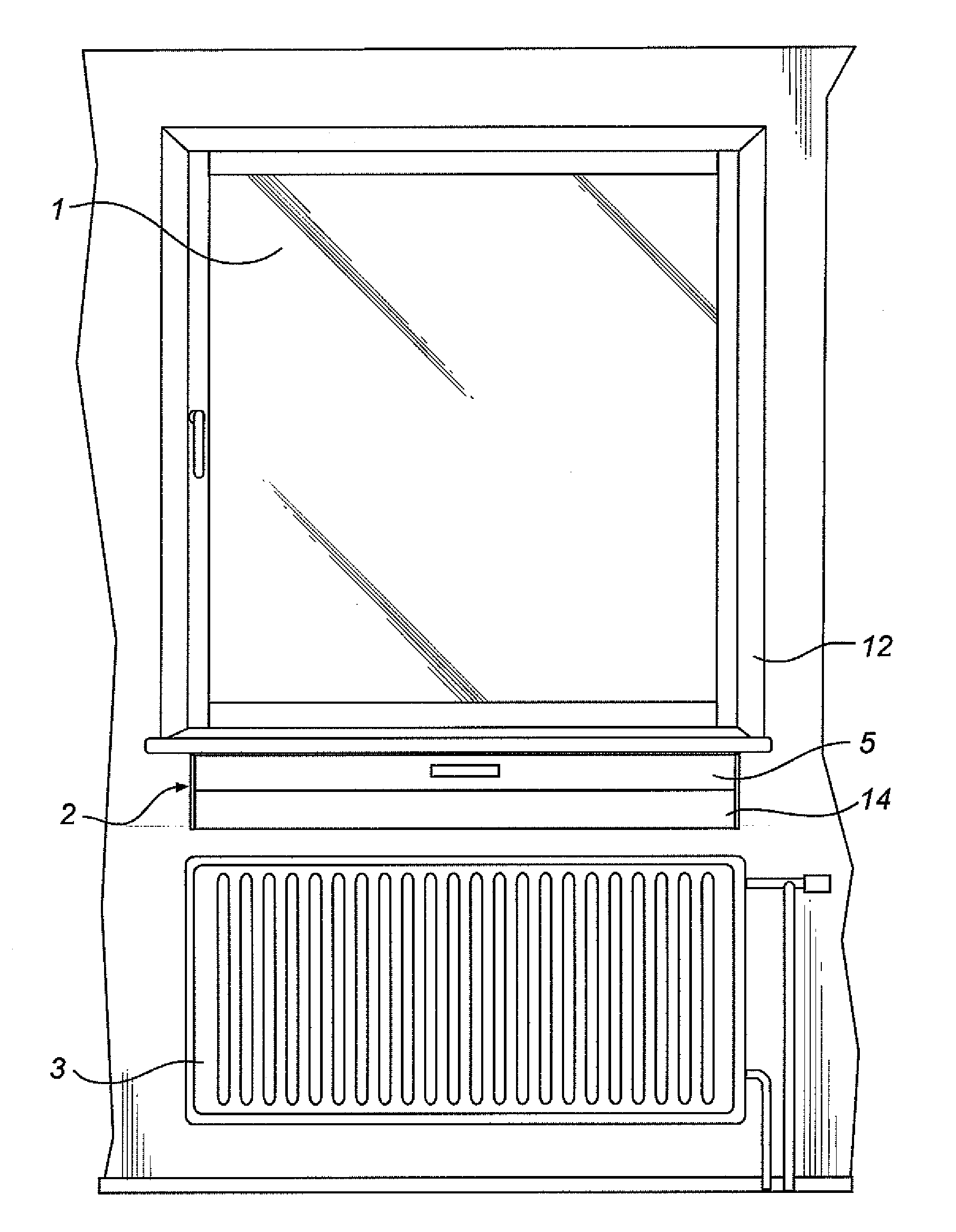

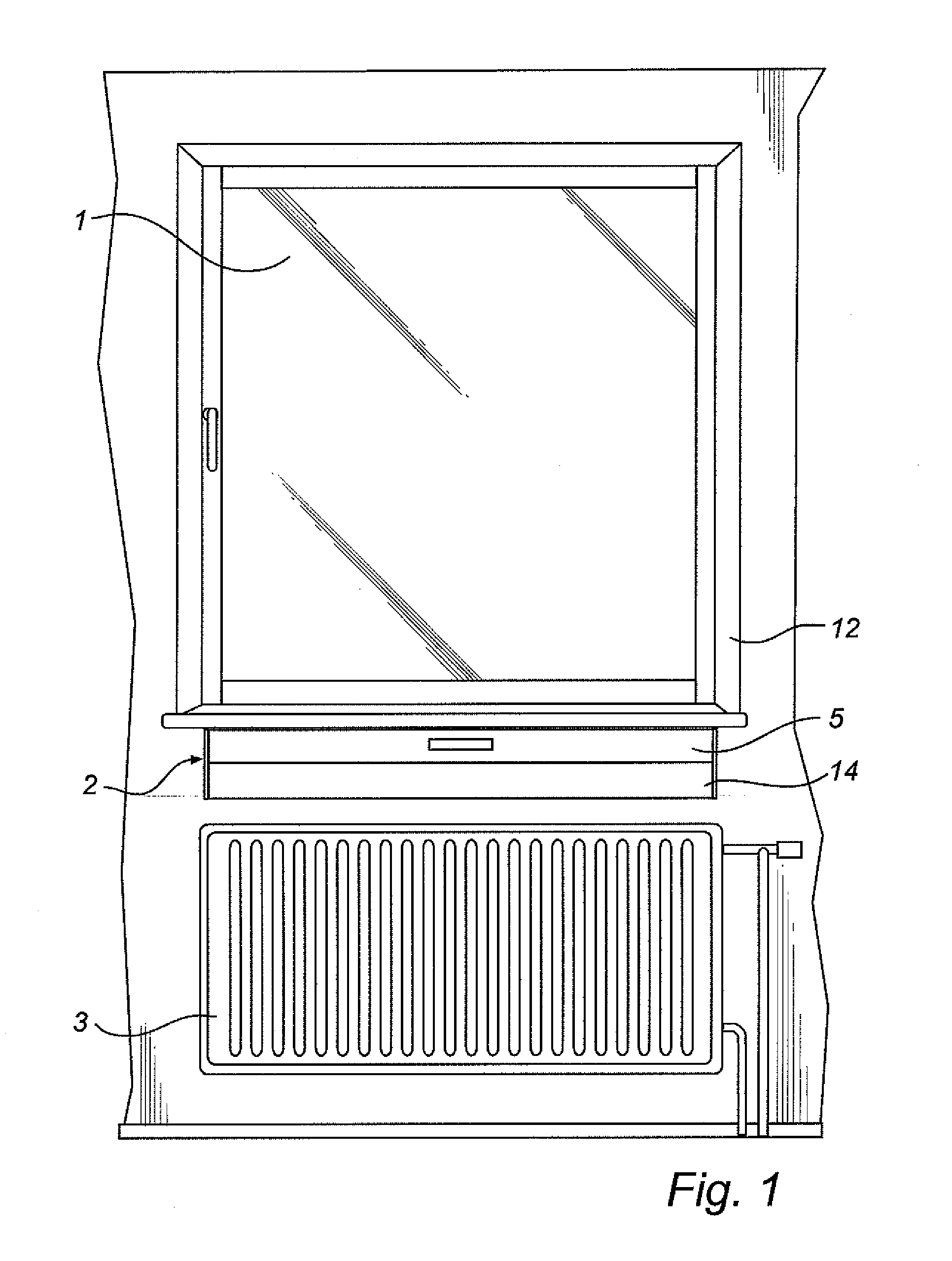

Ventilation air assembly

InactiveUS20100323603A1Avoid damageImprove comfortDucting arrangementsDispersed particle filtrationHeat spreaderWaste management

One embodiment of the present invention relates to a ventilation air assembly, including a filter holding unit the filter holding unit includes a housing having an inlet for ventilation air and an outlet for ventilation air, and a control member for controlling a ventilation air flow through the outlet. The filter holding unit is mounted at the wall surface. Furthermore, the ventilation air assembly includes a filter, which is arranged in the housing of the filter holding unit such that the ventilation air passes through the filter when flowing through the housing from the inlet to the outlet. Furthermore, the ventilation air assembly includes a wall portion having a wall surface, and a heater device, such as a radiator, which is mounted at the wall surface. The filter holding unit and the heater device are such positioned relative each other and the wall surface, and the control member is such adjustable, that the ventilation air flow exiting the outlet is directed towards a space between the wall surface and the heater device. The embodiment of the present invention does also relate to a filter holding unit for use in such a ventilation air assembly.

Owner:CAMFIL AB

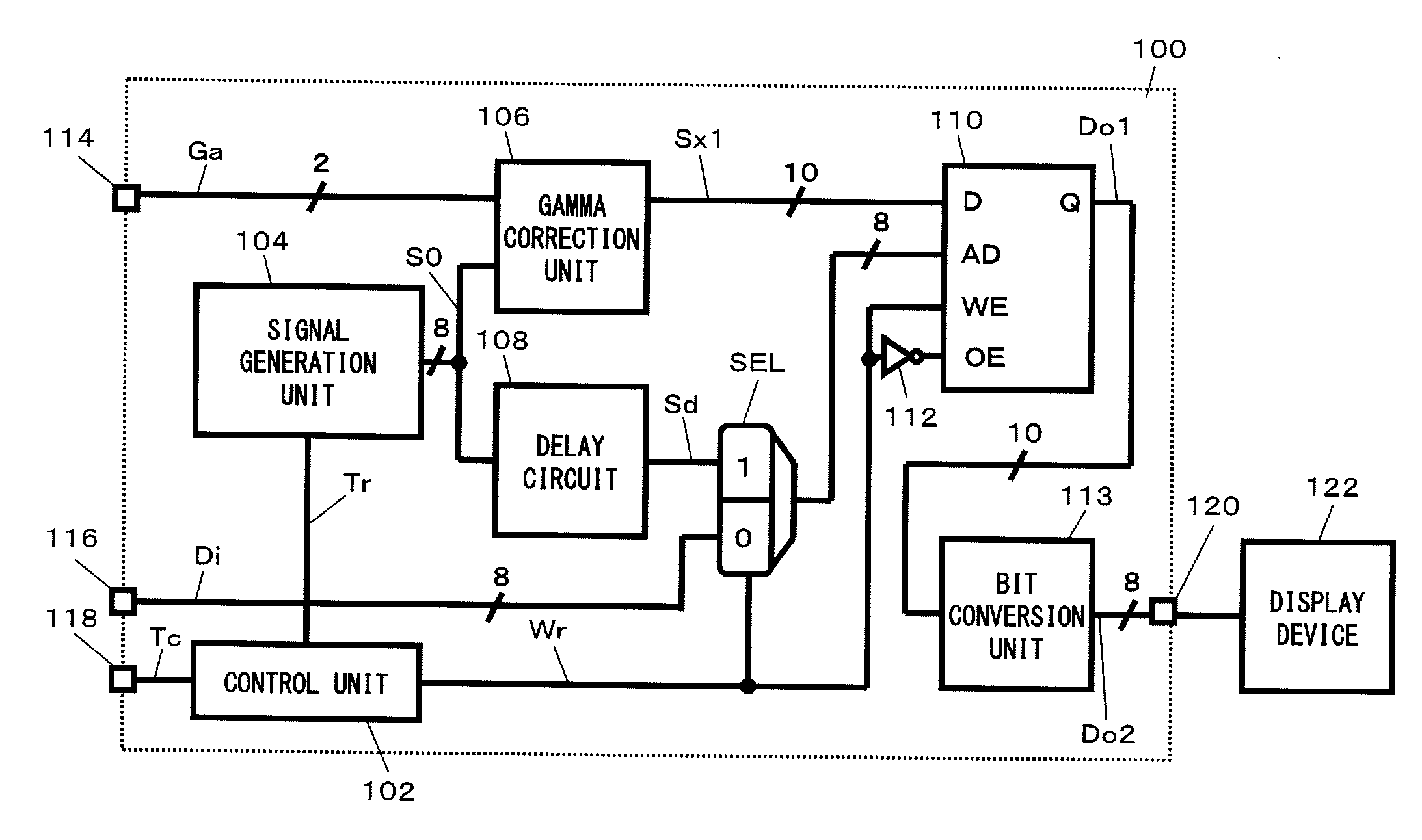

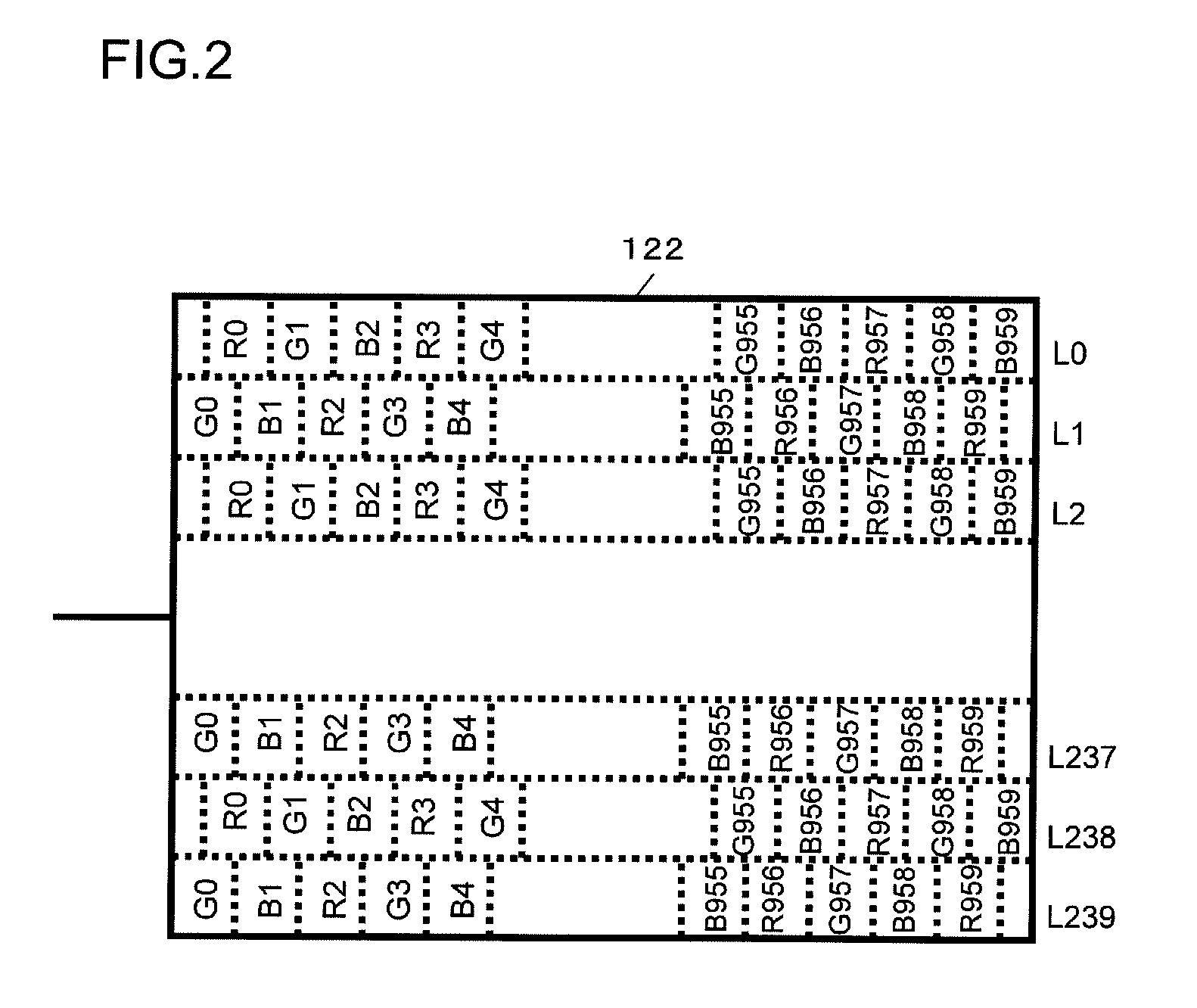

Image processing circuit

InactiveUS20110148911A1Reduce power consumptionEliminate processingCathode-ray tube indicatorsImaging processingZ-RAM

The image processing circuit 400 is provided with R RAM 418, G RAM 420, and B RAM 422. During the vertical blanking interval of a display device 122, tone correction results corresponding to all values which can be inputted as the input signal Di are stored as a lookup table (LUT) in each RAM. When an image is displayed in the display device 122, tone correction of the input signal Di is indirectly performed by referencing the LUT. Redundant computation can thereby be avoided, and power consumption can be reduced.

Owner:ROHM CO LTD

Apparatus for generating clock pulses using a direct digital synthesizer

InactiveUS7912882B2Many changeFlexible changePulse automatic controlGenerating/distributing signalsPhase noiseSquare waveform

The present invention relates to an apparatus for generating clock pulses using a Direct Digital Synthesizer (DDS). The present invention seeks to solve the problems of the conventional clock generator using a Phase Locked Loop (PLL) circuit where the output clock frequency cannot be varied and the output clock signal is degraded because of jitter and phase noise. The claimed apparatus comprises a phase accumulator, a phase-to-magnitude converter, a Digital-to-Analog (DA) converter, a band pass filter, and a comparator, which are serially connected. A 10×PLL multiplier provides a 196.608 MHz clock signal to the phase accumulator, the phase-magnitude converter and the digital analog converter, respectively. The phase accumulator also receives a Frequency Tuning Word (FTW) and using this FTW and the 196.608 MHz clock, outputs a desired specific frequency value. This frequency value is processed through the phase-magnitude converter, the digital analog converter, a band pass filter and a comparator in order to become a square wave of a desired frequency with a low jitter.

Owner:TRANSPACIFIC SONIC

Variable valve operating device

Owner:TOYOTA JIDOSHA KK

Head-mounted display device and control method for head-mounted display device

ActiveUS9823473B2Increase awarenessImprove ease of useInput/output for user-computer interactionCathode-ray tube indicatorsDisplay deviceVisual perception

A head-mounted display device that enables a user to visually recognize a virtual image and an outside scene includes an image display unit configured to cause the user to visually recognize the virtual image, a detecting unit configured to detect a visual line direction of the user, and a display switching unit configured to switch, according to the detected visual line direction, display of the virtual image by the image display unit between outside scene preferential display for preferentially displaying the outside scene and virtual image preferential display for preferentially displaying the virtual image.

Owner:SEIKO EPSON CORP