Patents

Literature

55results about How to "Mitigate, alleviate or eliminate one or more" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

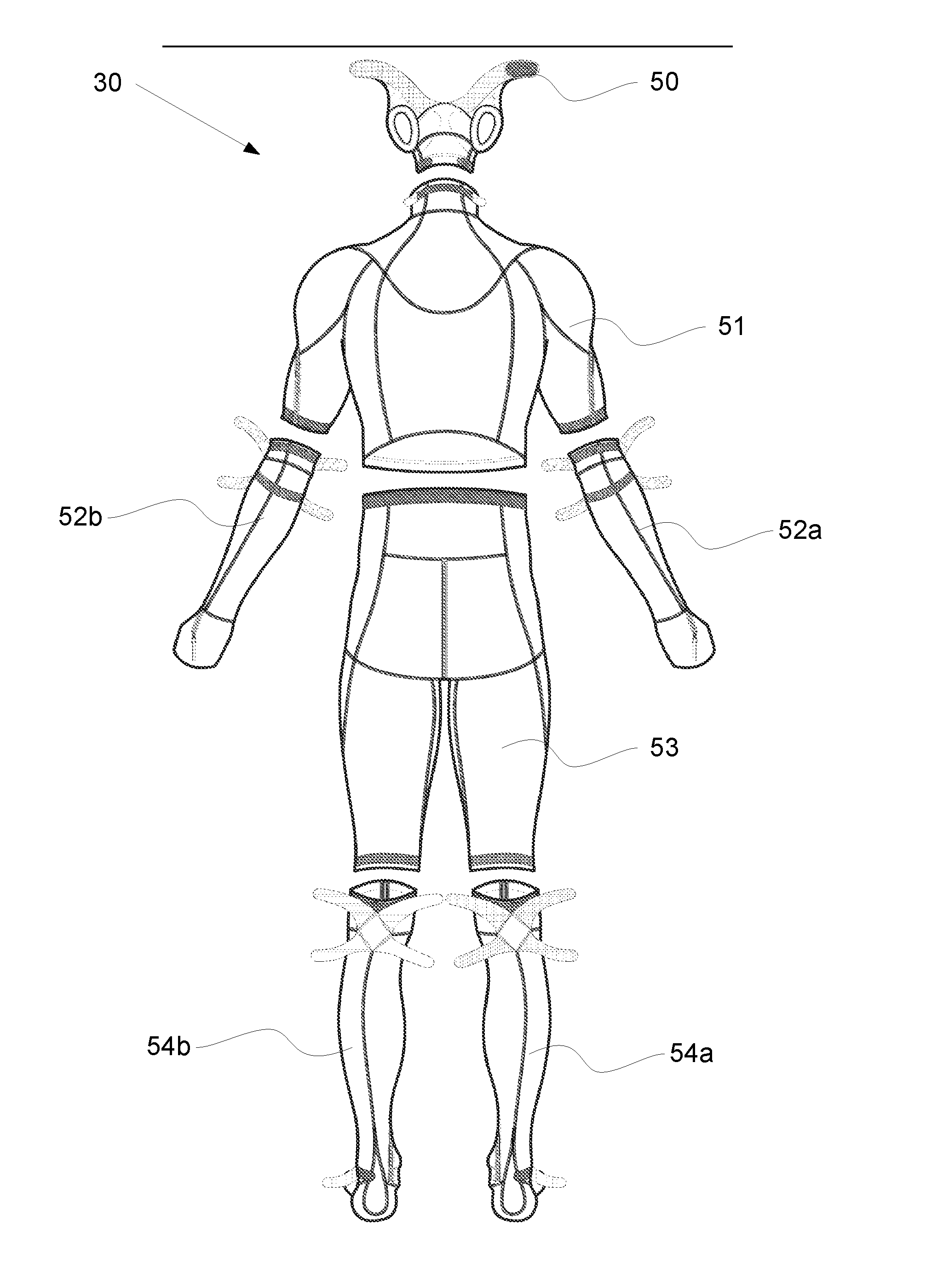

System And Garment For Muscle Relaxation Of A Spastic Muscle

InactiveUS20120245483A1Improve muscle relaxationMitigate, alleviate or eliminate one or moreElectrotherapyElectromyographyDiseaseMuscle relaxation

The present invention relates generally to muscle relaxation. Muscle relaxation is desired in many disease states, including spastic paresis and biomechanical and neuromuscular dysfunction. More specifically, the invention relates to a system that causes muscle relaxation by reducing muscular spasticity through the stimulation of joints and muscles. The system consists of a garment with electrodes, a hardware unit and software controlling the stimulation.

Owner:INERVENTIONS

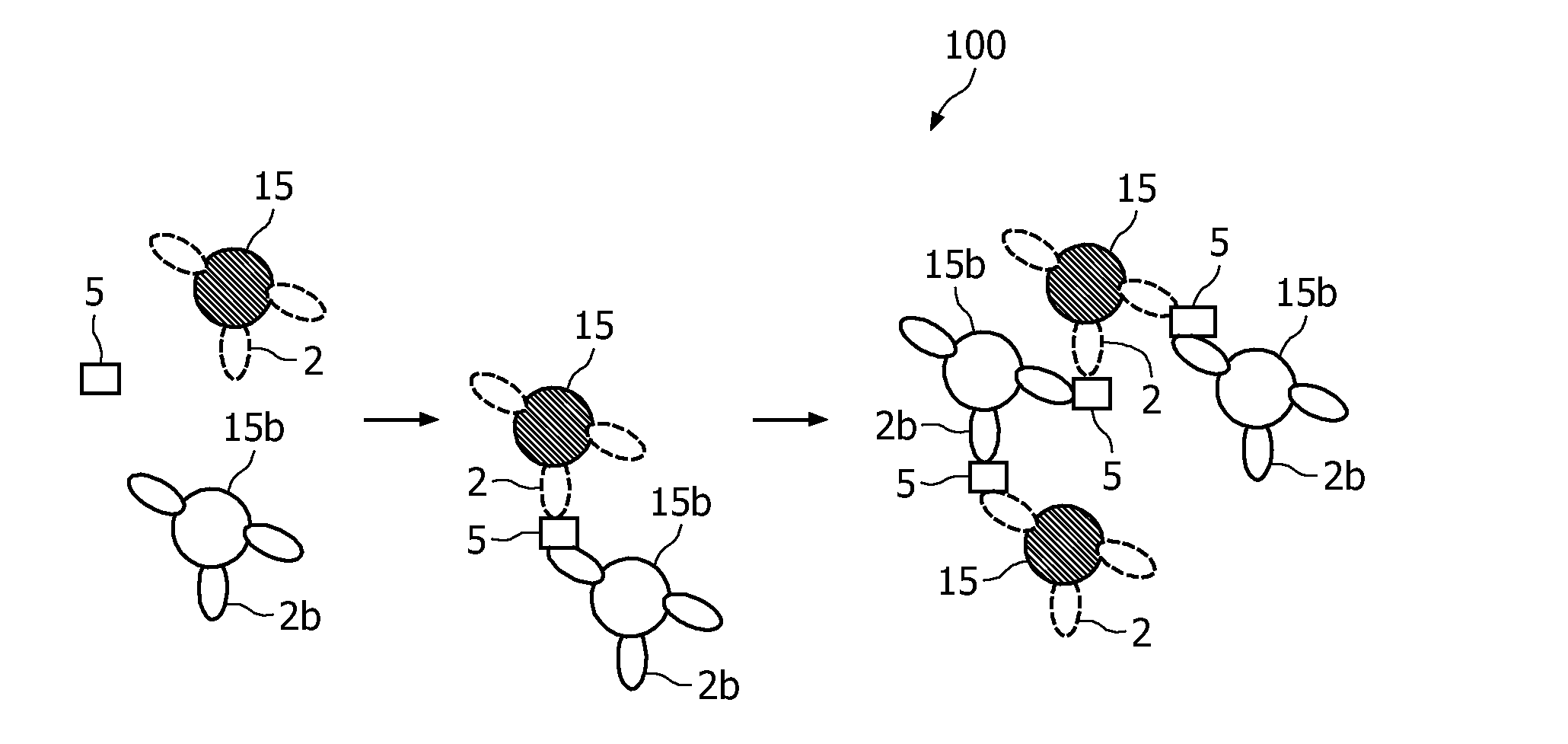

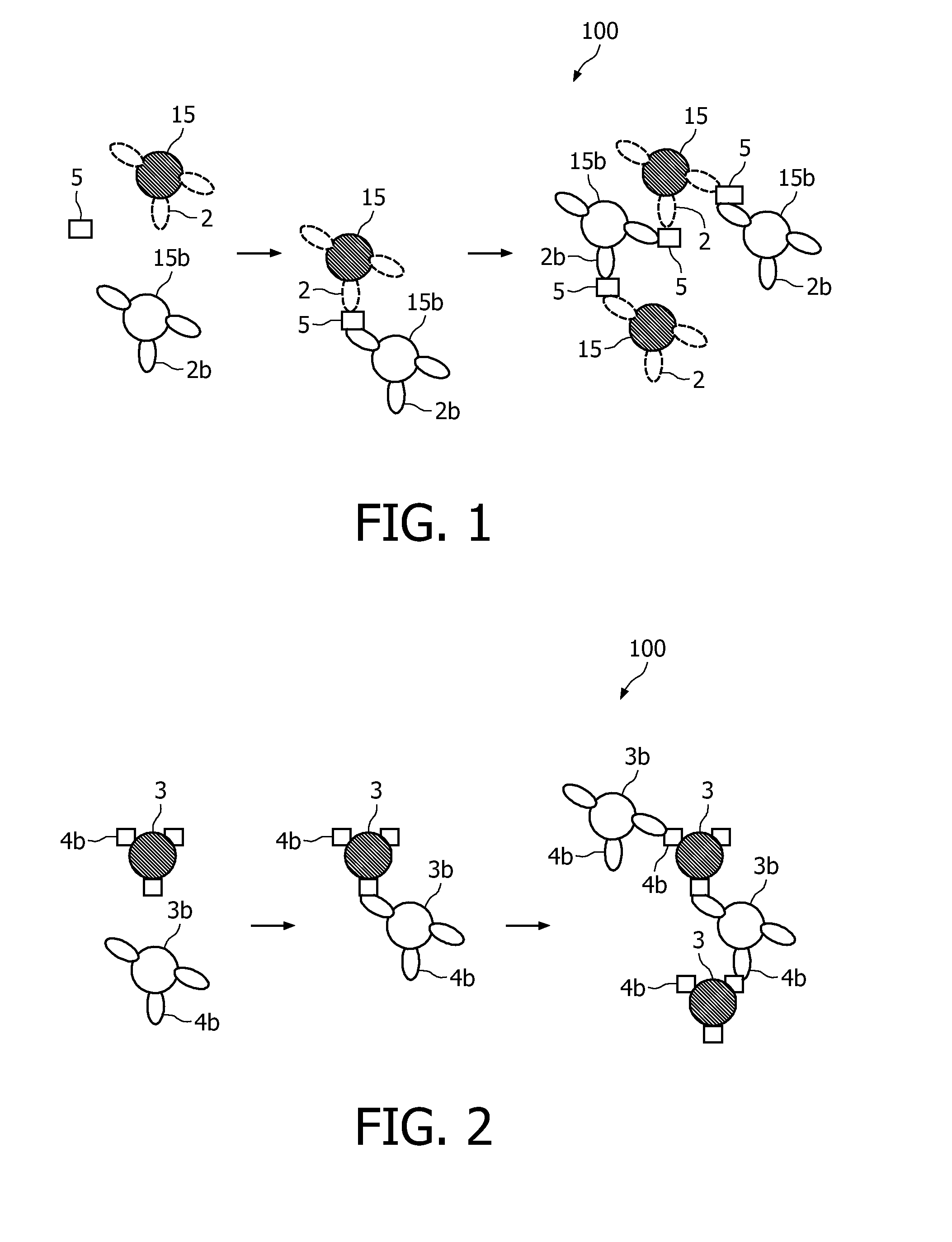

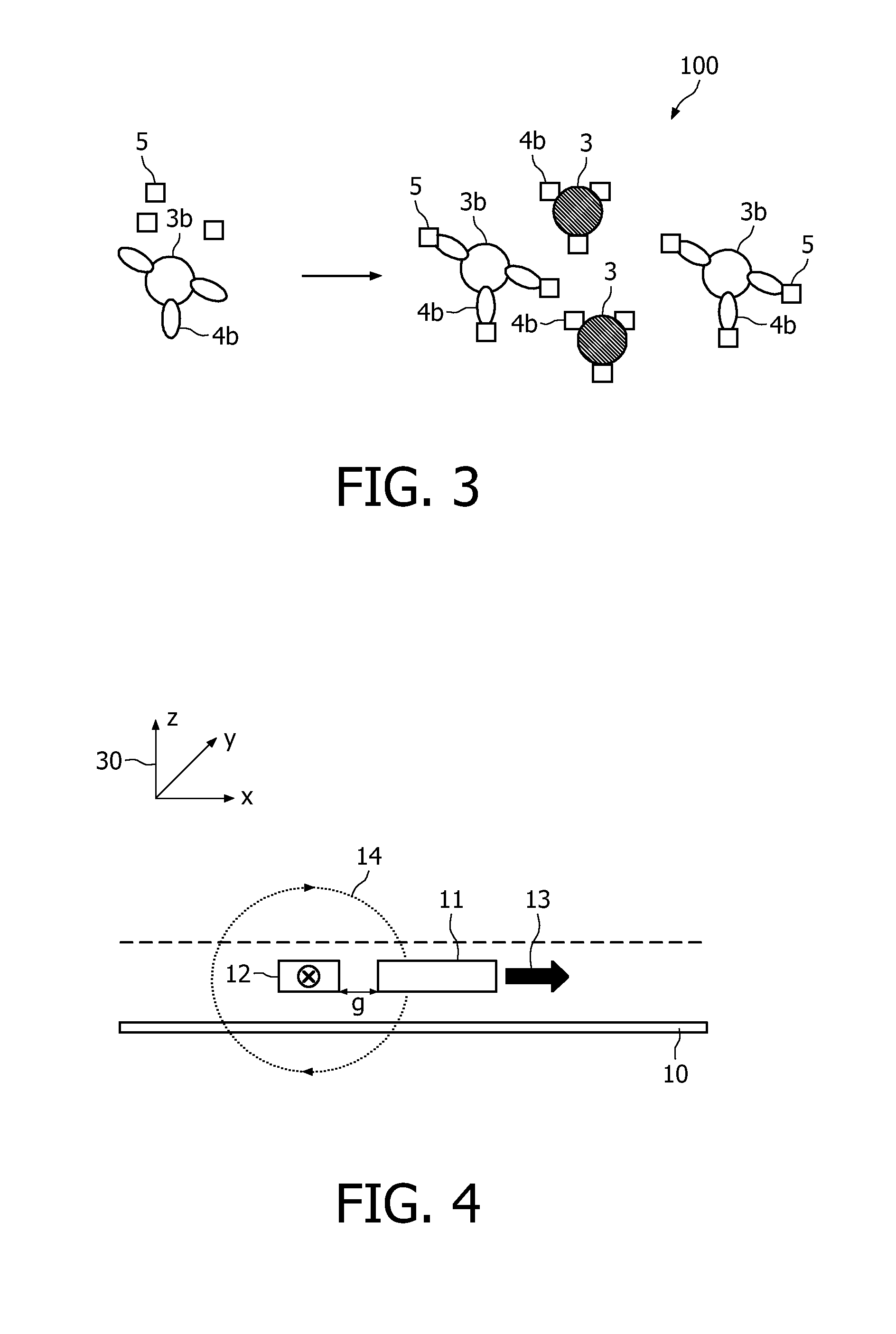

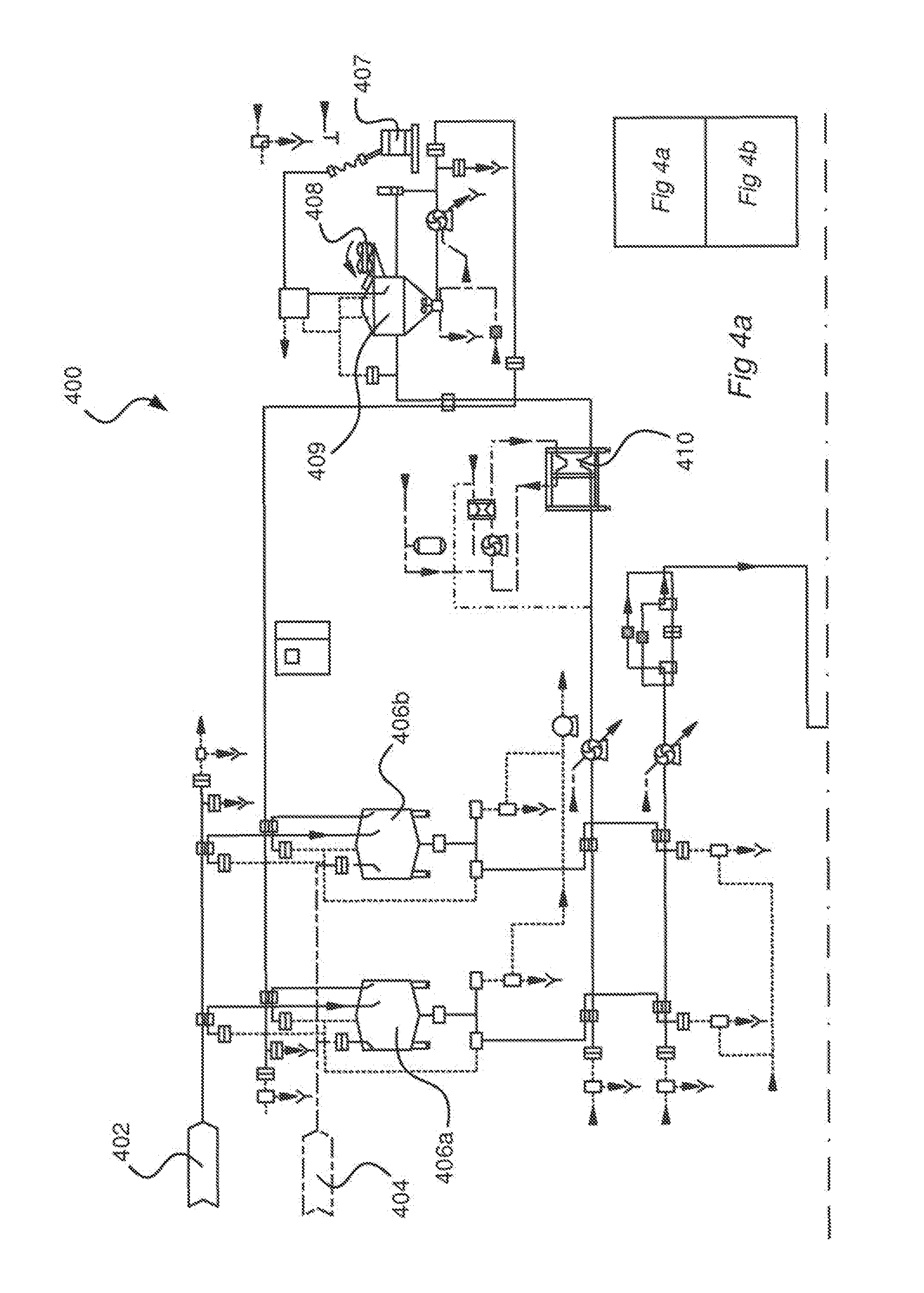

Measuring agglutination parameters

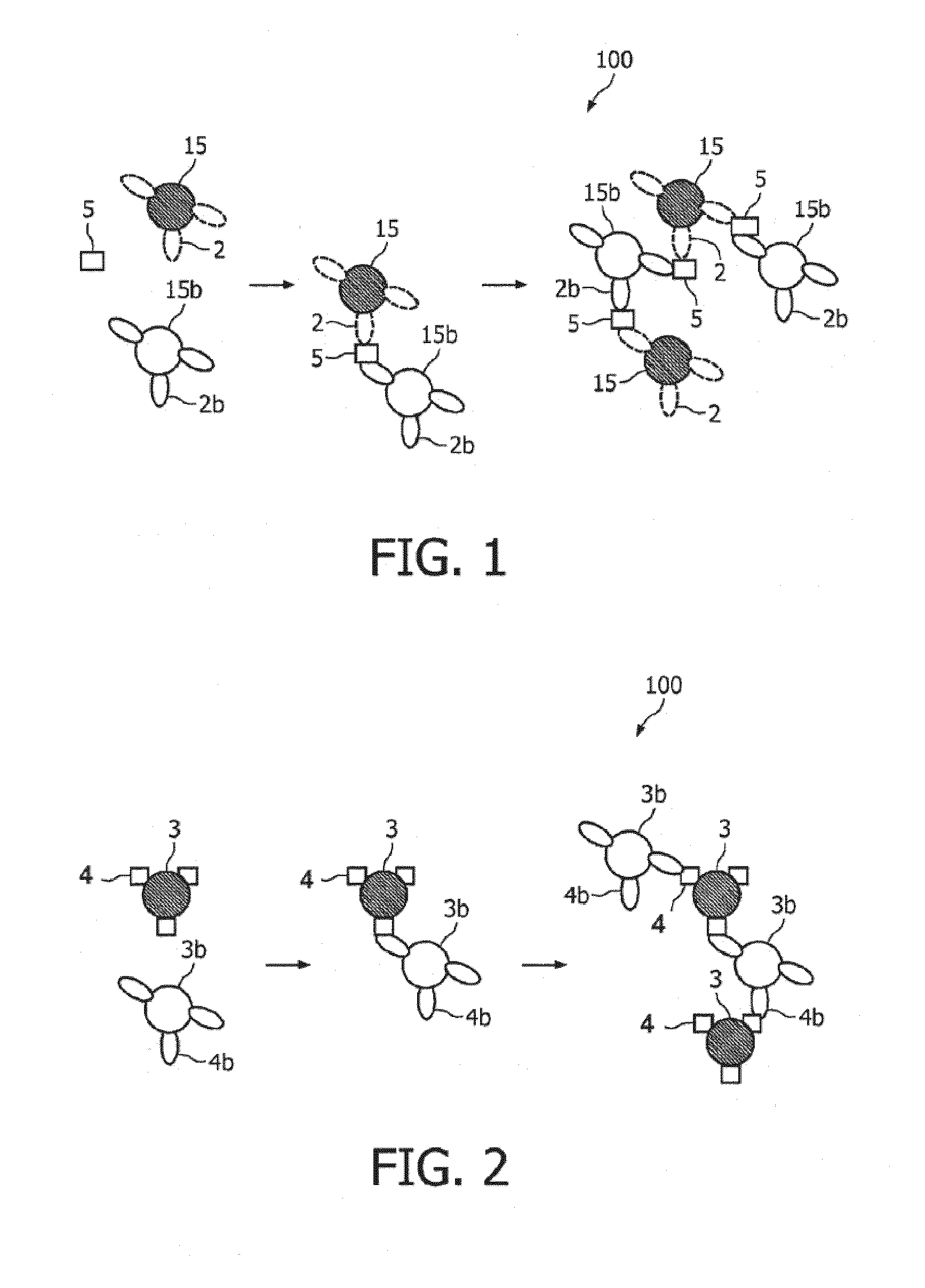

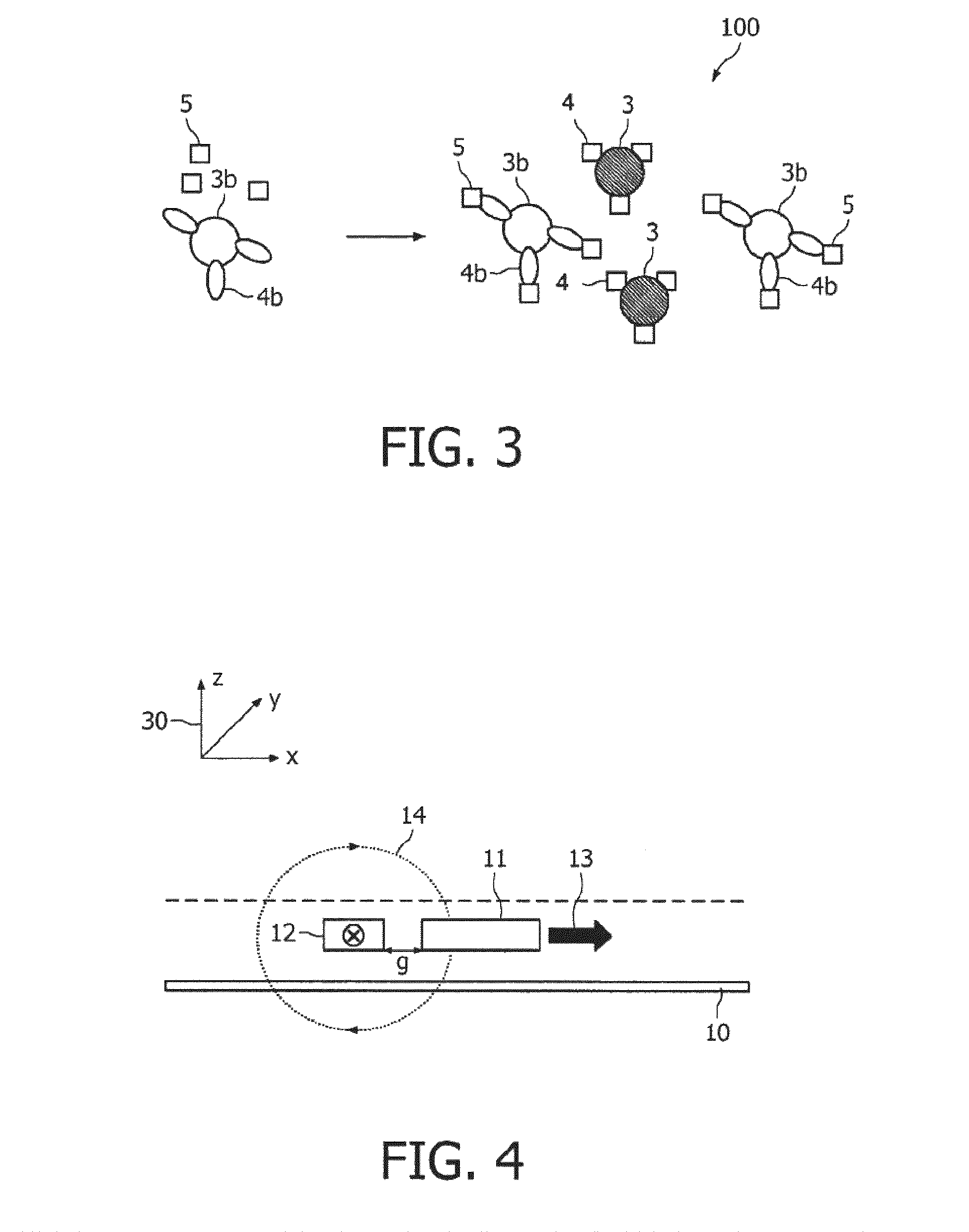

ActiveUS20100033158A1Mitigate, alleviate or eliminate one or moreImprove throughputBioreactor/fermenter combinationsNanomagnetismAgglutination assayAgglutination

A method and system are described for measuring agglutination in a target-induced agglutination assay with one or more magnetic particles performed in a reaction chamber. After the magnetic particles (3, 15), which are capable of binding to a target (5) are provided in the assay, an agglutination process resulting in agglutinated particles (100) comprising at least one magnetic particle is performed. The method then further comprises applying an alternating current magnetic field (HAC) to the assay and—measuring an effect of the HAC on the one or more magnetic particles (3,15) unattached to any surface. The measured effect is indicative of one or more agglutination parameters.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

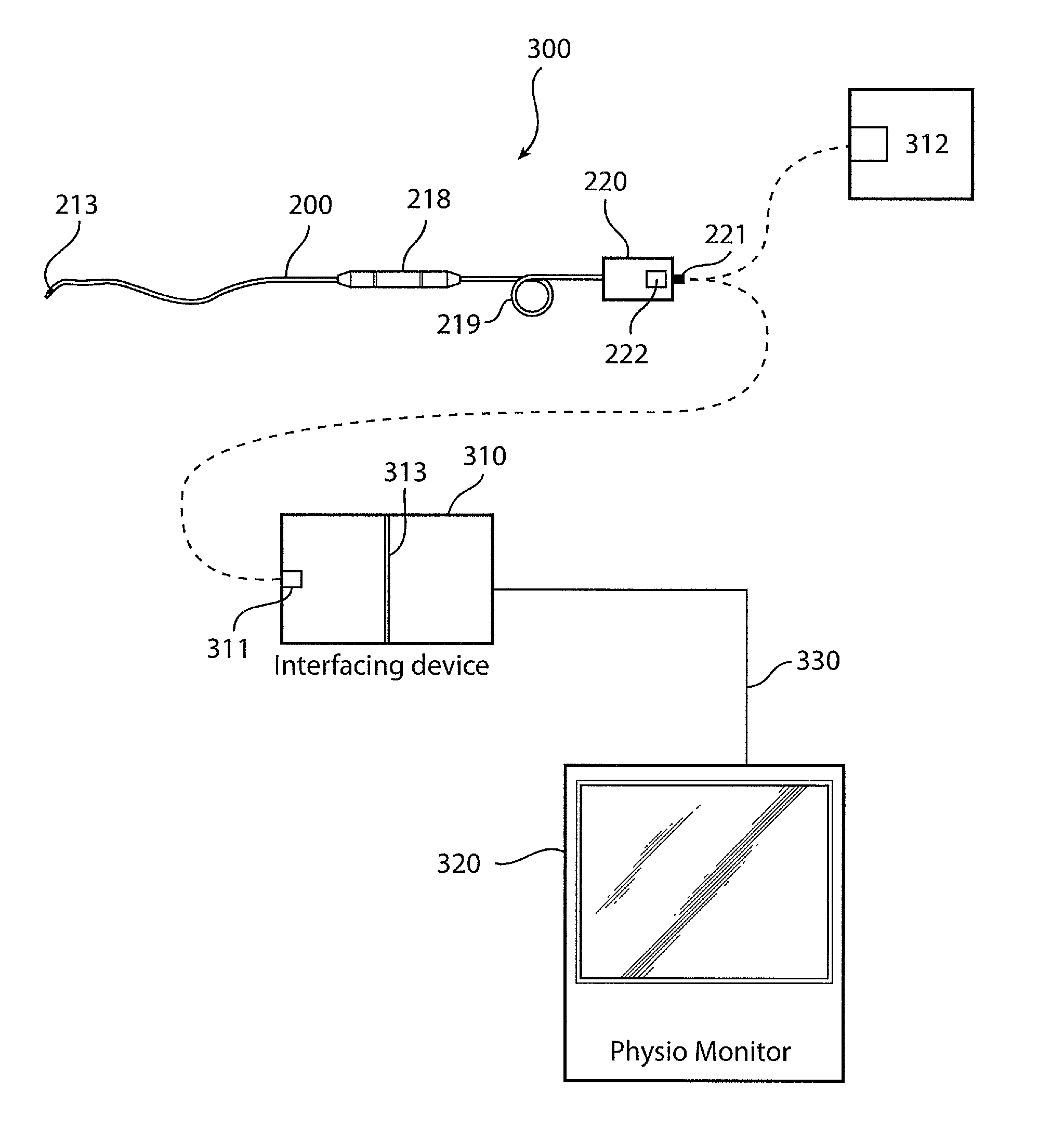

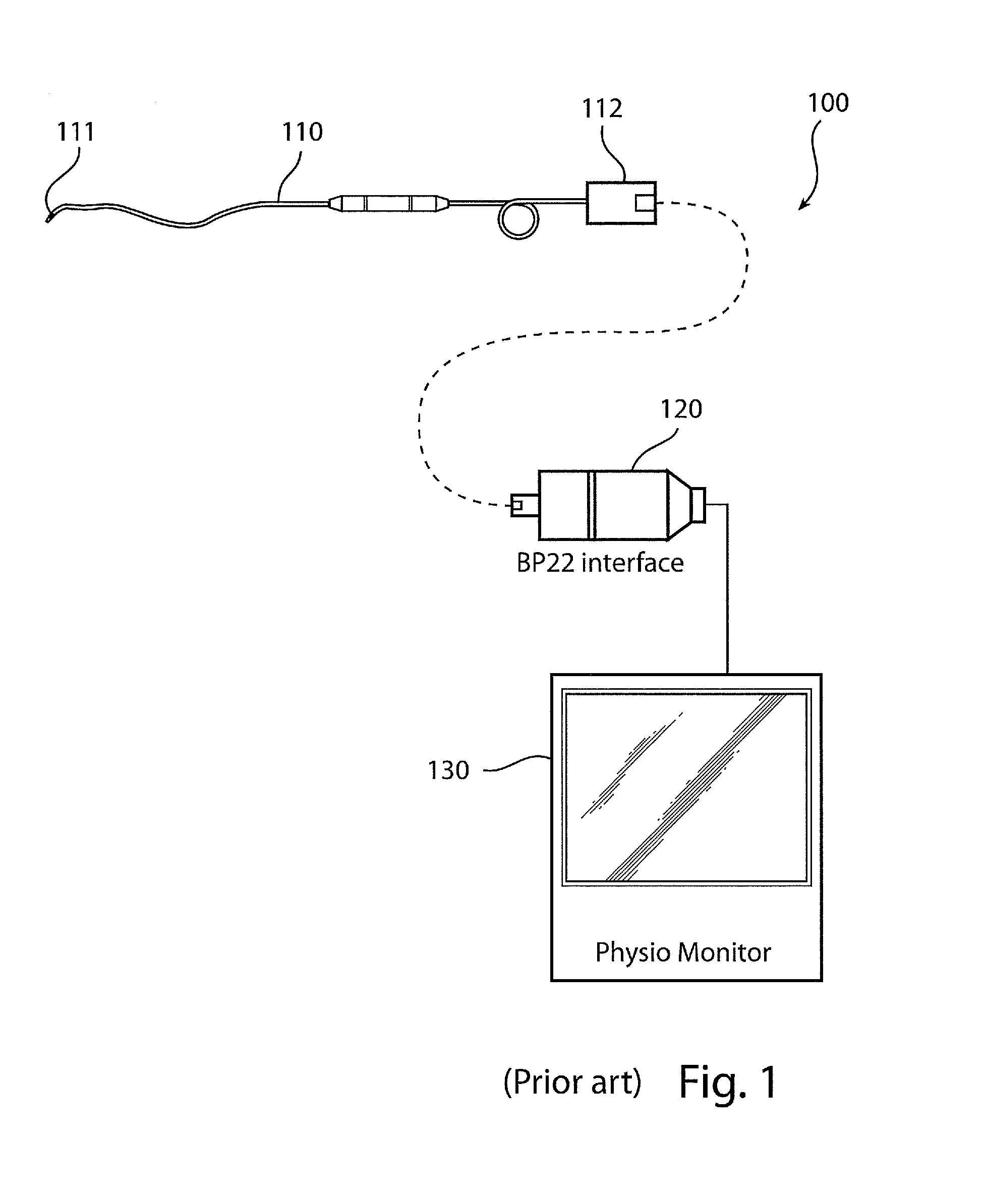

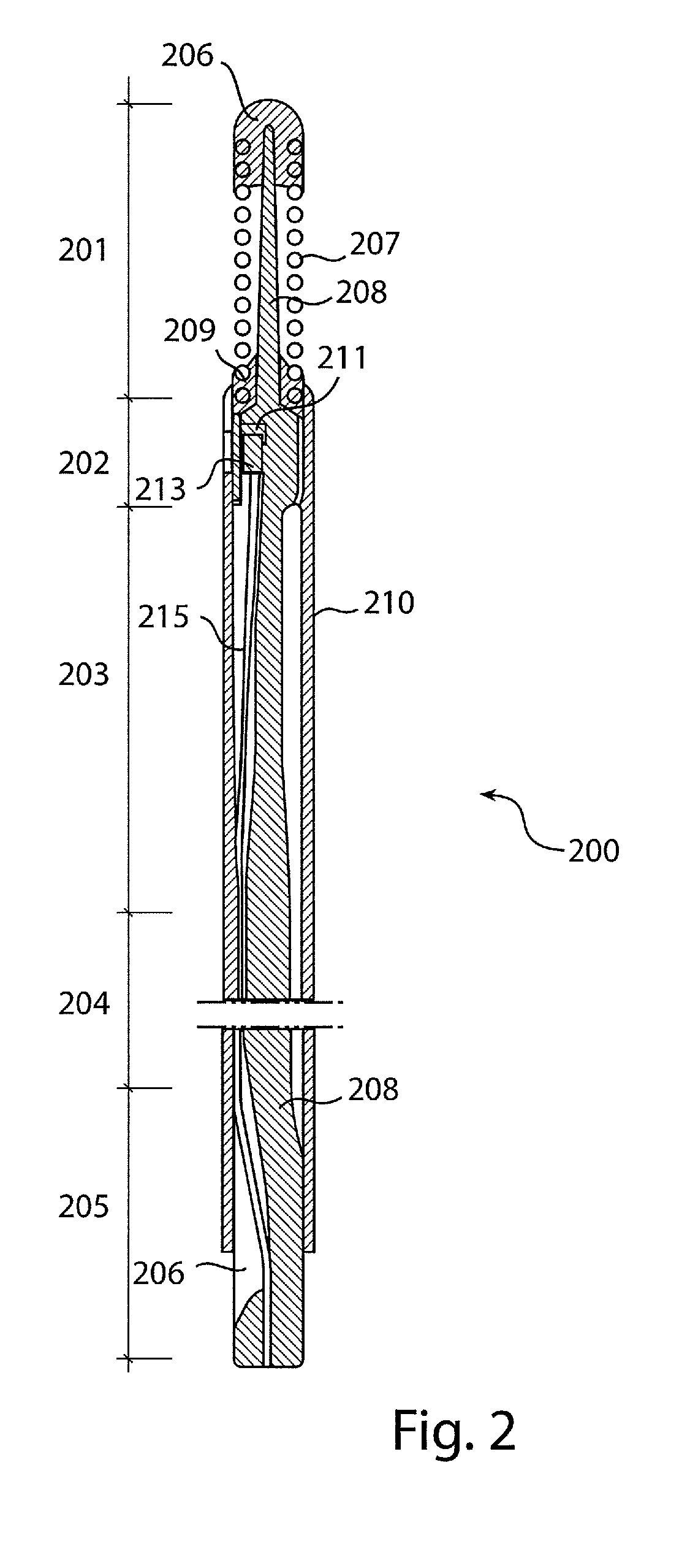

Sensor guide wire device and system including a sensor guide wire device

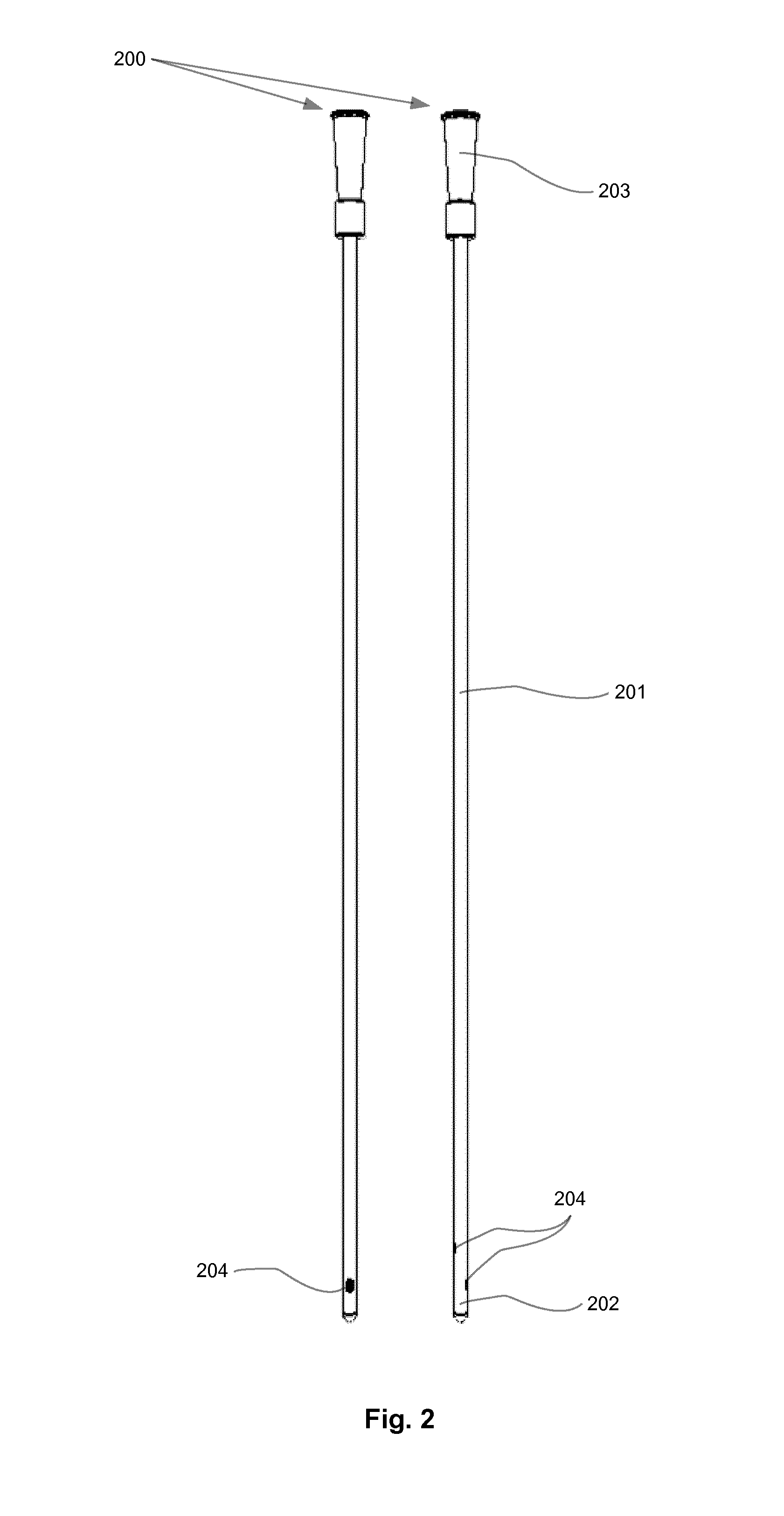

ActiveUS20120289808A1Minimized and at least reduced riskMitigate, alleviate or eliminate one or moreGuide wiresSensorsLiving bodyGuide wires

A sensor guide wire device (200) for intravascular measurements of a physiological variable in a living body is disclosed. The sensor guide wire (200) may comprise a sensor element (213) and a connector unit (220). The connector unit (220) is attachable to a signal converting device (310). The sensor element (213) provides the signal converting device (310) with a signal indicative of a physiological variable sensed by the sensor element (213). Furthermore, the connector unit (220) comprises a battery (222). A system (300) comprising the sensor guide wire device (200) and the signal converting device (310) is also disclosed.

Owner:ST JUDE MEDICAL COORDINATION CENT

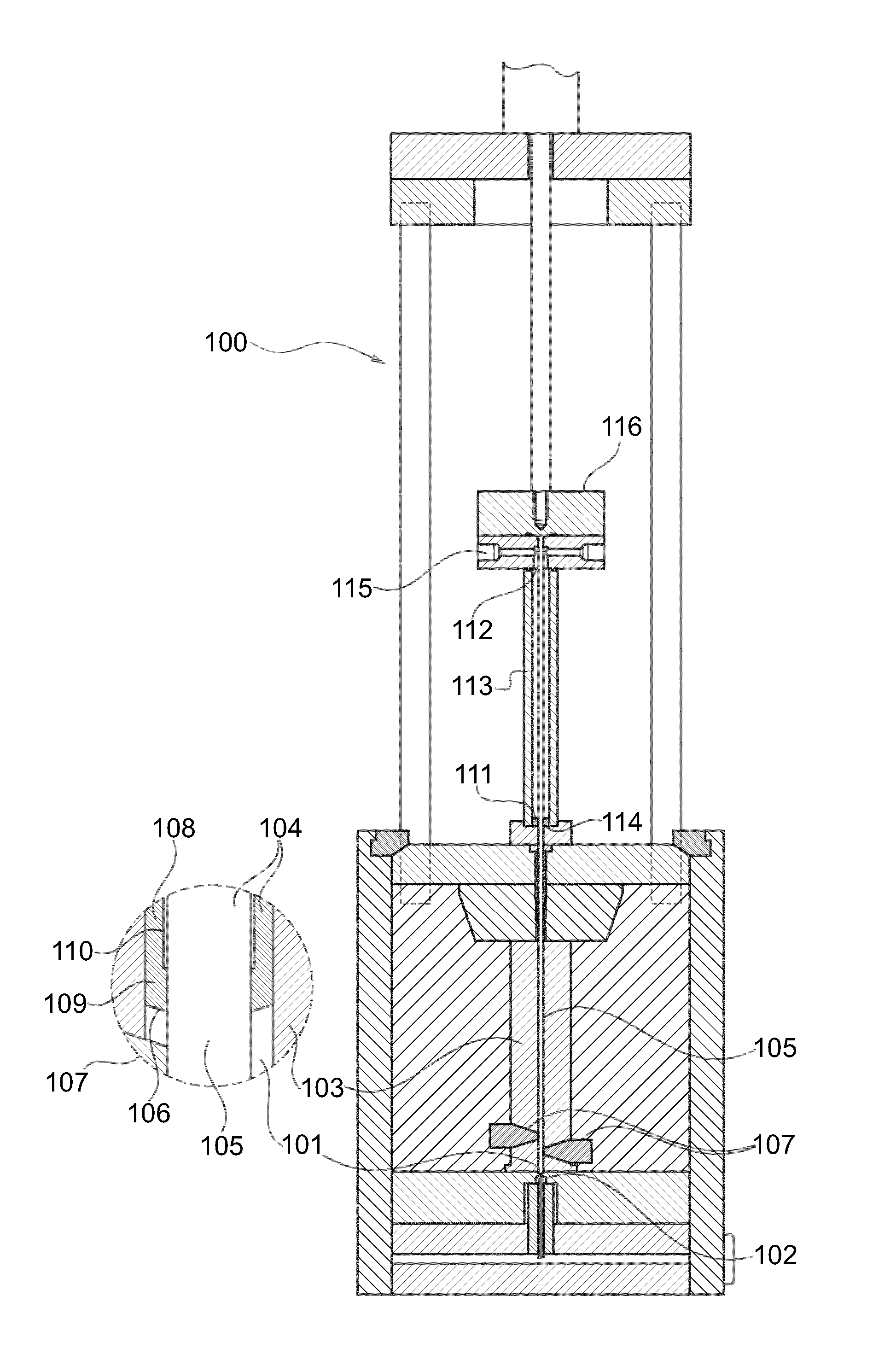

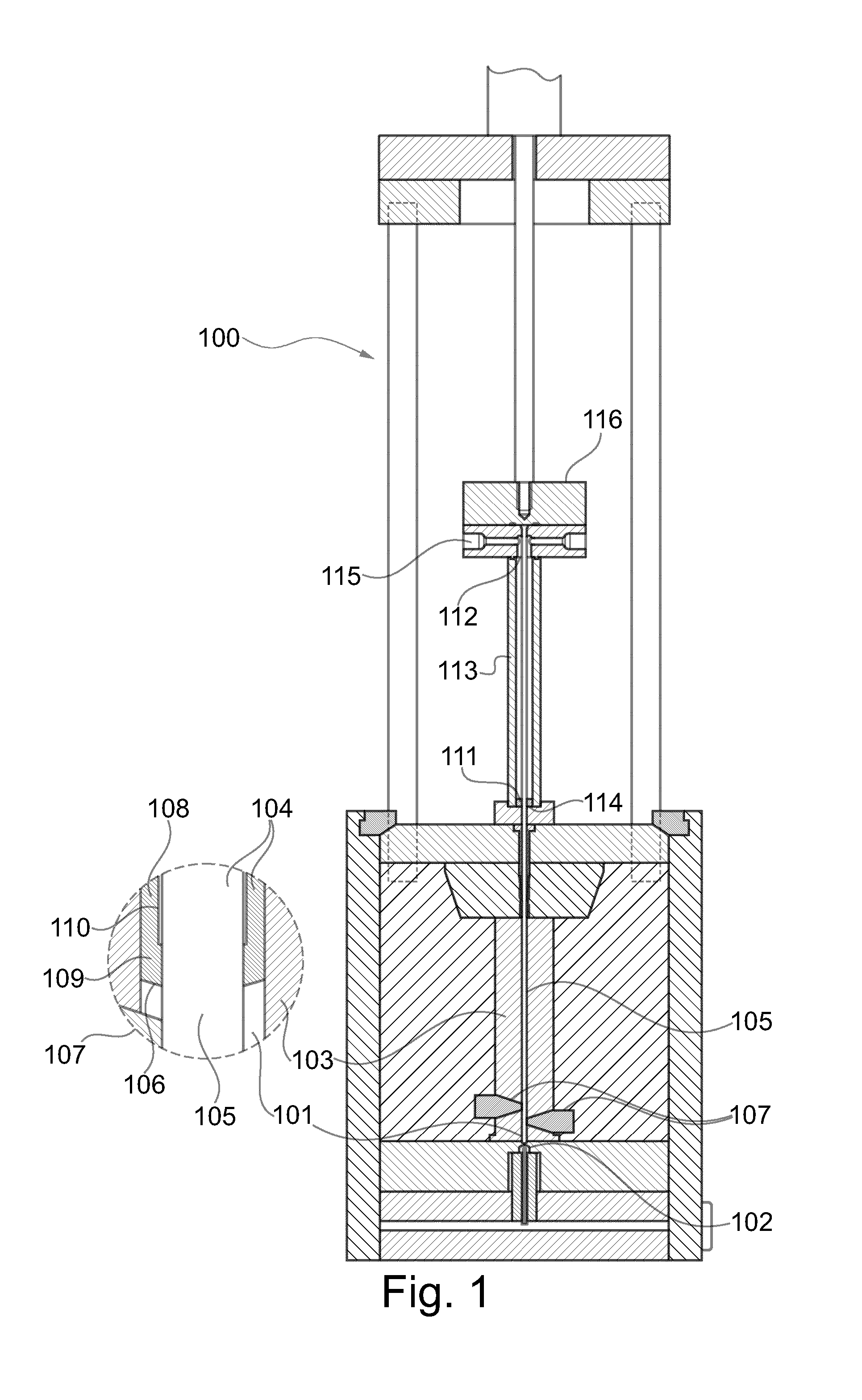

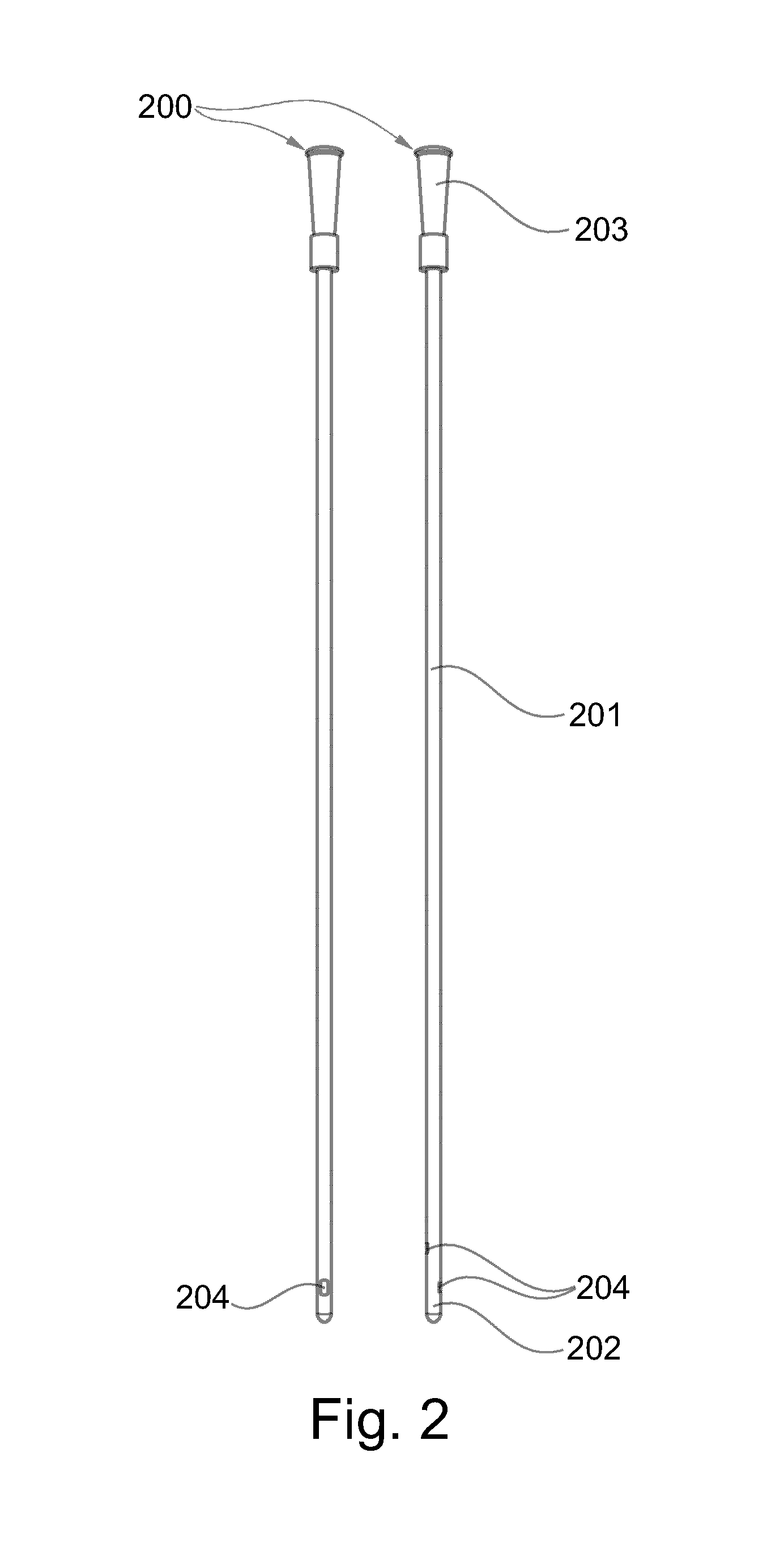

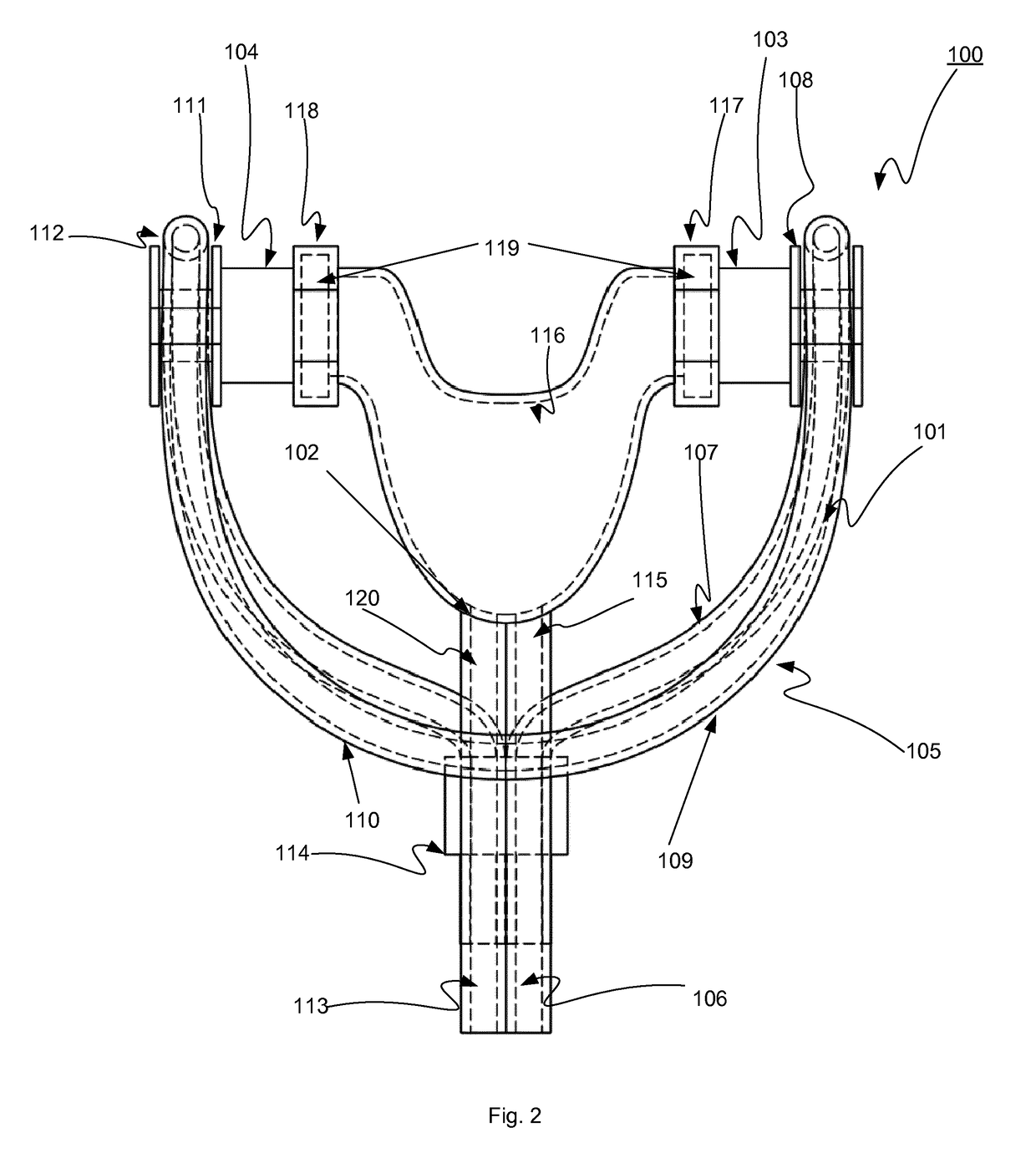

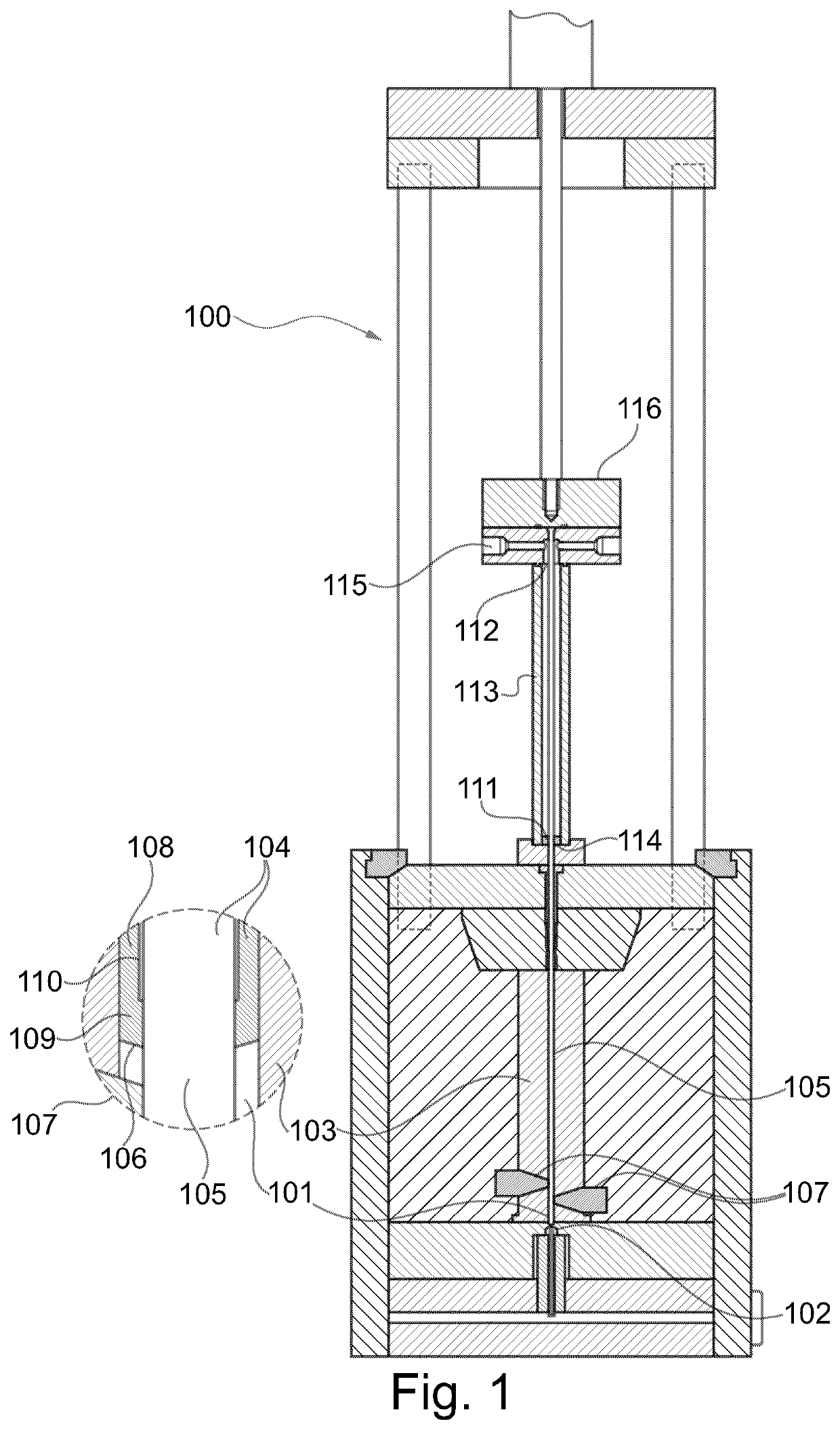

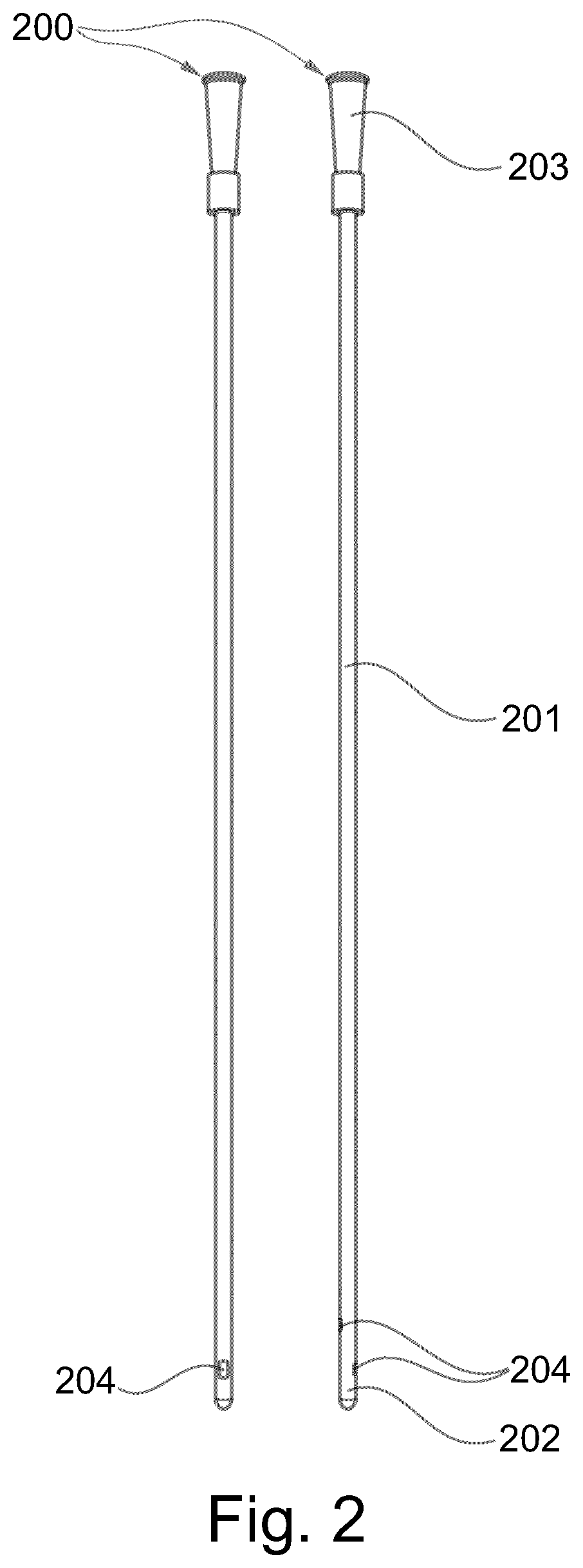

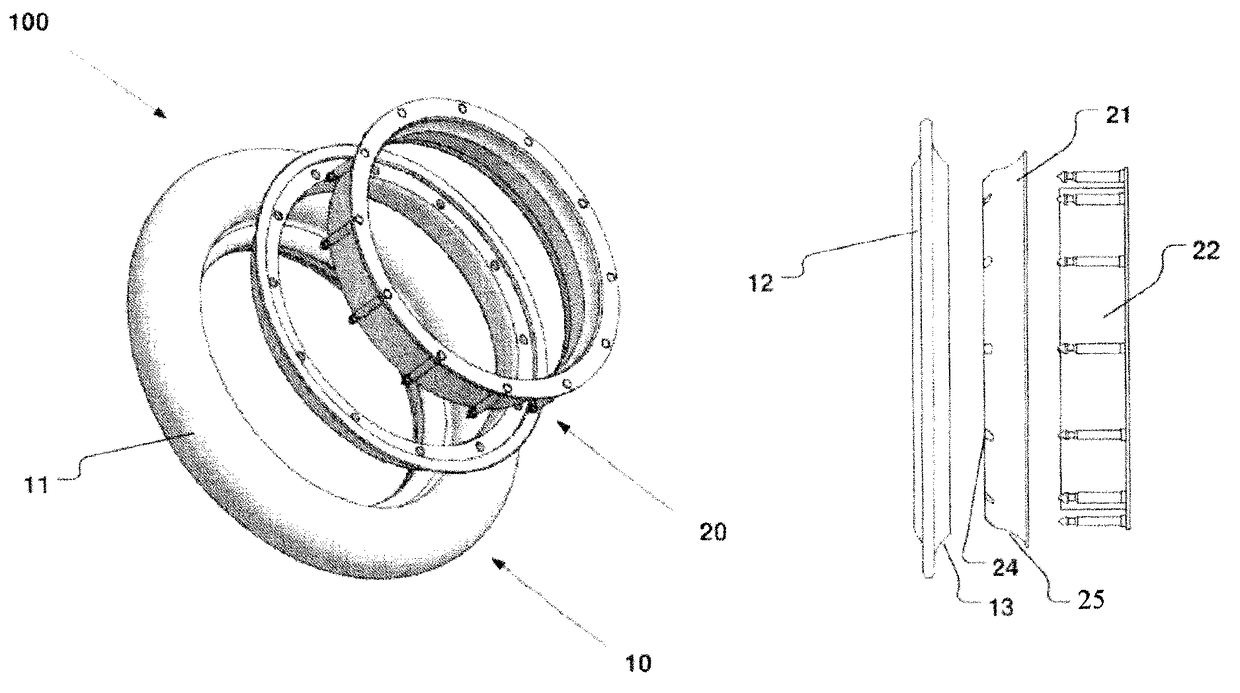

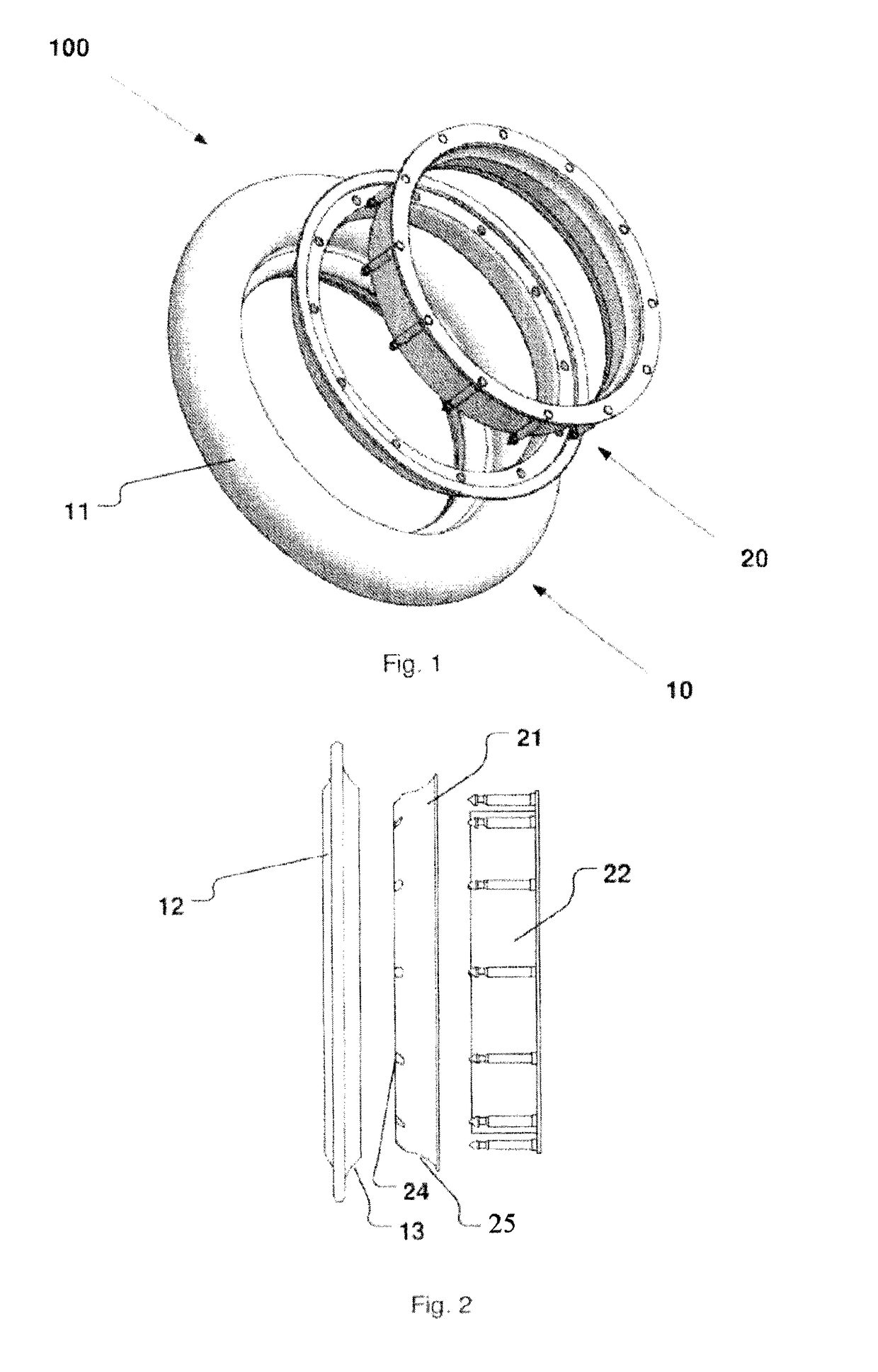

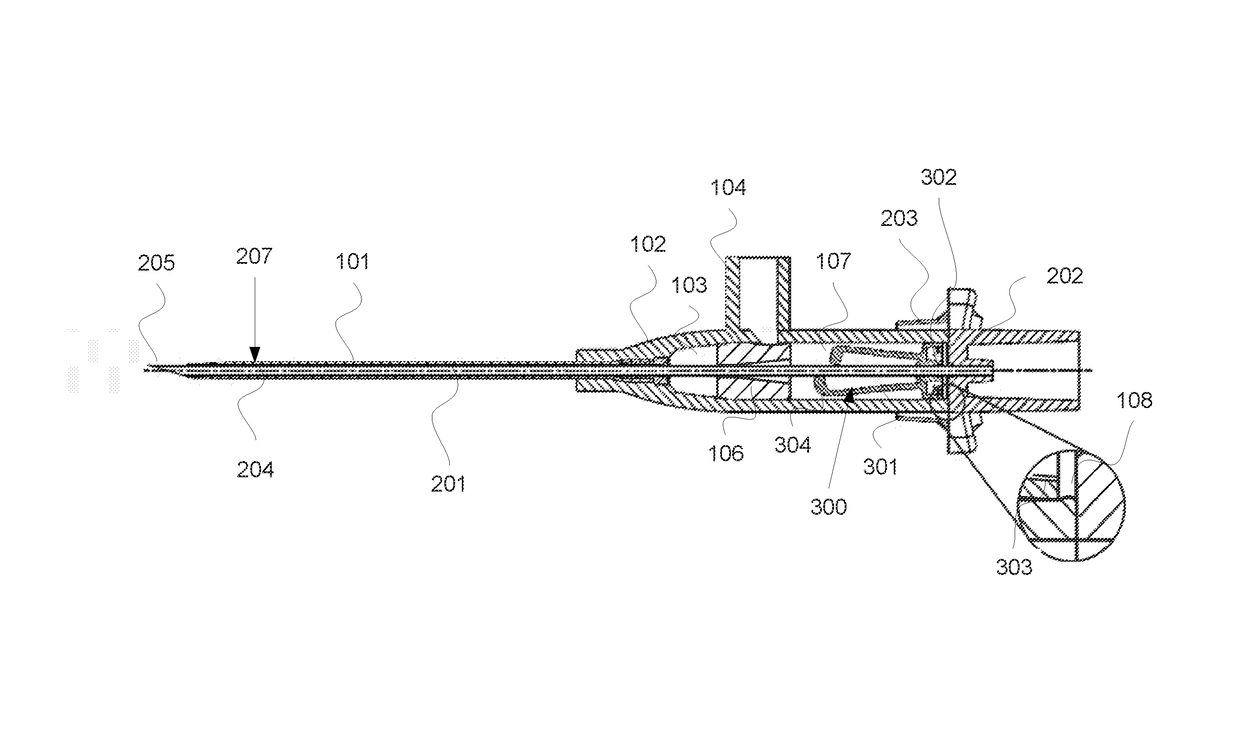

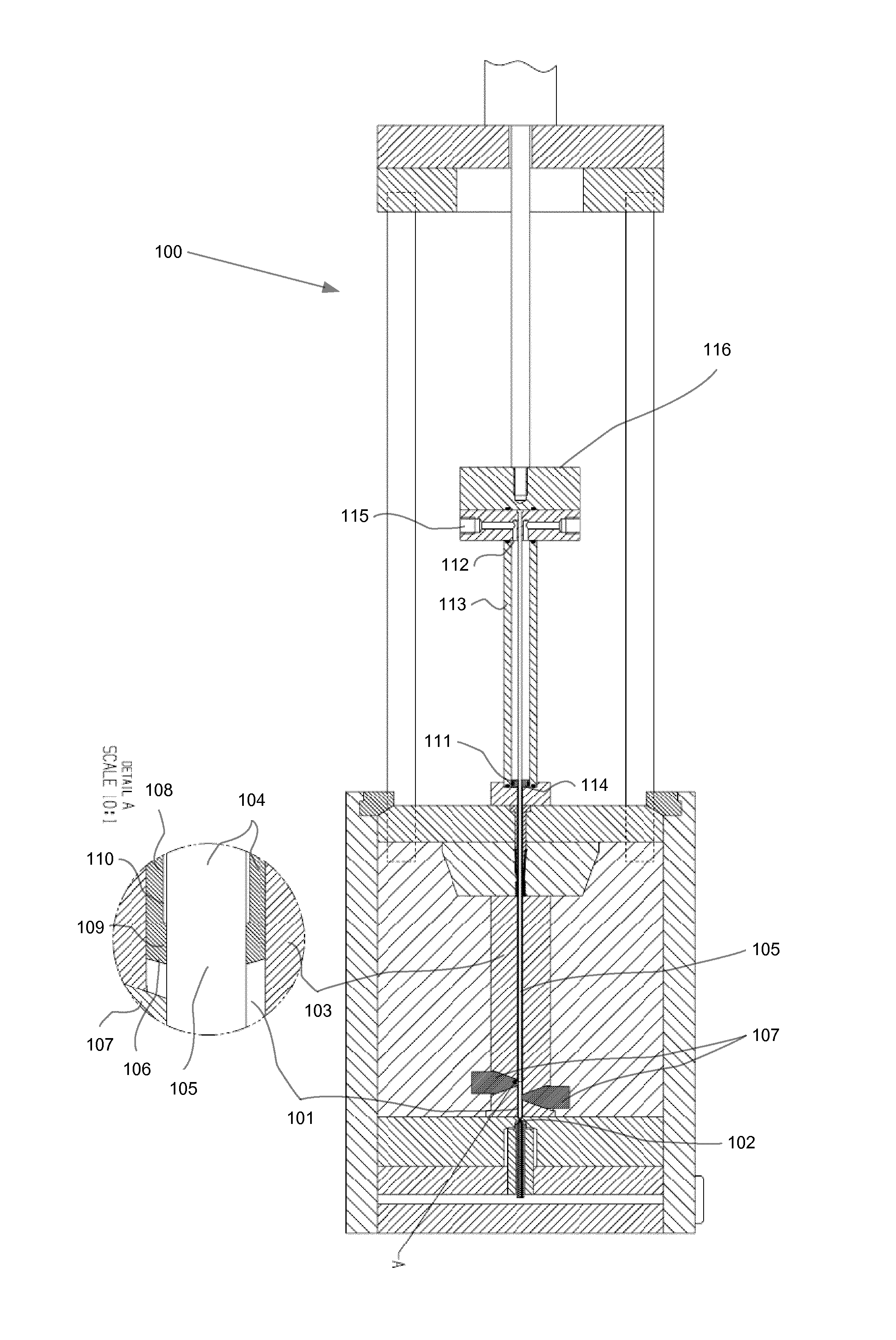

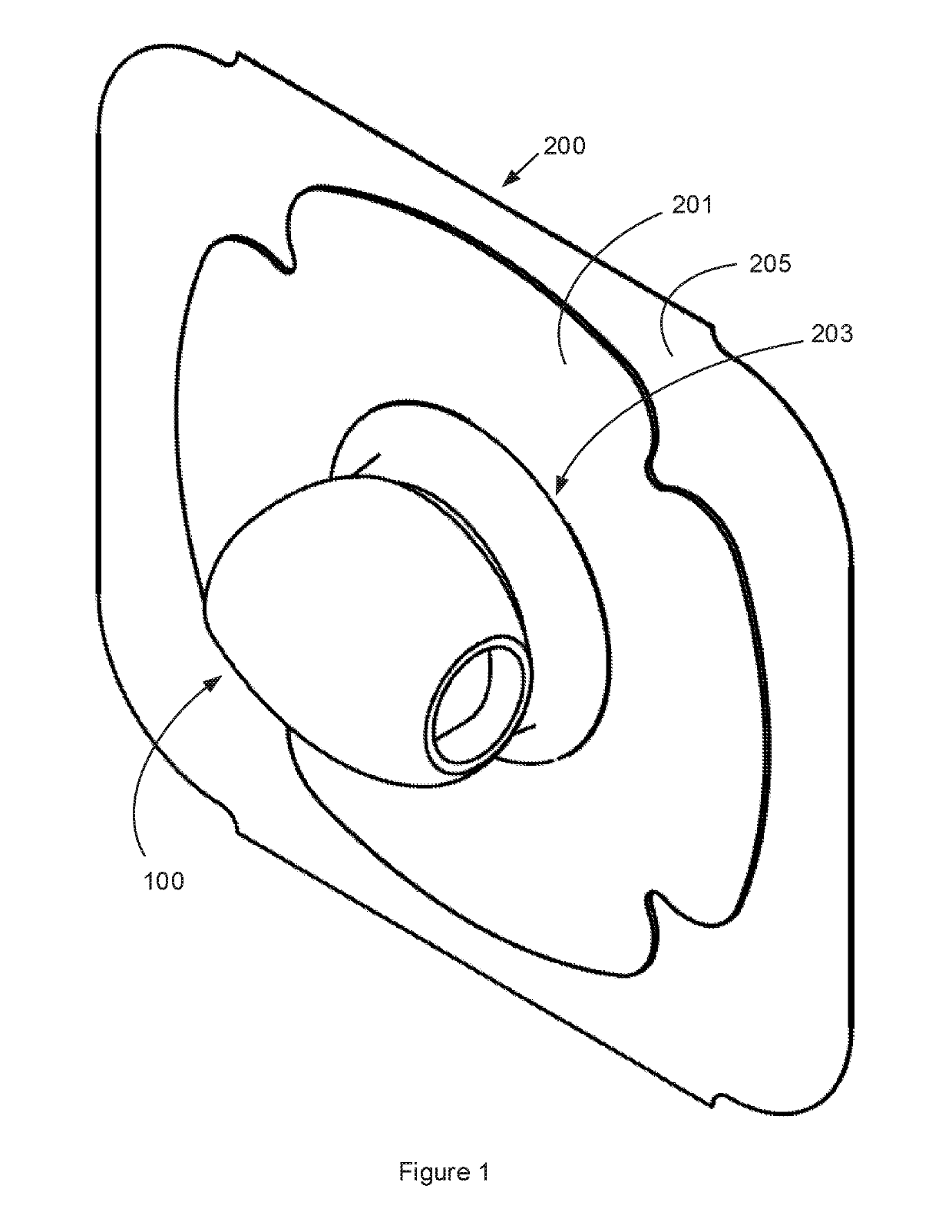

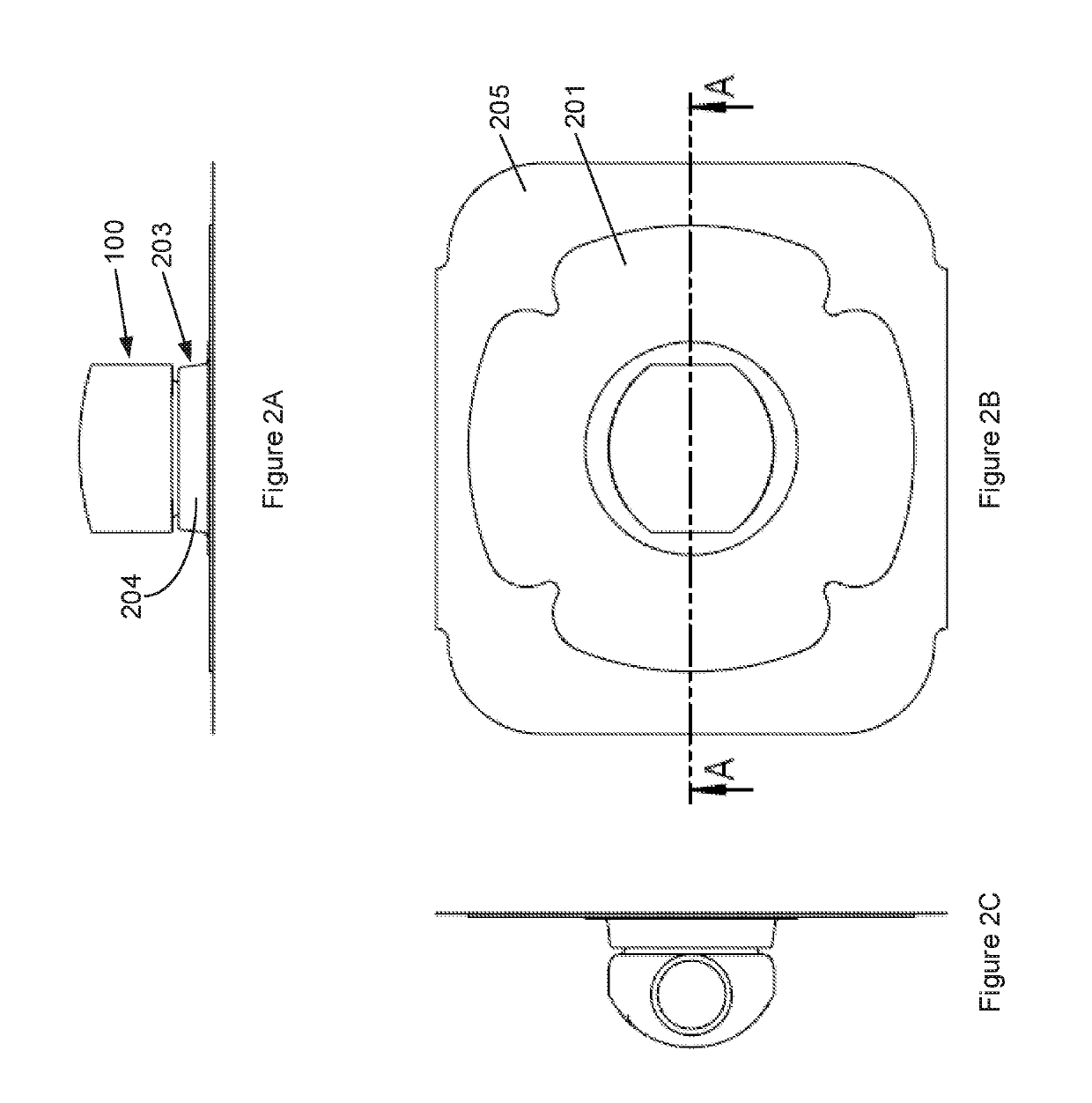

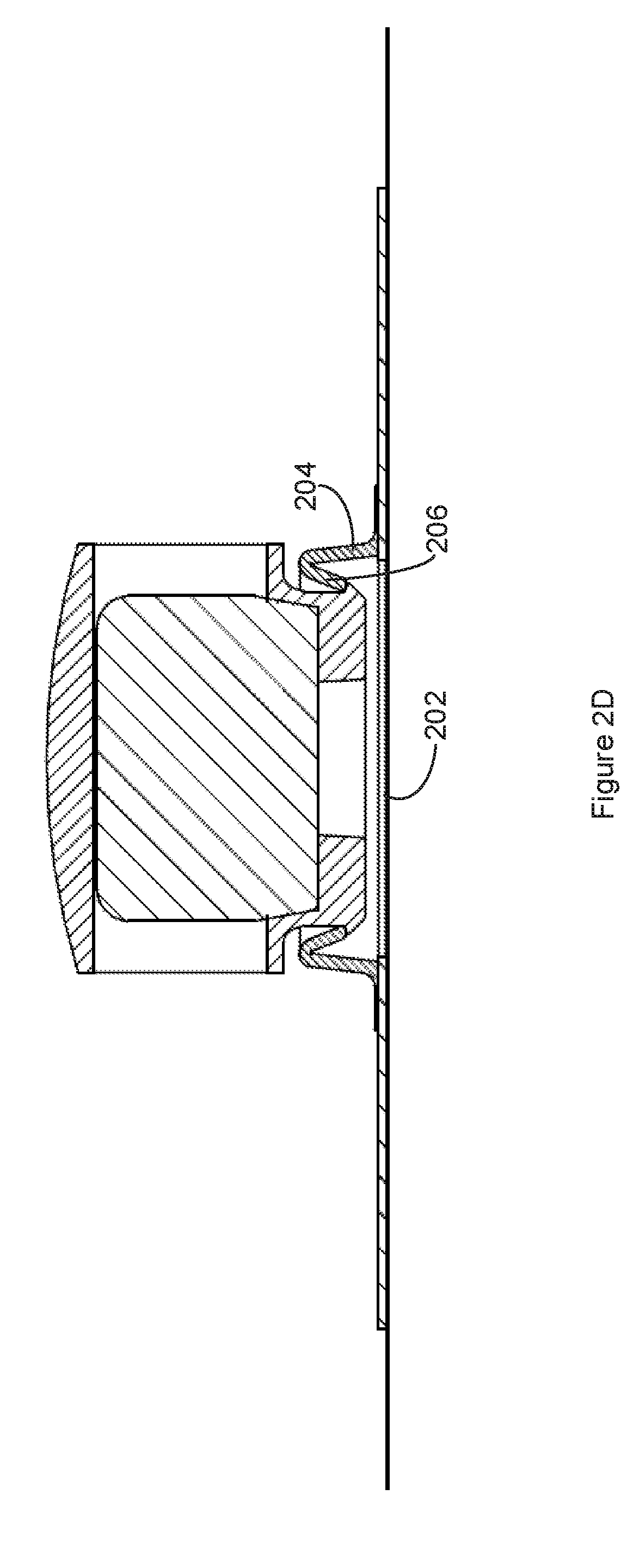

Method for manufacturing of urinary catheters

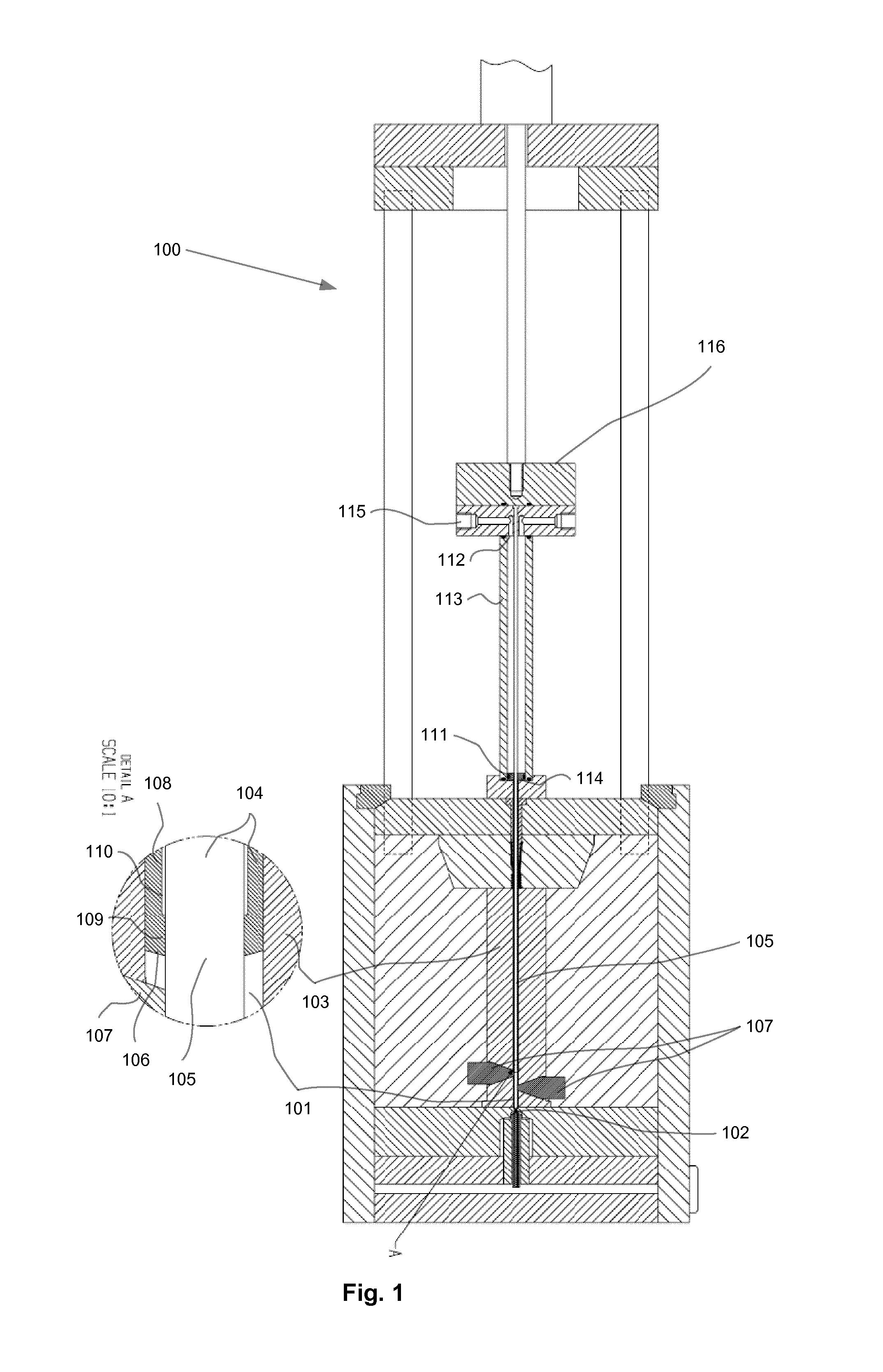

ActiveUS20150051587A1Increase cavity volumeMitigate, alleviate or eliminate one or moreWound drainsMedical devicesUrinary catheterCavity wall

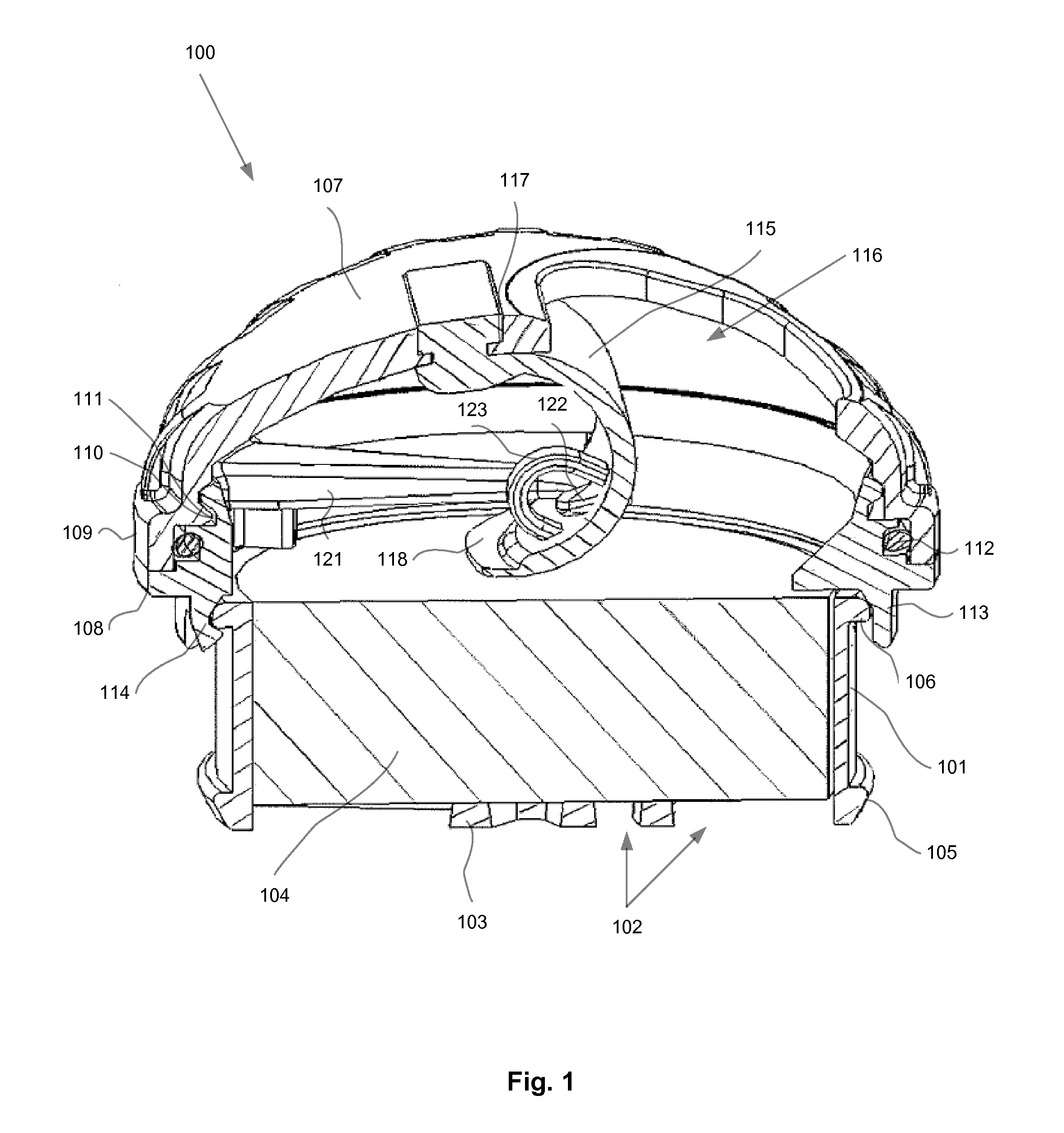

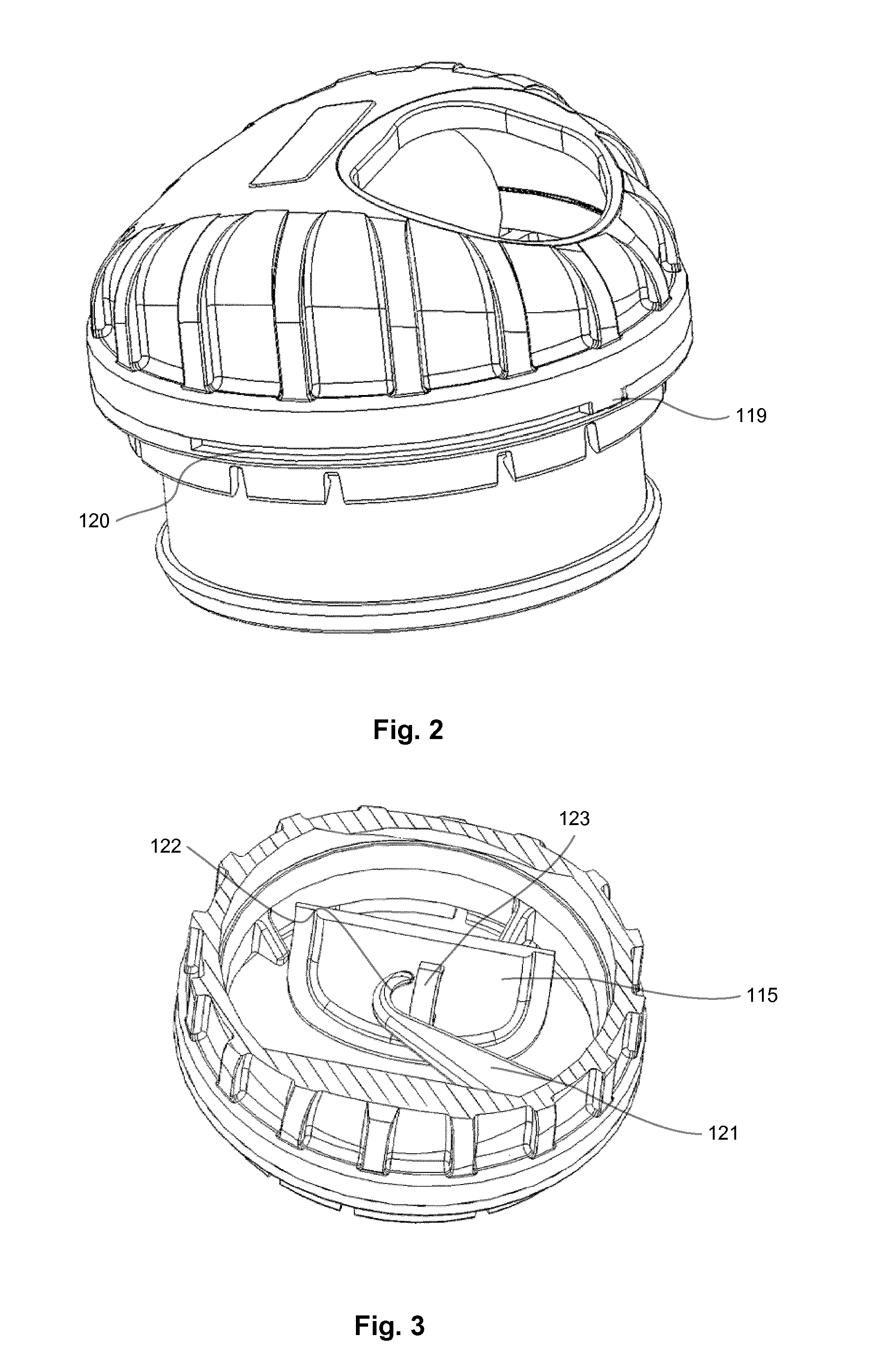

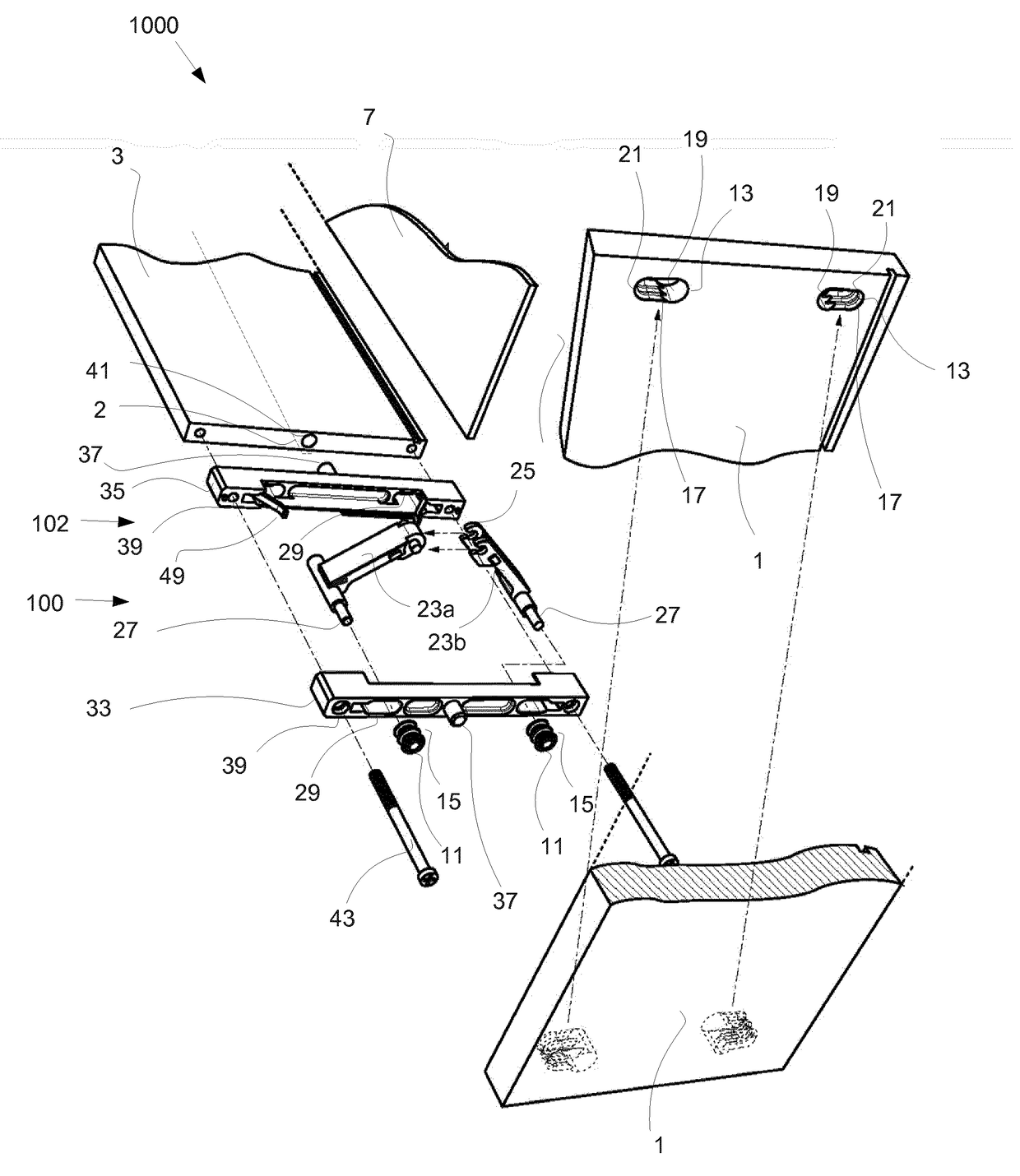

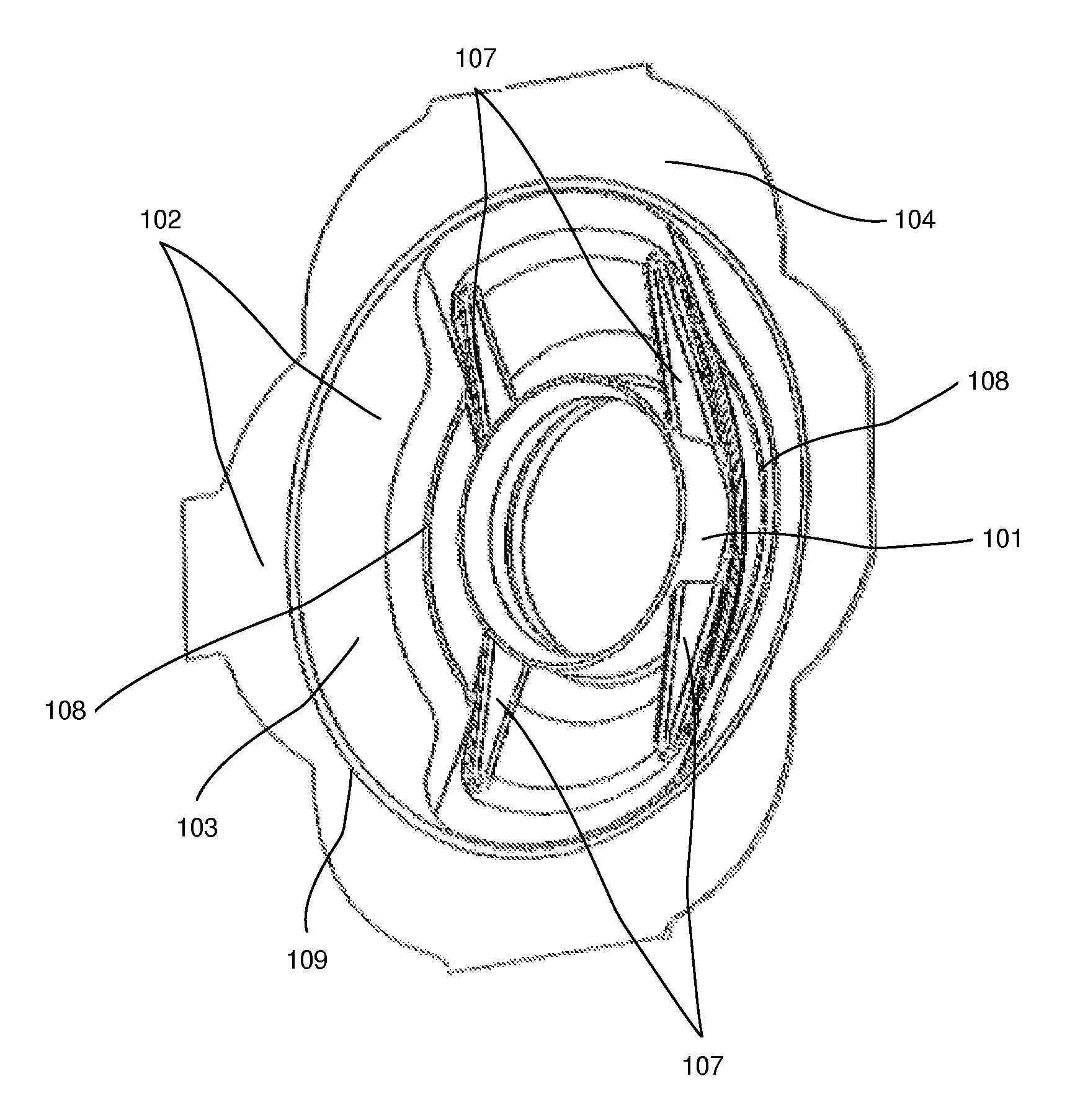

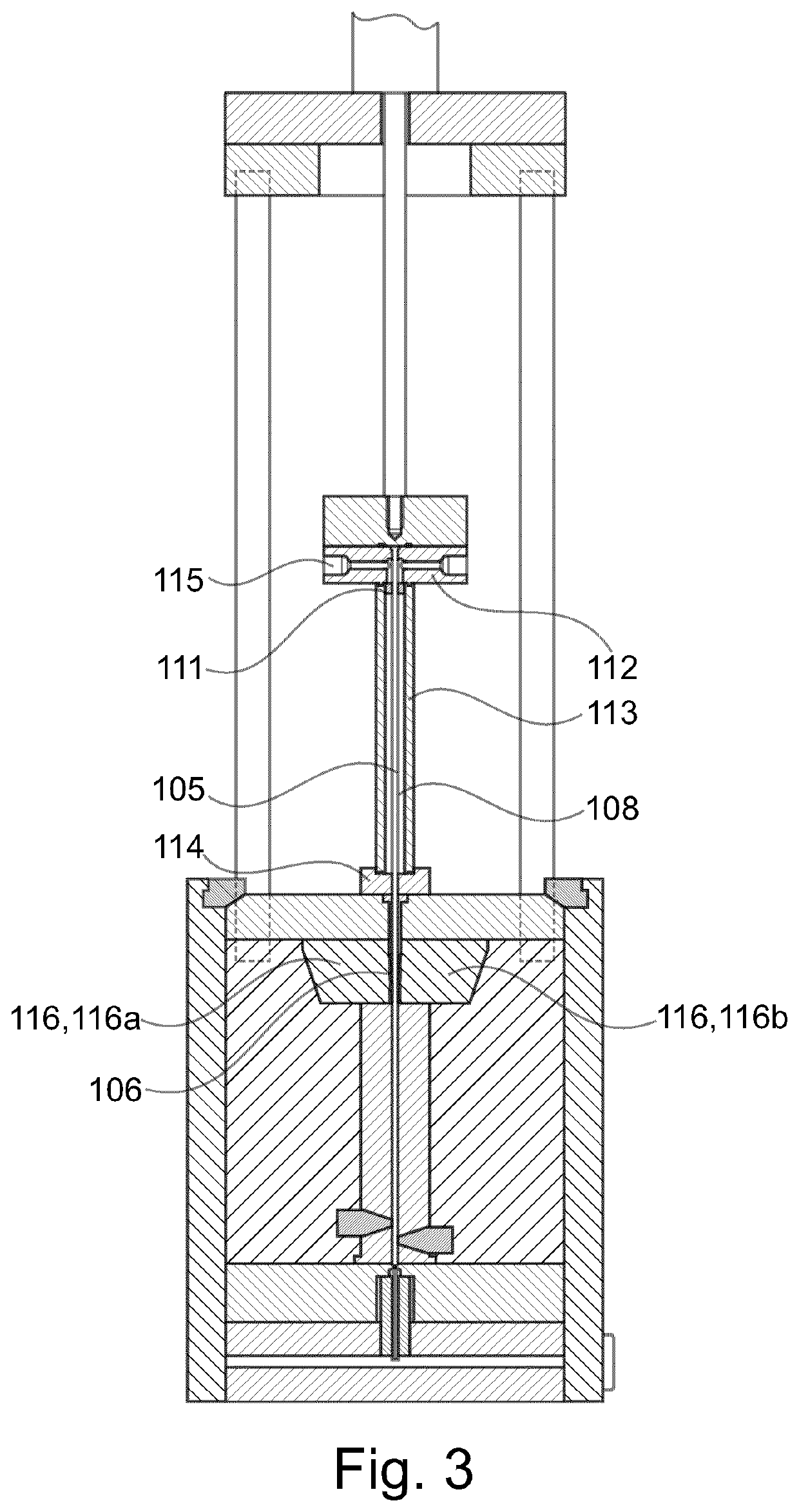

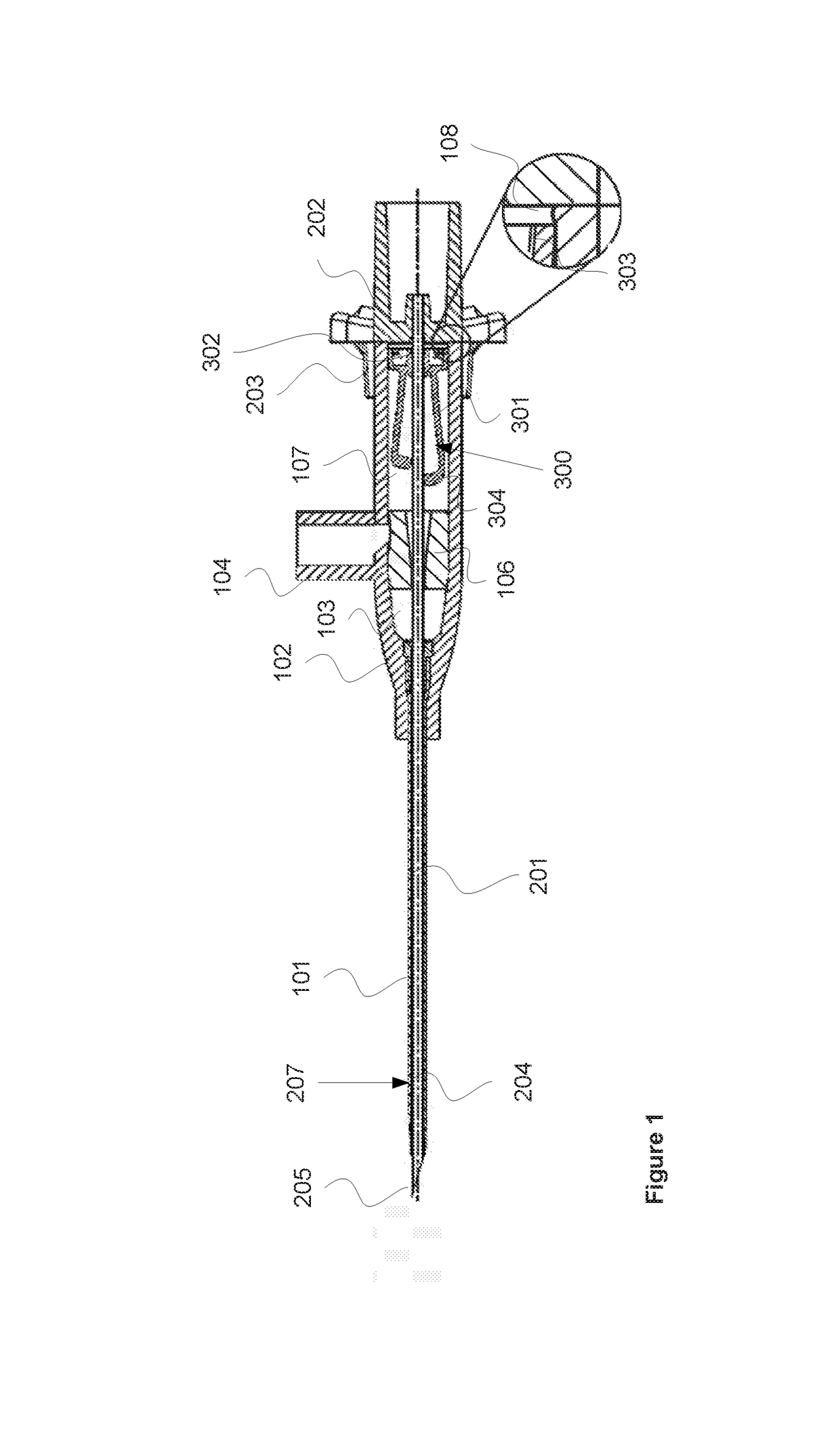

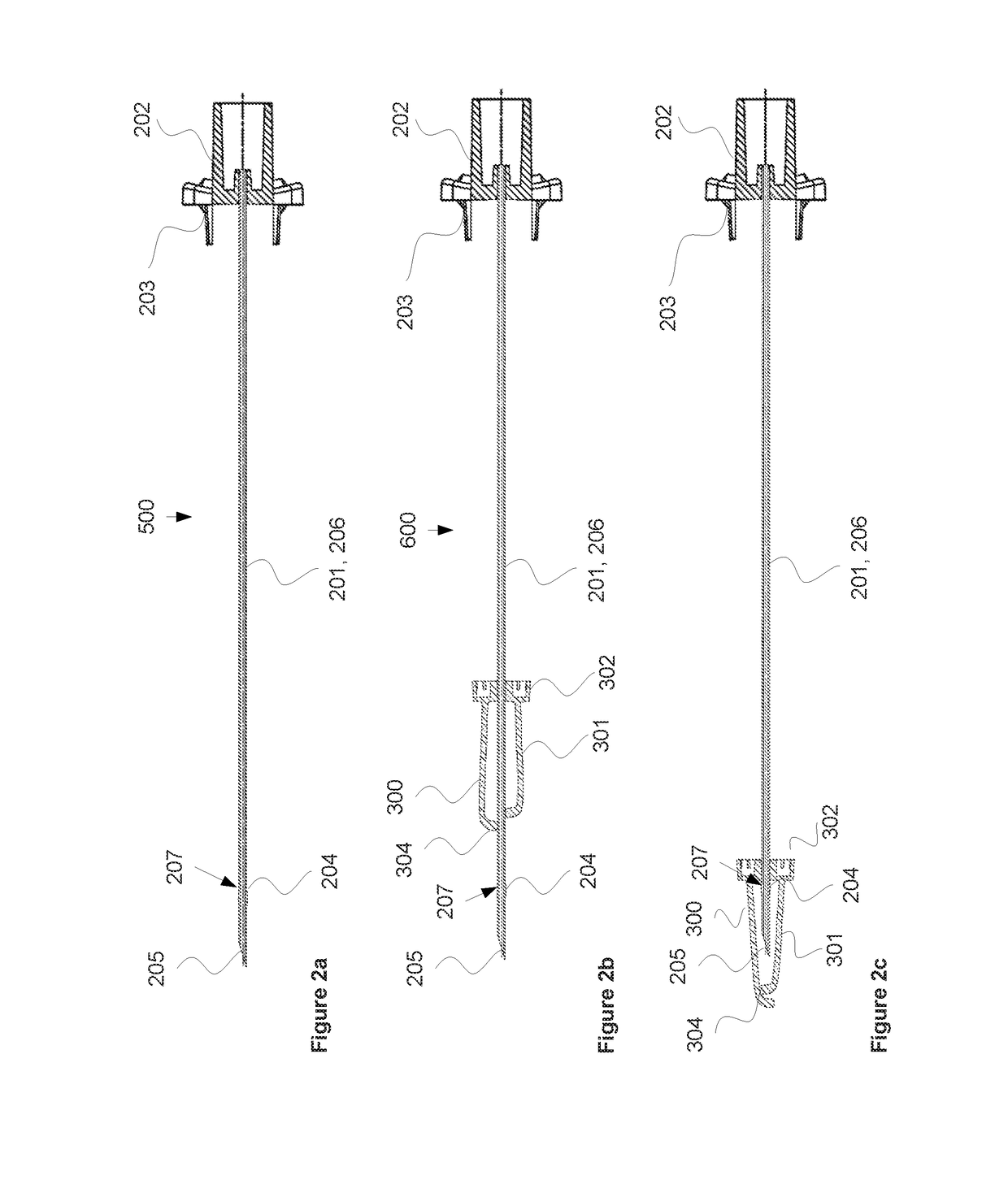

A method for manufacturing an elongated element (200) is provided. The method comprises arranging a molding cavity (101), defined by a mold (103) and a mold insert (104), said mold insert (104) comprising a mold core (105) and a displaceable mold cavity wall (106), said displaceable mold cavity wall (106) being arranged between the mold (103) and the mold core (105), such that the molding cavity has a start volume in a start position of the displaceable mold cavity wall (106). Then a liquid material is injected into a proximal end (102) of the molding cavity (101), where after the displaceable mold cavity wall (106) is displaced in relation to and along with the mold (103) and the mold core (105), distally during said injection, to increase the molding cavity volume from the start volume into an end volume at an end position of the displaceable mold cavity wall (106), wherein the molding cavity (101) in said end position of the displaceable mold cavity wall (106) corresponds to the elongated element (200). The liquid material is solidified, such that the elongated element (200) is formed, and the elongated element (200) and mold insert (104) is removed from said mold (103), where after the elongated element (200) is removed from said mold insert (104). An elongated element and a mold assembly for the manufacture thereof are also provided.

Owner:COLOPLAST AS

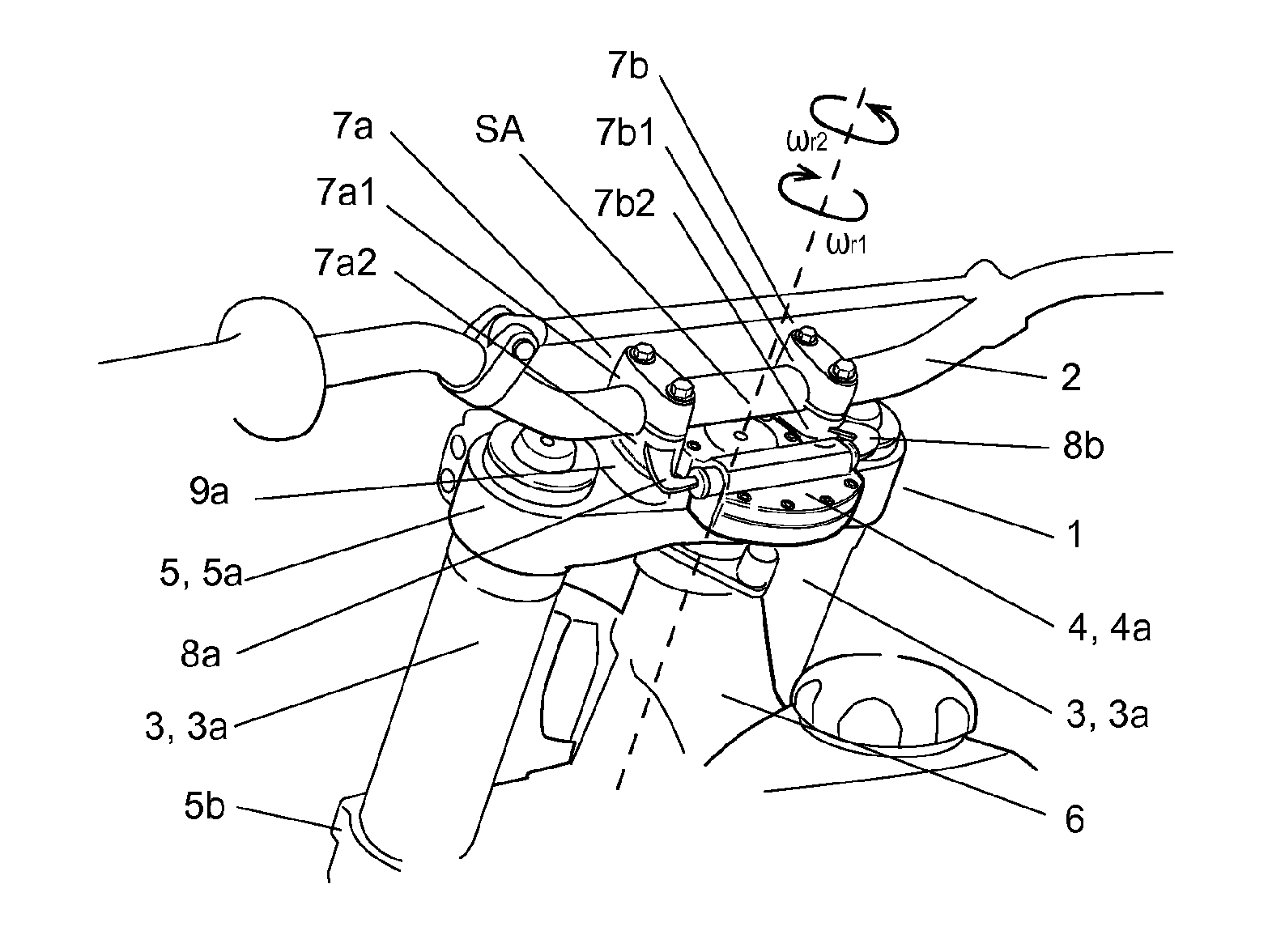

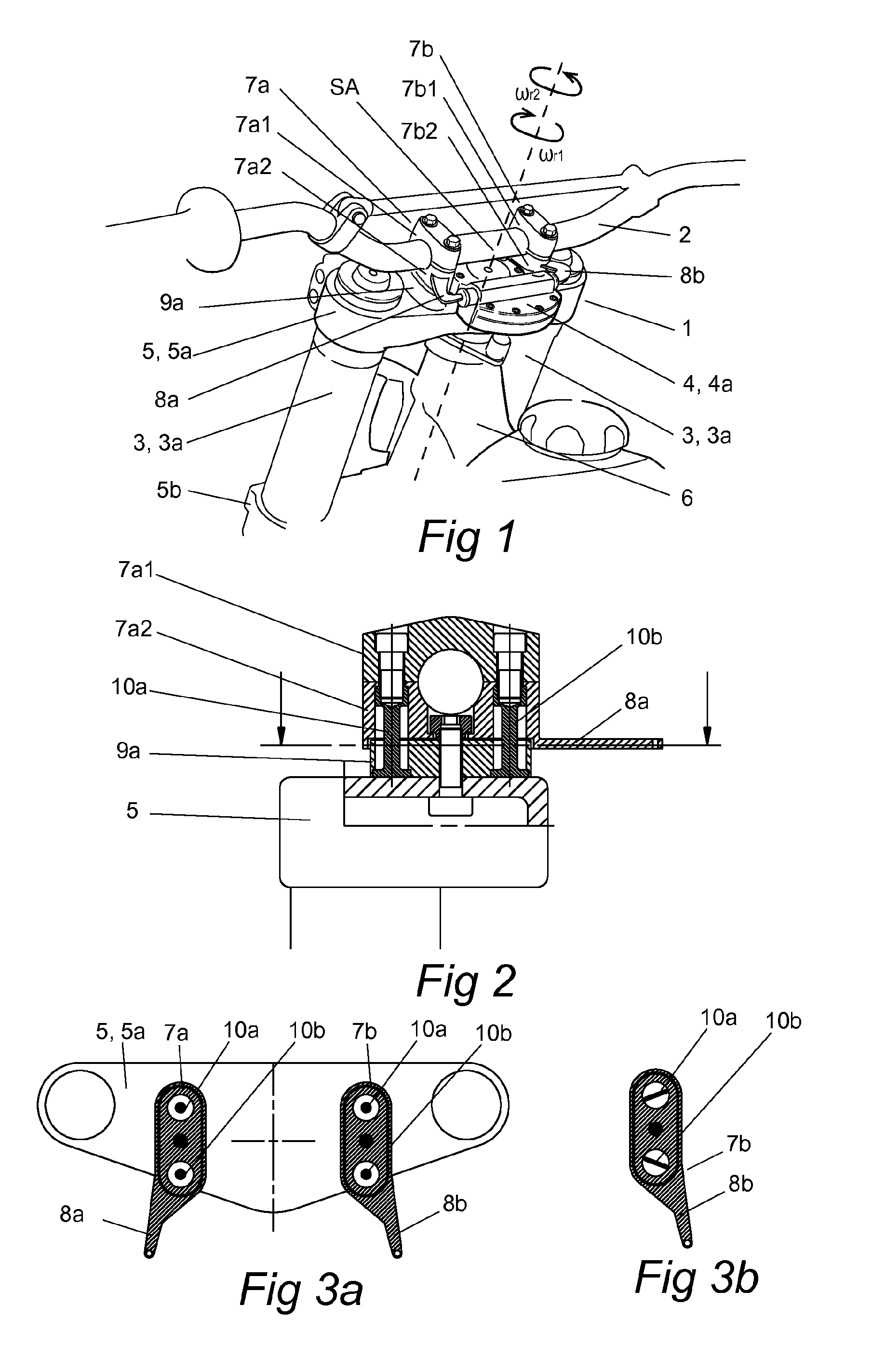

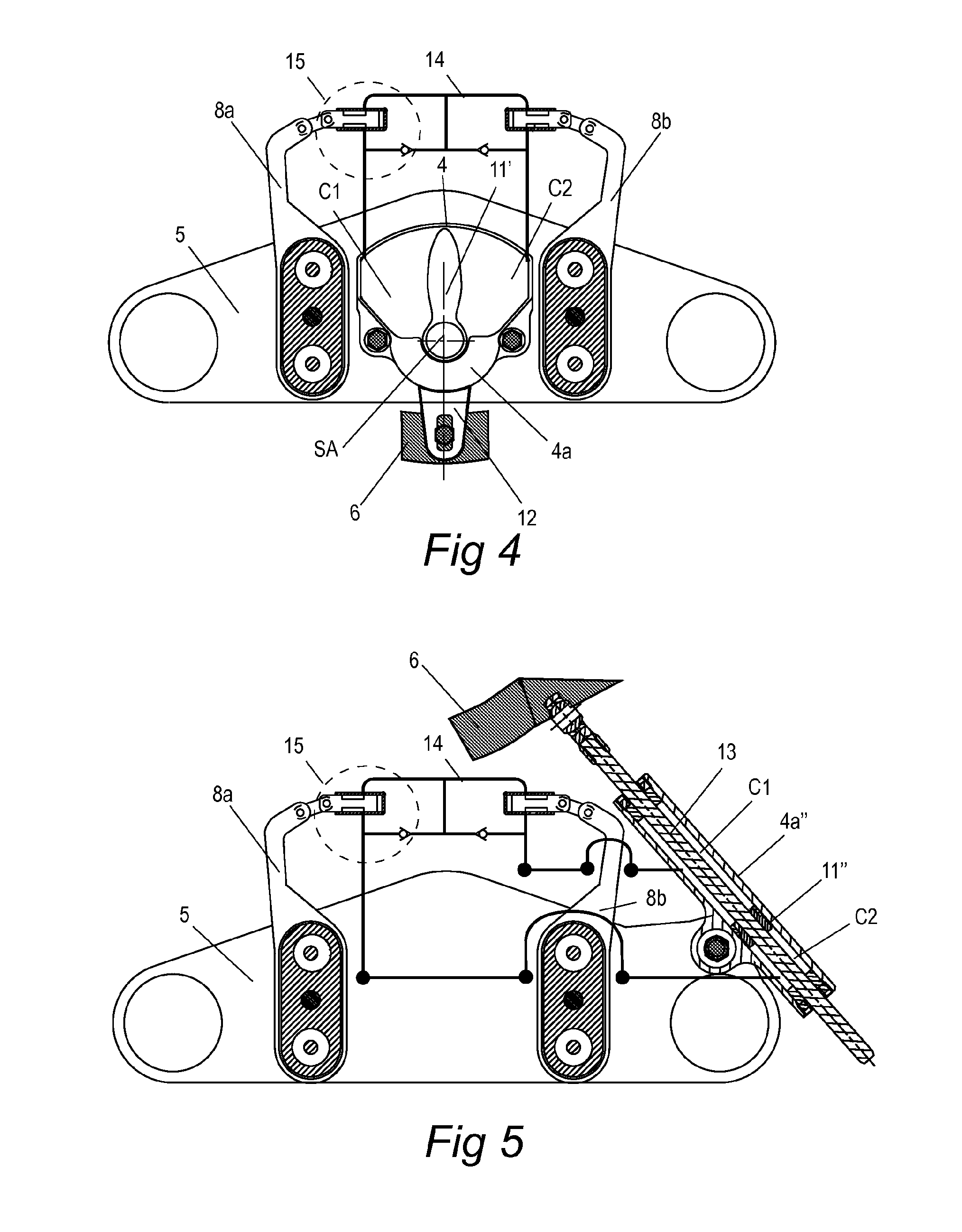

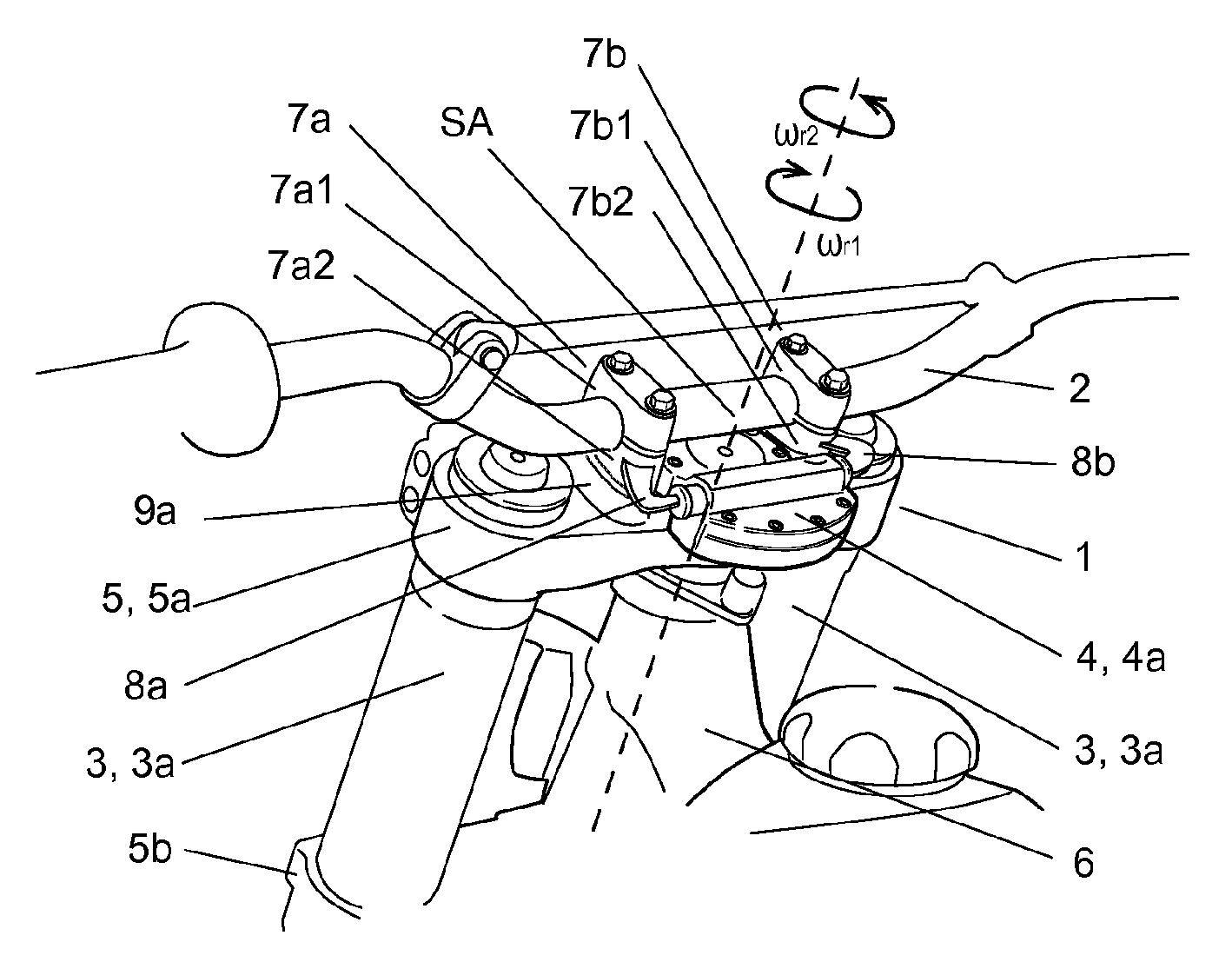

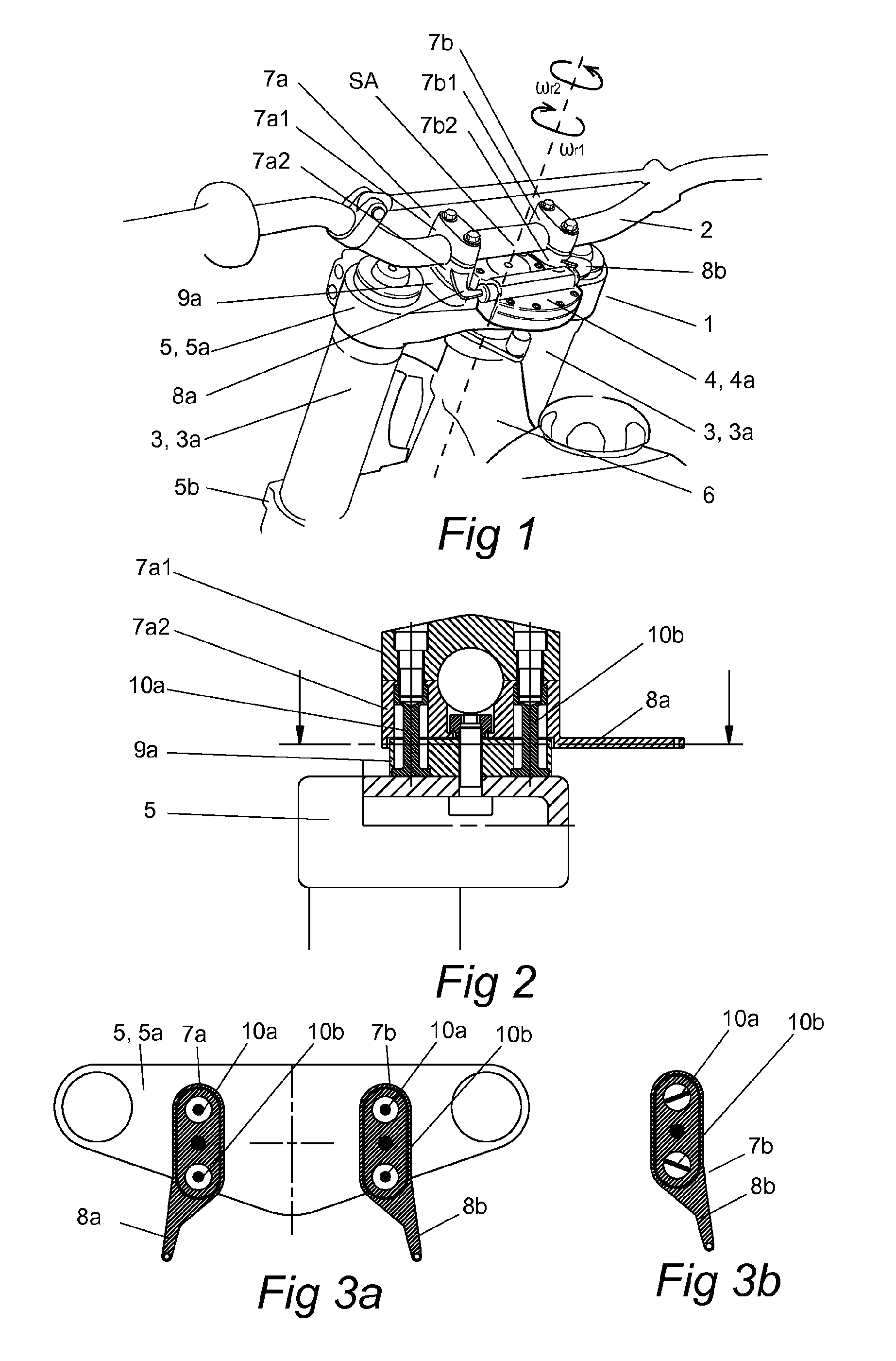

Steering damper with active adjustment of damping characteristics

ActiveUS20140249720A1Mitigates and/or alleviatesRobust and reliable methodDigital data processing detailsAutomatic steering controlRelative motionHydraulic fluid

A device adjusts the rotational damping of a steering device such that the rotational damping varies depending on whether the rotational motion about a steering axis is caused by a force acting on the steering device of the vehicle or a force acting on the part(s) of the vehicle contacting the ground. The flow of hydraulic fluid in the steering damper partly or wholly is adjusted by a main valve unit that is coupled together with both an attaching part and a steering device. The opening area of the main valve unit is determined by a relative motion between the attaching part and the steering device such that the flow of the hydraulic fluid in a direction from and to the respective damping chambers of the steering damper is controlled depending on the cause of the rotational movement.

Owner:OHLINS

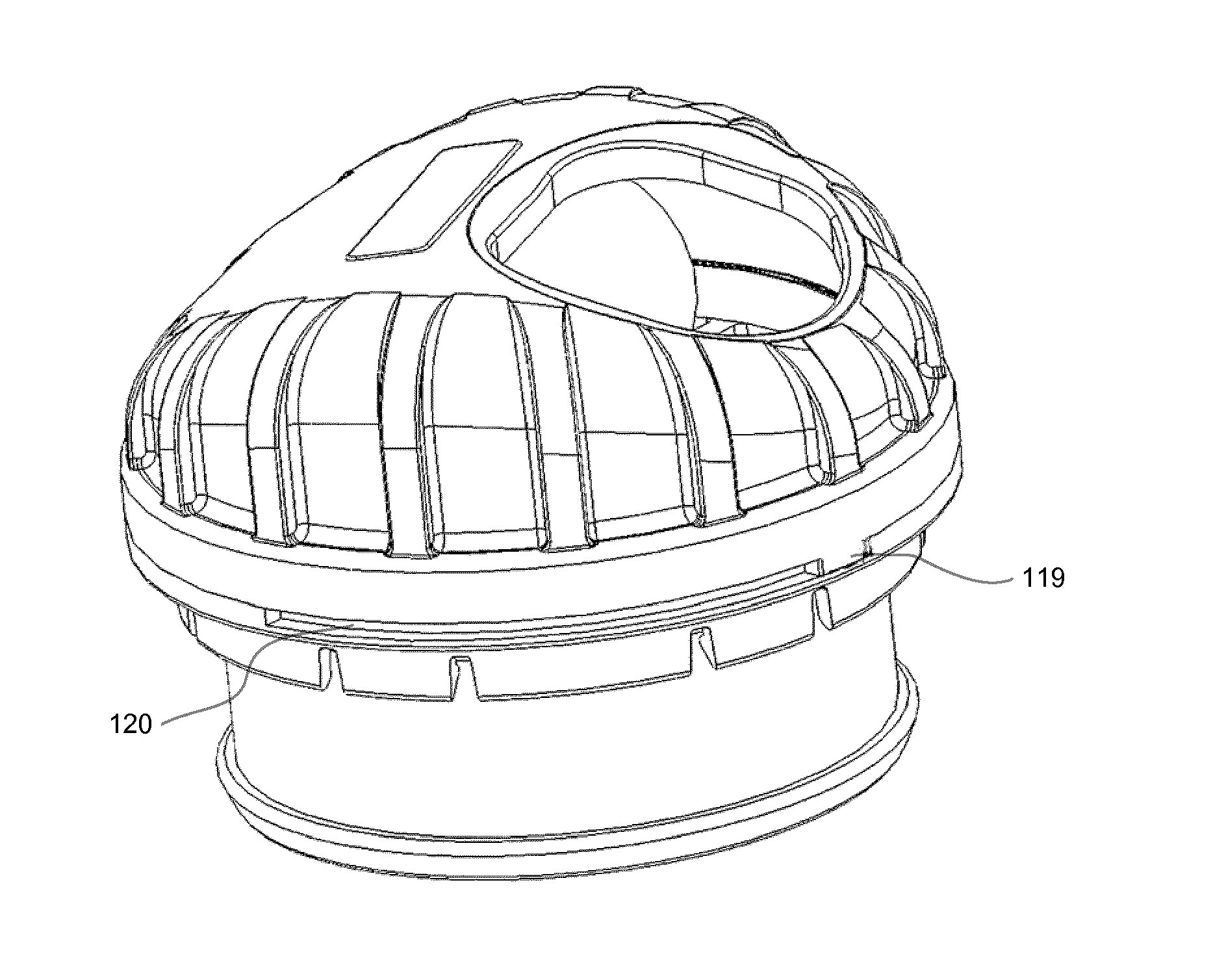

Tracheostoma valve

ActiveUS20150083119A1Mitigate, alleviate or eliminate one or moreTracheal tubesBreathing masksMedicineExhaled air

A tracheostoma valve for attachment to a tracheostoma valve plaster may include a tubular base portion with a proximal opening through which inhaled and exhaled air enters and exits, respectively. A distal lid portion may be arranged distally of the tubular base portion. The distal lid portion may have a distal opening through which inhaled and exhaled air enters and exits, respectively. The tracheostoma valve may have a valve flap member for closing the distal opening via interaction between a front side of the valve flap member and an edge of the distal opening. A valve retaining arm may be included for interaction with the valve flap member to prevent the valve flap member from interacting with the distal opening.

Owner:COLOPLAST AS

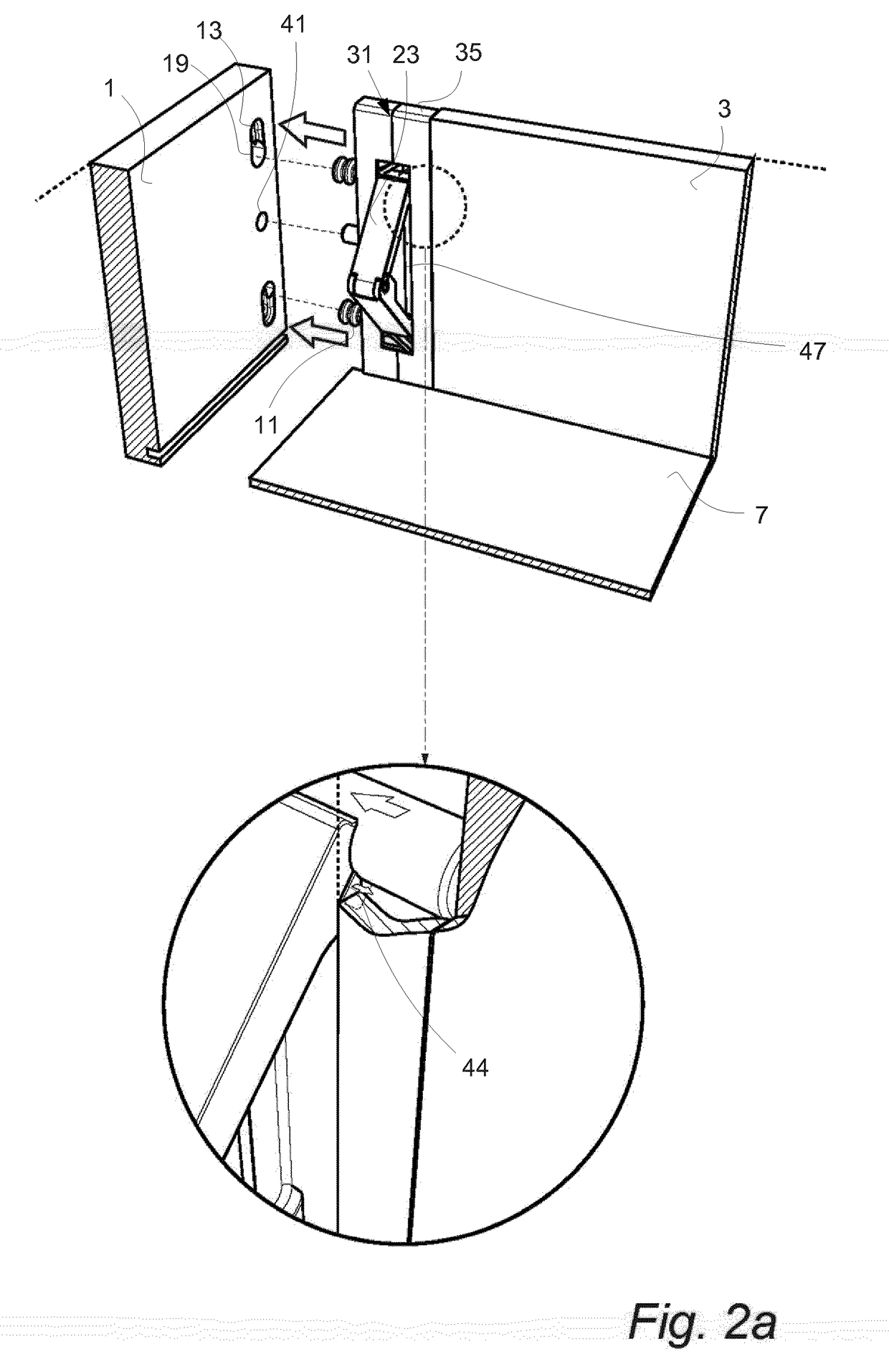

Fastening device for a furniture panel

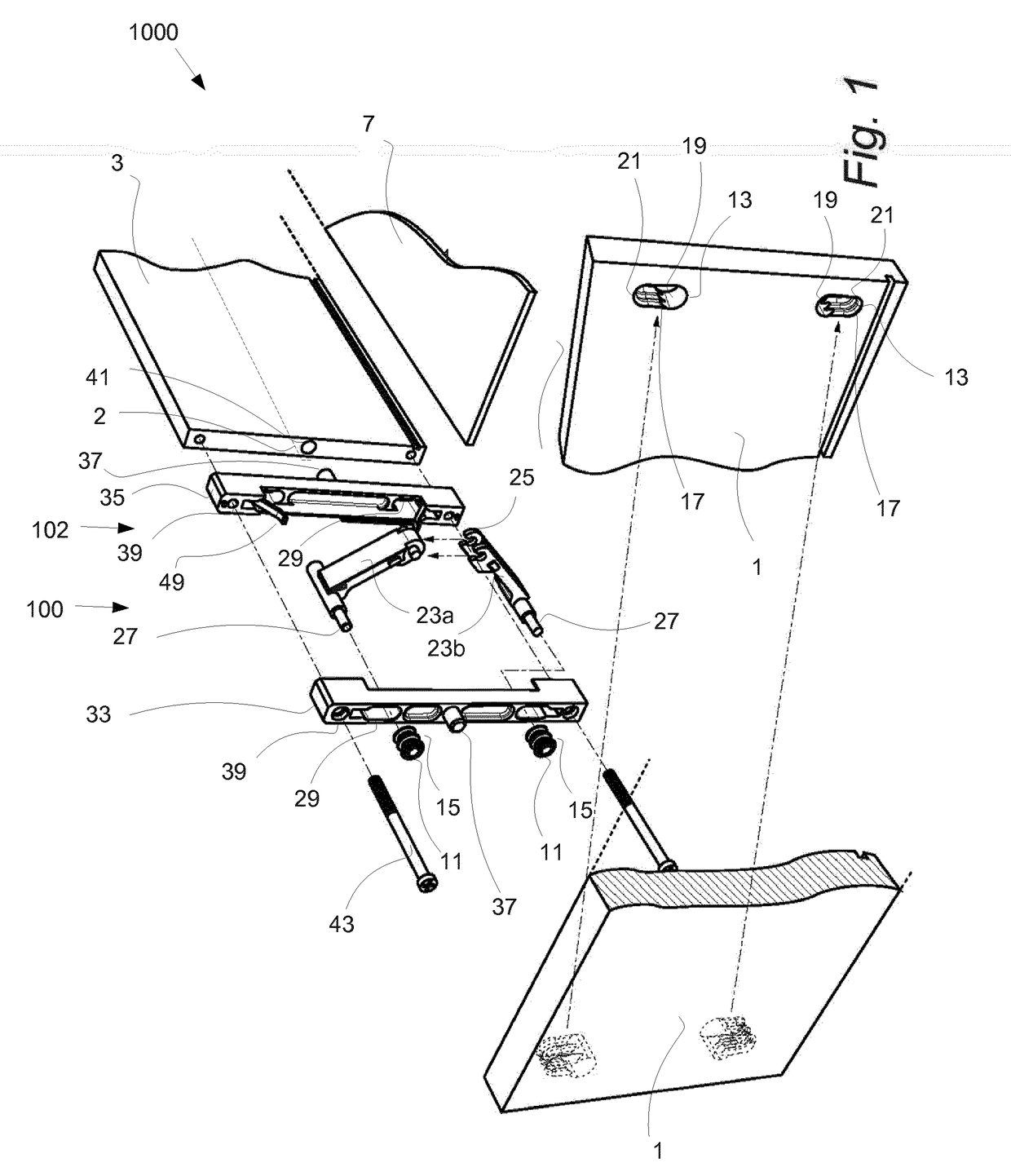

ActiveUS20180017091A1Mitigate, alleviate or eliminate one or moreDrawersFurniture joiningEngineeringHinge joint

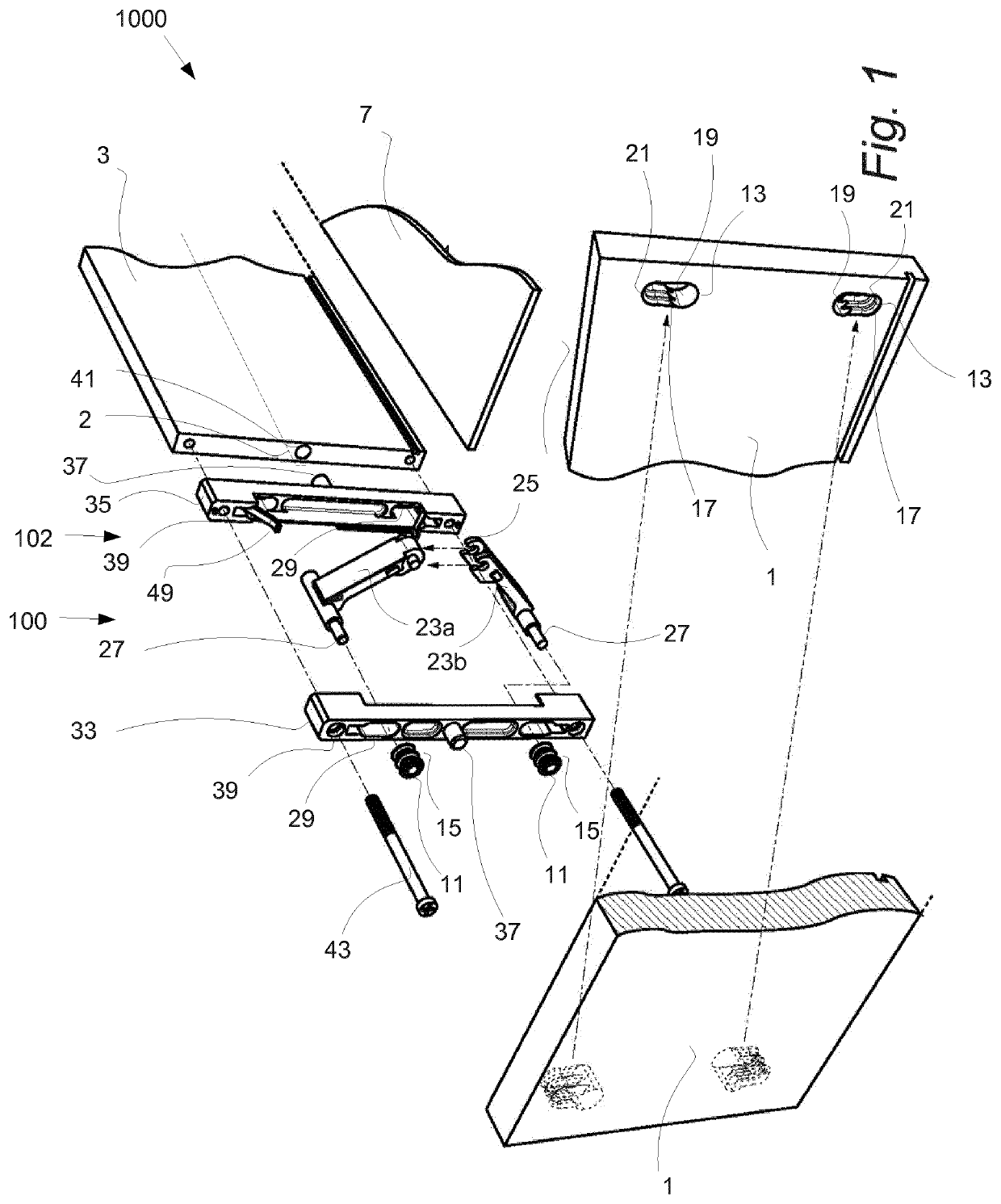

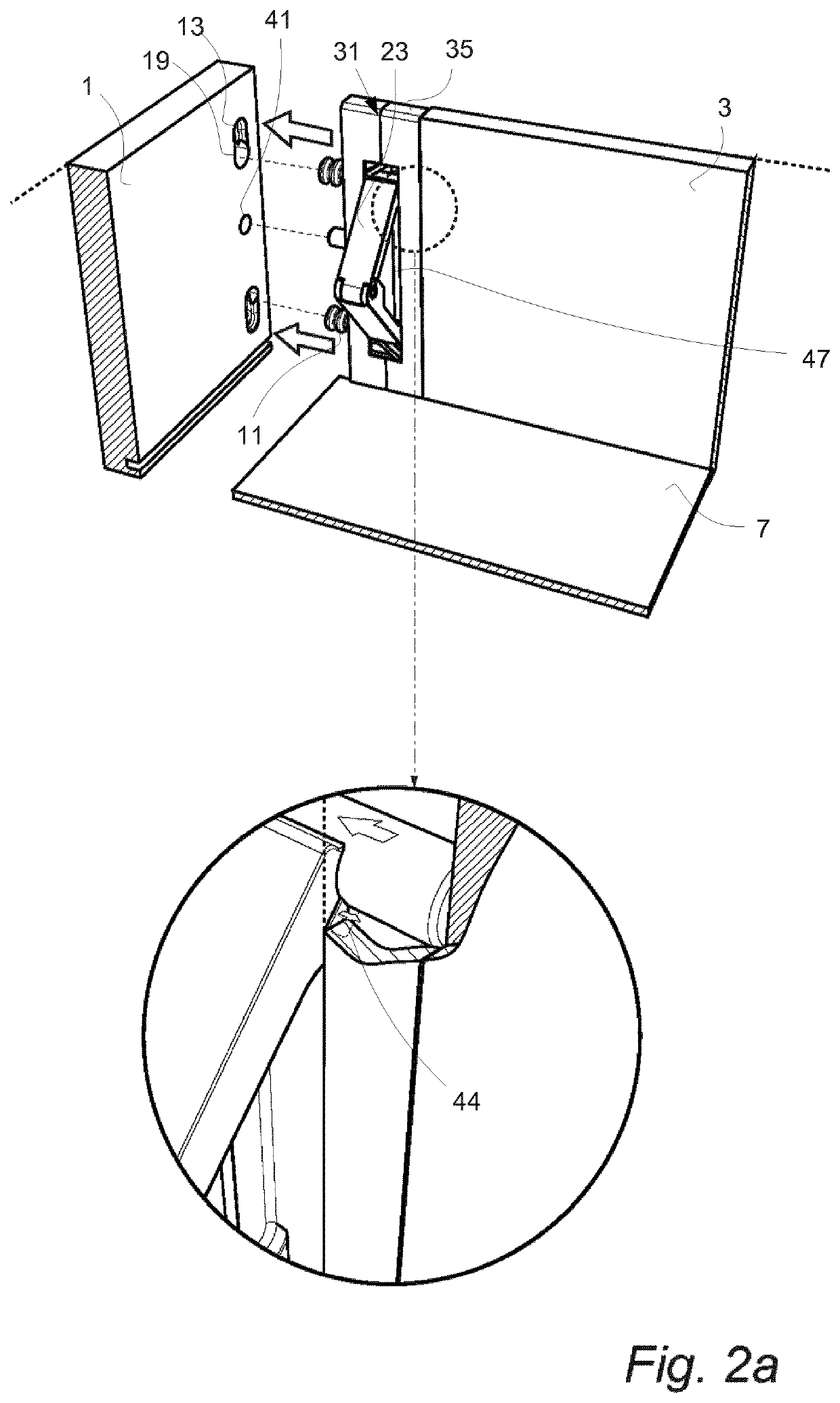

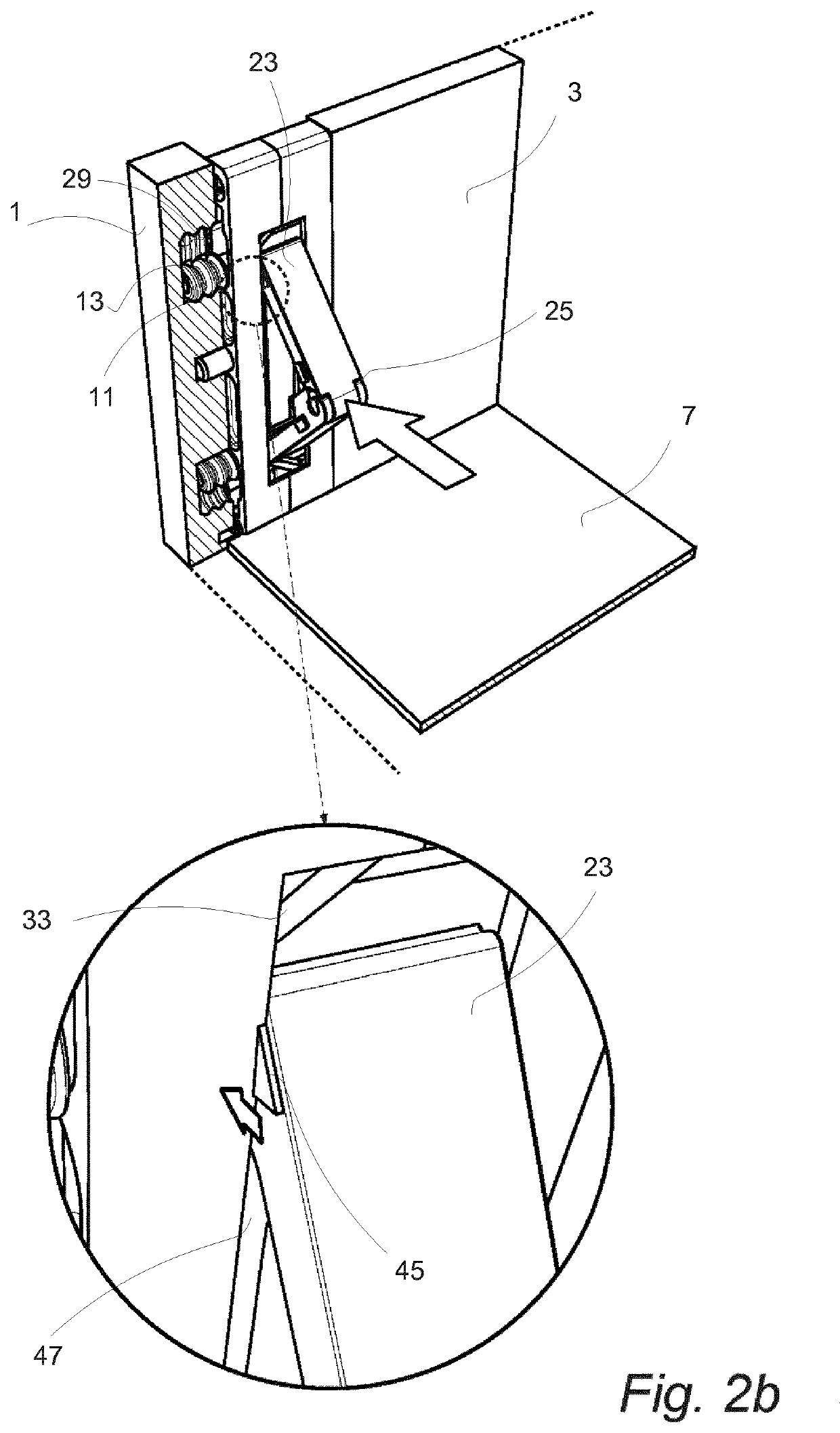

The present invention relates to a fastening device for fastening to a furniture panel. The fastening device comprises at least two dowels for reception in furniture panel recesses. The dowels are each connected to lateral ends of lever arms. The lever arms are centrally connected to each other at a hinge joint. One dowel may be displaced in relation to the other dowel between a furniture panel fastening position and a furniture panel releasing position of the fastening device. A fastening system for joining furniture parts, comprising the fastening device, is also disclosed. A method for using the fastening system is described as well as furniture assemblies using the system.

Owner:INTER IKEA SYST

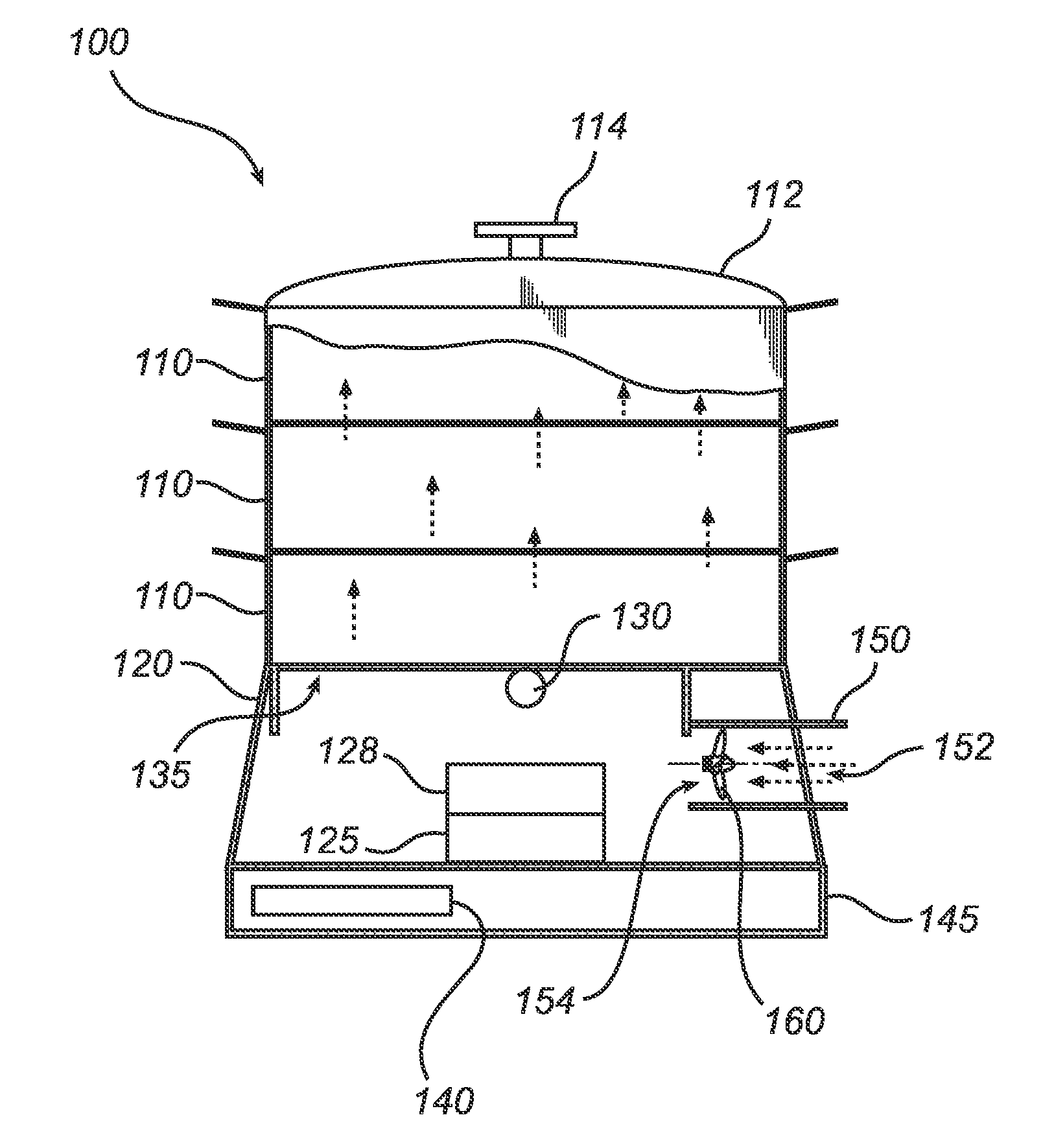

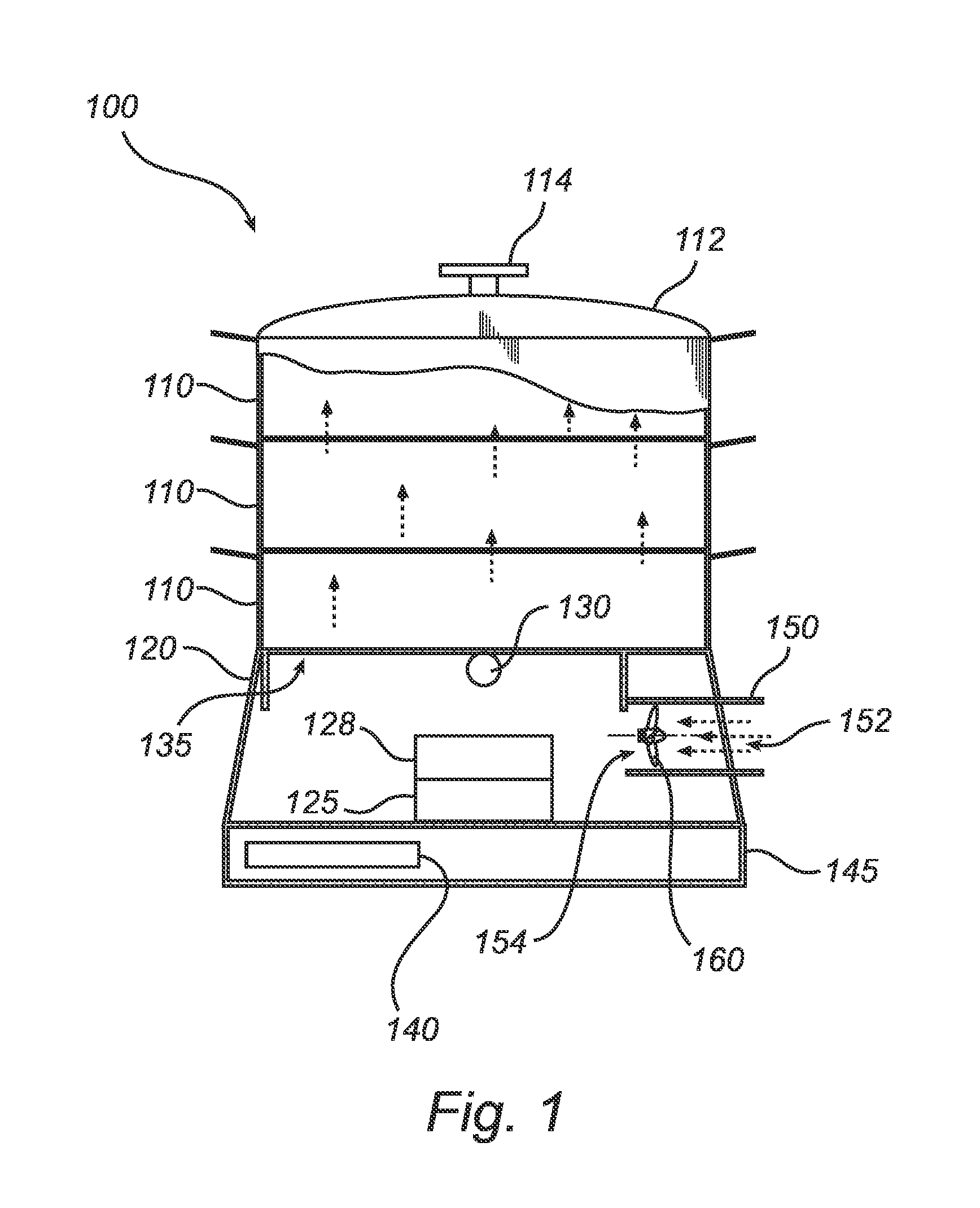

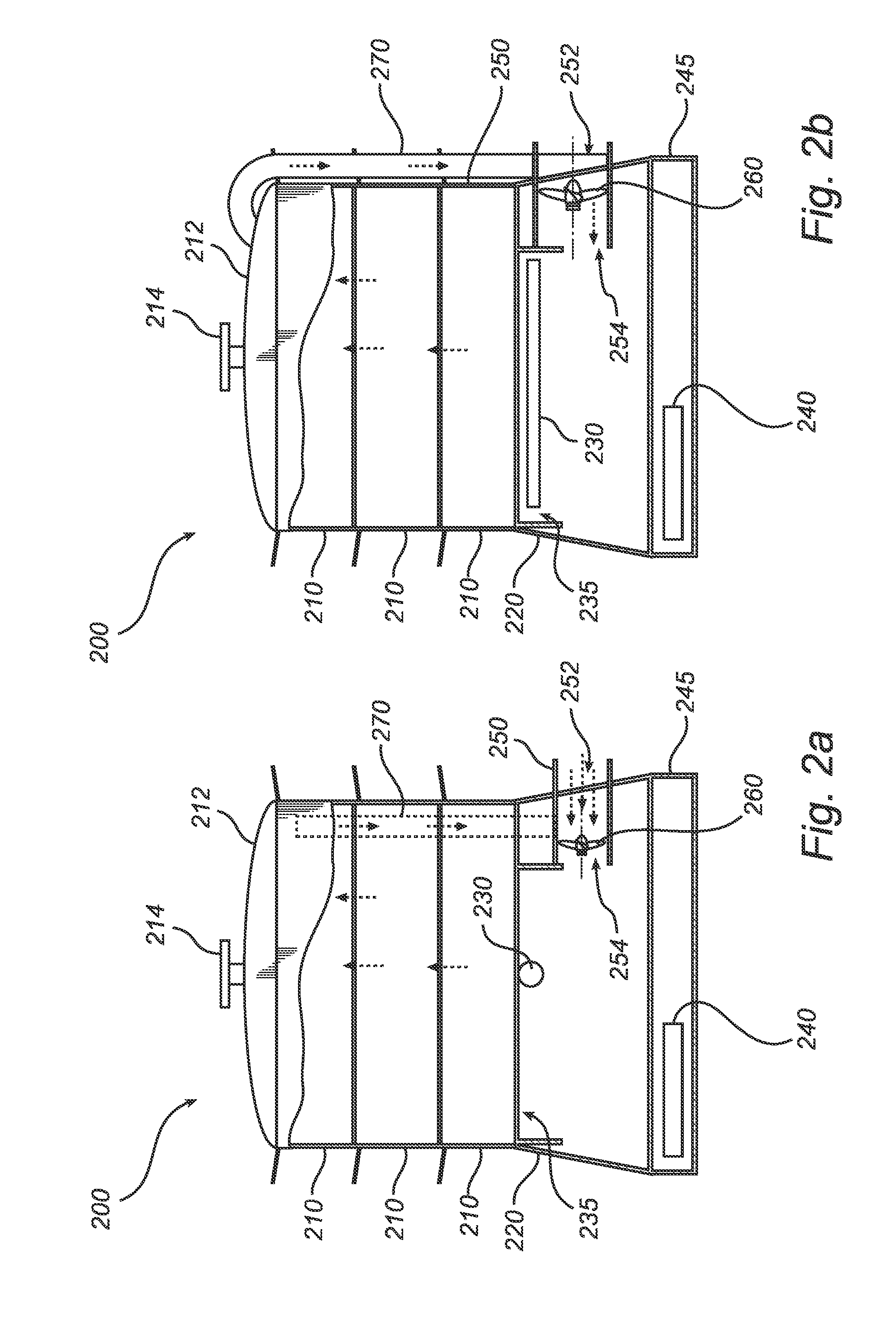

Device for steaming food

InactiveUS20120247342A1Reduce energy consumptionQuick compensationSteam cooking vesselsDeep fat fryersEngineeringProcess engineering

A device (100) for heating a food is disclosed. The device (100) comprises at least one heating chamber (110) and a variable-power steam-generating unit (120) configured to generate steam. The variable-power steam-generating unit (120) is fluidly connected with at least one heating chamber (110). On basis of difference between temperature sensed in the device (100) and a predetermined temperature, power of the variable-power steam-generating unit (120) can be adjusted such as to enable attaining a desired heating temperature in the heating process of the device (100).

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

Light system for emphasizing objects

InactiveUS20130169796A1Enhancing and suppressing appearanceMitigate, alleviate or eliminate one or moreElectroluminescent light sourcesColor television detailsEngineeringLighting system

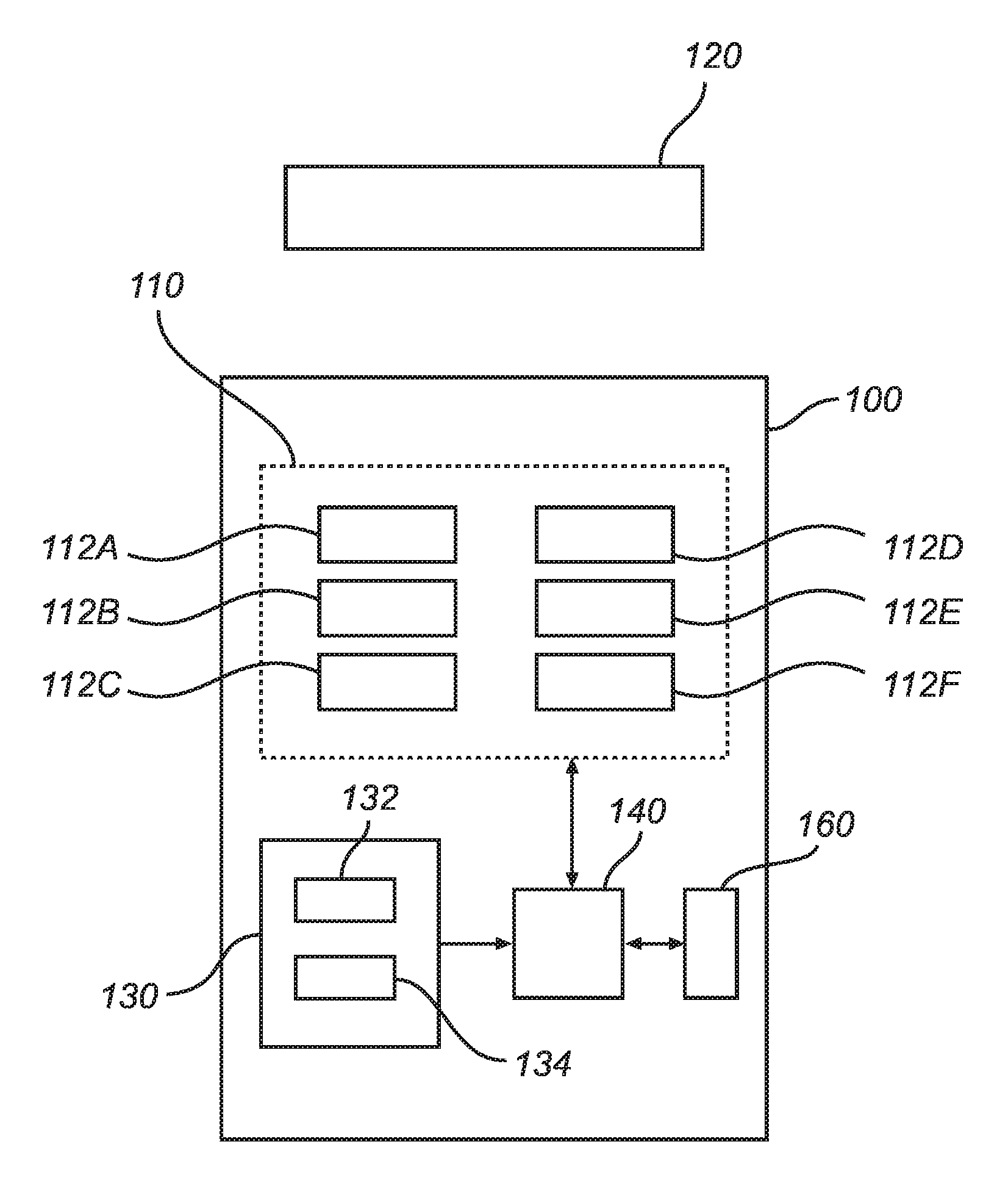

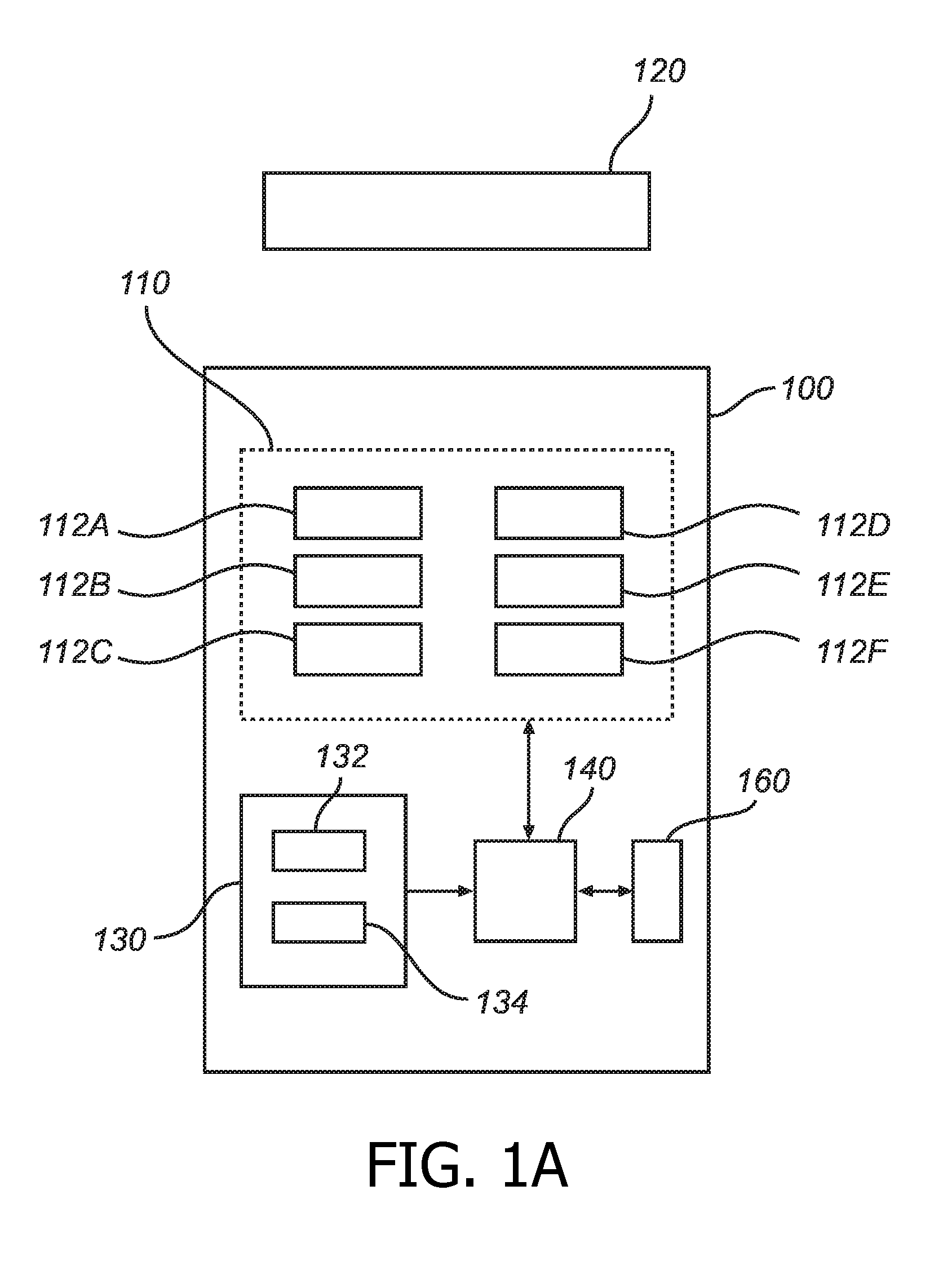

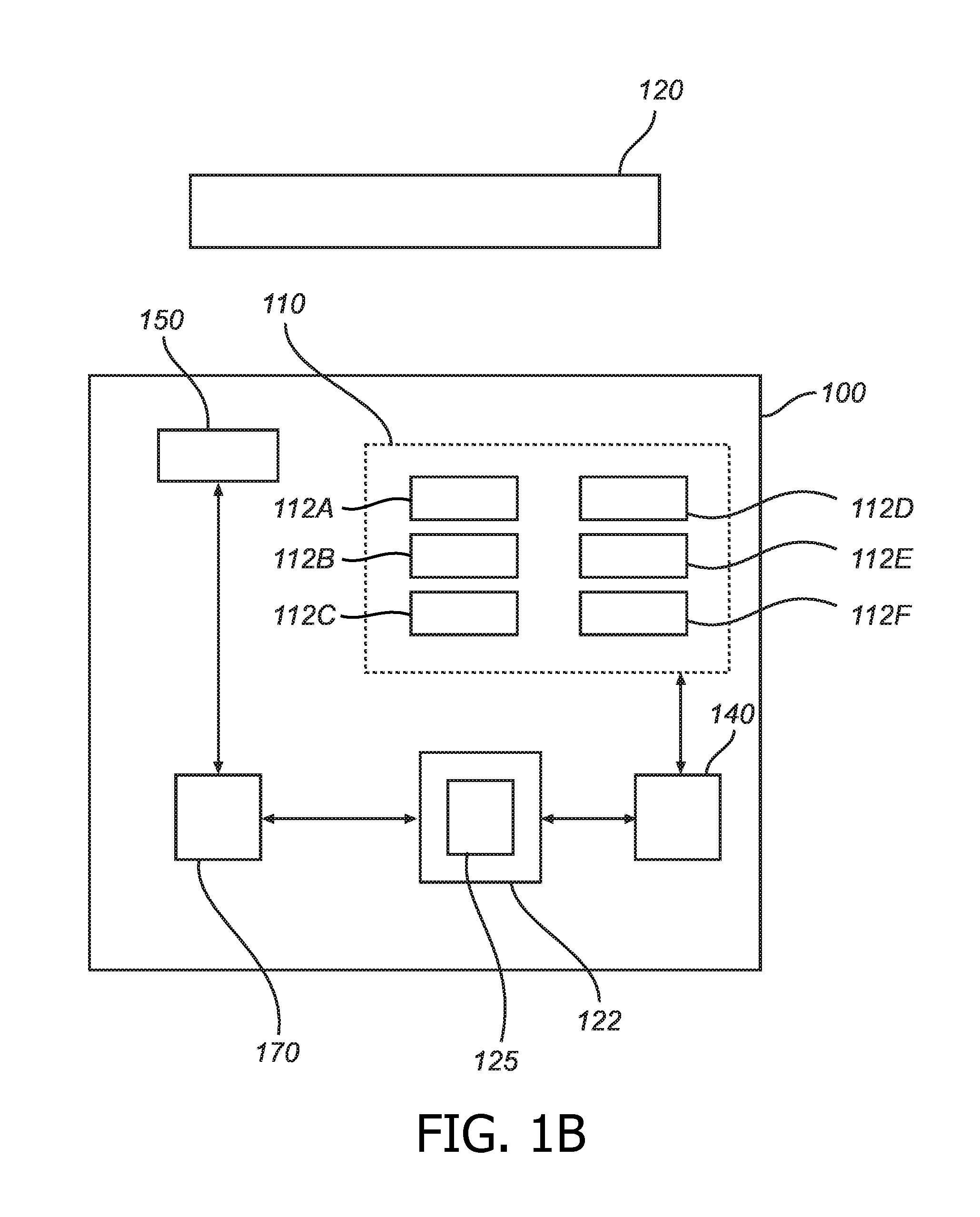

Light-emitting devices (100) and methods for operating light-emitting devices are disclosed. Each of the light-emitting devices (100) comprises a plurality of light sources (112A-112F) for illuminating a target (120), wherein each of the light sources is configured to emit light within a predetermined color range. Each of the light-emitting devices comprises means (140) for automatically adjusting the spectral power distribution of light-emitted by the light-emitting device on basis of the color of the target or a region of the target illuminated by the light-emitting device, such that light emitted by the light-emitting device is made increasingly compliant or even compliant with a criteria of a predetermined color characteristics.

Owner:SIGNIFY HLDG BV

Tracheostoma plaster

ActiveUS20110247629A1Mitigate, alleviate or eliminate one or moreTracheal tubesRespiratory apparatusProximal pointMedicine

A device for holding a tracheostoma device over a tracheostoma of a patient including a passage having a distal and a proximal opening for receiving the tracheostoma device at the distal opening thereof. A flange may extend laterally, caudially, and cranially from the passage. The flange may have a proximal side facing the tracheostoma of the patient and a distal side facing outwardly from the patient. At least a part of said proximal side may include skin adhesive. The flange may have a higher moment of resistance in the caudal / cranial direction than in the lateral / medial direction for said device by having a higher moment of resistance in the caudal / cranial direction than in the lateral / medial direction for at least a part of said flange.

Owner:COLOPLAST AS

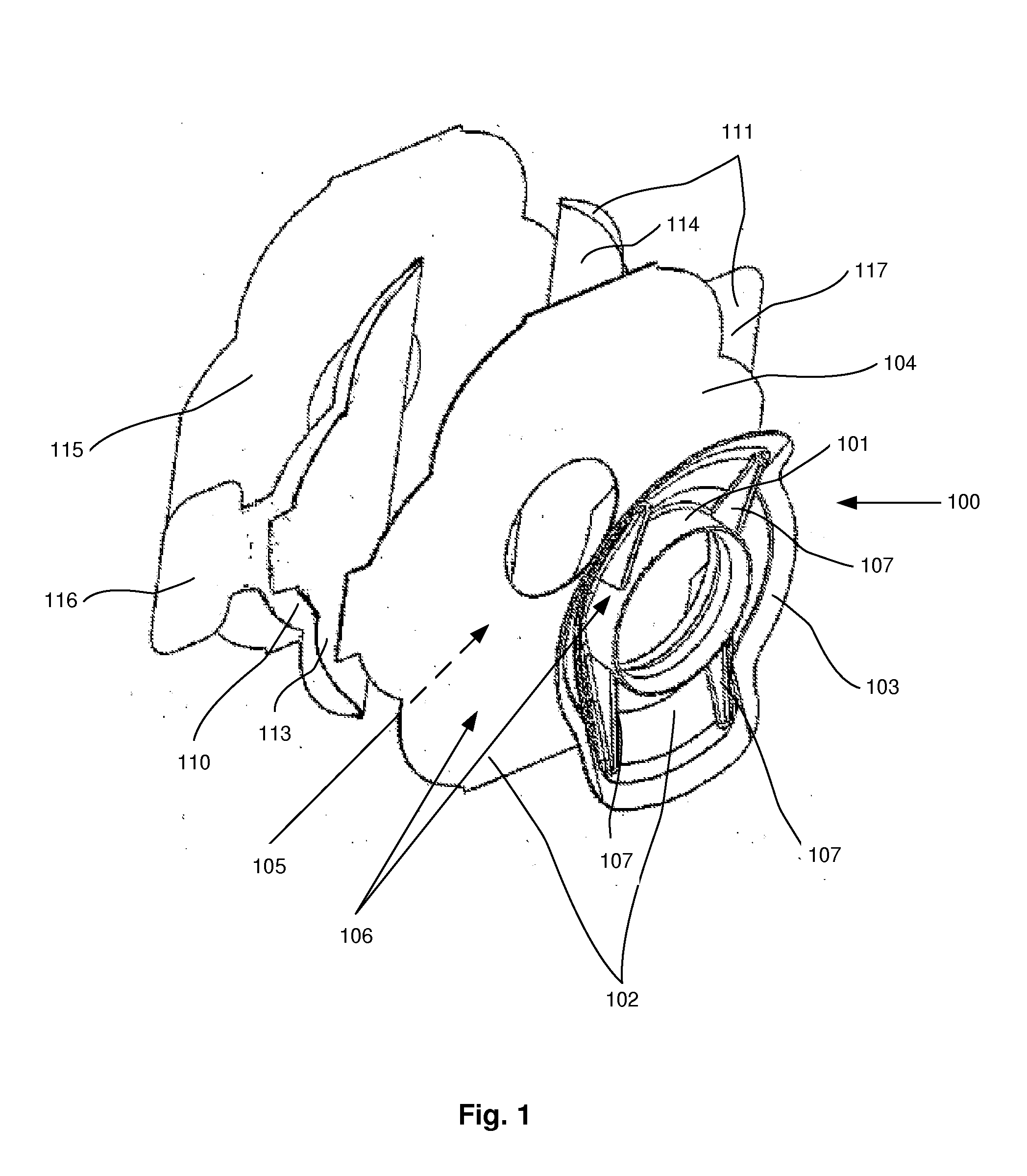

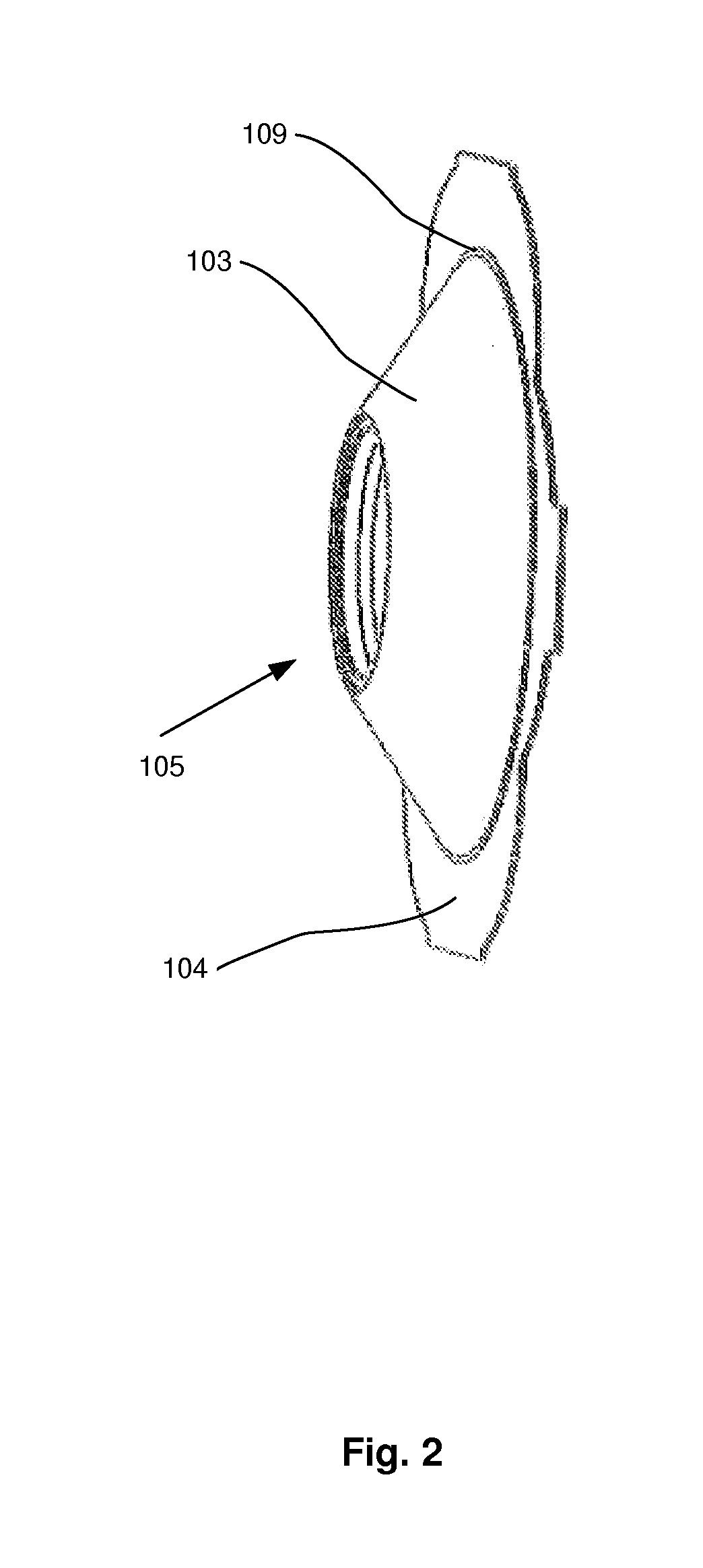

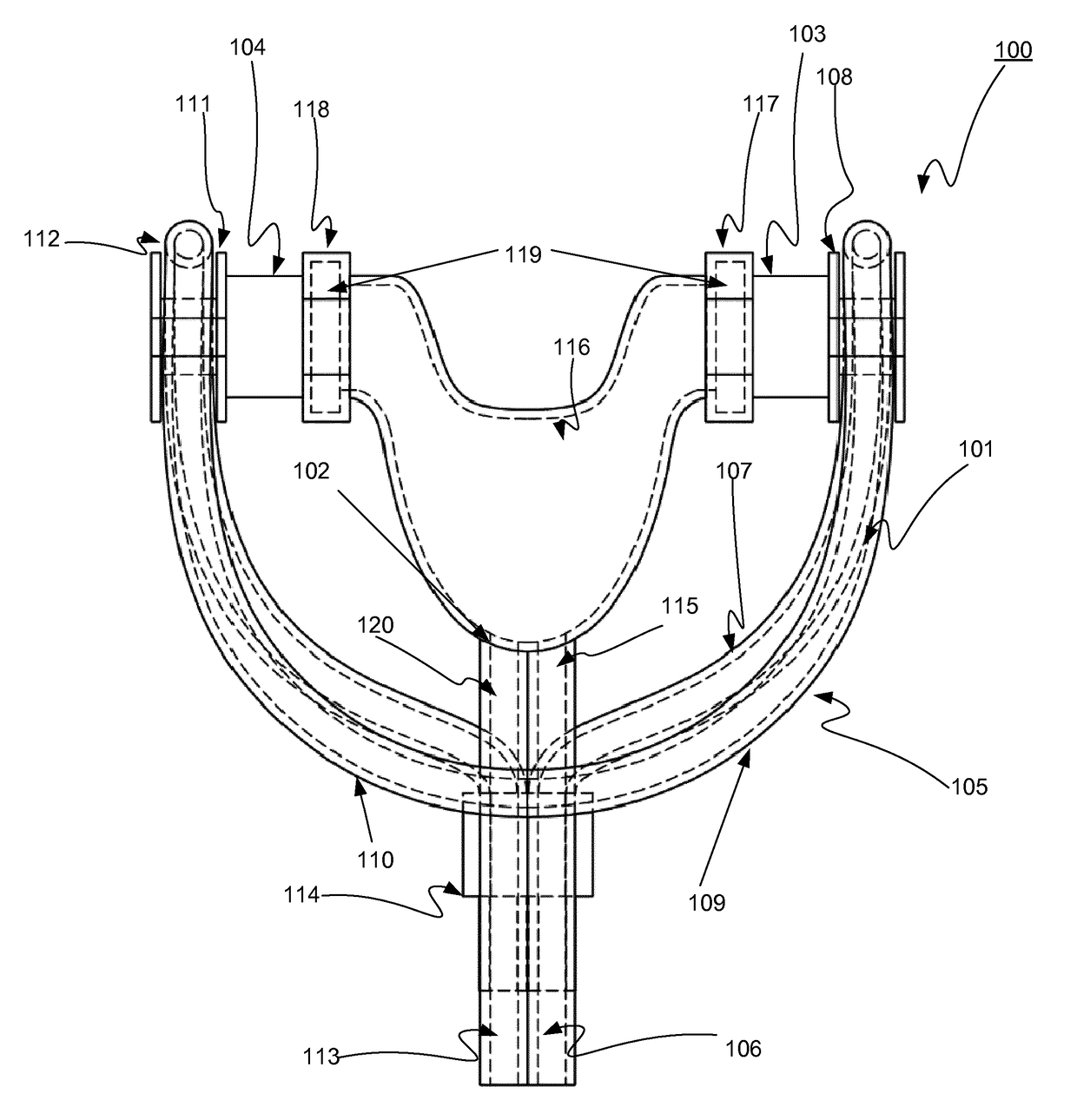

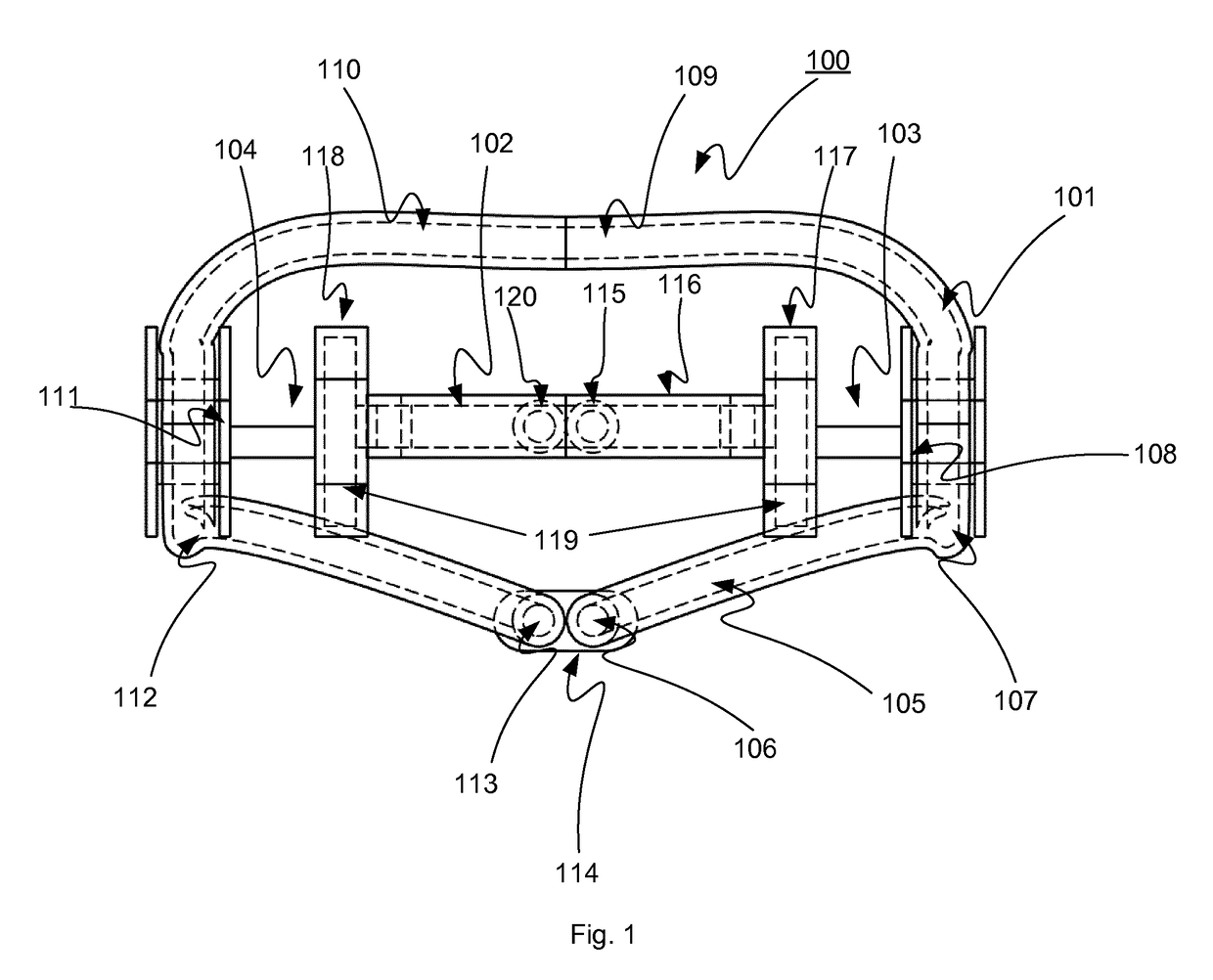

Mouth cooler

ActiveUS20170231815A1Mitigate, alleviate or eliminate one or moreRespiratorsAnaesthesiaOrthodonticsOral cavity

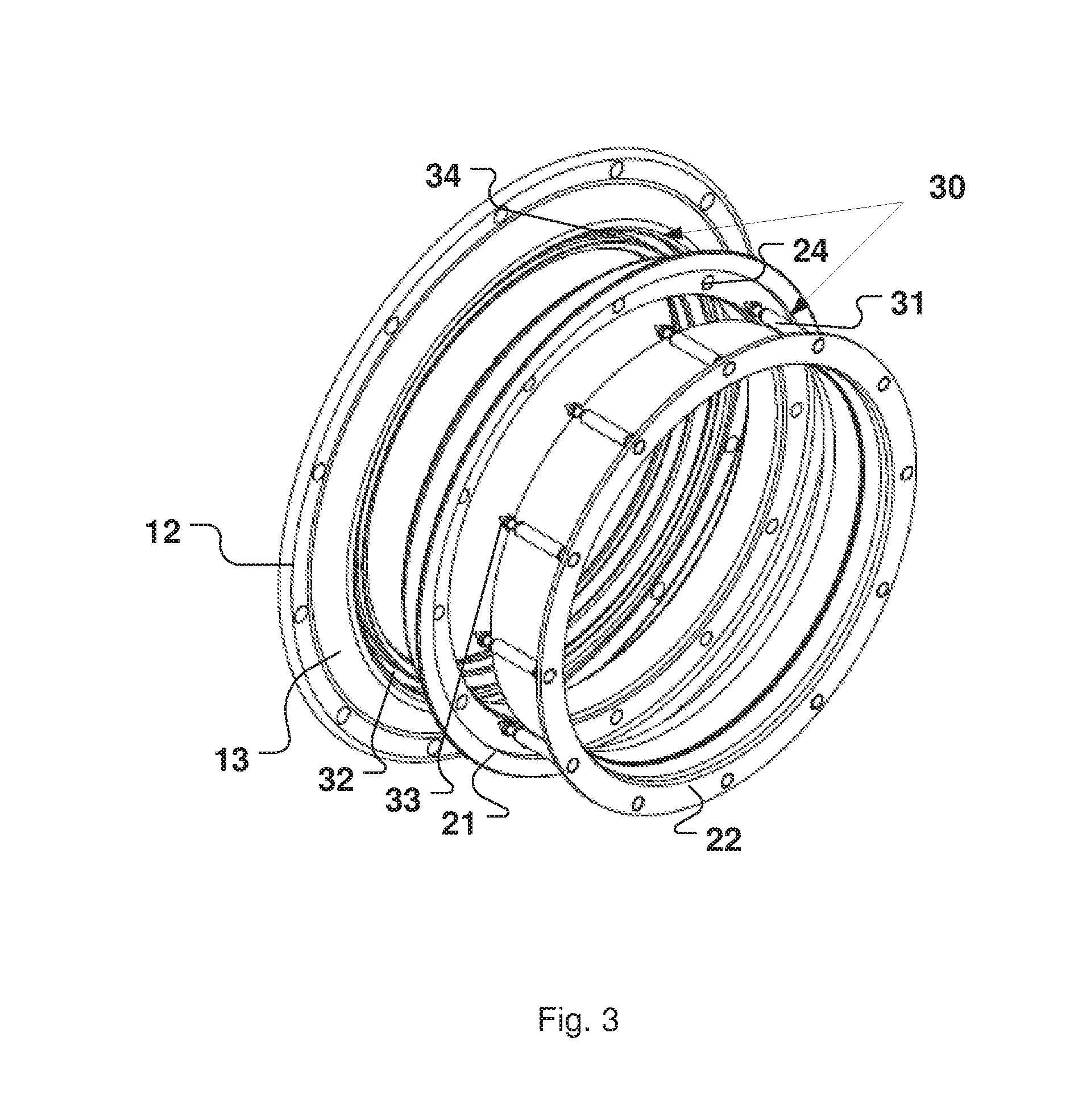

A mouth cooler is provided. The mouth cooler comprises a first peripheral cooling winding shaped and dimensioned to cool the lower and upper jaw, and at least one second cooling winding in arrangement with the peripheral cooling winding shaped and dimensioned to cool at least the blood entry to the tongue.

Owner:BRAINCOOL

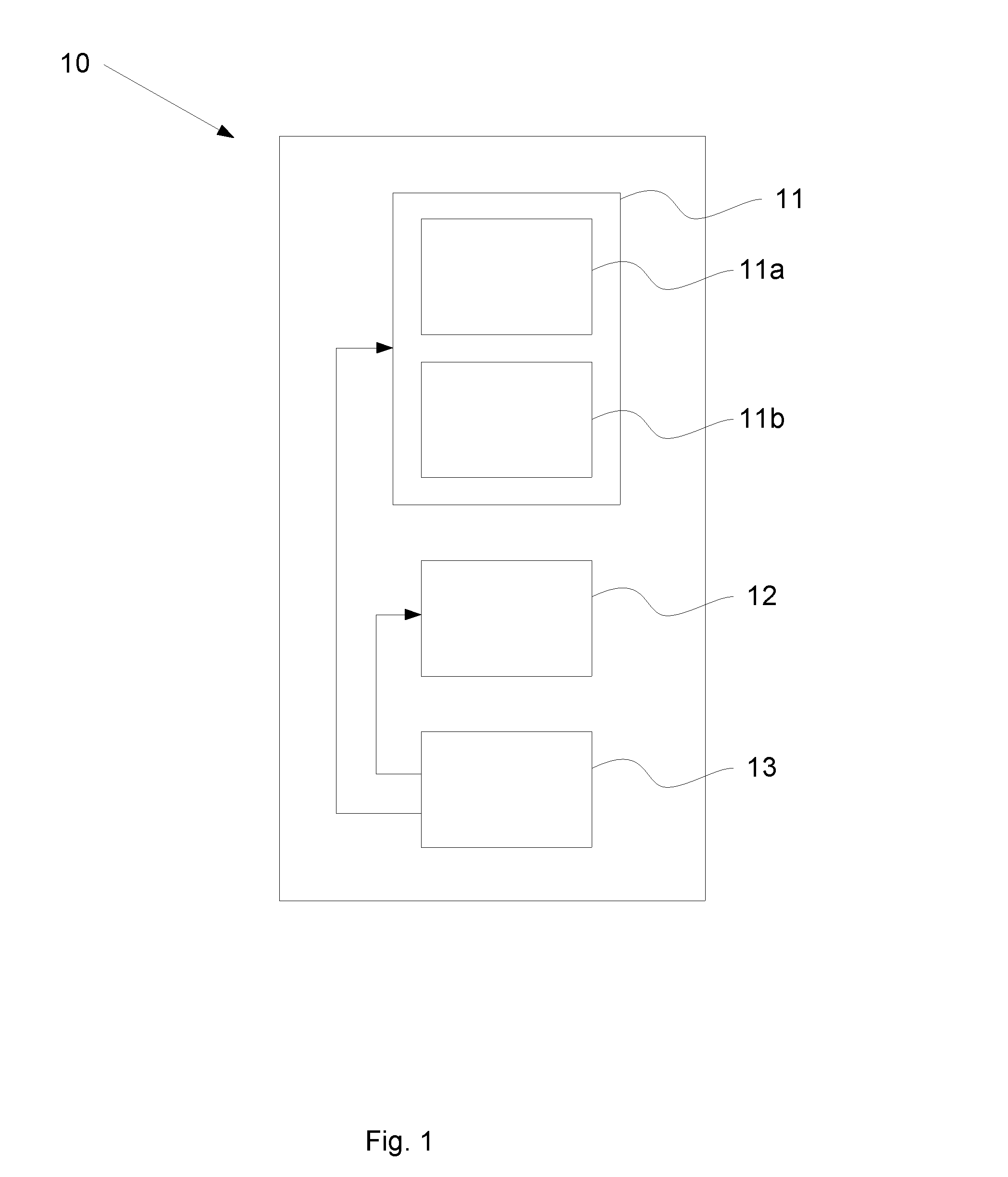

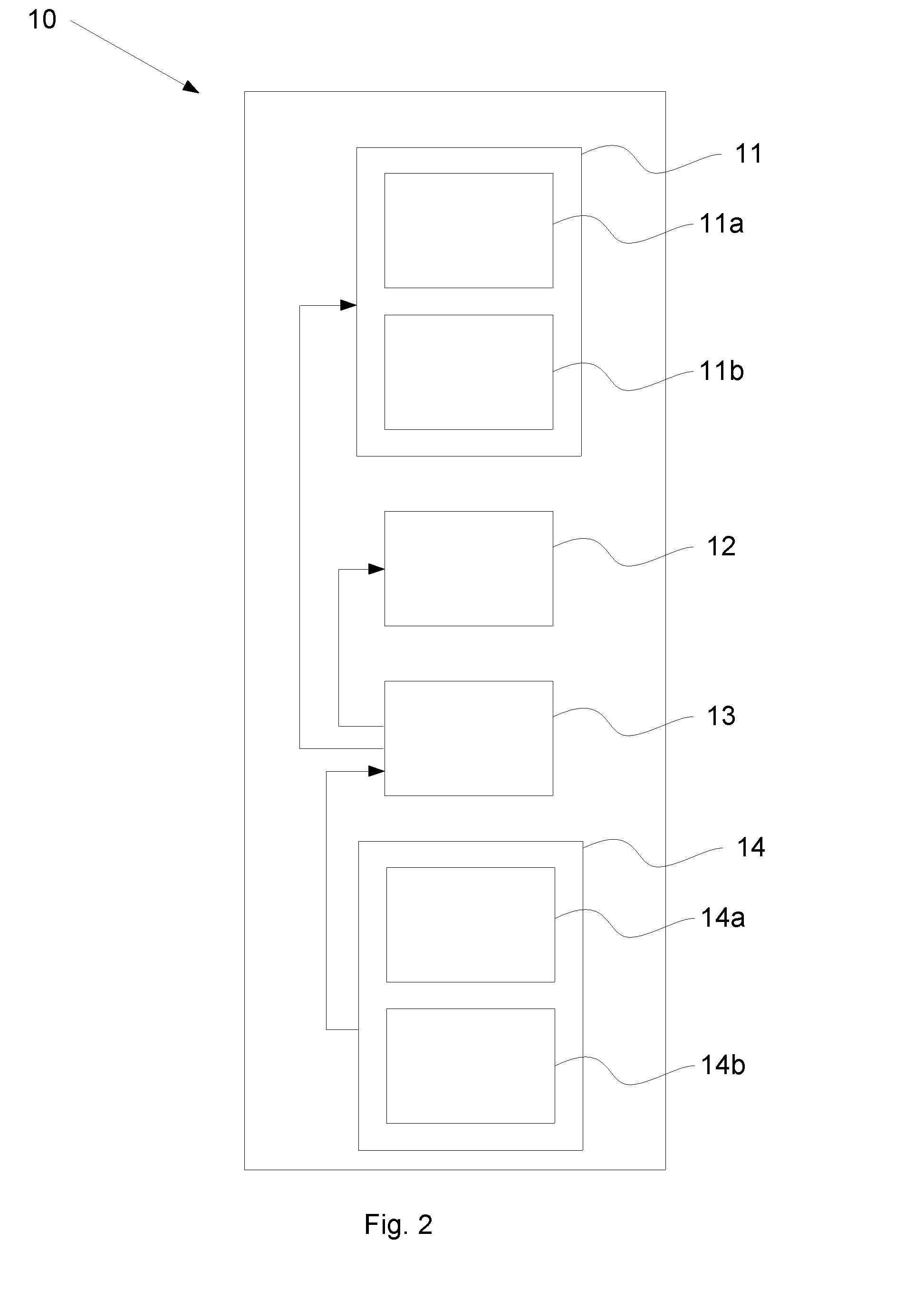

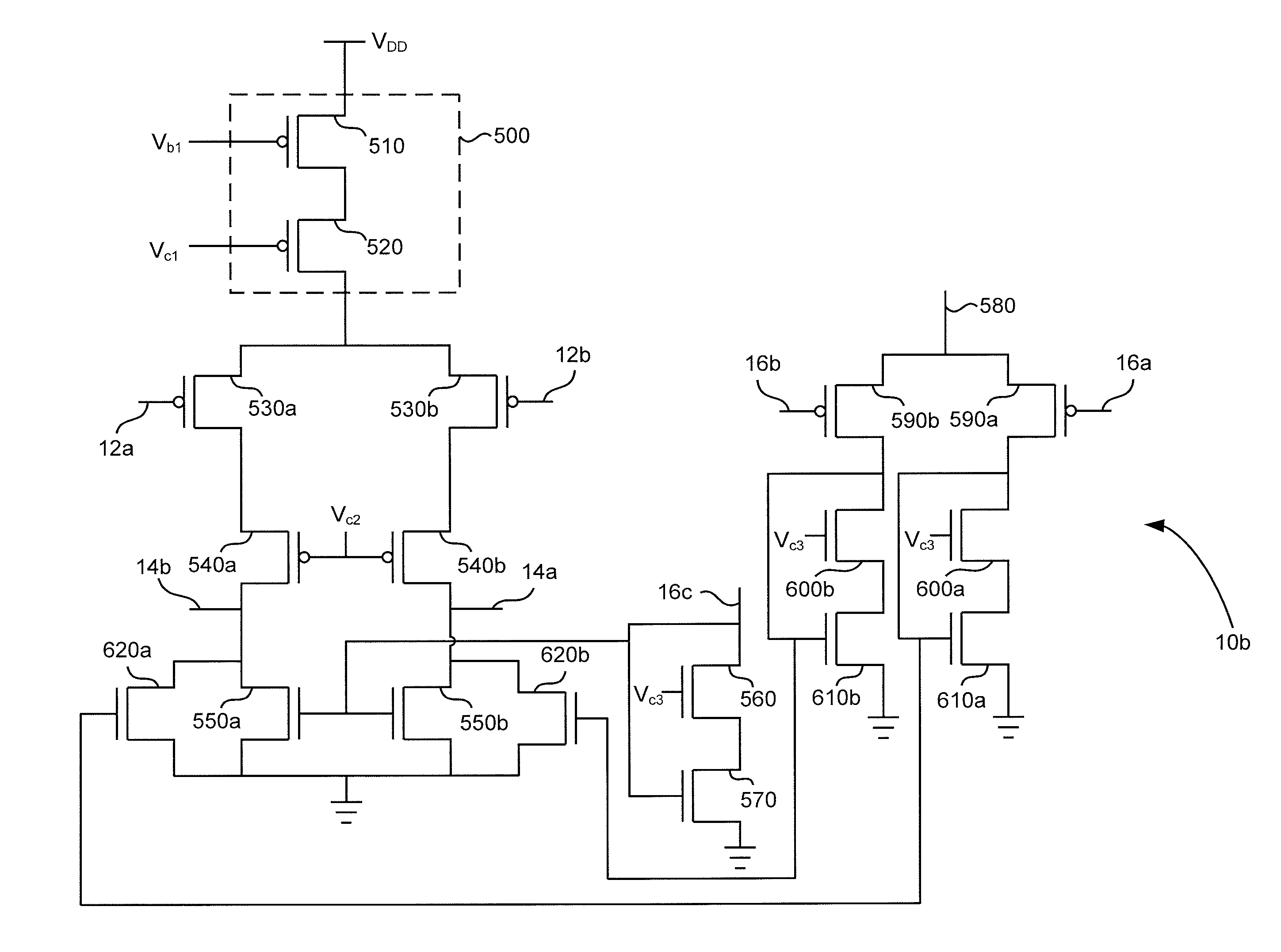

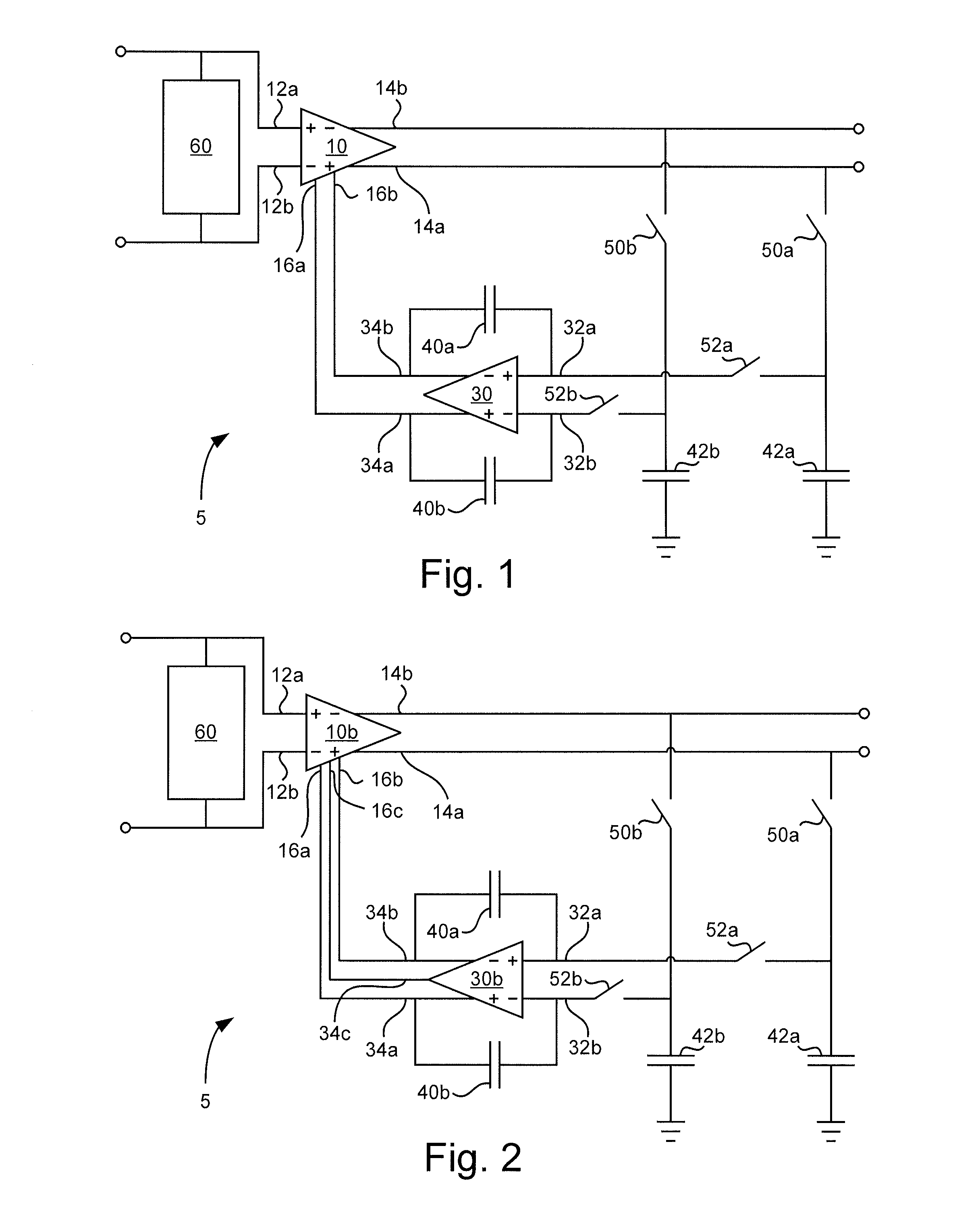

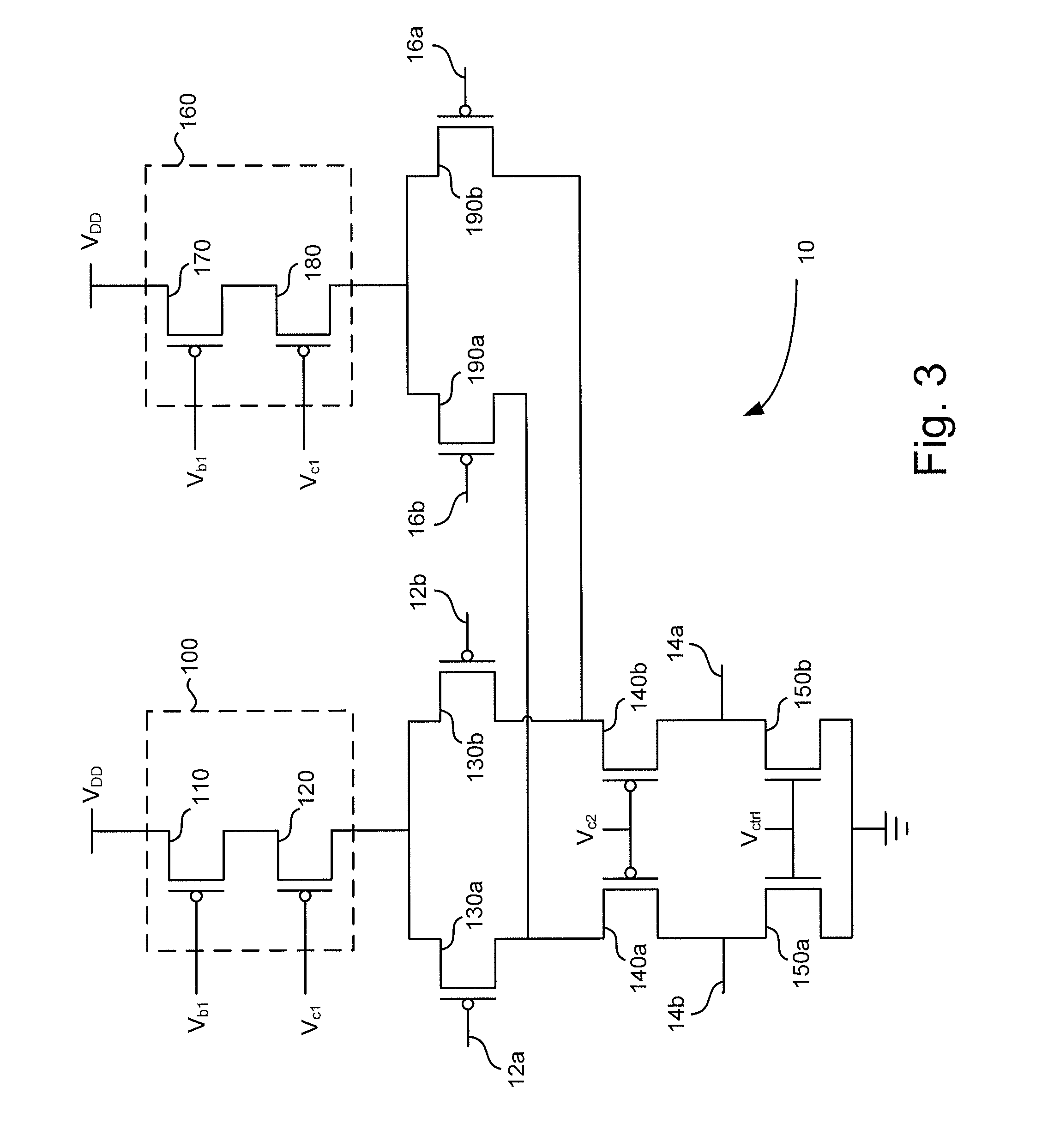

Comparator circuit

InactiveUS20110204978A1Mitigate, alleviate or eliminate one or moreHigh bandwidthMultiple input and output pulse circuitsAmplifier modifications to raise efficiencyAudio power amplifierComparators circuits

A comparator circuit (5) comprising a fully differential main amplifier unit (10, 10b). The main amplifier unit (10, 10b) comprises a control port and is adapted to control a bias current of a first branch of the main amplifier unit (10, 10b) and / or a bias current of a second branch of the main amplifier unit (10, 10b) in response to one or more control voltages supplied to the control port of the main amplifier unit (10, 10b). The comparator circuit (5) comprises circuitry (60) for balancing the voltages at the positive and negative input terminals (12a, 12b) of the main amplifier unit (10, 10b) during a first clock phase of the comparator circuit (5). Furthermore, the comparator circuit (10, 10a) comprises a switched-capacitor accumulator unit with a differential input. The switched-capacitor accumulator unit is operatively connected to the positive and negative output terminals (14a, 14b) of the main amplifier unit (10, 10b) for sampling voltages at the positive and negative output terminals (14a, 14b) of the main amplifier unit (10, 10b) during the first clock phase, and operatively connected to the control port of the main amplifier unit (10, 10b) for supplying said one or more control voltages.

Owner:CSR TECH INC

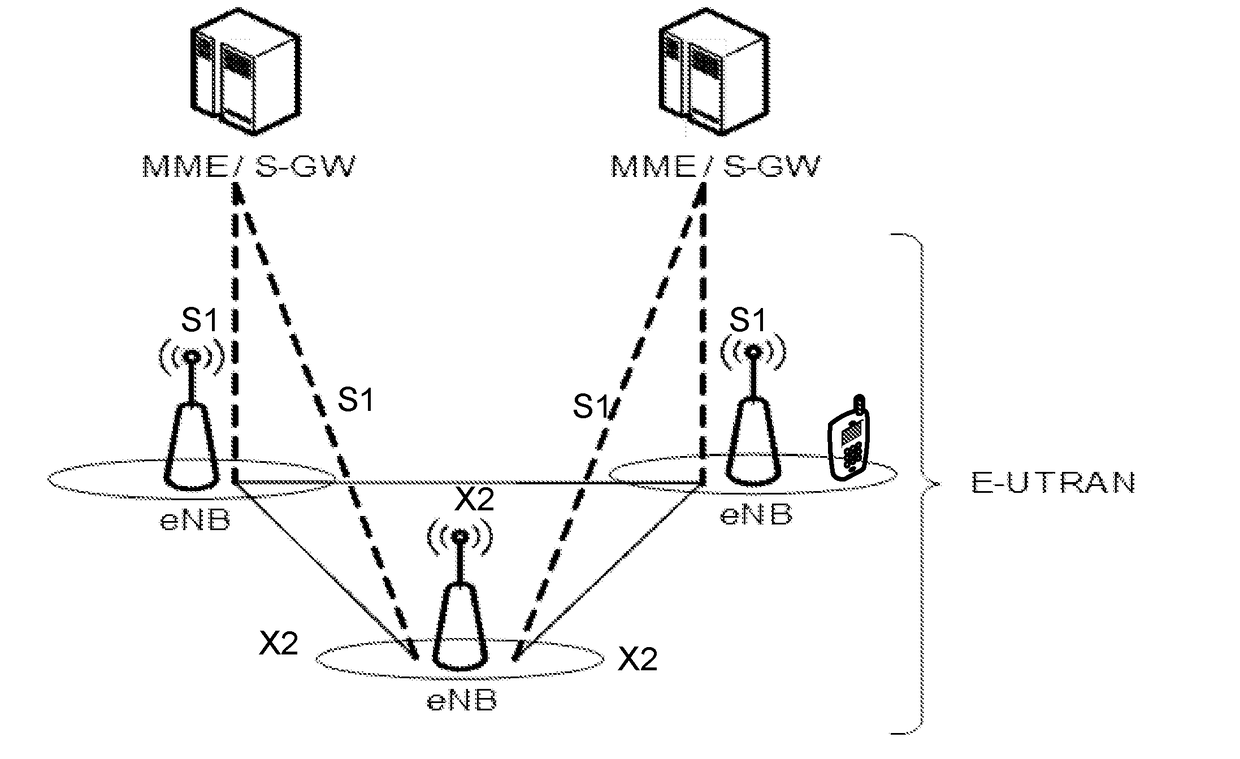

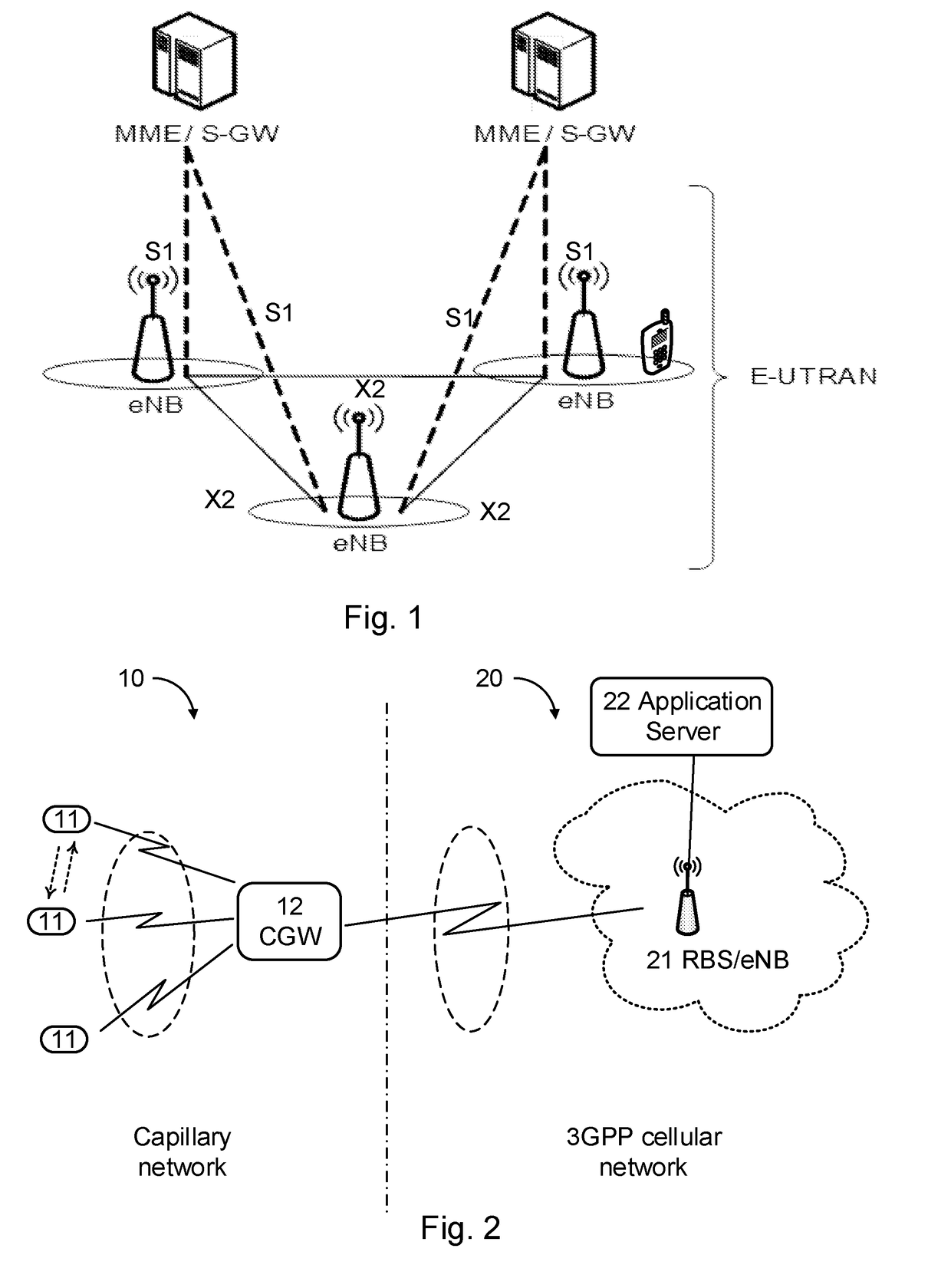

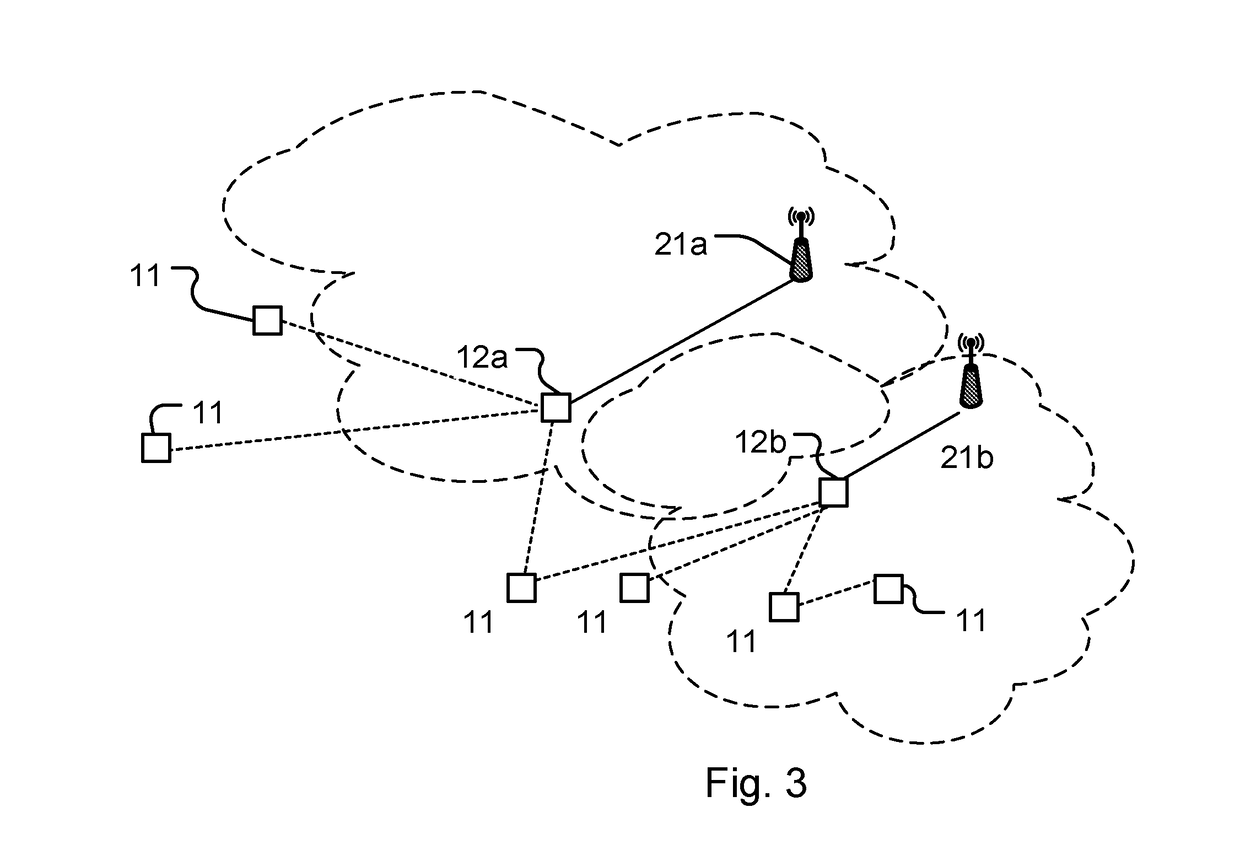

Selection of Capillary Network Gateway to a Cellular Network

InactiveUS20170071024A1Efficient traffic processingEfficient communicationNetwork traffic/resource managementAssess restrictionCapillary networkCellular radio

The present disclosure relates to the capillary network gateway selection in a capillary network. In particular, the present disclosure relates to a methods and arrangements for selecting a capillary network gateway, CGW, for linking of a machine device, MD, arranged to operate in a capillary network, to a cellular network. The cellular network is arranged to operate according to a radio access technology different from the radio access technology of the capillary network, the capillary network including a plurality of CGWs, each of which CGWs being adapted to forward traffic between the capillary network and a radio base station, RBS, of the cellular network. The method comprises, for at least two CGWs of the plurality of CGWs, to gather (S51) data related to cells of RBSs having a cellular radio connection to the respective CGW in the capillary network, and to control (S52) selection of at least one CGW out of the at least two CGWs based on the gathered data.

Owner:TELEFON AB LM ERICSSON (PUBL)

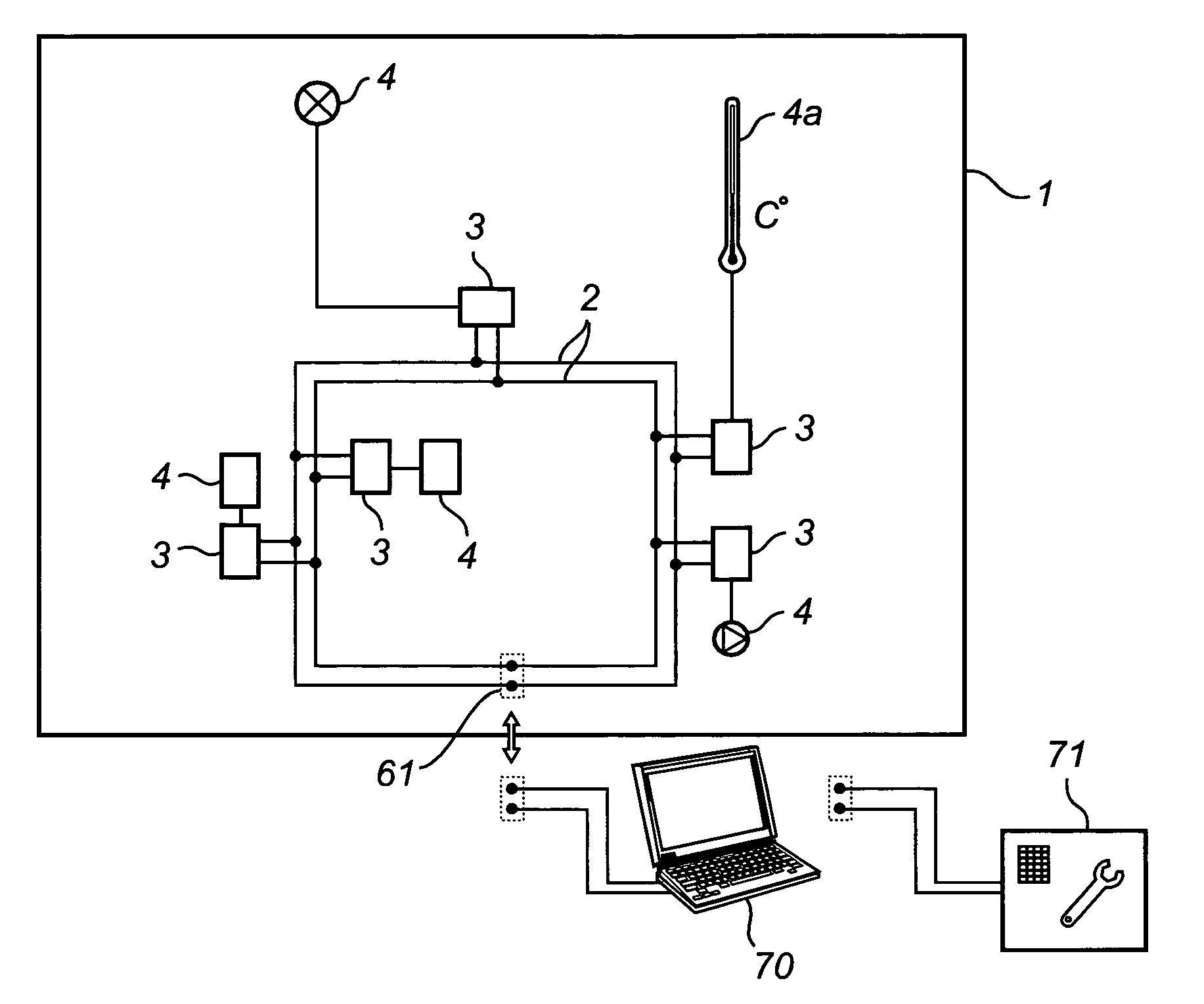

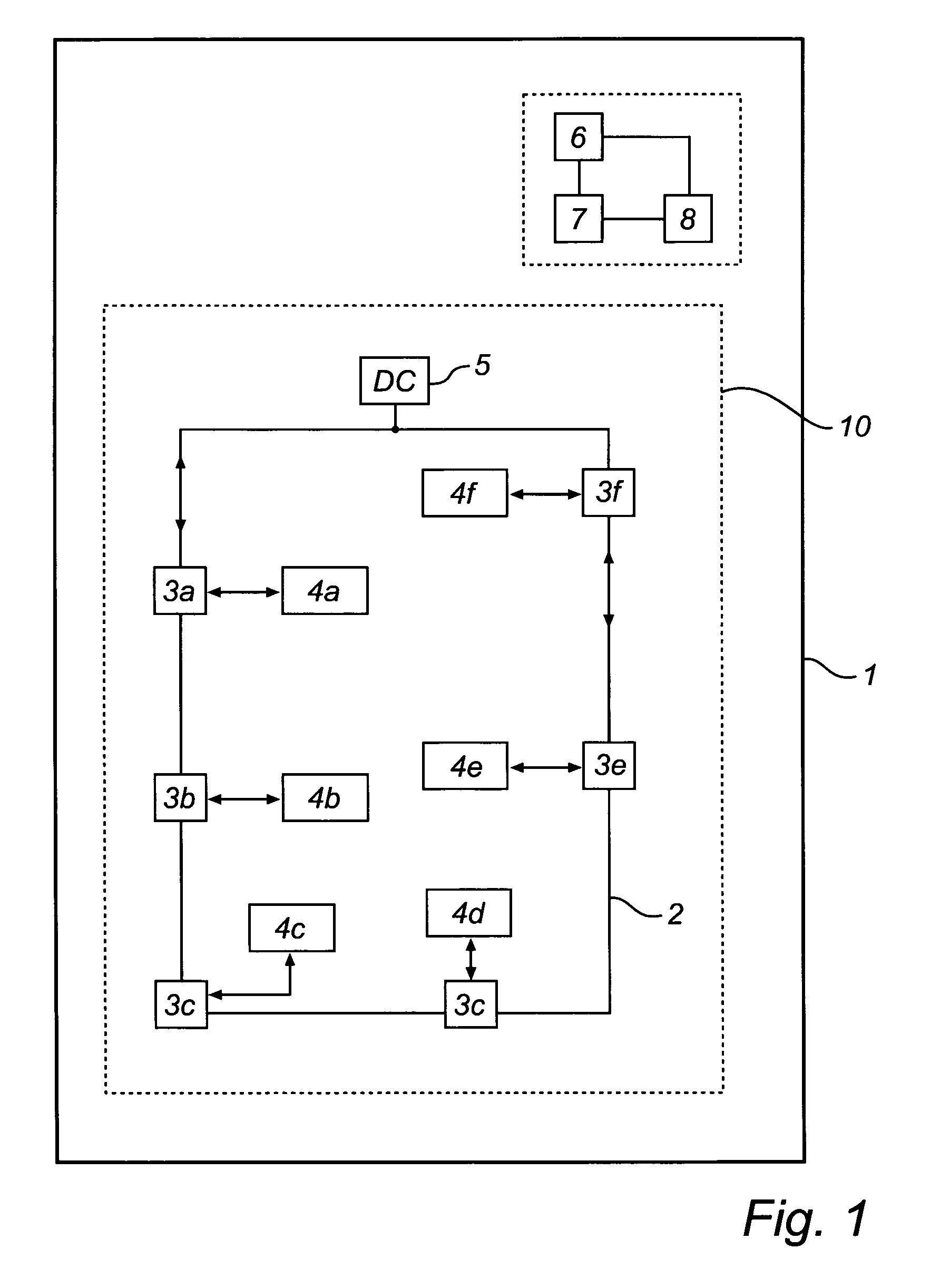

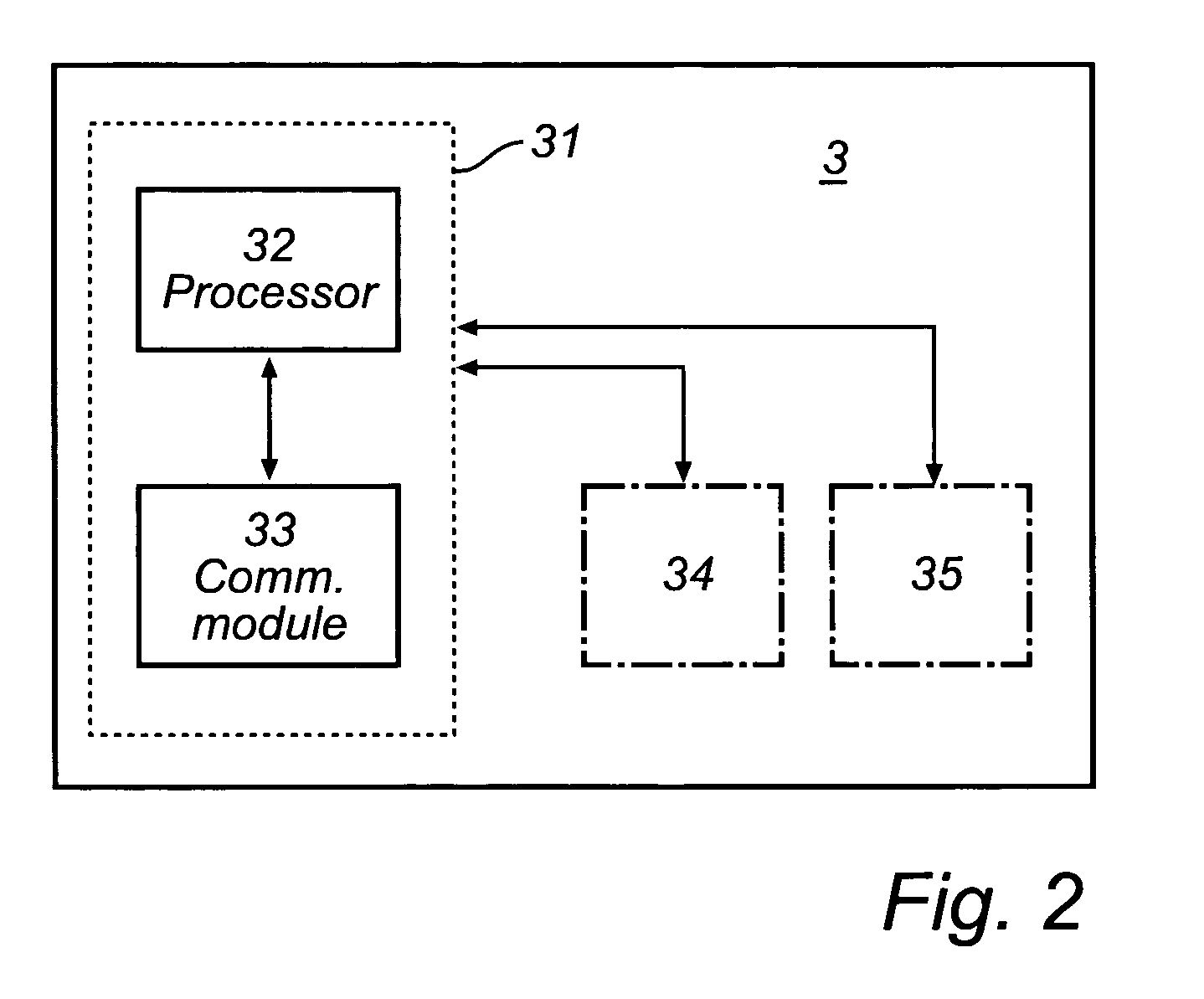

Bus control for a domestic appliance

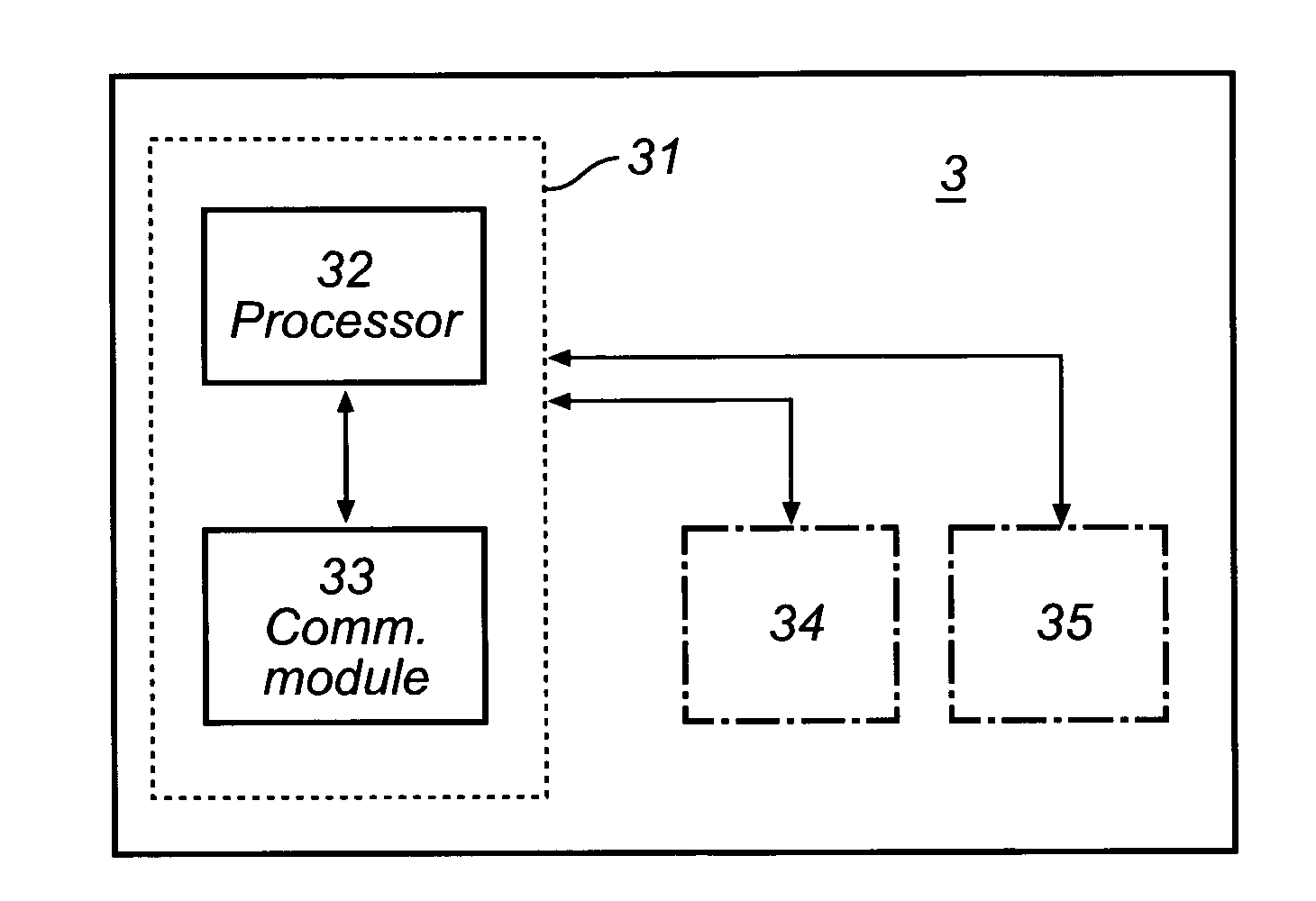

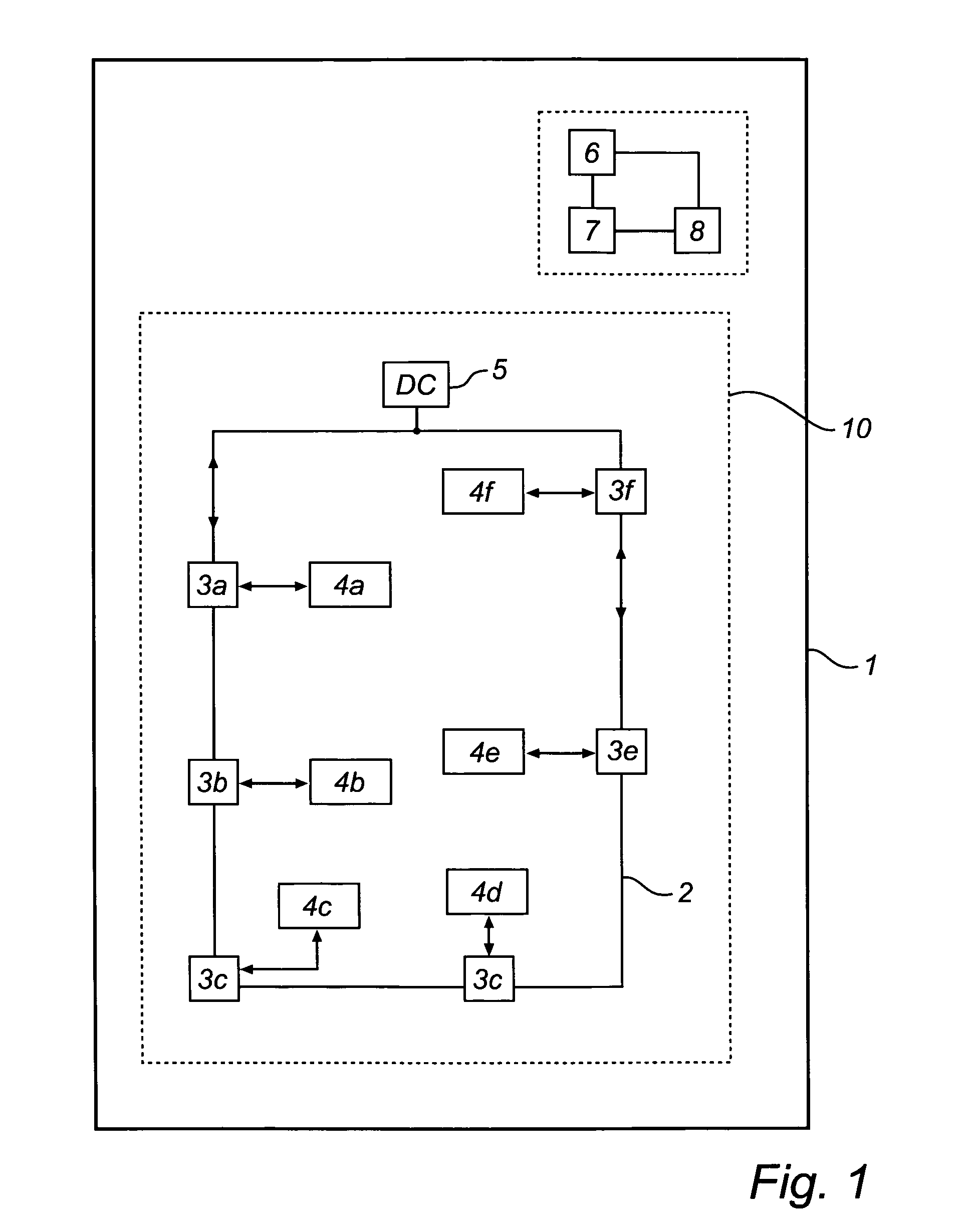

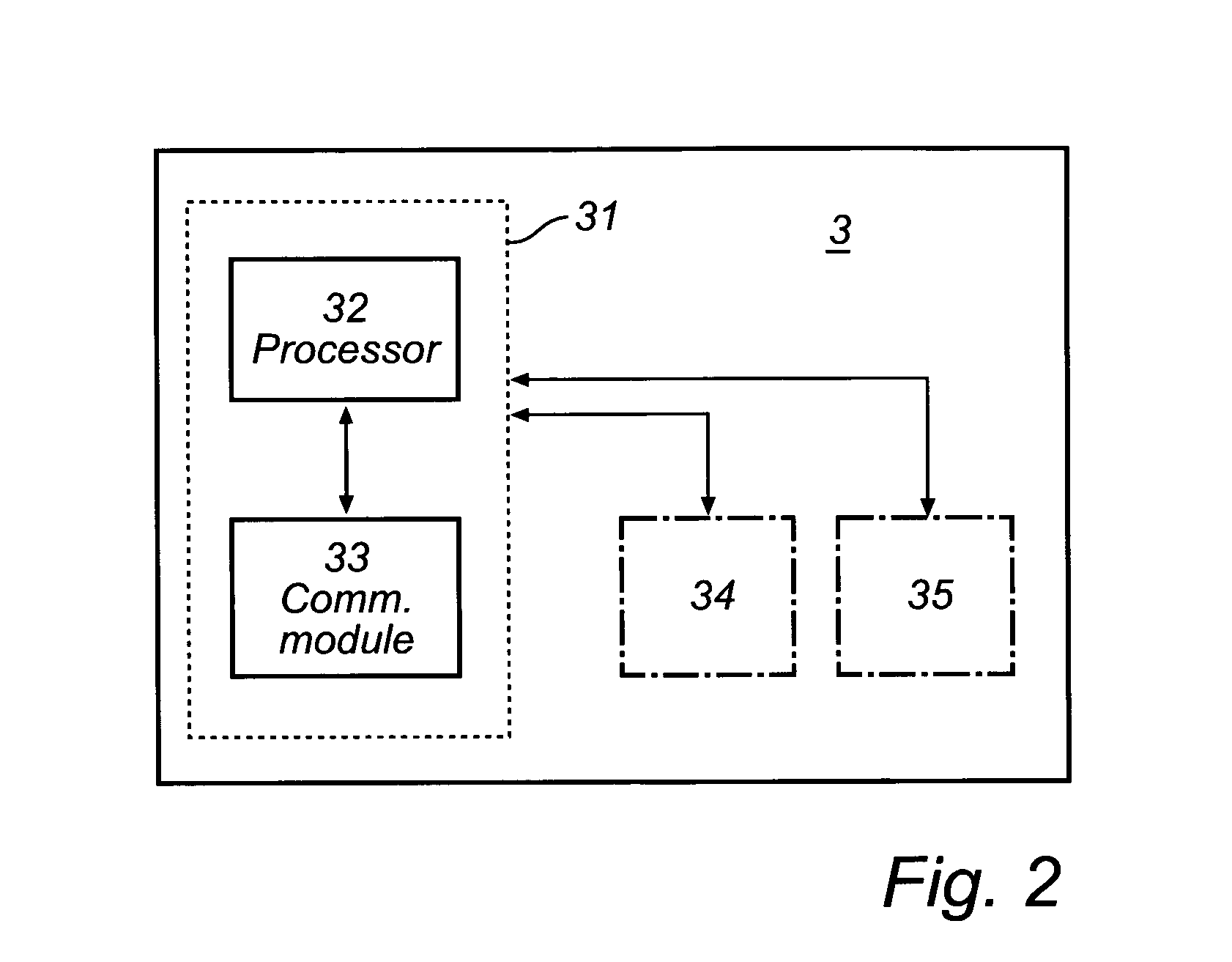

InactiveUS20120239840A1Guaranteed operational reliabilityIncrease productivityPrecision positioning equipmentSubstation remote connection/disconnectionData memoryEmbedded system

A domestic appliance (1) with a bus (2) is disclosed. A plurality of modules (3) are connected to the bus, each controlling an operational component (4). Initial programming of the modules may take place from a single connection point (61). The modules may be configured to control the domestic appliance jointly and non-hierarchically. Suitably, all modules are identical up to content of a data memory provided therein.

Owner:ELECTROLUX HOME PROD CORP NV

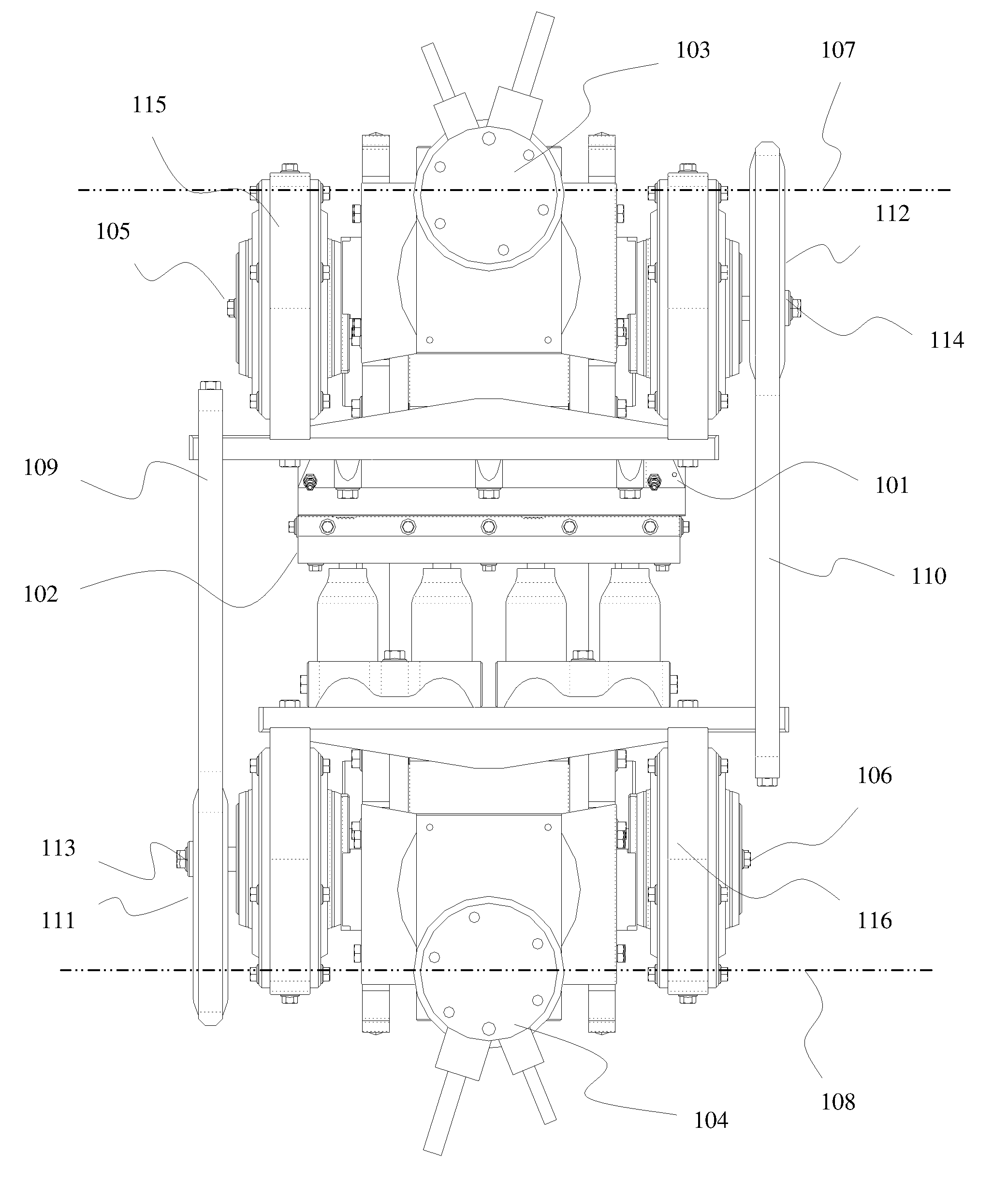

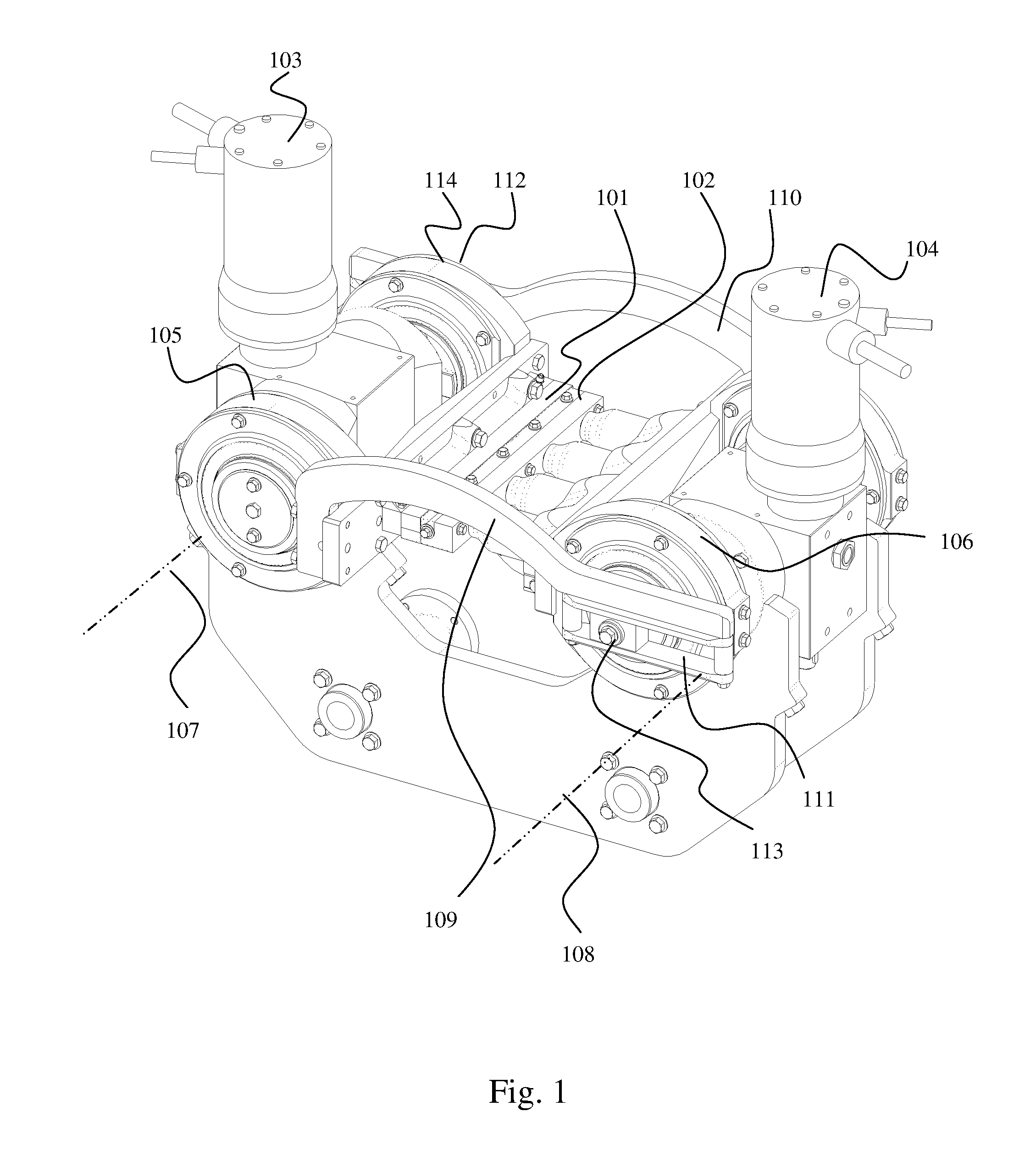

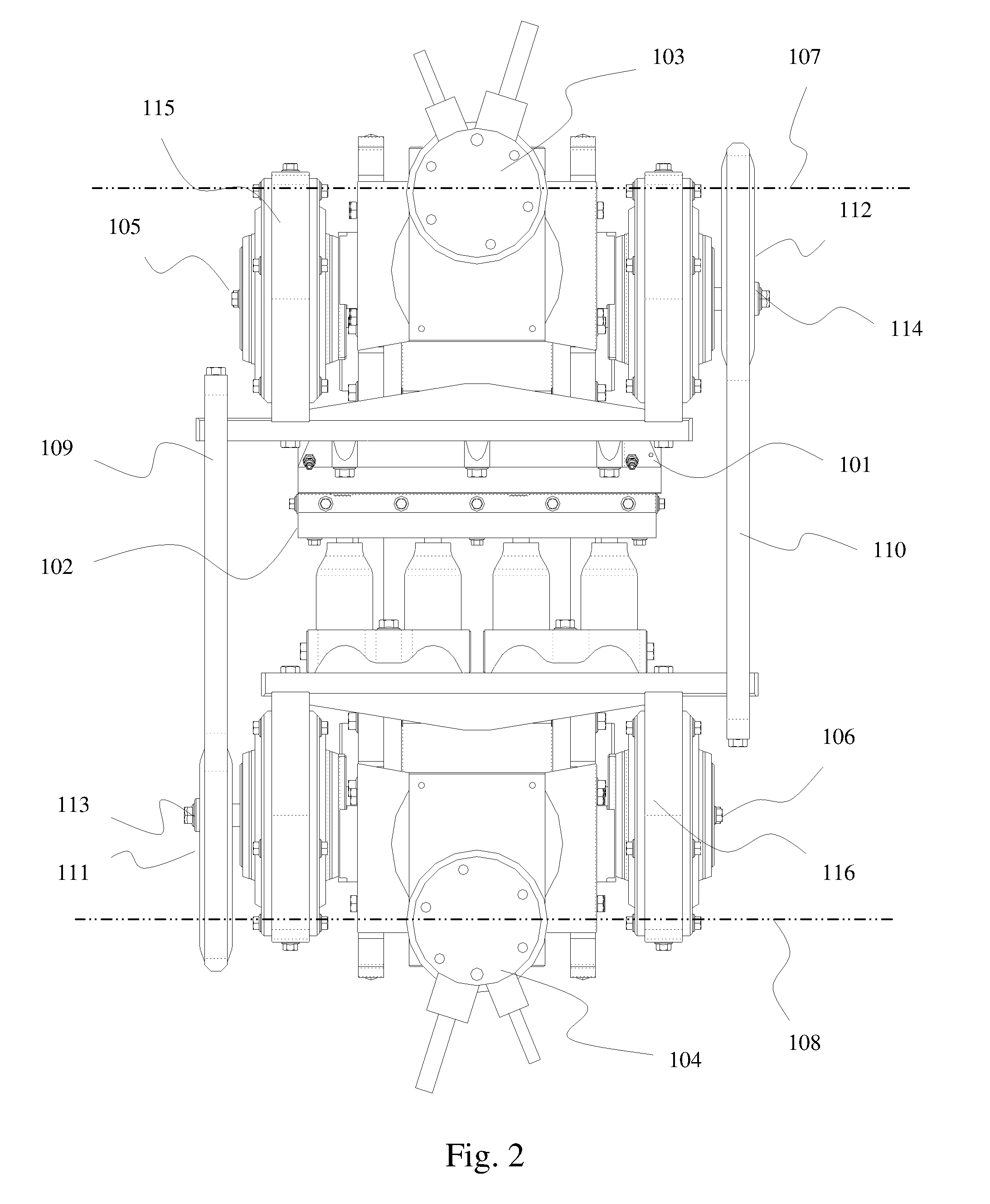

Method for manufacturing of urinary catheters

ActiveUS10807287B2Mitigate, alleviate or eliminate one or moreIncrease cavity volumeMedical devicesCatheterUrinary catheterEngineering

A method for manufacturing an elongated element (200) is provided. The method comprises arranging a molding cavity (101), defined by a mold (103) and a mold insert (104), said mold insert (104) comprising a mold core (105) and a displaceable mold cavity wall (106), said displaceable mold cavity wall (106) being arranged between the mold (103) and the mold core (105), such that the molding cavity has a start volume in a start position of the displaceable mold cavity wall (106). Then a liquid material is injected into a proximal end (102) of the molding cavity (101), where after the displaceable mold cavity wall (106) is displaced in relation to and along with the mold (103) and the mold core (105), distally during said injection, to increase the molding cavity volume from the start volume into an end volume at an end position of the displaceable mold cavity wall (106), wherein the molding cavity (101) in said end position of the displaceable mold cavity wall (106) corresponds to the elongated element (200). The liquid material is solidified, such that the elongated element (200) is formed, and the elongated element (200) and mold insert (104) is removed from said mold (103), where after the elongated element (200) is removed from said mold insert (104). An elongated element and a mold assembly for the manufacture thereof are also provided.

Owner:COLOPLAST AS

Fastening device for a furniture panel

ActiveUS10557491B2Mitigate, alleviate or eliminate one or moreDrawersFurniture joiningClassical mechanicsEngineering

Owner:INTER IKEA SYST

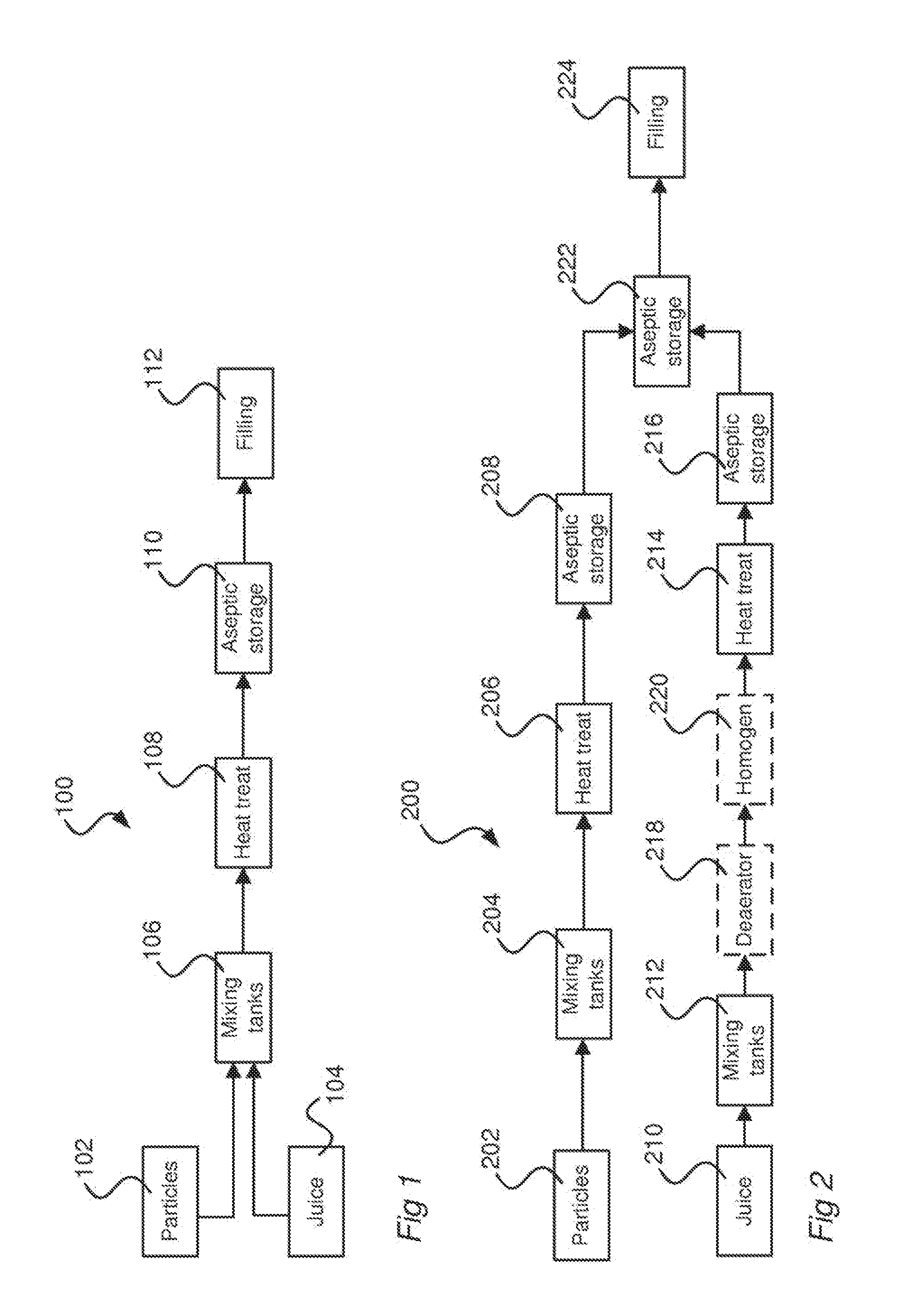

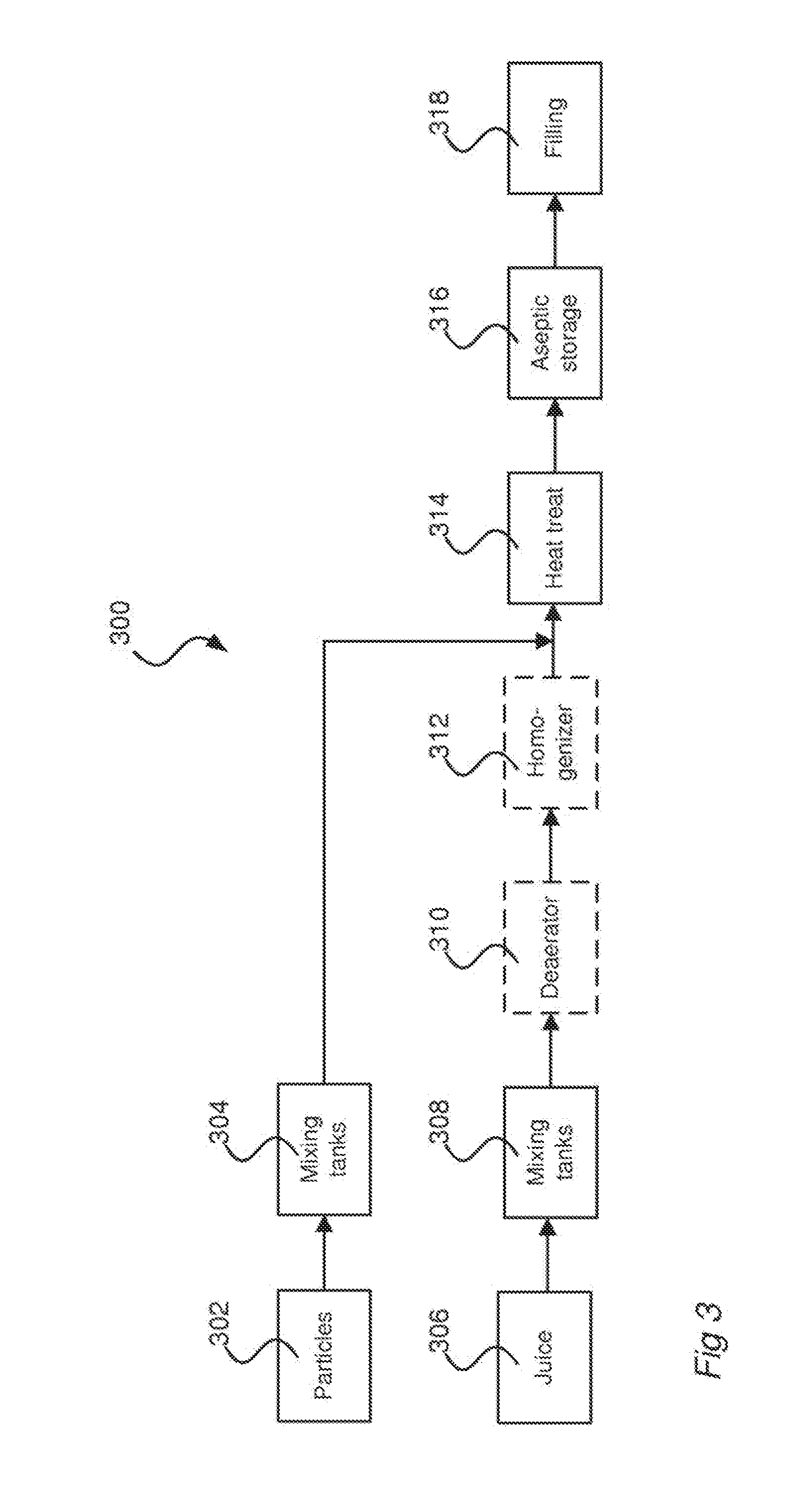

System and method for processing liquid or semi-liquid food products with particles

InactiveUS20170042199A1Reduce eliminateMitigate, alleviate or eliminate one or moreFood preservationLiquid productHigh concentration

It is provided a processing system for processing a liquid or semi-liquid food product. The food product is a composition of a first sub-composition having a low concentration of particles and a second sub-composition having a high concentration of particles. The high concentration is greater than said low concentration. The processing system comprises a first mixing tank for mixing said first sub-composition, a second mixing tank for mixing said second sub-composition, and a heat treatment apparatus arranged to receive said first sub-composition and said second sub-composition and to heat treat said first sub-composition and said second sub-composition.

Owner:TETRA LAVAL HLDG & FINANCE SA

Measuring agglutination parameters

ActiveUS8217647B2Mitigate, alleviate or eliminate one or moreImprove throughputBioreactor/fermenter combinationsNanomagnetismAgglutination assayAgglutination

Owner:KONINK PHILIPS ELECTRONICS NV

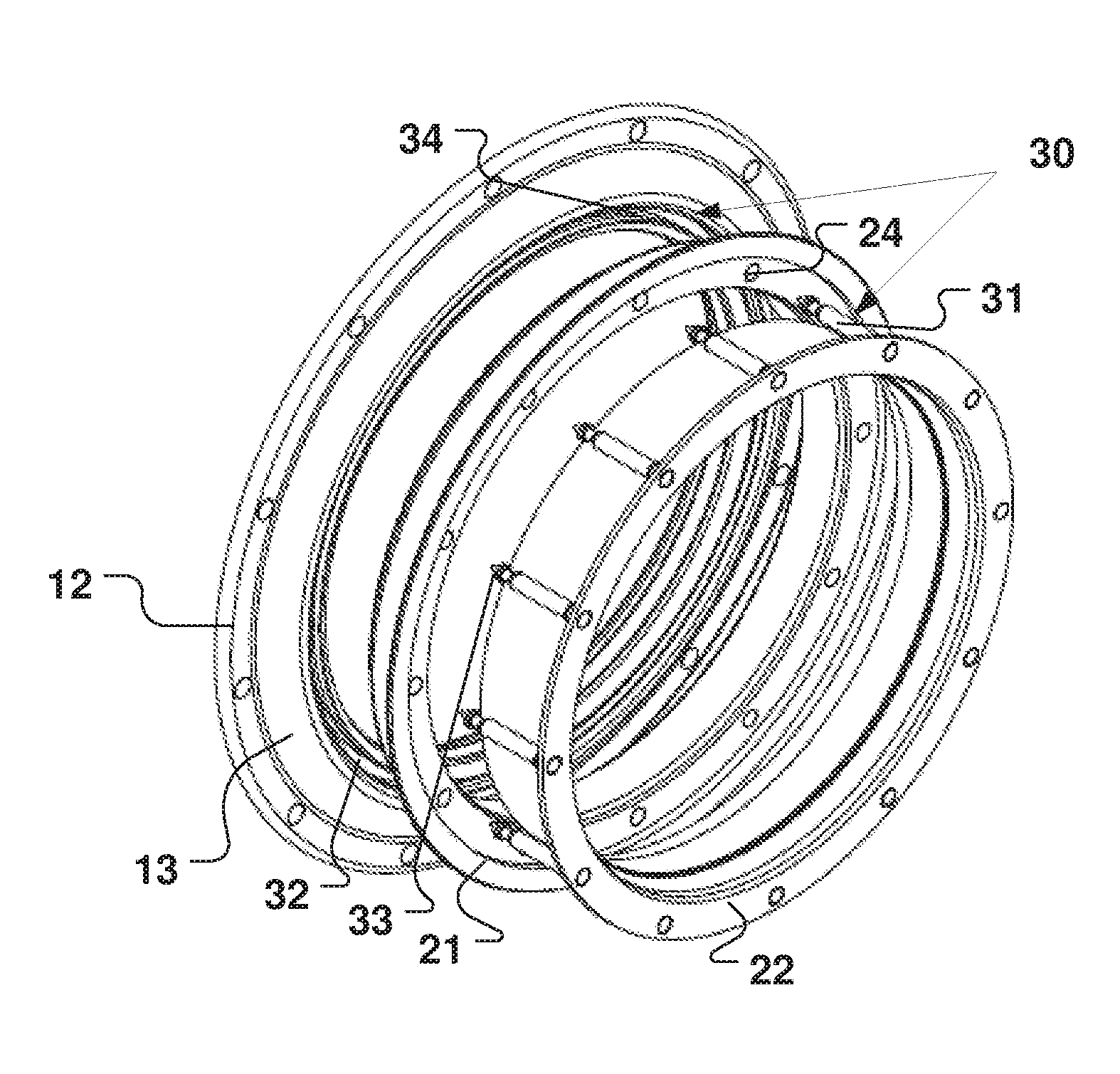

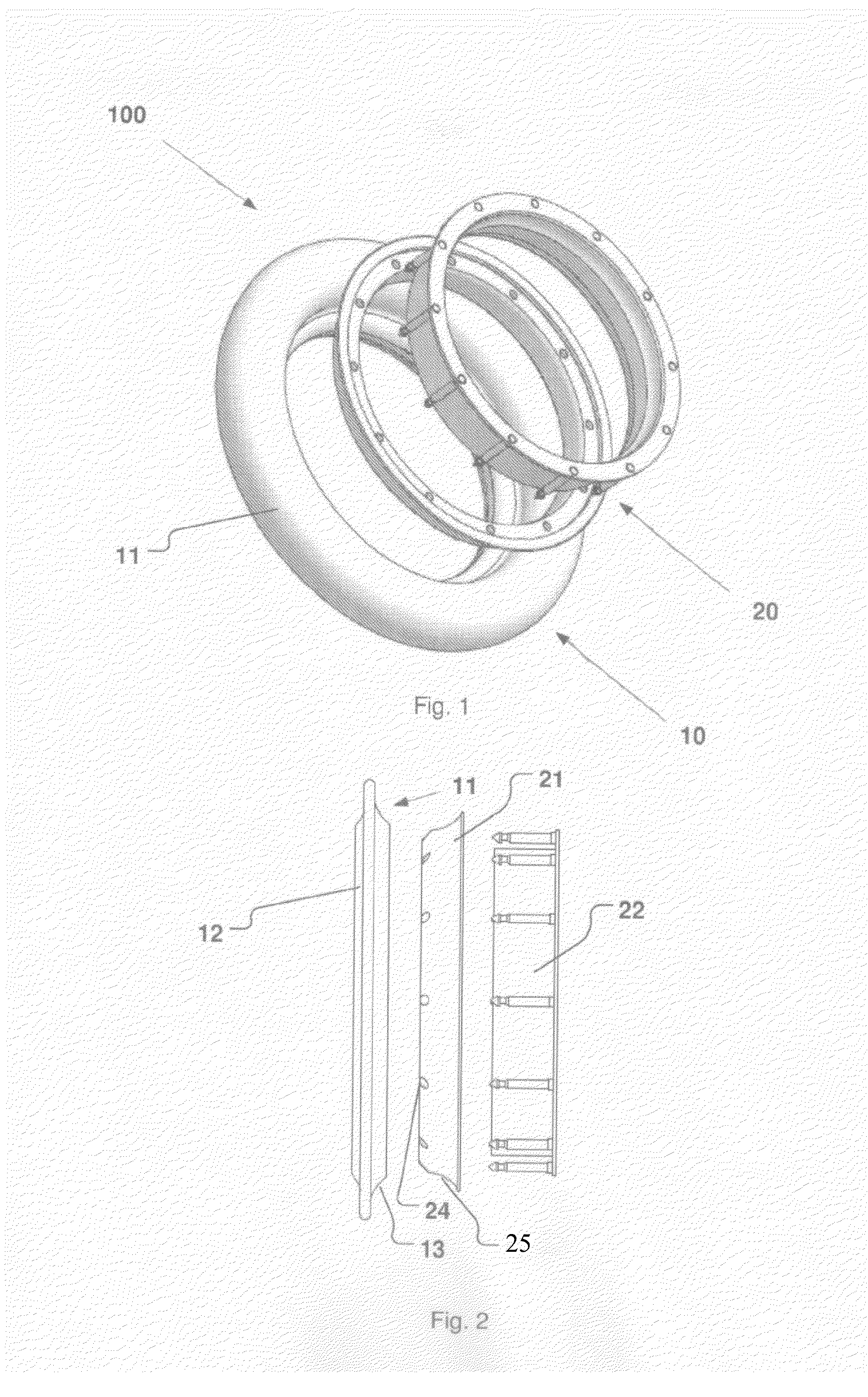

Device and a method for anastomosis

ActiveUS9743931B2Mitigate, alleviate or eliminate one or moreEvenly distributedStaplesNailsIntestine wallsEngineering

Owner:CARPONOVUM AB

Steering damper with active adjustment of damping characteristics

ActiveUS9409588B2Robust and reliable methodPrecise changeSpringsSteering deviceRelative motionHydraulic fluid

A device adjusts the rotational damping of a steering device such that the rotational damping varies depending on whether the rotational motion about a steering axis is caused by a force acting on the steering device of the vehicle or a force acting on the part(s) of the vehicle contacting the ground. The flow of hydraulic fluid in the steering damper partly or wholly is adjusted by a main valve unit that is coupled together with both an attaching part and a steering device. The opening area of the main valve unit is determined by a relative motion between the attaching part and the steering device such that the flow of the hydraulic fluid in a direction from and to the respective damping chambers of the steering damper is controlled depending on the cause of the rotational movement.

Owner:OHLINS

Needle hub and iv catheter system comprising such needle hub

ActiveUS20170361070A1Increase the friction surfaceMitigate, alleviate or eliminate one or moreGuide needlesInfusion needlesCatheter hubIV catheter

Disclosed herein is an IV catheter system., comprising a catheter hub (100), a needle hub (200) and a needle shield (300), wherein the needle of the needle hub is provided with a high friction surface part (207). Furthermore, an open and closed IV catheter system is described. Also disclosed is a needle hub (200) and a shielded needle system (600).

Owner:GREINER BIO ONE GMBH

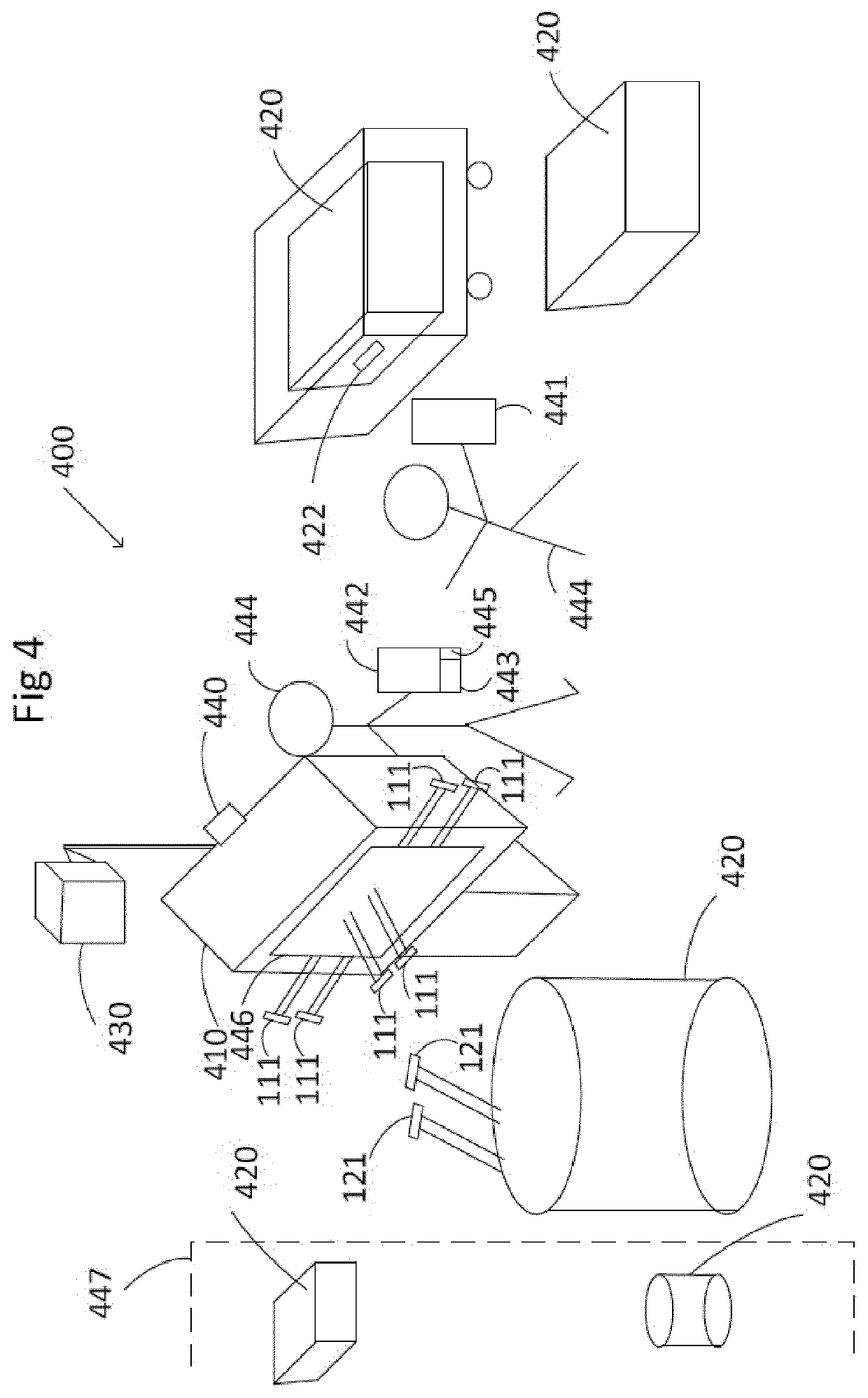

Monitoring System and Method for Biopharmaceutical Products

PendingUS20210313033A1Improve robustnessEasy to zoom inProgramme controlData processing applicationsMonitoring systemProcess engineering

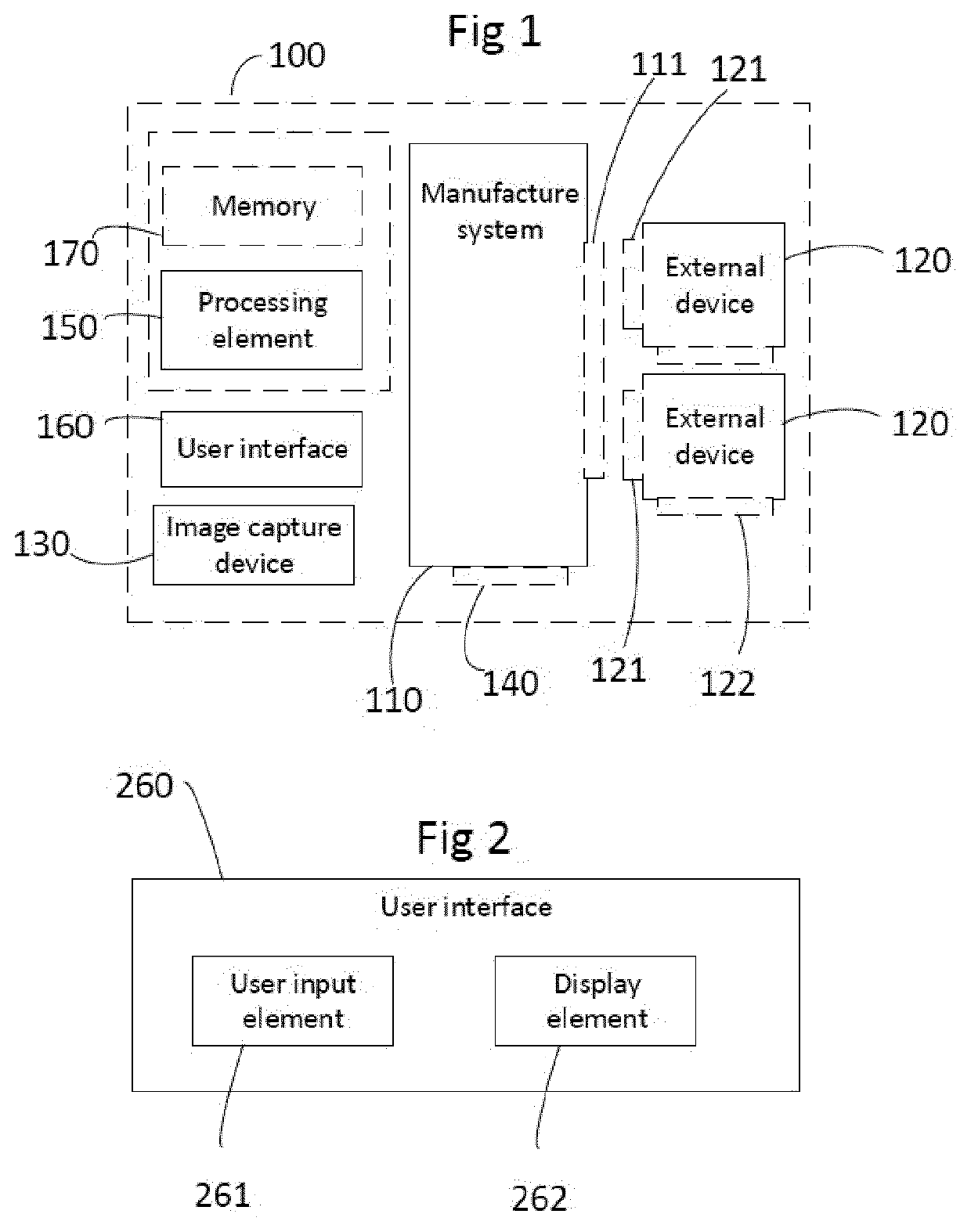

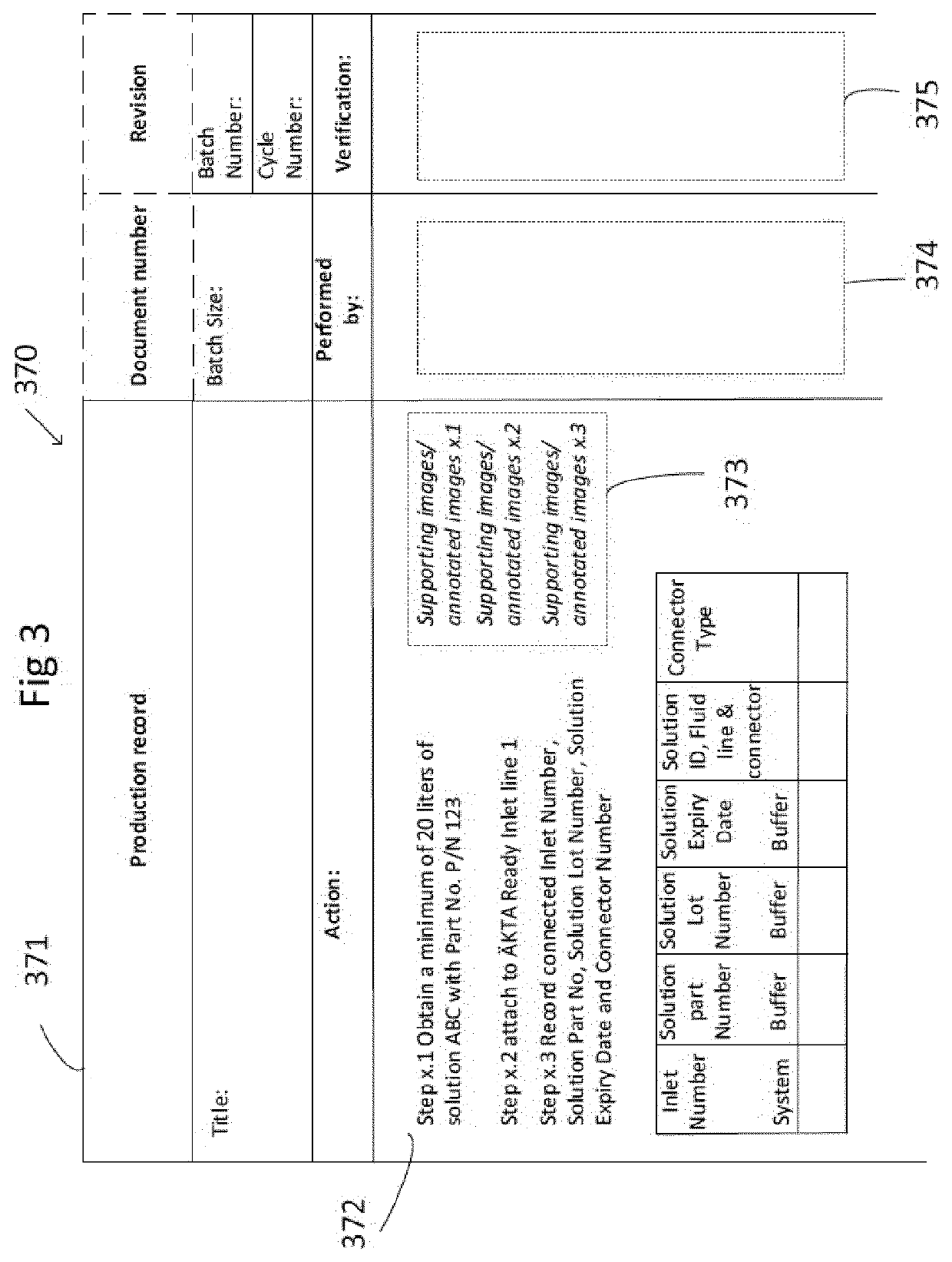

A monitoring system comprises a manufacture system with capability to manufacture a plurality of biopharmaceutical products, at least one image capture device arranged to capture a scene comprising the manufacture system, and a processing element connected to said at least one image capture device and arranged to process images captured by said at least one image capture device to track operator interactions and / or a result of operator interactions within the scene. The processing element is further is arranged to compare a predefined workflow process scheme relating to the selected biopharmaceutical product to at least a part of the tracked operator interactions with the manufacture system and / or to at least a part of the result of the tracked operator interactions with the manufacture system, and determine whether at least one pre-set criterion set by the workflow process scheme is fulfilled based on the comparison.

Owner:CYTIVA SWEDEN AB

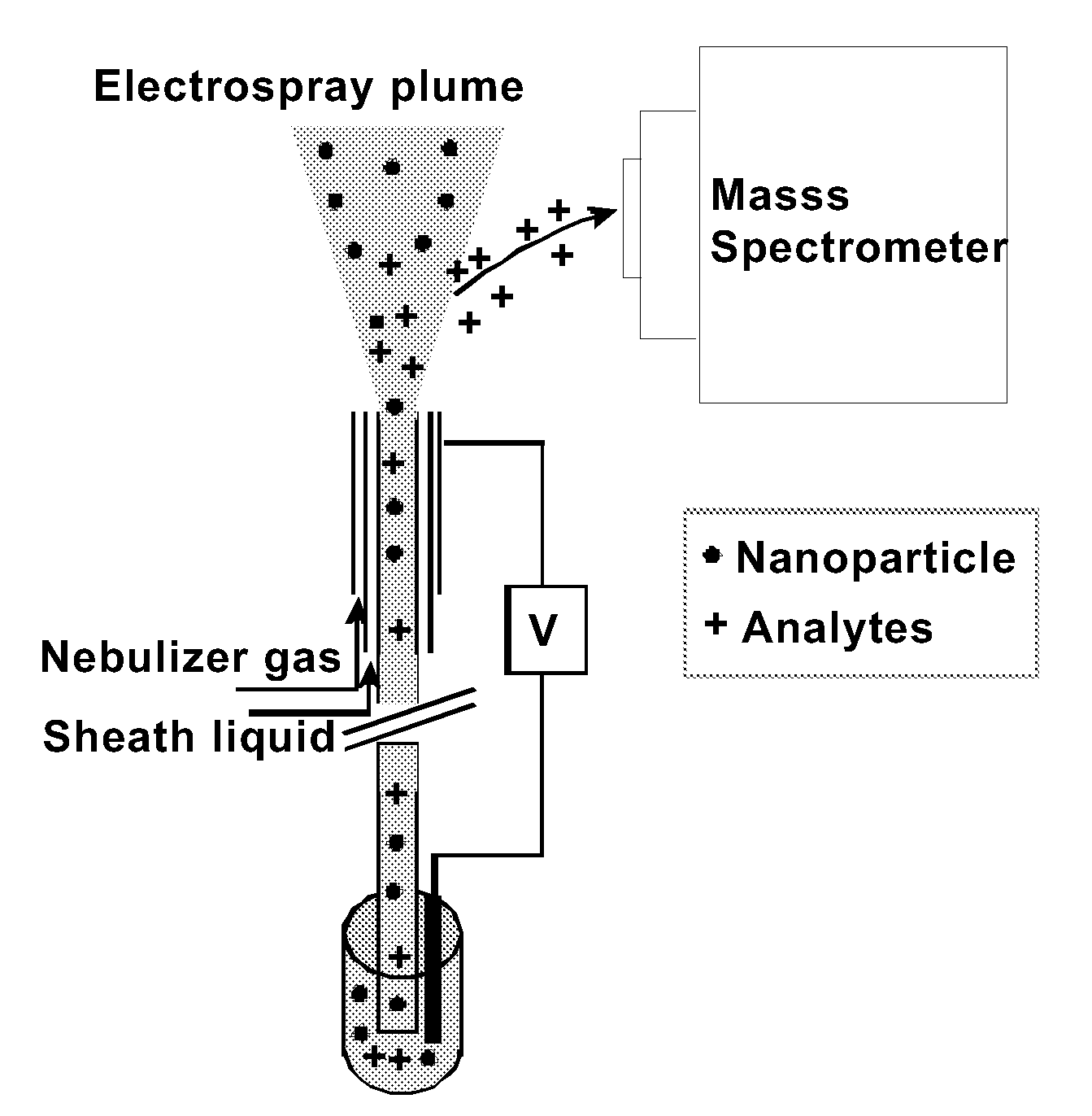

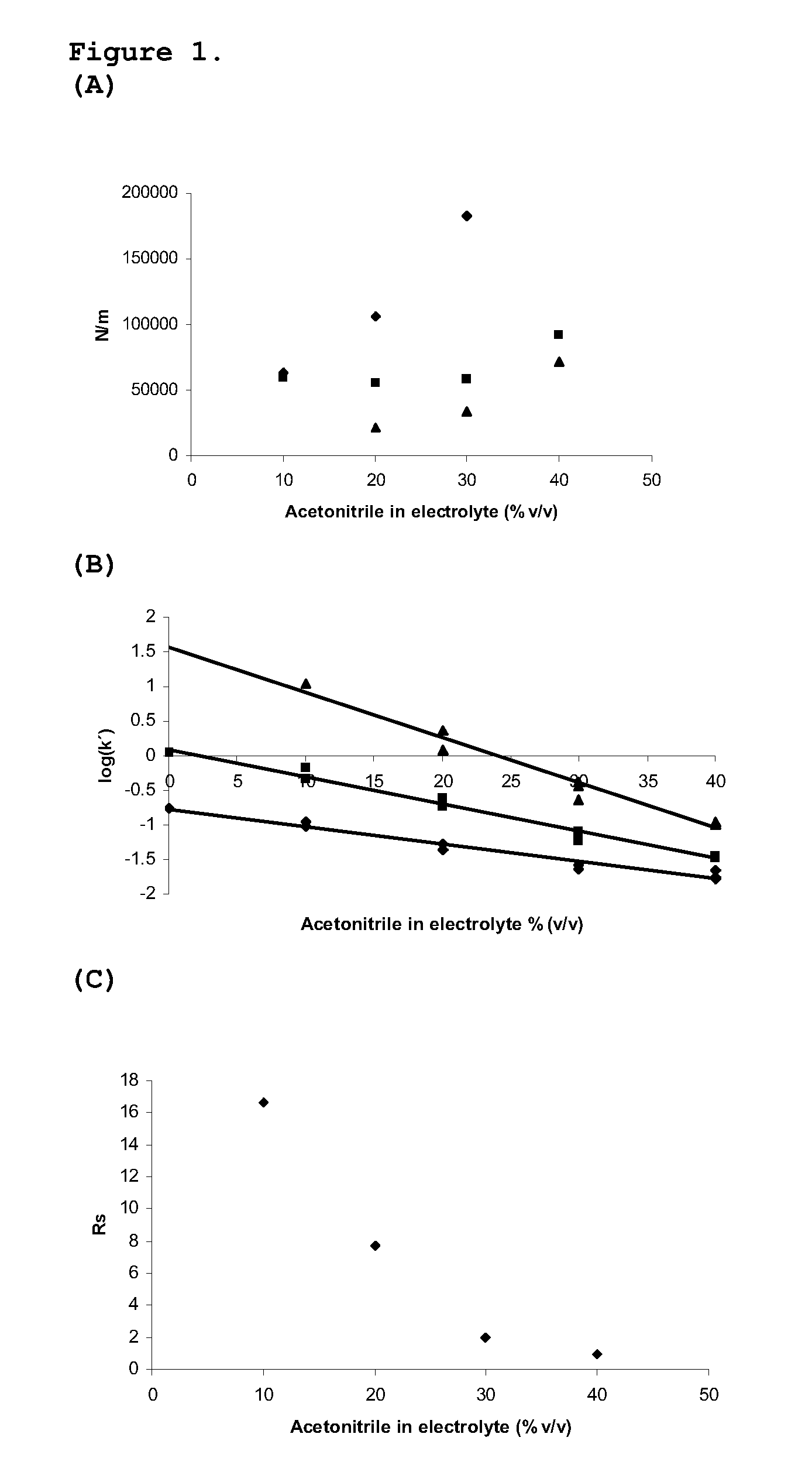

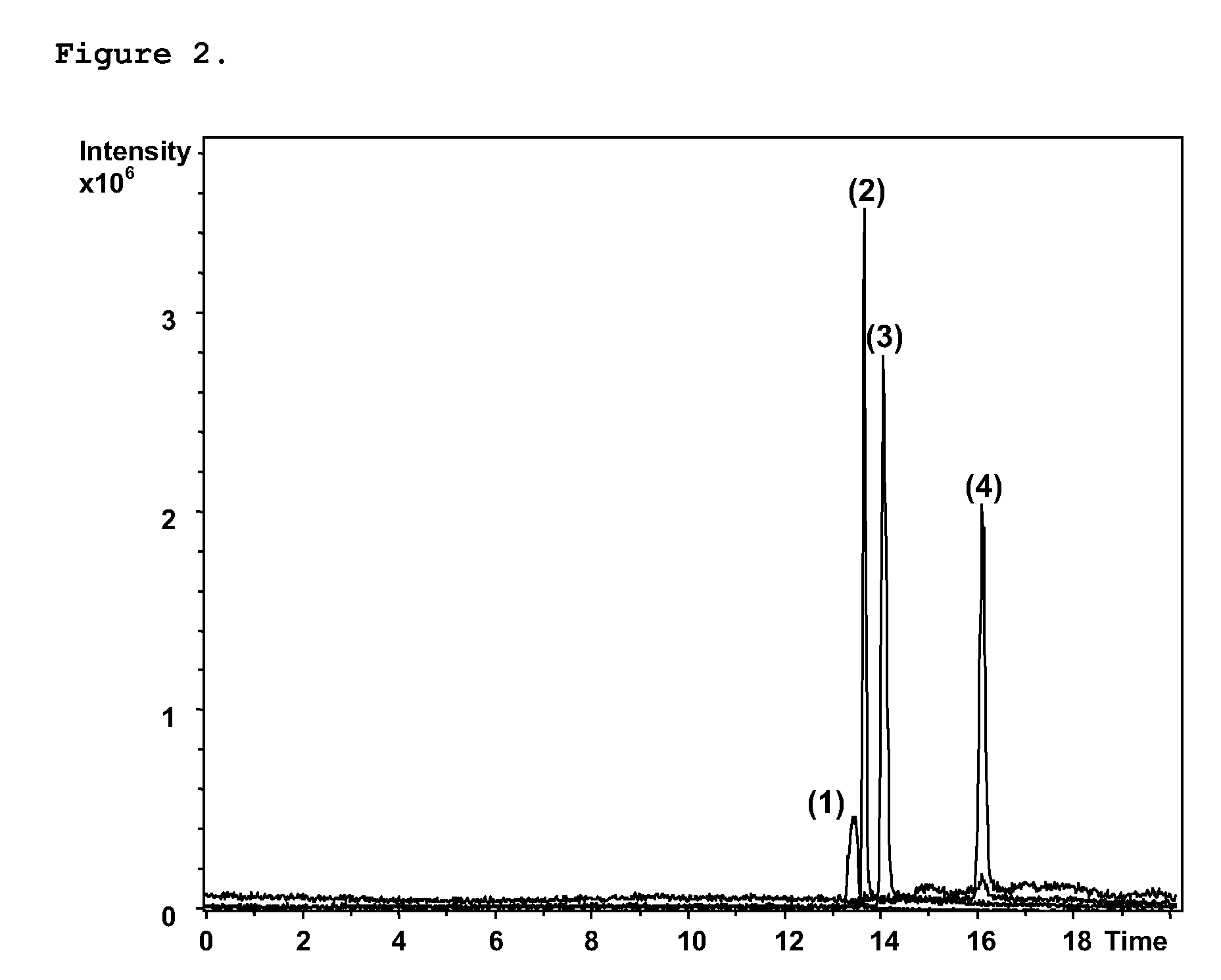

Particles

InactiveUS20090236519A1Prevents flocculation and aggregationMitigate, alleviate or eliminate one or moreLiquid surface applicatorsParticle separator tubesIonizationSolid phases

Particles in a mobile solid phase for chromatographic separation of sample components are disclosed. These particles comprise a core and a coating, wherein said core interacts with at least one analyte and said coating essentially prevents flocculation or aggregation. The core is preferably a polymer and the analyte is preferably detected with a mass analyzer with an angled ionization source.

Owner:NANOSEP AB

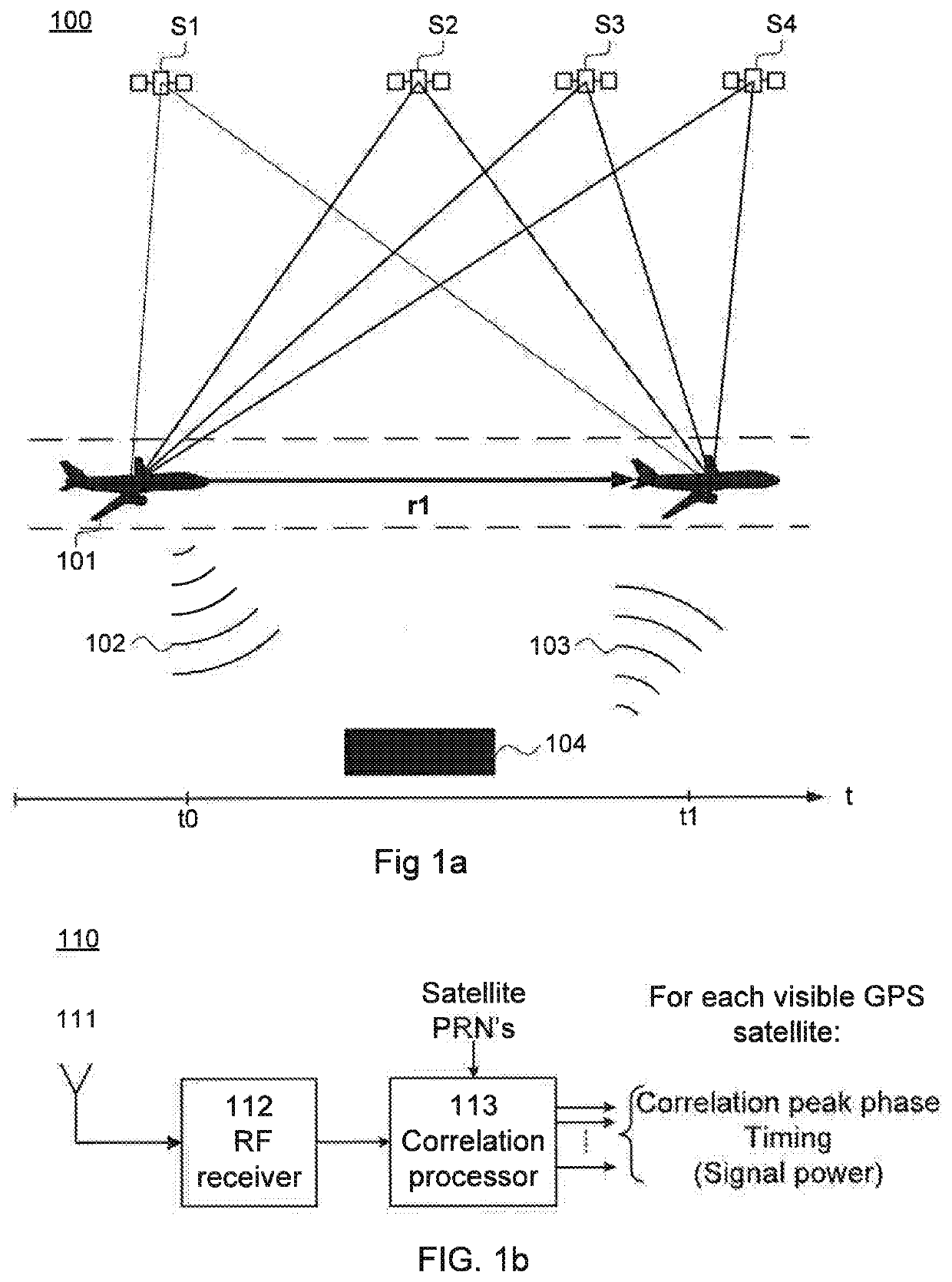

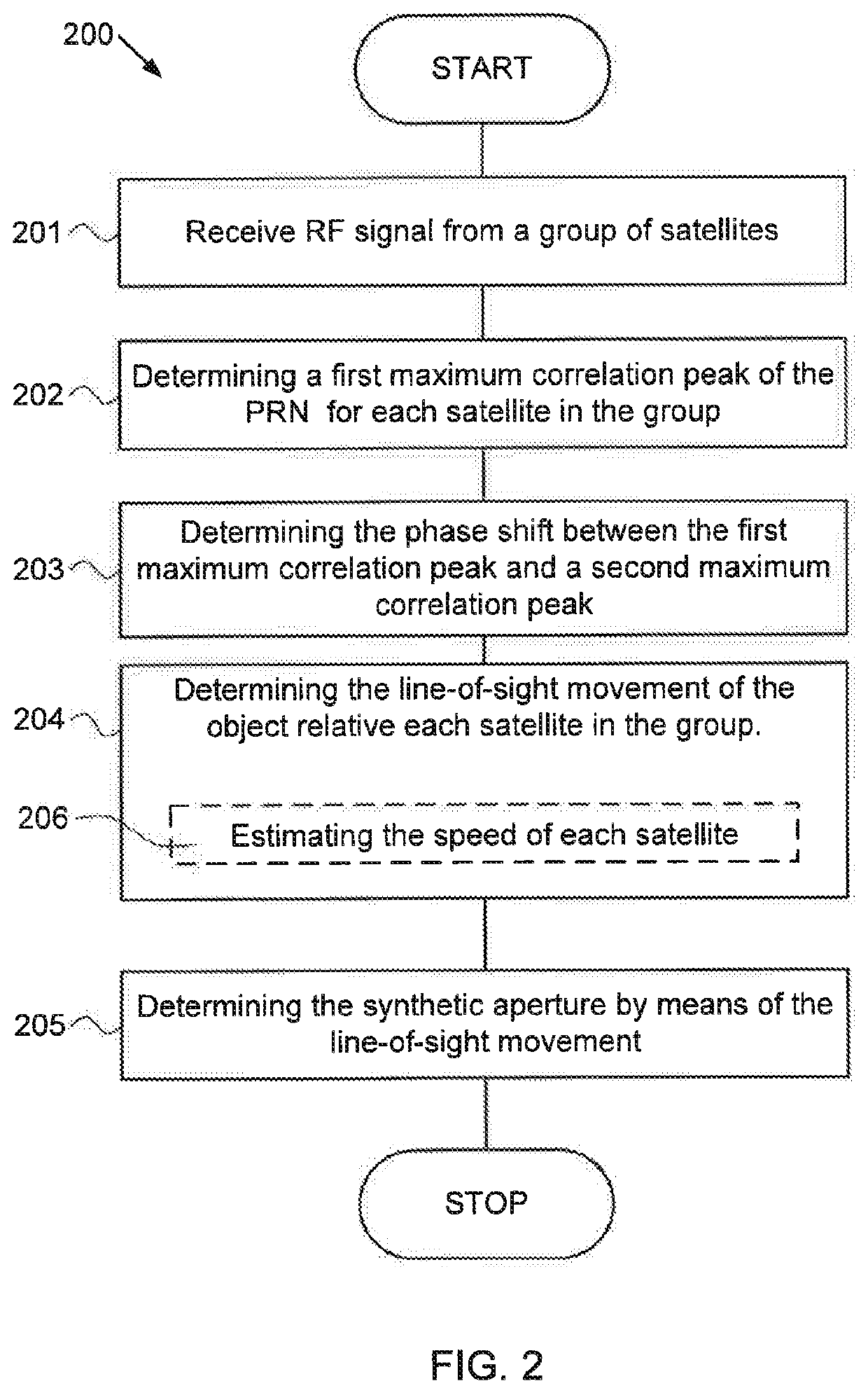

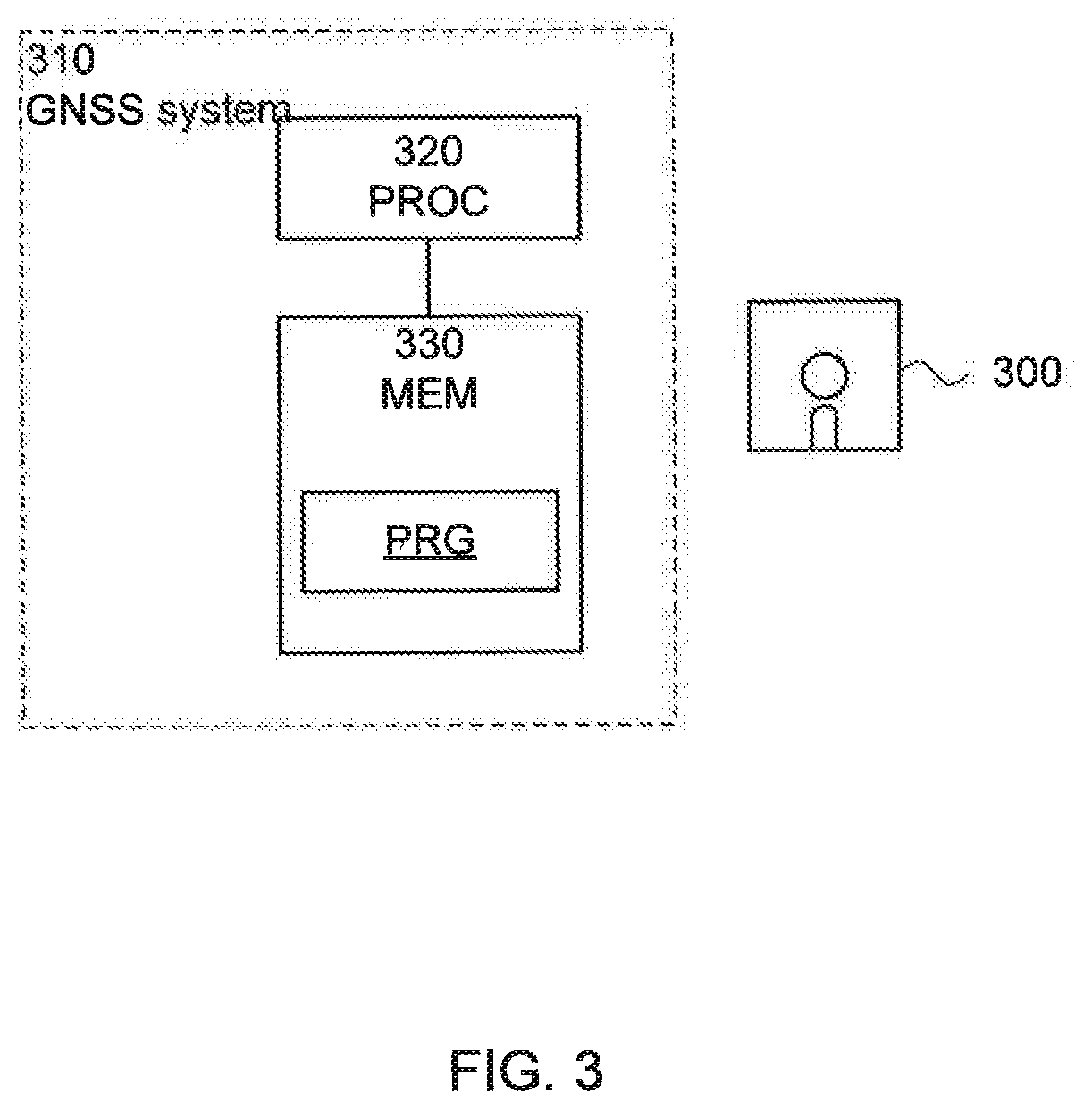

A method for determining the base line for a synthetic aperture of a SAR using GNSS

ActiveUS20200225360A1Mitigate, alleviate, or eliminate one or moreSatellite radio beaconingRadio wave reradiation/reflectionSynthetic aperture radarRadio frequency signal

The present invention relates to a method for determining a synthetic aperture of a synthetic aperture radar, SAR, system using information from a global navigation satellite system, GNSS, which includes a plurality of satellites each transmitting a radio frequency signal comprising a unique pseudo random number, PRN. The method comprises: receiving the radio frequency signal from a group of satellites in the GNSS, determining a first maximum correlation peak of the PRN of the received radio frequency signal from each satellite in the group of satellites, determining the phase shift between the first determined maximum correlation peak and a second determined maximum correlation peak of a received PRN from the same satellite at a later time, for each satellite in the group of satellites, determining a line-of-sight, LOS, movement of the SAR system relative each of the satellites in the group of satellites by means of the determined phase shift for each satellite in the group of satellites, and determining a synthetic aperture using the LOS movement relative each satellite in the group of satellites.

Owner:SAAB AB

Method for manufacturing of urinary catheters

InactiveUS20150018804A1Increase cavity volumeMitigate, alleviate or eliminate one or moreWound drainsCatheterUrinary catheterCavity wall

A method for manufacturing an elongated element (200) is provided. The method comprises arranging a molding cavity (101), defined by a mold (103) and a mold insert (104), said mold insert (104) comprising a mold core (105) and a displaceable mold cavity wall (106), said displaceable mold cavity wall (106) being arranged between the mold (103) and the mold core (105), such that the molding cavity has a start volume in a start position of the displaceable mold cavity wall (106). Then a liquid material is injected into a proximal end (102) of the molding cavity (101), where after the displaceable mold cavity wall (106) is displaced in relation to and along with the mold (103) and the mold core (105), distally during said injection, to increase the molding cavity volume from the start volume into an end volume at an end position of the displaceable mold cavity wall (106), wherein the molding cavity (101) in said end position of the displaceable mold cavity wall (106) corresponds to the elongated element (200). The liquid material is solidified, such that the elongated element (200) is formed, and the elongated element (200) and mold insert (104) is removed from said mold (103), where after the elongated element (200) is removed from said mold insert (104). An elongated element and a mold assembly for the manufacture thereof are also provided.

Owner:ROLSTED MOLD SYST APS

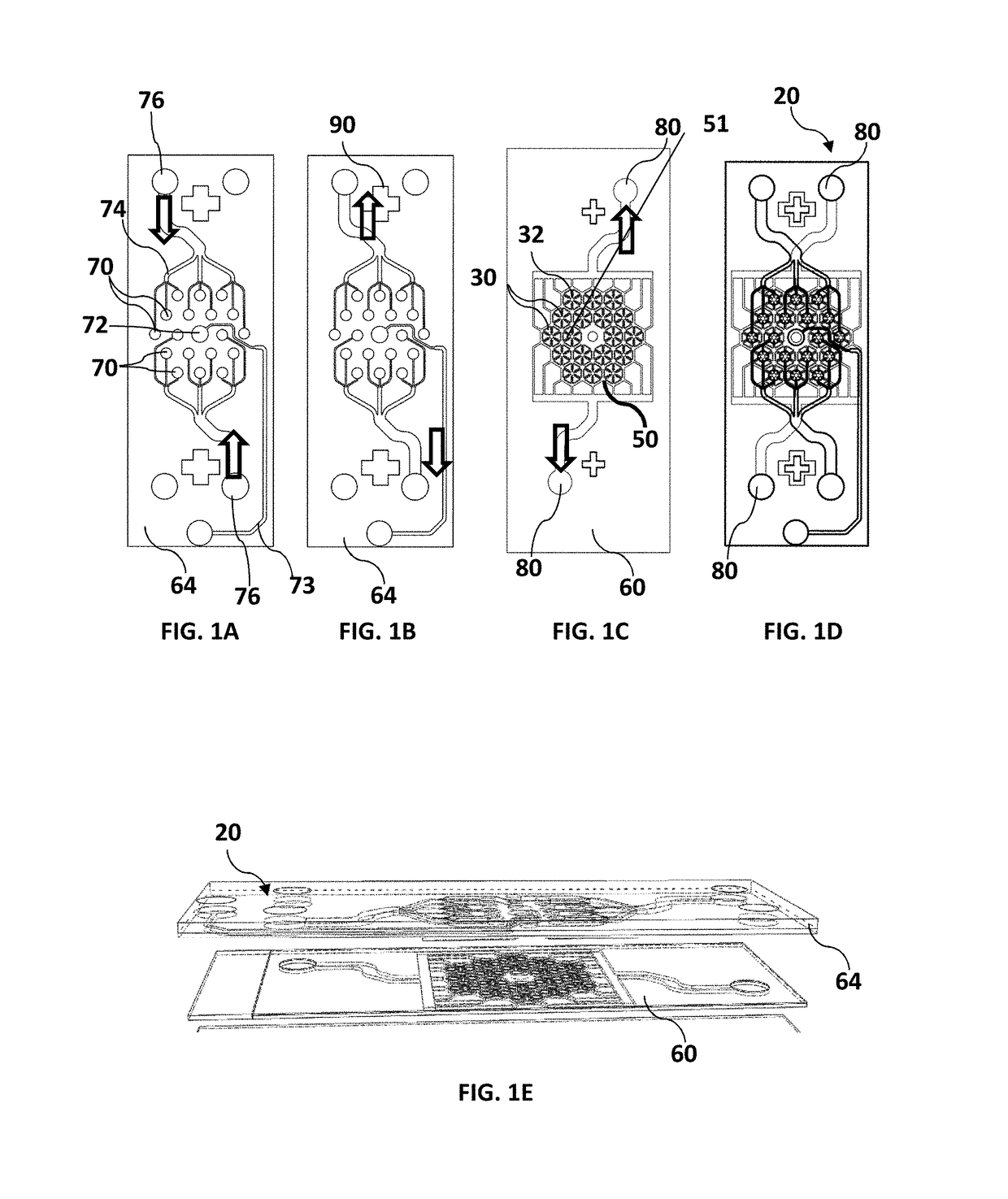

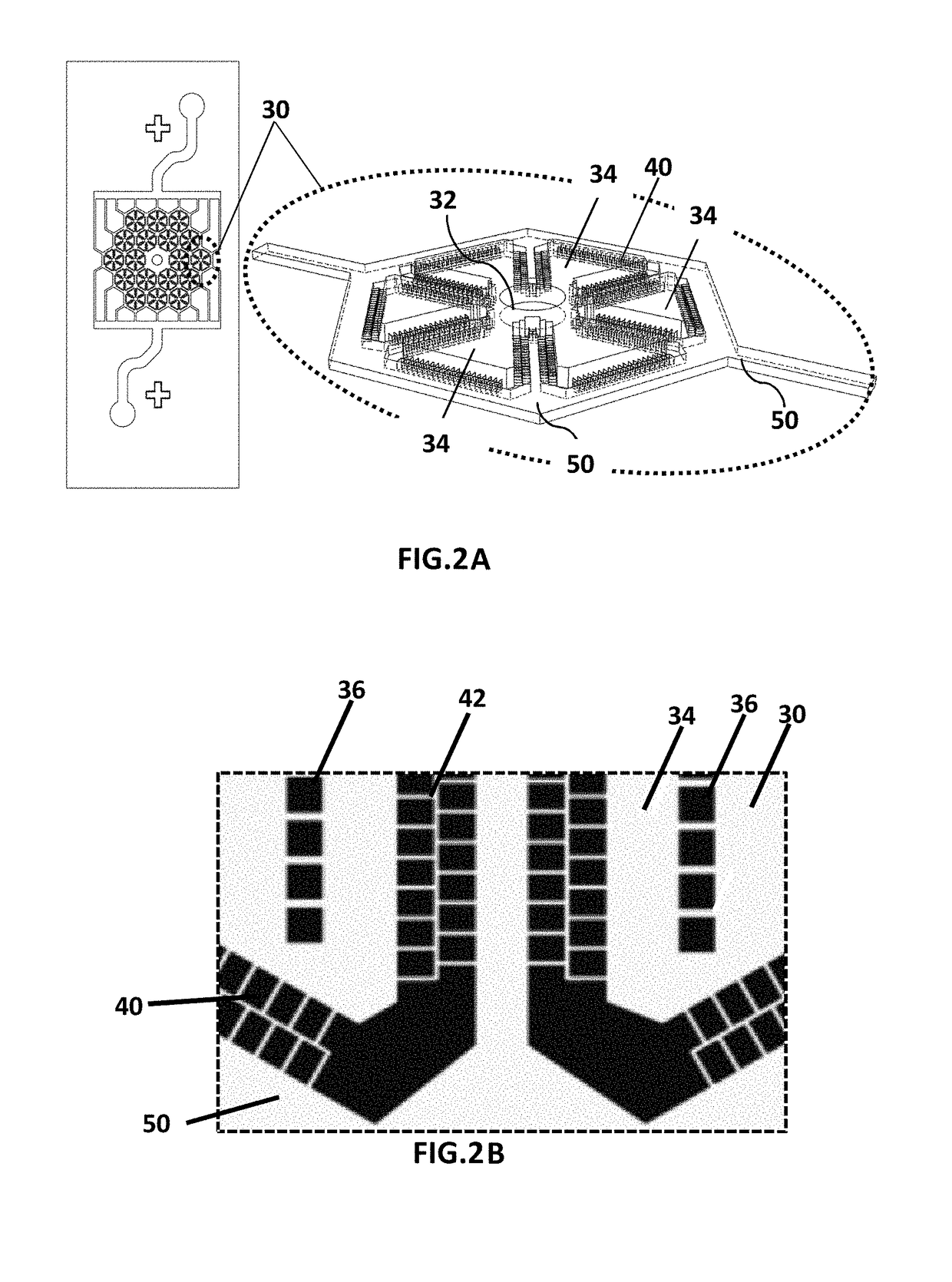

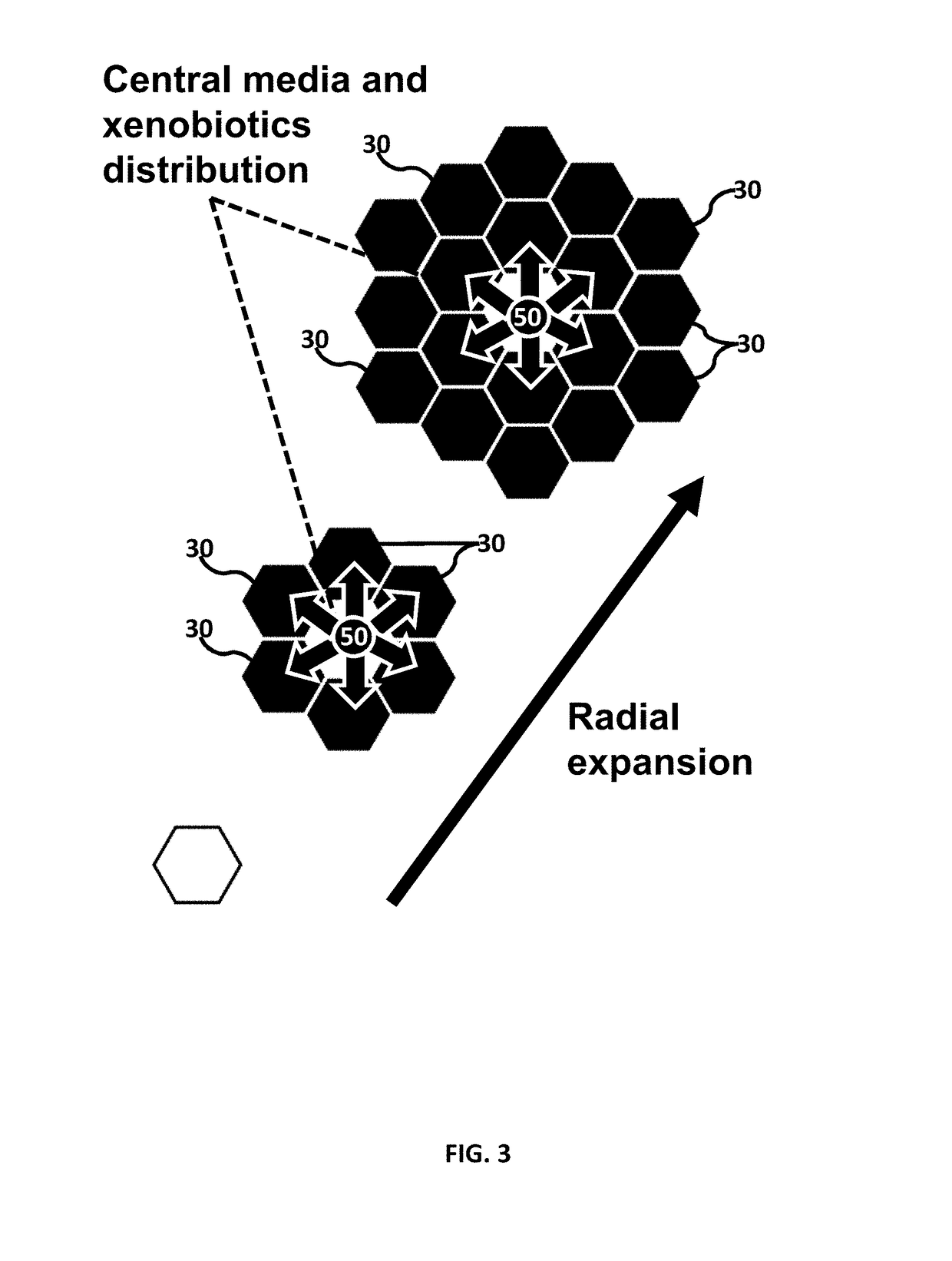

Microfluidic device for culturing cells

InactiveUS20190062686A1Mitigate, alleviate or eliminate one or moreImprove performanceBioreactor/fermenter combinationsBiological substance pretreatmentsCulture cellChannel network

A microfluidic device (10) for culturing and / or analysing at least one cell type is disclosed. The device (10) comprises a plurality of chambers (30), arranged in a radial expansion model. Chambers (30) have a central aperture (32) for receiving and / or removing the first cell type into the chamber (30) . The device (10) comprises a wall (40) on the perimeter of each chamber (30), and a feed channel network (50) outside each chamber adjacent to the wall (40) for conveying culture medium, reagents and / or a second cell type. The feed channel network (50) is provided with a central port (51) and configured such that culture medium, reagents, and / or a second cell type provided to the central port are distributed symmetrically in a radial fashion in the feed channel network (50). The wall (40) of the device (10) has a plurality of microfluidic diffusion channels (42) for allowing flow of the culture medium, reagents and / or the second cell type from the feed channel (50) into each chamber (30). Methods of culturing cells using such a device are also disclosed.

Owner:BANAEIYAN AMIN A +3

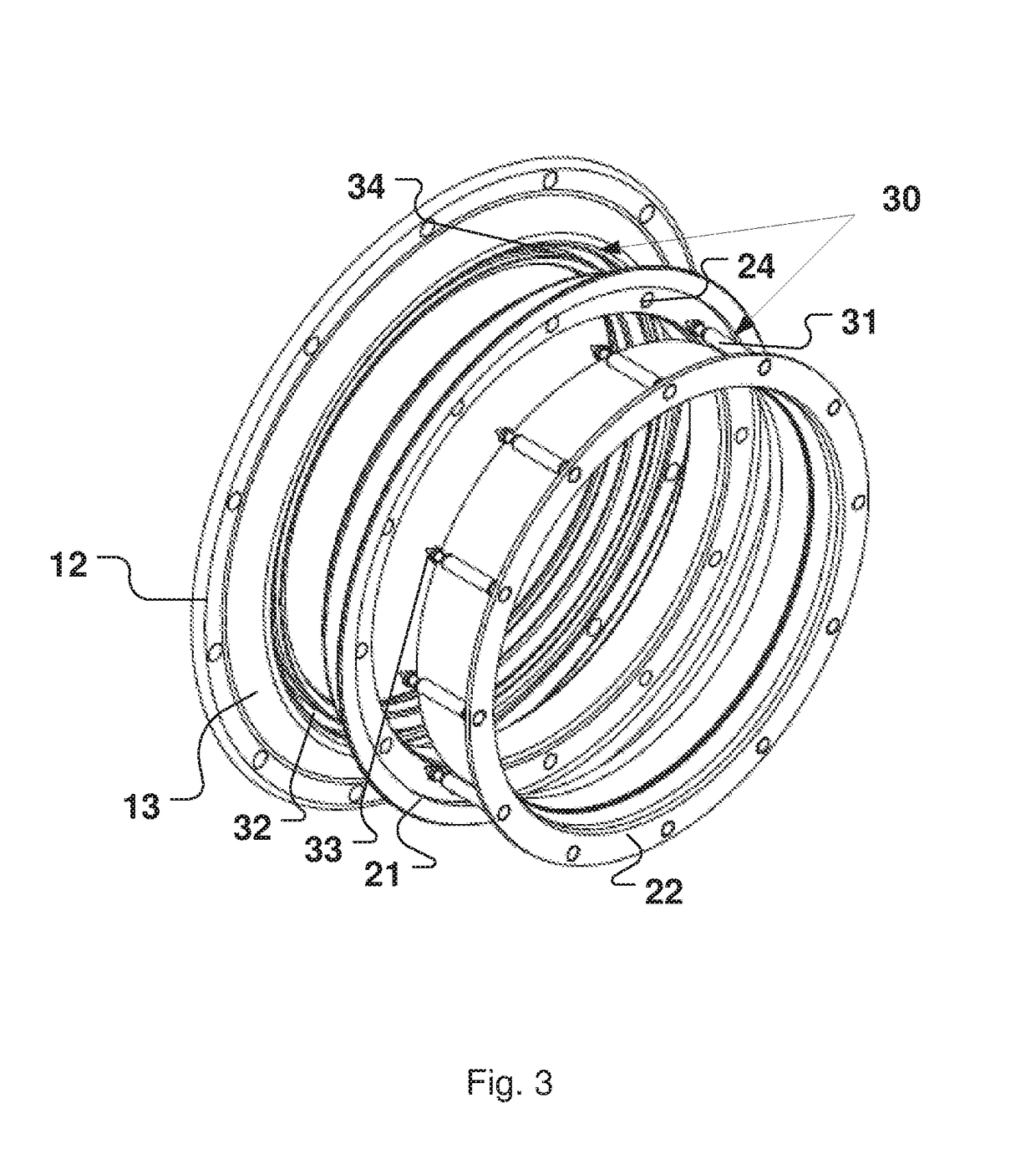

Apparatus for sealing an open end of a container

ActiveUS20130145726A1Reduce eliminateMitigate, alleviate or eliminate one or moreWrapper twisting/gatheringDomestic articlesRotational axisEngineering

An apparatus for sealing an open end of a package comprises a first longitudinally extending sealing jaw, bearing mounted on a first eccentric shaft rotatable around a first rotational axis, and a second longitudinally extending sealing jaw, bearing mounted on a second eccentric shaft rotatable around a second rotational axis, the second sealing jaw being parallel with the first sealing jaw. At least one motor drives rotation around the first and second rotational axis in opposite directions, wherein the first and the second sealing jaws oppose each other, and are allowed to oscillate between sealing and open positions by moving towards and away from each other. A first and second transversally extending guiding bar cooperate with the first and second eccentric shaft via guiding pins running in guiding grooves, such that transverse play between the first and the second eccentric shaft and the first and second sealing jaw is allowed.

Owner:TETRA LAVAL HLDG & FINANCE SA

Bus control for a domestic appliance

InactiveUS20120246365A1Guaranteed operational reliabilityLess laborPrecision positioning equipmentSubstation remote connection/disconnectionData memoryEmbedded system

A domestic appliance (1) with a bus (2) is disclosed. A plurality of modules (3) are connected to the bus, each controlling an operational component (4). Initial programming of the modules may take place from a single connection point (61). The modules may be configured to control the domestic appliance jointly and non-hierarchically. Suitably, all modules are identical up to content of a data memory provided therein.

Owner:ELECTROLUX HOME PROD CORP NV

Tracheostoma valve

ActiveUS20190111225A1Mitigate, alleviate or eliminate one or moreTracheal tubesMoistureBiomedical engineering

A tracheostoma device for cooperation with a tracheostoma device holder superimposed on a tracheostoma of a person is provided. The tracheostoma device comprises a tubular body and a container. Said tubular being at the proximal end of the tracheostoma device, comprising at least one inlet upon exhalation through the tracheostoma device, and being adapted for cooperation with the tracheostoma device holder. The container being at the distal end of the tracheostoma device, comprising at least one outlet upon exhalation through the tracheostoma device, and being adapted for housing a heat and moisture exchanging foam. The tubular body and the container may have a hardness of less than and including 100 Shore A.

Owner:COLOPLAST AS

Device and a method for anastomosis

ActiveUS20150201942A1Mitigates and alleviatesUniform distributionSurgical staplesWound clampsDistal anastomosisEngineering

Owner:CARPONOVUM AB

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com