Patents

Literature

81results about How to "Robust solution" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

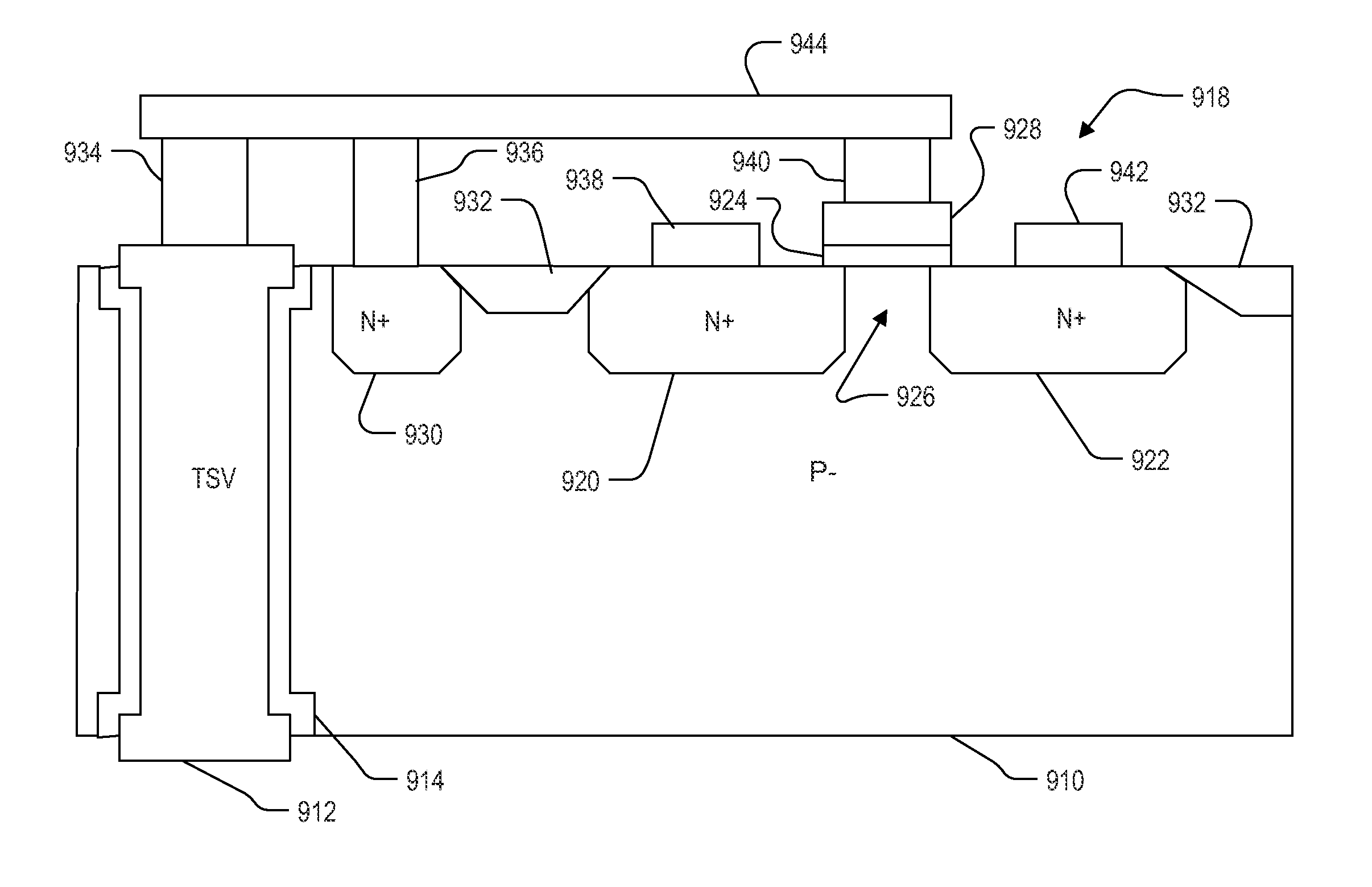

ESD/antenna diodes for through-silicon vias

ActiveUS8264065B2High yieldMore powerful circuits, components and systemsSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorExclusion zone

Roughly described, an antenna diode is formed at least partially within the exclusion zone around a TSV, and is connected to the TSV by way of a metal 1 layer conductor at the same time that the TSV is connected to either the gate poly or a diffusion region of one or more transistors placed outside the exclusion zone.

Owner:SYNOPSYS INC

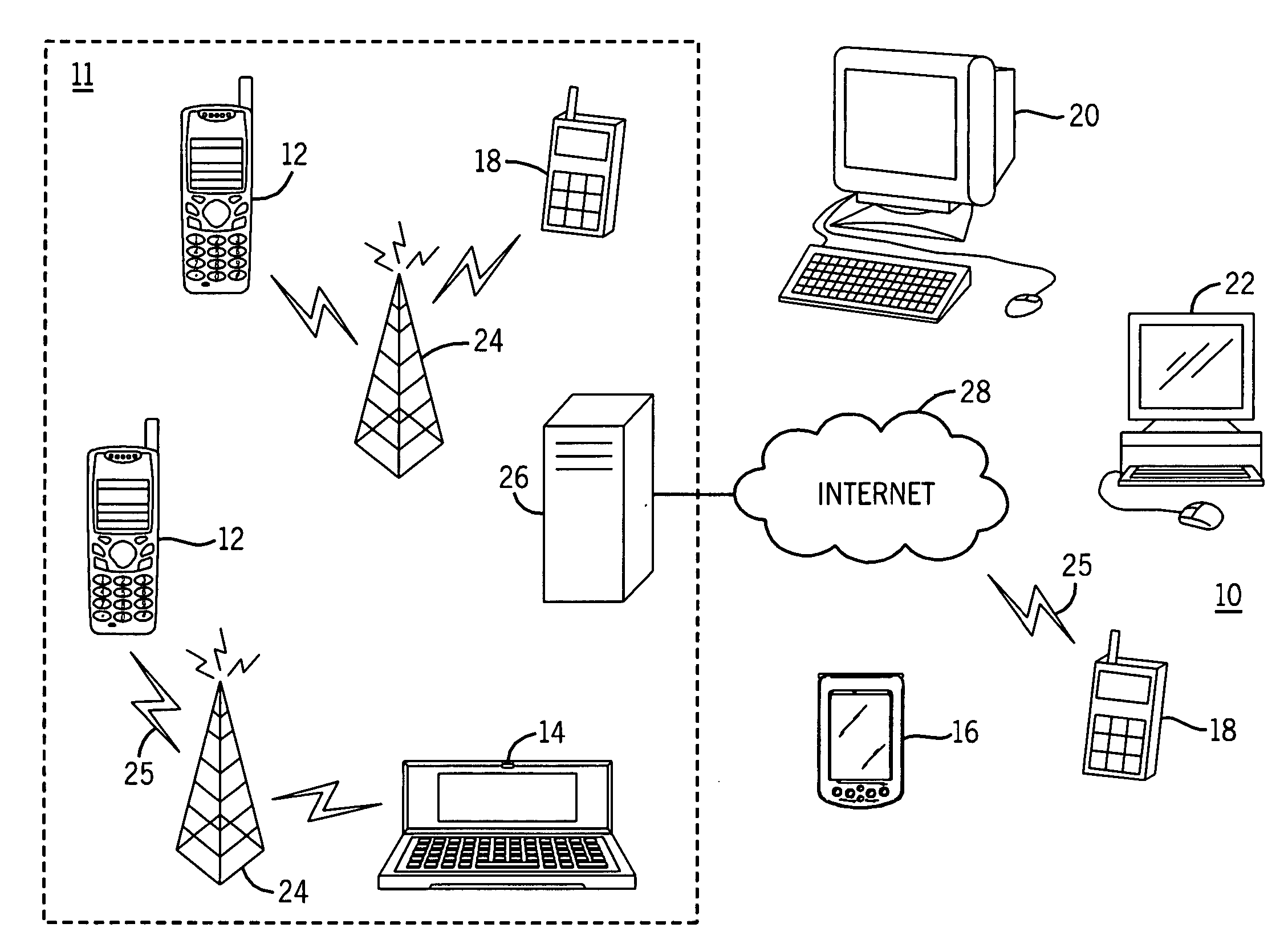

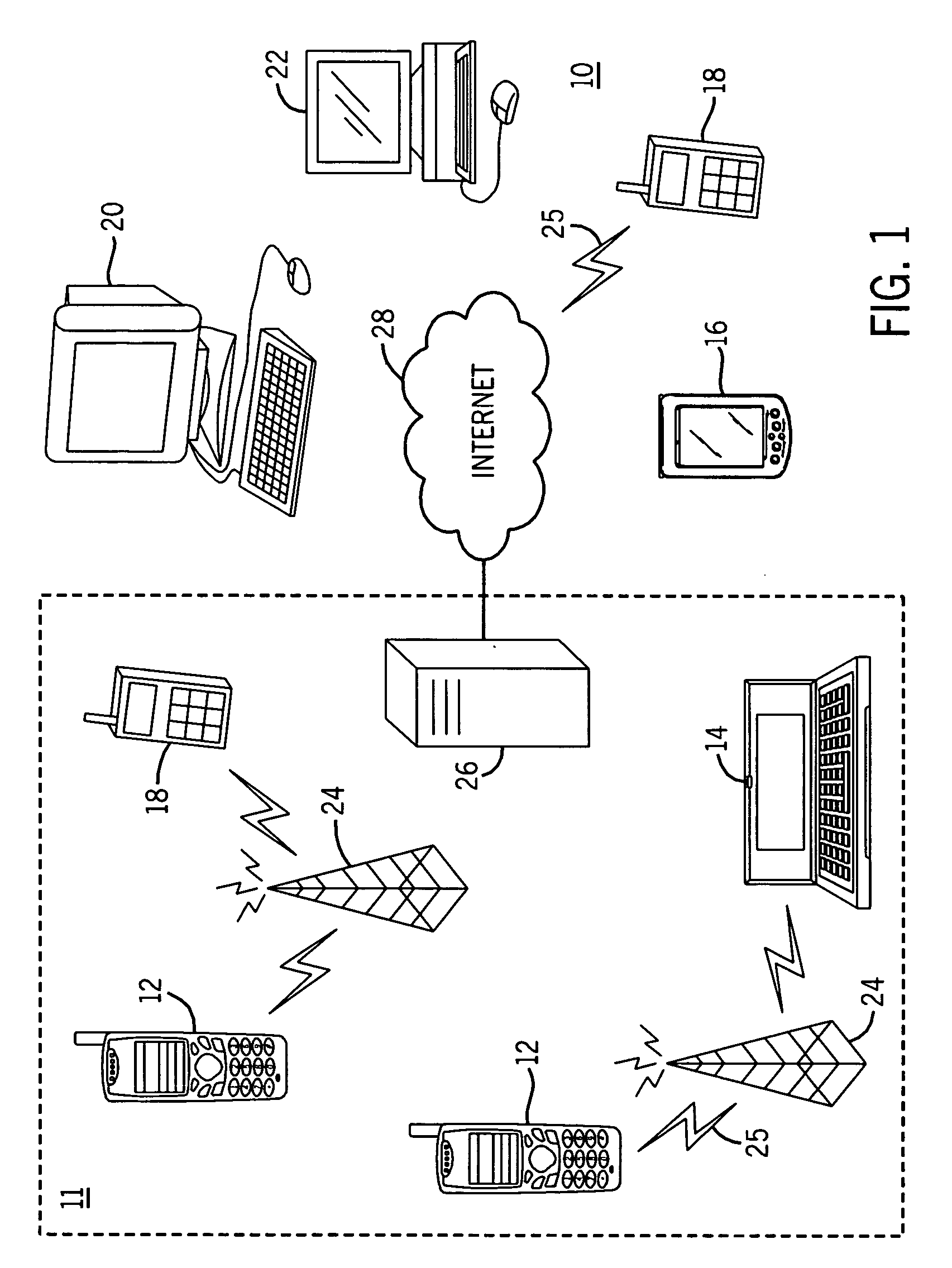

Method and apparatus for bi-layer segmentation

ActiveUS20130230237A1Robust solutionMinimized volumeImage enhancementImage analysisImage basedColor data

A method and an apparatus for bi-layer segmentation of an image or a sequence of images are described. A classifier is derived based on depth data of the image and another classifier is derived based on color data of the image. The image is then segmented by maximizing a weighted sum of matching scores derived from the classifiers based on depth data and color data of the image. The classifier based on color data of the image is derived using color sampling subsequent to generating an initial segmentation of the image.

Owner:INTERDIGITAL VC HLDG INC

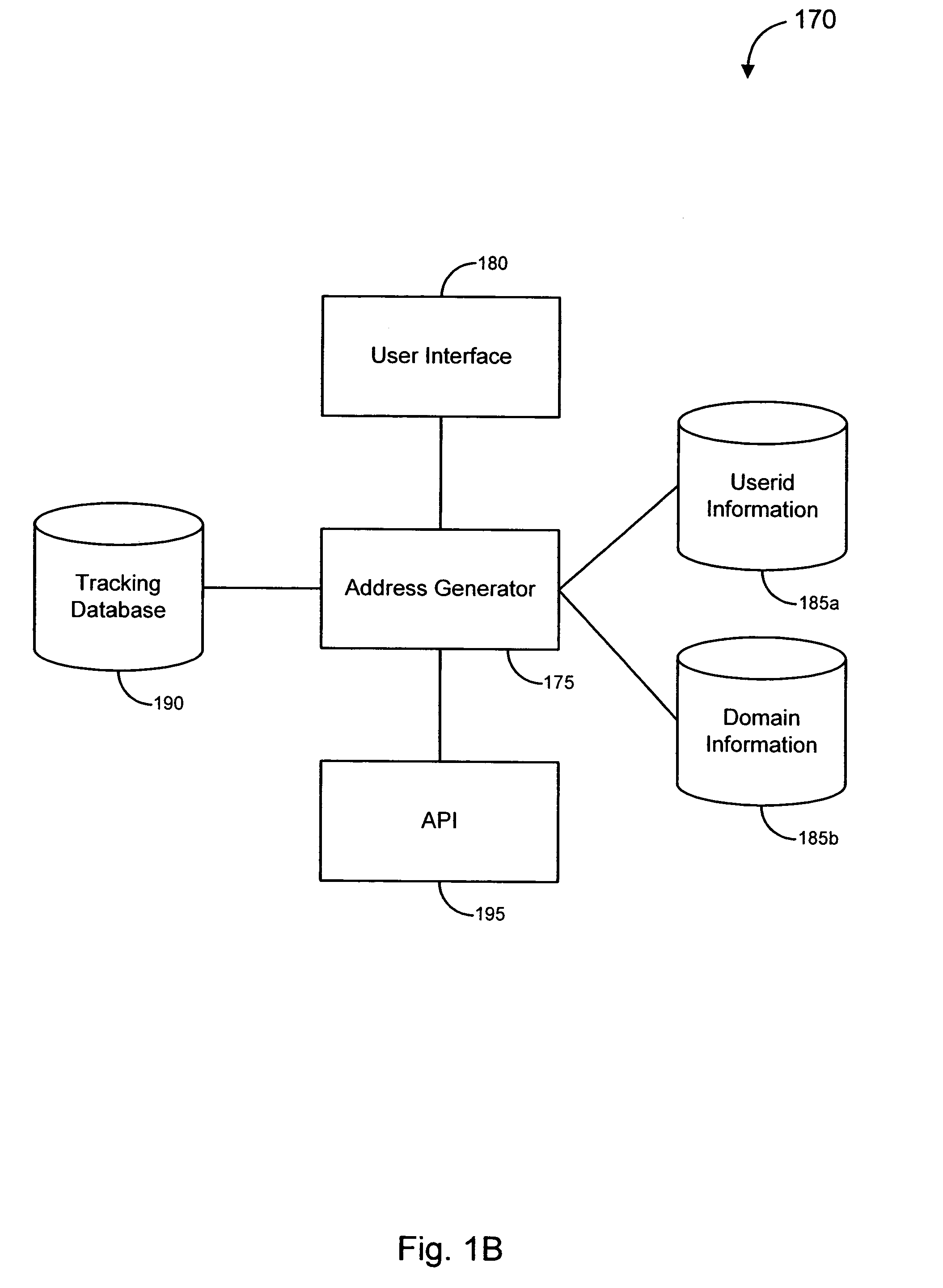

System and method for identifying segments in a web resource

ActiveUS20060282758A1Beneficial interaction modelImprove performanceDigital data information retrievalCharacter and pattern recognitionInternet contentSemantics

A robust, lightweight, bottom-up segmentation method for Internet content. According to the present invention, individual segments are created based upon weights assigned according to document structure and markup elements and semantics. Smaller segments are then merged into larger segments by determining which portions of the content page are related to each other. The remaining segments are then intelligently divided based upon device constraints.

Owner:III HLDG 3

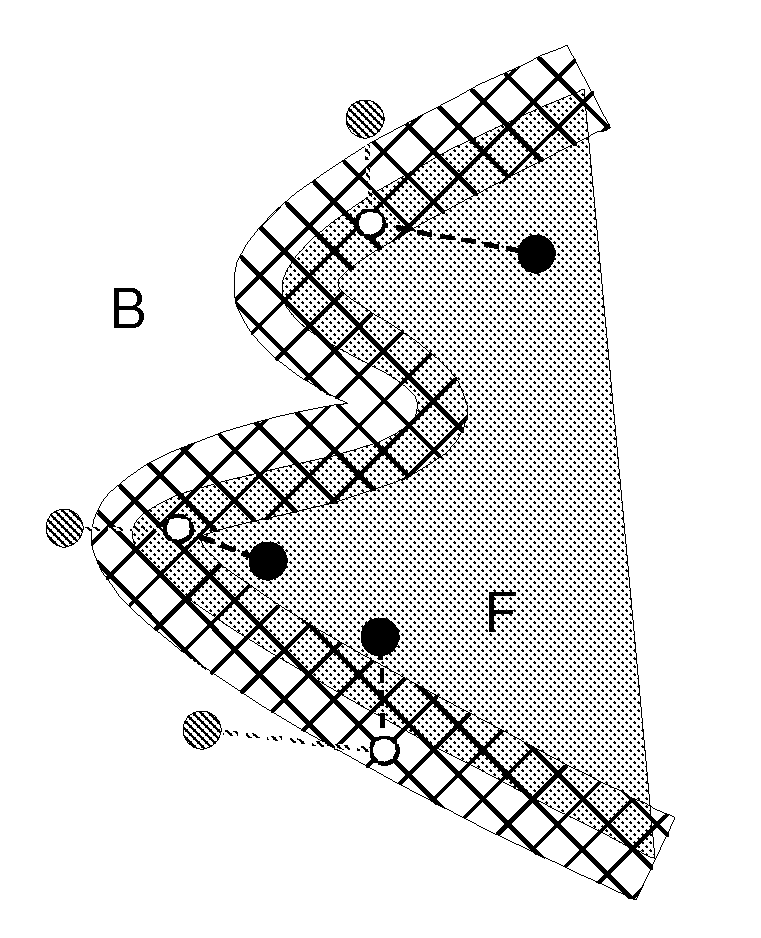

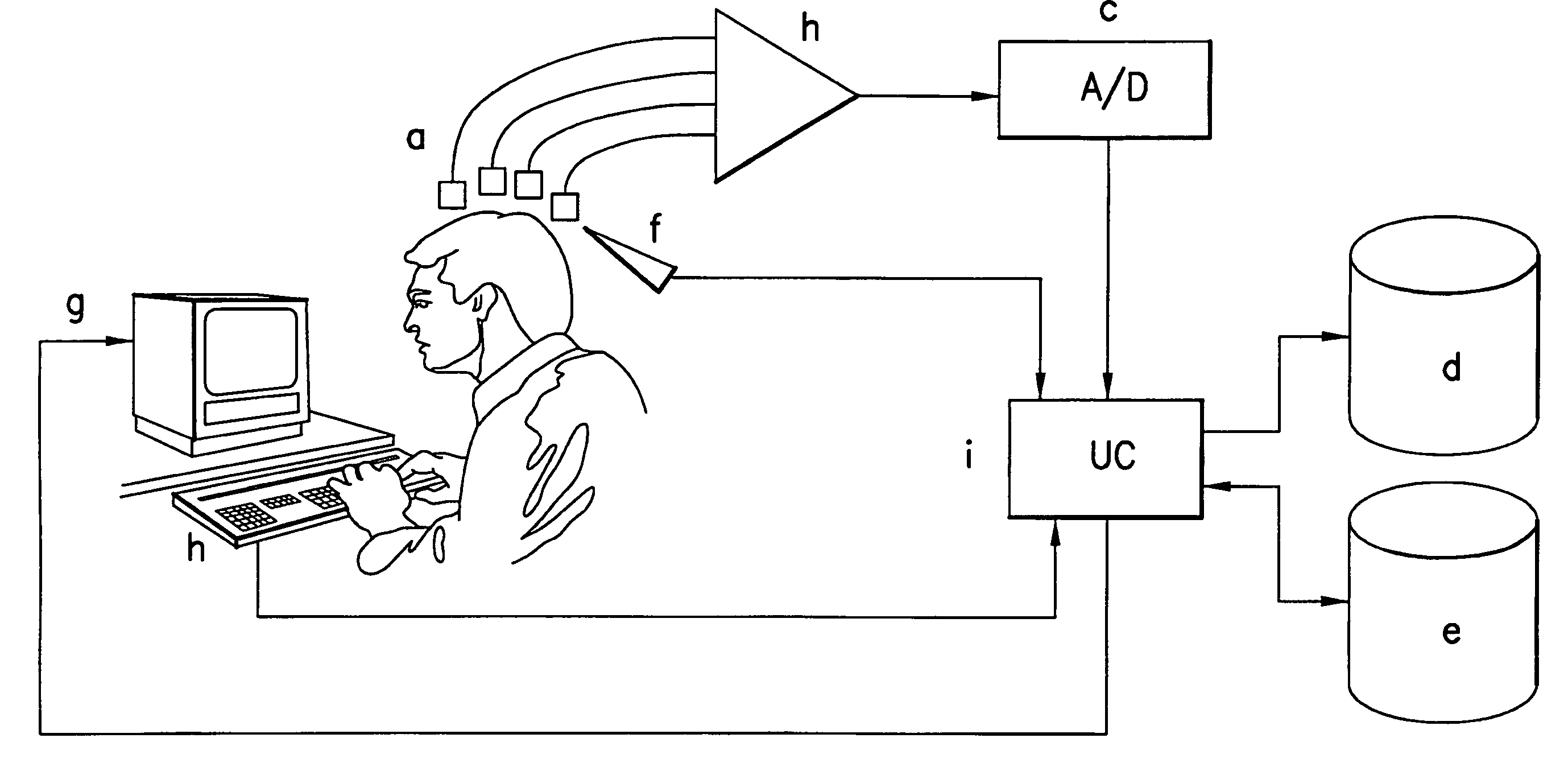

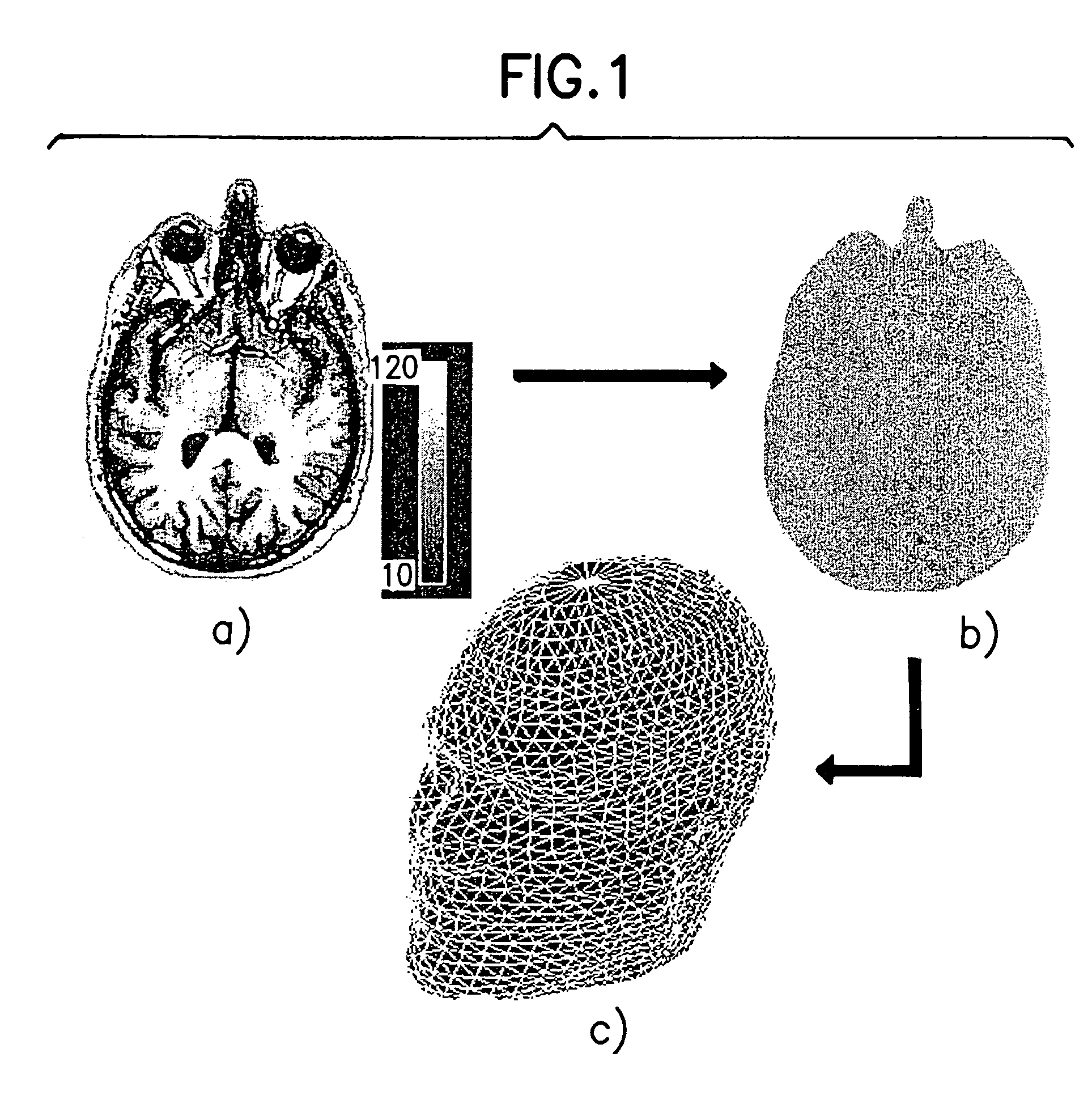

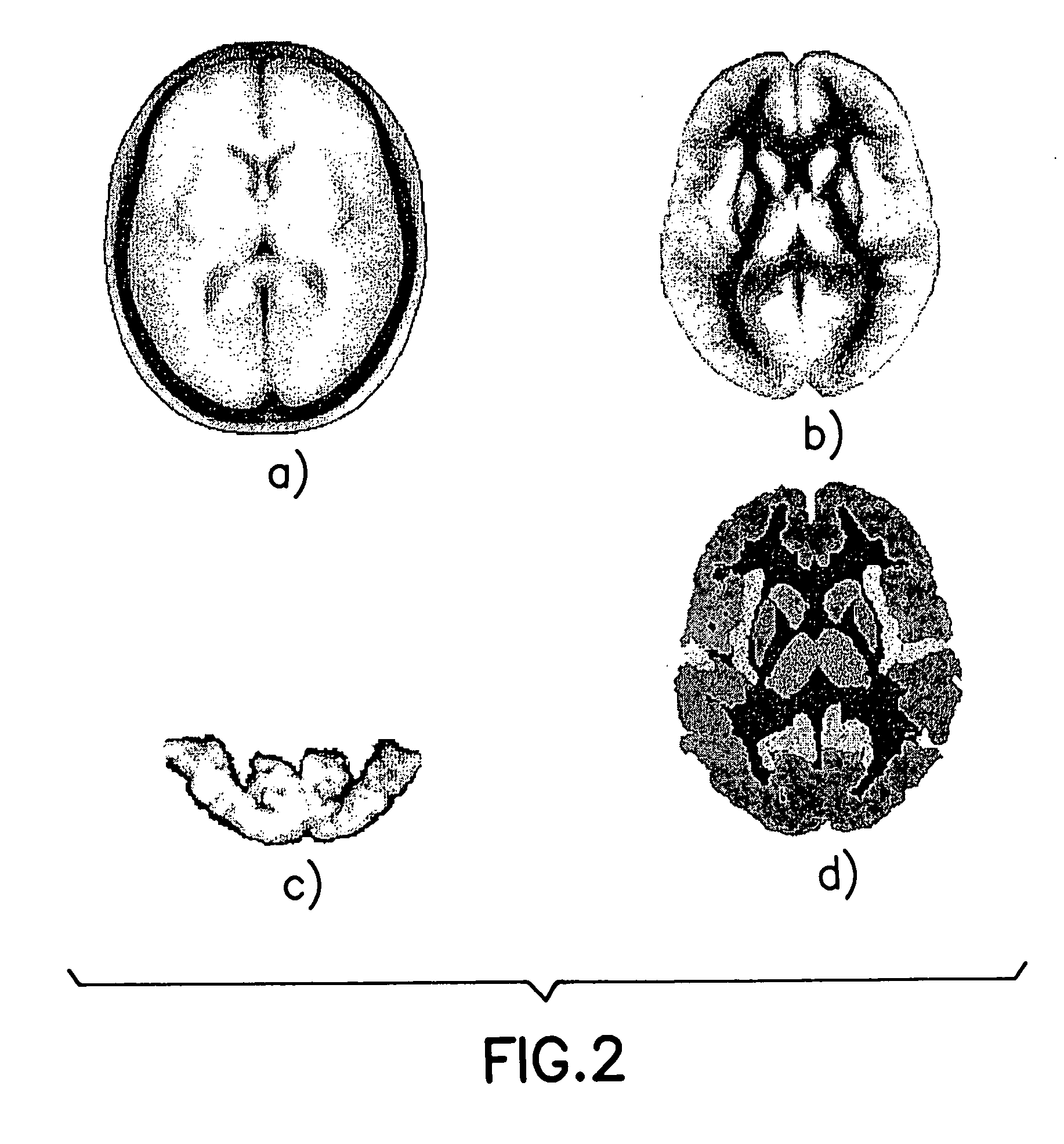

System and method for the tomography of the primary electric current of the brain and of the heart

InactiveUS7092748B2Low costReduce errorsBioelectric signal measurementSensorsTomographyFunctional space

A three-dimensional map of the probability of brain or heart functional states is obtained based on electric or magnetic signals, or a combination of both measured in the surface of body. From signals, the statistical descriptive parameters are obtained and a map of its distribution is calculated. The map is the inverse solution of the problem based upon: a) the restriction of the solution to structures with high probability of generating electric activity using for this restriction an Anatomical Atlas and b) imposing that the solution belong to a pre-specified functional space. The probability is determined that this map belongs to a test group. The spatial and temporal correlations of the map are modeled as well as their dependence on experimental covariables. The resulting probabilities are coded in a pseudocolor scale and they are superimposed on a Anatomical Atlas for their interactive three-dimensional visualization.

Owner:CENT NACIONAL DE INVESTIGACIONES CIENTIFICAS (CINC)

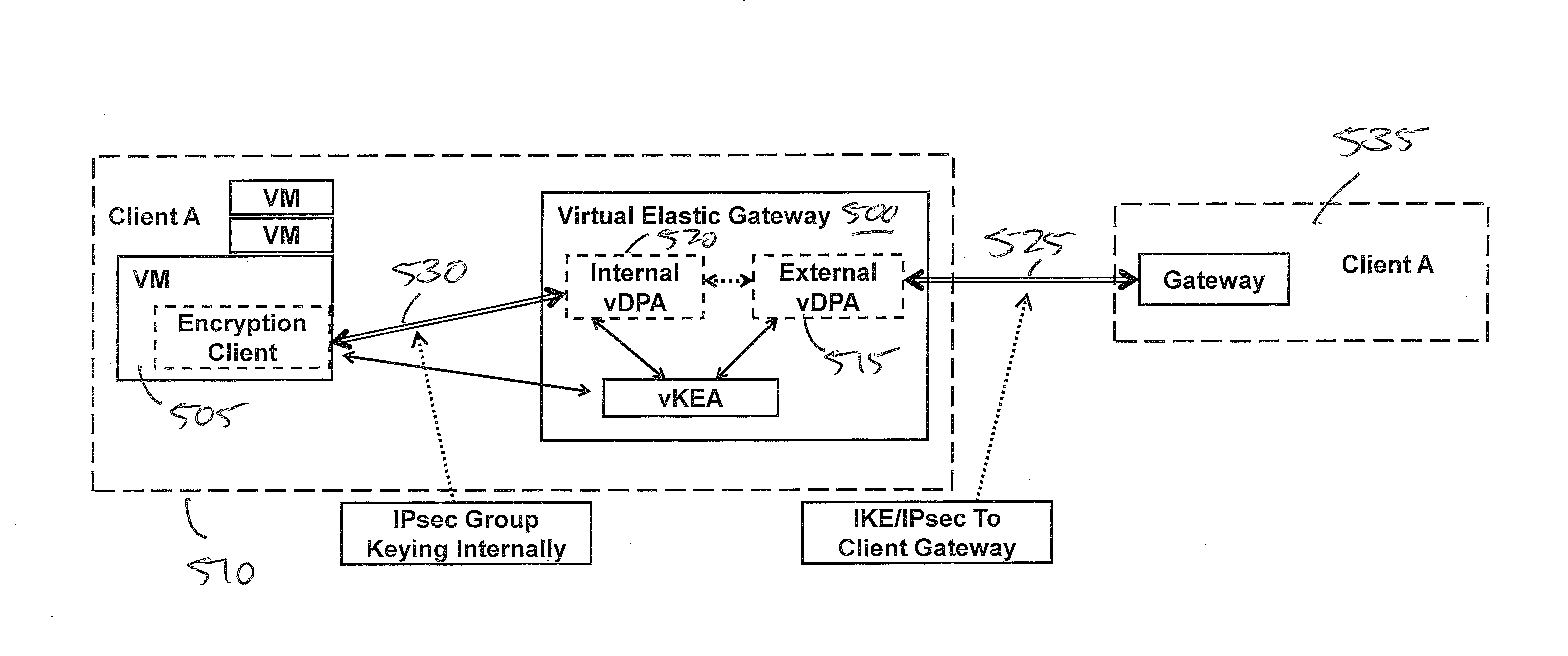

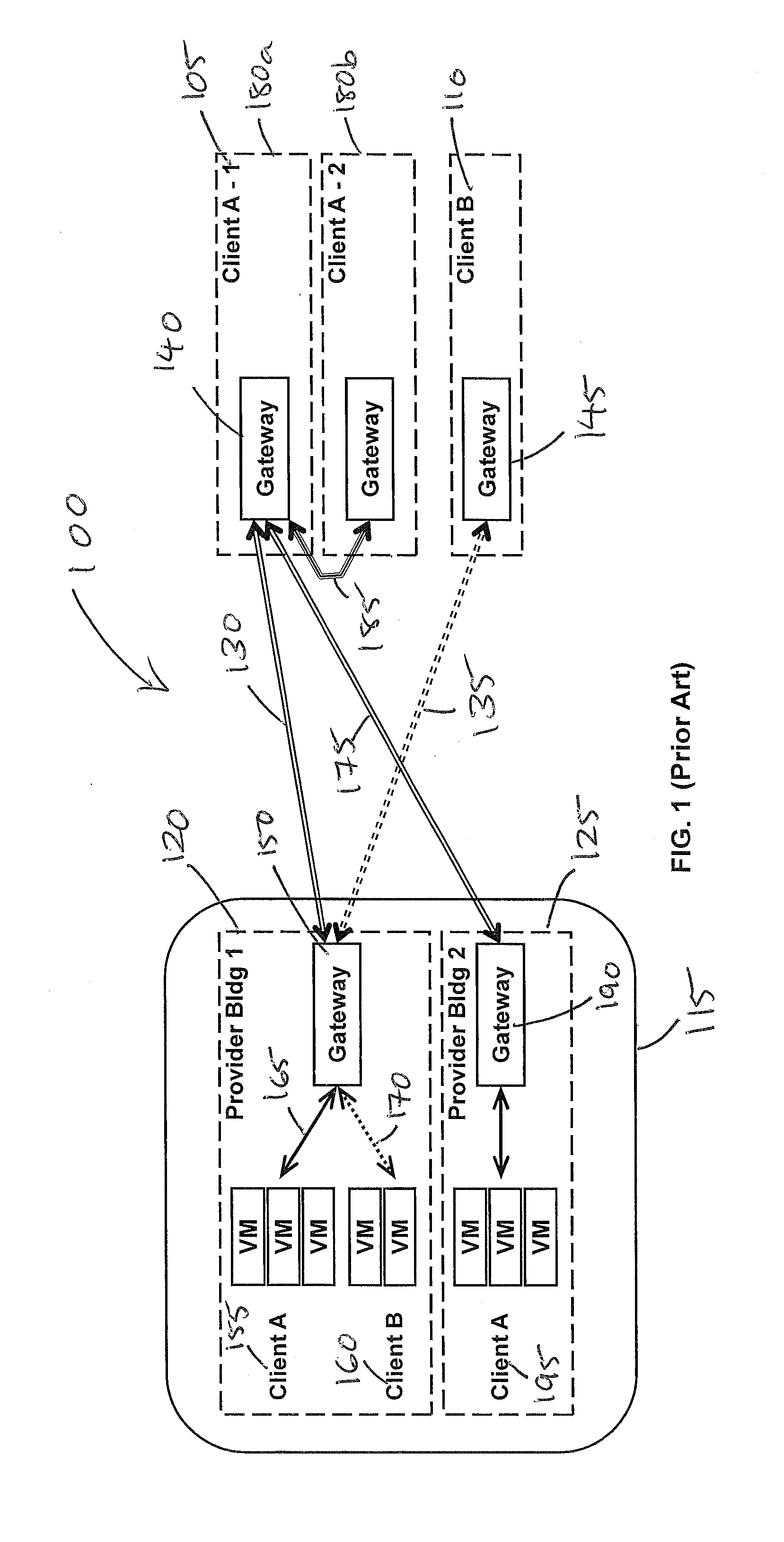

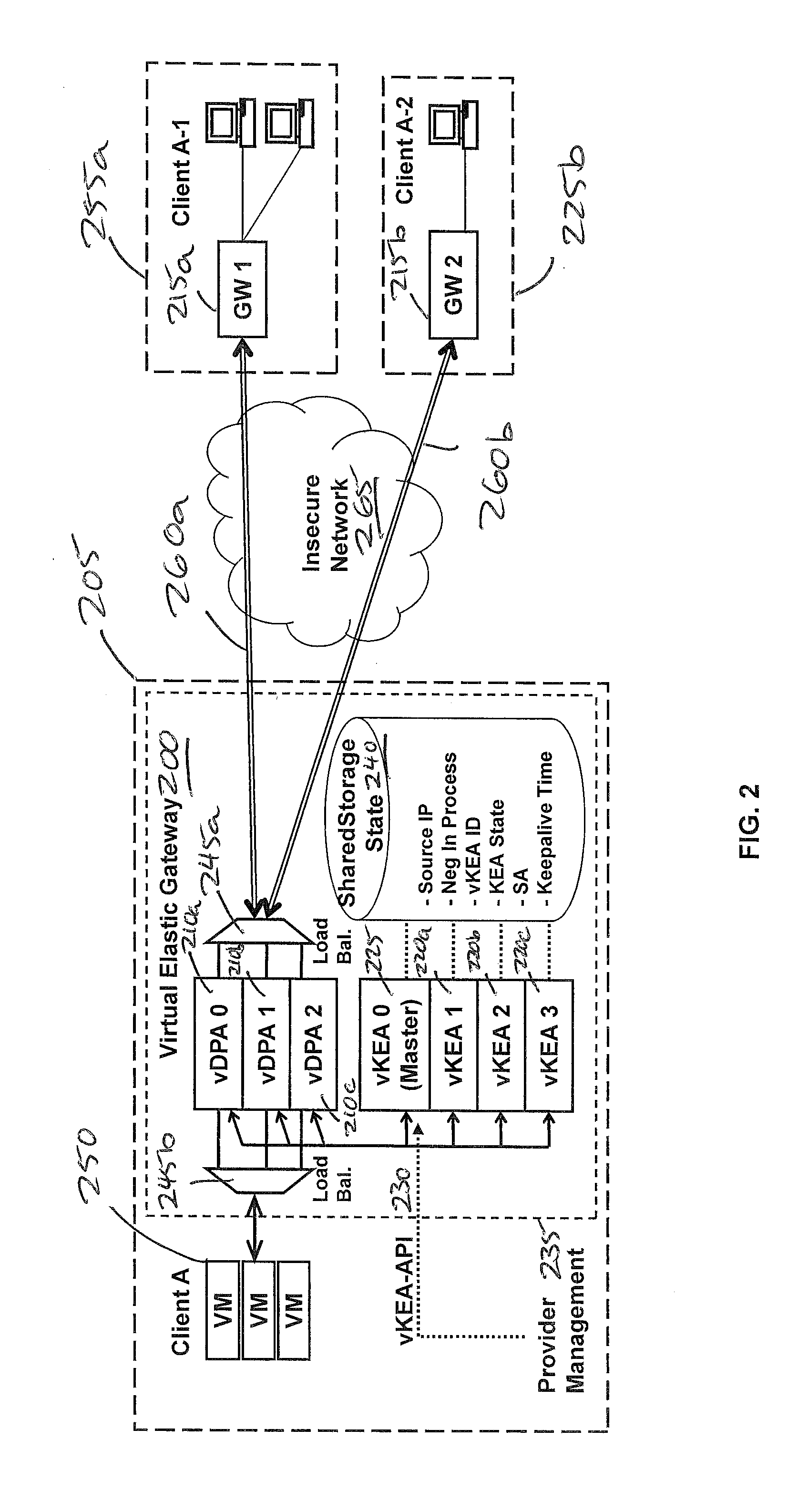

Dynamically scalable virtual gateway appliance

InactiveUS20120096269A1Improve availabilityRobust solutionUser identity/authority verificationDynamic ExtensionClient-side

A Virtual Elastic Gateway Appliance (VEGA) that implements all the capability of a security gateway in a set of virtual appliances for operation in a virtualized, cloud environment is provided. The virtual appliances are divided into various components to provide key exchange and data protection in separate virtual appliances allowing each to be scaled elastically and independently. Security management of the virtual gateway is under control of the client while the cloud provider can meter use of virtual resources. Shared state operation and tunneled key exchange ensure robust operation in a dynamic environment.

Owner:CIPHEROPTICS

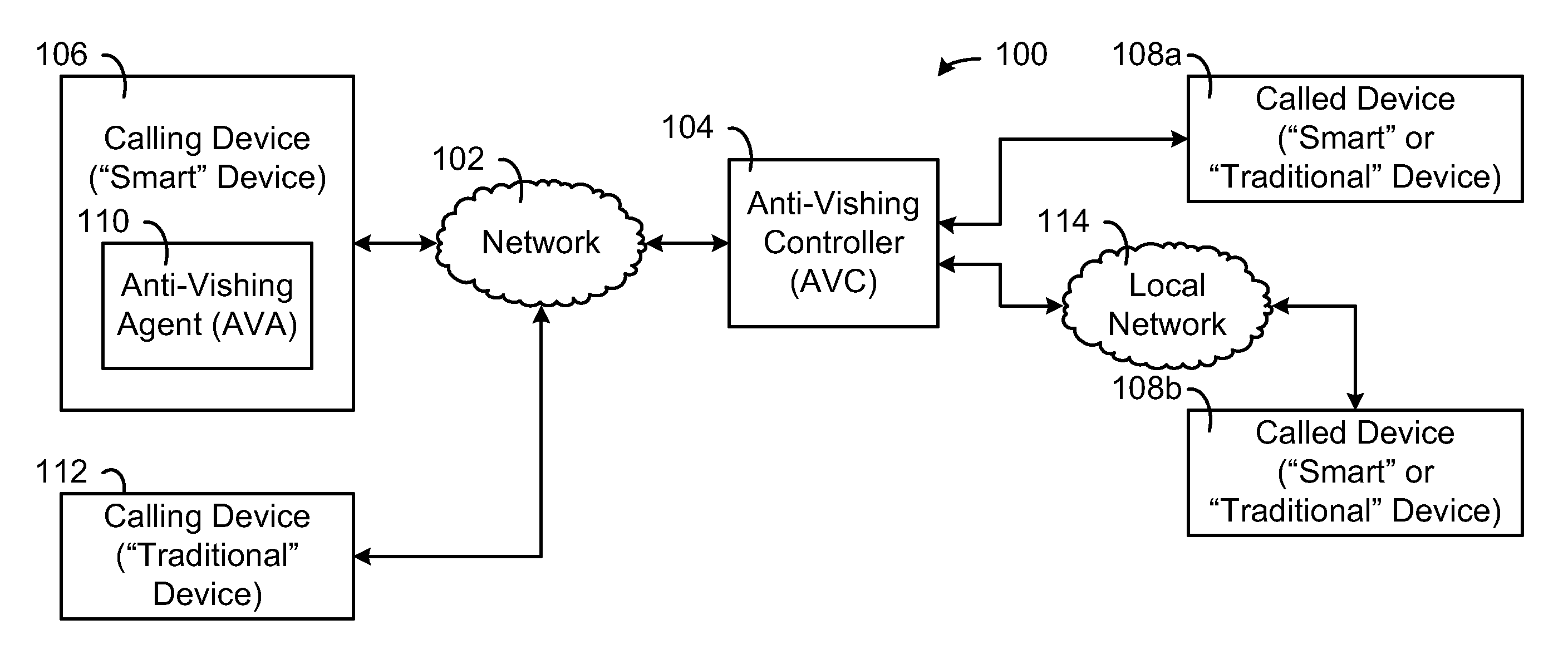

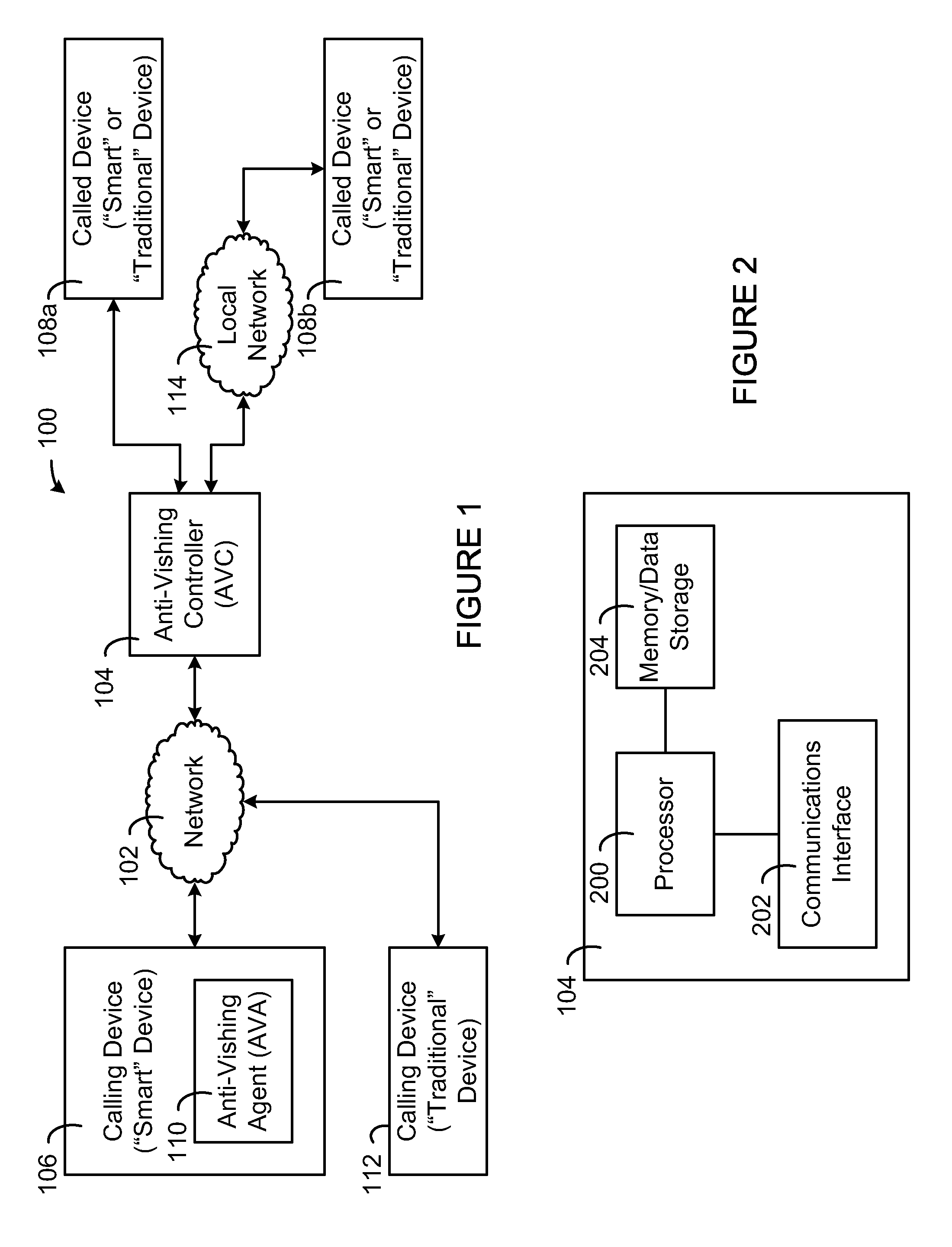

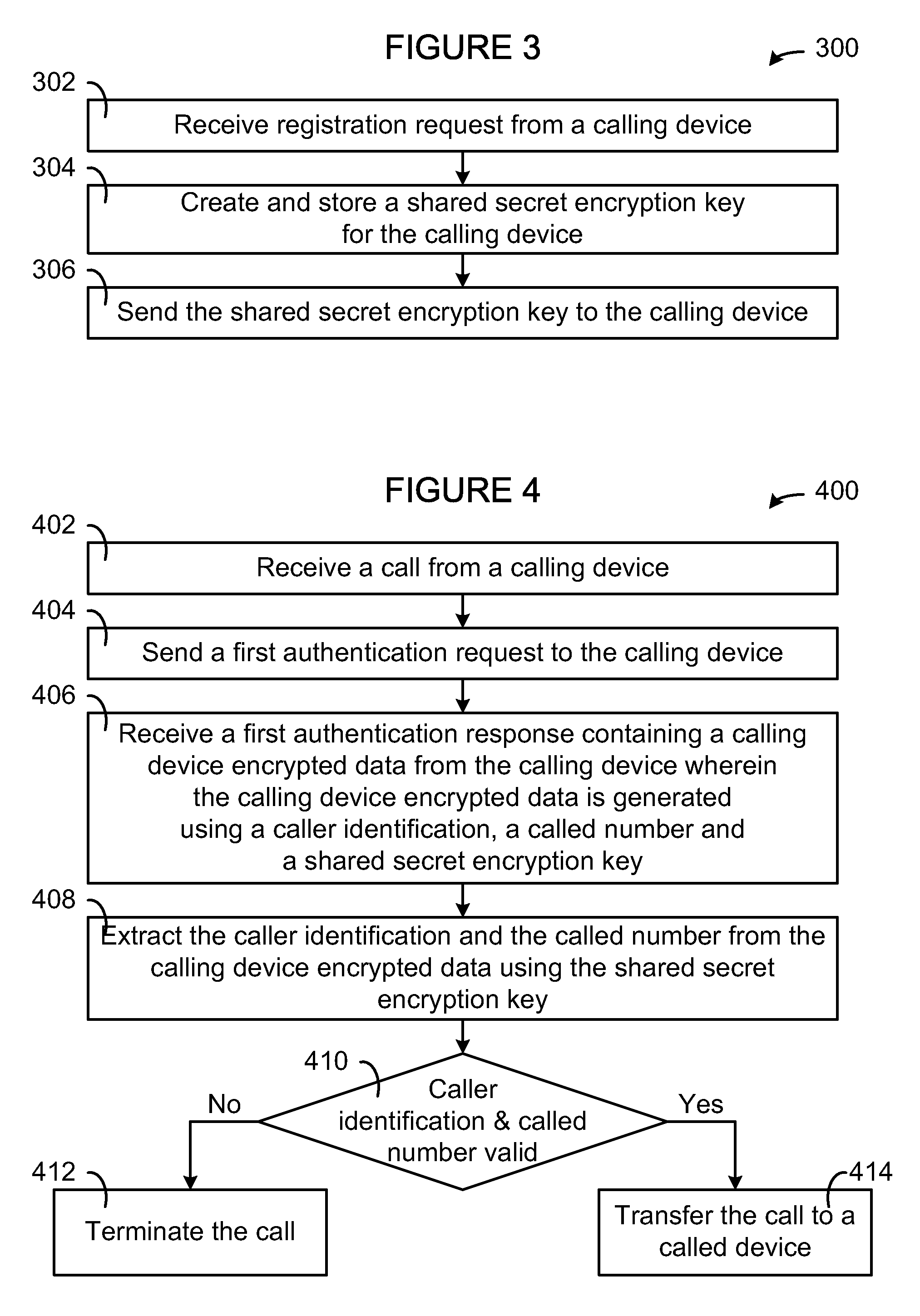

System, Method and Apparatus for Authenticating Calls

ActiveUS20090217039A1Little impact on user experienceReduce the impactDigital data processing detailsUser identity/authority verificationApplication softwareCommunication device

The present invention provides a system, method and apparatus for authenticating calls that is a robust Anti-vishing solution. The present invention can identify Caller ID spoofing, verify dialed number to detect man-in-the middle and verify called party against dialed digits to detect impersonation. This solution can handle calls coming from any phone any where with little impact on user experience. Two separate solutions are tailored for smart phones (communication devices capable of running application software) and traditional phones to reduce the impact to user experience while providing robust verification.

Owner:AVAYA INC

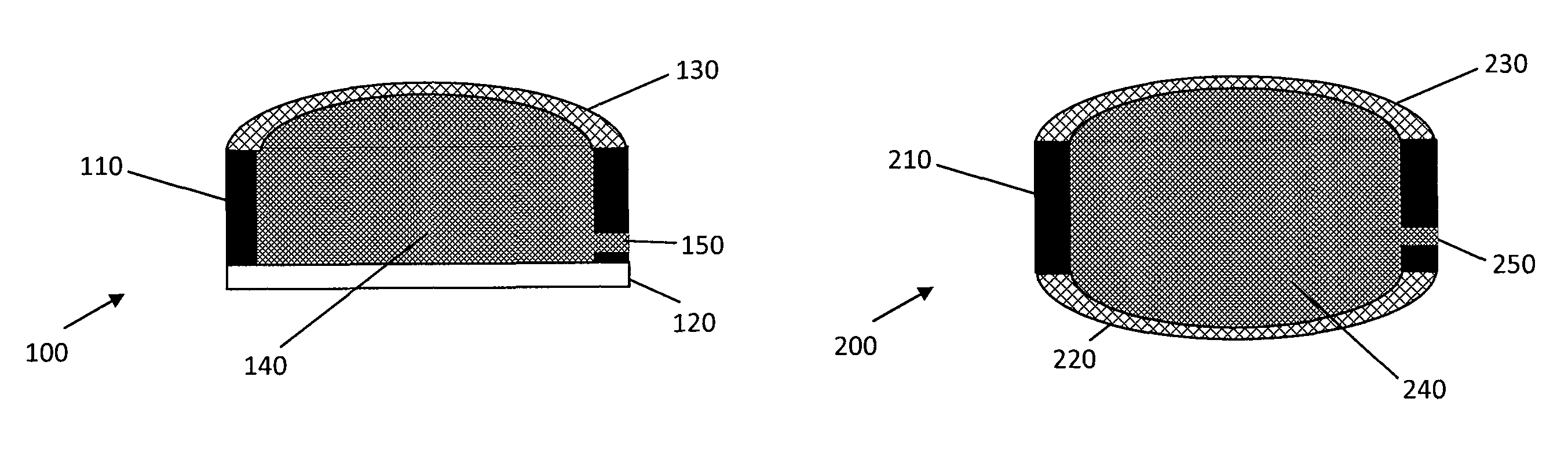

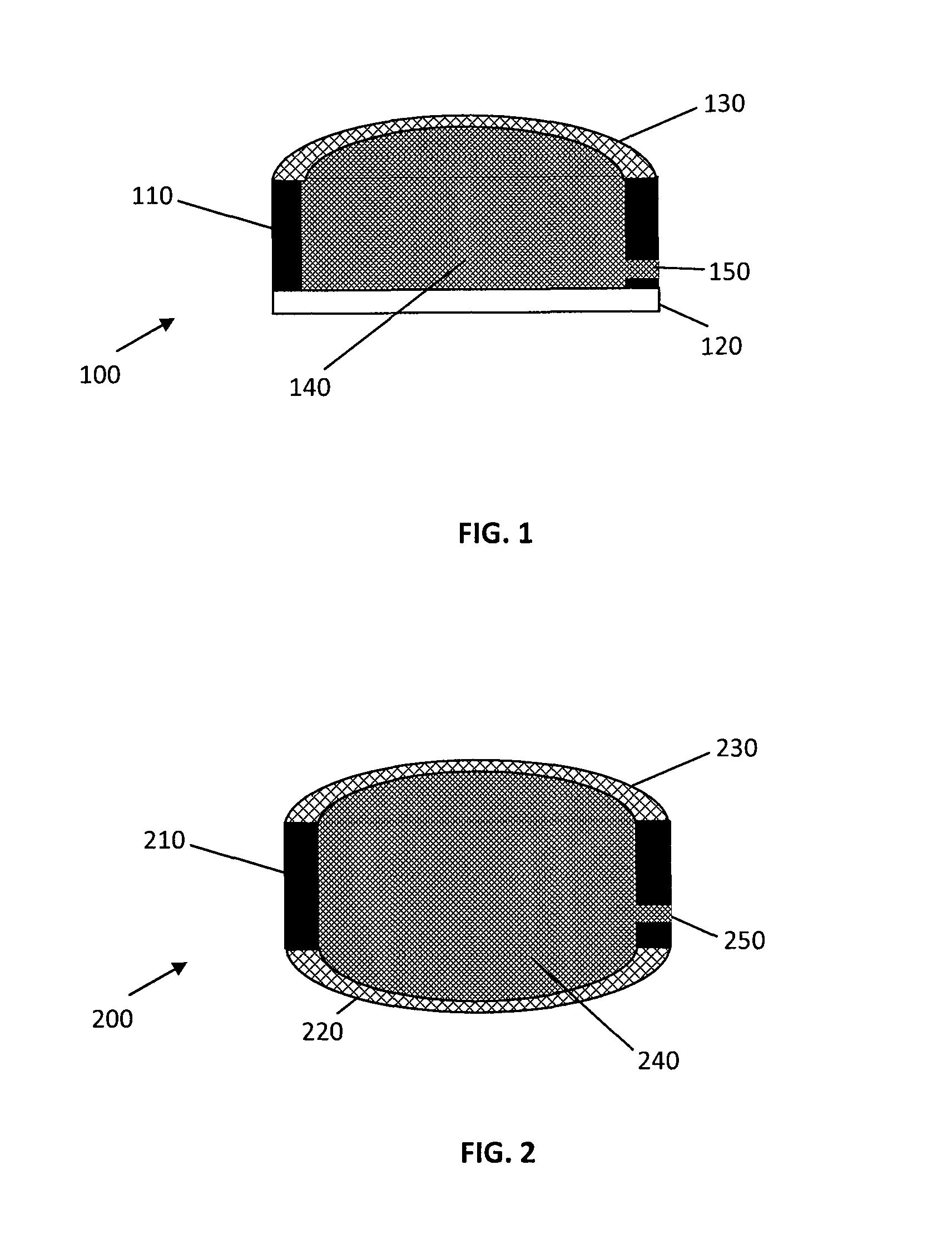

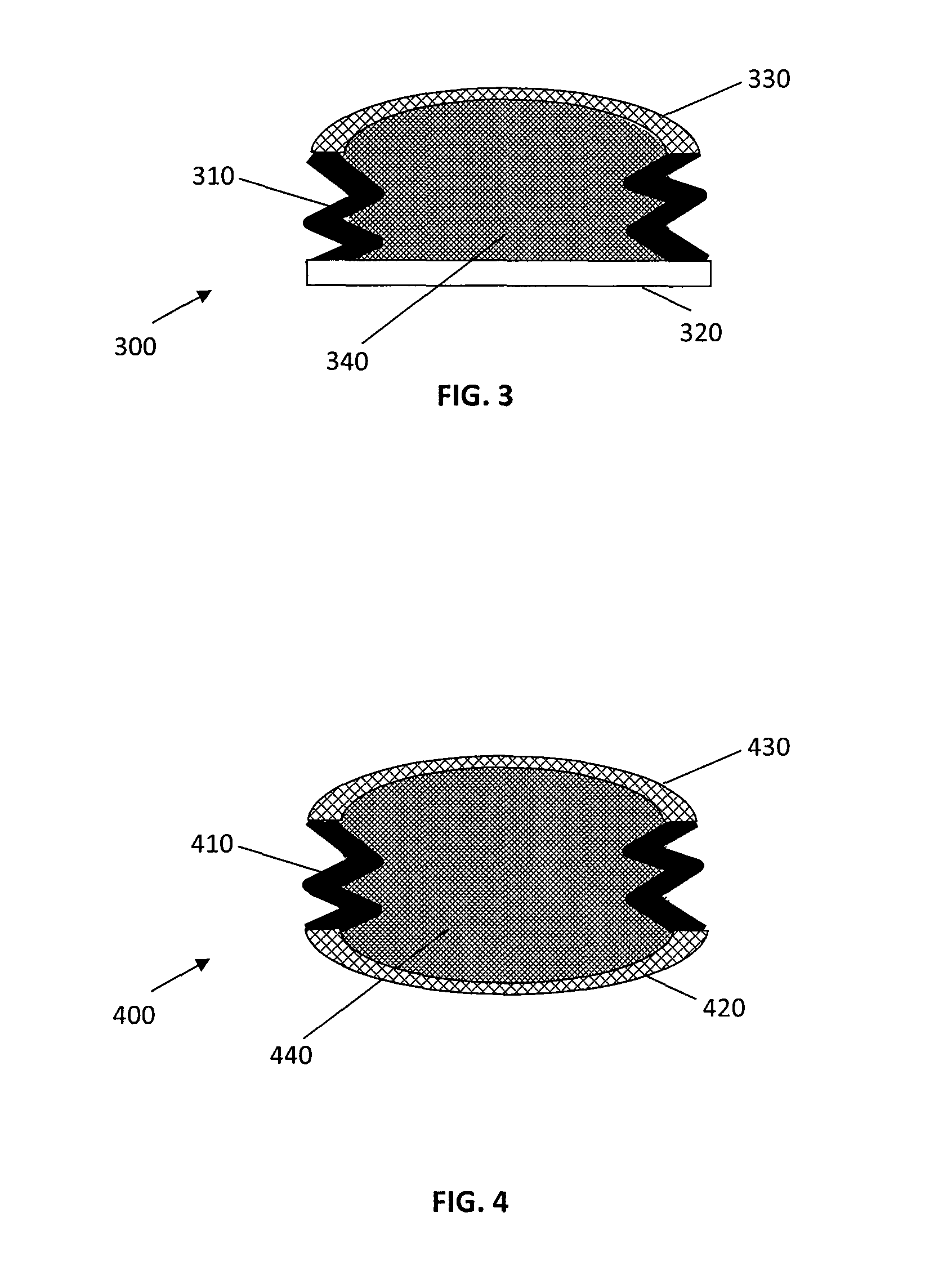

Fluidic adaptive lens with a lens membrane having suppressed fluid permeability

InactiveUS8254034B1Eliminate and slow down fluid permeationRobust solutionLensElastomerSelf adaptive

Fluidic adaptive lens devices containing impermeable elastomer membrane, and systems employing such lens devices, along with methods of fabricating such lens devices, are disclosed. In the embodiments, processes and techniques of creating transparent, impermeable elastomer membranes are disclosed. The membranes thus produced display no or extremely slow permeation for at least one fluid suitable for the fluidic adaptive lenses.

Owner:RHEVISION TECH

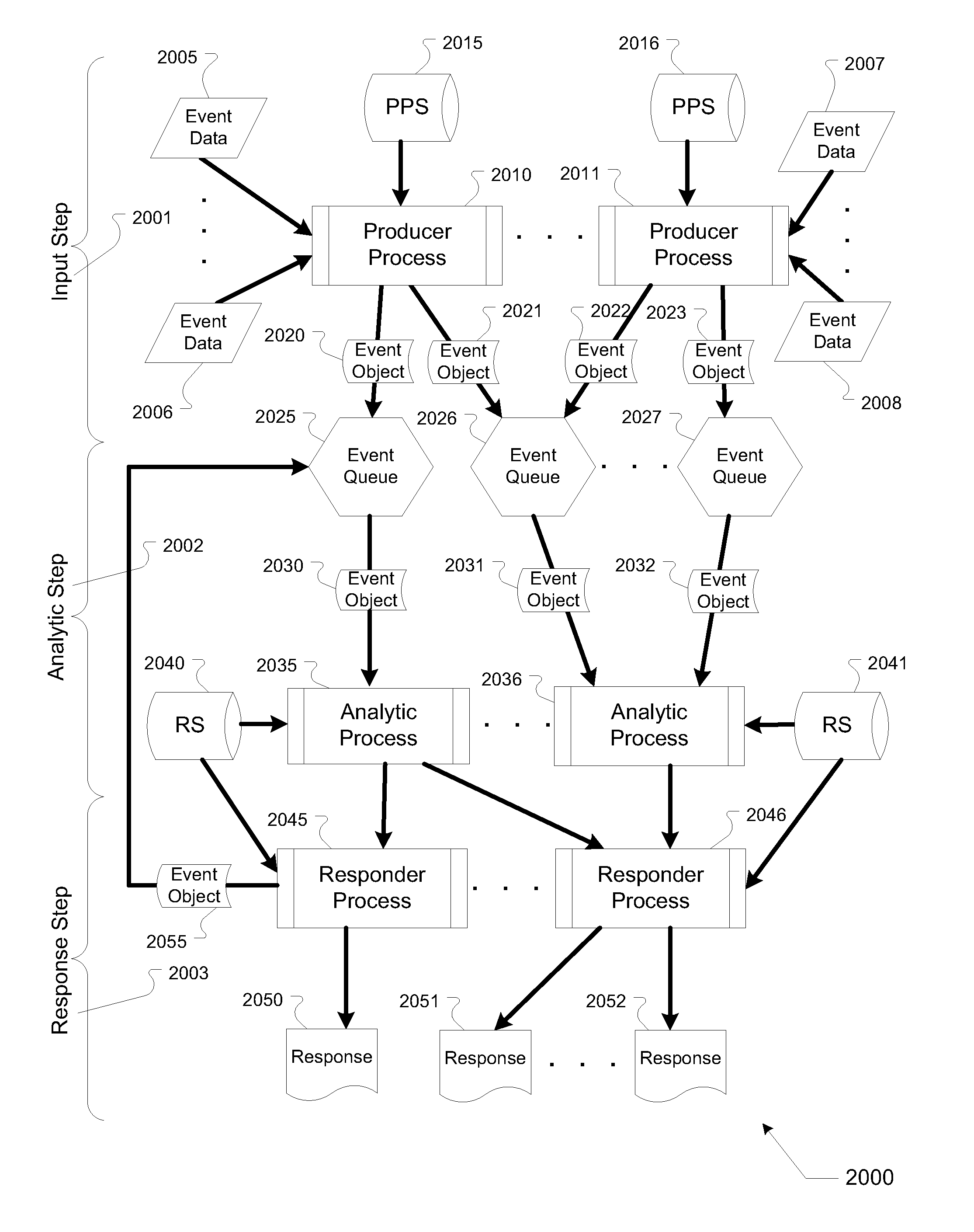

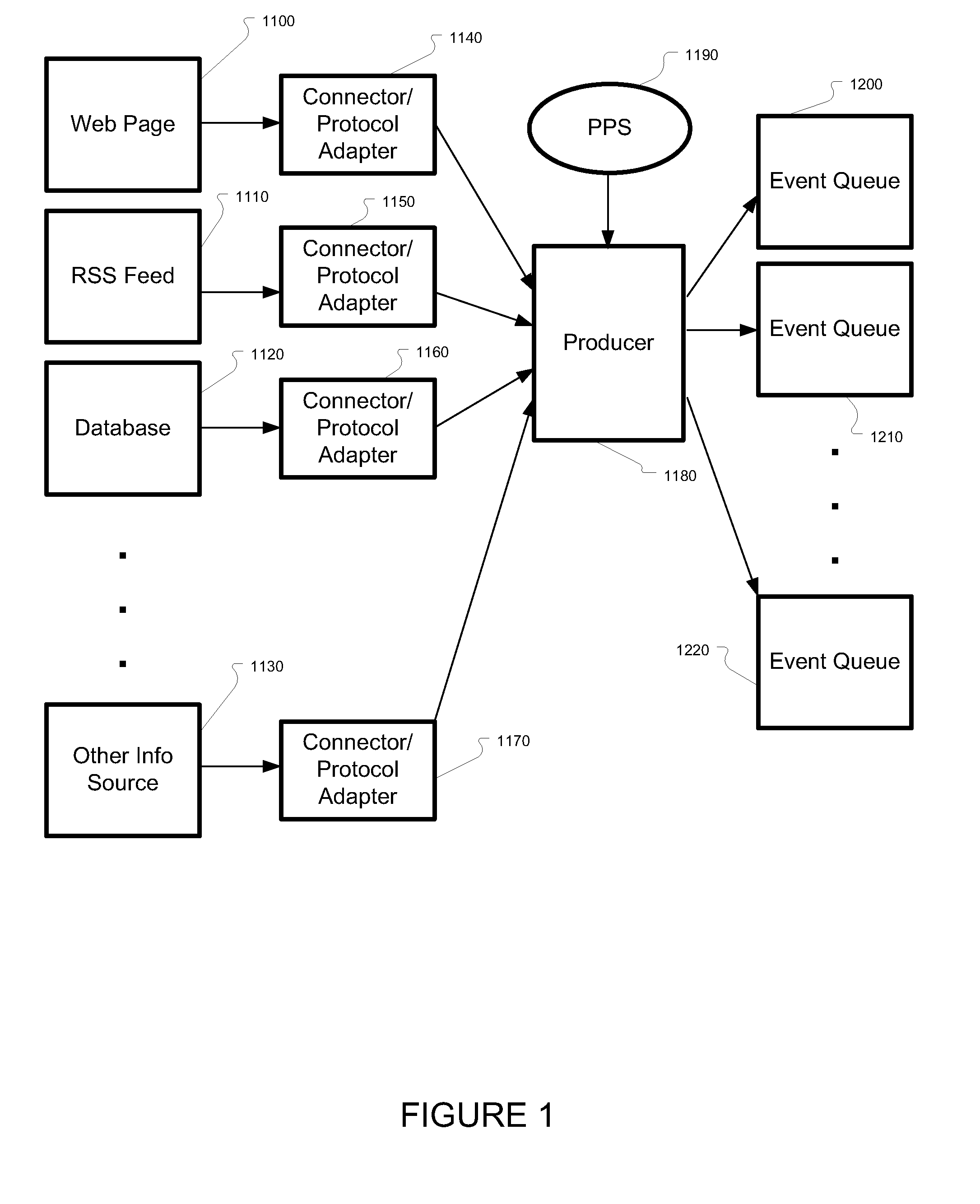

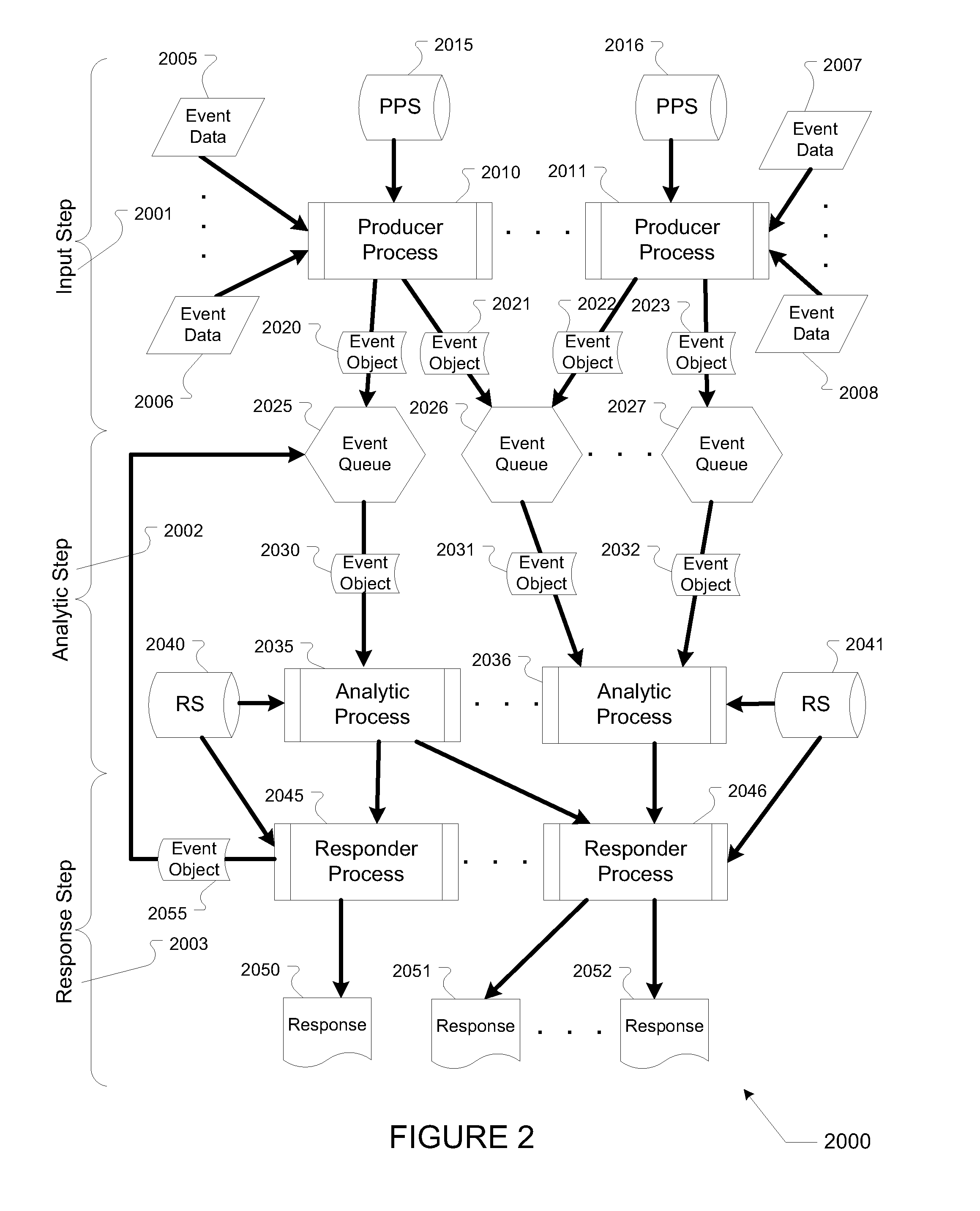

Workspace system and method for monitoring information events

ActiveUS20110167433A1Robust solutionDigital data information retrievalMultiprogramming arrangementsComputerized systemWorkspace

A system and method for monitoring information events partitions sets of information and processing steps into one or more workspaces. The workspaces include sharable portable specifications for implementing event monitoring by a plurality of users or computer systems. Workspaces may be bindable computing resources to establish controls between the computing resources and the workspaces.

Owner:INFORMATICA CORP

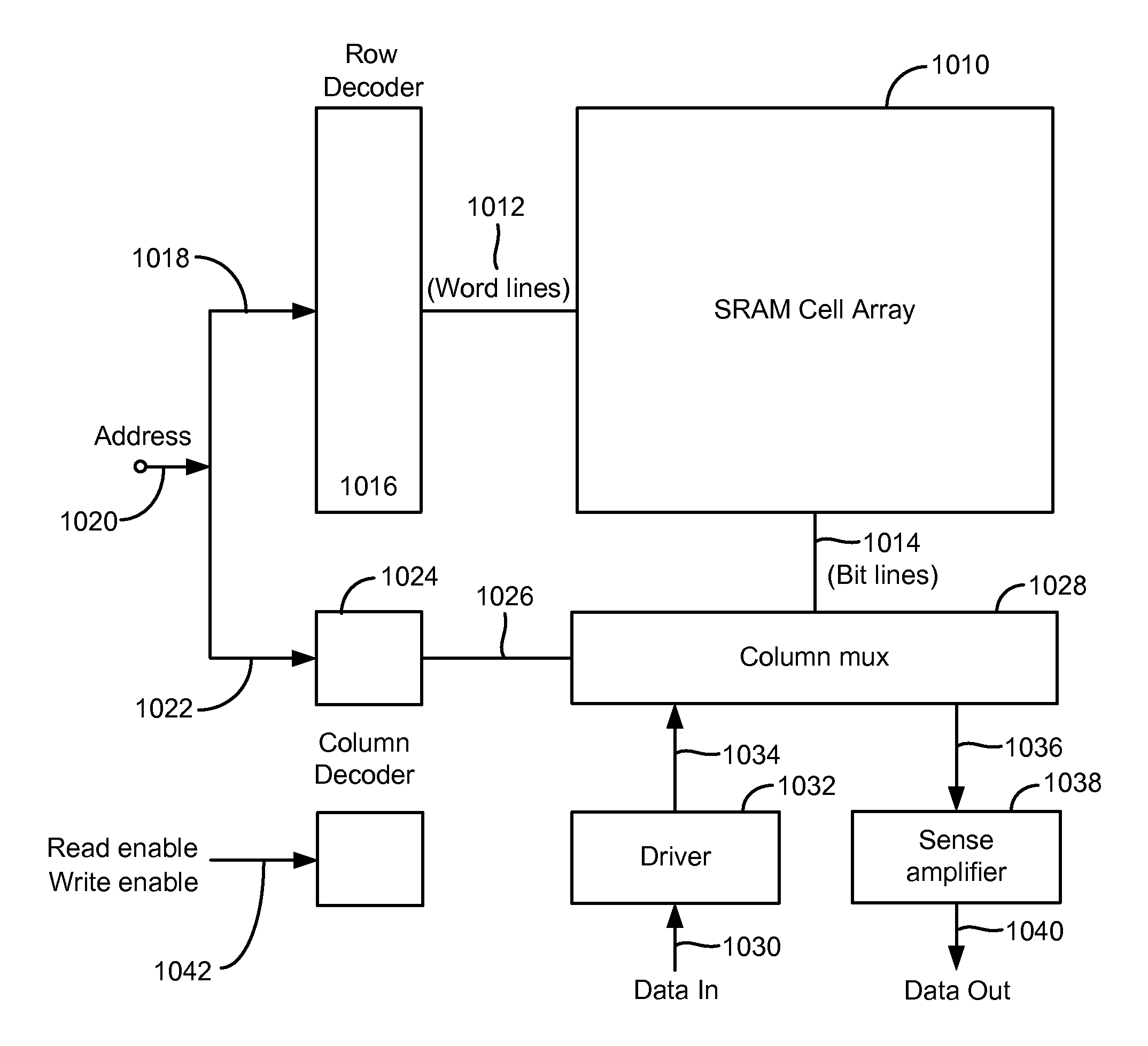

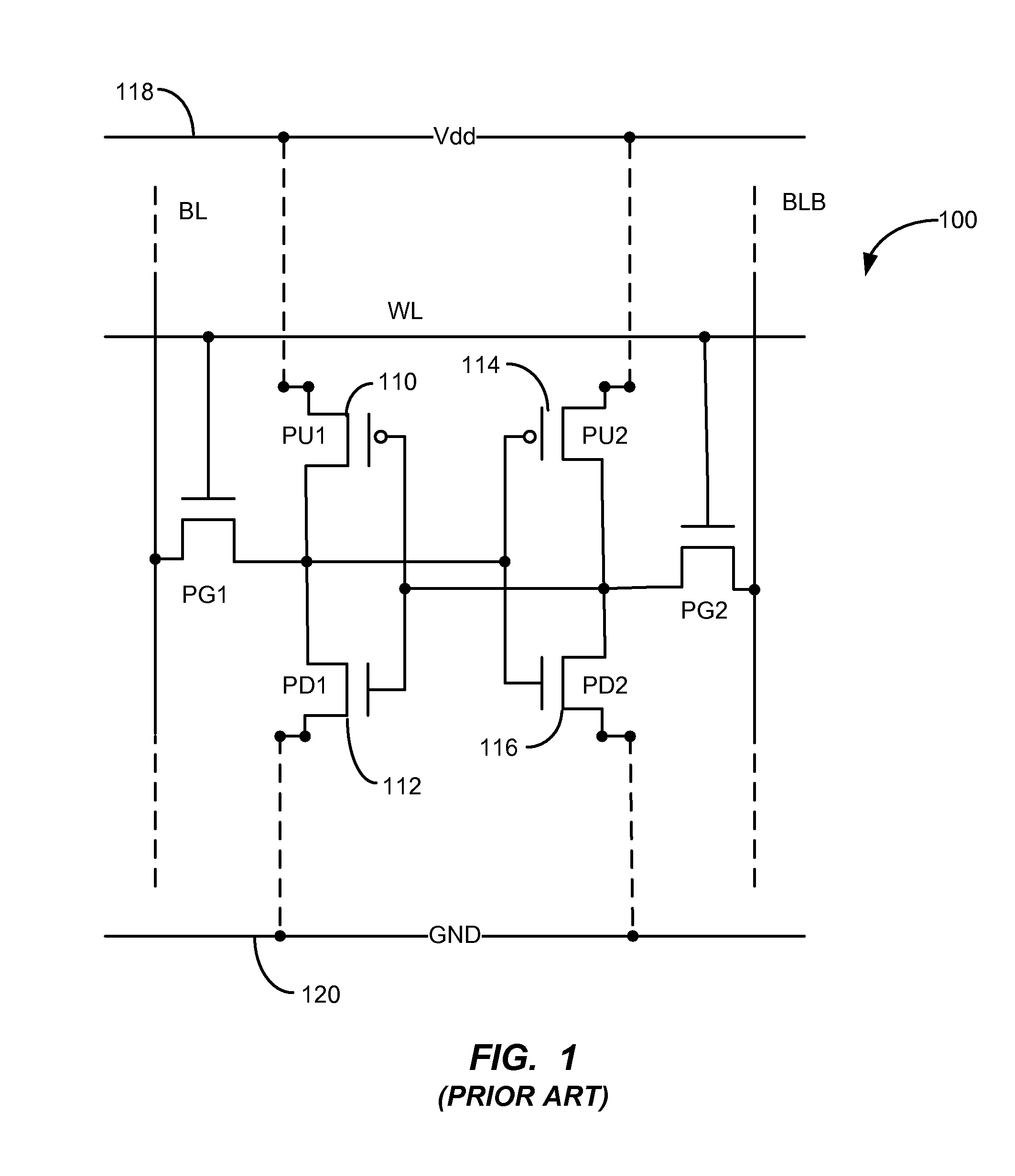

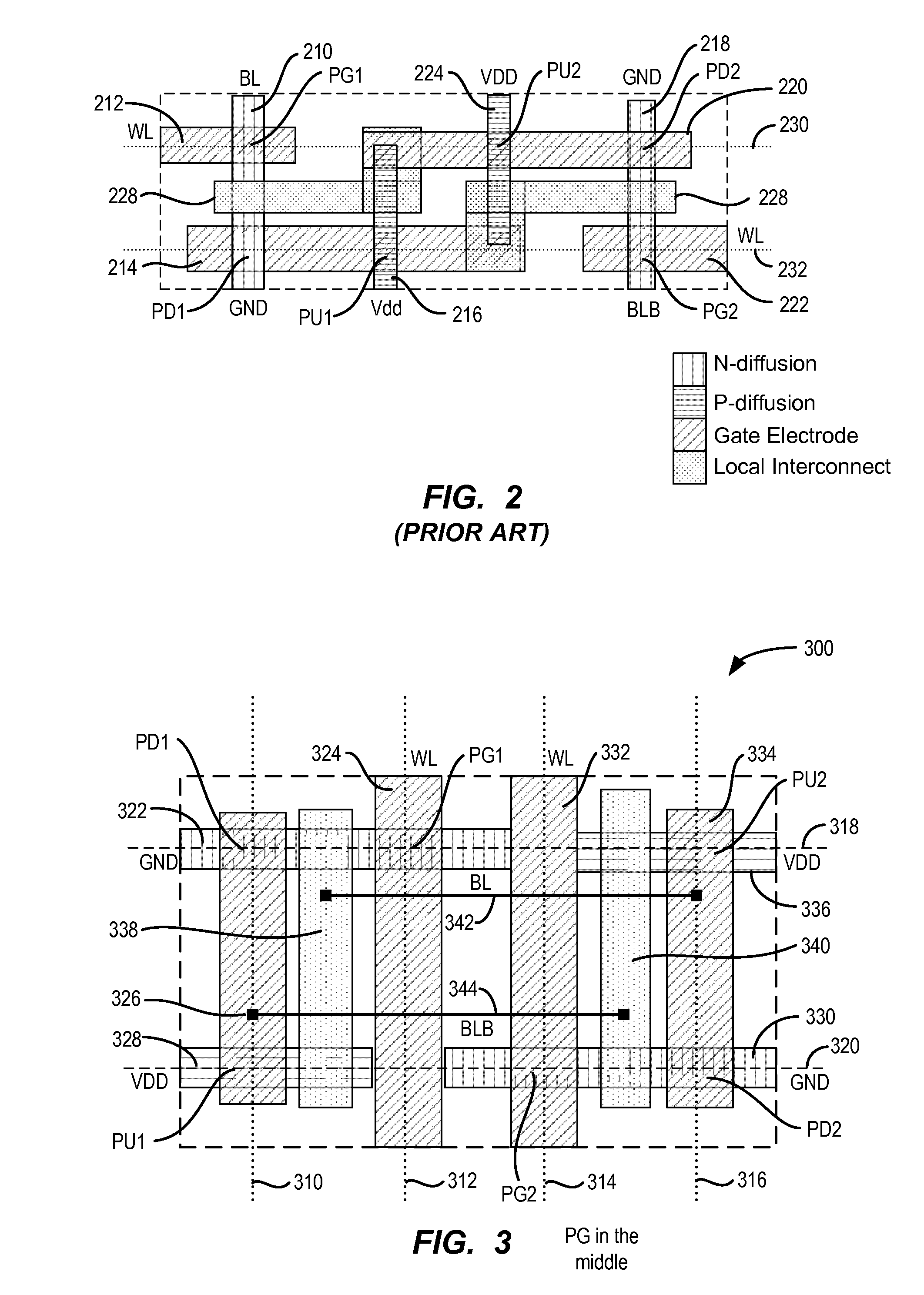

SRAM layouts

ActiveUS20140003133A1Robust solutionSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringMacrocell

Roughly described, the cell layout in an SRAM array is re-arranged such that the gate electrodes for transistors for which flexibility to use one channel length is desired, are formed along a different track from those for transistors for which flexibility to use a different channel length is desired. Not only does such a re-arrangement permit optimization of device ratios, but also in certain implementations can also reduce, rather than increase, cell area. Specific example layouts are described. The invention also involves layout files, macrocells, lithographic masks and integrated circuit devices incorporating these principles, as well as fabrication methods.

Owner:SYNOPSYS INC

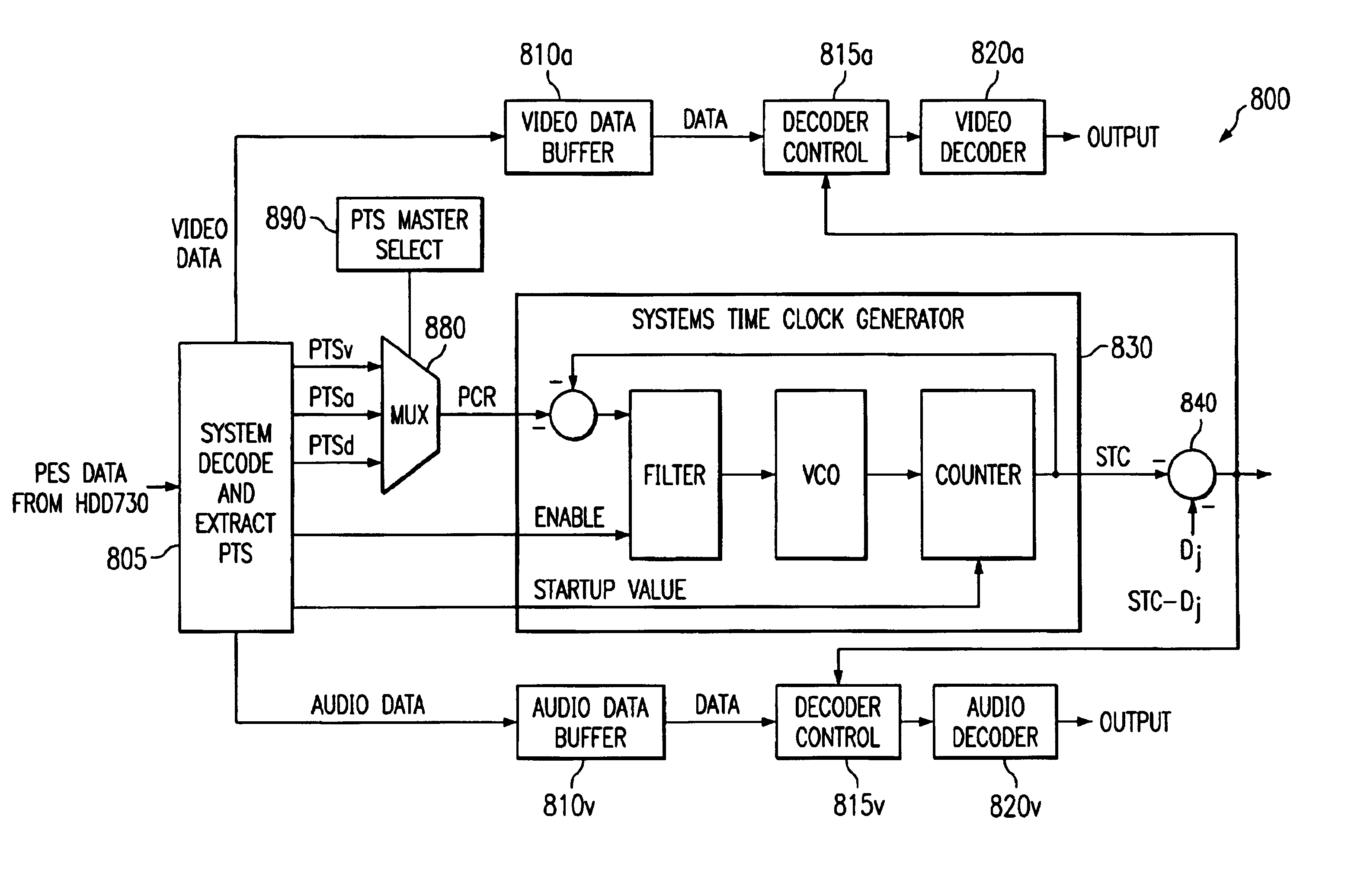

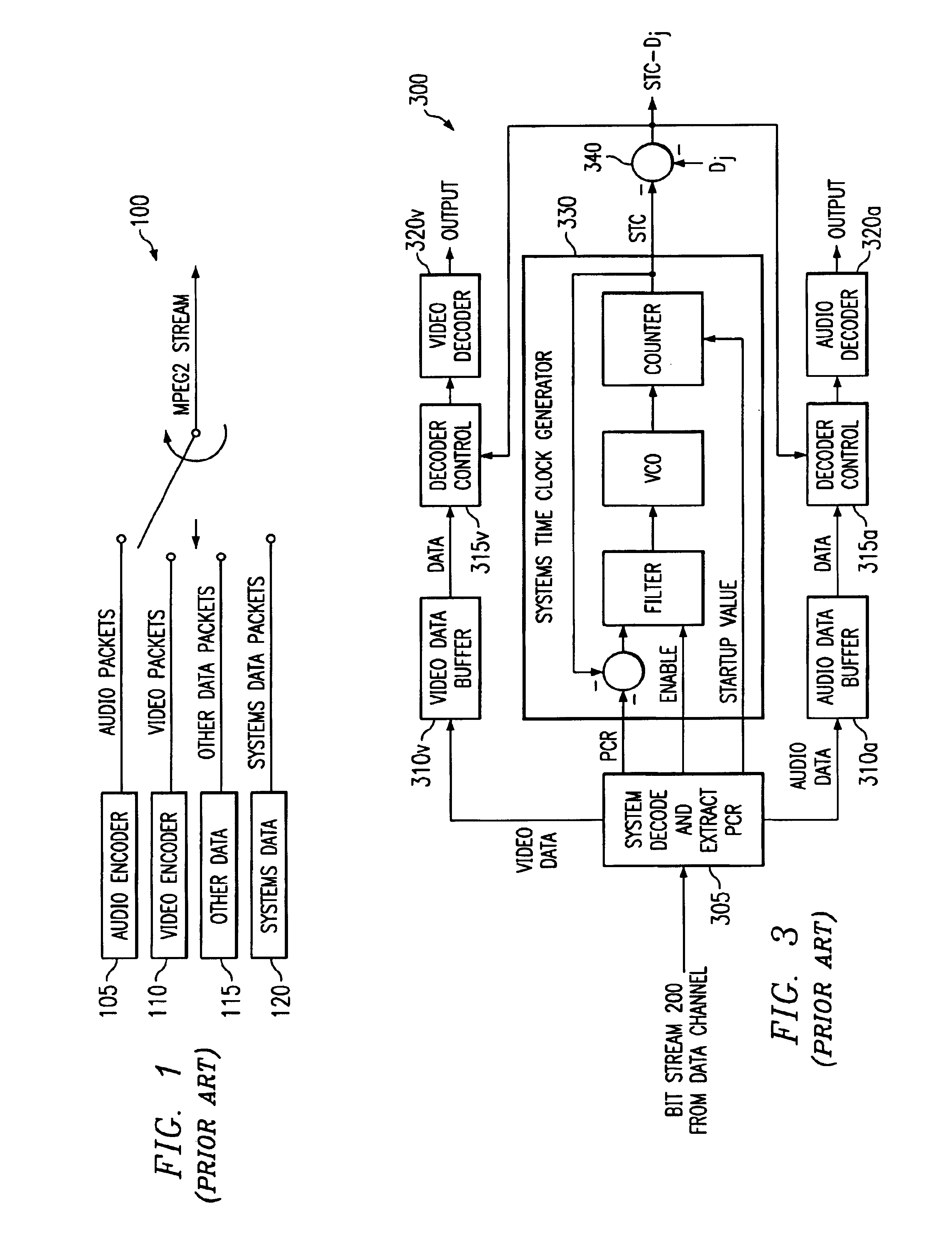

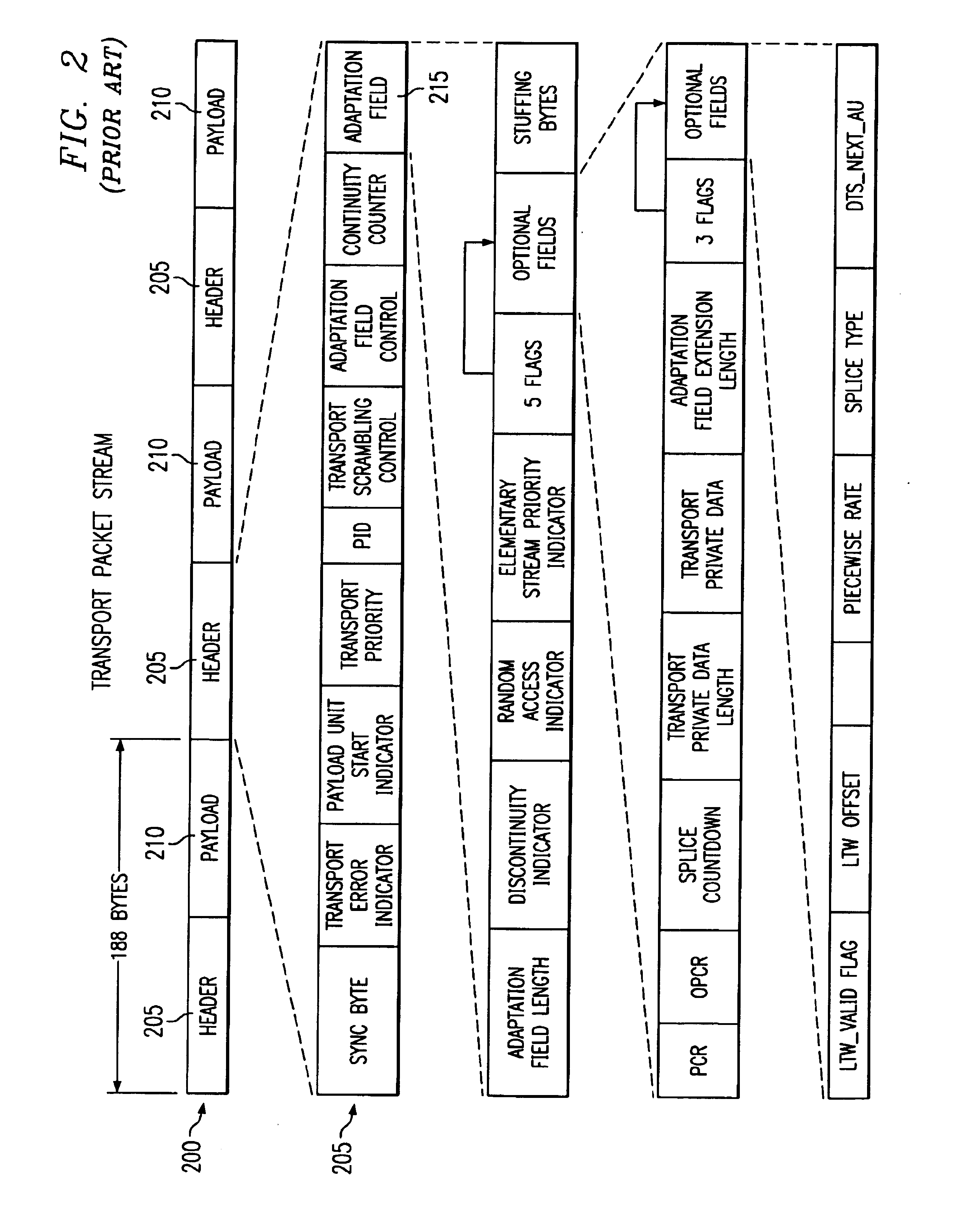

Apparatus and method for synchronizing video and audio MPEG streams in a video playback device

InactiveUS6931071B2Robust solutionTelevision system detailsPulse modulation television signal transmissionPacketized elementary streamElementary stream

There is disclosed an MPEG decoder comprising: 1) a packetized elementary stream (PES) interface for receiving a plurality of packetized elementary streams associated with a single video program; 2) a presentation time stamp (PTS) detection circuit for detecting presentation time stamps in the packetized elementary streams and extracting the presentation time stamps therefrom; and 3) a selection circuit for selecting presentation time stamps associated with a first one of the plurality of packetized elementary streams and transmitting the selected presentation time stamps to a clock generation circuit, wherein the clock generation circuit generates a first reference clock signal used by a first decoder to decode the first packetized elementary stream. The clock generation circuit further generates a second reference clock signal synchronized to the first reference clock signal, wherein the second reference clock signal is used by a second decoder to decode a second packetized elementary stream in synchronization with the first packetized elementary stream.

Owner:STMICROELECTRONICS SRL

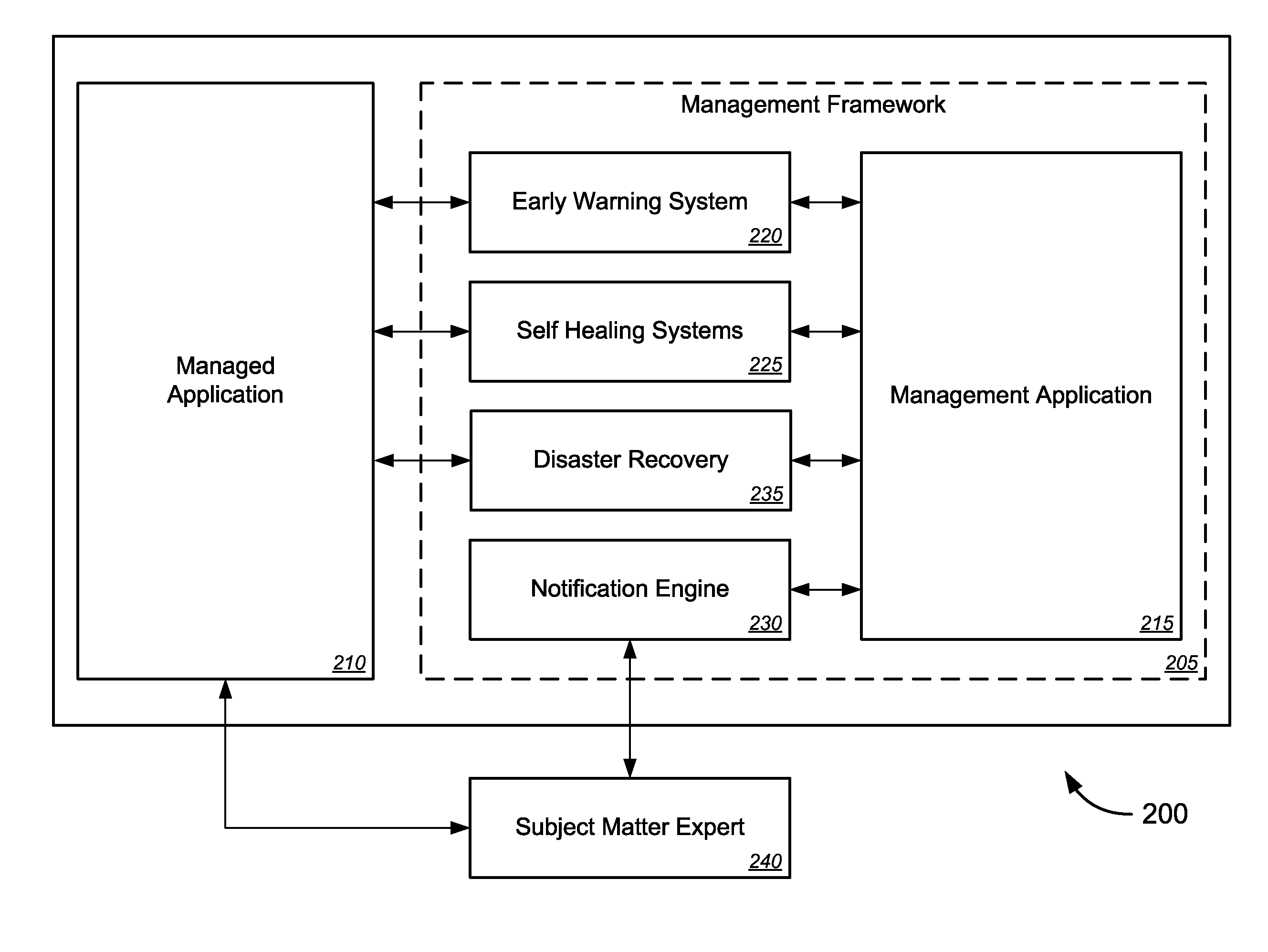

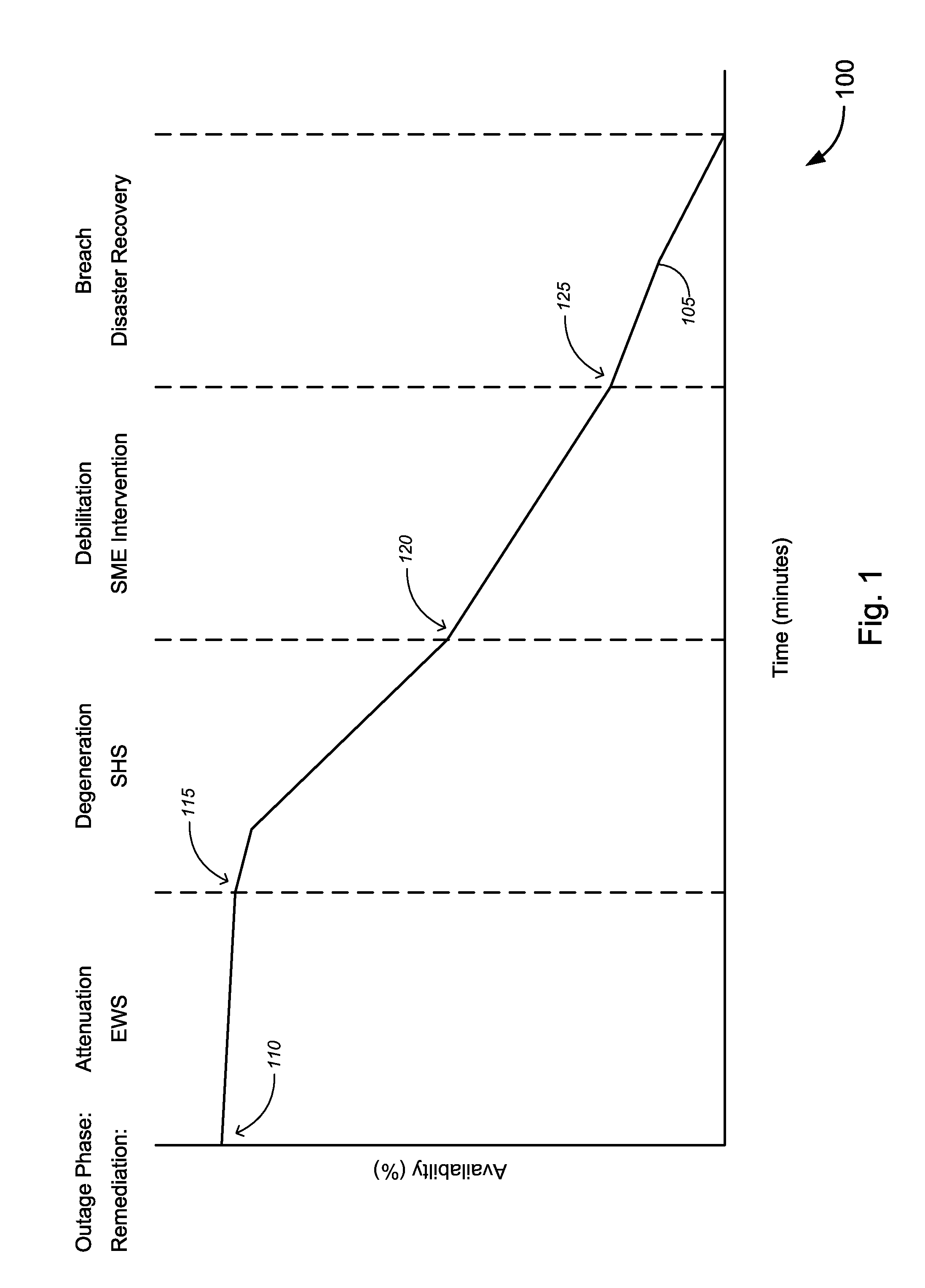

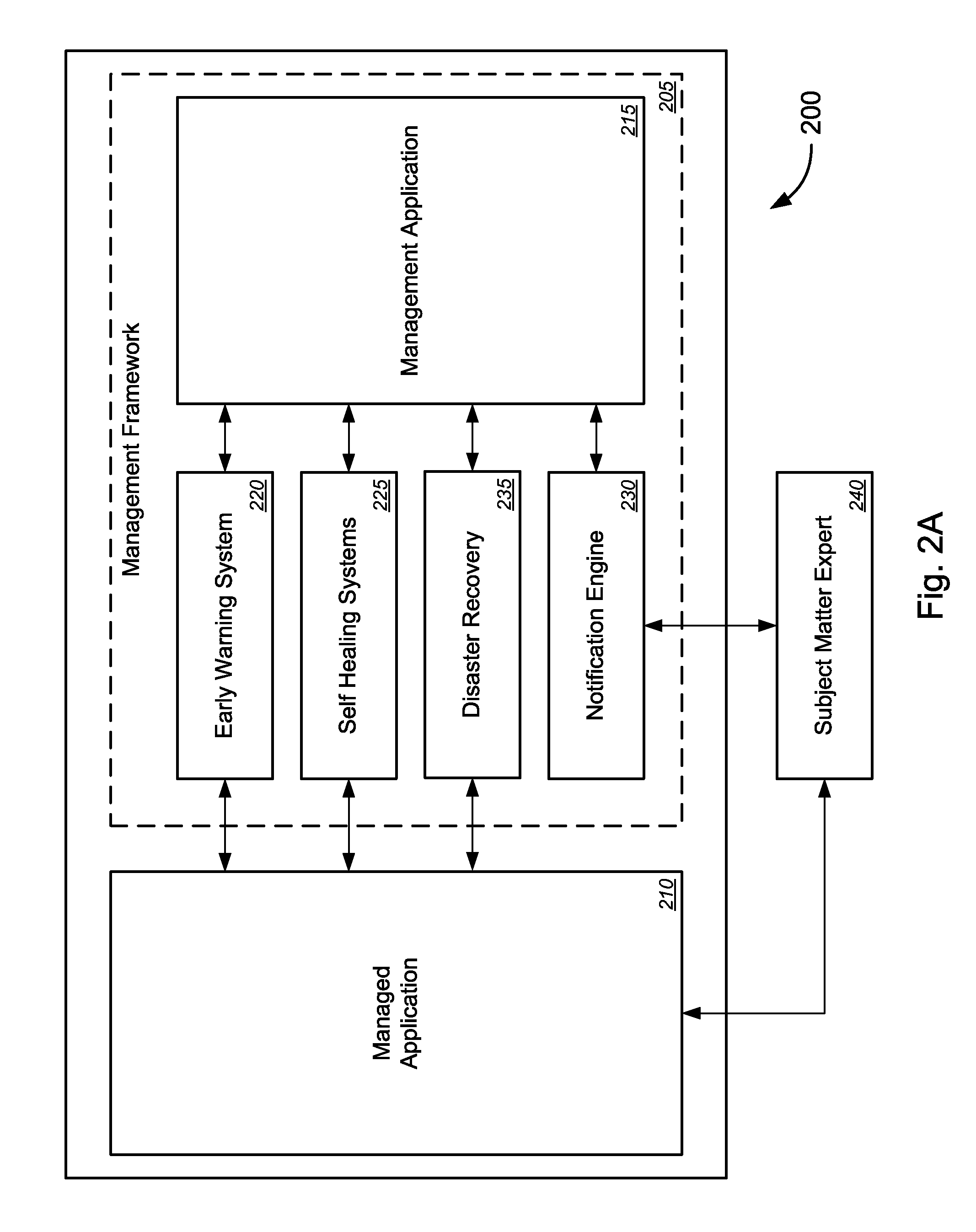

Autonomous Service Management

ActiveUS20140310564A1Robust solutionPreventing potential downtimeHardware monitoringNon-redundant fault processingApplication lifecycle managementStrong solutions

Novel tools and techniques that offer more robust solutions for application service management. Some such solutions provide a service management framework for managing a software application. In some cases, the framework can include multiple tools to detect and / or remedy application problems at a variety of different levels. In another aspect, some solutions can define multiple application lifecycle phases, ranging from minor impairment to catastrophic failure. For each of such phases, the service management framework can define one or more diagnostic criteria and / or one or more corrective actions that can be taken to remedy a suboptimal condition of the application.

Owner:CENTURYLINK INTPROP

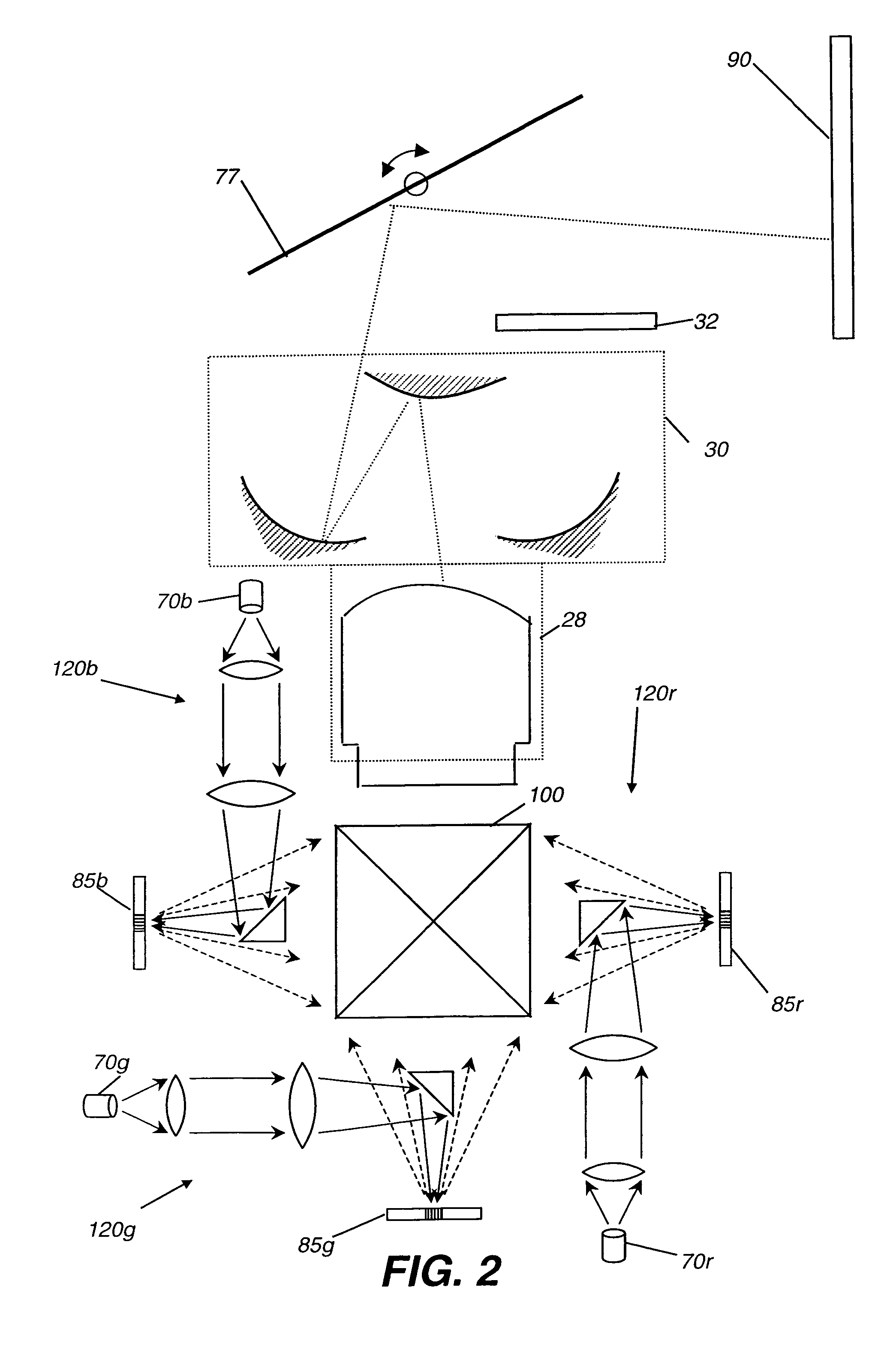

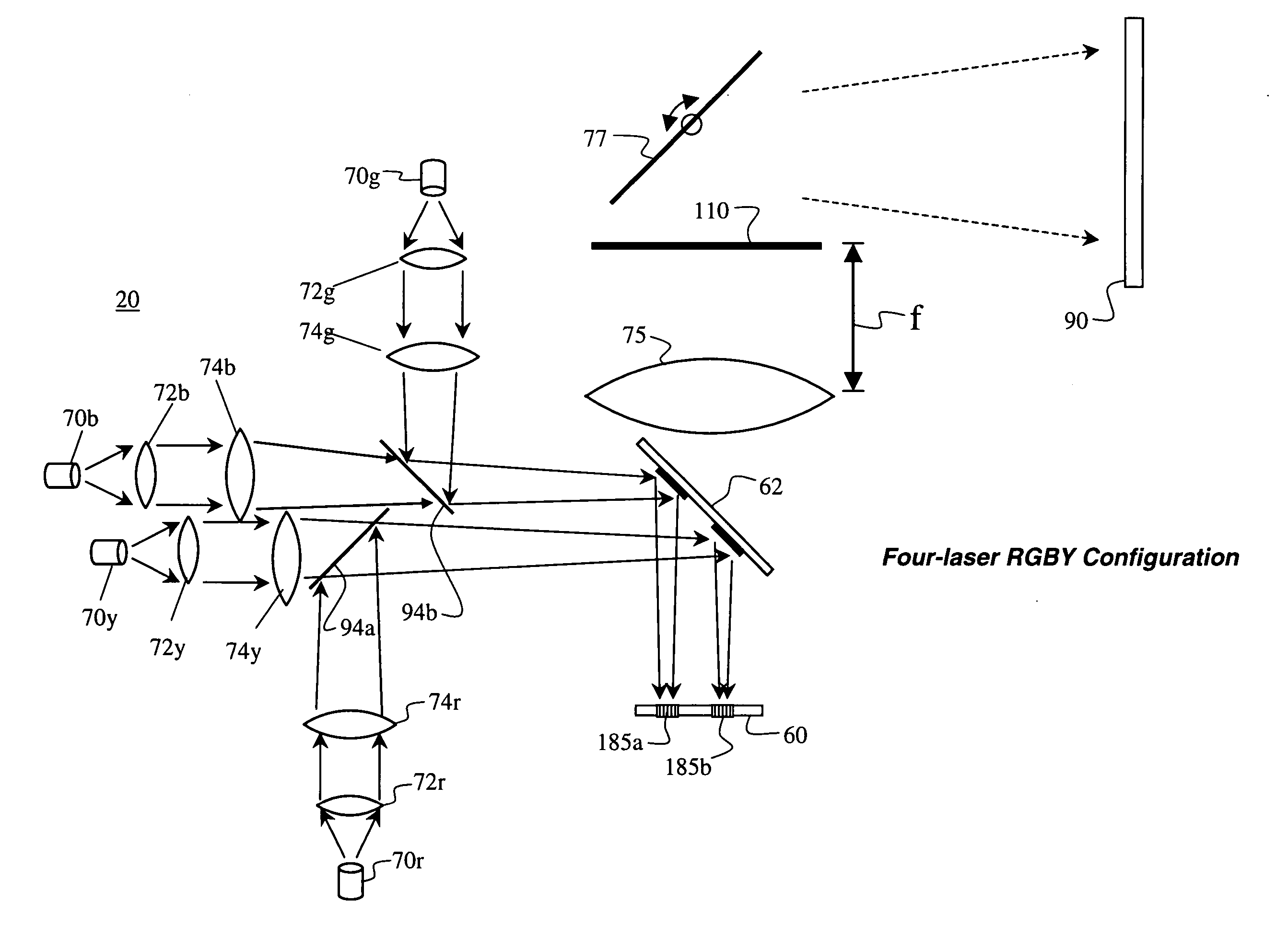

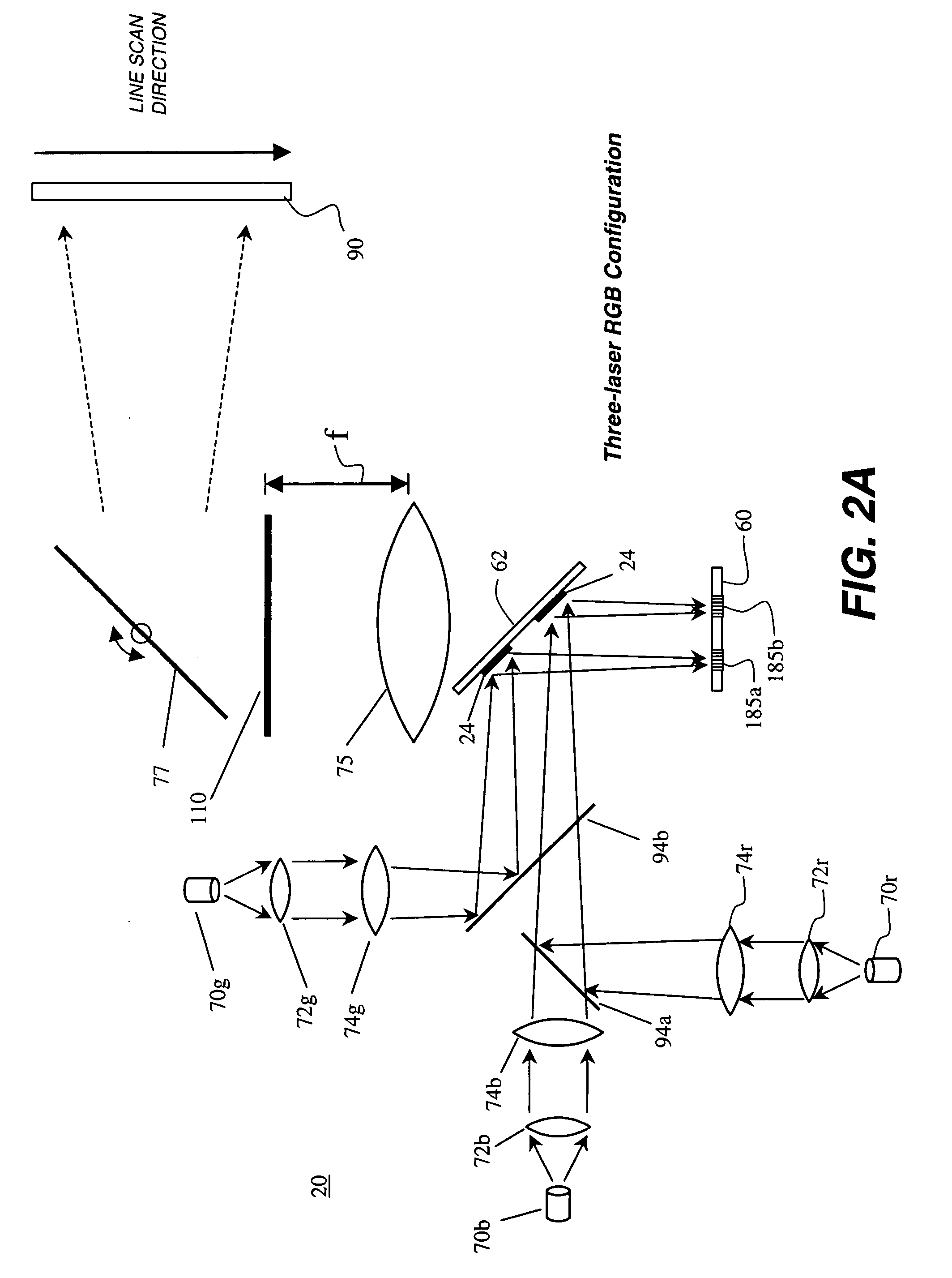

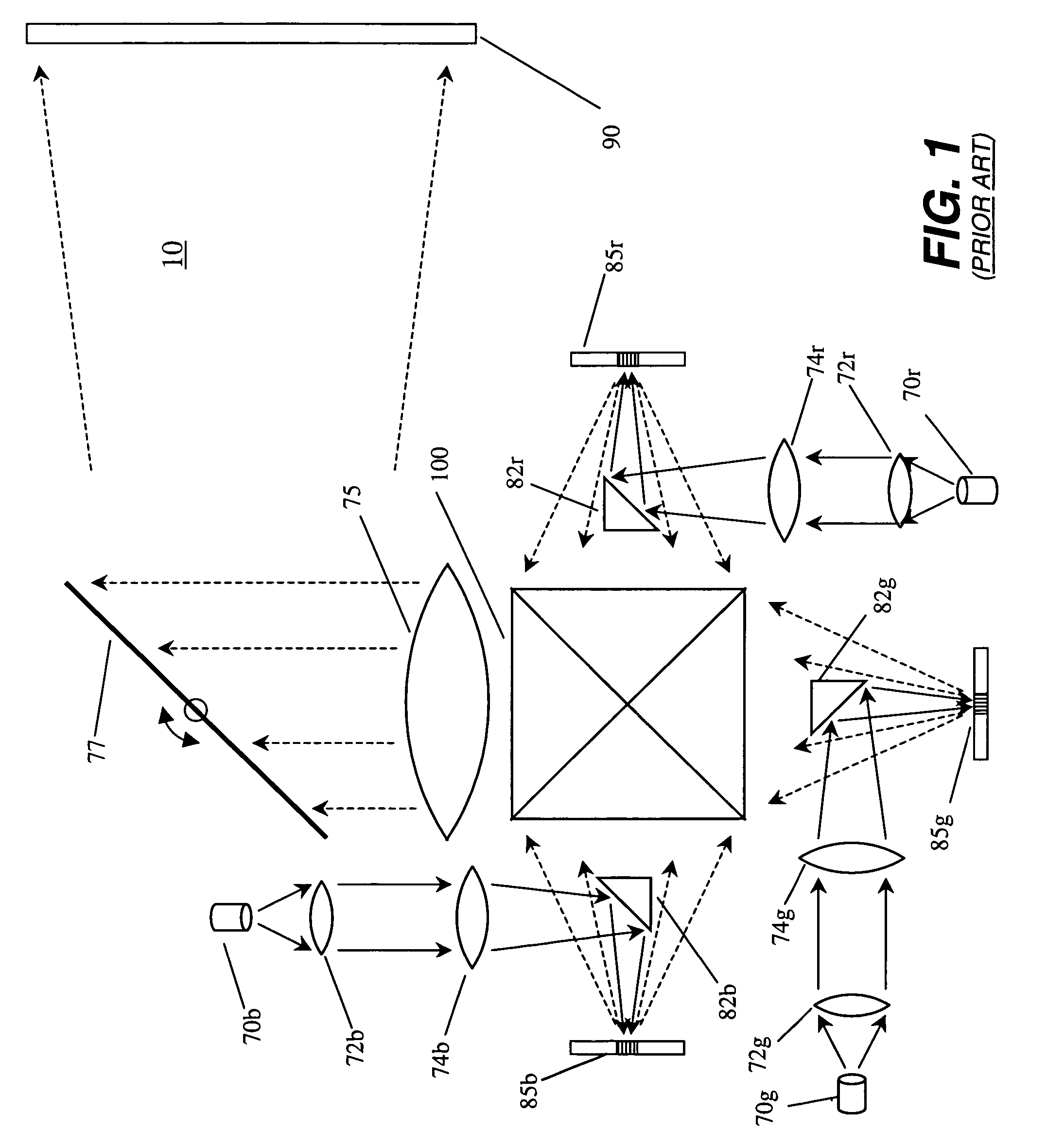

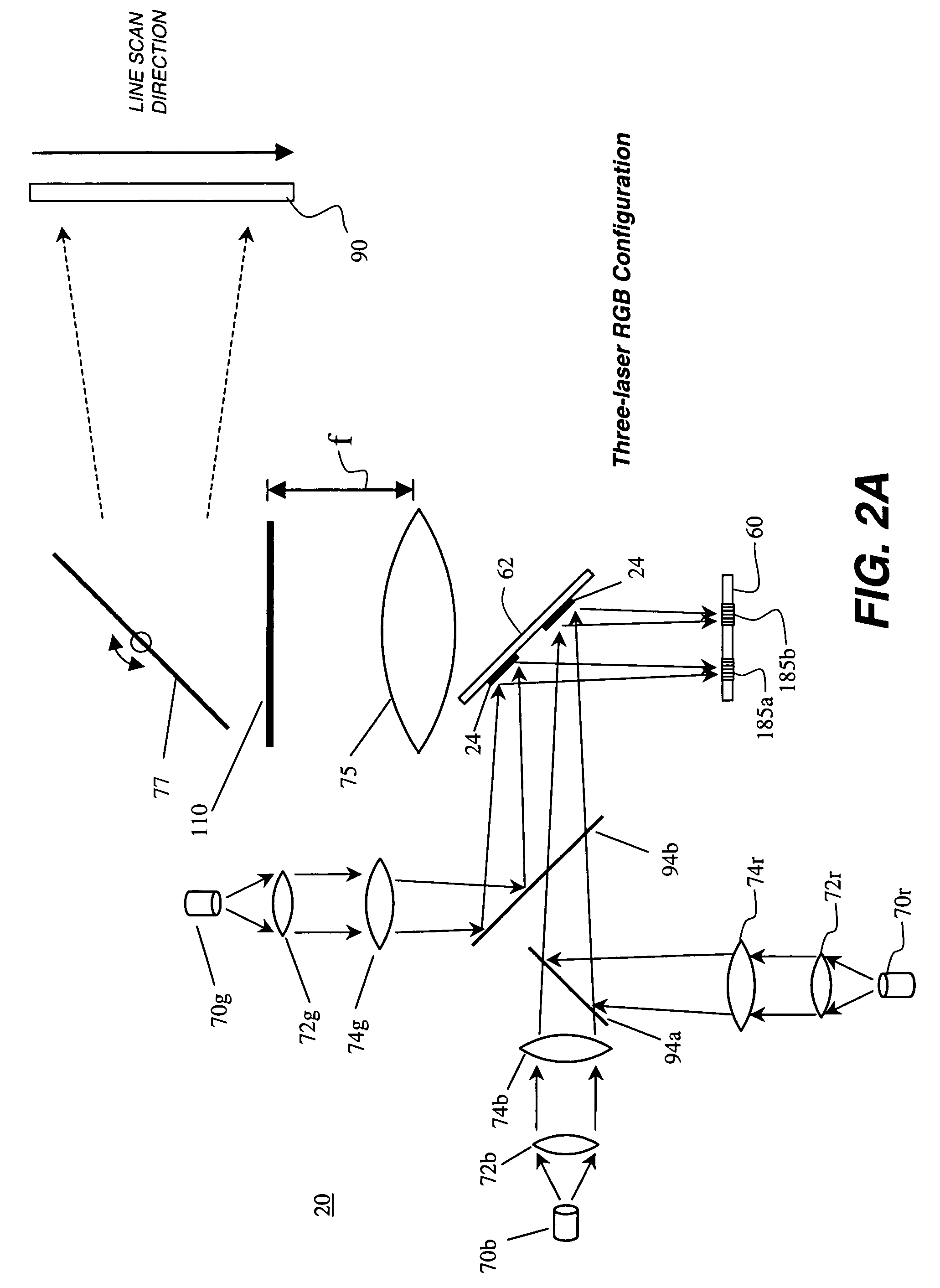

Display system incorporating trilinear electromechanical grating device

InactiveUS7274500B2Reduce in quantityMinimizing adjustingTelevision system detailsStatic indicating devicesGratingScanning mirror

A display system comprises a light modulator having at least three linear arrays of light modulating devices on a common substrate, at least one light source producing at least three colors of light for illuminating the at least three linear arrays, a lens for creating line images of the at least three linear arrays on a display surface, and a scanning mirror for scanning the line images to create a two-dimensional image on the display surface.

Owner:EASTMAN KODAK CO

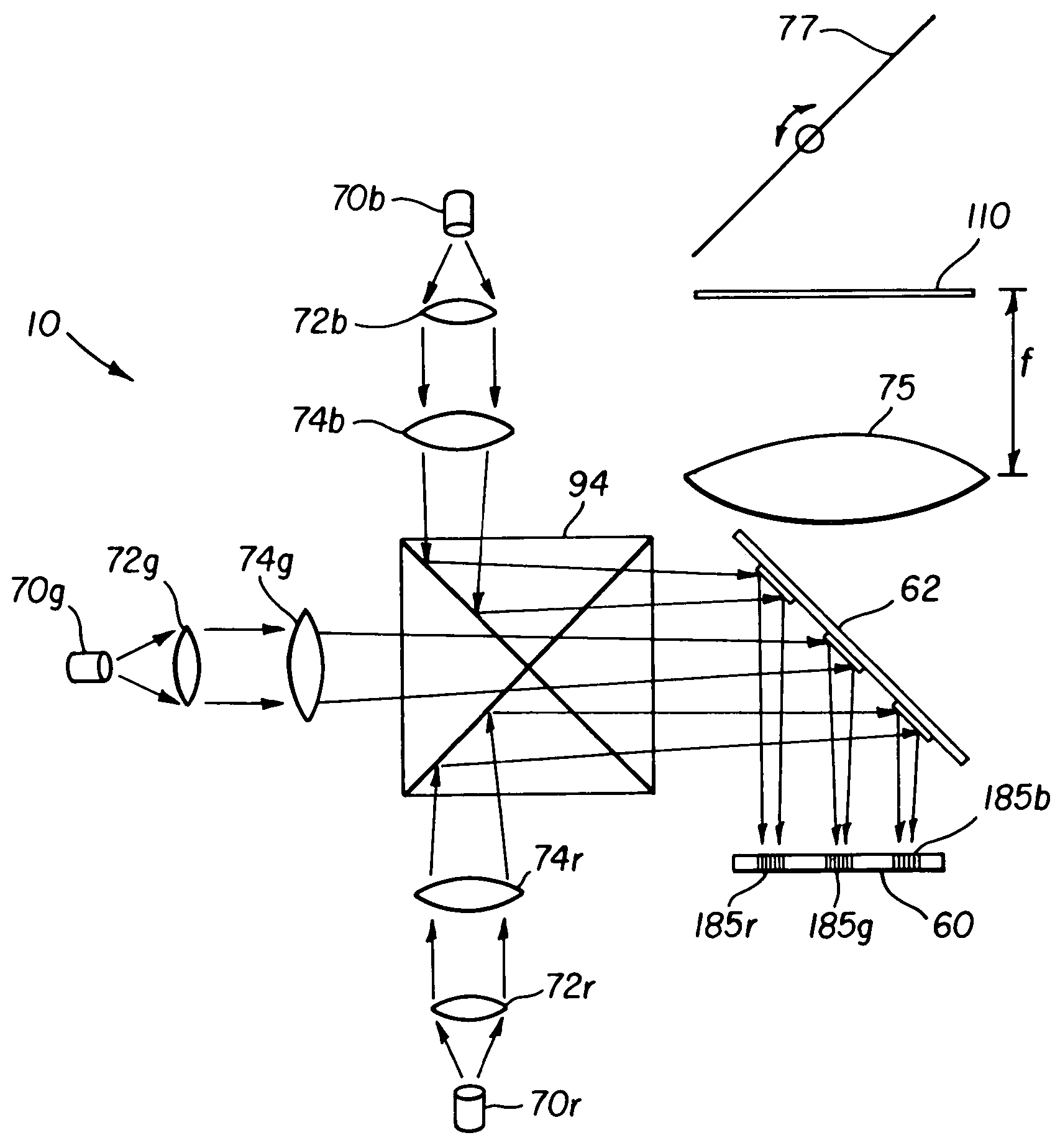

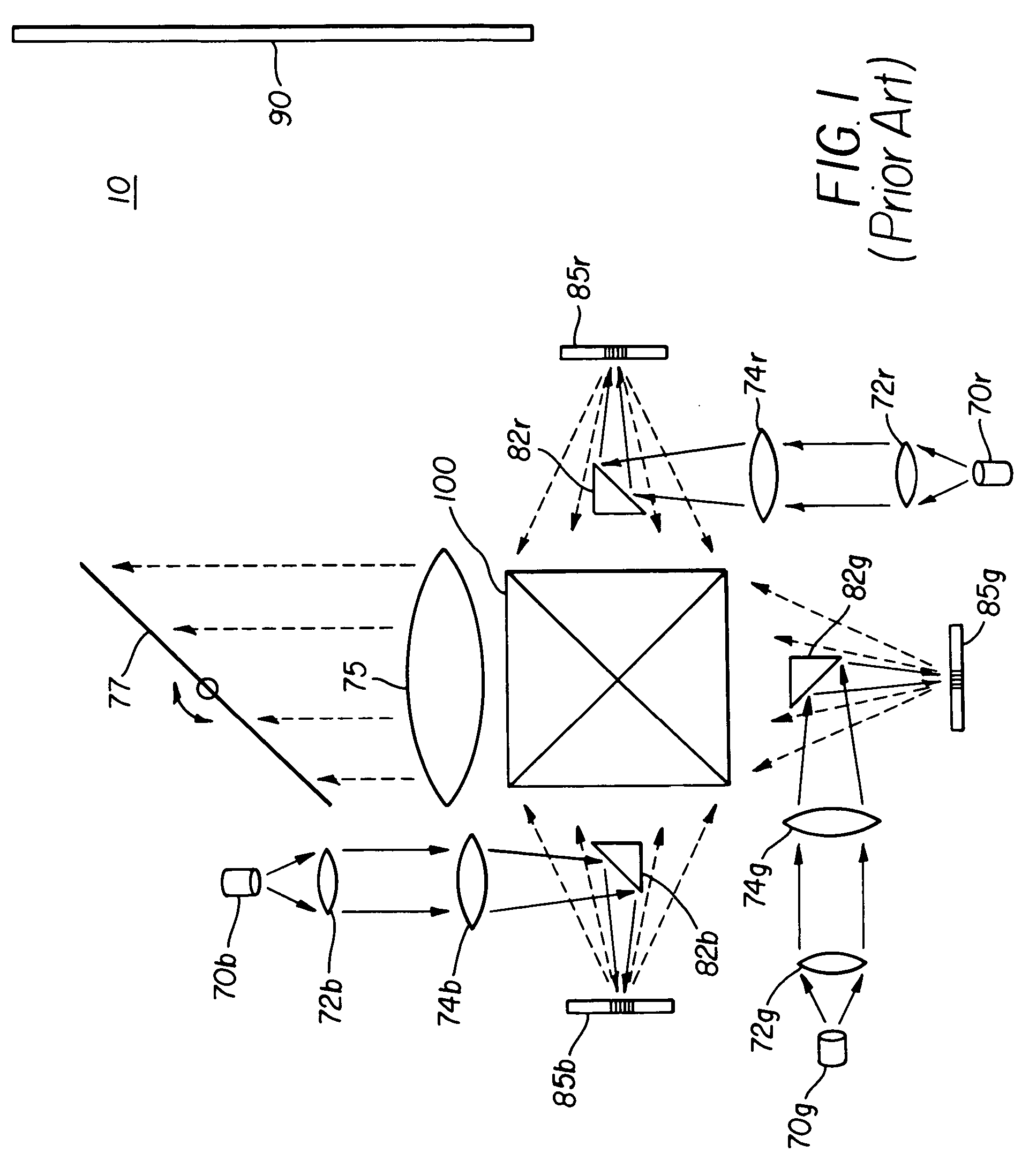

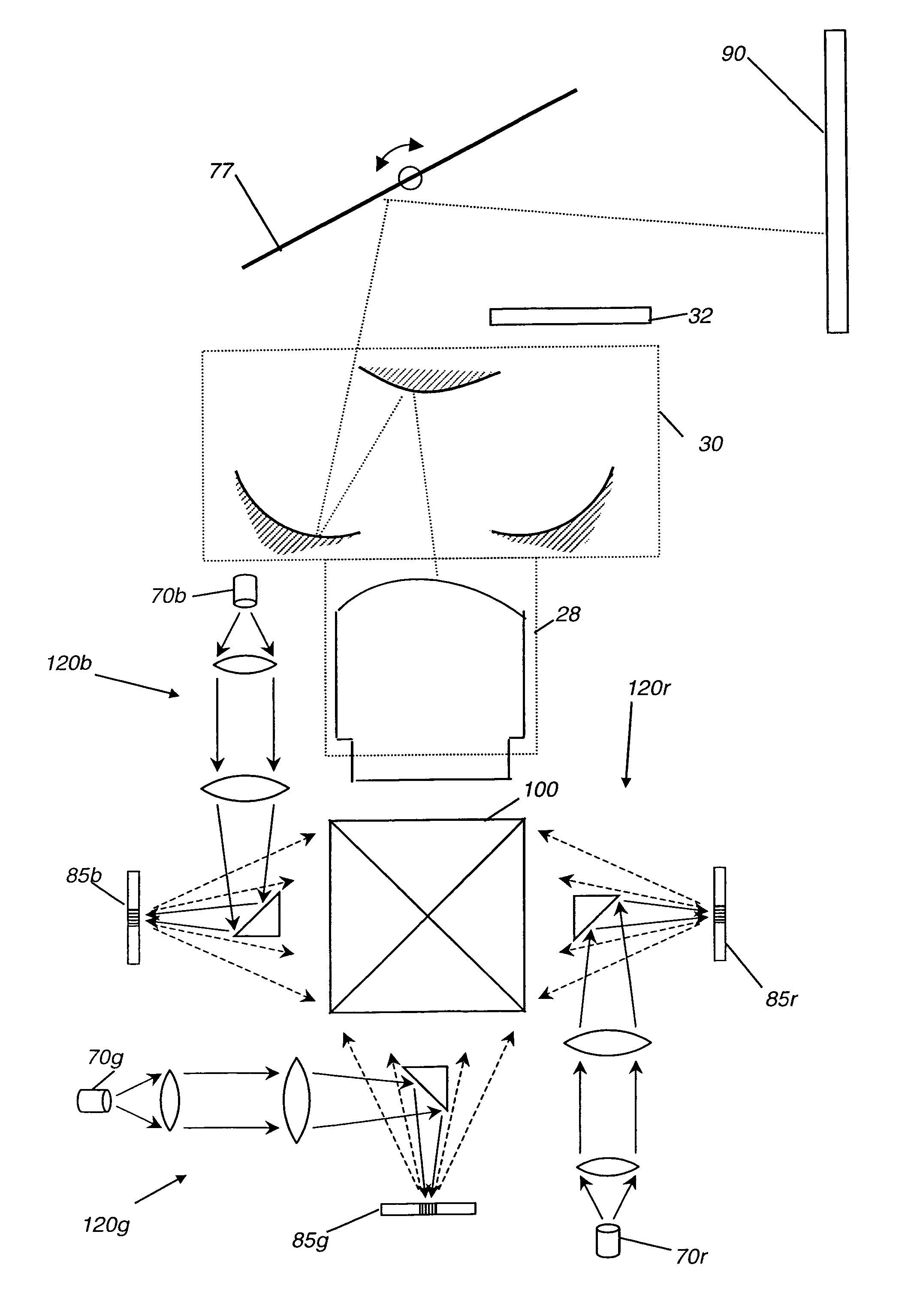

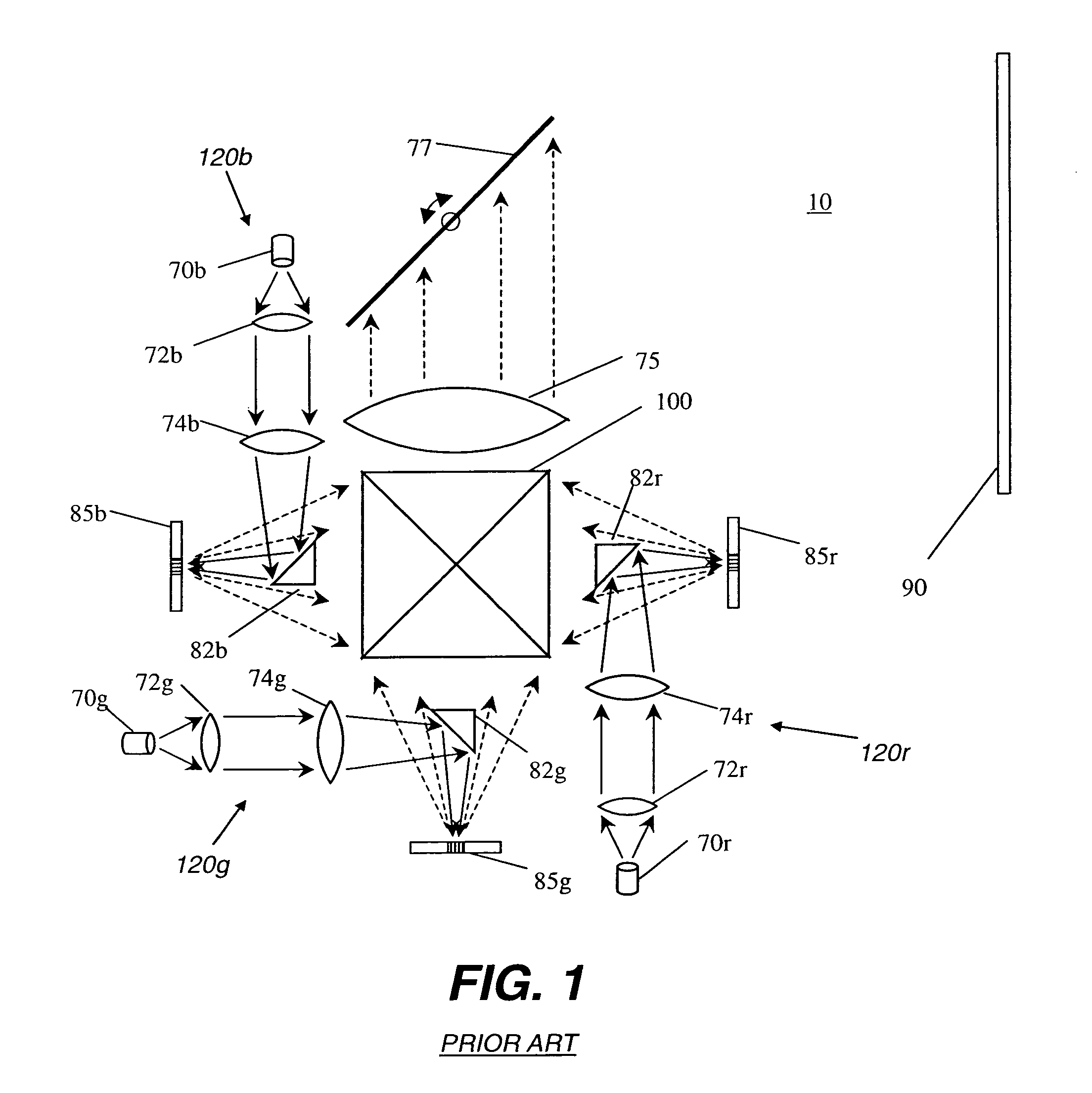

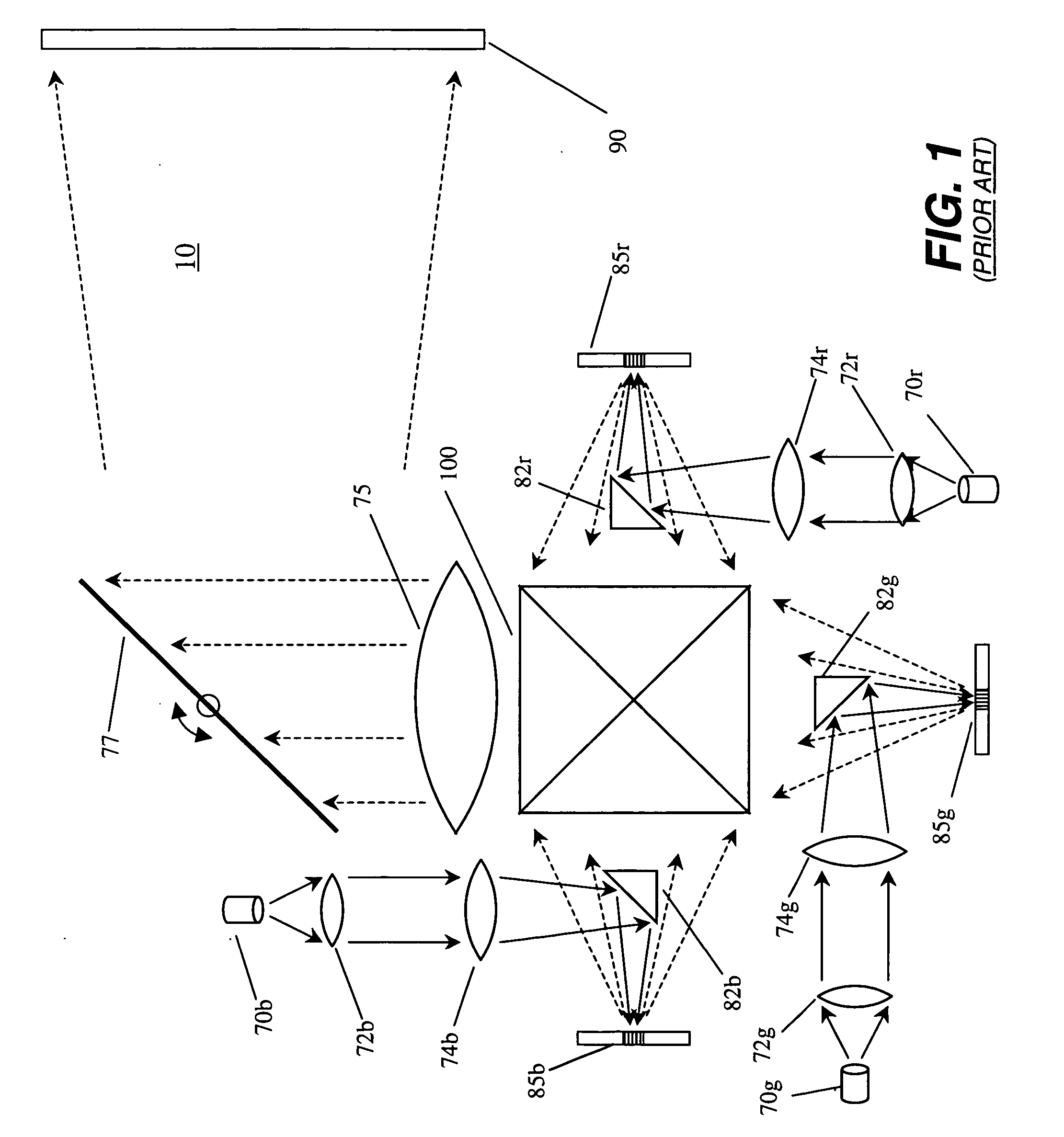

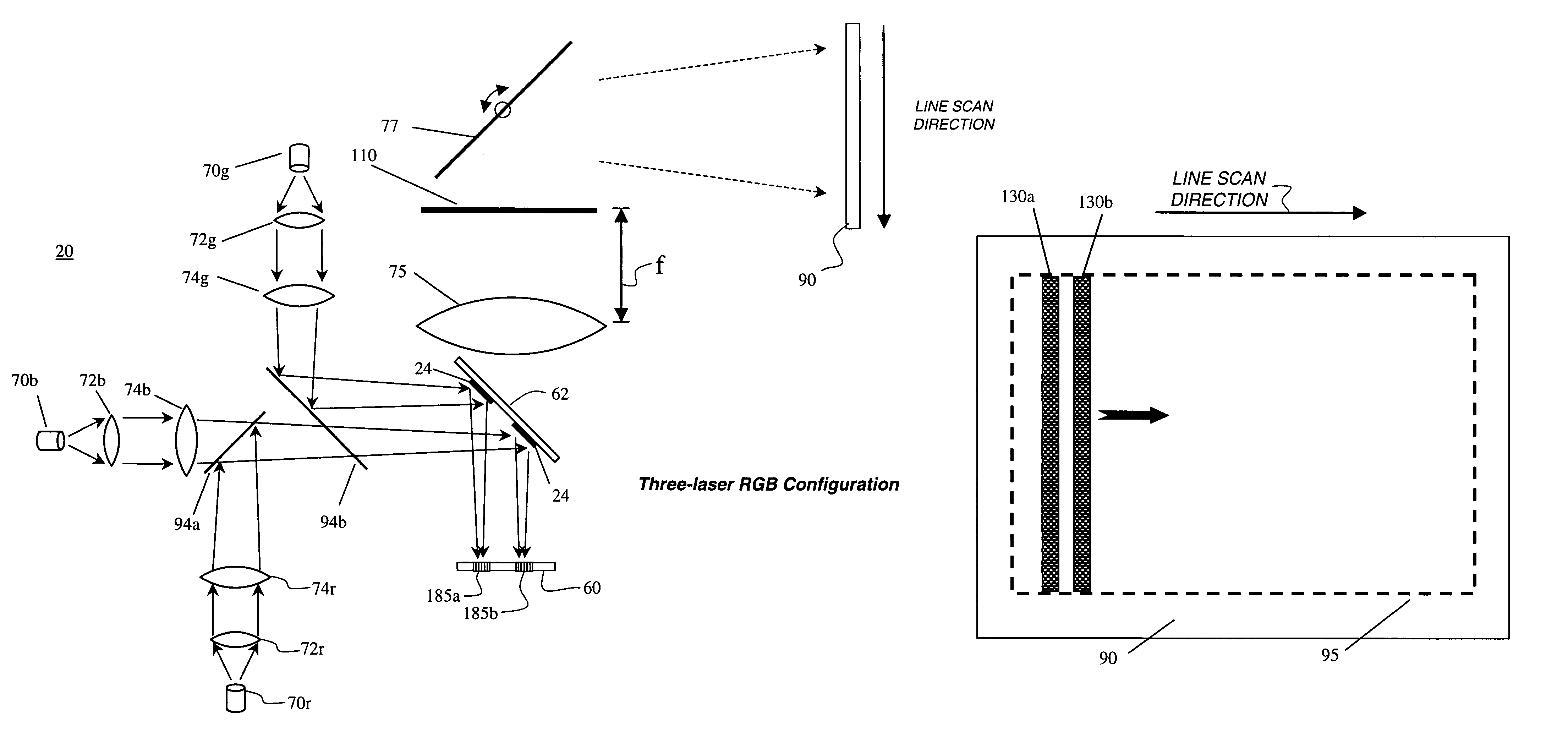

Speckle reduction for display system with electromechanical grating

InactiveUS7119936B2Lower Level RequirementsReduce in quantityTelevision system detailsStatic indicating devicesGratingLight beam

A display system (10) with reduced speckle has a light source (70) providing an illumination beam and a linear light modulator (85) having at least one linear array of light modulating devices for forming a modulated beam. The modulated beam has a plurality of orders of diffracted light. An obstructing element (82r,82g,82b) blocks a zeroeth order reflected light from the modulated beam. An angle-transforming optical assembly (30) anamorphically conditions the modulated beam. A scanning element (77) scans the modulated beam toward a display surface (90) for forming a two-dimensional image thereon.

Owner:EASTMAN KODAK CO

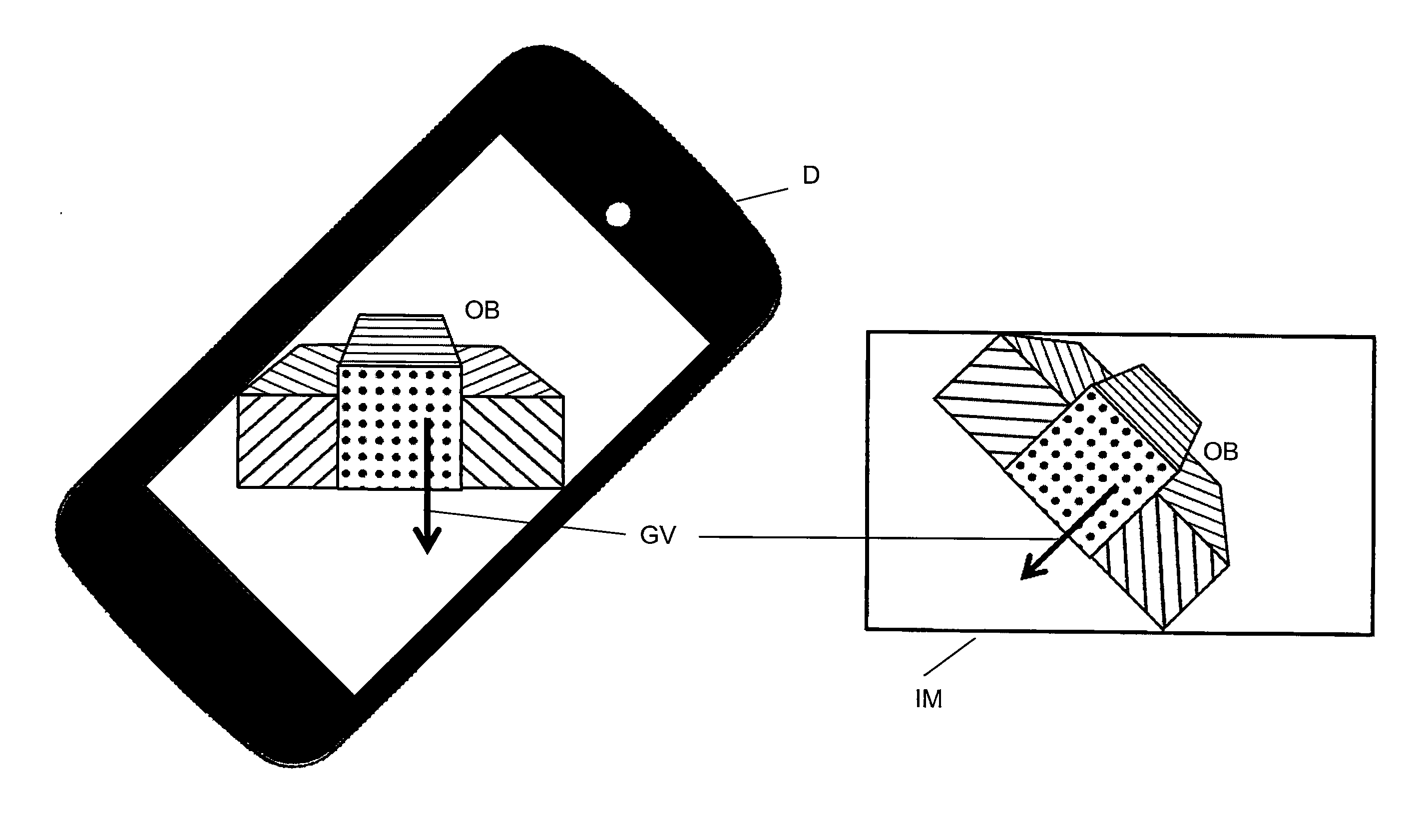

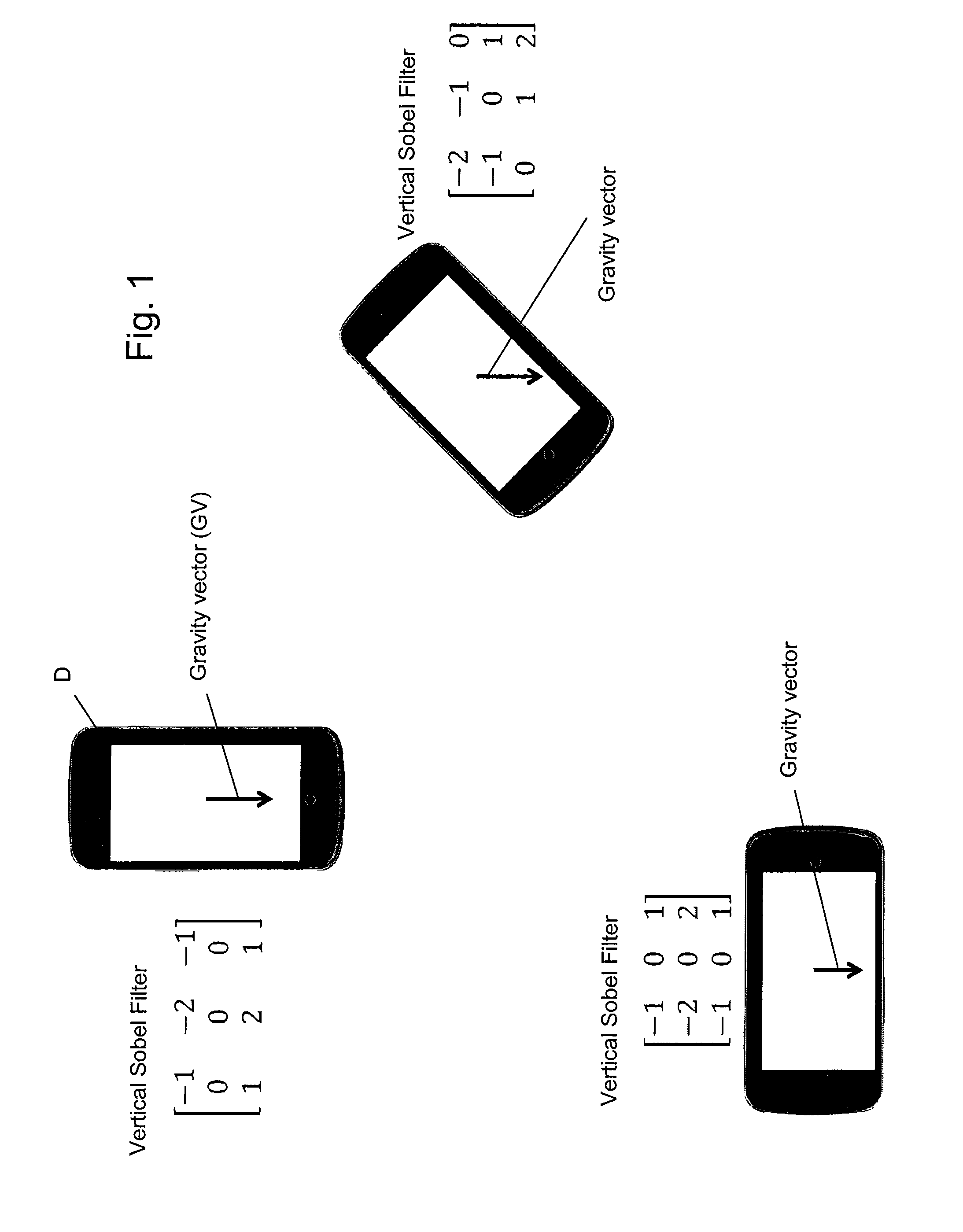

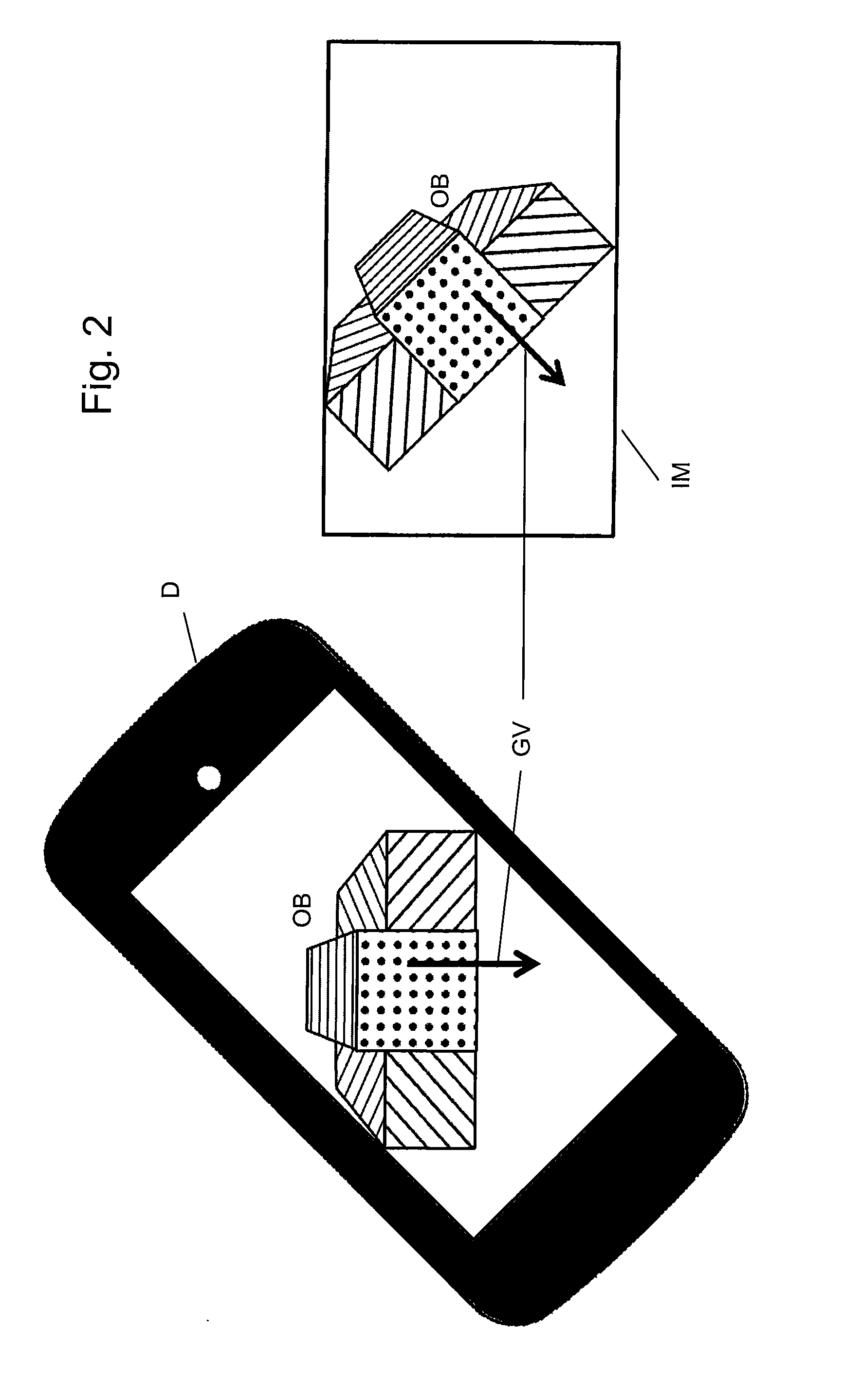

Image processing method, particularly used in a vision-based localization of a device

ActiveUS20150245020A1ConfidenceRobust solutionImage enhancementImage analysisImaging processingVision based

An image processing method includes the steps of providing at least one image of at least one object or part of the at least one object, and providing a coordinate system in relation to the image, providing at least one degree of freedom in the coordinate system or at least one sensor data in the coordinate system, and computing image data of the at least one image or at least one part of the at least one image constrained or aligned by the at least one degree of freedom or the at least one sensor data.

Owner:APPLE INC

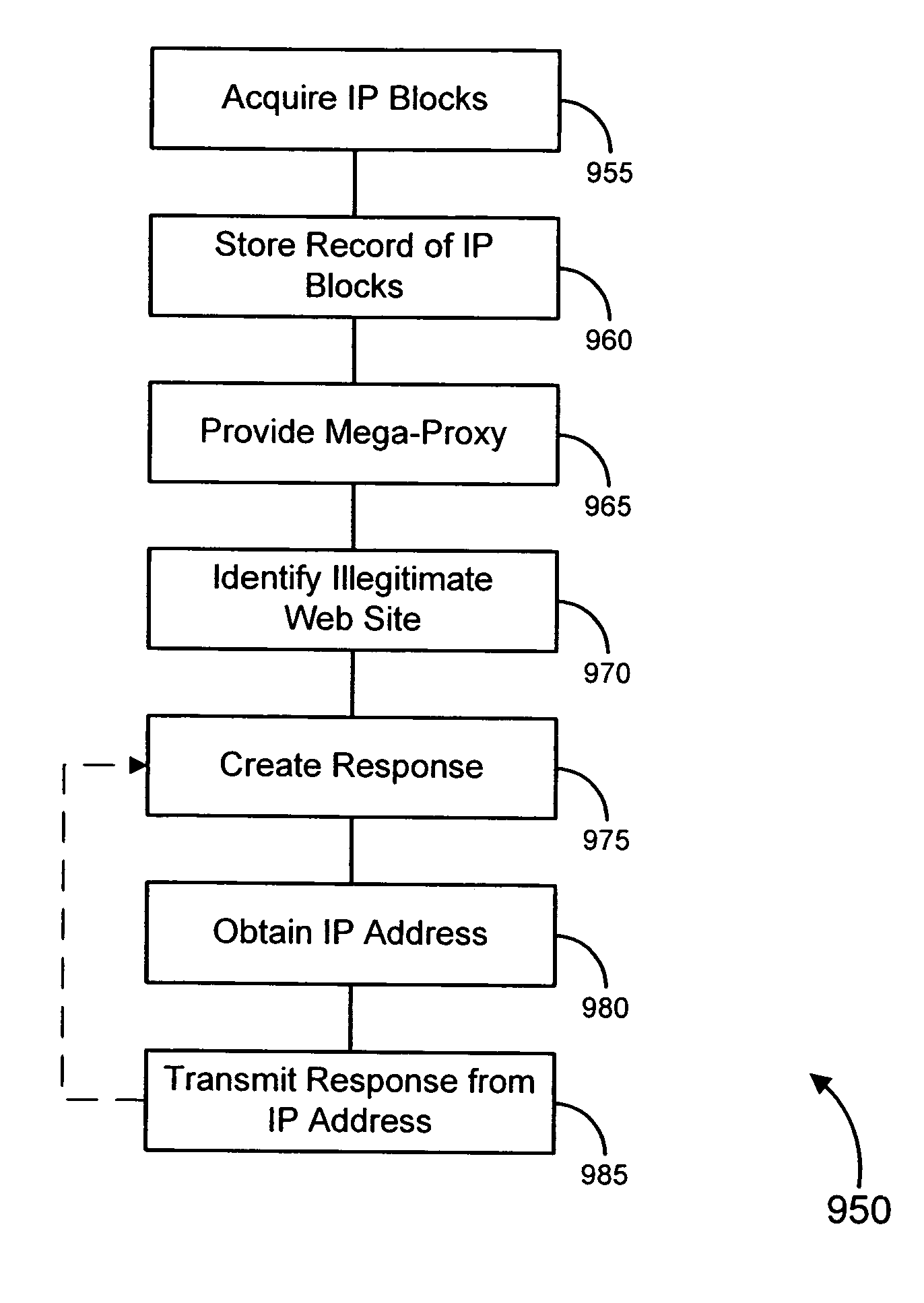

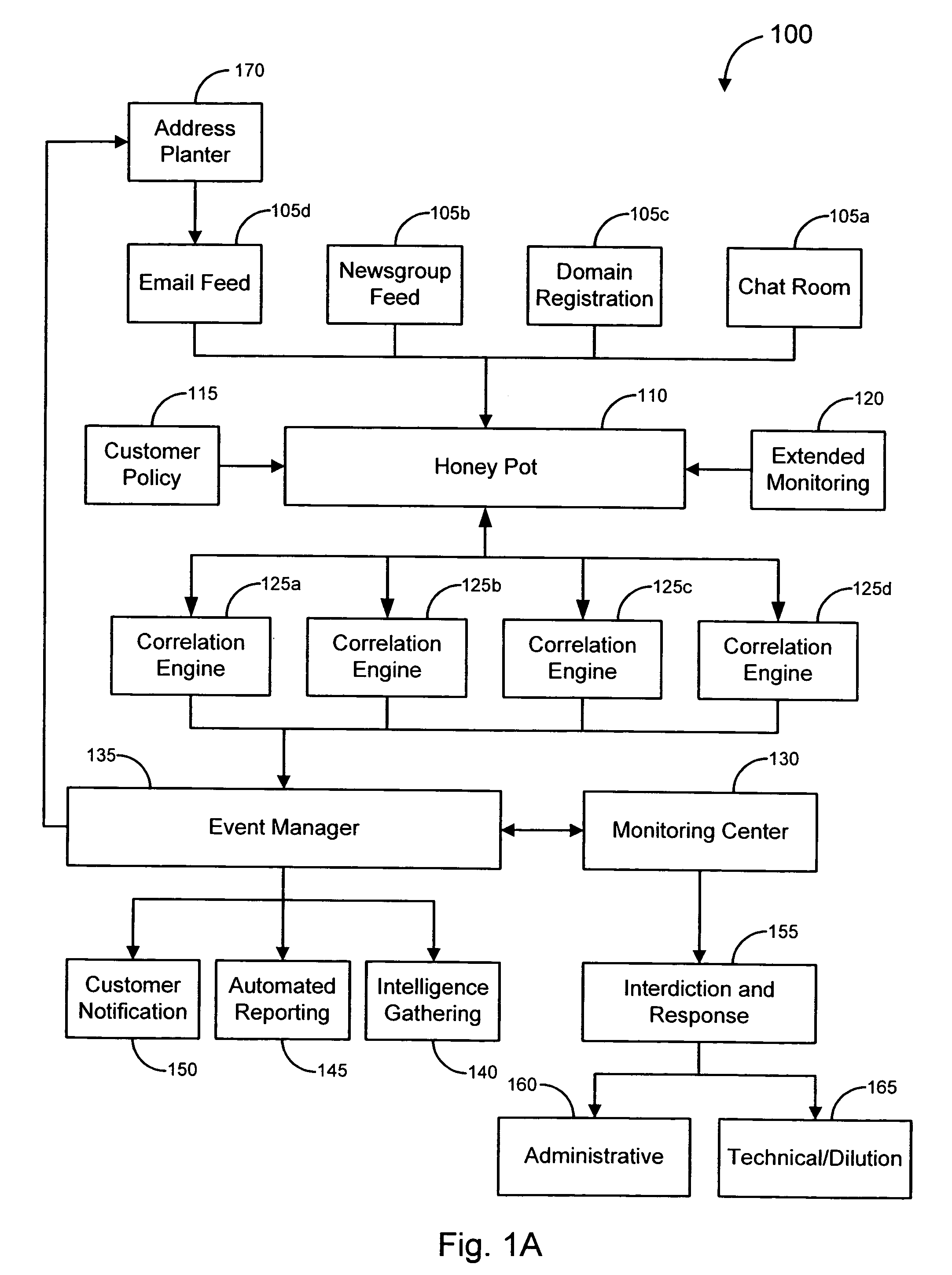

Enhanced responses to online fraud

ActiveUS7992204B2Reduced effectivenessImprove responseMemory loss protectionDigital data processing detailsResponse strategyData science

Solutions (including inter alia, systems, methods and software) for dealing with online fraud. Certain of these solutions provide enhanced responses to an identified instance of online fraud. Such enhanced responses can incorporate one or more of a variety of strategies for defeating an attempt by a server to filter and / or otherwise avoid responses to its fraudulent activity. Merely by way of example, responses may be disguised (e.g., by transmitting the responses from a variety of computers, by transmitting responses that appear to originate from a computer different than the actual source of the responses, etc.). In some cases, a response strategy may be implemented that forces the server (and / or an operator thereof) to choose between accepting the responses and blocking potential responses from the targets of the fraudulent scheme.

Owner:OPSEC ONLINE LTD

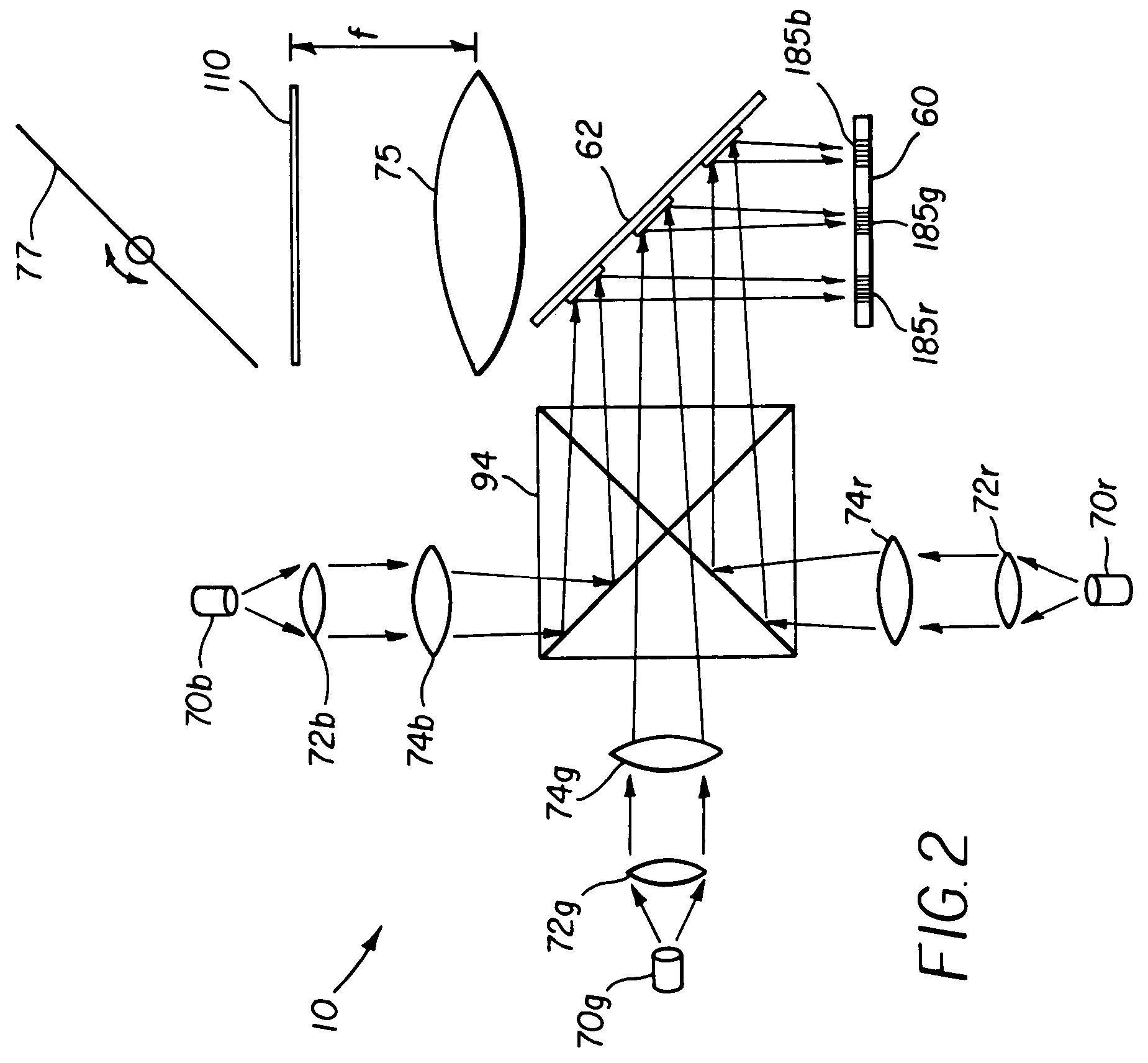

Display system incorporating bilinear electromechanical grating device

InactiveUS20070047061A1Reduce in quantityMinimizing adjustingProjectorsColor television detailsGratingScanning mirror

A line scanned display system includes at least three different colors of illumination provided by one or more light sources, and at least one directional illumination optical system for directing the three different colors of illumination. Also in the system is a bilinear array, having two linear arrays of light modulating devices, situated on a common substrate for receiving and modulating two different colors of illumination at any one time that are obtained from the three different colors of illumination. Finally, a lens for creating line images of the two linear arrays on a screen and a scanning mirror for scanning the line images across the screen to form an area image complete the system.

Owner:EASTMAN KODAK CO

Secure distributed storage system and method

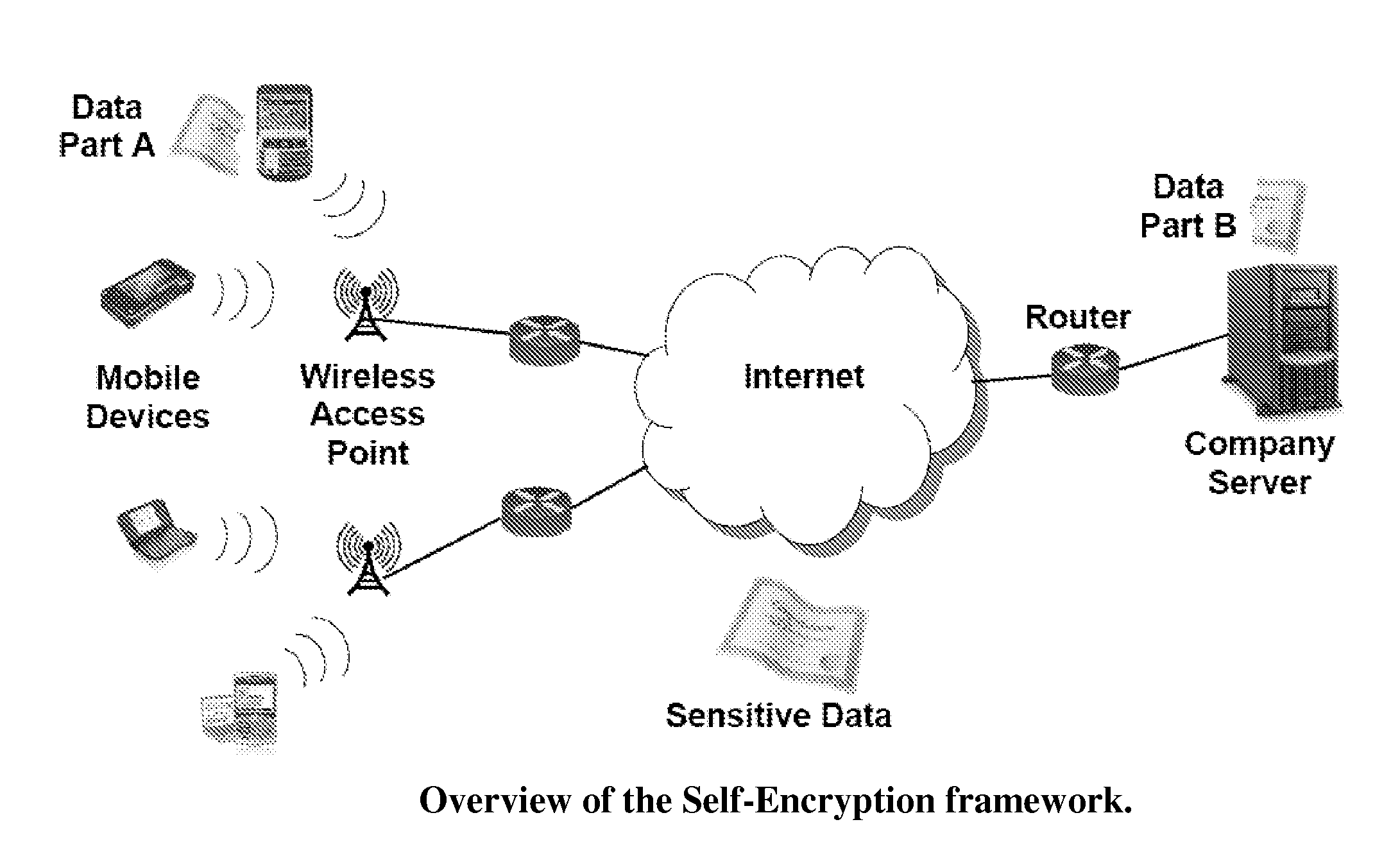

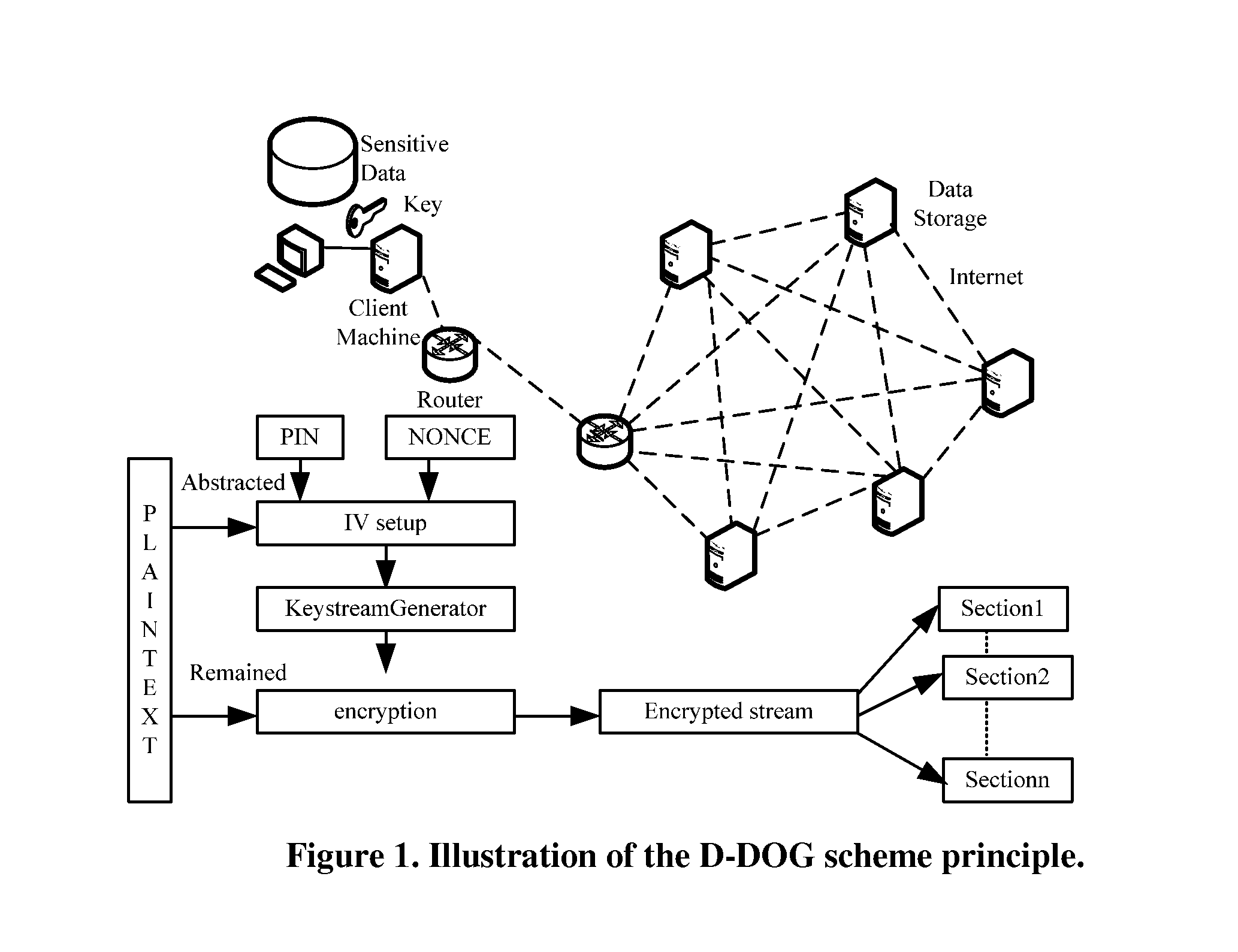

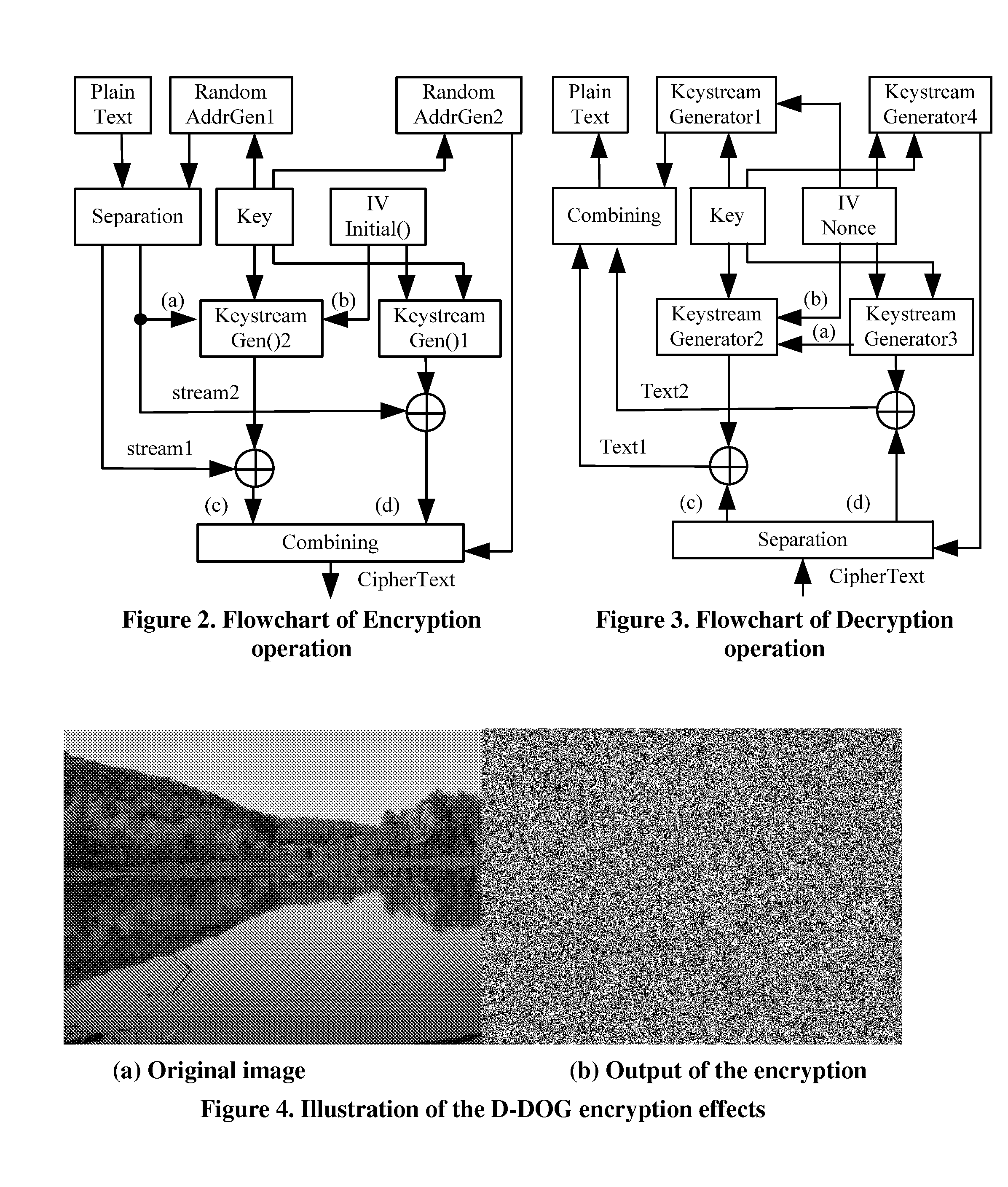

ActiveUS20110197056A1Less and less-robustProtect informationSecuring communicationOriginal dataKeystream

Moving from server-attached storage to distributed storage brings new vulnerabilities in creating a secure data storage and access facility. The Data Division and Out-of-order keystream Generation technique provides a cryptographic method to protect data in the distributed storage environments. In the technique, the Treating the data as a binary bit stream, our self-encryption (SE) scheme generates a keystream by randomly extracting bits from the stream. The length of the keystream depends on the user's security requirements. The bit stream is encrypted and the ciphertext is stored on the mobile device, whereas the keystream is stored separately. This makes it computationally not feasible to recover the original data stream from the ciphertext alone.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK

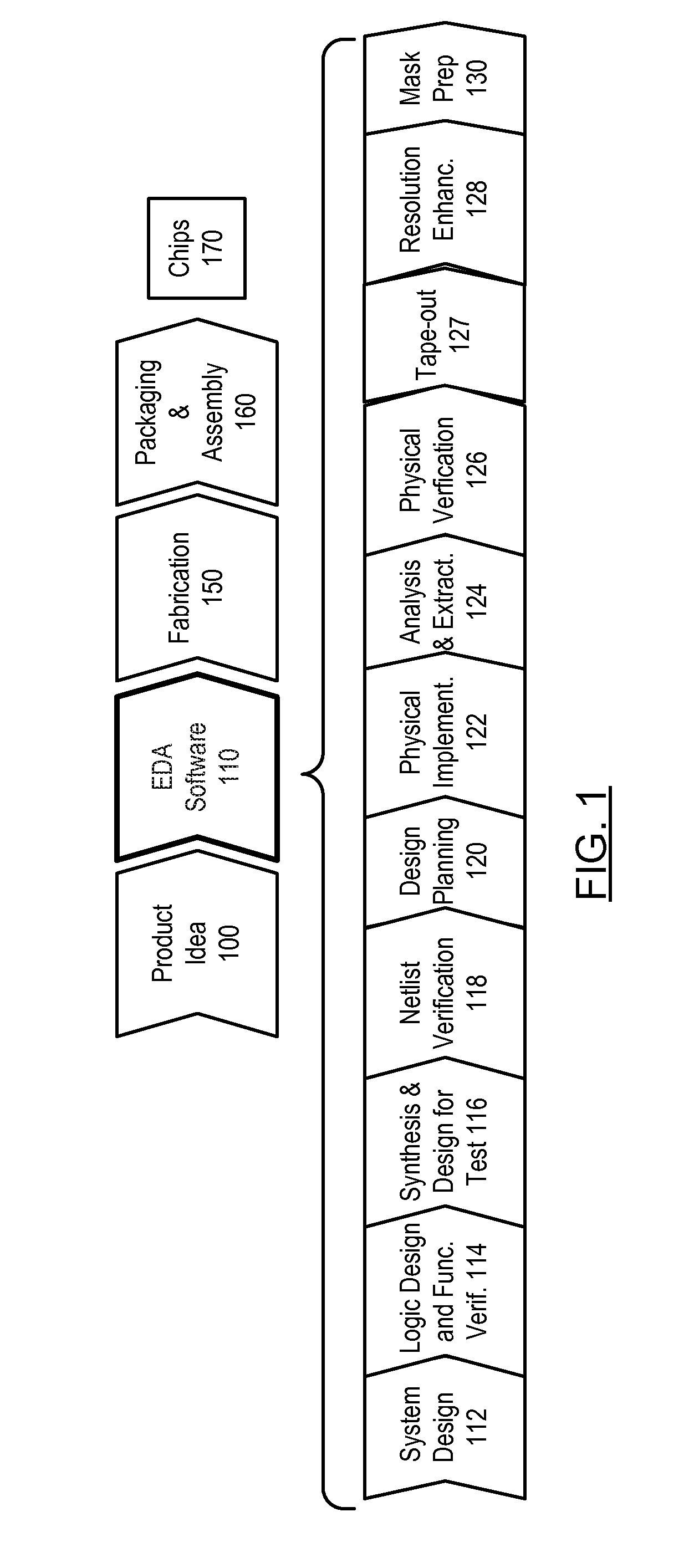

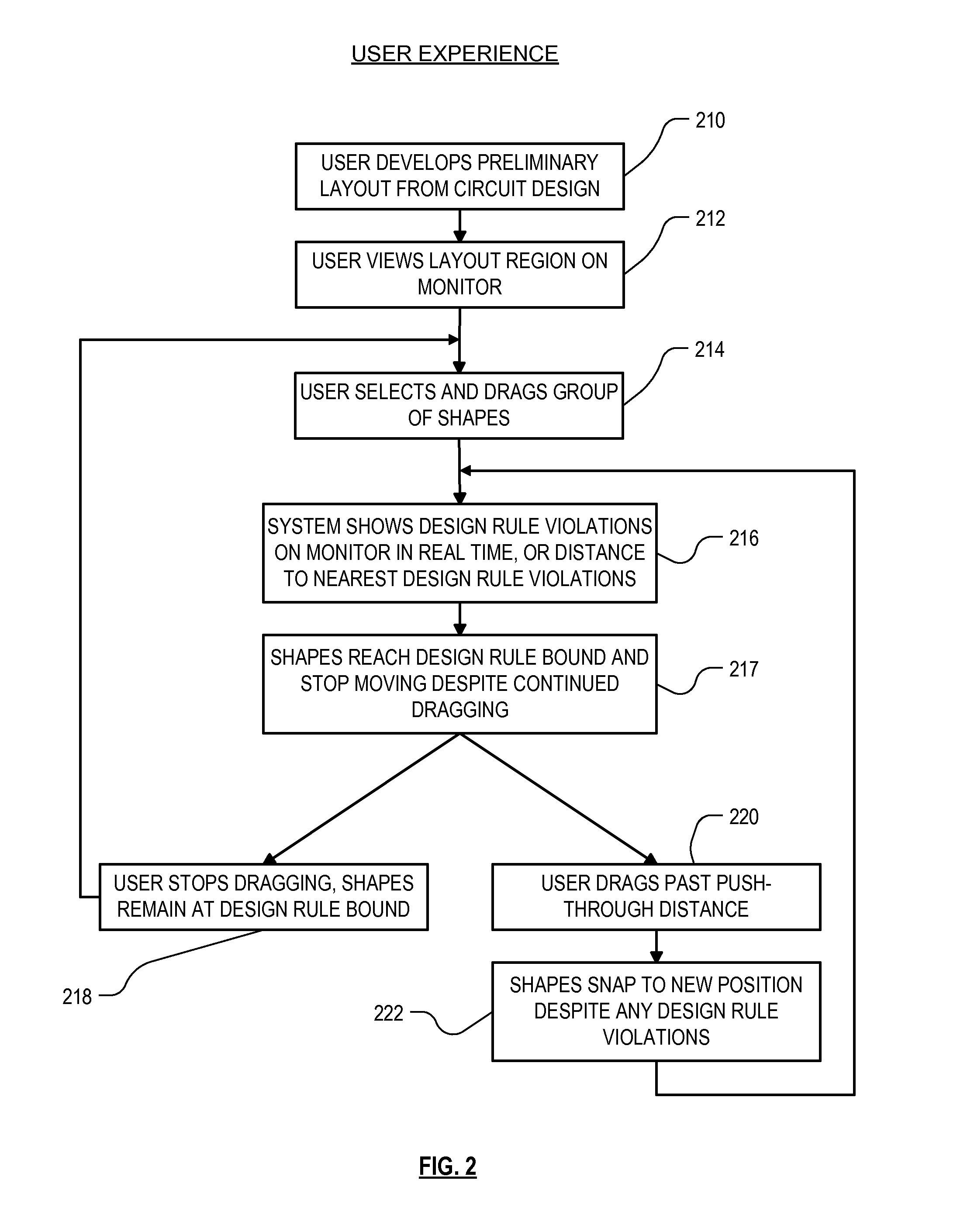

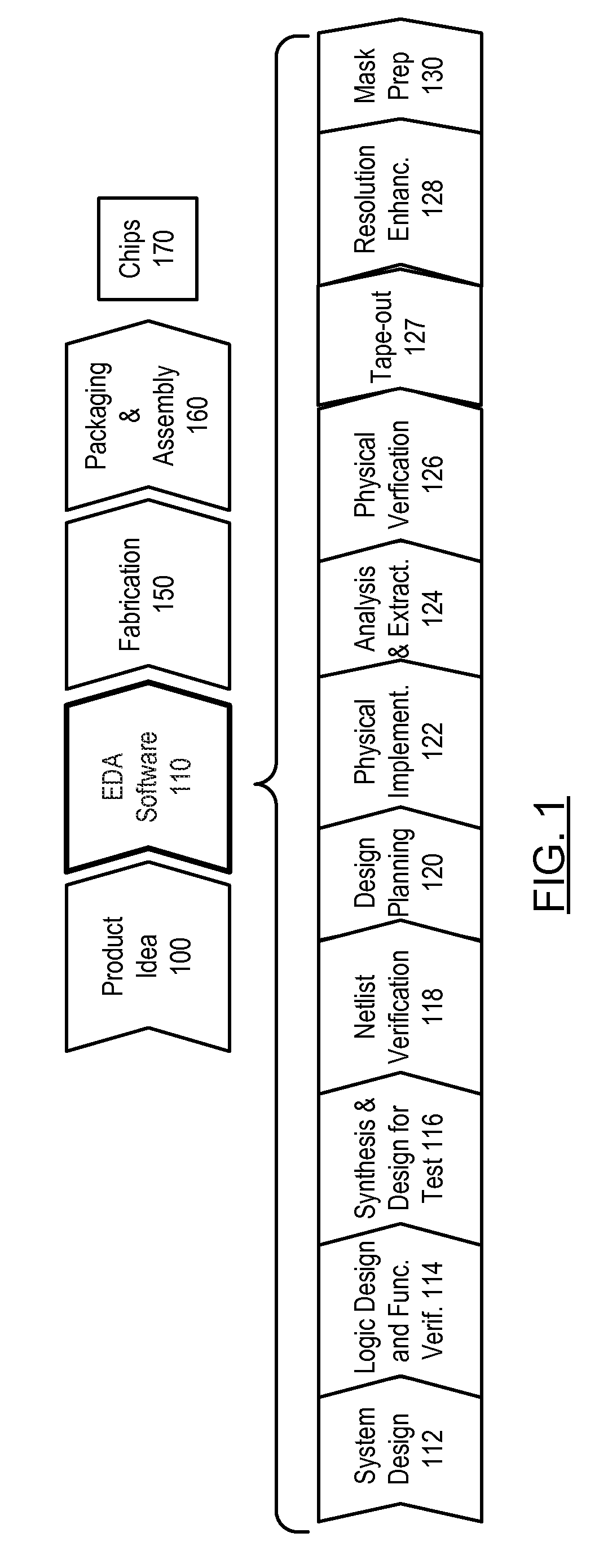

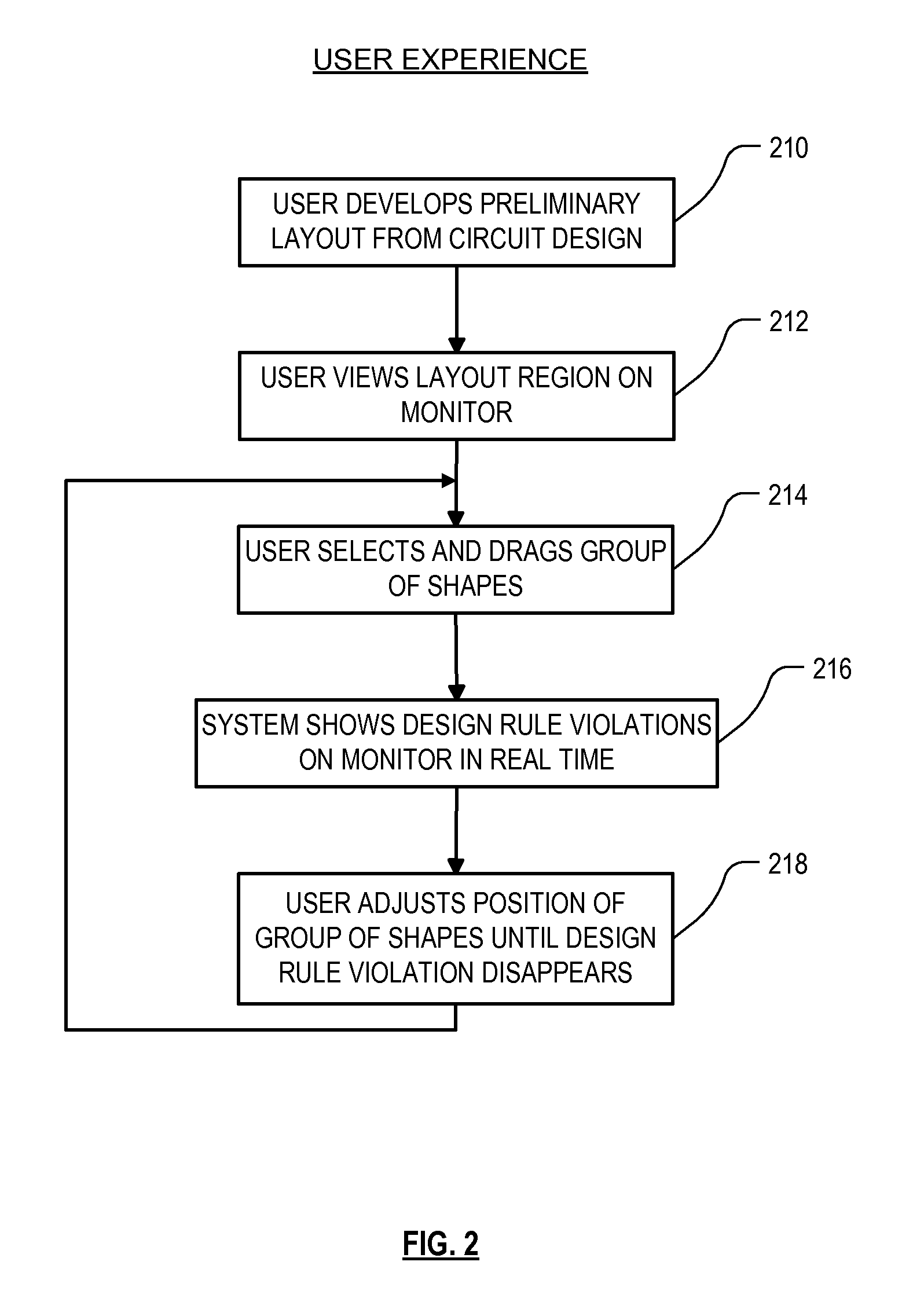

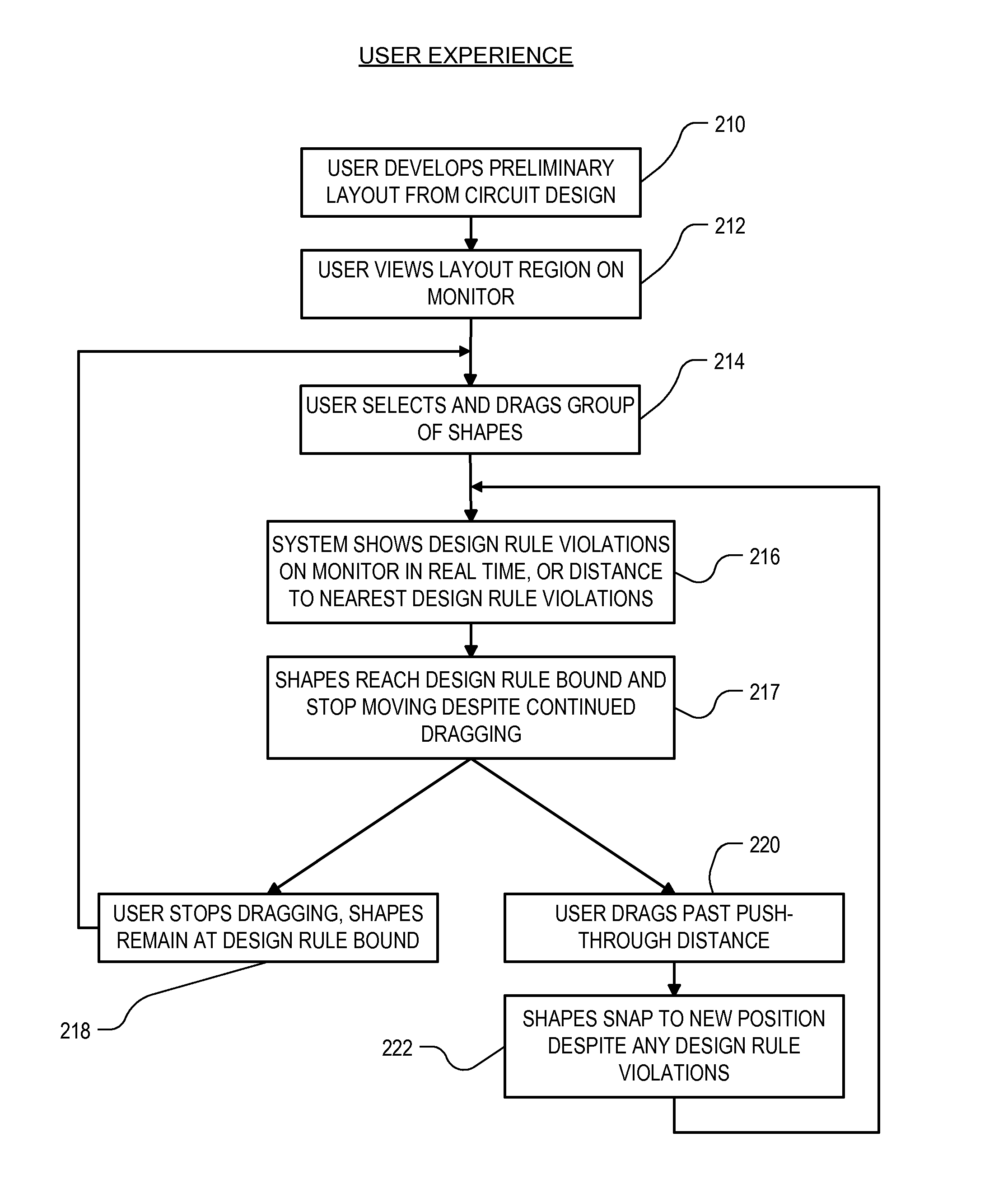

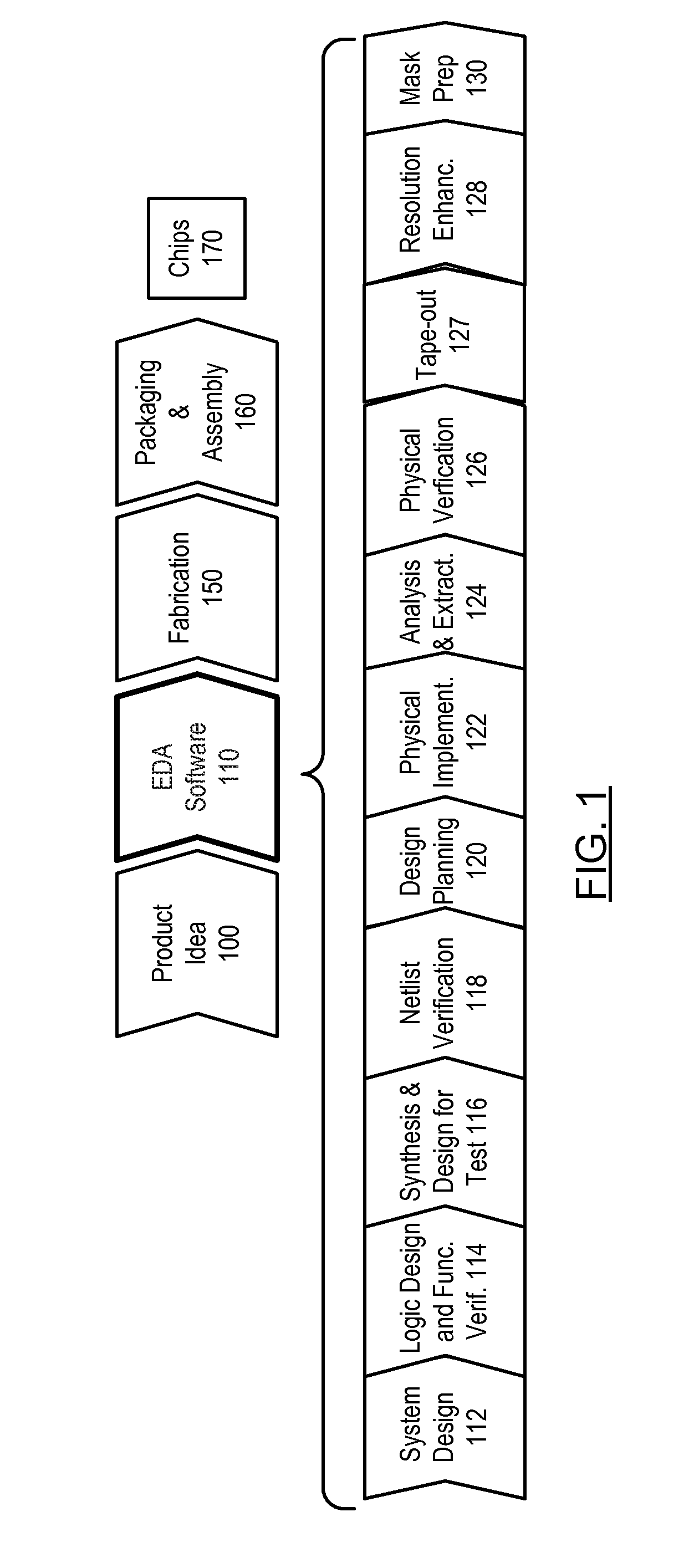

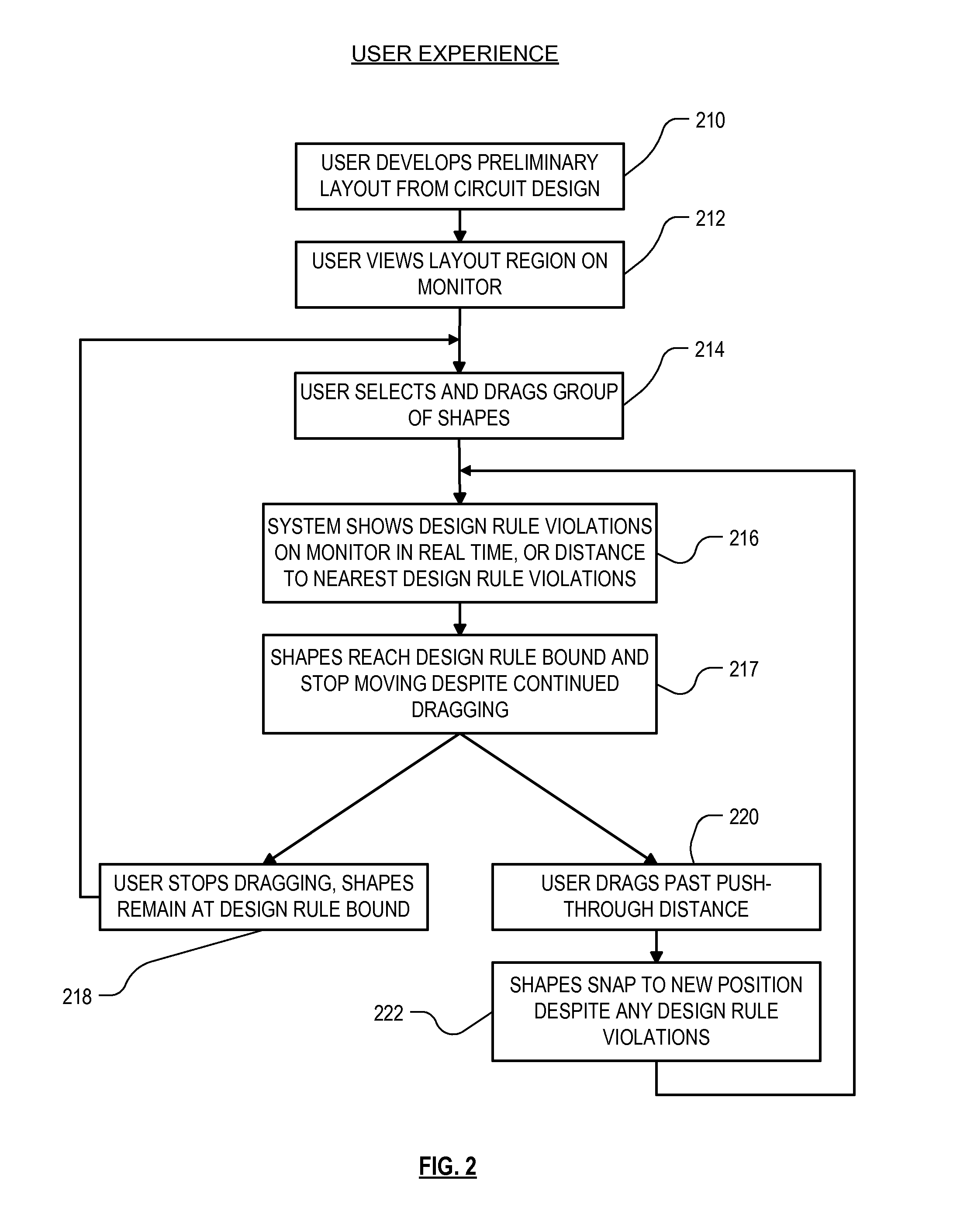

Real time drc assistance for manual layout editing

ActiveUS20120227023A1Robust solutionHigh altitude layout editingComputer programmed simultaneously with data introductionCAD circuit designComputer graphics (images)

Roughly described, while manually dragging shapes during IC layout editing, editing operations determine which edges of which shapes are moving at what speed ratios. Based on the edge information and the DRC rules, the system calculates and keeps track of the minimum of the maximum distance the edges are allowed to move with the cursor without violating DRC rules, in four linear directions and all corner directions. Once a next cursor destination point is known, a DRC clean destination point is calculated based on the linear and corner bounds. If the next cursor position is beyond a the push-through distance ahead of the new DRC clean point, the editing objects are moved to the user's destination point. Otherwise, the editing objects are moved to the new DRC clean destination point, thereby stopping movement at that point.

Owner:SYNOPSYS INC

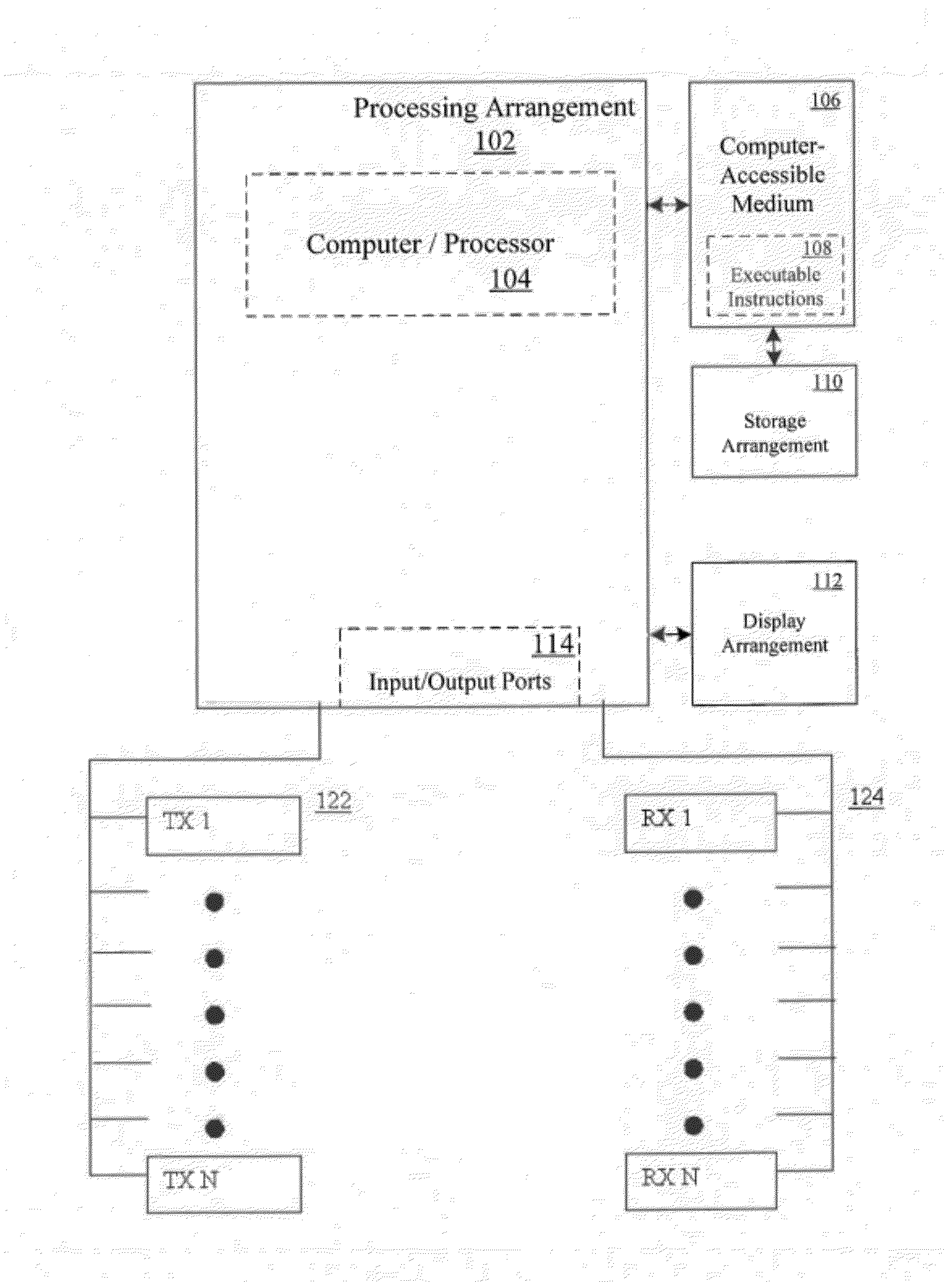

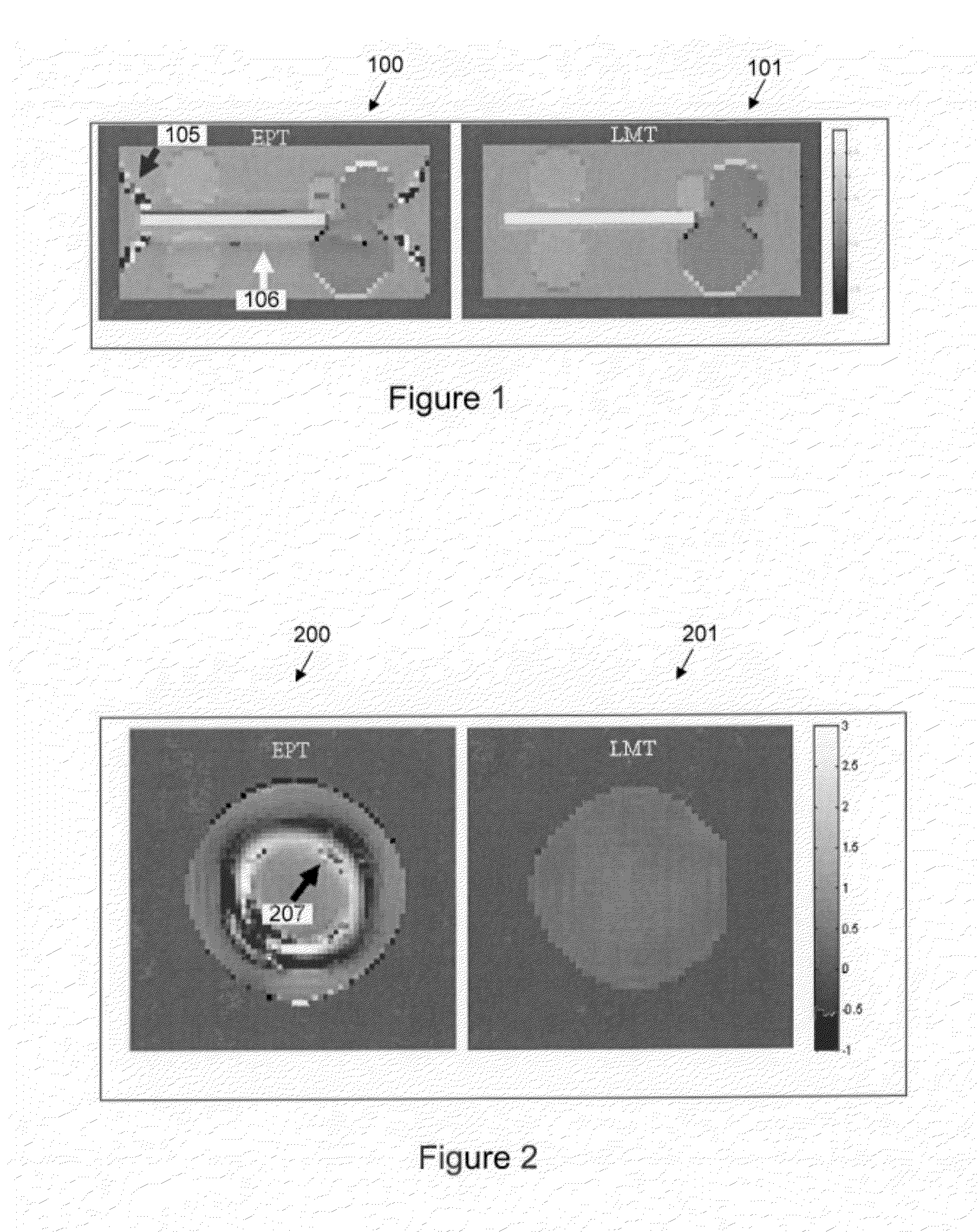

Apparatus, method and computer-accessible medium for noninvasive determination of electrical properties of tissues and materials

ActiveUS20120150458A1OptimizationImprove the situationMagnetisation measurementsResistance/reactance/impedenceElectricityTarget Response

Apparatus, method, and computer-accessible medium embodiments for a noninvasive mapping of electrical properties of tissues or materials. For example, it is possible to apply a plurality of stimulations to a target. It is possible to receive at least one signal from the target in response to the applied stimulations. Further, it is possible to process the at least one signal to determine electromagnetic-field-related quantities associated with the stimulations and the target response. Also, it is possible to supply the electromagnetic-field-related quantities to a system of equations relating these quantities to a plurality of electrical property values and residual field-related unknown values of the at least one target. It is also possible to determine a solution to the system of equations, including determining at least one electrical property of the at least one target.

Owner:NEW YORK UNIV

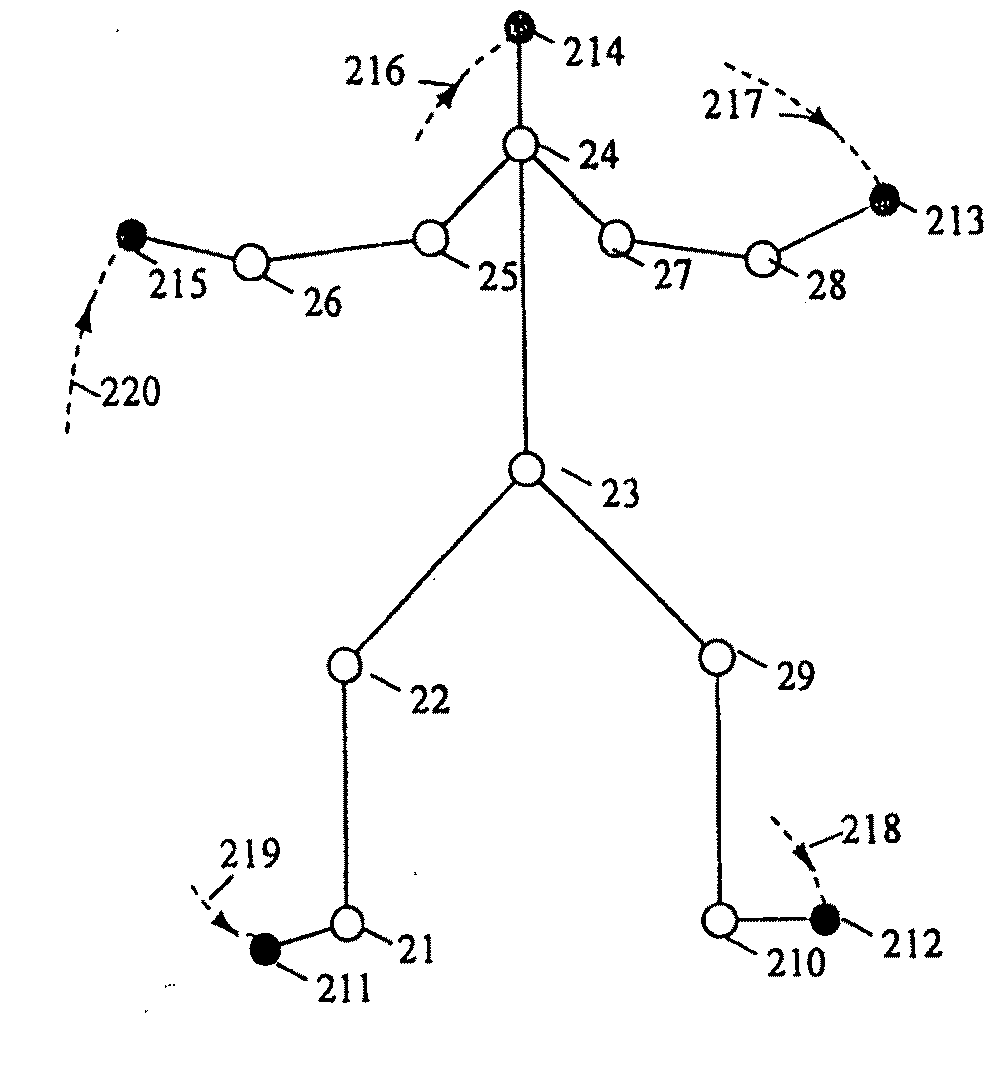

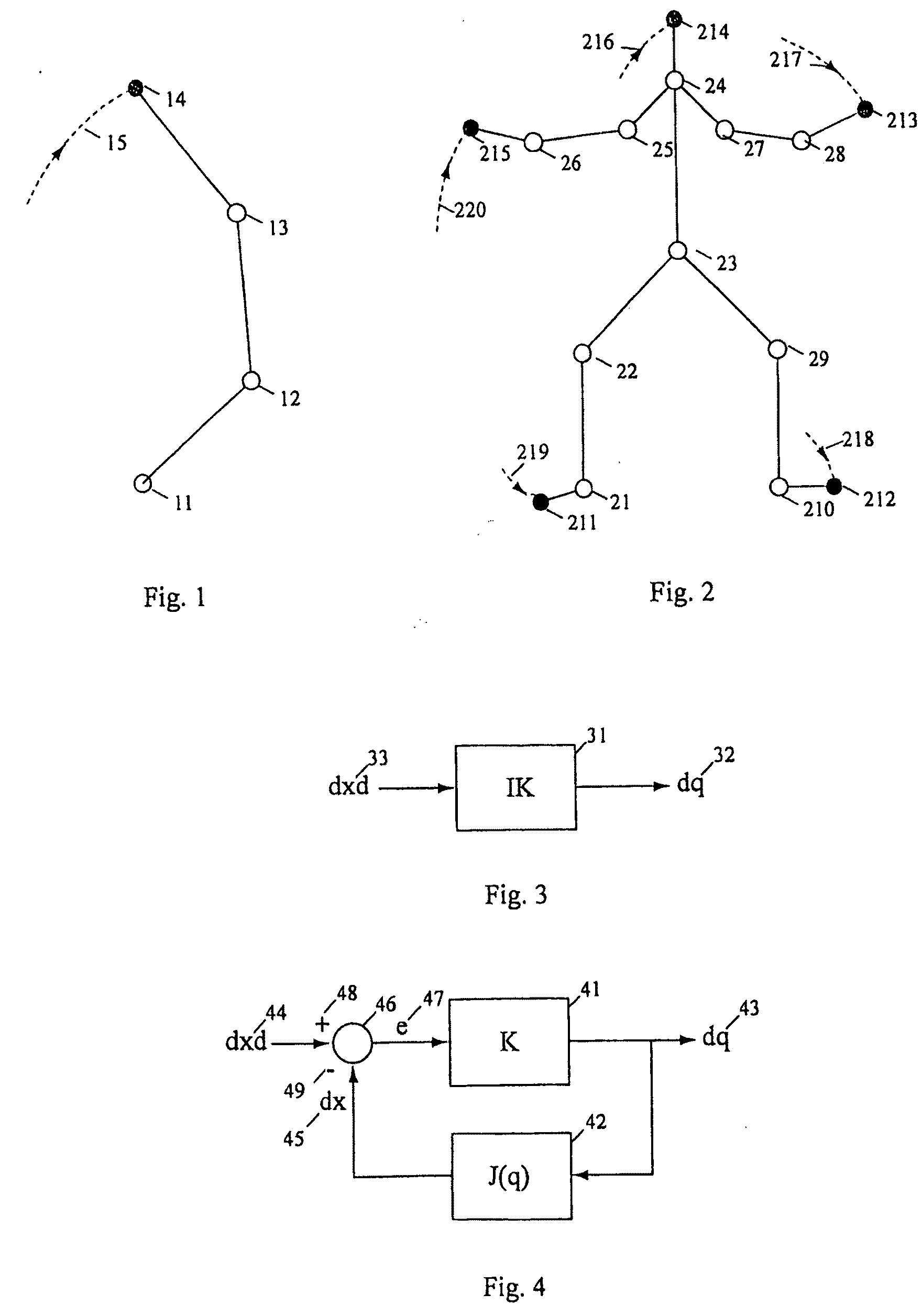

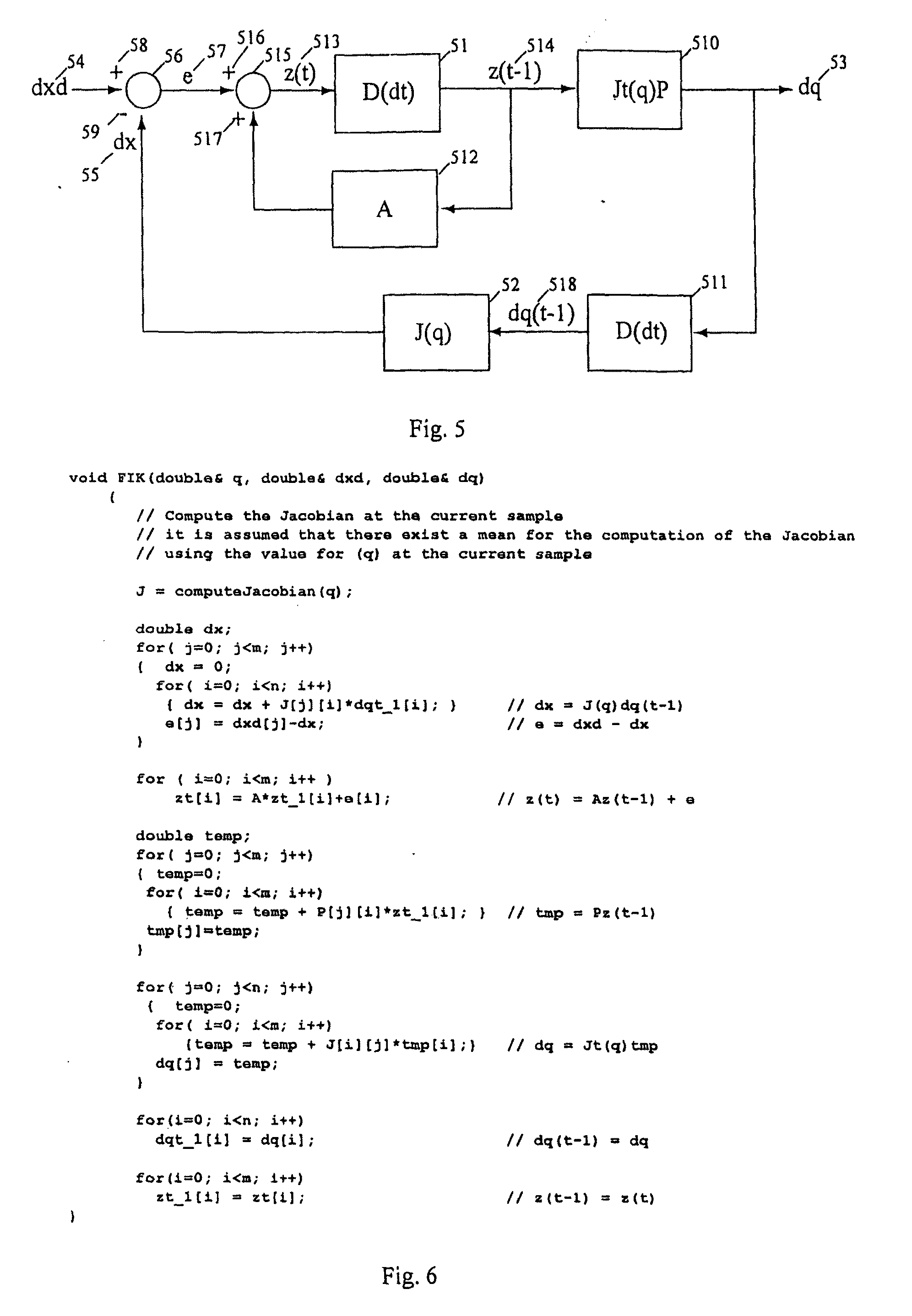

Inverse kinematics

ActiveUS20100228396A1Computationally efficientRobust solutionProgramme controlProgramme-controlled manipulatorTransfer matrixEngineering

A real-time method for controlling a system, the system including a plurality of controlling means each having at least one variable parameter (q) and a controlled element having a trajectory which is controlled by the controlling means, wherein the trajectory is related to the variable parameters by a variable matrix, the method comprising defining a control transfer matrix (K) relating the variable parameters dq to the trajectory dx, and using a feedback loop in which a feedback term is computed that is dependent on an error (e) which is the difference between the desired trajectory (dxd) which can have an arbitrary dimension specified as (m) and a current trajectory (dx).

Owner:APPLE INC

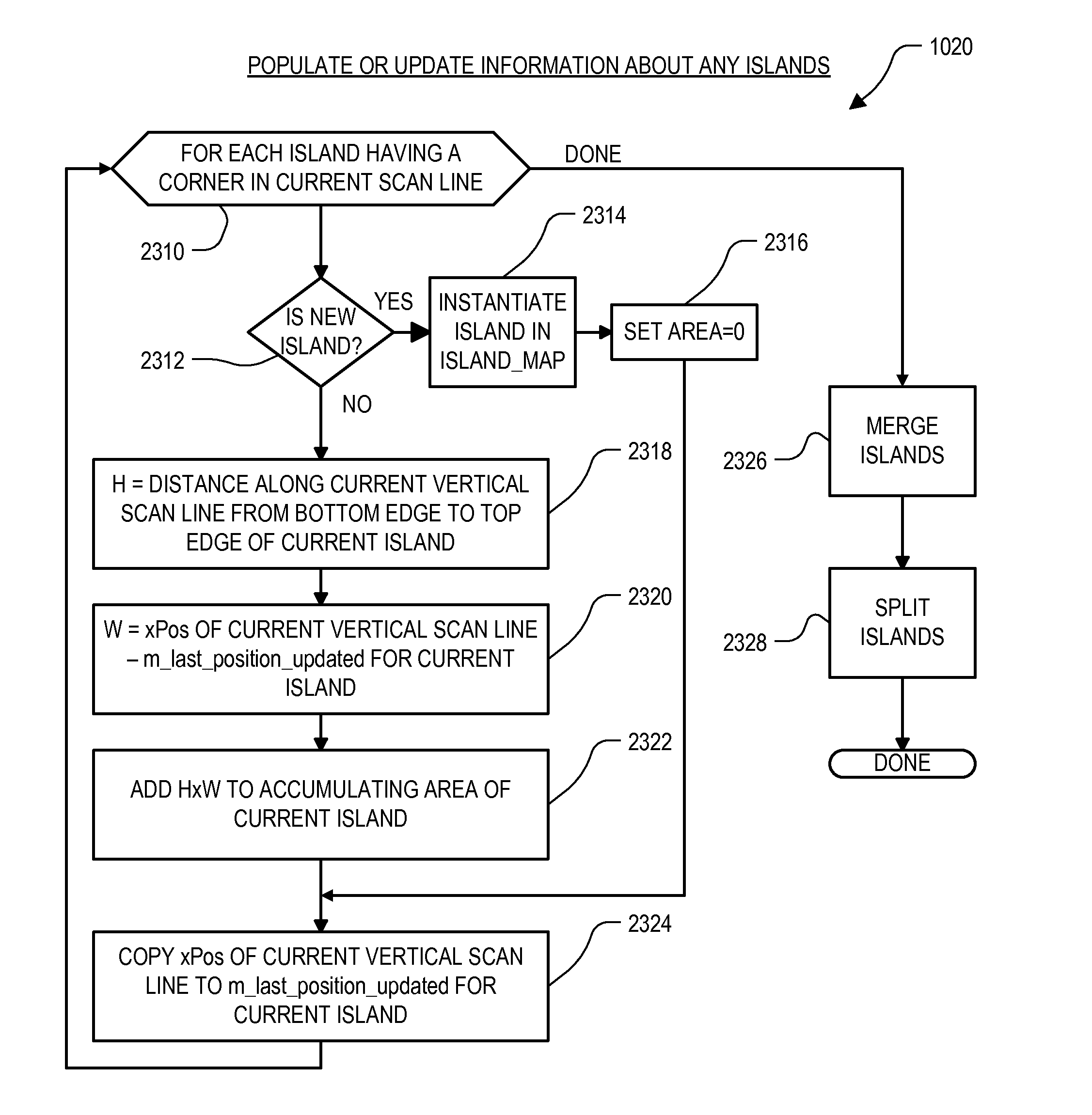

High performance design rule checking technique

ActiveUS20120144355A1Robust solutionConstraint-based CADSoftware simulation/interpretation/emulationData setComputer architecture

Roughly described, a design rule data set is developed offline from the design rules of a target fabrication process. A design rule checking method involves traversing the corners of shapes in a layout region, and for each corner, populating a layout topology database with values that depend on respective corner locations. After the layout topology database is populated, the values are compared to values in the design rule data set to detect any design rule violations. Violations can be reported in real time, while the user is manually editing the layout. Preferably corner traversal is performed using scan lines oriented perpendicularly to edge orientations, and scanning in the direction of the edge orientations. Scans stop only at corner positions and populate the layout topology database with what information can be gleaned based on the current scan line. The different scans need not reach each corner simultaneously.

Owner:SYNOPSYS INC

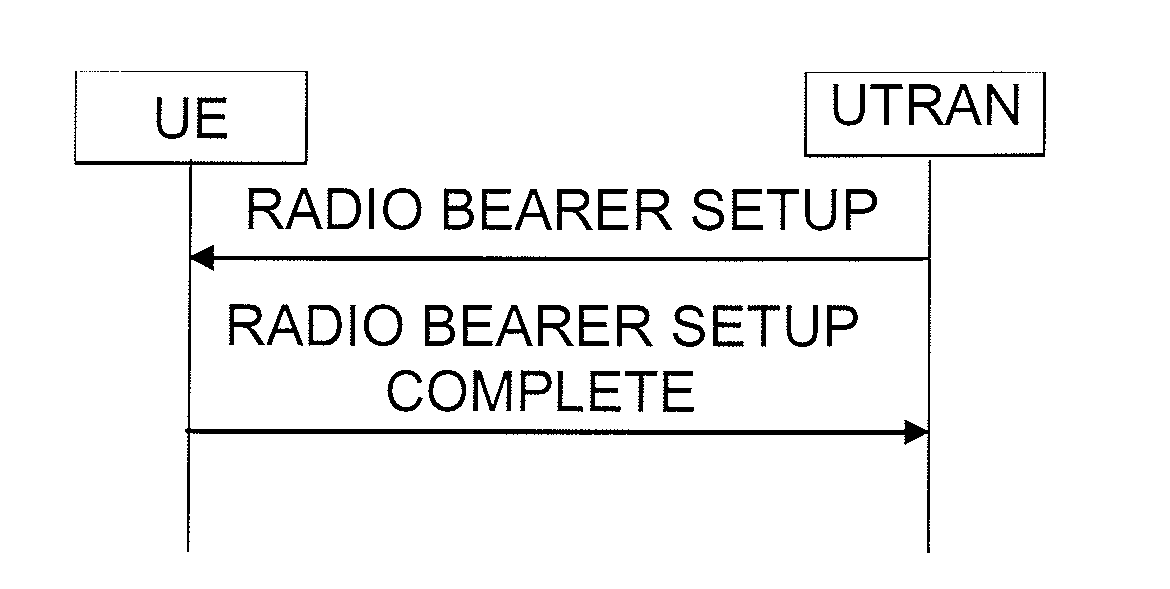

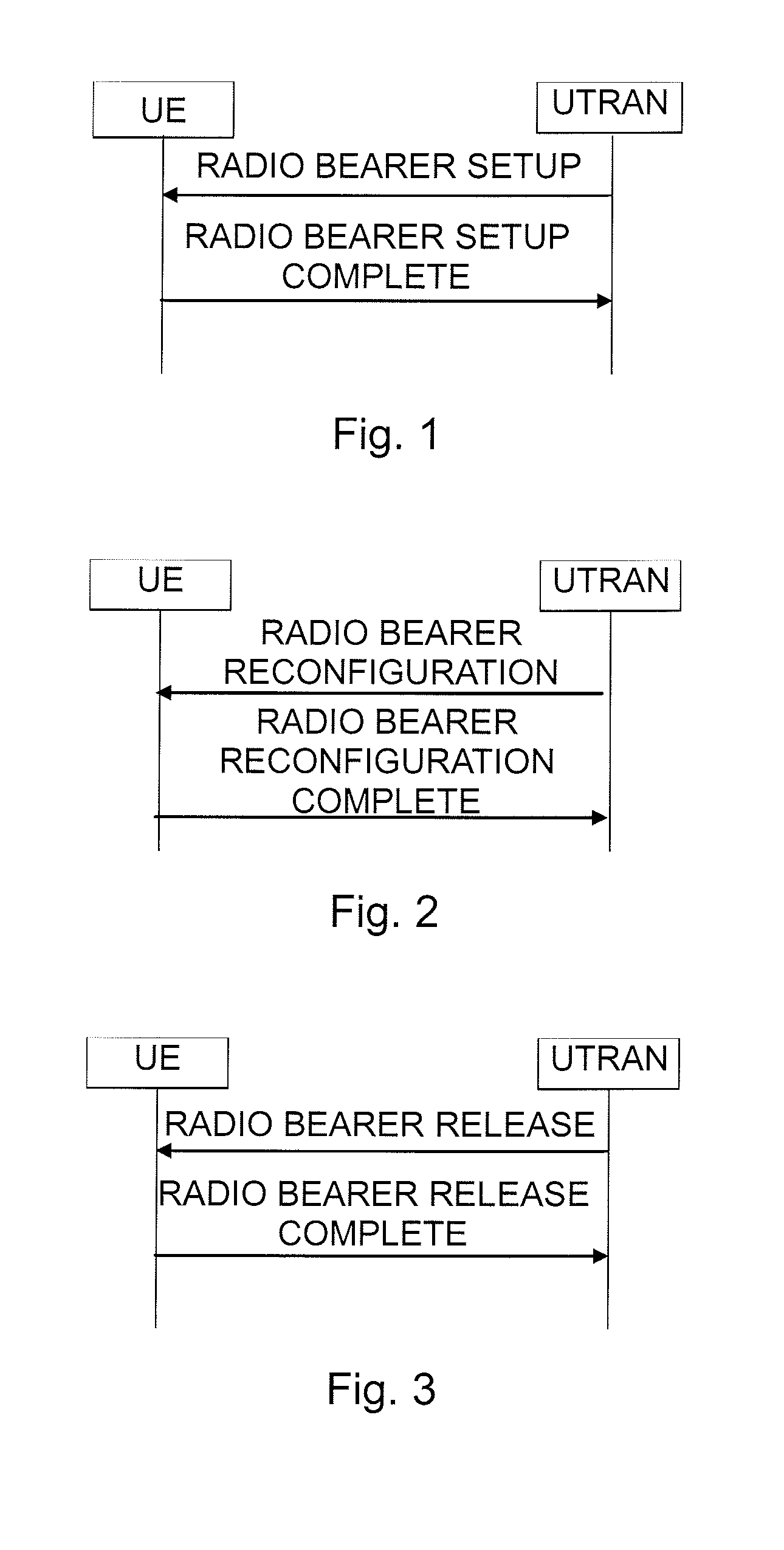

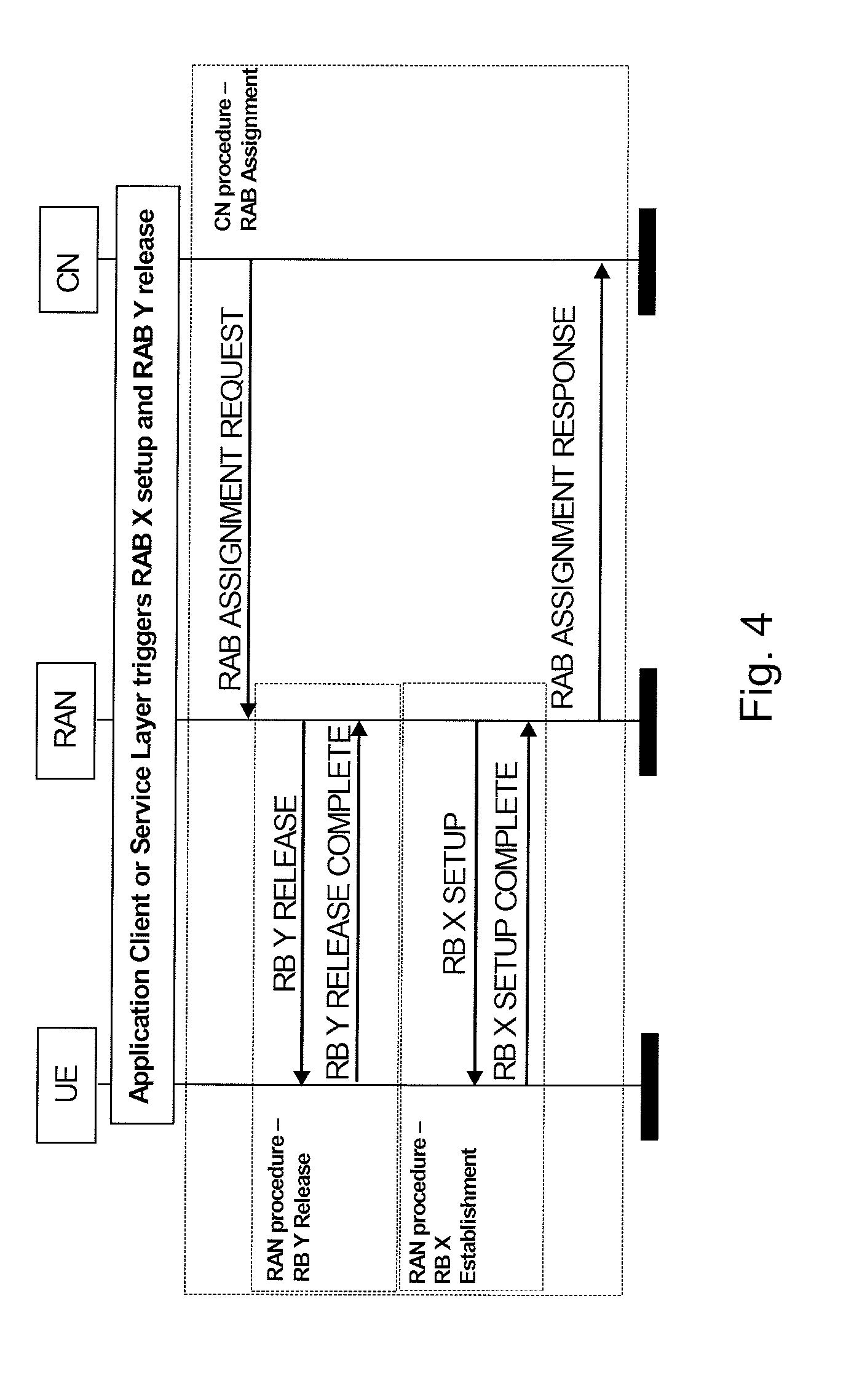

Unique radio bearer (RB) procedure

InactiveUS20110009124A1Easy to carryEasy maintenanceConnection managementRadio transmissionTelecommunicationsAir interface

The present invention is related to a method for radio resource handling in a wireless communication network comprising the steps: -receiving via a transport network interface a request for assignment of one or more radio resources over an air interface of the wireless communication network; -transmitting via the air interface a radio resource assignment message for one or more one radio resources in the wireless communication network; -receiving a radio resource assignment confirmation message over the air interface; -transmitting a radio resource assignment confirmation message over the transport network interface, wherein the radio resource assignment message transmitted via the air interface comprises a single radio resource assignment message configured to simultaneously perform establishment, release and modification of one or more radio resources provided by over the air interface. This method may be implemented by a computer program comprising instruction sets for each method step. Also, the present invention comprises a radio base station and a mobile terminal where the method according to the present invention may be executed.

Owner:UNWIRED PLANET

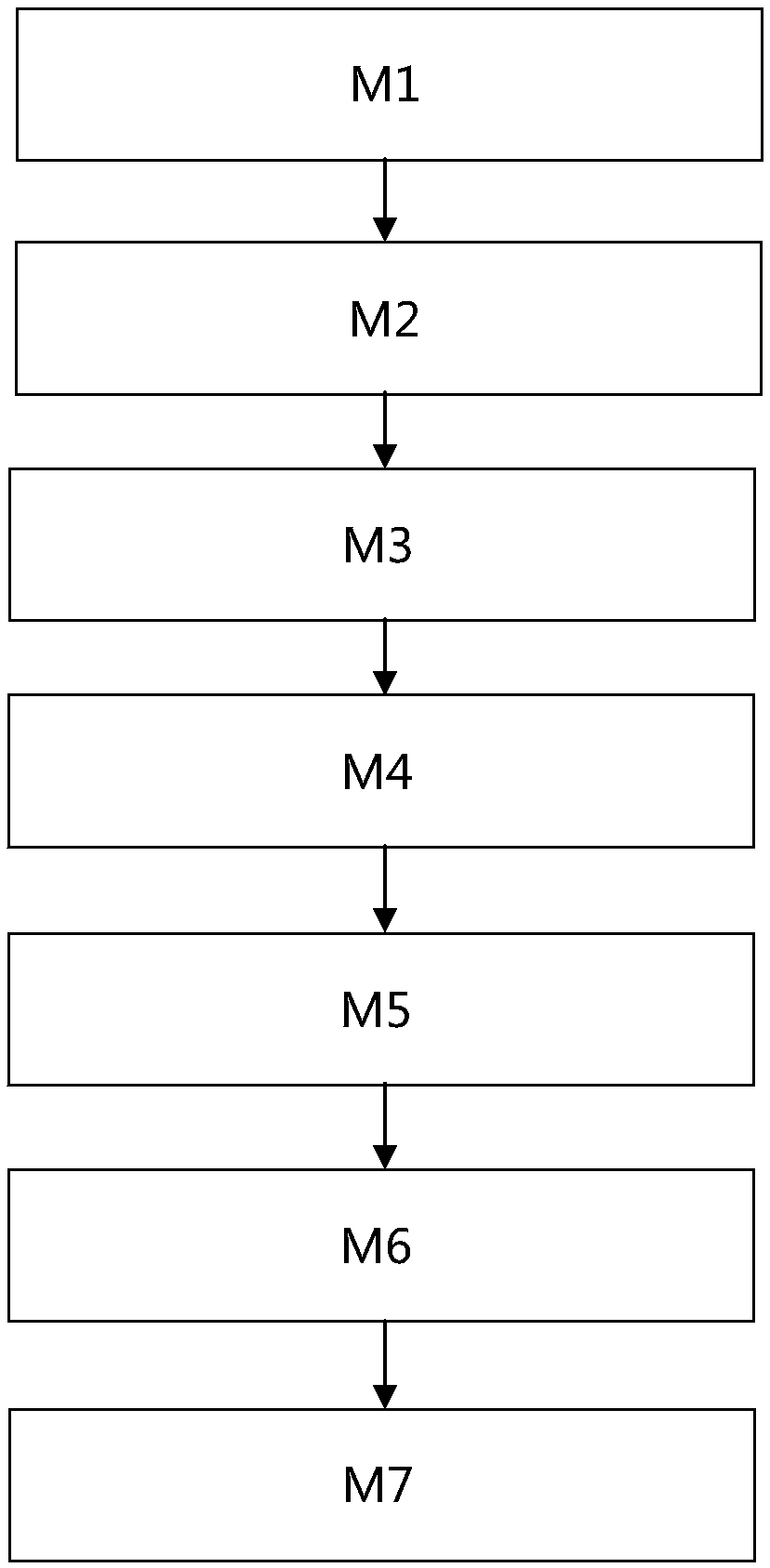

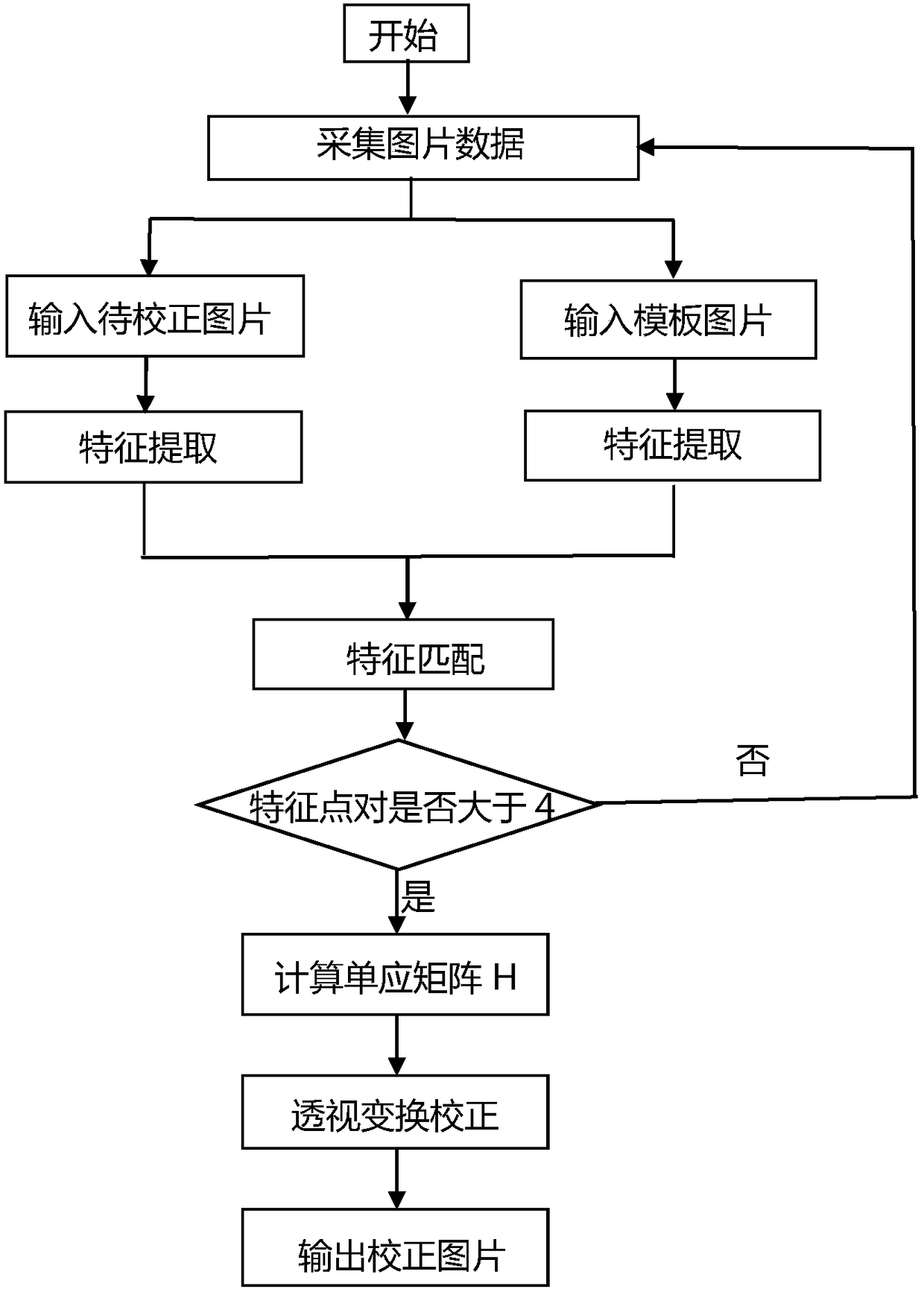

Picture correction method and system based on ORB algorithm

PendingCN108596867ARotation invariantImprove Calibration AccuracyImage enhancementImage analysisPerspective transformationFeature point matching

The invention discloses a picture correction method and system based on an ORB algorithm. The ORB algorithm and perspective transformation are combined in use. The method comprises the specific operation steps of S1, feature point detection; S2, feature point description; S3, feature point matching; S4, preliminary screening of matching point pairs; S5, acquisition of first N optimal point pairs;S6, calculation of a homographic matrix H; and S7, image registration and correction. Compared with existing methods, the method has the remarkable advantages that operation speed is 100 times that ofa SIFT algorithm and 10 times that of a SURF algorithm, correction precision is higher than that of the SIFT algorithm and slightly lower than that of the SURF algorithm, the method has rotation invariance, and the noise sensitivity problem is solved, so that the final correction effect is certainly ideal; and during calculation of the homographic matrix H, a random sampling consensus (RANSAC) algorithm is adopted, so that the homographic matrix H is solved more robustly, and mistaken matching points are eliminated.

Owner:WUYI UNIV

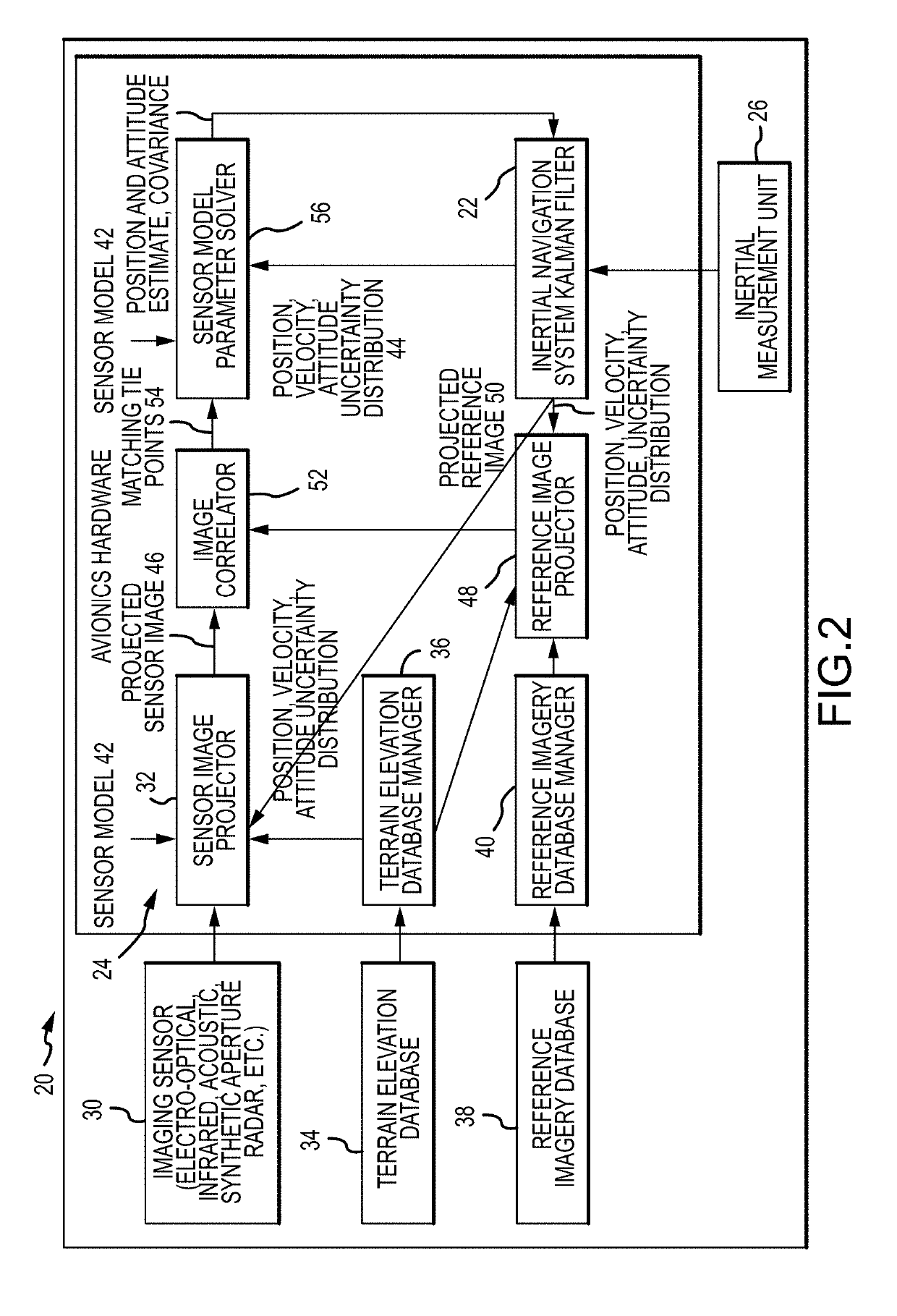

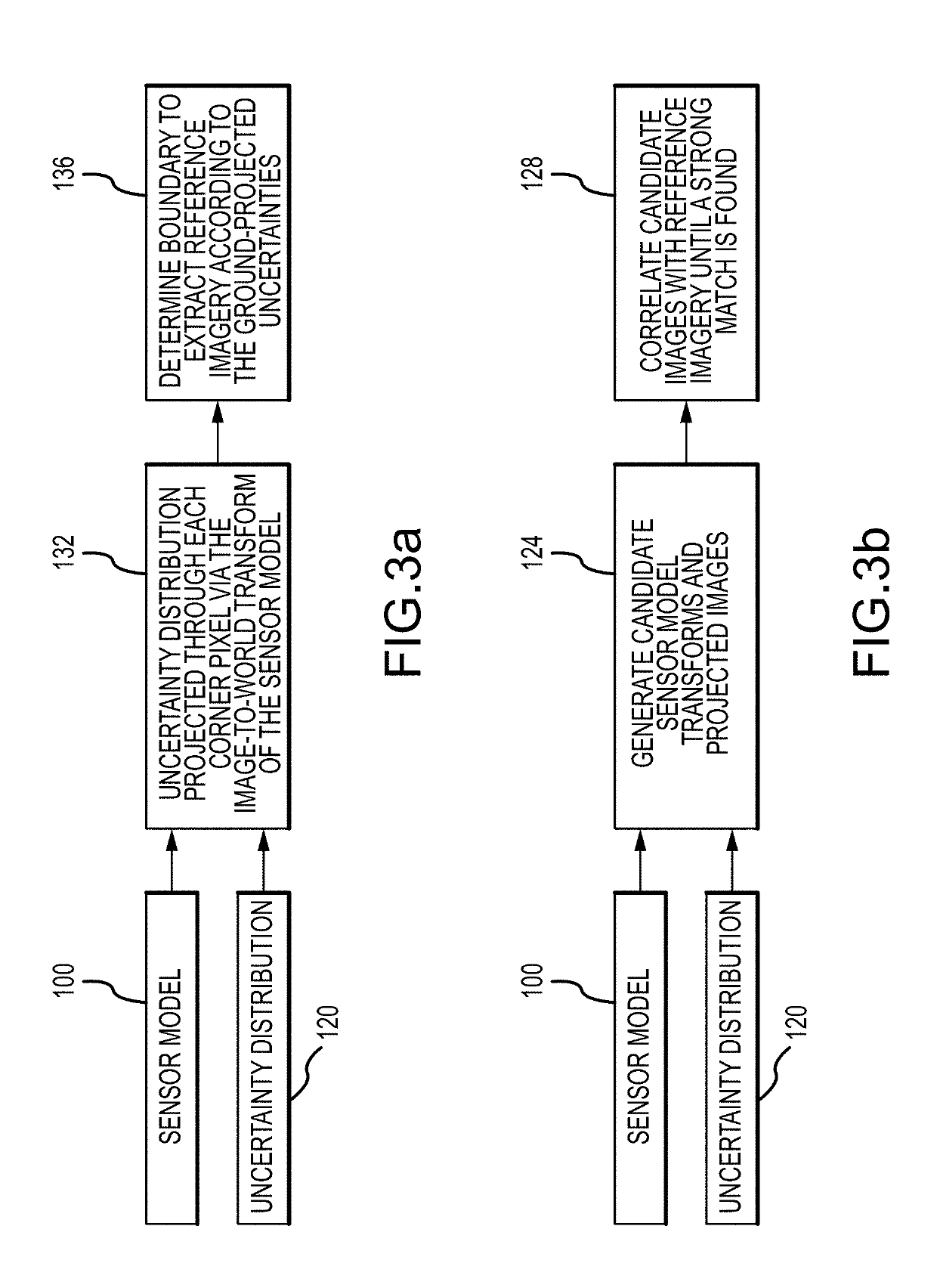

Image geo-registration for absolute navigation aiding using uncertainy information from the on-board navigation system

ActiveUS20190242711A1Improve computing efficiencyAccurate updateInstruments for road network navigationDirection controllersAviationDiagnostic Radiology Modality

A system and method for feeding back and incorporating the uncertainty distribution of the state estimate output by the INS in the image geo-registration process to handle larger navigation errors, provide a full six degree of freedom position and attitude absolute navigation update for the navigation system and provide a more accurate update for autonomous aerial, underwater or ground vehicles. Generating the update simultaneously for multiple images may provide a more robust solution to address any observability issues that may be present, the ability to fuse different sensor modalities and in general more accurate updates. Key frames may be used to improve the computational efficiency of the method.

Owner:RAYTHEON CO

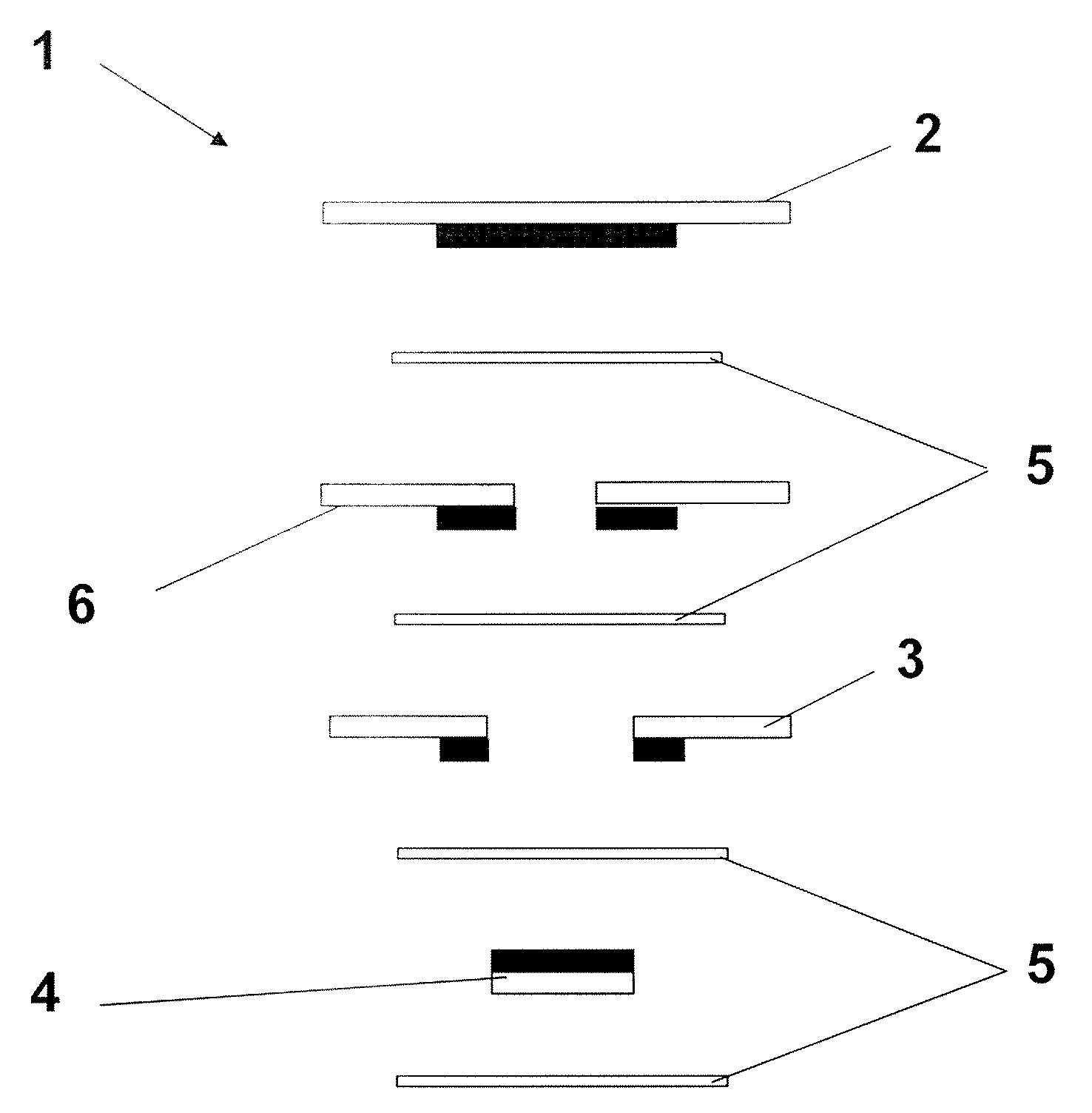

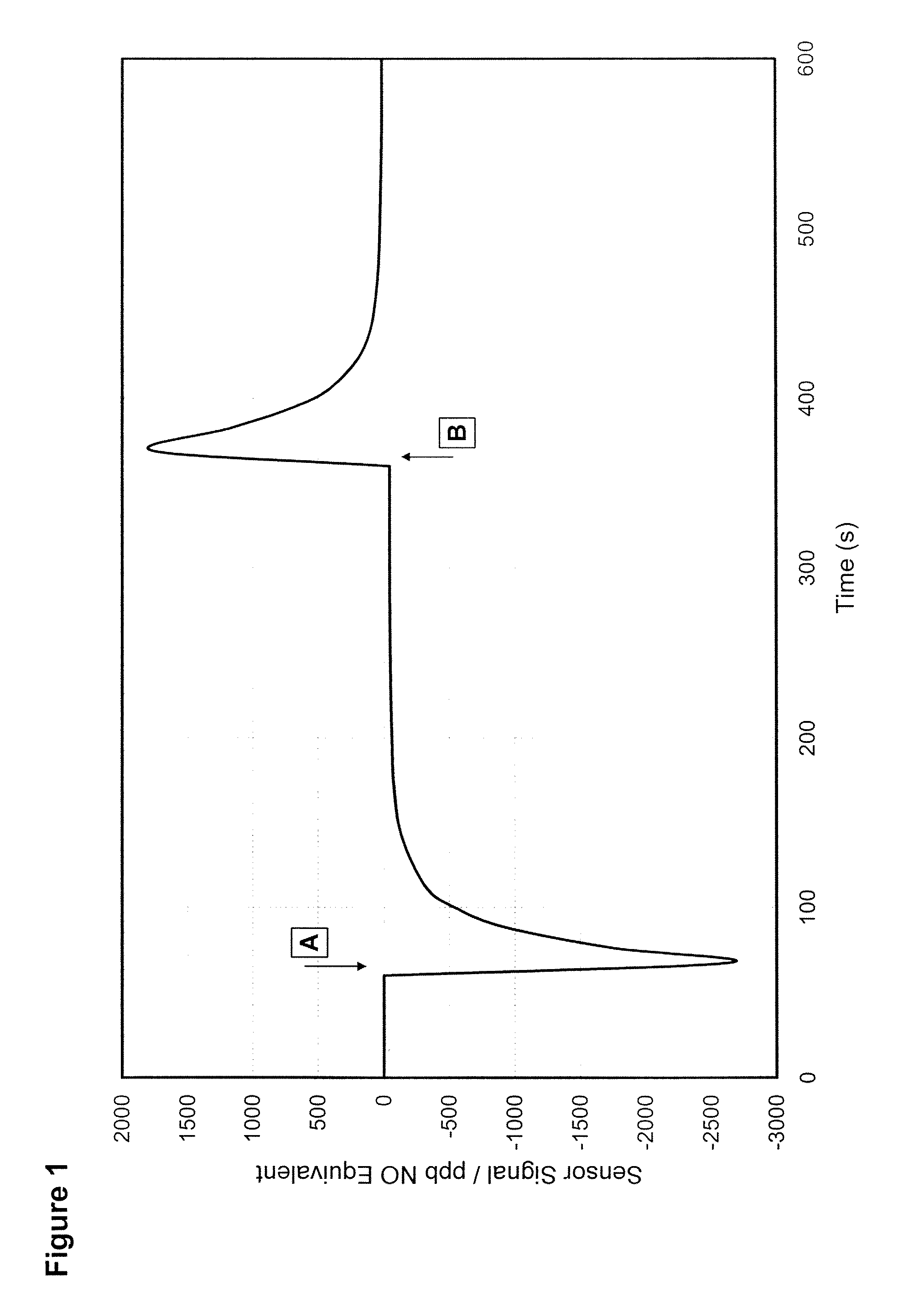

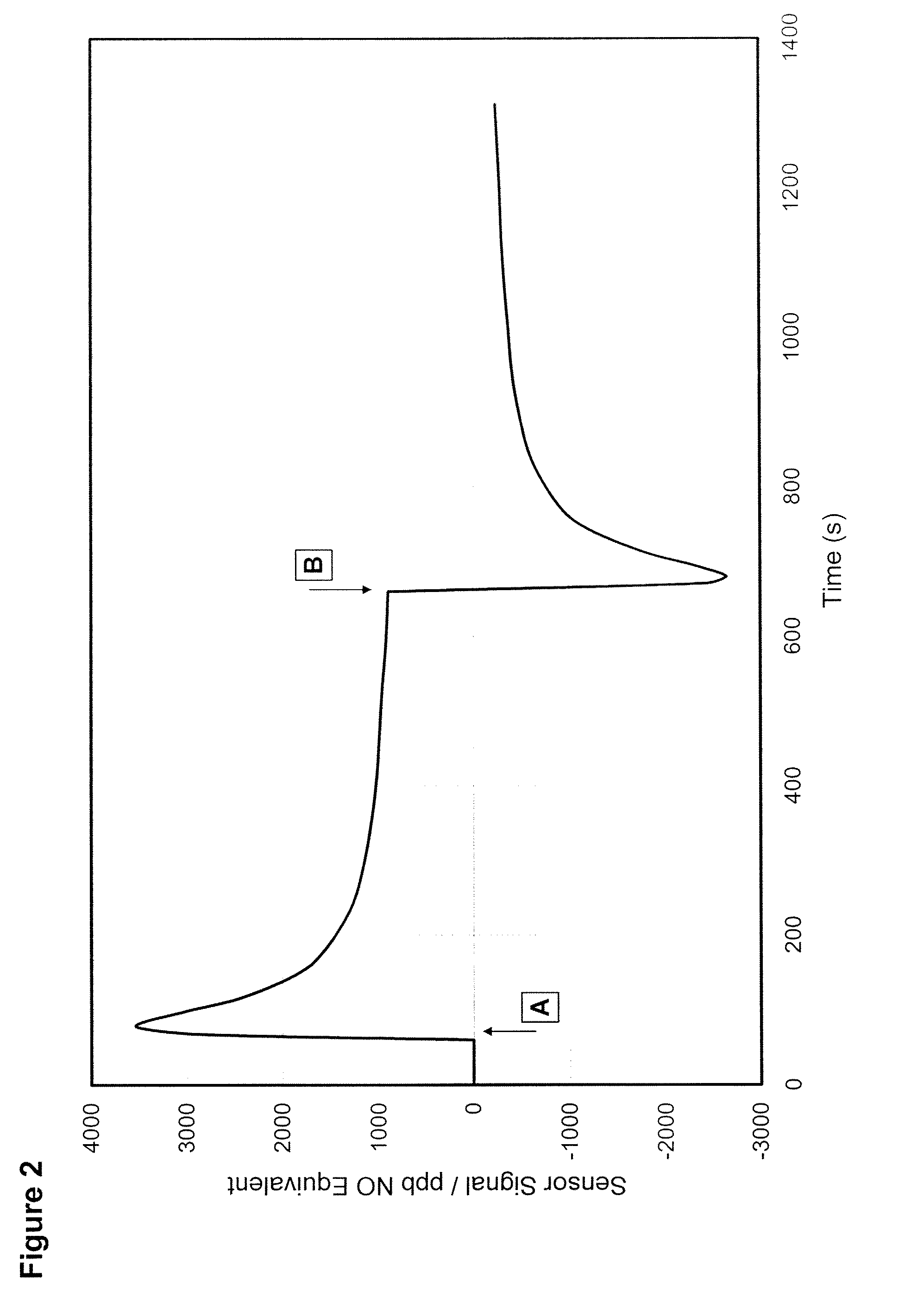

Gas Sensor

ActiveUS20080277290A1Reduce and cancel effectSimple robust solutionWeather/light/corrosion resistanceVolume/mass flow measurementElectrochemical gas sensorProduct gas

The present invention provides a unique solution to the problems of both steady-state and transient signals produced by a variety of interfering stimuli, including humidity, which relies upon the inclusion in a gas sensing electrode in an electrochemical gas sensor of a catalyst material in addition to a first catalyst material reactive to the target gas, the additional, or second, catalyst material producing a response to an interfering stimulus which is of the opposite polarity to that generated by the first catalyst material.

Owner:LIFE SAFETY DISTRIBUTION

Display system incorporating bilinear electromechanical grating device

InactiveUS7411722B2Reduce in quantityMinimizing adjustingProjectorsColor television detailsCamera lensGrating

Owner:EASTMAN KODAK CO

Real time DRC assistance for manual layout editing

ActiveUS8453103B2Robust solutionHigh altitude layout editingComputer programmed simultaneously with data introductionCAD circuit designComputer graphics (images)Edge based

Roughly described, while manually dragging shapes during IC layout editing, editing operations determine which edges of which shapes are moving at what speed ratios. Based on the edge information and the DRC rules, the system calculates and keeps track of the minimum of the maximum distance the edges are allowed to move with the cursor without violating DRC rules, in four linear directions and all corner directions. Once a next cursor destination point is known, a DRC clean destination point is calculated based on the linear and corner bounds. If the next cursor position is beyond a the push-through distance ahead of the new DRC clean point, the editing objects are moved to the user's destination point. Otherwise, the editing objects are moved to the new DRC clean destination point, thereby stopping movement at that point.

Owner:SYNOPSYS INC

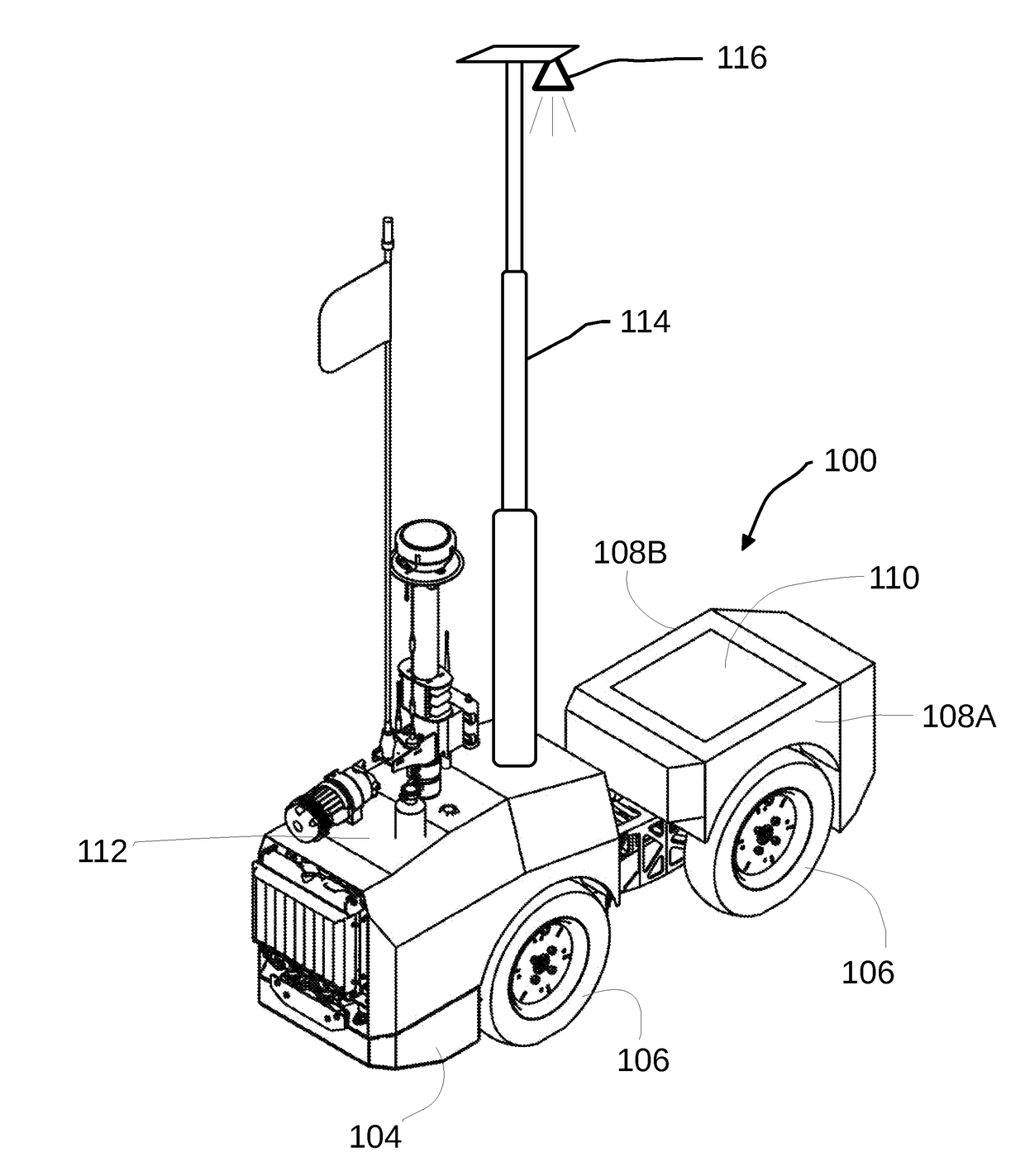

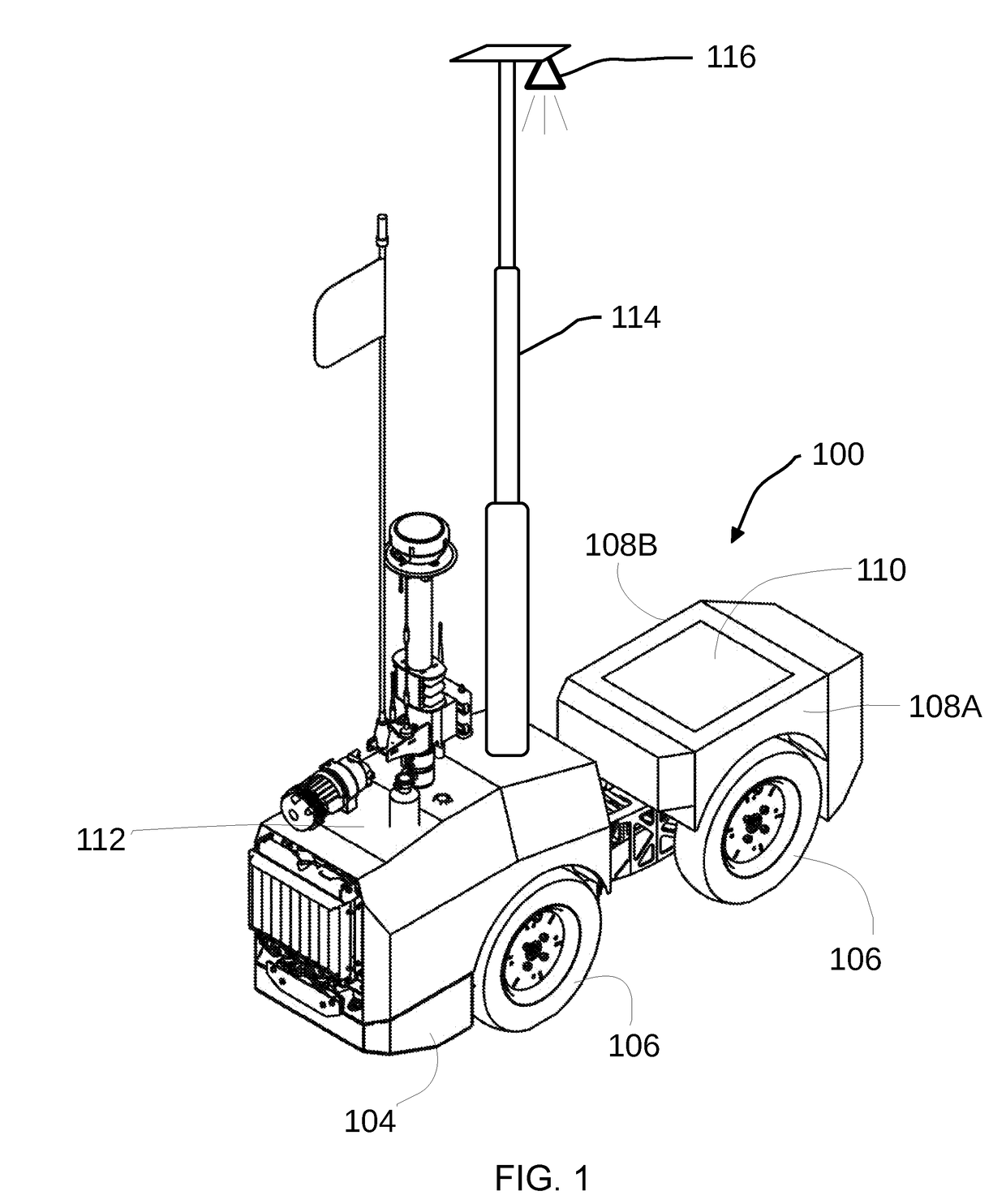

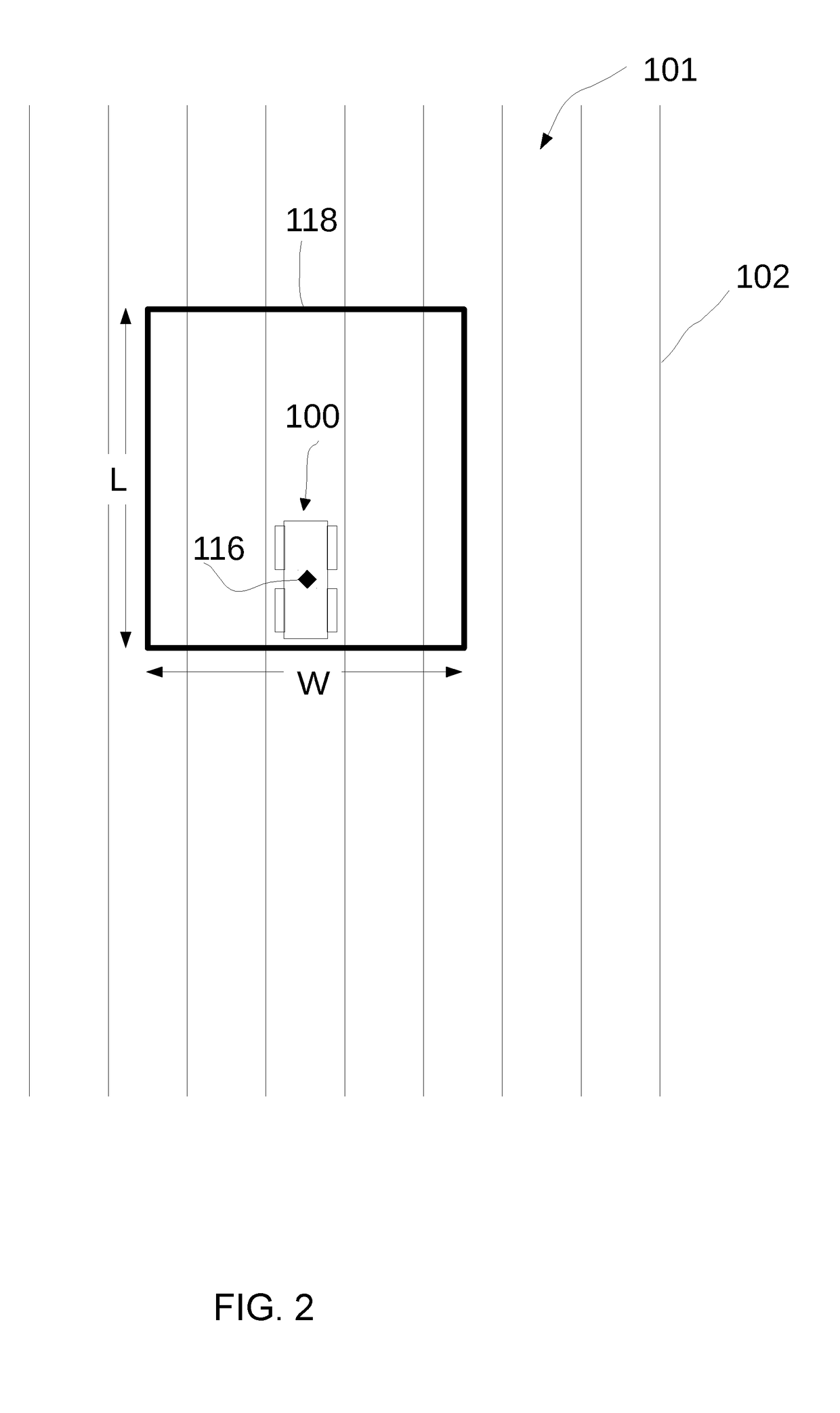

Real-time field mapping for autonomous agricultural platform

ActiveUS20170223889A1Robust solutionControl damageAutonomous decision making processFertilising methodsAgricultural scienceAgricultural engineering

A method of using an unmanned agricultural robot to generate an anticipatory geospatial data map of the positions of annual crop rows planted within a perimeter of an agricultural field, the method including the step of creating a geospatial data map of an agricultural field by plotting actual annual crop row positions in a portion of the geospatial data map that corresponds to a starting point observation window, and filling in a remainder of the geospatial data map with anticipated annual crop row positions corresponding to the annual crop rows outside of the starting point observation window, and refining the geospatial data map by replacing the anticipated annual crop row positions with measured actual annual crop row positions when an unexpected obstacle is encountered.

Owner:ROWBOT SYST

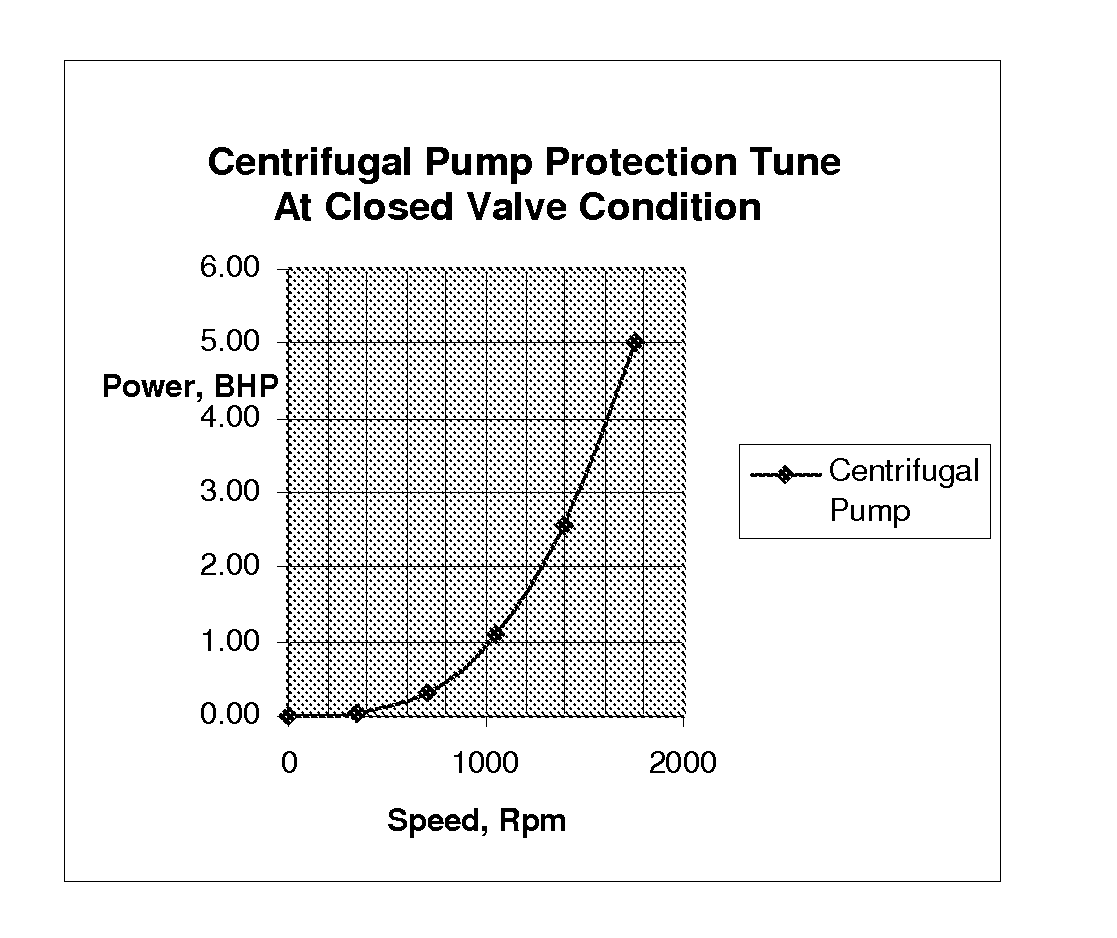

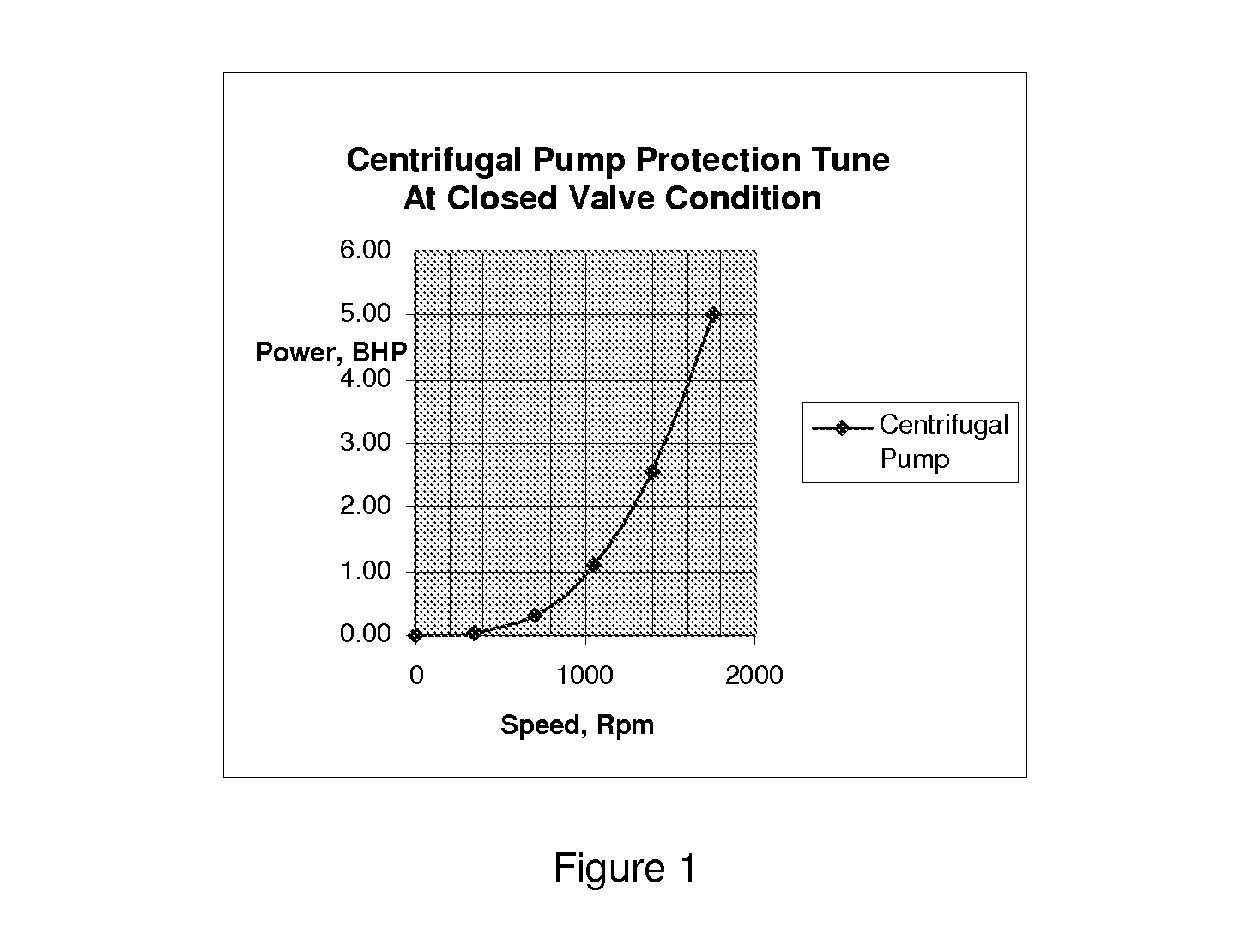

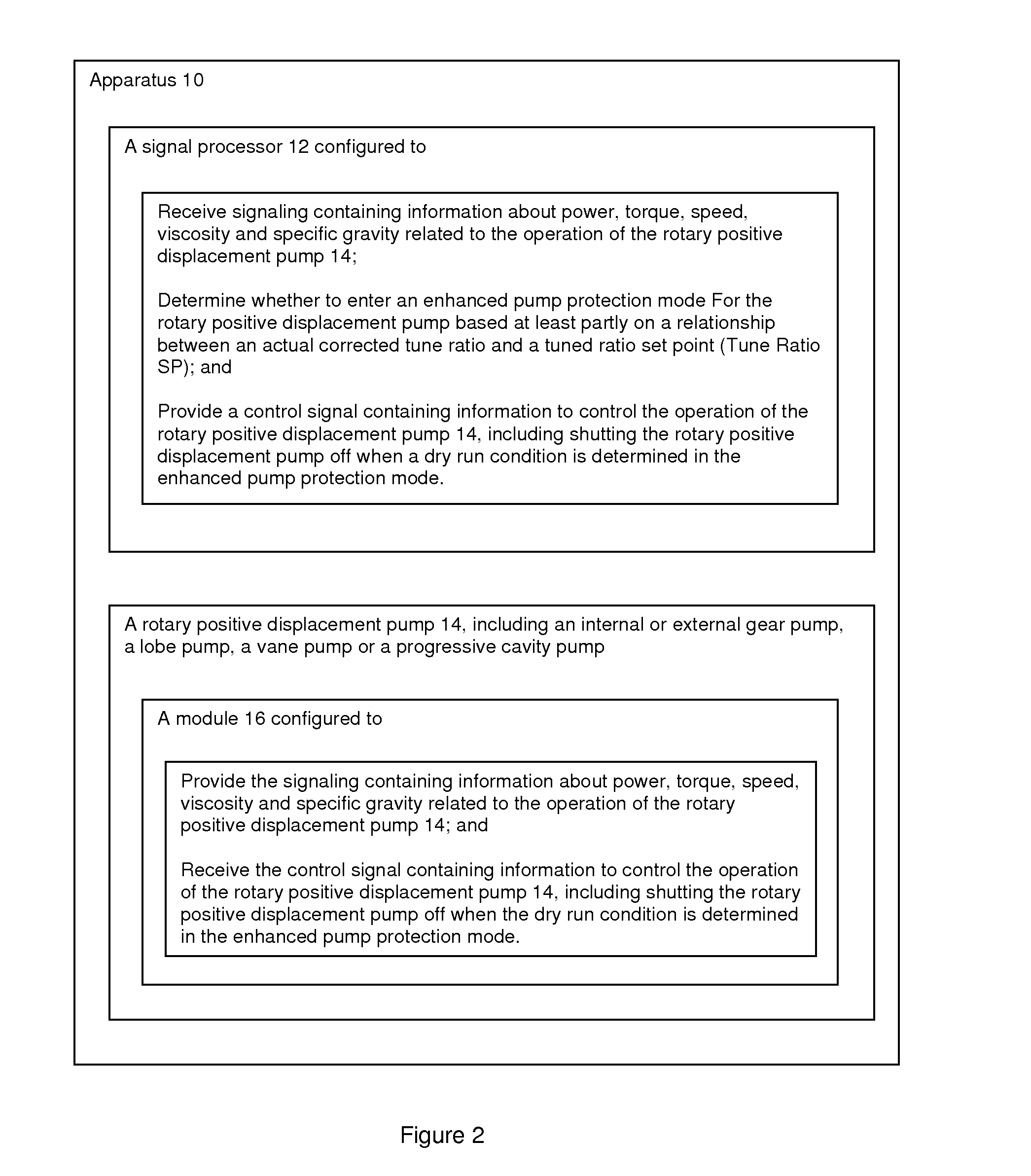

Method for rotary positive displacement pump protection

InactiveUS20140119966A1Short response timeImprove robustnessOscillating piston enginesRotary piston pumpsProtected modeViscosity

Techniques are provided for protecting a rotary positive displacement pump. The techniques include apparatus featuring a signal processor configured to receive signaling containing information about power, torque, speed, viscosity and specific gravity related to the operation of a pump; and determine whether to enter an enhanced pump protection mode for the rotary positive displacement pump based at least partly on a relationship between an actual corrected tune ratio and a tuned ratio set point (Tune Ratio SP). The signal processor may determine if the actual corrected tune ratio is less than or equal to the actual corrected tune ratio set point (Tune Ratio SP), and if so, then to enter the enhanced pump protection mode, else to continue to use a basic pump protection mode, and may also determine the actual corrected tune ratio based at least partly on a ratio of an actual corrected power (PAcorr) divided by a tuned corrected power (PTcorr) at a specific operating speed

Owner:ITT MFG ENTERPRISES LLC