Patents

Literature

309 results about "Delta-sigma modulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

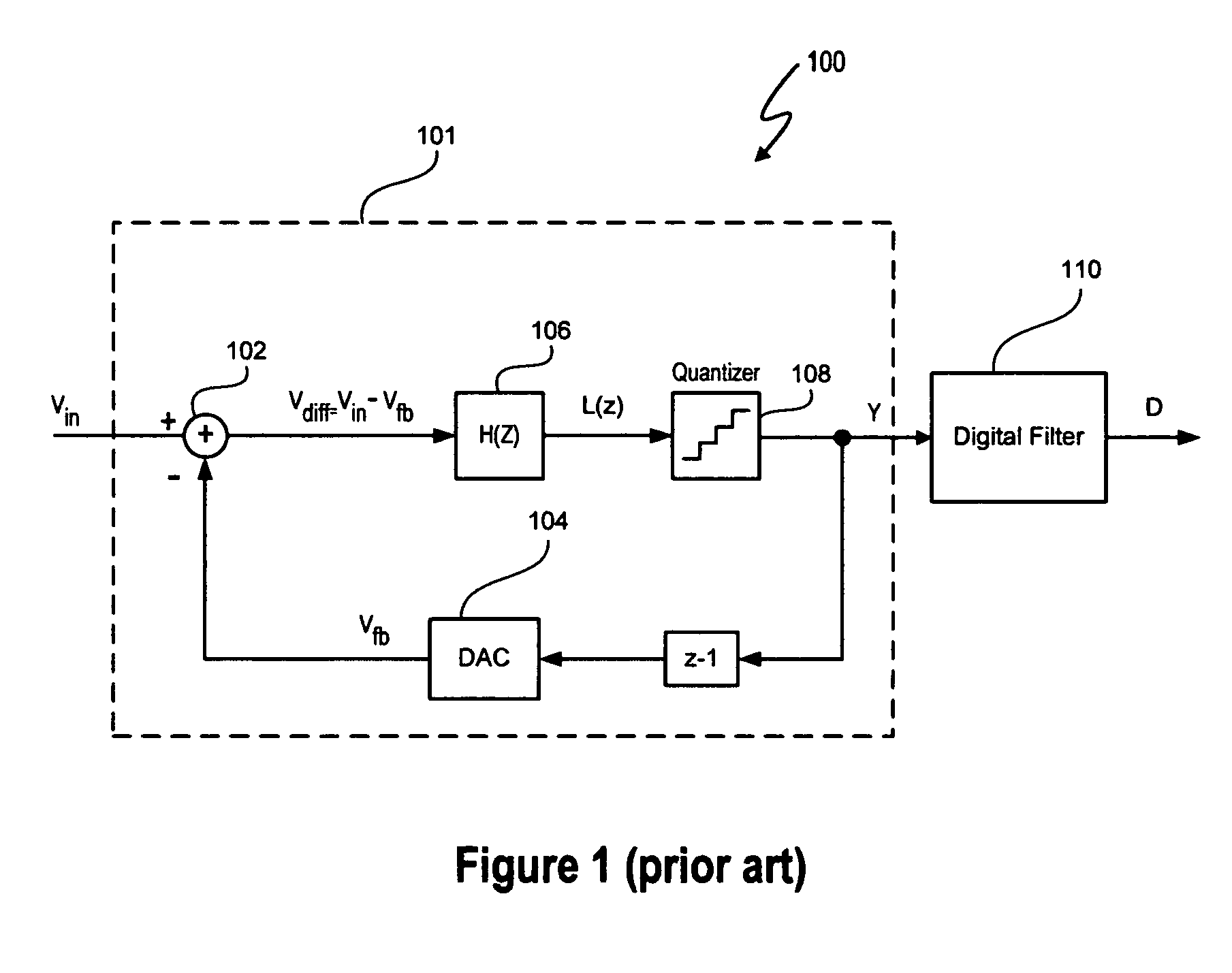

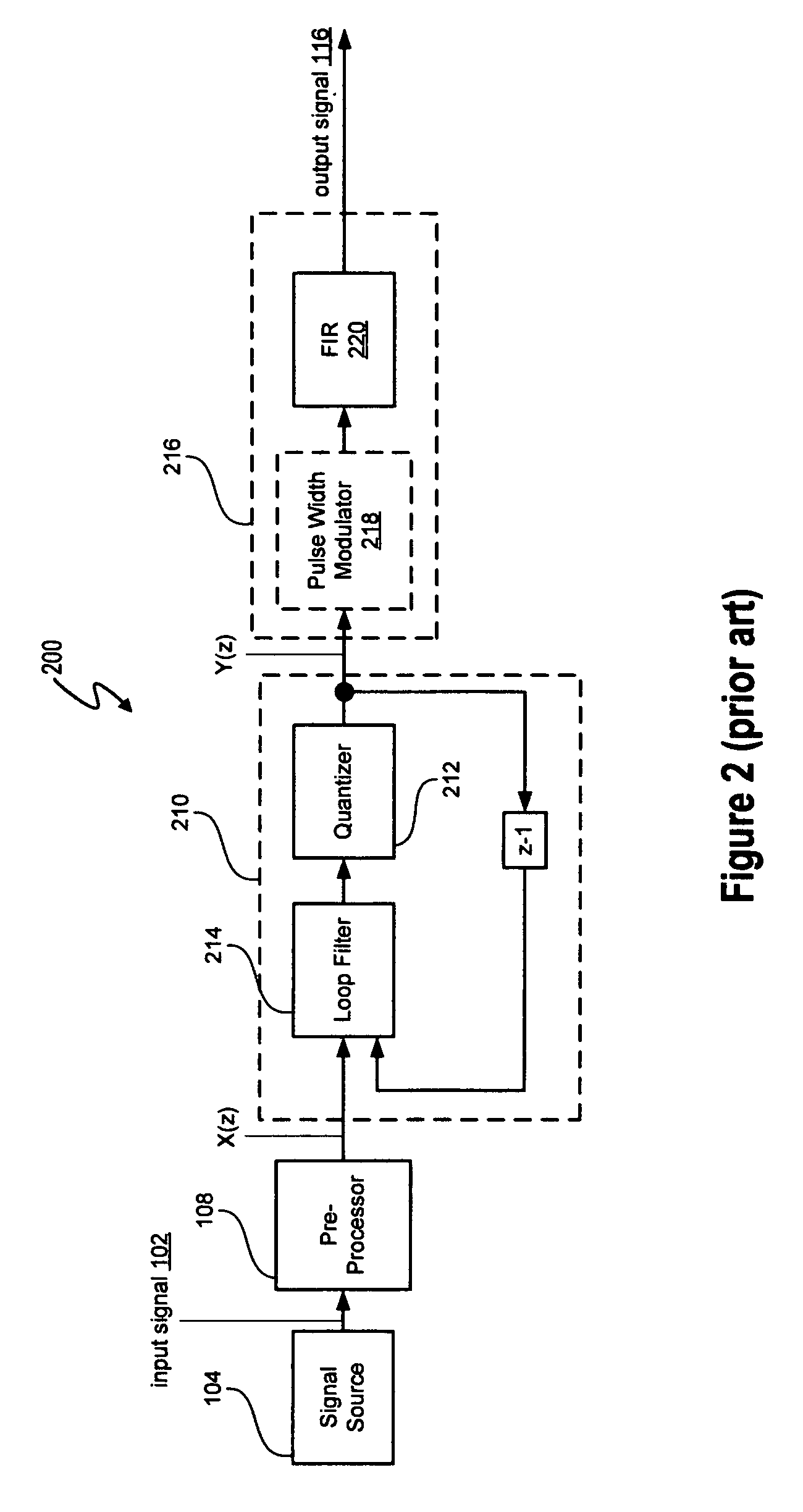

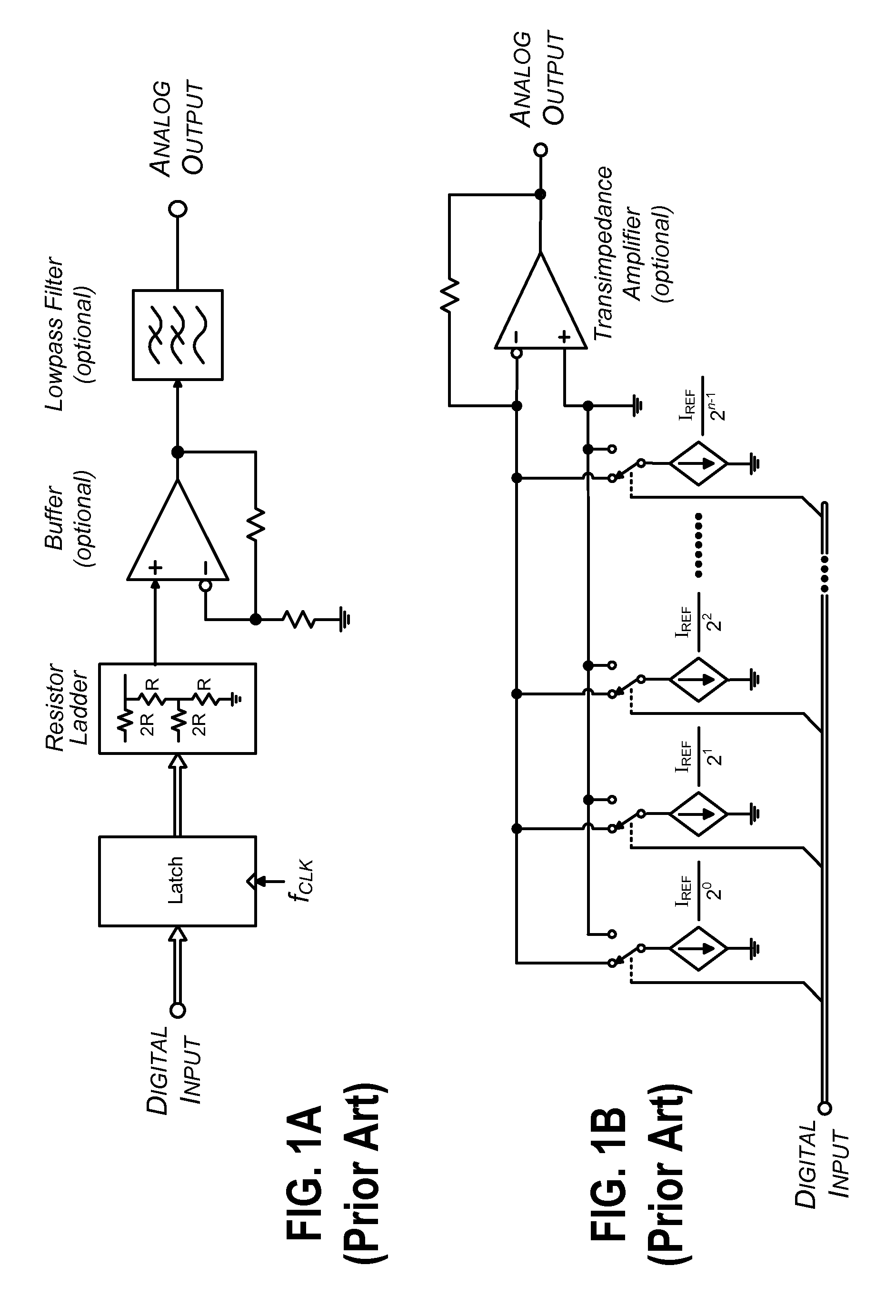

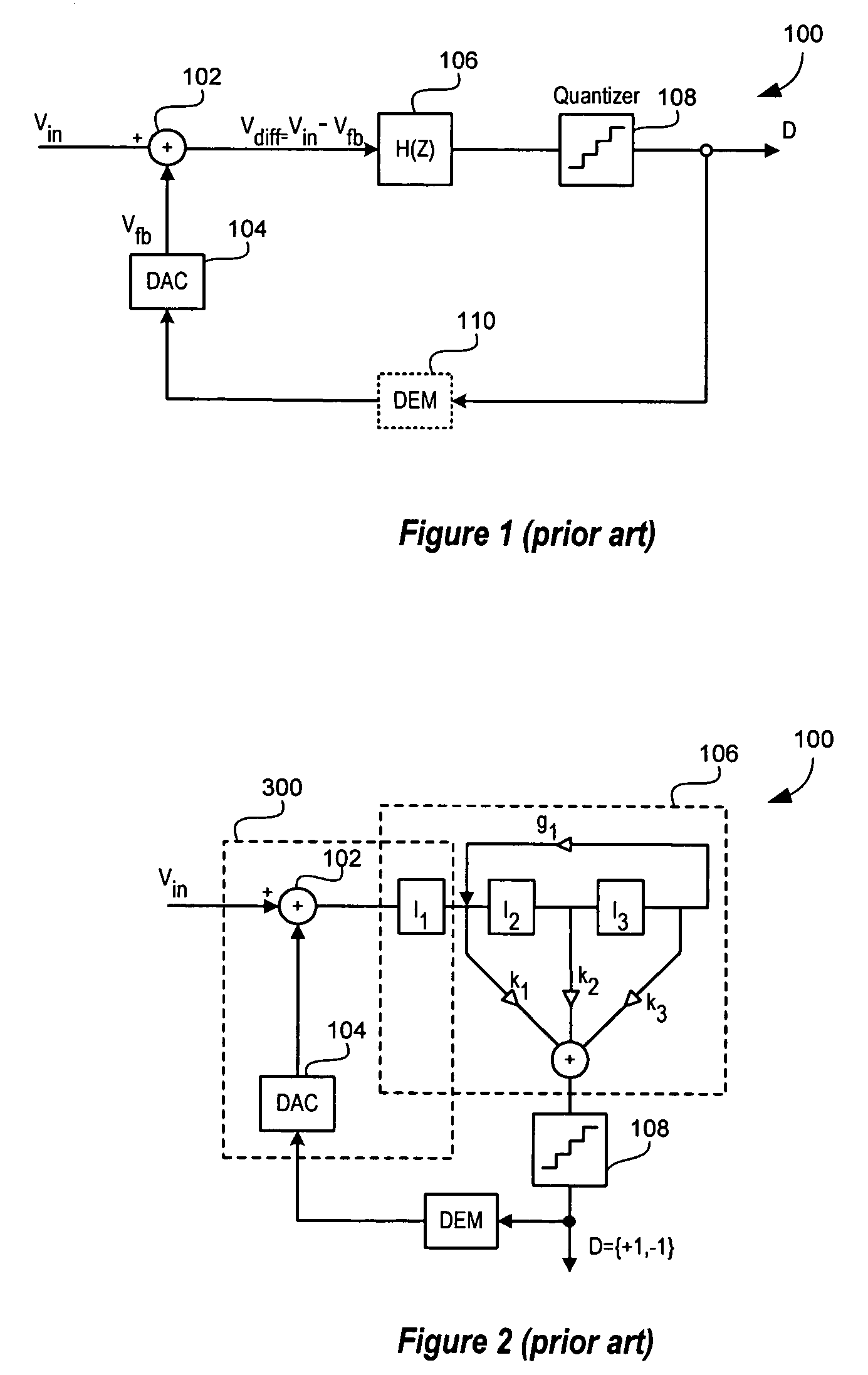

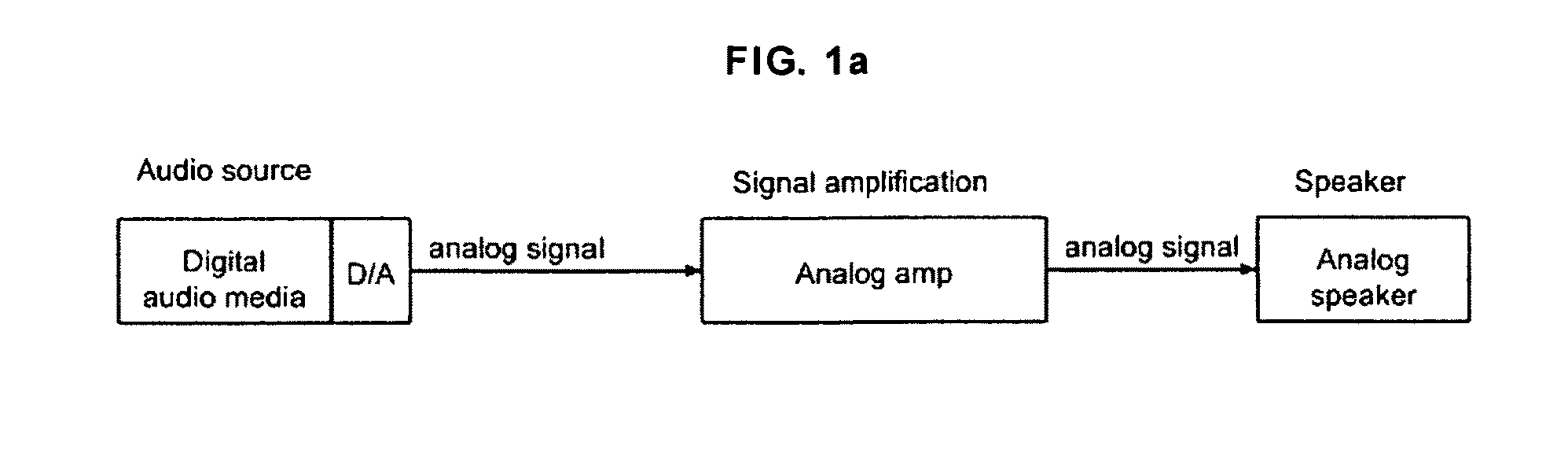

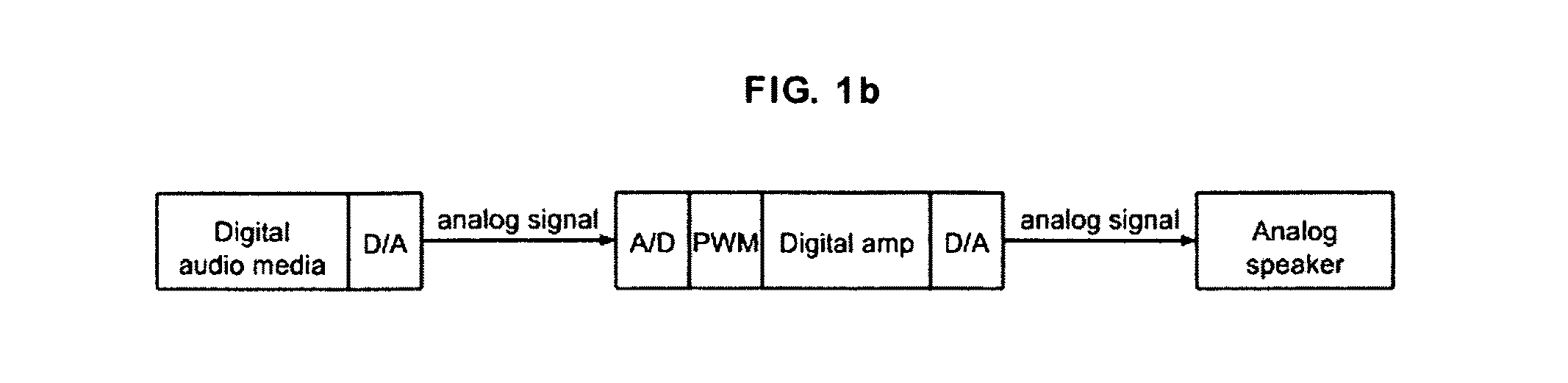

Delta-sigma (ΔΣ; or sigma-delta, ΣΔ) modulation is a method for encoding analog signals into digital signals as found in an analog-to-digital converter (ADC). It is also used to convert high bit-count, low-frequency digital signals into lower bit-count, higher-frequency digital signals as part of the process to convert digital signals into analog as part of a digital-to-analog converter (DAC).

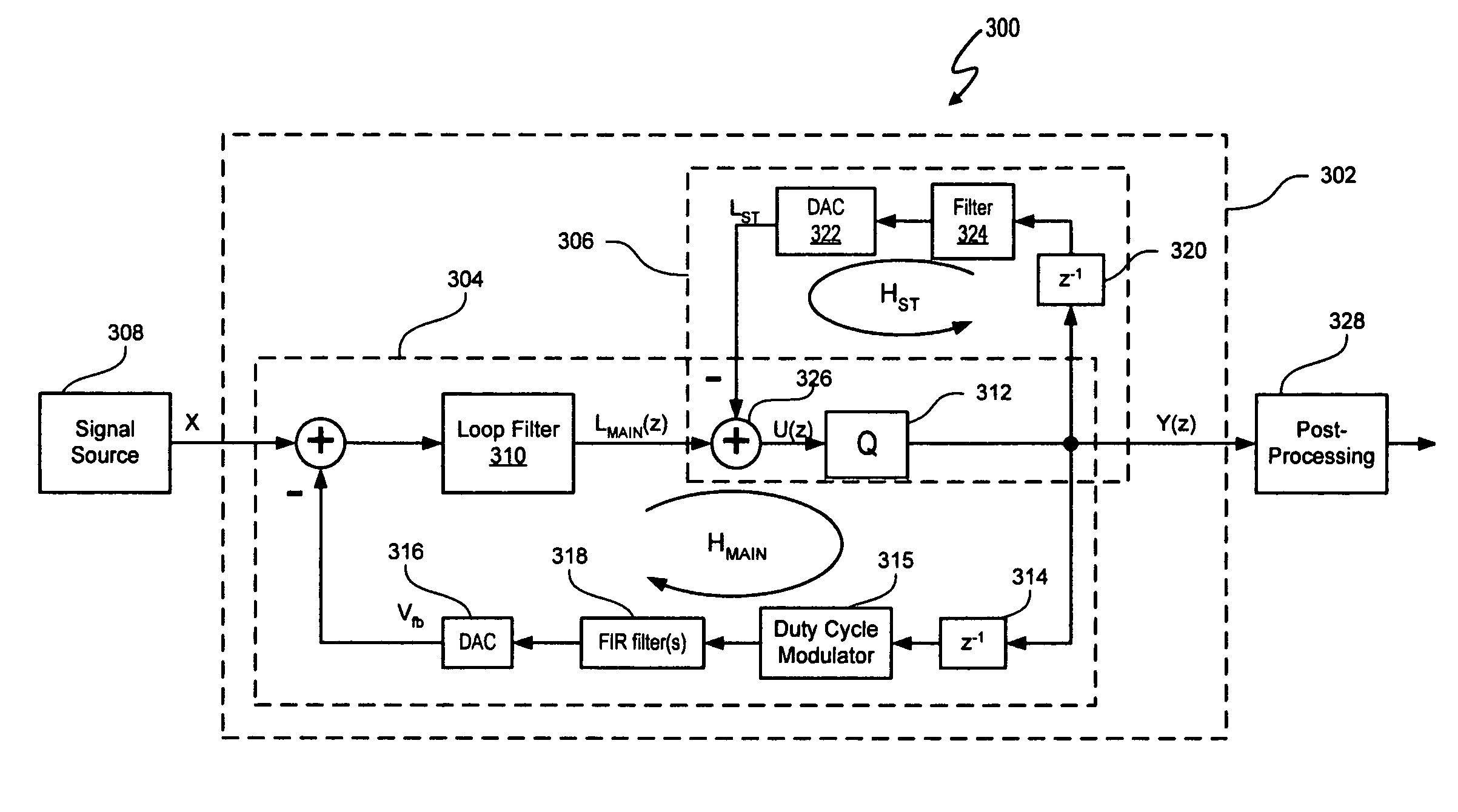

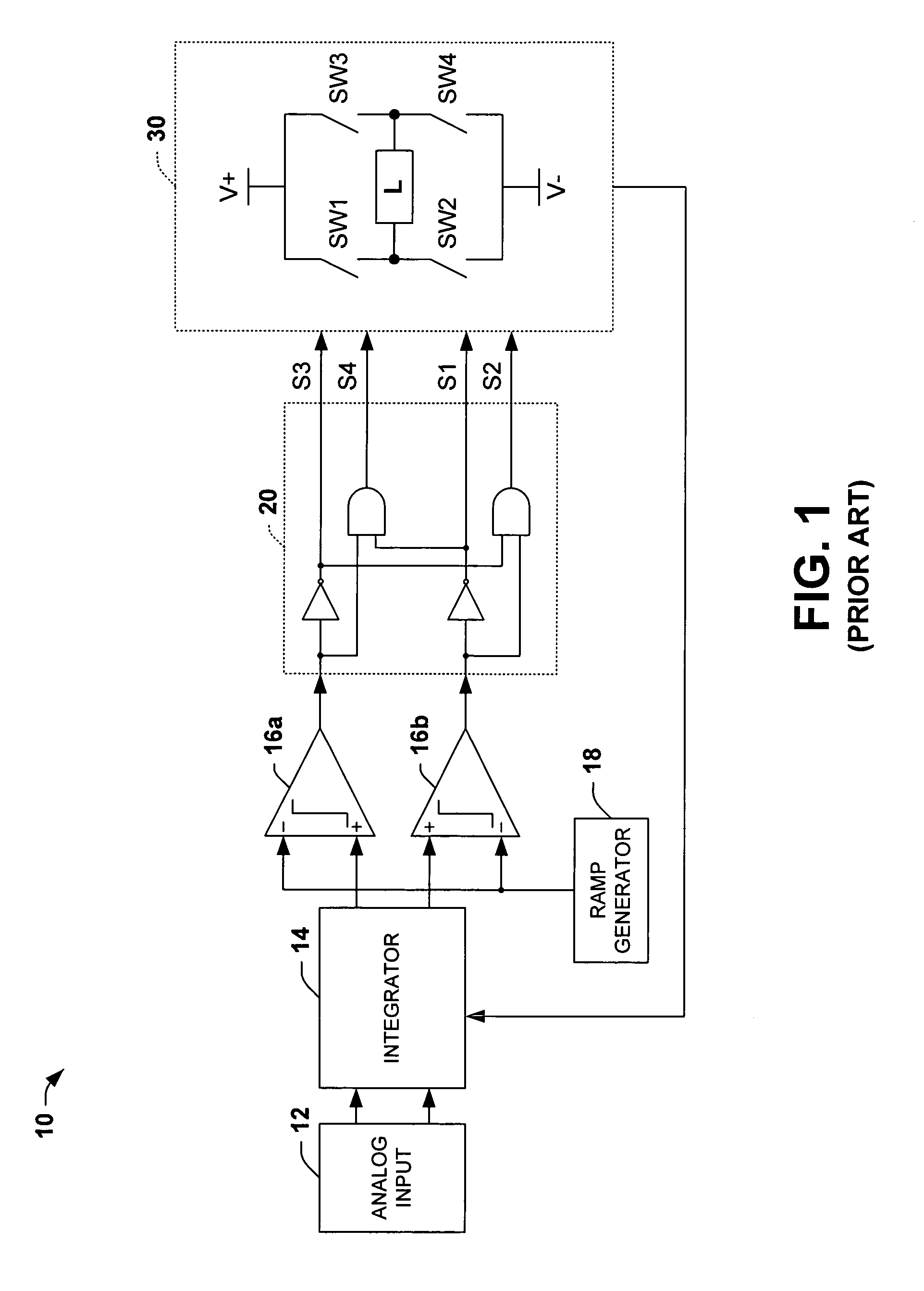

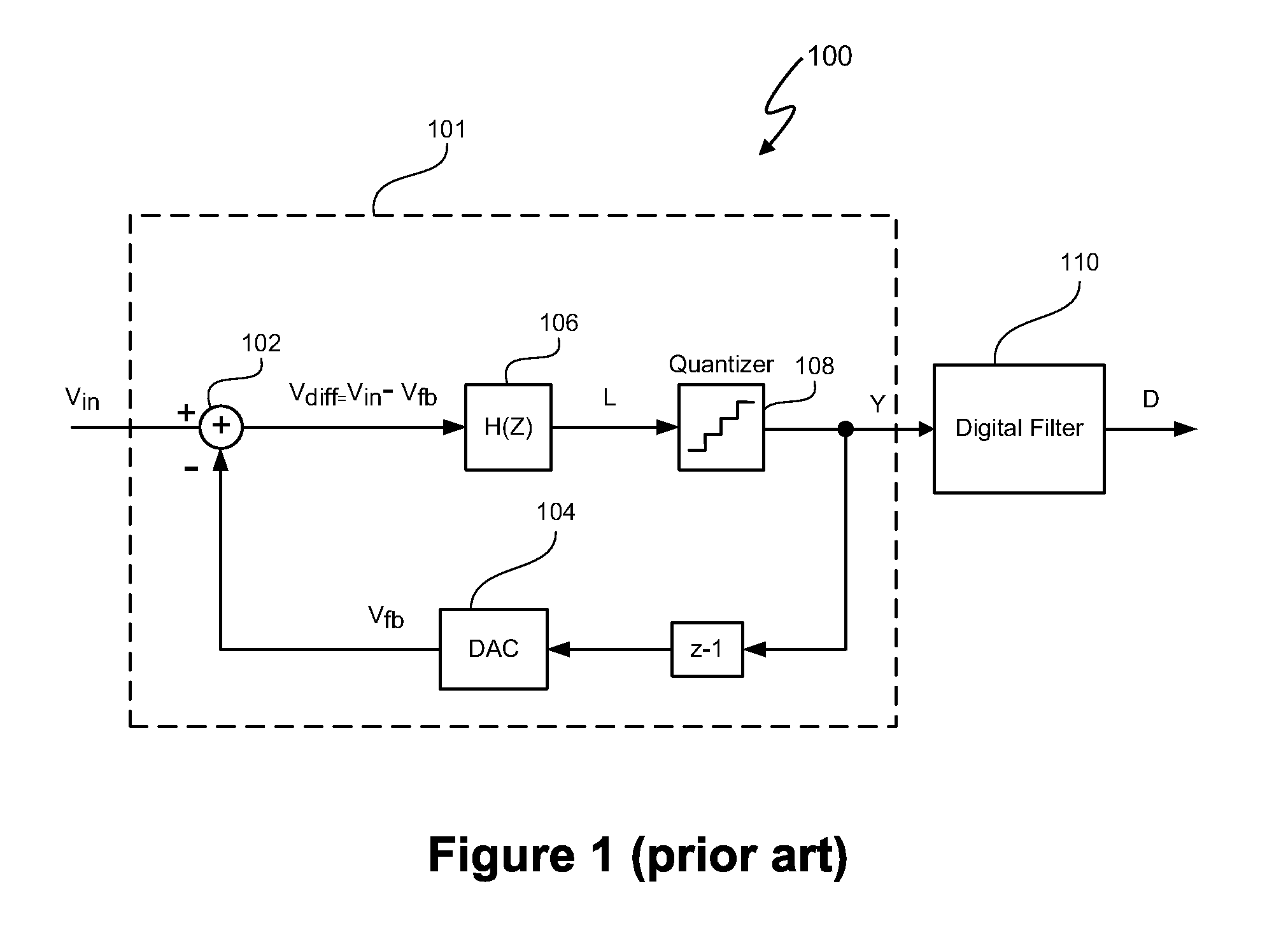

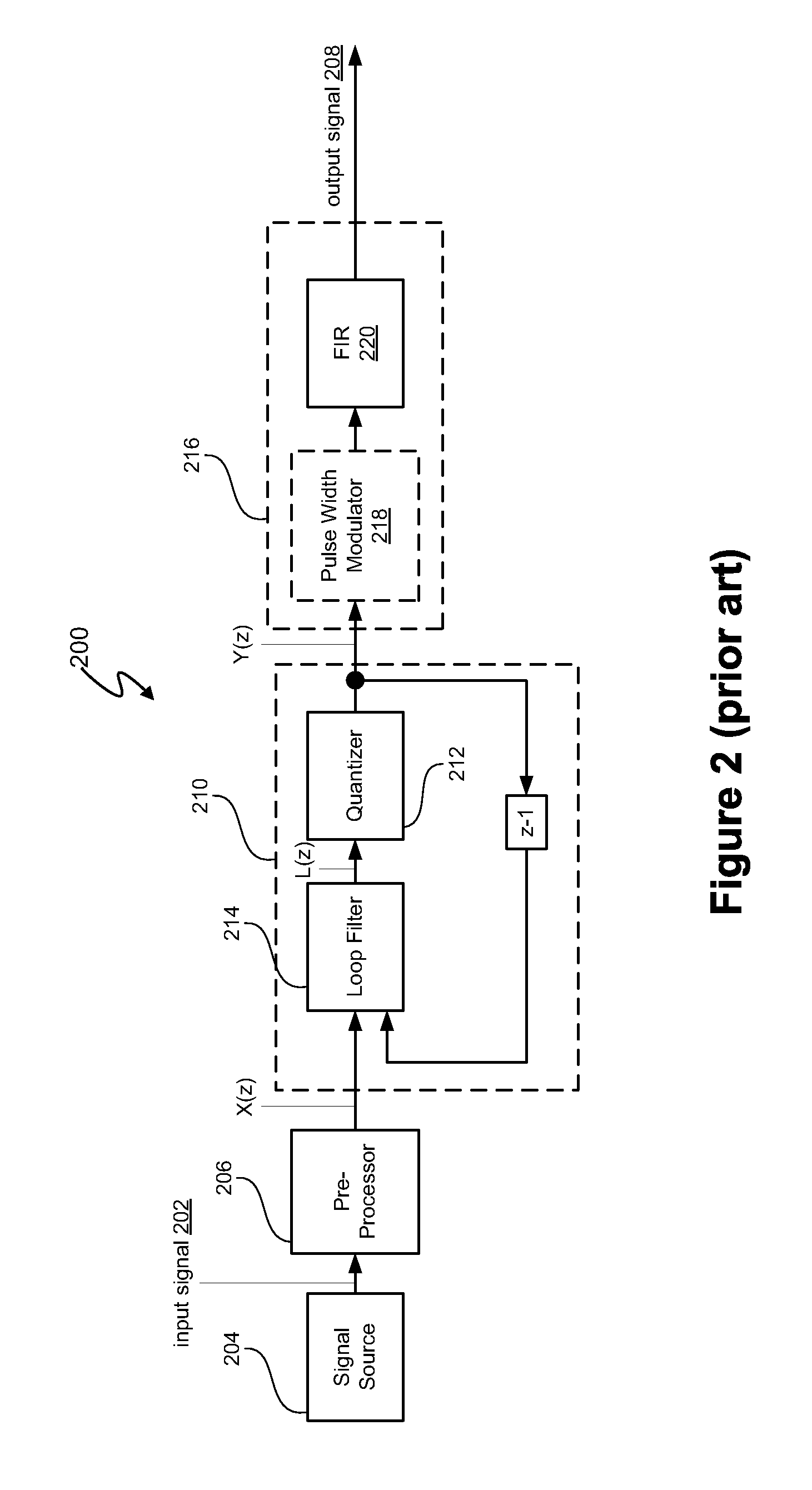

Signal processing system with analog-to-digital converter using delta-sigma modulation having an internal stabilizer loop

ActiveUS7183957B1Electric signal transmission systemsAnalogue conversionDelta-sigma modulationInstability

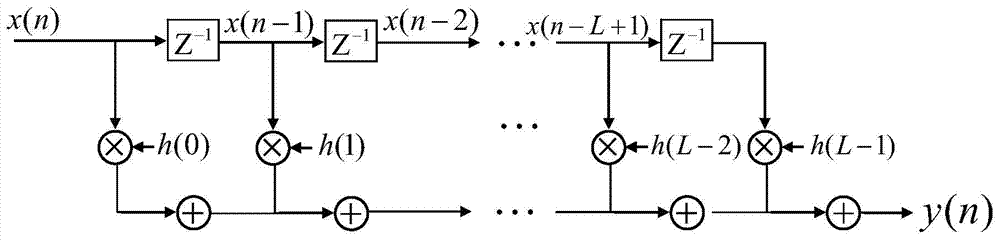

A signal processing system includes an analog-to-digital delta sigma modulator with a duty cycle modulator and a finite impulse response (FIR) filter in a main loop feedback path of the delta sigma modulator. The duty cycle modulator and FIR filter can provide high performance filtering in the main loop feedback path. To prevent instability in the main loop caused by the duty cycle modulator and FIR filter, the delta sigma modulator also includes a stabilizer loop. Transfer functions of the main loop and the stabilizer loop combine to achieve a target transfer function for the analog-to-digital delta sigma modulator that provides for stable operation of the analog-to-digital delta sigma modulator.

Owner:CIRRUS LOGIC INC

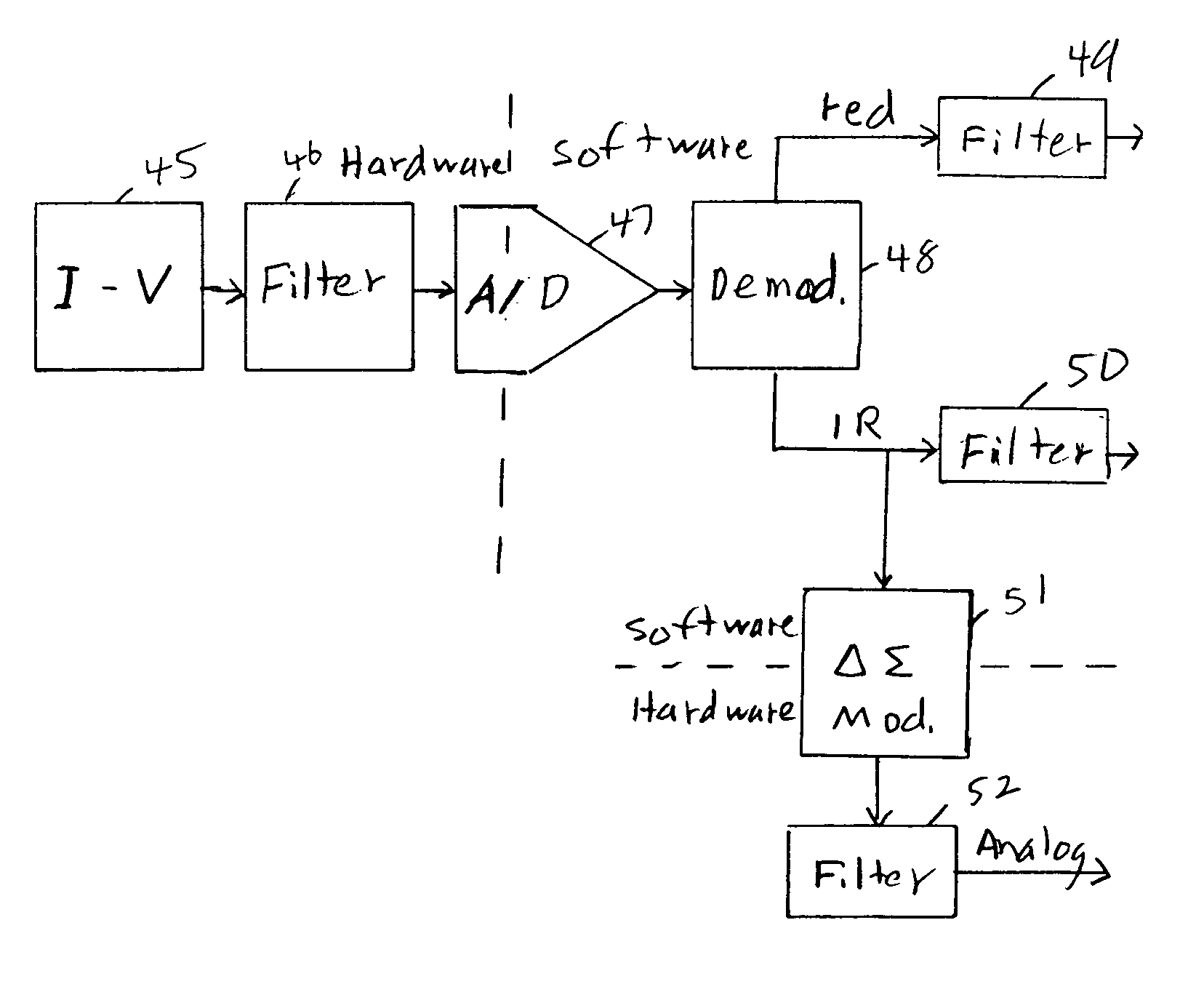

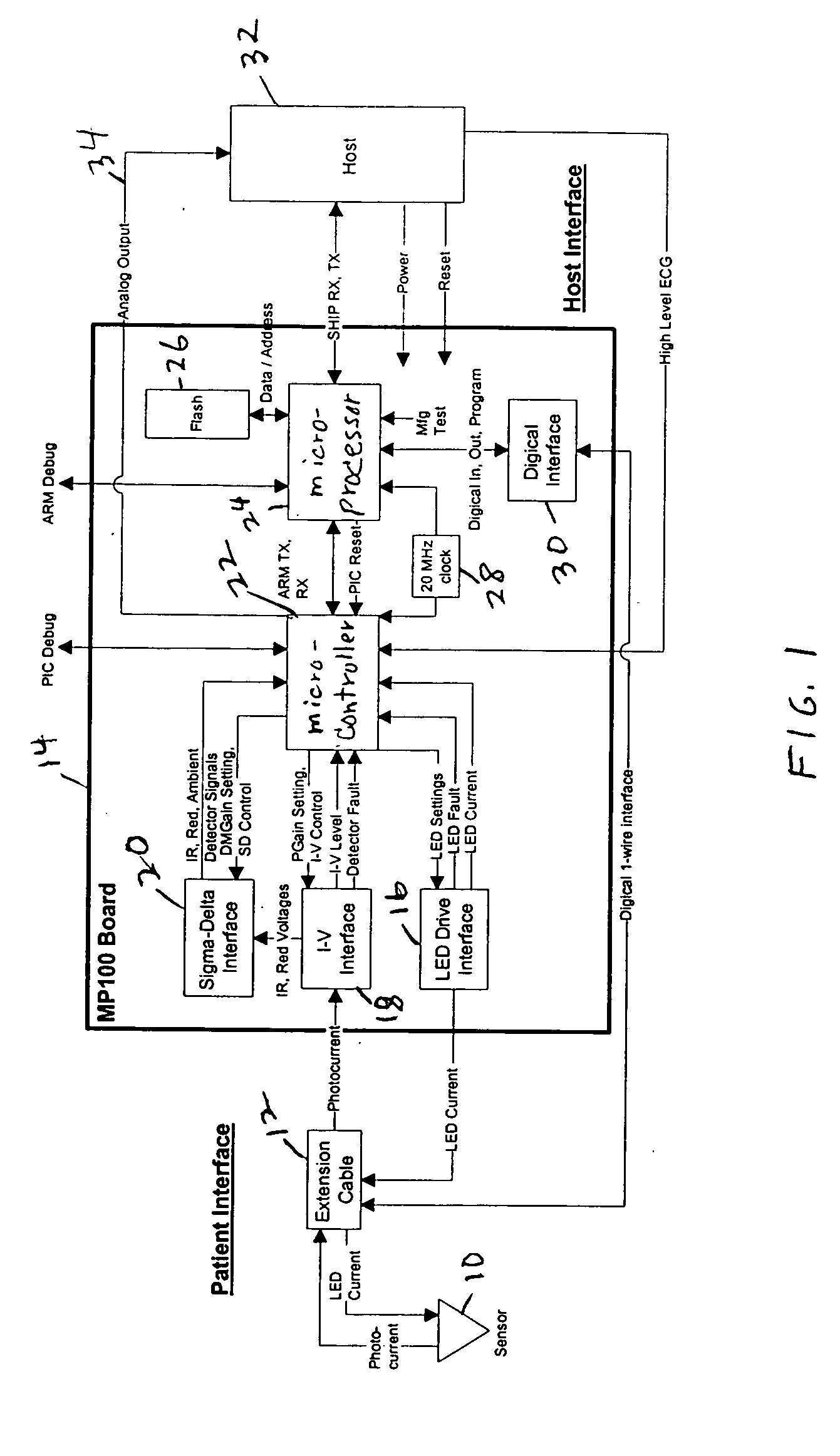

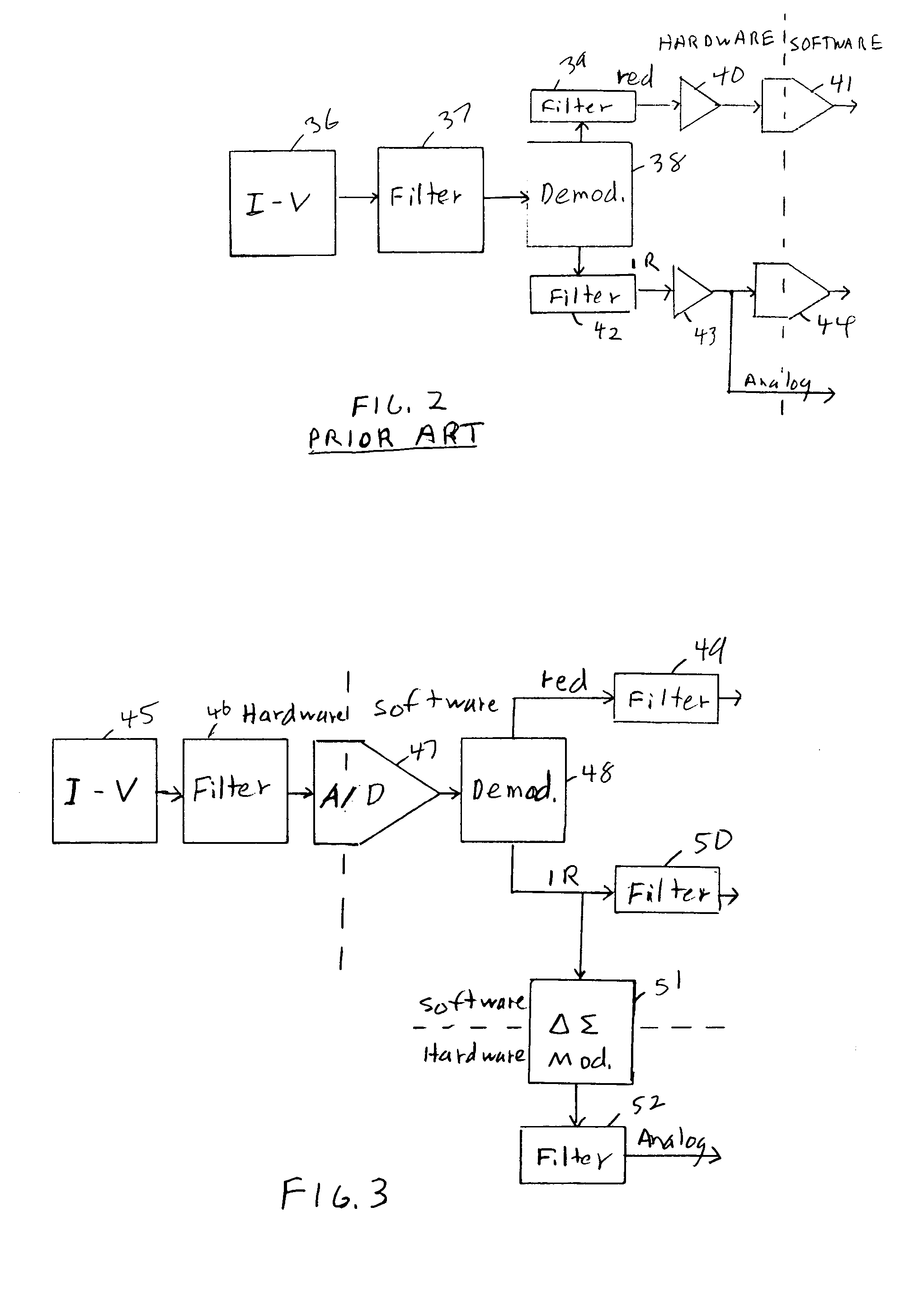

Delta-sigma modulator for outputting analog representation of physiological signal

ActiveUS20050187453A1Quick conversionReduce noiseCatheterDiagnostic recording/measuringWave shapeGreek letter sigma

A method and apparatus for providing a substantially real-time representation of an analog representation of a physiological signal. The waveform signal from the sensor is converted into digital form. A delta-sigma modulator is used as a simple Digital-to-analog Converter (ADC). The output can then be provided through a simple hardware filter to give an analog output signal in nearly real-time, which can be used for other instruments, synchronization, display, etc.

Owner:TYCO HEALTHCARE GRP LP

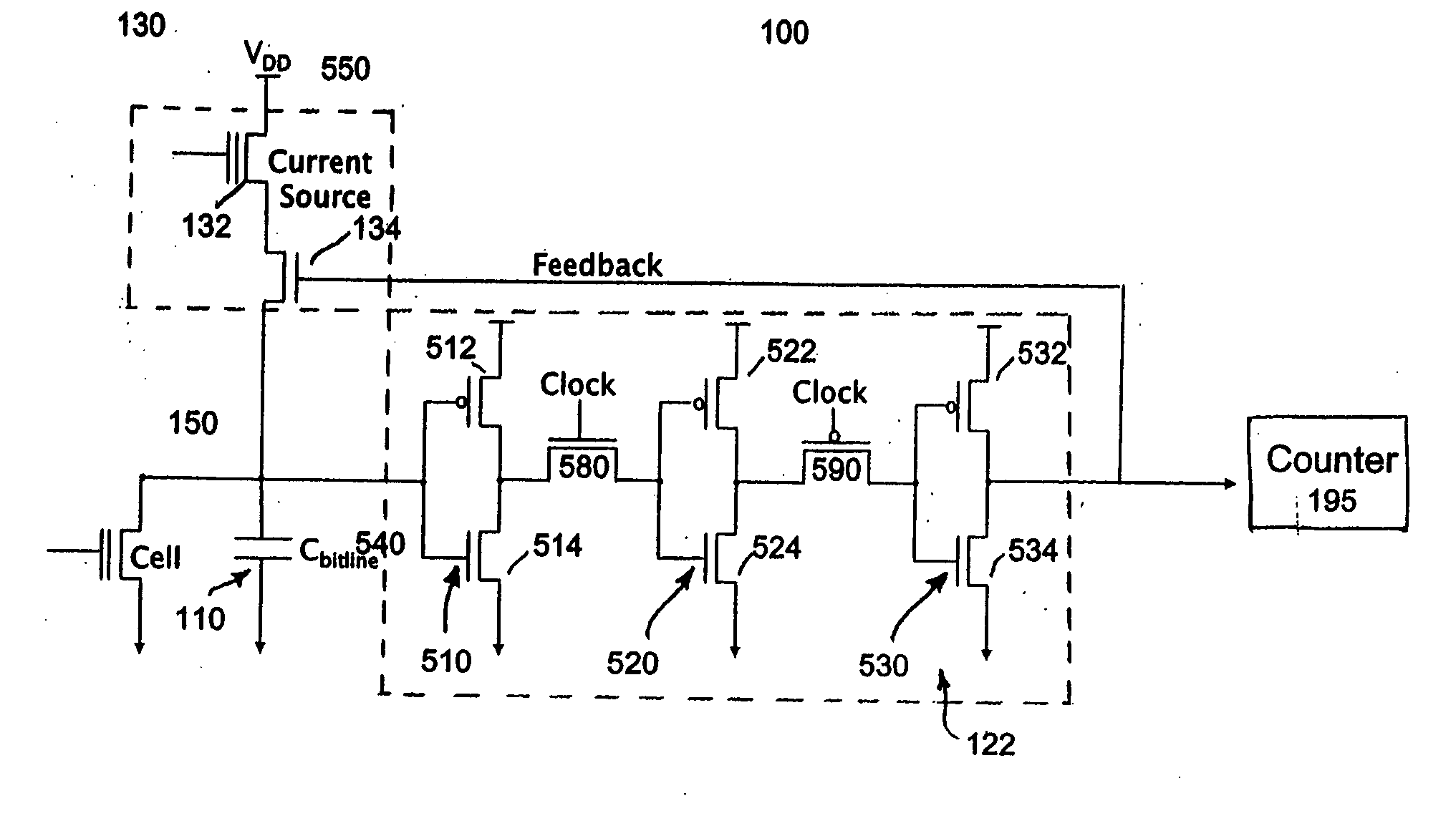

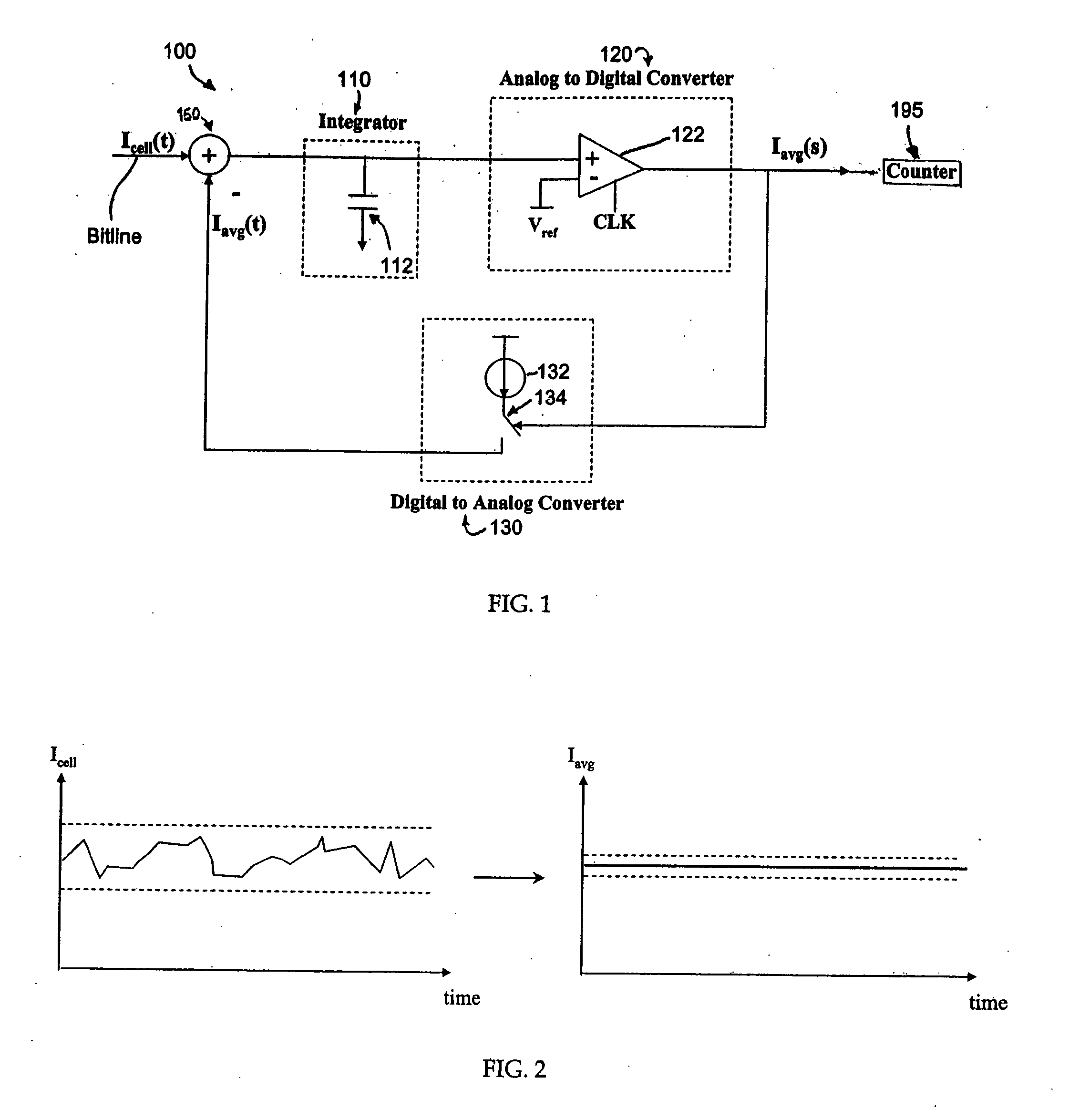

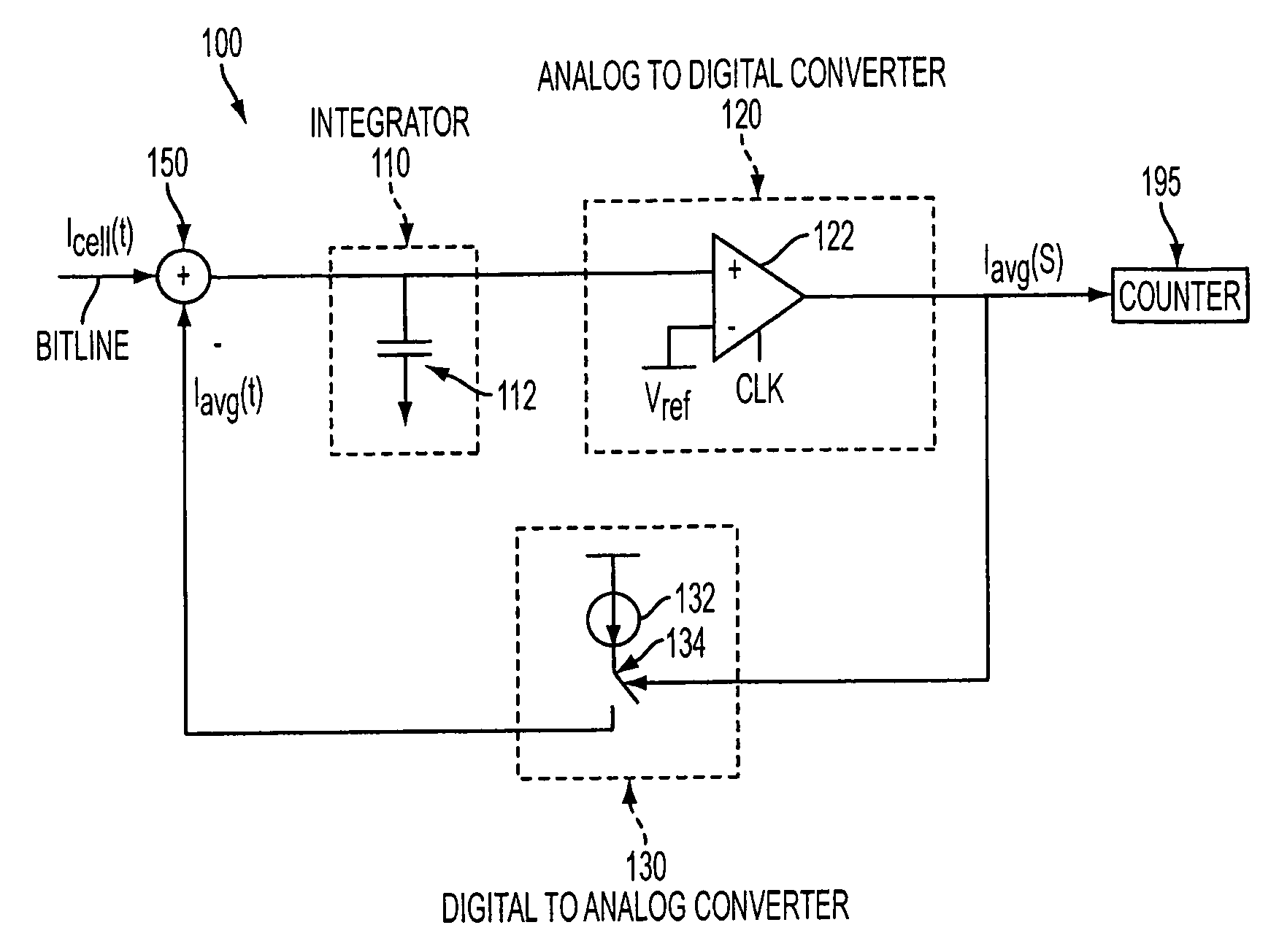

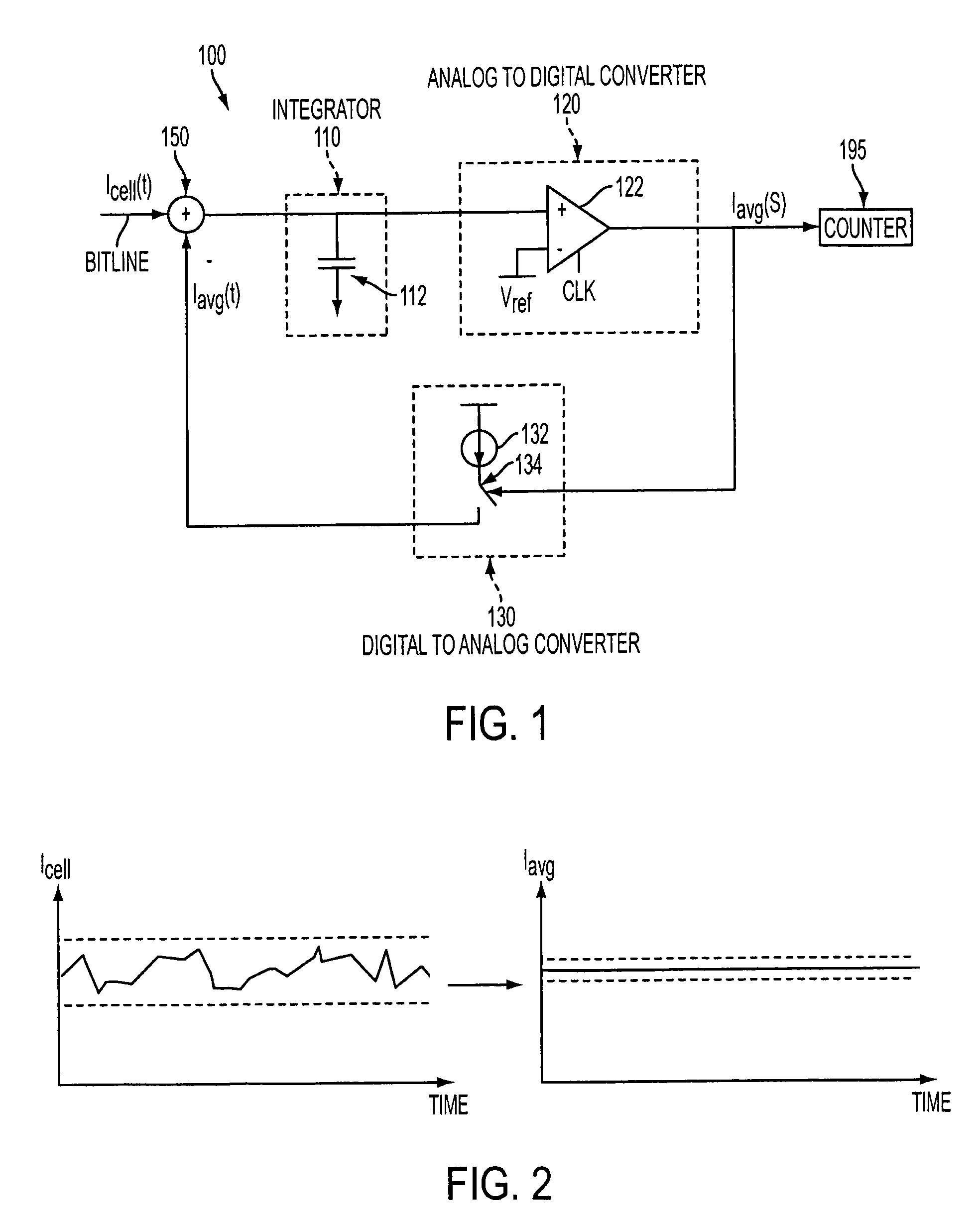

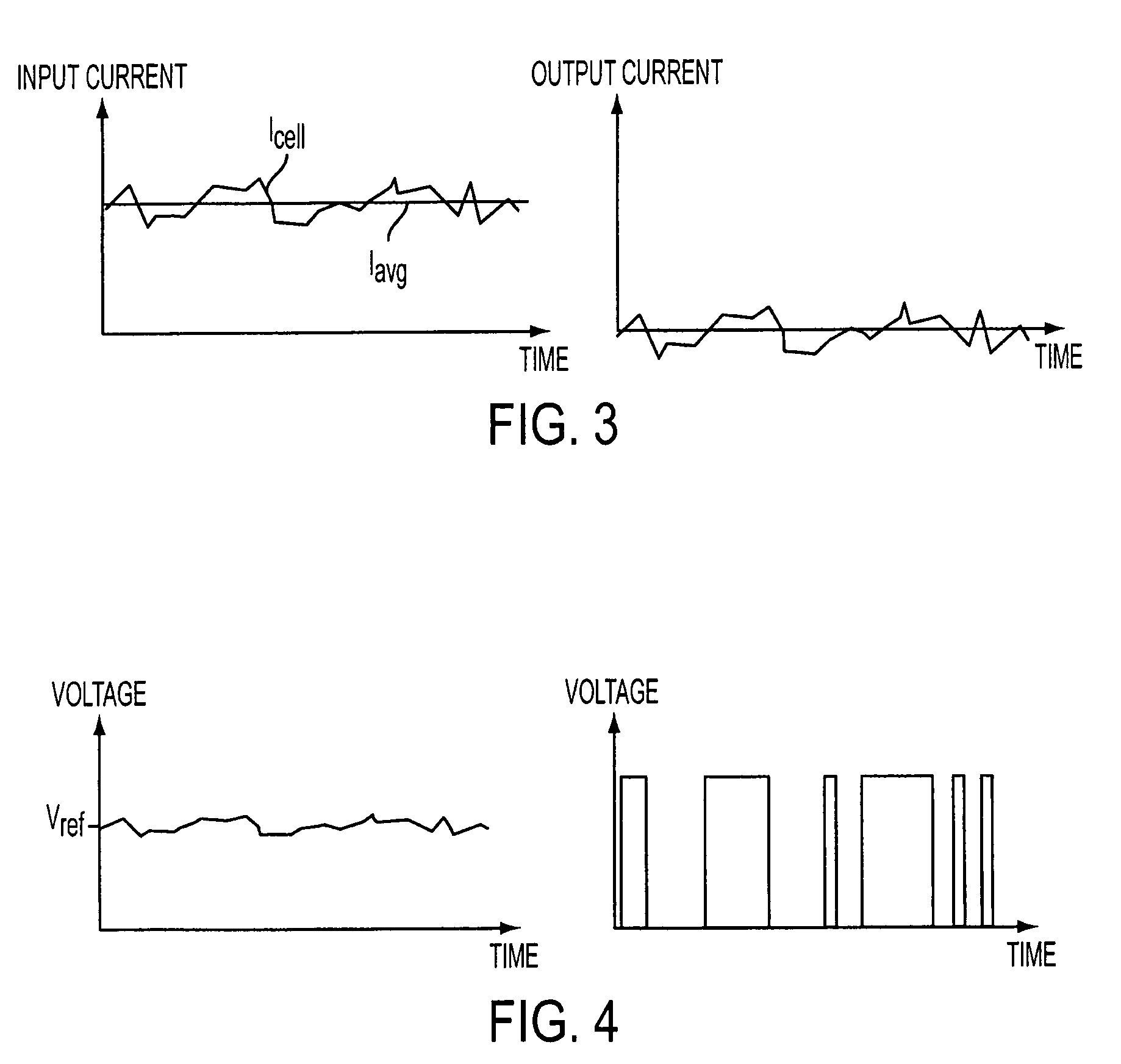

Method and apparatus for sensing flash memory using delta sigma modulation

ActiveUS20060250853A1Accurate inductionHigh circuitryRead-only memoriesDigital storageConvertersAverage current

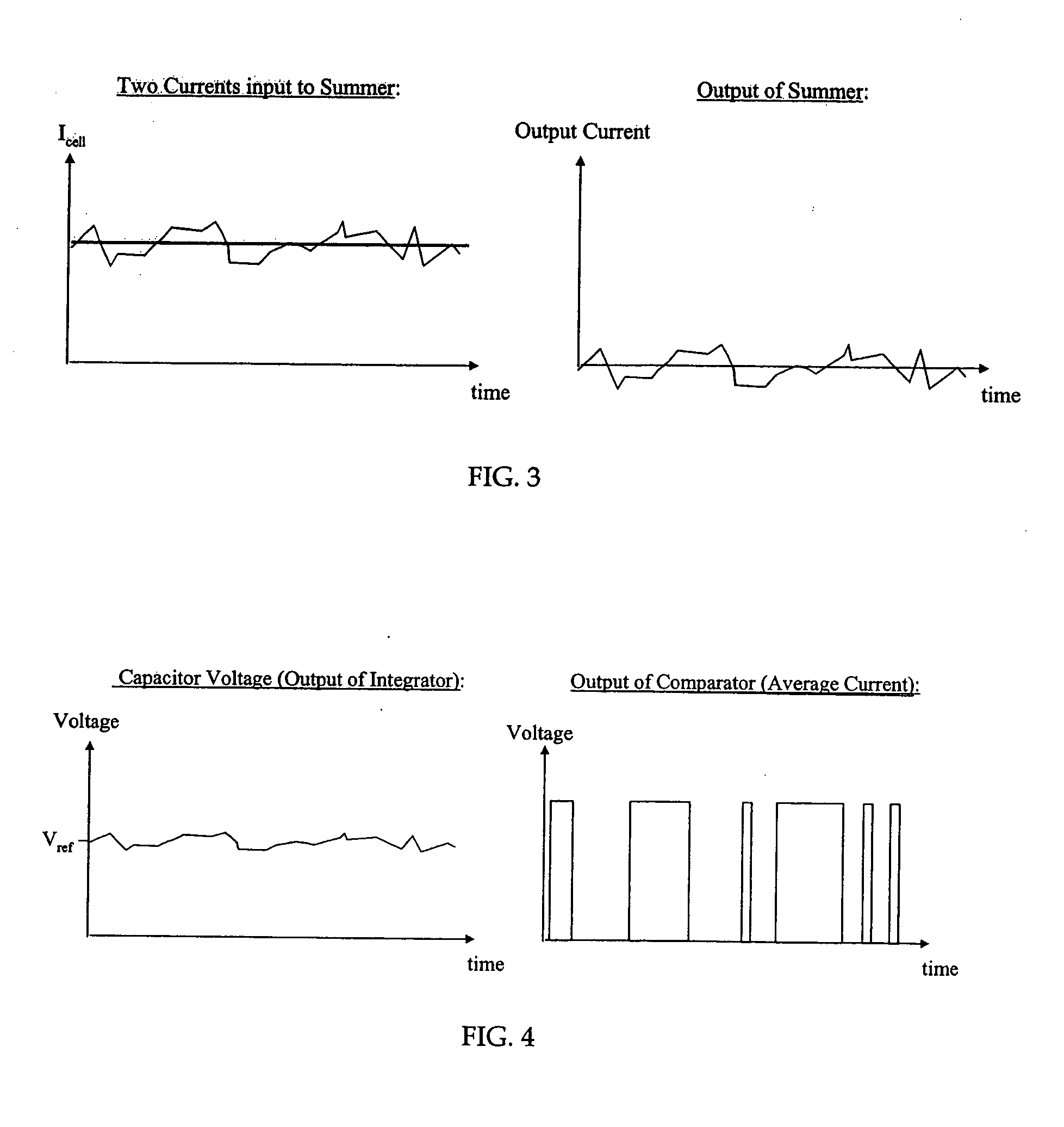

A simple method and device for accurately measuring flash memory cell current. The sensing scheme comprises an integrator, an analog to digital converter, and a digital to analog converter. The method comprises the acts of applying an input current and a feedback output current to a summer, integrating the resulting summer output over time, passing the integrated output to a clocked comparator, outputting a comparator output which controls a feedback circuit that keeps the integrator's voltage at the same level as a reference voltage, and outputting a digital average current to a counter. Delta sigma modulation (averaging) is employed to cancel out noise that would otherwise affect the cell current measurement.

Owner:MICRON TECH INC

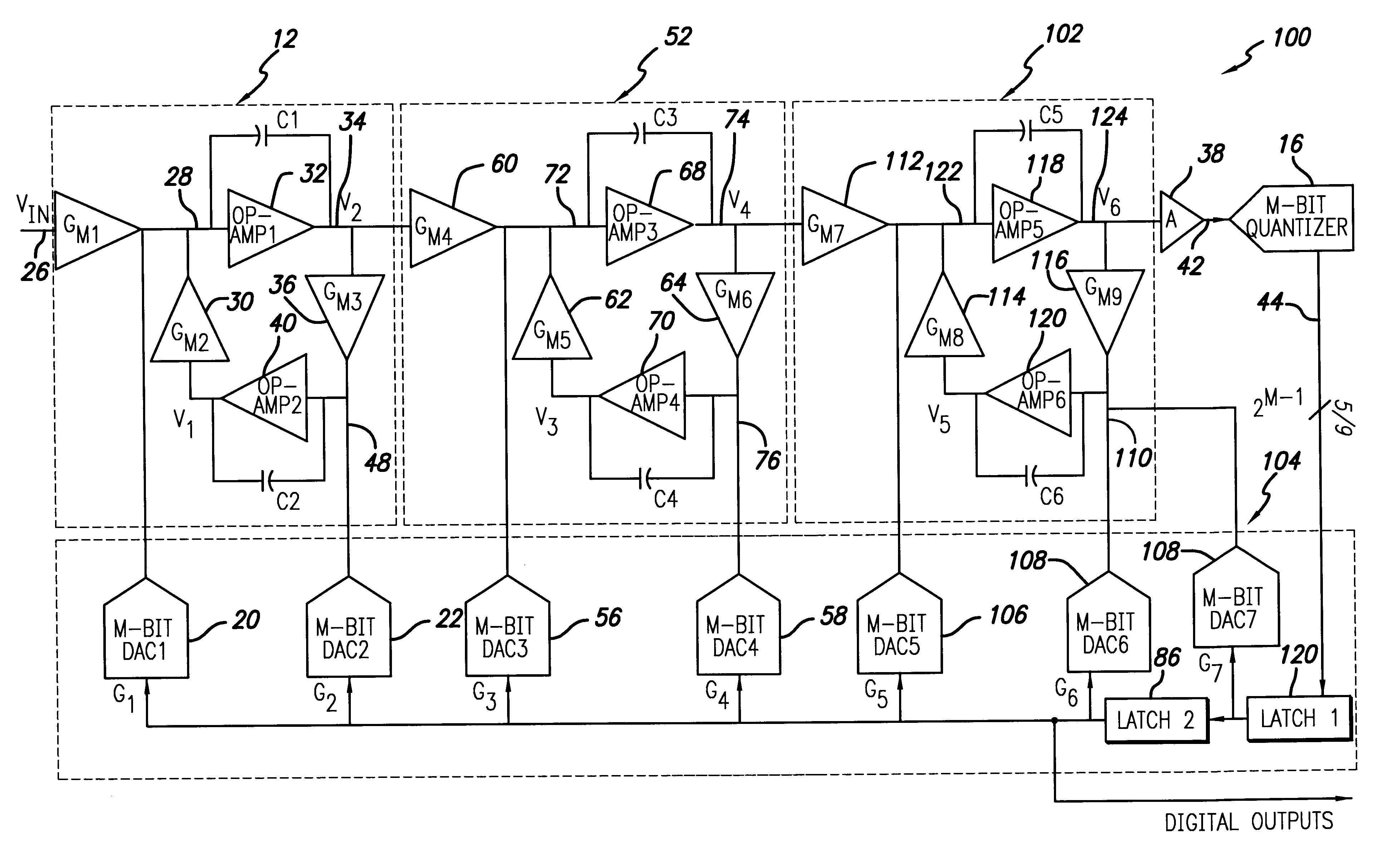

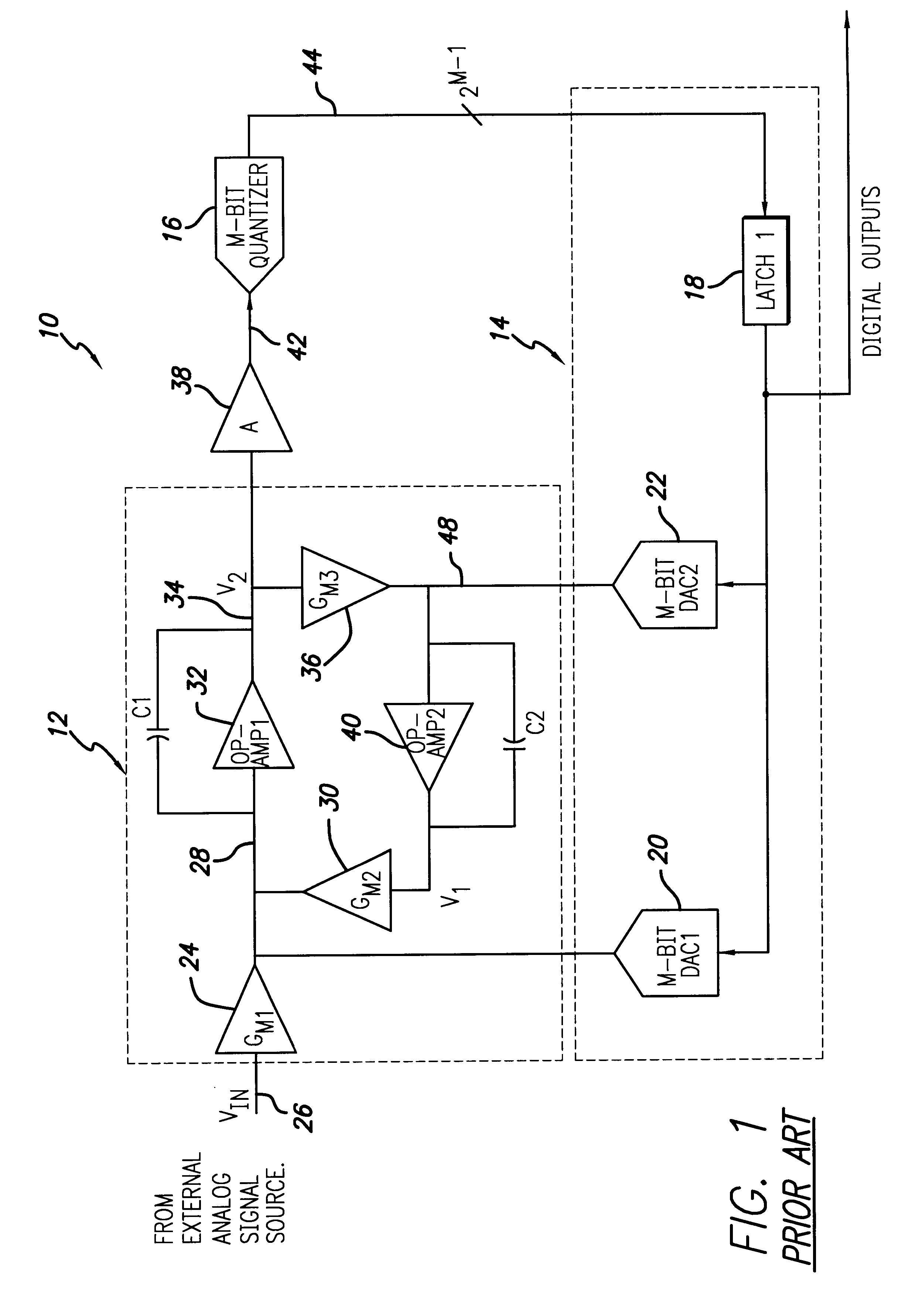

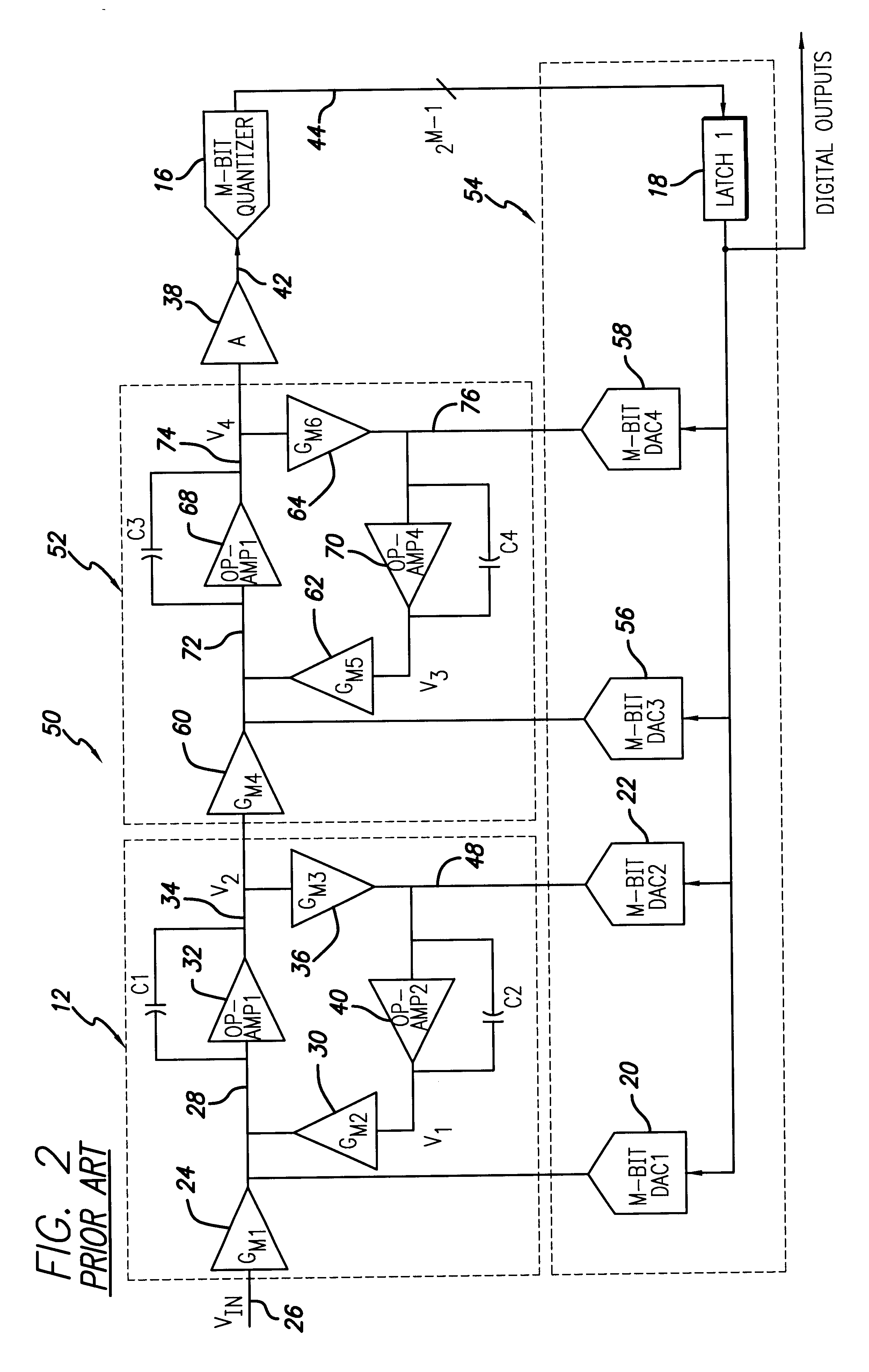

Excess delay compensation in a delta sigma modulator analog-to-digital converter

InactiveUS6414615B1Electric signal transmission systemsDelta modulationDigital analog converterAnalog signal

A high-performance delta sigma analog-to-digital converter. The high-performance delta sigma analog-to-digital converter includes a first mechanism for converting an input analog signal to a digital output signal. The first mechanism is characterized by a transfer function that is altered relative to an ideal transfer function. A second mechanism compensates for the alteration in the transfer function via a single additional digital-to-analog converter. In a specific embodiment, the alteration includes an additional pole and an additional zero induced by feedback delays in the first mechanism. The feedback delays include signal dependent jitter delay and feedback digital-to-analog converter cell switching delays. The second mechanism includes an additional latch that compensates for the signal dependent jitter delay. The first mechanism includes a resonator and a quantizer. The second mechanism includes a feedback path from an output of the quantizer to the resonator. The feedback path includes a first latch positioned between an output of the quantizer and the additional digital-to-analog converter. The additional latch is positioned at an output of the first latch and eliminates signal dependent jitter delay in the analog-to-digital converter. The additional feedback digital-to-analog converter is a non-return-to-zero digital-to-analog converter, an output of which is connected to the resonator.

Owner:RAYTHEON CO

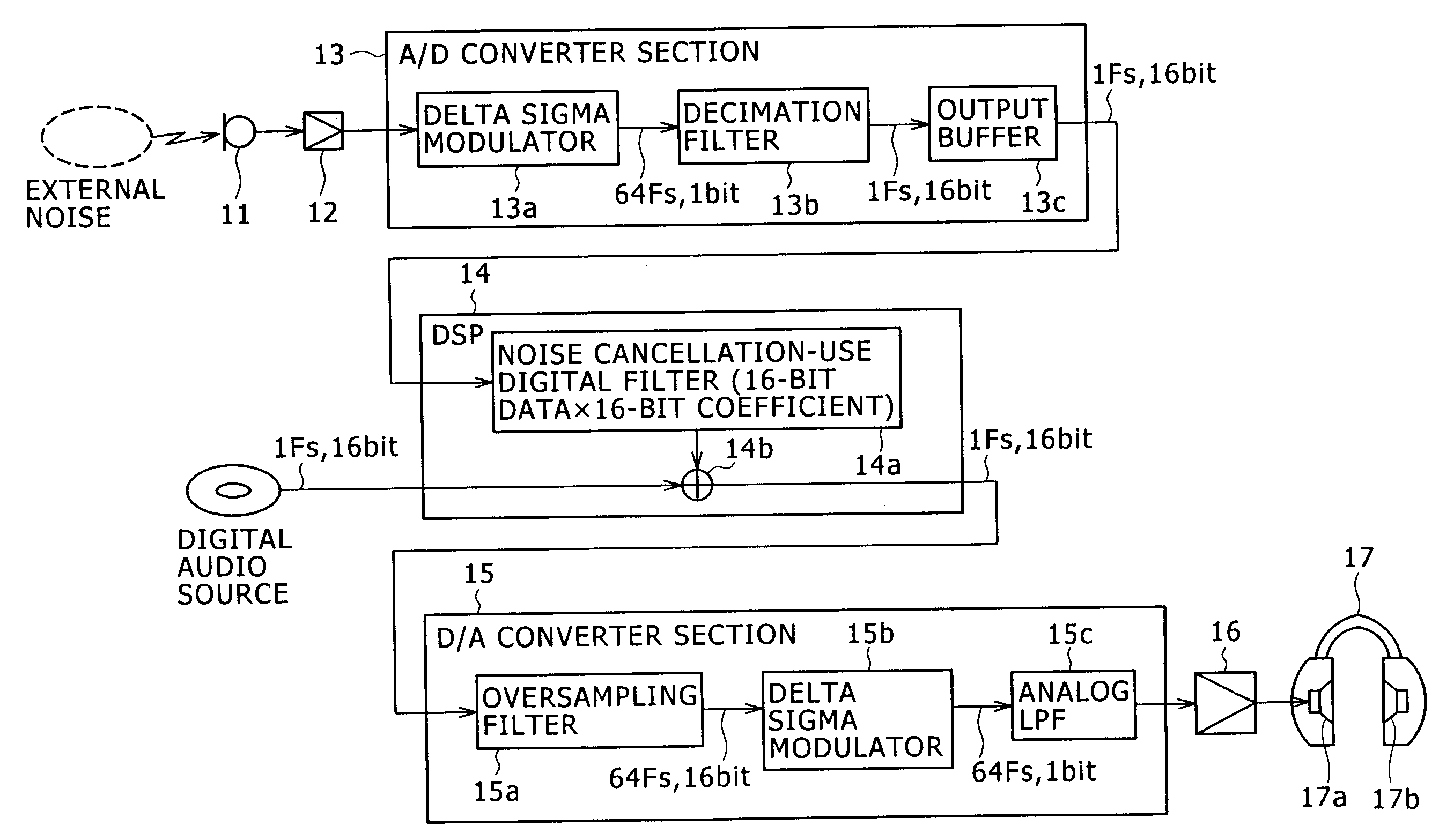

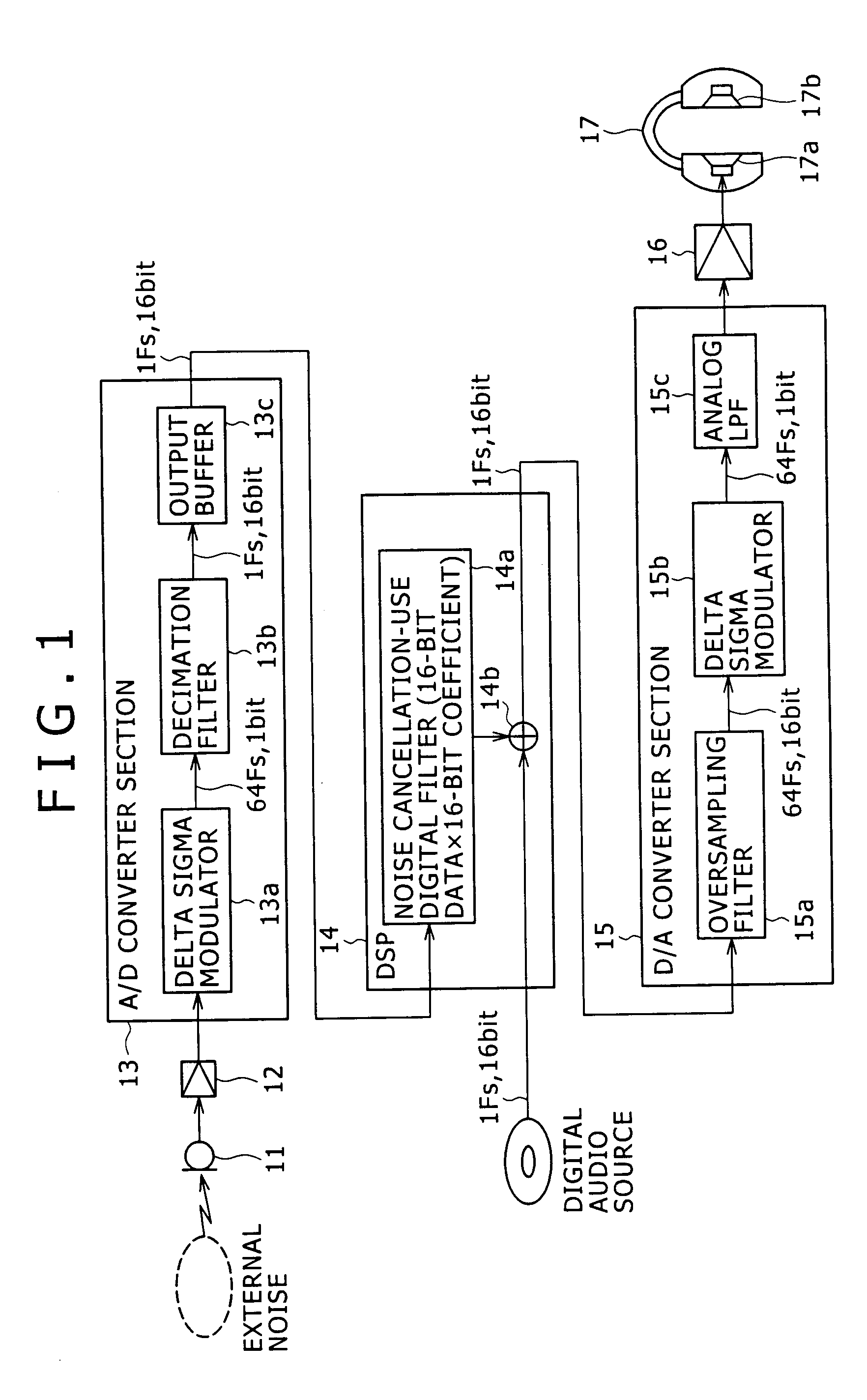

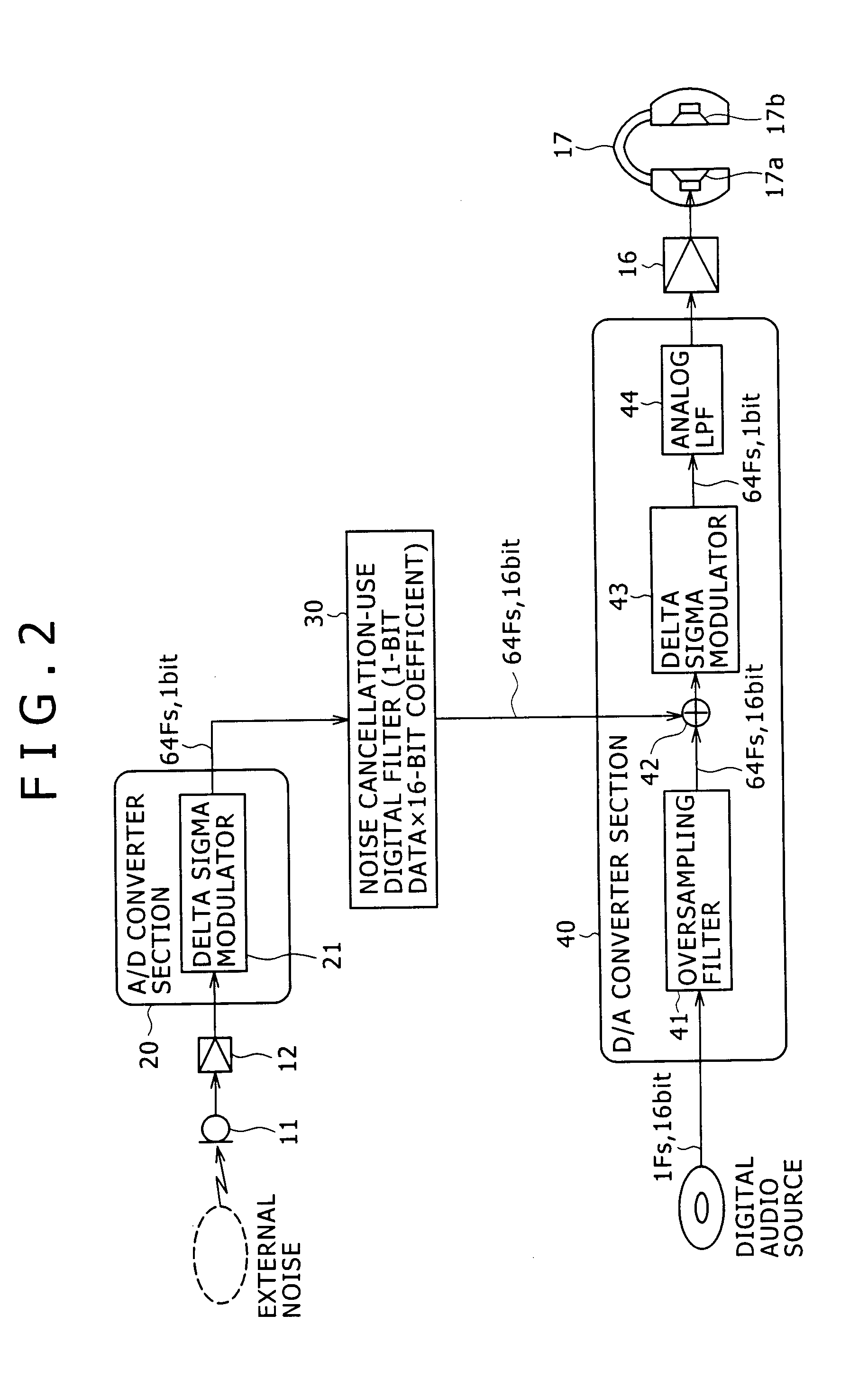

Signal processing apparatus and signal processing method

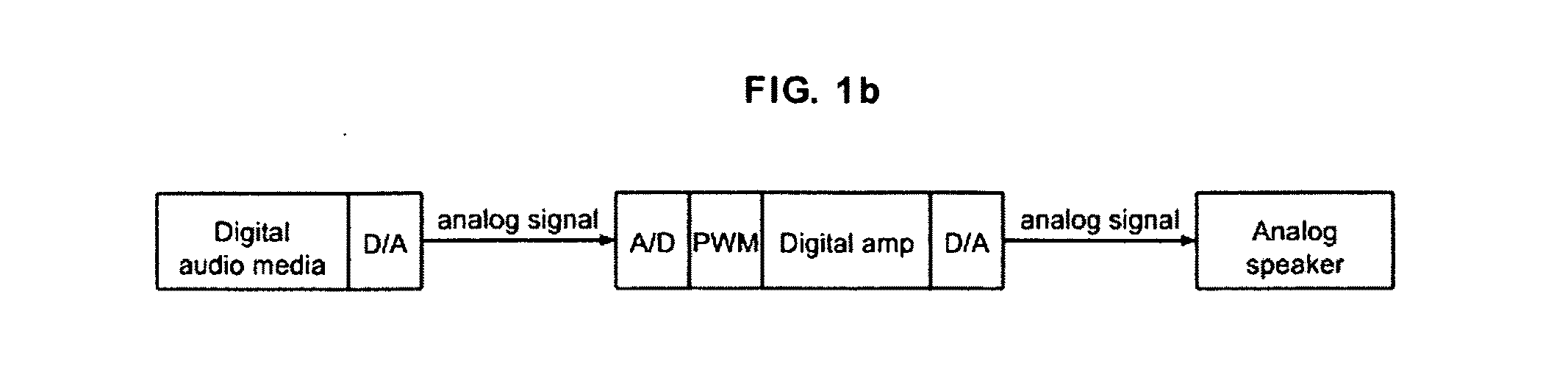

ActiveUS20080186218A1Improve sound qualityImprove practicalityElectric signal transmission systemsAnalogue conversionDigital filterAnalog signal

Disclosed herein is a signal processing apparatus including: analog-to-digital conversion means for performing delta sigma modulation of generating a digital signal having a predetermined sampling frequency and a predetermined quantization bit rate of one or more bits based on an input analog signal; signal processing means including a digital filter having a characteristic for outputting a digital signal having a sampling frequency n×Fs (Fs is a reference sampling frequency) and a quantization bit rate of a bits (a is a natural number greater than one) based on the above digital signal; and digital-to-analog conversion means including a part for performing delta sigma modulation for outputting a digital signal having a sampling frequency n×Fs and a quantization bit rate of b bits (b is a natural number greater than zero and less than a) based on a digital signal outputted from the signal processing means.

Owner:SONY CORP

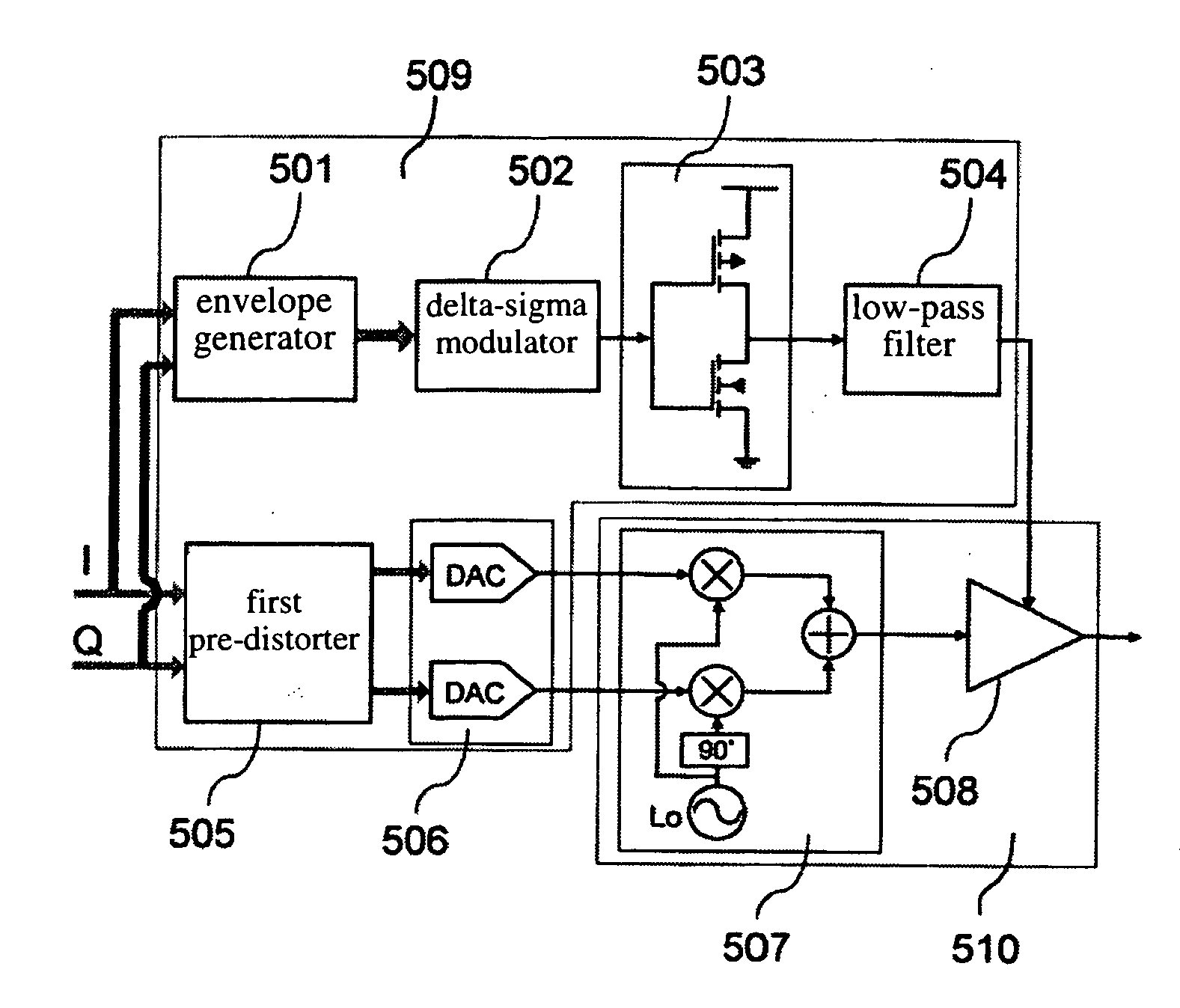

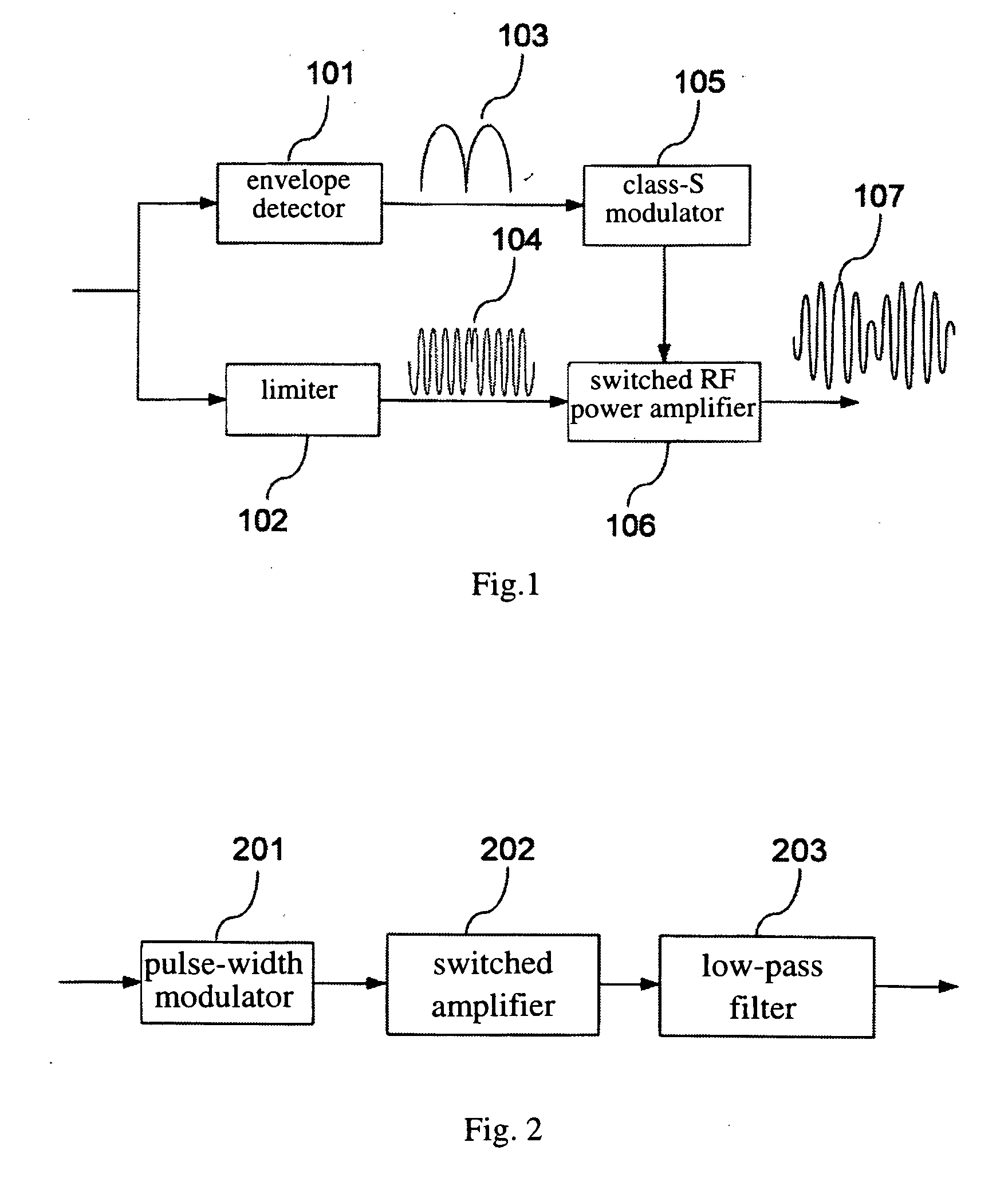

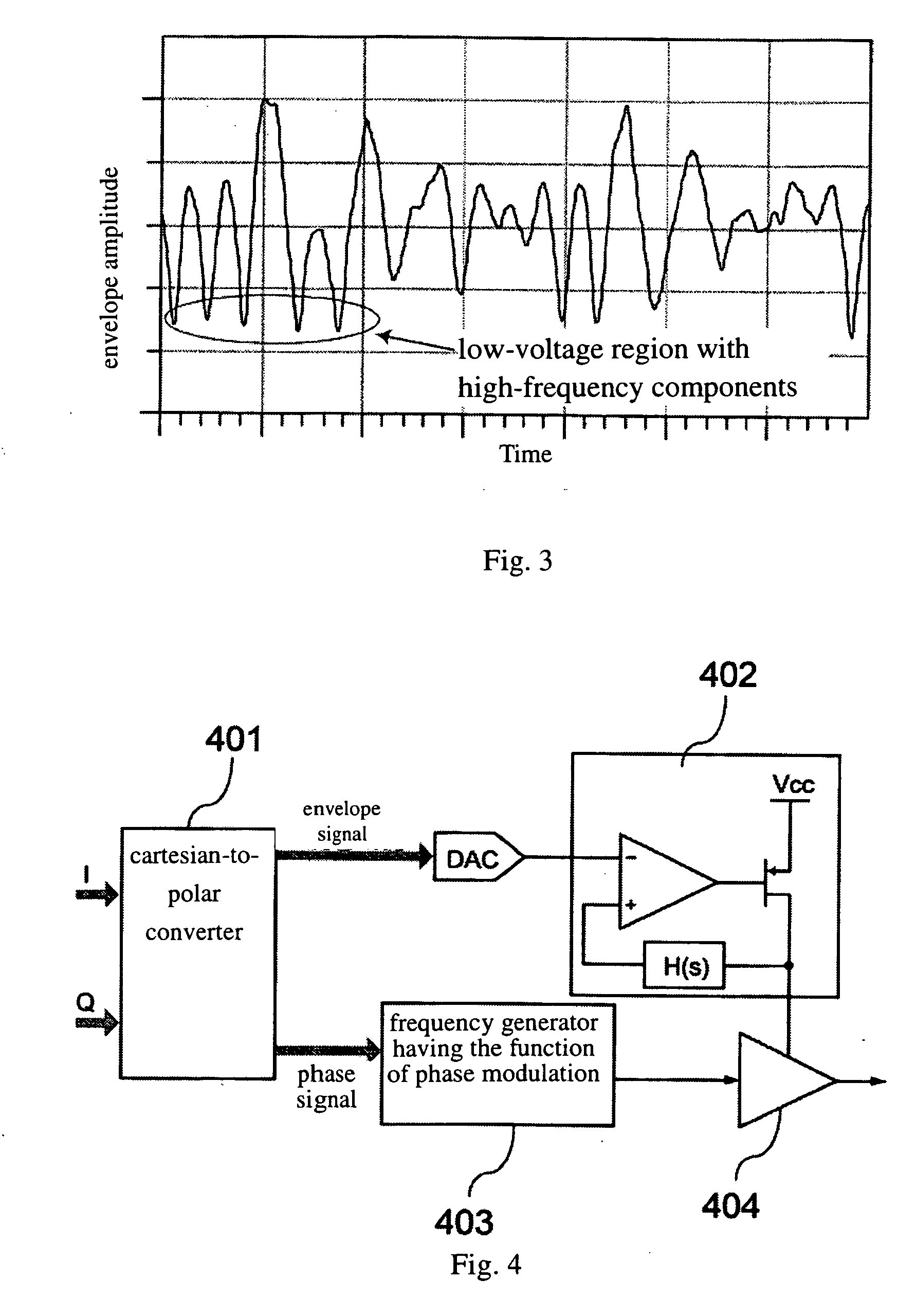

Microwave transmitter and the method for increasing envelope bandwidth

InactiveUS20070018718A1Low efficiencyPower flexibleAmplifier detailsDc amplifiers with modulator-demodulatorCarrier signalEngineering

The microwave transmitter of the present invention can perform two-terminal dynamic modulation with respect to the voltage supply terminal and the RF input terminal of a RF power amplifier. The microwave transmitter of the present invention comprises a first modulator and a second modulator. The first modulator uses the baseband digital delta-sigma modulation technique to process the envelope signal and outputs this signal to the voltage supply terminal of the RF power amplifier as a supply voltage. The second modulator uses the baseband digital pre-distortion technique to process the IQ-modulated carrier and outputs this signal to the RF input terminal of the RF power amplifier as a RF input signal. Thereby, the RF power amplifier can highly efficiently reconstruct the power-amplified RF modulated carrier without distortion at the RF output terminal. In addition, the baseband digital processing techniques used in the two modulators make the microwave transmitter of the present invention suitable for multi-mode operation.

Owner:NAT SUN YAT SEN UNIV +1

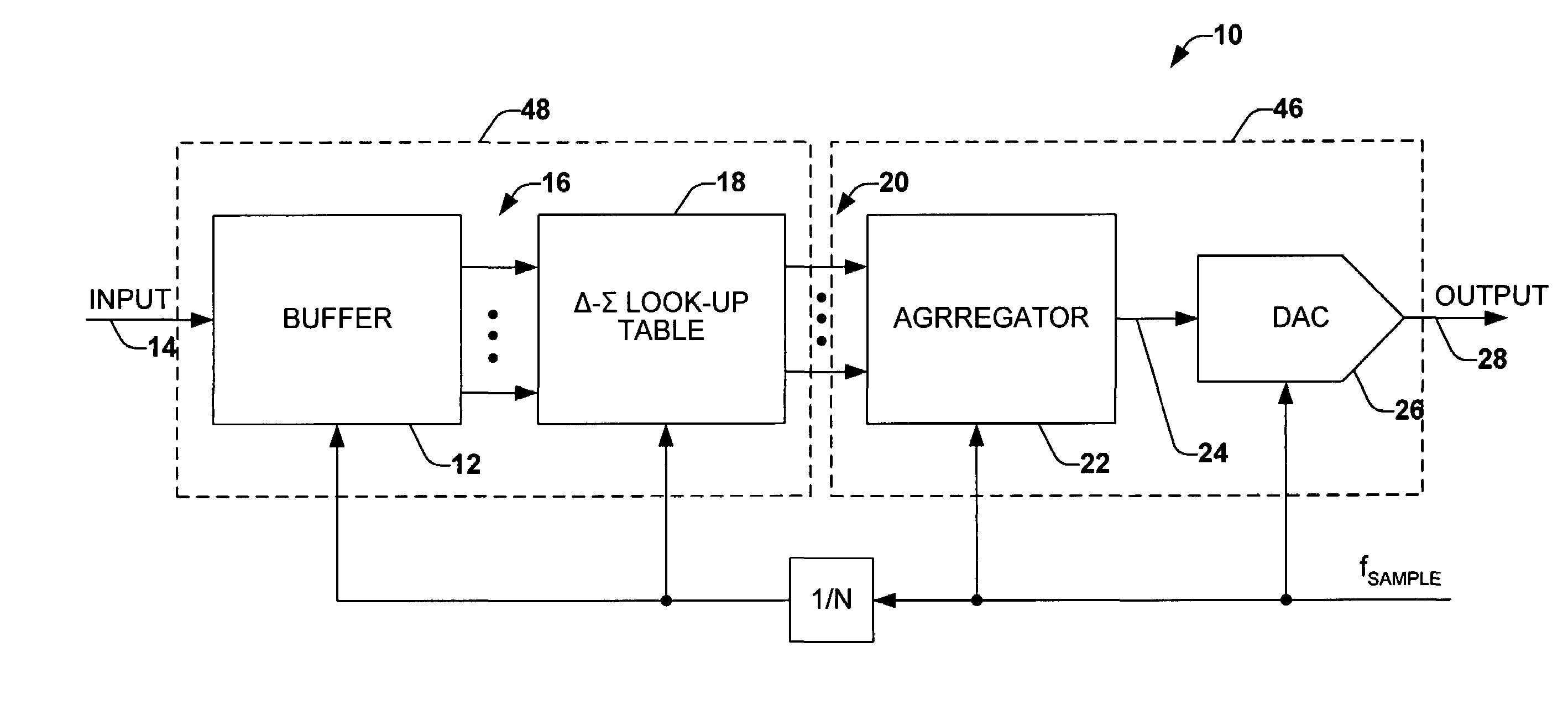

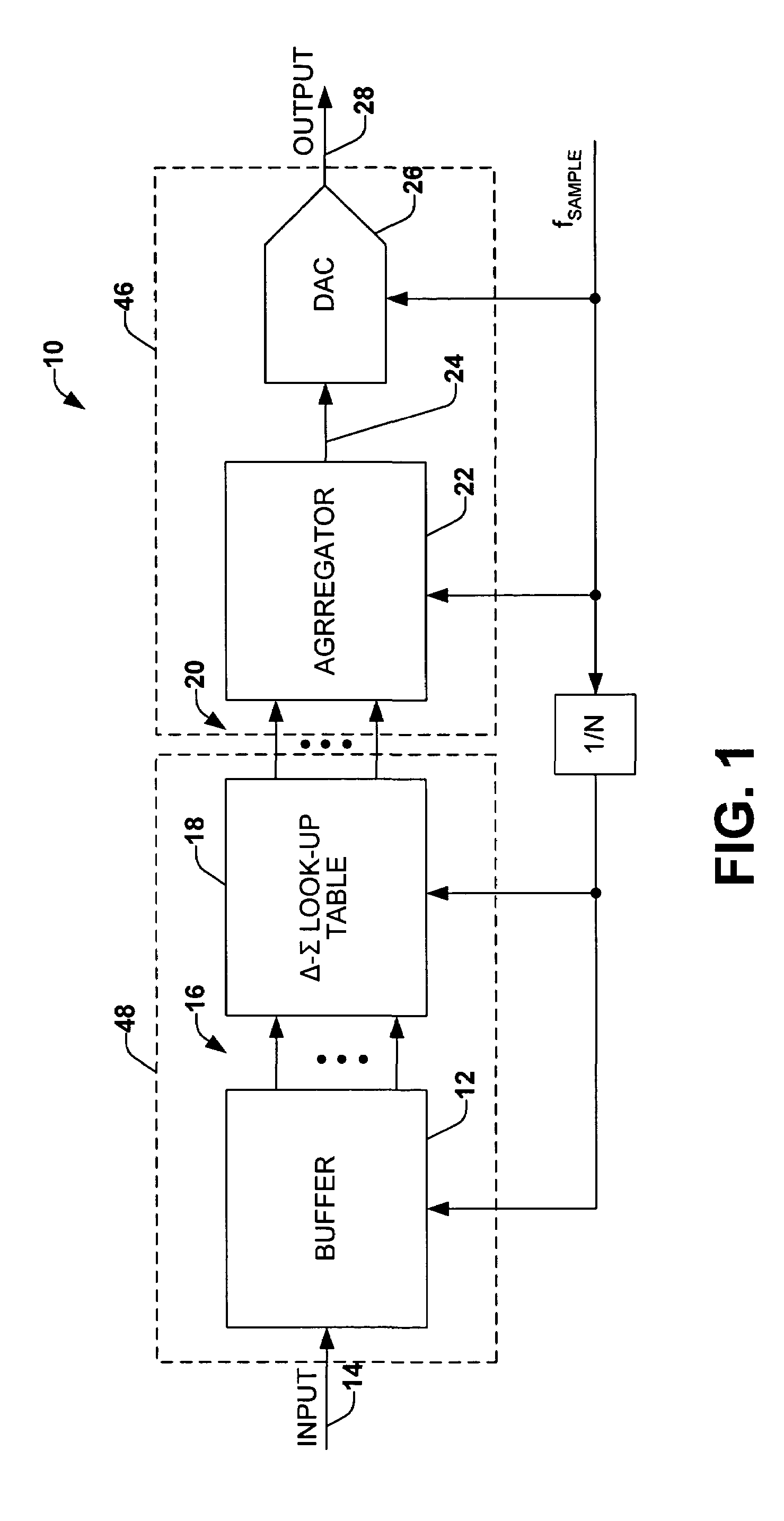

Look-up table delta-sigma conversion

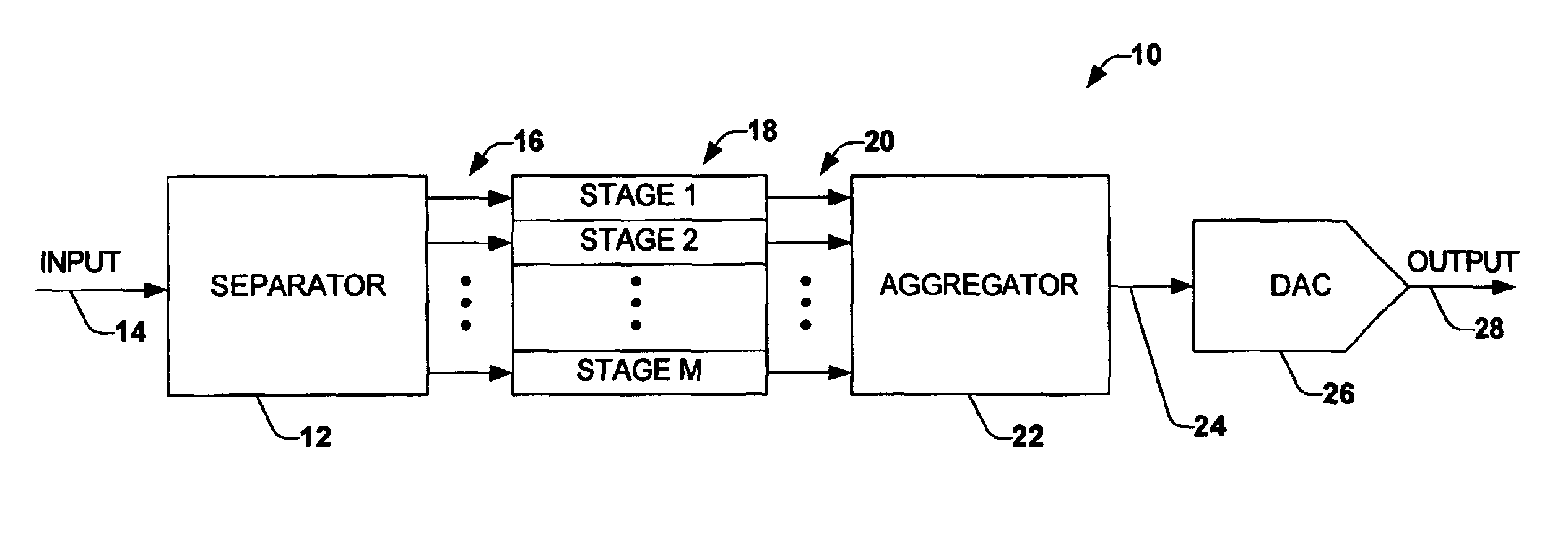

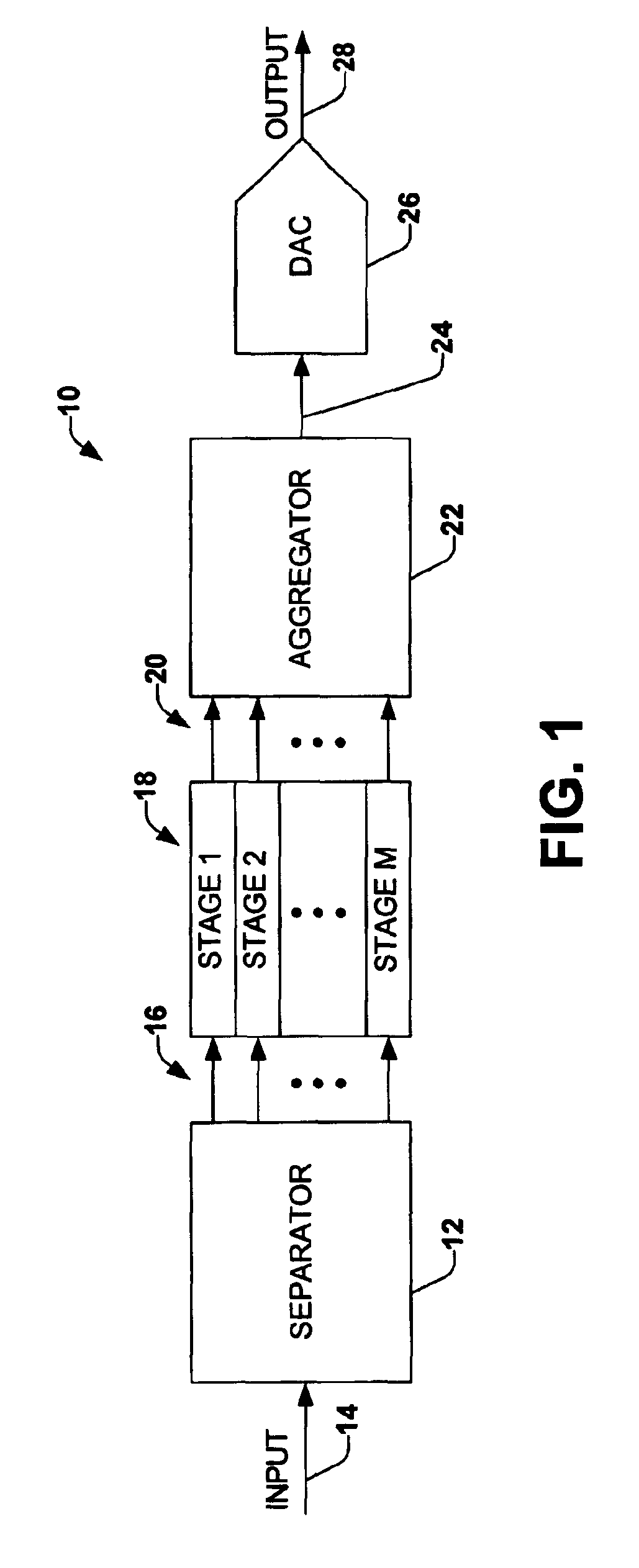

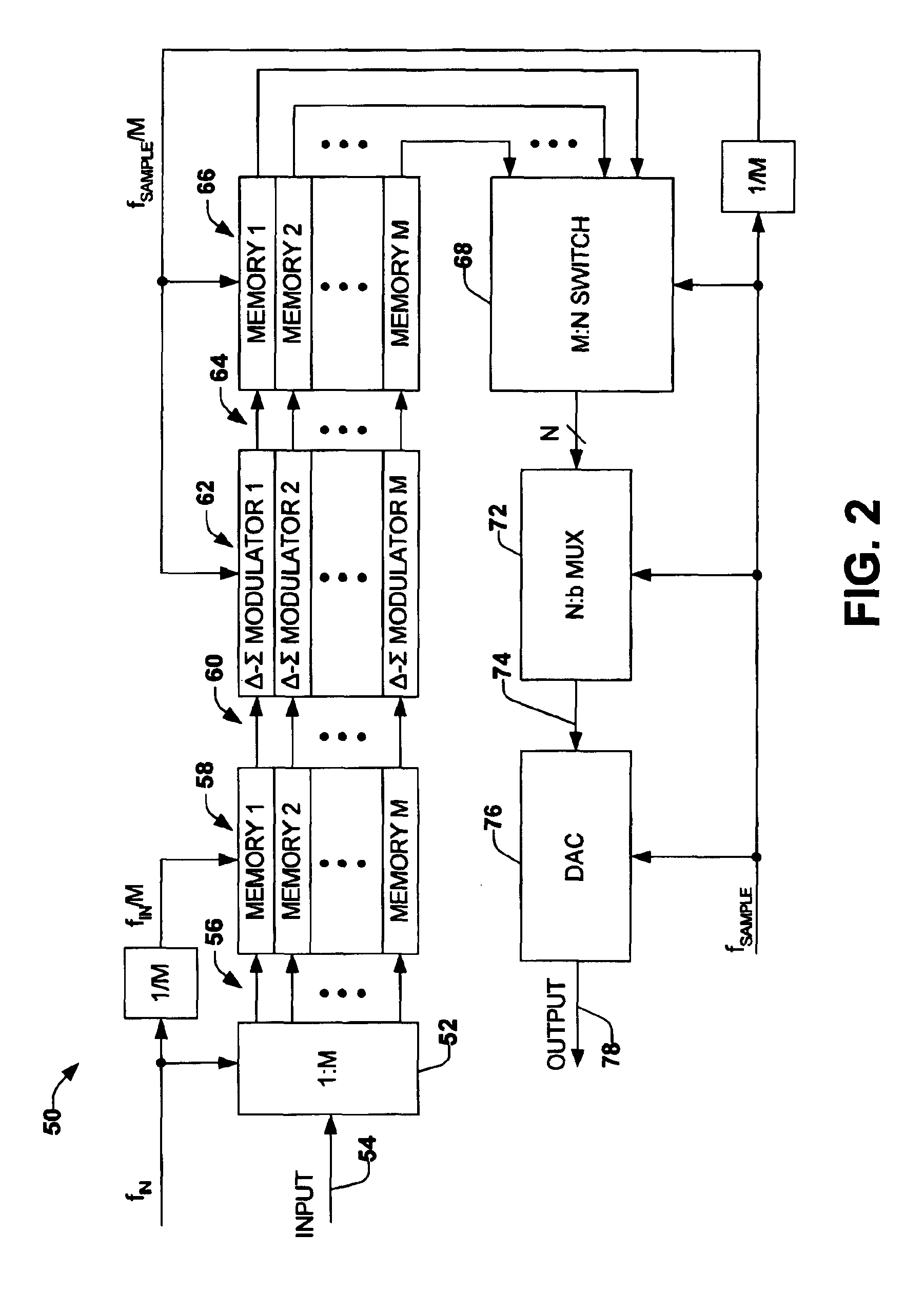

Signal conversion is implemented employing a memory system operating as a look-up table that stores a plurality of sets of output samples associated with each of a plurality of respective input samples. The look-up table thus can generate a corresponding set of output samples in response to a given input sample, thereby emulating desired digital upsampling and delta-sigma modulation. The output samples can be aggregated, such as by multiplexing, to provide an output data stream at a desired sample rate.

Owner:NORTHROP GRUMMAN SYST CORP

Conversion of a discrete time quantized signal into a continuous time, continuously variable signal

ActiveUS8294605B1Limit can be overcomeMinimize amplitudeElectric signal transmission systemsAnalogue conversionMulti bandAnalog signal

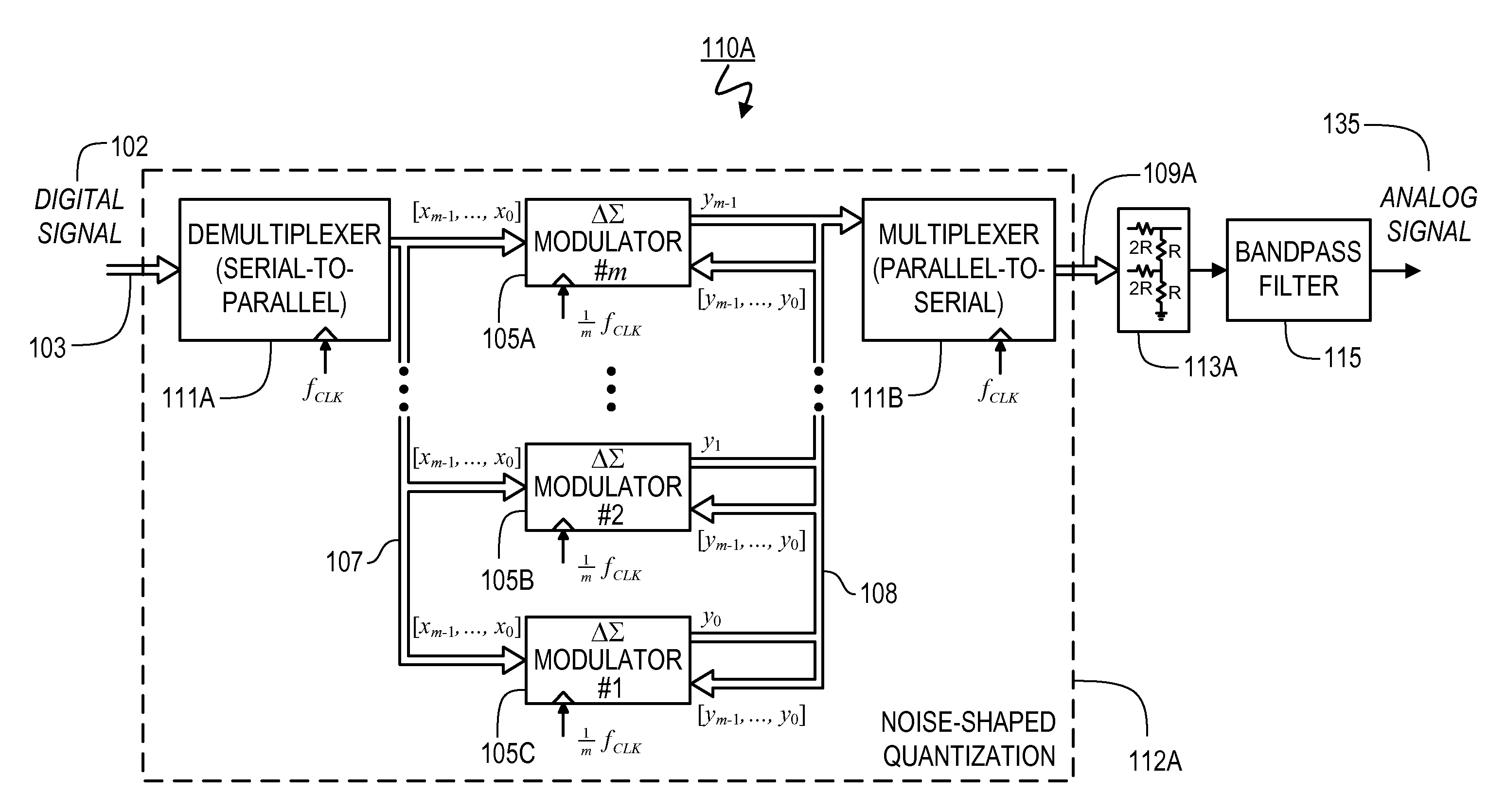

Provided are, among other things, systems, apparatuses, methods and techniques for converting a discrete-time quantized signal into a continuous-time, continuously variable signal. An exemplary converter preferably includes: (1) multiple oversampling converters, each processing a different frequency band, operated in parallel; (2) multirate (i.e., polyphase) delta-sigma modulators (preferably second-order or higher); (3) multi-bit quantizers; (4) multi-bit-to-variable-level signal converters, such as resistor ladder networks or current source networks; (5) adaptive nonlinear, bit-mapping to compensate for mismatches in the multi-bit-to-variable-level signal converters (e.g., by mimicking such mismatches and then shifting the resulting noise to a frequently range where it will be filtered out by a corresponding bandpass (reconstruction) filter); (6) multi-band (e.g., programmable noise-transfer-function response) bandpass delta-sigma modulators; and / or (7) a digital pre-distortion linearizer (DPL) for canceling noise and distortion introduced by an analog signal bandpass (reconstruction) filter bank.

Owner:PAGNANELLI FAMILY TRUST

Conversion employing delta-sigma modulation

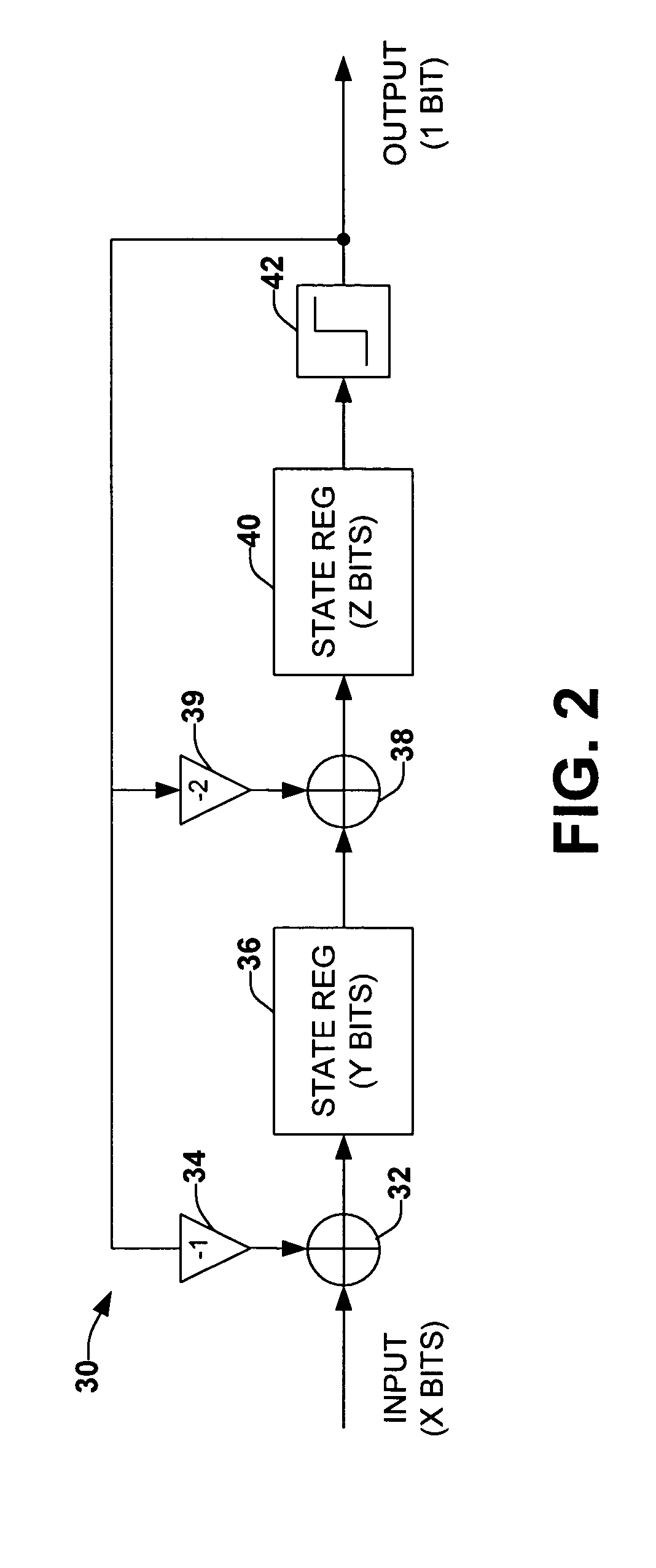

InactiveUS6873280B2Efficient implementationImprove performanceElectric signal transmission systemsDelta modulationNoise shapingData rate

Signal conversion of an input signal can be achieved by processing portions of the signal through plural parallel paths, which collectively approximate a desired infinite impulse response (IIR) filter, either alone or implemented with other signal processing functions. In one aspect, each of the paths can perform filtering, noise-shaping and / or quantization on a respective portion of the input signal to provide a corresponding representation of the respective portion of the input signal, for example, a coarser representation at a higher data rate. The corresponding representations from the parallel paths can be aggregated and further processed in a desired manner, such as conversion to an analog signal.

Owner:NORTHROP GRUMMAN SYST CORP

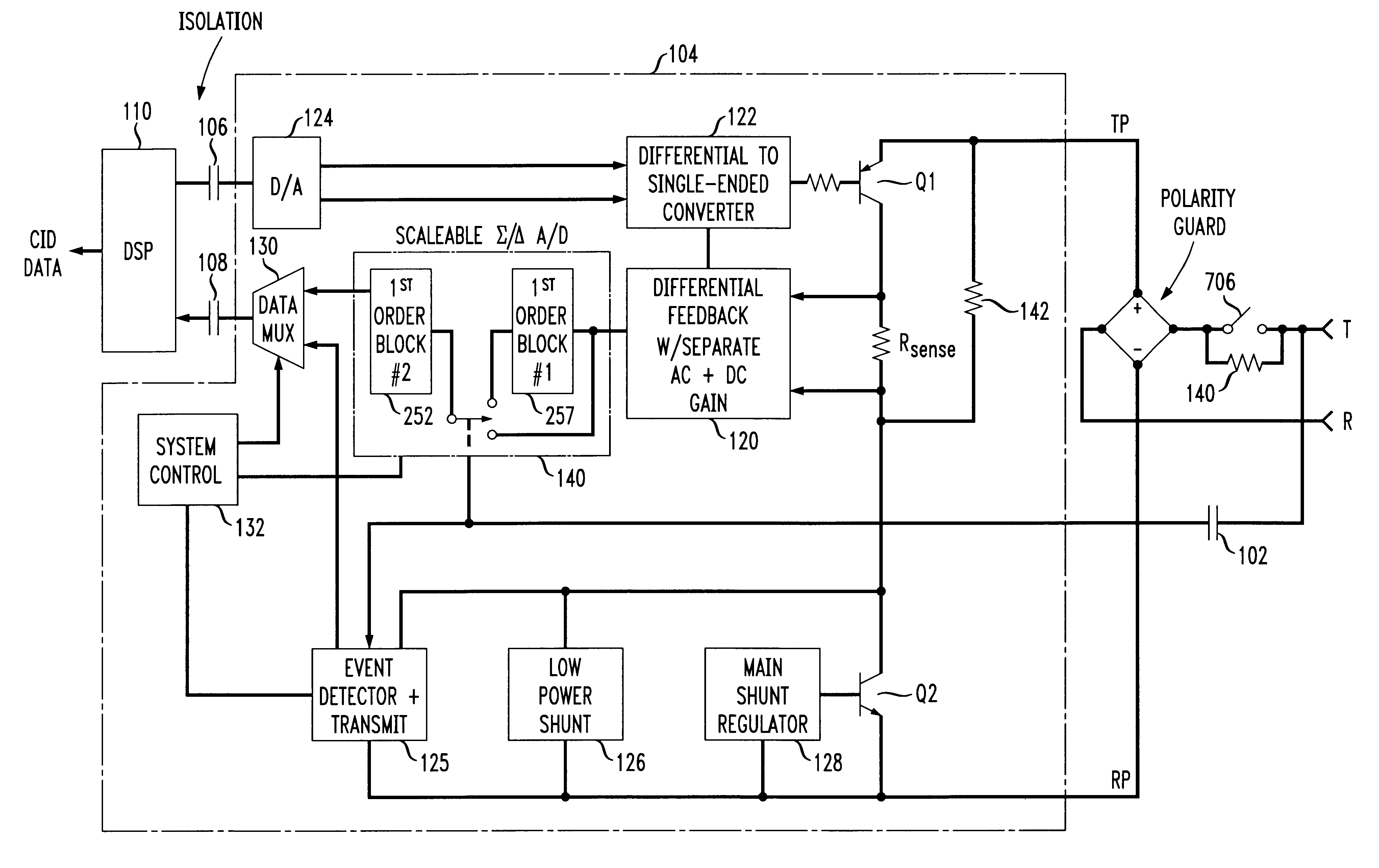

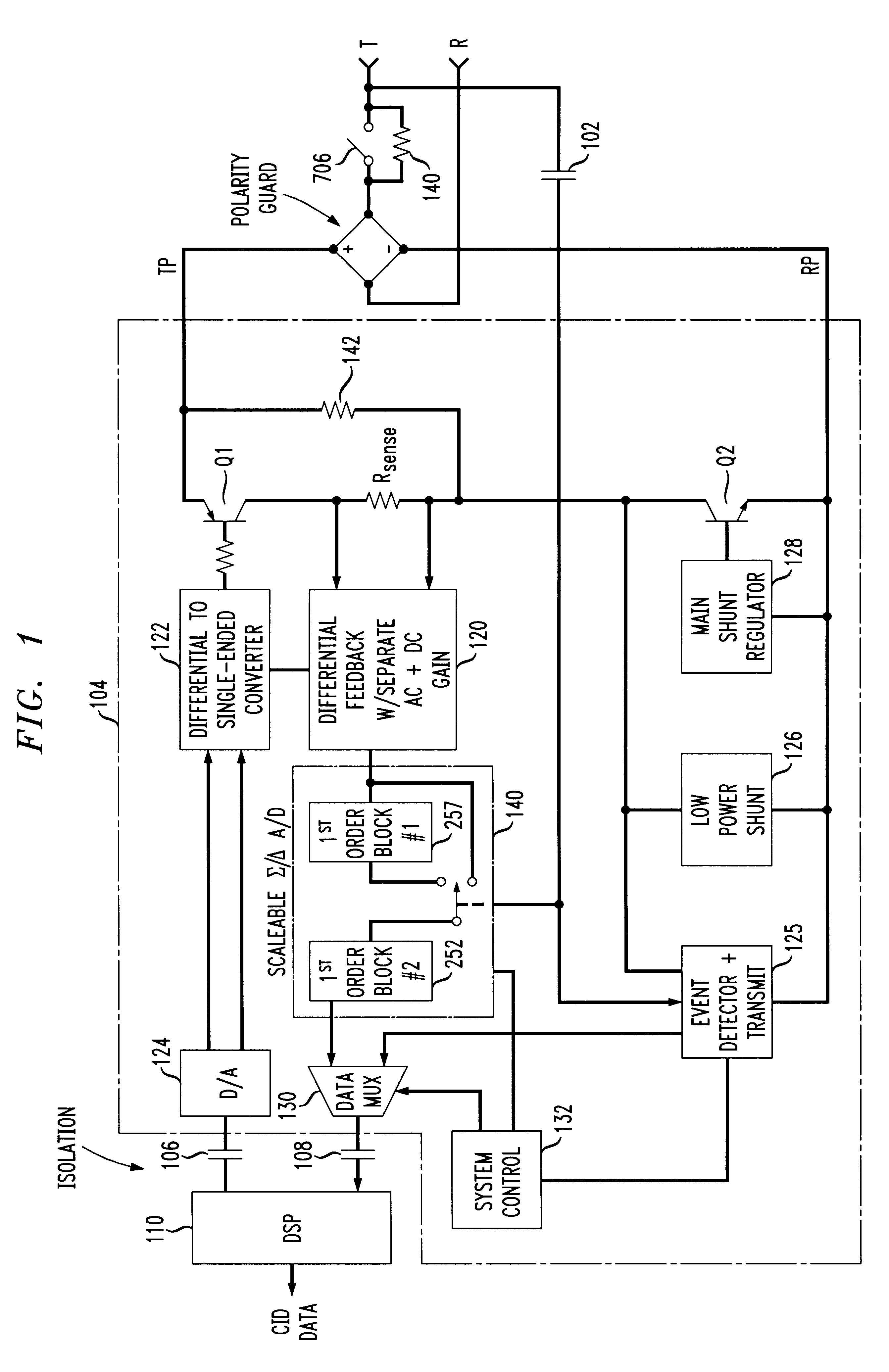

Call related information reception using sigma/delta modulation

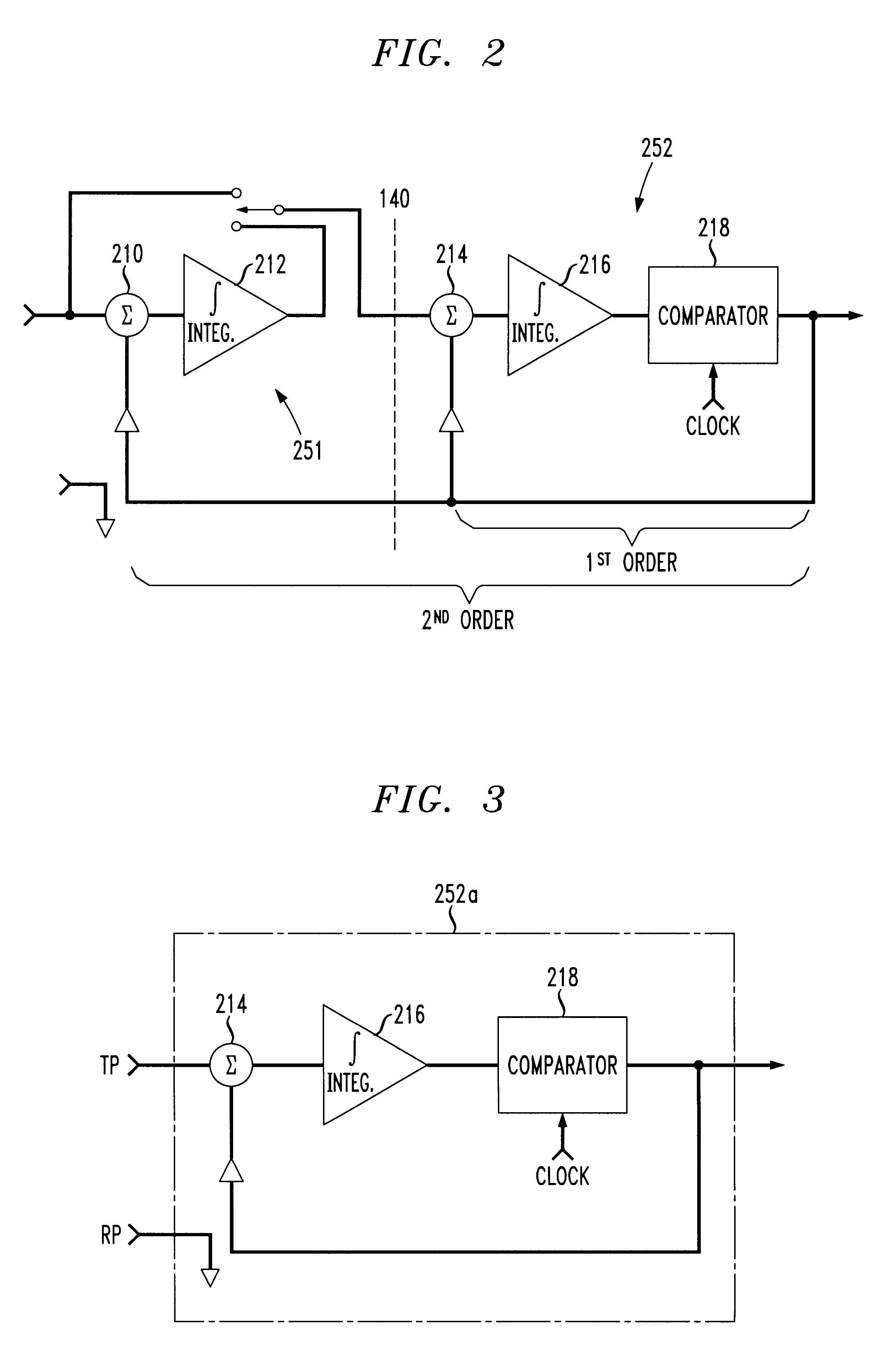

InactiveUS6205219B1Interconnection arrangementsUnauthorised/fraudulent call preventionGreek letter sigmaDigitization

A method and apparatus to receive and demodulate call related information, e.g., Caller ID information, in an audio codec placed on the line side and powered by current drawn from the telephone line. The audio codec includes a 1st order SIGMA / DELTA A / D converter to digitize the signal from the telephone line with SIGMA / DELTA modulation. The 1st order SIGMA / DELTA A / D converter may be a scaleable component capable of alternative operation in a 2nd order. The SIGMA / DELTA encoded digitized signal is digitally processed by a DSP including an amplifier module, a digital filter, a limit / slice module, and an FSK decoder to receive and output the call related information. Placement of the audio codec on the line side and the scaleable SIGMA / DELTA A / D converter provides significantly reduced power requirements for the audio codec, thus allowing operation from power derived from the telephone line. In another embodiment, to further reduce power consumption of the audio codec, the 1st order SIGMA / DELTA A / D converter is sampled at a slower rate than is conventional, e.g., by first dividing or otherwise providing a slower sampling clock.

Owner:LUCENT TECH INC +1

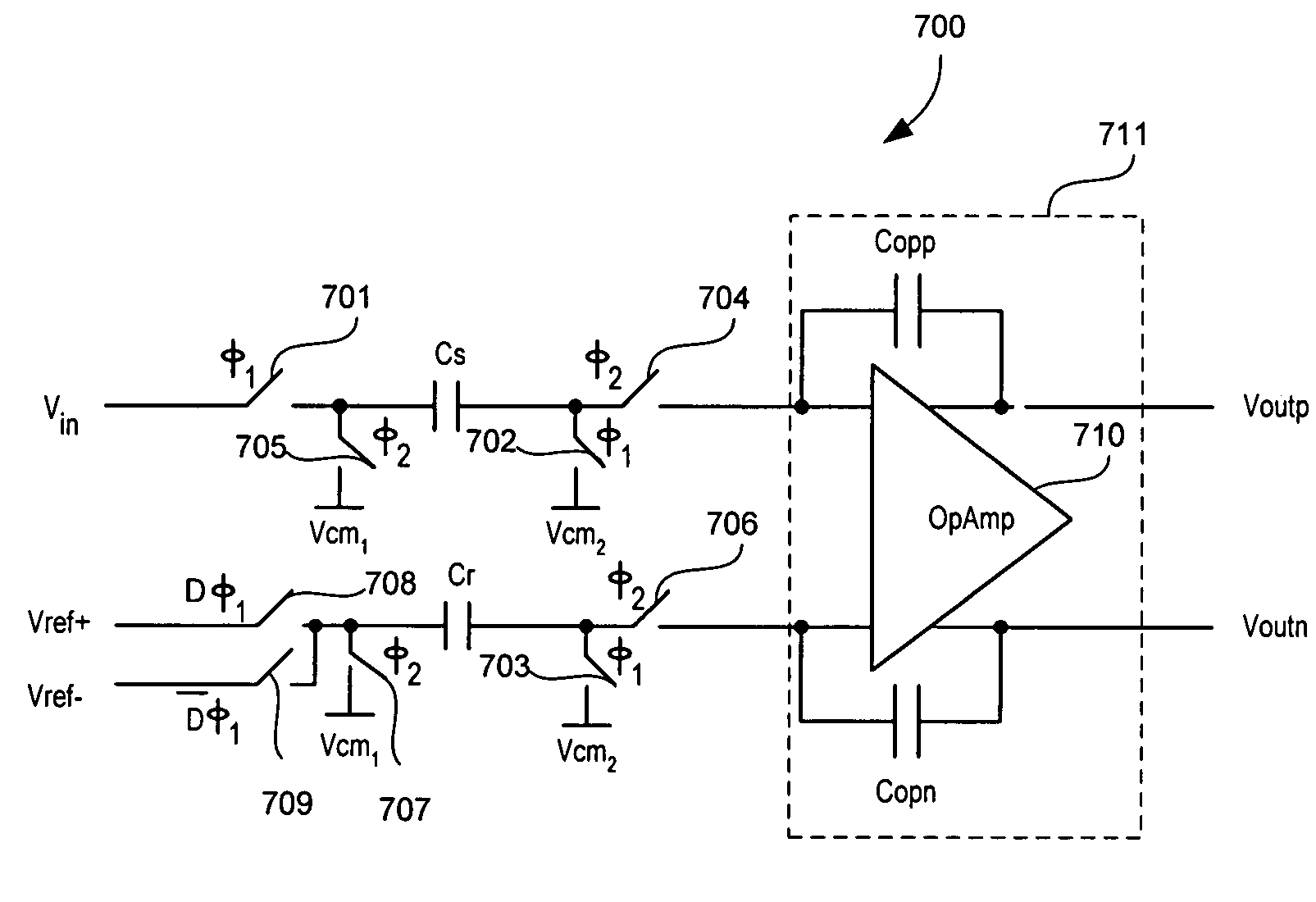

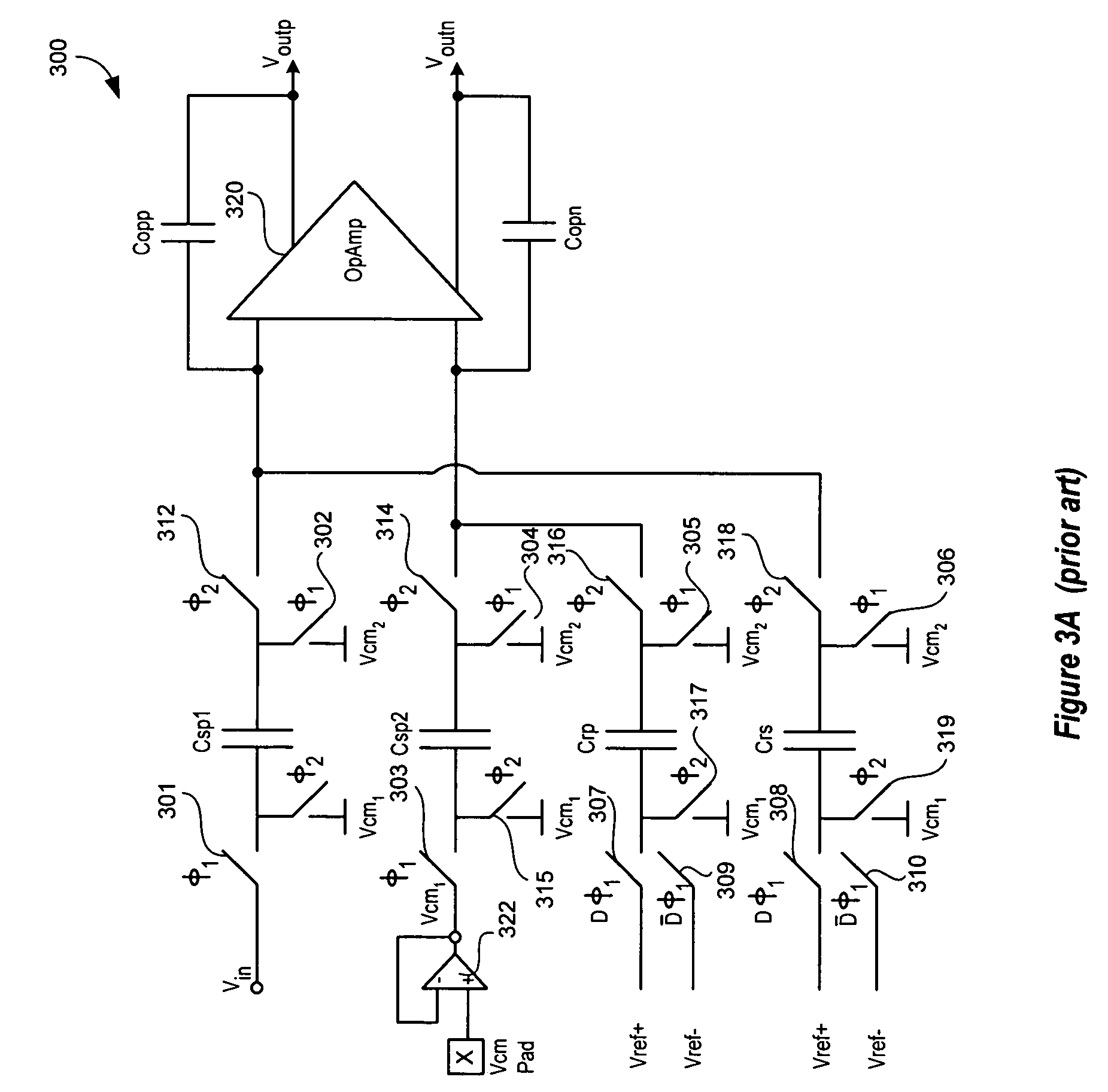

Signal processing system having an ADC delta-sigma modulator with single-ended input and feedback signal inputs

ActiveUS6972705B1Electric signal transmission systemsDifferential modulationAnalog feedbackEngineering

Signal processing systems described herein include an analog-to-digital delta sigma modulator to process a single-ended input signal using a single-ended analog feedback reference signal. The delta sigma modulator includes a switched capacitor circuit that integrates a difference between the single-ended input signal and the single-ended analog feedback signal derived from a quantization output of the delta sigma modulator. Embodiments of the switched capacitor circuit allow the delta sigma modulator to be implemented with fewer switches, less complicated reference signal generators, and smaller capacitors relative to conventional counterparts. Thus, embodiments of the delta sigma modulator described herein can cost less to build and use less power. Embodiments of the signal processing systems can be implemented in single and multi-bit delta sigma modulators and various sampling topologies, including single and double sampling topologies.

Owner:CIRRUS LOGIC INC

Method and apparatus for sensing flash memory using delta sigma modulation

ActiveUS7366021B2Accurate inductionHigh circuitryRead-only memoriesDigital storageIntegratorAverage current

Owner:MICRON TECH INC

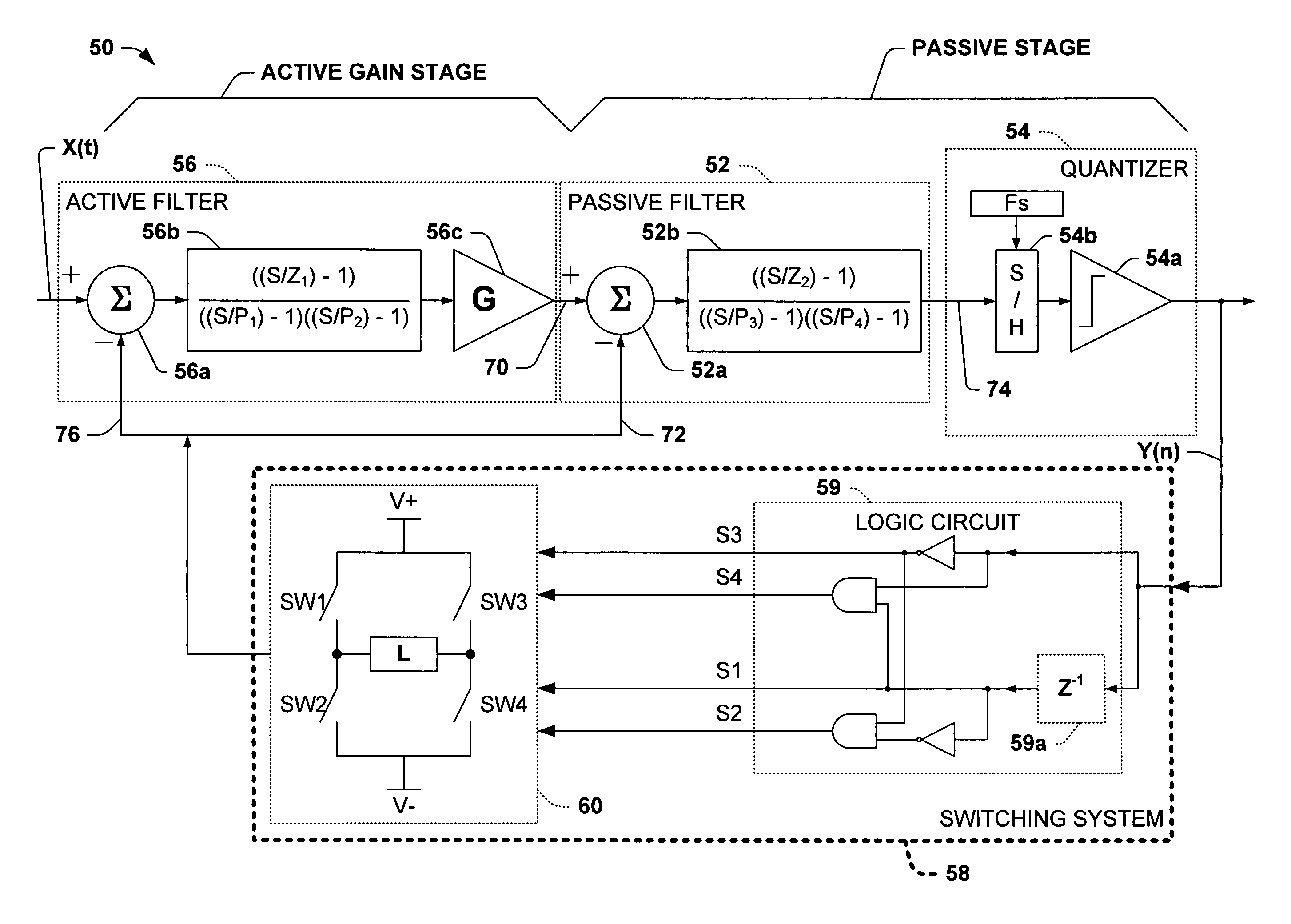

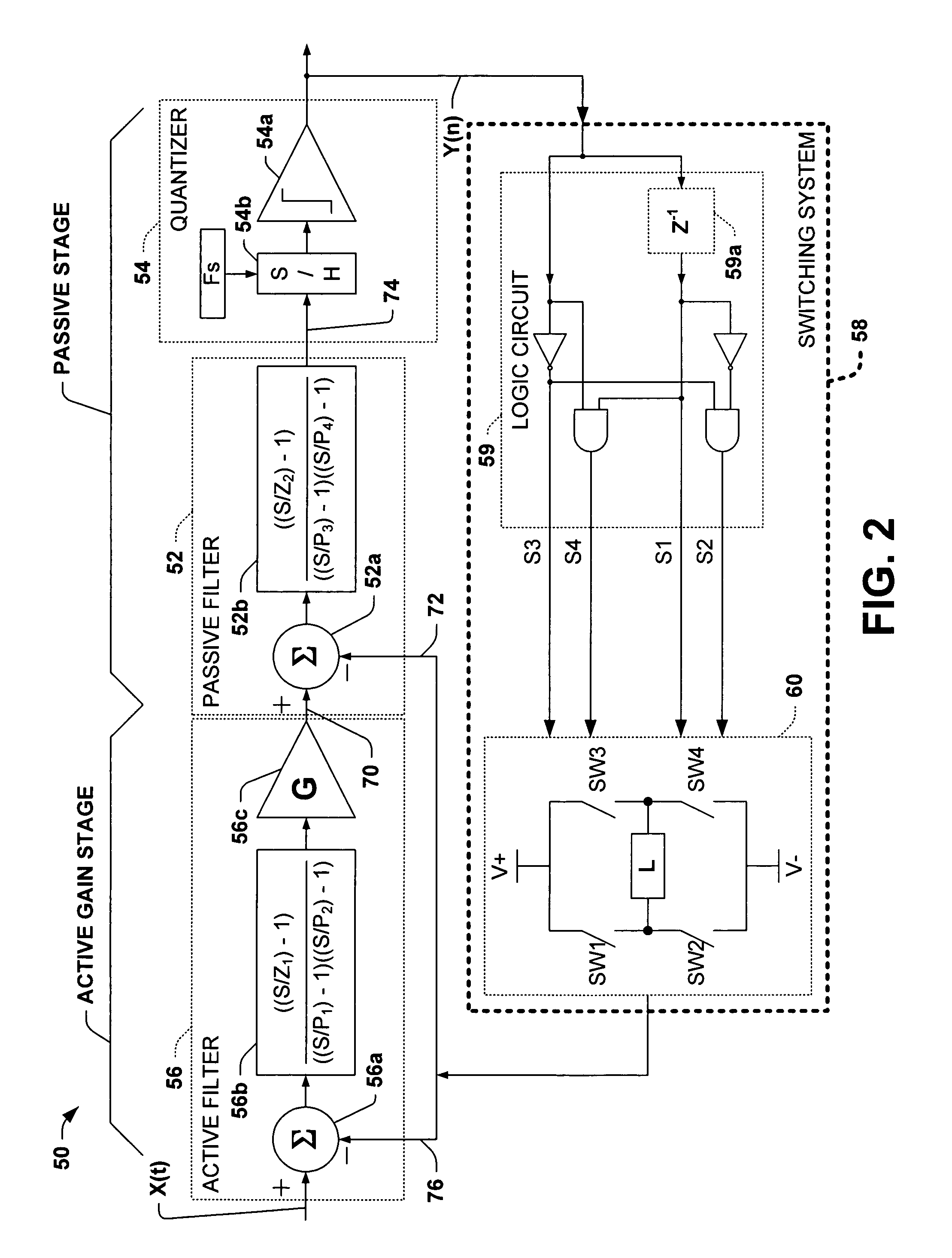

Amplifier using delta-sigma modulation

ActiveUS6998910B2Reduce adverse effectsSacrificing power consumption advantageAnalogue conversionDc amplifiers with modulator-demodulatorDriver circuitAudio power amplifier

An amplifier and a driver circuit therefor are presented for driving a load according to a system analog input. The amplifier comprises a passive delta-sigma modulator with a passive filter providing a first filtered signal according to a passive filter input and according to a feedback signal, a quantizer coupled with the passive filter and providing a quantized output according to the first filtered signal, and a switching system coupled with the the passive filter and the quantizer. The switching system selectively providing power to a load according to the quantized output and provides the feedback signal to the passive input, wherein a gain amplifier is provided in a feedback loop around the passive delta-sigma modulator.

Owner:TEXAS INSTR INC

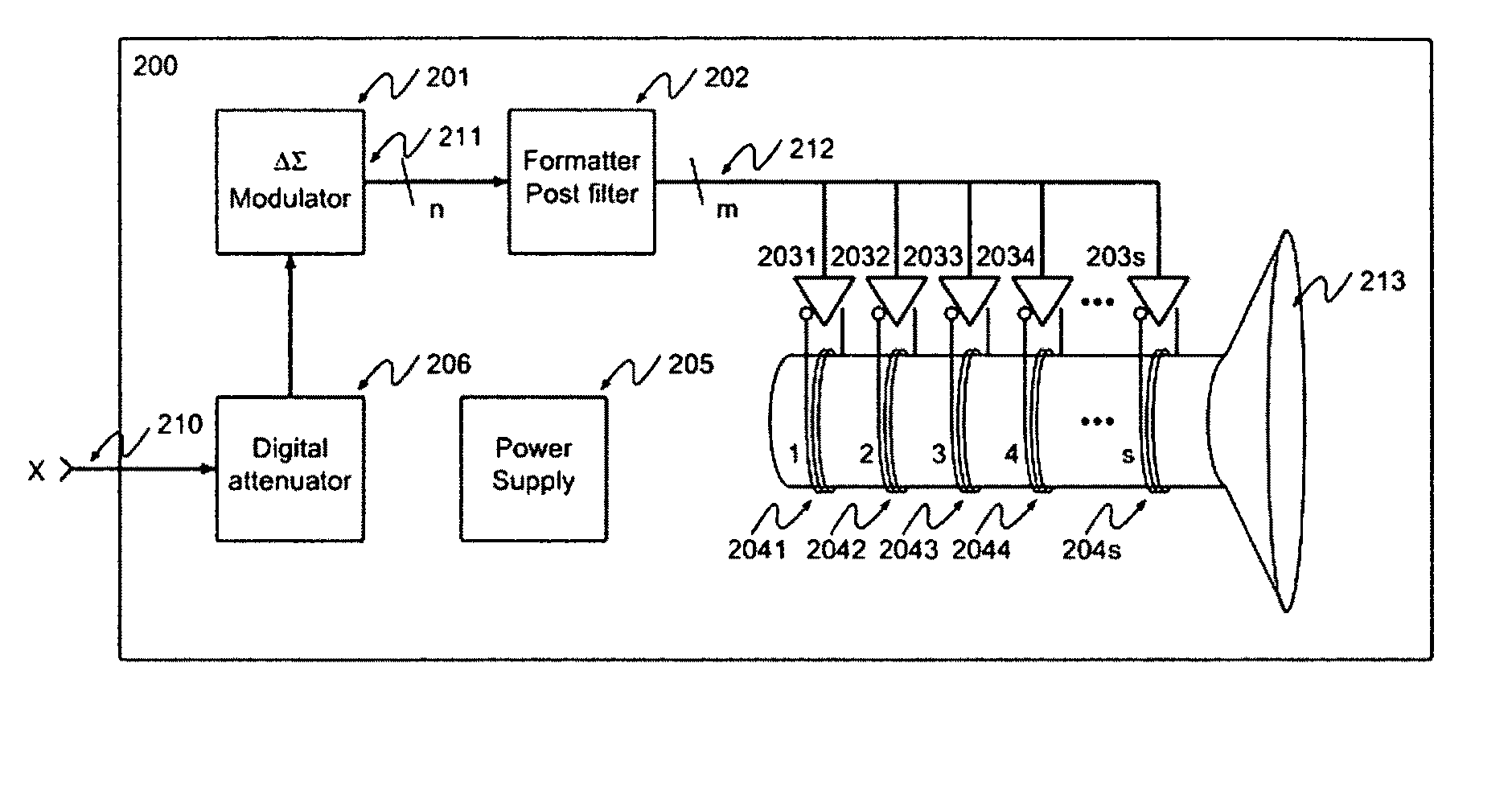

Digital speaker driving apparatus

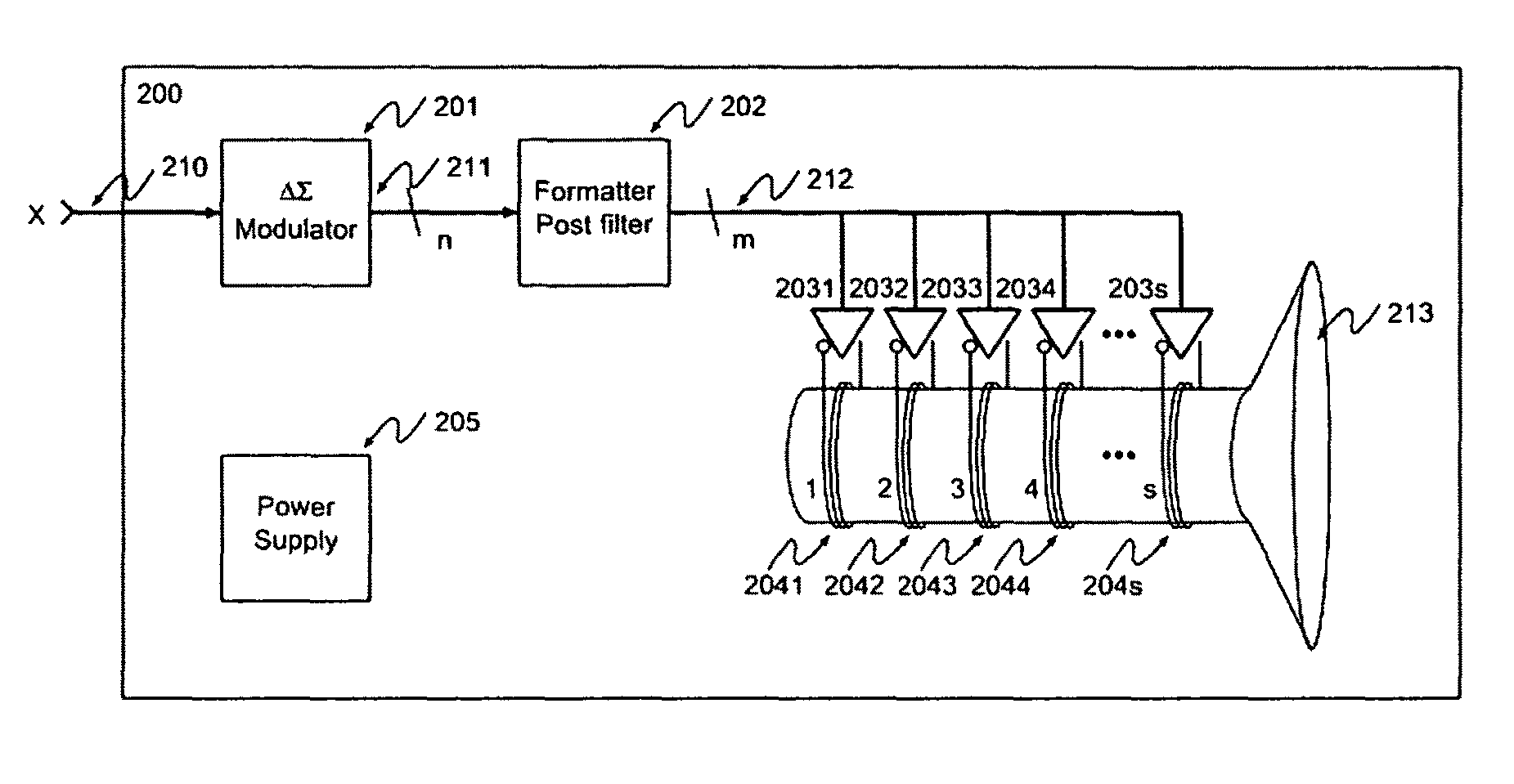

ActiveUS20100239101A1Low costLarge sound pressureDigitally weighted transducing elementsEar treatmentDelta-sigma modulationLoudspeaker

A digital sound system suitable for a digital speaker device for directly converting analog sound by a circuit using a ΔΣ modulator and a mismatch shaping filter circuit to output a plurality of digital signals and a plurality of speakers driven by the plurality of digital signals. A digital speaker driving device includes a ΔΣ modulator, a post filter, s driving circuits, and a power supply circuit to supply power to the ΔΣ modulator, the post filter and the s driving elements and the s driving circuits are adapted to s digital signal terminals.

Owner:TRIGENCE SEMICONDUCTOR INC

Multi-bit Delta-Sigma modulation-based digital speaker system implementation method and device

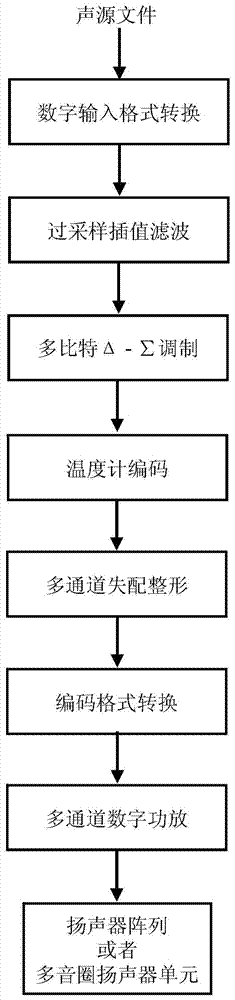

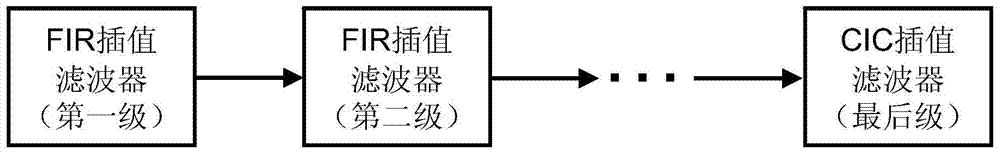

ActiveCN103701465AImprove battery lifeSave electricityDigitally weighted transducing elementsPower amplifiersLow voltageGreek letter sigma

The invention discloses a multi-bit Delta-Sigma modulation-based digital speaker system implementation method and device. The method comprises the following steps: 1) converting digital input formats; 2) performing oversampling interpolation filtering; 3) performing multi-bit Delta-Sigma modulation; 4) encoding a thermometer; 5) performing multi-channel mismatch-shaping; 6) converting encoding formats; 7) performing multi-channel digital power amplification; 8) driving a speaker array or a multi-voice coil speaker unit to phonate. The device comprises a digital input interface, an oversampling interpolation filter, a multi-bit Delta-Sigma modulator, a thermometer encoder, a multi-channel mismatch-shaper, an encoding format converter, a multi-channel digital amplifier, and a speaker array or multi-voice coil speaker unit which are sequentially connected. By adopting the method and the device, the high-power output under low-voltage power supply can be realized; the power consumption is reduced; the single chip integration of a multi-channel playback system is realized; the volume weight and the implementation cost of the system are reduced; the quality of playback voice is improved.

Owner:SUZHOU SONAVOX ELECTRONICS

Digital speaker driving apparatus

ActiveUS8306244B2Low costInhibit deteriorationSignal processingDigitally weighted transducing elementsEngineeringDelta-sigma modulation

A digital sound system suitable for a digital speaker device for directly converting analog sound by a circuit using a ΔΣ modulator and a mismatch shaping filter circuit to output a plurality of digital signals and a plurality of speakers driven by the plurality of digital signals. A digital speaker driving device includes a ΔΣ modulator, a post filter, s driving circuits, and a power supply circuit to supply power to the ΔΣ modulator, the post filter and the s driving elements and the s driving circuits are adapted to s digital signal terminals.

Owner:TRIGENCE SEMICONDUCTOR INC

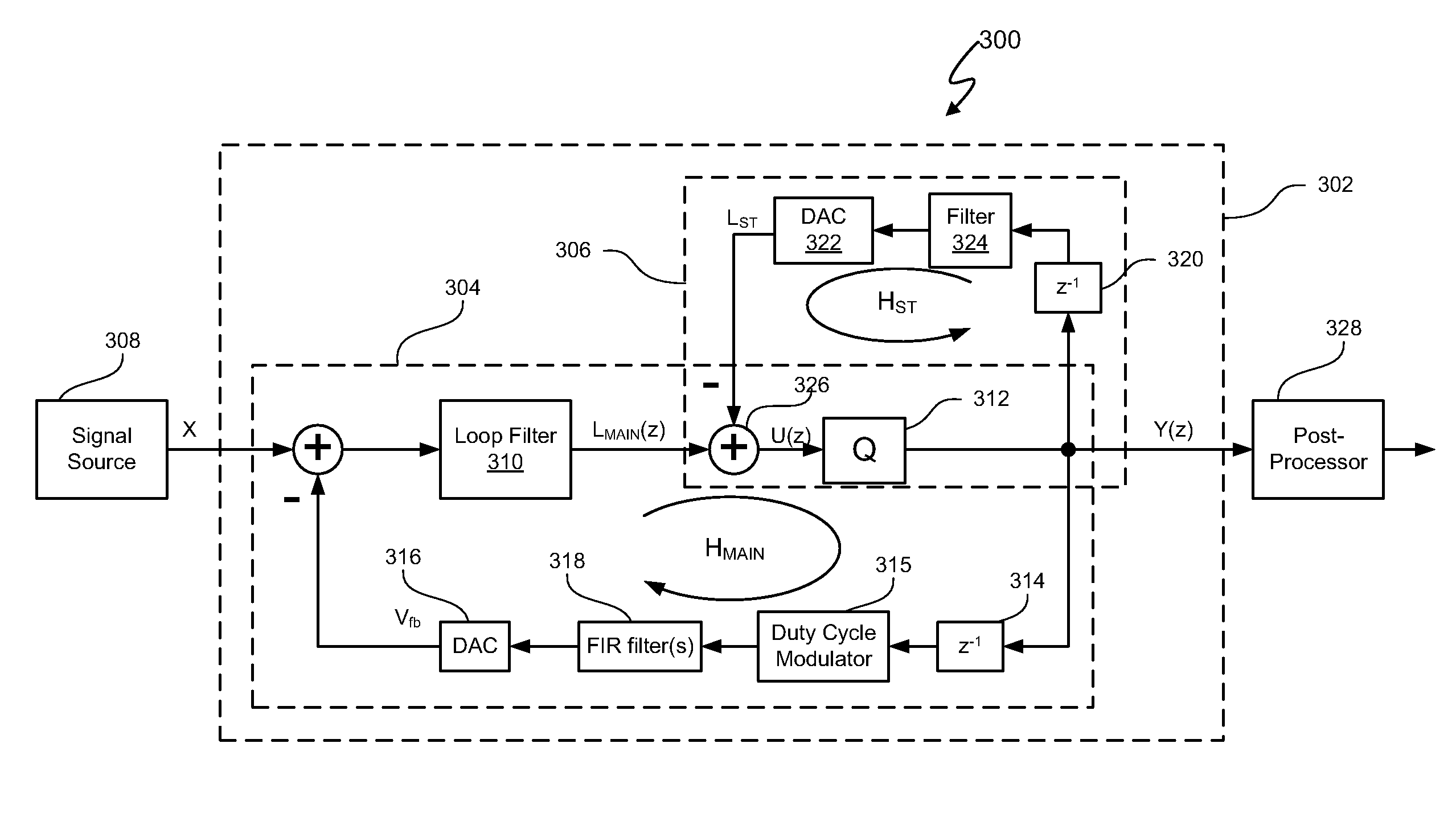

Signal processing system using delta-sigma modulation having an internal stabilizer path with direct output-to-integrator connection

ActiveUS7696913B2Electric signal transmission systemsEfficient power electronics conversionFinite impulse responseLoop filter

A signal processing system includes an analog-to-digital delta sigma modulator with a duty cycle modulator and a finite impulse response (FIR) filter in a main loop feedback path of the delta sigma modulator. The duty cycle modulator and FIR filter can provide high performance filtering in the main loop feedback path. To prevent instability in the main loop caused by the duty cycle modulator and FIR filter, the delta sigma modulator also includes a stabilizer loop. Transfer functions of the main loop and the stabilizer loop combine to achieve a target transfer function for the analog-to-digital delta sigma modulator that provides for stable operation of the analog-to-digital delta sigma modulator. In at least one embodiment, the stabilizer loop includes a stabilizer path that provides output data directly to an integrator of the main loop filter.

Owner:CIRRUS LOGIC INC

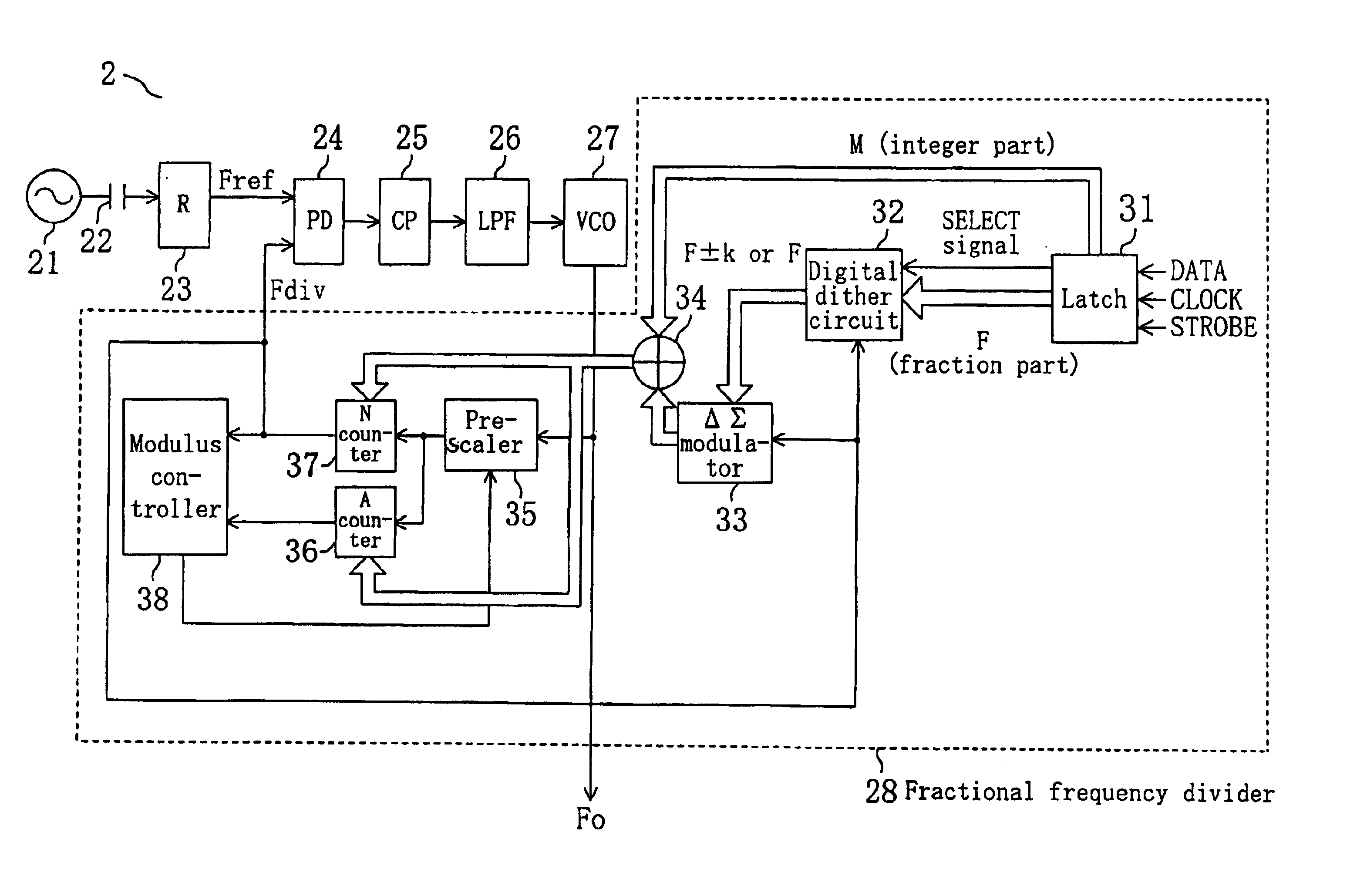

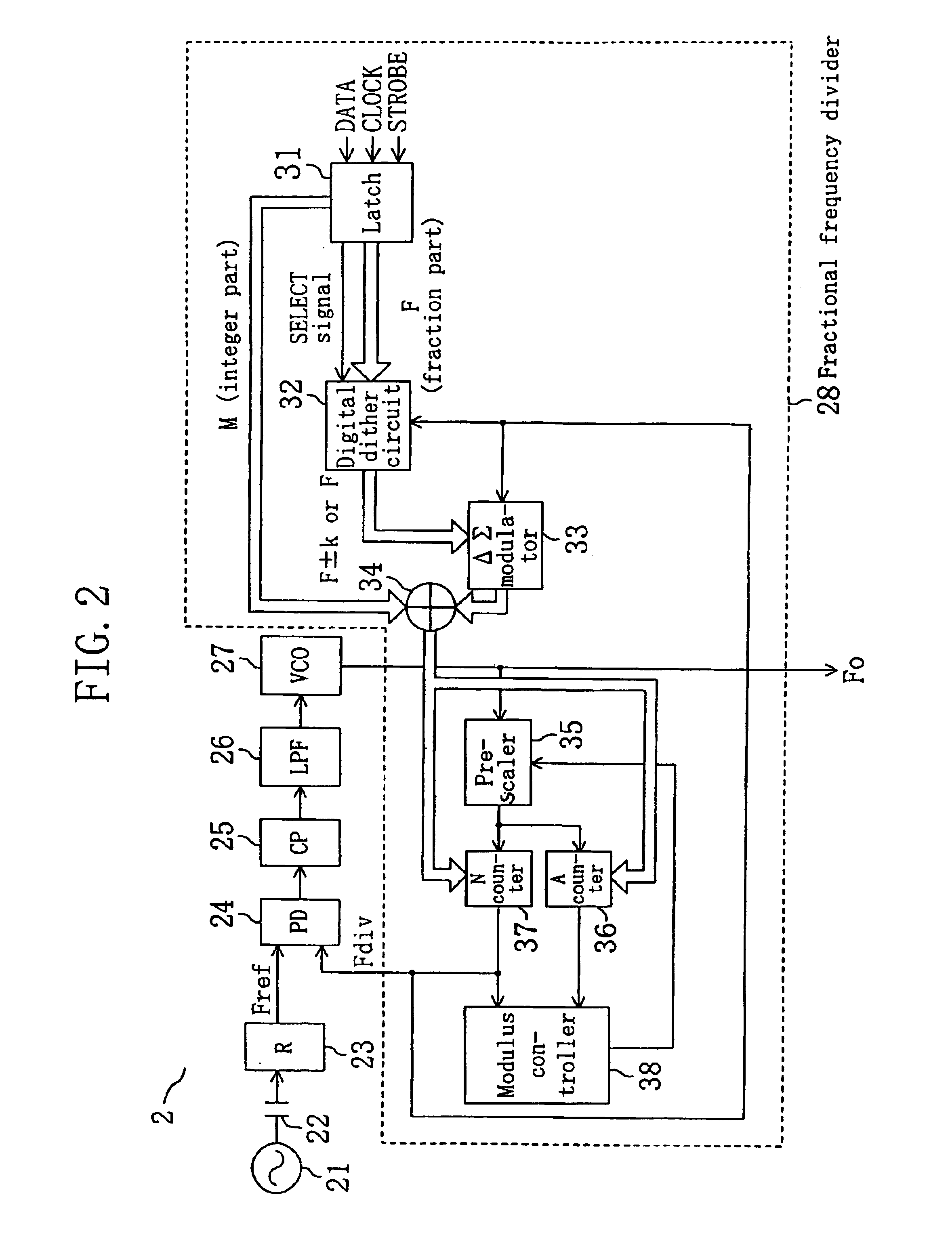

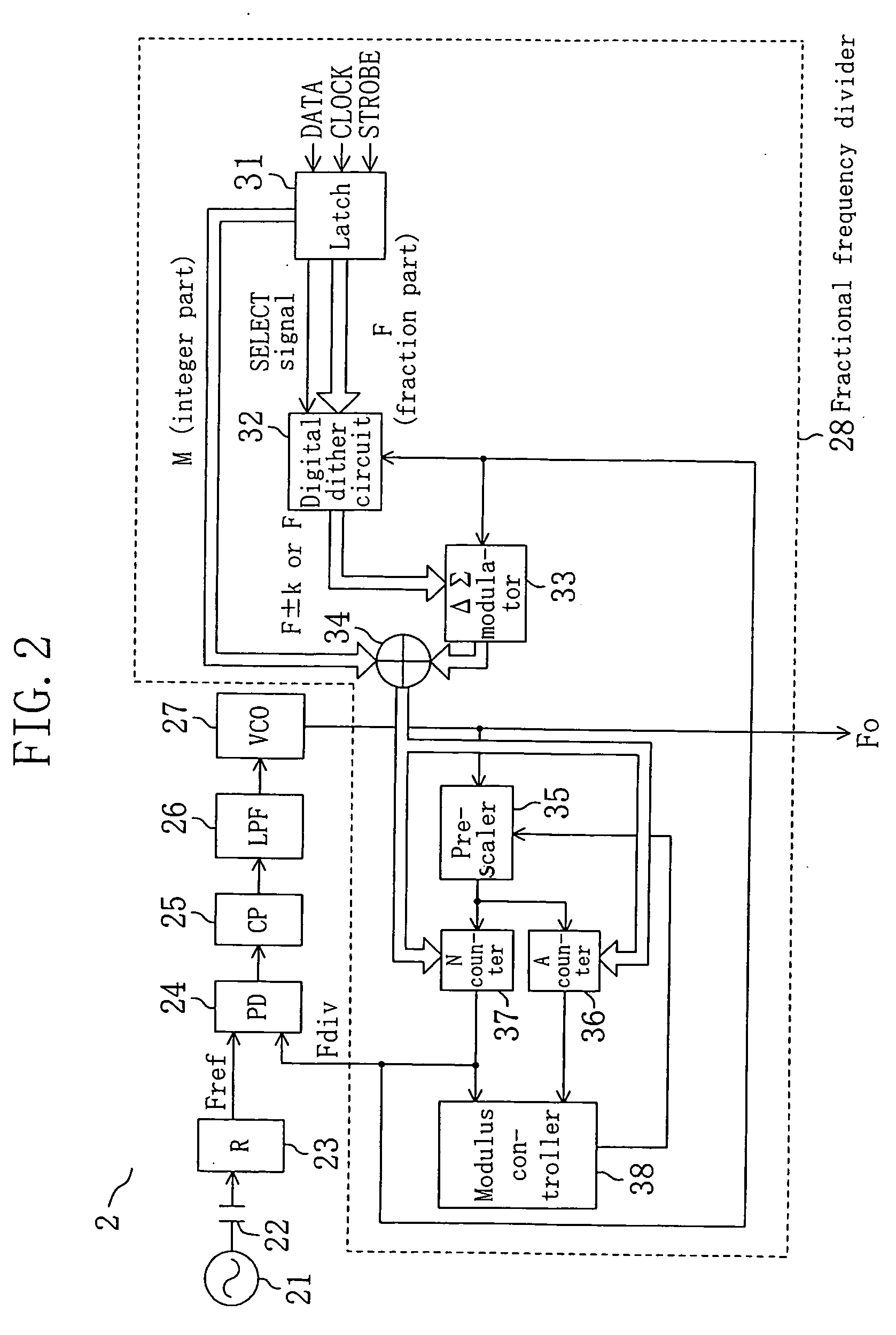

Signal processing device, signal processing method, delta-sigma modulation type fractional division PLL frequency synthesizer, radio communication device, delta-sigma modulation type D/A converter

InactiveUS6917317B2Suppress concentration of quantization noiseSuppress noiseElectric signal transmission systemsPulse automatic controlFrequency synthesizerEngineering

A fractional frequency divider (28) includes a latch (31) for holding frequency division data, a ΔΣ modulator (33), a digital dither circuit (32) for receiving a digital input F representing fraction part of the frequency division data from the latch (31) and supplying a digital output alternately changing between F+k and F−k (where k is an integer) or a F value itself to the ΔΣ modulator (33), and circuit means (34 through 38) for executing fractional frequency division based on integer part (M value) of the frequency division data and an output of the ΔΣ modulator (33). The digital dither circuit (32) is useful for suppressing a spurious signal generated as a result of concentration of quantization noise at a particular frequency when the ΔΣ modulator (33) receives a particular F value (e.g., F=2n−1).

Owner:PANASONIC CORP

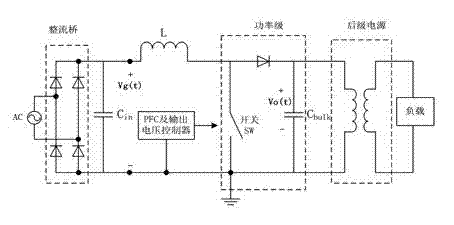

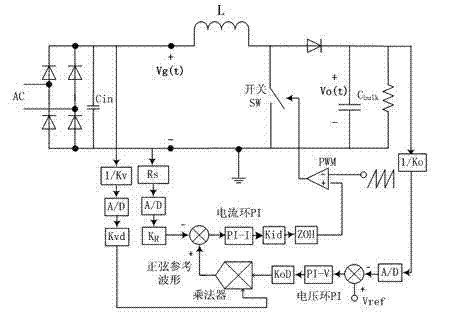

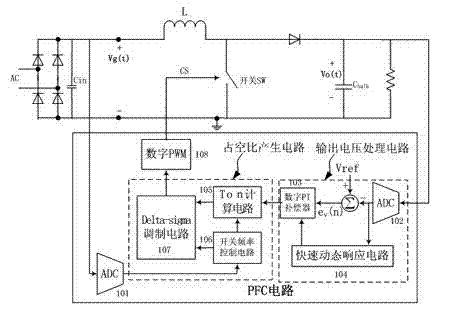

PFC (power factor correction) circuit based on delta-sigma modulation technique and duty ratio control method thereof

InactiveCN102255490AQuick responseIncrease powerEfficient power electronics conversionPower conversion systemsFrequency spectrumActive power factor correction

The invention provides a PFC (power factor correction) circuit based on a delta-sigma modulation technique and a duty ratio control method thereof. The PFC circuit comprises an input voltage ADC (analog to digital converter), a duty ratio generation circuit, an output voltage processing circuit and a digital pulse width modulation circuit in electrical connection, wherein the duty ratio generation circuit comprises a switching frequency control circuit, a Ton counting circuit and a delta-sigma modulation circuit in electrical connection; and the output voltage processing circuit comprises an output voltage ADC, a digital PI (proportional integral) compensator and a rapid dynamic response circuit in electrical connection. The delta-sigma modulation technique is utilized in the PFC circuit to realize the duty ratio control method. According to the invention, the response speed of the input voltage change can be improved, the iL waveform of the input inductive current is adjusted, the frequency spectrum of the pulse width signal is shaped, the power factor is improved and the output voltage is stabilized.

Owner:佛山市南海赛威科技技术有限公司

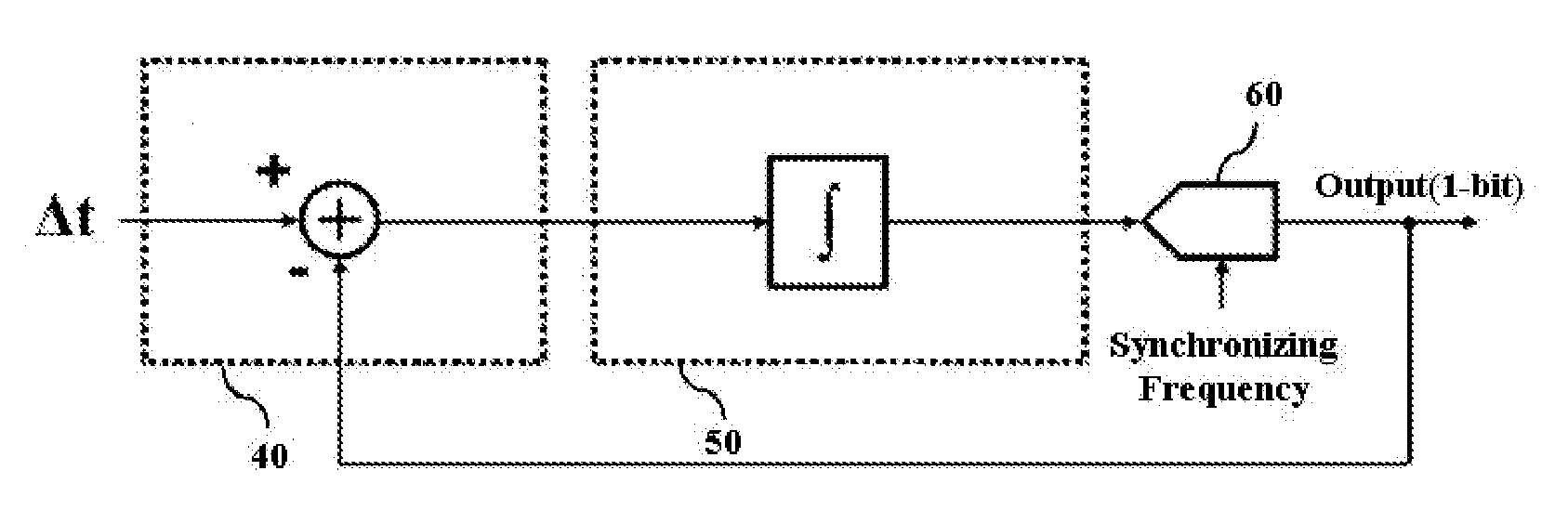

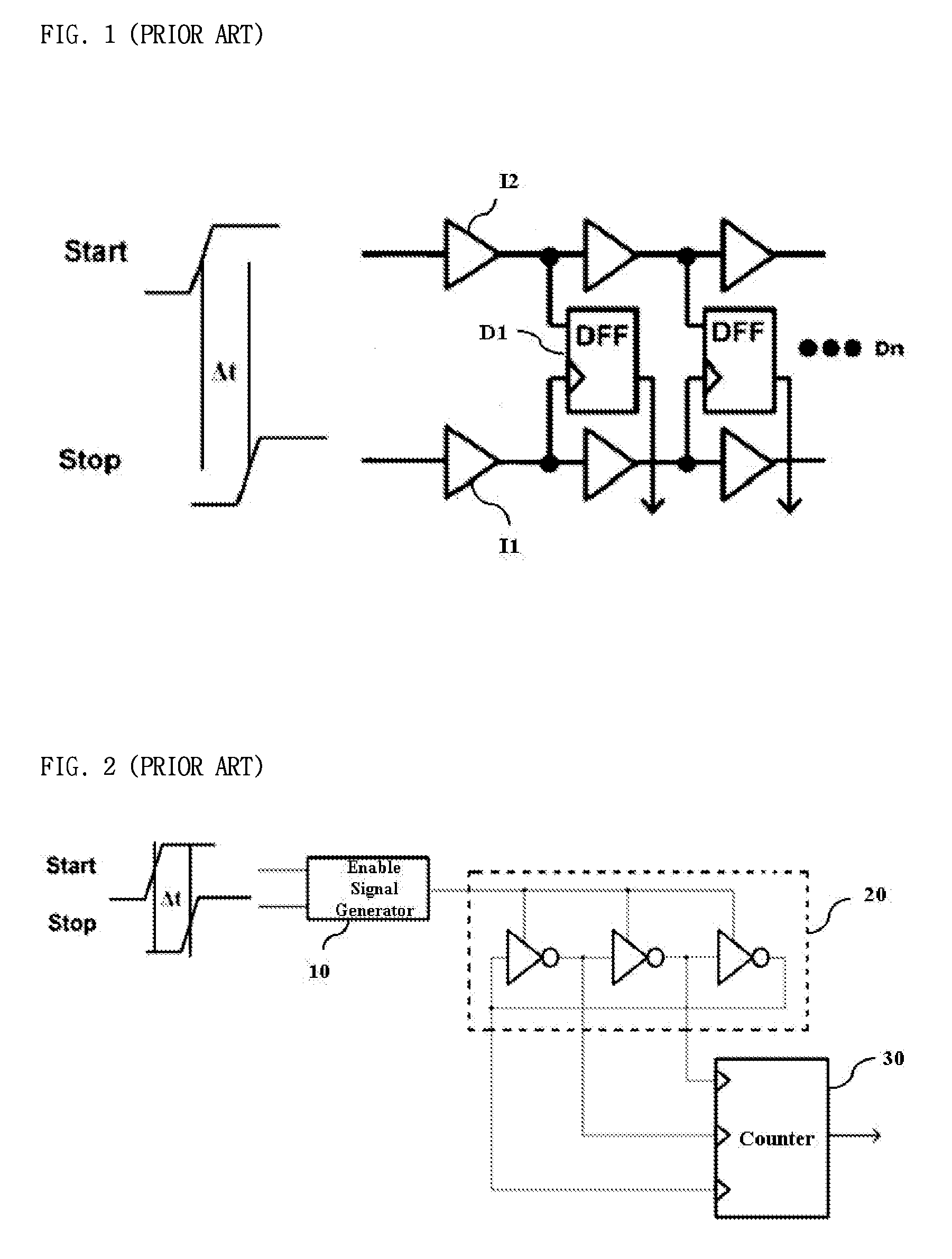

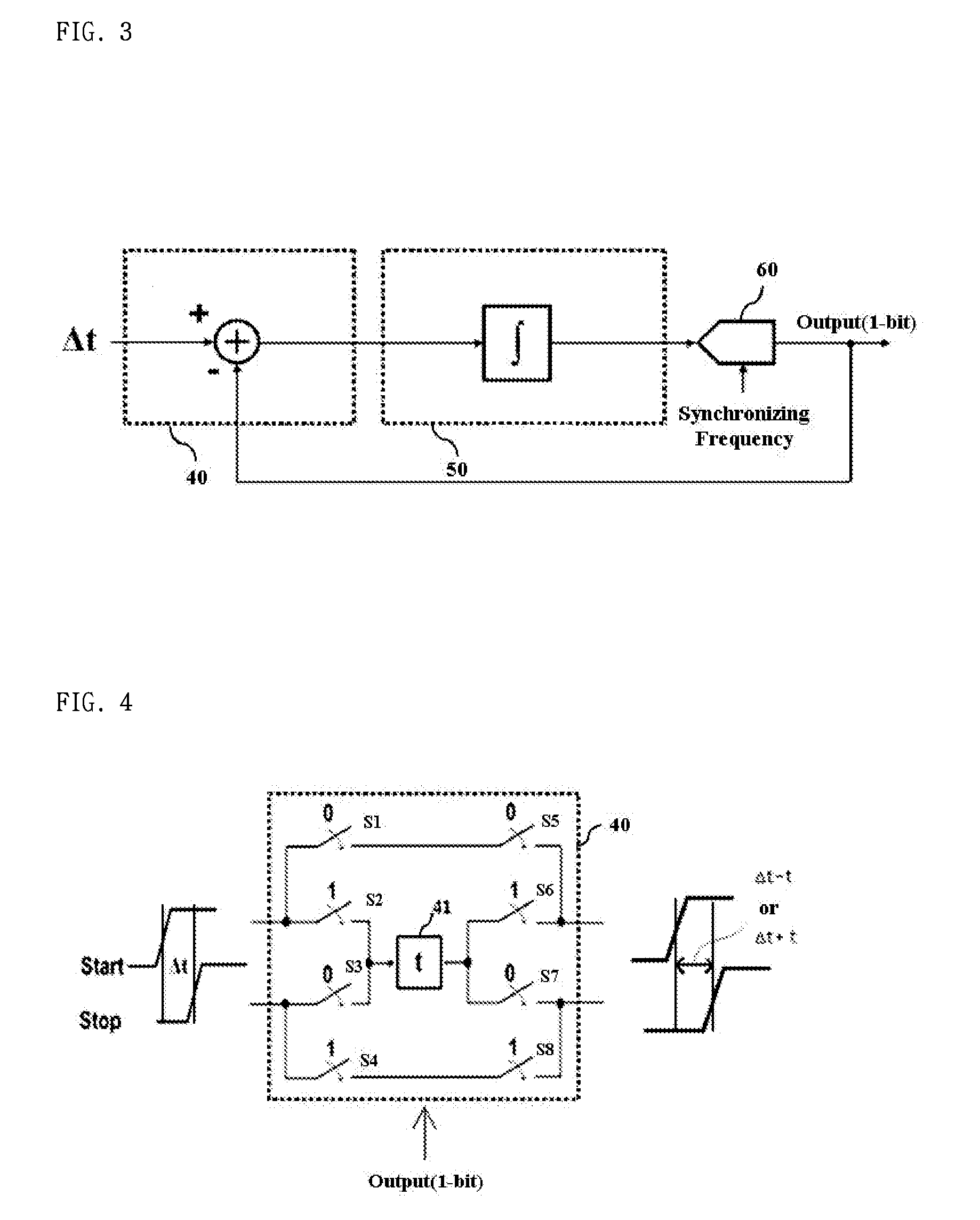

Noise-shaping time to digital converter (TDC) using delta-sigma modulation method

InactiveUS8421661B1Electric signal transmission systemsDelta modulationDigital down converterDelayed time

The present invention relates to a time digital converter, and more particularly, to a noise-shaping time to digital converter (TDC) that has a 1-bit output and uses a delta-sigma modulation method. The noise-shaping time to digital converter (TDC) that has the 1-bit output and uses the delta-sigma modulation method in accordance with the present invention eliminates the need for a large number of D flip-flops or counters and a plurality of delay units connected in series to one another because the time to digital converter is fabricated such that a delay element has a resolution of the effective delay time in a semiconductor process, unlike the conventional time to digital converter. Therefore, the time to digital converter of the present invention has an advantage in that an extremely high resolution and high linearity can be achieved with an efficient circuit configuration and low power consumption.

Owner:POSTECH ACAD IND FOUND

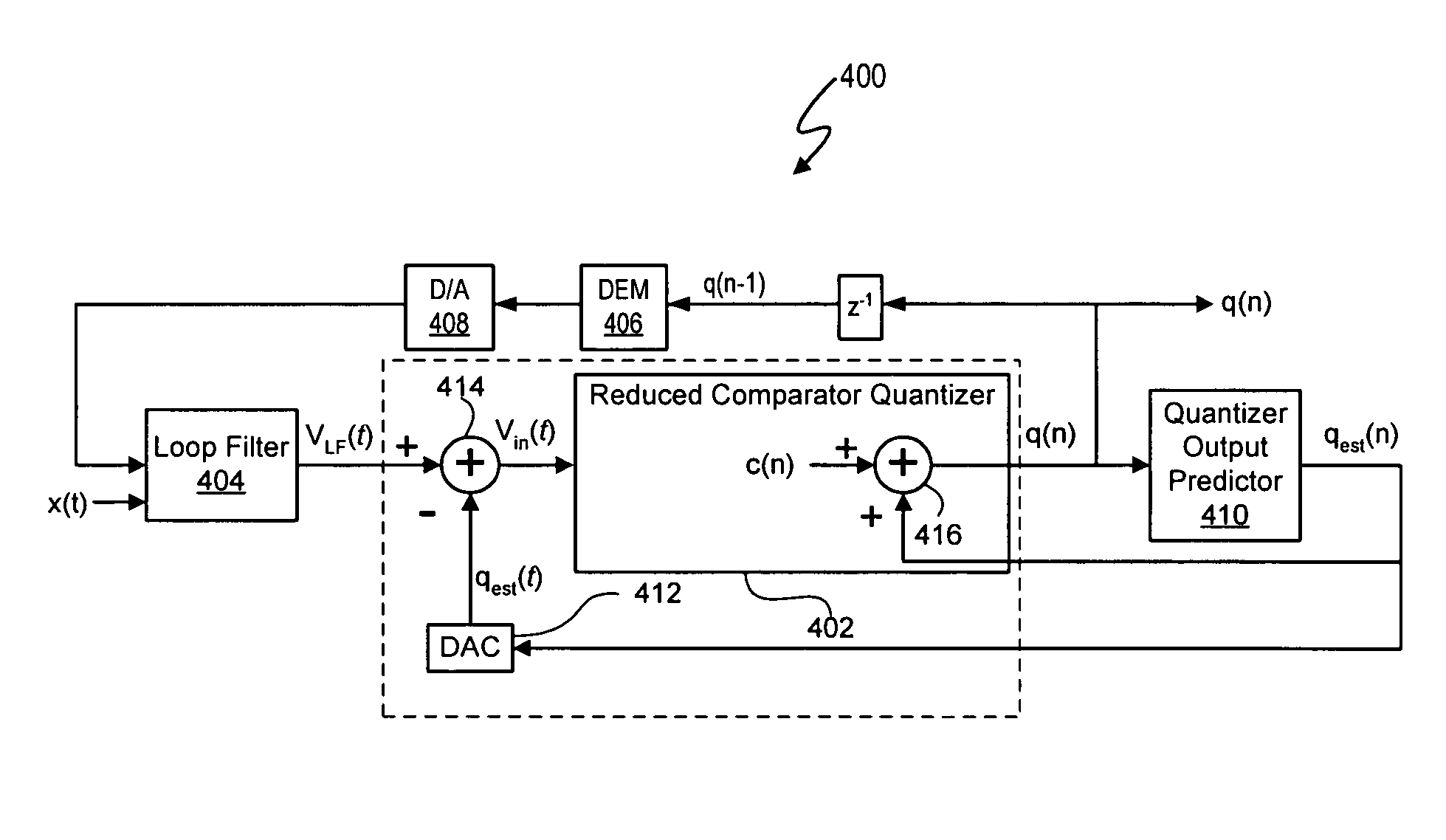

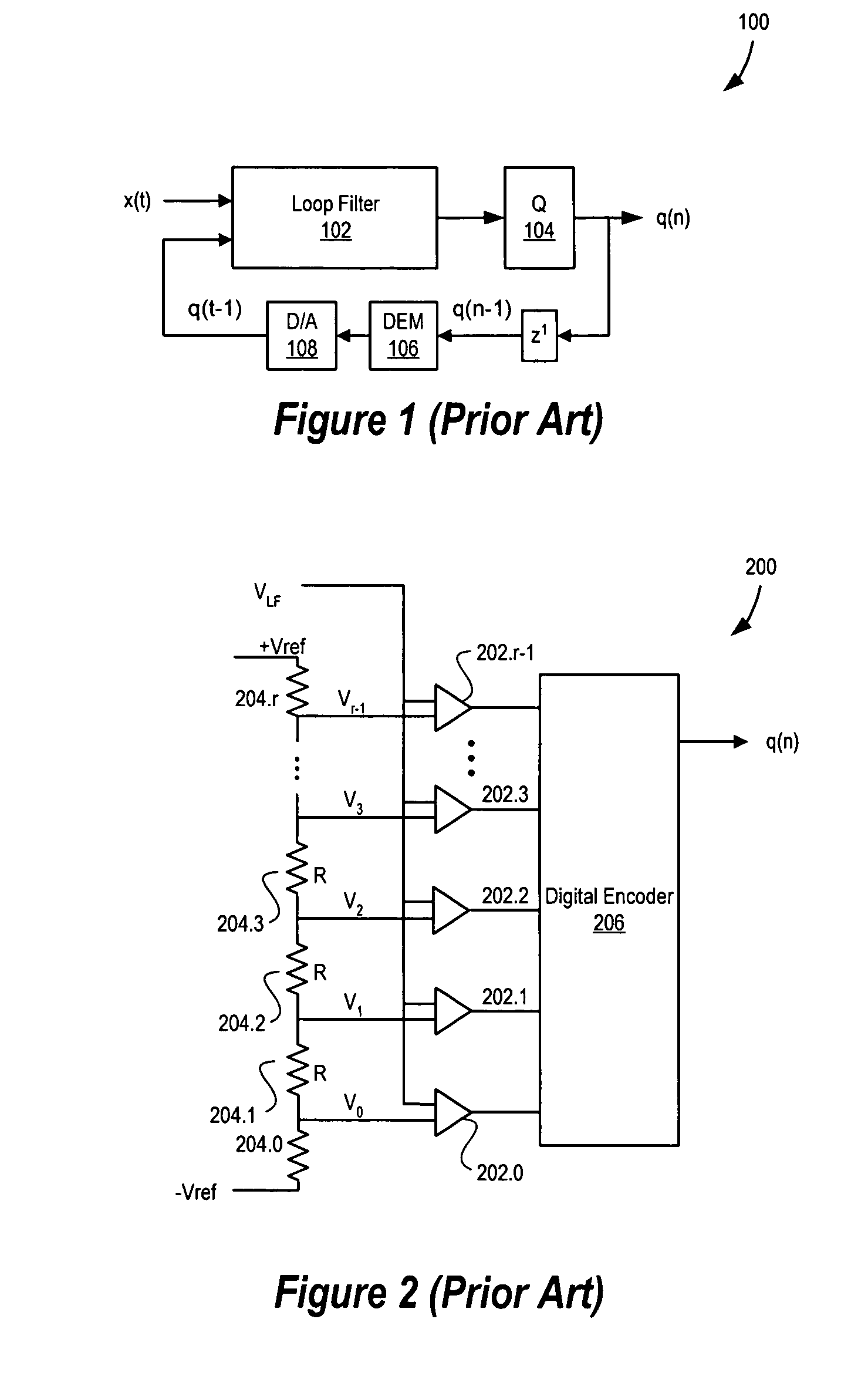

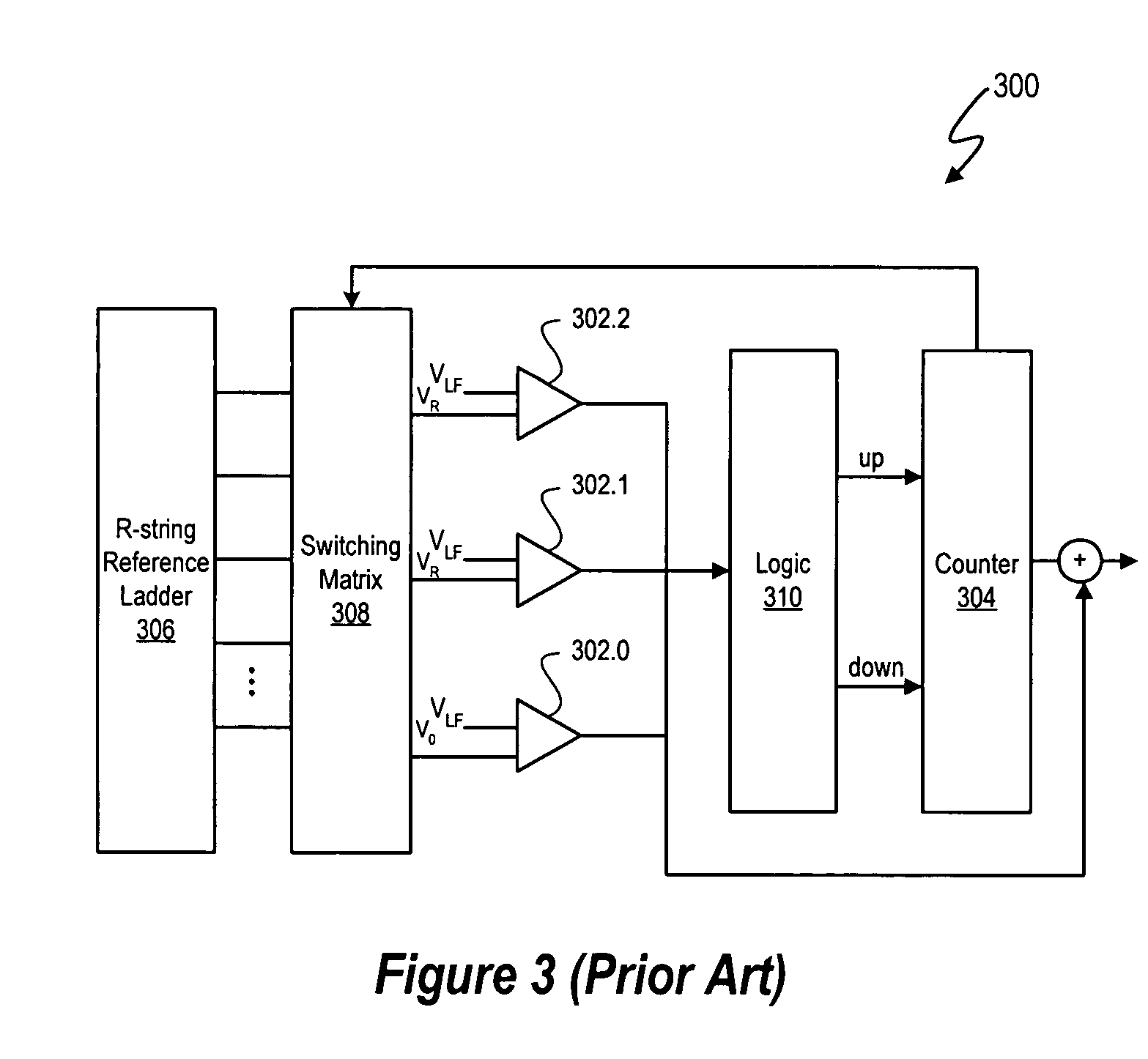

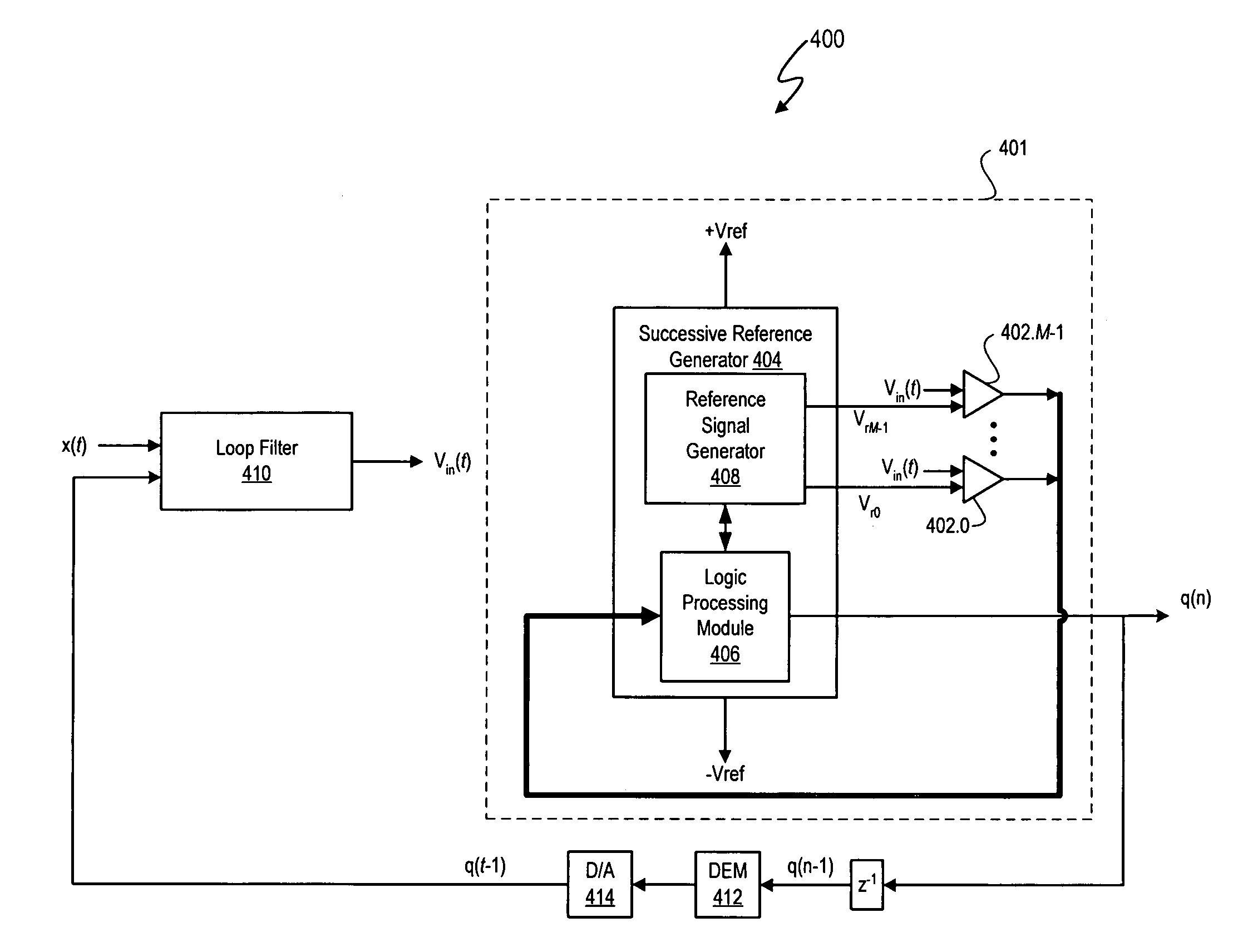

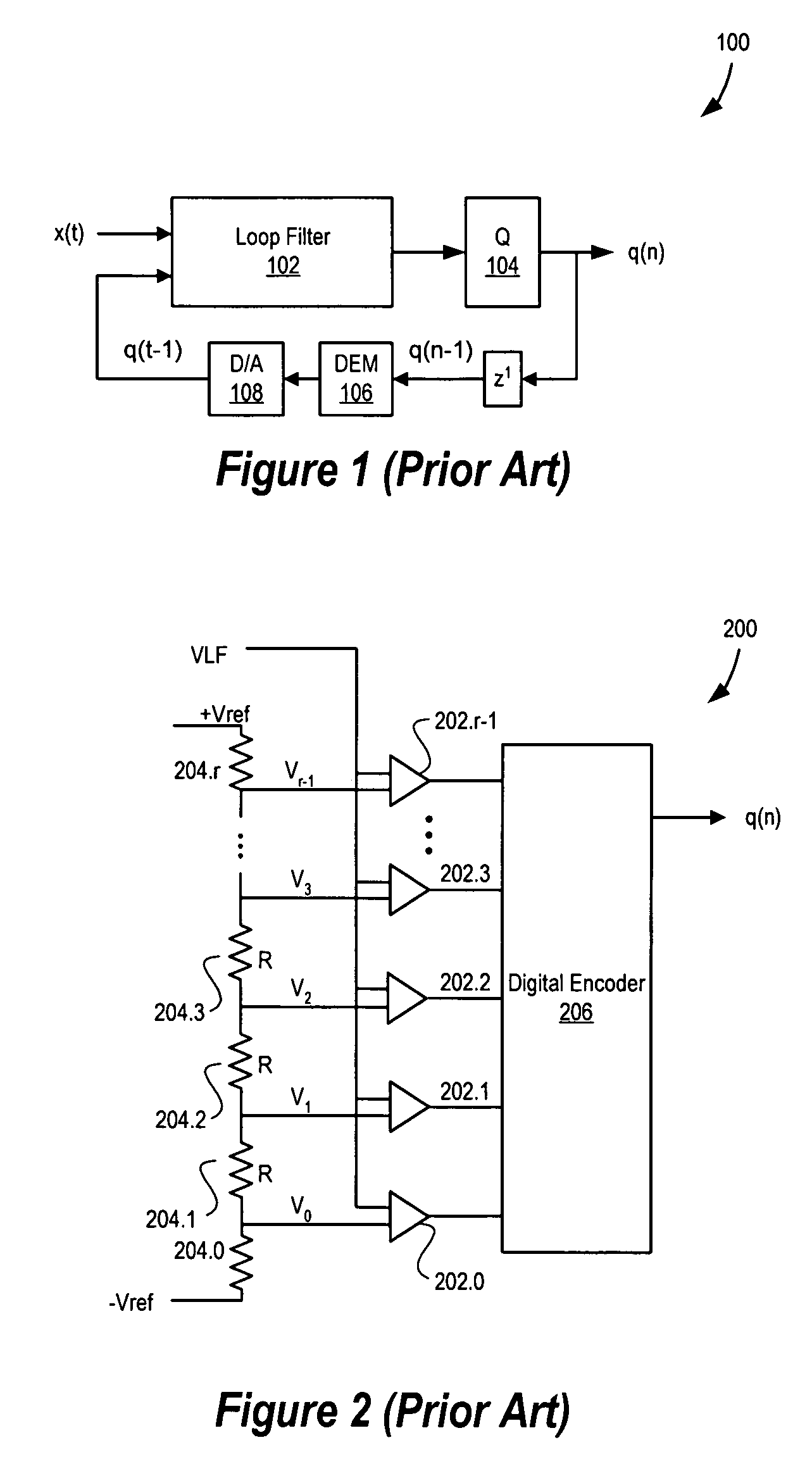

Delta sigma modulator analog-to-digital converters with quantizer output prediction and comparator reduction

ActiveUS7298305B2Reduce settingsElectric signal transmission systemsSpeech analysisLoop filterA d converter

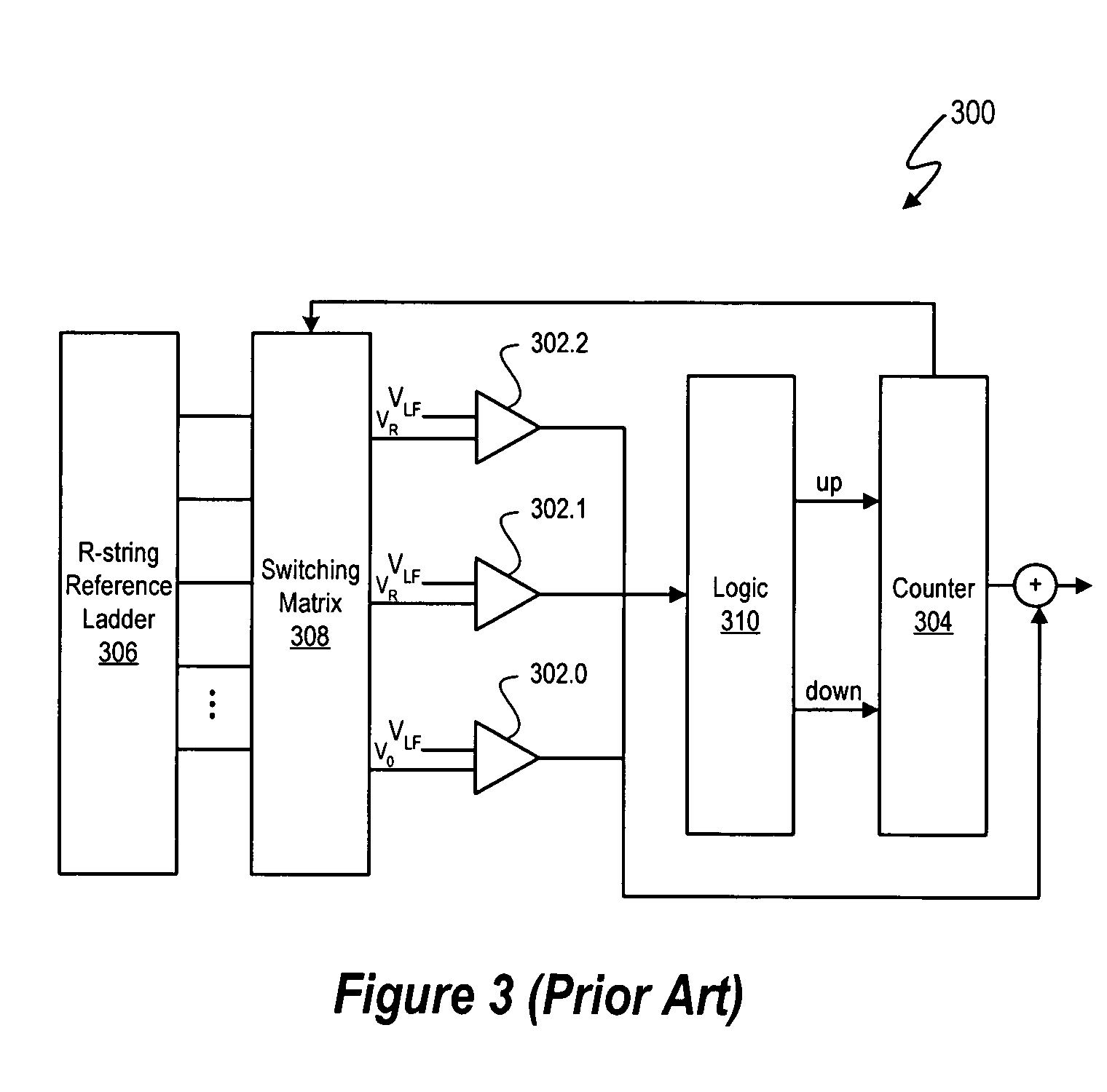

The quantizers of delta sigma modulators in the signal processing systems described herein use a reduced set of comparators for quantization by predetermining and maintaining a maximum per cycle deviation d between a loop filter output signal VLF(t) and a predicted quantizer output signal qest. In at least one embodiment, a maximum quantizer level deviation d is defined in terms of a number of quantization levels. Thus, the number of comparators in a quantizer needed to quantize the quantizer input signal Vin(t) is based on the maximum quantizer level deviation d. In addition to using fewer comparators than available quantization output levels N, the quantizers can use an even number of comparators M, in contrast to comparable conventional reduced comparator ADC tracking quantizer designs using M+1 number of comparators, where N and Mare integers and M<N.

Owner:CIRRUS LOGIC INC

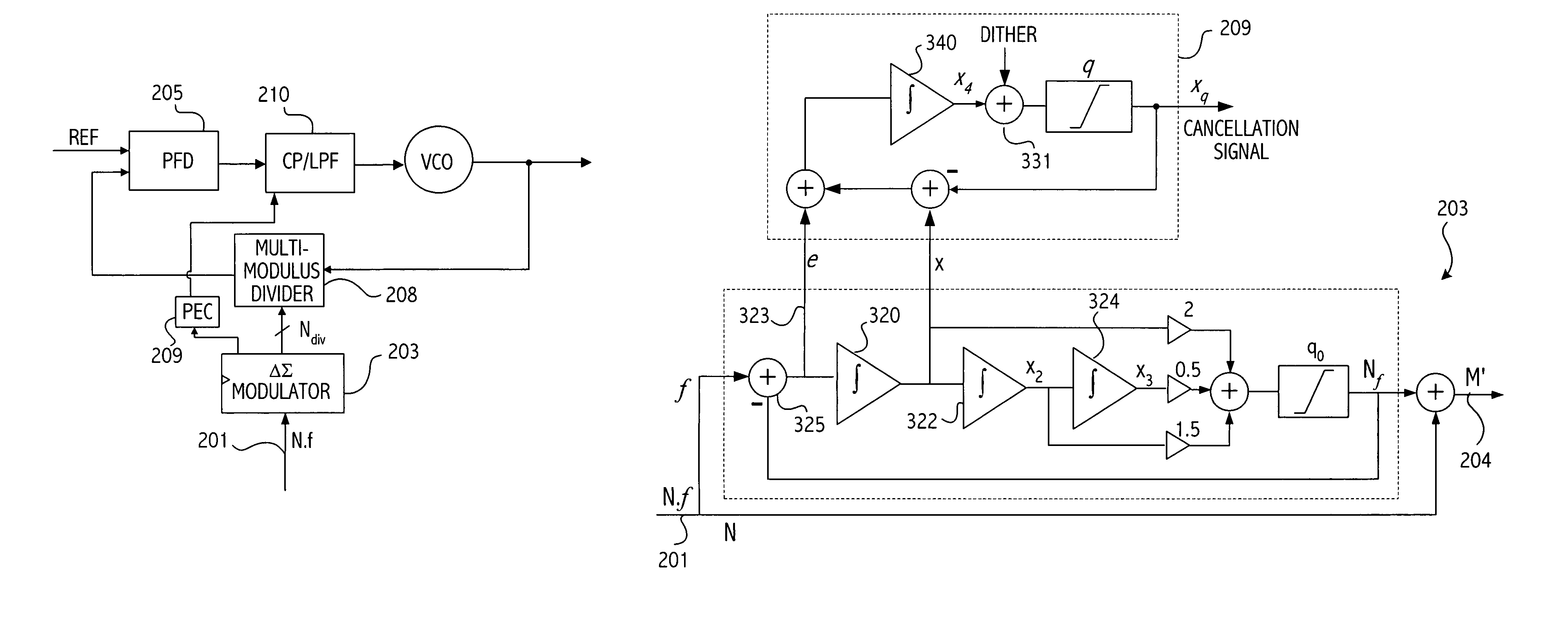

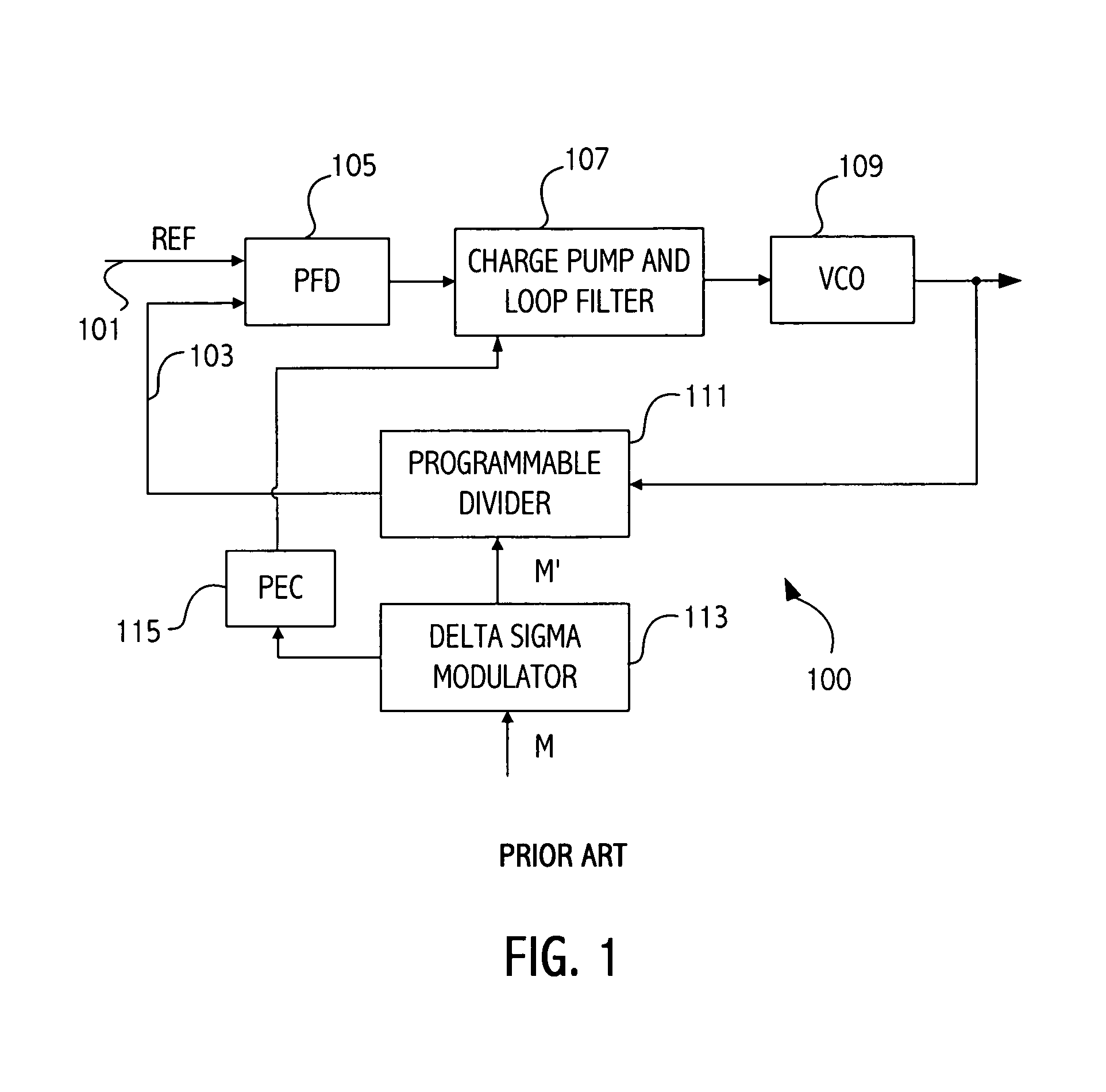

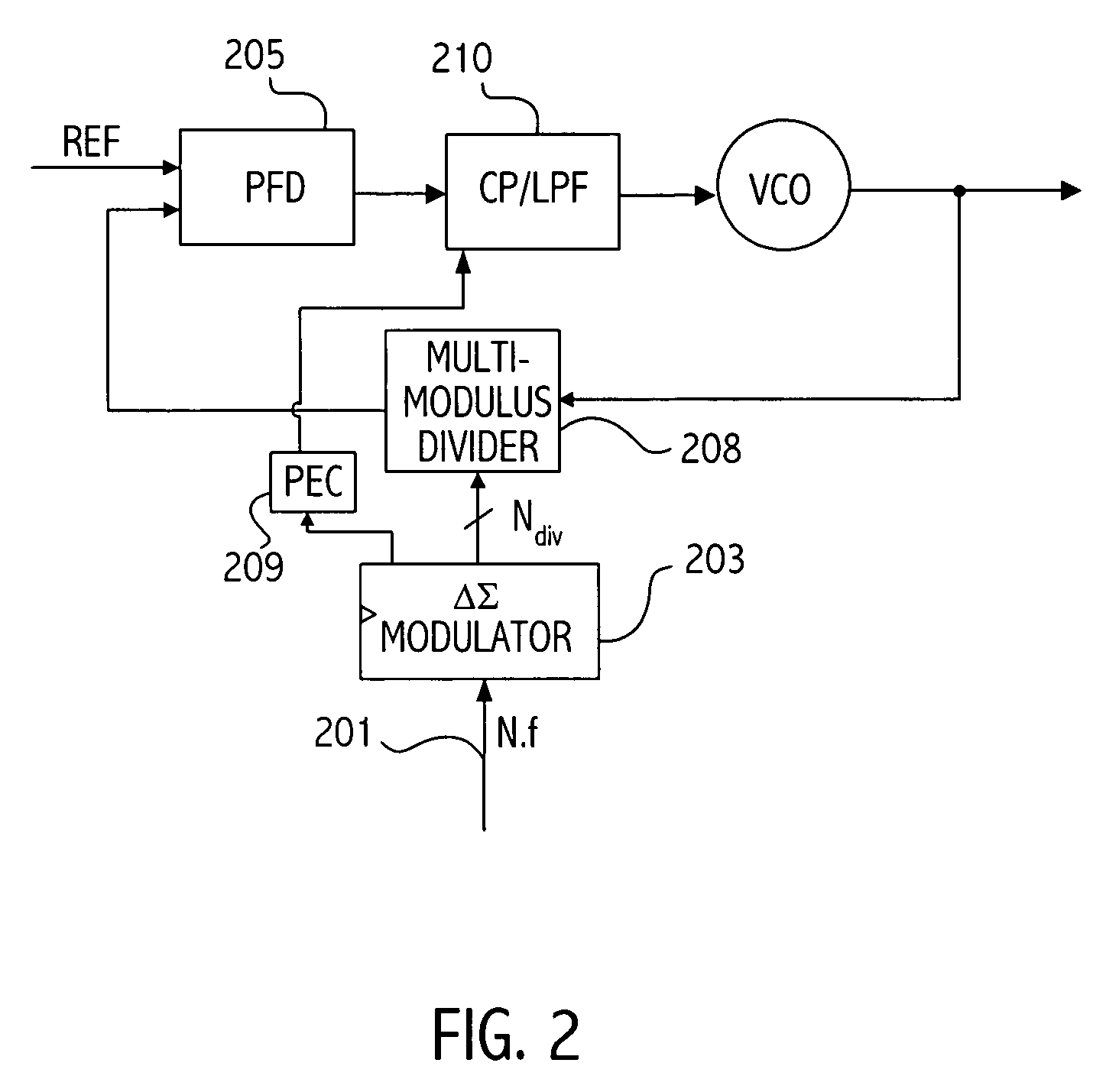

Phase error cancellation

A noise cancellation signal is generated for a fractional-N phase-locked loop by supplying a divide value to a first delta sigma modulator and generating a divide control signal in a first delta sigma modulator to control a divide value of a feedback divider in the phase-locked loop. The first delta sigma modulator integrates an error term indicative of a difference between a value of the generated divide control signal and the divide value supplied to the first delta sigma modulator. A phase error cancellation signal is generated by quantizing the integrated error term using a second delta sigma modulator. The error term can be used by the second delta sigma modulator while quantizing the integrated error term, thereby limiting the low pass filter effects of the second delta sigma modulator in the cancellation signal.

Owner:SKYWORKS SOLUTIONS INC

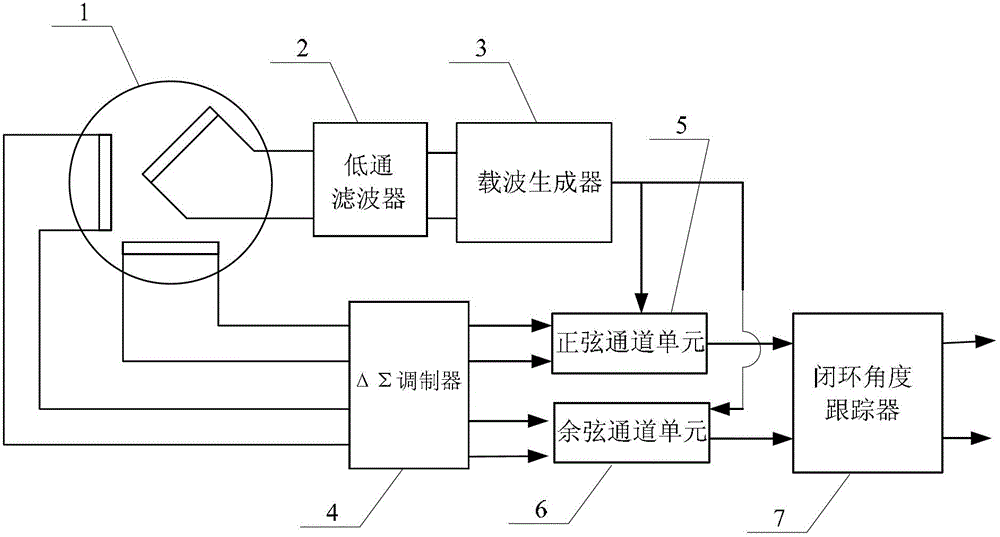

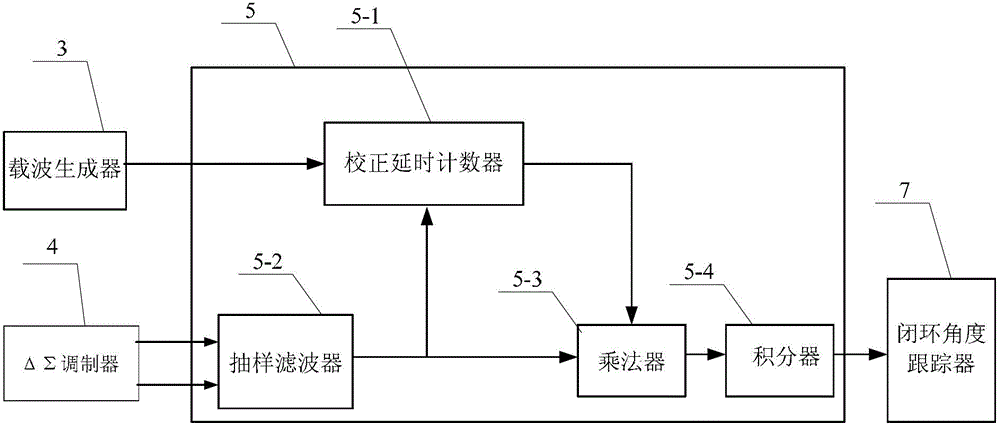

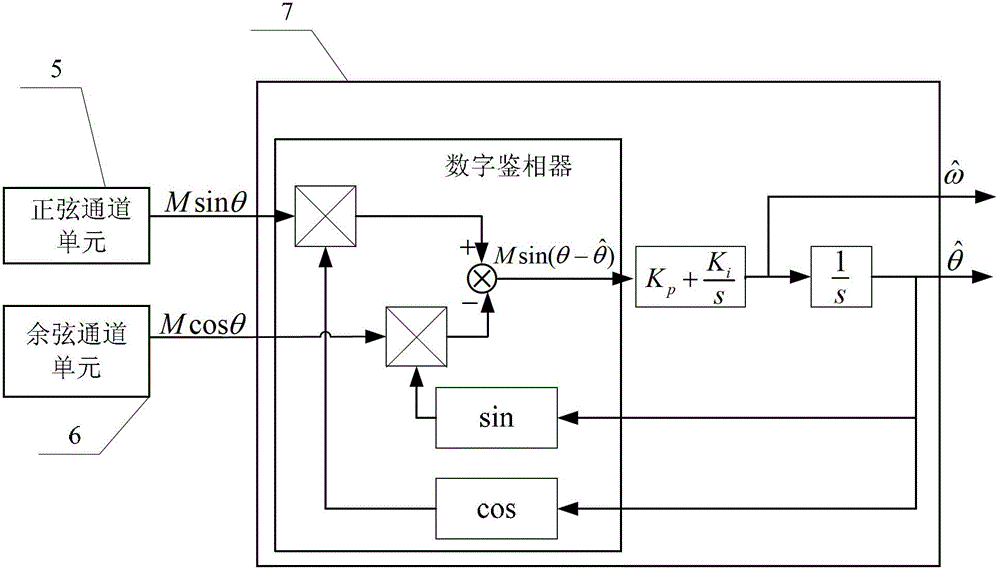

Delta-Sigma modulation principle based digital switching device and method for rotary transformer

InactiveCN102751991AReal-time digital conversionLow costAnalogue-digital convertersLow-pass filterCarrier signal

The invention provides a Delta-Sigma modulation principle based digital switching device and method for a rotary transformer, which belongs to the technical field of digital switching of a rotary transformer output signal, and solves the current problems of digitally converting an analog signal outputted by the rotary transformer by means of calculation with a specialized chip and the high cost. The device comprises a rotary transformer, and also includes a low pass filter, a carrier wave generator, a Delta-Sigma modulator, a sine channel unit, a cosine channel unit and a closed loop angle tracker. The method includes the steps of converting the analog signal returned by the rotary transformer to a digital signal based on the Delta-Sigma A / D converter with an oversampling principle, wherein the digital signal has a delay correcting function, multiplying the digital signal being sampled and filtered with a delay marking signal to compensate the whole system, calculating the inputted signal by the closed loop angle tracker, and obtaining an angle signal and an angular speed signal of the motor measured by the rotary transformer. The device and the method provided by the invention are suitable for the digital conversion of the signals outputted by the rotary transformer.

Owner:HARBIN INST OF TECH

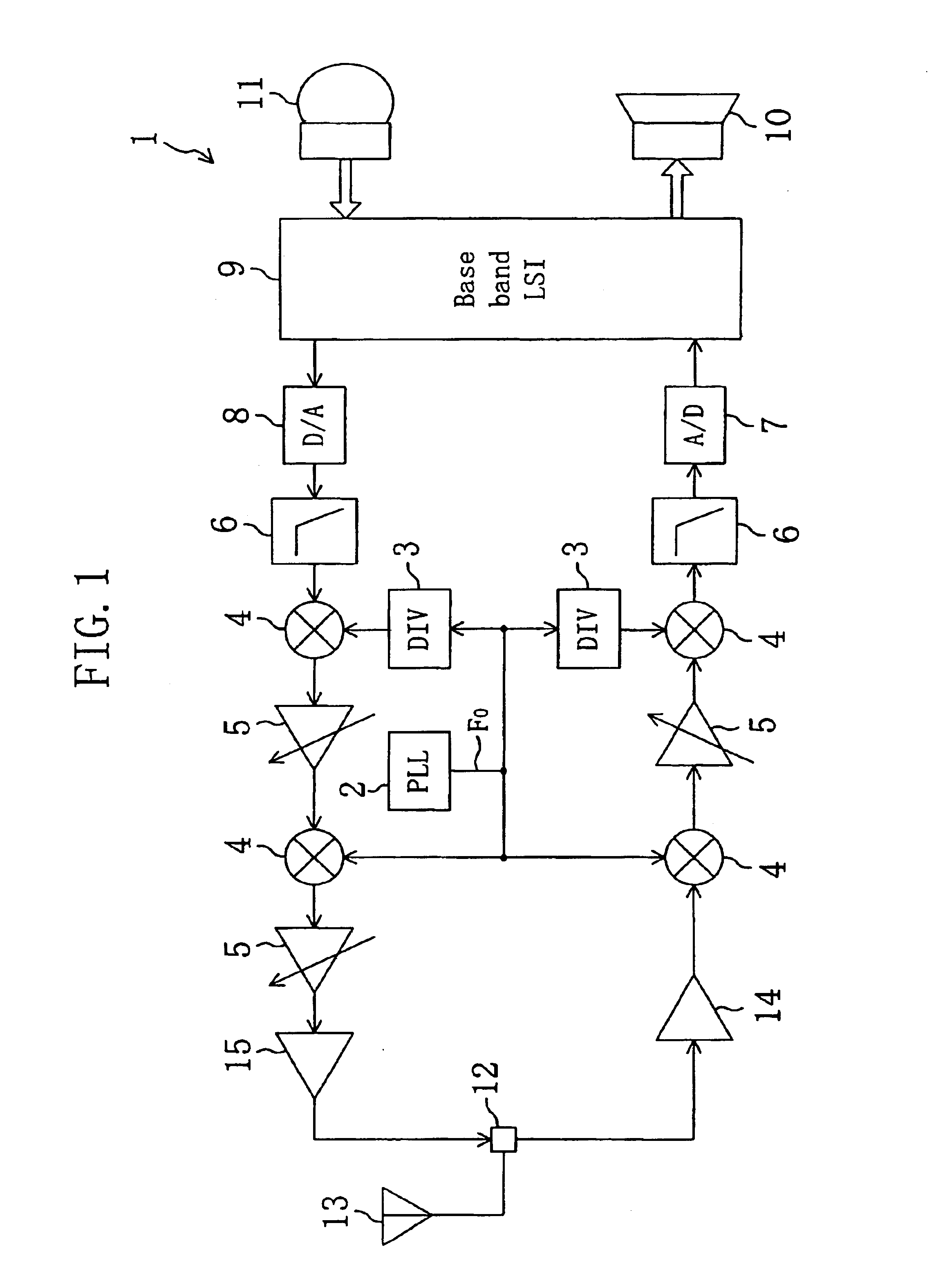

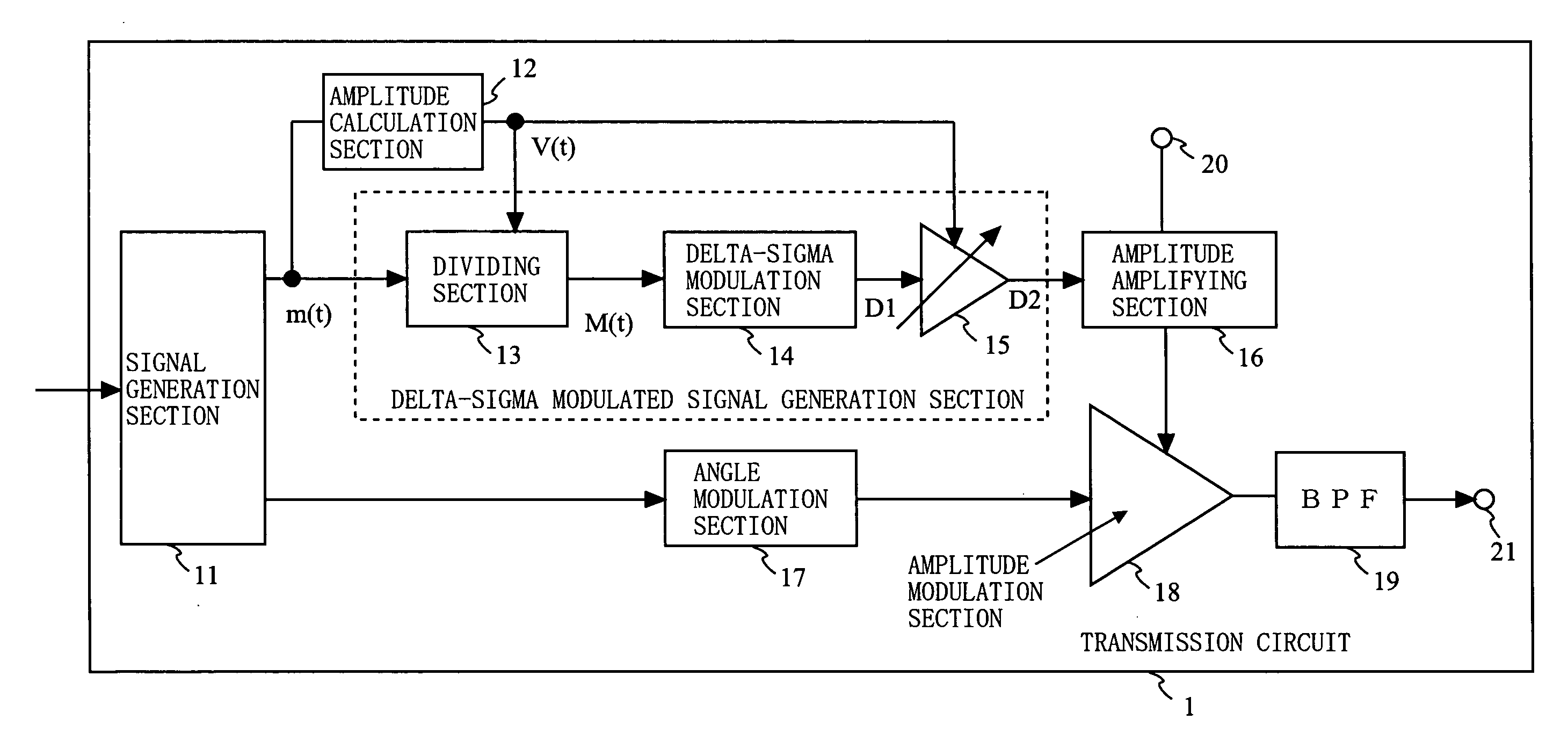

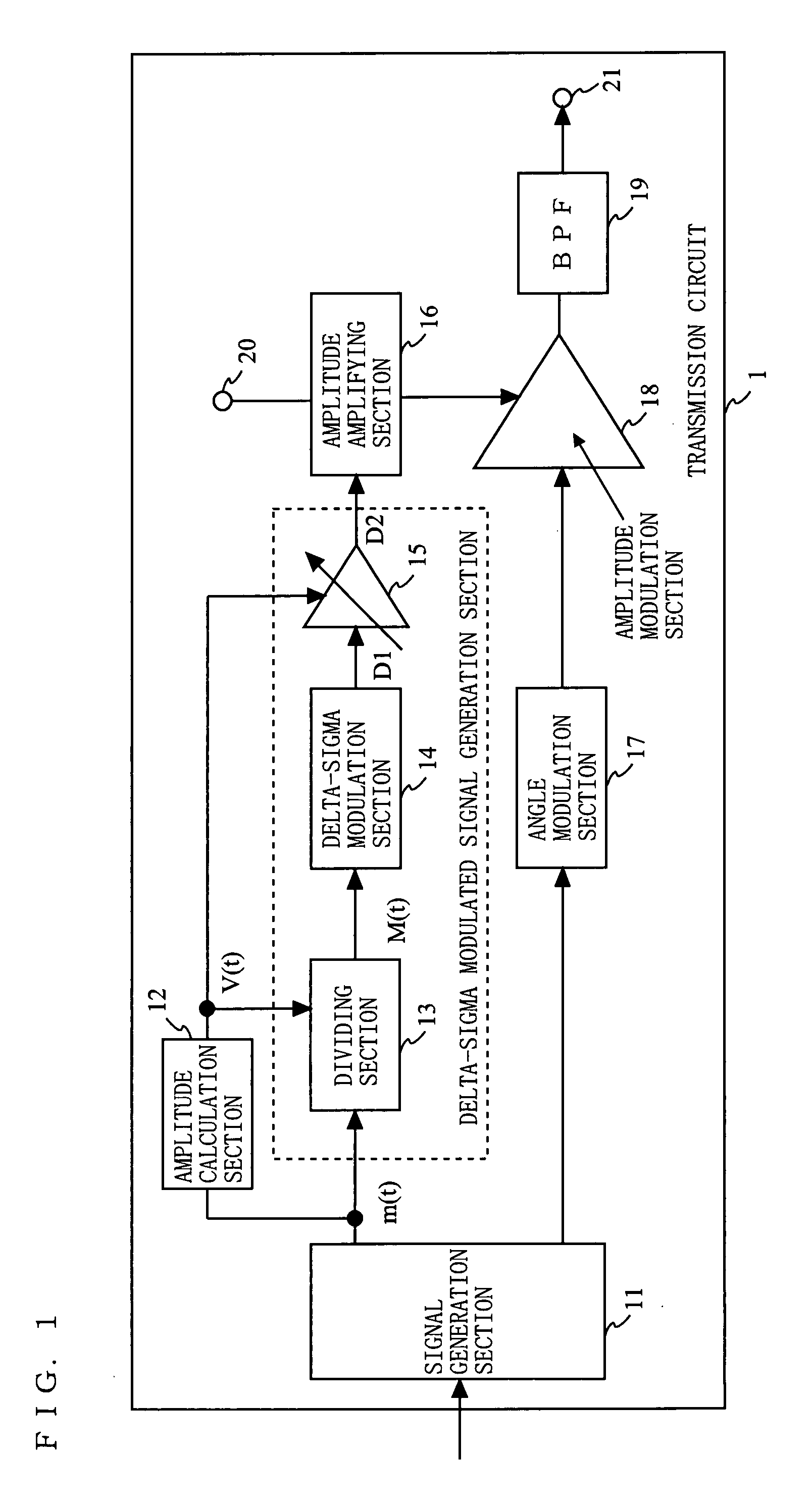

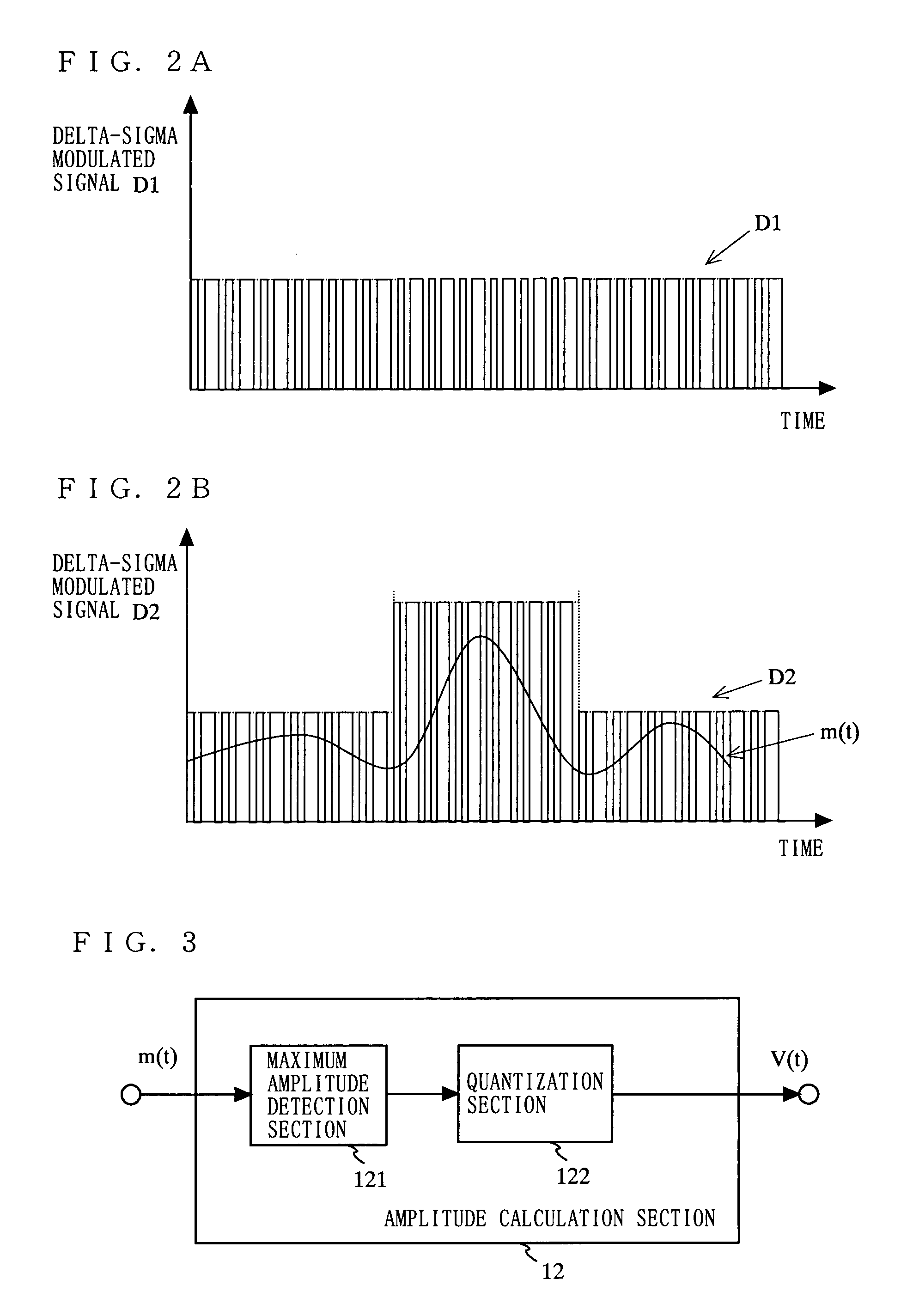

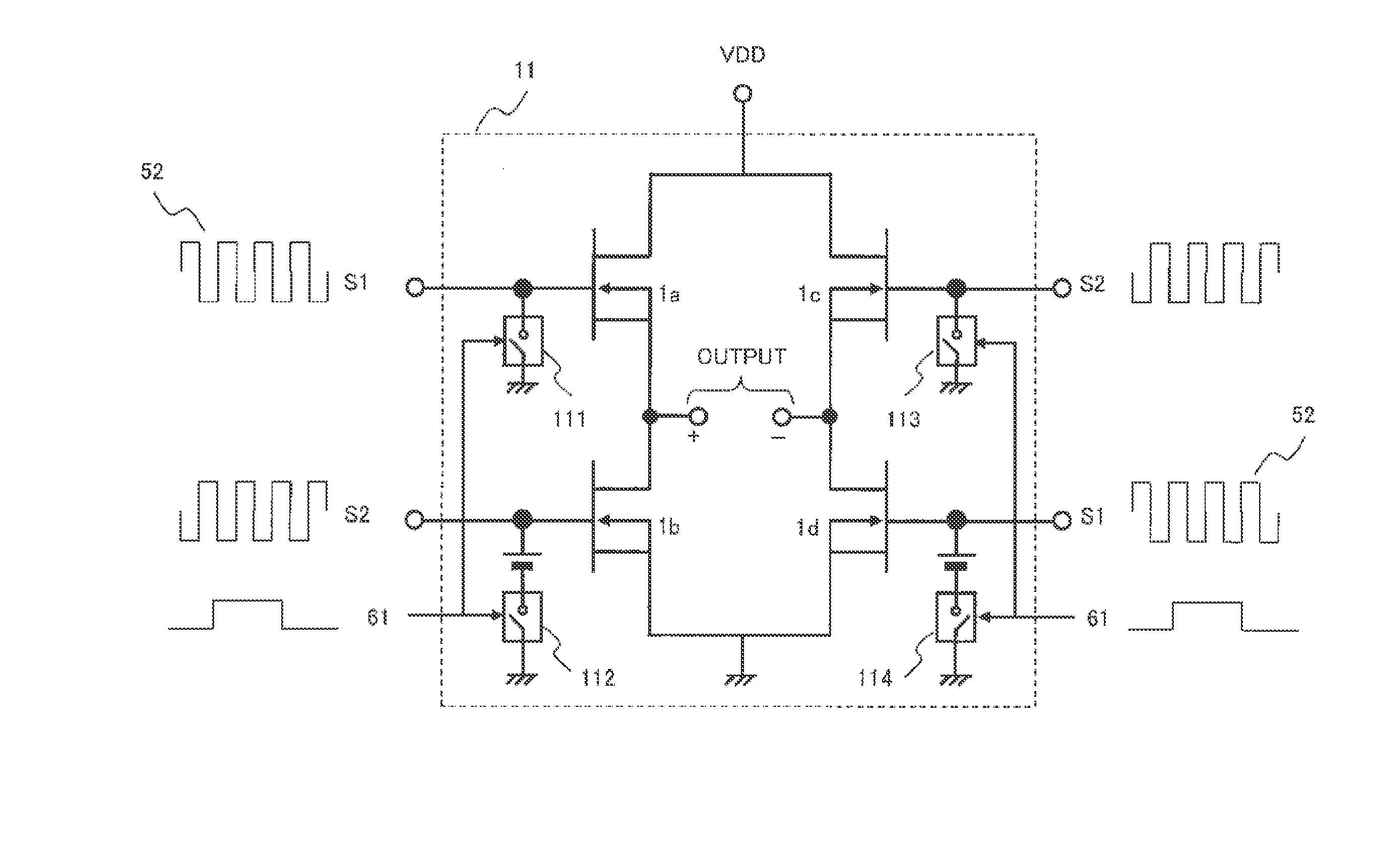

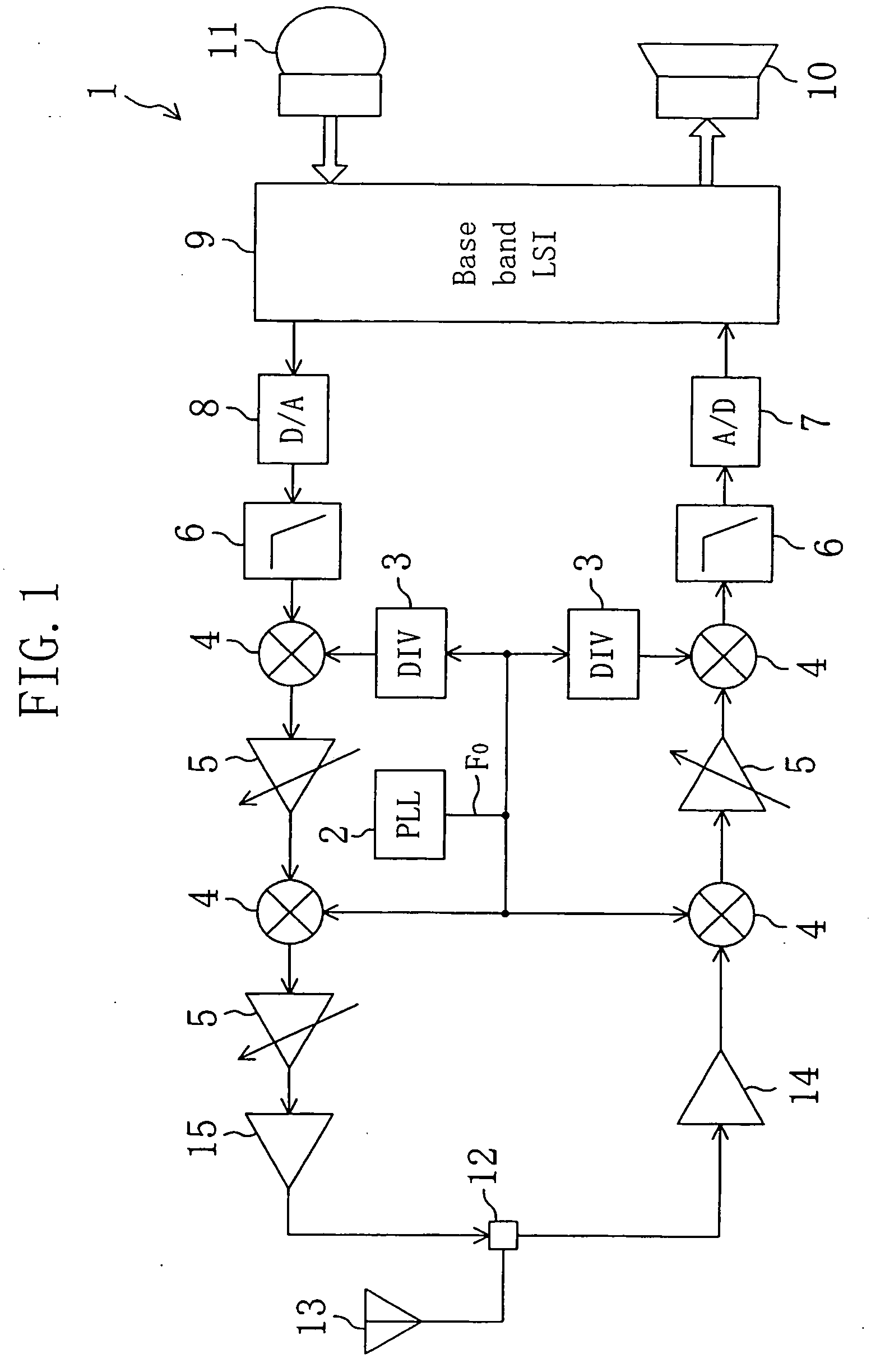

Transmission circuit and communication device

ActiveUS20080068240A1Small sizeImprove efficiencyHigh frequency amplifiersModulation with suppressed carrierAudio power amplifierVariable-gain amplifier

Provided is a transmission circuit which is small in size, operates with high efficiency, and outputs a transmission signal having high linearity. A signal generation section 11 generates an amplitude signal m(t) and a phase signal. An angle modulation section 17 angle-modulates the phase signal to output an angle-modulated signal. An amplitude calculation section 12 outputs a discrete value signal V(t) having a plurality of discrete values corresponding to a magnitude of the amplitude signal m(t). A dividing section 13 divides the amplitude signal m(t) by the discrete value signal V(t) to output an amplitude signal M(t). A delta-sigma modulation section 14 delta-sigma modulates the amplitude signal M(t) to output a delta-sigma modulated signal. A variable gain amplifier section 15 amplifies the delta-sigma modulated signal by a gain corresponding to the discrete value signal V(t). An amplitude amplifying section 16 supplies, to an amplitude modulation section 18, a voltage corresponding to a magnitude of the delta-sigma modulated signal. The amplitude modulation section 18 amplitude-modulates the angle-modulated signal by the voltage supplied from the amplitude amplifying section 16, to output a modulation signal.

Owner:INTERDIGITAL PATENT HLDG INC

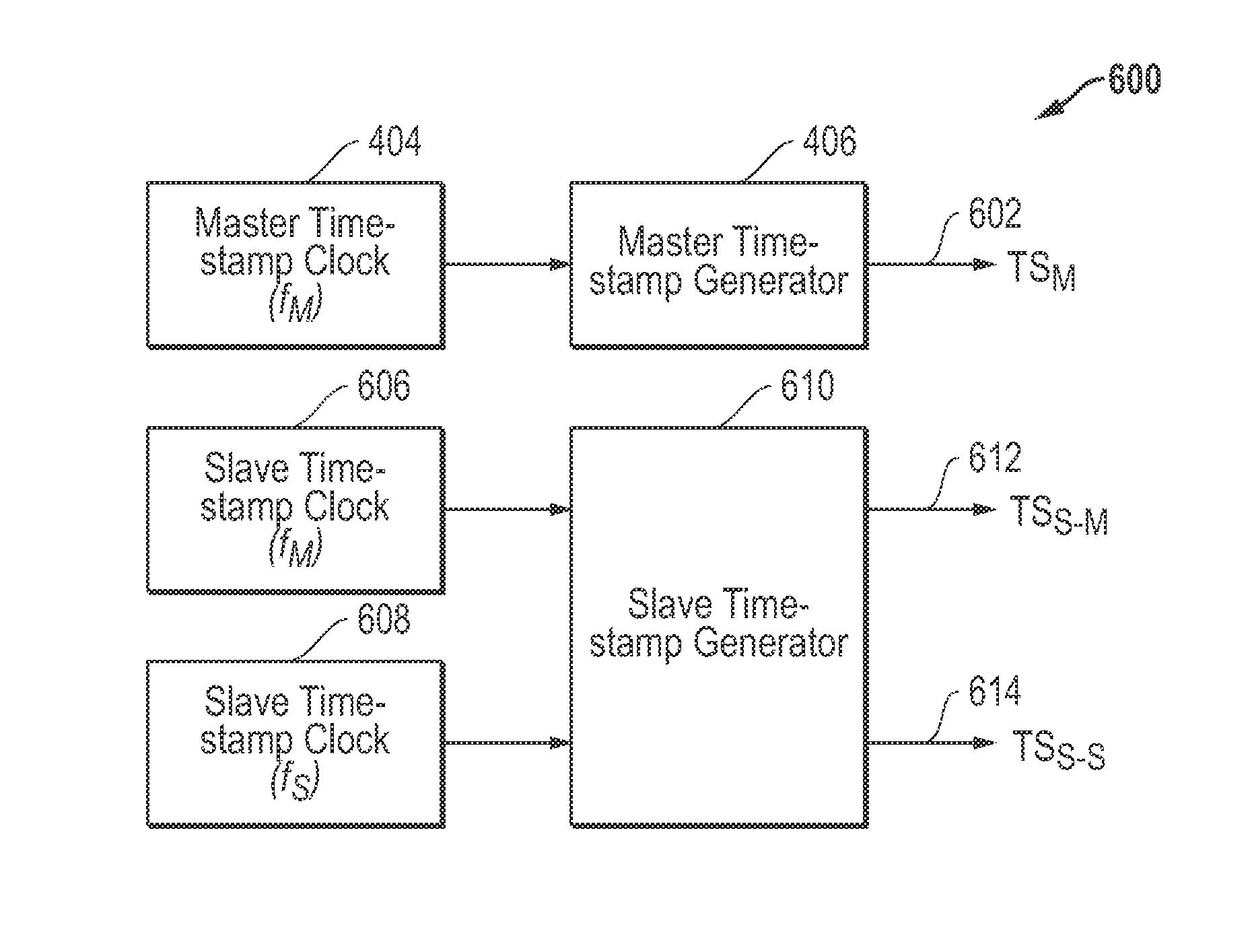

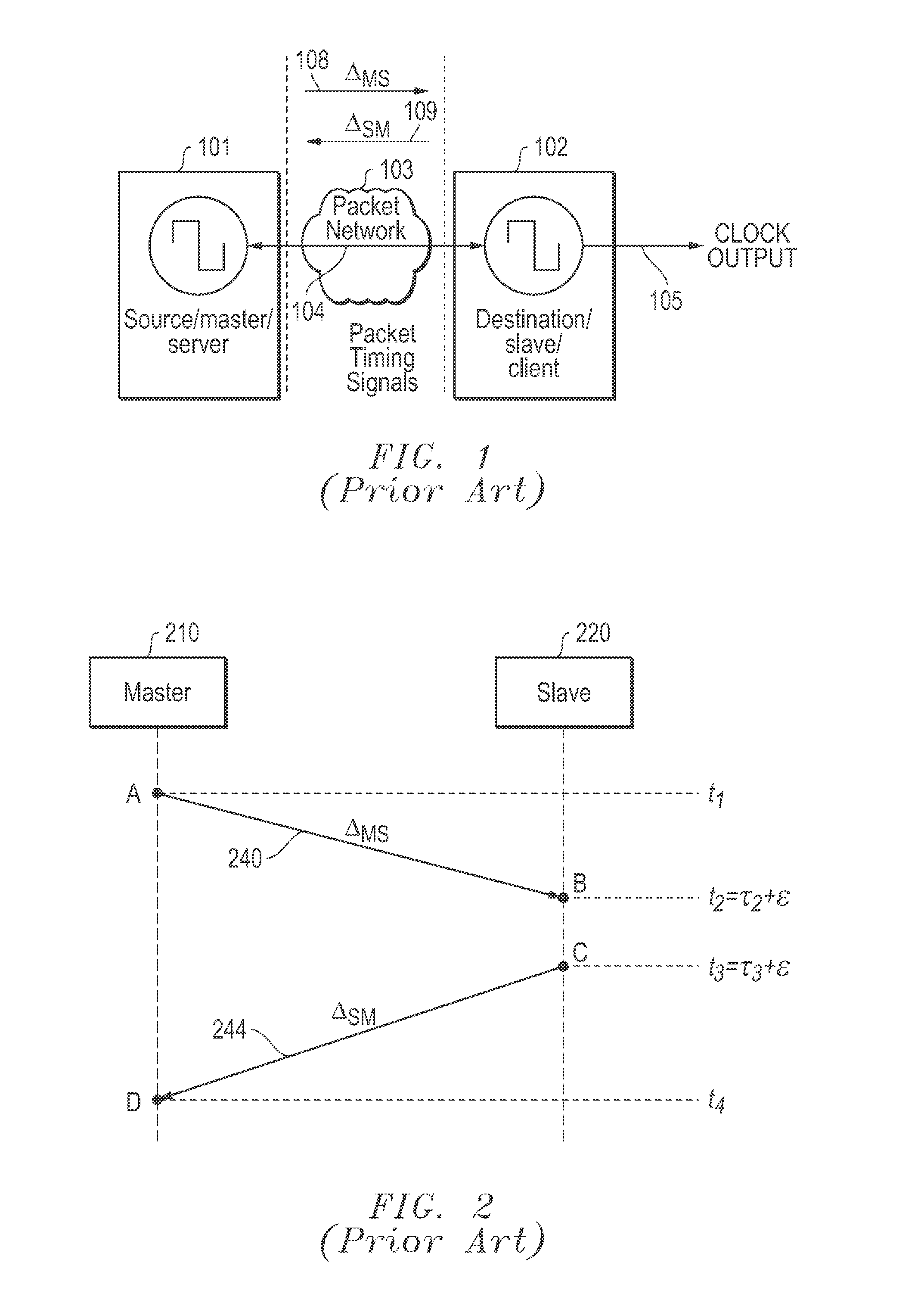

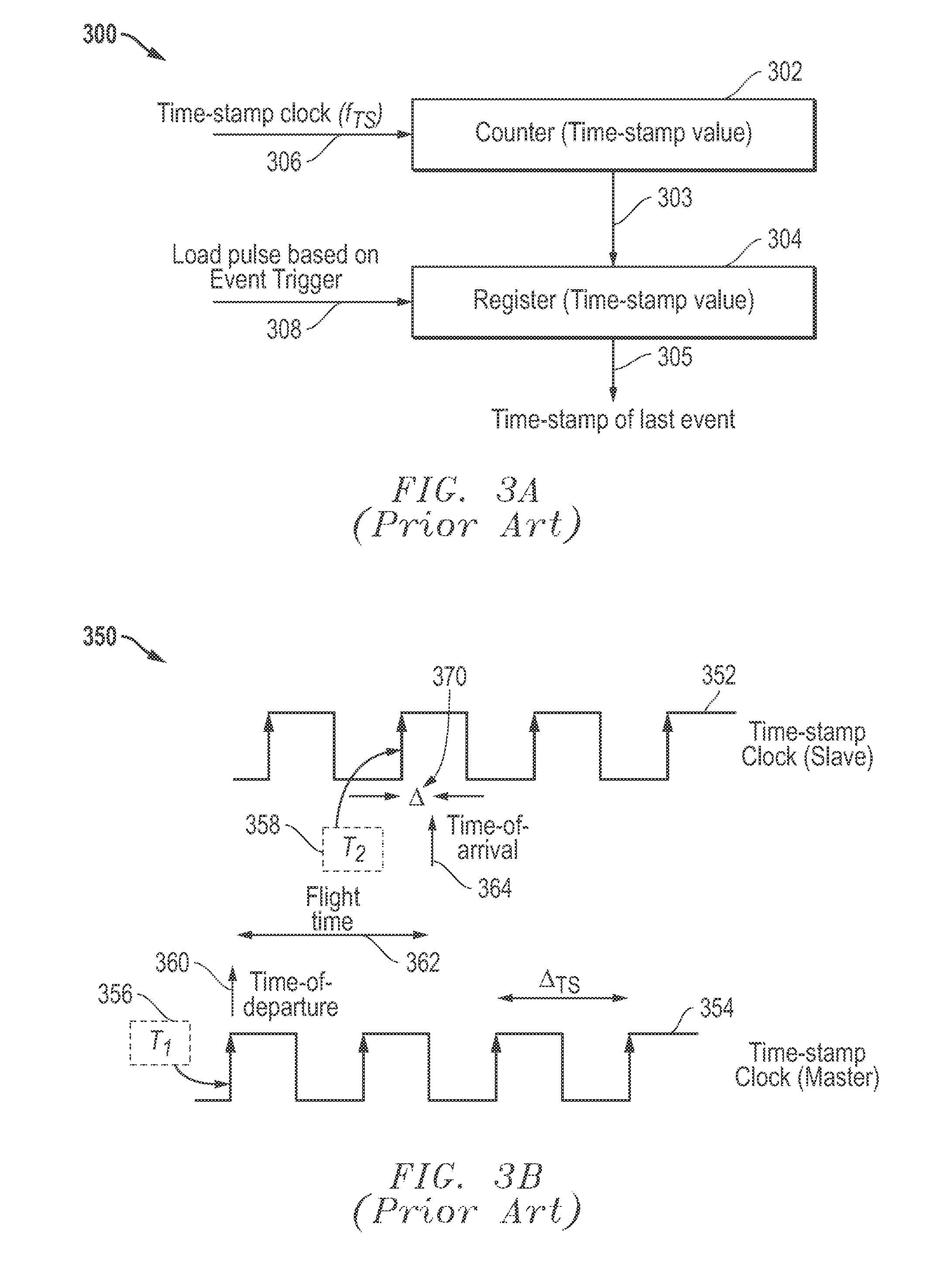

Systems and methods utilizing randomized clock rates to reduce systematic time-stamp granularity errors in network packet communications

Systems and methods are disclosed for utilizing slave (receive) time-stamp clock rates that are different from master (sender) time-stamp clock rates to randomize and thereby reduce systematic time-stamp granularity errors in the communication of network packets. The slave (receive) time-stamp clock rate for some embodiments is set to be a fixed value that has a relationship with the master (sender) time-stamp clock rate such that the ratio of the slave (receive) clock rate to the master (sender) clock rate is a rational number. Other embodiments use a time-varying frequency for the slave (receive) time-stamp clock rate to randomize the slave (receive) time-stamp clock with respect to the master (sender) time-stamp clock. Additional time-stamps can also be generated using a slave (receive) time-stamp clock having a rate set to equal the rate of the master (sender) time-stamp clock signal. Further spread spectrum and / or delta-sigma modulation techniques can be applied to effectively randomize the slave (receive) time-stamp clock.

Owner:KEYSIGHT TECH SINGAPORE (SALES) PTE LTD

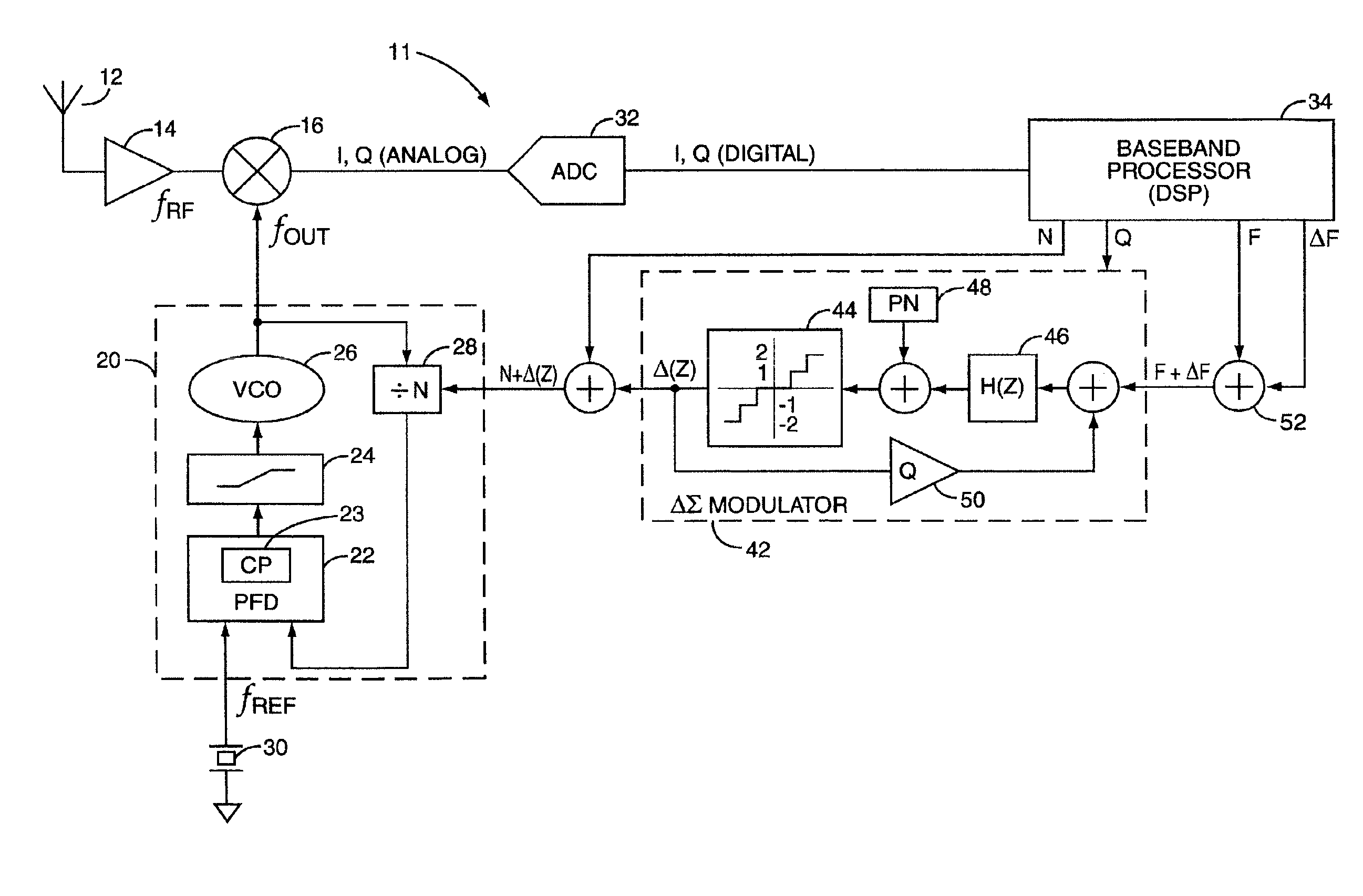

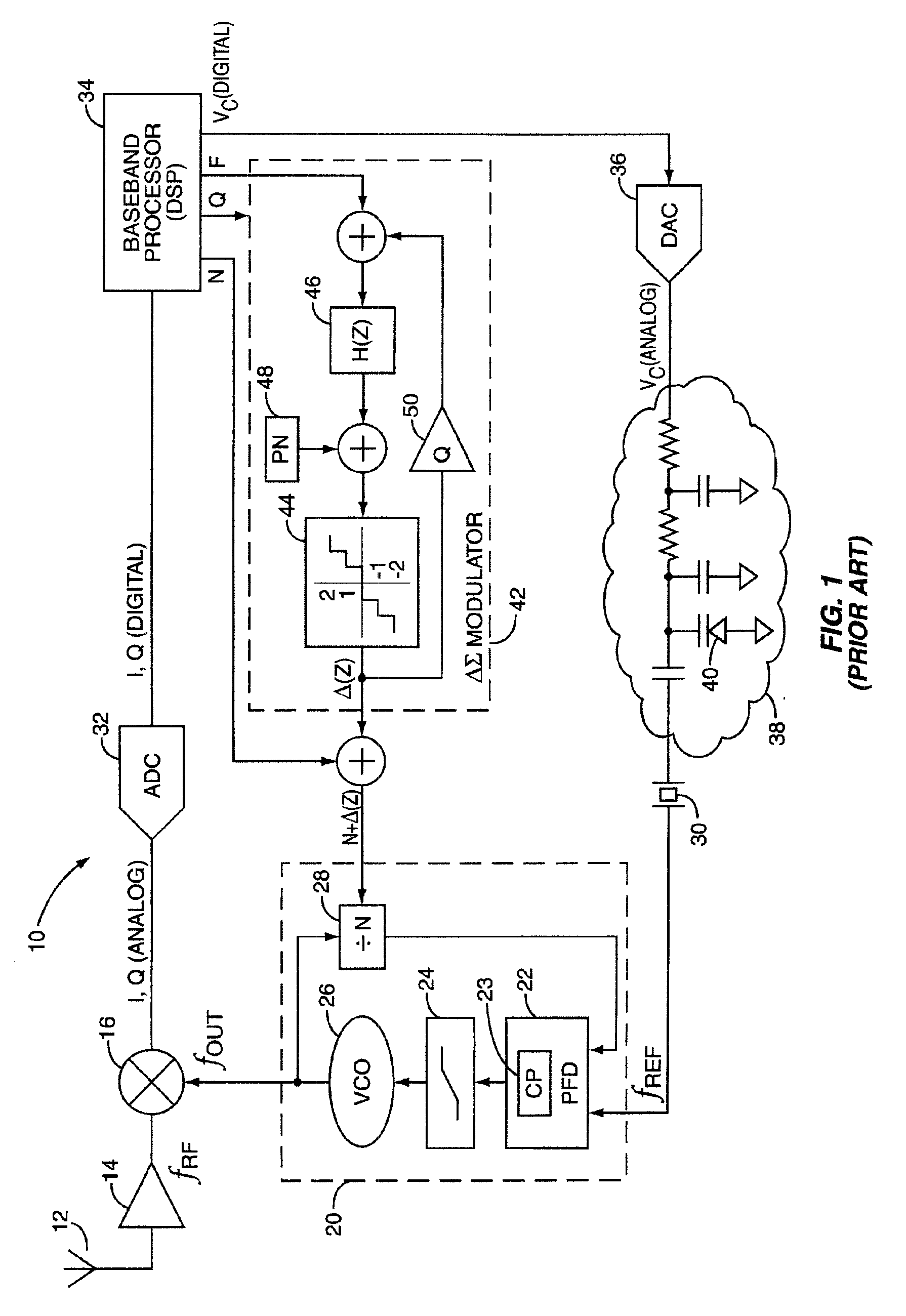

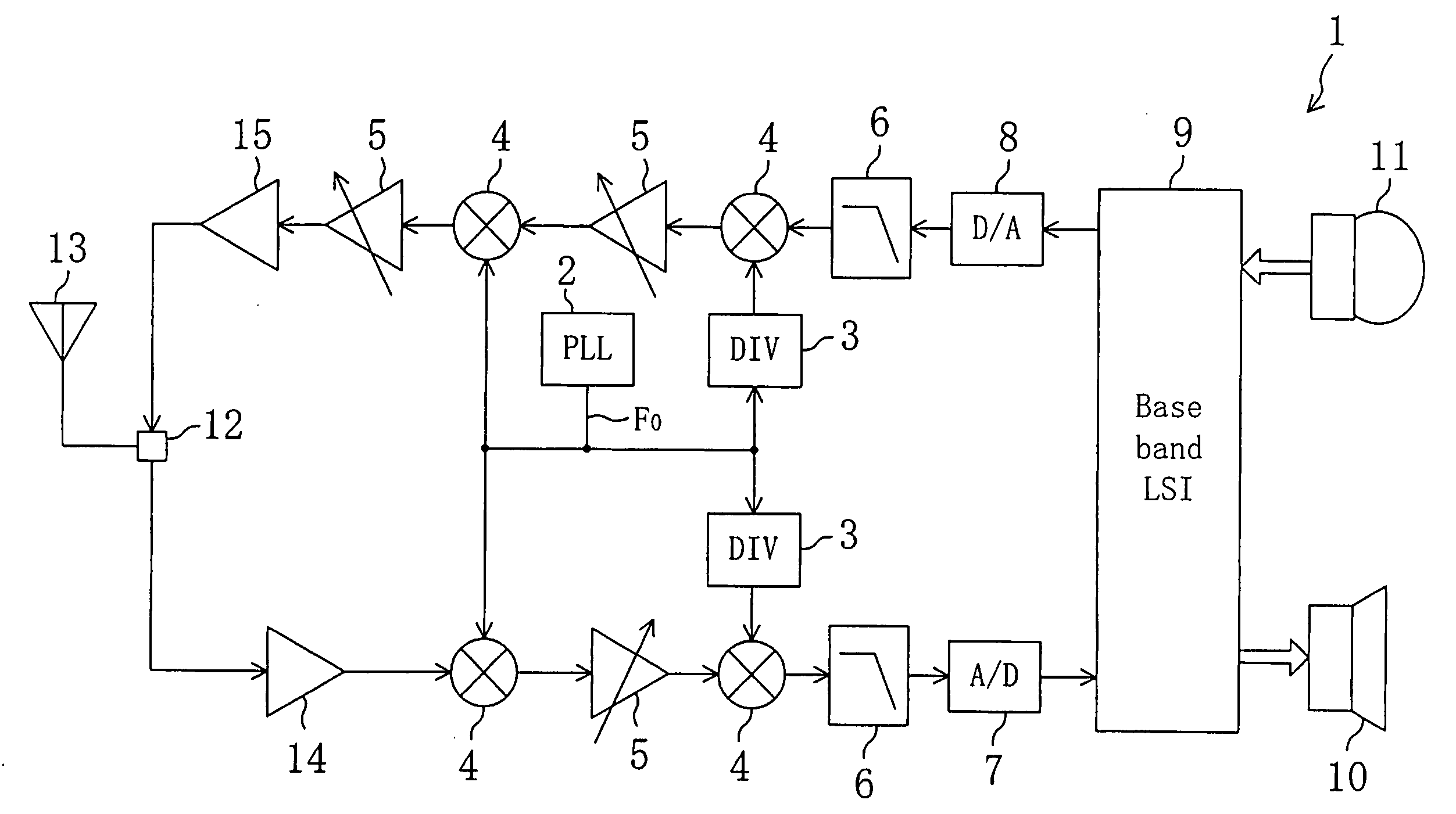

Direct automatic frequency control method and apparatus

InactiveUS6856791B2Reduce errorsAutomatic controlPulse automatic controlRadio transmissionFrequency spectrumEngineering

An Automatic Frequency Control (AFC) circuit for a mobile terminal employs a fractional-N Phase Locked Loop (PLL) to directly reduce errors in the synthesized frequency, such as due to component tolerances, temperature drift, and the like. The frequency error is detected by the average speed of rotation of the I,Q constellation. A corresponding offset is added to the tuning frequency selection word prior to encoding, such as in a ΔΣ modulator, to generate an effective non-integer PLL frequency division factor over a specified duration. The ΔΣ modulator may include dithering the different integer values by a pseudo-random number to minimize noise in the output frequency spectrum introduced by the fractional-N division. Component and parameter selection allow a high degree of resolution in frequency control of the fractional-N PLL. By directly controlling for the frequency error, a DAC and XTAL oscillator tuning circuit may be eliminated from the AFC circuit.

Owner:OPTIS WIRELESS TECH LLC

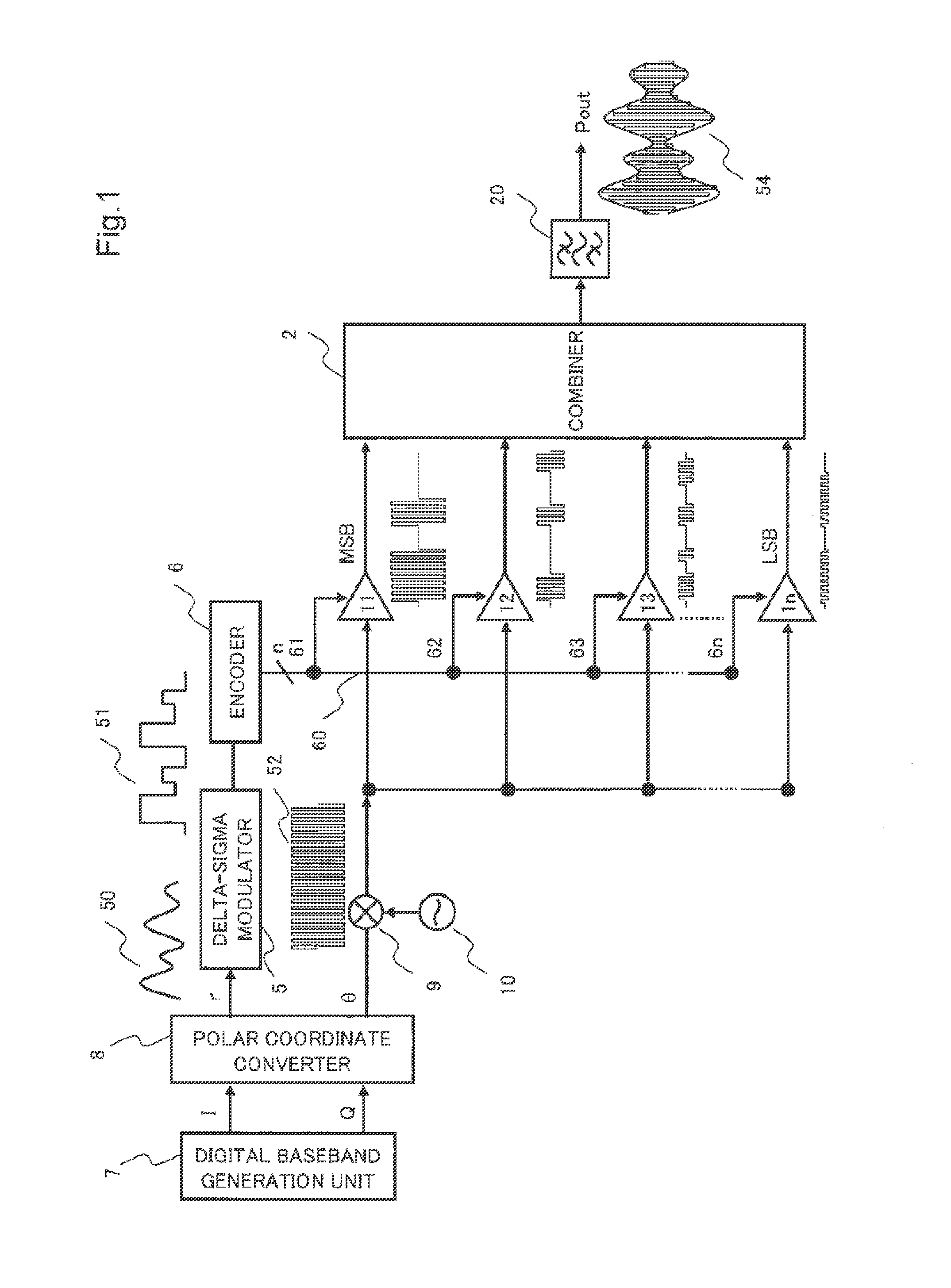

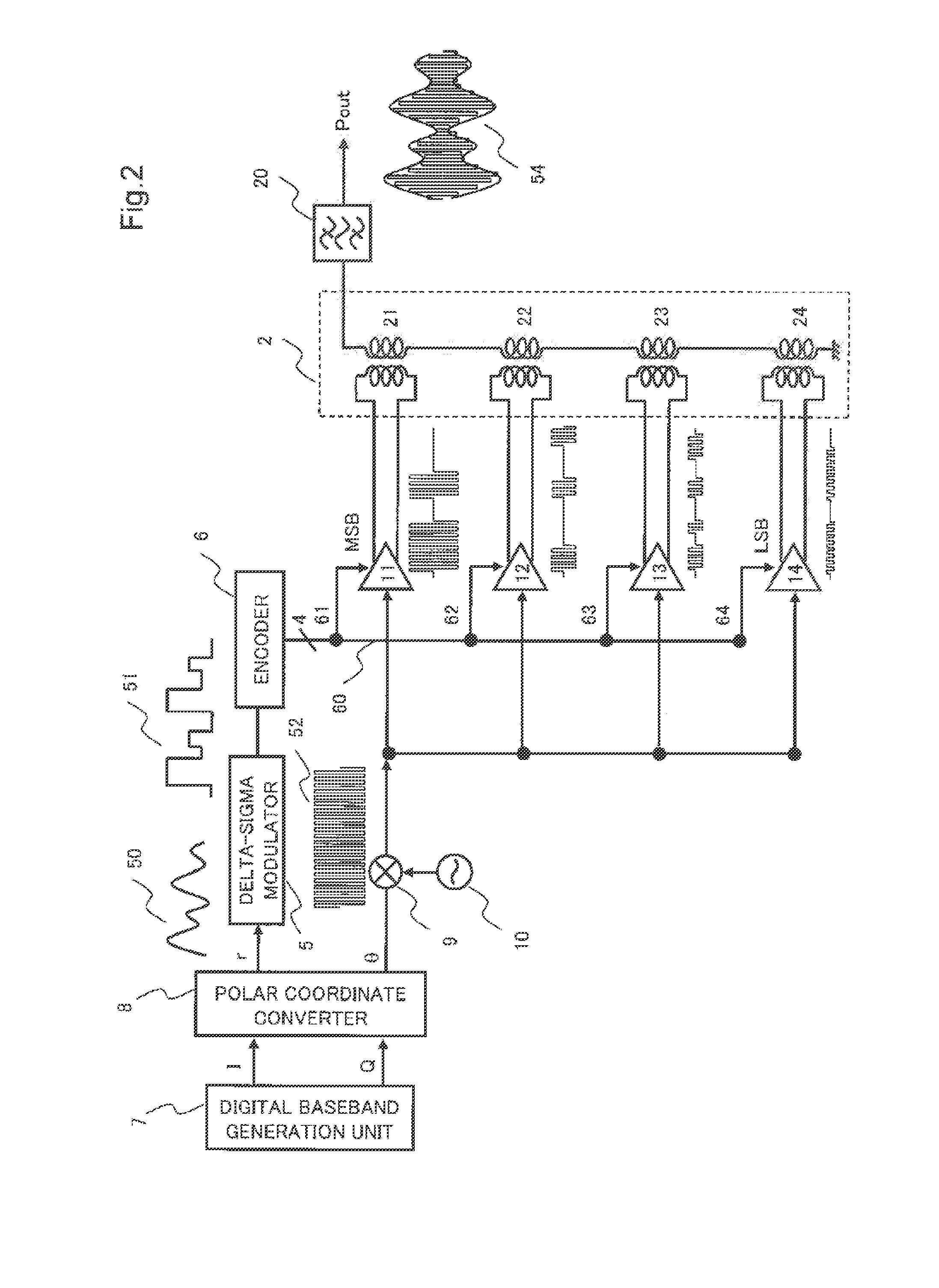

Power amplification device

ActiveUS20140218104A1Improve power efficiencyIncrease consumptionGated amplifiersAmplifier detailsAudio power amplifierControl signal

An object of the present invention is to provide a power amplification device having high power efficiency for an input signal even in a power region in a large back-off.A power amplification device of the present invention includes a delta-sigma modulator which performs a multilevel delta sigma modulation on amplitude signals of input signals, a plurality of power amplifiers which amplify carrier signals, an encoder which generates a first control signal that controls ON / OFF of the outputs from said plurality of power amplifiers in accordance with the output from said delta-sigma modulator, and a combiner which combines at least two power output from said plurality of power amplifiers in accordance with said first control signal.

Owner:NEC CORP

Signal processing device, signal processing method, delta-sigma modulation type fractional division pll frequency synthesizer, radio communication device, delta-sigma modulation type d/a converter

InactiveUS20050017887A1Suppress concentration of quantization noiseSuppress noiseElectric signal transmission systemsPulse automatic controlDelta-sigma modulationEngineering

A fractional frequency divider (28) includes a latch (31) for holding frequency division data, a ΔΣ modulator (33), a digital dither circuit (32) for receiving a digital input F representing fraction part of the frequency division data from the latch (31) and supplying a digital output alternately changing between F+k and F−k (where k is an integer) or a F value itself to the ΔΣ modulator (33), and circuit means (34 through 38) for executing fractional frequency division based on integer part (M value) of the frequency division data and an output of the ΔΣ modulator (33). The digital dither circuit (32) is useful for suppressing a spurious signal generated as a result of concentration of quantization noise at a particular frequency when the ΔΣ modulator (33) receives a particular F value (e.g., F=2n−1).

Owner:PANASONIC CORP

Delta sigma modulator analog-to-digital converters with multiple threshold comparisons during a delta sigma modulator output cycle

ActiveUS7221303B1Electric signal transmission systemsDifferential modulationEngineeringDelta-sigma modulation

The analog-to-digital (ADC) delta sigma modulators in the signal processing systems described utilize comparator number reduction techniques to improve a delta sigma modulator quantizer. The delta sigma modulator generates one quantization output signal per delta sigma modulator output cycle. A quantizer of the delta sigma modulator includes one or more comparators, that each makes at least two comparisons per delta sigma modulator output cycle. The one or more comparators compare a quantizer input signal against one or more thresholds. A successive reference generator determines the one or more thresholds for the one or more comparators wherein each of the one or more thresholds during a later one of the at least two comparisons is in conformity with results of an earlier one of the at least two comparisons. Redundant and other iterative comparison techniques and threshold generation techniques are used to efficiently reduce the number of comparators in the quantizer while maintaining accuracy.

Owner:CIRRUS LOGIC INC

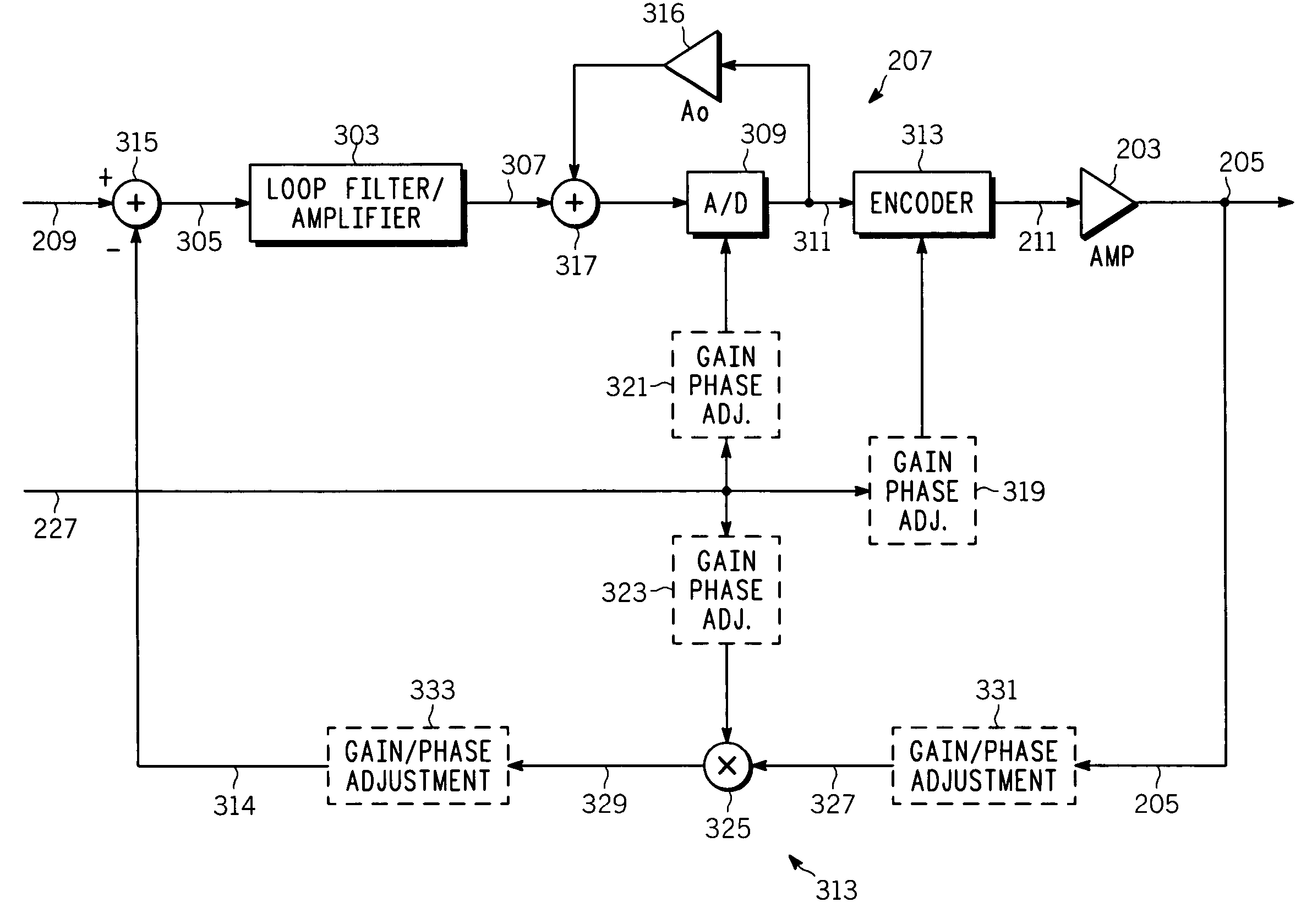

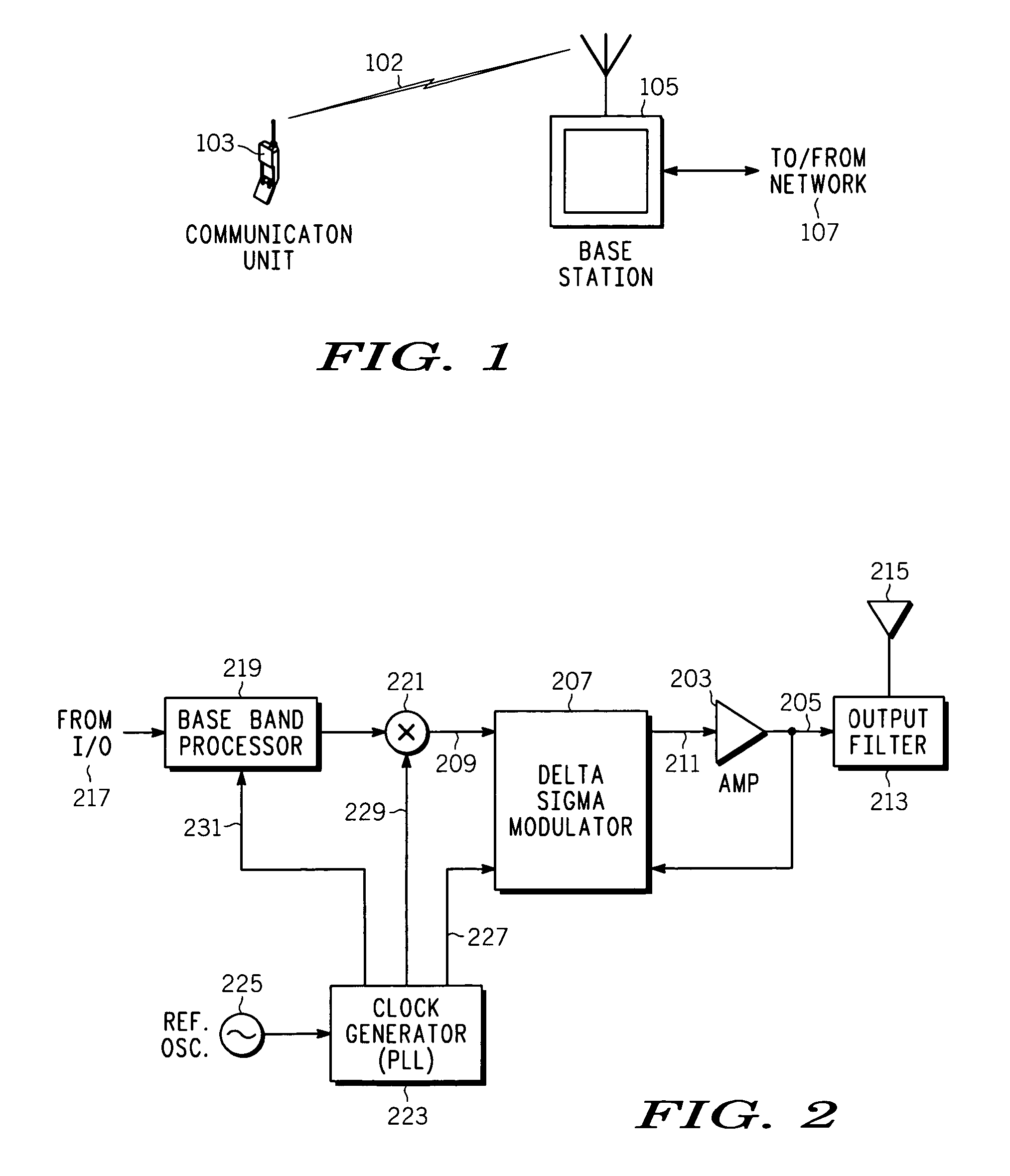

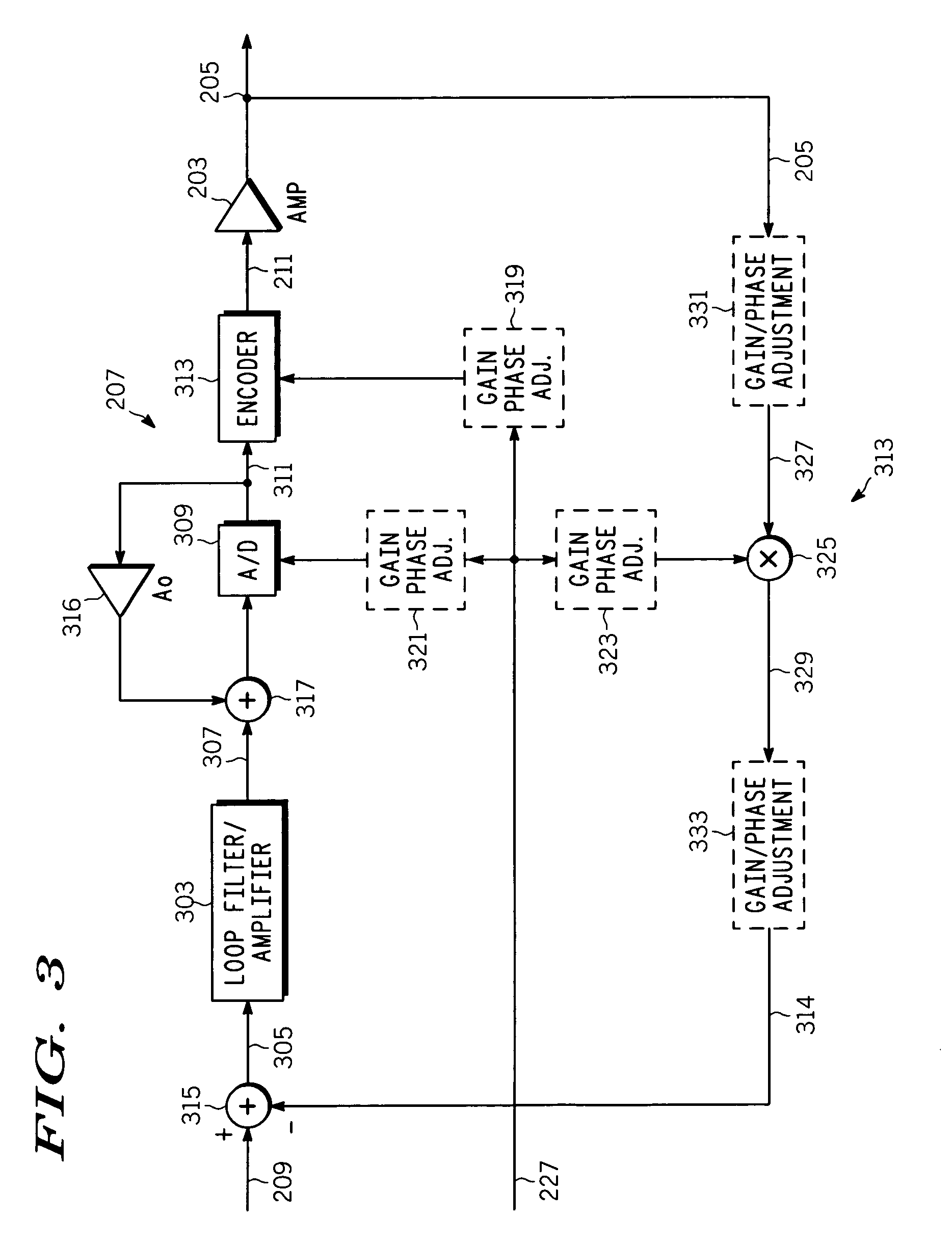

Switching power amplifier using a frequency translating delta sigma modulator

InactiveUS7023267B2Negative-feedback-circuit arrangementsModulation transferenceAudio power amplifierIntermediate frequency

A radio frequency (RF) switching power amplifier comprises: a switching amplifier 203 to provide an amplified signal within an RF band; and a delta signal modulator (DSM) 207 that is operable; to control the switching amplifier in a feedback configuration, to process an input signal within an intermediate frequency (IF) band where the input signal corresponds to a base band signal and the amplified signal, and to provide an output signal within the RF band to drive the switching amplifier. Certain embodiments allow for or compensate for a floating or variable IF band and multiple RF bands.

Owner:PWRF