Patents

Literature

873results about "Printed circuit simultaneous processing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

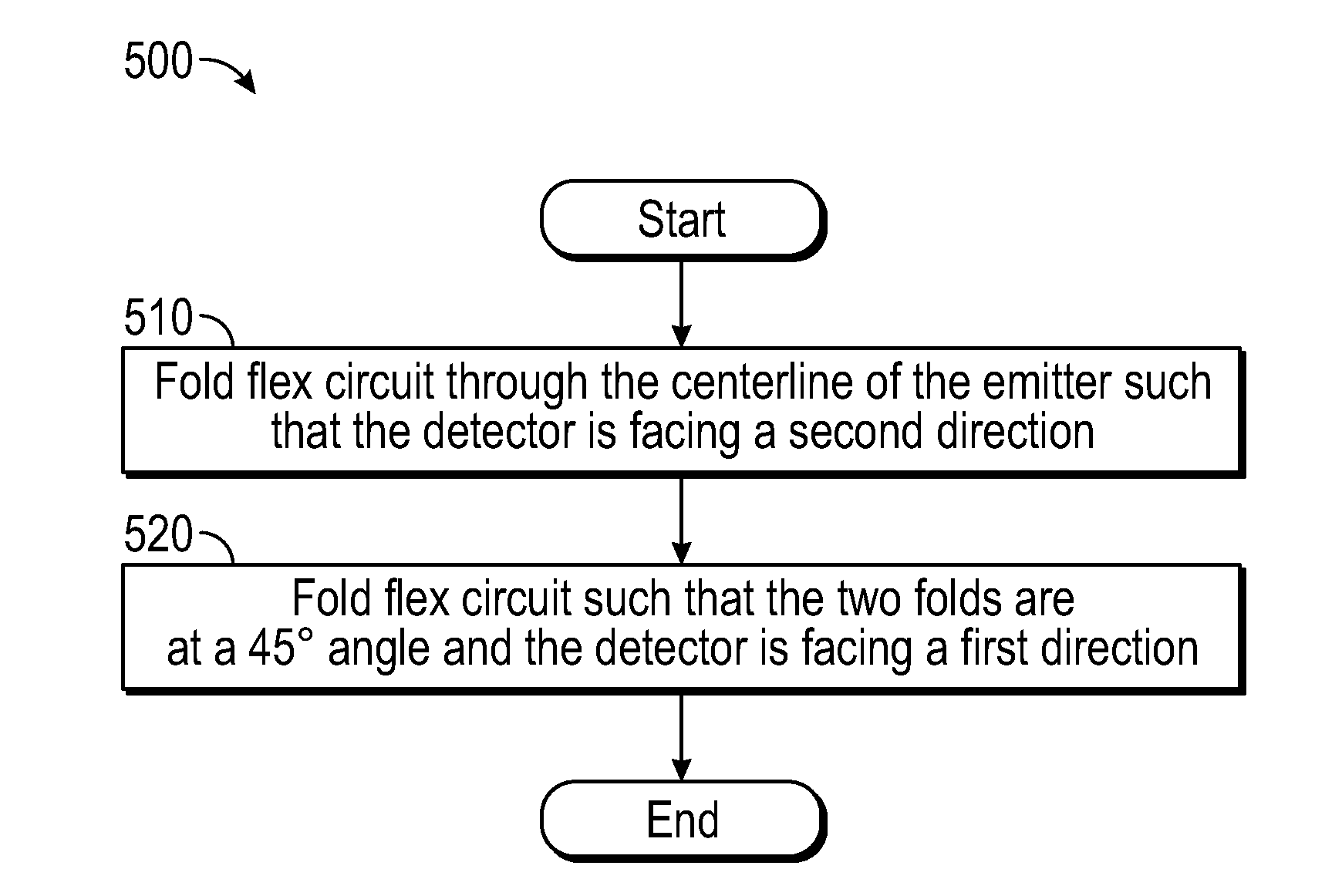

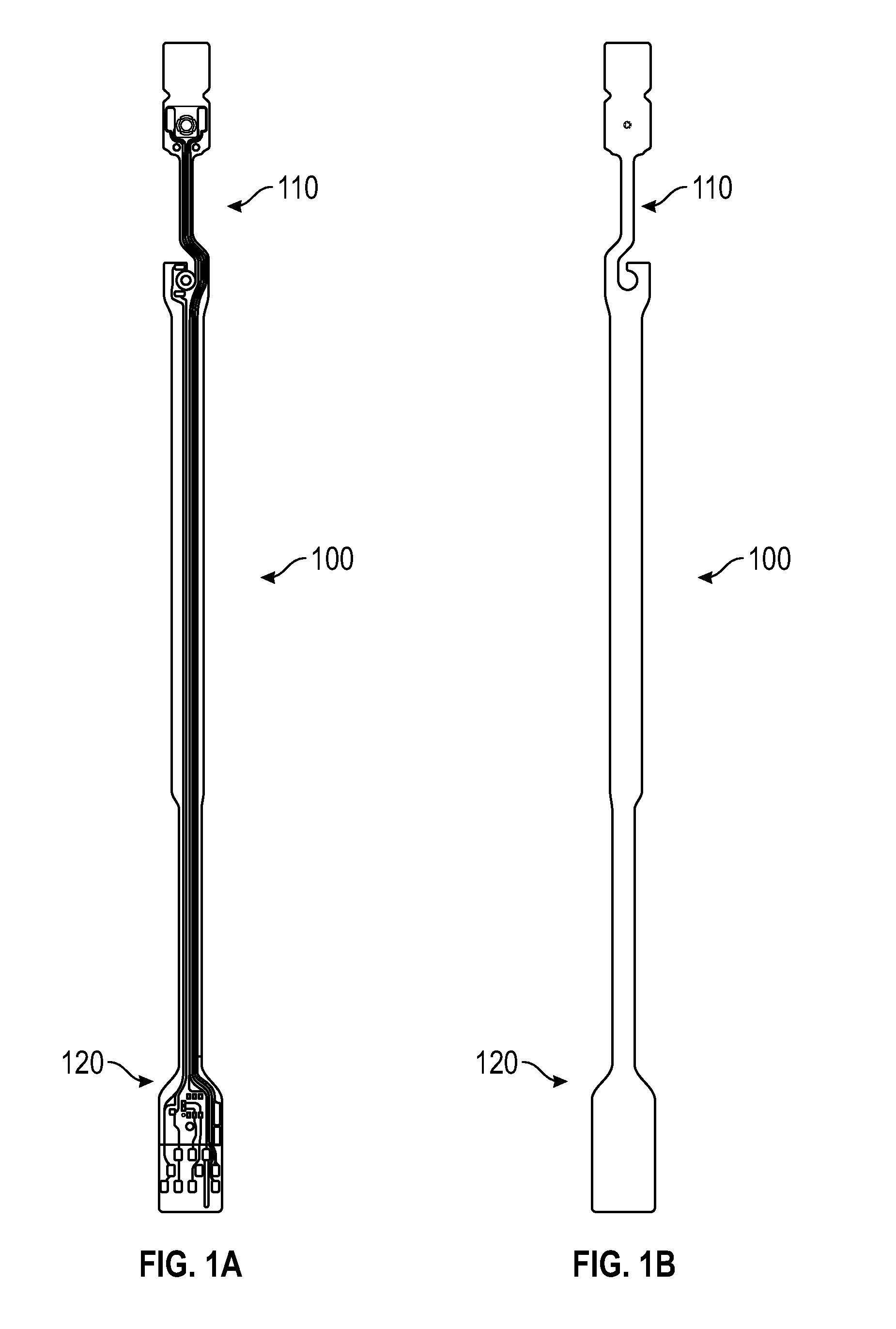

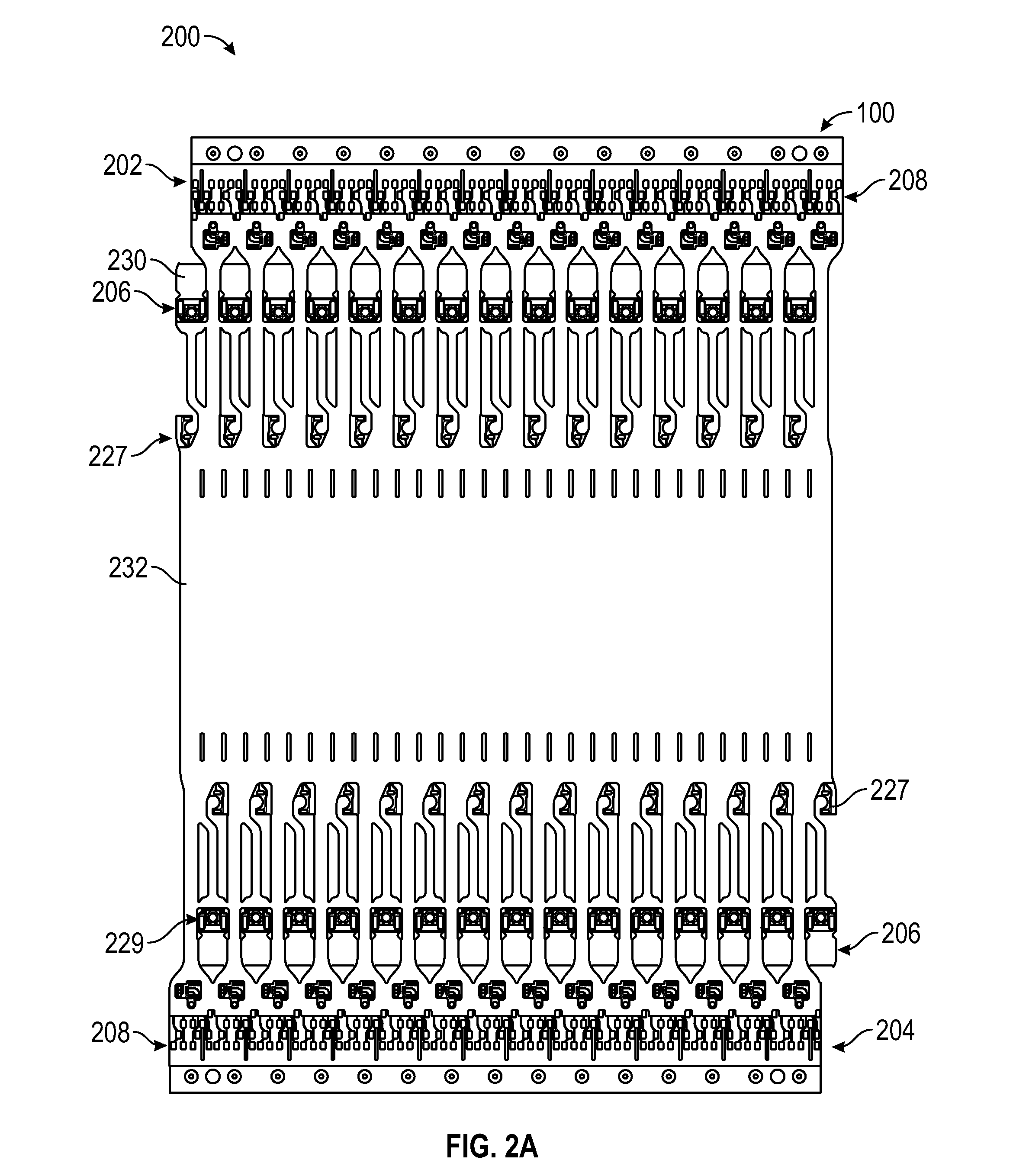

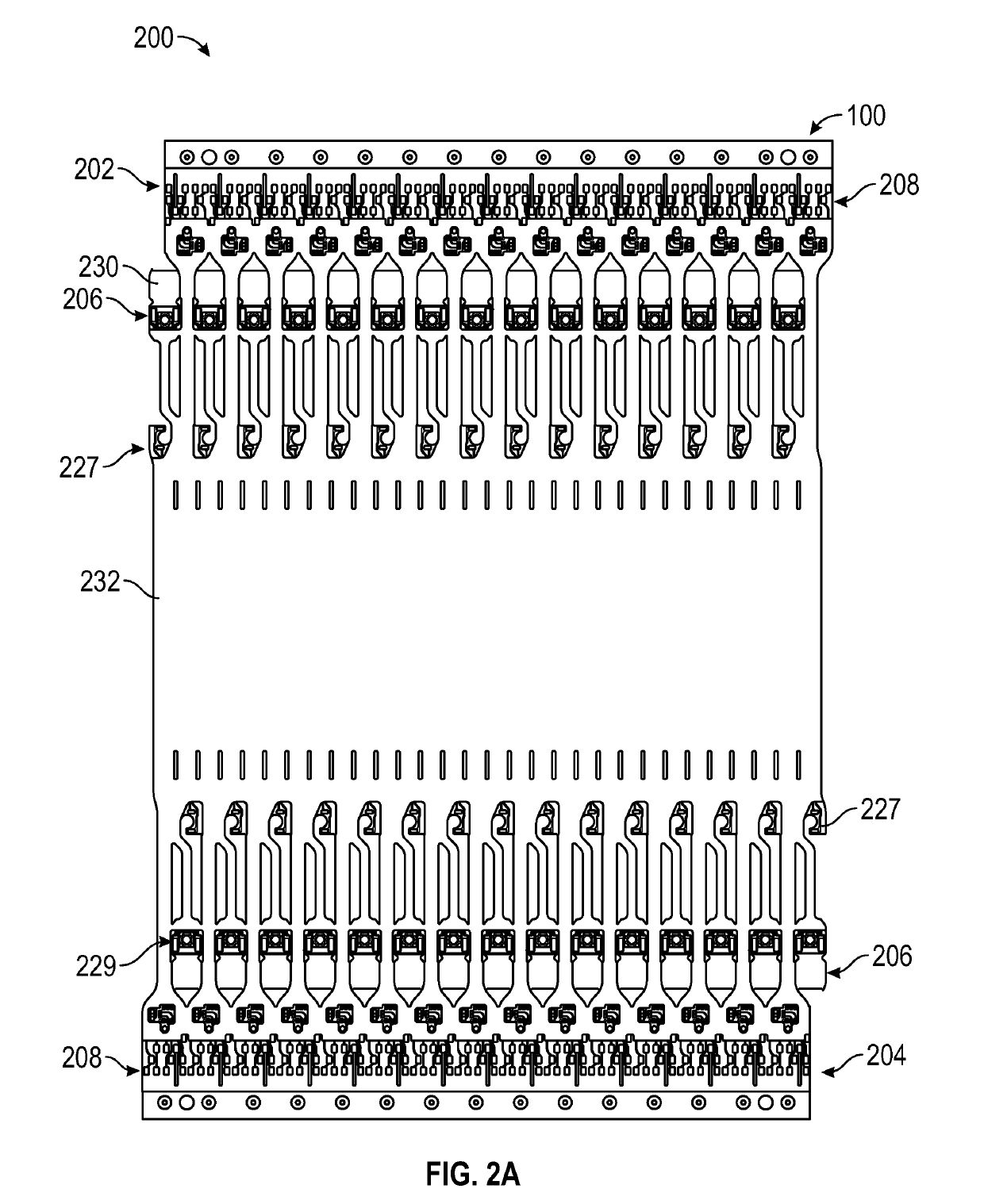

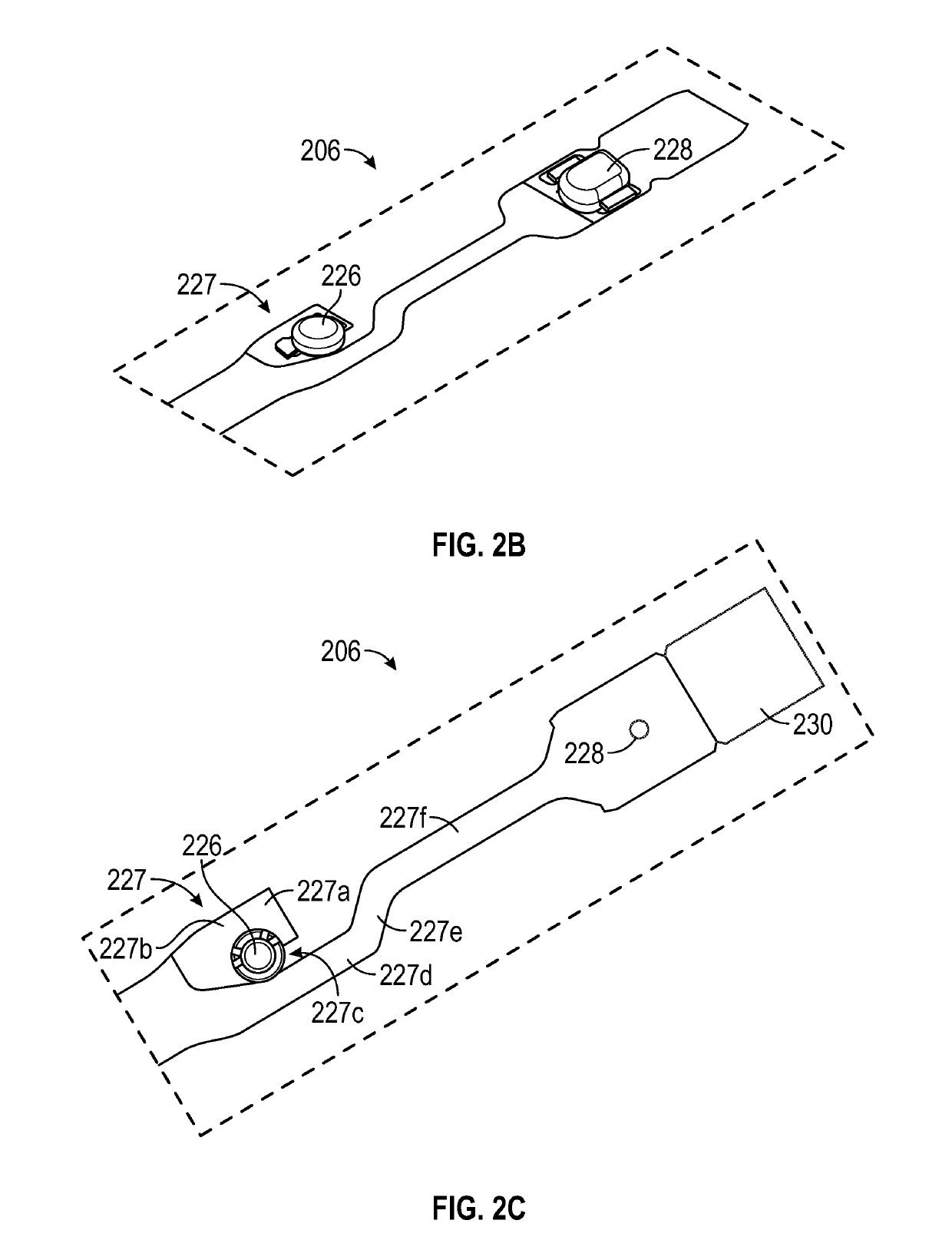

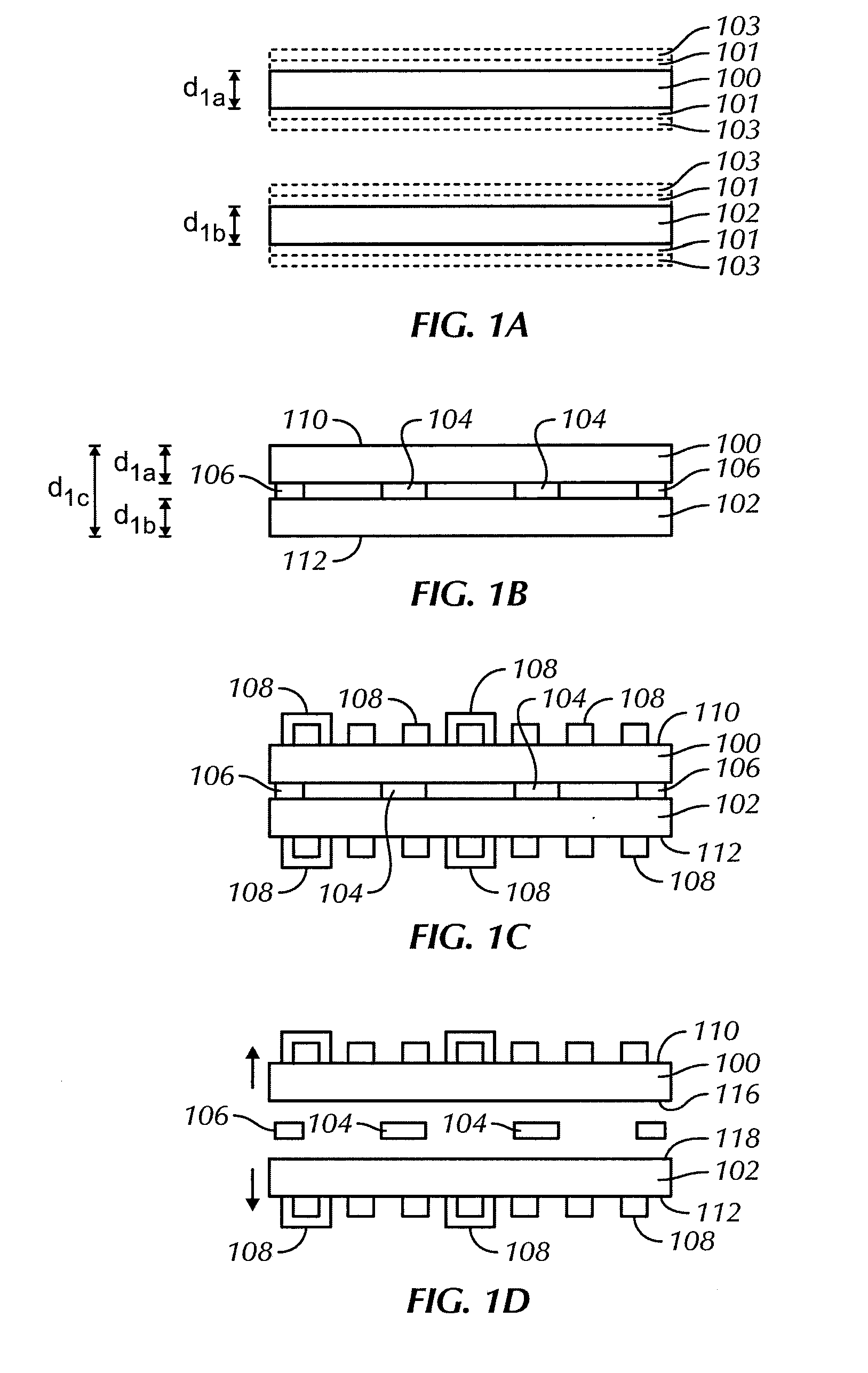

Fold flex circuit for lnop

ActiveUS20160234944A1Low costOptimized material usageDiagnostics using lightPrinted circuit aspectsFolded formFold-forming

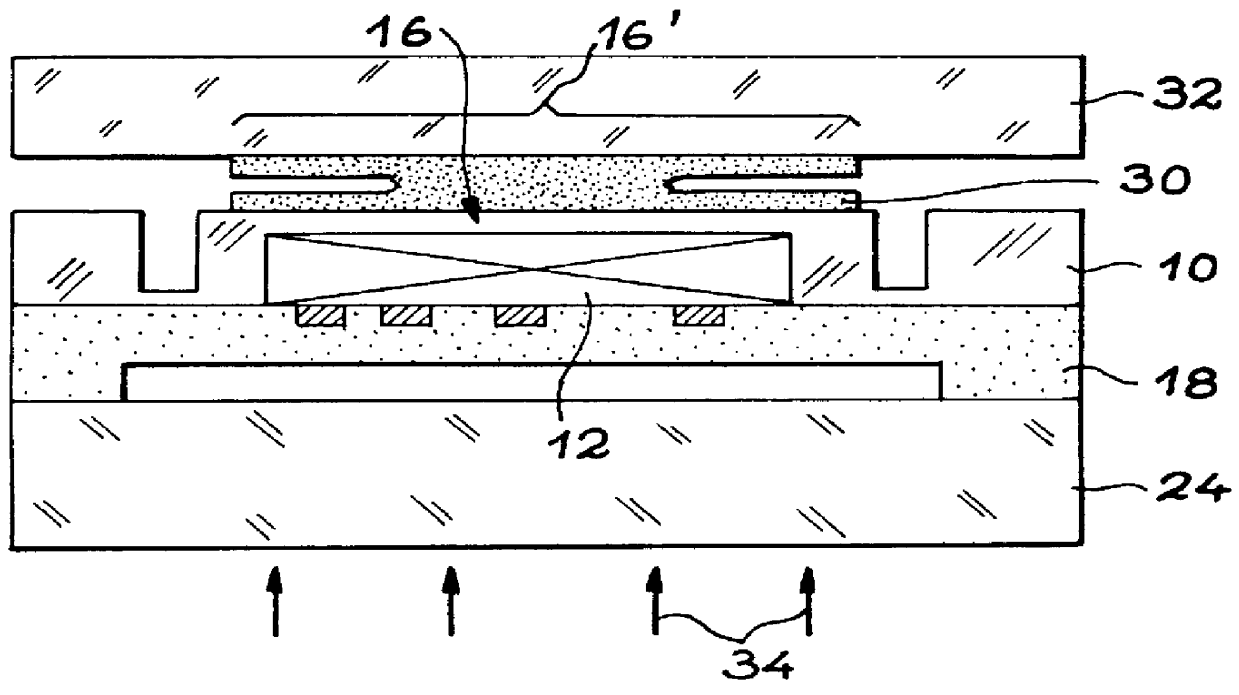

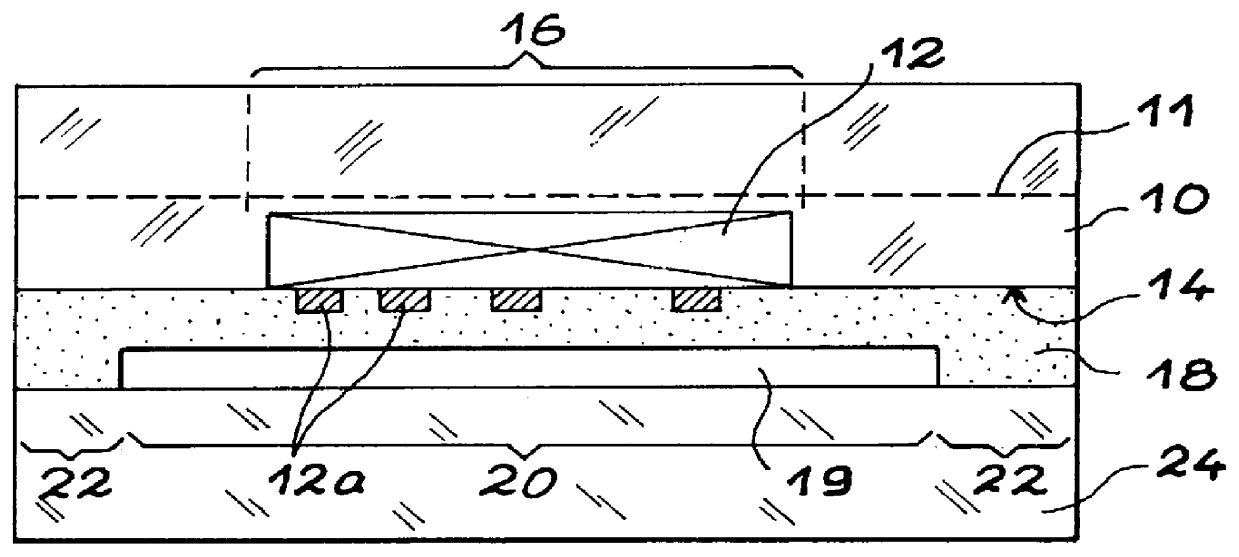

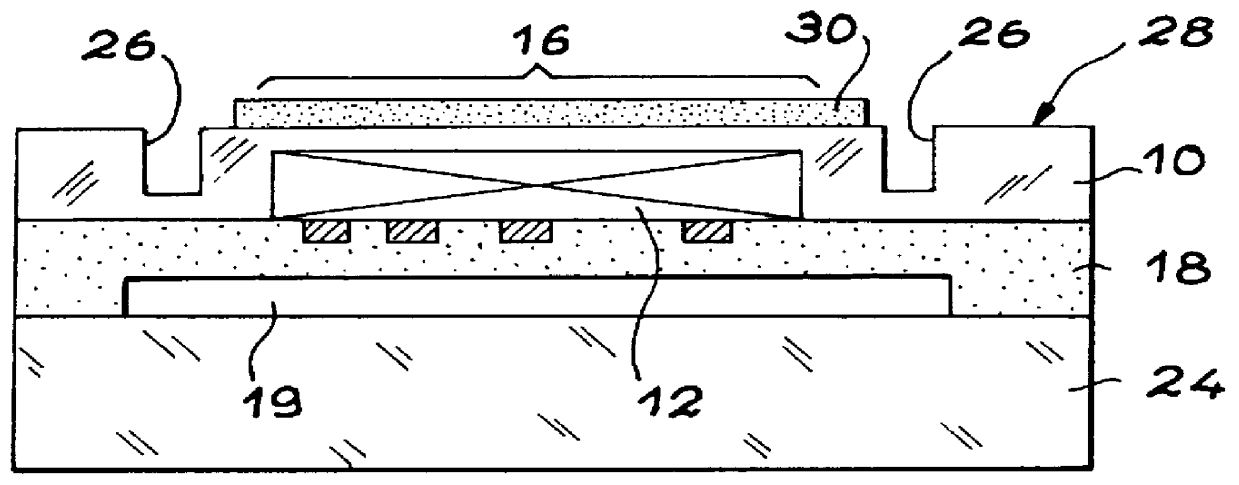

Various sensors and methods of assembling sensors are described. In some embodiments, the sensor assembly includes a first end, a body portion, and a second end. The first end can include a neck portion and a connector portion and the second end can include a flap, a first component, a neck portion, and a second component. A method is also described for sensor folding. The method can include using a circuit with an attached emitter and a detector that is separated by a portion of the circuit. The method can also include folding the portion of the circuit such that a first fold is created through the emitter and folding the portion of the circuit such that a second fold is created such that the first fold and second fold form an angle.

Owner:MASIMO CORP

Fold flex circuit for LNOP

ActiveUS10327337B2Low costMaximize amount of materialDiagnostics using lightPrinted circuit aspectsFolded formEngineering

Various sensors and methods of assembling sensors are described. In some embodiments, the sensor assembly includes a first end, a body portion, and a second end. The first end can include a neck portion and a connector portion and the second end can include a flap, a first component, a neck portion, and a second component. A method is also described for sensor folding. The method can include using a circuit with an attached emitter and a detector that is separated by a portion of the circuit. The method can also include folding the portion of the circuit such that a first fold is created through the emitter and folding the portion of the circuit such that a second fold is created such that the first fold and second fold form an angle.

Owner:MASIMO CORP

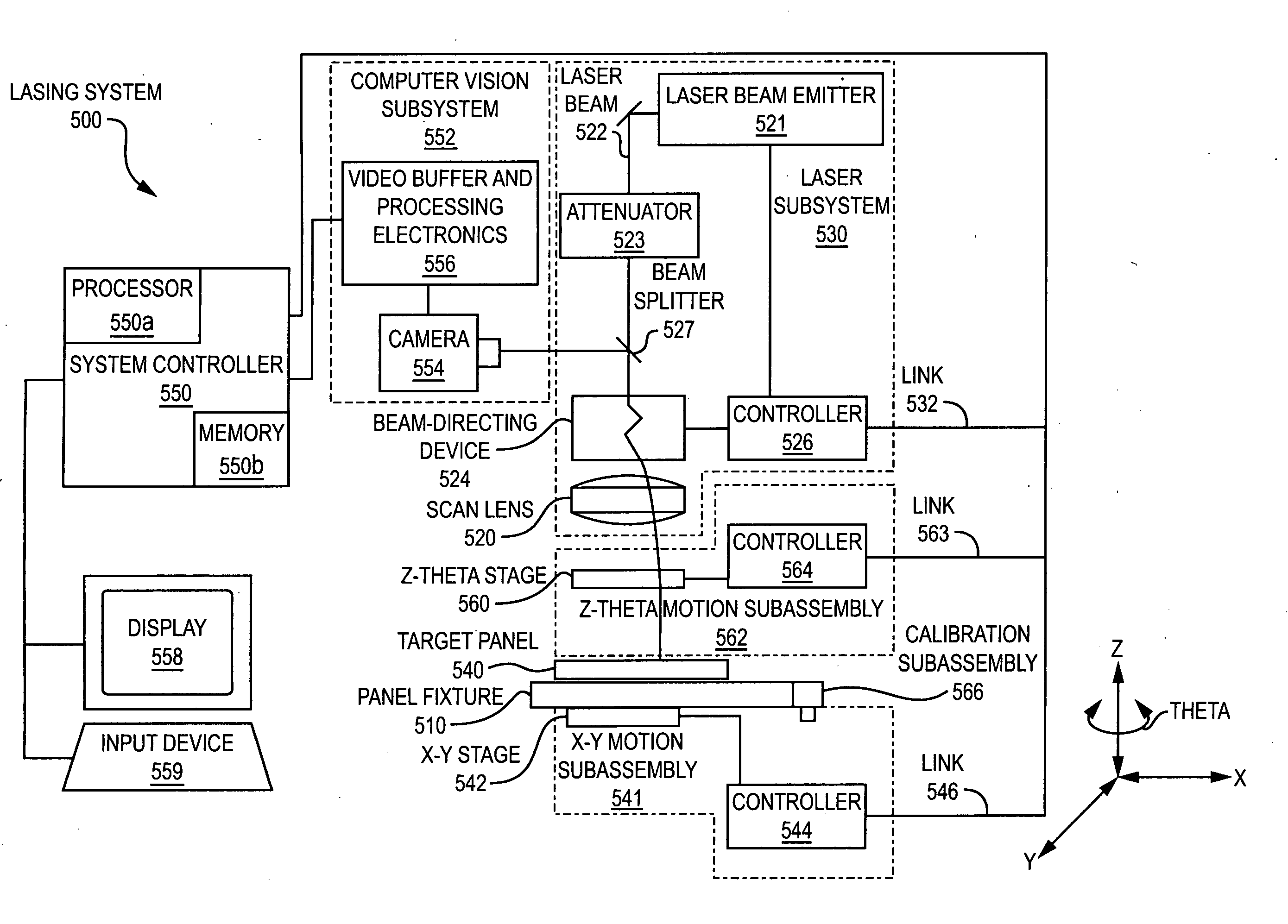

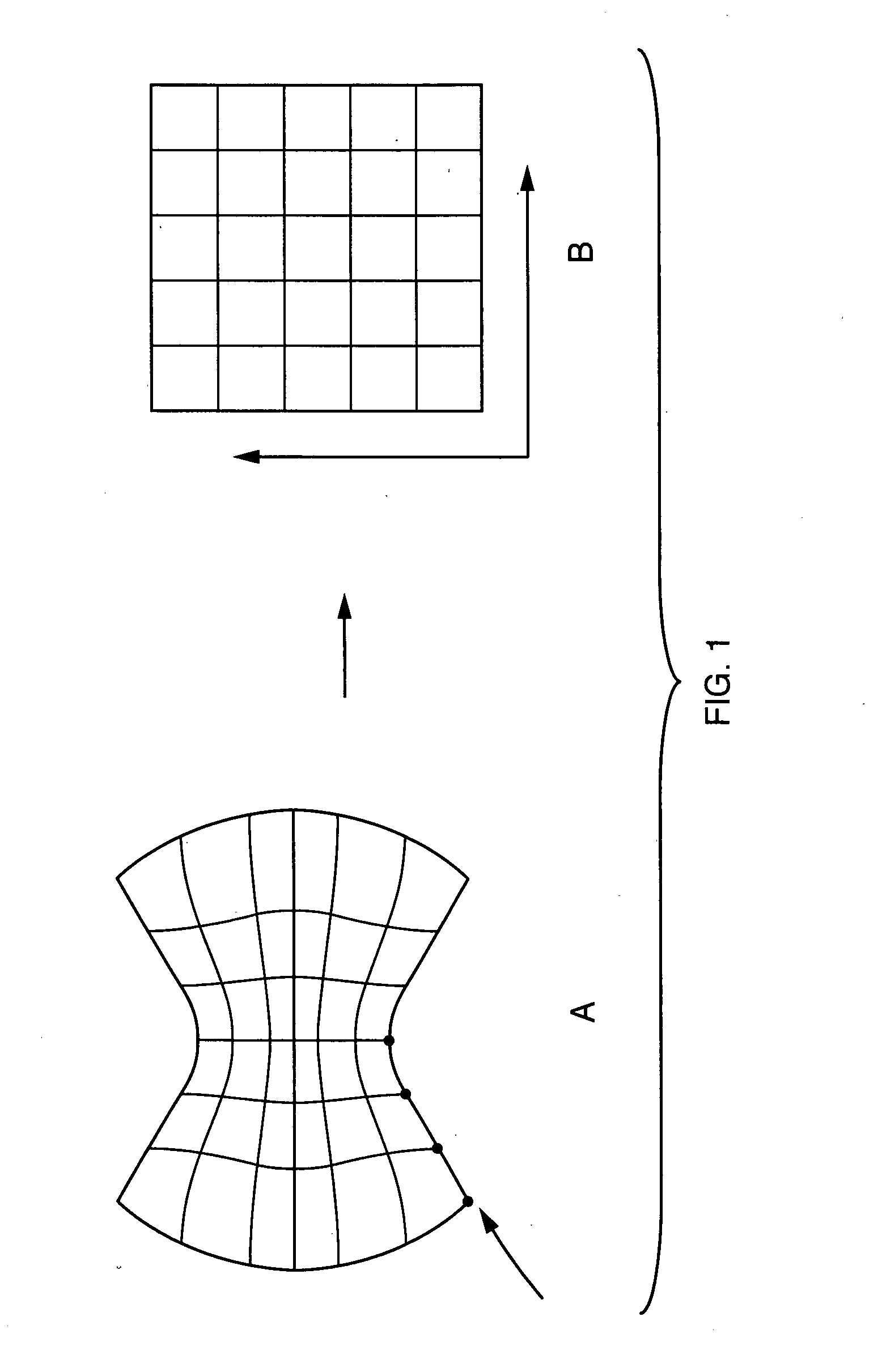

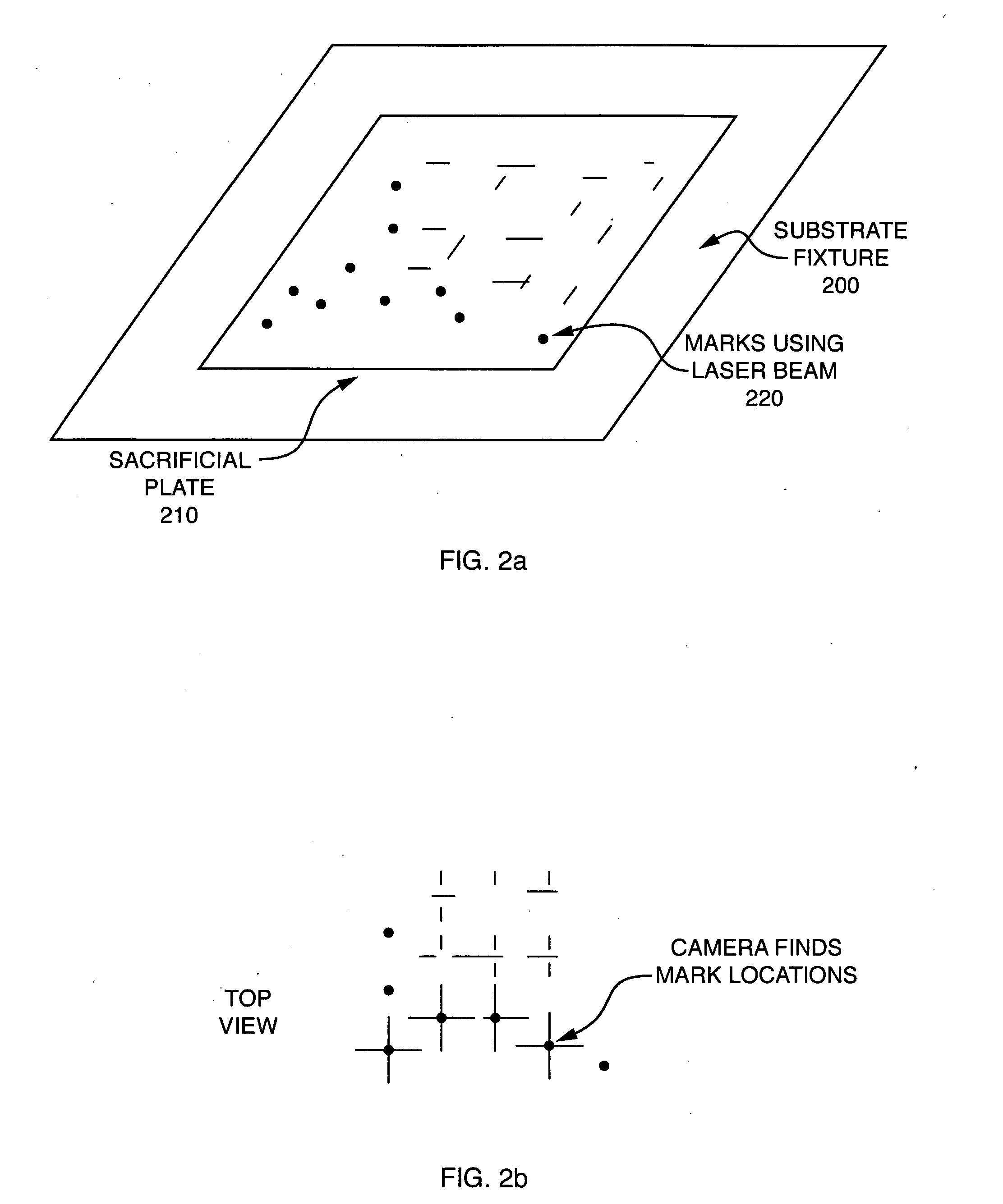

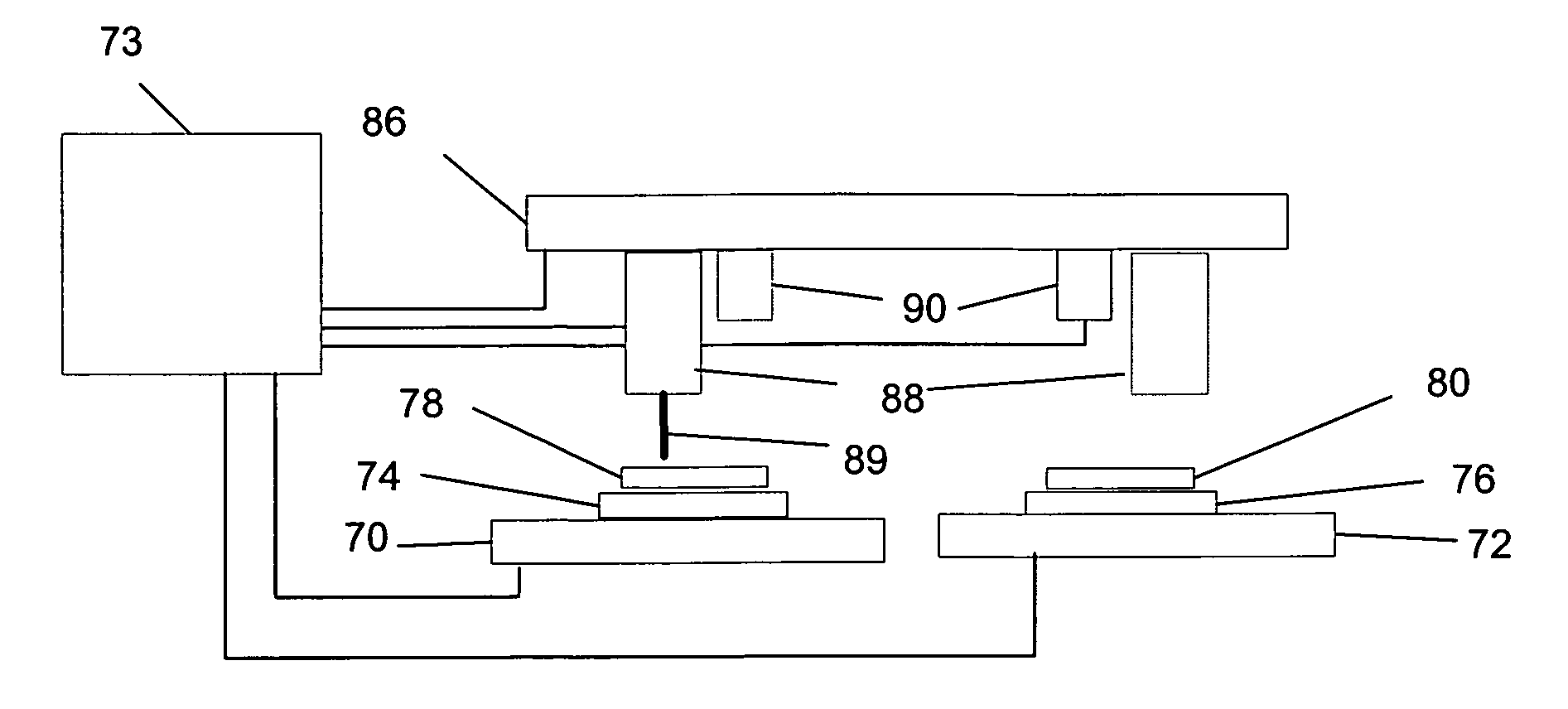

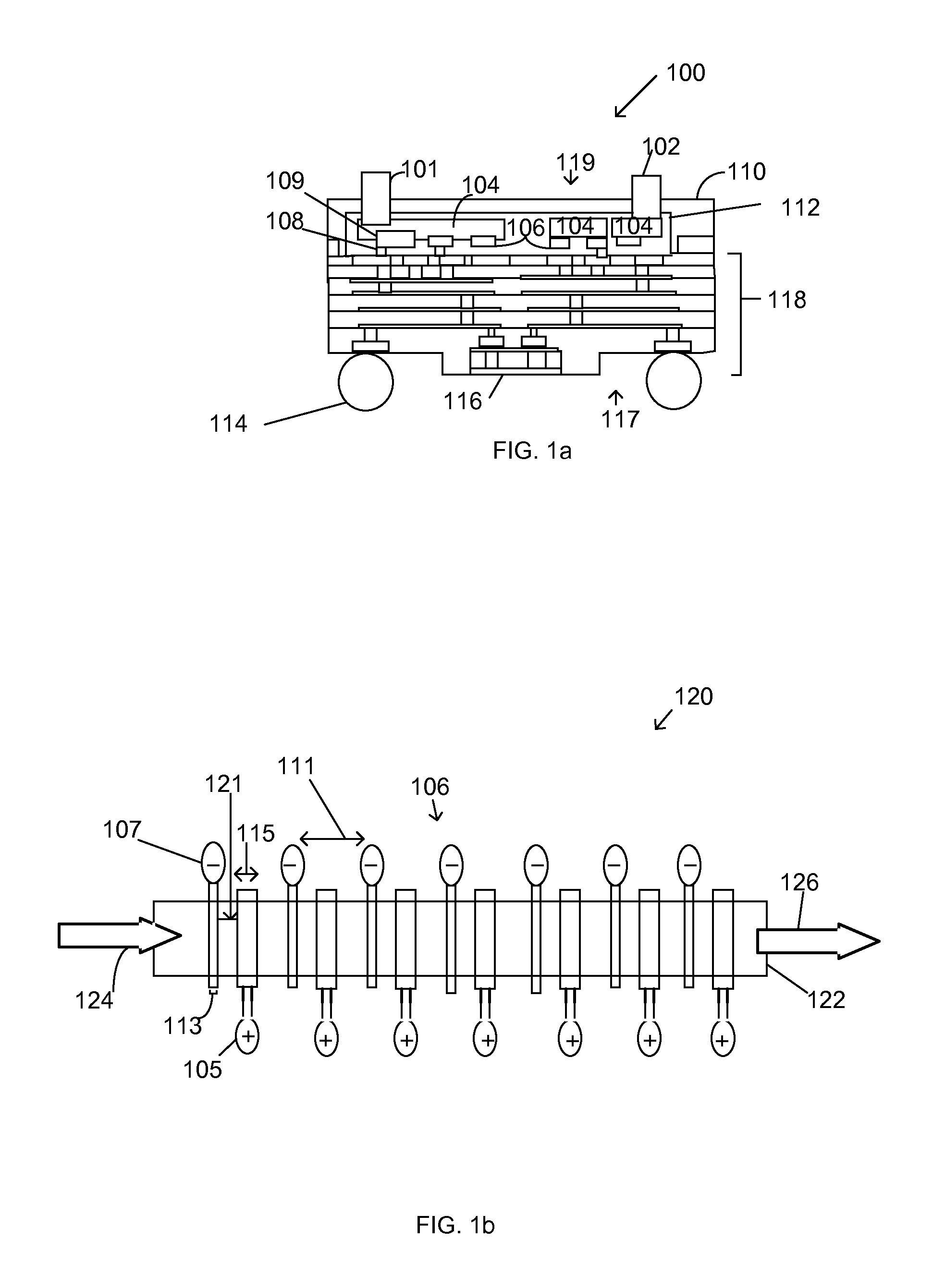

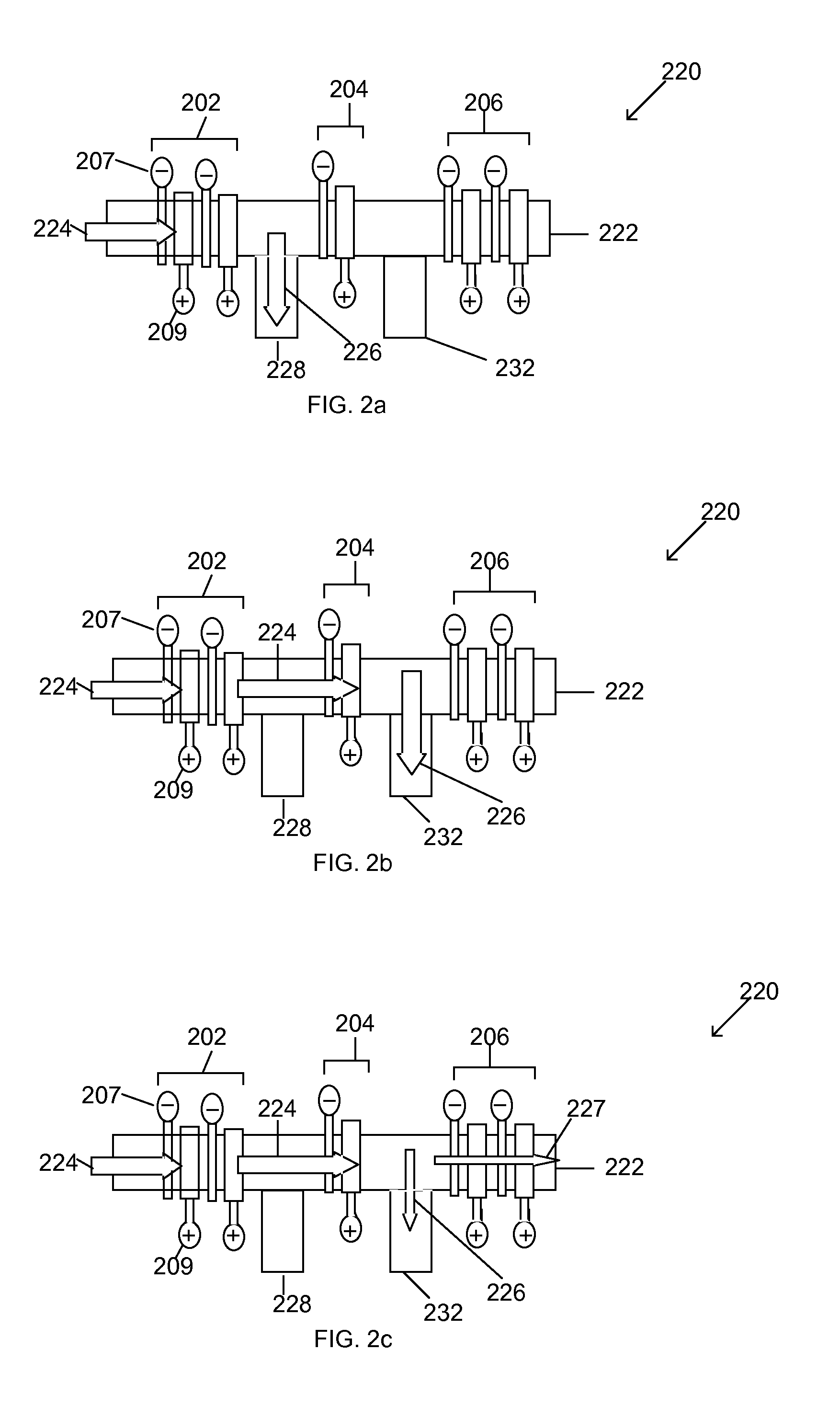

Laser trim motion, calibration, imaging, and fixturing techniques

InactiveUS20050205778A1Optimal lasing procedureOptimal procedureMaterial analysis using wave/particle radiationPrinted circuit aspectsBiomedical engineeringLaser trimming

A system for probing circuit elements, includes a panel fixture, probe holder and stage. The fixture has a platen surface to support a work piece having work piece surface. The work piece surface is substantially parallel to the platen surface and has a target element thereon. The probe holder is configured to support a probe for detecting a characteristic of the target element. A stage rotates the probe holder about an axis substantially orthogonal to the platen surface, to align the probe with probe locations associated with the circuit element, so that the characteristic of the circuit element can detected by the probe. Fixturing motion can be optimized for efficient work piece manufacturing. Calibration and vision subassemblies are also provided.

Owner:THE GSI GRP LLC

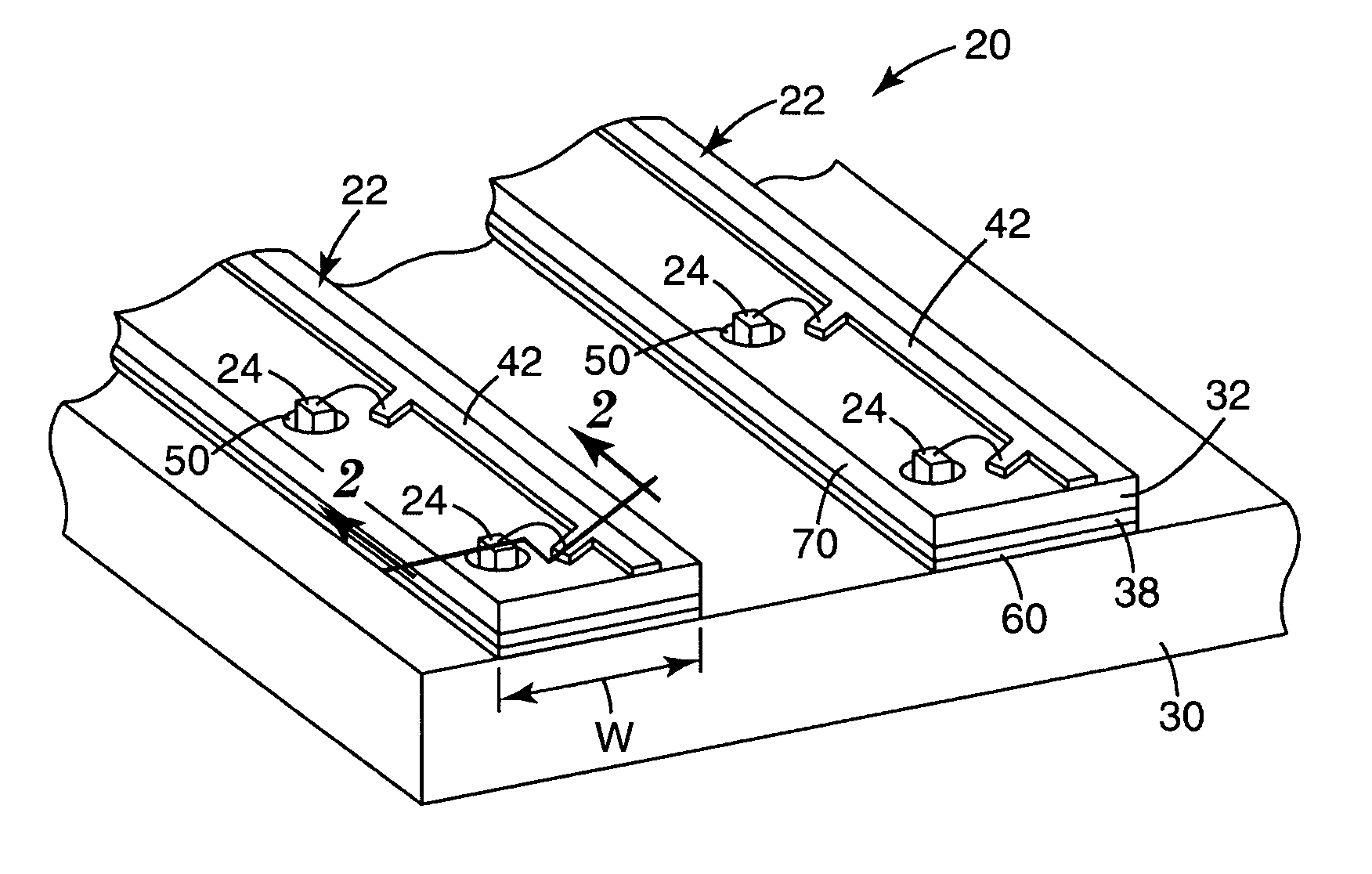

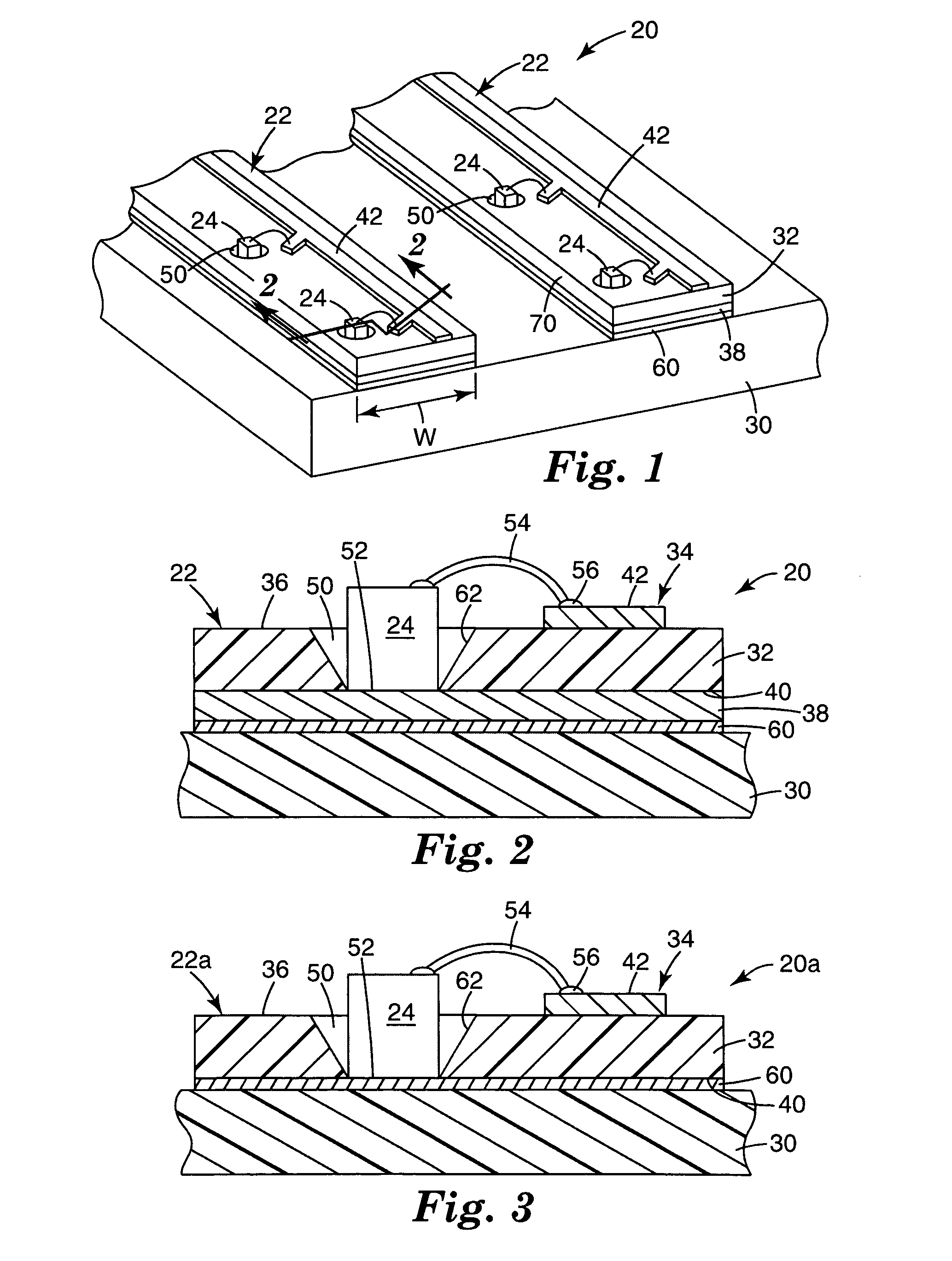

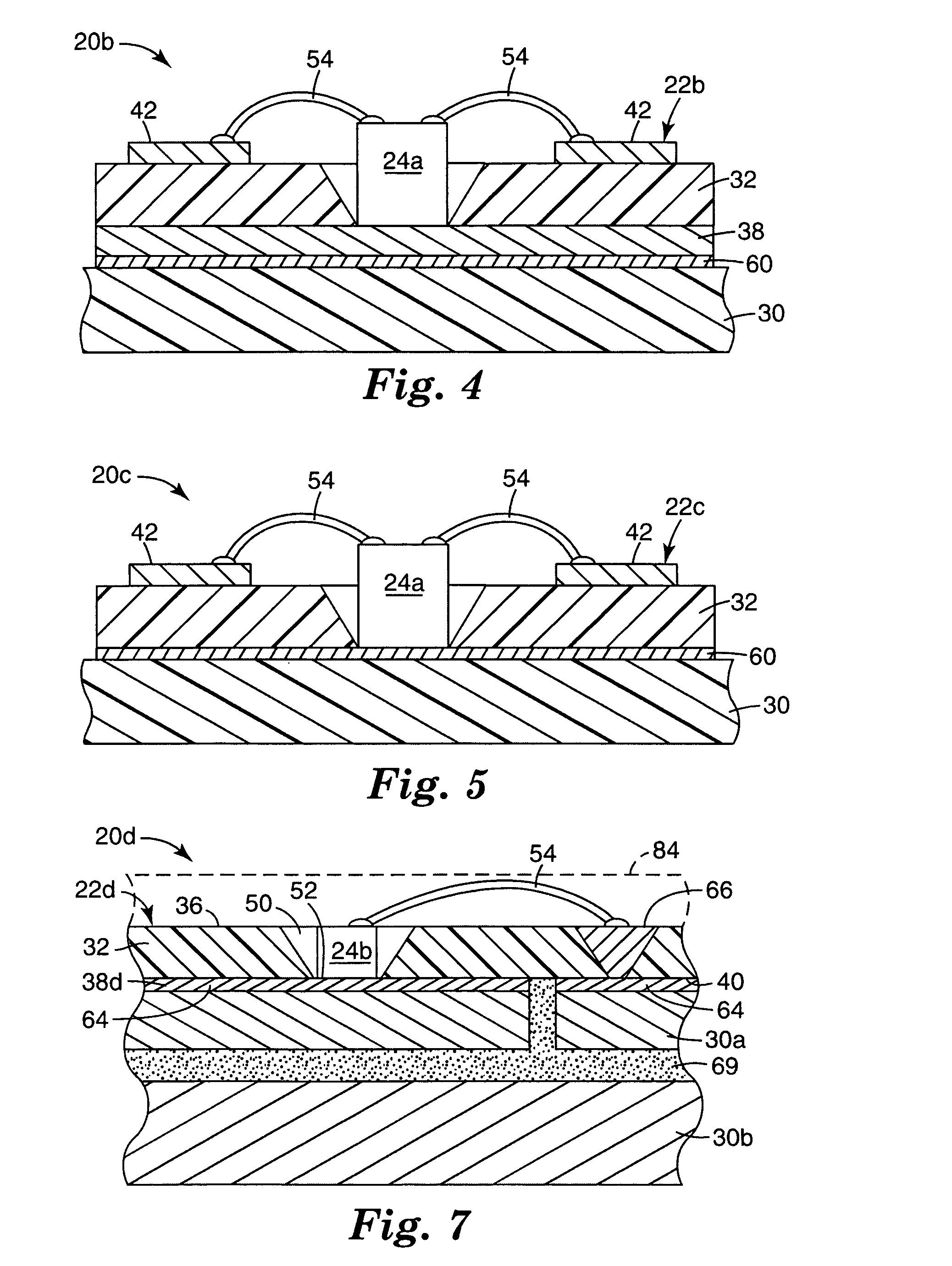

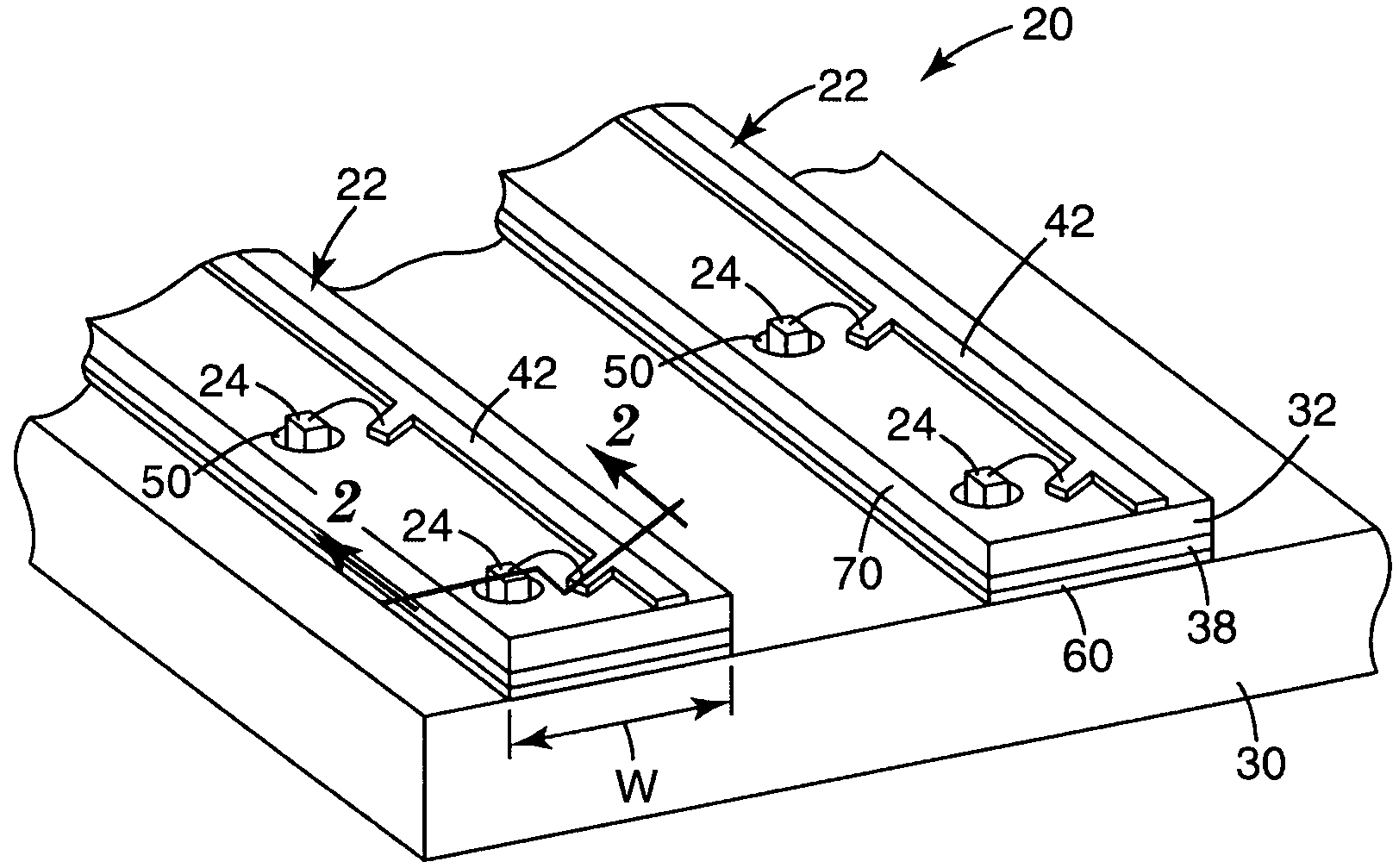

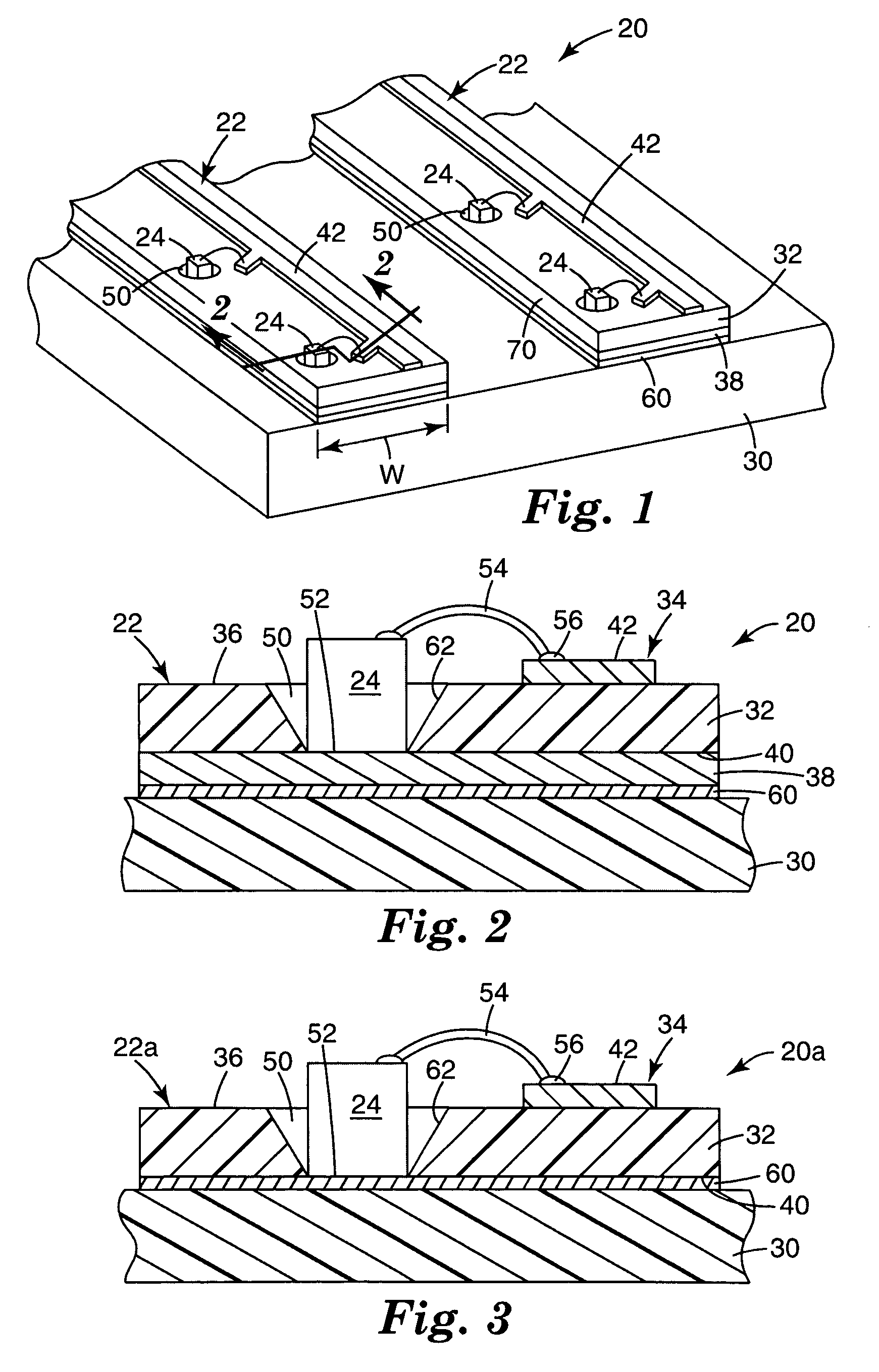

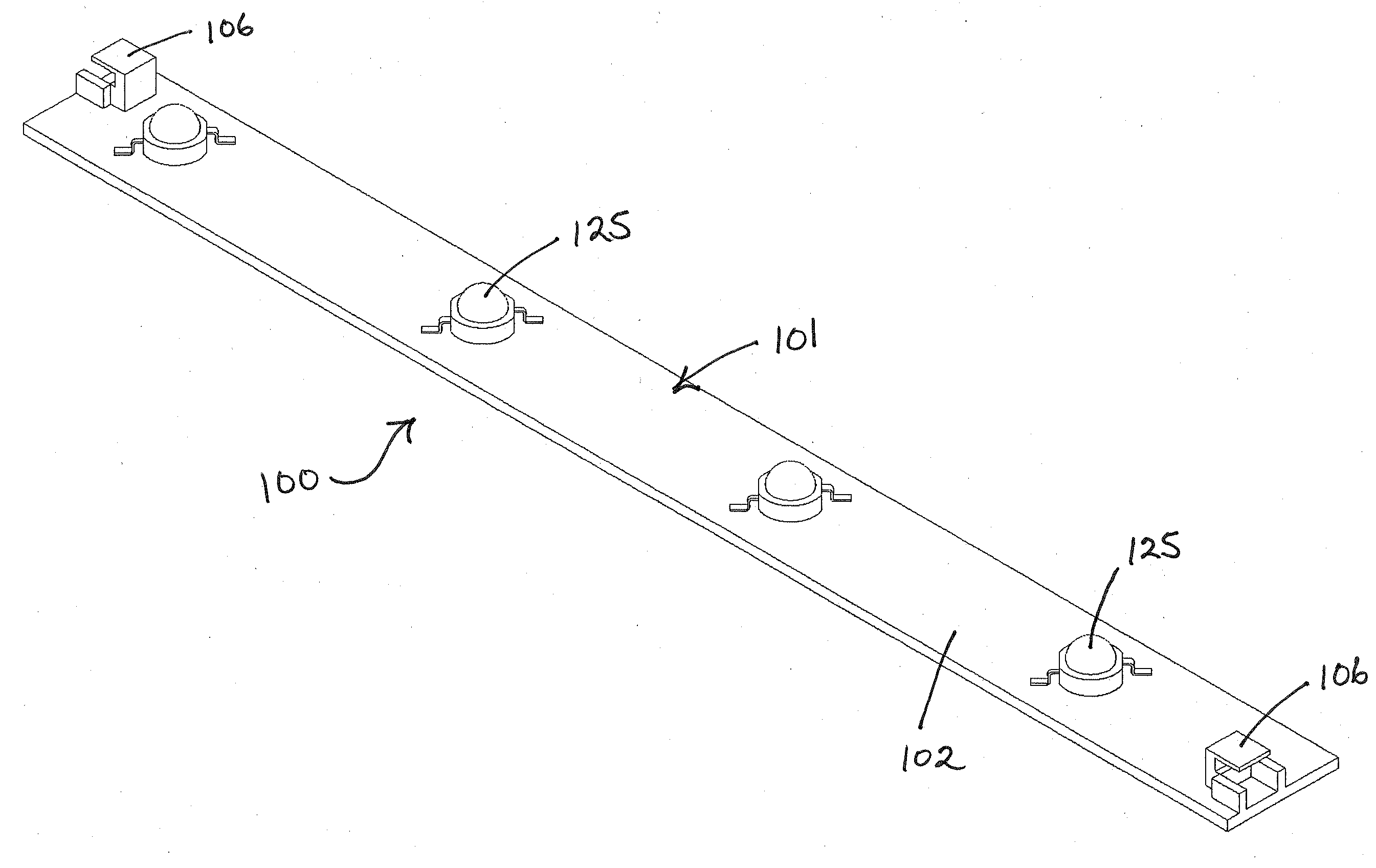

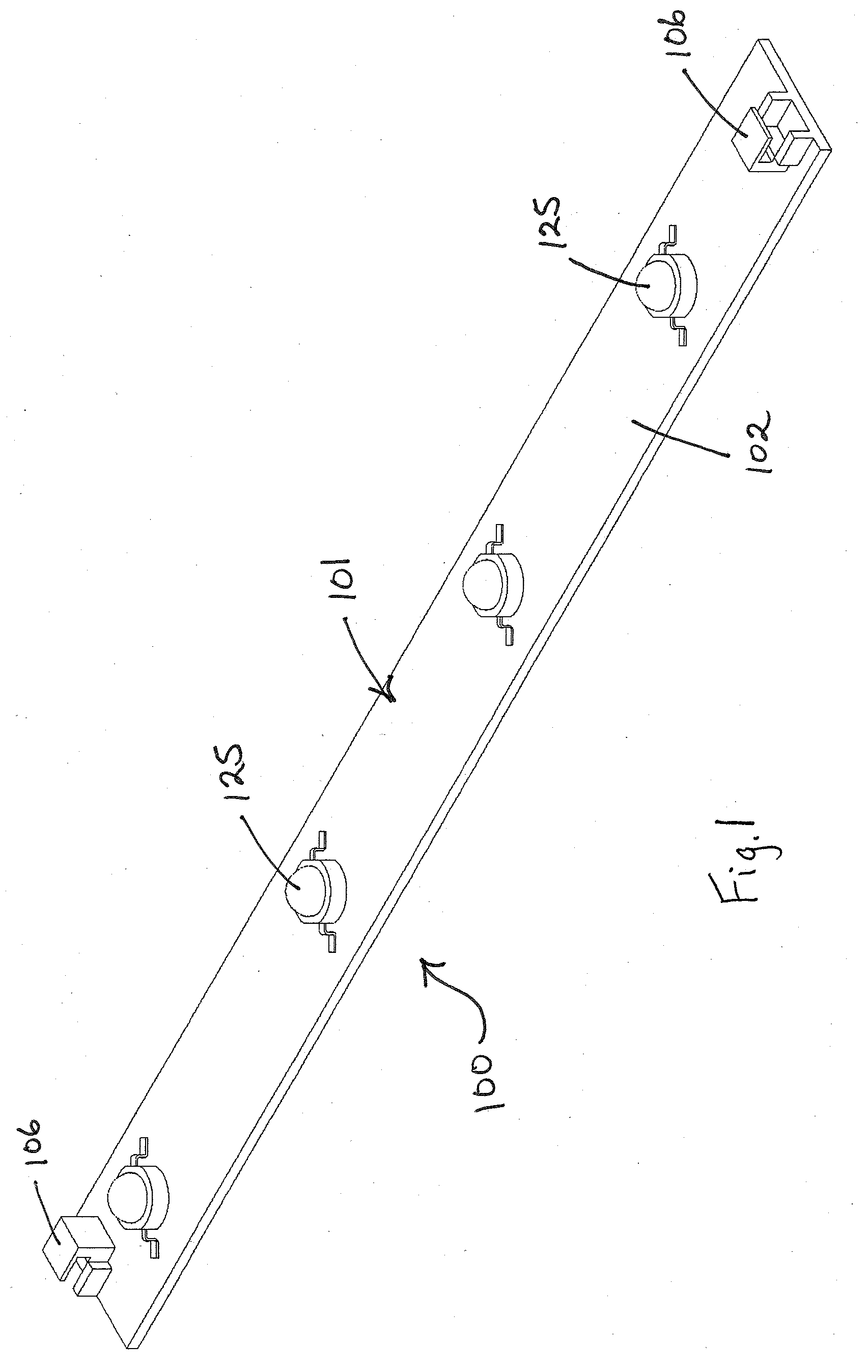

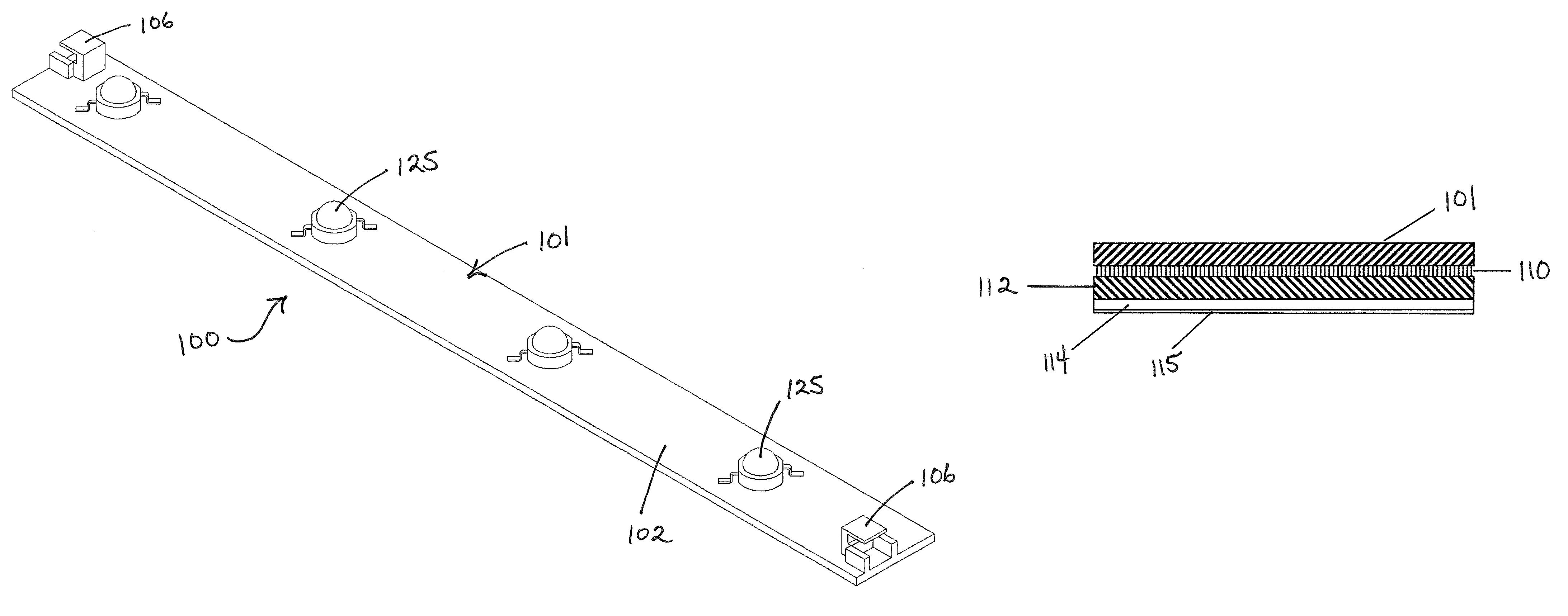

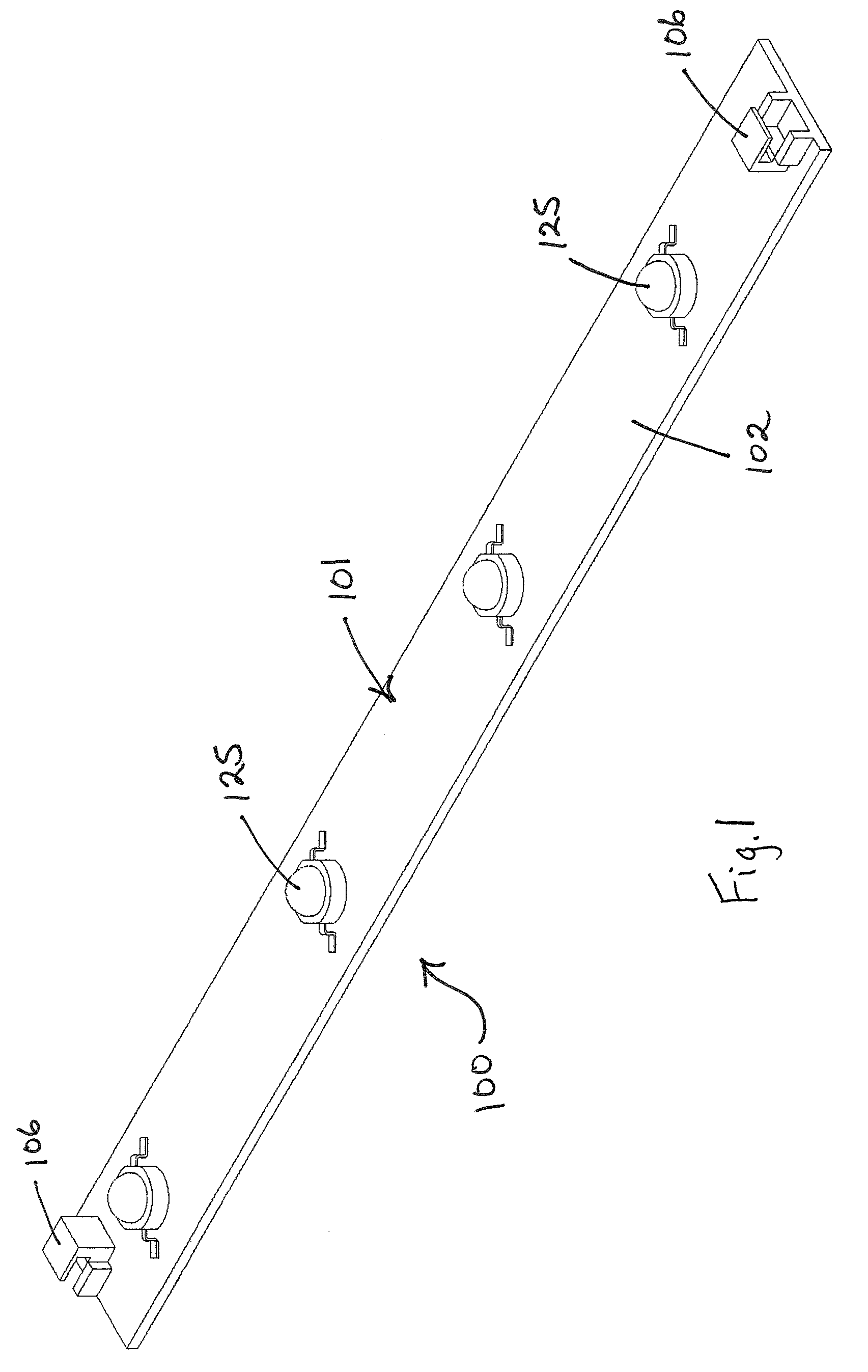

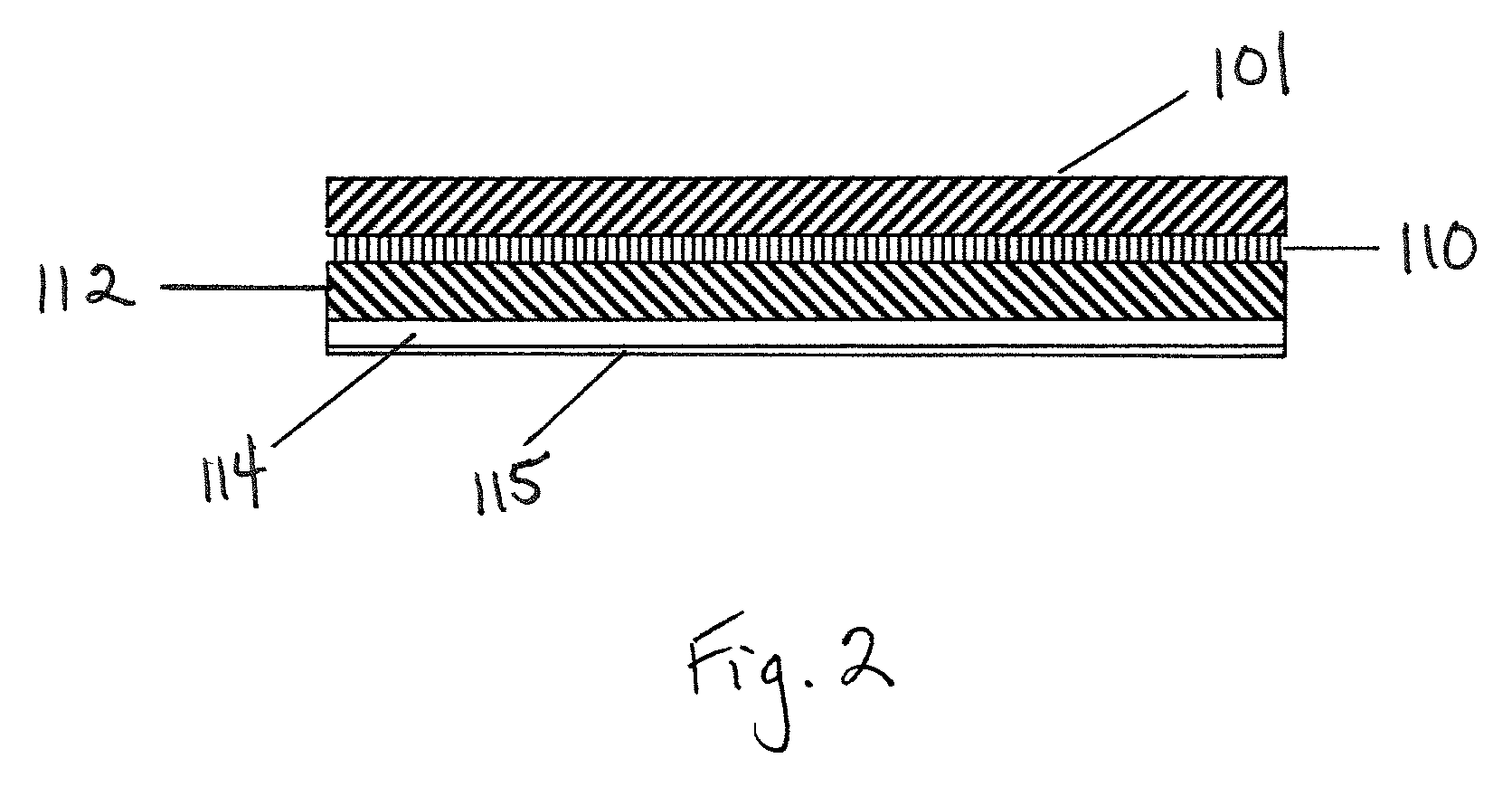

Illumination assembly using circuitized strips

ActiveUS20060098438A1Lighting support devicesLighting heating/cooling arrangementsLight-emitting diode

An illumination assembly includes a heat dissipating member having a plurality of circuitized strips disposed thereon a spaced relationship. Each circuitized strip includes an electrically insulative substrate having at least one circuit trace on a first side of the substrate and an electrically and thermally conductive layer on a second side of the substrate, such that the at least one circuit trace is electrically insulated from the second side of the substrate. The circuitized strips have a plurality of vias extending from the first side to the second side of the substrate. A plurality of LEDs are disposed in the plurality of vias, such that each LEDs is disposed on the electrically and thermally conductive layer on the second side of the substrate and electrically connected to the at least one circuit trace on the first side of the substrate.

Owner:3M INNOVATIVE PROPERTIES CO

Illumination assembly using circuitized strips

ActiveUS7303315B2Lighting support devicesLighting heating/cooling arrangementsElectricityEngineering

An illumination assembly includes a heat dissipating member having a plurality of circuitized strips disposed thereon a spaced relationship. Each circuitized strip includes an electrically insulative substrate having at least one circuit trace on a first side of the substrate and an electrically and thermally conductive layer on a second side of the substrate, such that the at least one circuit trace is electrically insulated from the second side of the substrate. The circuitized strips have a plurality of vias extending from the first side to the second side of the substrate. A plurality of LEDs are disposed in the plurality of vias, such that each LEDs is disposed on the electrically and thermally conductive layer on the second side of the substrate and electrically connected to the at least one circuit trace on the first side of the substrate.

Owner:3M INNOVATIVE PROPERTIES CO

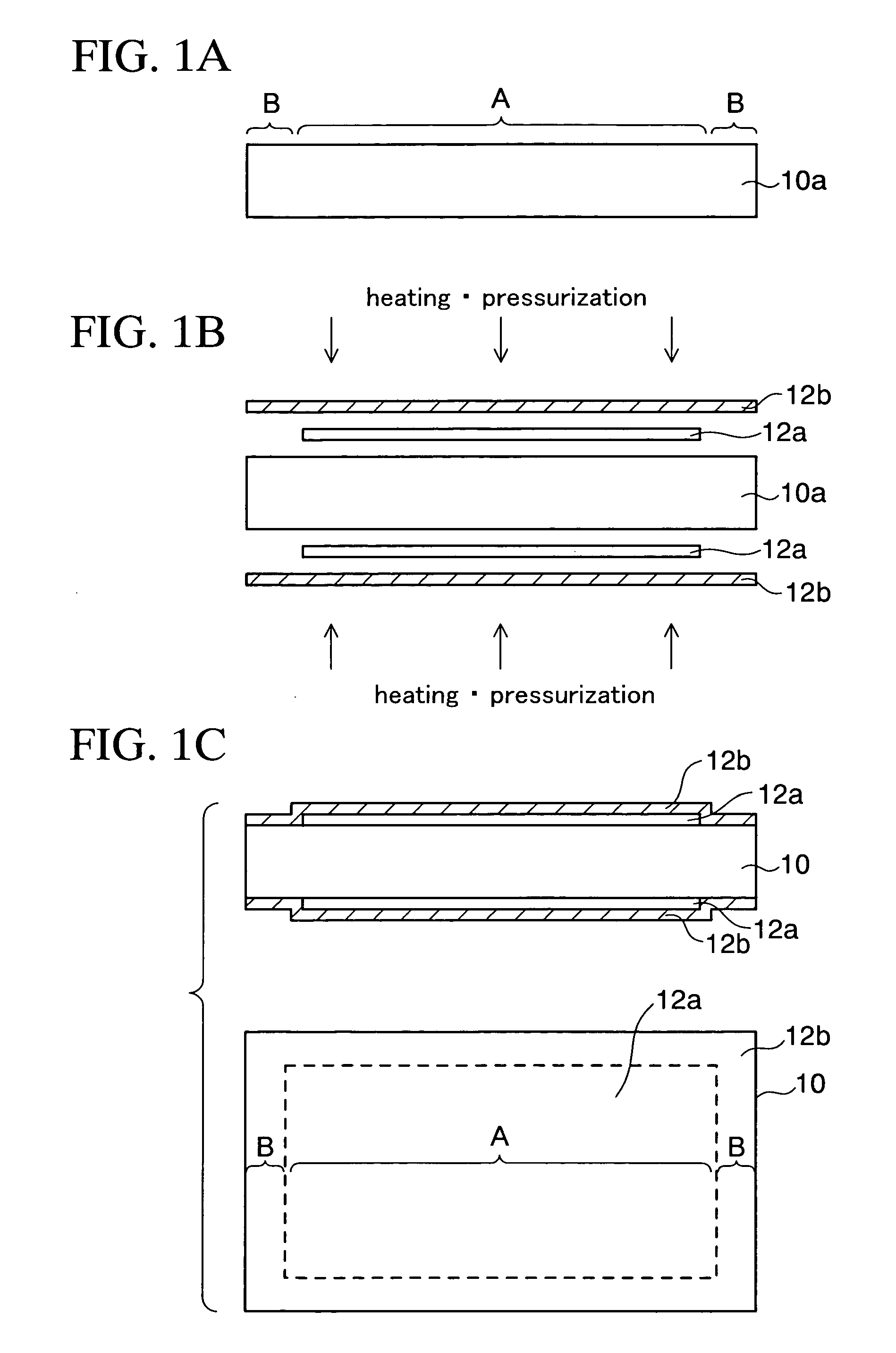

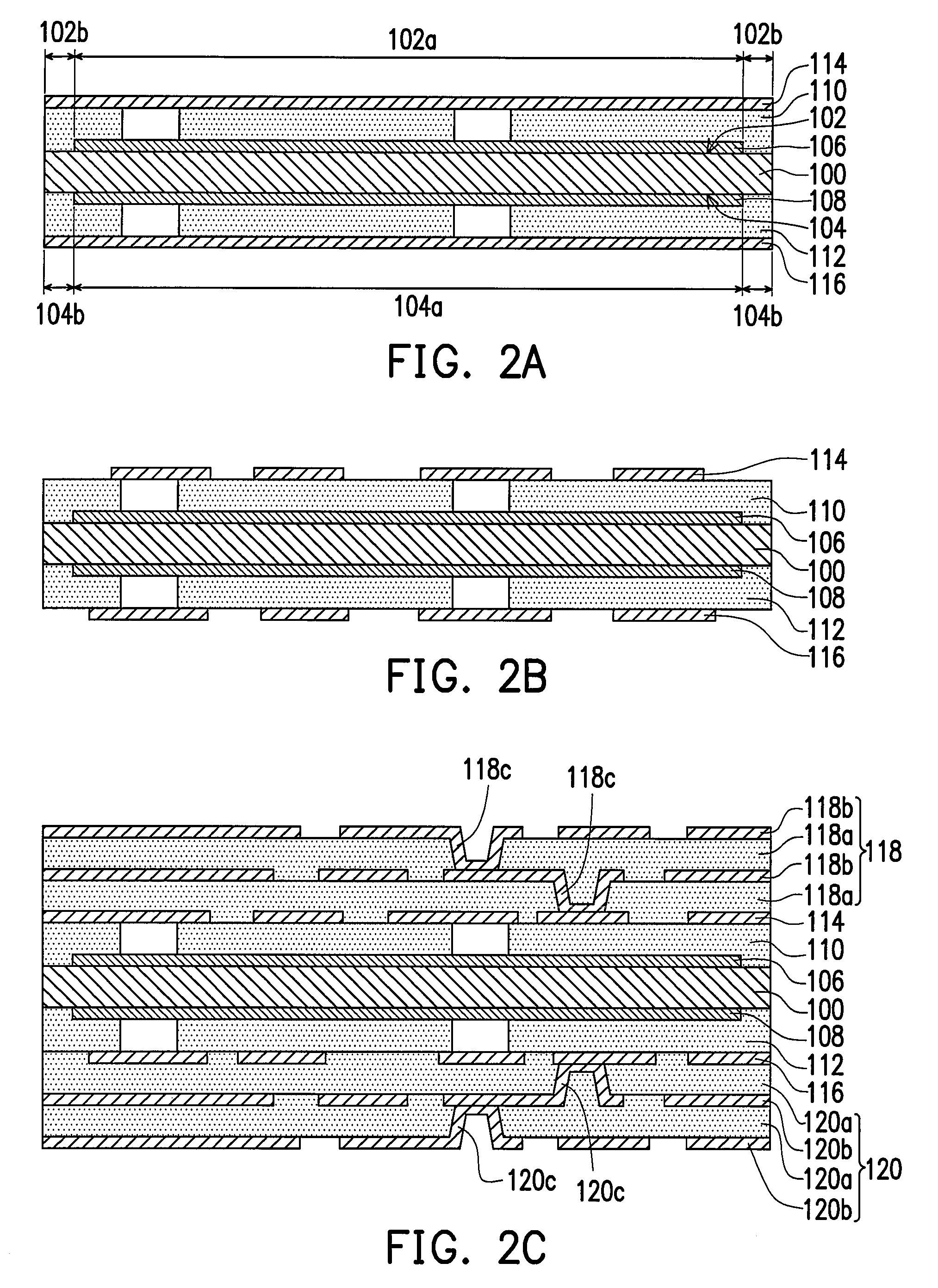

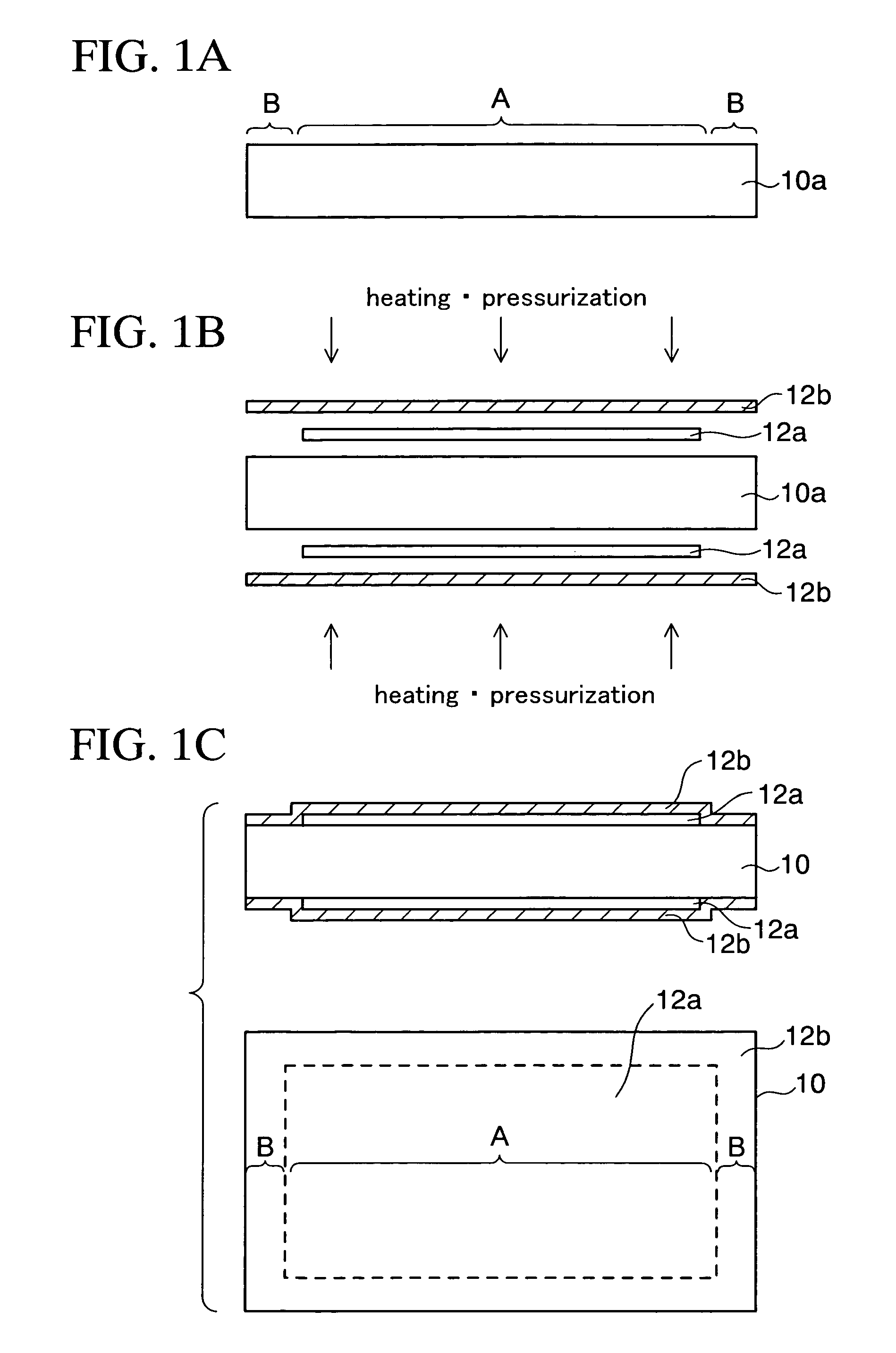

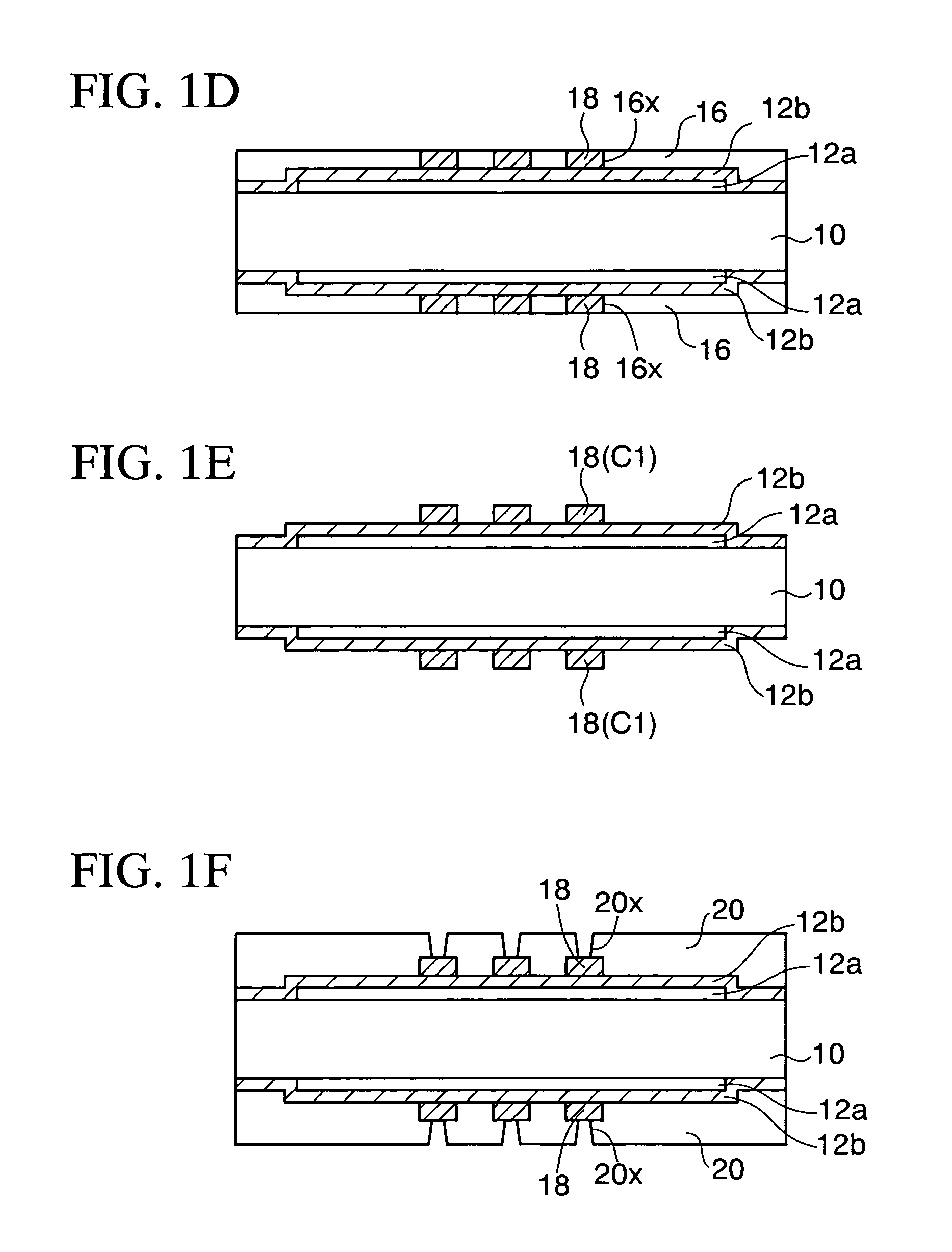

Method of manufacturing wiring substrate and method of manufacturing electronic component mounting structure

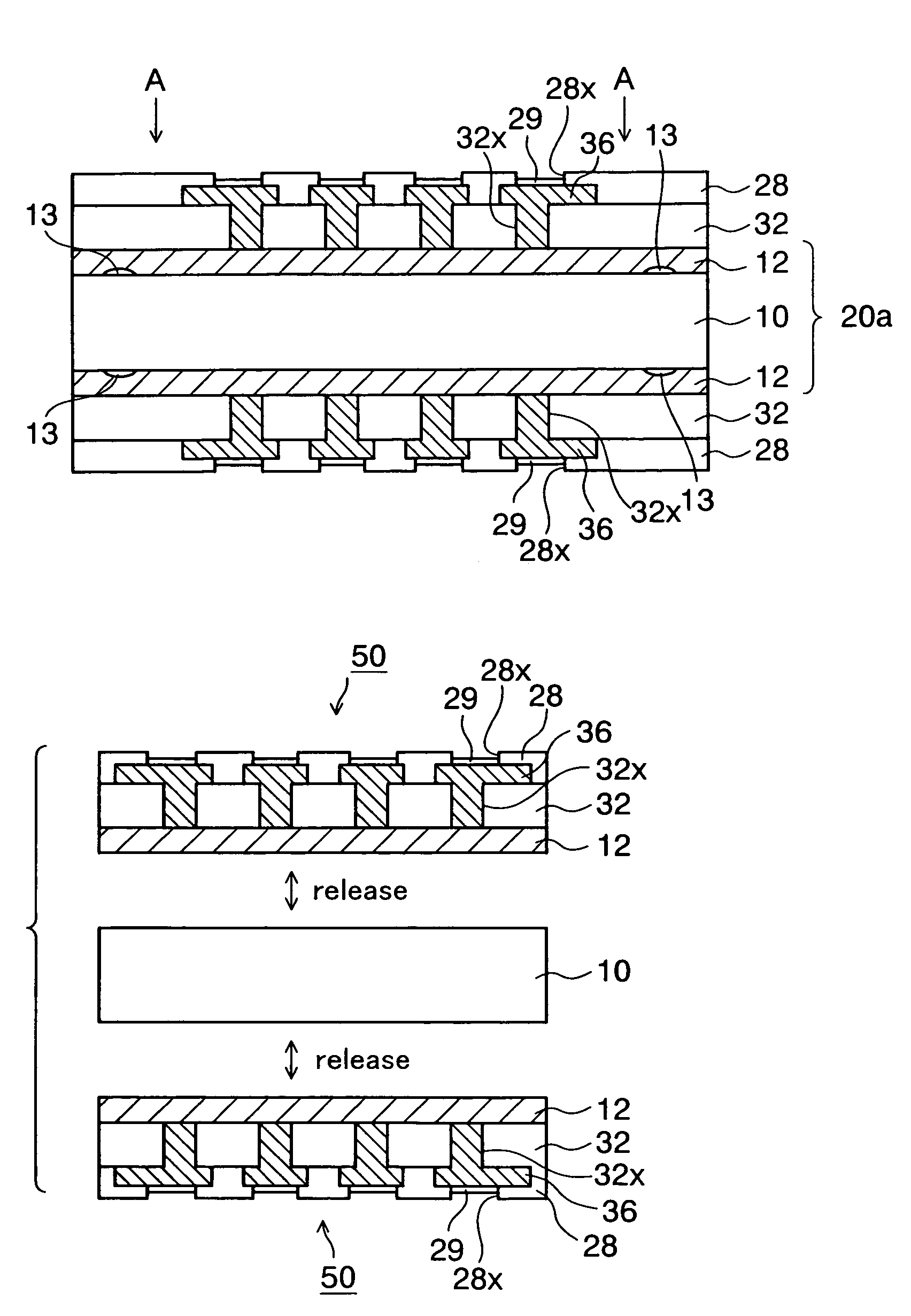

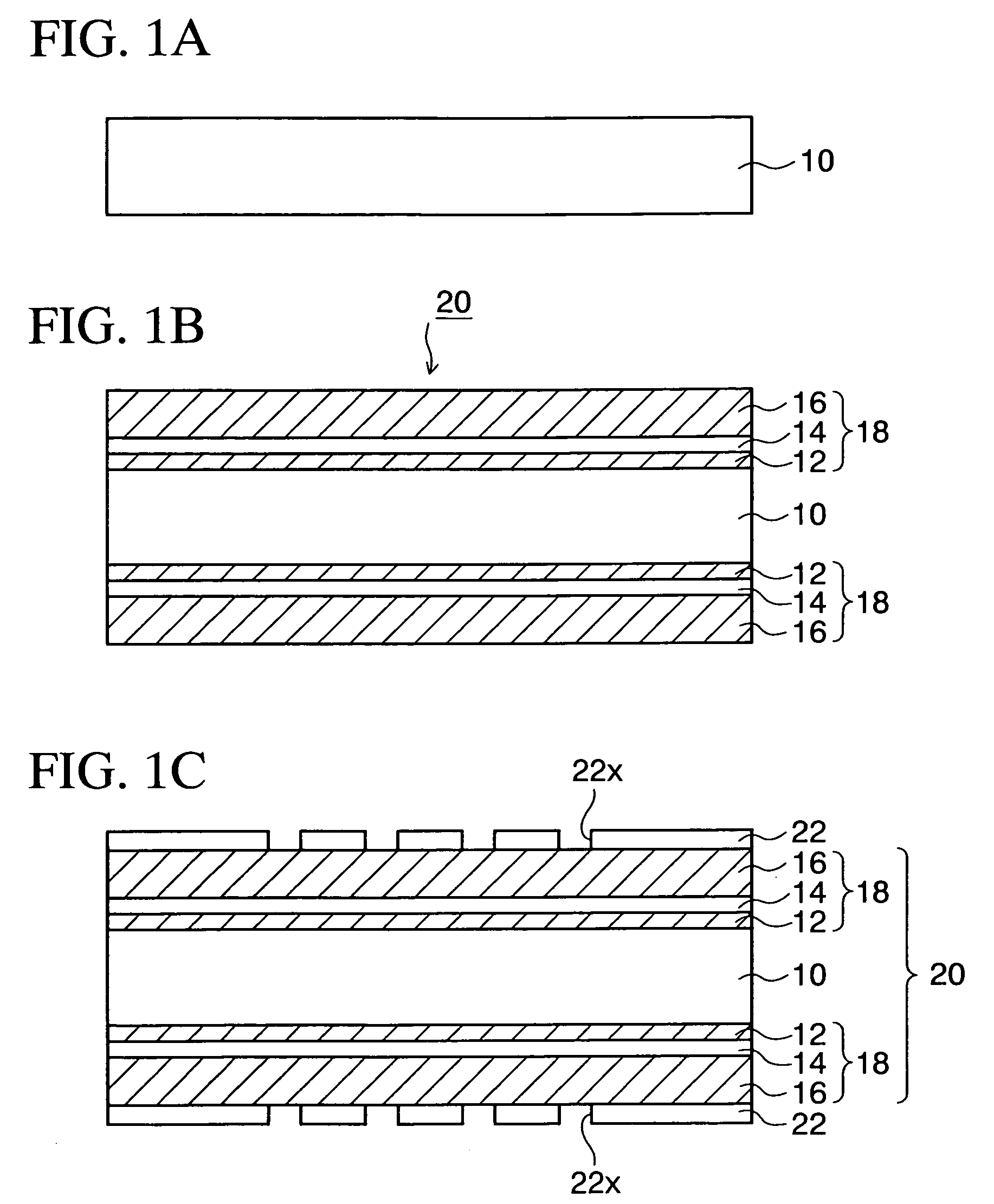

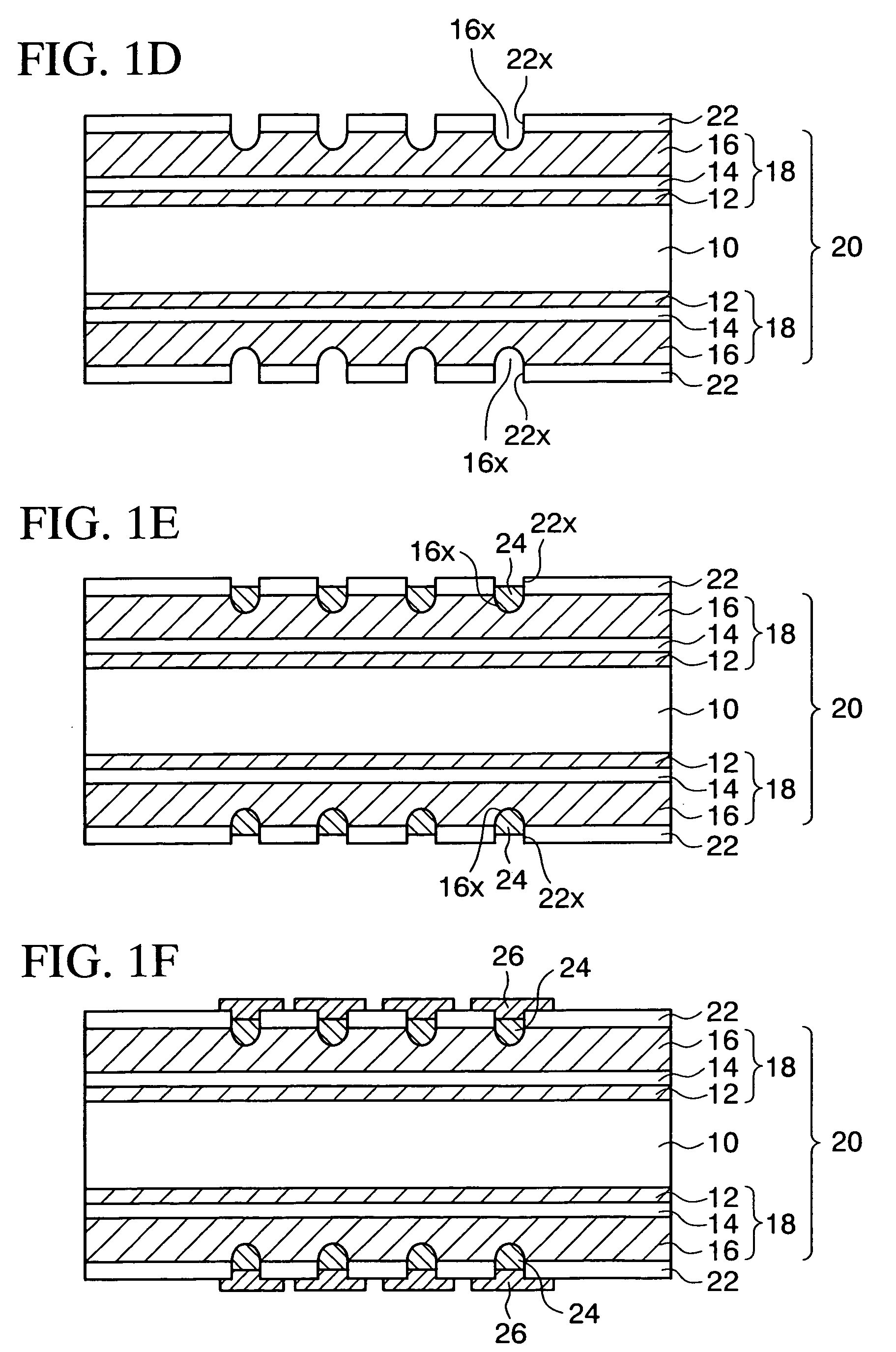

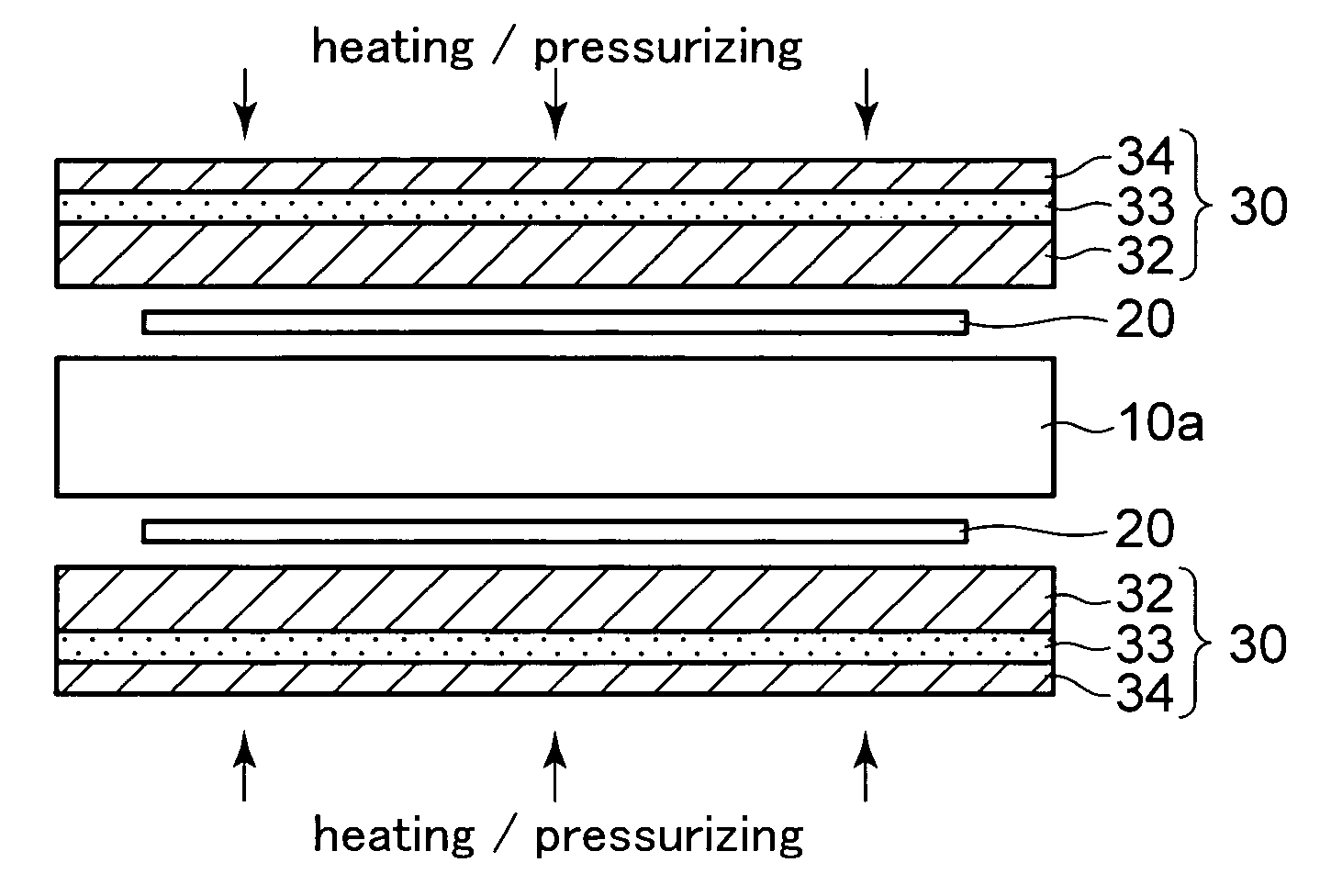

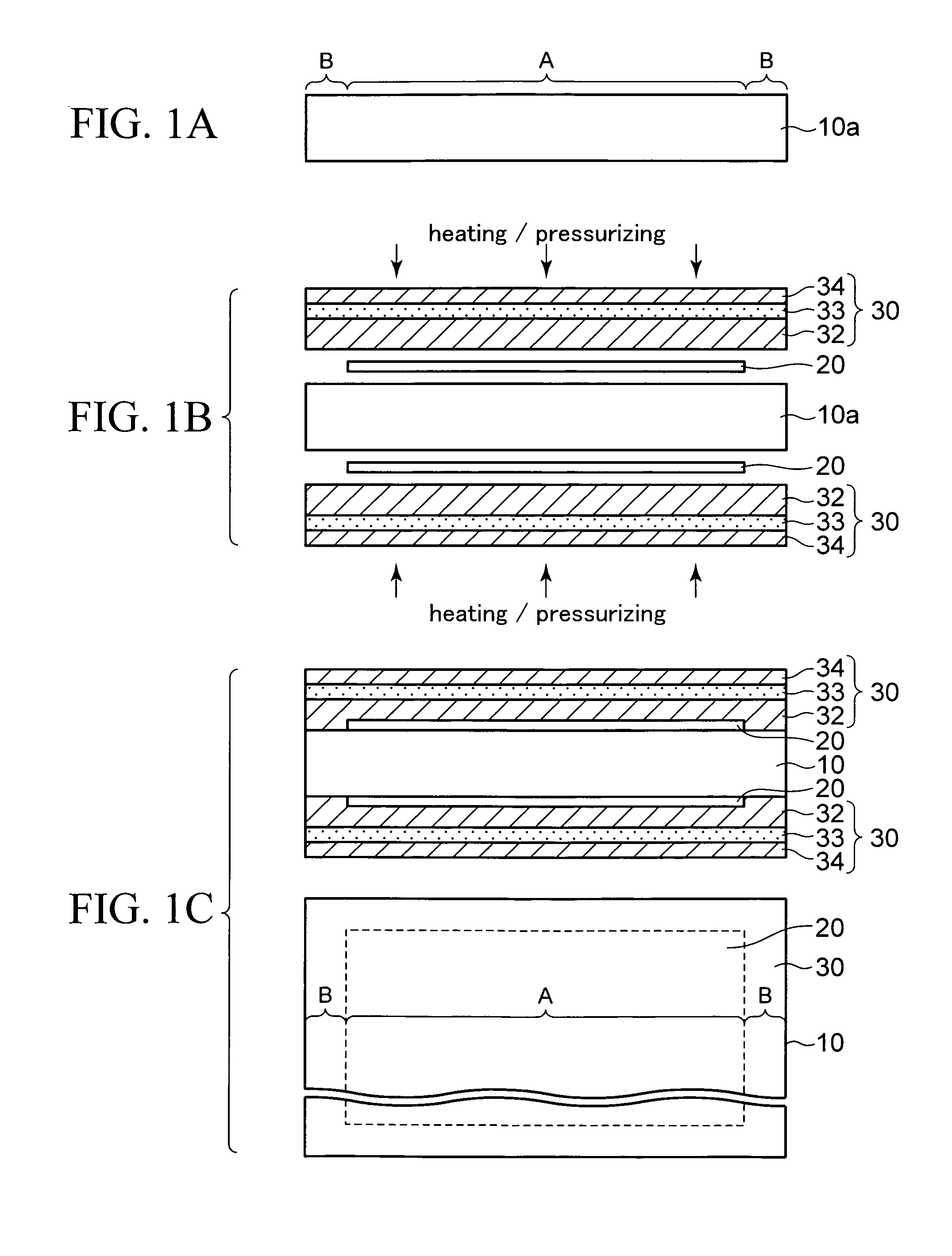

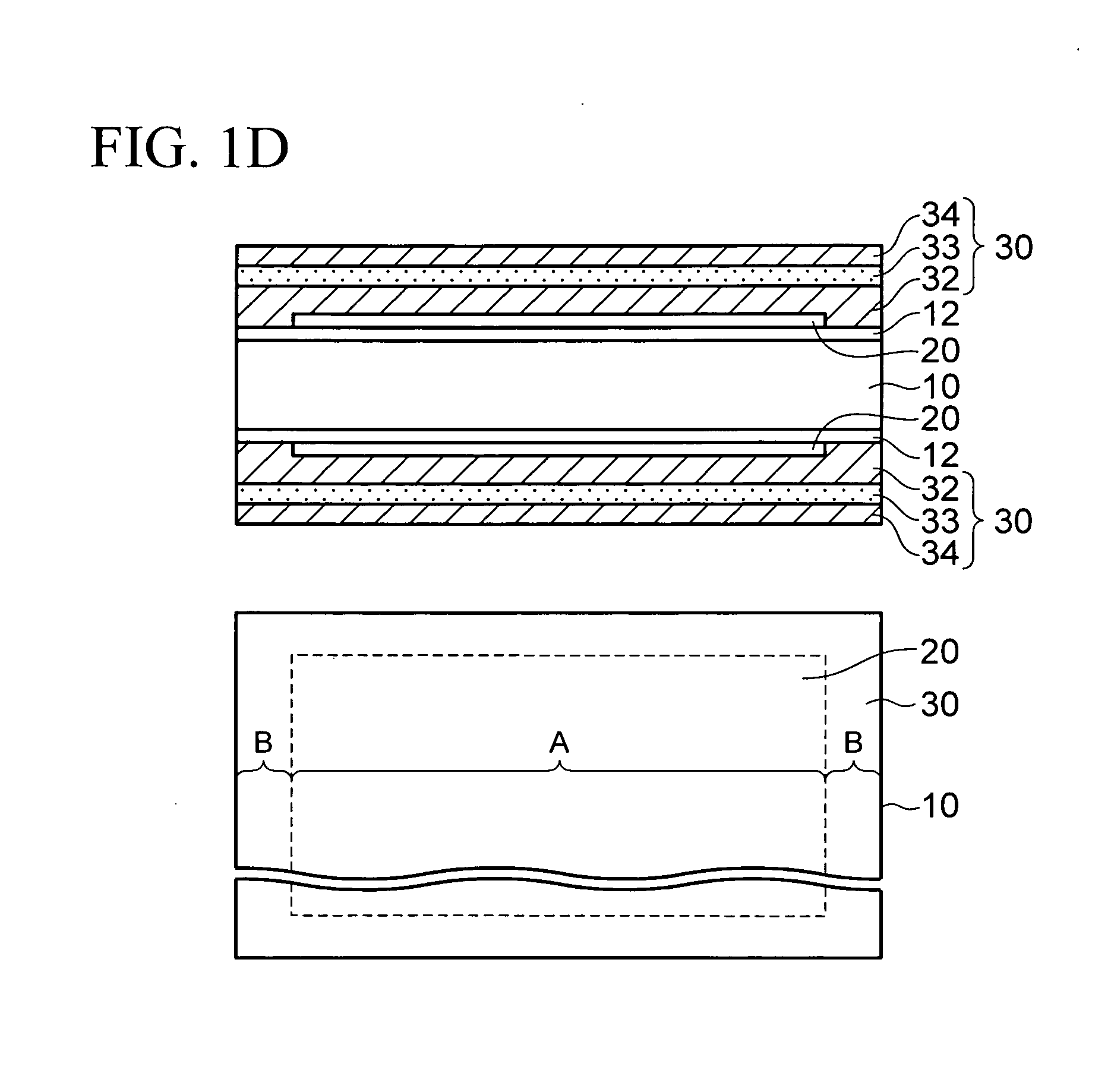

ActiveUS20070124924A1Easy to conveyEasy to handlePrinted circuit assemblingLine/current collector detailsMetal foilEngineering

A method of manufacturing a wiring substrate including the steps of, obtaining a temporary substrate from a prepreg, and concurrently attaching a metal foil onto at least one surface of the temporary substrate, by disposing the metal foil on a prepreg through a underlying layer interposed between them, in a way that the underlying layer is disposed in a wiring formation region on the prepreg, and the metal foil having a size larger than that of the underlying layer is caused to contact with an outer peripheral portion of the wiring formation region, and then by hardening the prepreg with heating and pressurization, forming a build-up wiring layer on the metal foil, and obtaining a wiring member in which the build-up wiring layer is formed on the metal foil, by cutting out a portion of structure in which the underlying layer, the metal foil and the build-up wiring layer are formed on the temporary substrate, the portion corresponding to a peripheral portion of the underlying layer, and thus by separating the metal foil from the temporary substrate.

Owner:SHINKO ELECTRIC IND CO LTD

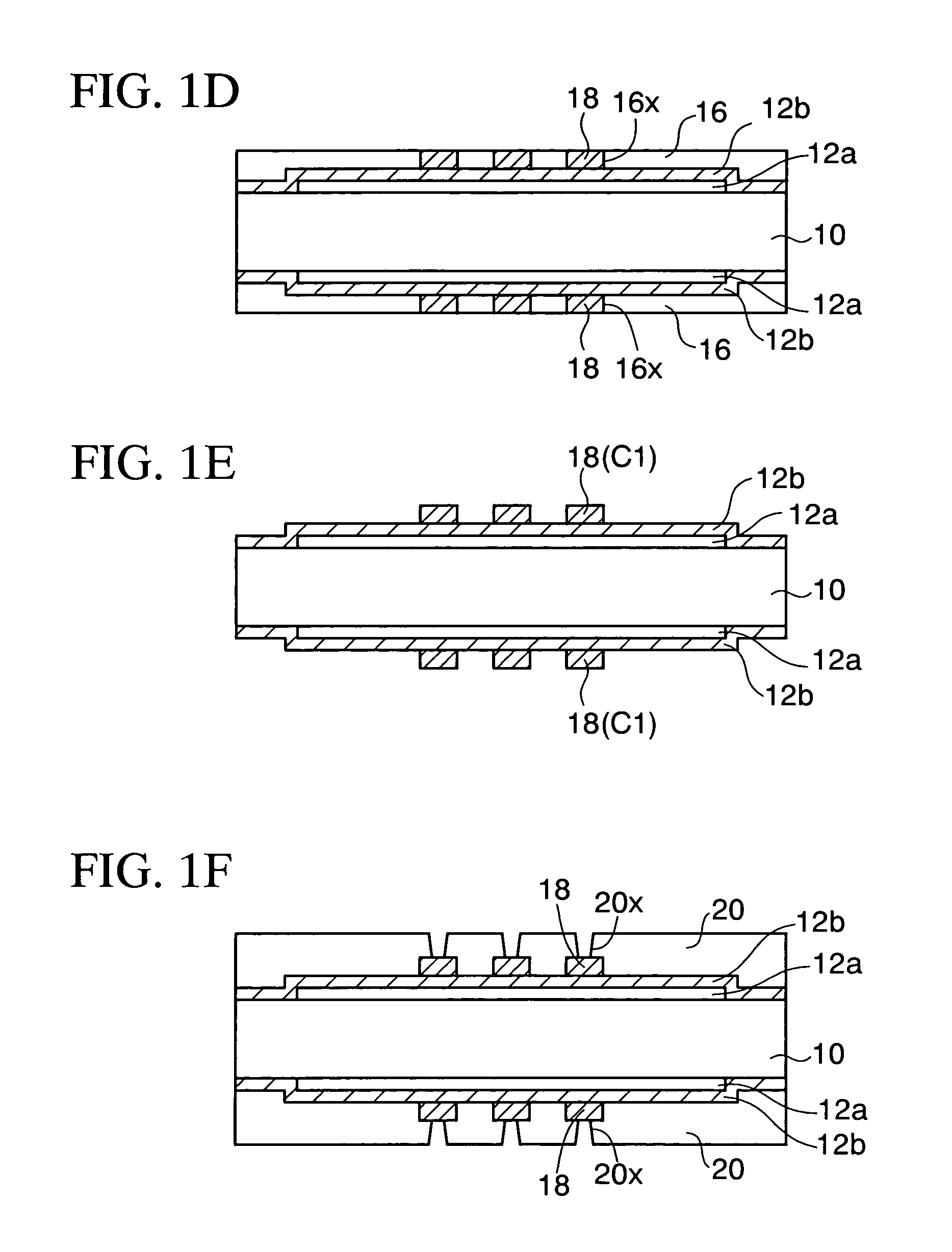

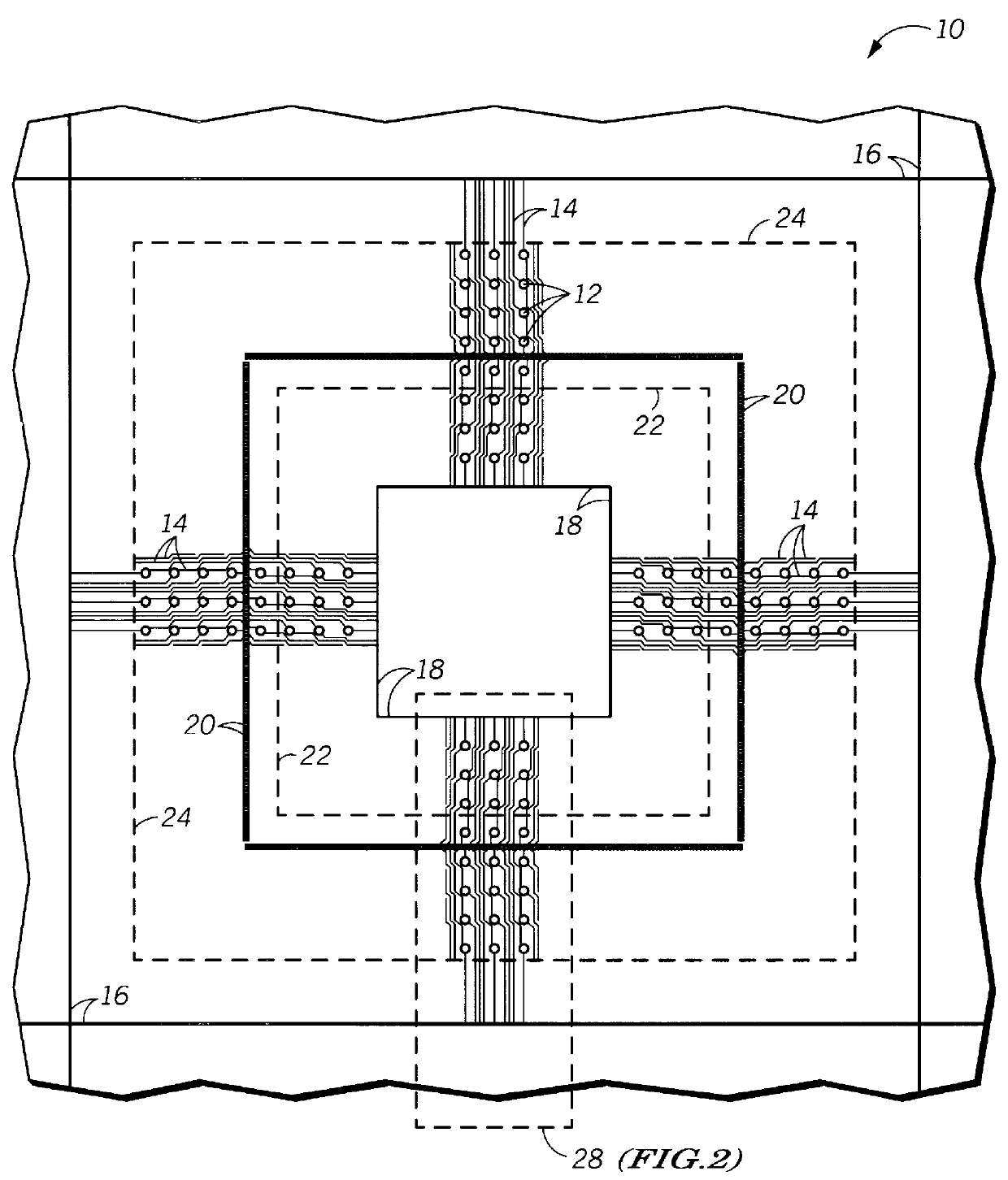

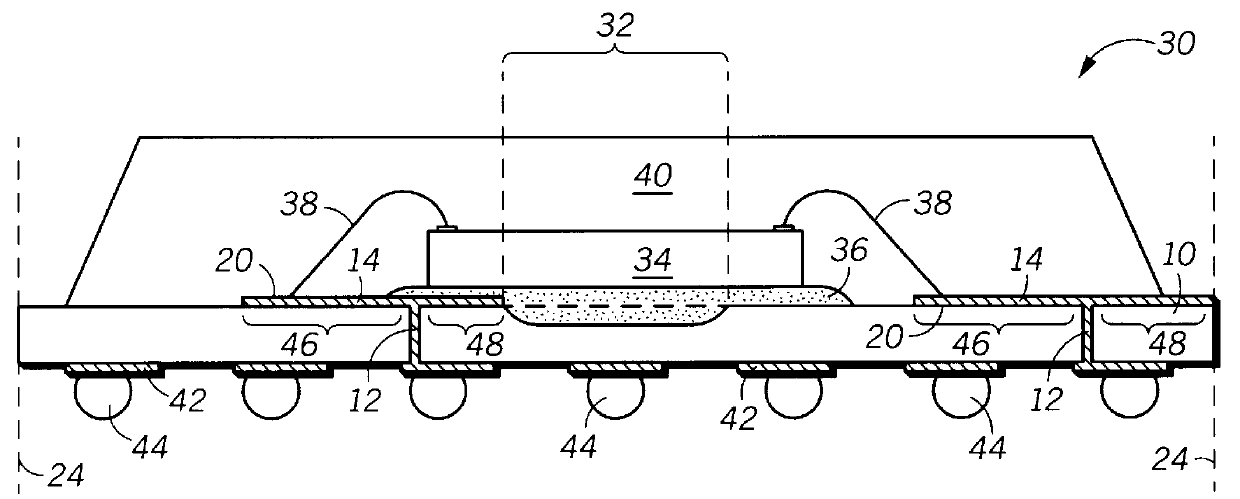

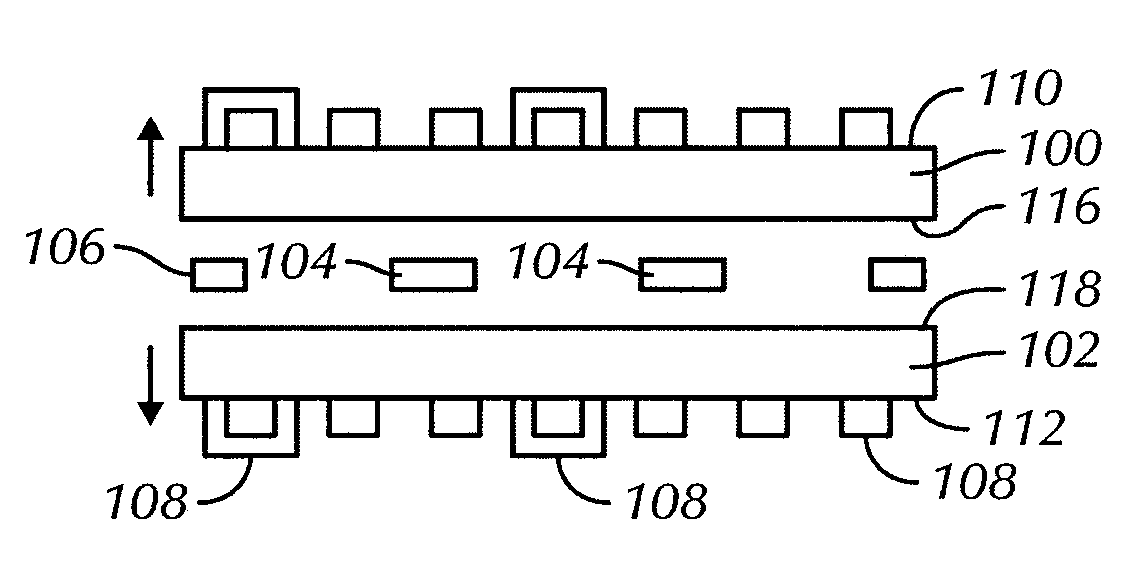

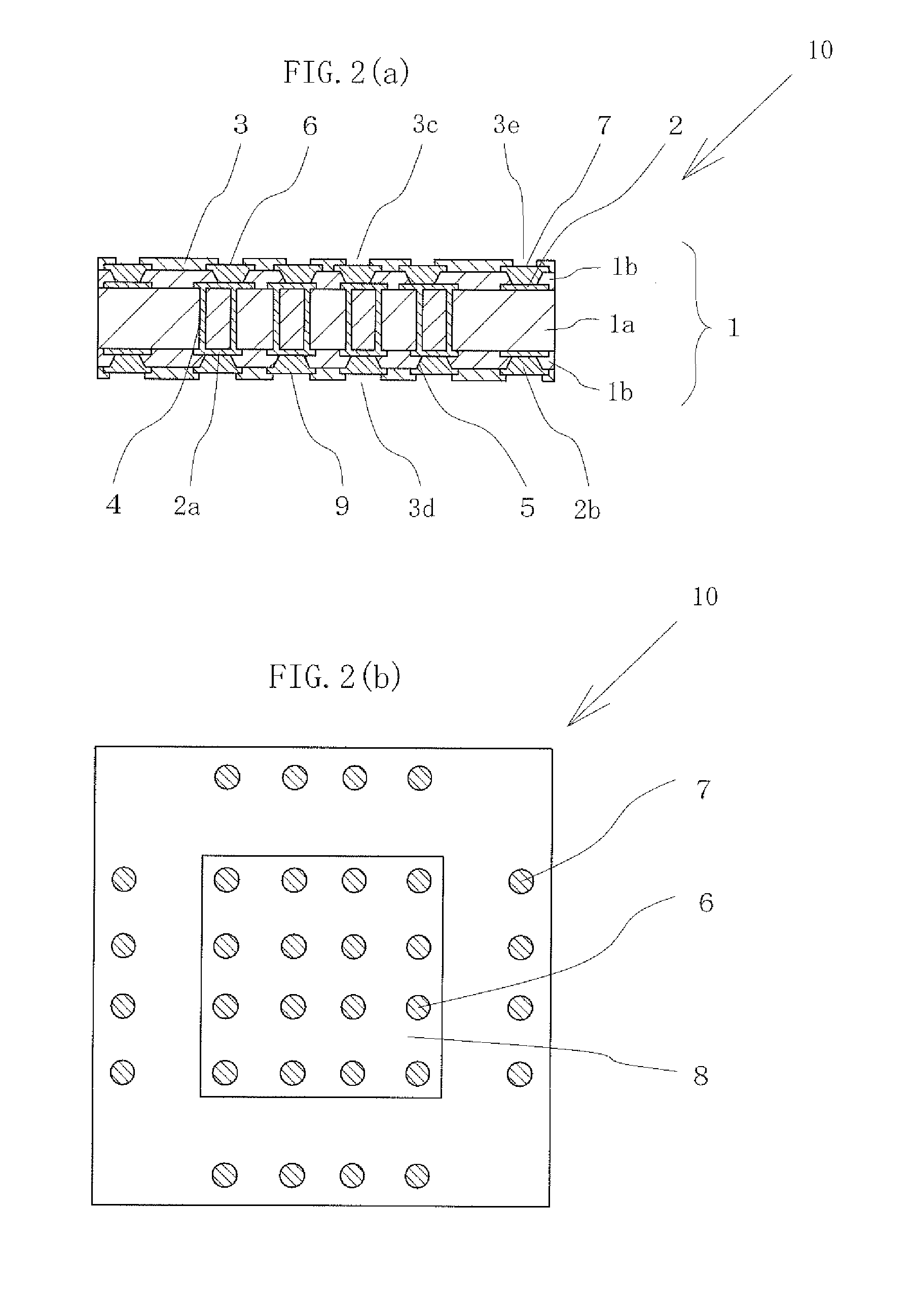

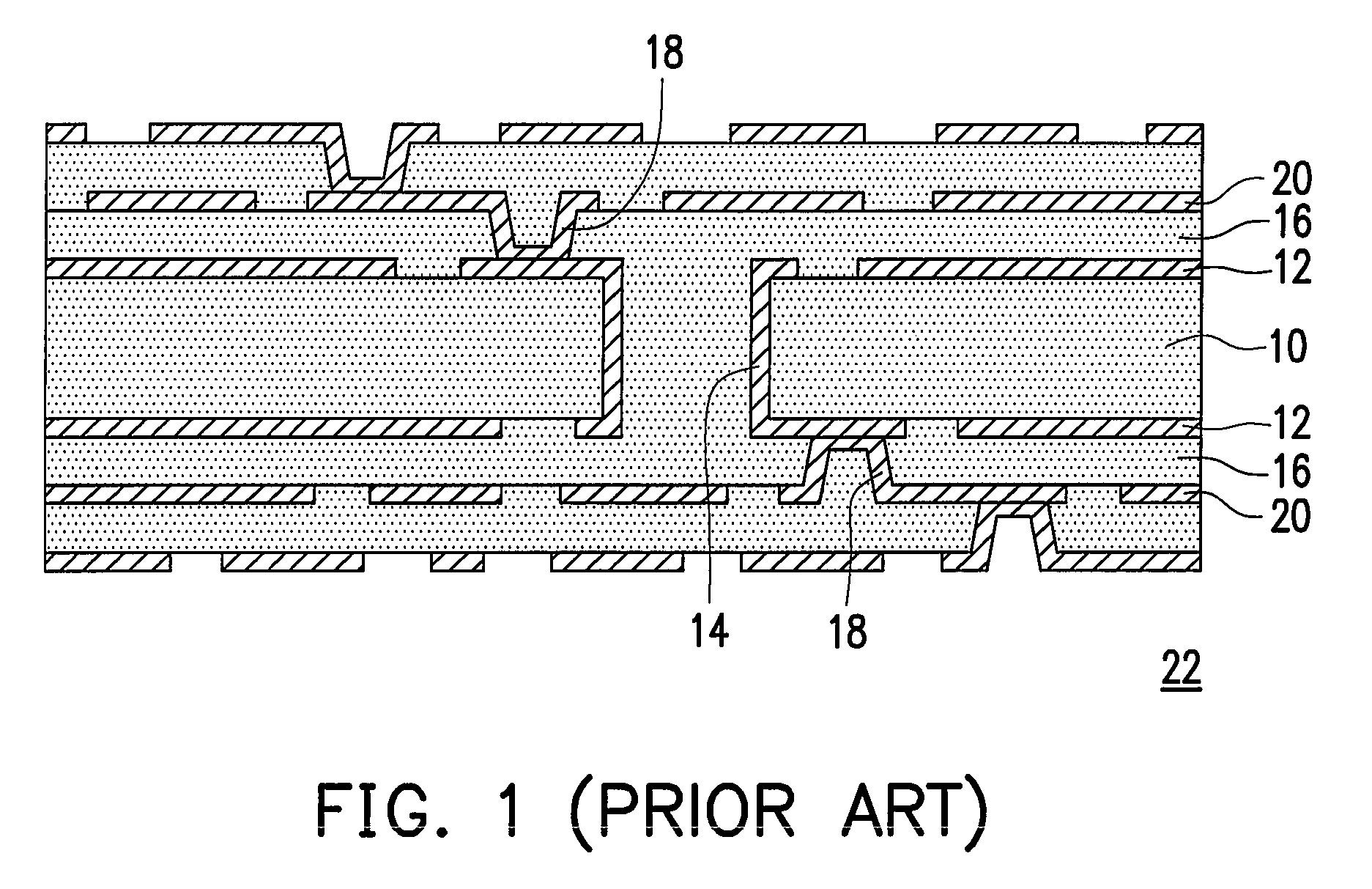

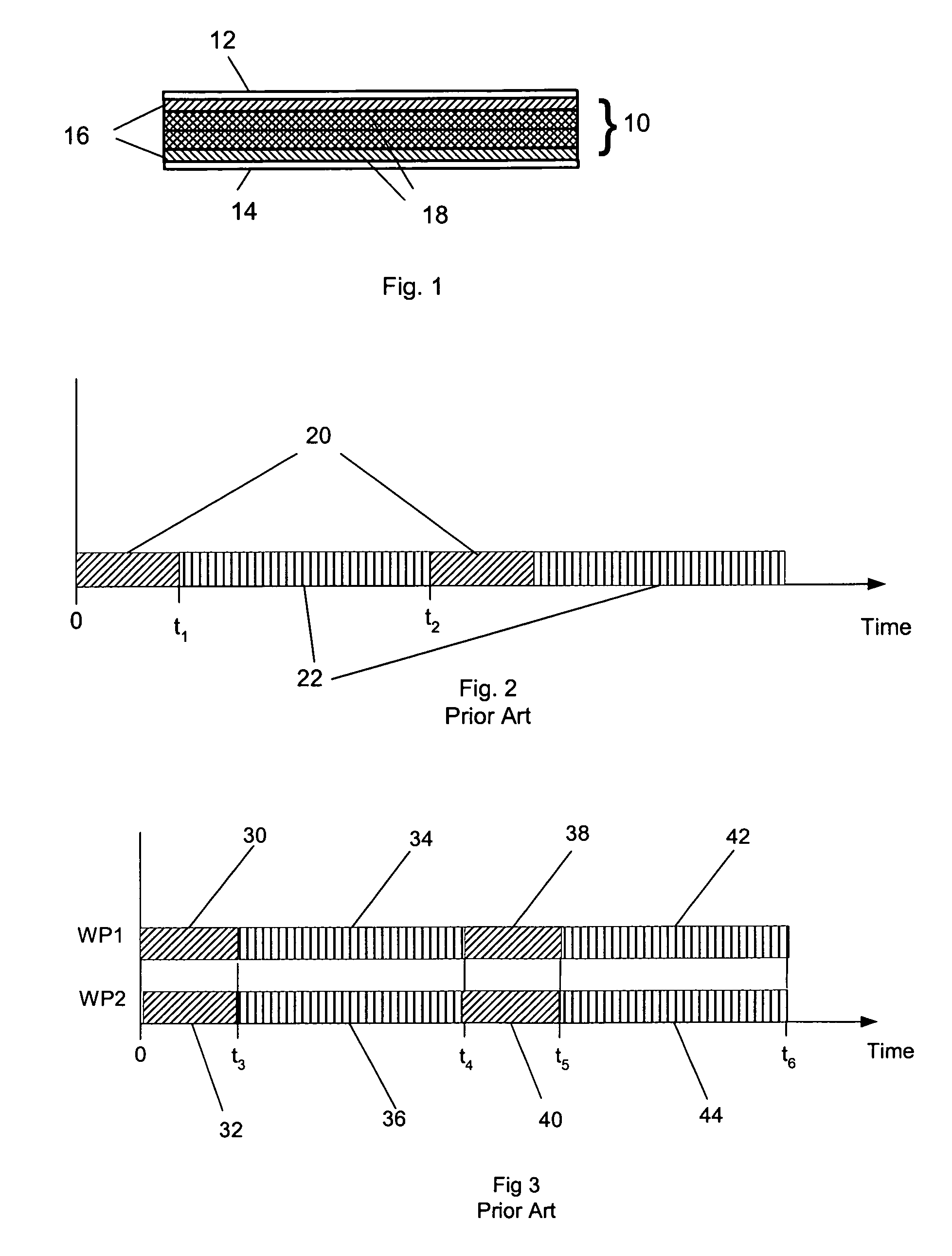

Method for plating using nested plating buses and semiconductor device having the same

InactiveUSRE36773E1Printed circuit assemblingElectrically conductive connectionsEngineeringElectroplating

Routing density of a wiring substrate (10) is increased by providing a nested plating bus (18) as a supplement to an external plating bus (16). A first group of conductive traces (14) is connected to the nested plating bus, while another group of traces is connected to the external plating bus. After the conductive elements are plated, the nested plating bus is removed by etching, milling, or stamping techniques. Use of a nested plating bus increases I / O count for a given substrate area and / or reduces the need to have routing on more than one layer of the substrate.

Owner:FREESCALE SEMICON INC

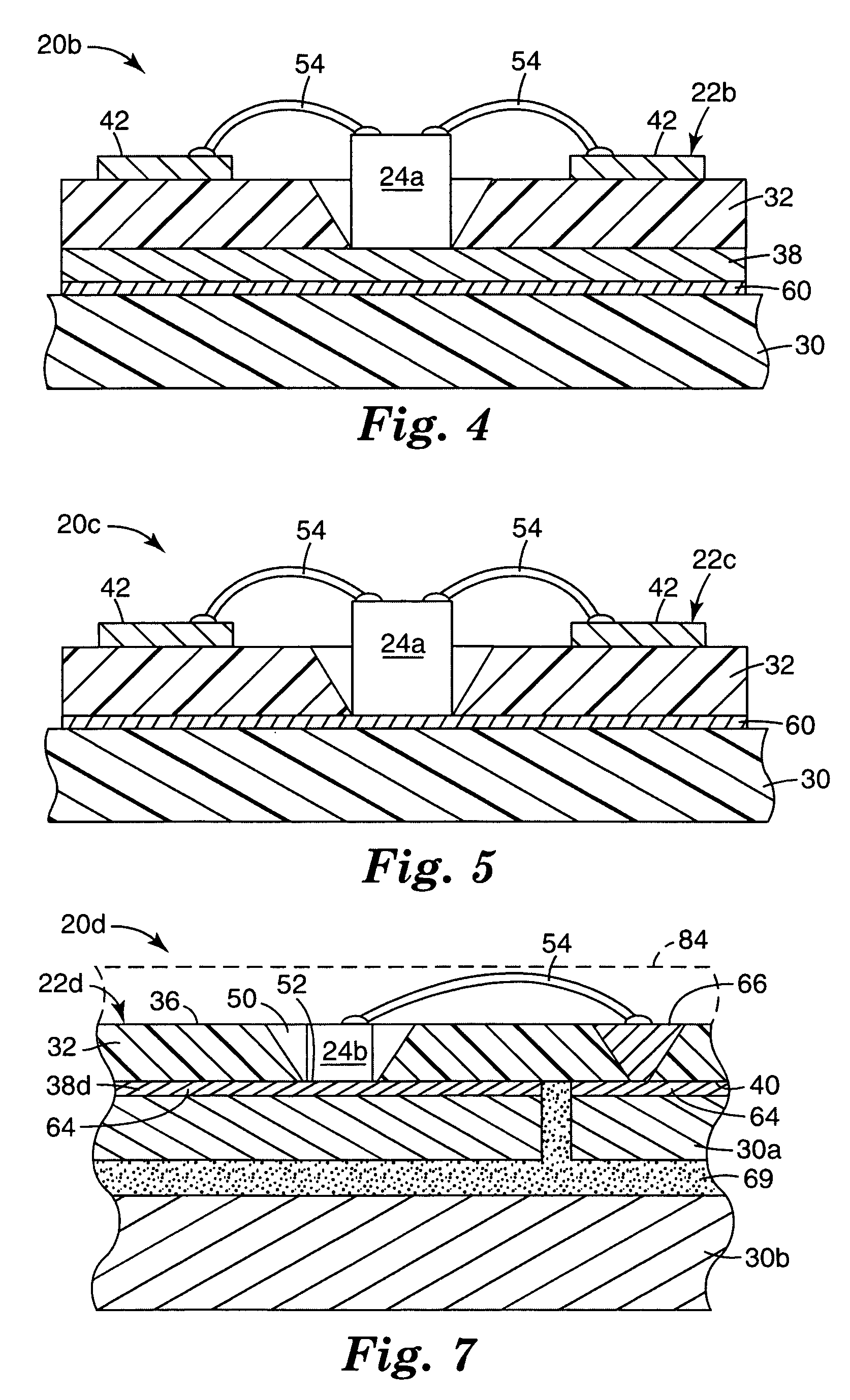

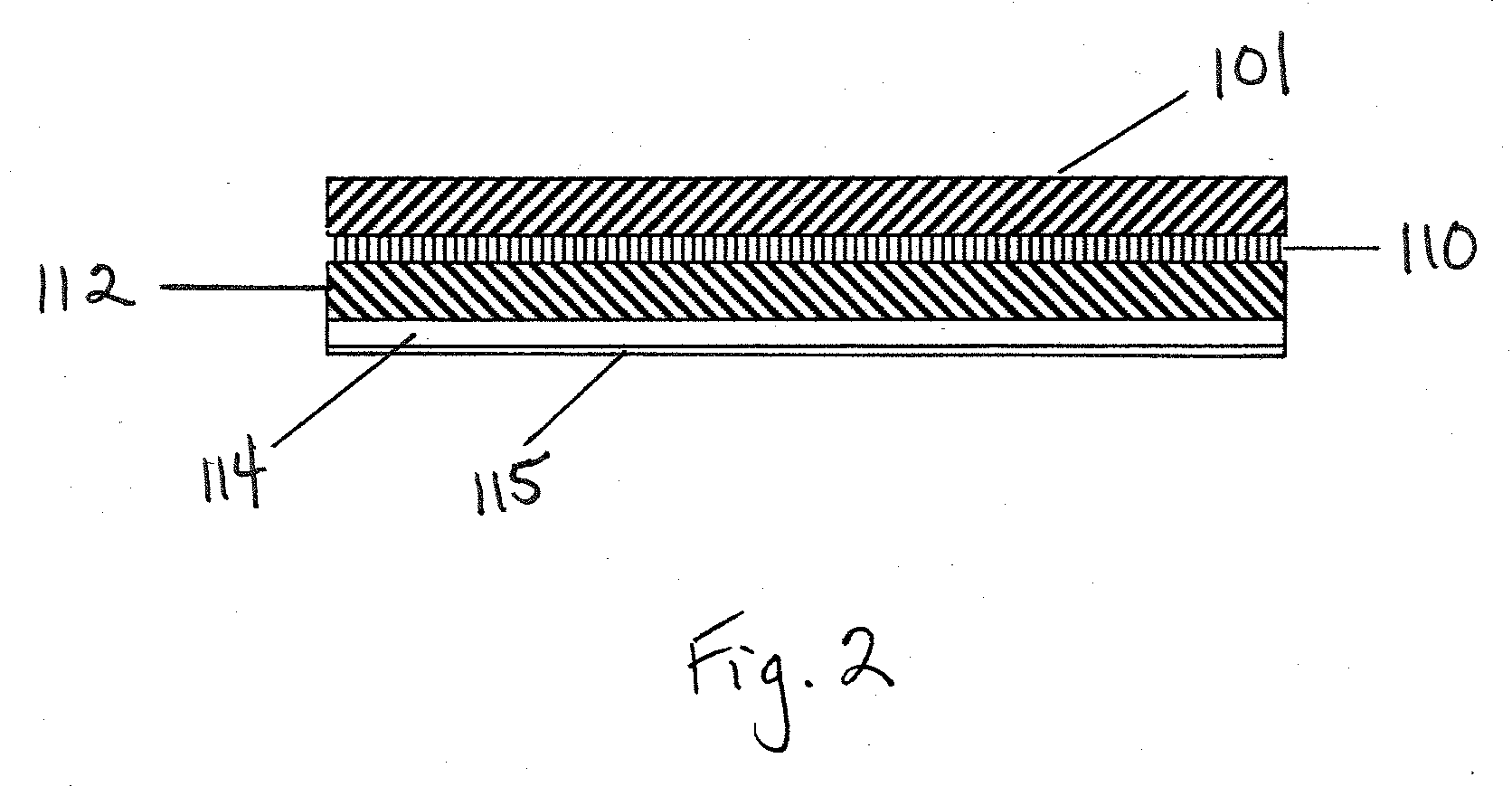

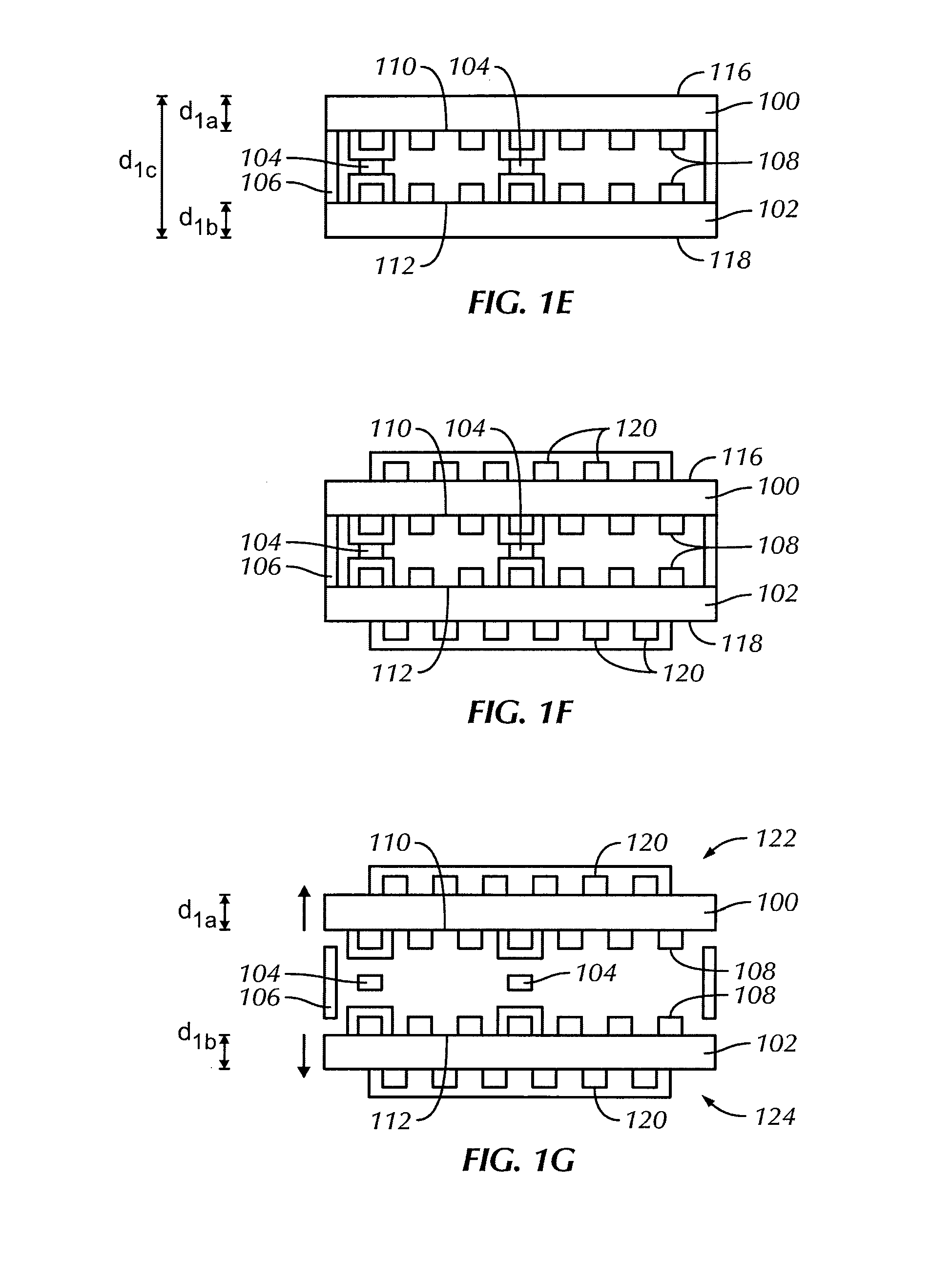

Layered structure for use with high power light emitting diode systems

A layered structure for use with a high power light emitting diode system comprises an electrically insulating intermediate layer interconnecting a top layer and a bottom layer. The top layer, the intermediate layer, and the bottom layer form an at least semi-flexible elongate member having a longitudinal axis and a plurality of positions spaced along the longitudinal axis. The at least semi-flexible elongate member is bendable laterally proximate the plurality of positions spaced along the longitudinal axis to a radius of at least 6 inches, twistable relative to its longitudinal axis up to 10 degrees per inch, and bendable to conform to localized heat sink surface flatness variations having a radius of at least 1 inch. The top layer is pre-populated with electrical components for high wattage, the electrical components including at least one high wattage light emitting diode at least 1.0 Watt per 0.8 inch squared.

Owner:METROSPEC TECH

Embedded circuit substrate and manufacturing method thereof

Owner:ADVANCED SEMICON ENG INC

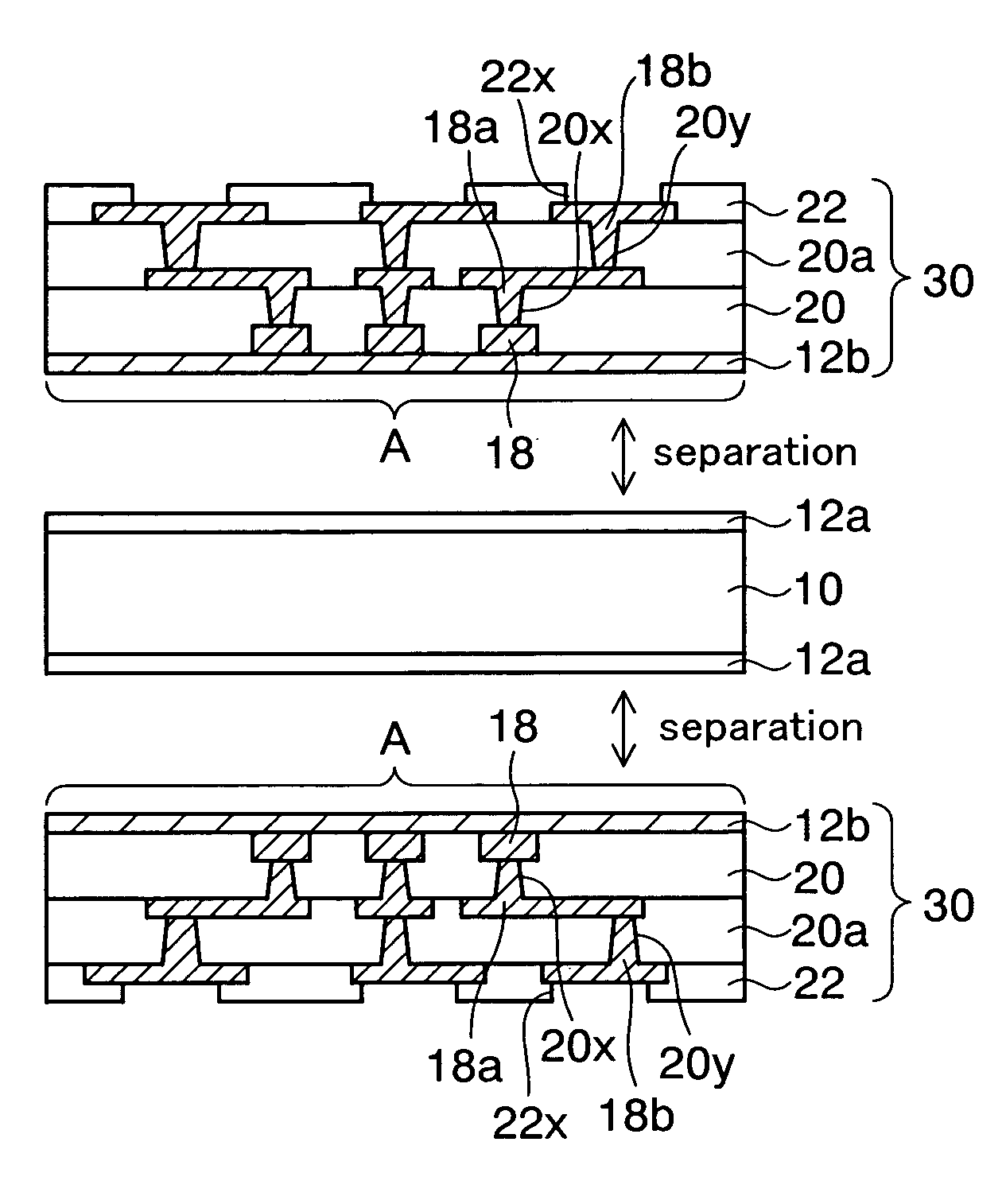

Method for fabricating thin touch sensor panels

A method for fabricating thin DITO or SITO touch sensor panels with a thickness less than a minimum thickness tolerance of existing manufacturing equipment. In one embodiment, a sandwich of two thin glass sheets is formed such that the combined thickness of the glass sheets does not drop below the minimum thickness tolerance of existing manufacturing equipment when thin film process is performed on the surfaces of the sandwich during fabrication. The sandwich may eventually be separated to form two thin SITO / DITO panels. In another embodiment, the fabrication process involves laminating two patterned thick substrates, each having at least the minimum thickness tolerance of existing manufacturing equipment. One or both of the sides of the laminated substrates are then thinned so that when the substrates are separated, each is a thin DITO / SITO panel having a thickness less than the minimum thickness tolerance of existing manufacturing equipment.

Owner:APPLE INC

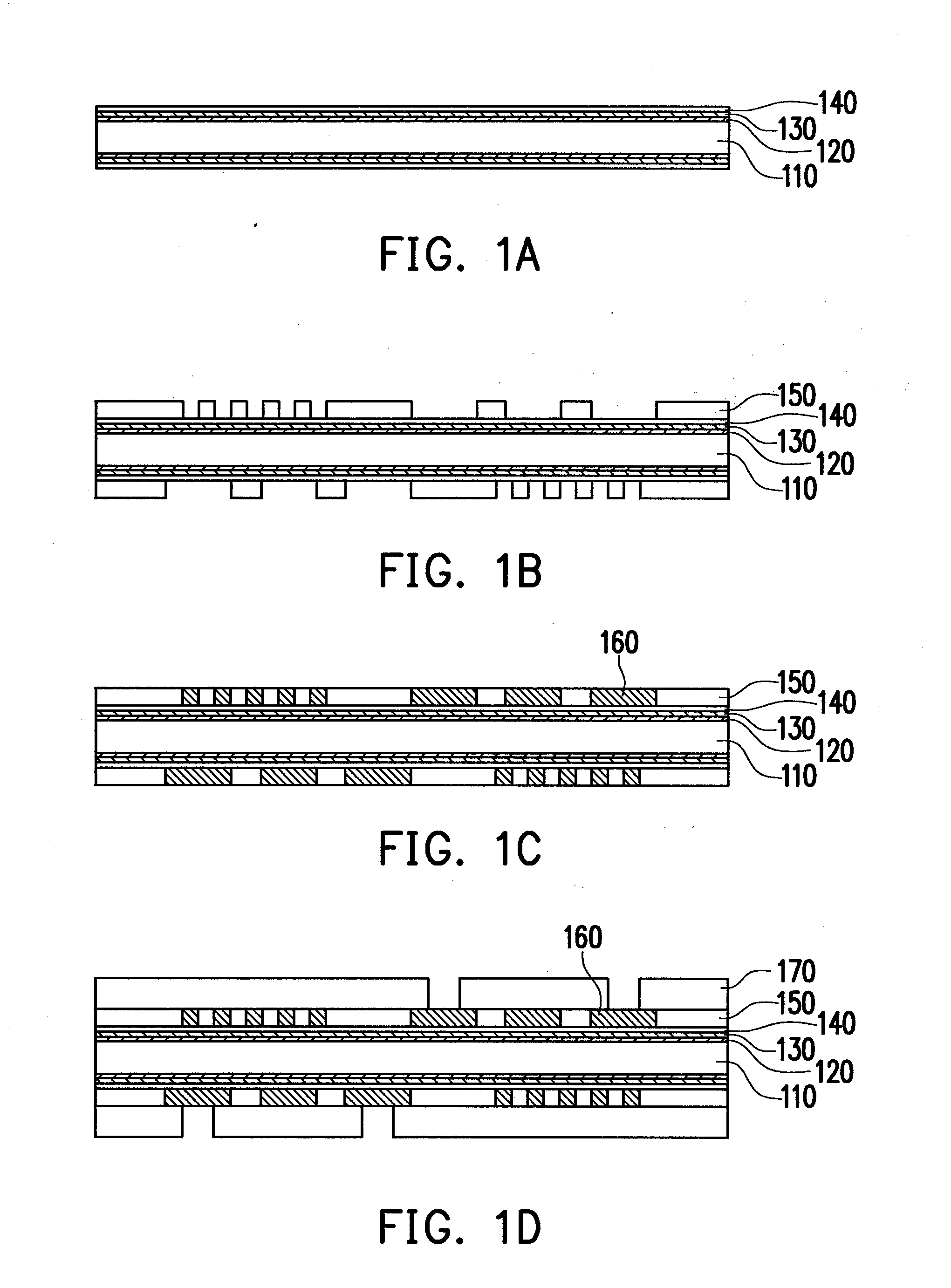

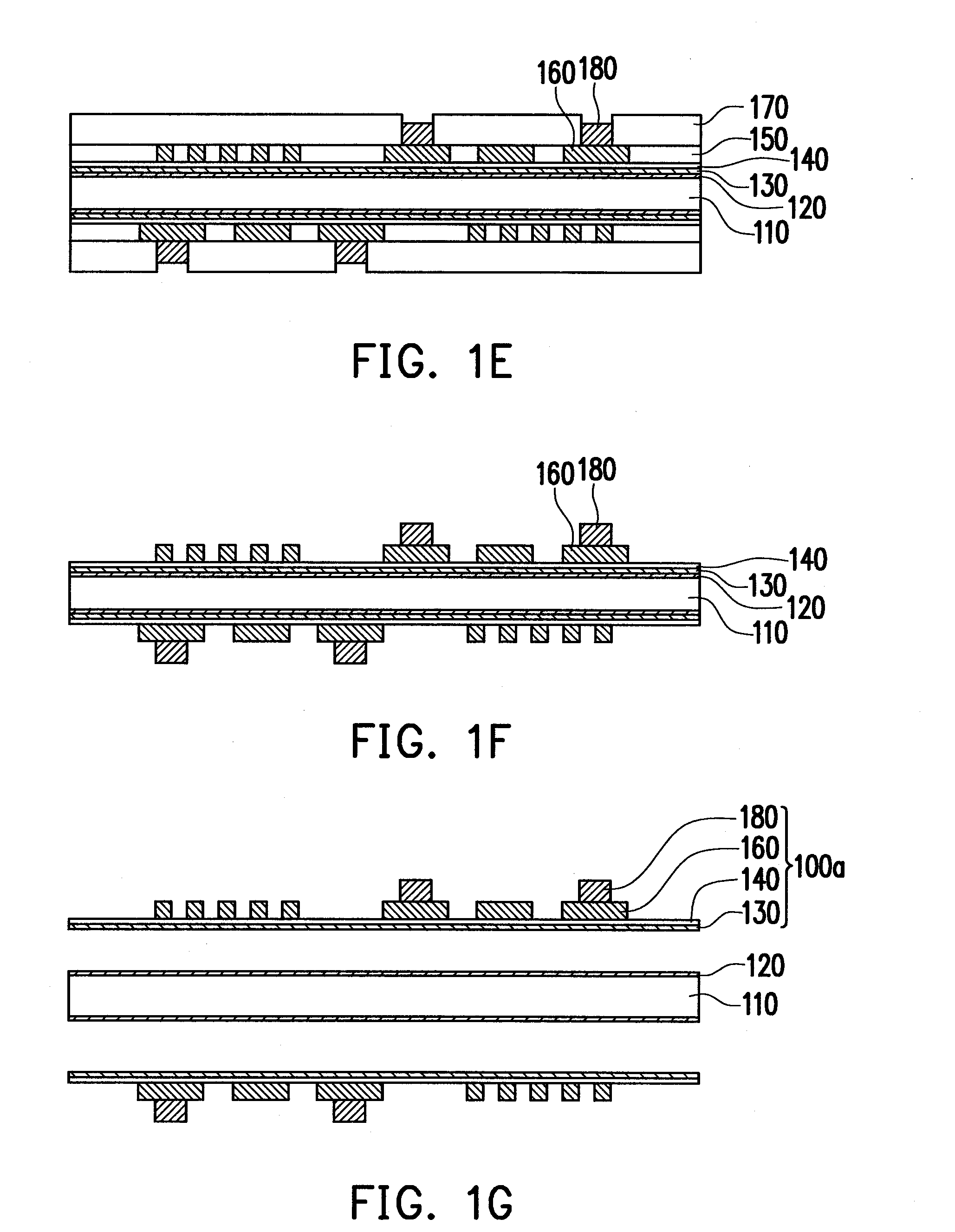

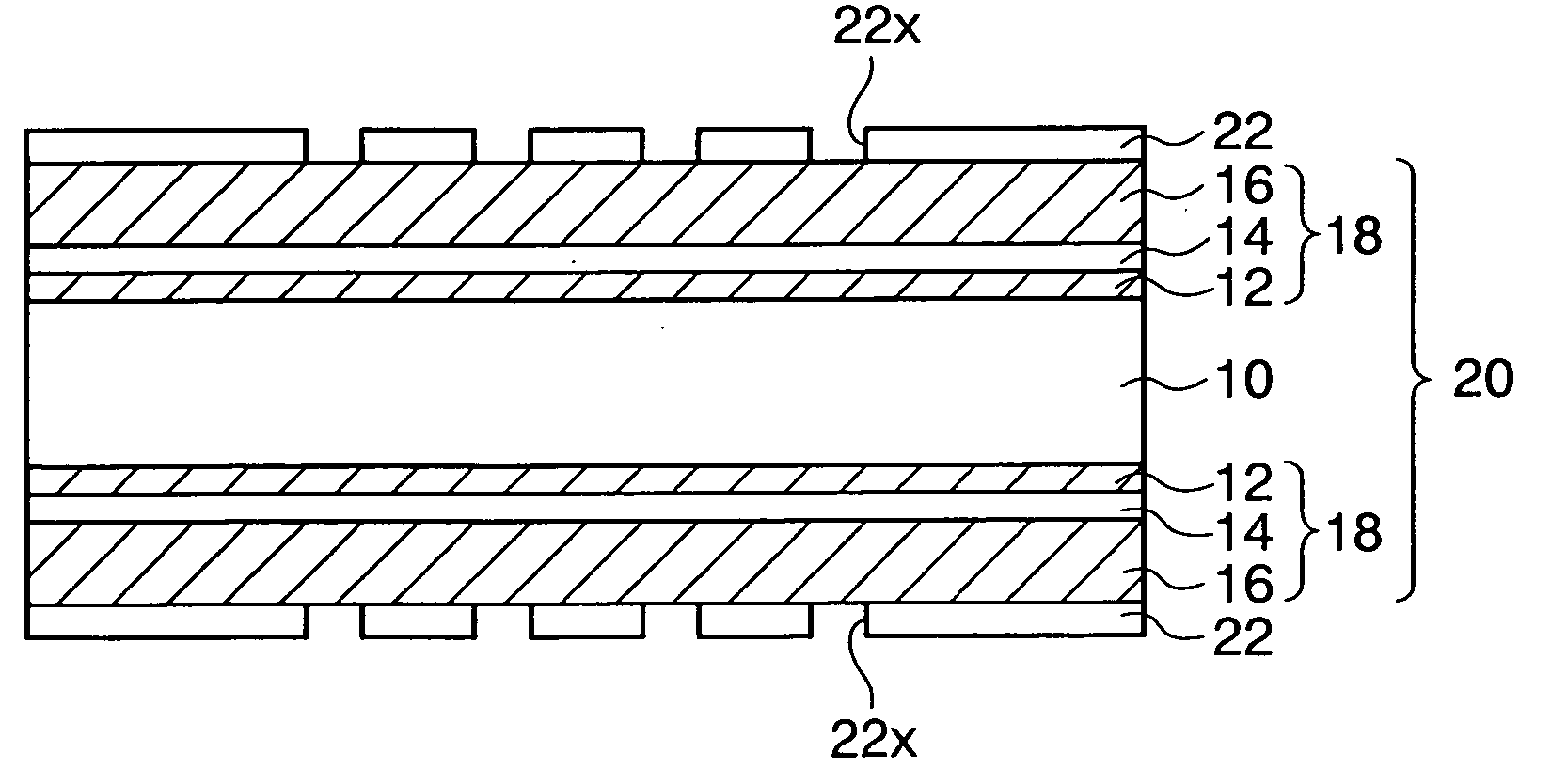

Circuit substrate manufacturing method

ActiveUS20050155222A1Improve workabilityLow costPaper/cardboard articlesLaminating printed circuit boardsMetallic foilOptoelectronics

A circuit substrate manufacturing method of the present invention includes the steps of preparing a substrate on which a metallic foil made of a first metal (copper) is formed in a releasable state, forming a build-up wiring including a metal layer made of a second metal (solder) on the metallic foil, obtaining a circuit member having a structure that the build-up wiring is formed on the metallic foil by releasing the metallic foil from the substrate, and exposing the metal layer by removing selectively the metallic foil of the circuit member with respect to the metal layer.

Owner:SHINKO ELECTRIC IND CO LTD

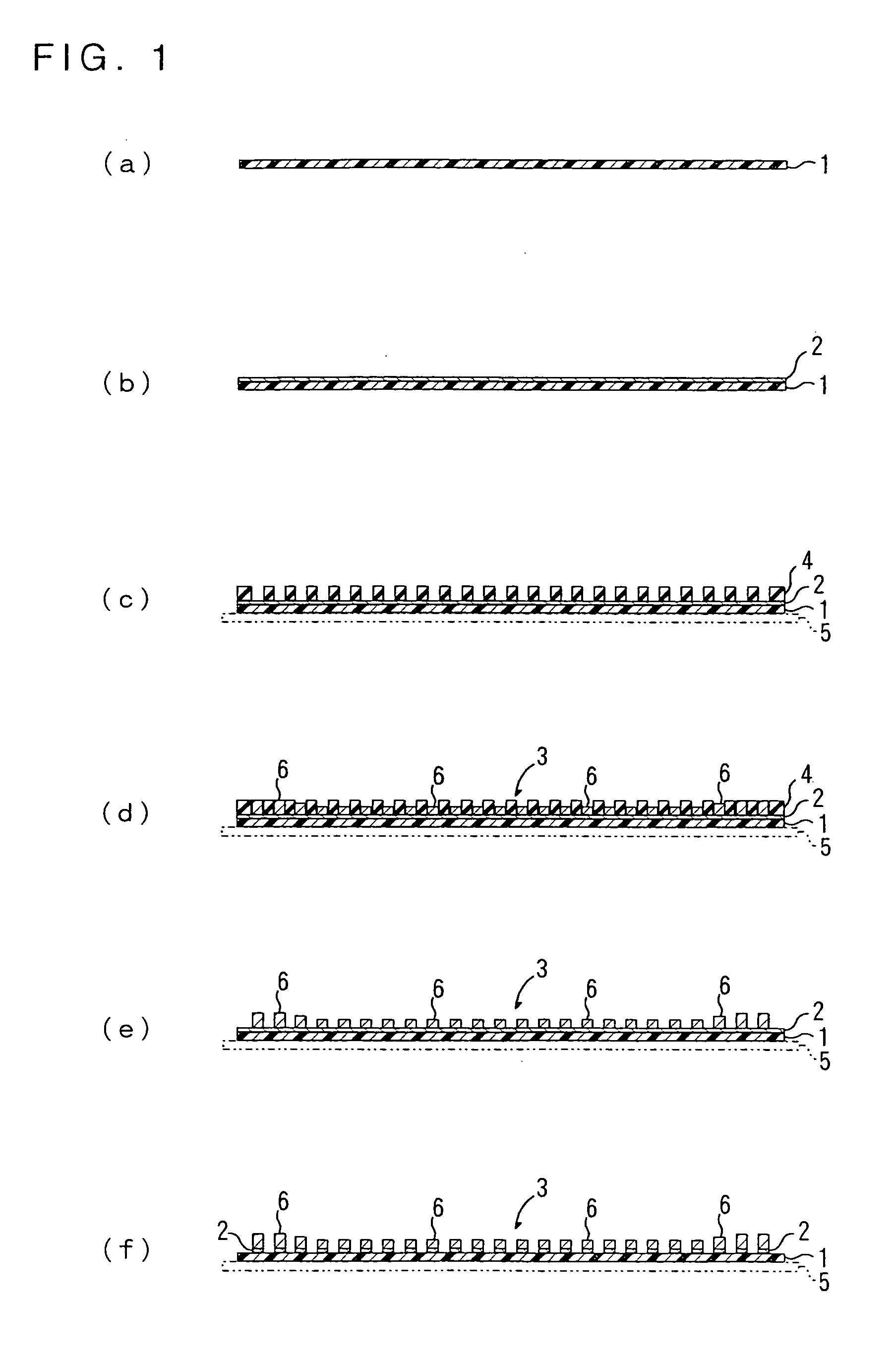

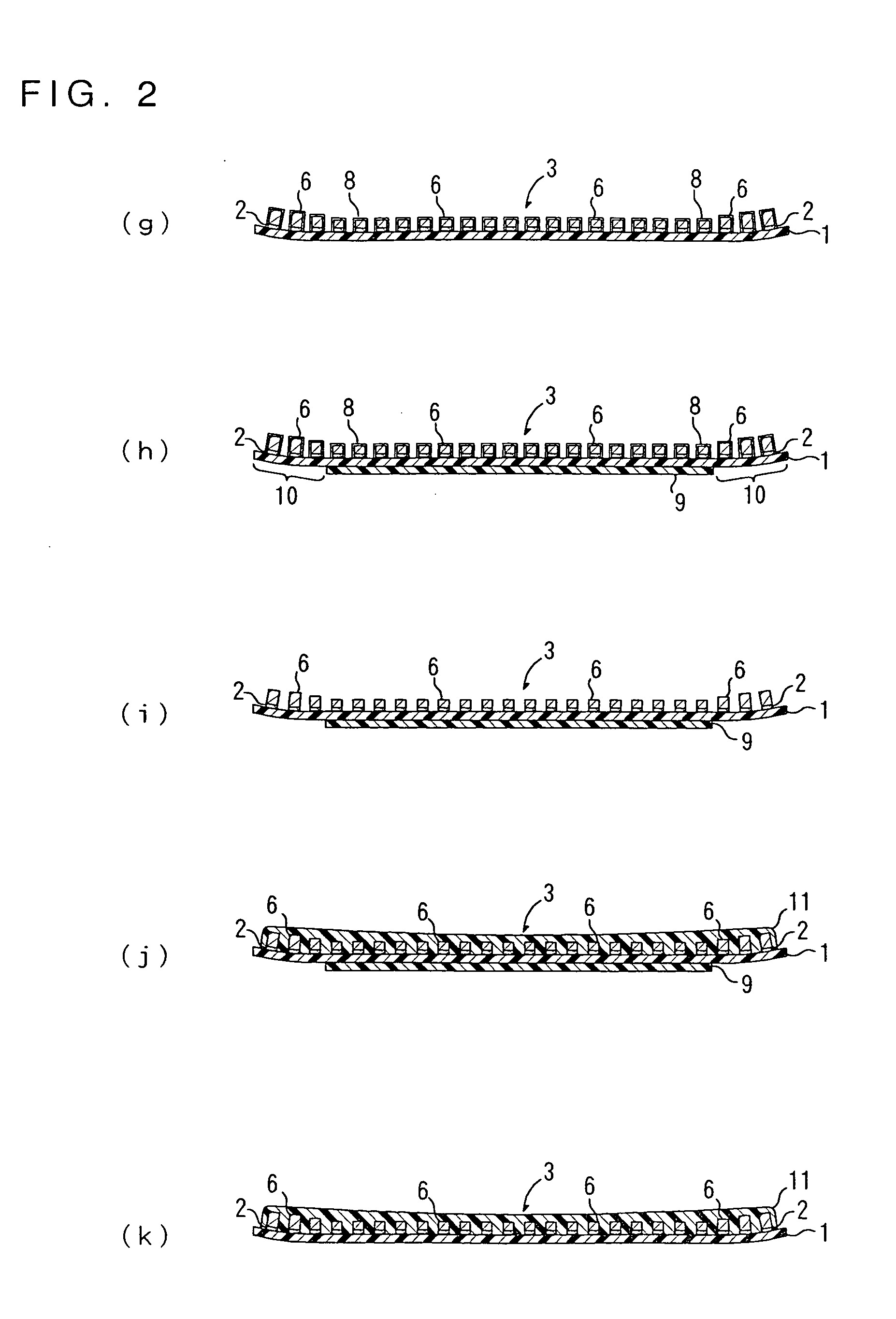

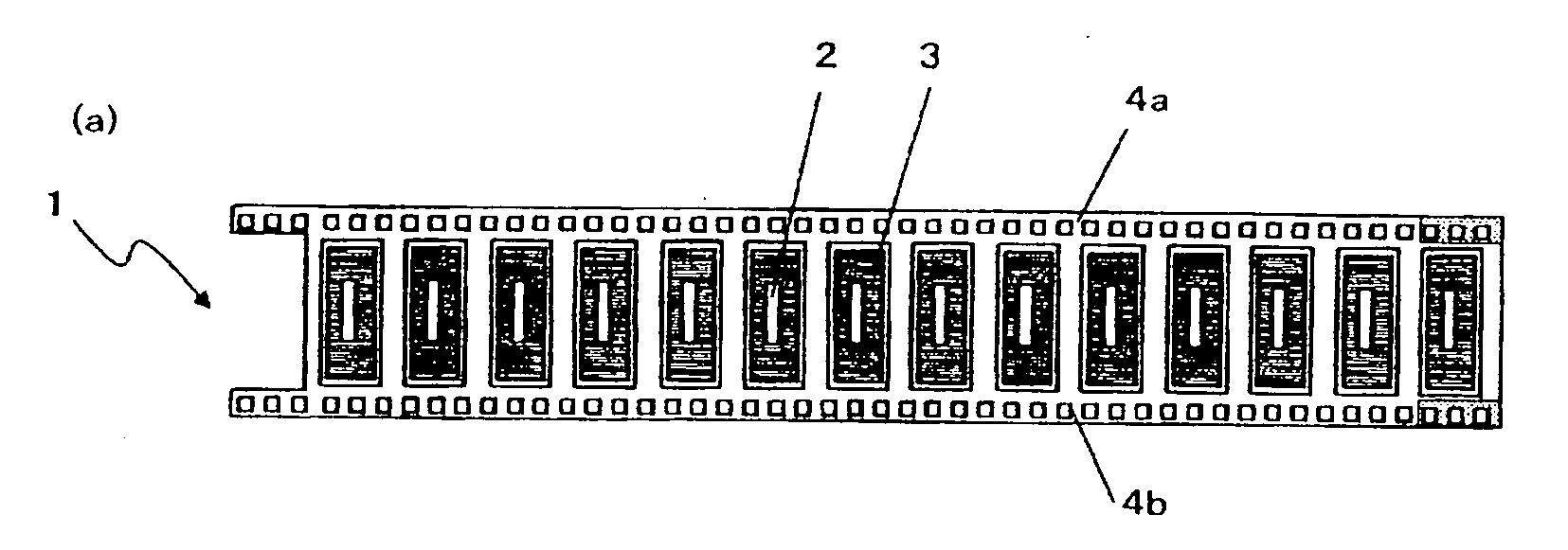

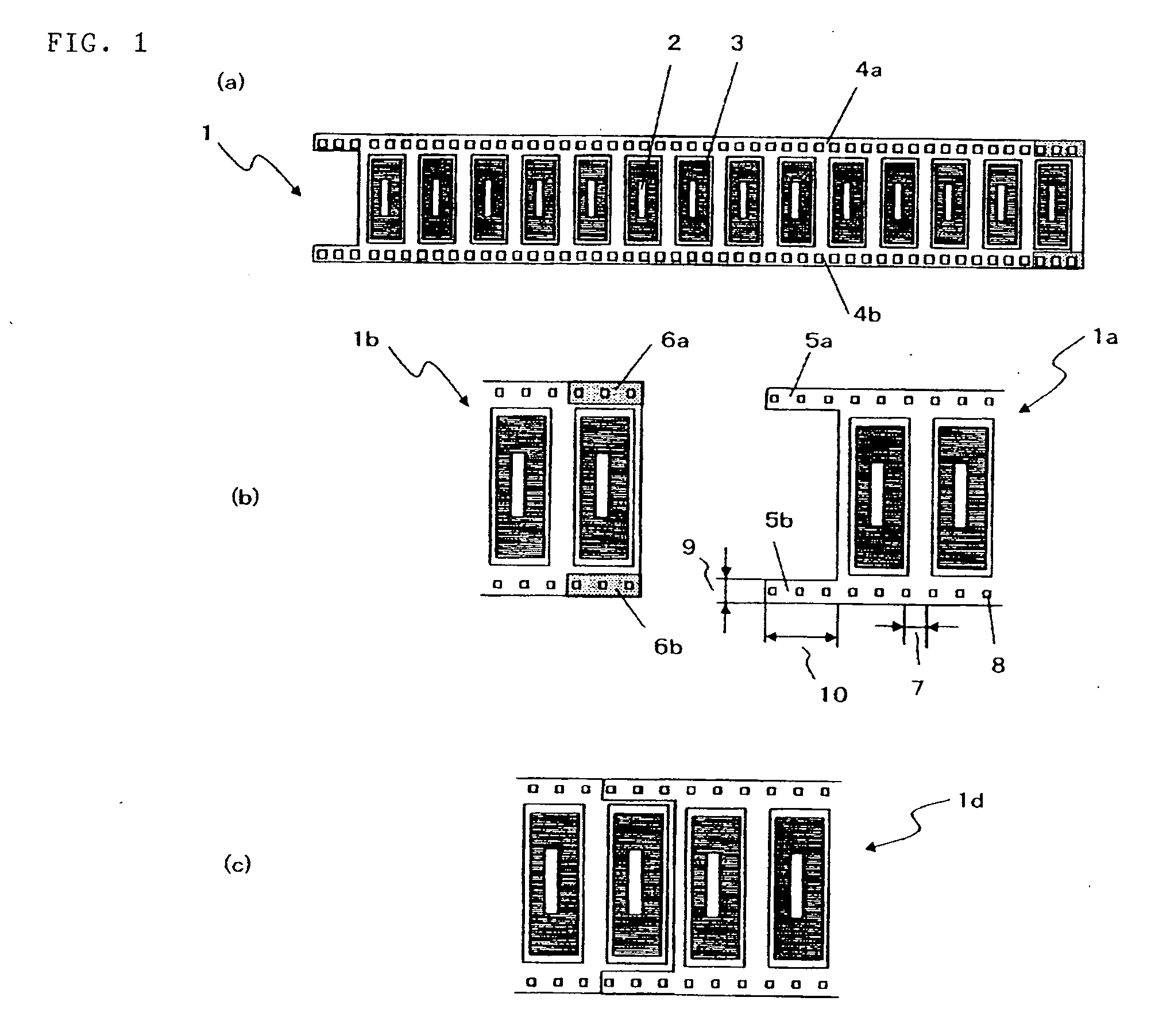

Producing method of flexible wired circuit board

InactiveUS20050067293A1Large thicknessAvoid it happening againPrinted circuit detailsDecorative surface effectsResistElectrolysis

A producing method of a flexible wired circuit board that can prevent the formation of a gap between an elongate substrate and a stiffener sheet bonded thereto to prevent contamination of the flexible wired circuit board obtained. In the process subsequent to the process of forming a conductive pattern 3 on a surface of the elongate substrate 1 by the semi-additive process using electrolysis plating and then annealing the elongate substrate 1 with the conductive pattern 3 in its wound up state, a stiffener sheet 9 having a width narrower than the elongate substrate 1 is bonded to the back side of the elongate substrate 1. Thereafter, an oxidized film formed on a surface of the conductive pattern 3 is removed and then a solder resist 11 is formed thereon. This prevents the strip of the stiffener sheet 9 from the elongate substrate 1 and in turn prevents etching solution or developing solution from entraining in a gap therebetween.

Owner:NITTO DENKO CORP

Process for selective transfer of a microstructure formed on an initial substrate to a final substrate

InactiveUS6159323APrinted circuit assemblingLamination ancillary operationsMaterials scienceSelective transfer

Process for transfer of a microstructure (12) from an initial substrate (10) to a final substrate (32). The process includes the following steps in sequence: bonding between the initial substrate (10) and an intermediate substrate (24), the microstructure facing the intermediate substrate, formation of at least one layer (30) of bond material on at least one selected region (16) of the initial substrate including the microstructure bring the said selected region (16) into contact with the final substrate, treatment of the bond material in an area corresponding to the selected region (16), to increase the bond force, breaking the selected region (16) of the initial substrate, from the intermediate substrate (24).

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

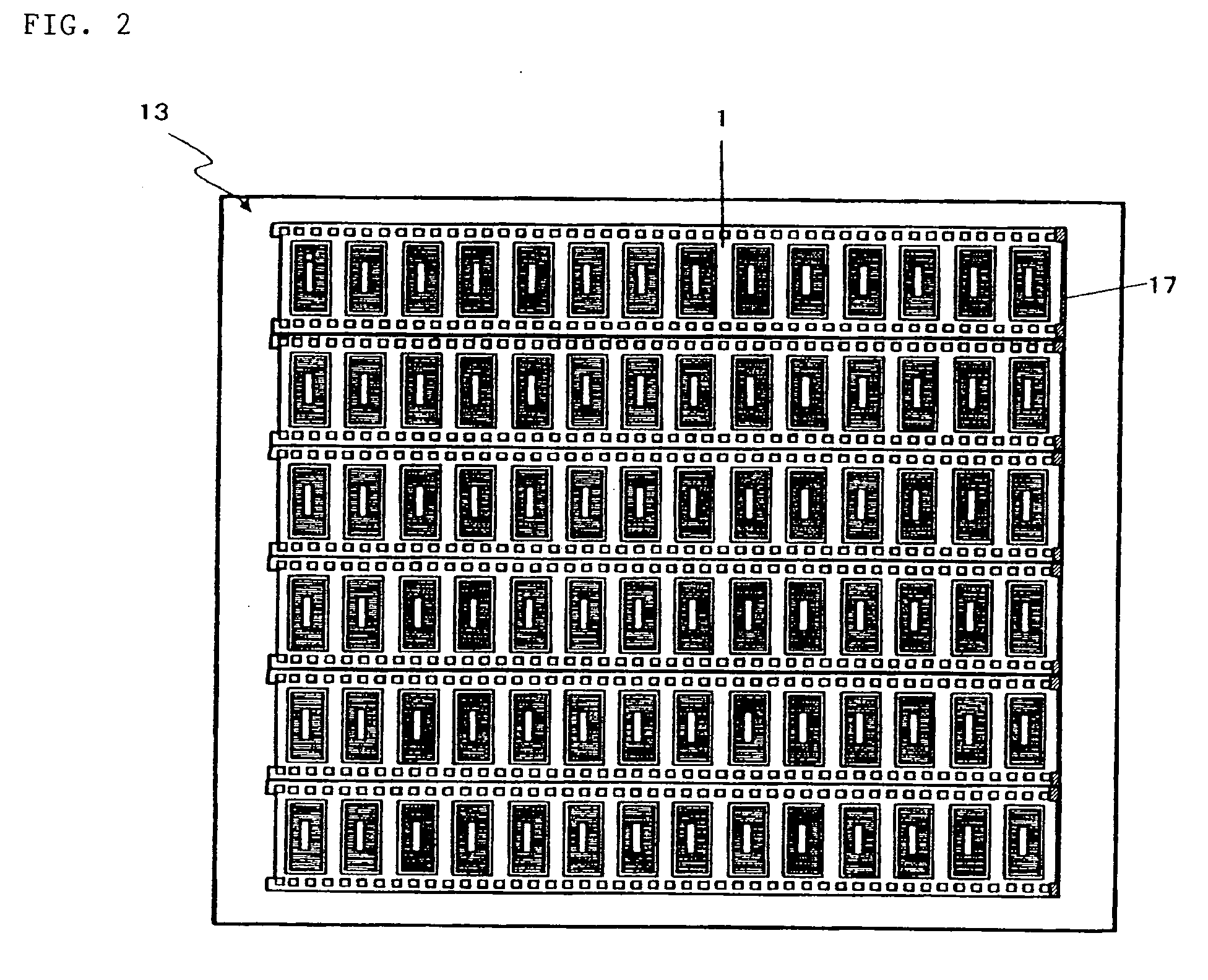

Collective printed circuit board

ActiveUS20120081864A1High yieldNumberSemiconductor/solid-state device detailsSolid-state devicesPrinted circuit boardSemiconductor components

There is provided a collective printed circuit board including a plurality of printed circuit boards each having a mounting unit on which a semiconductor element is mounted at an upper-surface central portion, and a frame having a plurality of through holes having sizes to surround the mounting portion. Upper-surface peripheral edge portions of the printed circuit boards and a through-hole peripheral portion of the frame are bonded to each other such that the mounting units are exposed from the through holes.

Owner:KYOCERA CORP

Tape-Style Flexible Circuit Board, and Manufacturing Method and Manufacturing Apparatus for the Same

InactiveUS20080259575A1Reduce lossesEasy to handleLamination ancillary operationsPrinted circuit aspectsFlexible circuitsEngineering

Owner:TORAY IND INC

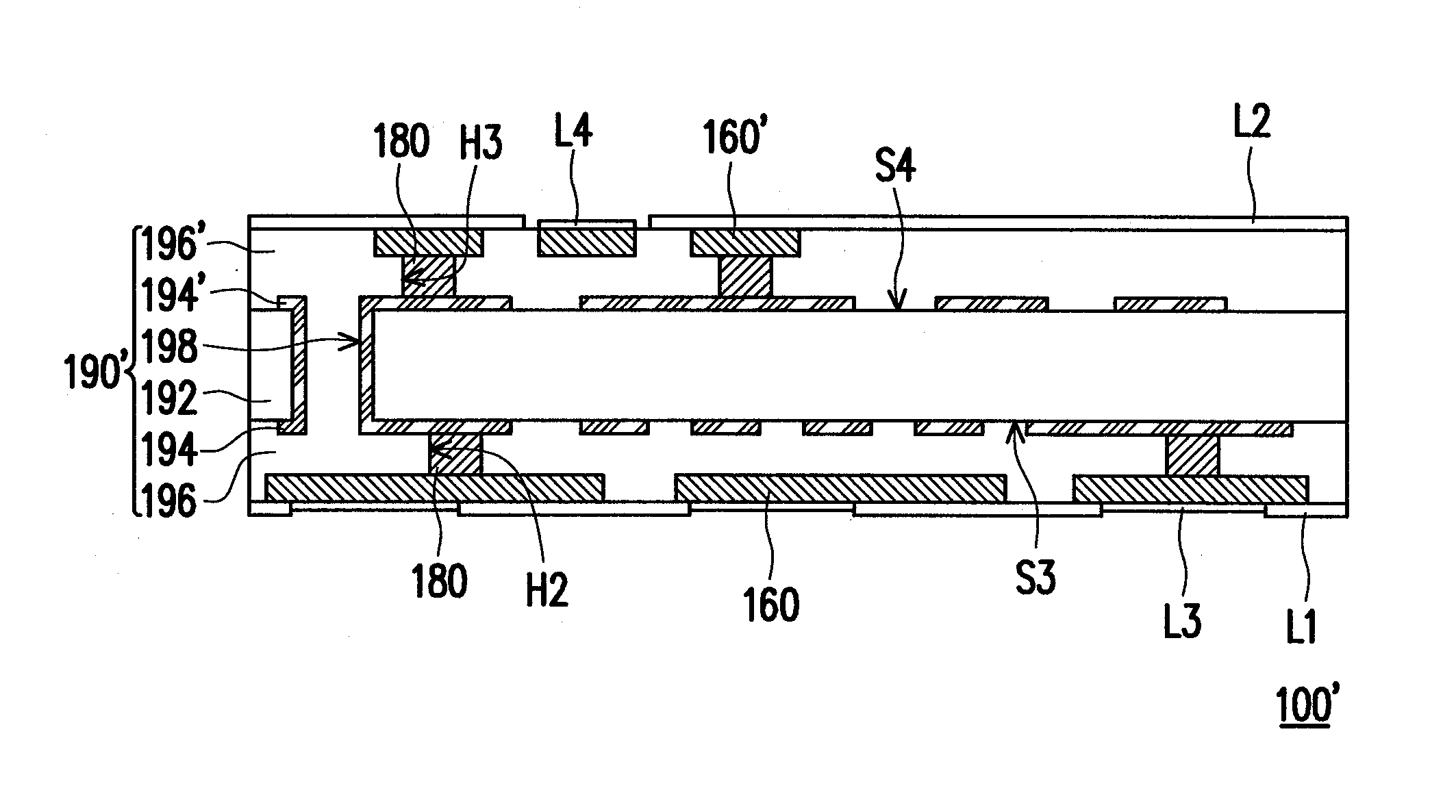

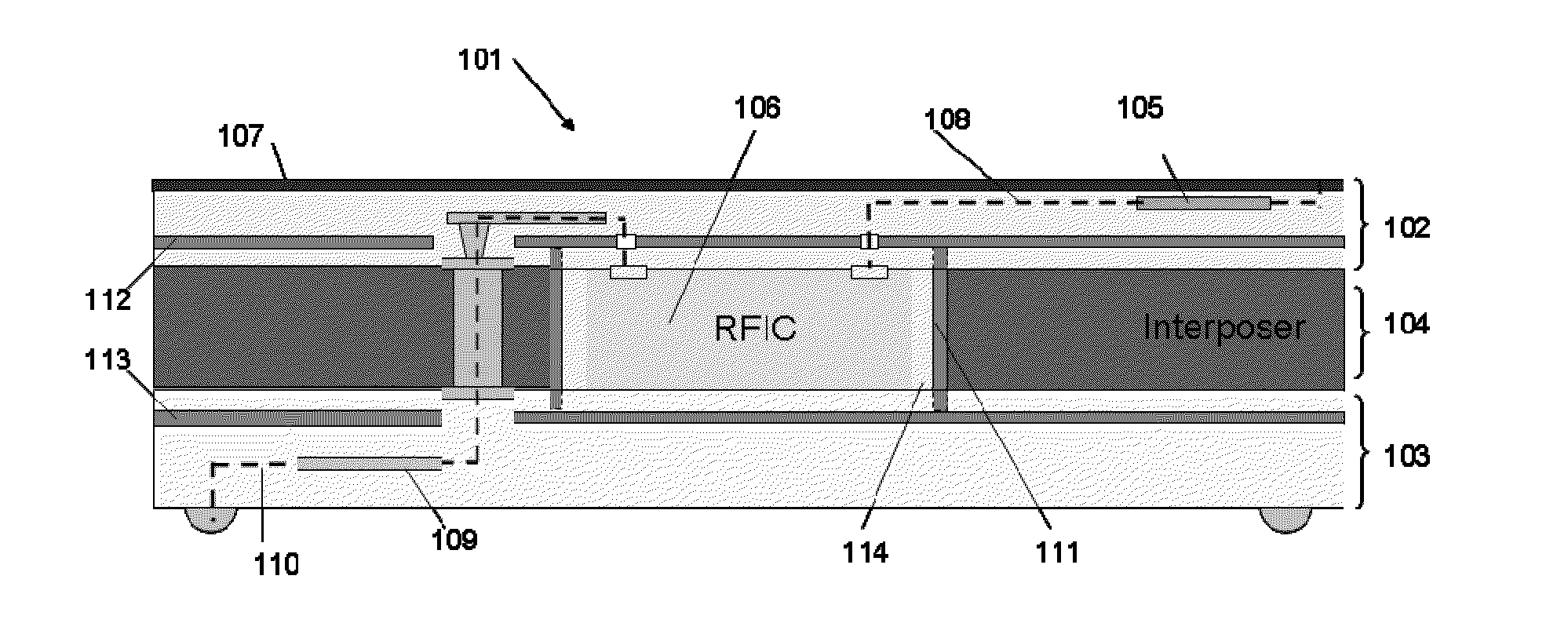

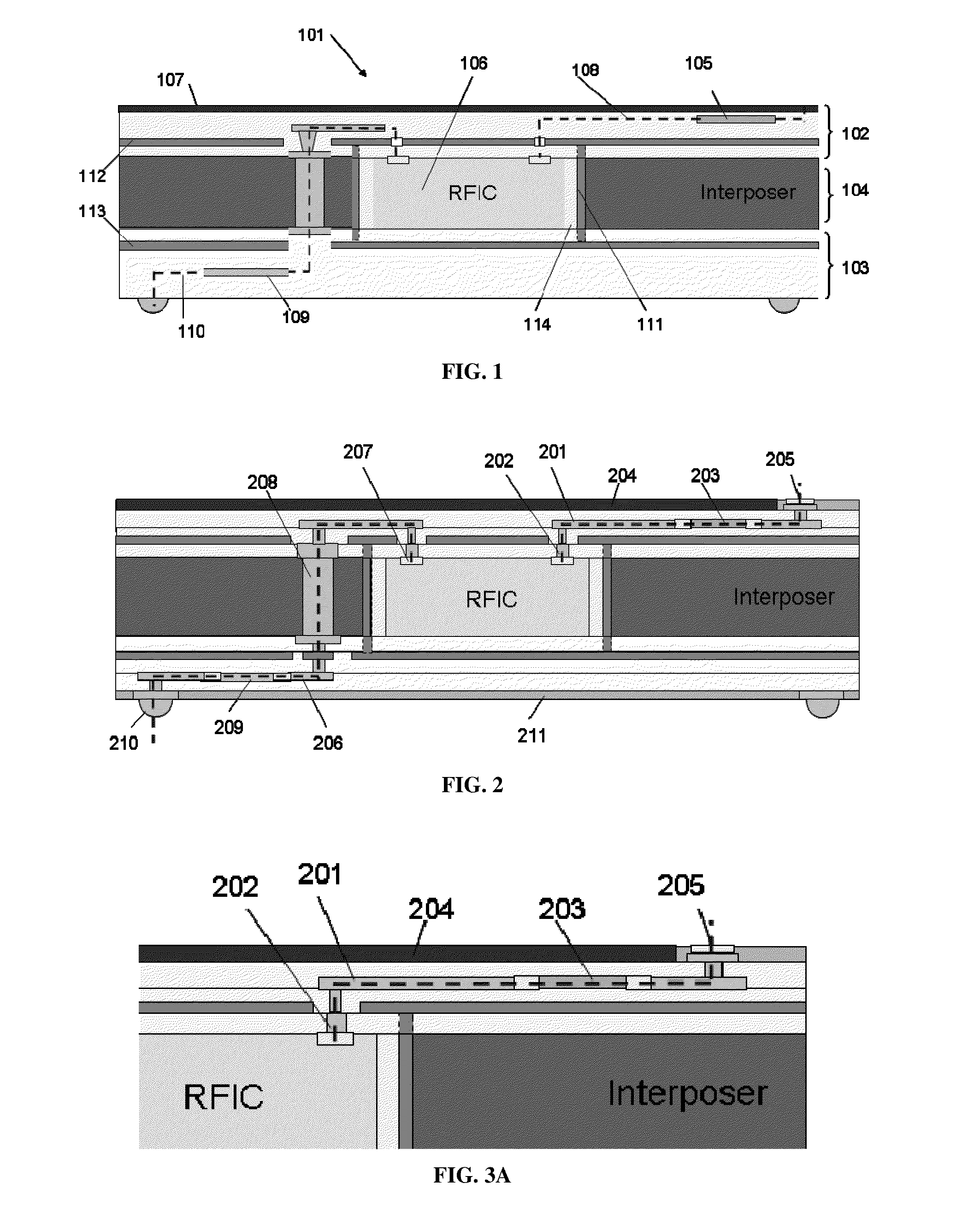

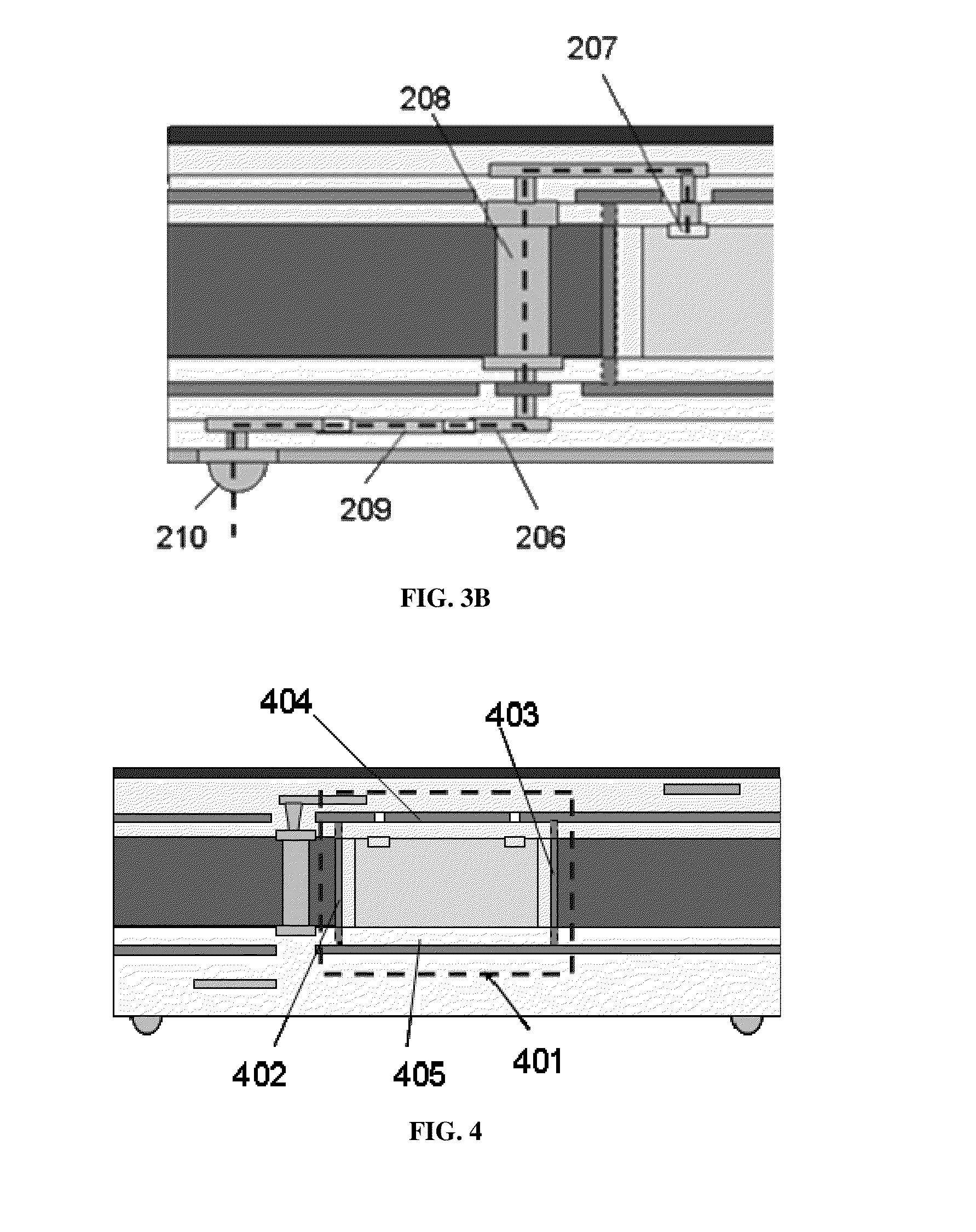

Partitioned Hybrid Substrate for Radio Frequency Applications

InactiveUS20150016078A1Improve signal integrityReduce manufacturing costLaminating printed circuit boardsSolid-state devicesManufacturing cost reductionRadio frequency

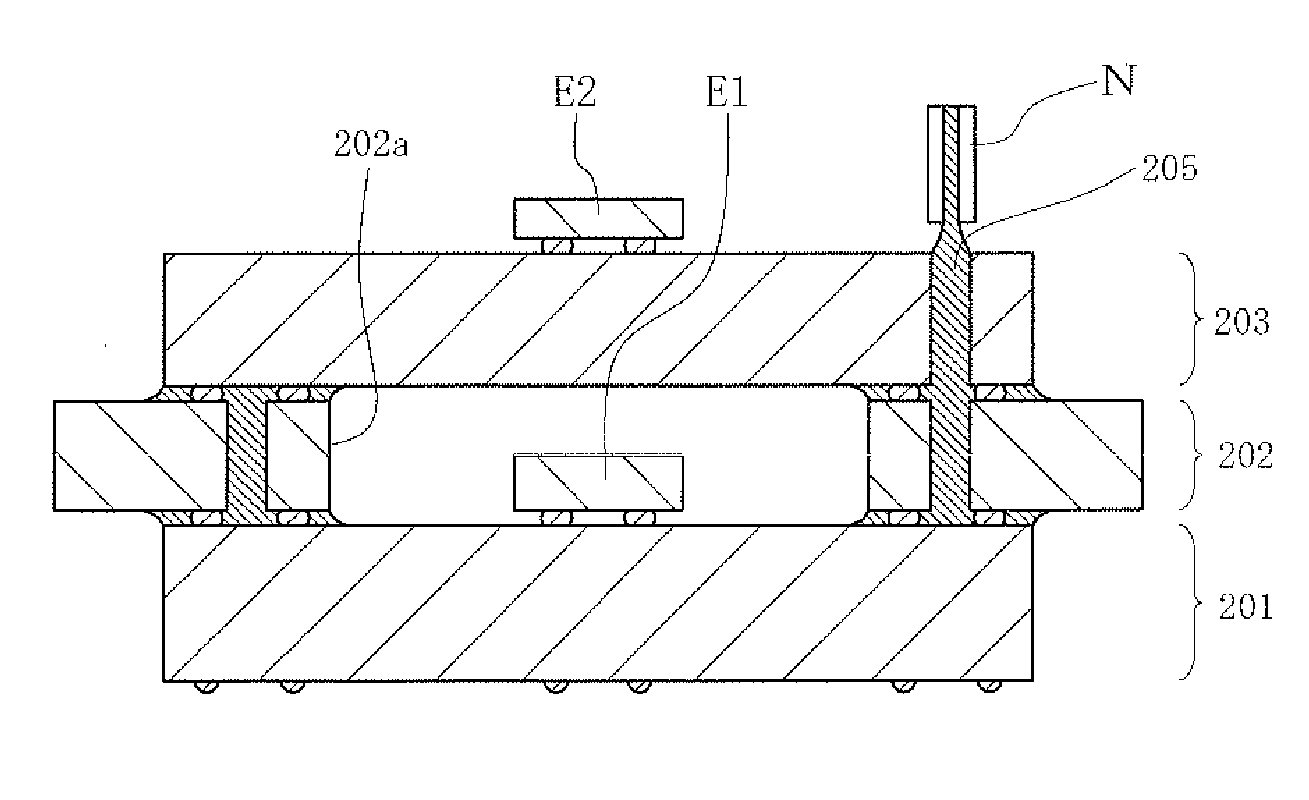

The presently claimed invention is to provide a package for compact RF signal system, and a method to form the package thereof in order to miniaturize the size of package, improve signal integrity, and reduce manufacturing cost. The package comprises a hybrid substrate with a sandwiched structure, in which the hybrid substrate comprises an upper layer and a lower layer with different dielectric properties being separated by an interposer for improving electrical isolation and mechanical stiffness. Metal layers are formed on the sidewalls of the opening to surround an active component, such that the metal sidewalls together with two ground plates in the upper and lower layers constitute a self-shielding enclosure inside the package to protect the active component.

Owner:HONG KONG APPLIED SCI & TECH RES INST

Circuit substrate manufacturing method

ActiveUS7222421B2Low costImprove workabilityPaper/cardboard articlesLaminating printed circuit boardsMetallic foilOptoelectronics

A circuit substrate manufacturing method including the steps of preparing a substrate on which a metallic foil is formed in a releasable state, forming a build-up wiring on the metallic foil, obtaining a circuit member having a structure that the build-up wiring is formed on the metallic foil by releasing the metallic foil from the substrate, and exposing a lowest wiring layer of the build-up wiring by removing the metallic foil of the circuit member.

Owner:SHINKO ELECTRIC IND CO LTD

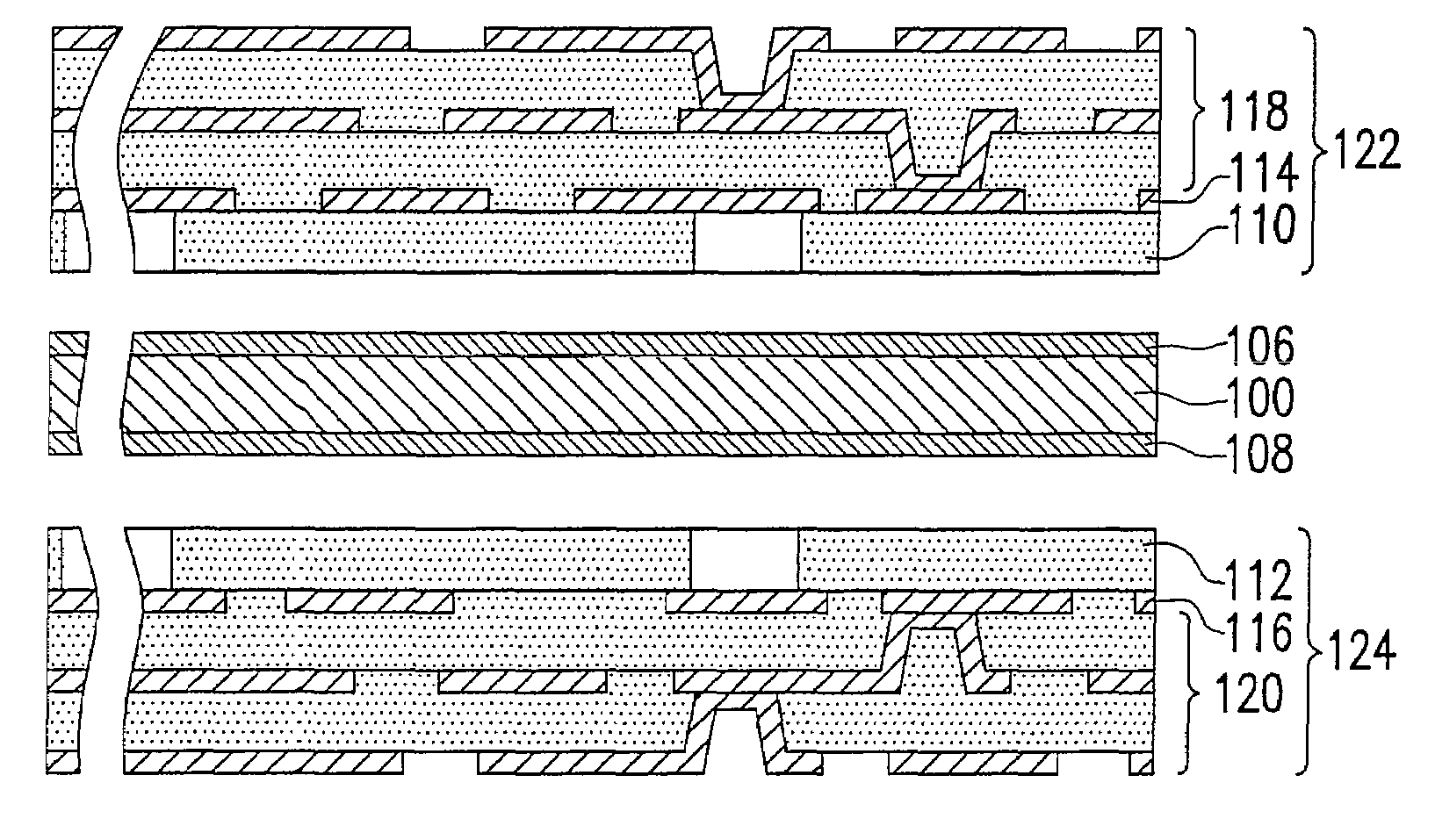

Method of manufacturing wiring substrate and method of manufacturing electronic component device

ActiveUS20080202661A1Trouble in manufactureHigh yieldPaper/cardboard articlesSemiconductor/solid-state device detailsMetal foilEngineering

In a method of manufacturing a wiring substrate of the present invention, first, a structure in which an underlying layer is arranged in a wiring forming area of a temporary substrate and a peelable multi-layer metal foil that is larger in size than the underlying layer is arranged on the underlying layer and is adhered partially to an outer peripheral portion of the wiring forming area of the temporary substrate, and the peelable multi-layer metal foil is constructed by temporary adhering a first metal foil and a second metal foil with peelable. Then, a built-up wiring layer is formed on the peelable multi-layer metal foil, and the peelable multi-layer metal foil is separated from the temporary substrate by cutting a portion of such a structure that the underlying layer, the peelable multi-layer metal foil, and the built-up wiring layer are formed on the temporary substrate, the portion corresponding to a peripheral portion the underlying layer, whereby a wiring member in which the built-up wiring layer is formed on the peelable multi-layer metal foil is obtained.

Owner:SHINKO ELECTRIC IND CO LTD

Multilayer wiring substrate and method for manufacturing the same

InactiveUS20100132997A1Improve reliabilityImprove connection reliabilitySemiconductor/solid-state device detailsPrinted circuit aspectsElectrical conductorOptoelectronics

A multilayer wiring substrate is manufactured through a recess forming step, a gold-diffusion-prevention-layer forming step, a terminal forming step, resin-insulating-layer forming step, a conductor forming step, and a metal-layer removing step. In the recess forming step, a copper foil layer is half-etched so as to form recesses. In the gold-diffusion-prevention-layer forming step, a gold diffusion prevention layer is formed in each recess. In the terminal forming step, a gold layer, a nickel layer, and a copper layer are stacked in sequence on the gold diffusion prevention layer to thereby form a surface connection terminal. In the resin-insulating-layer forming step, a resin insulating layer is formed, and, in the conductor forming step, via conductors and conductor layers are formed. In the metal-layer removing step, the copper foil layer and the gold diffusion prevention layer are removed so that the gold layer projects from the main face of the laminated structure.

Owner:NGK SPARK PLUG CO LTD

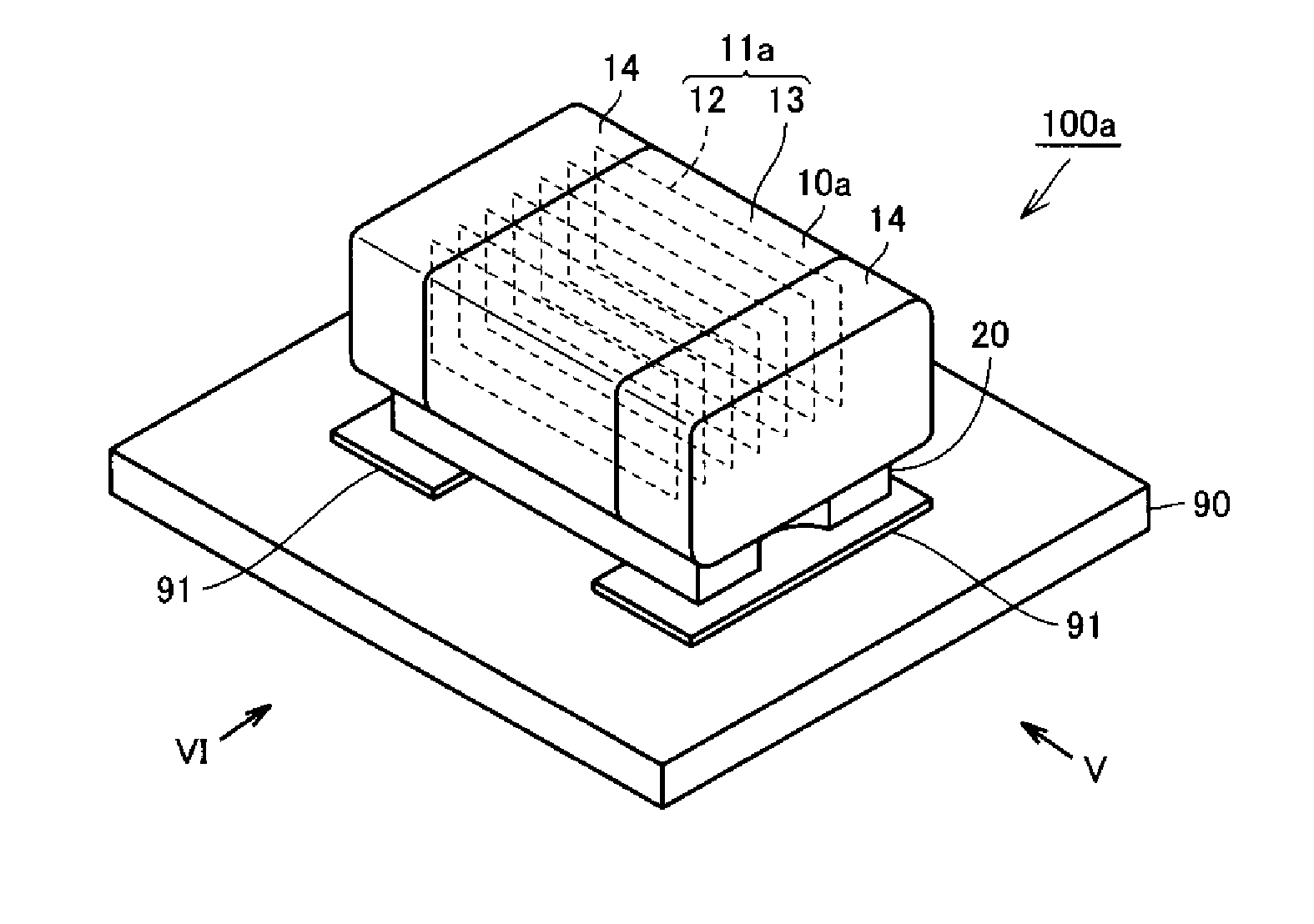

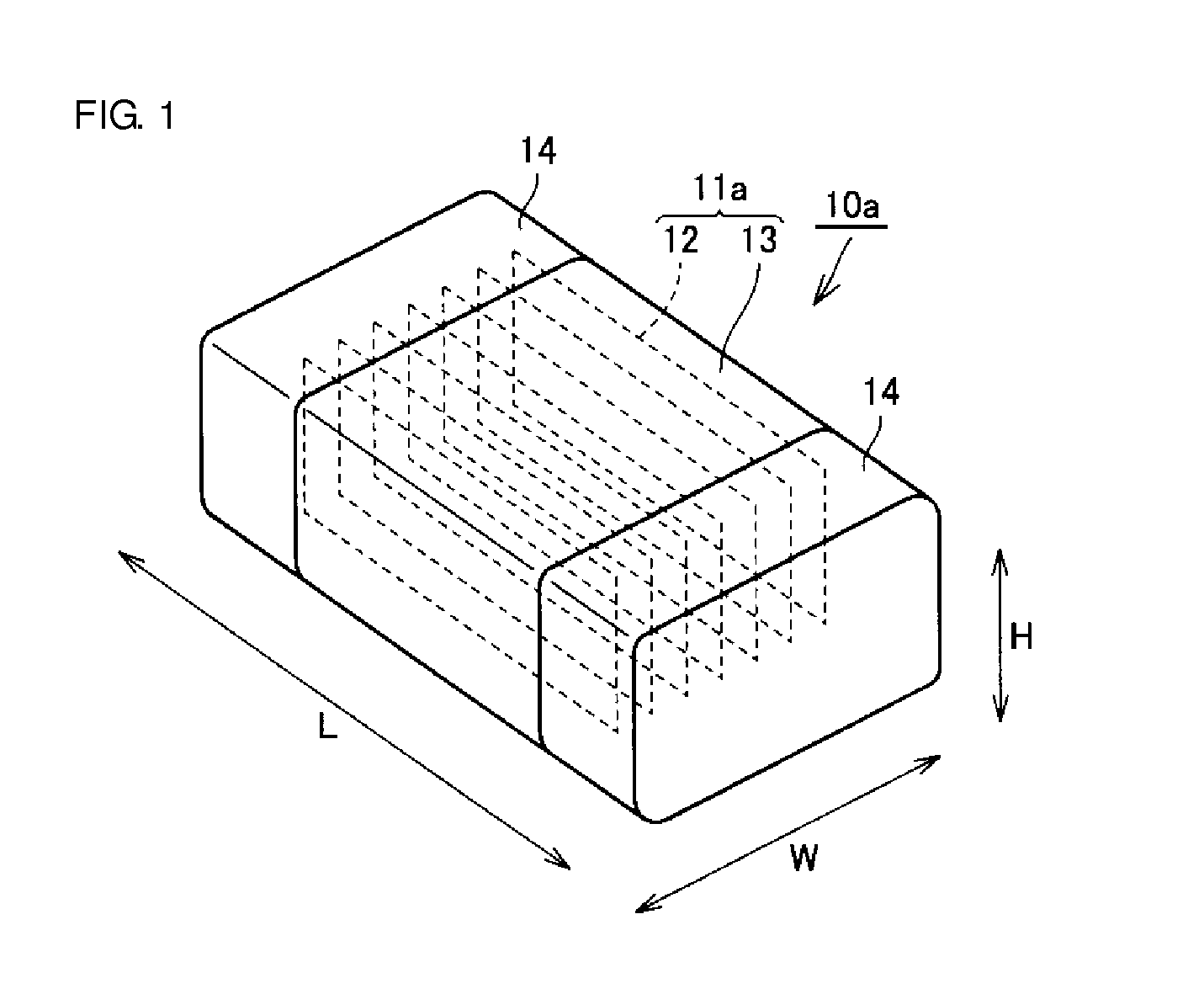

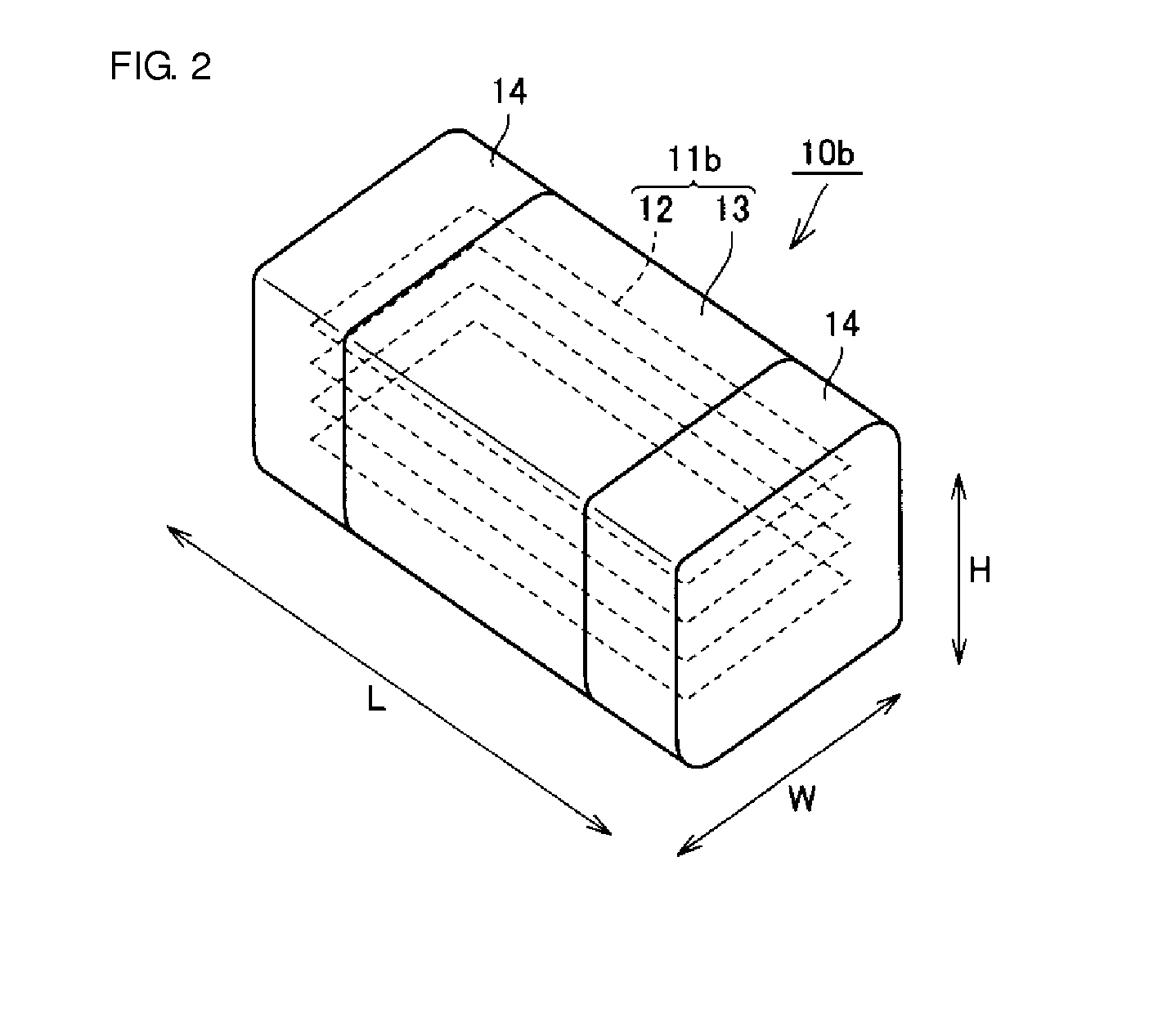

Electronic component

ActiveUS20150270068A1OccurrenceAvoid glitchesResistor terminals/electrodesFixed capacitor dielectricEngineeringElectronic component

An electronic component includes an electronic element including external electrodes on a surface and a substrate terminal on which the electronic element is mounted. The substrate terminal includes a first main surface, a second main surface opposite the first main surface, and a peripheral surface joining the first main surface and the second main surface. The substrate terminal includes mounting electrodes provided on the second main surface and electrically connected to the external electrodes of the electronic element, and connection electrodes provided on the first main surface and electrically connected to lands of a circuit substrate. A maximum width of the connection electrodes is greater than a maximum width of the mounting electrodes.

Owner:MURATA MFG CO LTD

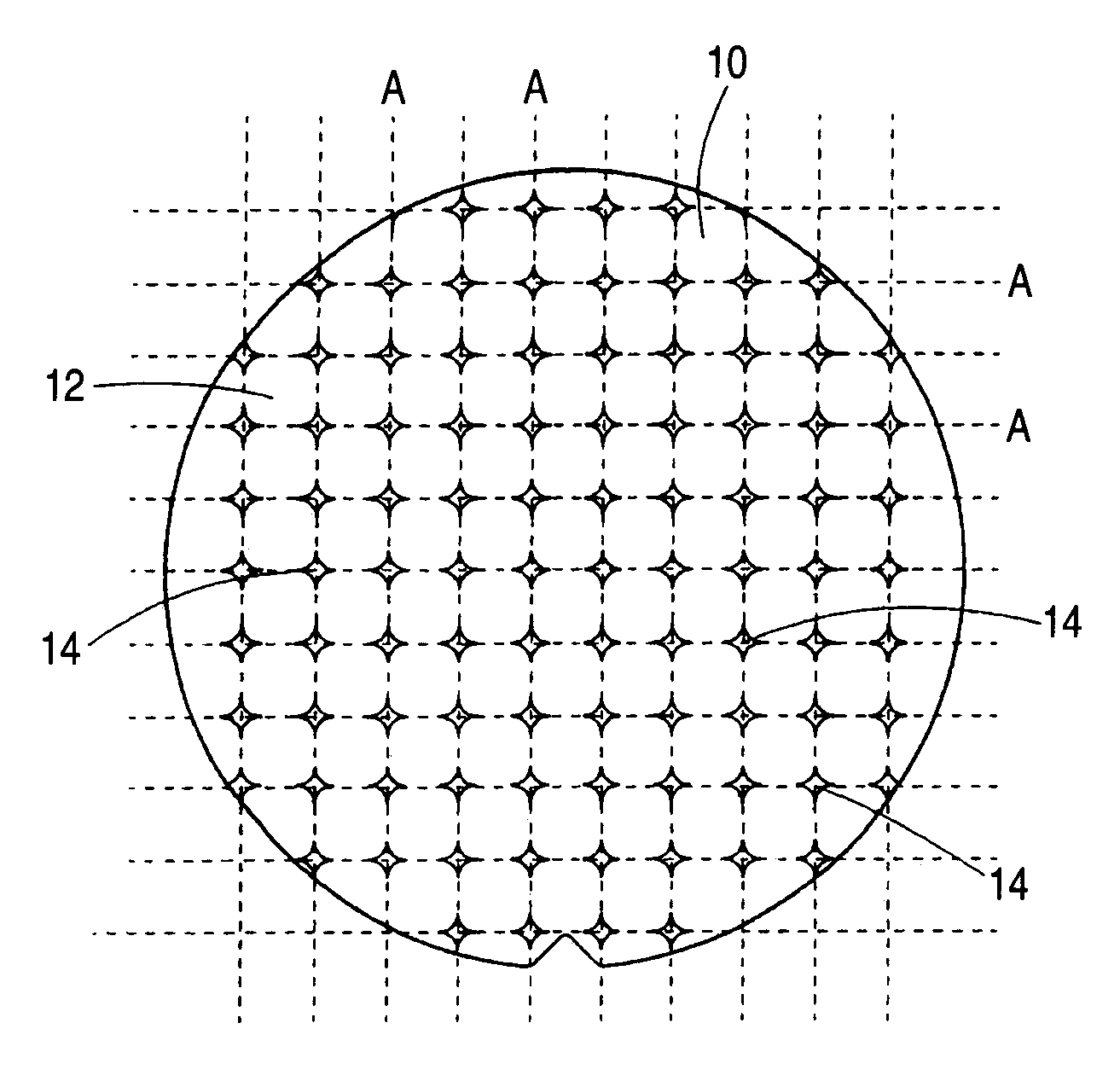

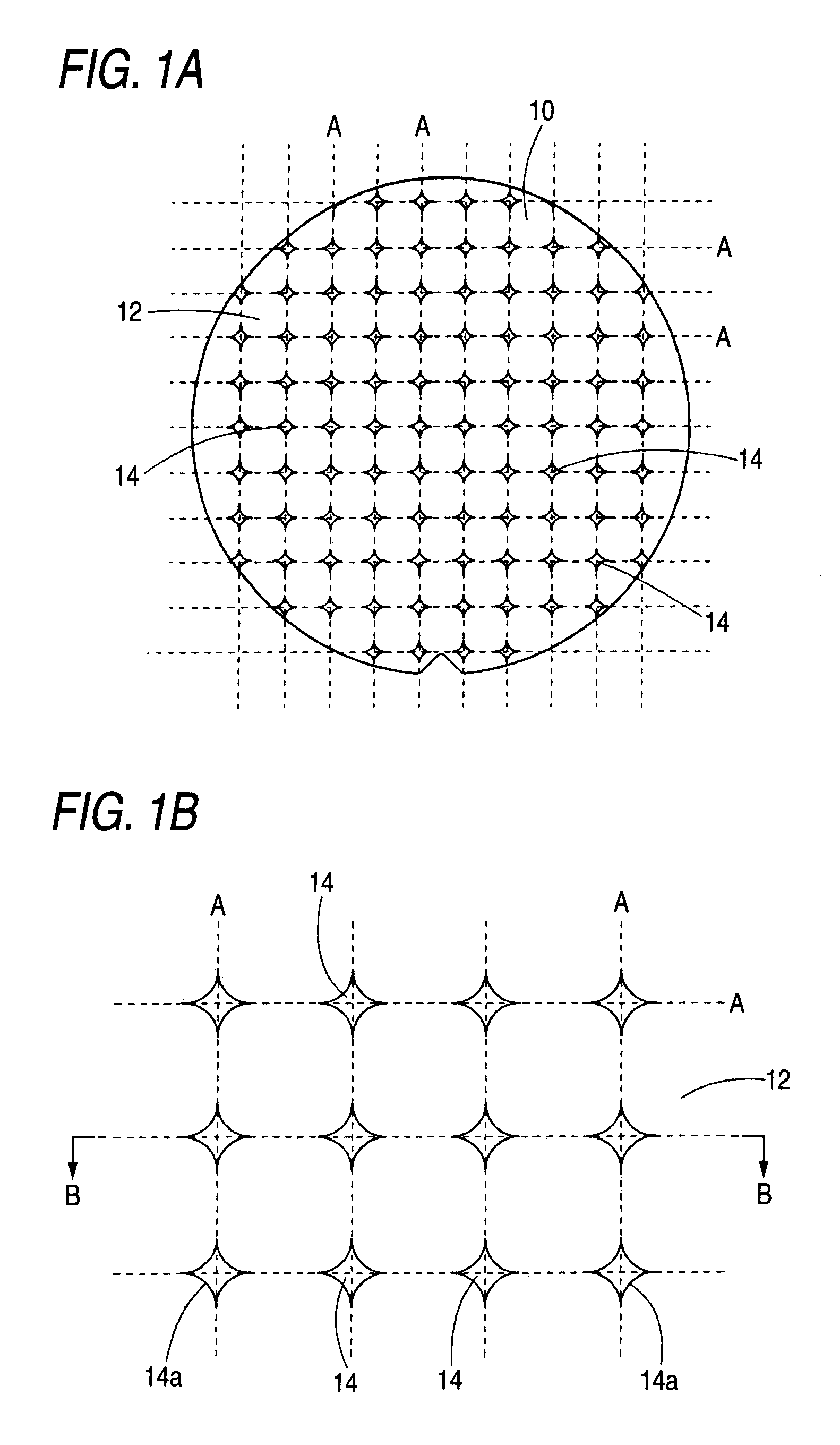

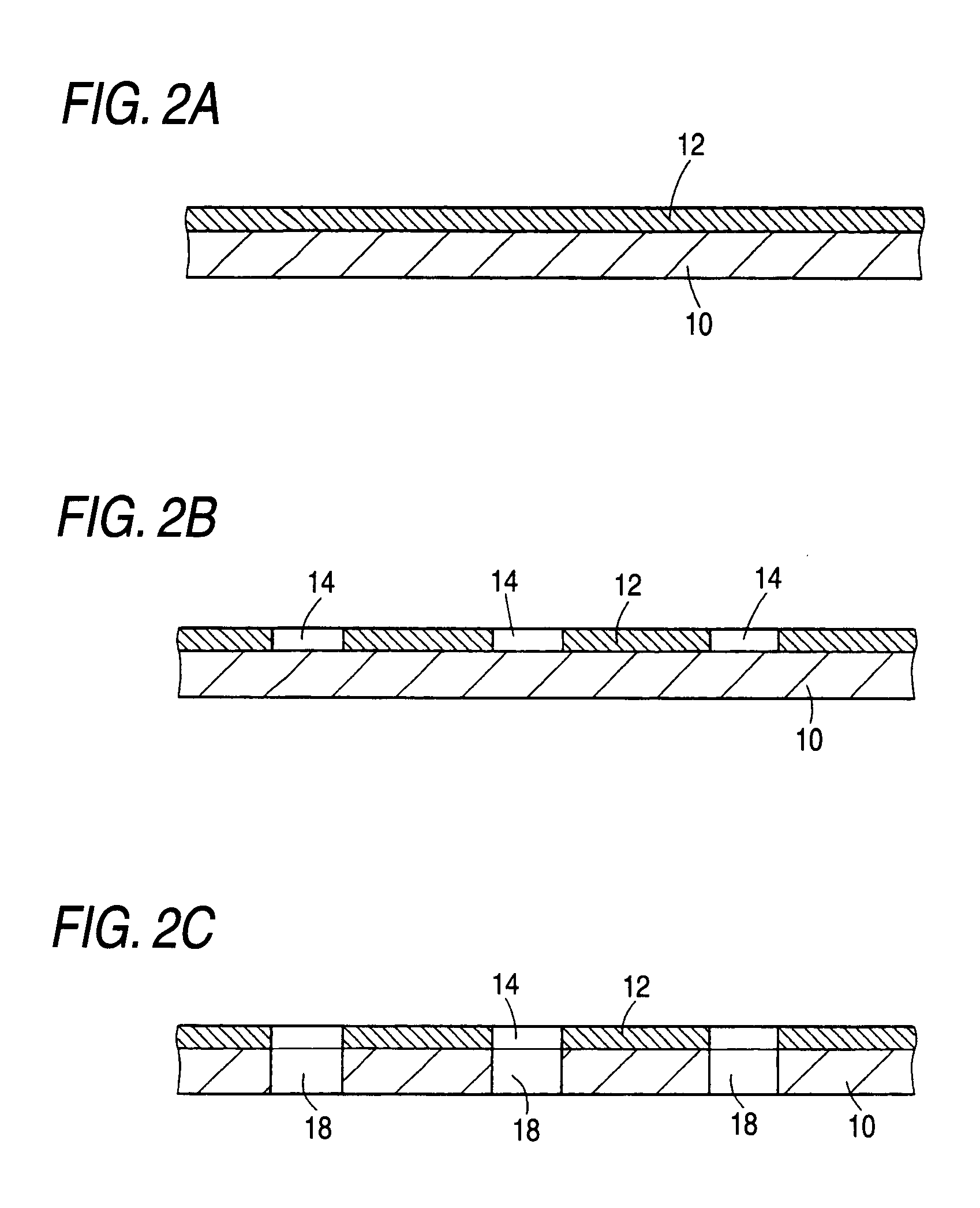

Substrate dividing method

InactiveUS20090098712A1High strengthEasy to handlePrinted circuit aspectsSemiconductor/solid-state device manufacturingSplit linesEngineering

A method of dividing a substrate 10 into individual pieces by setting dividing lines A used to dividing the substrate 10 into individual pieces at a predetermined interval in a vertical direction and a horizontal direction and then dividing the substrate 10 along the dividing lines A, includes a step of forming chamfering patterns 14 to form through holes, which are used to chamfer corner portions of individual pieces of the substrate, in respective intersection points between the dividing lines on the substrate, a step of forming chamfering through holes by etching the substrate 10, and a step of obtaining the individual pieces of the substrate by separating the substrate in the vertical direction and the horizontal direction along the dividing lines A respectively.

Owner:SHINKO ELECTRIC IND CO LTD

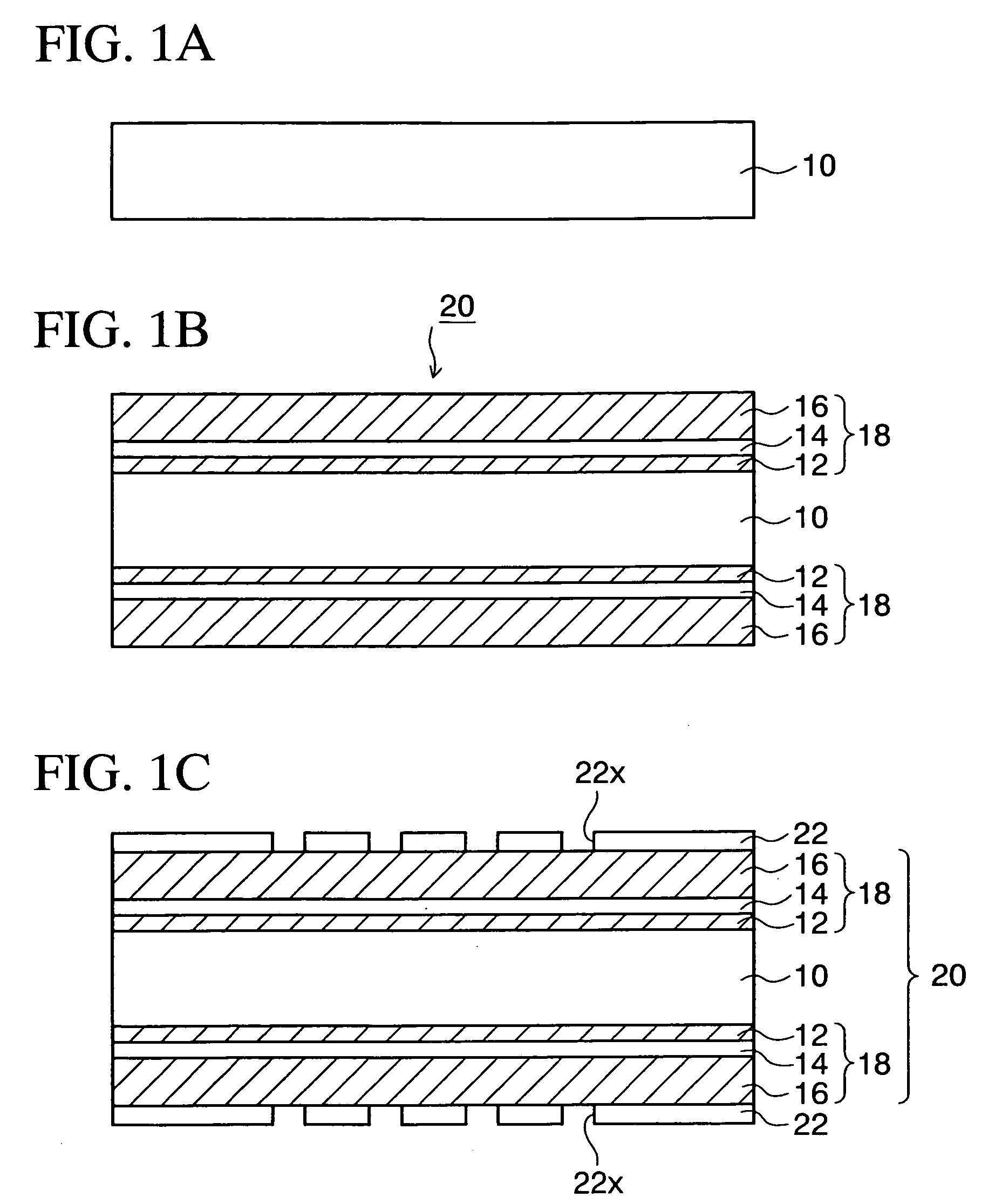

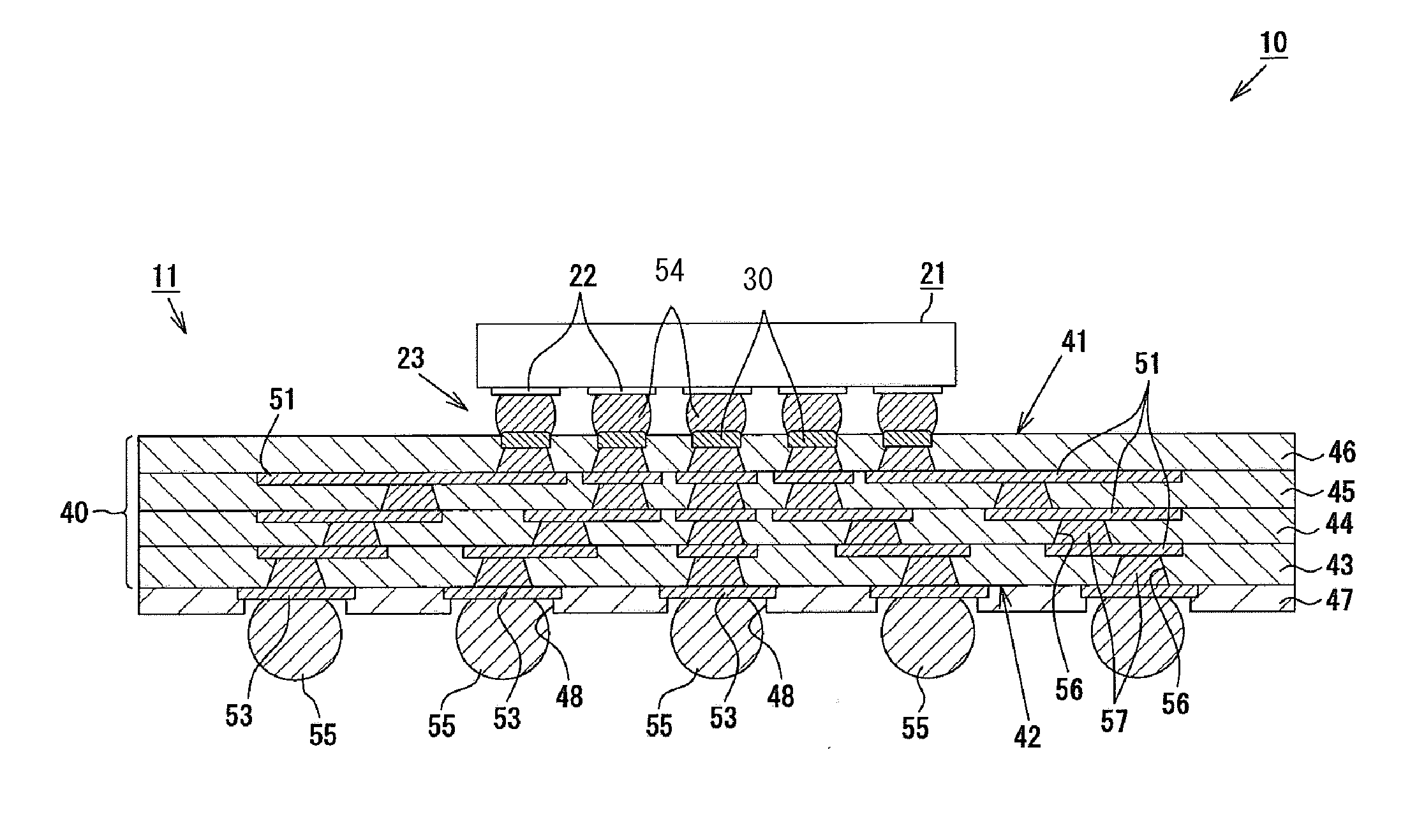

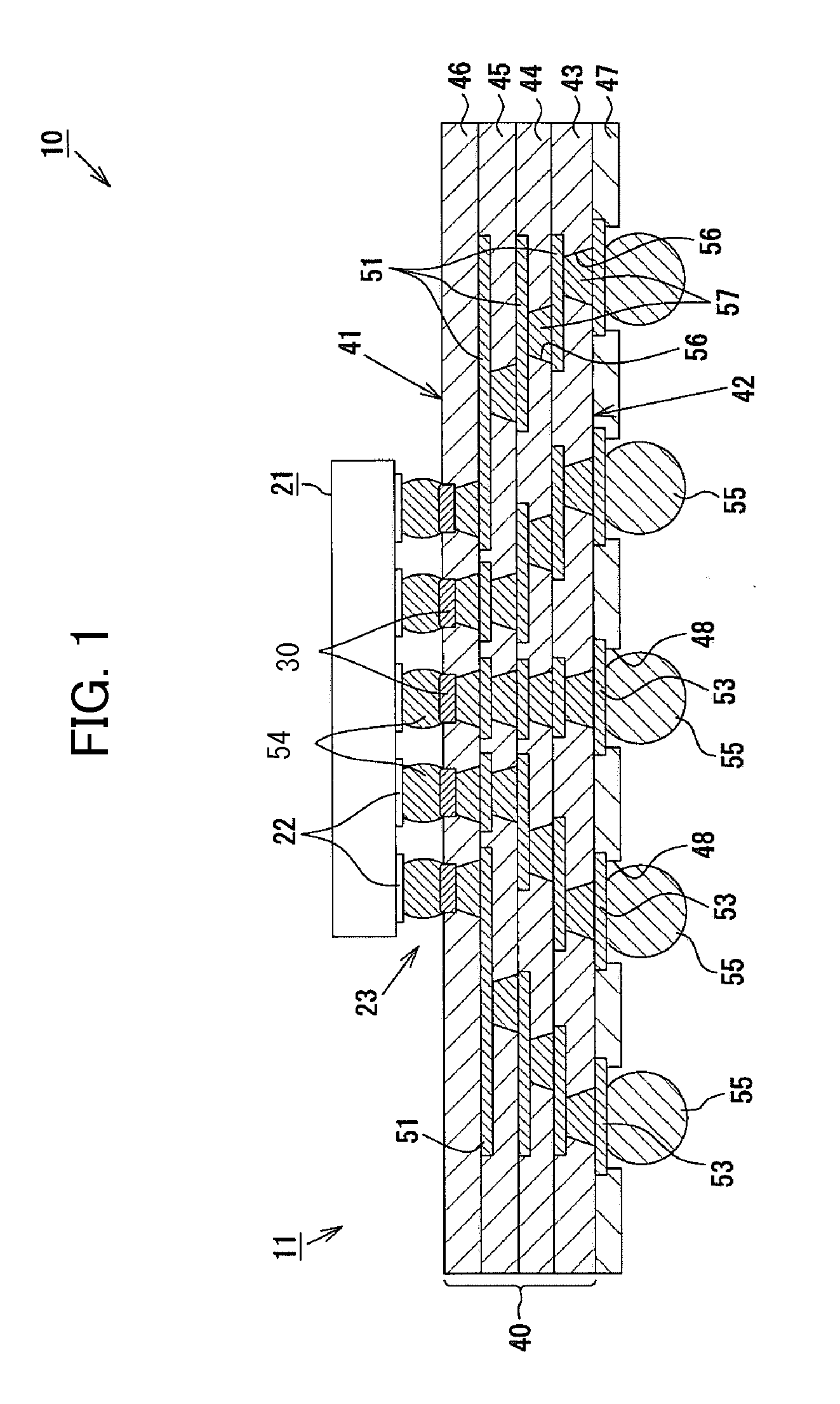

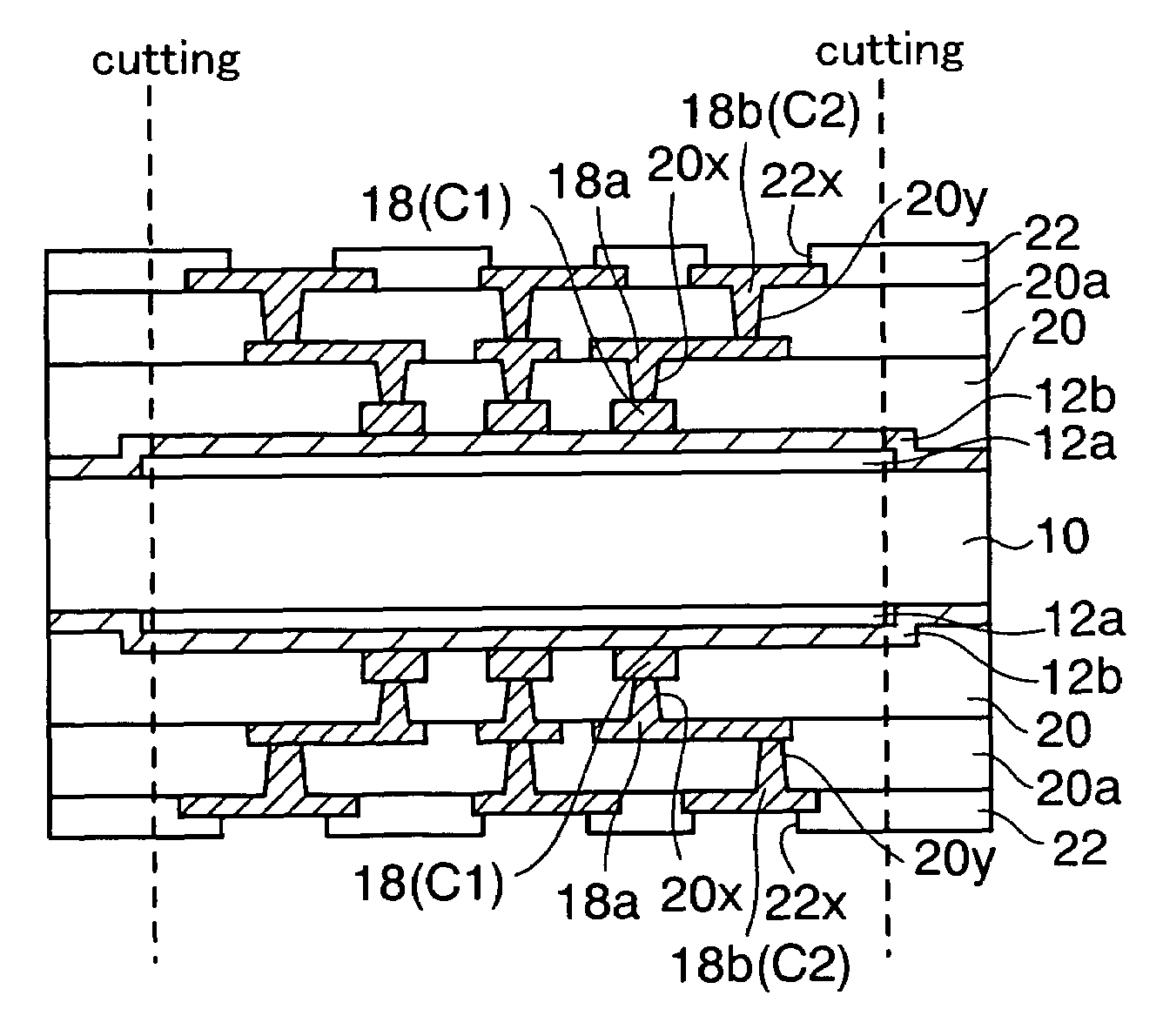

Printed wiring board and method of fabricating the same

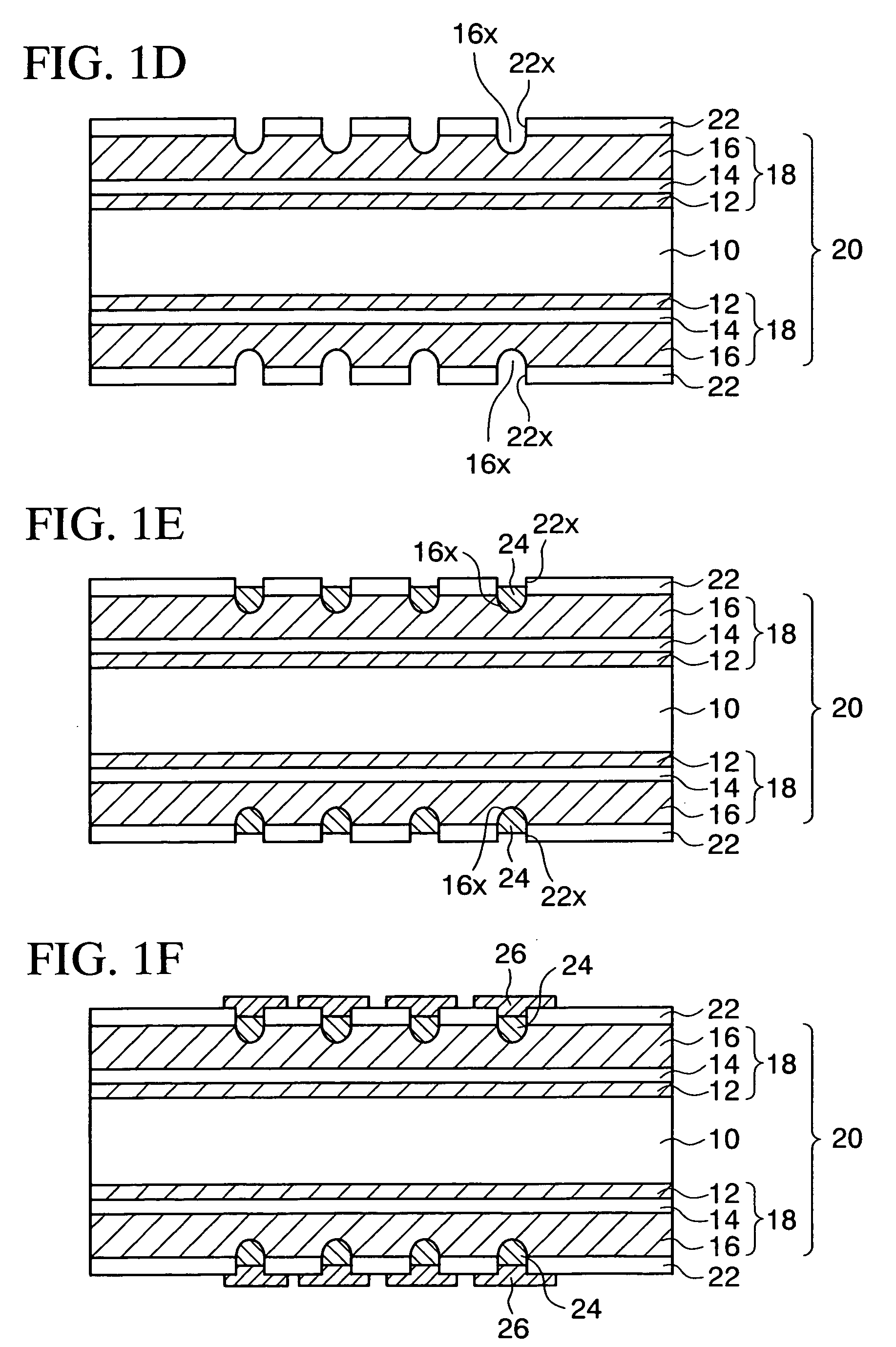

ActiveUS7223687B1Reduce thicknessHighly integratedPrinted circuit assemblingLaminating printed circuit boardsEngineeringDielectric layer

A method of fabricating a printed wiring board comprising the following steps is provided. A portion of each of two dielectric layers or metal layers bonds to both sides of a carrier plate, respectively. Two build-up wiring structures are respectively formed on the dielectric layers or the metal layers by a build-up process. The portions of the dielectric layers or metal layers bonded to the carrier plate are removed such that the dielectric layers or metal layers and the build-up wiring structures formed thereon are released from the carrier plate to form two printed wiring boards.

Owner:SUBTRON TECH

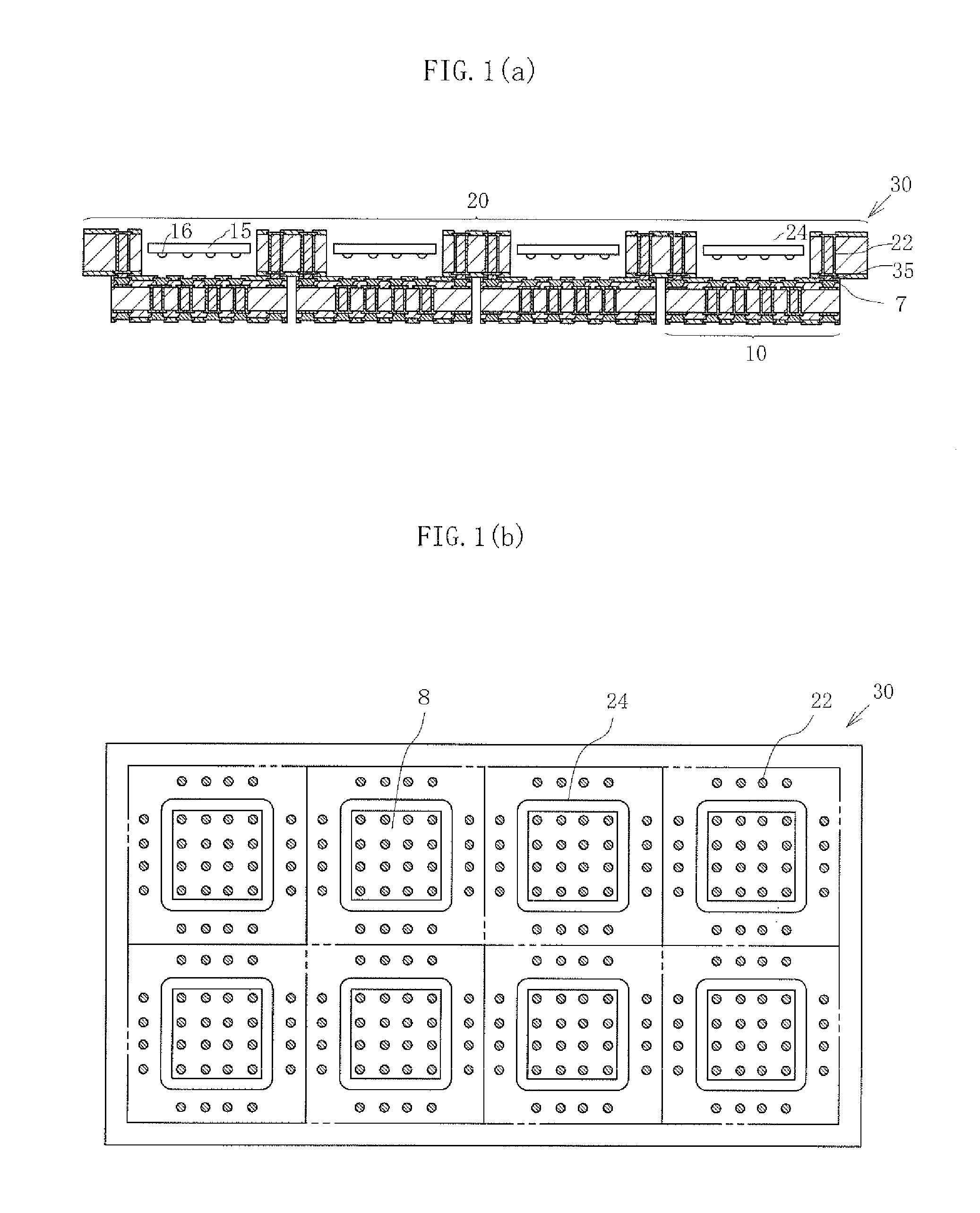

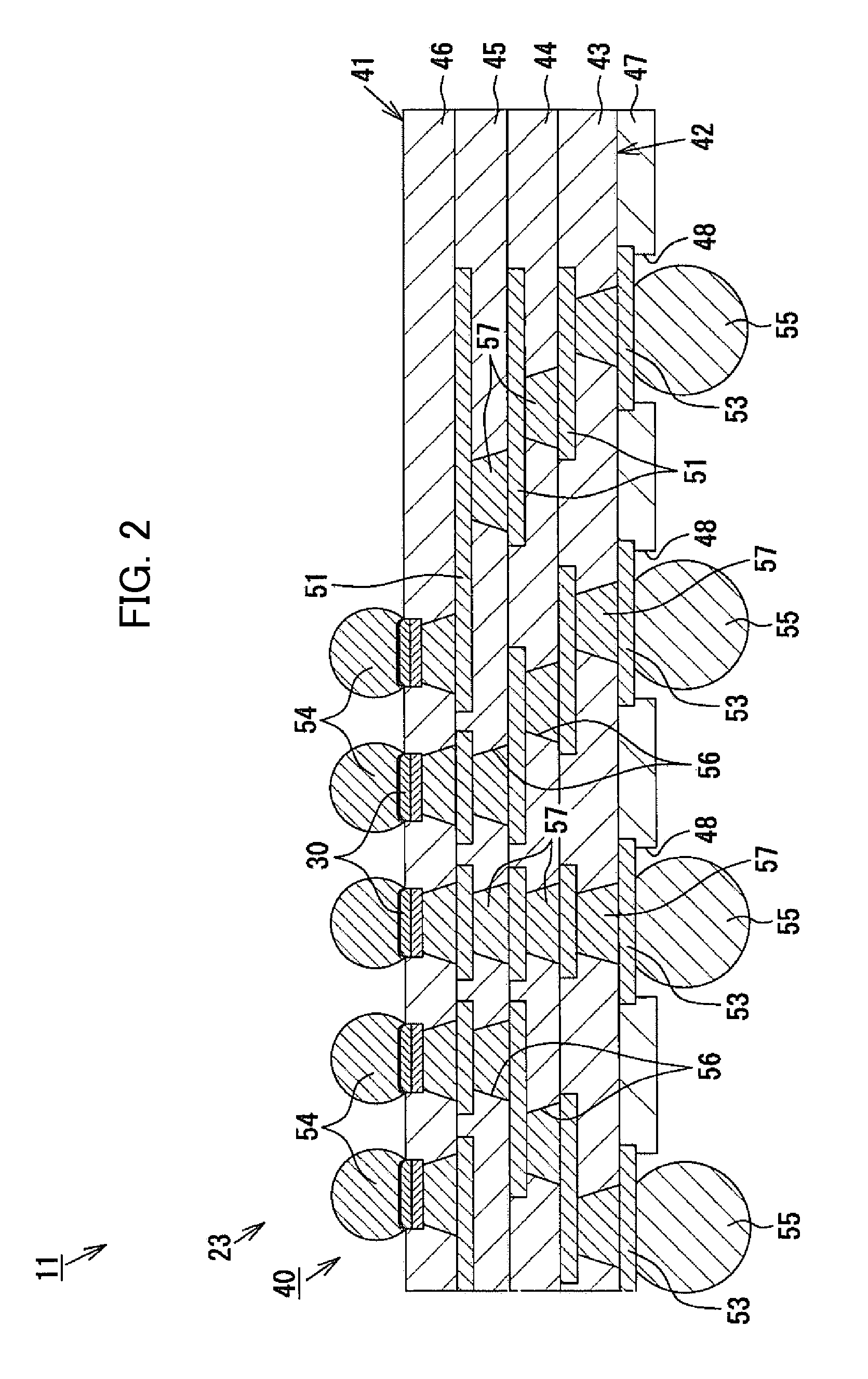

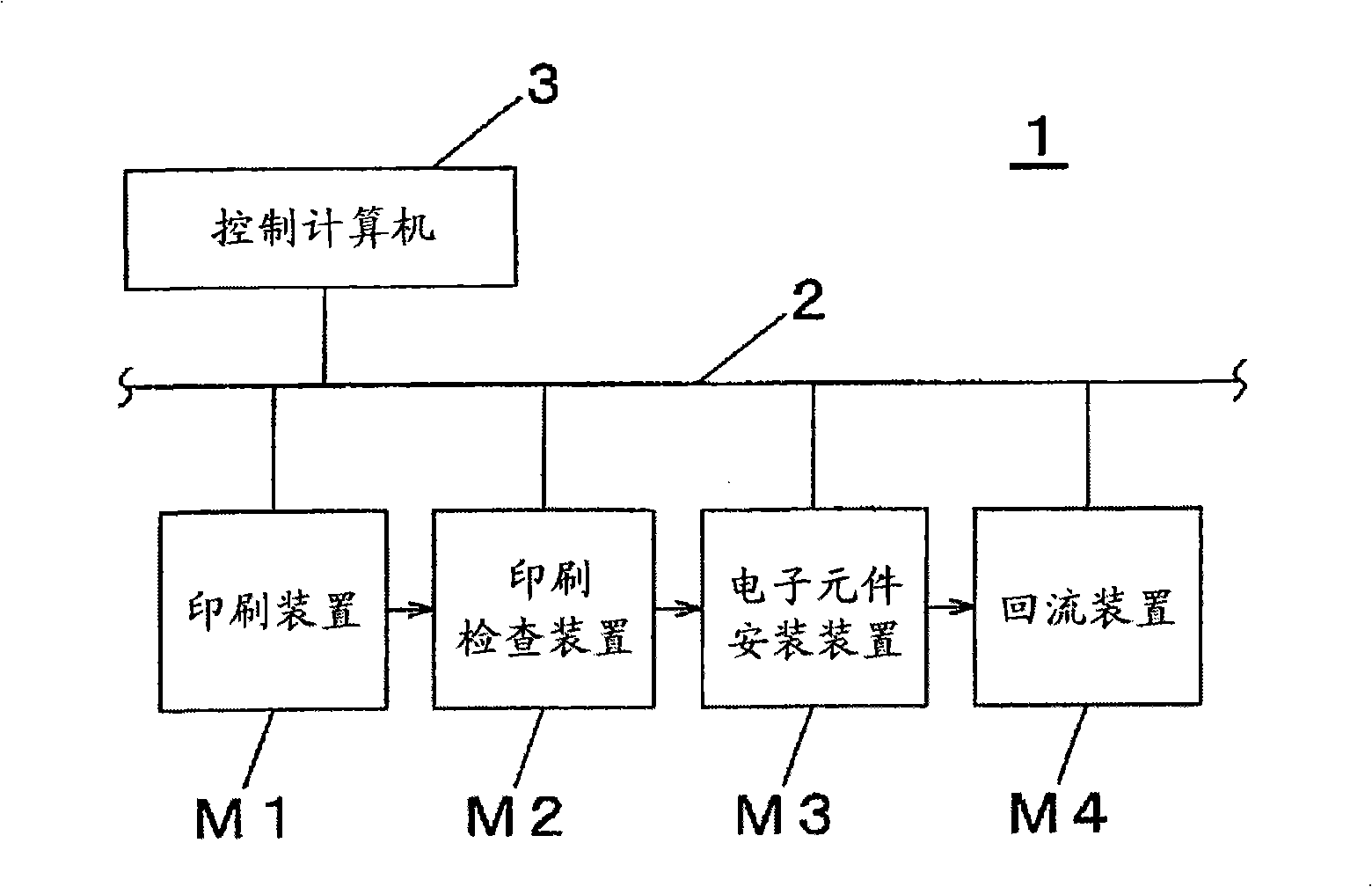

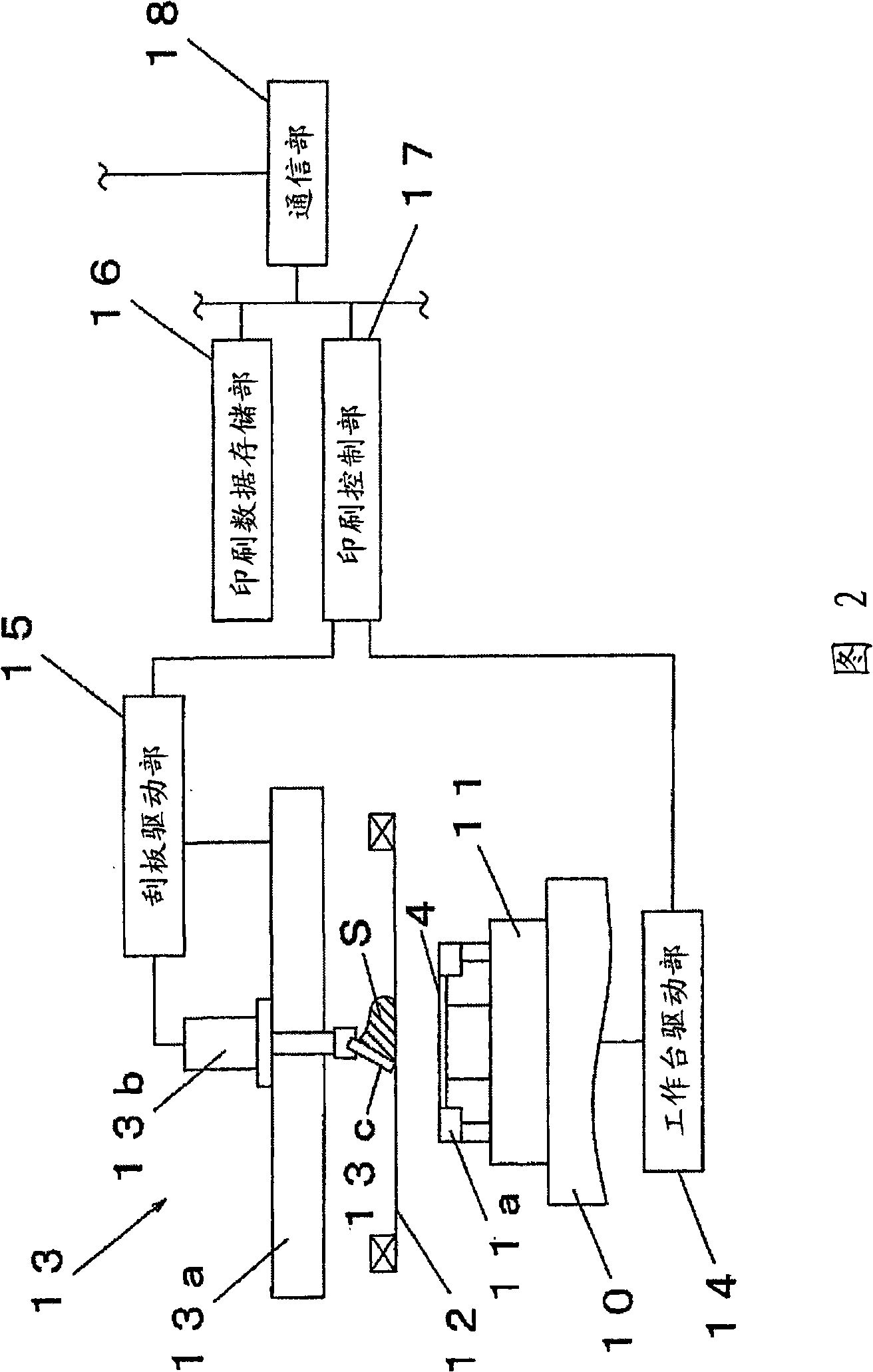

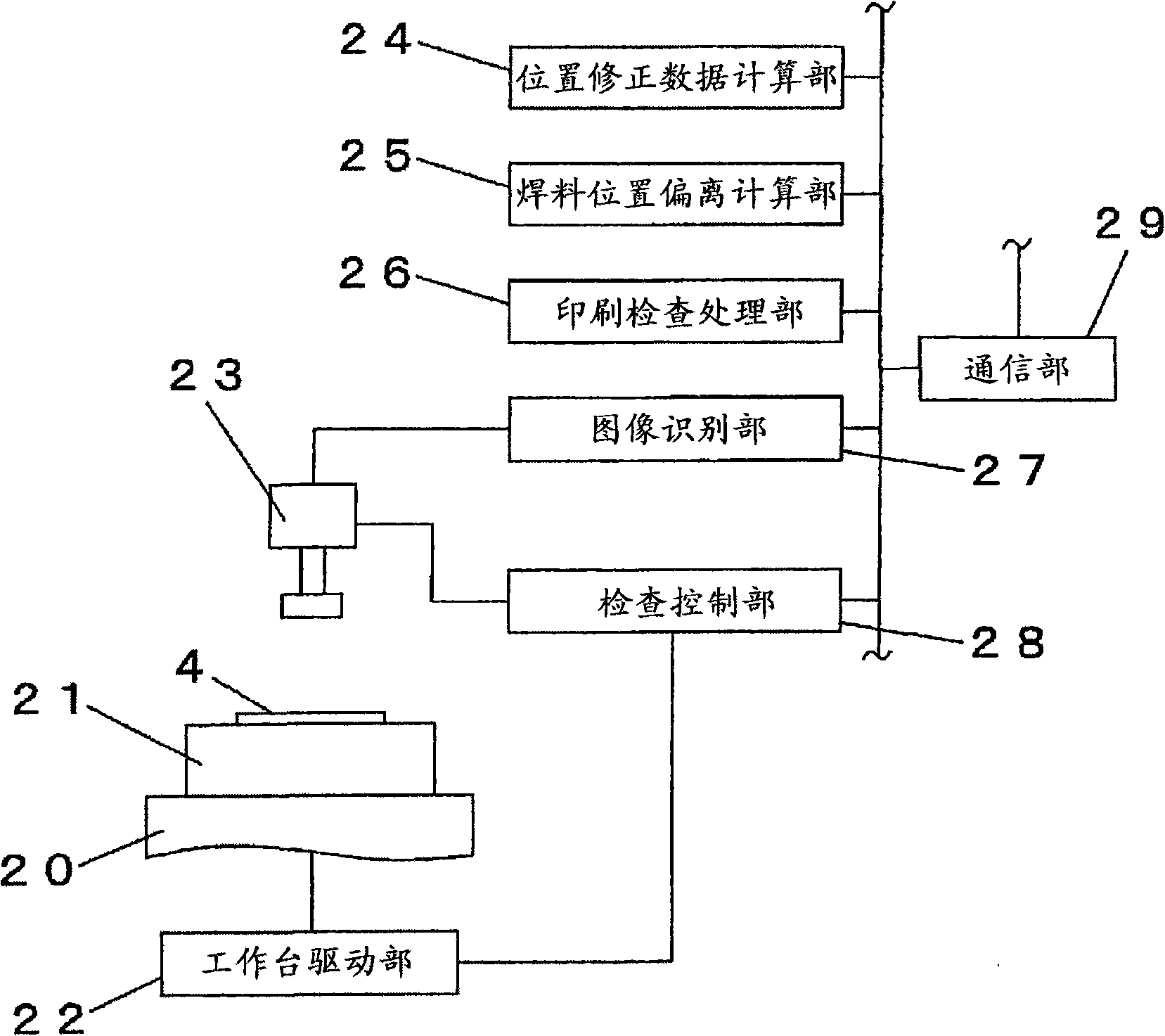

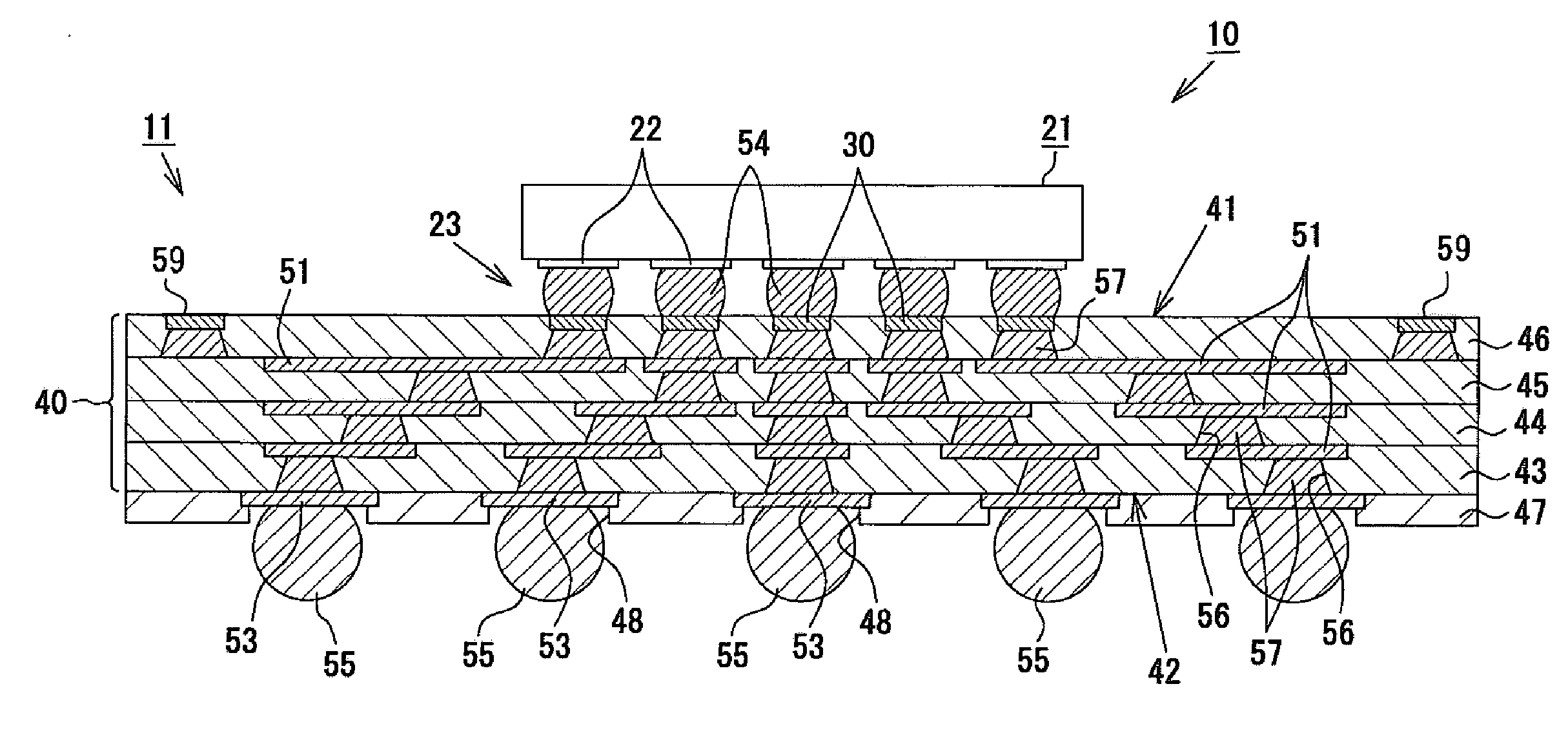

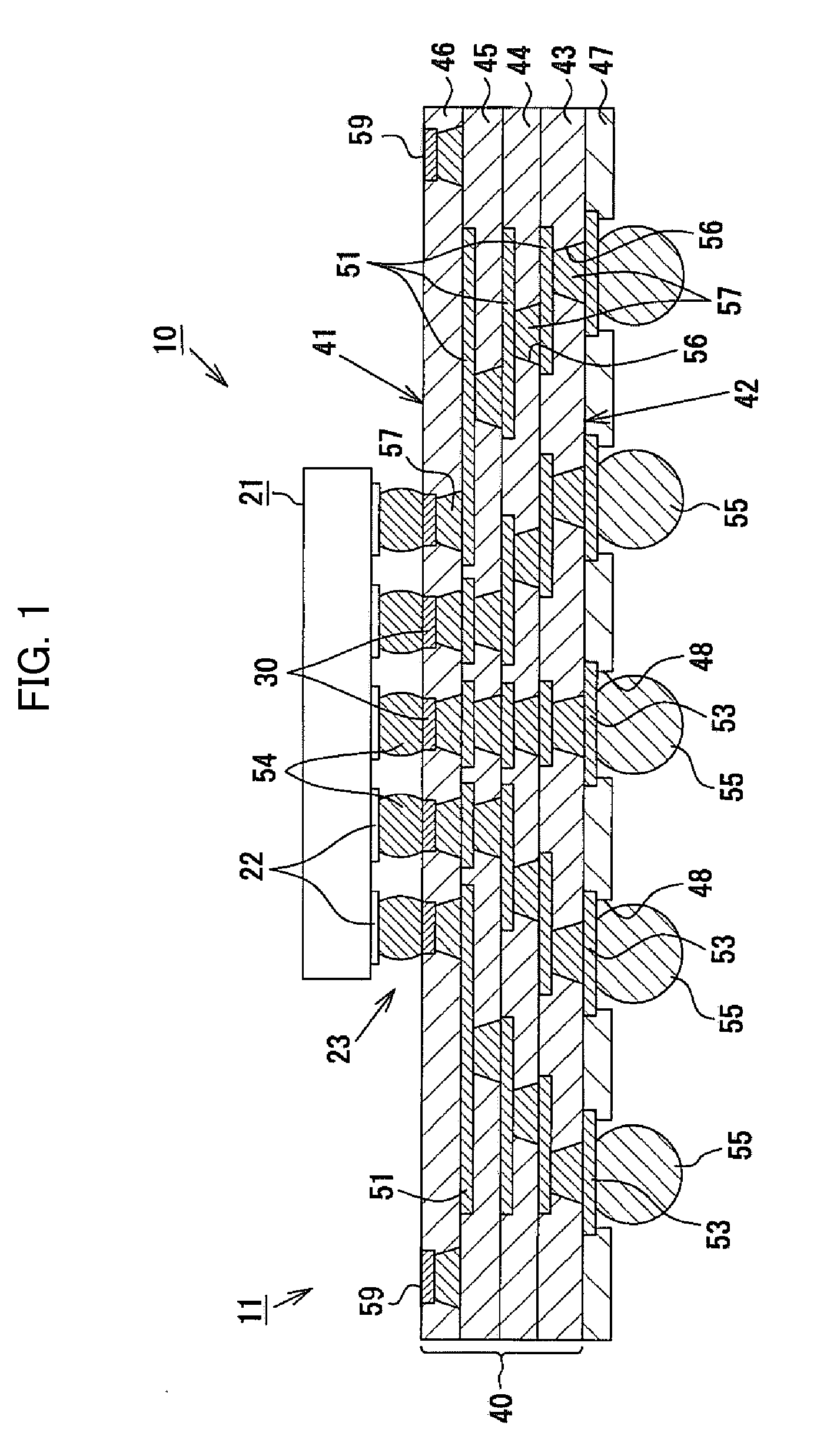

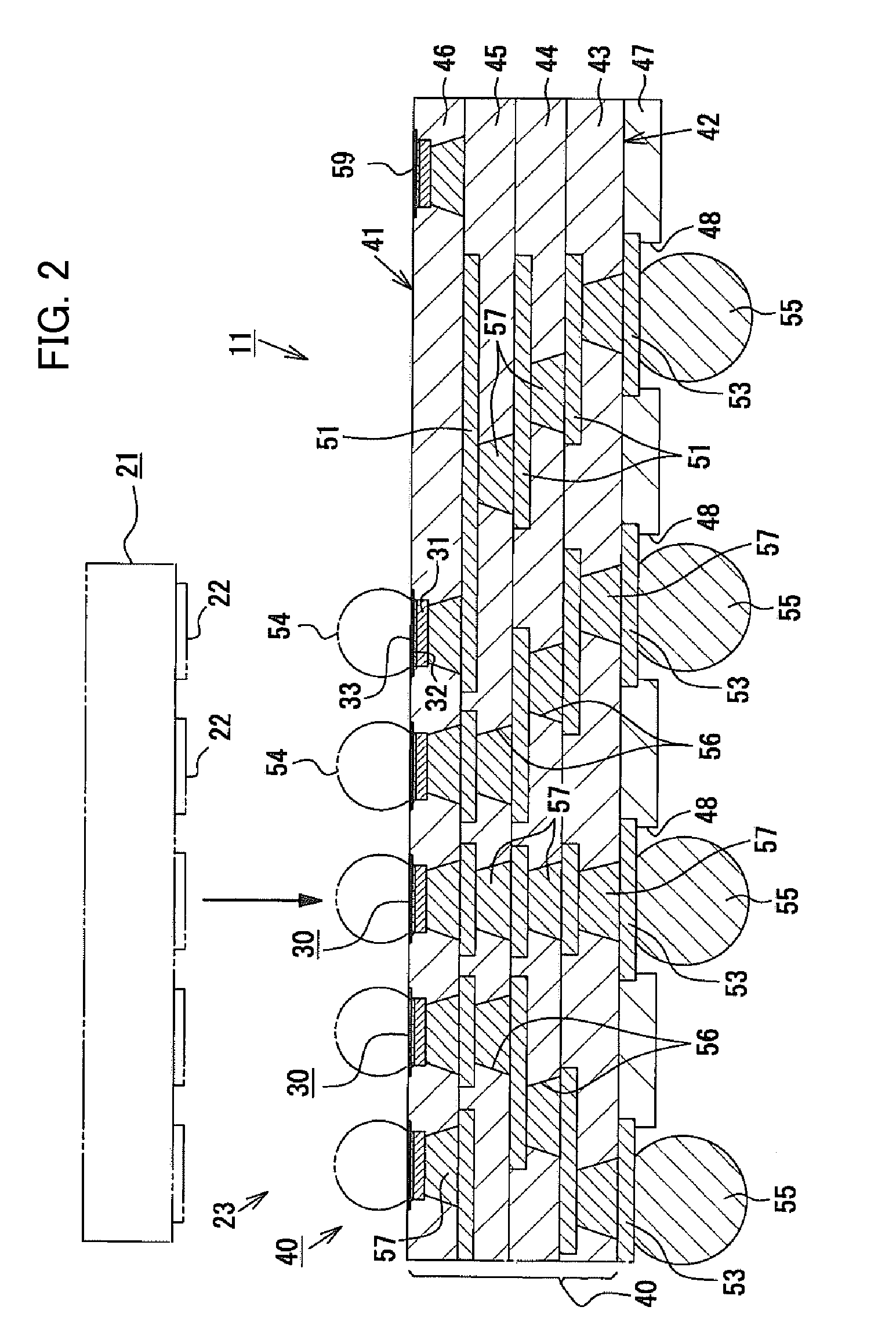

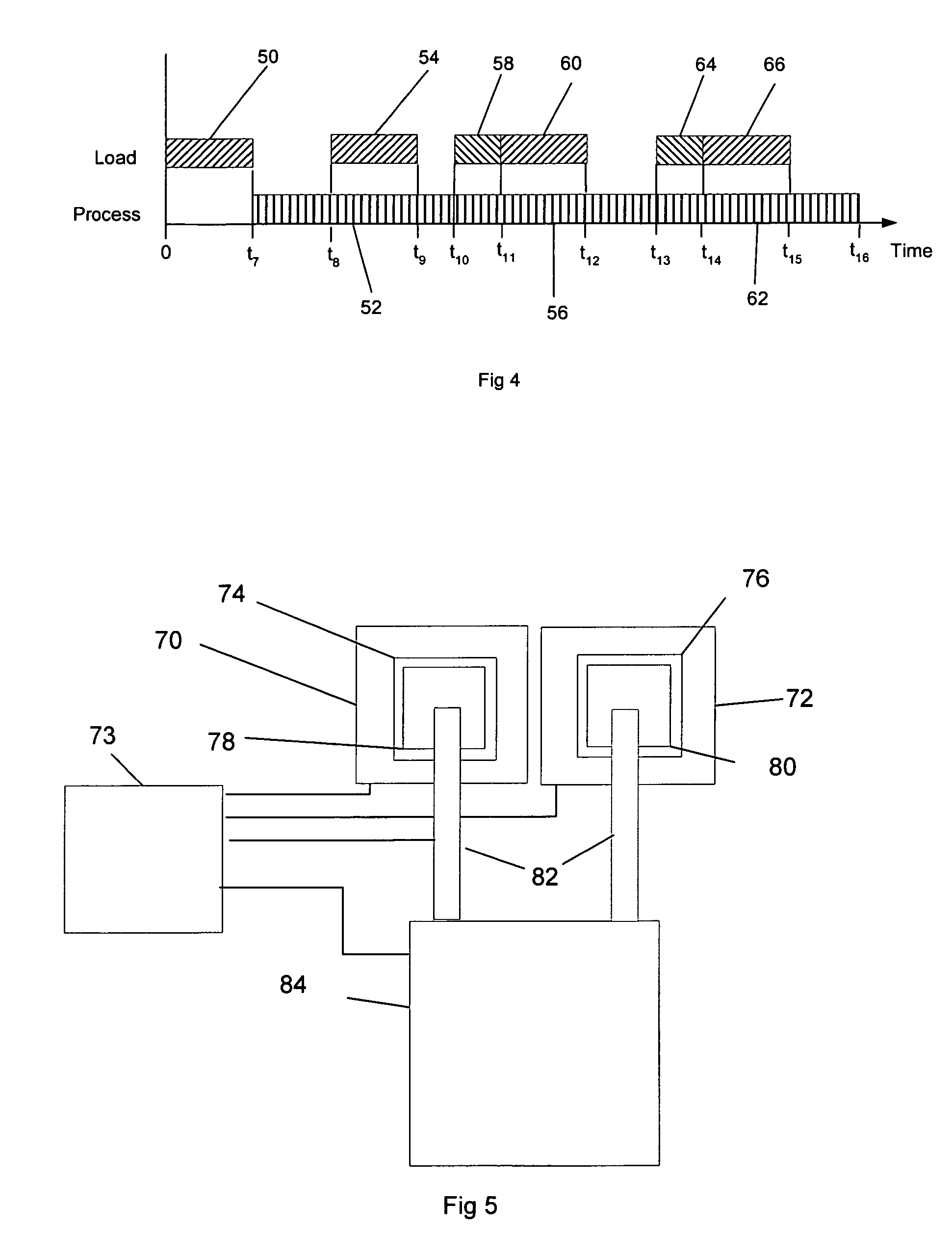

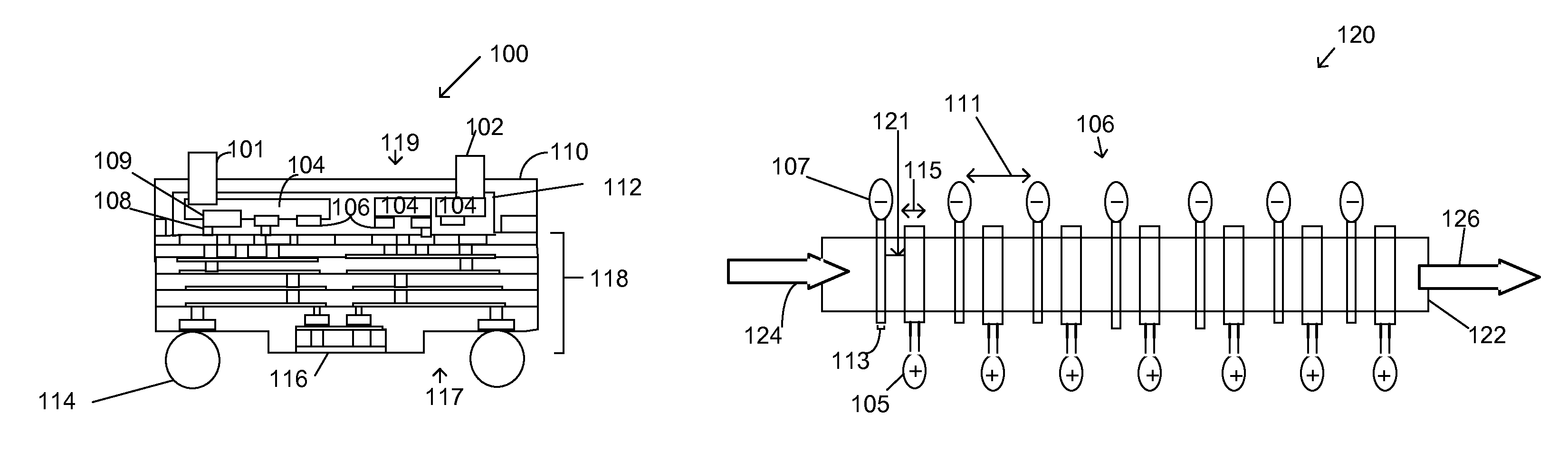

Electronic component mounting system and electronic component mounting method

ActiveCN101312137APrinted circuit assemblingSemiconductor/solid-state device testing/measurementEngineeringElectronic component

In electronic component mounting for a plurality of individual substrates held on a carrier, solder position deviation data is calculated for each individual substrate based on a mark position recognition result on a carrier after solder printing, a solder position recognition result, and electrode position information indicating the position of an electrode on each individual substrate, an operation of calculating position correction data, which is used to correct the positional deviation to mount electronic components at proper positions, is performed for each individual substrate based on the calculated solder position deviation data and the calculated position correction data is feed-forwarded to an electronic component mounting apparatus, and an electronic component mounting operation of a component mounting mechanism is controlled based on the mark position recognition result and the position correction data.

Owner:PANASONIC CORP

Layered structure for use with high power light emitting diode systems

A layered structure for use with a high power light emitting diode system comprises an electrically insulating intermediate layer interconnecting a top layer and a bottom layer. The top layer, the intermediate layer, and the bottom layer form an at least semi-flexible elongate member having a longitudinal axis and a plurality of positions spaced along the longitudinal axis. The at least semi-flexible elongate member is bendable laterally proximate the plurality of positions spaced along the longitudinal axis to a radius of at least 6 inches, twistable relative to its longitudinal axis up to 10 degrees per inch, and bendable to conform to localized heat sink surface flatness variations having a radius of at least 1 inch. The top layer is pre-populated with electrical components for high wattage, the electrical components including at least one high wattage light emitting diode at least 1.0 Watt per 0.8 inch squared.

Owner:METROSPEC TECH

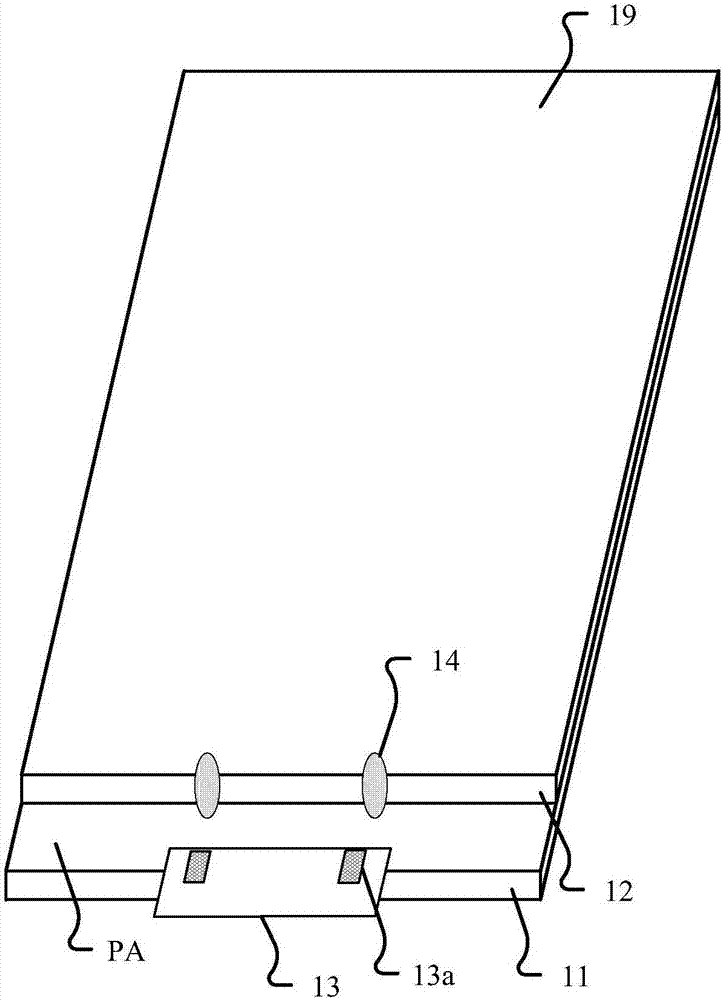

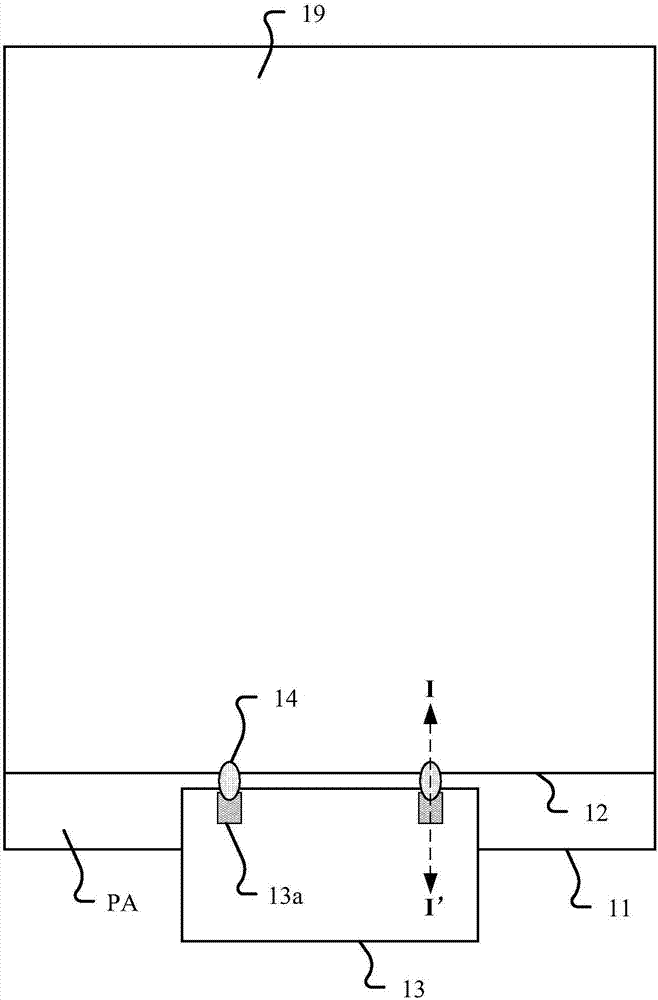

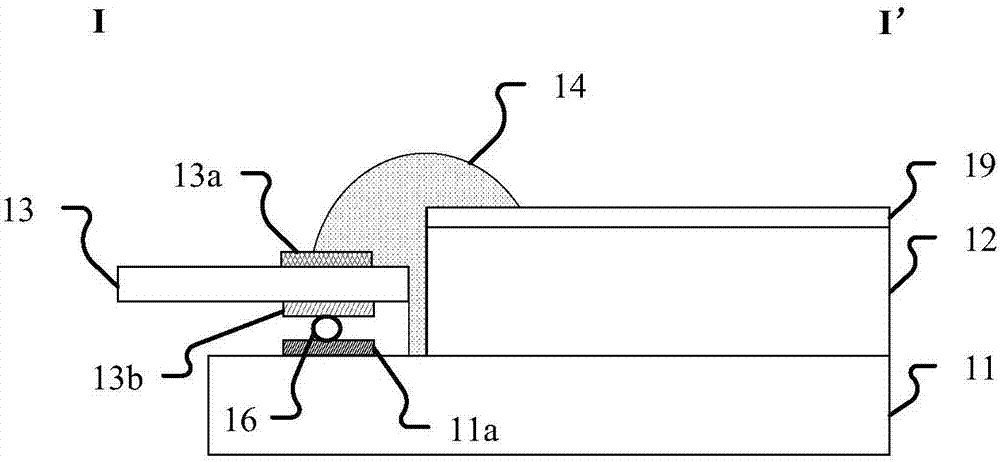

Display panel and display device

ActiveCN107247373AConducive to narrow borderReduce areaPrinted circuit groundingSemiconductor/solid-state device detailsChip on filmDisplay device

The invention discloses a display panel and a display device, and belongs to the field of display technologies. The display panel comprises electrically conductive adhesion bodies, a chip on film, an electrically conductive layer, a first substrate and a second substrate. The first substrate is opposite to the second substrate, the chip on film is adhered at a step region of the first substrate, and the electrically conductive layer is positioned on the side, which is far away from the first substrate, of the second substrate; the chip on film comprises a grounding bonding pad, and the grounding bonding pad is arranged on the side, which is far away from the first substrate, of the chip on film; the electrically conductive adhesion bodies are electrically connected with the electrically conductive layer and are electrically connected with the grounding bonding pad. According to the technical scheme, the display panel and the display device have the advantages that the grounding bonding pad is arranged on the side, which is far away from the first substrate, of the chip on film, accordingly, the occupied area of the step regions can be reduced while static electricity is prevented, and frames of the display panel can be advantageously narrowed.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

Multilayer wiring substrate and method for manufacturing the same

ActiveUS20100208437A1Low connection reliabilityDeterioration of surface shapeEarth drilling toolsDrill bitsElectrical conductorEngineering

A multilayer wiring substrate of the present invention has a laminated structure composed of conductor layers and resin insulating layers stacked alternately. A plurality of surface connection terminals to which terminals of a chip component are to be surface-connected are formed on a main face of the laminated structure. A plurality of via conductors connected to the plurality of surface connection terminals are formed in the resin insulating layers. Each of the plurality of surface connection terminals has a structure in which a copper layer, a nickel layer, and a gold layer are stacked in this sequence. The gold layer is larger in diameter than at least the copper layer. The gold layer has an overhanging portion which extends radially outward from a circumference of the copper layer.

Owner:NGK SPARK PLUG CO LTD

Method of manufacturing wiring substrate and method of manufacturing electronic component mounting structure

ActiveUS7594317B2Reduce manufacturing costEasy to installPrinted circuit assemblingLine/current collector detailsMetal foilEngineering

A method of manufacturing a wiring substrate including the steps of, obtaining a temporary substrate from a prepreg, and concurrently attaching a metal foil onto at least one surface of the temporary substrate, by disposing the metal foil on a prepreg through a underlying layer interposed between them, in a way that the underlying layer is disposed in a wiring formation region on the prepreg, and the metal foil having a size larger than that of the underlying layer is caused to contact with an outer peripheral portion of the wiring formation region, and then by hardening the prepreg with heating and pressurization, forming a build-up wiring layer on the metal foil, and obtaining a wiring member in which the build-up wiring layer is formed on the metal foil, by cutting out a portion of structure in which the underlying layer, the metal foil and the build-up wiring layer are formed on the temporary substrate, the portion corresponding to a peripheral portion of the underlying layer, and thus by separating the metal foil from the temporary substrate.

Owner:SHINKO ELECTRIC IND CO LTD

Method and apparatus for laser processing

InactiveUS7834293B2Reduce eliminateShorten the timeSolid-state devicesSemiconductor/solid-state device manufacturingLaser processingLight beam

Owner:ELECTRO SCI IND INC

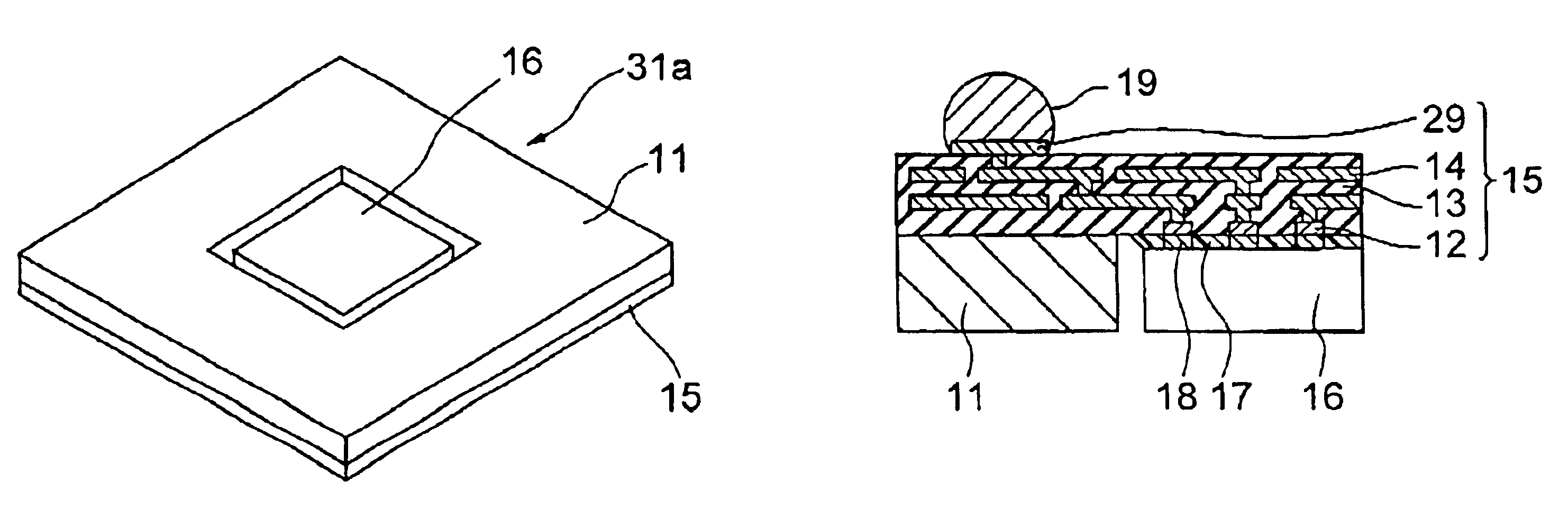

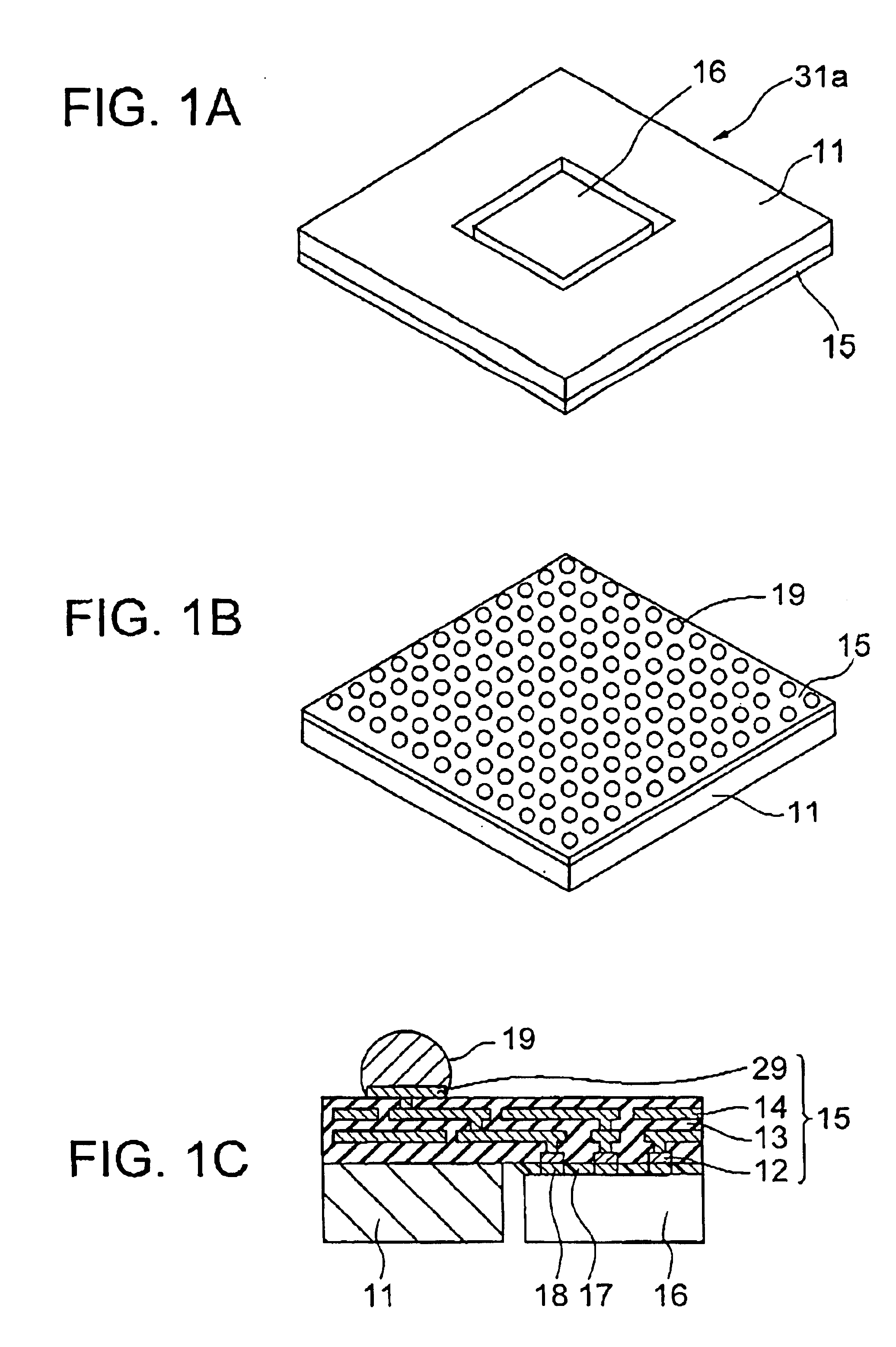

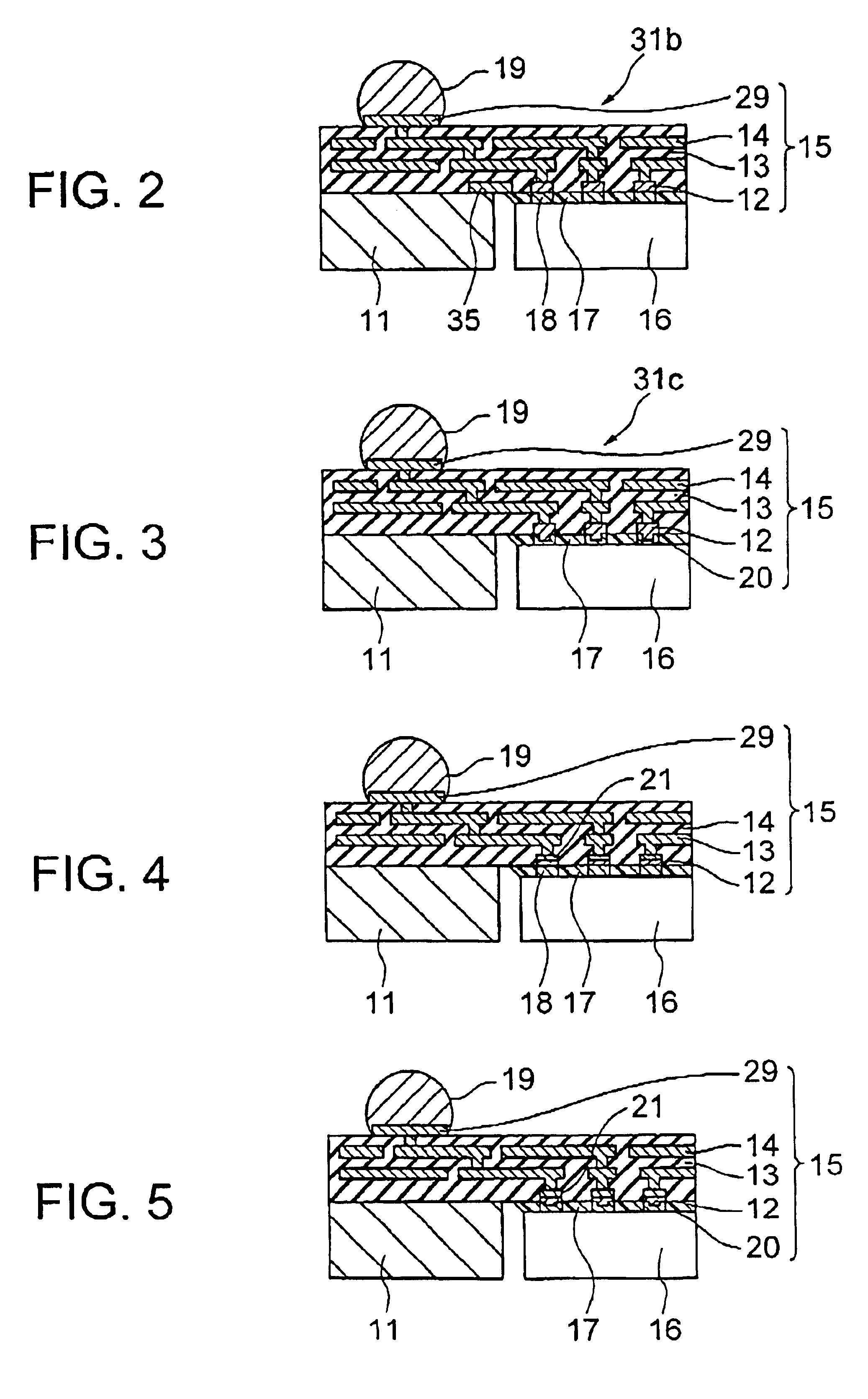

Semiconductor package board using a metal base

InactiveUS6841862B2Improve smoothnessImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor chip

A semiconductor package board for mounting thereon a semiconductor chip includes a metal base having an opening for receiving therein the semiconductor chip and a multilayer wiring film layered onto the metal base. The semiconductor chip is flip-chip bonded onto the metal pads disposed on the multilayer wiring film within the opening. The surface of the metal base is flush with the top surface of the semiconductor chip received in the opening. The resultant semiconductor device has a larger number of external pins and a smaller deformation without using a stiffener.

Owner:NEC CORP

Heterogeneous integration of microfluidic devices in package structures

ActiveUS20140083858A1Sludge treatmentSolid-state devicesElectrical and Electronics engineeringElectrode

Methods of forming a microelectronic packaging structure and associated structures formed thereby are described. Those methods may include attaching a microfluidic die to a package structure, wherein the microfluidic die comprises a plurality of asymmetric electrodes that may be coupled with signal pads disposed within the package structure.

Owner:INTEL CORP

Popular searches

Insulating layers/substrates working Optical sensors Printed circuit secondary treatment Printed circuit simultaneous processing Measuring/recording heart/pulse rate Blood flow measurement Printed circuit non-printed electric components association Circuit board tools positioning Inspection/indentification of circuits Welding/soldering/cutting articles