Patents

Literature

30results about How to "Increase processing bandwidth" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

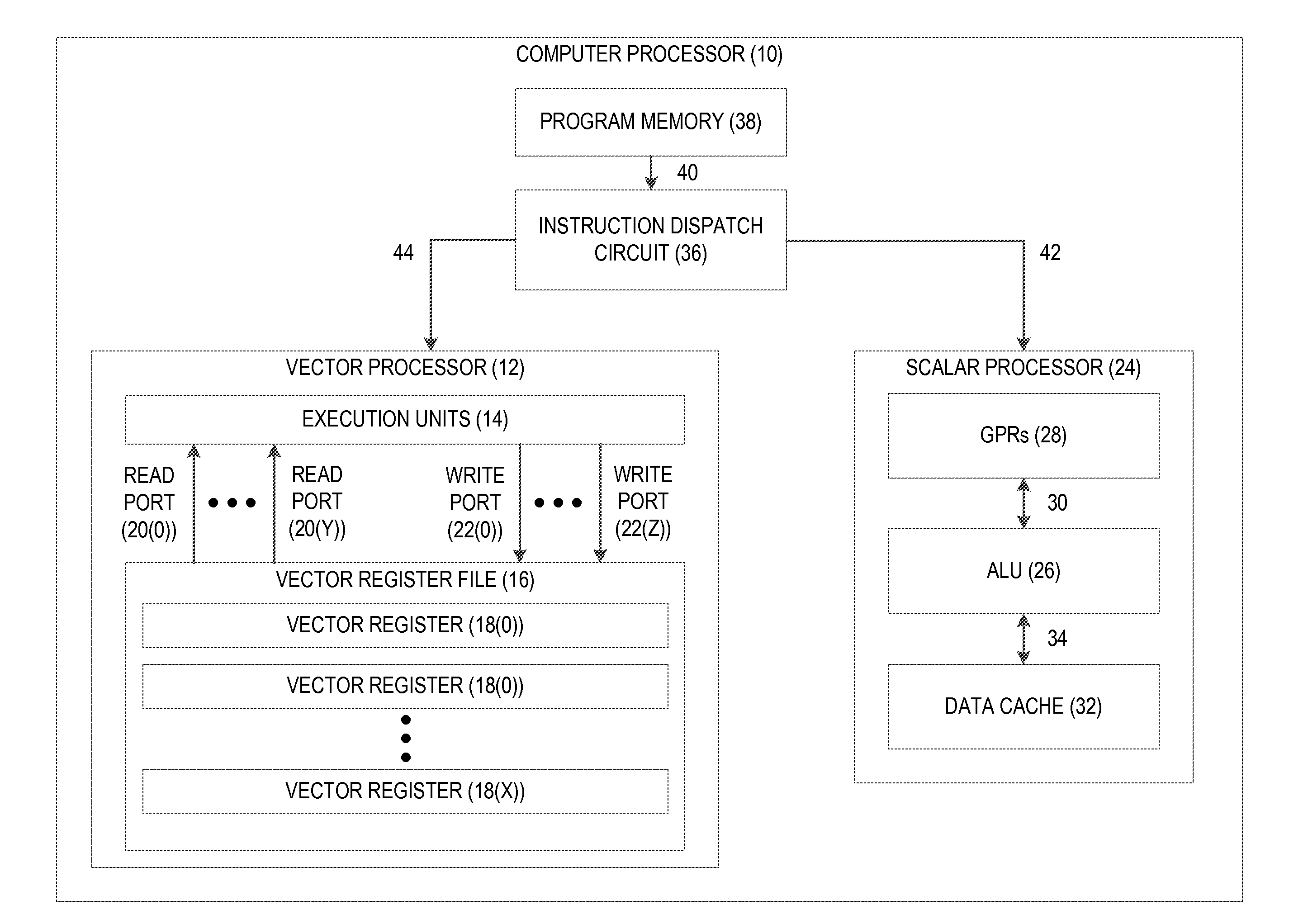

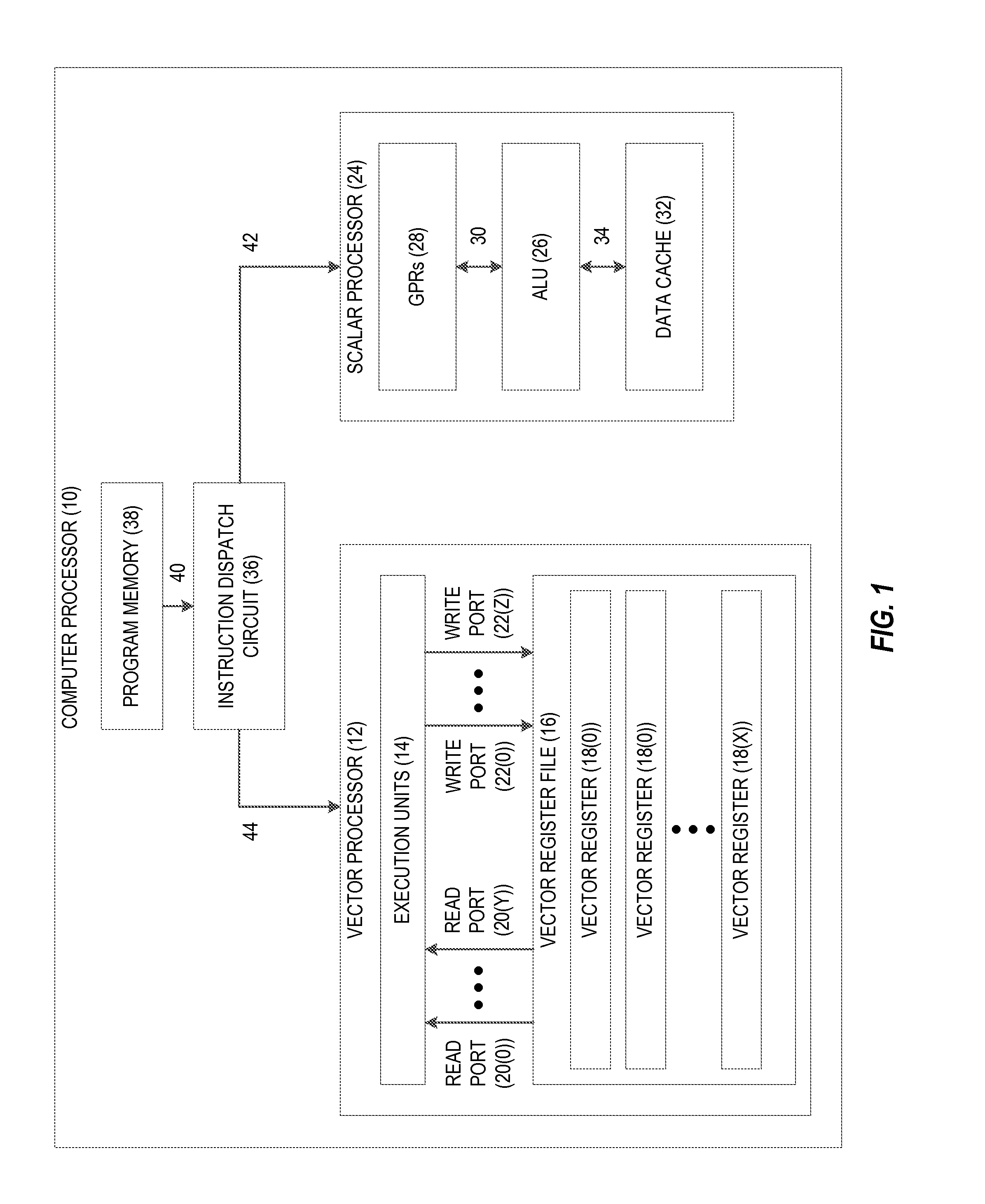

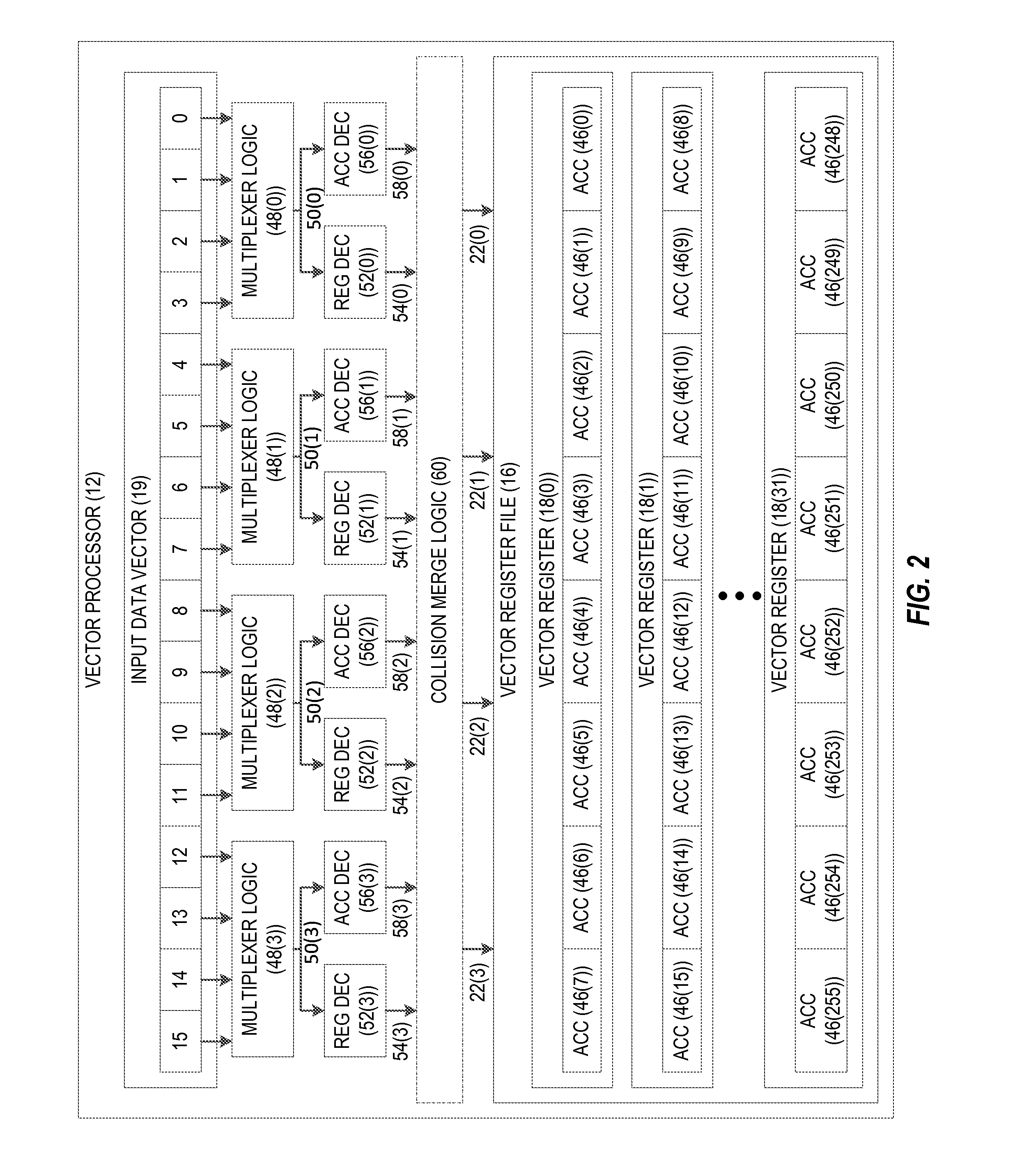

Parallelization of scalar operations by vector processors using data-indexed accumulators in vector register files, and related circuits, methods, and computer-readable media

InactiveUS20160026607A1Increase processing bandwidthImprove processing performanceRegister arrangementsGeneral purpose stored program computerData valueData vector

Parallelization of scalar operations by vector processors using data-indexed accumulators in vector register files, related circuits, methods, and computer-readable media are disclosed. In one aspect, a vector processor comprises a vector register file providing a plurality of write ports and a plurality of vector registers each providing a plurality of accumulators. The vector processor receives an input data vector. For each of the plurality of write ports, the vector processor executes vector operation(s) for accessing an input data value of the input data vector, and determining, based on the input data value, a register index for a vector register among the plurality of vector registers, and an accumulator index for an accumulator among the plurality of accumulators of the vector register. Based on the register index, a register value is retrieved from the register index, and a scalar operation is performed based on the register value and the accumulator index.

Owner:QUALCOMM INC

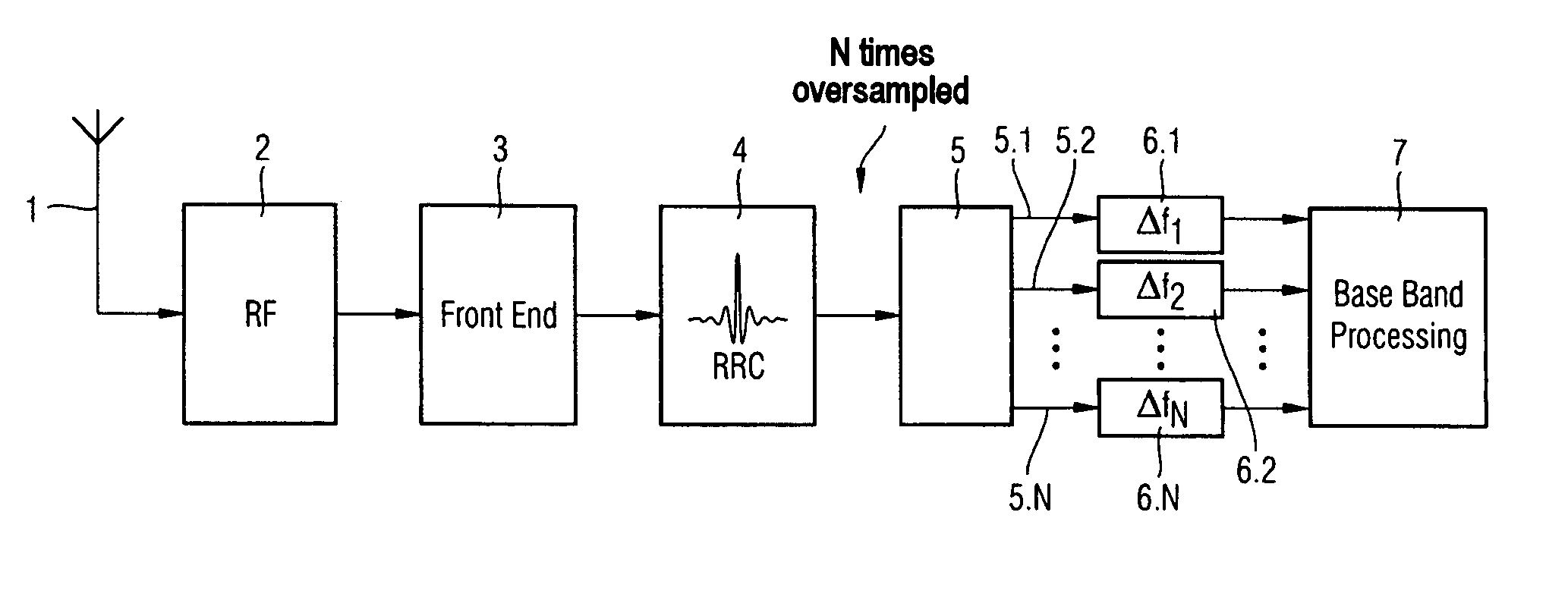

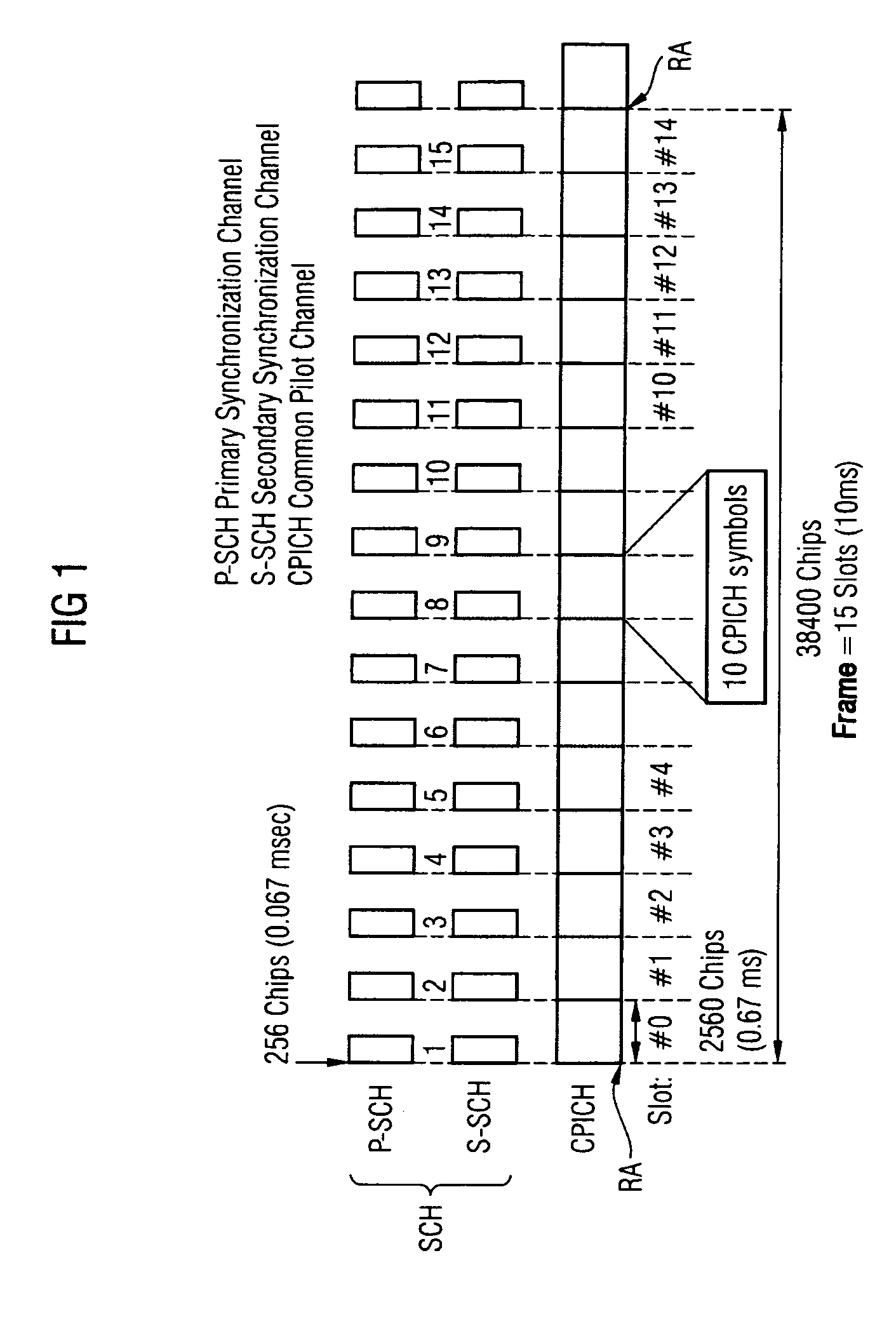

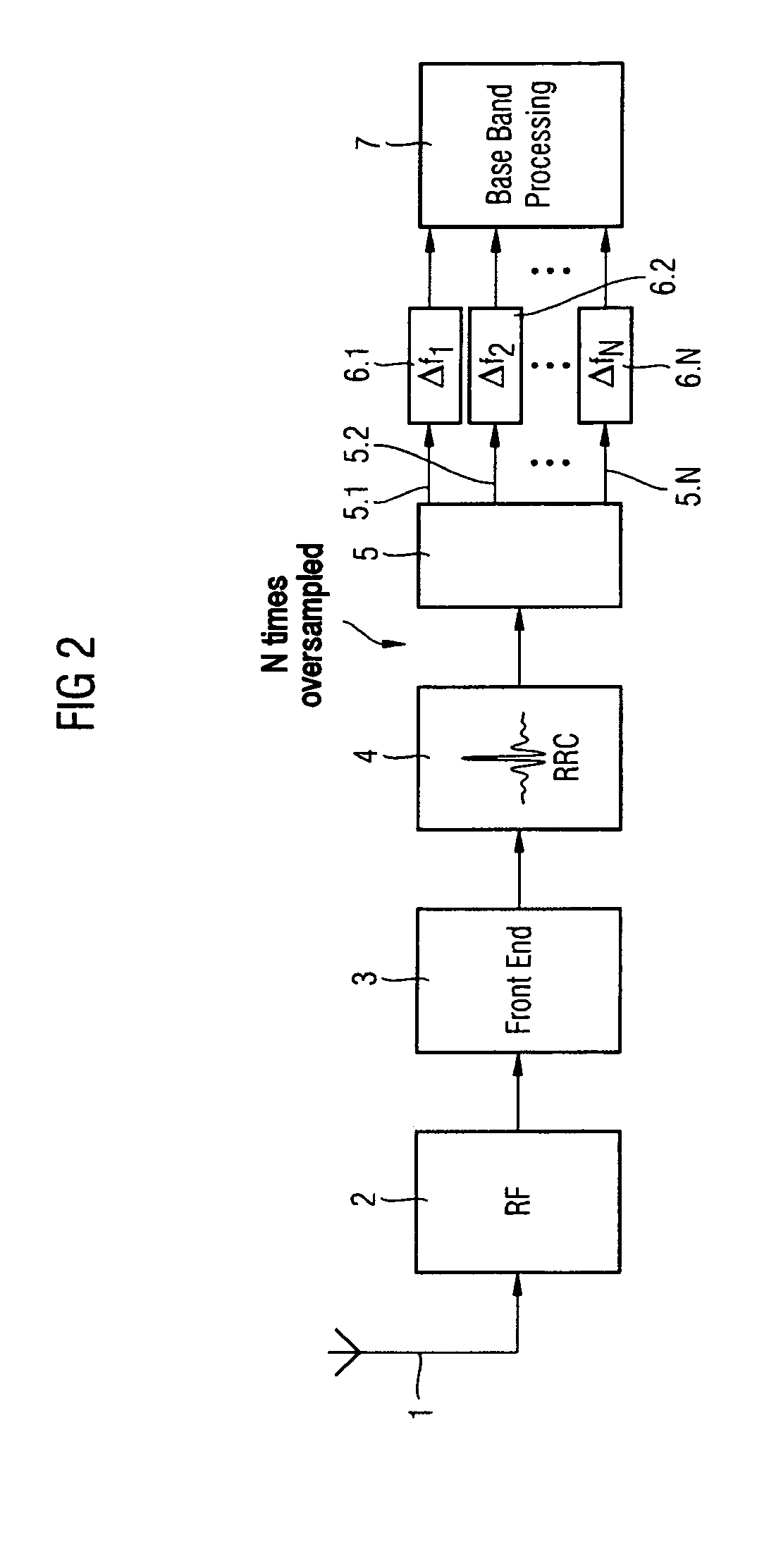

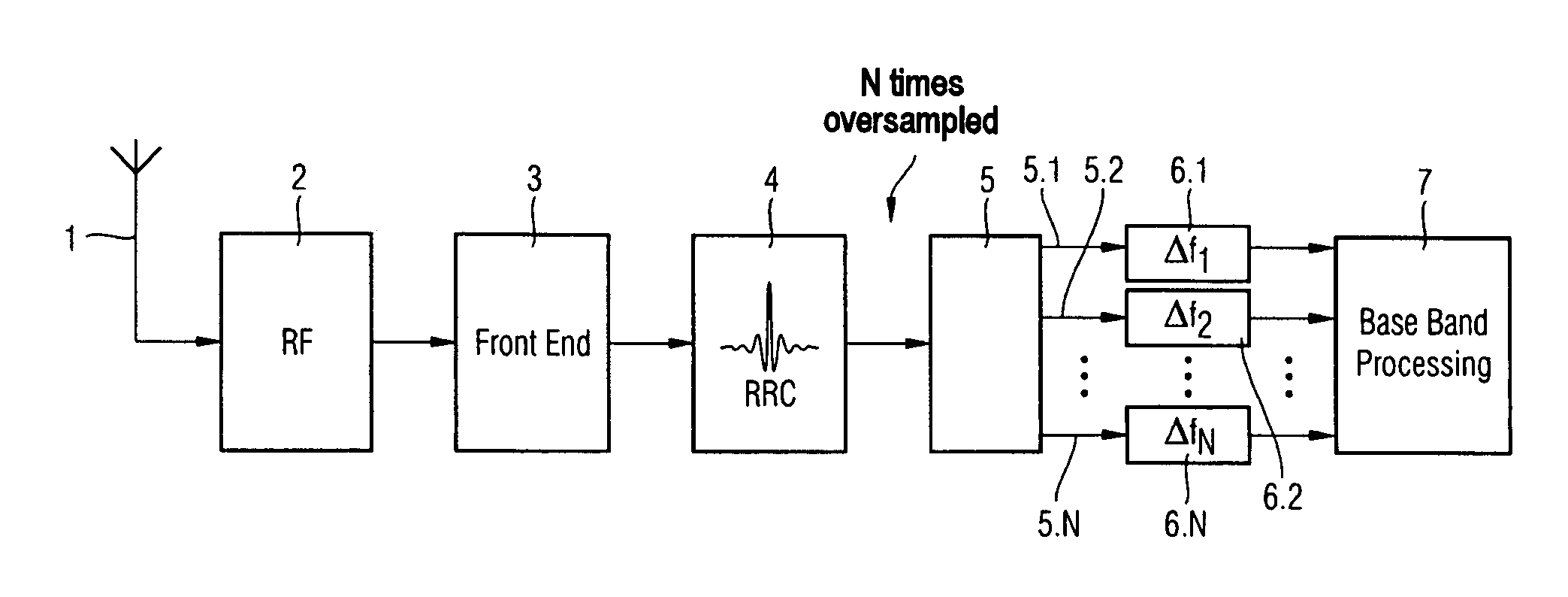

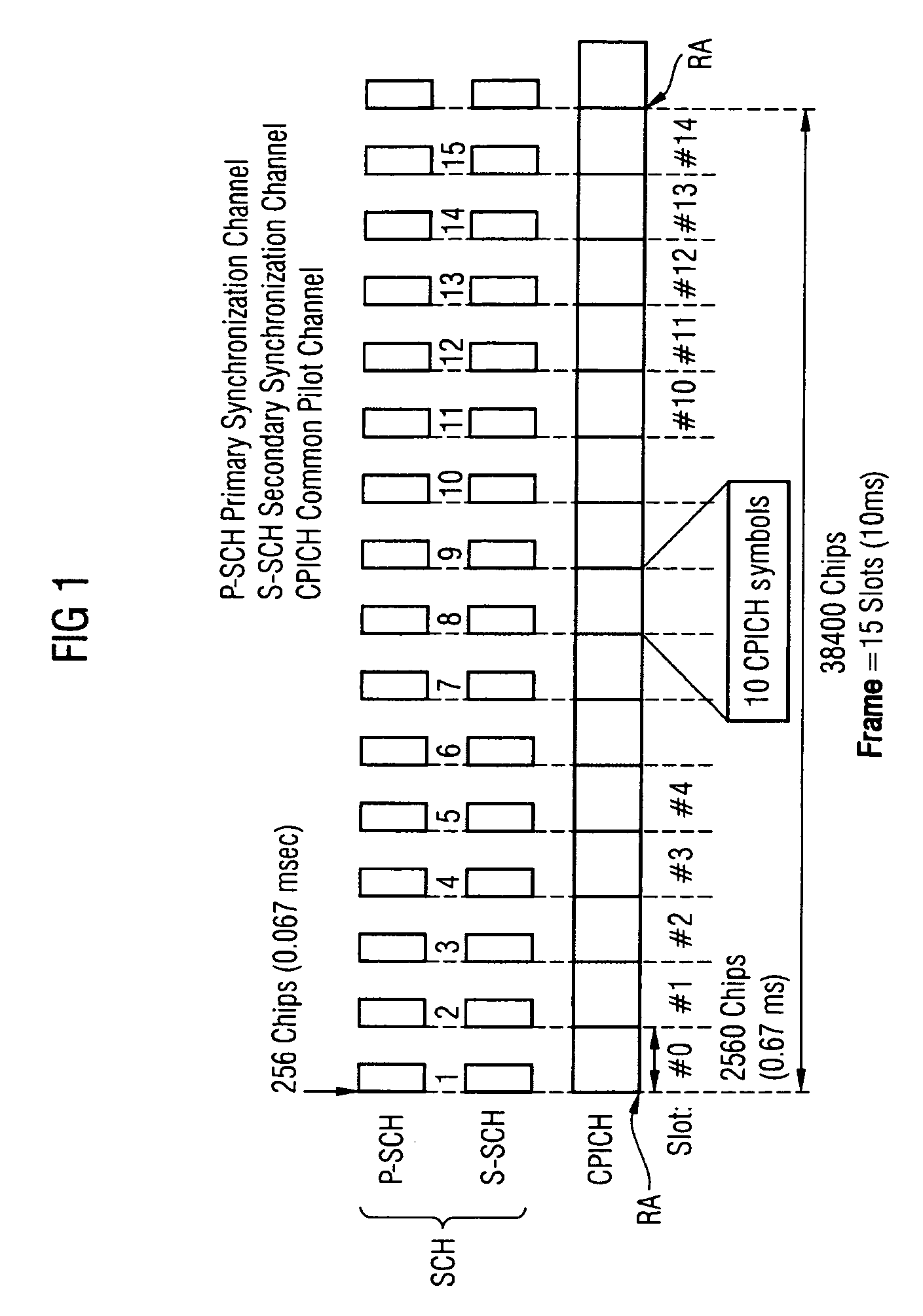

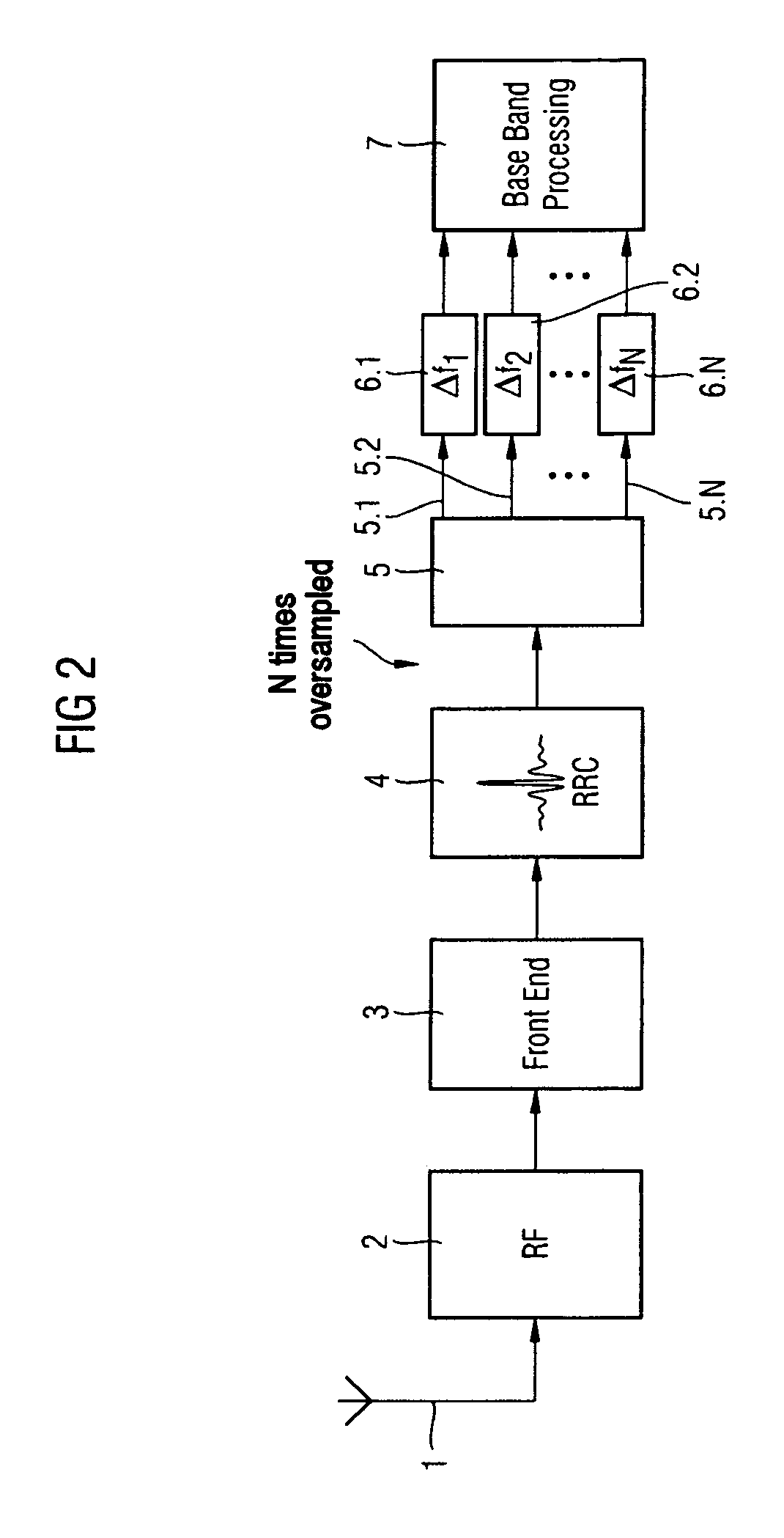

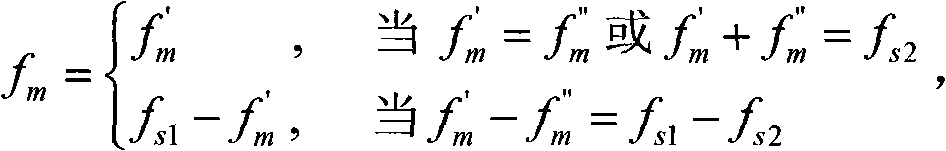

Method and apparatus for synchronization of a mobile radio receiver to a base station

InactiveUS20050117679A1Improve performanceProcess bandwidth be increaseRadio/inductive link selection arrangementsPulse position modulationPhase correlationFrequency offset

In a method for synchronization of a mobile radio receiver to a base station, the received signal is sampled using oversampling, by which means sample values are obtained from different sampling phases. The oversampled signal is correlated with a local code, with sample values that are associated with a first sampling phase being processed with a frequency offset with respect to sample values that are associated with a second sampling phase.

Owner:INTEL CORP

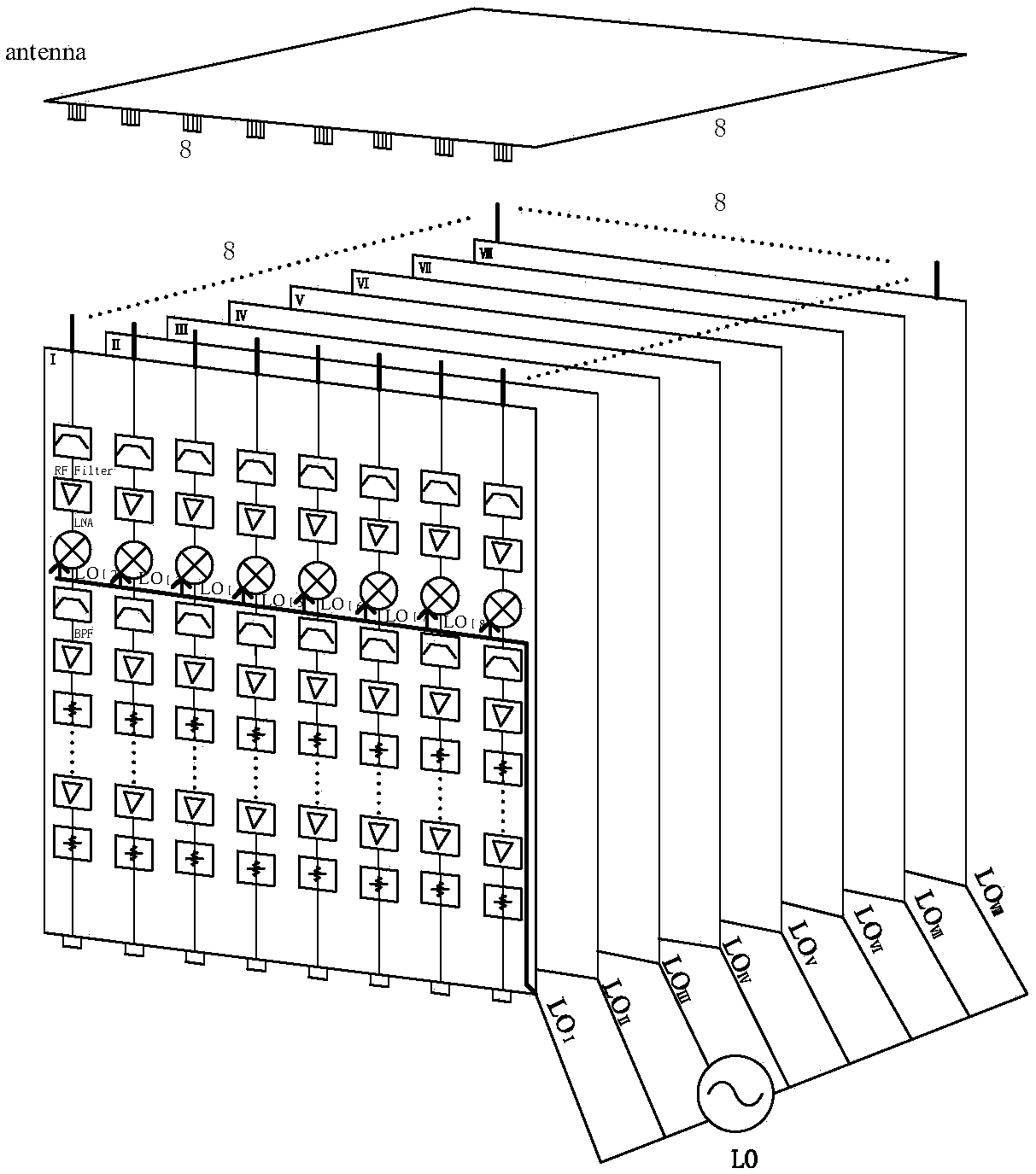

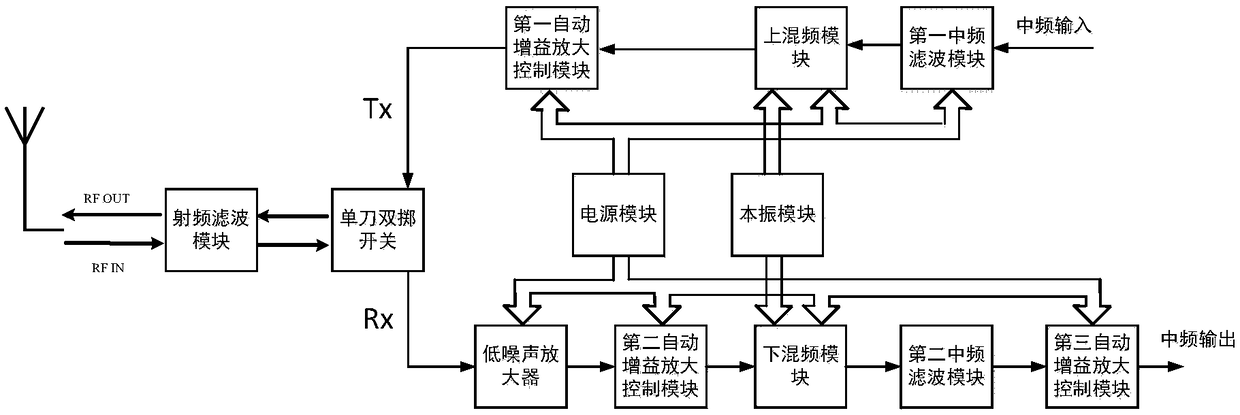

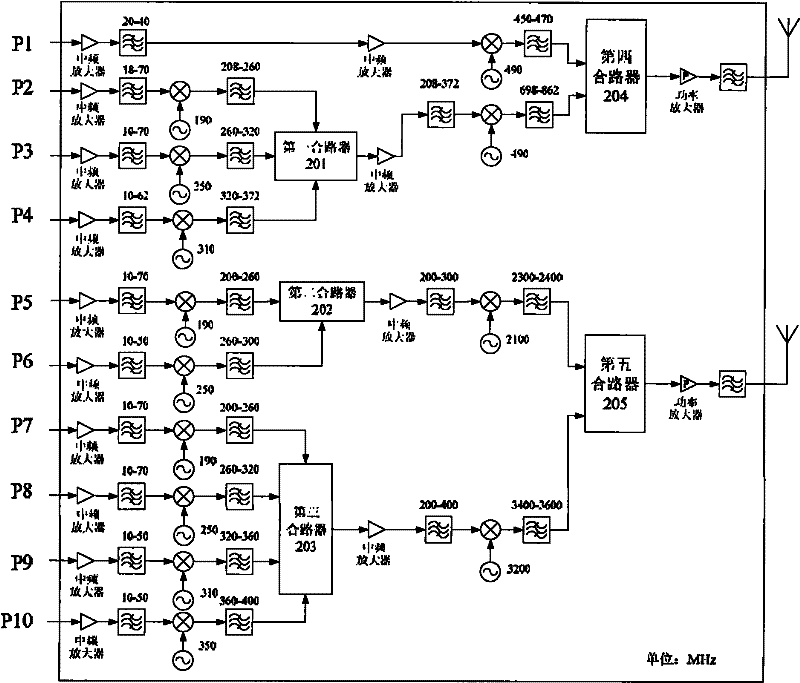

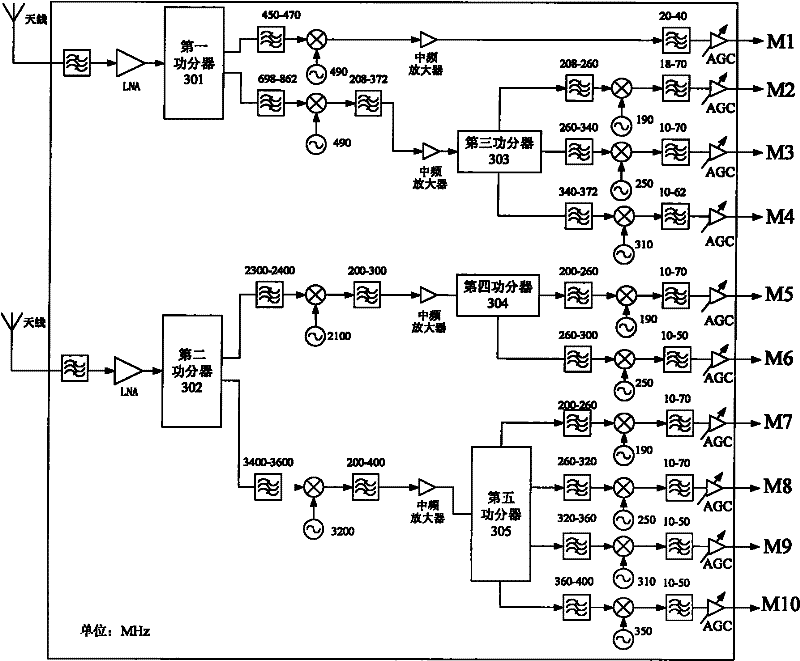

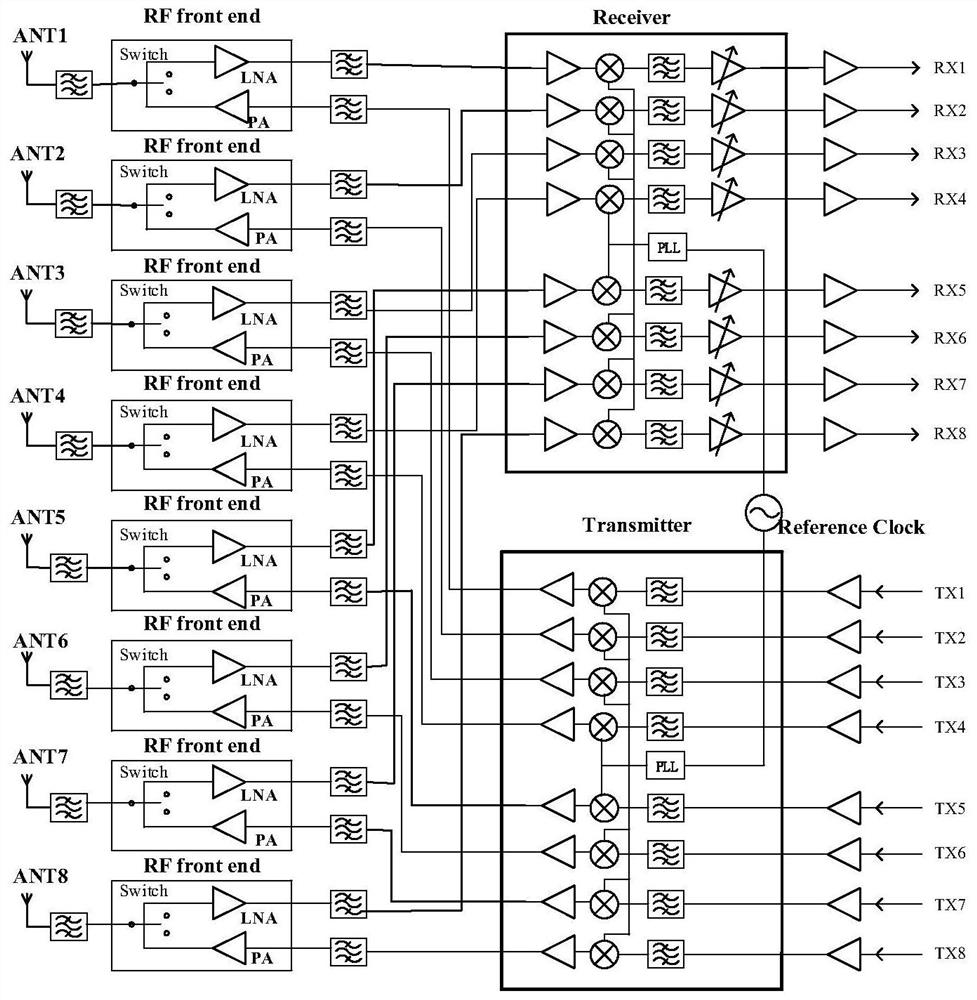

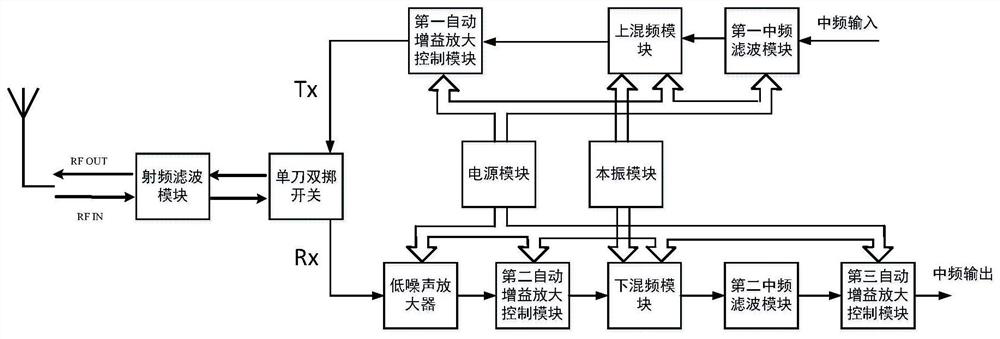

High performance channel simulator radio frequency transceiver applied to 5G communication

ActiveCN108429594AReduce complexityReduced Power RequirementsTransmission monitoringLocal oscillator signalTransceiver

The invention discloses a high performance channel simulator radio frequency transceiver applied to 5G communication. The transceiver comprises a transmission link and a receiving link, in the transmission link, an intermediate frequency signal is signally transmitted out via a first intermediate frequency, an upper mixing module, a first automatic gain amplification control module, a single-poledouble-throw switch and a radio frequency filtering module in sequence; in the receiving link, a radio frequency signal is finally received via a radio frequency filtering module, the single-pole double-throw switch, a low noise amplifier, a second automatic gain control amplification module, a lower mixing module, a second intermediate frequency filtering module and a third automatic gain amplification control module in sequence; in addition, the transceiver also comprises a local oscillator module for providing local oscillator signals to the upper mixing module and the lower mixing module.According to the transceiver provided by the invention, the complexity of the channel simulator can be effectively reduced, the requirement on power of the signal channel in 5G research is reduced, the power consumption is lowered, and meanwhile the transceiver has the characteristics of large processing bandwidth, small area and good performance.

Owner:SOUTHEAST UNIV

Method and apparatus for synchronization of a mobile radio receiver to a base station

InactiveUS7668273B2Extended processing timeGood synchronizationRadio/inductive link selection arrangementsPulse position modulationPhase correlationOversampling

Owner:INTEL CORP

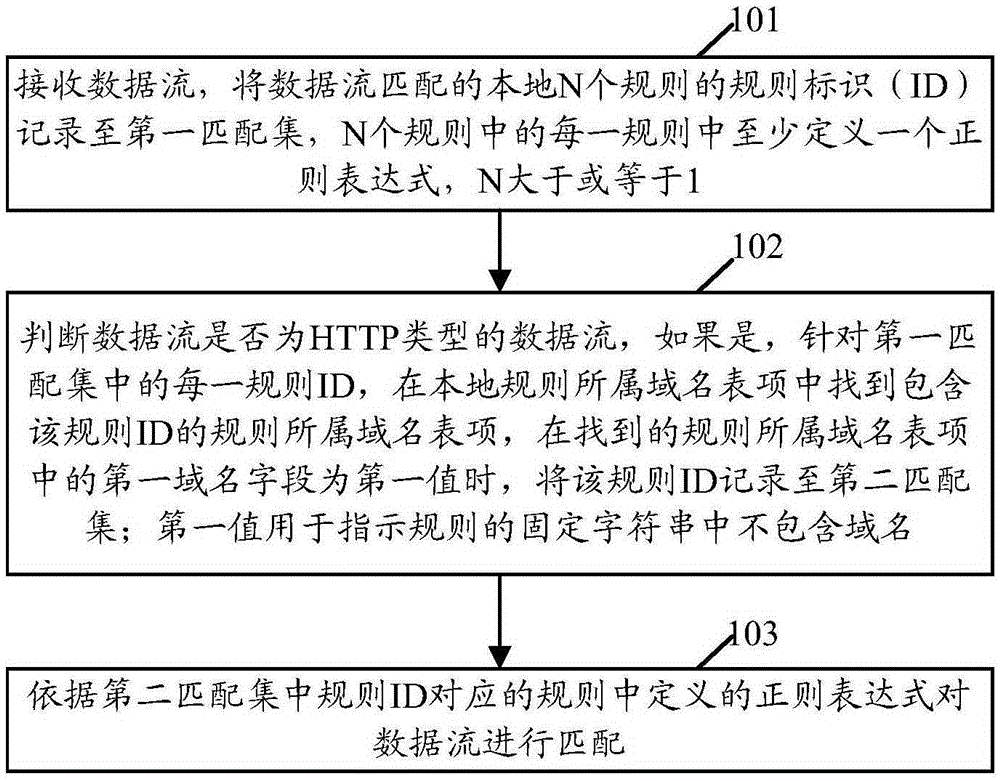

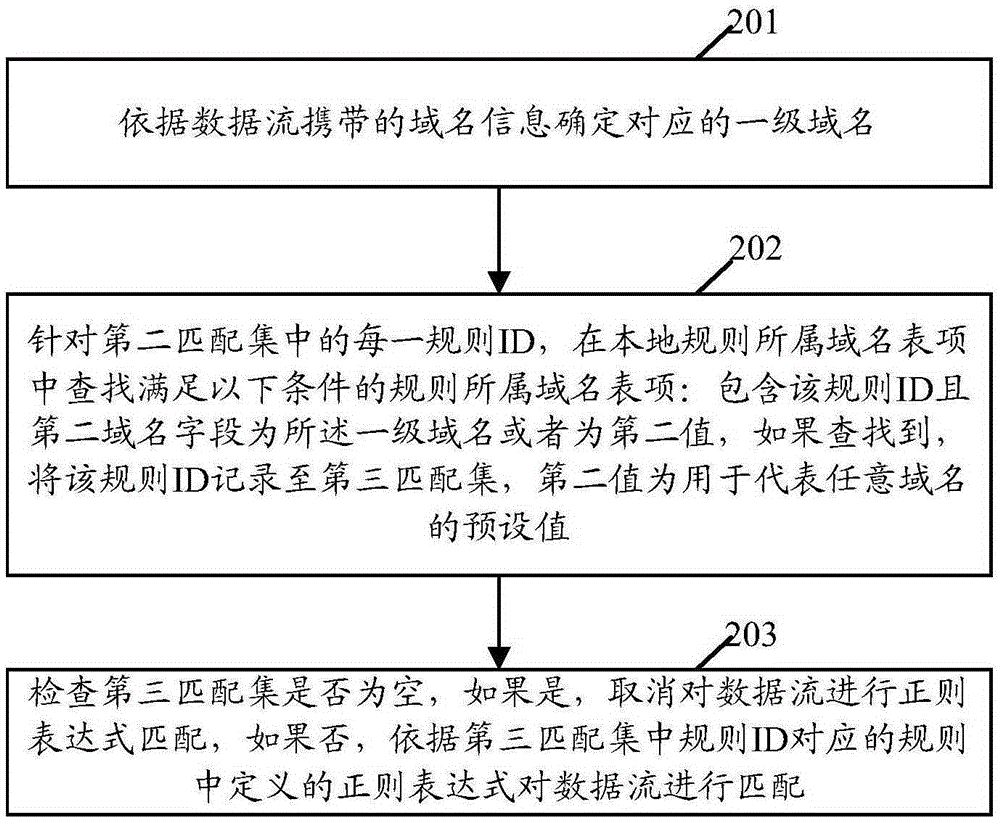

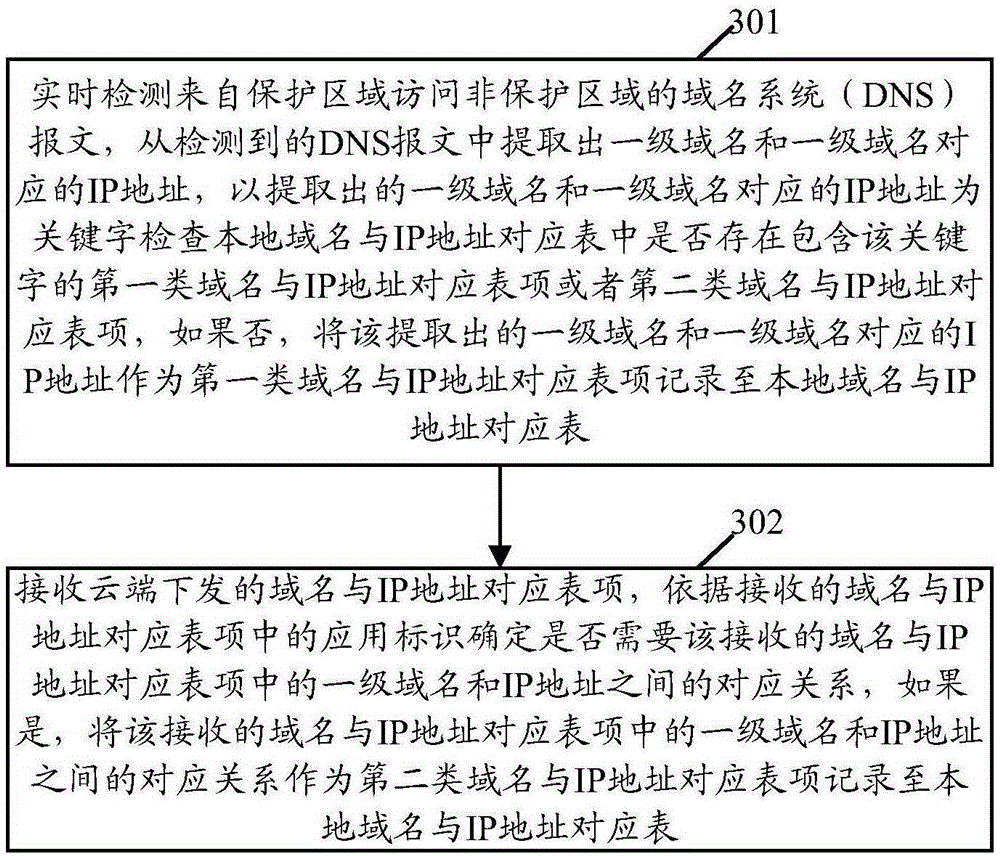

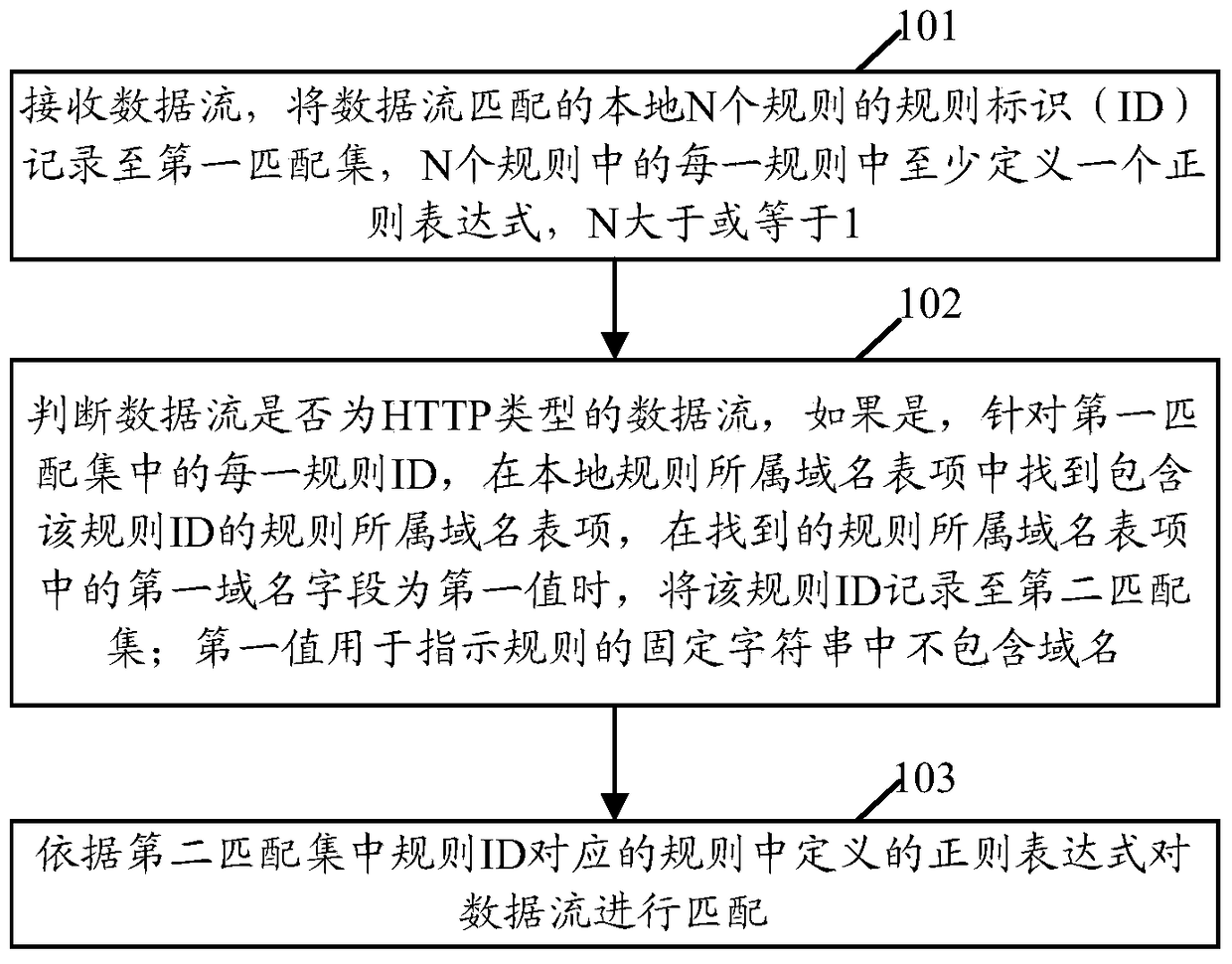

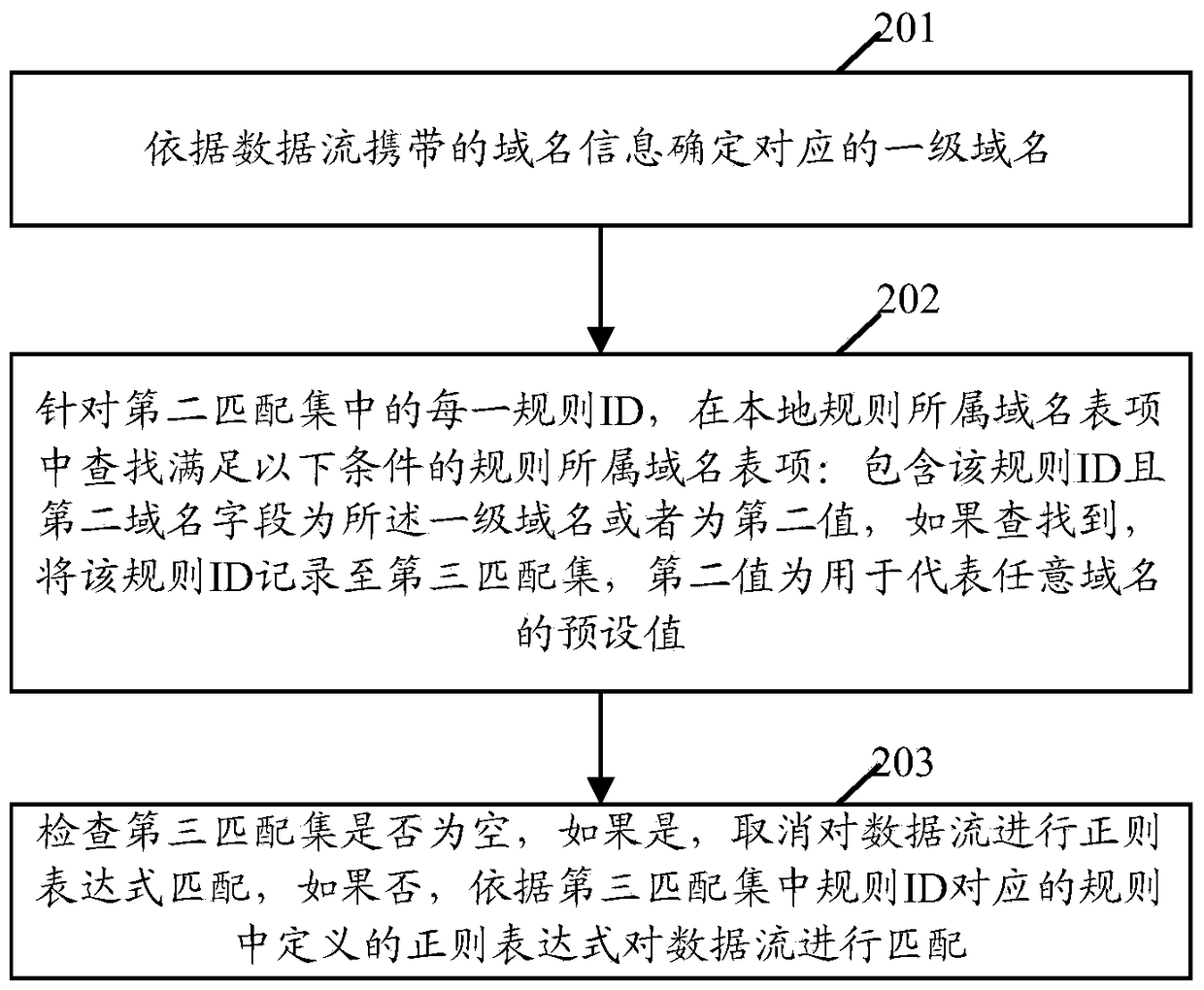

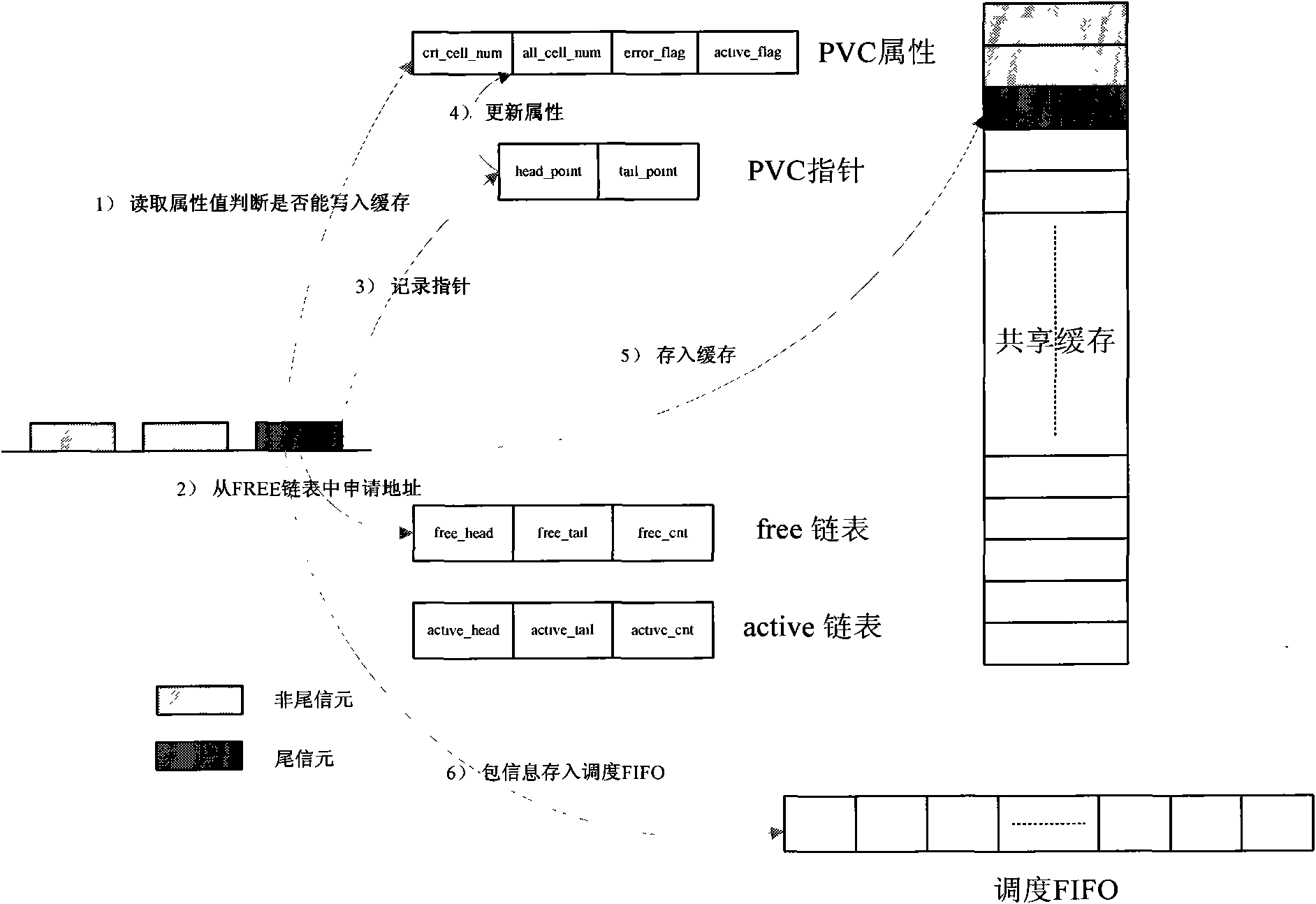

Data flow detection method and device

ActiveCN105591836AReduce the number of timesIncrease processing bandwidthData switching networksData streamData mining

The invention provides a data flow detection method and a data flow detection device. According to the data flow detection method and the data flow detection device, rules finally matched with a data flow are filtered, and the final remaining rules are less than the rules finally matched with the data flow, namely, the number of times of carrying out regular expression matching on the data flow finally is reduced, the performance overhead of equipment on regular expression matching is greatly decreased, and the processing bandwidth of the data flow detection equipment is broadened on the premise that hardware is unchanged.

Owner:NEW H3C TECH CO LTD

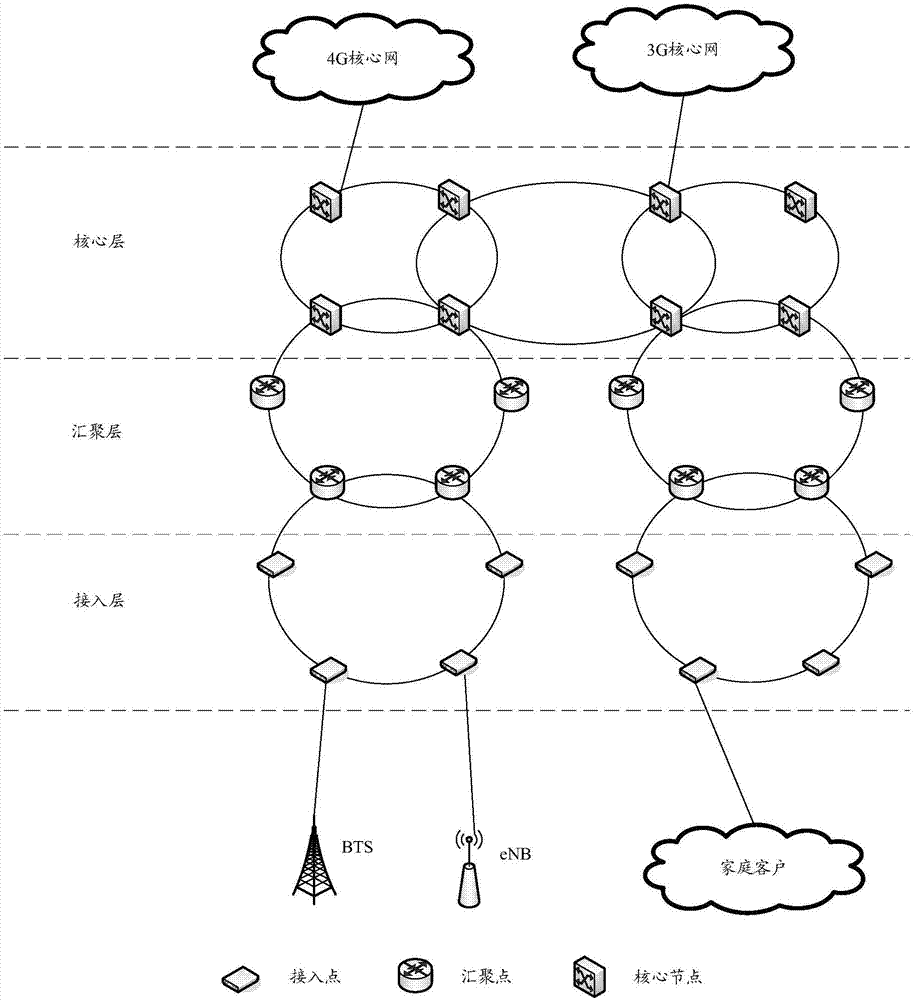

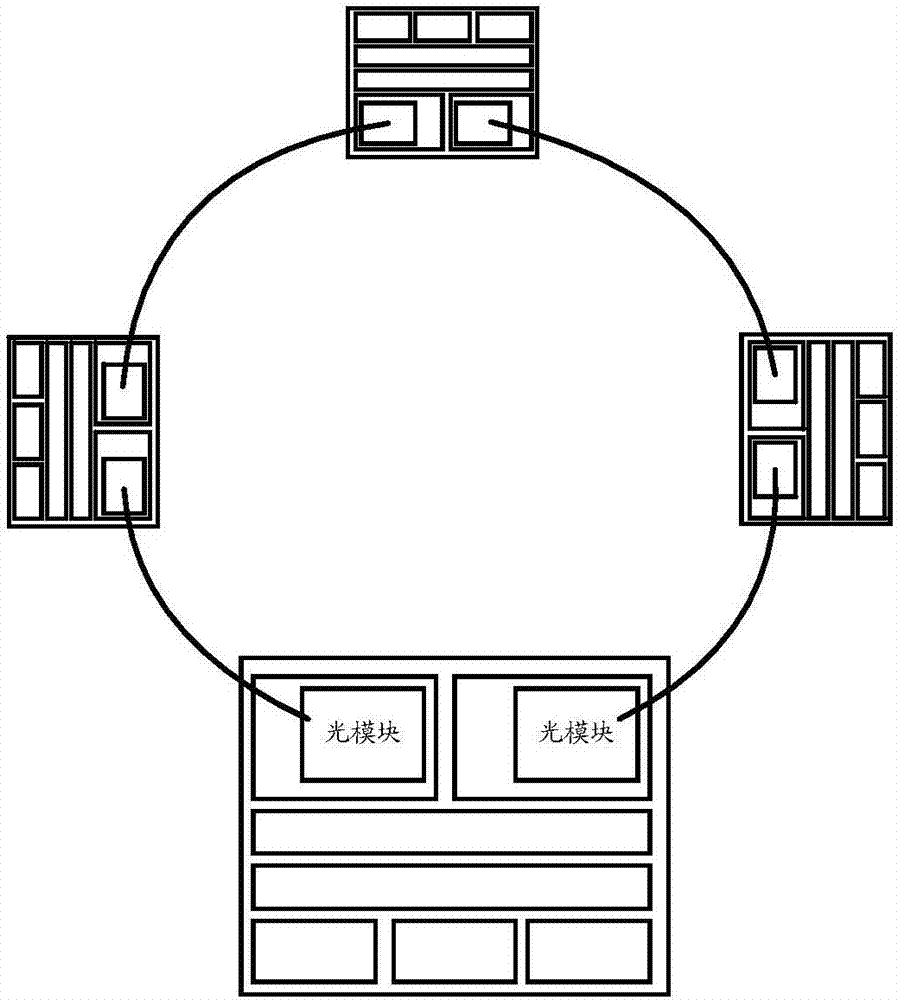

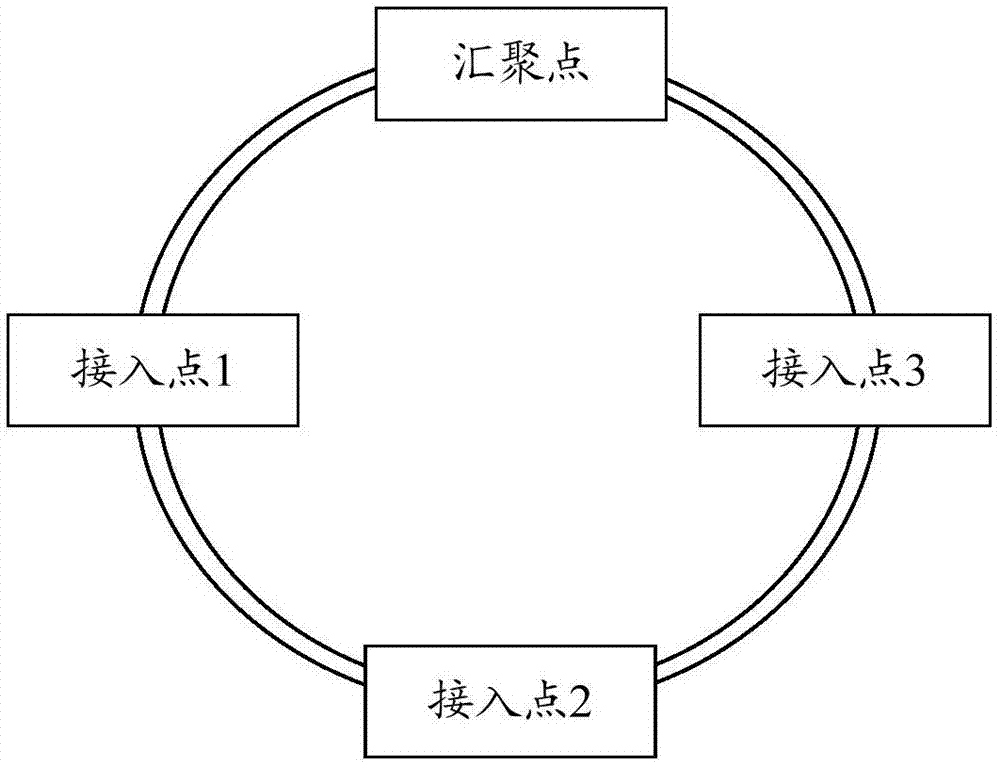

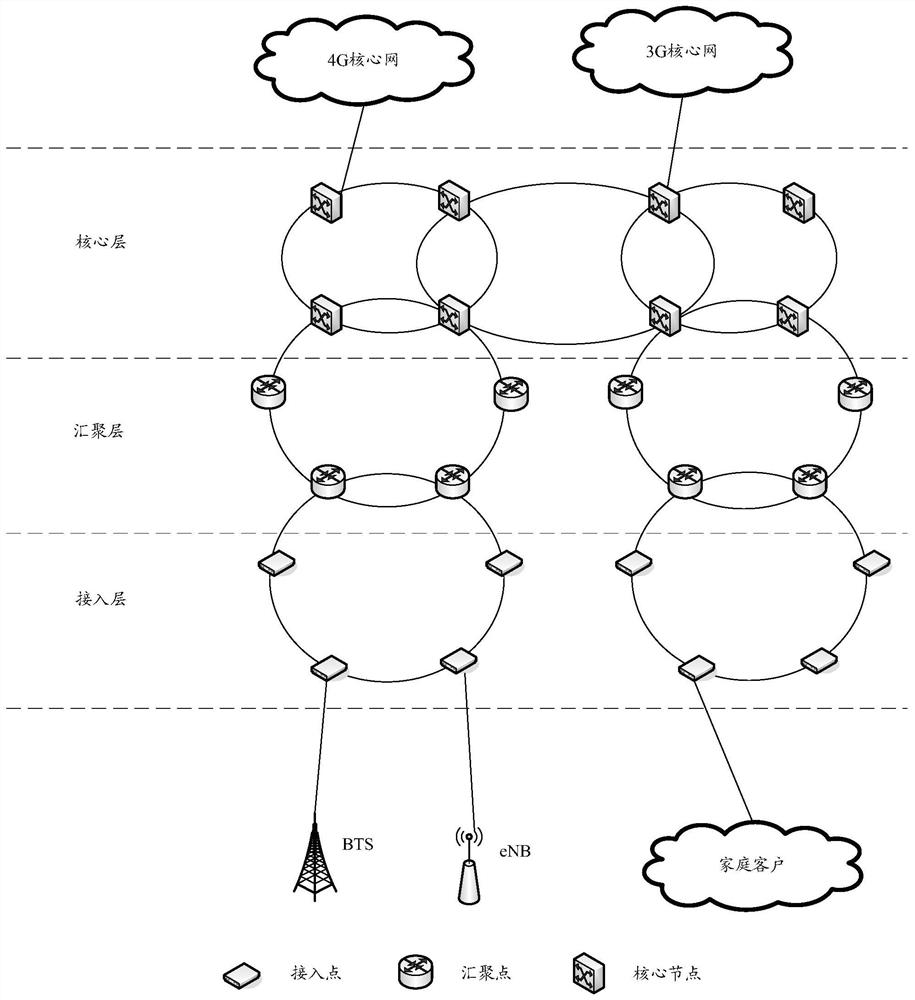

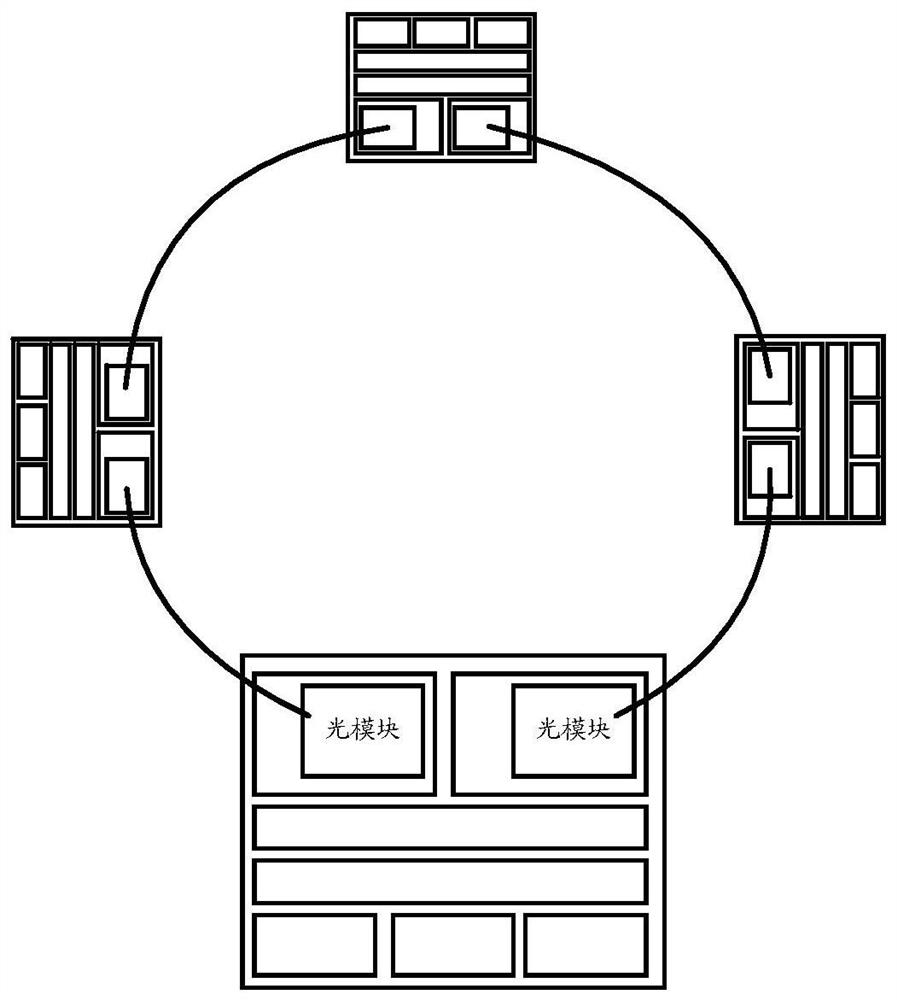

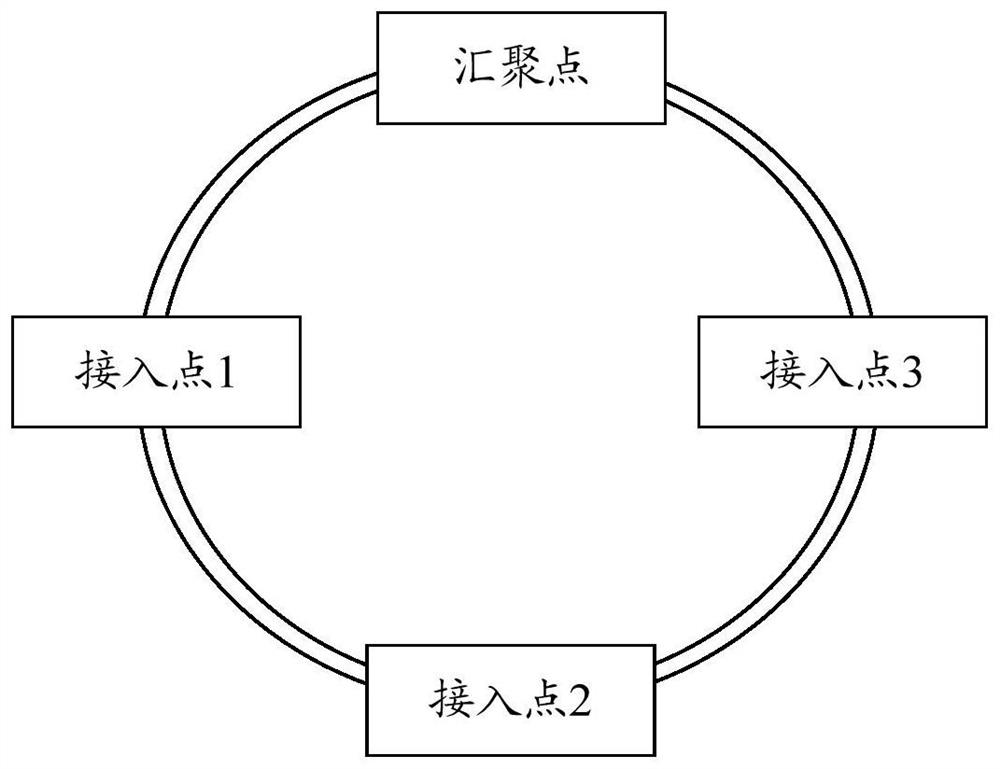

Optical module and network equipment

ActiveCN107342821ARelieve stressIncrease processing bandwidthMultiplex system selection arrangementsData switching by path configurationOptical receiversOccupancy rate

The invention discloses an optical module and network equipment and aims to solve a problem of a relatively high processing bandwidth occupancy rate of an optical module in the prior art. The optical module is arranged at first network equipment of an access ring, the access ring comprises second network equipment and third network equipment, the second network equipment and the third network equipment are in optical connection with the first network equipment, the first network equipment is applied to an access point, the optical module comprises a first multi / demultiplexer and an optical receiver, wherein the first multi / demultiplexer is used for receiving first optical signals from the second network equipment, separating second optical signals having first wavelengths from the first optical signals and transmitting the second optical signals to the light receiver, the first multi / demultiplexer is further used for transmitting third optical signals to the third network equipment, the third optical signals are other optical signals which are separated from the first optical signals and have other wavelengths except the first wavelengths, and the light receiver is used for receiving the second optical signals.

Owner:HUAWEI TECH CO LTD

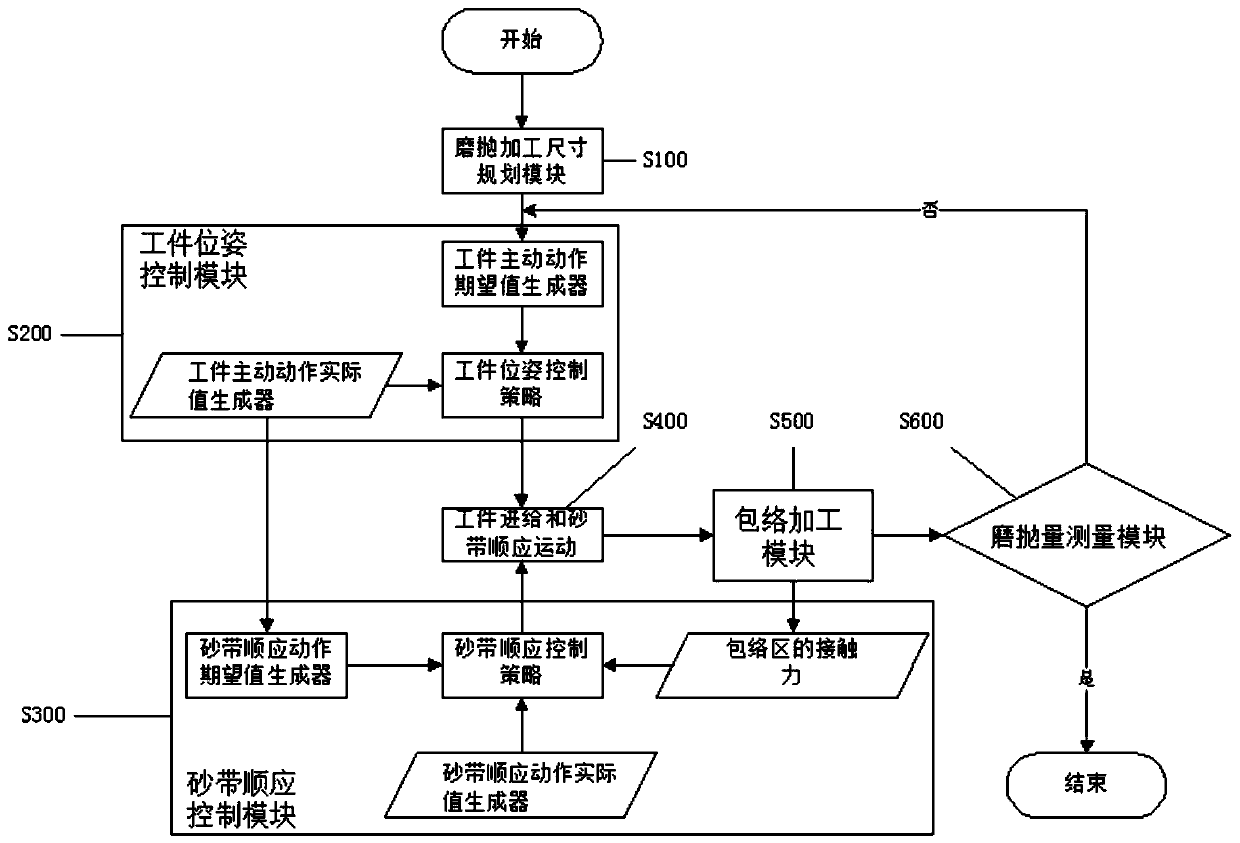

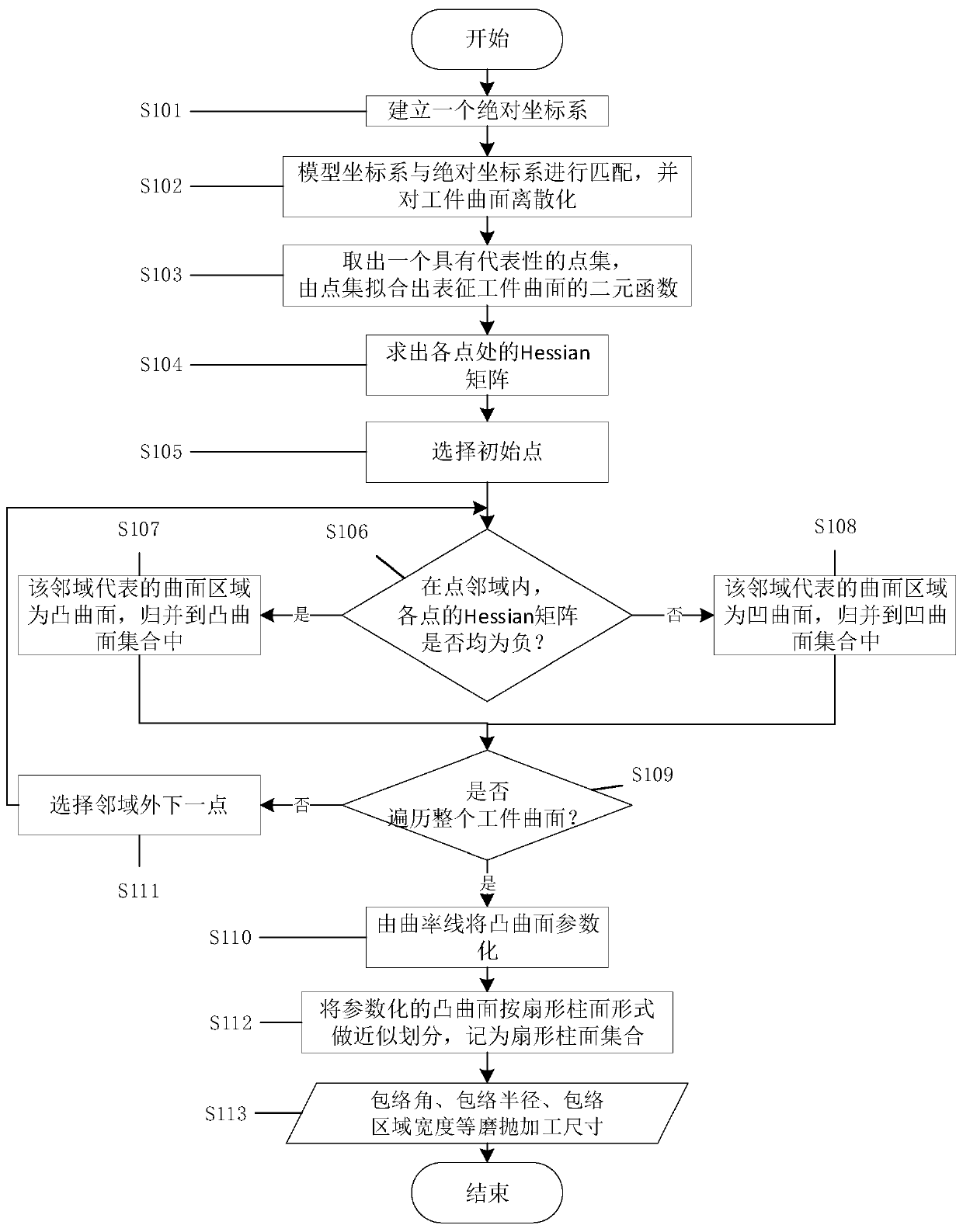

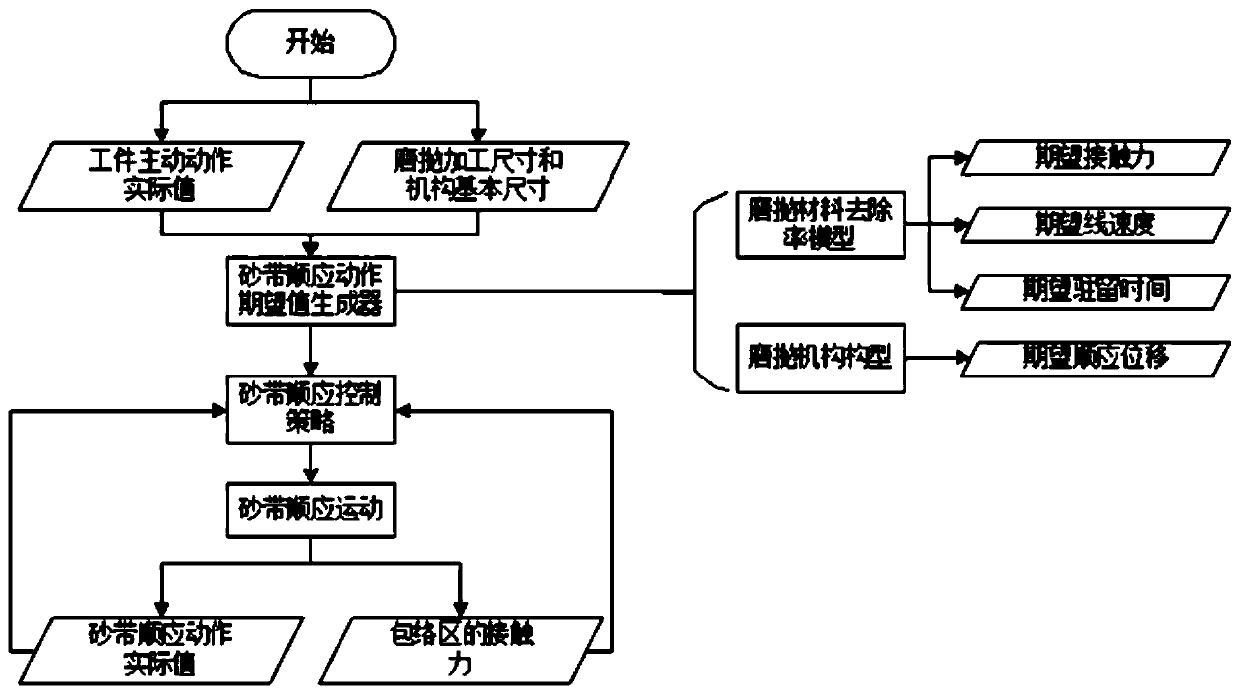

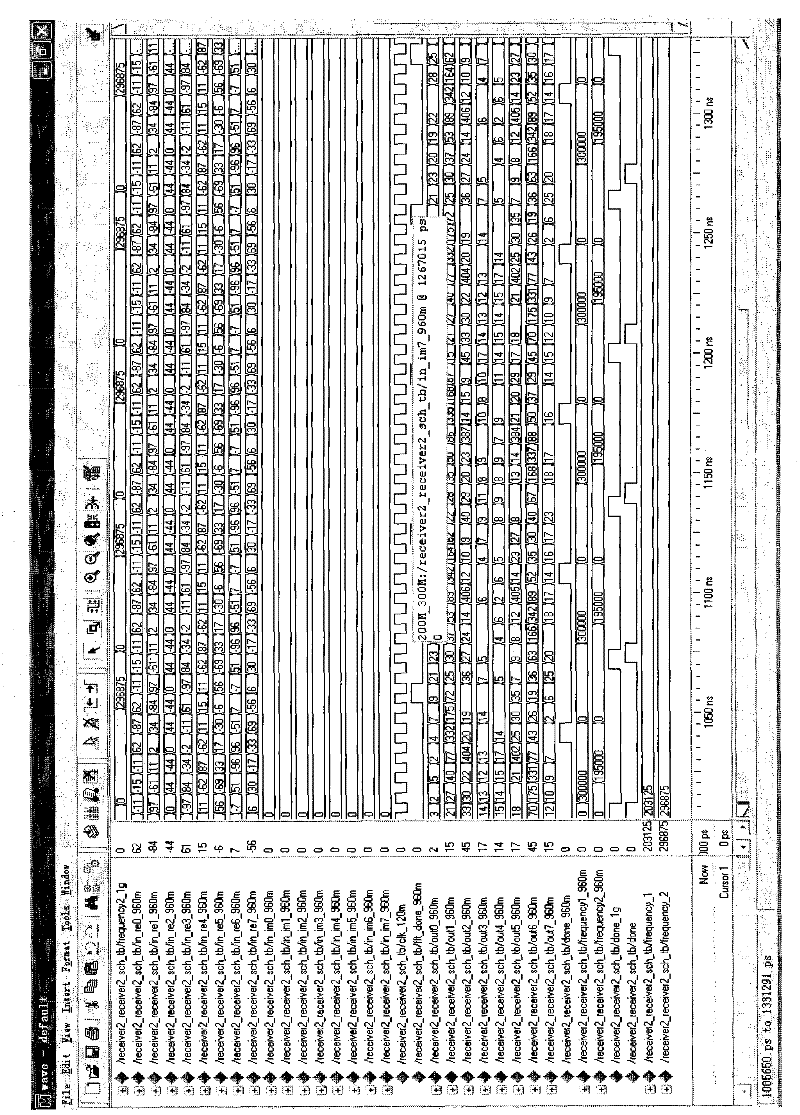

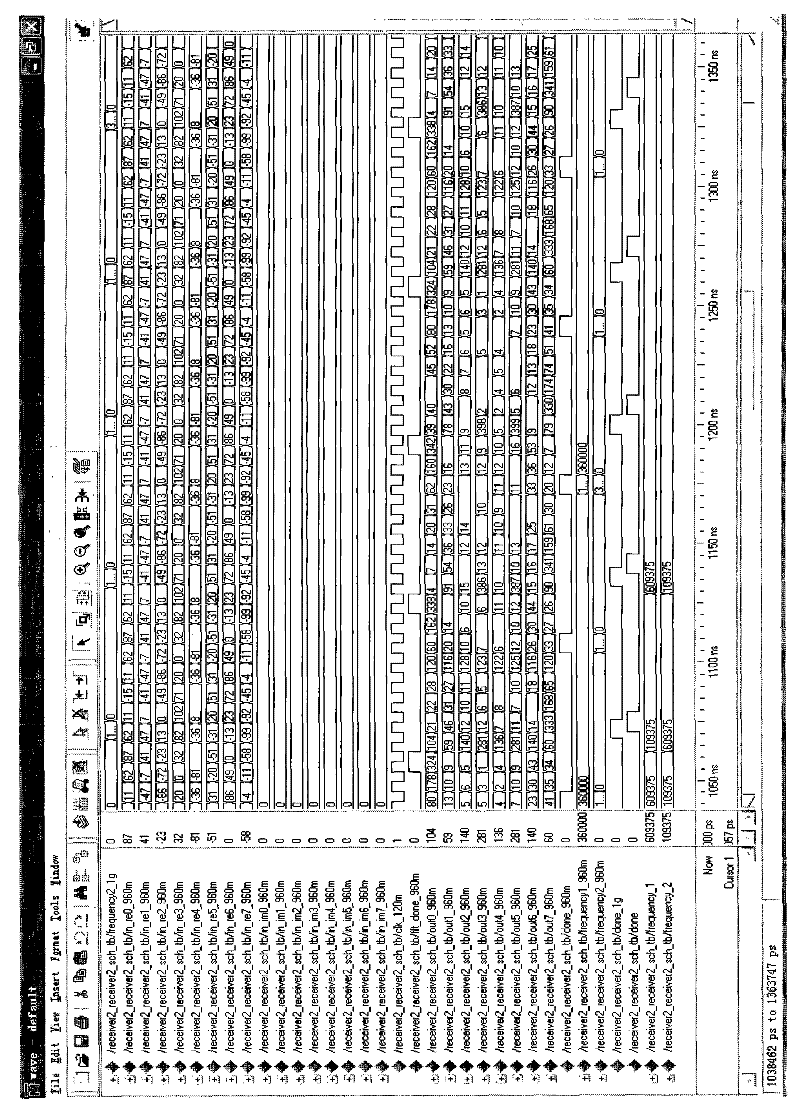

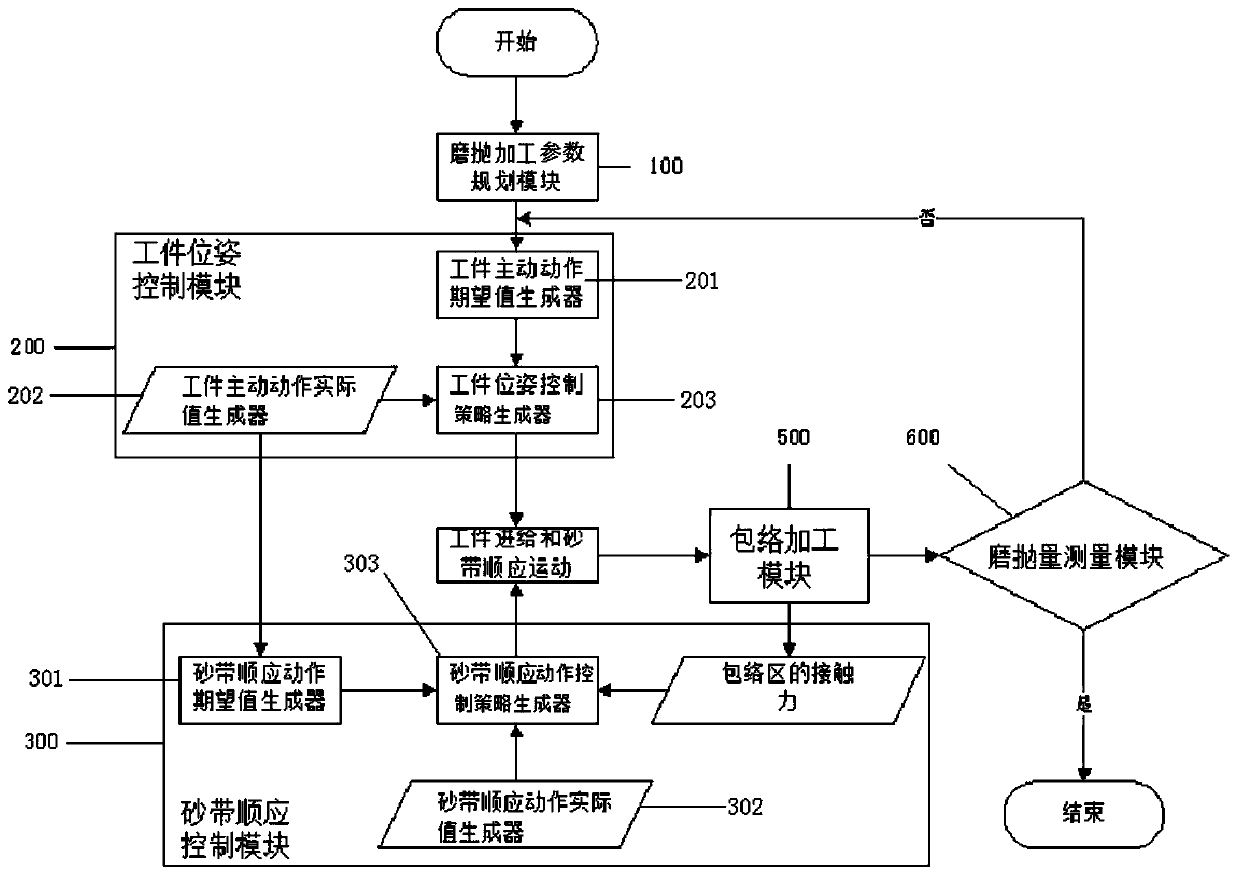

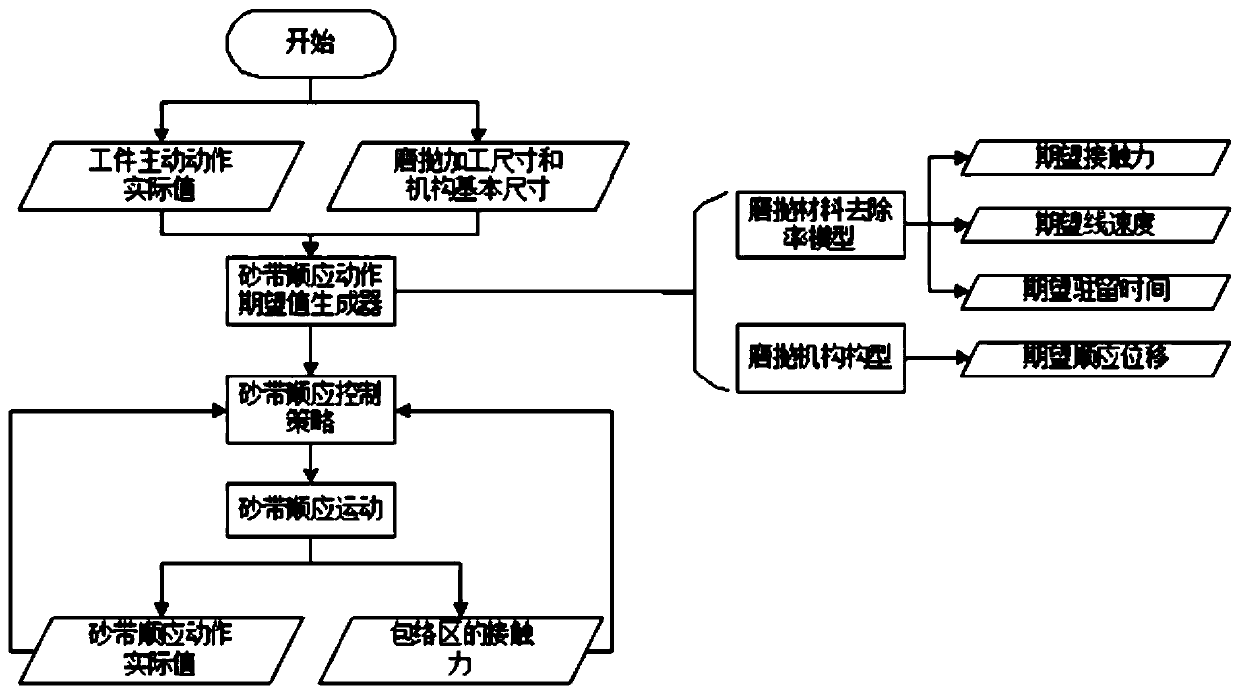

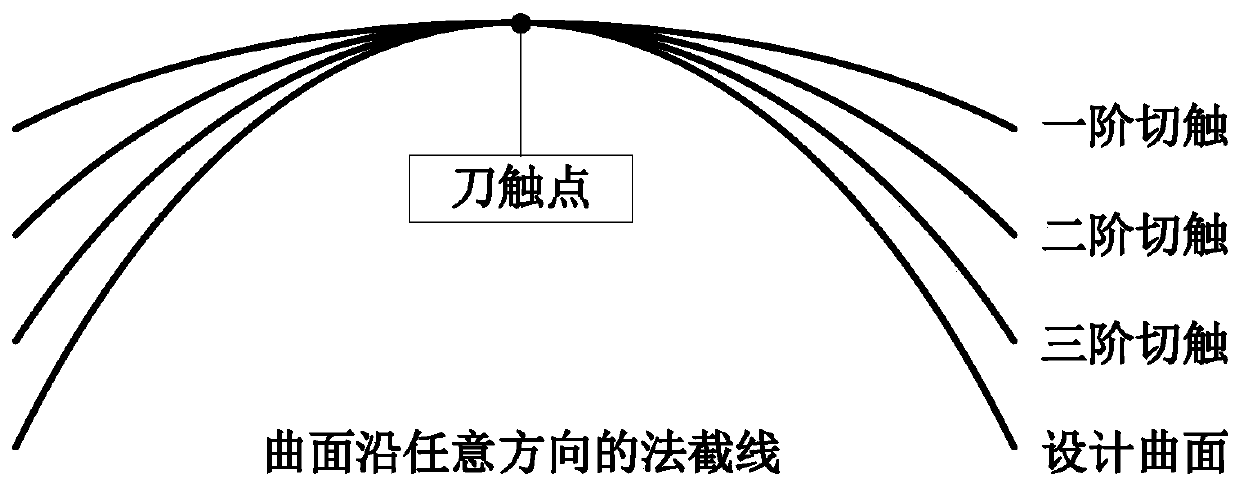

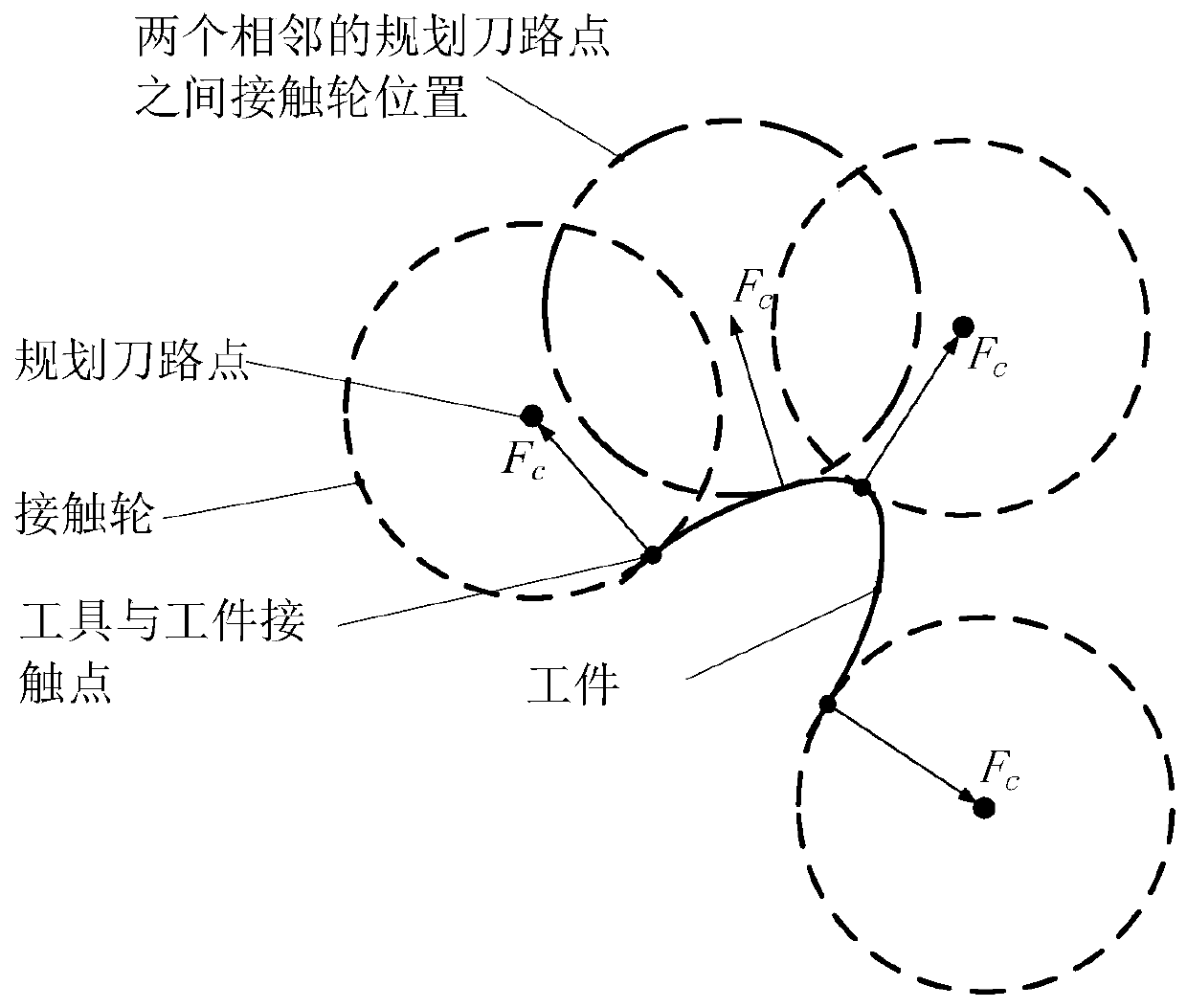

High-order tangent contact enveloping type polishing machining control system and method

ActiveCN110153851ARealize closed-loop controlEnvelope guaranteeBelt grinding machinesGrinding feed controlManufacturing technologyMachine control

The invention belongs to the technical field of intelligent polishing machining and manufacturing, and particularly relates to a high-order tangent contact enveloping type polishing machining controlsystem and method. The control system comprises a polishing machining parameter planning module, a workpiece pose control module, an abrasive belt compliance control module, an enveloping machining module and a polishing amount measuring module, wherein the polishing machining parameter planning module is used for identifying a convex curved surface in a workpiece curved surface, the workpiece pose control module and the abrasive belt compliance control module act cooperatively so as to adjust the pose of a workpiece and the contact force of the enveloping machining module and a sector-shapedcolumn surface in real time, and polishing machining on the workpiece is conducted under the condition; and the polishing amount measuring module is used for judging whether a polishing process is finished or not. The invention further discloses a corresponding method. According to the system, high-order cutting and enveloping on the machined workpiece are realized, meanwhile, the the workpiece pose control module and the abrasive belt compliance control module act cooperatively to achieve the synergistic effect, so that closed-loop control is realized, and the stability, rapidity and accuracyof system response are ensured.

Owner:HUAZHONG UNIV OF SCI & TECH

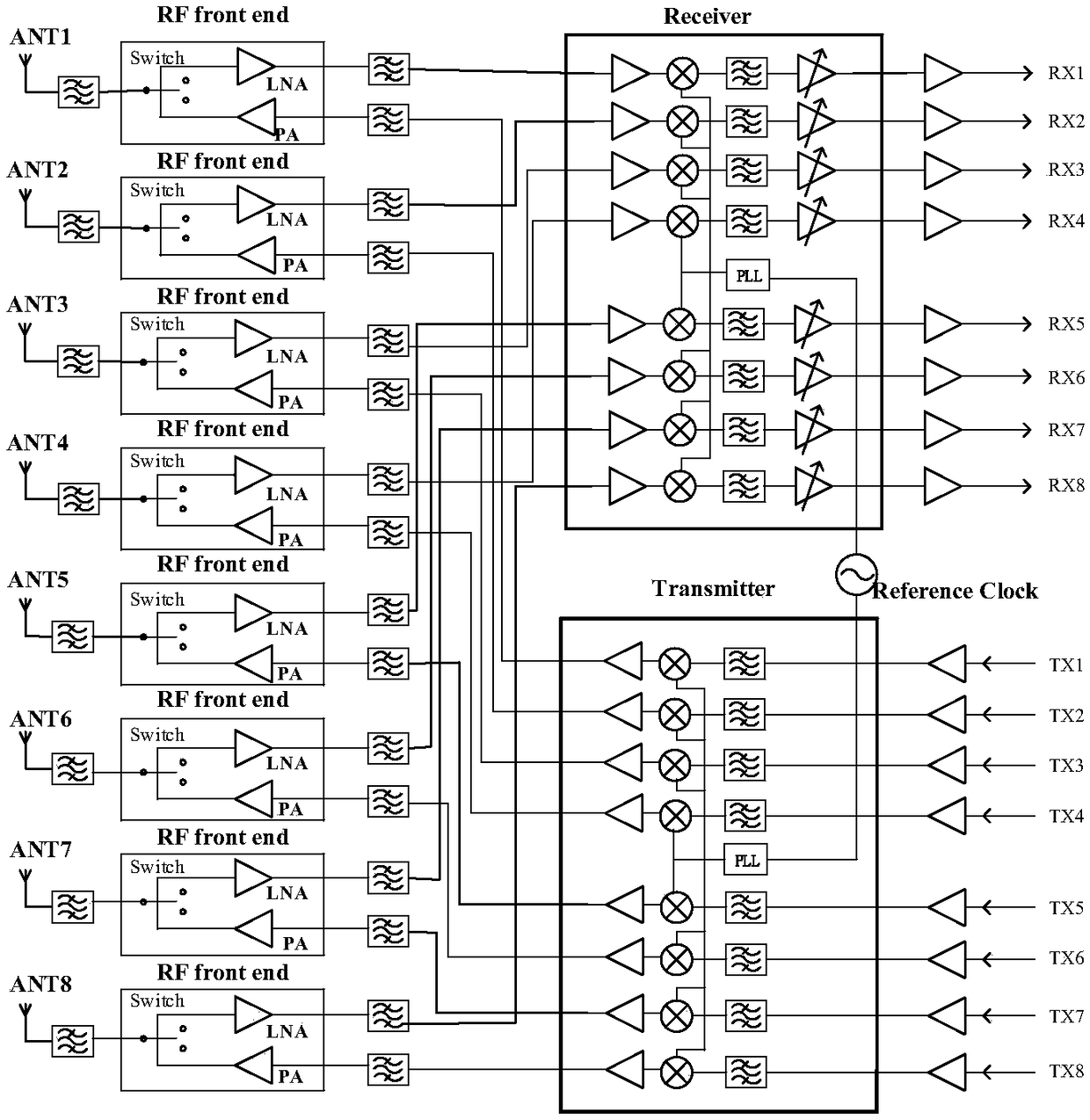

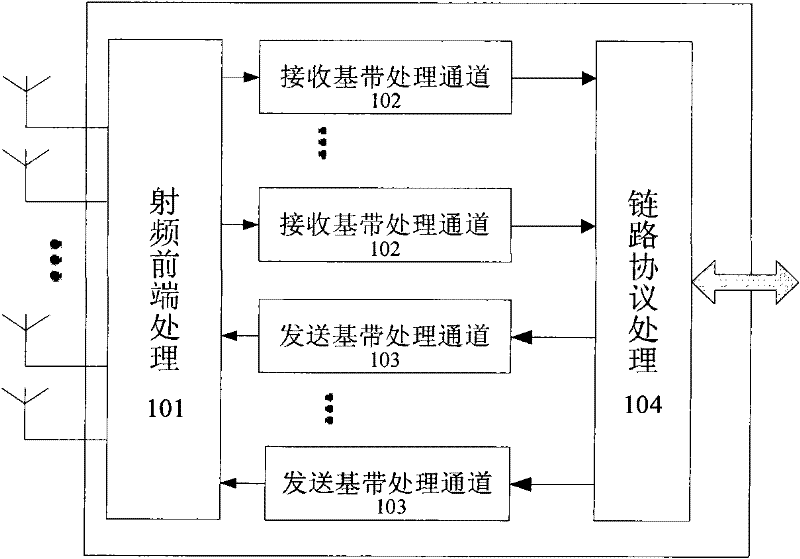

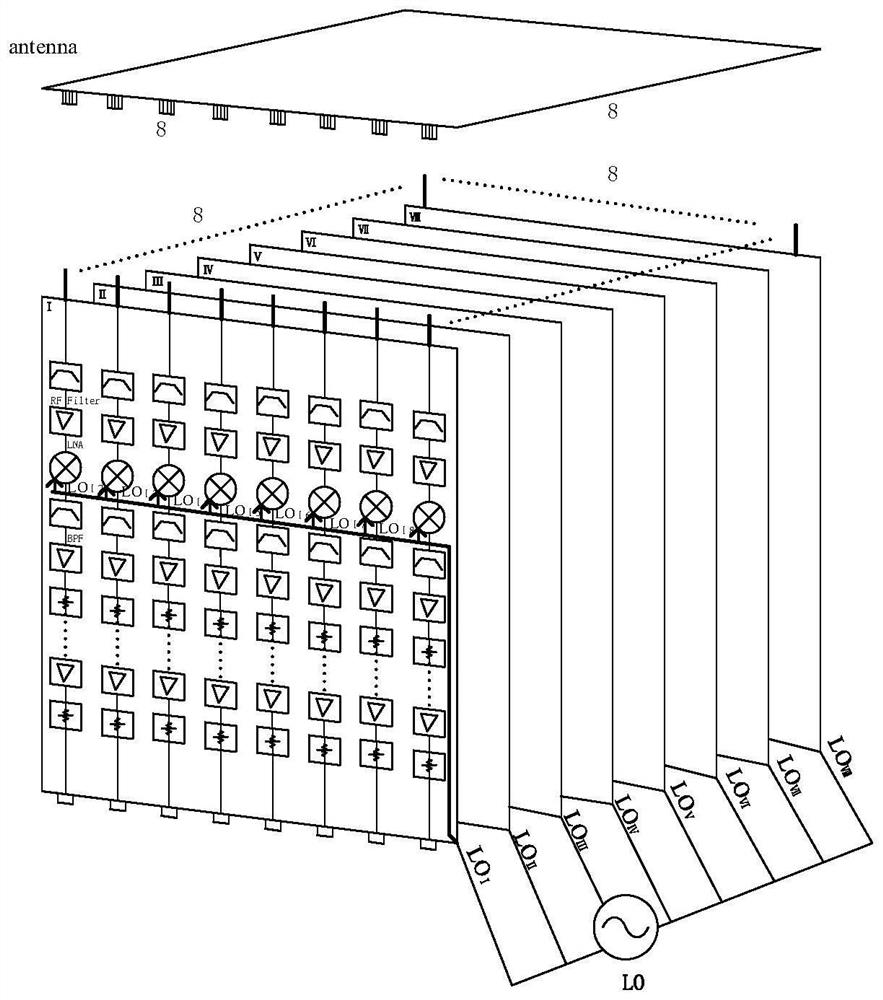

Multi-band frequency spectrum aggregating wireless transmitter-receiver device

InactiveCN101741803BIncrease processing bandwidthIncrease data transfer rateWireless network protocolsRadio transmission for post communicationMulti bandFrequency spectrum

The invention discloses a multi-band frequency spectrum aggregating wireless transmitter-receiver device which is characterized in that multi-band simulating radio frequency front ends are aggregated; different radio frequencies are divided into 20 MHz and 60 MHz processing frequency bands; analog-to-digital conversion while receiving a base-band signal and digital-to-analogue conversion while sending are performed in low and intermediate frequencies; and a signal treatment relative to a base-band NC-OFDM modulation-demodulation is performed by a sending base-band processing channel and a receiving base-band processing channel which are dynamically arranged. The invention solves the problem that the prior mobile communication terminal cannot work in multi-band at the same time during the communication process and only can use continuous frequency spectrums. The frequency spectrum aggregating function of the transmitter-receiver device realizes a data rate required by an IMT-Advanced system.

Owner:UNIV OF SCI & TECH OF CHINA

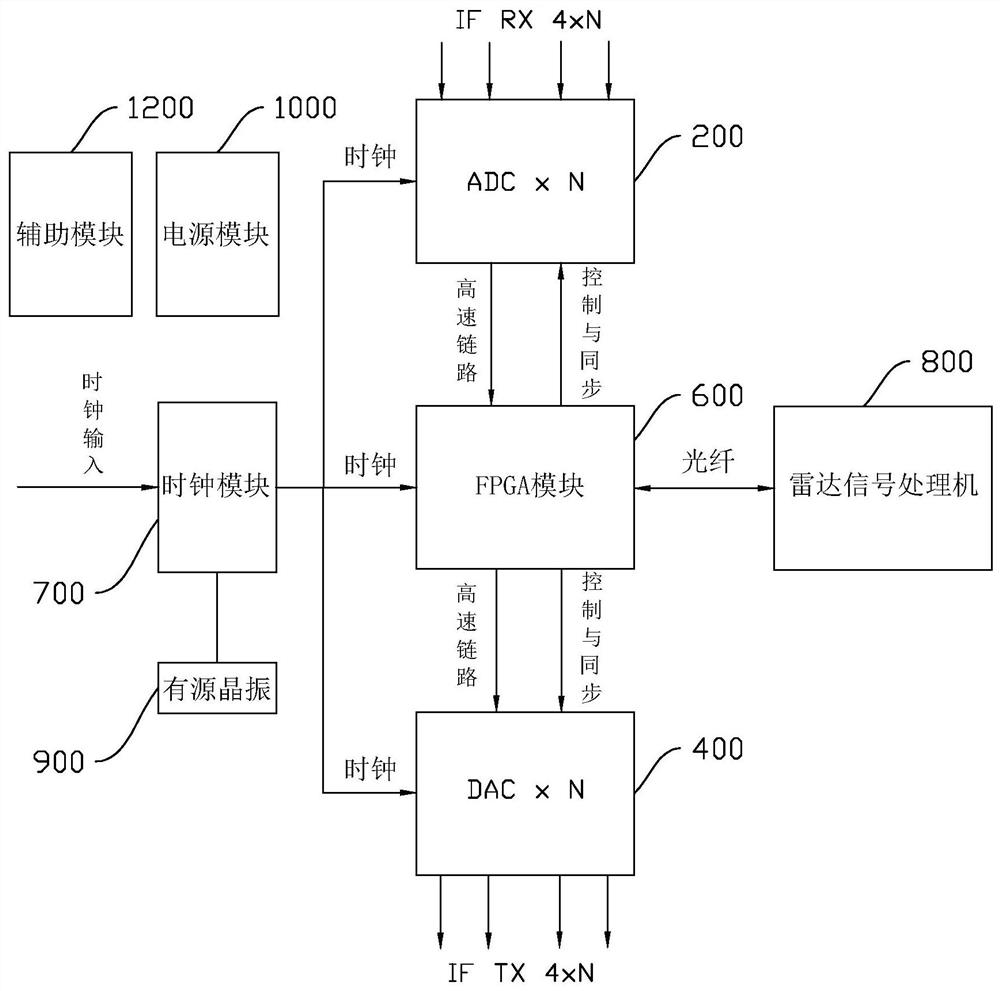

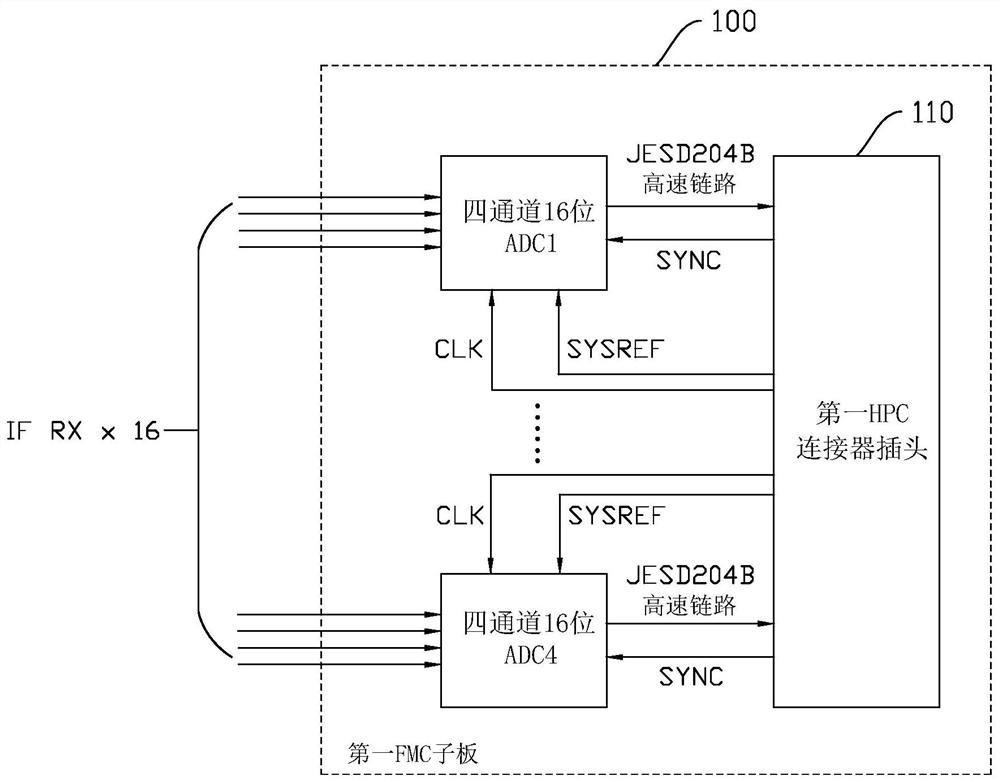

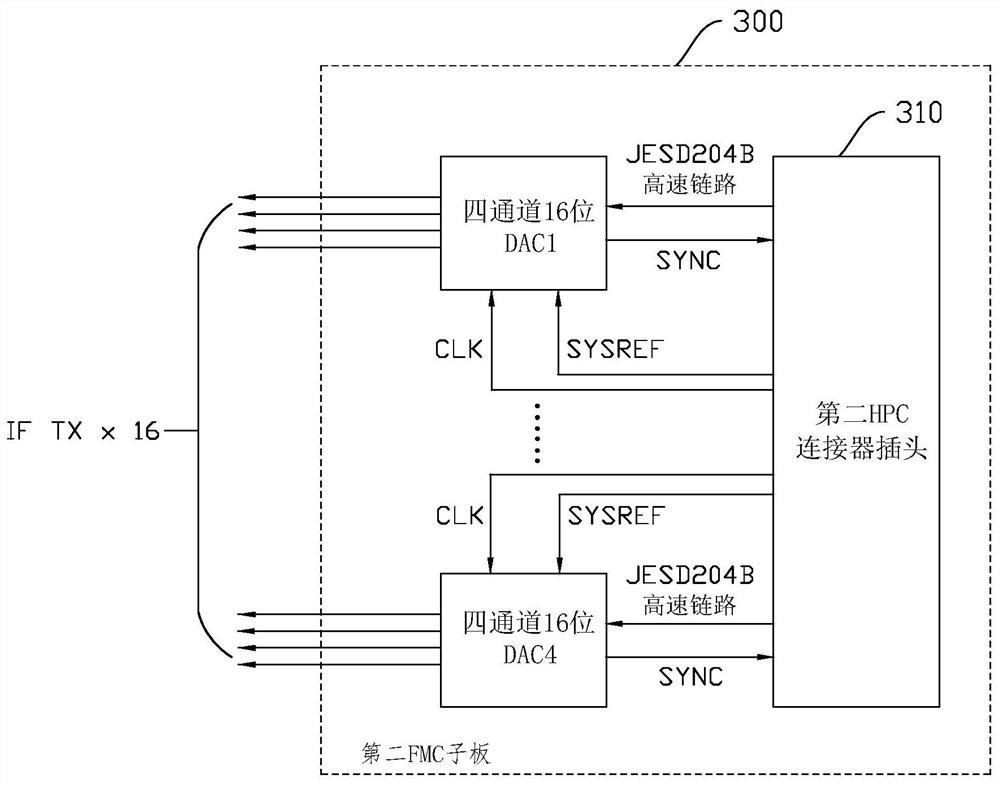

Intermediate frequency signal processing unit and digital phased array radar with same

PendingCN112946583AHighly integratedIncrease processing bandwidthRadio wave reradiation/reflectionChannel dataIntermediate frequency

The invention discloses an intermediate frequency signal processing unit and a digital phased array radar with the same. The intermediate frequency signal processing unit comprises a first FMC daughter board, a second FMC daughter board and a carrier board, the first FMC daughter board is provided with a first HPC connector plug, the second FMC daughter board is provided with a second HPC connector plug, and the carrier board is provided with a first HPC connector socket corresponding to the first HPC connector plug and a second HPC connector socket corresponding to the second HPC connector plug; the first FMC daughter board is provided with an ADC module, and the ADC module comprises N multi-channel ADC chips; the second FMC daughter board is provided with a DAC module, and the DAC module comprises N multi-channel DAC chips; an FPGA module and a clock module are arranged on the carrier plate, the FPGA module is electrically connected with the ADC module and the DAC module, and the clock module is electrically connected with the ADC module, the FPGA module and the DAC module. According to the intermediate frequency signal processing unit, synchronous transmission of multi-channel data can be achieved, the integration level is high, and expansion is easy.

Owner:XTR SOLUTIONS

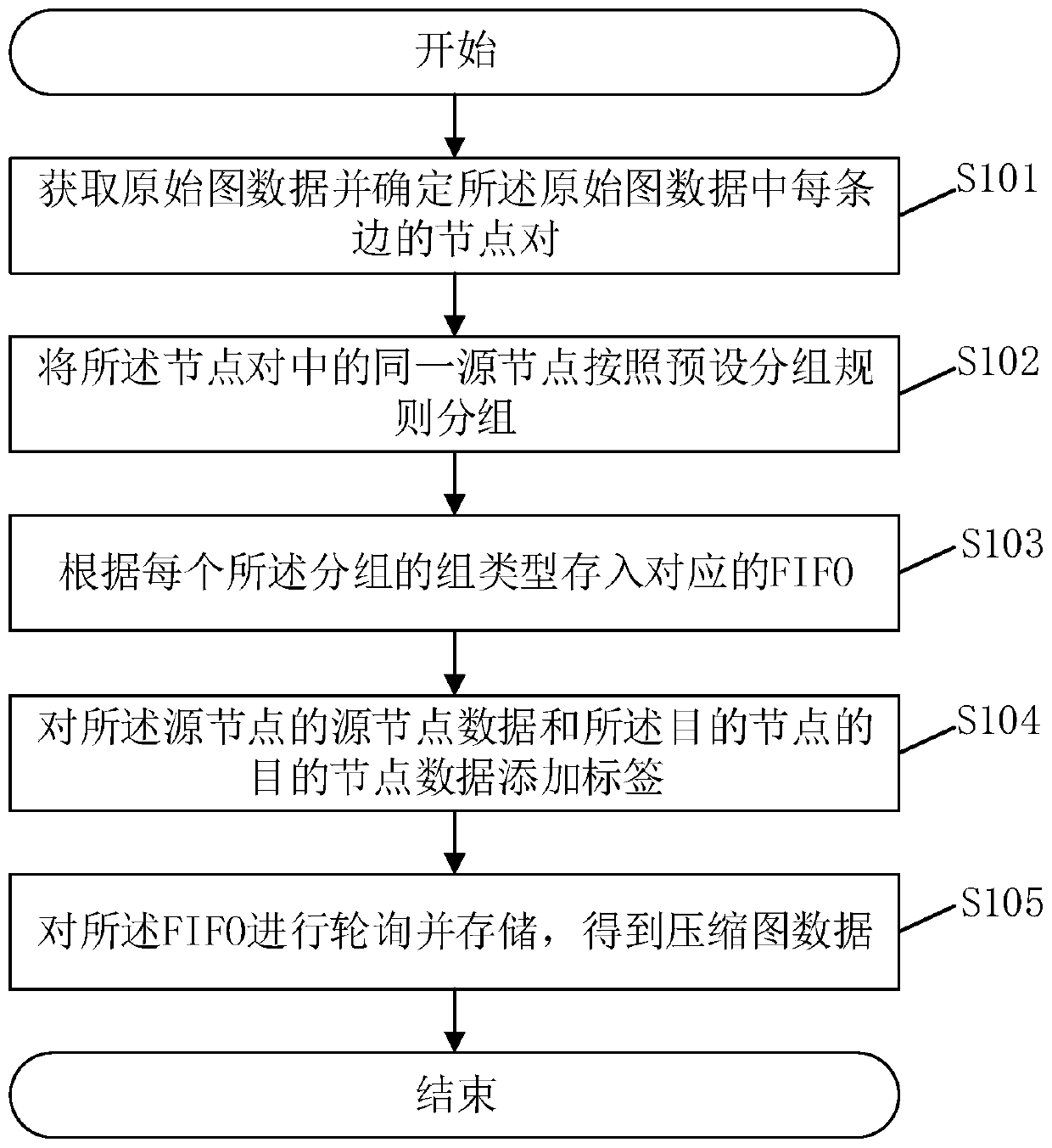

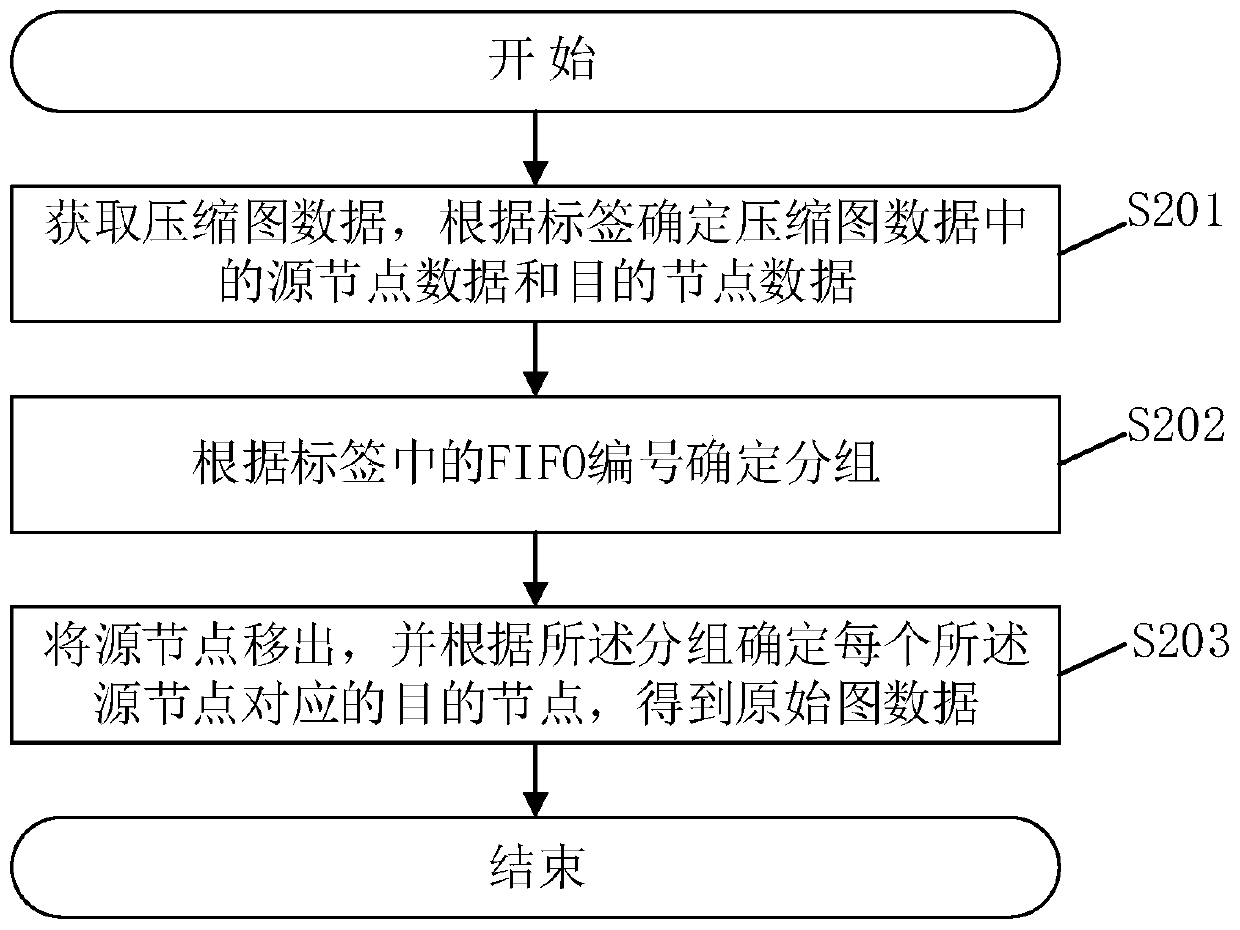

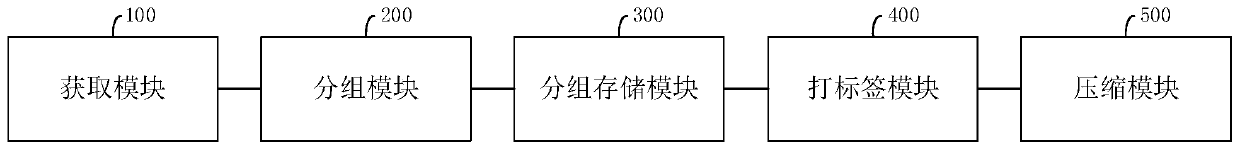

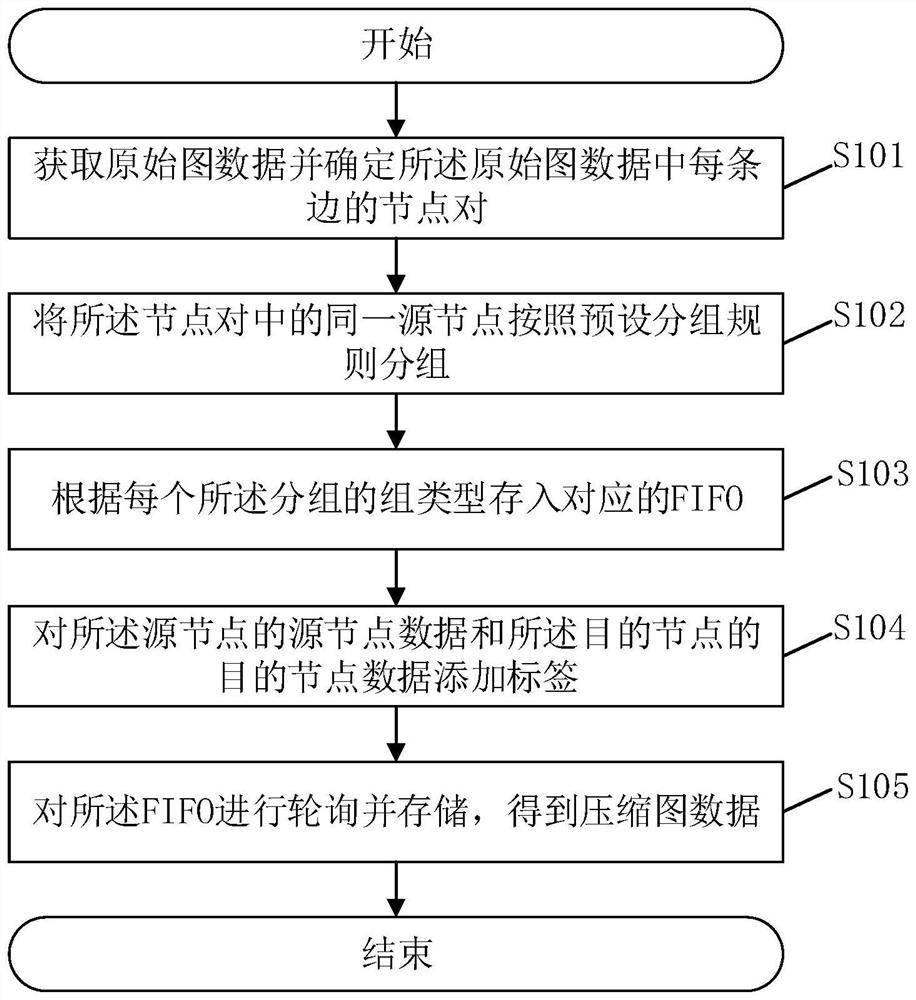

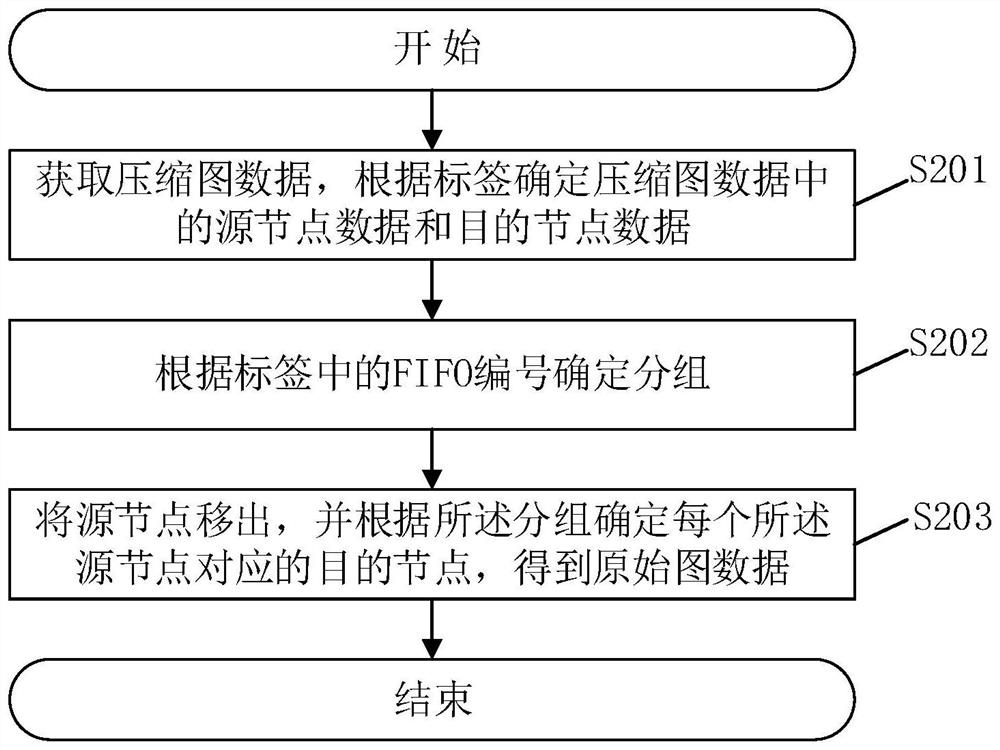

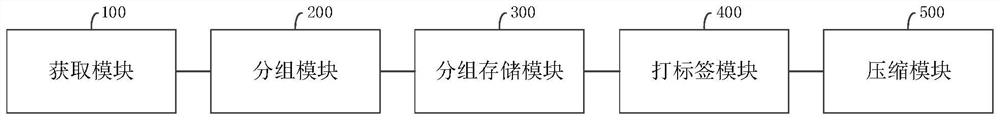

Data compression method, data decompression method, data compression system, and related devices for graph data

ActiveCN111046002AIncrease processing bandwidthSpecial data processing applicationsFile system functionsData compressionTheoretical computer science

The invention provides a graph data compression method. The method comprises the steps of obtaining original graph data and determining a node pair of each edge in the original graph data; grouping the same source nodes in the node pairs according to a preset grouping rule, wherein one source node is reserved in each group; storing the data into the corresponding FIFO according to the group type of each group; adding labels to the source node data of the source node and the destination node data of the destination node; and polling and storing the FIFO to obtain compressed graph data. According to the method, different compression ratios are adopted for the source nodes with different numbers corresponding to the destination nodes, only one source node is reserved in the same group, and repeated source nodes do not need to be stored; and large-scale parallel decompression of the graph data can be supported, and the processing bandwidth of the graph data is greatly increased. The invention further provides a data compression system of a graph calculation system, a computer readable storage medium and a data compression terminal, which have the above beneficial effects.

Owner:INSPUR BEIJING ELECTRONICS INFORMATION IND

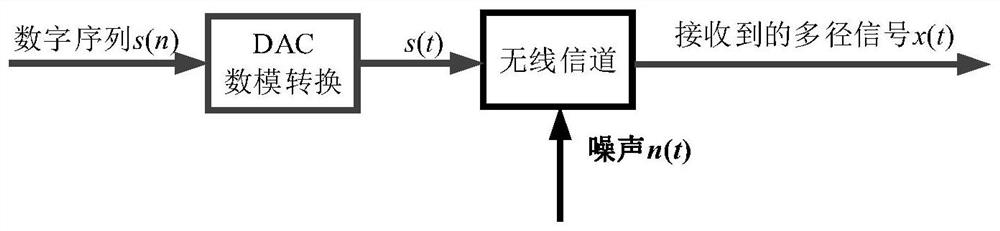

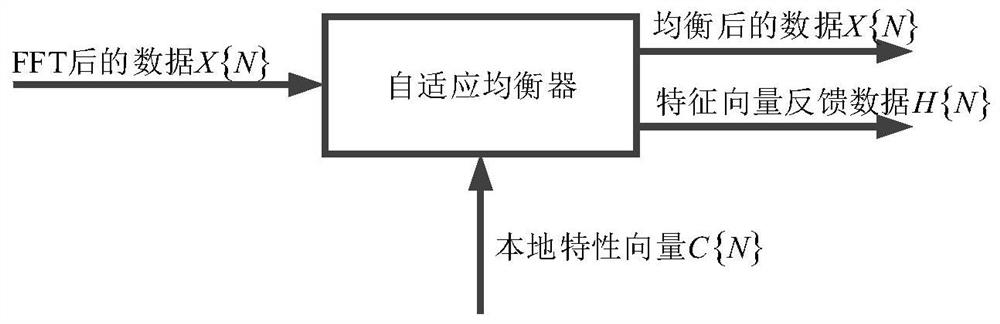

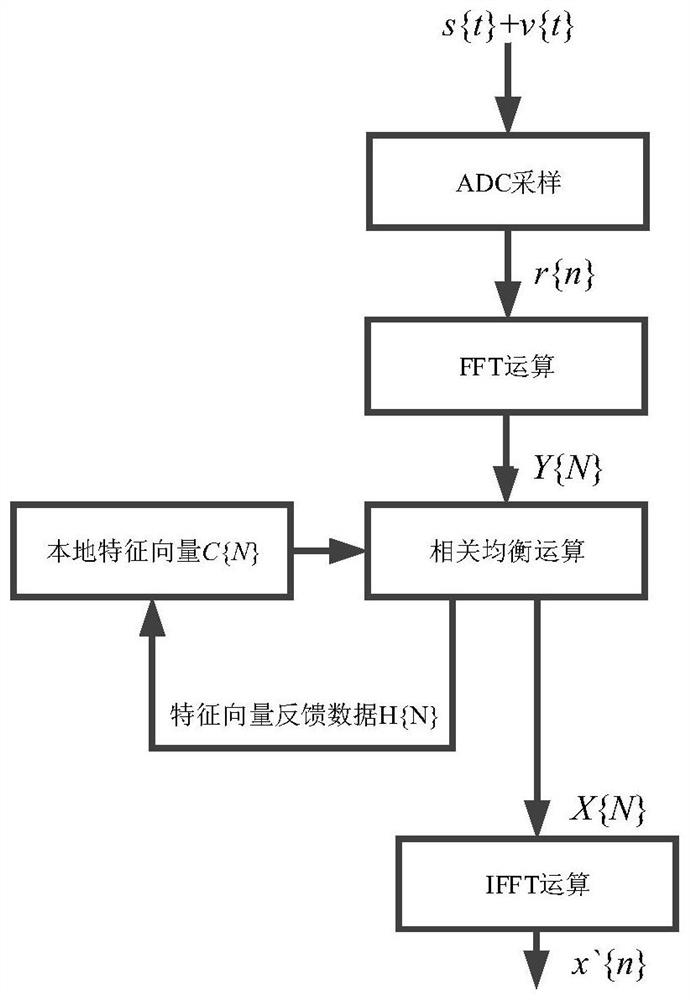

A frequency domain adaptive equalization transmission data processing method, data receiving end and storage medium

ActiveCN110855588BIncrease processing bandwidthLower latencyTransmitter/receiver shaping networksTime domainFeature vector

Owner:BEIJING JUN MAO GUO XING TECH CO LTD

A High Performance Channel Simulator RF Transceiver for 5G Communications

ActiveCN108429594BReduce complexityReduced Power RequirementsTransmission monitoringLow noiseLocal oscillator signal

The invention discloses a high-performance channel simulator radio frequency transceiver applied to 5G communication, which includes a transmission link and a reception link; in the transmission link, the intermediate frequency signal passes through the first intermediate frequency filtering module, the up-mixing module, The first automatic gain amplification control module, single-pole double-throw switch and radio frequency filter module are finally transmitted; in the receiving link, the radio frequency signal passes through the radio frequency filter module, single-pole double-throw switch, low noise amplifier, second automatic gain control amplification module, The down-mixing module, the second intermediate frequency filtering module and the third automatic gain amplification control module finally receive back; in addition, a local oscillator module providing local oscillator signals for the up-mixing module and the down-mixing module is also included. The invention can effectively reduce the complexity of the channel simulator, reduce the power demand for a single channel in 5G research, reduce power consumption, and has the characteristics of large processing bandwidth, small area, and good performance.

Owner:SOUTHEAST UNIV

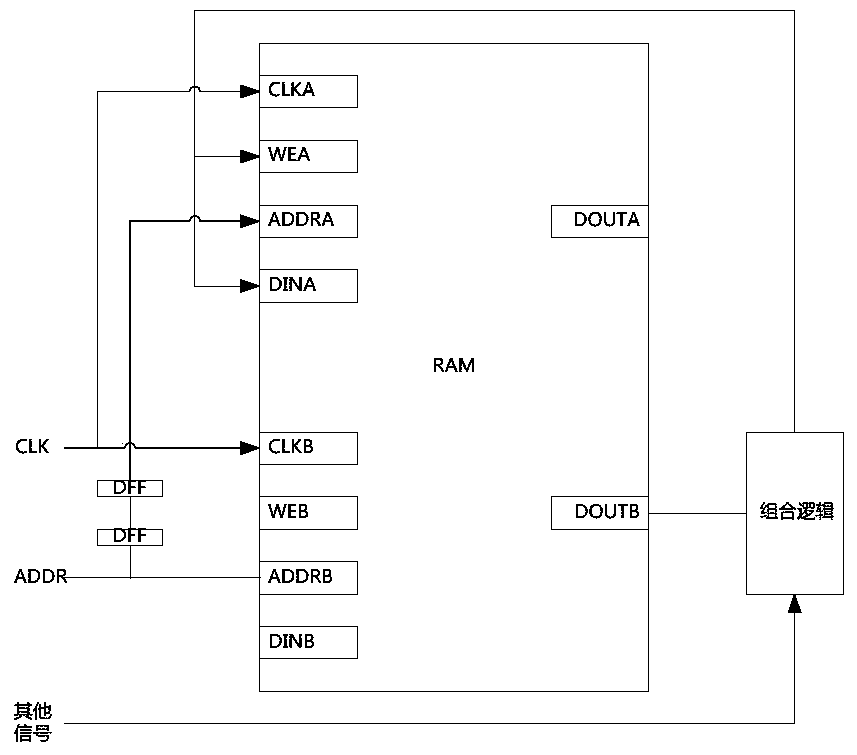

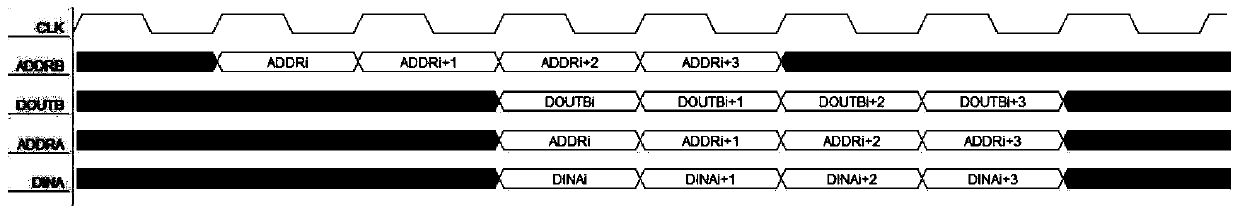

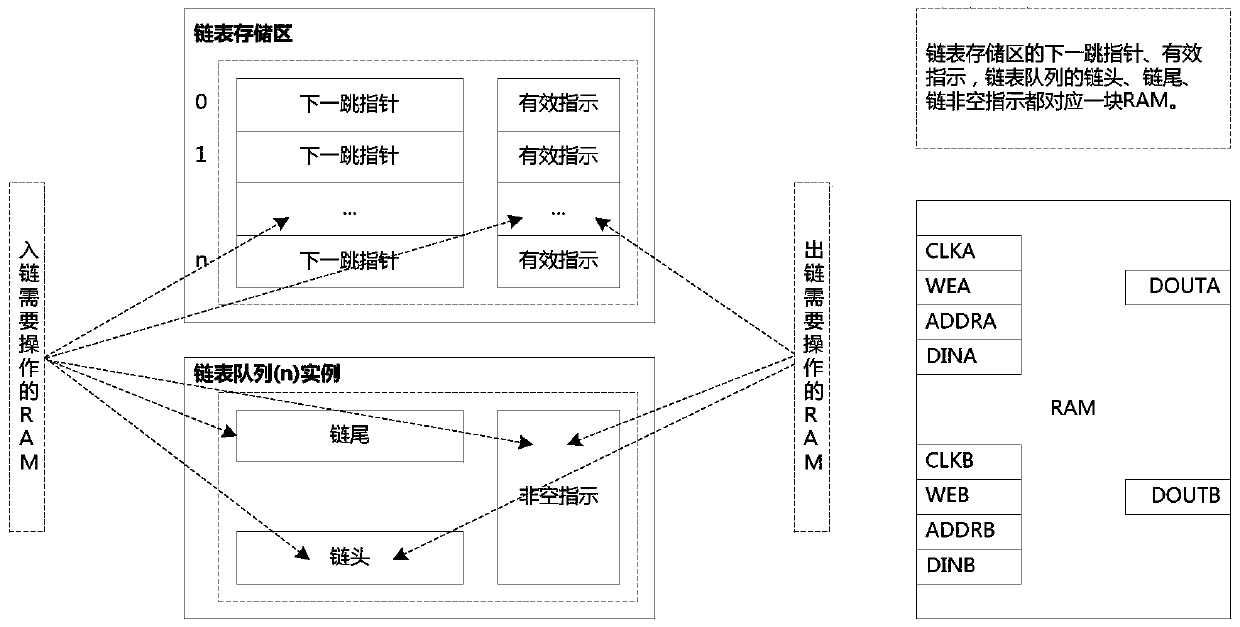

A circuit structure and operation method for realizing chained list pipeline operation

ActiveCN106126435BIncrease processing bandwidthMemory adressing/allocation/relocationLinked listSoftware

The invention provides a circuit structure for achieving chain table pipeline operation. The circuit structure comprises a chain table storage area and a chain table queue. The chain table storage area comprises a next-hop pointer and next-hop pointer effective indication. The chain table queue comprises a chain head, a chain tail and non-idle indication of the chain head. The circuit structure is characterized in that the next-hop pointer effective indication status 0[1:0] is expressed by 2 bits, and the 2 bits of the indication are expressed as status 0[0] and status 0[1] respectively; the chain table queue further comprises a reboot chain head and an indication state of the reboot chain head, and the indication state status 1[1:0] of the reboot chain head is expressed by 2 bits; the chain tail contains status 0[0]information corresponding to the chain table storage area. The problem that software and universal hardware chain tables can not process chain inlet and chain outlet at the same time for each clock cycle is solved; processing bandwidth is increased.

Owner:众邦同力(武汉)技术有限公司

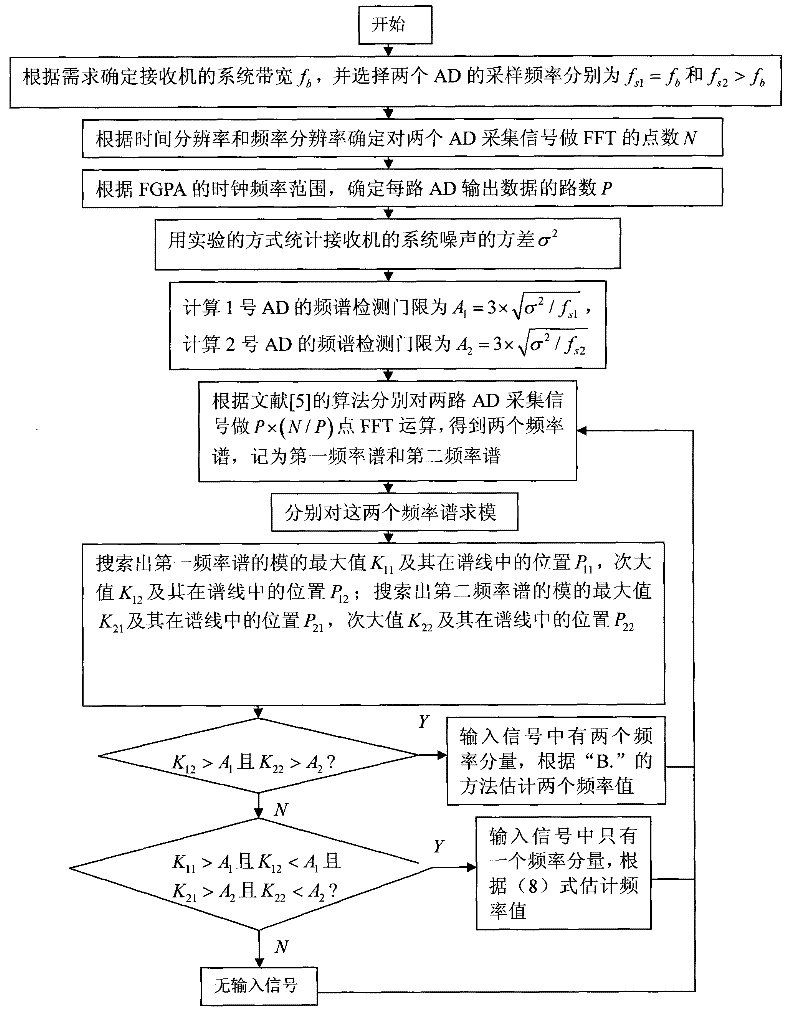

Electronic reconnaissance broadband digital receipt signal processing method based on under sampling

InactiveCN101793952BSmall amount of calculationIncrease processing bandwidthWave based measurement systemsFrequency spectrumBroadband

The invention discloses an electronic reconnaissance broadband digital receipt signal processing method based on under sampling. The method of the invention includes that: system bandwidth of a receiver is determined, and two sampling ADs are selected; according to Winograd algorithm, FFT operation is respectively carried out on the two AD acquisition signals, so as to obtain a first frequency spectrum of a first sampling AD and a second frequency spectrum of a second sampling AD; modulus of the two frequency spectrums are obtained; maximum of modulus of the two frequency spectrums and position thereof in spectral line as well as sub-maximum of modulus and position thereof in spectral line are searched, and finally frequency value of primary sinusoid component is obtained. The invention can cause the processing bandwidth of the receiver to breakthrough half of sampling frequency of AD device without using complex signal and improves the processing bandwidth.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

A control system and method for high-order tangential contact enveloping grinding and polishing

ActiveCN110153851BRealize closed-loop controlEnvelope guaranteeBelt grinding machinesGrinding feed controlLoop controlControl system

The invention belongs to the technical field of intelligent polishing machining and manufacturing, and particularly relates to a high-order tangent contact enveloping type polishing machining controlsystem and method. The control system comprises a polishing machining parameter planning module, a workpiece pose control module, an abrasive belt compliance control module, an enveloping machining module and a polishing amount measuring module, wherein the polishing machining parameter planning module is used for identifying a convex curved surface in a workpiece curved surface, the workpiece pose control module and the abrasive belt compliance control module act cooperatively so as to adjust the pose of a workpiece and the contact force of the enveloping machining module and a sector-shapedcolumn surface in real time, and polishing machining on the workpiece is conducted under the condition; and the polishing amount measuring module is used for judging whether a polishing process is finished or not. The invention further discloses a corresponding method. According to the system, high-order cutting and enveloping on the machined workpiece are realized, meanwhile, the the workpiece pose control module and the abrasive belt compliance control module act cooperatively to achieve the synergistic effect, so that closed-loop control is realized, and the stability, rapidity and accuracyof system response are ensured.

Owner:HUAZHONG UNIV OF SCI & TECH

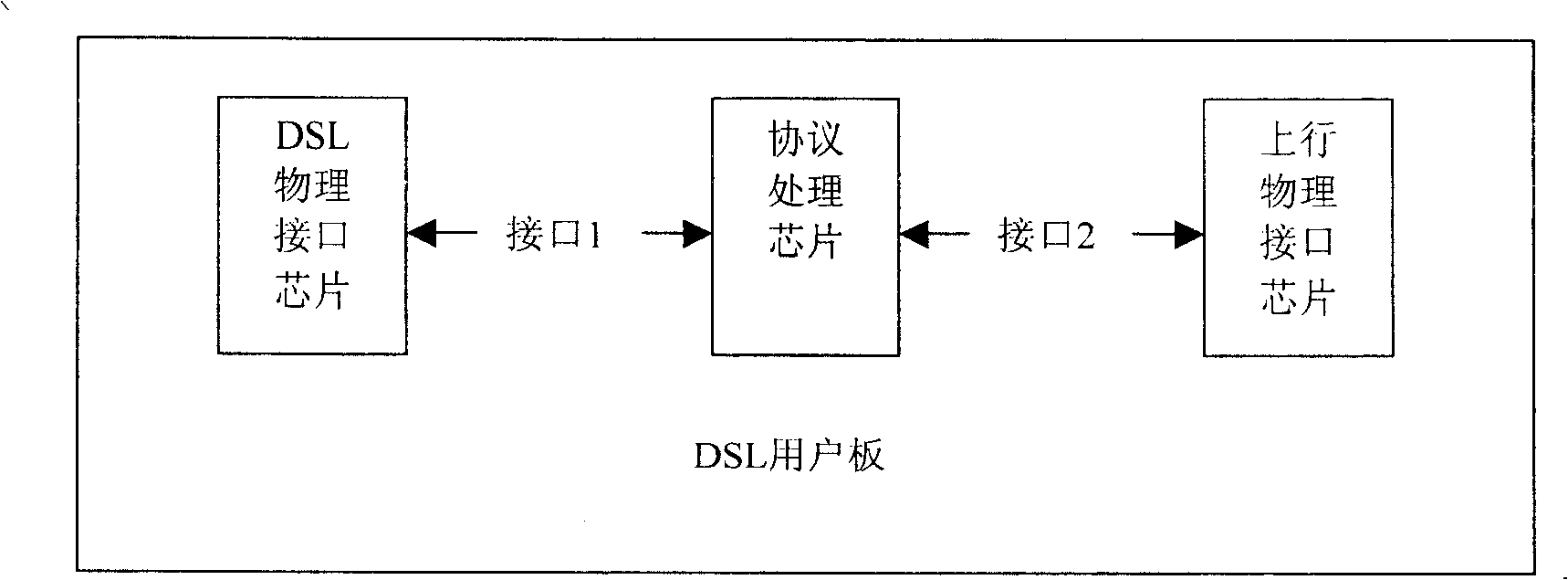

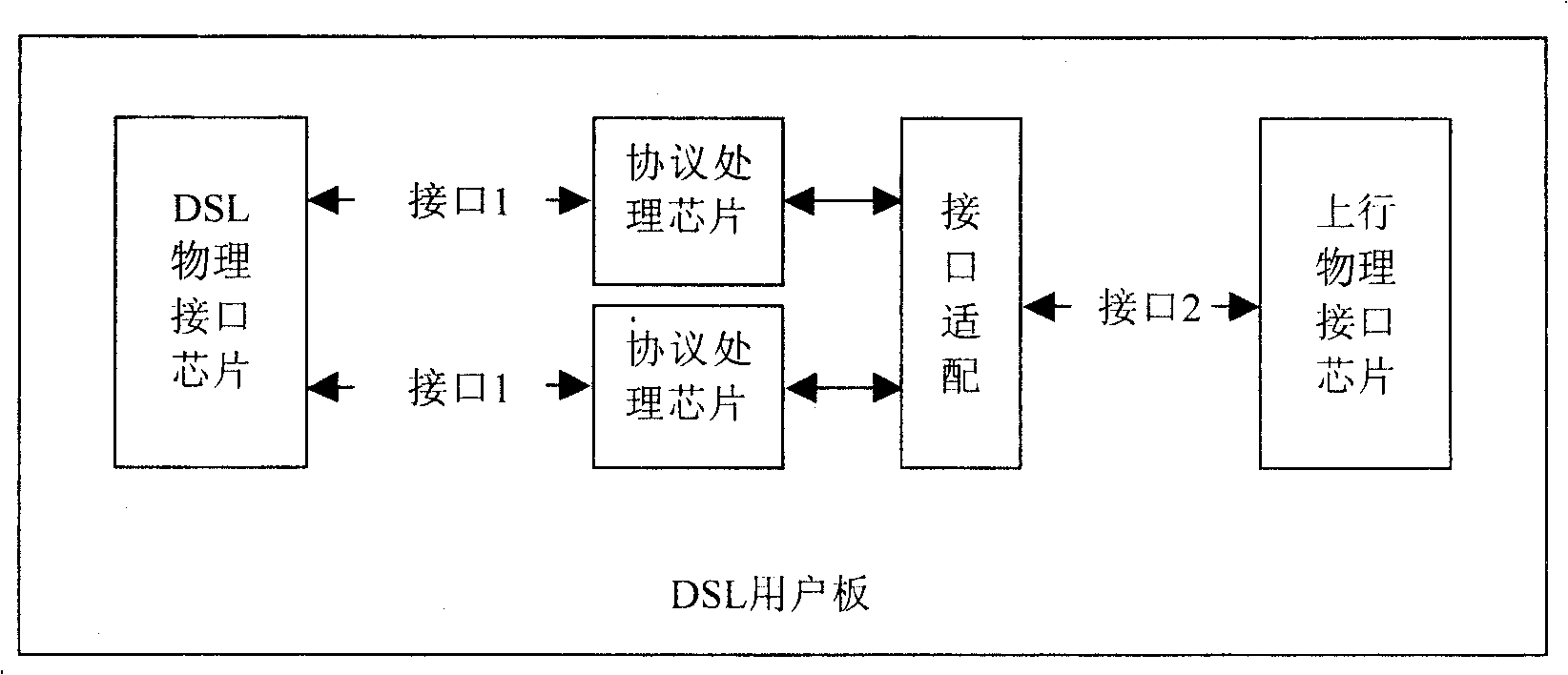

Method for improving DSL user board bandwidth and DSL user board using the same

InactiveCN100433621CIncrease processing bandwidthHigh densityMultiplex system selection arrangementsData switching detailsClock rateDistributed computing

The invention discloses an improving DSL user board bandwidth method, which raises interface bandwidth between DSL user board chips to the scheduled bandwidth according to the bandwidth value which needs to improve, when the DSL user board bandwidth needs to improve. The invention comprises the following modes: increasing interface quantity; improving interface broad band rate; or improving interface clock frequency. The invention can improve processing bandwidth of DSL user board, which reduces the cost.

Owner:HUAWEI TECH CO LTD

Data compression method, decompression method, system and related device for graph data

ActiveCN111046002BIncrease processing bandwidthFile system functionsSpecial data processing applicationsData compressionTheoretical computer science

The present application provides a method for compressing graph data, including: obtaining original graph data and determining a node pair of each edge in the original graph data; grouping the same source nodes in the node pair according to preset grouping rules; A source node; store the corresponding FIFO according to the group type of each group; add labels to the source node data of the source node and the destination node data of the destination node; poll and store the FIFO to obtain compressed graph data. The present application enables source nodes with different numbers of corresponding destination nodes to adopt different compression rates, only one source node is reserved in the same group, and there is no need to store duplicate source nodes. It can support large-scale parallel decompression of graph data and greatly increase the bandwidth of graph data processing. The present application also provides a data compression system for a graph computing system, a computer-readable storage medium, and a data compression terminal, which have the above beneficial effects.

Owner:INSPUR BEIJING ELECTRONICS INFORMATION IND

Electronic reconnaissance broadband digital receipt signal processing method based on under sampling

InactiveCN101793952AMeet the interceptionMeet processing needsWave based measurement systemsFrequency spectrumComputer science

The invention discloses an electronic reconnaissance broadband digital receipt signal processing method based on under sampling. The method of the invention includes that: system bandwidth of a receiver is determined, and two sampling ADs are selected; according to Winograd algorithm, FFT operation is respectively carried out on the two AD acquisition signals, so as to obtain a first frequency spectrum of a first sampling AD and a second frequency spectrum of a second sampling AD; modulus of the two frequency spectrums are obtained; maximum of modulus of the two frequency spectrums and position thereof in spectral line as well as sub-maximum of modulus and position thereof in spectral line are searched, and finally frequency value of primary sinusoid component is obtained. The invention can cause the processing bandwidth of the receiver to breakthrough half of sampling frequency of AD device without using complex signal and improves the processing bandwidth.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Data flow detection method and device

ActiveCN105591836BReduce the number of timesIncrease processing bandwidthData switching networksData streamData mining

Owner:NEW H3C TECH CO LTD

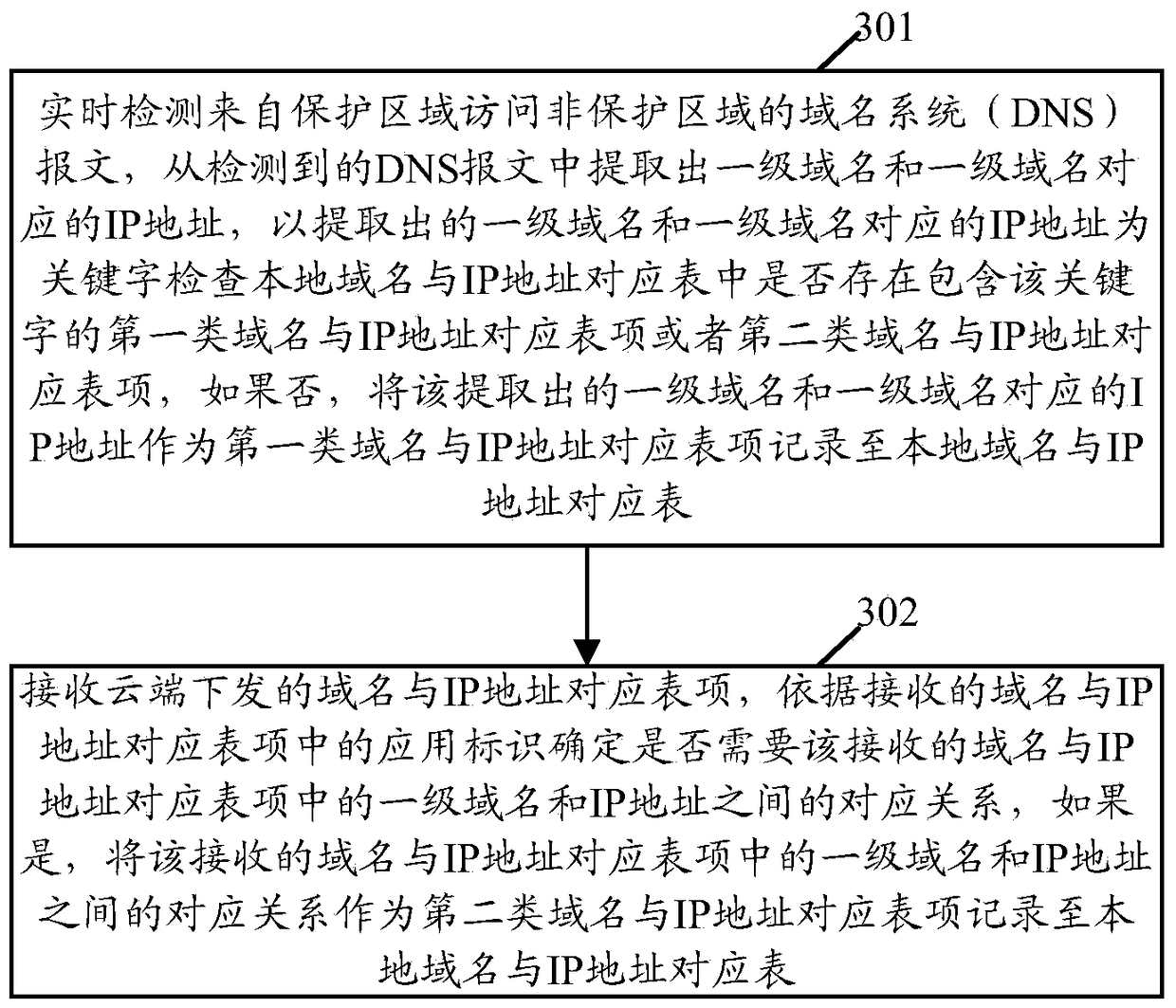

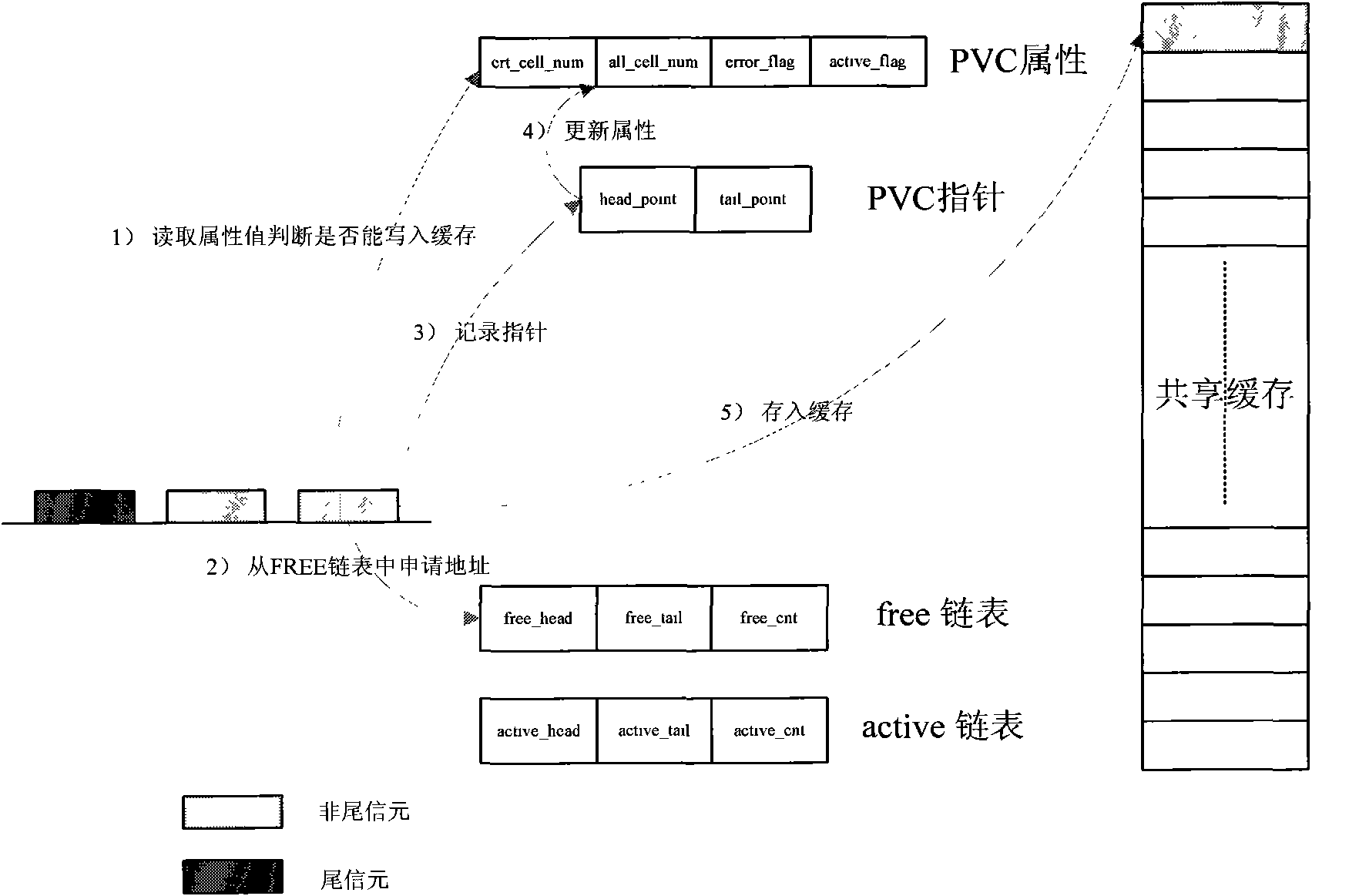

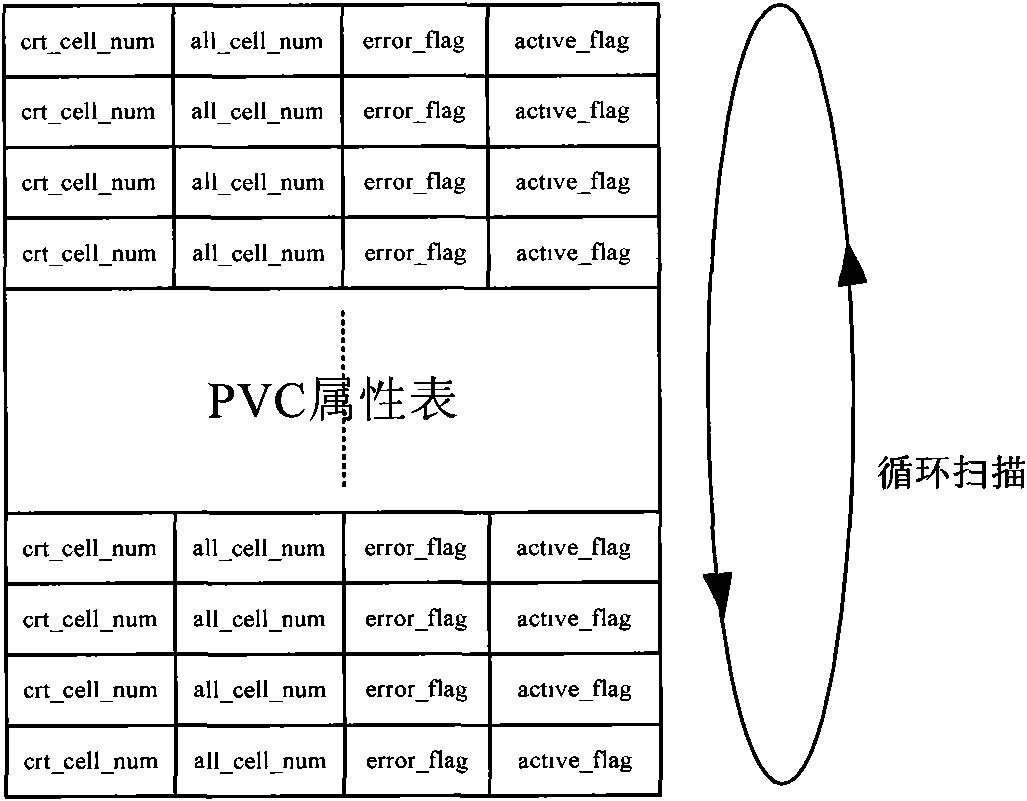

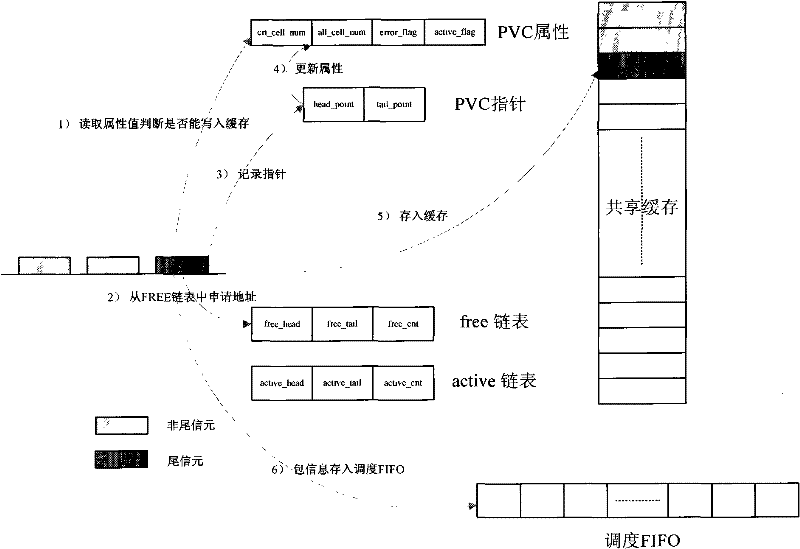

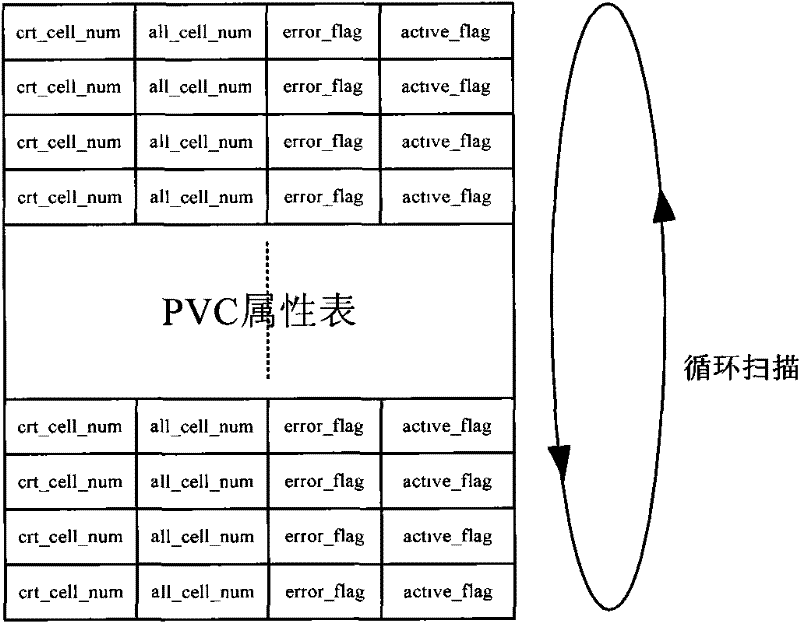

Asynchronous transfer mode (ATM) cell recombination and sharing buffer memory system and realization method thereof

InactiveCN102347882BSimple implementation logicCache management is fair and reasonableData switching networksStatic random-access memoryAsynchronous Transfer Mode

Owner:高通创锐讯通讯科技(上海)有限公司

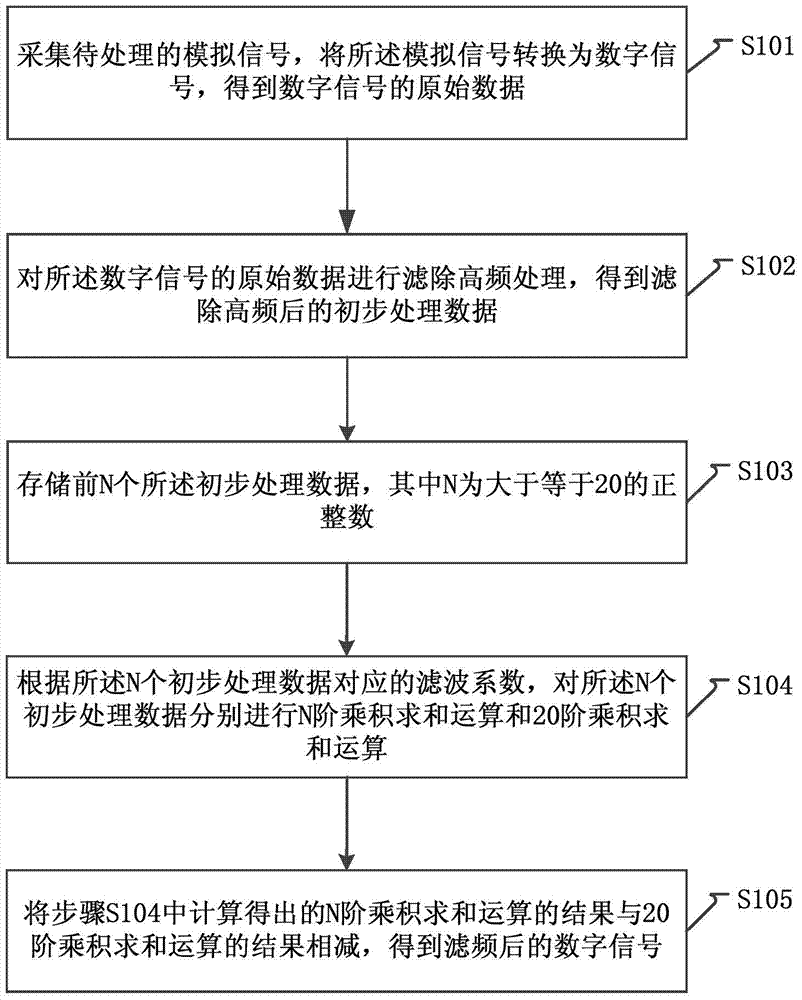

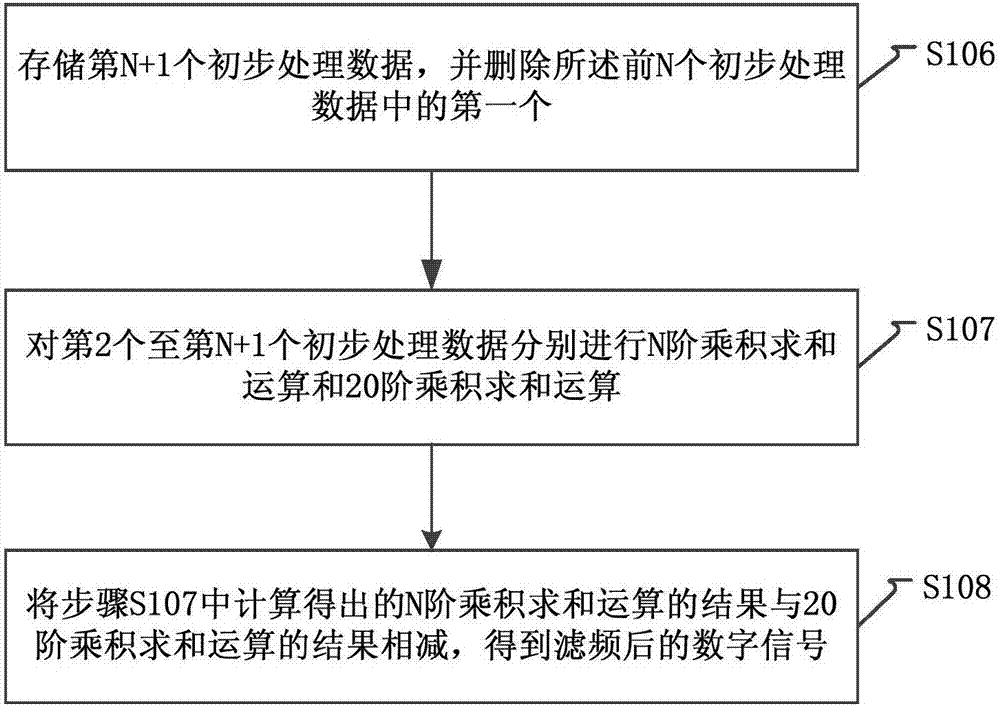

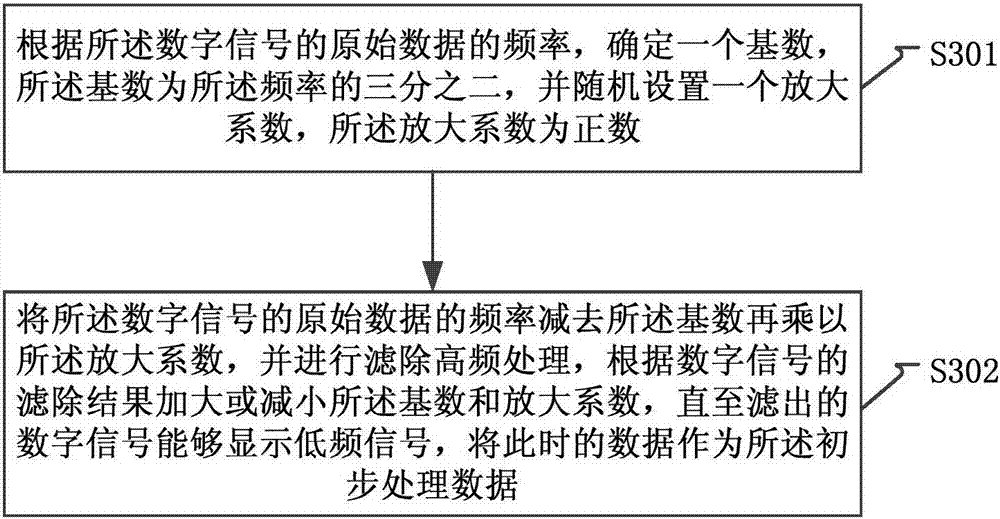

An RC filter method and RC filter for blood pressure and heart rate test

ActiveCN104779934BHigh precisionIncrease flexibilityDigital technique networkOriginal dataBlood pressure

The invention discloses an RC filter method and an RC filter for testing blood pressure and heart rate, wherein the method includes: step A: collecting an analog signal to be processed, converting the analog signal into a digital signal, and obtaining a digital signal raw data; step B: filter out the high-frequency processing on the original data of the digital signal, and obtain the preliminary processed data after filtering out the high frequency; step C: store the first N described preliminary processed data, wherein N is greater than A positive integer equal to 20; step D: according to the filter coefficients corresponding to the N preliminary processing data, respectively perform N-order product summation and 20-order product summation operations on the N preliminary processing data; Step E: The result of the N-order product summation operation is subtracted from the result of the 20-order product summation operation to obtain a frequency-filtered digital signal. The RC filtering method and the RC filter of the present invention eliminate the influence of external factors, improve precision and flexibility, and increase processing bandwidth.

Owner:合肥矽景电子有限责任公司

Optical module, network equipment, optical system and communication system

ActiveCN107342821BRelieve stressIncrease processing bandwidthMultiplex system selection arrangementsData switching by path configurationOptical ModuleCommunications system

Owner:HUAWEI TECH CO LTD

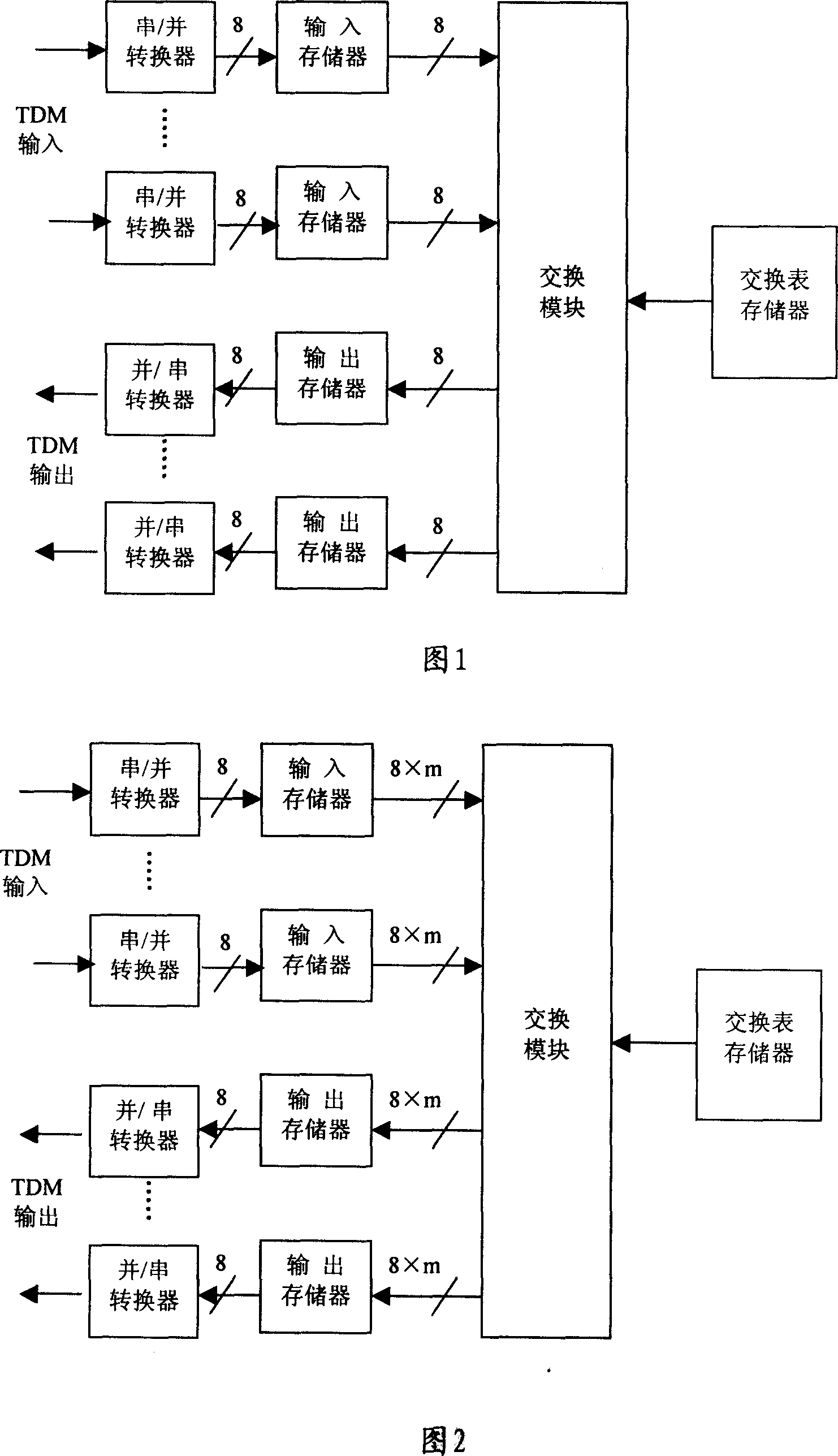

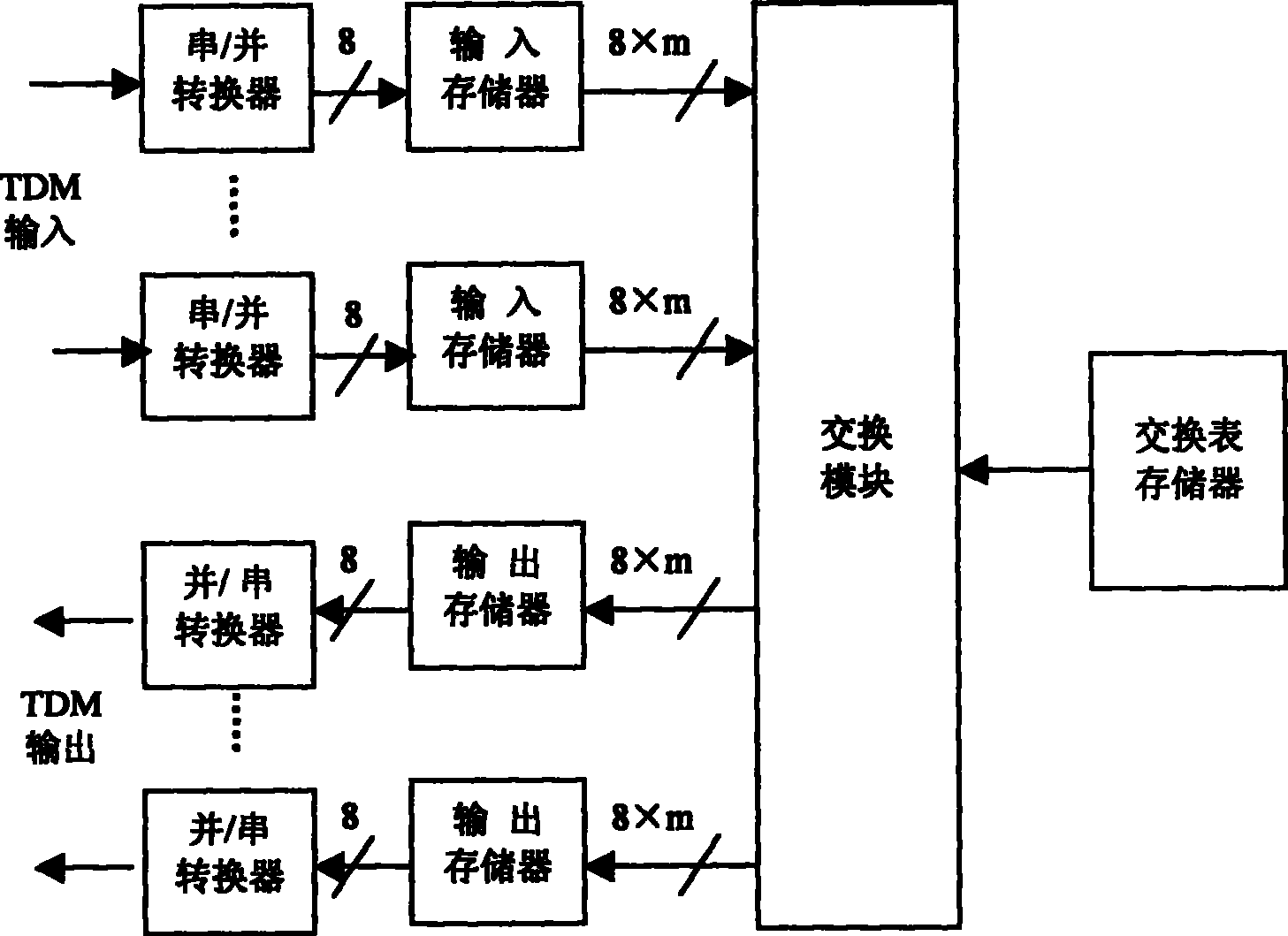

Mass TDMA complex switching chip data processing method

ActiveCN1855783BIncrease processing bandwidthLarge capacityTime-division multiplexMultiplexingParallel computing

Owner:HUAWEI TECH CO LTD

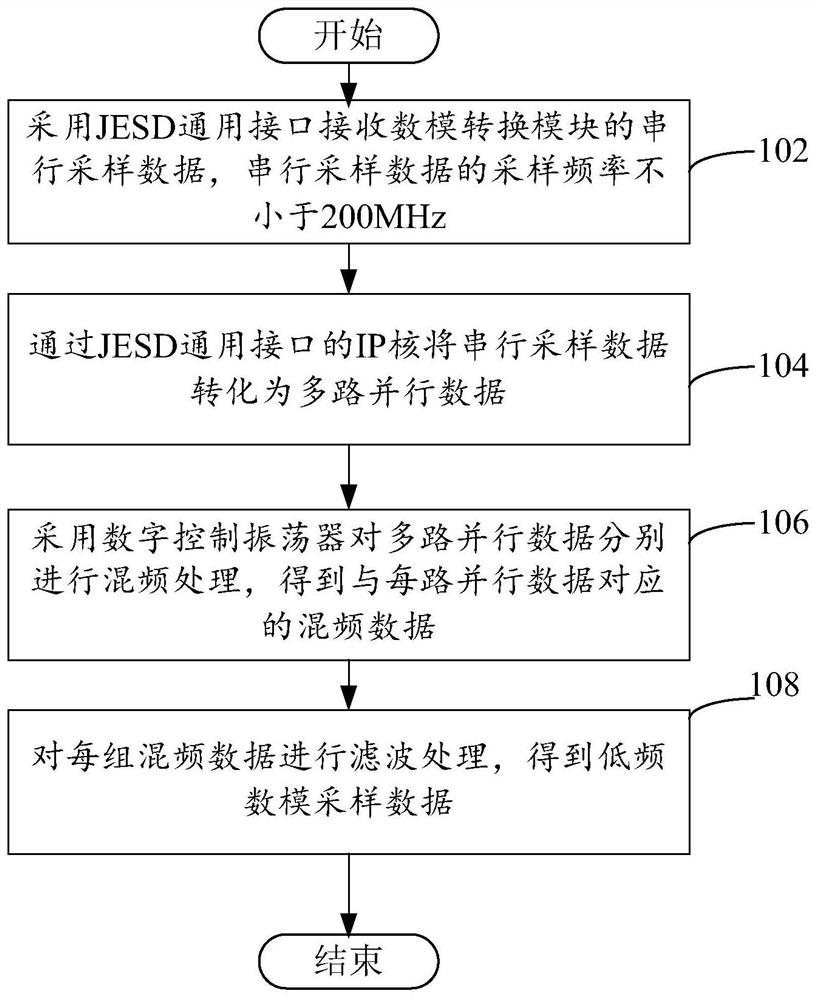

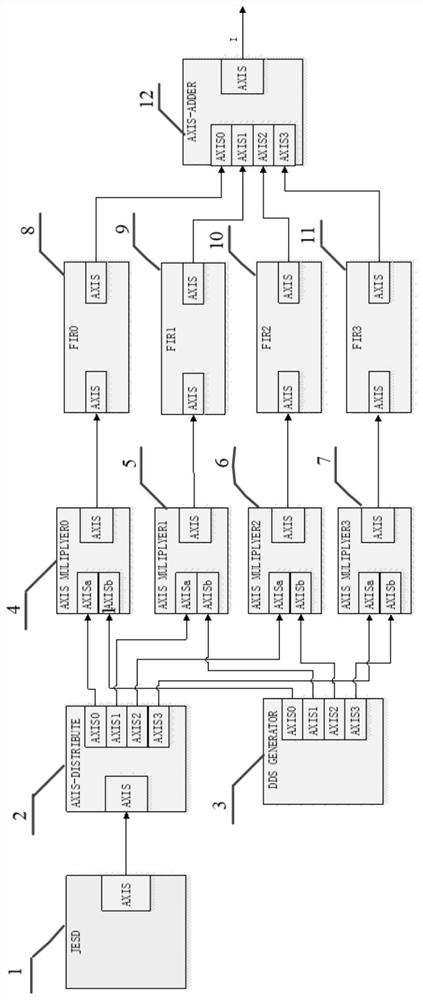

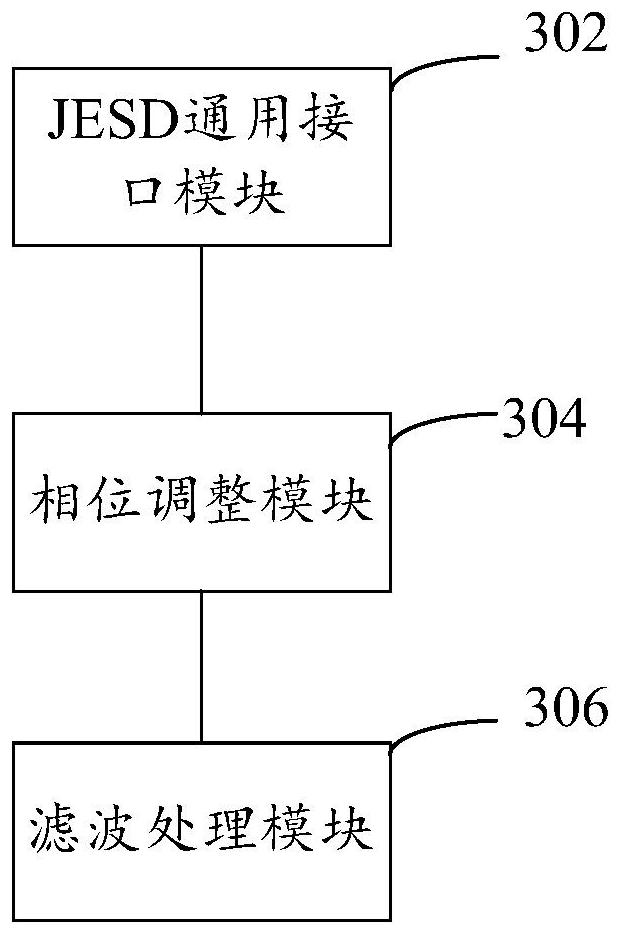

FPGA chip data processing method, chip, computer equipment and storage medium

InactiveCN112083674AMeet miniaturizationMeet multi-channel integrationProgramme controlWave based measurement systemsComputer hardwareComputer architecture

The invention provides an FPGA chip data processing method, a chip, computer equipment and a storage medium, and belongs to the field of radar AD front-end digital processing. The method particularlycomprises the following steps: receiving serial sampling data of a digital-to-analog conversion module by adopting a JESD universal interface, the sampling frequency of the serial sampling data beingnot less than 200MHz; converting the serial sampling data into multiple paths of parallel data through an IP core of the JESD universal interface; respectively carrying out frequency mixing processingon the multiple paths of parallel data by adopting a digital control oscillator to obtain frequency mixing data corresponding to each path of parallel data; and performing filtering processing on each group of frequency mixing data to obtain low-frequency digital-analog sampling data. Through the processing scheme disclosed by the invention, the FPGA chip is simple in design, strong in processingcapacity and easy for engineering practice.

Owner:LEIHUA ELECTRONICS TECH RES INST AVIATION IND OF CHINA

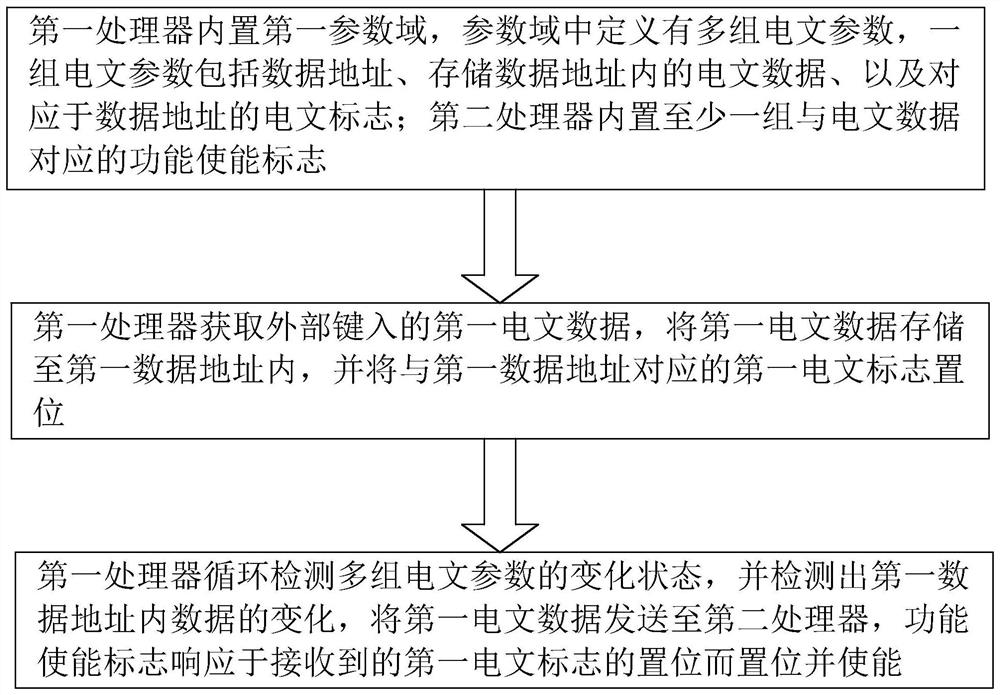

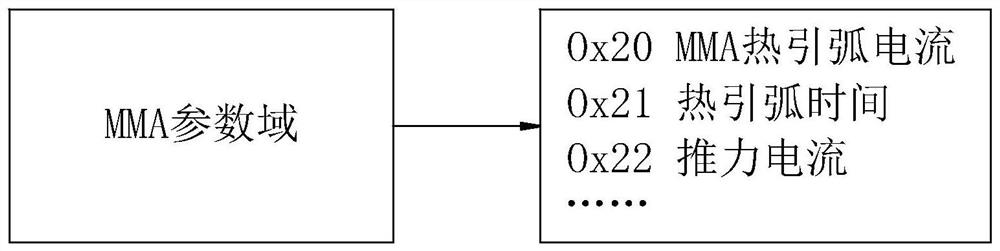

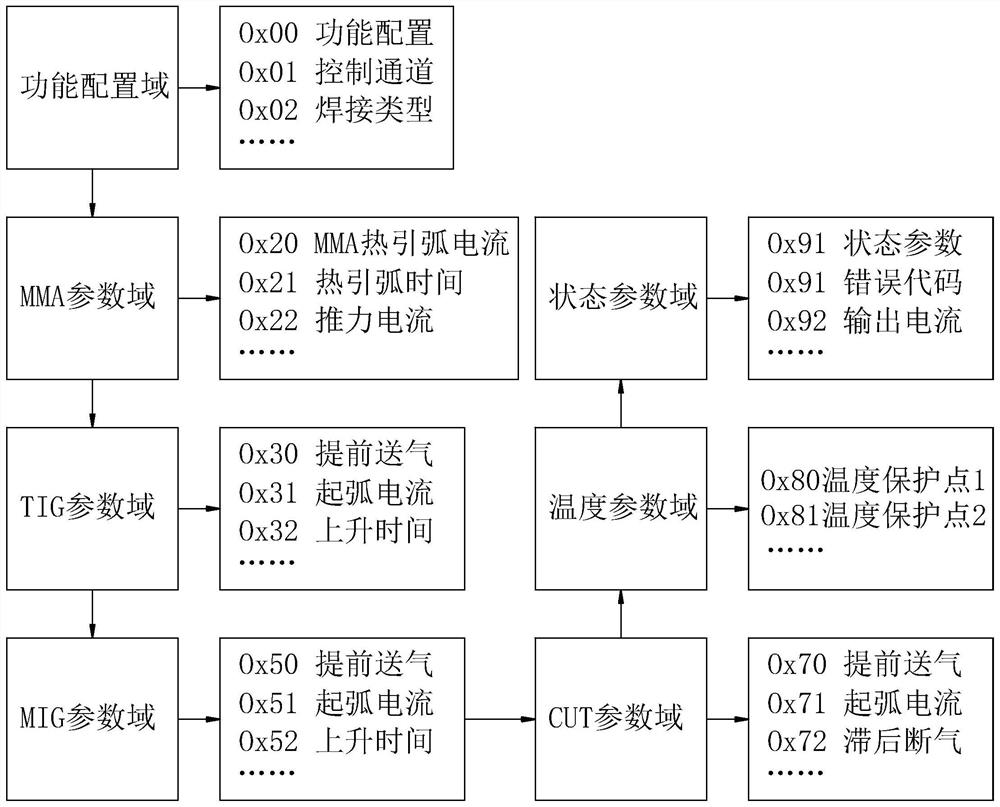

Arc welding machine communication protocol configuration method, system, device and storage medium thereof

ActiveCN111673234BIntegrity guaranteedImprove unityArc welding apparatusComputer hardwareCommunications protocol

The invention relates to a communication protocol configuration method and system for an arc welding machine. The method includes: a first processor has a built-in first parameter domain, and a plurality of sets of telegram parameters are defined in the parameter domain. The electronic text data and the electronic text flag corresponding to the data address; the second processor has built-in at least one set of function enabling flags corresponding to the electronic text data; obtains the first electronic text data entered from the outside, and stores the first electronic text data in the first electronic text data. In the data address, and set the first message flag corresponding to the first data address; cyclically detect the change status of multiple groups of message parameters, and detect the change of the data in the first data address, and send the first message data to the first data address. In the second processor, the function enable flag is set and enabled in response to the setting of the received first message flag. The problem of product unreliability is solved, and the unified correspondence between telegram data and function enable flag is beneficial to improve the effect of product reliability.

Owner:SHANGHAI HUGONG ELECTRIC WELDING MACHINE MFG

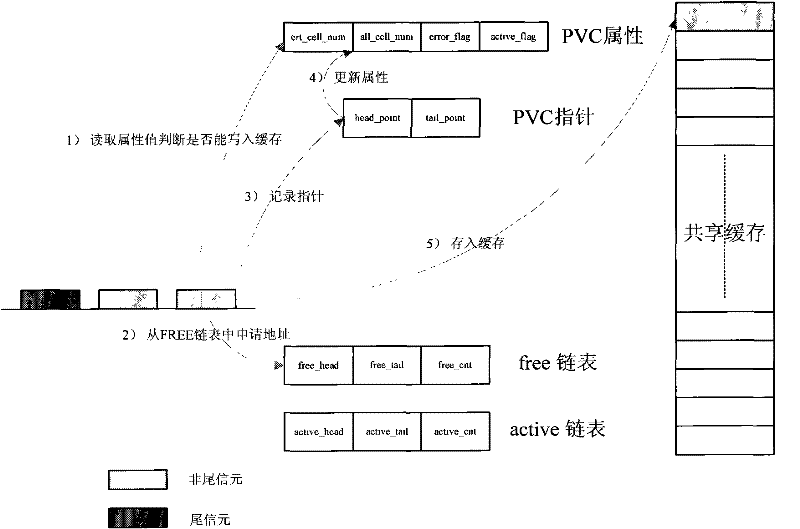

Asynchronous transfer mode (ATM) cell recombination and sharing buffer memory system and realization method thereof

InactiveCN102347882ASimple implementation logicCache management is fair and reasonableData switching networksStatic random-access memoryAsynchronous Transfer Mode

The invention discloses an asynchronous transfer mode (ATM) cell recombination and sharing buffer memory system, which comprises a permanent virtual circuit (PVC), a chain table, a scanner and a first-in first-out device (FIFO), wherein the PVC is used for receiving cells, an on-chip static random-access memory (SRAM) is used as a receiving buffer memory, the PVC shares the buffer memory, the chain table comprises a FREE chain table for indicating the buffer memory rest space and an ACTIVE chain table for representing the space occupied by a buffer memory packet, the FREE chain table is used for receiving requests of the PVC, transferring the address in the FREE chain table to the PVC and storing the address into the buffer memory through the PVC, the scanner is used for visiting the attribute value and the chain table of the PVC in a fixed time sequence, and the FIFO has the effect that the information of the PVC packet is written into the FIFO after the PVC receives the tail cells of a certain PVC packet. In addition, the invention also discloses a realization method of the ATM cell recombination and sharing buffer memory. The unnecessary cells can be cleared, simultaneously, the operation of releasing the corresponding buffer space is completed, the buffer memory management is fairer and more reasonable, the processing bandwidth is high, and the logic realization is simple.

Owner:高通创锐讯通讯科技(上海)有限公司

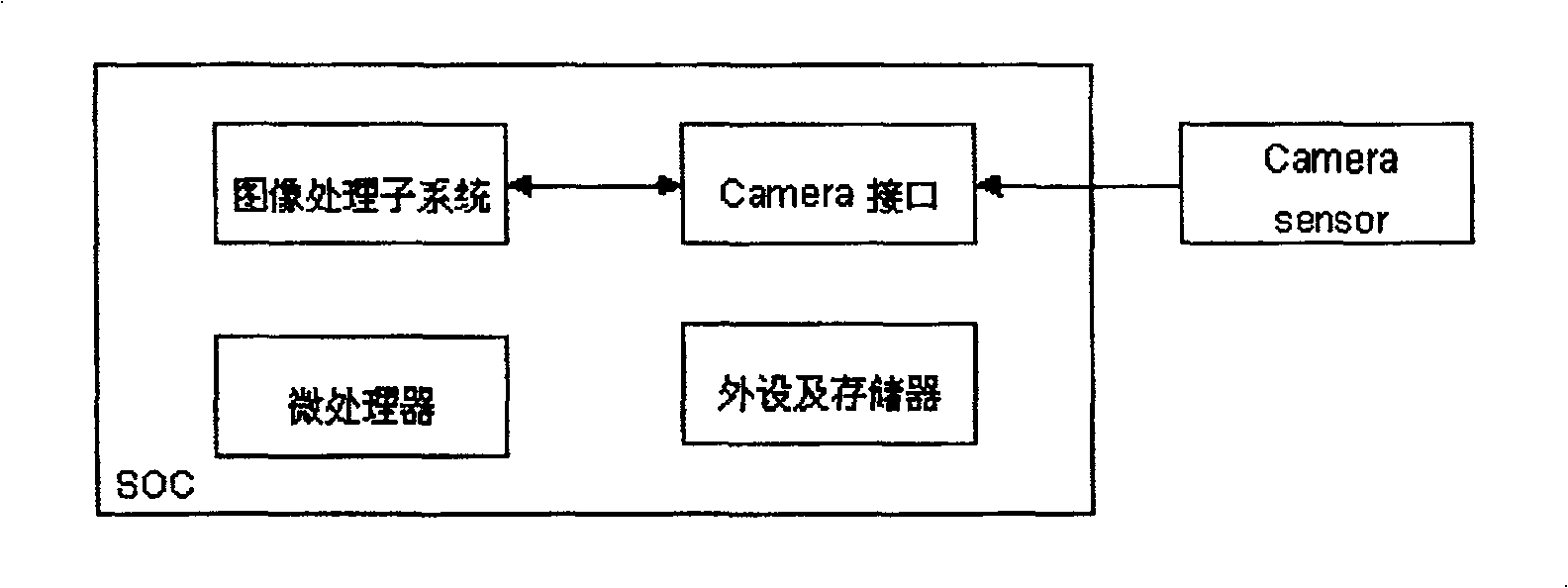

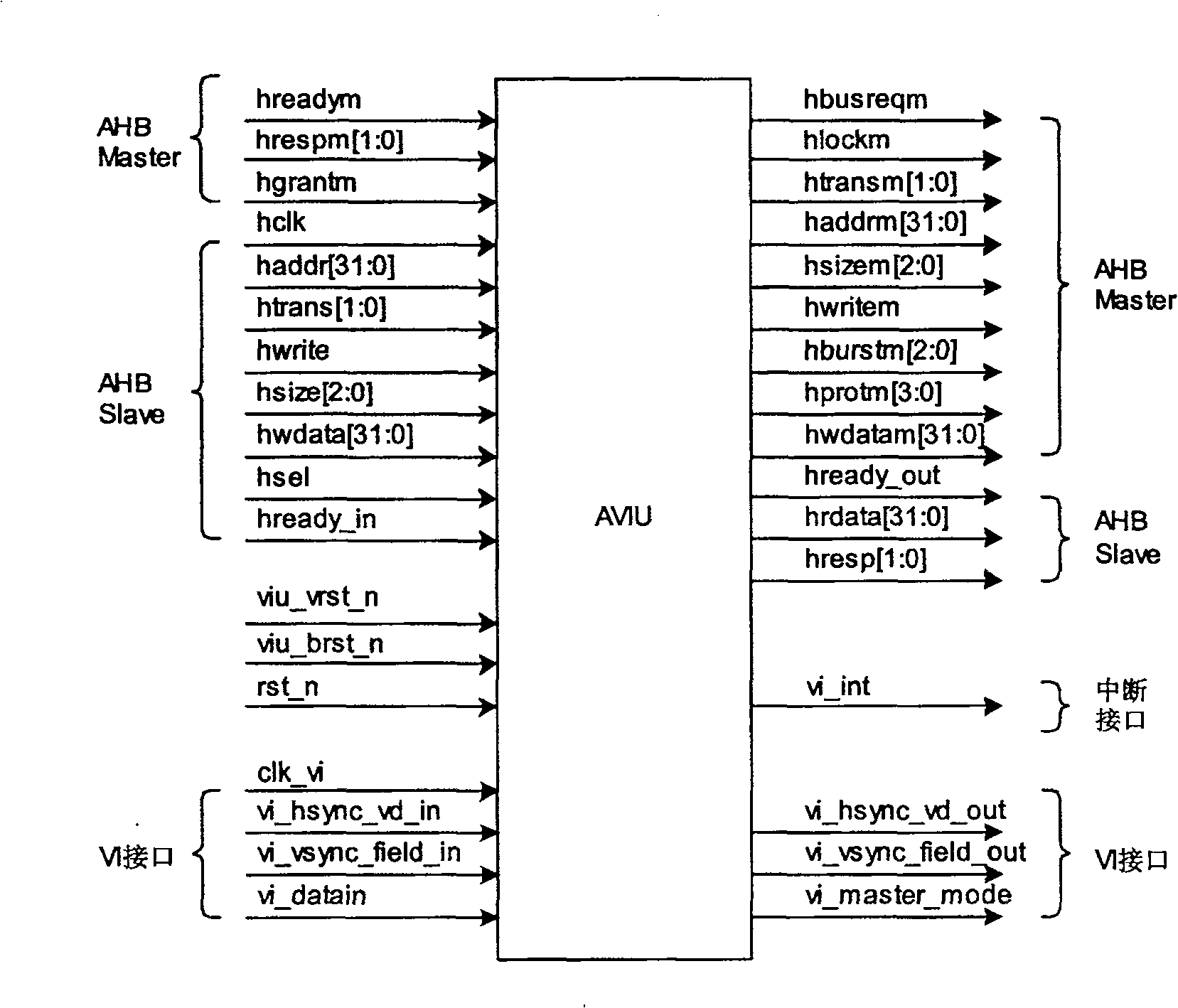

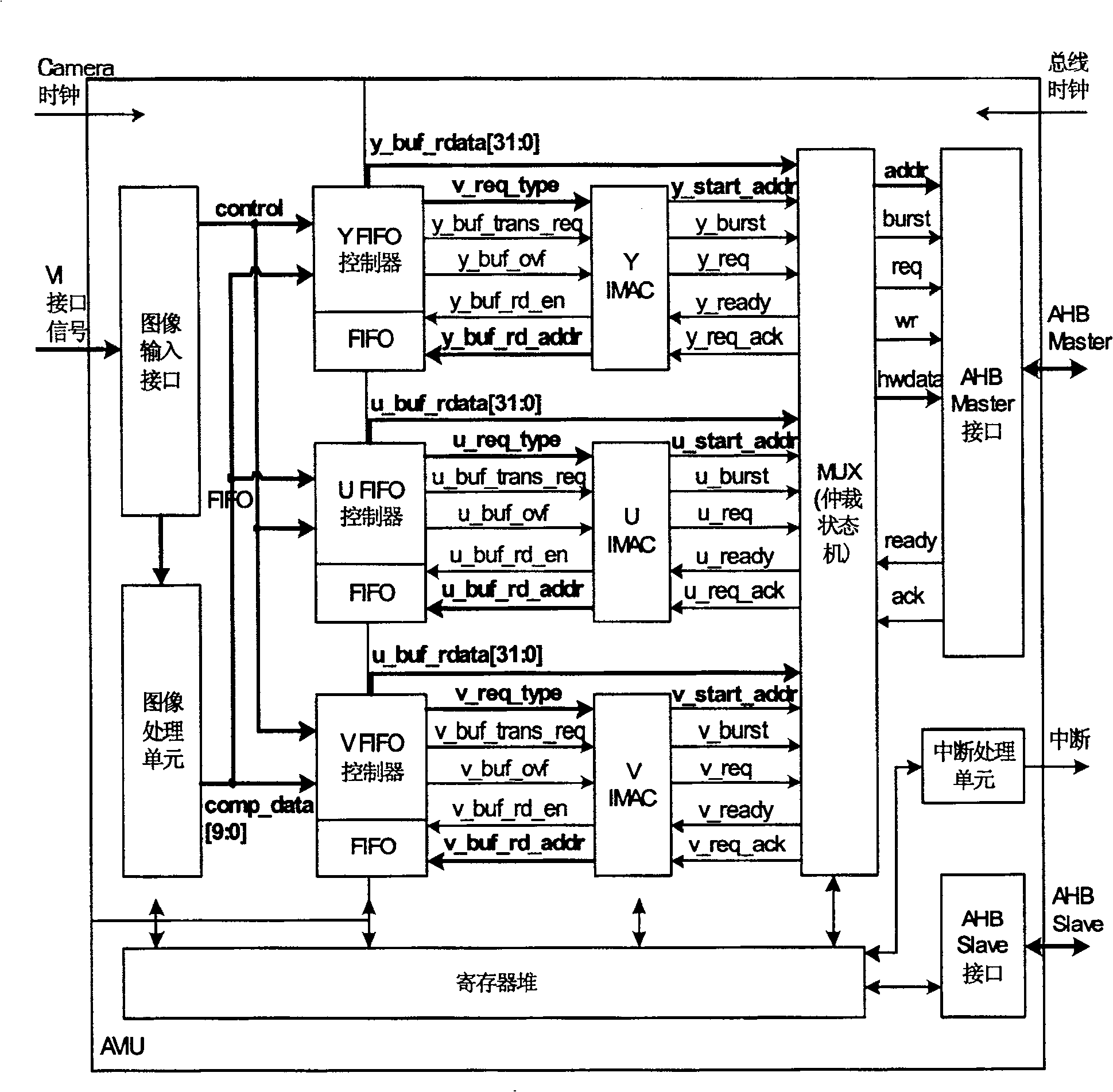

Device, method and chip and cell phone for realizing image data collection

ActiveCN100531311CEasy to controlHigh selectivityTelevision system detailsColor television detailsProcessor registerData acquisition

Owner:HUAWEI TECH CO LTD

A kind of antibacterial pa66/abs composite material and preparation method thereof

Owner:ZHUZHOU TIMES NEW MATERIALS TECH

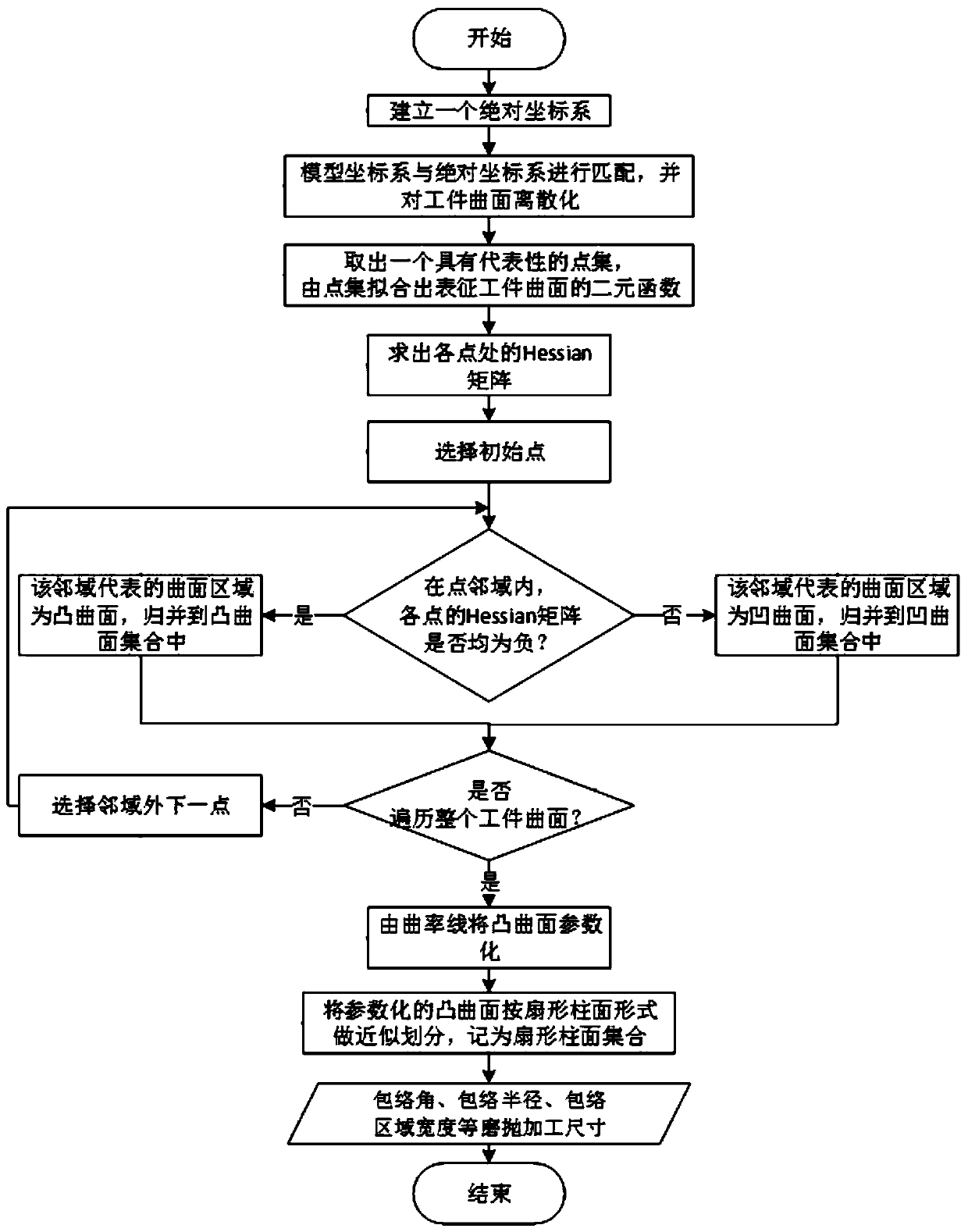

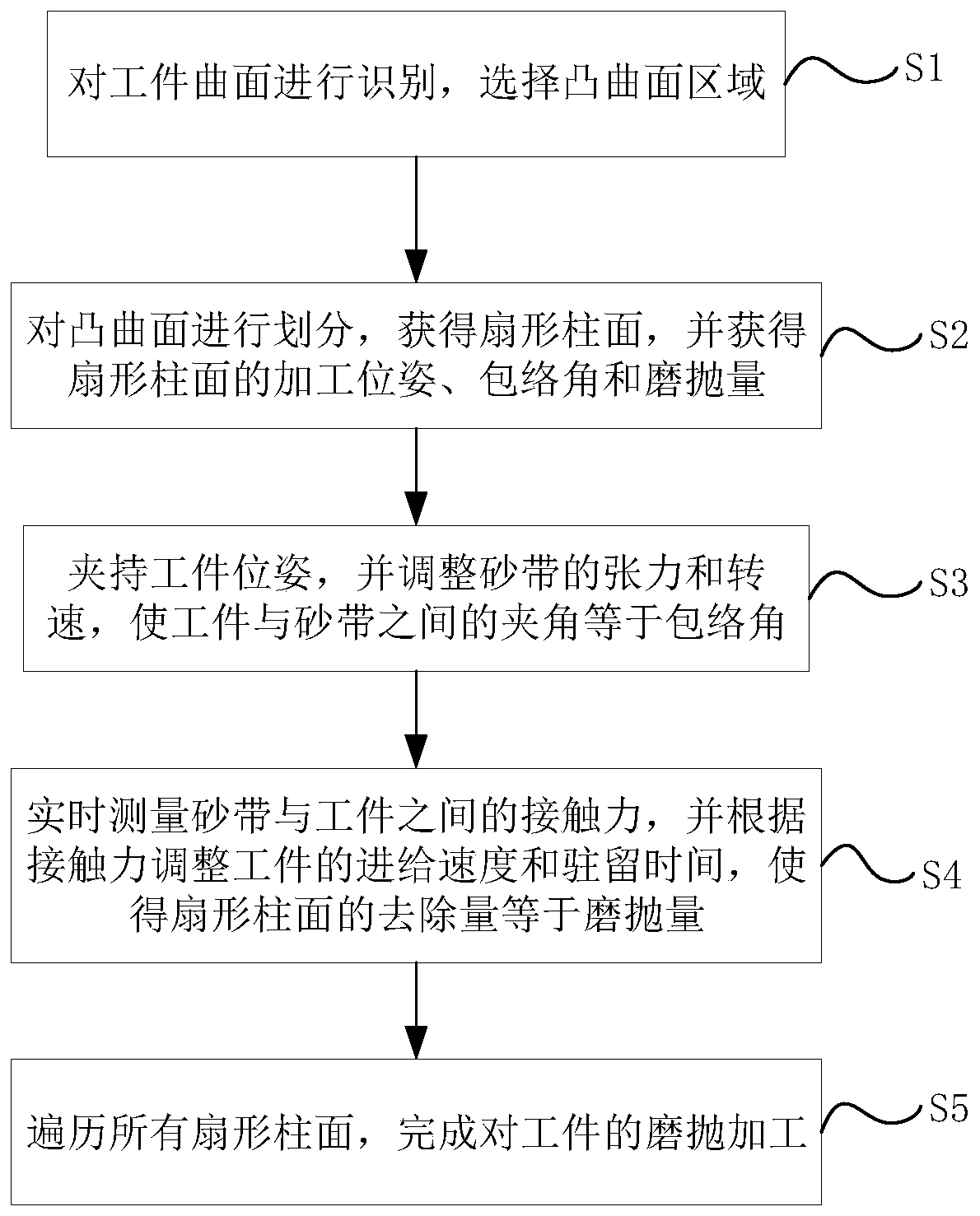

A kind of high-order tangential enveloping grinding and polishing processing method and its application

ActiveCN110227994BFeed speed controlRealize high-order contact enveloping grinding and polishingBelt grinding machinesGrinding feed controlPolishingEngineering

The invention belongs to the technical field of intelligent grinding and polishing manufacturing, in particular to a high-order cutting contact enveloping grinding and polishing method and applicationthereof. The method comprises the steps of 1, identifying curve faces of a workpiece and selecting a convex curved face area; 2, dividing the convex curved face area to obtain multiple sector cylinders and the machining poses, the enveloping angles [alpha] and the grinding and polishing quantities of the sector cylinders; 3, enabling one of the sector cylinders to make contact with a sanding belt, and adjusting the corresponding machining pose of the sector cylinder to make the angle of enveloping segmental arc between the workpiece and the sanding belt be equal to the enveloping angle [alpha]; 4, measuring the contact force of the sanding belt and the sector cylinders in real time until the removal amount of the sector cylinder is equal to the grinding and polishing quantity; and 5, repeating the step 3 and the step 4 until each sector cylinder is adjusted in the same way to complete the grinding and polishing of the workpiece. According to the method and the application thereof, theworkpiece is ground and polished in high-order cutting contact enveloping manner, and the machining is high in precision, good in quality, and high in efficiency.

Owner:HUAZHONG UNIV OF SCI & TECH

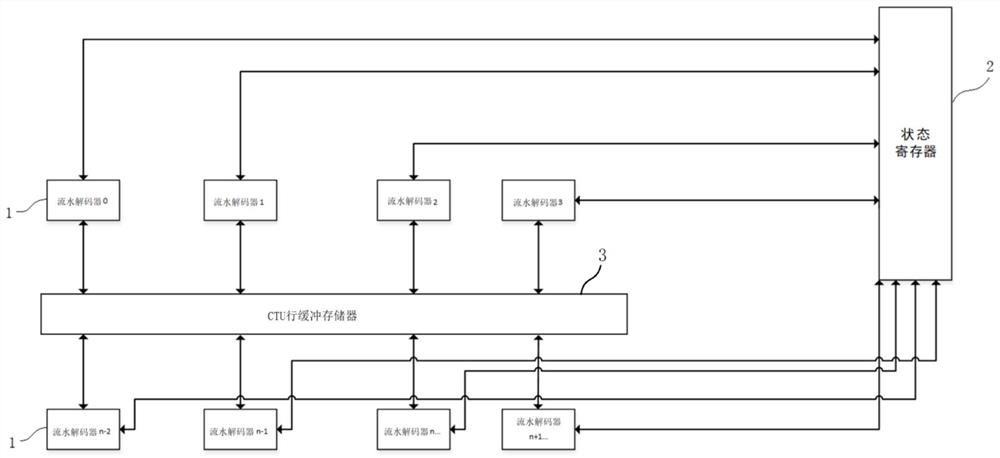

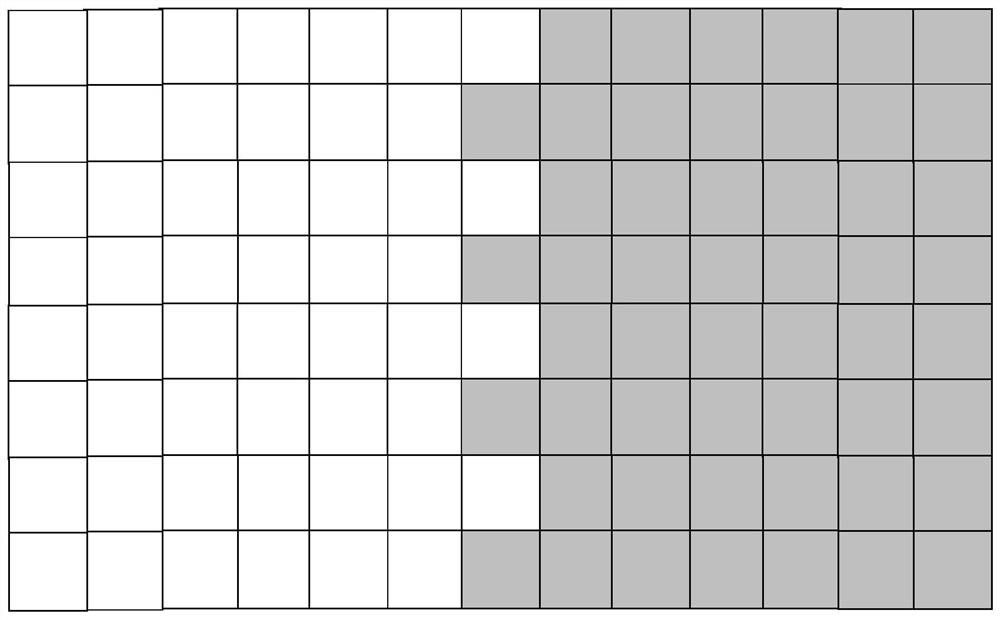

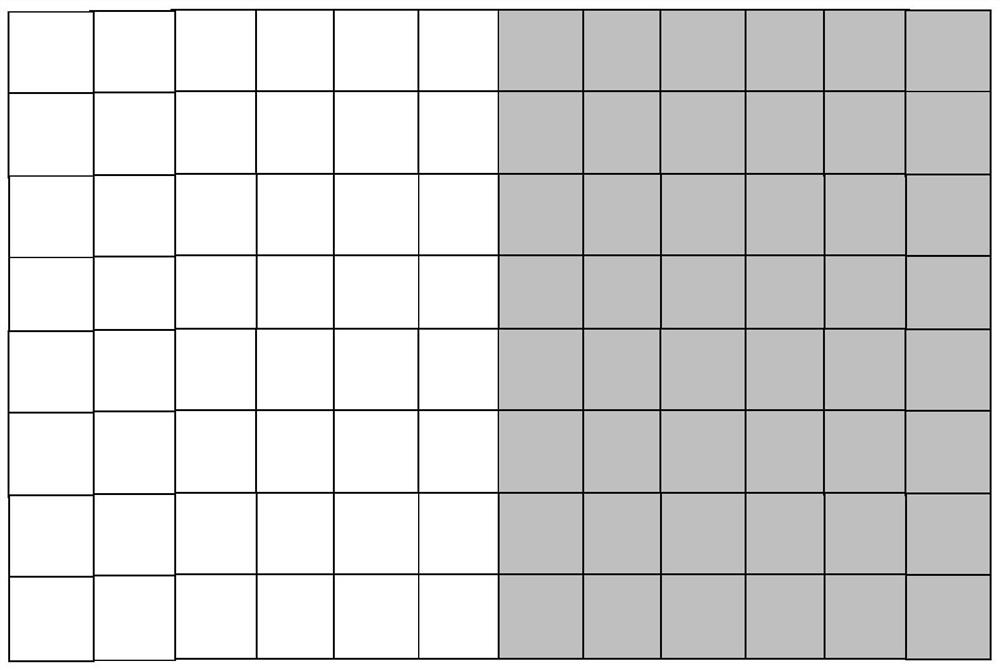

Intra-frame decoding method and intra-frame decoding module

ActiveCN112218091AIncrease processing bandwidthReduce Synchronous ControlDigital video signal modificationDecoding methodsComputer architecture

The invention discloses an intra-frame decoding method and an intra-frame decoding module. The intra-frame decoding method comprises steps of obtaining an image frame syntax element, and obtaining thenumber n of CTUs (Coding Tree Units) in each row of the image frame syntax element; selecting a corresponding decoding mode for decoding according to the value of n; the CTU row buffer memory enabling each pipeline decoder to obtain own reasonable memory space according to the configuration of the state register; the multistage pipeline decoders sharing the CTU row buffer memory, and the pipelinedecoders deciding the read-in positions of themselves and the decoding starting time according to the configuration of the state register. According to the method, the processing bandwidth of the decoders can be effectively increased, synchronous control between the decoders is effectively reduced, and the intra-frame decoding speed is improved.

Owner:博流智能科技(南京)有限公司