Patents

Literature

89 results about "Dataflow computation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

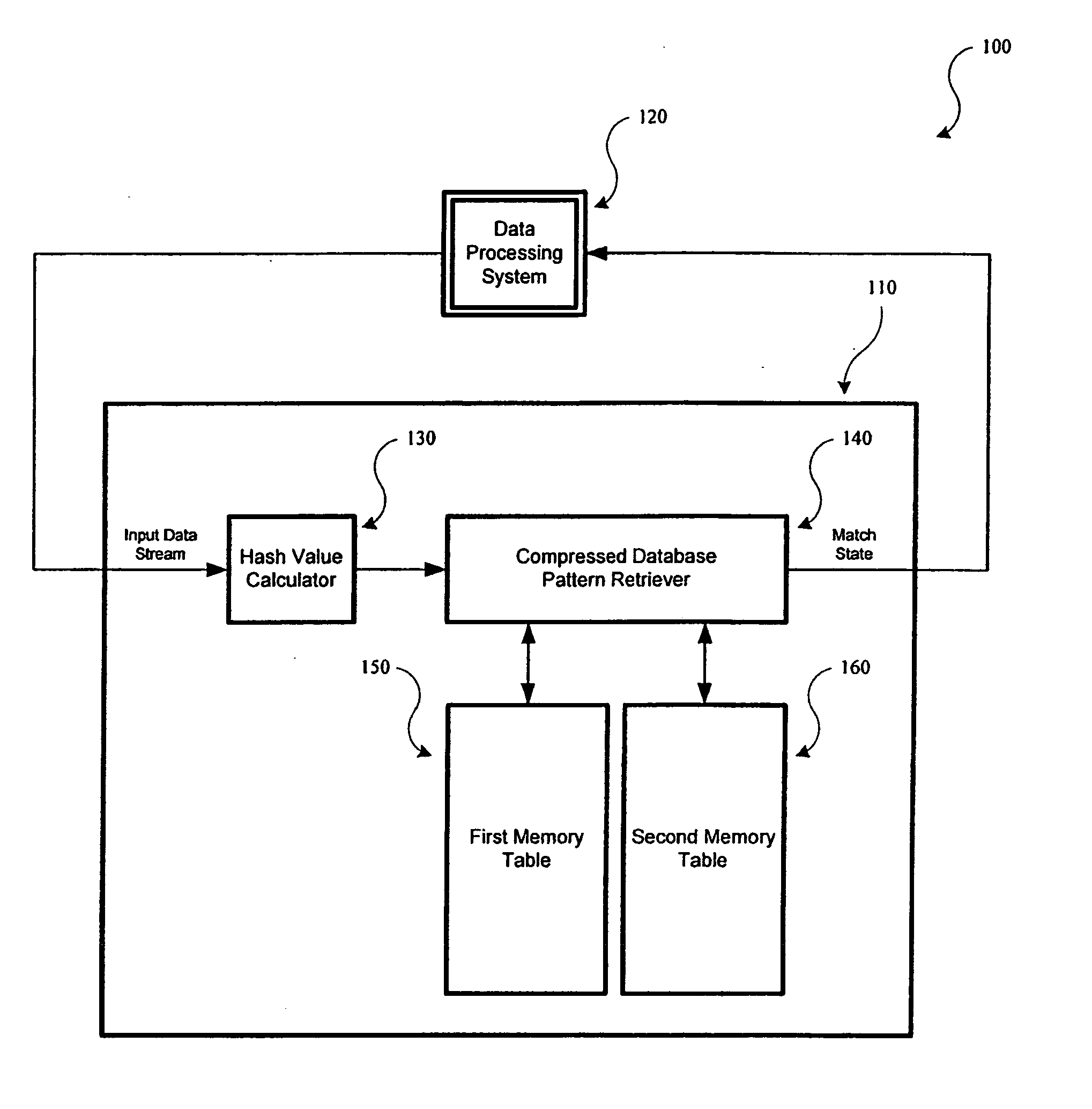

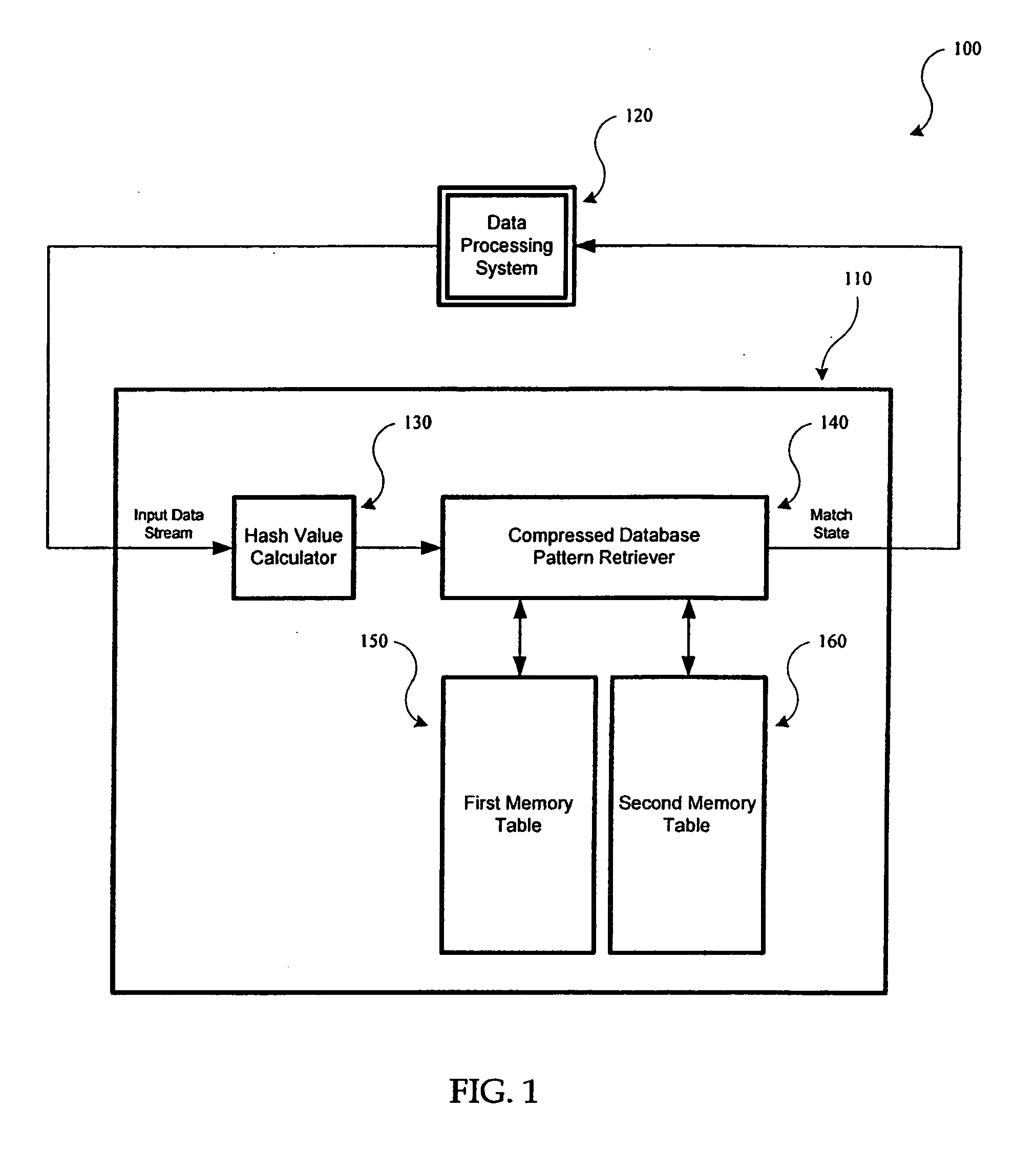

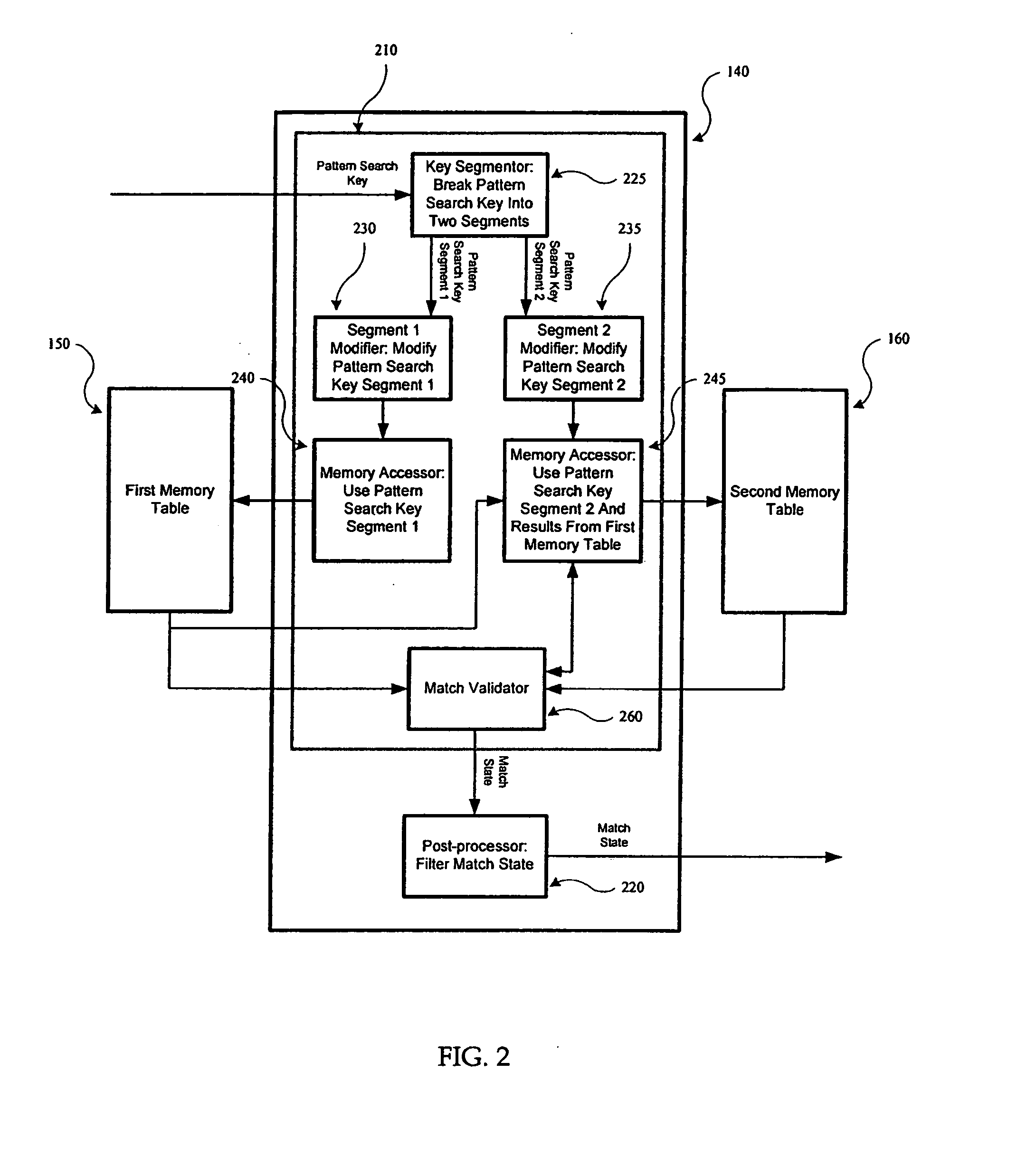

Fast pattern matching using large compressed databases

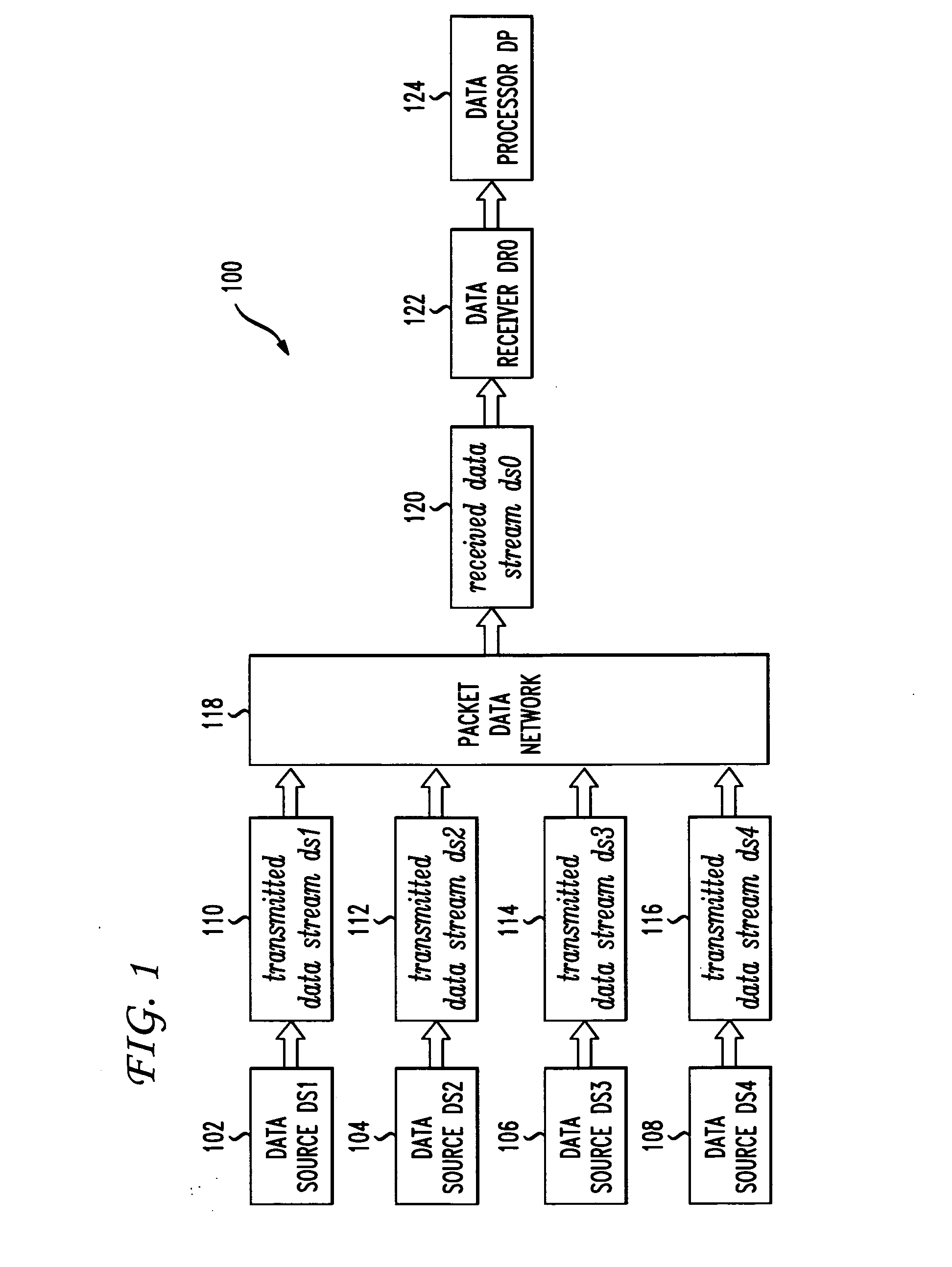

InactiveUS20060193159A1Improve performanceDigital data information retrievalDigital storageData streamPattern matching

A pattern matching system includes, in part, a multitude of databases each configured to store and supply compressed data for matching to the received data. The system divides each data stream into a multitude of segments and optionally computes a data pattern from the data stream prior to the division into a multitude of segments. Segments of the data pattern are used to define an address for one or more memory tables. The memory tables are read such that the outputs of one or more memory tables are used to define the address of another memory table. If during any matching cycle, the data retrieved from any of the successively accessed memory tables include an identifier related to any or all previously accessed memory tables, a matched state is detected. A matched state contains information related to the memory location at which the match occurs as well as information related to the matched pattern, such as the match location in the input data stream.

Owner:SENSORY NETWORKS +1

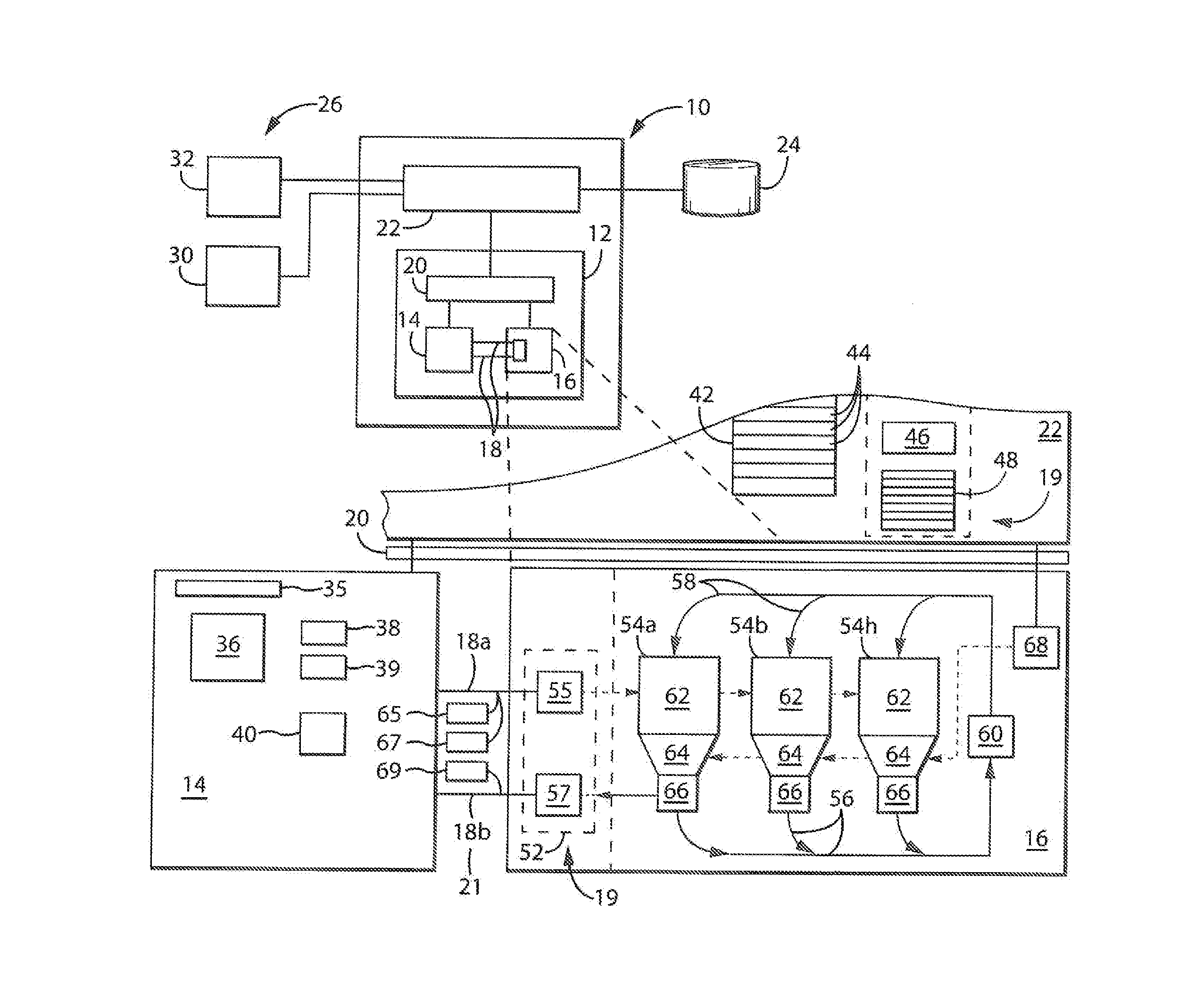

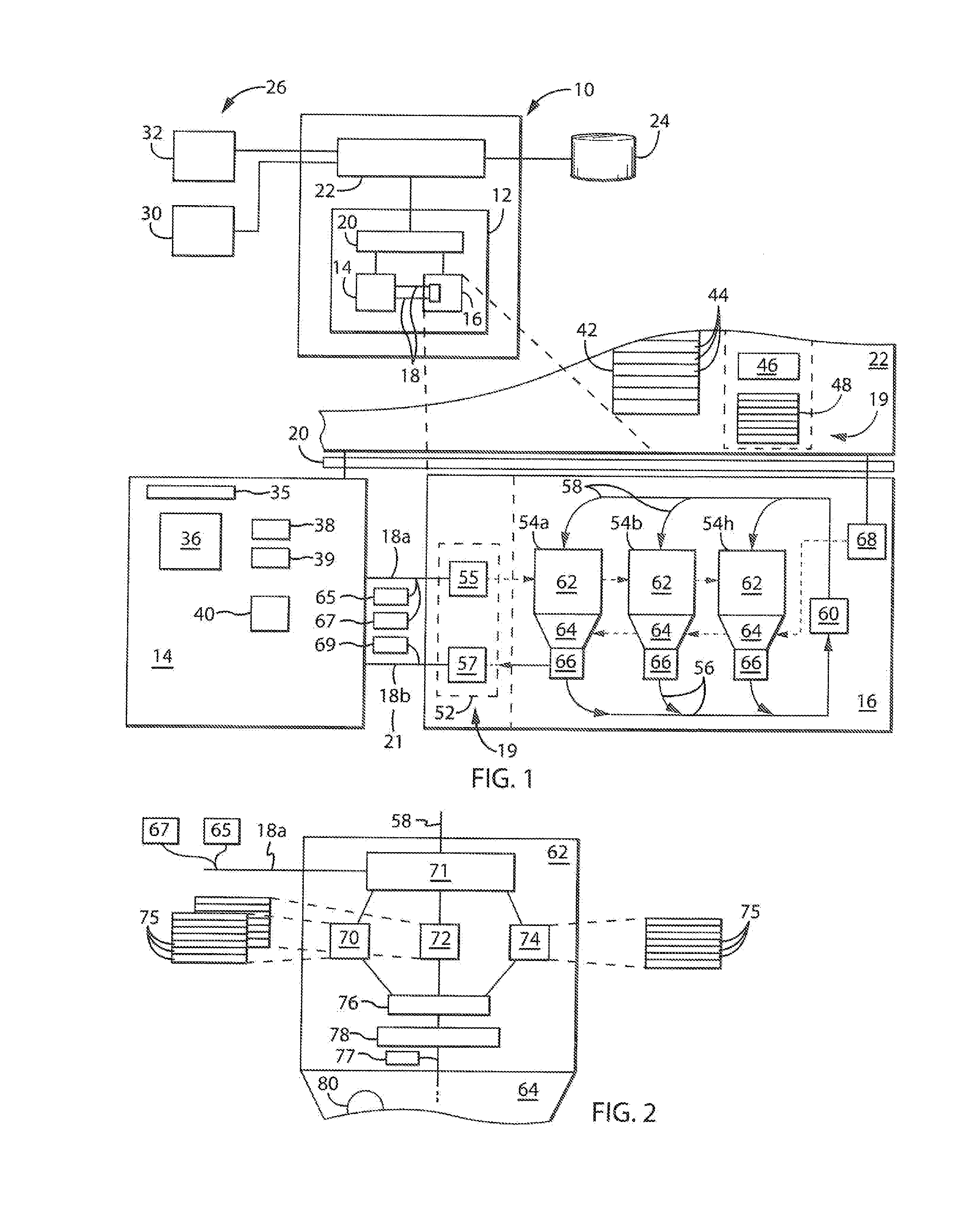

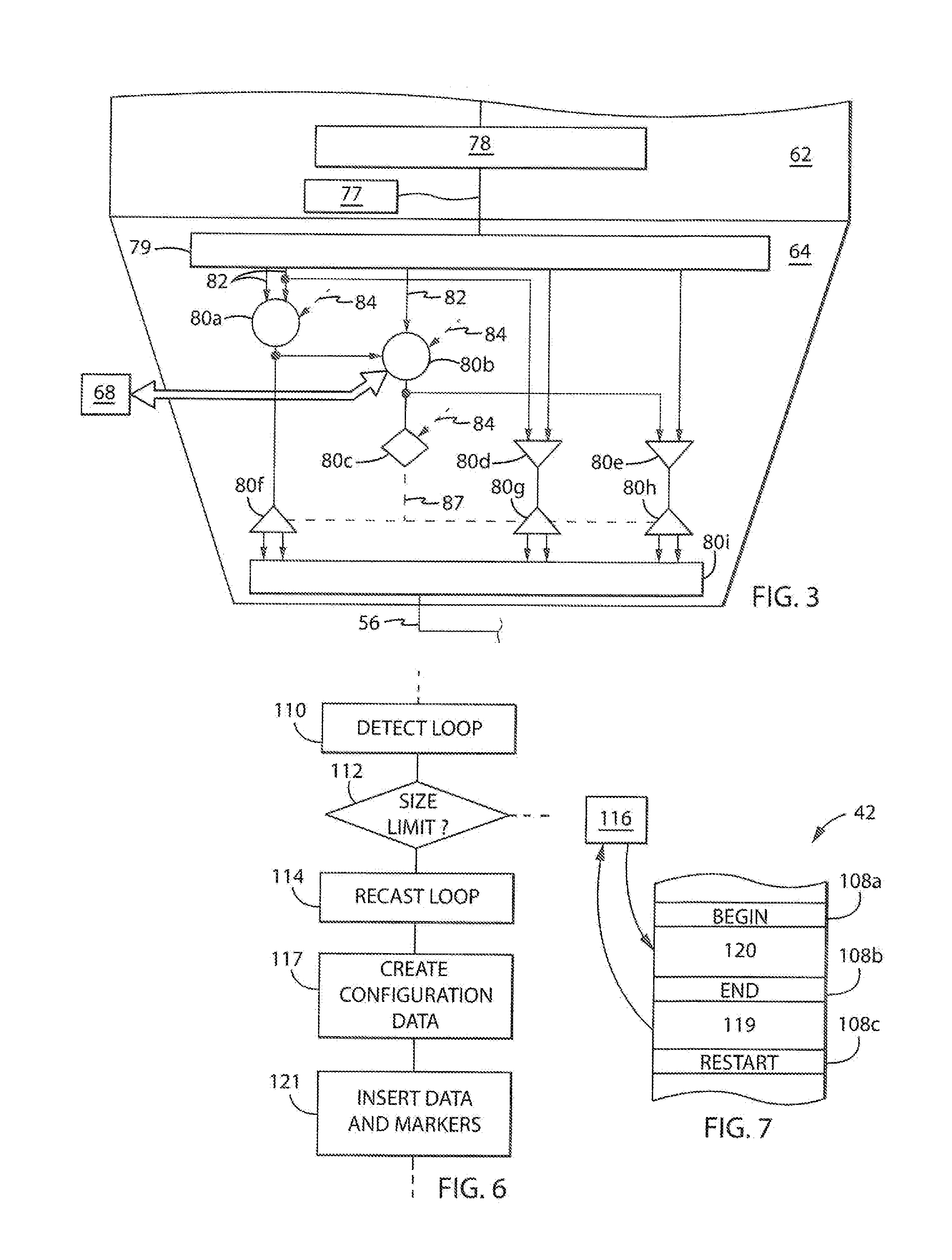

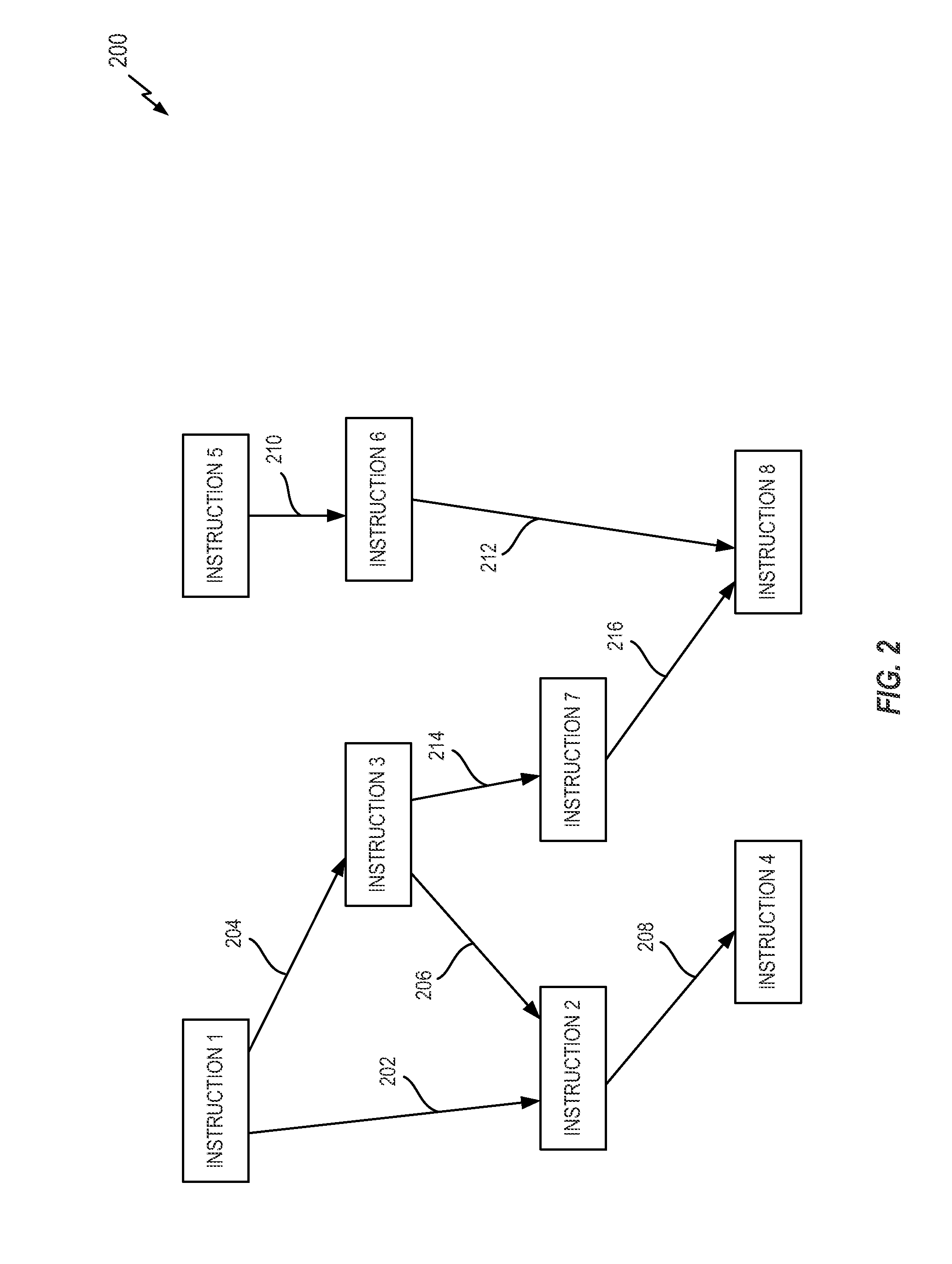

Computer with Hybrid Von-Neumann/Dataflow Execution Architecture

ActiveUS20170031866A1Simple control processAvoid problemsDataflow computersInstruction analysisData stream processingGeneral purpose computer

A dataflow computer processor is teamed with a general computer processor so that program portions of an application program particularly suited to dataflow execution may be transferred to the dataflow processor during portions of the execution of the application program by the general computer processor. During this time the general computer processor may be placed in partial shutdown for energy conservation.

Owner:WISCONSIN ALUMNI RES FOUND

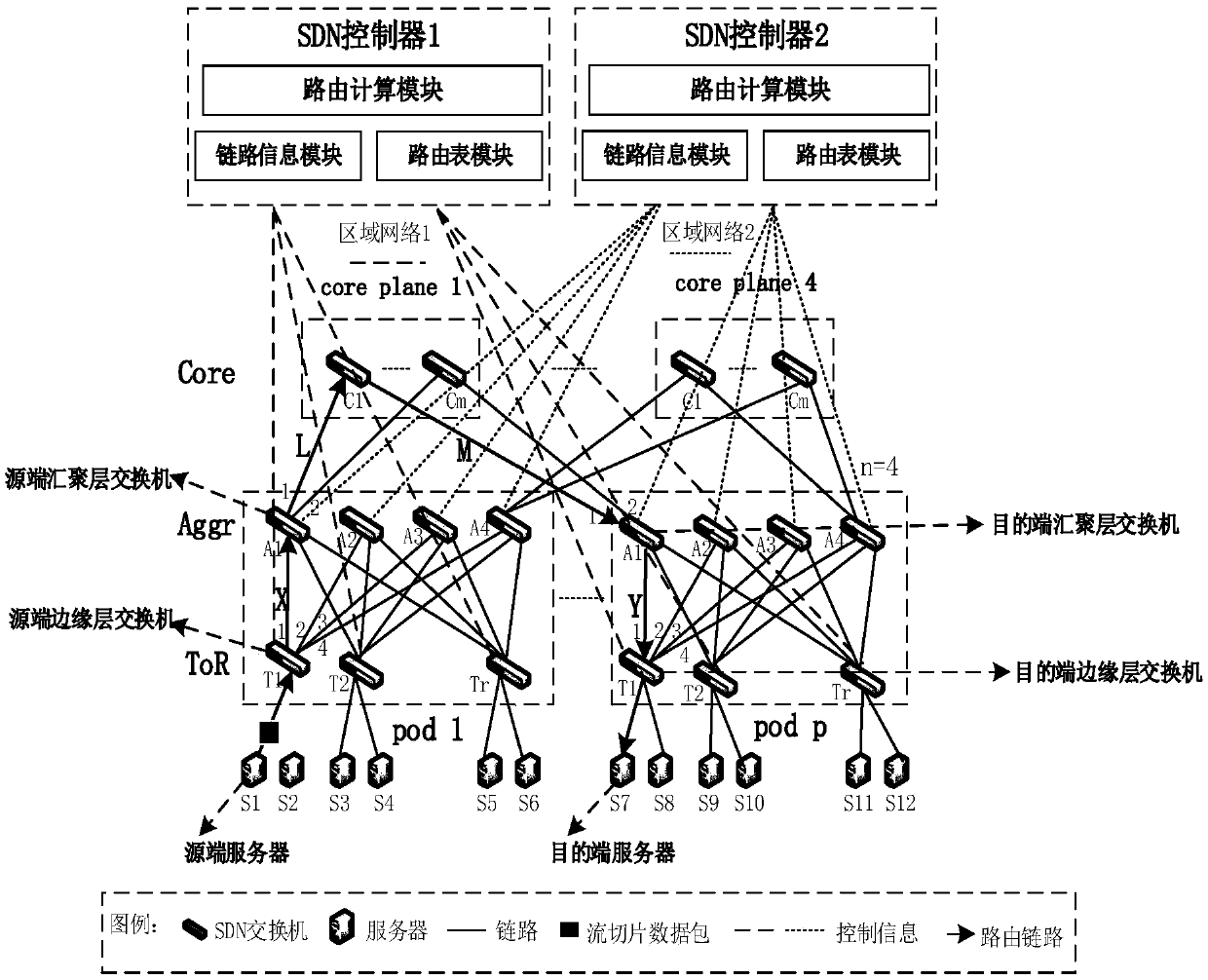

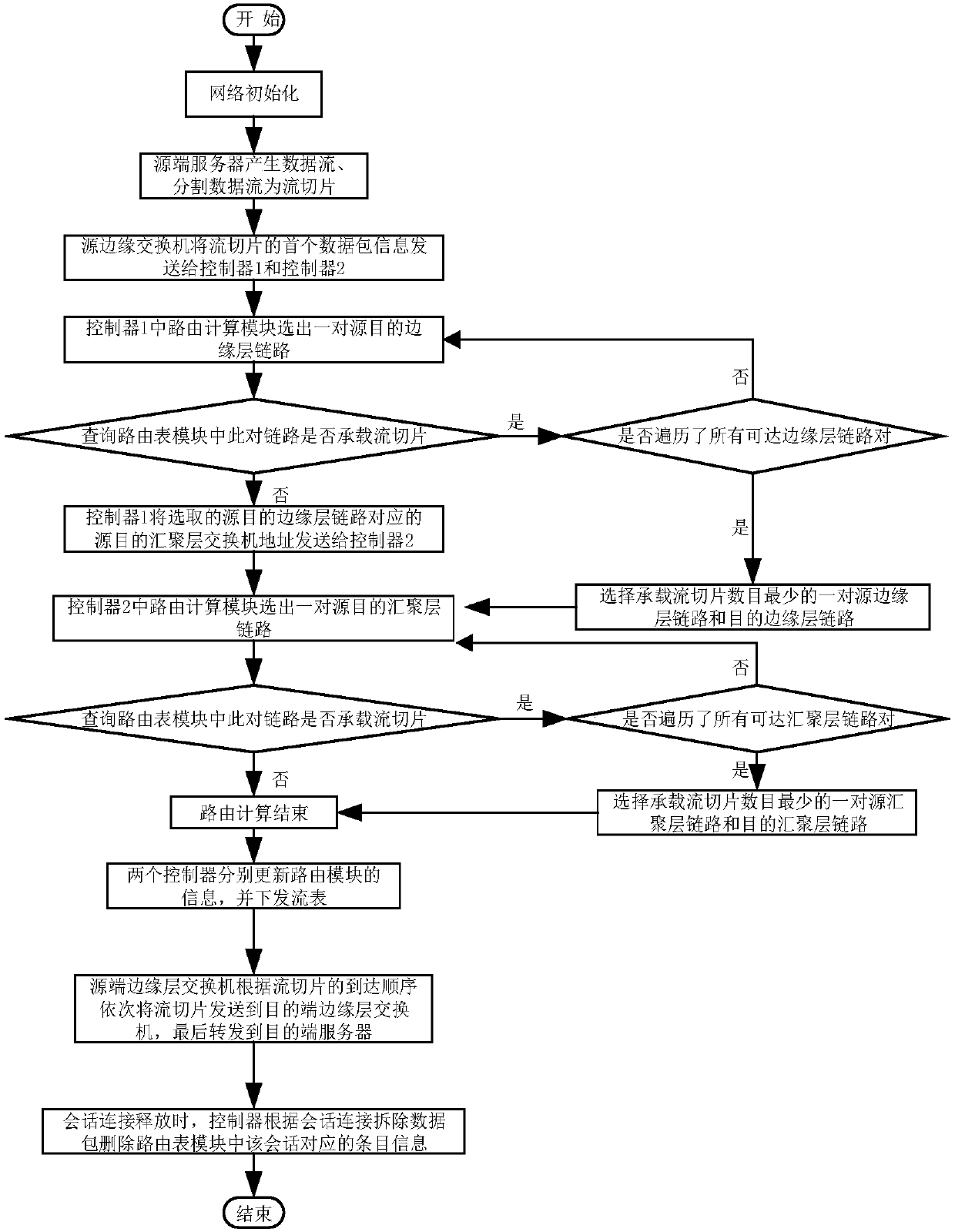

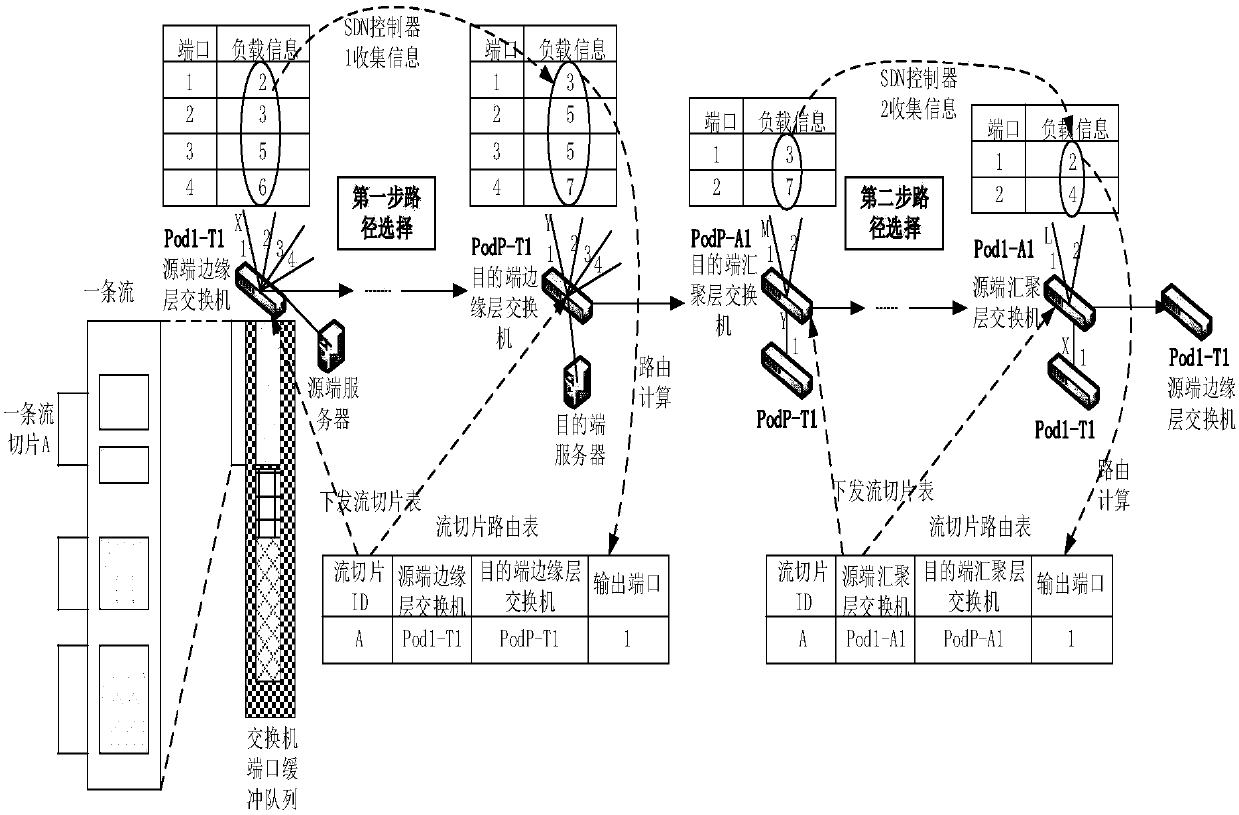

SDN based distributed control load balancing system and method

ActiveCN107819695AOvercoming the Distributed Scaling ProblemOvercome overheadData switching networksData streamRouting table

The invention discloses an SDN based distributed control load balancing system and method, aiming at mainly solving the problems of distributed extension, network overheads, uneven load and link congestion in existing small-scale single data center networks. The system disclosed by the invention comprises a three-layer Clos underlying network and two SDN controllers, wherein the SDN controller isadditionally provided with link information, a routing table and a routing calculation module, and the above modules act together to calculate a path for a data stream. The load balancing method includes the following steps: adopting two-step path selection, partitioning the data stream into stream slices in a buffer area of an end host, separately monitoring and collecting local link informationof two local area networks by using the two controllers, and taking a queuing delay of each port of a switch as the link information to optimize the selection of routing links. According to the schemeof the invention, the distributed multi-controller and two-step path selection are adopted in the three-layer Clos network, and a significant network balancing effect can be achieved; and the schemecan be used for load balancing control of large-scale single data center networks.

Owner:XIDIAN UNIV +1

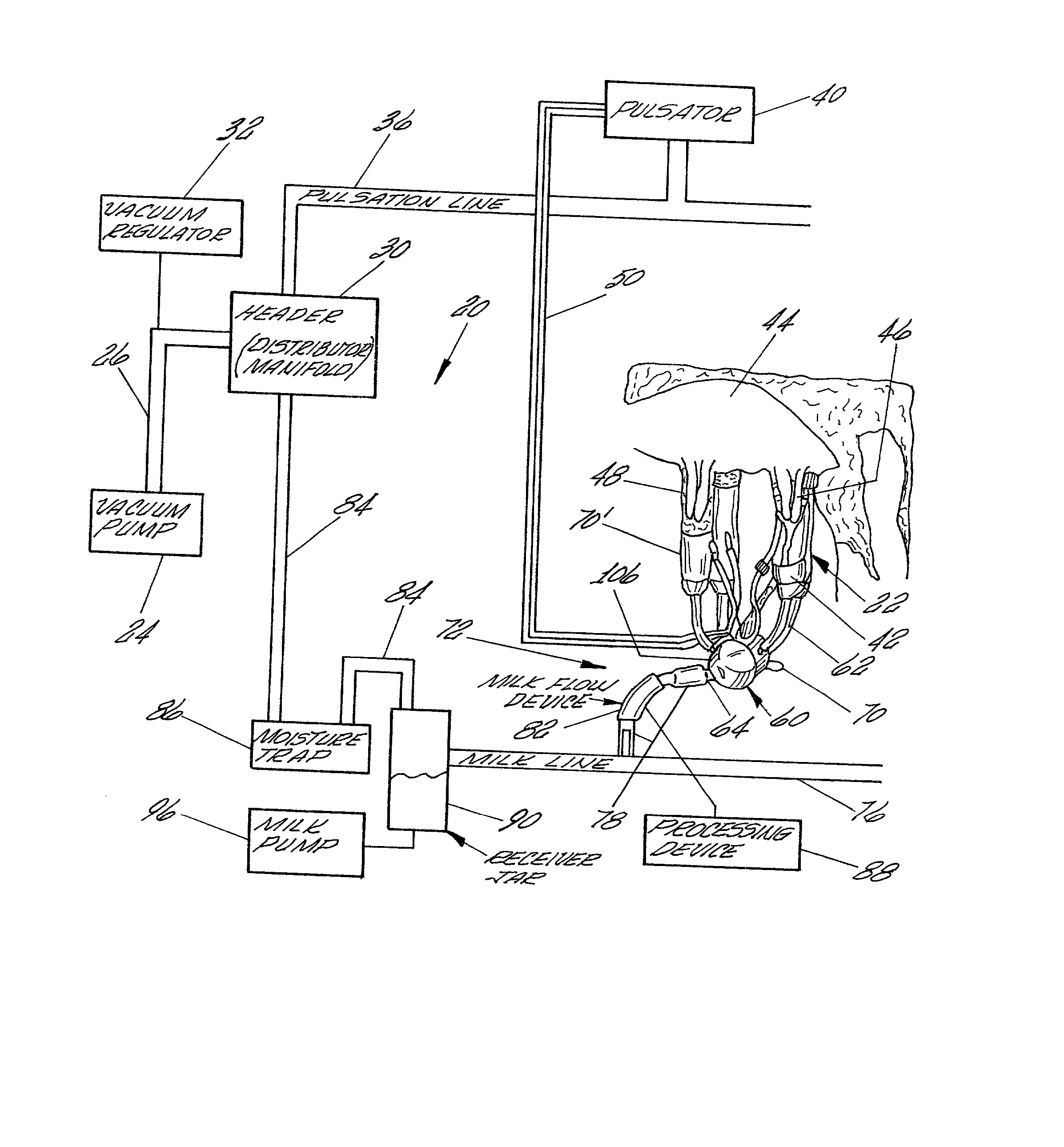

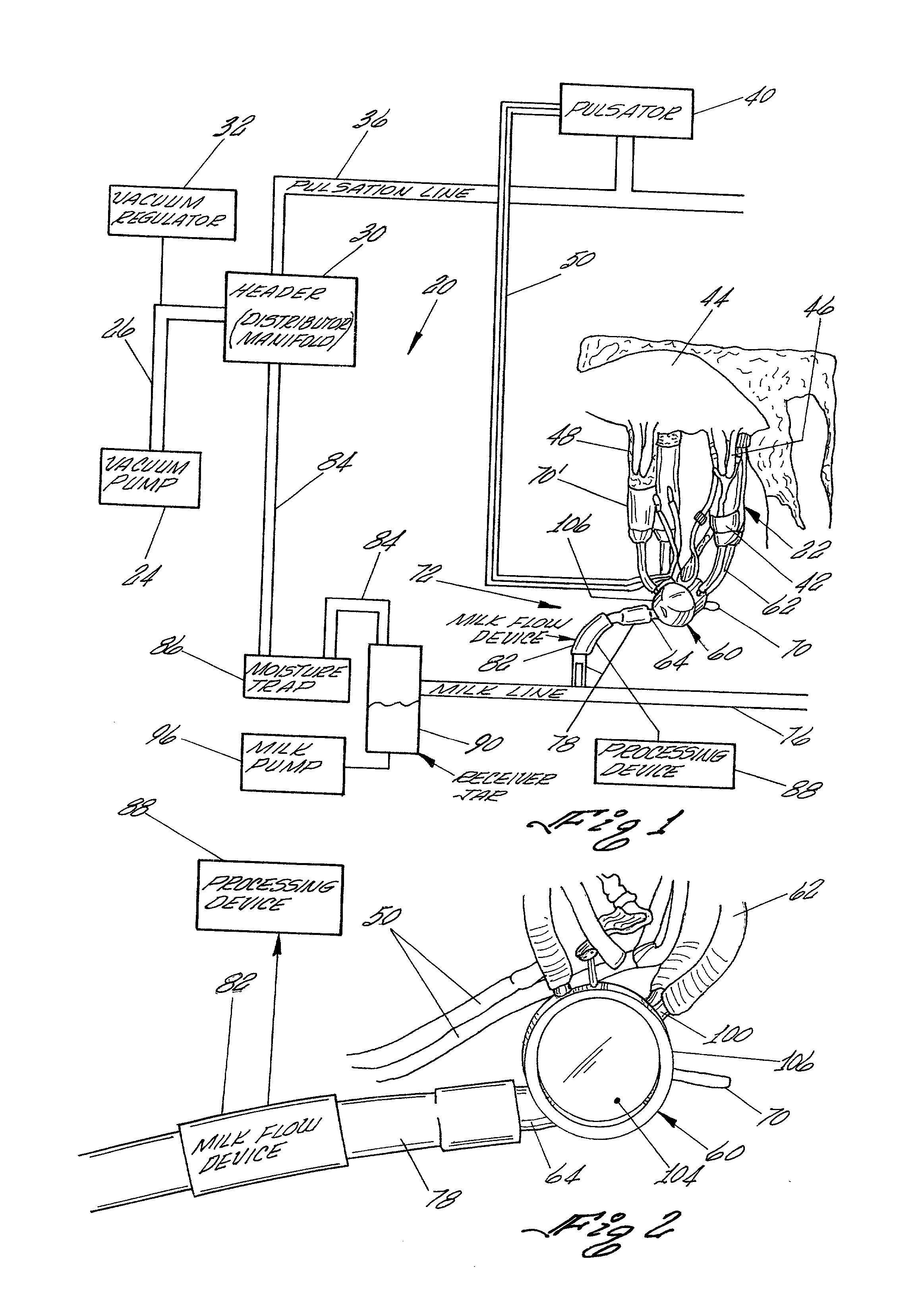

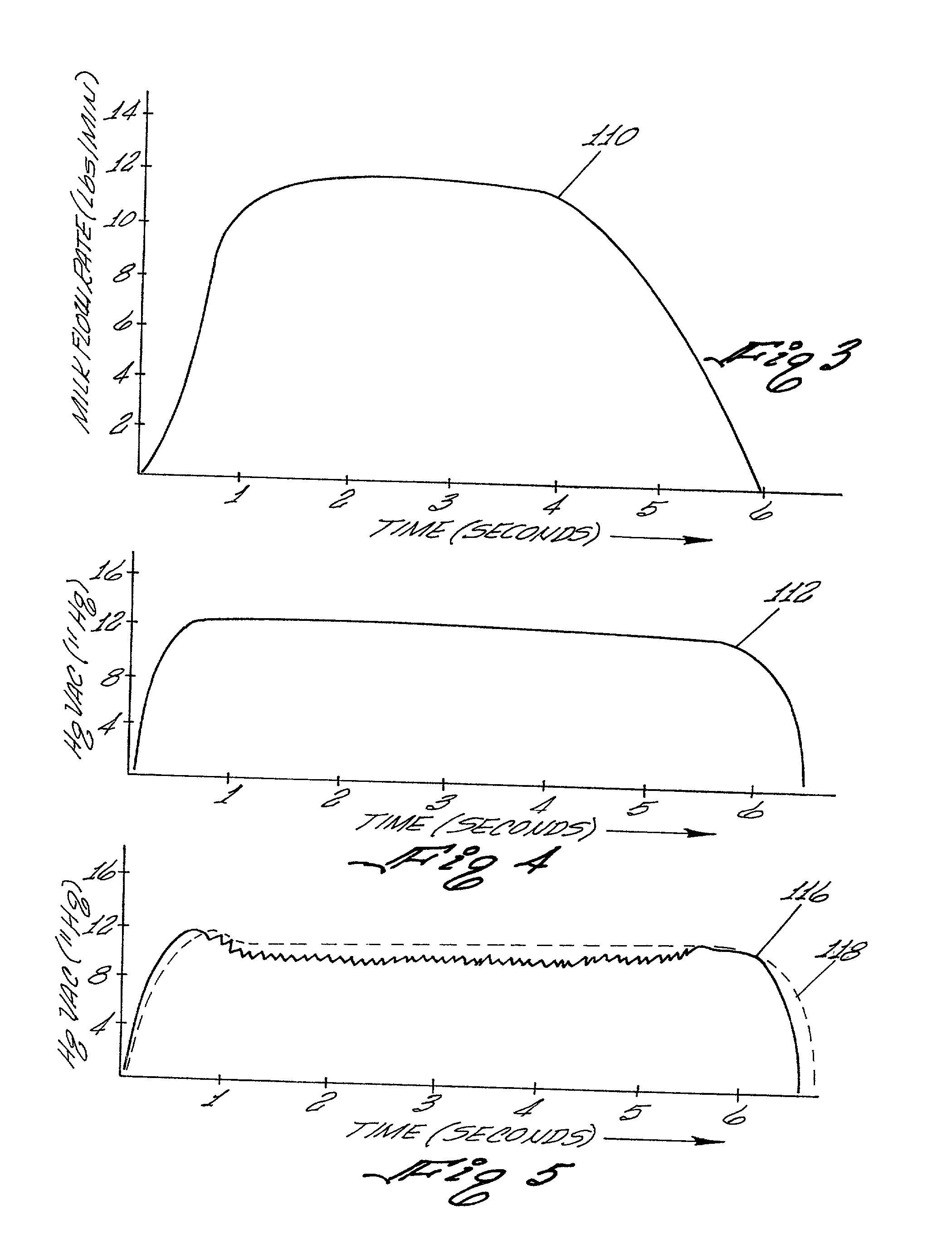

Method for measuring flow rate of a continuous fluid flow

InactiveUS20020156589A1Stable vacuumGood for healthTesting/calibration apparatusFlow propertiesTraffic capacityData stream

A method for measuring flow rate of a continuous fluid flow is shown. The method comprises the steps of generating a first signal at a first predetermined location representing a height of a selected section of the continuous fluid flow at the first predetermined location and for generating a second signal at a second predetermined location located in a selected direction and a known distance representing that the selected section of the continuous fluid flow has traversed from the first predetermined location to the second predetermined location; generating a third signal representing the conductivity of the fluid; receiving the first signal, the second signal and the third signal and creating a data stream therefrom; calculating from the data stream an elapsed time for the selected section of the continuous fluid flow to traverse the known distance; calculating from the data stream an average conductivity of the fluid from the data stream; deriving the cross-sectional area of the selected section from the height of the selected section compensated for variance in conductivity; calculating the volume of fluid flow using the cross-sectional area and elapsed time; and generating an output signal representing the calculated volume of fluid flow.

Owner:TECH HLDG +1

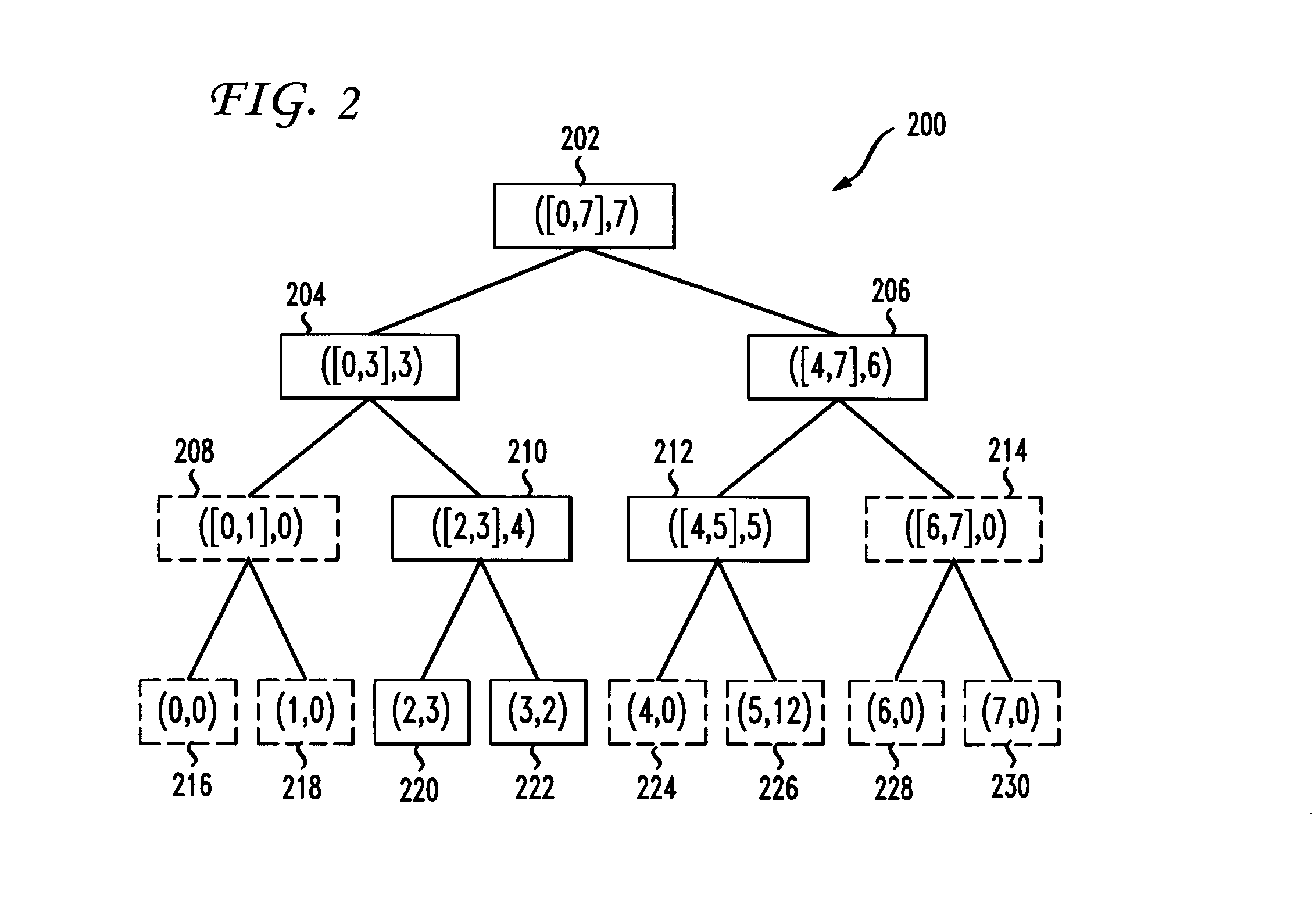

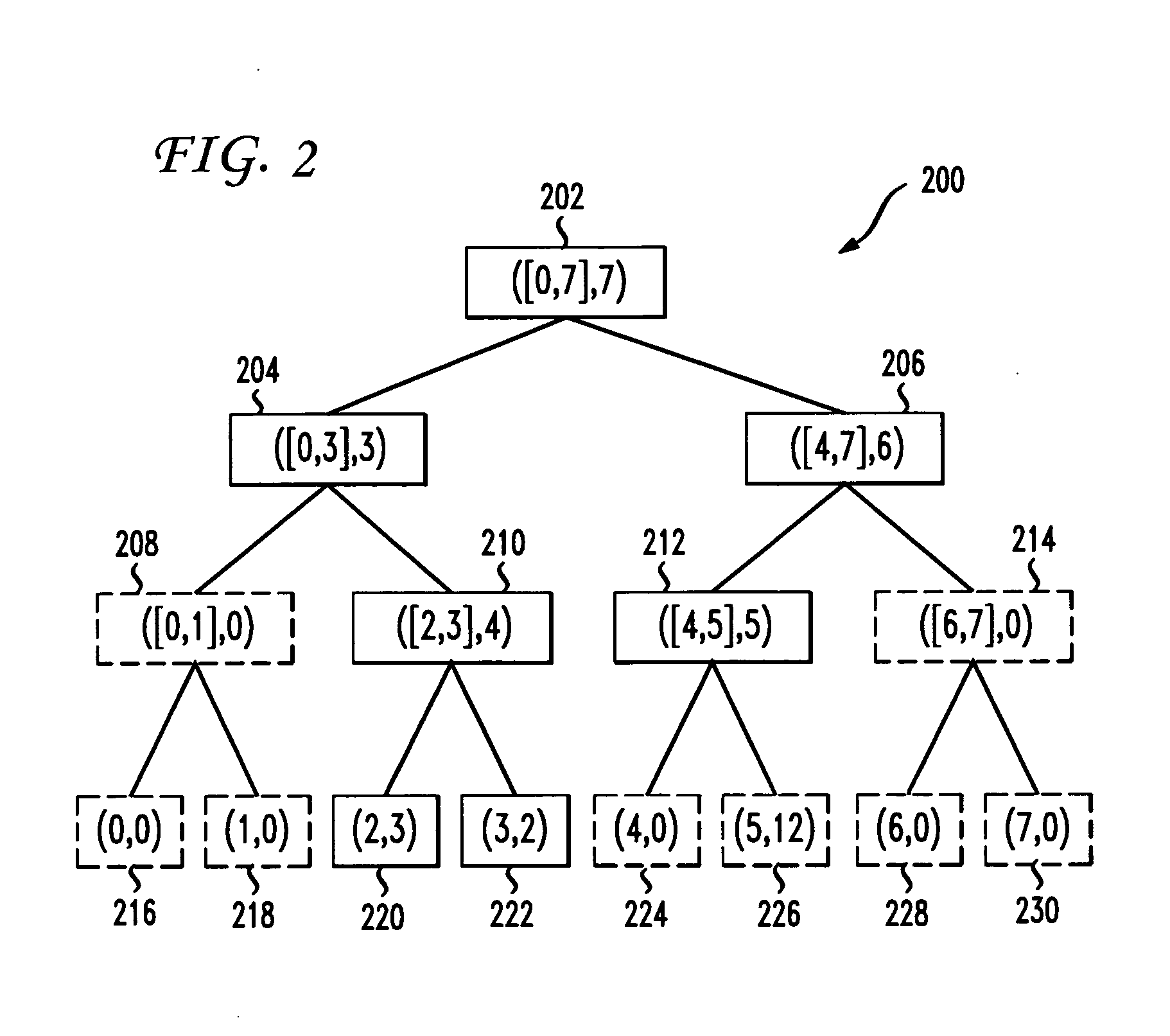

Computing time-decayed aggregates in data streams

InactiveUS20090172059A1Increase weightReduced computing resourceError preventionFrequency-division multiplex detailsTimestampData stream

Aggregates are calculated from a data stream in which data is sent in a sequence of tuples, in which each tuple comprises an item identifier and a timestamp indicating when the tuple was transmitted. The tuples may arrive out-of-order, that is, the sequence in which the tuples arrive are not necessarily in the sequence of their corresponding timestamps. In calculating aggregates, more recent data may be given more weight by multiplying each tuple by a decay function which is a function of the timestamp associated with the tuple and the current time. The tuples are recorded in a quantile-digest data structure. Aggregates are calculated from the data stored in the quantile-digest data structure.

Owner:IOWA STATE UNIV RES FOUND +1

Computing time-decayed aggregates under smooth decay functions

ActiveUS20090172058A1Reduce decreaseEffective calculationTransmissionDigital function generatorsData streamTimestamp

Aggregates are calculated from a data stream in which data is sent in a sequence of tuples, in which each tuple comprises an item identifier and a timestamp indicating when the tuple was transmitted. The tuples may arrive at a data receiver out-of-order, that is, the sequence in which the tuples arrive are not necessarily in the same sequence as their corresponding timestamps. In calculating aggregates, more recent data may be given more weight by a decay function which is a function of the timestamp associated with the tuple and the current time. The statistical characteristics of the tuples are summarized by a set of linear data summaries. The set of linear data summaries are generated such that only a single linear data summary falls between a set of boundaries calculated from the decay function and a set of timestamps. Aggregates are calculated from the set of linear data summaries

Owner:AT&T INTPROP I L P +1

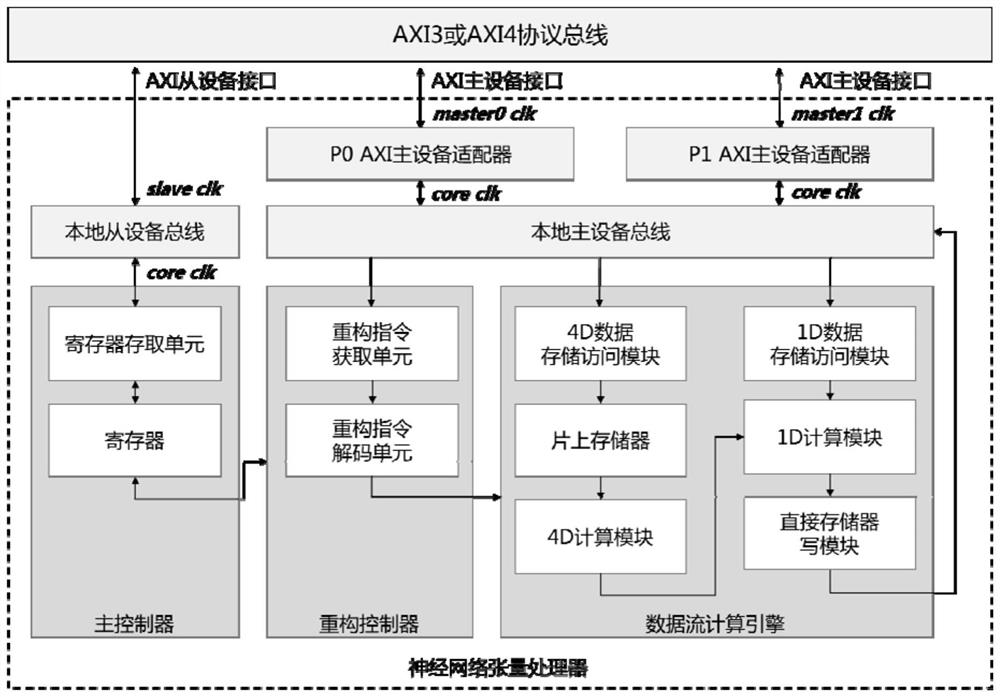

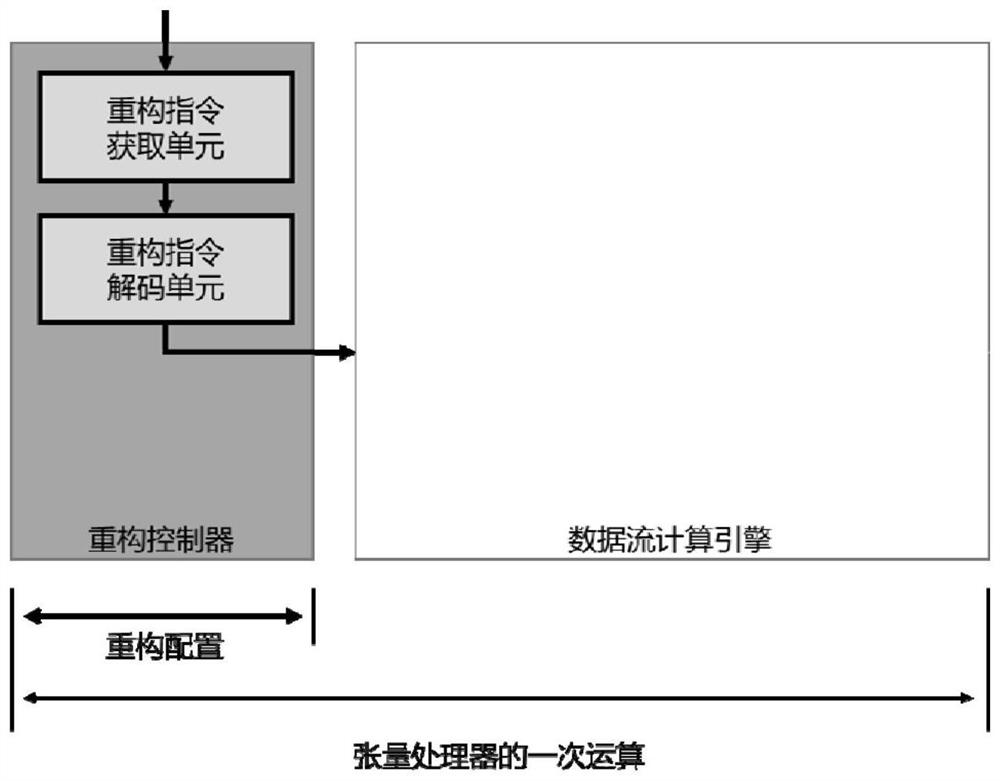

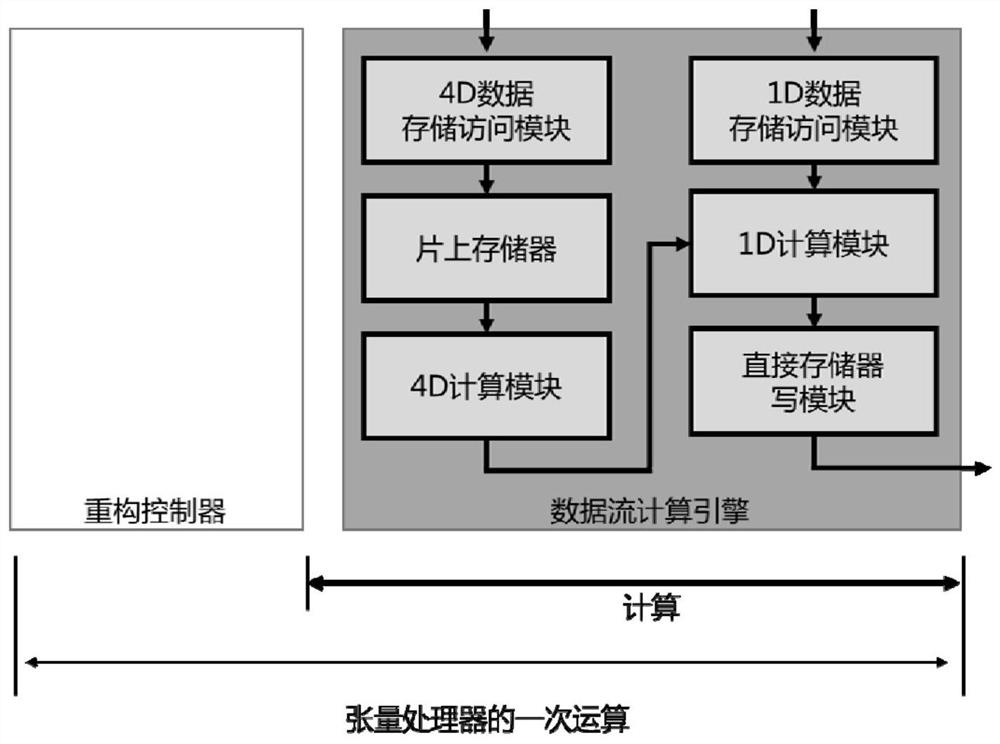

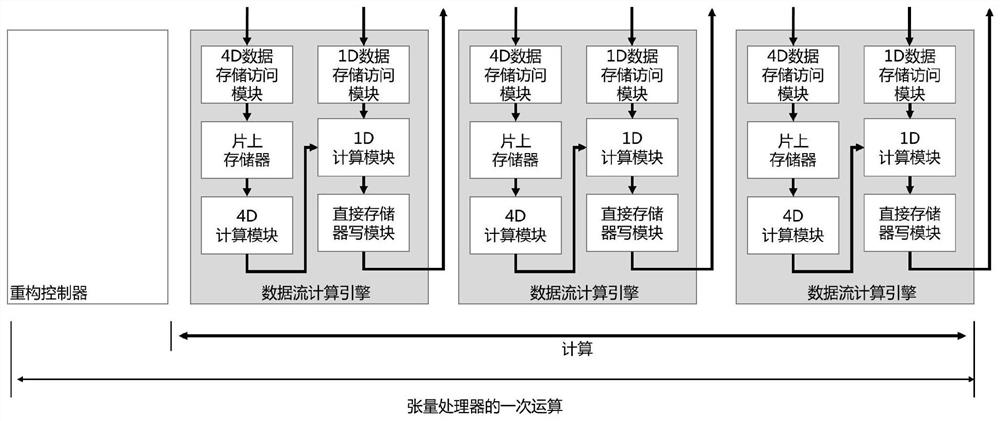

Neural network tensor processor

PendingCN112381220AImprove computing efficiencyPhysical realisationEnergy efficient computingExternal storageData stream

The invention discloses a neural network tensor processor. The neural network tensor processor comprises a main controller, a reconstruction controller and a data flow calculation engine, the main controller is used for providing a control and state interface of the neural network tensor processor for an external control unit, and providing first configuration information and a first initial signal for the reconstruction controller, the reconstruction controller receives the first configuration information and the first starting signal, obtains a reconstruction instruction of an external memory after the first starting signal is valid, and analyzes the reconstruction instruction to generate second configuration information and a second starting signal, and the data flow calculation enginereceives the second configuration information and the second initial signal, performs function configuration according to the second configuration information, acquires data and parameters of the external memory to execute operation after the second initial signal is valid, and writes a calculation result into the external memory. The tensor processor provided by the invention is suitable for carrying out centralized calculation on a neural network algorithm, and has universality and expandability.

Owner:厦门壹普智慧科技有限公司

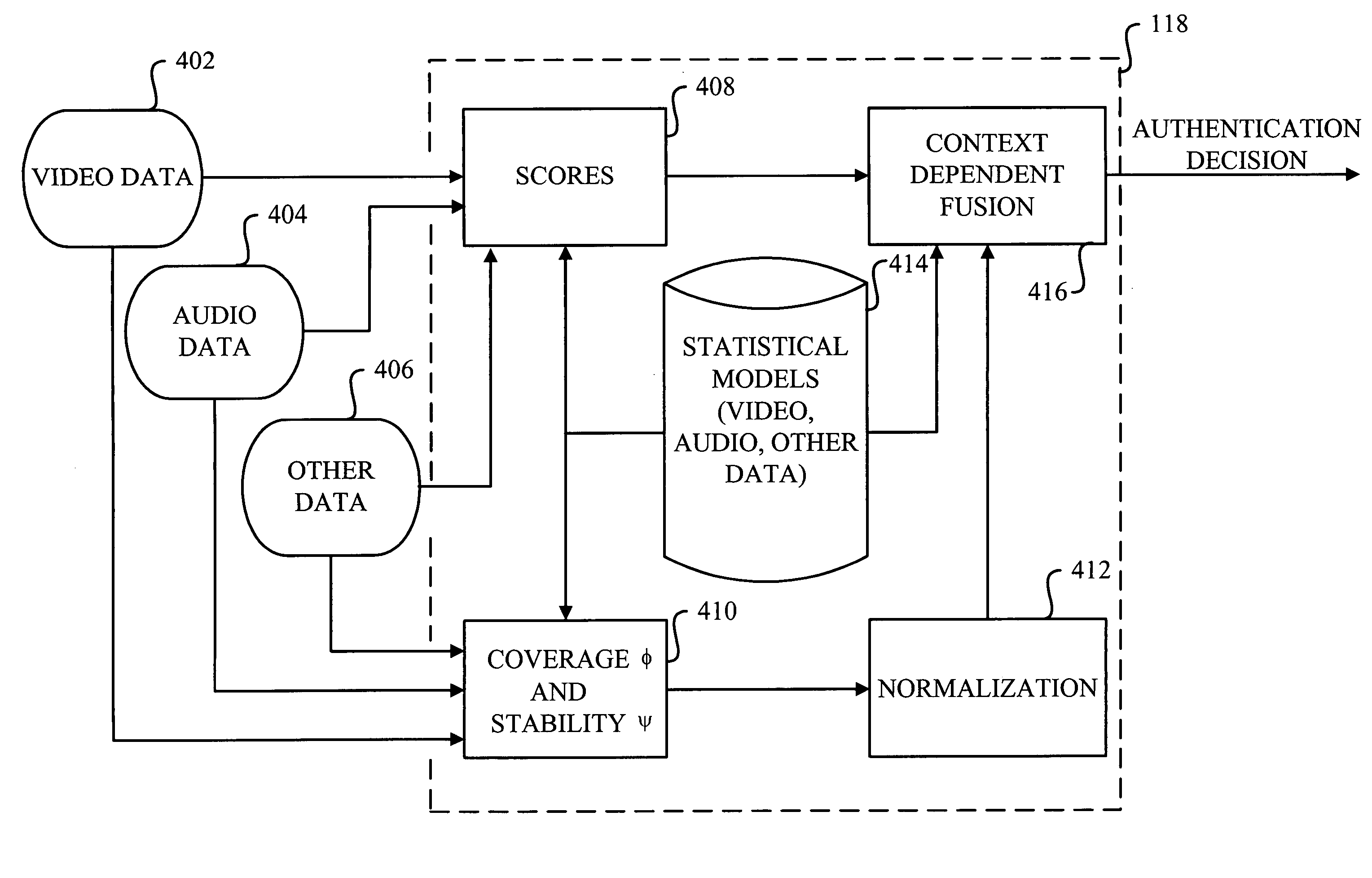

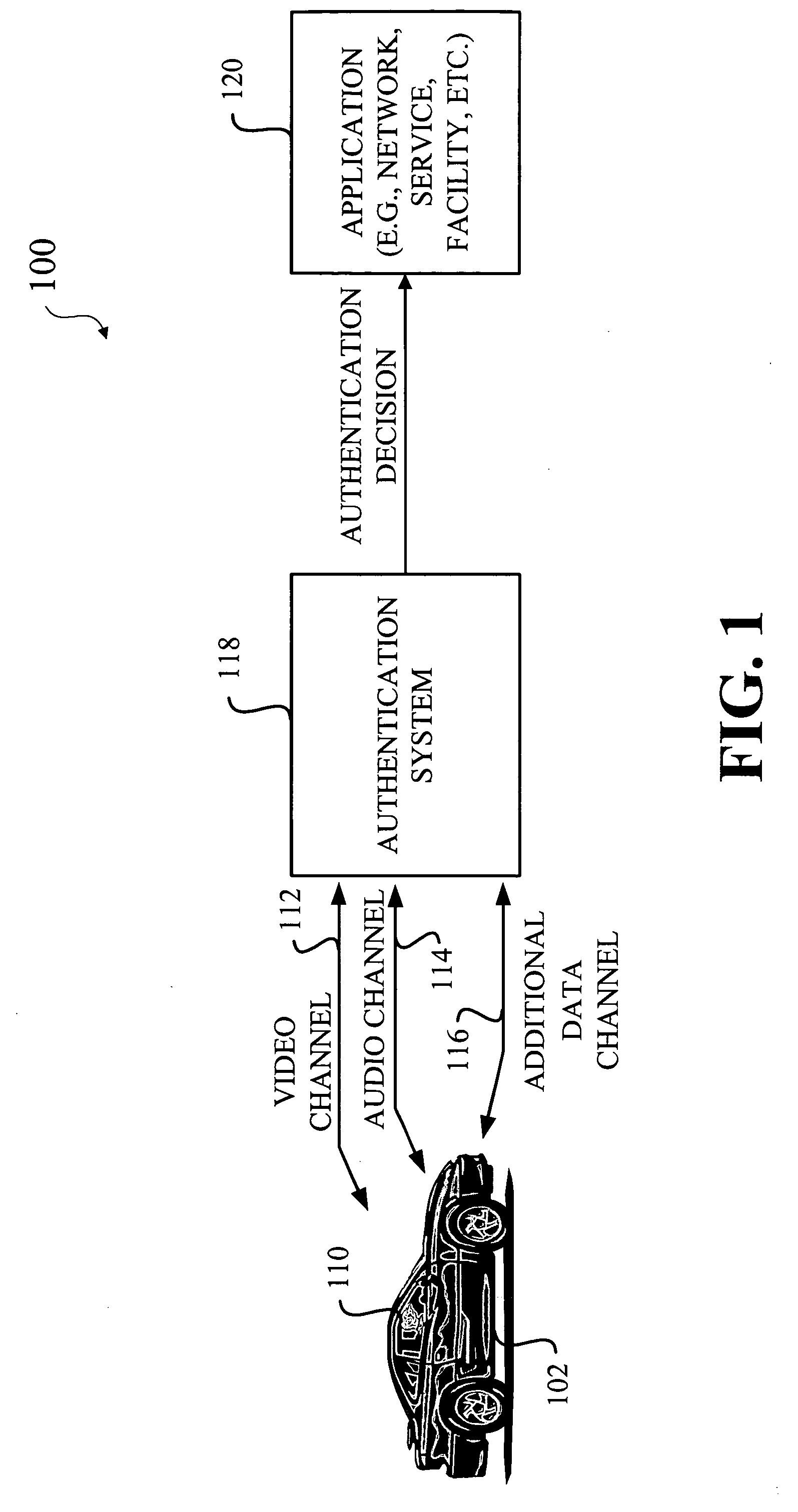

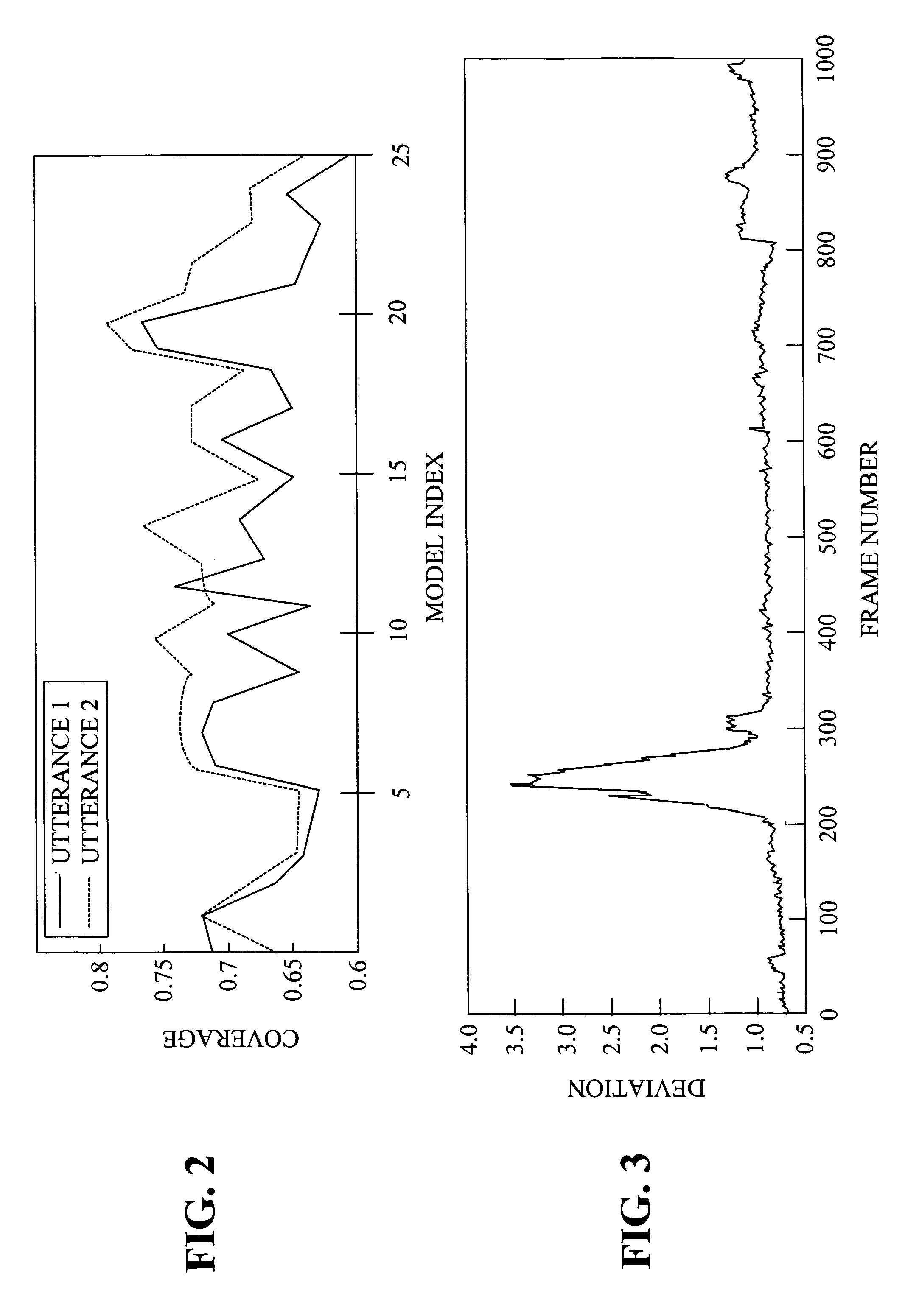

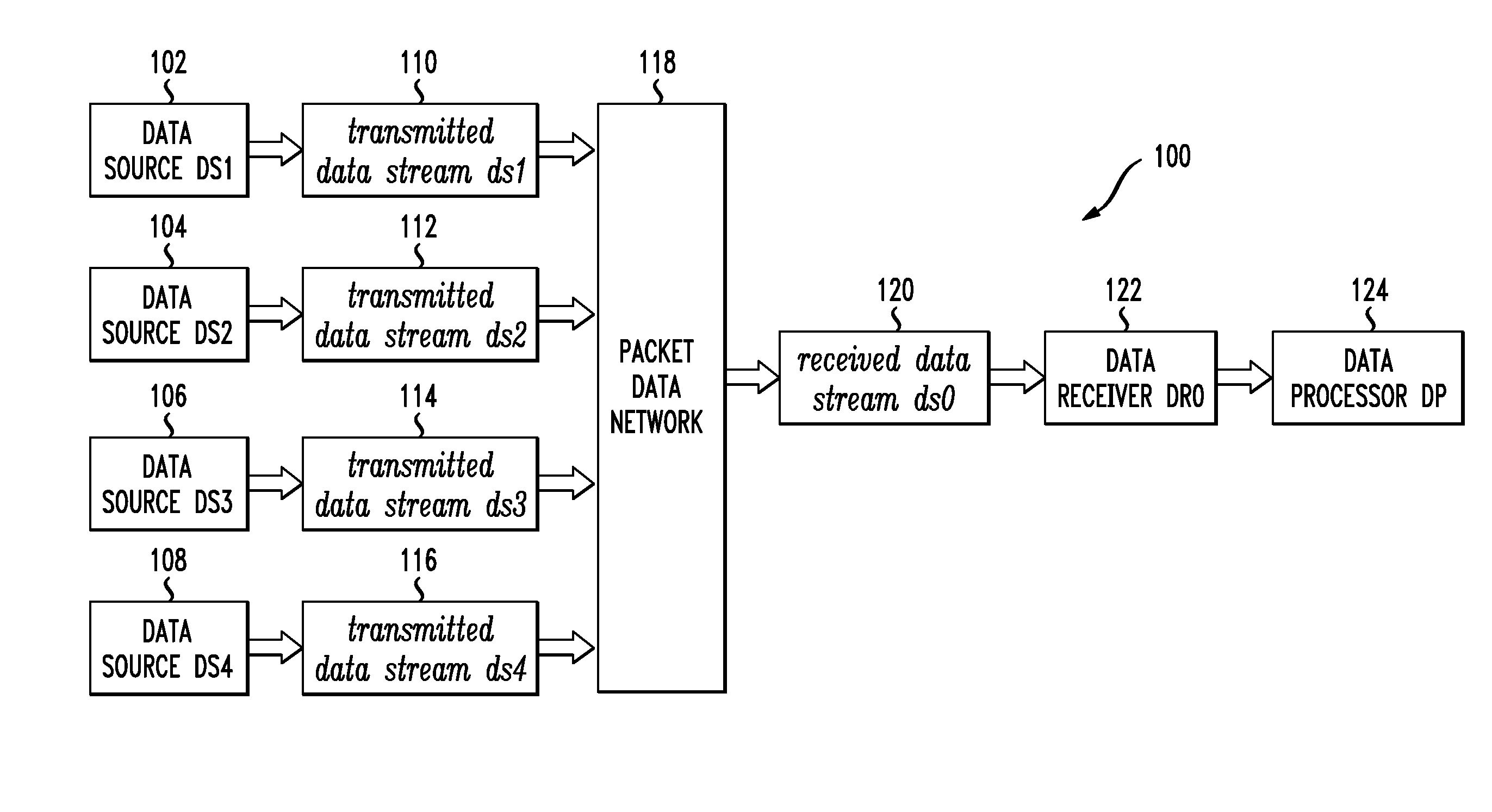

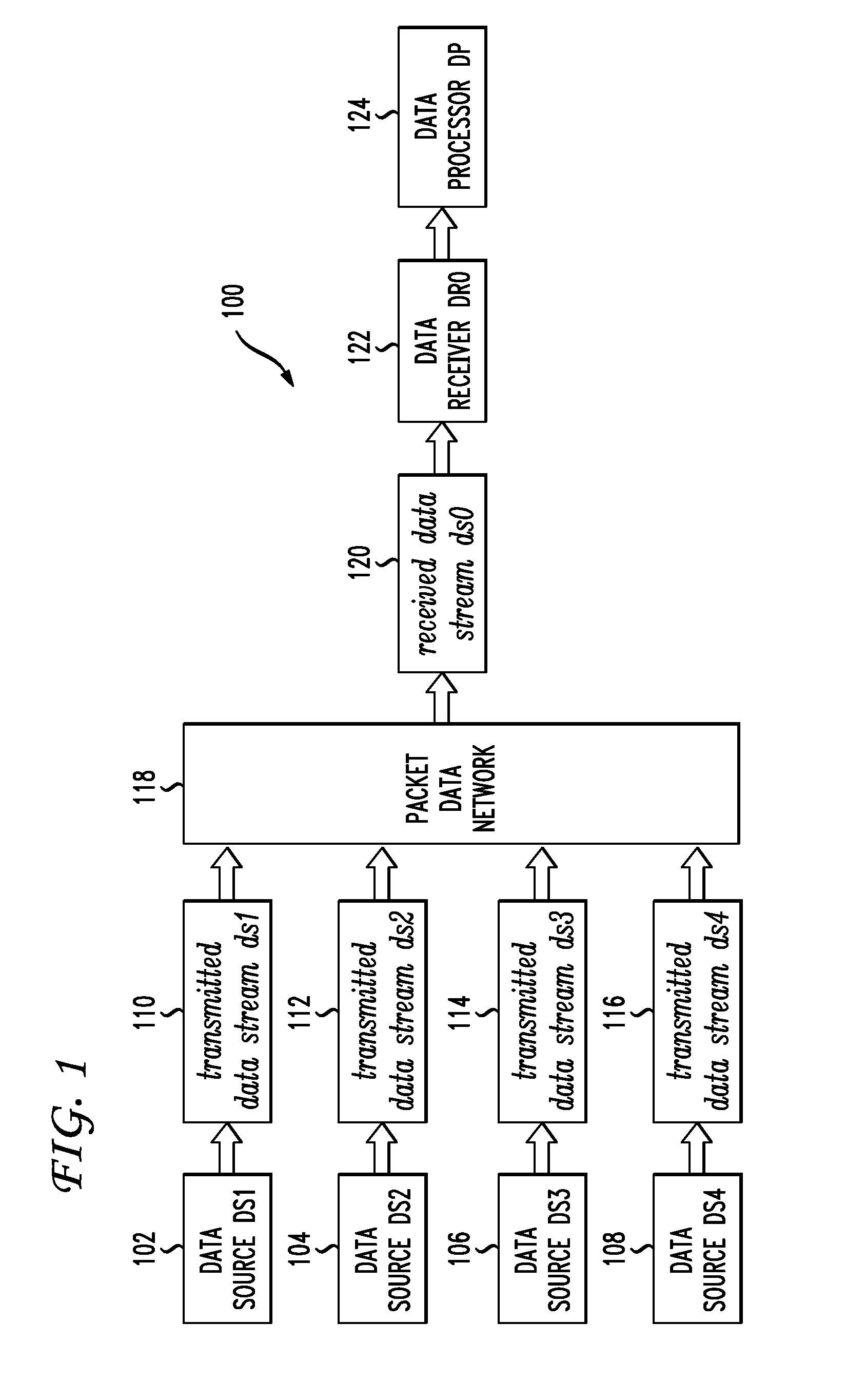

Automated decision making using time-varying stream reliability prediction

Automated decision making techniques are provided. For example, a technique for generating a decision associated with an individual or an entity includes the following steps. First, two or more data streams associated with the individual or the entity are captured. Then, at least one time-varying measure is computed in accordance with the two or more data streams. Lastly, a decision is computed based on the at least one time-varying measure. One form of the time-varying measure may include a measure of the coverage of a model associated with previously-obtained training data by at least a portion of the captured data. Another form of the time-varying measure may include a measure of the stability of at least a portion of the captured data. While either measure may be employed alone to compute a decision, preferably both the coverage and stability measures are employed. The technique may be used to authenticate a speaker.

Owner:IBM CORP

High Integrity Data Network System and Method

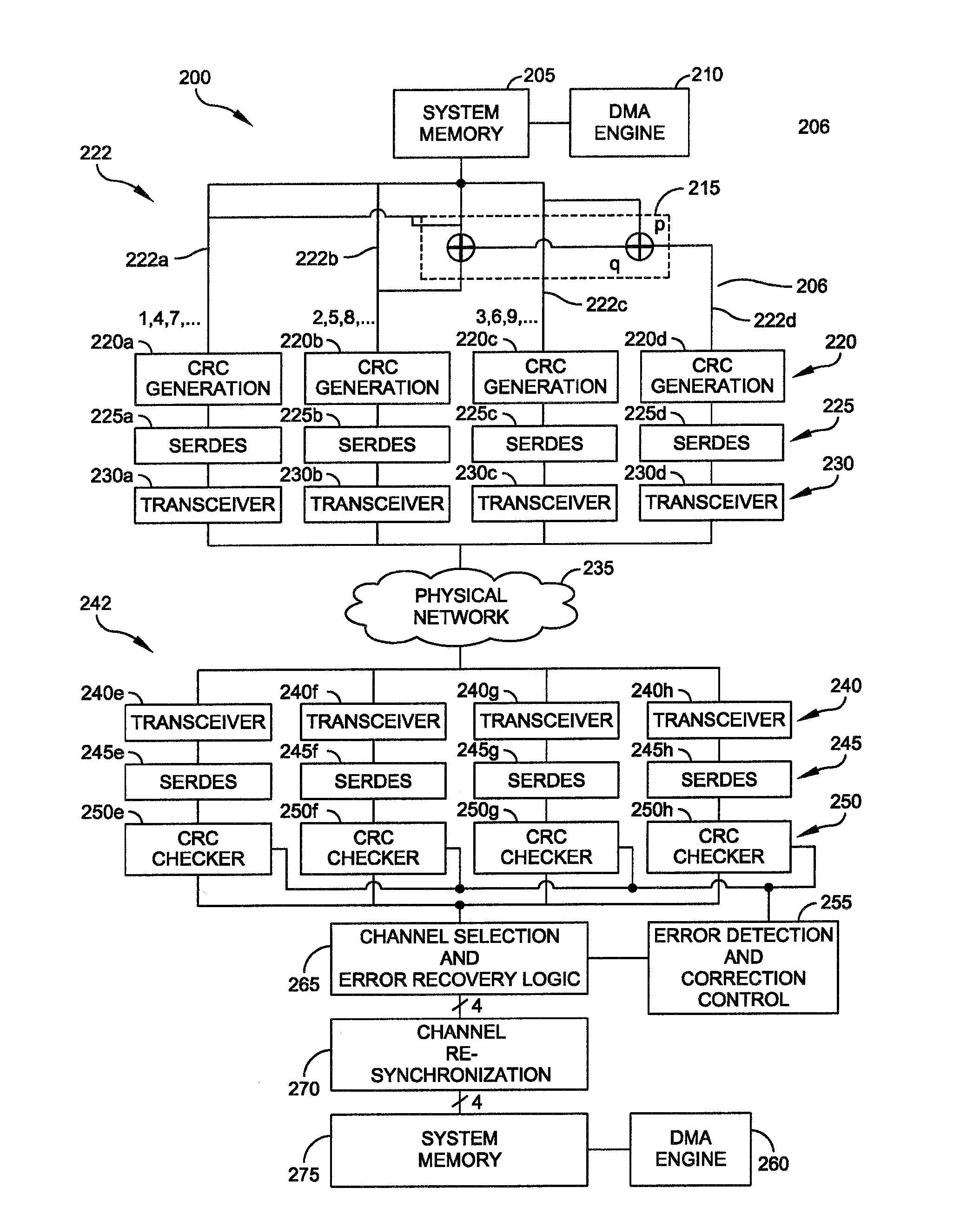

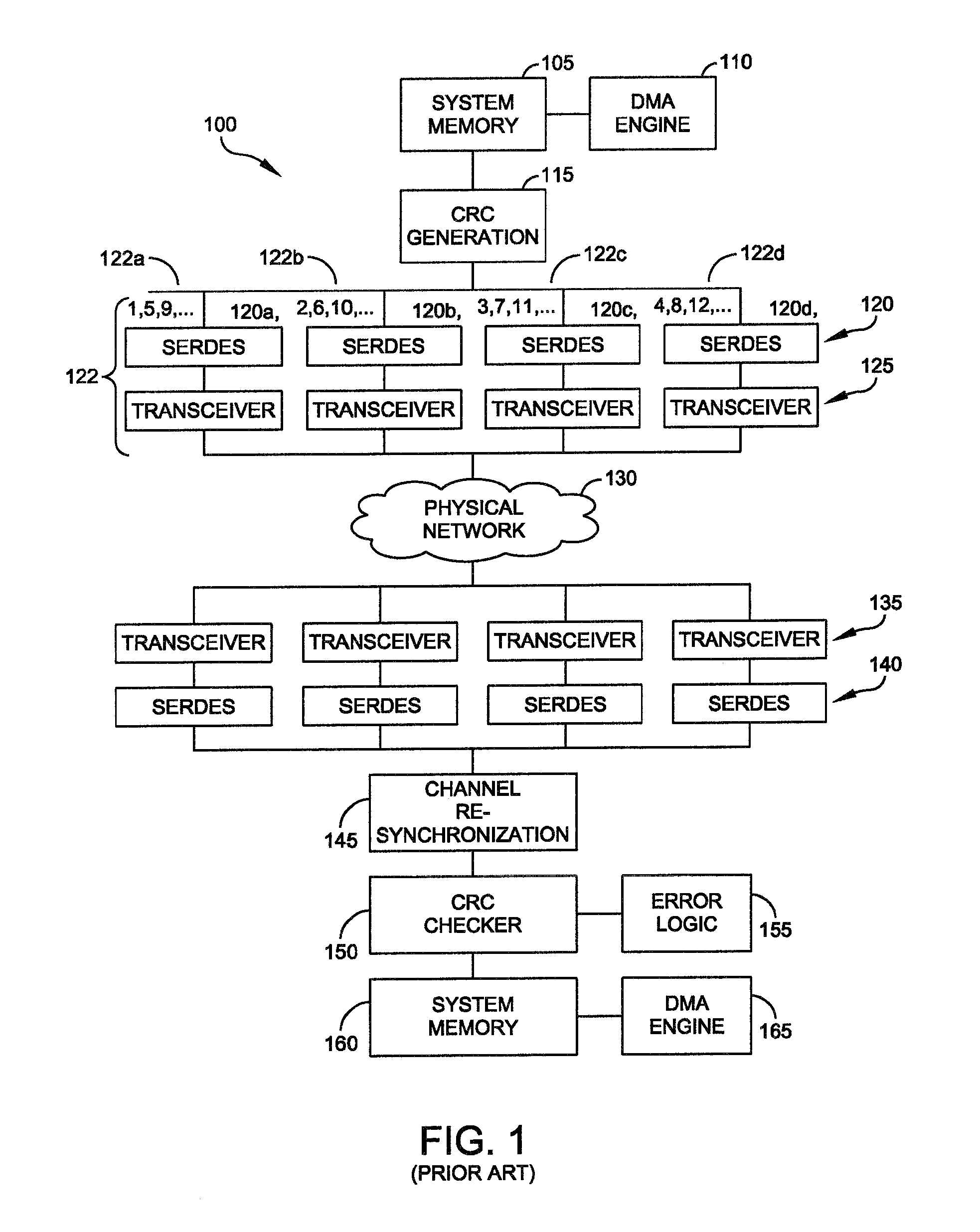

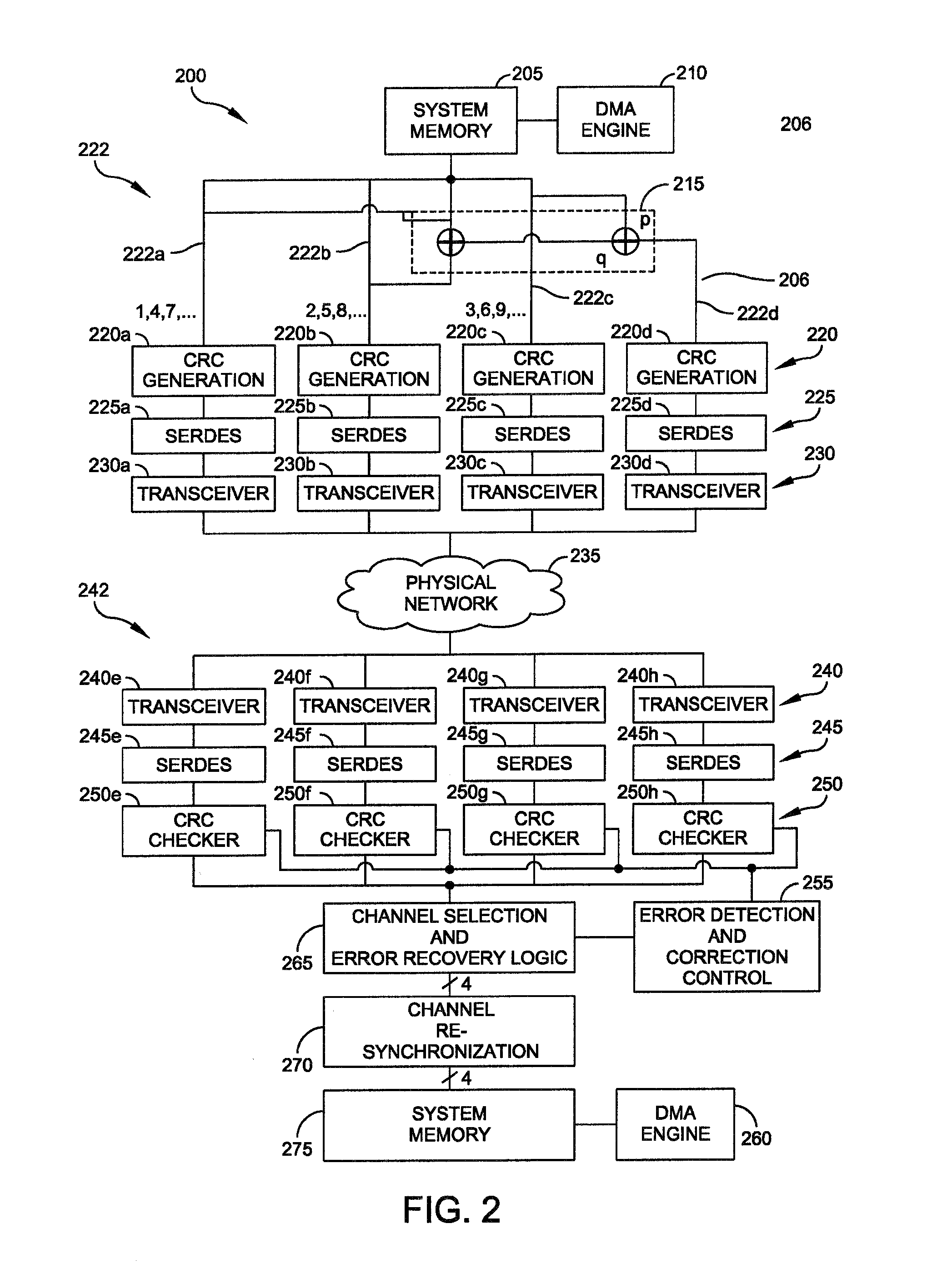

InactiveUS20100262887A1Code conversionError correction/detection using block codesSerial transferData stream

A system for transmitting information data packets over a network includes a plurality of parallel transmission channels, each receiving interleaved data words constituting the data packets. Each channel includes a corresponding check sum data generator to compute check sum data for a corresponding sequence of data words. A logic circuit responsive to the interleaved data words from each channel performs an arithmetic operation on the data words from those channels to generate a parity data stream onto a separate channel. A check sum data generator computes checksum data based on the parity data stream. An encoder device downstream from each checksum data generator encodes the data and checksum from each channel for serial transmission over a network.

Owner:LOCKHEED MARTIN CORP

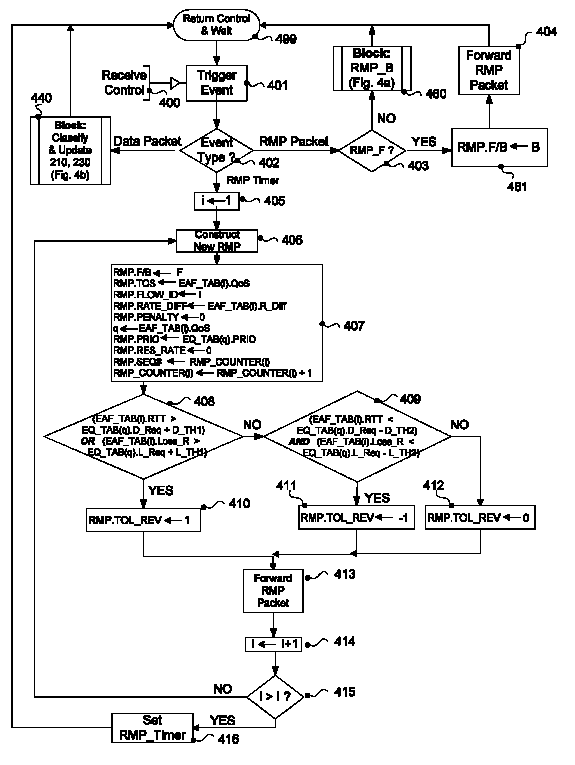

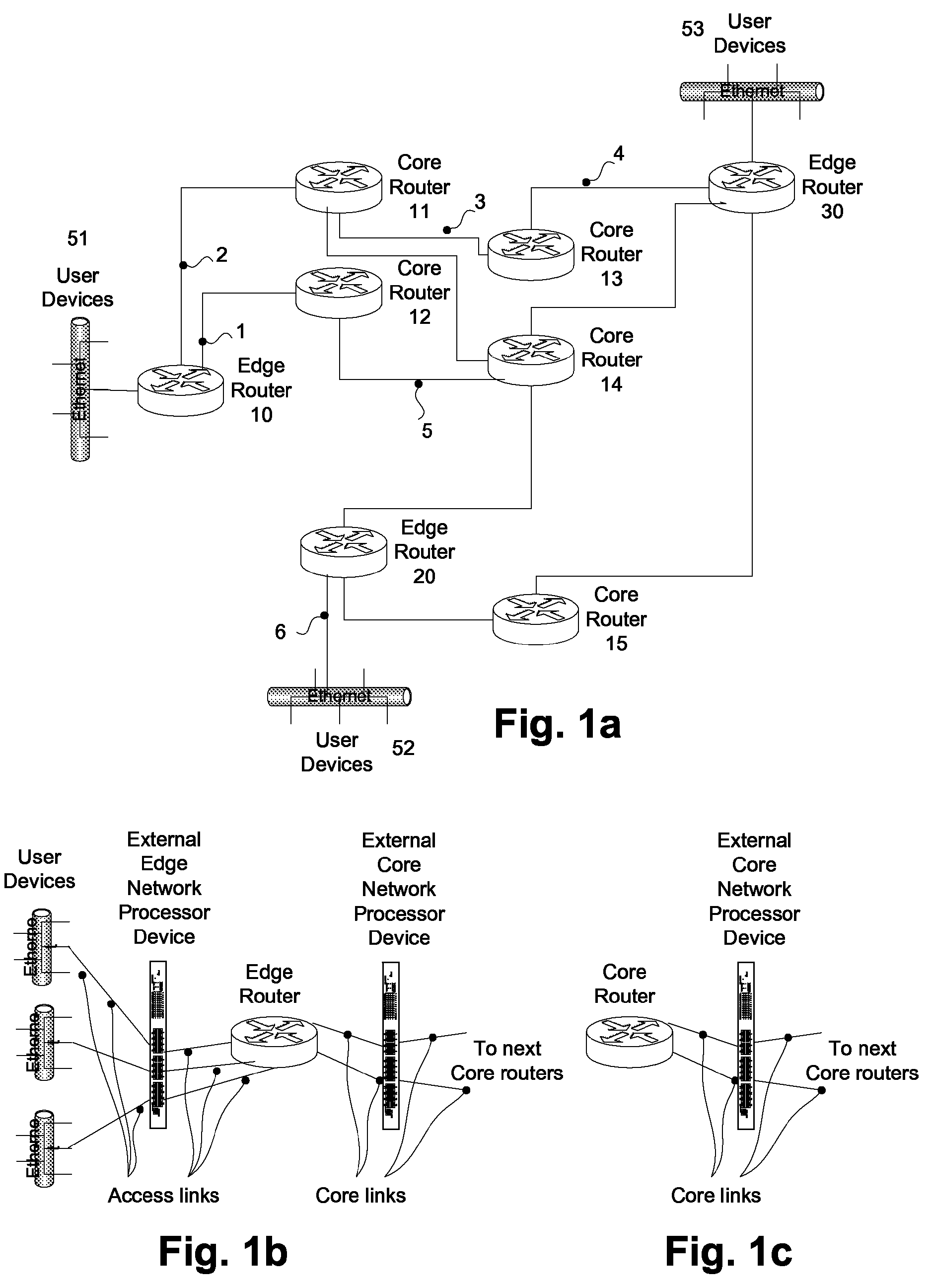

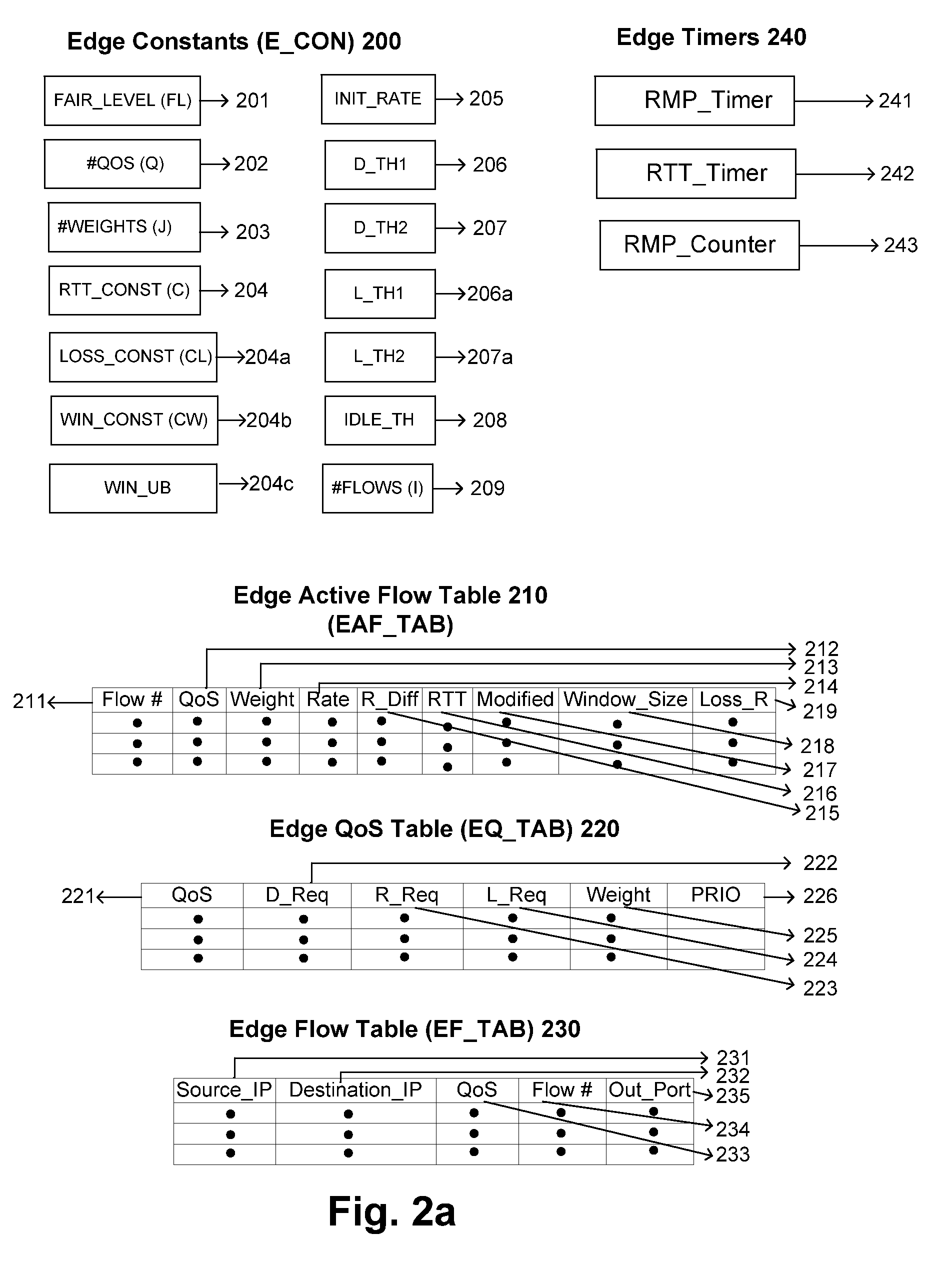

Method and apparatus for fair flow control and congestion avoidance supporting multiple QoS class requirements

Owner:ROSBERG ZVI

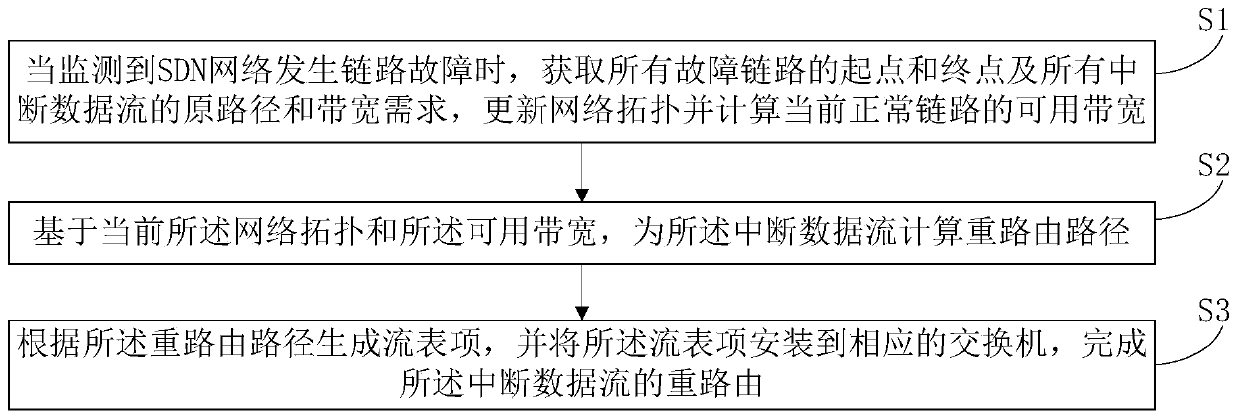

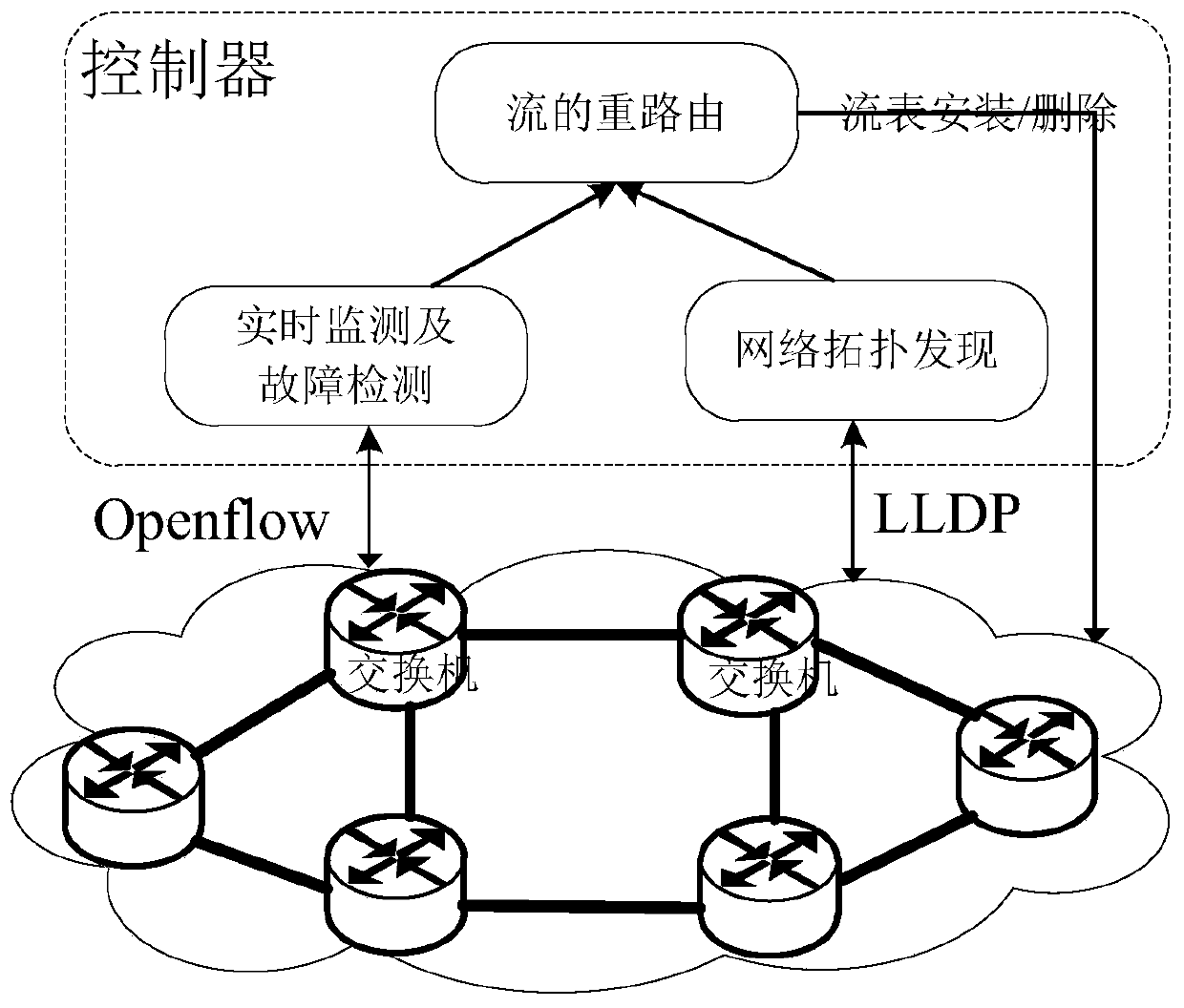

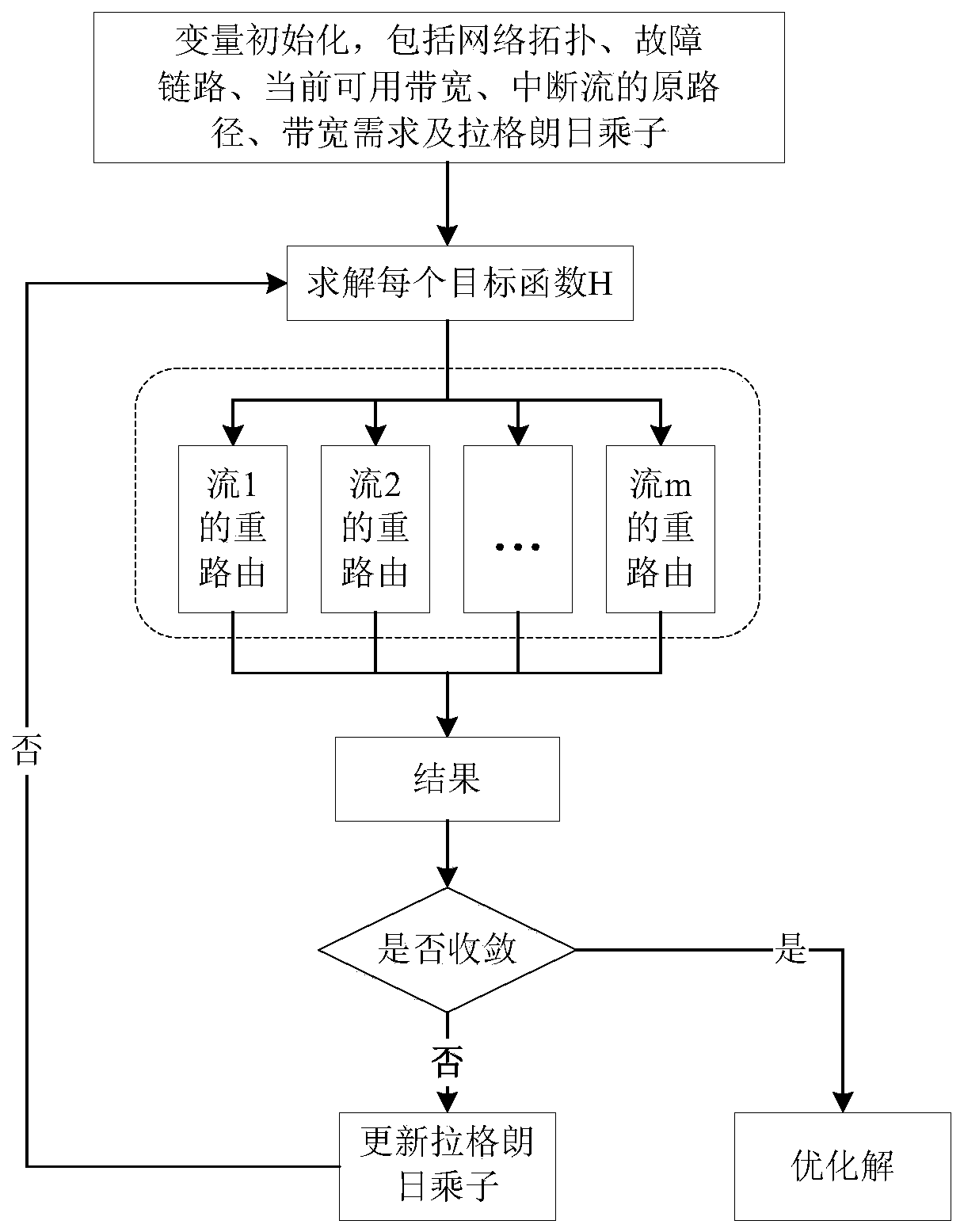

SDN network multi-link fault recovery method and system for multi-stream coexistence

ActiveCN109768924ASave on installation costsEnsure continuityData switching networksRecovery methodData stream

The invention relates to an SDN network multi-link fault recovery method and system for multi-flow coexistence. The method comprises the steps that when it is monitored that a link fault occurs in anSDN network, acquiring starting points and ending points of all faulted links and original paths and bandwidth requirements of all interrupted data streams, updating a network topology, and calculating the available bandwidth of a current normal link; calculating a rerouting path for the interrupted data stream based on the current network topology and the available bandwidth; and generating a flow table entry according to the rerouting path, and installing the flow table entry to a corresponding switch to complete rerouting of the interrupted data flow. The method and the device are suitablefor scenes where multiple link faults exist in the SDN network and multiple data streams pass through each faulted link; in order to minimize the communication cost of a controller and a switch, an original optimization problem is decomposed into a plurality of sub-problems which can be executed in parallel, so that rapid recovery of faults is realized, the installation cost of flow table items isreduced, the service interruption time is shortened, the continuity of data flow is ensured, and the performance of the SDN is improved.

Owner:SHANDONG COMP SCI CENTNAT SUPERCOMP CENT IN JINAN

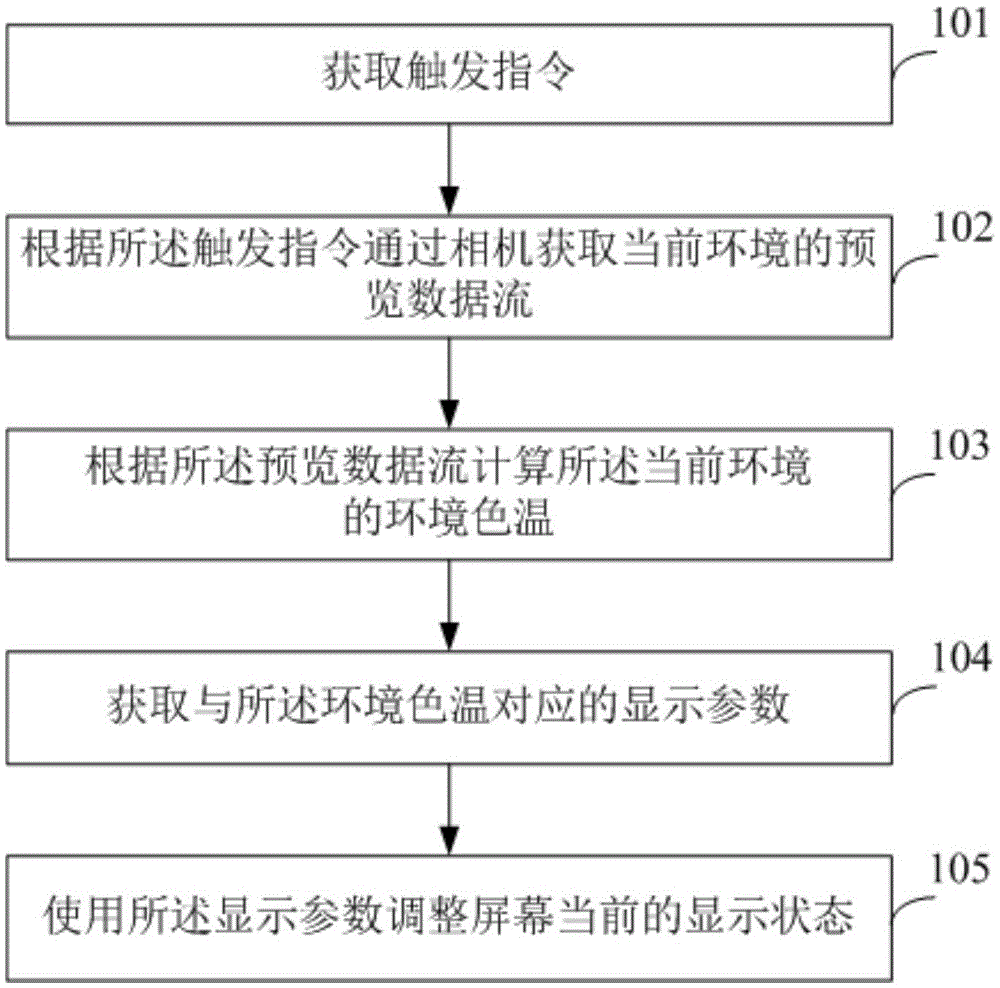

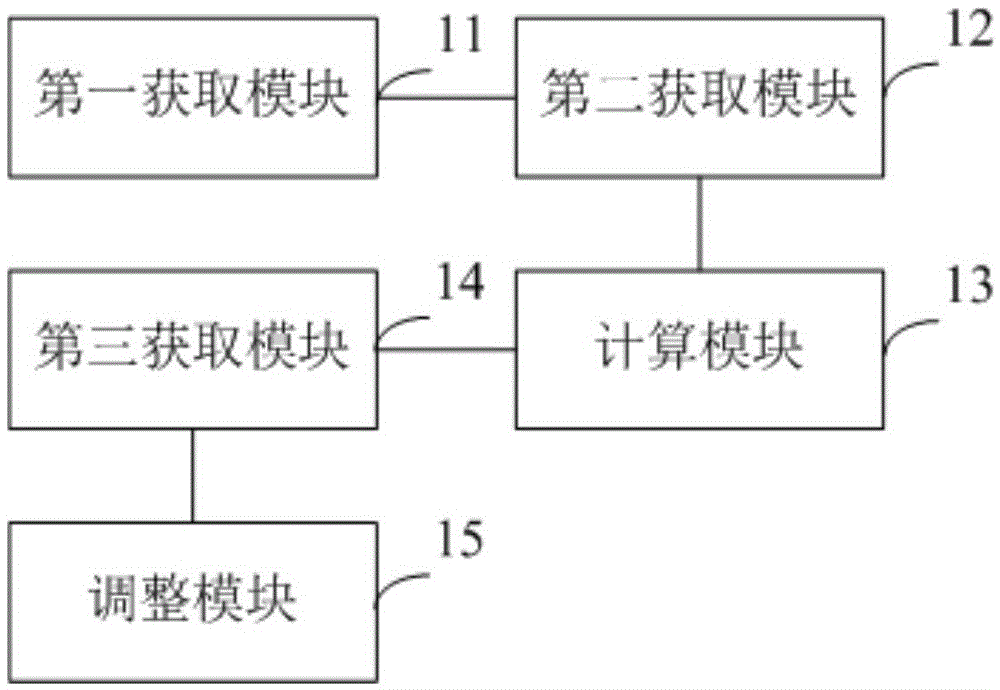

Screen display method and device

InactiveCN105892965AImprove convenienceImprove intelligenceDigital output to display deviceData streamOn-screen display

The invention provides a screen display method and device. Through the acquisition of a trigger instruction, according to the trigger instruction, the preview data stream of the current environment is obtained through a camera, the environment color temperature of the current environment is calculated according to the preview data stream, a display parameter corresponding to the environment color temperature is obtained, and the current display state of the screen is regulated by the display parameter. On the basis of the environment color temperature of the current environment, the display parameter matched with the color temperature is automatically acquired, the screen is regulated to the display state corresponding to the display parameter, convenience and intelligentization for regulating the screen are improved, a screen display effect can be more similar to the current environment since the screen is regulated on the basis of the color temperature, and user experience is improved.

Owner:LEMOBILE INFORMATION TECH BEIJING

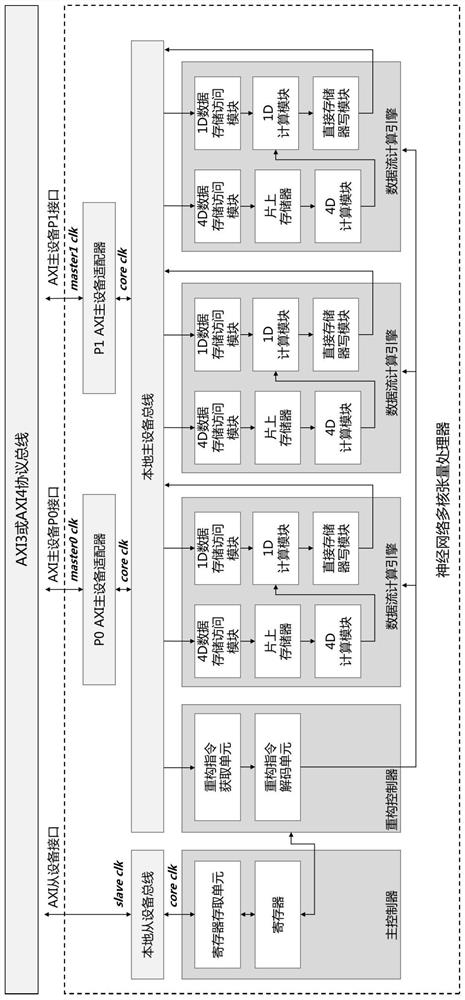

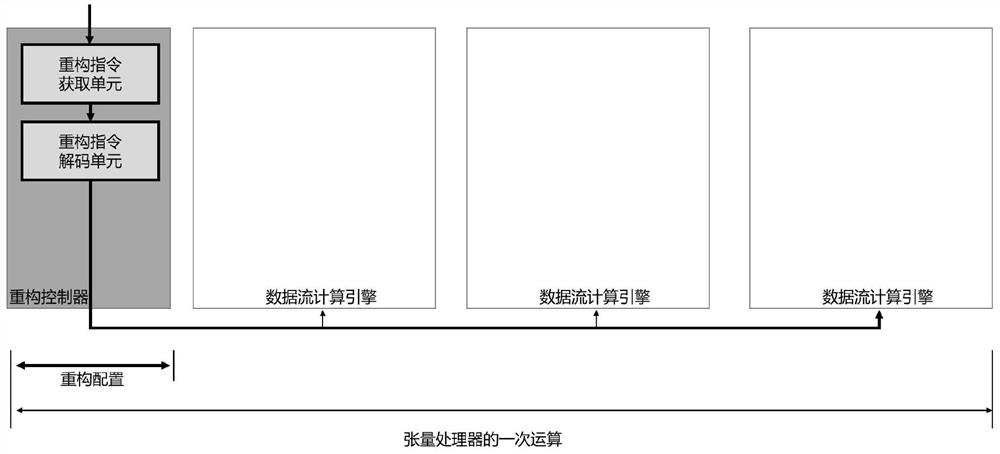

Multi-core tensor processor of neural network

The invention discloses a multi-core tensor processor of a neural network. The multi-core tensor processor comprises a main controller, a reconstruction controller and a plurality of data flow calculation engines, the main controller is used for providing a control and state interface of the neural network tensor processor for an external control unit, and providing first configuration informationand a first initial signal for the reconstruction controller; the reconstruction controller receives the first configuration information and the first starting signal, obtains a reconstruction instruction of an external memory after the first starting signal is valid, and analyzes the reconstruction instruction to generate multiple groups of second configuration information and second starting signals; and each data flow calculation engine respectively receives the corresponding second configuration information and the second initial signal, performs function configuration according to the second configuration information, acquires data and parameters of the external memory to execute operation after the second initial signal is valid, and writes a calculation result into the external memory. The multi-core tensor processor is suitable for performing centralized calculation on a neural network algorithm, and has universality and expandability.

Owner:厦门壹普智慧科技有限公司

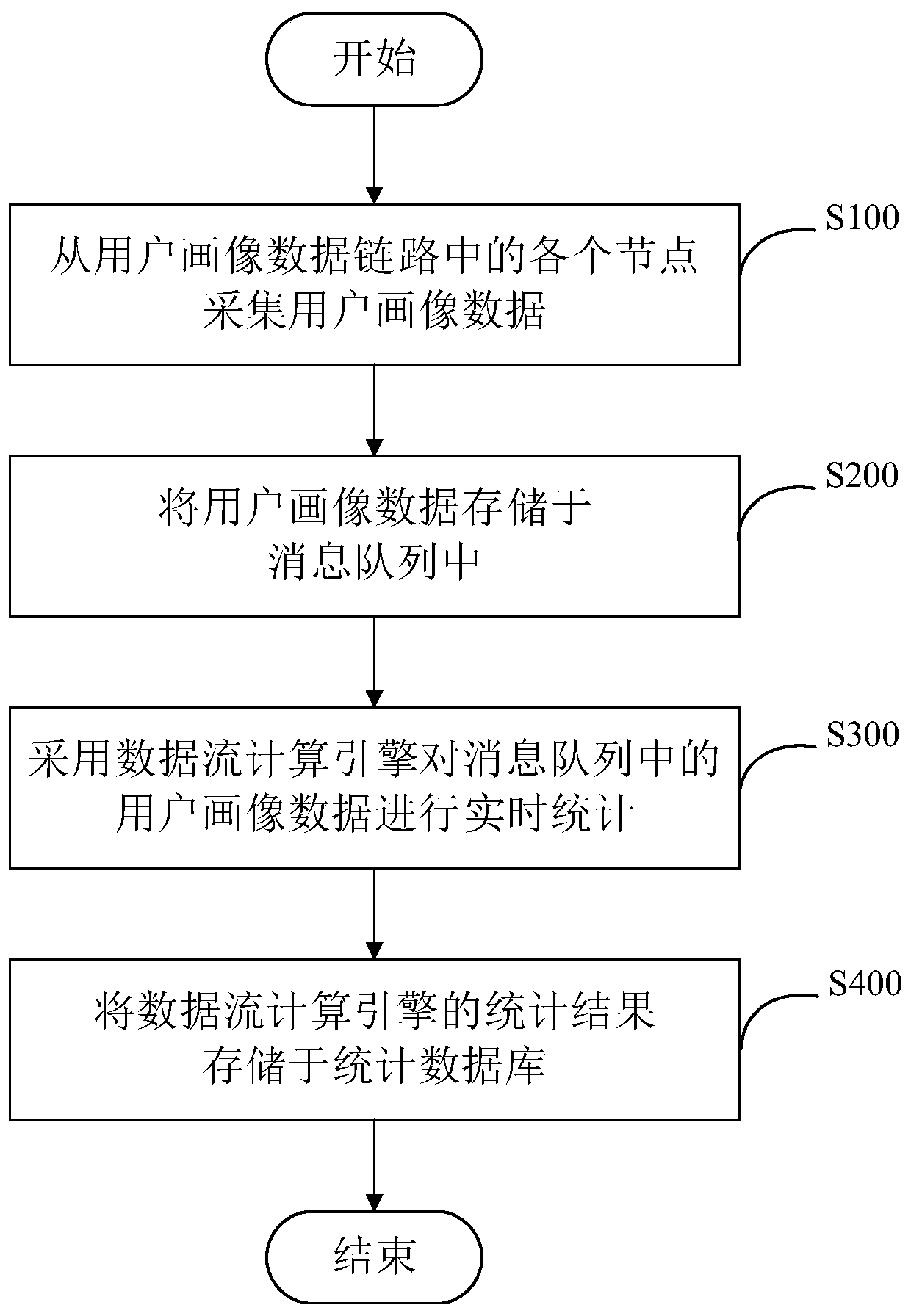

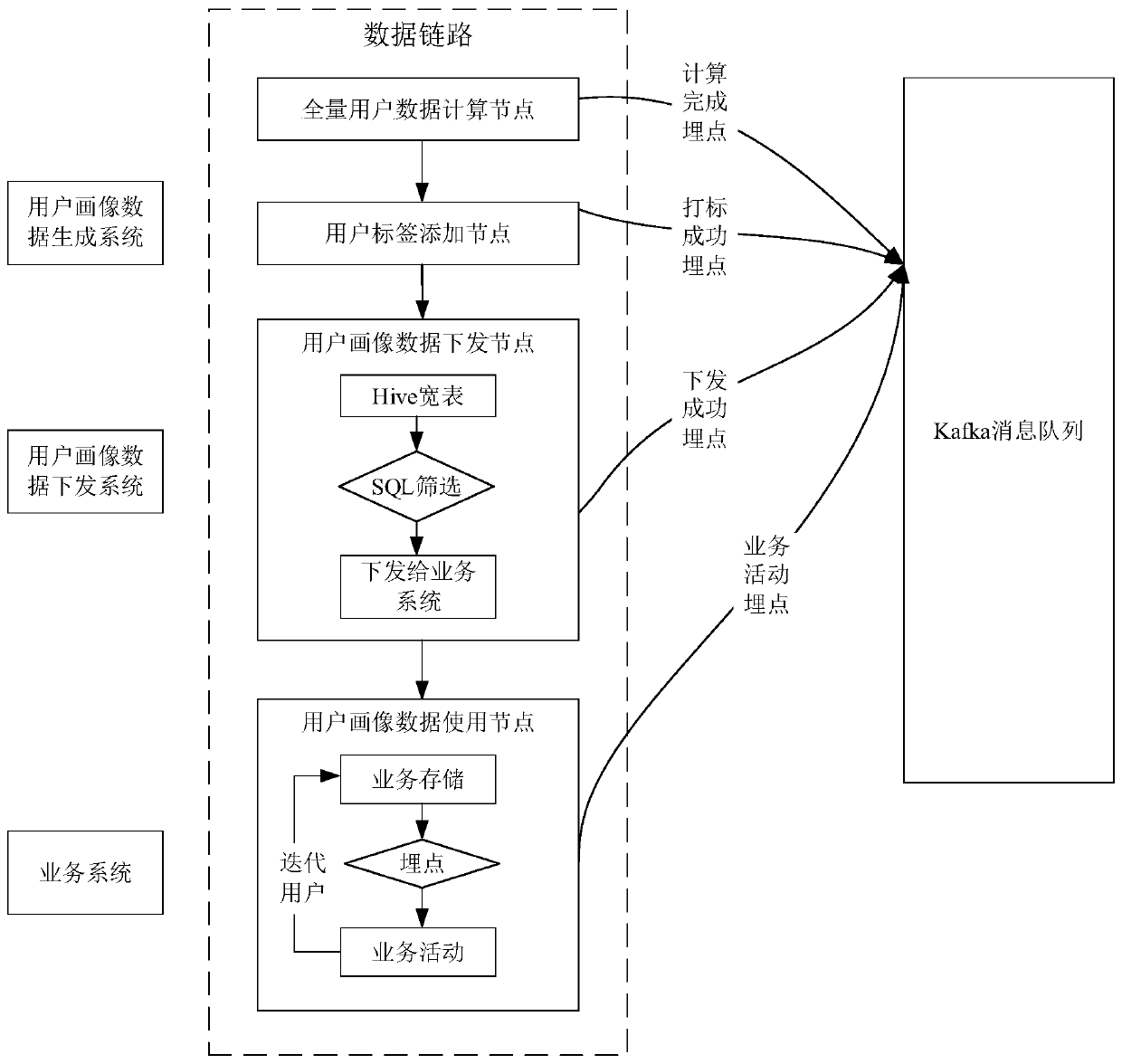

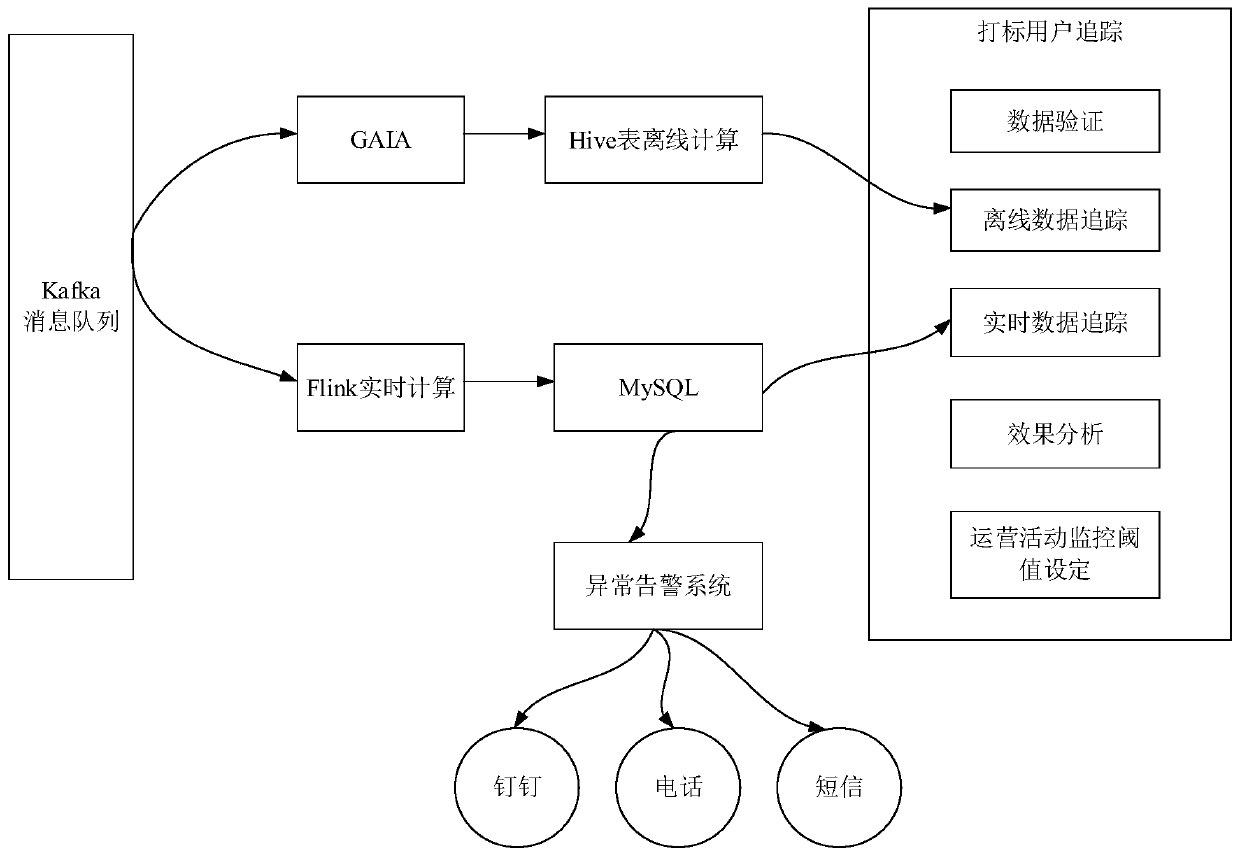

User portrait data monitoring method, system and device and storage medium

ActiveCN110908883AWill not affect normal workImprove the efficiency of data statisticsDigital data information retrievalHardware monitoringStatistical databaseMessage queue

The invention provides a user portrait data monitoring method, system and device and a storage medium. The user portrait data monitoring method comprises the following steps: collecting user portraitdata from each node in a user portrait data link; storing the user portrait data in a message queue; performing real-time statistics on the user portrait data in the message queue by adopting a data flow calculation engine; and storing a statistical result of the data flow calculation engine in a statistical database. By adopting the scheme of the invention, full-link monitoring is carried out onthe user portrait data link, and the data statistics efficiency is improved by combining the message queue and the data flow calculation engine, so that the data of each node in the user portrait datalink can be captured and analyzed in time, and problems can be found in time.

Owner:JIANGSU MANYUN SOFTWARE TECH CO LTD

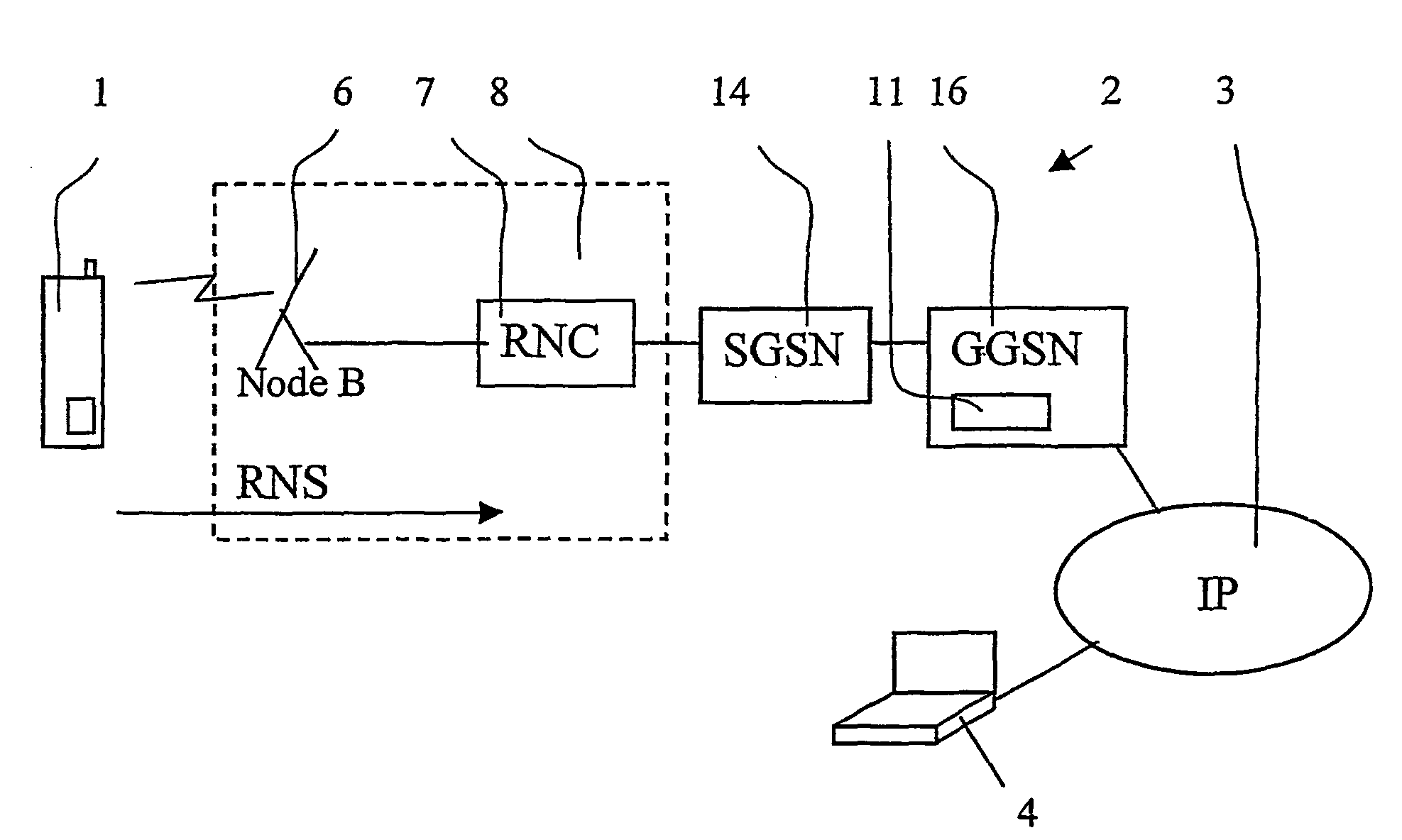

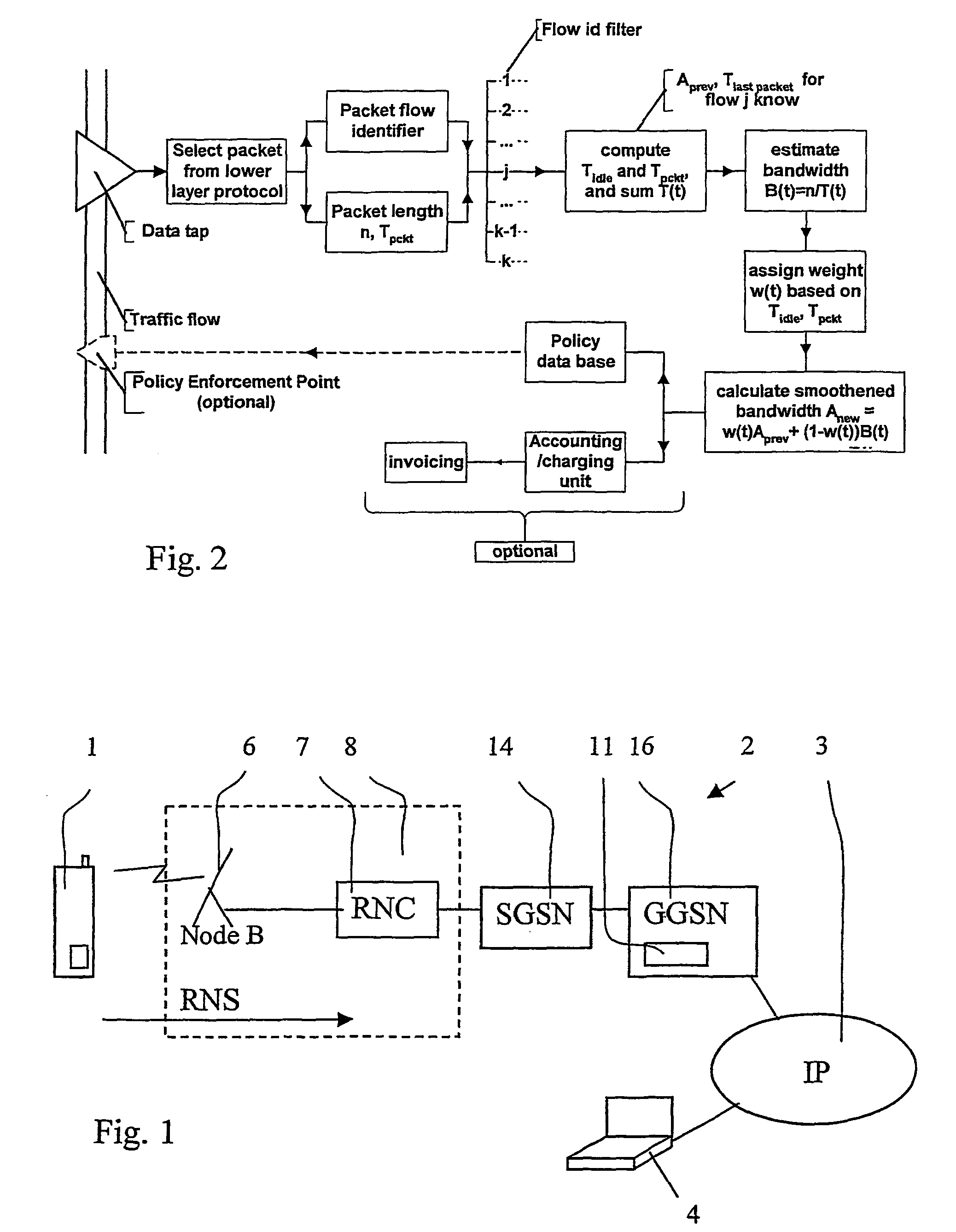

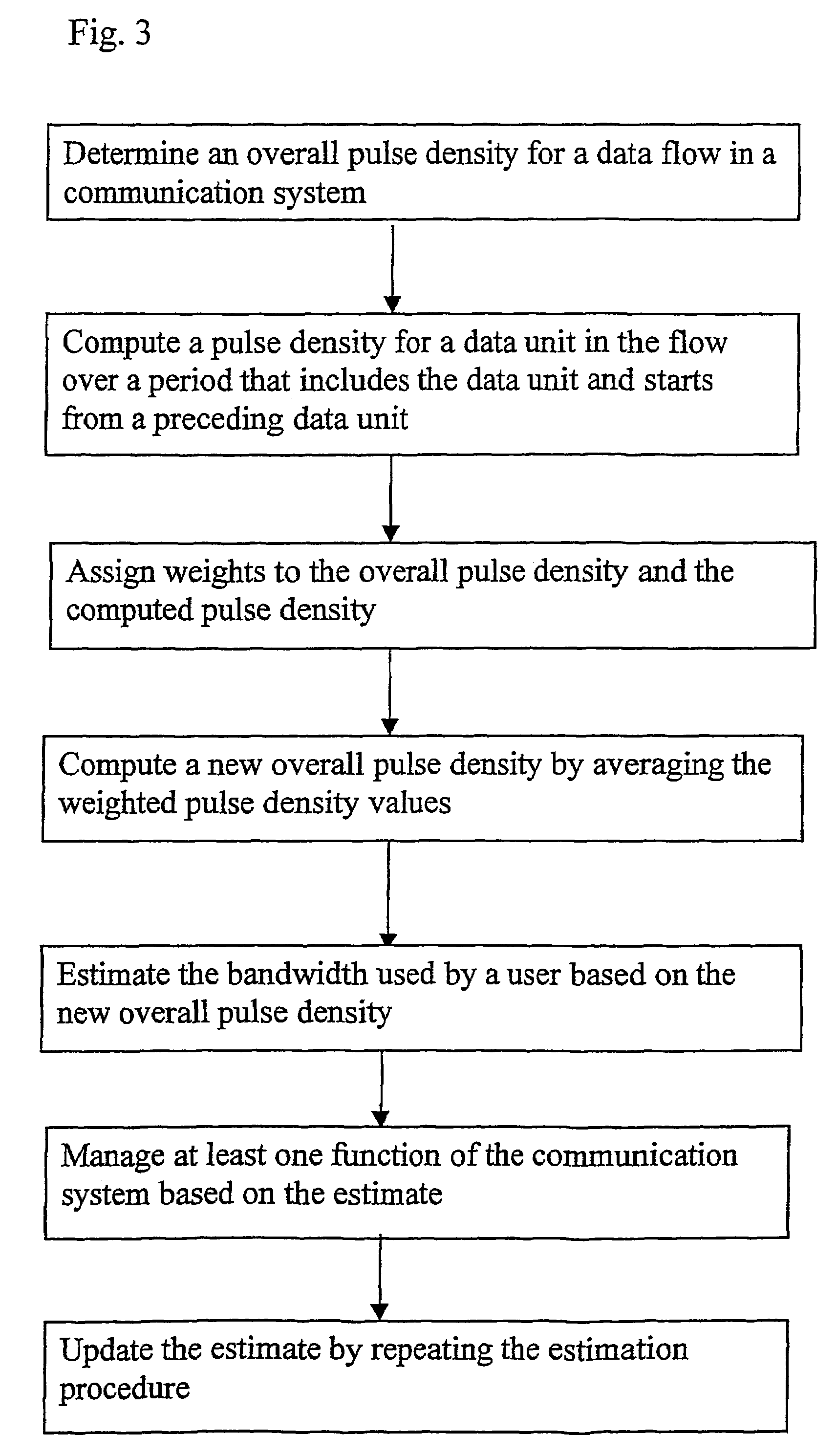

Bandwidth estimation

InactiveUS7315514B2Great awarenessIncrease awarenessError preventionTransmission systemsCommunications systemData stream

A bandwidth estimation in a resource of a data communication system. After a data unit in a data flow has been received, a recent pulse density for the data flow over a period that includes the received data unit and starts from a time point that precedes the received data unit in the flow is computed. An overall pulse density is computed based on the computed recent pulse density and a previous overall pulse density computed earlier for the data flow. The computation of the overall pulse density is based on values of the computed recent pulse density and the previous overall pulse density. The values are weighted relative to each other. The used bandwidth is estimated based on the weighted overall pulse density.

Owner:NOKIA CORP

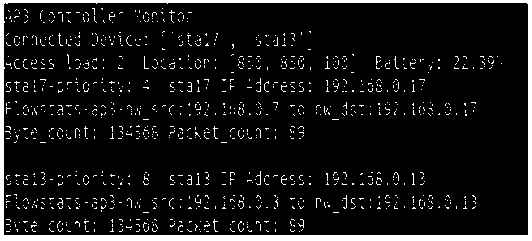

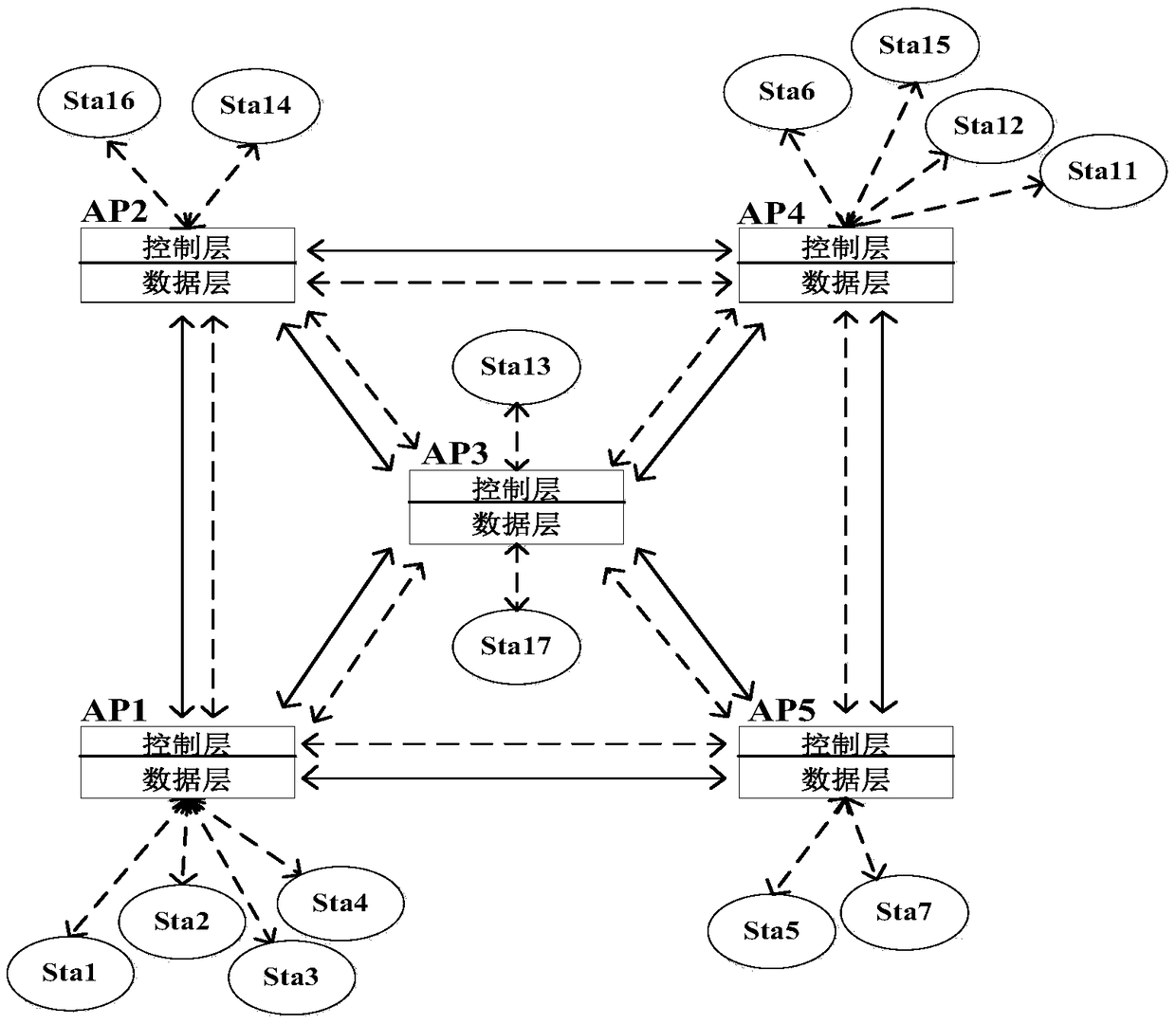

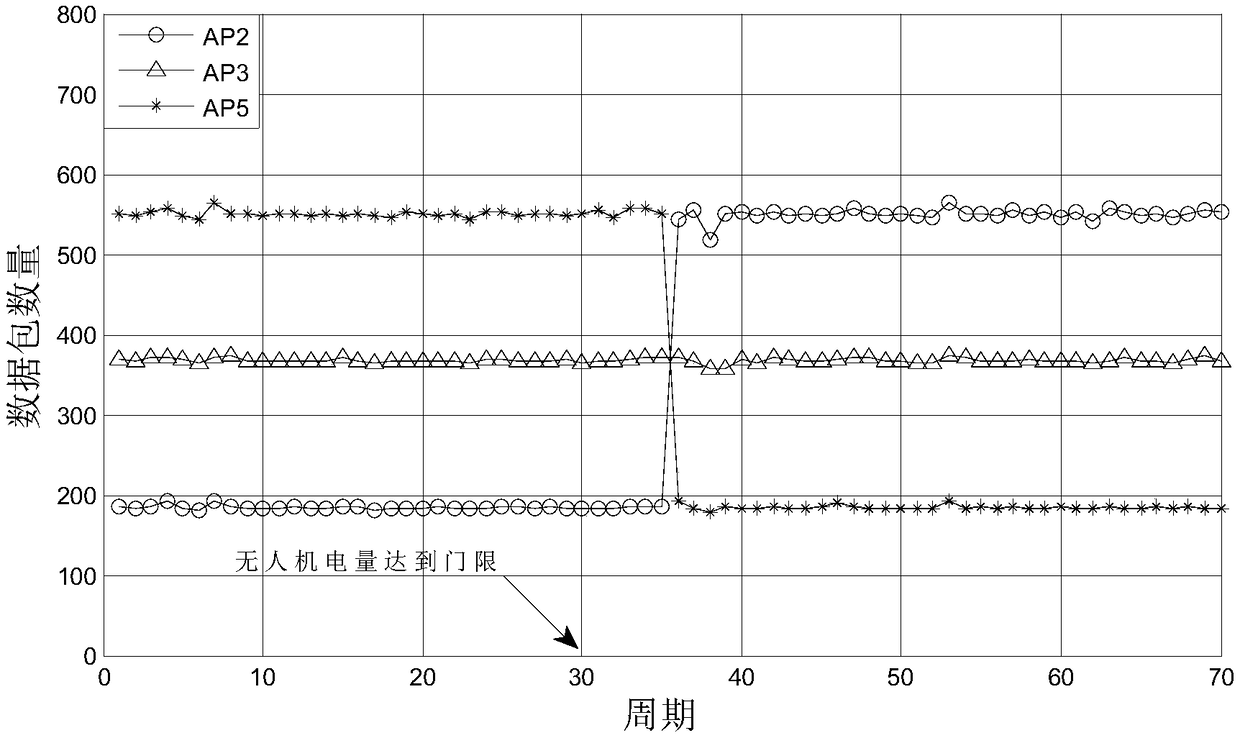

A method and a system for configuring network traffic of an unmanned aerial vehicle based on SDN distributed control

ActiveCN109089294AGuaranteed continuous communicationEasy to implementData switching networksNetwork data managementTraffic capacityData stream

The invention provides an SDN distributed control unmanned aerial vehicle network flow configuration method and a system thereof. According to the data flow information, the original node and the target node of the new path are obtained, and the local network topology table is transformed into a directed graph with weights. According to the link weights in the directed graph, the original node andthe target node are used to calculate the new path for the data flow. Sending a MOD message to a UAV node controller on the new path according to the data stream information priority. The UAV node controller that receives the MOD message replies to the corresponding ACK message, completes the route switching, and realizes the traffic configuration. In order to solve the problem of communication interruption caused by UAV leaving the network due to power exhaustion in the network, by distinguishing the priority of data stream, the high-level users can finish the traffic planning first to realize the communication.

Owner:NAT UNIV OF DEFENSE TECH

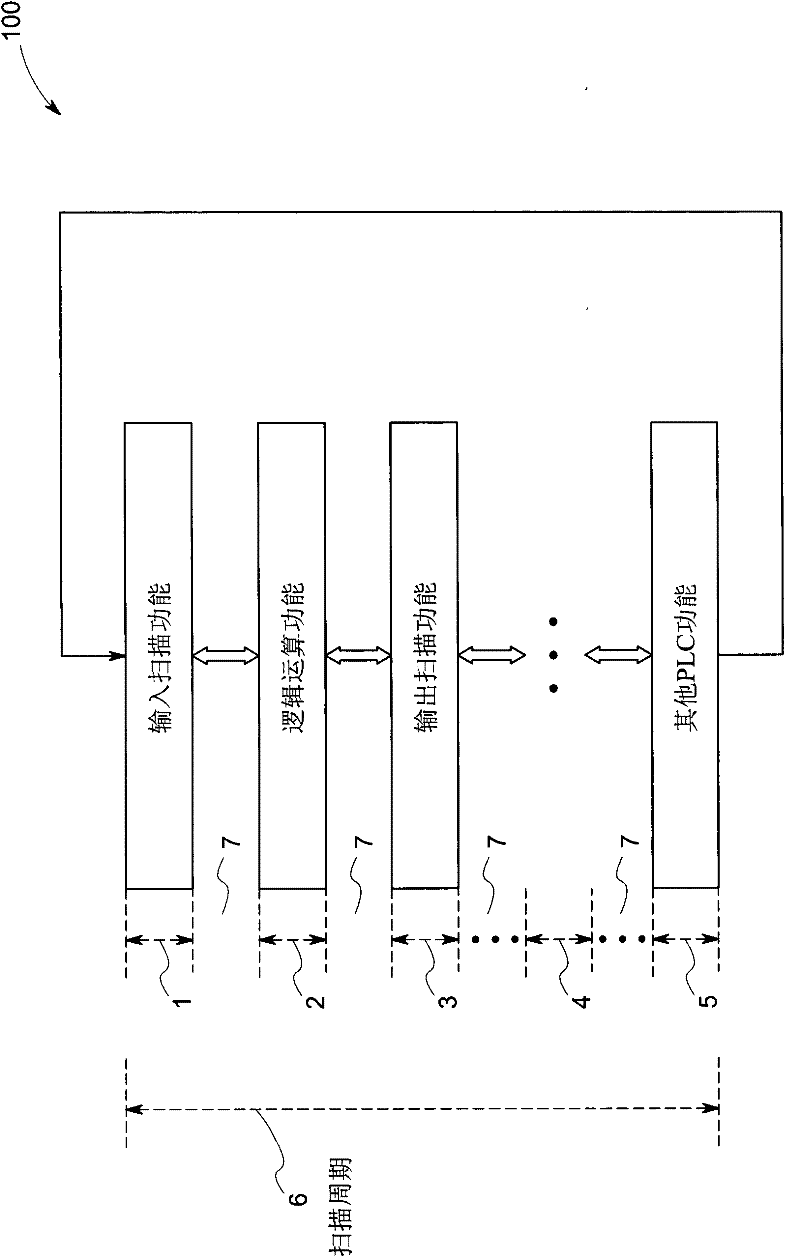

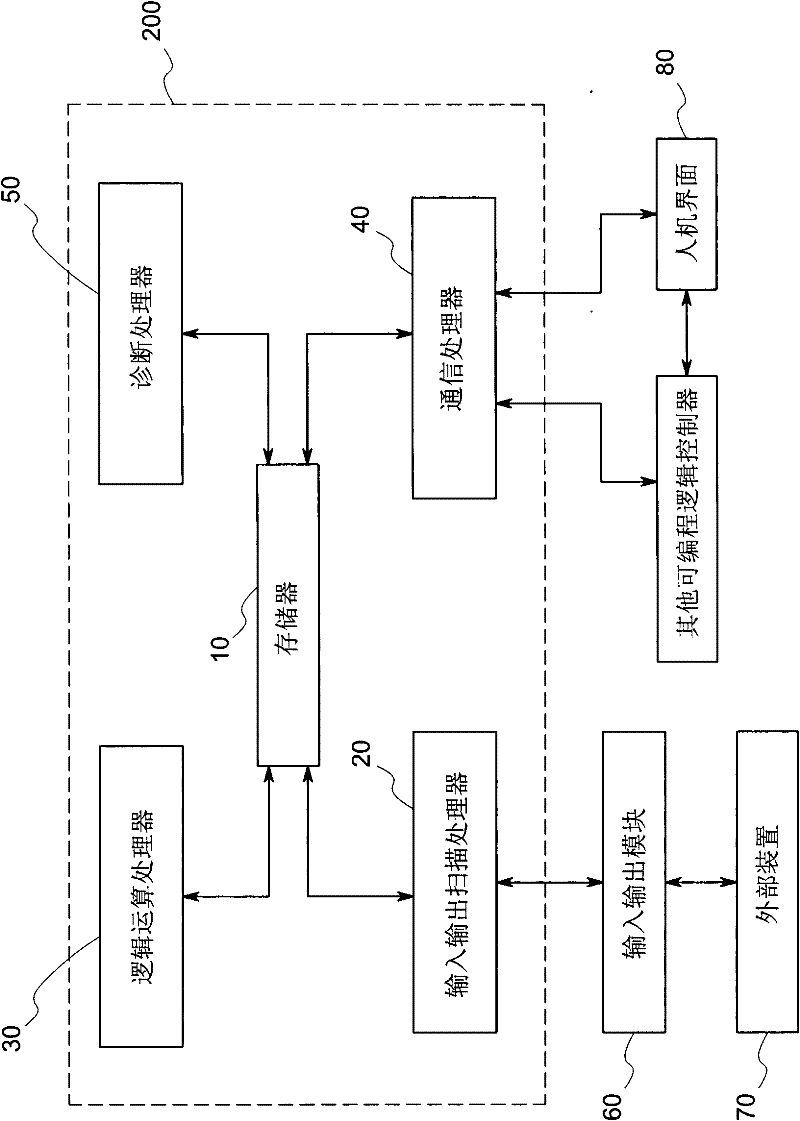

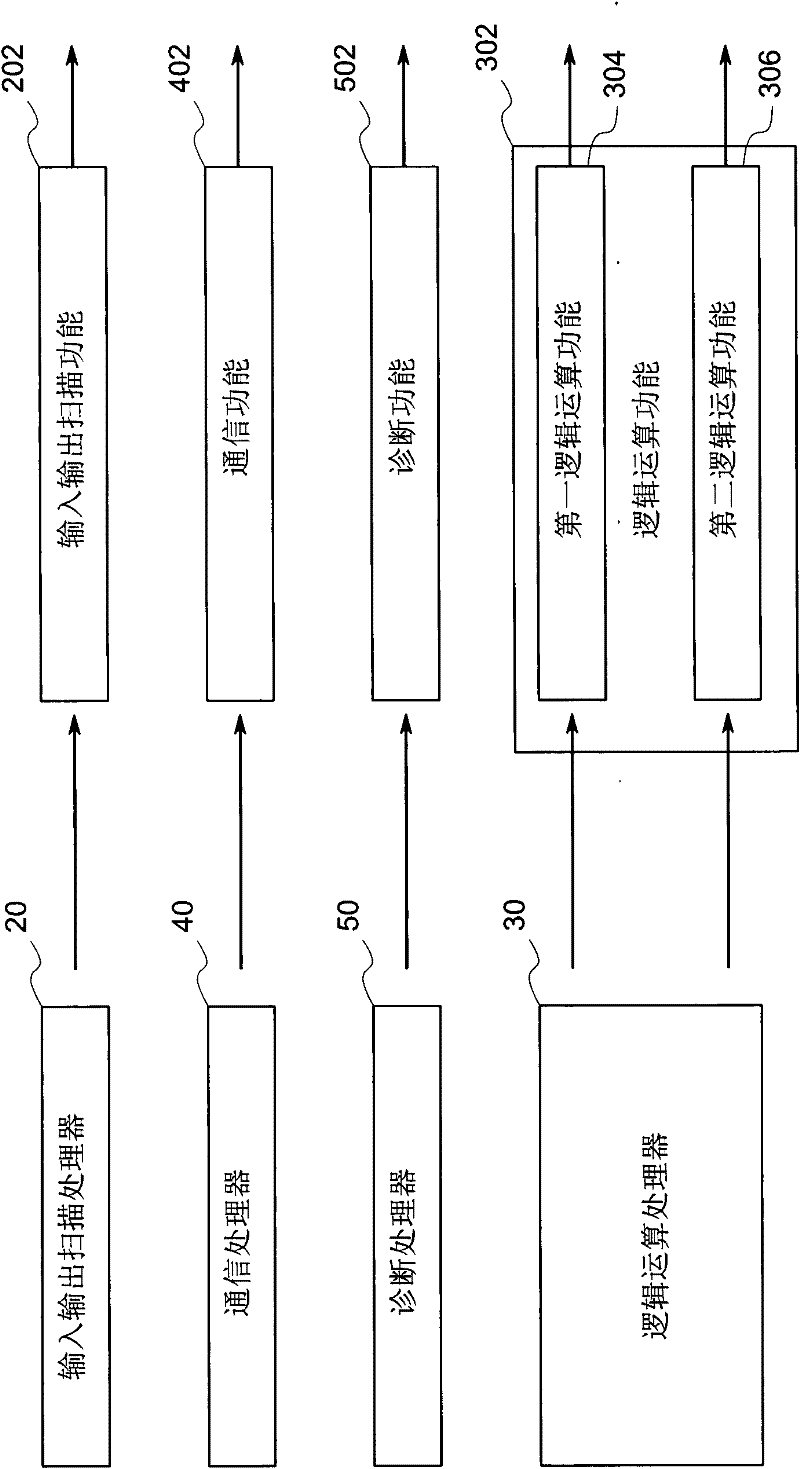

Programmable controller and operation method thereof

InactiveCN102540952ASolve technical problems with low execution efficiencyImprove execution efficiencyProgramme control in sequence/logic controllersData streamProgrammable logic controller

The invention discloses a programmable controller and an operation method thereof. The programmable controller comprises a logical operation processor and a function processor, wherein the logical operation processor is used for executing a logical operation instruction according to a data stream computer architecture; the function processor is used for communicating with the logical operation processor to exchange data and used for executing a function instruction based on the data stream computer architecture; and the function instruction and the logical operation instruction are respectively executed by the function processor and the logical operation processor in a basically parallel mode. By adoption of the programmable controller and the operation method thereof, the instructions based on the data stream computer architecture are executed, the technical problem of low execution efficiency caused by sequential execution of the instructions in the conventional programmable controller is solved, and a technical effect of improving instruction execution efficiency is achieved.

Owner:GENERAL ELECTRIC CO

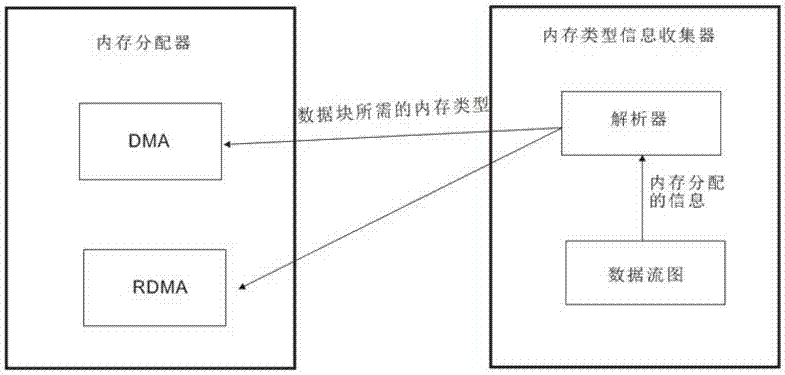

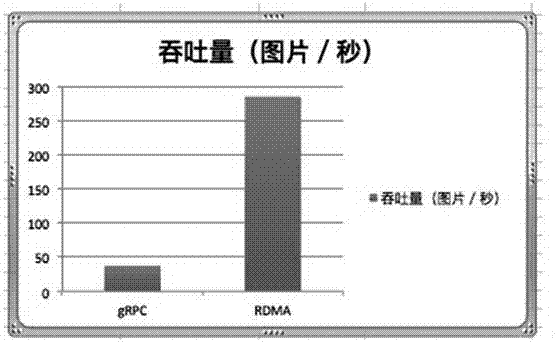

Zero copy data flow based on RDMA

The invention discloses zero copy data flow based on RDMA. The zero copy data flow mainly comprises a memory allocator and an information collector; the memory allocator is used for achieving allocation rules of different memories; the memory classification information collector is used for analyzing a data flow calculation graph and calculating a data source and a data receiving node according to every side in the data flow calculation graph to determine a buffering area management rule of every step. The zero copy data flow based on the RDMA has the advantages that the high tensor transmission speed and high-speed extension of a GPU can be achieved and unnecessary memory copy is eliminated.

Owner:CLUSTAR TECH LO LTD

Two input differential cyclic accumulator

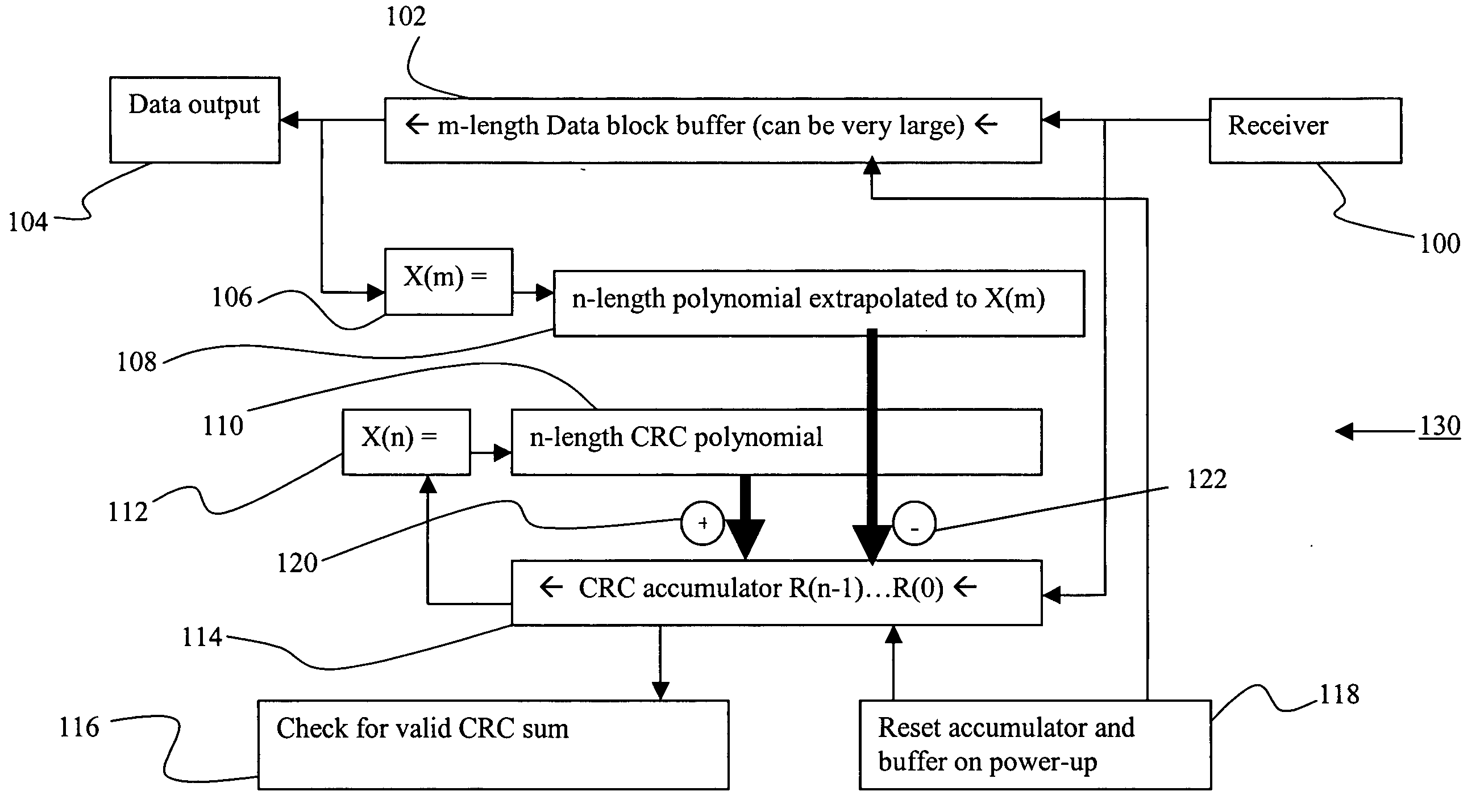

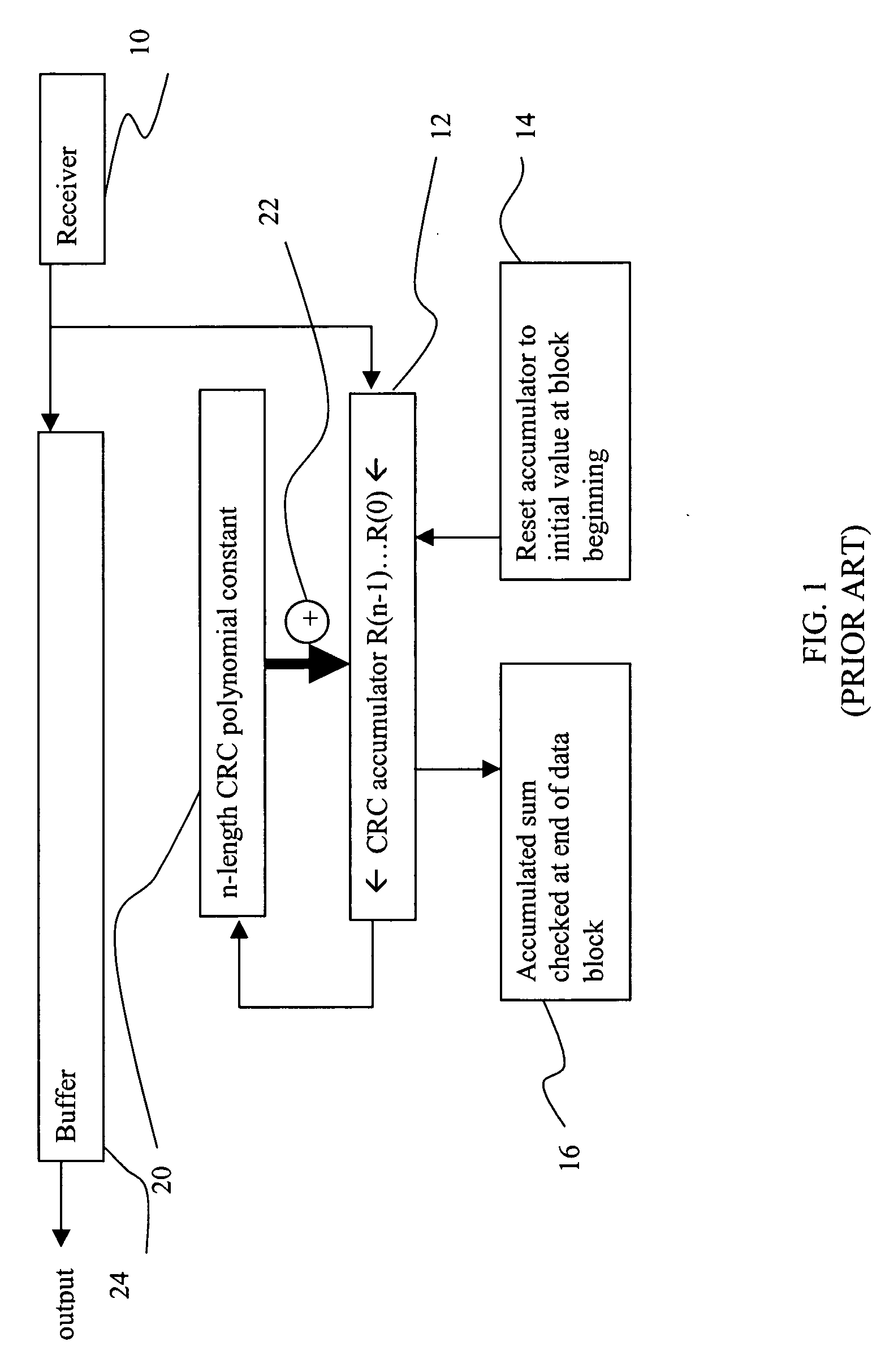

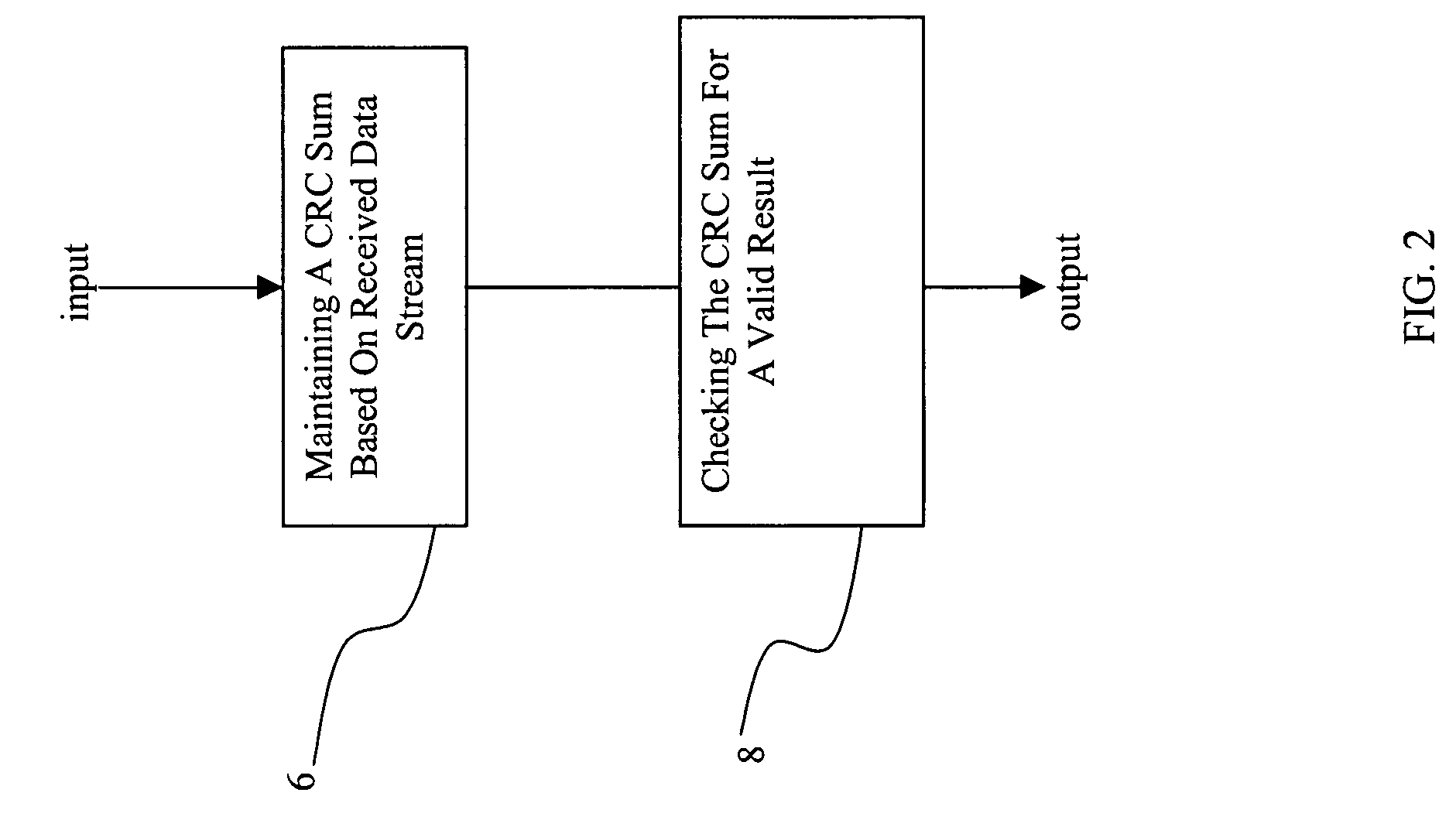

An apparatus and method to find CRC protected data packets by updating a cyclic redundancy checks (CRC) sum calculated from a data stream of CRC protected packets by adding new data while subtracting an effect of old data, and checking the updated CRC sum for a predetermined result. The apparatus includes a m-length memory to store a data stream an n-length accumulator to accumulate a CRC sum from the data. The apparatus includes a remainder circuit to feedback the data leaving the accumulator to the accumulator based on a predetermined CRC polynomial and a subtraction circuit to remove the effect of data leaving the memory from the accumulator. A CRC sum validation circuit checks the CRC sum for a valid result to indicate that the data packet protected by the CRC is located.

Owner:AGILENT TECH INC

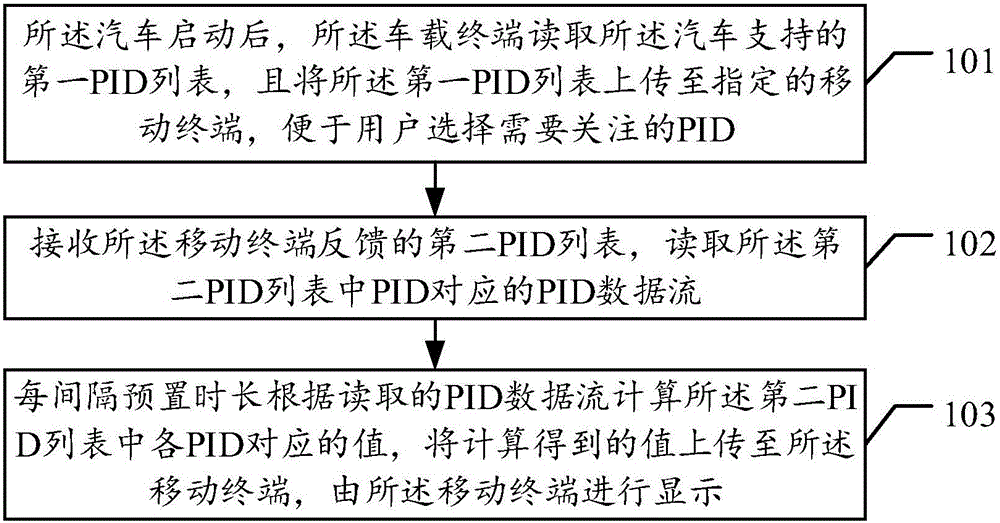

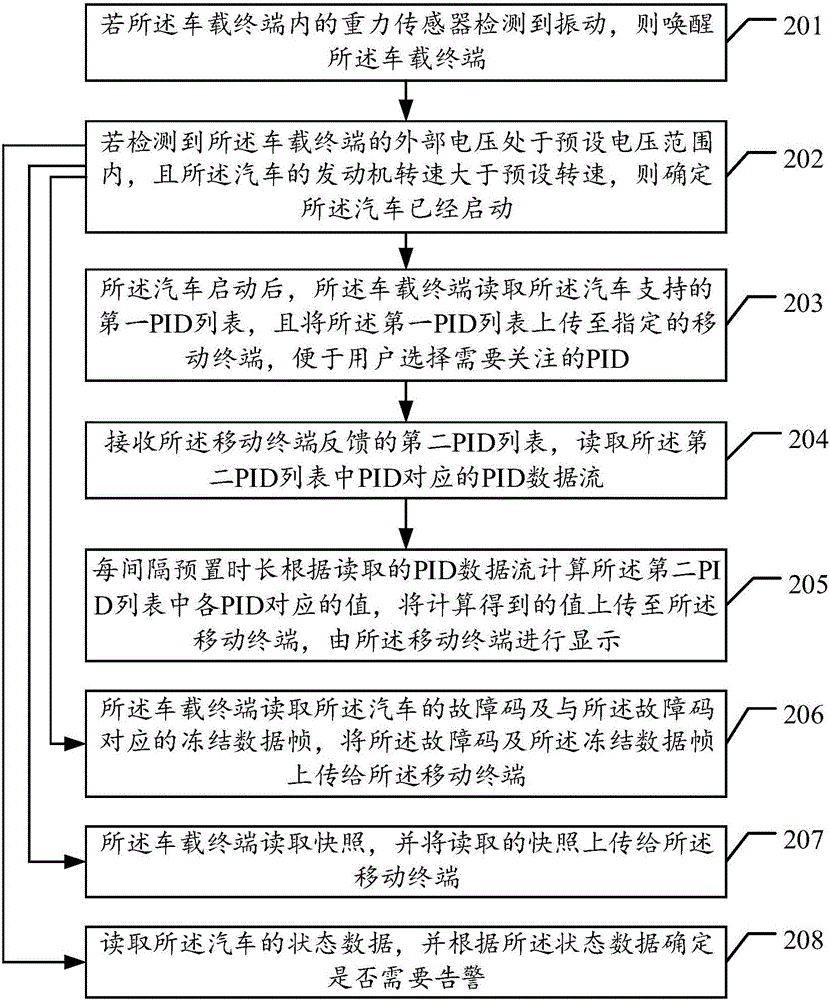

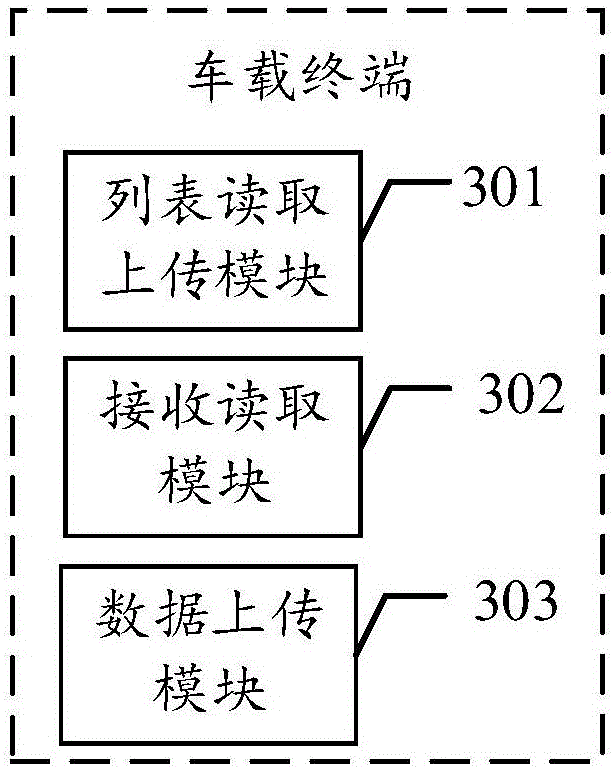

Vehicle data processing method and vehicle terminal

InactiveCN106204799AMeet the needs of useImprove user experienceRegistering/indicating working of vehiclesPersonalizationComputer science

The invention discloses a vehicle data processing method. The method is applied to a vehicle terminal, and the vehicle terminal is connected with a vehicle through an OBD interface. The method comprises the following steps: the vehicle terminal reads a first PID list supported by the vehicle after the vehicle starts, uploads the first PID list to an assigned mobile terminal convenient for a user to select the needed PID, receives a second PID list fed back by the mobile terminal, and reads PID dataflow corresponding to PIDs in the second PID list, values corresponding to all the PIDs in the second PID list are calculated according to the read PID dataflow every preset time, and the values obtained after calculation are uploaded to the mobile terminal and are displayed by the mobile terminal. The invention also discloses the vehicle terminal. The vehicle terminal effectively realizes users' customized settings, meets users' user demands, and improves users' use experiences.

Owner:SHENZHEN CASTEL WIRELESS TELECOMM

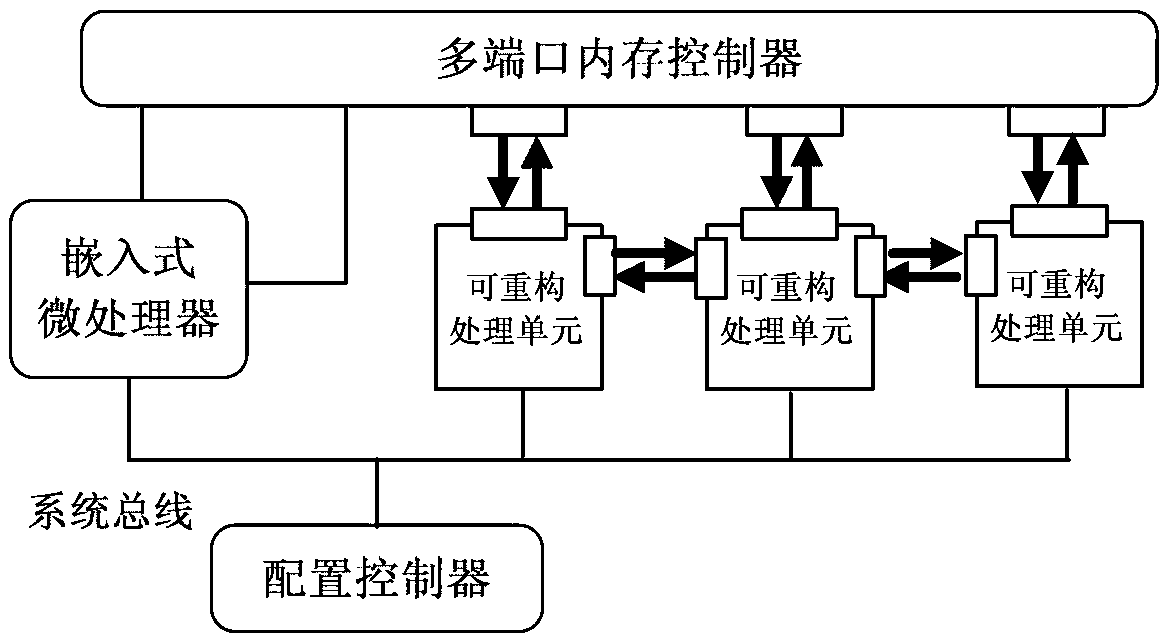

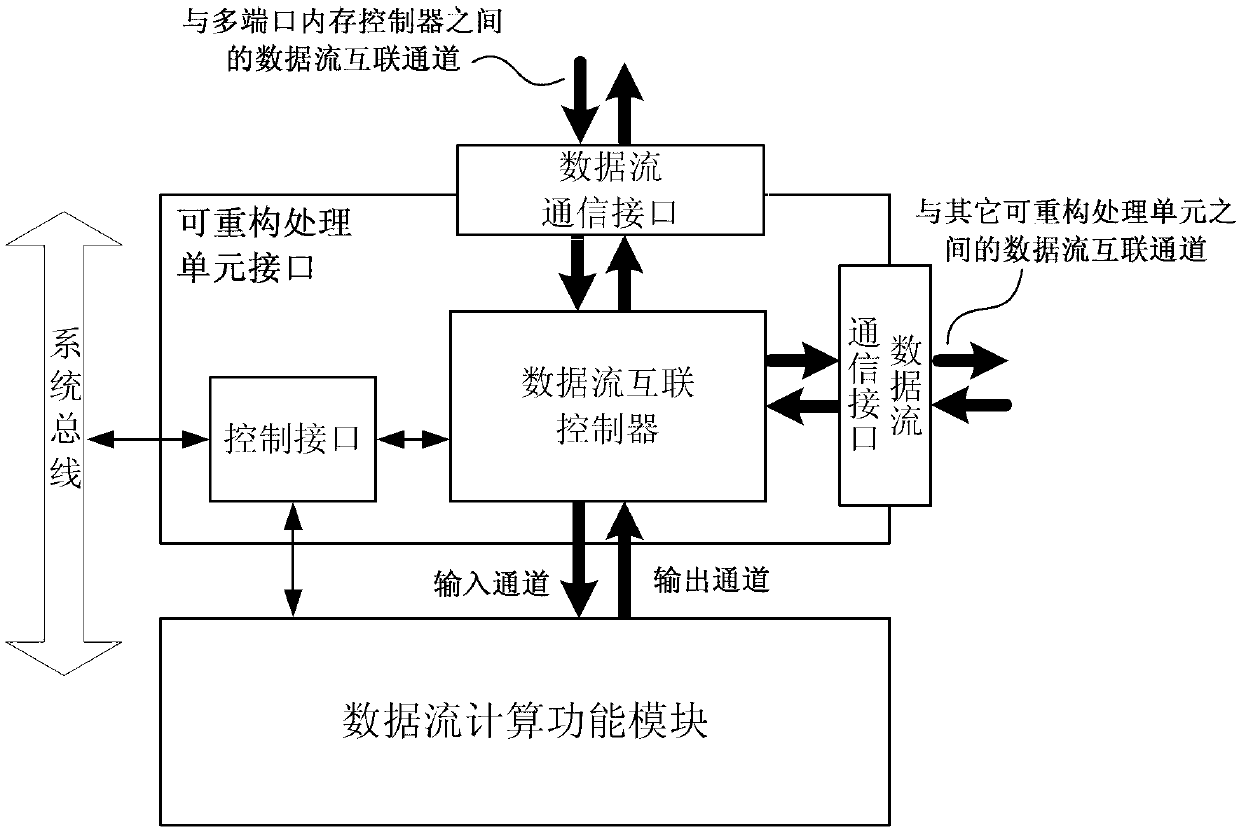

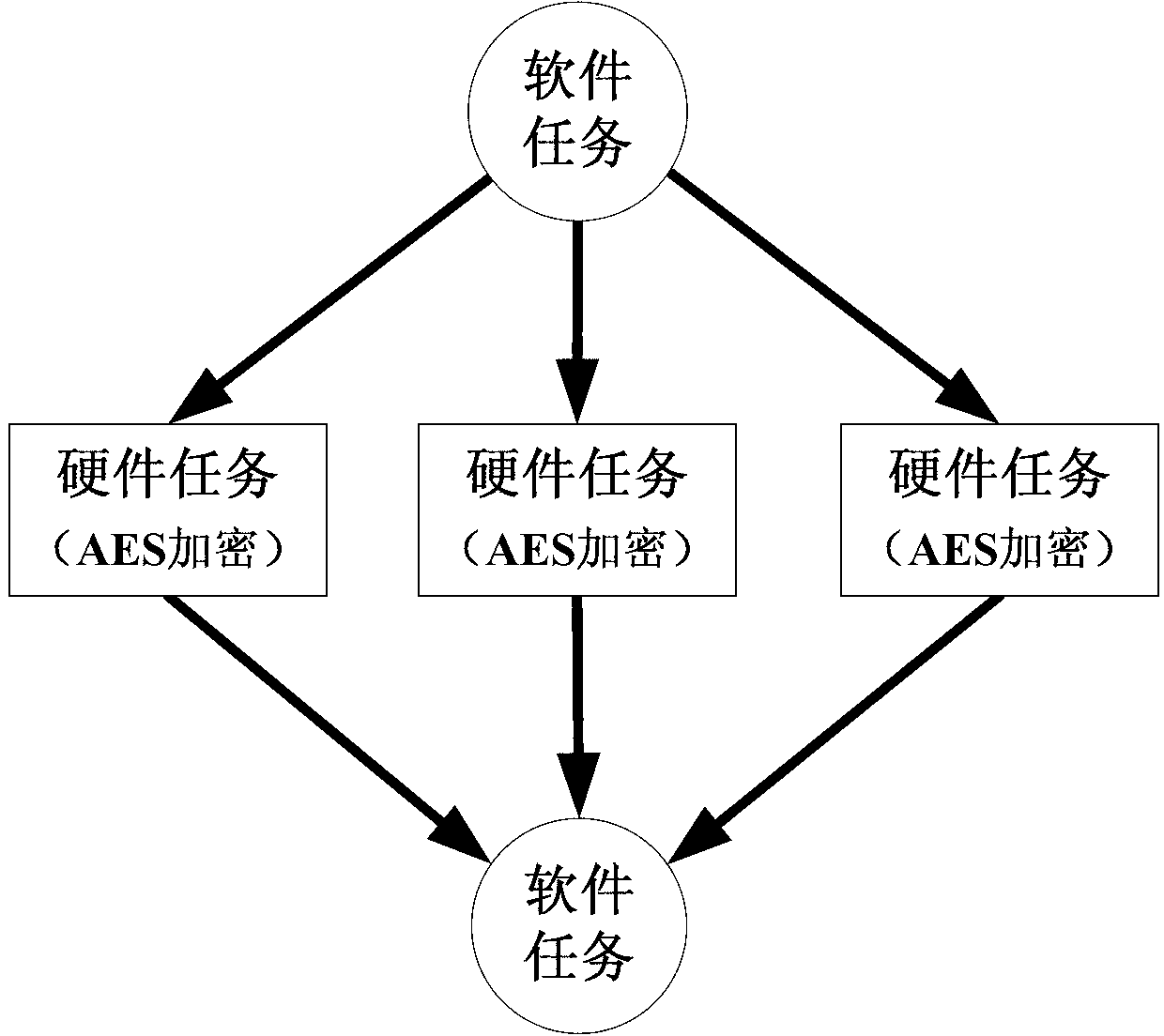

Dynamic reconfigurable system adaptable to plurality of dataflow computation modes and operating method

InactiveCN103218345AEasy to handleImprove adaptabilityDigital computer detailsElectric digital data processingReconfigurabilityCommunication interface

The invention relates to the technical field of reconfigurable circuits and systems, and discloses a dynamic reconfigurable system adaptable to a plurality of dataflow computation modes and an operating method. The dynamic reconfigurable system comprises an embedded microprocessor, a configuration controller, a multi-port memory controller and a plurality of reconfigurable processing units. A dataflow communication interface and a control interface, which can be separated, are adopted for each reconfigurable processing unit, so that the embedded microprocessor can be used for dynamically configuring the functions and interconnection structure of each reconfigurable processing unit to be adapted to the dataflow computation modes. Compared with the conventional system with a bus and a fast simplex link (FSL) structure, the system has the advantages that the resource reconfigurability of a field programmable gate array (FPGA) is fully utilized, and functions and structures, which are matched with the dataflow computation modes, are configured during operation to improve a communication bandwidth and the processing performance of dataflow driving application; and moreover, the system is high in structural adaptability and expansibility, and the invention is significant for a dataflow processing-oriented dynamic reconfigurable system.

Owner:SHANGHAI ANLOGIC INFOTECH CO LTD

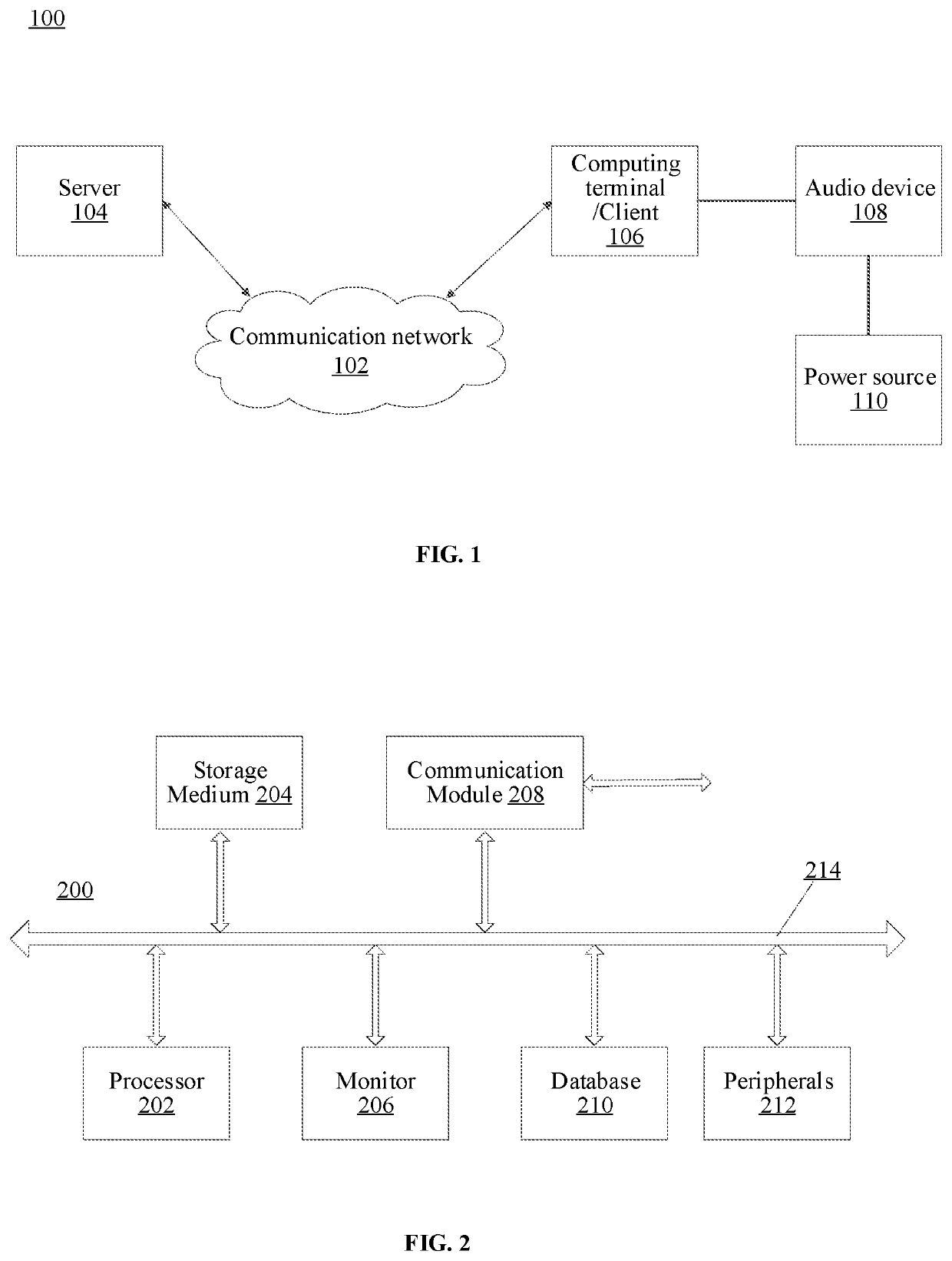

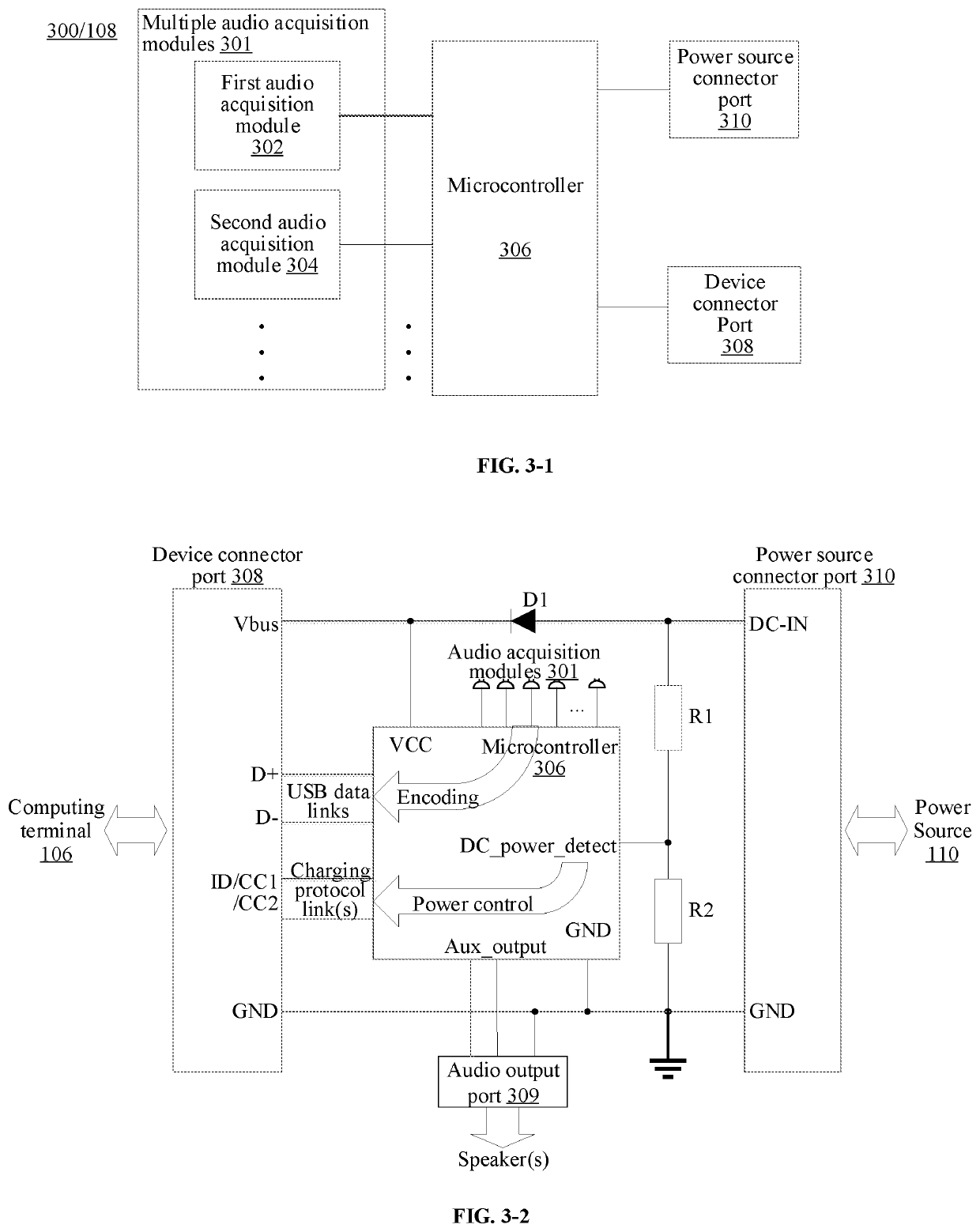

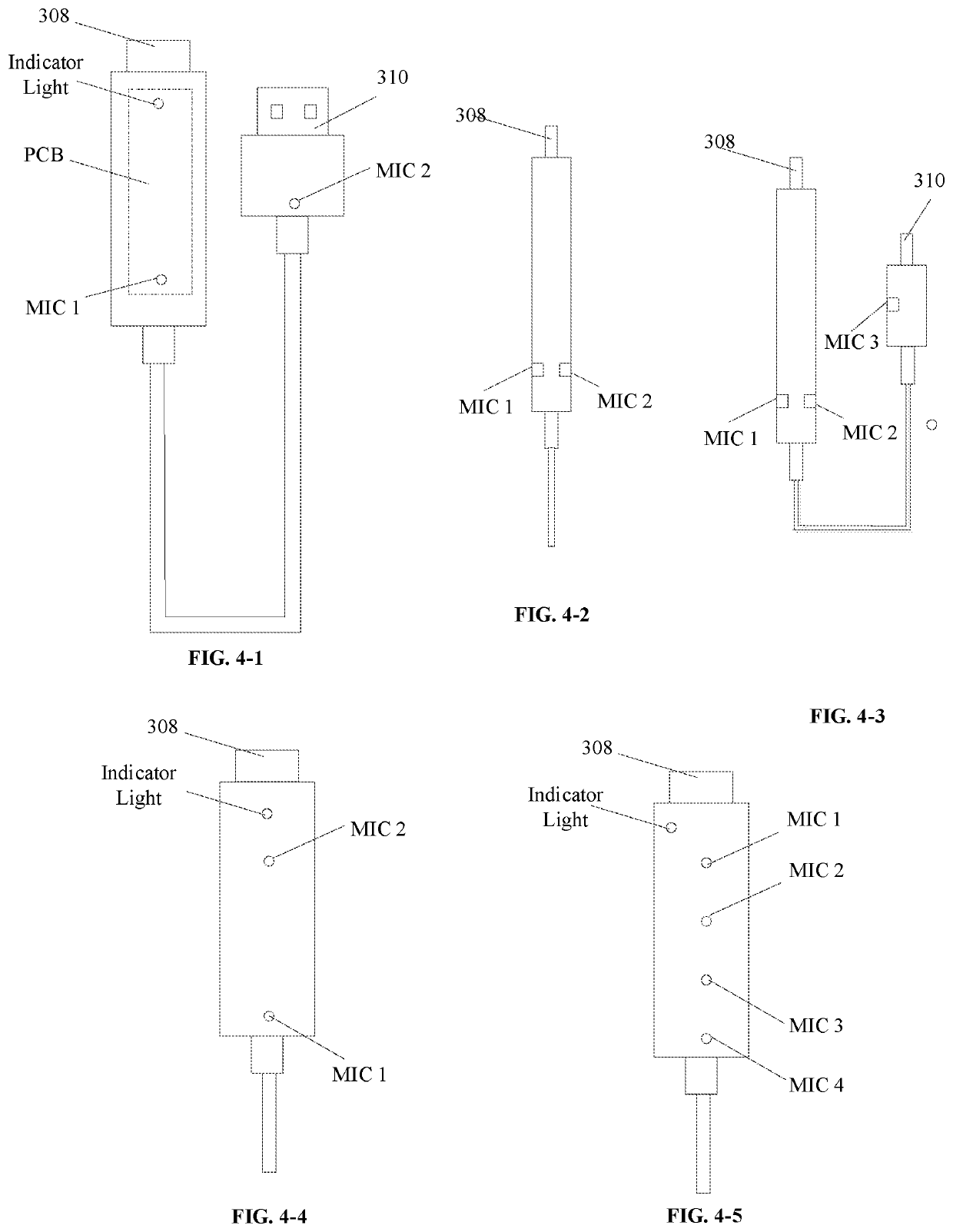

Audio device and audio processing method

The present disclosure provides an audio device and an audio processing method based on the charger cable. The audio device includes: at least two microphones configured to collect audio signals; and a microcontroller configured to, process the audio signals collected by the at least two microphones to generate one data stream; and when the audio device is connected to a computing terminal, send the data stream to the computing terminal, the data stream being further processed by the computing terminal to perform an action. Each of the at least two microphones is respectively connected to the microcontroller.

Owner:KIKAGO LTD

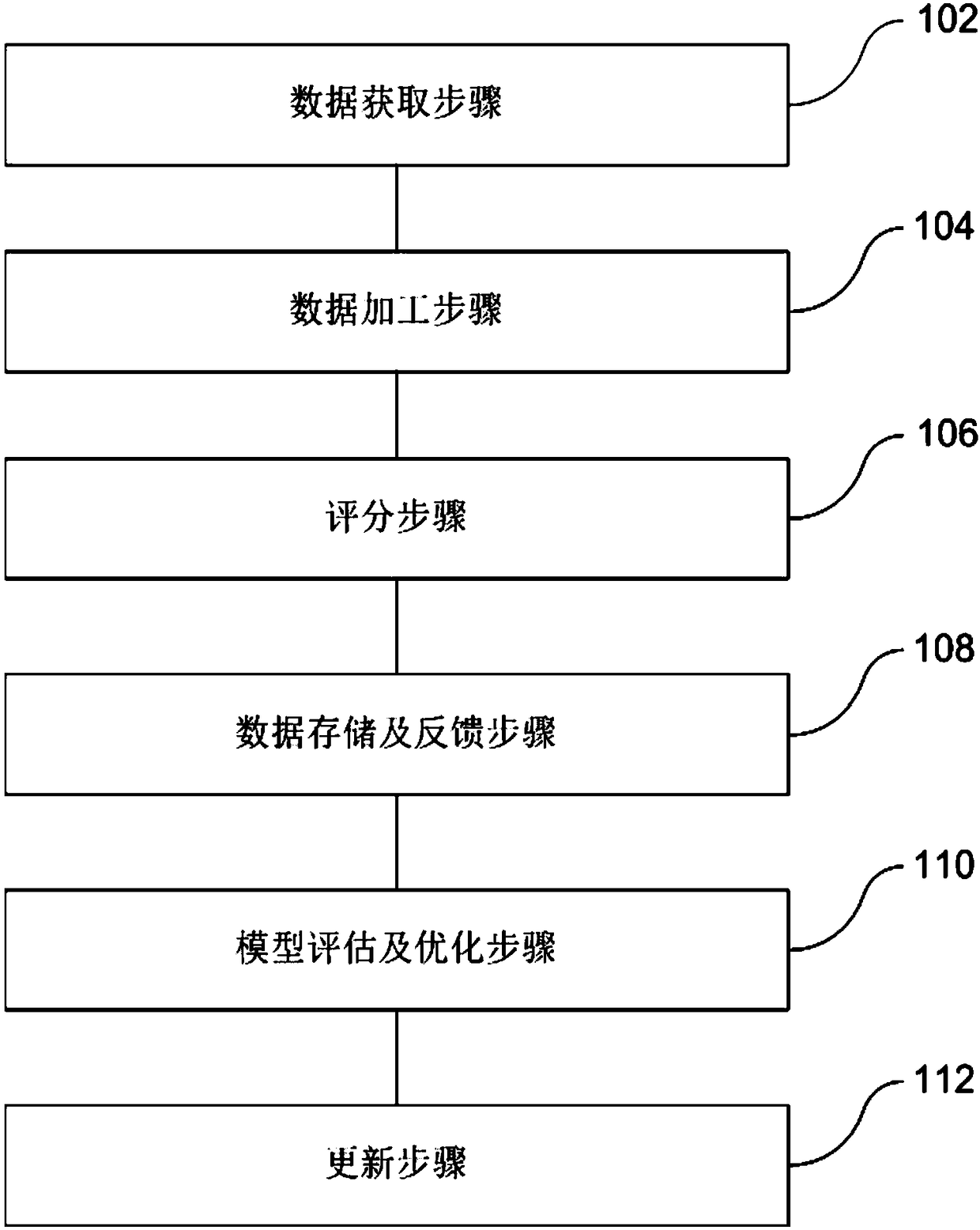

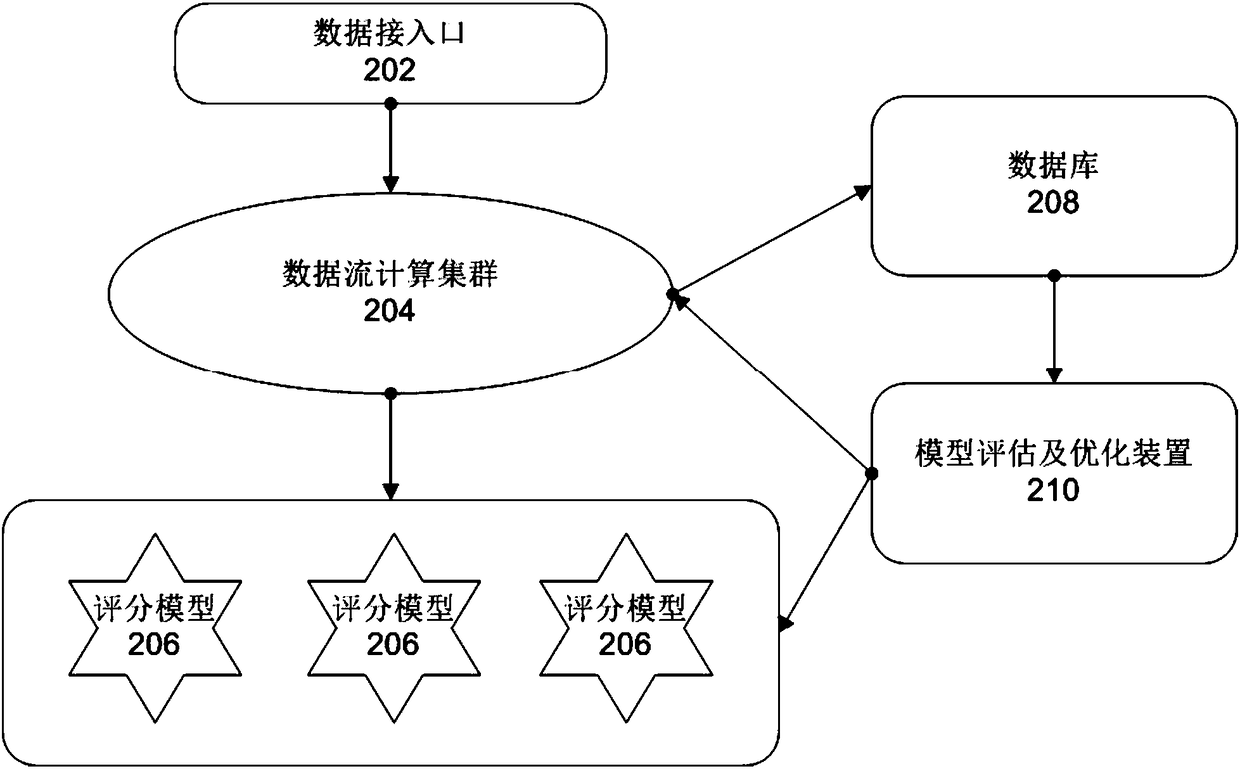

Real-time grading method and grading system for credit of users

InactiveCN108446291AStrong data theory supportFinanceWeb data retrievalReal-time dataData acquisition

The invention brings forward a real-time grading method for credit of users. The method comprises the following steps: a data acquisition step of acquiring basic data of users through internet, a dataprocessing step of importing acquired basic data into dataflow computation cluster for real-time data processing, a grading step of importing processed basic data into one or multiple grading modelsand grading the processed basic data, wherein one or multiple grading models is / are established according to existing data, a data storage and feedback step of saving the basic data, the processed basic data and grades into a database and acquiring feedback information, a model evaluation and optimization step of evaluating and optimizing the one or multiple grading models and the dataflow computation cluster according to the saved basic data, the processed basic data, the grades and the feedback information, and an update step of updating the applied one or multiple grading models and the dataflow computation cluster according to optimized one or multiple grading models and the dataflow computation cluster. The invention also puts forward a real-time grading system for credit of users.

Owner:深圳萨摩耶数字科技有限公司

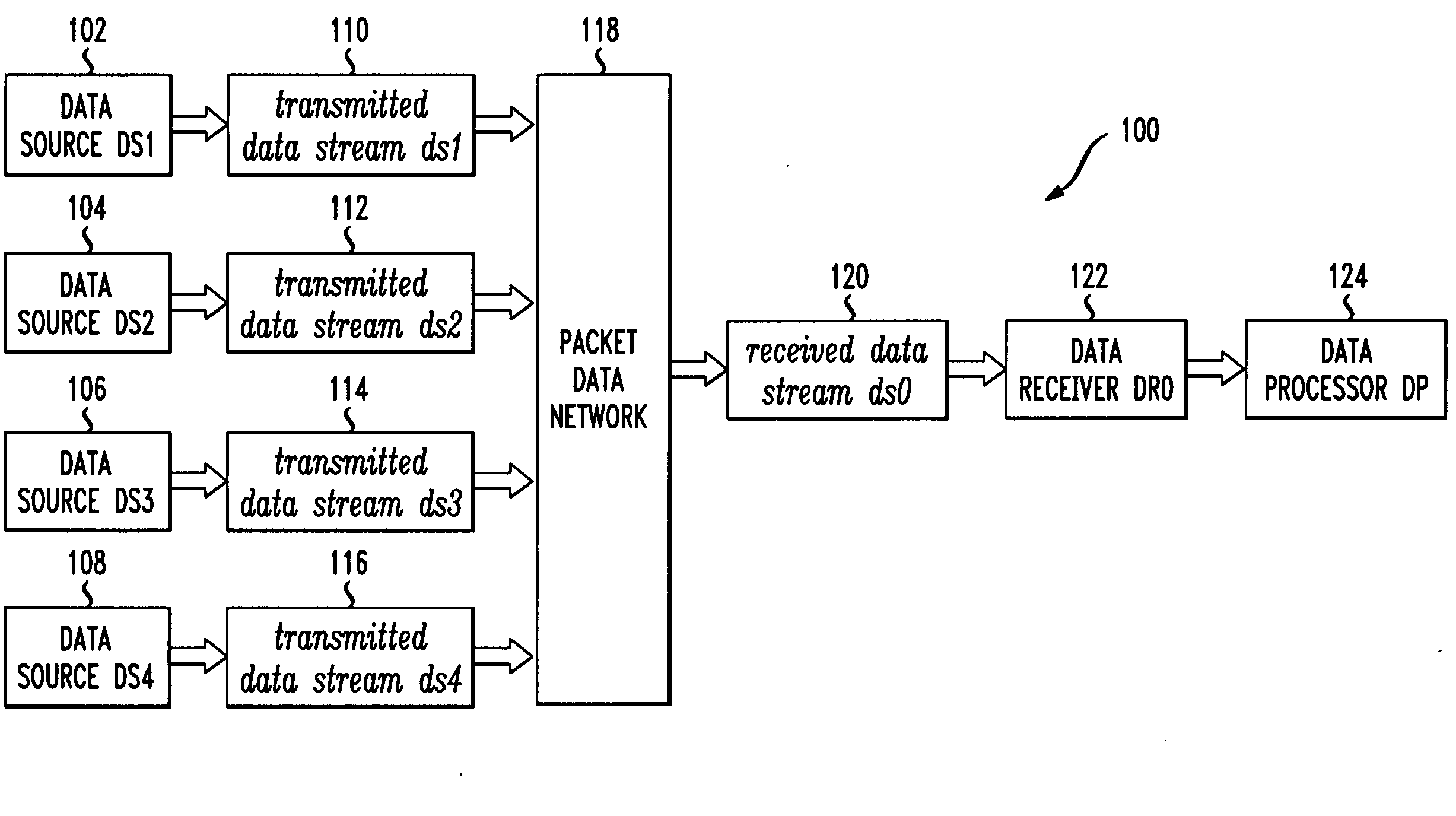

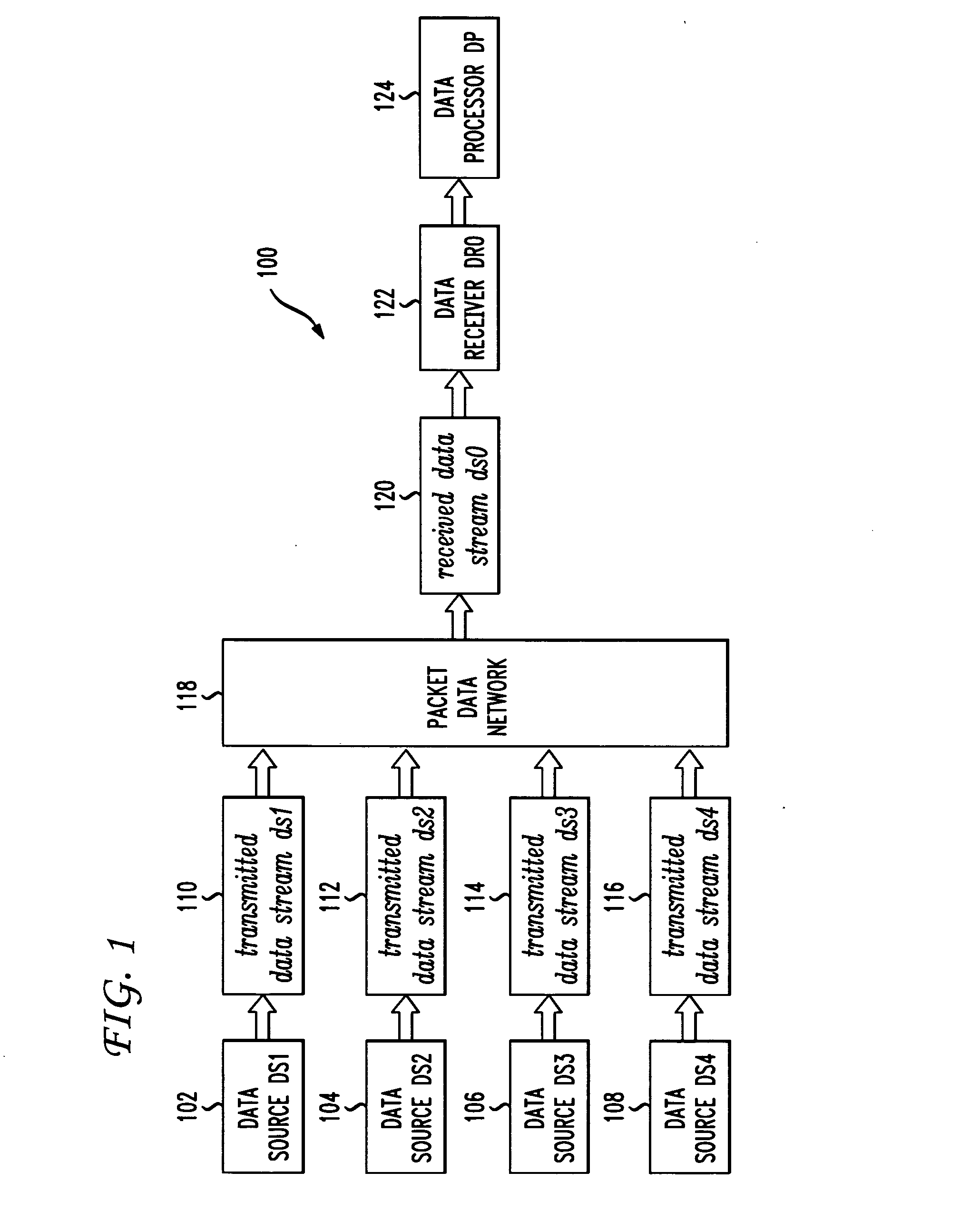

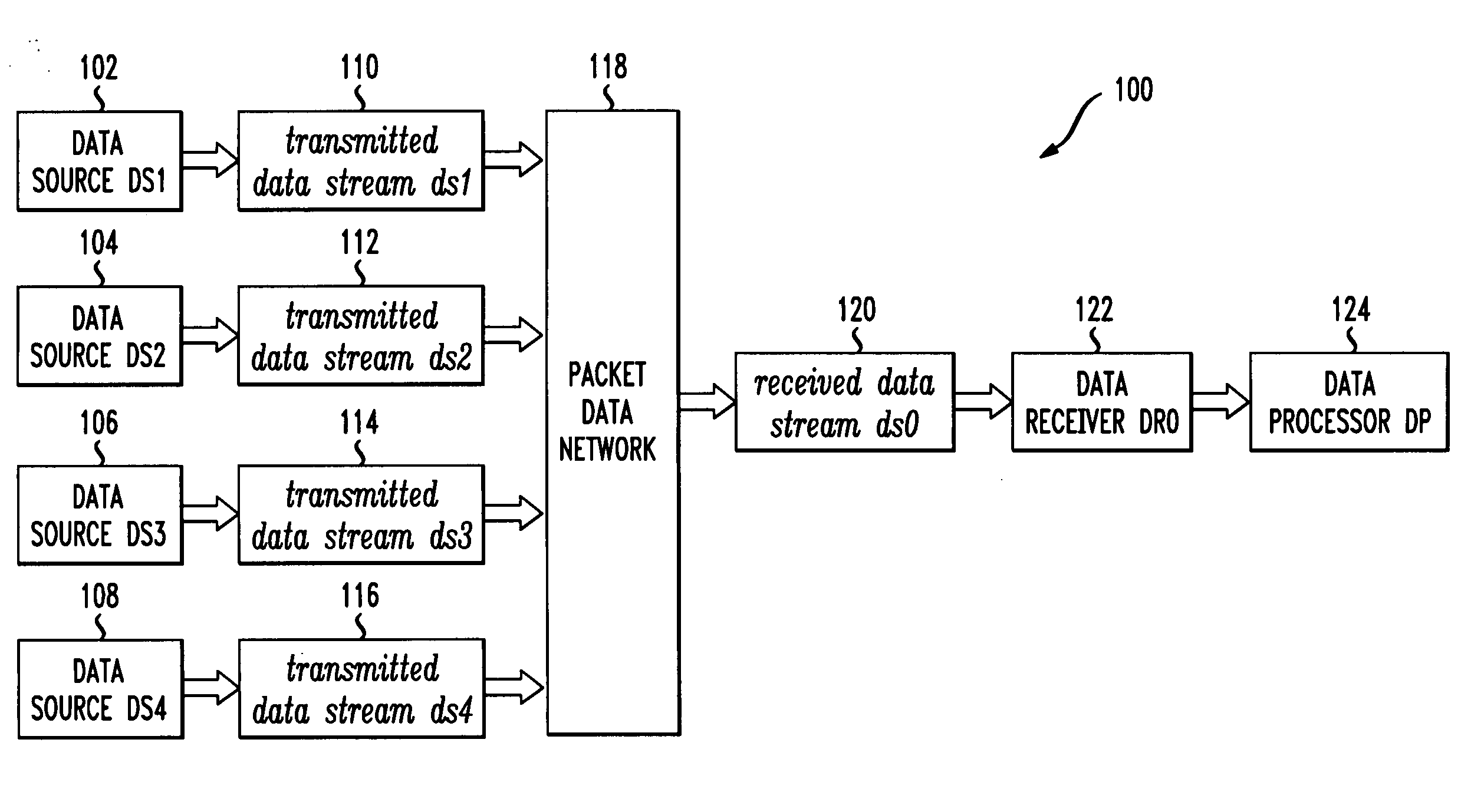

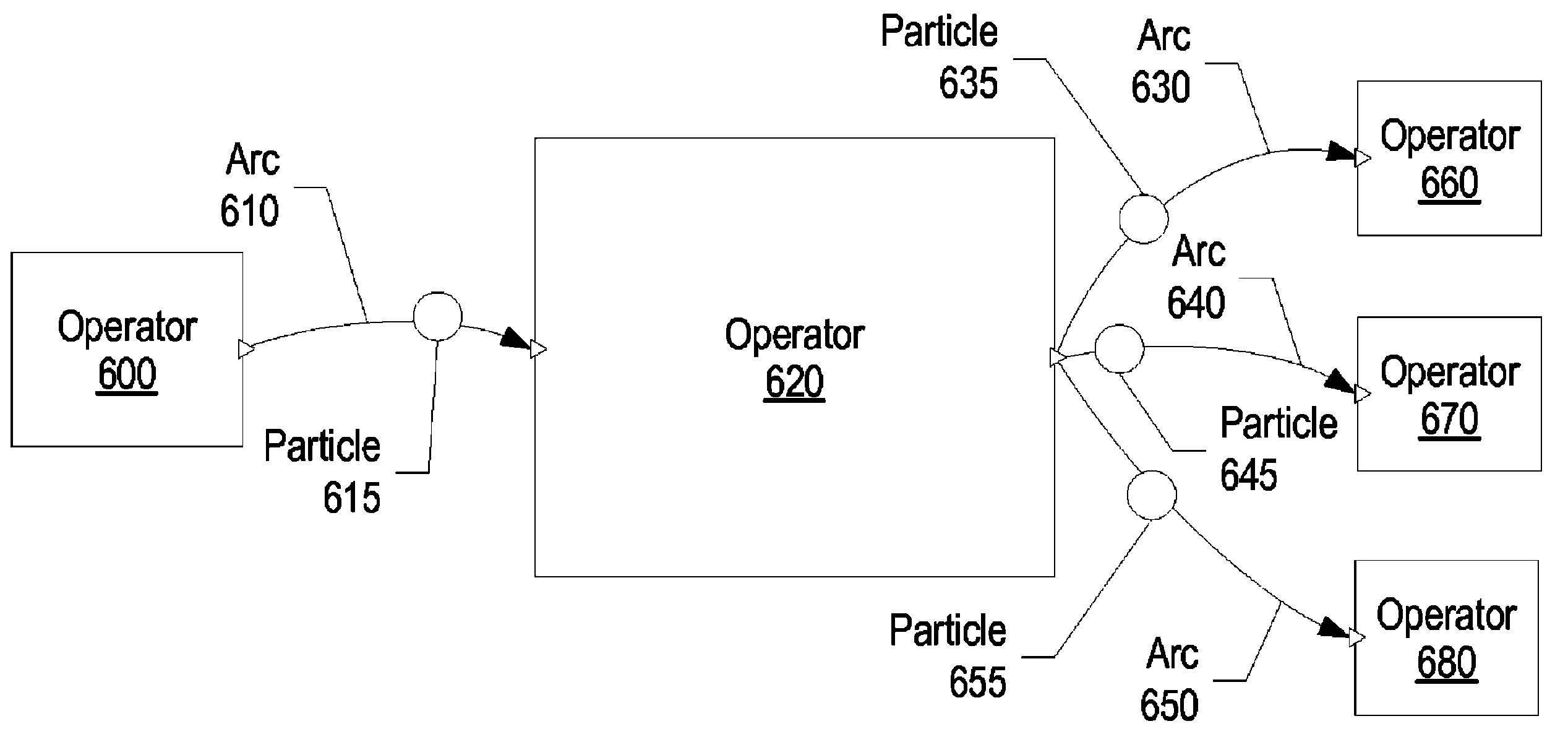

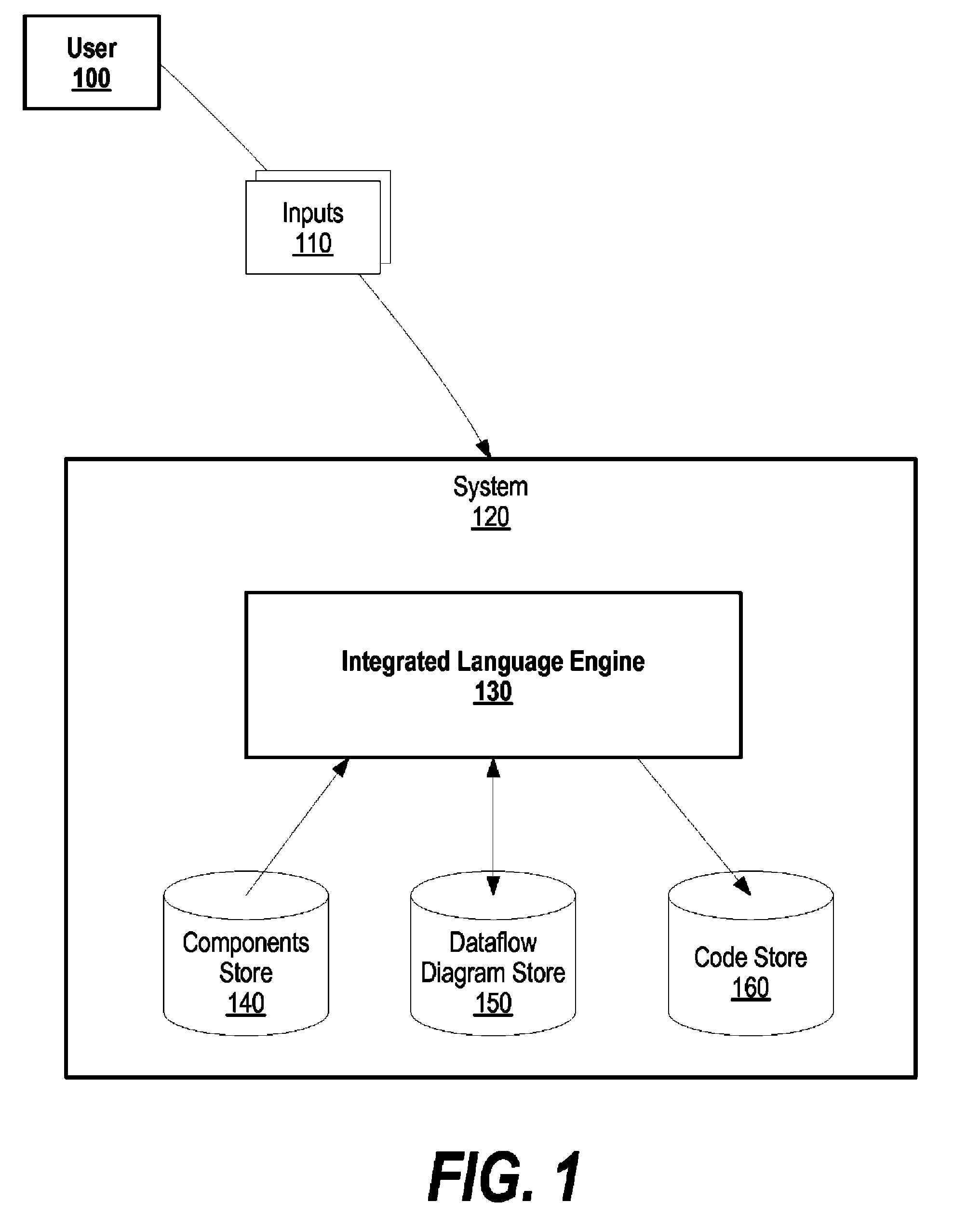

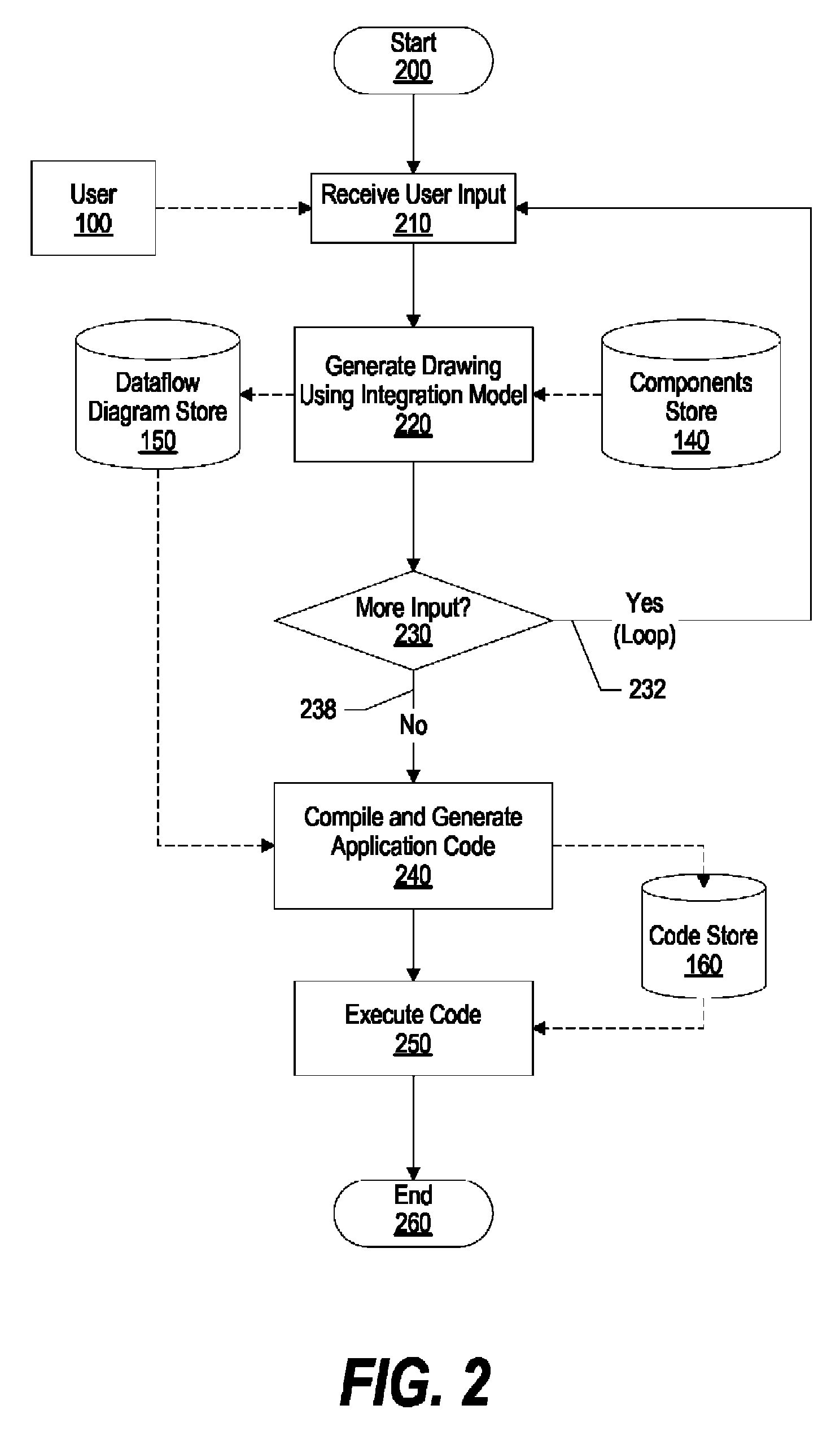

System and method for simulating data flow using dataflow computing system

InactiveUS7774189B2Analogue computers for electric apparatusGeneral purpose stored program computerControl flowData stream

A system and method for implementing a unified model for integration systems is presented. A user provides inputs to an integrated language engine for placing operator components and arc components onto a dataflow diagram. Operator components include data ports for expressing data flow, and also include meta-ports for expressing control flow. Arc components connect operator components together for data and control information to flow between the operator components. The dataflow diagram is a directed acyclic graph that expresses an application without including artificial boundaries during the application design process. Once the integrated language engine generates the dataflow diagram, the integrated language engine compiles the dataflow diagram to generated application code.

Owner:LINKEDIN

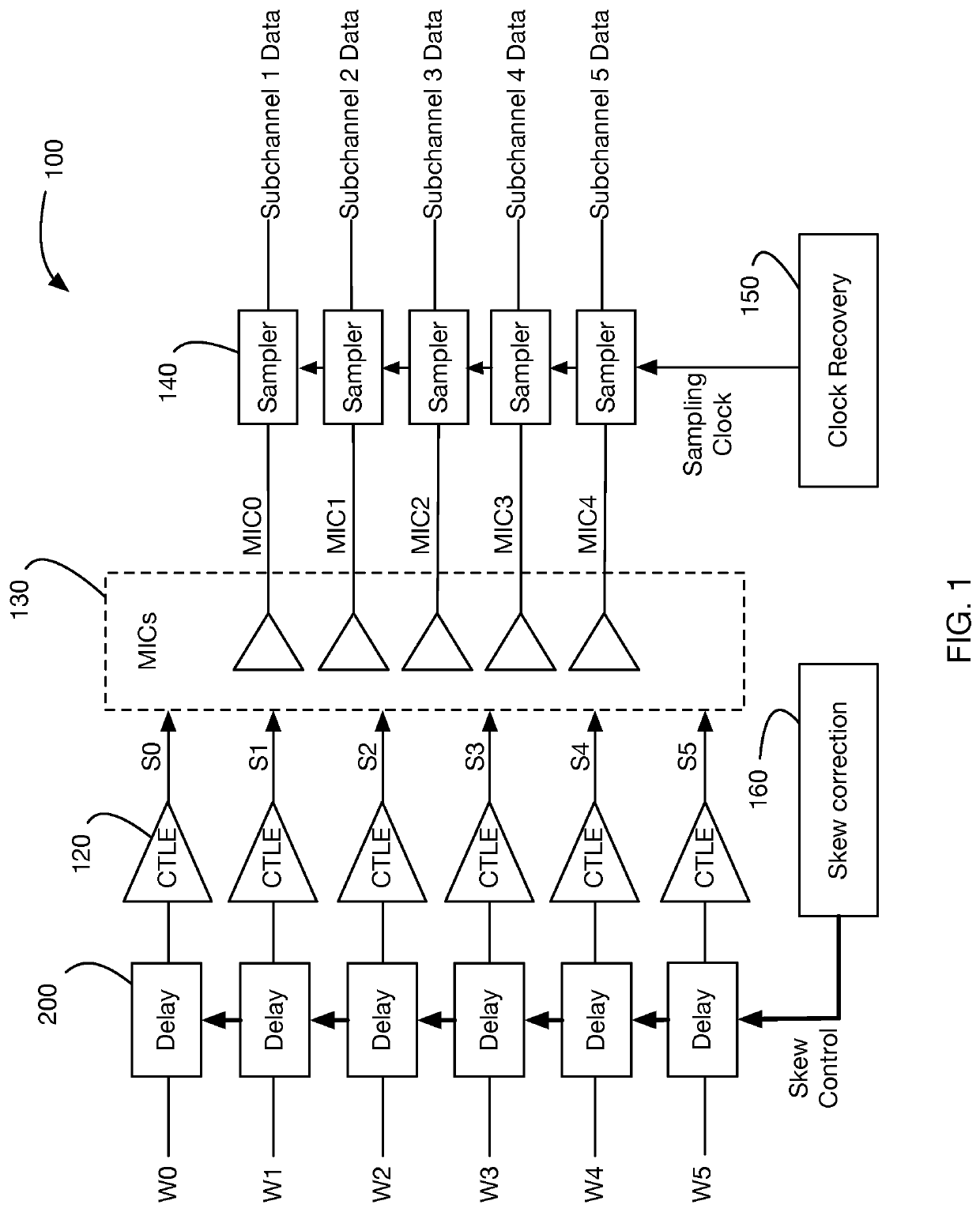

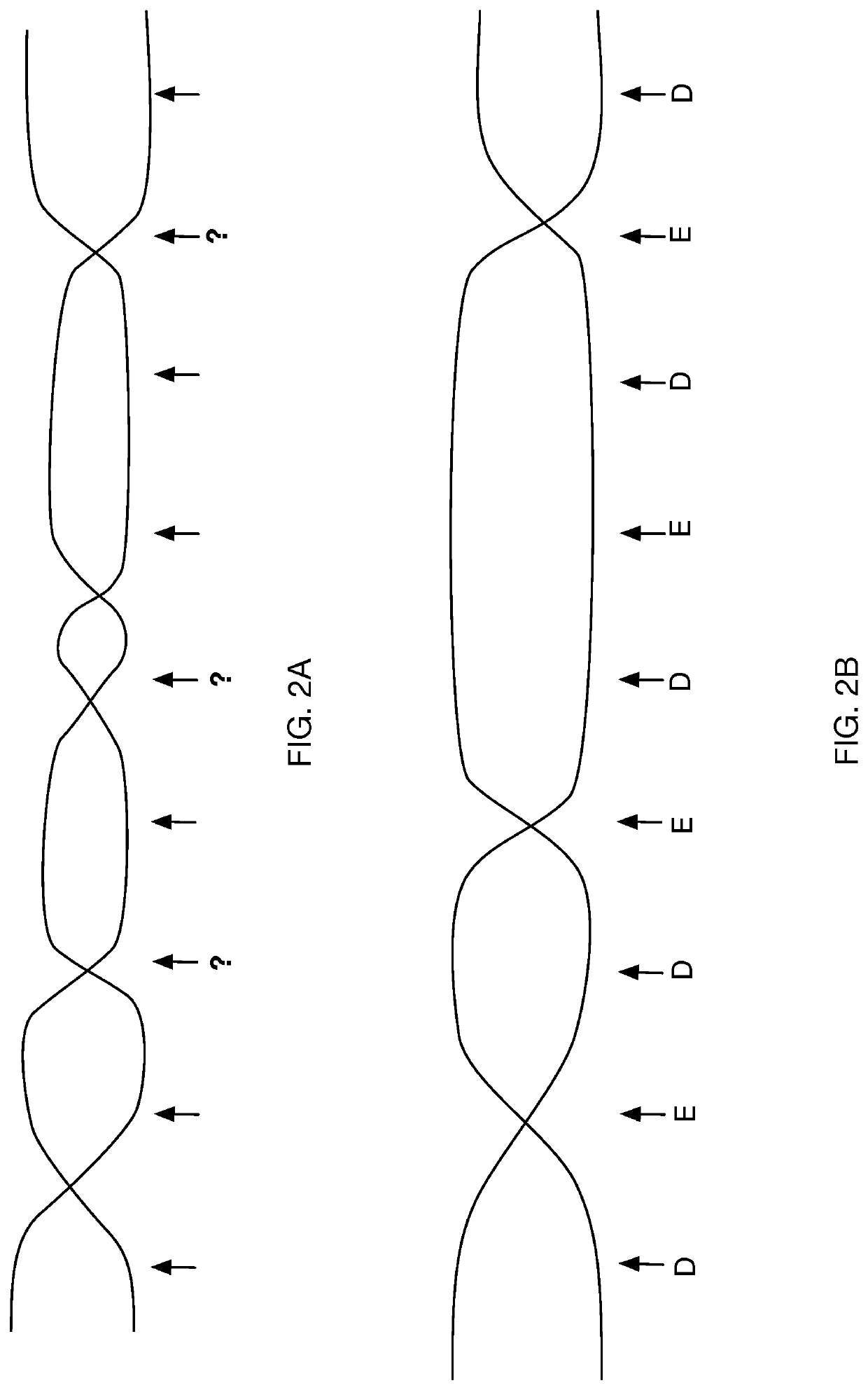

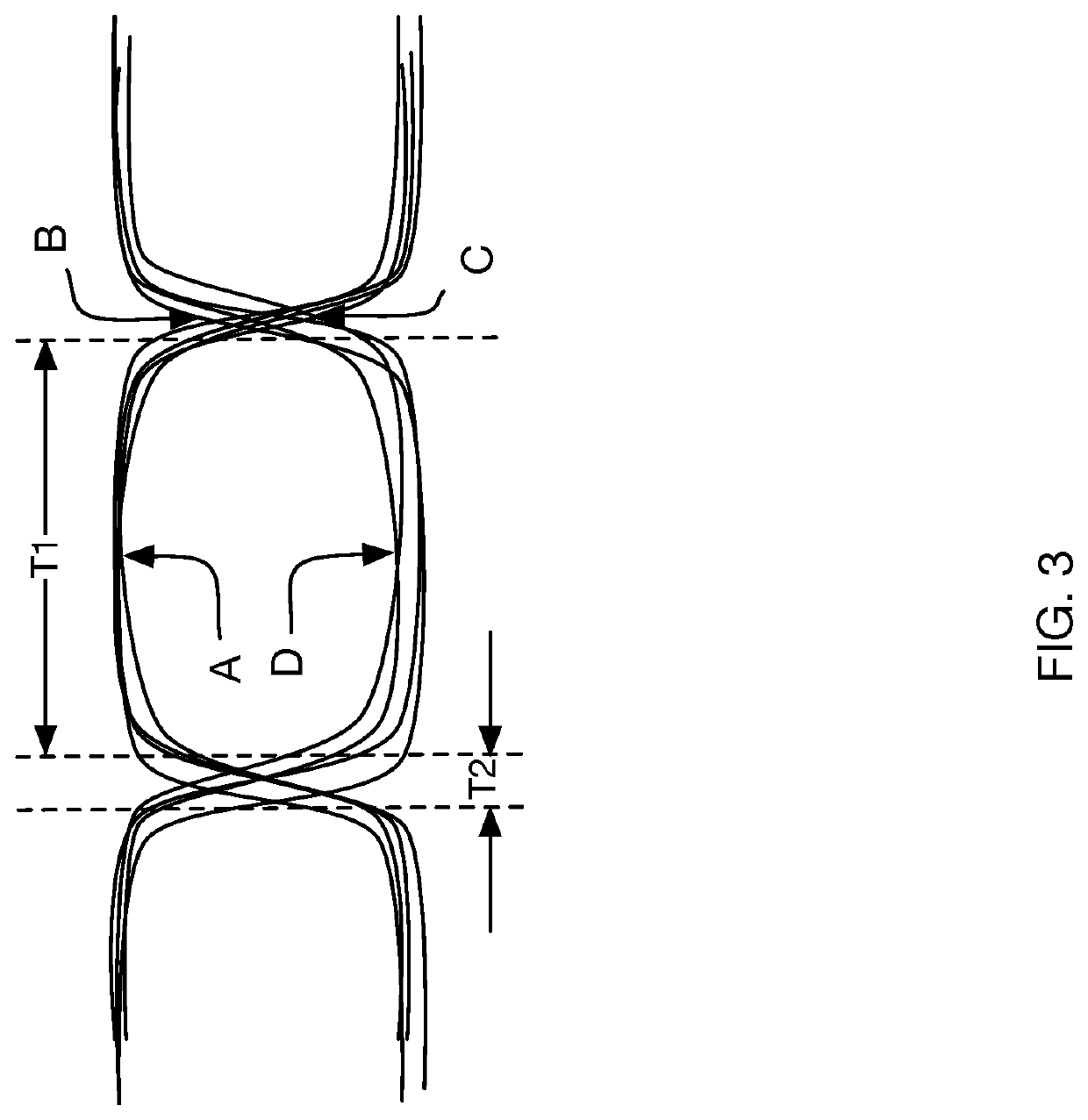

Method for measuring and correcting multiwire skew

ActiveUS20200119901A1Reliable detectionAccurate interpretationSynchronisation information channelsError detection/correctionData streamAlgorithm

Methods and systems are described for sequentially obtaining a plurality of data streams, the plurality of data streams comprising a data stream in a current condition, a data stream in a skewed-forward condition, and a data stream in a skewed-backward condition, calculating, for each data stream in the plurality of data streams, a corresponding set of cost-function values by obtaining a corresponding set of eye measurements, the eye measurements obtained by adjusting a sampling threshold of a sampler generating a plurality of samples of the data stream, the plurality of samples comprising edge samples and data samples, wherein the data stream is sampled at a rate equal to twice a rate of the data stream and calculating the corresponding set of cost-function values based on the corresponding set of eye measurements, and generating a skew control signal based on a comparison of the sets of calculated cost-function values.

Owner:KANDOU LABS

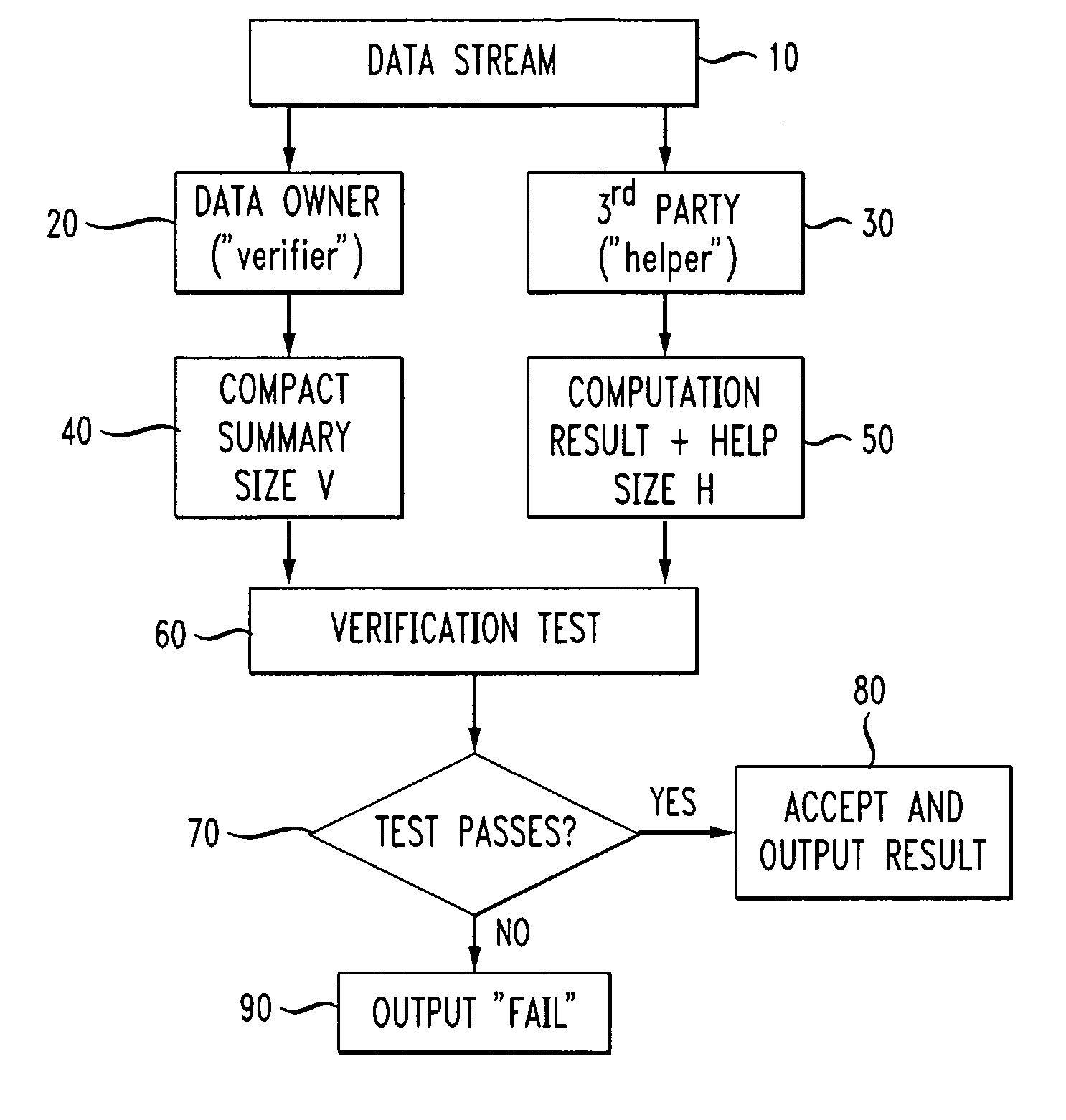

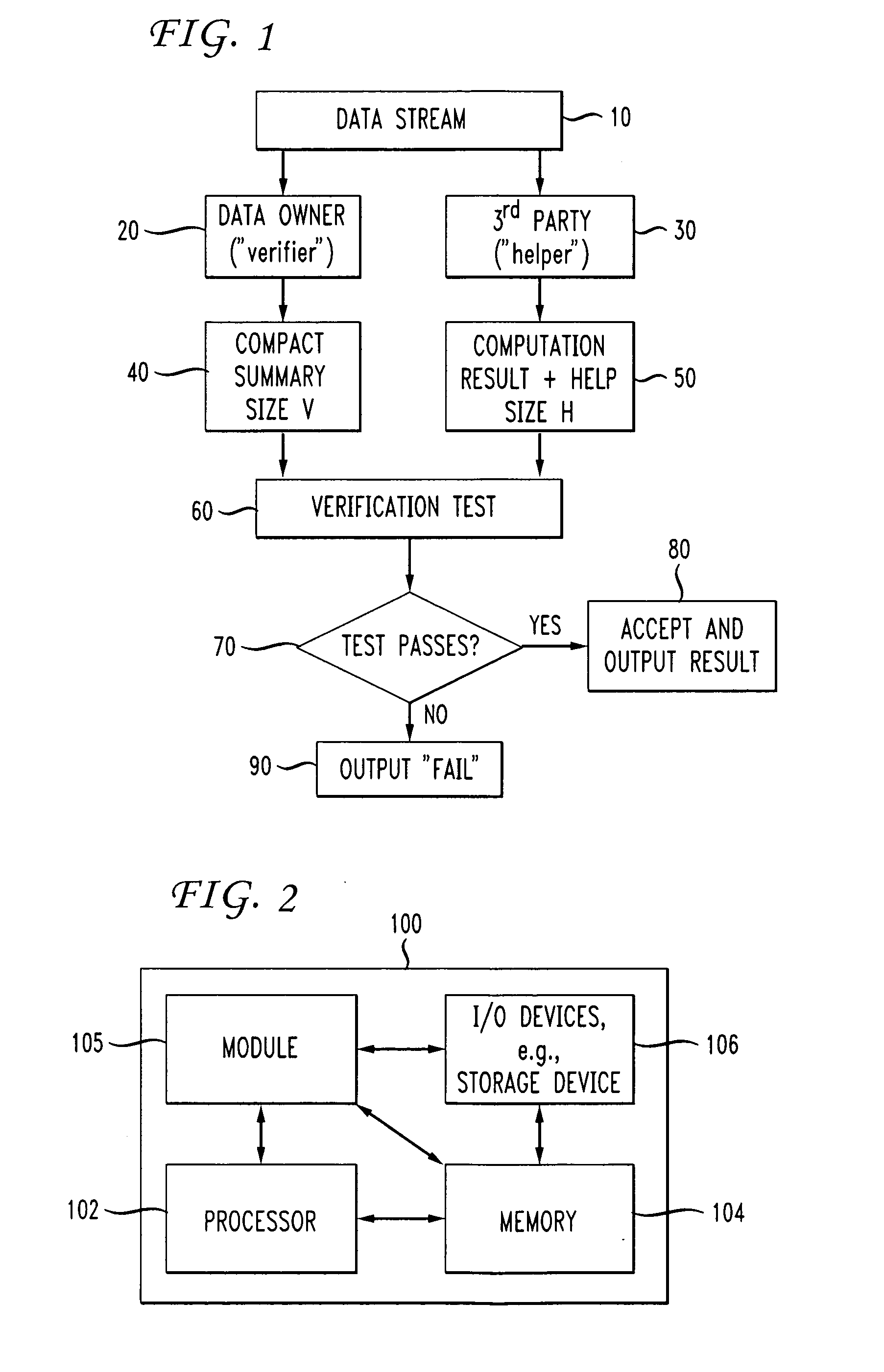

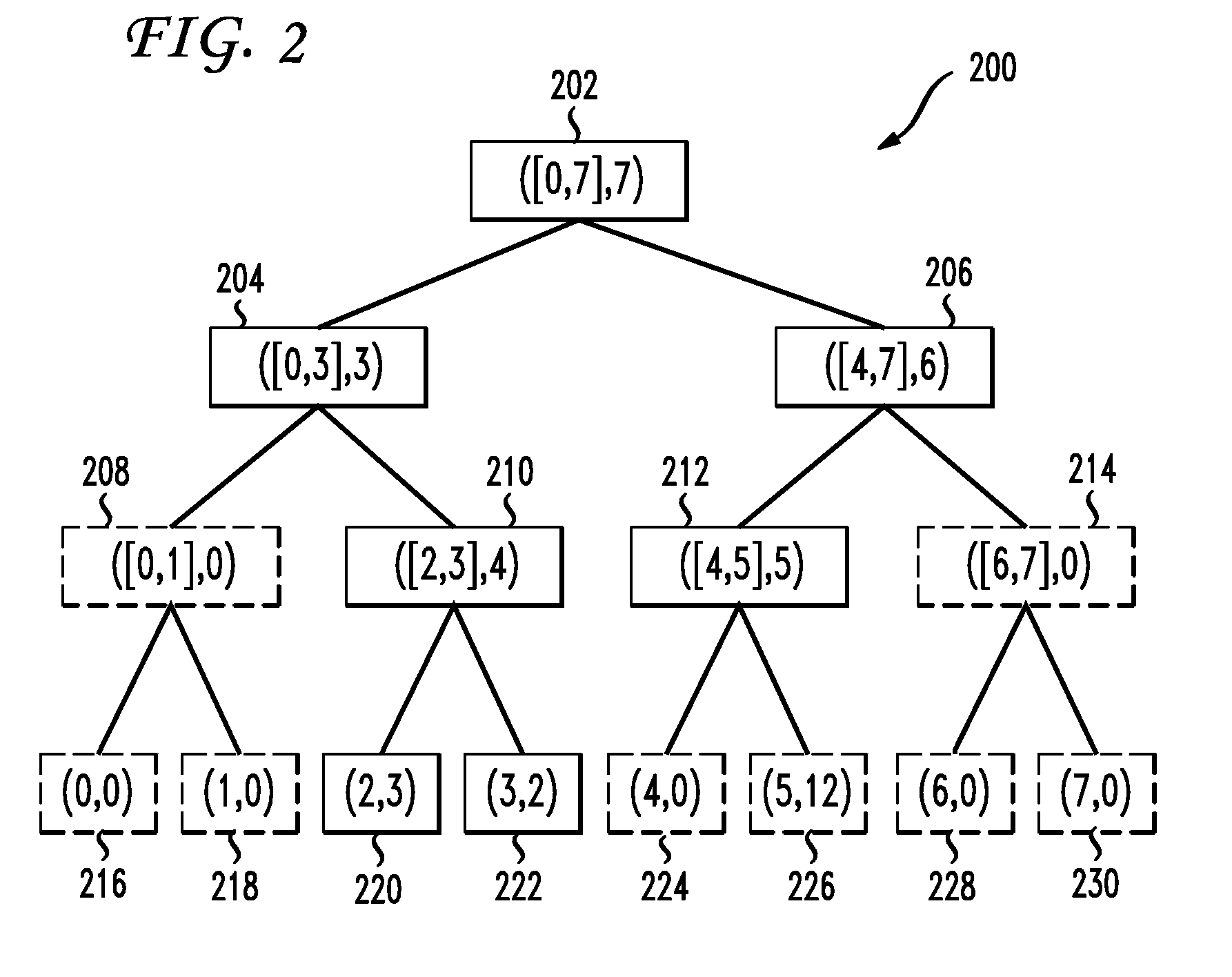

Verification Of Data Stream Computations Using Third-Party-Supplied Annotations

A third party that performs data stream computation is requested to return not only the solution to the computation, but also “annotations” to the original data stream. The annotations are then used by the data owner (in actuality, a “verifier” associated with the data owner) to check the results of the third party's computations. As implemented, the verifier combines the annotations with the original data, performs some computations, and is then assured of the correctness of the provided solution. The cost of verification is significantly lower to the data owner than the cost of fully processing the data “in house”.

Owner:TRUSTEES OF DARTMOUTH COLLEGE THE +1

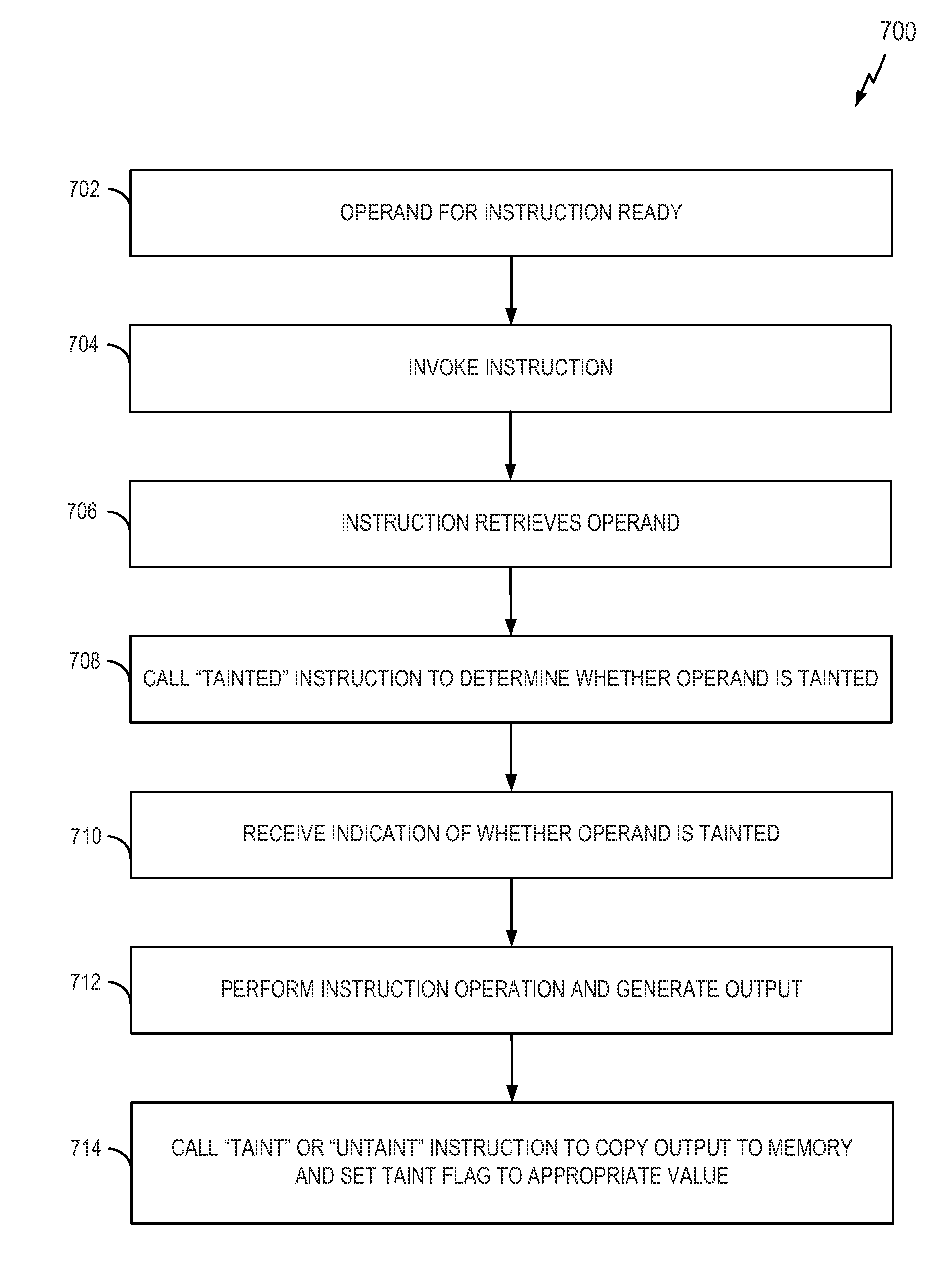

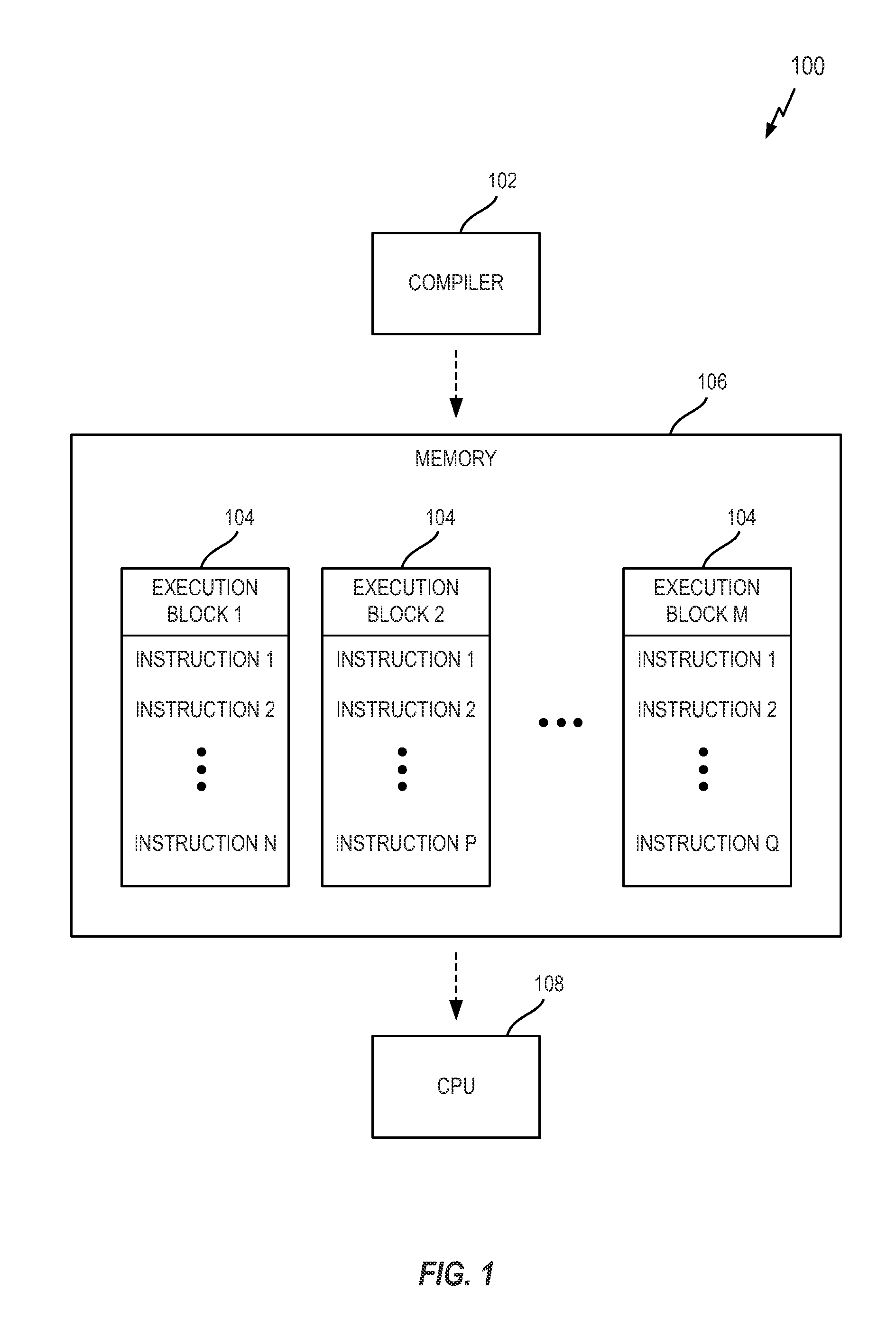

Mechanism for tracking tainted data

InactiveUS20160232346A1Non-macromolecular adhesive additivesPolarising elementsData integrityData storing

The disclosure relates in some aspects to protecting systems and data from maliciously caused destruction. Data integrity is maintained by monitoring data to detect and prevent potential attacks. A mechanism for tracking whether data is tainted is implemented in a Data Flow computer architecture or some other suitable architecture. In some aspects, a taint checking mechanism is implemented within a register file, memory management, and an instruction set of such an architecture. To this end, an indication of whether the data stored in a given physical memory location is tainted is stored along with the physical memory location. For example, a register can include a bit for a corresponding taint flag, a memory page can include a bit for a corresponding taint flag, and an input / output (I / O) port can include a bit for a corresponding taint flag.

Owner:QUALCOMM INC

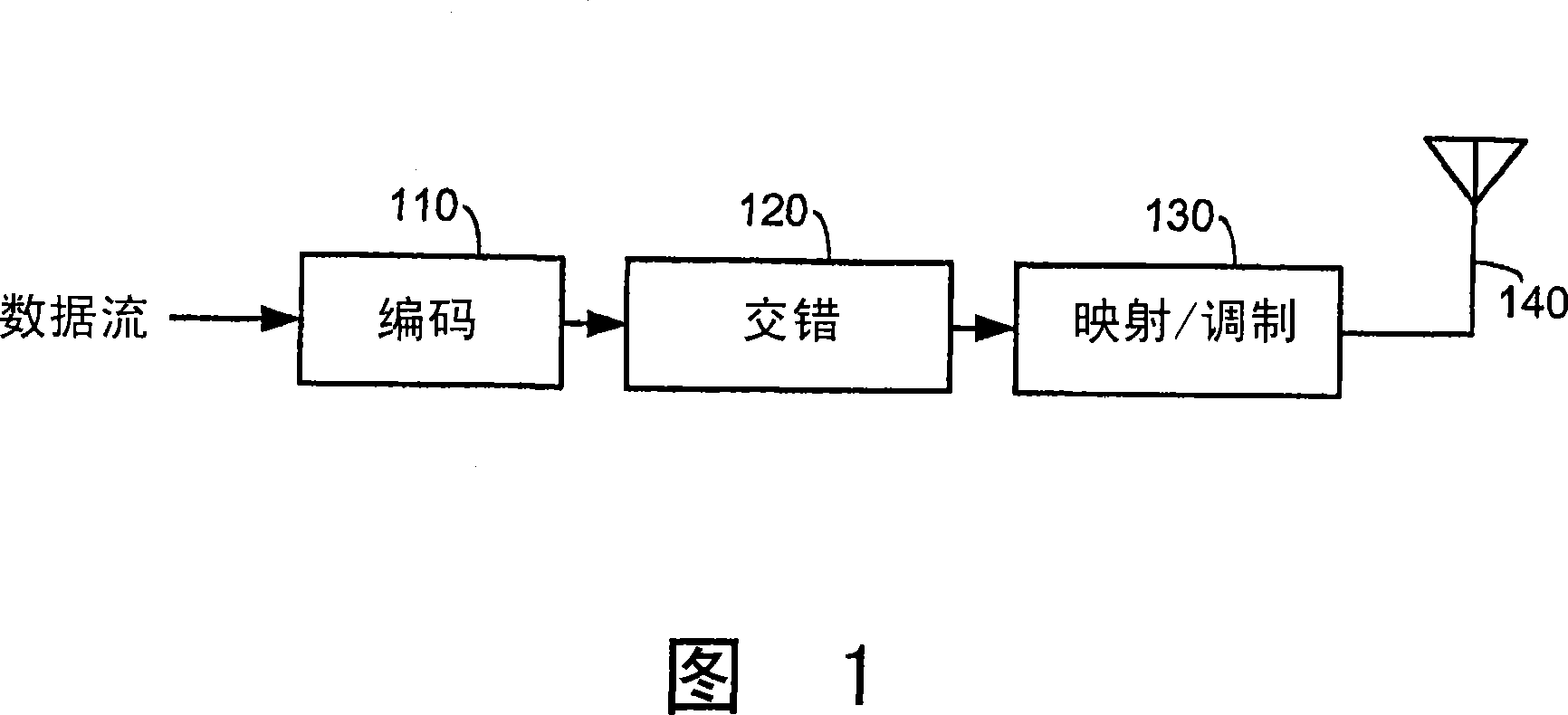

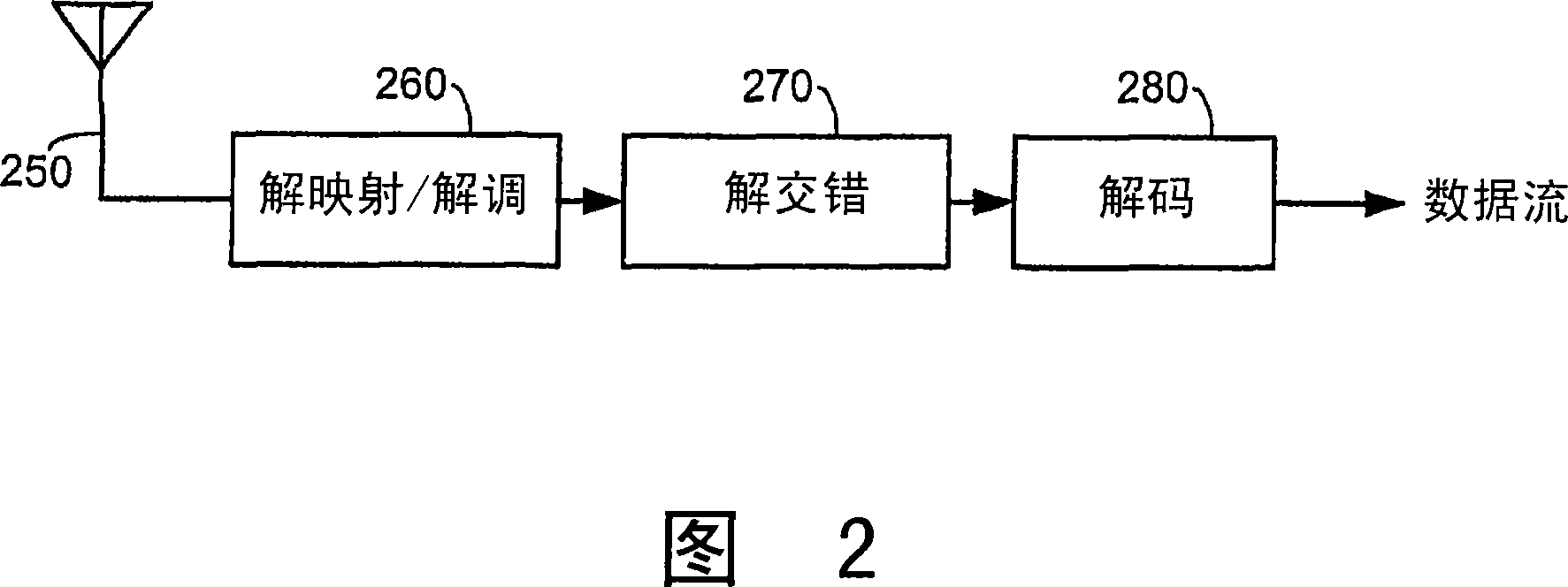

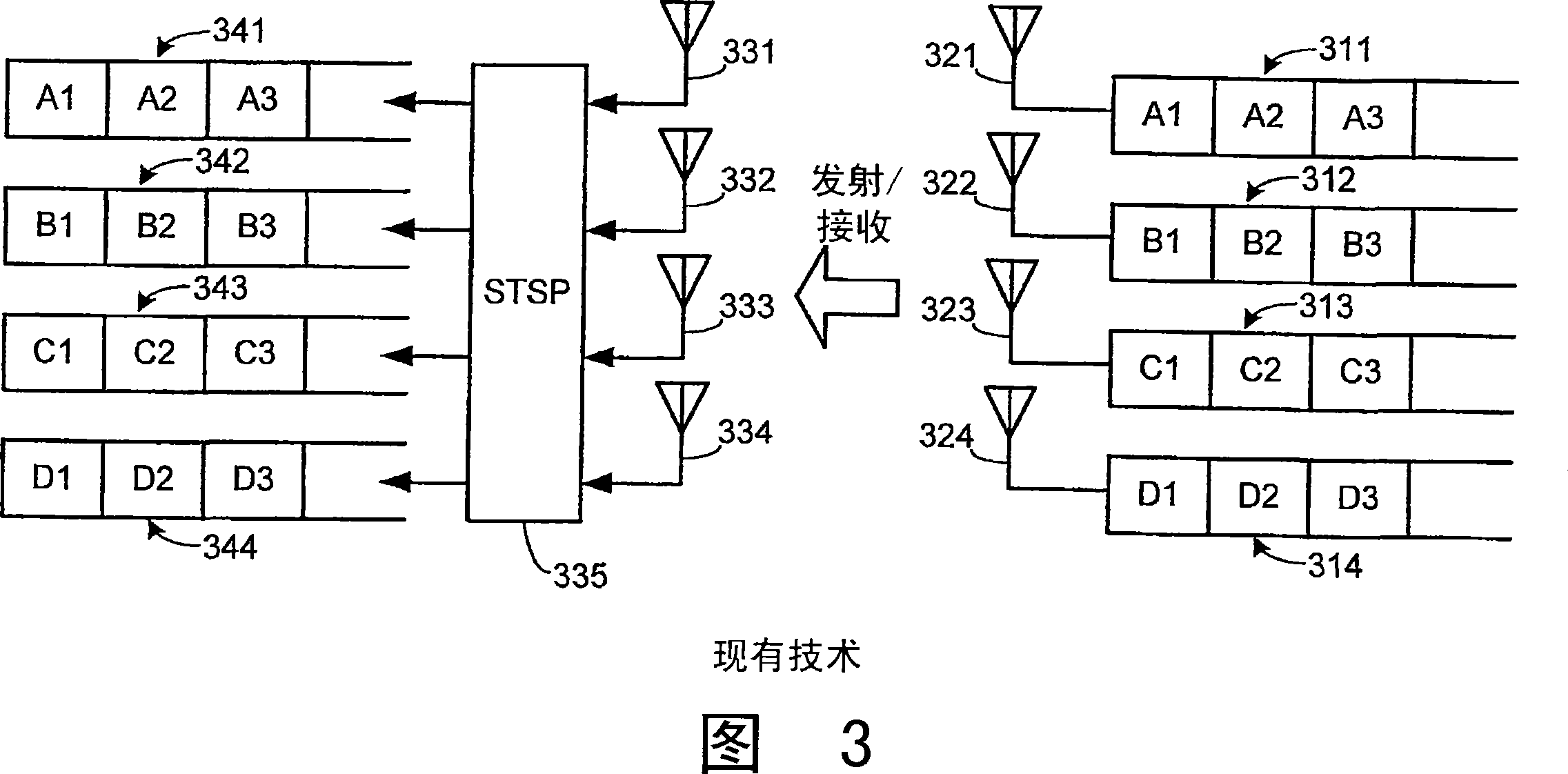

Systems and methods for reducing uplink resources to provide channel performance feedback for adjustment of downlink mimo channel data rates

ActiveCN101160770AReduce the amount of resourcesImprove performanceSpatial transmit diversityError detection/prevention using signal quality detectorData streamCommunications system

Systems and methods for improving the performance of a MIMO wireless communication system by reducing the amount of uplink resources that are needed to provide channel performance feedback for the adjustment of data rates on the downlink MIMO channels. In one embodiment, a method comprises encoding each of a set of data streams according to corresponding data rates, permuting the data streams on a set of MIMO channels according to a full permutation of combinations, transmitting the permuted data streams, receiving the permuted data streams, decoding and determining an SNR for each of the data streams, computing a condensed SNR metric for the set of data streams, providing the condensed metric as feedback, determining a set of individual SNR metrics for the data streams based on the condensed SNR metric, and adjusting the data rates at which the data streams are encoded based on the individual SNR metrics.

Owner:QUALCOMM INC

Computing Time-Decayed Aggregates in Data Streams

ActiveUS20130155892A1Increase weightReduced computing resourceError preventionTransmission systemsData streamTimestamp

Aggregates are calculated from a data stream in which data is sent in a sequence of tuples, in which each tuple comprises an item identifier and a timestamp indicating when the tuple was transmitted. The tuples may arrive out-of-order, that is, the sequence in which the tuples arrive are not necessarily in the sequence of their corresponding timestamps. In calculating aggregates, more recent data may be given more weight by multiplying each tuple by a decay function which is a function of the timestamp associated with the tuple and the current time. The tuples are recorded in a quantile-digest data structure. Aggregates are calculated from the data stored in the quantile-digest data structure.

Owner:IOWA STATE UNIV RES FOUND INC +1

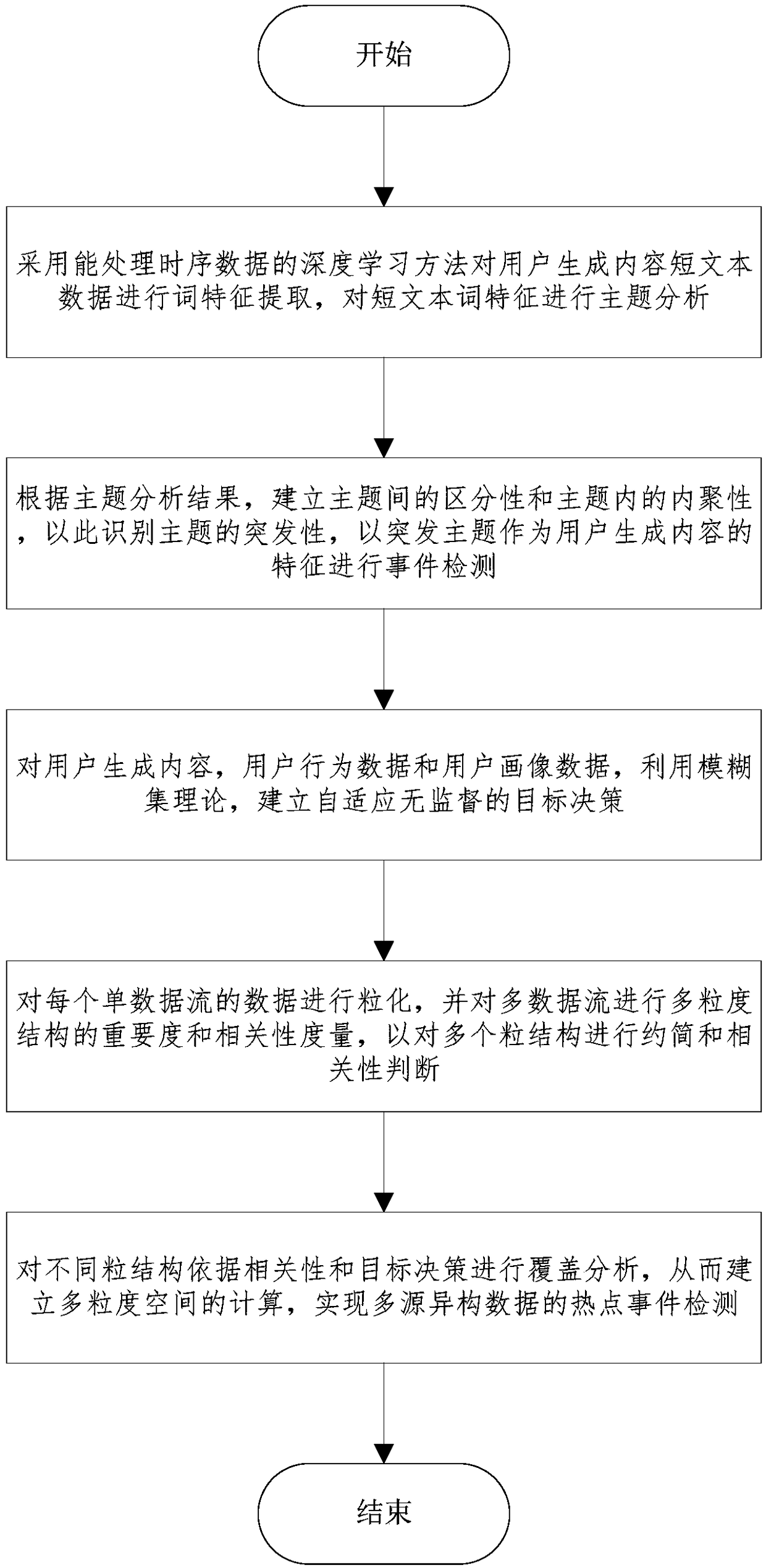

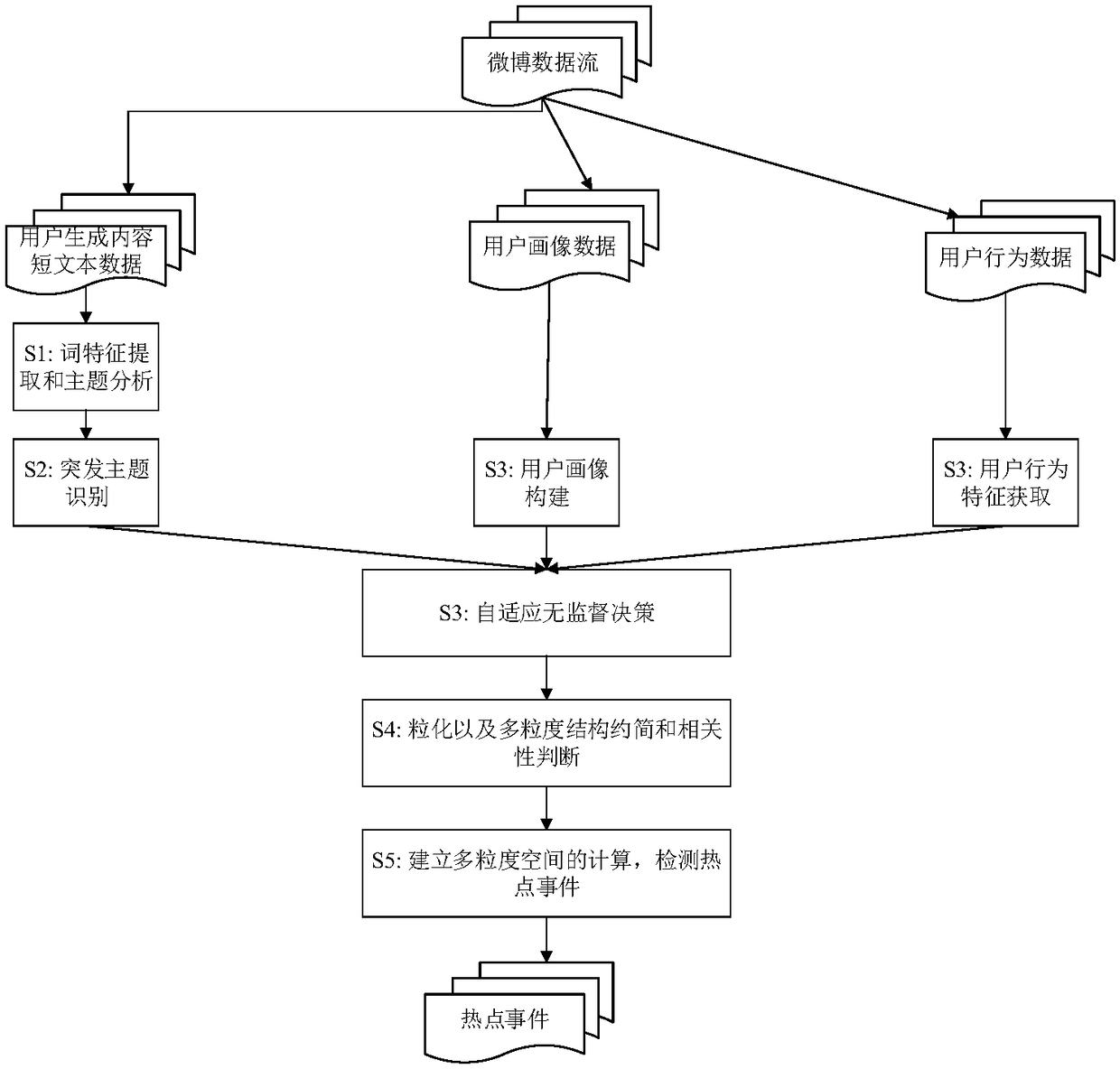

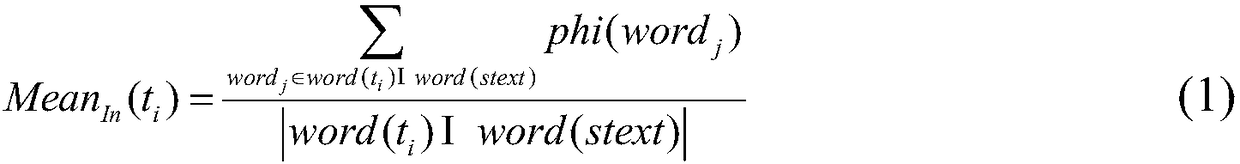

Hot event detection method for social network based on multiple data stream calculation

ActiveCN108519993AImplement hotspot event detectionSolve timing problemsSpecial data processing applicationsSubject analysisData stream

The invention discloses a hot event detection method for social network based on multiple data stream calculation. The hot event detection method comprises the following steps: extracting word features of short text data of user-generated content and making a subject analysis of the word features; establishing differentiations between themes and cohesion within themes and taking sudden themes as features of the user-generated content; establishing self-adaptive unsupervised target decisions with a fuzzy set theory; granulating data of each single data stream and measuring importance and relevance of a multi-granularity structure of multiple data streams in order to reduce and determine relevance of multiple granular structures; and making a coverage analysis of different granule structuresaccording to relevance and target decisions in order to establish calculation of a multi-granularity space and detect hot events. With the hot event detection method, unsupervised and self-adaptive decisions can be made. Multi-source heterogeneous data can be calculated. Hot events in social network can be effectively detected.

Owner:SOUTH CHINA UNIV OF TECH