Patents

Literature

125results about How to "Effectively lead to differentiation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

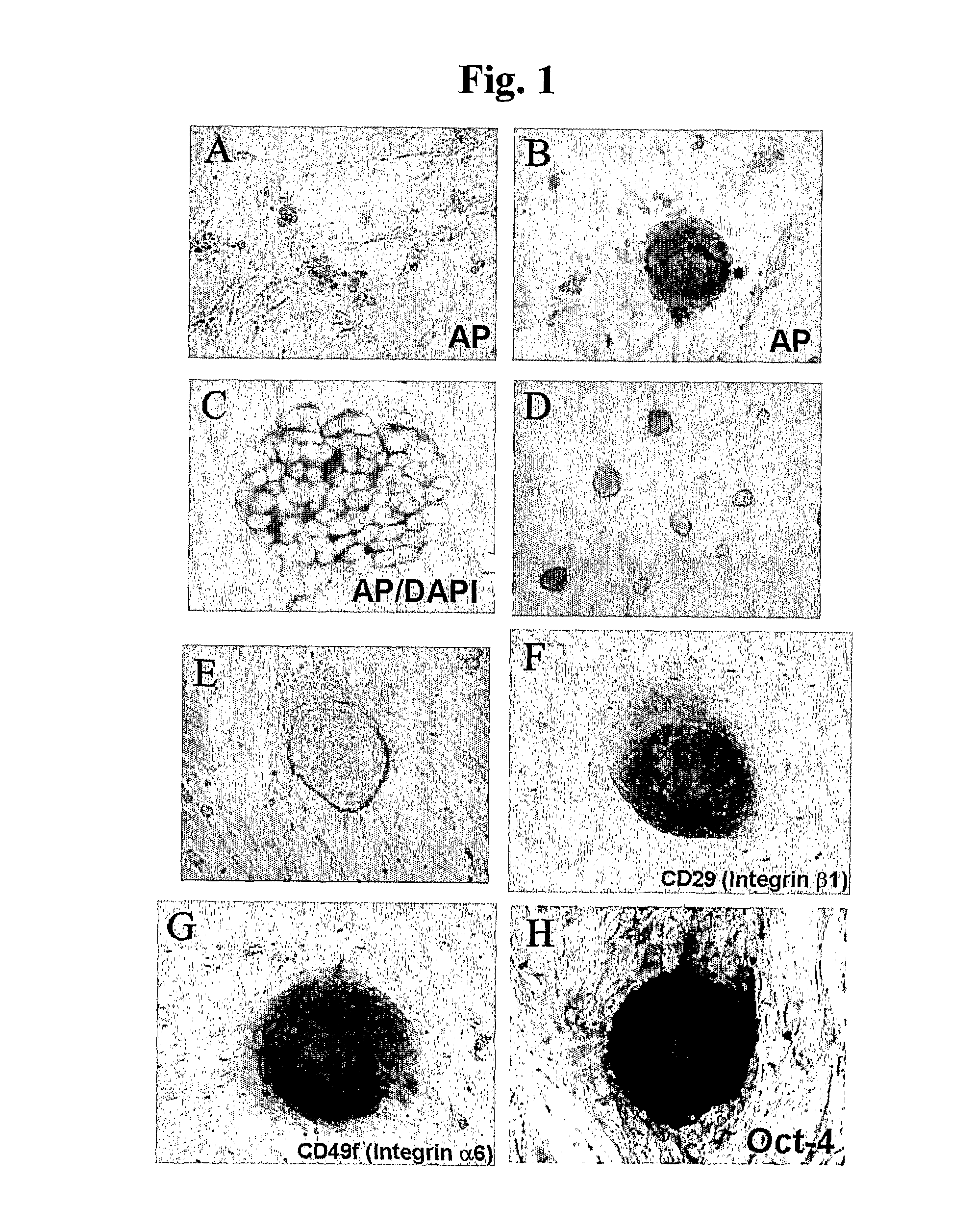

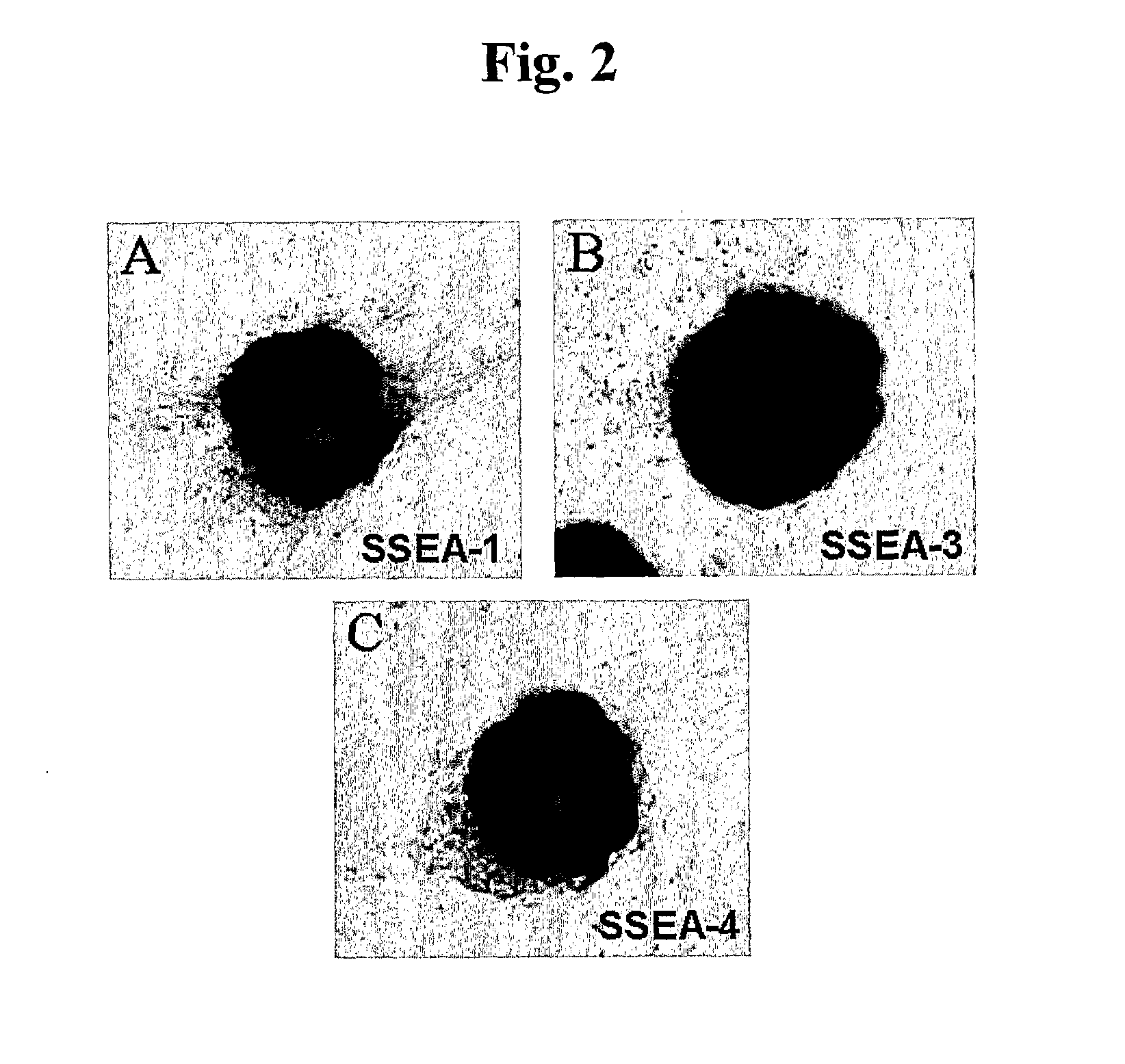

Compositions And Methods For Self-Renewal And Differentiation In Human Embryonic Stem Cells

ActiveUS20070281355A1Efficient productionEffectively lead to differentiationPeptide/protein ingredientsMetabolism disorderGerm layerFeeder Layer

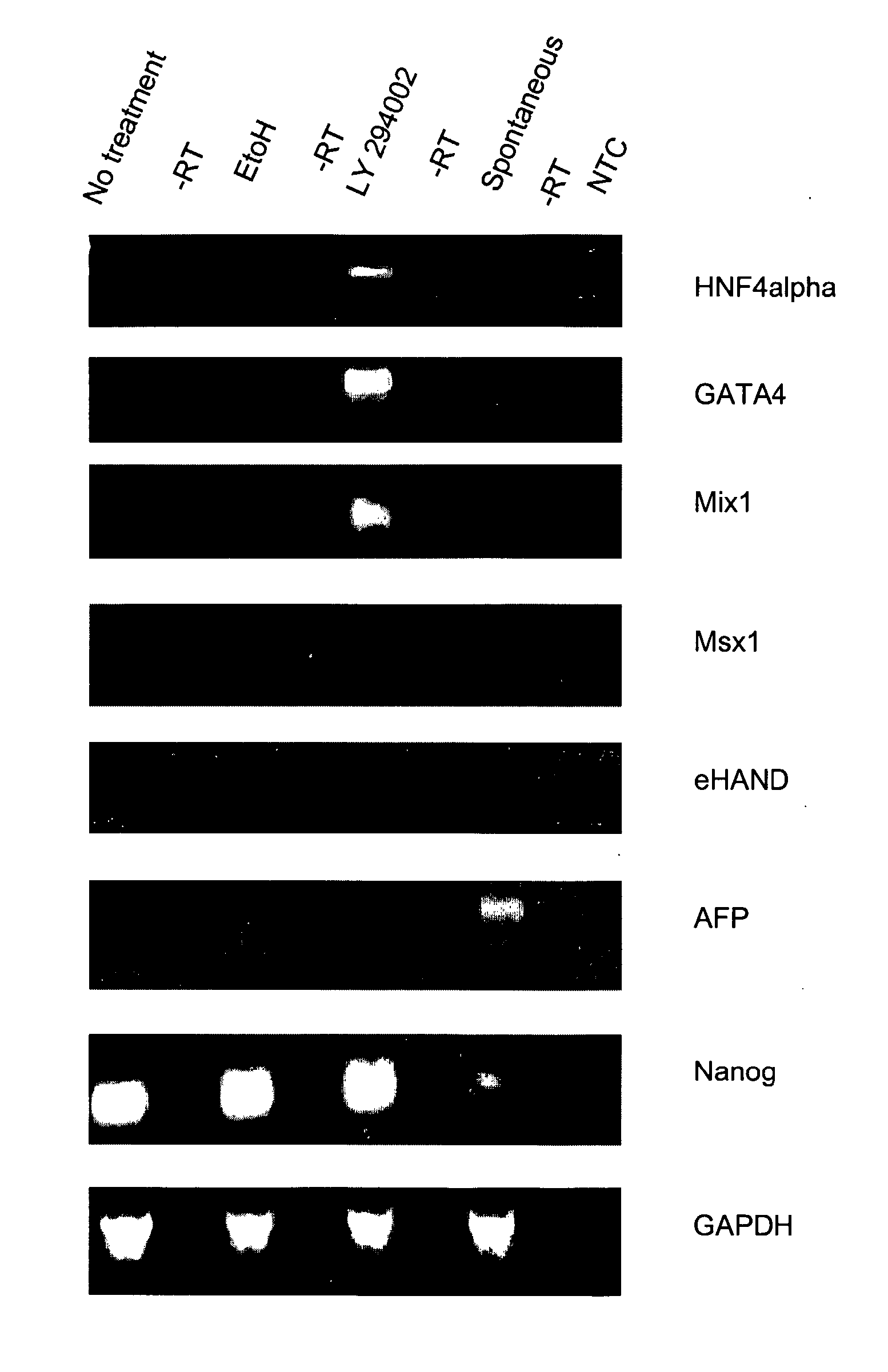

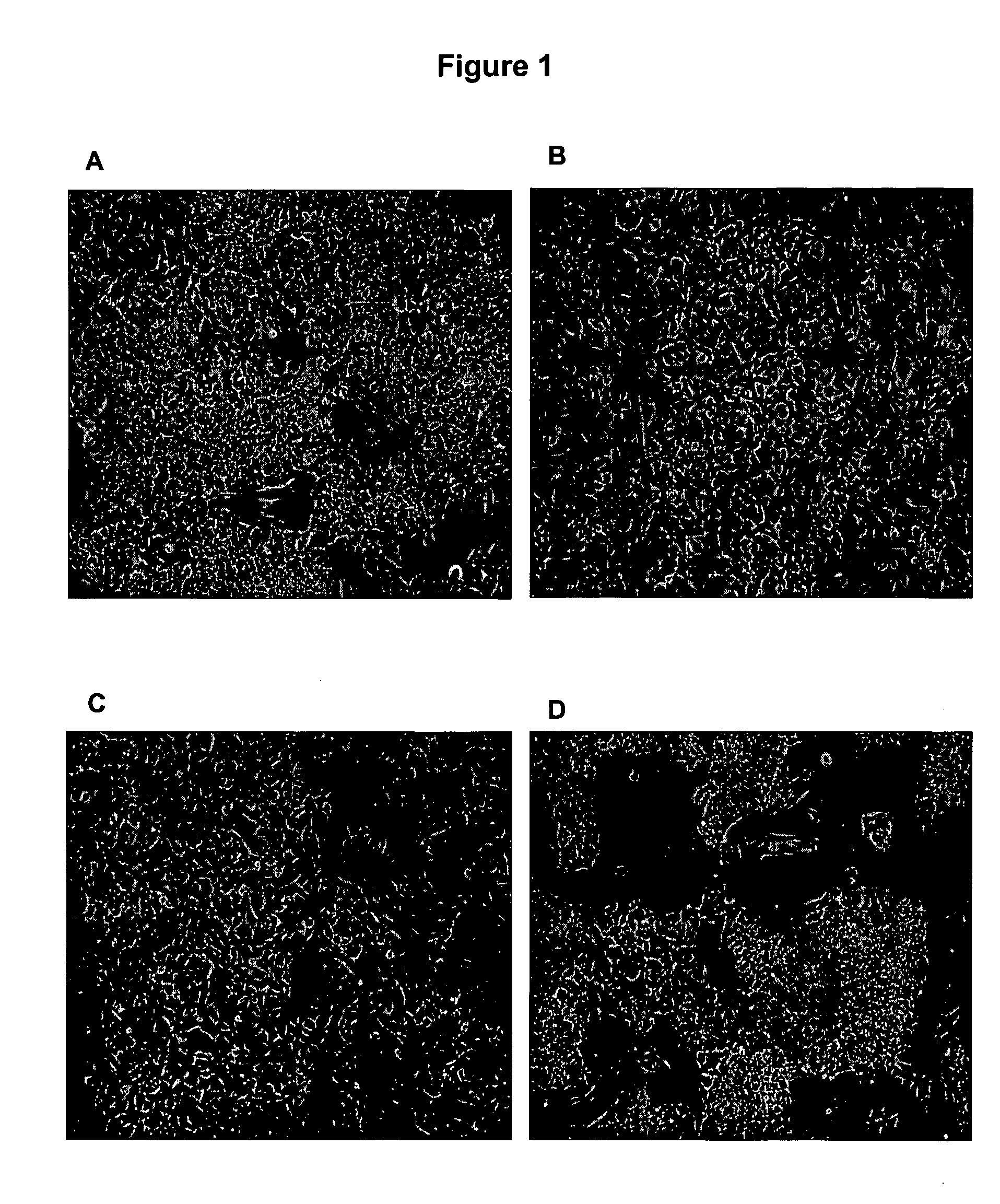

The present invention provides compositions and methods for the production of differentiated mammalian cells. More particularly, the present invention provides cellular differentiation methods employing culturing the cells on a feeder layer or under feeder-free conditions in cell culture and further contacting the cells with an inhibitor of the PI3-kinase pathway for the generation of differentiated mammalian cells from pluripotent mammalian stem cells. Preferably, the differentiated cell is selected from the group consisting of a mesendodermal cell, a mesodermal cell, and an endodermal cell.

Owner:UNIV OF GEORGIA RES FOUND INC +1

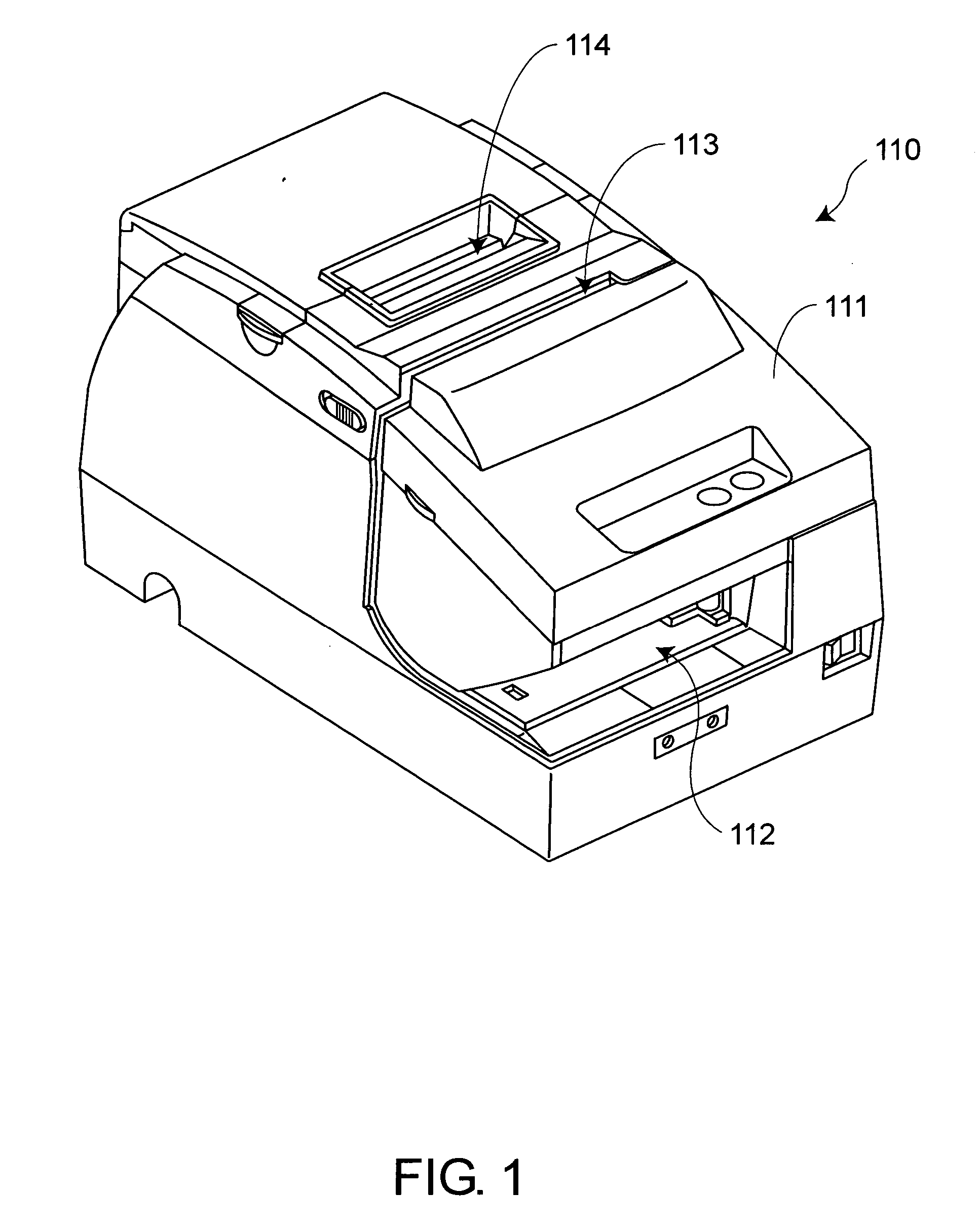

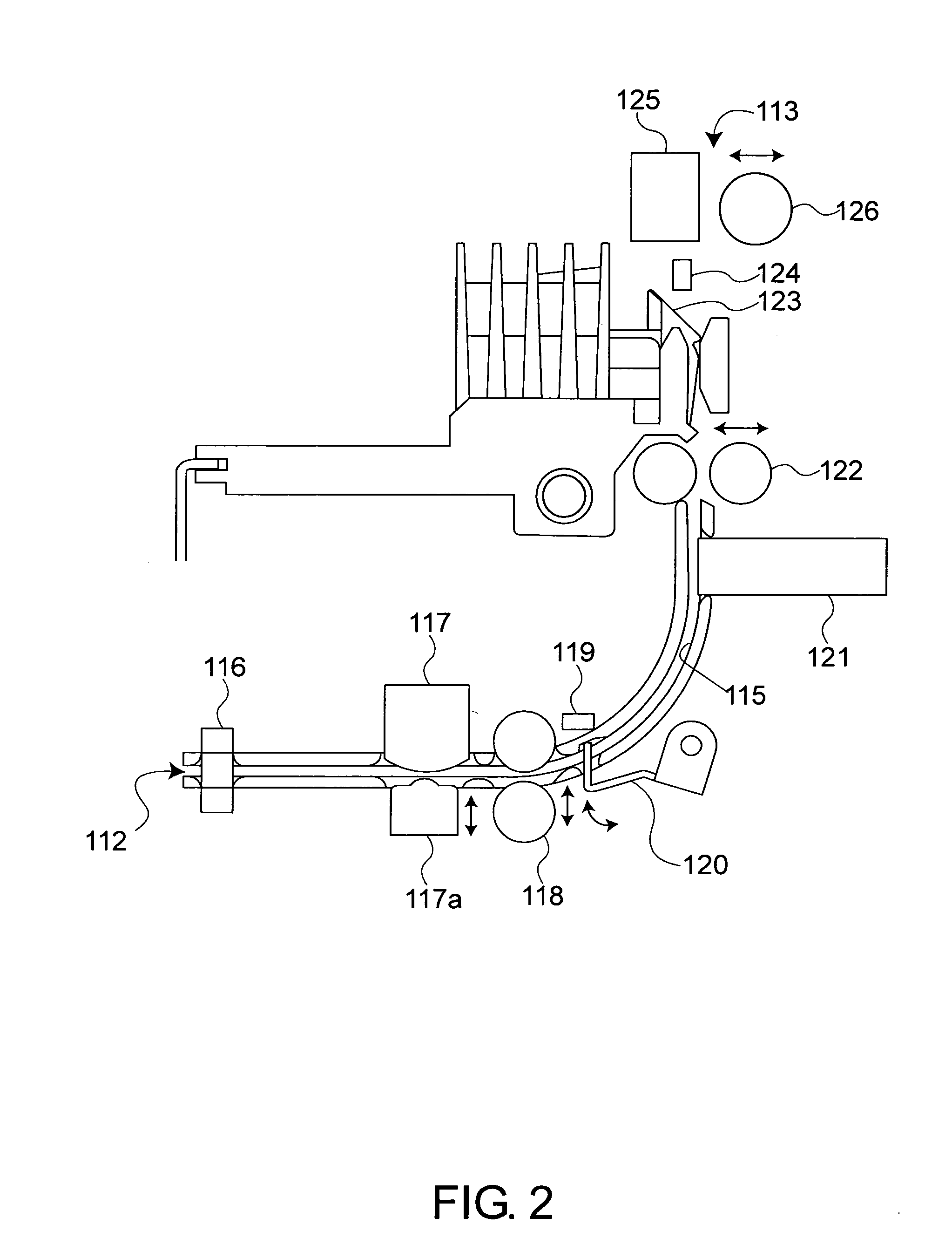

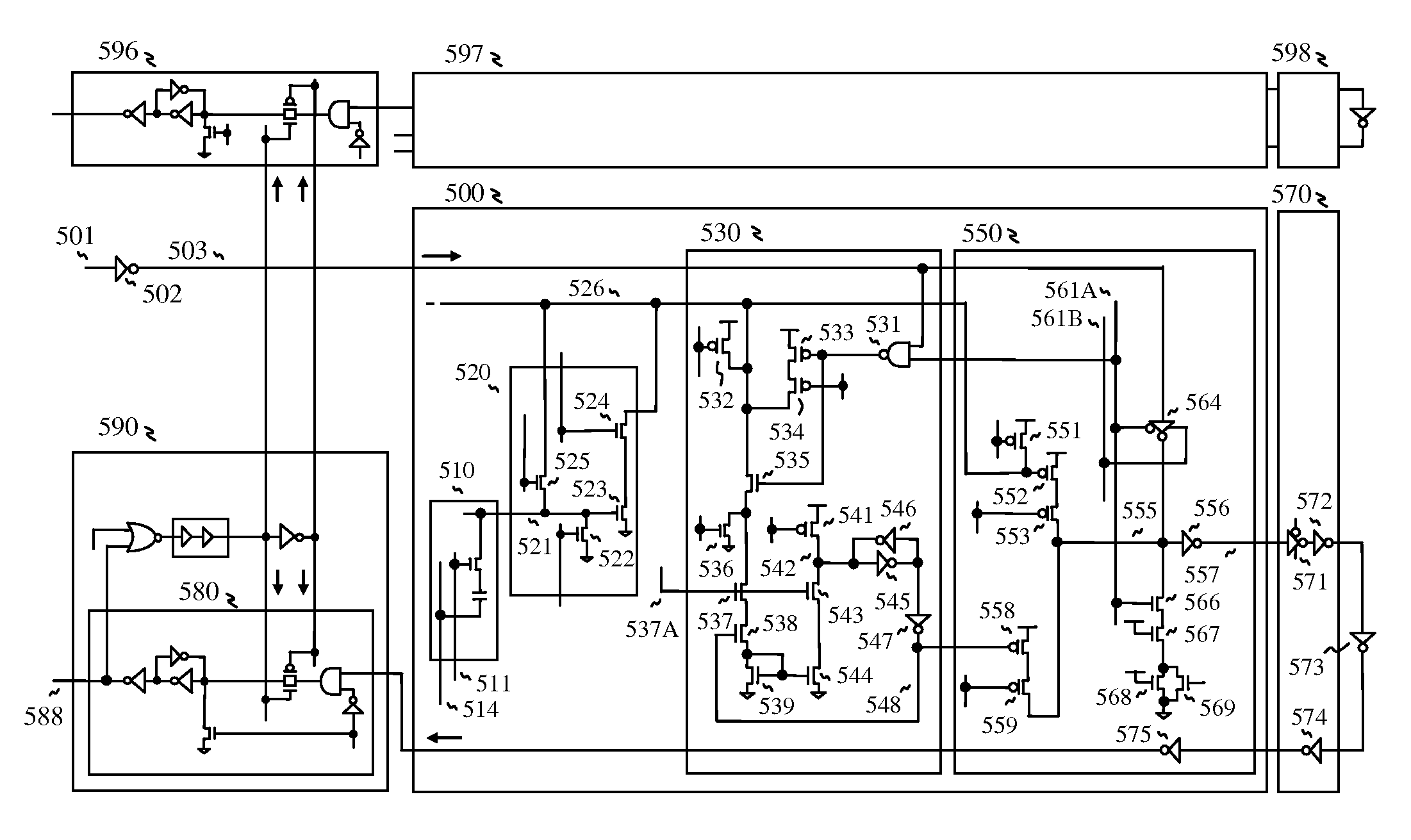

Negotiable instrument processing apparatus

InactiveUS20060115141A1Efficient captureEffectively lead to differentiationImage enhancementPaper-money testing devicesPaymentValue set

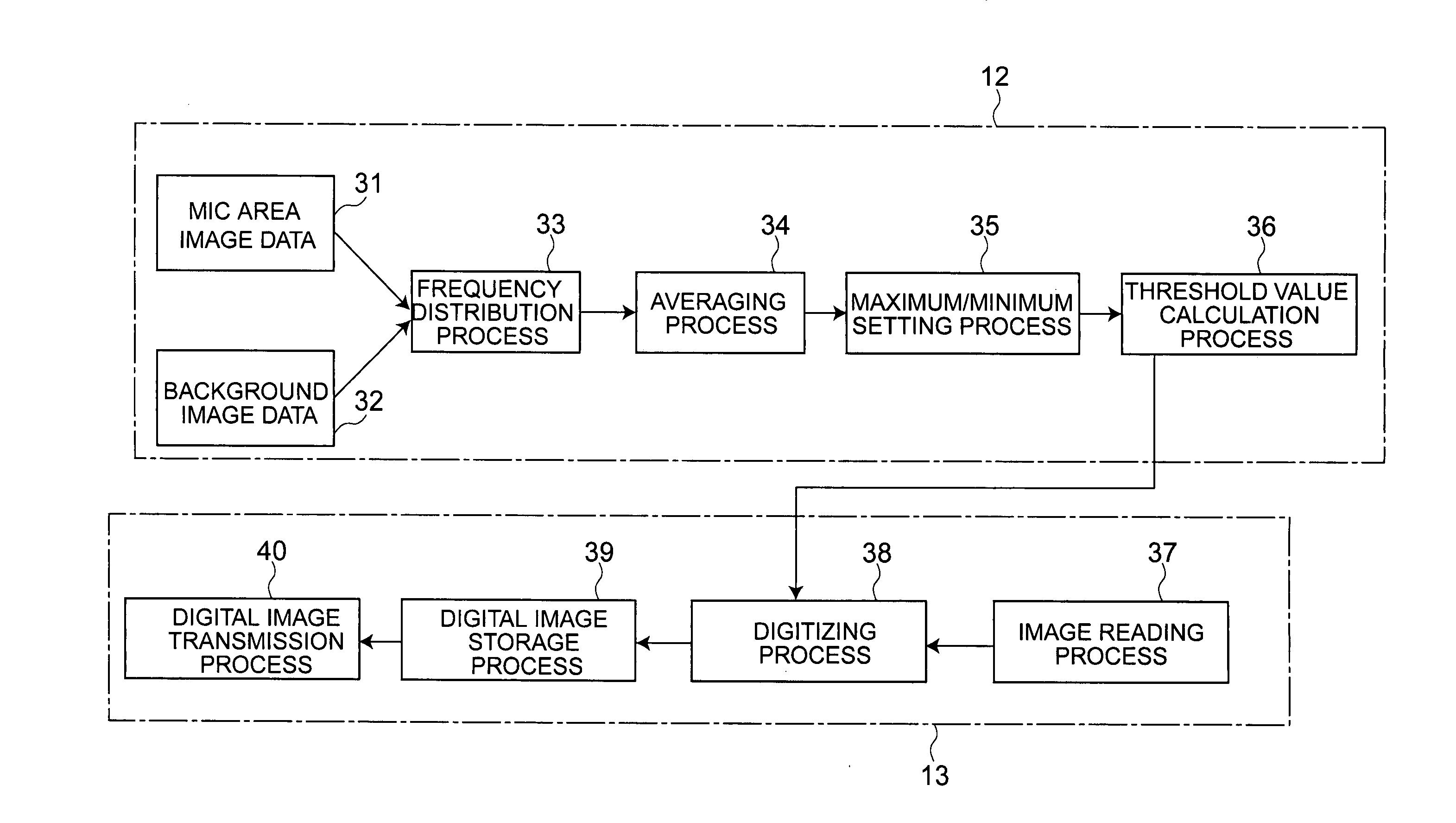

An apparatus and a method for processing checks and other negotiable instruments efficiently captures MICR data required for electronic payment and an image of the check or negotiable instrument enabling the amount, payee, and other information printed or written on the check face to be clearly read. The image reading unit 11 of the check processing apparatus 110 scans and outputs a gray scale image of the check. A threshold value determination unit 12 sets a threshold value for digitizing the image data based on the density level frequency distribution of primary gray scale image data obtained by the image data reading unit scanning a first scanning area T. This first scanning area contains part of a printed text area 127 where text is printed on the negotiable instrument and part of the background 49 of the negotiable instrument. A digital image processor 20 digitizes and converts secondary gray scale image data to digital image data based on the threshold value set by the threshold value determination unit 12. The secondary gray scale image data is generated by the image reading unit 11 scanning a predefined second scanning area of the negotiable instrument.

Owner:SEIKO EPSON CORP

Methods for increasing definitive endoderm differentiation of pluripotent human embryonic stem cells with PI-3 kinase inhibitors

ActiveUS8187878B2Efficient productionEffectively lead to differentiationPeptide/protein ingredientsMetabolism disorderGerm layerFeeder Layer

Owner:UNIV OF GEORGIA RES FOUND INC +1

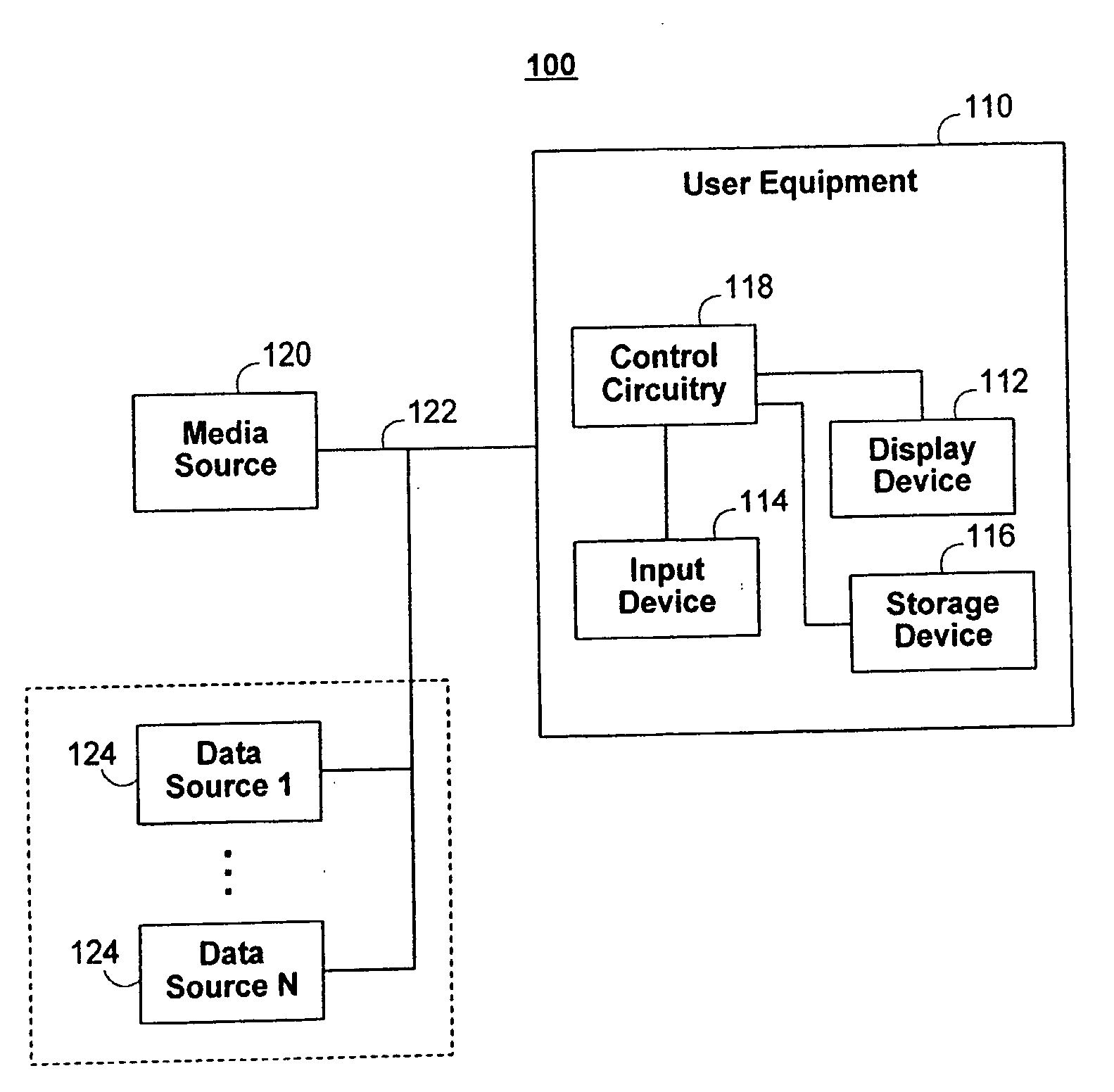

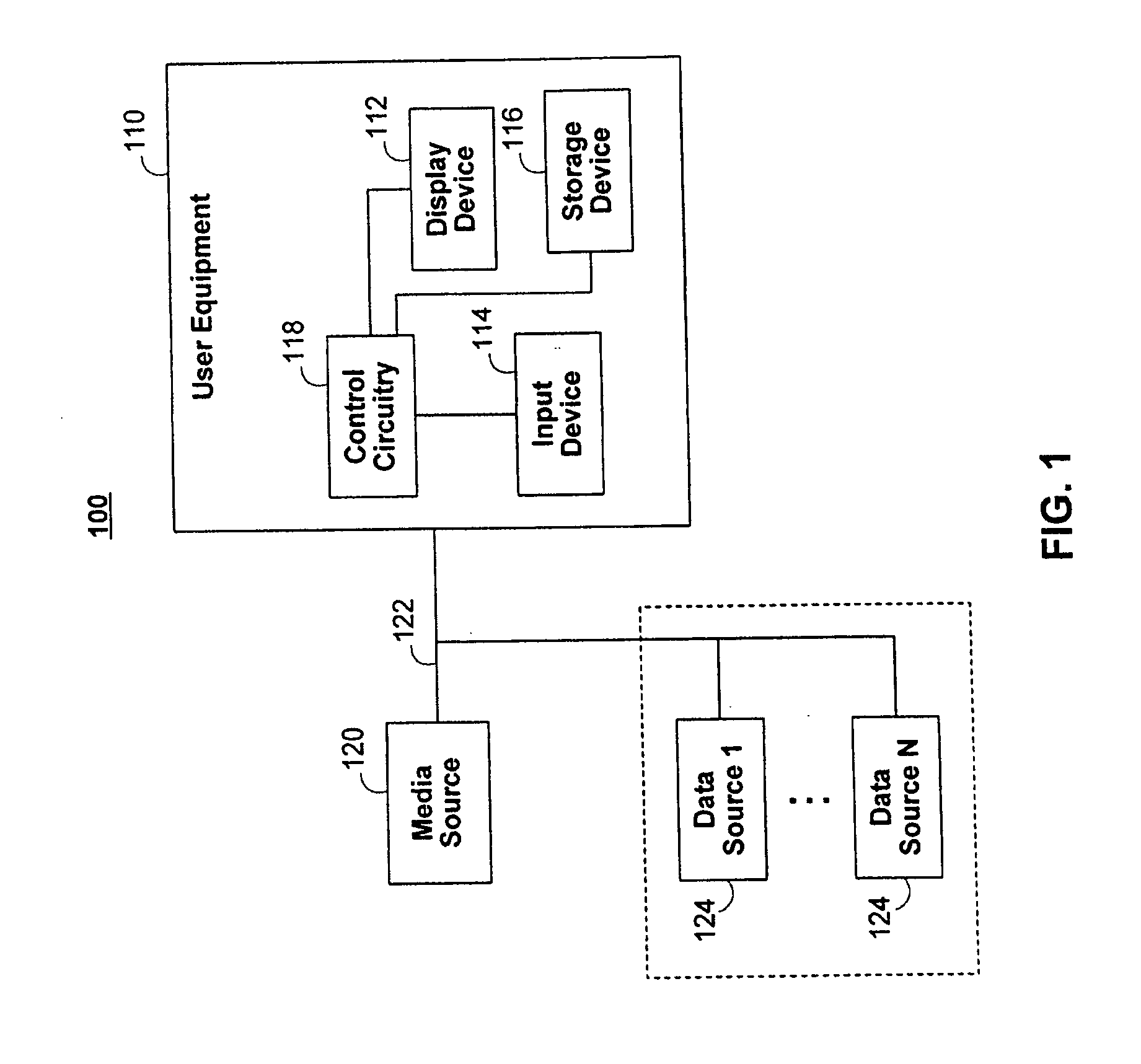

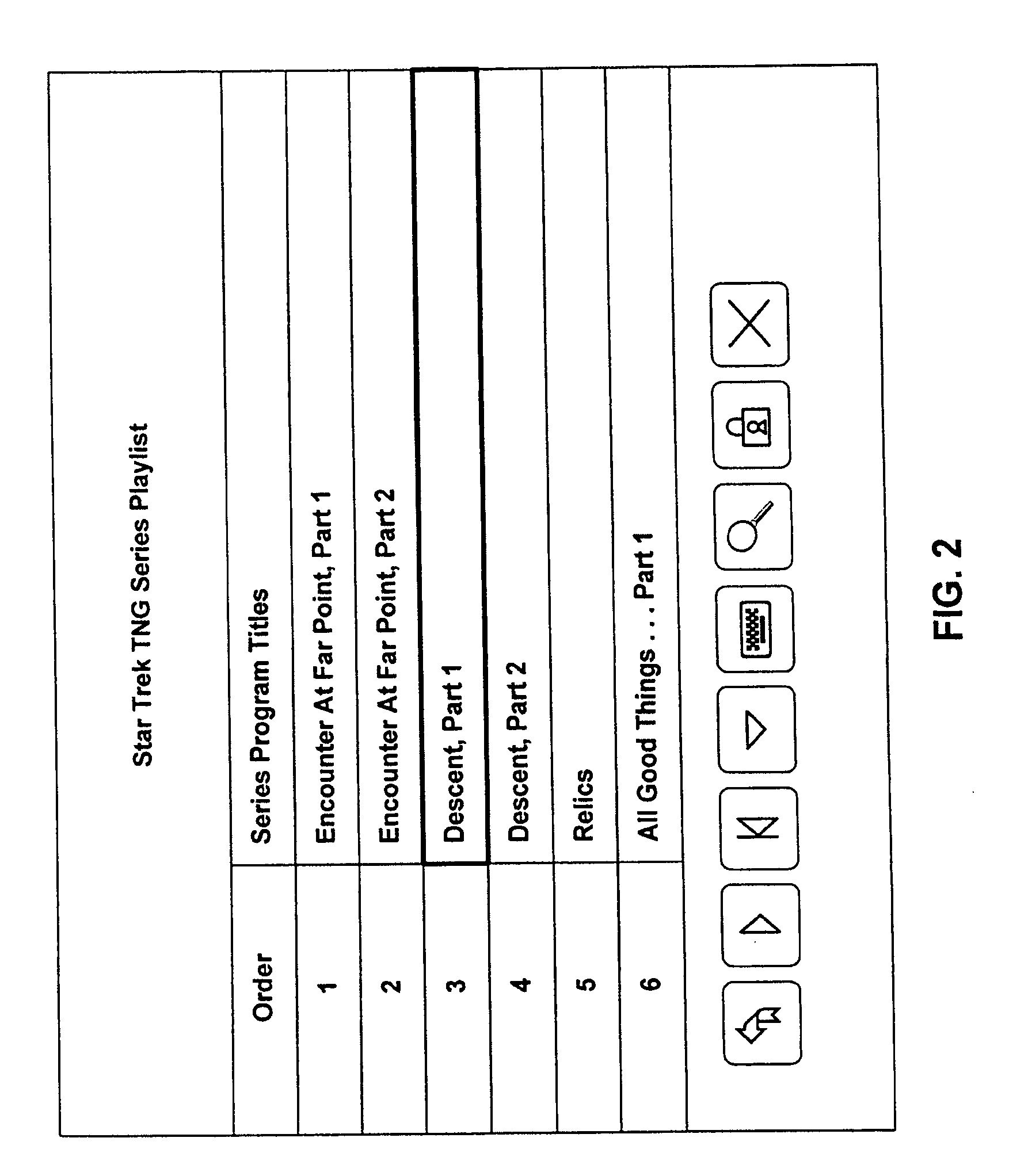

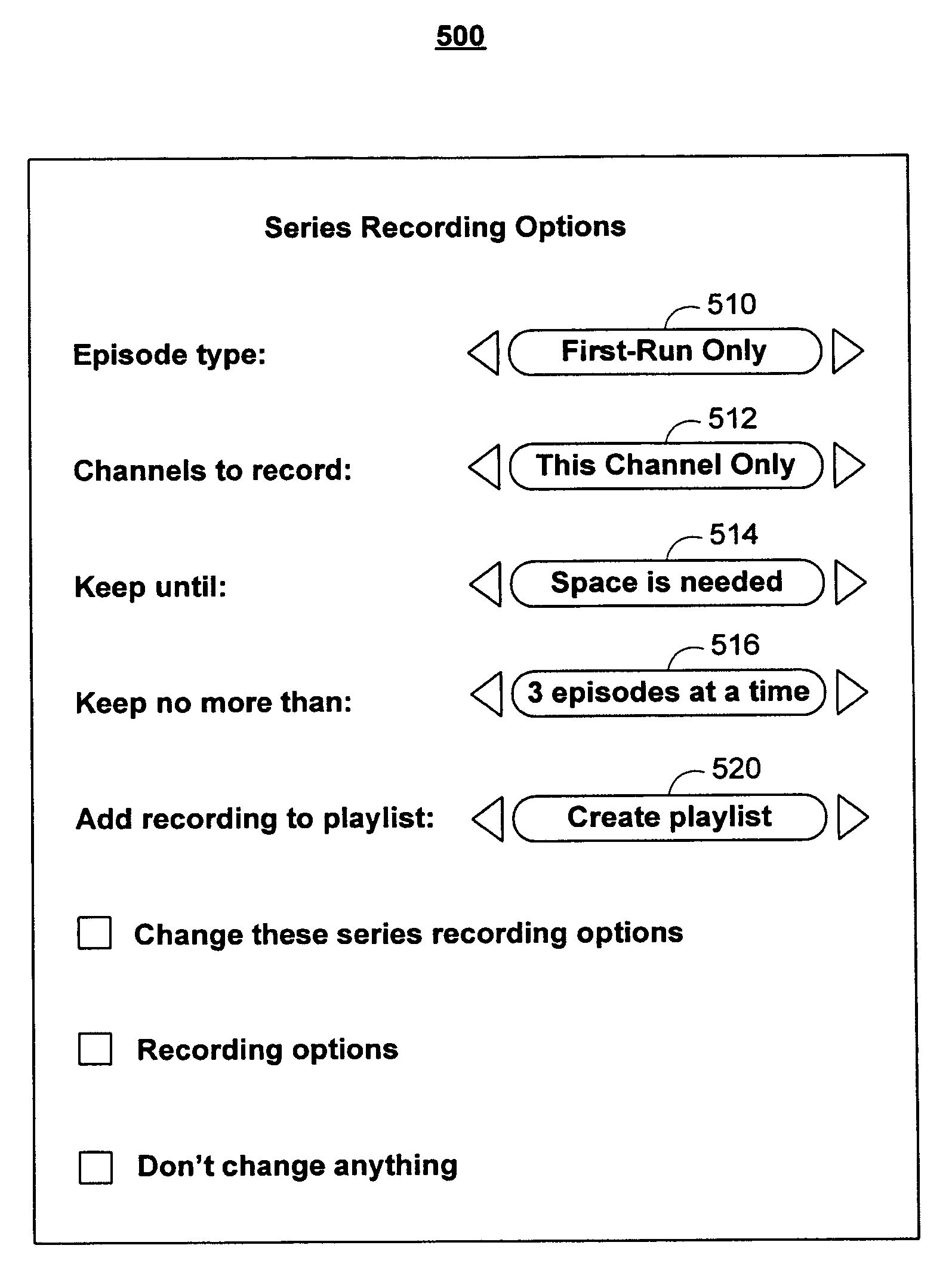

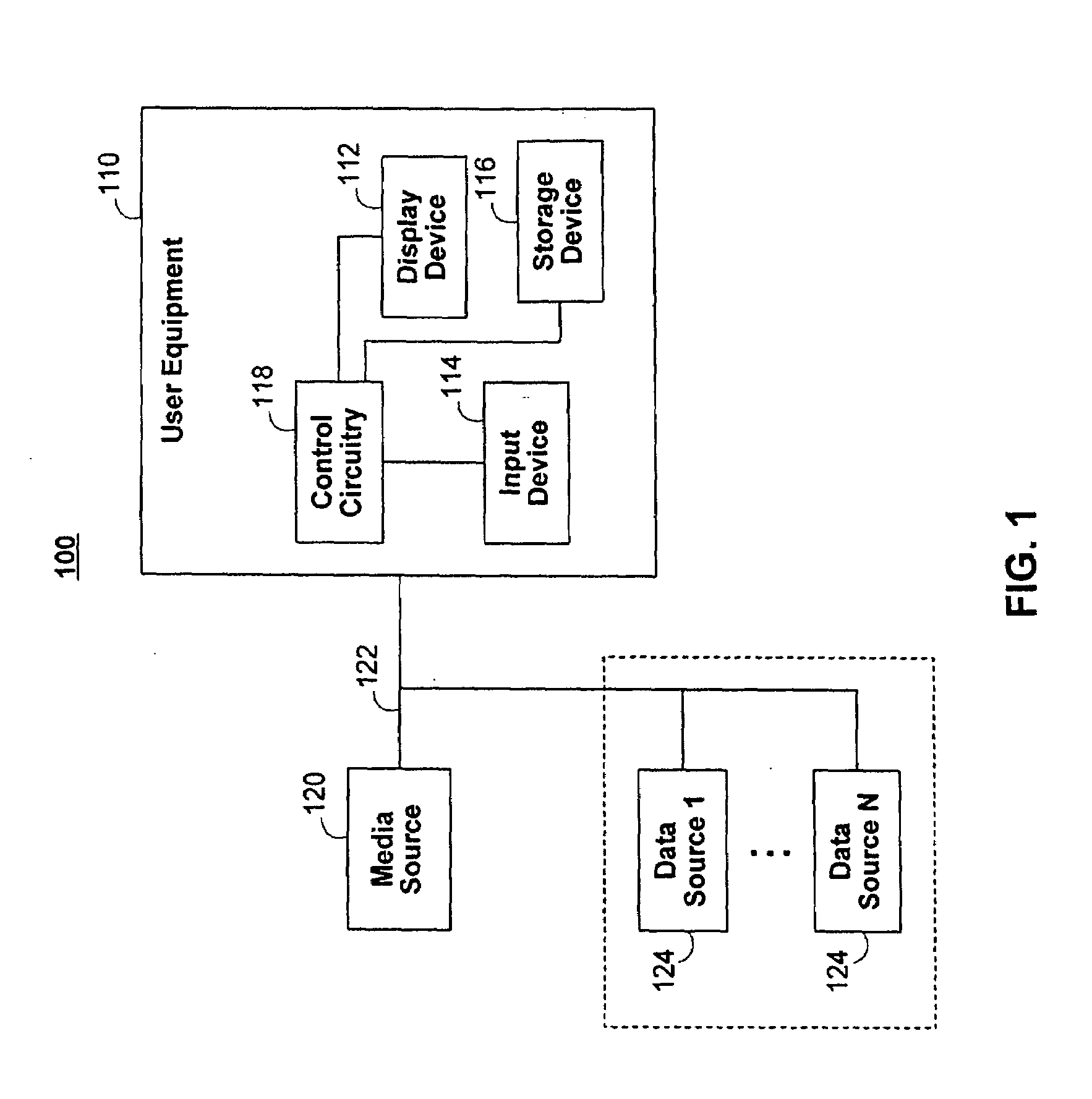

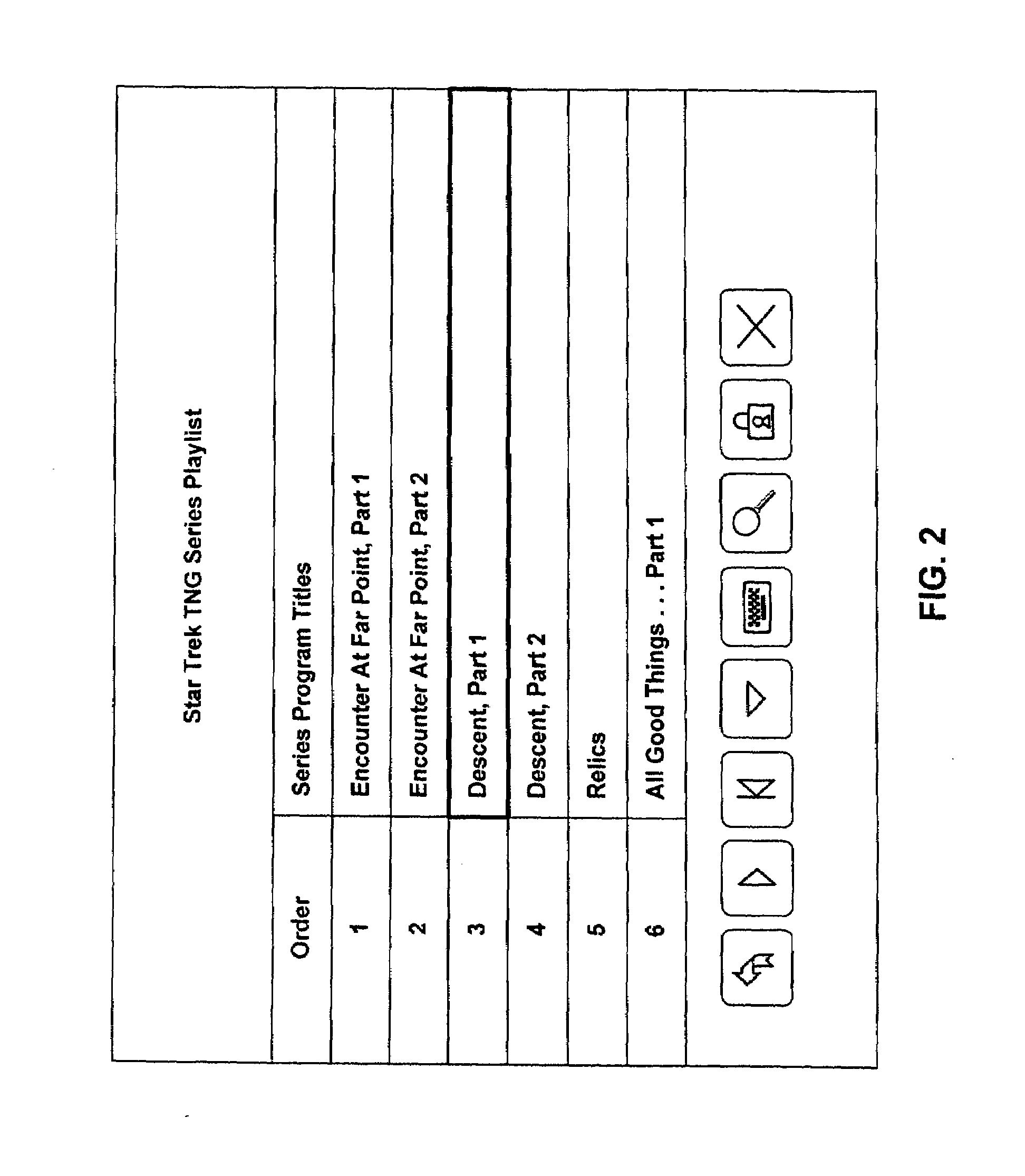

Systems and methods for using playlists

InactiveUS20080115173A1Easily select parameterEffectively lead to differentiationTelevision system detailsColor television detailsApplication softwareCluster based

Systems and methods for automatically generating a playlist of series assets and systems and methods for grouping assets of a playlist in clusters are provided. In one embodiment, series assets may automatically be included into a playlist for that series. In another embodiment, an interactive media guidance application may group assets in clusters based on one or more user selected parameters or may group assets in cluster based on automatically determined parameters. In yet another embodiment, the interactive media guidance application may group assets in clusters and display at least one identifier in connection with each cluster to indicate a basis for forming the cluster. The identifier may be a key word or catch phrase that succinctly identifies a trait or characteristic of assets in a particular cluster associated with the identifier.

Owner:UNITED VIDEO PROPERTIES +1

Systems and methods for using playlists

InactiveUS20080114794A1Easily select parameterEffectively lead to differentiationMetadata video data retrievalSelective content distributionApplication softwareCluster based

Systems and methods for automatically generating a playlist of series assets and systems and methods for grouping assets of a playlist in clusters are provided. In one embodiment, series assets may automatically be included into a playlist for that series. In another embodiment, an interactive media guidance application may group assets in clusters based on one or more user selected parameters or may group assets in cluster based on automatically determined parameters. In yet another embodiment, the interactive media guidance application may group assets in clusters and display at least one identifier in connection with each cluster to indicate a basis for forming the cluster. The identifier may be a key word or catch phrase that succinctly identifies a trait or characteristic of assets in a particular cluster associated with the identifier.

Owner:ROVI GUIDES INC +1

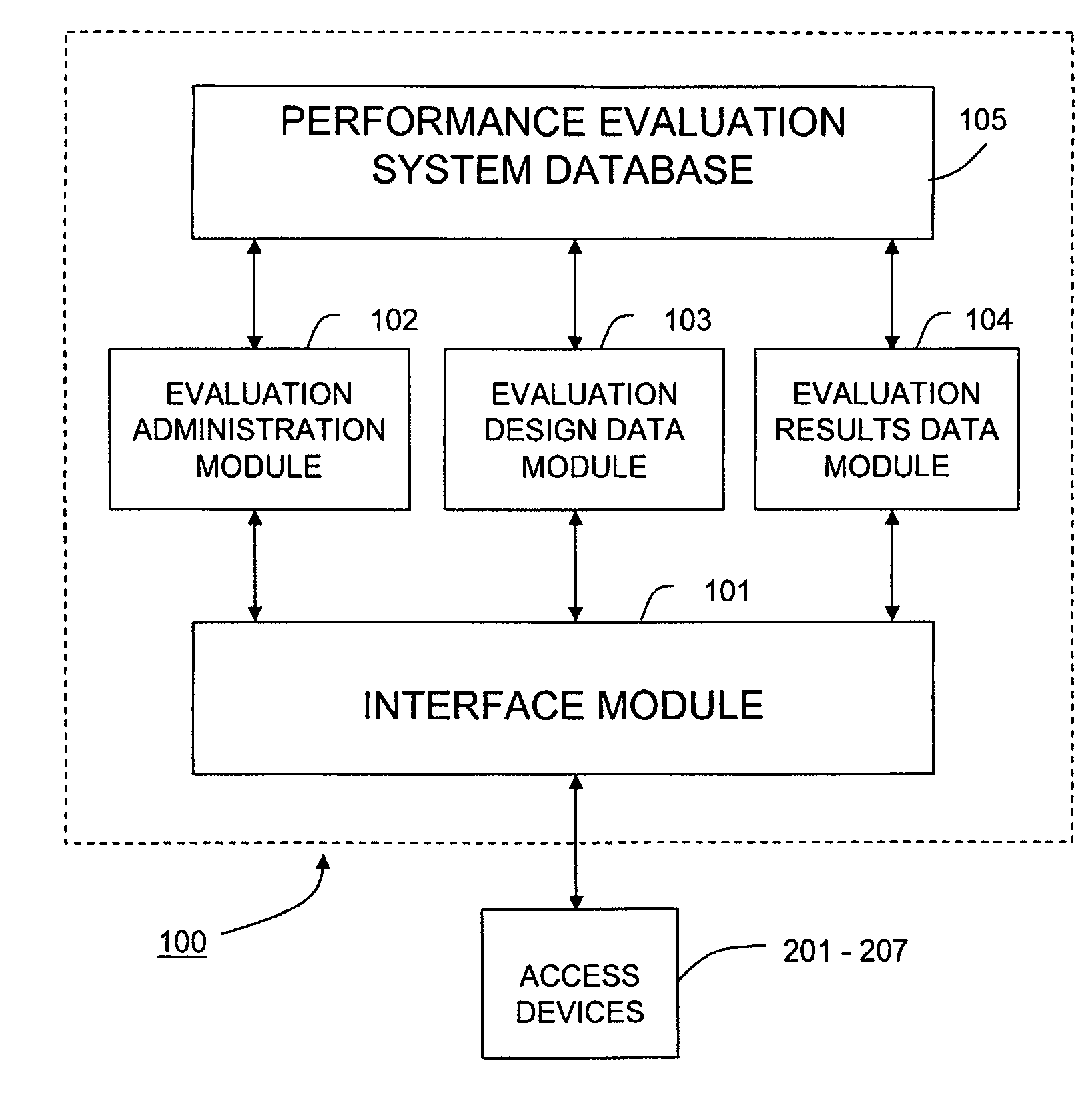

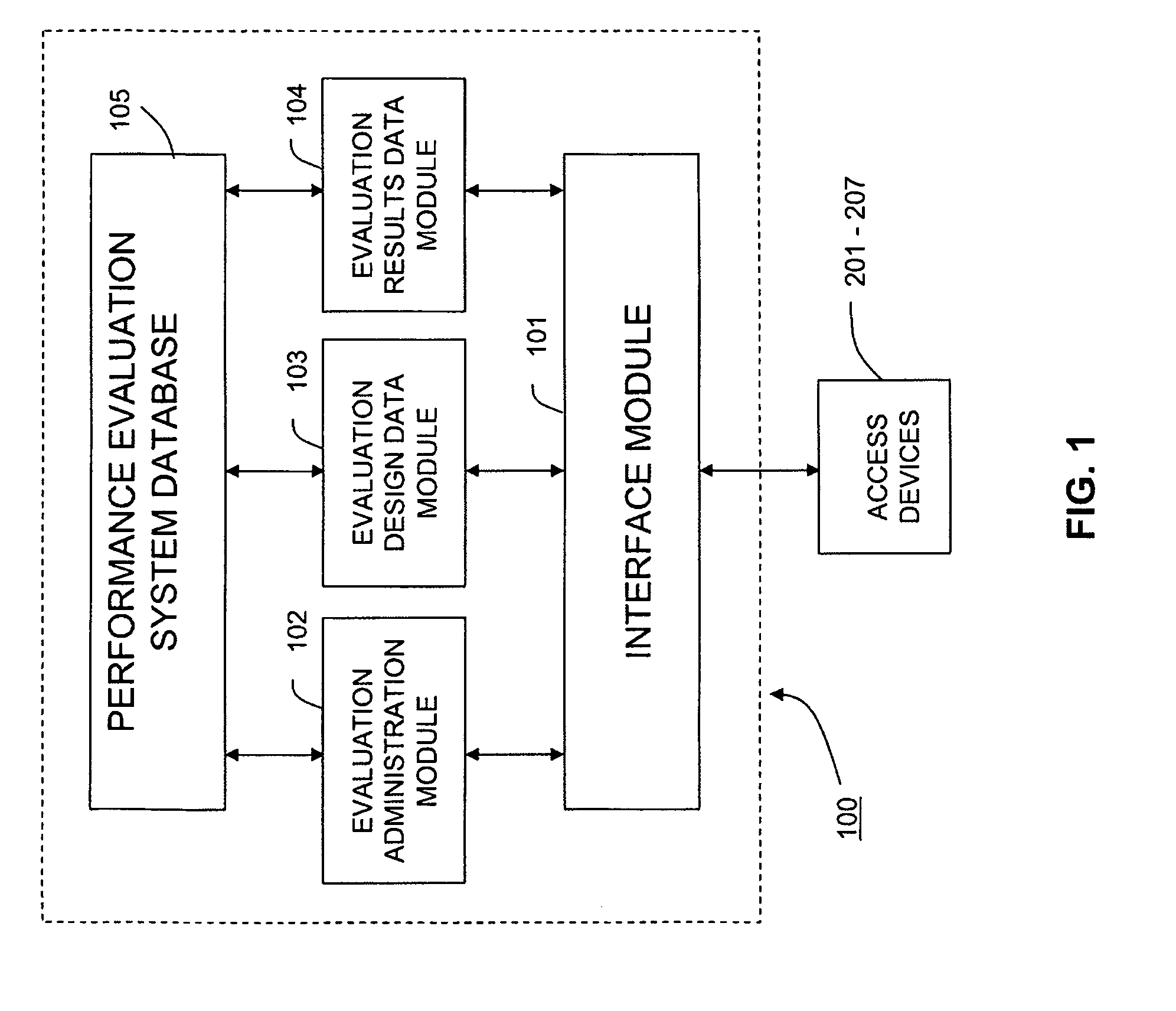

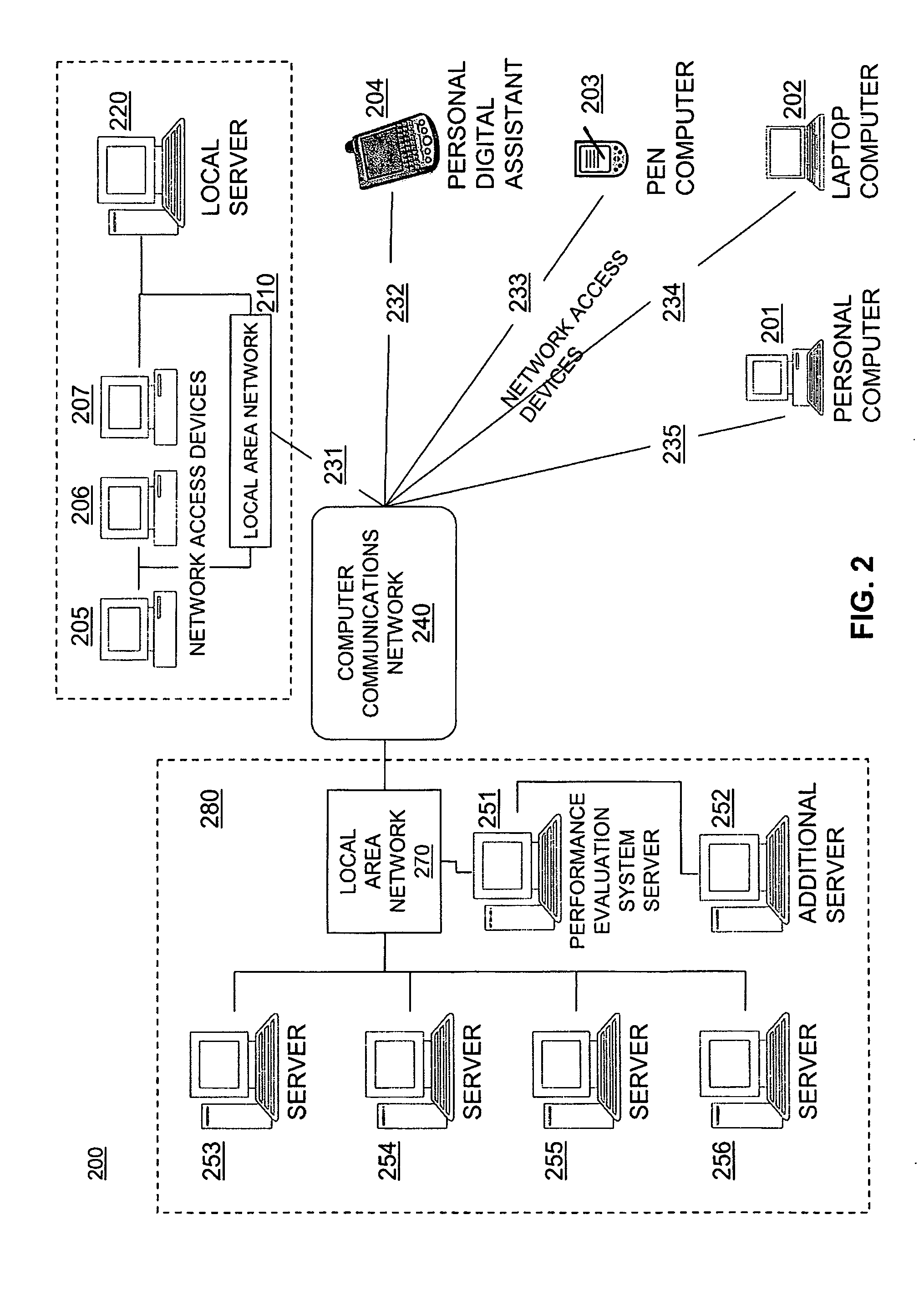

System and method for rating performance

InactiveUS20080114608A1Performance accurately and reliably and efficientlyPromote differentiationData processing applicationsWorld Wide WebData science

Owner:BASTIEN RENE

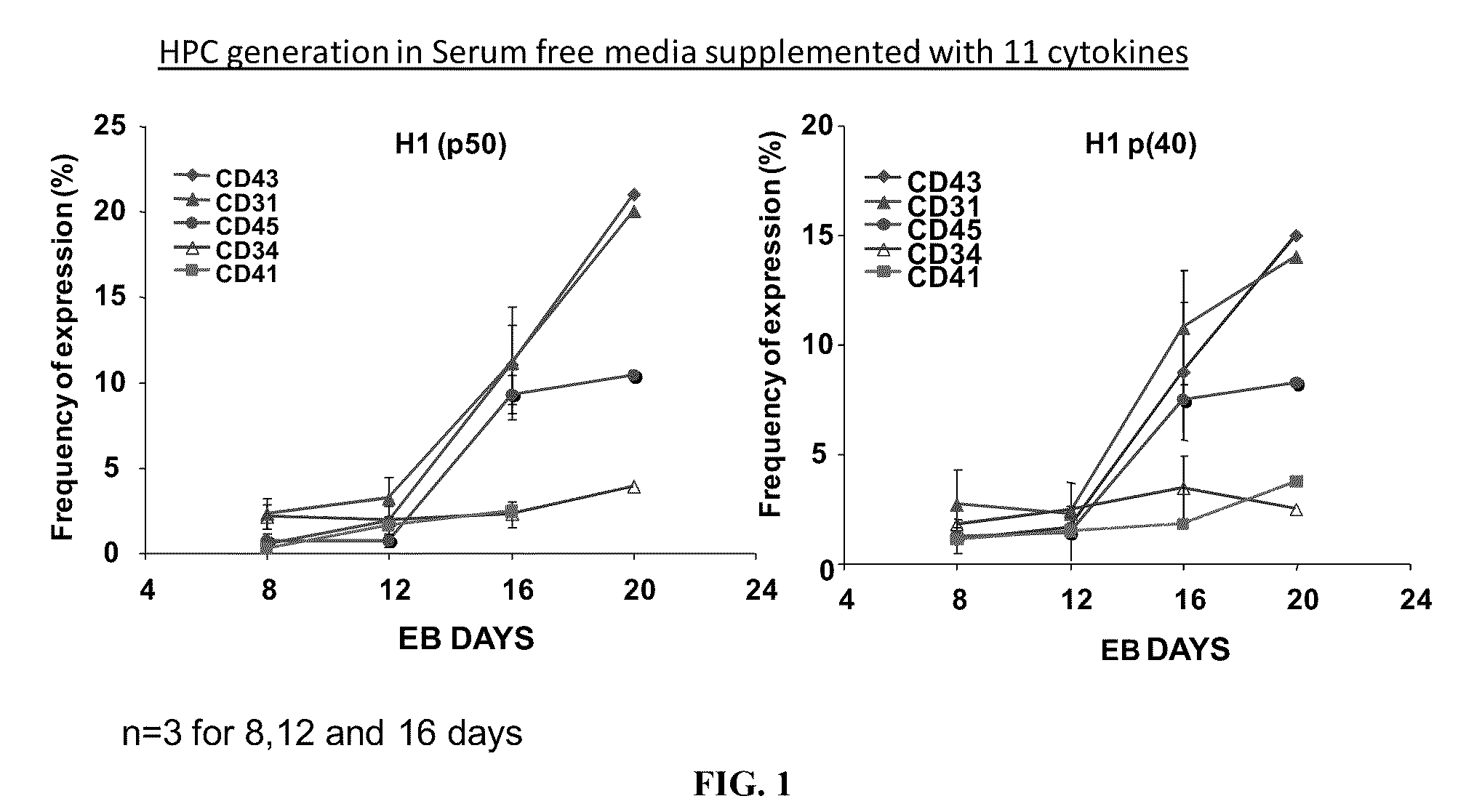

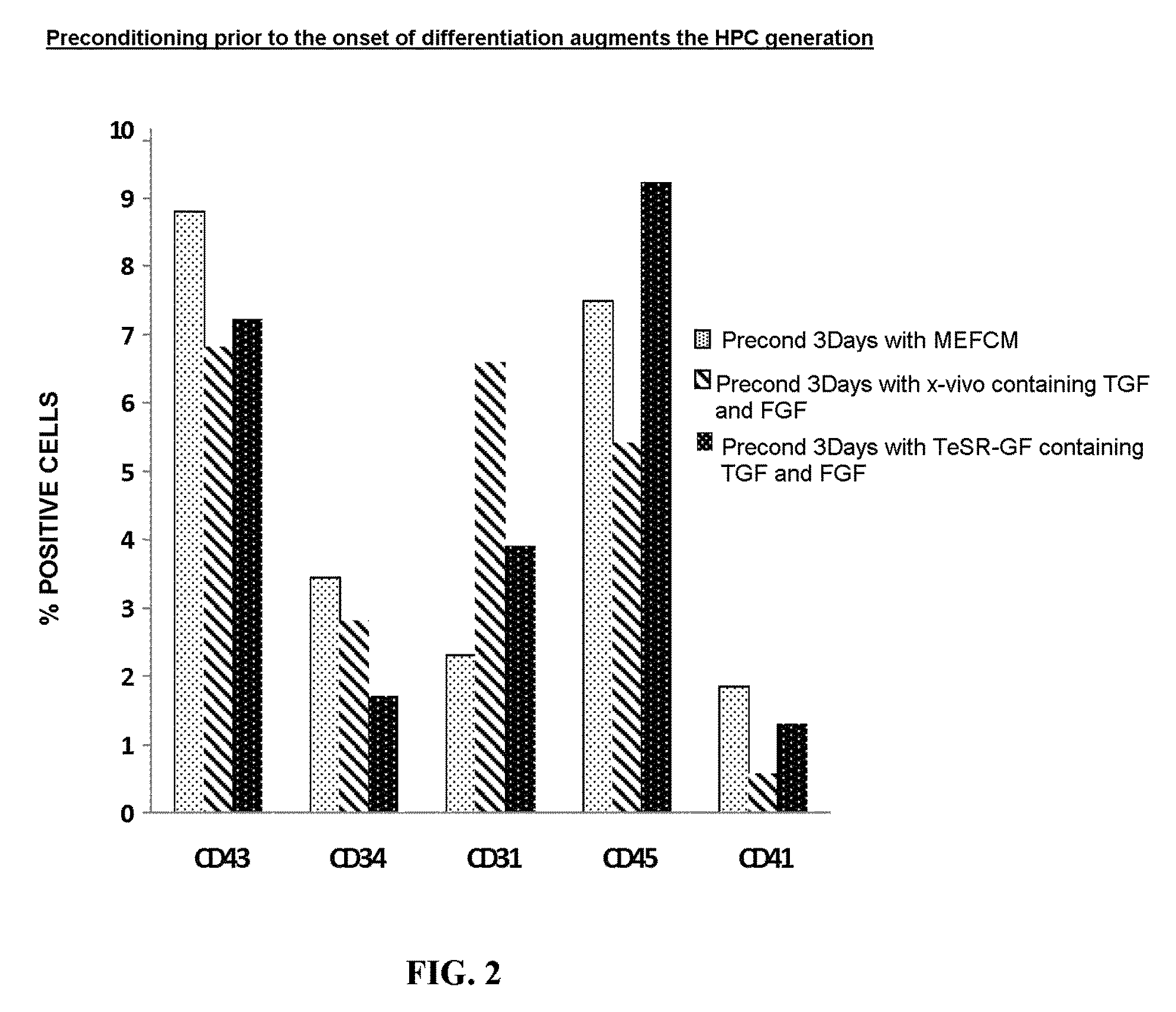

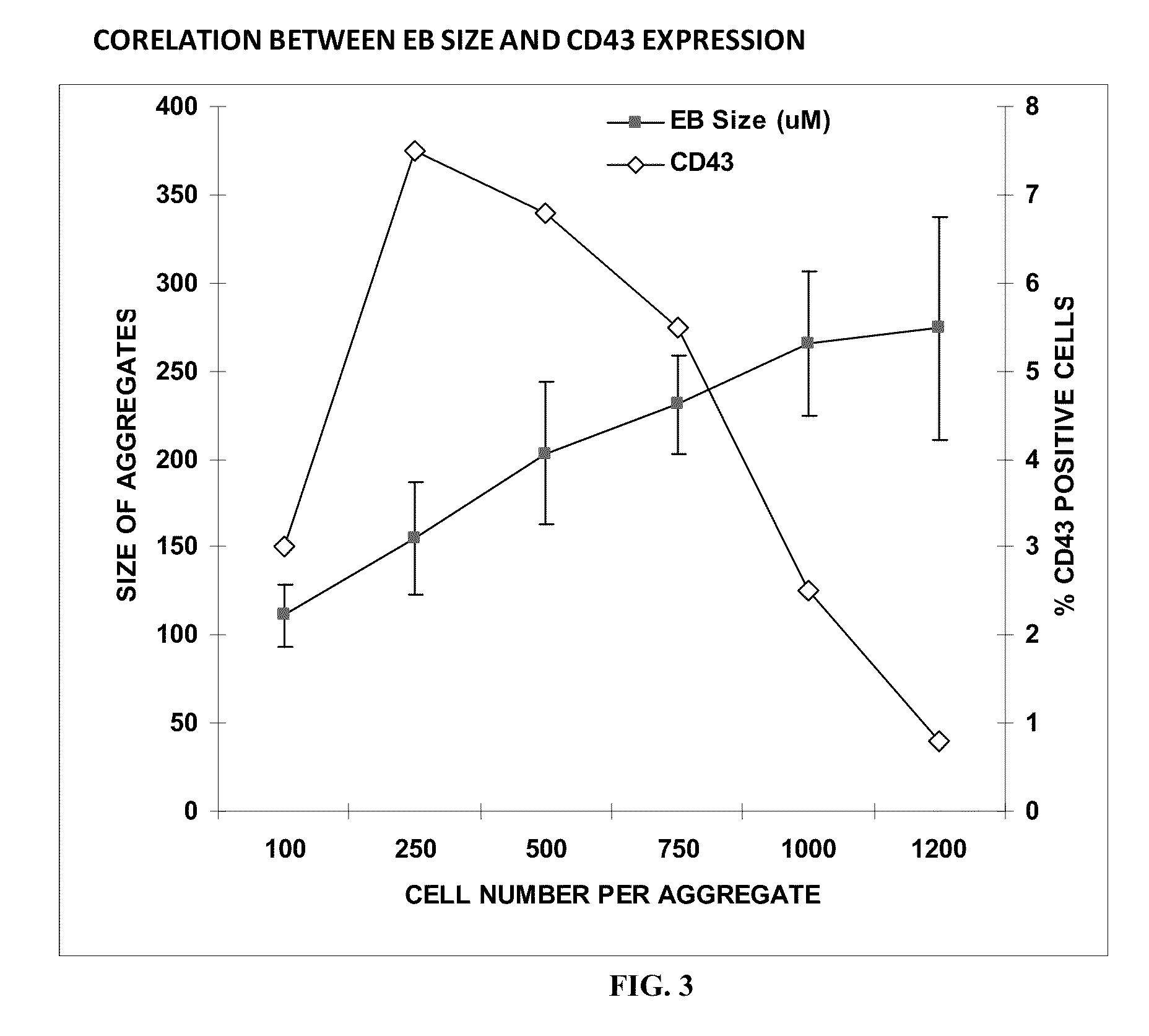

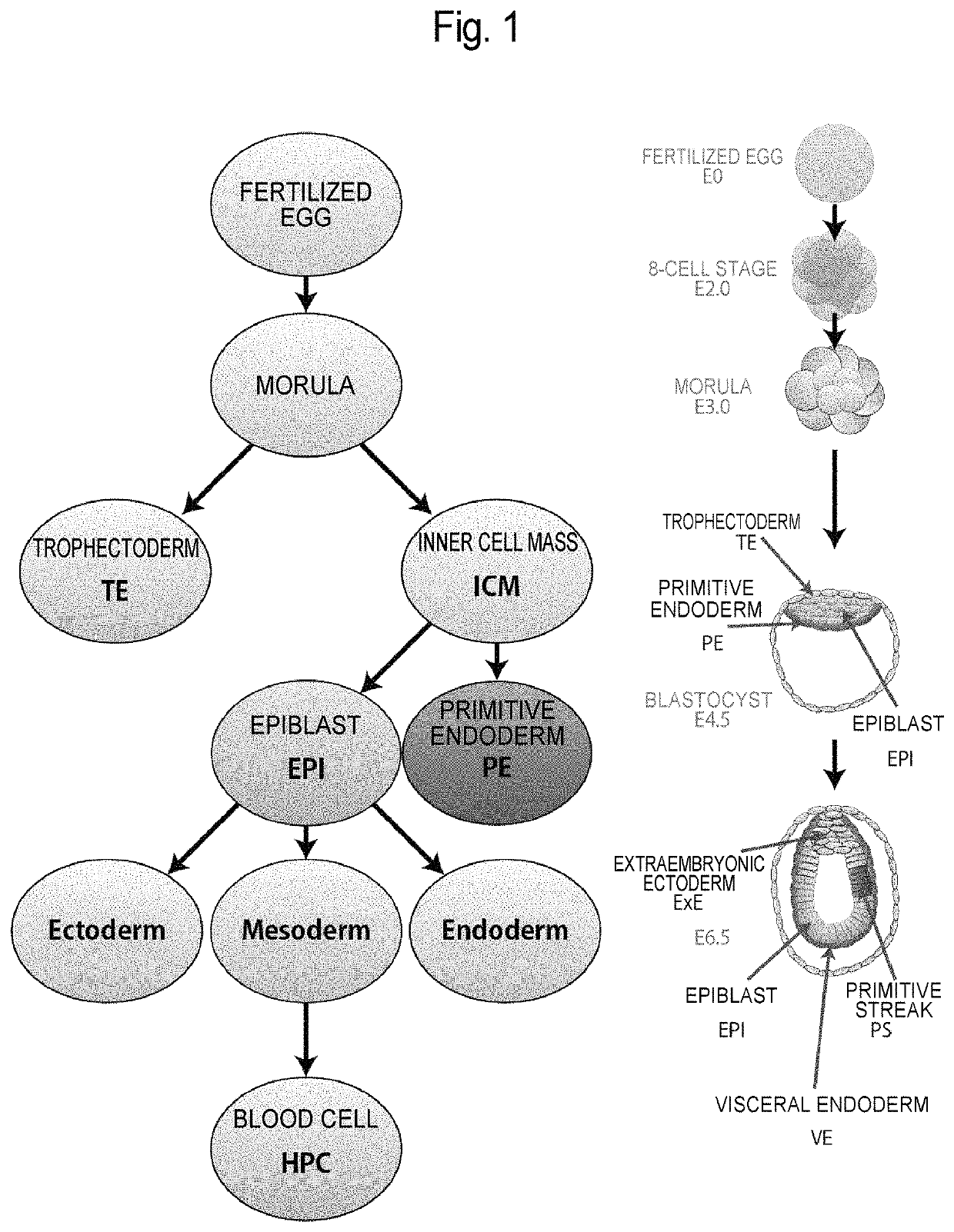

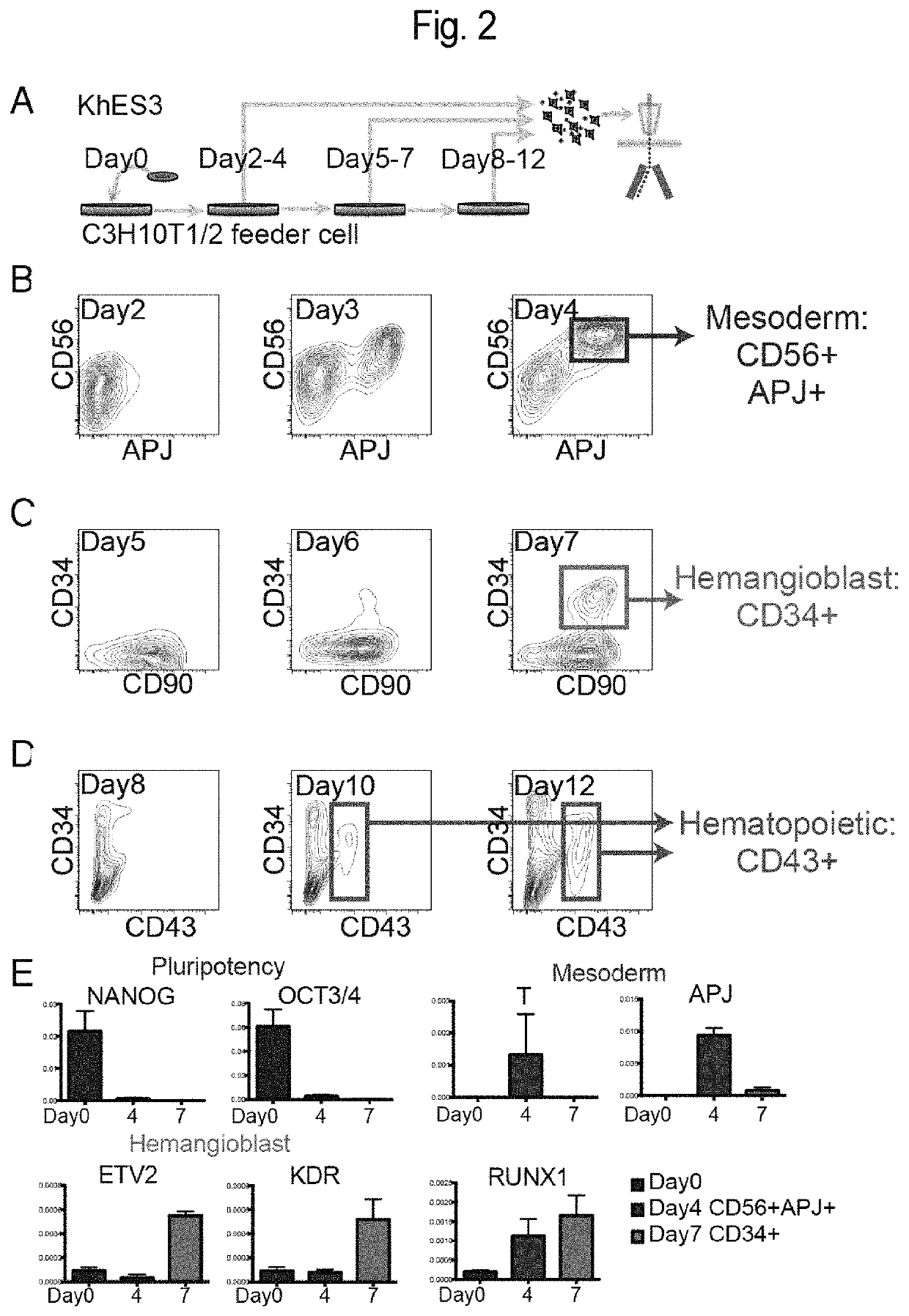

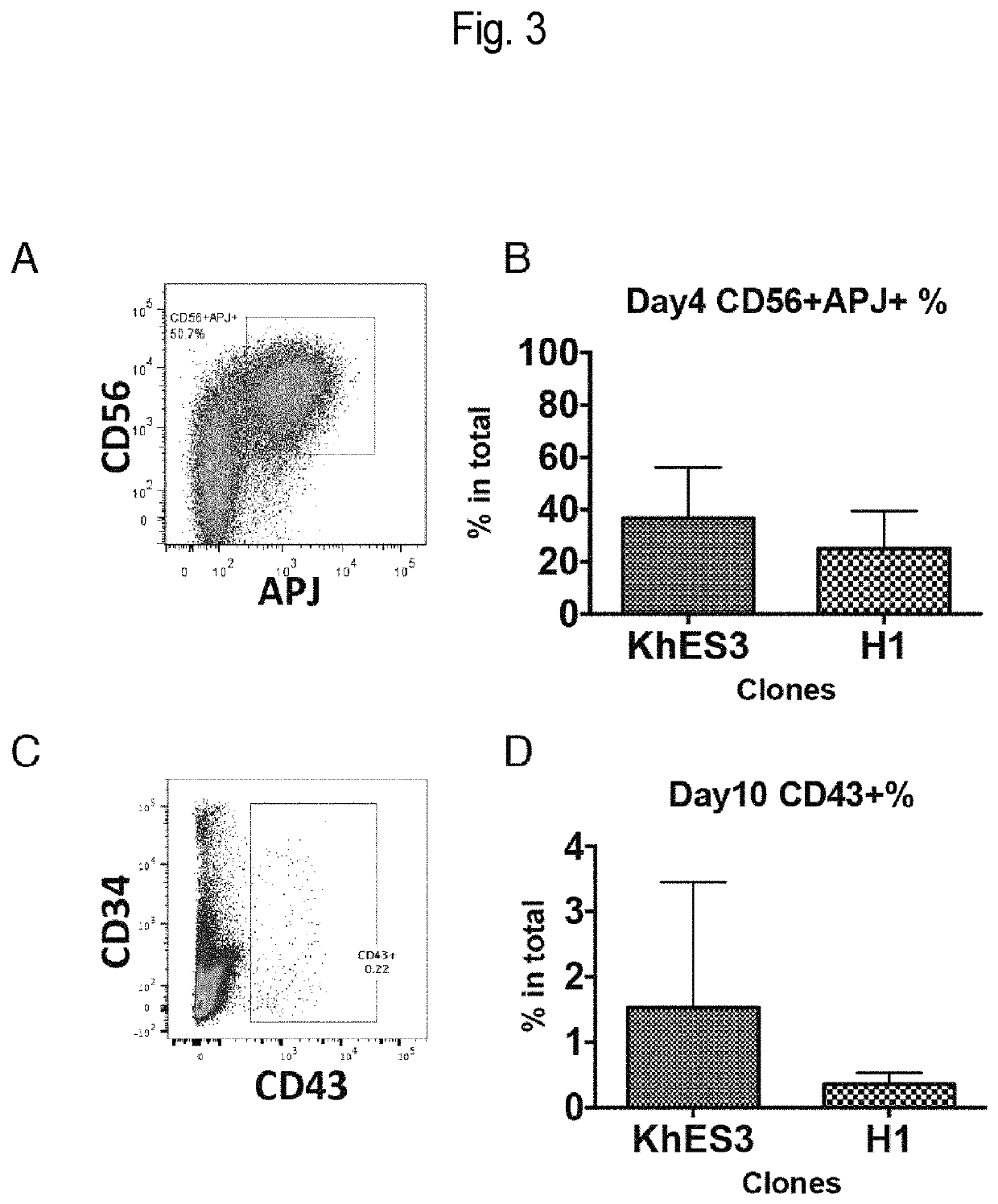

Differentiation of pluripotent cells

ActiveUS8372642B2Promote differentiationPromote cell differentiationNervous disorderCulture processBiologyBone marrow

Provided herein are methods for the in vitro maintenance, expansion, culture, and / or differentiation of pluripotent cells, such as human embryonic stem cells (hESC) or induced pluripotent cells (iPSC), into hematopoietic precursor cells or endothelial cells. The pluripotent cells may be maintained and differentiated under defined conditions; thus, the use of mouse feeder cells or serum is not required in certain embodiments for the differentiation of the pluripotent cells into hematopoietic precursor cells or endothelial cells. The resulting hematopoietic precursor cells may be further differentiated into various myeloid or lymphoid lineages.

Owner:FUJIFILM CELLULAR DYNAMICS INC

Method of Inducing the Differentiation of Embryonic Stem Cells Into Nerve by Serum-Free Suspension Culture

ActiveUS20080044901A1Effectively lead to differentiationEfficient inductionNervous system cellsEmbryonic cellsSerum free mediaNervous system

The present invention provides a clinically applicable method of inducing differentiation of embryonic stem cells, particularly a method of inducing differentiation of embryonic stem cells into forebrain neurons. More specifically, the present invention provides a method of inducing differentiation of embryonic stem cells, comprising culturing the embryonic stem cells as a floating aggregate in a serum-free medium, particularly a method of inducing differentiation of the embryonic stem cells into nervous system cells such as forebrain neurons and cerebellar neurons and sensory organ cells; a floating aggregate of embryonic stem cells obtained by culturing the embryonic stem cells as a floating aggregate in a serum-free medium; and cells derived from a floating aggregate of embryonic stem cells, particularly nervous system cells such as forebrain neurons and cerebellar neuron, sensory organ cells such as retinal precursor cells, and the like.

Owner:RIKEN

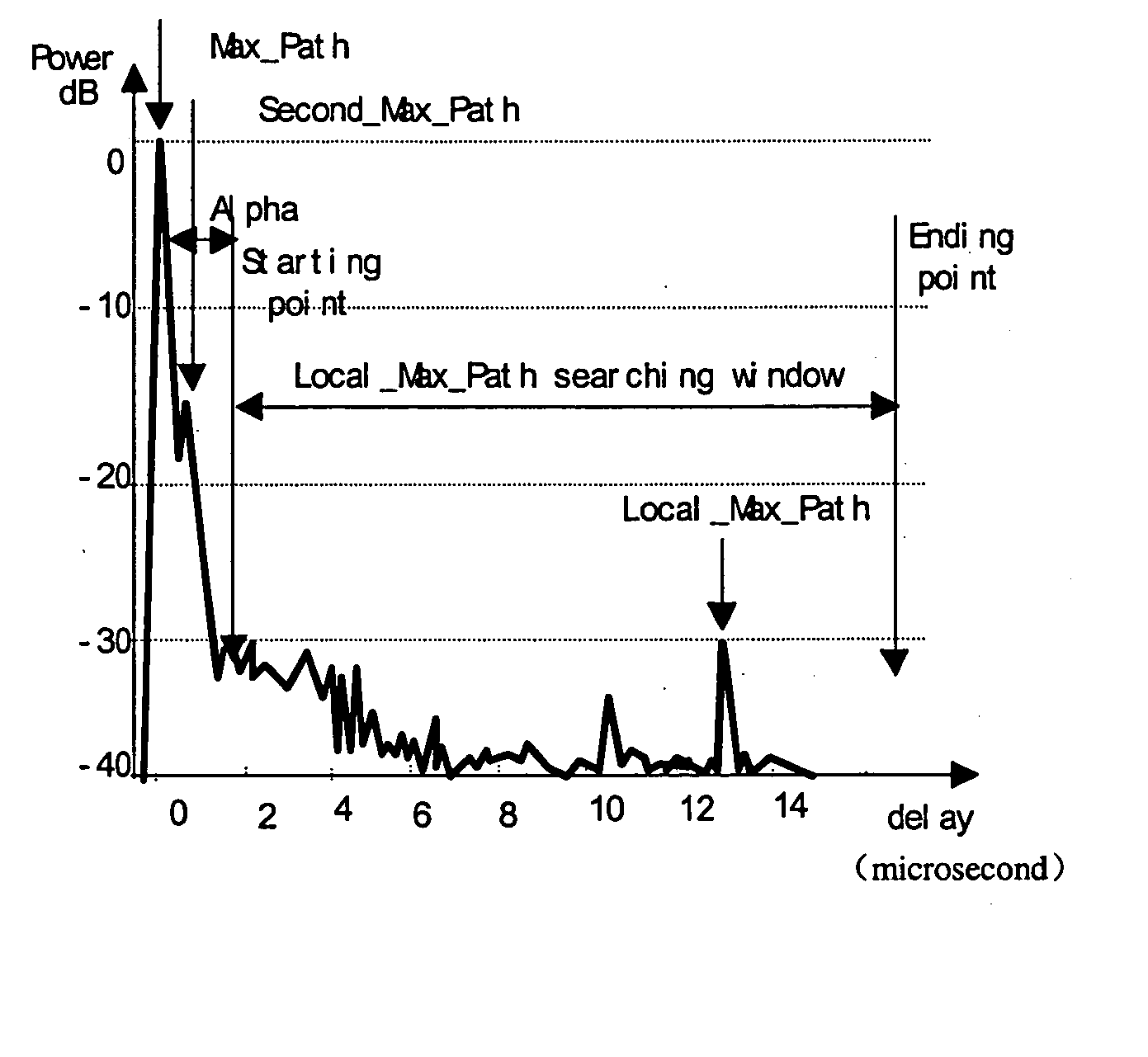

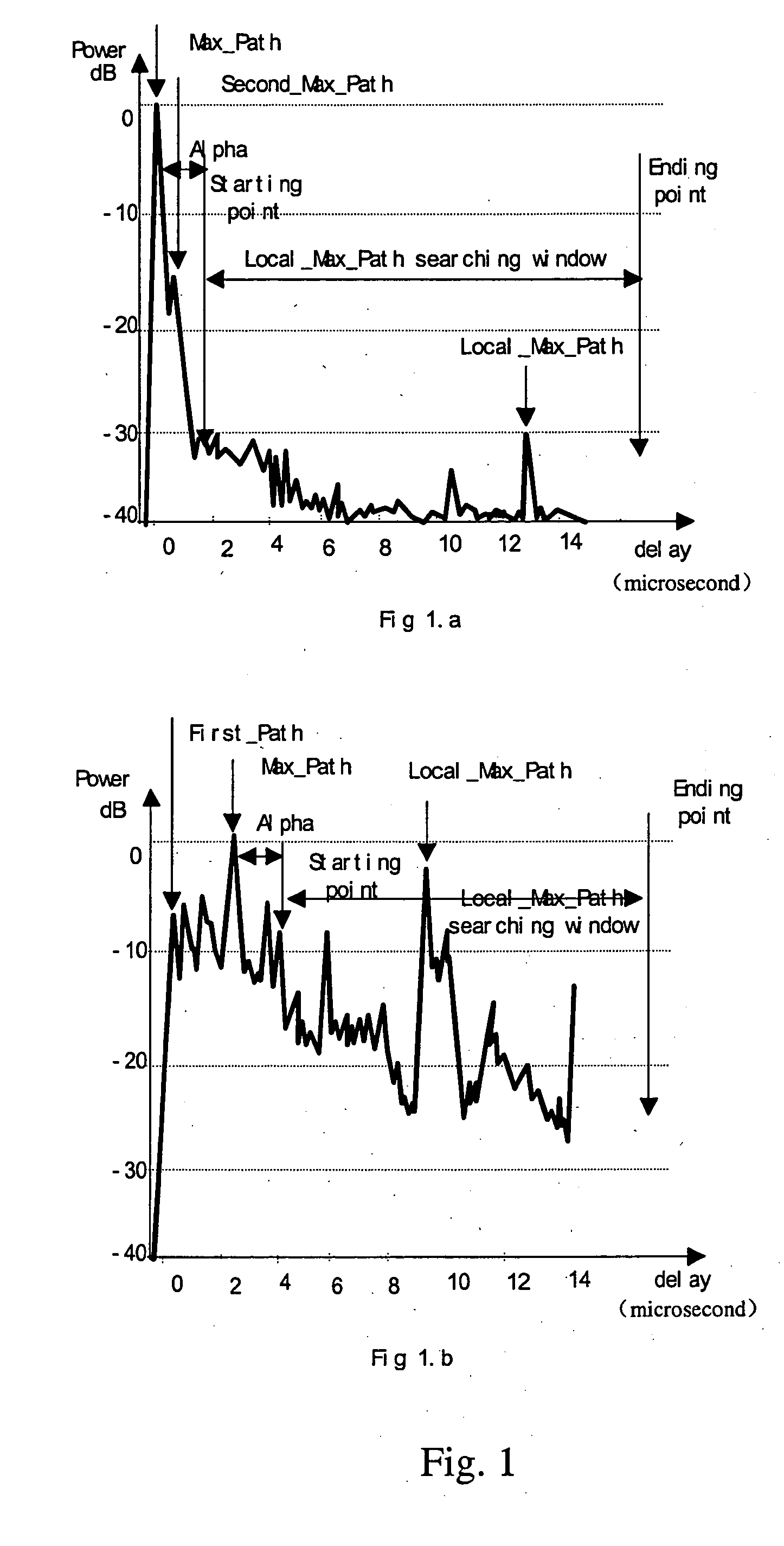

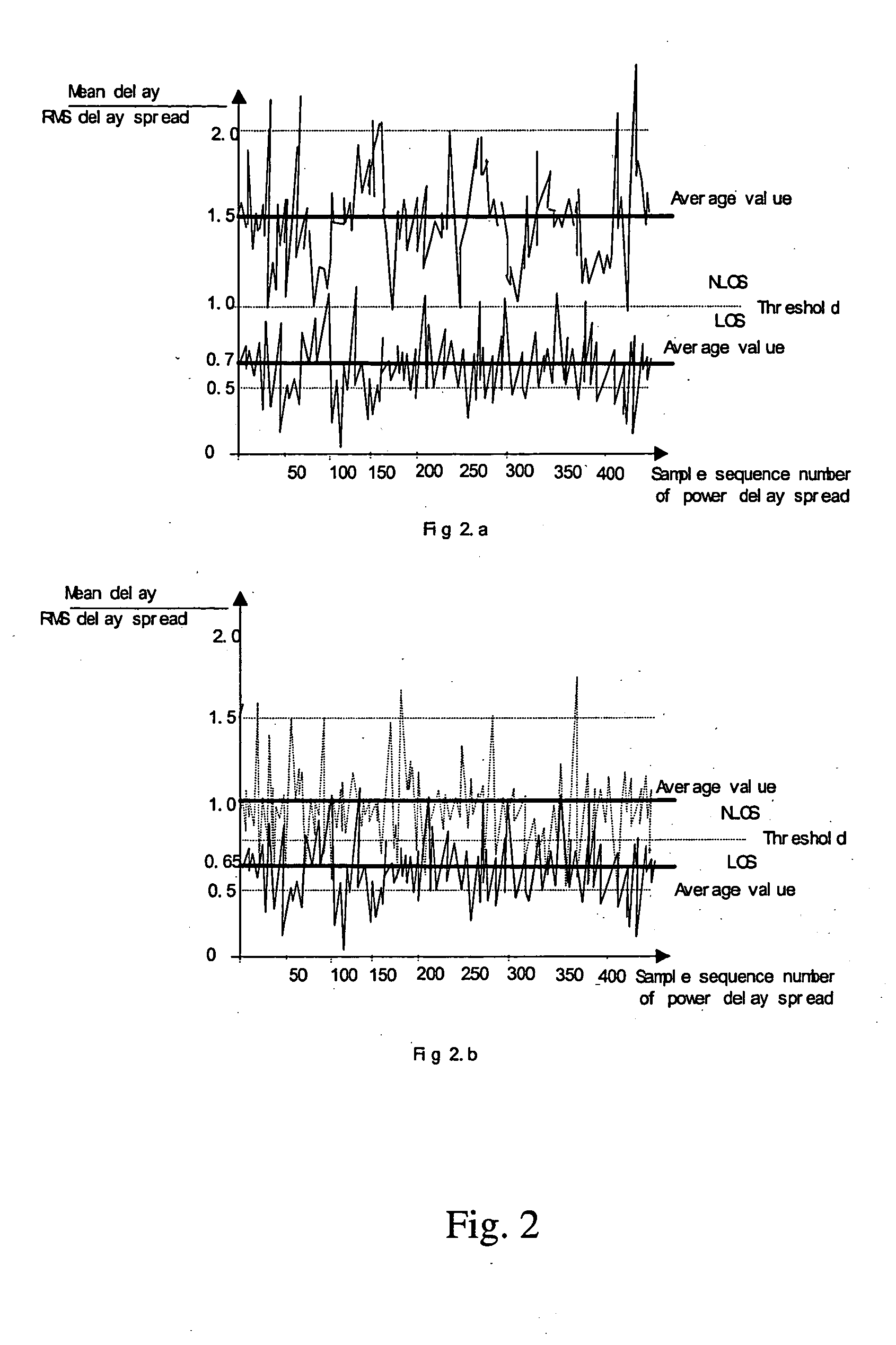

Method distinguishing line of sight (los) from non-line of sight (nlos) in cdma mobile communication system

InactiveUS20050124368A1Effectively lead to differentiationHigh positioning accuracyPosition fixationRadio/inductive link selection arrangementsPower delay profileDirect path

The invention discloses a method that identifies whether a channel is LOS or NLOS in a mobile communication system. After coherent accumulation and non-coherent accumulation have been made by the system, first the method takes power difference between the direct path and the non-direct path in a same power delay profile to identify a channel; and then the result is further determined by {overscore (τ)} / σ difference of a LOS channel and a NLOS channel (where {overscore (τ )}and σ is the mean delay and the RMS delay spread of a multipath power profile, respectively). A channel is determined as a LOS channel, if the power ratio of the Maximum Path to the Local Maximum Path is greater than a threshold K, and simultaneously the arrival time difference between the First Path and said Maximum Path is less than a time interval T; otherwise it is a NLOS channel. The method is easier to implement and compatible with the present mobile communication system.

Owner:HUAWEI TECH CO LTD

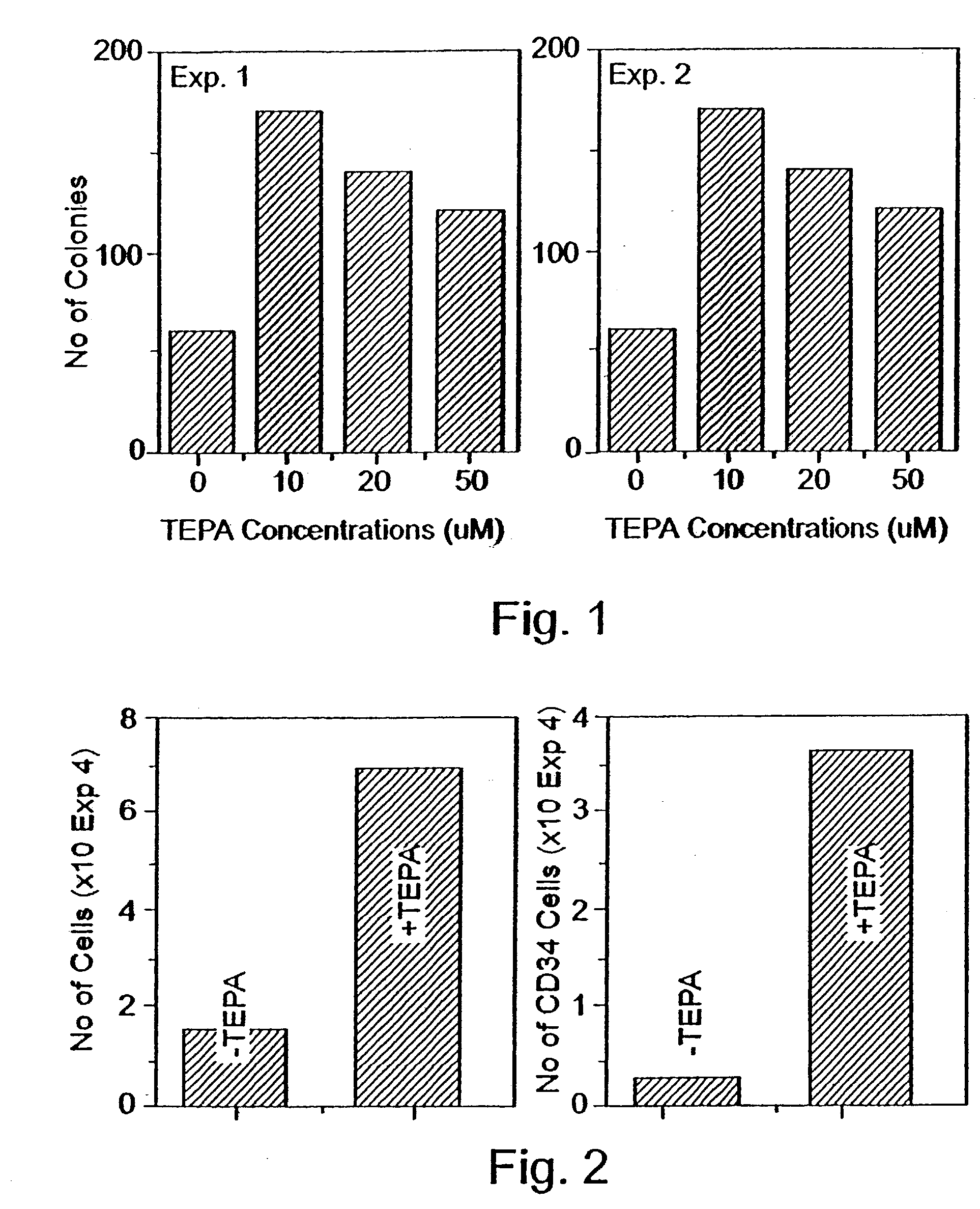

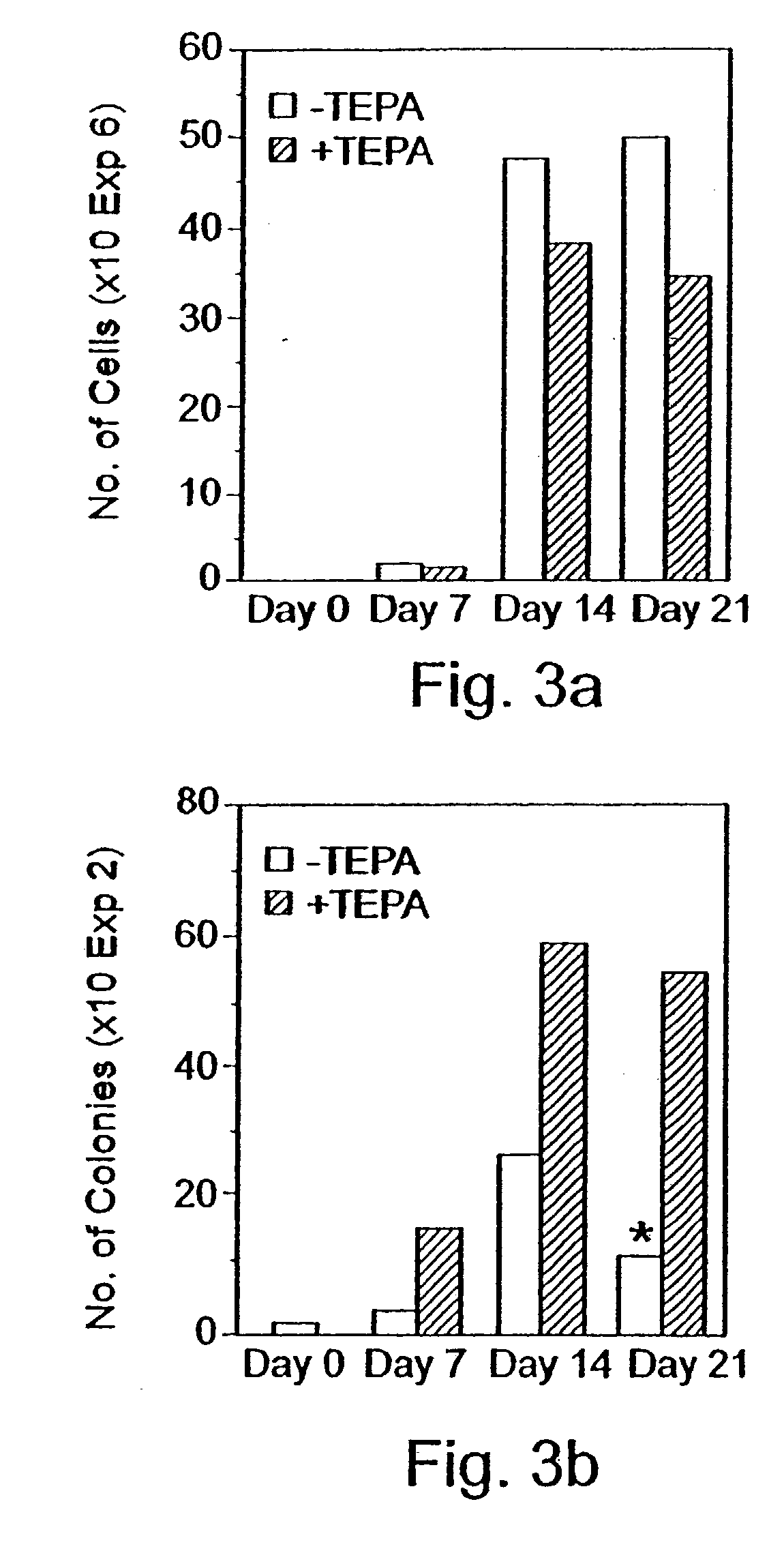

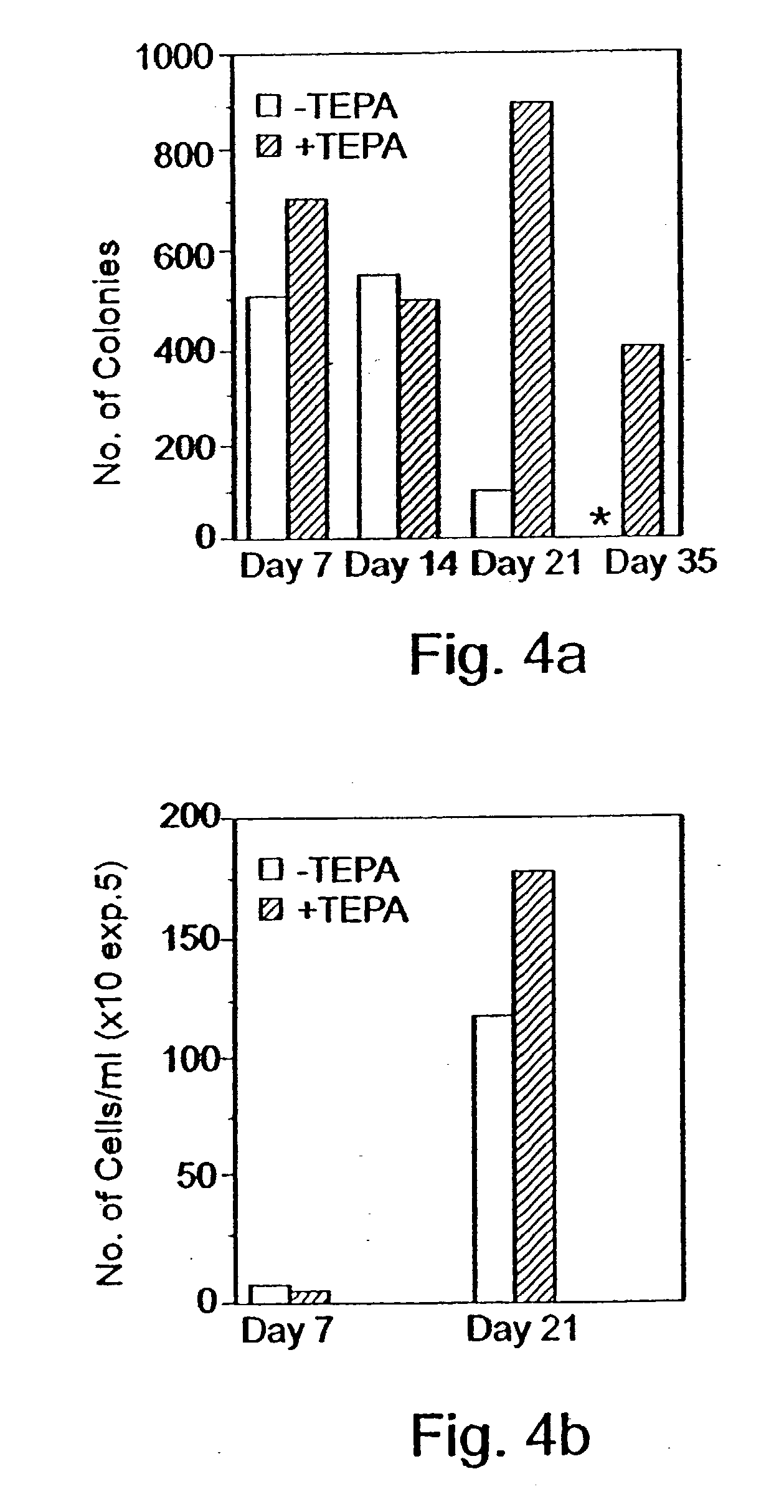

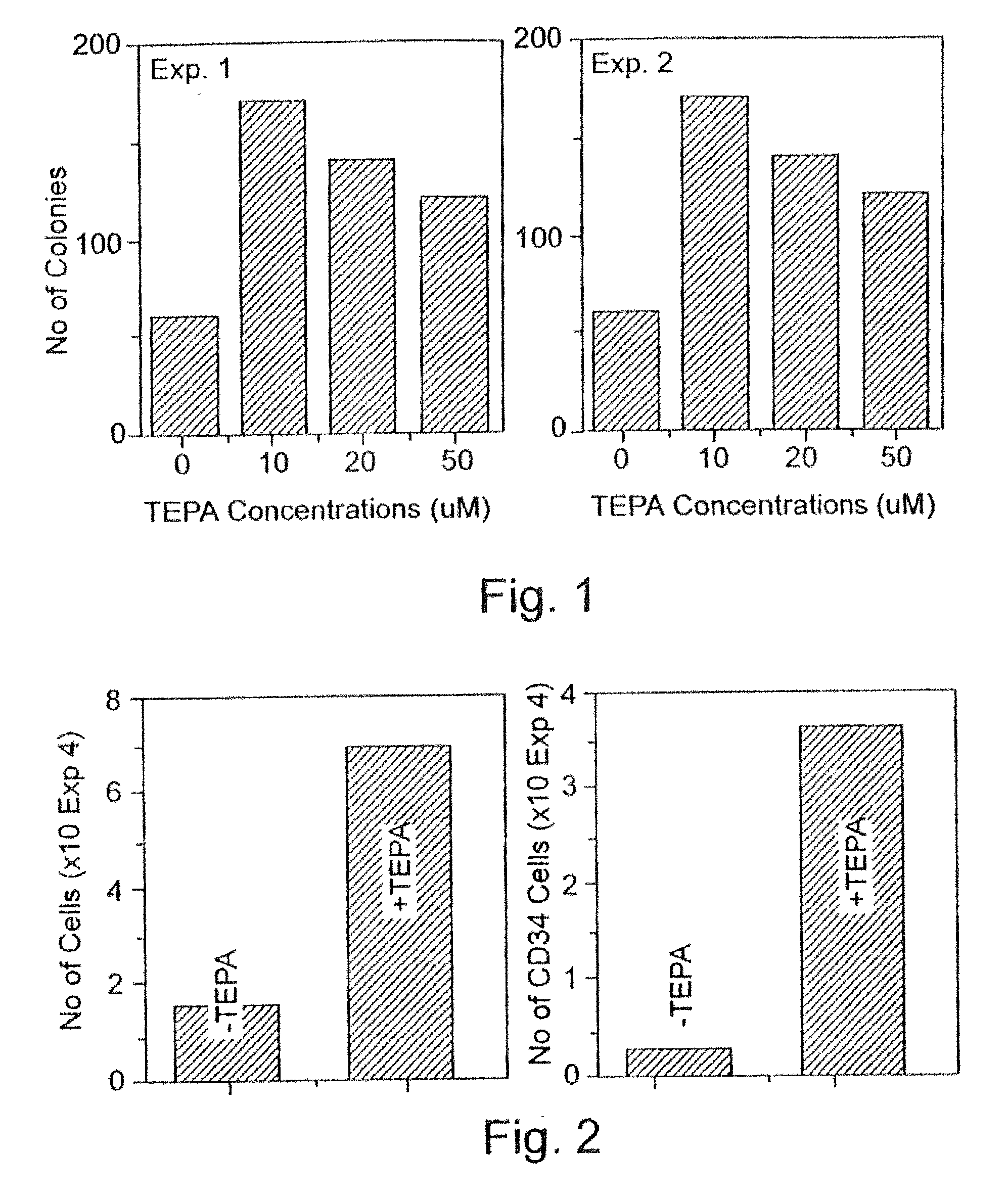

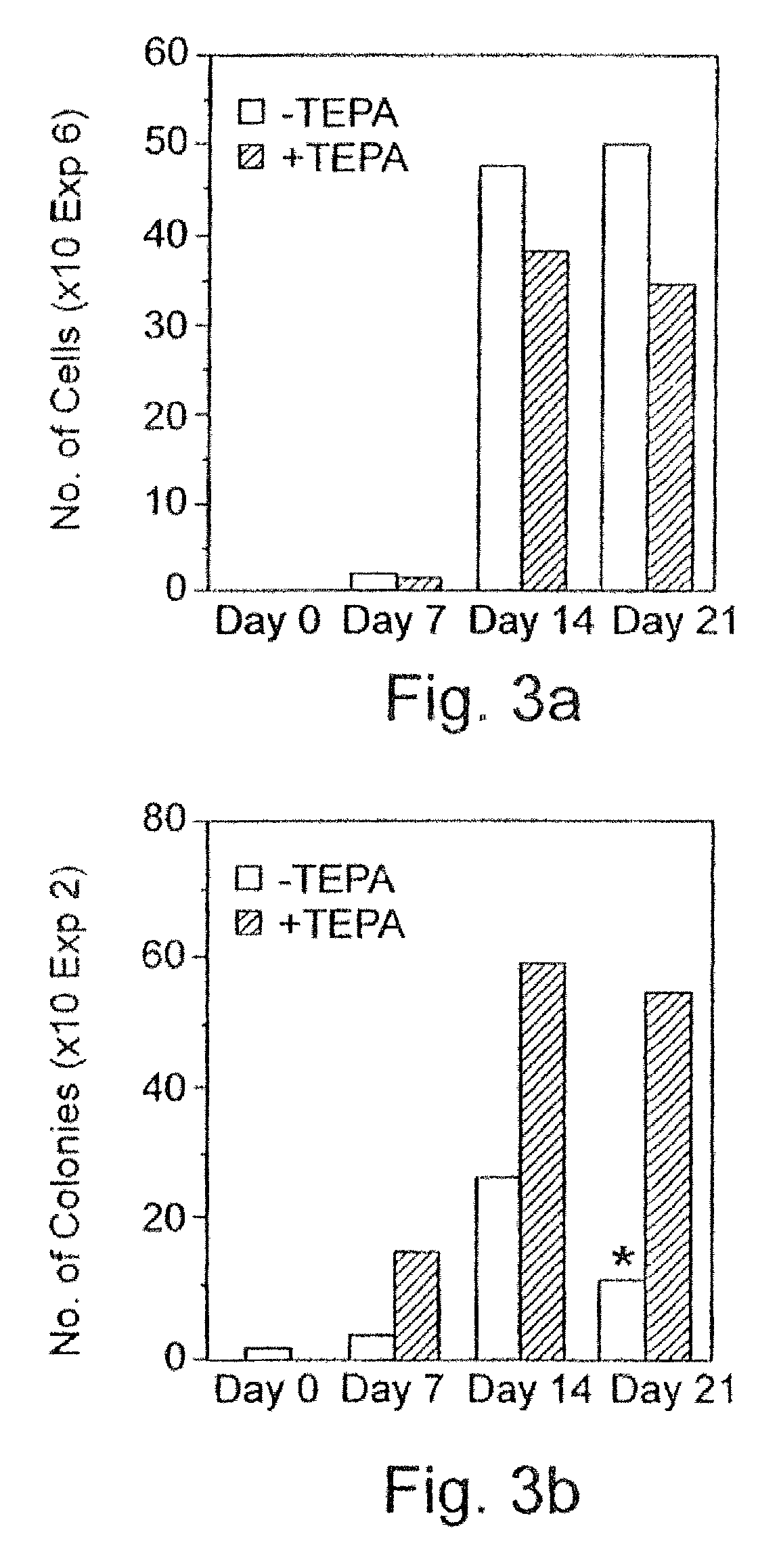

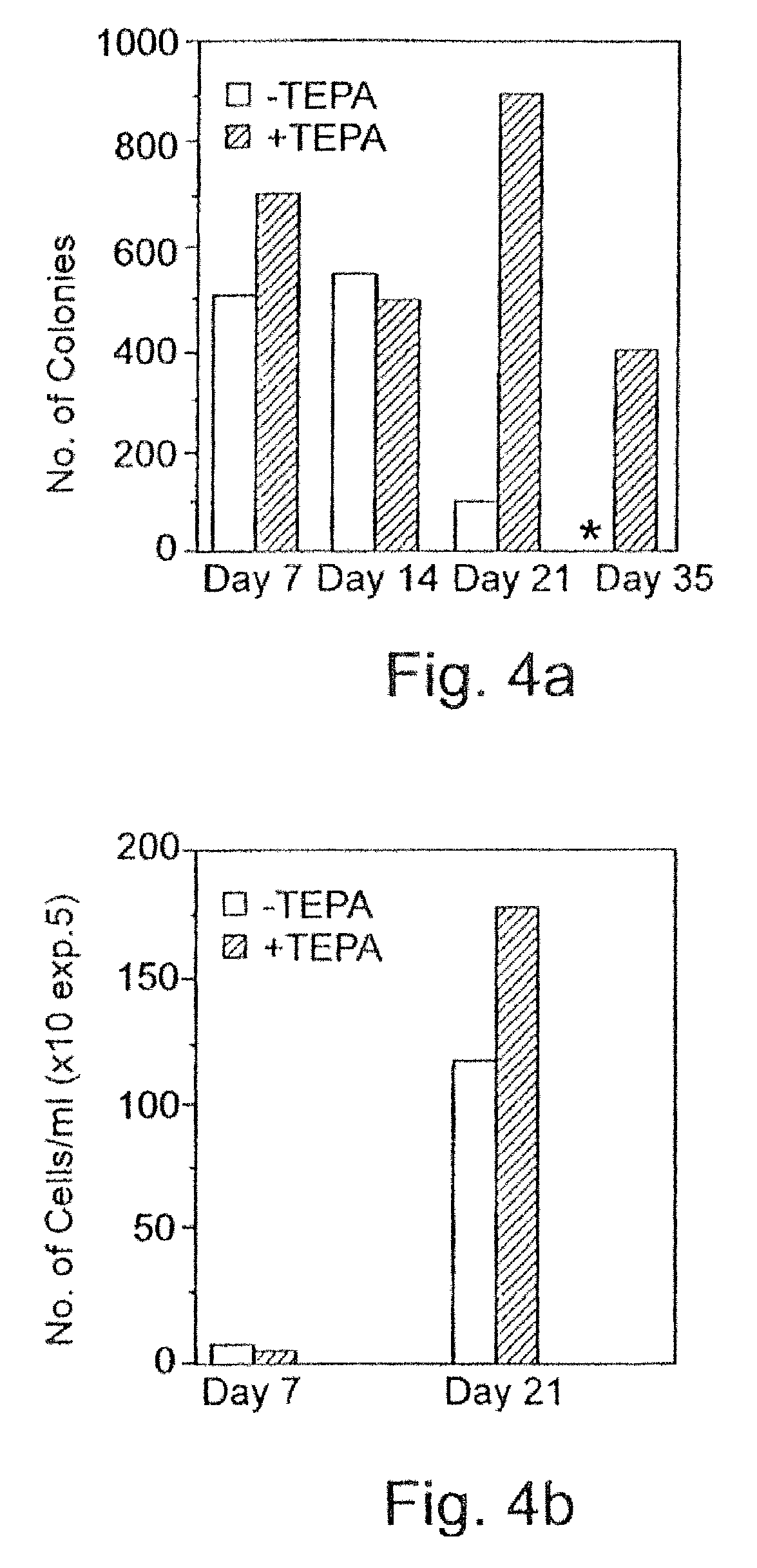

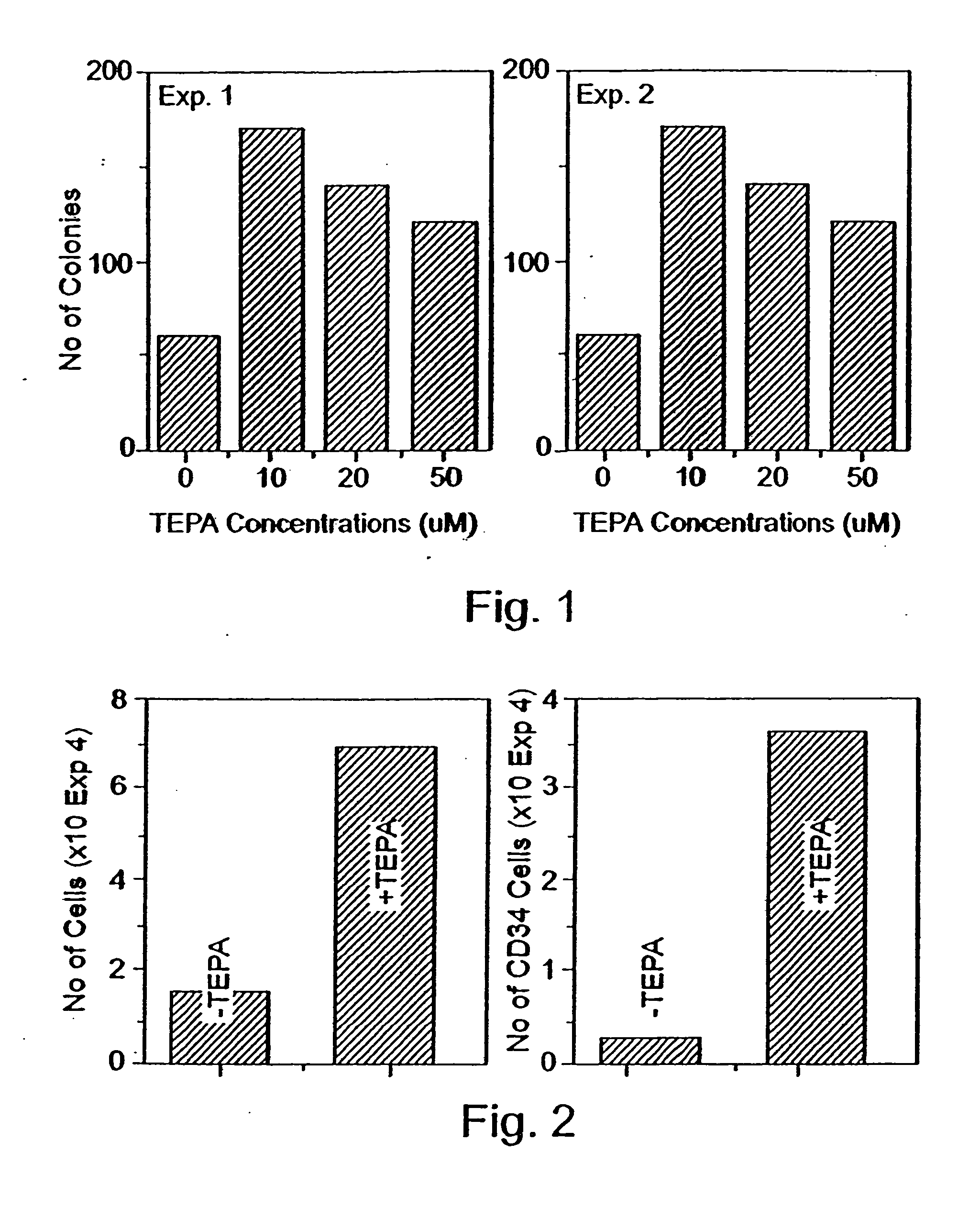

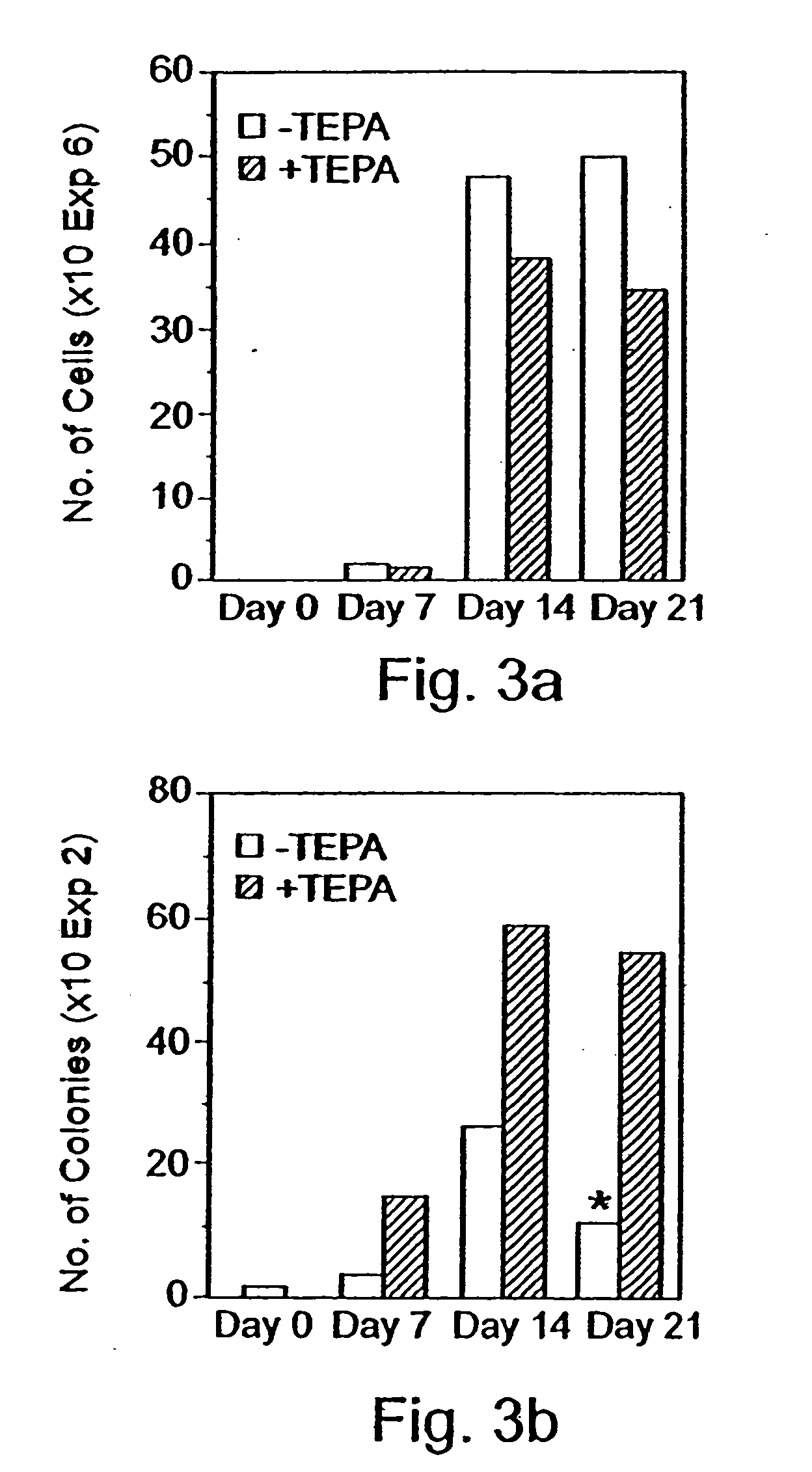

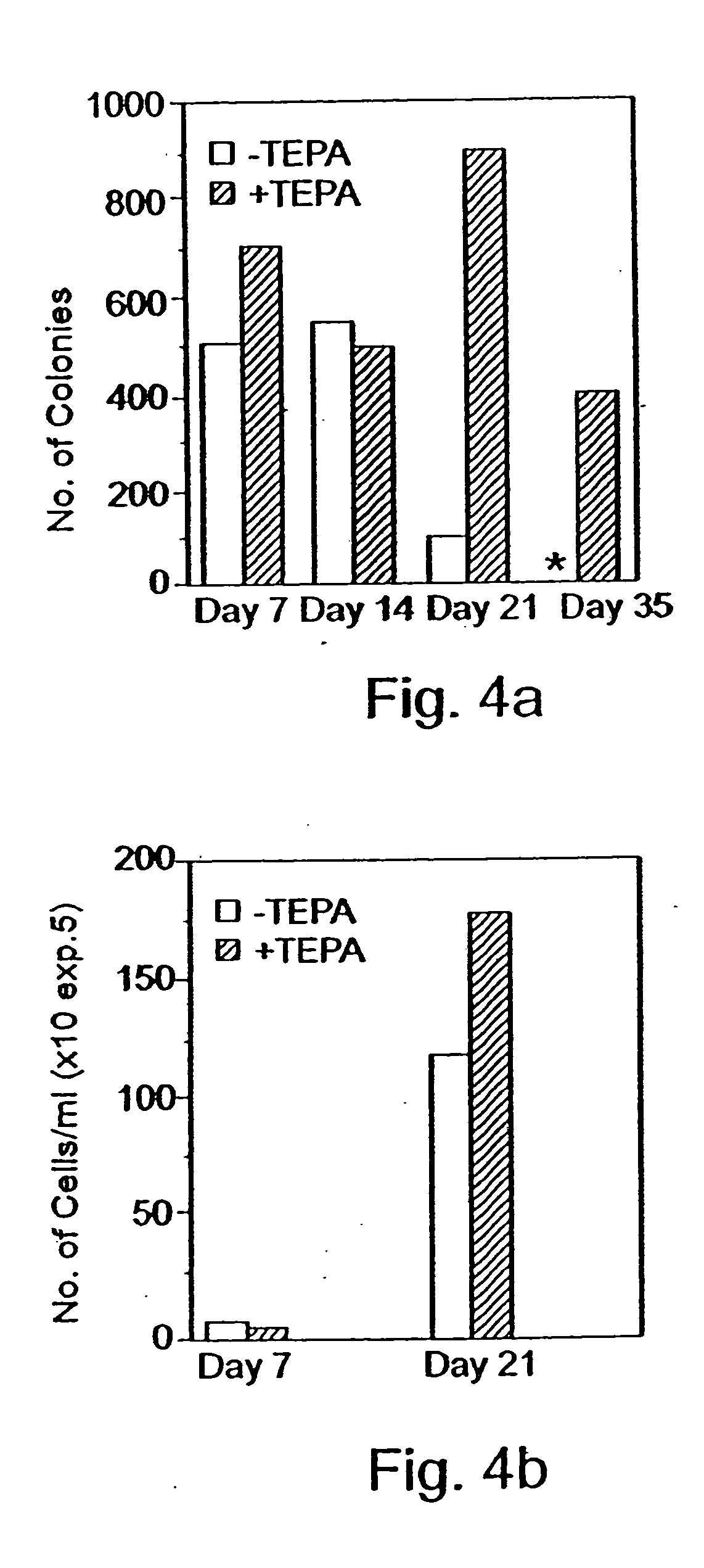

Methods of controlling proliferation and differentiation of stem and progenitor cells

InactiveUS20050031595A1Reduce capacityExpand the populationBiocidePeptide/protein ingredientsProgenitorCopper Chelator

A method of ex-vivo expanding a population of stem cells, while at the same time inhibiting differentiation of the stem cells. The method comprises ex-vivo providing the stem cells with conditions for cell proliferation and with at least one copper chelator in an amount and for a time period for permitting the stem cells to proliferate and, at the same time, for reducing a capacity of the stem cells to differentiate

Owner:GAMIDA CELL +1

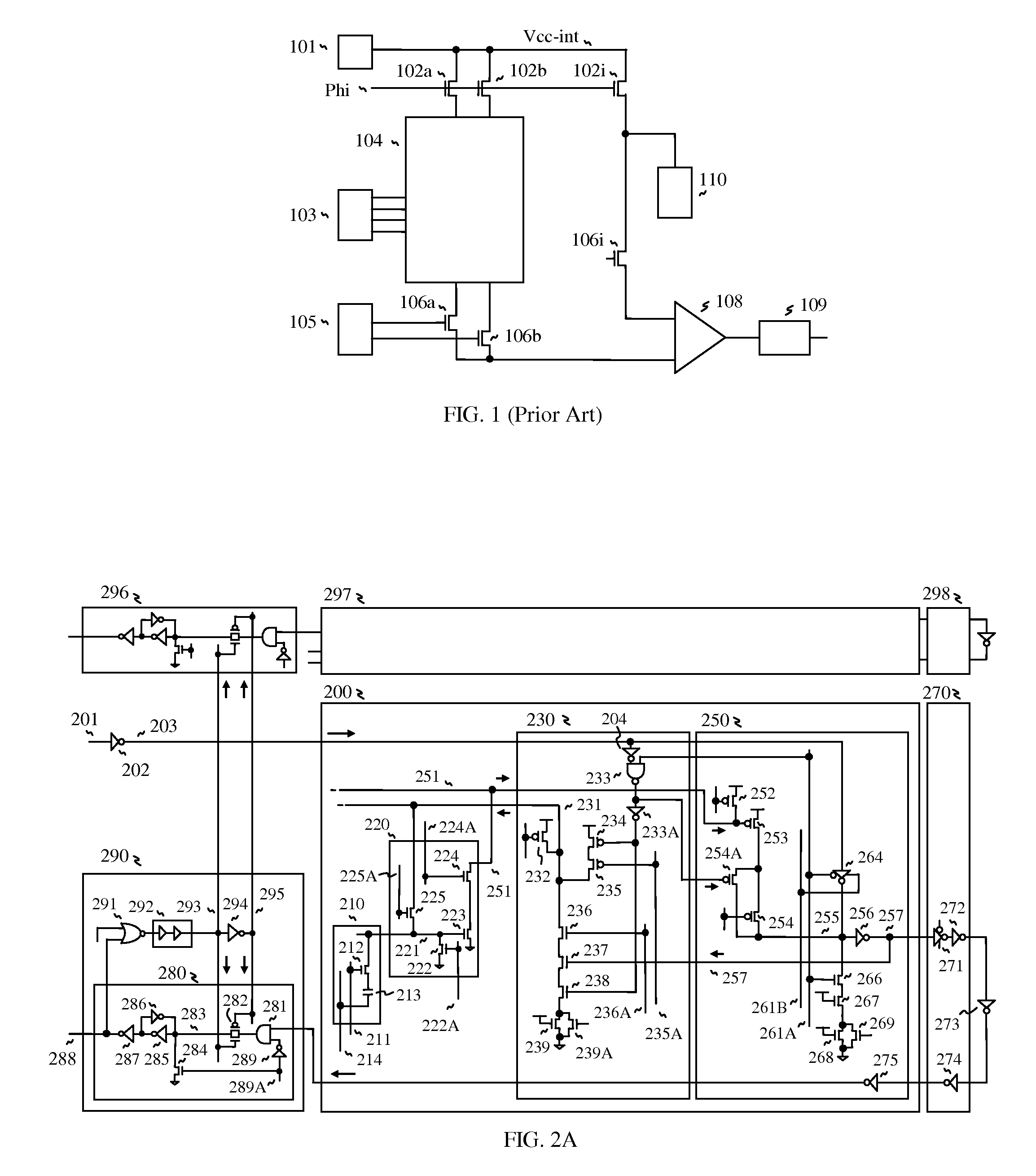

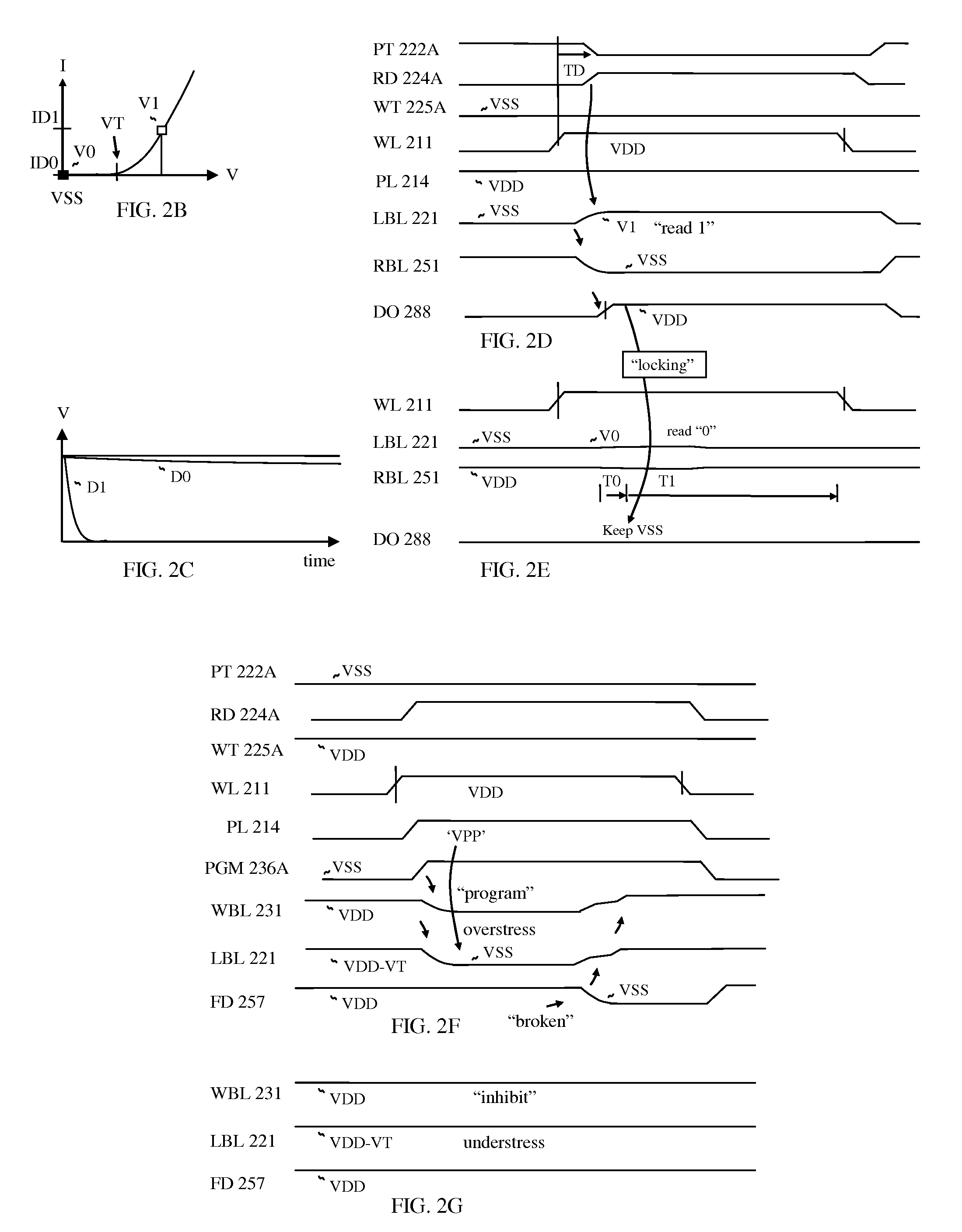

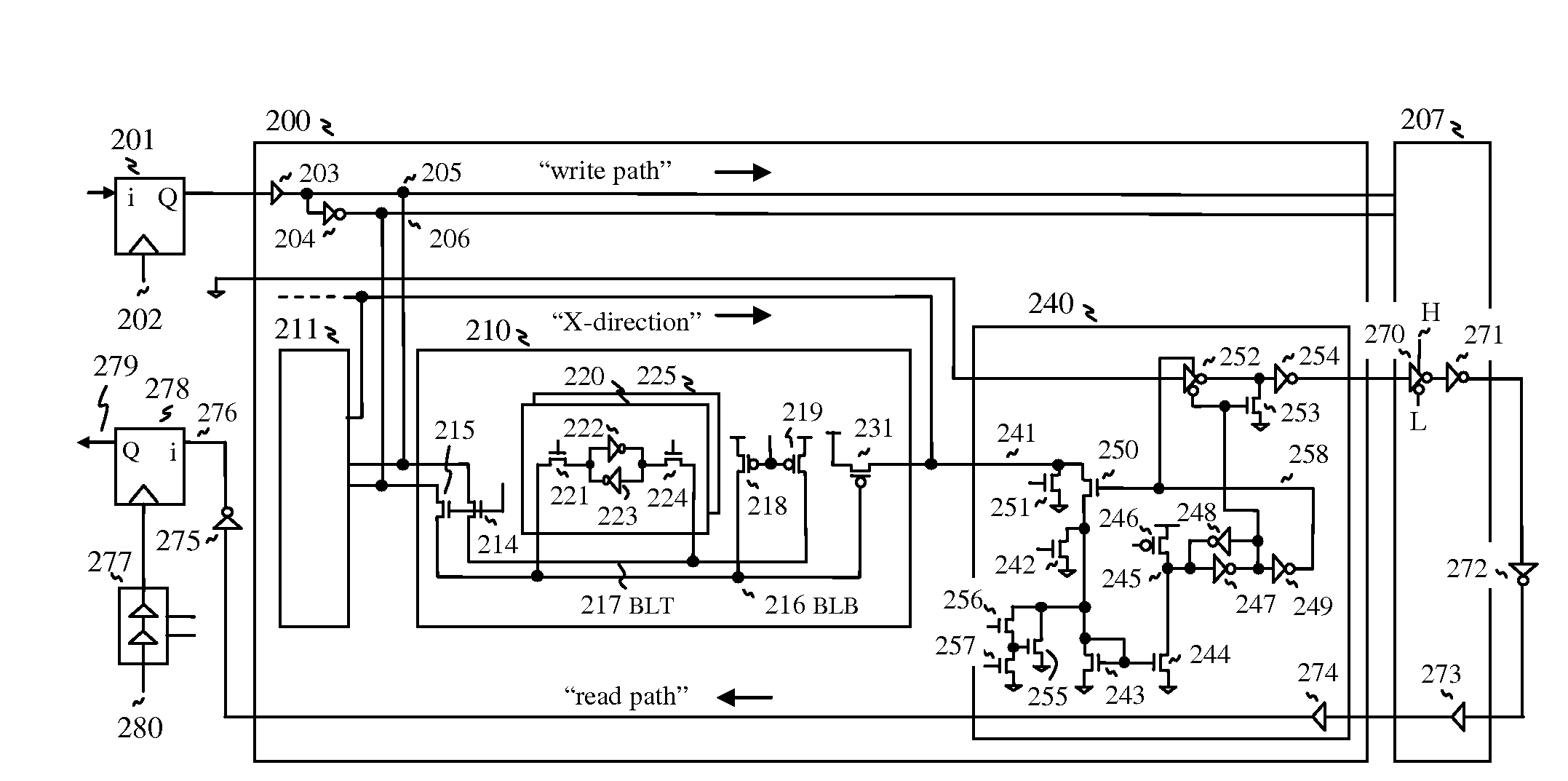

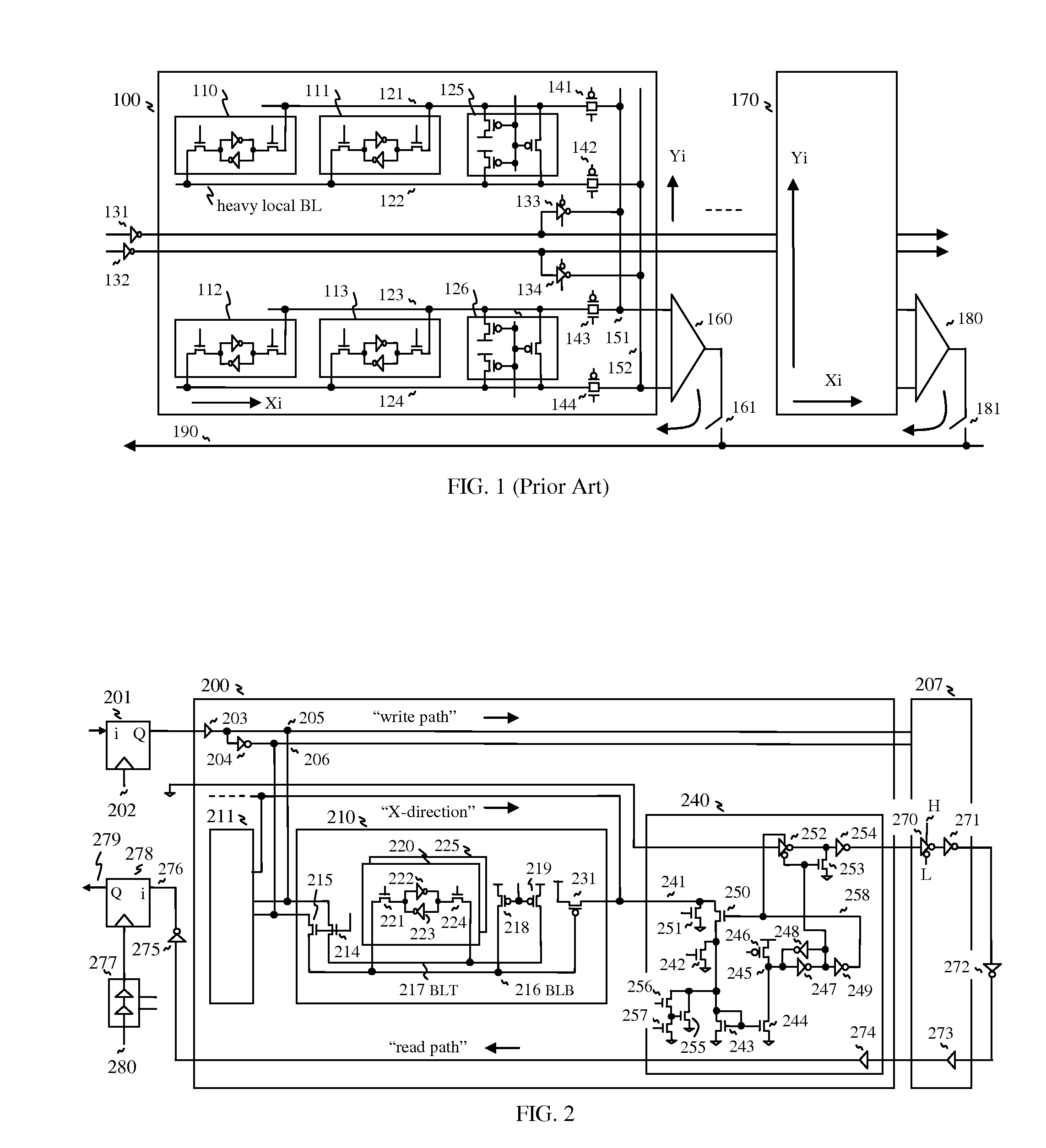

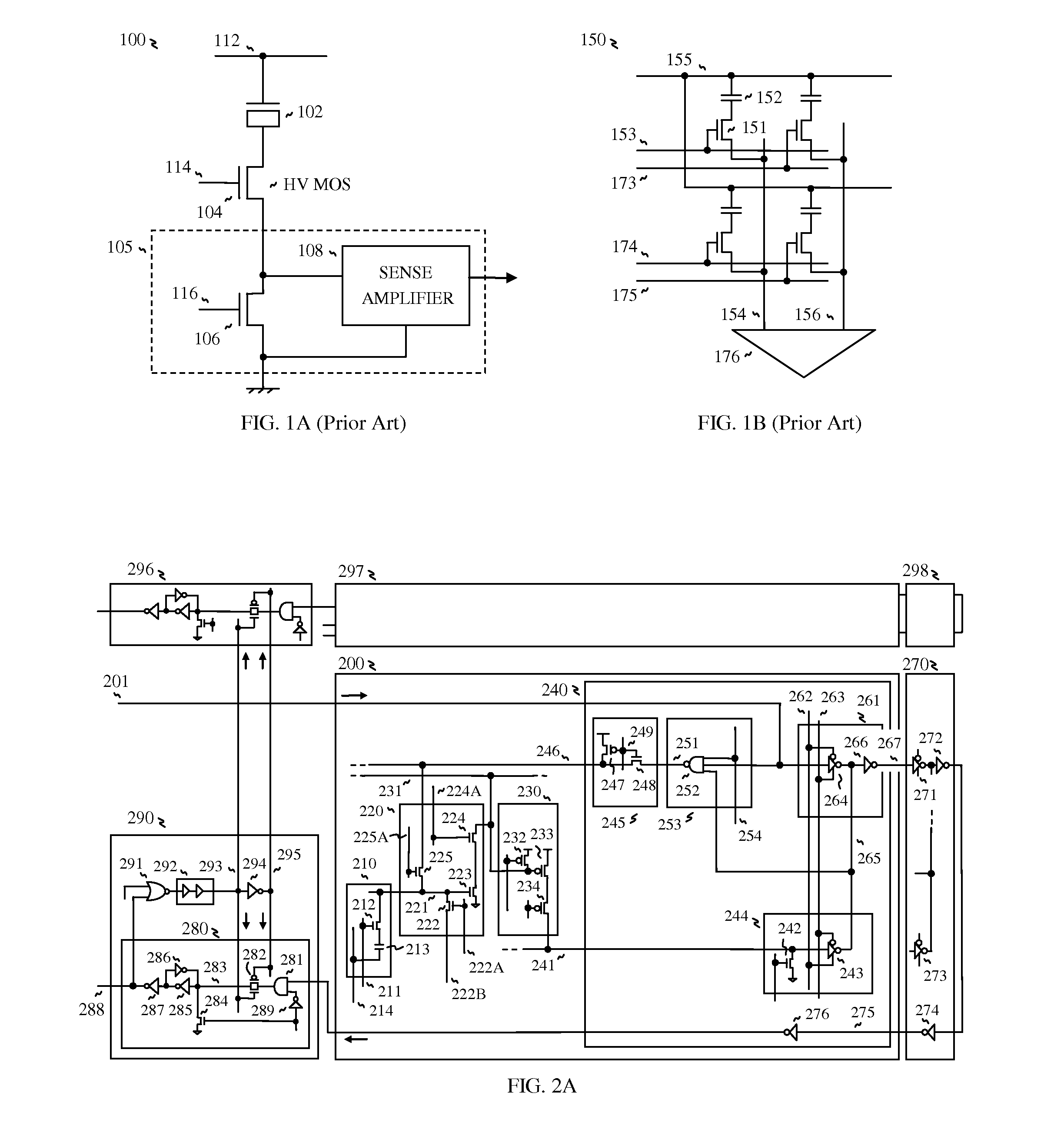

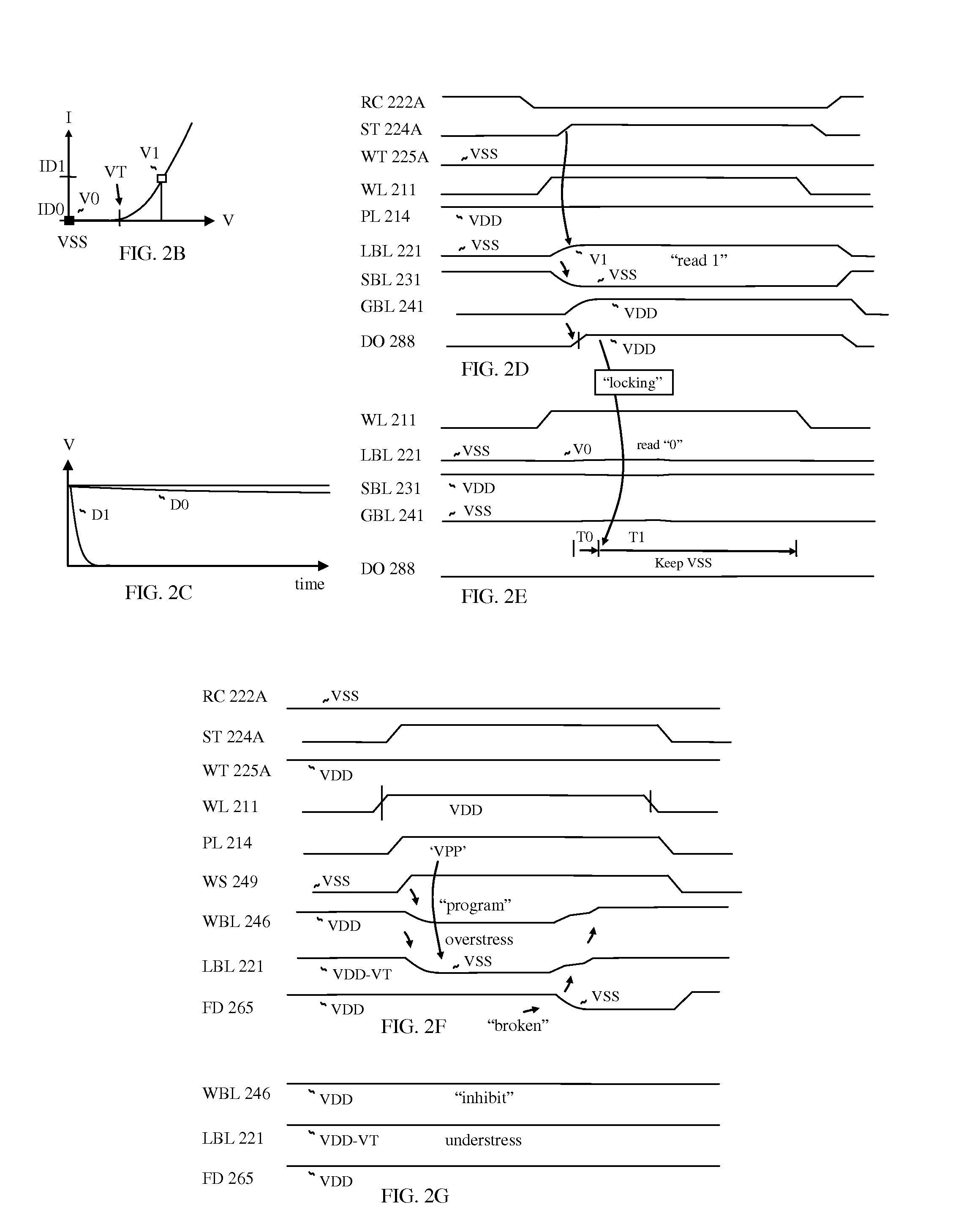

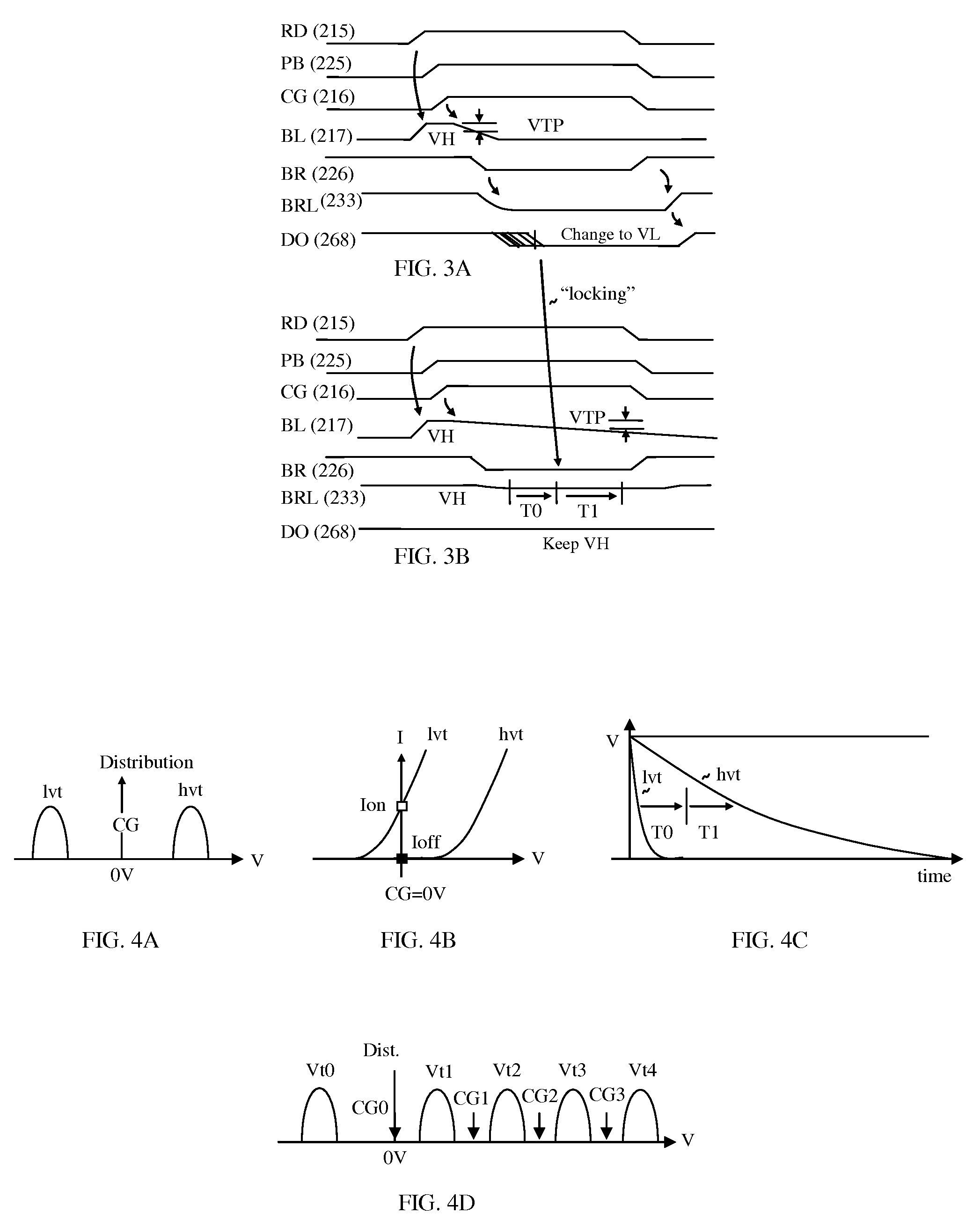

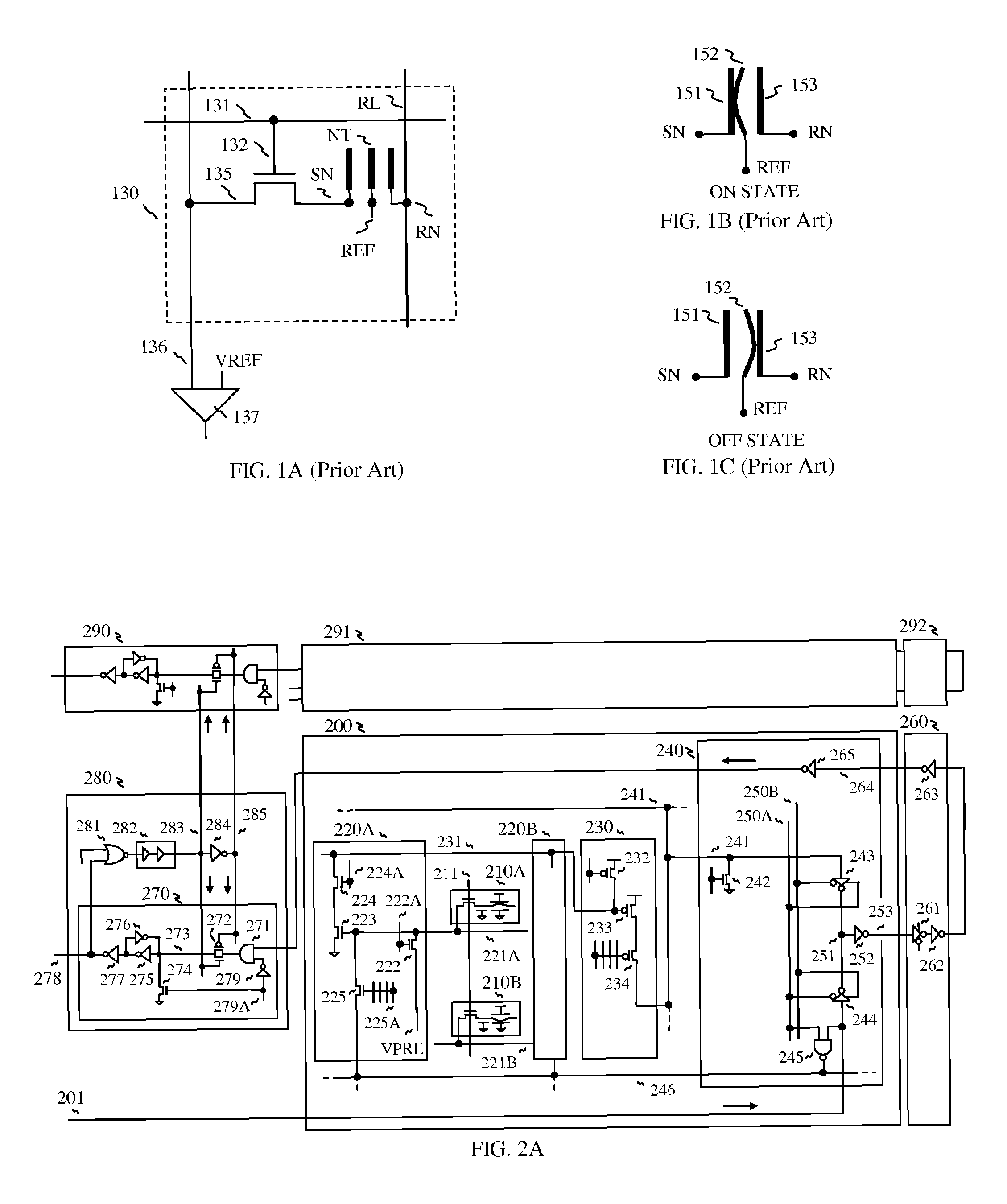

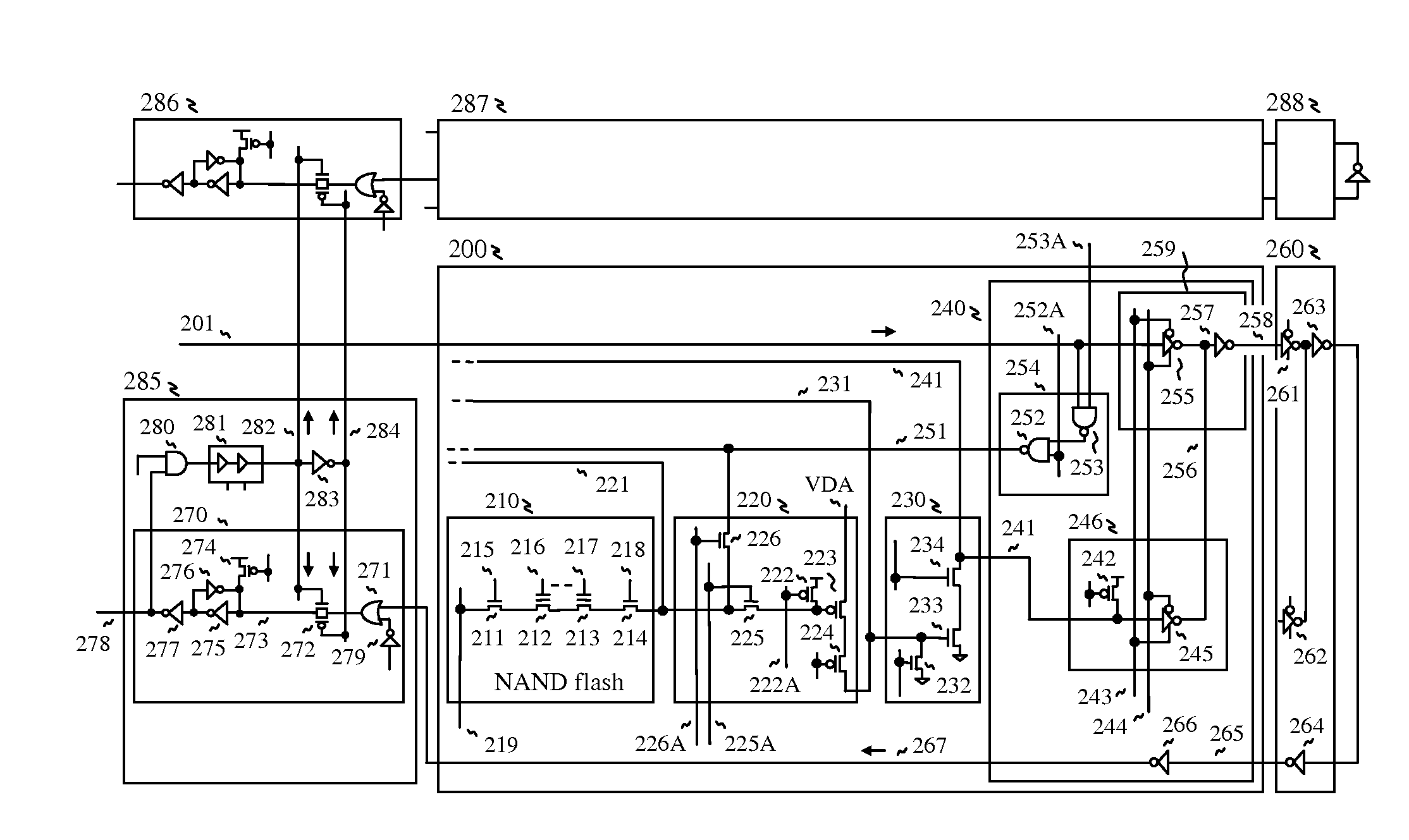

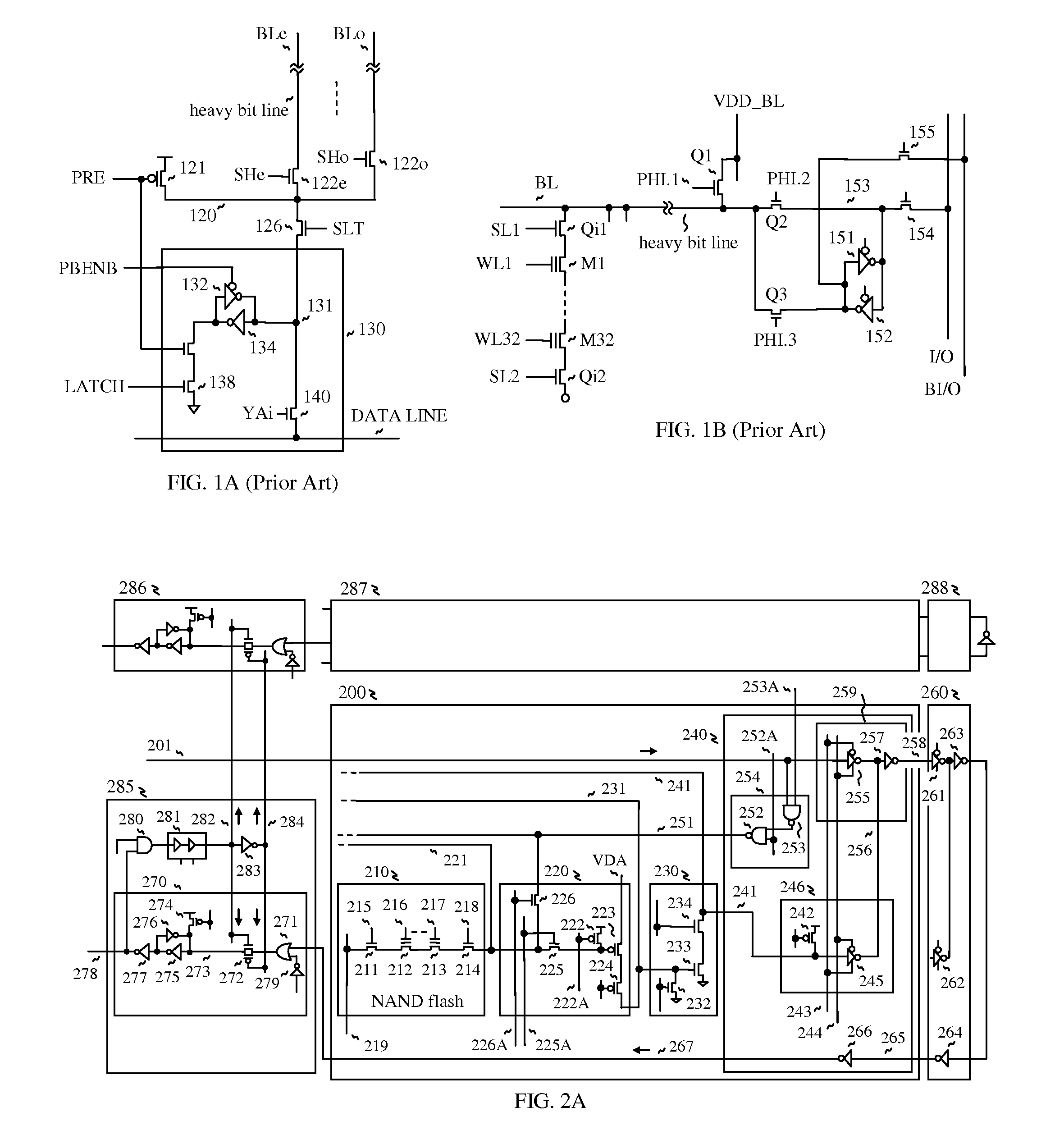

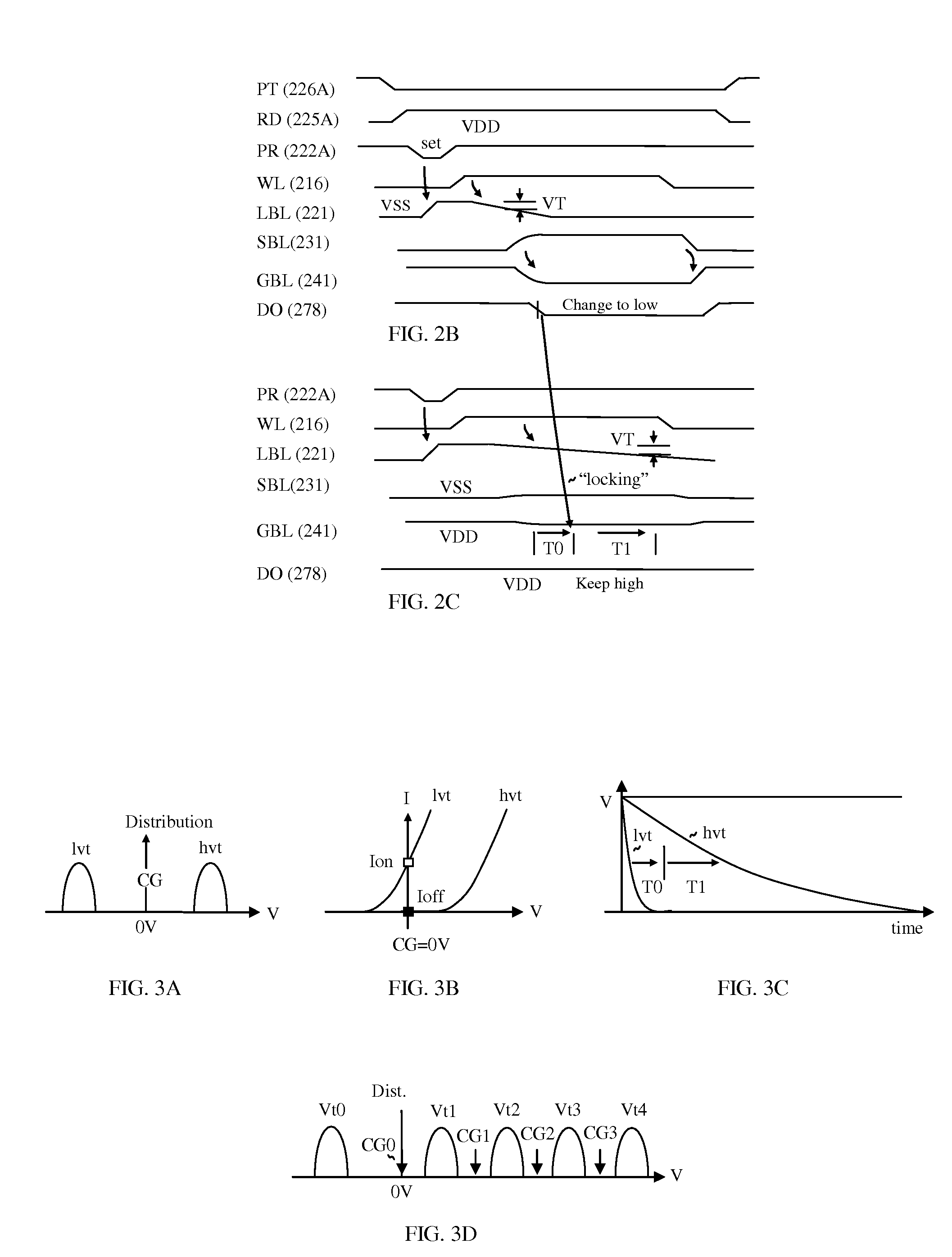

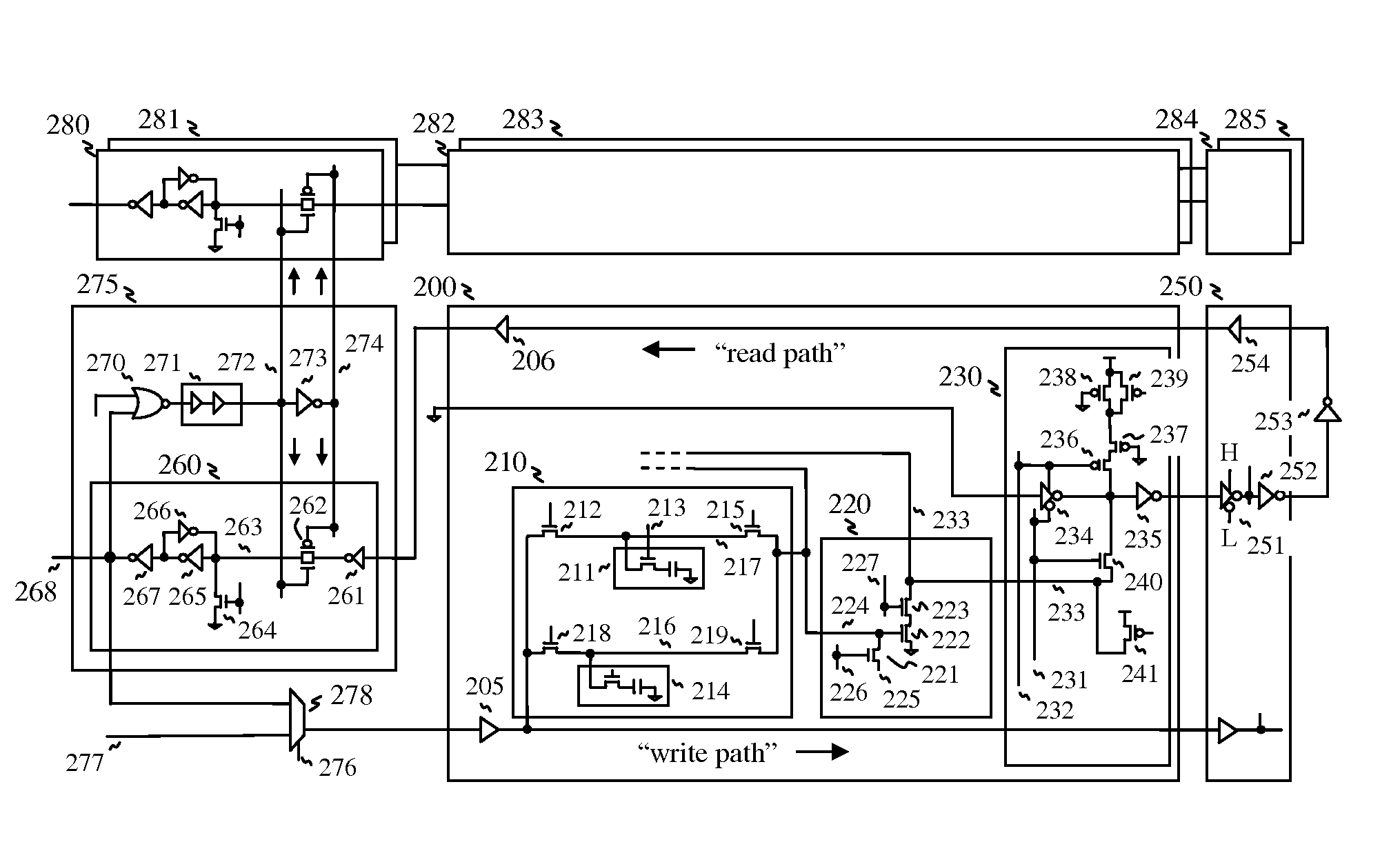

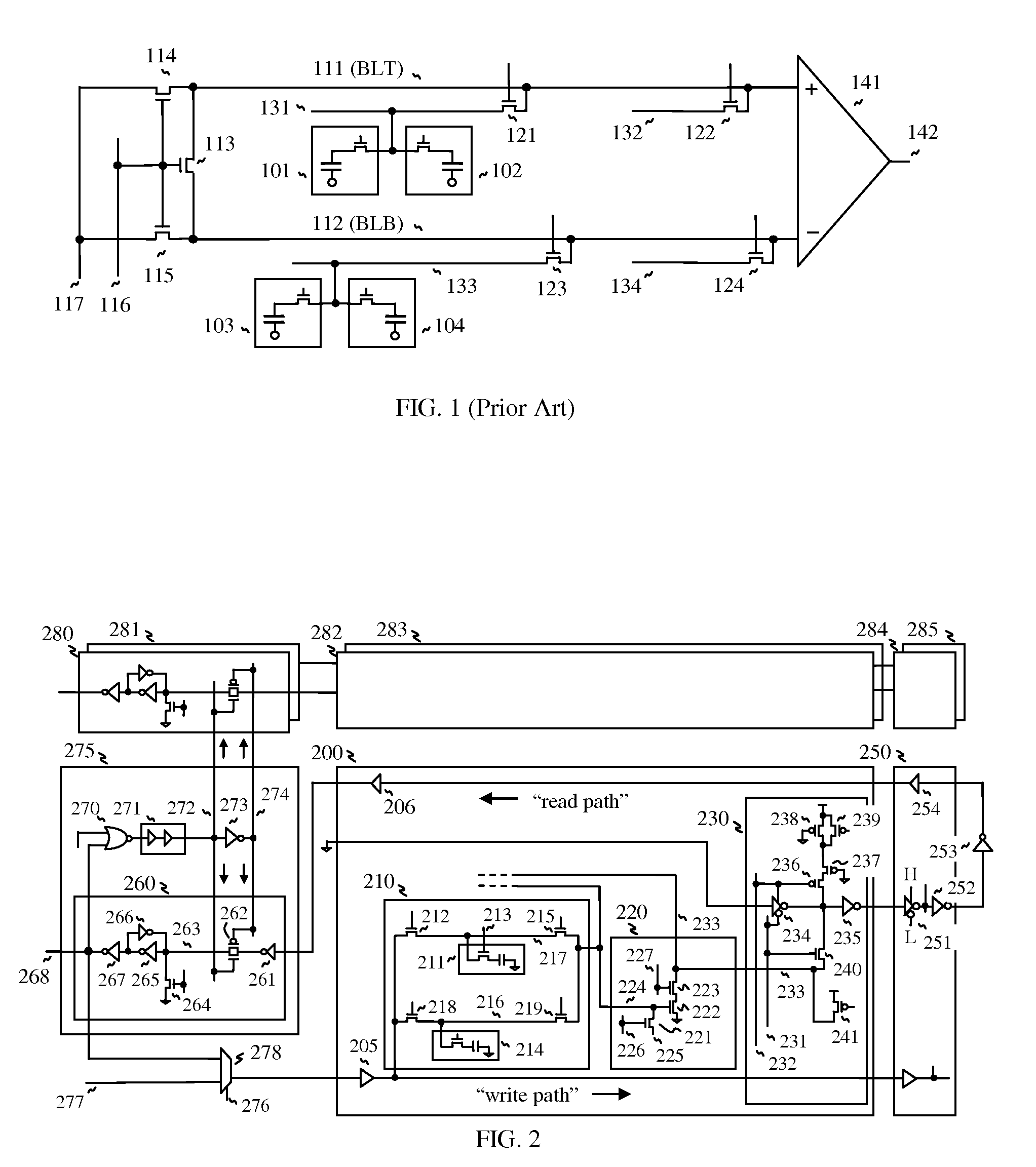

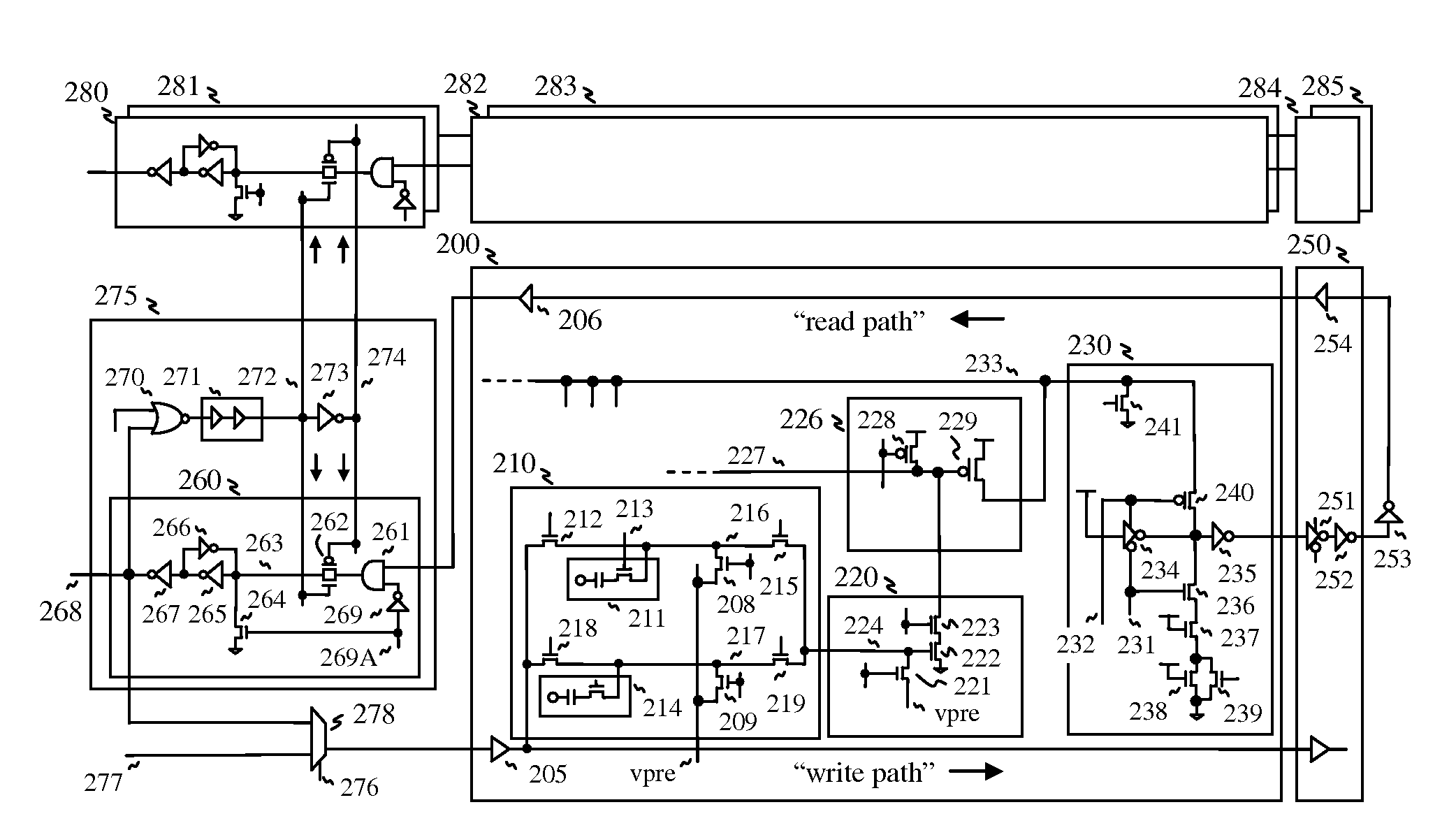

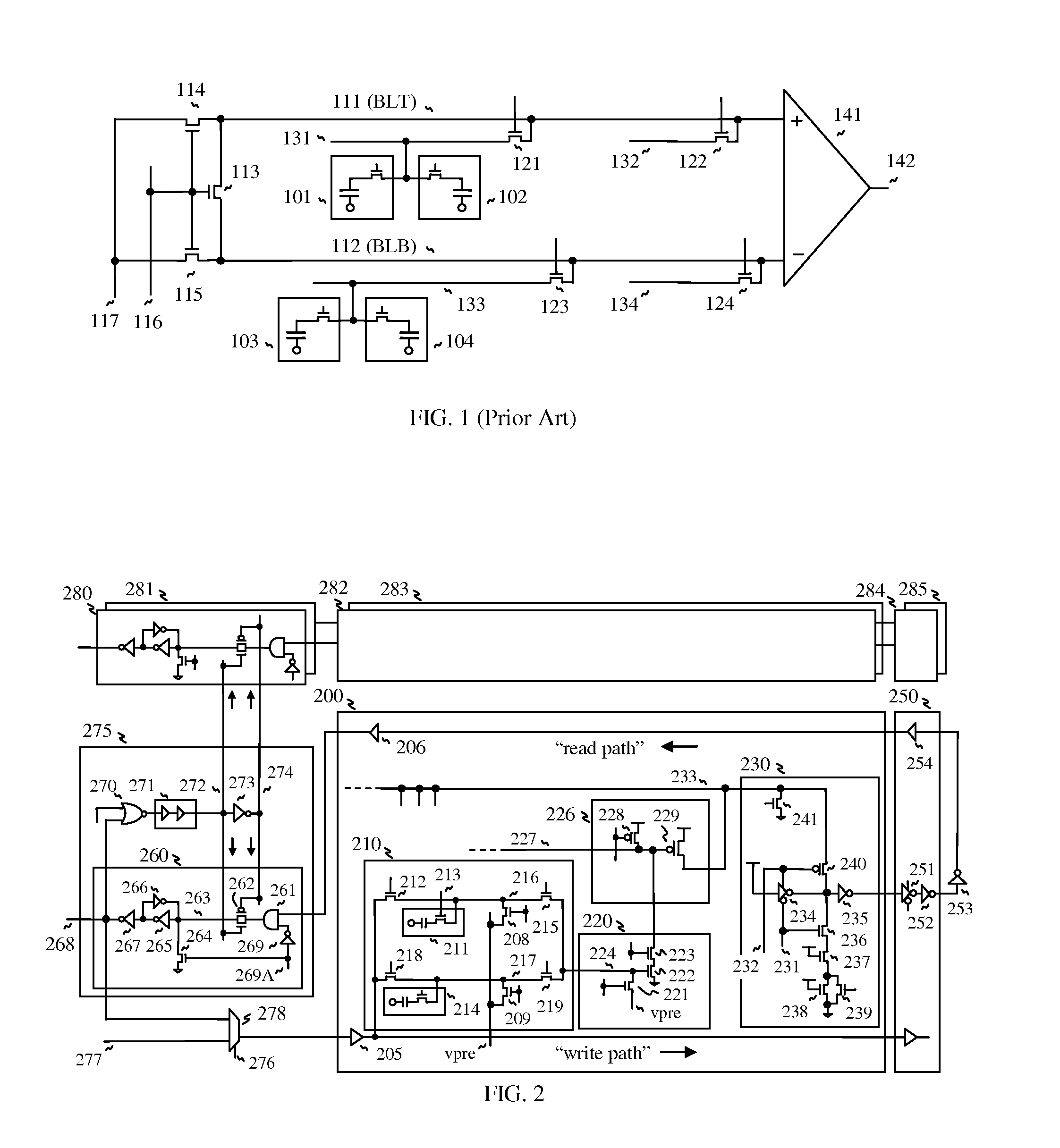

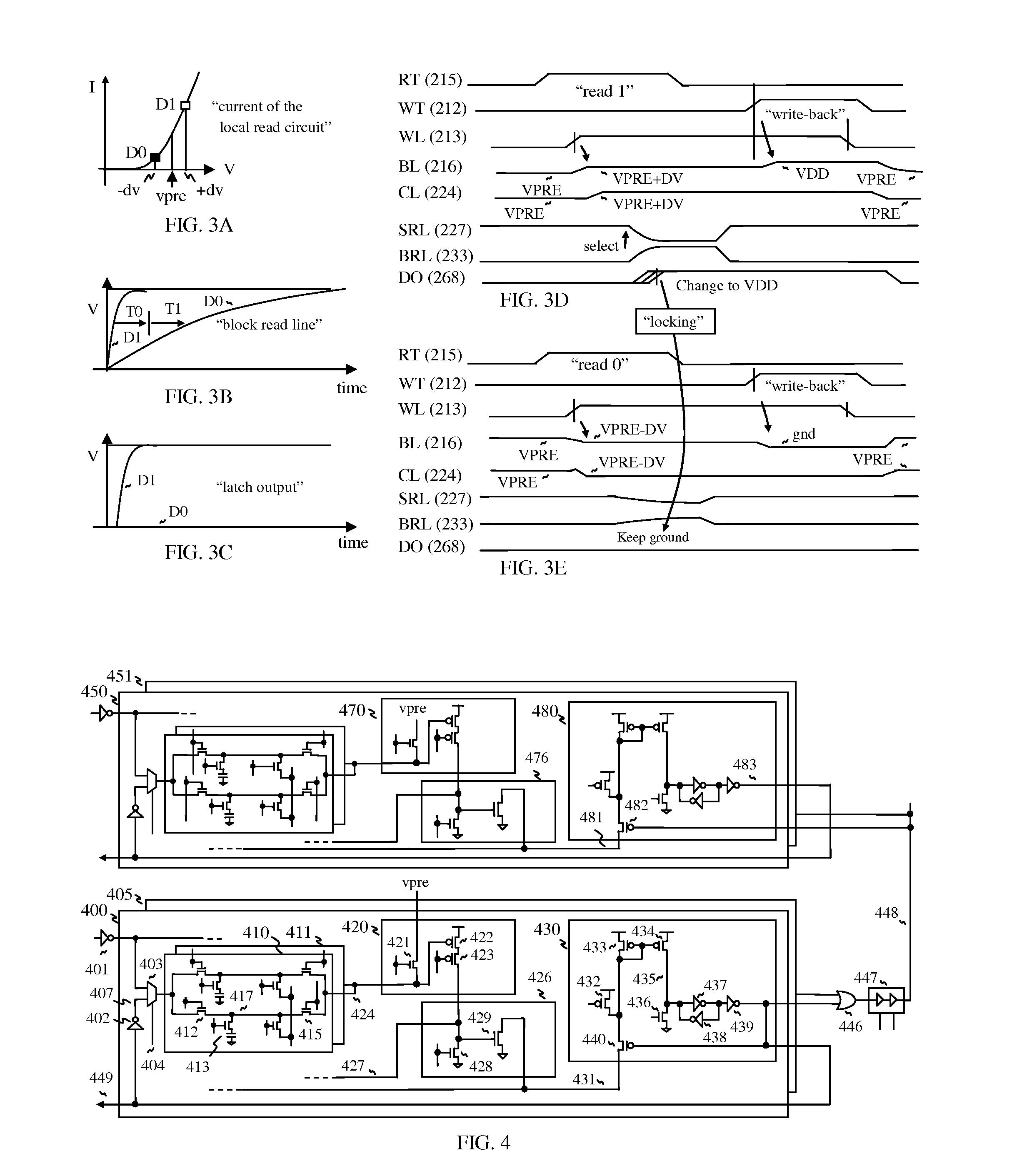

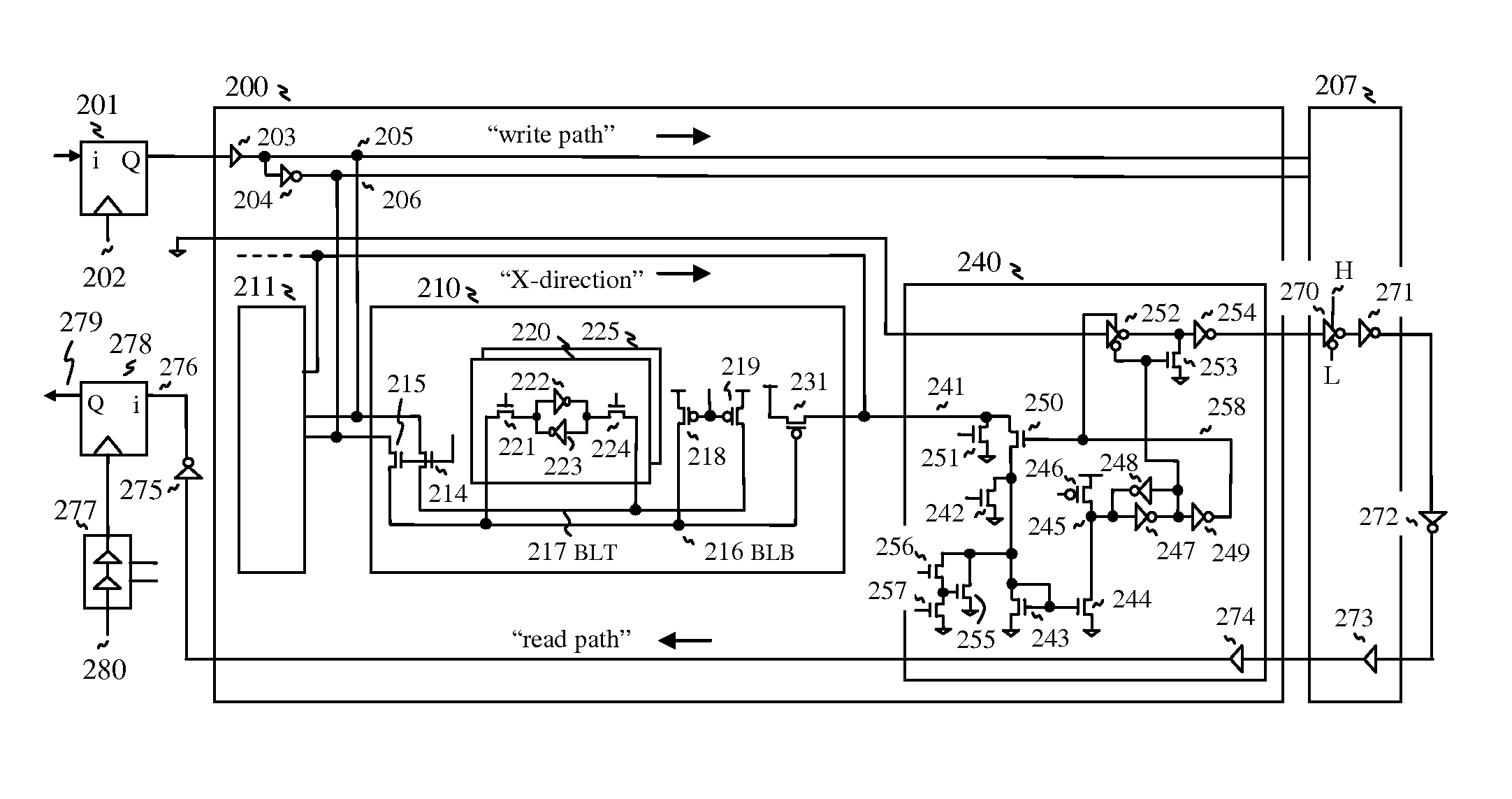

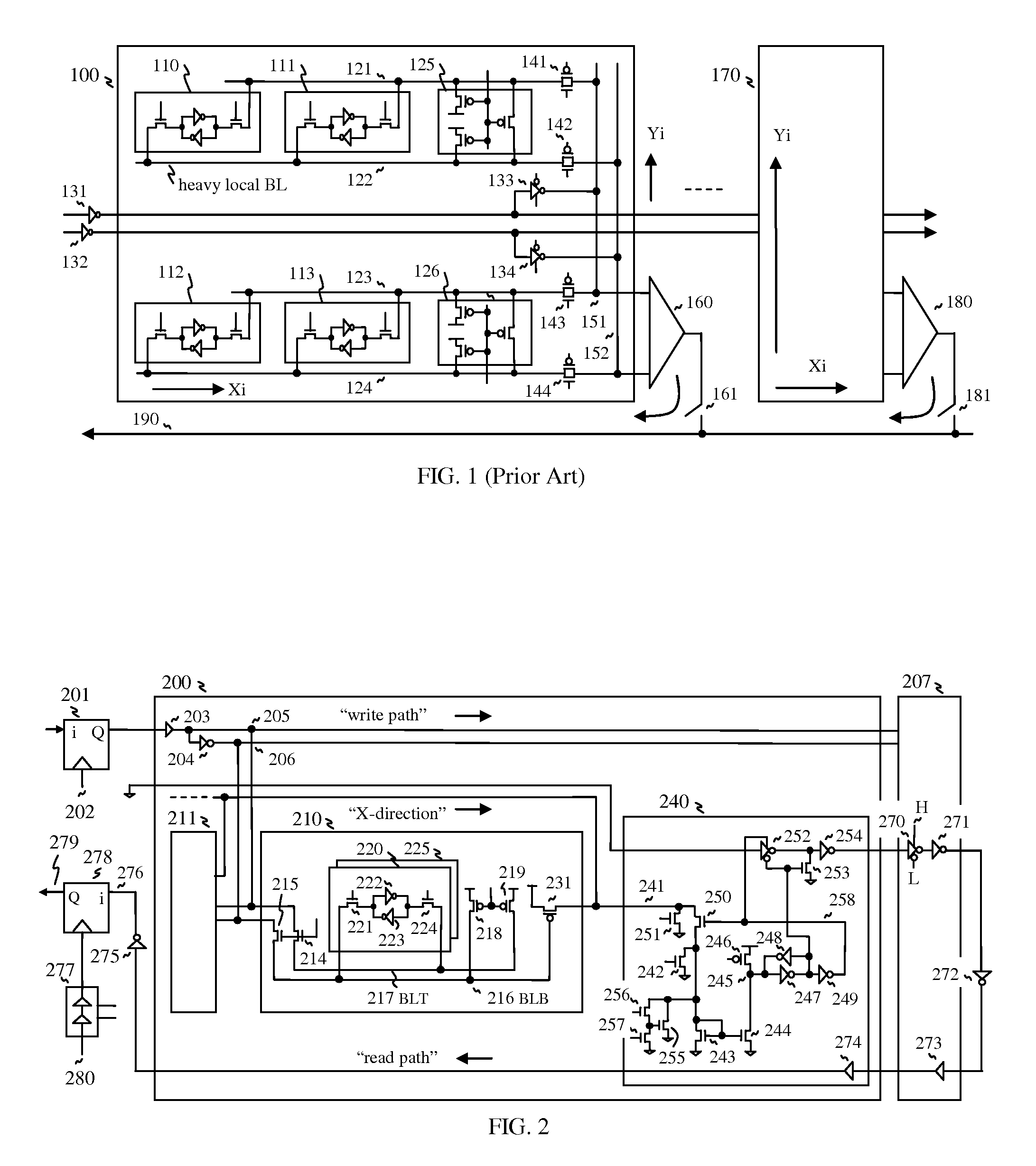

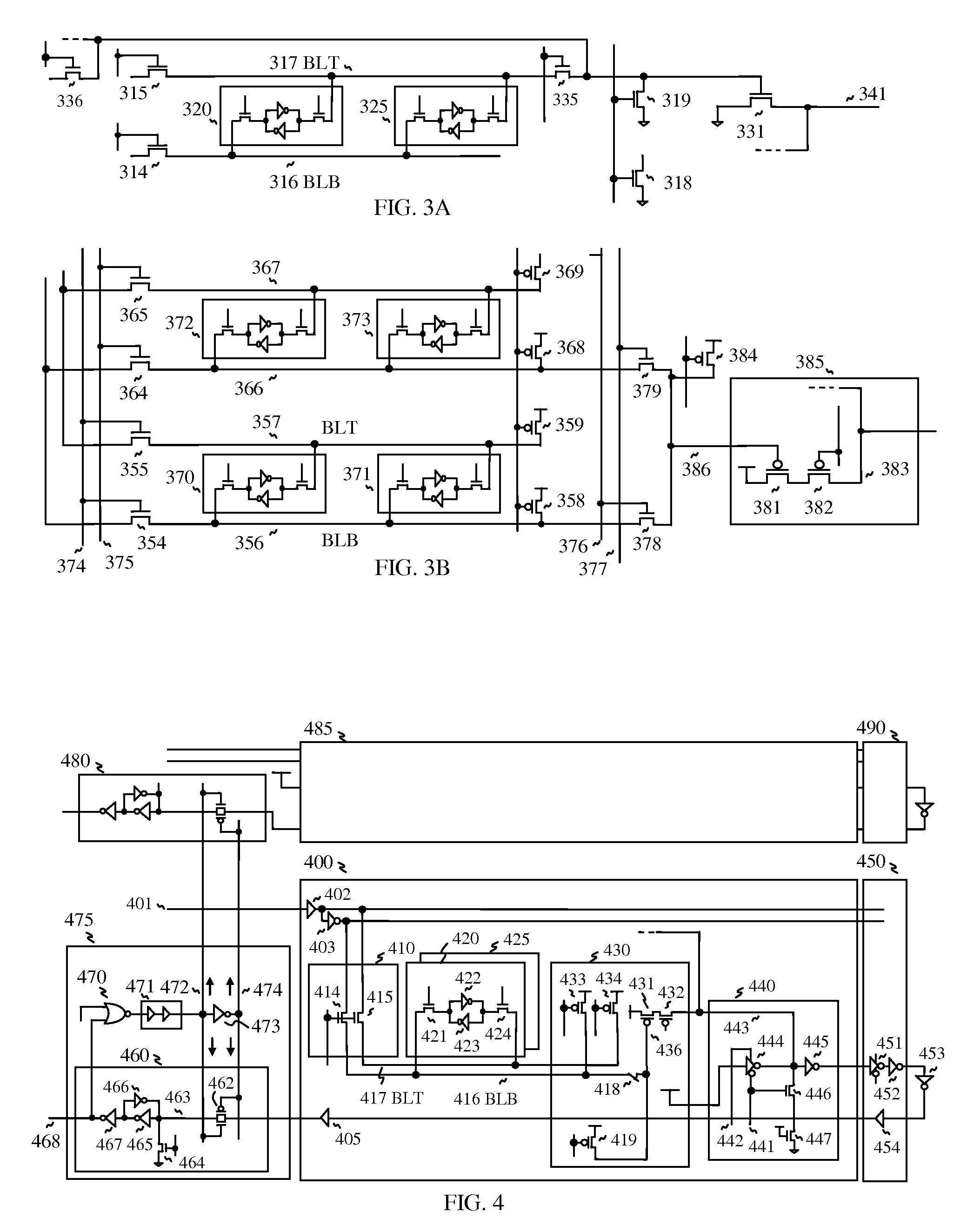

Mask ROM with light bit line architecture

InactiveUS7715246B1Configuring memory is more flexibleReduce in quantityTransistorSolid-state devicesCapacitanceBit line

For improving performance of mask ROM, bit line is multi-divided for reducing capacitance, so that multi-stage sense amps are used for reading, wherein a local sense amp receives an output from a memory cell through the bit line, and a global sense amp receives the local sense amp output. By the sense amps, a voltage difference in the bit line is converted to a time difference for differentiating data “1” and data “0”. For example, data “1” is quickly transferred to an output latch circuit through the sense amps with high gain, but data “0” is rejected by a locking signal based on data “1” as a reference signal. Furthermore, a buffered data path is used for transferring data wherein the buffered data path includes a forwarding write line and a returning read line. Additionally, alternative circuits and memory cell structures for implementing the mask ROM are described.

Owner:KIM JUHAN

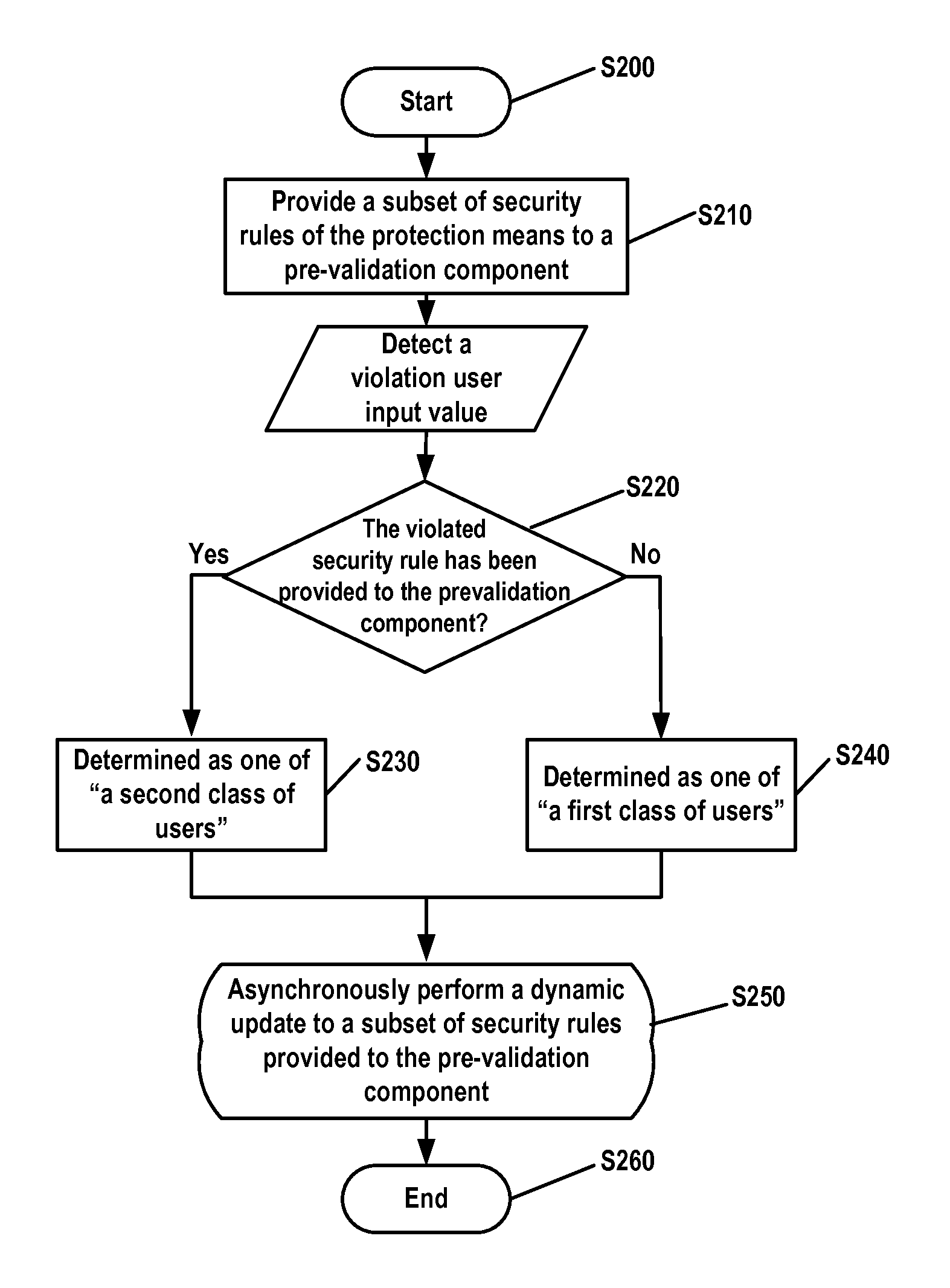

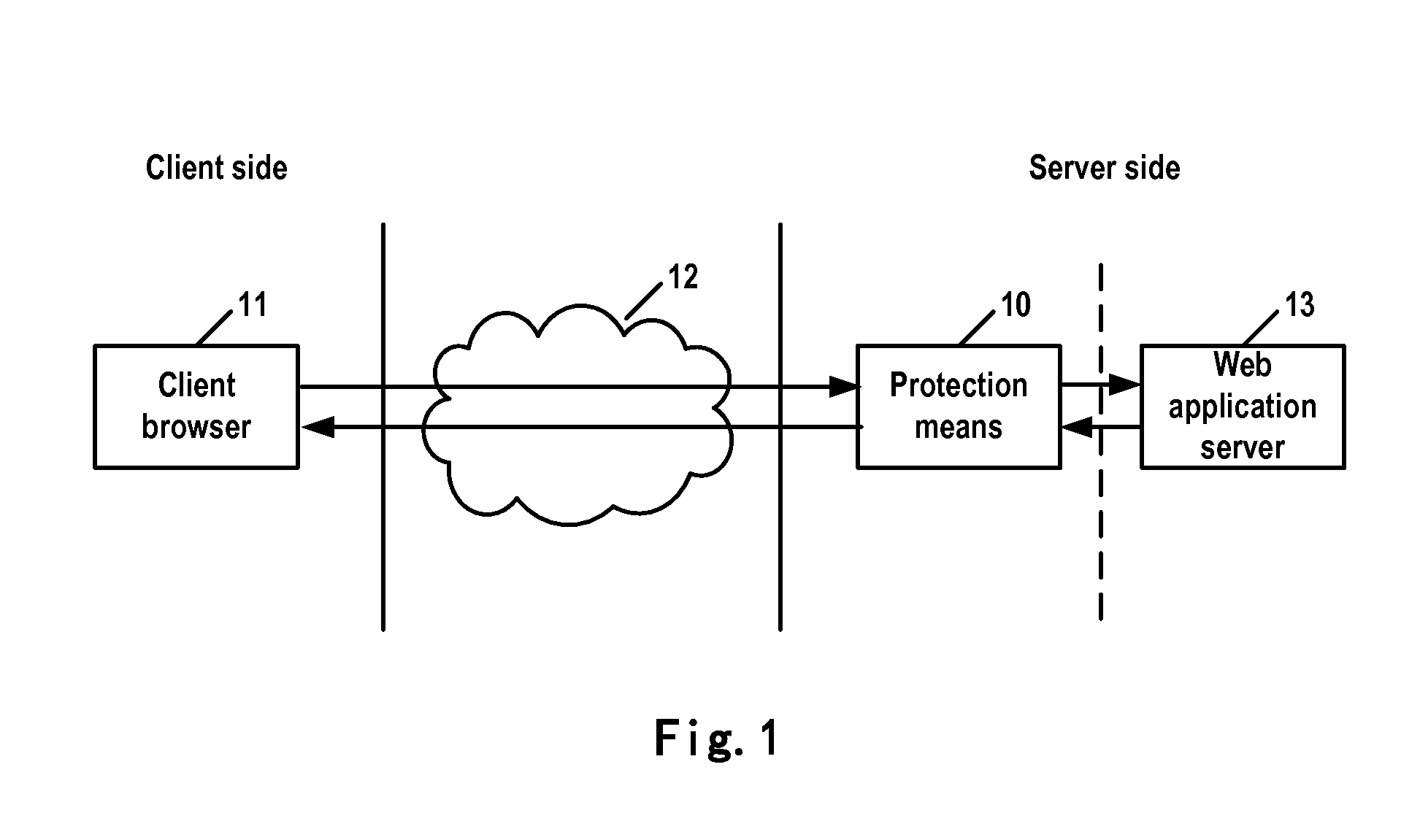

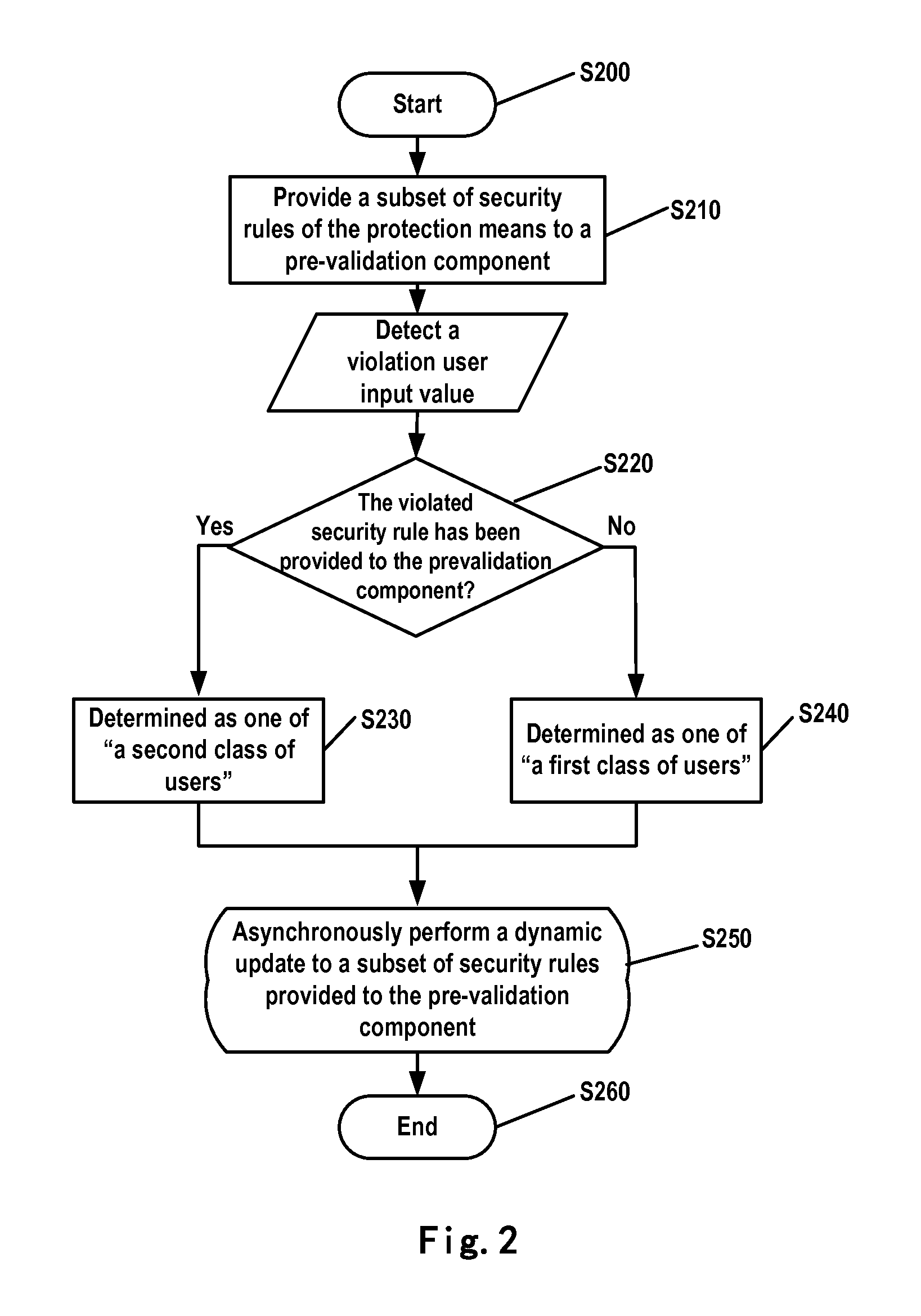

Method and apparatus for security validation

ActiveUS20120304249A1Increase experienceEffectively lead to differentiationDigital data authenticationPlatform integrity maintainancePre validationUser input

A computer-implemented method, apparatus, and article of manufacture for security validation of a user input in a computer network application. The method includes: providing a subset of security rules of a server-side protection means to a pre-validation component deployed at a client side, so as to enable security validation of a user input on the client side by the pre-validation component; validating the user input based on at least one of the security rules; determining, in response to detecting a user input violation and that a violated security rule has not been provided to the pre-validation component, the user as a first class of users; determining, in response to detecting the user input violation and that the violated security rule has been provided to the pre-validation component, the user as a second class of users; and performing different security protection actions to the first and second class of users.

Owner:IBM CORP

Methods of controlling proliferation and differentiation of stem and progenitor cells

InactiveUS20020159981A1Reduce capacityExpand the populationBiocidePeptide/protein ingredientsProgenitorCulture mediums

A cell population cultured ex-vivo in a culture medium under conditions permitting cells of the cell population to proliferate and, at the same time, reducing a capacity of the cells in utilizing cooper, the cells are hence expanded yet not further differentiated as compared to ex-vivo seeded cells from which the cell population developed.

Owner:GAMIDA CELL

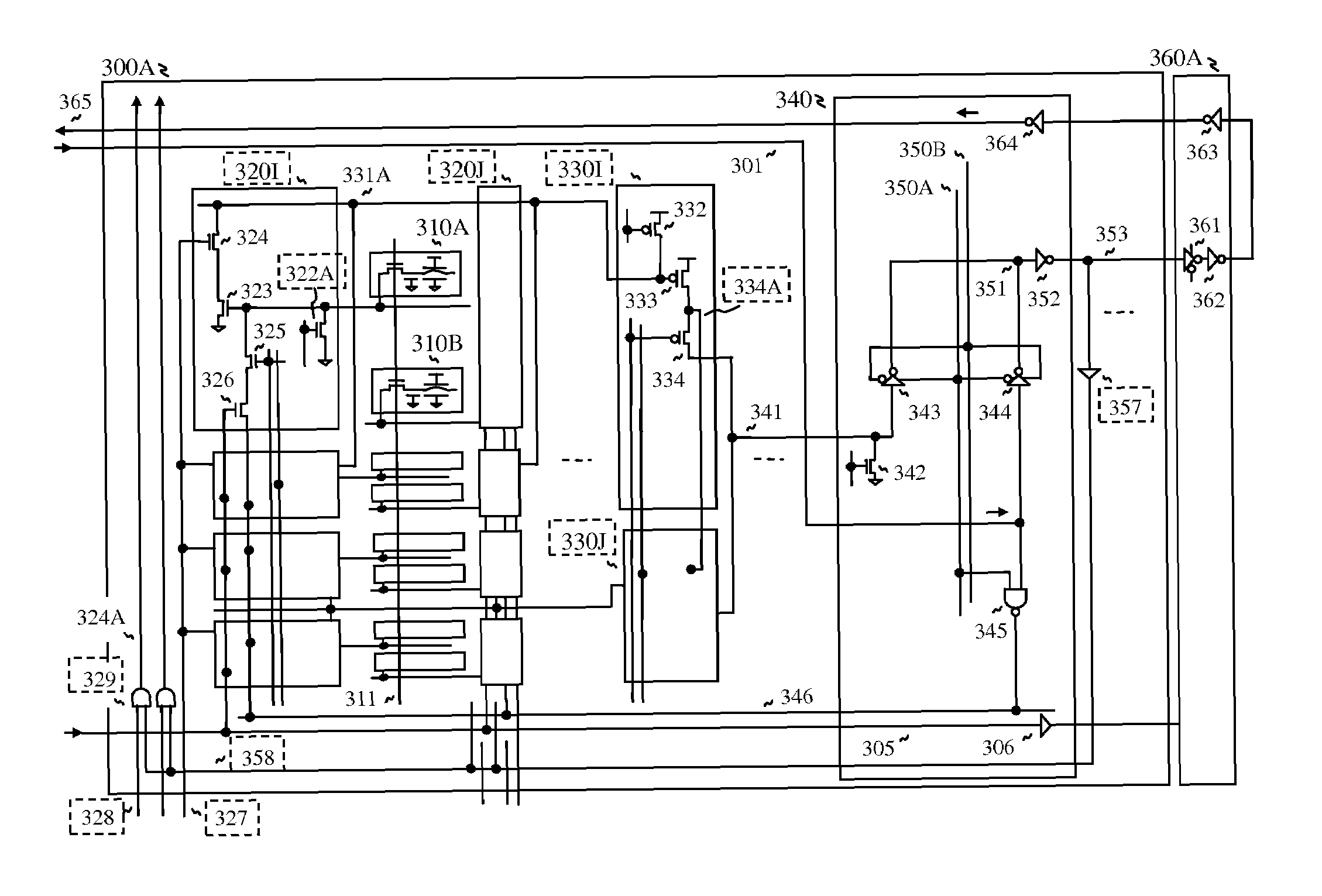

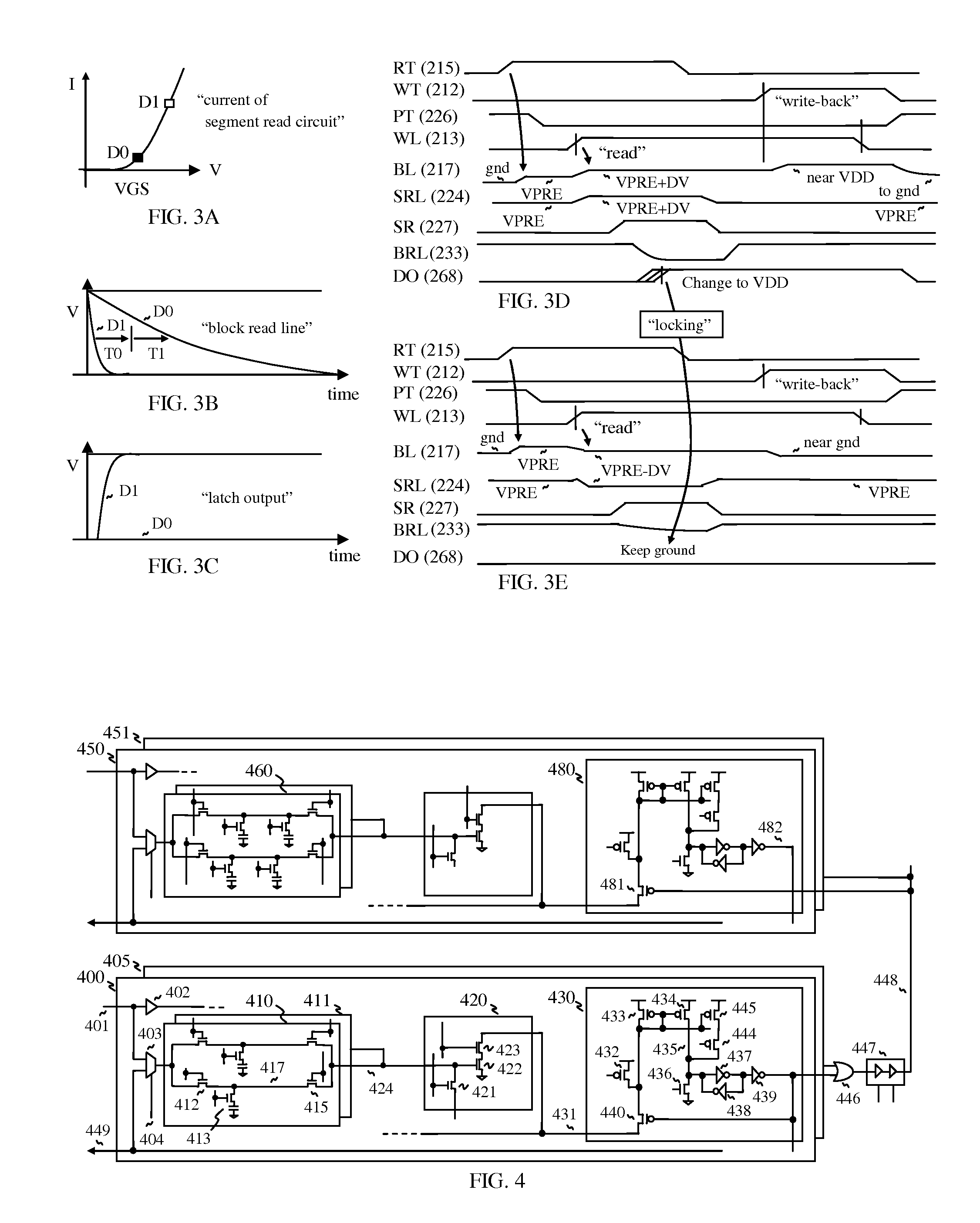

SRAM including bottom gate transistor

Bit lines in SRAM array are multi-divided, so that a segment read circuit is connected to local bit line, which circuit serves as amplifying transistor of an amplifier with load device of a block read circuit. Thus the amplified voltage is latched by a current mirror which serves as another amplifier in the block read circuit, such that one data is latched early but another data is latched later because the amplifier changes its output quickly or slowly depending on the local bit line voltage. In this manner, time-domain sensing scheme is introduced to differentiate fast data and slow data, where the locking signal is generated by a read enable signal or a reference signal based on fast data. Particularly, memory cell includes bottom gate transistor as a pull-up device to reduce area. Additionally, alternatives are described, such as stacked memory cell structure and CAM application.

Owner:KIM JUHAN

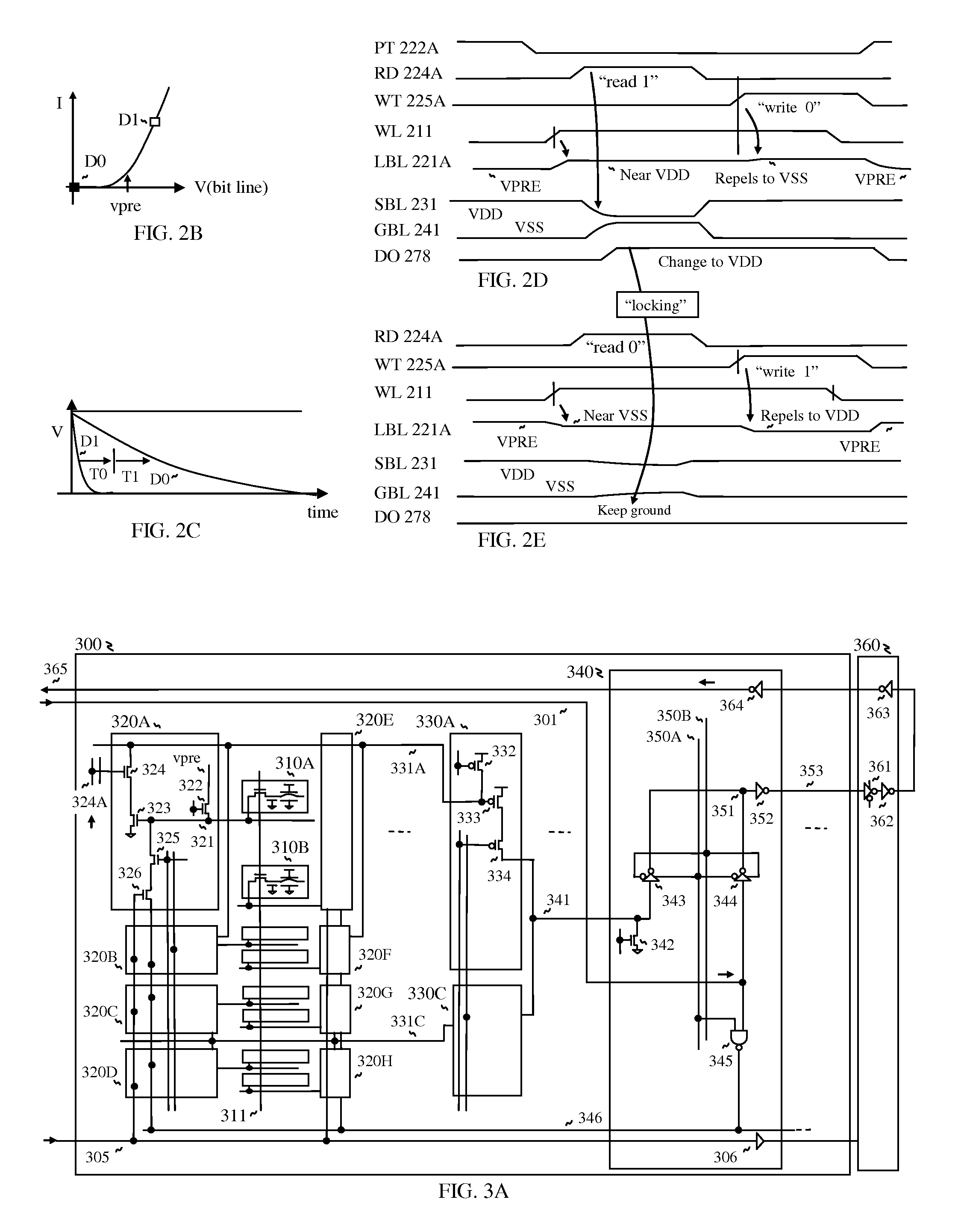

One-time programmable read only memory

InactiveUS20100061137A1Reduce sensitivityLow currentRead-only memoriesDigital storageData transmissionCapacitance

For realizing high speed one time programmable memory, bit line is multi-divided for reducing capacitance, so that the bit line is quickly charged when reading and multi-stage sense amps are used for connecting divided bit line, wherein the multi-stage sense amps are composed of a first dynamic circuit serving as a local sense amp for reading the memory cell, a second dynamic circuit serving as a segment sense amp for reading the local sense amp, and a tri-state inverter serving as an amplify circuit of a global sense amp for reading the segment sense amp. When reading data, a voltage difference in the bit line is converted to a time difference for differentiating high data (programmed) and low data (unprogrammed) by the multi-stage sense amps. And buffered data path is connected to the global sense amp for realizing fast data transfer. Additionally, alternative circuits and memory cell structures are described.

Owner:KIM JUHAN

NOR flash memory including bipolar segment read circuit

A bipolar segment read circuit is applied for reading NOR flash memory such that cell current is converted to voltage by discharging bit line, which voltage is amplified by the bipolar segment read circuit, and then the voltage difference is converted to time difference by a block read circuit. In this manner, a reference signal is generated by reference cells storing low threshold data, which signal is delayed by a tunable delay circuit for generating a locking signal. Thus the locking signal effectively rejects latching high threshold data in latch circuits because high threshold data is arrived later. Furthermore, by adopting multi-divided bit line architecture, discharging time of bit line is reduced. And the memory cell can be formed from single crystal silicon or thin film polysilicon because the memory cell only drives lightly loaded bit line, even though thin film transistor can flow relatively low current, which realizes multi-stacked memory.

Owner:KIM JUHAN

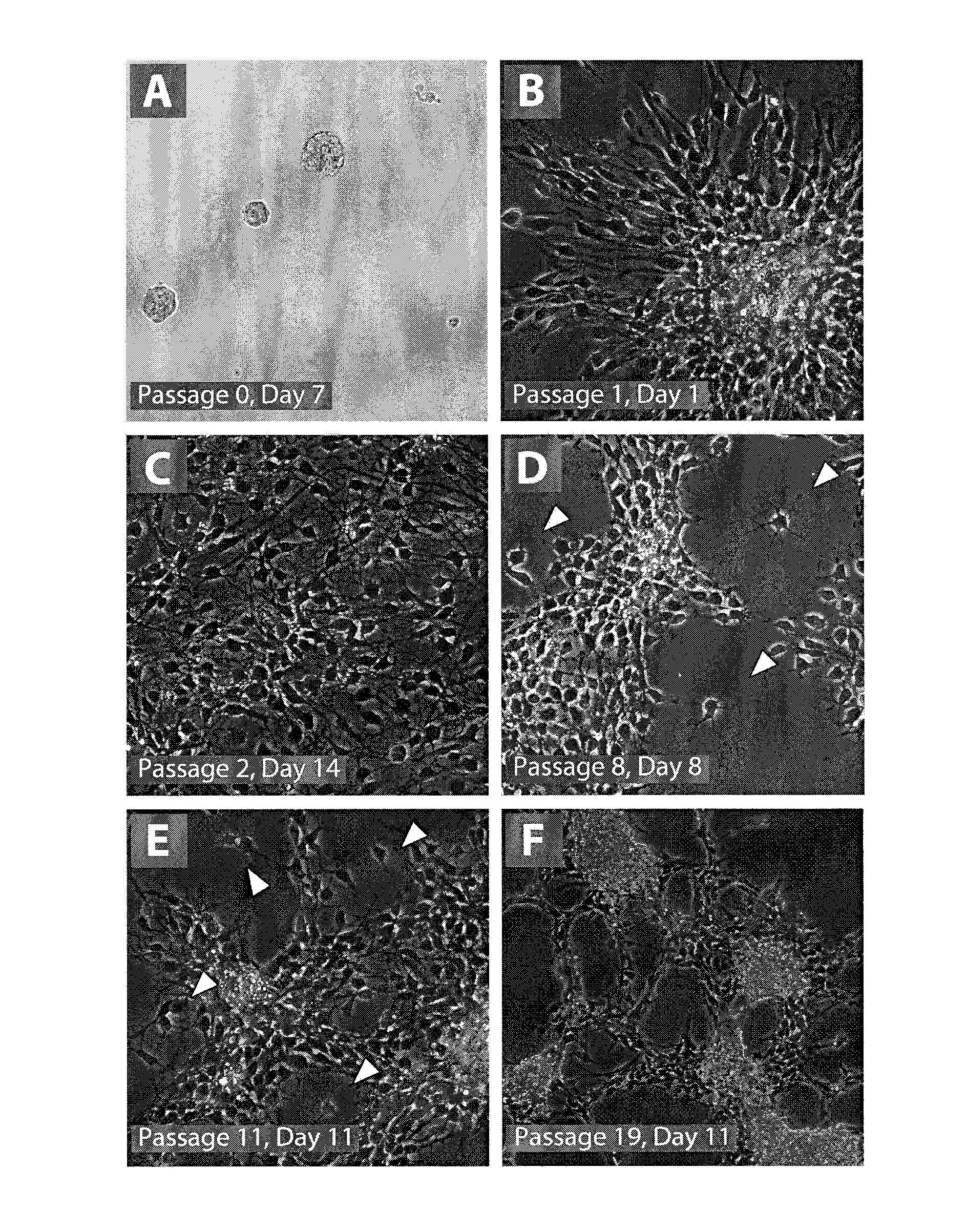

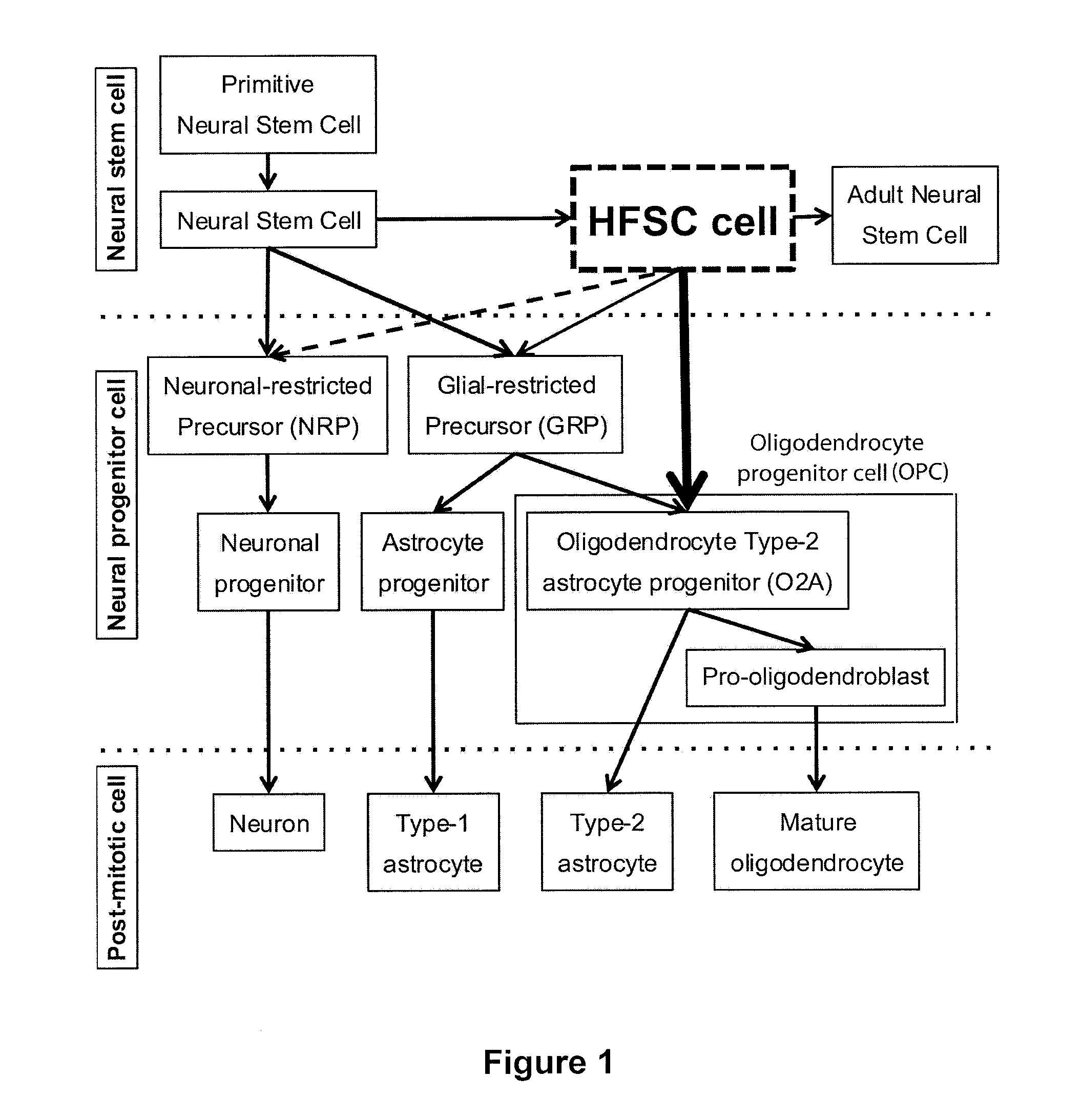

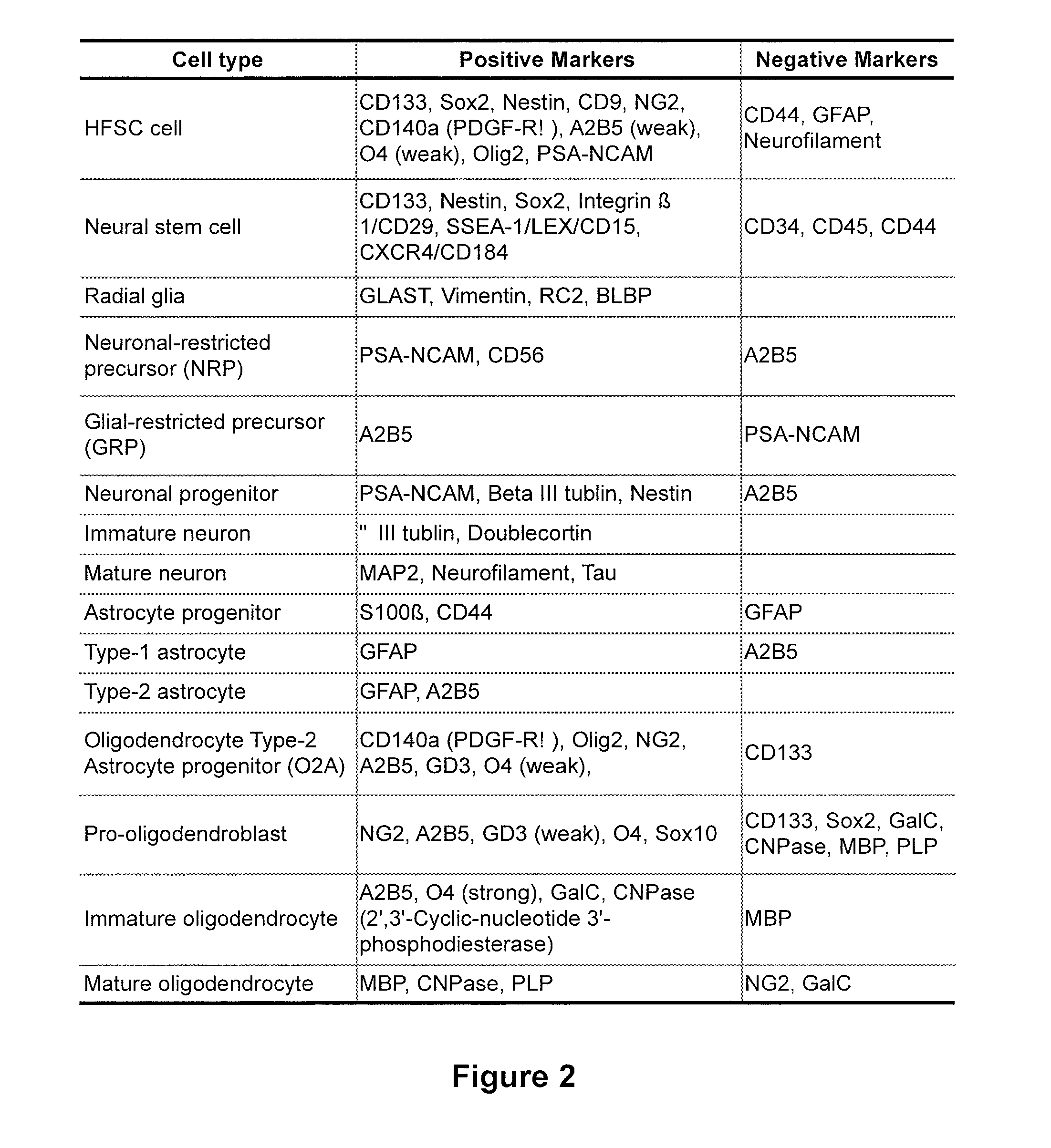

Culture method to obtain and maintain a pure or enriched population of mammalian neural stem cells and/or neural/progenitor cells that are prone to differentiate into oligodendrocyte-lineage cells in vitro

An isolated expandable human neural stem or progenitor cell wherein the cell is a progenitor cells or stem cell, maintains its capability to differentiate into neurons, astrocytes, and oligodendrocytes, maintains its ability to differentiate into oligodendrocyte lineage cells efficiently throughout subsequent passages, and the cell expresses at least cell surface antigens CD133 and CD140α. Also provided is a method of in vitro culturing an expandable neural progenitor or stem cell isolated from a mammalian central nervous system, and the culture itself, wherein said cell maintains its capability to differentiate into neurons, astrocytes, and oligodendrocytes and its ability to differentiate into oligodendrocyte-lineage cells efficiently. In addition, a method of treating a condition caused by a loss of myelin or a loss of oligodendrocytes is provided as is a composition comprising an isolated expandable neural stem cell or one cultured by the methods of the invention.

Owner:KIDO TSUNEO

Low power carbon nanotube memory

InactiveUS7675768B1Reduce operating powerTotal current dropNanoinformaticsDigital storageBit lineAudio power amplifier

Low power carbon nanotube memory is realized such that a first dynamic circuit serves as a local sense amp for reading a memory cell through a lightly loaded local bit line, a second dynamic circuit serves as a segment sense amp for reading the local sense amp, a first tri-state inverter serves as an inverting amplifier of a global sense amp, and a second tri-state inverter serves as a bypass circuit for bypassing output from previous memory block. When reading, a voltage difference in the local bit line is converted to a time difference for differentiating high data and low data by the sense amps for realizing low power with dynamic operation. In particular, amplify transistor of the sense amps is composed of relatively long channel transistor for reducing turn-off current. And buffered data path is used for achieving fast data transfer. Additionally, alternative circuits and memory cell structures are described.

Owner:FRONTEON

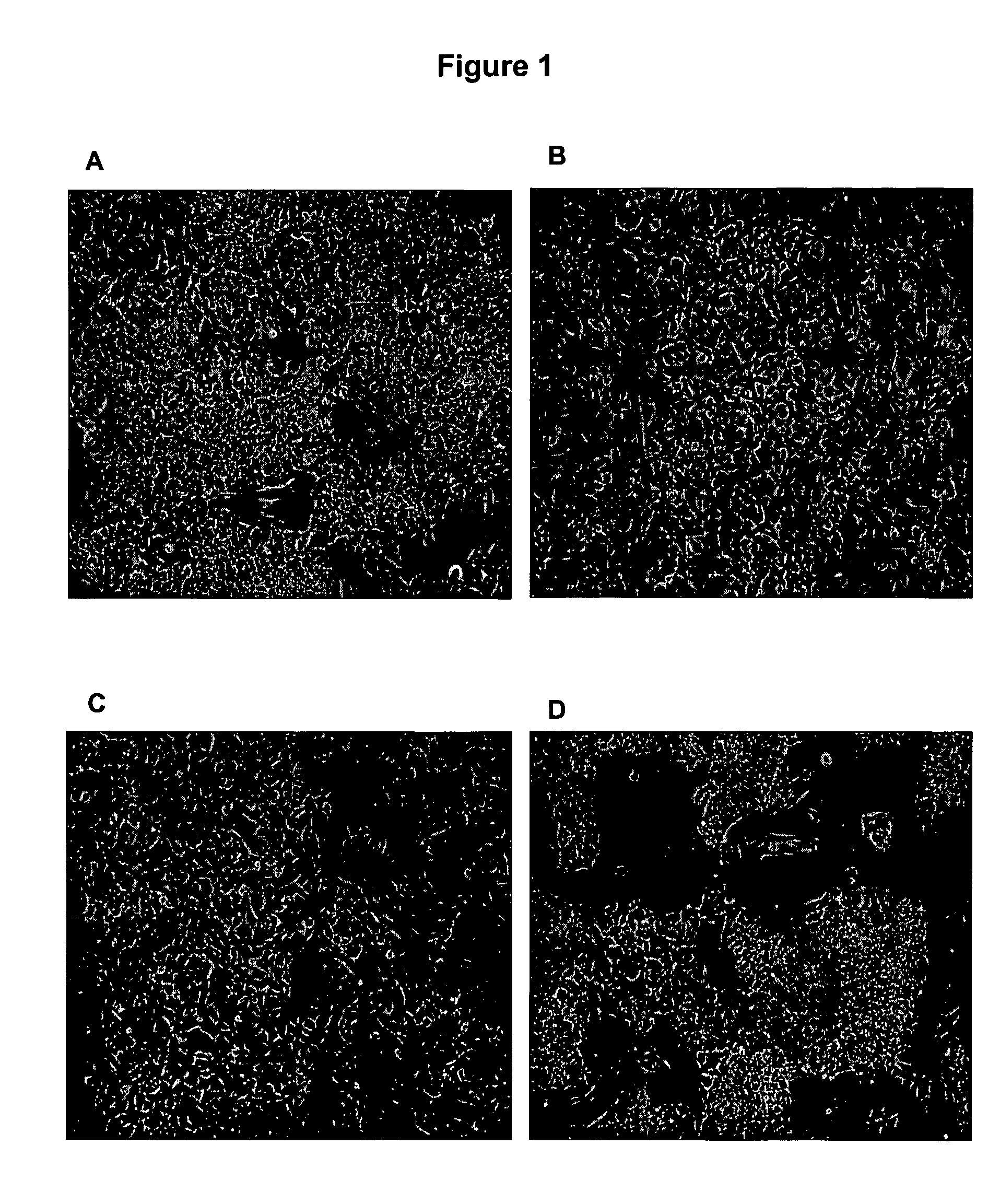

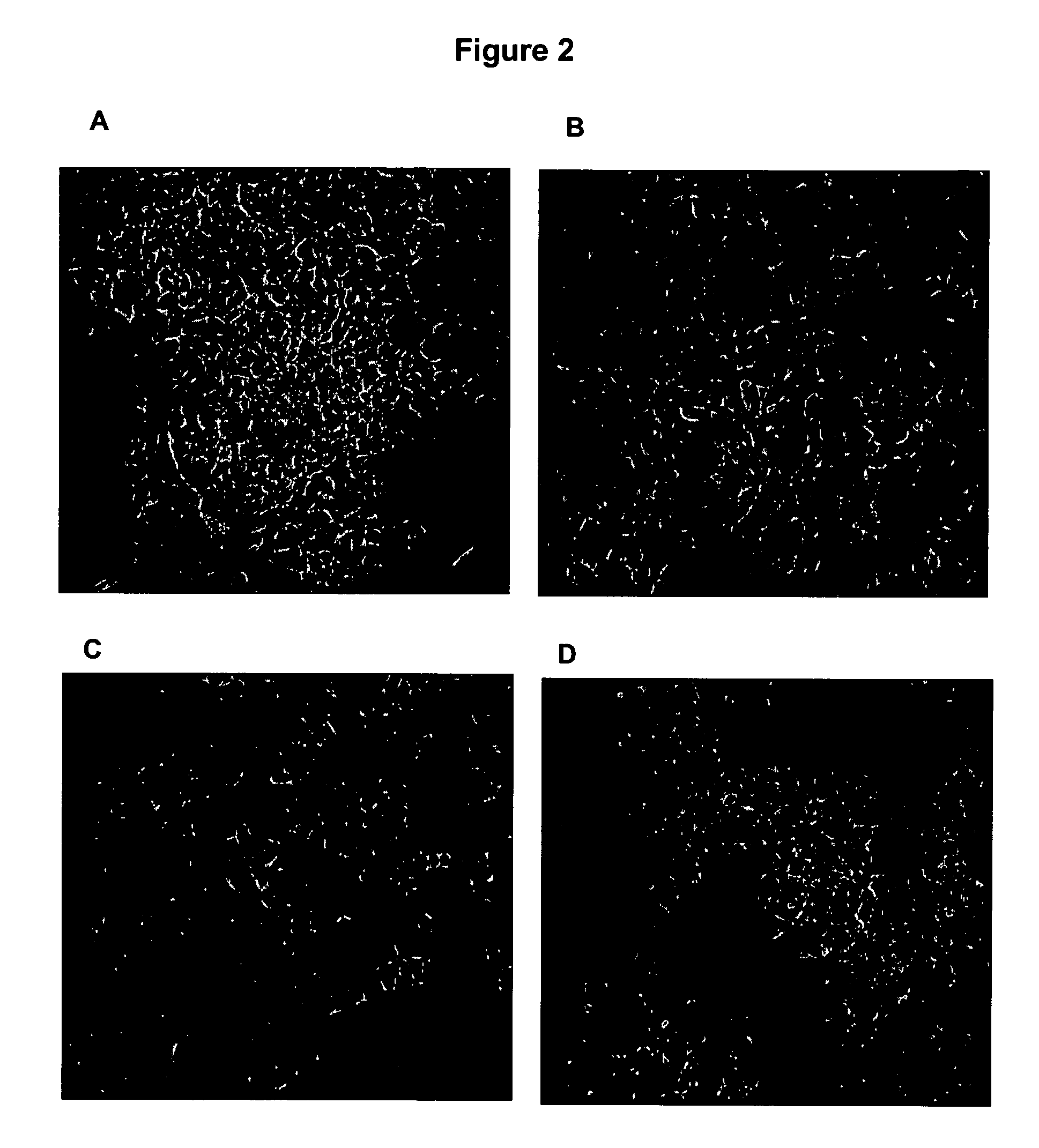

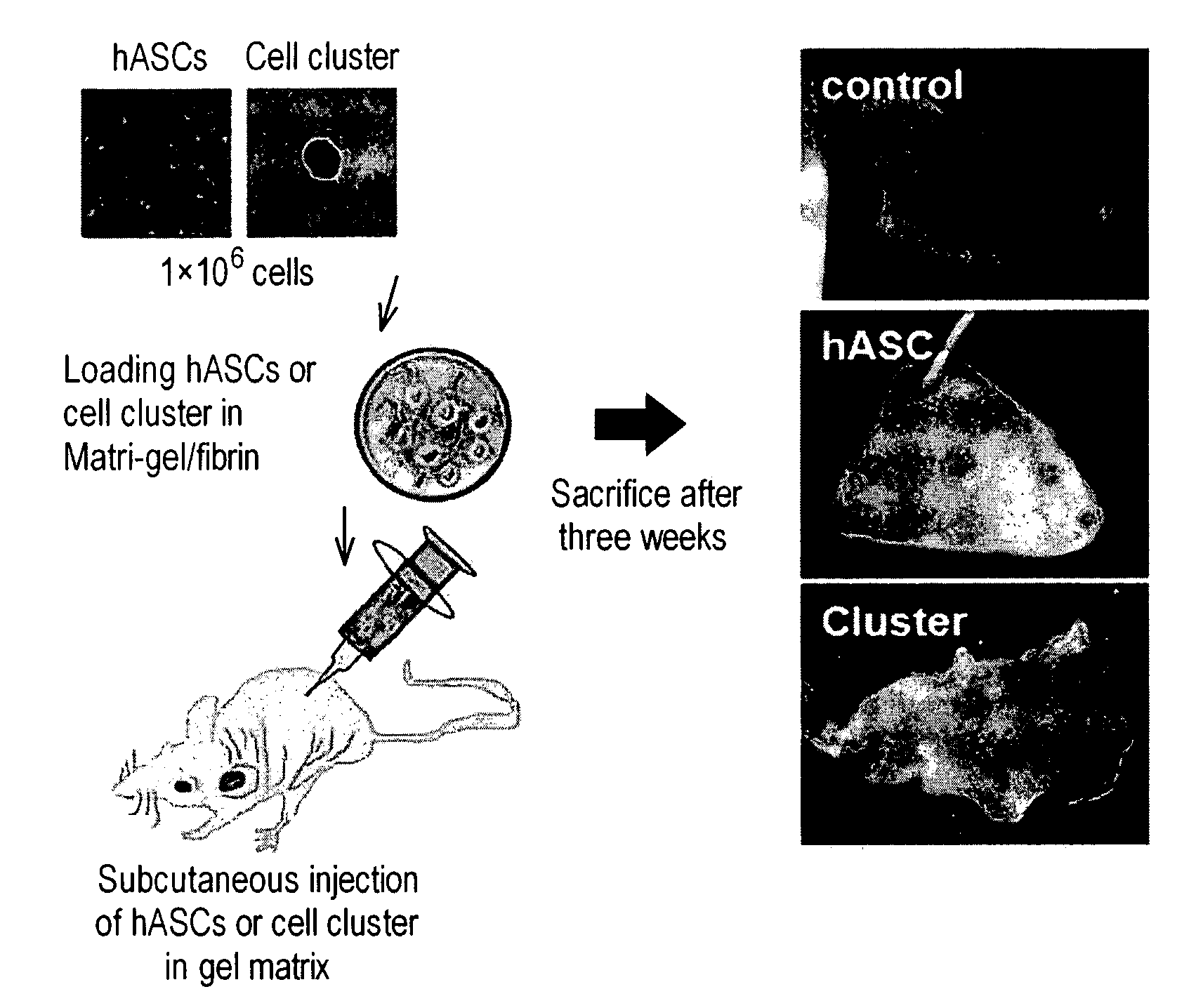

Method for differentiation of stem cells into vascular cells and the induction of angiogenesis using the same

ActiveUS20120134965A1Effectively lead to differentiationEfficiently formedBiocideNervous disorderAngiogenesis growth factorCell cluster

The present invention relates to a method for differentiating stem cells into vascular cells by culturing them in the form of a three-dimensional cell cluster and the use of the three-dimensional cell cluster for angiogenesis. Specifically, the present invention teaches a method for differentiating stem cells into vascular cells comprising culturing stem cells by adhering them onto a culture plate with a surface having a hydrophobic property or a culture plate onto which a growth factor is immobilized, wherein the cultured stem cells are later detached from the culture plate as their density increases to form a three-dimensional cell cluster and grown in the form of a three-dimensional cell cluster while differentiating into vascular cells. Also disclosed is the use of a three-dimensional cell cluster composed of the vascular cells differentiated from stem cells by the above method as a cell therapy agent for angiogenesis.

Owner:S-BIOMEDICS CO LTD

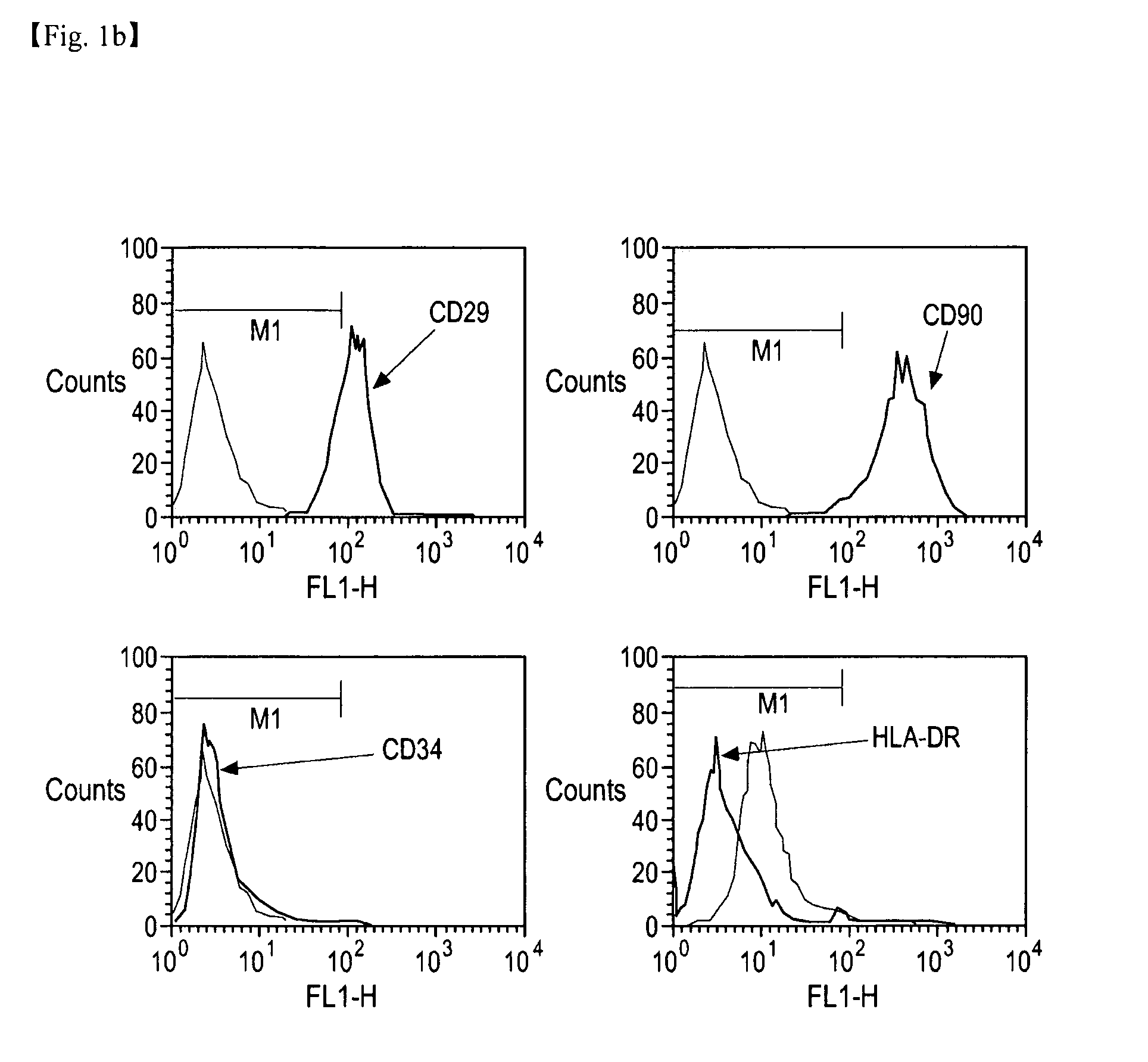

Mesenchymal stem cell and method for production thereof

InactiveUS20110111499A1Efficiently and in large quantity producingEffectively lead to differentiationBiocideMuscular disorderMesenchymal stem cellMyocyte

The present invention provides a method for producing a mesenchymal stem cell having an ability to differentiate into a myoblast by culturing a pluripotent stem cell derived from a human or animal, including: i) preparing the pluripotent stem cell that has been cryopreserved, ii) sub-culturing the prepared pluripotent stem cell in an undifferentiated state for a prescribed number of times, iii) culturing the subcultured pluripotent stem cell under conditions that enable induction of differentiation into an adipocyte in vitro, and iv) separating and collecting a CD105-positive cell during the culturing process.

Owner:NAGOYA UNIVERSITY

Methods of controlling proliferation and differentiation of stem and progenitor cells

InactiveUS20050118150A1Reduce capacityExpand the populationOrganic active ingredientsPeptide/protein ingredientsProgenitorCopper Chelator

A method of ex-vivo expanding a population of stem cells, while at the same time inhibiting differentiation of the stem cells. The method comprises ex-vivo providing the stem cells with conditions for cell proliferation and with at least one copper chelator in an amount and for a time period for permitting the stem cells to proliferate and, at the same time, for reducing a capacity of the stem cells to differentiate

Owner:GAMIDA CELL +1

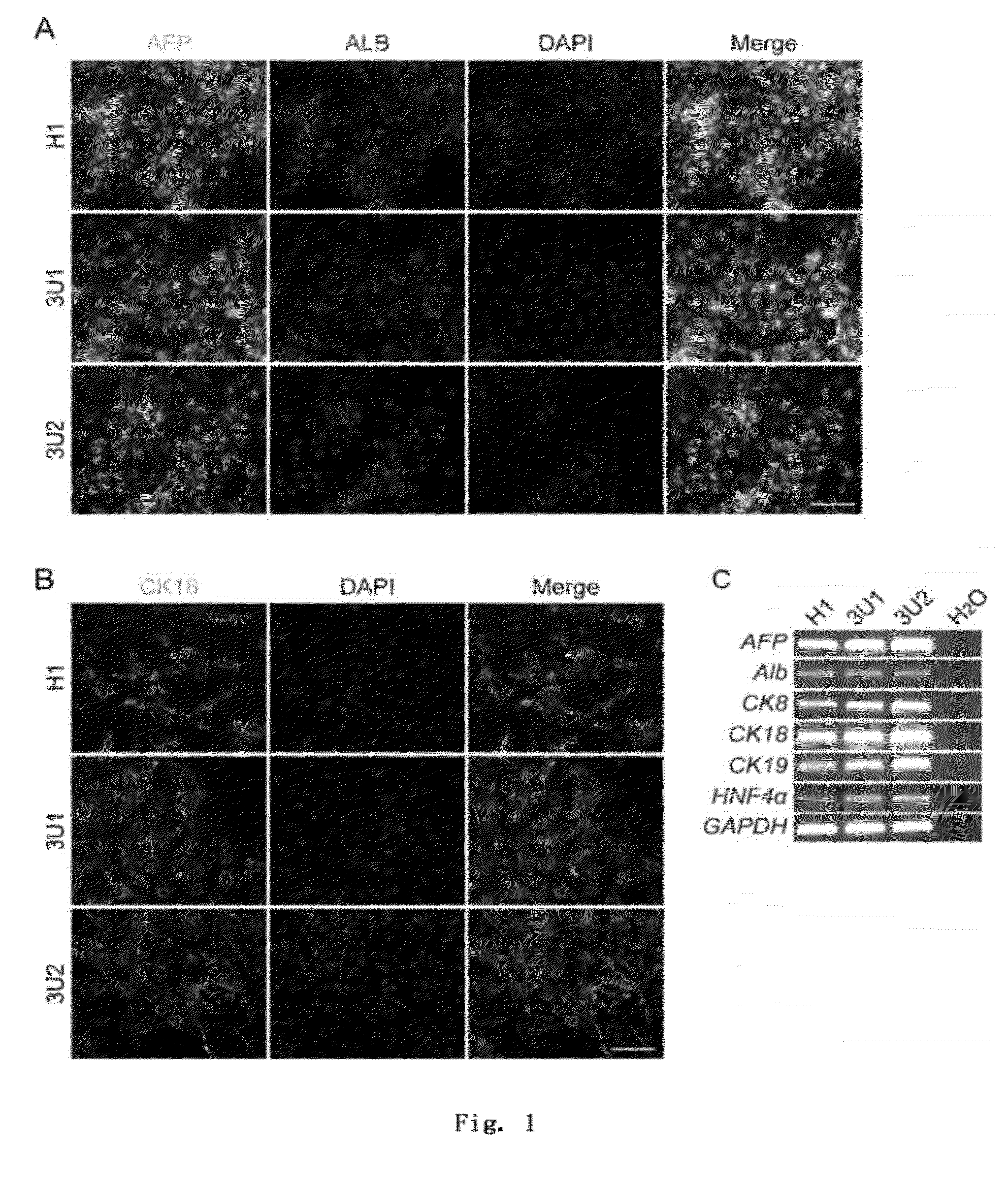

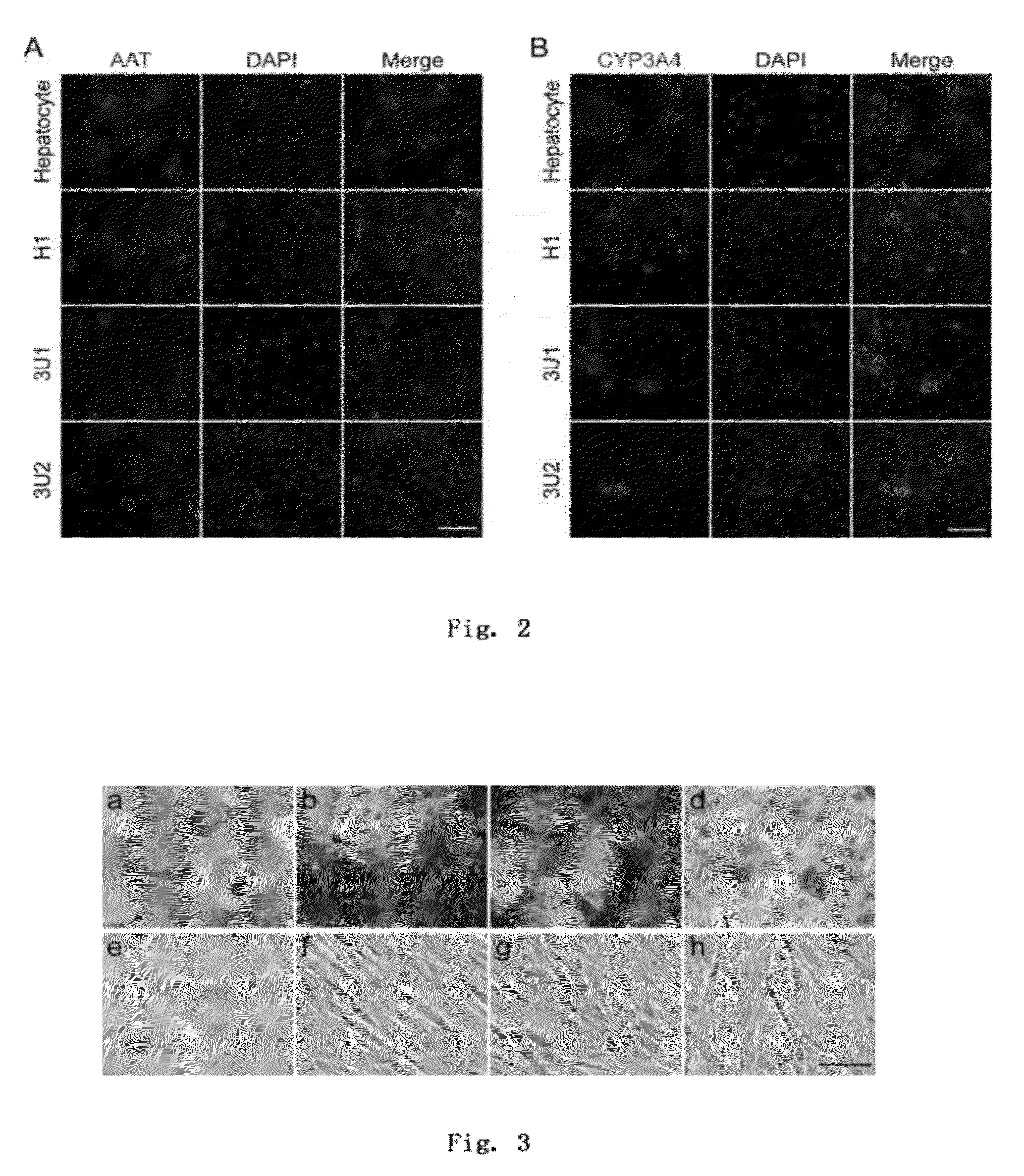

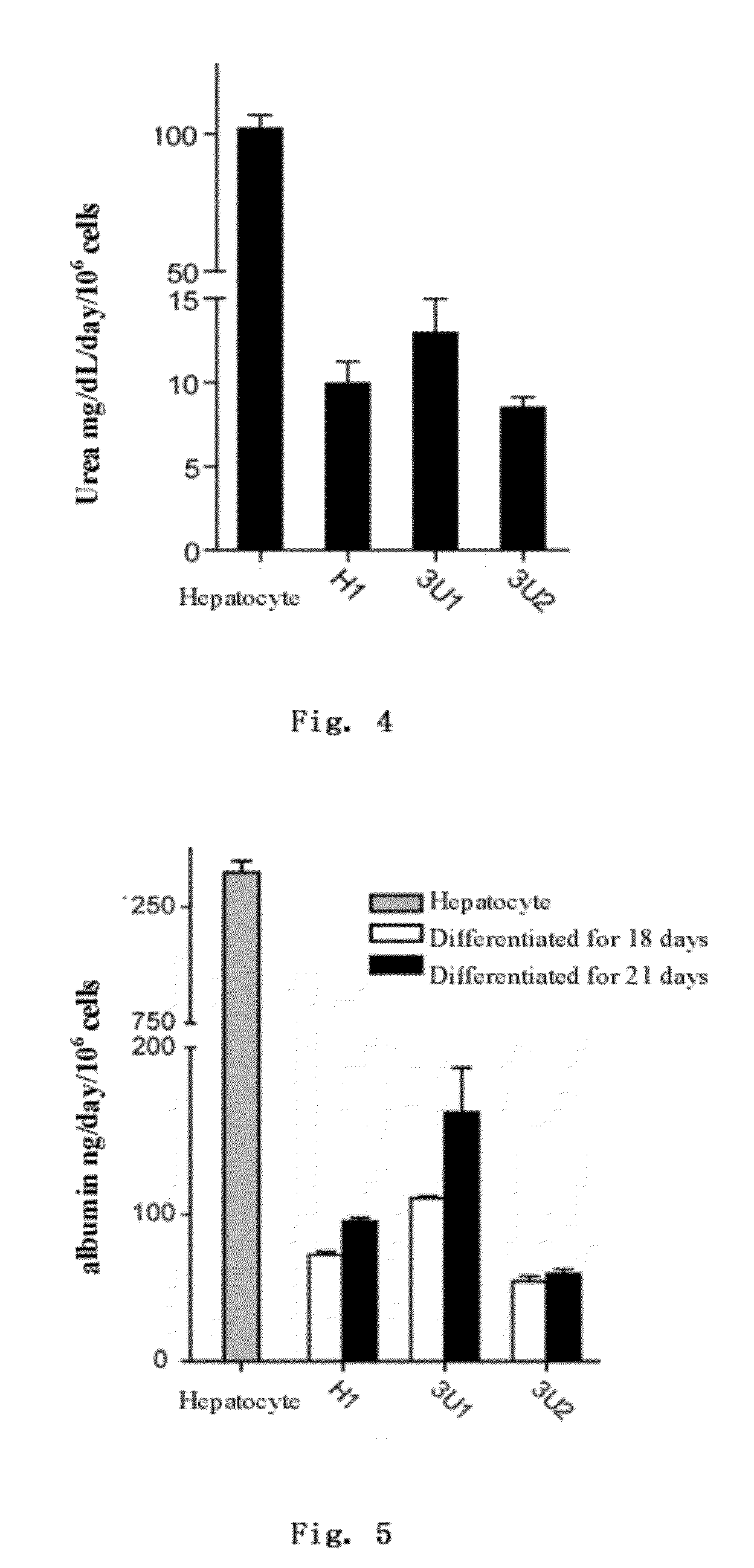

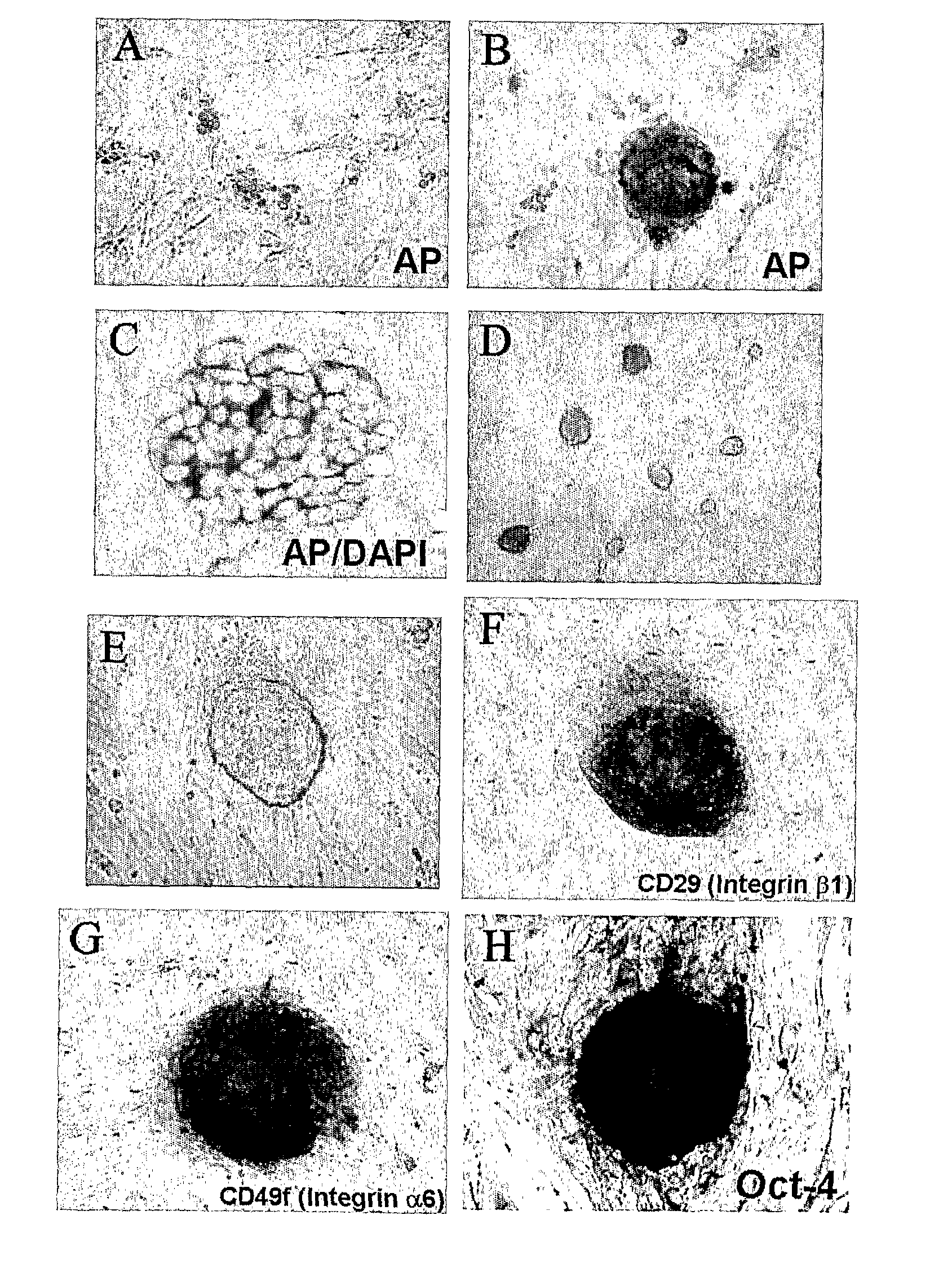

Methods for obtaining hepatocytes, hepatic endoderm cells and hepatic progenitor cells by induced differentiation

InactiveUS20120190059A1Improve proliferative abilityEfficient representationHepatocytesMicrobiological testing/measurementGerm layerProgenitor

The present invention discloses a method for inducing the differentiation of embryonic stem cells (ESC) or induced pluripotent stem cells (iPS cells) into hepatocytes, a method for inducing the differentiation of embryonic stem cells or induced pluripotent stem cells into hepatic endoderm cells, and a method for inducing the differentiation of embryonic stem cells (ESC) or induced pluripotent stem cells into hepatic progenitor cells. The present invention also provides the hepatocytes, hepatic endoderm cells and hepatic progenitor cells obtained by above methods, and the uses of these cells.

Owner:BEIJING HUAYUANBOCHUANG TECH

In Vitro Method for Isolating, Proliferating and Differentiating Germ-Line Stem Cells

InactiveUS20080044395A1Achieve isolationAchieve proliferationBiocideGenetic material ingredientsMale infertilityBiology

The present invention discloses methods for isolating, proliferating and differentiating germ-line stem cell in vitro. More specifically, the present invention discloses a method for the in vitro isolation and proliferation of mammalian germ-line stem cells, characterized in culturing cells isolated from mammalian testis in an embryonic stem cell culture medium, and for the in vitro differentiation, characterized in encapsulating mammalian germ-line stem cells and Sertoli cells with calcium alginate and co-culturing with peritubular cells. Also, the present invention discloses germ-line stem cells obtained by above methods, a composition for the treatment of male infertility, comprising the germ-line stem cells, and a method for the treatment of male infertility by the use of the germ-line stem cells.

Owner:COLLEGE OF MEDICINE POCHON CHA UNIV IND

High speed flash memory

InactiveUS20100054039A1Total current dropReduce power consumptionSolid-state devicesRead-only memoriesBit lineAudio power amplifier

Owner:KIM JUHAN

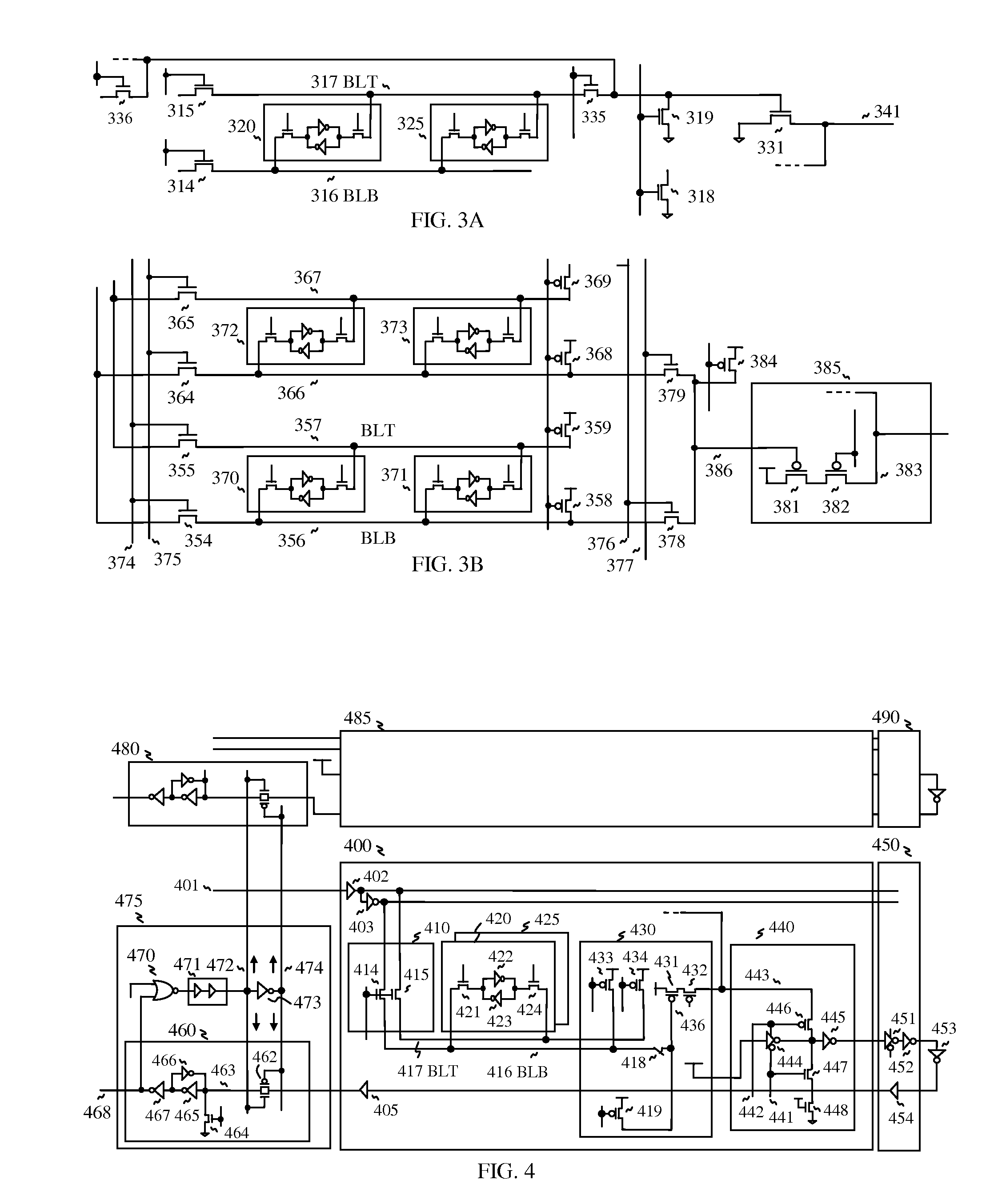

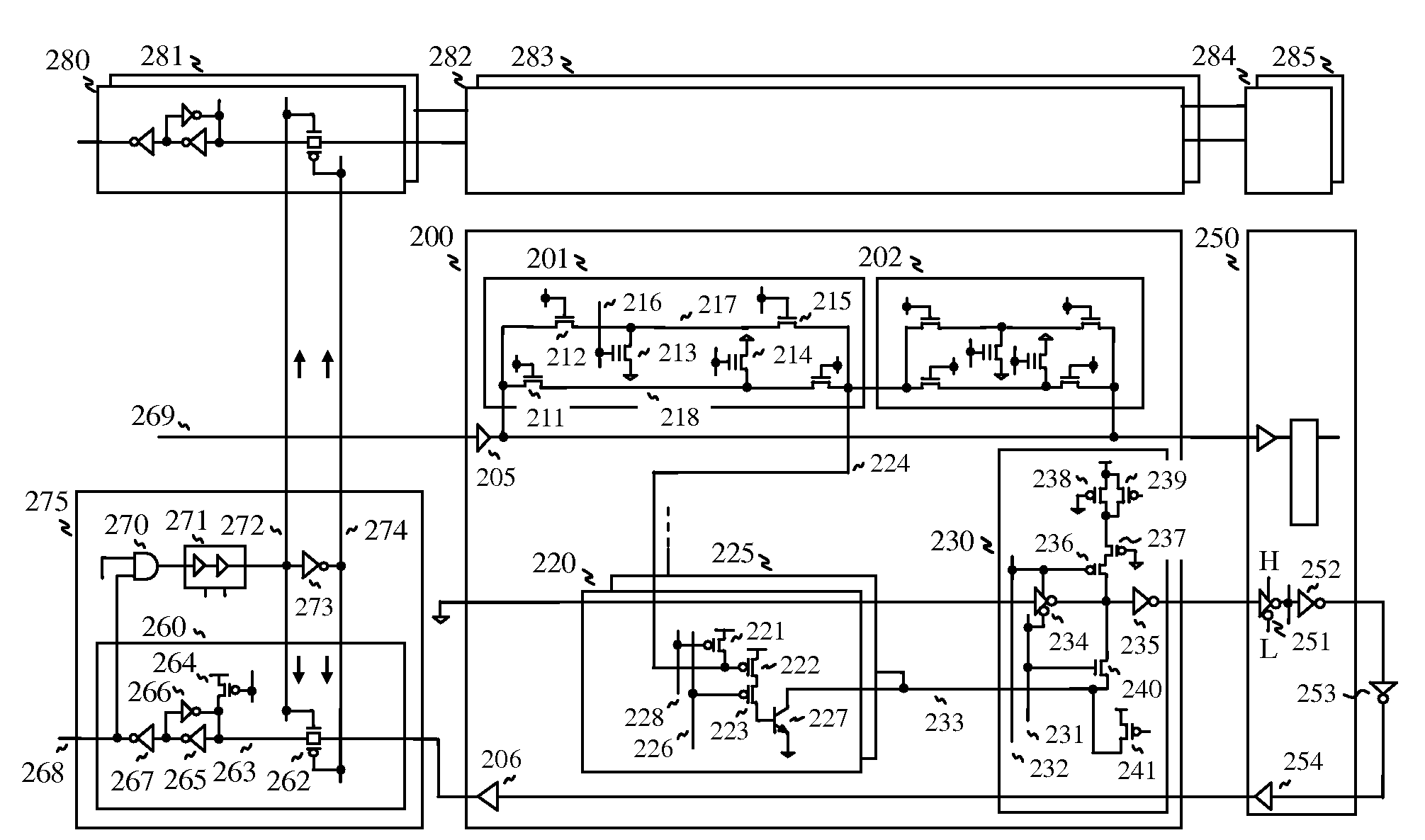

DRAM including segment read circuit

InactiveUS7443714B1Reduce parasitic capacitanceReducing bit line loadingDigital storageTime domainBit line

A time-domain sensing scheme is introduced for reading a DRAM cell and bit lines are multi-divided for reducing parasitic loading. Thereby lightly loaded bit line is quickly charged by a selected memory cell when reading data “1”. The charged voltage is amplified by a segment read circuit, which quickly changes an output of a block read circuit. In contrast, the bit line is discharged when reading data “0”, so that impedance of the segment read circuit is increased, which slowly changes the output of a block read circuit. Hence, data “1” is arrived early but data “0” is not arrived to a latch circuit, because the latch is locked by a locking signal based on data “1”. Furthermore storage capacitor is reduced to drive short bit line only. Additionally, various alternatives are described.

Owner:KIM JUHAN

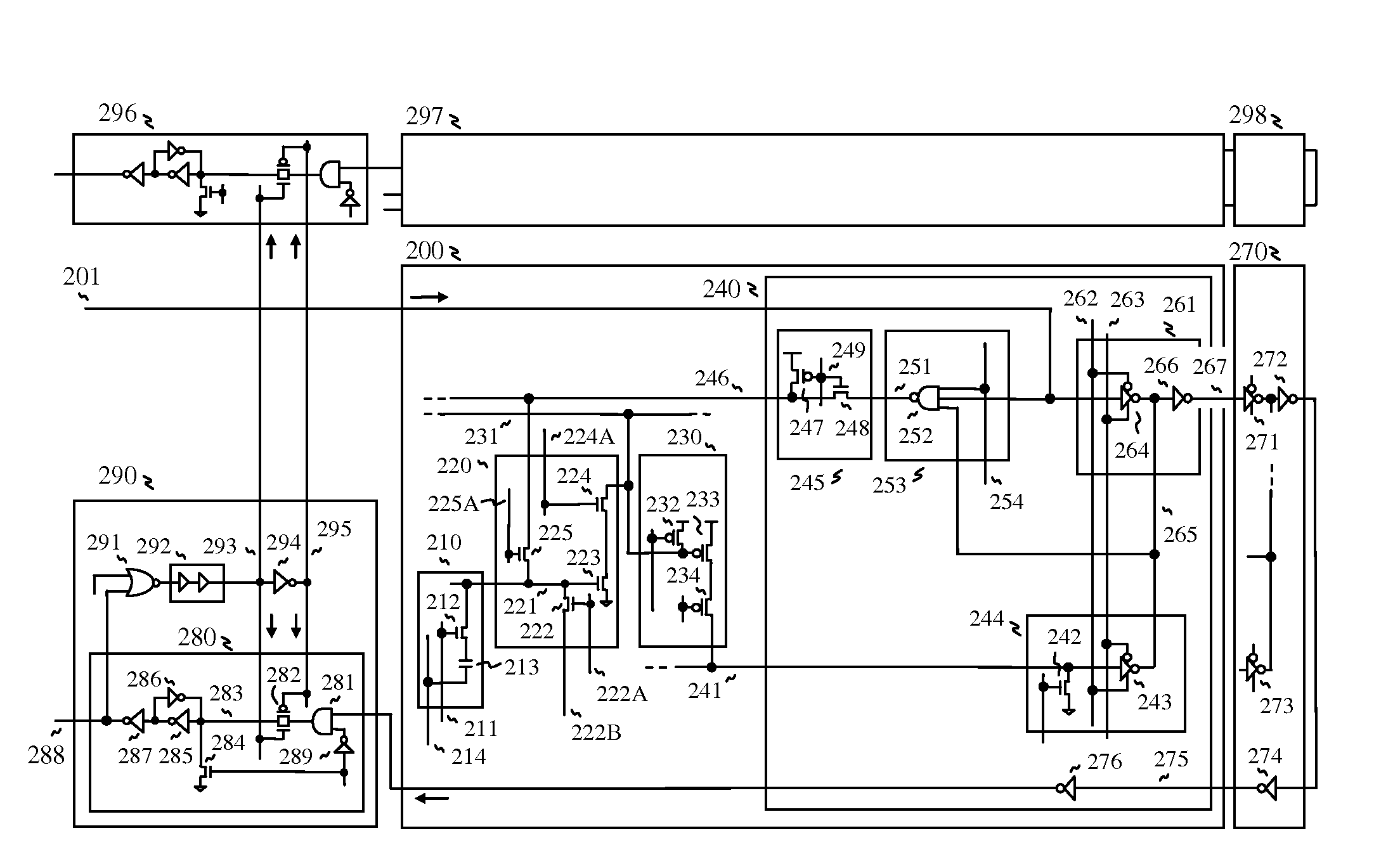

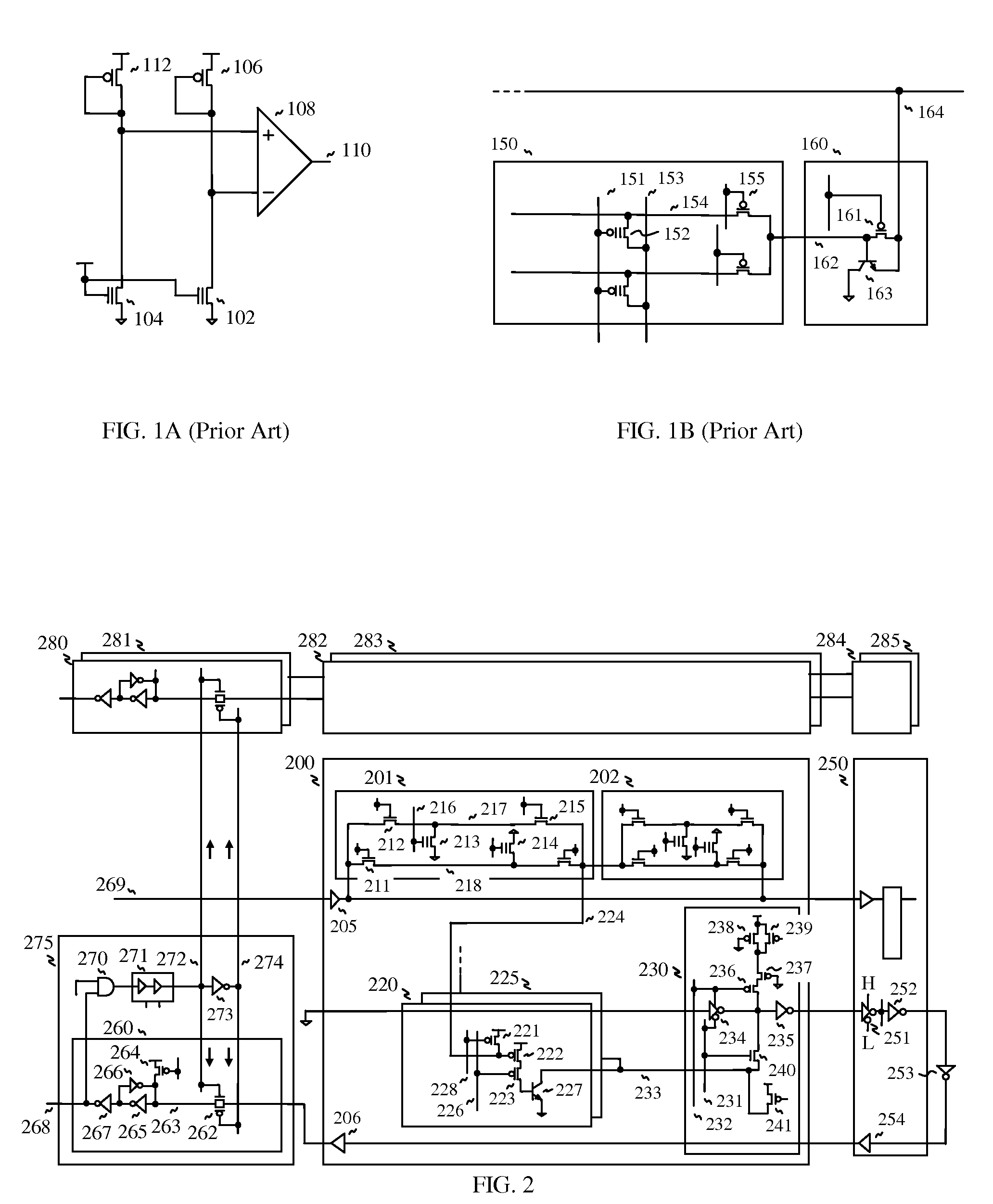

High-speed DRAM including hierarchical read circuits

DRAM includes hierarchical read circuits with multi-divided bit lines, wherein a local read circuit receives an output from a memory cell through a bit line, a segment read circuit receives an output from one of multiple local read circuits through a segment read line, and a block read circuit receives an output from one of multiple segment read circuits through a block read line. Thus a voltage difference is converted to a time difference by the read circuits. In this manner, a time-domain sensing scheme is realized to differentiate high data and low data. For instance, high data is quickly transferred to a latch circuit through the read circuits with high gain, but low data is rejected by a locking signal based on high data as a reference signal. Additionally, various alternatives are described. And structures for the memory cell and layouts for the read circuits are illustrated.

Owner:KIM JUHAN

Neuronal differentiation-inducing peptide and use thereof

A neuronal differentiation inducer provided by the present invention contains an artificially synthesized peptide which includes an amino acid sequence constituting a signal peptide in amyloid precursor protein (APP), or a partial sequence of the amino acid sequence constituting this signal peptide.

Owner:TOAGOSEI CO LTD

Mesoderm induction method having high blood cell differentiation capacity

ActiveUS11136547B2Efficient inductionPromote differentiationPeptide/protein ingredientsMammal material medical ingredientsPluripotential stem cellMedicine

Provided is a method for inducing mesoderm, comprising a step of bringing pluripotent stem cells into contact with bone morphogenetic protein 4 (BMP4) or CHIR for at least 3 days.

Owner:KYOTO UNIV +1

Stacked SRAM including segment read circuit

InactiveUS7542332B1Reduce parasitic capacitanceReducing bit line loadingDigital storageTime domainBit line

Bit lines in SRAM array are multi-divided, so that a segment read circuit is connected to local bit line, which circuit serves as amplifying transistor of an amplifier with load device of a block read circuit. Thus the amplified voltage is latched by a current mirror which serves as another amplifier in the block read circuit, such that one data is latched early but another data is latched later because the amplifier changes its output quickly or slowly depending on the local bit line voltage. In this manner, time-domain sensing scheme is introduced to differentiate fast data and slow data, where the locking signal is generated by a read enable signal or a reference signal based on fast data. Additionally, alternatives and applications are described. And memory cell is formed from polysilicon because the memory cell drives lightly loaded bit line even though polysilicon transistor can flow low current, which realizes stacked memory.

Owner:KIM JUHAN

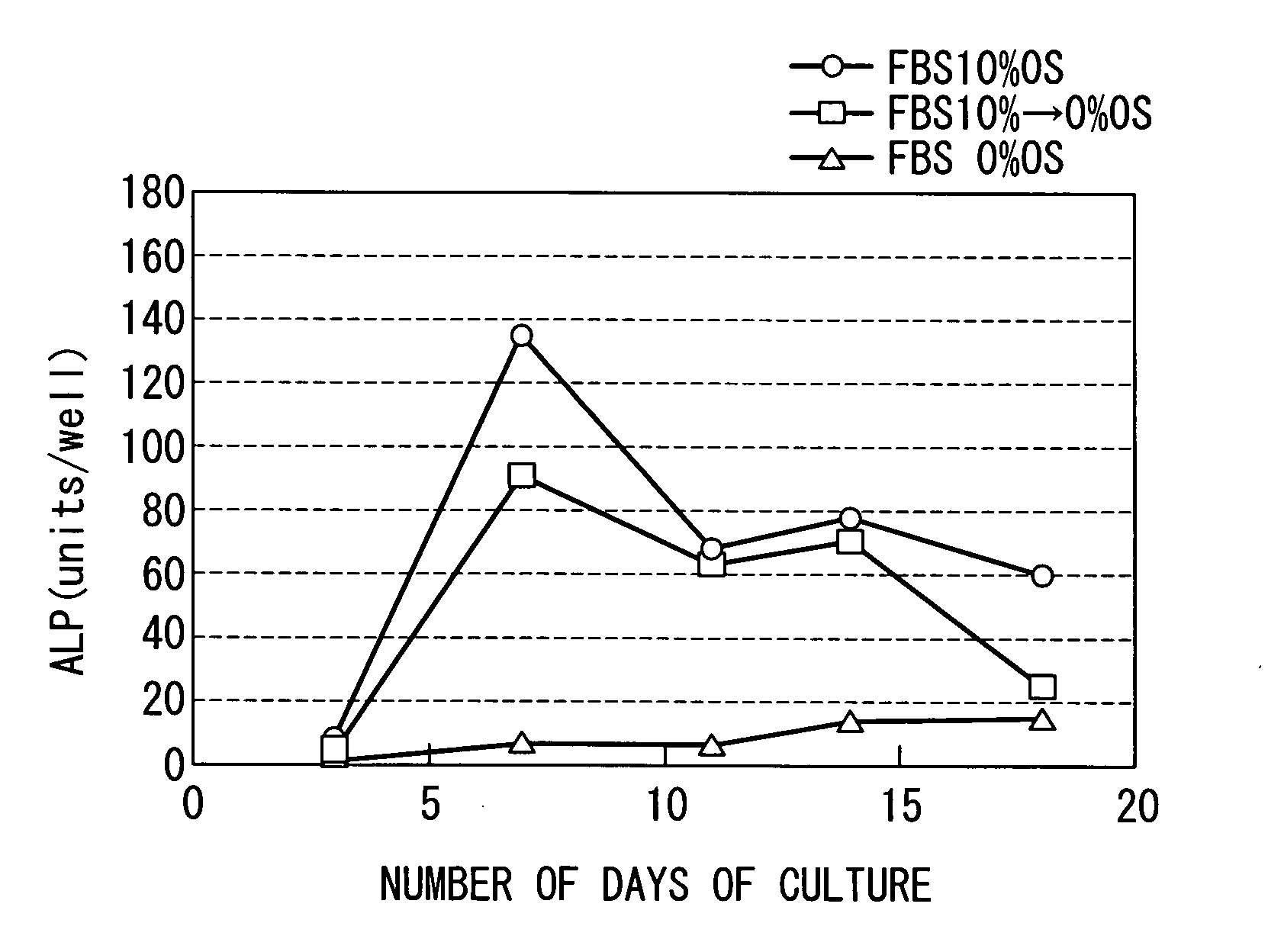

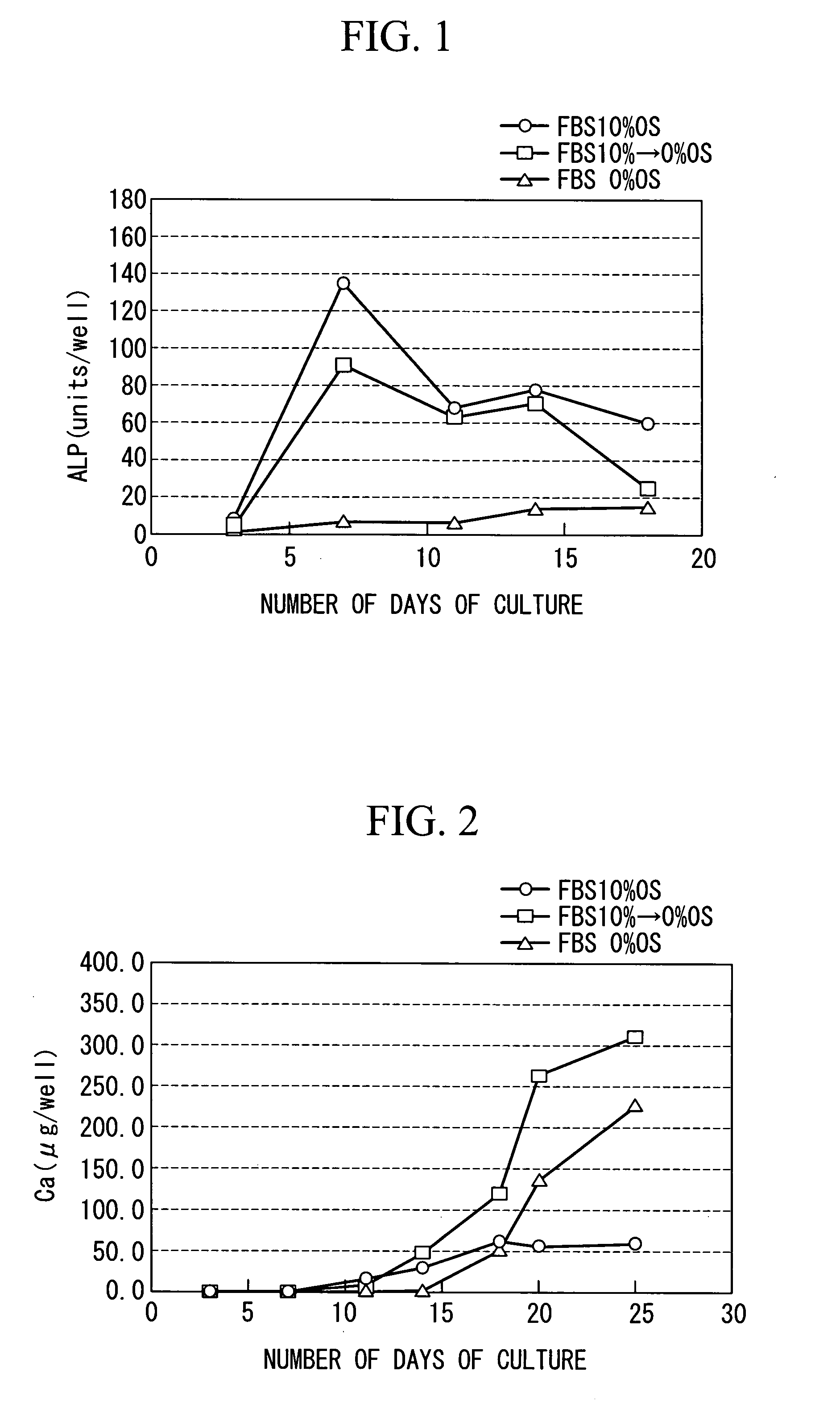

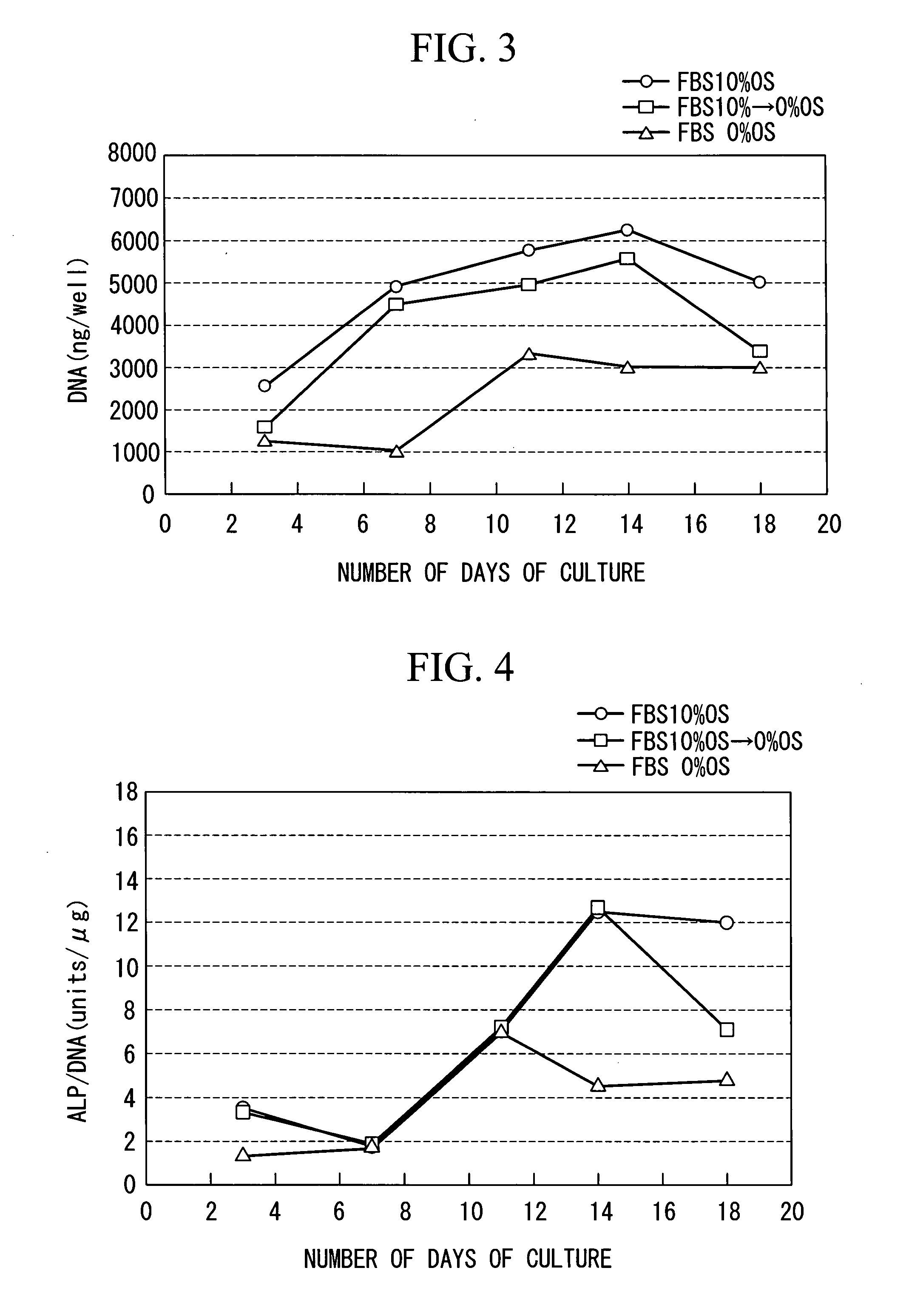

Method for culturing mesenchymal stem cell and method for producing biological tissue prosthesis

InactiveUS20100028997A1Reduce concentrationReduce harmCulture processArtificial cell constructsProsthesisMesenchymal stem cell proliferation

The purpose is to proliferate a mesenchymal stem cell to a sufficient degree while reducing the amount of blood serum contained in a biological tissue progenitor cell to be grafted, and to efficiently differentiate the mesenchymal stem cell into the biological tissue progenitor cell. There is provided a method for culturing a mesenchymal stem cell, comprising: a first culture step of proliferating a mesenchymal stem cell in a medium containing blood serum; and a second culture step of differentiating the mesenchymal stem cell into a biological tissue progenitor cell in a medium containing blood serum at a lower concentration than that in the medium used in the first culture step.

Owner:OLYMPUS CORP