Patents

Literature

46results about How to "Few switch" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

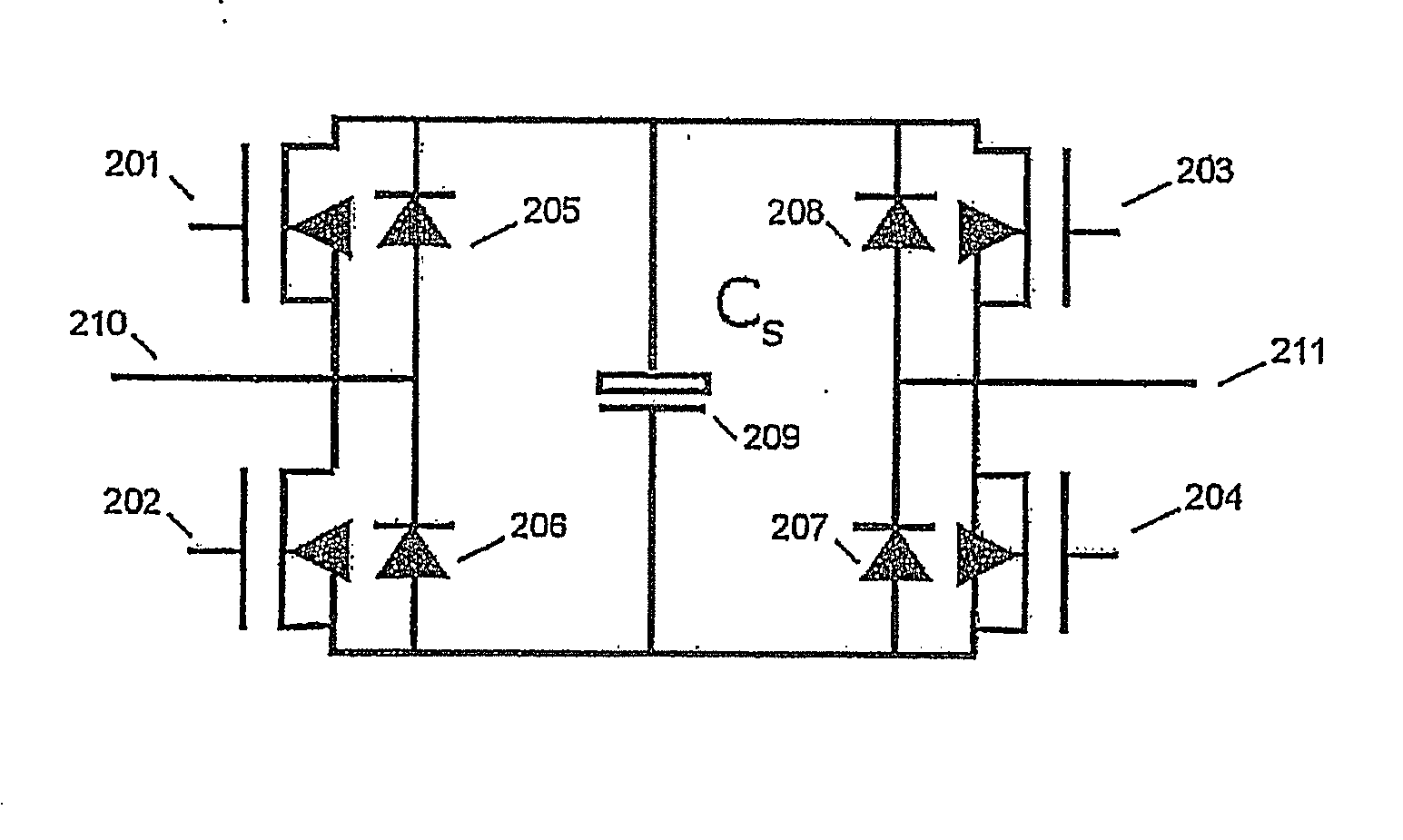

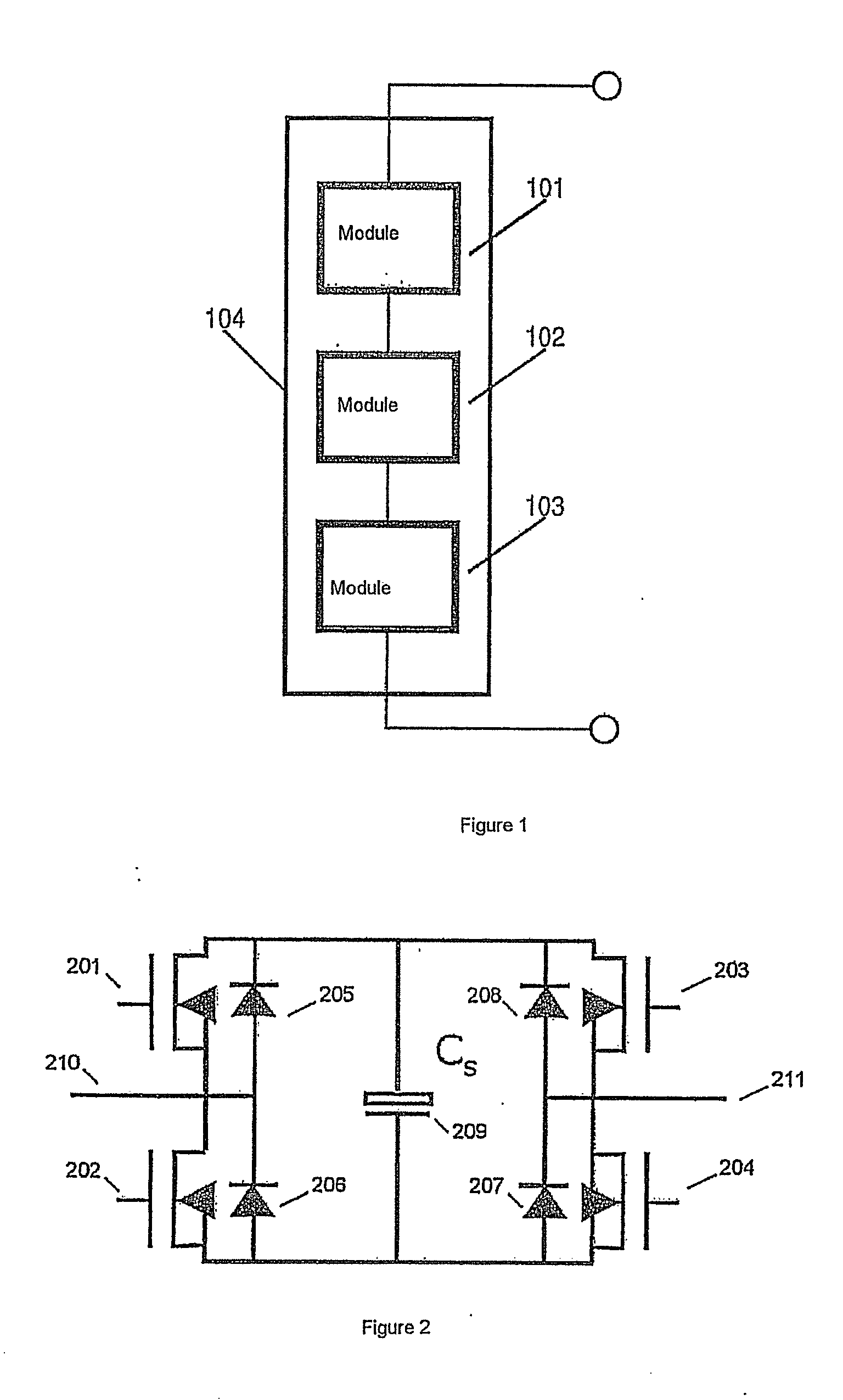

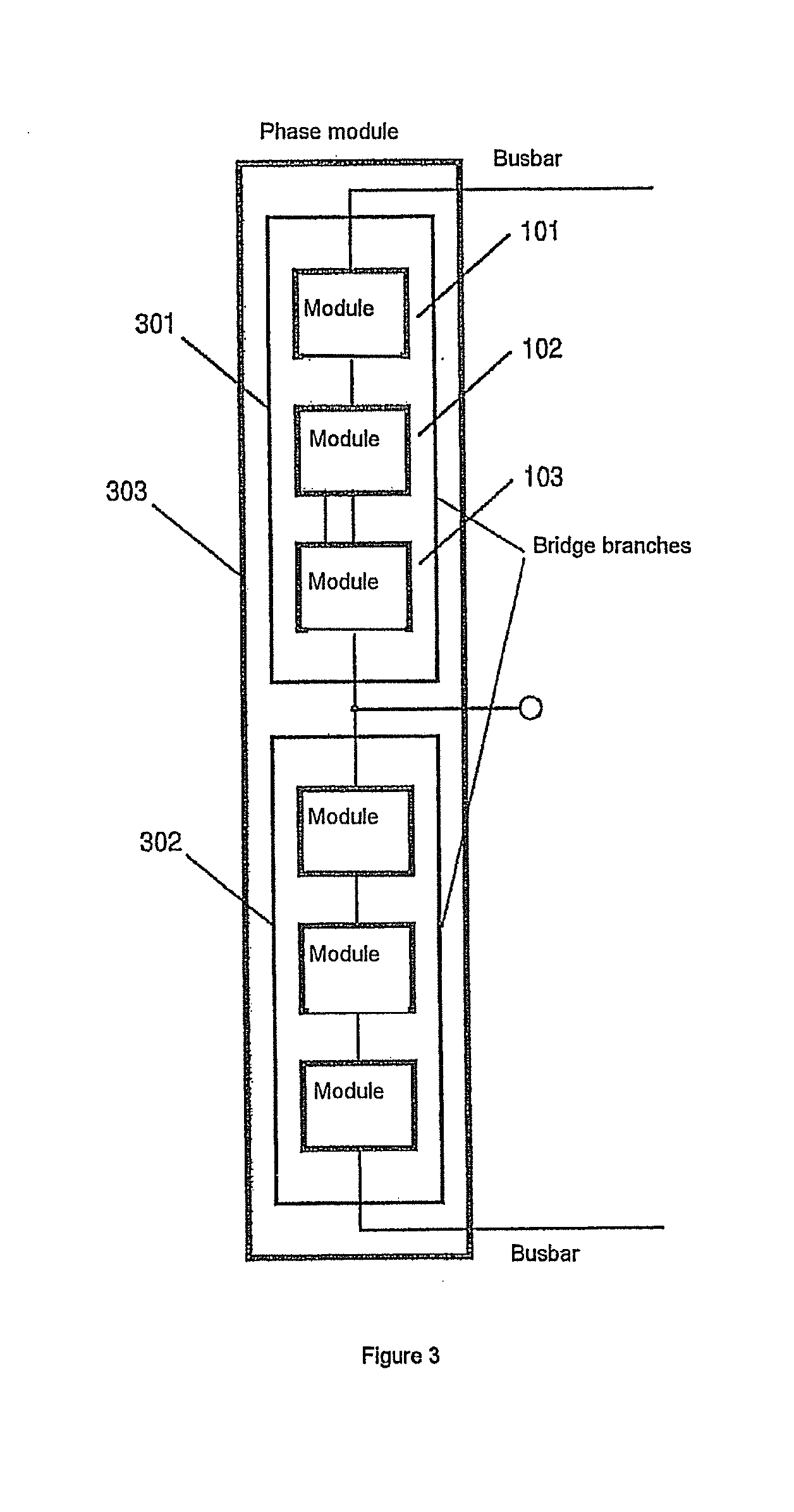

Novel multi-level converter topology with the possibility of dynamically connecting individual modules in series and in parallel

ActiveUS20140049230A1Reduced functionalityFew switchDc-ac conversion without reversalElectric variable regulationLevel converterEnergy storage

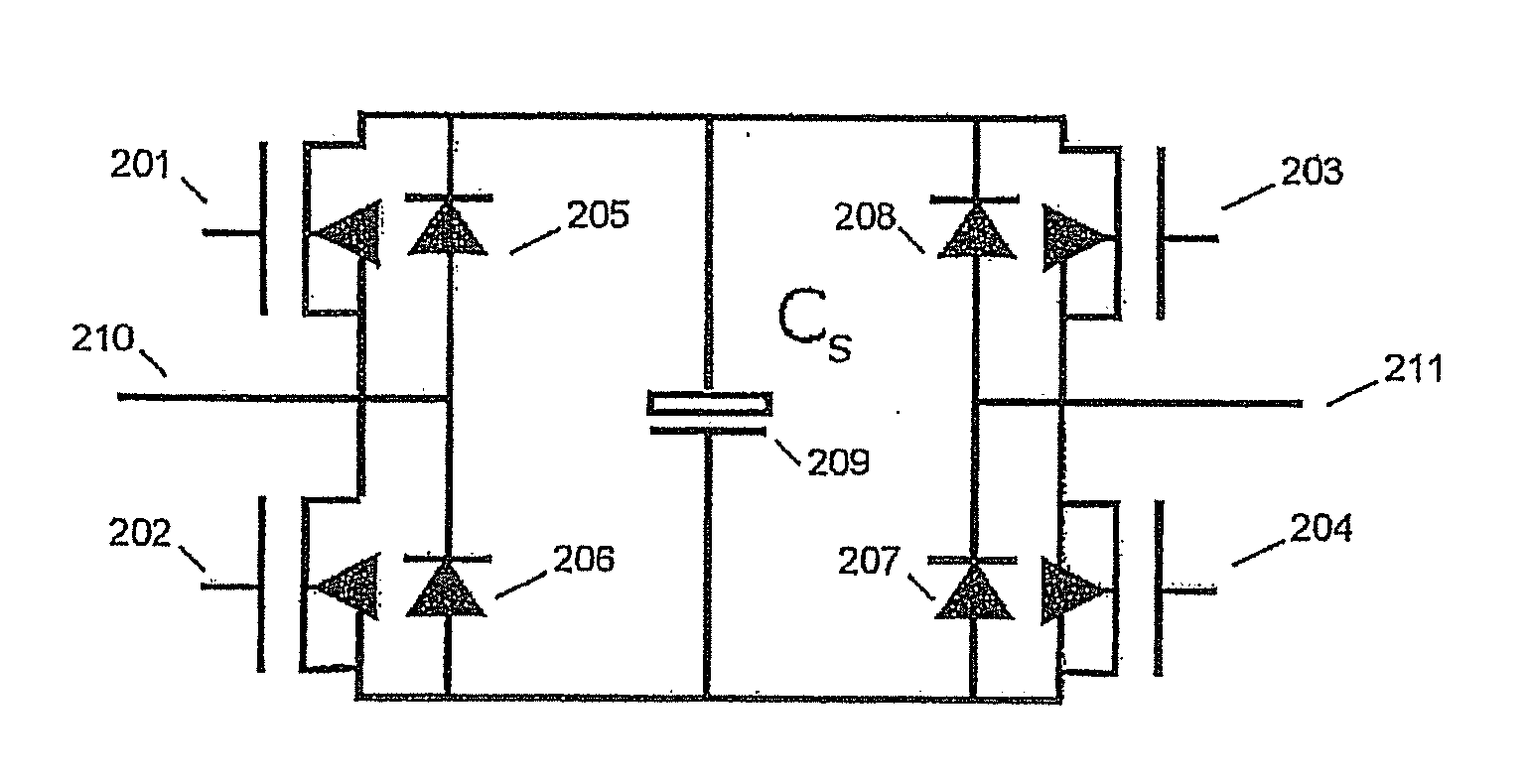

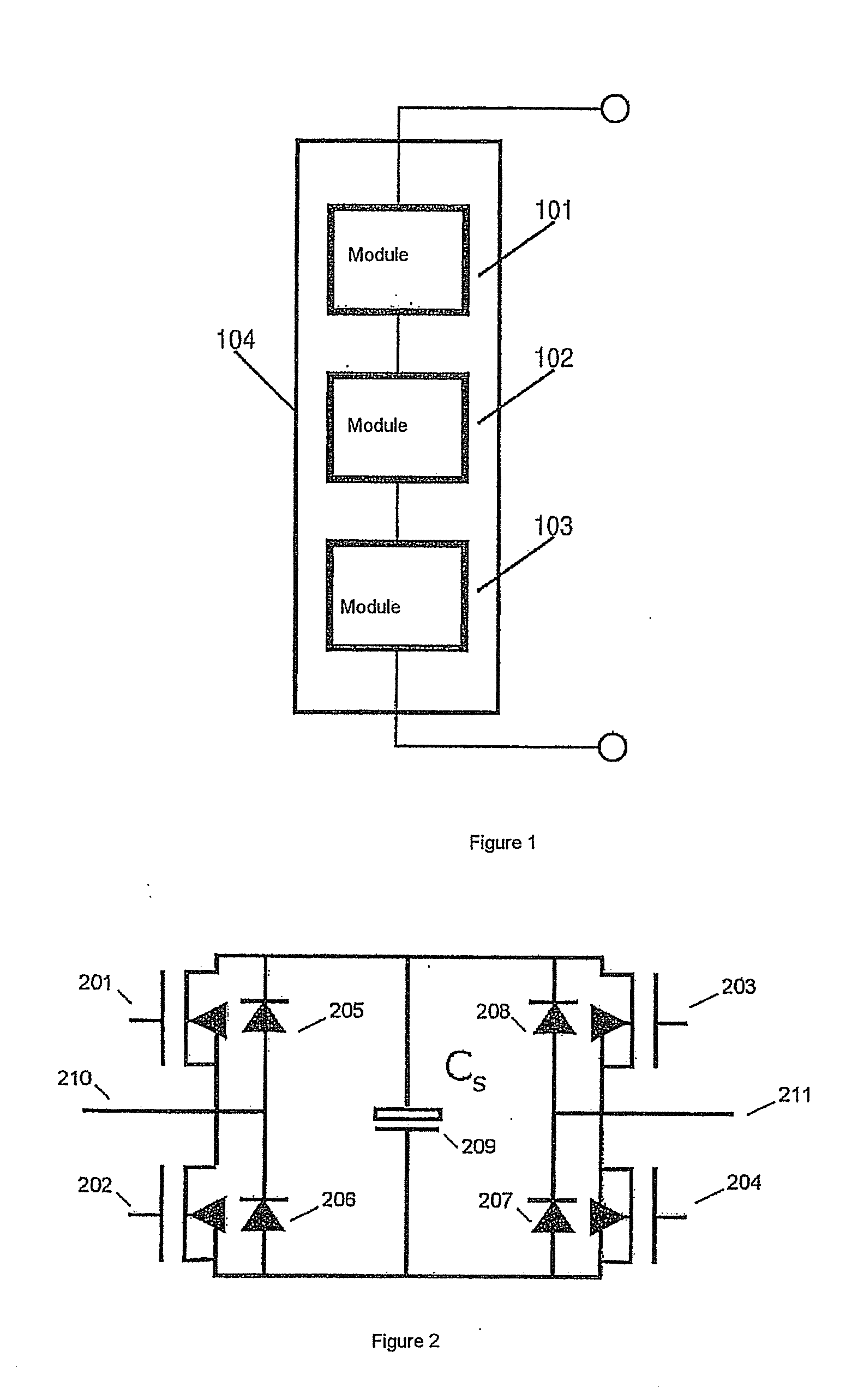

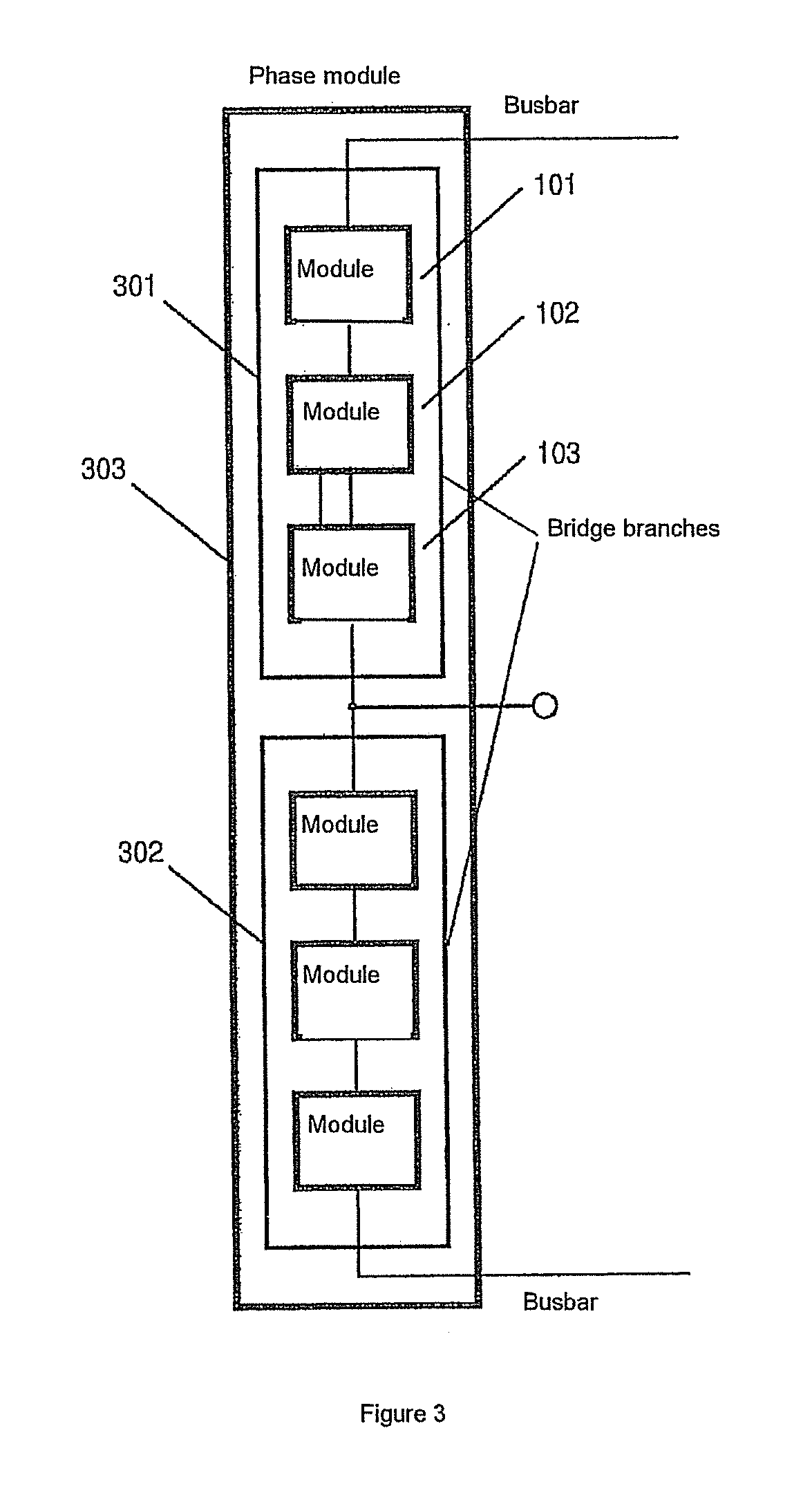

The present invention describes an electrical converter system for power supply systems, comprising at least two identical individual modules connected consecutively, characterised in that each individual module have at least four internal switching elements, at least one energy storage element and at least four connectors, wherein the connectors are paired and serve as a first and a second terminal pair; the internal switching elements of each individual module are designed in such manner that they are able to selectively connect one or both connectors of each terminal pair to the energy storage element; the cascaded connection of at least two individual modules is made in such manner that the connectors in the second terminal pair of a preceding individual module are each connected to the connectors of the first terminal pair in the respective following individual module, and at least one terminal of the first terminal pair of the first individual module of the cascaded connection and at least one terminal of the second terminal pair of the last individual module of the cascaded connection serve as terminals for the cascaded connection; and wherein the switching elements of the respective individual modules in the cascaded connection of at least two individual modules connect their respective energy storage element to the terminals of the cascaded connection in such manner that a selective serial or parallel connection of the energy storage elements is made.

Owner:TECH UNIV MUNCHEN

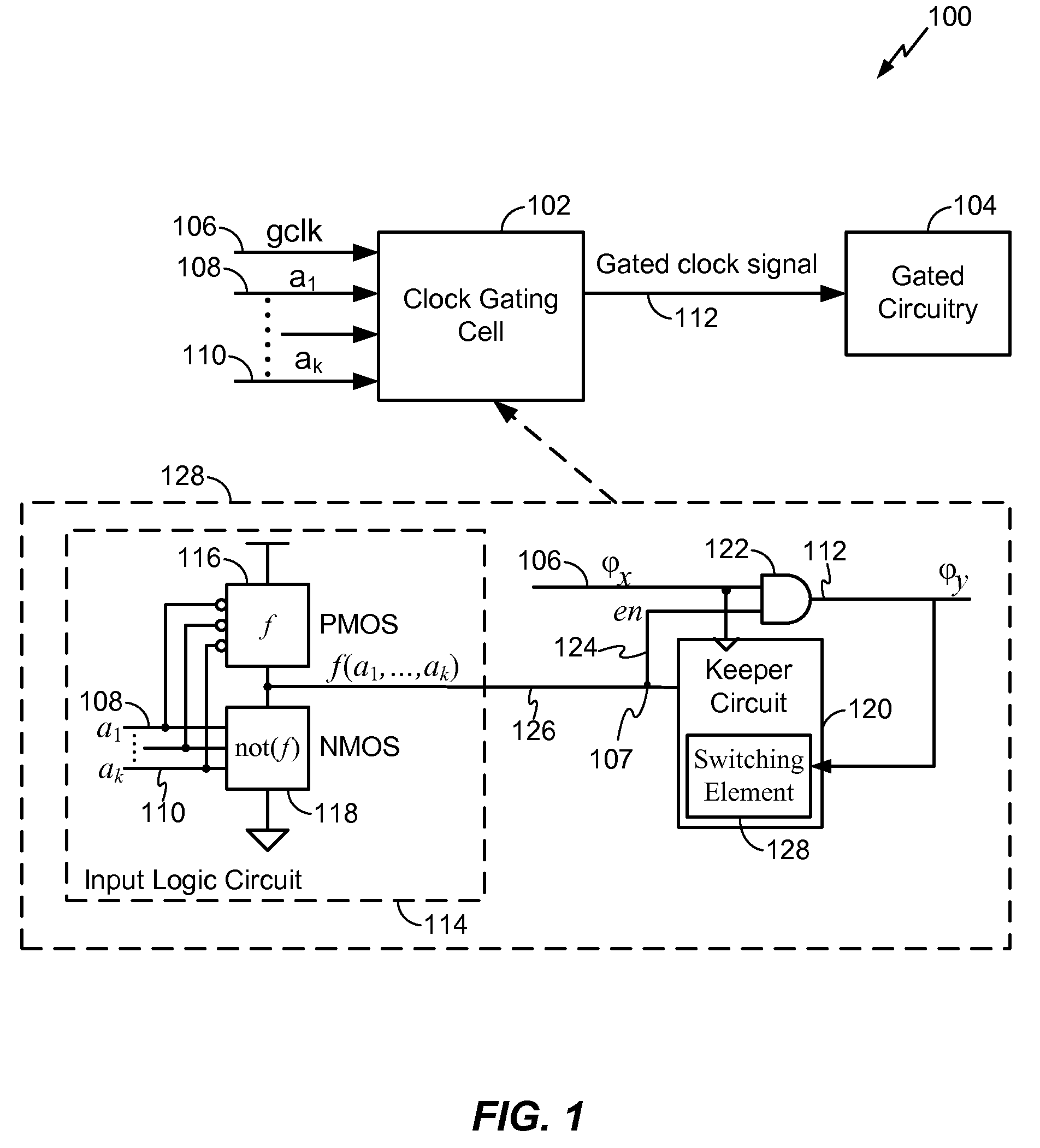

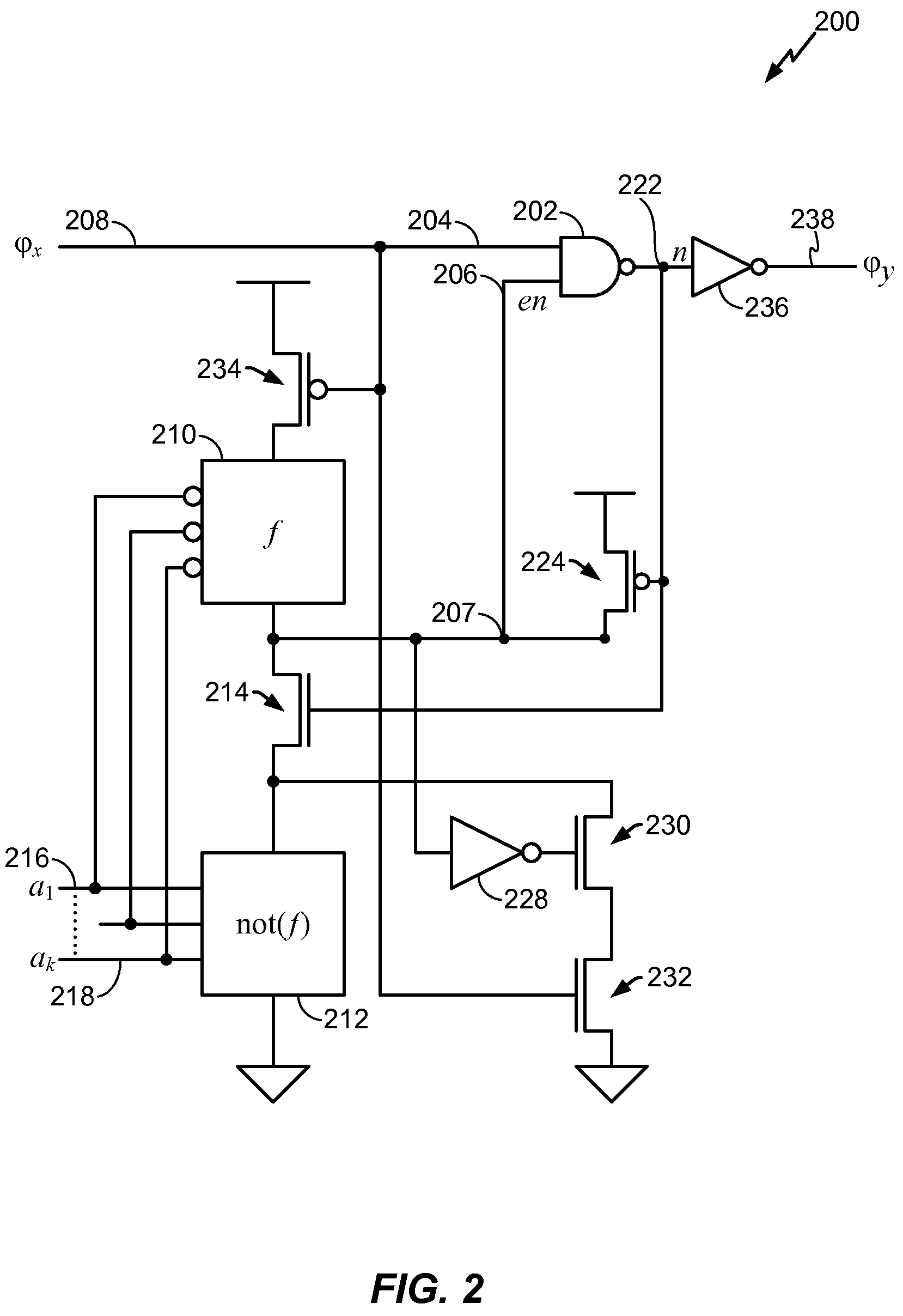

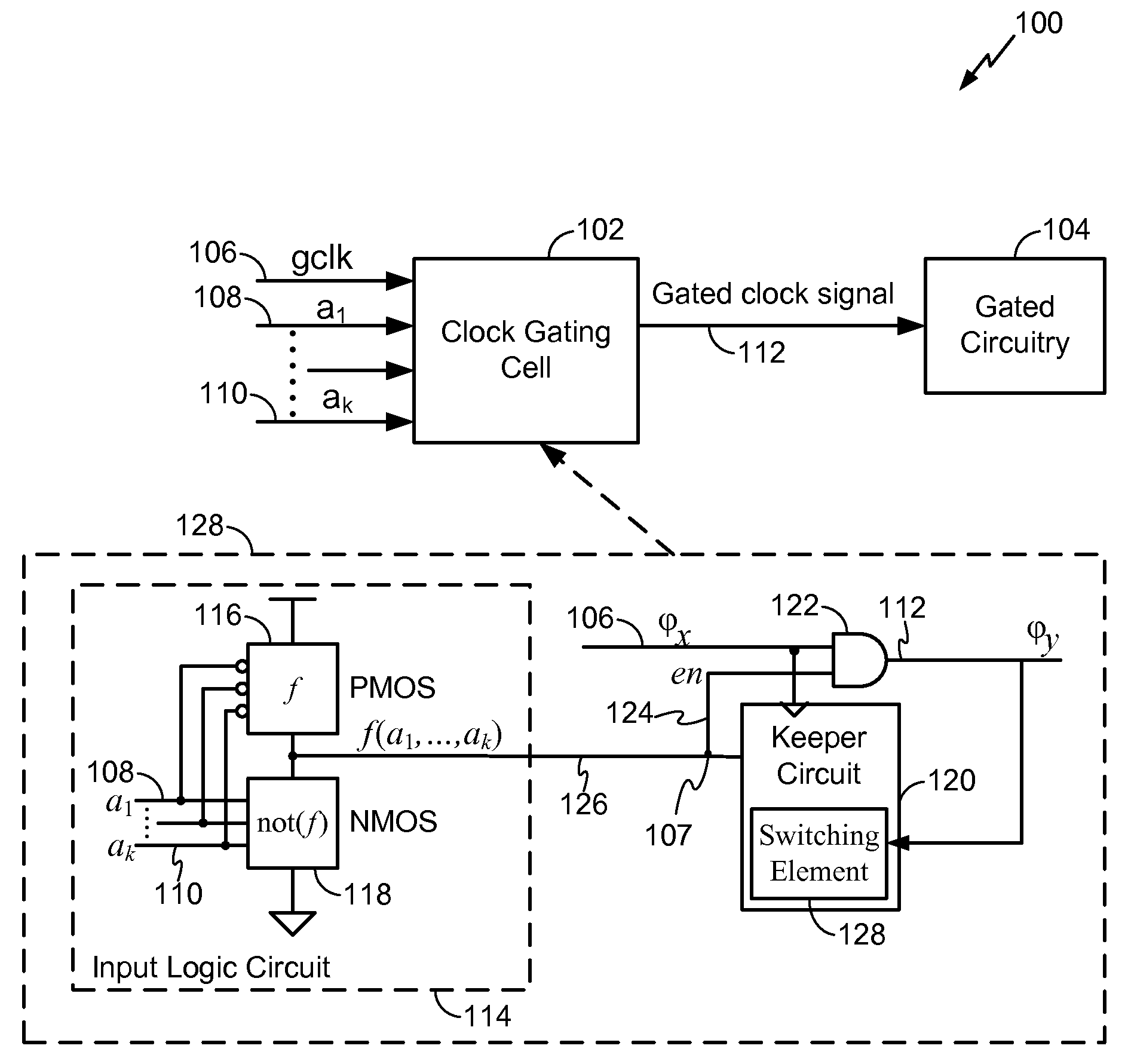

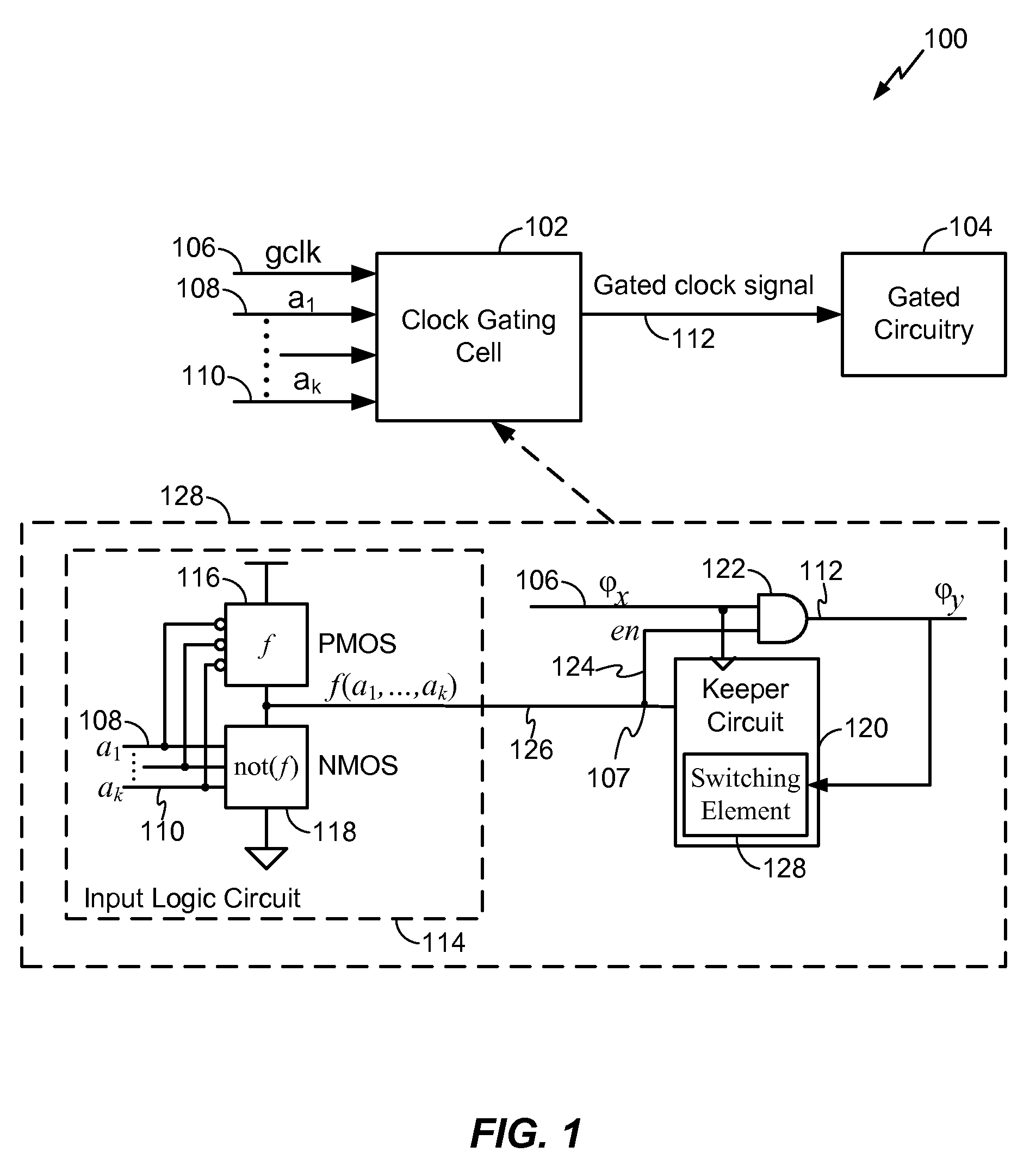

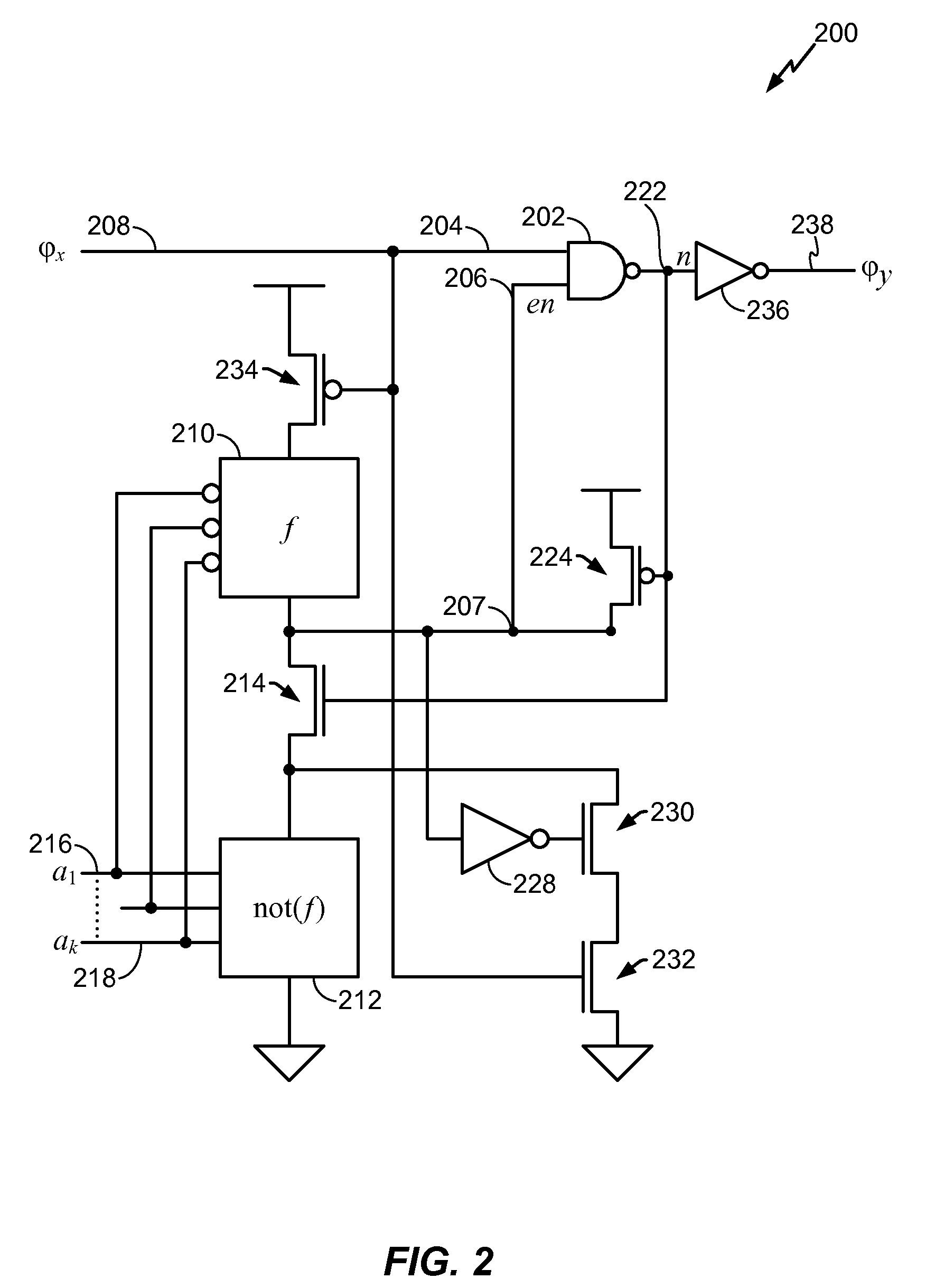

Clock gating system and method

ActiveUS7902878B2Reduce in quantityReduce areaPower reduction by control/clock signalGenerating/distributing signalsEngineeringLogic circuitry

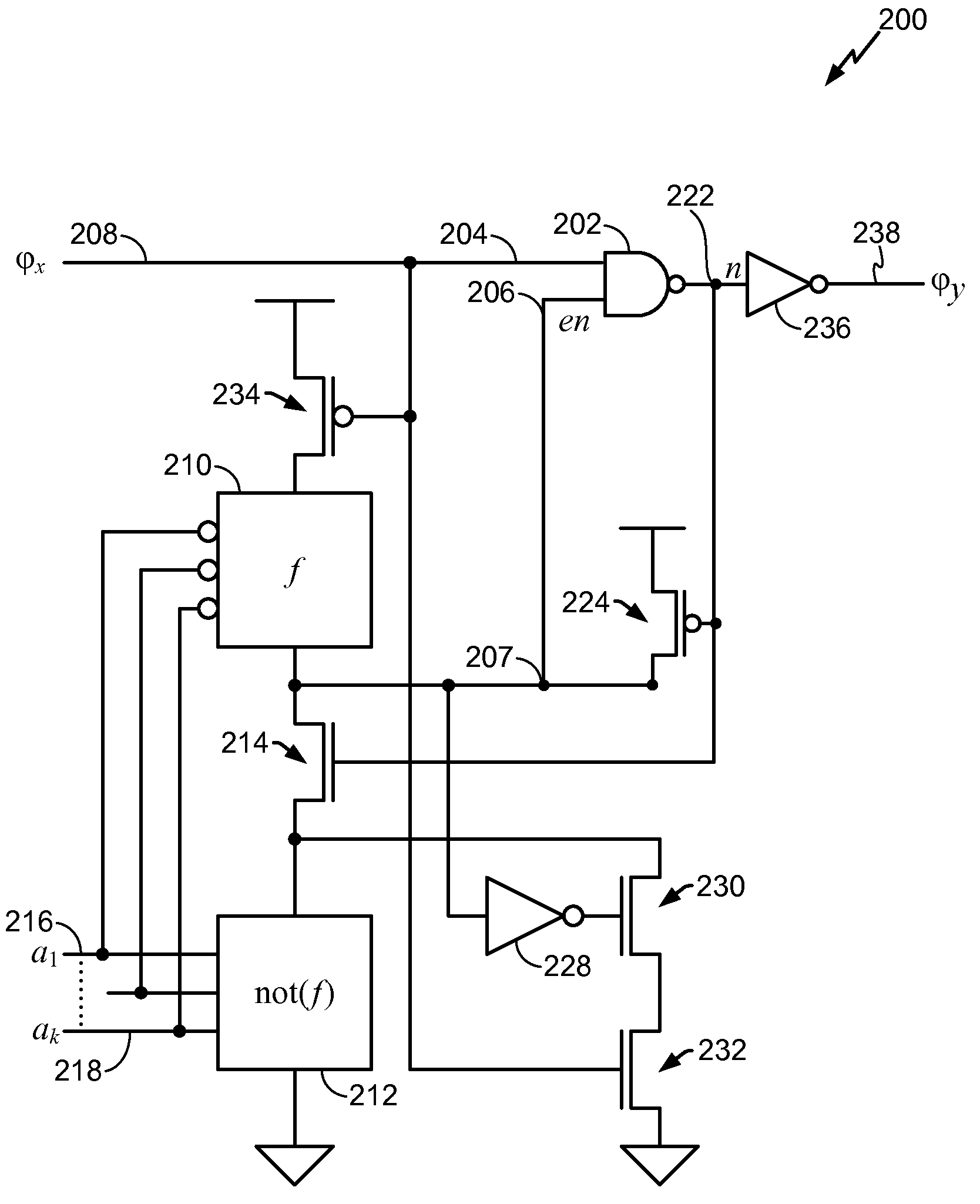

A clock gating system and method is disclosed. In a particular embodiment, the system includes an input logic circuit having at least one input to receive at least one input signal and having an output at an internal enable node. A keeper circuit includes at least one switching element that is responsive to a gated clock signal and is coupled to the internal enable node to selectively hold a logical voltage level at the internal enable node. The system further includes a gating element responsive to an input clock signal and to the logical voltage level at the internal enable node to generate the gated clock signal.

Owner:QUALCOMM INC

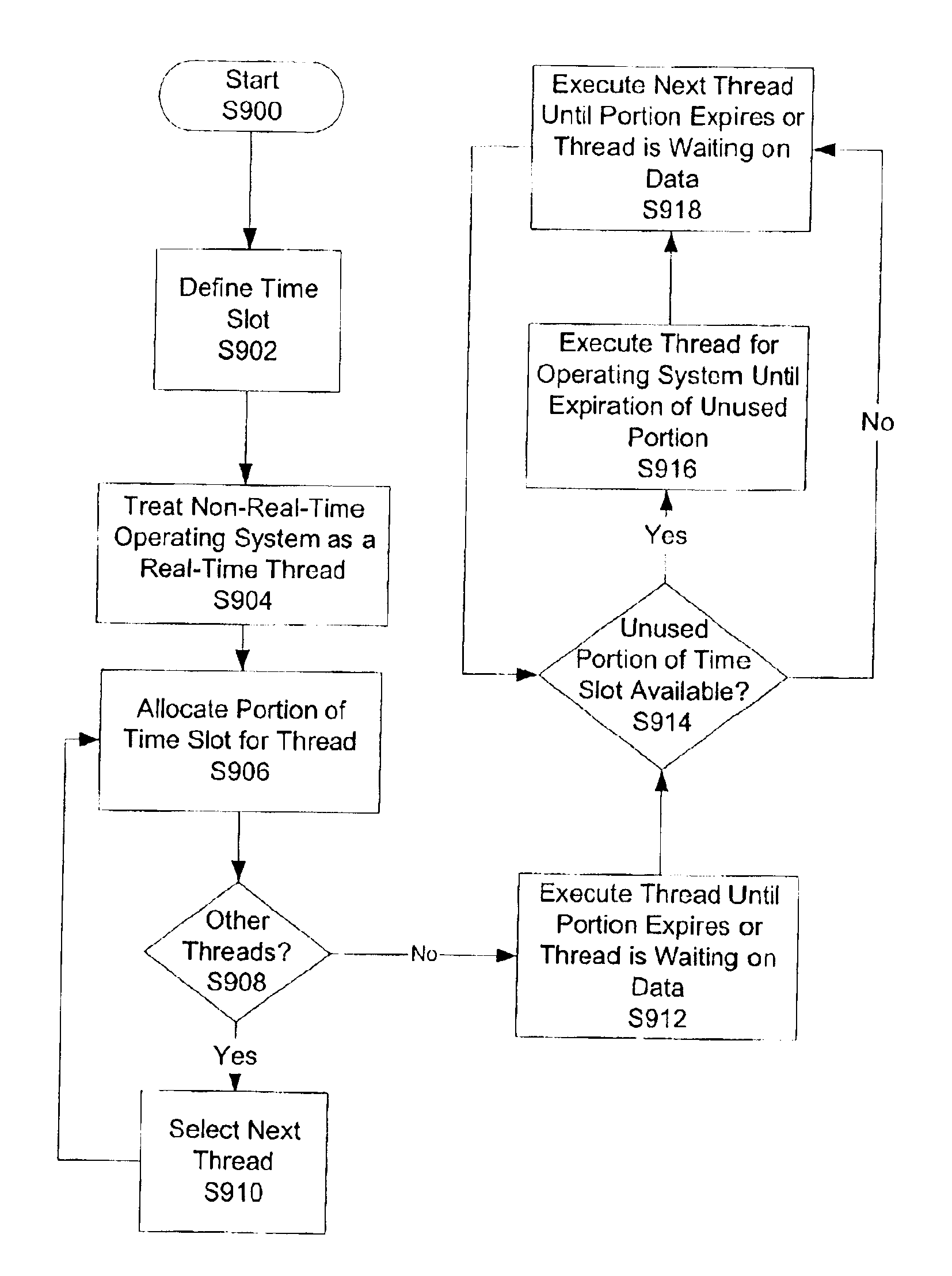

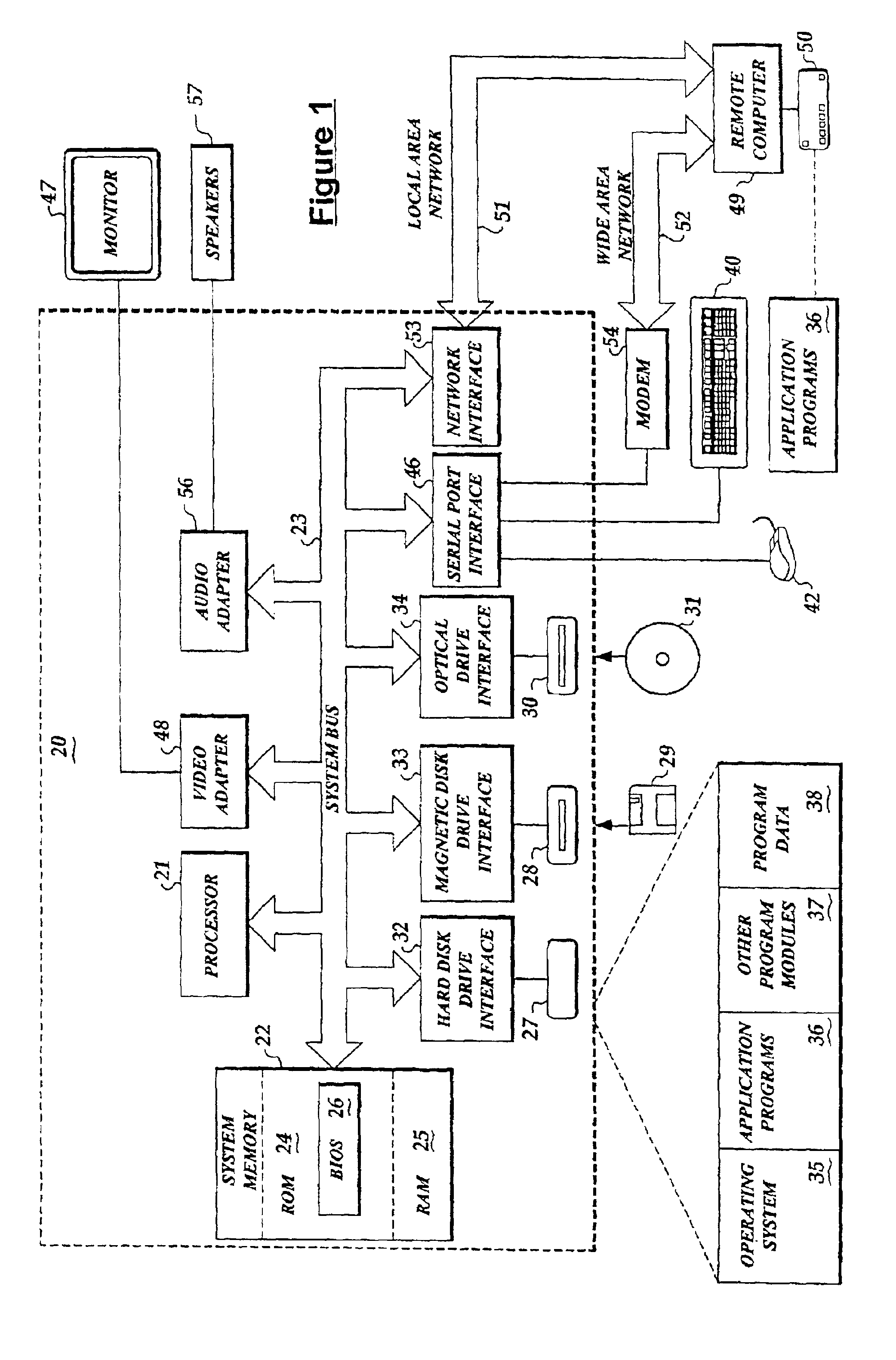

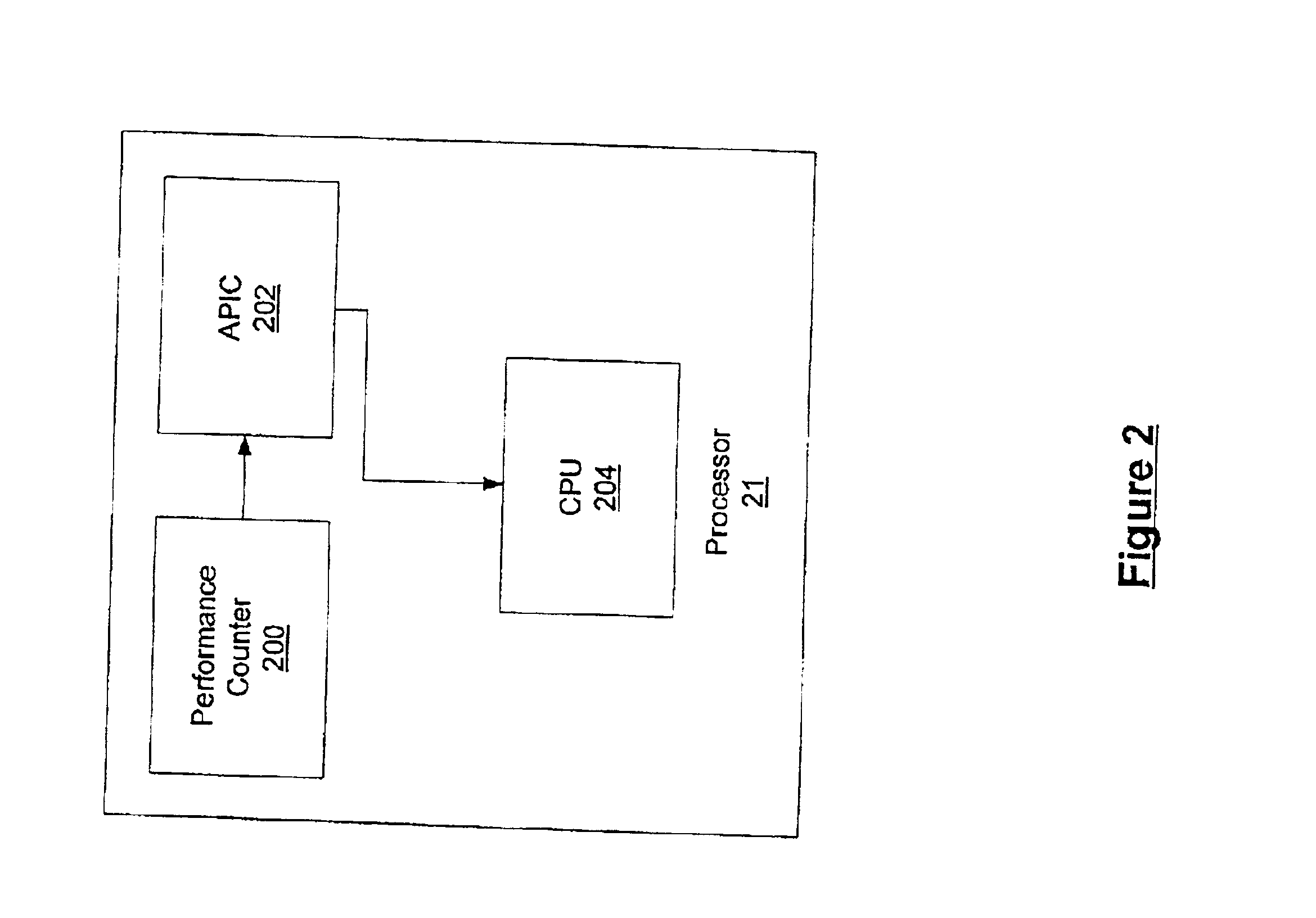

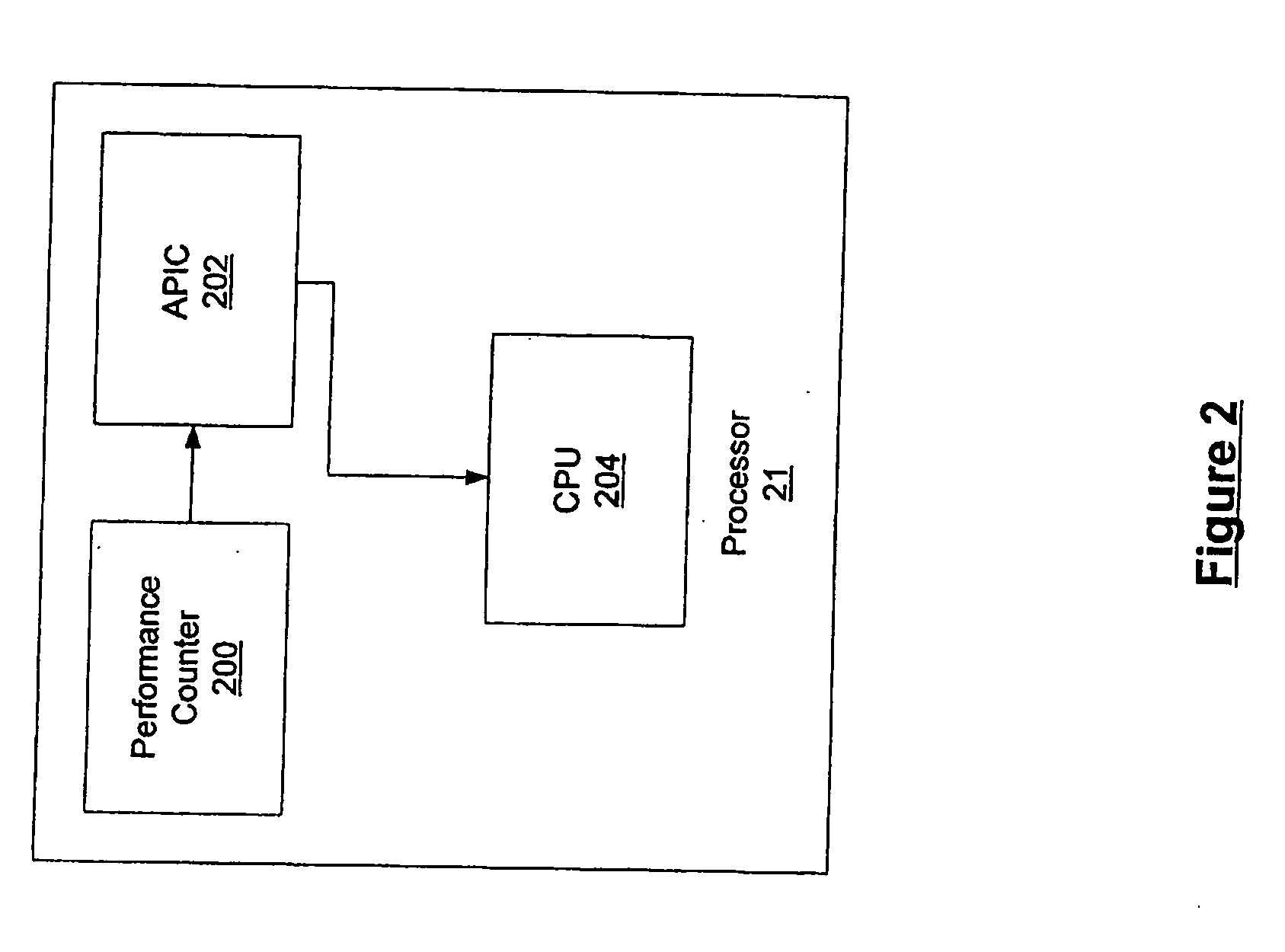

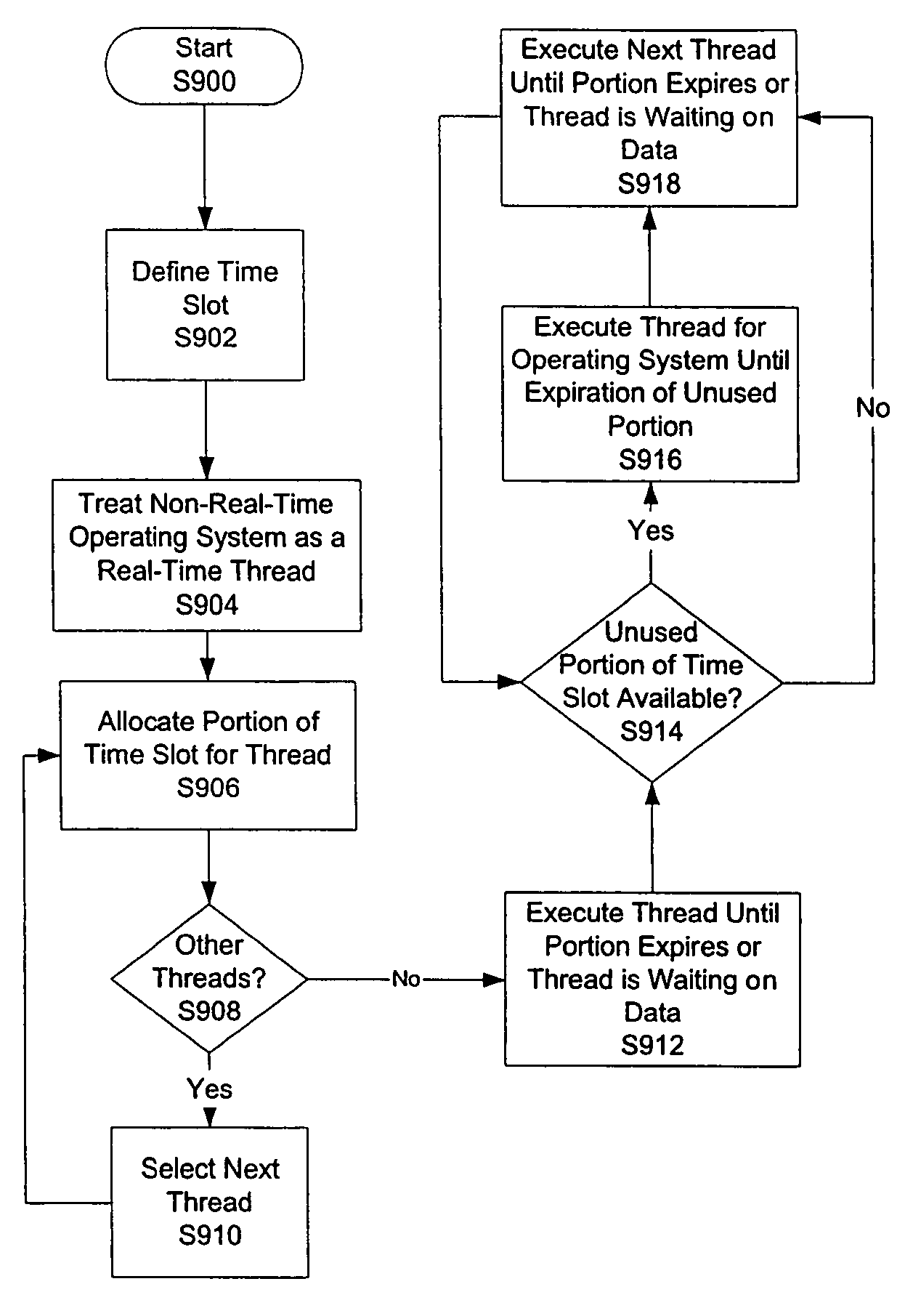

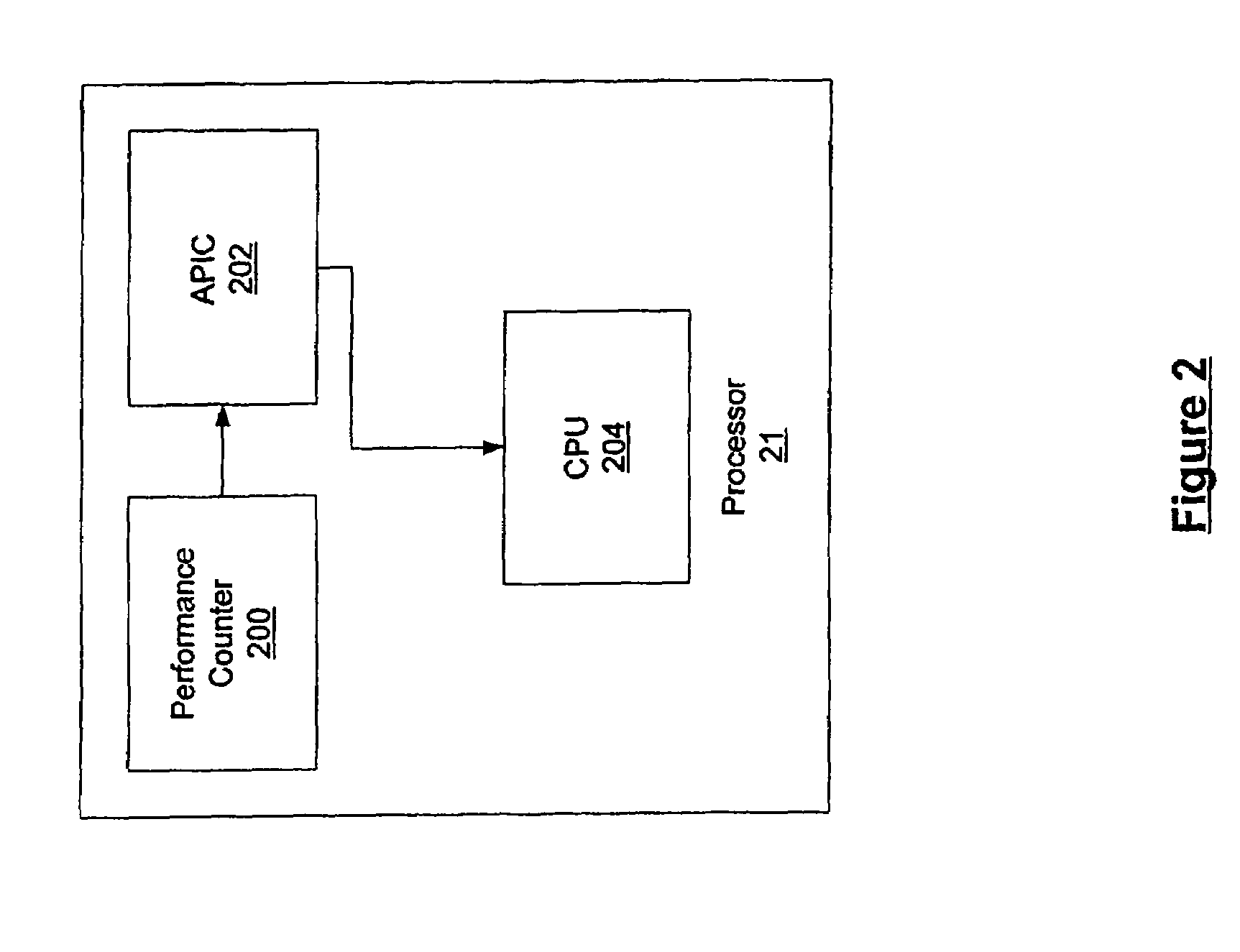

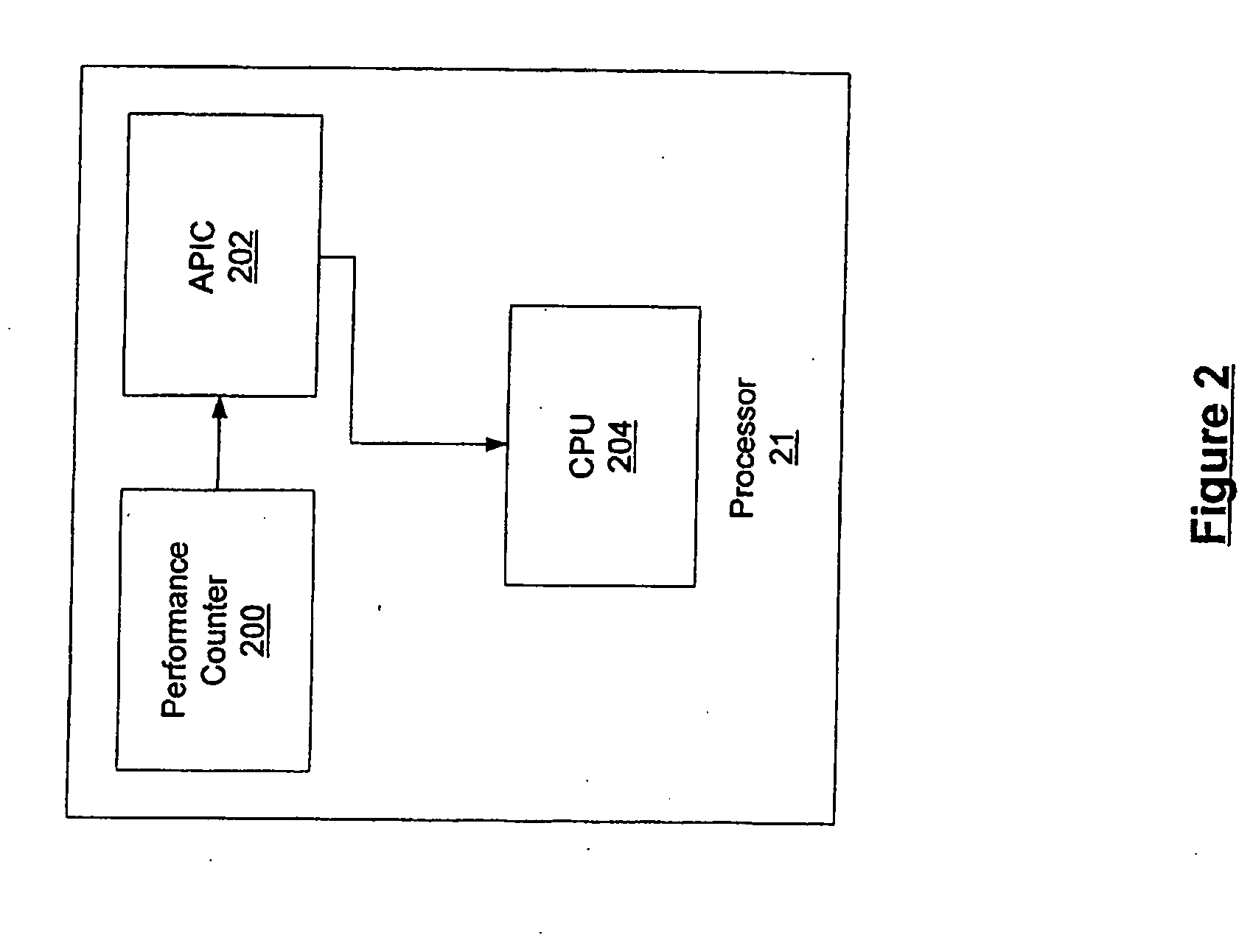

Real-time scheduler

InactiveUS6957432B2Facilitates real-time schedulingSpeed of execution of operatingProgram initiation/switchingResource allocationTime scheduleNon real time

Methods and computer-executable components for real-time scheduling of CPU resources are disclosed. A performance counter determines when to allocate CPU resources to a thread. When it is time to allocate the CPU resources, the performance counter issues a maskable or non-maskable interrupt to an advanced programmable interrupt controller (APIC). The APIC then issues a maskable non-maskable interrupt to the CPU. In response to receiving the non-maskable interrupt, the CPU allocates resources to the thread. In addition, the disclosed methods and computer-executable components also: (a) allow scheduling of CPU resources such that real-time threads are guaranteed respective portions of time slots, (b) enable real-time scheduling on a non-real-time operating system, and (c) provide scheduling of CPU resources on a uni-processor machine such that at least first and second real-time threads dependent on one another are synchronized.

Owner:MICROSOFT TECH LICENSING LLC

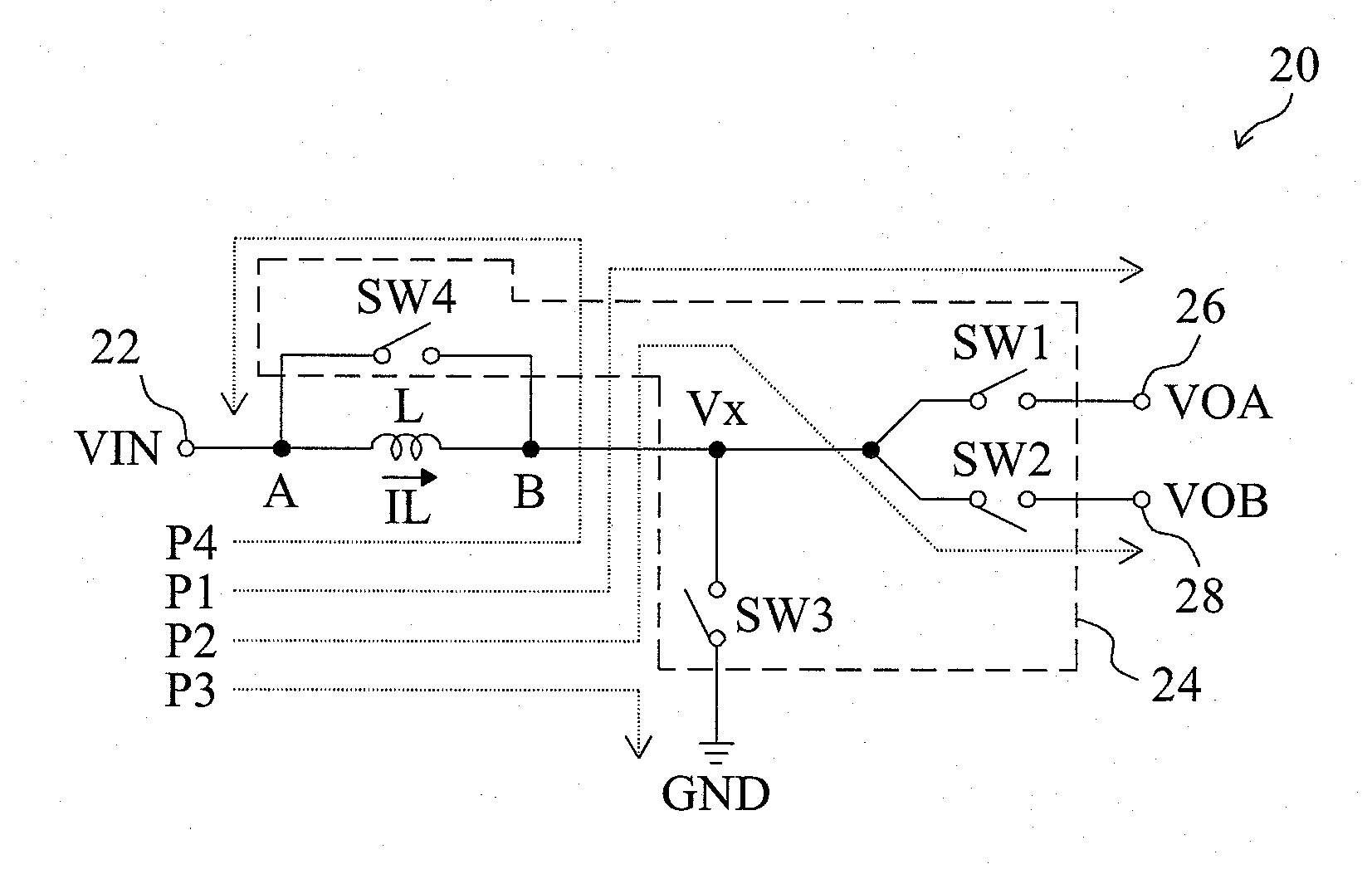

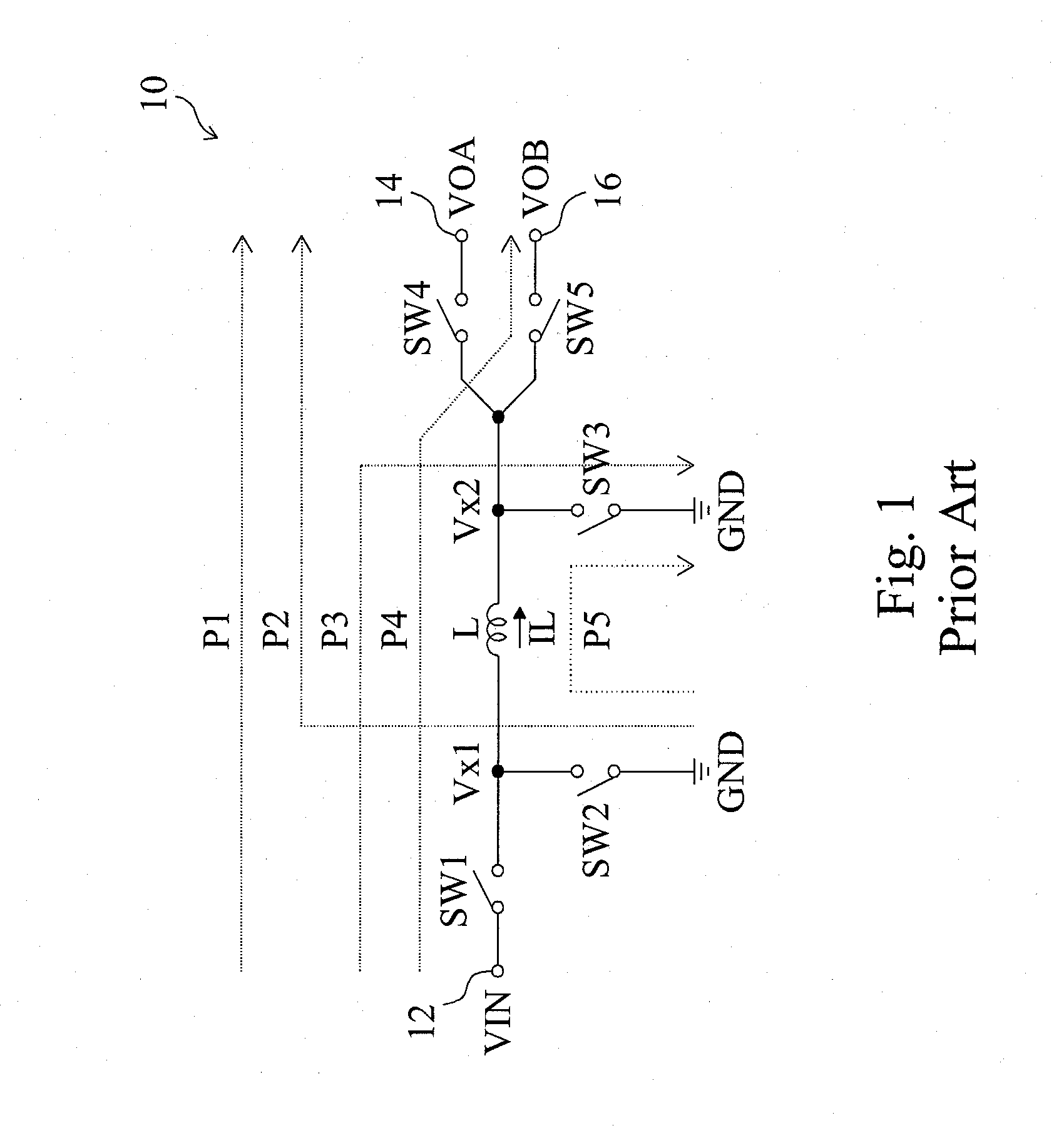

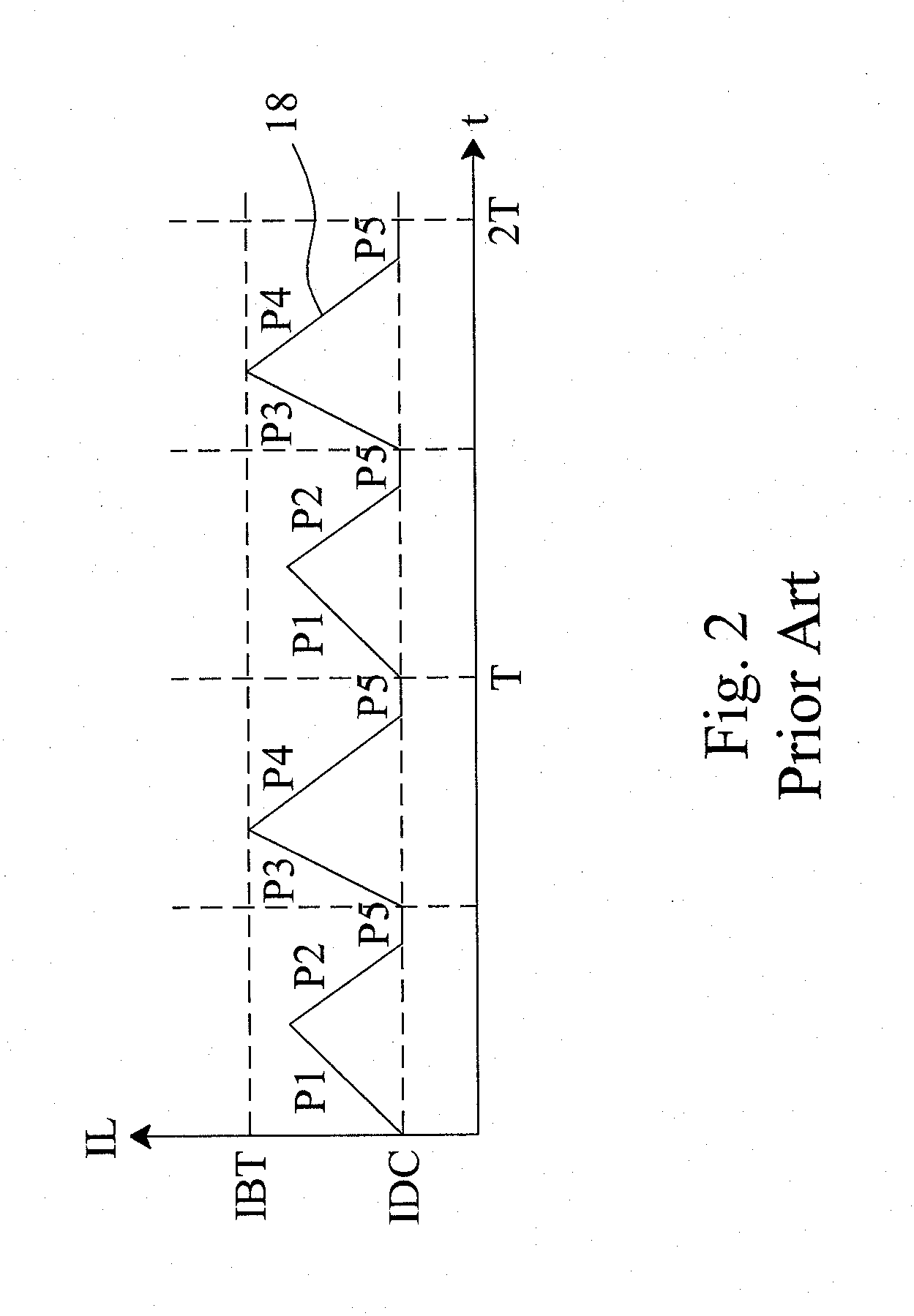

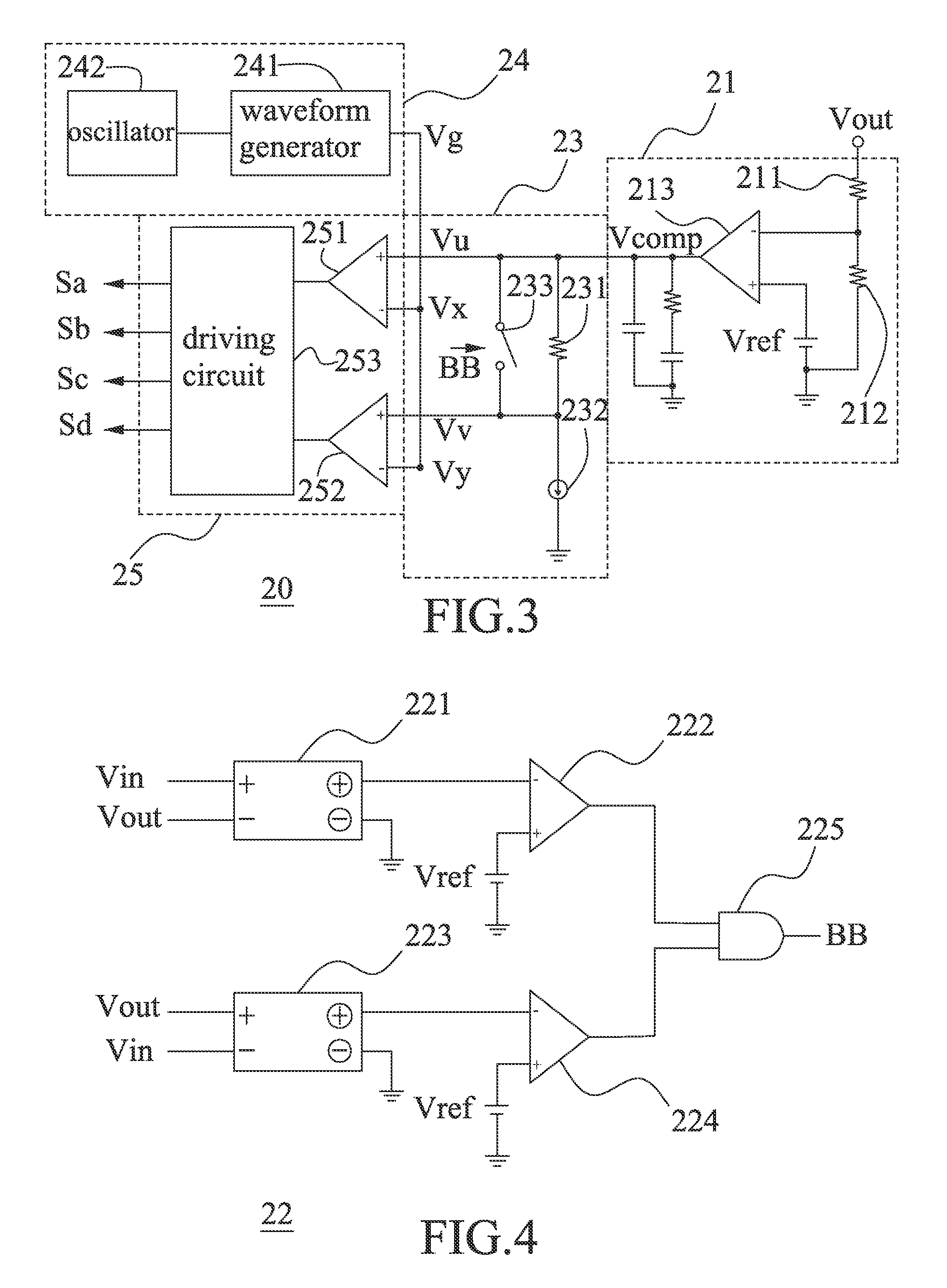

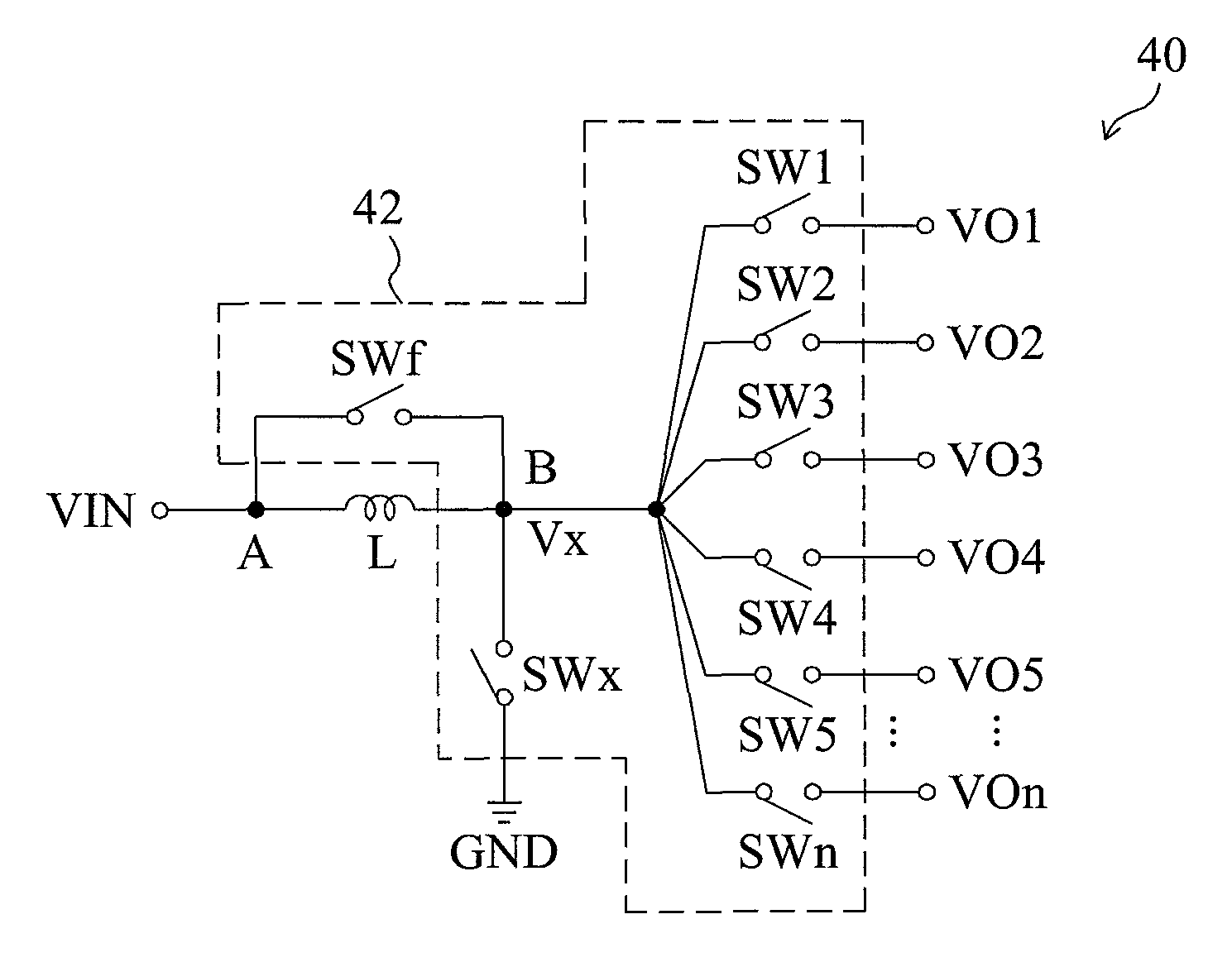

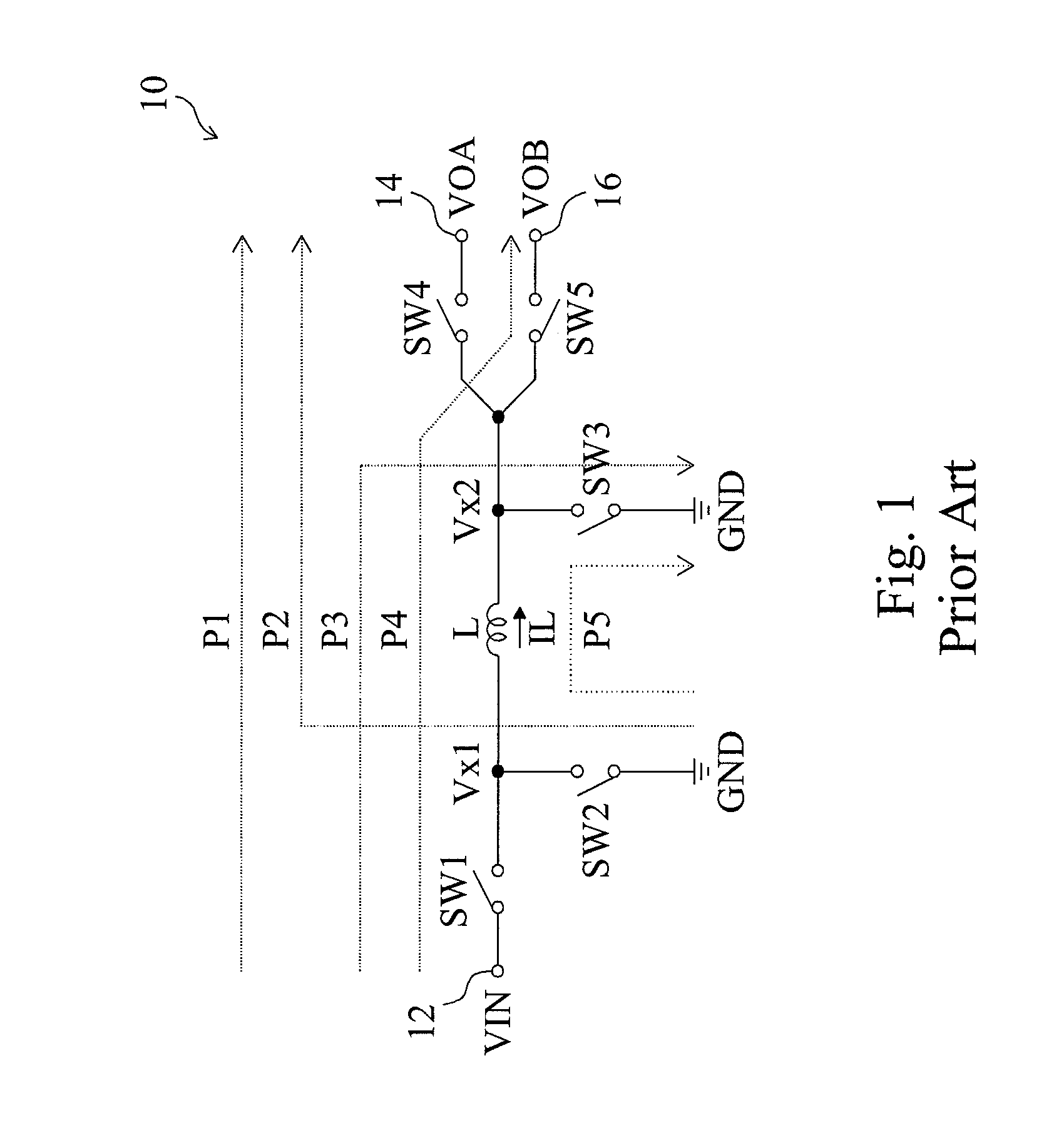

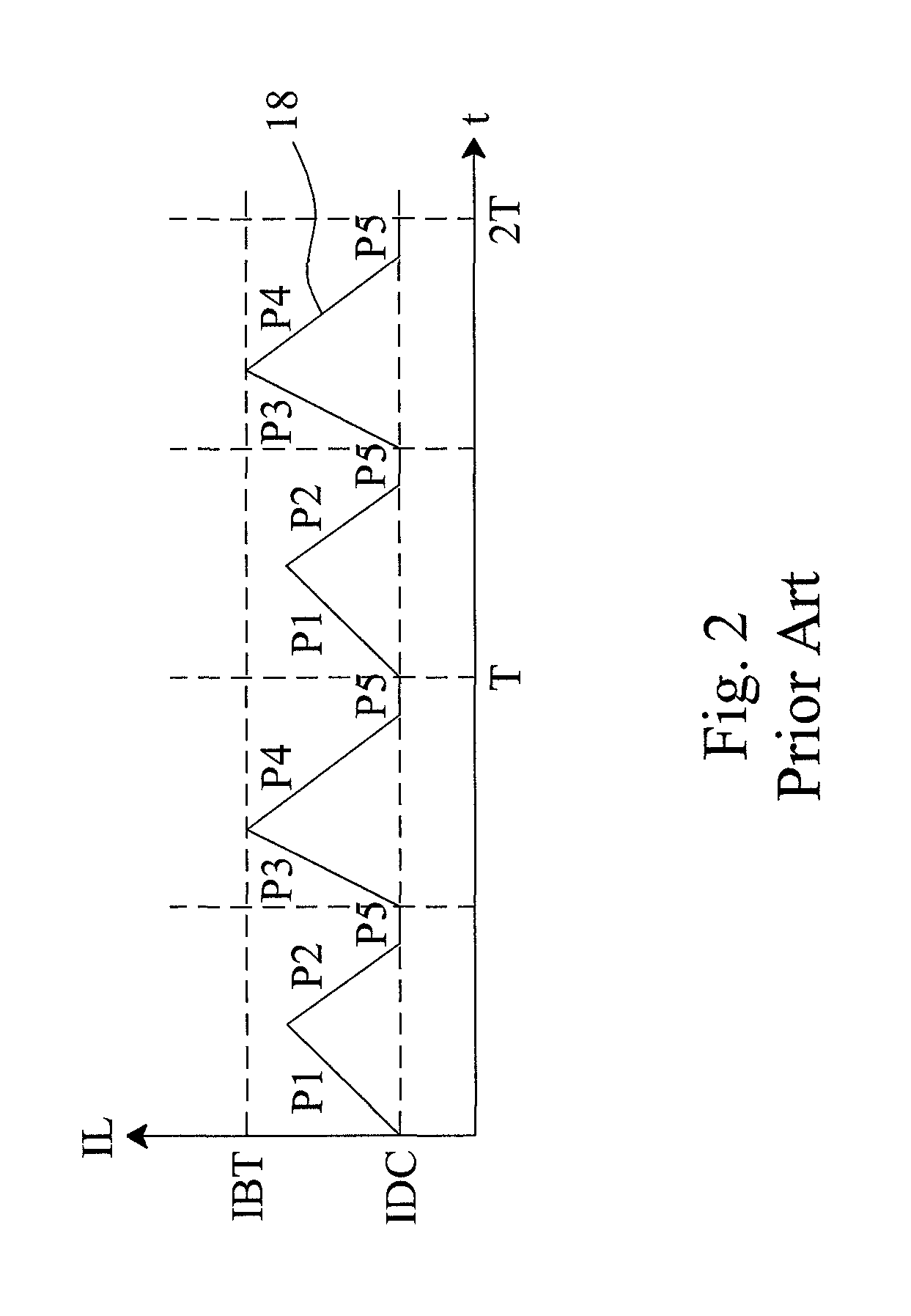

Single-inductor multiple-output power converter

ActiveUS20100231186A1Few switchLow costDc-dc conversionElectric variable regulationEngineeringInductor

A single-inductor multiple-output power converter includes an inductor having a first terminal and a second terminal. The first terminal of the inductor is coupled to a power input terminal, and the second terminal of the inductor is switched to either of the first terminal of the inductor, multiple power output terminals, and a ground terminal. By switching the second terminal of the inductor between the first terminal of the inductor, the power output terminals, and the ground terminal, the power converter may provide multiple output voltages at the power output terminals respectively, in a less loss and thereby higher efficiency manner.

Owner:RICHTEK TECH

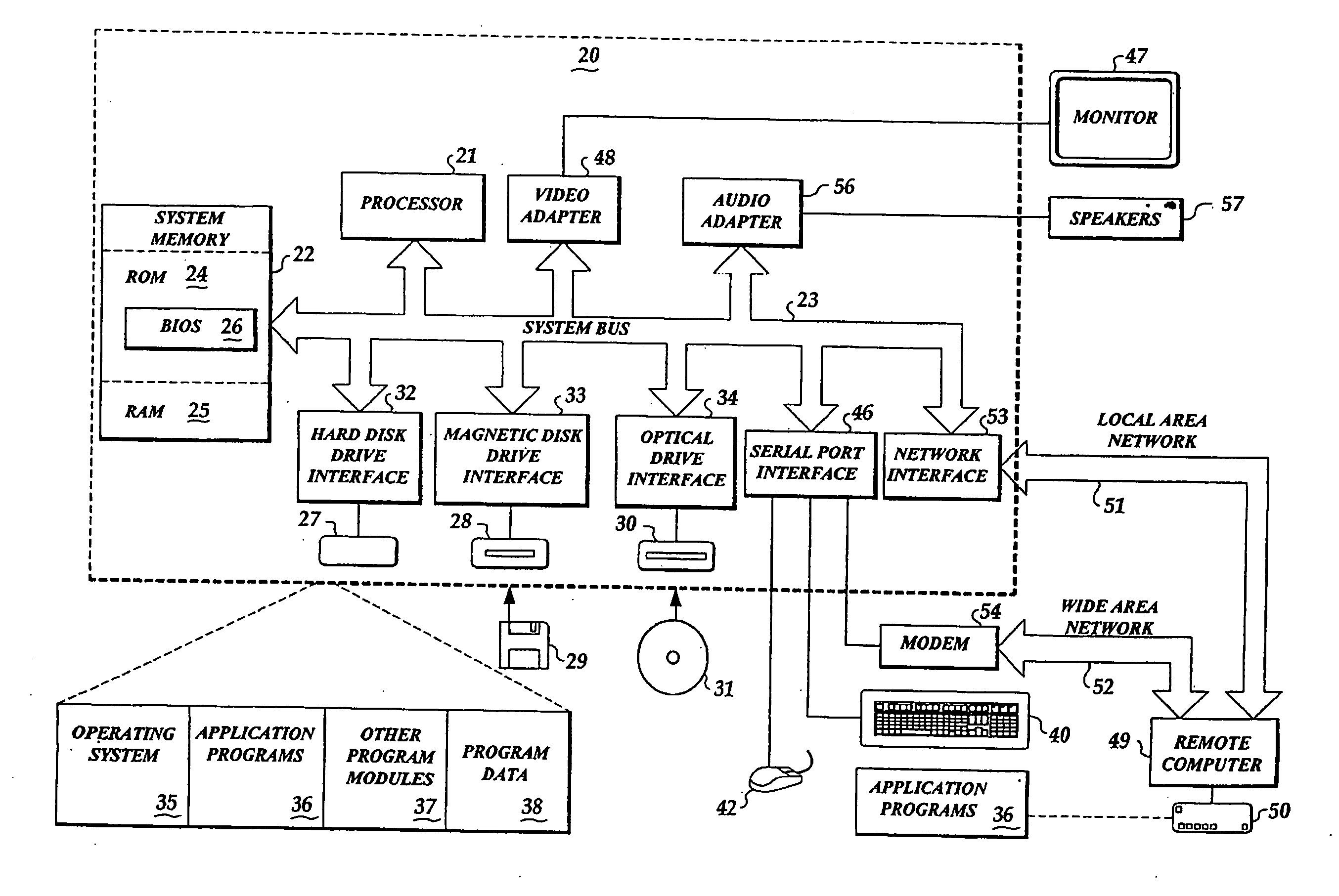

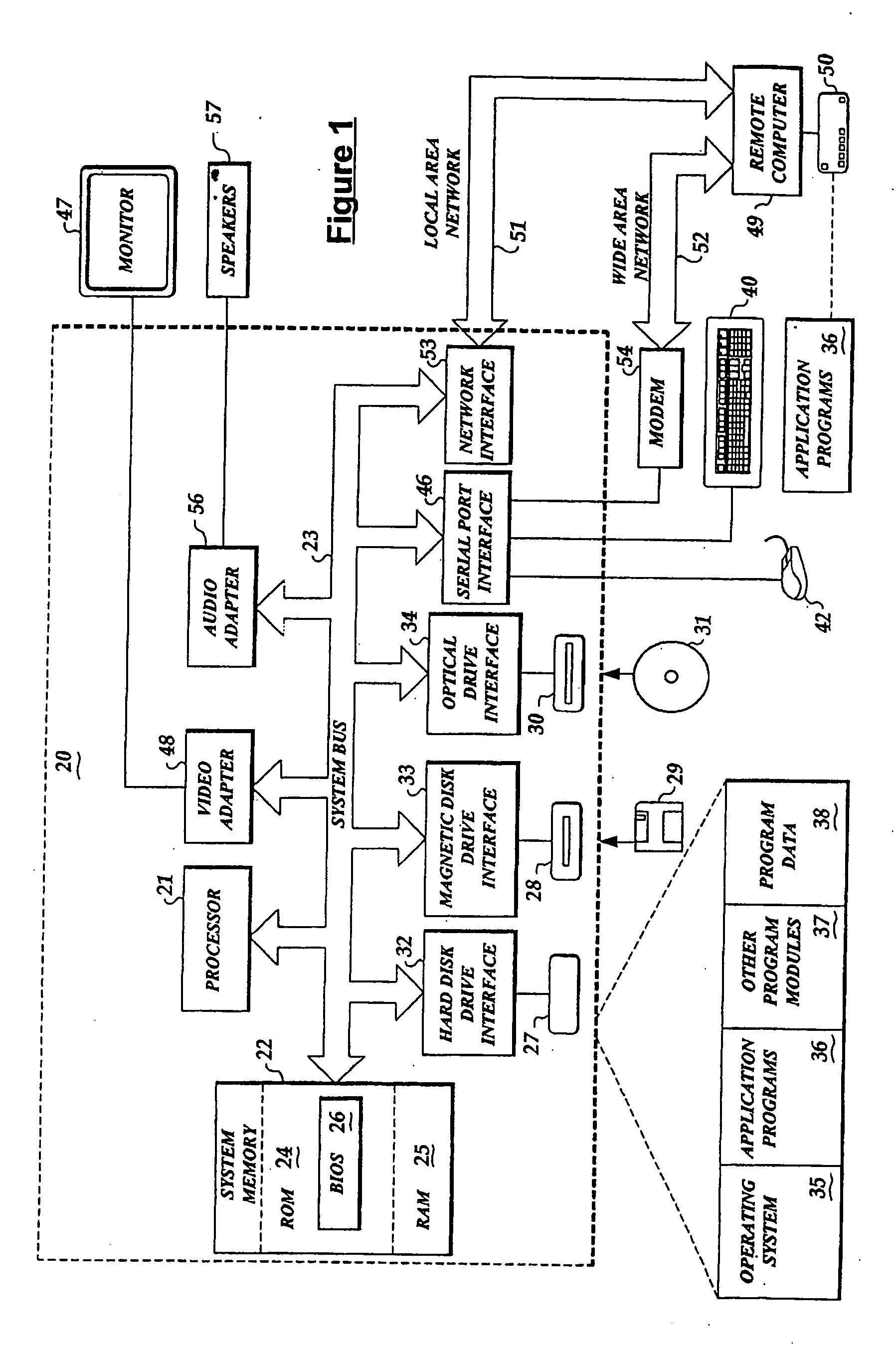

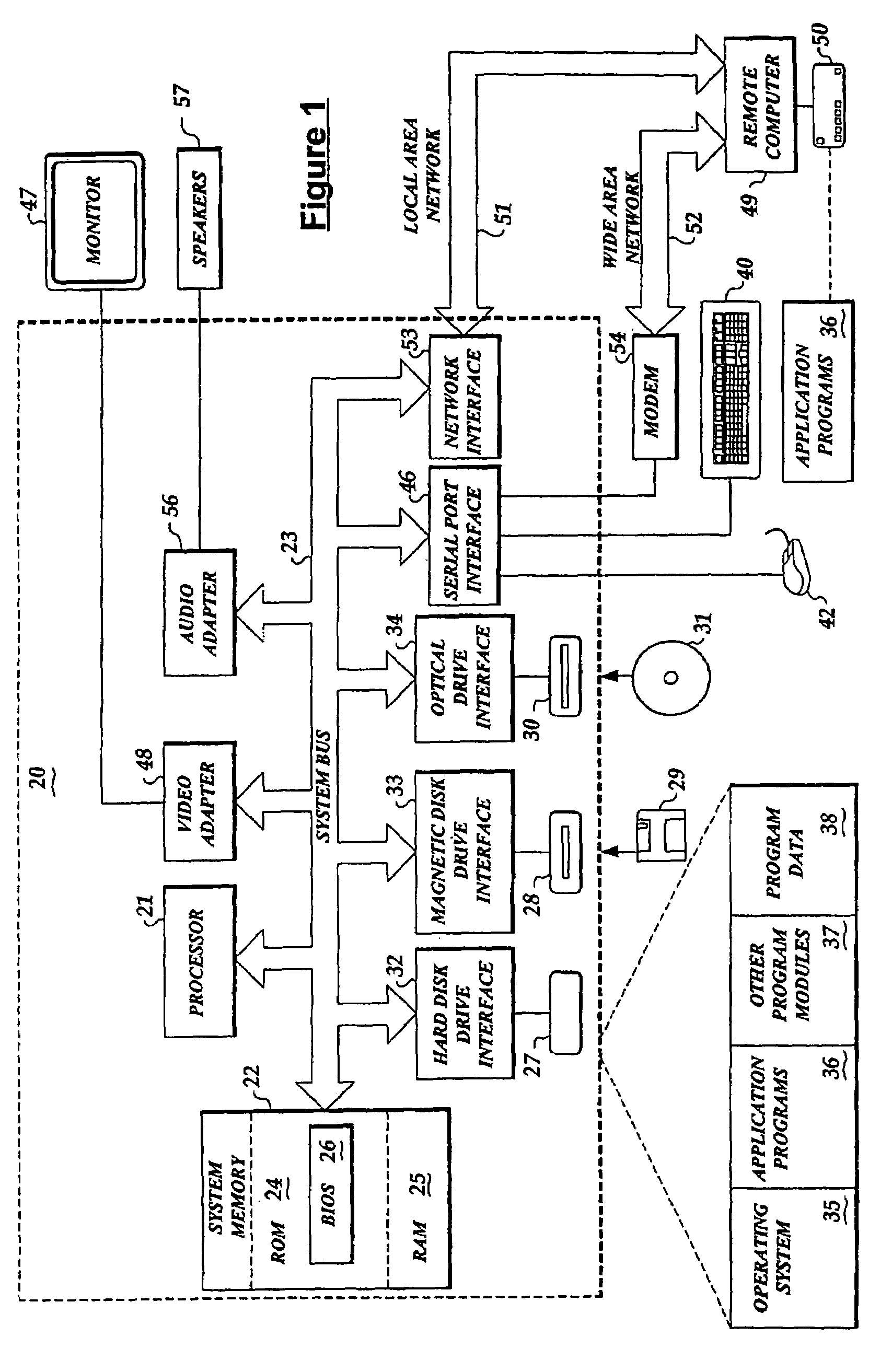

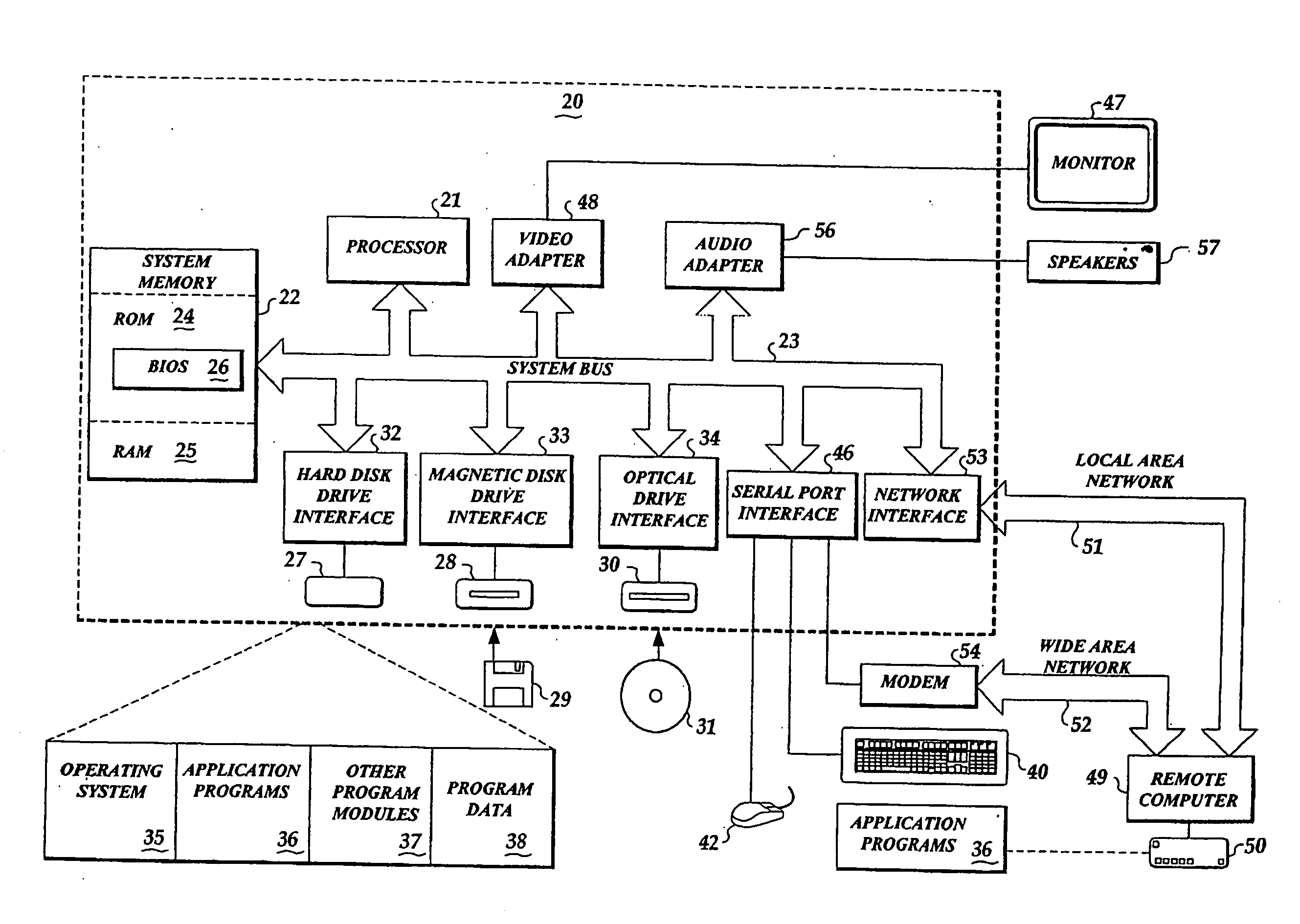

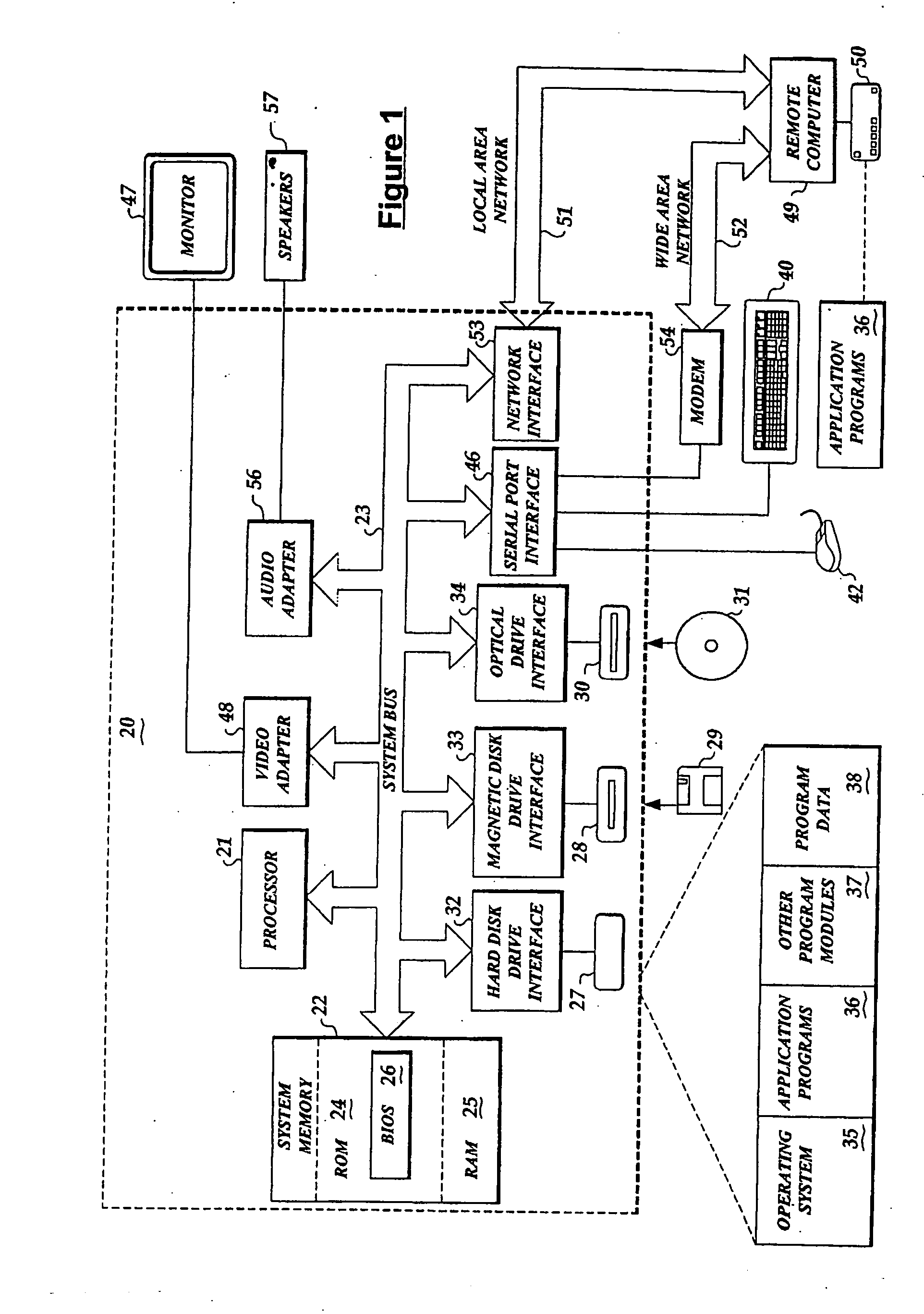

Method and system for real time scheduler

InactiveUS20050229179A1Facilitates real-time schedulingSpeed of execution of operatingProgram initiation/switchingResource allocationTime scheduleNon-maskable interrupt

Methods and computer-executable components for real-time scheduling of CPU resources are disclosed. A performance counter determines when to allocate CPU resources to a thread. When it is time to allocate the CPU resources, the performance counter issues a maskable or non-maskable interrupt to an advanced programmable interrupt controller (APIC). The APIC then issues a maskable non-maskable interrupt to the CPU. In response to receiving the non-maskable interrupt, the CPU allocates resources to the thread. In addition, the disclosed methods and computer-executable components also: (a) allow scheduling of CPU resources such that real-time threads are guaranteed respective portions of time slots, (b) enable real-time scheduling on a non-real-time operating system, and (c) provide scheduling of CPU resources on a uni-processor machine such that at least first and second real-time threads dependent on one another are synchronized.

Owner:MICROSOFT TECH LICENSING LLC

Clock Gating System and Method

ActiveUS20090267649A1Reduce power consumptionReduced footprintPower reduction by control/clock signalGenerating/distributing signalsEngineeringLogic circuitry

A clock gating system and method is disclosed. In a particular embodiment, the system includes an input logic circuit having at least one input to receive at least one input signal and having an output at an internal enable node. A keeper circuit includes at least one switching element that is responsive to a gated clock signal and is coupled to the internal enable node to selectively hold a logical voltage level at the internal enable node. The system further includes a gating element responsive to an input clock signal and to the logical voltage level at the internal enable node to generate the gated clock signal.

Owner:QUALCOMM INC

Method and system for realtime scheduler

InactiveUS6990665B2Facilitates real-time schedulingSpeed of execution of operatingProgram initiation/switchingResource allocationTime scheduleNon real time

Methods and computer-executable components for real-time scheduling of CPU resources are disclosed. A performance counter determines when to allocate CPU resources to a thread. When it is time to allocate the CPU resources, the performance counter issues a maskable or non-maskable interrupt to an advanced programmable interrupt controller (APIC). The APIC then issues a maskable non-maskable interrupt to the CPU. In response to receiving the non-maskable interrupt, the CPU allocates resources to the thread. In addition, the disclosed methods and computer-executable components also: (a) allow scheduling of CPU resources such that real-time threads are guaranteed respective portions of time slots, (b) enable real-time scheduling on a non-real-time operating system, and (c) provide scheduling of CPU resources on a uni-processor machine such that at least first and second real-time threads dependent on one another are synchronized.

Owner:MICROSOFT TECH LICENSING LLC

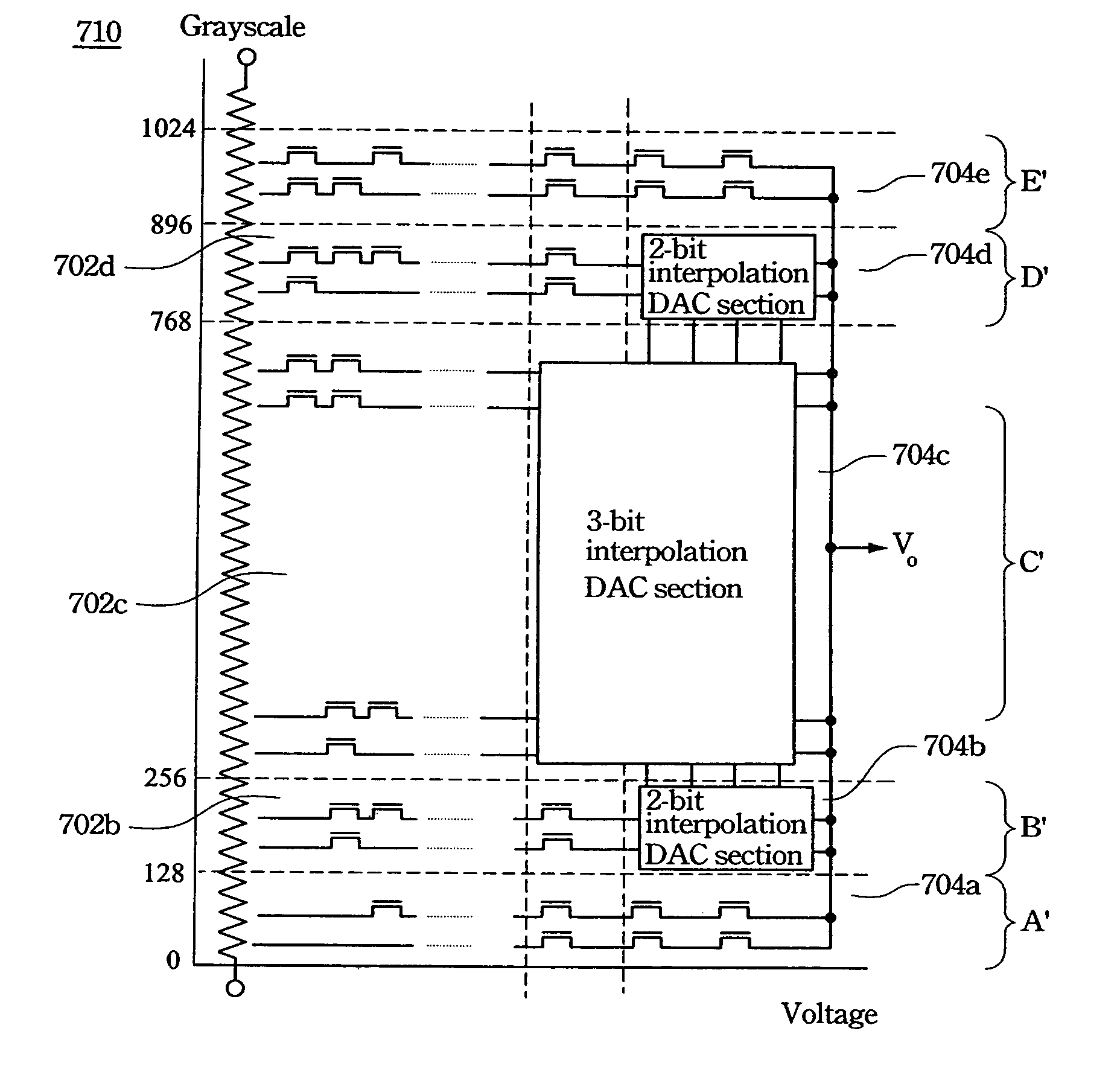

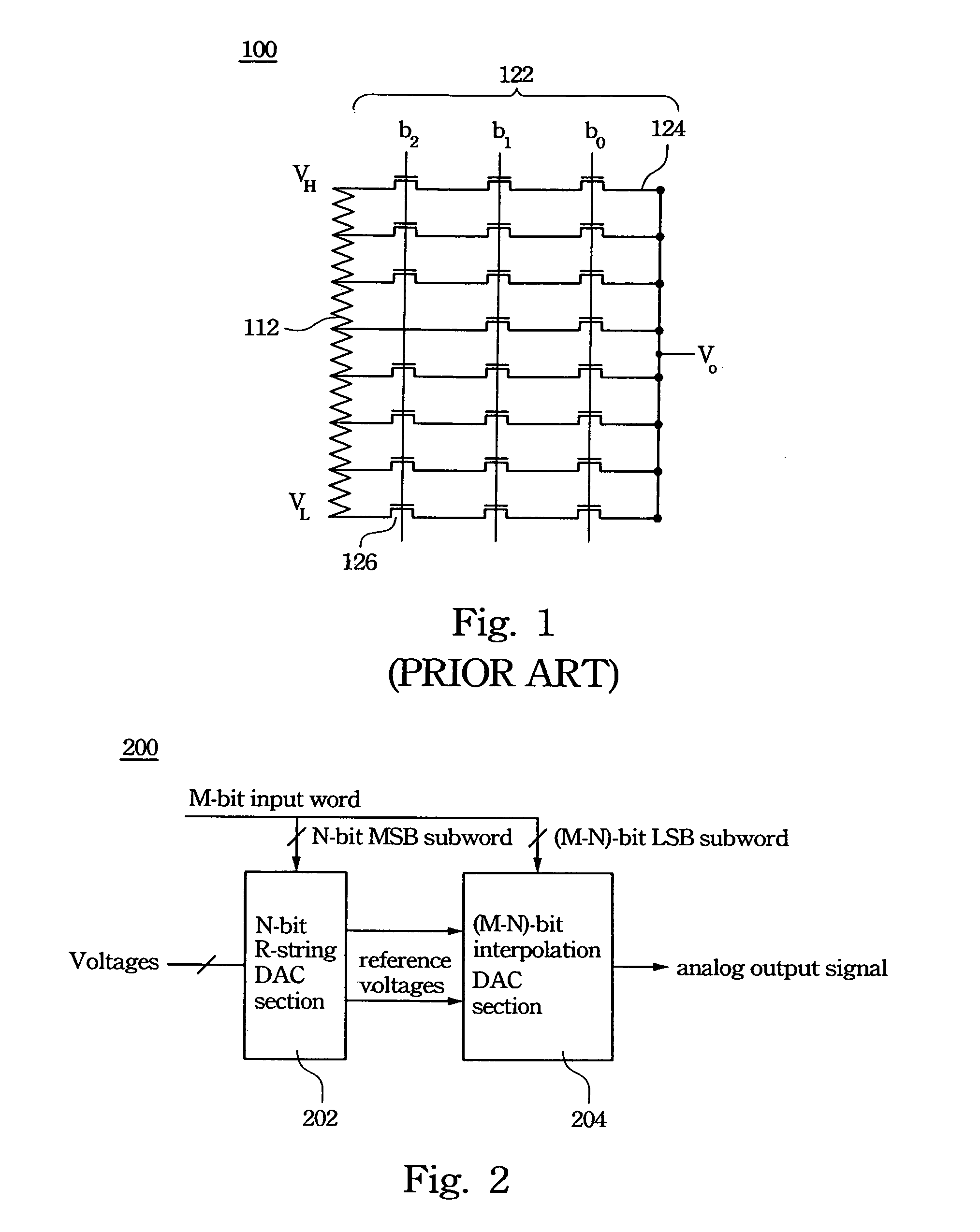

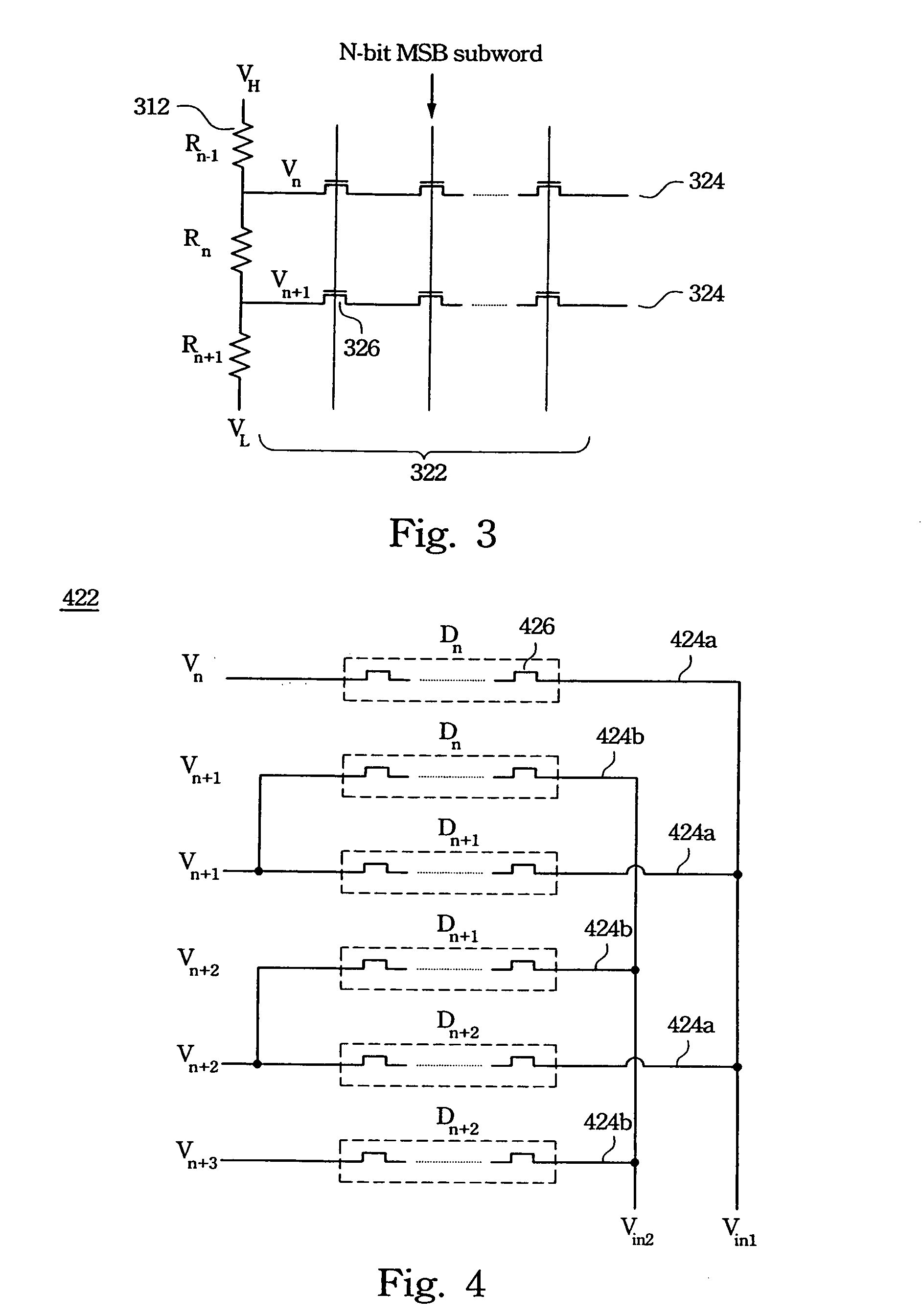

Digital-to-analog converter

ActiveUS7161517B1Reduce loadReduce layout areaElectric signal transmission systemsDigital-analogue convertorsDigital analog converterEngineering

Owner:HIMAX TECH LTD

Method and system for real time scheduler

InactiveUS20050229178A1Facilitates real-time schedulingSpeed of execution of operatingProgram initiation/switchingResource allocationTime scheduleNon-maskable interrupt

Methods and computer-executable components for real-time scheduling of CPU resources are disclosed. A performance counter determines when to allocate CPU resources to a thread. When it is time to allocate the CPU resources, the performance counter issues a maskable or non-maskable interrupt to an advanced programmable interrupt controller (APIC). The APIC then issues a maskable non-maskable interrupt to the CPU. In response to receiving the non-maskable interrupt, the CPU allocates resources to the thread. In addition, the disclosed methods and computer-executable components also: (a) allow scheduling of CPU resources such that real-time threads are guaranteed respective portions of time slots, (b) enable real-time scheduling on a non-real-time operating system, and (c) provide scheduling of CPU resources on a uni-processor machine such that at least first and second real-time threads dependent on one another are synchronized.

Owner:MICROSOFT TECH LICENSING LLC

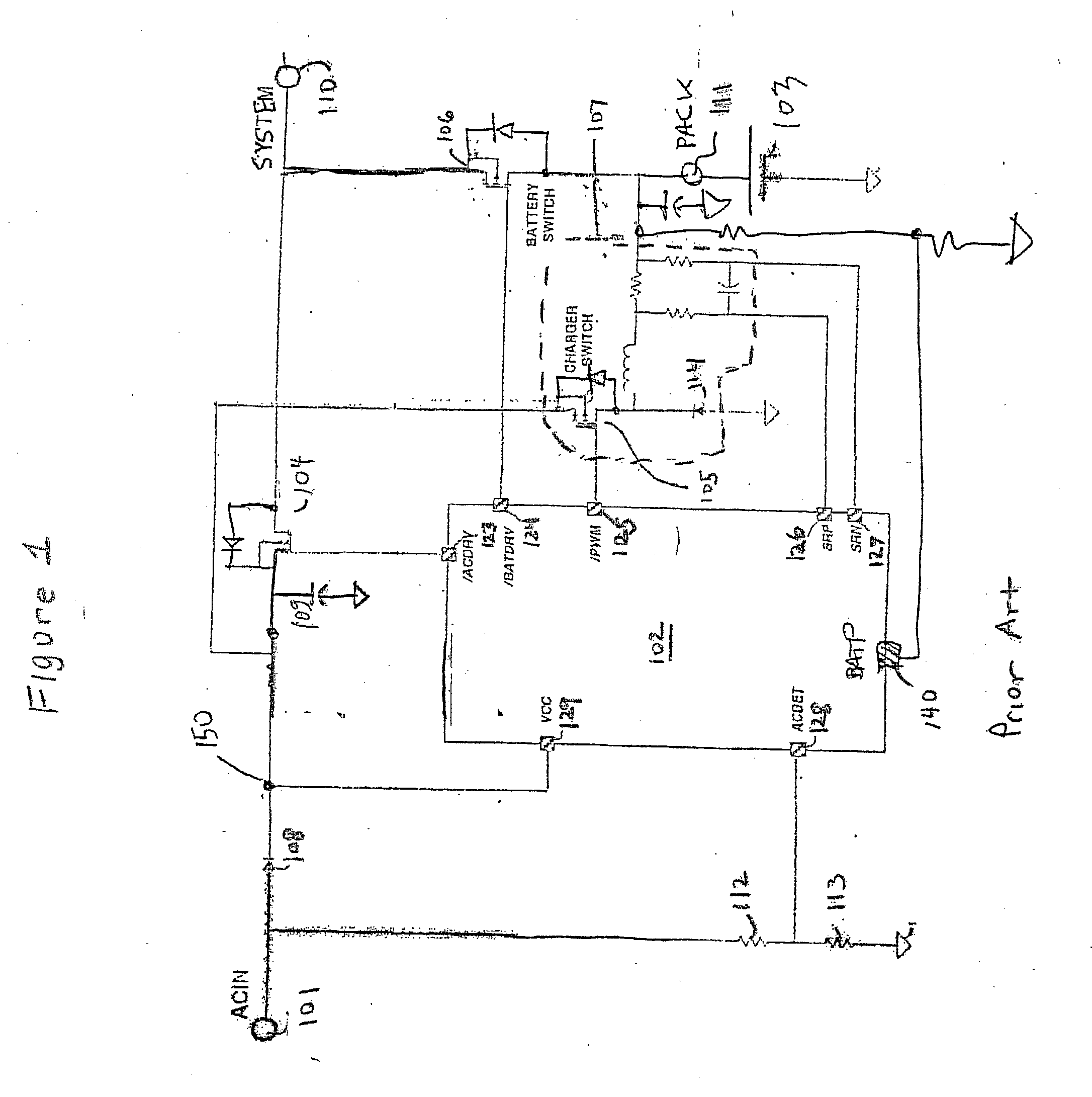

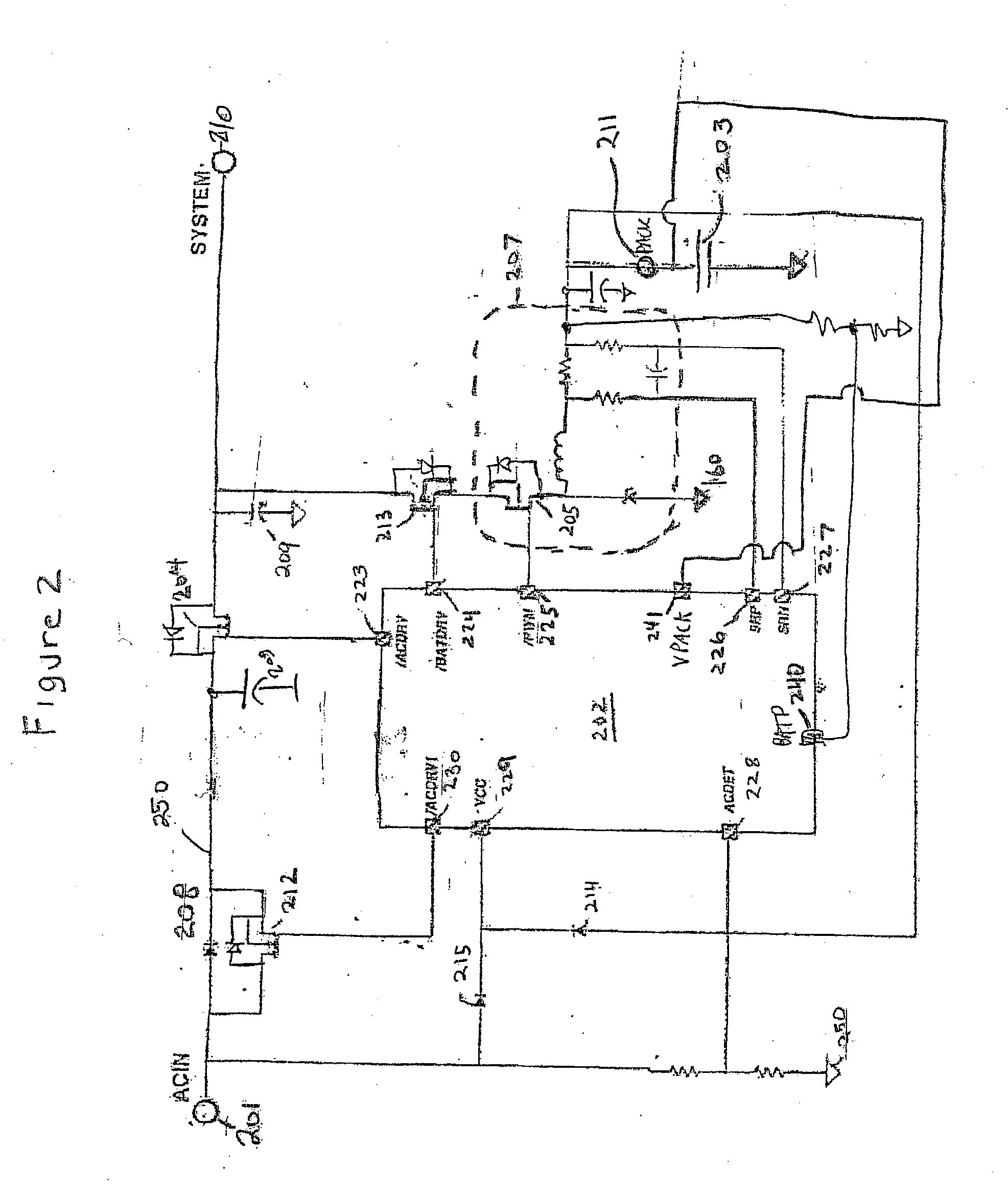

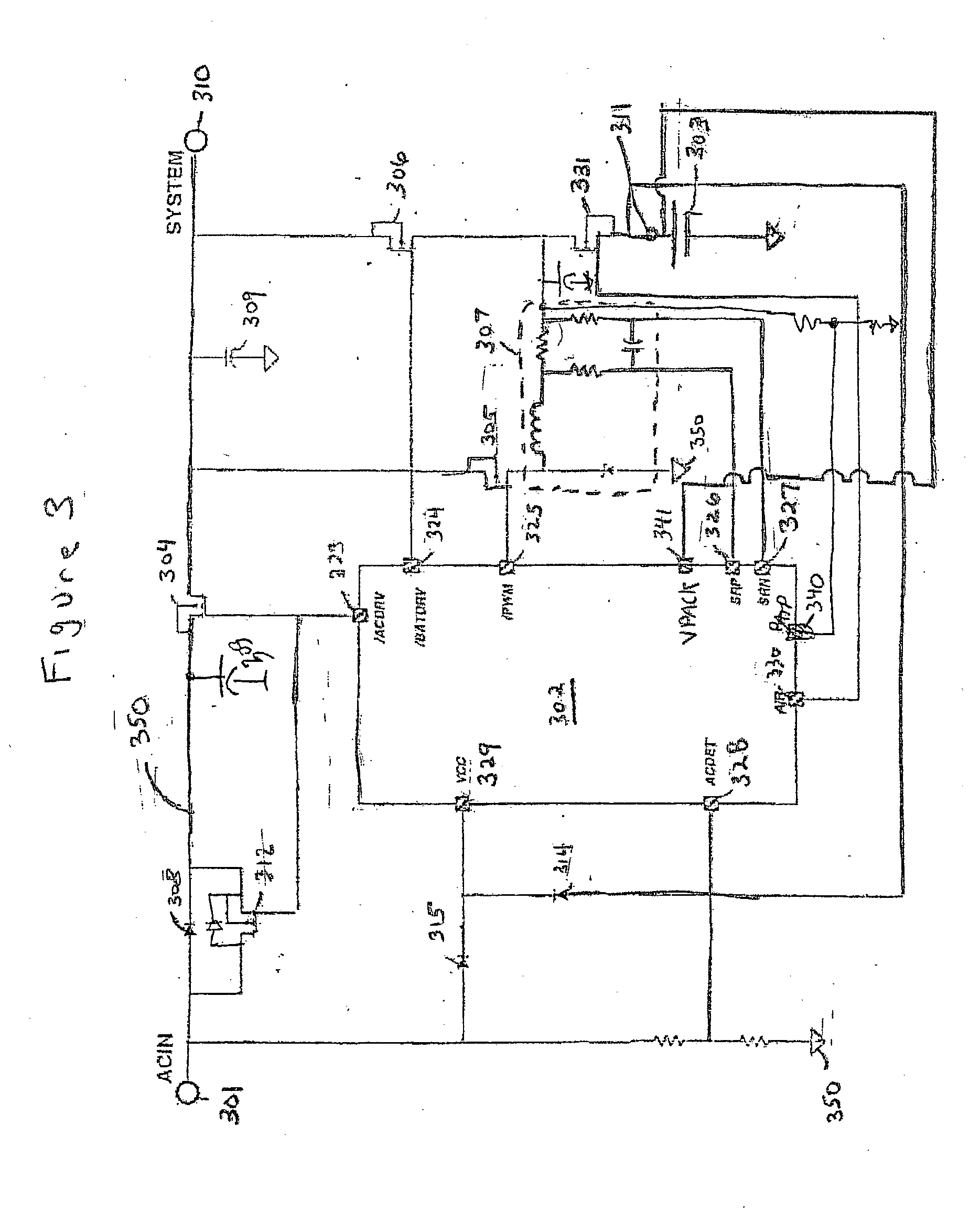

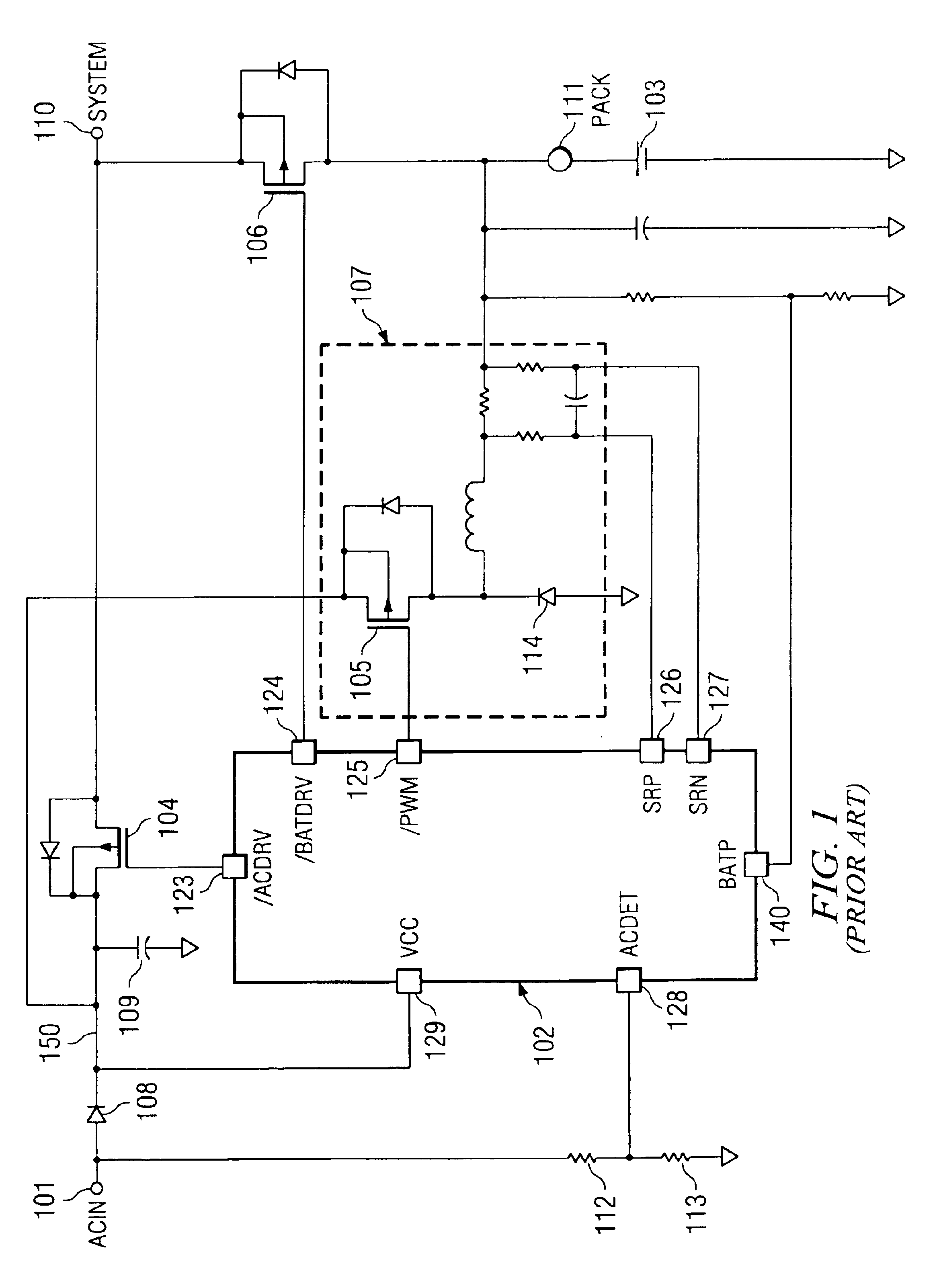

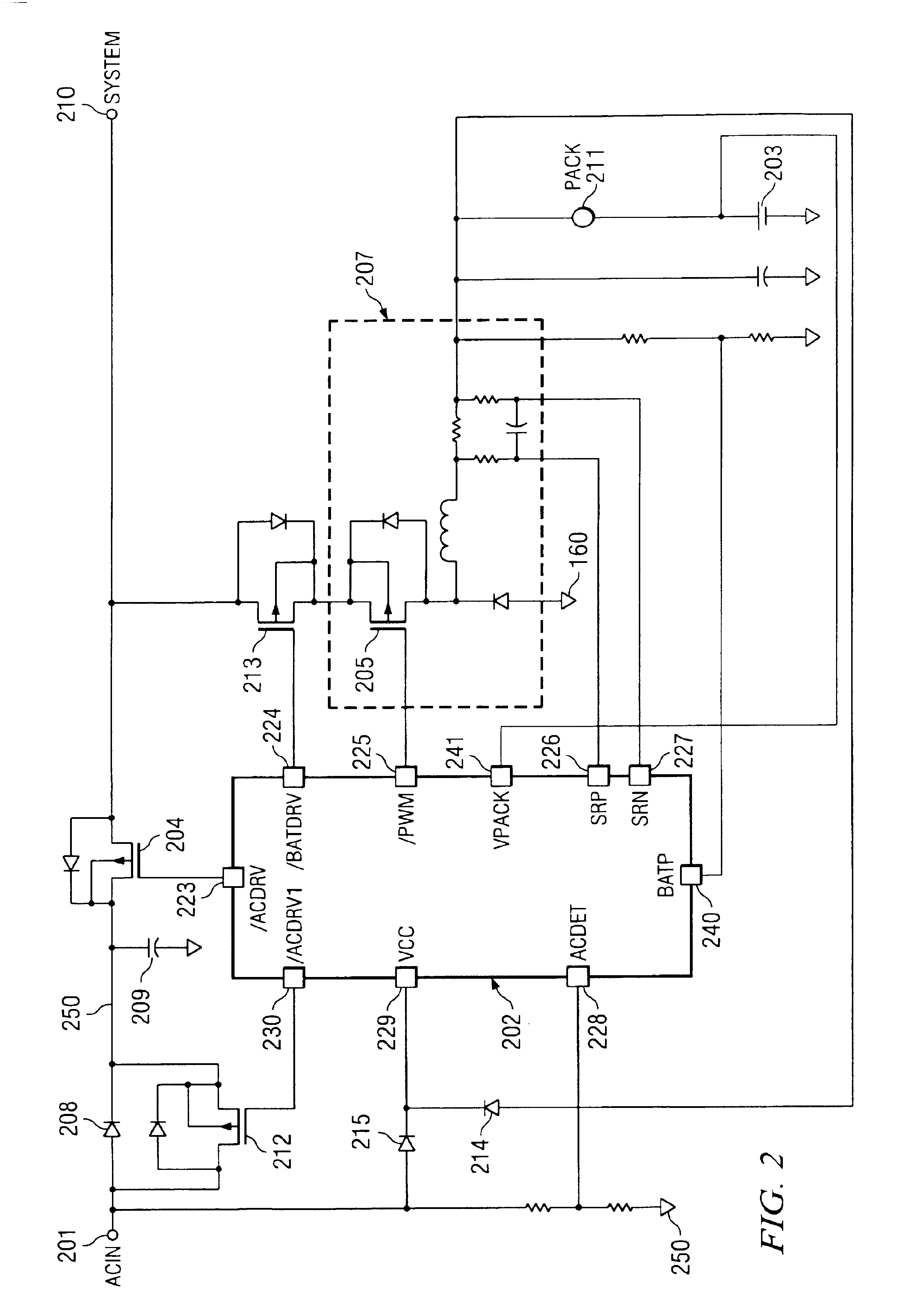

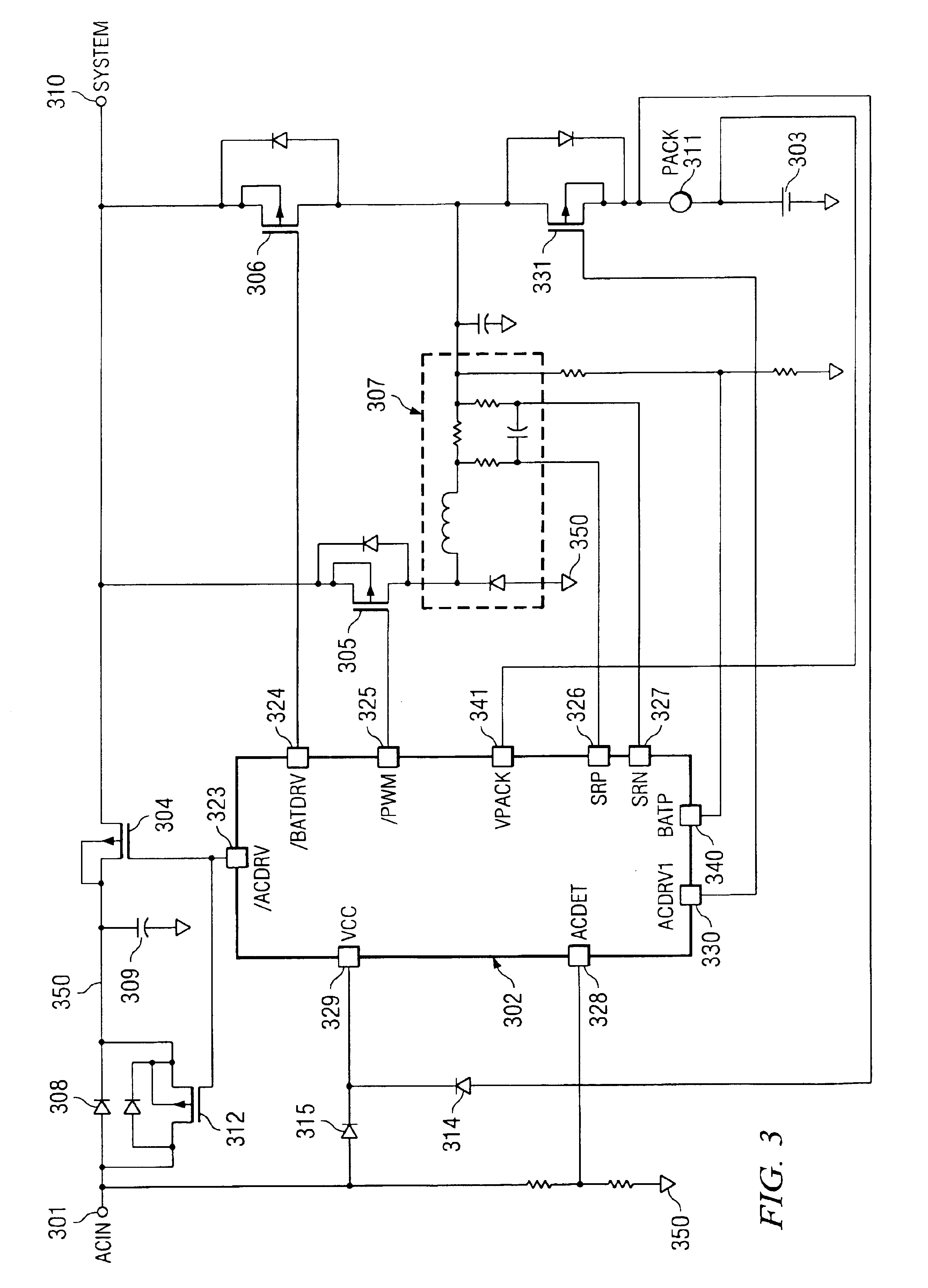

Architecture for switching power source to load in battery powered system

InactiveUS20050017766A1Reduce power consumptionFew switchAc-dc conversion without reversalVolume/mass flow measurementMicrocontrollerAC adapter

The present invention comprises a combination of a new circuit topology utilizing microcontroller (202, 302) and a modified logic control circuit which enables the replacement of a Schottky diode, commonly used in series with AC adapter, by a MOS transistor switch (212, 312) to implement airline mode operation of a system, with the added benefits of more efficient power dissipation and minimization of sparking or arcing at the power input terminal.

Owner:TEXAS INSTR INC

Architecture for switching between an external and internal power source

InactiveUS6969972B2Reduce power consumptionFew switchAc-dc conversion without reversalVolume/mass flow measurementMicrocontrollerAC adapter

The present invention comprises a combination of a new circuit topology utilizing microcontroller (202, 302) and a modified logic control circuit which enables the replacement of a Schottky diode, commonly used in series with AC adapter, by a MOS transistor switch (212, 312) to implement airline mode operation of a system, with the added benefits of more efficient power dissipation and minimization of sparking or arcing at the power input terminal.

Owner:TEXAS INSTR INC

Novel multi-level converter topology with the possibility of dynamically connecting individual modules in series and in parallel

ActiveUS20150077069A2Lower internal resistanceKeep energy smallElectric variable regulationDc-ac conversion without reversalComputer moduleComputer terminal

The present invention describes an electrical converter system for power supply systems, comprising at least two identical individual modules connected consecutively, characterised in that each individual module have at least four internal switching elements, at least one energy storage element and at least four connectors, wherein the connectors are paired and serve as a first and a second terminal pair; the internal switching elements of each individual module are designed in such manner that they are able to selectively connect one or both connectors of each terminal pair to the energy storage element; the cascaded connection of at least two individual modules is made in such manner that the connectors in the second terminal pair of a preceding individual module are each connected to the connectors of the first terminal pair in the respective following individual module, and at least one terminal of the first terminal pair of the first individual module of the cascaded connection and at least one terminal of the second terminal pair of the last individual module of the cascaded connection serve as terminals for the cascaded connection; and wherein the switching elements of the respective individual modules in the cascaded connection of at least two individual modules connect their respective energy storage element to the terminals of the cascaded connection in such manner that a selective serial or parallel connection of the energy storage elements is made.

Owner:TECH UNIV MUNCHEN

Multiprocessing transaction recovery manager

InactiveUS8499298B2Quantity minimizationMaximizes timeDigital data information retrievalSpecial data processing applicationsResource managementApplication software

Owner:INT BUSINESS MASCH CORP

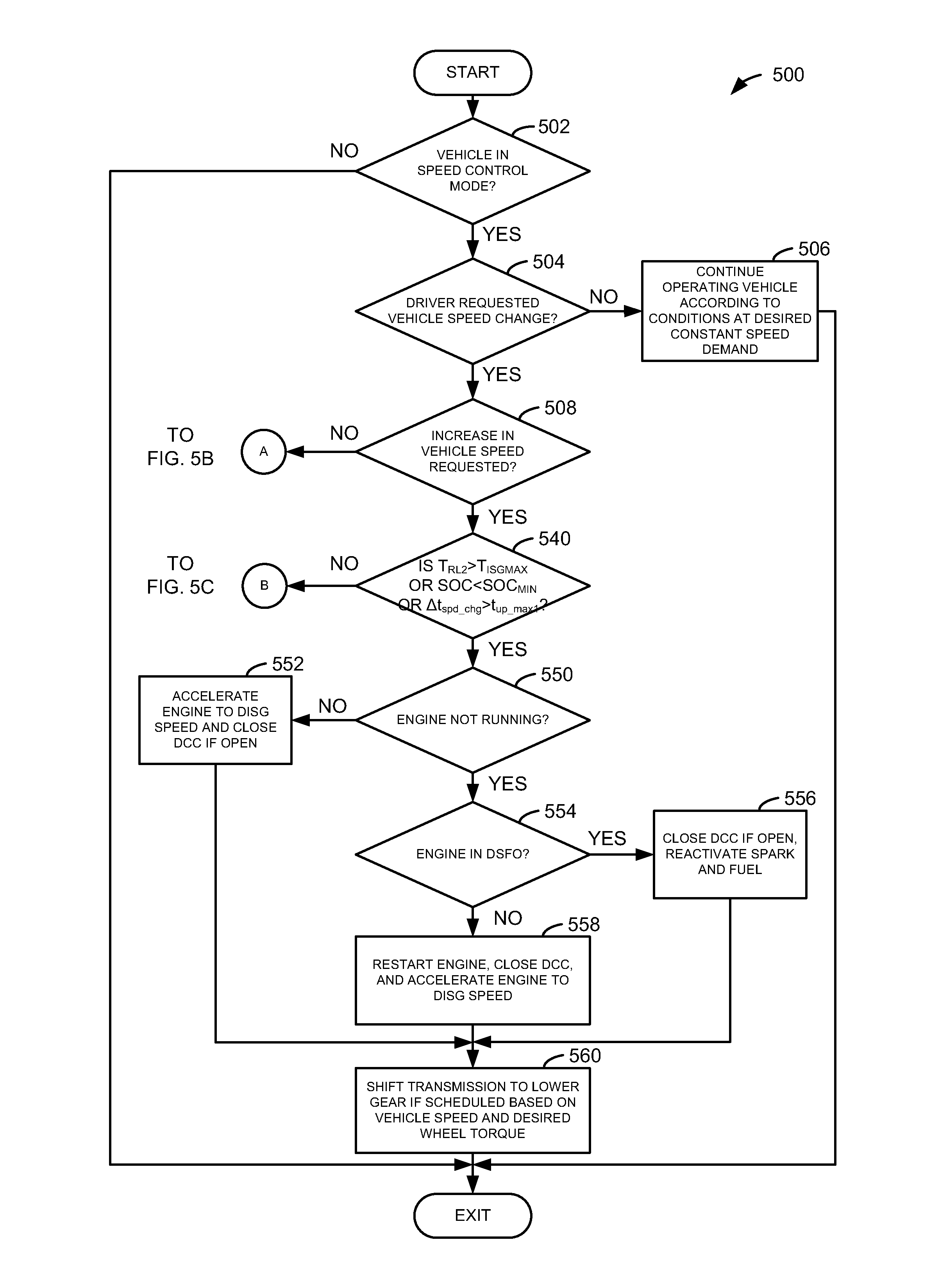

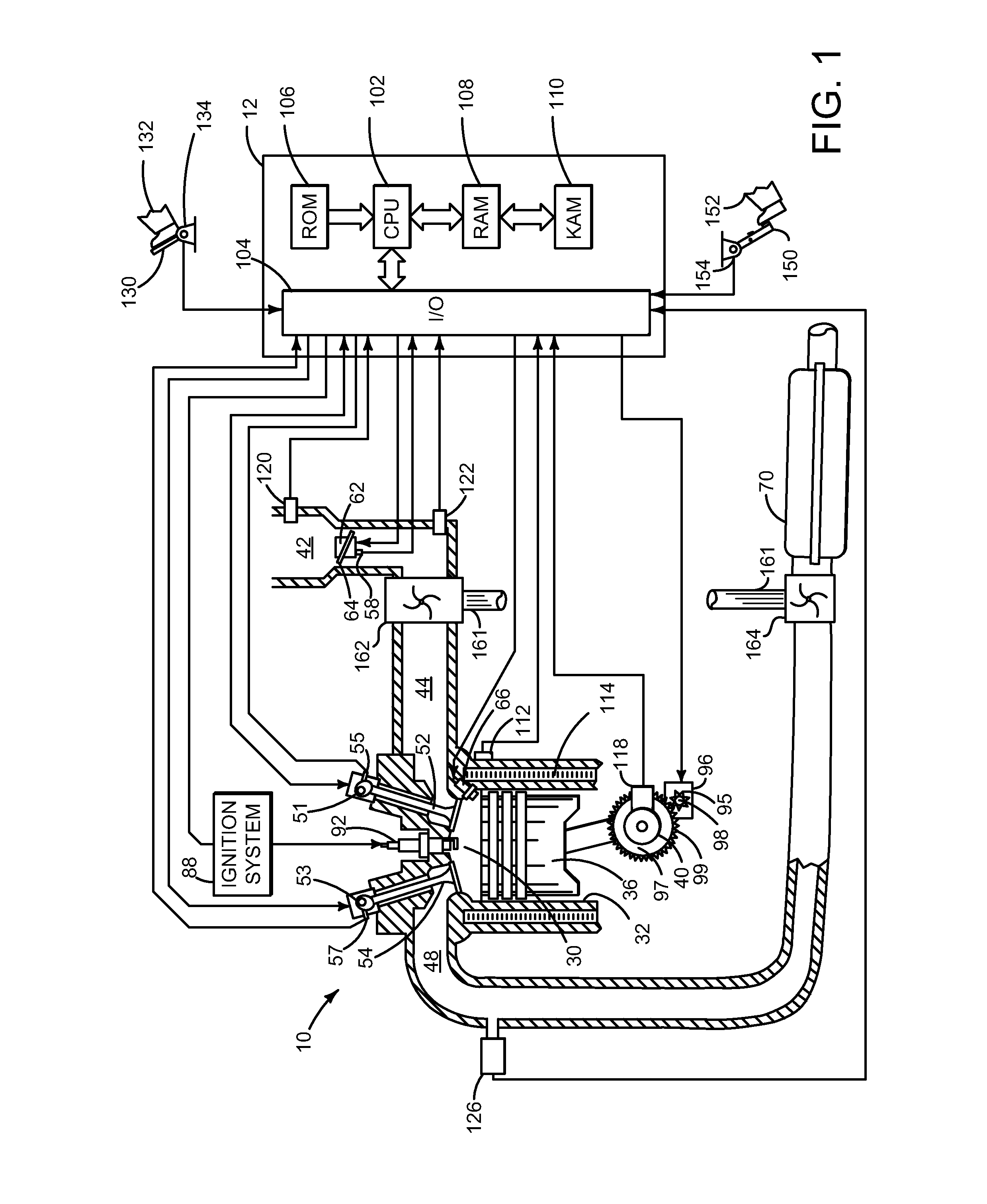

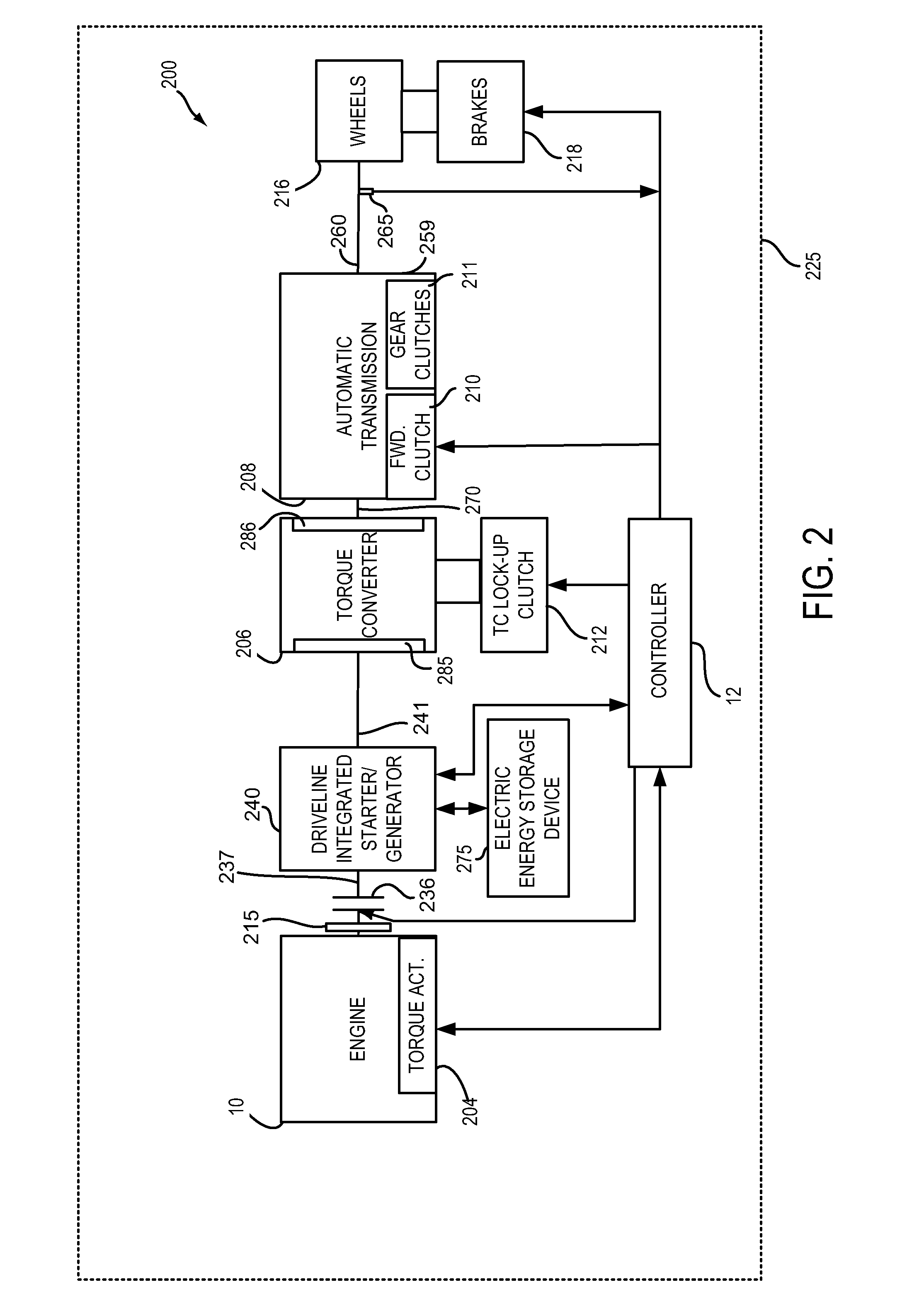

Methods and system for operating a hybrid vehicle in cruise control mode

ActiveUS20160114792A1Improve efficiencyReduced durabilityHybrid vehiclesDigital data processing detailsCruise controlMode change

Systems and methods for reducing driveline mode change busyness for a hybrid vehicle are presented. The systems and methods may delay a driveline mode change in response to a time since a change from a first desired vehicle speed to a second vehicle speed, or alternatively, driveline mode changes may be initiated in response to an estimated time to change from the first desired vehicle speed to the second desired vehicle speed.

Owner:FORD GLOBAL TECH LLC

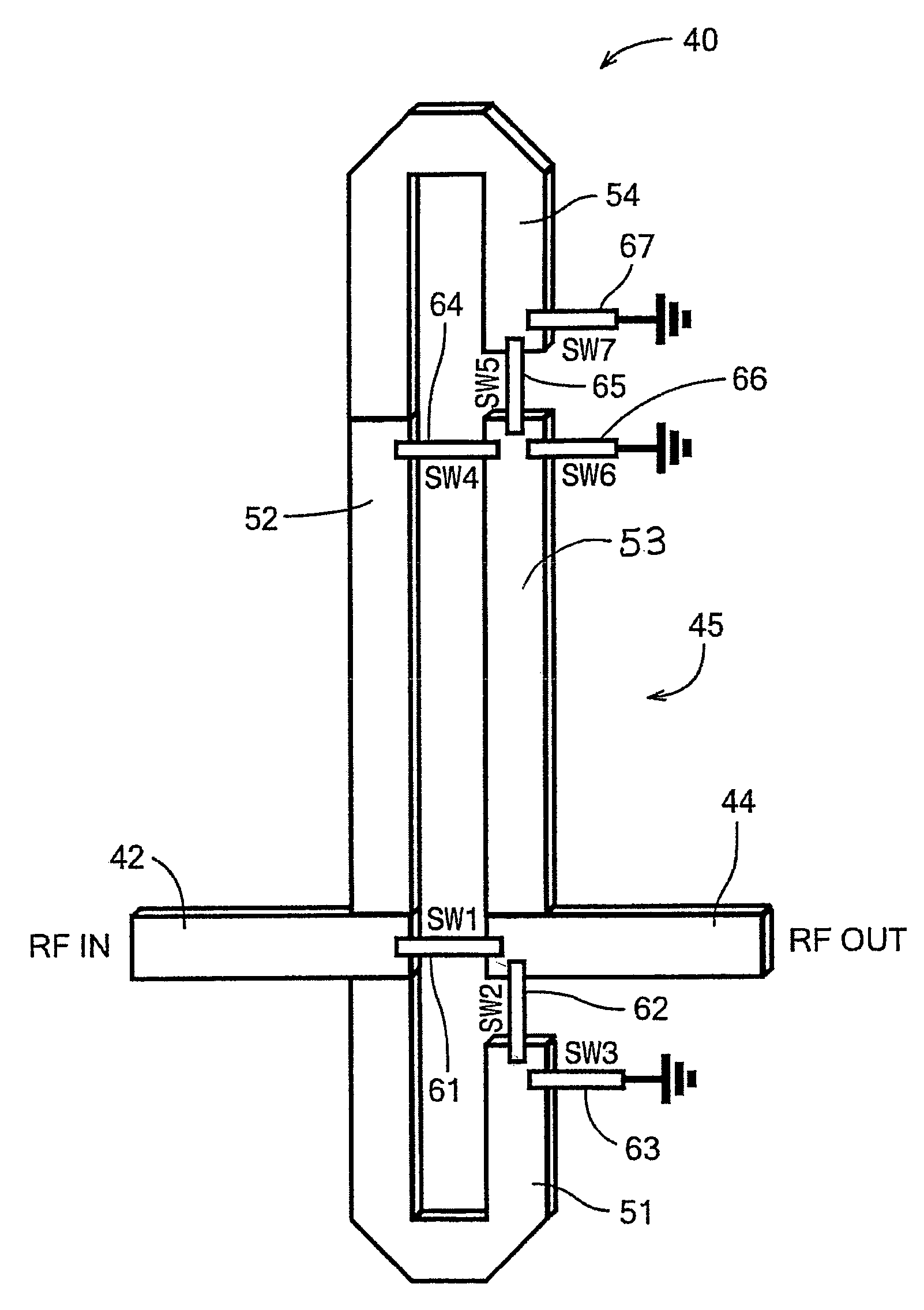

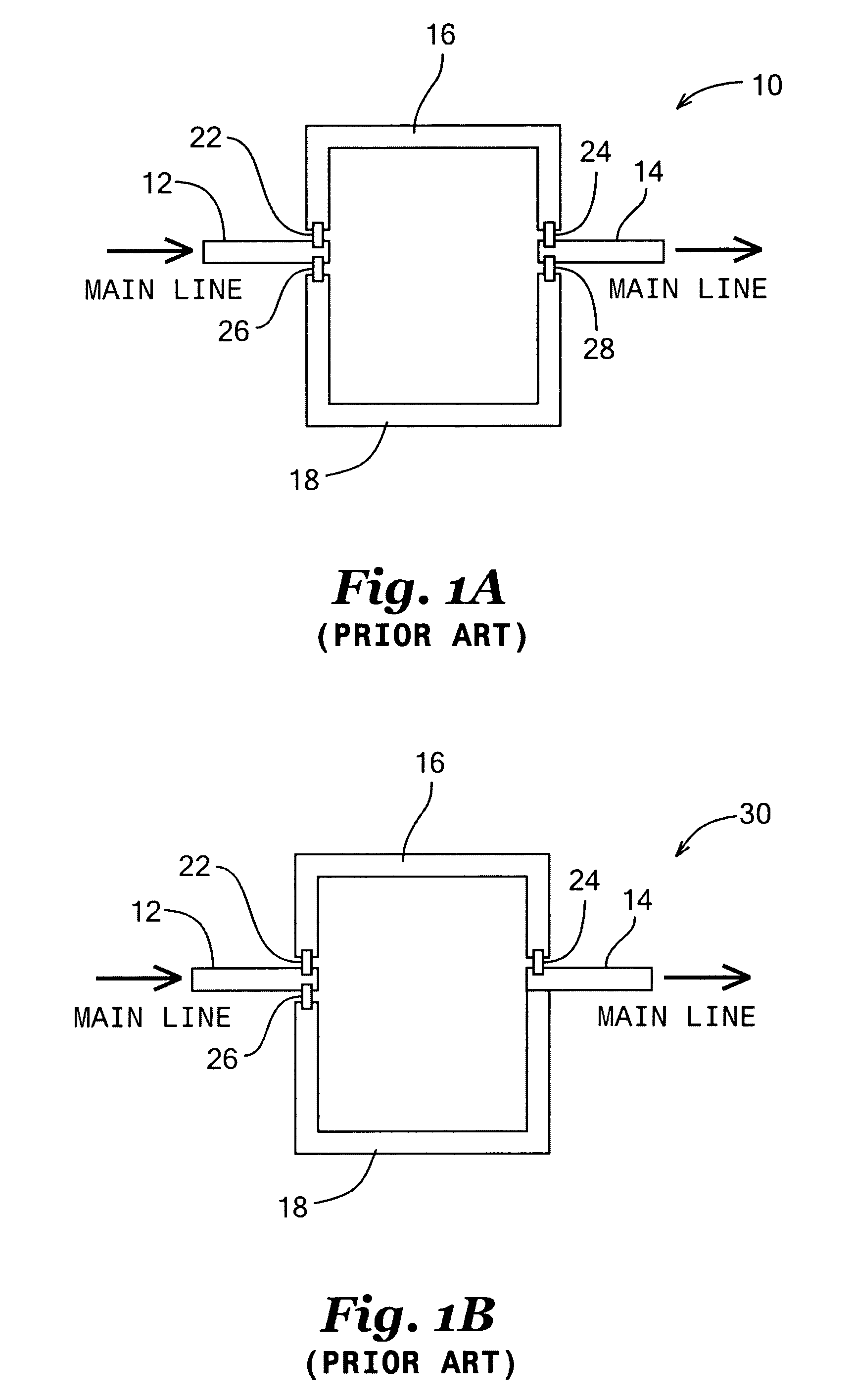

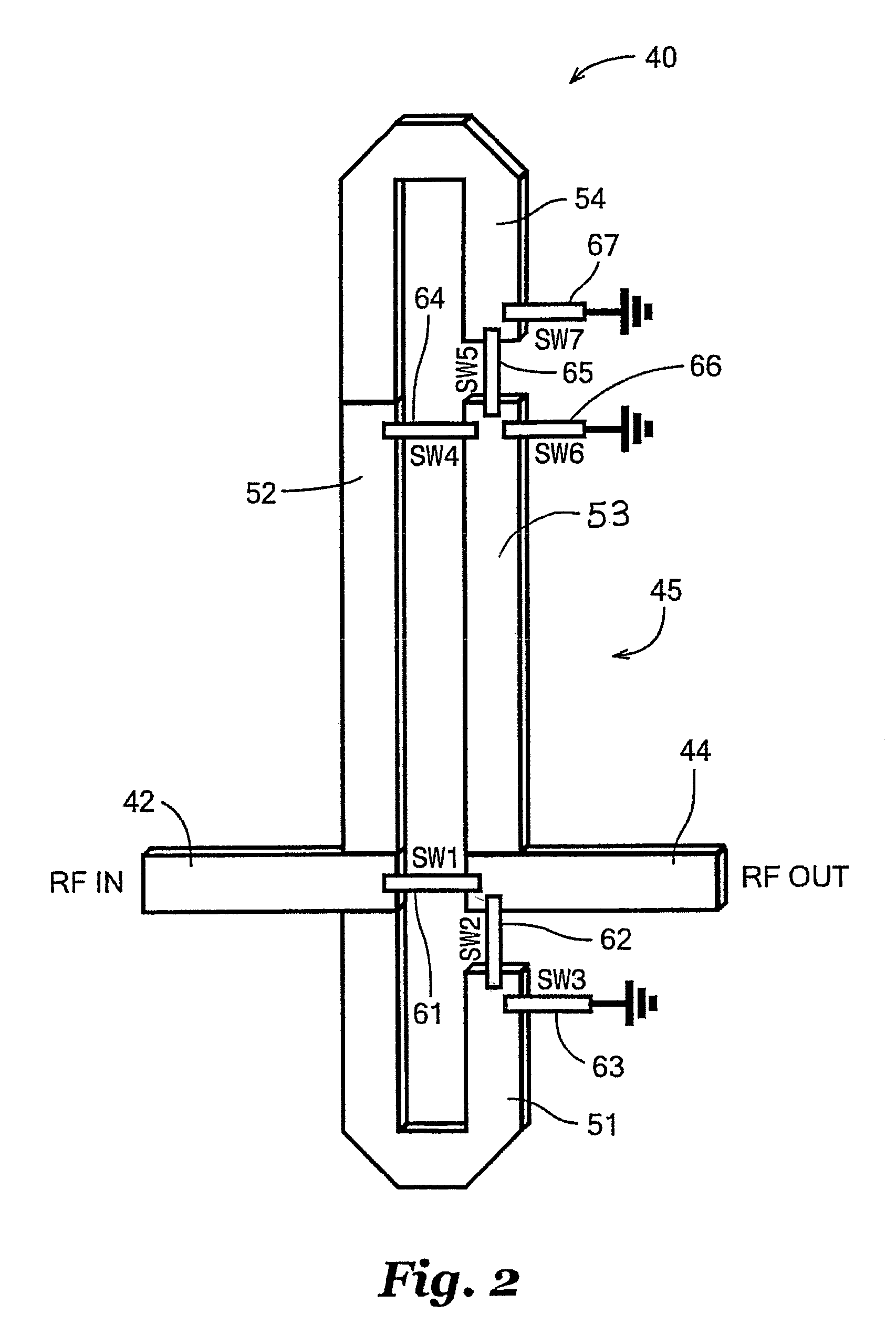

Phase shifter providing multiple selectable phase shift states

InactiveUS7315225B2Small sizeReduced insertion lossMultiple-port networksDelay linesPhase shiftedLength wave

A single-structure, two-bit phase shifter useful for steering the beam of an antenna such as an aeronautical antenna. The phase shifter includes an input line, an output line, a plurality of switched lines such as quarter-wavelength microstrip lines connected directly or indirectly between the input line and the output line, and a plurality of switches for selectively and controllably connecting one or more of the switched lines between the input line and the output line. The phase shifter controllably connects one or more of the switched lines in series between the input line and the output line, thus providing phase shifts of an input radio frequency (RF) signal between one of four discrete phase shift amounts. Using up to three quarter-wavelength switched lines, the phase shifter provides phase shifts in increments of ninety degrees, e.g., phase shifts of zero, ninety, one hundred eighty, and two hundred seventy degrees (0°, 90°, 180°, and 270°). The inventive phase shifter is formed as a single two-bit structure, rather than two one-bit structures; thus it has a relatively smaller size than conventional two-bit phase shifters. Also, the inventive two-bit phase shifter may be configured such that the input signal passes through only one closed switch in any phase shift configuration, which reduces the overall insertion loss by reducing the insertion loss caused by passing the input signal through multiple switches.

Owner:EMS TECH CANADA

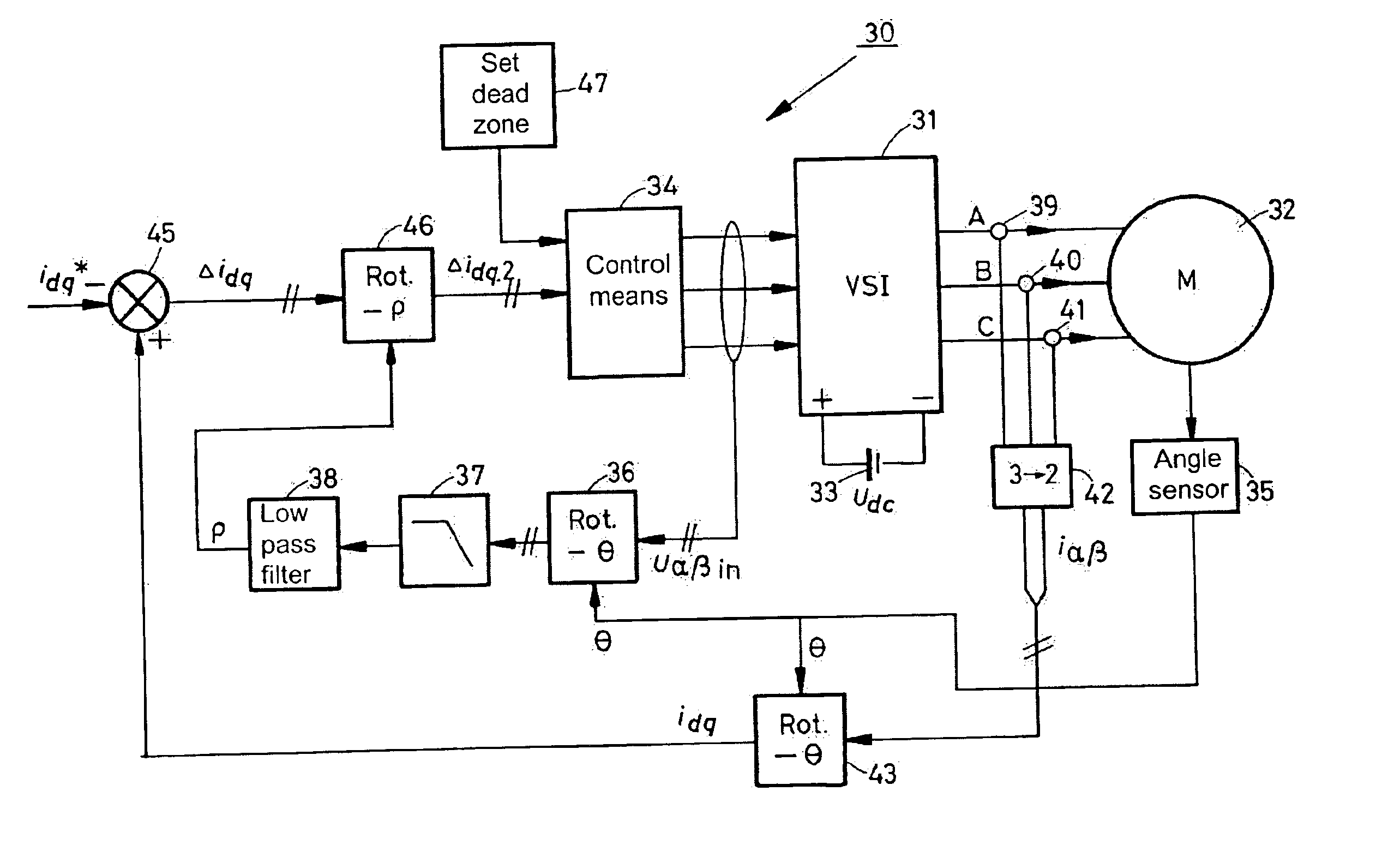

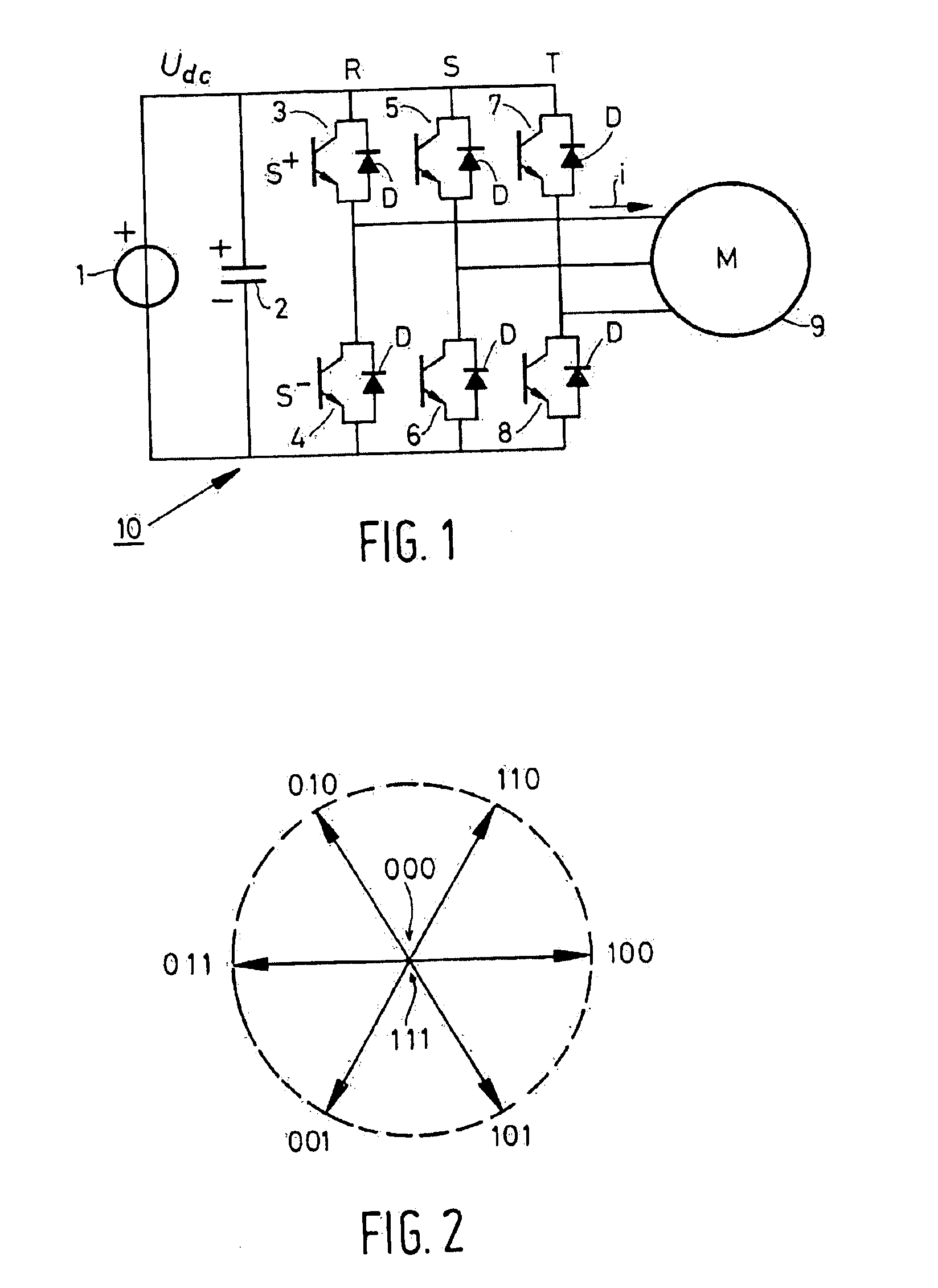

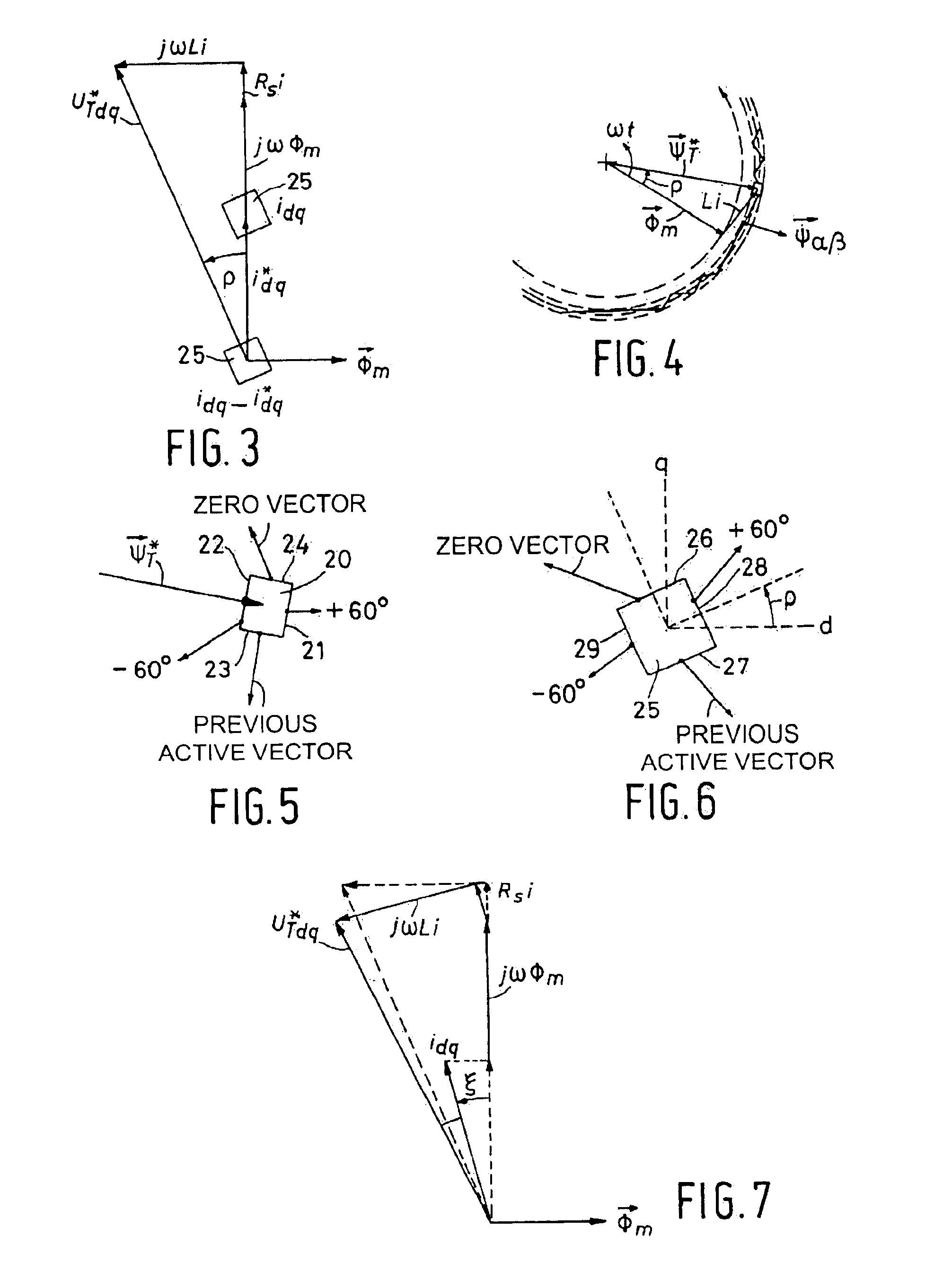

Method and device for controlling an electric load connected to a multiphase switchable DC/AC frequency convertor

InactiveUS6864660B2Short timeEasy to implementAC motor controlDC motor speed/torque controlFrequency changerEngineering

A method and a device for realizing an effective value of a quantity to be varied in an electrical load connected to a multi-phase switchable DC / AC frequency convertor comprising a plurality of controllable switches. The value is realized by varying a current or a voltage delivered by the DC / AC frequency convertor through suitable switching of the switches thereof, and wherein the quantity exhibits a load angle which, averaged in time, leads or lags the voltage or current being delivered. The method and / or the device is arranged for carrying out the steps comprising the defining of a dead zone having dimensions that are representative of an allowable amplitude and phase angle deviation in the quantity to be realized; the orienting of the dead zone with respect to the voltage or current delivered by the DC / AC frequency convertor by rotating the dead zone through the load angle in the direction of the delivered voltage or current; and the switching of one or more of the switches on the basis of the manner in which the deviation in the quantity to be realized extends beyond the dead zone, for the purpose of realizing the quantity during operation with an amplitude and phase deviation ranging within the dead zone.

Owner:ENGIE ELECTROPROJECT BV

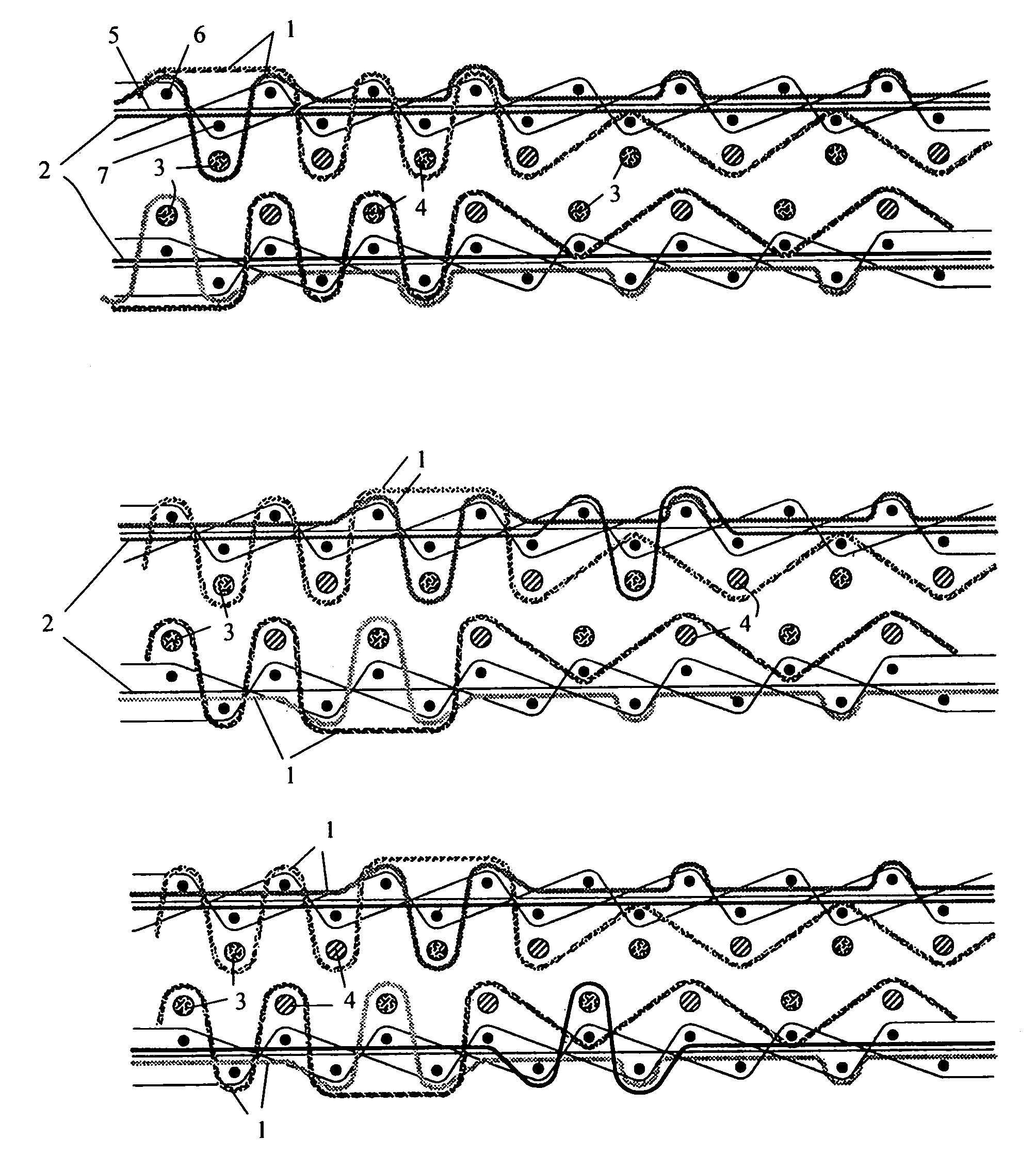

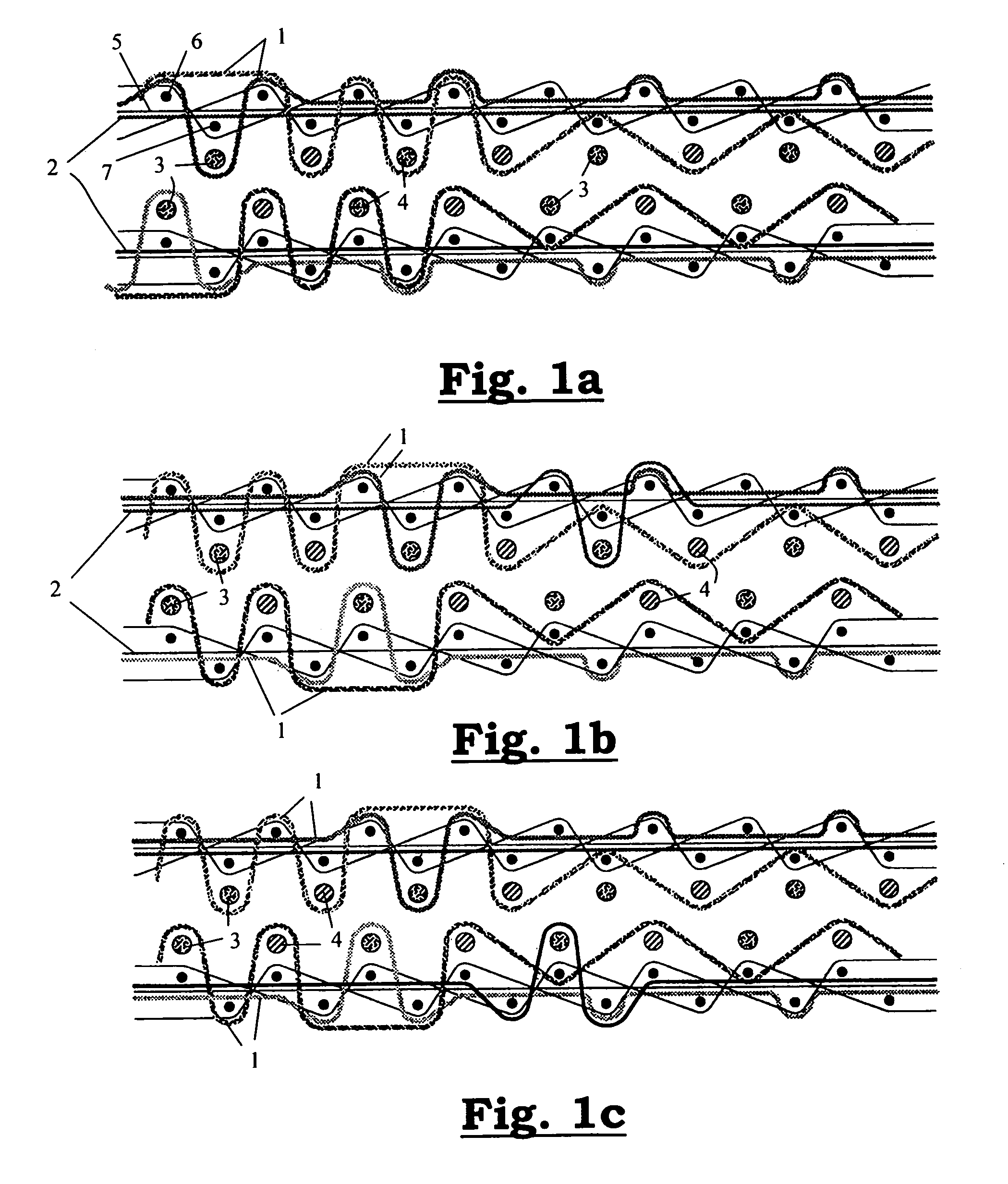

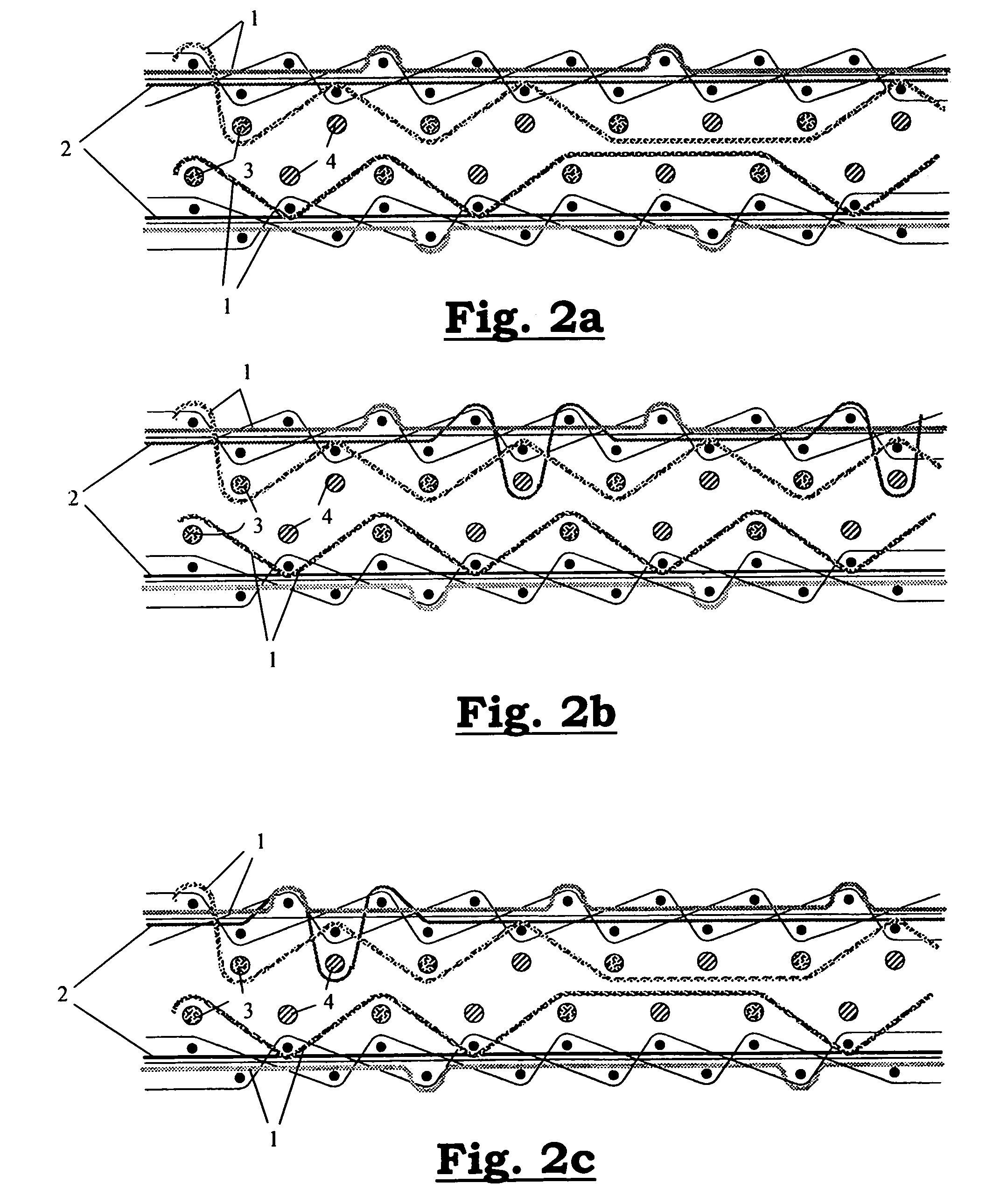

Method for weaving fabrics with areas having a corded structure with a large variety of colour effects

A method for weaving a pile fabric with areas having a corded structure, a backing fabric being woven on a weaving machine by inserting backing weft yarns during successive weft insertion cycles between binding and tension warp yarns, while pattern-weft yarns are inserted outside the backing fabric, and are covered by pile warp yarns forming cords. Successive series of different pattern-weft yarns are inserted into the pile fabric in areas having a corded structure and at least one pattern-weft yarn of each series is running essentially above the warp yarns in a first part of its trajectory and is forming the pattern, and is covered by pile warp yarns essentially forming cords in a second part of its trajectory, so that a predetermined pattern or design is formed. This enables the color palette and / or the effect palette to be modified across the width of the weaving machine with weft effects.

Owner:N V MICHEL VAN DE WIELE

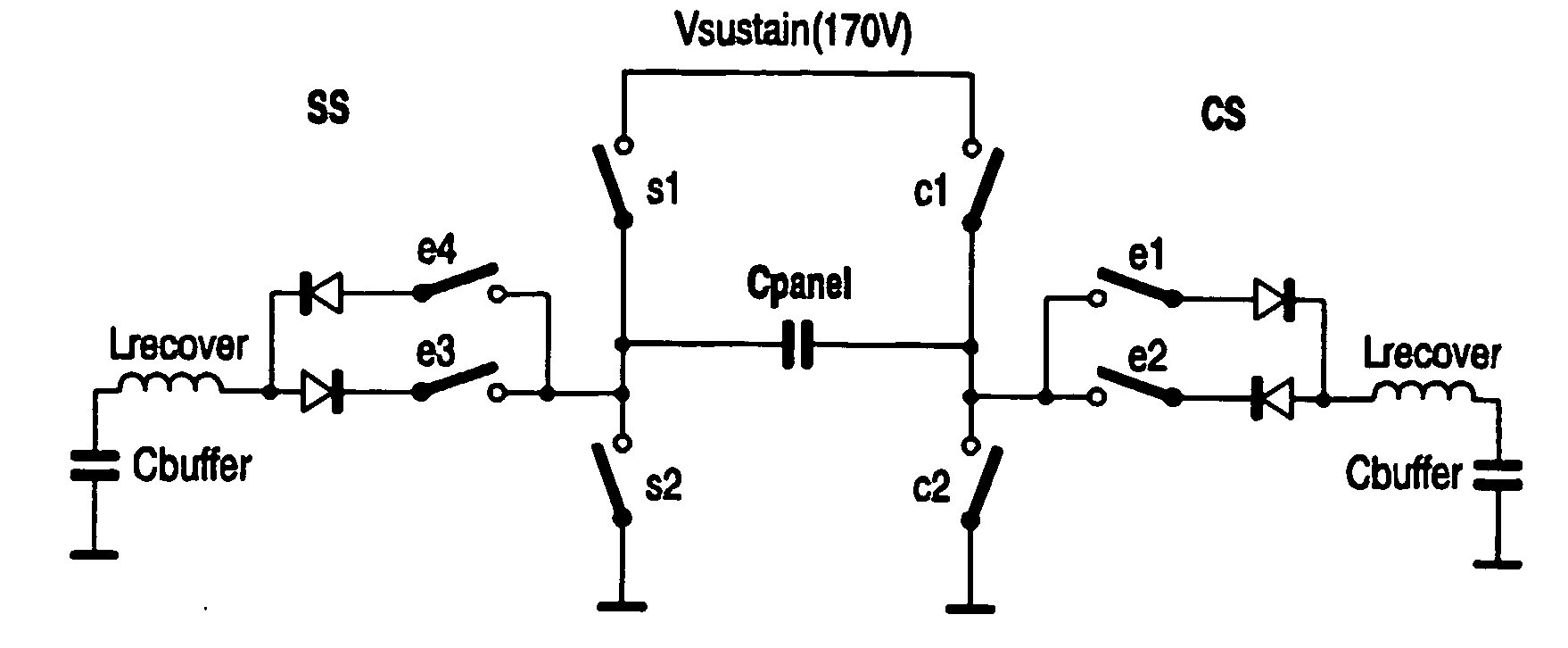

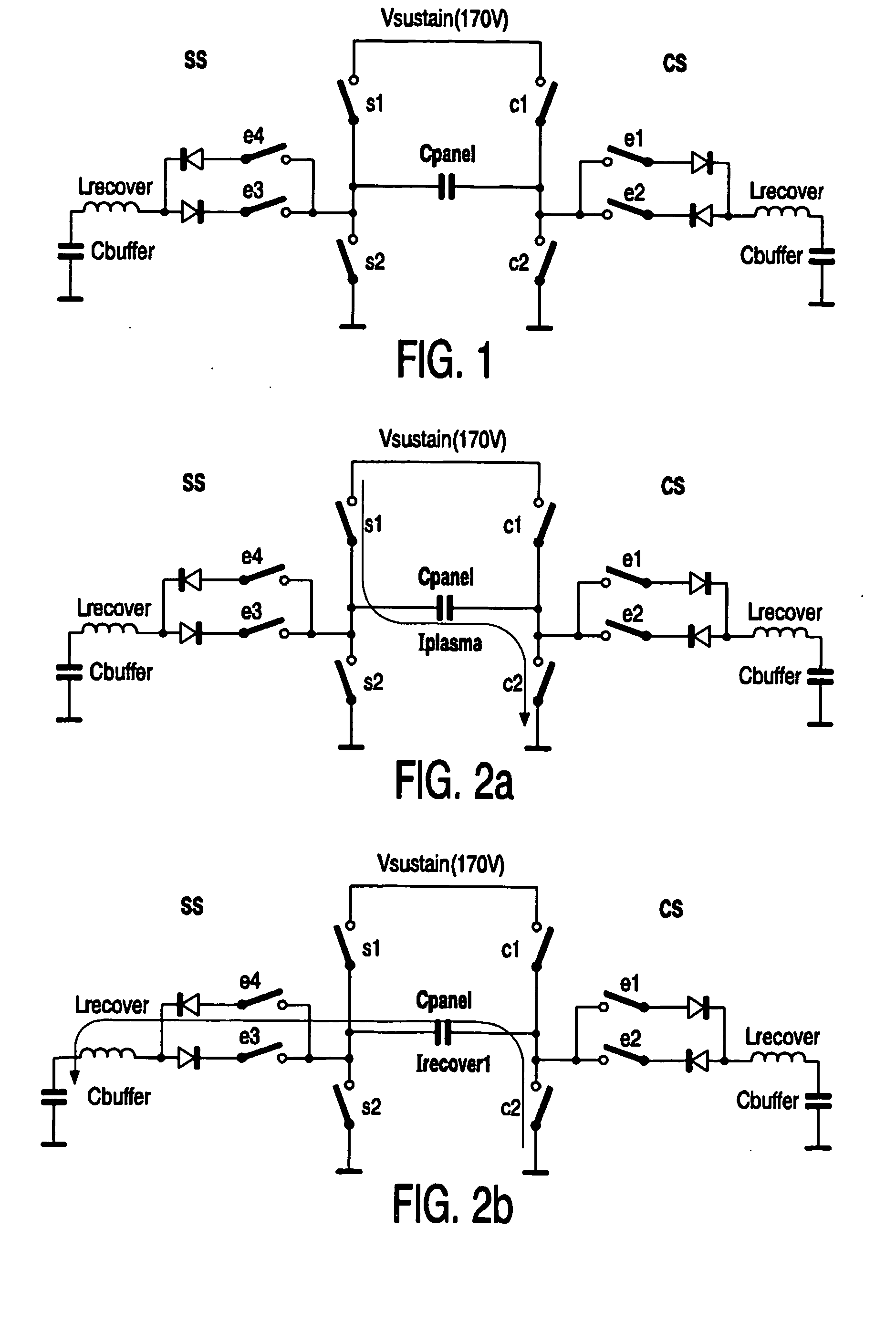

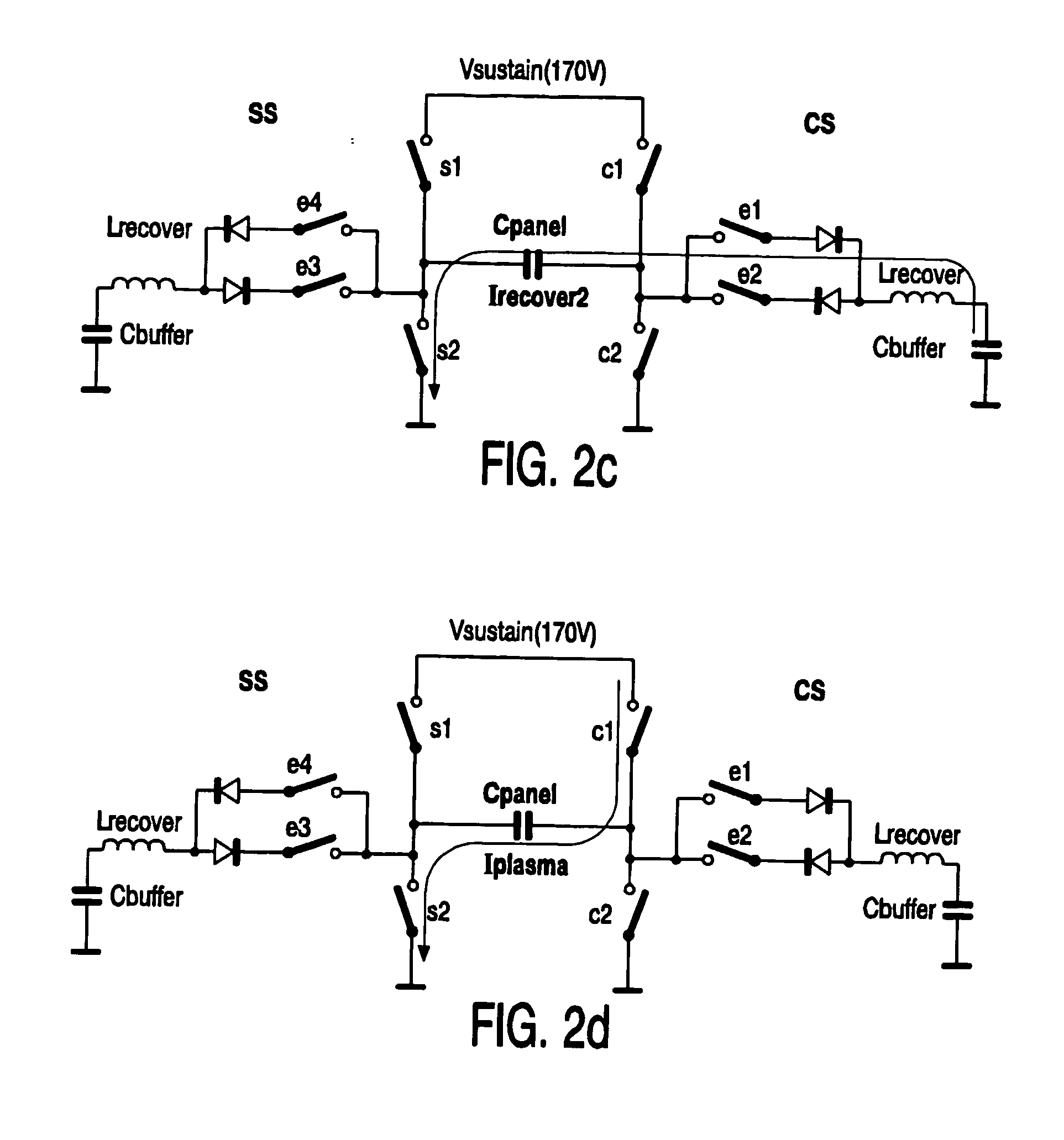

Energy recovery device for plasma display panel

InactiveUS20060250327A1Reduce lossesEasy constructionStatic indicating devicesEnergy recoveryEngineering

Disclosed is an energy recovery device for recovering energy in a display panel, in particular a plasma display panel, wherein an energy recovery storing unit (Lrecover) is coupled with the display panel during an energy recovery period following a sustain period. The particularity of the invention is that the energy recovery recover storing unit (Lrecover) is charged in said sustain step.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

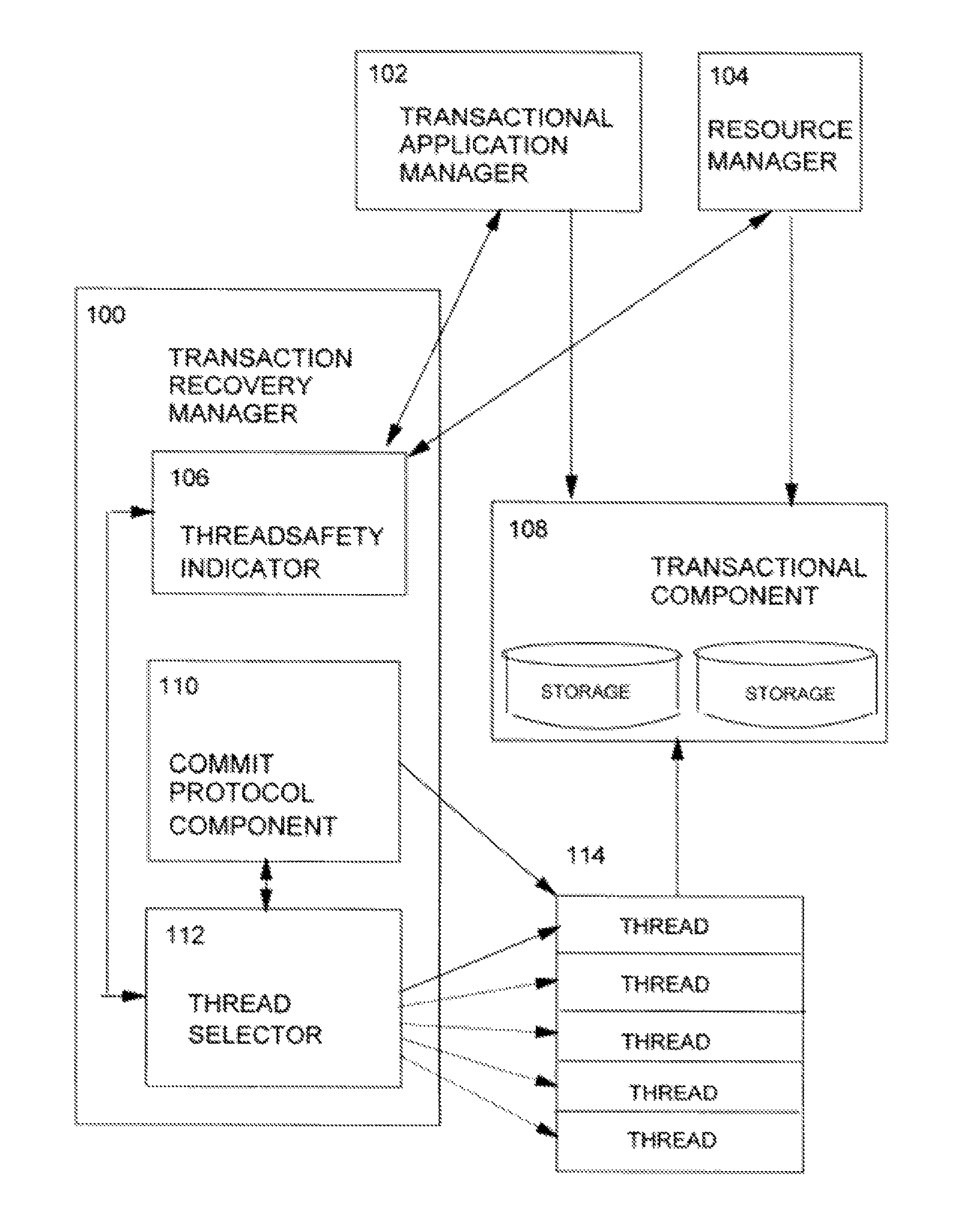

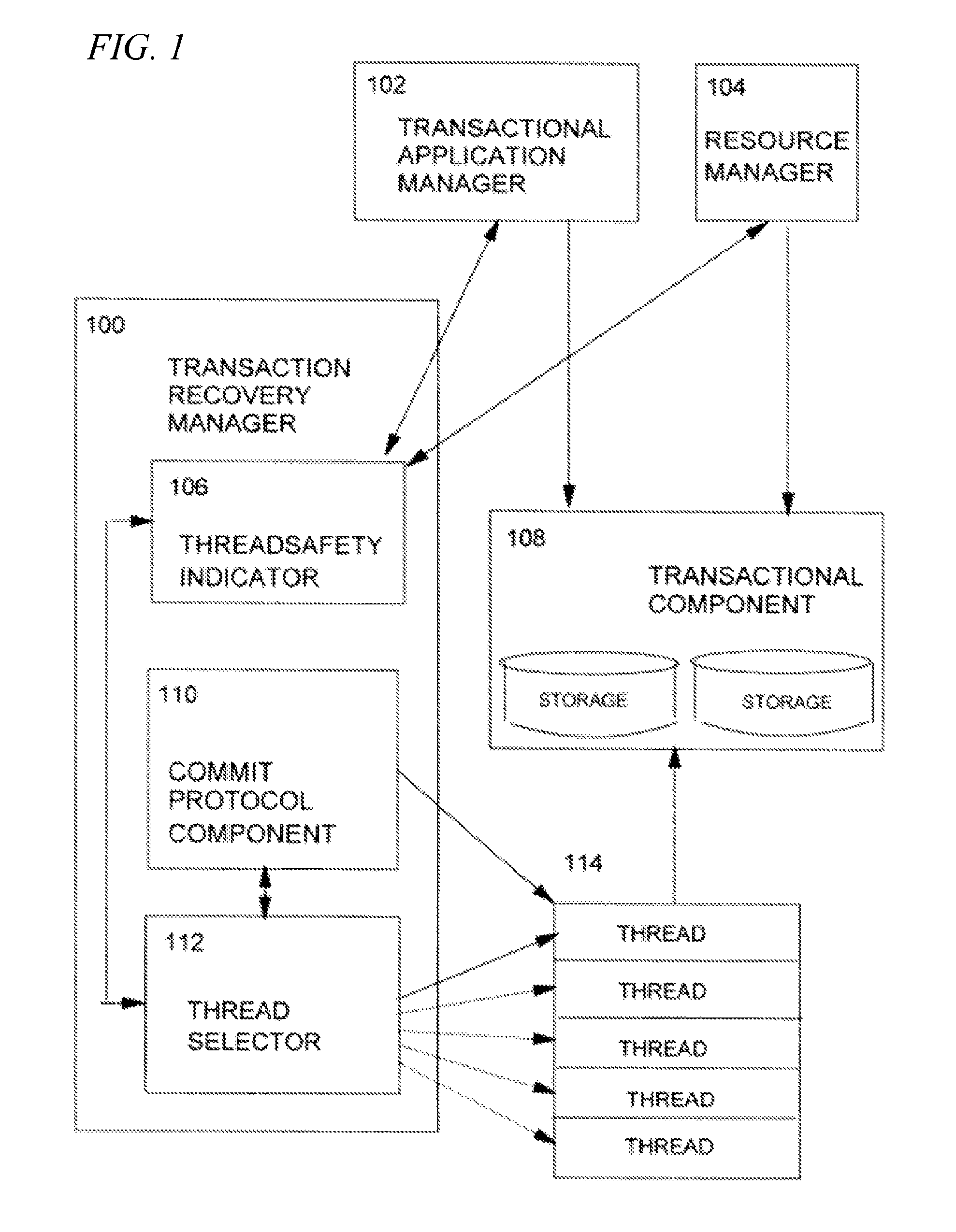

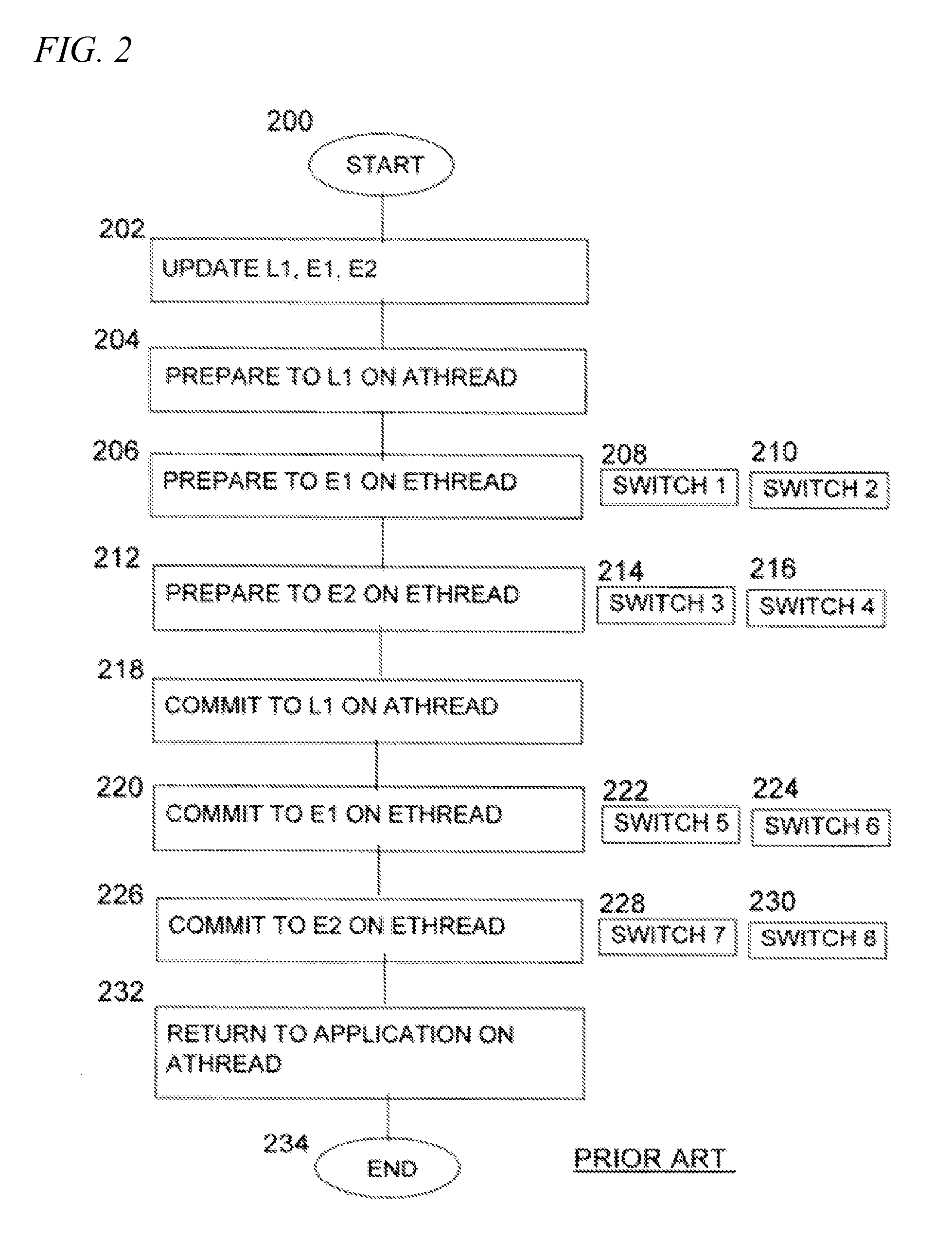

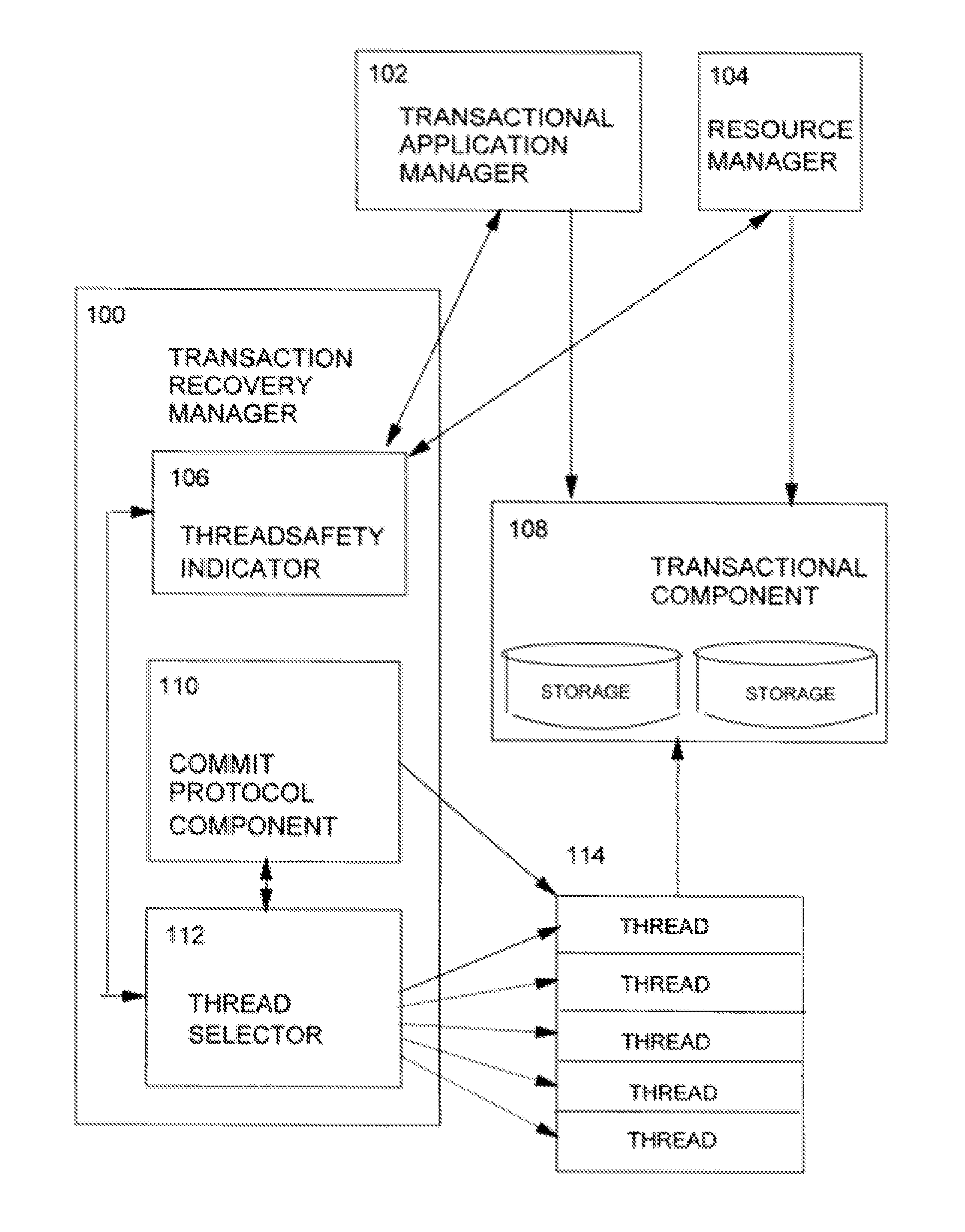

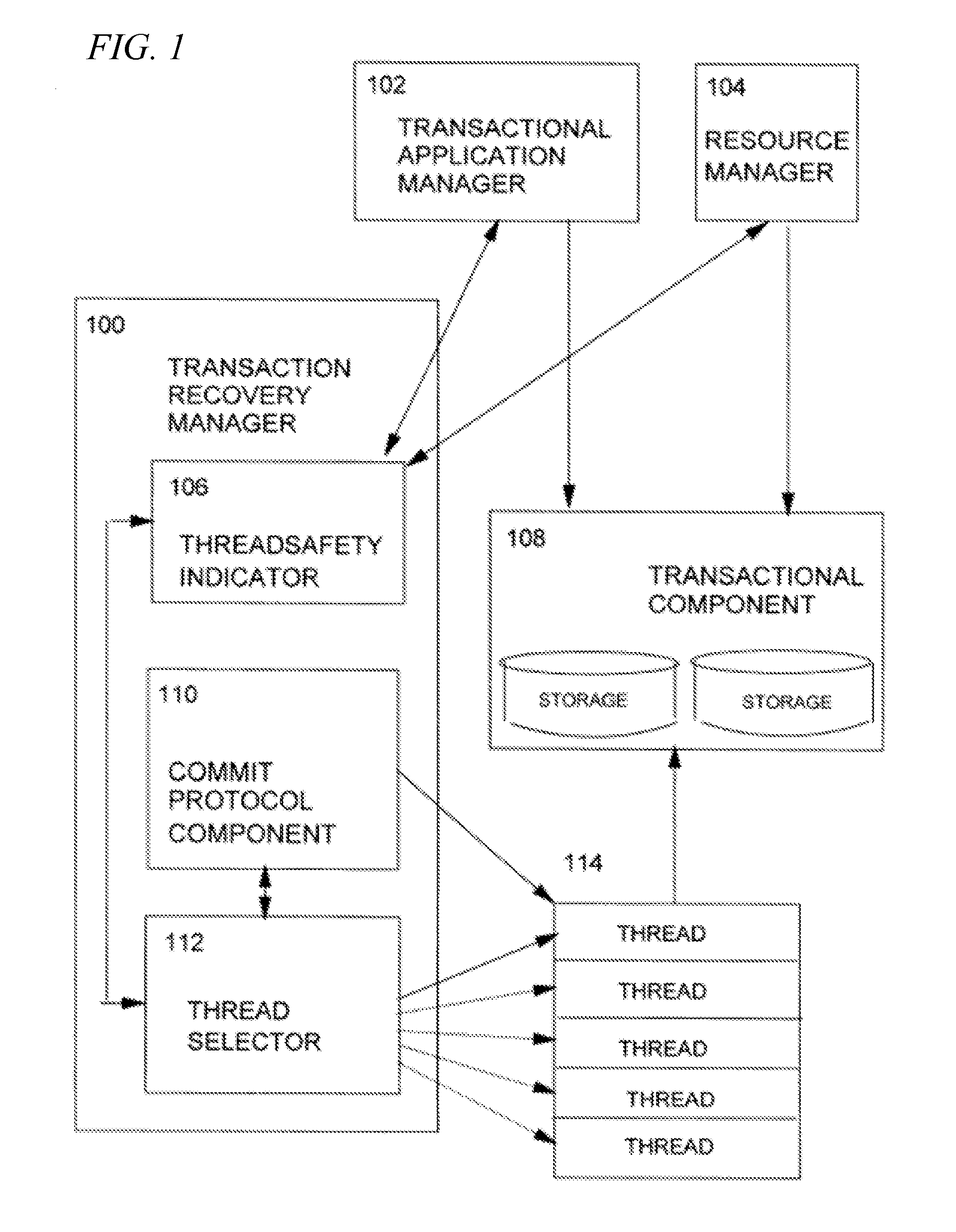

Multiprocessing transaction recovery manager

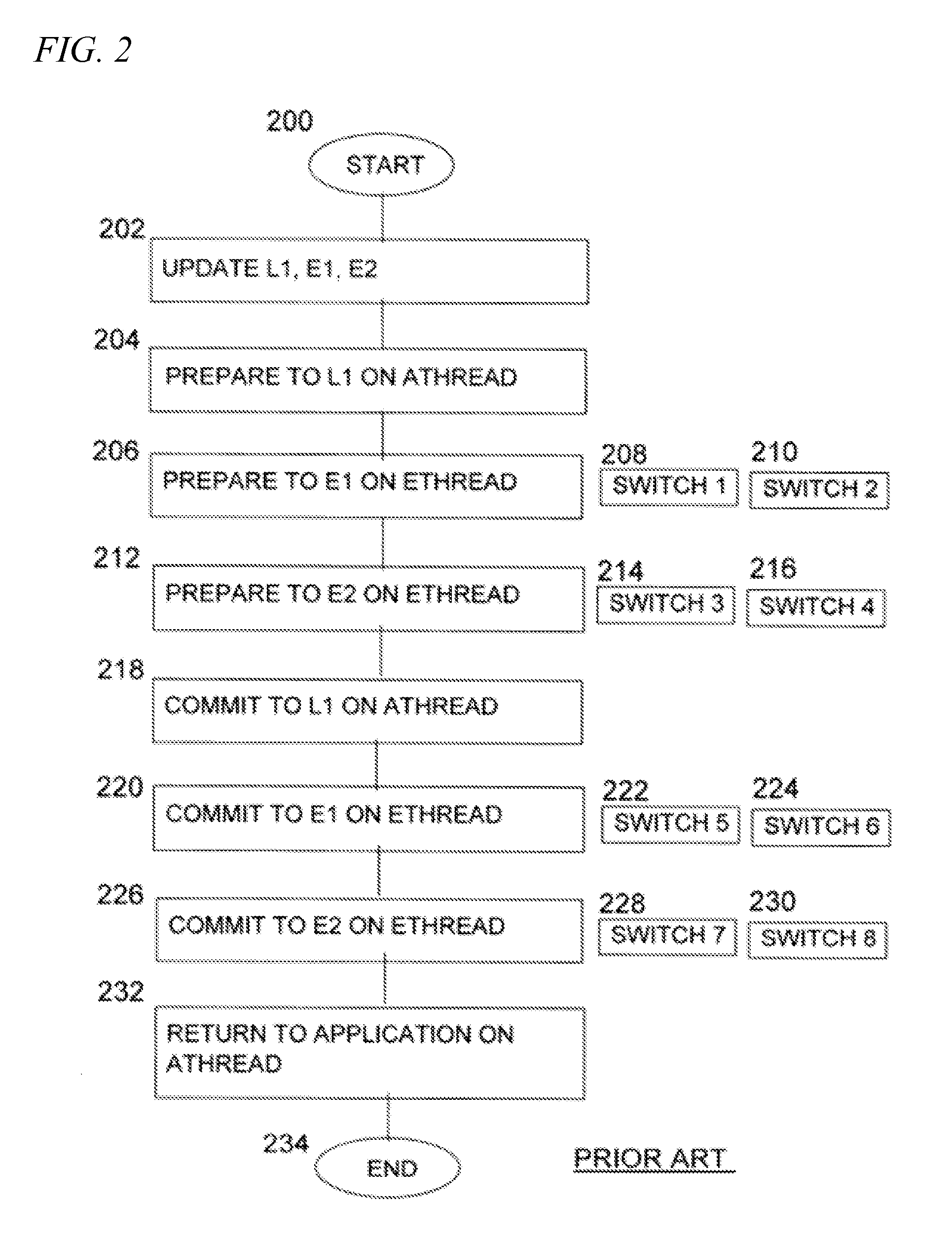

InactiveUS20110185360A1Quantity minimizationMaximizes timeDigital data information retrievalSpecial data processing applicationsResource managementApplication software

A multiprocessing transaction recovery manager, operable with a transactional application manager and a resource manager, comprises a threadsafety indicator for receiving and storing positive and non-positive threadsafety data of at least one transactional component managed by one of the transactional application manager and the resource manager; a commit protocol component for performing commit processing for the at least one transactional component; and a thread selector responsive to positive threadsafety data for selecting a single thread for the commit processing to be performed by the commit protocol component. The thread selector is further operable to select plural threads for the commit processing to be performed by the commit protocol component responsive to non-positive threadsafety data.

Owner:IBM CORP

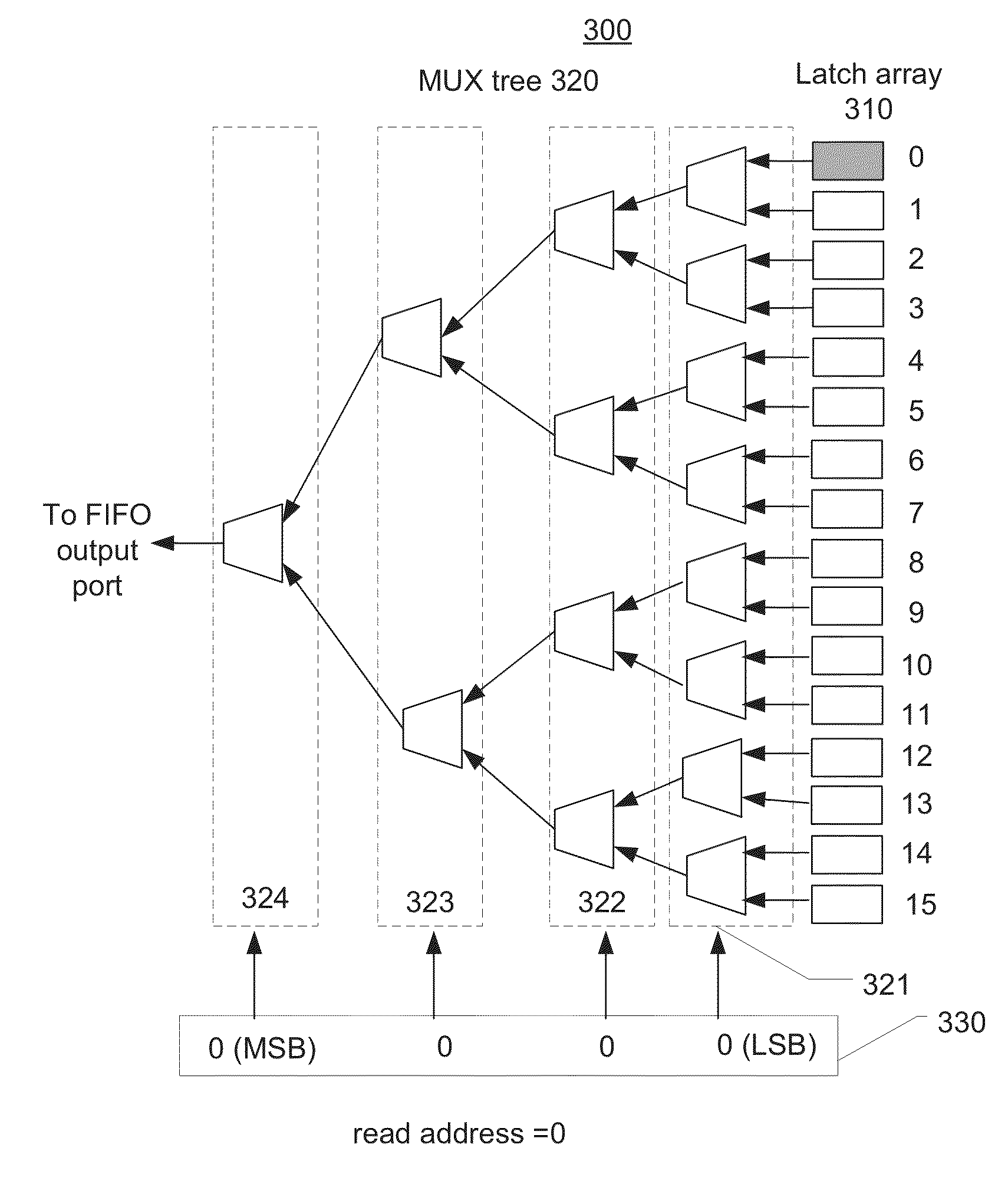

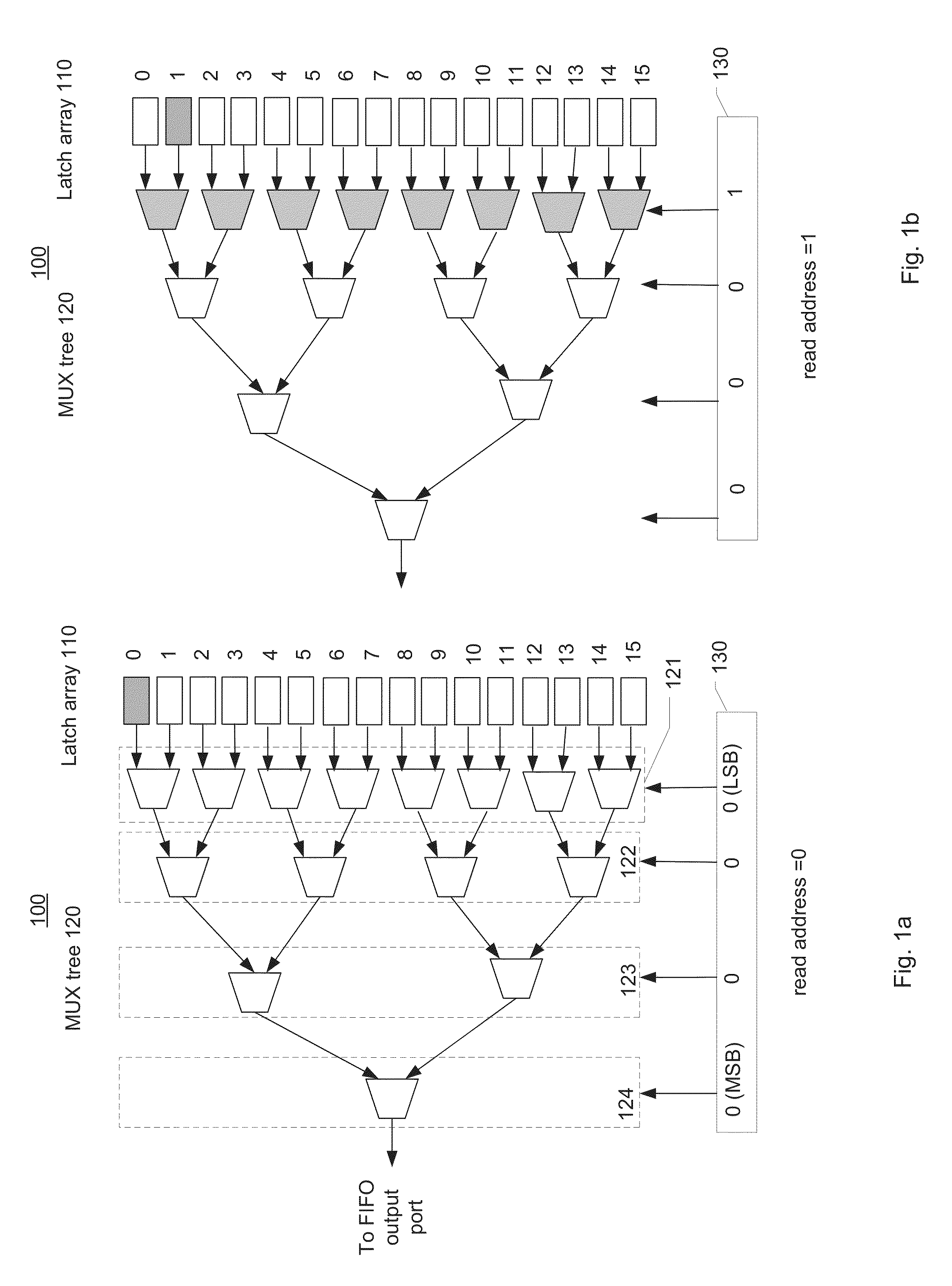

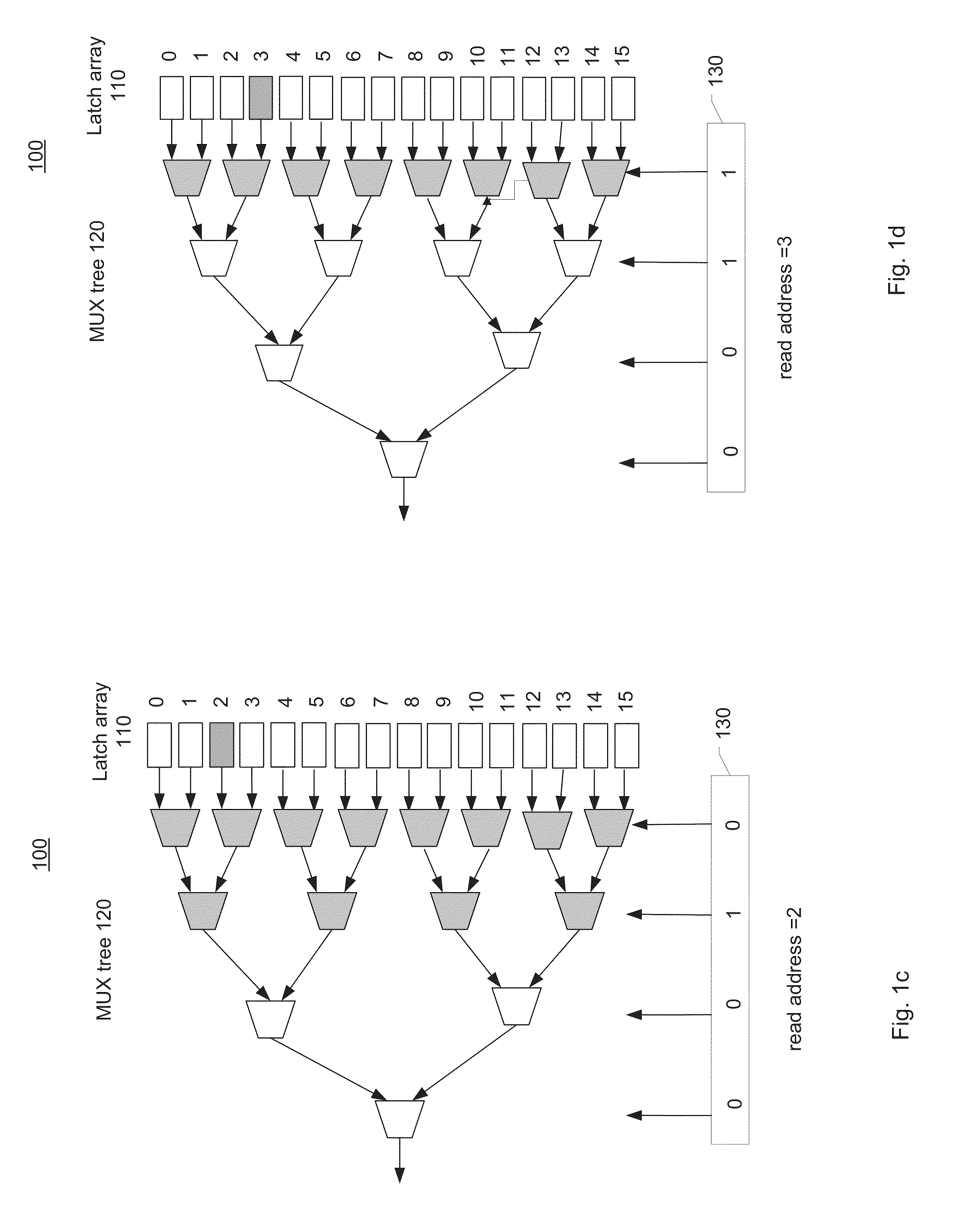

Power conservation using gray-coded address sequencing

ActiveUS20140184268A1Reduce dynamic power consumptionReduced activityPower consumption reductionComputer aided designMultiplexerLinearity

A multiplexer tree operable to control an output a sequence of data stored in a plurality of storage units in accordance with a non-linear address sequence that has less bit transition counts than a linear address sequence. The non-linear address sequence is provided to the selection inputs of the multiplexer tree and causes the levels having greater numbers of multiplexers to toggle less frequently than the levels having smaller numbers of multiplexers. The non-linear address sequence may comprise a Gray code sequence where every two adjacent addresses differ by a single bit. The non-linear address sequence may be optimized to minimize transistor switching in the multiplexer tree.

Owner:NVIDIA CORP

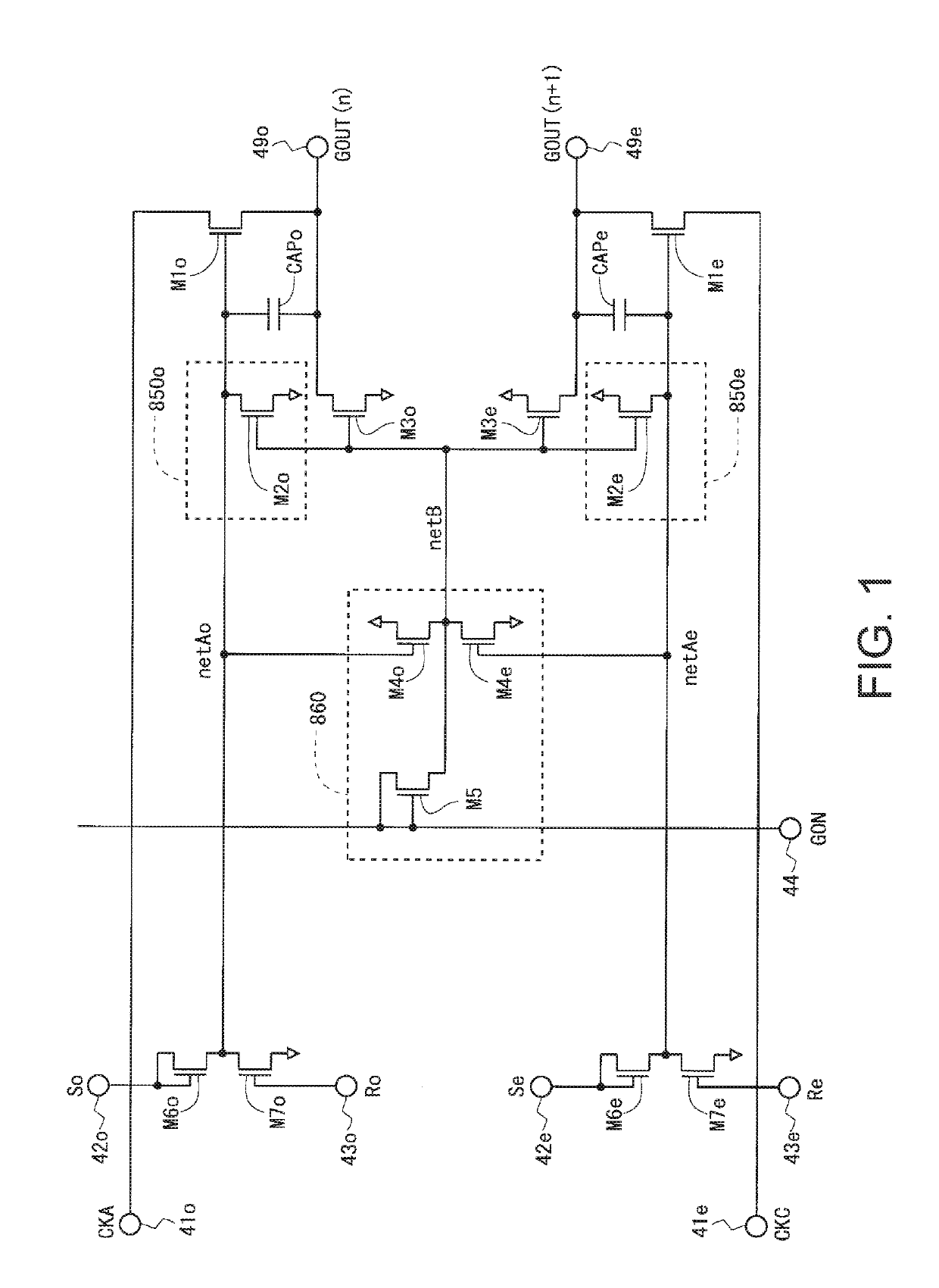

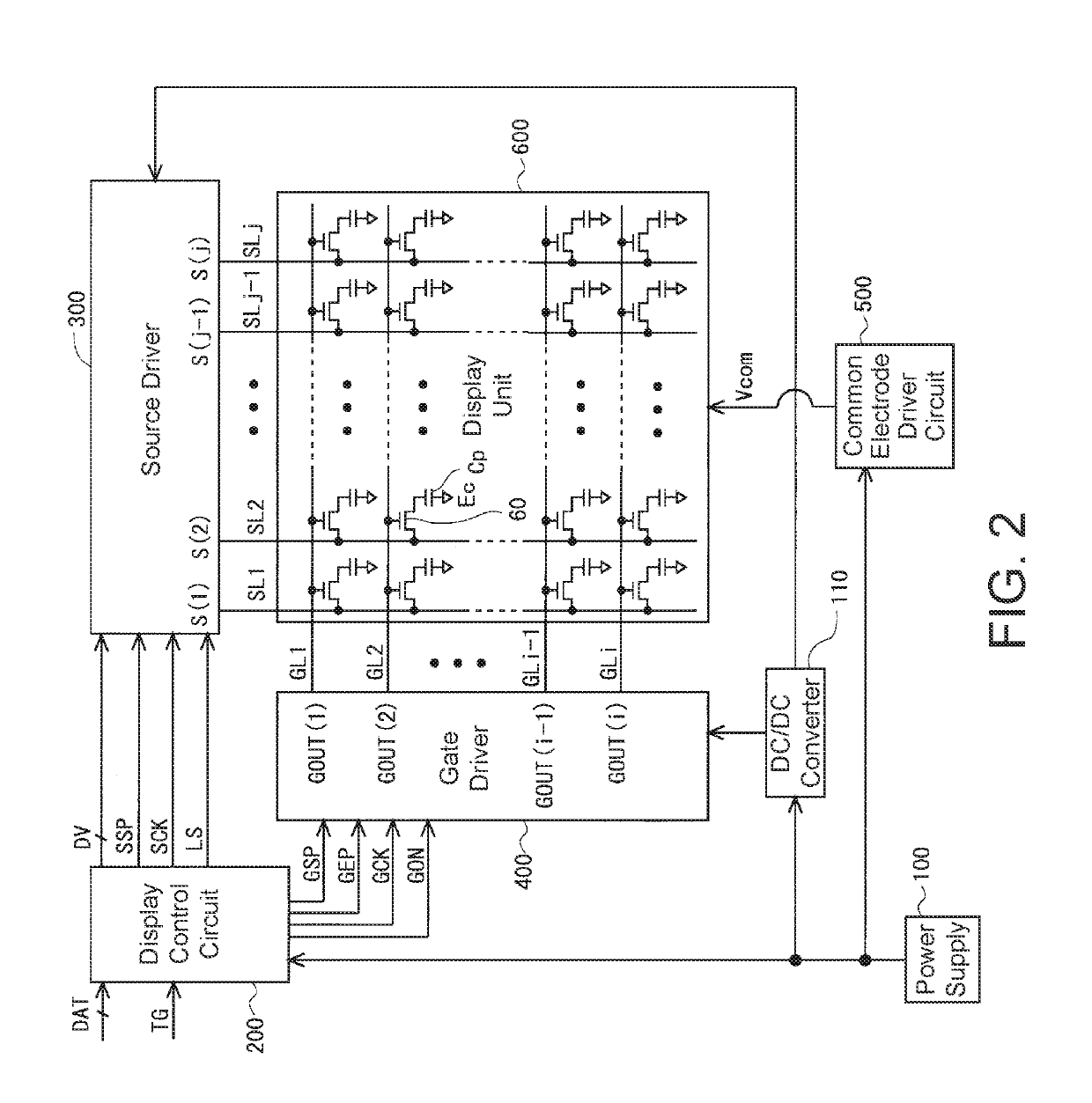

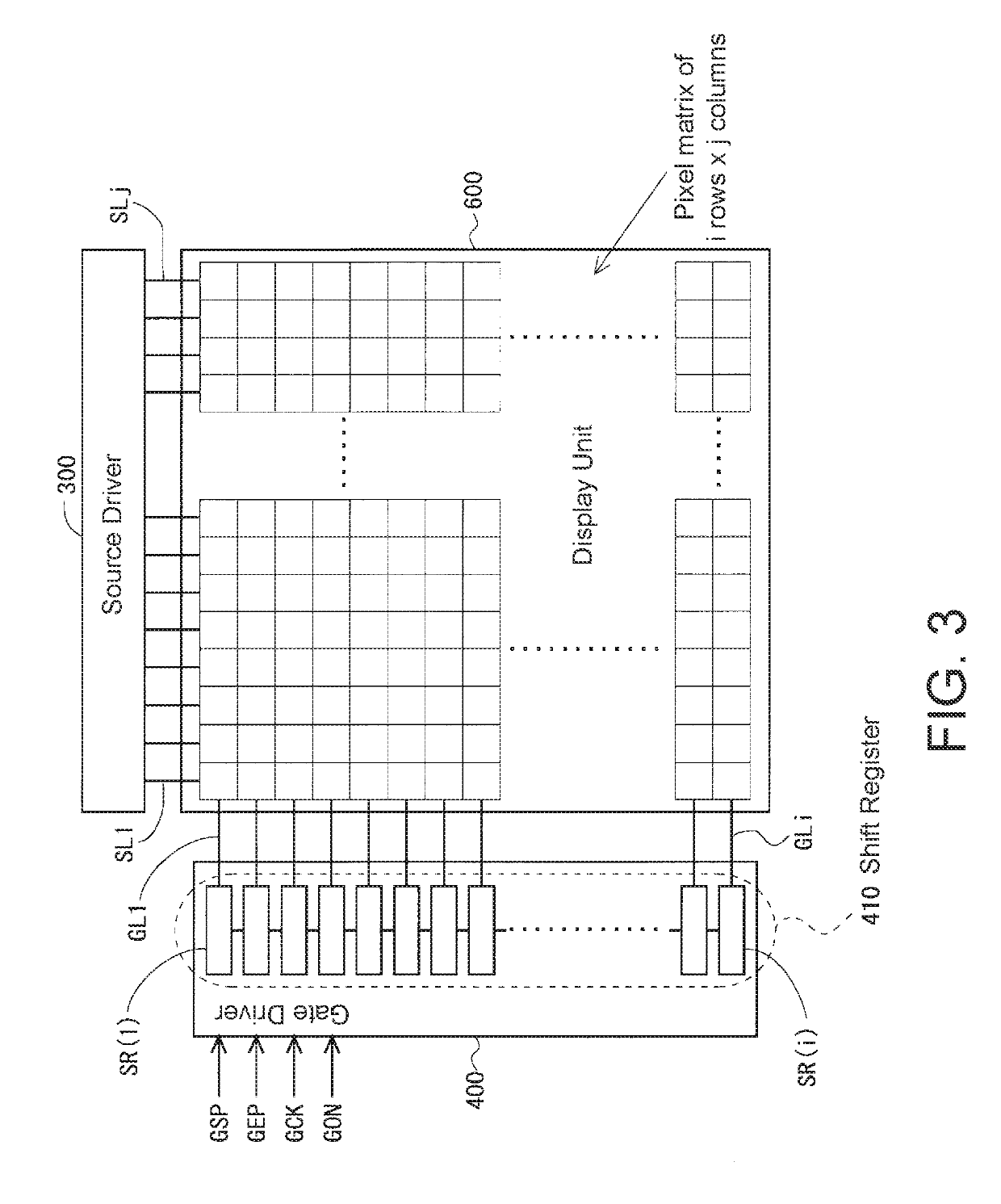

Shift register, display device provided with same, and method for driving shift register

ActiveUS10473958B2Reduce problem sizeReduce thicknessStatic indicating devicesDigital storageShift registerProcessor register

The present invention provides a monolithic gate driver that includes fewer elements than in conventional configurations. In one aspect, a plurality of stages included in a shift register are divided into a plurality of stage circuit groups, where each stage circuit group includes the stage circuits of P adjacent stages (two stages, for example). Each stage circuit group includes a stabilization node and a stabilization node controller that controls the voltage of the stabilization node. The stabilization node controller includes: thin-film transistors in which the gate terminals thereof are connected to output control nodes, the drain terminals thereof are connected to the stabilization node, and the source terminals thereof are connected to an input terminal for a DC supply voltage; and a thin-film transistor for changing the voltage of the stabilization node to a high level.

Owner:SHARP KK

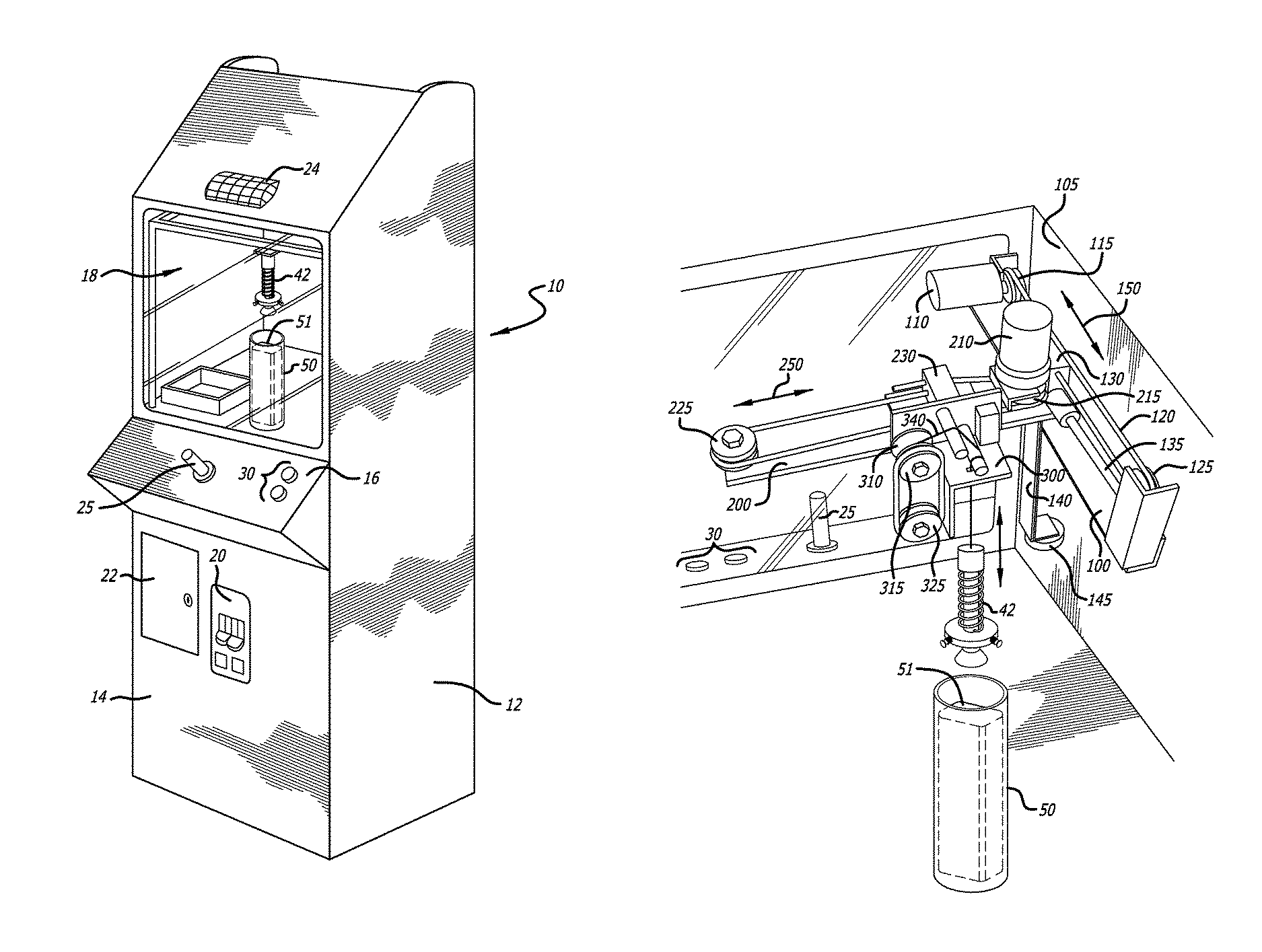

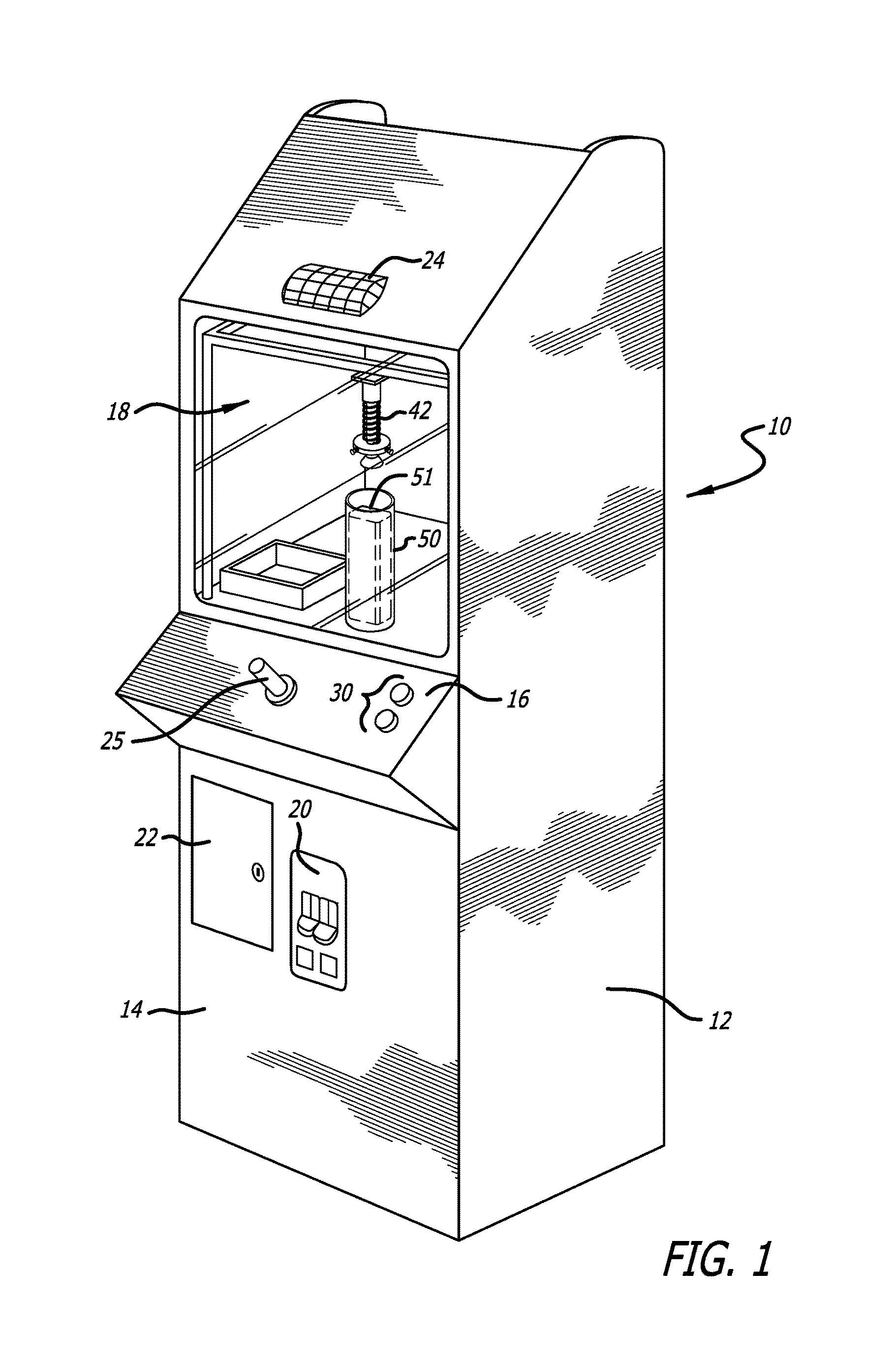

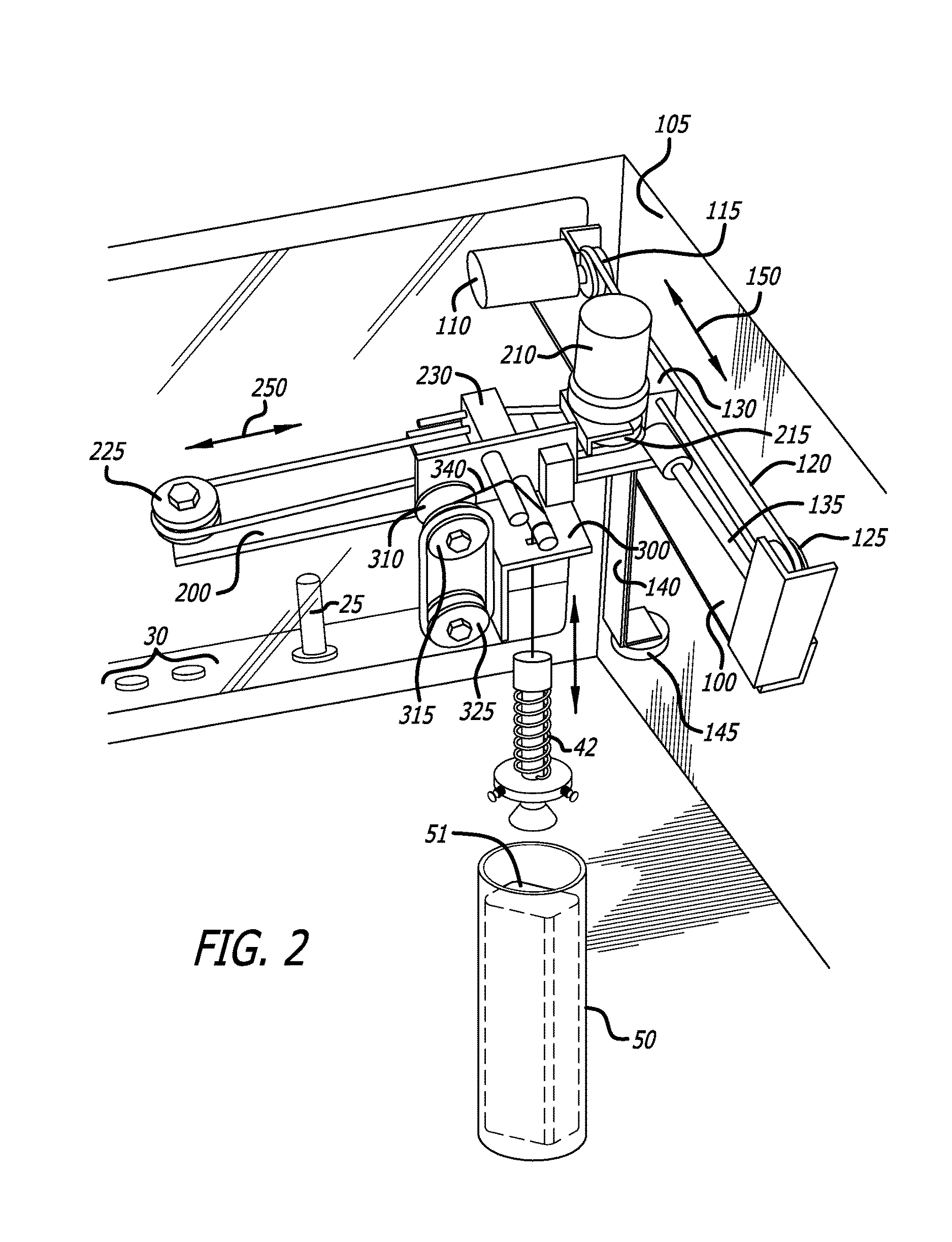

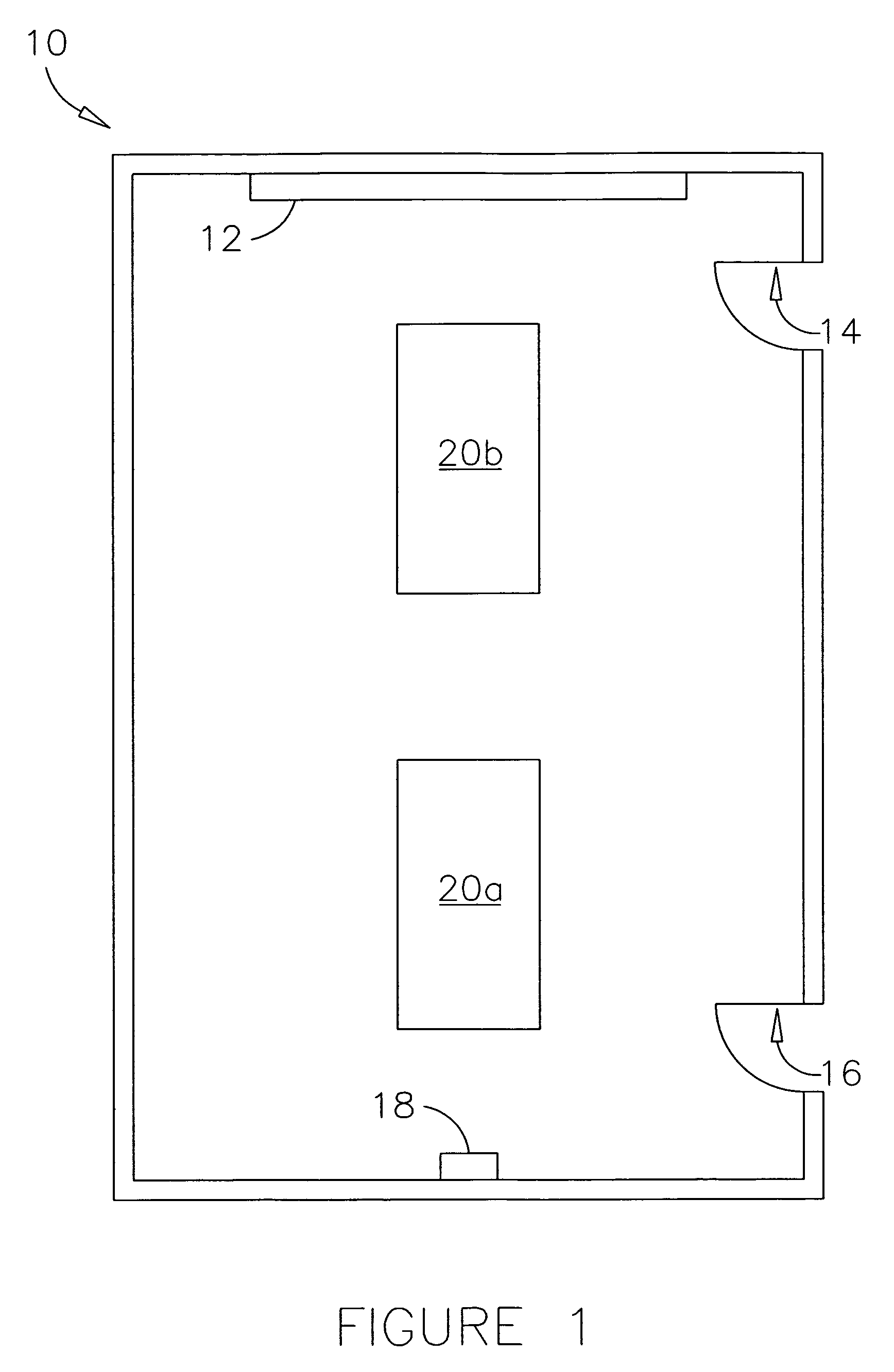

Crane game with modified pulley system

ActiveUS9539496B1Few switchLess wiringIndoor gamesApparatus for meter-controlled dispensingClutchEngineering

An arcade game is disclosed having a modified three dimensional control of an acquisition device using three motors, pulleys, and belts that maneuver the acquisition device in three directions. Each belt is located in a pair of pulley wheels that have a “grooved section that allows the belt to slip when the motor reaches an end of its cycle, eliminating the need for switches and clutches.

Owner:STEPHEN P SHOEMAKER TRUST

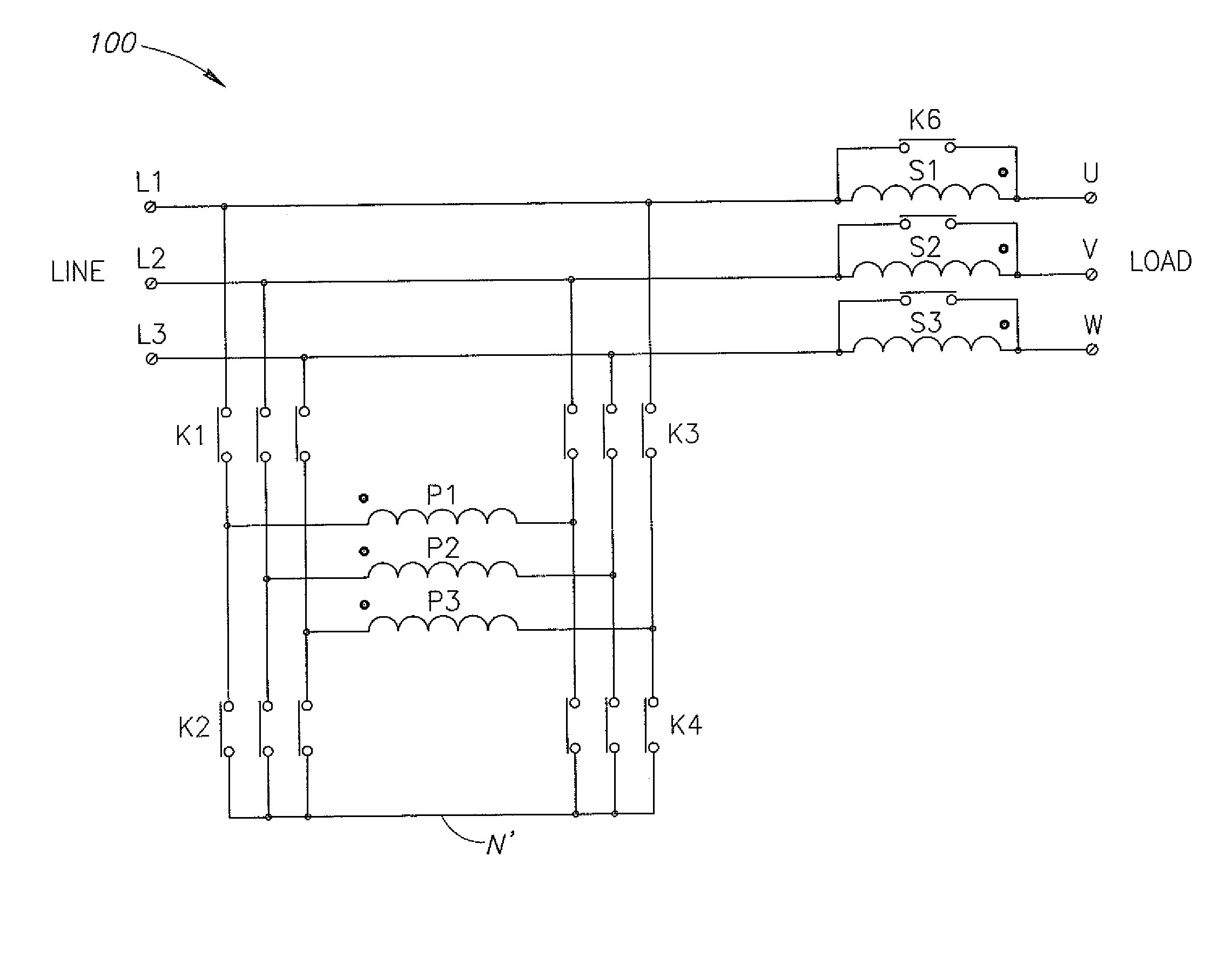

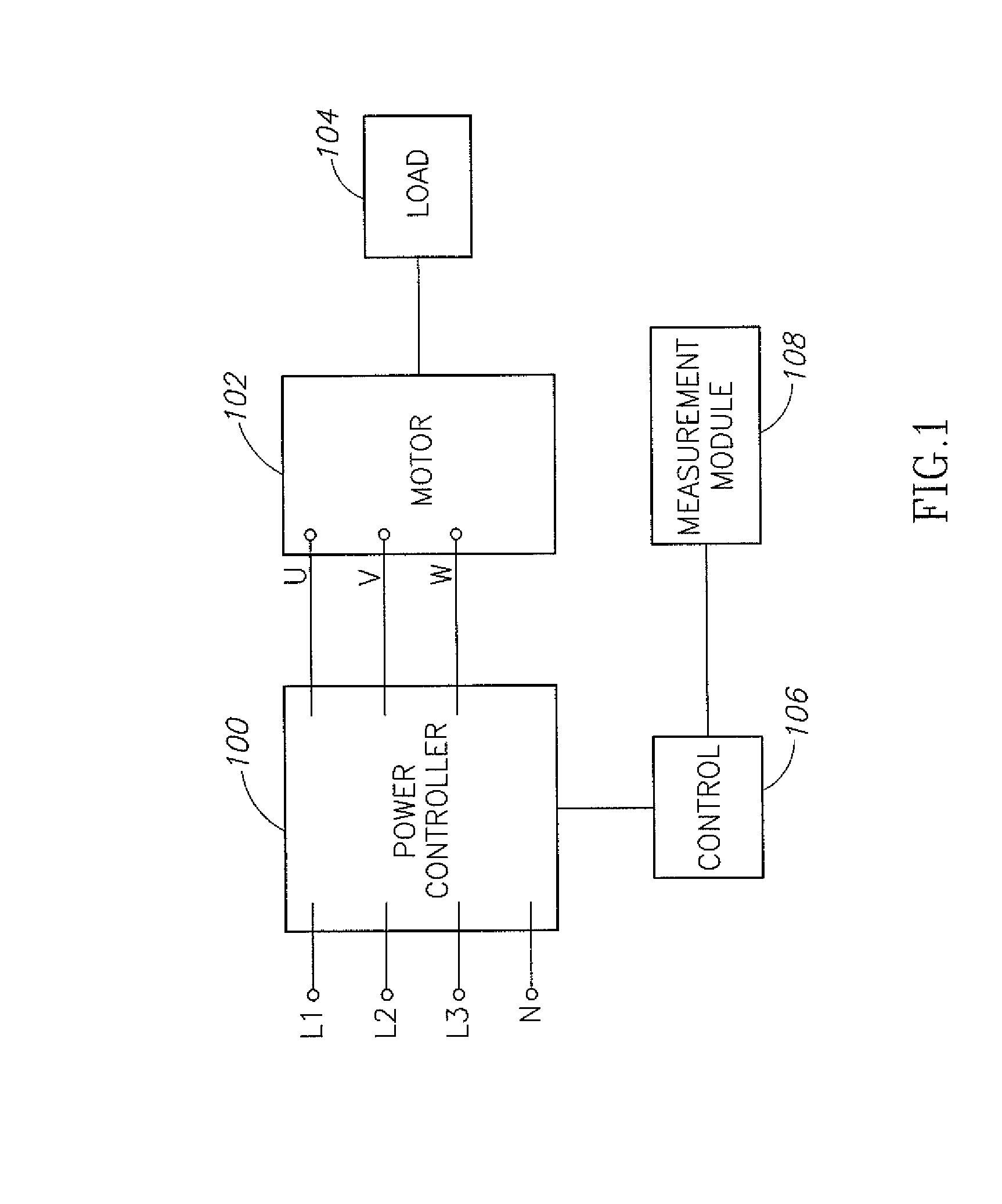

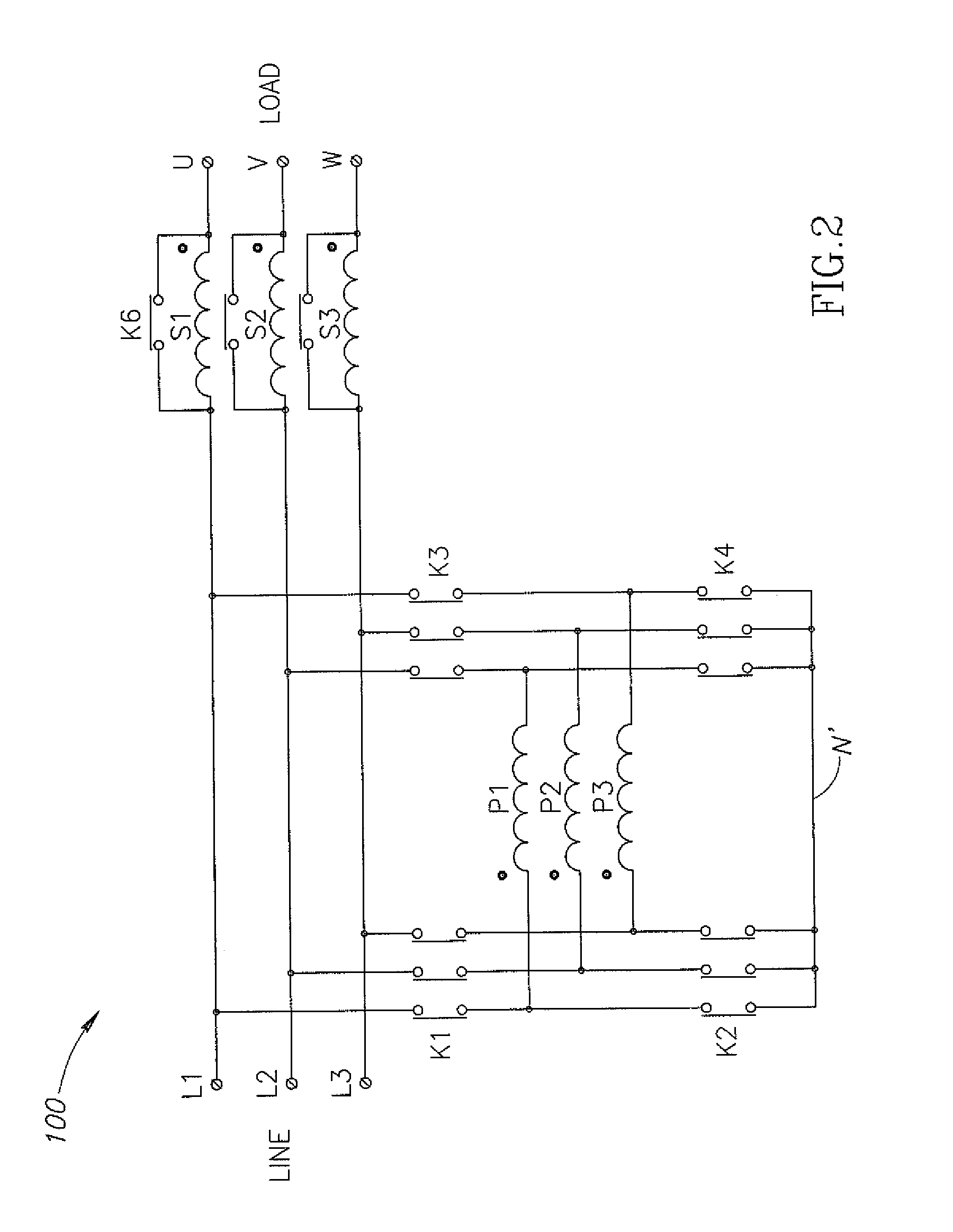

Variable voltage supply system

ActiveUS20090309536A1Significant problemFew switchMultiple-port networksAC motor controlEngineeringConductor Coil

Apparatus for controlling the voltage supplied to a load, comprising:a multi-phase transformer having a primary and a secondary winding for each phase, each secondary being connected in series between an input line and an output directed to the load; andthe primary is configurable by switches such that the phase of the voltage of the secondary is different from the line to which it is connected by a phase different from 0 and 180 degrees.

Owner:ORTEA SPA

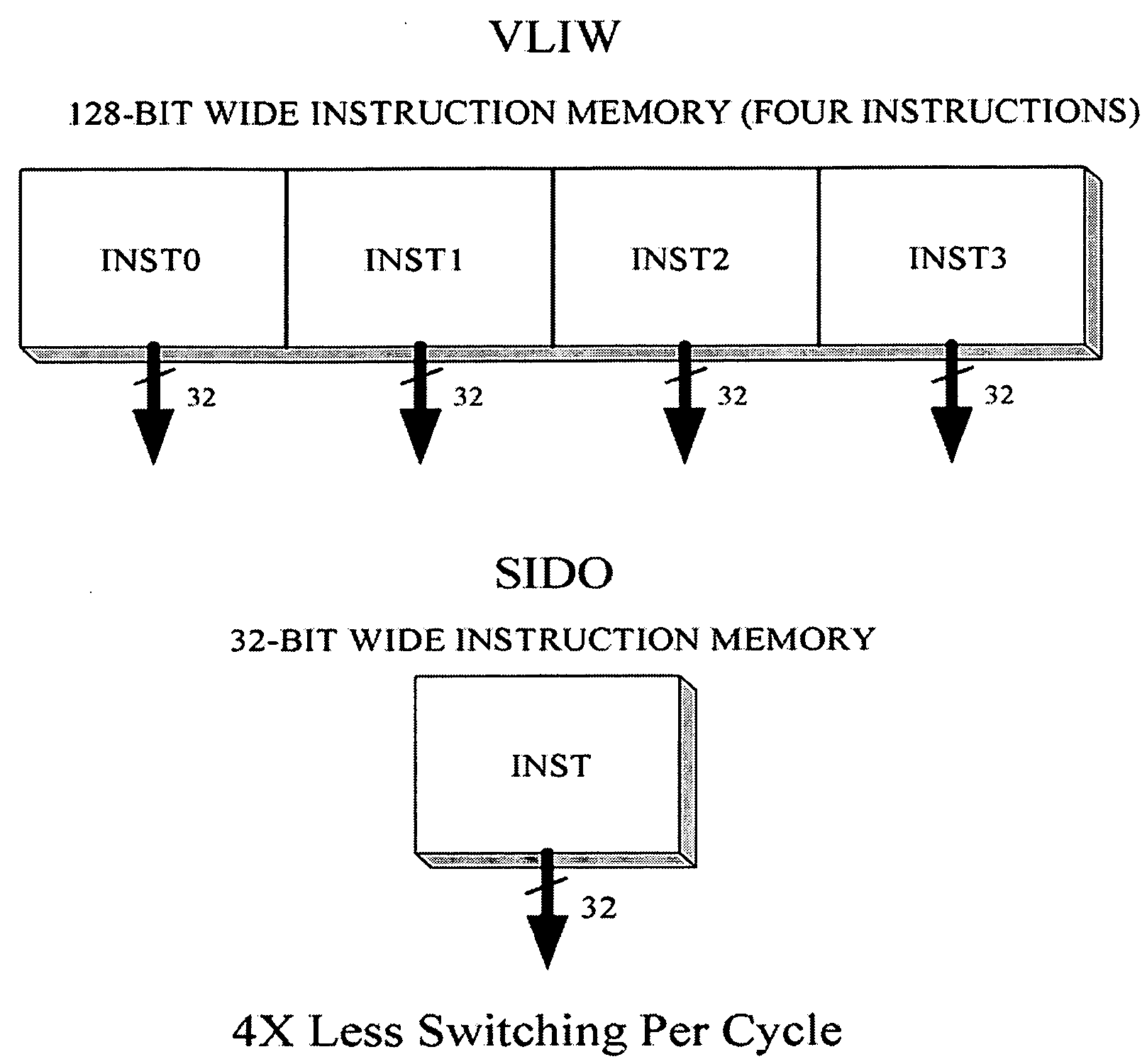

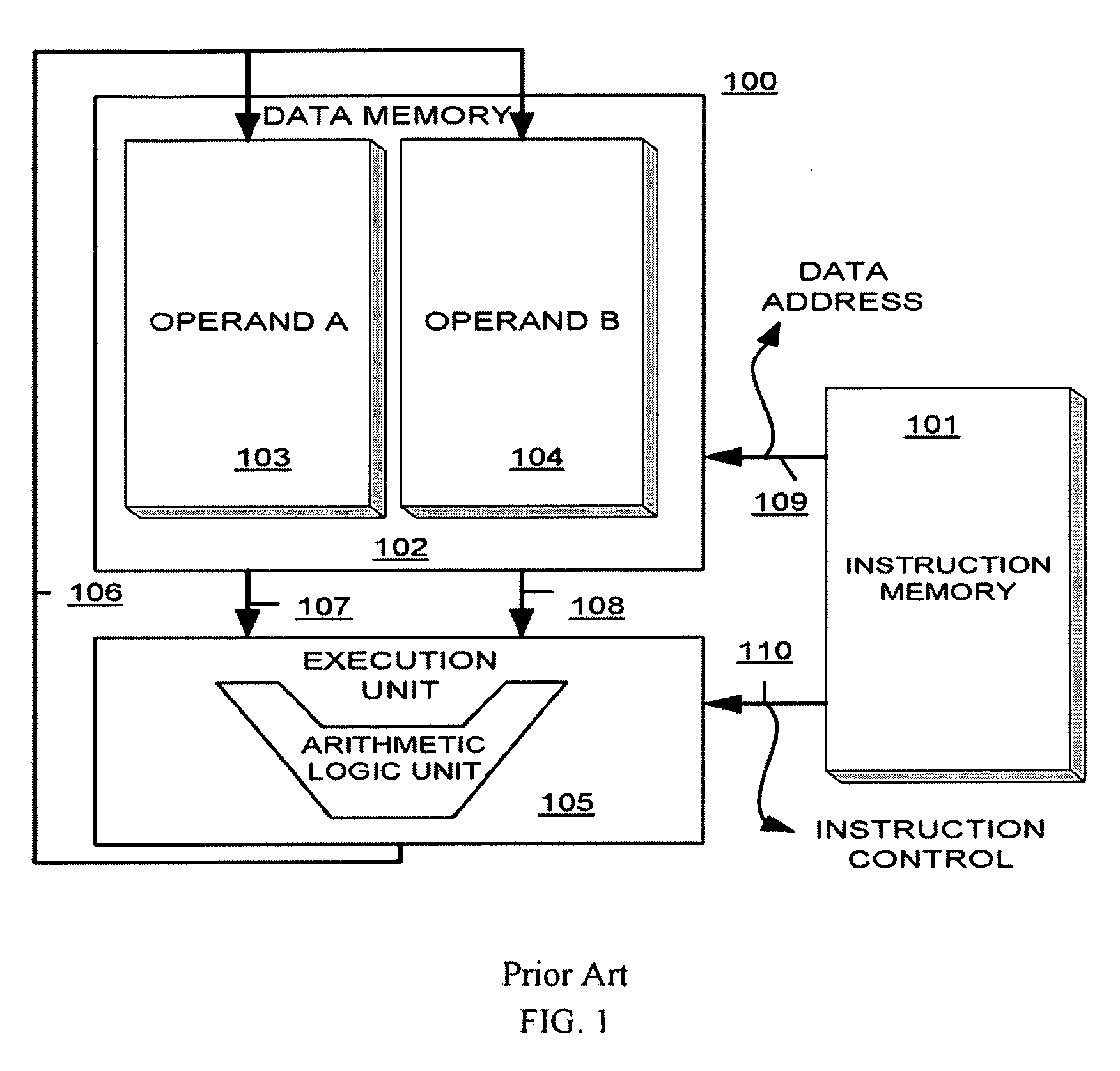

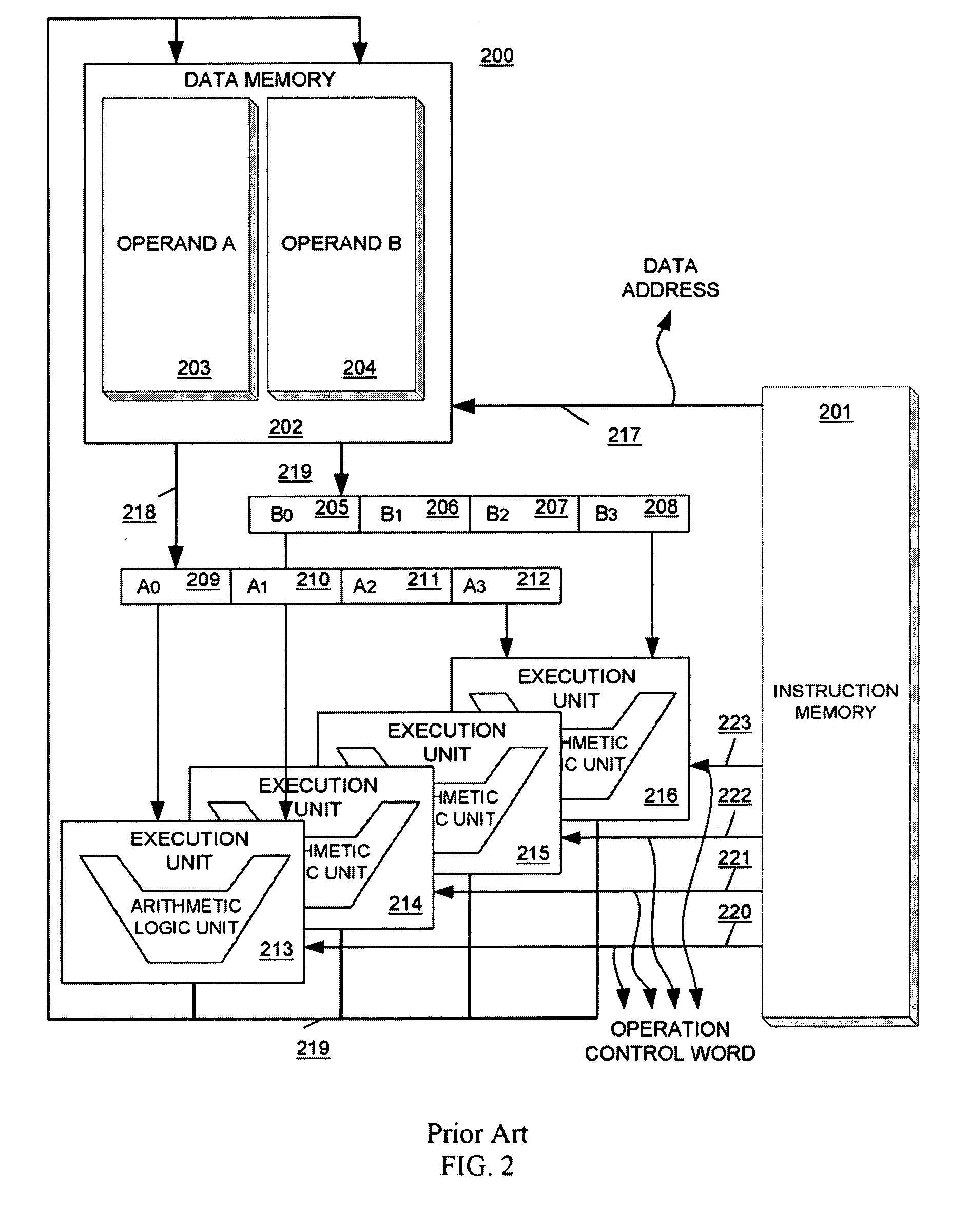

Same instruction different operation (SIDO) computer with short instruction and provision of sending instruction code through data

InactiveUS20090031117A1Powerful number crunching engineShort flexibilityDigital computer detailsSpecific program execution arrangementsData operationsExecution unit

A same instruction different operation (SIDO) processor is disclosed in which the instruction control word is supplied using data bus as one operand and the data to be operated is supplied through another operand. Also disclosed is a method for the provision of operation-code along with data / operands using a short instruction word. With all the execution units working in parallel on multiple data operands, a variety of operations can be performed in parallel. This allows short instruction format and flexibility to dynamically program the processor on the fly by changing data / operand words, and supports basic integer operations using very simple and efficient hardware execution units.

Owner:FAROOQUI AAMIR A +1

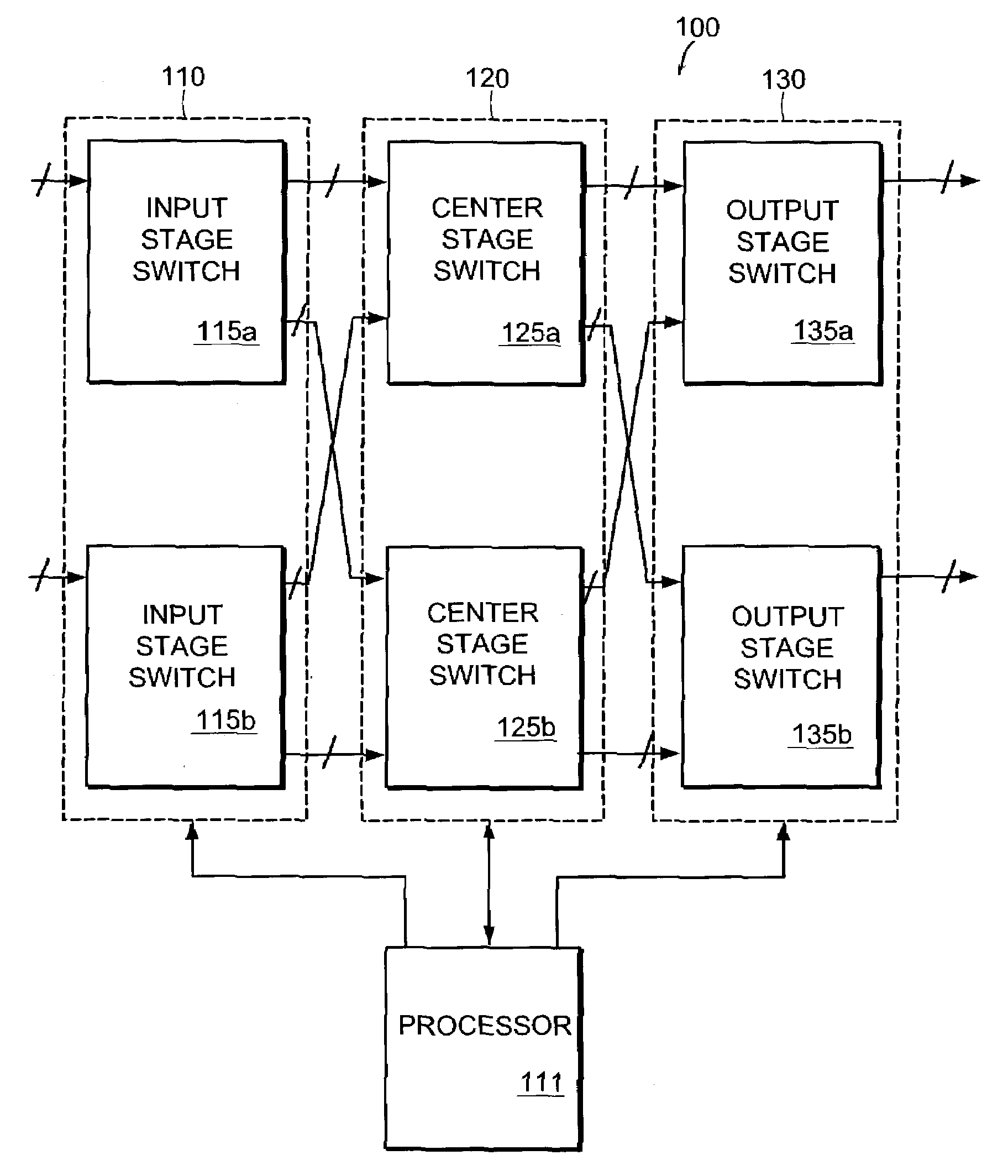

Scheduling connections in a multi-stage switch to retain non-blocking properties of constituent switching elements

InactiveUS7346049B2Minimize the differenceQuickly reconfiguredMultiplex system selection arrangementsCircuit switching systemsDistributed computing

A scheduling algorithm is provided that may be implemented in a multi-stage switch requiring less switching elements than known switching architectures in order to increase bandwidth and to retain the non-blocking properties of the constituent switching elements for incoming traffic, including multicast traffic. A scheduling algorithm is also provided for incremental scheduling of connections being added or removed from the switch.

Owner:INTEL CORP

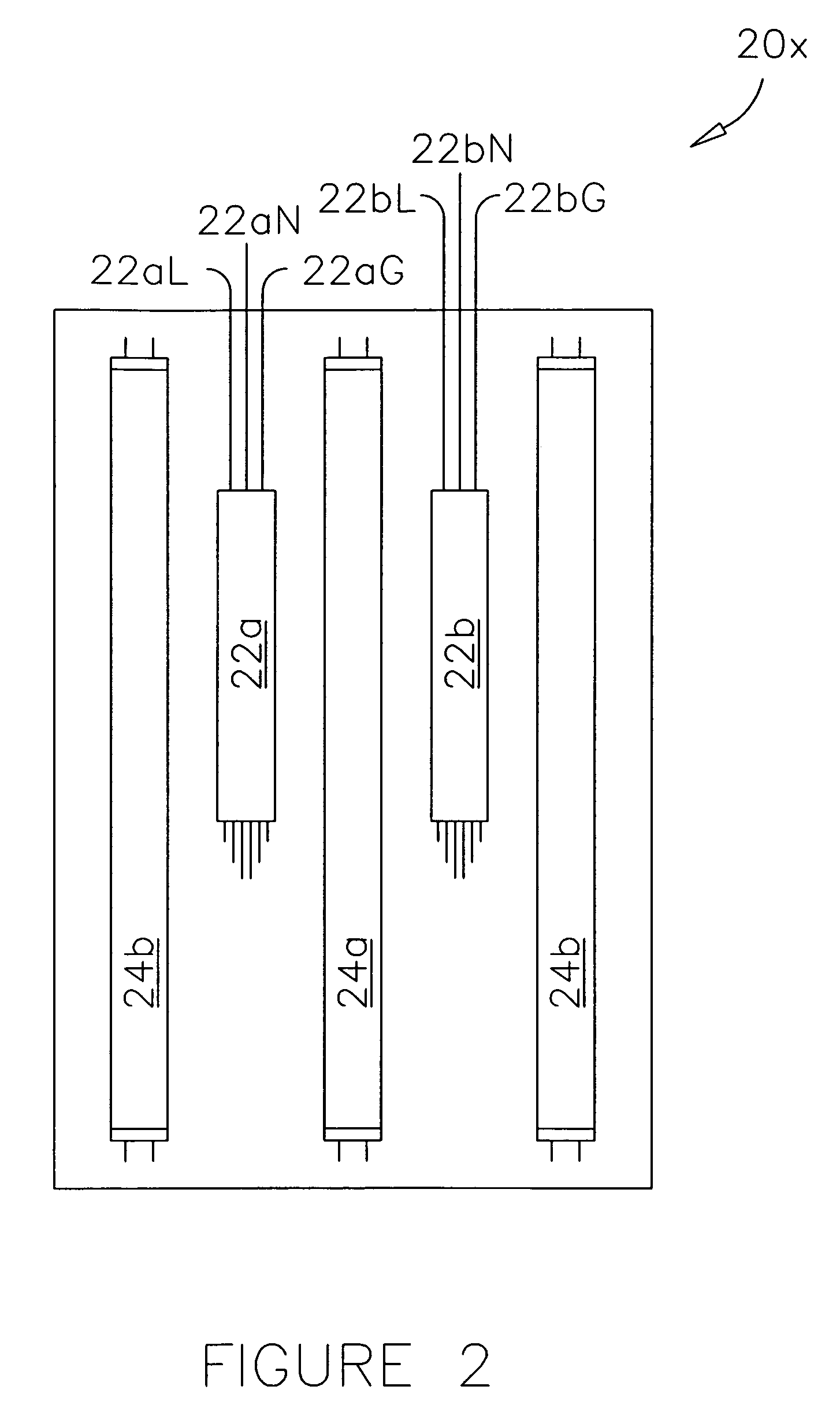

Simplified lighting control system

ActiveUS8148851B2Facilitates multiple modes of lighting configurationsEasy to operateDc network circuit arrangementsBoards/switchyards circuit arrangementsLow voltagePower switching

The invention offers an improvement in lighting control systems by providing a simplified power switching control system (i.e., using direct AC line voltage or DC current power switches instead of low voltage switches that control higher-current-capable relays) that controls the power to the power supplies that drive the light producing devices in a plurality of luminaires or lighting fixtures in a given installation. The lighting control system facilitates multiple modes of lighting configurations while requiring fewer switches that the prior art and also being easier to operate. The system supports the simultaneous use of multiple lighting technologies. Other embodiments showing extensions to the invention are also disclosed.

Owner:LITECONTROL

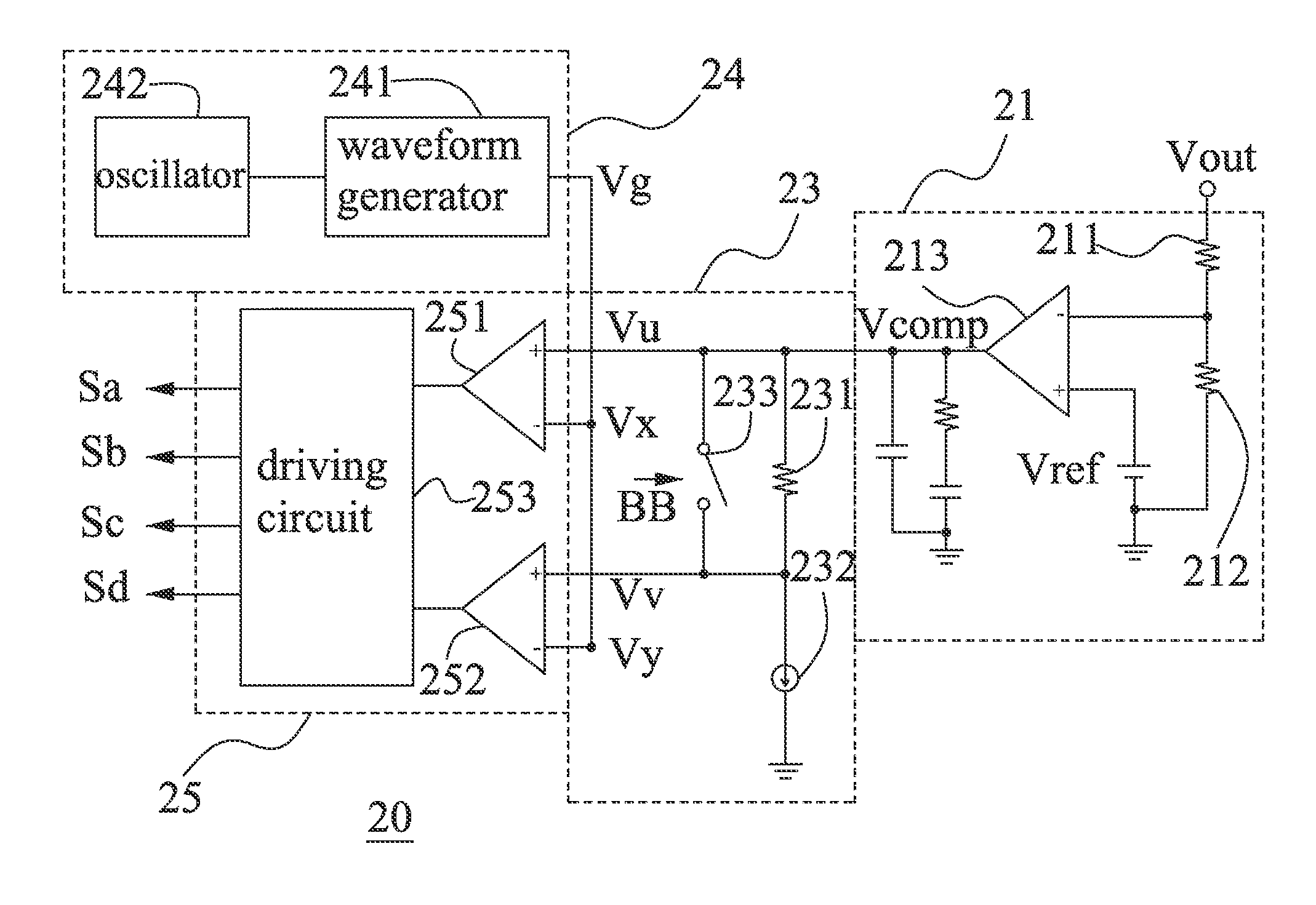

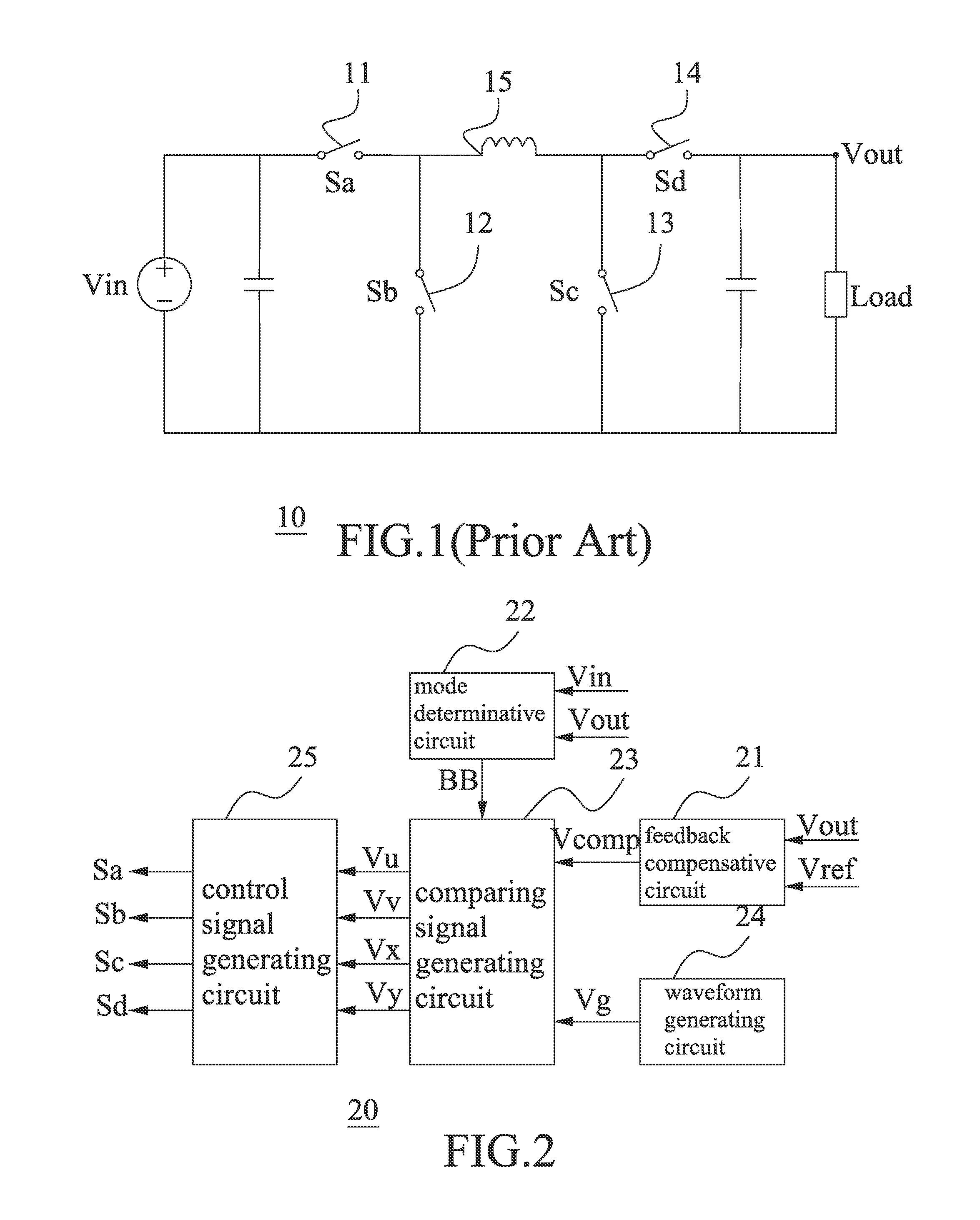

Control circuit and method for a buck-boost switching converter

InactiveUS8823340B2Improve efficiencyEasy to operateDc-dc conversionElectric variable regulationControl signalEngineering

Owner:RICHTEK TECH

Single-inductor multiple-output power converter

A single-inductor multiple-output power converter includes an inductor having a first terminal and a second terminal. The first terminal of the inductor is coupled to a power input terminal, and the second terminal of the inductor is switched to either of the first terminal of the inductor, multiple power output terminals, and a ground terminal. By switching the second terminal of the inductor between the first terminal of the inductor, the power output terminals, and the ground terminal, the power converter may provide multiple output voltages at the power output terminals respectively, in a less loss and thereby higher efficiency manner.

Owner:RICHTEK TECH

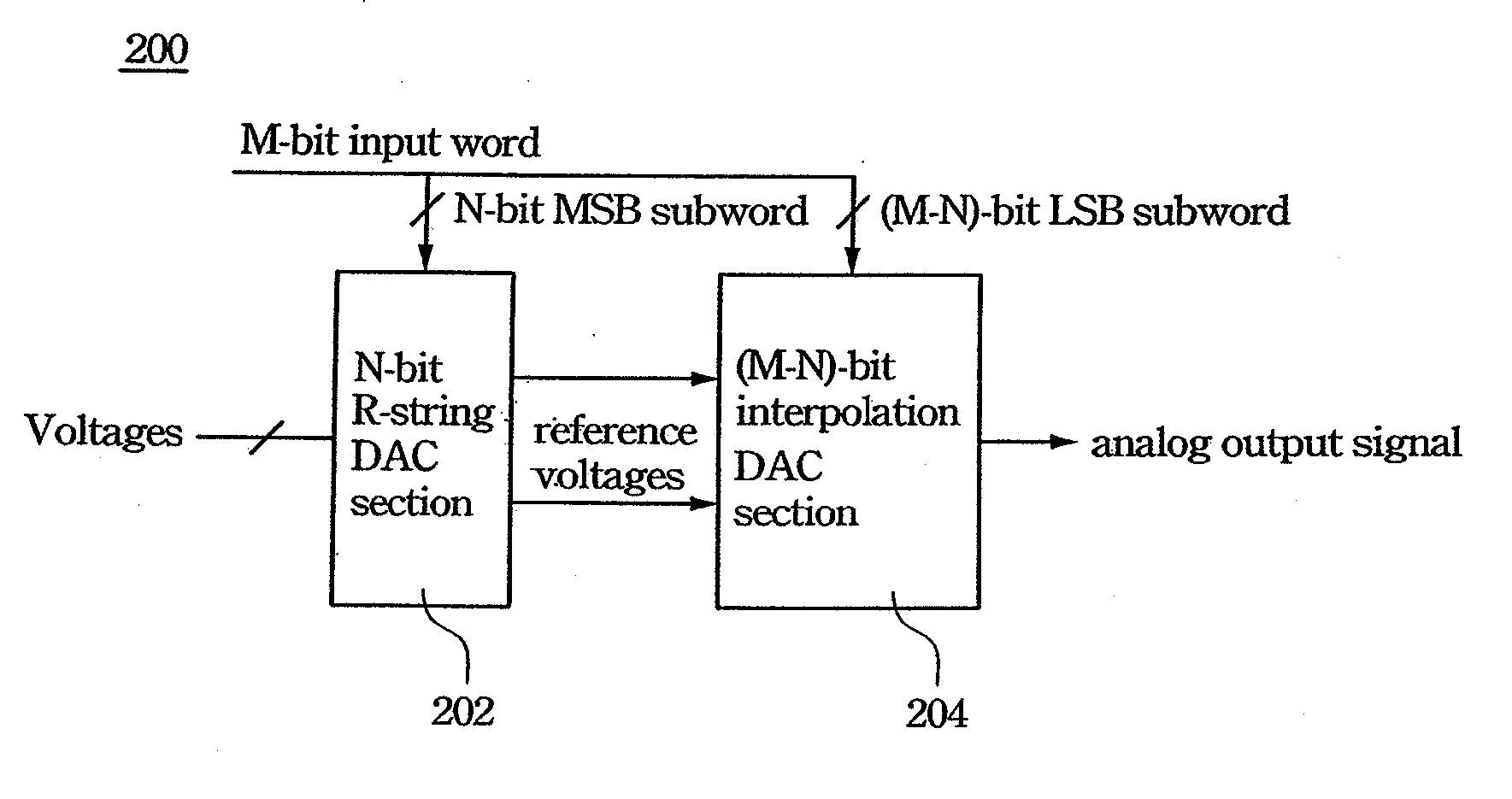

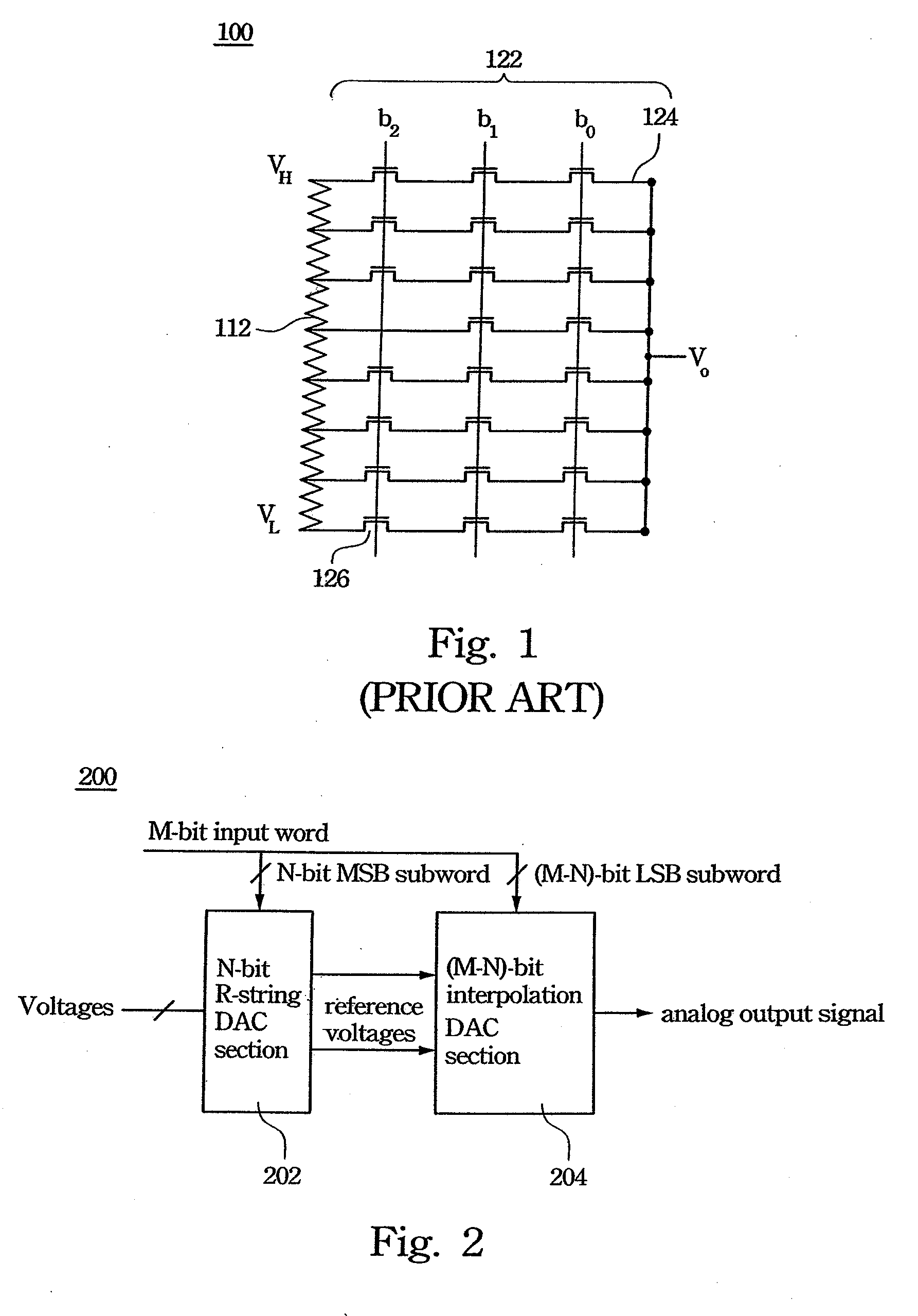

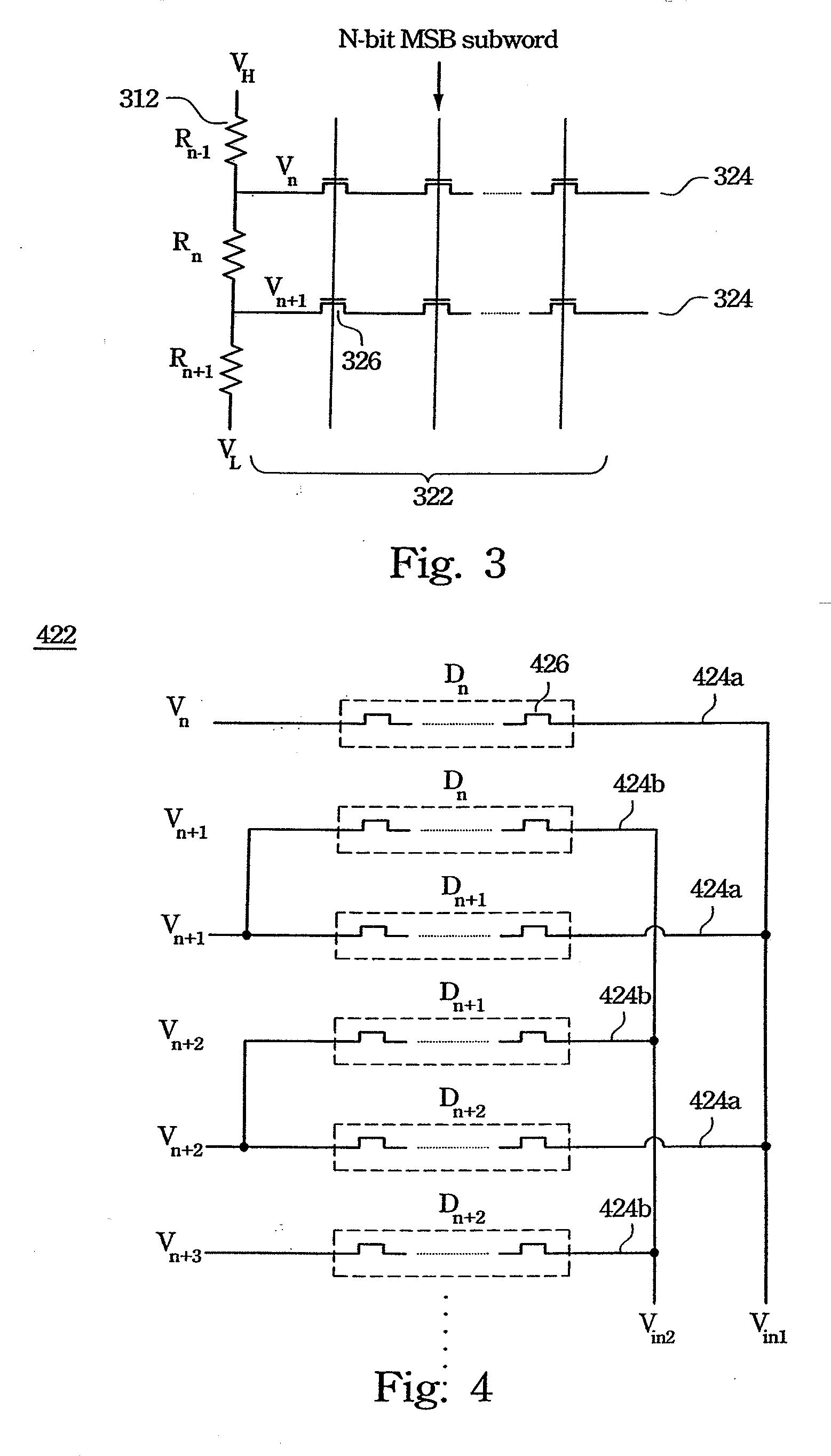

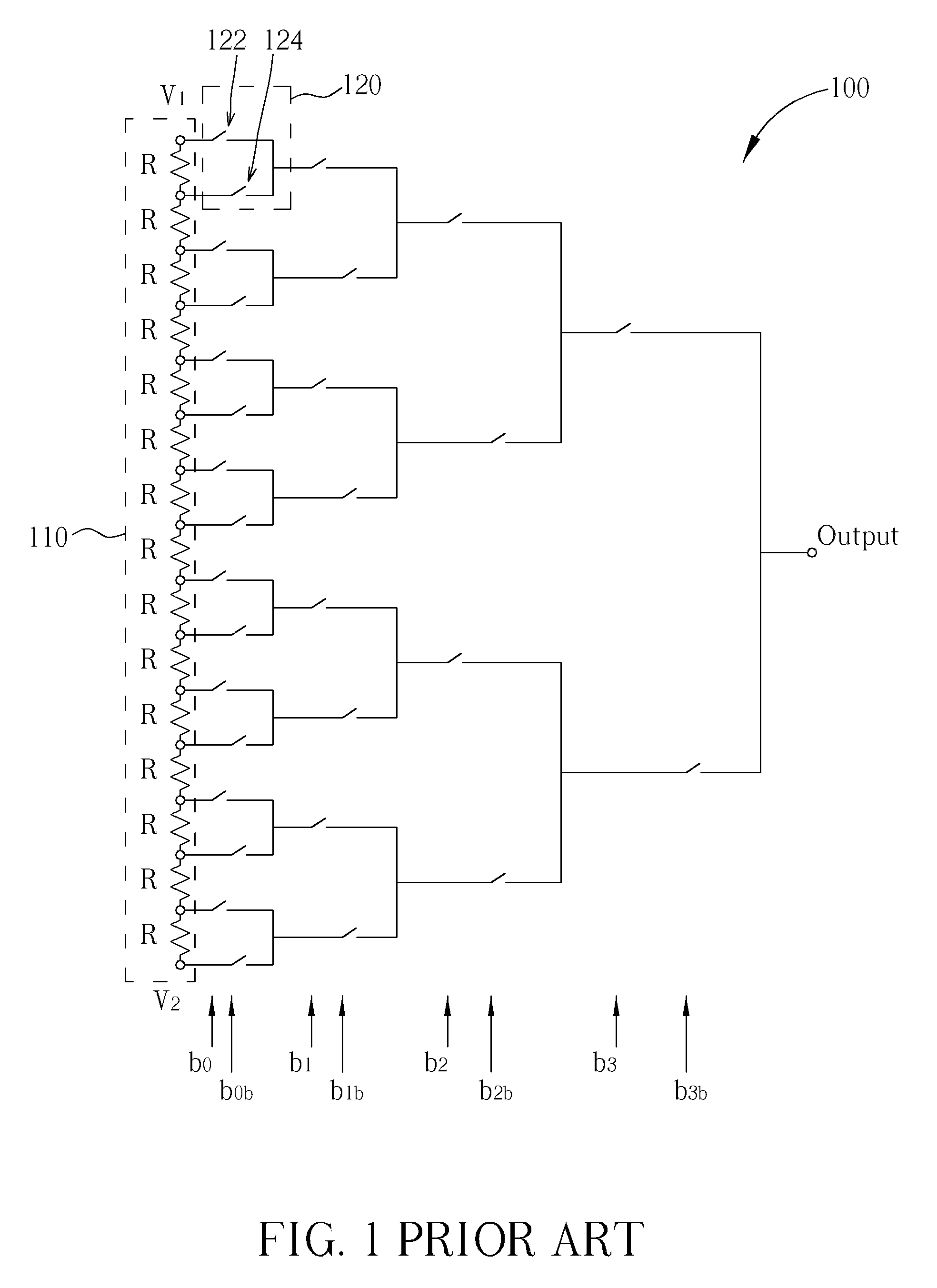

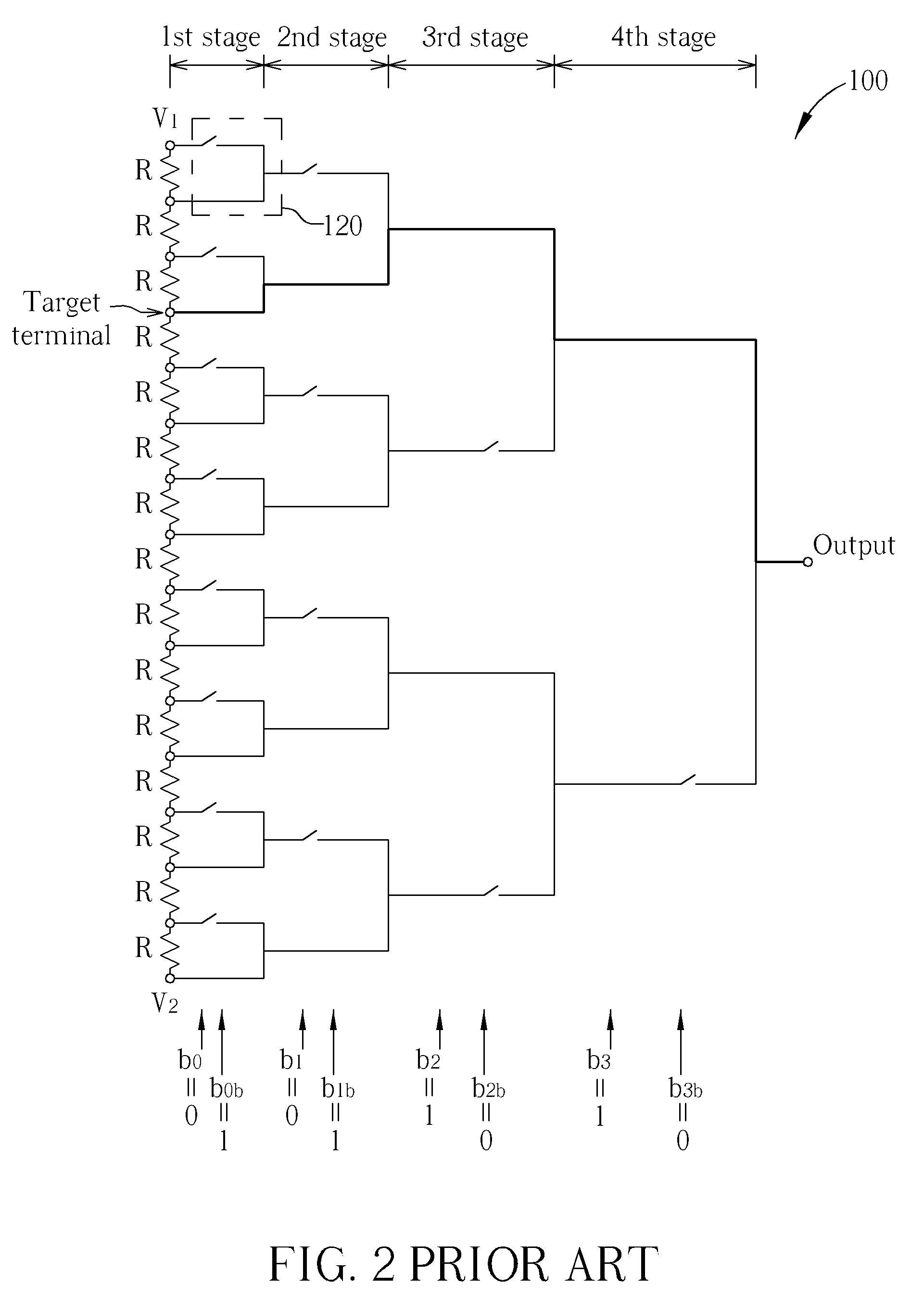

Digital-to-Analog Converter

ActiveUS20070001885A1Circuit loading is loweredReduce layout areaElectric signal transmission systemsDigital-analogue convertorsEngineeringResistor

A DAC has an N-bit R-string DAC section and an (M-N)-bit interpolation DAC section. The N-bit R-string DAC section has a plurality of resistors and a 2-of-N selector. The resistors are electrically connected in series to provide a plurality of voltage levels. The 2-of-N selector is coupled to the series-connected resistors, and is arranged to select two neighboring voltage levels according to an N-bit MSB subword. The (M-N)-bit interpolation DAC section is coupled to the N-bit R-string DAC section, and is arranged to interpolate an analog output signal from the two neighboring voltage levels according to an (M-N)-bit LSB subword.

Owner:HIMAX TECH LTD

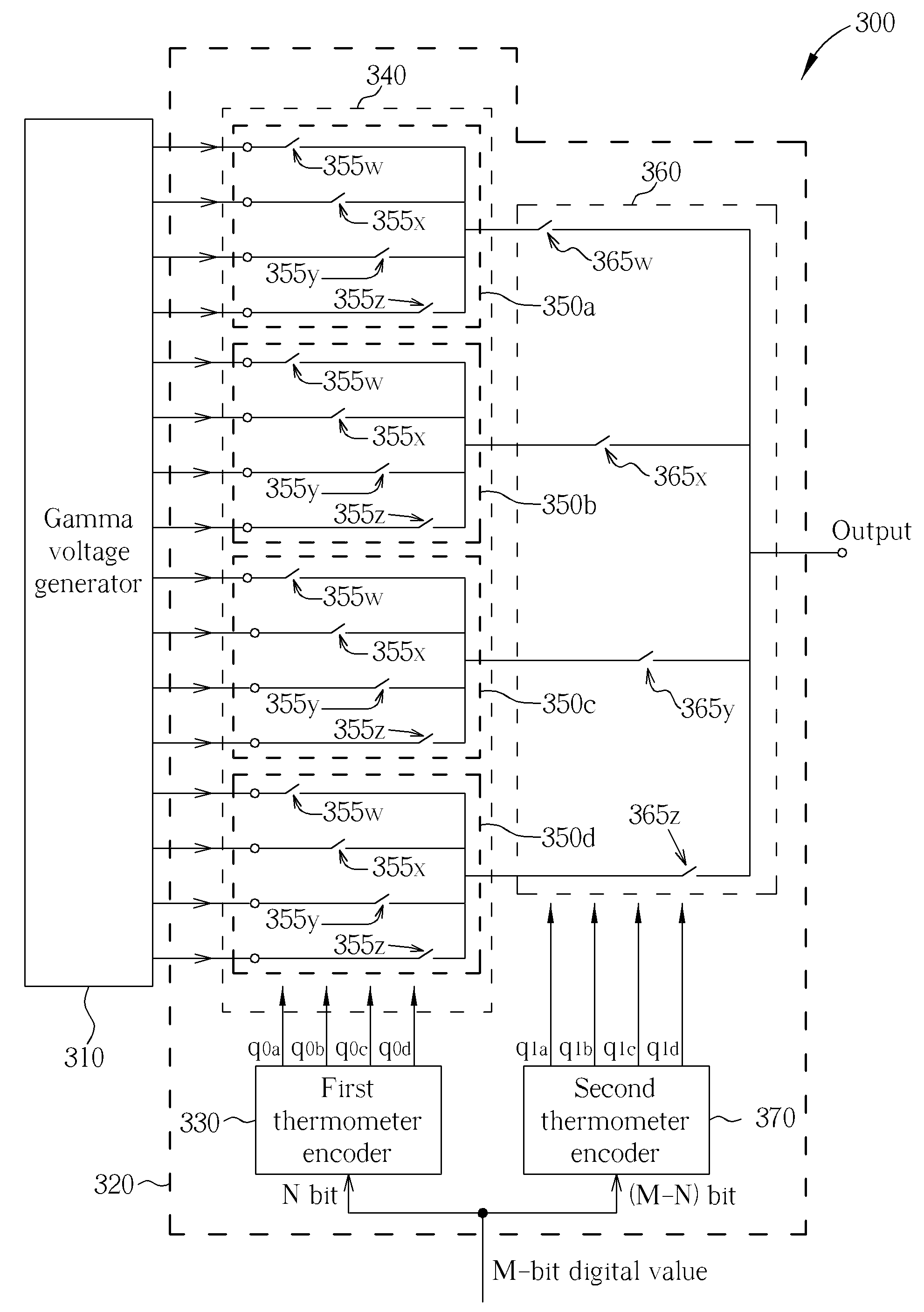

Digital-to-analog converter having efficient switch configuration

ActiveUS20100141494A1Efficient configurationReduce power consumptionElectric signal transmission systemsAnalogue-digital convertersVoltage generatorEngineering

A DAC includes a gamma voltage generator for generating a plurality of gamma voltages, and a decoder for receiving an M-bit digital value for selecting one of the gamma voltages, wherein the decoder comprises a first thermometer encoder, a first selector and a second selector. The first thermometer encoder is utilized to receive N bits of the digital value to generate a first thermometer code with 2N bits, wherein N is smaller than M, and M and N are positive integers. The first selector has a plurality of selecting groups, each selecting group having 2N switches controlled by the first thermometer code to output one gamma voltage, where the second selector receives the gamma voltages outputted by the selecting groups of the first selector and outputs one gamma voltage selected from the received gamma voltages based on the (M−N) bit of the digital value.

Owner:HIMAX TECH LTD