Patents

Literature

63results about How to "Reduce electrostatic discharge" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

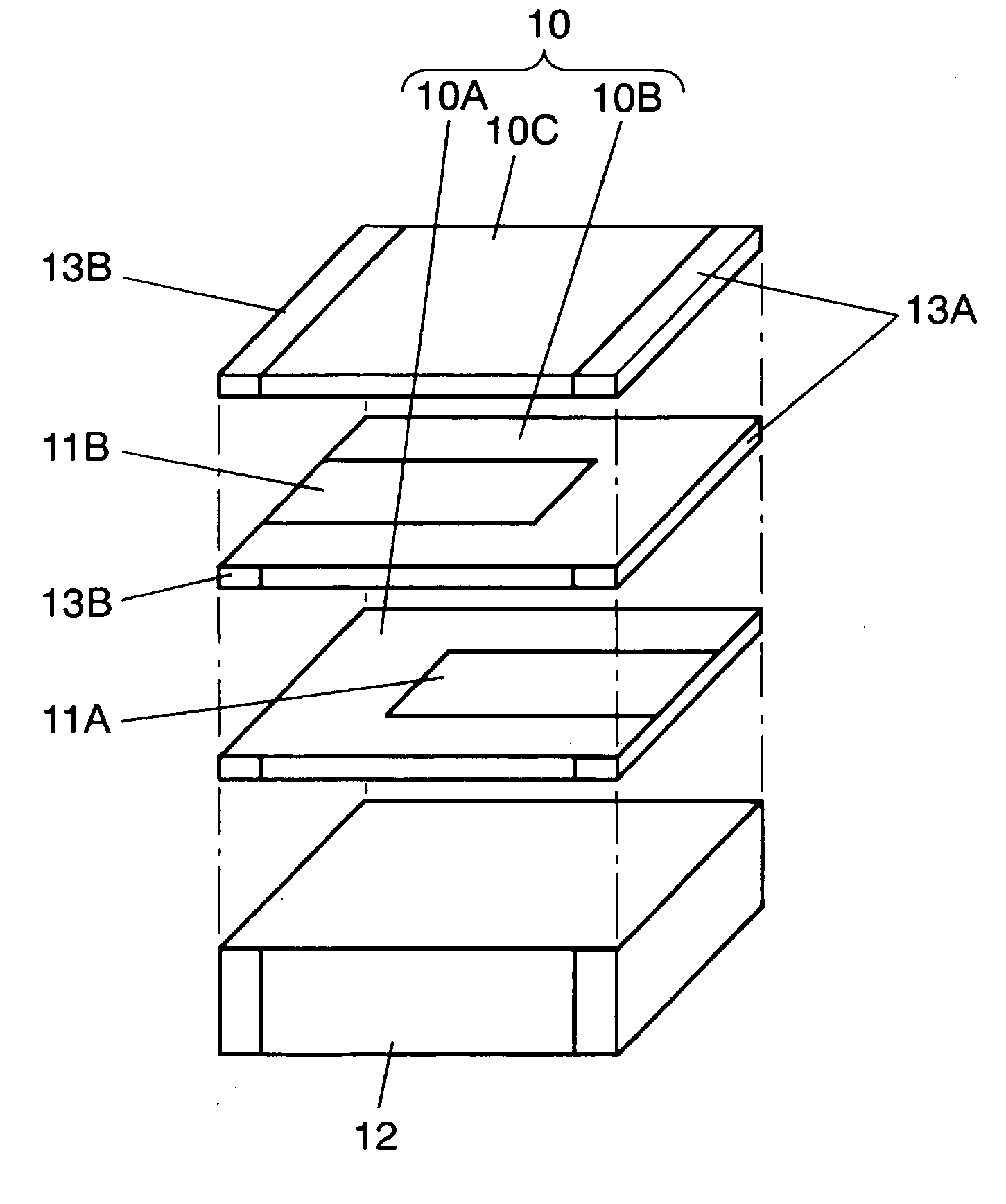

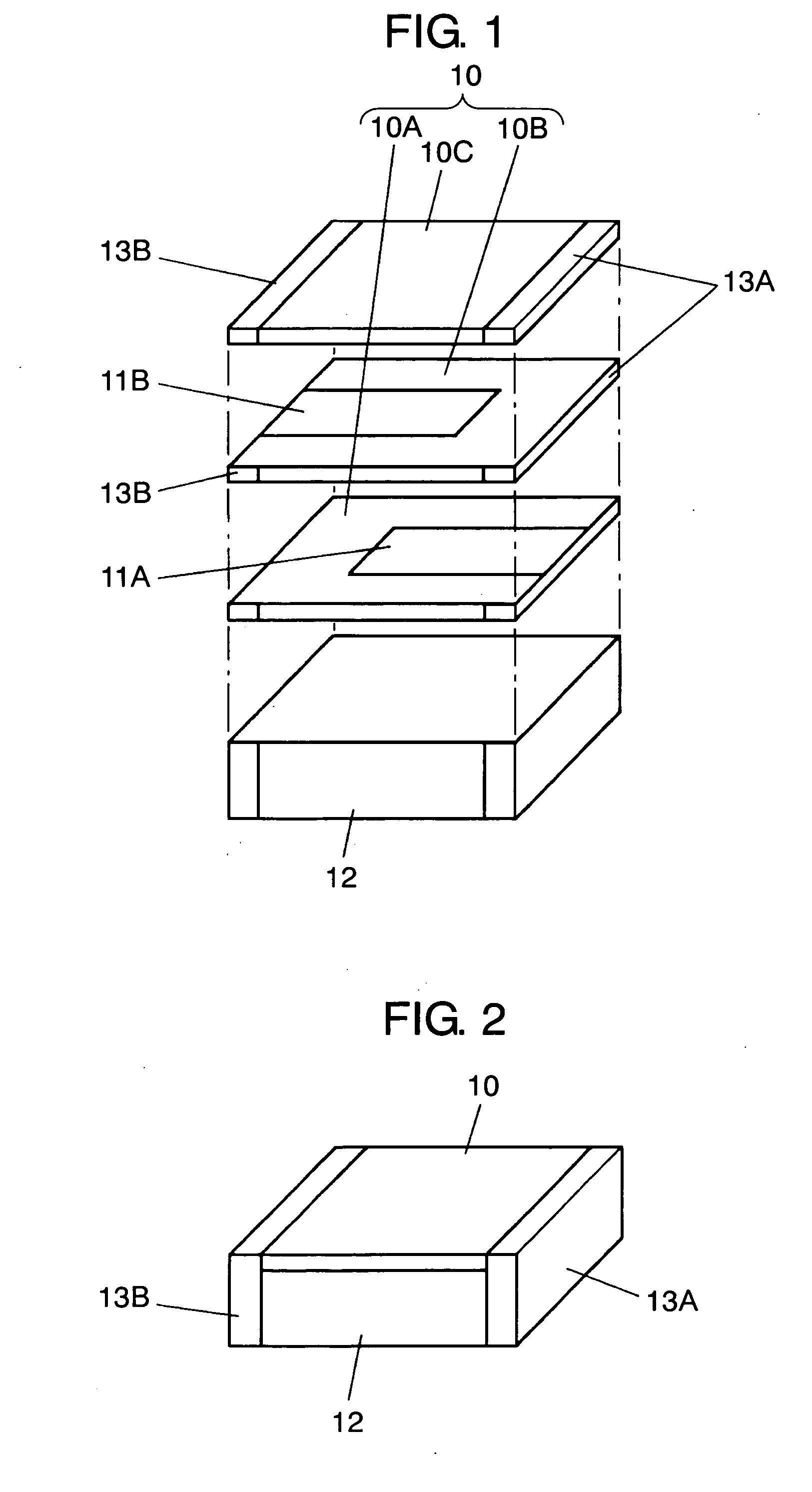

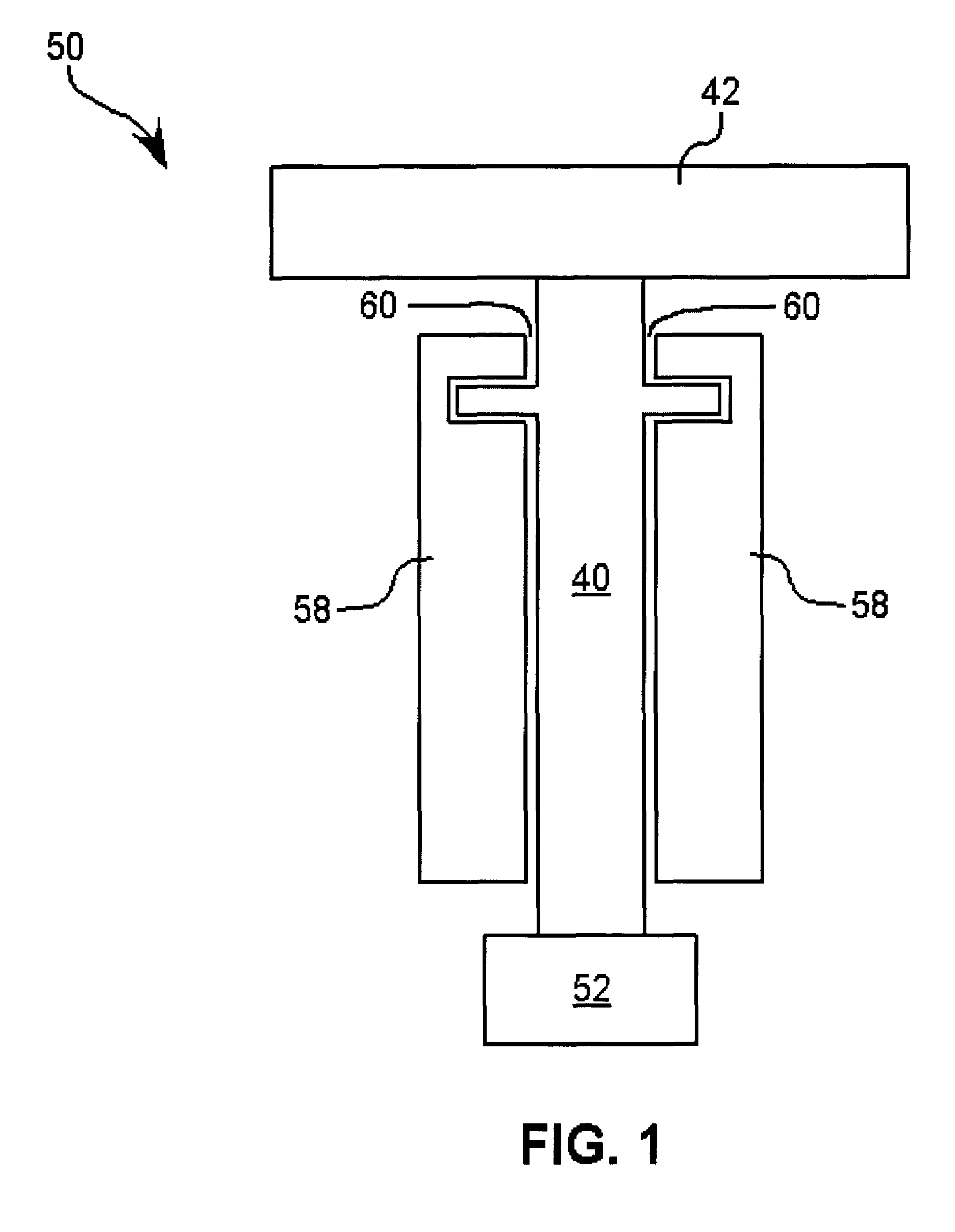

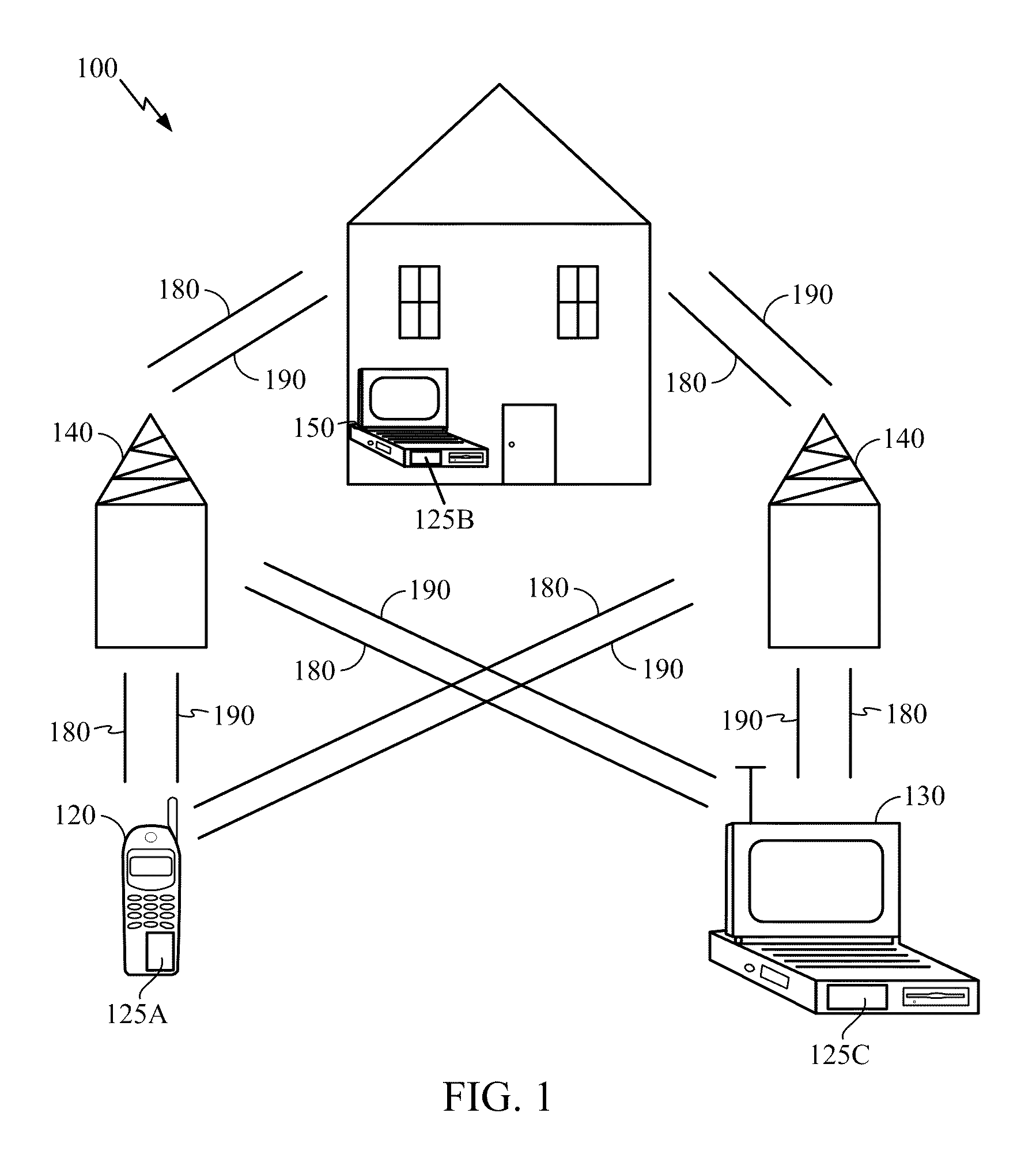

Reduced Susceptibility To Electrostatic Discharge During 3D Semiconductor Device Bonding and Assembly

InactiveUS20100258949A1Reduce electrostatic dischargePotential damagePrinted circuit assemblingSemiconductor/solid-state device detailsElectrostatic dischargeGround plane

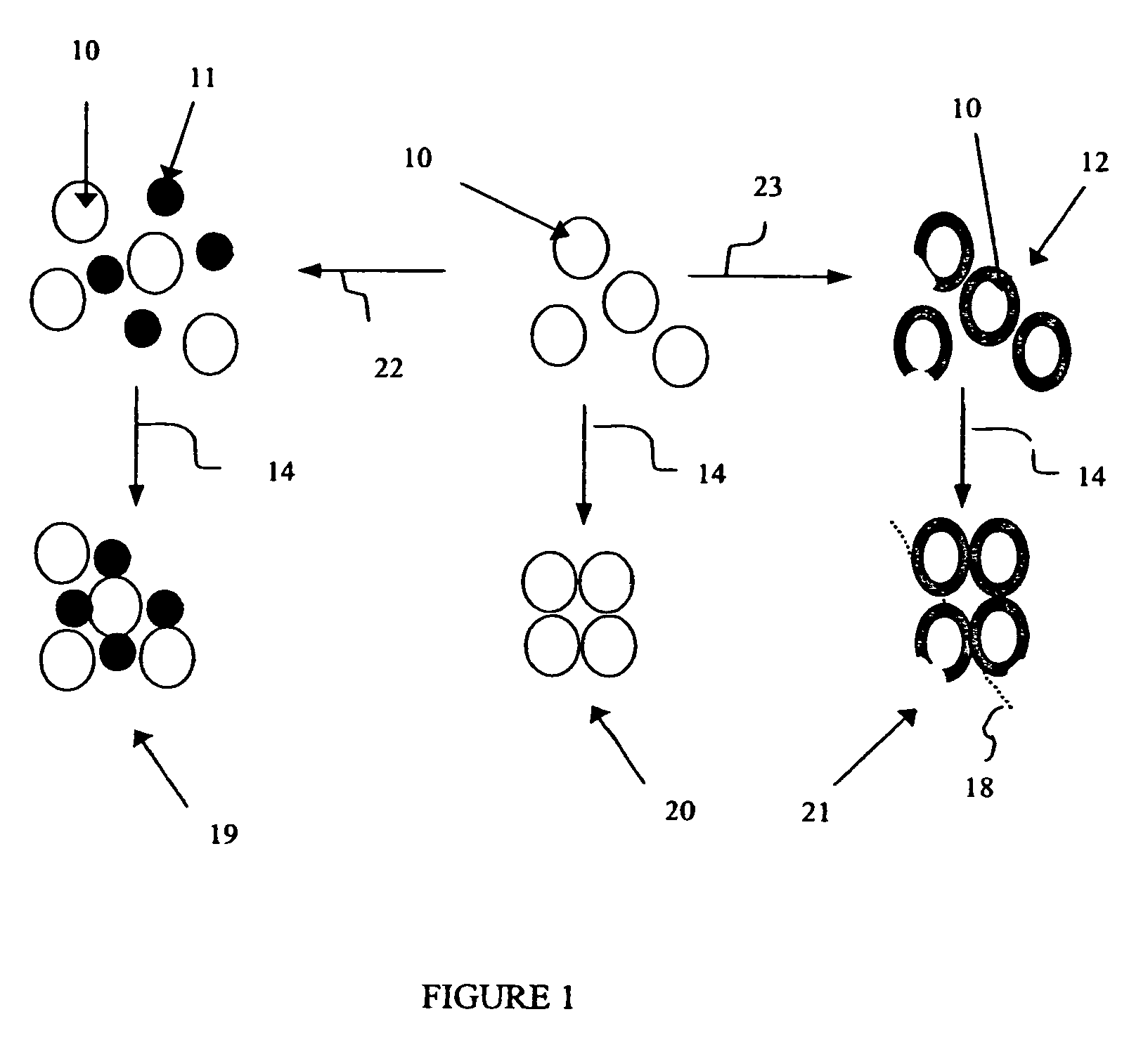

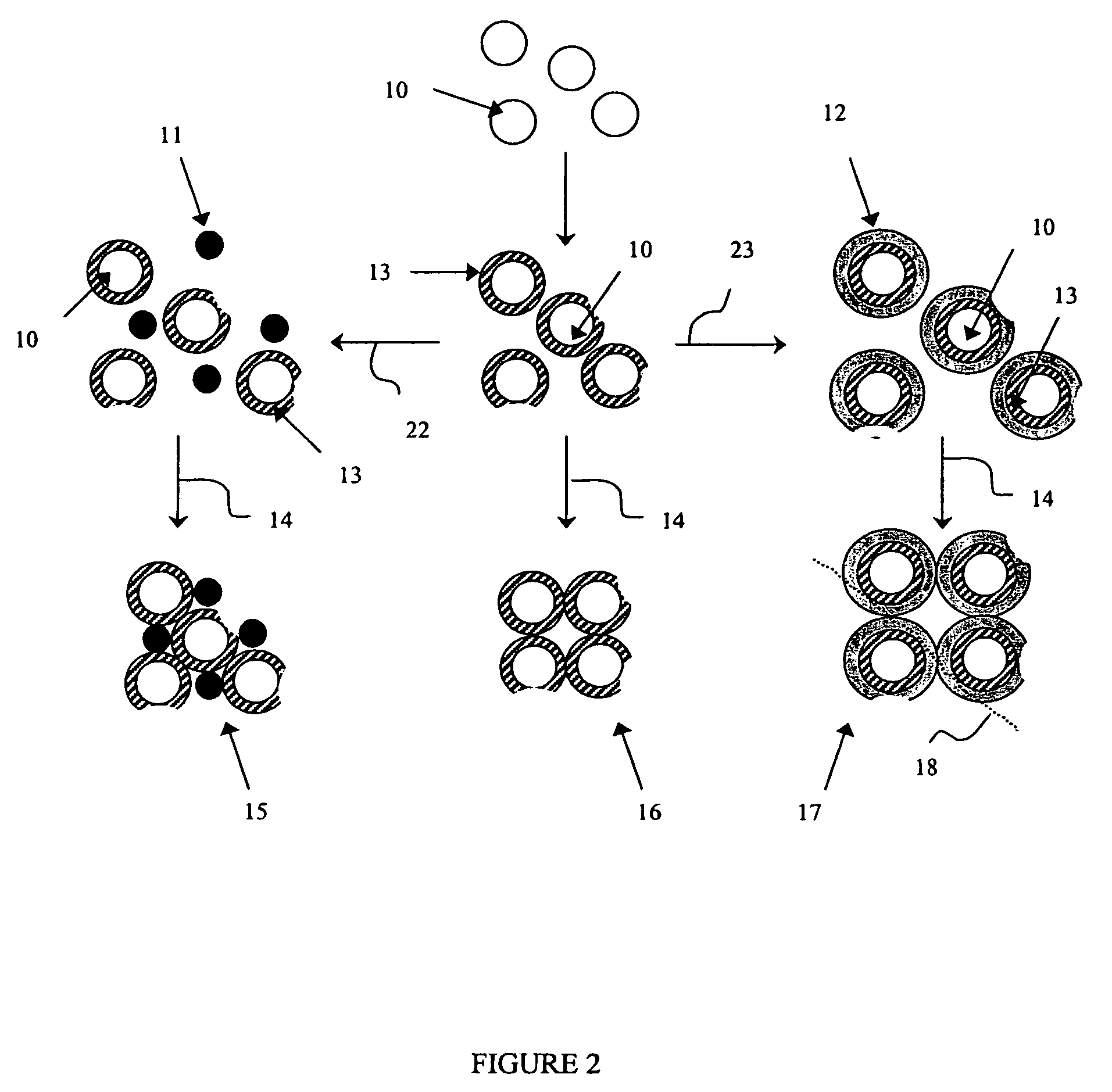

A method to reduce electrostatic discharge susceptibility when assembling a stacked IC device. The method includes coupling a ground plane of a first semiconductor device and a ground plane of a second semiconductor device to substantially a same electrical potential. Active circuitry on the first semiconductor device and active circuitry on the second semiconductor device are electrically coupled after the ground planes are coupled. Electrically coupling the ground planes of the first and the second semiconductor device creates a preferred electrostatic discharge path to ground, thus minimizing potential damage to sensitive circuit elements.

Owner:QUALCOMM INC

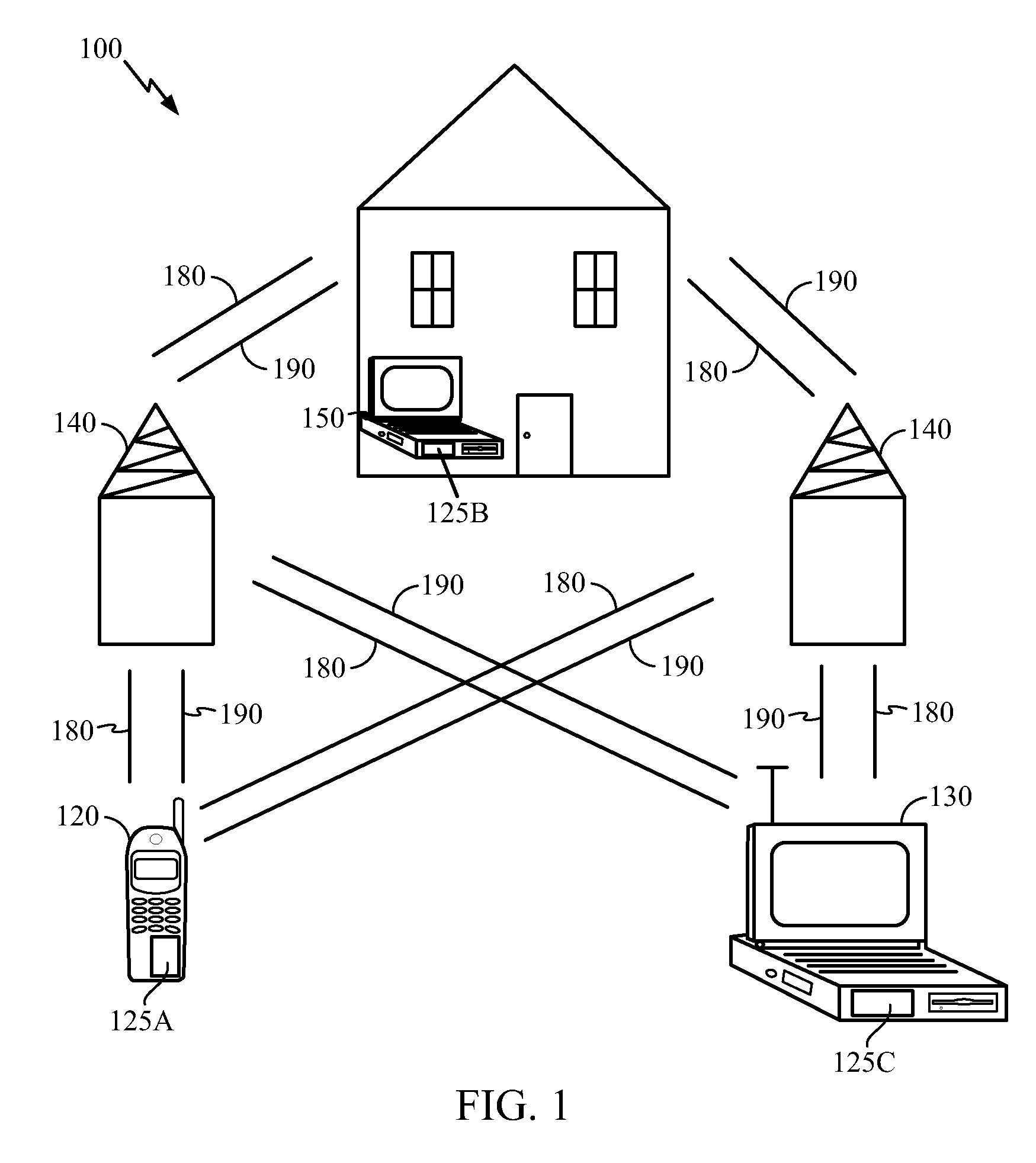

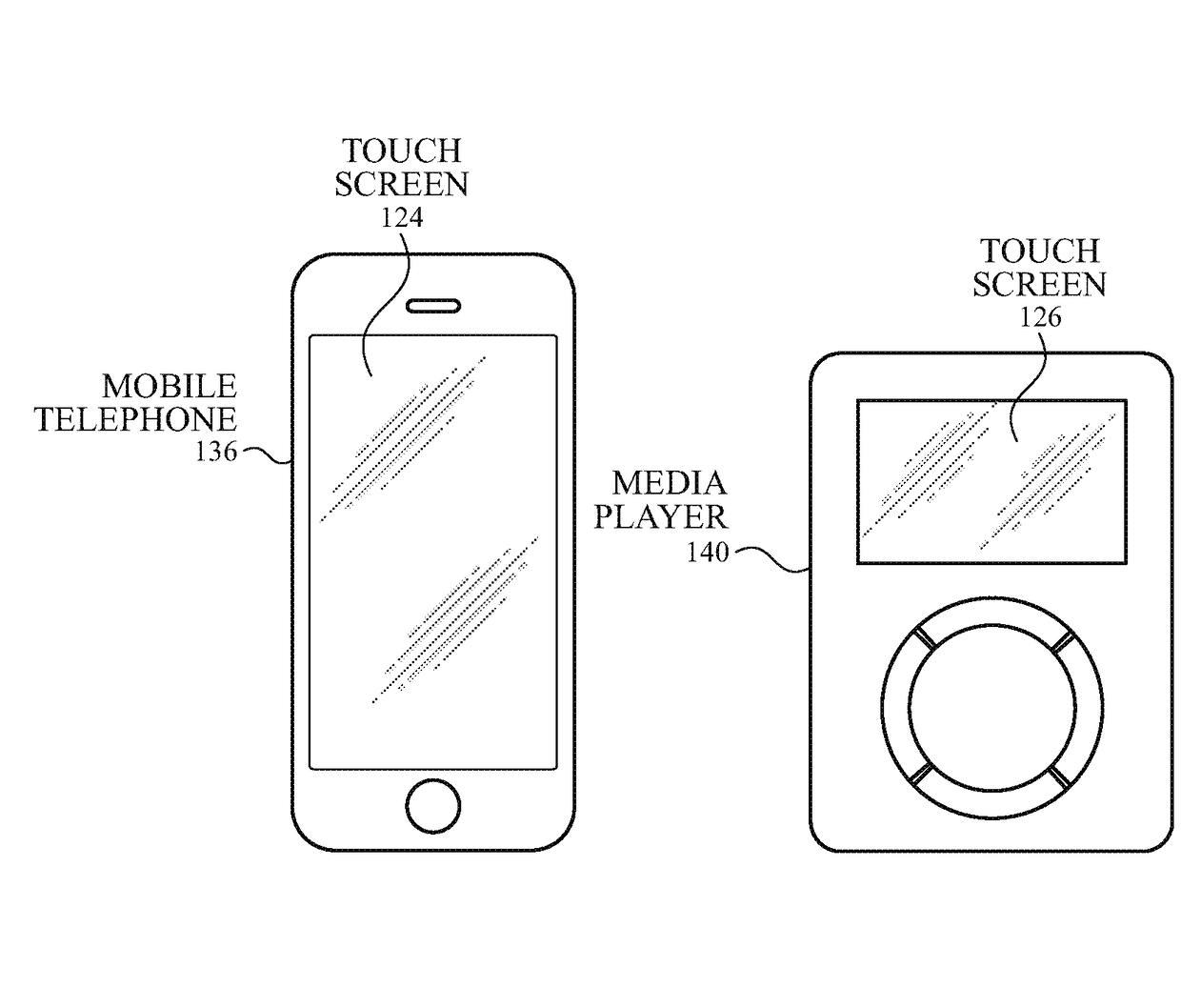

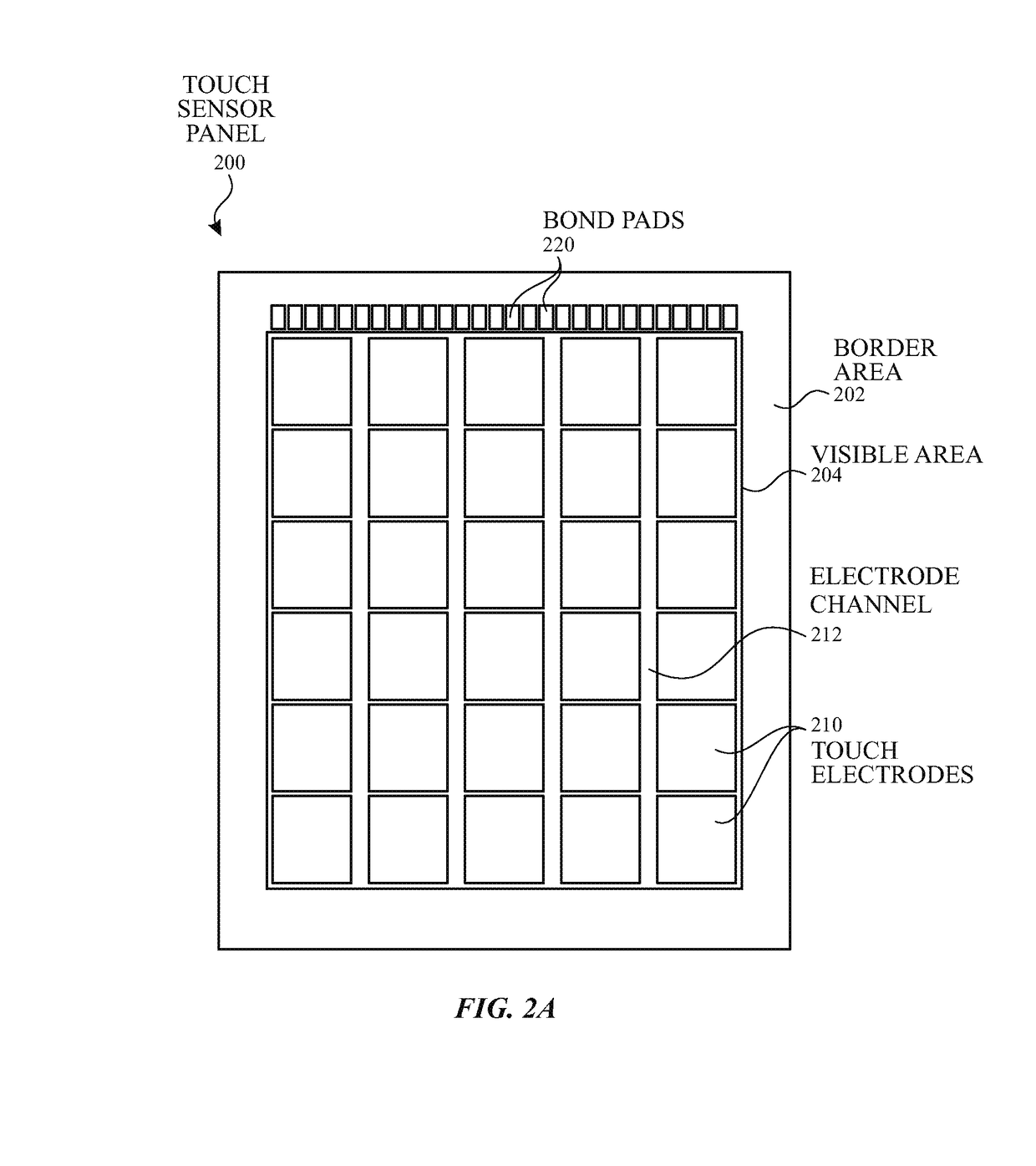

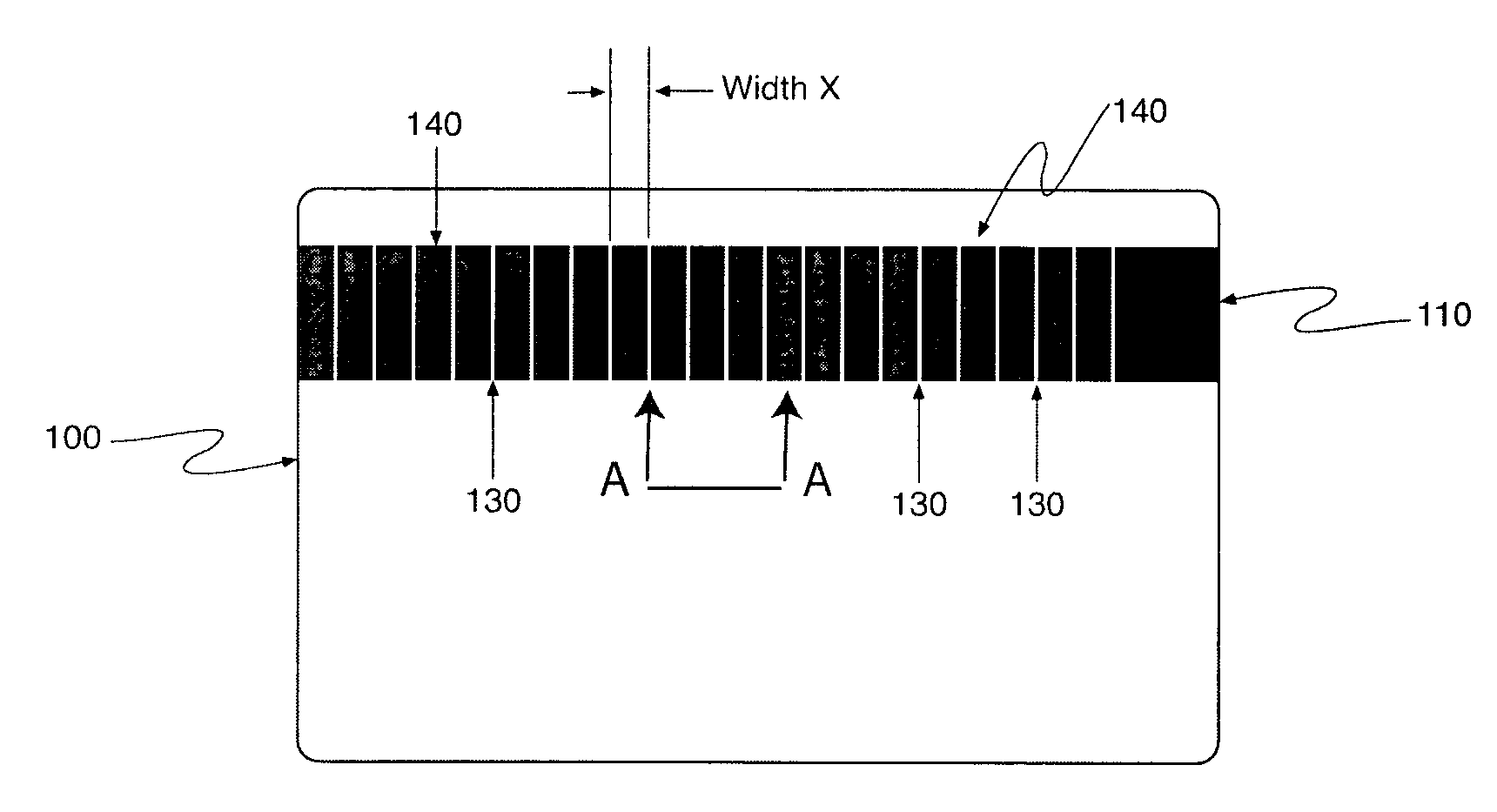

Back of cover touch sensors

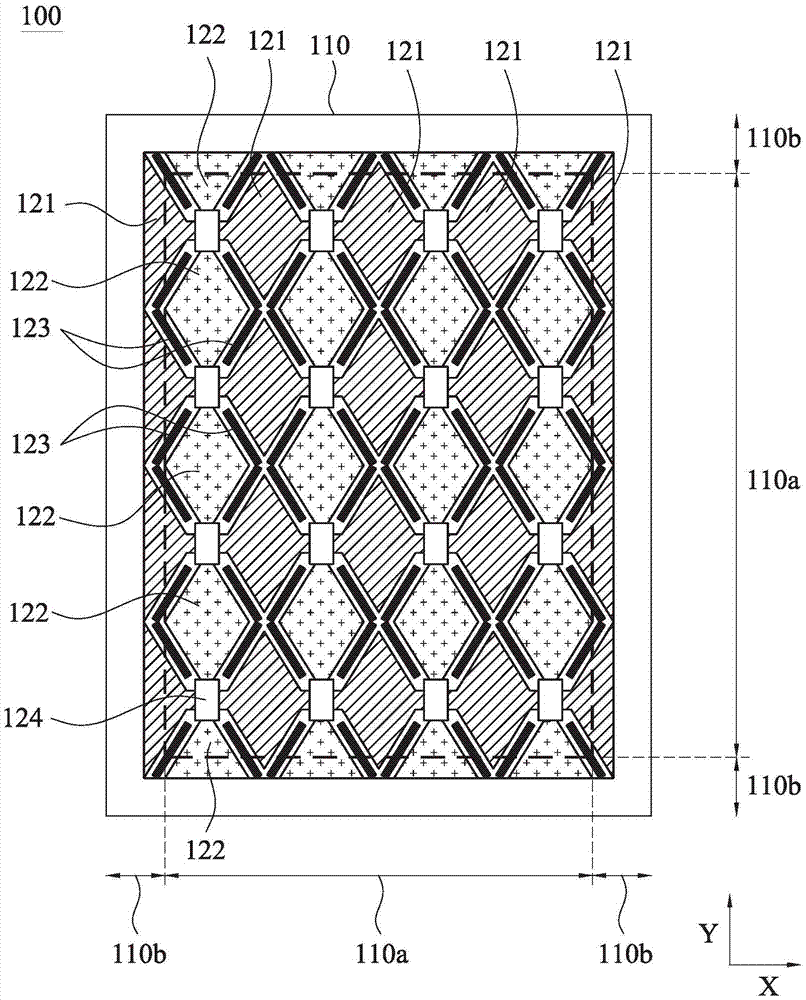

ActiveUS20180067584A1Reduce electrostatic dischargeAffects overall performance of sensorDevices with sensorSubstation equipmentEngineeringBoundary region

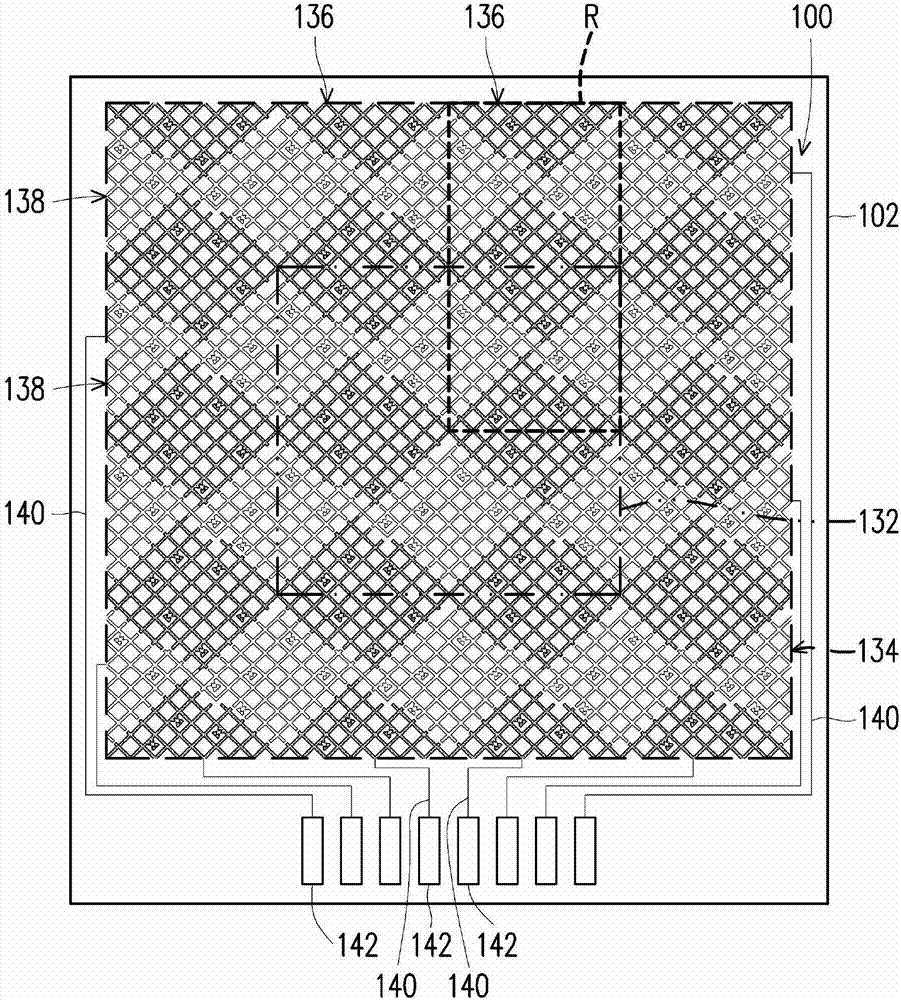

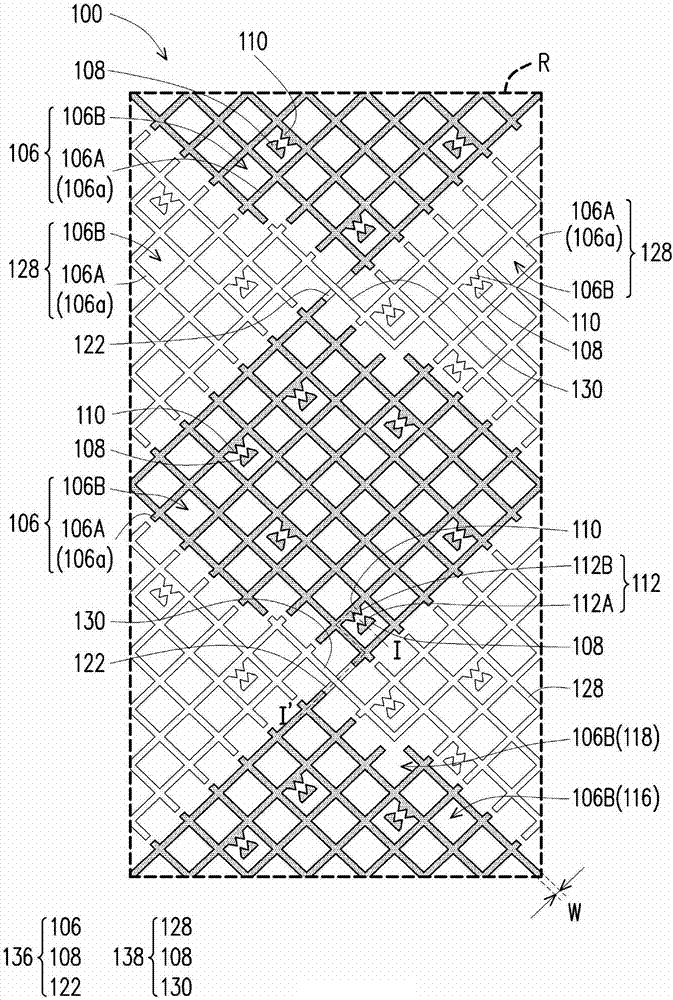

Touch sensor configurations for reducing electrostatic discharge events in the border area of a touch sensor panel is disclosed. Touch sensors (e.g., electrodes formed on the cover material and / or the opaque mask) can be susceptible to certain events such as arcing and discharge / joule heating, which may negatively affect touch sensor performance. Examples of the disclosure can include increasing the trace width, spacing, and / or thickness in the border area relative to the trace width, spacing, and / or thickness in the visible / active area along one or more sides of the touch sensor panel. In some examples, touch electrodes can be located exclusively in the visible / active areas along one or more sides of the touch sensor panel, while dummy sections can be included in both the border and visible / active areas. Additionally or alternatively, one or more gaps between adjacent touch electrodes in the border area or serpentine routing can be included.

Owner:APPLE INC

Method for fabricating organic light emitting display device

ActiveUS20090311824A1Reduced responseAvoid damageElectroluminescent light sourcesSolid-state devicesDisplay deviceLight-emitting diode

A fabricating method of an organic light emitting display device including performing a sheet test as a sheet unit on a mother board formed with panels and sheet wires for supplying test signals to the panels on the mother board, the method including: forming drive elements for driving the panels in each of the panels and forming sheet wires electrically coupled to at least a portion of the drive elements and shorting bar electrically coupling all of the sheet wires; forming organic light emitting diodes in each of the panels and isolating the sheet wires from each other by etching open regions of the shorting bar apart from contact regions of the shorting bar for coupling the shorting bar to the sheet wires; performing the sheet test on the plurality of panels by supplying the test signals to the sheet wires; and separating the panels by scribing the mother board.

Owner:SAMSUNG DISPLAY CO LTD

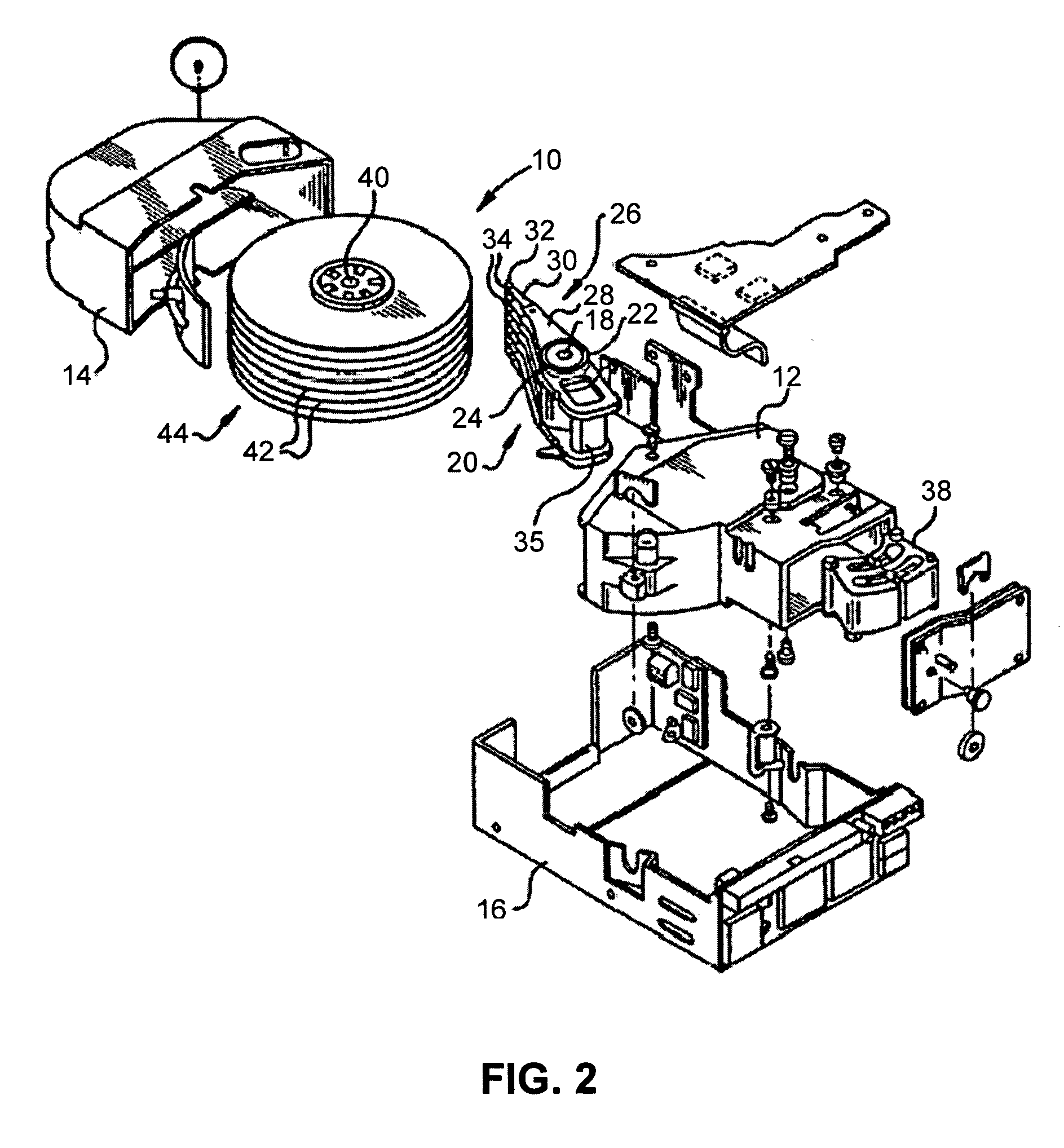

Low permittivity lubricant for magnetic disk drive systems

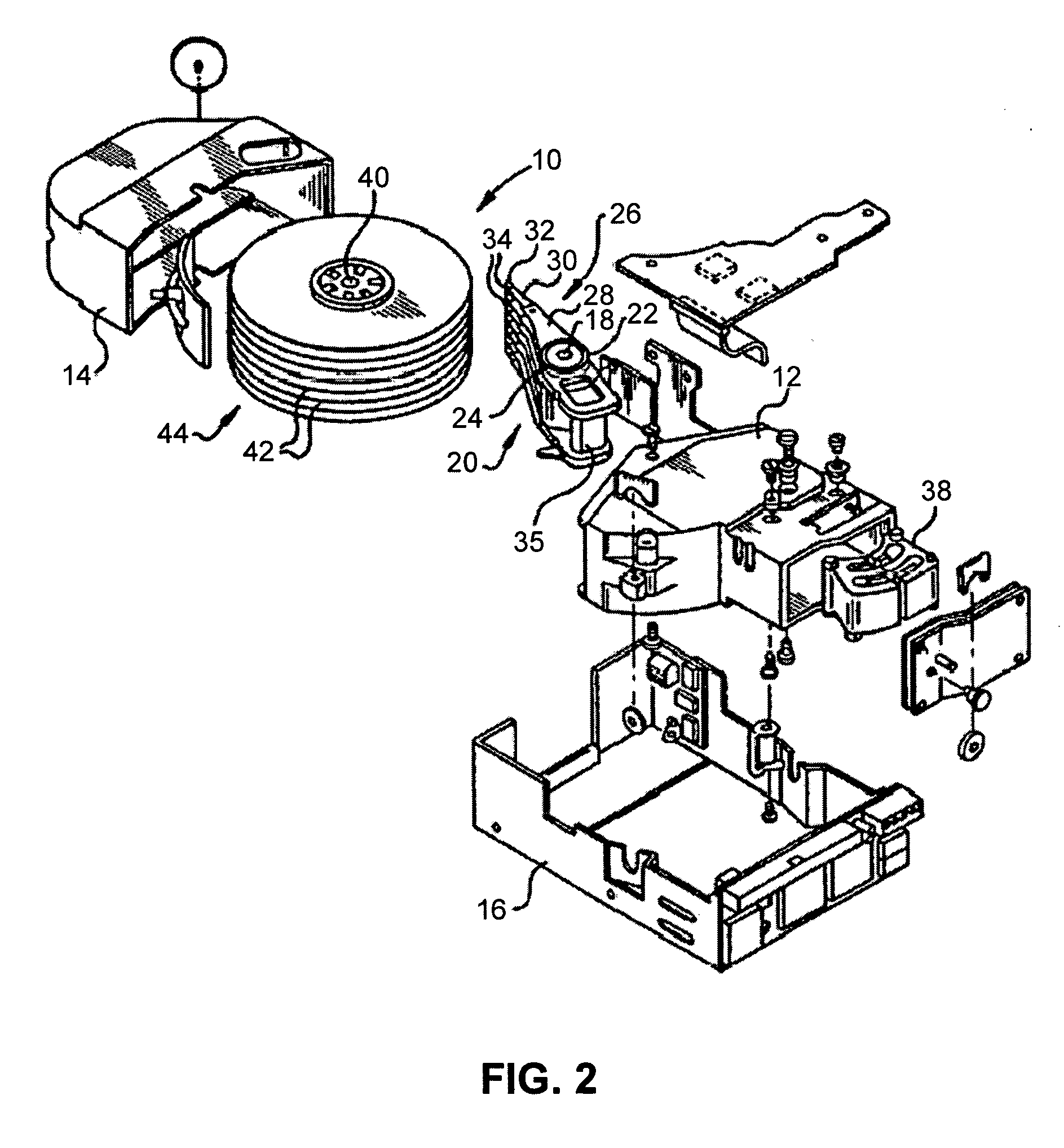

InactiveUS20050068667A1Lower relative electrical permittivityReduce electrostatic dischargeShaftsRecord information storageCharge controlEngineering

An improved disk drive system that employs a lubricant with improved charge control is provided. The disk drive system is comprised of a rotatably mounted magnetic disk. A rotor is coupled to the disk and rotatably retained by a stator. A bearing is formed that serves as an interface between the stator and the rotor. A motor coupled to the rotor rotates the magnetic disk via the rotor. Located in the bearing is a lubricant having a low relative electrical permittivity.

Owner:WESTERN DIGITAL TECH INC

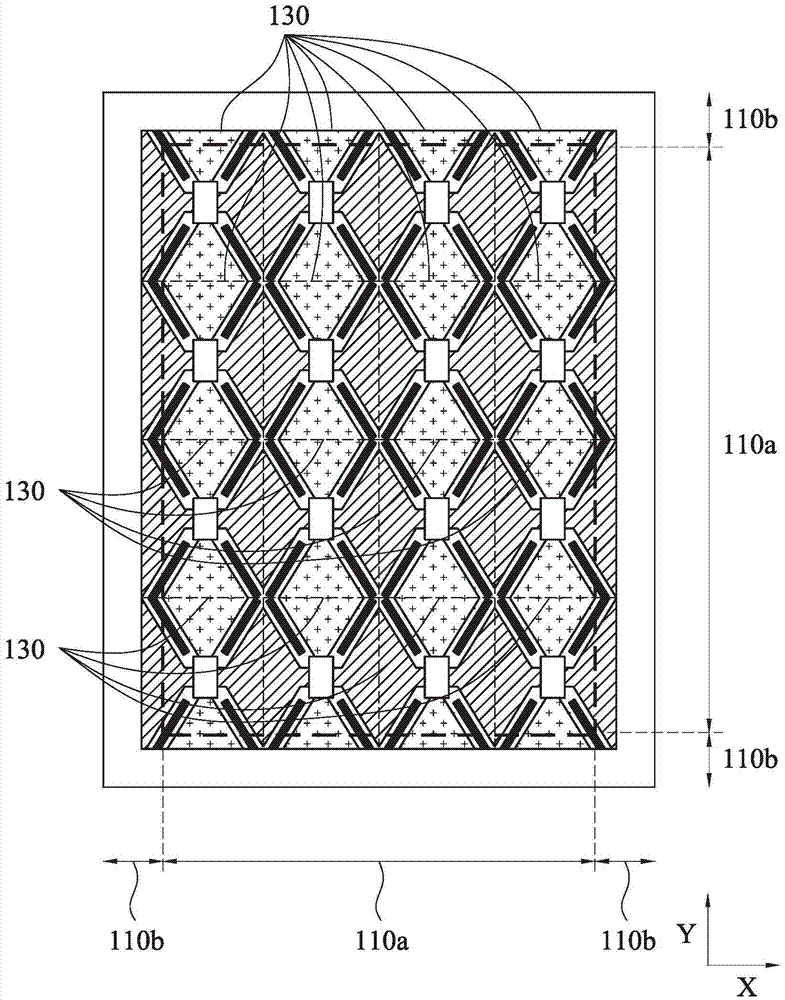

Touch panel and electronic apparatus

ActiveCN106933398AReduce electrostatic dischargeInput/output processes for data processingComputer scienceTouch panel

The invention discloses a touch panel and an electronic apparatus. The touch panel comprises a substrate, a plurality of first electrode blocks and a plurality of second electrode blocks. The substrate has a display region and a non display region. The first electrode blocks and the second electrode blocks are formed on the substrate, and the second electrode blocks are arranged around the first electrode blocks. Each first electrode block is completely arranged in the display region, and at least one part of each second electrode block is located in the non display region. Each first electrode block comprises a first touch electrode pattern and a first virtual electrode pattern. Each of the second electrode blocks comprises a second touch electrode pattern and a second region; at least one part of the second region comprises at least one second virtual electrode pattern; and the area of the second virtual electrode pattern is smaller than that of the first virtual electrode pattern. According to the touch panel and the electronic apparatus, the electrostatic discharge probability can be reduced.

Owner:HANNSTAR DISPLAY CORPORATION

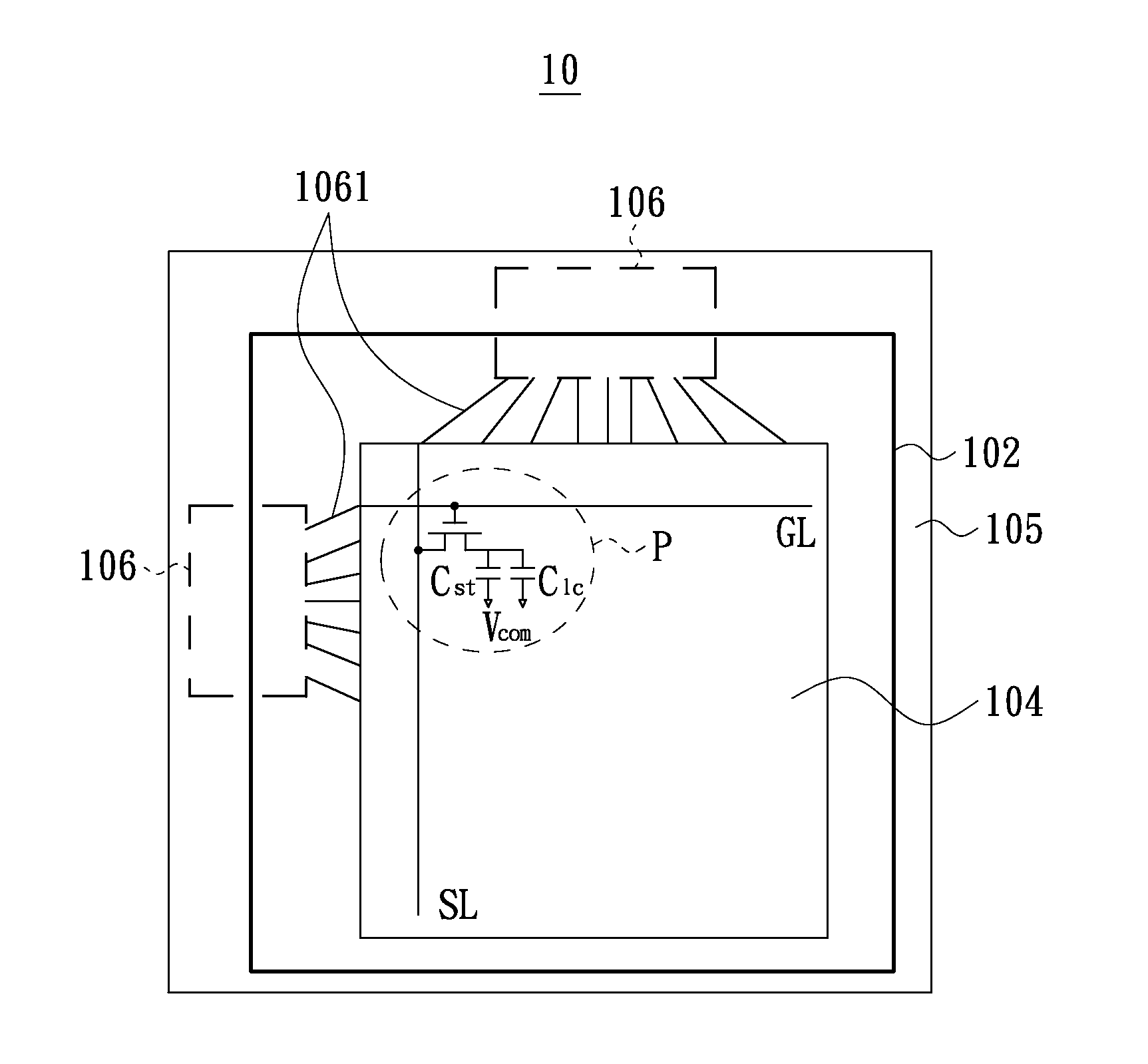

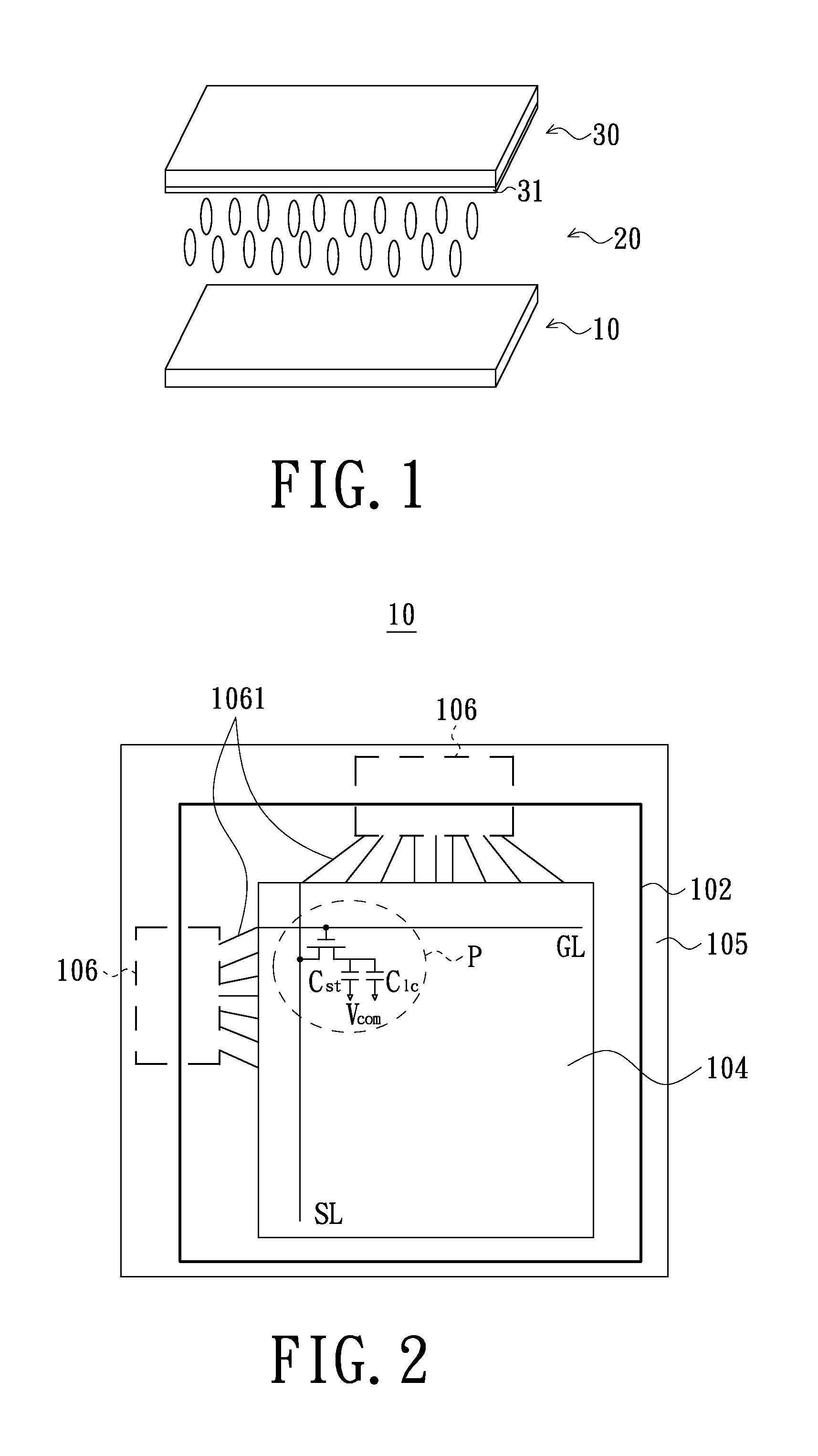

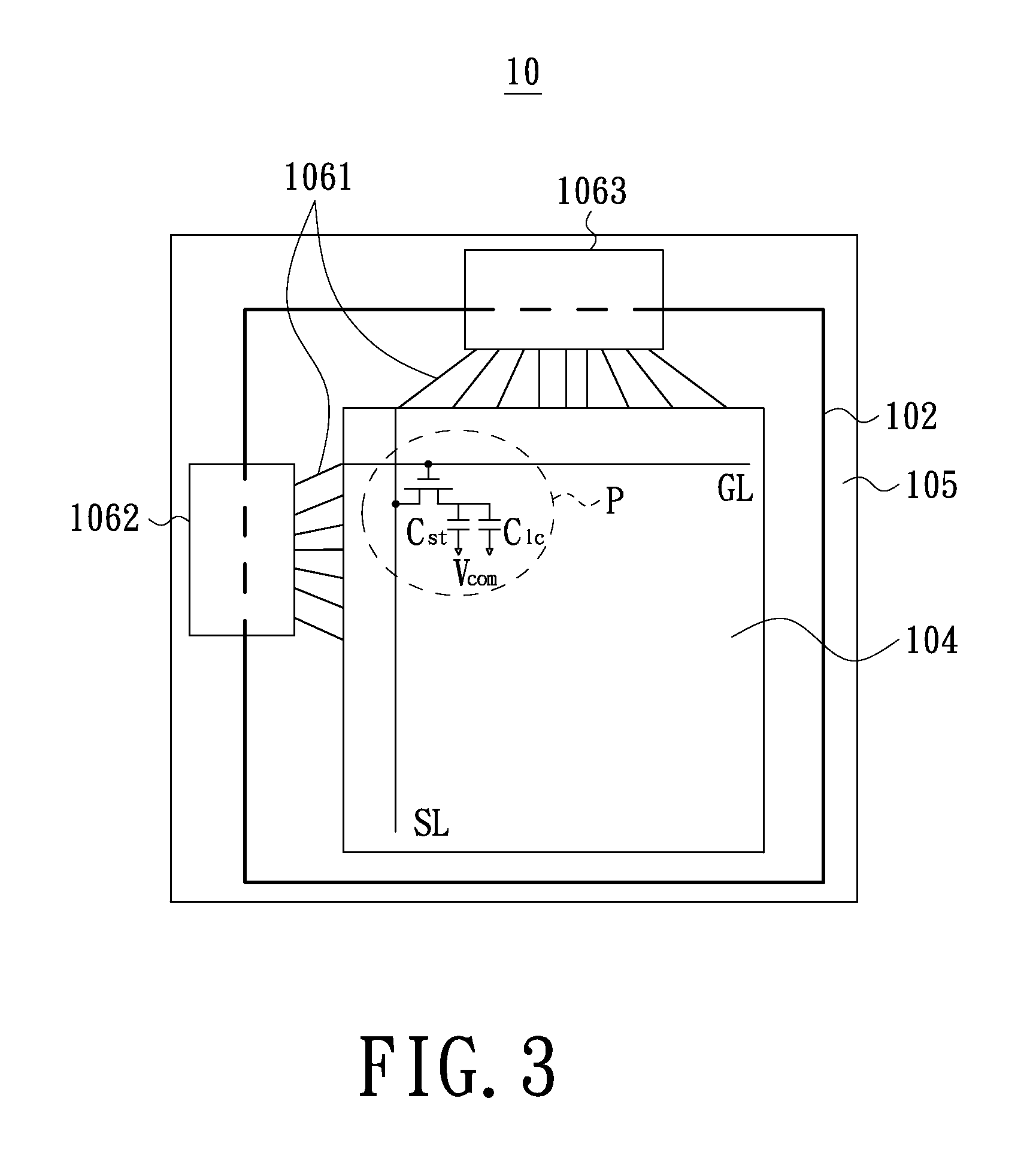

Display device and display array substrate

ActiveUS20120281159A1Reduce electrostatic dischargeEnhanced ESD protectionStatic indicating devicesNon-linear opticsDisplay deviceOptoelectronics

A display device comprises a display array substrate, a common substrate and a display layer. The display array substrate comprises a display region and a periphery region, and at least one chip-bonding area is formed in the periphery region. The display layer is sandwiched between the display array substrate and the common-electrode substrate. A conductive loop is disposed in the periphery region of the display array substrate, and passes through the chip-bonding area.

Owner:E INK HLDG INC

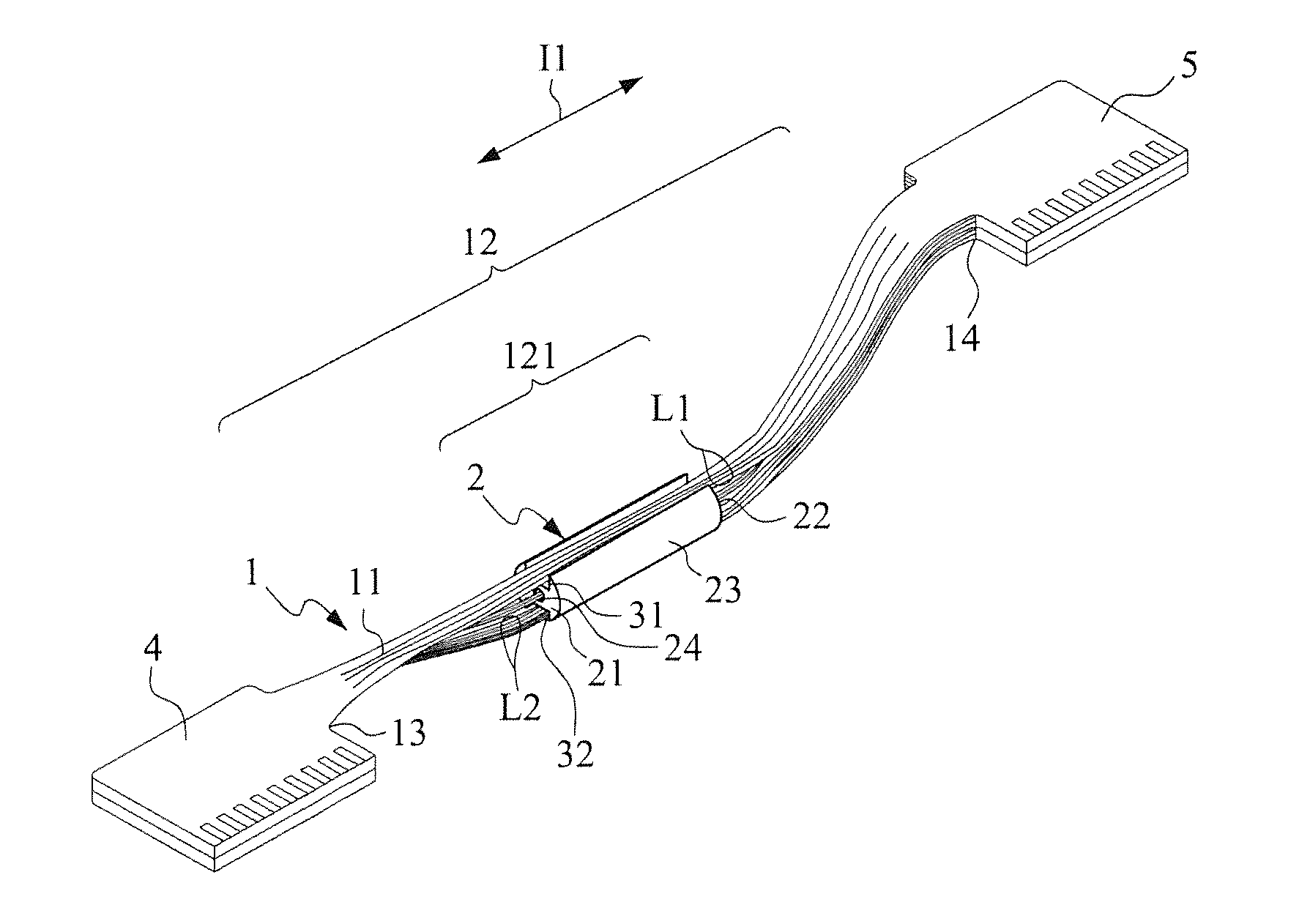

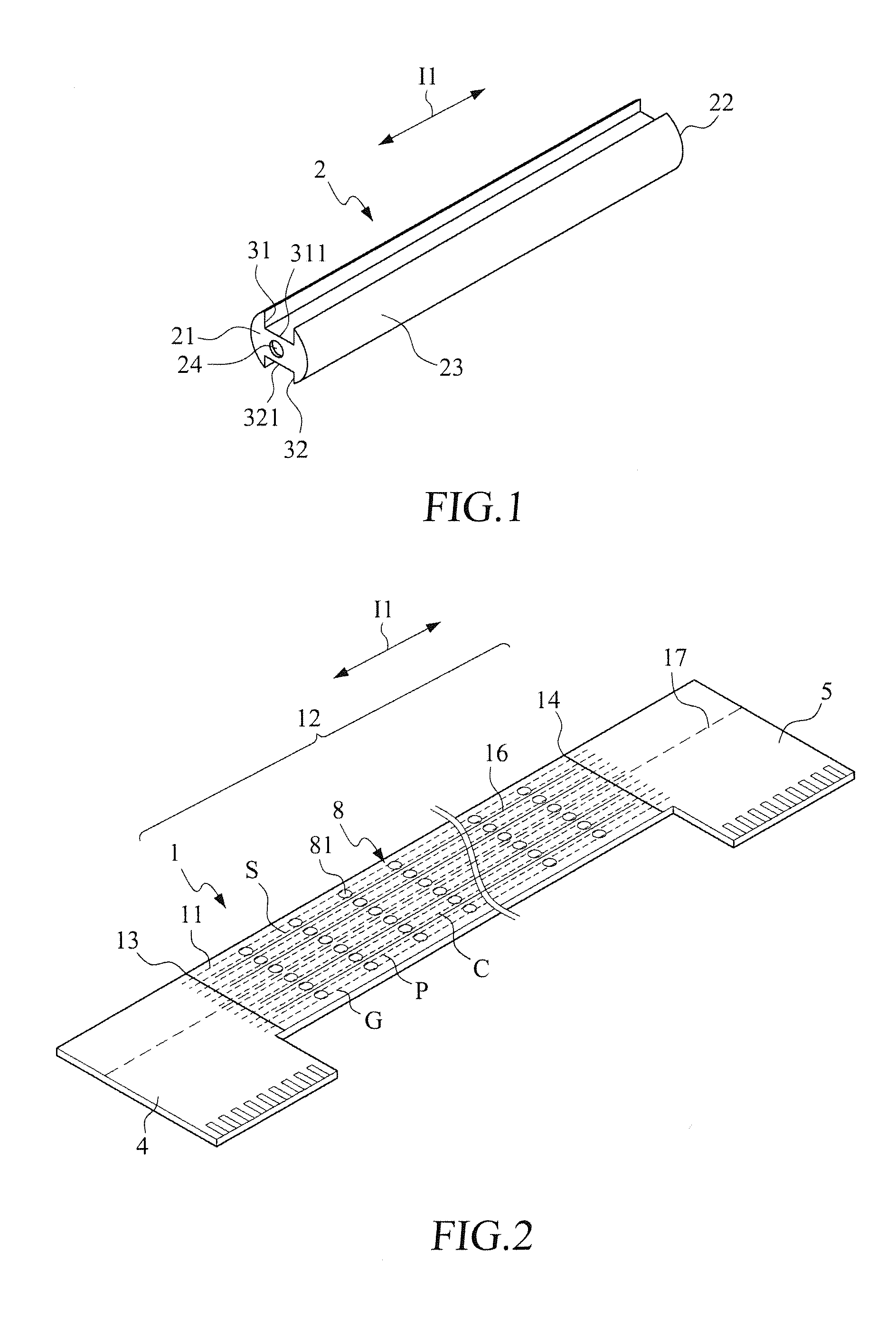

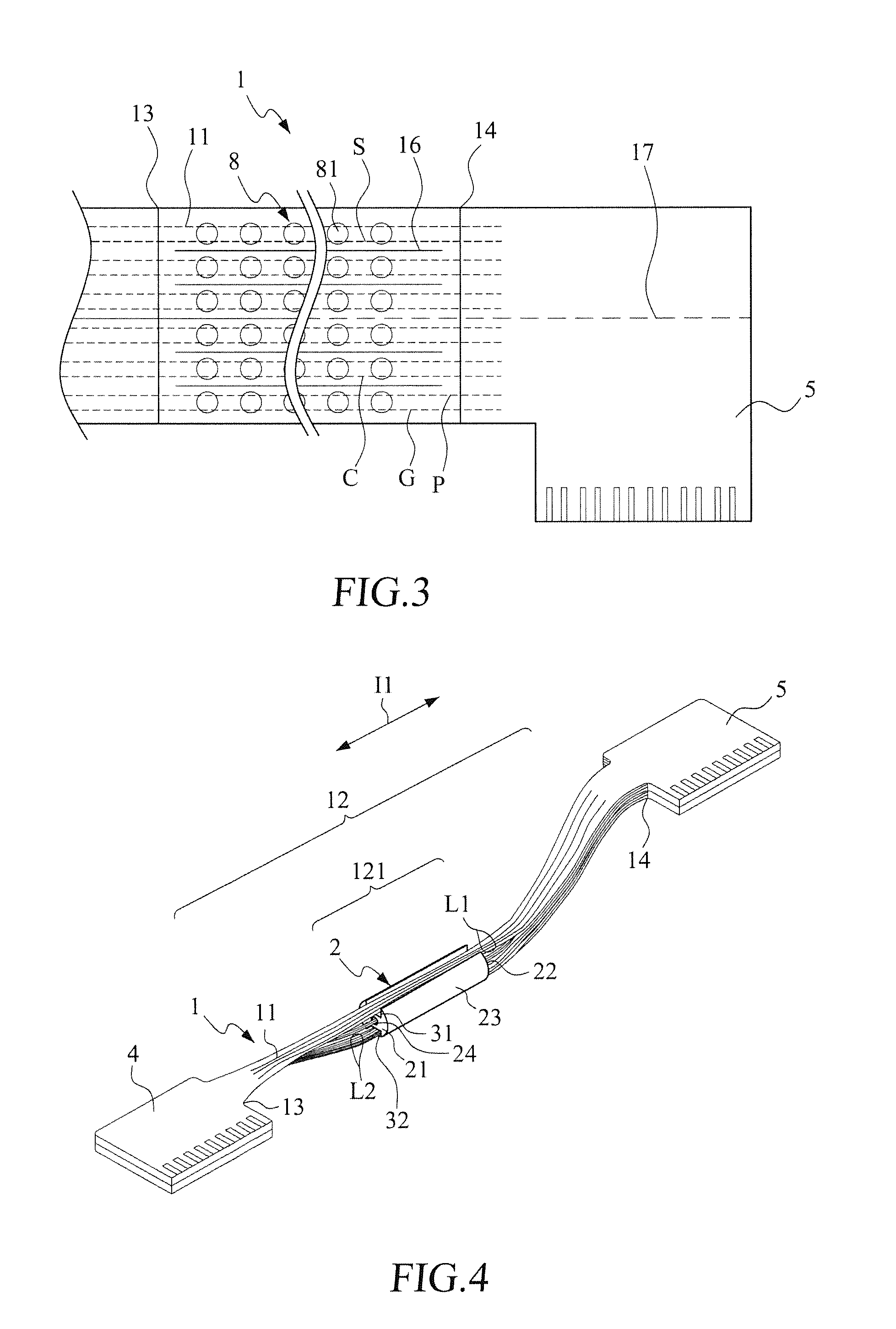

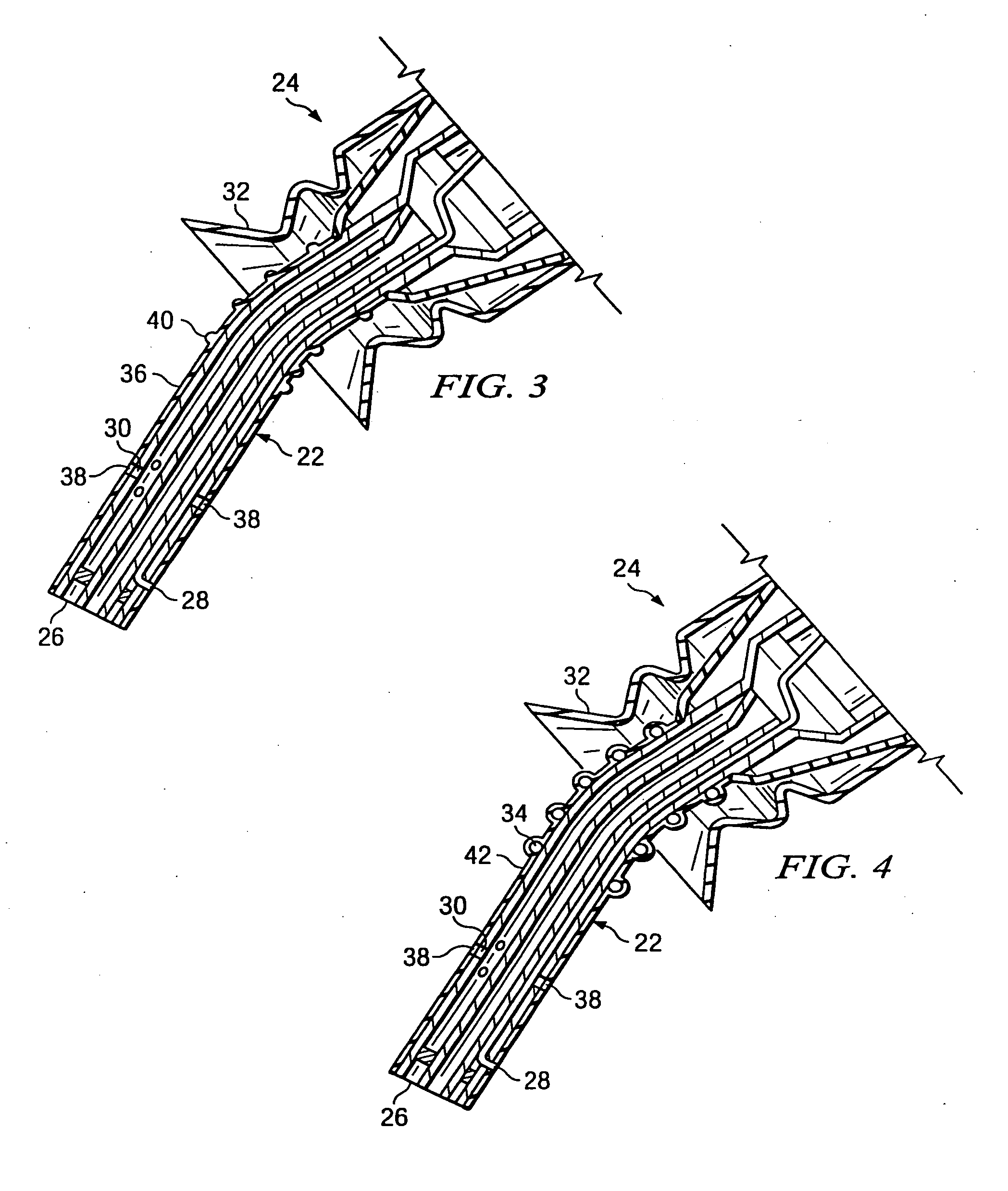

Bundle division structure for flexible circuit cable

InactiveUS20140097021A1Reduce mutual interferenceReduce electrostatic dischargePrinted circuit aspectsHigh frequency circuit adaptationsElectrical conductorFlexible circuits

Owner:ADVANCED FLEXIBLE CIRCUITS

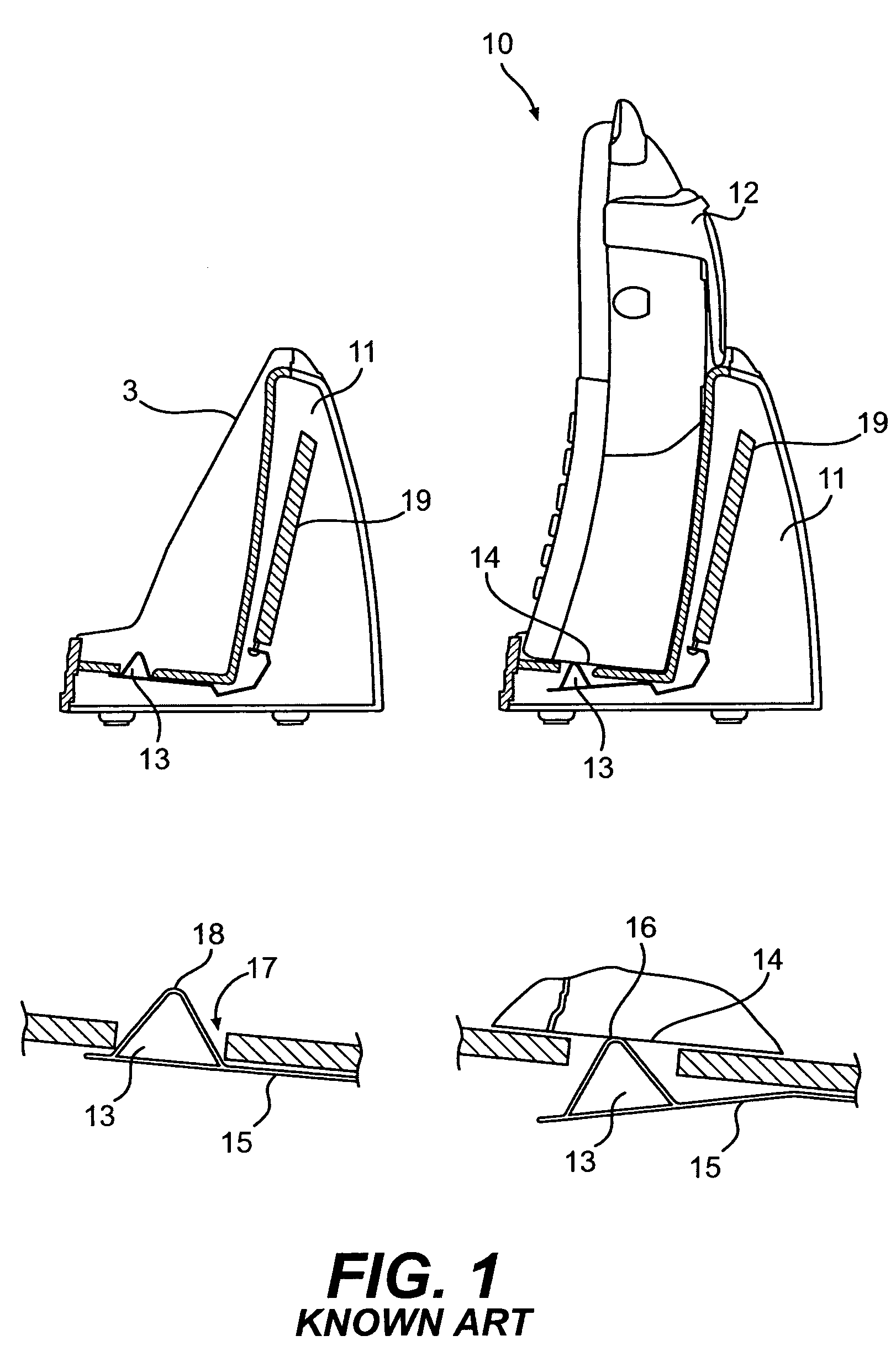

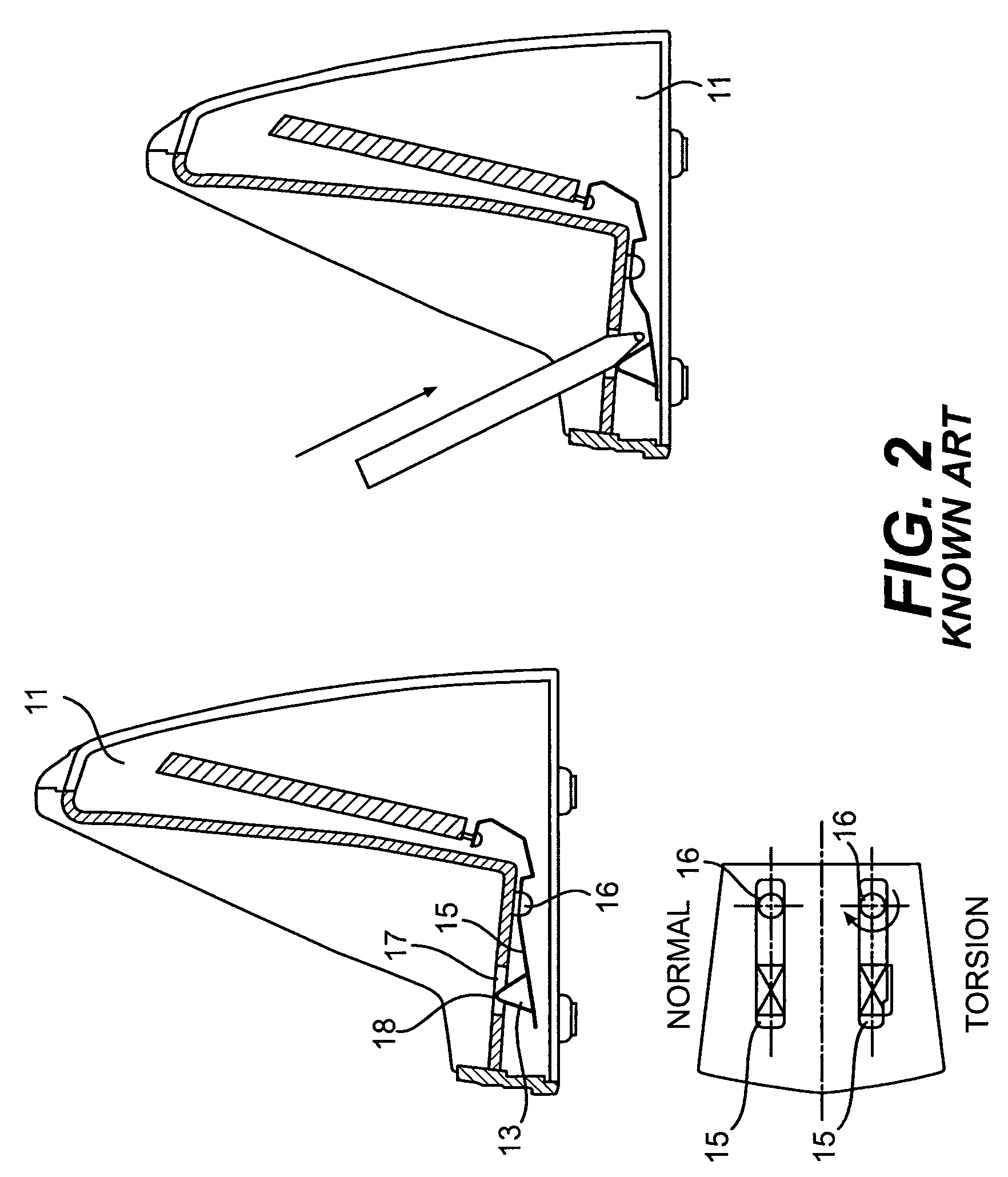

Electrostatic discharge enhanced charge contact design

ActiveUS7316592B2Reduce electrostatic dischargeBatteries circuit arrangementsCoupling contact membersElectrostatic dischargeHandset

Owner:VTECH TELECOMM

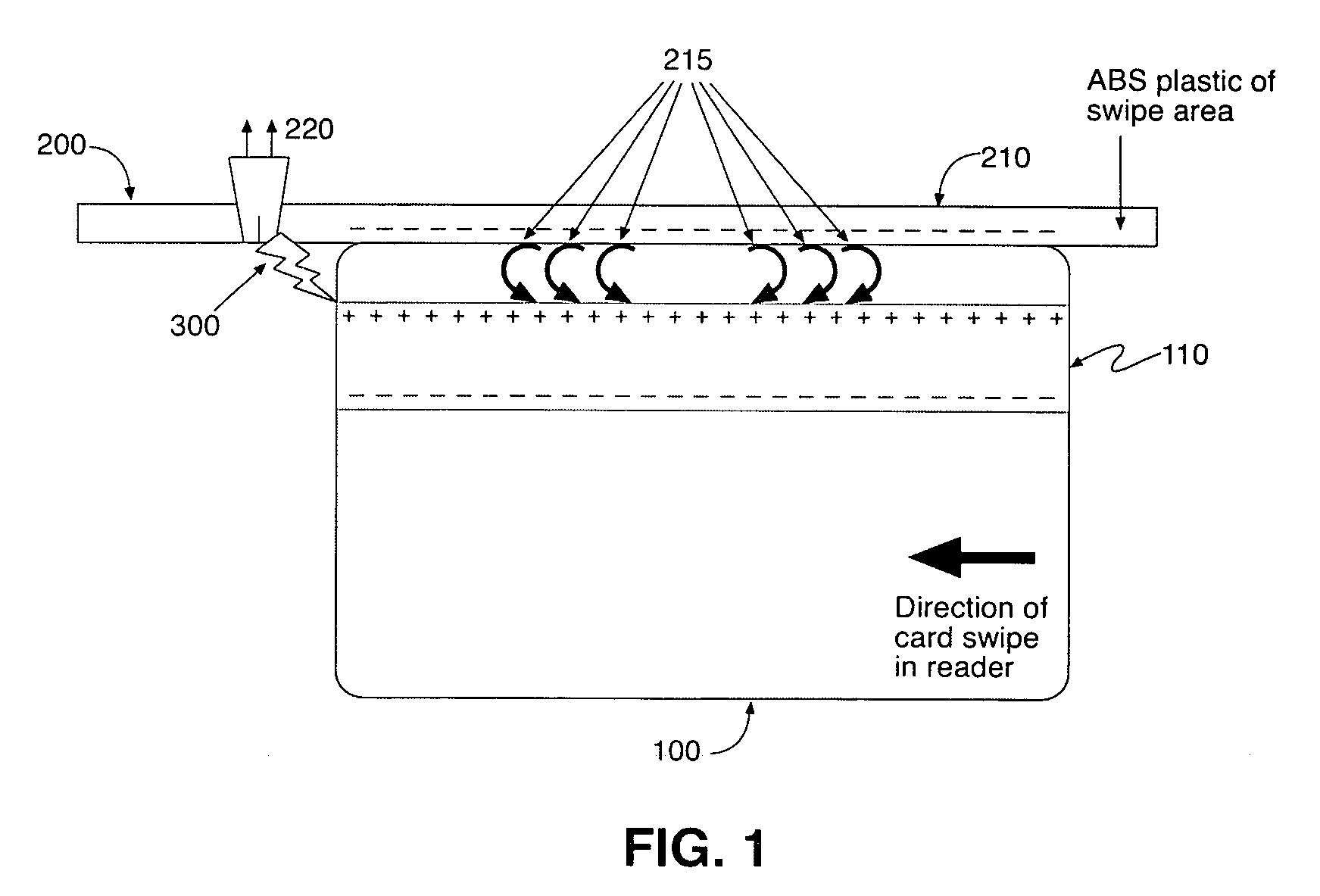

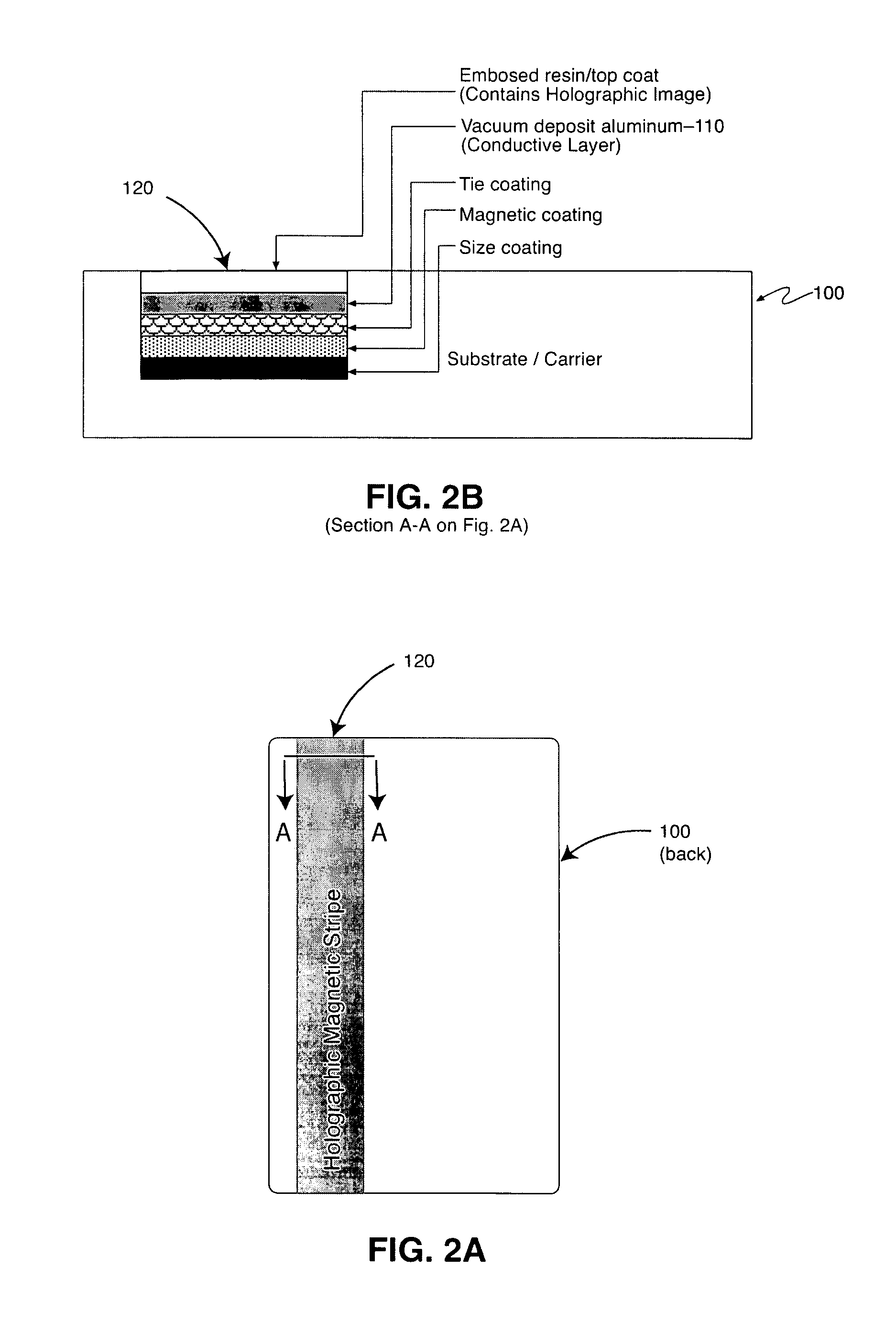

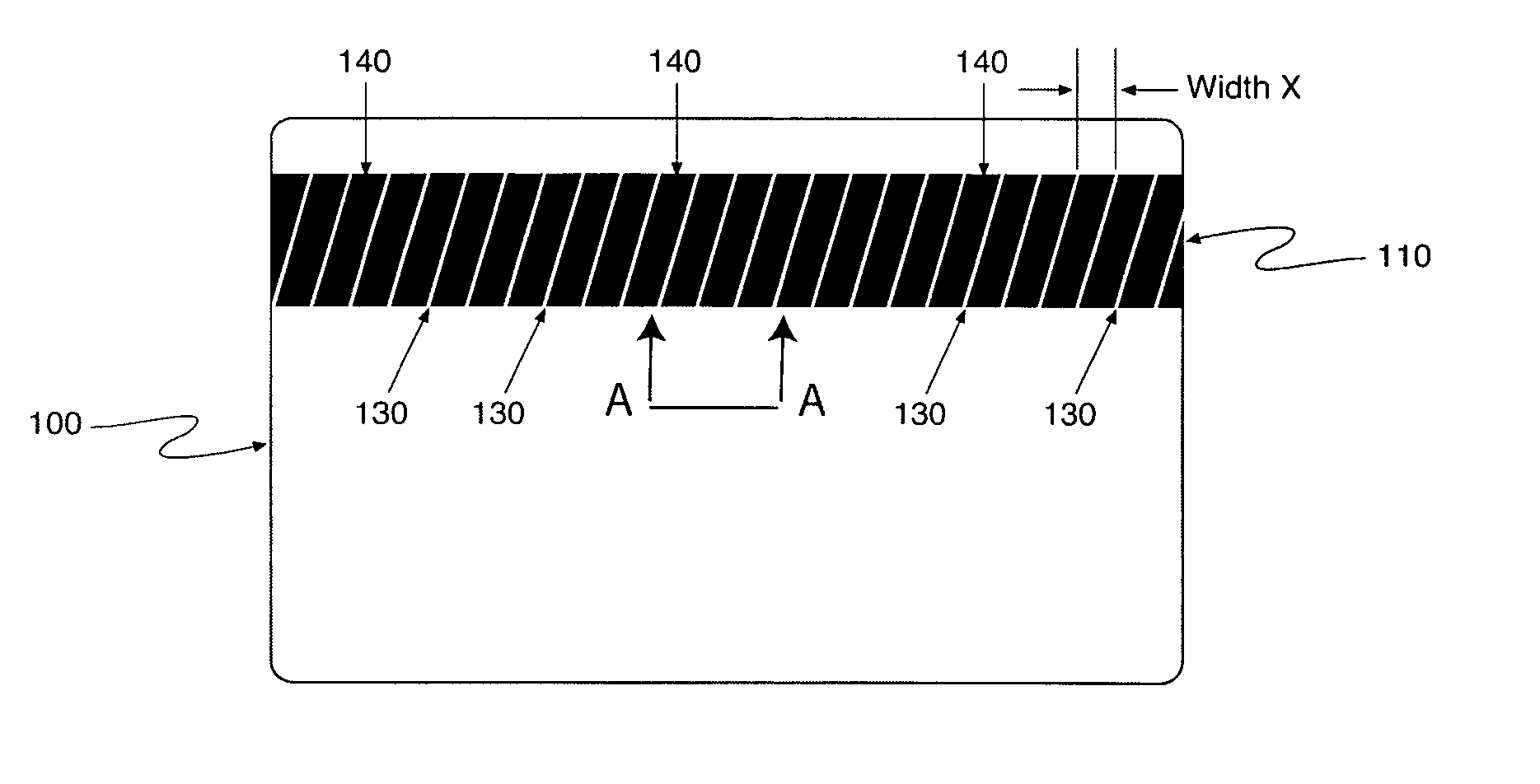

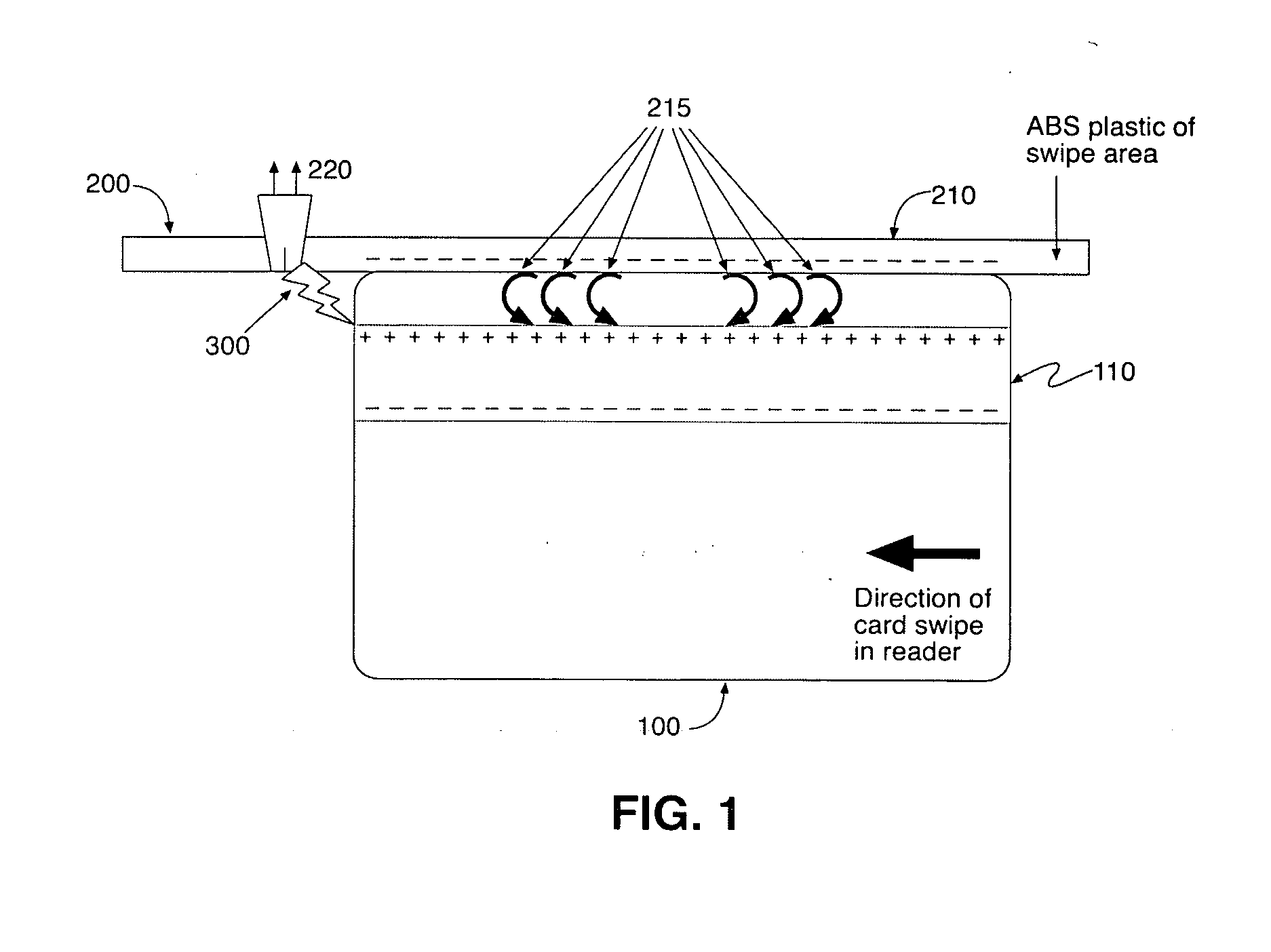

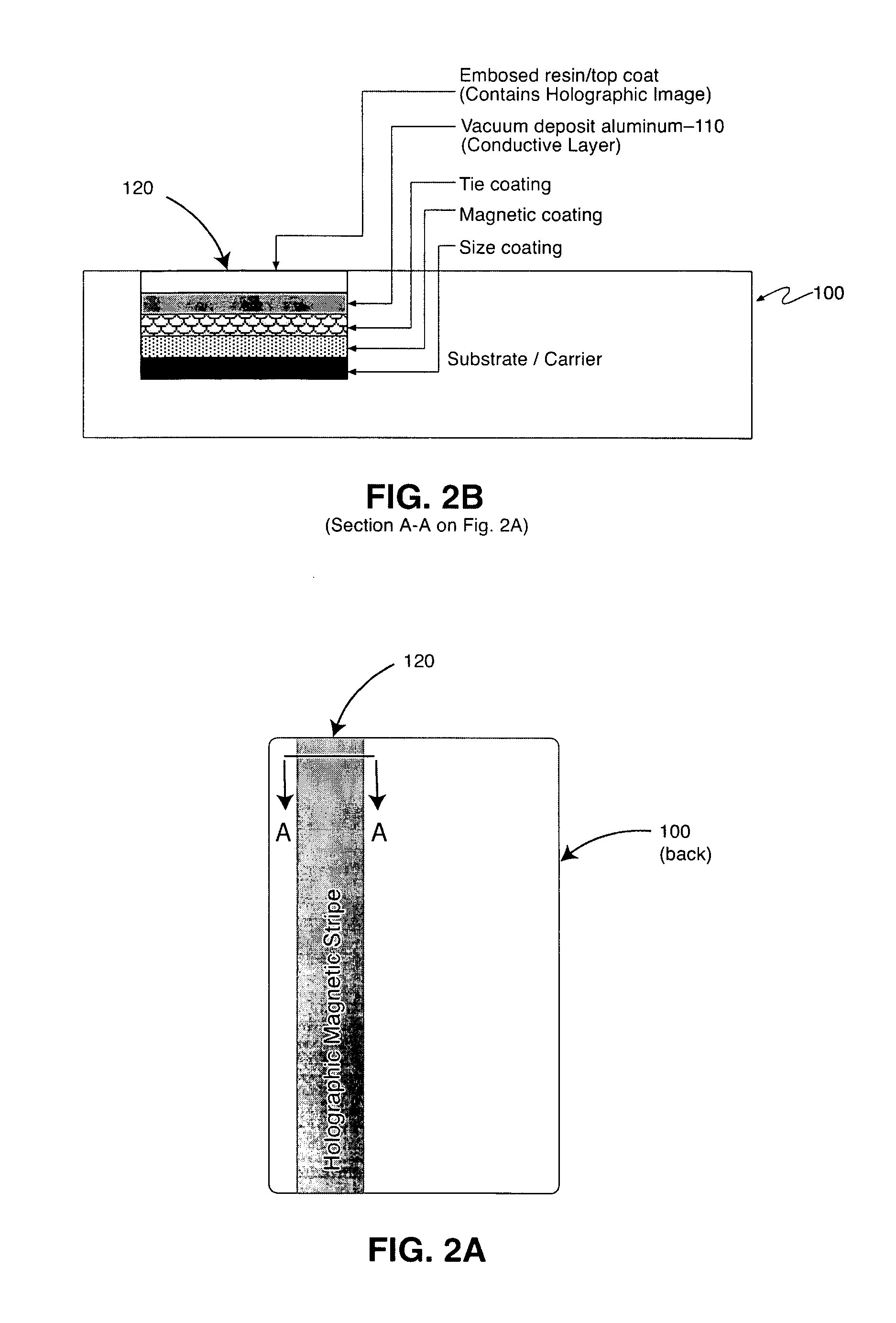

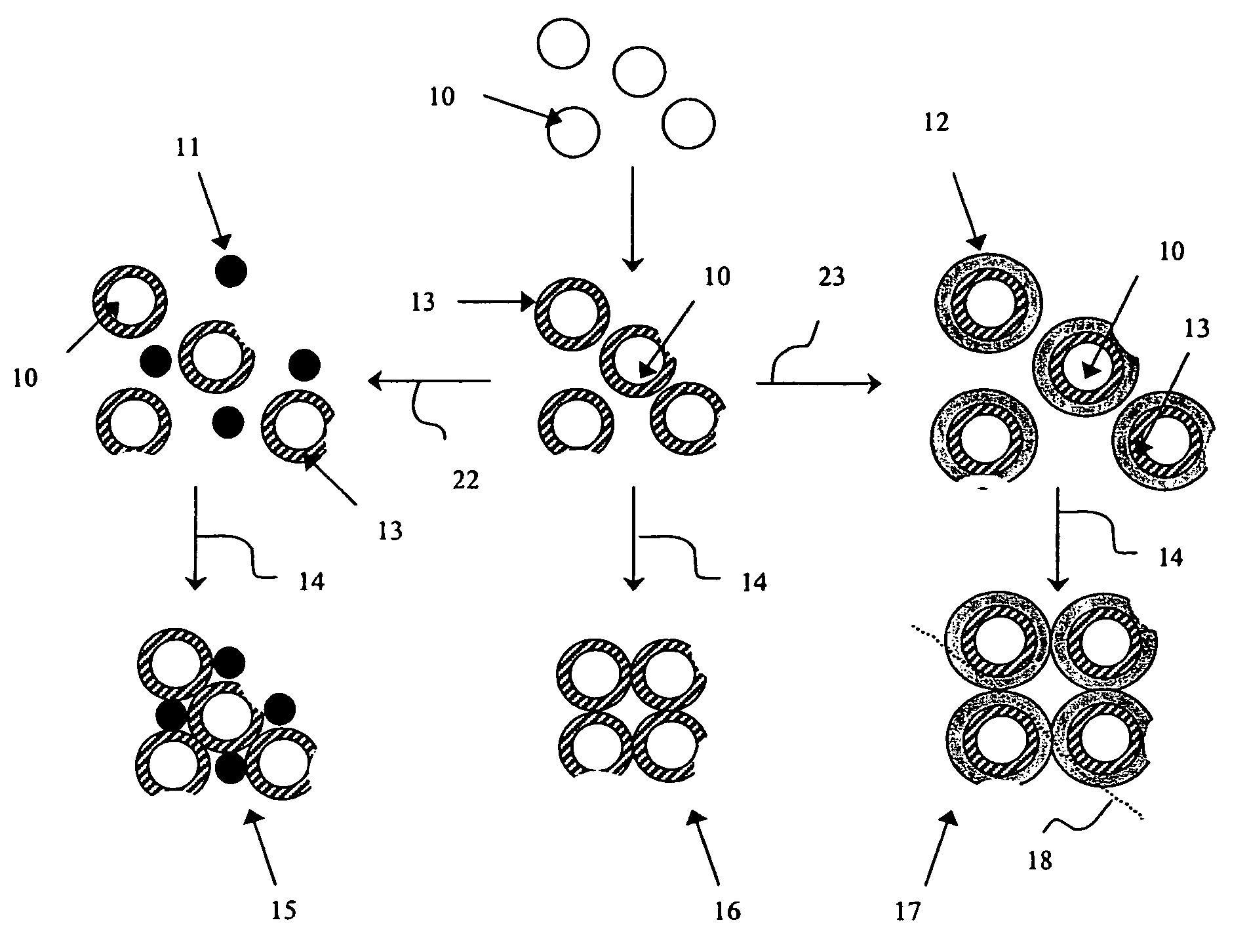

Method of reducing electro-static discharge (ESD) from conductors on insulators

InactiveUS7677462B2Eliminate or reduce the amount of electrostatic charge carried or storedFacilitate conductionProtective coatings for layersCharacter printing data arrangement from carrierElectrical conductorEngineering

A non-conductive carrier having a conductive component comprising a plurality of sections to disrupt the conductive component's conductive path. Each section is isolated from other sections such that a charge accumulated in one section cannot combine with the charge accumulated in another section, thereby minimizing any potential electrostatic discharge from the carrier.

Owner:OPSEC SECURITY GROUP

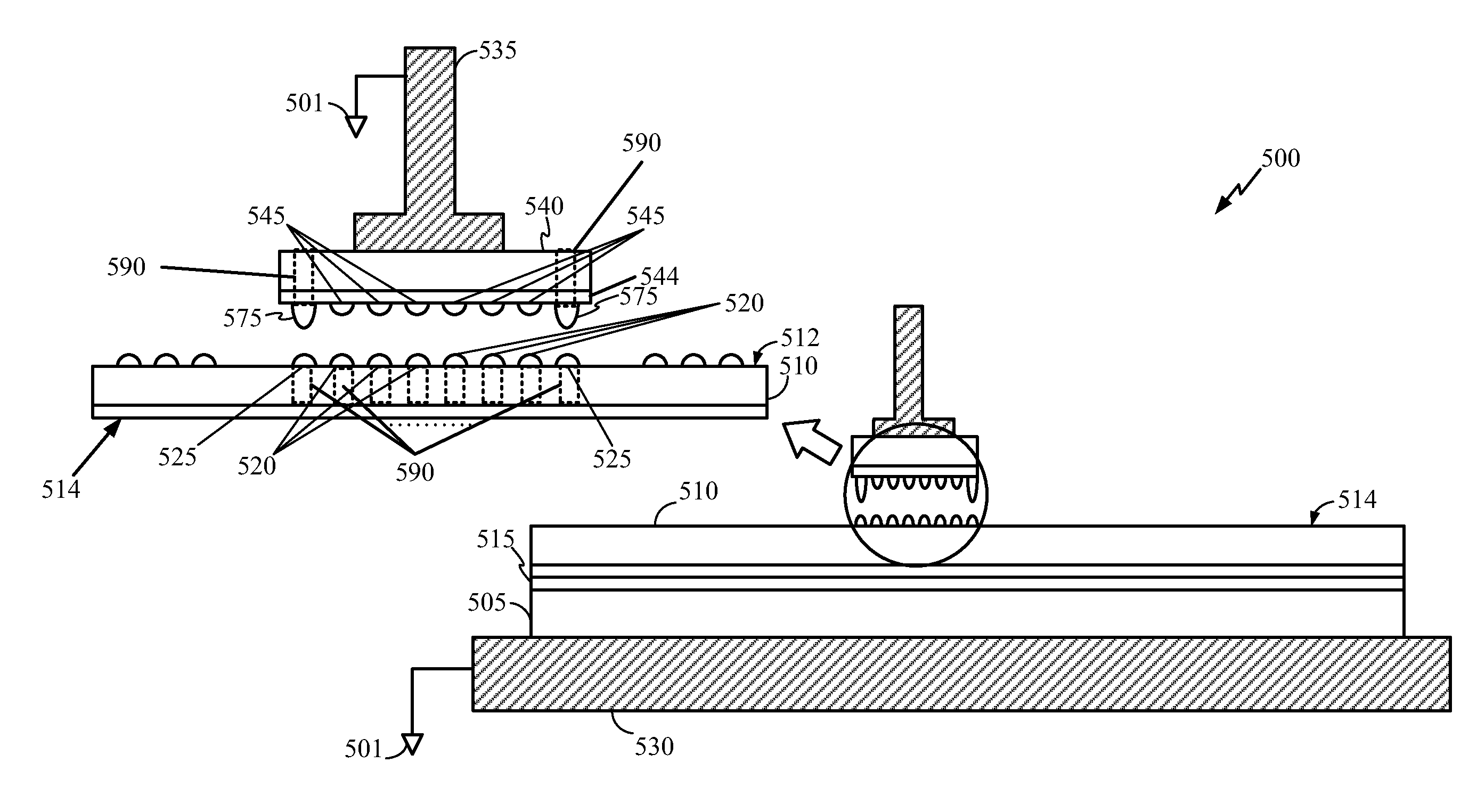

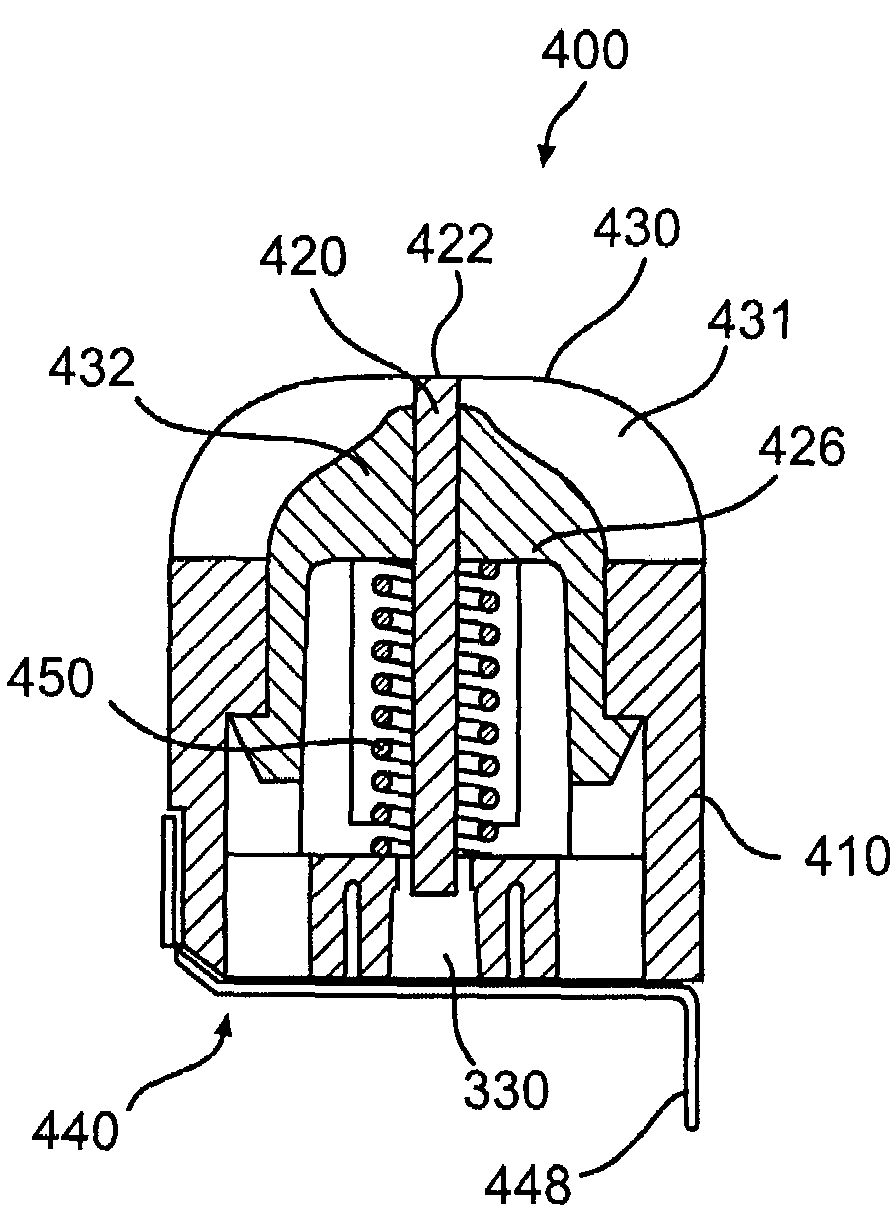

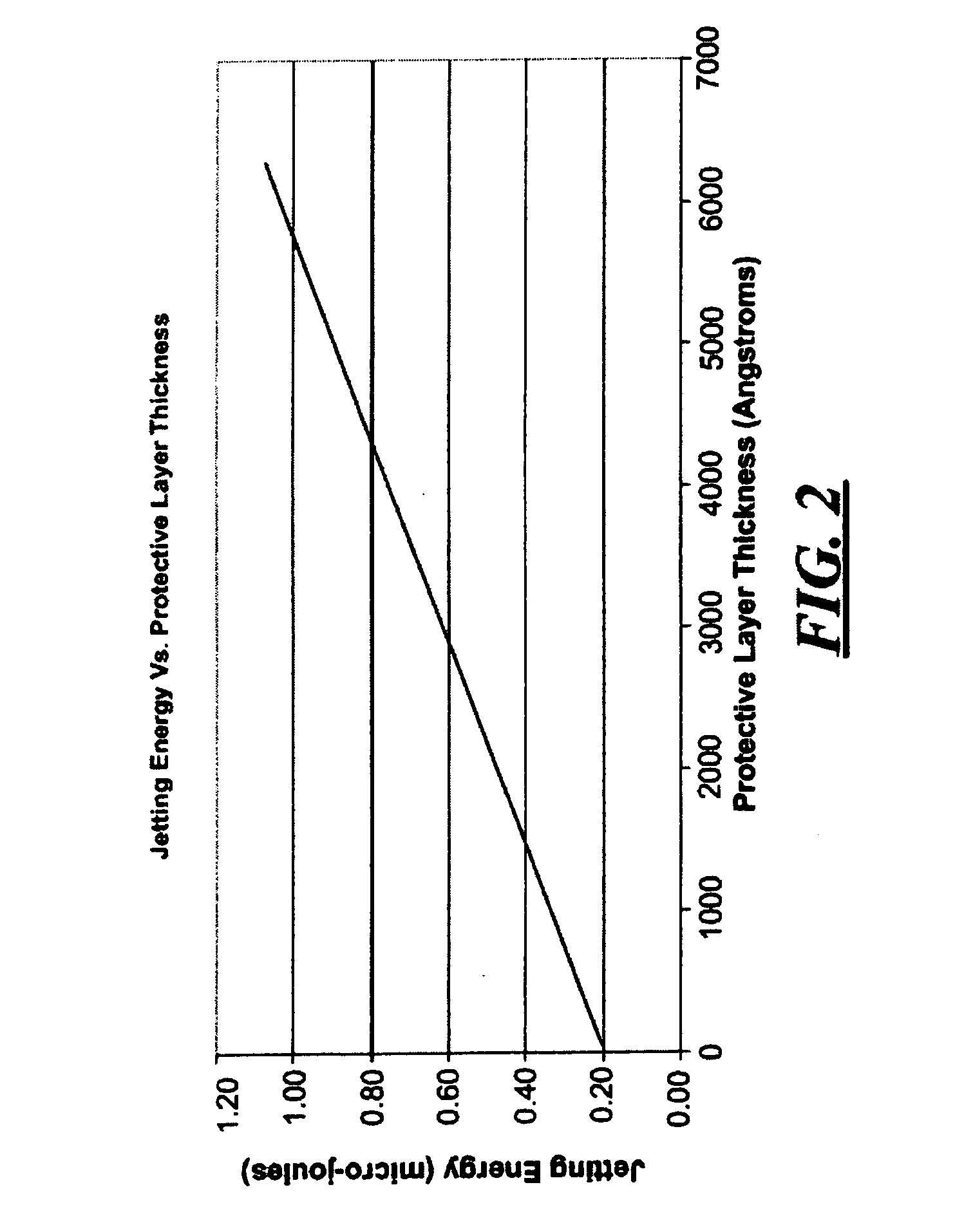

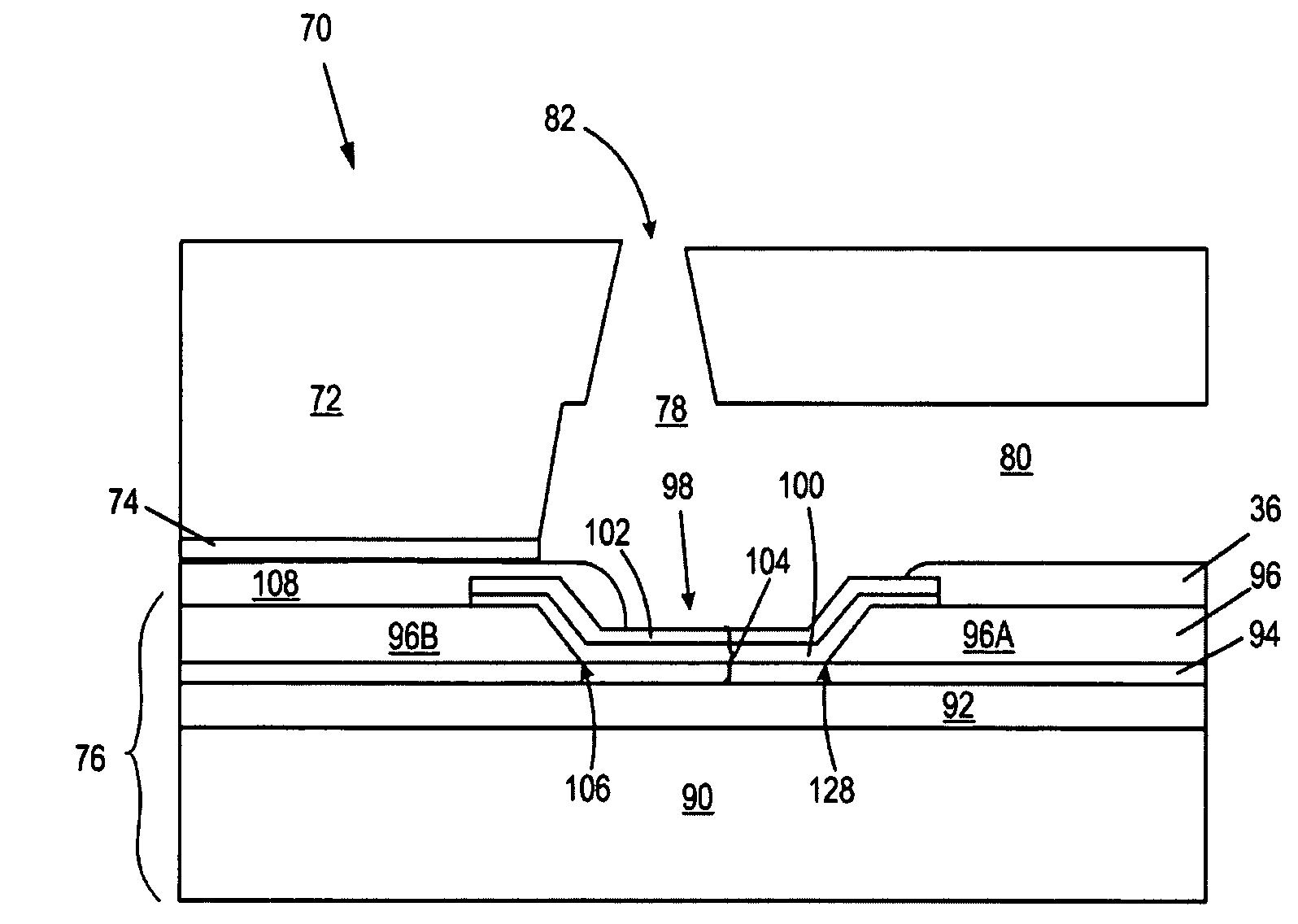

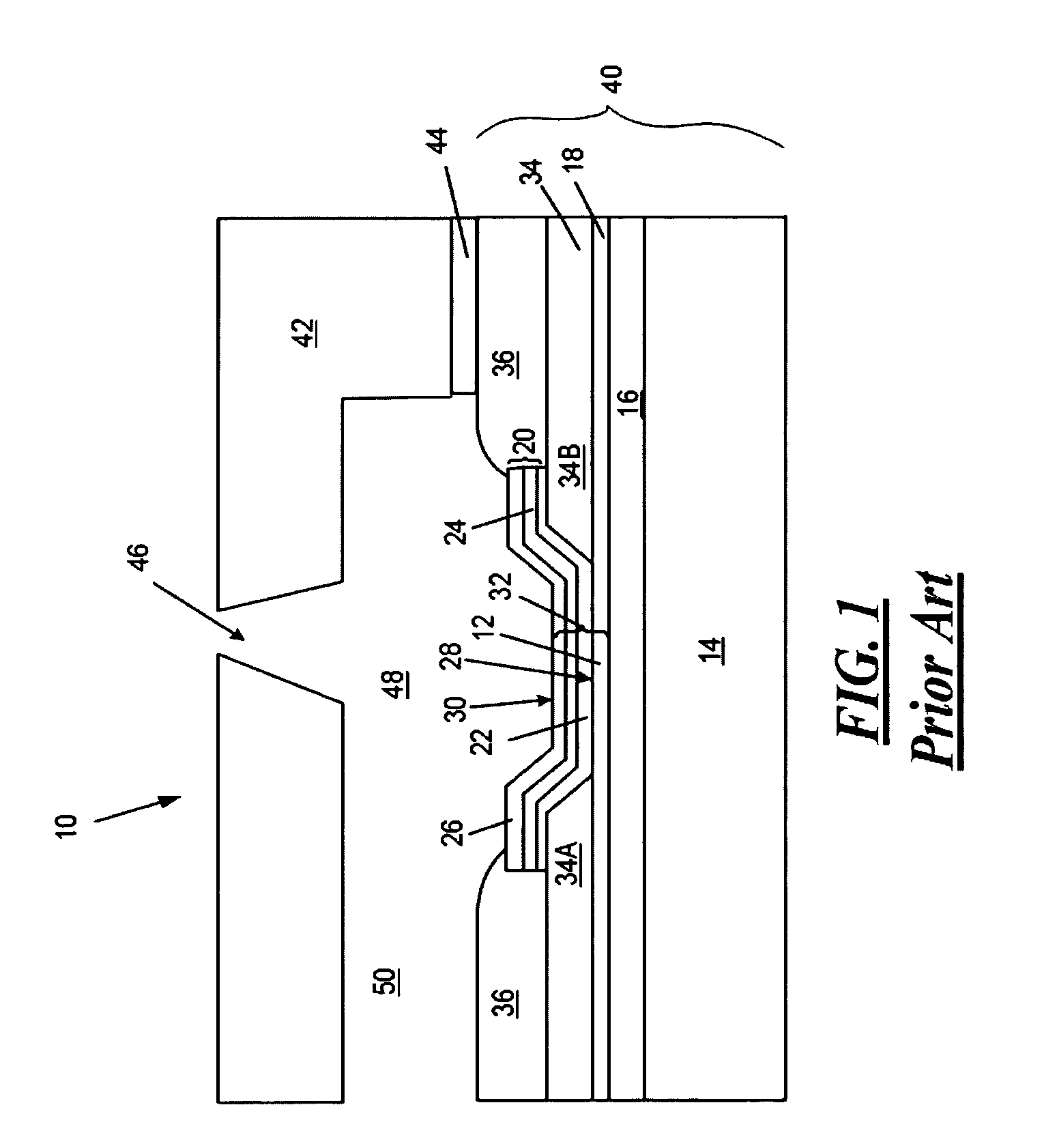

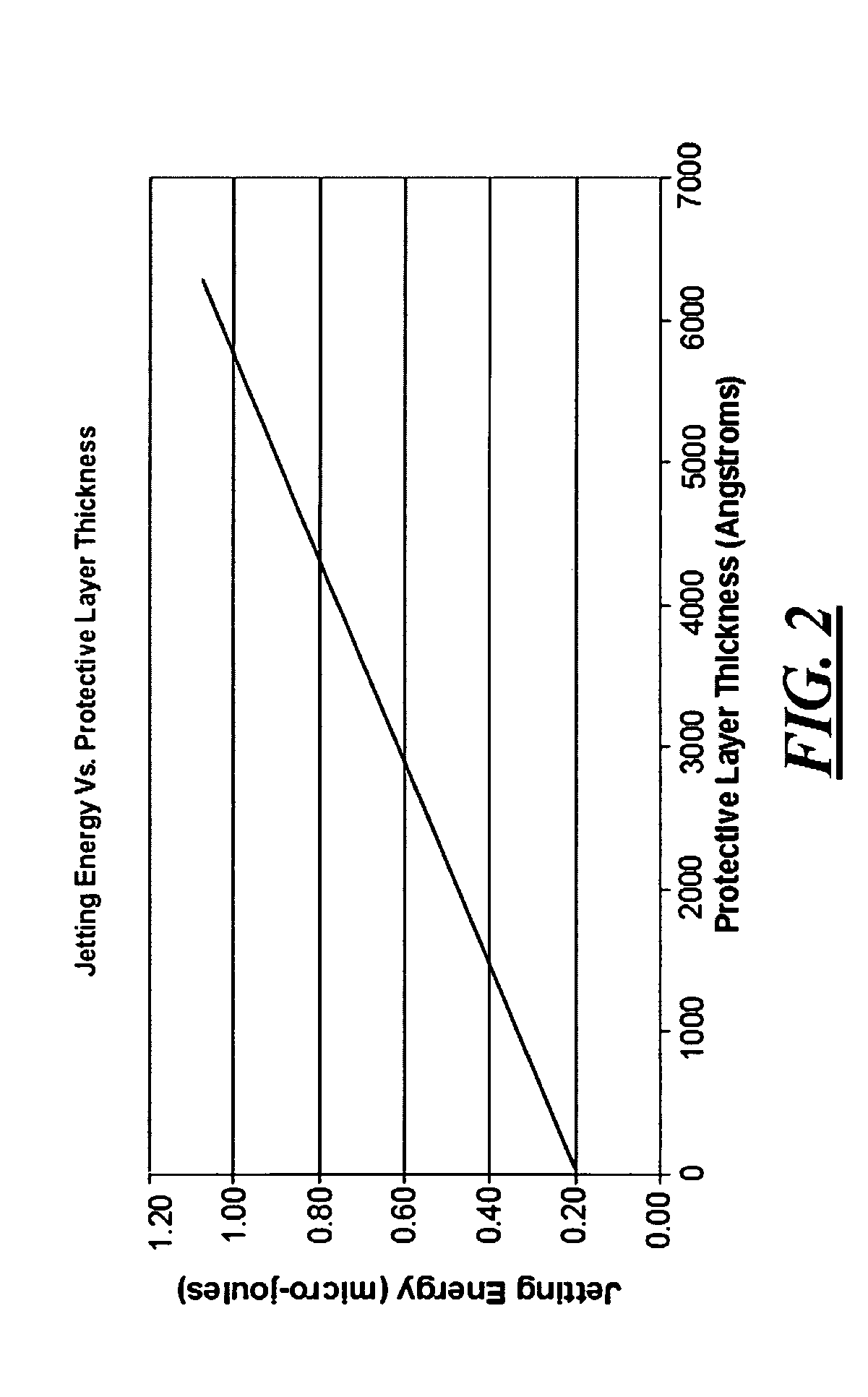

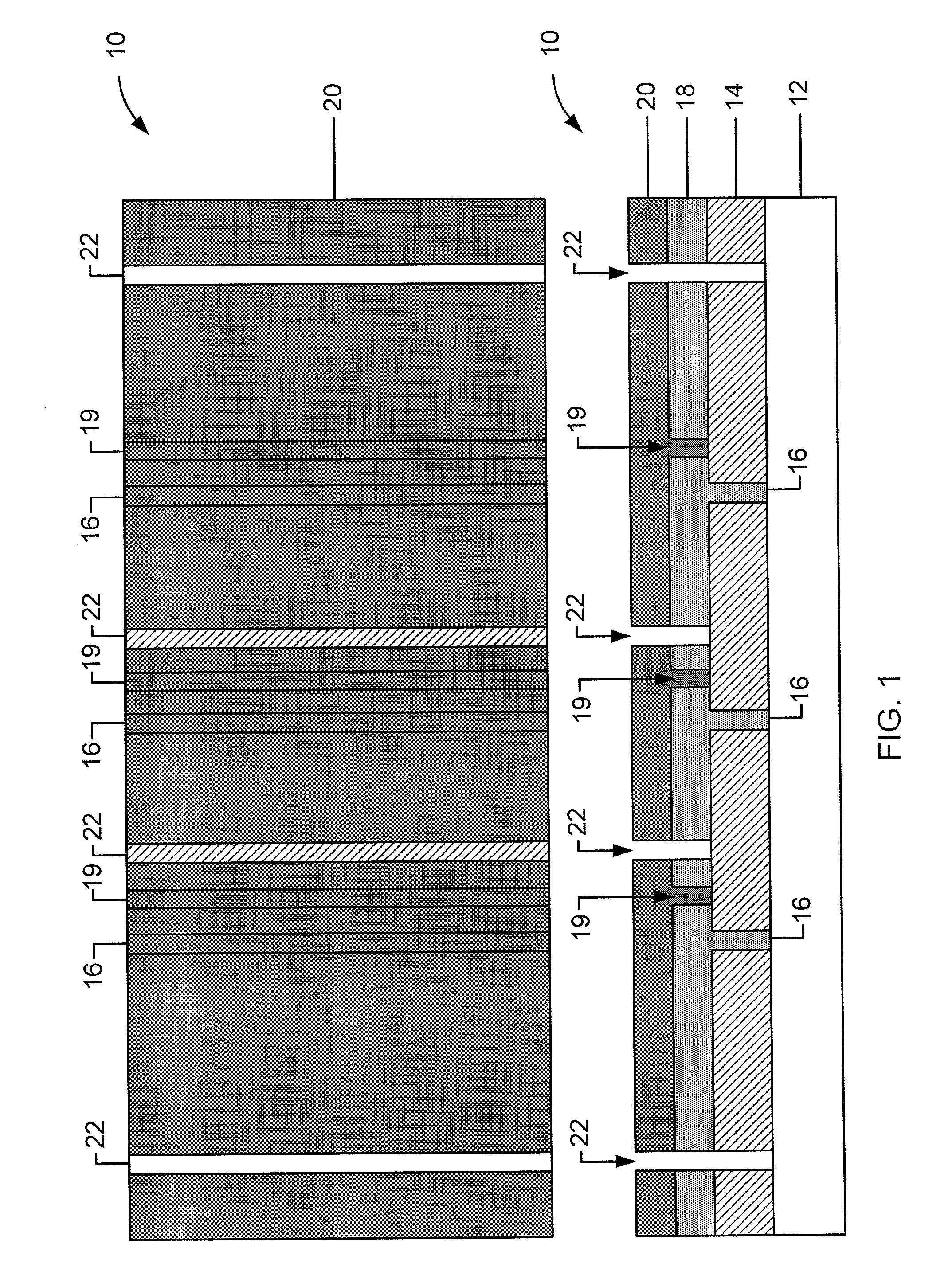

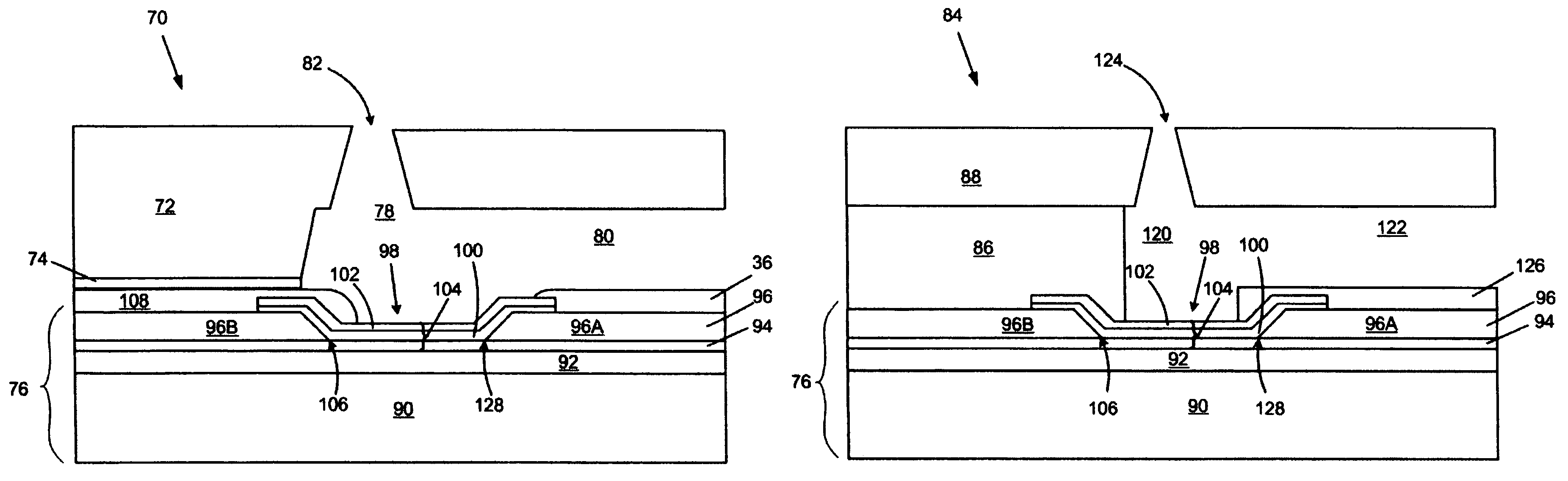

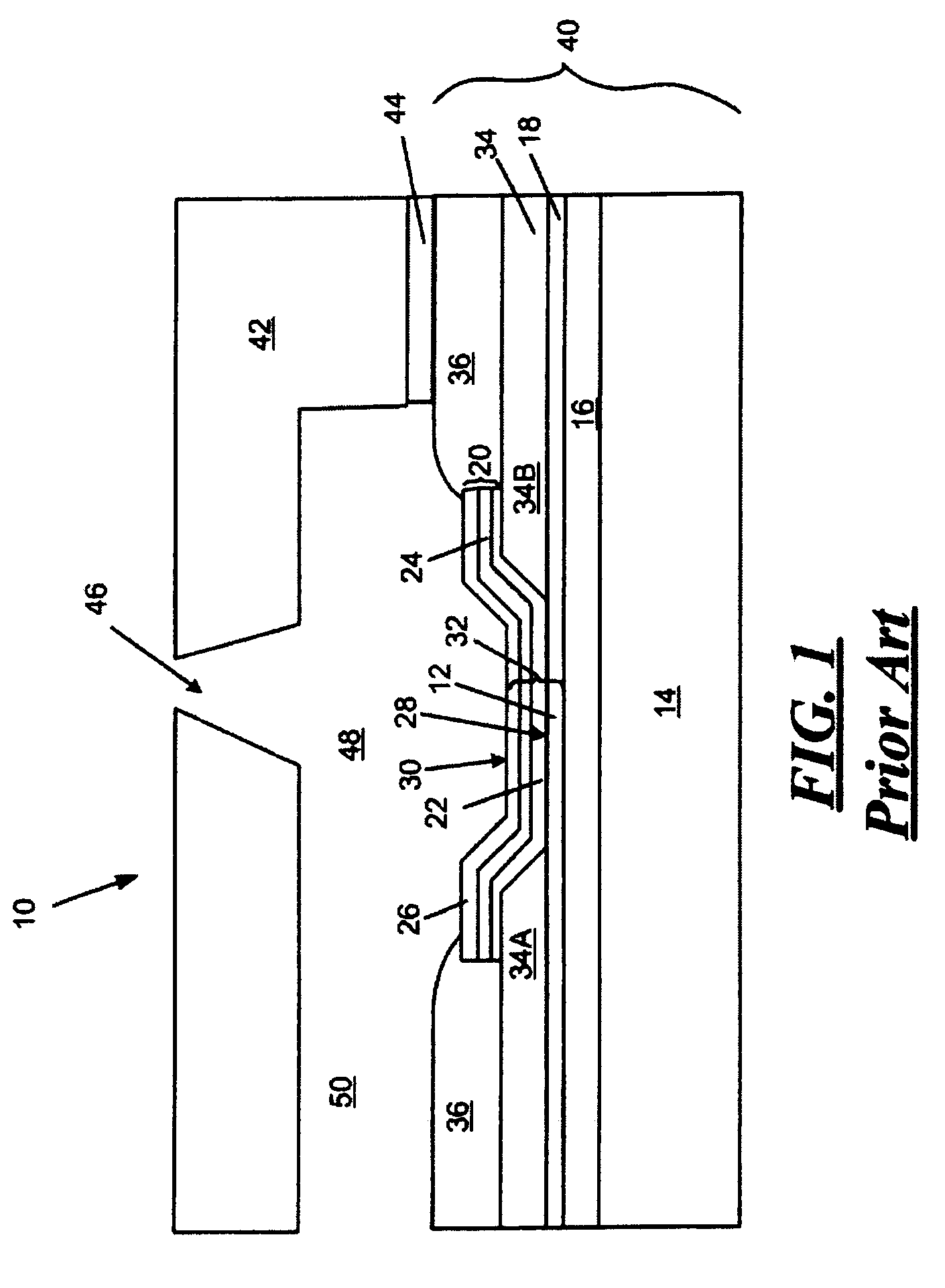

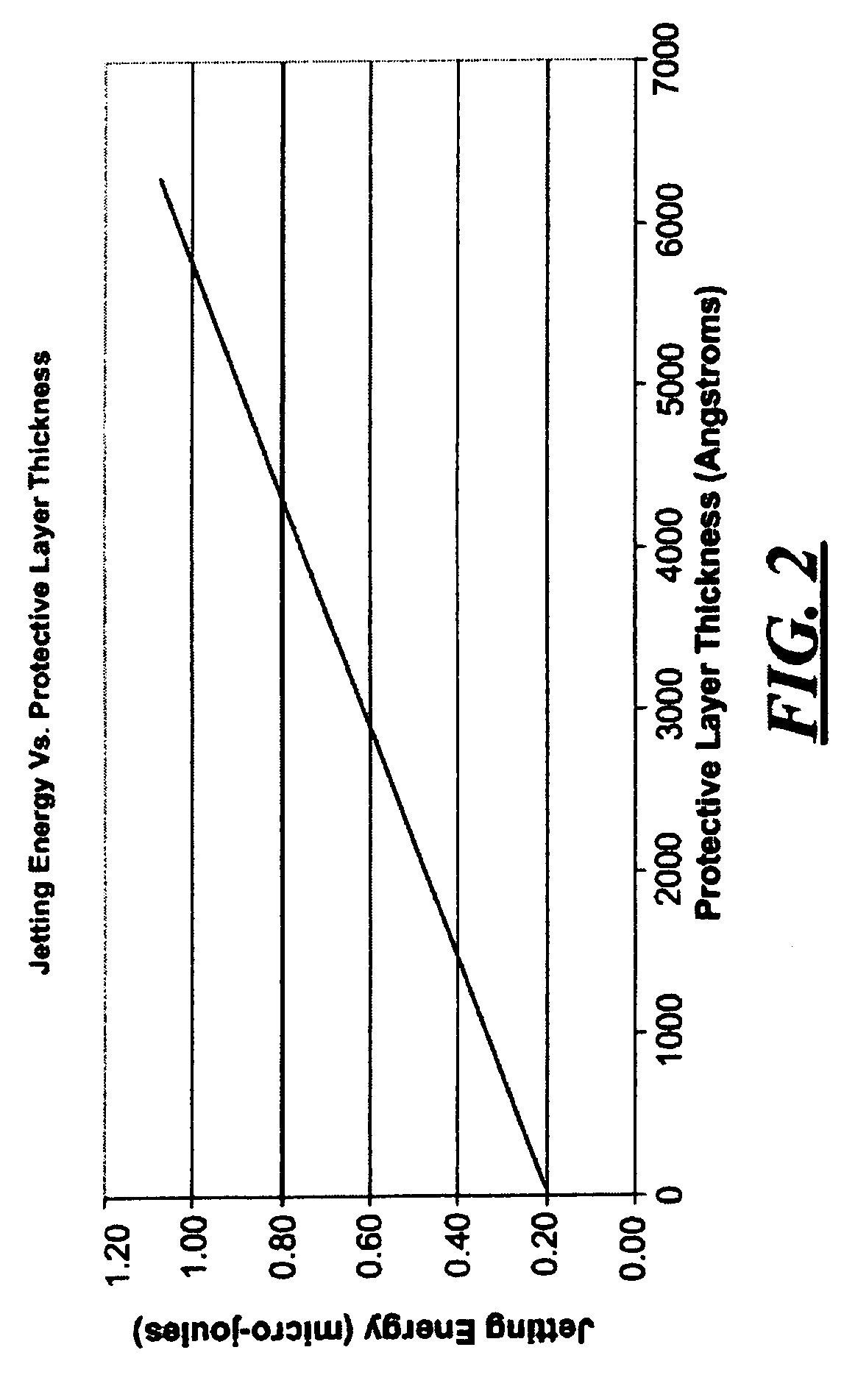

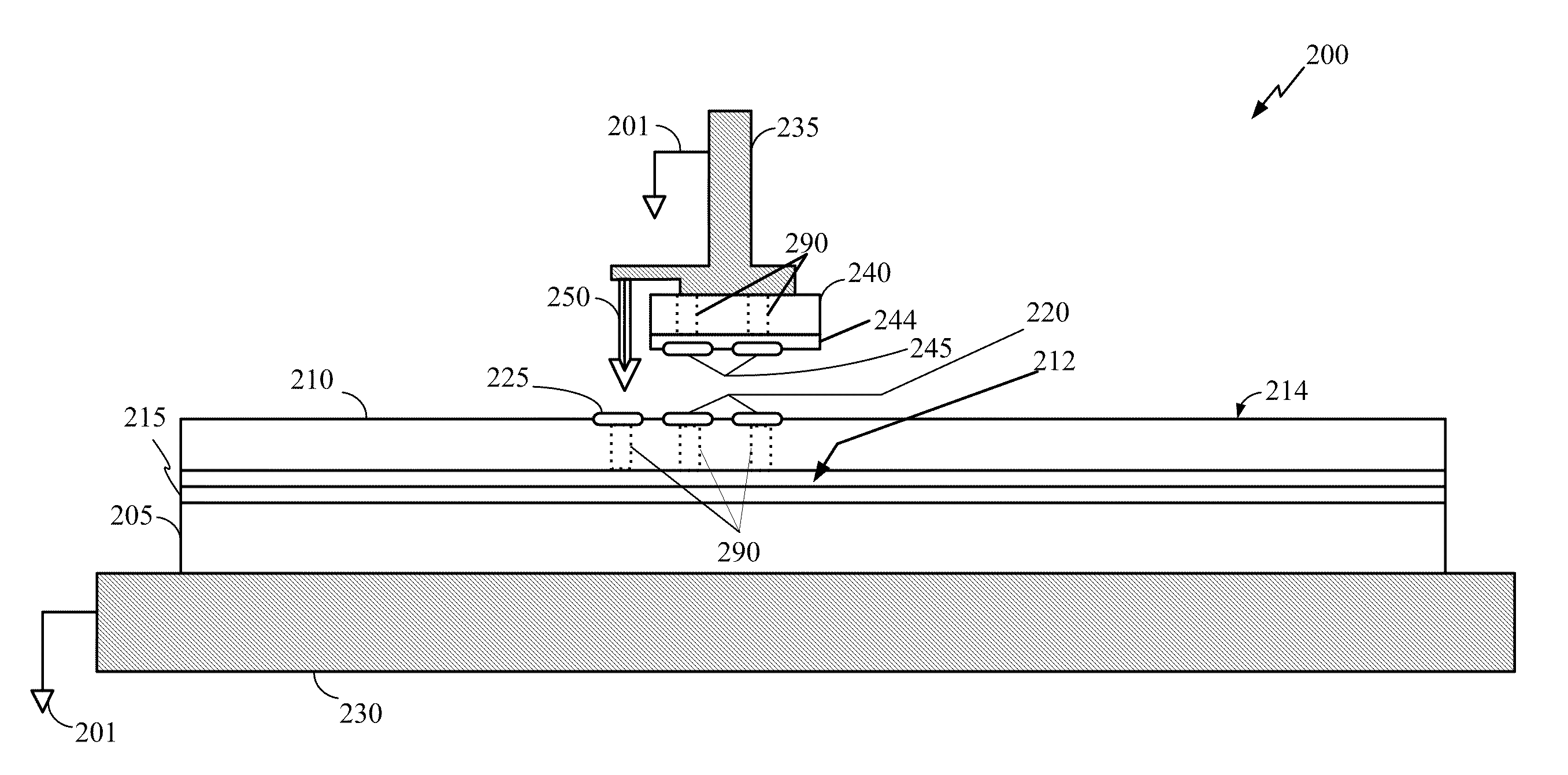

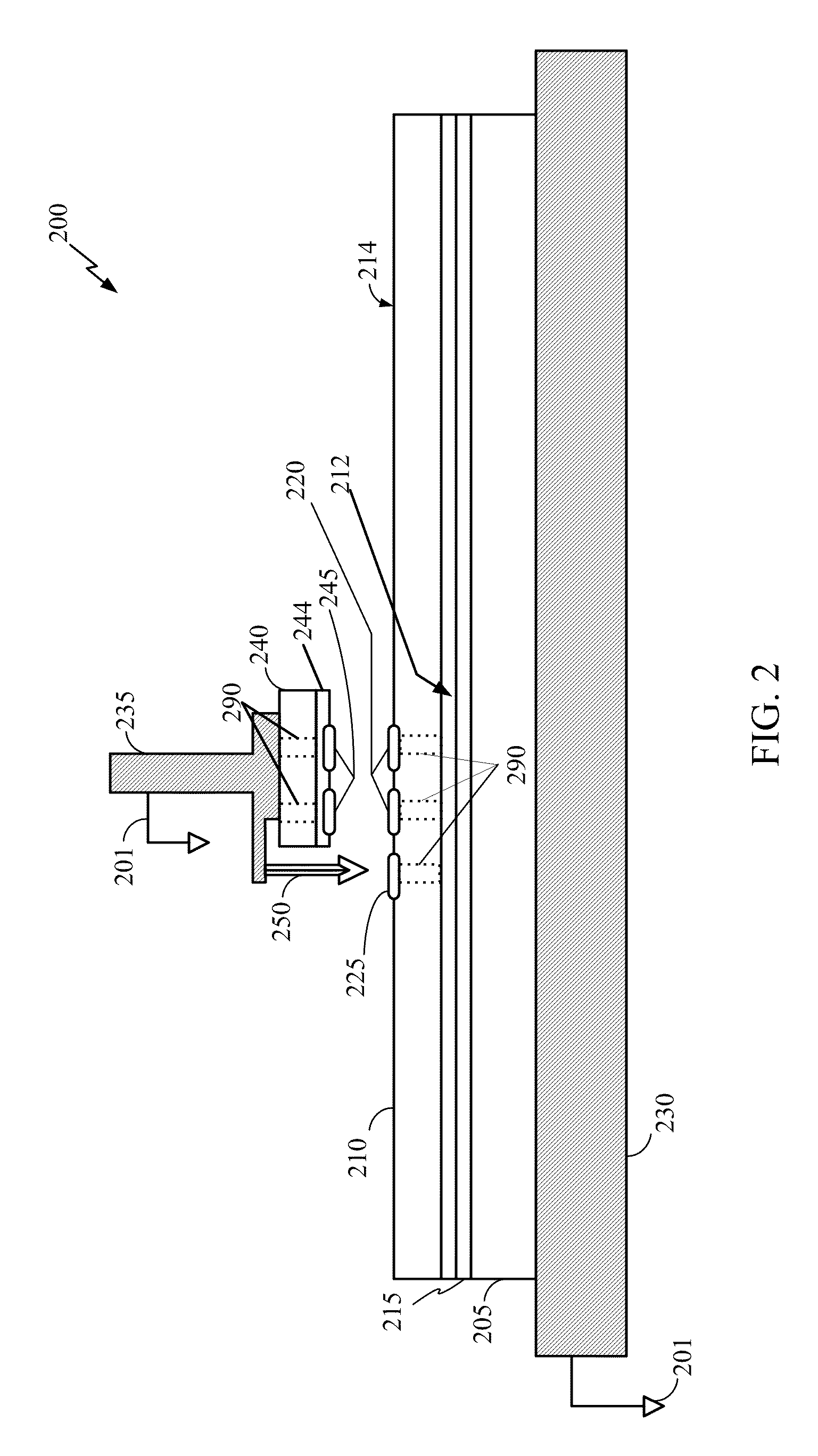

Low energy, long life micro-fluid ejection device

ActiveUS20070146436A1Weaken energyProlong lifePrintingElectrical resistance and conductanceEngineering

Micro-fluid ejection heads and methods for extending the life of micro-fluid ejection heads. One such micro-fluid ejection head includes a substrate having a plurality of thermal ejection actuators. Each of the thermal ejection actuators has a resistive layer and a protective layer thereon. A flow feature member is adjacent the substrate and defines a fluid feed channel, a fluid chamber associated with at least one of the actuators and in flow communication with the fluid feed channel, and a nozzle. The nozzle is offset to a side of the chamber opposite the feed channel. A polymeric layer having a degradation temperature of less than about 400° C. overlaps a portion of the at least one actuator associated with the fluid chamber and positioned less than about five microns from at least an edge of the at least one actuator opposite the fluid feed channel.

Owner:SLINGSHOT PRINTING LLC

Low energy, long life micro-fluid ejection device

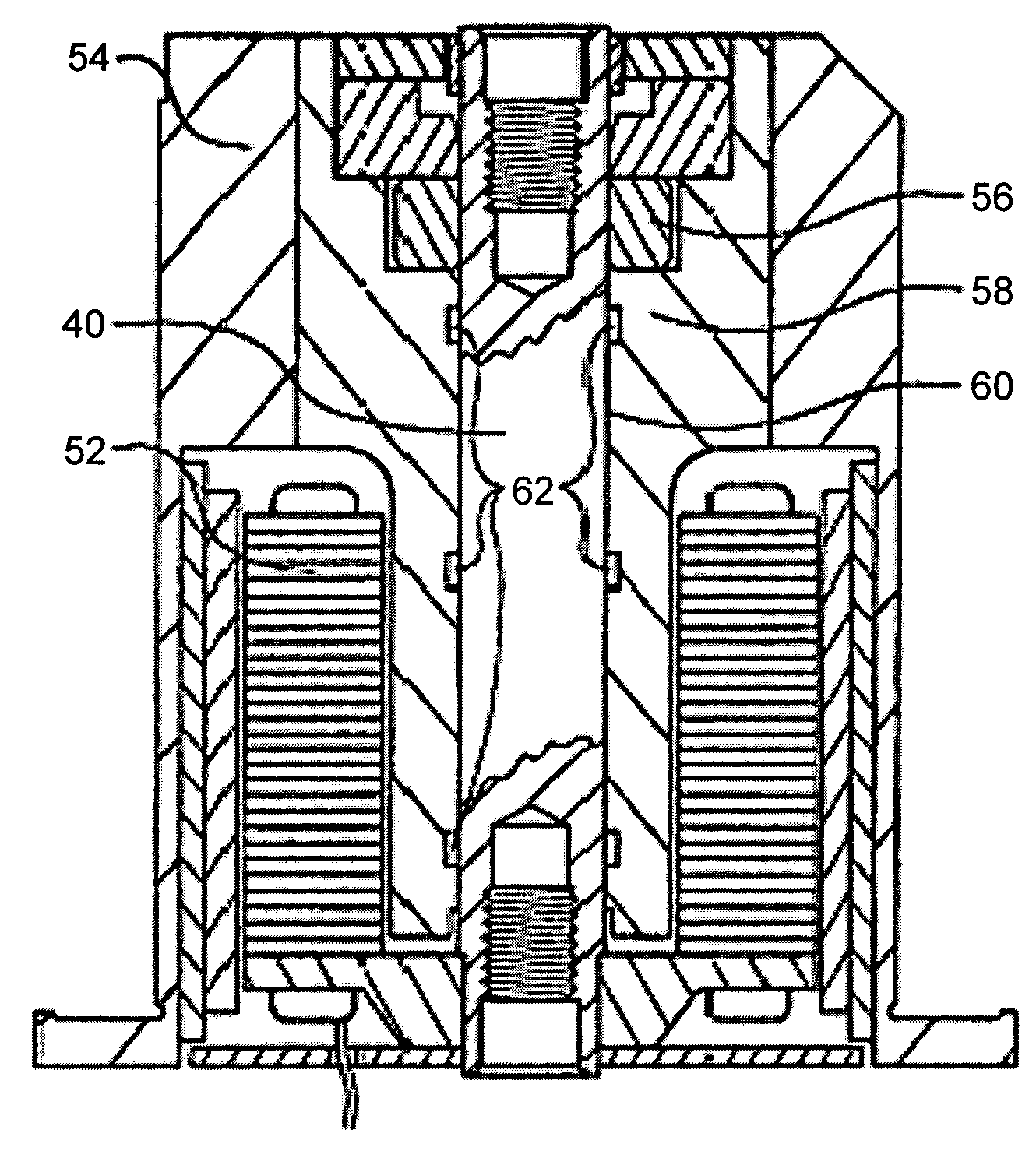

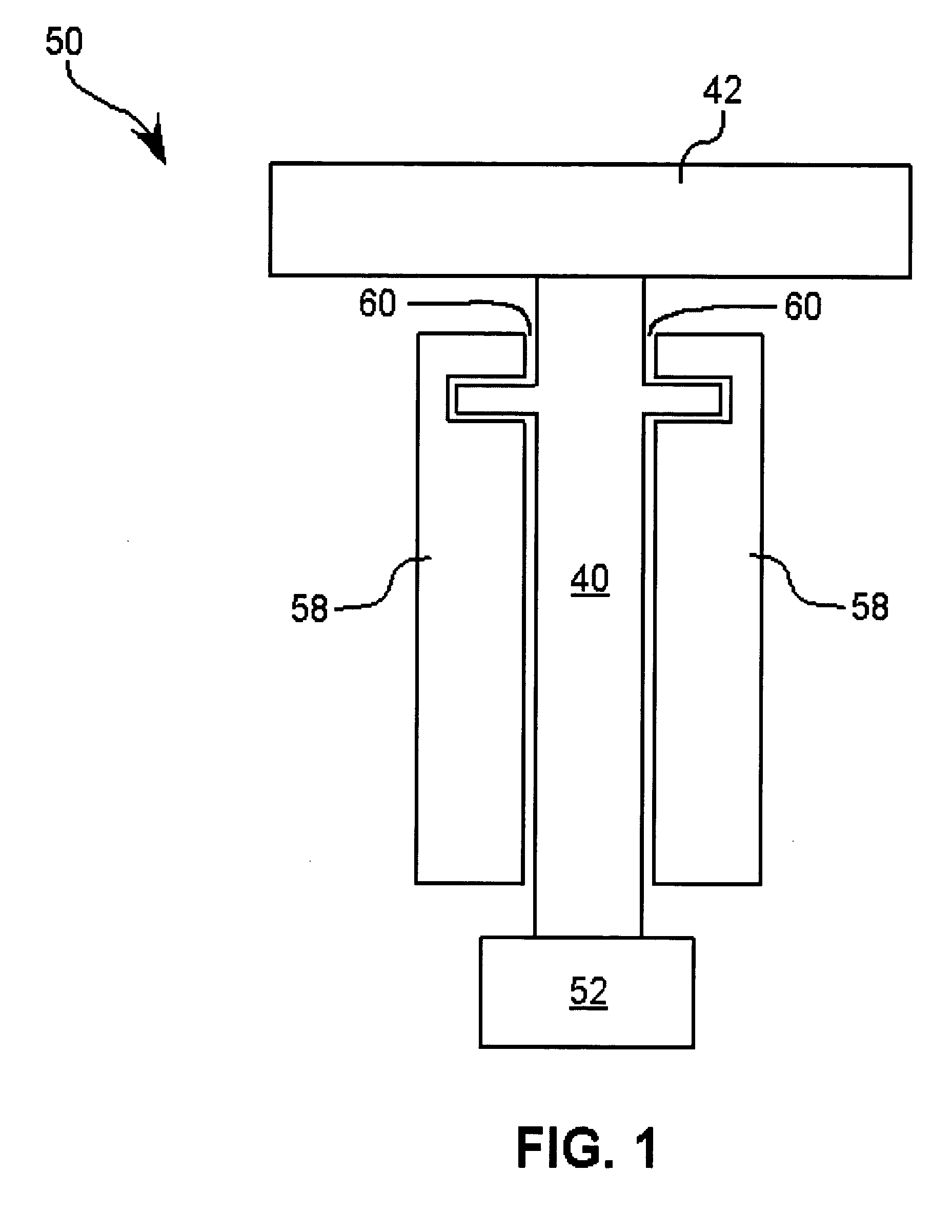

ActiveUS20080259131A1Thickness minimizationReduce cavitation effectsPrintingActuatorProtection layer

Micro-fluid ejection heads and methods for extending the life of micro-fluid ejection heads. One such micro-fluid ejection head includes a substrate having a plurality of thermal ejection actuators. Each of the thermal ejection actuators has a resistive layer and a protective layer thereon. A flow feature member is adjacent the substrate and defines a fluid feed channel, a fluid chamber associated with at least one of the actuators and in flow communication with the fluid feed channel, and a nozzle. The nozzle is offset to a side of the chamber opposite the feed channel. A polymeric layer having a degradation temperature of less than about 400° C. overlaps a portion of the at least one actuator associated with the fluid chamber and positioned less than about five microns from at least an edge of the at least one actuator opposite the fluid feed channel.

Owner:SLINGSHOT PRINTING LLC

Method of reducing electro-static discharge (ESD) from conductors on insulators

InactiveUS20070201174A1Eliminate and reduce amountEliminate or reduce the amount of electrostatic charge carried or storedProtective coatings for layersCharacter printing data arrangement from carrierElectrical conductorElectrostatic discharge

A non-conductive carrier having a conductive component comprising a plurality of sections to disrupt the conductive component's conductive path. Each section is isolated from other sections such that a charge accumulated in one section cannot combine with the charge accumulated in another section, thereby minimizing any potential electrostatic discharge from the carrier.

Owner:OPSEC SECURITY GROUP

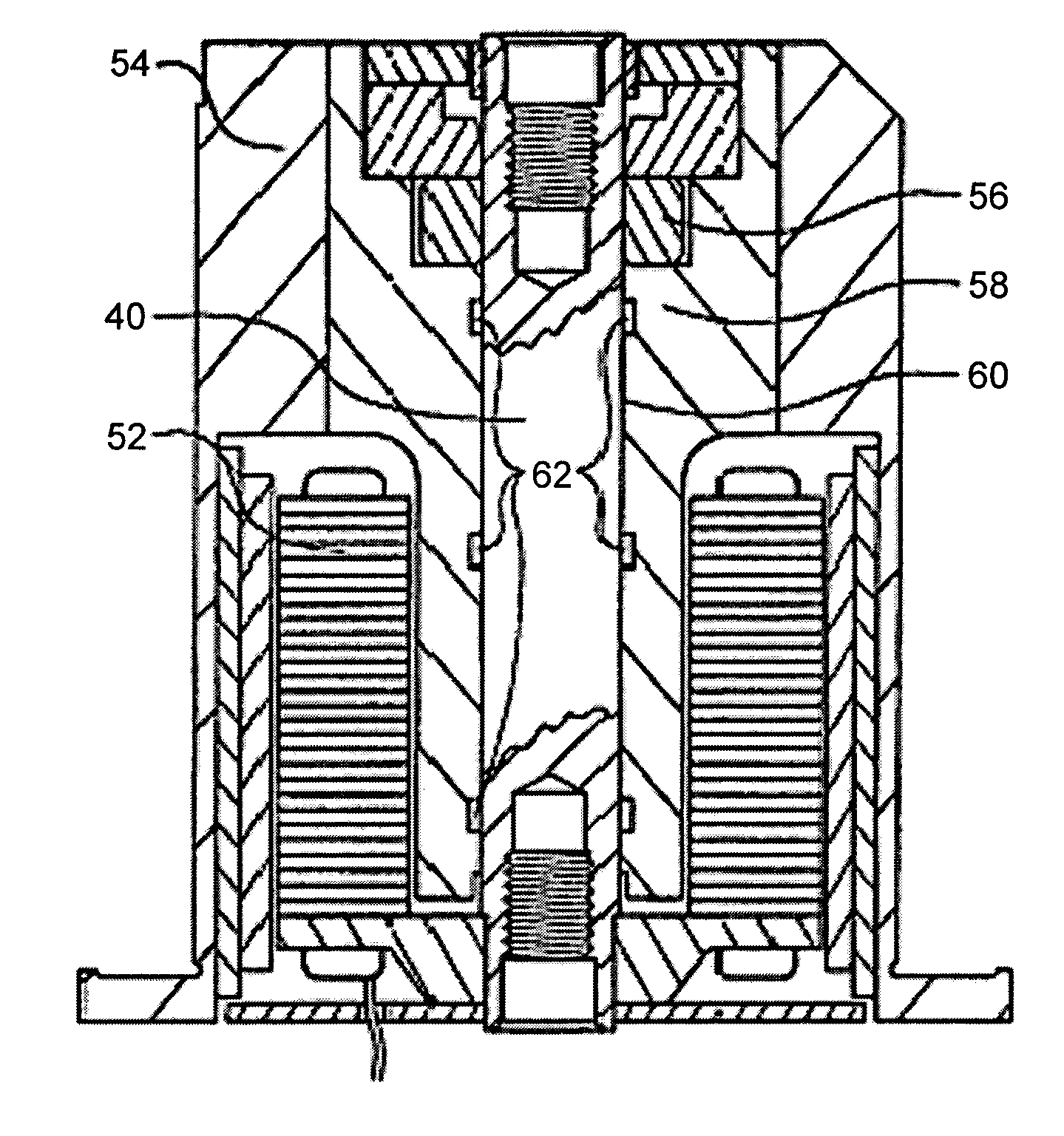

Conductive greases and methods for using conductive greases in motors

InactiveUS20050062350A1Reduce electrostatic dischargeReduce electrostatic discharge machiningAssociation with grounding devicesShaftsStatorEngineering

A motor including a frame, a stator fixed relative to the frame, and a bearing assembly fixed relative to the frame may be provided. The bearing assembly may include ball bearings at least partially encompassed by a conductive grease. The conductive grease may include grease and particles including at least one of carbon, metal and a combination thereof. At least one particle may be coated with a conductive polymer. A rotor may be supported by the bearing assembly for rotation relative to the stator.

Owner:A O SMITH

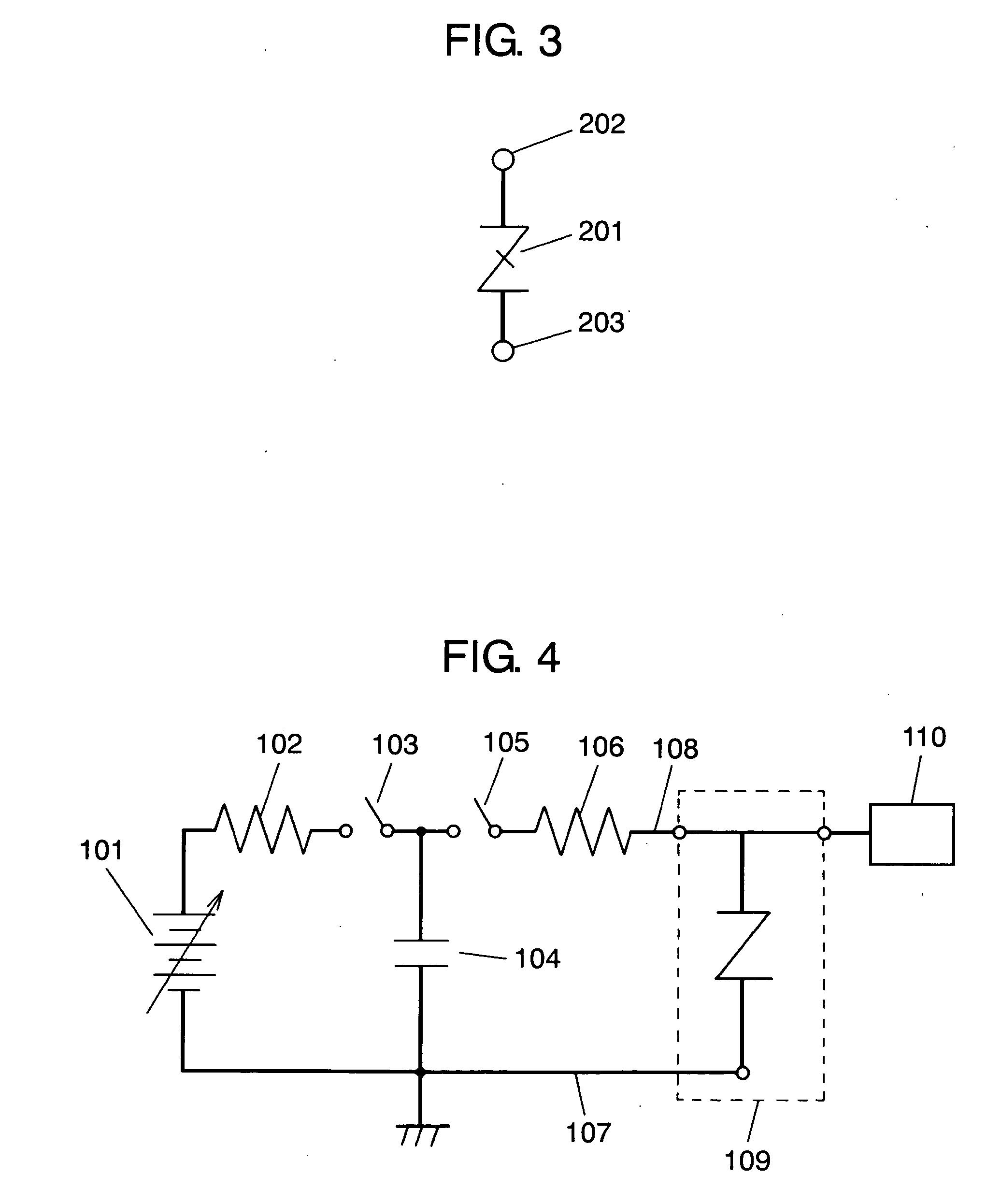

Static electricity countermeasure component

InactiveUS20060227473A1Reduce electrostatic dischargeSmall electrostatic capacityCurrent responsive resistorsEmergency protective arrangement detailsElectrostatic discharge protectionVaristor

It is possible to realize an electrostatic discharge protection component having a very small electrostatic capacity suited to a high-frequency equipment and comprising a ceramic insulating substrate, a varistor unit composed of a varistor layer and an internal electrode, which are sintered and integrated on the ceramic insulating substrate, and at least a pair of external electrodes provided on the varistor unit, the varistor unit being formed with a varistor.

Owner:PANASONIC CORP

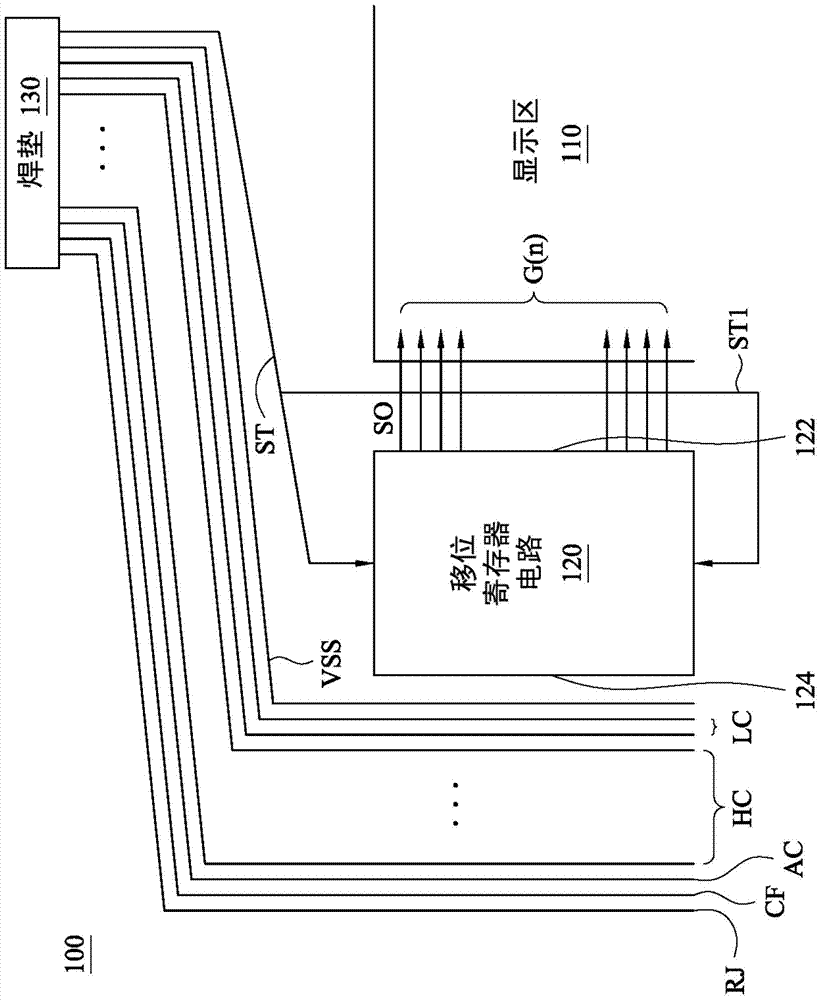

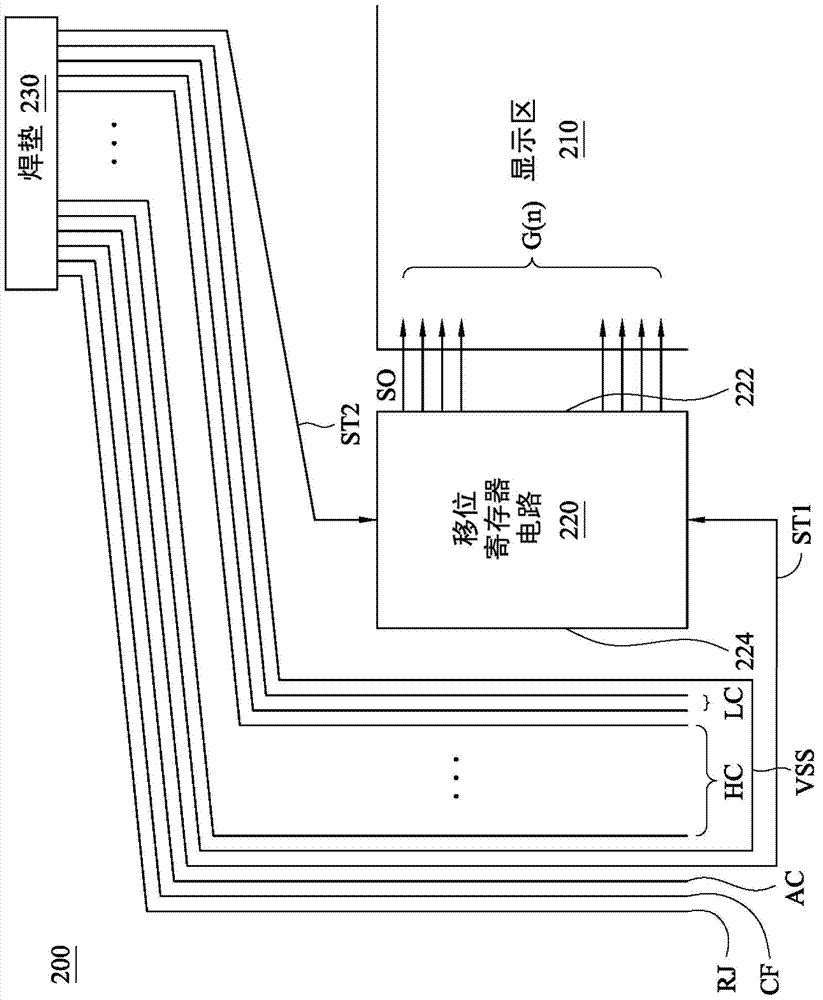

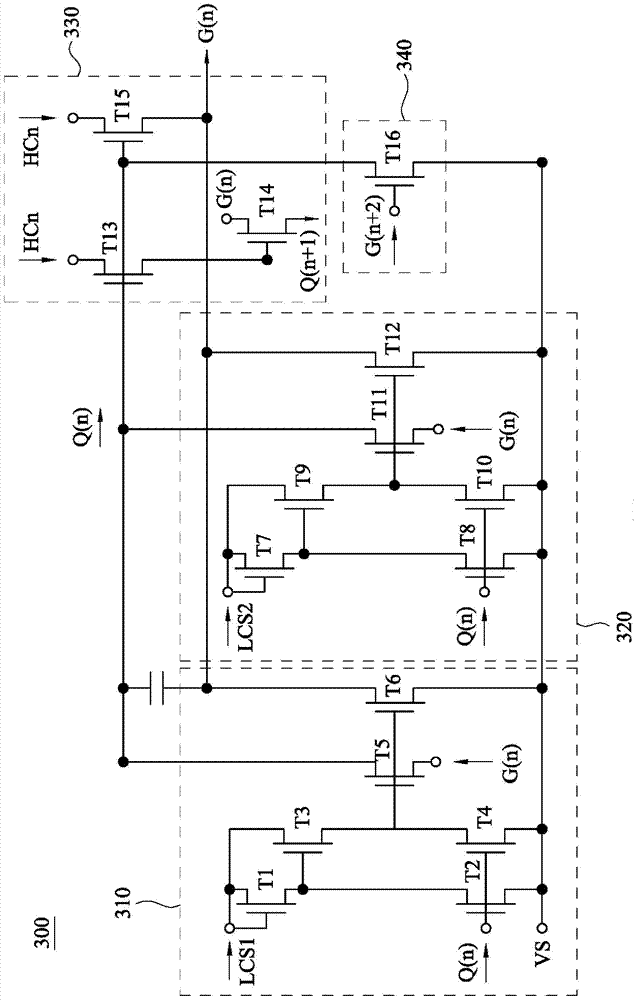

Display panel and its manufacturing method

ActiveCN103903547AImprove production yieldReduce line crossingStatic indicating devicesDigital storageShift registerHemt circuits

The invention provides a display panel and its manufacturing method. The display panel comprises a display area and a position moving storing circuit, a first start signal line and a second start signal line. The position moving storing circuit is electrically coupled to the display area through plural signal transmitting lines. The first start signal and the second start signal line are both electrically coupled with the position moving storing circuit wherein the first start signal and the second start signal line do not cross over the signal transmitting lines.

Owner:AU OPTRONICS CORP

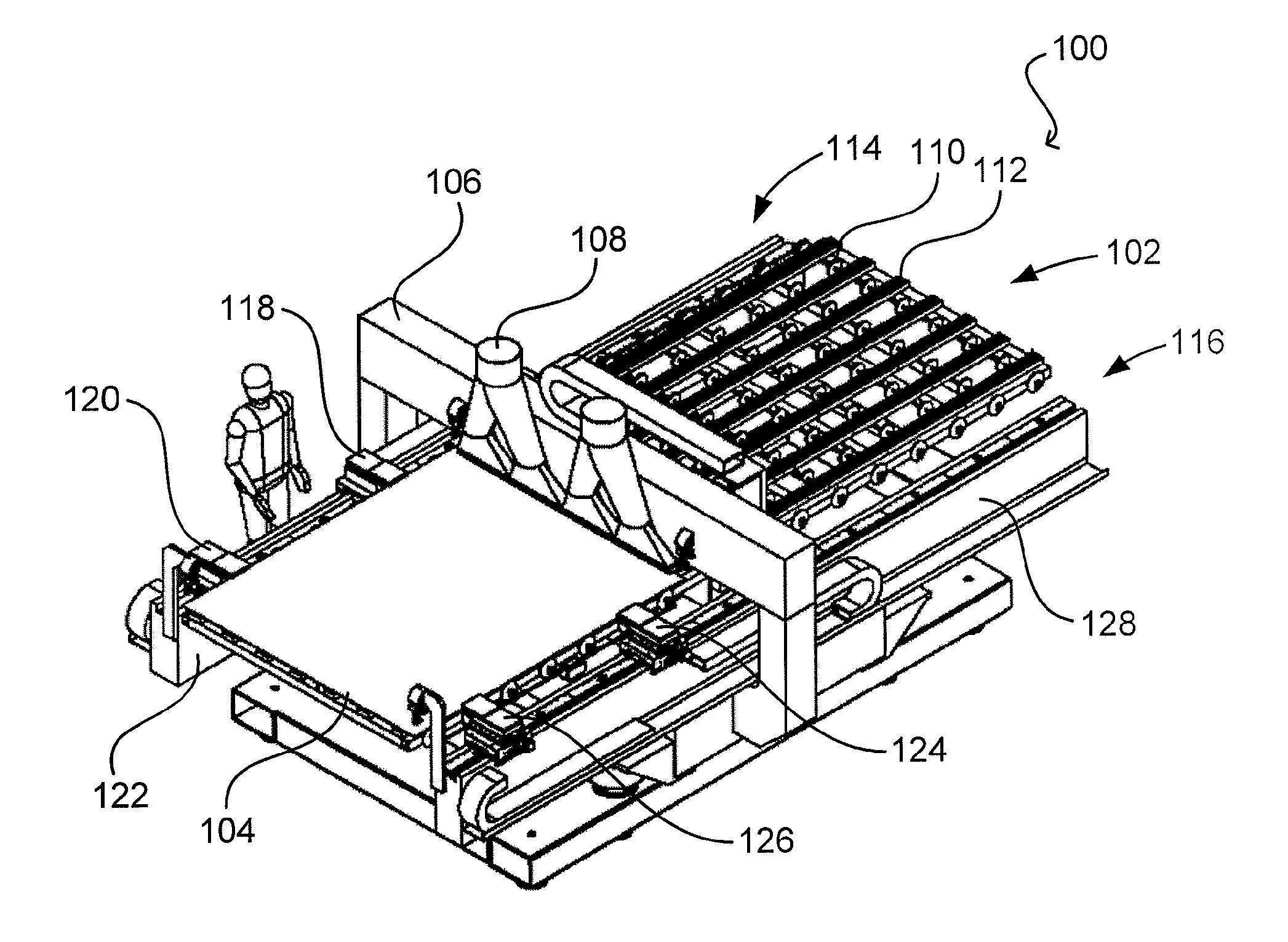

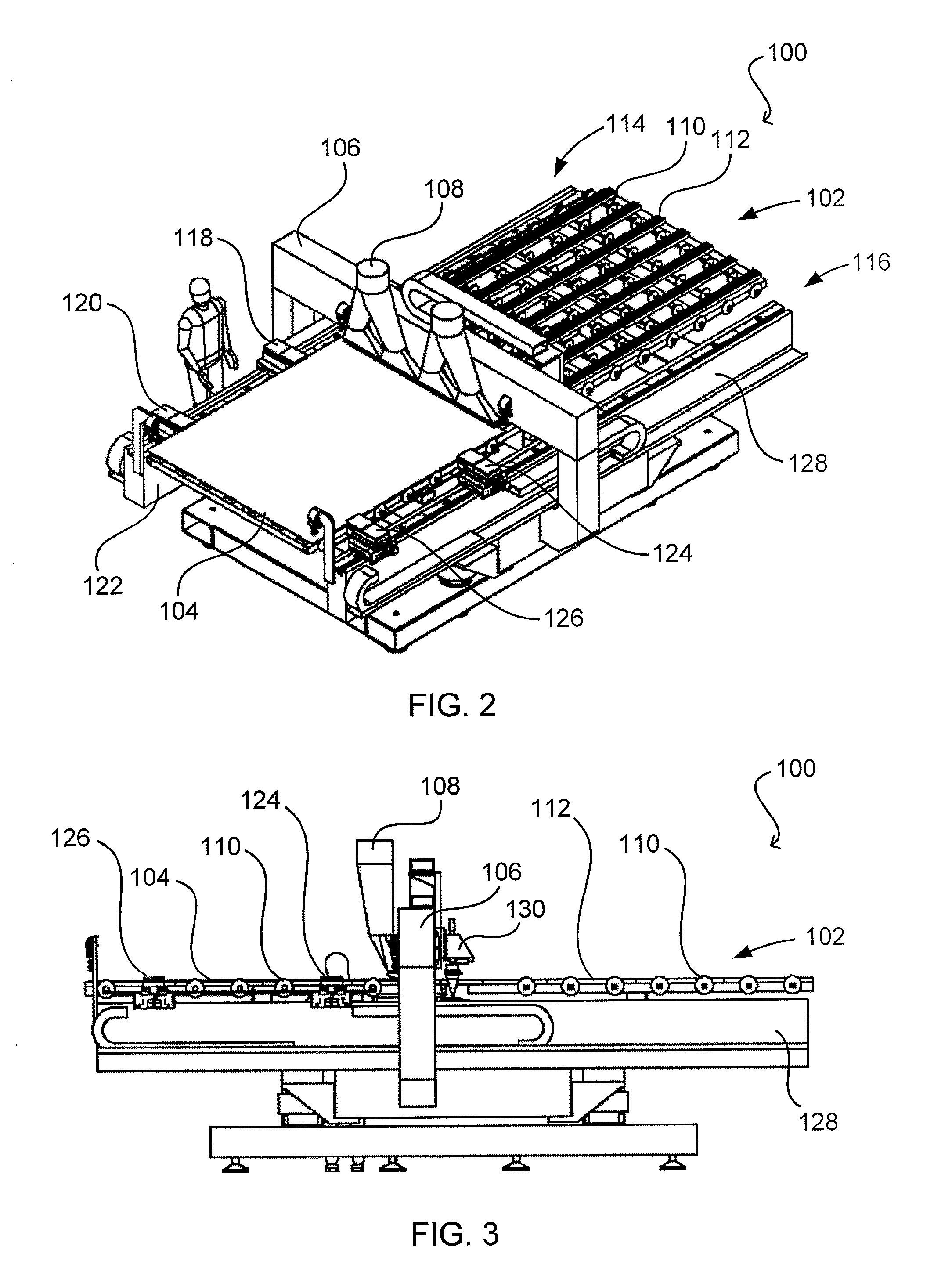

Laser modules and processes for thin film solar panel laser scribing

InactiveUS20110132884A1Easy to controlQuality improvementLaser beam welding apparatusSemiconductor devicesLaser scribingComputer terminal

Laser systems for laser scribing are provided. The systems include a remote module coupled to a laser module through a cable. The remote module includes a controller and a chiller. The laser module has at least a laser source and a cooling plate. The laser module is operable to remove material from at least a portion of a workpiece. The systems also include a plurality of termination modules coupled to the laser module through a plurality of optical fibers. Each of the termination modules includes a mechanical interface. The mechanical interface is coupled to a respective optical fiber. The systems further include a plurality of scanning devices operable to control a position of the output from the laser. Each of the scanning devices is coupled to a respective mechanical interface.

Owner:FORTIX

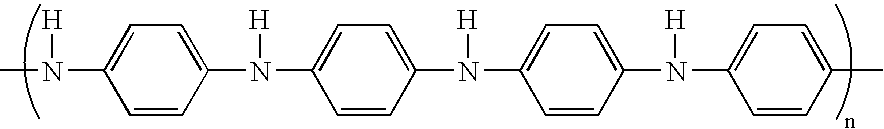

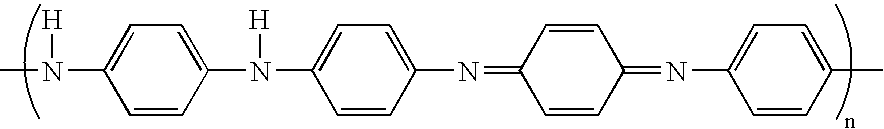

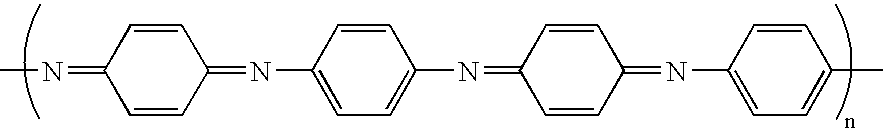

Disk drive system with hydrodynamic bearing lubricant having charge-control additive comprising dioctyldiphenylamine and/or oligomer thereof

InactiveUS7212376B2Lower relative electrical permittivityReduce electrostatic dischargeShaftsRecord information storageOligomerCharge control

An improved disk drive system that employs a lubricant with improved charge control is provided. The disk drive system is comprised of a rotatably mounted magnetic disk. A rotor is coupled to the disk and rotatably retained by a stator. A bearing is formed that serves as an interface between the stator and the rotor. A motor coupled to the rotor rotates the magnetic disk via the rotor. Located in the bearing is a lubricant having a low relative electrical permittivity.

Owner:WESTERN DIGITAL TECH INC

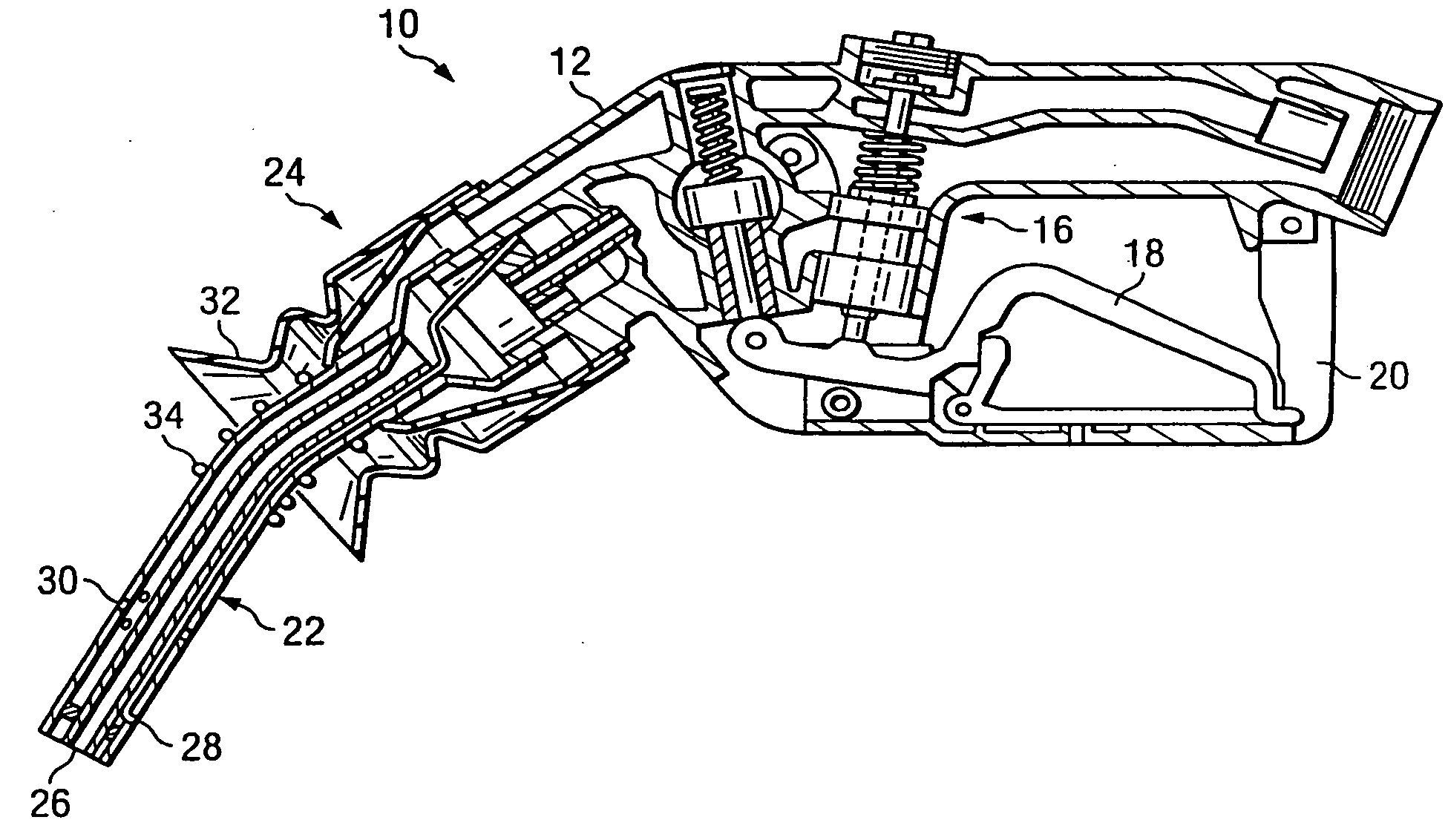

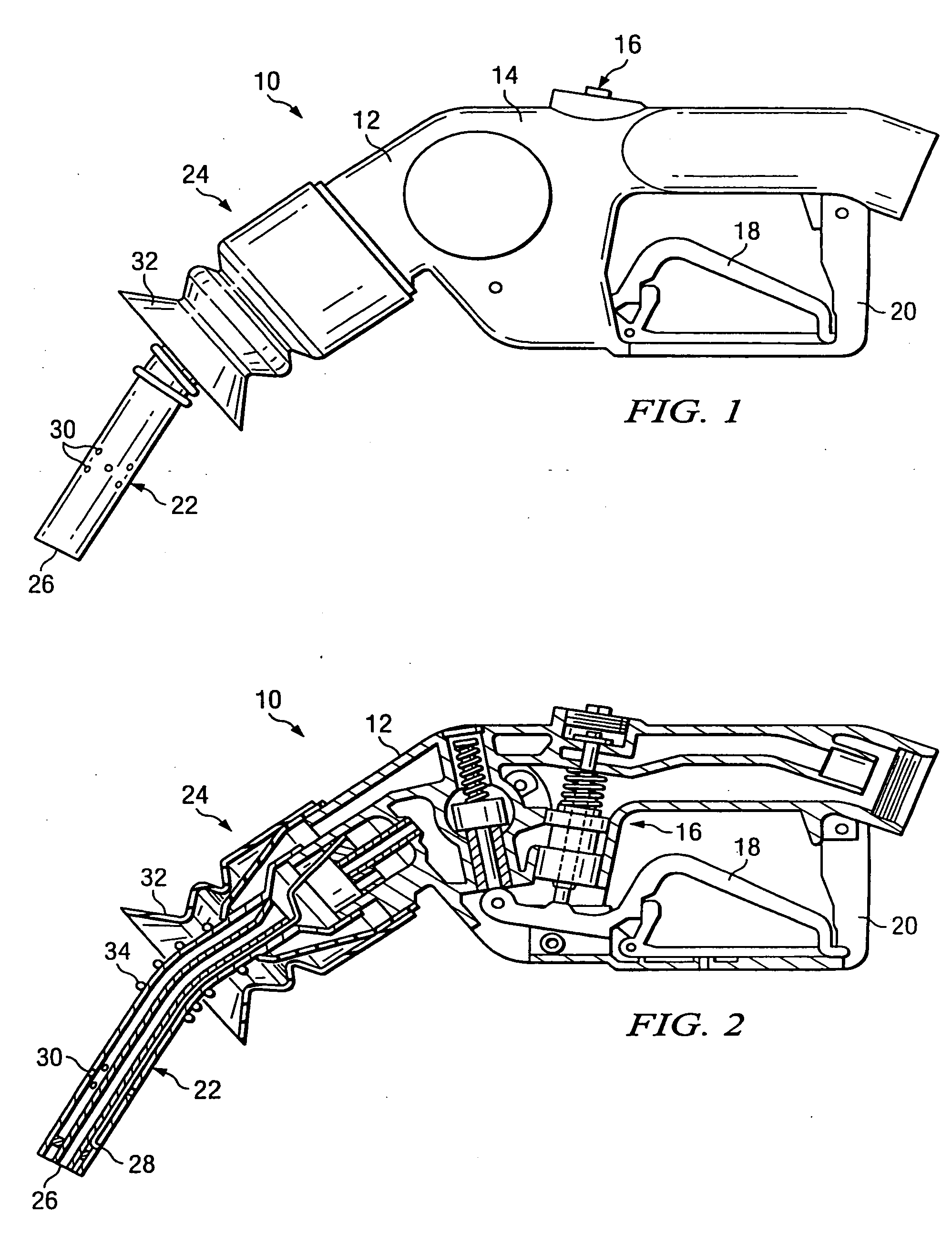

Static dissipative fuel dispensing nozzle

InactiveUS20050115631A1Reduce electrostatic dischargeLiquid fillingLiquid transferring devicesElectrostatic dischargeStatic electricity

A fuel dispensing nozzle includes a body, a handle connected to the body, a handle guard connected to the body and generally surrounding the handle, and a spout extending from the body. Parts of the nozzle are made of, or covered in, static dissipative materials. Additionally, a method for reducing static discharge in existing nozzle installations includes the application of static dissipative material to existing nozzles to address certain static discharge risks.

Owner:WAYNE FUELING SYST

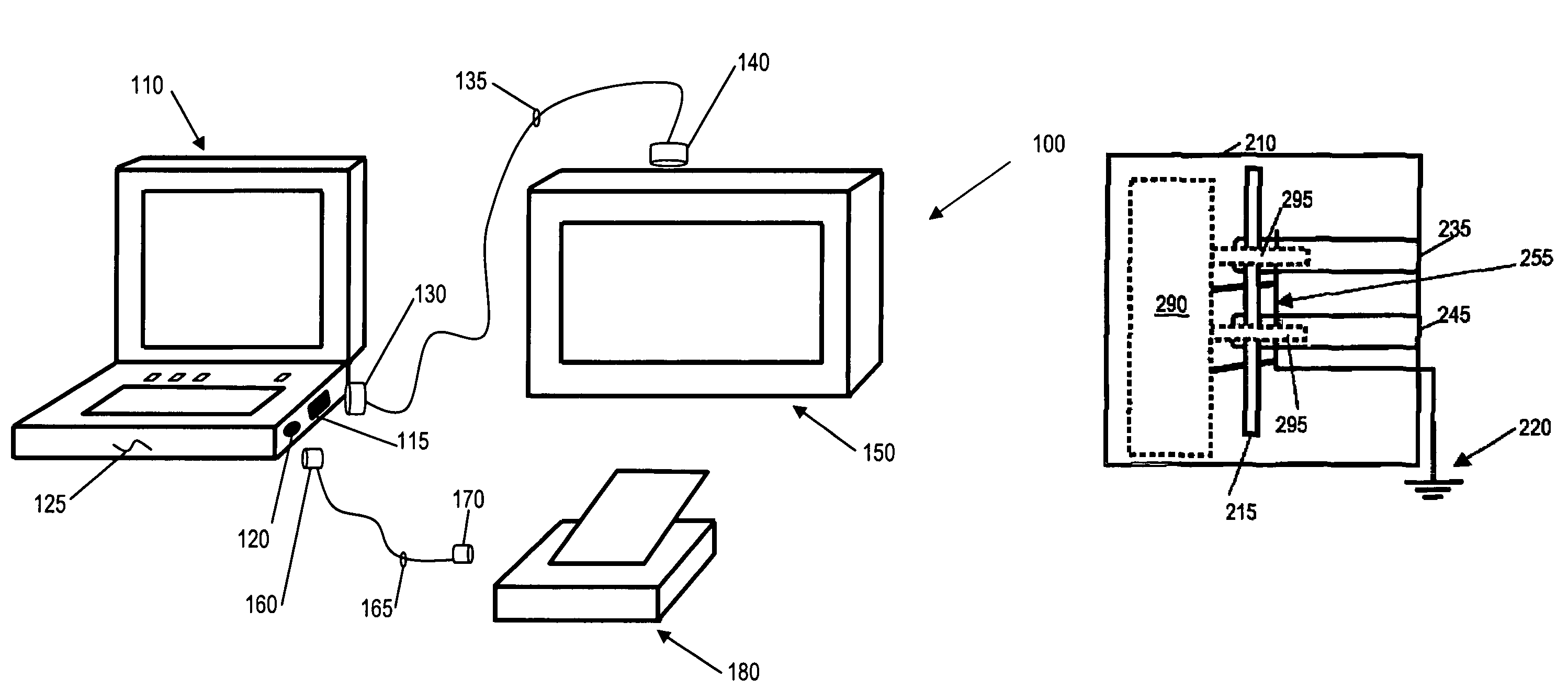

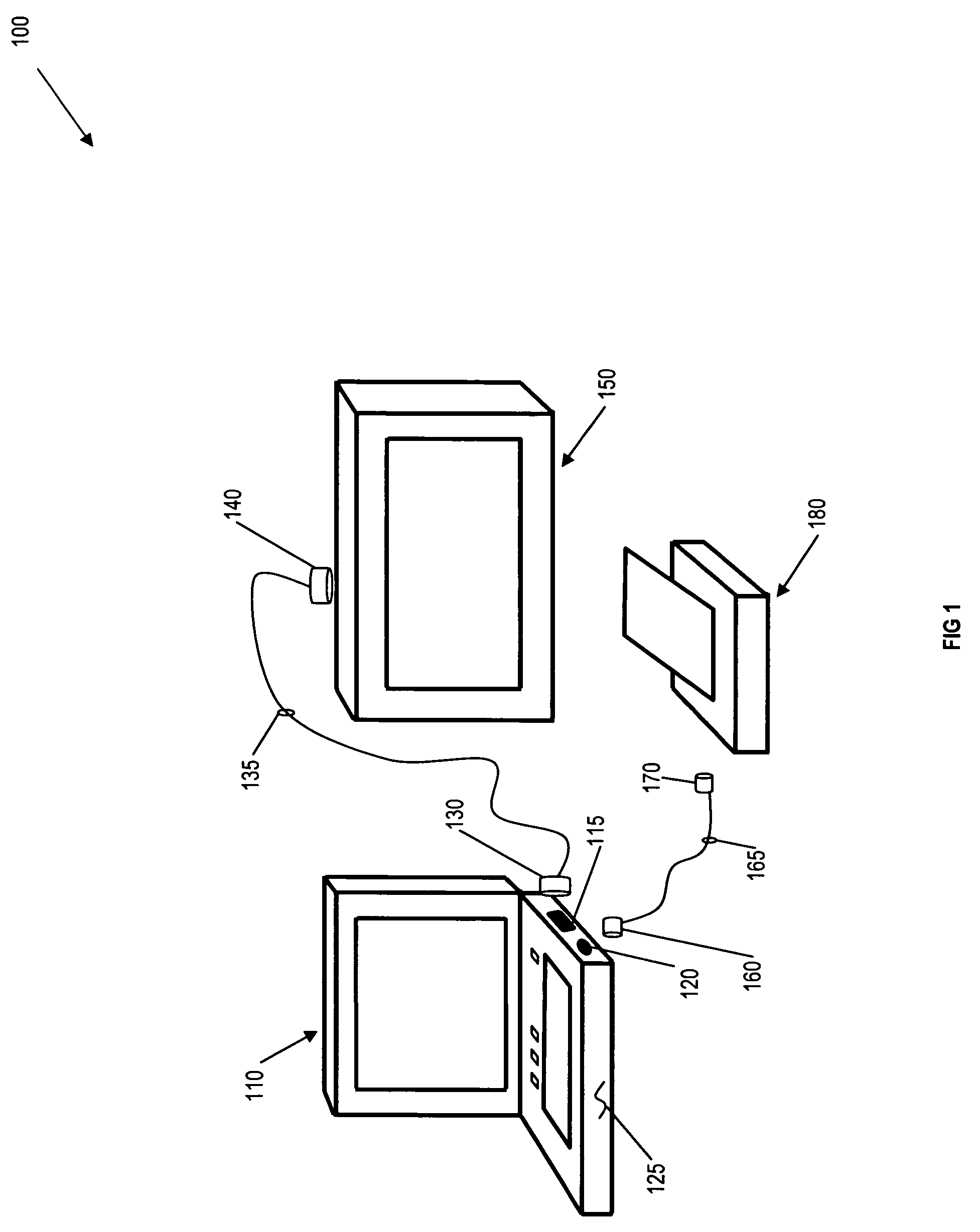

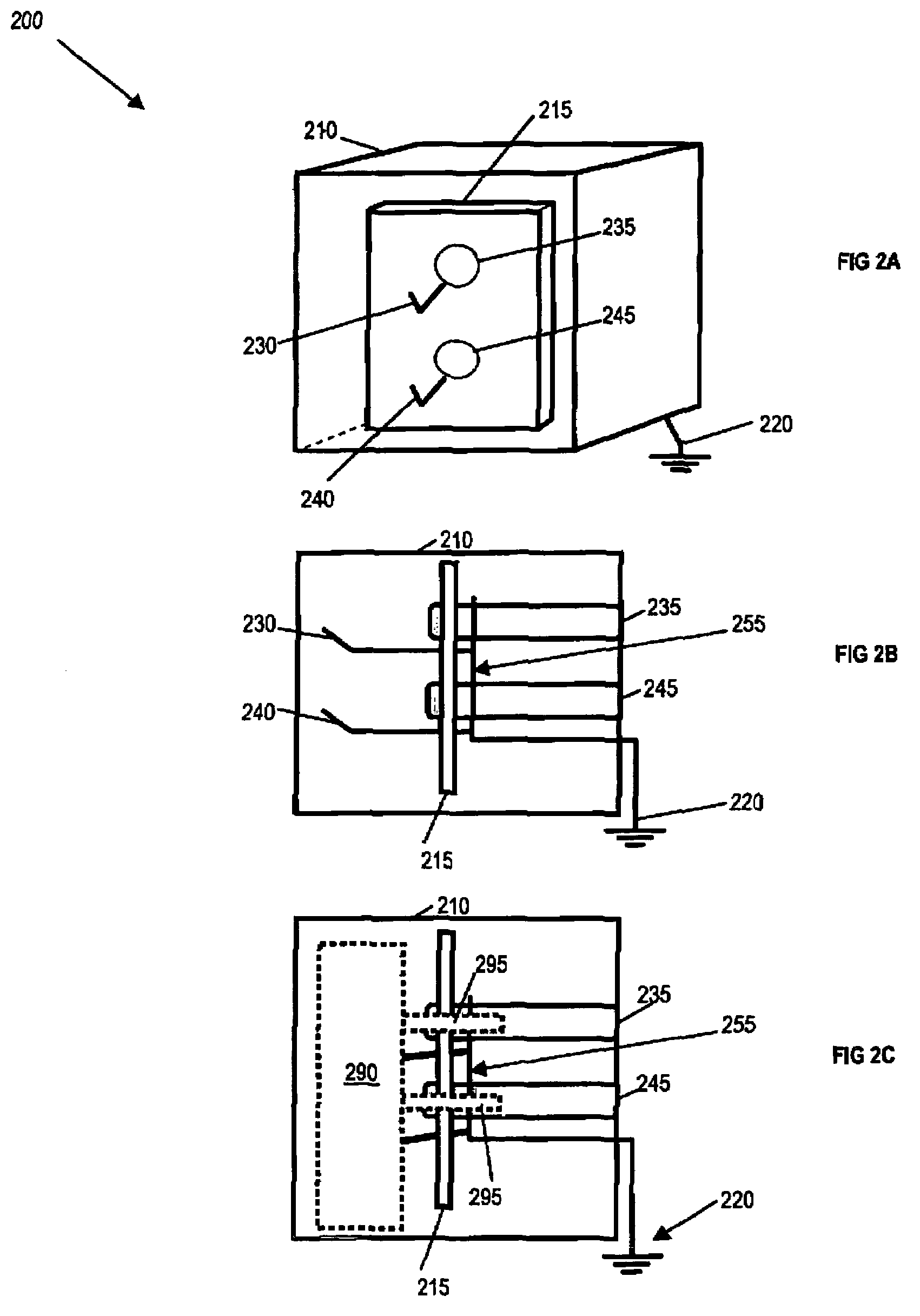

Methods and arrangements to attenuate an electrostatic charge on a cable prior to coupling the cable with an electronic system

InactiveUS7247038B2Reduce static chargeReduce electrostatic dischargeCouplings bases/casesConnection contact member materialElectrical conductorElectronic systems

Methods and arrangements to methods and arrangements to attenuate electrostatic discharges of a cable are disclosed. Embodiments may include connectors with discharge elements integrated into the connectors to interconnect conductors of a cable to attenuate or discharge an electrostatic charge built up on the conductors. In some embodiments, the conductors are momentarily connected to ground as the connector couples with another connector to interconnect a cable with, e.g., a computer. In further embodiments, the discharge elements interconnect the conductors of a cable to redistribute an electrostatic charge and thereby minimize the impact of a discharge when the cable couples with an electronic system such as a computer. Another embodiment comprises a male connector with discharge elements, which ground conductors of the cable as the cable is being inserted into the connector. The discharge elements are pushed out of the way of the conductors as the conductors couple with the connector.

Owner:INT BUSINESS MASCH CORP

Low energy, long life micro-fluid ejection device

ActiveUS7413289B2Thickness minimizationReduce cavitation effectsPrintingElectrical resistance and conductanceEngineering

Micro-fluid ejection heads and methods for extending the life of micro-fluid ejection heads. One such micro-fluid ejection head includes a substrate having a plurality of thermal ejection actuators. Each of the thermal ejection actuators has a resistive layer and a protective layer thereon. A flow feature member is adjacent the substrate and defines a fluid feed channel, a fluid chamber associated with at least one of the actuators and in flow communication with the fluid feed channel, and a nozzle. The nozzle is offset to a side of the chamber opposite the feed channel. A polymeric layer having a degradation temperature of less than about 400° C. overlaps a portion of the at least one actuator associated with the fluid chamber and positioned less than about five microns from at least an edge of the at least one actuator opposite the fluid feed channel.

Owner:SLINGSHOT PRINTING LLC

Electrostatic charge dissipation system statement regarding federally sponsored research or development

InactiveUS7815759B1Reduce susceptibilityOvercome lack of conductivityNon-explosive/non-thermic compositionsElectricityConductive polymer

An electrostatic charge reduction system including a composition having at least one energetic particle component with or without a non-conducting binder, and conducting polymer or electrically neutral polymer deposited on the energetic component in its oxidized form. The oxidation of the polymer occurs during or after the polymer deposition process.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

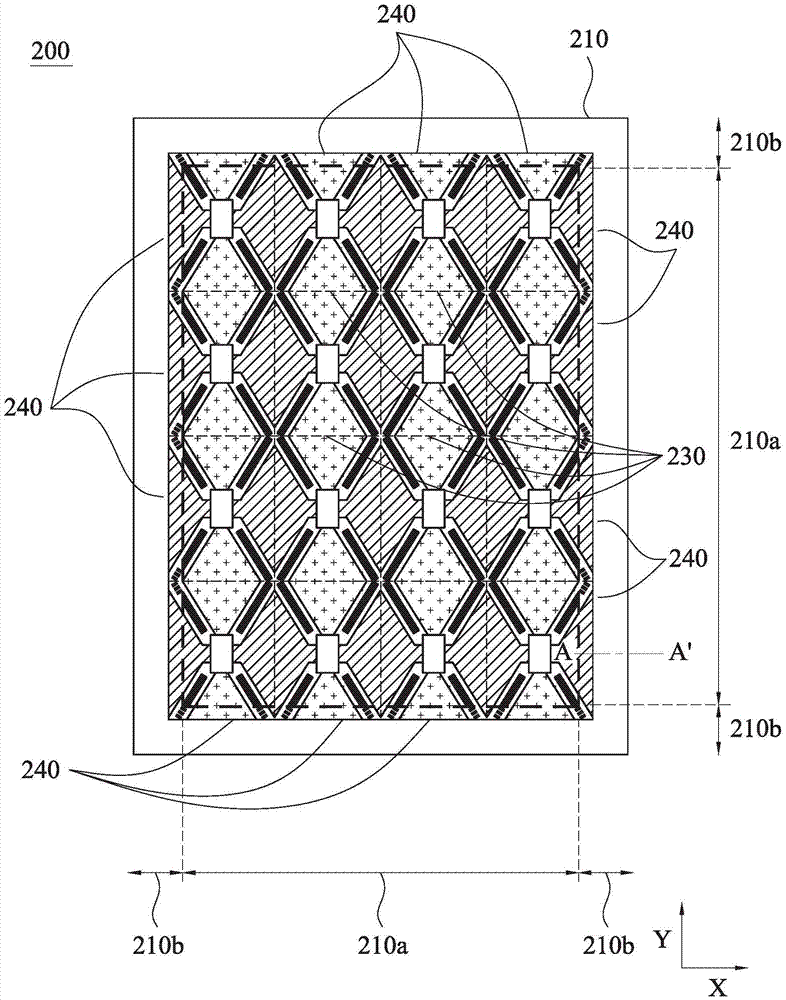

Touch electrode array and touch display device

InactiveCN107329641ALoss of touchIncreasing the thicknessInput/output processes for data processingDisplay deviceEngineering

A touch electrode array and a touch display device are disclosed. The touch electrode array is disposed on a substrate and includes at least one first sensing electrode and at least one guard electrode. The first sensing electrode is made of a mesh structure. The mesh structure includes a solid portion and at least one open portion defined by the solid portion. The at least one guard electrode overlaps the at least one open portion in one direction. additionally the touch display device comprising the touch electrode array is put forward.

Owner:AU OPTRONICS CORP

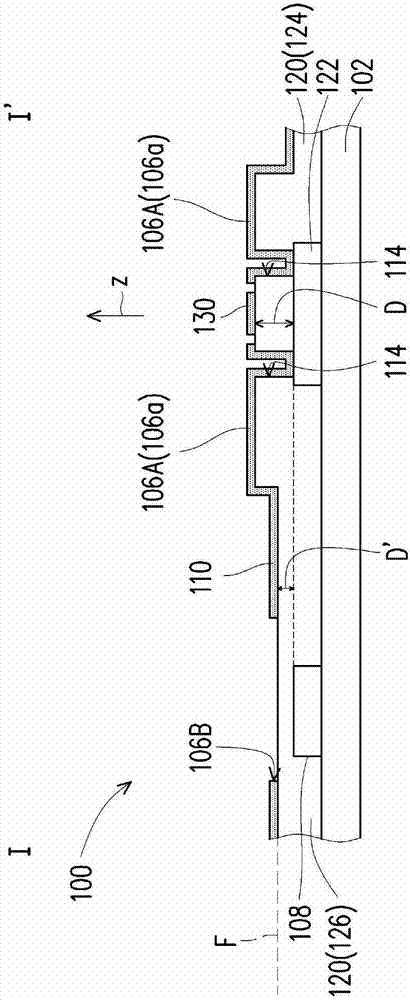

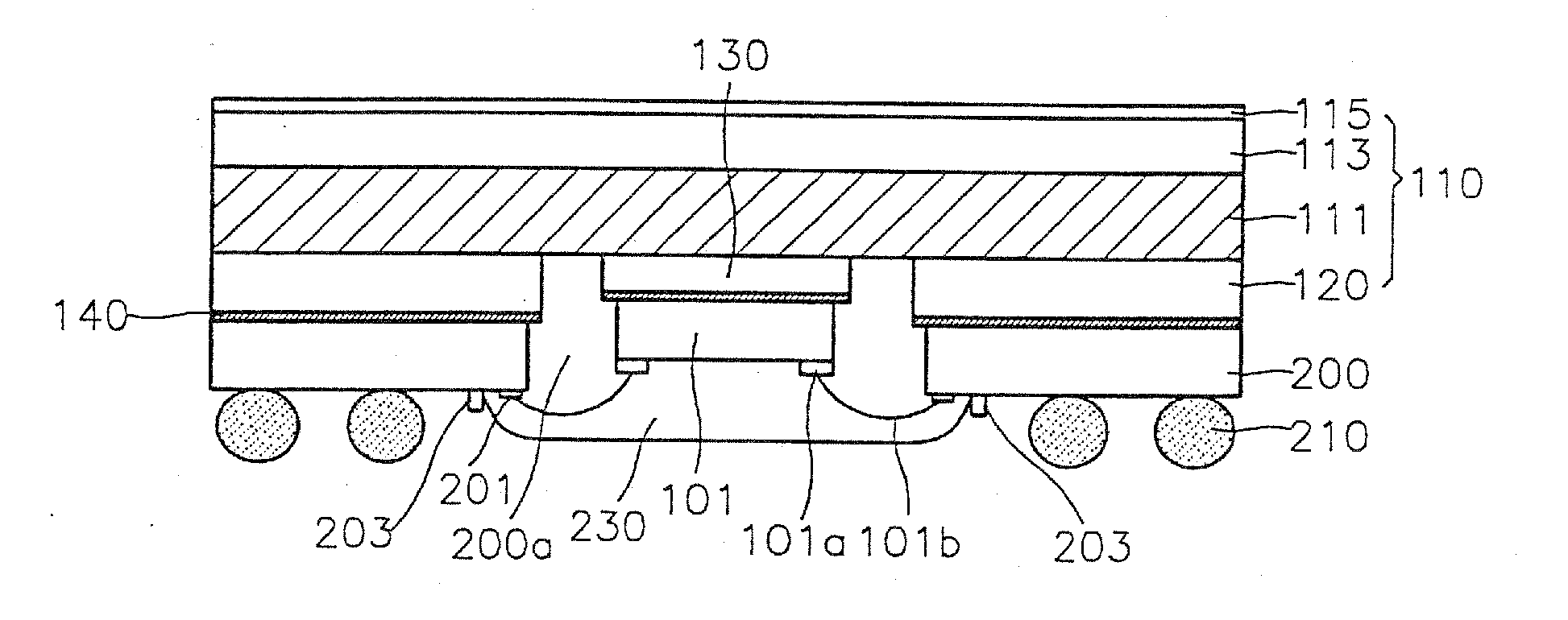

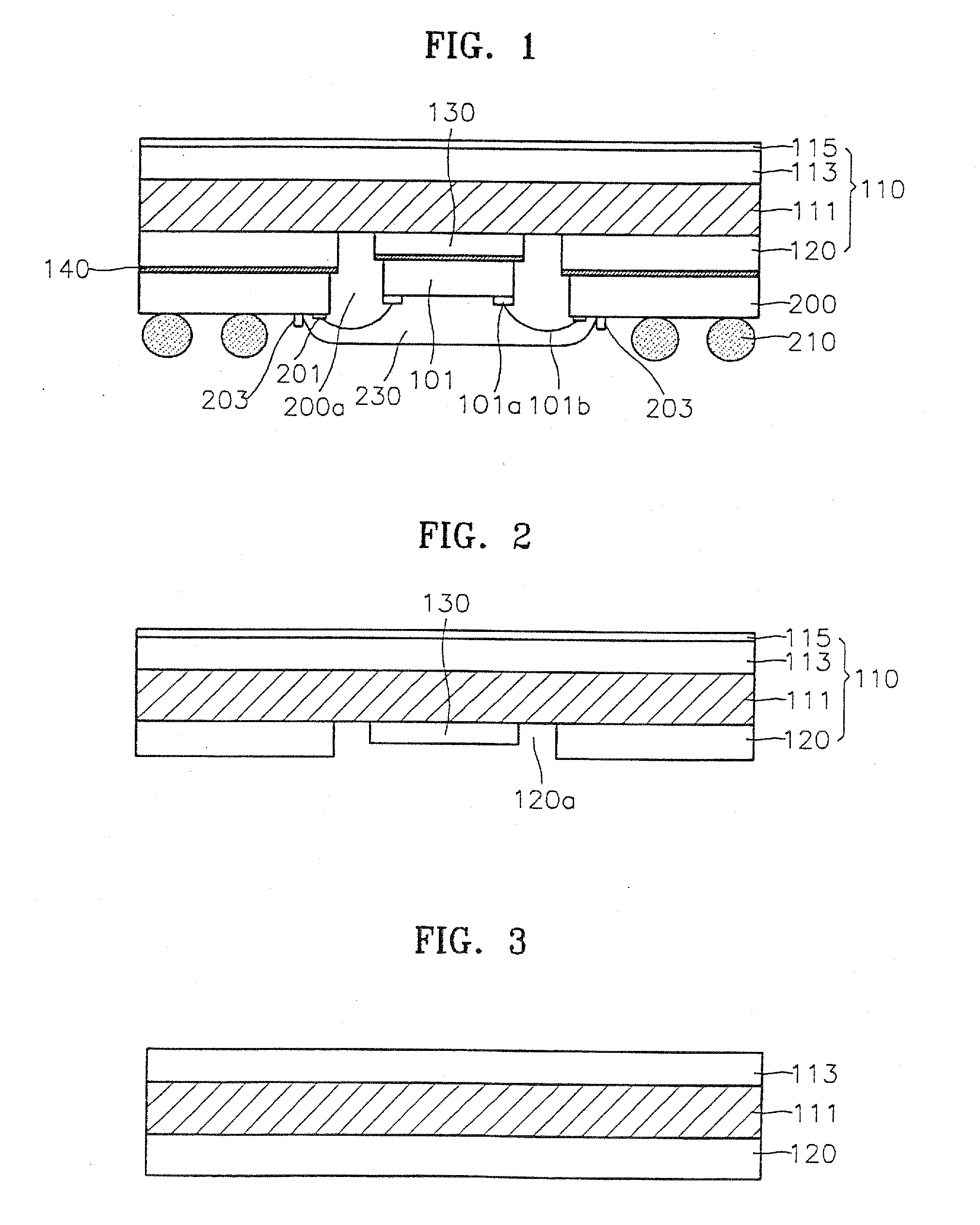

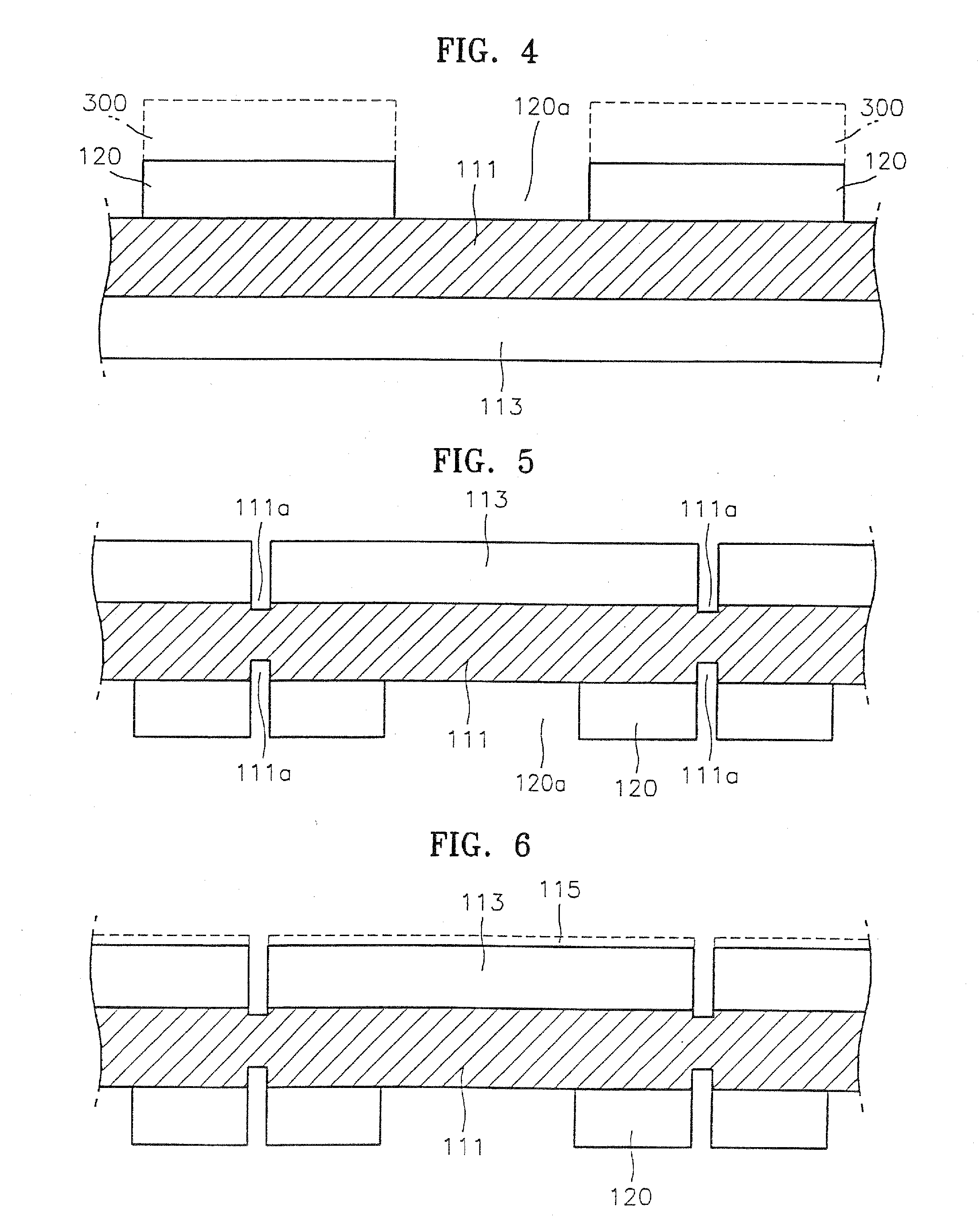

High-power ball grid array package, heat spreader used in the bga package and method for manufacturing the same

ActiveUS20070258215A1Reduce generationReduce conductivitySemiconductor/solid-state device detailsSolid-state devicesSolder ballSemiconductor chip

Provided are a high-power ball grid array (BGA) and a method for manufacturing the high-power BGA. The high-power BGA includes a printed circuit board which has a through hole at its center, connection pads which are formed on the bottom of the printed circuit board, matrix solder balls which surround the through hole and are adjacent to the connection pads on the bottom of the printed circuit board, a heat spreader which is formed on the top surface of the printed circuit board and includes an insulating layer of a high thermal conductivity, a semiconductor chip which is mounted downwardly on the bottom surface of the heat spreader, within the through hole, and includes a plurality of pads for bonding via gold wires with the connection pad, and a passive film which fills the through hole and is formed at the bottom of the semiconductor chip. By interposing a ceramic between the semiconductor chip and the heat spreader, for insulating, the generation of charges between the semiconductor chip and the heat spreader can be sharply reduced, and defects such as ESD (electrostatic discharge) can be reduced when testing for the ESD and mounting the package.

Owner:SAMSUNG ELECTRONICS CO LTD

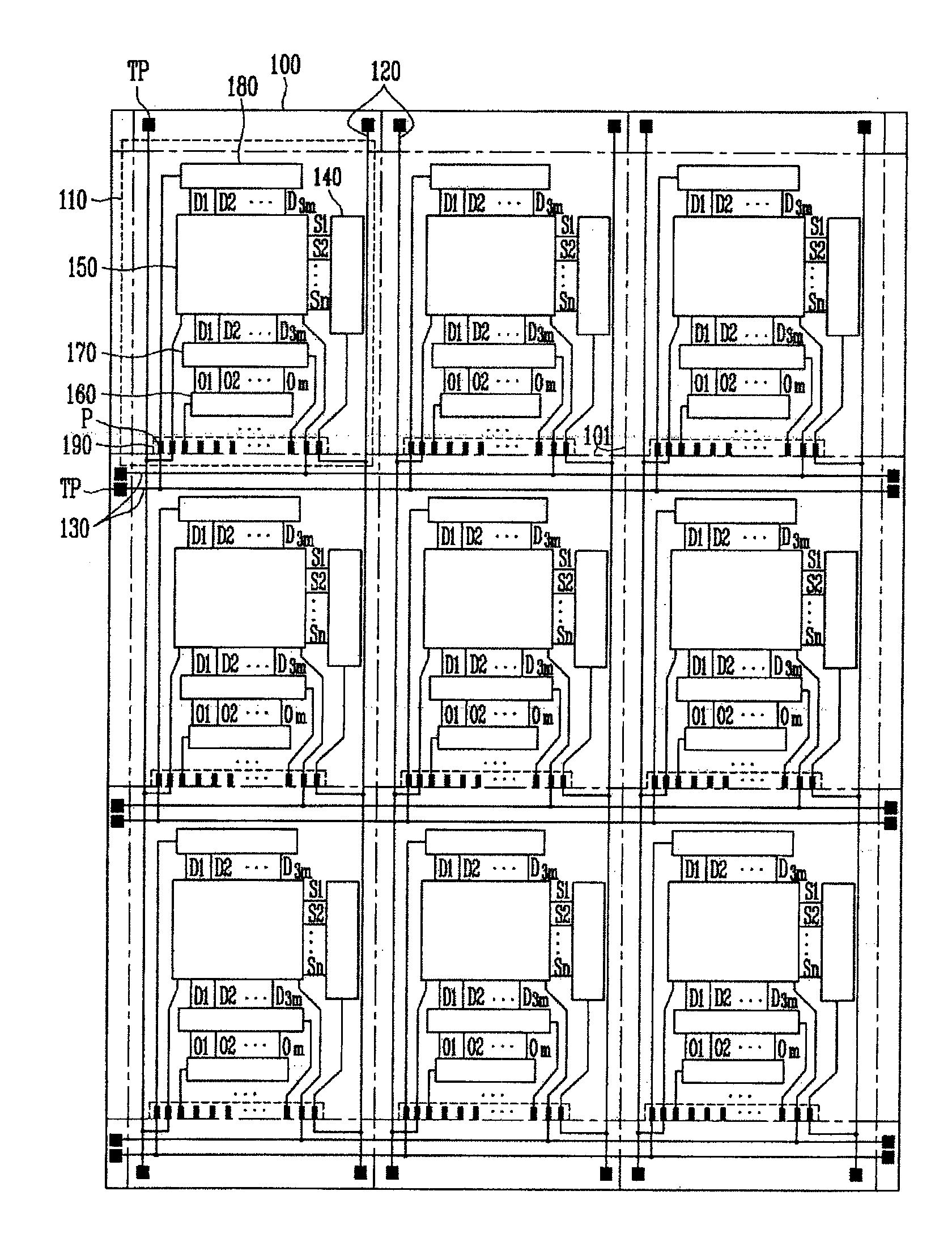

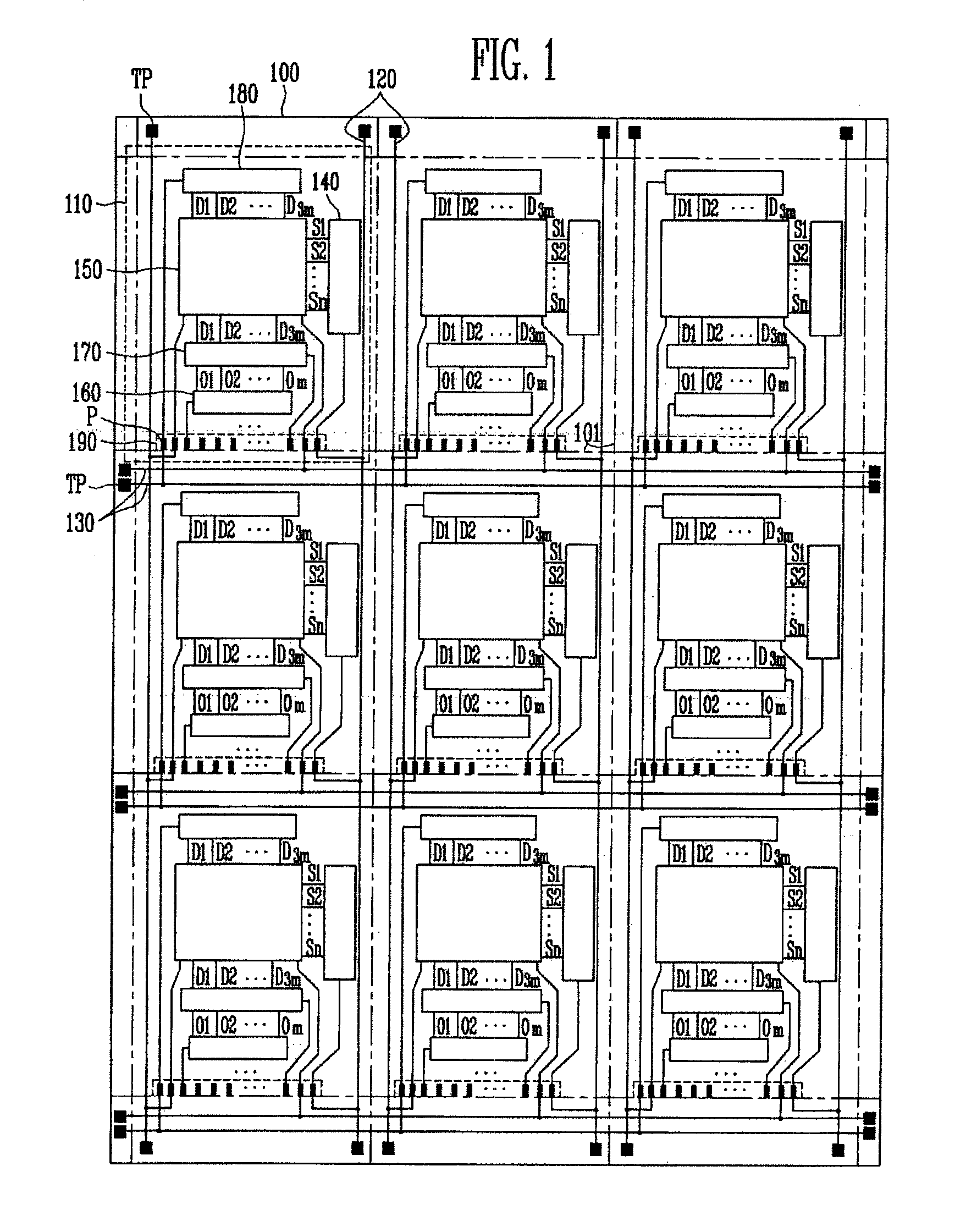

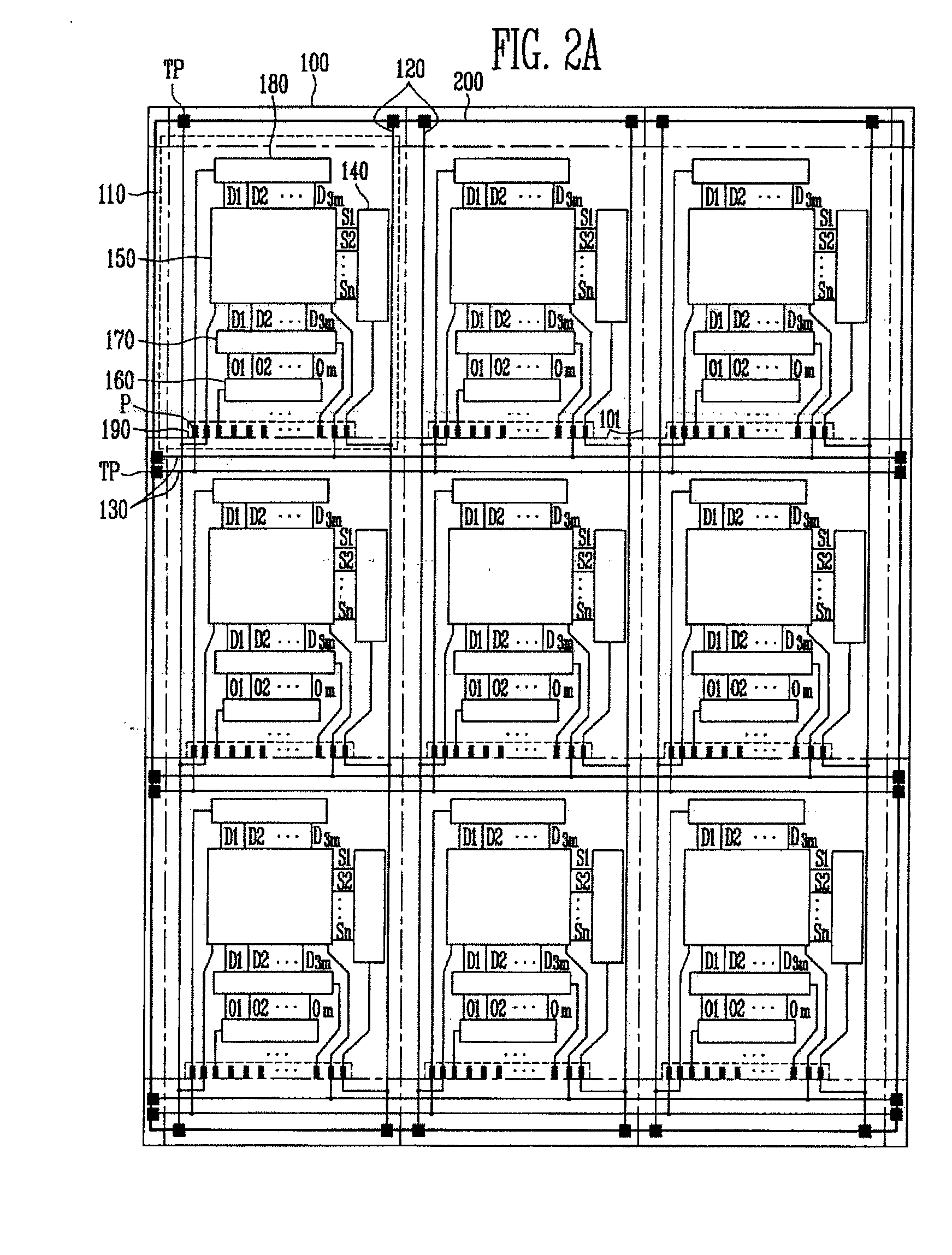

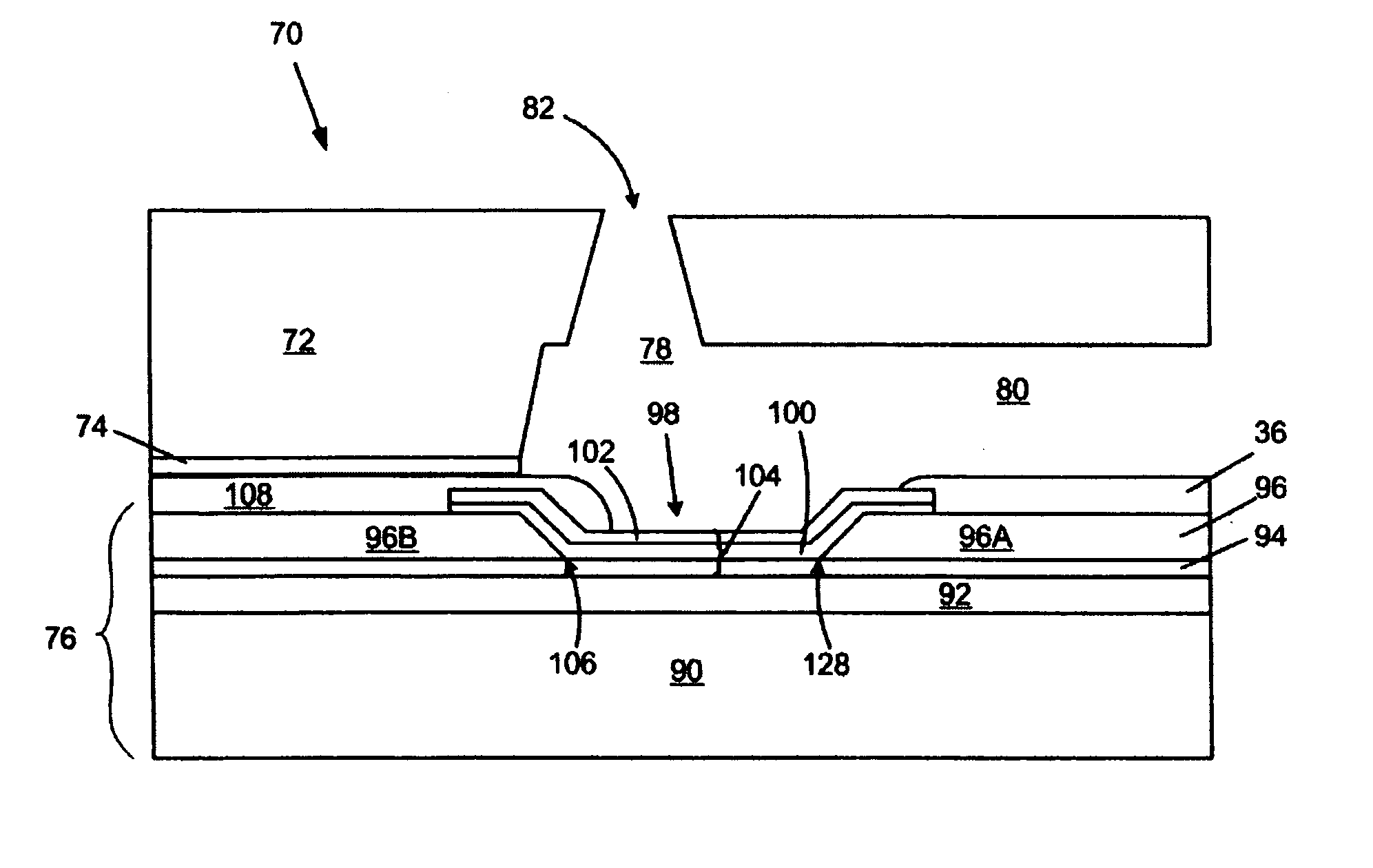

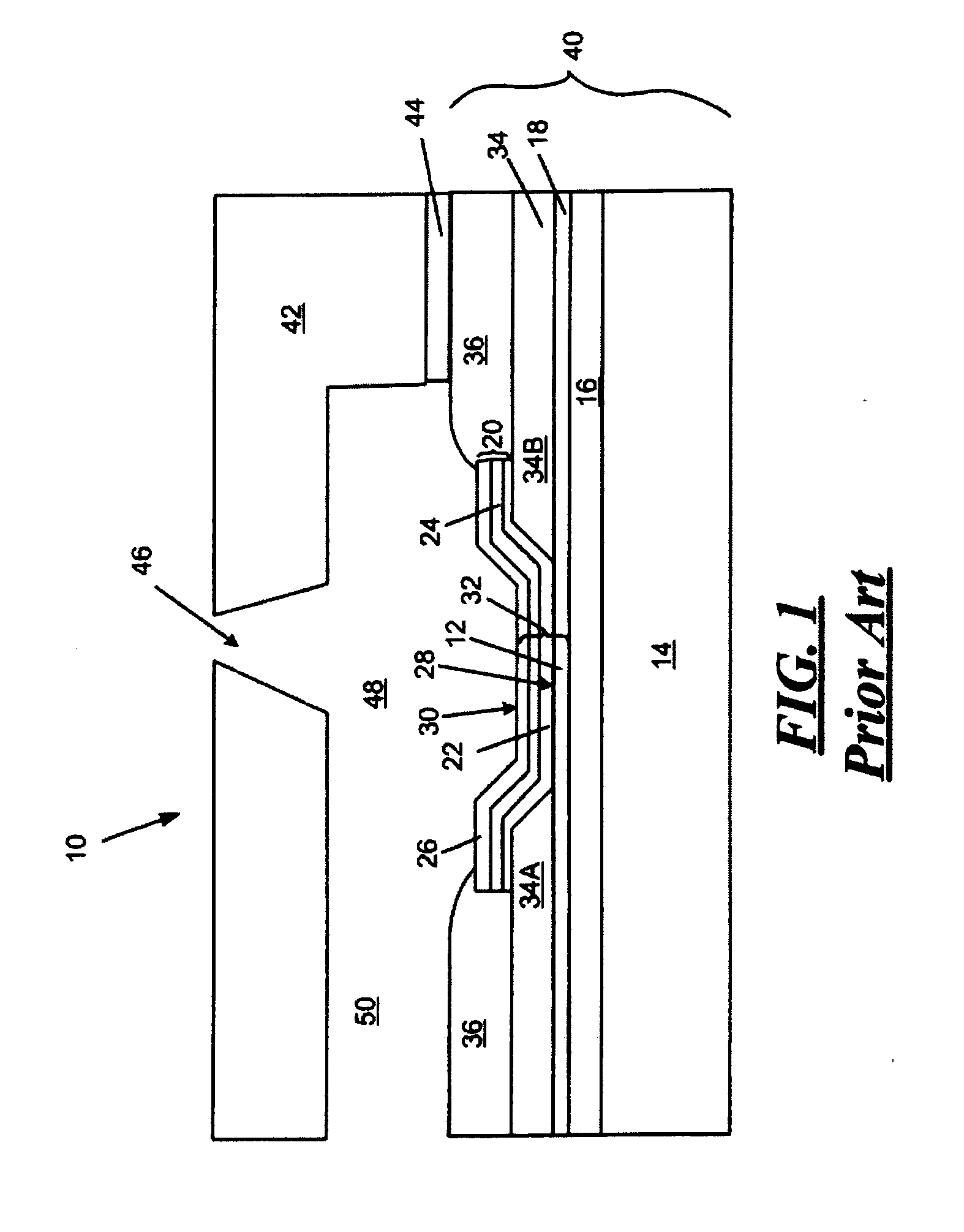

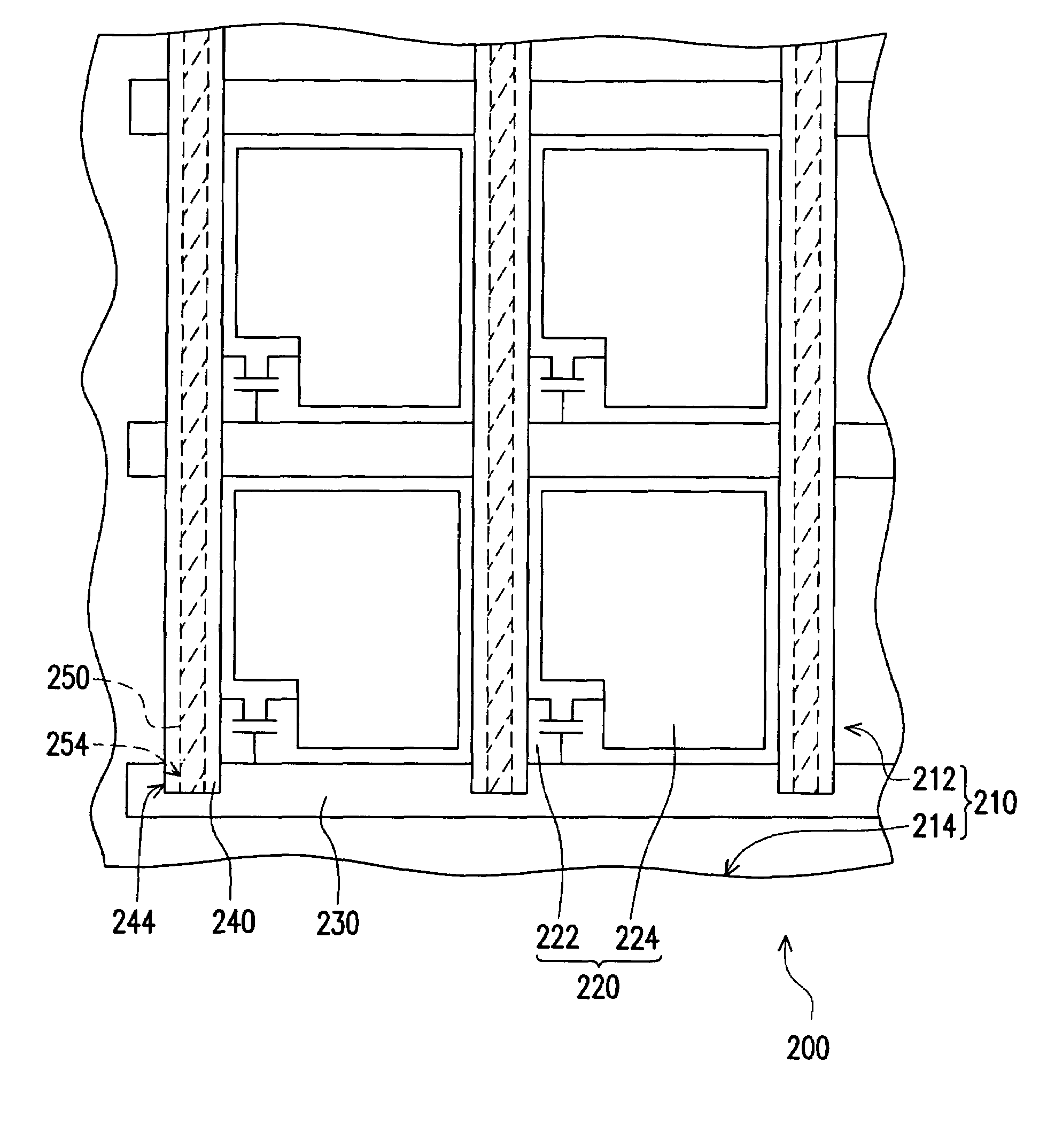

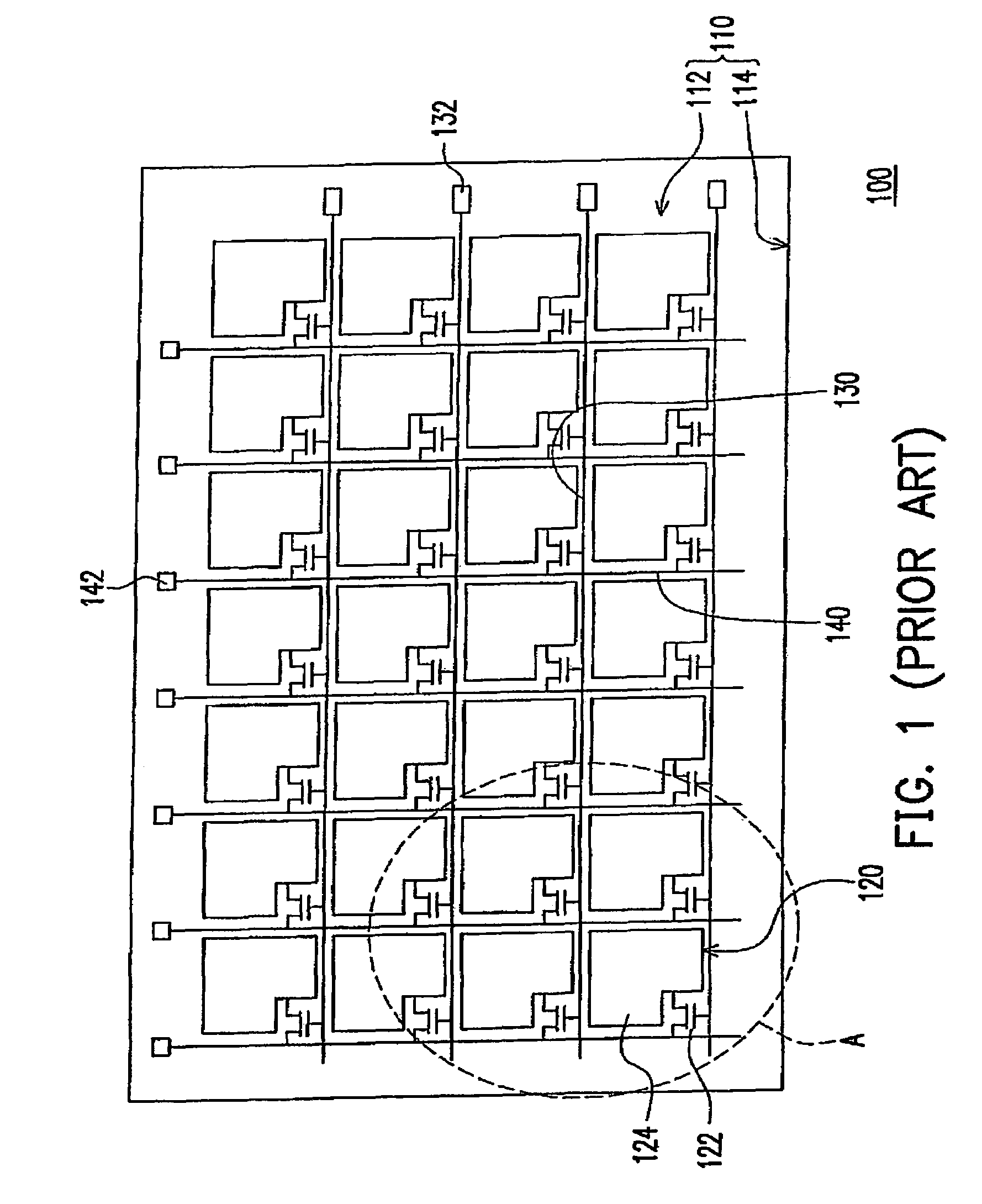

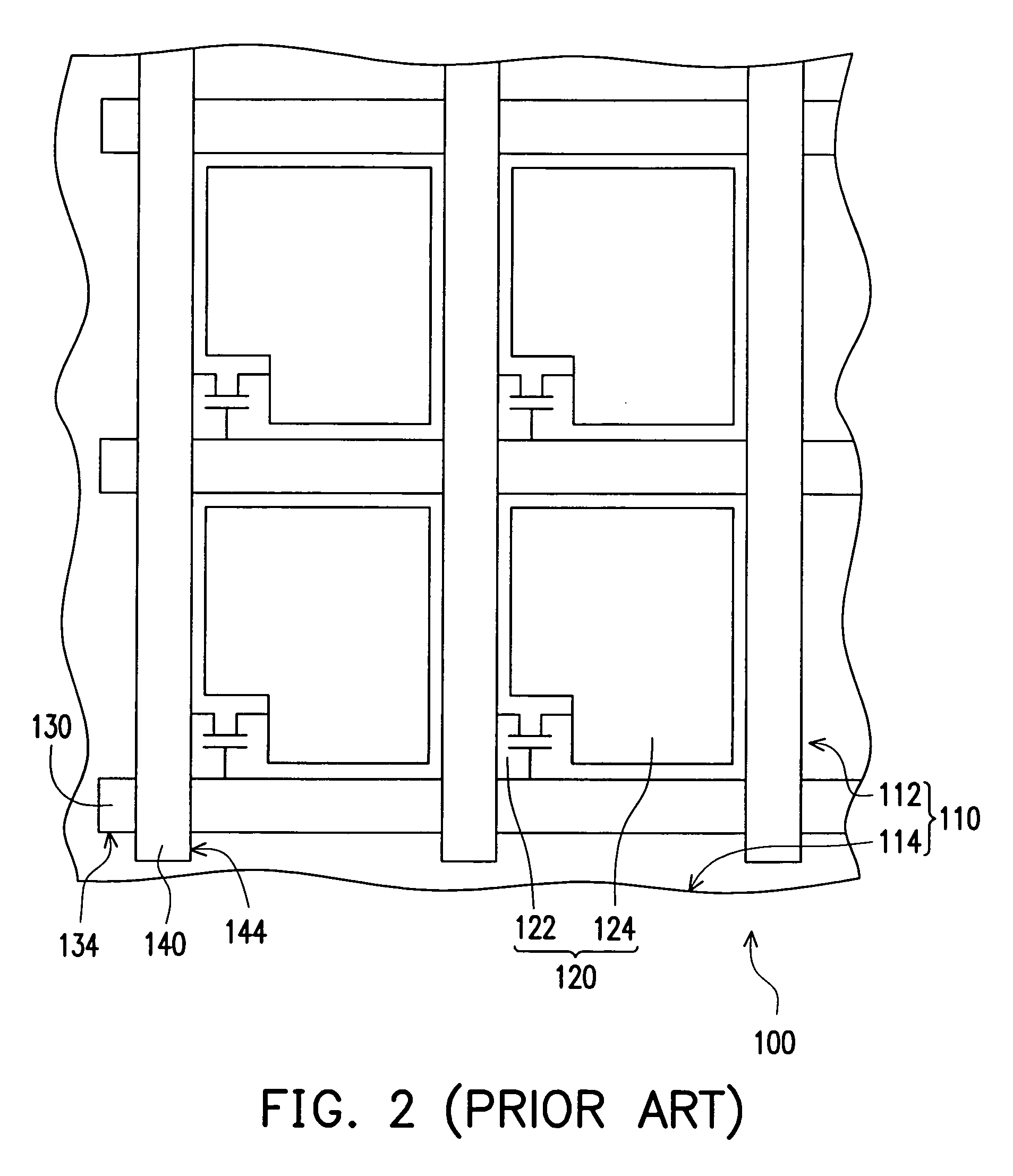

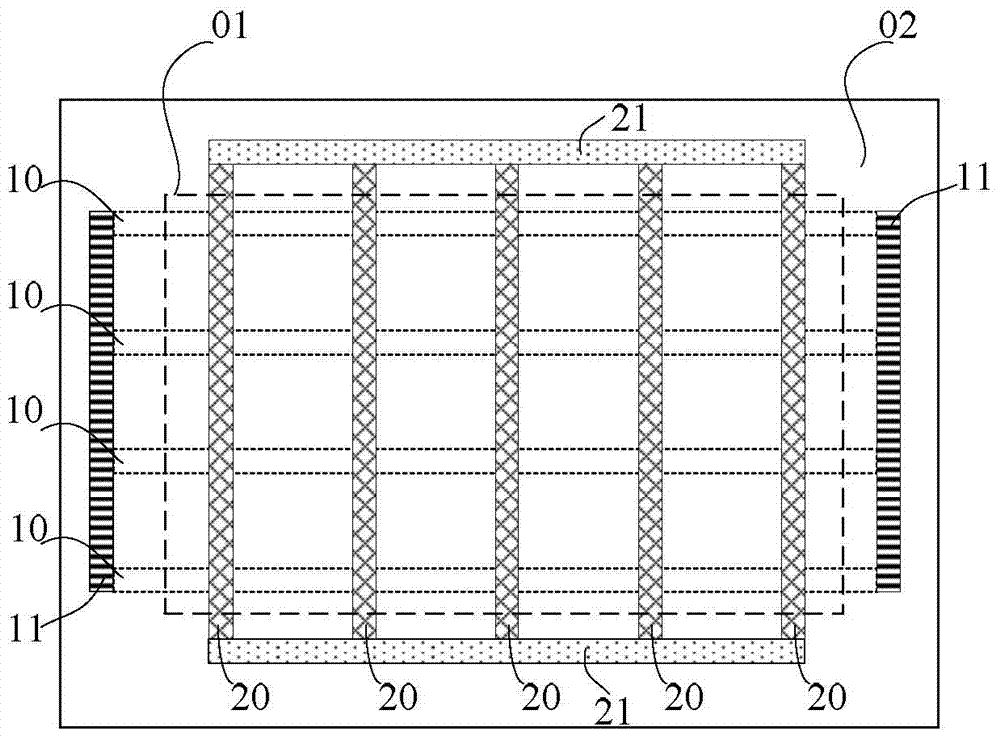

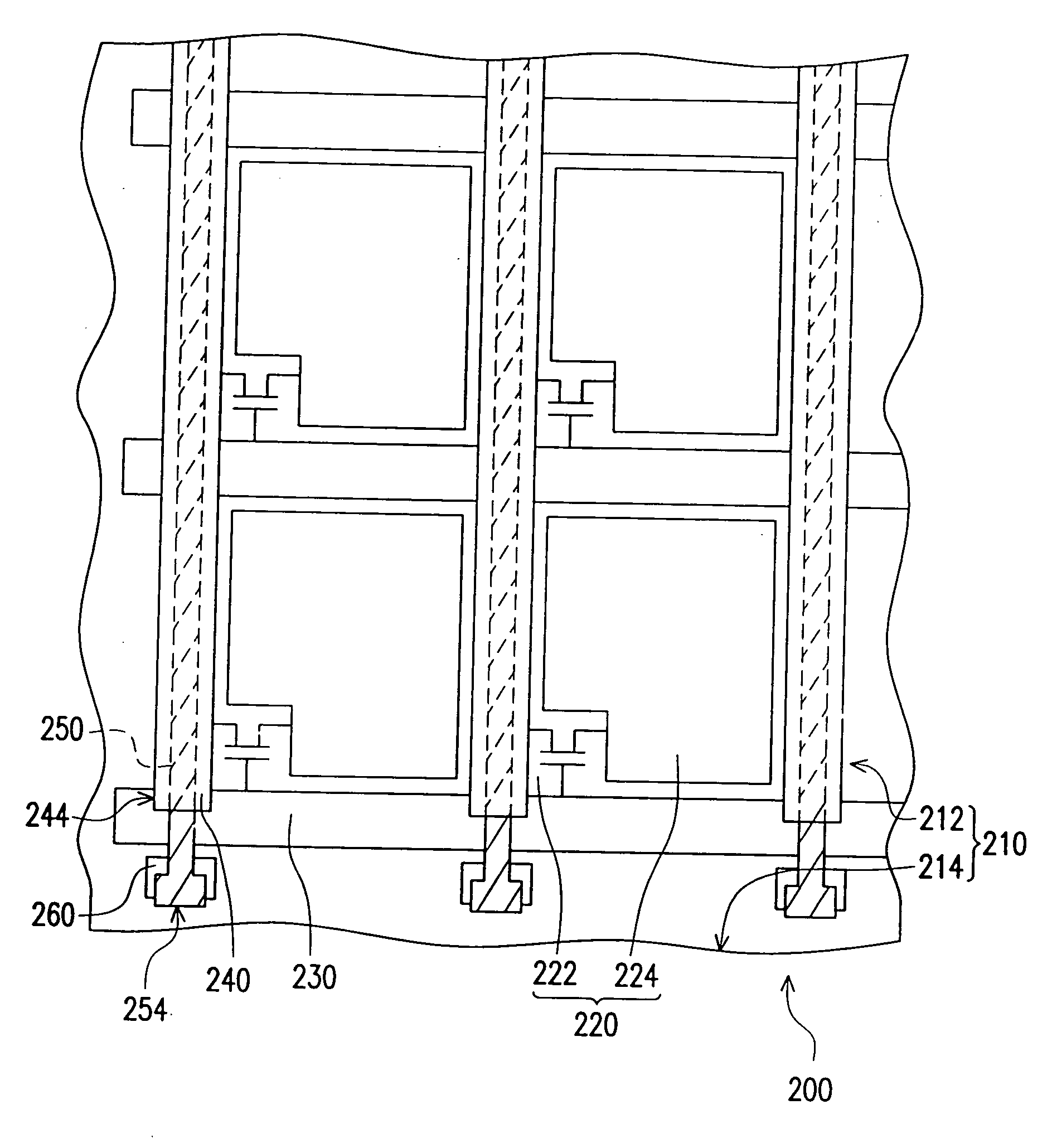

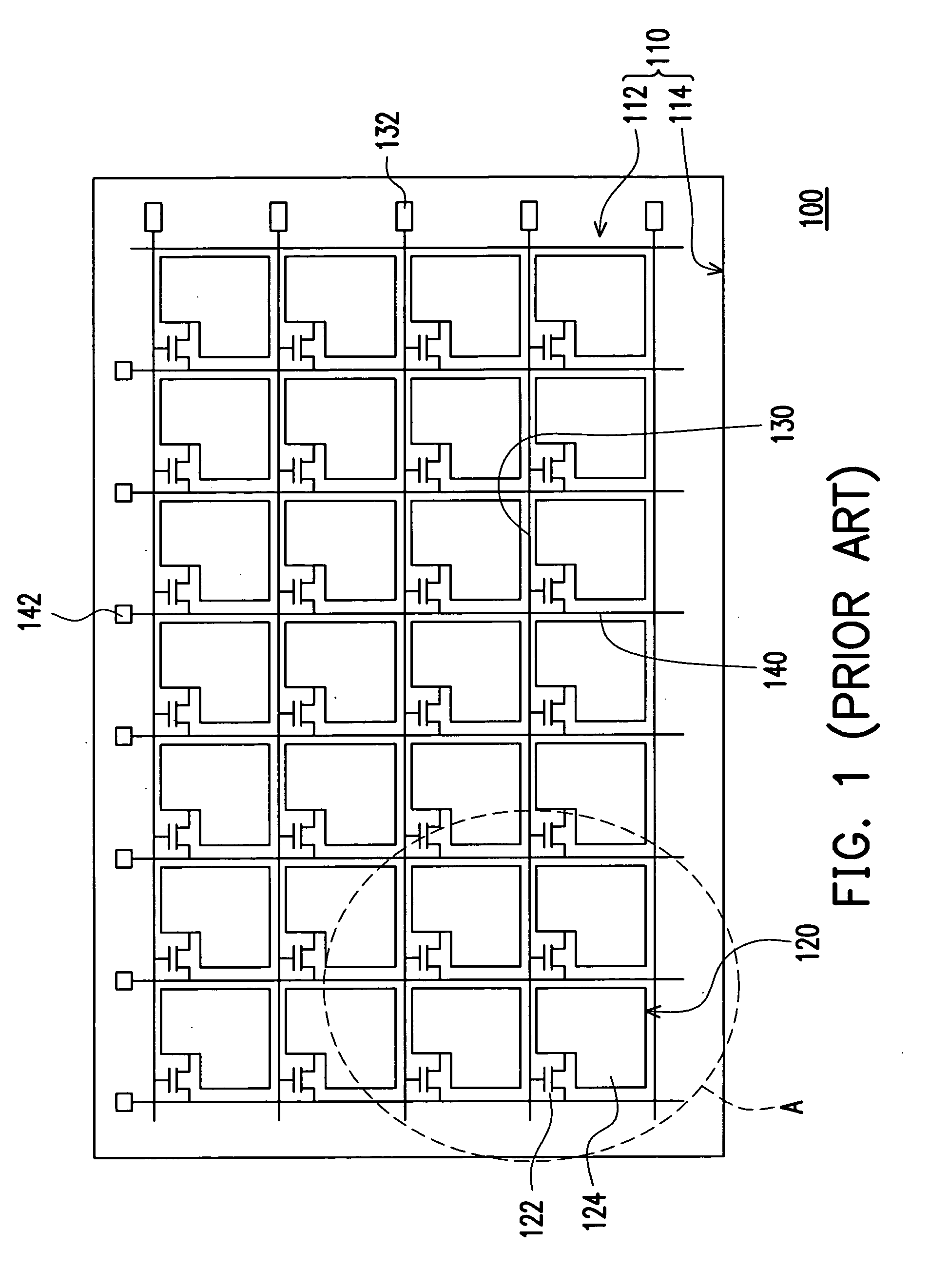

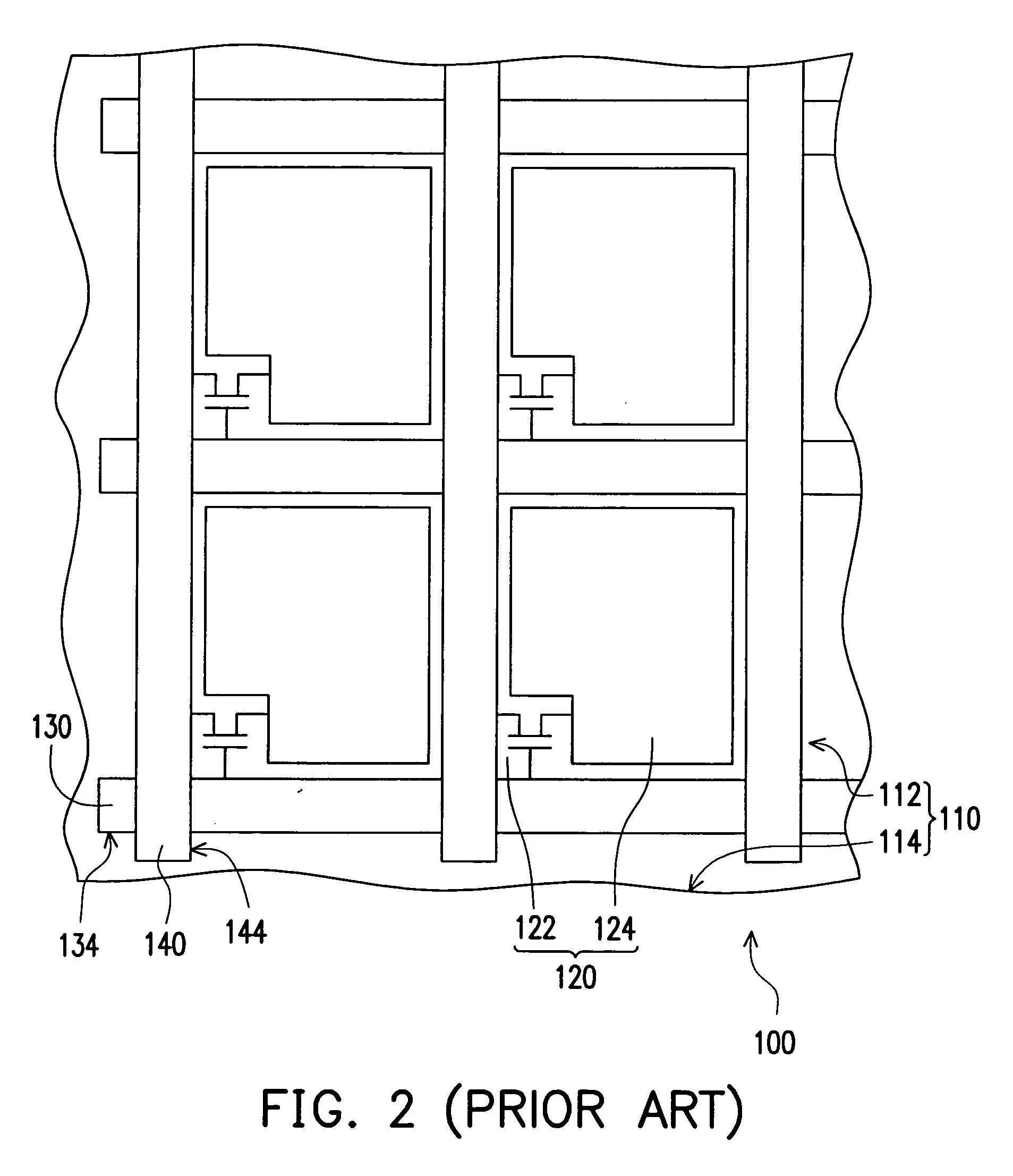

Thin film transistor array substrate having scan or data lines extending to peripheral area without exceeding respectively outmost data and scan lines for reducing electrostatic discharge damage

ActiveUS7489366B2Optimize layoutAvoid damageStatic indicating devicesSolid-state devicesScan lineEngineering

A thin film transistor (TFT) array substrate for reducing electrostatic discharge damage includes a substrate, a plurality of pixel units, scan lines and data lines. The substrate has a pixel area and a peripheral area adjacent to the pixel area. The pixel units are disposed in the pixel area. The scan lines and data lines are disposed in the pixel area of the substrate and electrically connected with the pixel units, wherein one end of each scan line extending to the peripheral area is a bonding pad for the scan line. One end of each data line extending to the peripheral area is a bonding pad for the data line. The other end of each data line extending to the peripheral area is an end part of the data line. Particularly, the end part of the data line does not exceed the outmost scan line.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

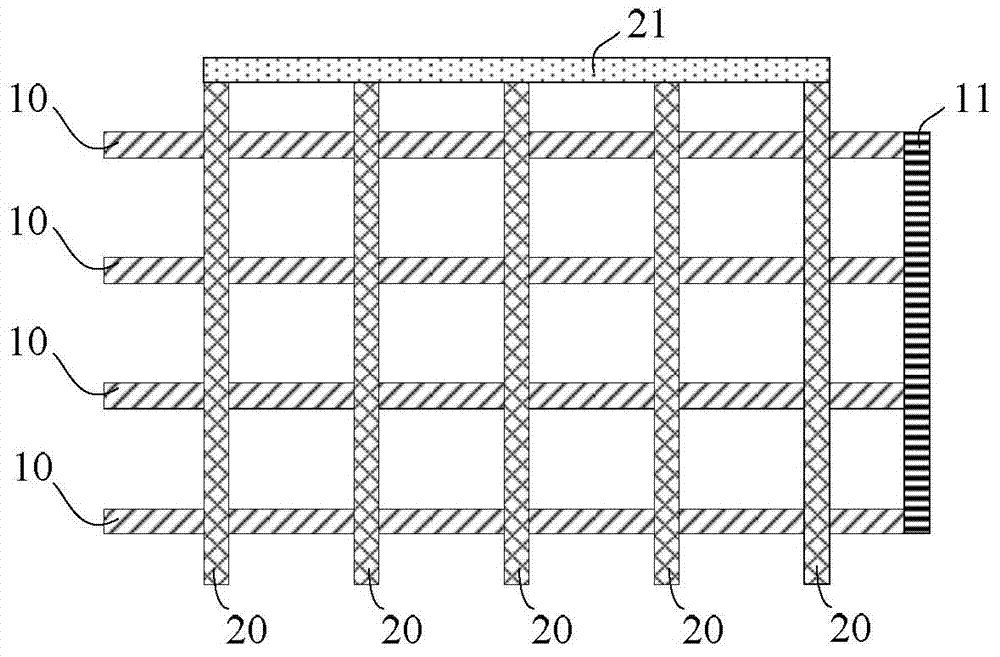

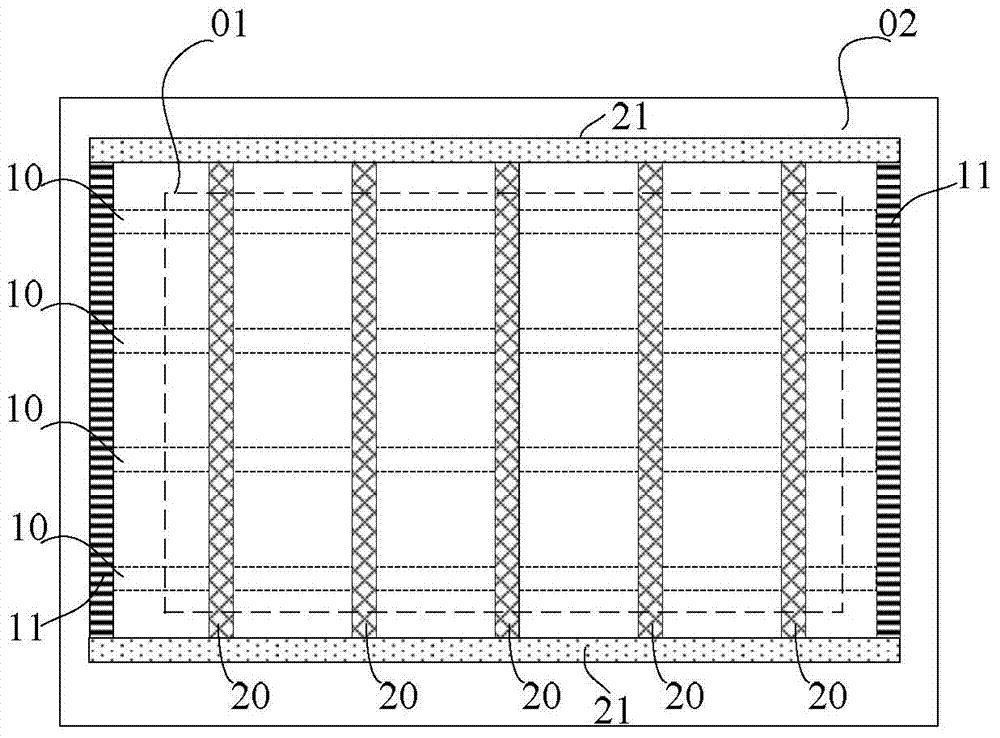

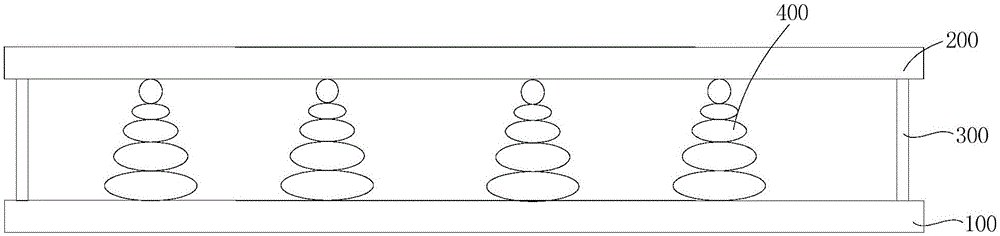

Array substrate, manufacturing method thereof and display device

ActiveCN104716146AReduce electrostatic dischargeImprove yieldSolid-state devicesSemiconductor/solid-state device manufacturingElectricityDisplay device

The embodiment of the invention provides an array substrate, a manufacturing method thereof and a display device, and relates to the technical field of display. The electrostatic discharge of the TFT array substrate in the manufacturing process can be effectively reduced, and the product yield is improved. The method includes the step of forming a thin film transistor and signal lines and further includes the step of forming a signal line communicating wire, wherein the signal line communicating wire at least makes the signal lines of the same type electrically connected. Before the last film layer is manufactured in the array substrate manufacturing process, the method further includes the step of etching via holes in the signal line communicating wire or the positions, close to the signal line communicating wires, of the signal lines, wherein the via holes are used for eliminating the electrical connection of the signal lines. The method is used for manufacturing the array substrate and the display device.

Owner:BOE TECH GRP CO LTD

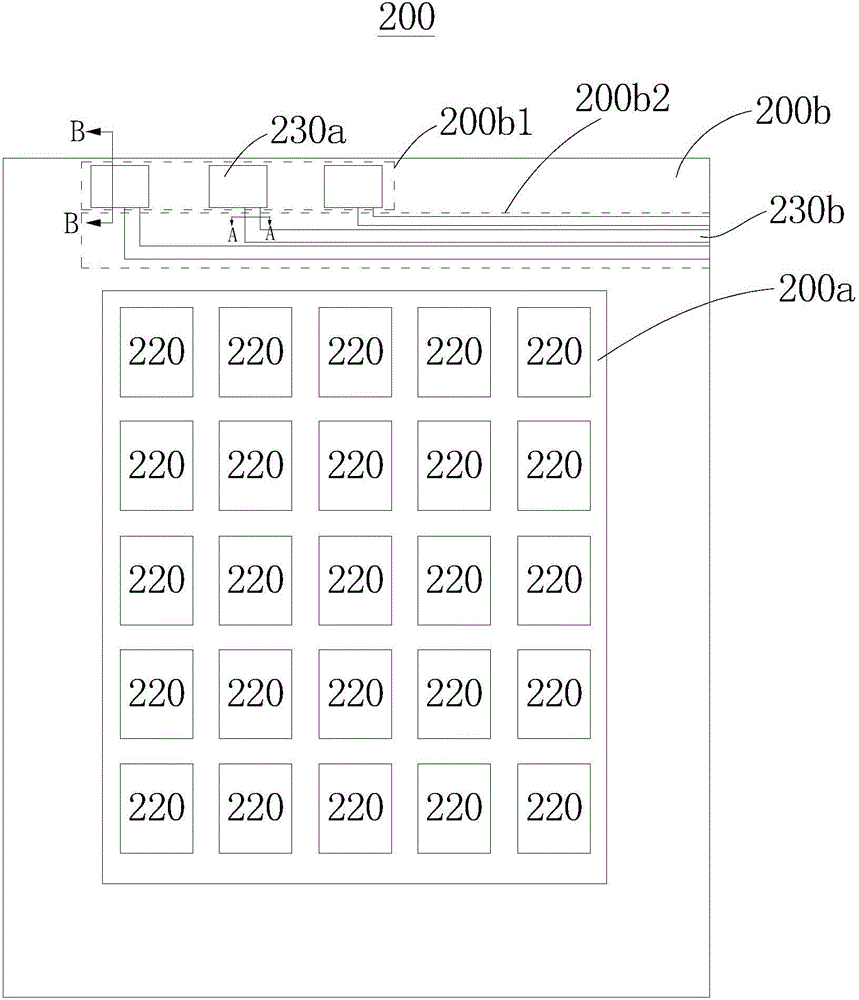

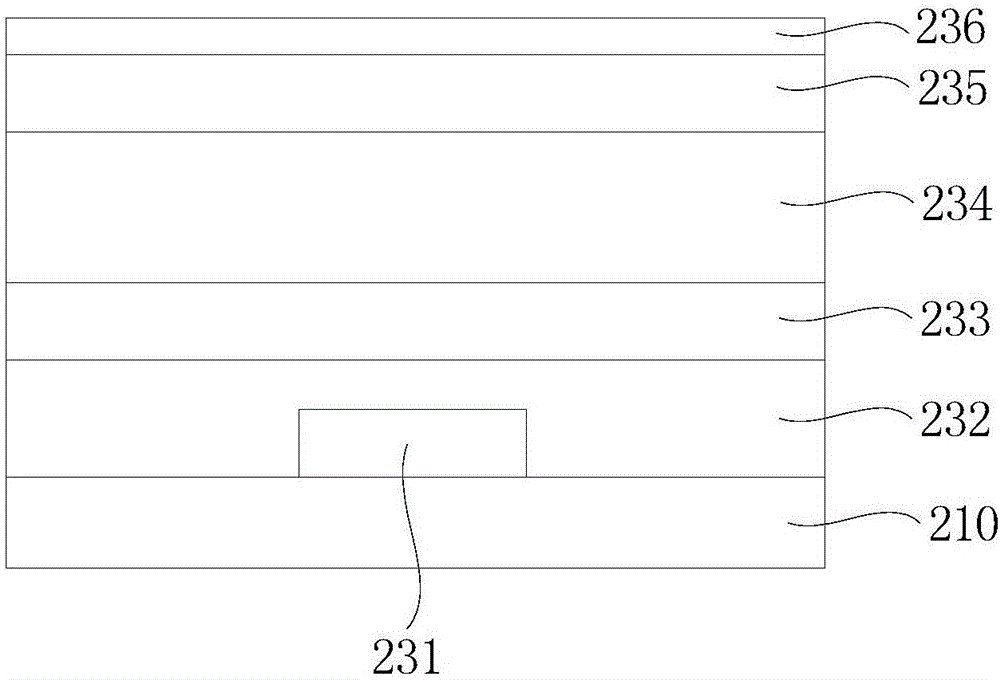

Array substrate, manufacturing method of routing line and test pad of array substrate as well as liquid crystal panel

InactiveCN106405962ARaise the threshold voltageReduce parasitic capacitanceNon-linear opticsInsulation layerLiquid-crystal display

The invention provides an array substrate. The array substrate comprises a test pad located in a test pad area and a routing line located in a routing area, wherein the routing line is connected with the test pad; the routing line comprises a first metal layer, a first insulation layer, a first passivation layer, a second insulation layer, a second passivation layer and a transparent electrode layer which are successively arranged on the substrate and are located in the routing area. The invention also provides a manufacturing method of the routing line and the test pad of the array substrate as well as a liquid crystal panel. In a routing structure of the array substrate, a second metal layer which is a source-drain metal layer of a thin film transistor is eliminated; a pixel electrode layer is in span connection with the first metal layer; a plurality of film layers are arranged between the pixel electrode layer and the first metal layer, and a long distance is formed between the pixel electrode layer and the first metal layer, thus the breakdown threshold voltage can be increased, and the stray capacitance can be reduced, so that the occurrence probability of electrostatic discharge can be reduced.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

Thin film transistor array substrate for reducing electrostatic discharge damage

ActiveUS20070131989A1Reducing electrostatic discharge damageOptimize layoutStatic indicating devicesSolid-state devicesScan lineEngineering

A thin film transistor (TFT) array substrate for reducing electrostatic discharge damage includes a substrate, a plurality of pixel units, scan lines and data lines. The substrate has a pixel area and a peripheral area adjacent to the pixel area. The pixel units are disposed in the pixel area. The scan lines and data lines are disposed in the pixel area of the substrate and electrically connected with the pixel units, wherein one end of each scan line extending to the peripheral area is a bonding pad for the scan line. One end of each data line extending to the peripheral area is a bonding pad for the data line. The other end of each data line extending to the peripheral area is an end part of the data line. Particularly, the end part of the data line does not exceed the outmost scan line.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

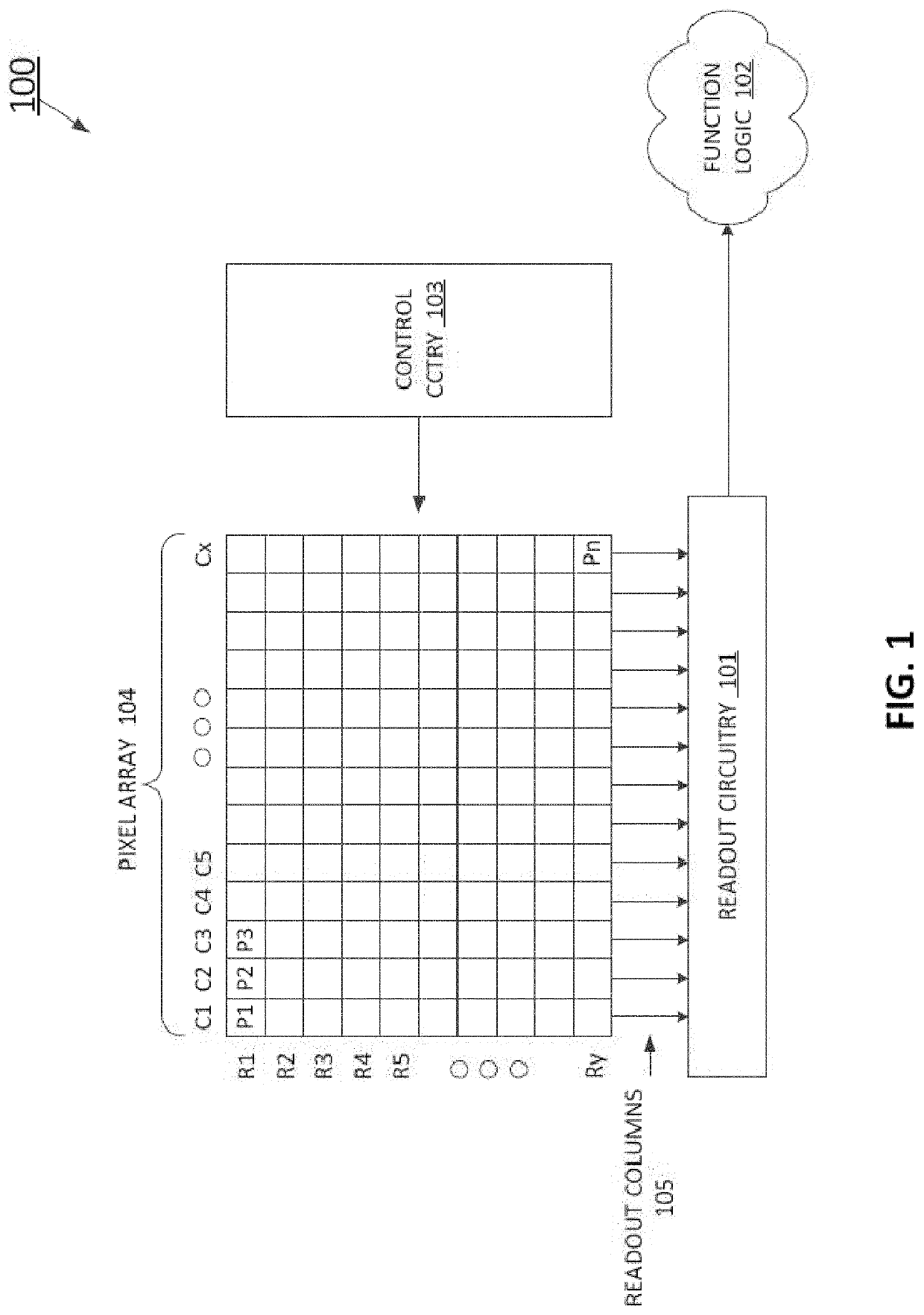

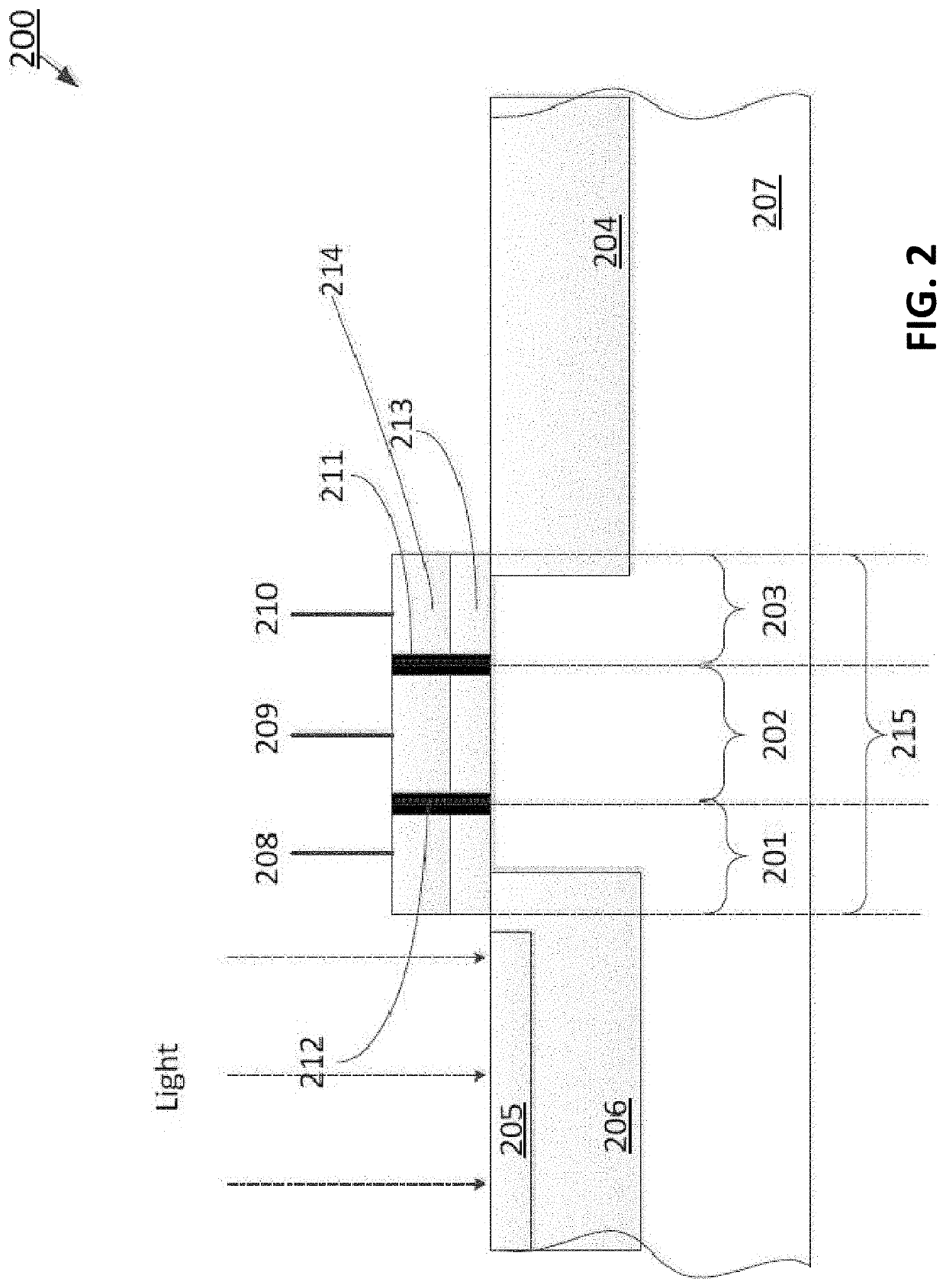

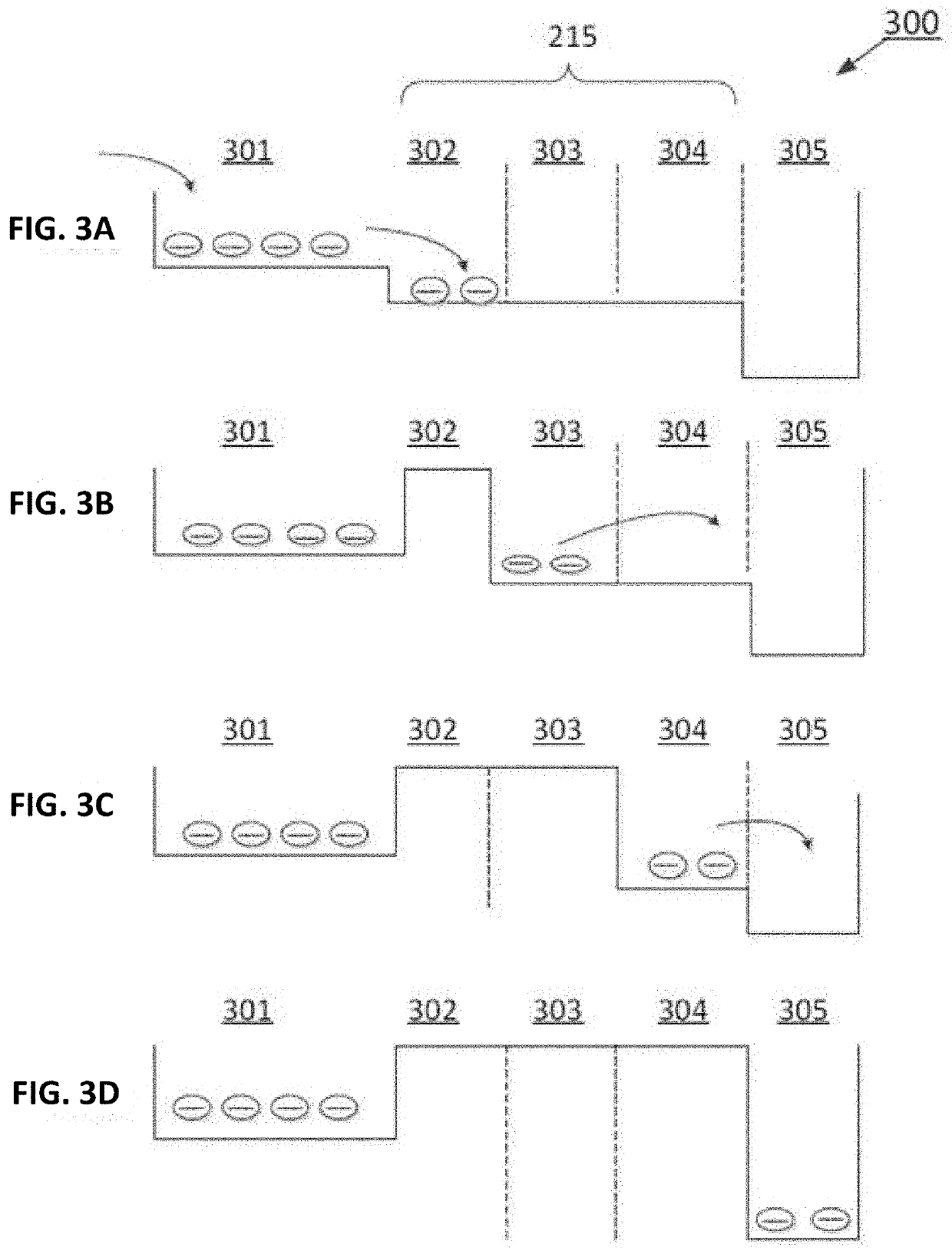

CMOS image sensor with multiple stage transfer gate

InactiveUS20200099878A1Raise the potentialReduce conversionTelevision system detailsSolid-state devicesTransmission gateCMOS

An image sensor pixel comprises a first charge storage node configured to have a first charge storage electric potential; a second charge storage node configured to have a second charge storage electric potential and receive charge from the first charge storage node, wherein the second charge storage electric potential is greater than the first charge storage electric potential; and a transfer circuit coupled between the first and the second charge storage nodes, wherein the transfer circuit comprises at least three transfer regions, wherein: a first transfer region is proximate to the first charge storage node and configured to have a first transfer electric potential greater than the first charge storage electric potential and lower than the second charge storage electric potential; a second transfer region is coupled between the first and a third transfer region and configured to have a second transfer electric potential greater than the first charge storage electric potential and lower than the second charge storage electric potential; and the third transfer region is proximate to the third charge storage node and configured to have a third transfer electric potential greater than the first charge storage electric potential and lower than the second charge storage electric potential. Charges are fully transferred from the first charge storage node to the second charge storage node after a plurality of transfer signal pulses.

Owner:OMNIVISION TECH INC

Reduced susceptibility to electrostatic discharge during 3D semiconductor device bonding and assembly

InactiveUS8198736B2Potential damageReduce electrostatic dischargeSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorGround plane

A method to reduce electrostatic discharge susceptibility when assembling a stacked IC device. The method includes coupling a ground plane of a first semiconductor device and a ground plane of a second semiconductor device to substantially a same electrical potential. Active circuitry on the first semiconductor device and active circuitry on the second semiconductor device are electrically coupled after the ground planes are coupled. Electrically coupling the ground planes of the first and the second semiconductor device creates a preferred electrostatic discharge path to ground, thus minimizing potential damage to sensitive circuit elements.

Owner:QUALCOMM INC

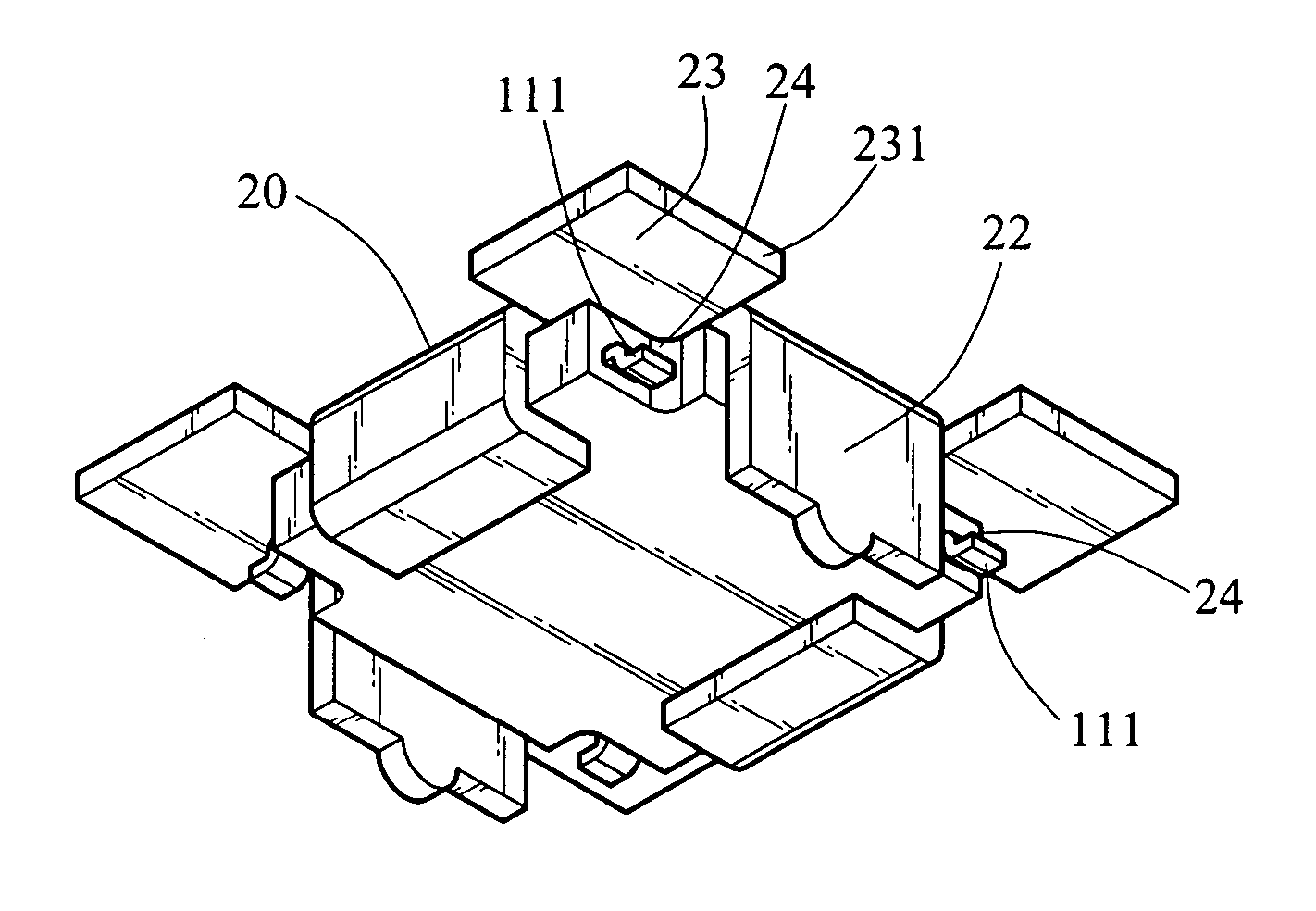

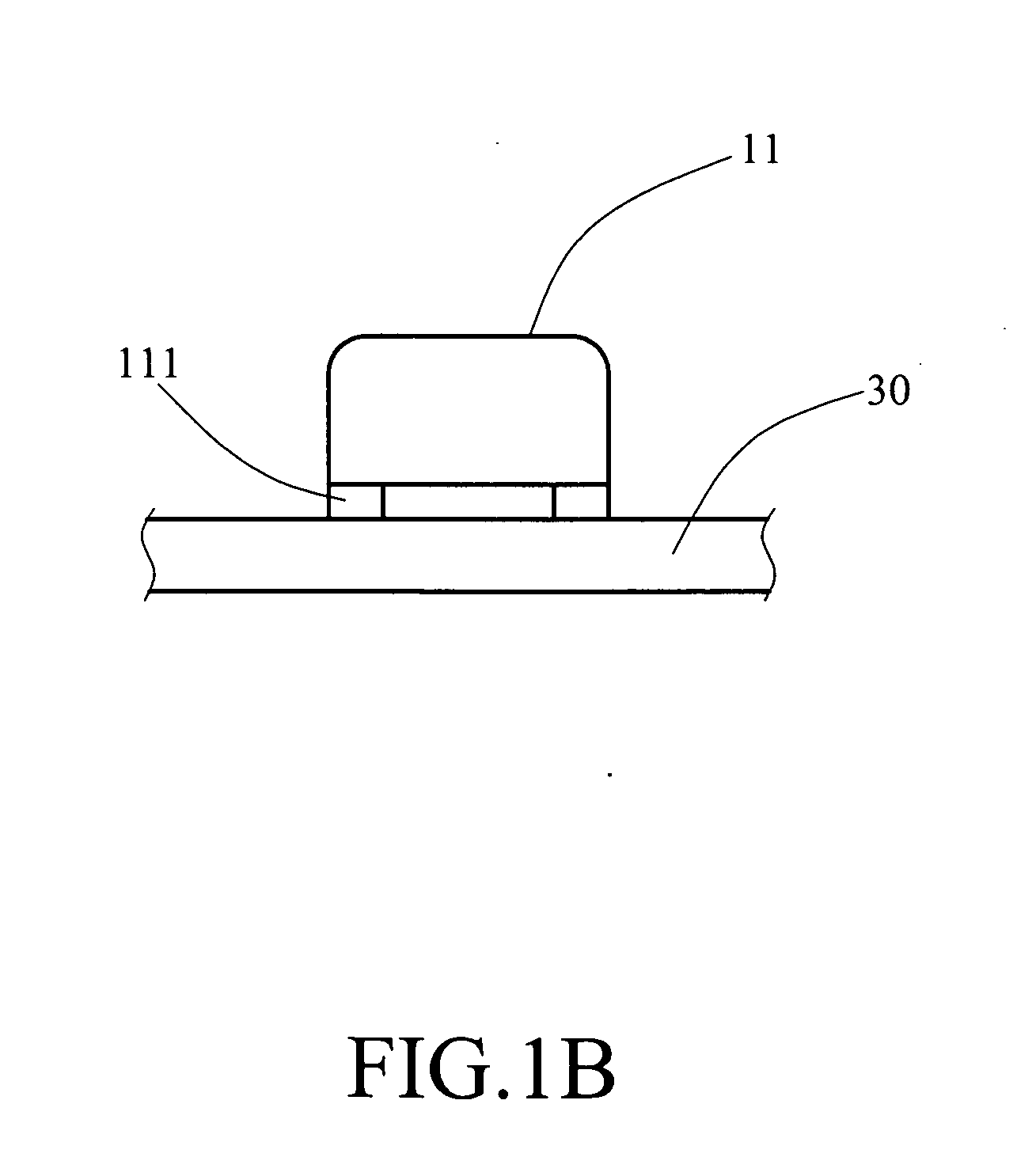

Protective structure for electrostatic discharge

InactiveUS20070247777A1Enhance functionImprove shieldingElectrostatic discharge protectionEmergency protective arrangement detailsElectrostatic discharge protectionElectrical and Electronics engineering

A protective structure for electrostatic discharge used to guide an electrostatic charge to a ground portion is provided, which comprises at least one press element and a masking piece, wherein an electrostatic charge near the press element is attracted by wrapping the press element with the masking piece, and then the attracted electrostatic charge is directed out of the press element, which greatly reduces the probability that the press element is interfered by the electrostatic charge and effectively shields the press element.

Owner:INVENTEC CORP