Patents

Literature

217results about How to "Simplify the communication process" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

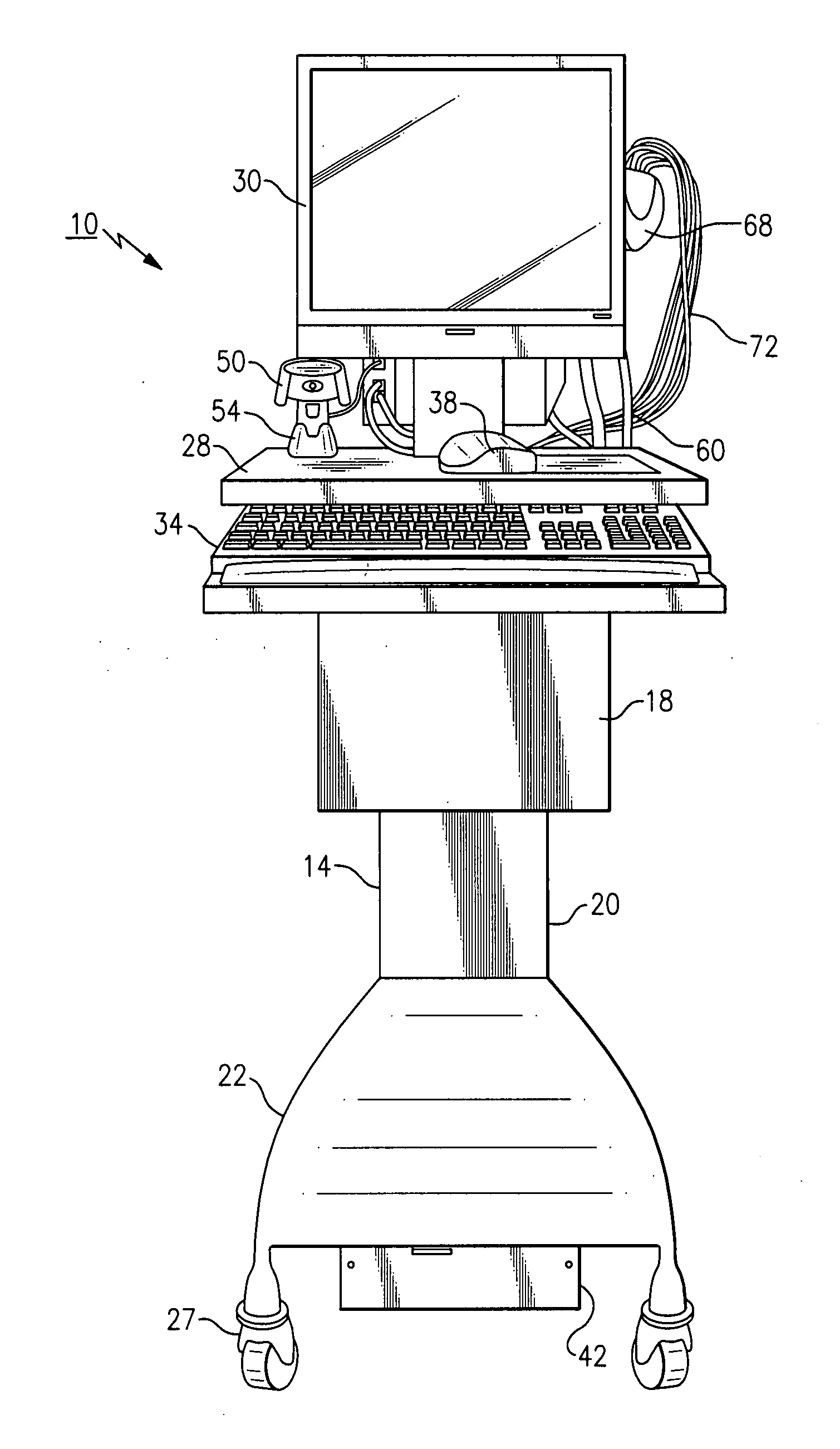

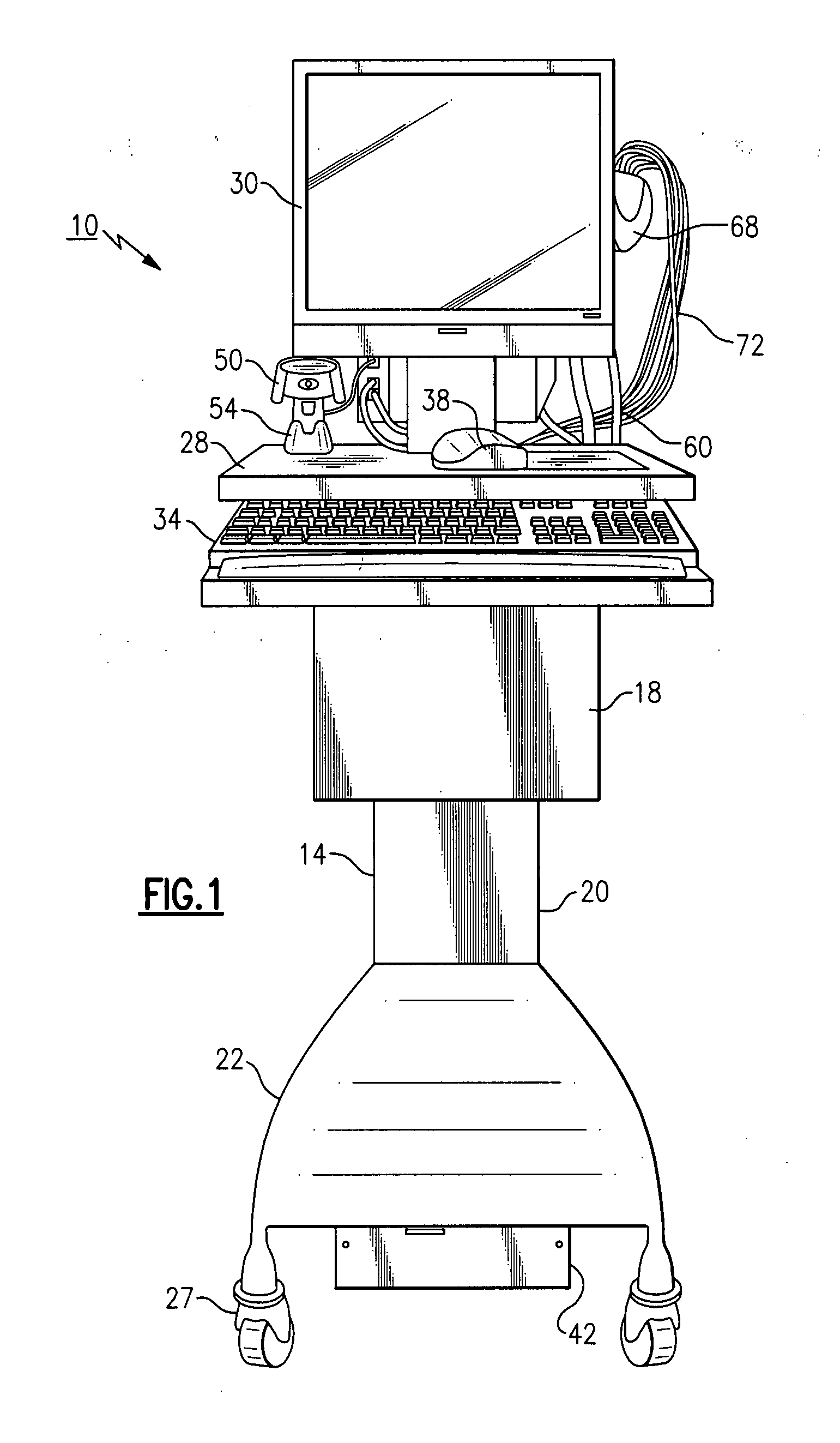

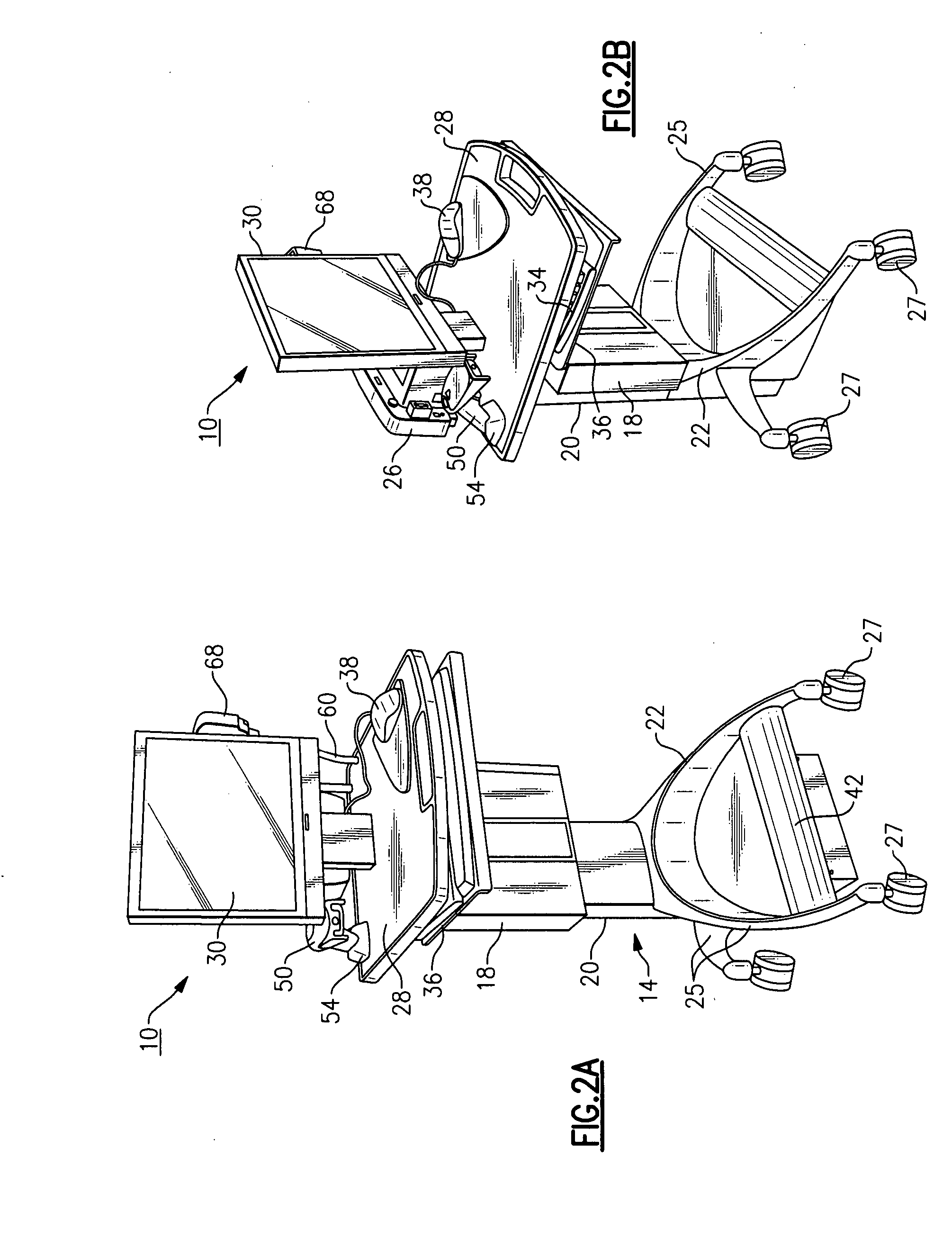

Information workflow for a medical diagnostic workstation

InactiveUS20070185390A1Effectively and reliably handleSimplify the communication processData processing applicationsElectrocardiographyWorkflowPatient record

An information workflow for a medical diagnostic workstation in which patient data is captured, arranged and displayed in predetermined formats for a user in the handling of patients. The workflow permits vitals capture and storage and creation of a comprehensive patient record in which the workstation can operate in a stand-alone or network connected mode.

Owner:WELCH ALLYN INC

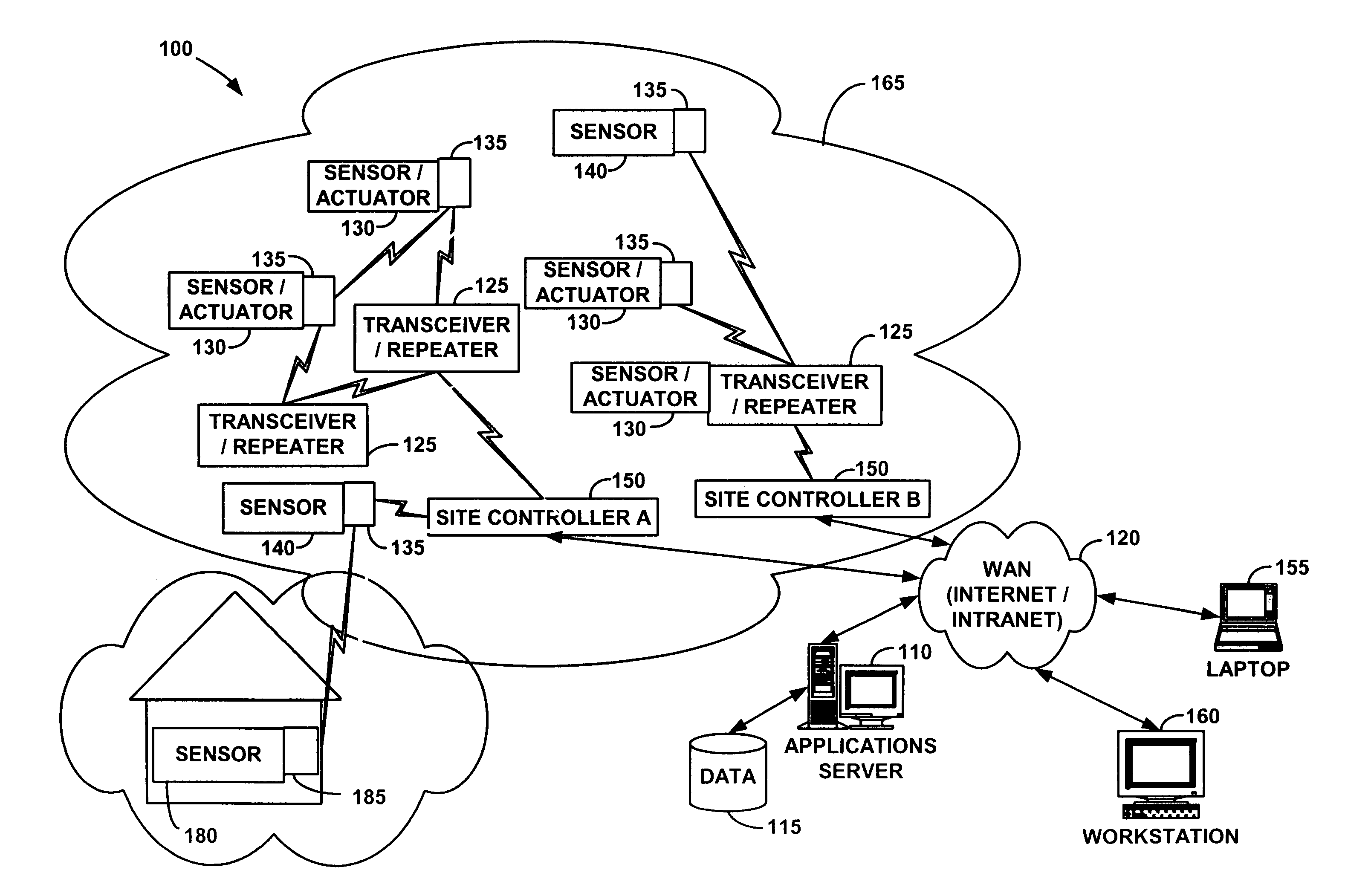

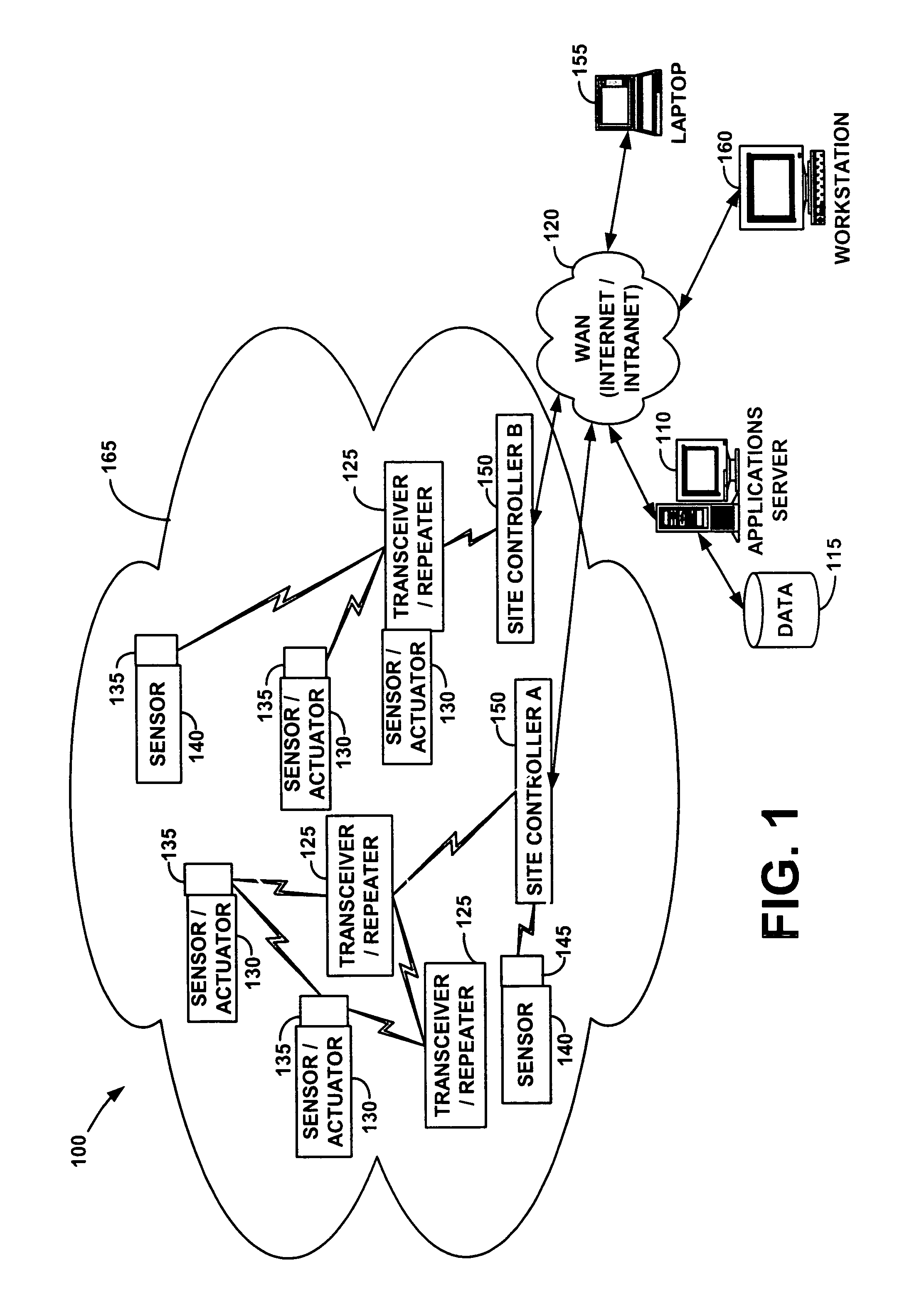

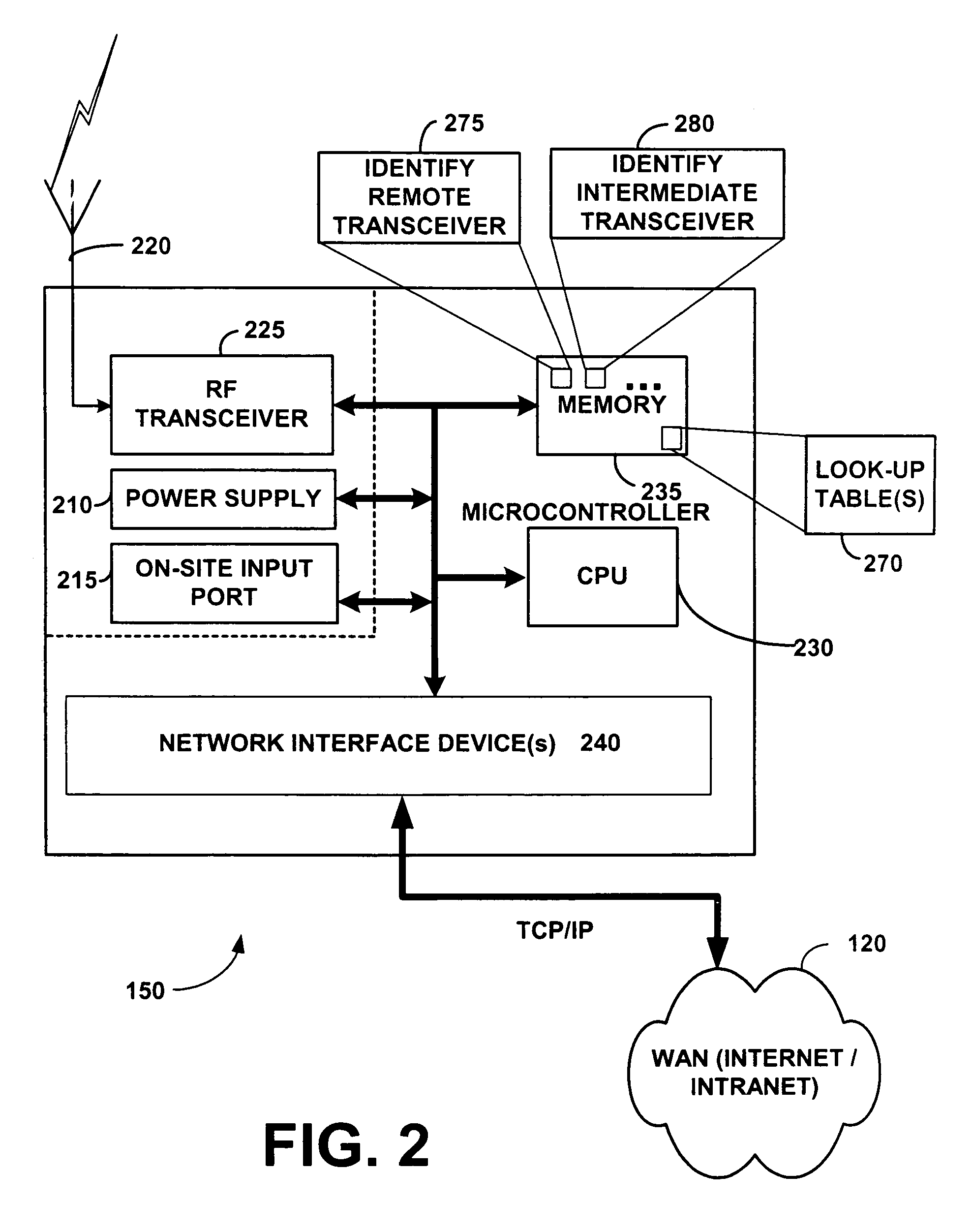

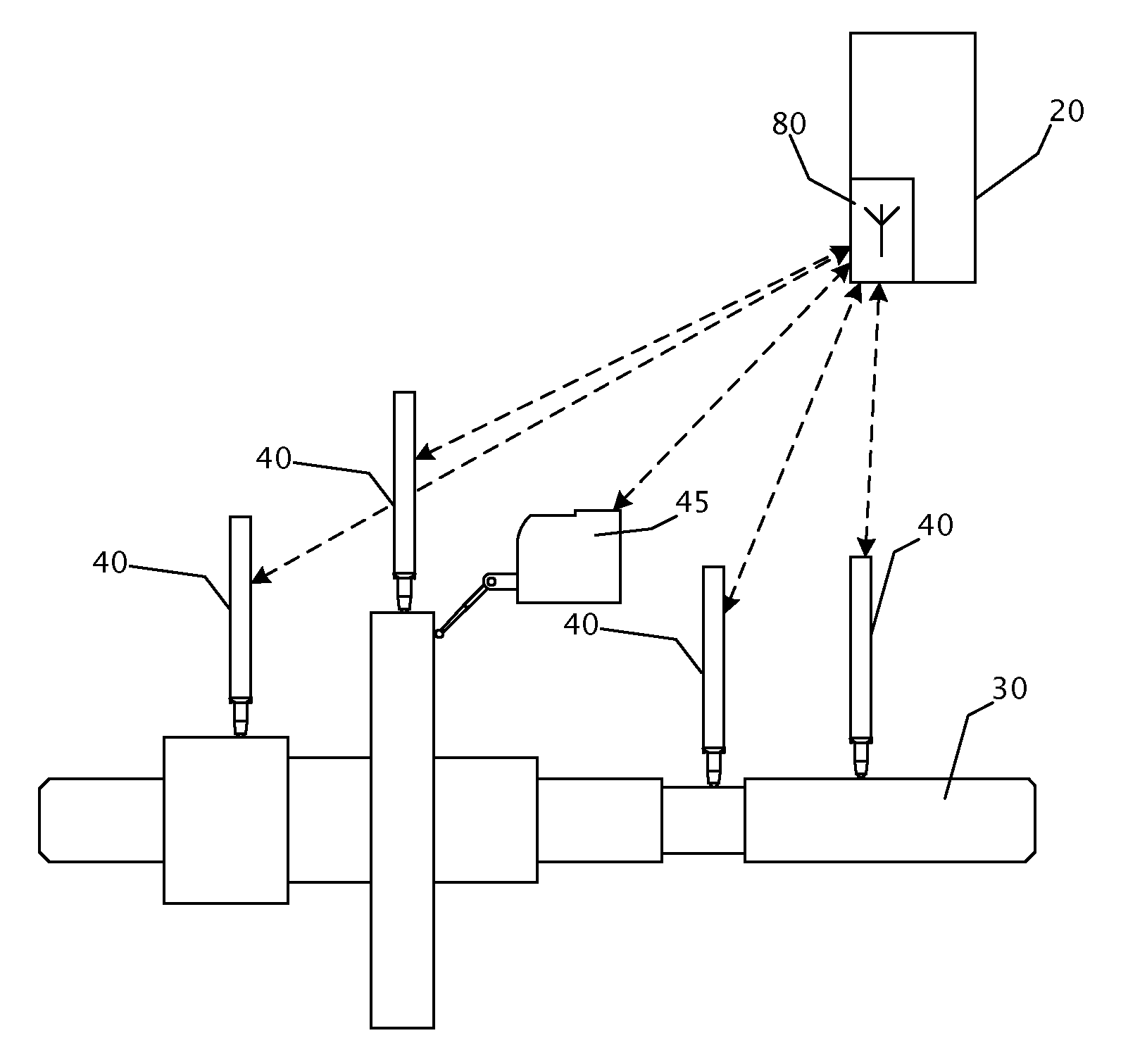

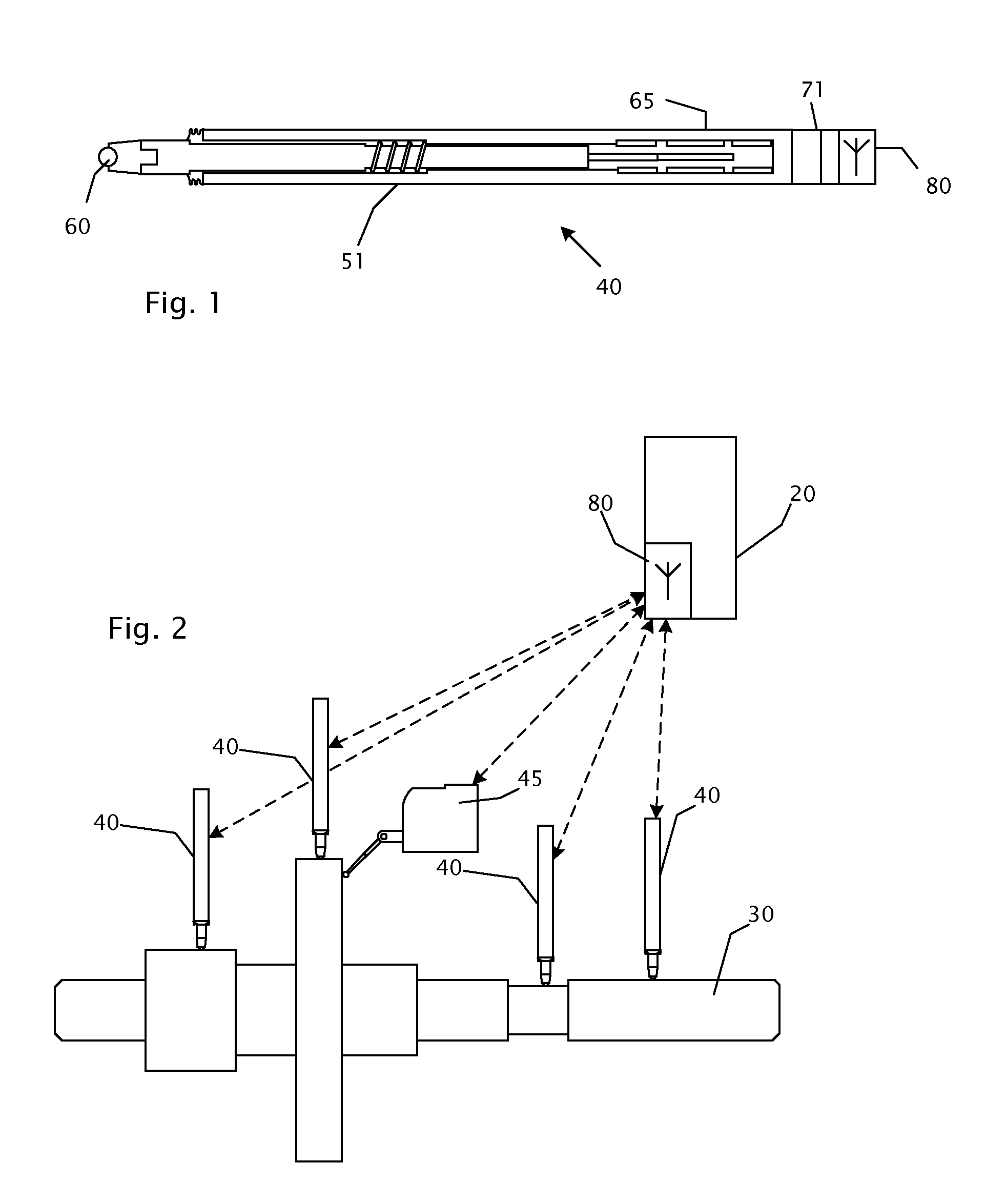

System and method for controlling communication between a host computer and communication devices associated with remote devices in an automated monitoring system

InactiveUS7650425B2Low costMinimize complexityAlarmsProgramme total factory controlTelecommunications linkTransceiver

A site controller adapted to be used in an automated monitoring system for monitoring and controlling a plurality of remote devices via a host computer connected to a first communication network is provided. The site controller is configured for controlling communication with the host computer and a plurality of communication devices that define a second communication network associated with the plurality of remote devices. Briefly described, in one embodiment, the site controller comprises a transceiver configured to communicate with the plurality of communication devices via the second communication network; a network interface device configured to communicate with the host computer via the first communication network; and logic configured to: manage communication with each of the plurality of communication devices, via a first communication protocol, based on one or more communication paths for each of the plurality of communication devices, each communication path comprising one or more communication devices involved in the communication link between the transceiver and each of the plurality of communication devices; and manage communication with the host computer via a second communication protocol.

Owner:SIPCO

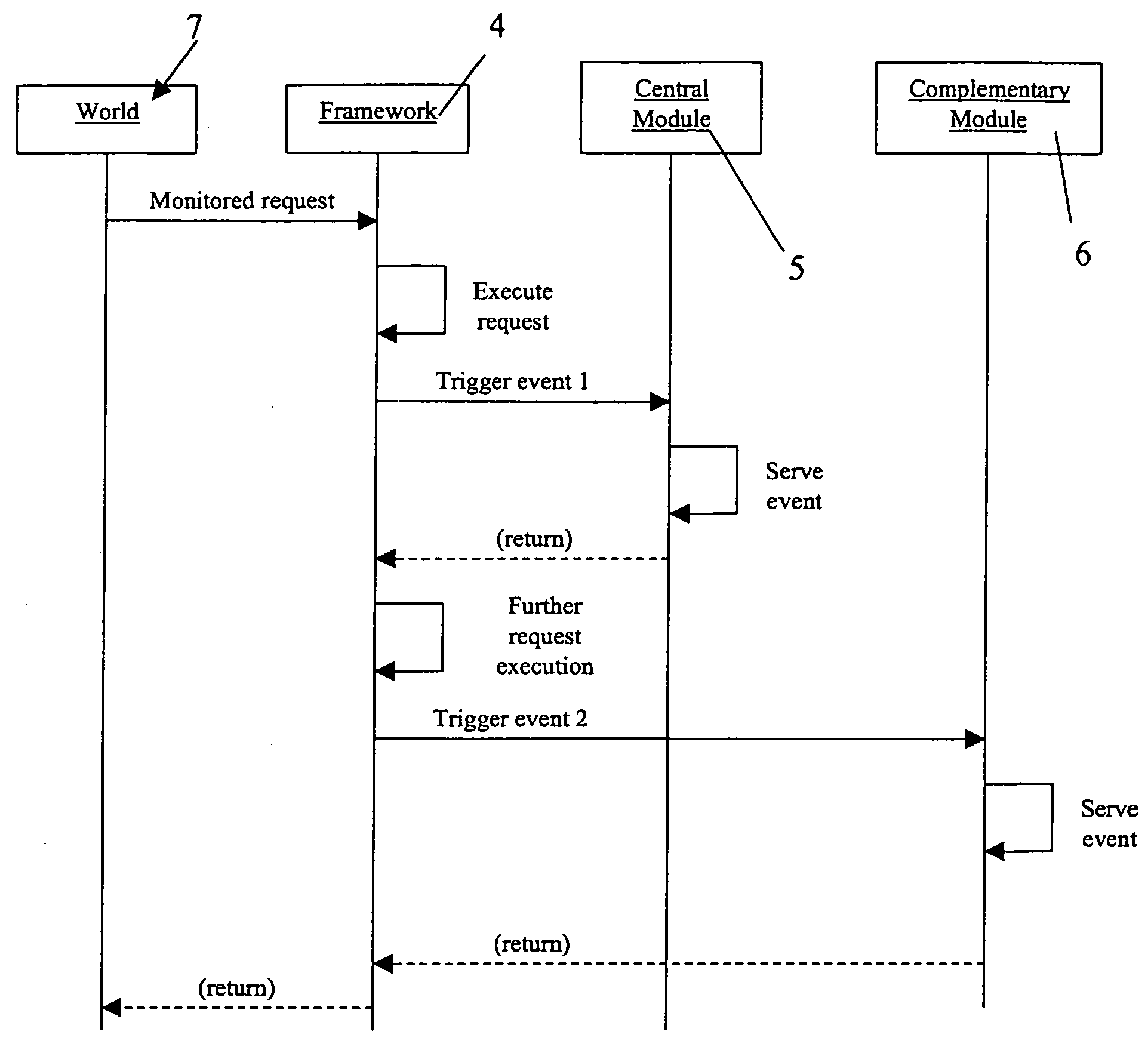

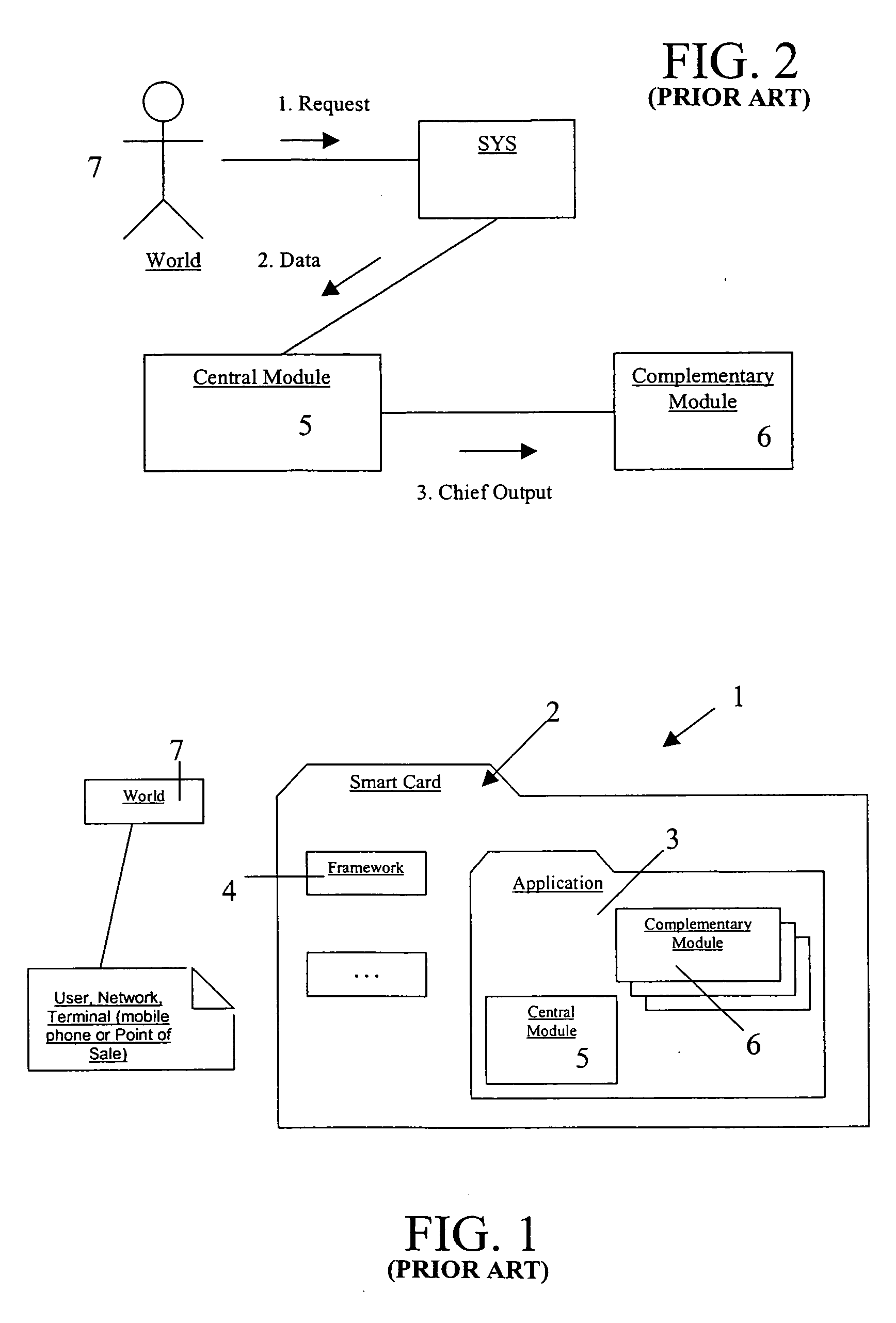

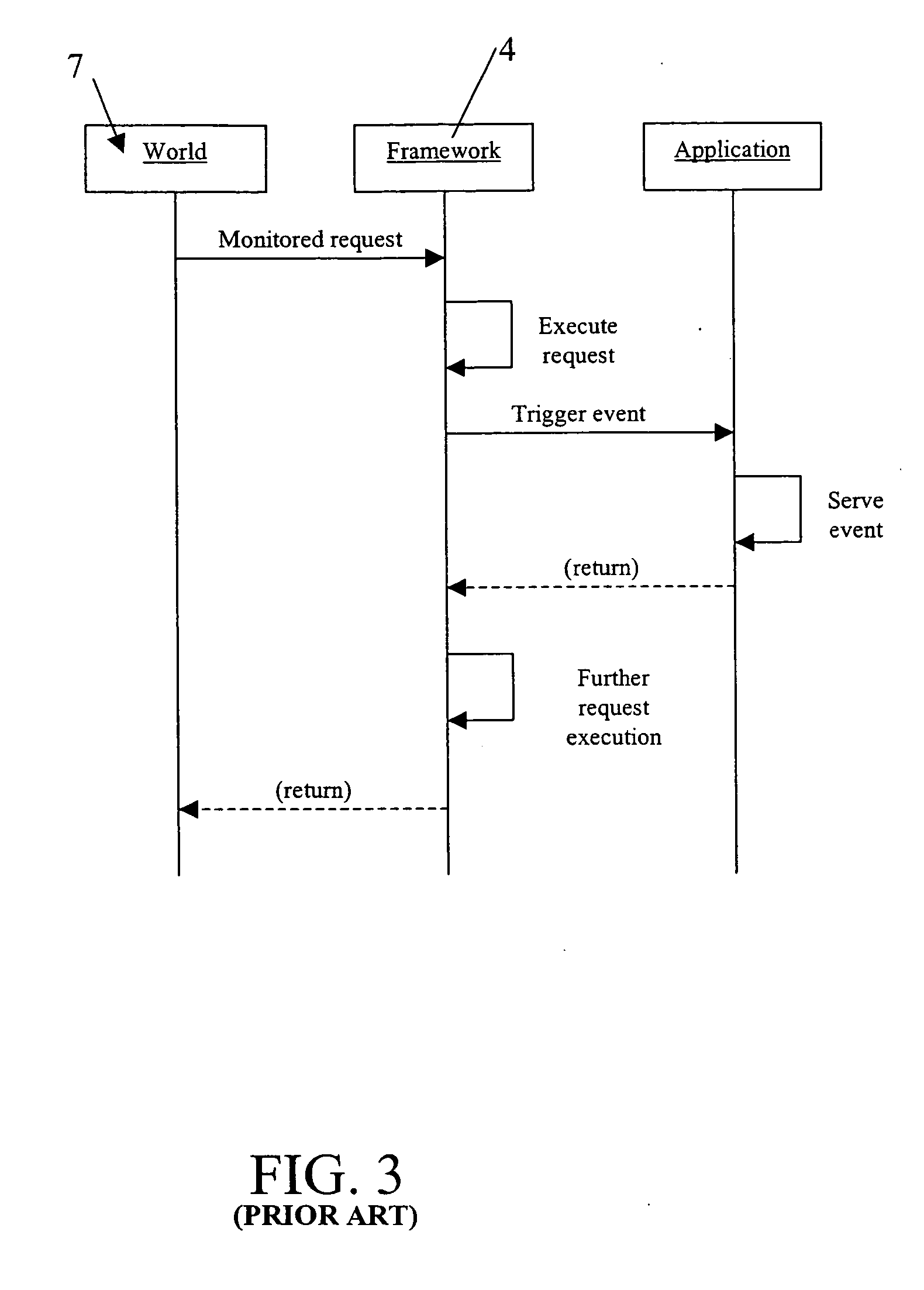

Method for the decomposition in modules of smart-card event-driven applications

ActiveUS20050119940A1Easy to separateSimplified inter-module communicationHand manipulated computer devicesProgram controlComputer architectureDecomposition

A method for separating an event-driven application in an electronic device is provided. The electronic device includes a smart-card, and the application resident in the smart-card may be separated in at least two modules: a central module and one or more complementary modules. The method includes managing the interaction between the modules by a framework of the smart-card, and generating new set of events by the framework at the end of execution of the central module. In this manner, the central module can be developed early in production and in any set of programming languages. It can access any card resources and even in an architecture dependent way.

Owner:STMICROELECTRONICS INT NV

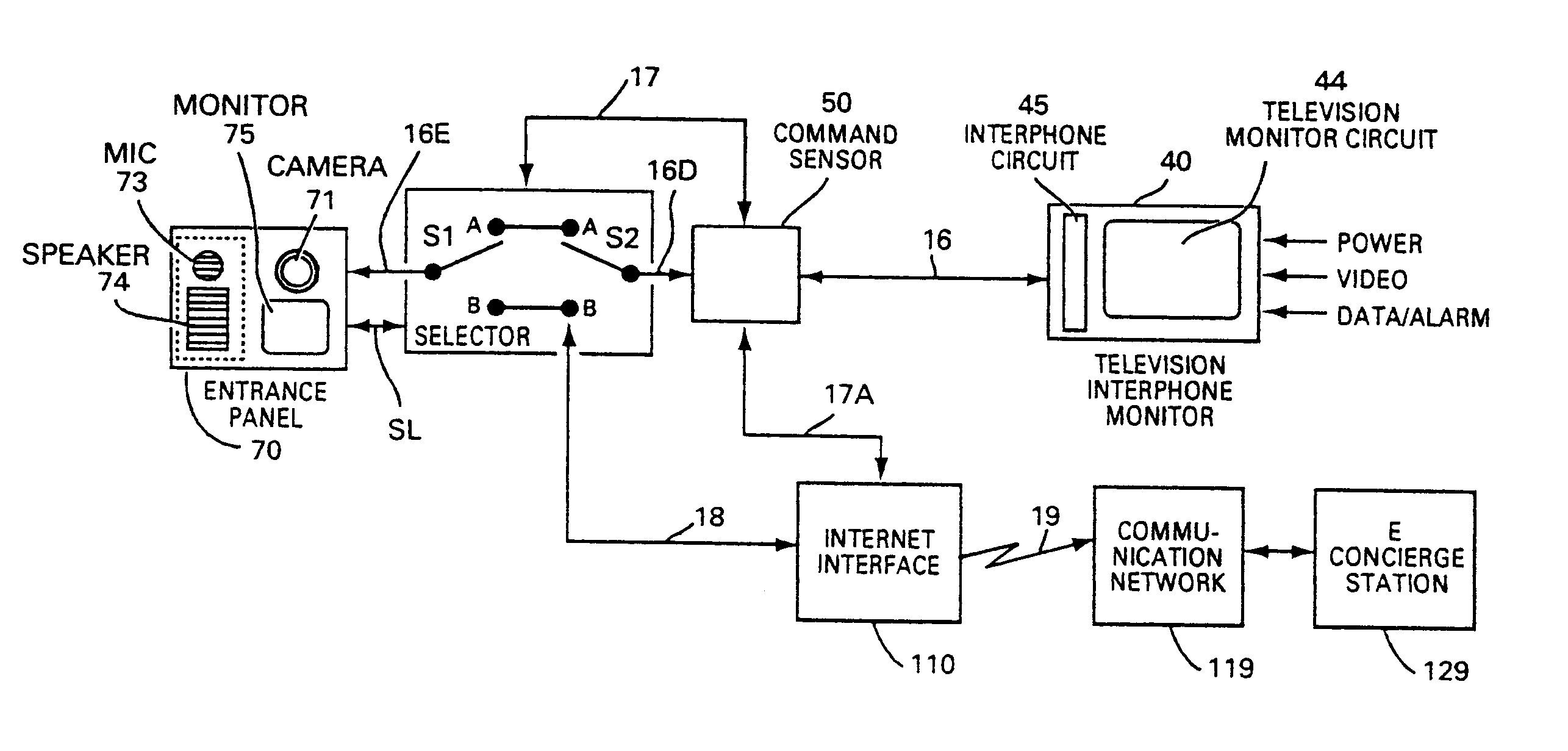

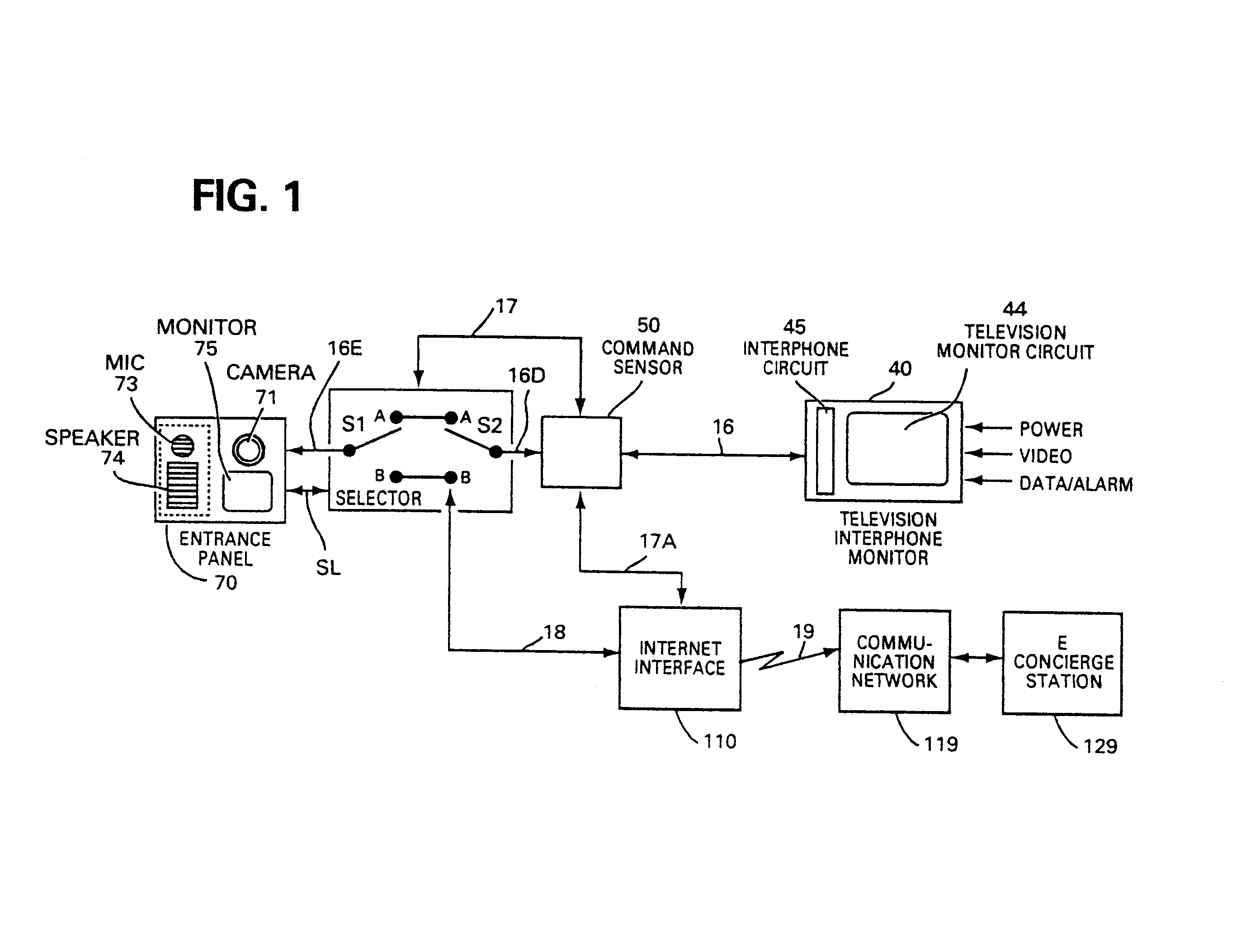

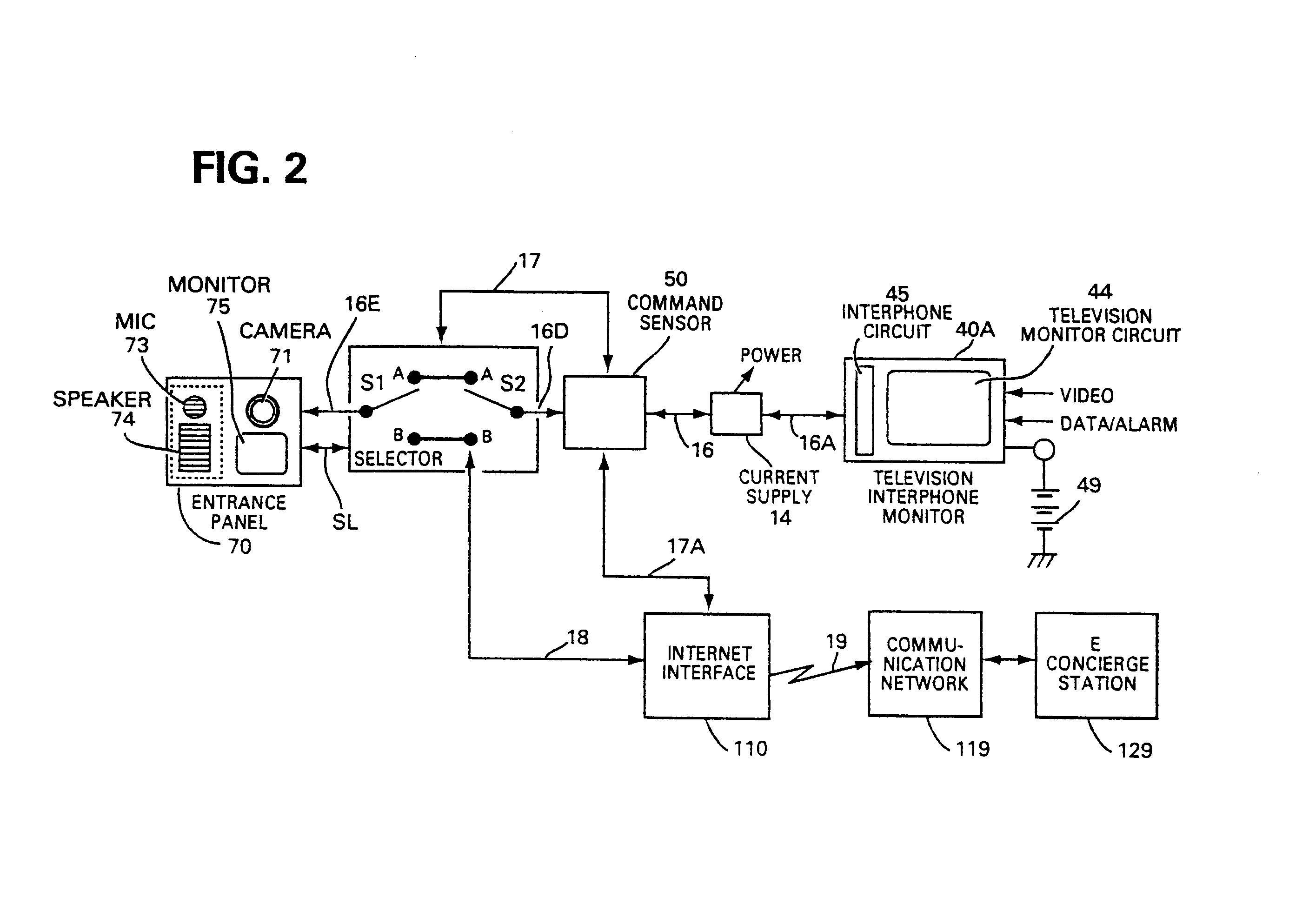

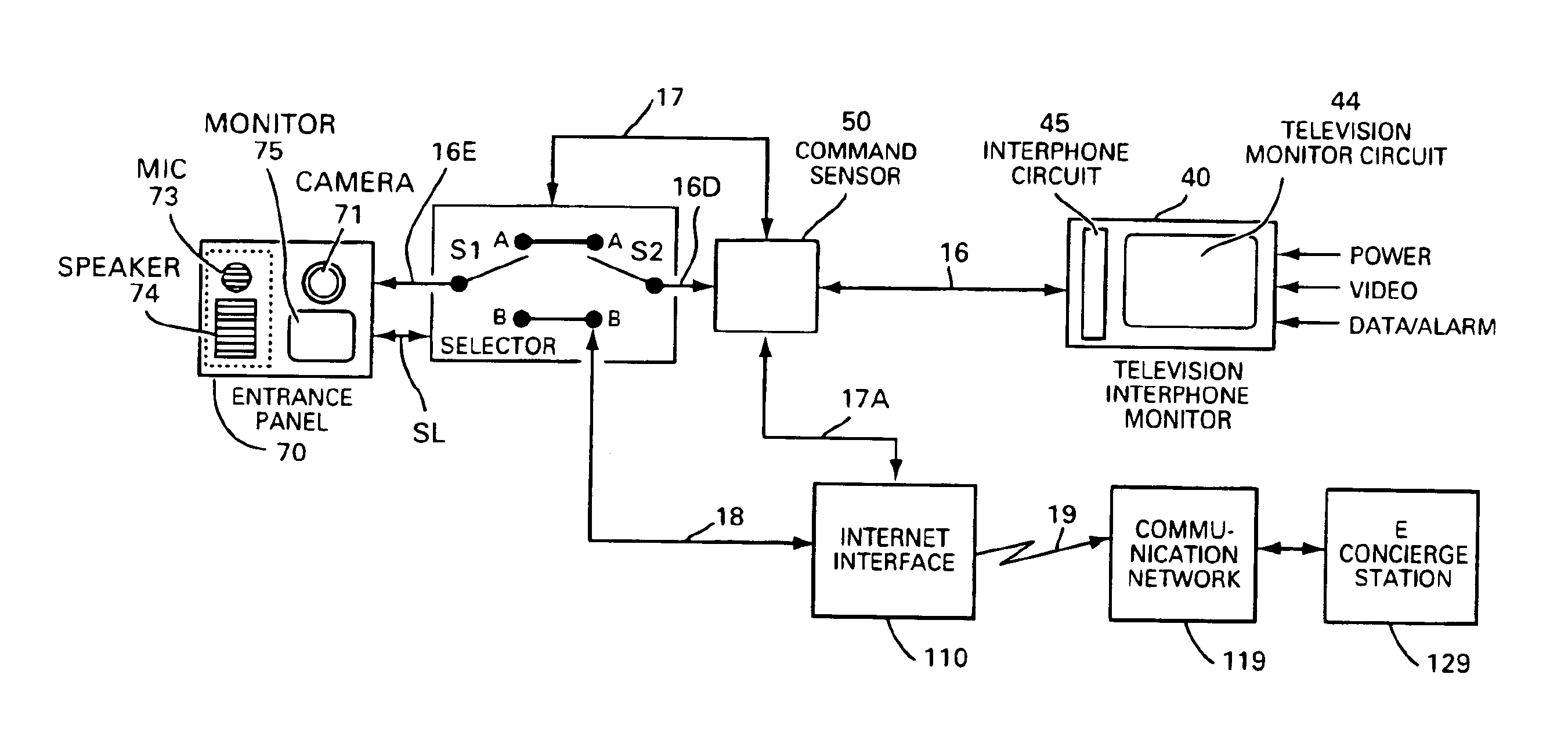

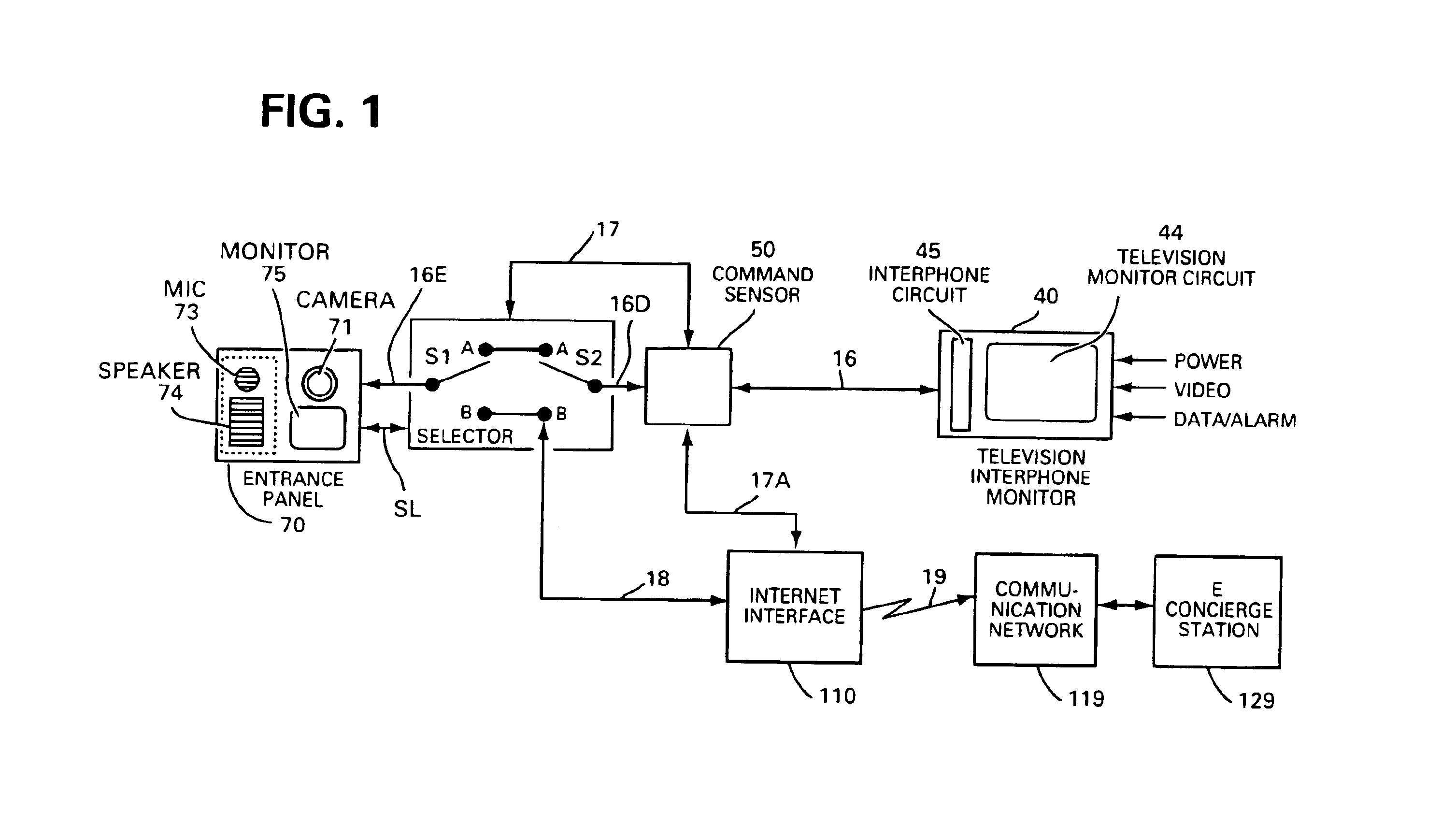

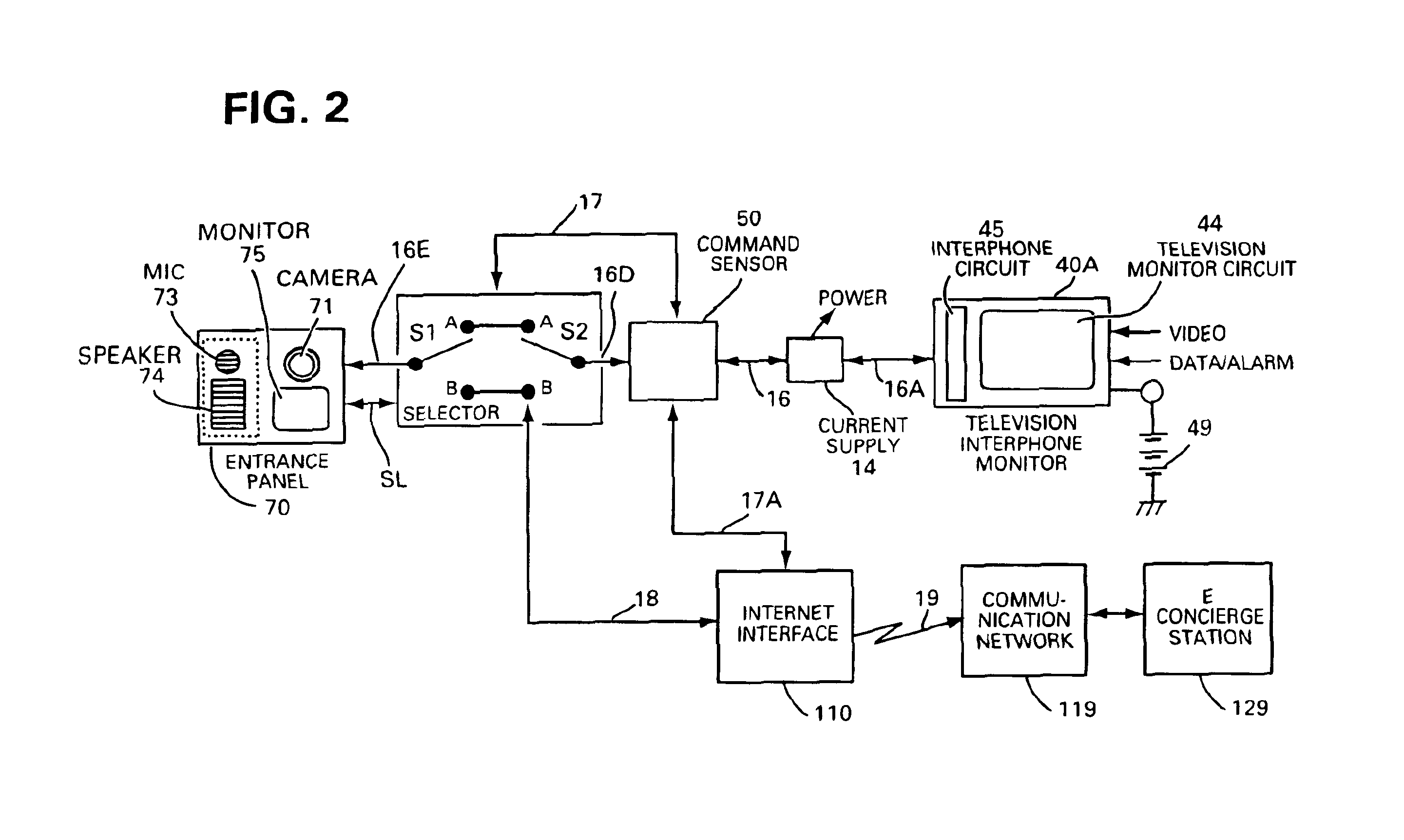

Method and apparatus for connecting a television interphone monitor system to a concierge station over the internet

InactiveUS6603842B2Simple recallSimplify the communication processTelephonic communicationColor television detailsPrivate networkThe Internet

A method and apparatus for connecting a television interphone monitor system including at least one television interphone monitor connected via internal communication lines and a matrix selector with at least one entrance panel, and with at least one interface unit to an E concierge station via a communication network selected from the group consisting of dedicated network, public network and the Internet.

Owner:ELBEX VIDEO LTD

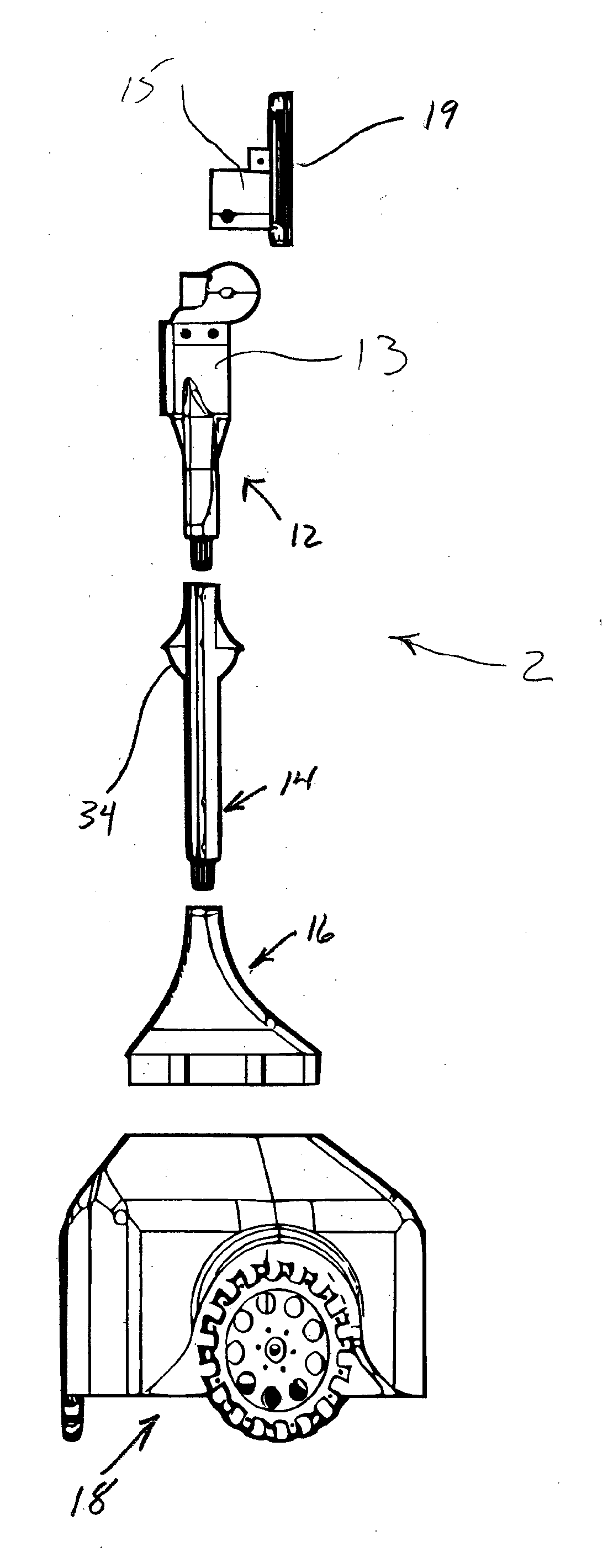

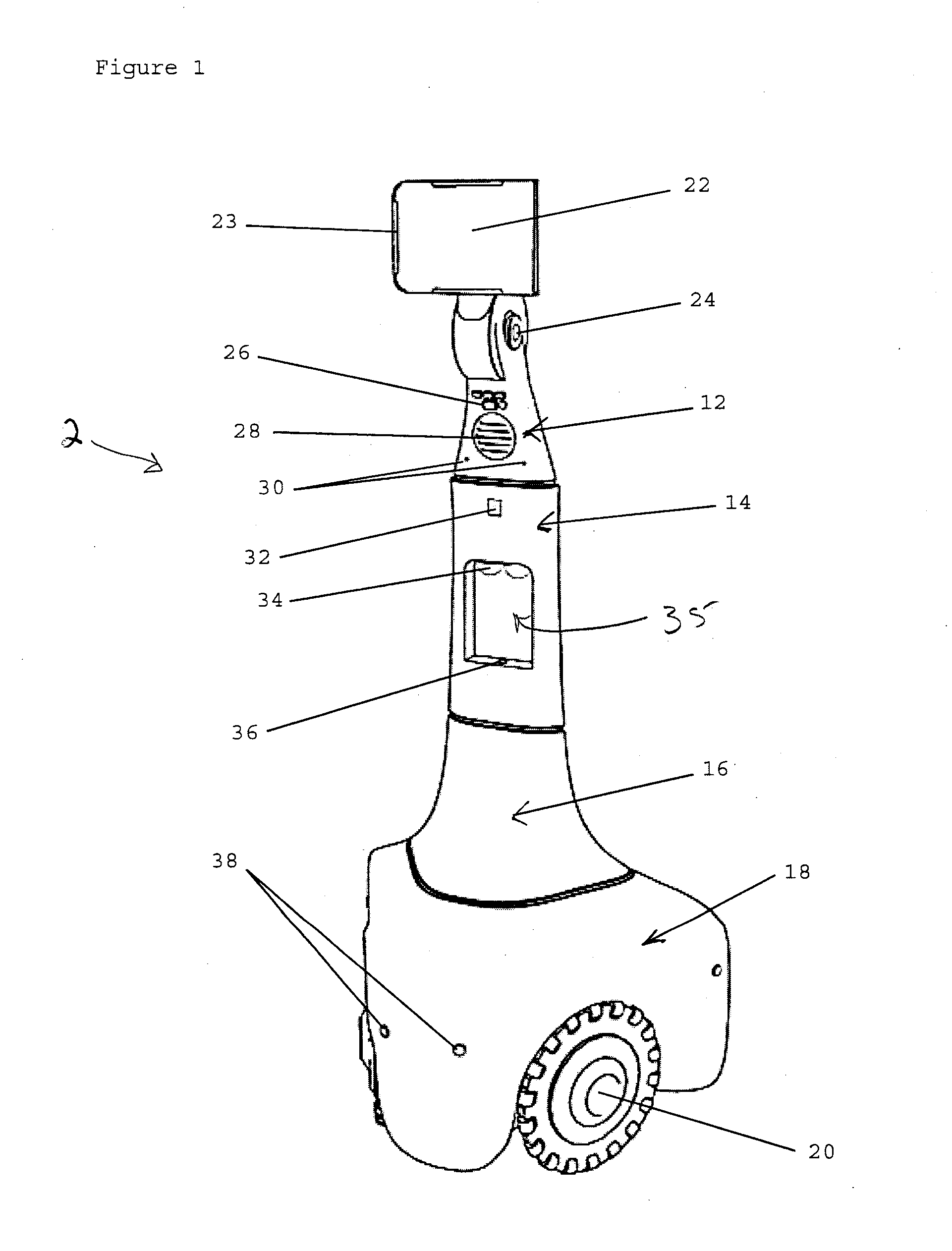

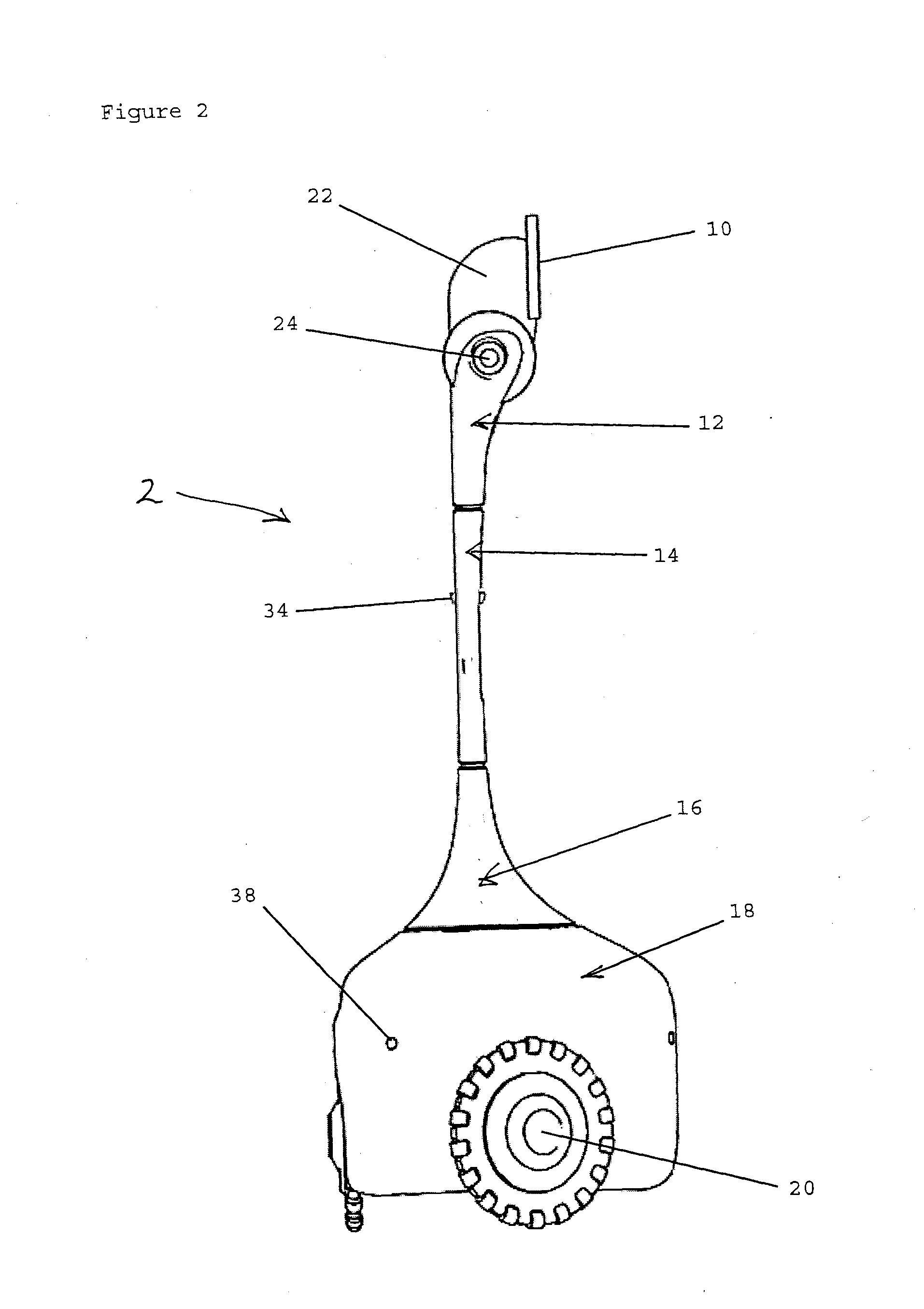

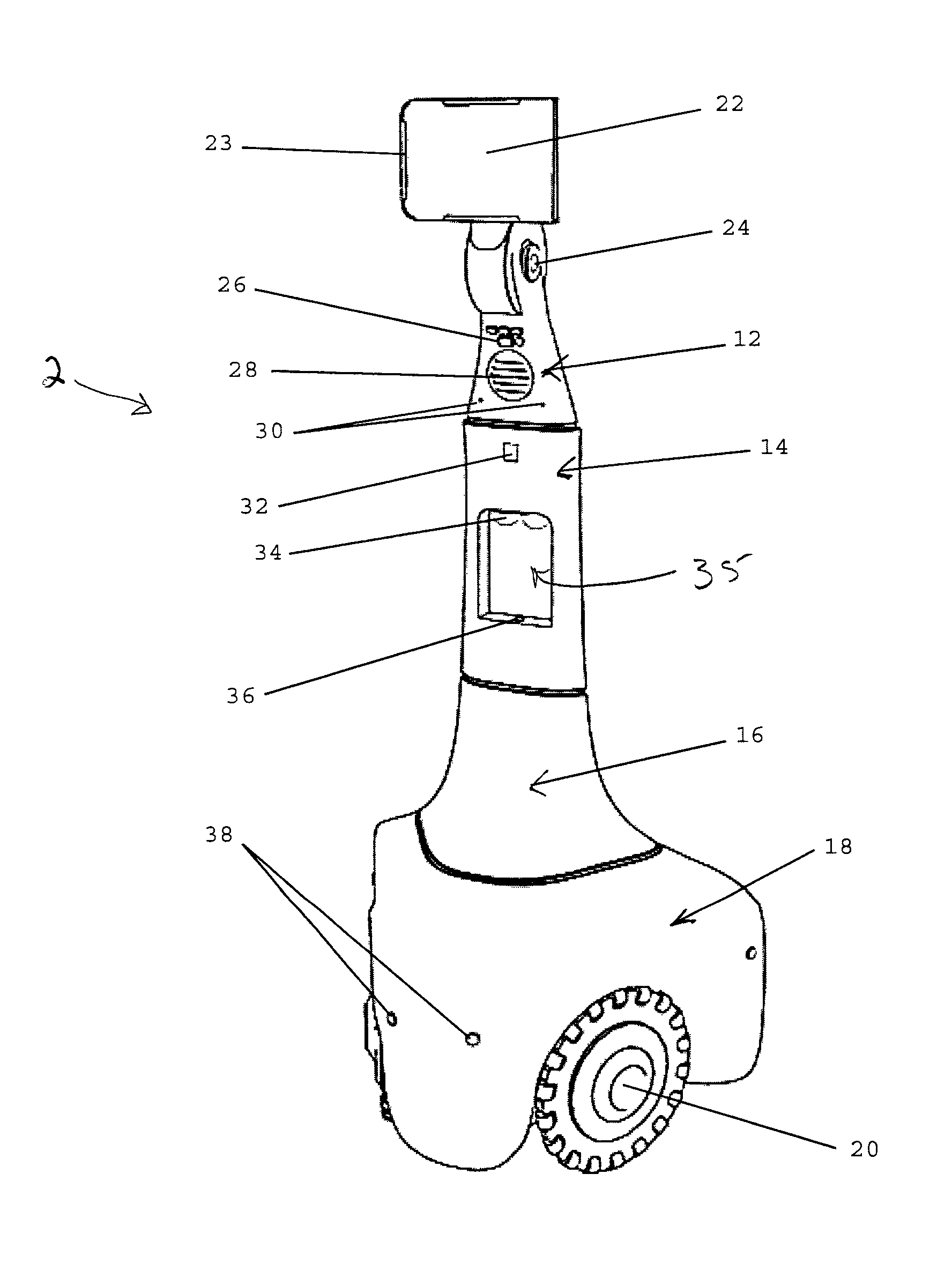

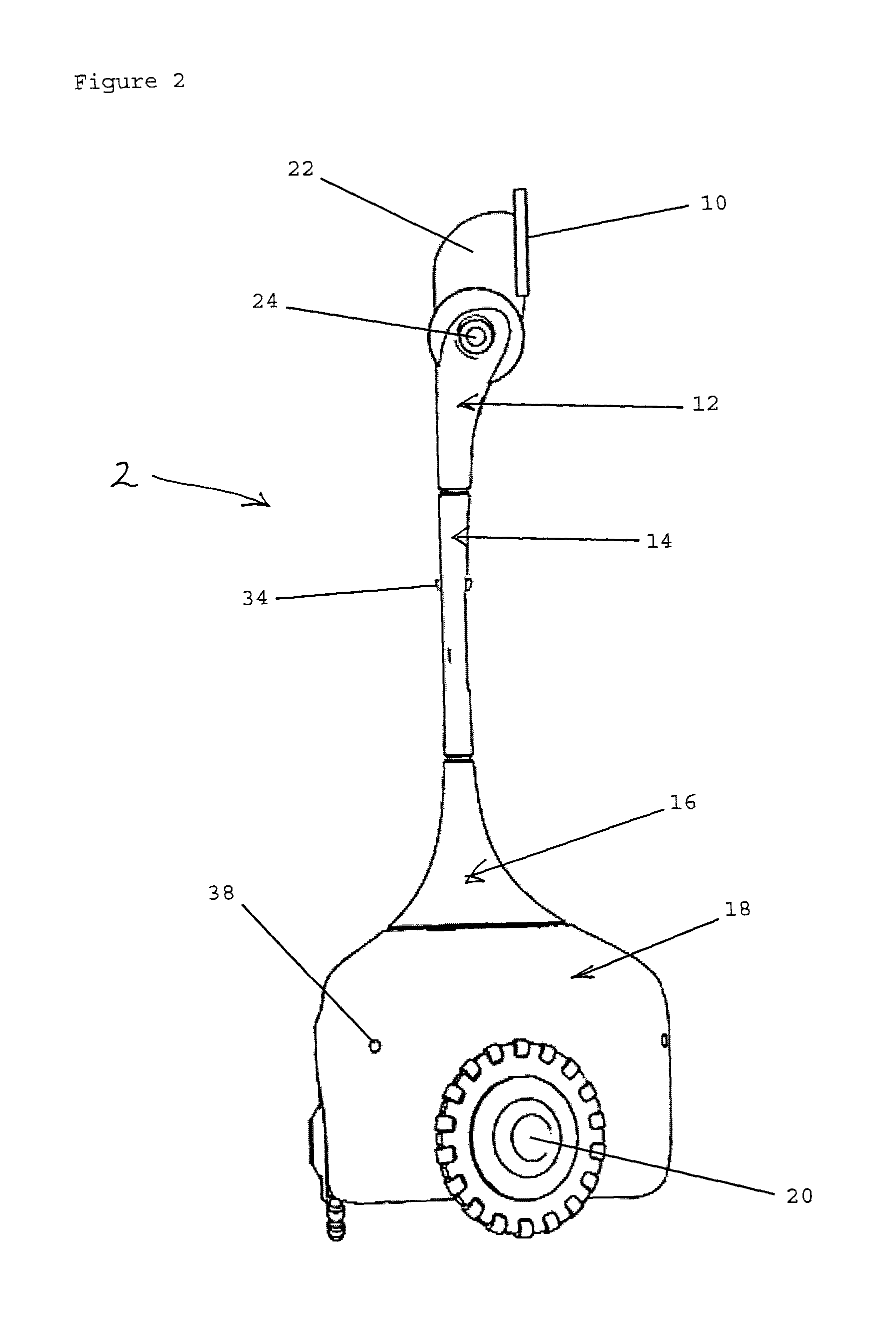

Customizable robotic system

ActiveUS20140009561A1Extend coverageImprove communicationProgramme-controlled manipulatorStands/trestlesRobotic systemsThird party

A telepresence robot uses a series of connectible modules and preferably includes a head module adapted to receive and cooperate with a third party telecommunication device that includes a display screen. The module design provides cost advantages with respect to shipping and storage while also allowing flexibility in robot configuration and specialized applications.

Owner:CROSSWING INC

Method and apparatus for connecting a television interphone monitor system to a concierge station over the internet

InactiveUS6940957B2Simple recallSimplify the communication processTelephonic communicationColor television detailsPrivate networkThe Internet

Owner:ELBEX VIDEO LTD

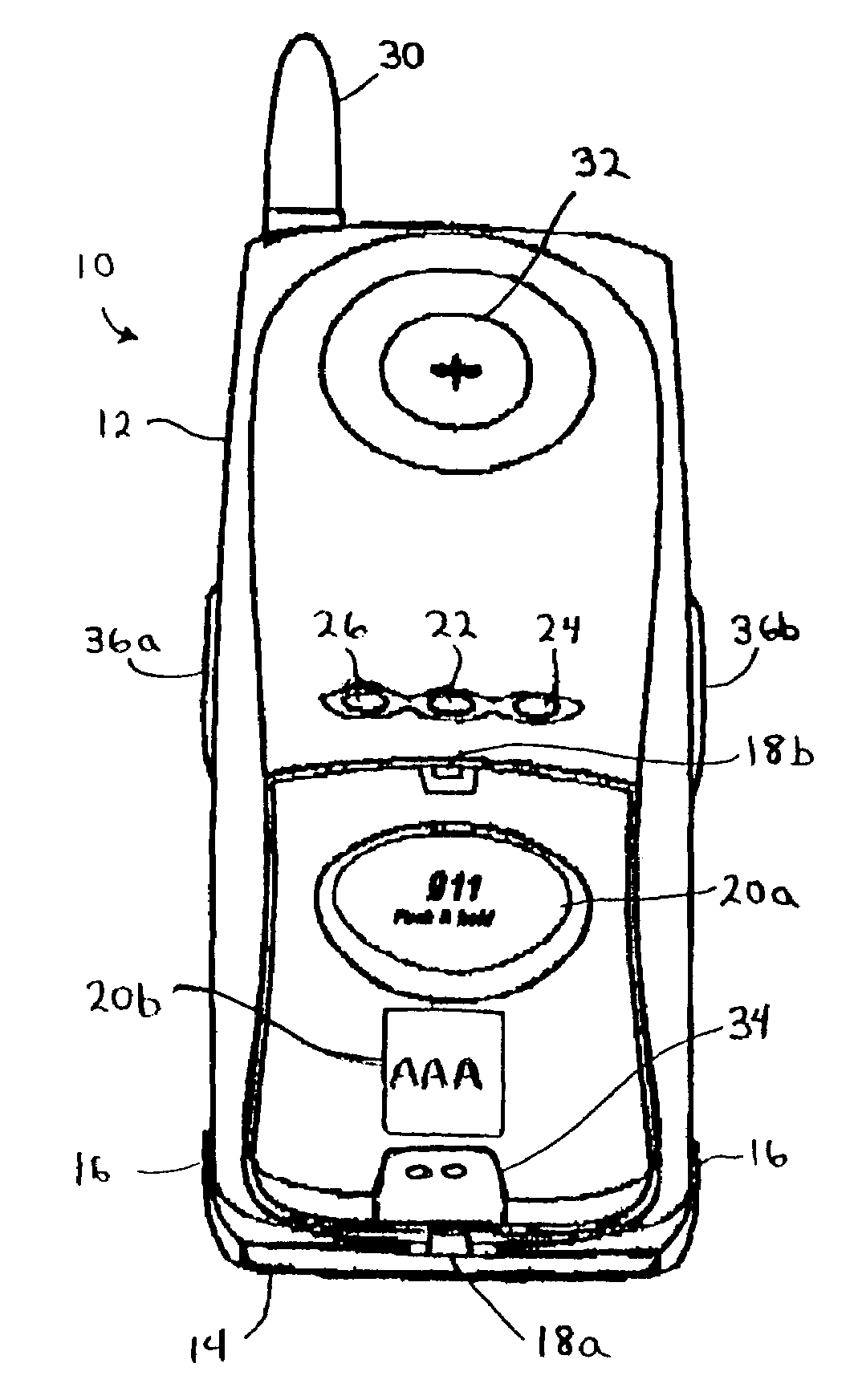

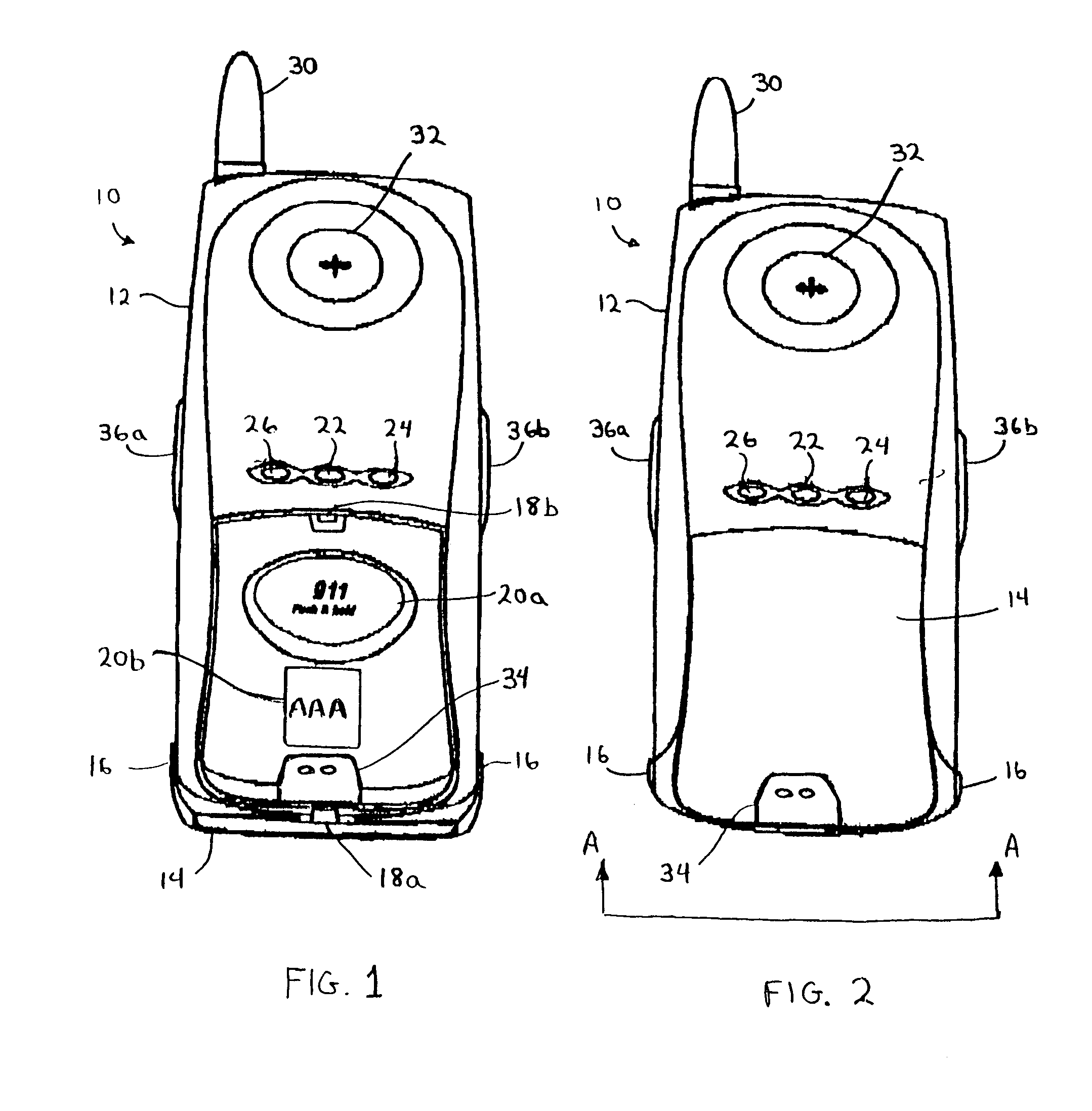

Emergency phone with alternate number calling capability

InactiveUS7092695B1Eliminates oversight and difficulty and disadvantageAvoid accidental activationAlarms using portable personal devicesEmergency connection handlingVoice communicationEngineering

An emergency-use-only cellular phone provides for contacting and establishing full-duplex voice communication with emergency personnel at either a public emergency response service or a private roadside assistance service. The phone automatically places a cellular call to the public emergency response service with a single press of a first activation button, and to the private roadside assistance service with a single press of a second activation button. When either activation button is pressed, the following functions are initiated: (1) electrical power from a power supply is provided to a cellular transmitter and receiver, (2) the cellular receiver is activated to search for an available channel from among A or B cellular system channels, (3) an emergency telephone number corresponding to the selected service is accessed from memory, and (4) the cellular transmitter is activated to establish communication with the selected emergency response service. Since all of these functions are initiated by pressing one button, communication with the selected emergency response service may be established simply and speedily, even under stressful conditions. The phone may include a modular GPS receiver unit for providing location information to the public emergency response service or a private roadside assistance service.

Owner:SECUREALERT INC

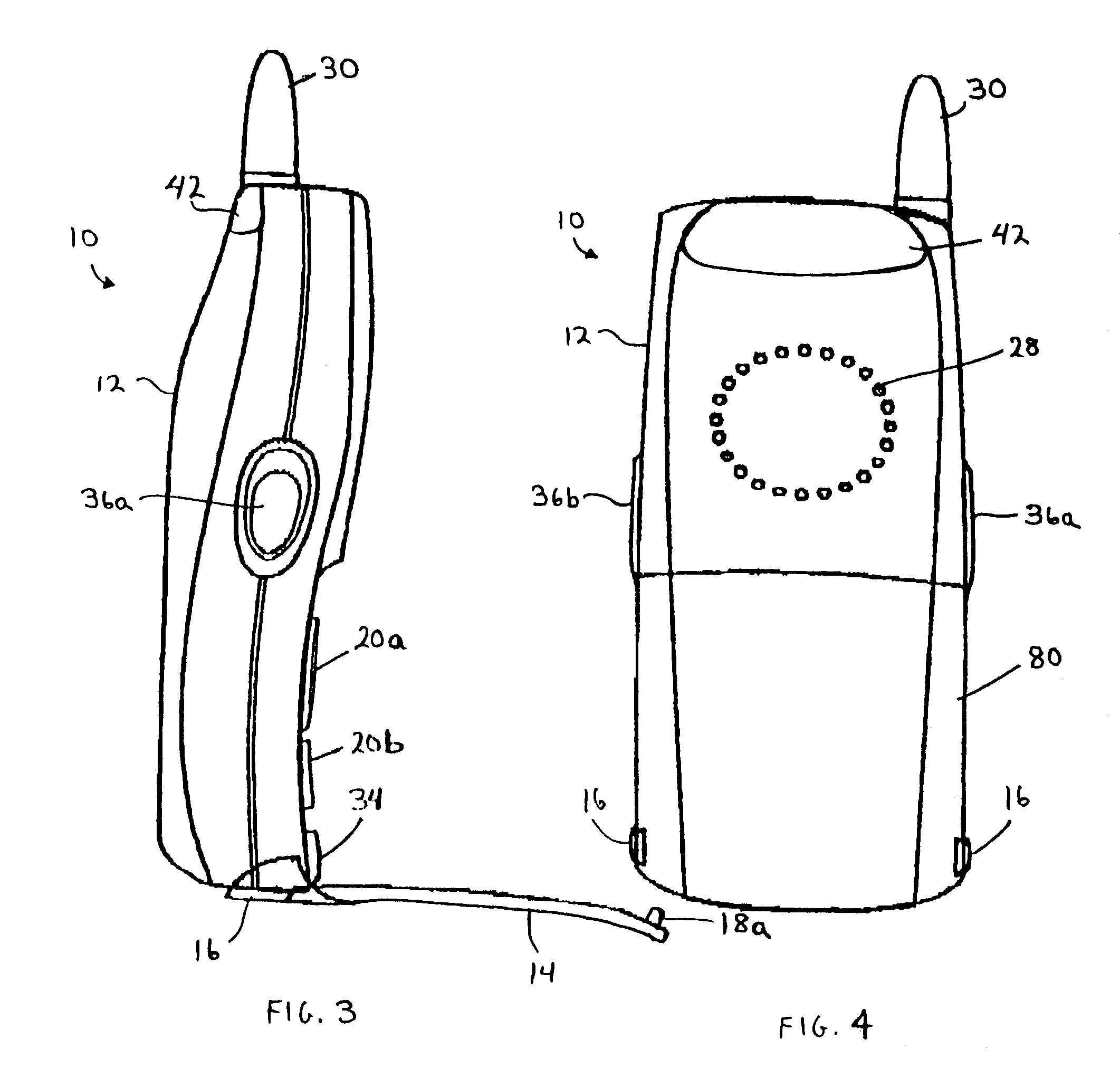

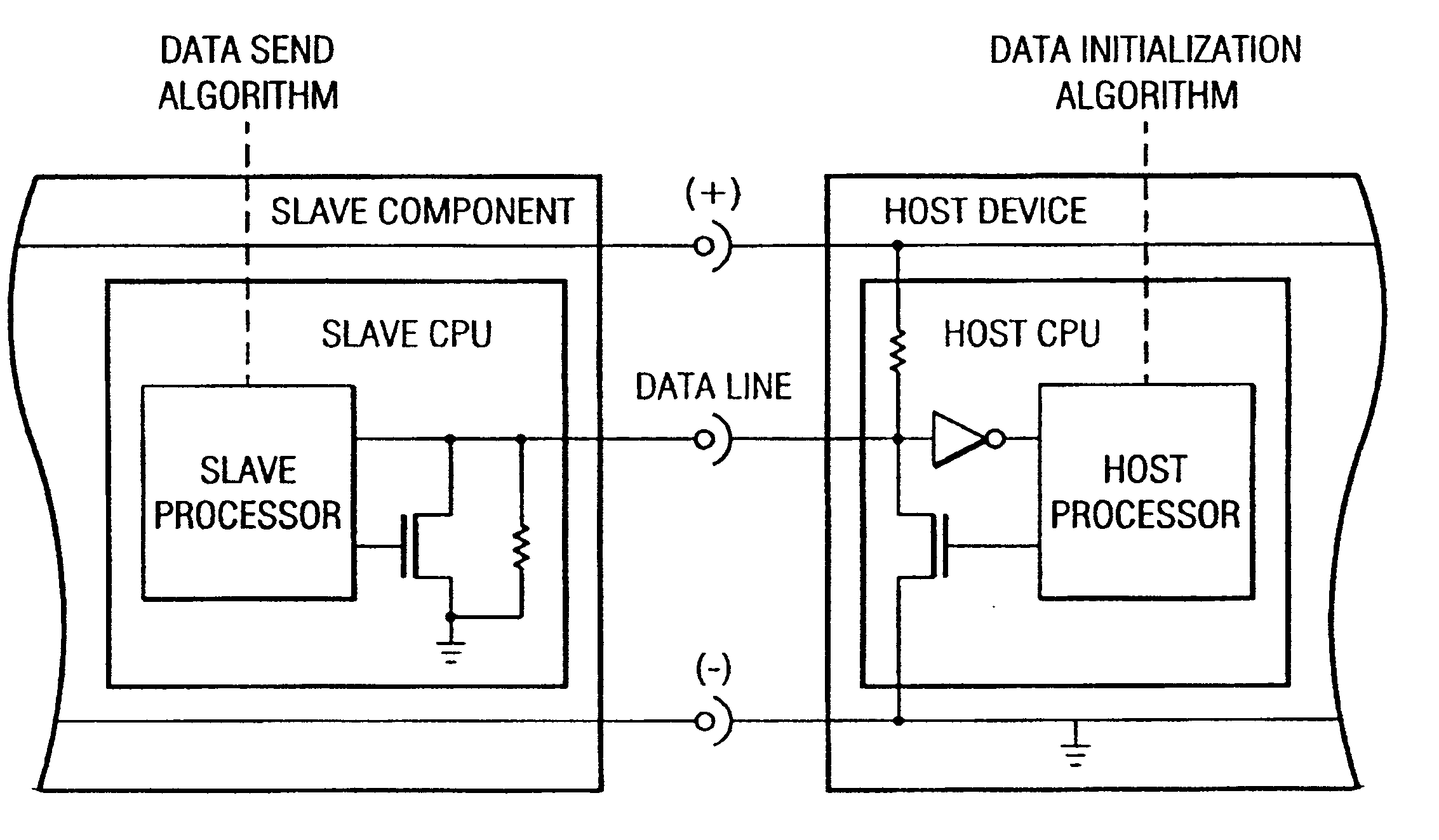

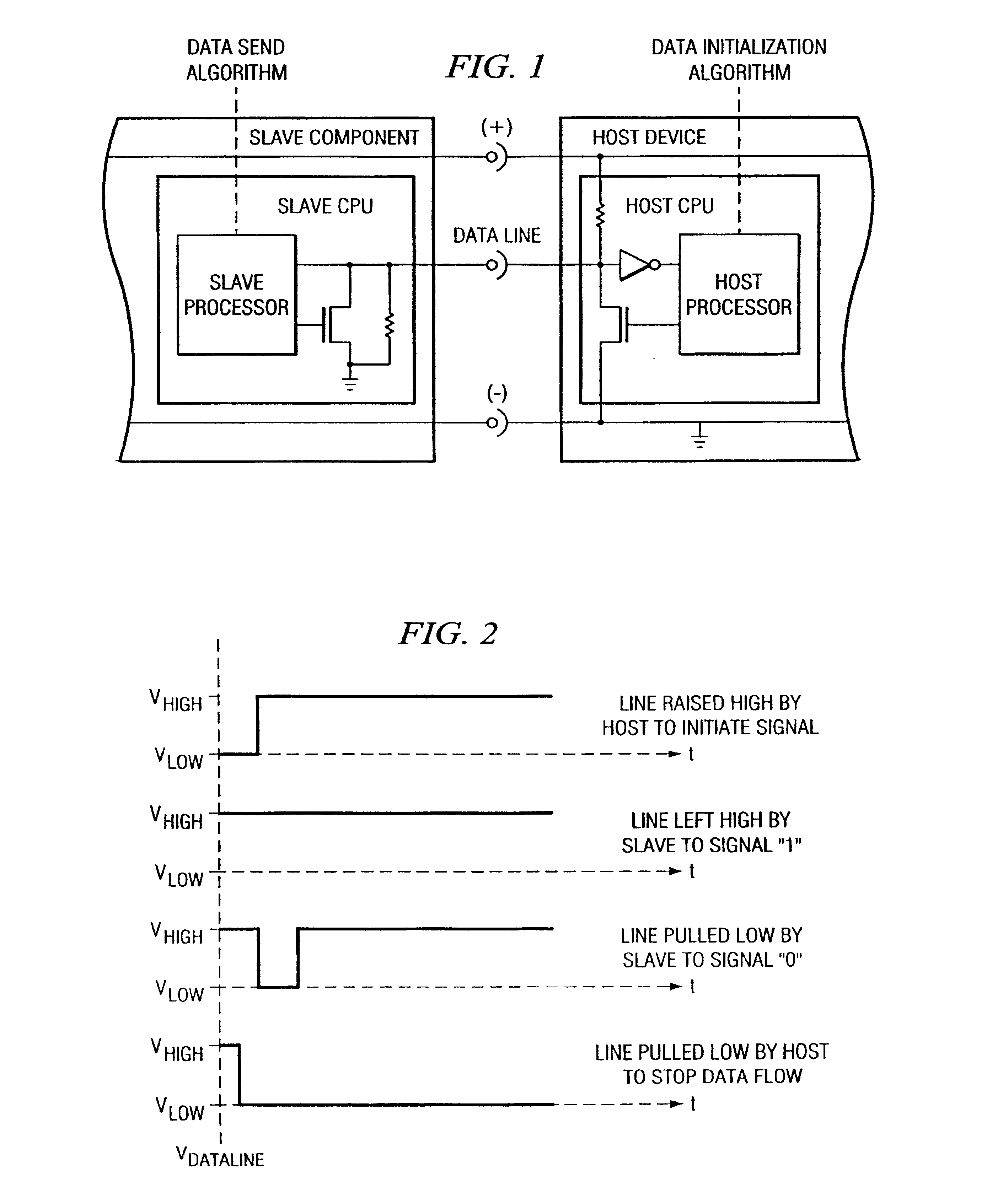

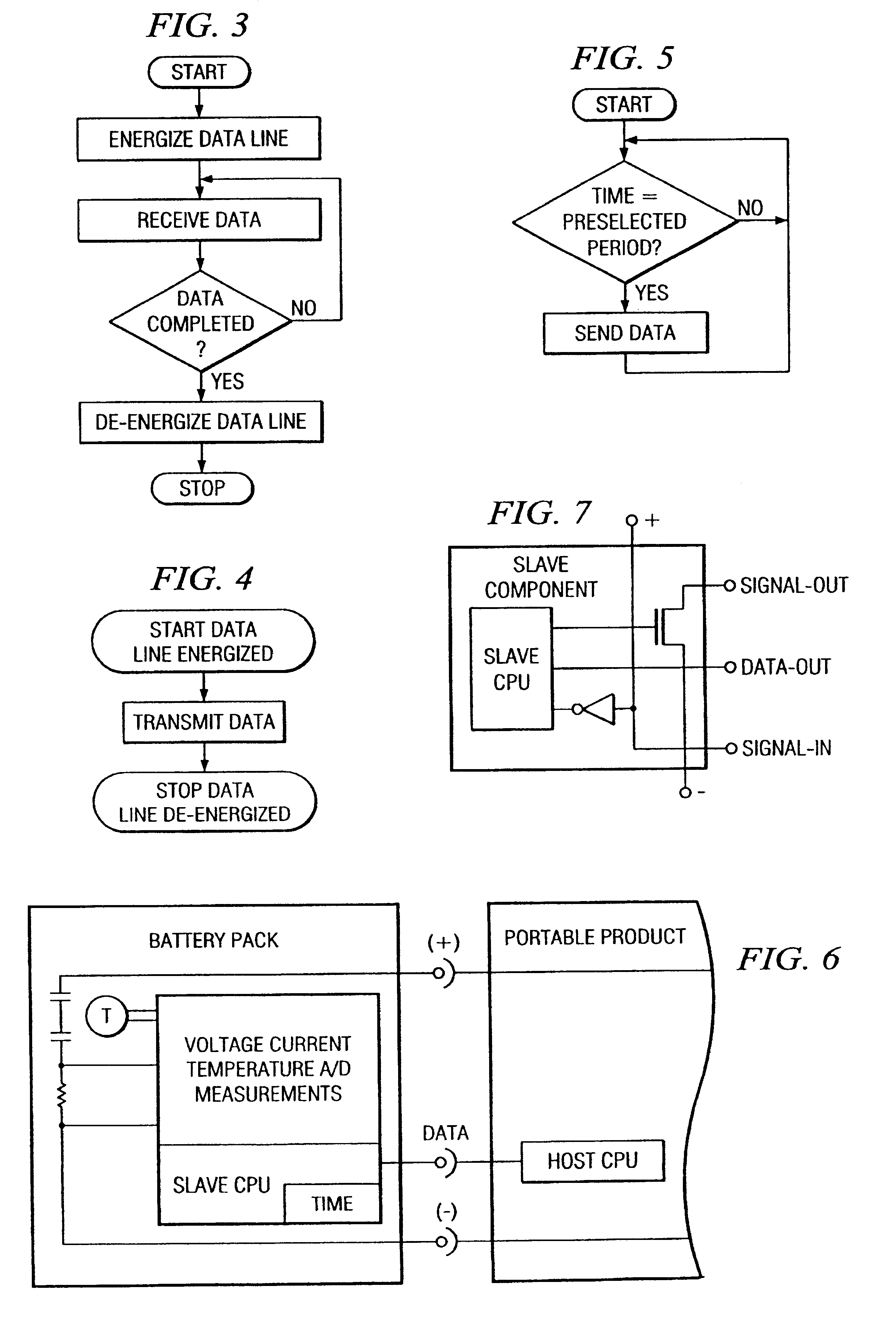

Data communication interface between host and slave processors

InactiveUS6697897B1Simplify the communication processReduce power consumptionElectric digital data processingDuplex signal operationCommunication interfaceMaster processor

A data communication interface for transferring at least one data bit to a host processor. The interface includes a one-wire data line, and a slave processor connected to the data line and including a pull-down circuit for varying voltage on the data line. The slave processor is passive and incapable of sampling data from the data line. The slave processor is programmed to vary voltage on the data line when the data line is energized, to signal at least one data bit.

Owner:MICROCHIP TECH INC

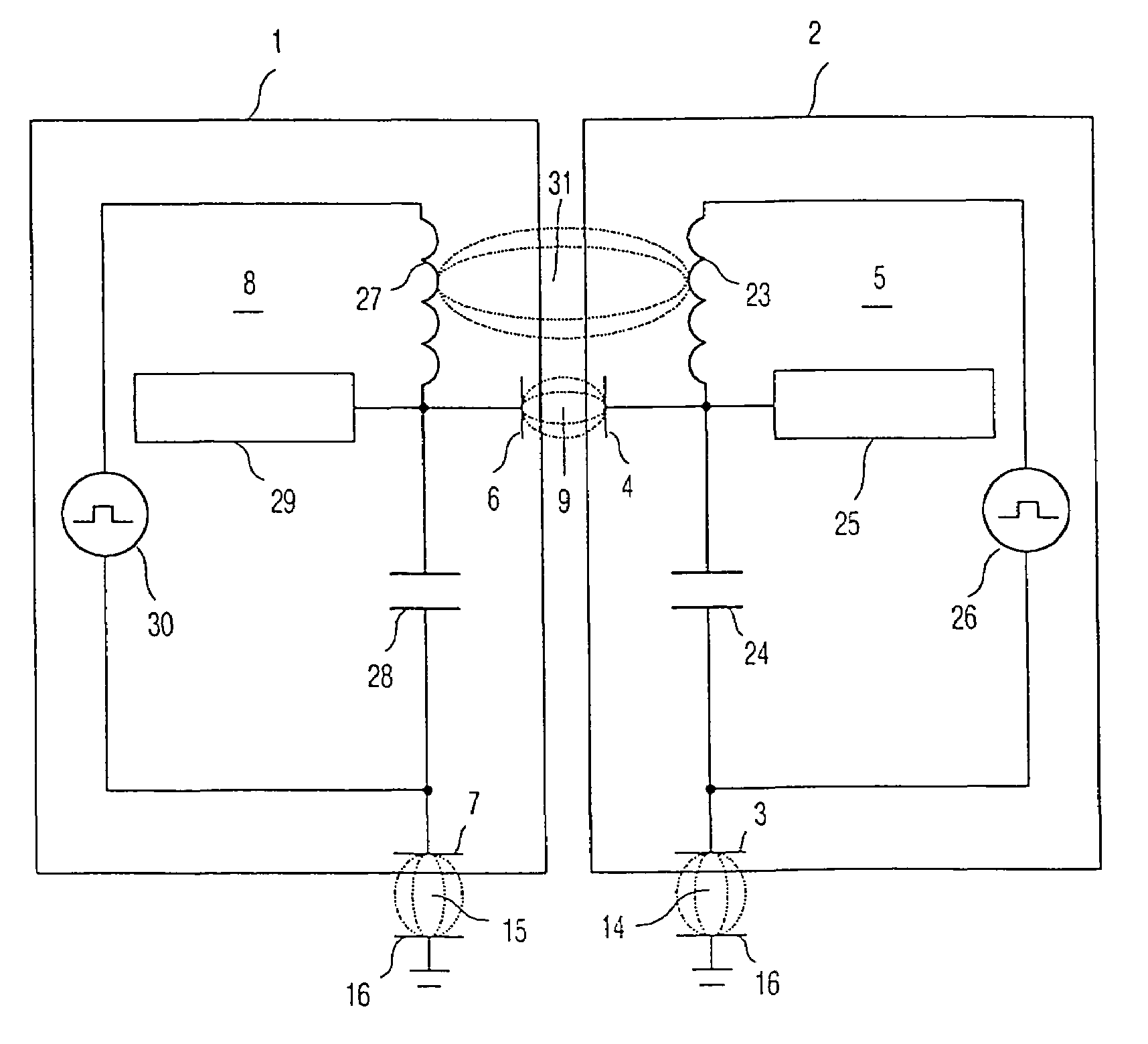

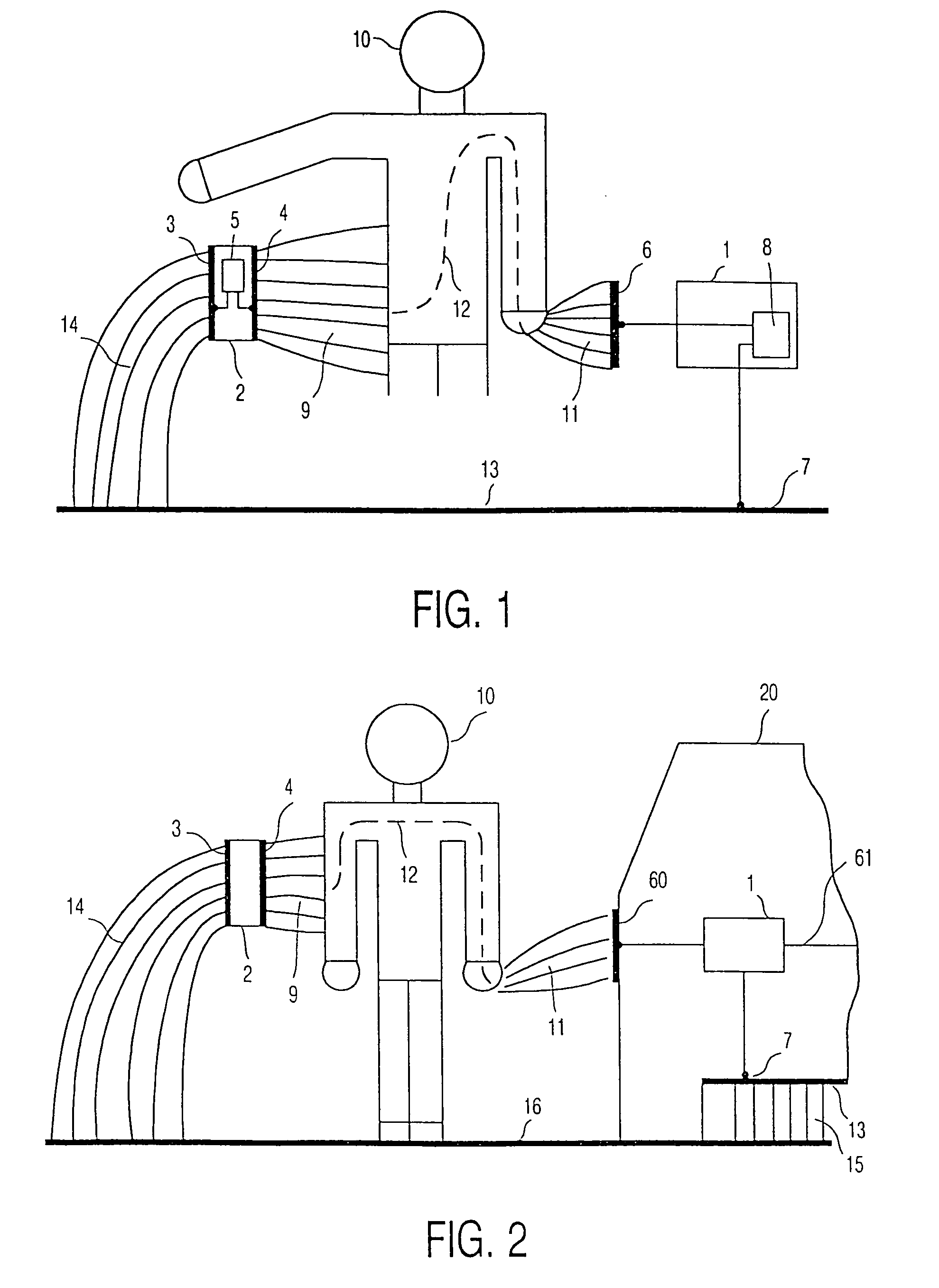

Electronic communications system

InactiveUS6992565B1Simple operationEasy to operateElectric signal transmission systemsLock applicationsElectronic communicationCar door

An electronic communication system for a vehicle, including a base station which is accommodated in the vehicle and at least one portable data carrier which is arranged to exchange data signals with the base station. A first coupling link is formed at least partly by the body of a user, whose skin is not required to be in physical contact with the data carrier, so that the body of the user contactlessly conducts displacement currents from the data carrier without contacting the data carrier. This permits the user to unlock a car door, or trunk, and / or start the vehicle, without using a key or having to touch a remote control device. The data carrier can be located in a briefcase and / or purse, and the ability to access the vehicle is not comprised even though there is no physical contact between the user and the data carrier.

Owner:NXP BV

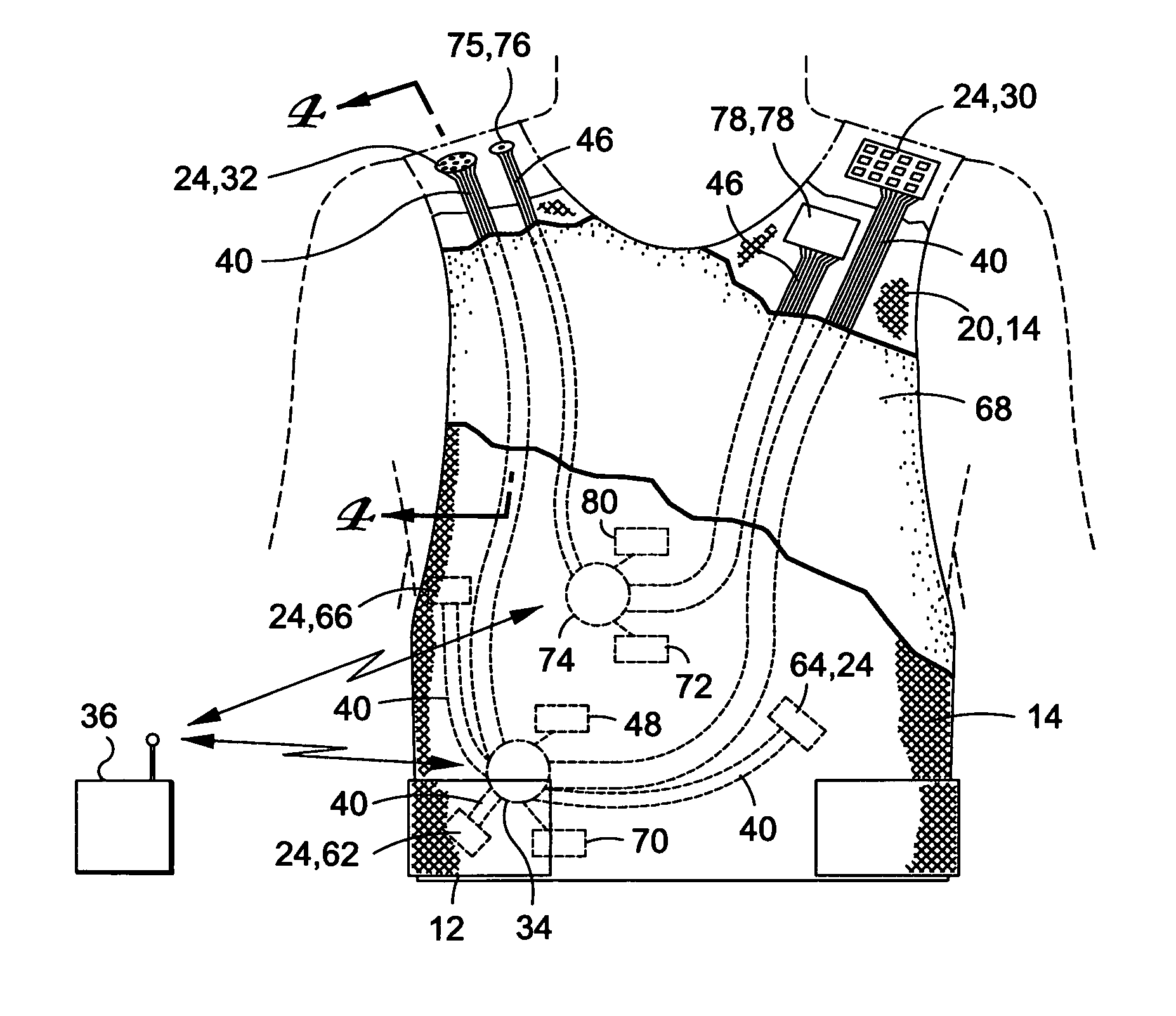

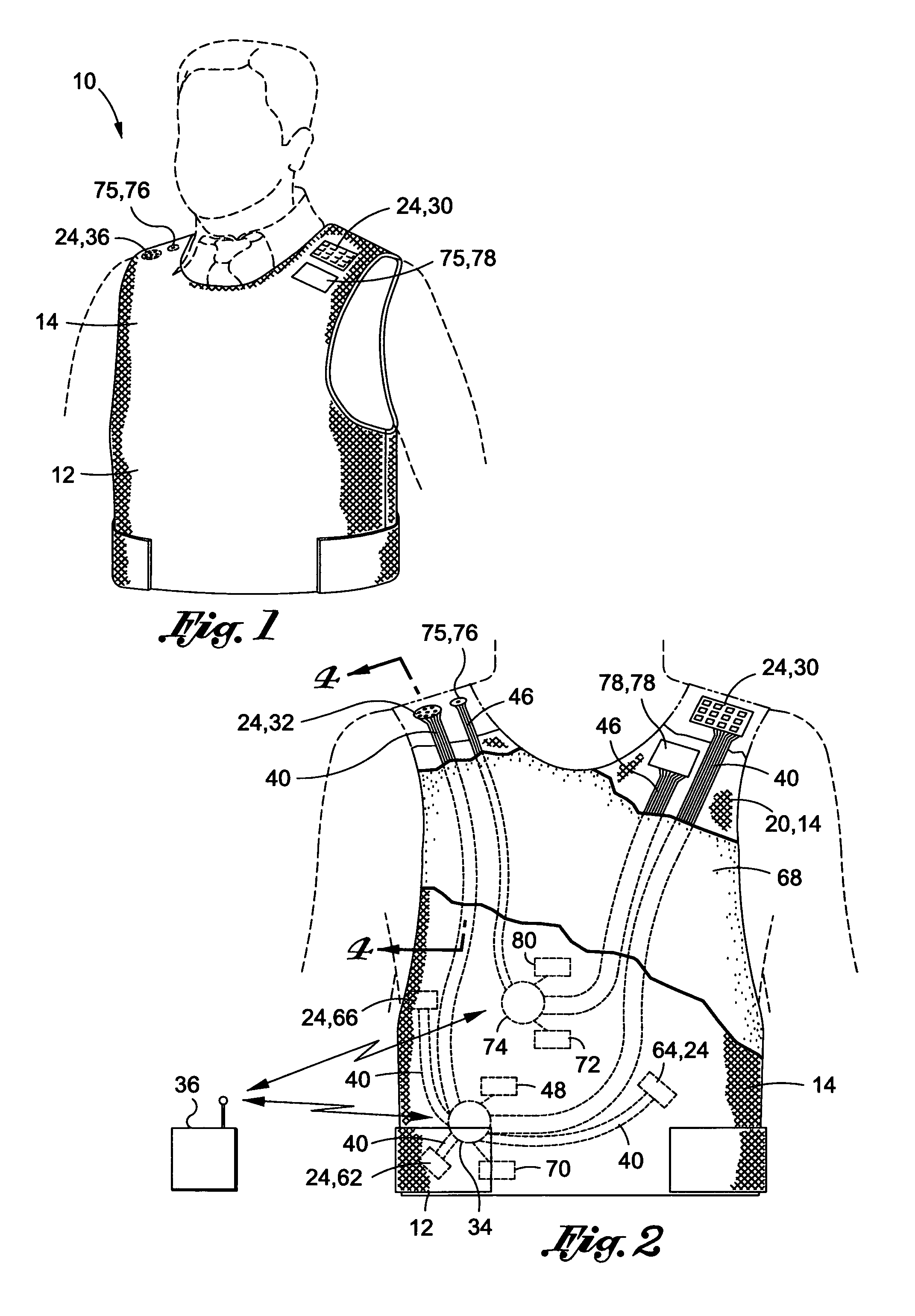

Safety vest assembly including a high reliability communication system

InactiveUS8341762B2Facilitate communicationSimplify the communication processSpace suitsFlying suitsElectricityCommunications system

Owner:BALZANO ALFIERO

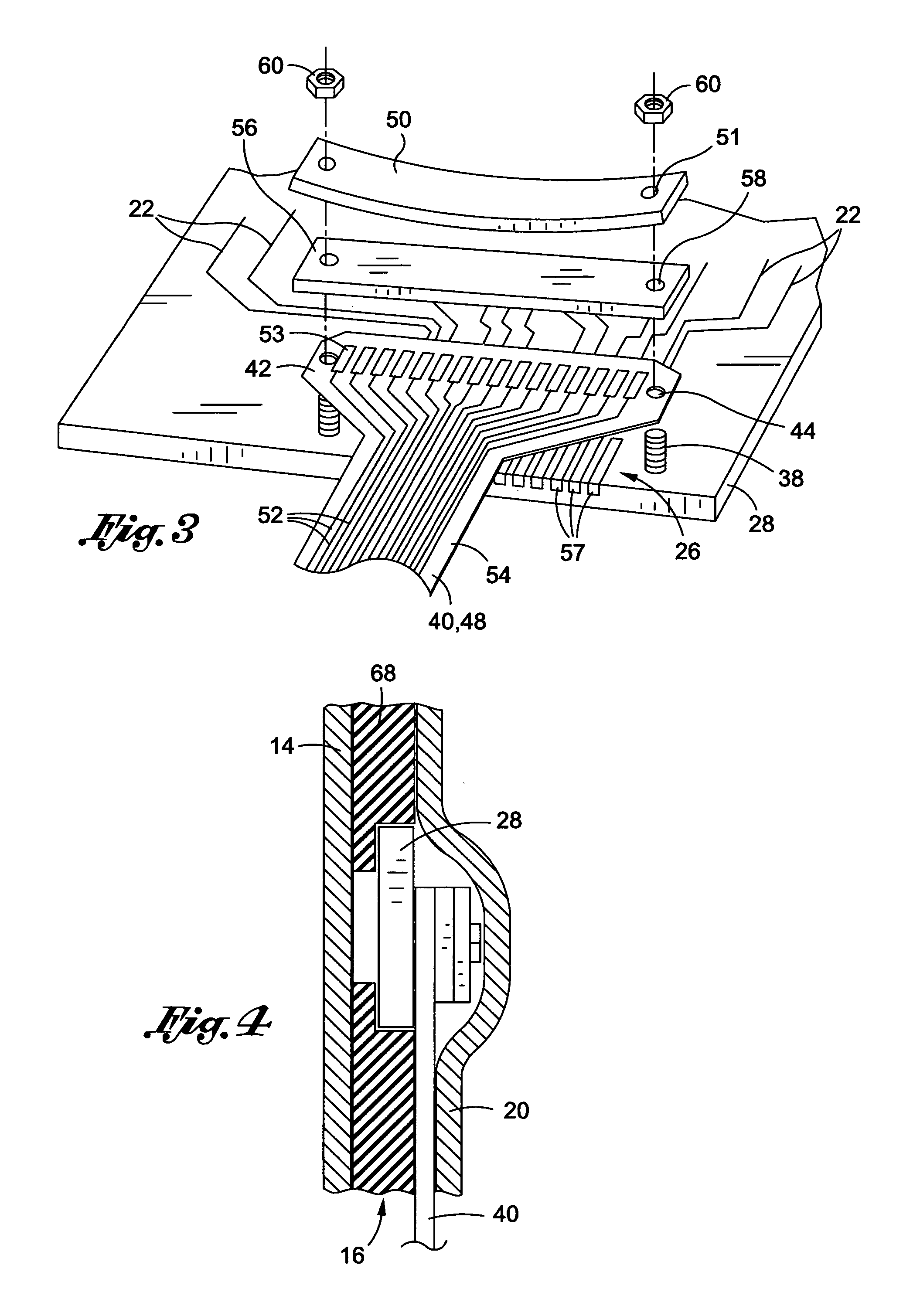

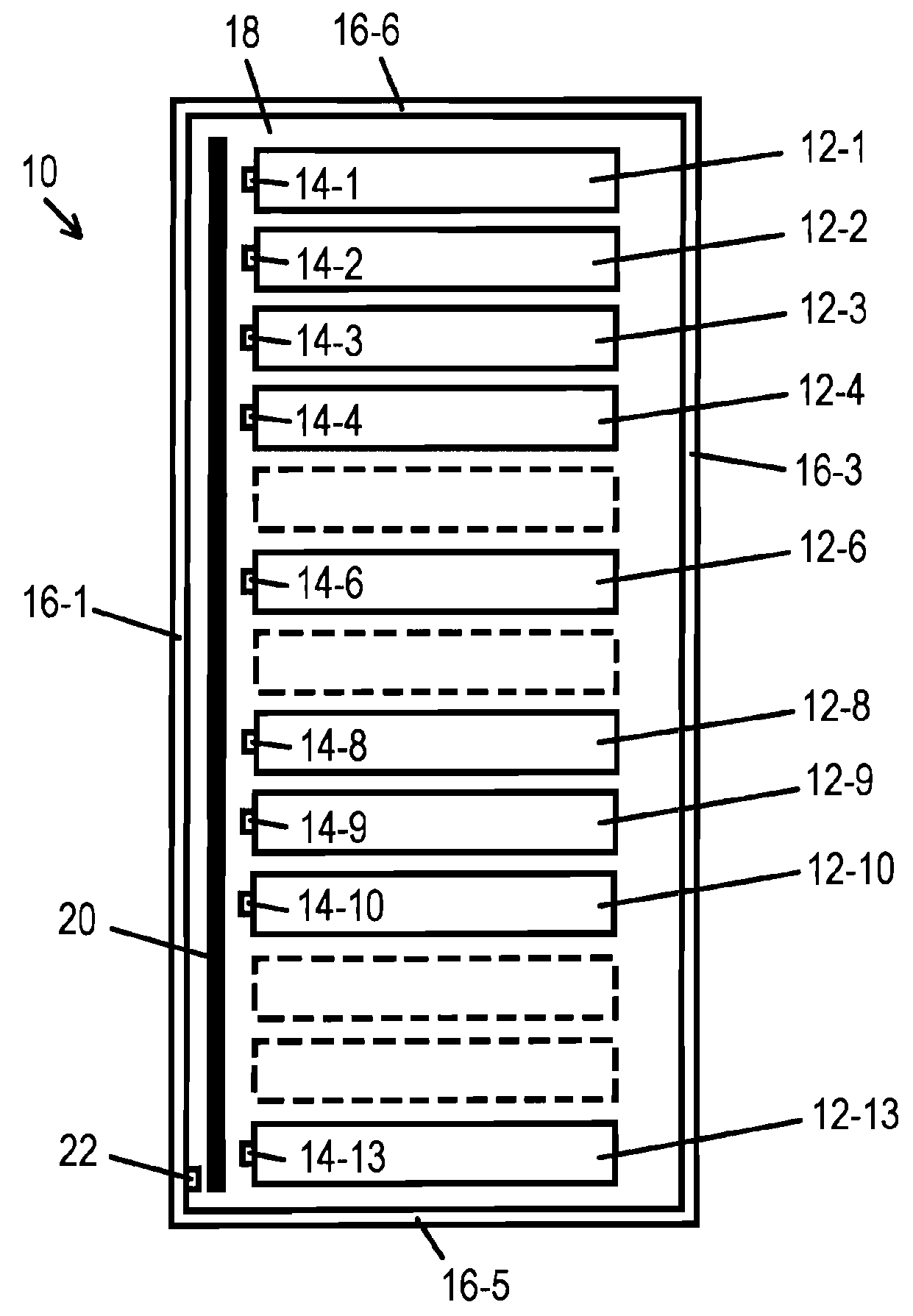

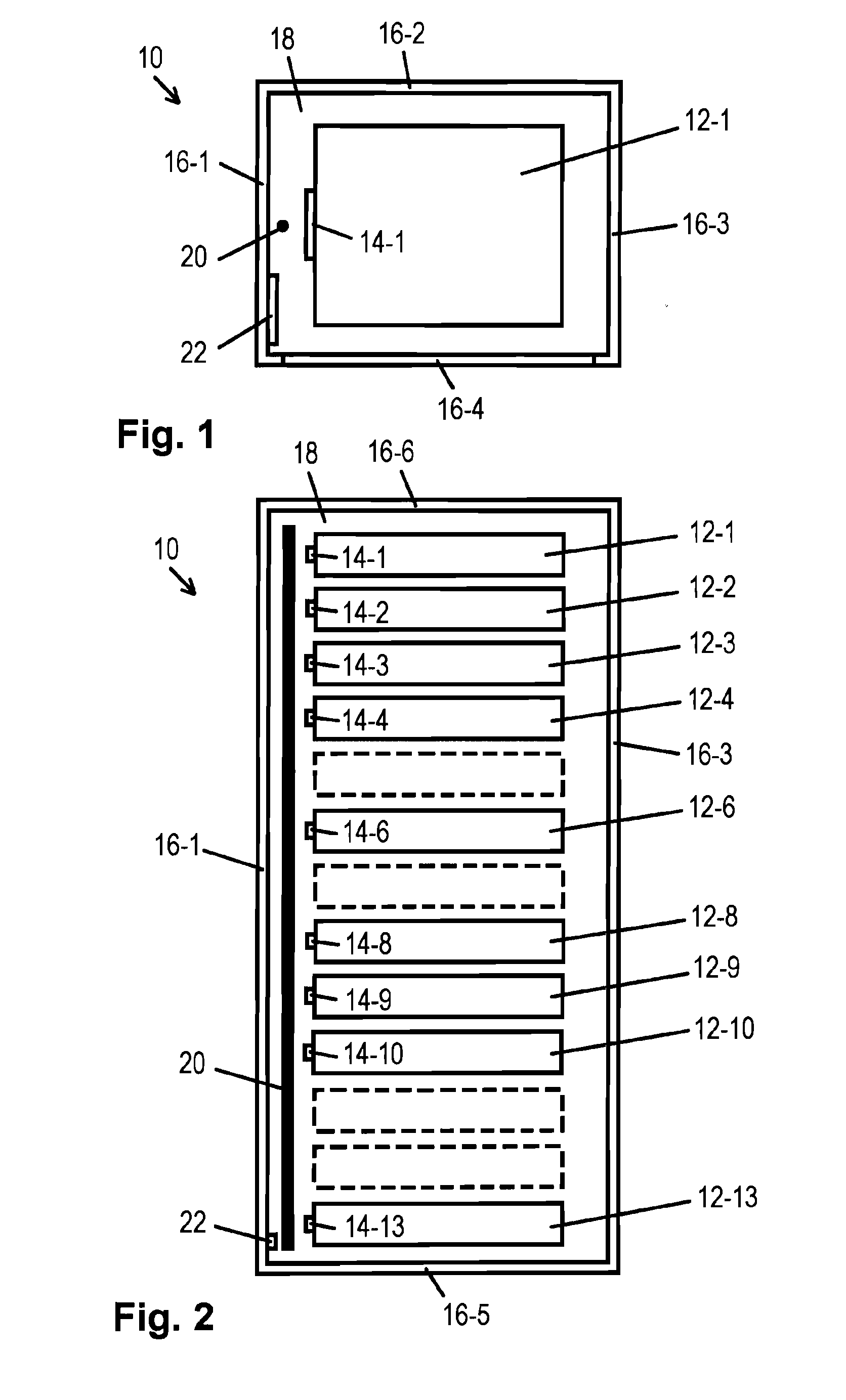

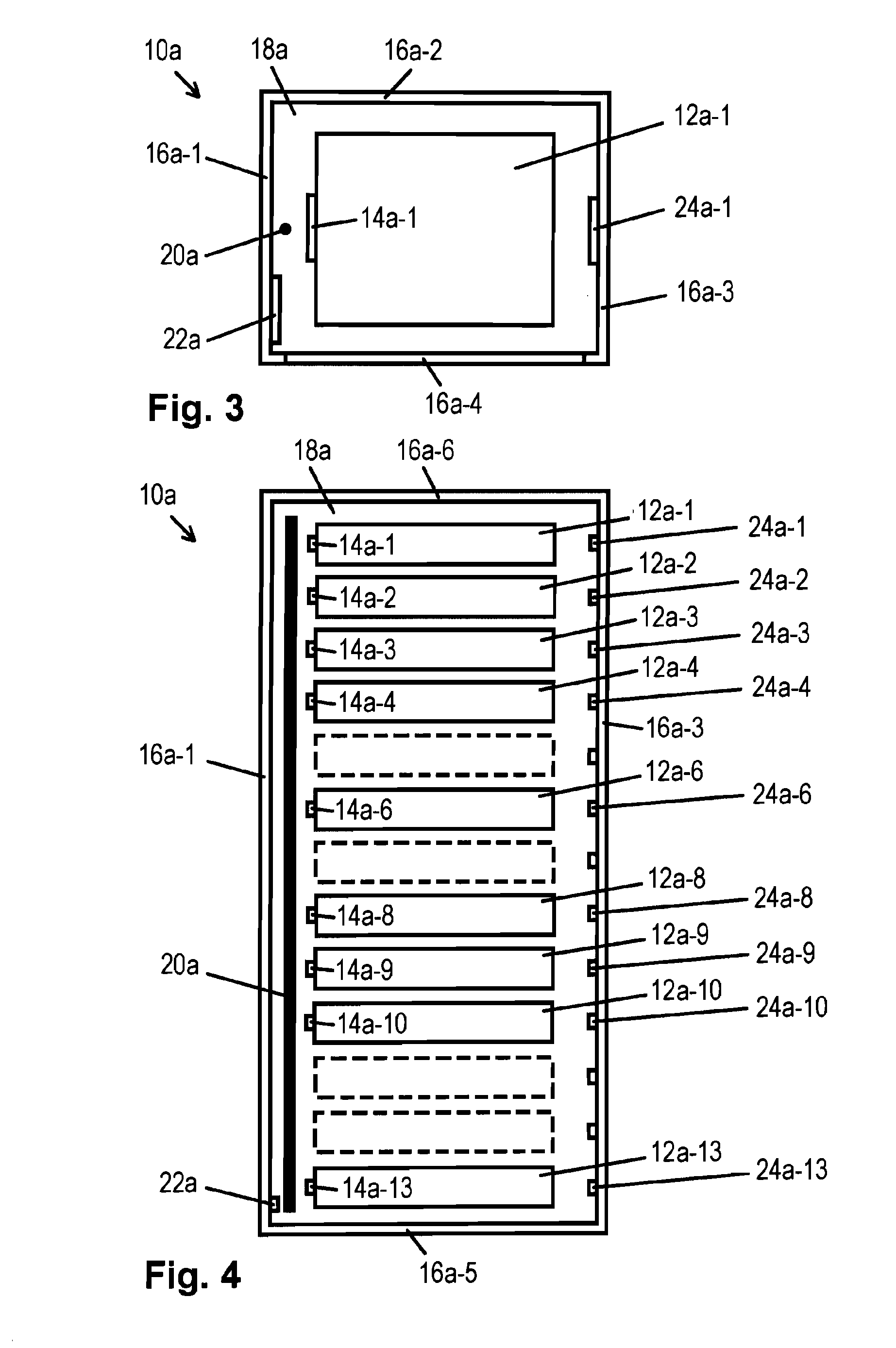

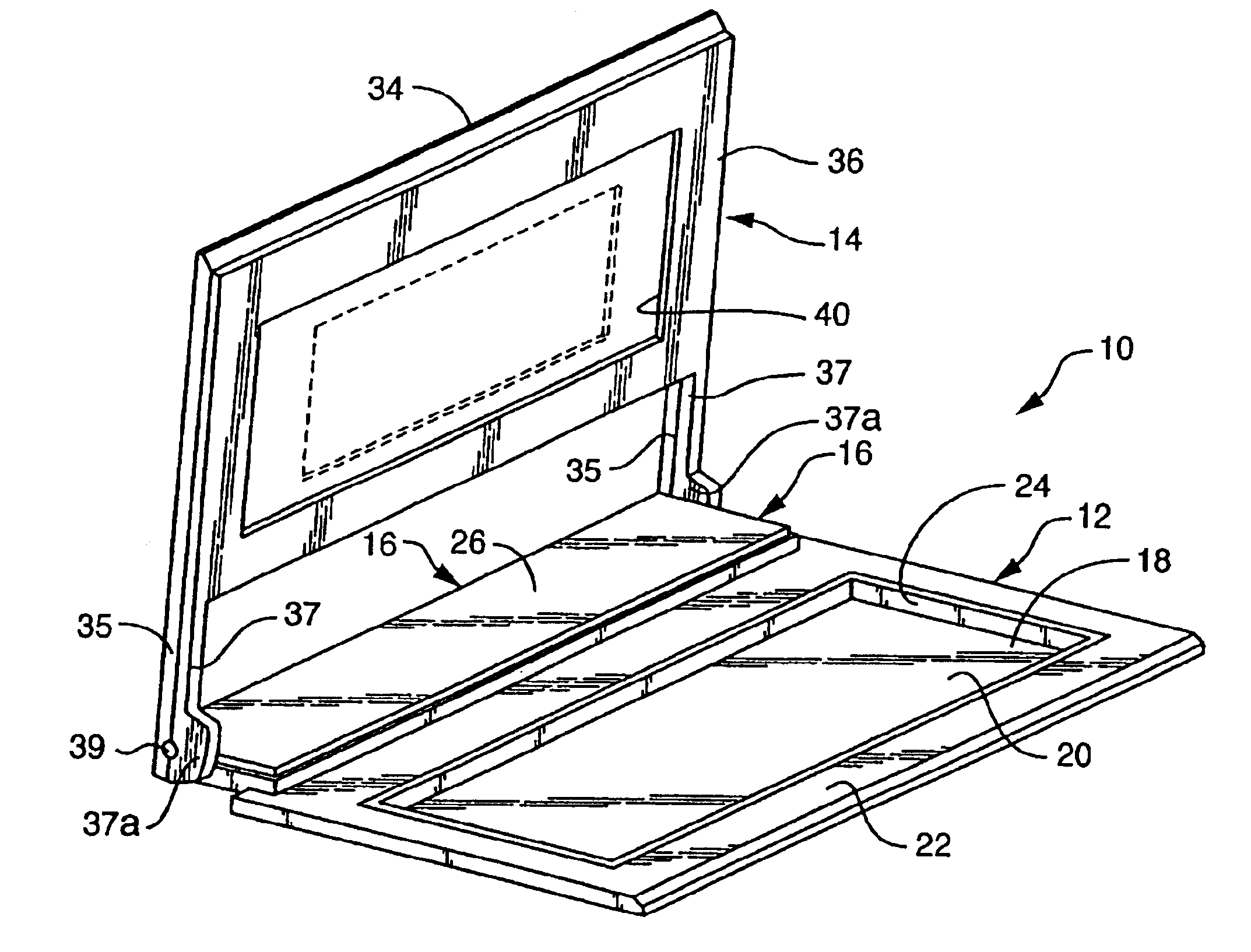

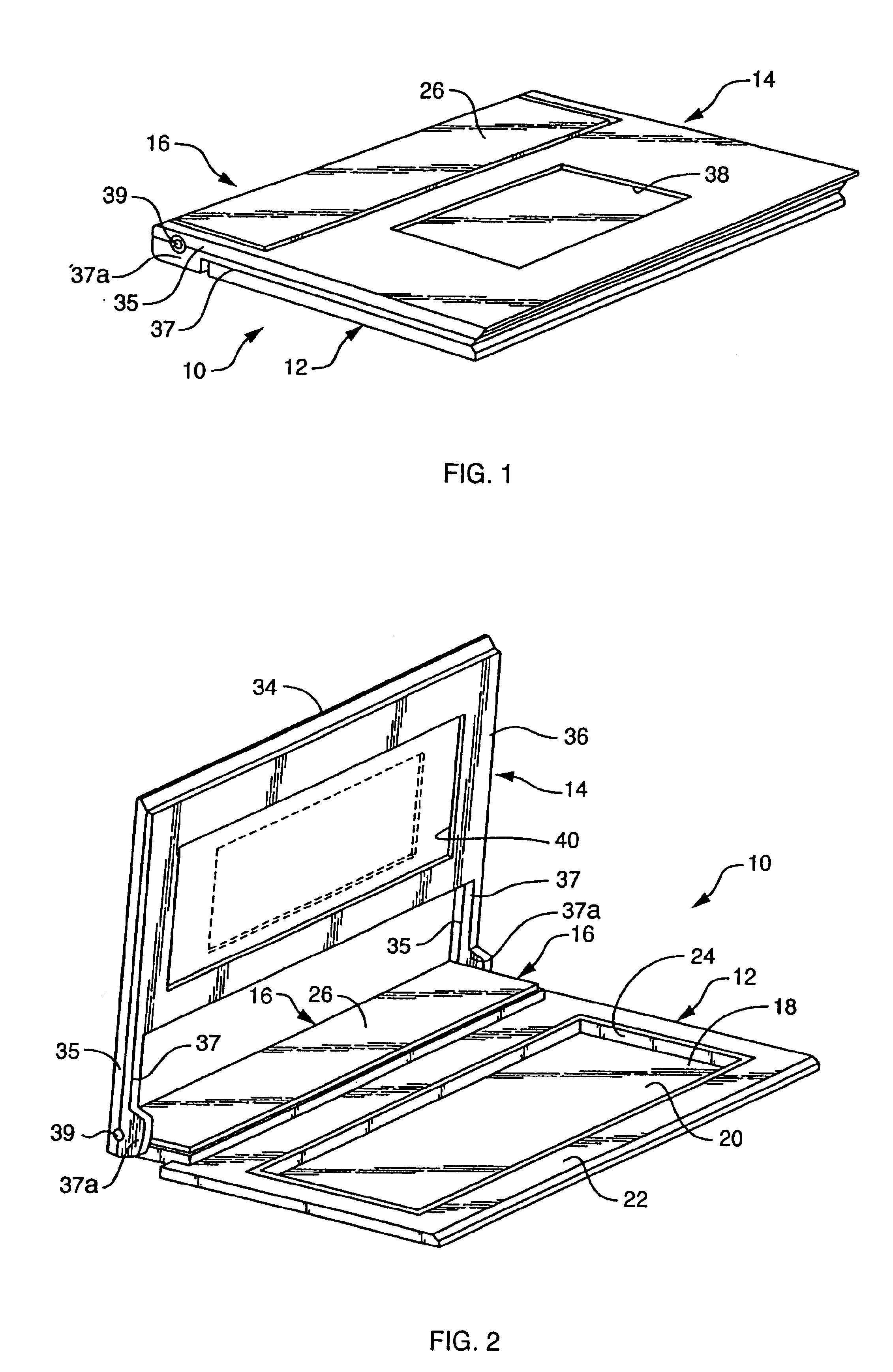

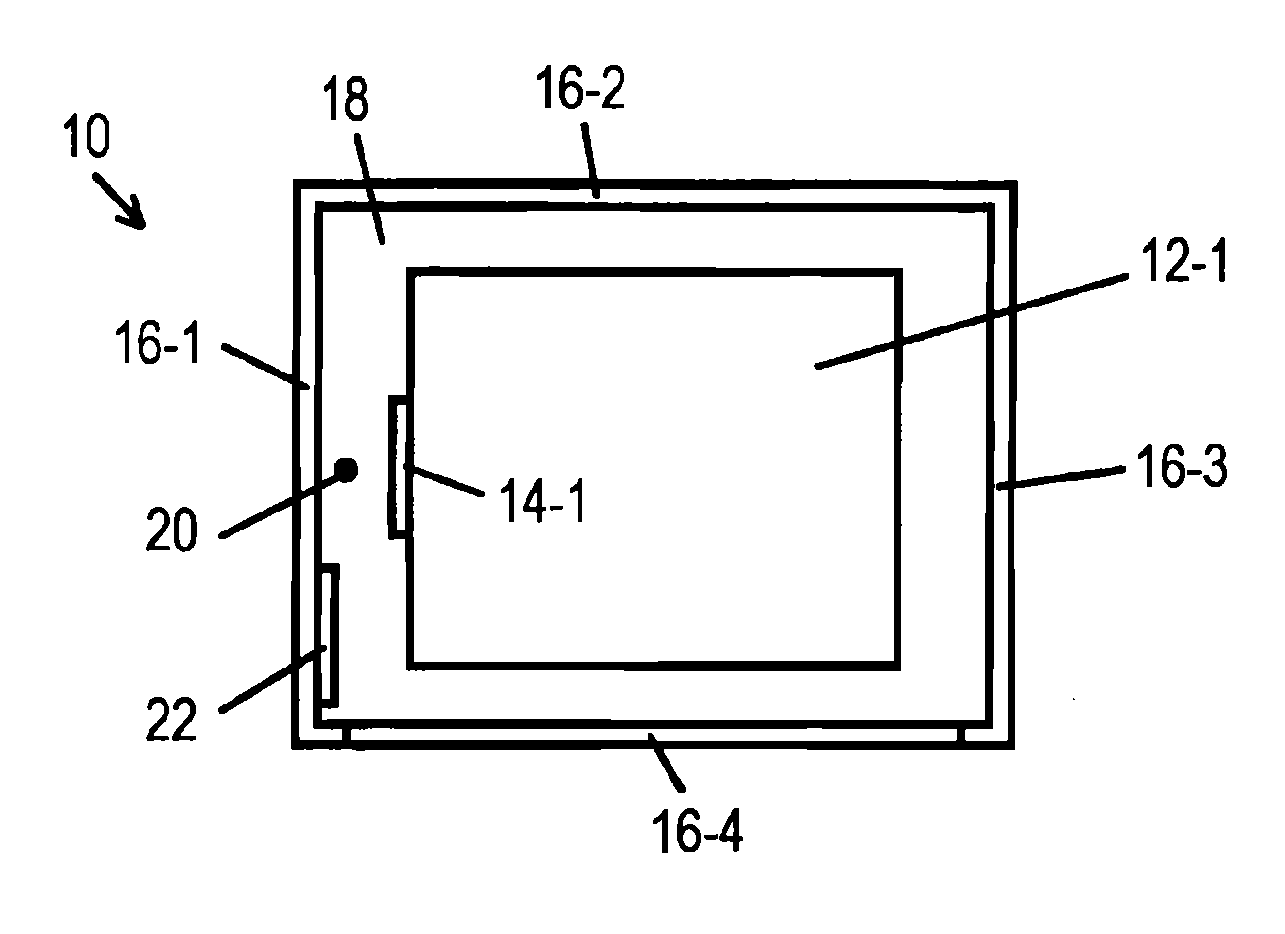

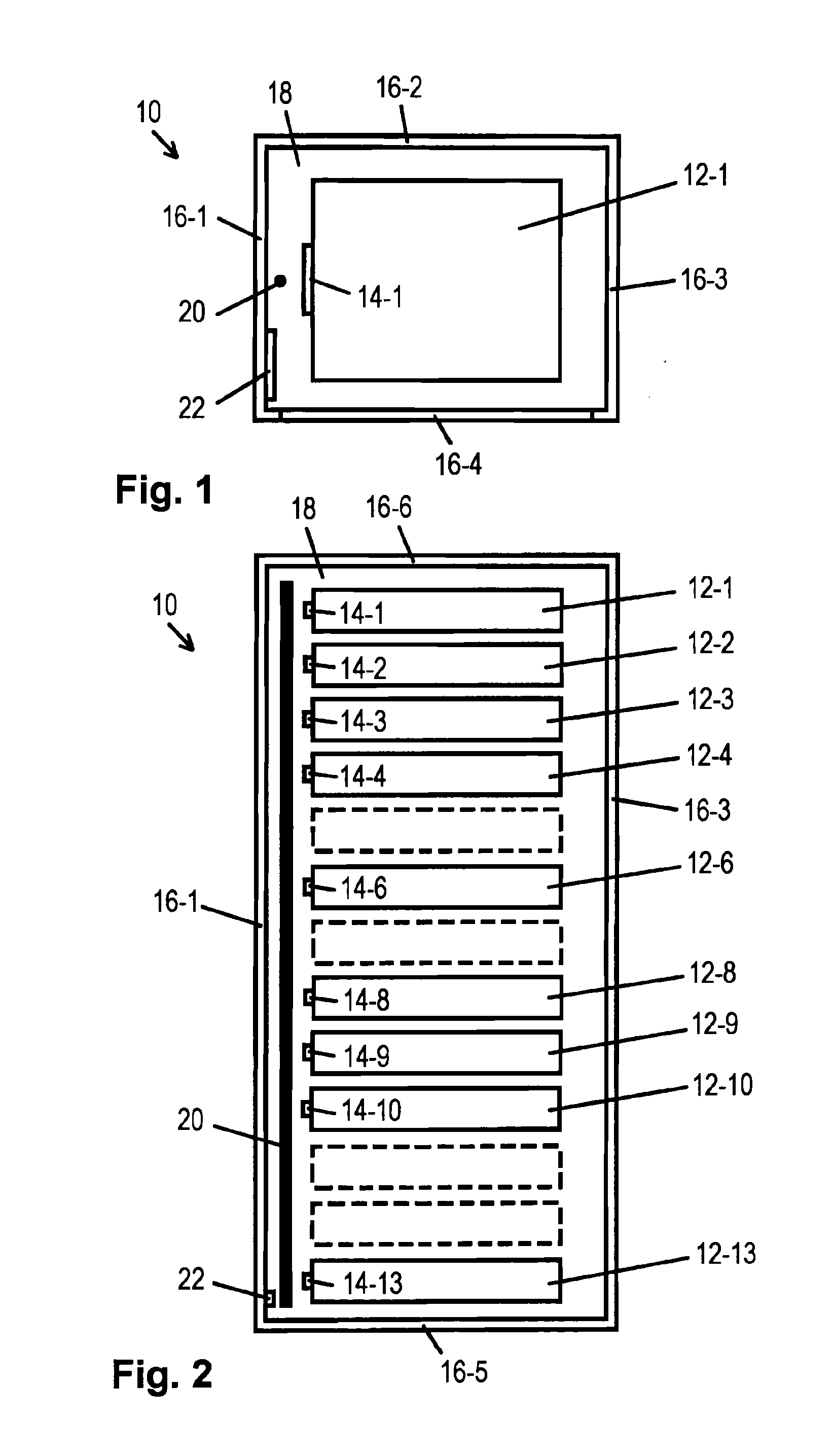

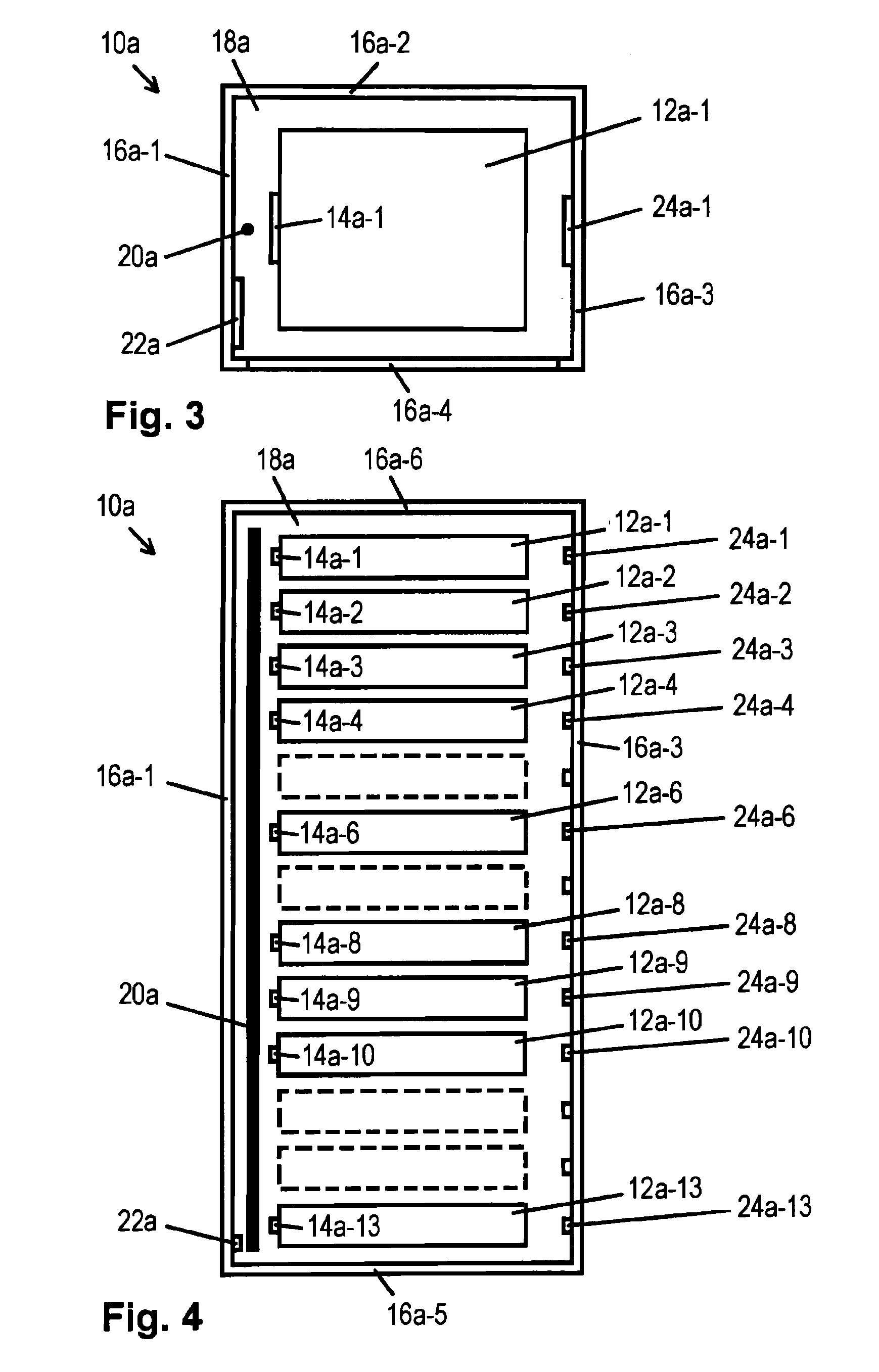

Container for receiving articles

InactiveUS20090256680A1Operation be restrictOperation be prohibitMemory record carrier reading problemsOther accessoriesEngineeringMechanical engineering

The invention provides a container (10) comprising a, a receiving compartment (18) for receiving articles (12) each provided with an RFID transponder (14), a shielding (16) for shielding of the receiving compartment (18), and an RFID antenna device (20) located in the receiving compartment (18) for communication with the transponders (14). Reliable identification of articles (12) located in the container (10) can thus be simplified considerably.

Owner:KILIAN DIETER

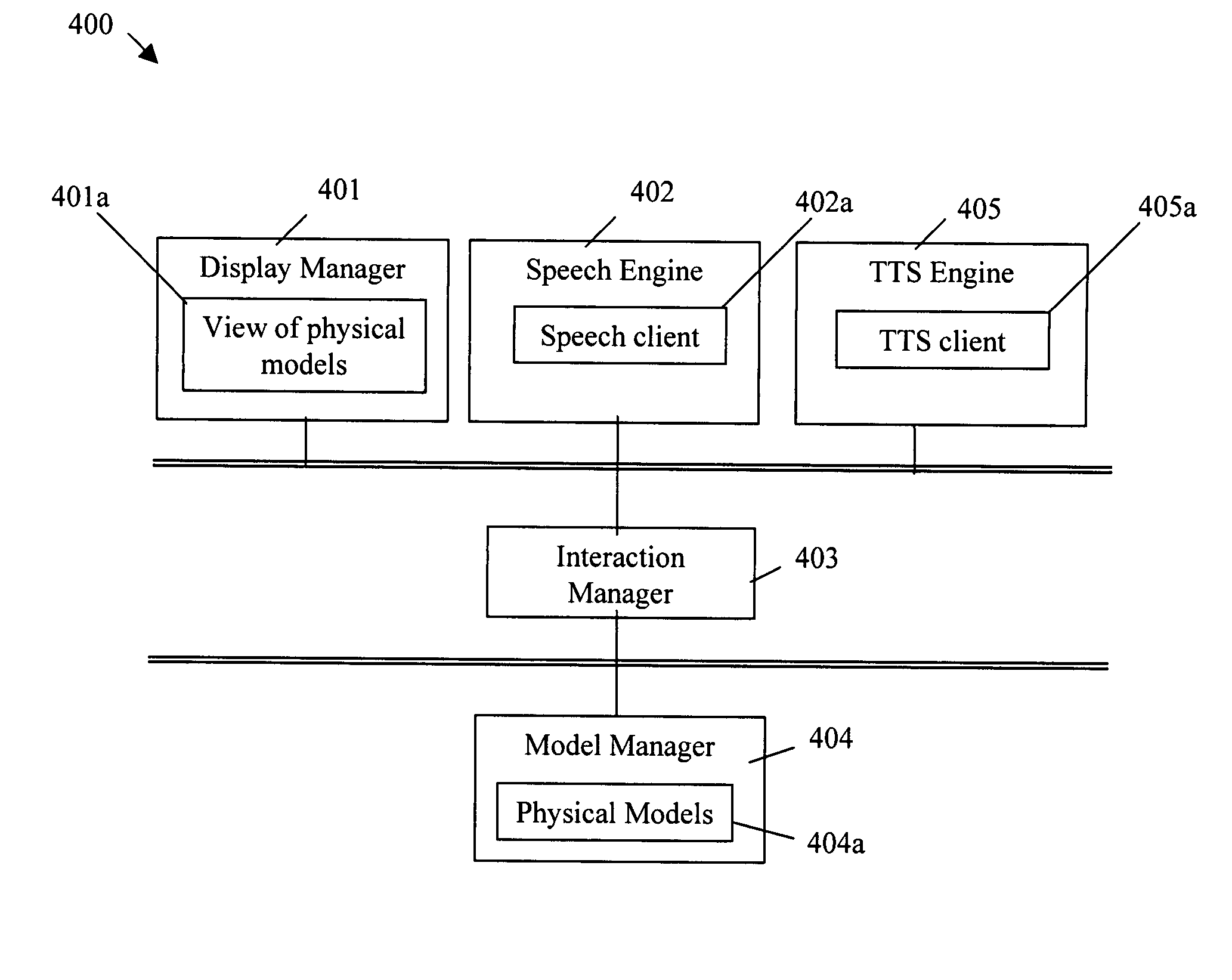

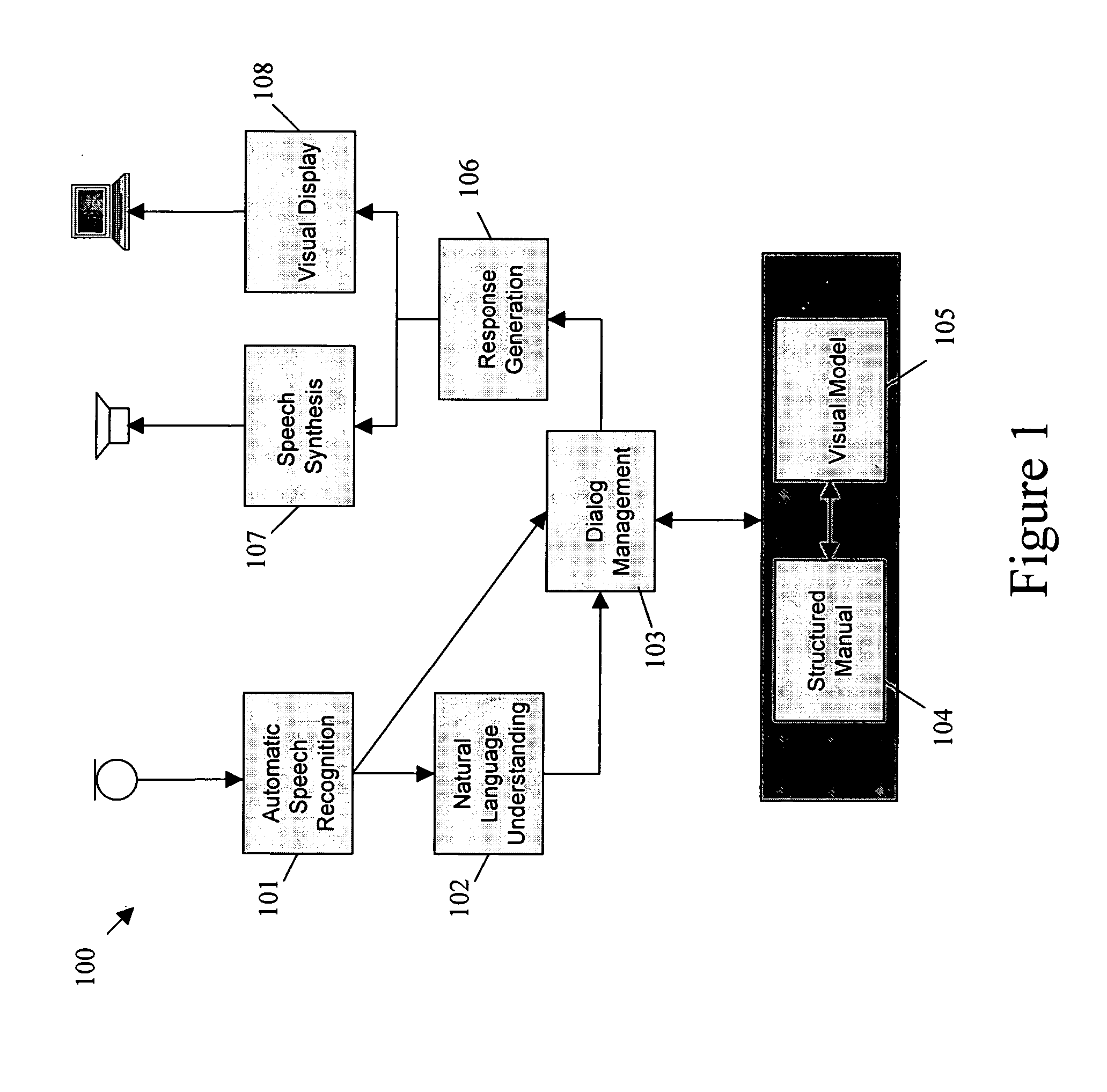

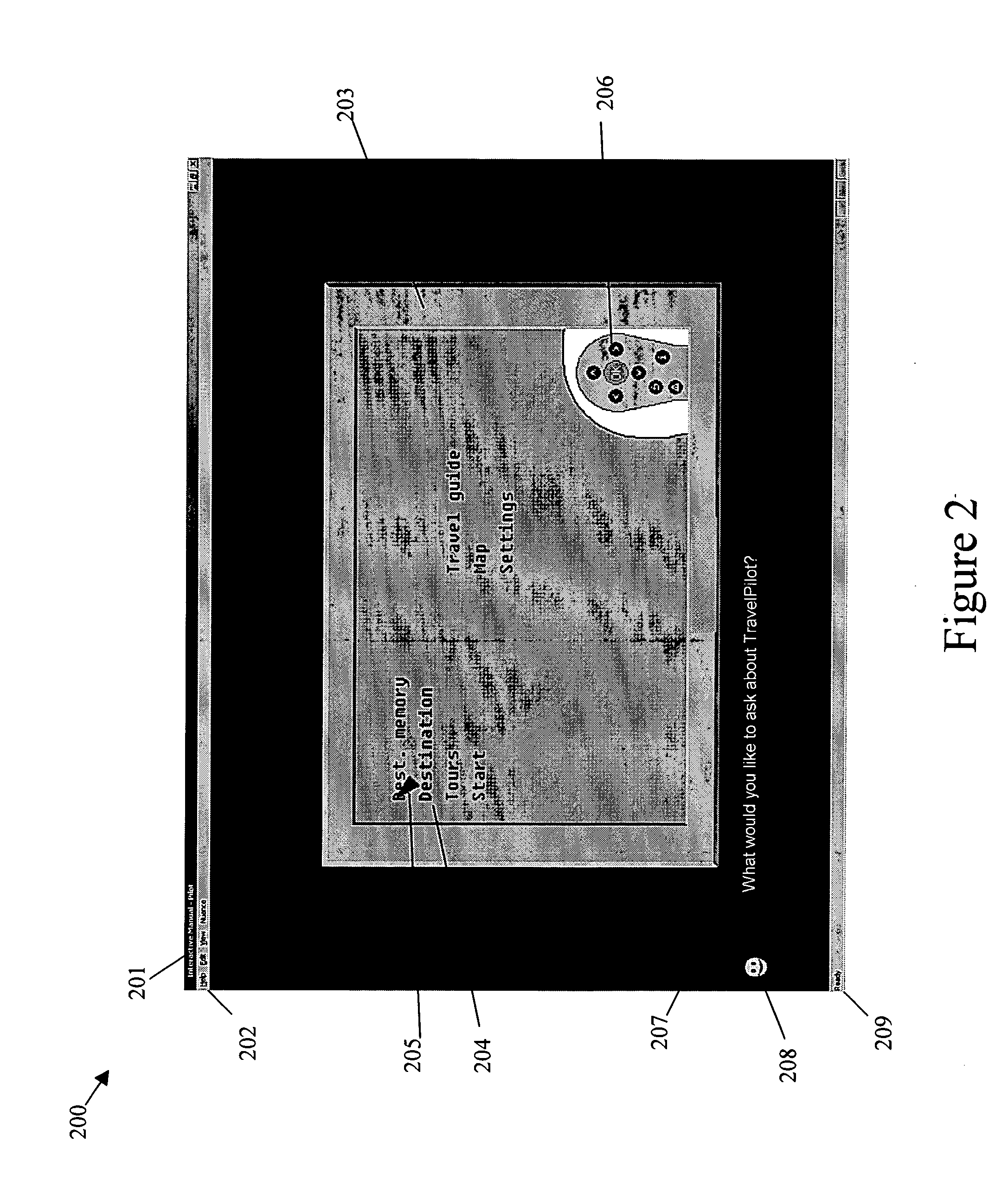

Interactive manual, system and method for vehicles and other complex equipment

A method and system of providing an interactive manual, including a speech engine to receive and process speech from a user, convert the speech into a word sequence, and identify meaning structures from the word sequence, a structured manual including information related to an operation of a device, a visual model to relate visual representation of the information, a dialog management arrangement to interpret the meaning structures in a context and to extract pertinent information and the visual representation from the structured manual and the visual model, and an output arrangement to output the information and visual representation.

Owner:ROBERT BOSCH GMBH

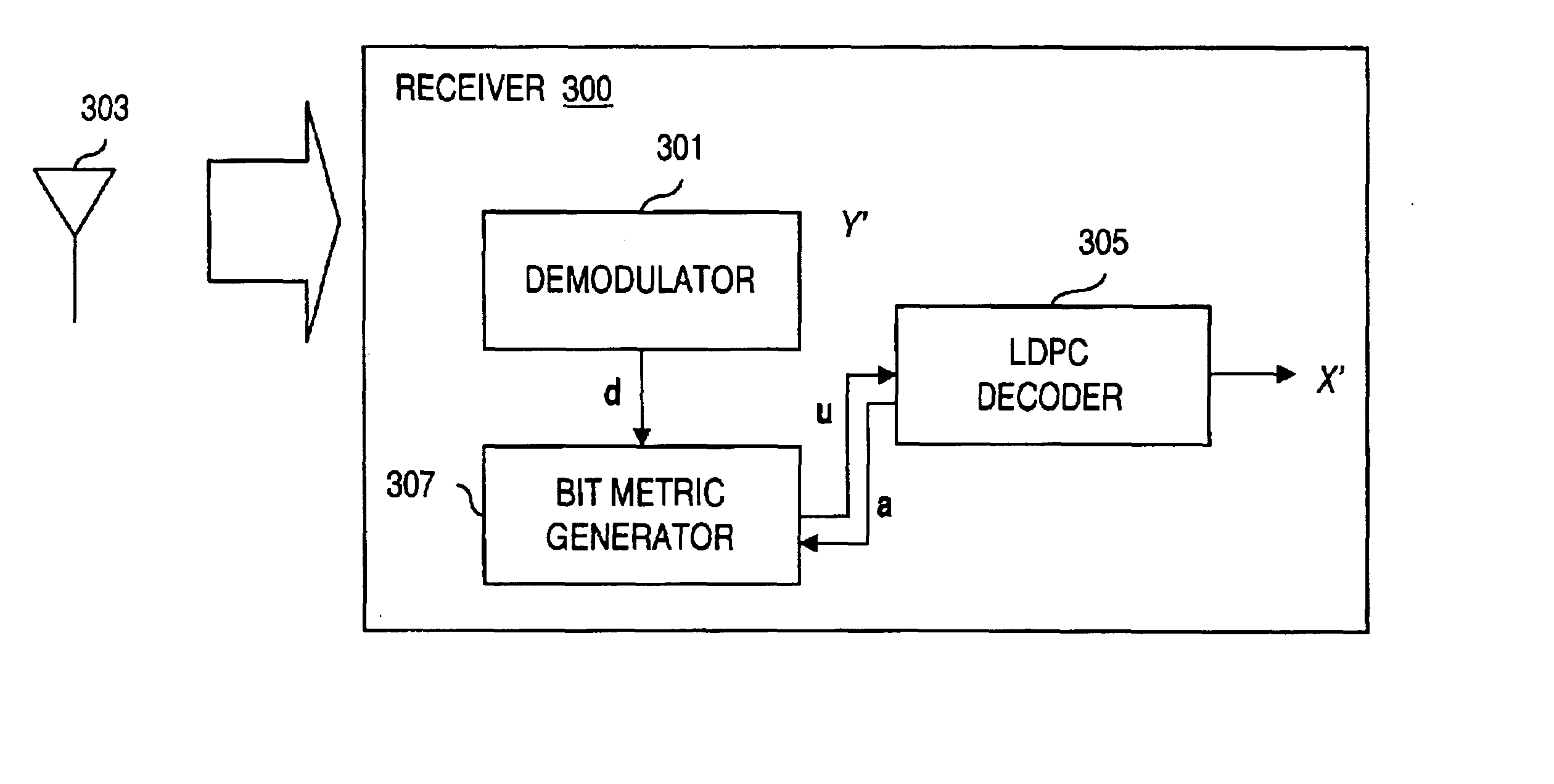

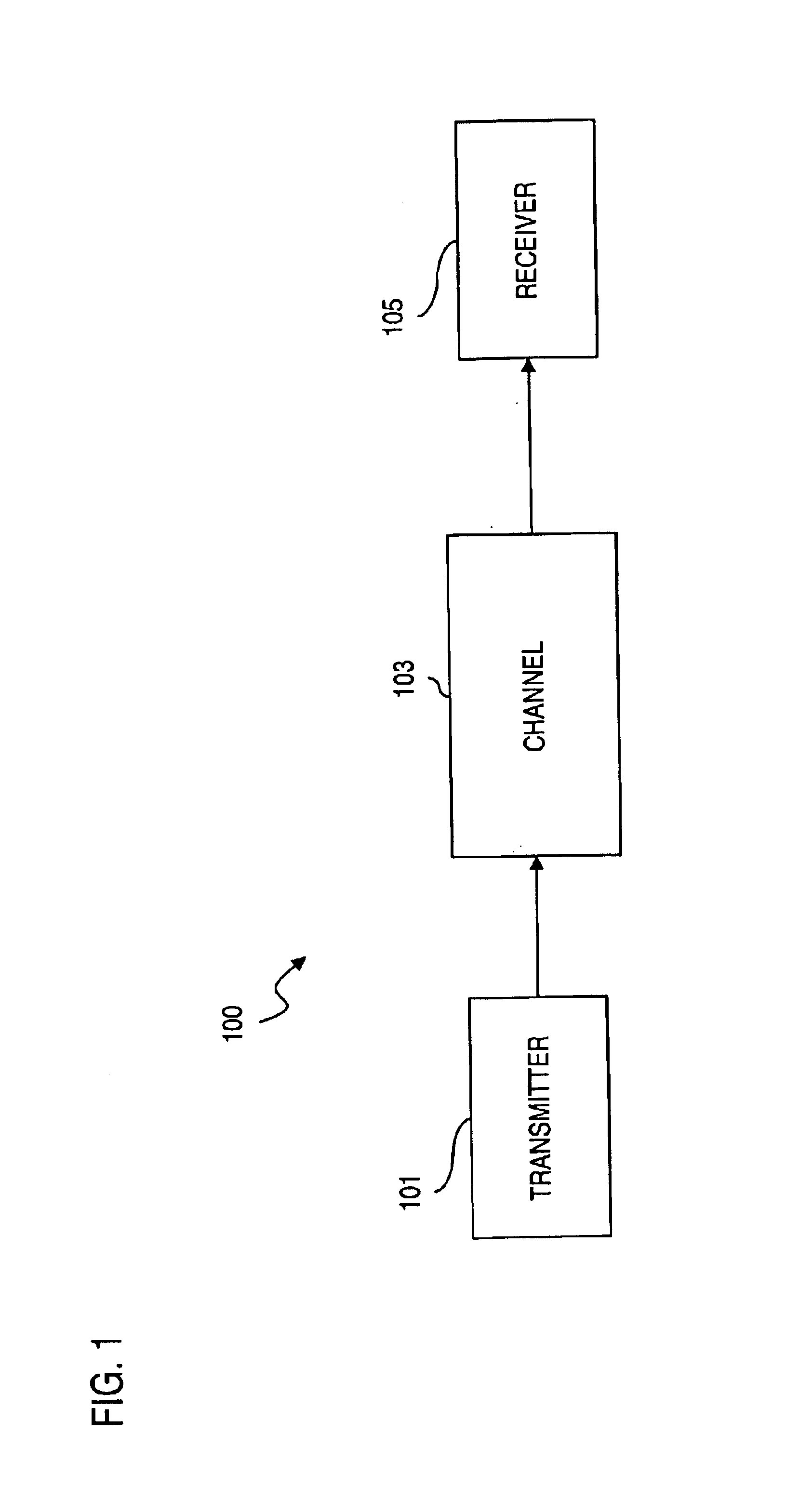

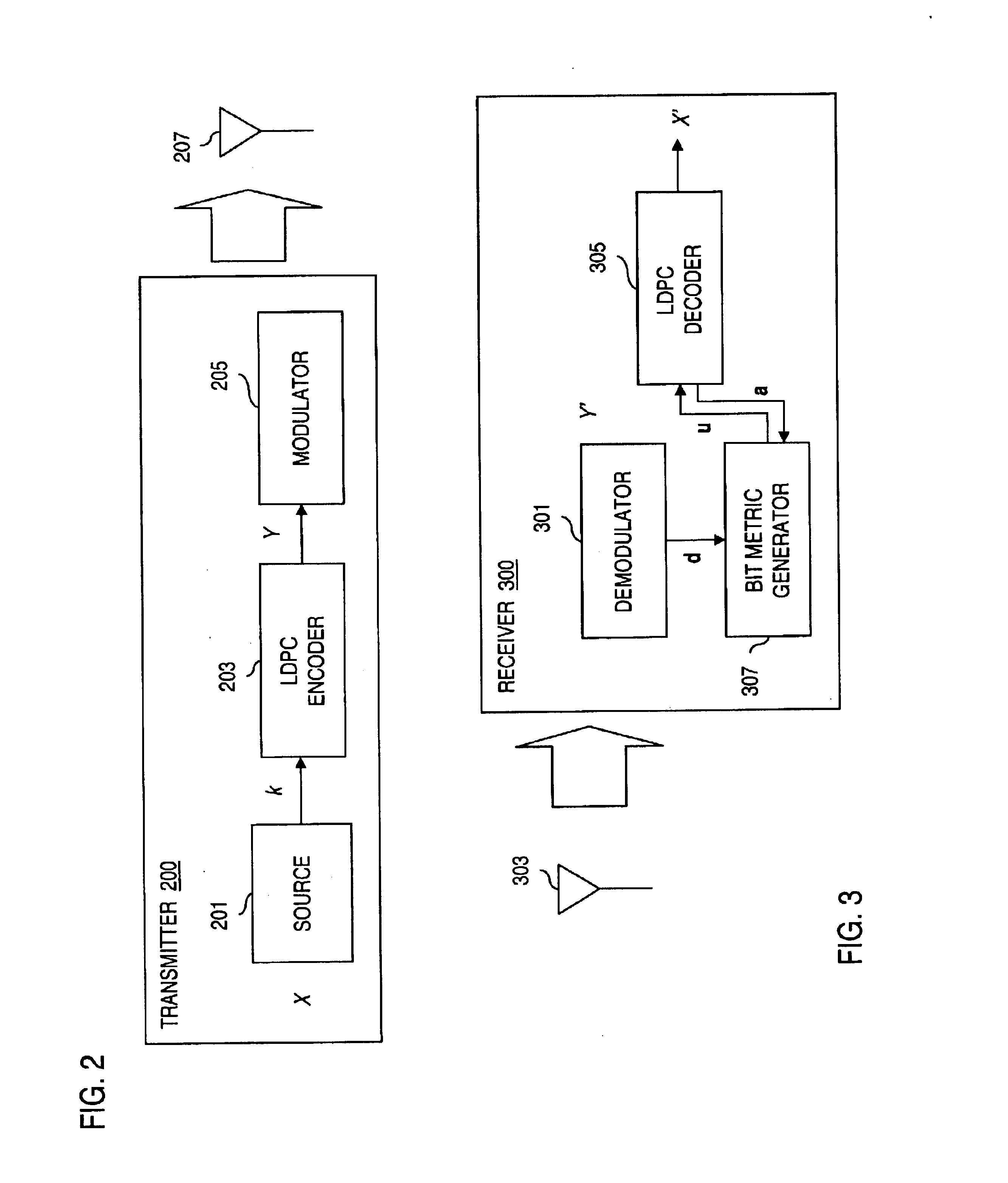

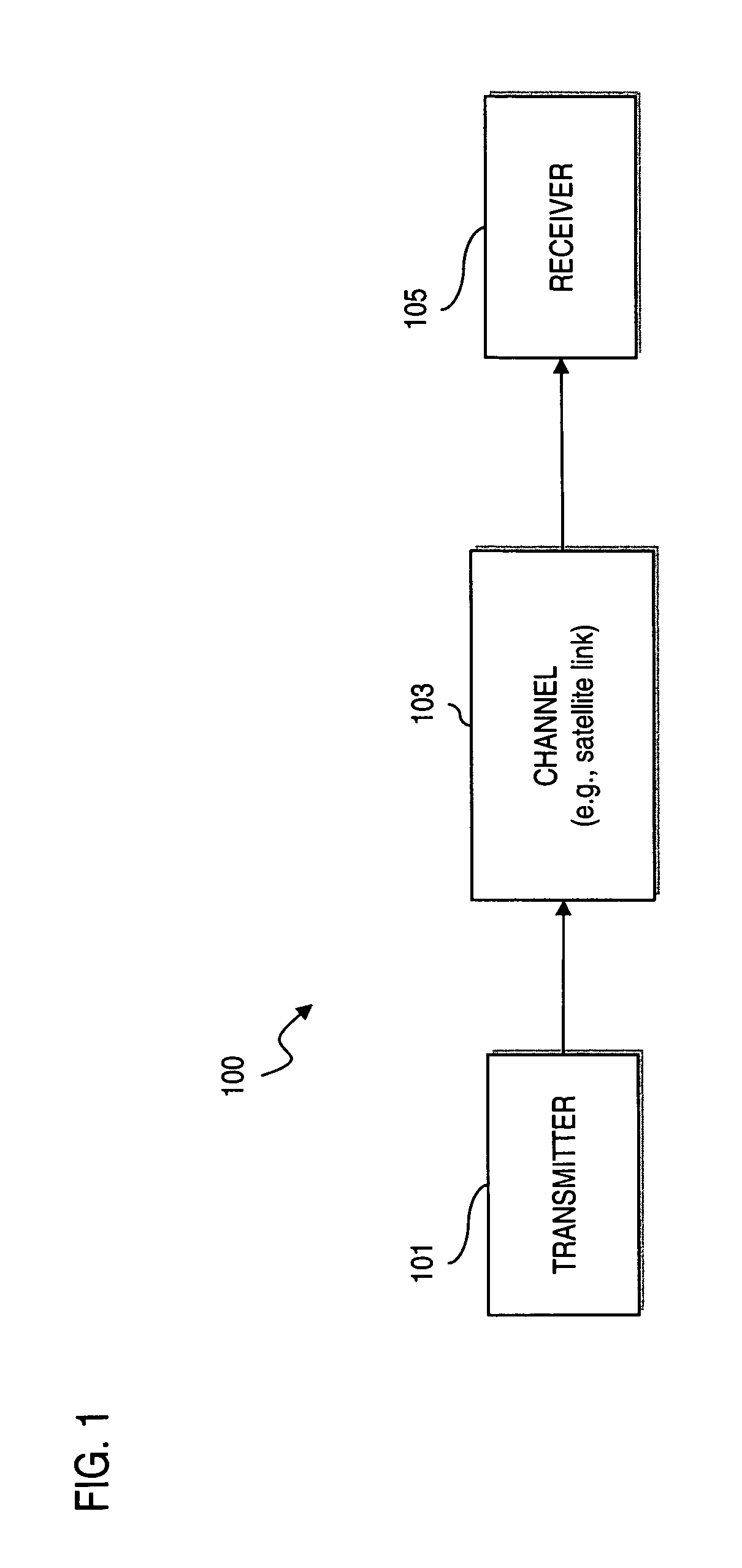

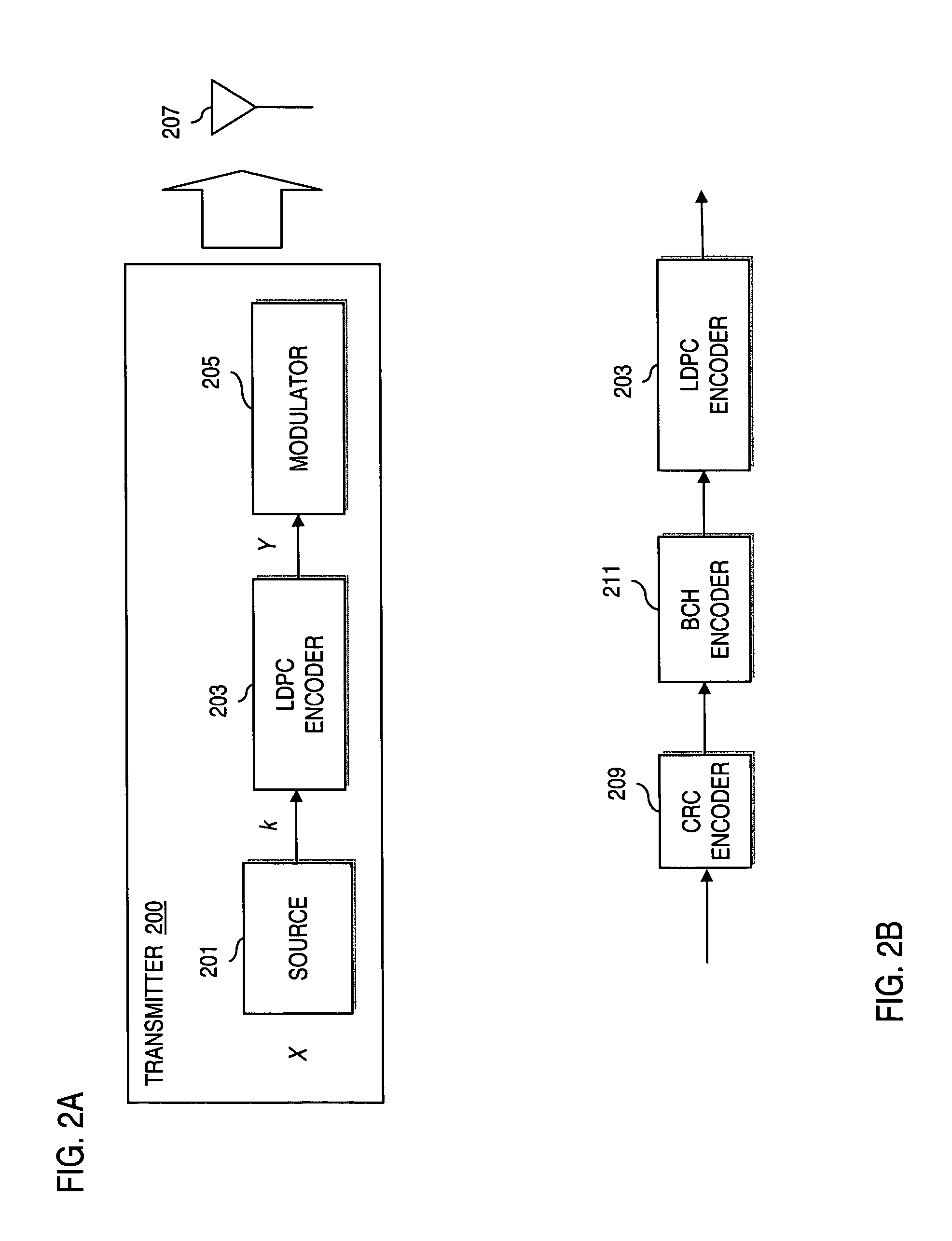

Method and system for decoding low density parity check (LDPC) codes

ActiveUS7020829B2Simplify the communication processSatellite broadcast receivingError correction/detection using LDPC codesCommunications systemParity-check matrix

An approach is provided for transmitting messages using low density parity check (LDPC) codes. Input messages are encoded according to a structured parity check matrix that imposes restrictions on a sub-matrix of the parity check matrix to generate LDPC codes. The LDPC codes are transmitted over a radio communication system (e.g., satellite network), wherein a receiver communicating over the radio communication system is configured to iteratively decode the received LDPC codes according to a signal constellation associated with the LDPC codes. The receiver is configured to iteratively regenerating signal constellation bit metrics after one or more decoding iterations.

Owner:DTVG LICENSING INC

Customizable robotic system

ActiveUS8994776B2Easy to reconfigureSimplify the communication processProgramme-controlled manipulatorCharacter and pattern recognitionThird partyRobotic systems

Owner:CROSSWING INC

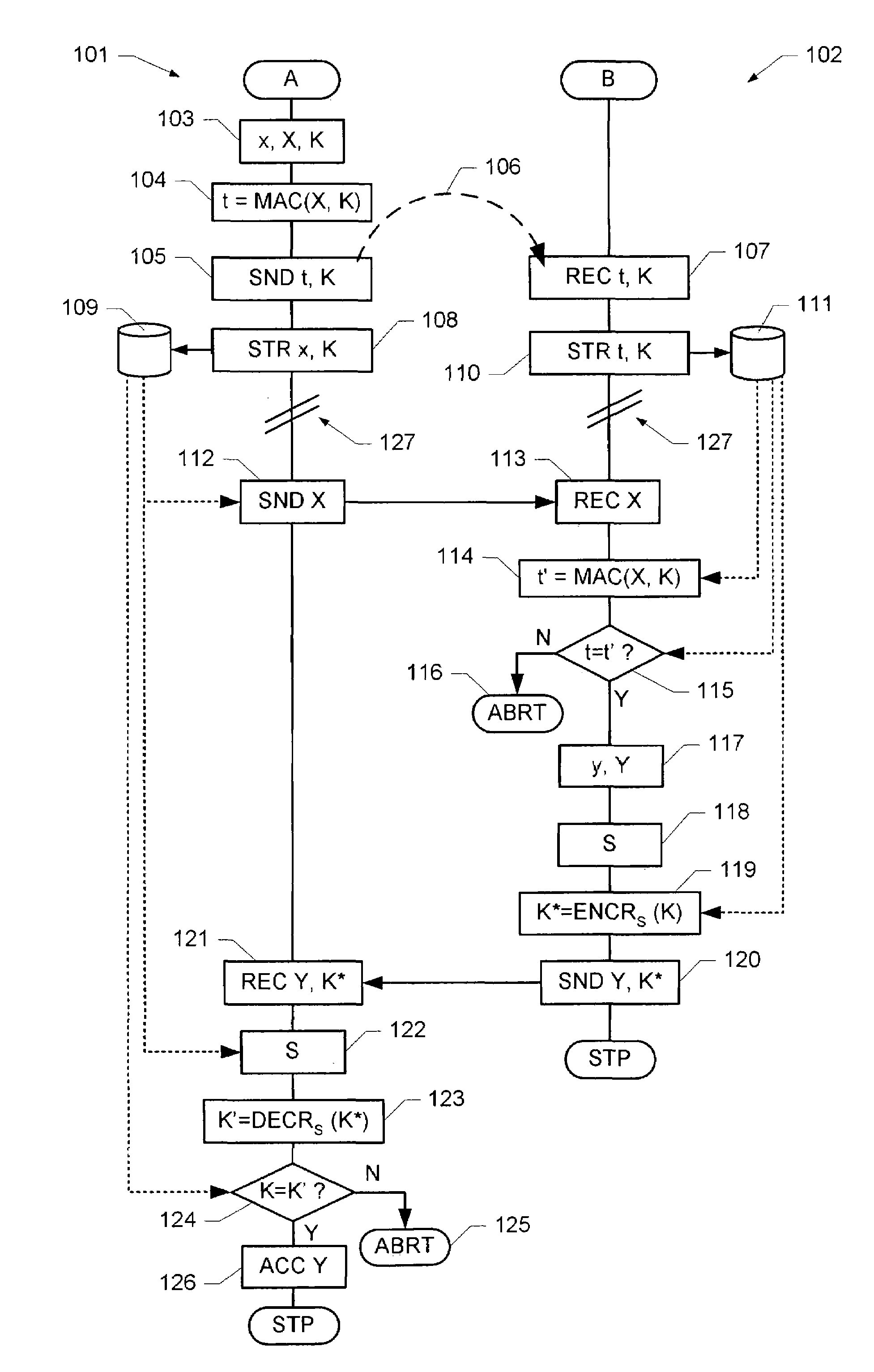

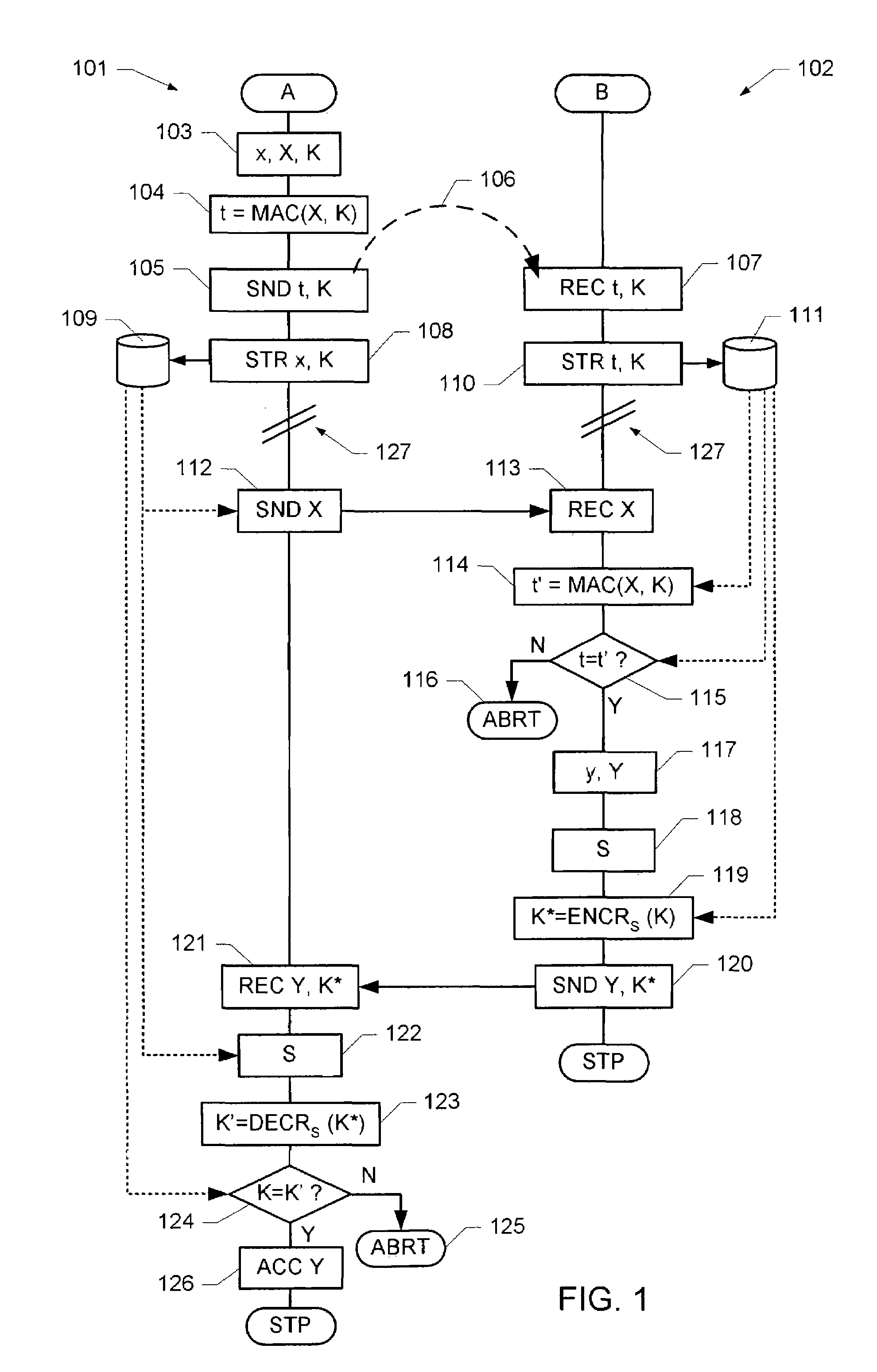

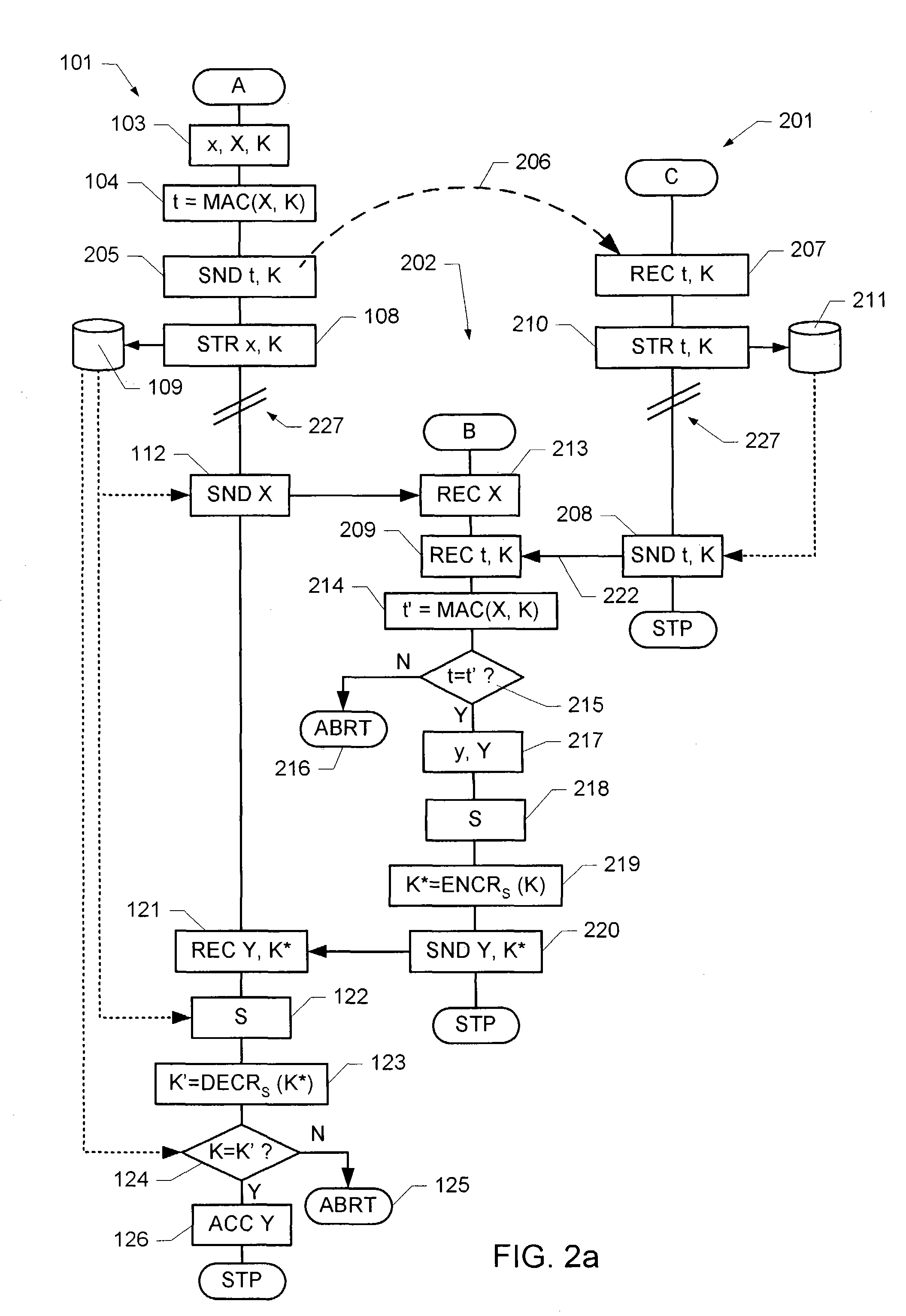

Secure communications

ActiveUS7284127B2High safetyHigh level of securityKey distribution for secure communicationPublic key for secure communicationSecure communicationComputer security

A method of providing secure communications between a first and a second communications unit comprising a key exchange between the communications units resulting in a shared secret key, the key exchange including a user interaction. The method includes the steps of providing, at least partly by means of a user interaction, a passcode to the first and second communications units; generating a first contribution to the shared secret key by the first communications unit and a second contribution to the shared secret key by the second communications unit, and transmitting each generated contribution to the corresponding other communications unit; authenticating the transmitted first and second contributions by the corresponding receiving communications unit based on at least the passcode; and establishing said shared secret key by each of the communications units from at least the corresponding received first or second contribution, only if the corresponding received contribution is authenticated successfully.

Owner:TELEFON AB LM ERICSSON (PUBL)

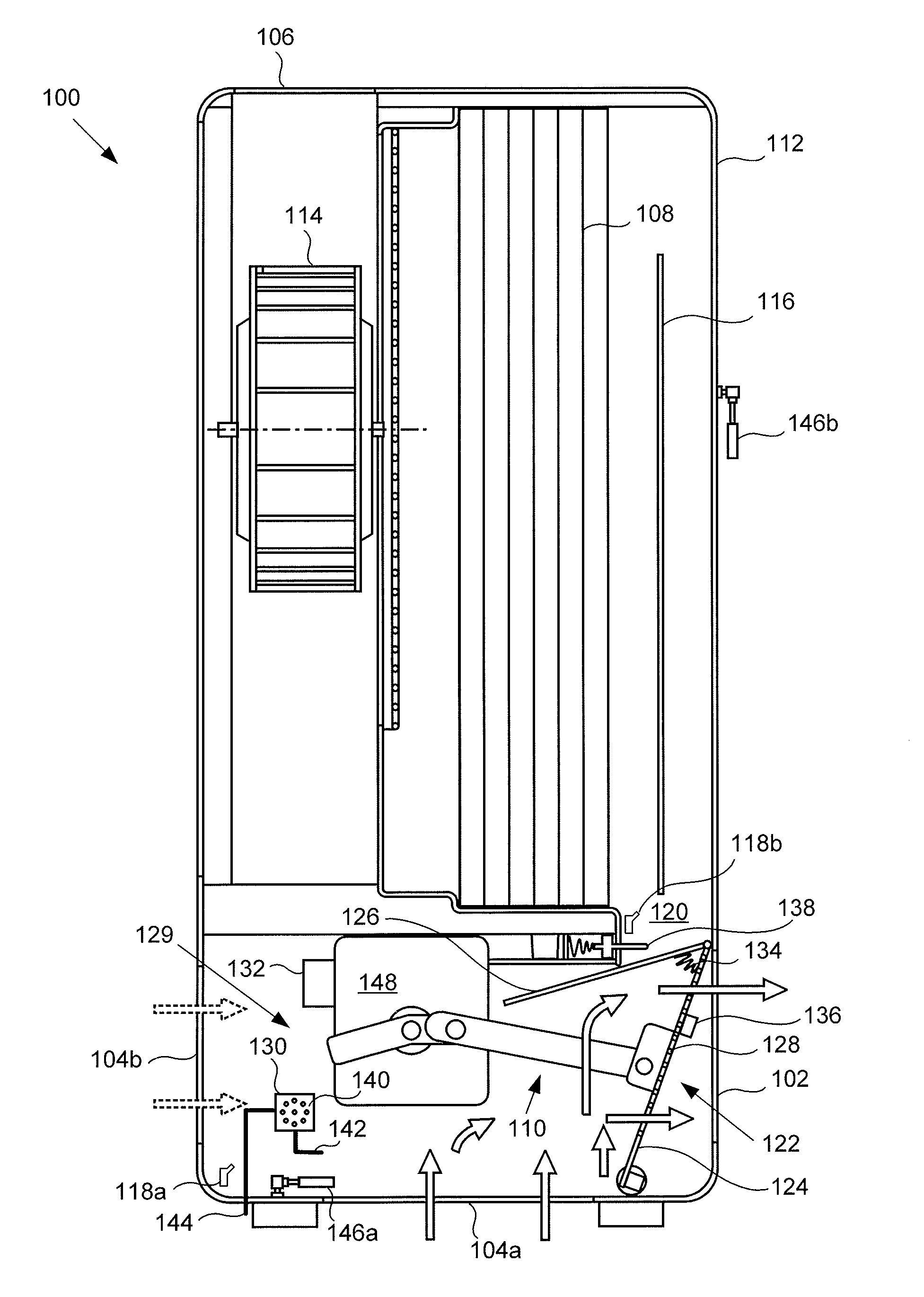

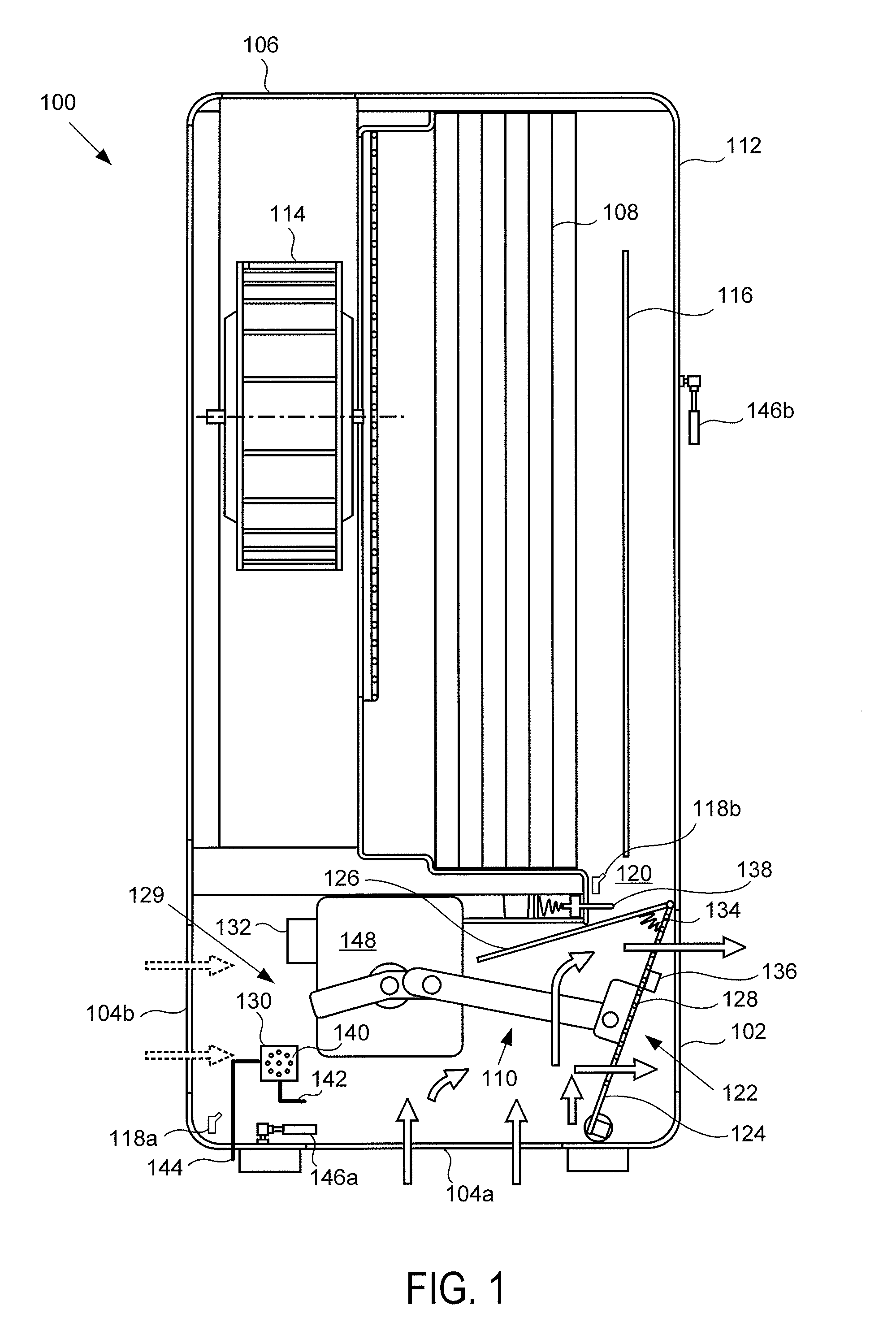

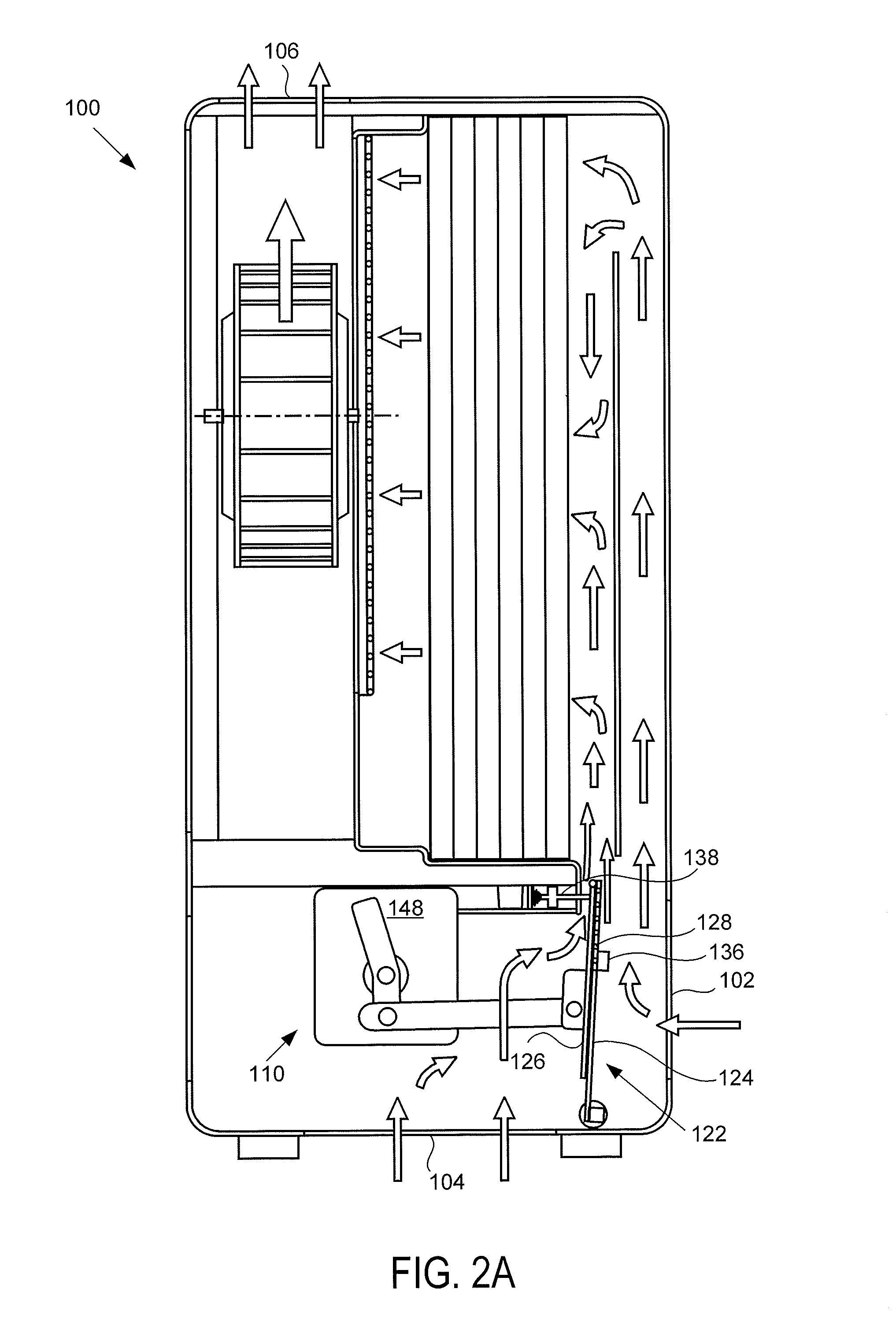

Room Air Purifier With Pressurization Relief

ActiveUS20150075373A1Extend filter lifeReduce pressureCombination devicesMechanical apparatusRoom air cleanersAir purifiers

Systems and methods are provided for an air purifier with over pressurization relief, including the following components. A room air inlet is configured to fluidly receive air from a room. A supply duct inlet is configured to fluidly receive air from a forced air system. An air filter and or air purification means is configured to filter / purify air. An outlet is configured to expel filtered / treated air into the room. A bypass damper system has at least one air filtering mode position and a bypass mode position. A pressure control mechanism is configured to automatically allow the bypass damper system to move from at least one air filtering mode position to a bypass mode position when the air received from the supply duct inlet exceeds a bypass threshold. The bypass mode position guides air from the supply duct inlet into the room without requiring passage through the filter and the outlet.

Owner:MILLER GREGORY R

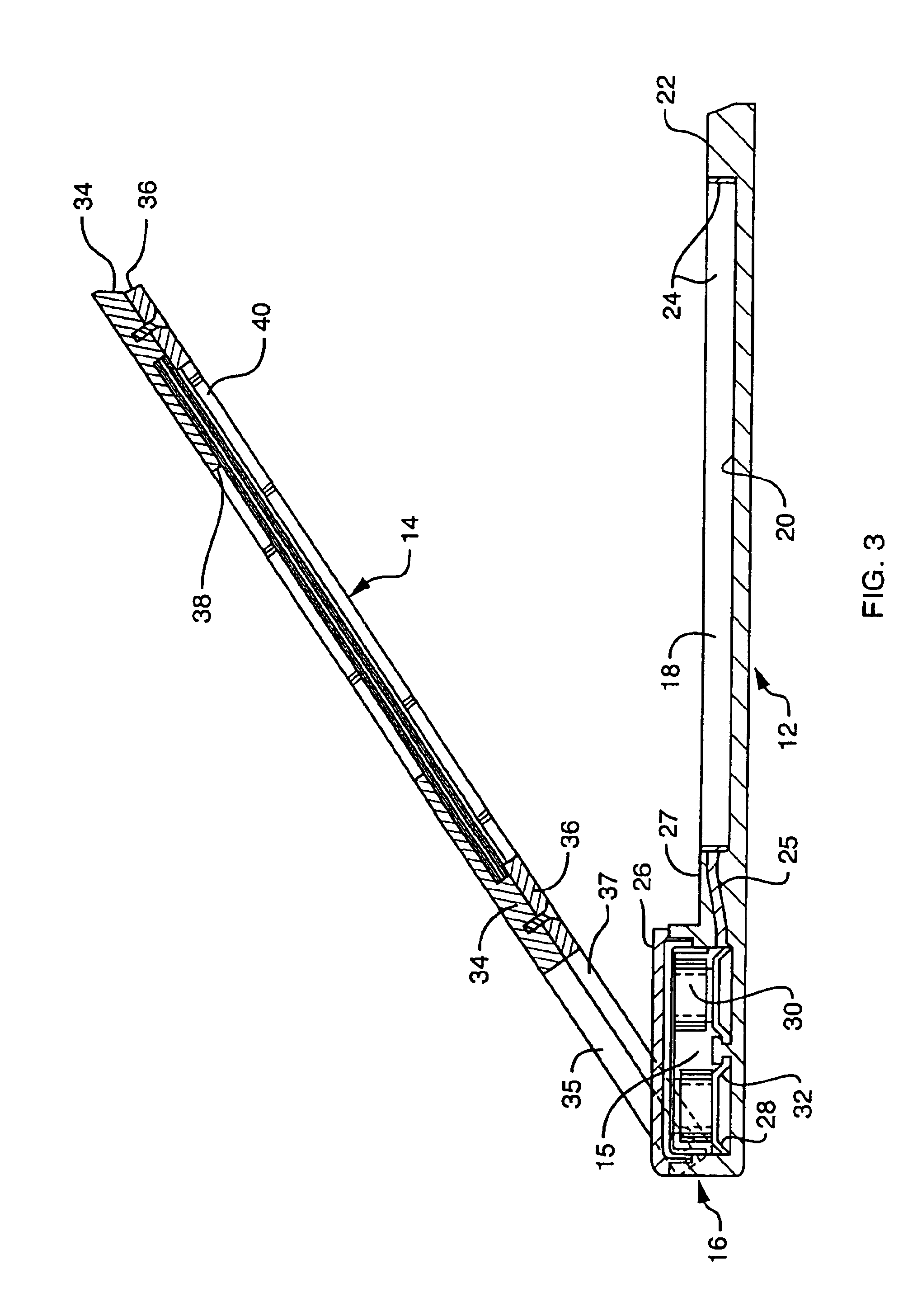

Transaction tray with communications means

InactiveUS6850767B1Simplify the communication processDigital data processing detailsLighting elementsWired communicationComputer science

A transaction tray comprises a surface having a first writing portion, a display screen and communications means for receiving information to be displayed on the display screen, wherein the information which is received by the communications means is received from a source remote from said apparatus. The communications means may be a wireless communications means, a two-way communications means or a hard wired communications means. Further, a transaction tray comprises a tray portion and a hinged lid portion, lighting means associated with the tray portion, a first transparent window is provided in the outer surface of the lid and a second transparent window in the inner surface. A first translucent advertising substrate is displayed in the first window and a second translucent advertising substrate is displayed in the second window. Communications means is provided to receive information to be displayed on the first and second translucent advertising substrates, wherein said information is received by said communications means from a source remote from said transaction tray.

Owner:MAXYMYCH PETER NICHOLAS

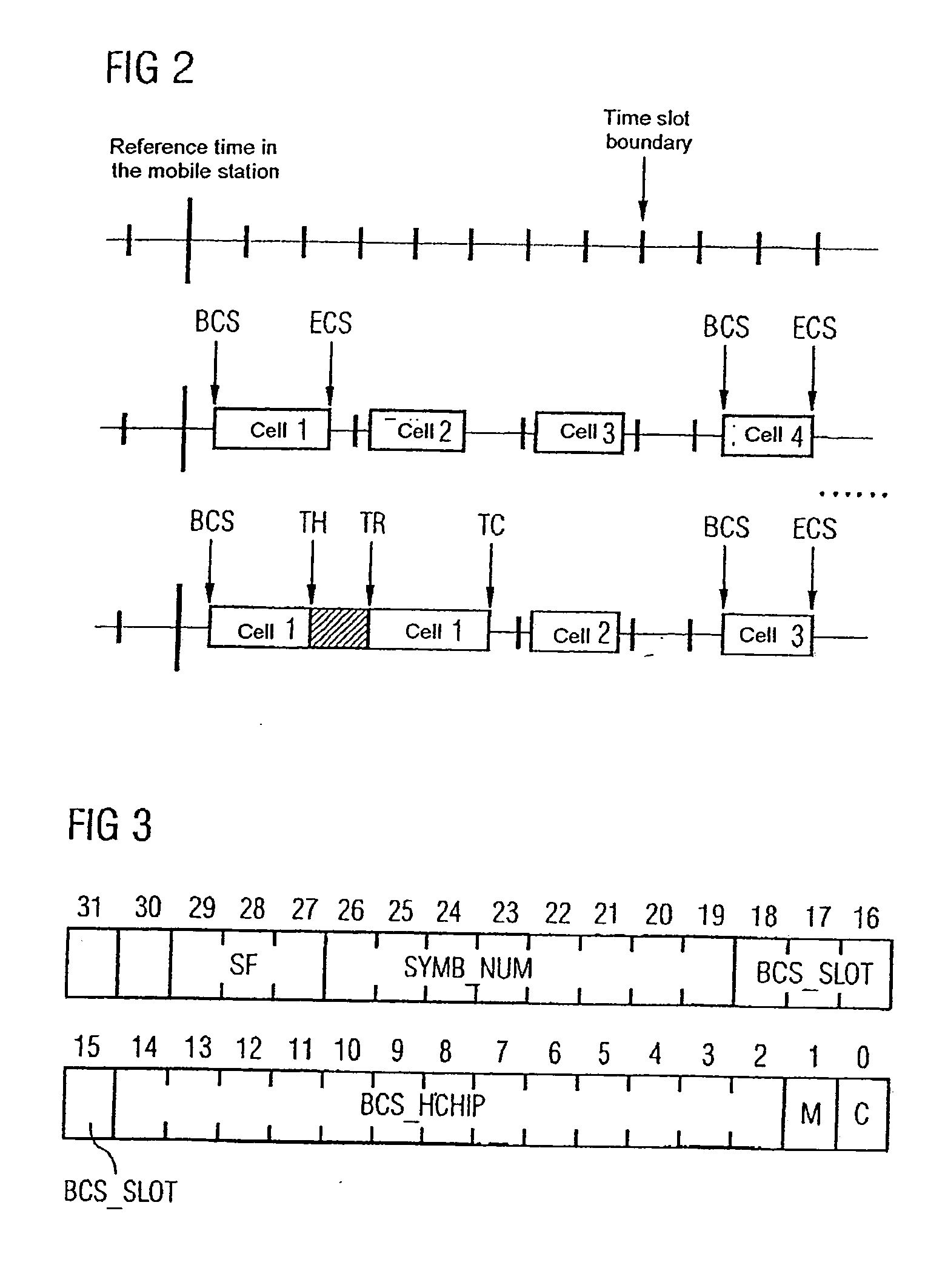

Apparatus and method for time control of the processing of a radio signal in a mobile station

InactiveUS20050008040A1High degree of flexibilitySimplify communicationTime-division multiplexSubstation equipmentTime frameTime control

Owner:INTEL CORP

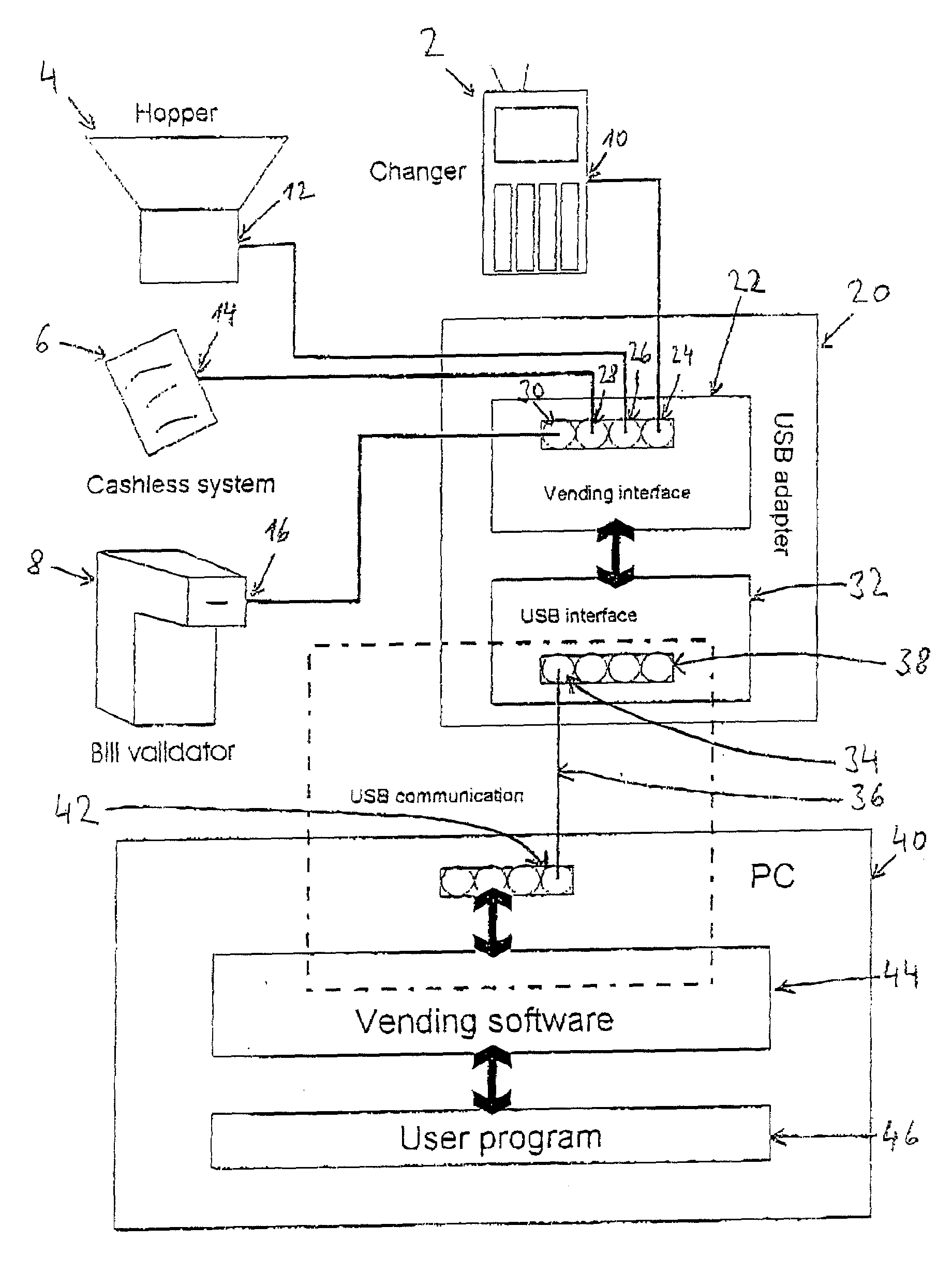

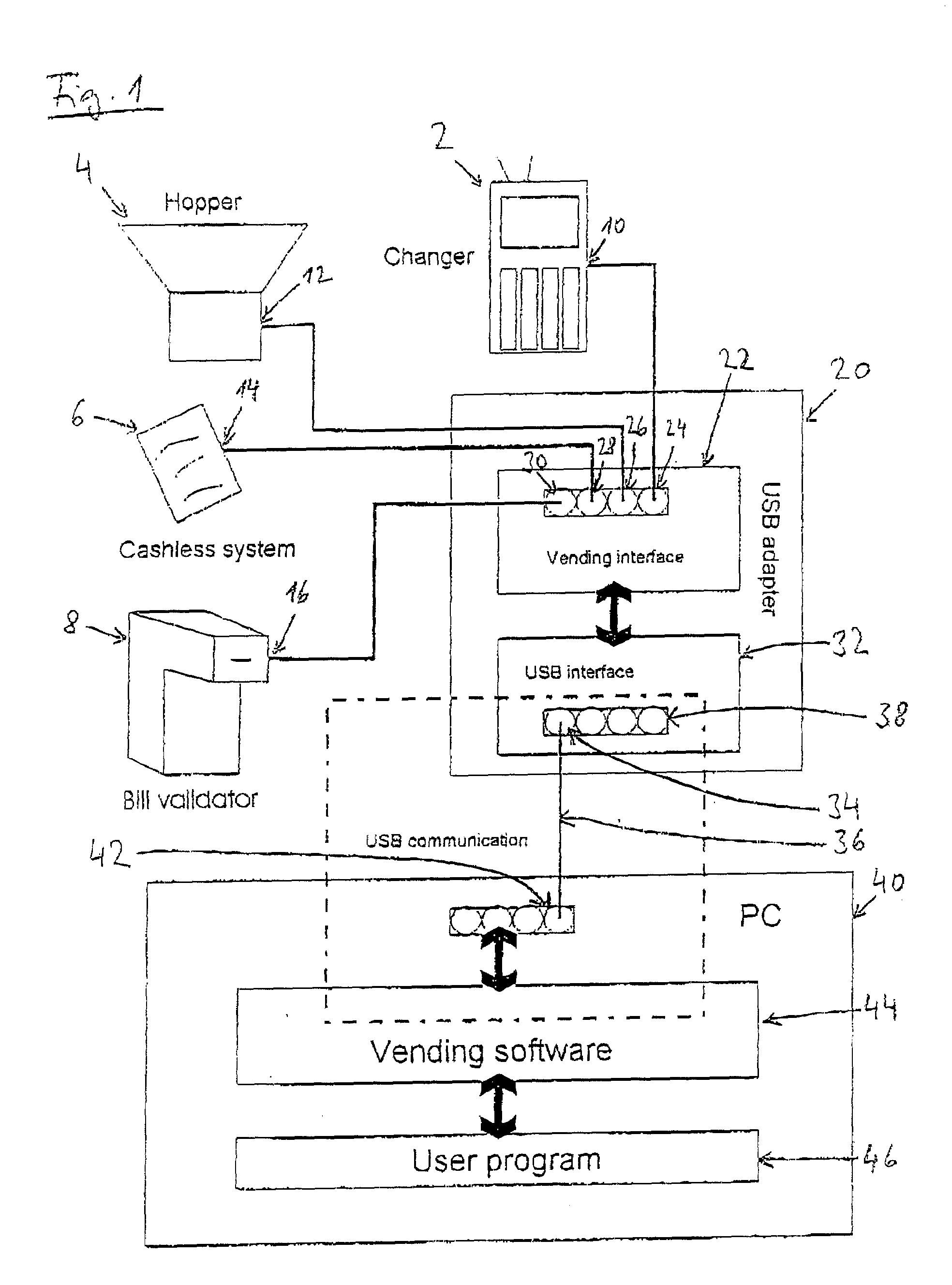

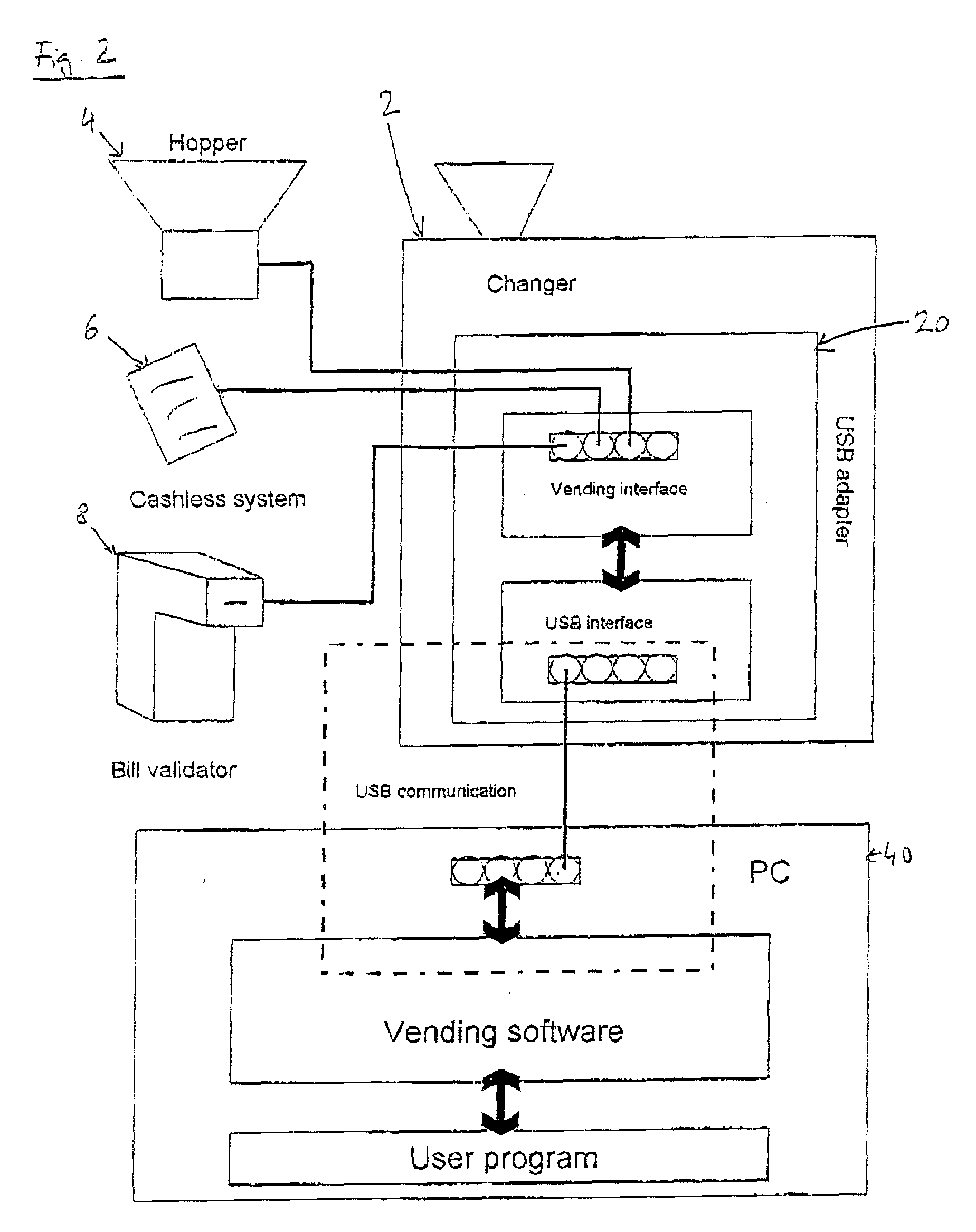

Payment system for a vending machine

InactiveUS20070227856A1Improve performanceGood priceControlling coin-freed apparatusCoin-freed apparatus detailsCard readerEmbedded system

Payment system for a vending machine with at least one money handling unit, for example a coin validator / money changer, bank note validator, card reader, hopper or the like, a PC, a single adaptor, which comprises a PC interface via which it may be connected to the PC, and which comprises a plurality of vending machine interfaces for different standards via which it may be connected to the money handing units, and PC software via which the money handling units are controlled.

Owner:NAT REJECTORS

Container for Receiving Articles

ActiveUS20120211397A1Avoid interferenceSimplify the communication processMemory record carrier reading problemsOther accessoriesEngineeringMechanical engineering

The invention provides a container (10) comprising a, a receiving compartment (18) for receiving articles (12) each provided with an RFID transponder (14), a shielding (16) for shielding of the receiving compartment (18), and an RFID antenna device (20) located in the receiving compartment (18) for communication with the transponders (14). Reliable identification of articles (12) located in the container (10) can thus be simplified considerably.

Owner:KILIAN DIETER

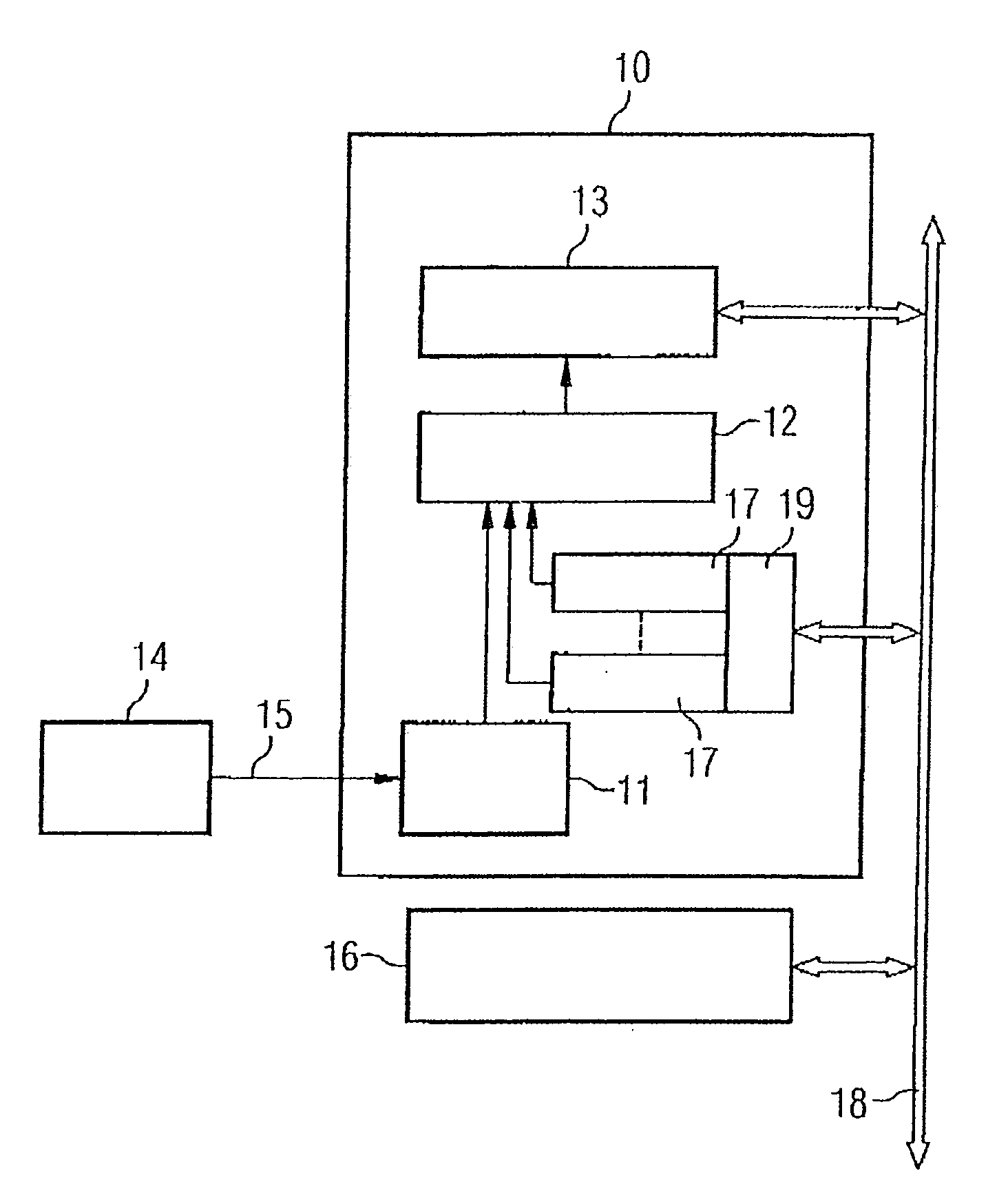

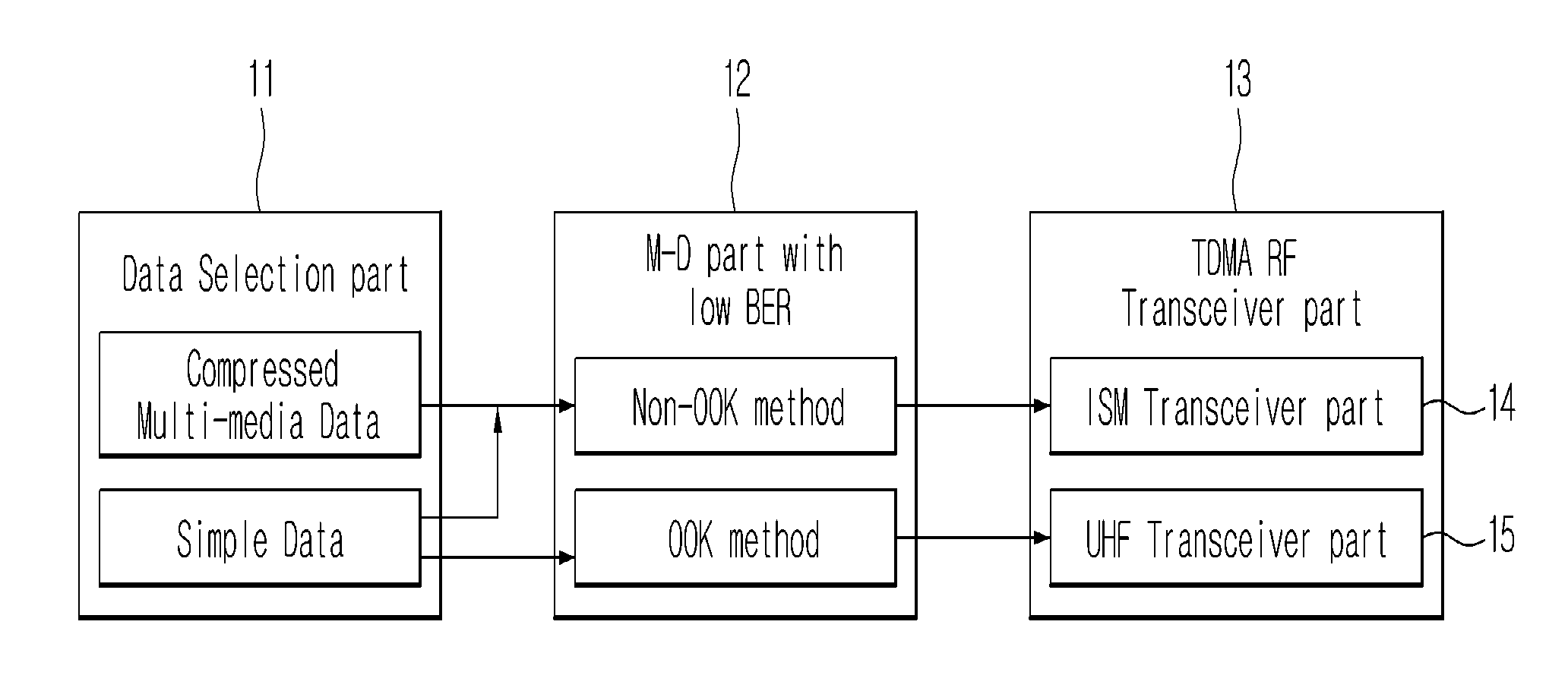

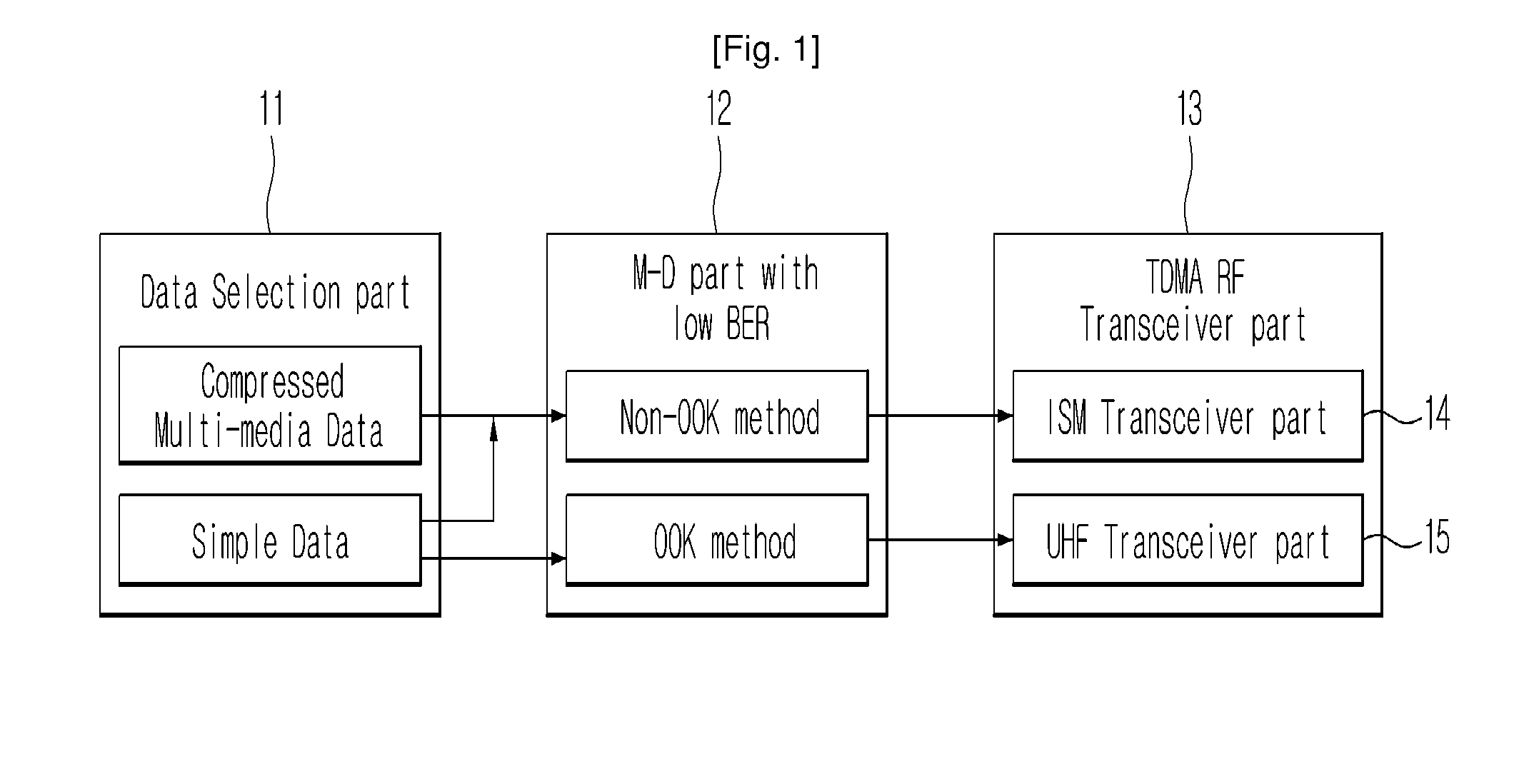

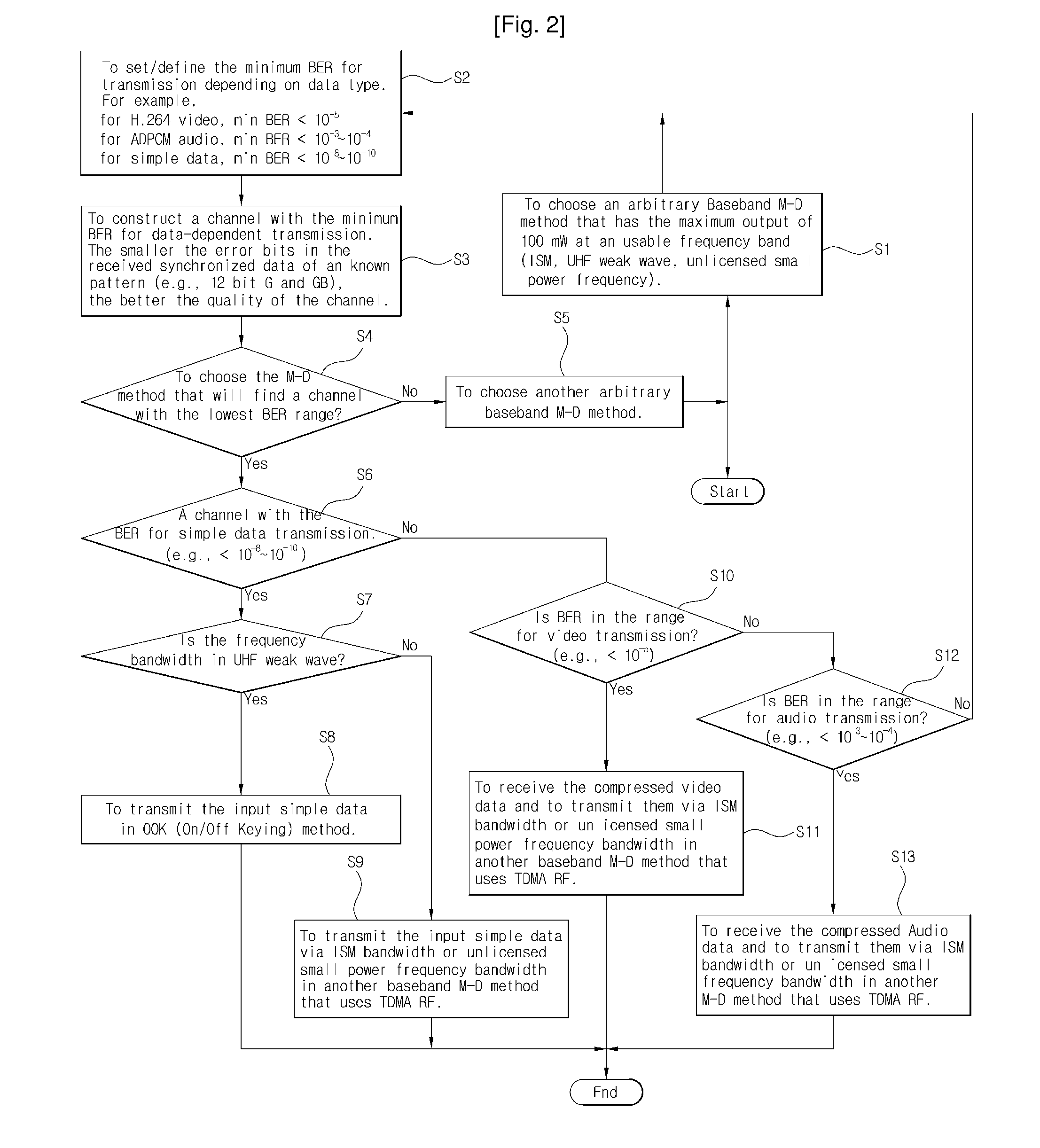

Wireless Robust Modulation-Demodulation Communication Methode & Device And Rear Viewing Device For Vehicle

InactiveUS20120155549A1Low error rateLower production costColor television with pulse code modulationPulse modulation television signal transmissionISM bandWave band

The invention concerns a wireless communication device making use of a robust wireless communication method (RWCM), and its application on a rear view monitoring system. More specifically, a robust wireless communication device (RWCD) consists of a Data Selection part (11), a Modulation-Demodulation (M-D) part (12) and a TDMA RF Transceiver part (13) that is made up of an ISM Transceiver part (14) and an UHF Transceiver part (15). The Data Selection part (11) sorts the input data into simple or multimedia data, and sends them to the M-D part (12). The simple data are separated into two types: data that do not use multi-media or UHF wave band, and data that do use the UHF band. The M-D method for the former does not include the OOK (On / Off Keying) process which does get used for the latter. In the ISM Transceiver part (14), the non-UHF band simple data and multi-media data are communicated via ISM band or free small-power frequency range. The UHF Transceiver part (15) transmits and receives the simple data that use the UHF band.

Owner:OH JUNE SOO

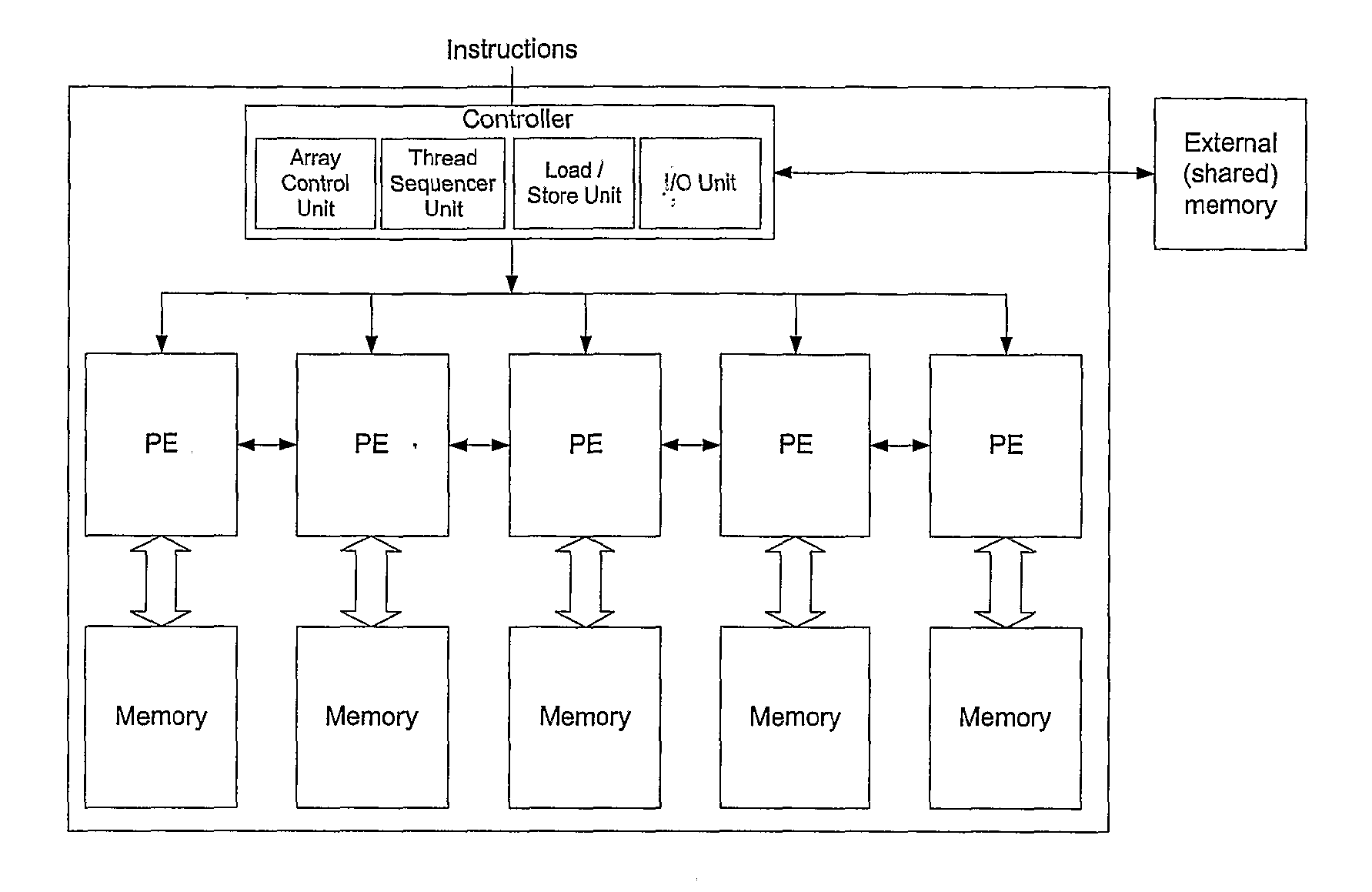

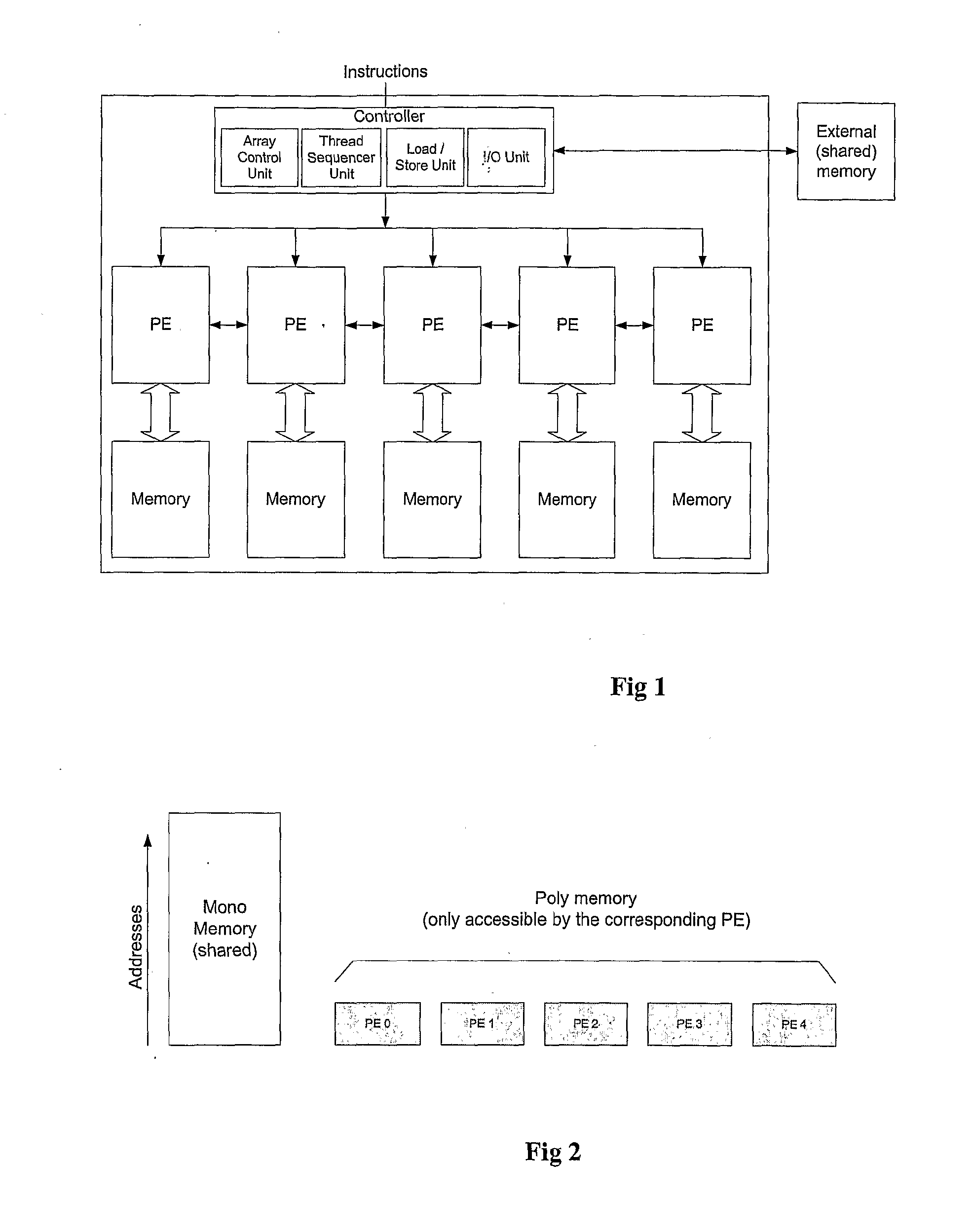

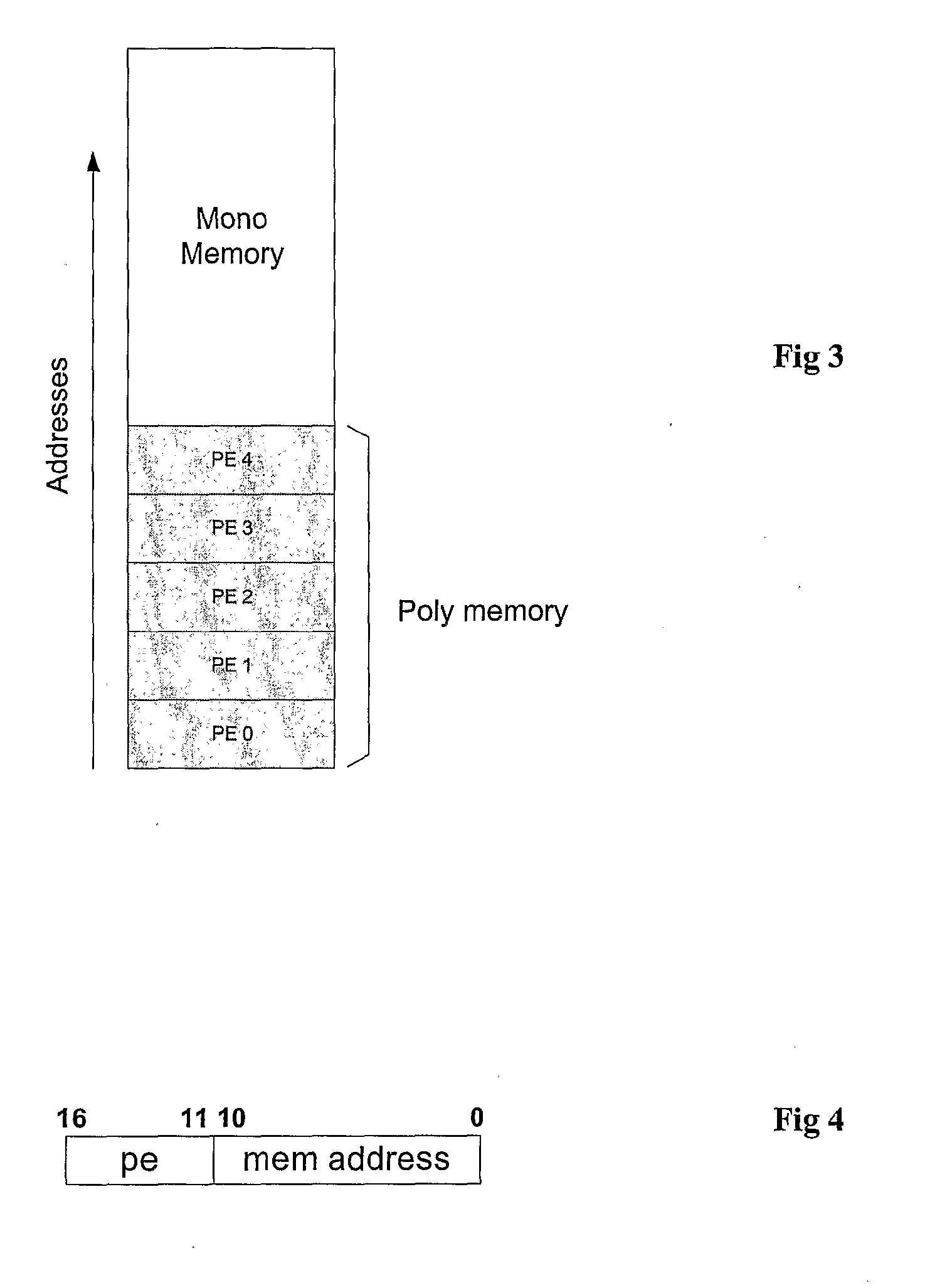

Processor memory system

InactiveUS20090164752A1Simple processRaise the potentialMemory architecture accessing/allocationSingle instruction multiple data multiprocessorsControl signalNetwork connection

A data processor comprises a plurality of processing elements (PEs), with memory local to at least one of the processing elements, and a data packet-switched network interconnecting the processing elements and the memory to enable any of the PEs to access the memory. The network consists of nodes arranged linearly or in a grid, e.g., in a SIMD array, so as to connect the PEs and their local memories to a common controller. Transaction-enabled PEs and nodes set flags, which are maintained until the transaction is completed and signal status to the controller e.g., over a series of OR-gates. The processor performs memory accesses on data stored in the memory in response to control signals sent by the controller to the memory. The local memories share the same memory map or space. External memory may also be connected to the “end” nodes interfacing with the network, eg to provide cache. One or more further processors may similarly be connected to the network so that all the PE memories from all the processors share the same memory map or space. The packet-switched network supports multiple concurrent transfers between PEs and memory. Memory accesses include block and / or broadcast read and write operations, in which data can be replicated within the nodes and, according to the operation, written into the shared memory or into the local PE memory.

Owner:RAMBUS INC

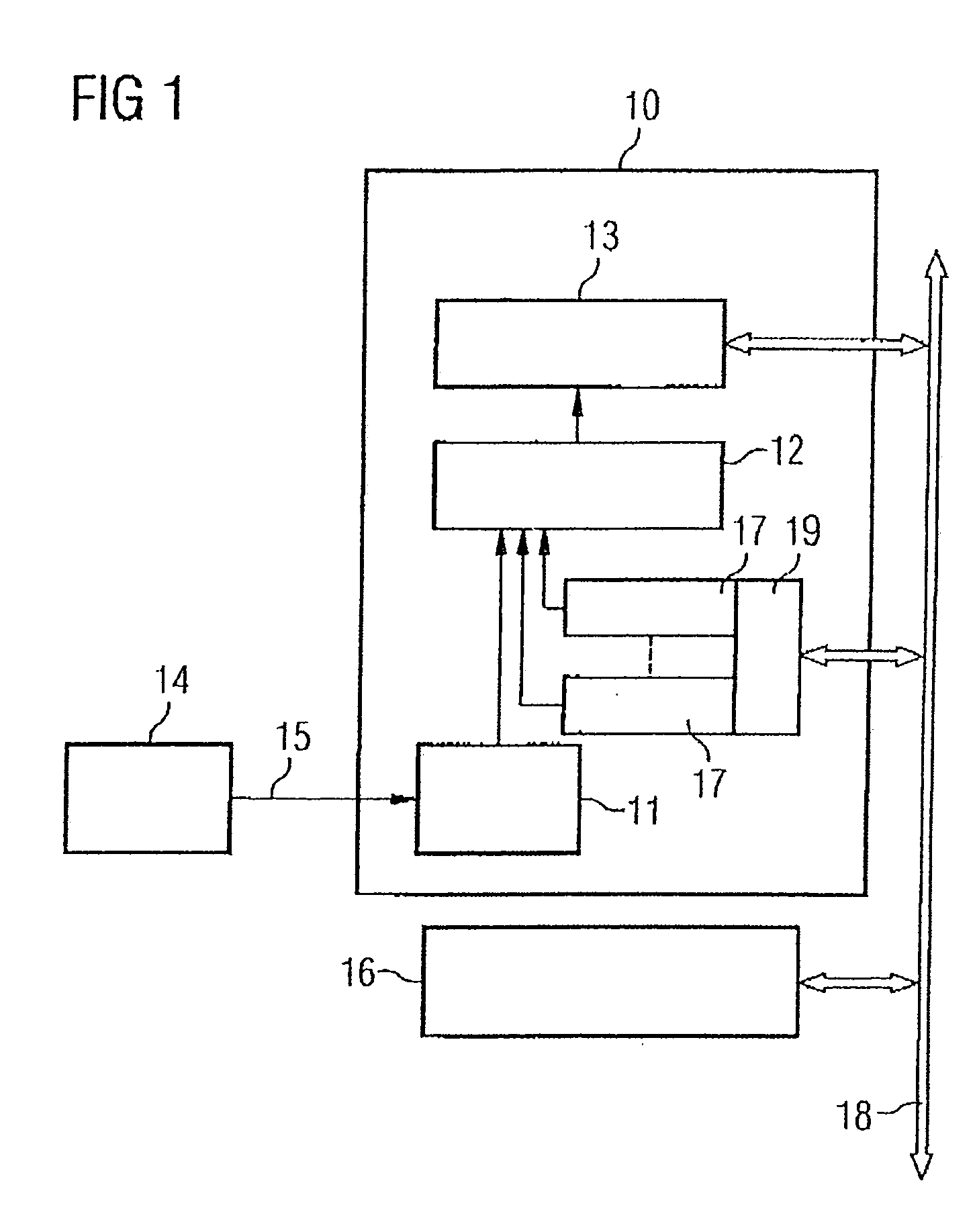

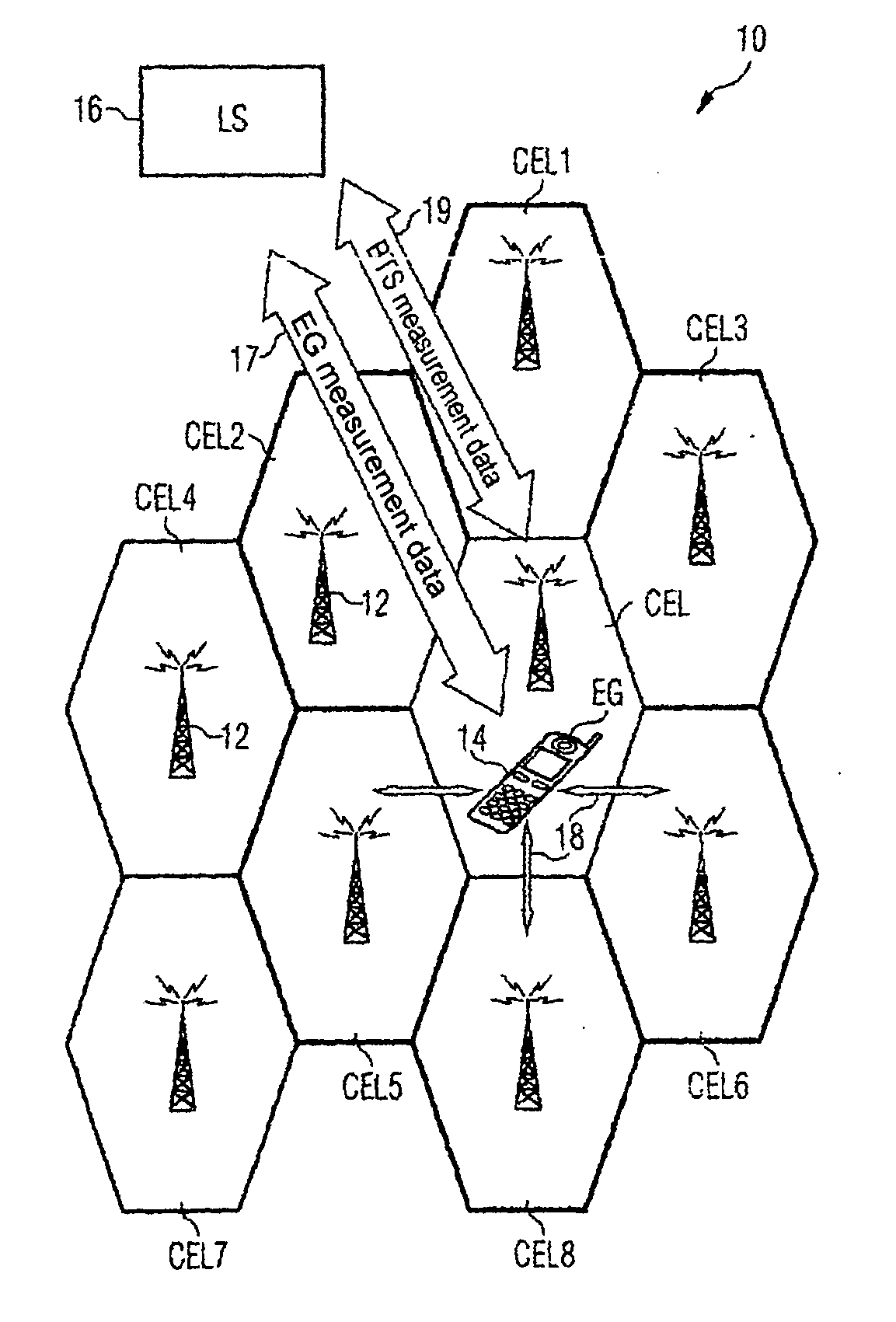

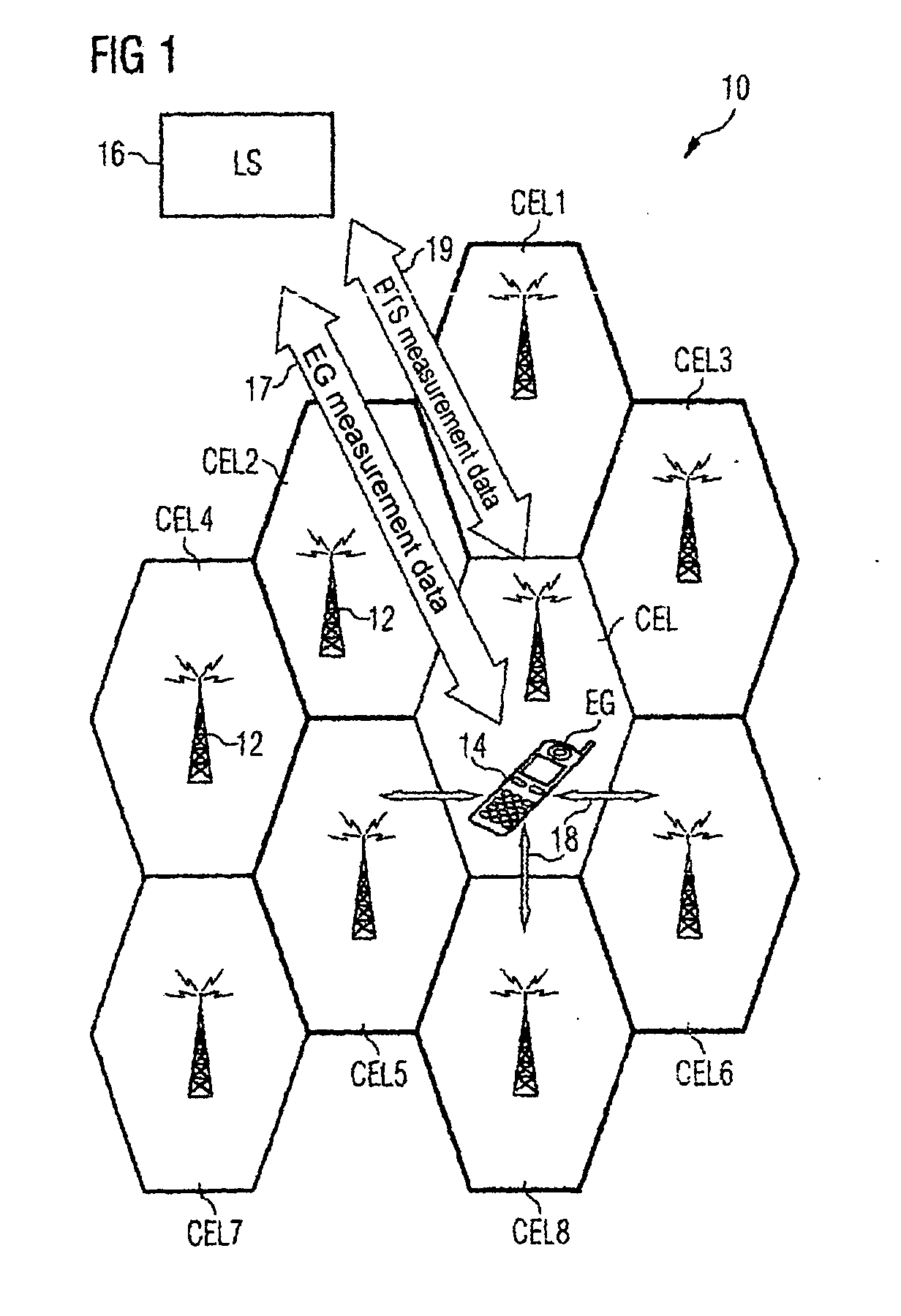

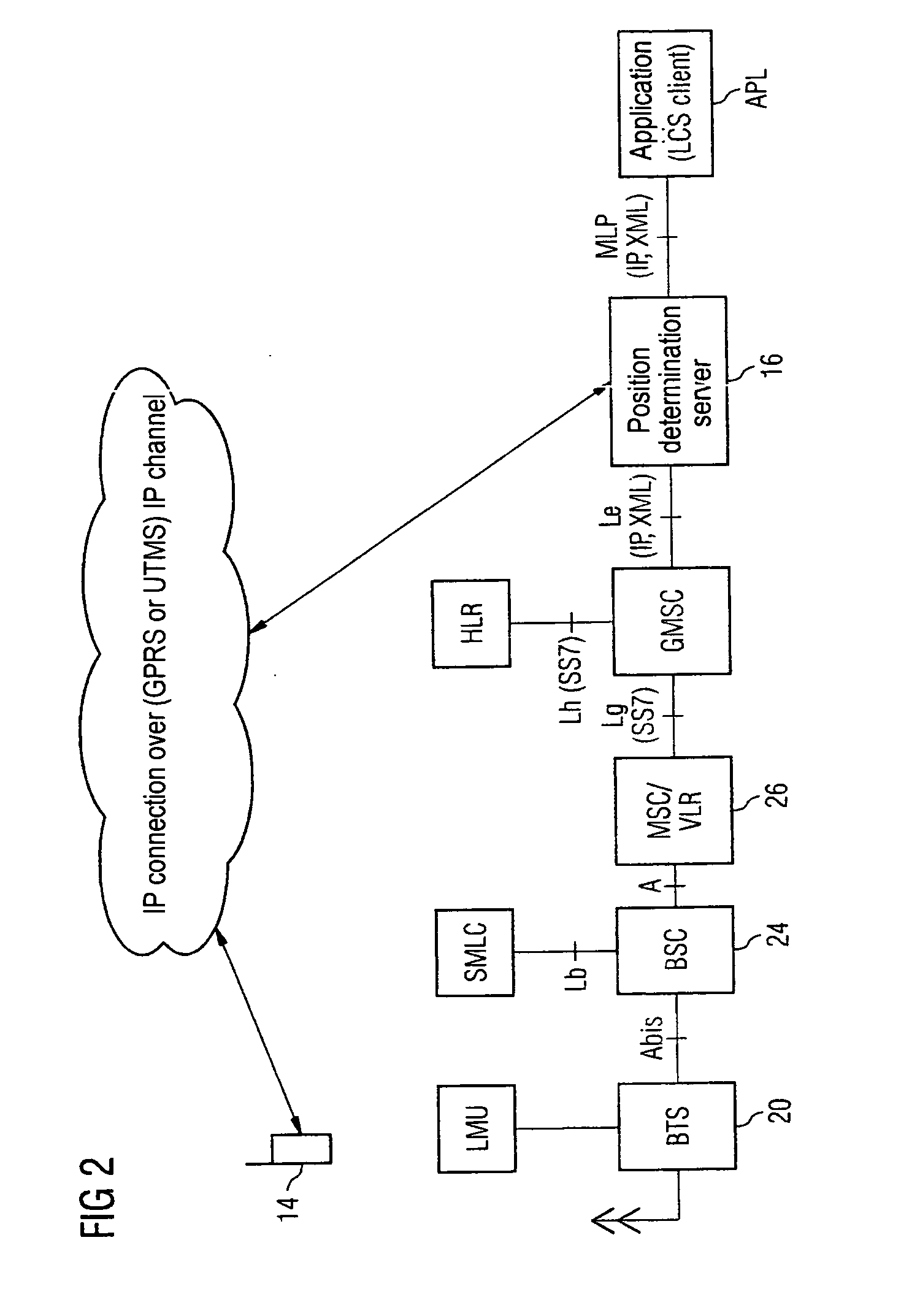

Method and device for determining the position of terminal in a cellular mobile radio network

InactiveUS20050192029A1Minimize the numberPrecise positioningRadio/inductive link selection arrangementsWireless communicationNetwork measurementData memory

Method for determining the position of a terminal (14) in a cellular mobile radio network (10). with network measurements being executed in the terminal (14) for selection of a service cell (CEL), with the following steps: transfer (S2) of a measurement data request message from a position determination server (16) to the terminal (14), reading out (S3) of measurement data determined by the network measurements from a measurement data memory (40) in the terminal (14) in response to the request message, transfer (S4) of a response message with the read out measurement data from the terminal (14) to the position determination server (16), calculation (S5) of the position of the terminal (14), based on the measurement data transferred, in the position determination server (16).

Owner:SIEMENS AG

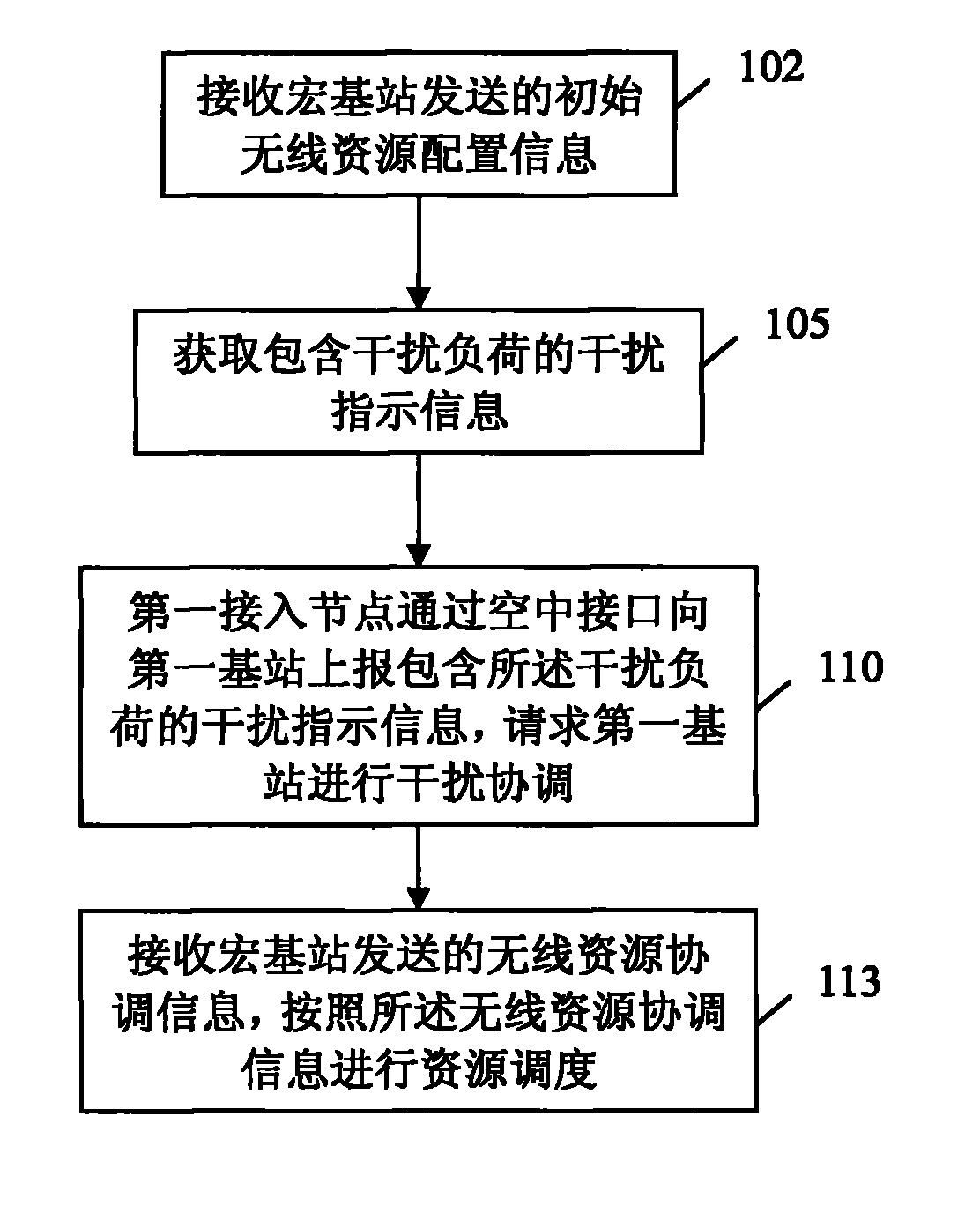

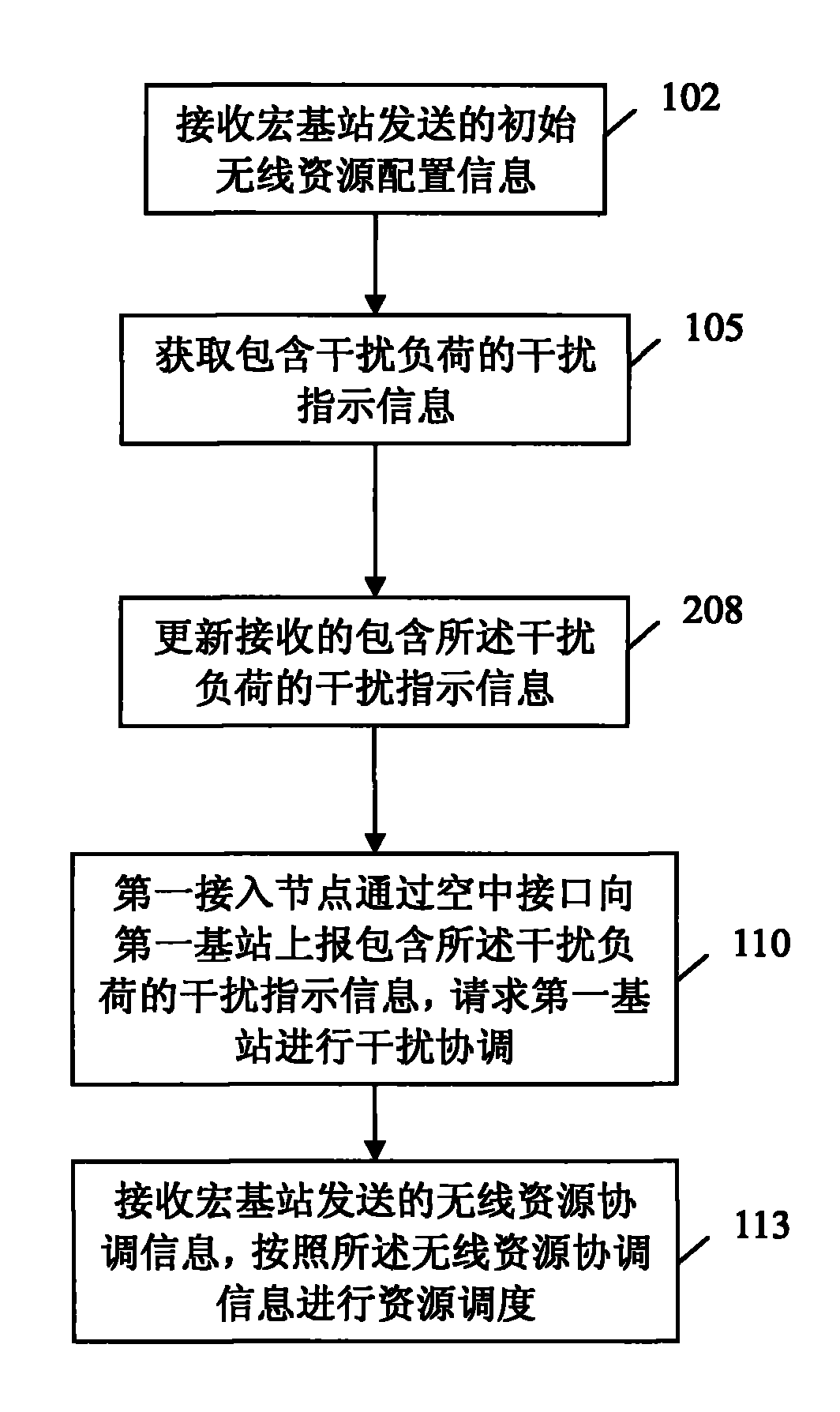

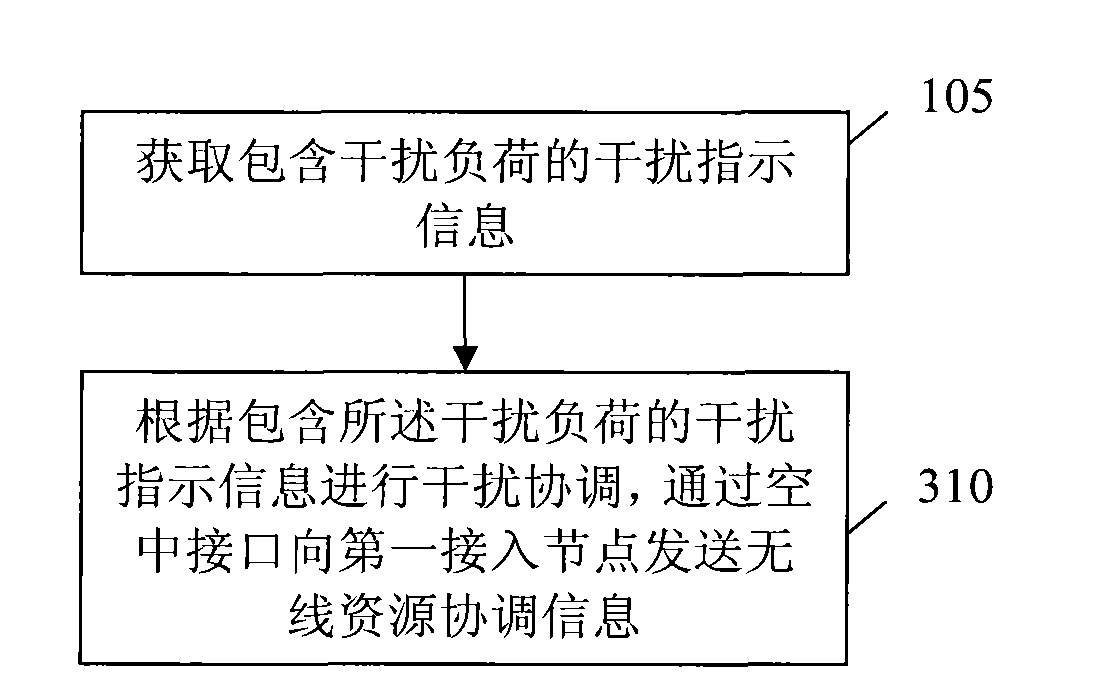

Coordination method of interference, equipment and system thereof

InactiveCN102202311ASimplify the communication processReduce time delayNetwork planningRemote radio headAir interface

The invention discloses a coordination method of interference, equipment and a system thereof. The method comprises the following steps: the interference indication information of an interference load is obtained; a first access node reports the interference indication information of the interference load to a first base station through an air interface and requests the first base station to carry out interference coordination, or the first base station carries out interference coordination according to interference indication information which comprises the interference load and sends wireless resource coordination information to the first access node through the air interface wherein the first access node comprises Relay NodeB, HeNB, PicoNodeB, Femto Cell or Remote Radio Head. According to the invention, the communication flow of the interference coordination process is simplified, the time delay of the process is reduced, the communication resource in the process of usage is reduced, and the user experience of the process is improved.

Owner:HUAWEI TECH CO LTD

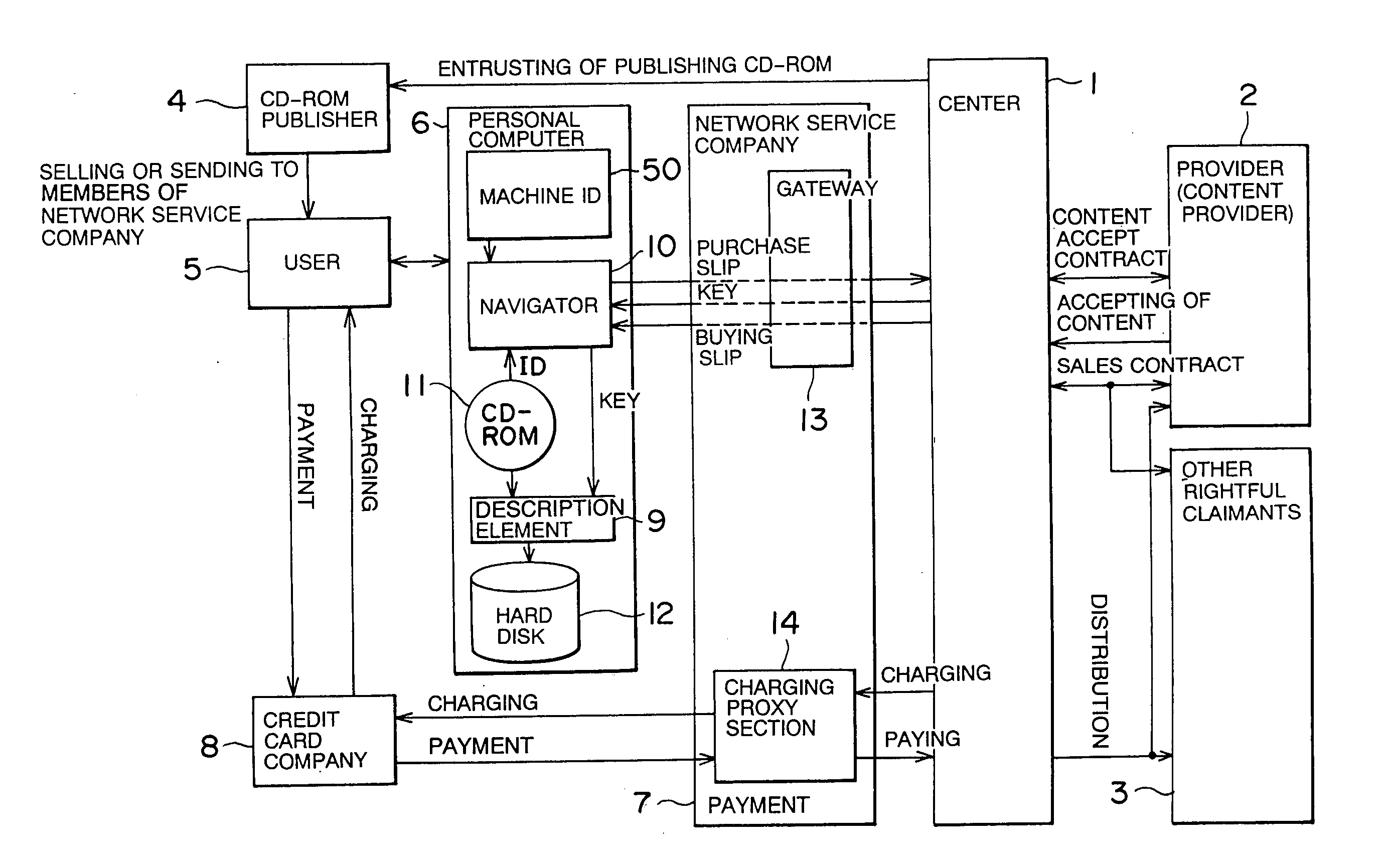

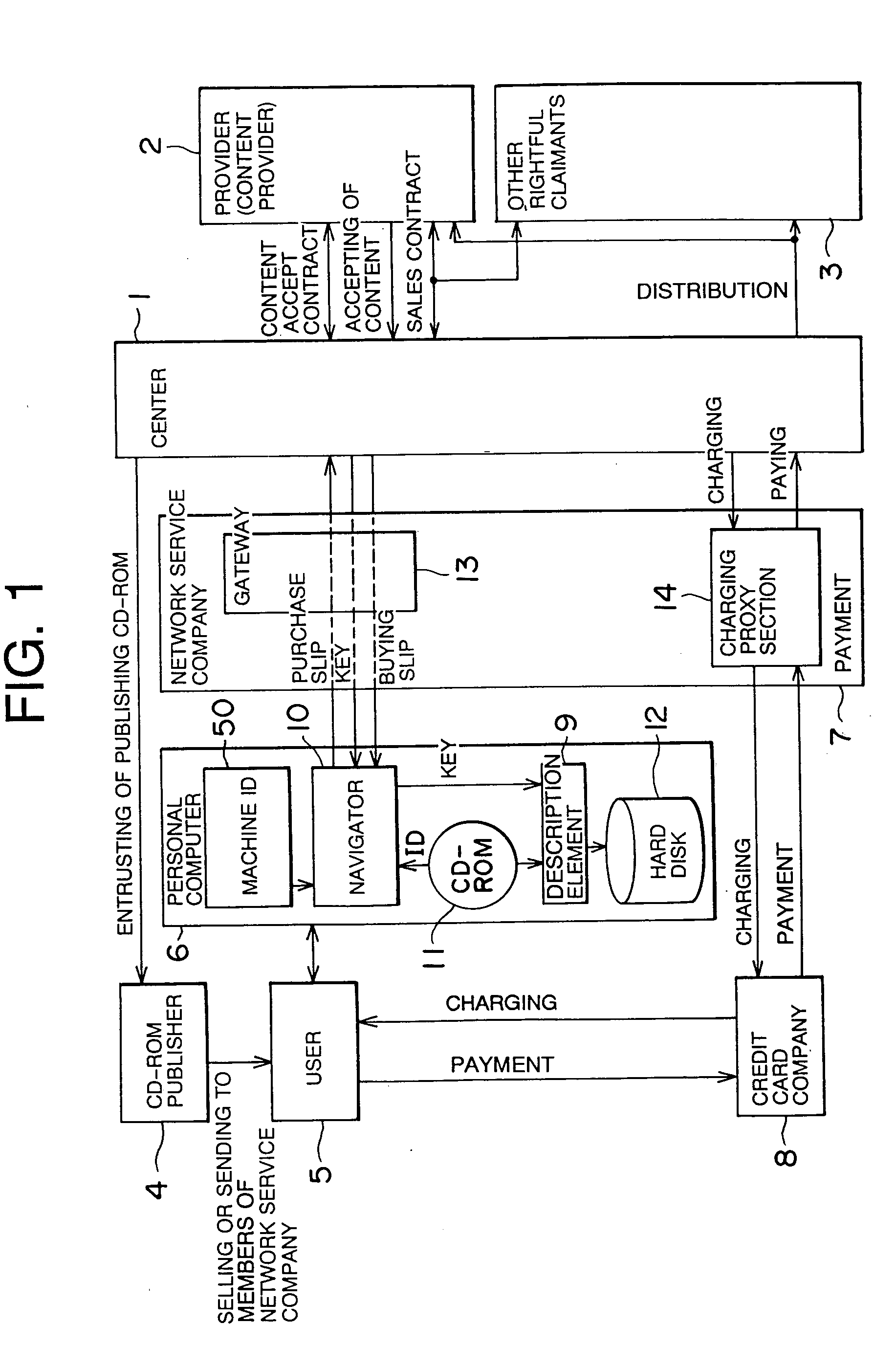

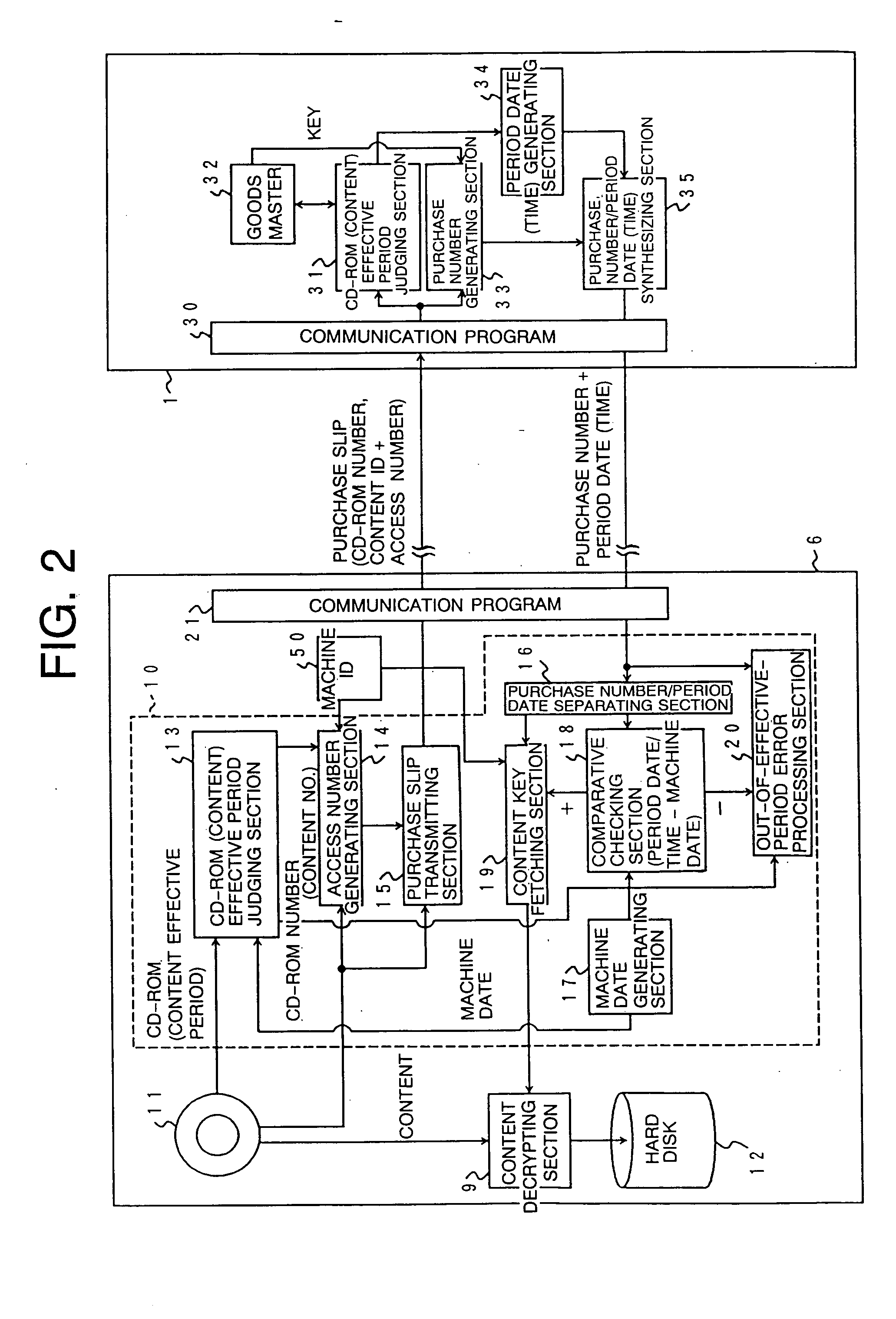

Content sales period verifying system and content decryption key effective period verifying system

InactiveUS20050071272A1Simplify the communication processEasy to operateUnauthorized memory use protectionDigital data protectionPrimary stationCD-ROM

A CD-ROM is recorded with a CD-ROM effective period and an effective period of a content stored in the CD-ROM. A CD-ROM effective period judging section of a personal computer reads the effective periods, compares these periods with a machine date generated by a machine date generating section and enables a purchase slip transmitting section to transmit a purchase slip only when the machine data falls within the effective periods. A CD-ROM effective period judging section of a center compares the present date with the CD-ROM effective period and the content effective period registered on a goods master, reads the key from the goods master and transmits the key to the personal computer only when both of a CD-ROM number and a content ID written onto the received purchase slip fall within the effective periods.

Owner:FUJITSU LTD

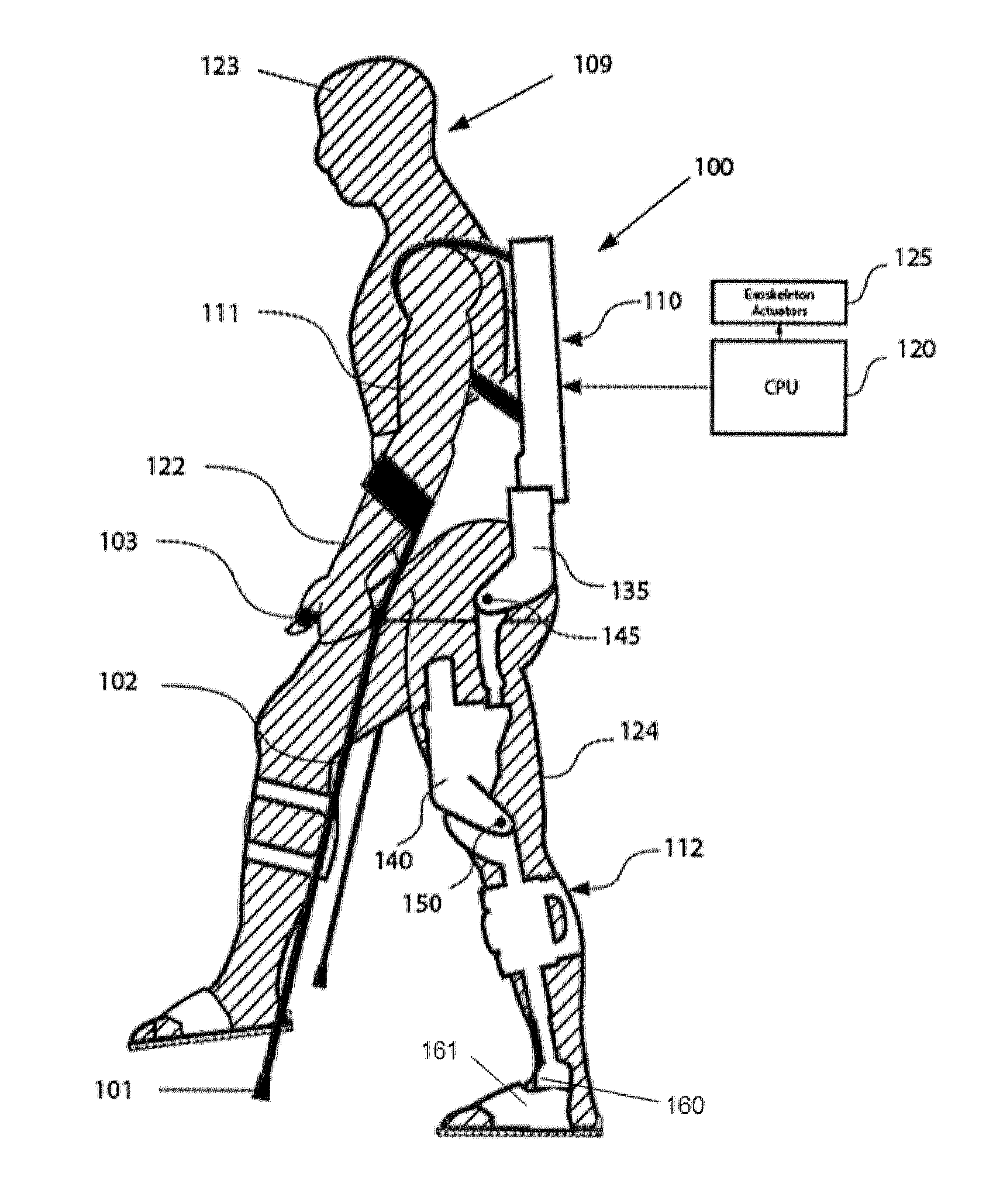

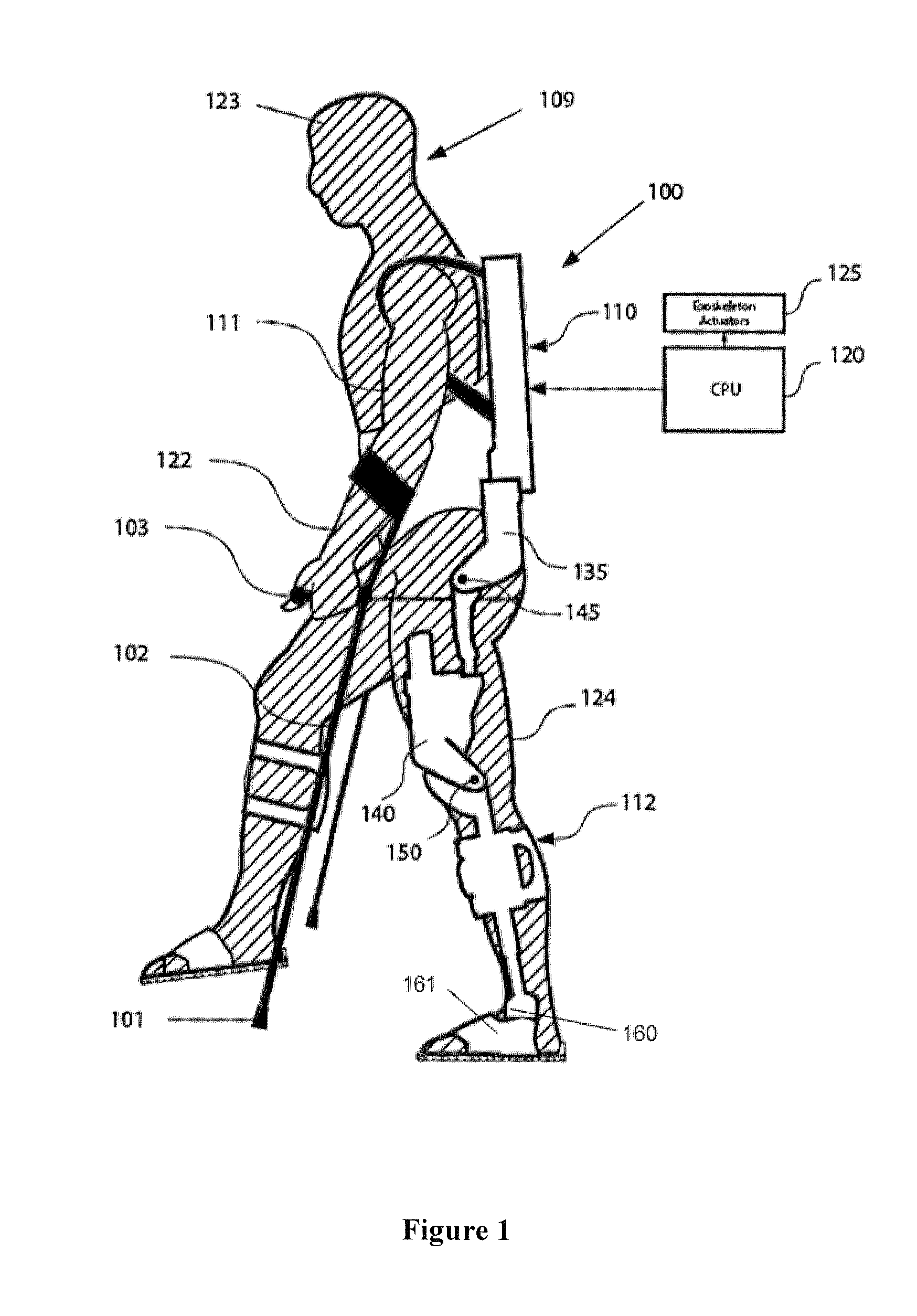

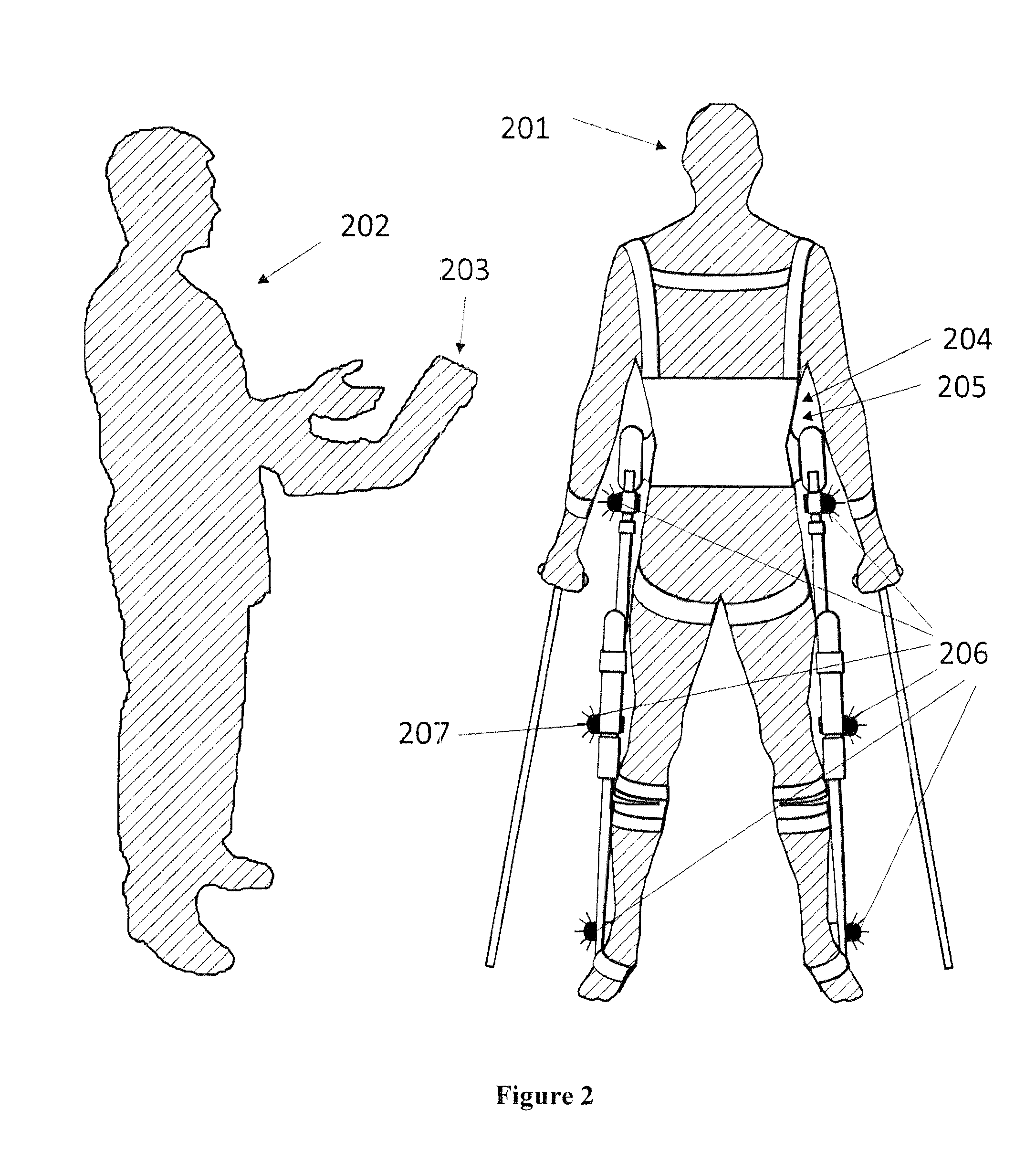

Machine to Human Interfaces for Communication from a Lower Extremity Orthotic

ActiveUS20160045386A1Maximizes therapeutic benefitBenefit maximizationWalking aidsDiagnostic recording/measuringHuman–machine interfaceControl system

An exoskeleton includes a control system which incorporates a feedback system used to establish and communicate orthosis operational information to a physical therapist and / or to an exoskeleton user. The feedback system can take various forms, including employing sensors to establish a feedback ready value and communicating the value through one or more light sources which can be in close proximity to joints of the exoskeleton joints.

Owner:EKSO BIONICS

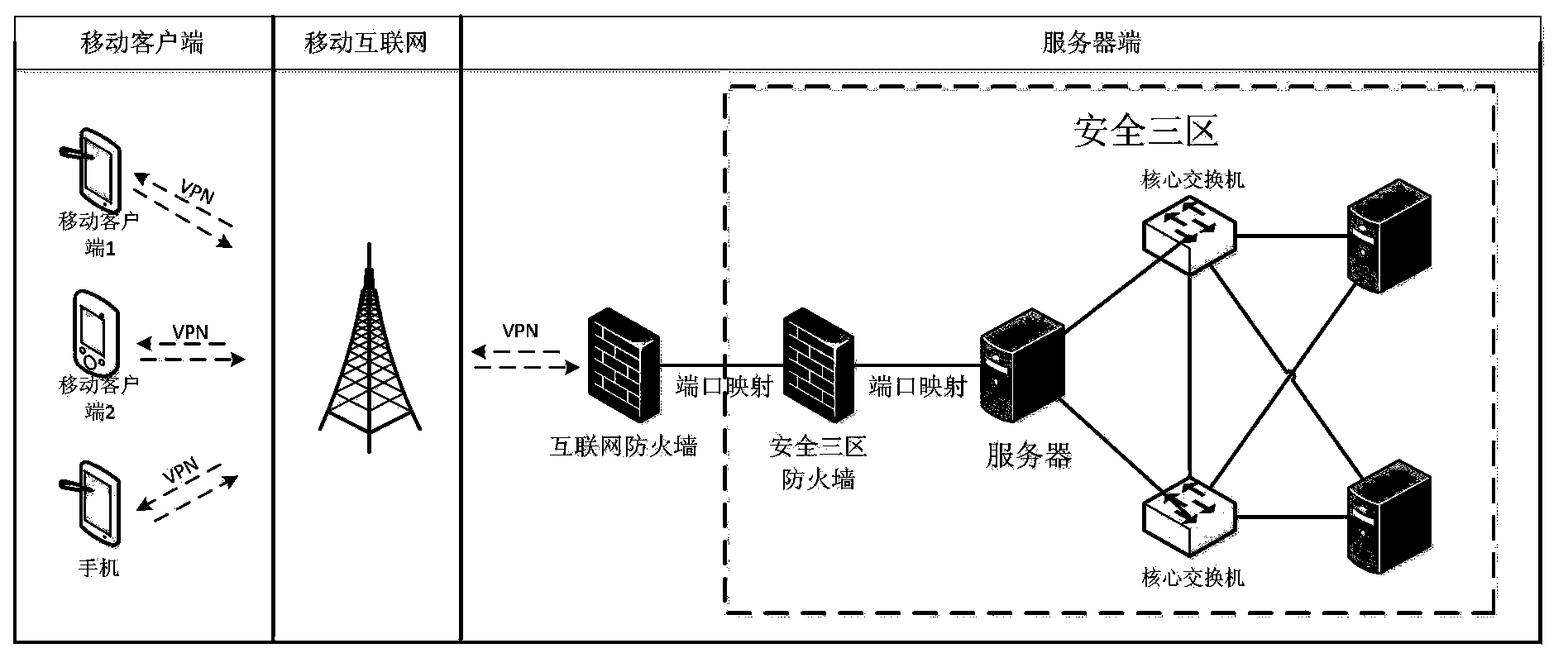

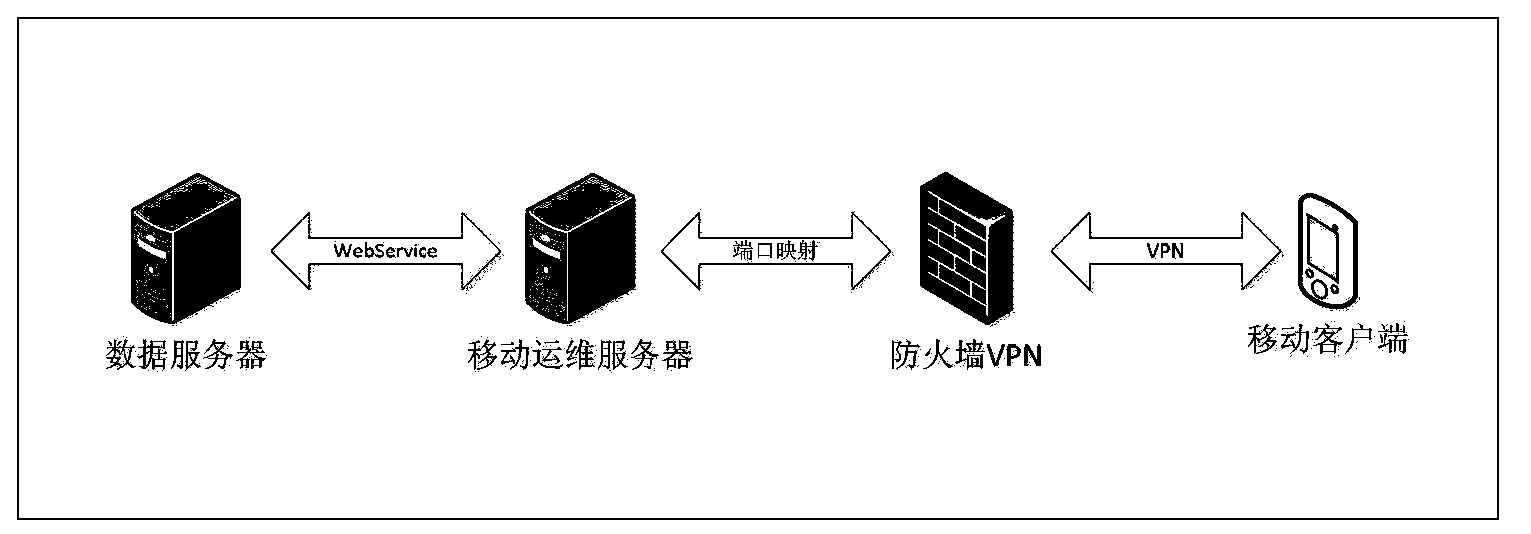

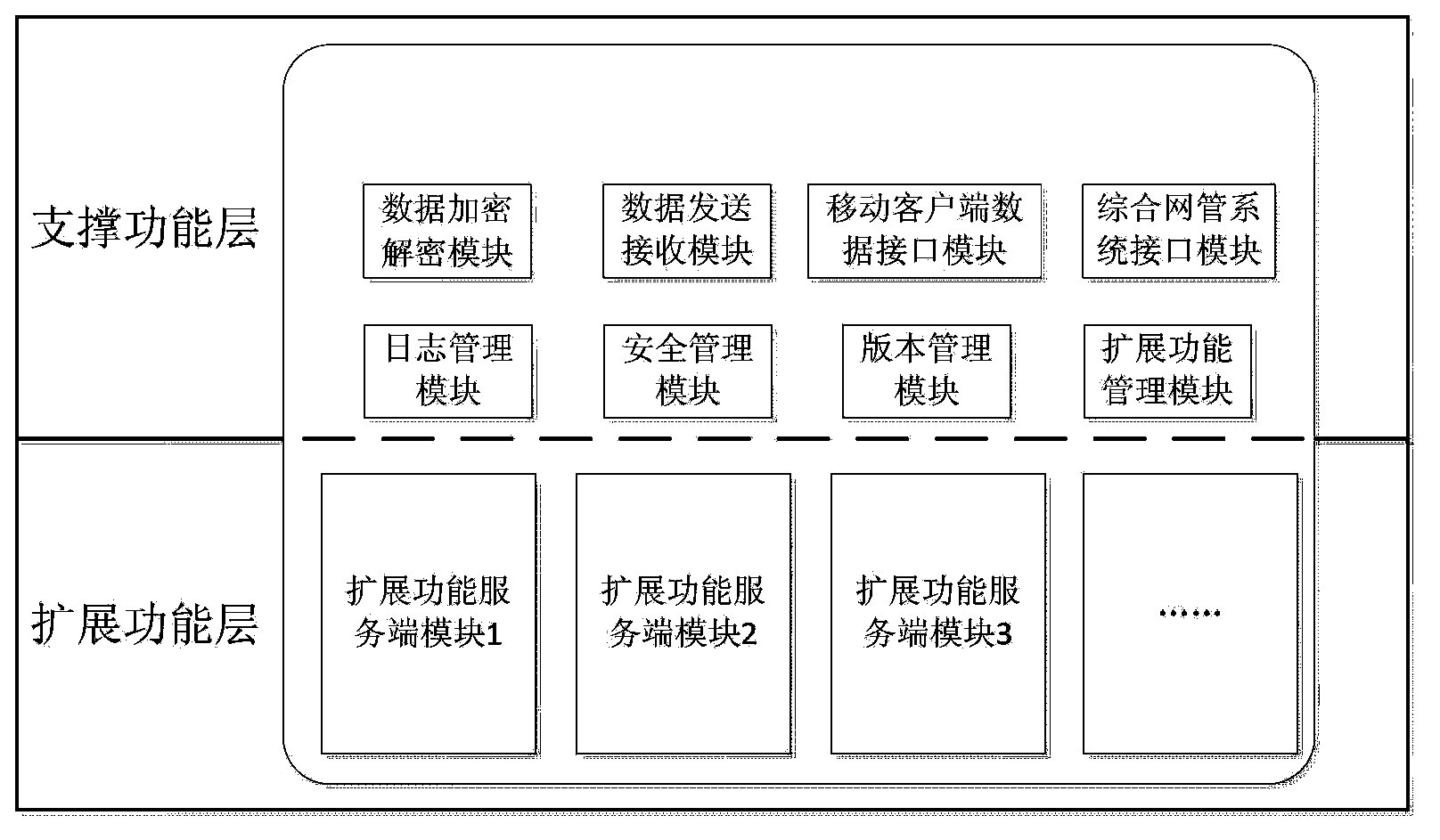

Power communication operation and maintenance mobile system and power communication operation and maintenance method

ActiveCN103685215AImprove work efficiencySimplify the communication processData switching networksData exchangeClient-side

The invention discloses a power communication operation and maintenance mobile system and a power communication operation and maintenance method which are designed for the inconvenient data exchange between outdoor people and the internal part of a company. The power communication operation and maintenance mobile system comprises a mobile client, a server end and a mobile Internet which is in wireless connection with the mobile client and the server end. The mobile client end is internally provided with communication operation and maintenance software used for carrying out data exchange about communication operation and maintenance with the server end. The server end is internally provided with communication operation and maintenance software used for carrying out data exchange about communication operation and maintenance with the mobile client. The power communication operation and maintenance method is that the mobile client carries out the data exchange about communication operation and maintenance with the server end according to a received outside command or a built-in command, and the server end carries out data exchange about communication operation and maintenance with the server end through the mobile Internet according to a received outside command, a built-in command or a mobile client request.

Owner:CHINA SOUTHERN POWER GRID COMPANY

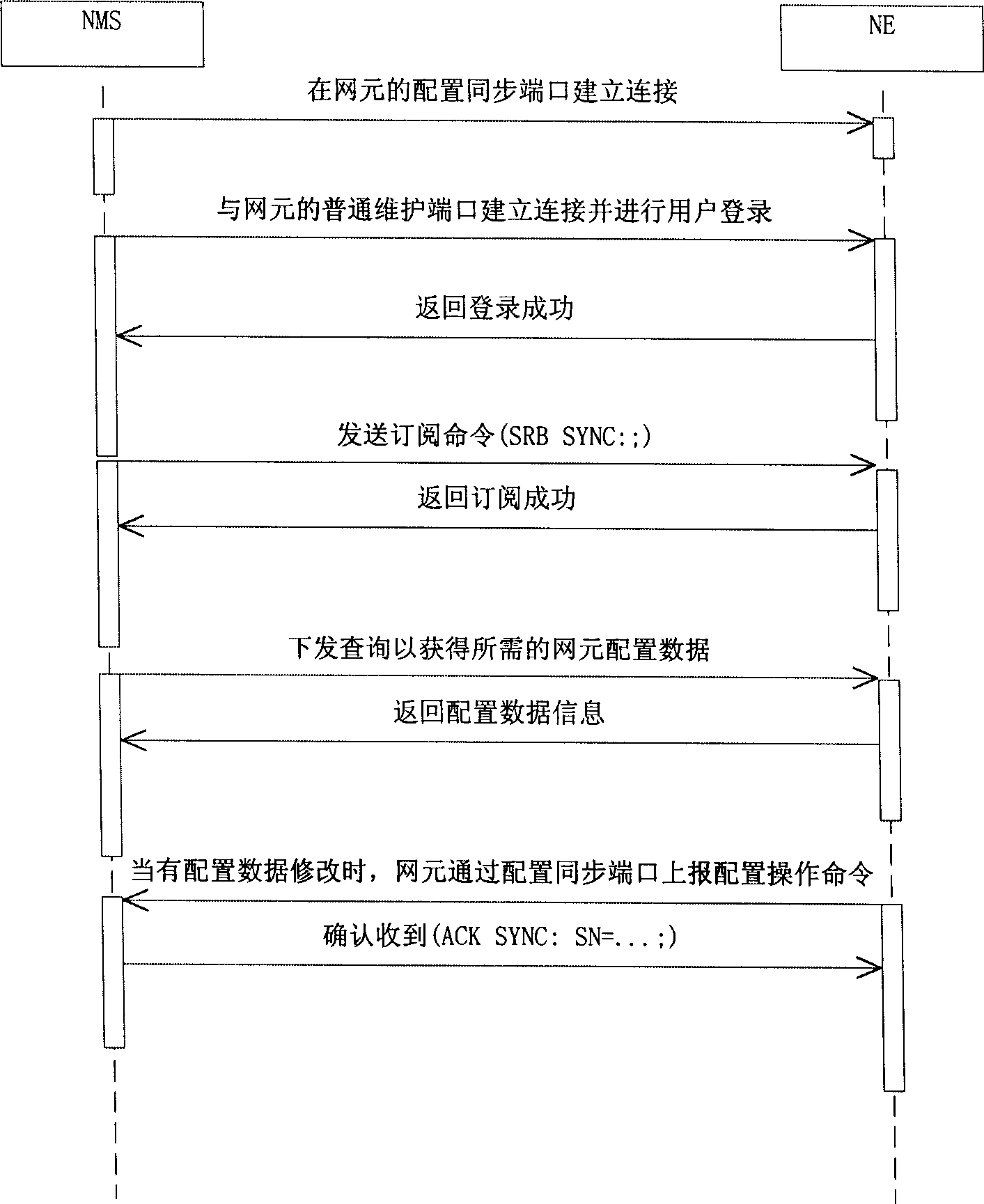

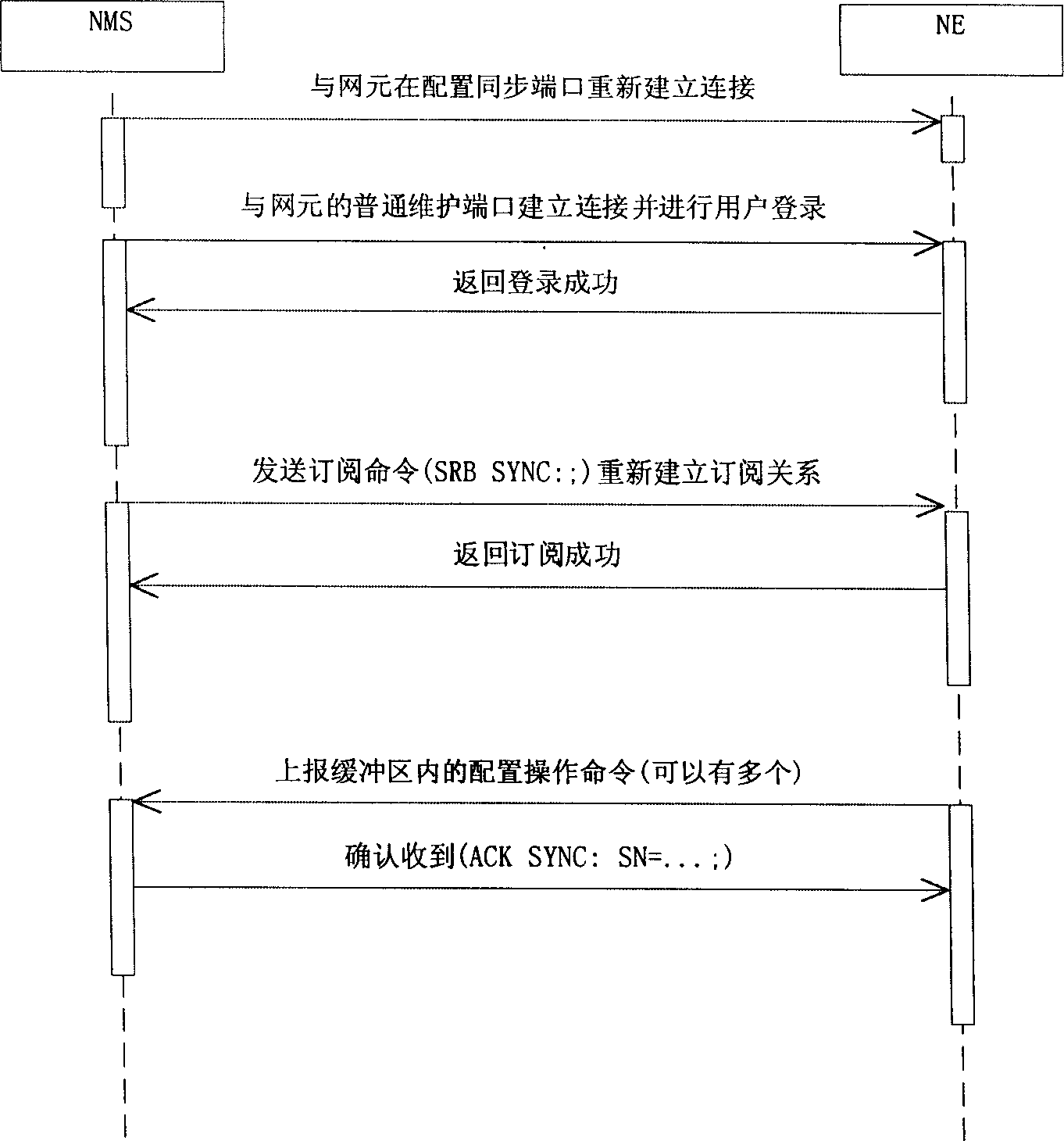

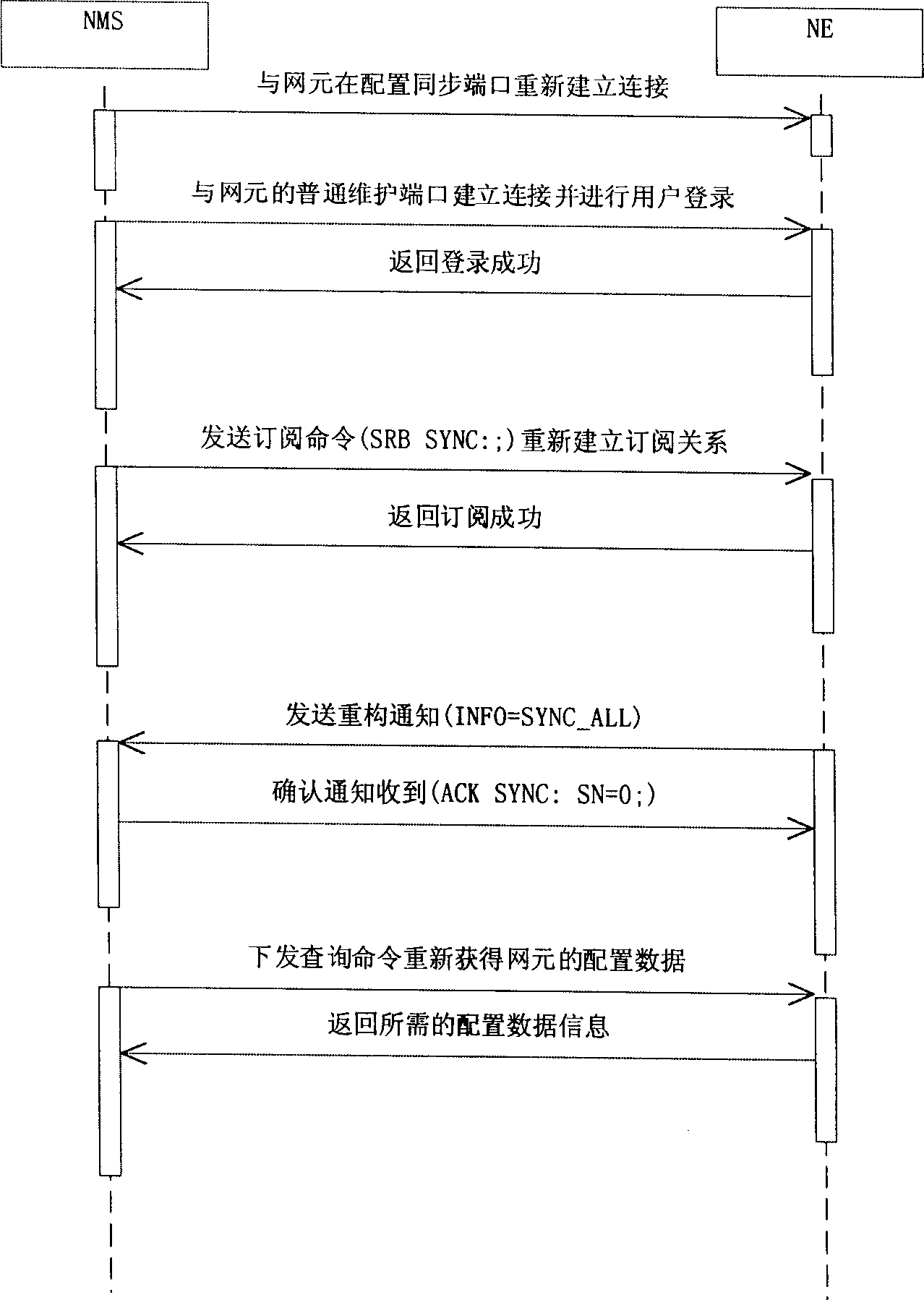

Method for realtime synchronisation of net element and telecommunication system

InactiveCN1482767AReal-time data synchronizationSolve the problem of synchronization delayData switching networksTelecommunications networkReal-time data

The invention discloses a real-time data synchronization method for the net element and telecommunication network administration system comprising, establishing connection between the network administration system and the configuration synchronization port of the network element, the administration system establishing connection on common maintenance port and login, the administration system sending subscription instruction to the network element through the common maintenance port for setting up subscription relation, the administration system sending layout data query instruction to the network element through the common maintenance port, acquiring the layout data of the network element, thus achieving the real-time data synchronization between the net element and telecommunication network administration system, and simplifying the communication flow path. íí

Owner:HUAWEI TECH CO LTD

Method and system for providing short block length low density parity check (LDPC) codes in support of broadband satellite applications

ActiveUS7237174B2Low Density Parity CheckMinimize resourceError preventionError correction/detection using LDPC codesDigital videoParity-check matrix

Owner:DTVG LICENSING INC

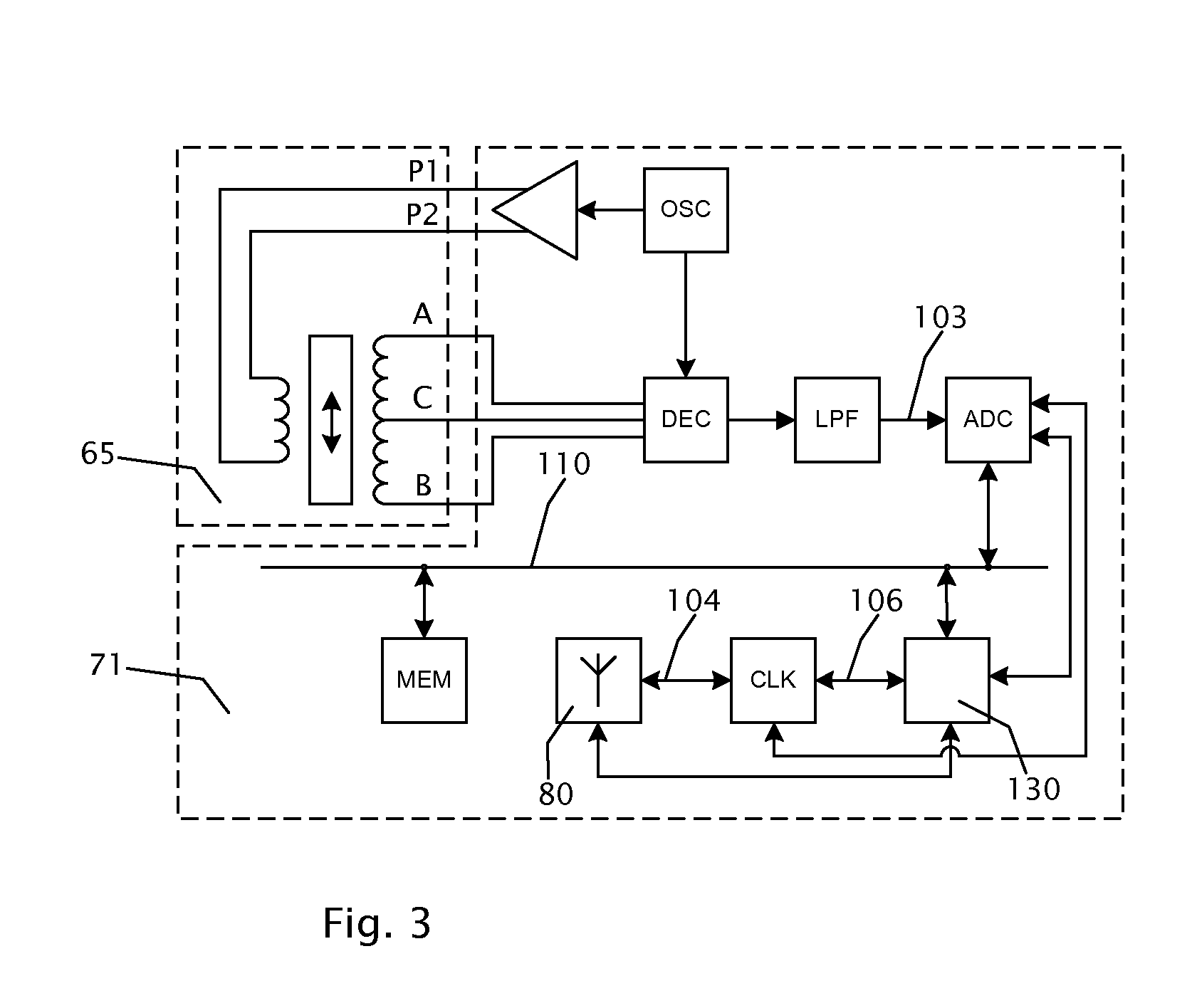

Device for measuring dimensions

ActiveUS20120004886A1Simplify communicationLimit consumption and perturbationFeeler-pin gaugesDigital computer detailsSize measurementTransducer

Measuring system having a plurality of probes for measuring lengths, each probe including a probe tip connected in removable fashion relative to a casing, a transducer supplying an electric signal that is representative of the position of said probe tip relative to the casing, a digital processing unit for sampling the signal from said transducer and transforming it into a digital representation of said position, and a bidirectional interface for a wireless communication network connecting said probes with a control unit. A method including a step during which the clocks of the digital processing units of the probes are synchronized through said bidirectional wireless interface and a step during which the control unit transmits commands determining the instant at which said electric signals are sampled.

Owner:TESA SE