Patents

Literature

51 results about "Bank switching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Bank switching is a technique used in computer design to increase the amount of usable memory beyond the amount directly addressable by the processor. It can be used to configure a system differently at different times; for example, a ROM required to start a system from diskette could be switched out when no longer needed. In video game systems, bank switching allowed larger games to be developed for play on existing consoles.

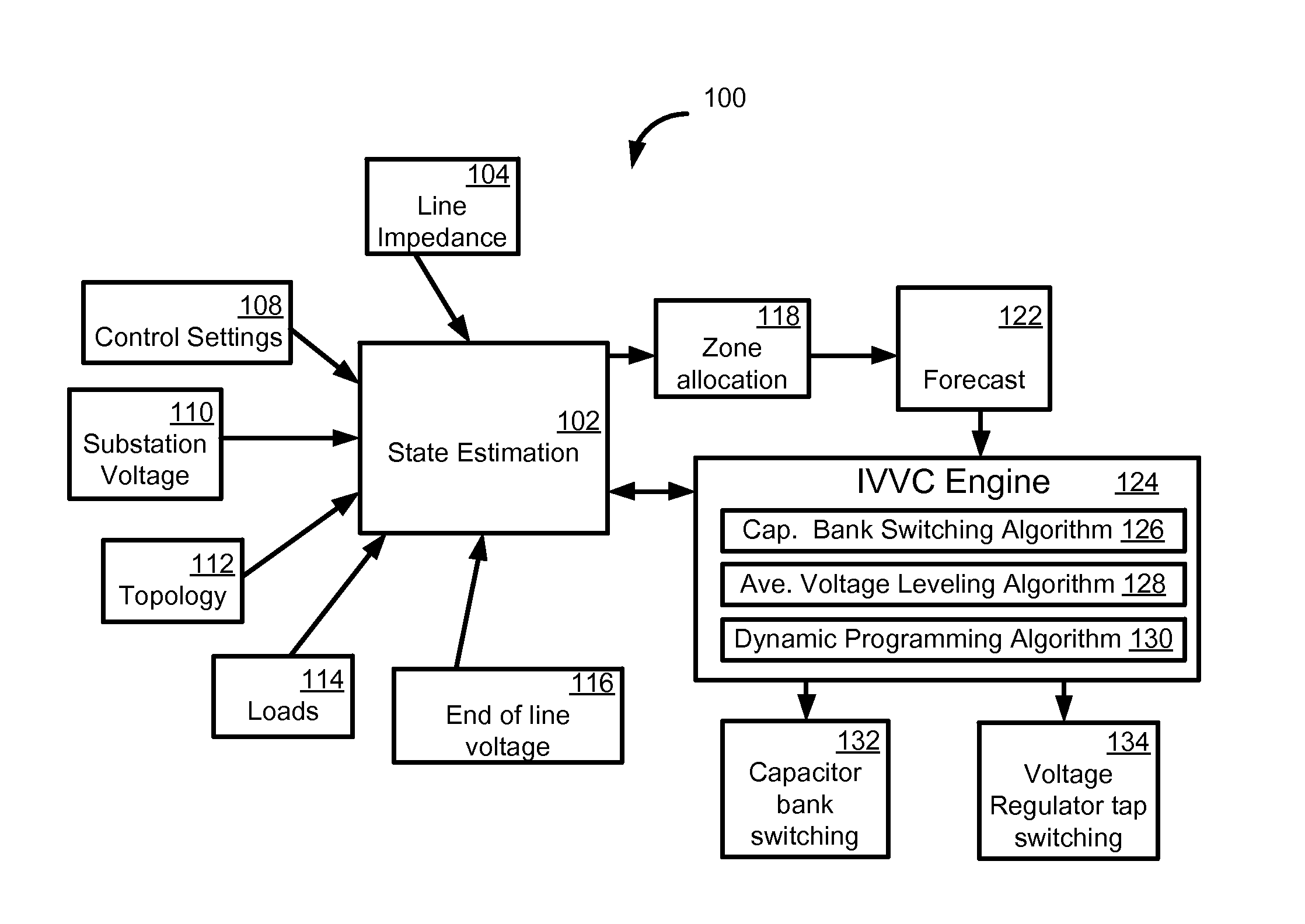

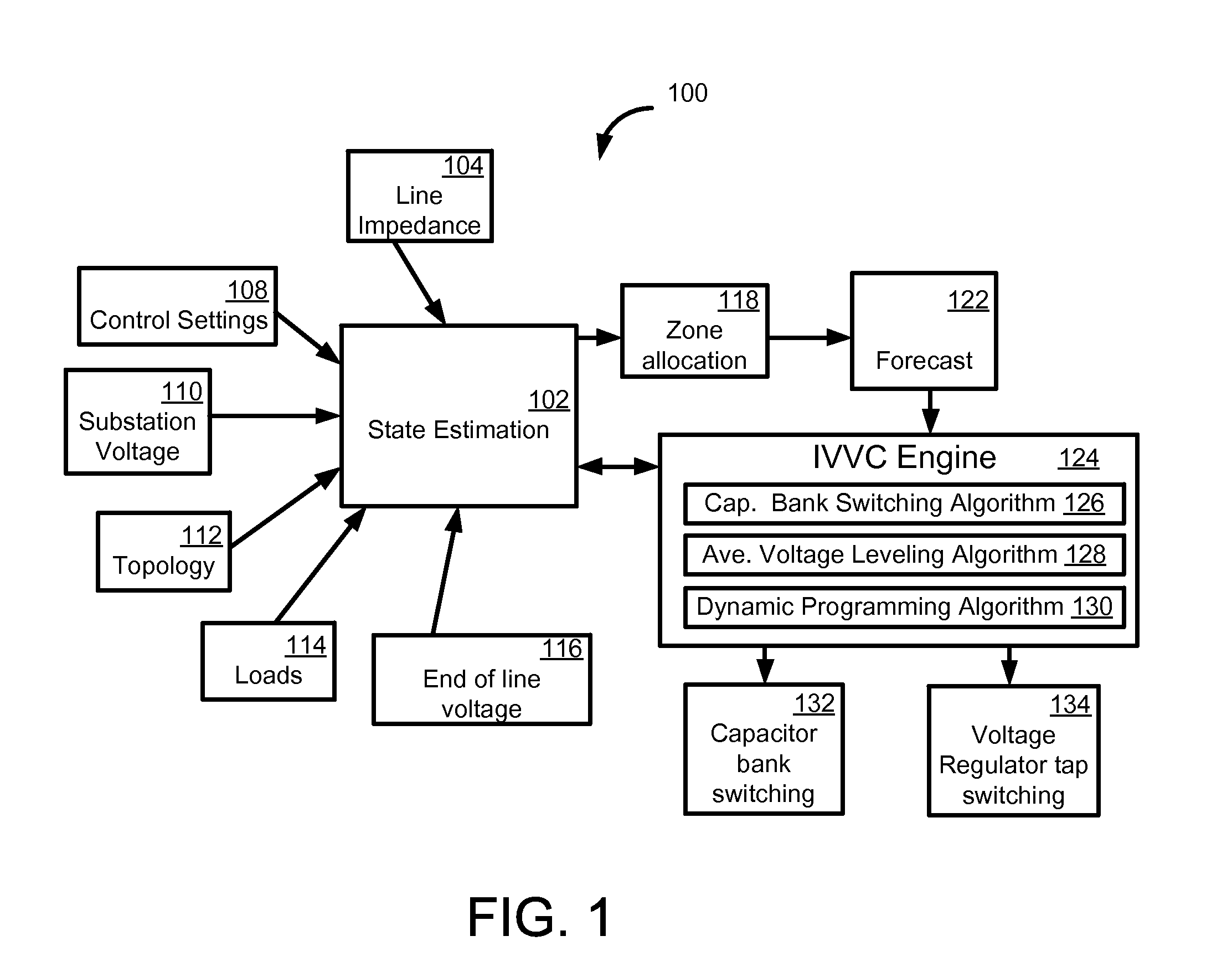

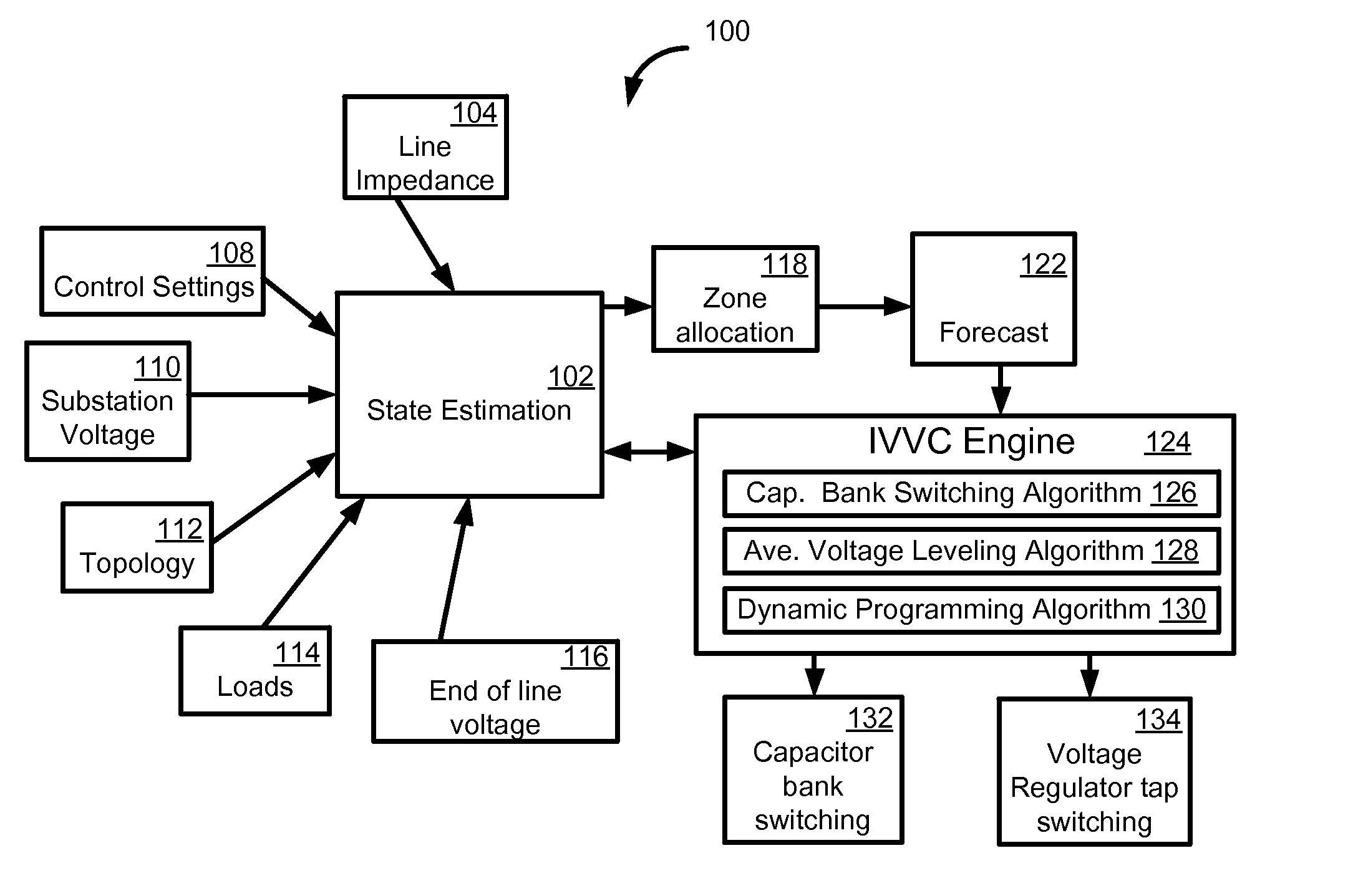

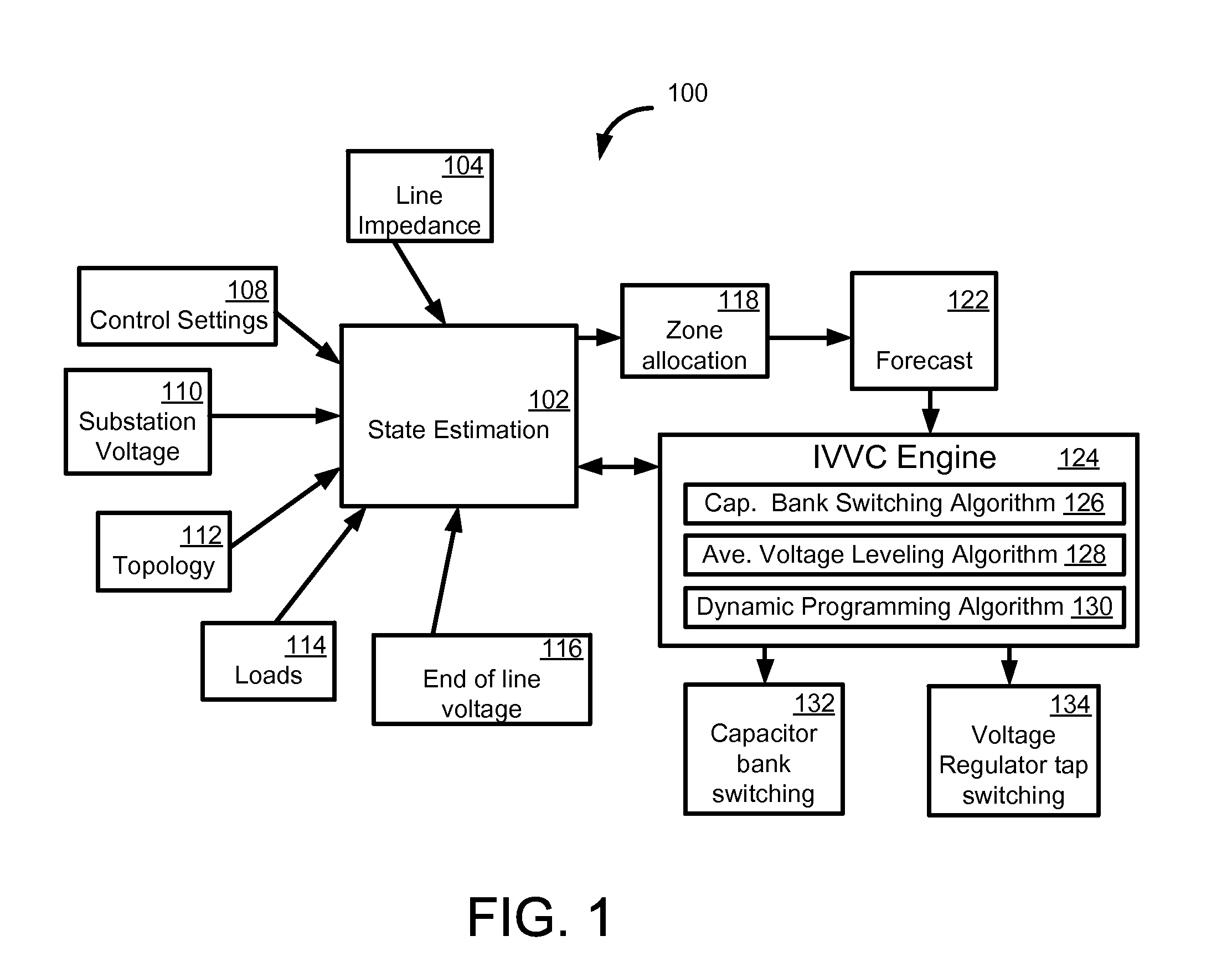

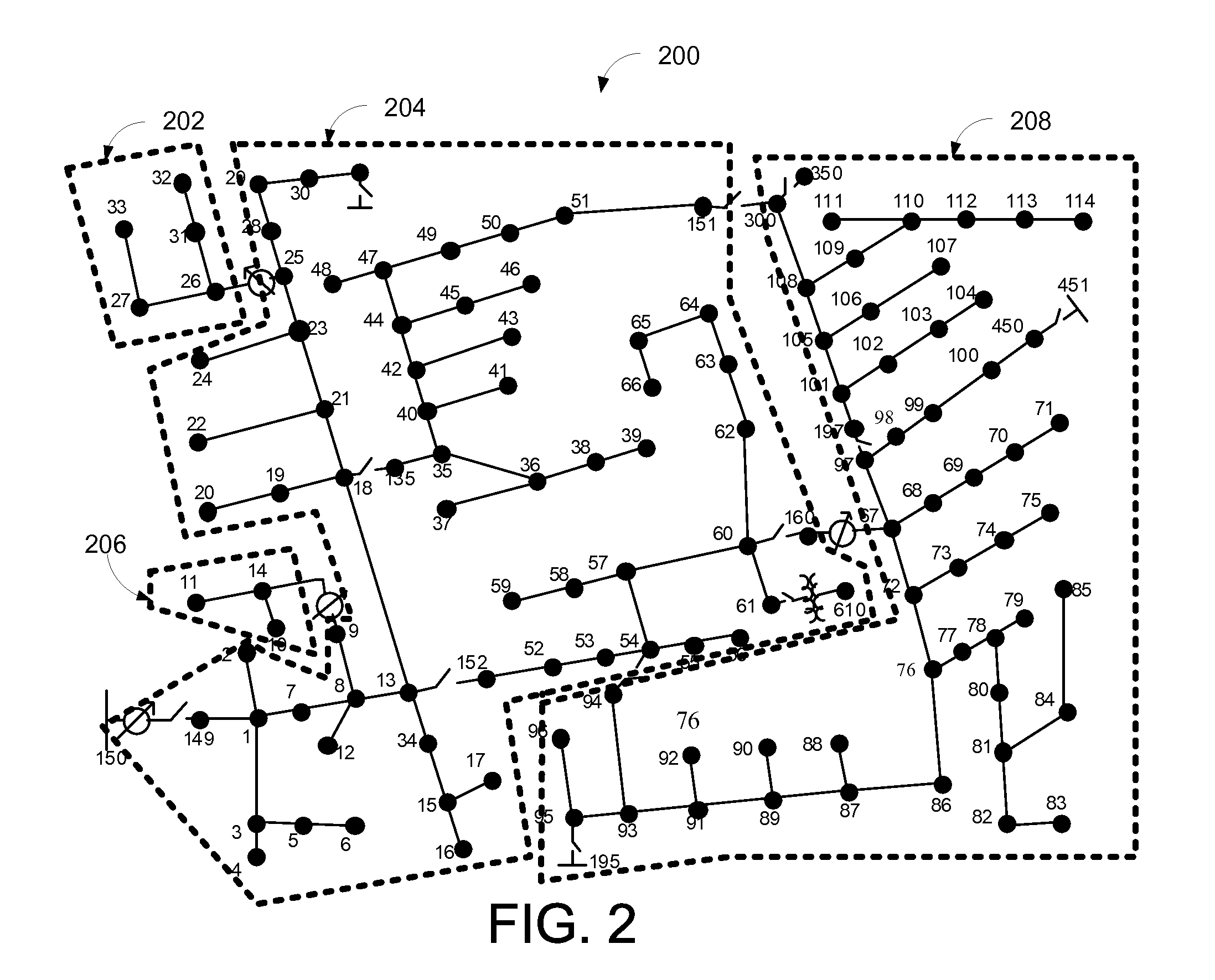

Systems, Methods, and Apparatus for Integrated Volt/VAR Control in Power Distribution Networks

ActiveUS20120193984A1Dc network circuit arrangementsLoad forecast in ac networkTime segmentElectric distribution network

Certain embodiments of the invention may include systems, methods, and apparatus for controlling voltage and reactive power in a distribution network. One method includes estimating at least one present state associated with a distribution network; allocating one or more load zones in the distribution network; predicting load profiles of each zone for a predetermined time period; determining capacitor bank switching schedules for a predetermined time period based at least in part on the at least one present state and the predicted load profiles; and switching capacitor banks according to the capacitor bank switching schedules.

Owner:GENERAL ELECTRIC CO

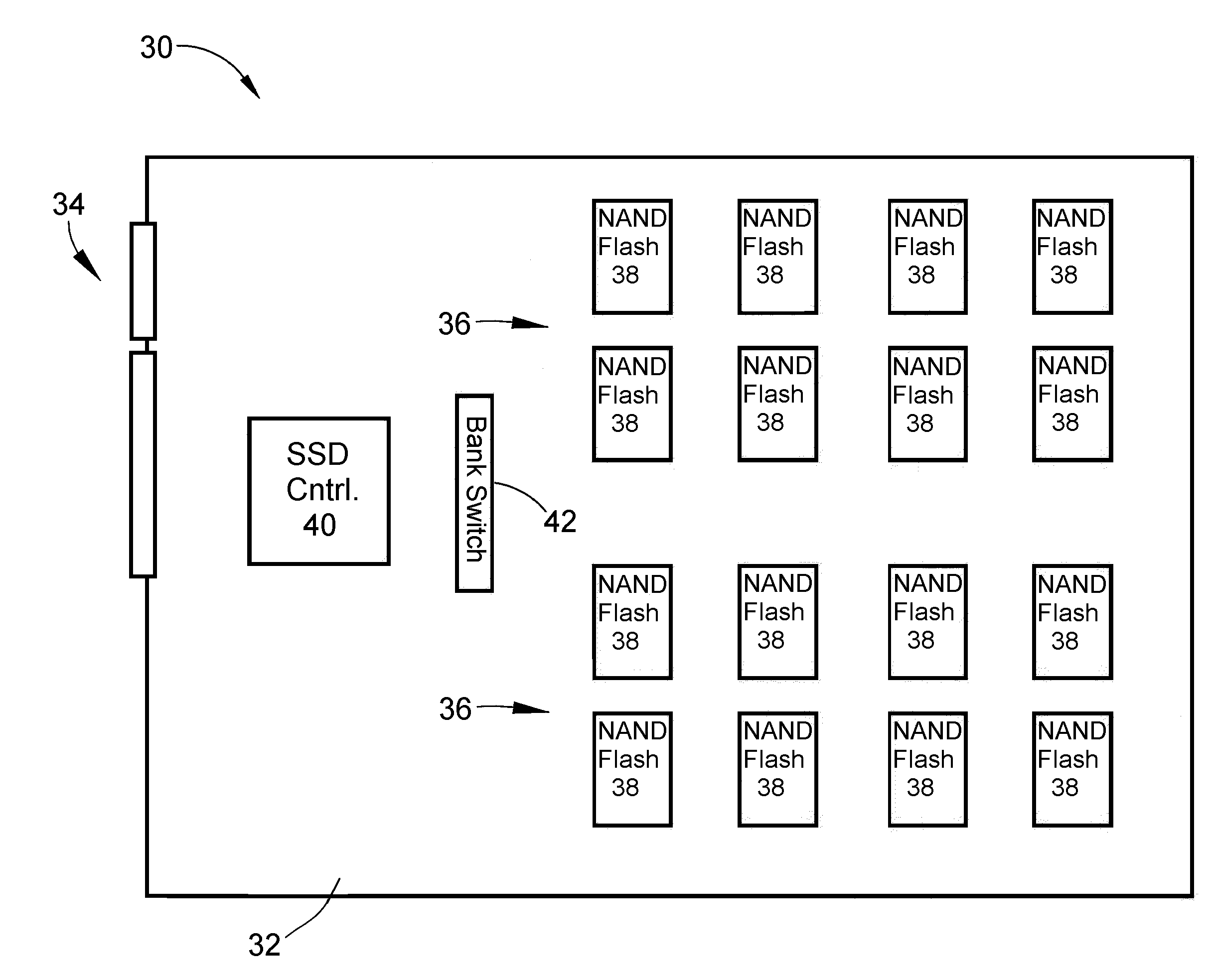

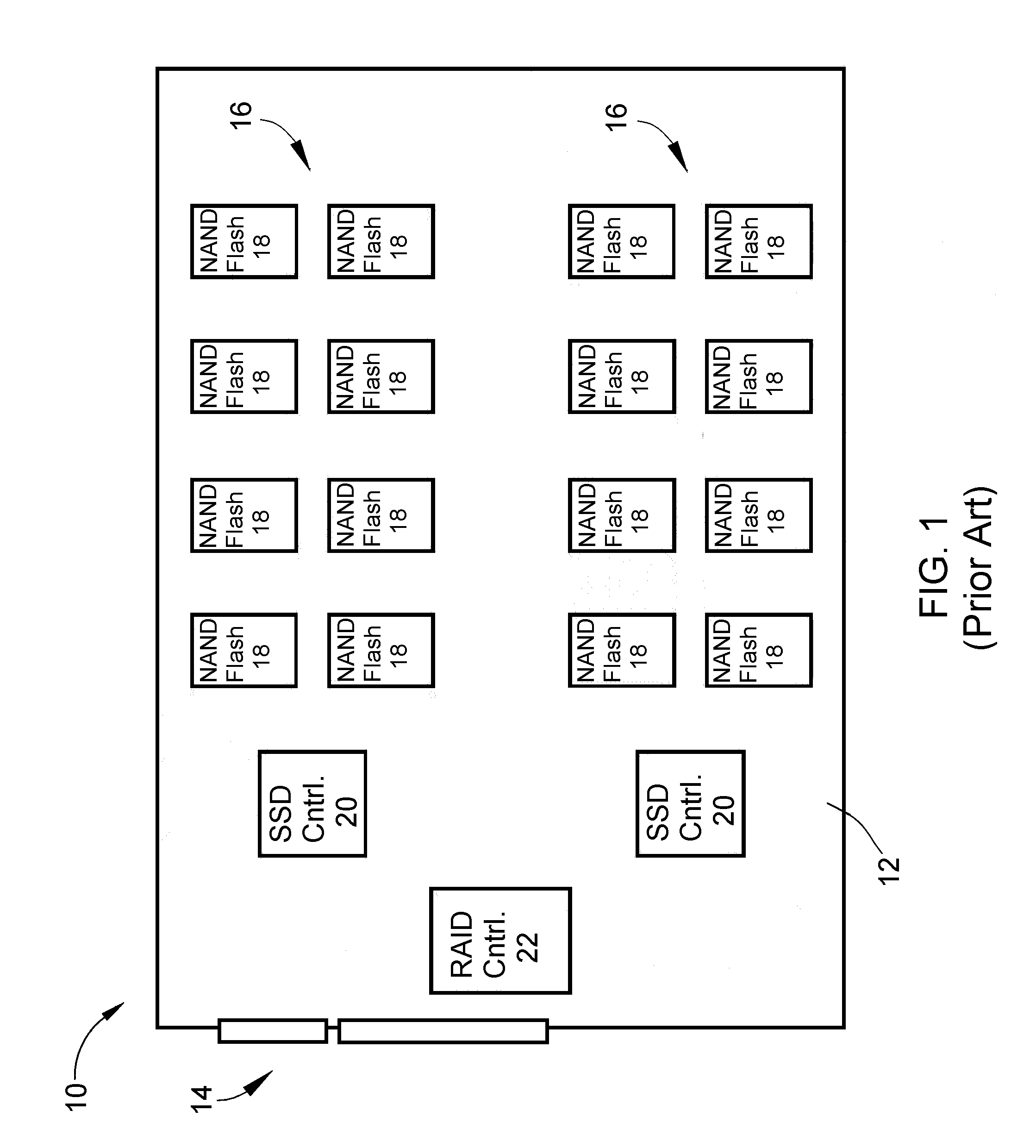

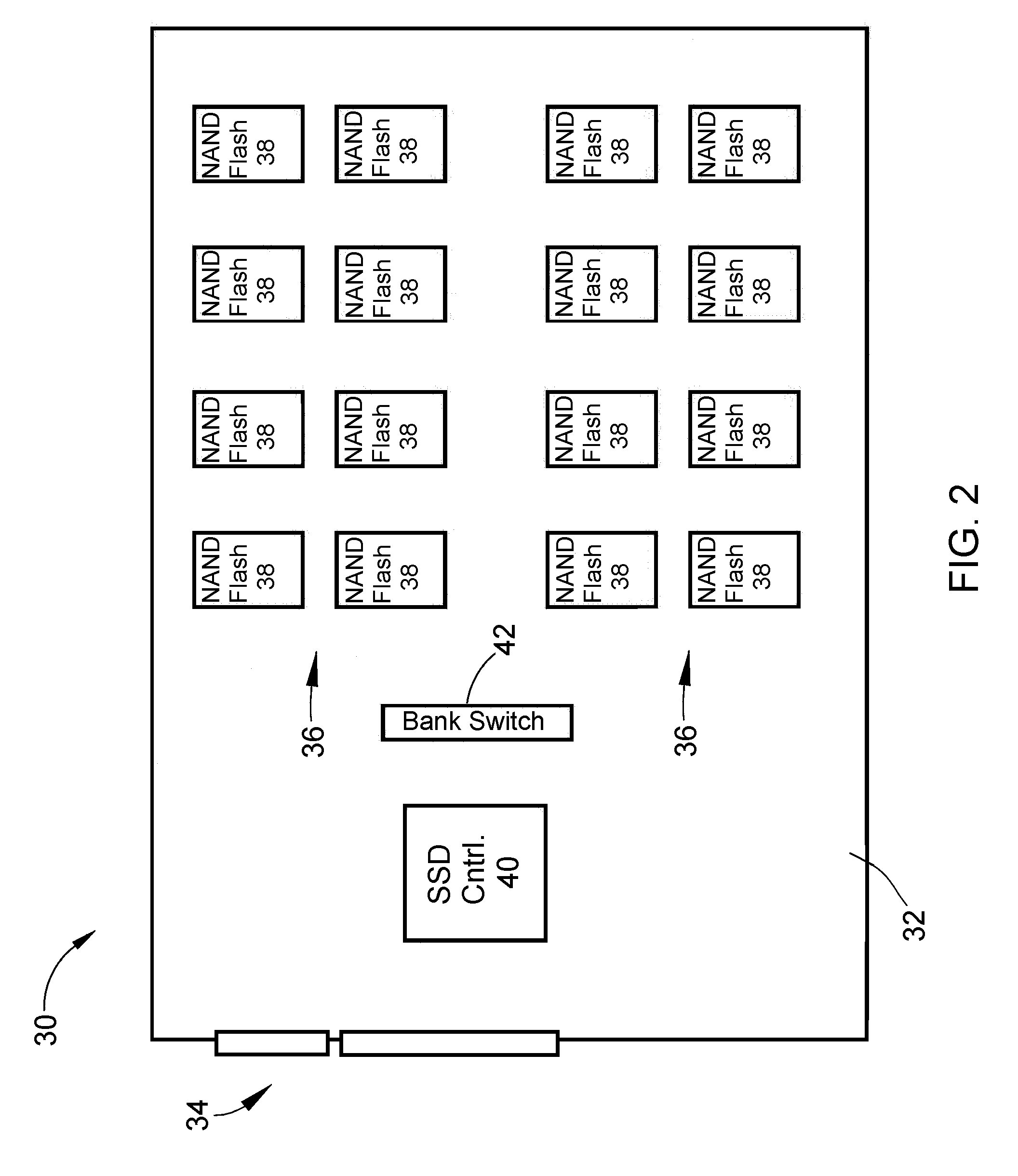

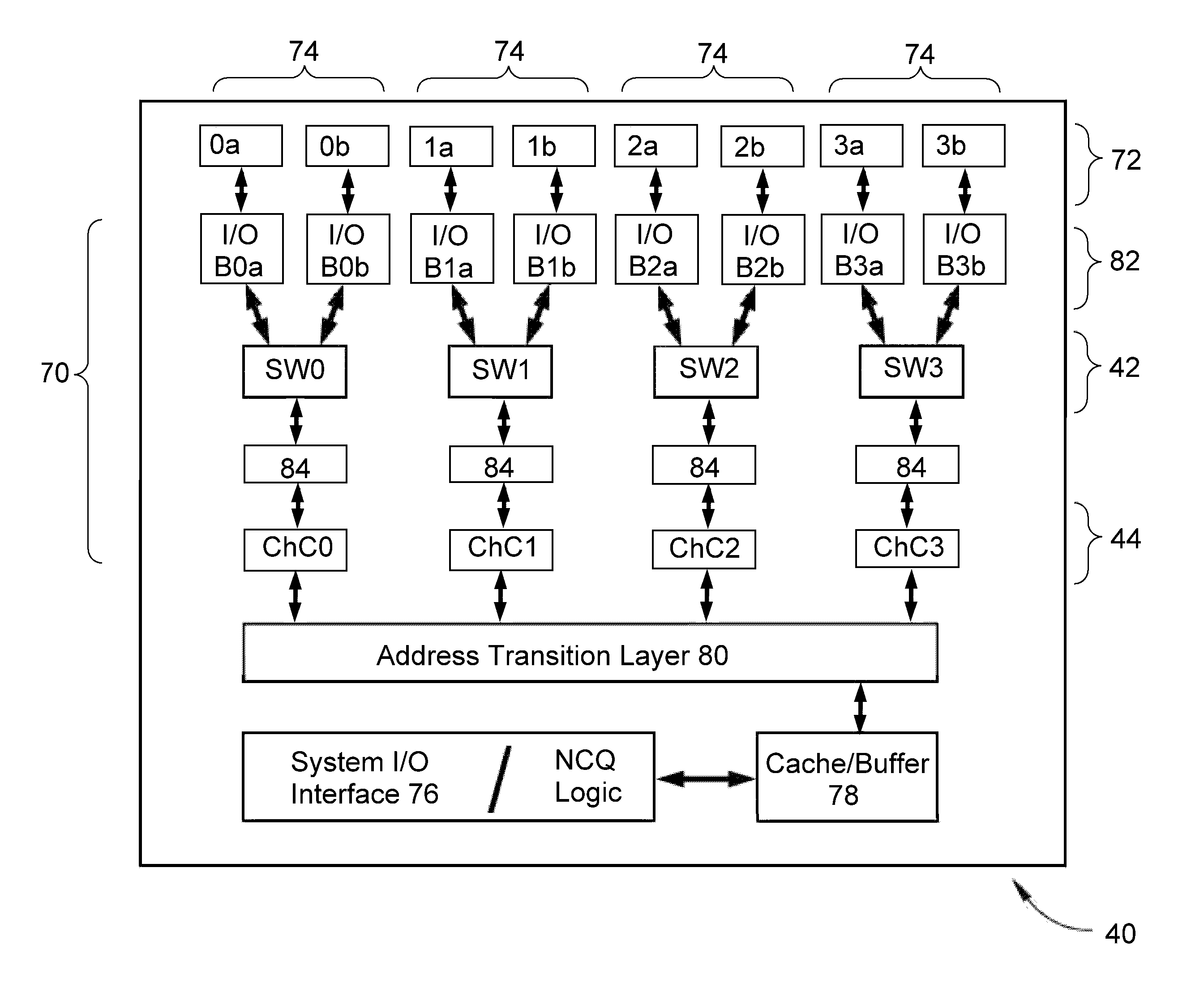

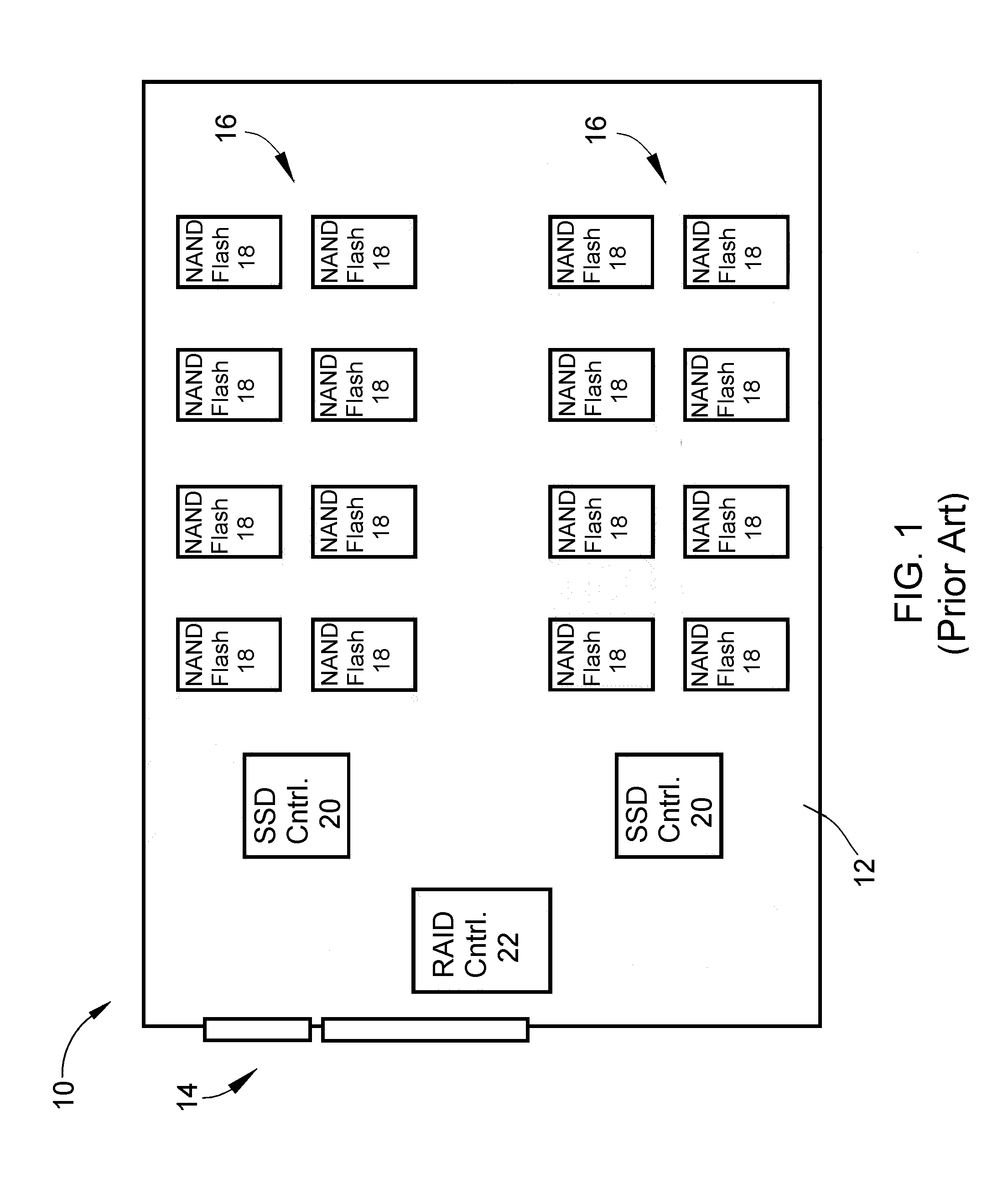

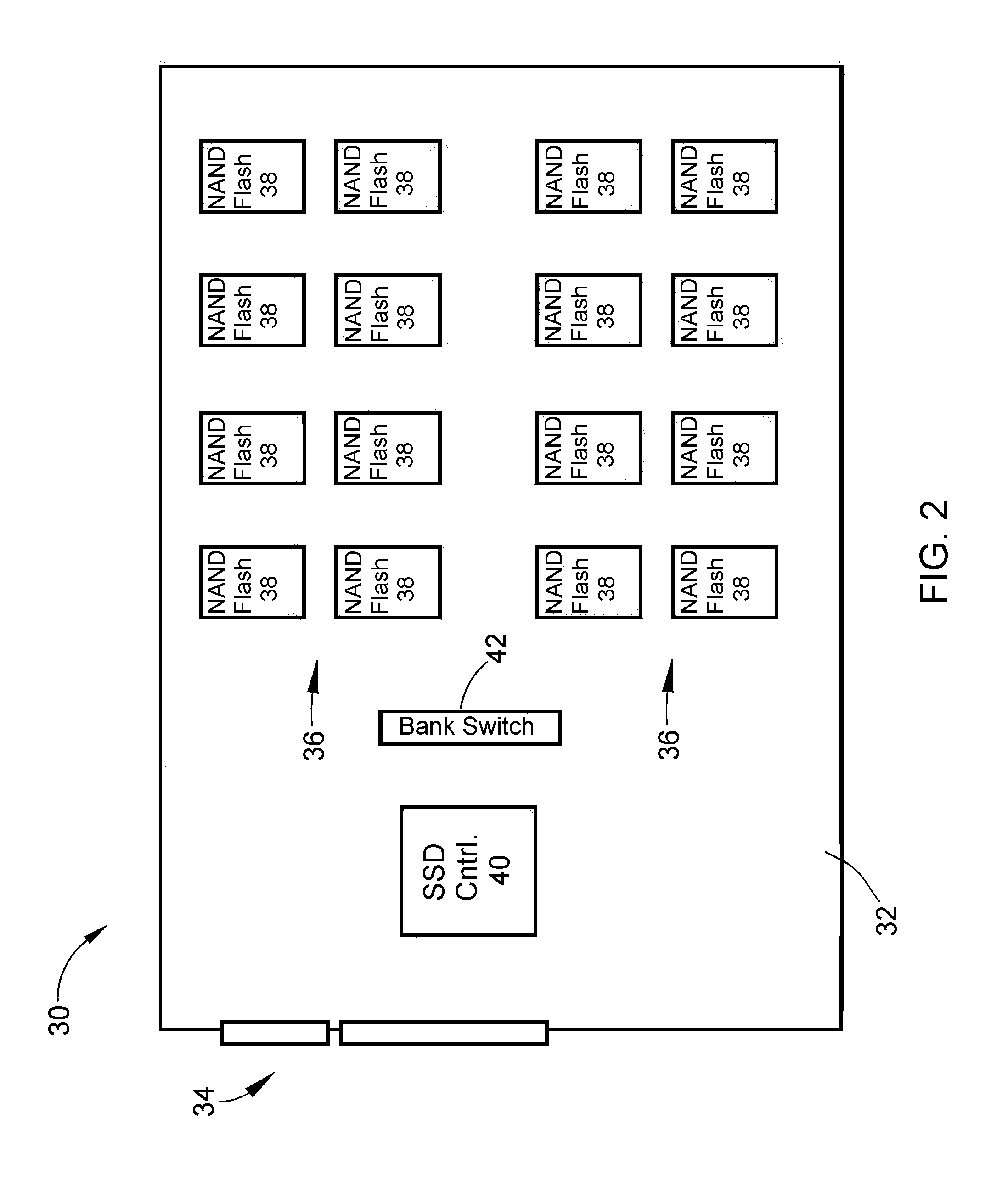

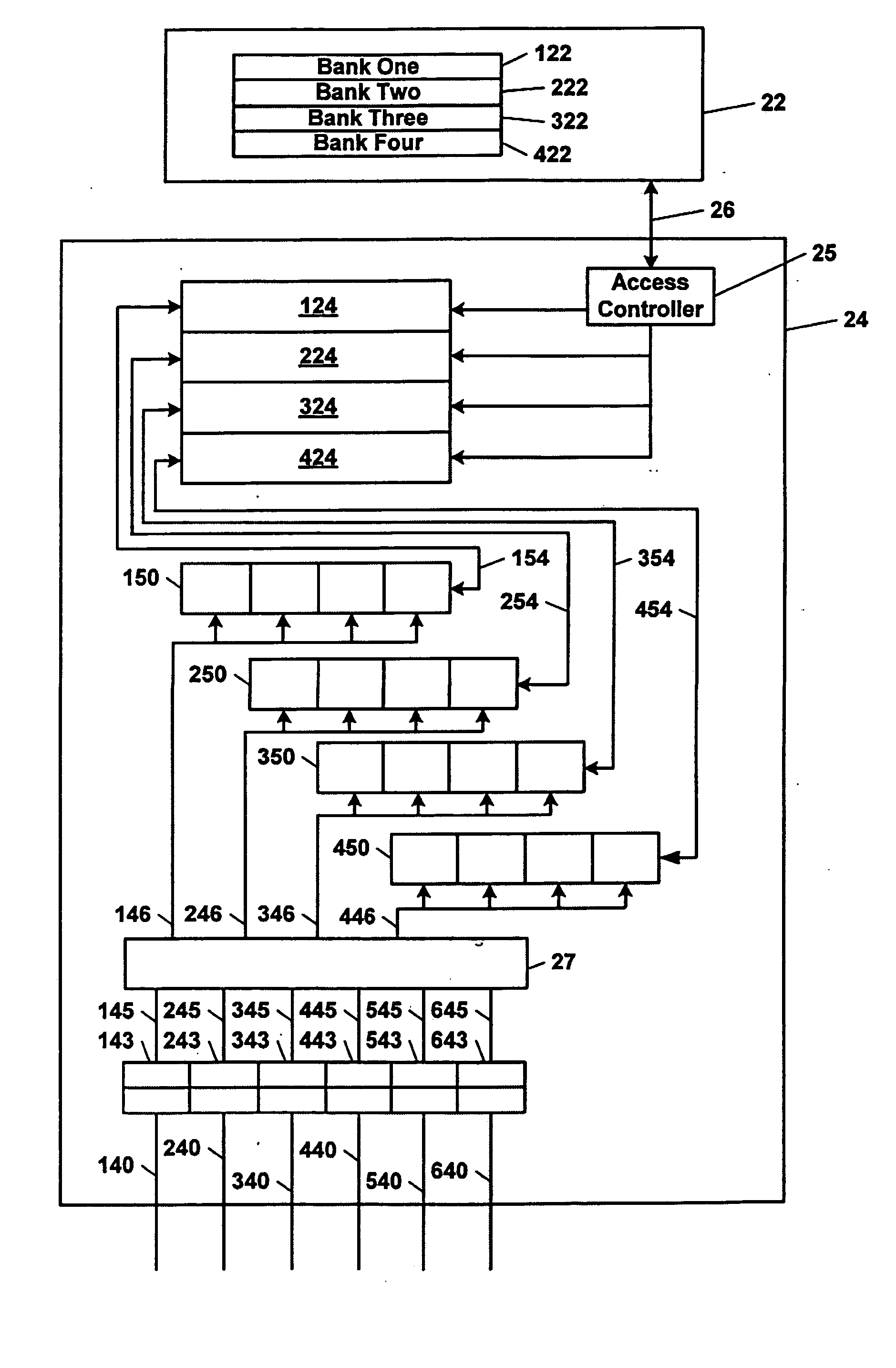

Large capacity solid-state storage devices and methods therefor

InactiveUS20110060869A1Large capacityMemory architecture accessing/allocationMemory adressing/allocation/relocationSolid-state storageControl store

Non-volatile storage devices and methods capable of achieving large capacity SSDs containing multiple banks of memory devices. The storage devices include a printed circuit board, at least two banks of non-volatile solid-state memory devices, bank switching circuitry, a connector, and optionally a memory controller. The bank switching circuitry is functionally interposed between the banks of memory devices and either the connector or the memory controller. The bank switching circuitry operates to switch accesses by a system logic or the memory controller among the at least two banks.

Owner:OCZ STORAGE SOLUTIONS

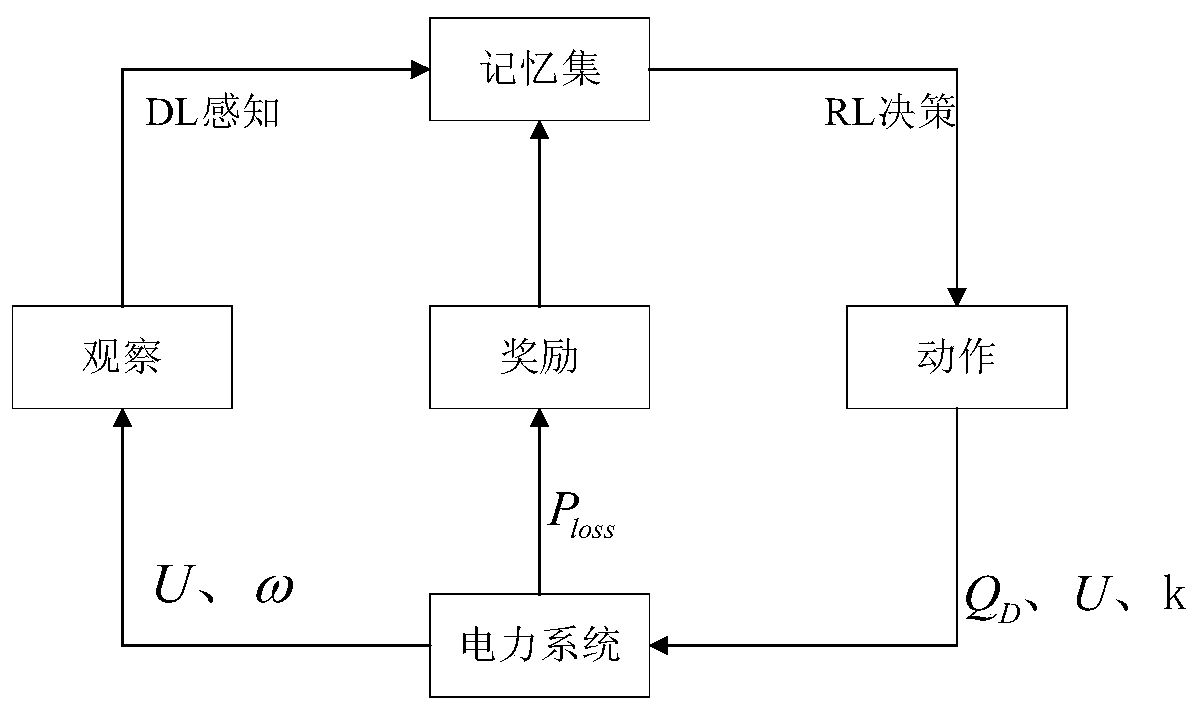

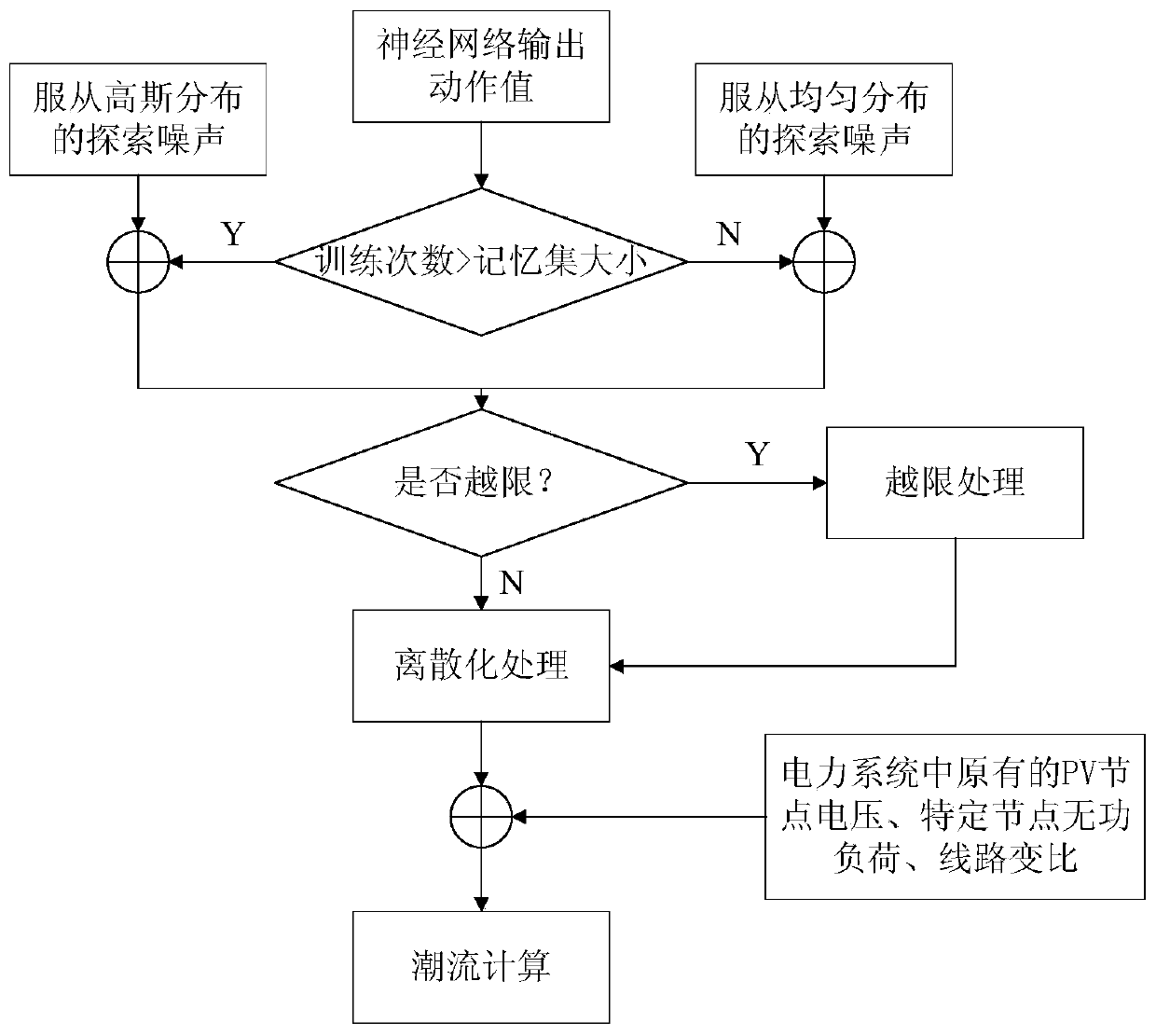

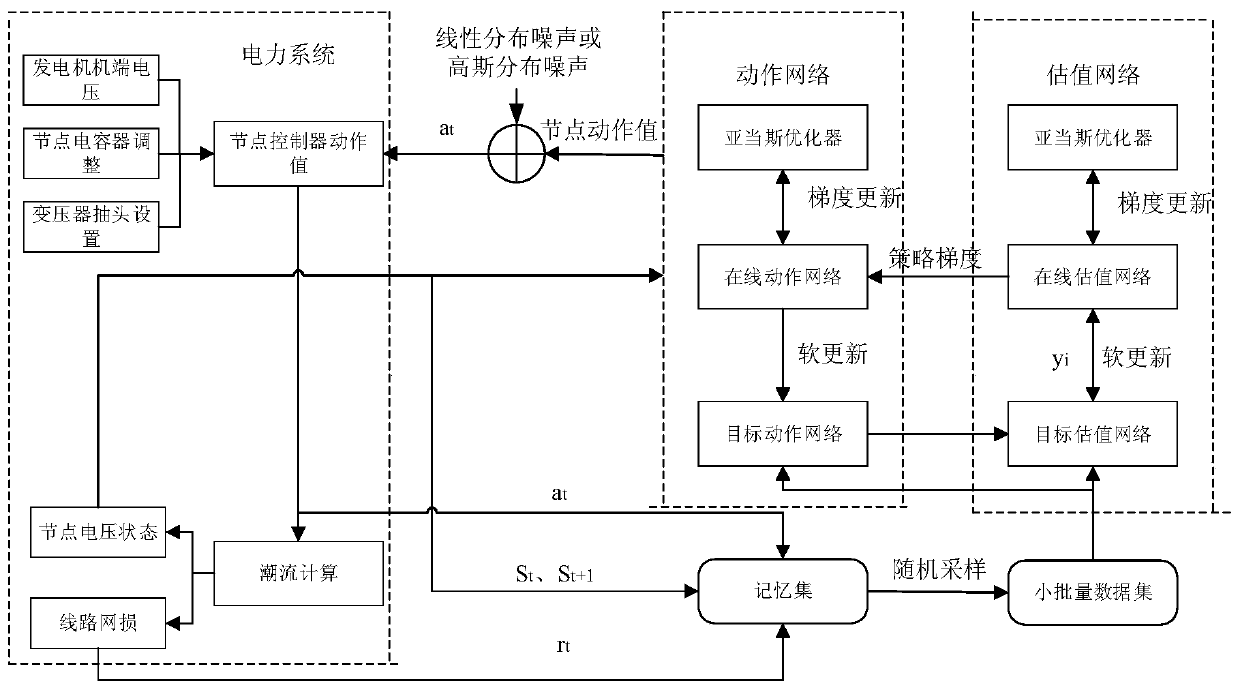

Power system reactive power optimization method based on depth determination strategy gradient reinforcement learning

ActiveCN110535146AAchieve information exchangeImprove power utilizationReactive power adjustment/elimination/compensationReactive power compensationTerminal voltageTransformer

The invention provides a power system reactive power optimization method based on depth determination strategy gradient reinforcement learning. A deterministic depth gradient strategy algorithm is applied to the traditional power system reactive power optimization problem. The voltage state of the power system is sensed through a depth neural network, a corresponding action decision is then made by using a reinforcement learning method, a correct generator terminal voltage adjustment action, a node capacitor bank switching action and a transformer tapping point adjustment action are made to adjust reactive power distribution in the power system, the active power network loss of the power system is minimized. As the neural network is divided into an online network and a target network, association between parameter updating and adjacent training in each training process of the neural network is avoided, and the problem that reactive power optimization of the power system is caught in local optimization is avoided. On the premise of conforming to the security constraint of the power system, the economical efficiency of the operation of the power system is improved by reducing the network loss of the power system.

Owner:HARBIN INST OF TECH +1

Systems, methods, and apparatus for integrated volt/VAR control in power distribution networks

ActiveUS8816531B2Electric signal transmission systemsDc network circuit arrangementsTime segmentElectric distribution network

Owner:GE DIGITAL HLDG LLC

Capacitor system

InactiveUS20050212493A1Reduce power lossImprove performanceDc network circuit arrangementsElectrolytic capacitorsCapacitanceTransfer switch

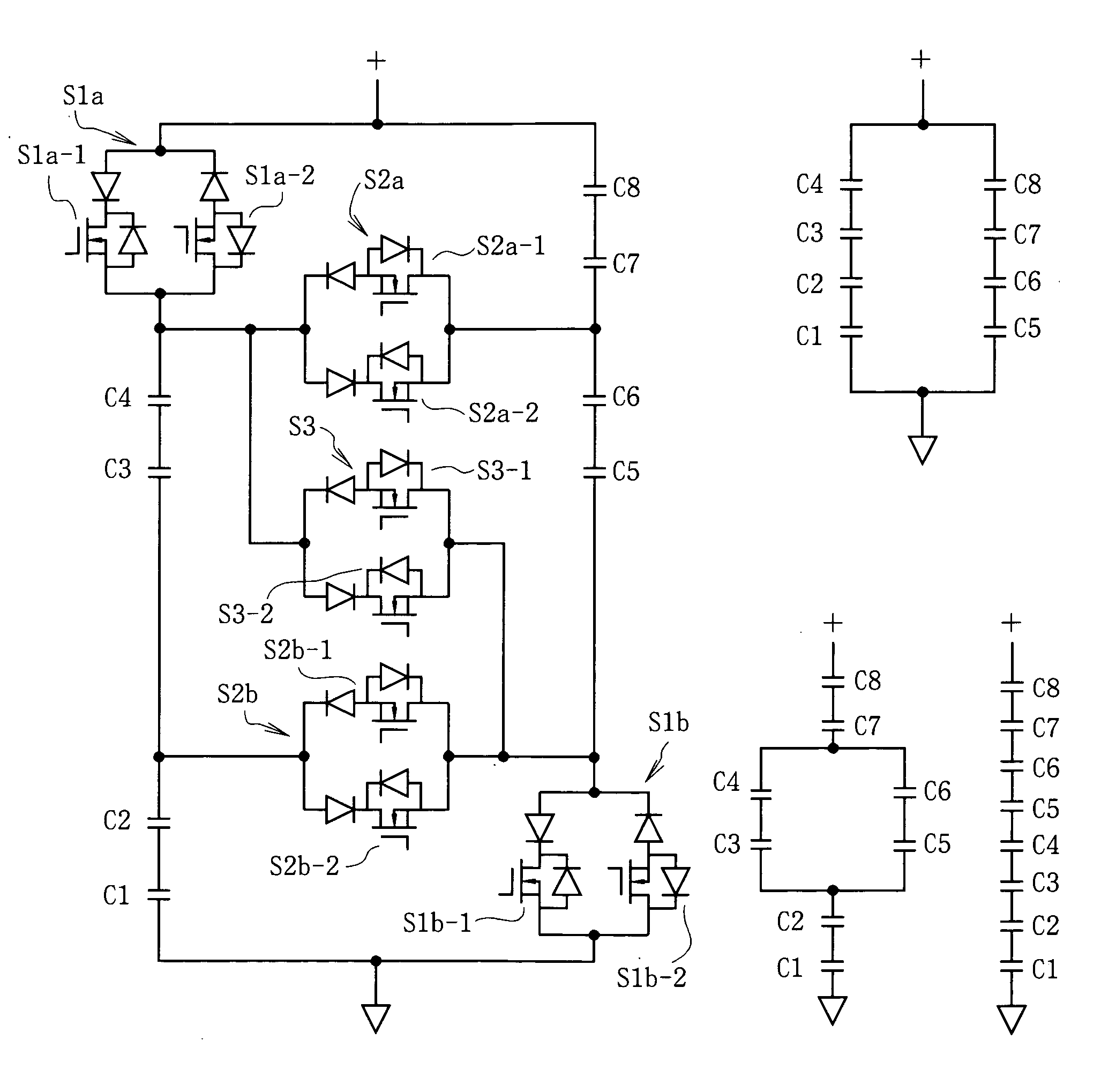

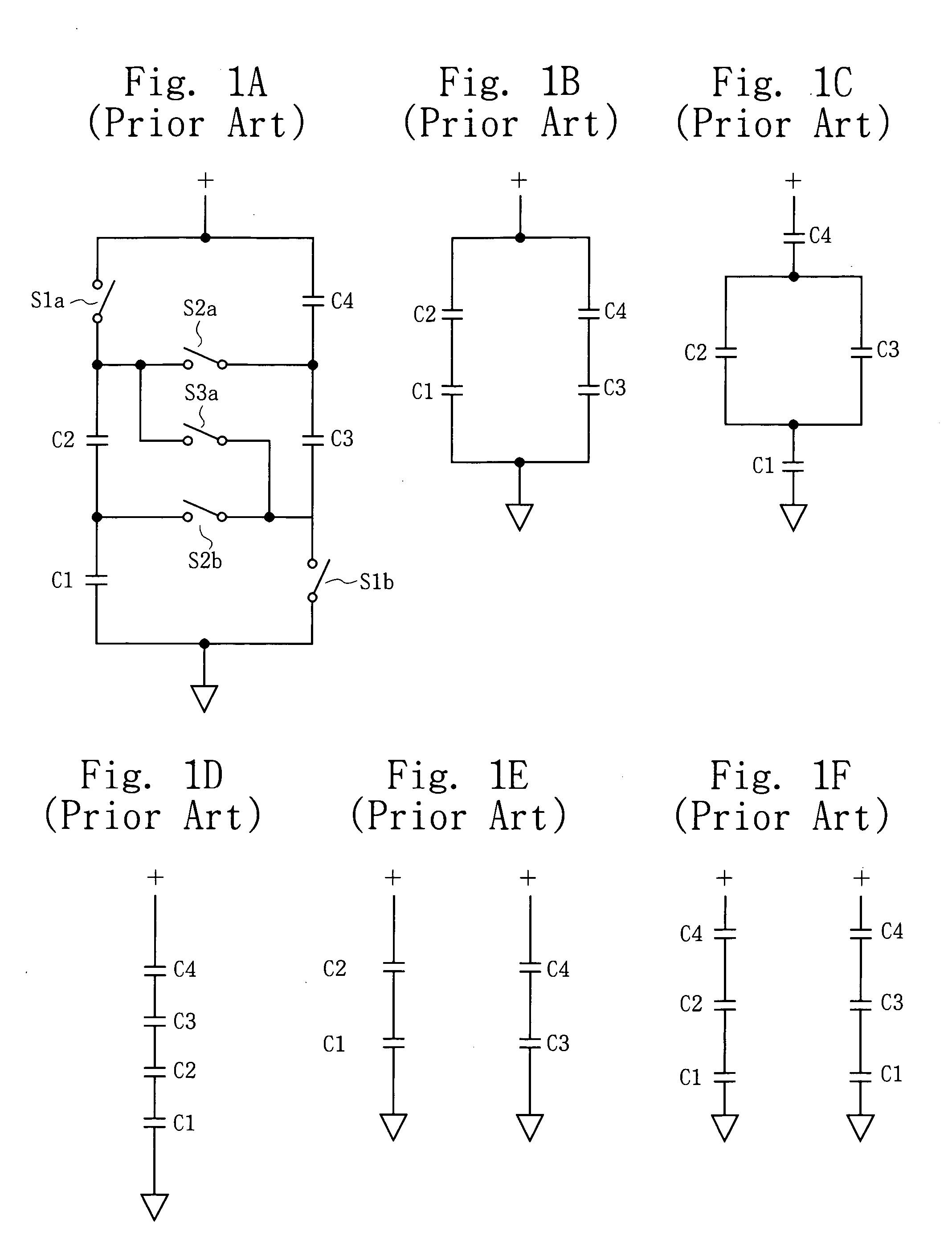

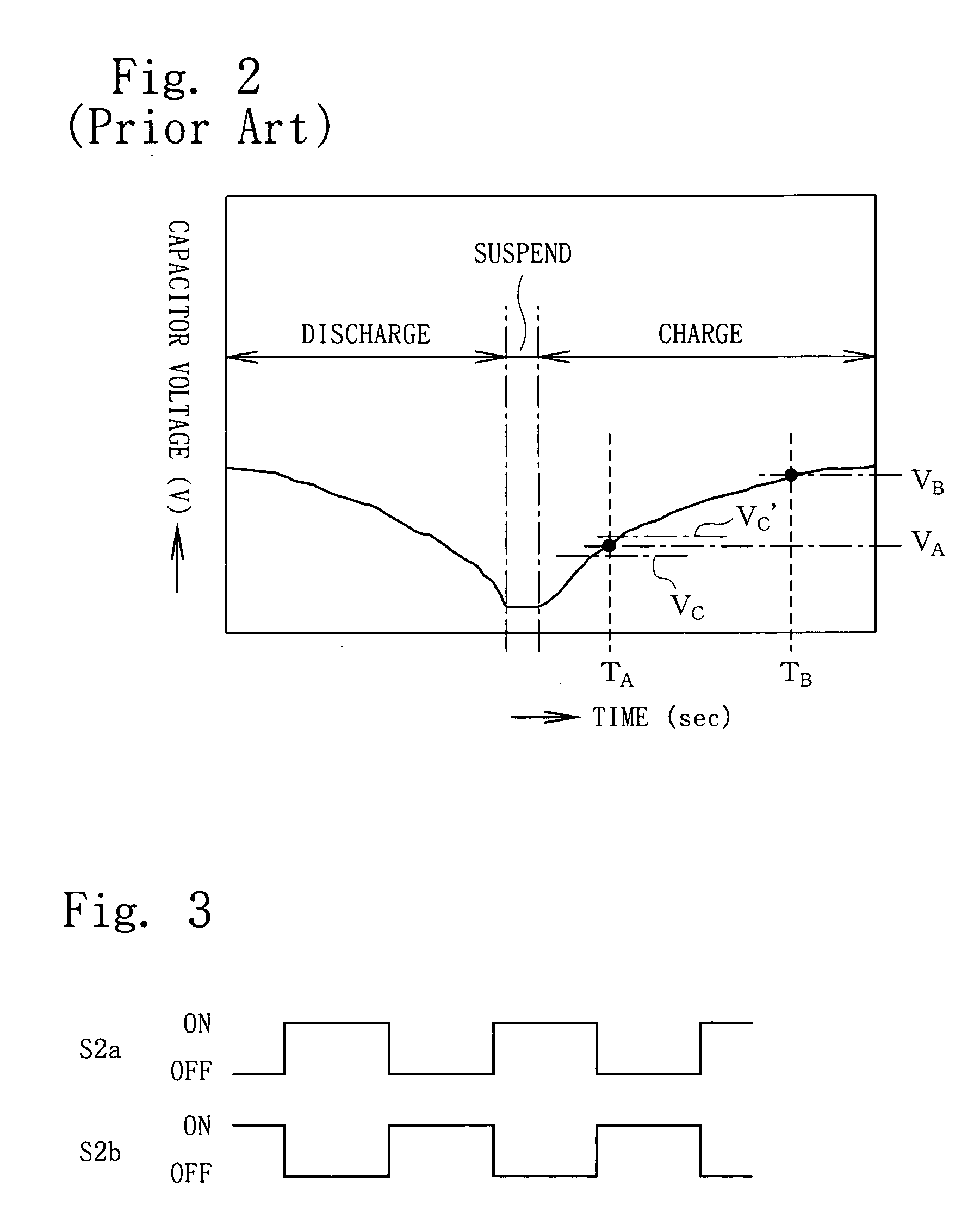

Provided is a capacitor system which makes the best use of the performance of capacitors while reducing power loss. The capacitor system includes a plurality of capacitors, parallel monitors which are respectively connected in parallel to the capacitors and initialize voltages of the capacitors to a predetermined value, a plurality of changeover switches which function to switch a connection state of the capacitors connected in series, and a bank switching function of switching the connection state of the capacitors by alternately turning the changeover switches on and off to provide a predetermined voltage. The changeover switches are alternately turned on and off while maintaining a simultaneous ON time to ensure continuous flow of a charge / discharge current.

Owner:TOKO ELECTRIC CORP +1

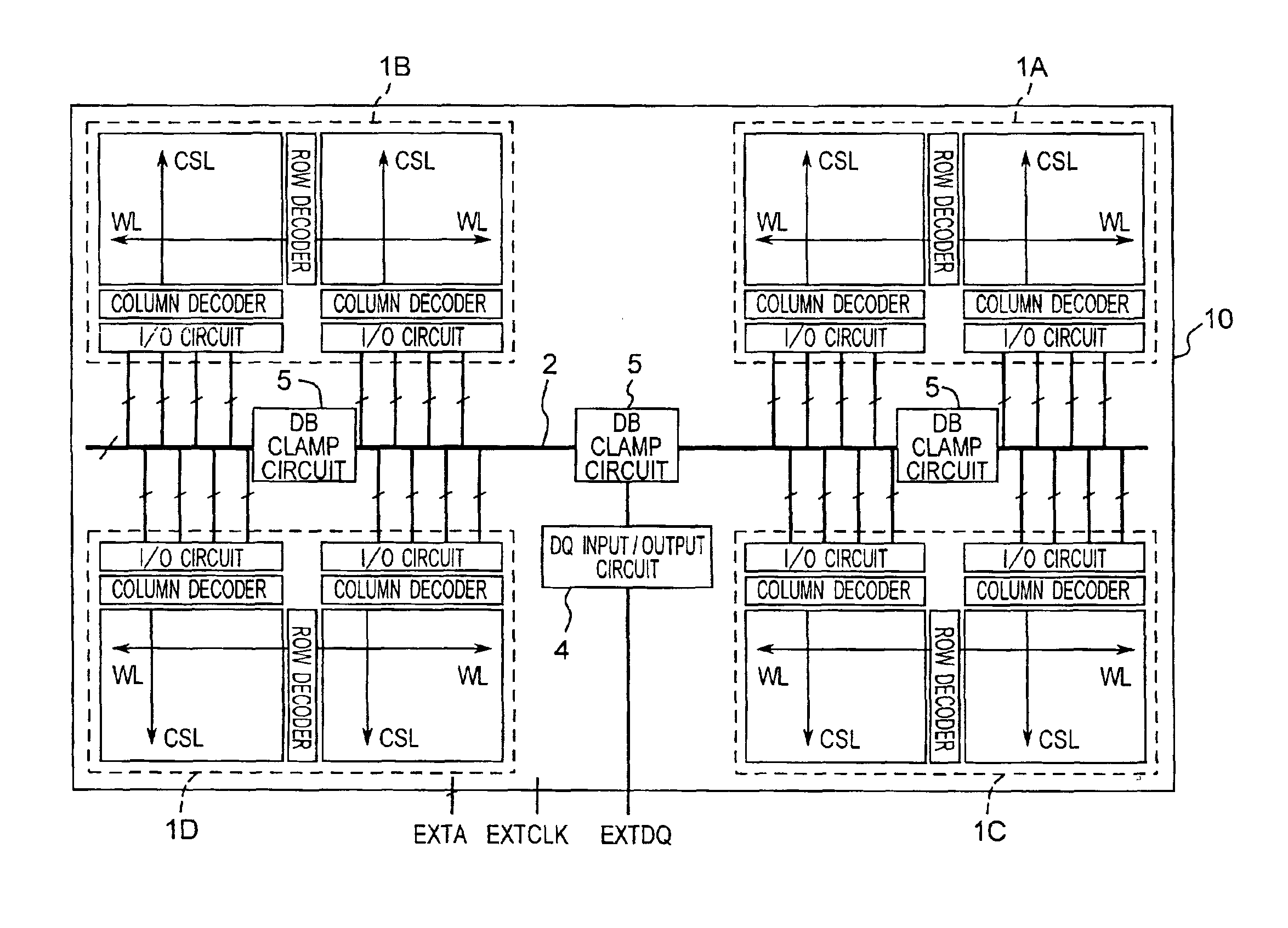

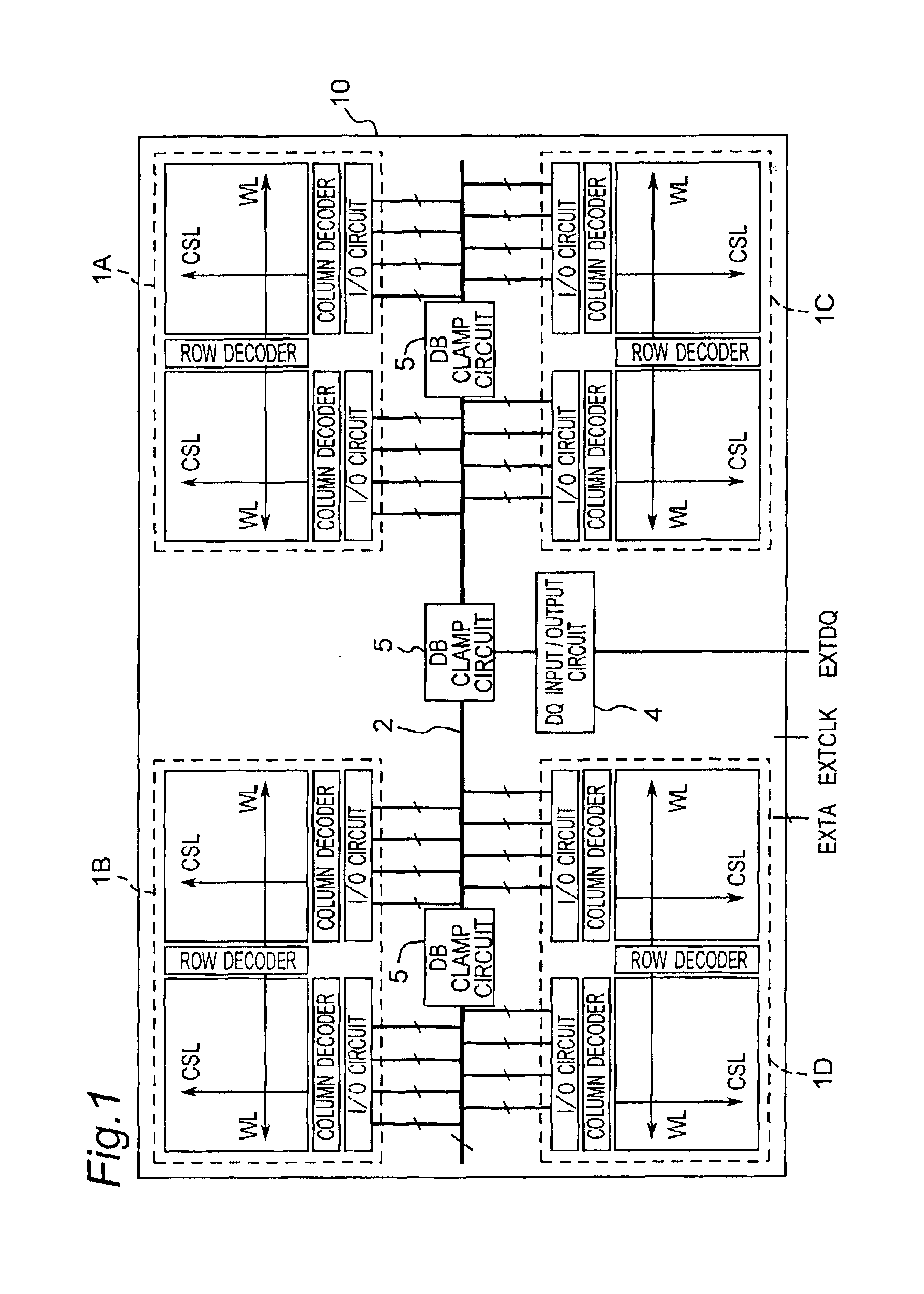

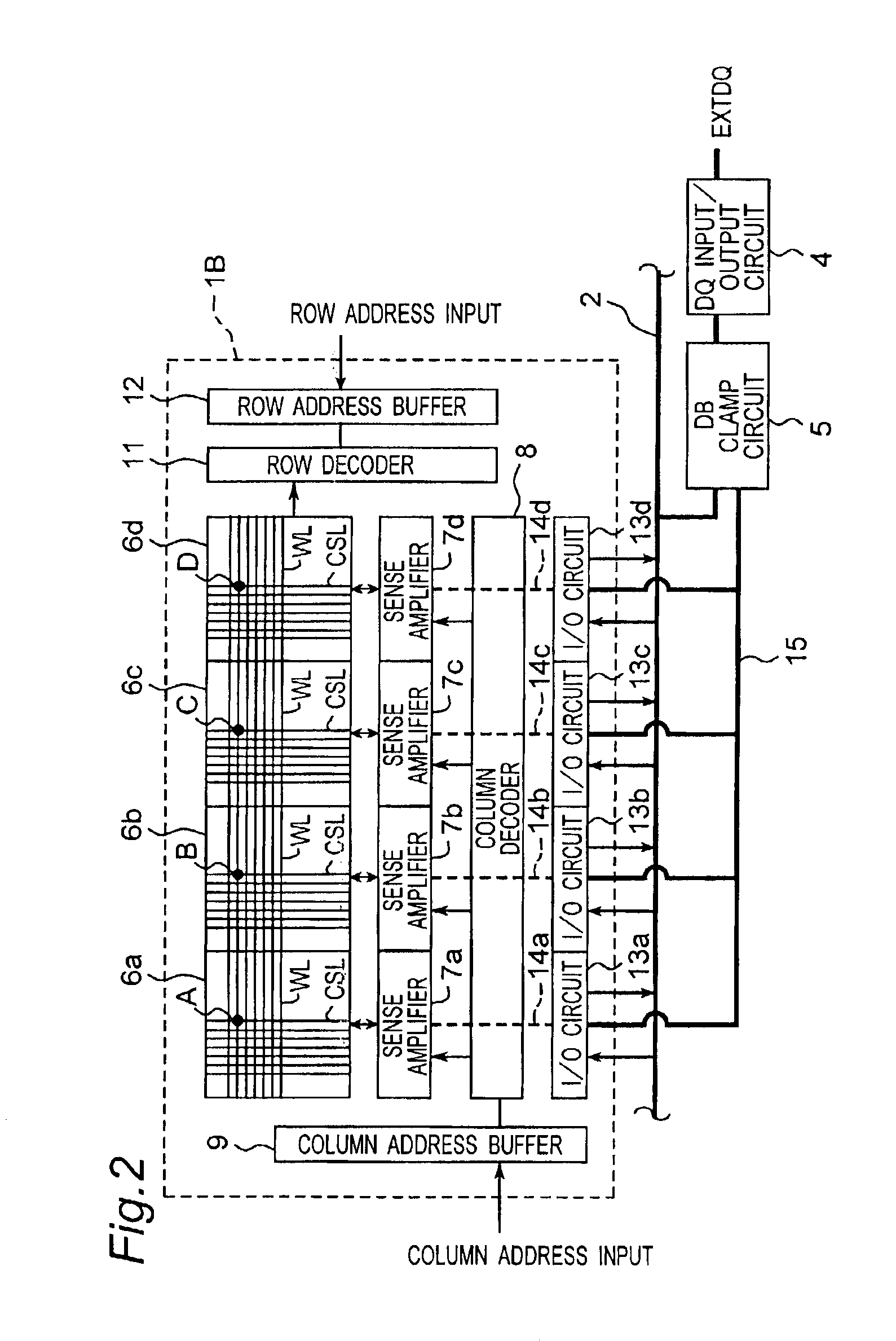

Semiconductor memory device and its testing method

A semiconductor memory device is of a bank switching type having a plurality of memory array banks provided in a memory chip which can be switched from one to another for storage operation. The semiconductor memory device includes: a plurality of memory arrays in the memory array banks; an input / output circuit for transmitting information data between the memory arrays and the outside; a data bus for connecting between the memory arrays and the input / output circuit; and N-channel transistors provided across the data bus. The data bus consists of a plurality of adjacent lines. Each of N-channel transistors is connected at their drain to the corresponding lines of the data bus while at their source to the ground. When a multi-bit test is commenced for writing and reading data on the memory arrays, the N-channel transistors are turned on to connect the lines of the data bus to the ground.

Owner:RENESAS ELECTRONICS CORP

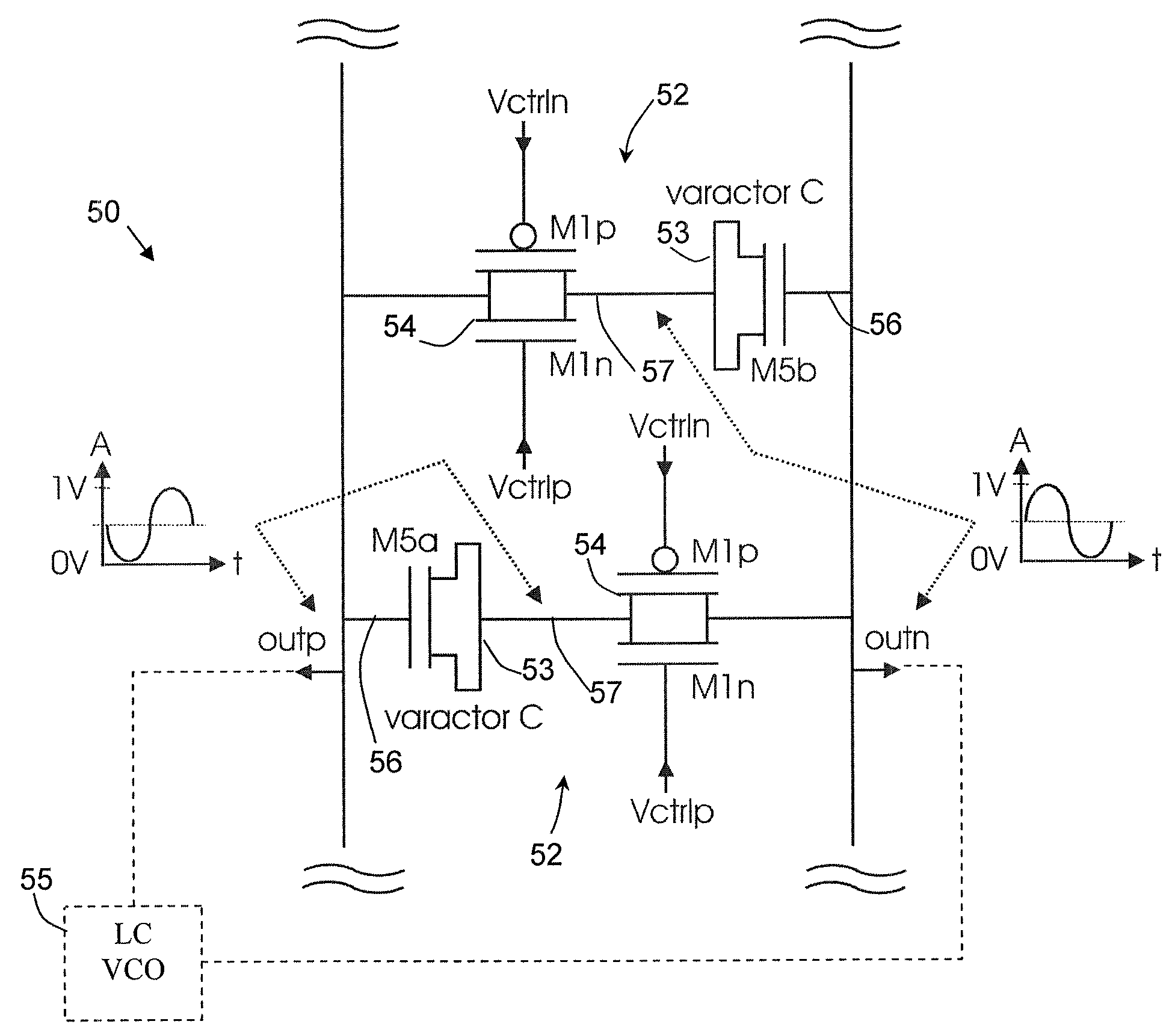

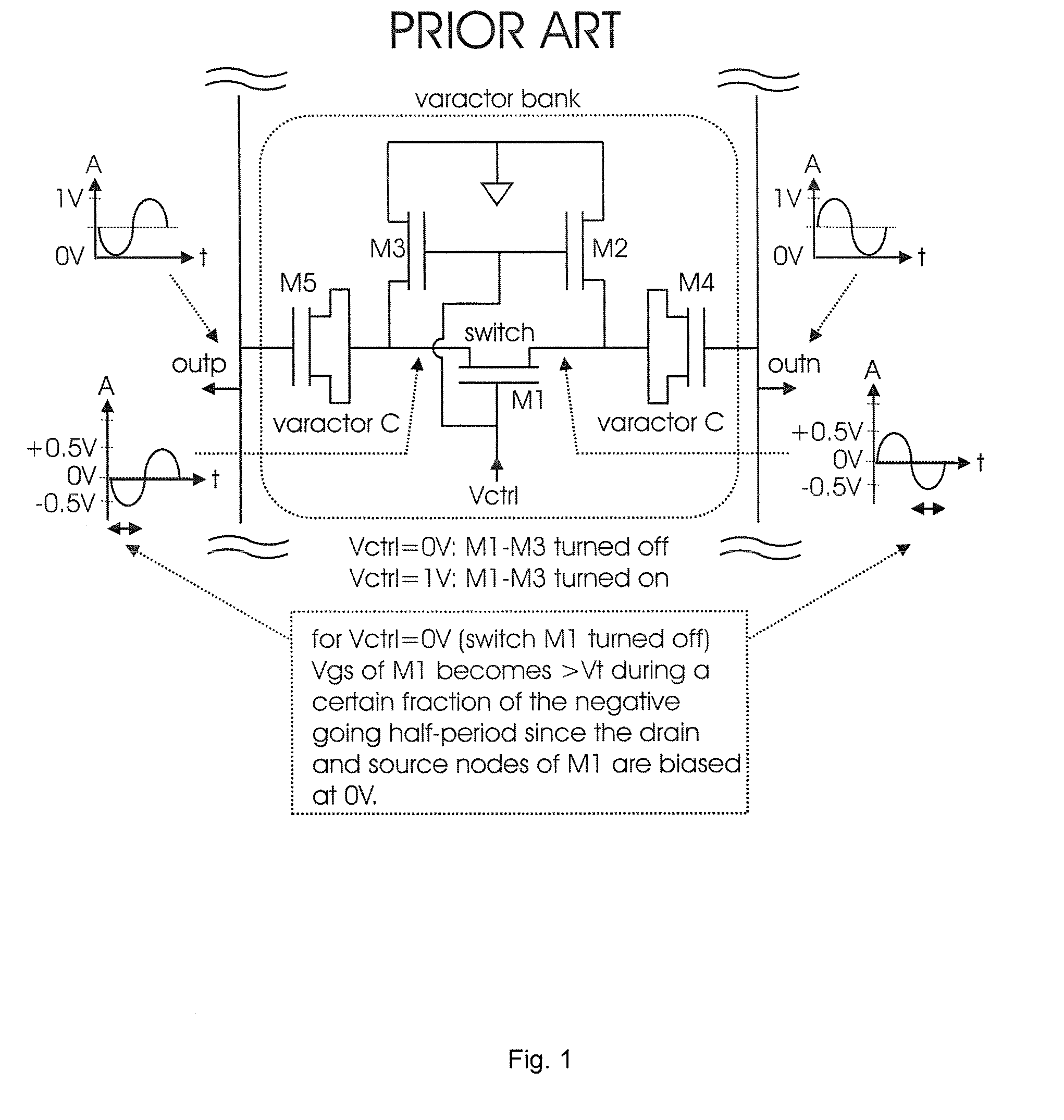

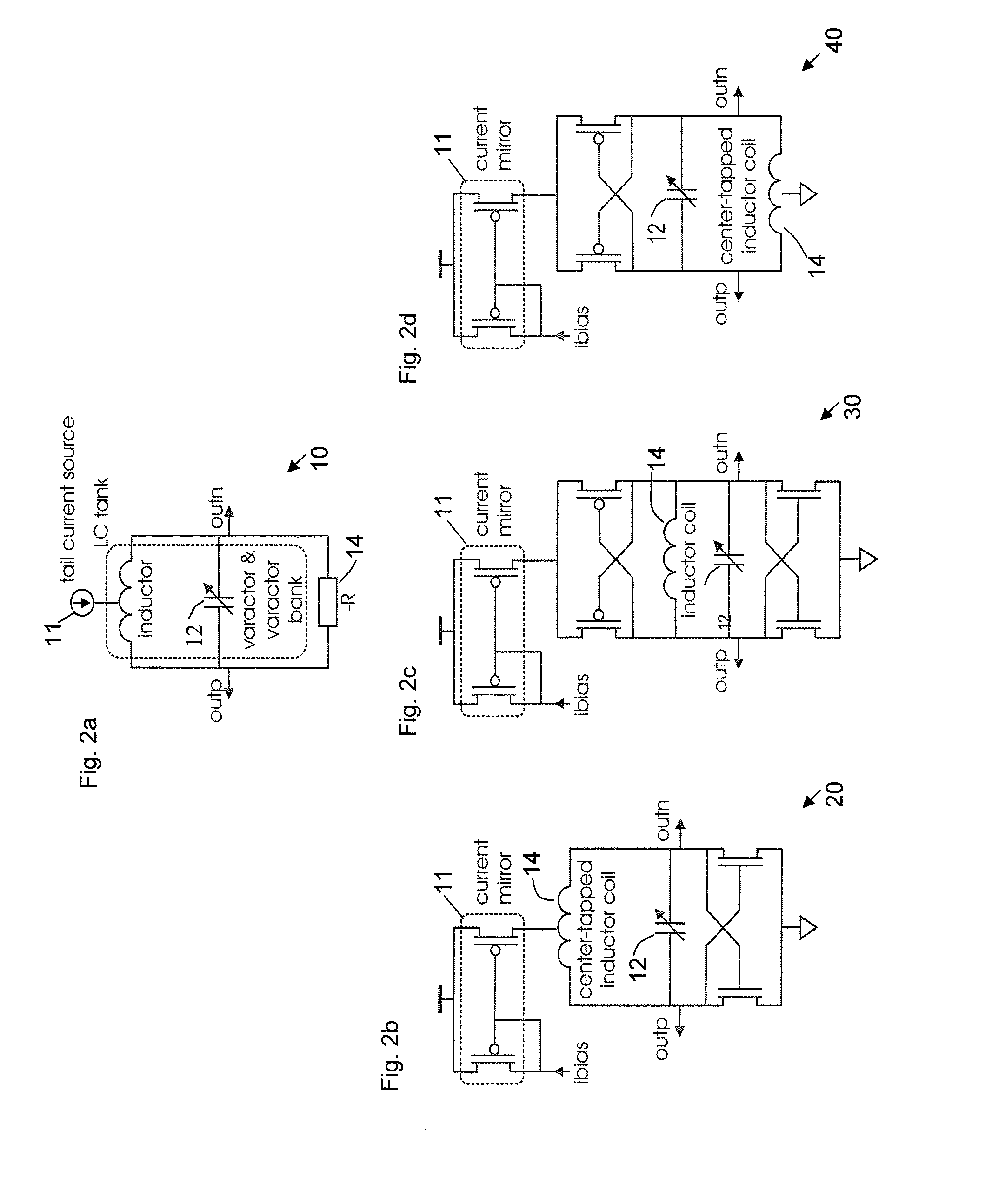

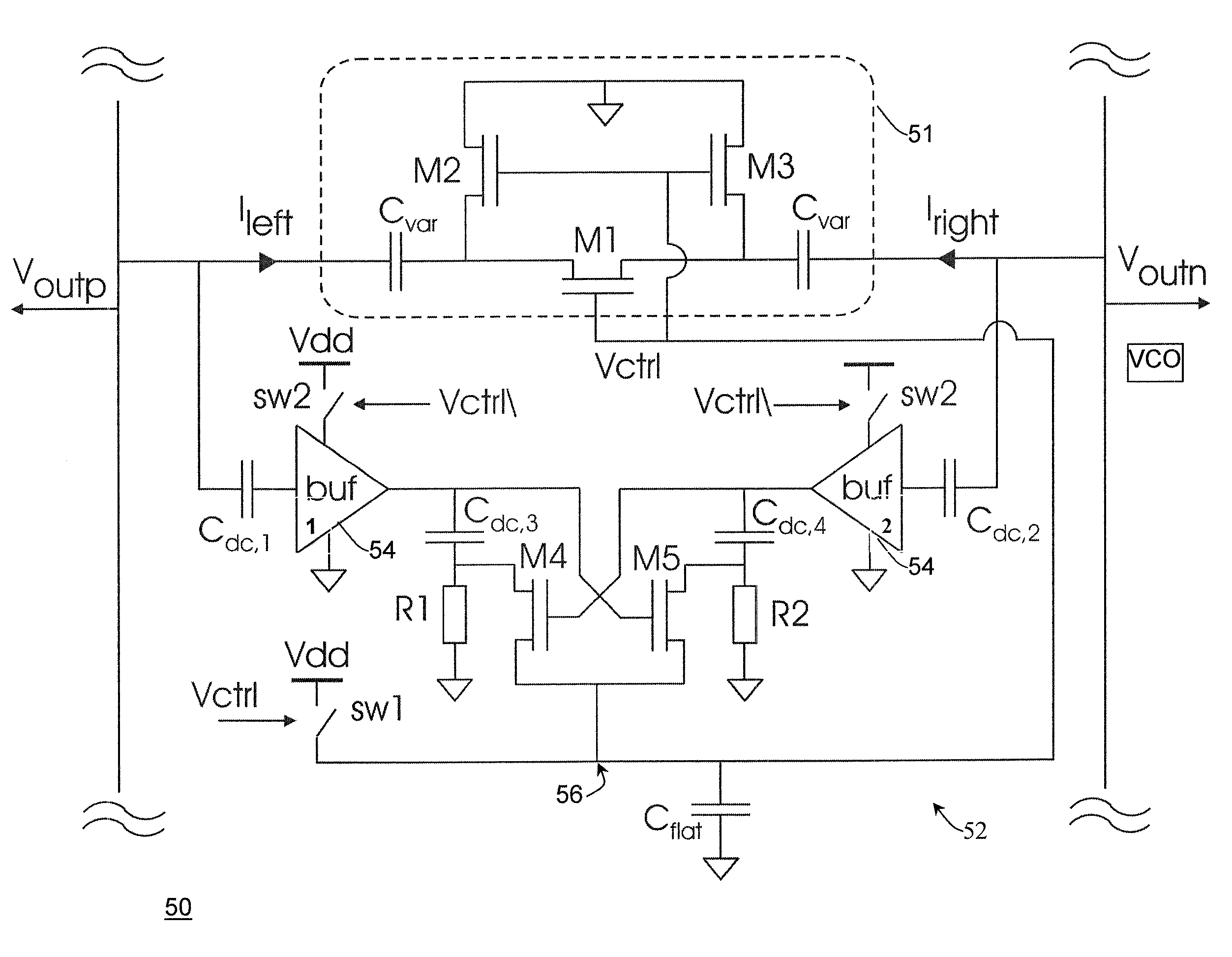

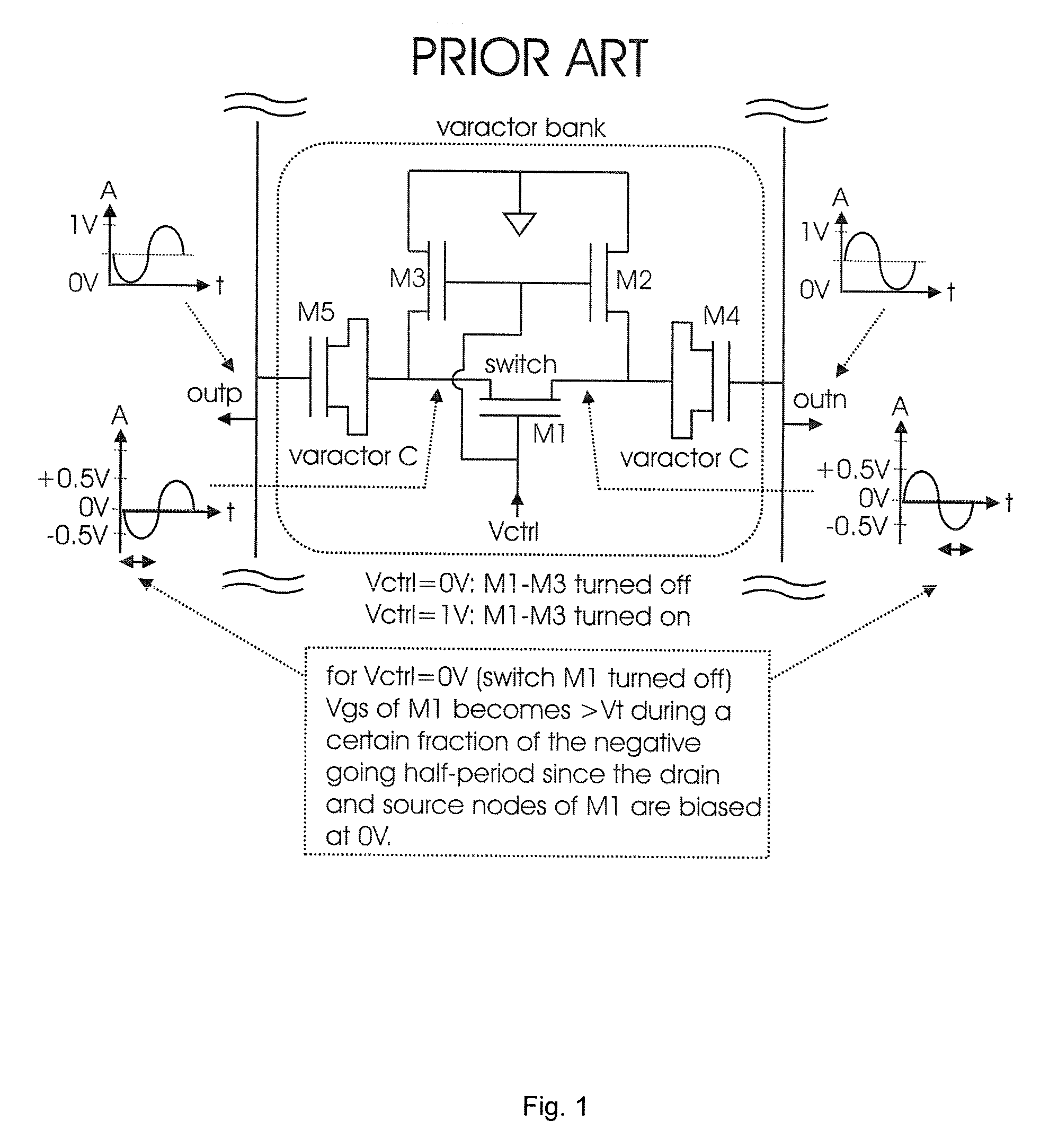

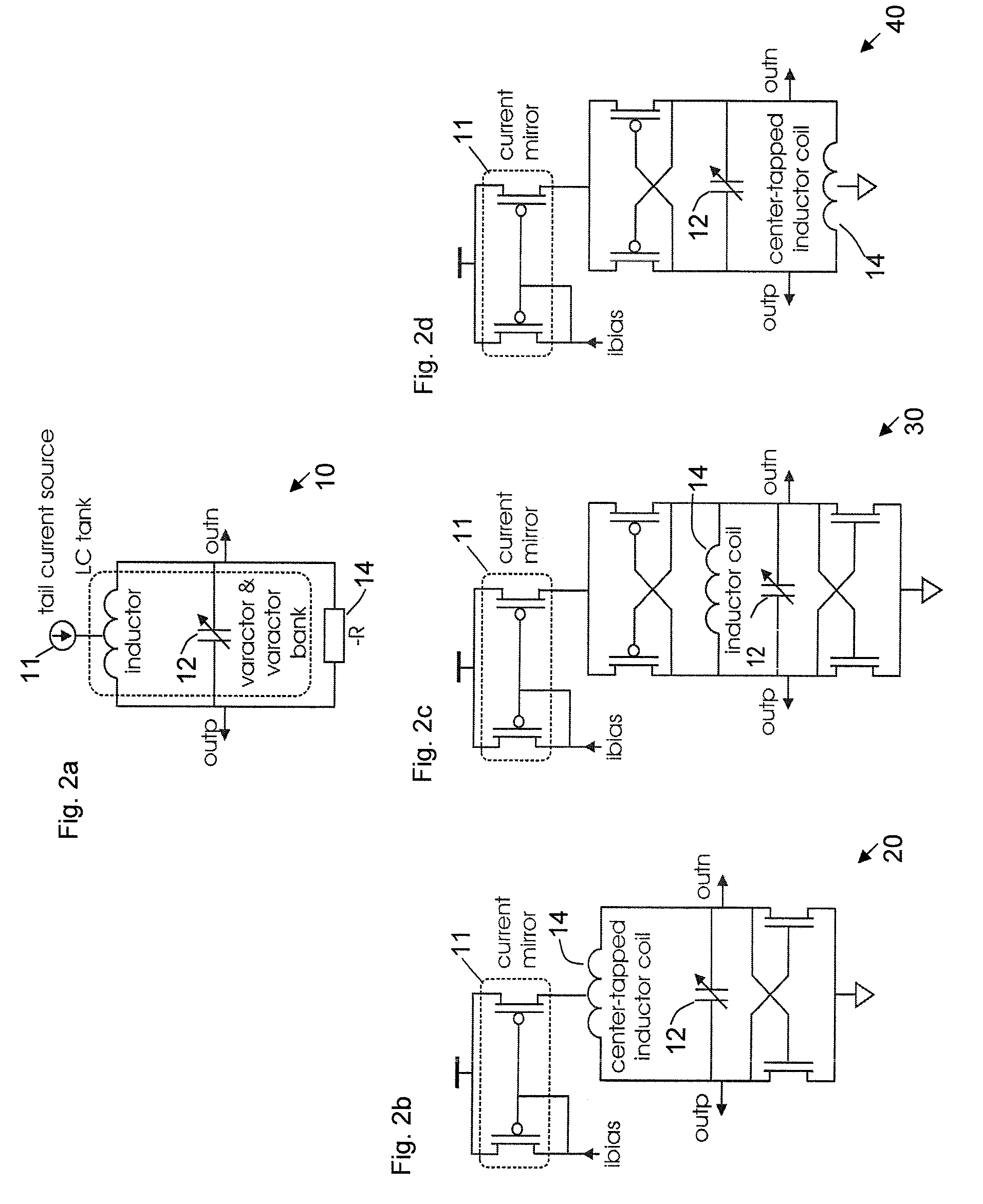

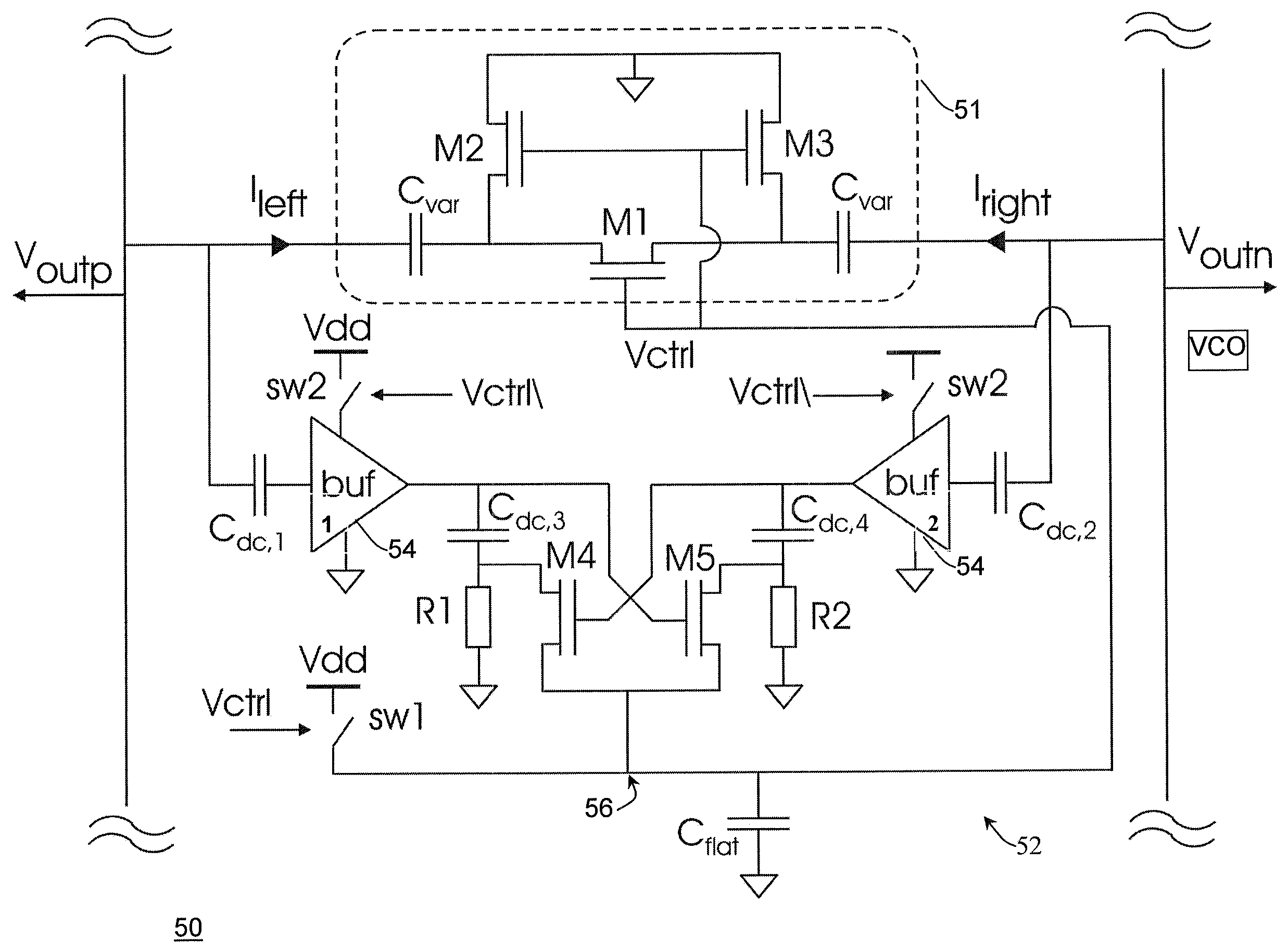

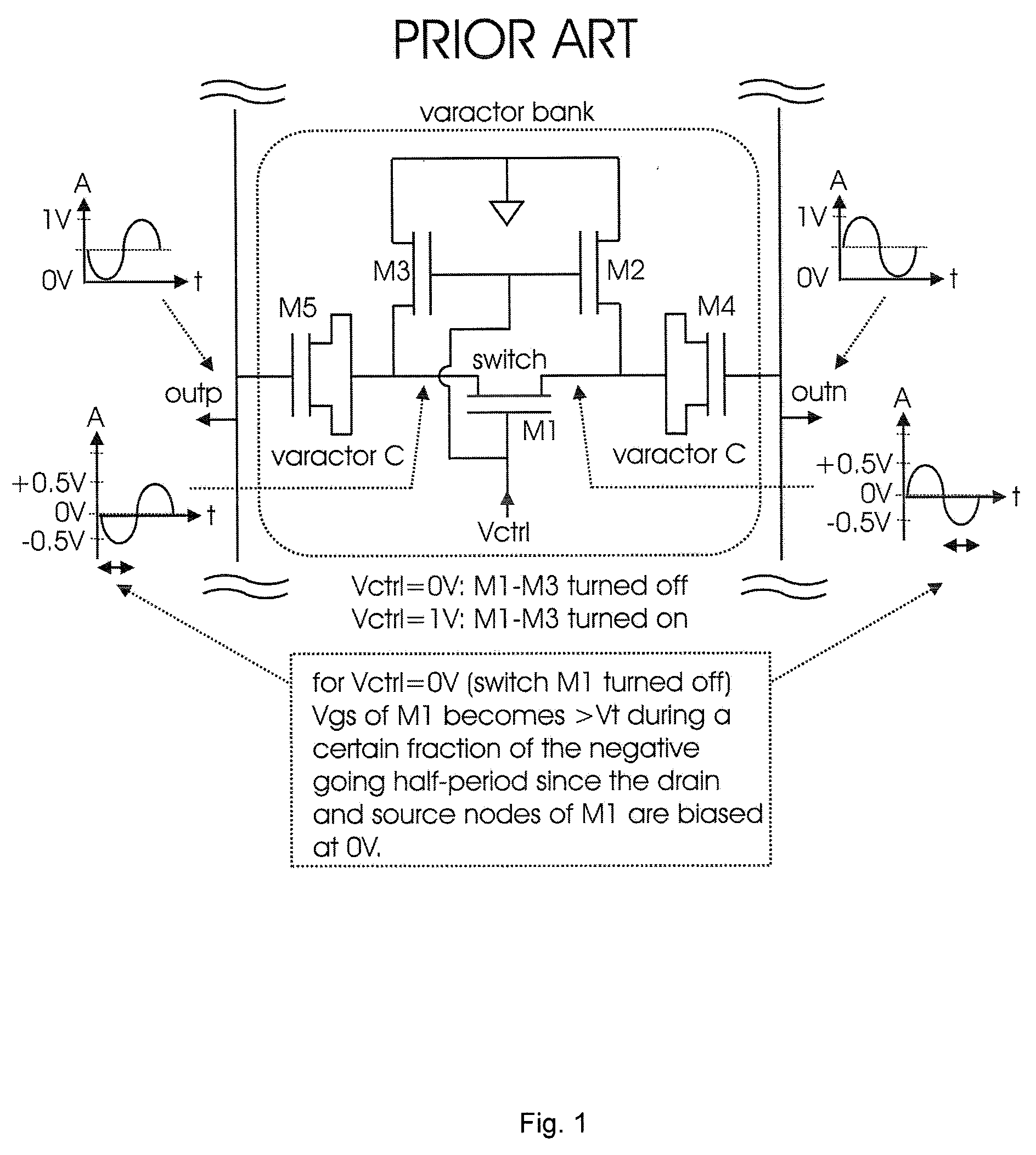

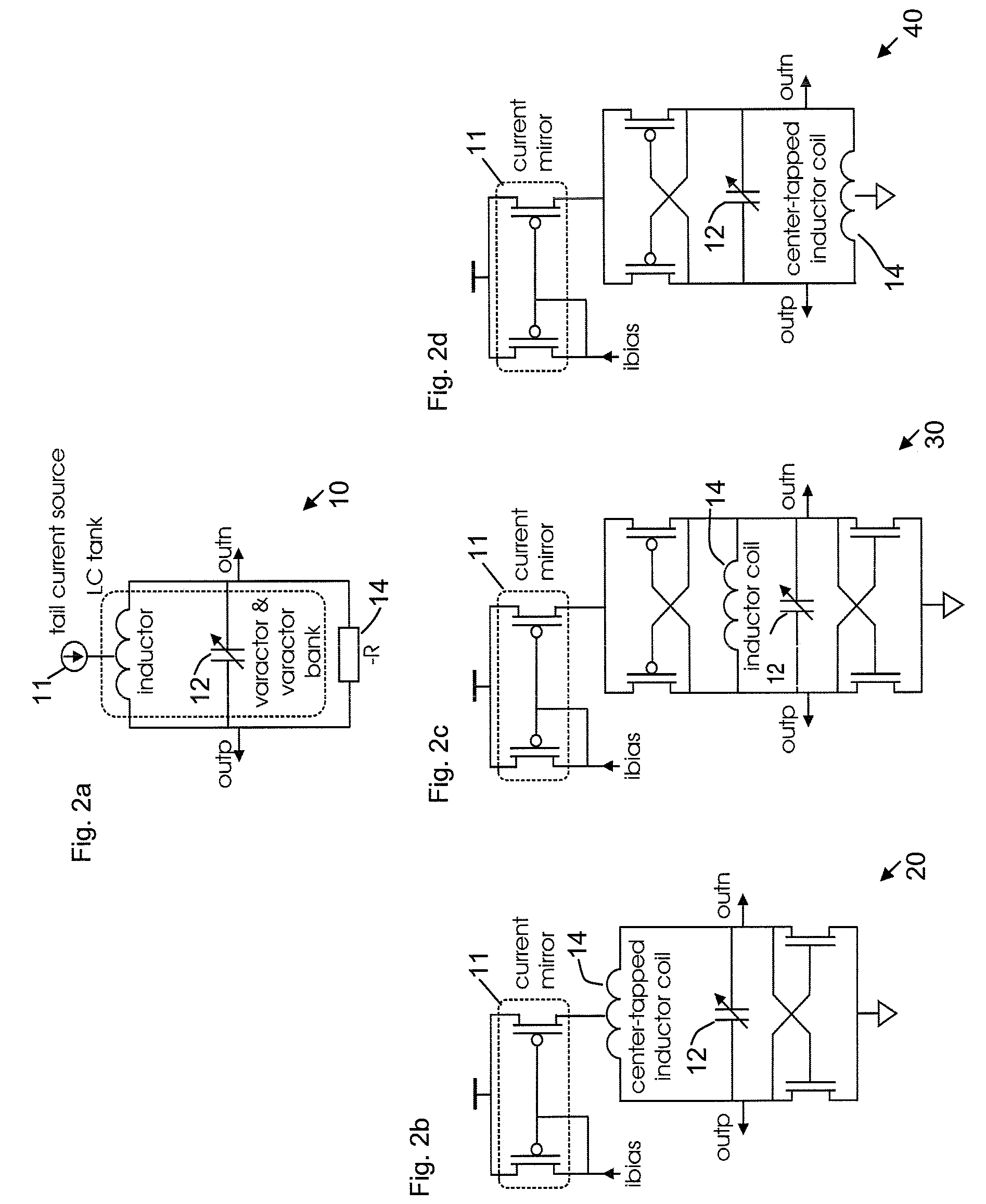

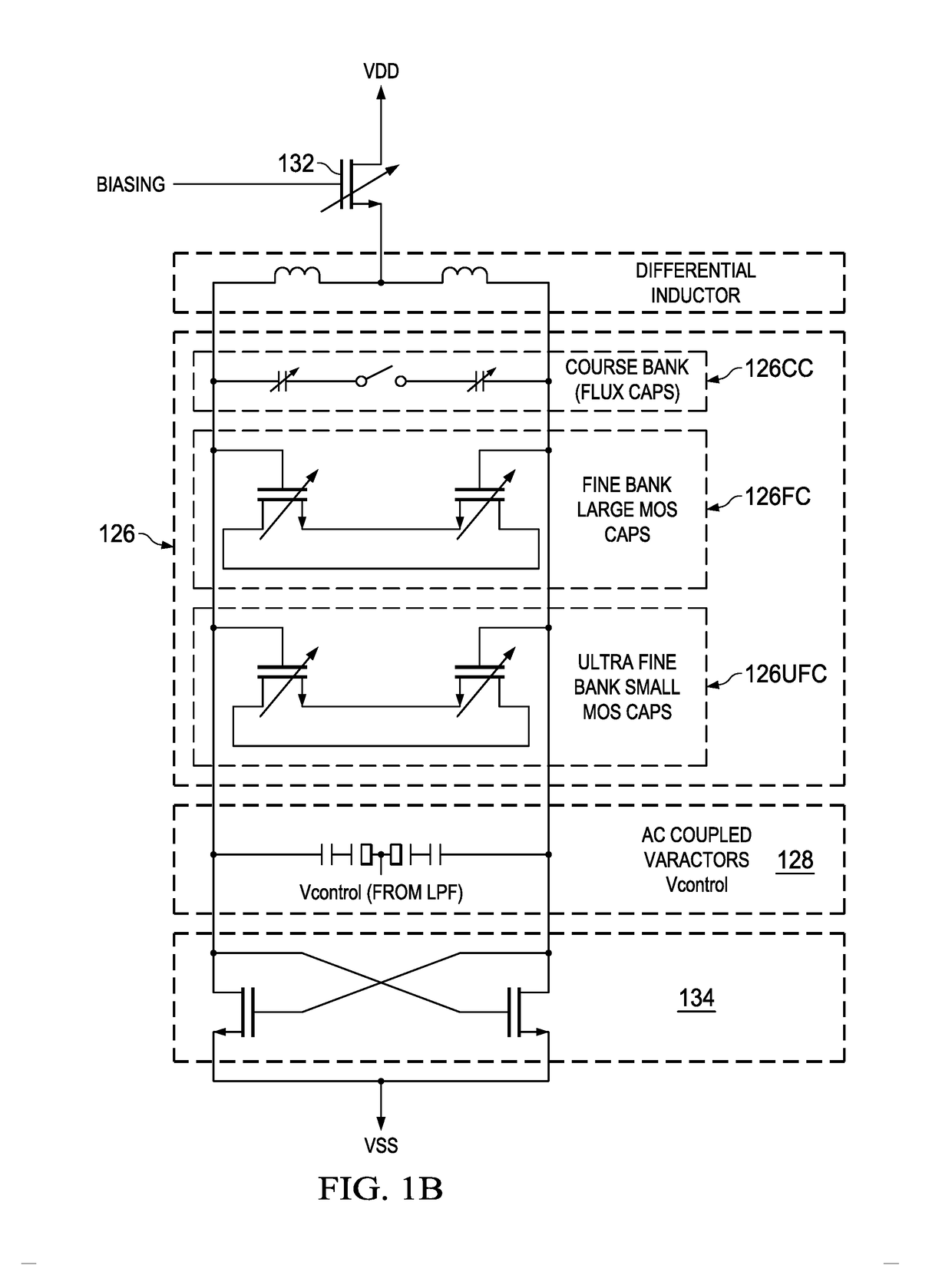

Varactor bank switching based on Anti-parallel branch configuration

A system and apparatus for varactor bank switching for a voltage controlled oscillator, is disclosed. Varactor bank switching involves partitioning a varactor bank switch into two anti-parallel branches, wherein each branch comprises a pass-gate circuit that is series-connected to a fixed varactor or capacitor; and maintaining an output common mode voltage of an actual oscillator signal at the varactor-side terminal of each pass-gate circuit, such that a threshold voltage of the switch transistor in the pass-gate circuit is not exceeded and the switch remains in an off-state.

Owner:IBM CORP

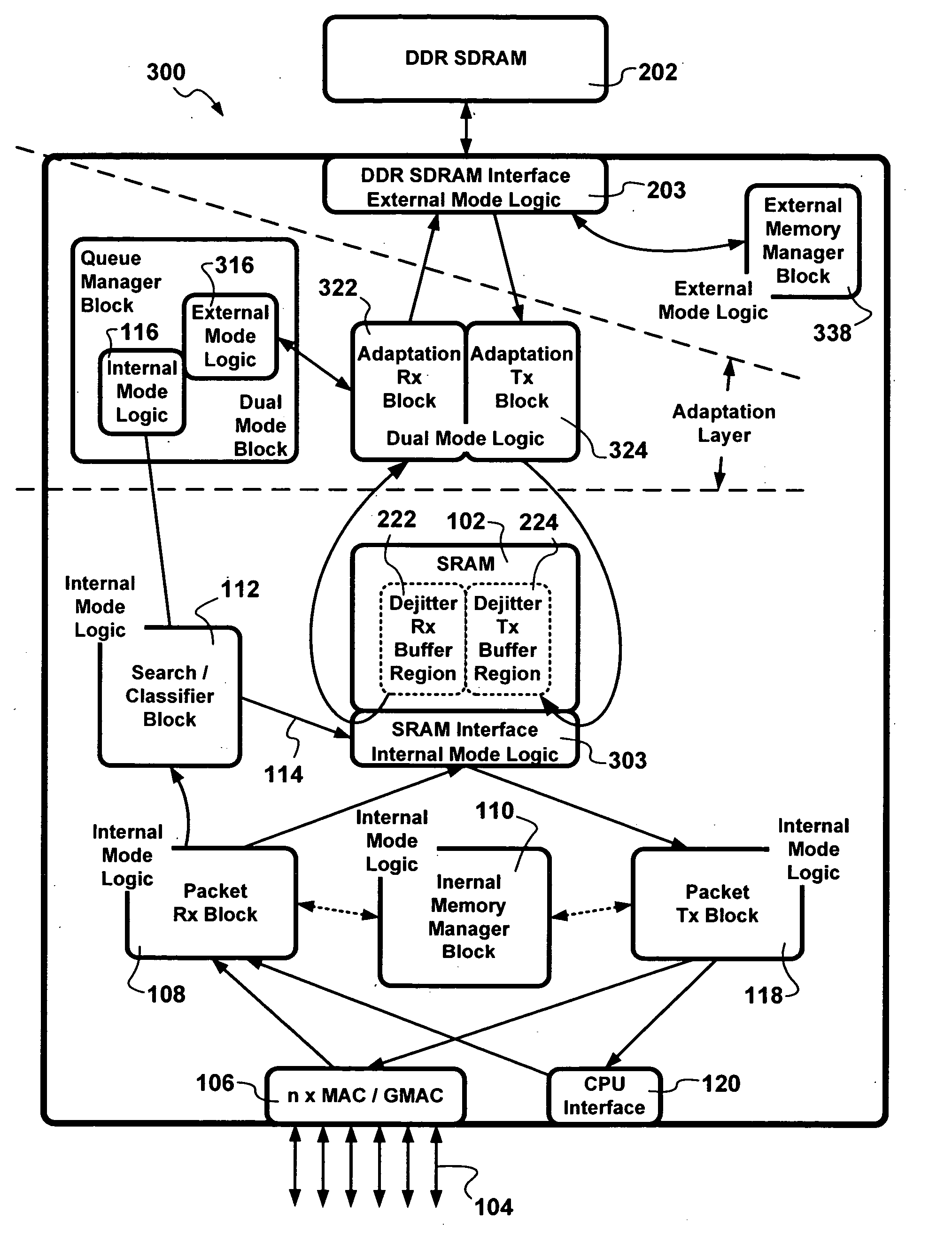

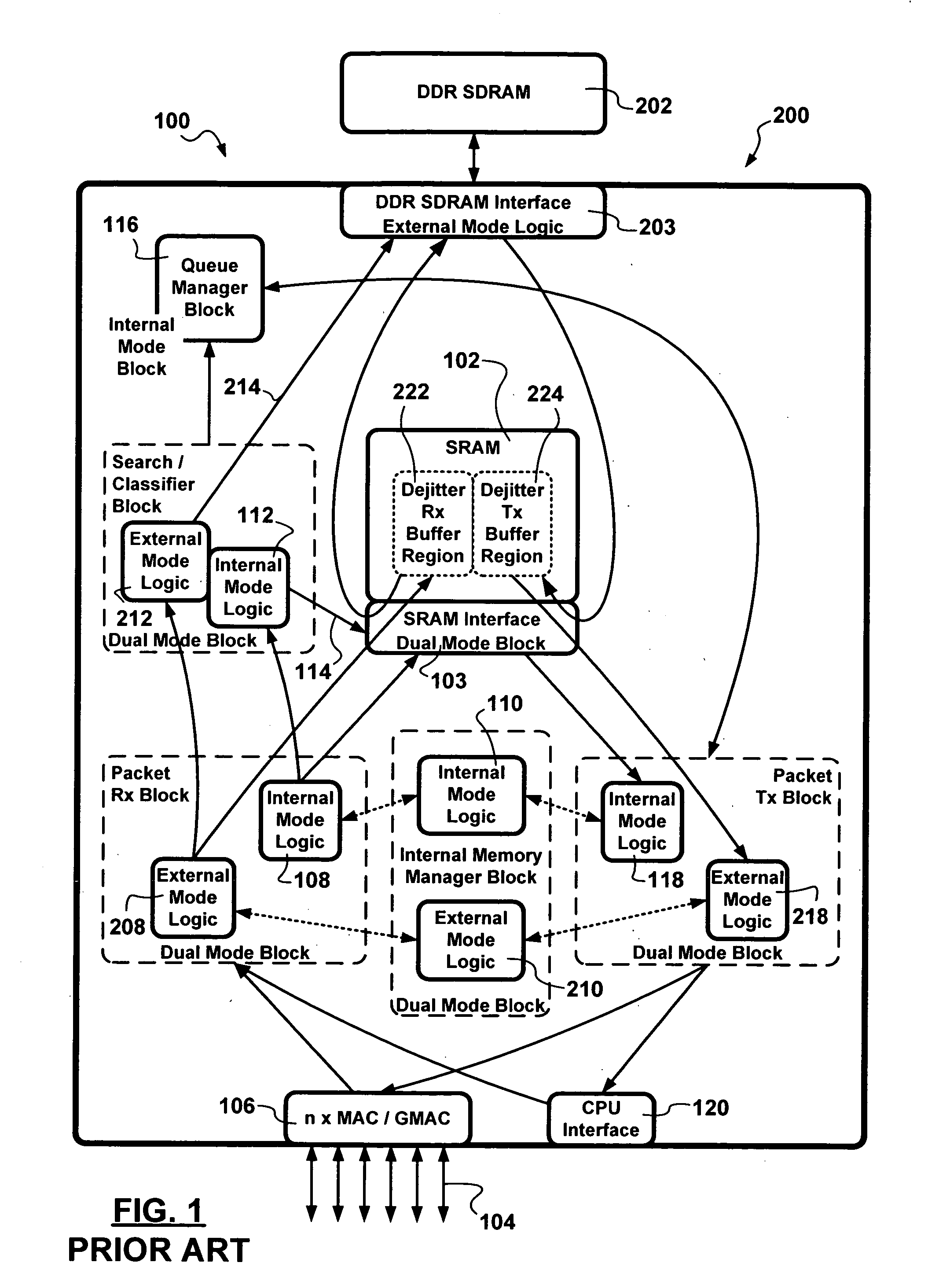

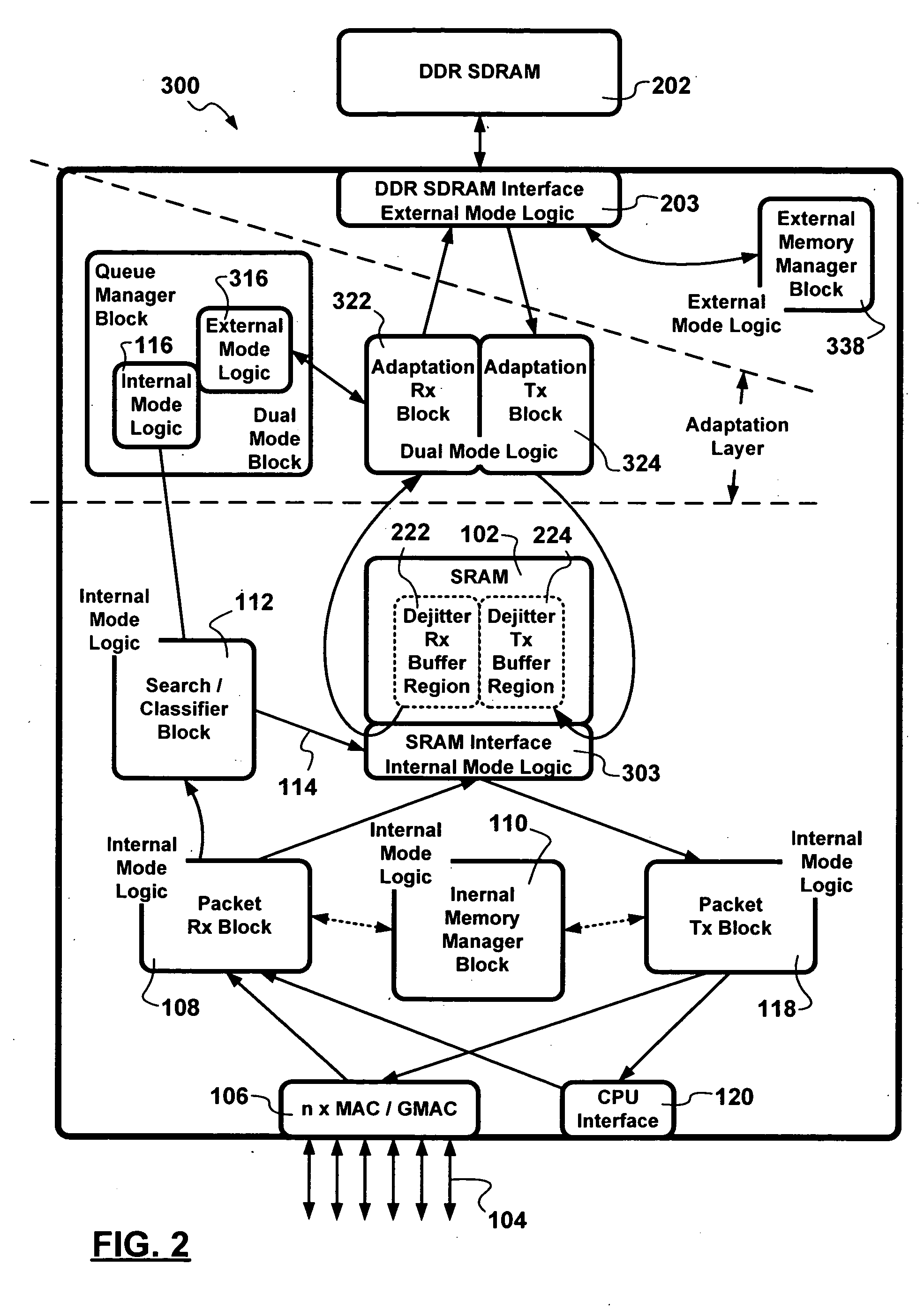

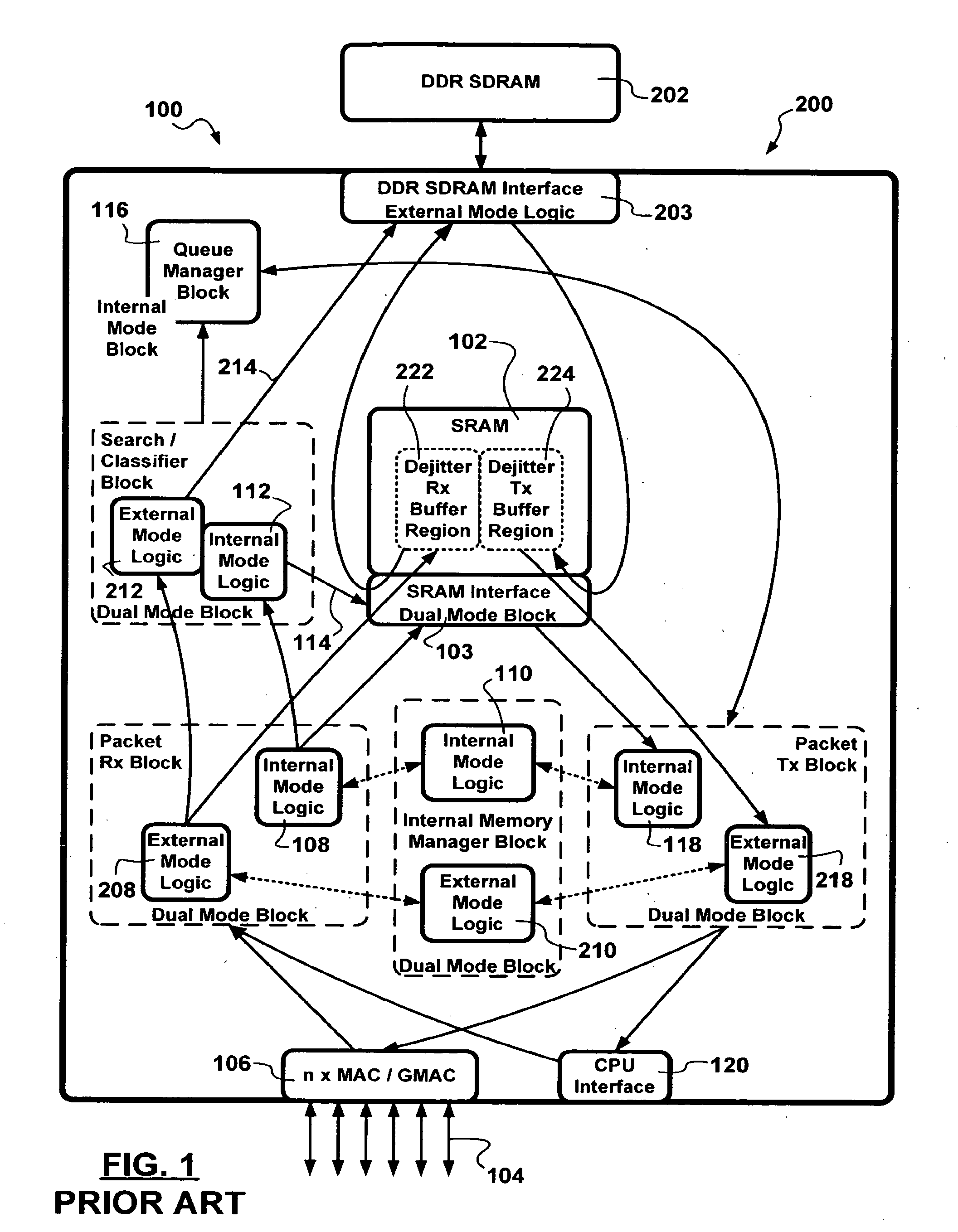

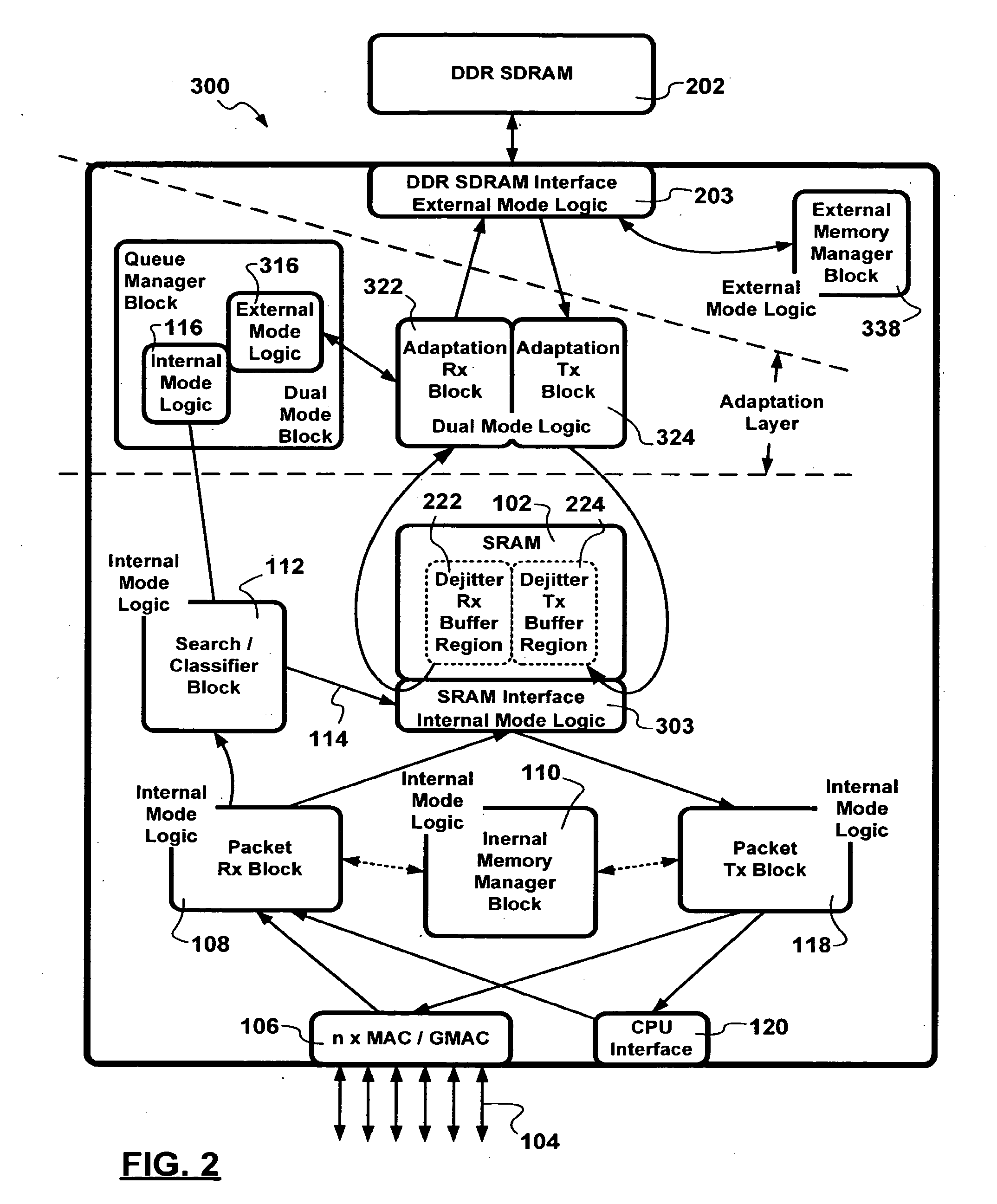

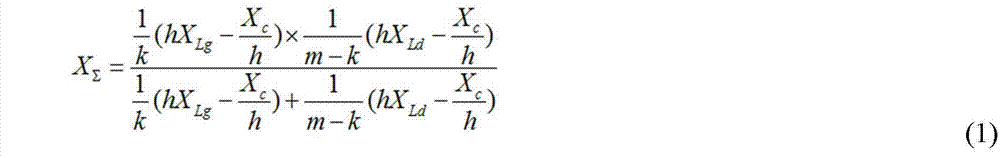

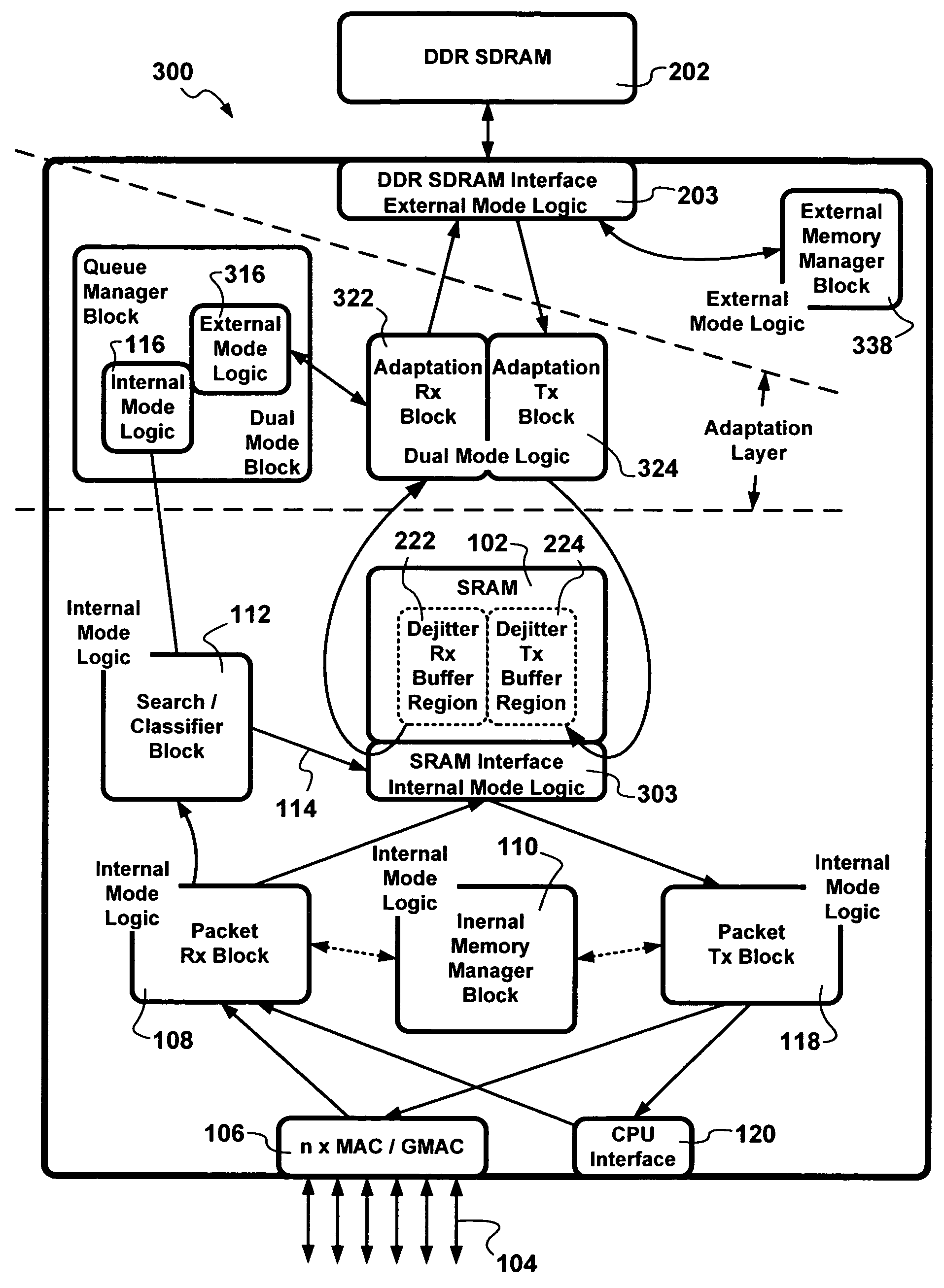

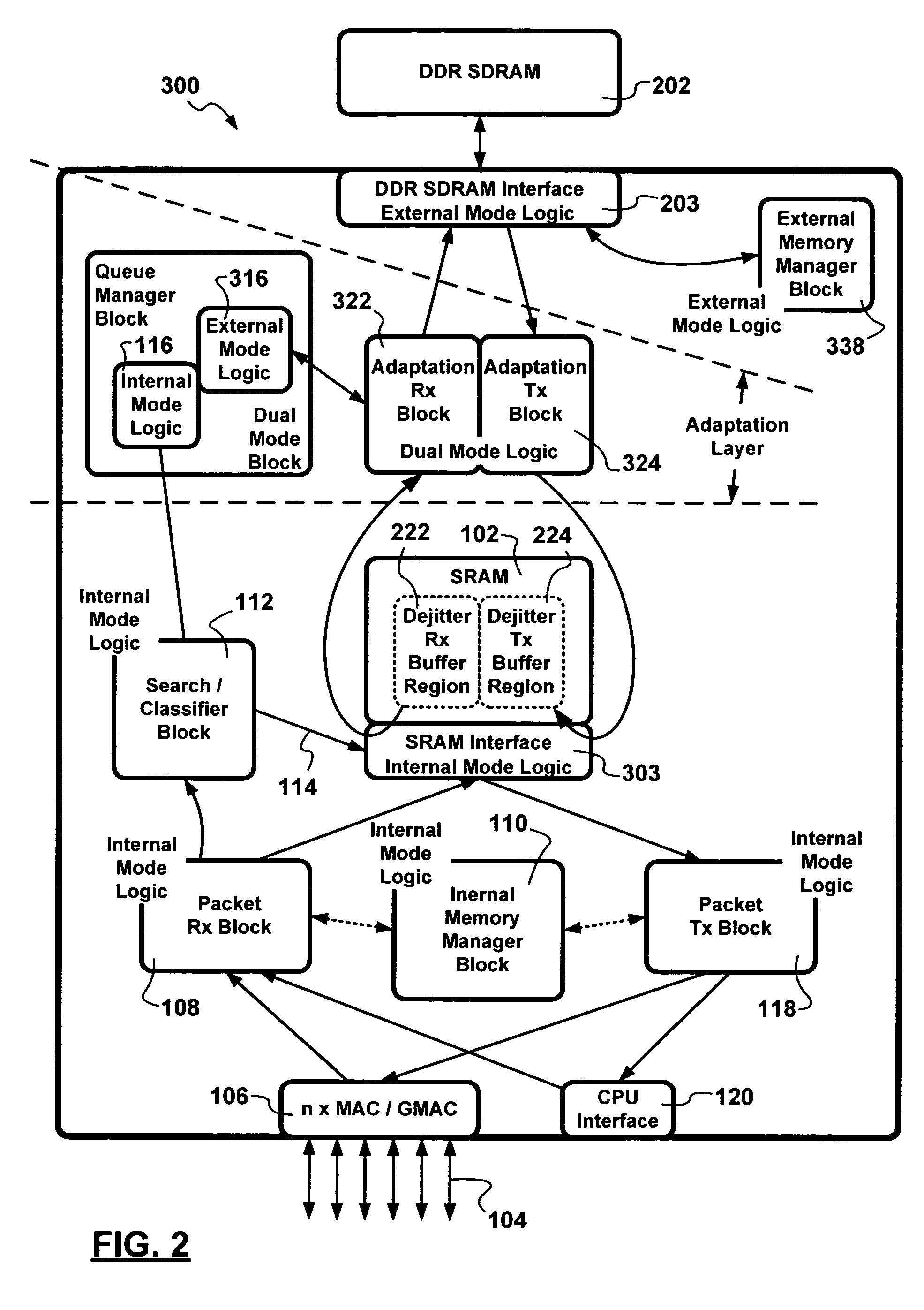

Compact packet switching node storage architecture employing double data rate synchronous dynamic RAM

A two-chip / single-die switch architecture and a method for accessing a DDR SDRAM memory store in a switching environment are presented. The two-chip / single-die architecture includes an internal memory storage block on the single-die, an external memory storage interface to a Double Data Rate Synchronous Dynamic Random Access Memory (DDR SDRAM), an external memory manager, and a packet data transfer engine effecting packet data transfers between an internal memory store and the external DDR SDRAM memory. The packet data transfer engine operates as an adaptation layer addressing issues related to employing appropriate: addressing schemes, granule sizes, memory transfer burst sizes, access timing, etc. The packet data transfer engine includes a minimal number of dual mode operational blocks such as: a queue manager, and adaptation receive and transmit blocks. The method relates to a packet data transfer discipline addressing random memory access latencies incurred in employing DDR SDRAM, using predictive bank switching to hide random access latencies, packet length dependent variable memory write burst lengths to minimize bank switching, and performing memory read and write operations during corresponding read and write windows. Advantages are derived from the a space-efficient two-chip / single-die switching node architecture implemented with a reduced amount of dual mode logic, and also from DDR SDRAM bandwidth utilization efficiencies.

Owner:IKANOS COMMUNICATIONS

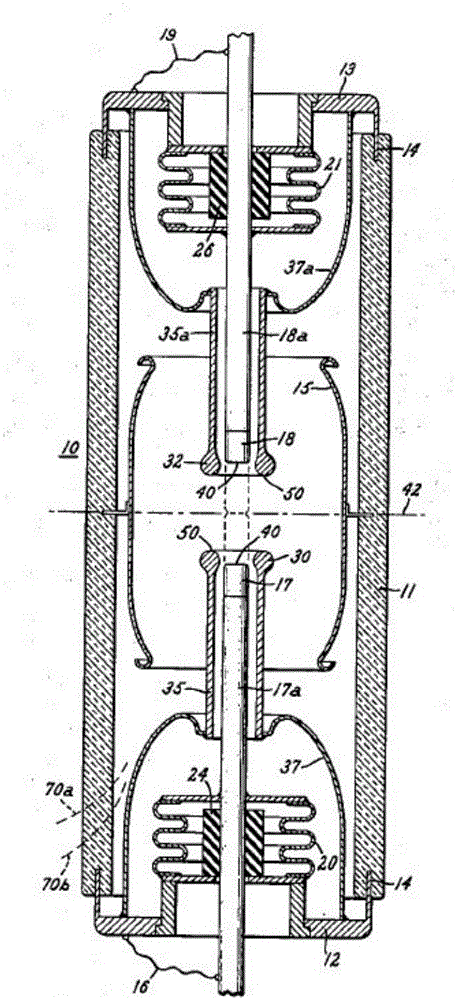

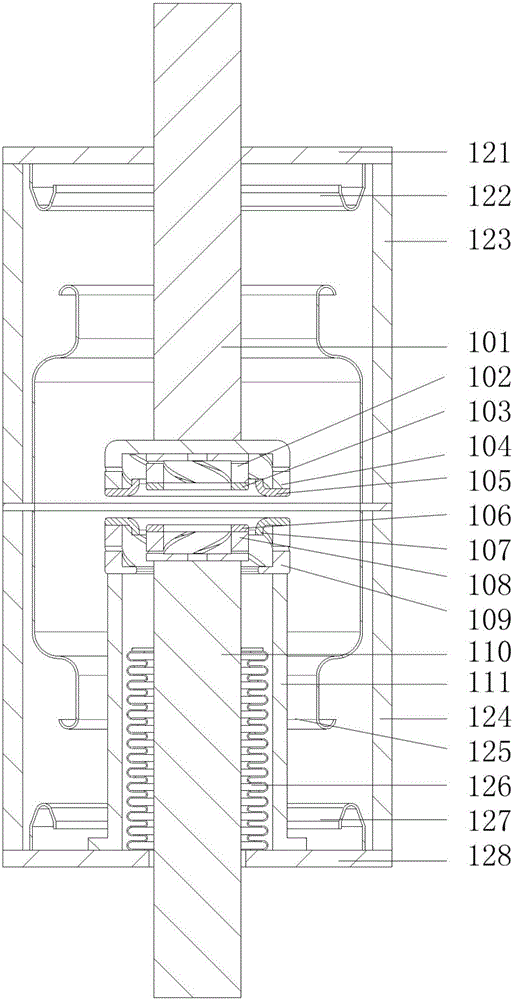

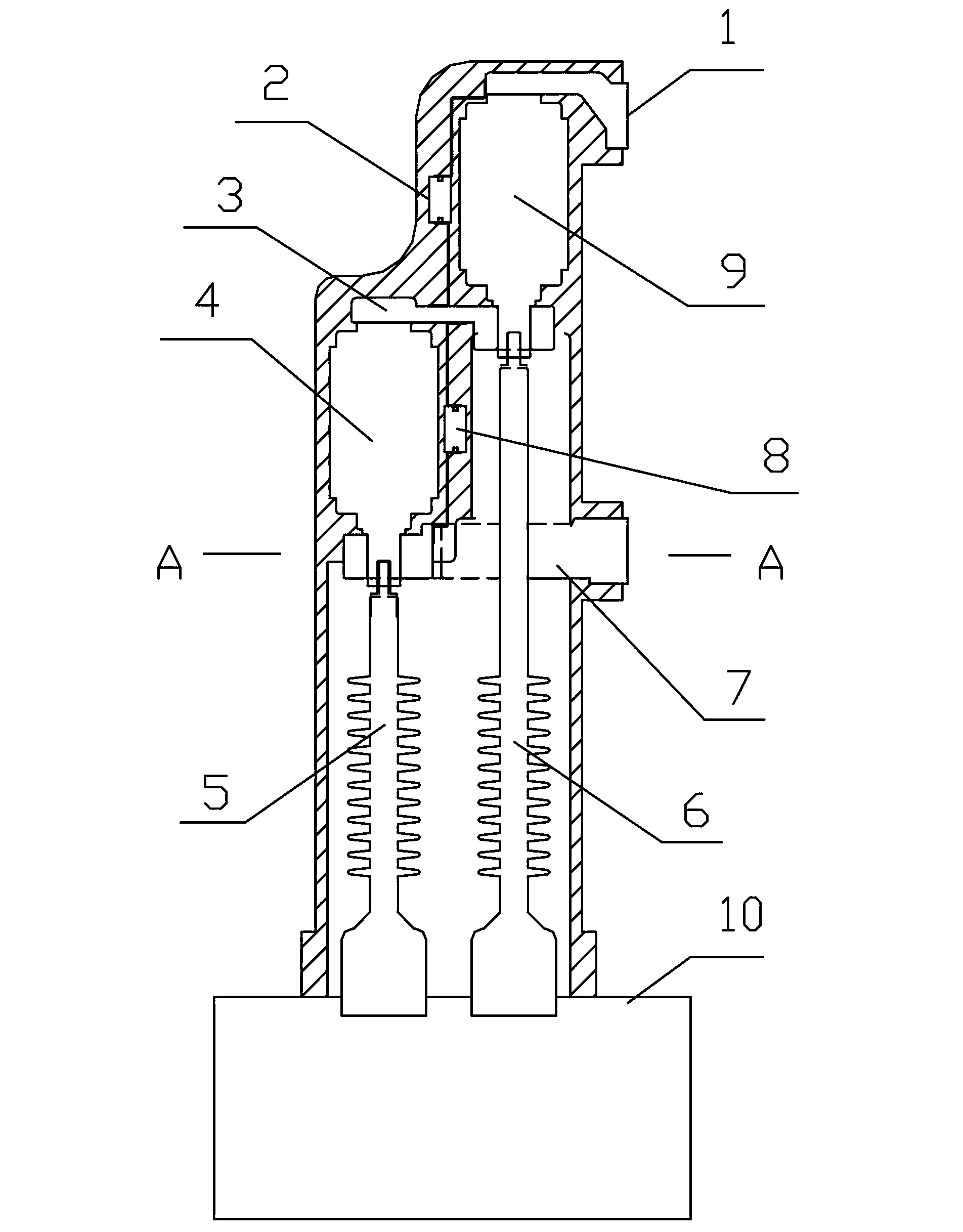

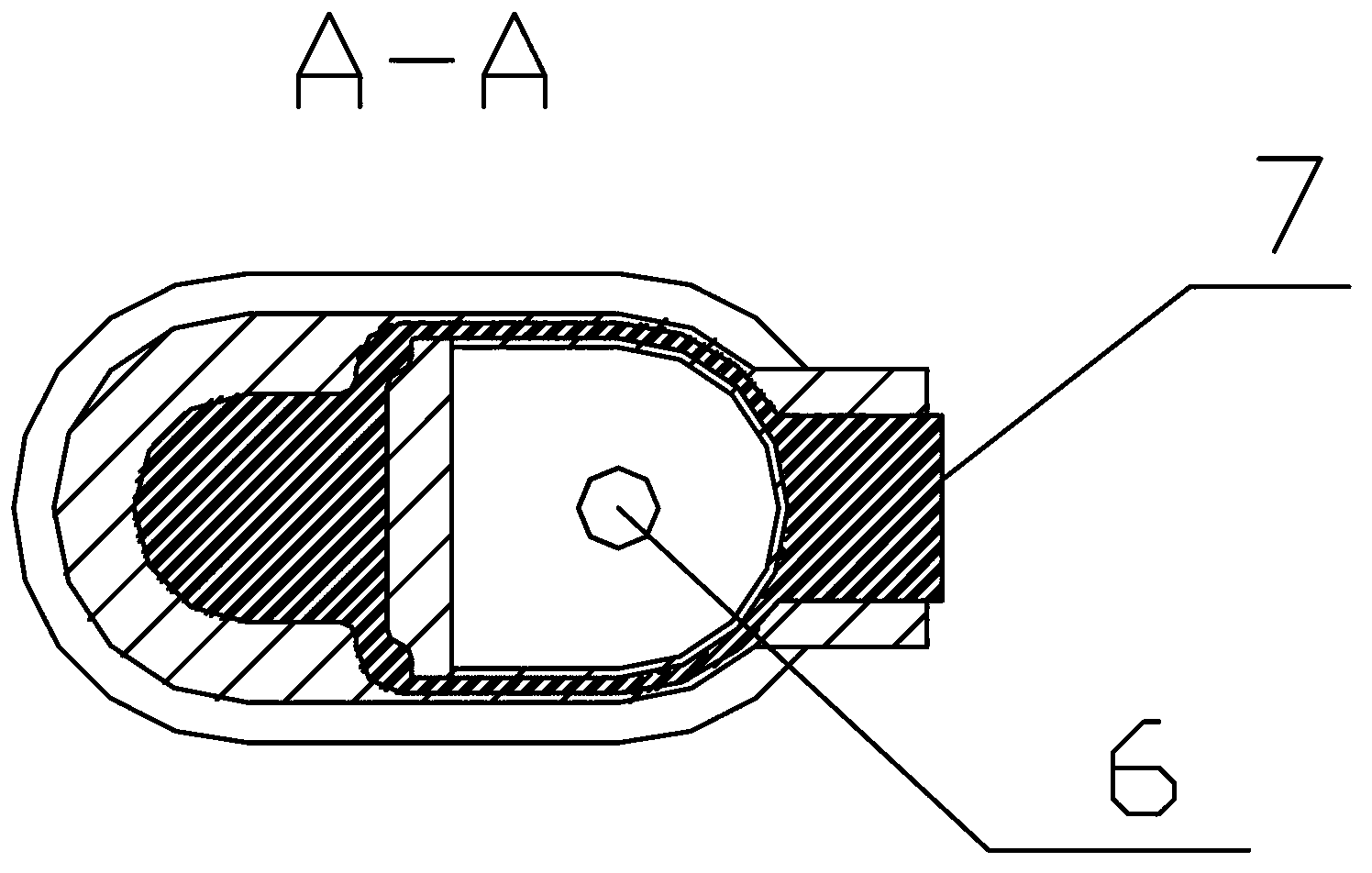

Contact with fixed fracture and having short-circuit current breaking capability and vacuum arc extinguishing chamber

ActiveCN105679597ARealization of breaking functionRealize functionHigh-tension/heavy-dress switchesAir-break switchesEngineeringCapacitive current

The invention relates to a contact with a fixed fracture and having short-circuit current breaking capability and a vacuum arc extinguishing chamber. The contact comprises a group of fixed fracture contact and a group of movable fracture contact, wherein the movable fracture contact is arranged inside the fixed fracture contact when being in a switching-off state. The vacuum arc extinguishing chamber comprises the contact, a shell and a shielding cover, and the contact is provided with the fixed fracture and has short-circuit current breaking capability. By the contact and the vacuum arc extinguishing chamber, the problems of structure complexity of a traditional composite magnetic field contact structure and other vacuum arc extinguishing chambers with regard to capacity current breaking design are solved, deficiency of magnetic field control on vacuum arc and the like are solved; the electric field shielding and protection of the fixed fracture contact on the movable fracture contact are achieved, and the influence of defects formed on the surface of the movable fracture contact on breakdown during the capacitive closing process is avoided; the breaking function and the insulation function are separated, the breaking function is achieved by the composite magnetic field contact, the insulation function is achieved by the fixed contact, and the contact can be used for breaking short-circuit current and also can be used for switching capacitive current such as reactive compensation field of capacitor bank switching and the like.

Owner:XI AN JIAOTONG UNIV

Varactor bank switching based on negative control voltage generation

InactiveUS7479839B1Angle modulation by variable impedencePulse automatic controlControl signalPass gate

A method and apparatus for varactor bank switching for a voltage controlled oscillator is disclosed. Varactor bank switching involves generating a negative bias voltage signal as a control signal for a varactor bank switch in an off-state, the varactor bank switch comprising a pass-gate circuit including switching transistors. Generating the negative bias voltage signal includes employing an active rectifier circuit running at the speed of an oscillation signal, the negative bias voltage signal maintaining the gate-source voltage of the pass-gate circuit below a threshold voltage to prevent said switching transistors from becoming conductive in an off-state.

Owner:GLOBALFOUNDRIES INC

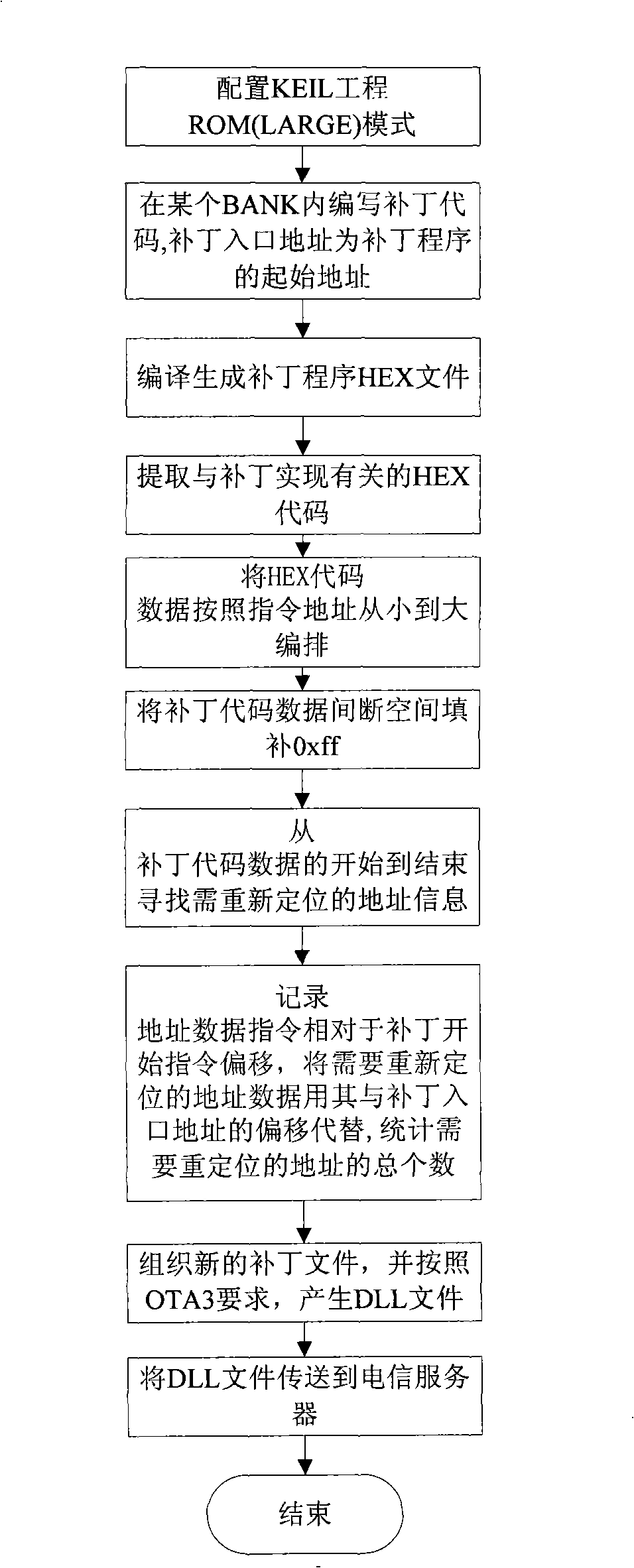

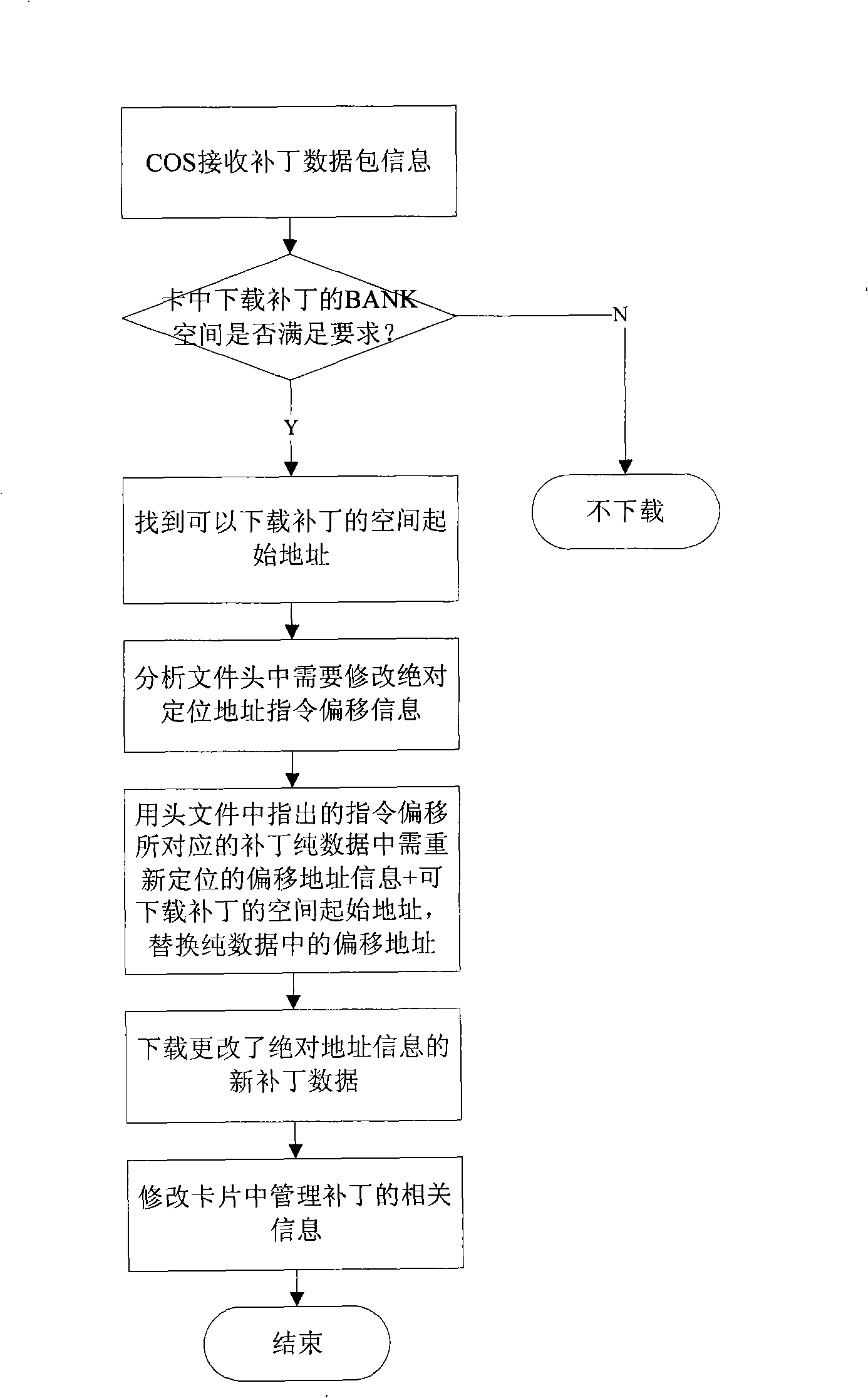

Scheme for electric communication card dynamically downloading patch program

ActiveCN101334734ASoftware testing/debuggingProgram loading/initiatingDynamic managementAnalysis tools

The invention provides a proposal for using a telecommunication card to dynamically download a patch; as the telecommunication card OTA3 carries out standard requirement to the patch which is downloaded by dynamic management and the patch can be put in any place without affecting the operation of the patch, the proposal is provided; with the continuous increase of the application complexity and the continuous enlargement of the patch, the patch is forced to use the instruction such as LCALL / LJMP which relates to an absolute address; after the patch is downloaded, as the entry address of each function which forms the patch changes, the absolute addressing can generate problems by the LCALL / LJMP instruction; the invention uses the chip provided with BANK switching mechanism as the object, analyzes the address information which needs to be repositioned by using a single analysis tool of the absolute address of the patch in virtue of the particular composing skills of KEIL tool software, and carries out information replacement to the address information which needs to be repositioned by using the patch management mechanism in the telecommunication card, thus realizing the dynamical download of the patch.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

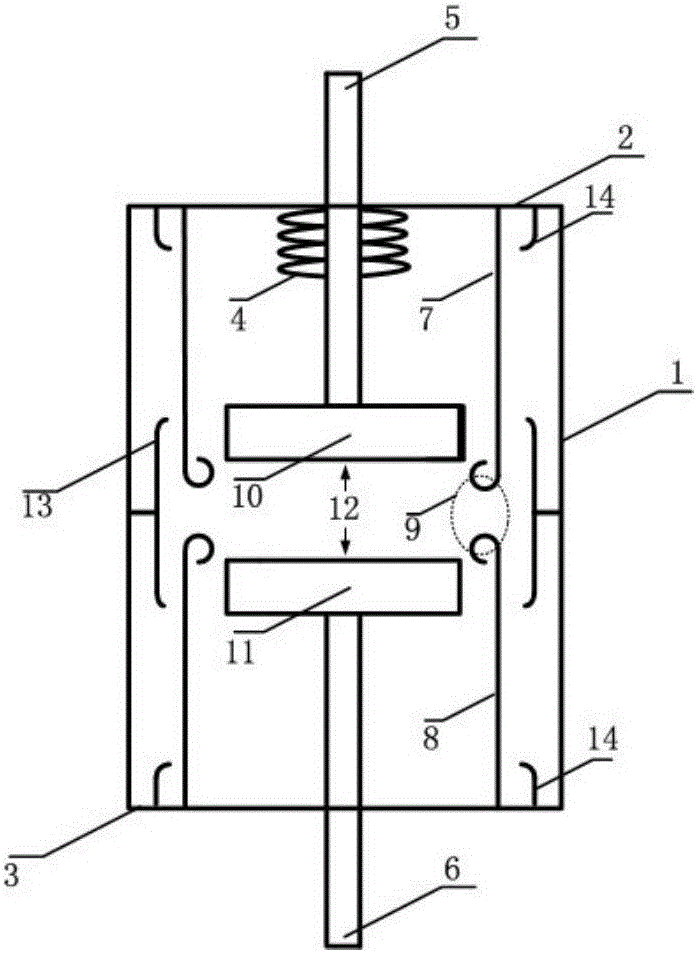

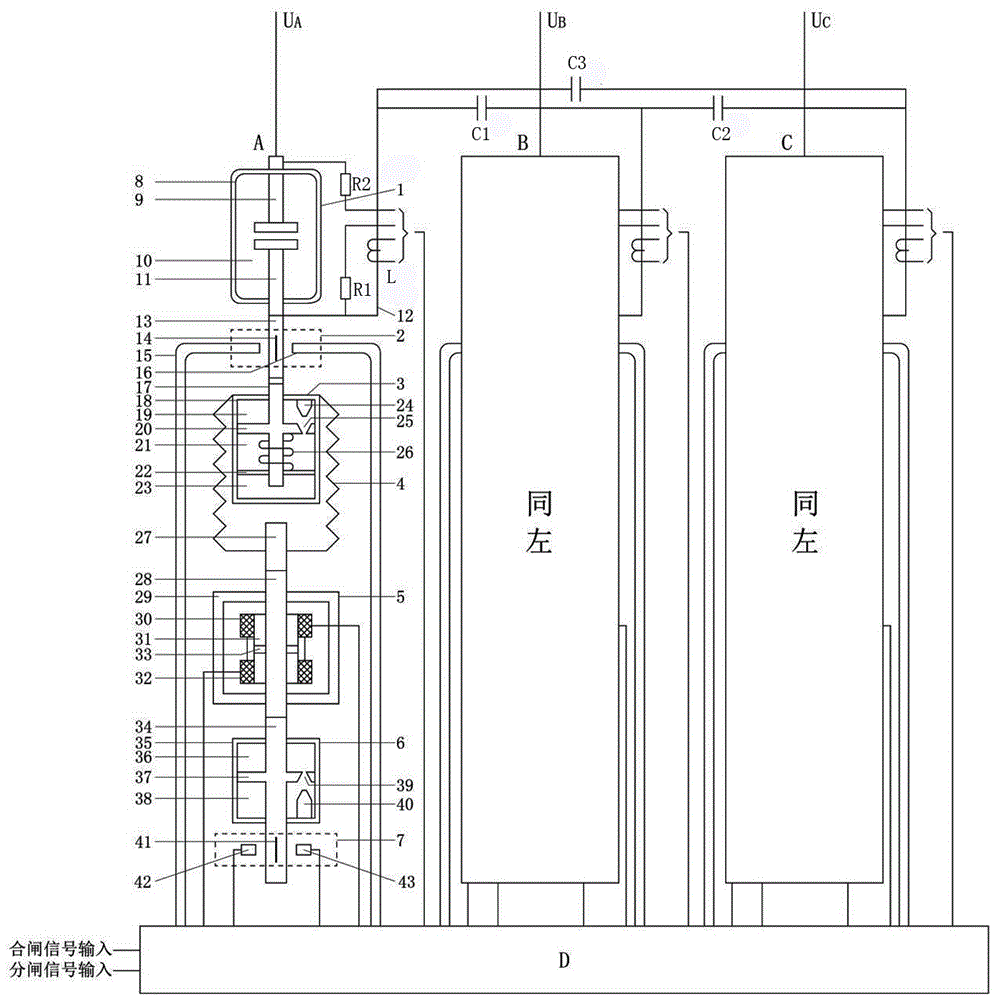

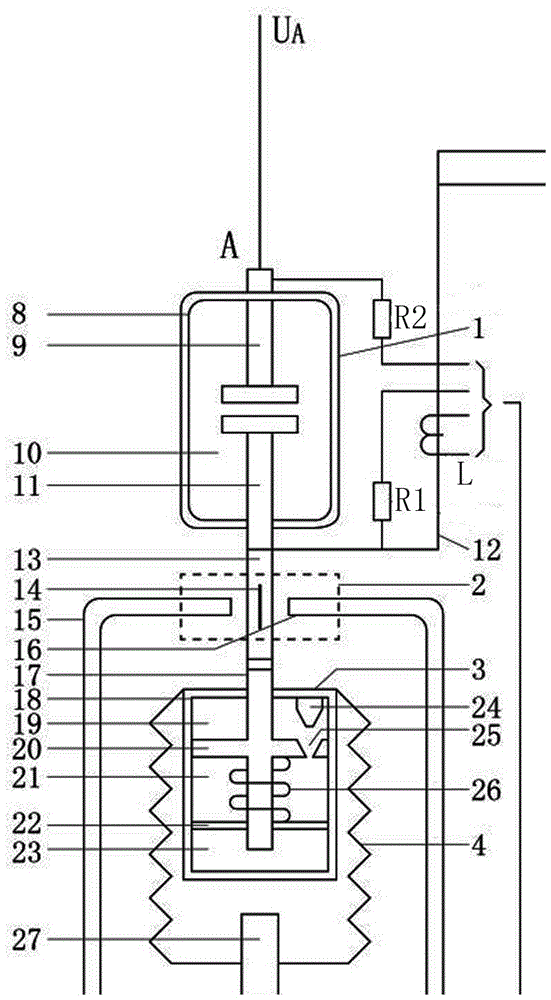

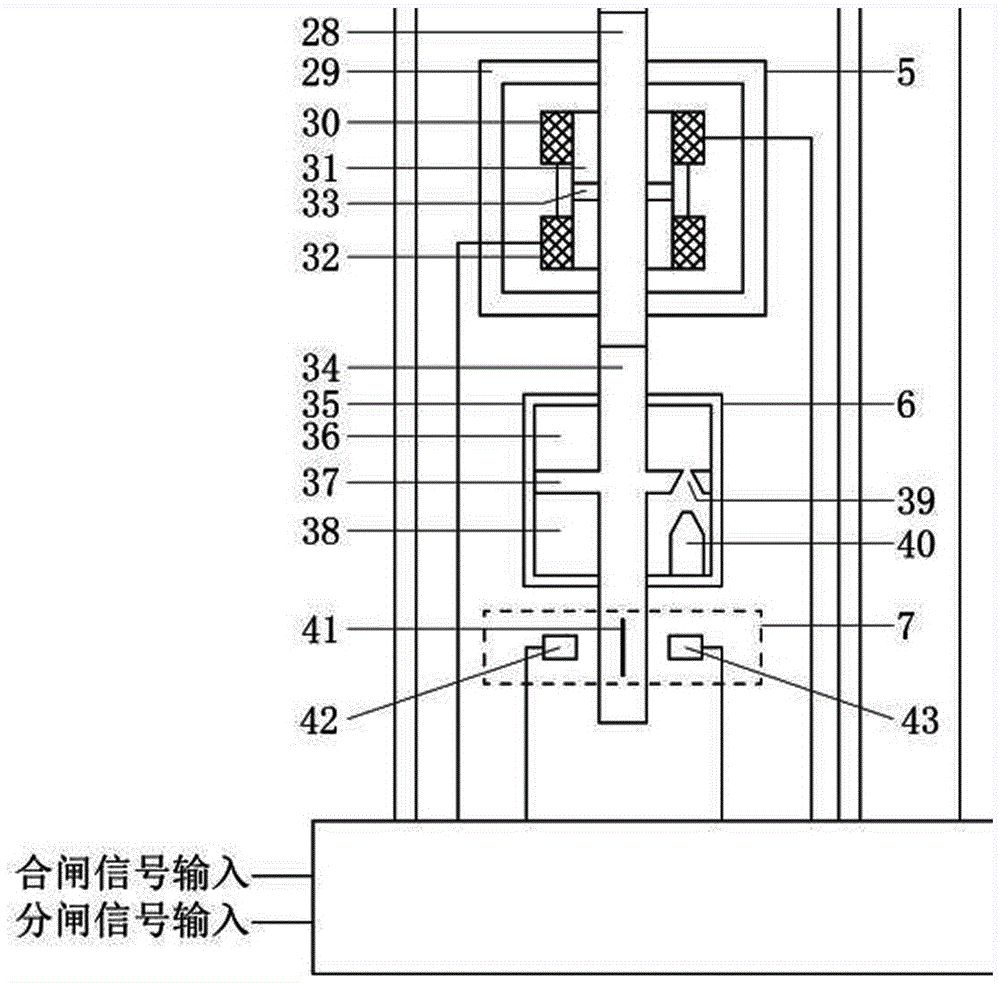

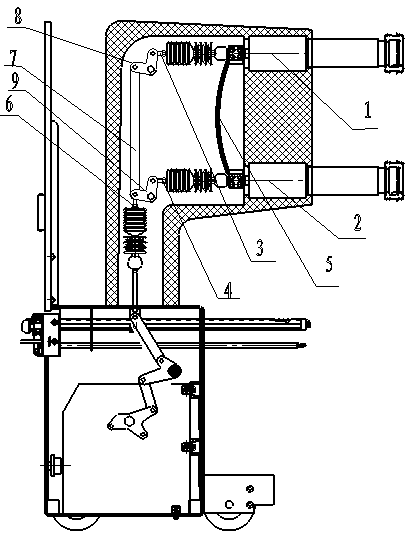

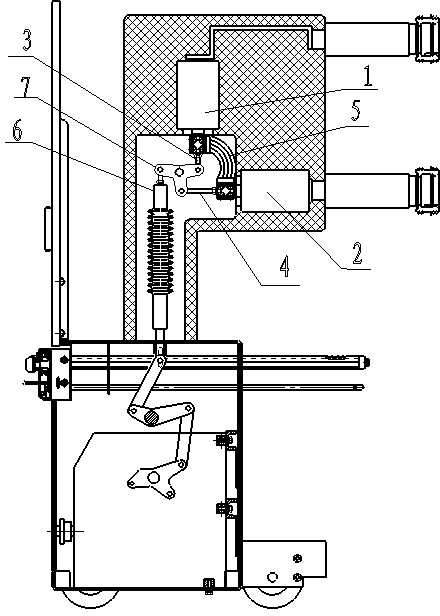

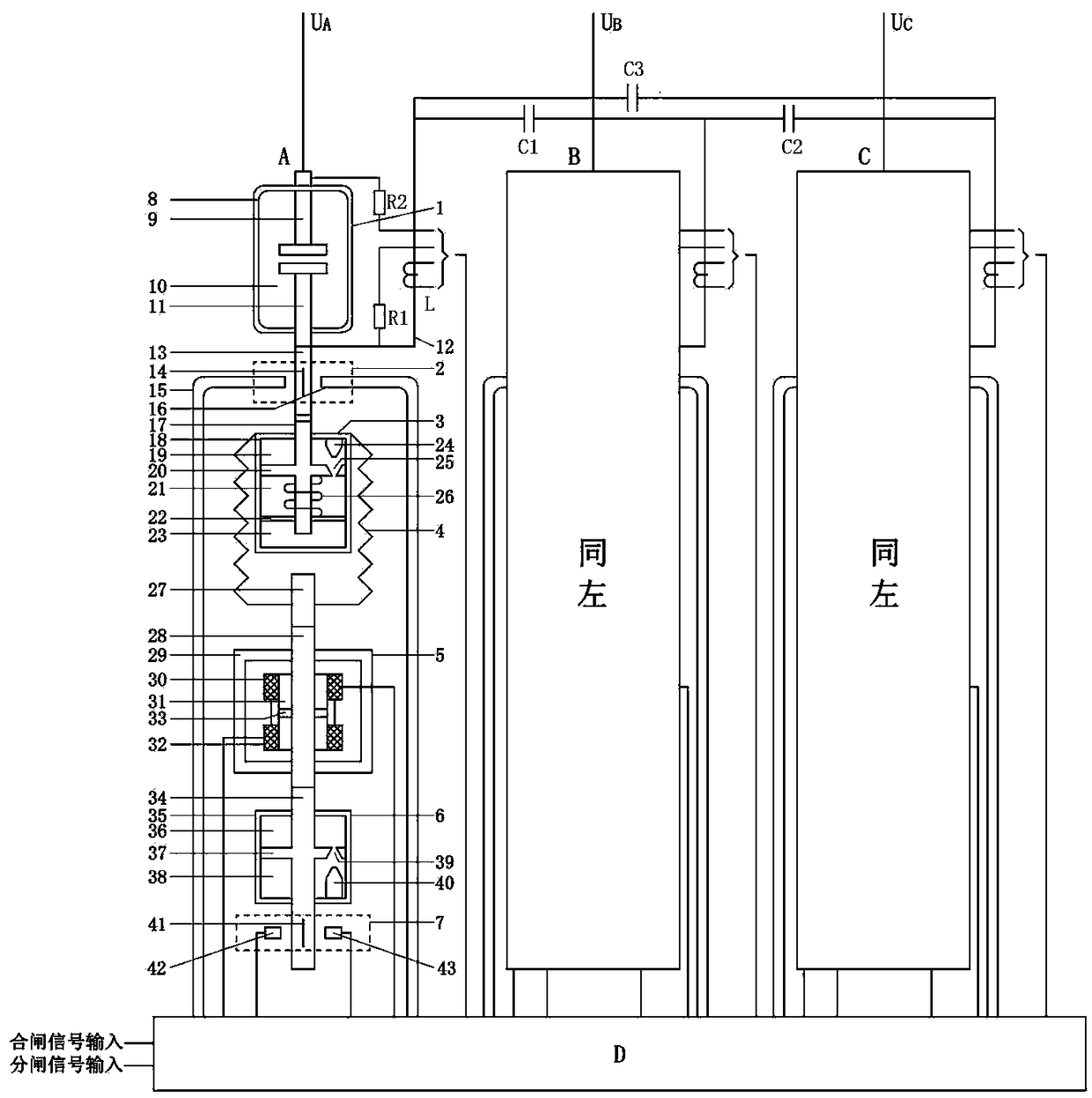

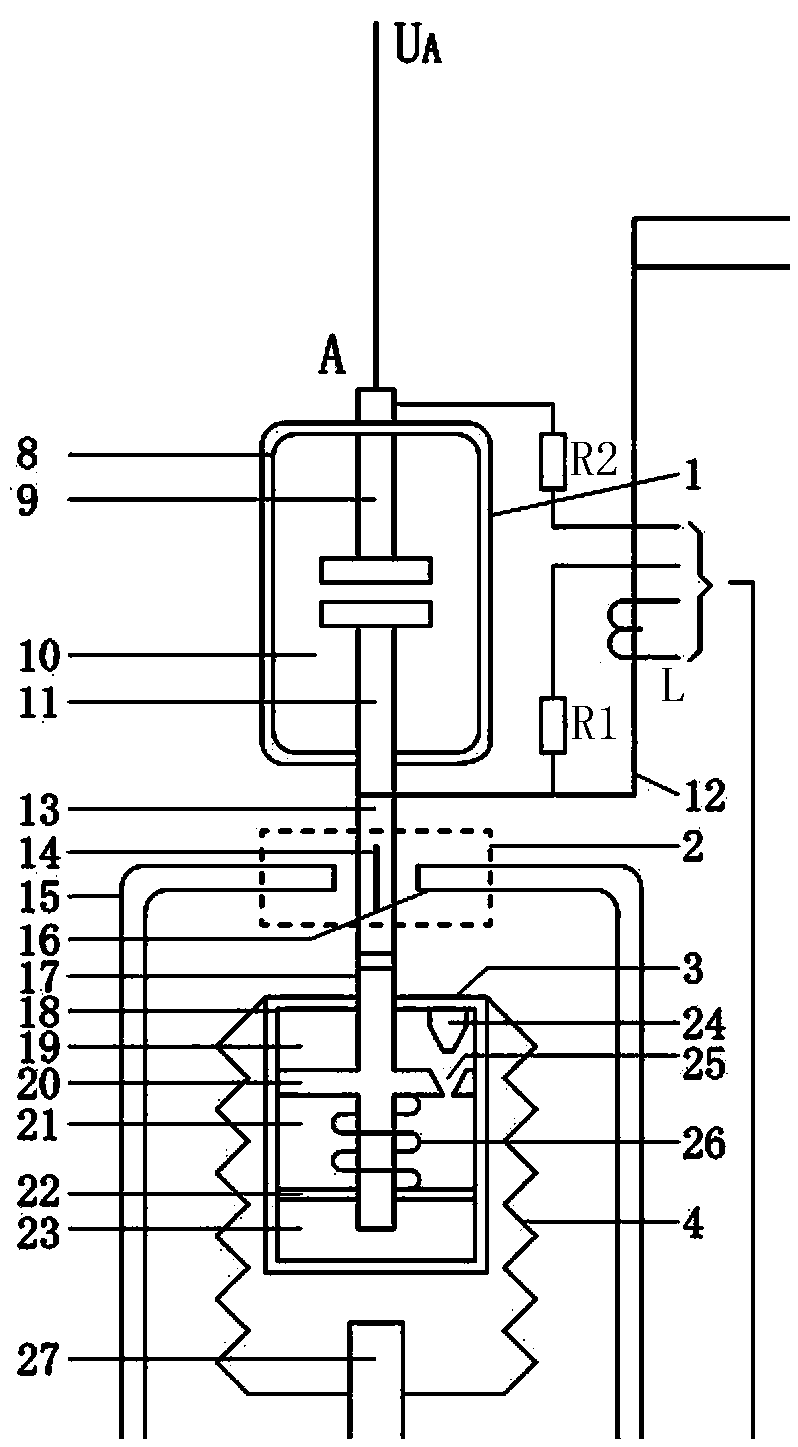

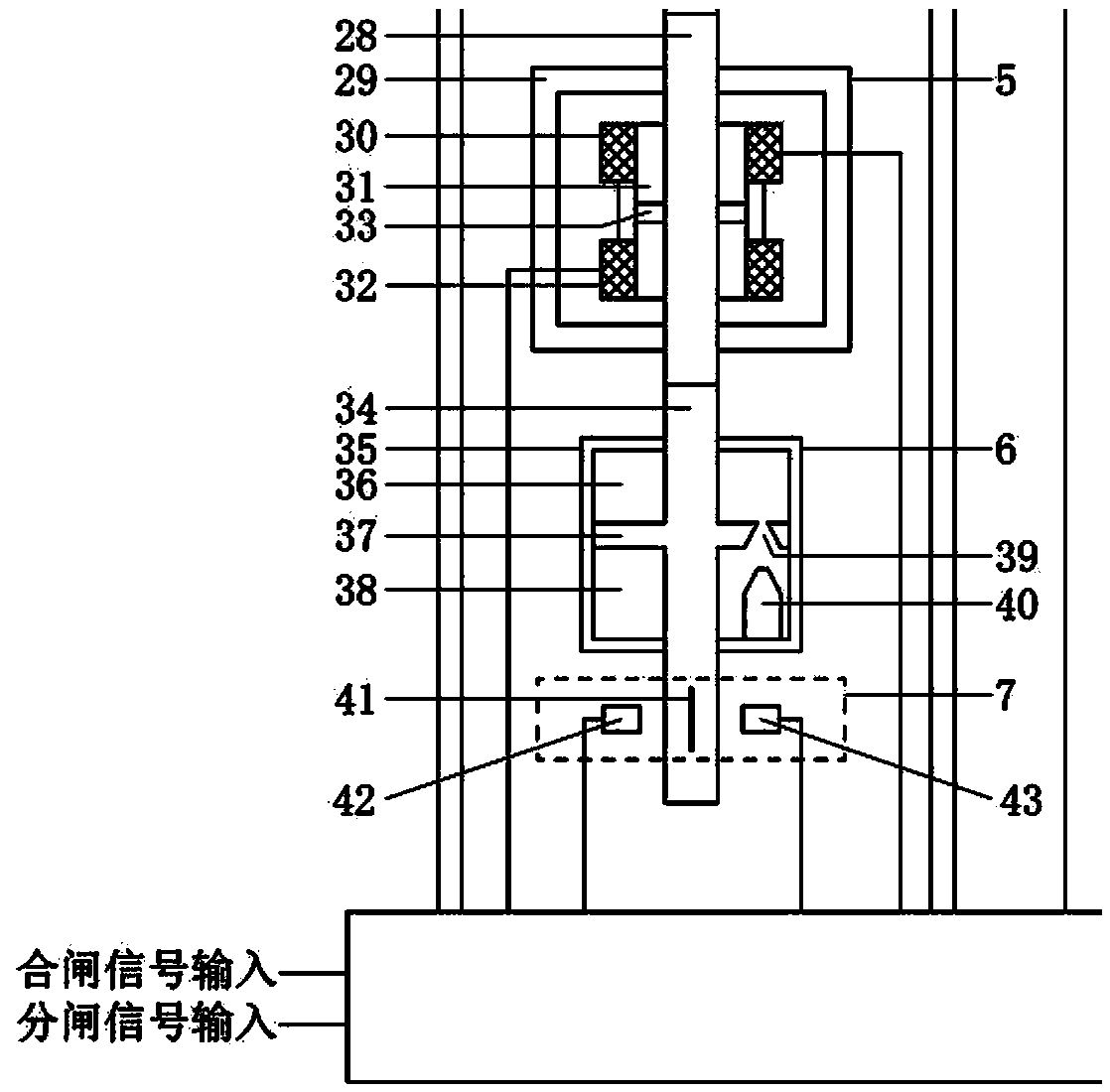

Intelligent circuit breaker for shunt capacitor bank switching based on flexible opening and closing technology

ActiveCN106024496AImprove energy savingImprove delivery capacityHigh-tension/heavy-dress switchesAir-break switchesPower qualityShunt capacitors

The invention discloses an intelligent circuit breaker for shunt capacitor bank switching based on a flexible opening and closing technology, which comprises three posts A, B and C and an intelligent controller D. Three phases of power supplies UA, UB and UC are respectively connected with the three posts A, B and C; two ends of a shunt capacitor C1 are respectively connected with the posts A and B; two ends of a shunt capacitor C2 are respectively connected with the posts B and C; two ends of a shunt capacitor C3 are respectively connected with the posts A and C; each of the three posts A, B and C comprises a conductive and arc-extinguishing component, a first stroke sensing unit, a closing damping component, a high-voltage insulated component, an opening and closing driving component, an opening damping component and a second stroke sensing unit sequentially in serial connection along the axial direction. The intelligent circuit breaker for shunt capacitor bank switching based on the flexible opening and closing technology has the beneficial effects that the structure is simple; the operation is reliable; the maintenance is convenient; the cost performance is high; the shunt capacitor bank can be switched frequently; and due to reactive power compensation equipment for shunt capacitor bank switching, effects of reducing loss, conserving energy, improving the transmission ability and improving the power quality of the power grid are achieved.

Owner:JIANGSU MODERN POWER CAPACITOR

Non-volatile storage devices, methods of addressing, and control logic therefor

ActiveUS8463979B2Increasing addressable memory spaceDoubling of the capacity of a solid state driveMemory architecture accessing/allocationMemory adressing/allocation/relocationSolid-state storageControl store

Non-volatile storage devices and methods capable of achieving large capacity solid state drives containing multiple banks of memory devices. The storage devices include a printed circuit board, at least two banks of non-volatile solid-state memory devices, bank switching circuitry, a connector, and a memory controller. The bank switching circuitry is integrated onto the memory controller and functionally interposed between the banks of memory devices and the front end of the memory controller. The bank switching circuitry operates to switch accesses by the memory controller among the at least two banks.

Owner:KIOXIA CORP

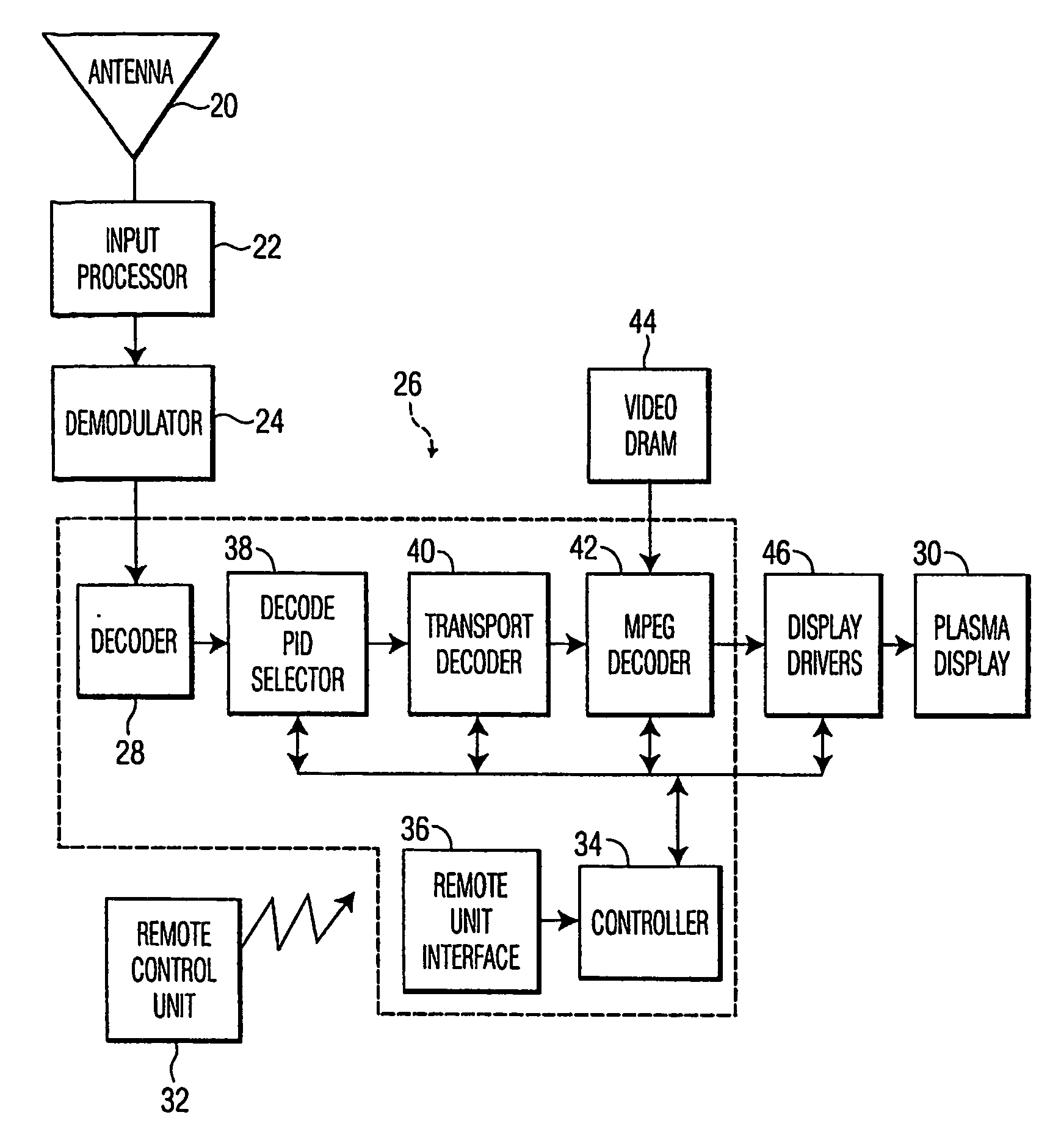

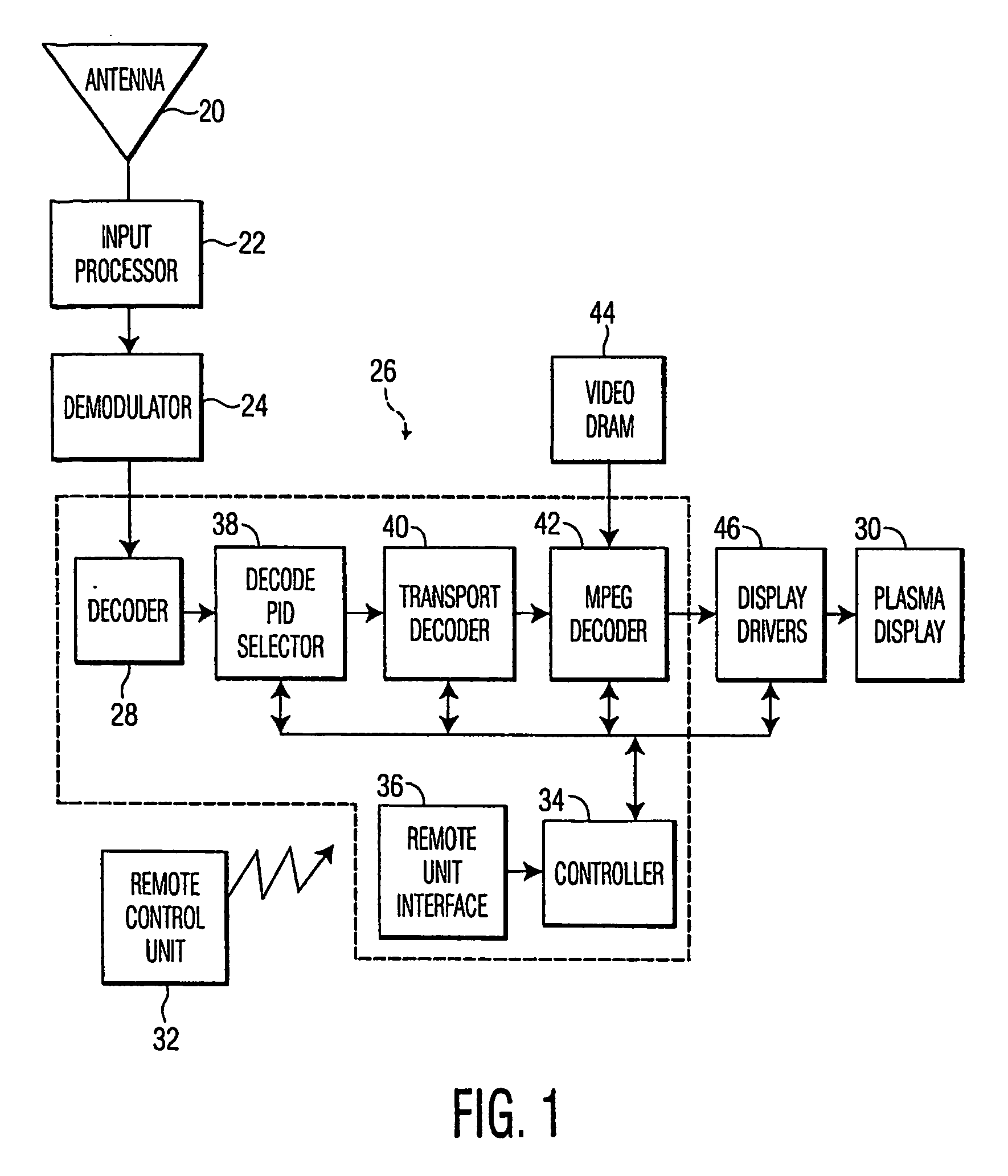

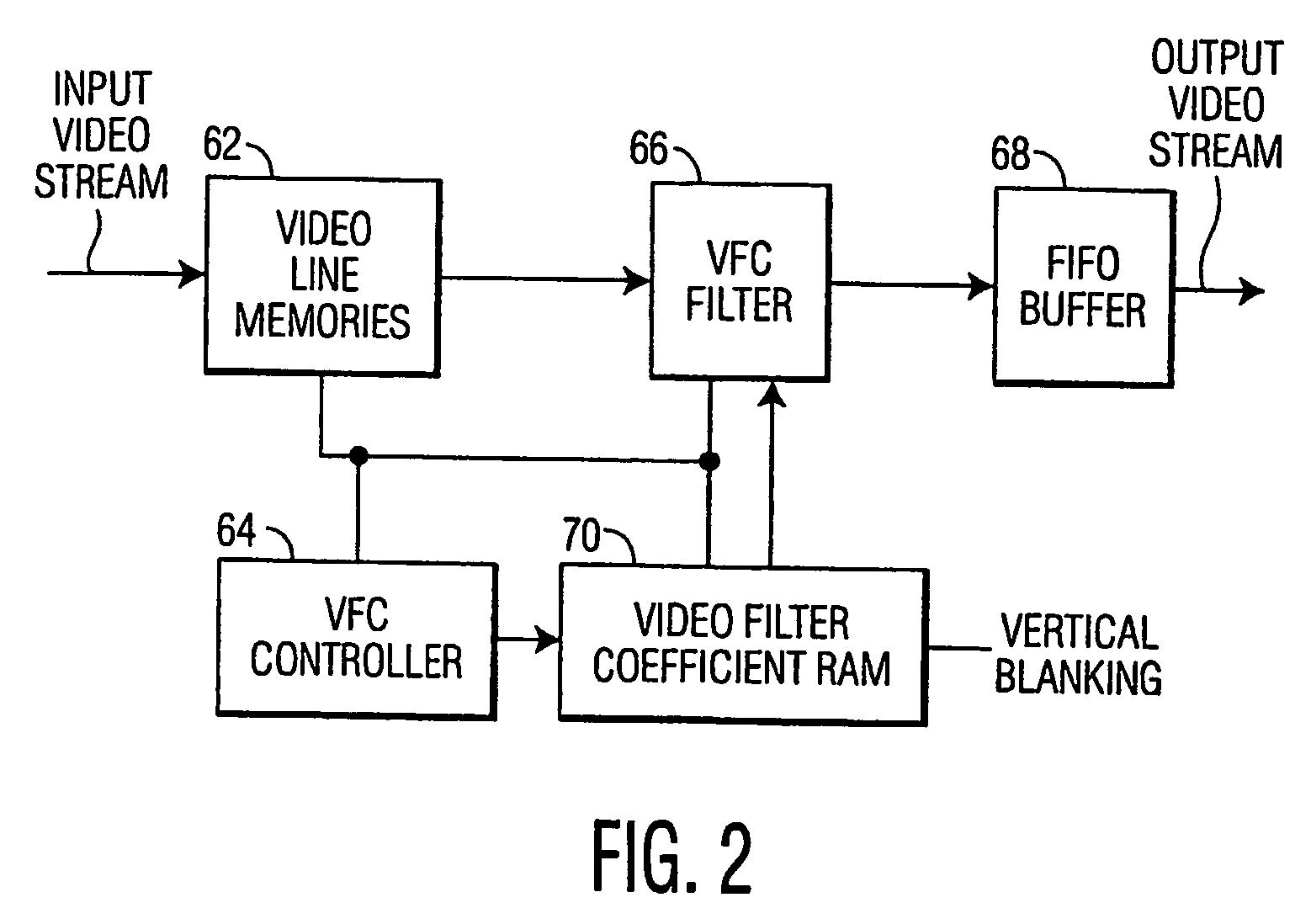

Method and system for detecting and performing automatic bank switching for a filter coefficient ram

InactiveUS20050237430A1Television system detailsTelevision system scanning detailsVertical blanking intervalComputer science

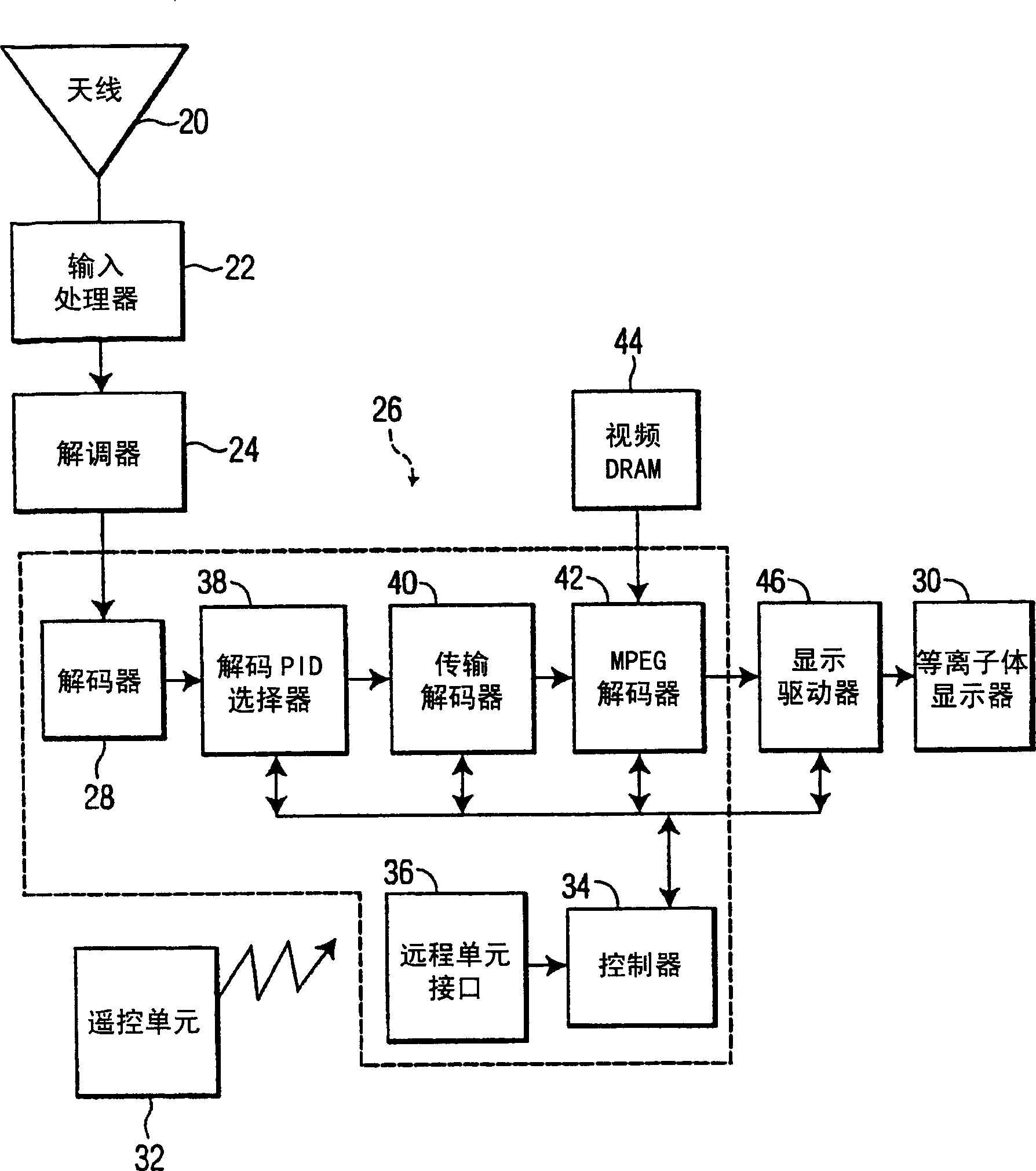

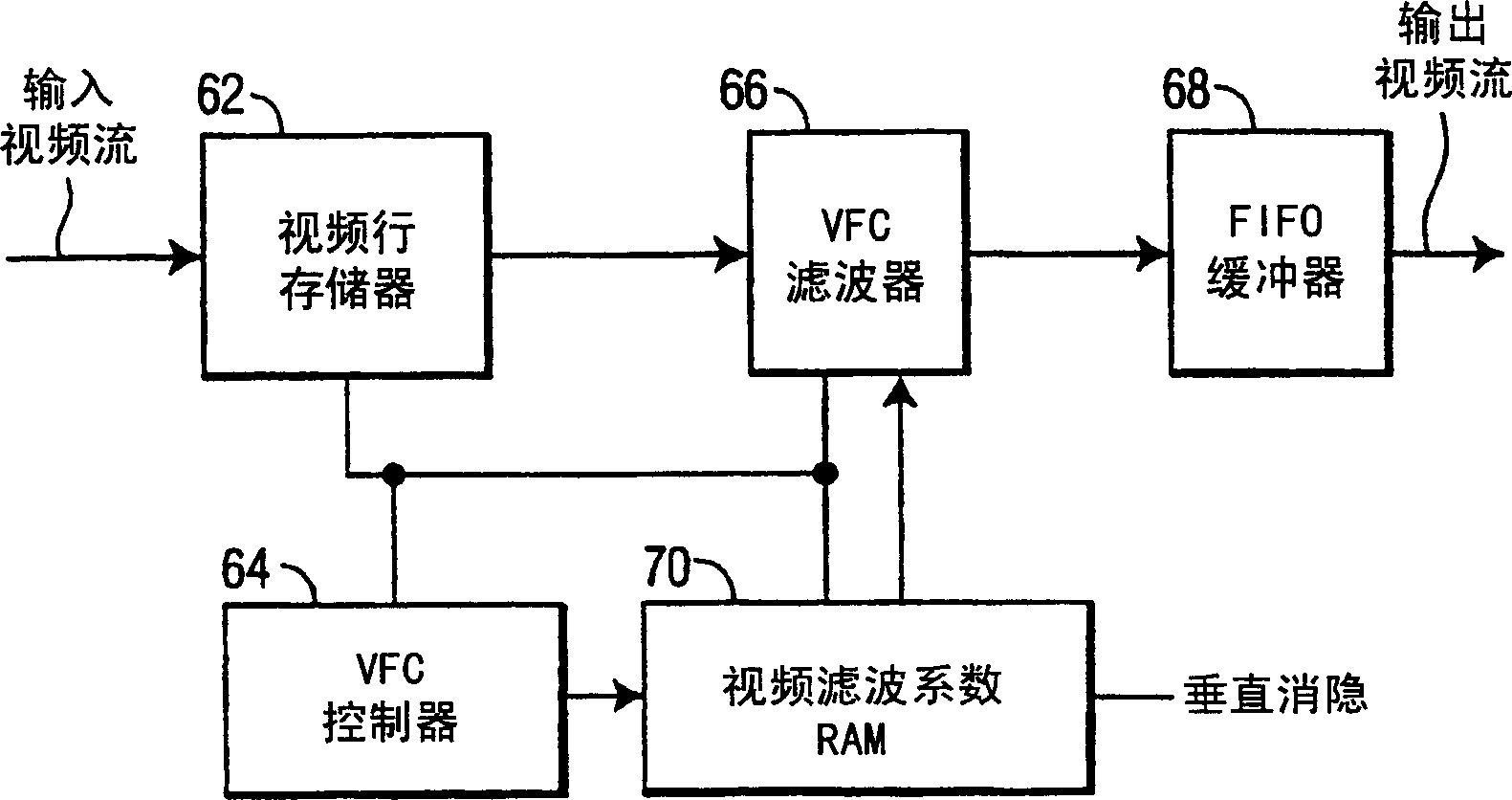

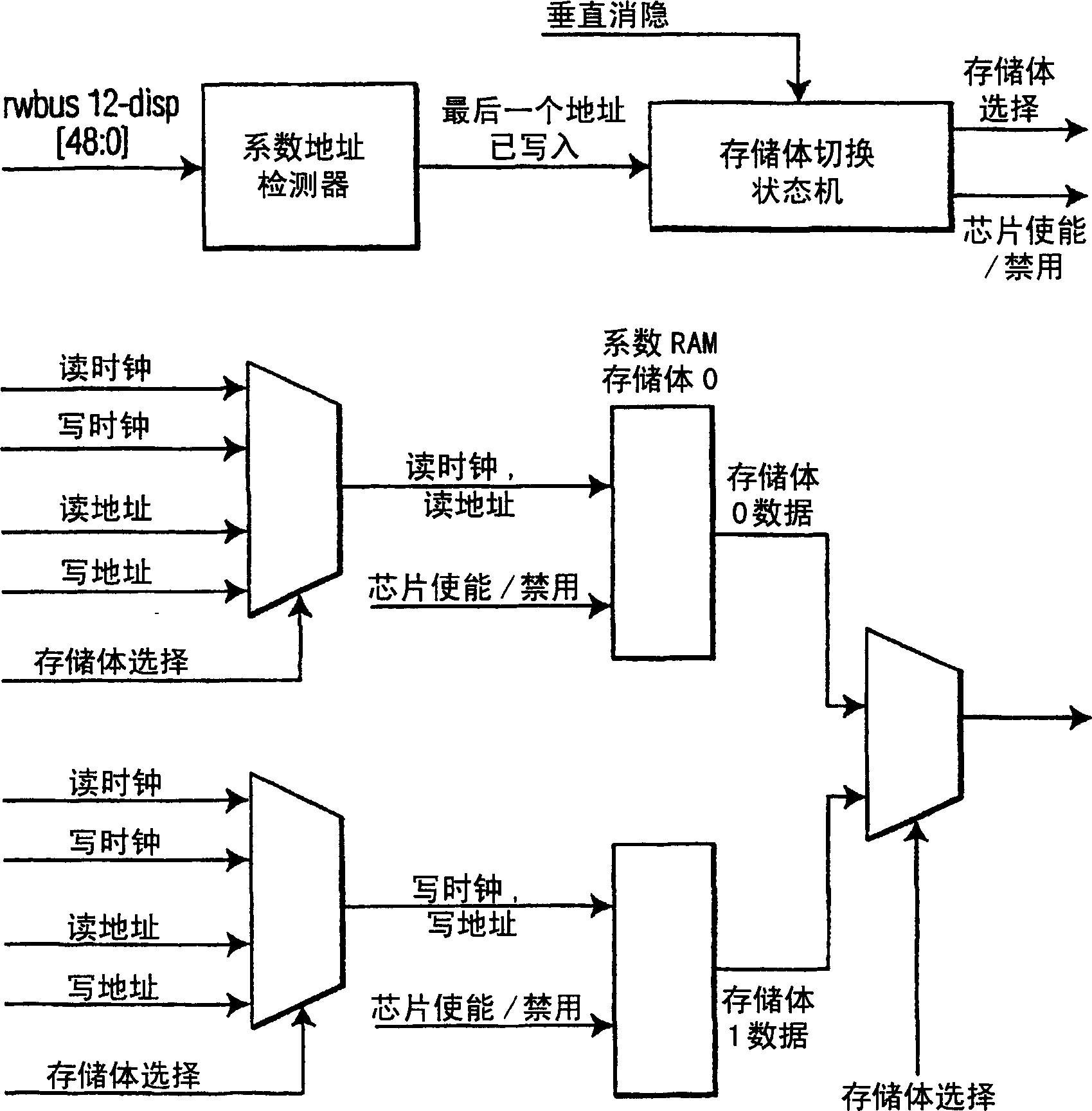

A method for facilitating a dual-bank filter coefficient RAM designed to switch banks automatically during the vertical blanking interval in a television application. The method and system of the present invention allows a micro controller to program a new set of filter coefficients in the memory bank not currently being used, automatically detect when all the coefficients have been written and then automatically switch banks during the vertical blanking interval in the television application.

Owner:INTERDIGITAL MADISON PATENT HLDG

Vacuum switch for medium-voltage switching capacitor bank

ActiveCN103325609AImprove securityImprove the withstand voltage levelHigh-tension/heavy-dress switchesAir-break switchesOvervoltageCapacitance

The invention relates to the field of medium-voltage power, in particular to a vacuum switch for a medium-voltage switching capacitor bank. The vacuum switch for the medium-voltage switching capacitor bank comprises a first arc-control chamber, a second arc-control chamber and a middle conductive piece, wherein the bottom end of the first arc-control chamber is connected in series with the top end of the second arc-control chamber through the middle conductive piece. The vacuum switch with double arc-control chambers is higher in voltage withstand level and can bear impact of switching overvoltage after capacitor bank switching. Commonly, in a 35kV power system, the reigniting probability of a vacuum fracture is about 2.5%, theoretically, the reigniting probability of the vacuum switch for the medium-voltage switching capacitor bank can be reduced to 0.0625%, reliability is high, and therefore safety of a medium-voltage power capacitance compensation device and system can be improved greatly.

Owner:厦门顾德益电气股份有限公司

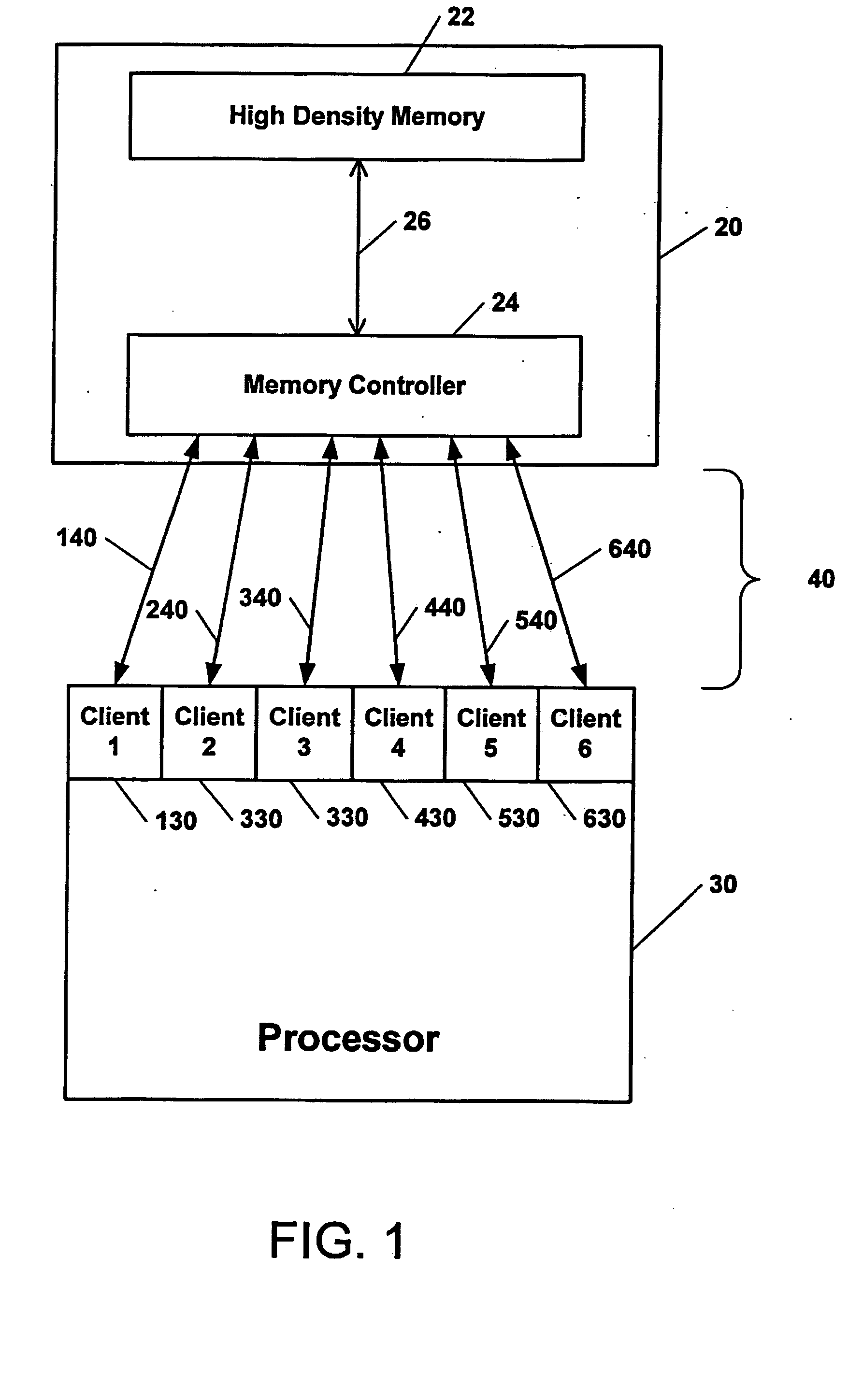

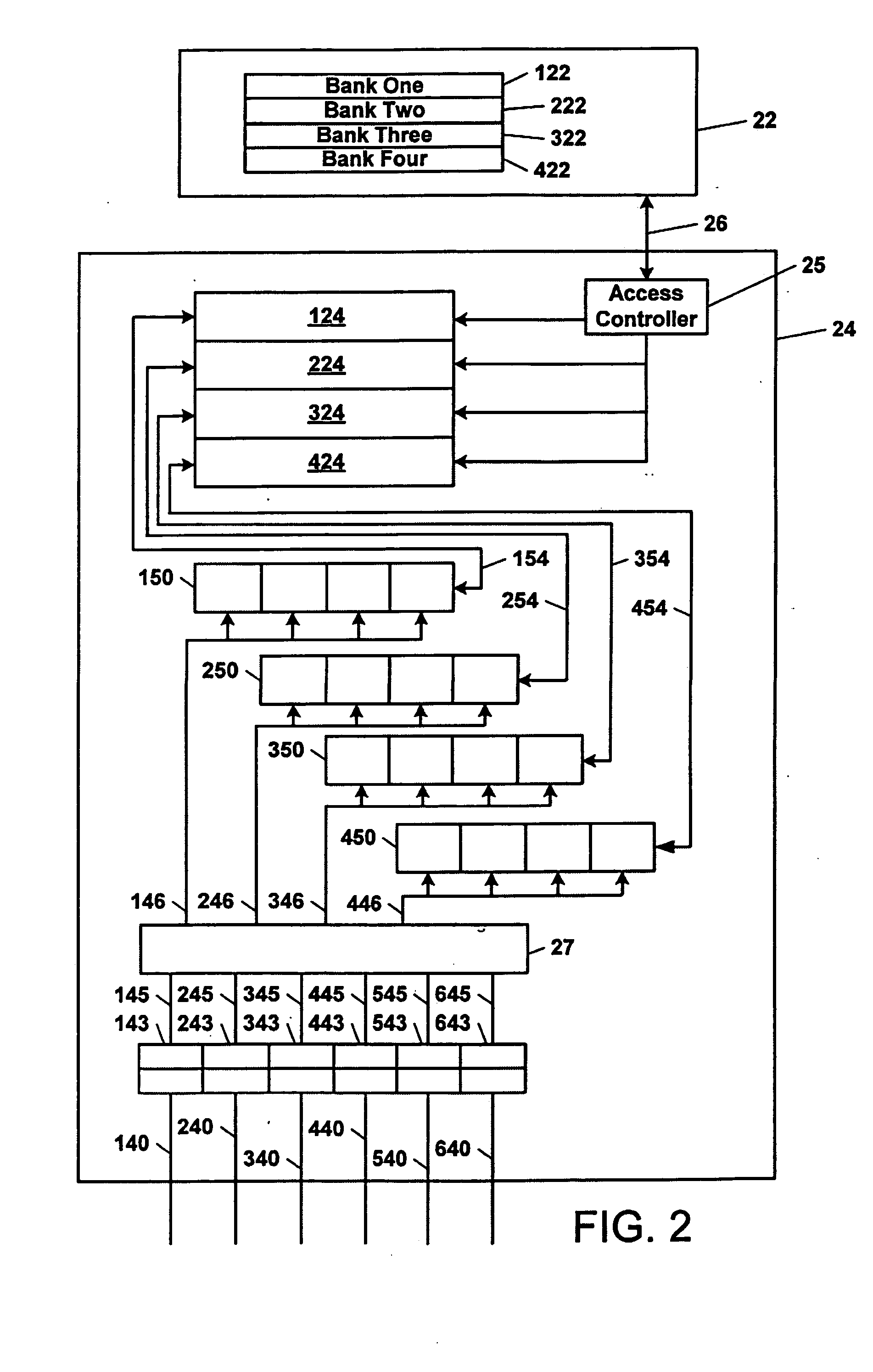

Device and method for small discontiguous accesses to high-density memory devices

InactiveUS20050108492A1Memory adressing/allocation/relocationDigital computer detailsHigh densityMemory architecture

A memory architecture design and strategy is provided using memory devices that would normally be considered disadvantageous, but by accommodating the data input, output, and other peripheral controller services, overall performance in this mode is optimized. The surprising result is that even though the choice of memory is inappropriate for the task based on the precepts of the prior art, the overall memory system is effective. Bank switching in DDR-SDRAM can be utilized to achieve technological feasibility without resorting to, for example, SRAM.

Owner:THALES E SECURITY +1

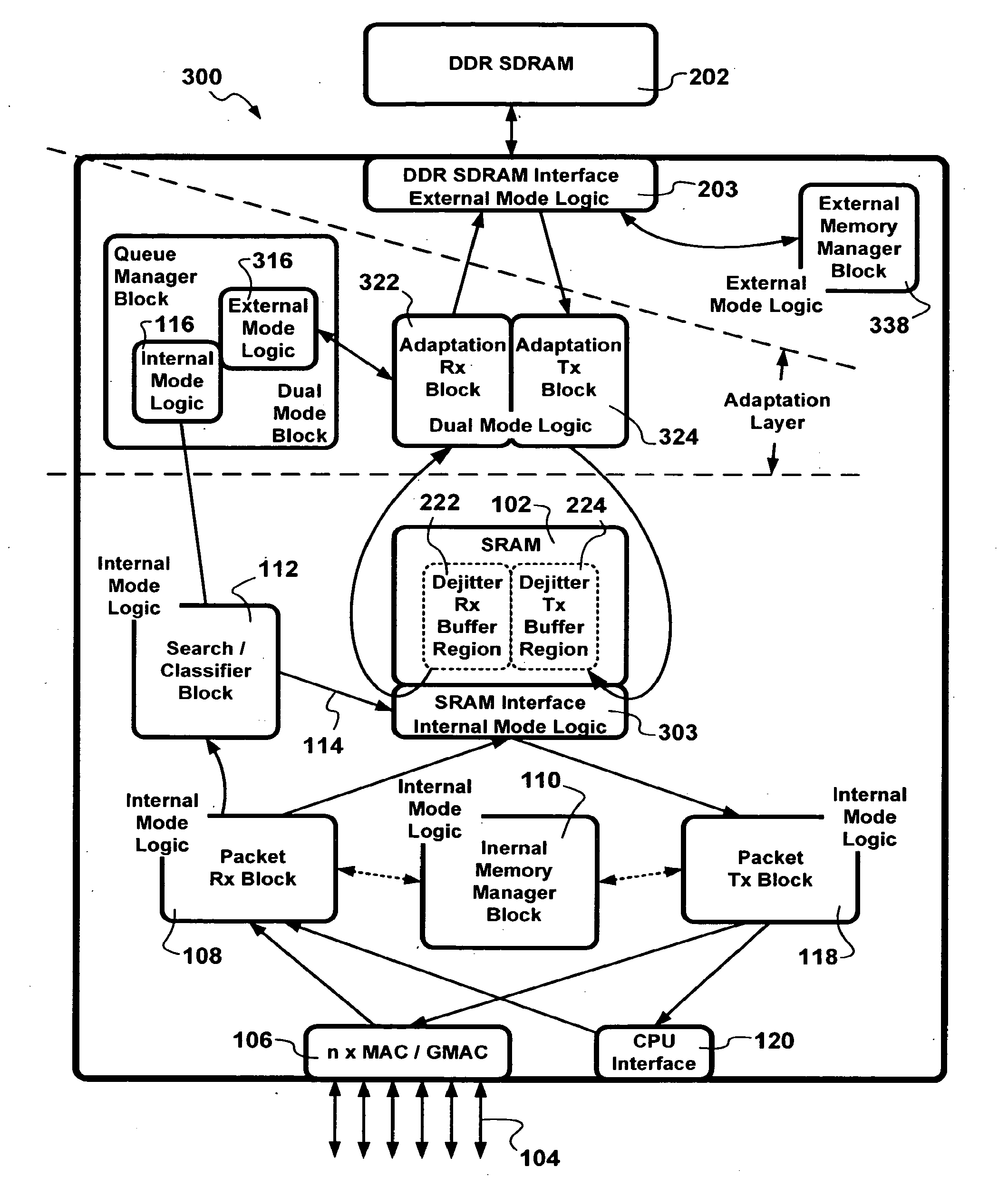

Compact Packet Switching Node Storage Architecture Employing Double Data Rate Synchronous Dynamic RAM

A two-chip / single-die switch architecture and a method for accessing a DDR SDRAM memory store in a switching environment are presented. The two-chip / single-die architecture includes an internal memory storage block on the single-die, an external memory storage interface to a Double Data Rate Synchronous Dynamic Random Access Memory (DDR SDRAM), an external memory manager, and a packet data transfer engine effecting packet data transfers between an internal memory store and the external DDR SDRAM memory. The packet data transfer engine operates as an adaptation layer addressing issues related to employing appropriate: addressing schemes, granule sizes, memory transfer burst sizes, access timing, etc. The packet data transfer engine includes a minimal number of dual mode operational blocks such as: a queue manager, and adaptation receive and transmit blocks. The method relates to a packet data transfer discipline addressing random memory access latencies incurred in employing DDR SDRAM, using predictive bank switching to hide random access latencies, packet length dependent variable memory write burst lengths to minimize bank switching, and performing memory read and write operations during corresponding read and write windows. Advantages are derived from the a space-efficient two-chip / single-die switching node architecture implemented with a reduced amount of dual mode logic, and also from DDR SDRAM bandwidth utilization efficiencies.

Owner:IKANOS COMMUNICATIONS

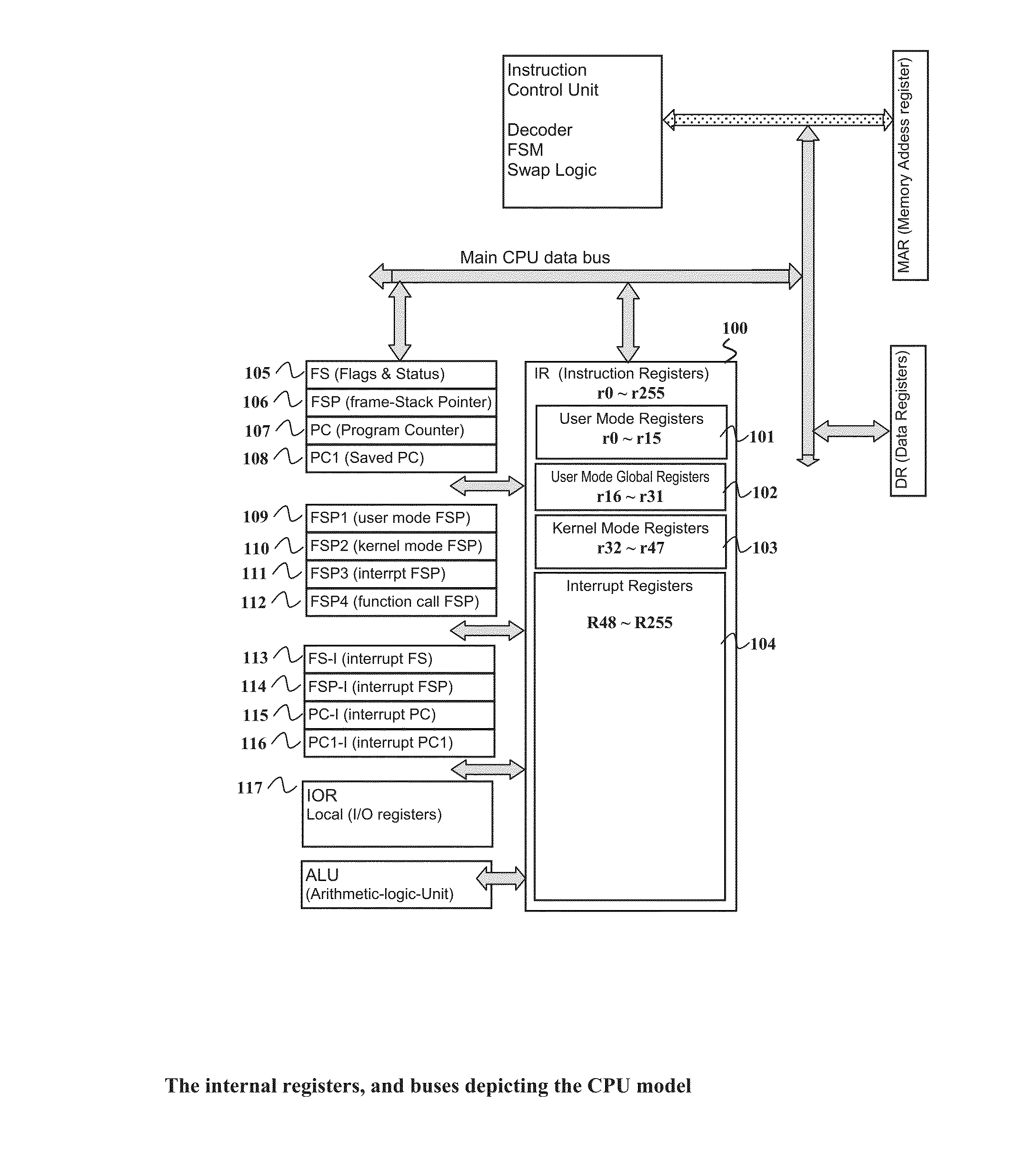

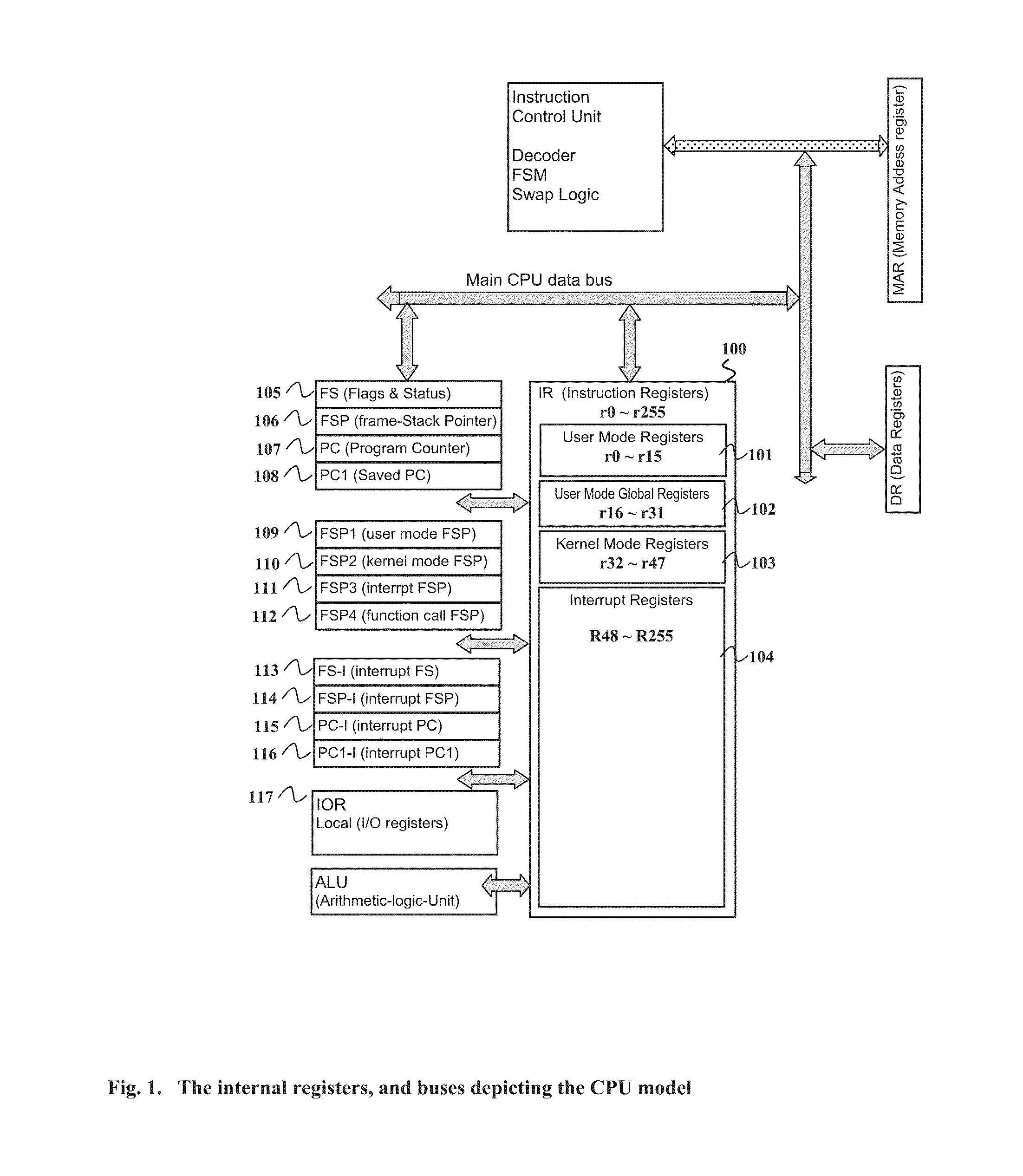

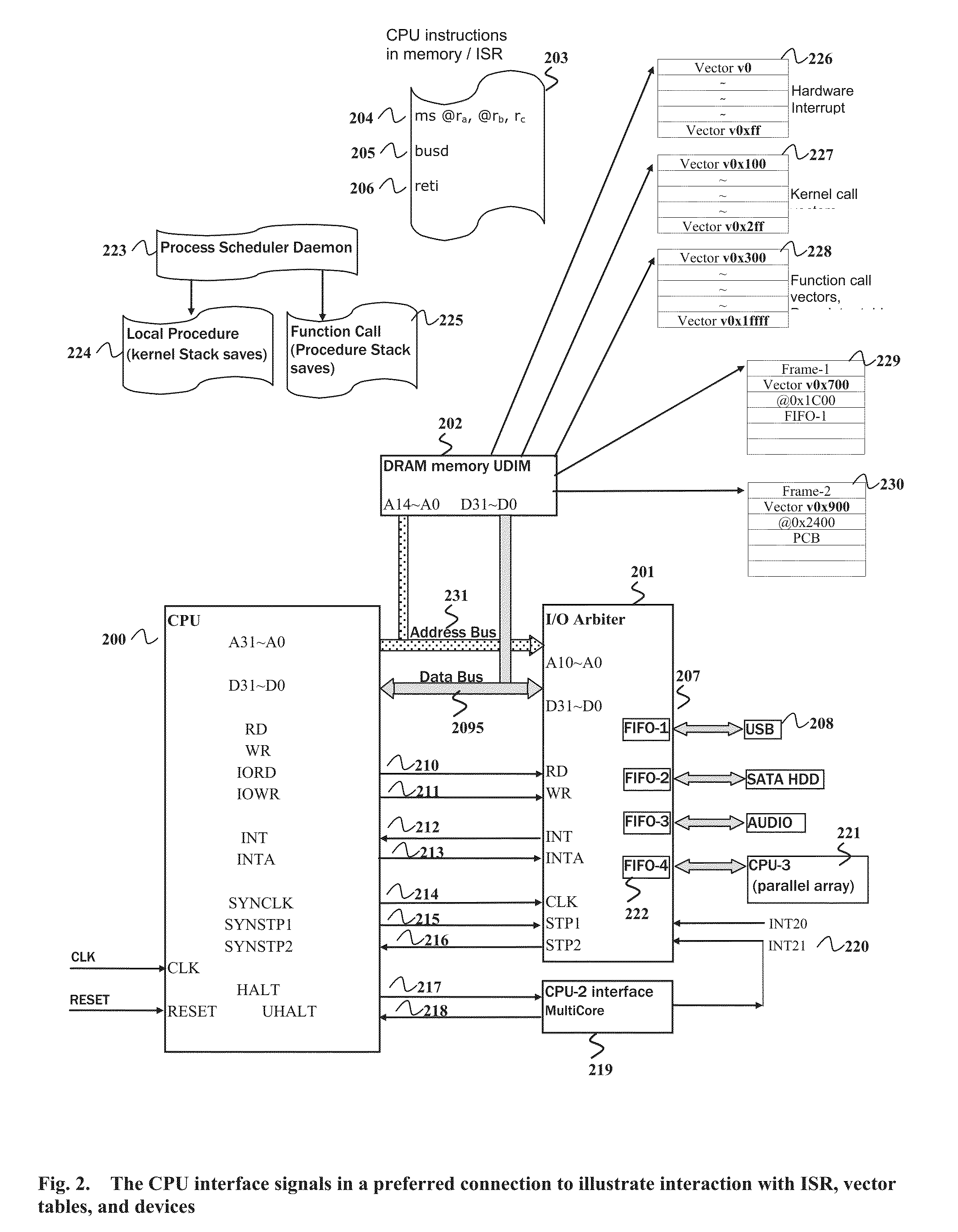

Processor model using a single large linear registers, with new interfacing signals supporting fifo-base I/O ports, and interrupt-driven burst transfers eliminating dma, bridges, and external I/O bus

InactiveUS20160224485A1Simple and powerful CPU architectureEfficient mappingElectric digital data processingProcessor modelSystems design

A processor or CPU architecture that implements many enabling technologies proven to enhance data through put supporting the synchronous burst data transfer. The Input-Output (I / O) is uniformly viewed and treated as an individual First-In-First-Out (FIFO) device. Pluralities of memory areas are implemented for user stack, kernel stack, interrupt stack and procedure call stack. Only one I / O arbiter is necessary for a CPU model that arbitrates between a plurality of FIFOs substituting data caches for on-chip implementation, thus eliminating traditional data transfer techniques using Direct-Memory-Access (DMA), bus control and lock signals leaving just the interrupt signals and the new synchronous signals for an easy and streamlined system design and CPU model. Supporting an interrupt-driven, FIFO-based I / O and synchronous burst data transfer the CPU employs a simple linear large register sets without bank switching.

Owner:UNIVERSITI TEKNOLOGI MALAYSIA +1

Varactor bank switching based on negative control voltage generation

InactiveUS20090243702A1Discontinuous tuning for band selectionElectronic switchingControl signalPass gate

Owner:GLOBALFOUNDRIES INC

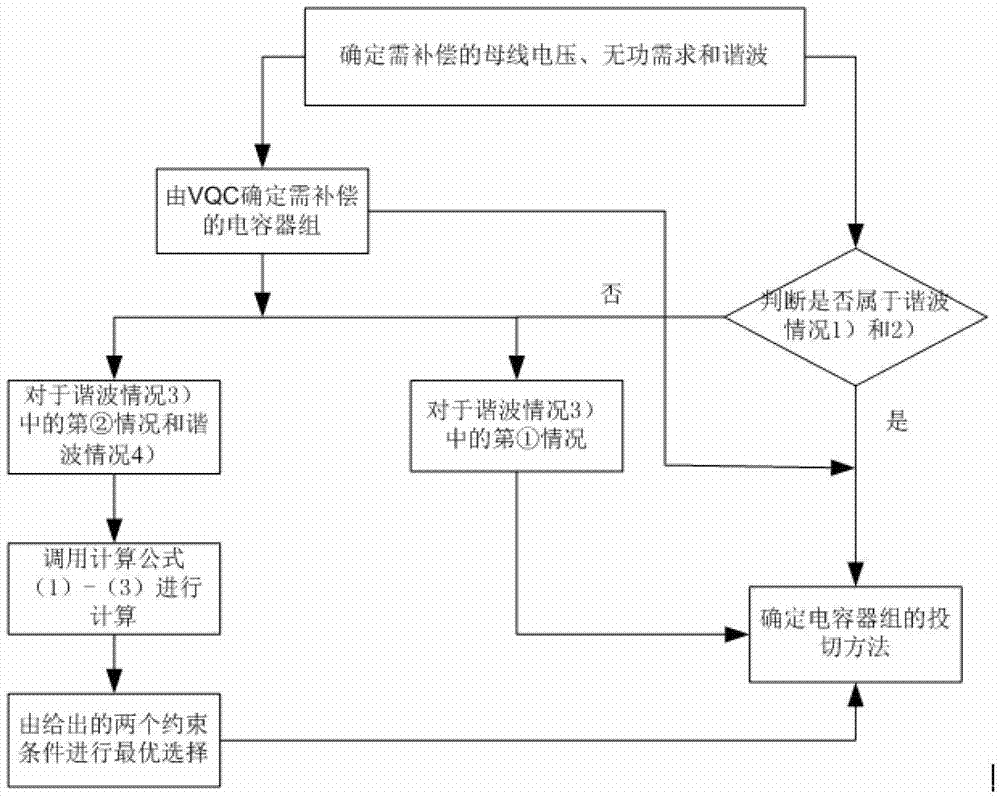

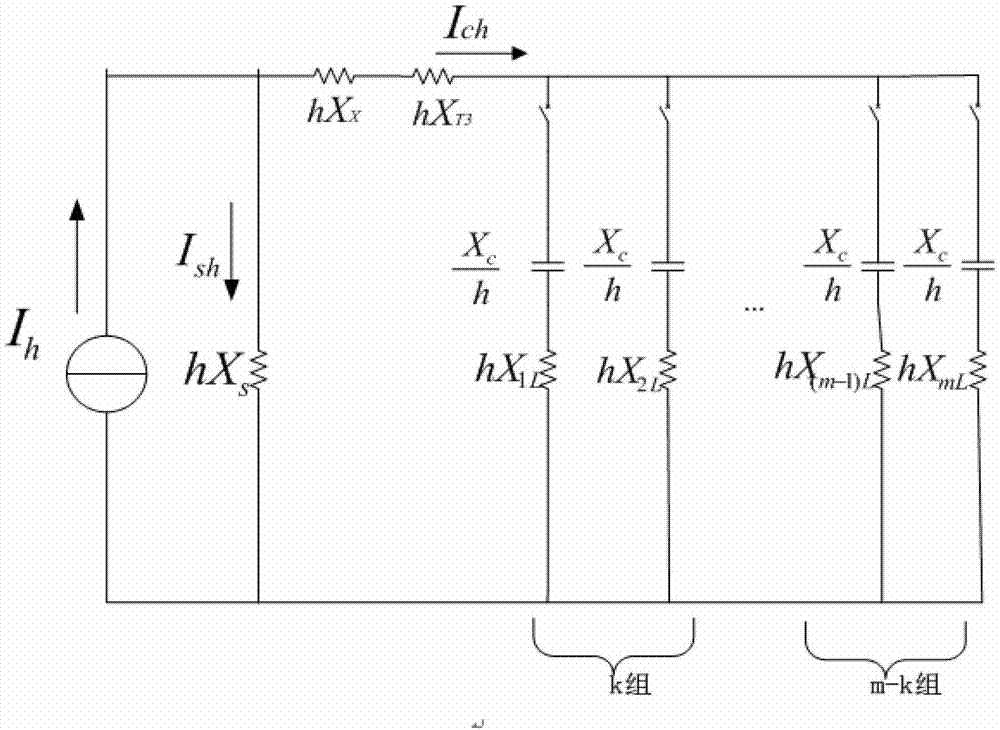

Capacitor bank switching method under harmonic conditions

InactiveCN103199536AEnhanced inhibitory effectMake up for the shortcomings of less harmonic considerationsHarmonic reduction arrangementAc network to reduce harmonics/ripplesCompensation effectMathematical model

The invention discloses a capacitor bank switching method under harmonic conditions, and belongs to the technical field of capacitor banks. Harmonic compensation is performed to a maximum extent. The technical scheme includes: firstly, a bus voltage, idle work requirements and harmonic conditions at the position, where compensation is needed, of a transformer substation are determined, and a capacitor bank needing to be compensated is determined through VQC; then an equivalent mathematical model of the transformer substation is given, wherein reactance values of a current limiting reactor and a third winding of a transformer are taken into account; and finally, the harmonic conditions of the transformer substation are summarized to four kinds, a corresponding considering and calculating method is given aiming at each harmonic condition so as to obtain the optimal compensation capacitor bank. The capacitor bank switching method under the harmonic conditions has the advantages that a switching strategy of the capacitor bank in the VQC of the transformer substation under various harmonic conditions, namely, under the various harmonic conditions, capacitor banks with different reactance rates are combined in an optimal mode, and under the premise that the VQC is met, the maximum compensation effects on harmonic waves are achieved.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING) +2

Compact packet switching node storage architecture employing Double Data Rate Synchronous Dynamic RAM

Owner:IKANOS COMMUNICATIONS

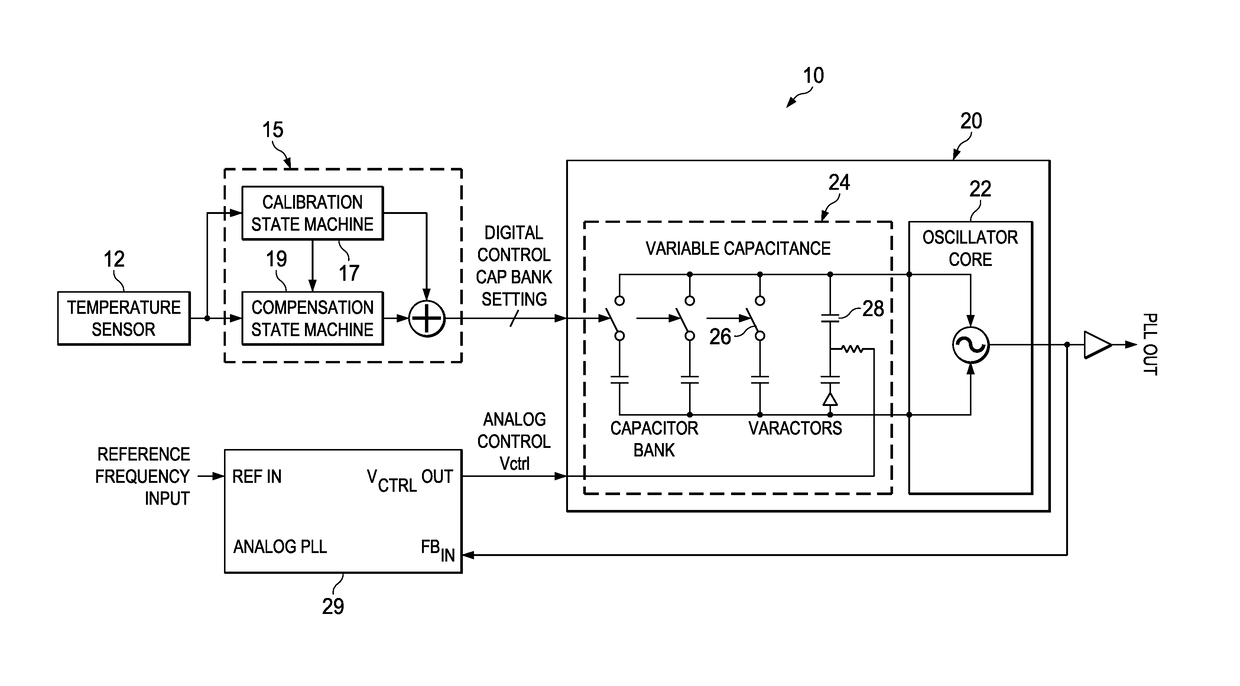

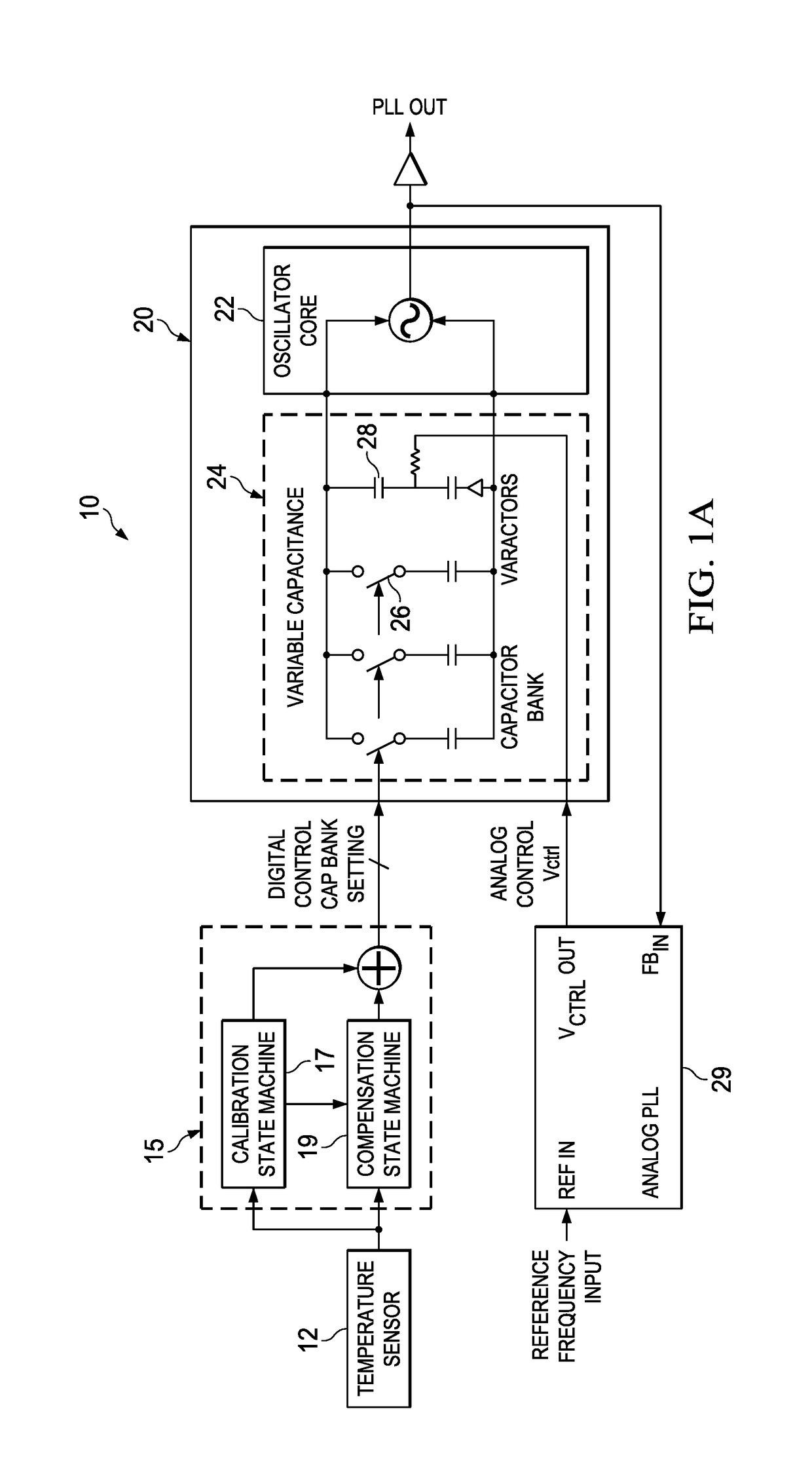

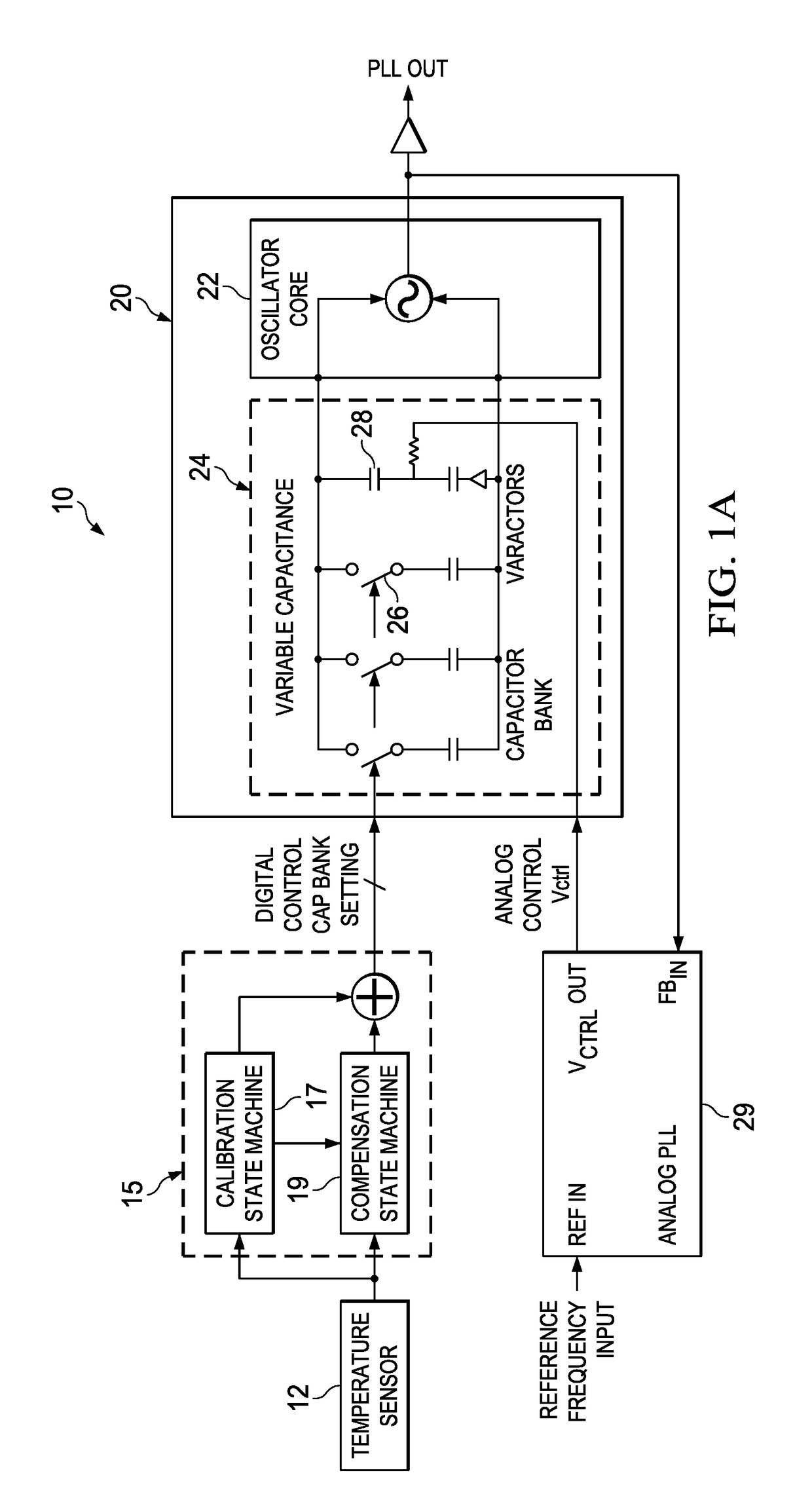

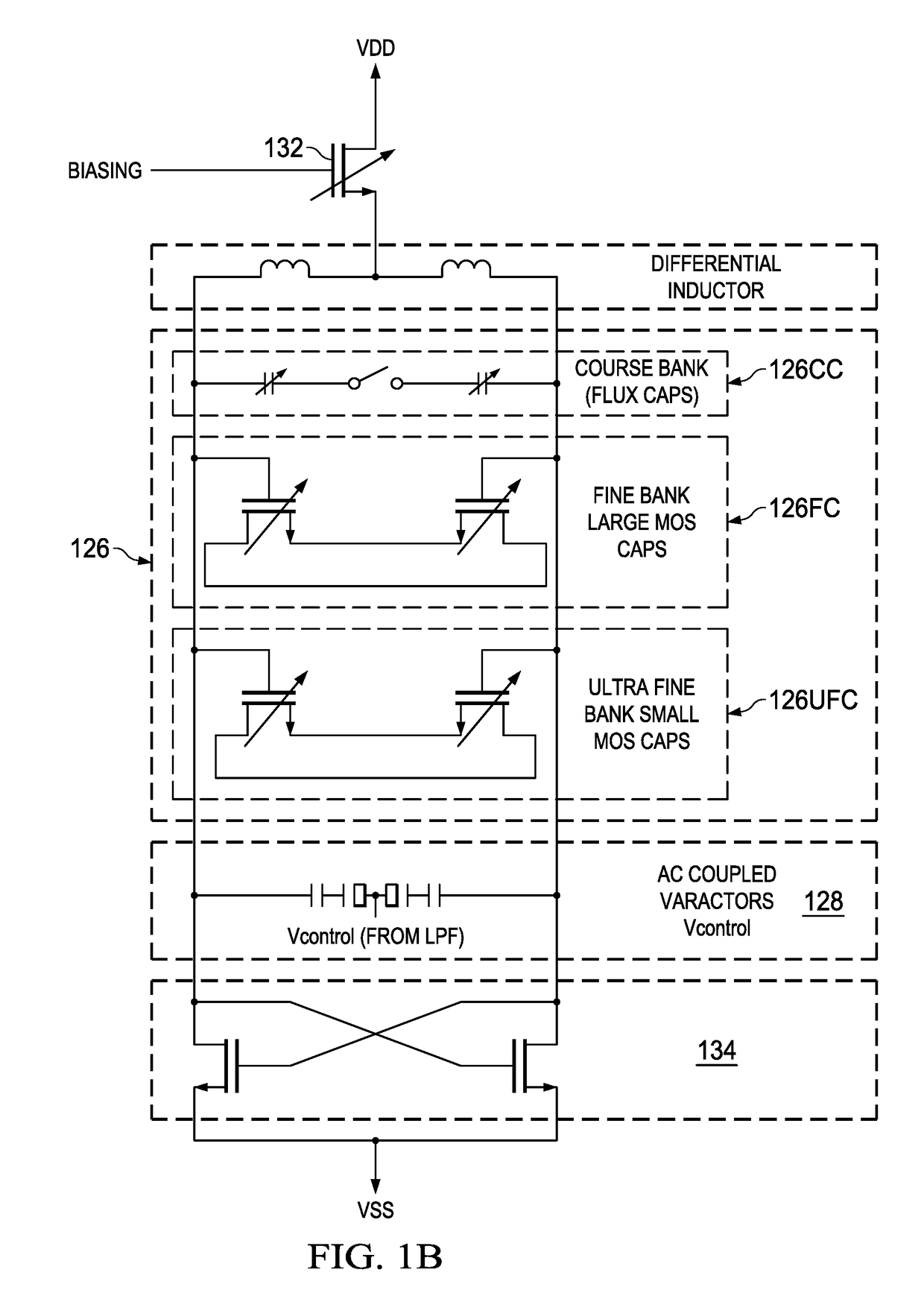

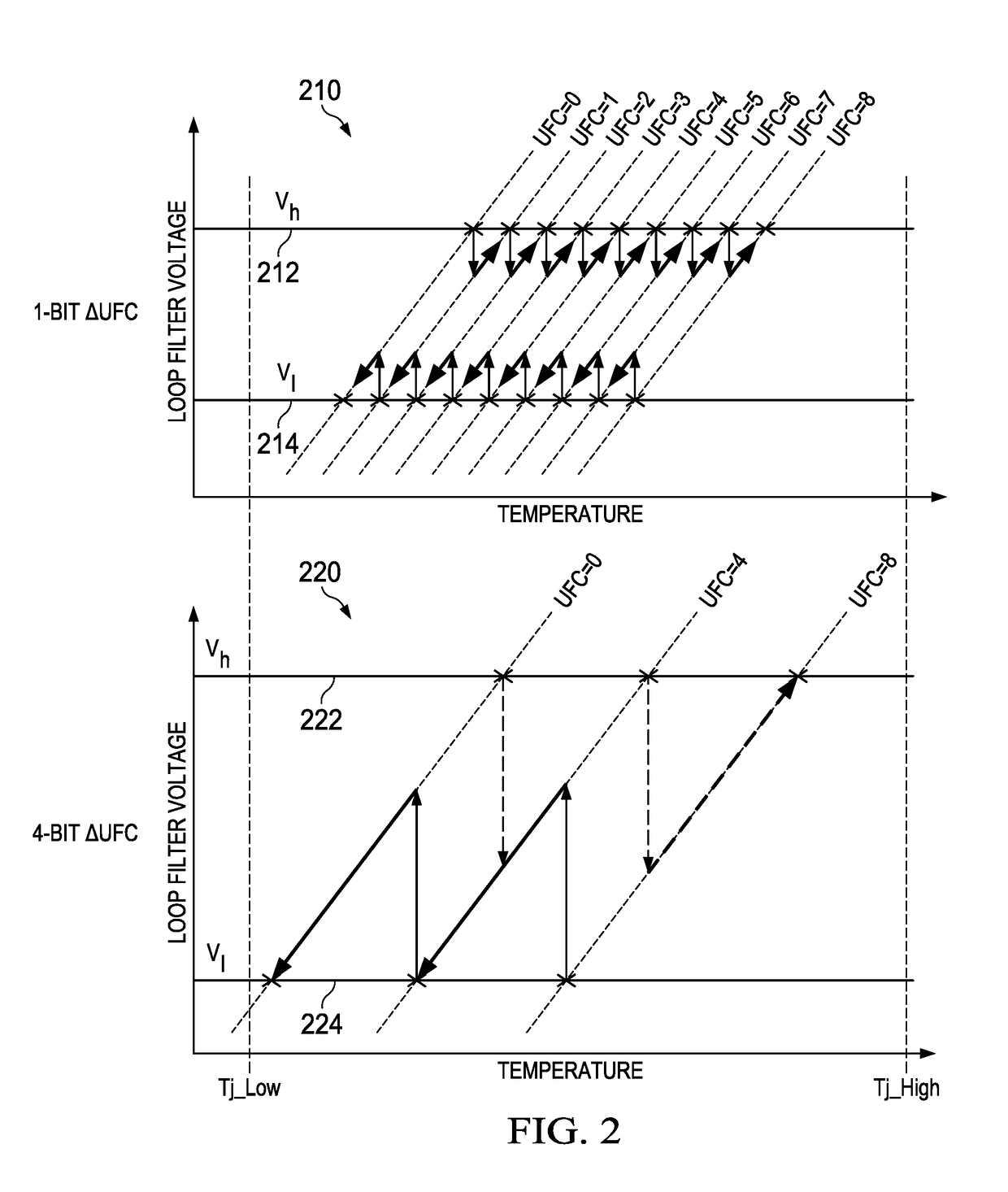

Pll lock range extension over temperature using dynamic capacitor bank switching

ActiveUS20170264302A1Increase lock rangeIncrease temperaturePulse automatic controlGenerator stabilizationResistor ladderCapacitor

A multi-ladder DAC includes first and second resistor ladders, with a switch-interconnect. The switch-interconnect includes a second set of switches connected between each node of the first ladder and the top and bottom tap points of the second ladder. All other second ladder tap points are part of a loop tied to the nodes above and below each resistor through a second set of switches. Because no current flows through the switches that tie the top and bottom second-ladder tap points to the nodes of the first ladder, avoiding IRswitch error, thereby improving DNL.

Owner:TEXAS INSTR INC

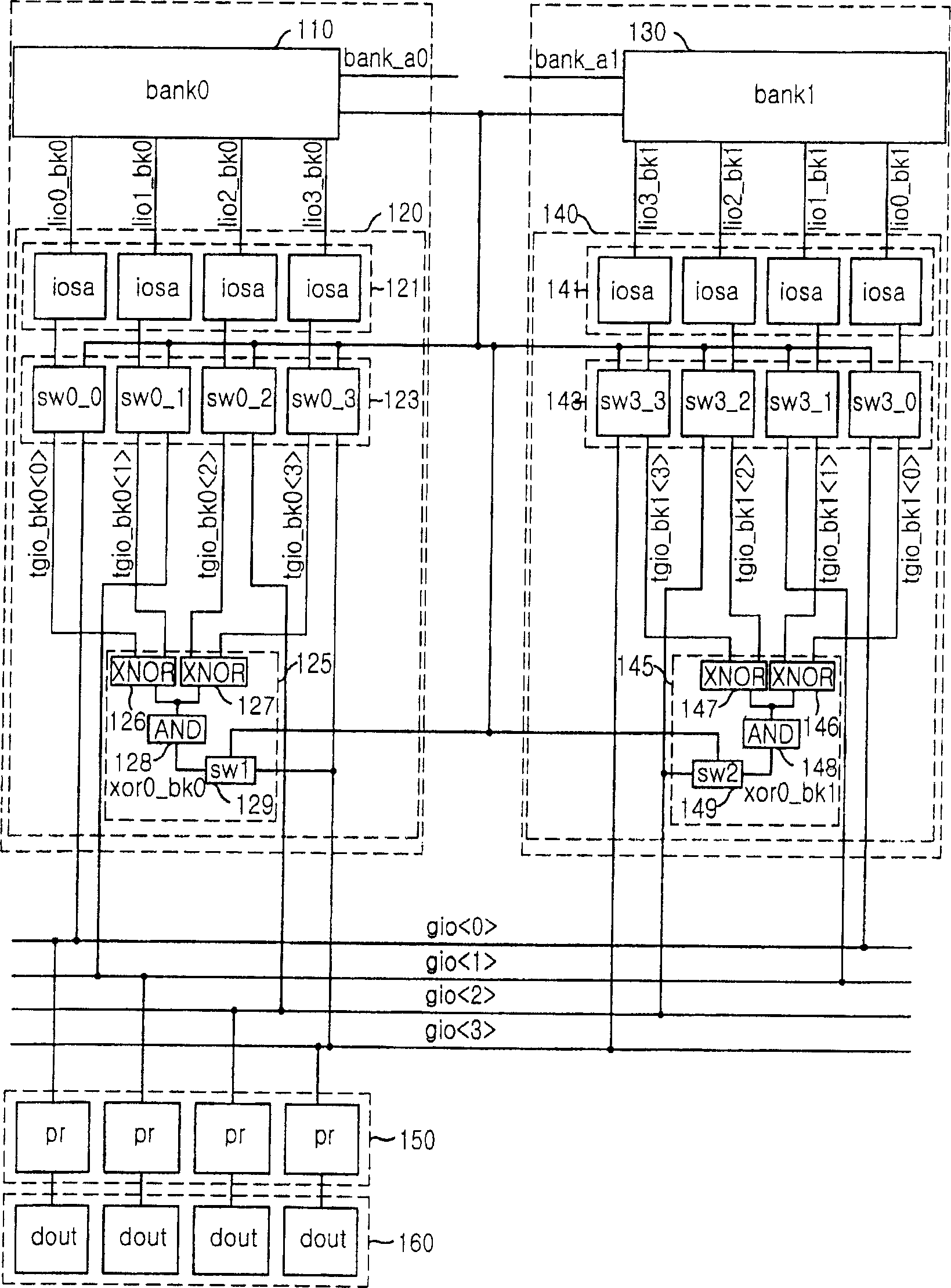

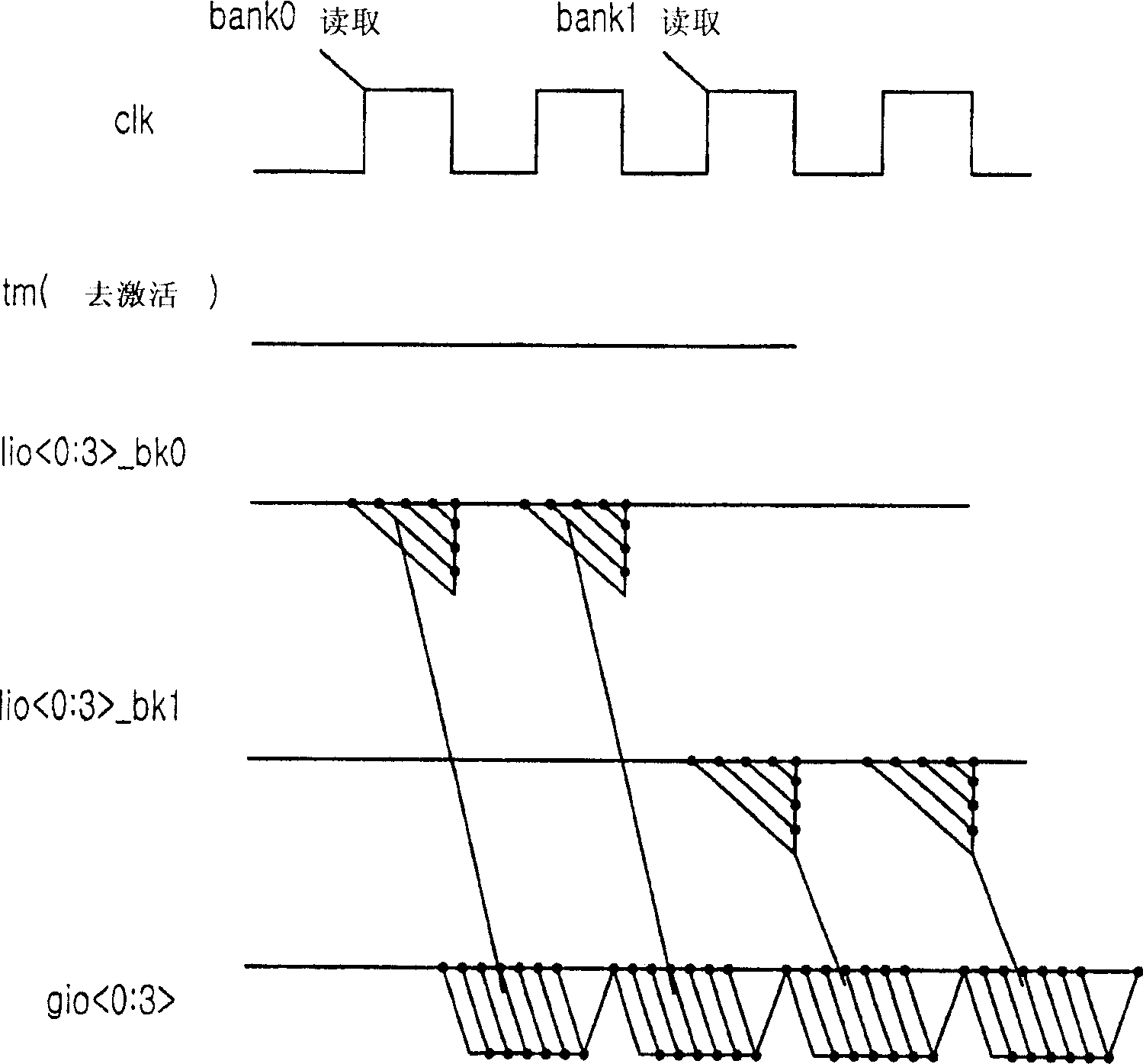

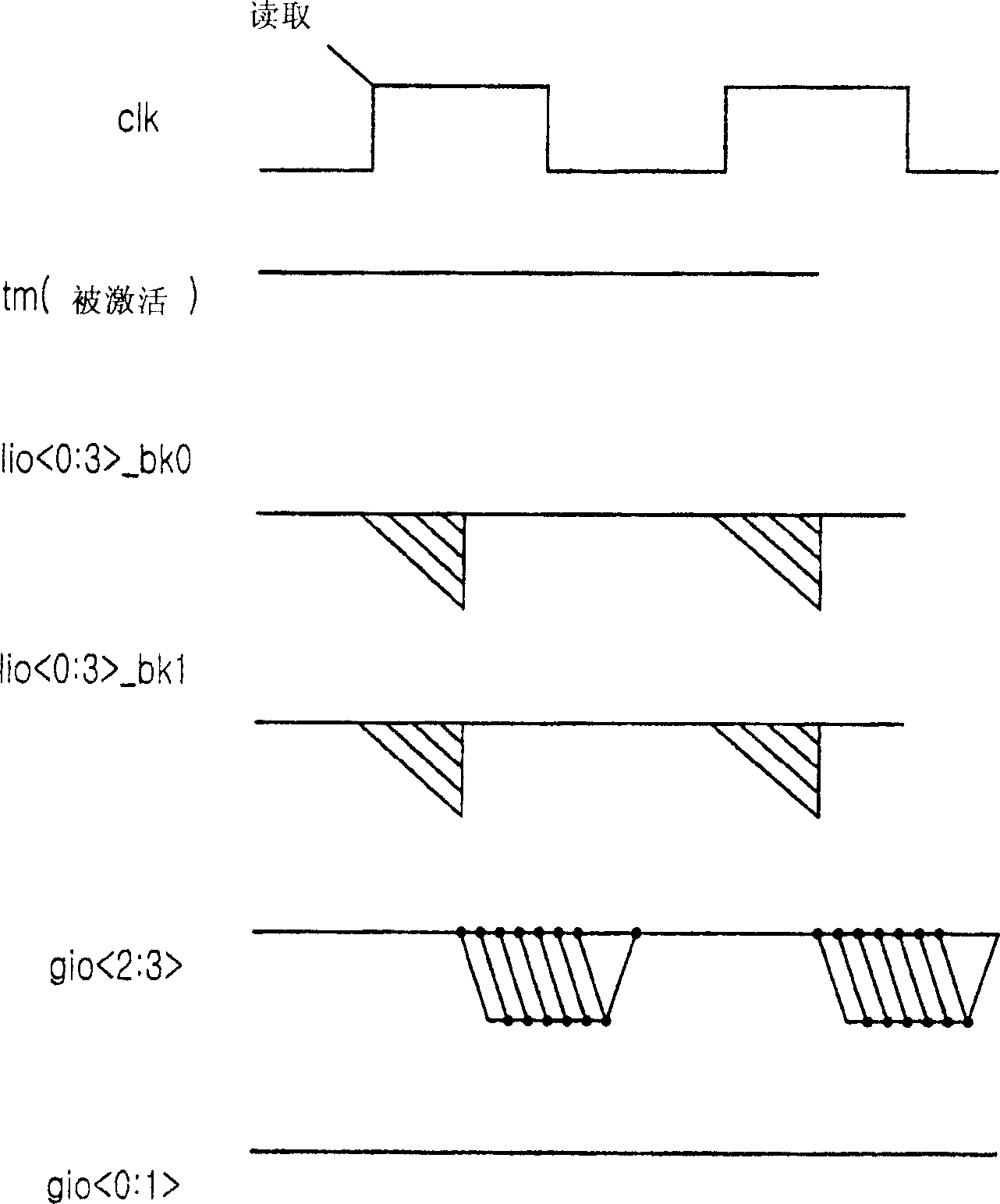

Memory cell test circuit for use in semiconductor memory device and its method

A memory cell test circuit for use in a semiconductor memory device having a plurality of banks connected to a plurality of global input / output lines, including: a plurality of bank switching units for transferring data outputted from the plurality of banks to the plurality of global input / output lines based on a test mode signal and a plurality of control clock signals; a logic operation unit for performing a logic operation to the data outputted to the plurality of global input / output lines and for outputting a result of the logic operation to a test global input / output line; and a switching unit coupled to the test global input / output line and the plurality of global input / output lines for selectively passing data of the test global input / output line and data of the global input / output lines based on the test mode signal and the plurality of control clock signals.

Owner:SK HYNIX INC

Capacitor bank switching vacuum circuit breaker

InactiveCN103560044ASolve the problem that the probability of rekindling remains highReduce breakdown rateHigh-tension/heavy-dress switchesAir-break switchesEngineeringCapacitor

The invention discloses a capacitor bank switching vacuum circuit breaker. The capacitor bank switching vacuum circuit breaker is sequentially provided with a conductive part, a transmission mechanism and a spring mechanism from top to bottom. An arc extinguish chamber I and an arc extinguish chamber II of each phase in the conductive part are vertically arranged left and right, a movable conductive rod I at the bottom of the arc extinguish chamber I is in short-circuited connection with a movable conductive rod II at the bottom of the arc extinguish chamber II in a flexible mode, the top end of an isolating pull rod in the transmission mechanism is connected with a connecting plate, and the connecting plate is connected with the movable conductive rod I and the movable conductive rod II. A serial connection fracture mode is adopted on a vacuum fracture, and the problem that the reignition probability is high when a common vacuum circuit breaker is used for switching a capacitor bank is solved.

Owner:SHANDONG TAIKAI VACUUM SWITCH

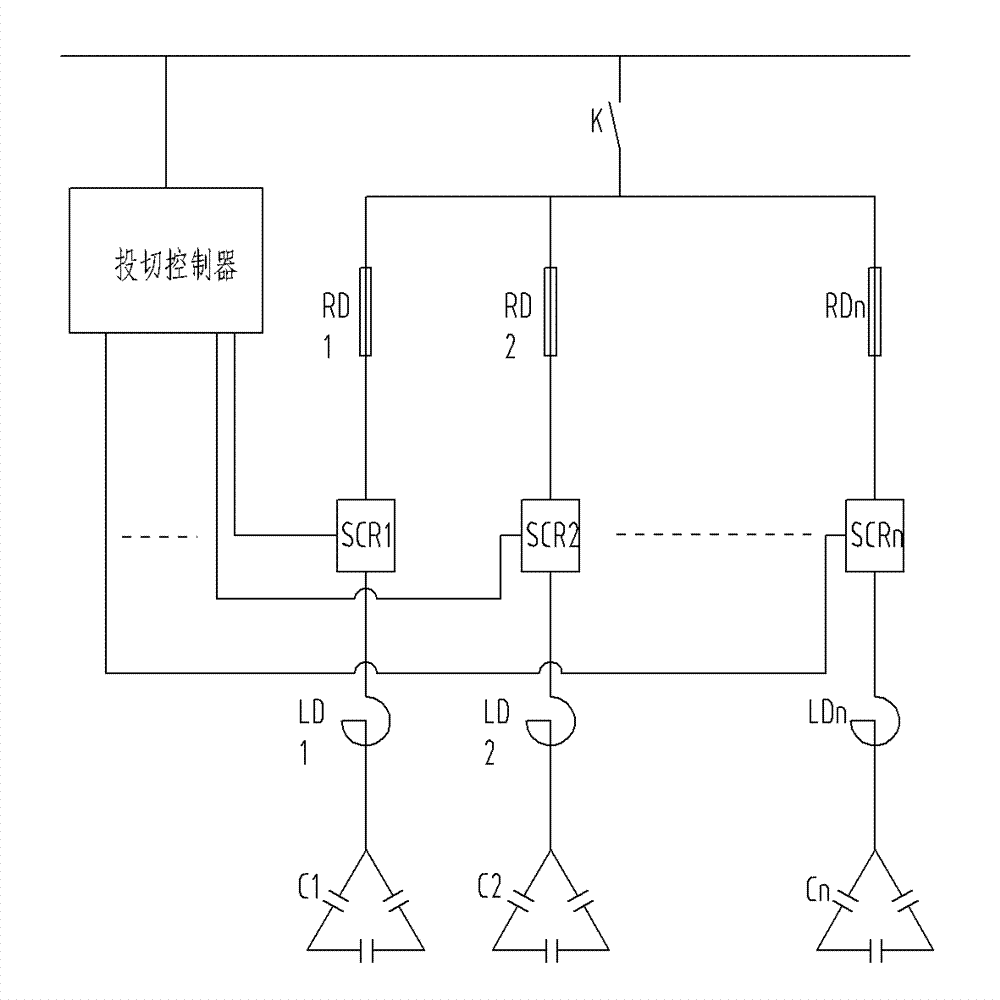

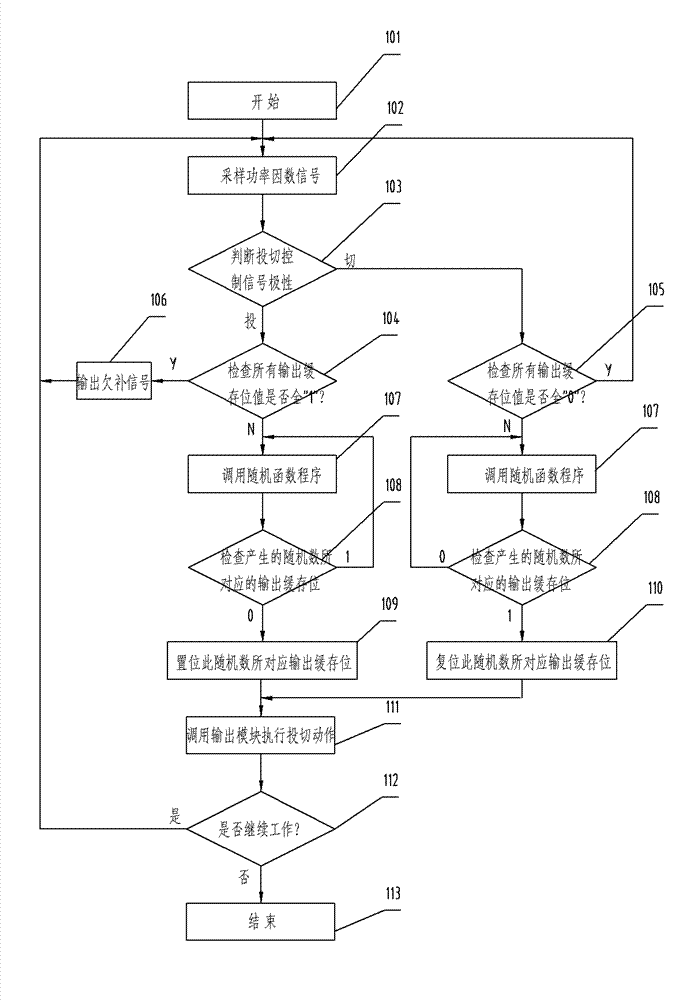

Compensating capacitor bank switching method and compensating capacitor bank switching device

InactiveCN102832628AExtend working lifeImprove mean time between failuresReactive power adjustment/elimination/compensationReactive power compensationElectricityPower compensation

The invention discloses a compensating capacitor bank switching method and a compensating capacitor bank switching device adopting the method. The method mainly includes: working out a random function program with output values serving as sequence numbers of compensating capacitor banks, and selecting compensating capacitor banks switched into a power grid and compensating capacitor banks switched out of the power grid according to the random function output values. The compensating capacitor bank switching device comprises a plurality of capacitor banks (6), a capacitor bank switching controller (8), capacitor bank switching control switches (5) and a power factor meter (7), and a microprocessor (15) of the capacitor bank switching controller (8) is connected with a signal output end of the power factor meter (7) through an input interface circuit (13) and is connected with a control signal end of each capacitor bank switching control switch (5) through an output interface circuit (14). Compared with the prior art, the compensating capacitor bank switching method and the compensating capacitor bank switching device are capable of effectively solving the problem of poor operating reliability of a reactive power compensation device.

Owner:LIUZHOU HAIGE ELECTRICAL

Method and system for detecting and performing automatic bank switching for a filter coefficient RAM

InactiveCN1666500ATelevision system detailsColor signal processing circuitsArray data structureVertical blanking interval

A method for facilitating a dual-bank filter coefficient RAM designed to switch banks automatically during the vertical blanking interval in a television application. The method and system of the present invention allows a micro controller to program a new set of filter coefficients in the memory bank not currently being used, automatically detect when all the coefficients have been written and then automatically switch banks during the vertical blanking interval in the television application.

Owner:THOMSON LICENSING SA

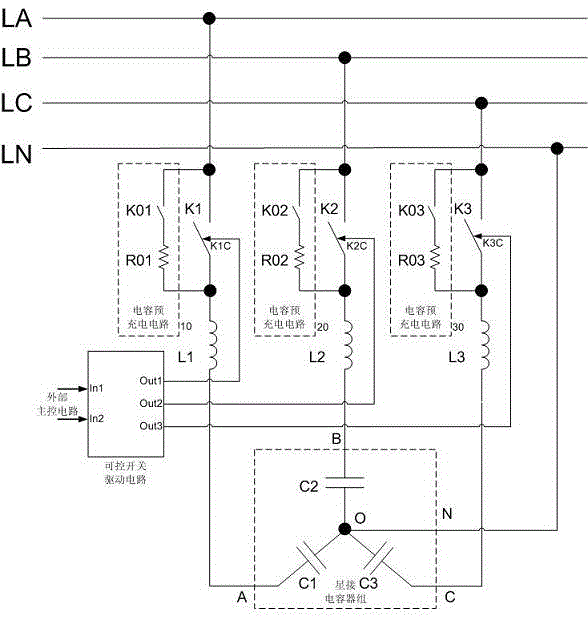

Star-connection capacitor bank switching module

ActiveCN105680455AReduce volumeLow costReactive power adjustment/elimination/compensationReactive power compensationCapacitanceSilicon-controlled rectifier

A star-connection capacitor bank switching module is disclosed. The star-connection capacitor bank switching module comprises a star-connection capacitor bank, three controllable switches K1, K2 and K3, three small inductors L1, L2 and L3, three capacitor pre-charging circuits 10, 20 and 30, and a silicon controlled rectifier driving circuit, wherein the N input terminal of the star-connection capacitor is connected with the null line LN of a distribution network line; A, B and C input terminals are connected with the first ends of the three small inductors respectively; the second ends of the three small inductors are connected with LA, LB and LC phase lines of the distribution network line through the three controllable switches respectively; the three capacitor pre-charging circuits are connected with the three controllable switches in parallel; and the three output ends of the controllable switch driving circuit are connected with the control ends of the three controllable switches respectively. The star-connection capacitor bank switching module is connected with the distribution network line; three-phase reactive power time-sharing compensation can be realized; the generation of surge current in the capacitor switching process can be effectively avoided; impact current that may be caused when the capacitor is connected to the power grid can be reduced; and the service life of the module is prolonged.

Owner:广州开能电气技术有限公司

PLL lock range extension over temperature

ActiveUS10187071B2Increase temperaturePulse automatic controlGenerator stabilizationJunction temperatureSwitched capacitor

Owner:TEXAS INSTR INC

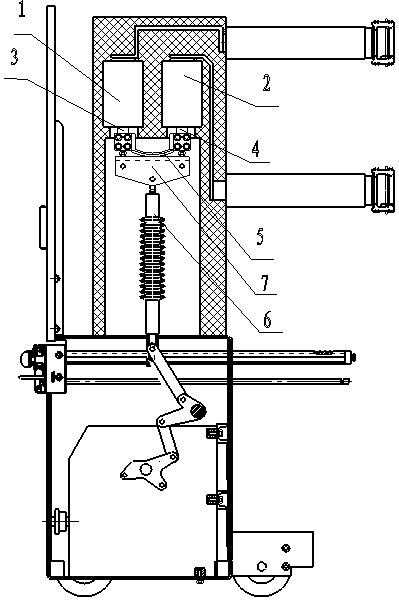

Intelligent circuit breaker for shunt capacitor bank switching based on flexible opening and closing technology

ActiveCN106024496BImprove power qualitySimple structureHigh-tension/heavy-dress switchesAir-break switchesShunt capacitorsEngineering

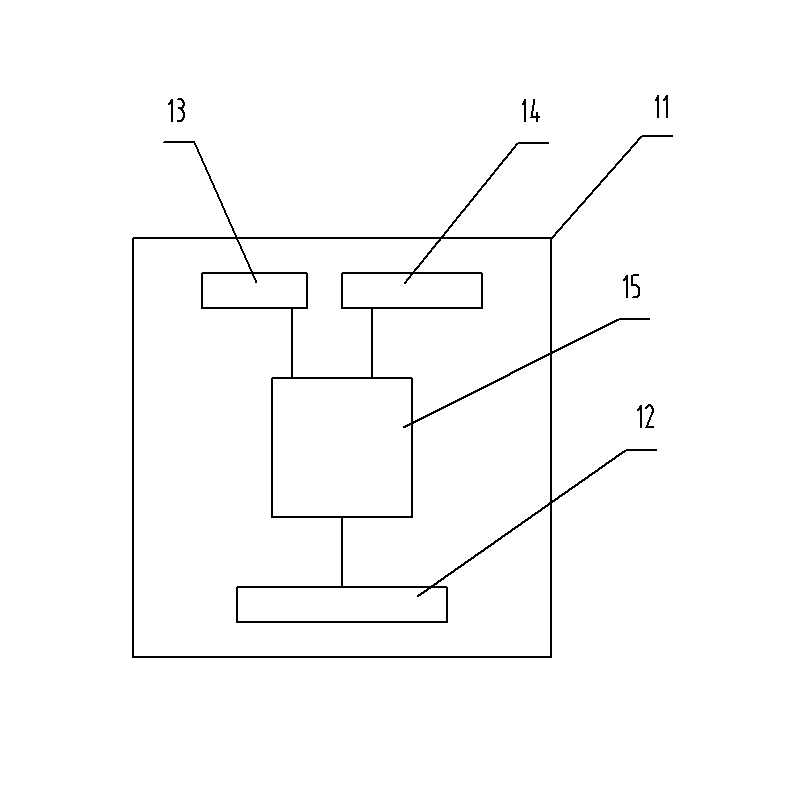

An intelligent circuit breaker for shunt capacitor bank switching based on a flexible opening and closing technology, comprising three poles A, B and C and an intelligent controller D. Three-phase power supplies UA, UB and UC are respectively connected with the three poles A, B and C; two ends of a shunt capacitor C1 are respectively connected with the poles A and B; two ends of a shunt capacitor C2 are respectively connected with the poles B and C; two ends of a shunt capacitor C3 are respectively connected with the poles A and C; each of the three poles A, B and C comprises a conductive and arc-extinguishing component (1), a first stroke sensing component (2), a closing damping component (3), a high-voltage insulated component (4), an opening and closing driving component (5), an opening damping component (6), and a second stroke sensing component (7) sequentially connected in series in an axial direction. The intelligent circuit breaker for shunt capacitor bank switching based on the flexible opening and closing technology features a simple structure, reliable operation, convenient maintenance, and a high price-performance ratio; a shunt capacitor bank can be switched frequently; the reactive power compensation equipment for shunt capacitor bank switching achieves effects of reducing loss and saving energy of a power grid, and improving the transmission capacity and electric energy quality of the power grid.

Owner:JIANGSU MODERN POWER CAPACITOR

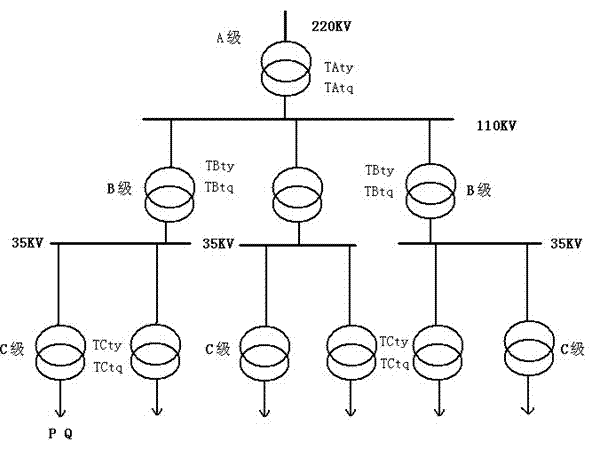

Voltage reactive comprehensive control method for step transformer substations

ActiveCN102082440BReduce switching oscillation problemsReactive power adjustment/elimination/compensationReactive power compensationTime delaysPower grid

The invention relates to a voltage reactive comprehensive control method for step transformer substations. Time delays are set in main transformer tap adjustment and reactive compensation capacitor switching control of the transformer substations of different voltage levels, wherein different time delays are set in the main transformer tap adjustment and the reactive compensation capacitor switching control of the transformer substations of the last stage and the main transformer tap adjustment and the reactive compensation capacitor switching control of the transformer substations of the next stage to realize time sequence fit of voltage reactive control of the transformer substations of different voltage levels; the same time delay is set in the voltage reactive control of the transformer substations of the same voltage level; and the operation time delay difference of the transformer substations of different voltage levels is at least greater than the required time of the operation. The method can realize reactive voltage optimization control of a global power grid, and can obviously reduce the ubiquitous problems of frequent main transformer tap adjustment and capacitor bank switching oscillation of the current transformer substations.

Owner:SHANDONG ELECTRIC POWER ENG CONSULTING INST CORP +1