Patents

Literature

41results about How to "Potential fluctuation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

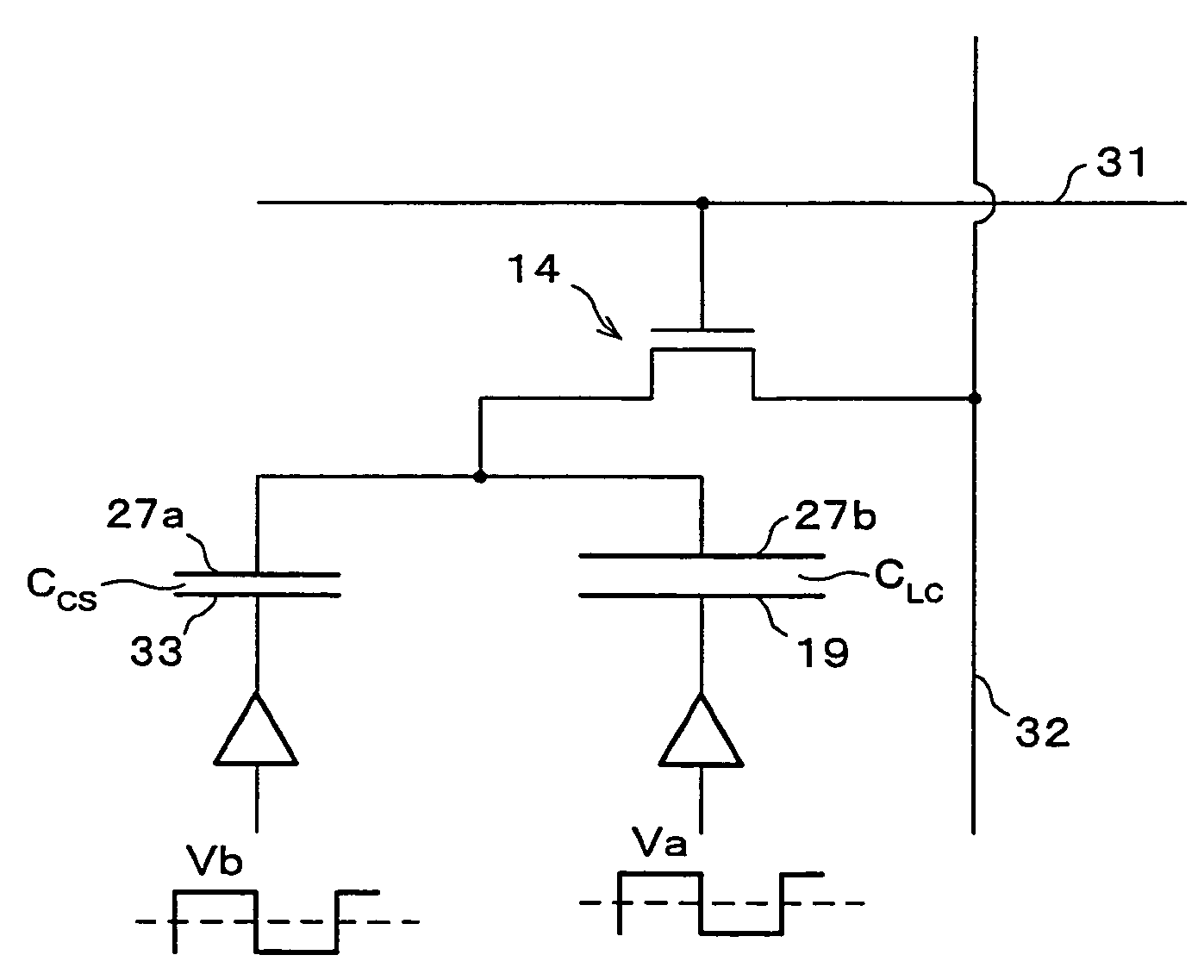

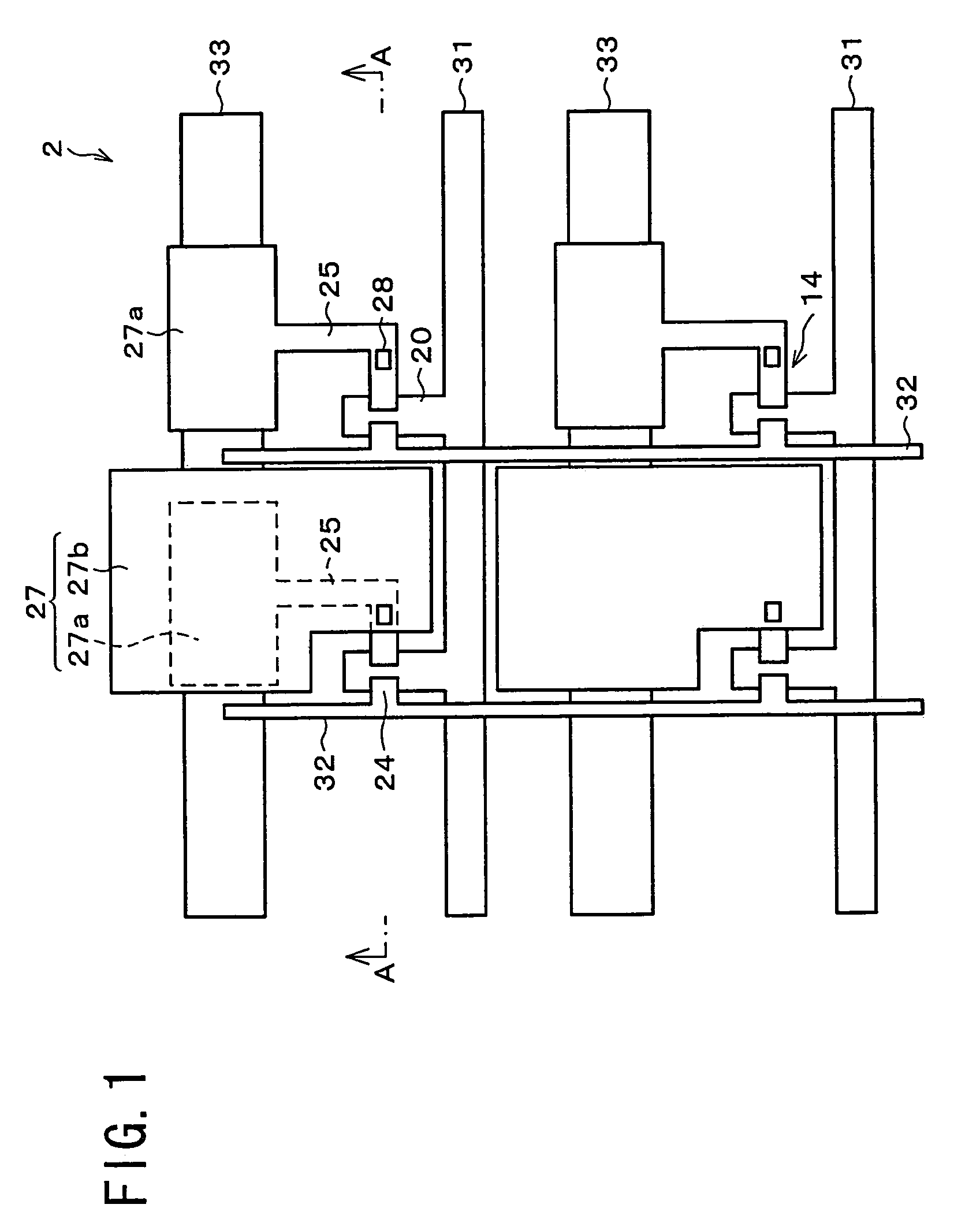

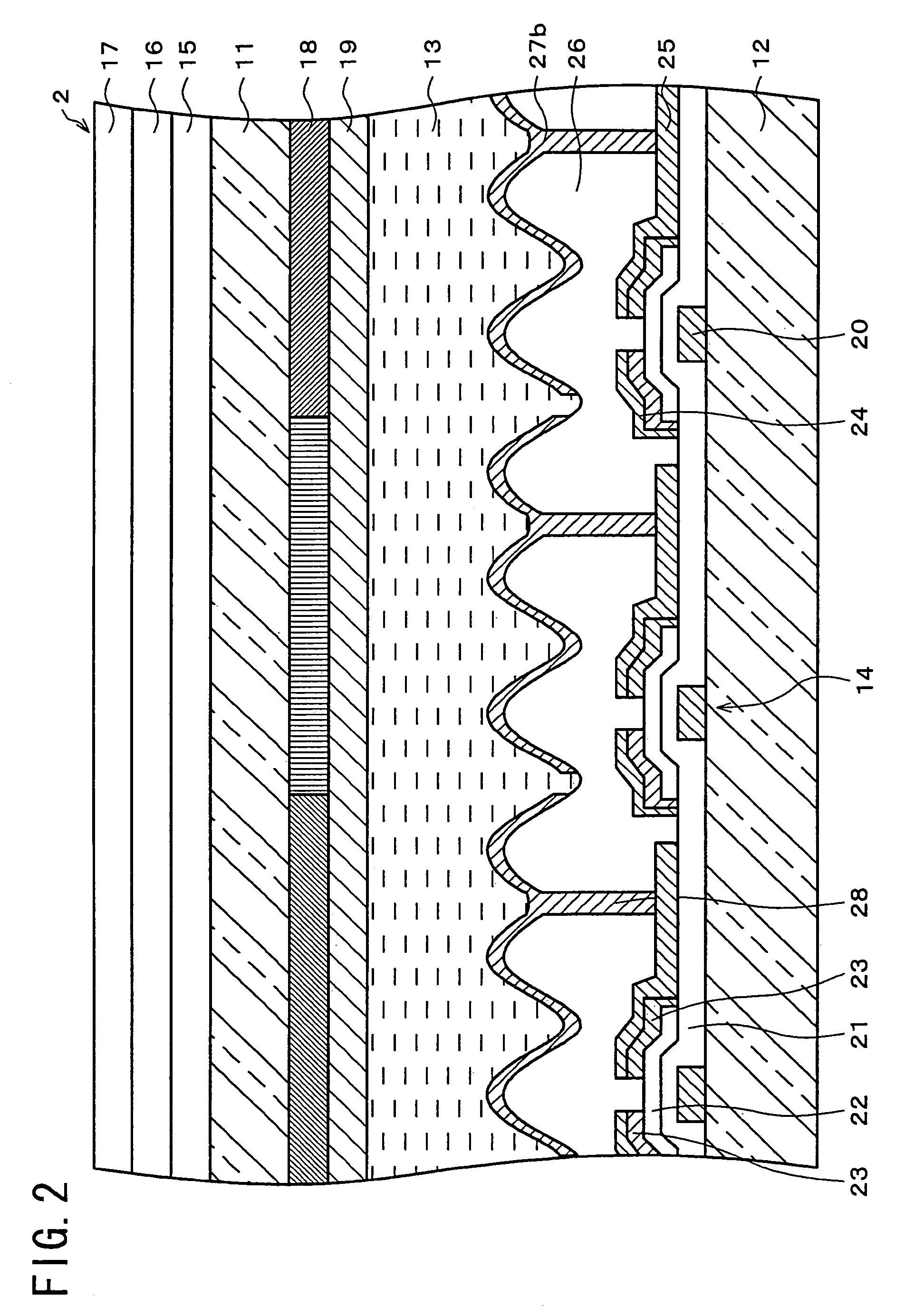

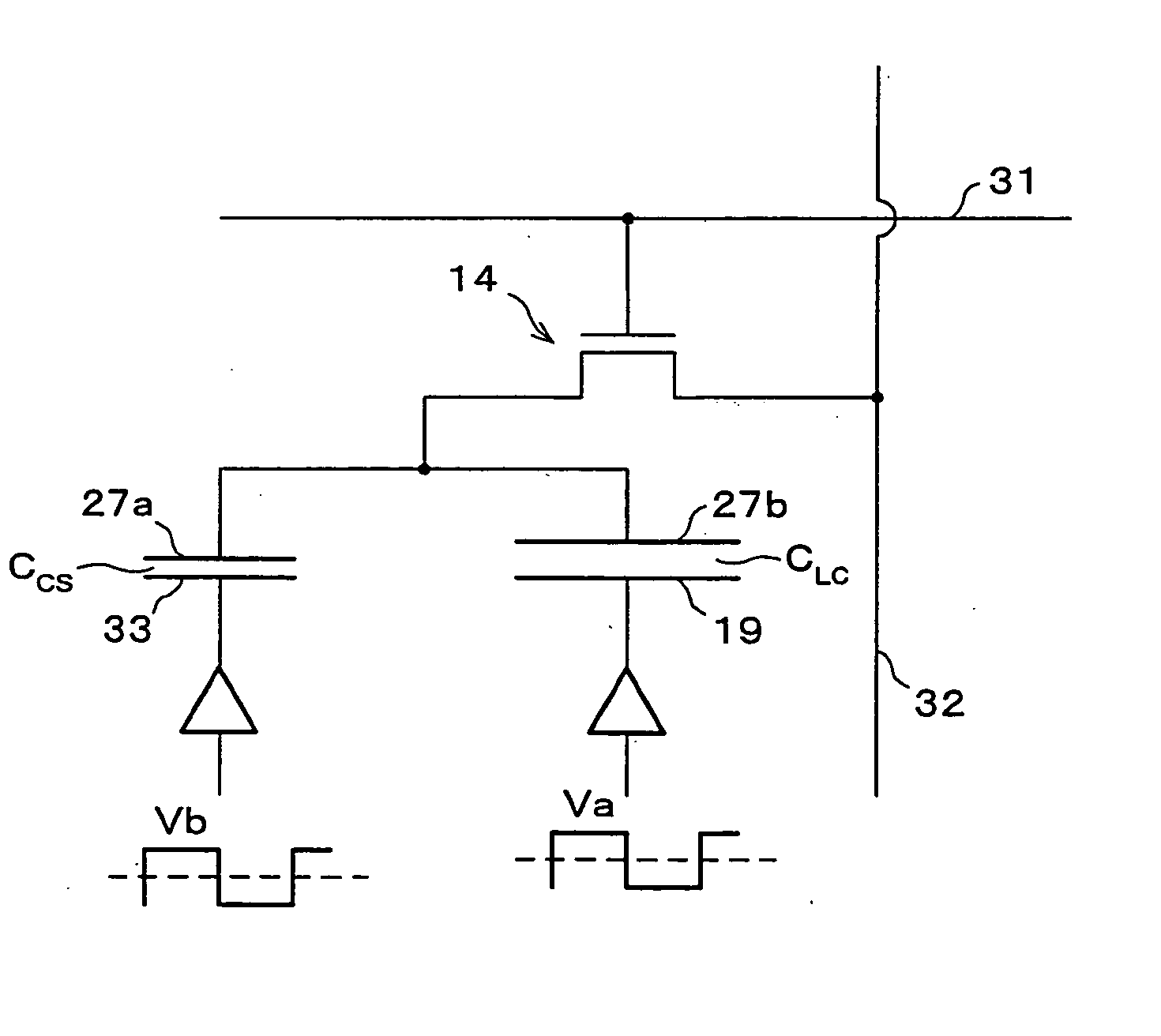

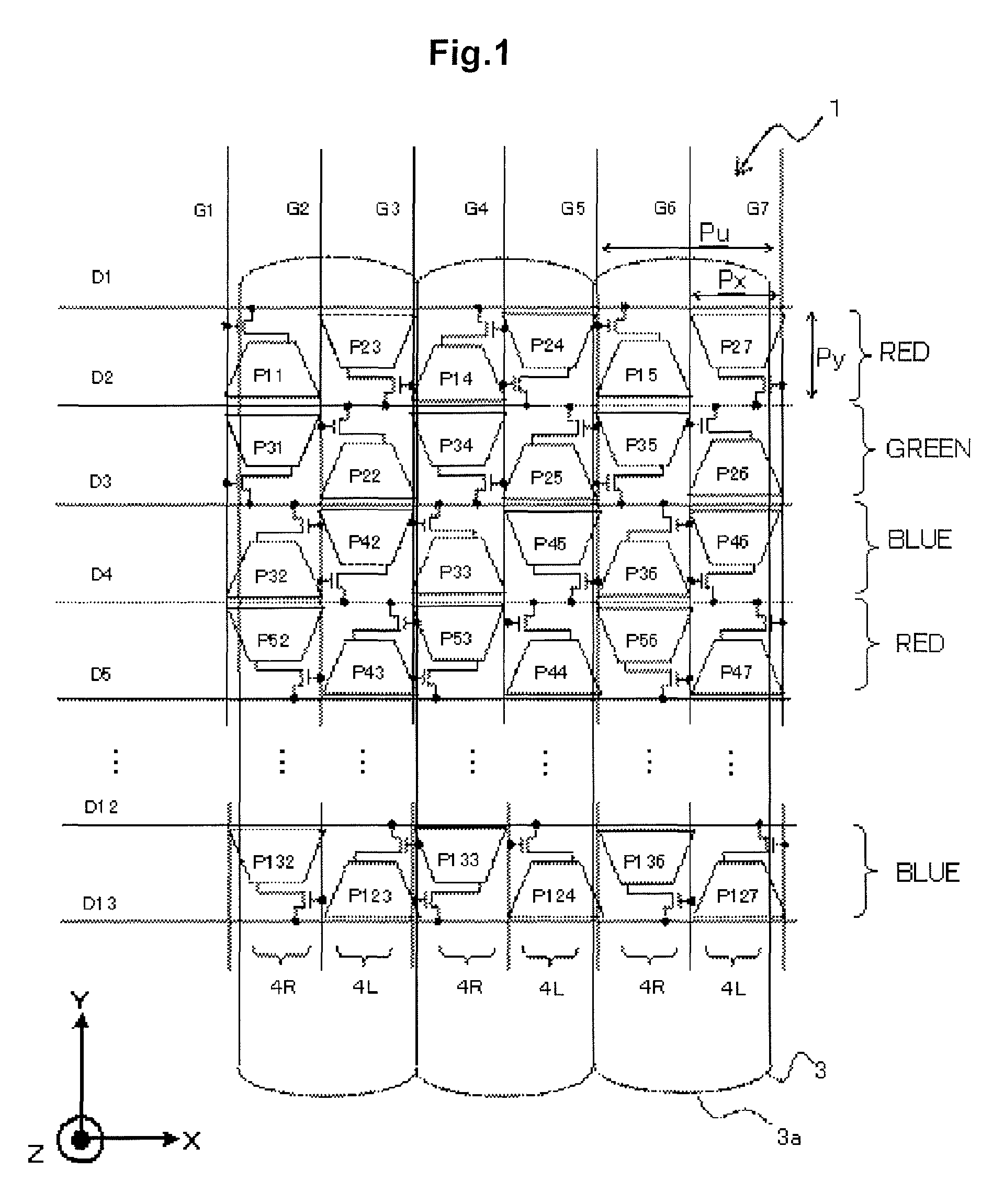

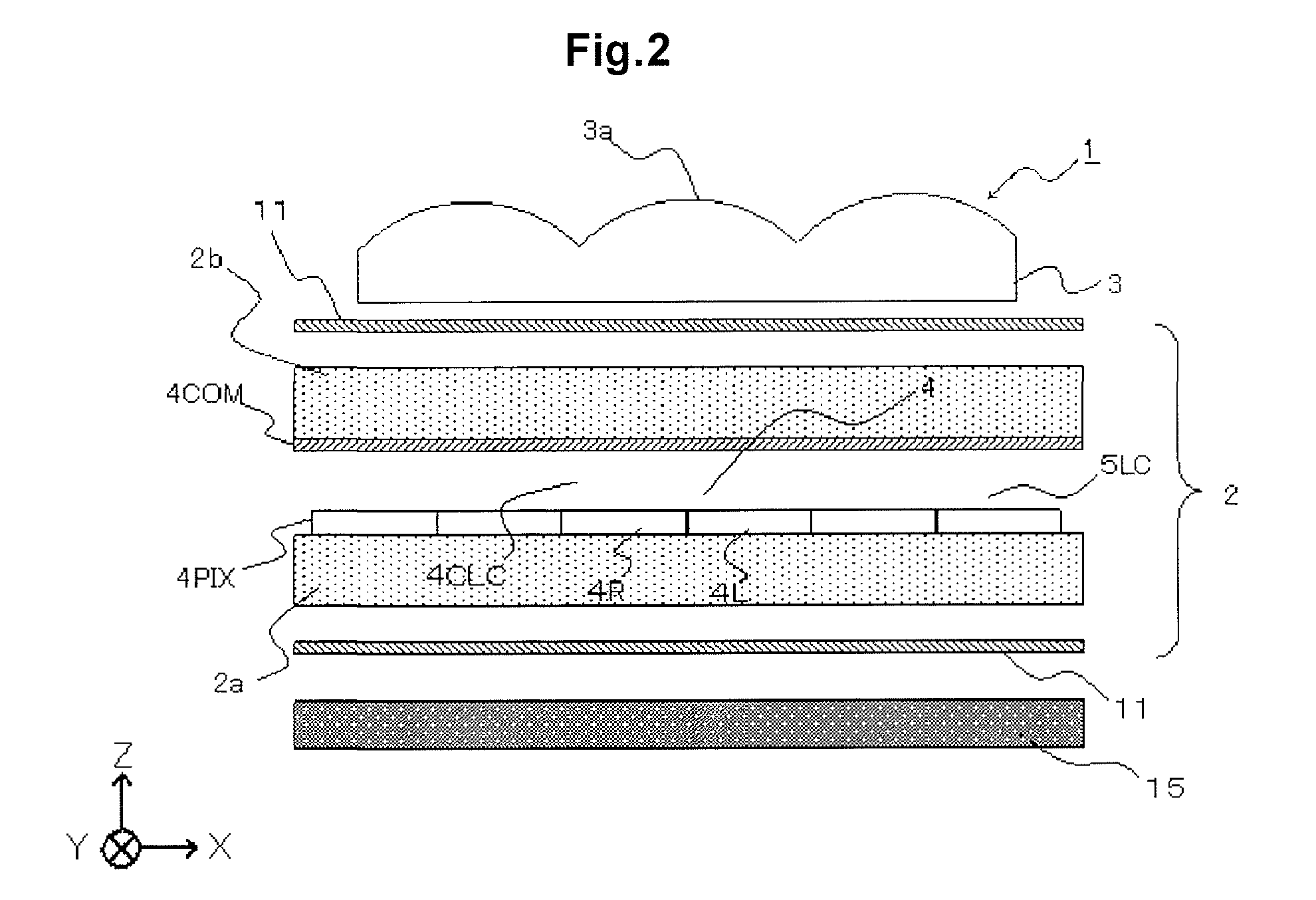

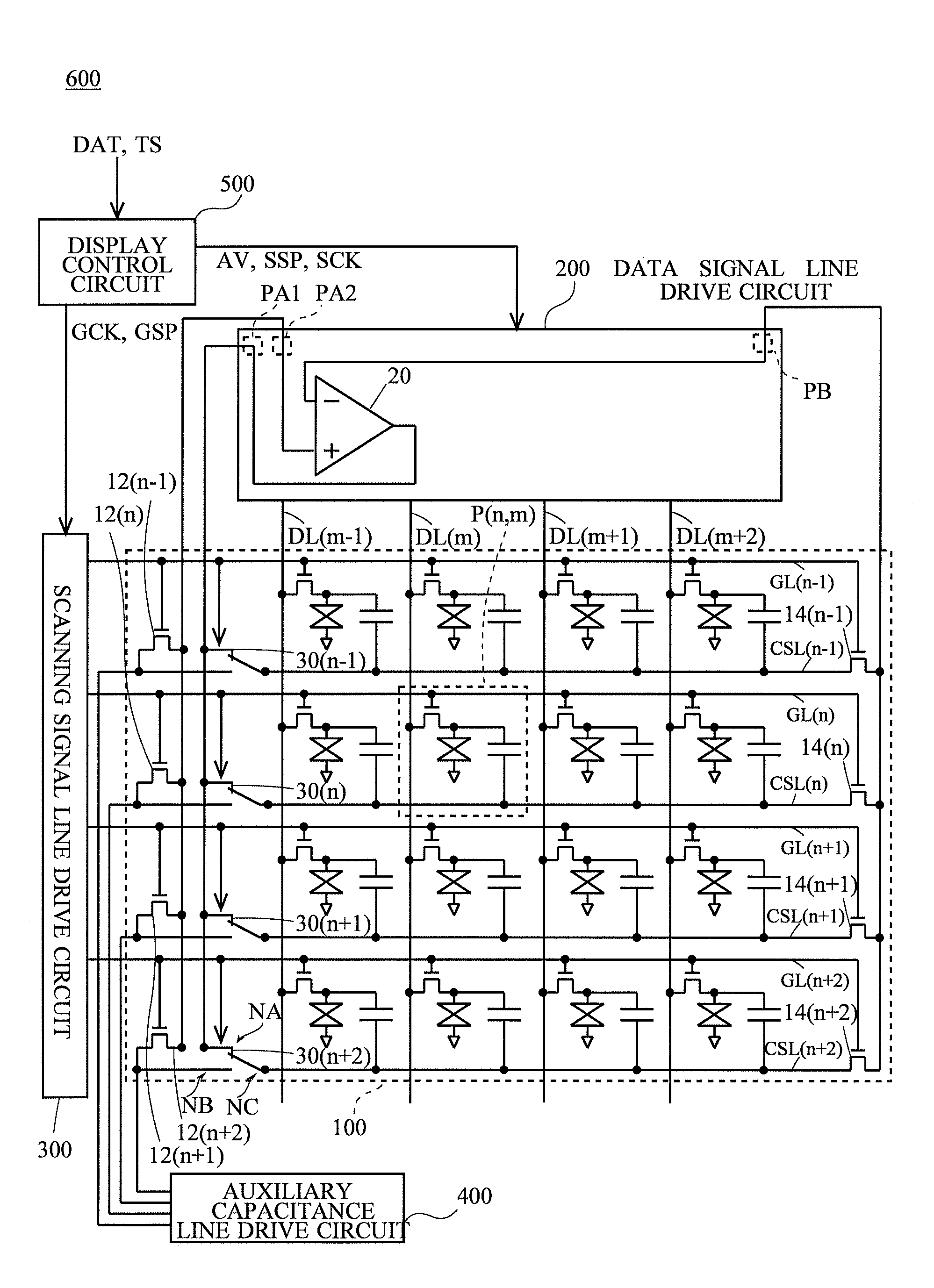

Display device, method of driving same and electronic device mounting same

InactiveUS7286108B2Potential fluctuationSuppress noiseStatic indicating devicesNon-linear opticsCapacitanceData signal

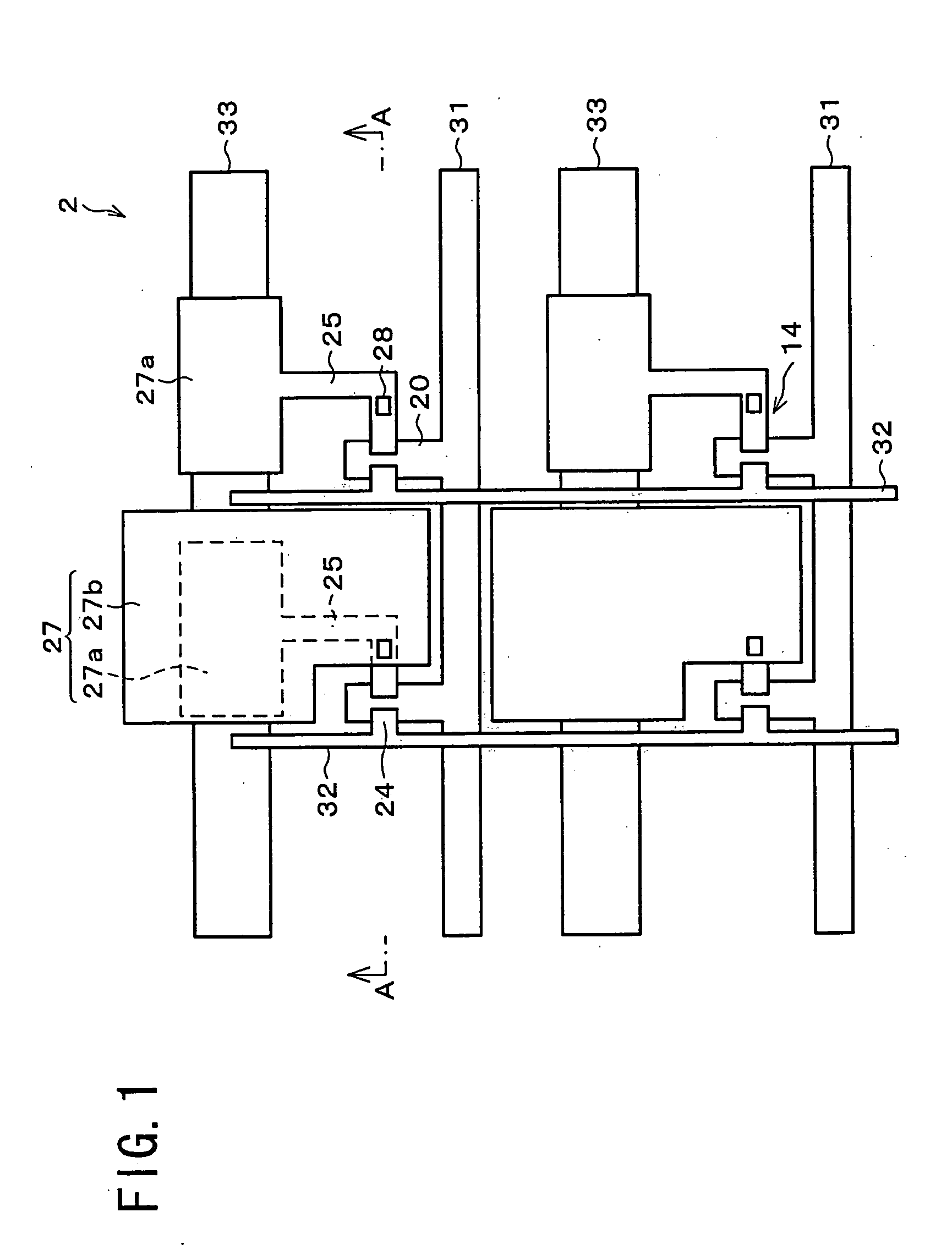

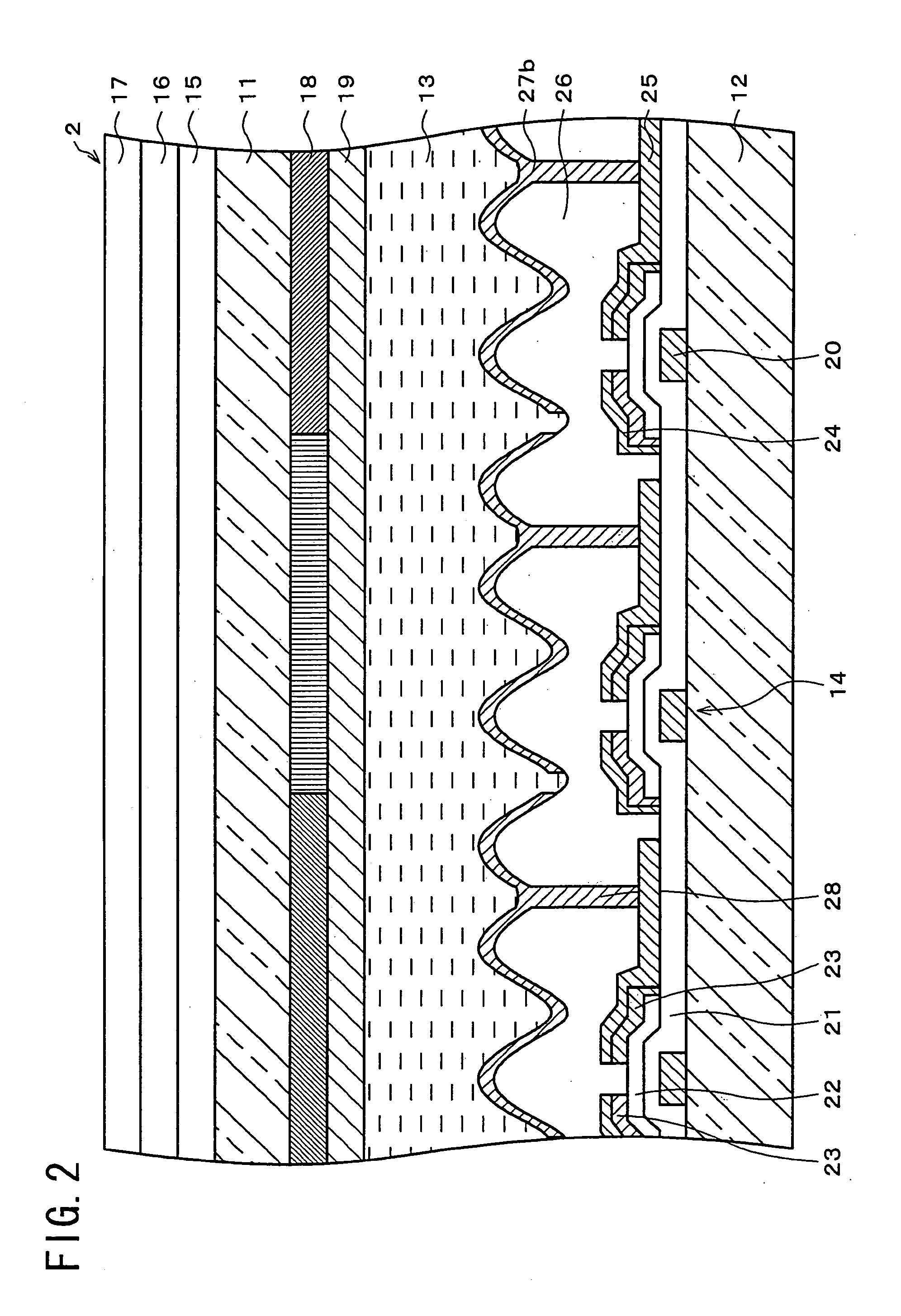

A liquid crystal panel (2) includes scanning signal lines (31) for supplying scanning signals to gate electrodes (20) of TFTs (14), and data signal lines (32) for supplying data signals to data electrodes (24) of TFTs. The liquid crystal panel further includes auxiliary capacitive electrode pads (27a) for use in forming auxiliary capacitance and an auxiliary capacitive lines (33) so as not to generate a capacitive bond with the scanning signal lines. The liquid crystal panel is driven at a rewriting frequency of a screen of not more than 30 Hz. As a result, the liquid crystal panel can be driven at a low consumption power while maintaining a desirable display quality of the liquid crystal panel.

Owner:SHARP KK

Display device, method of driving same and electronic device mounting same

InactiveUS20050140632A1Reduce power consumptionIncreased power consumptionStatic indicating devicesNon-linear opticsCapacitanceDisplay device

A liquid crystal panel (2) includes scanning signal lines (31) for supplying scanning signals to gate electrodes (20) of TFTs (14), and data signal lines (32) for supplying data signals to data electrodes (24) of TFTs. The liquid crystal panel further includes auxiliary capacitive electrode pads (27a) for use in forming auxiliary capacitance and an auxiliary capacitive lines (33) so as not to generate a capacitive bond with the scanning signal lines. The liquid crystal panel is driven at a rewriting frequency of a screen of not more than 30 Hz. As a result, the liquid crystal panel can be driven at a low consumption power while maintaining a desirable display quality of the liquid crystal panel.

Owner:SHARP KK

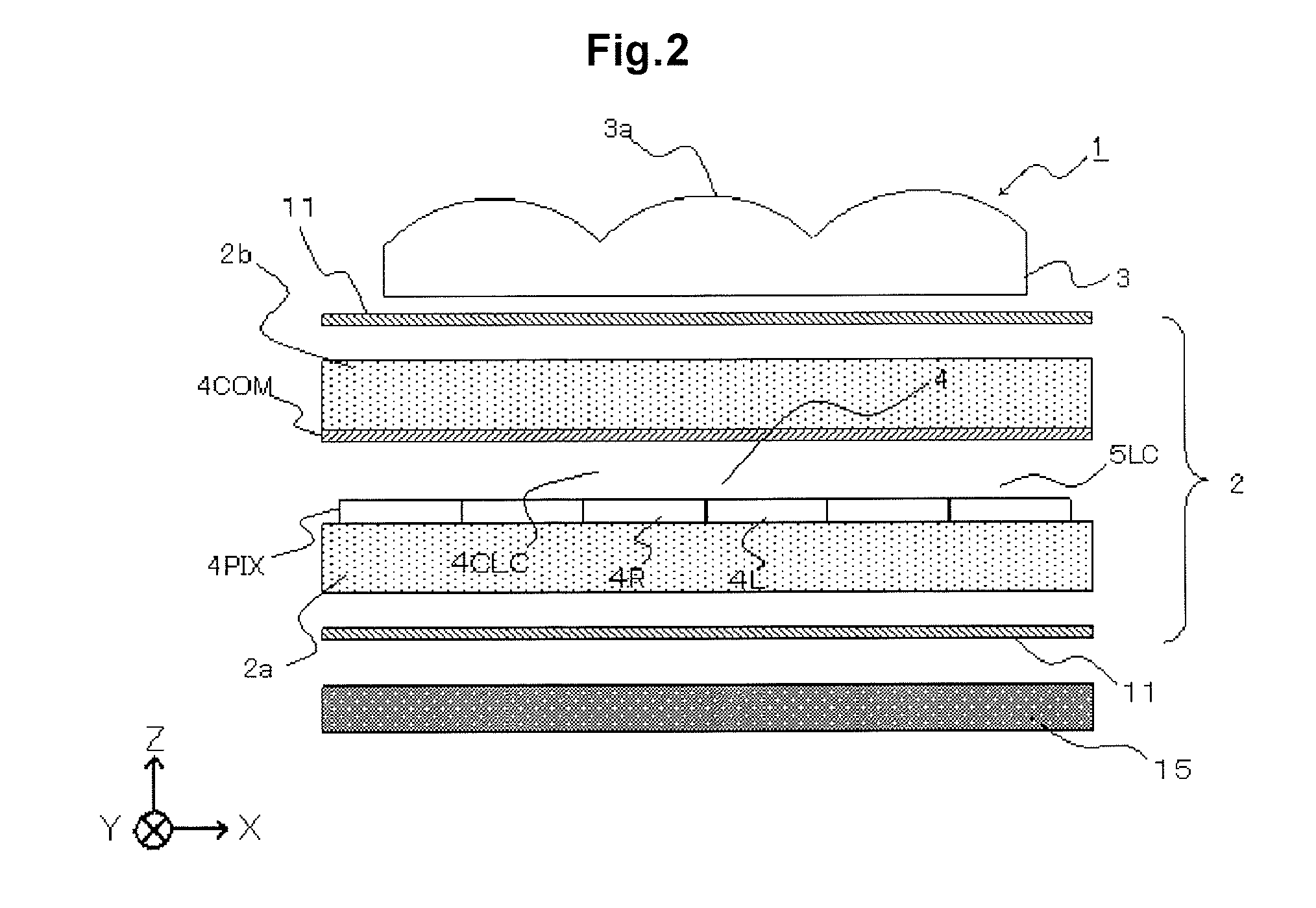

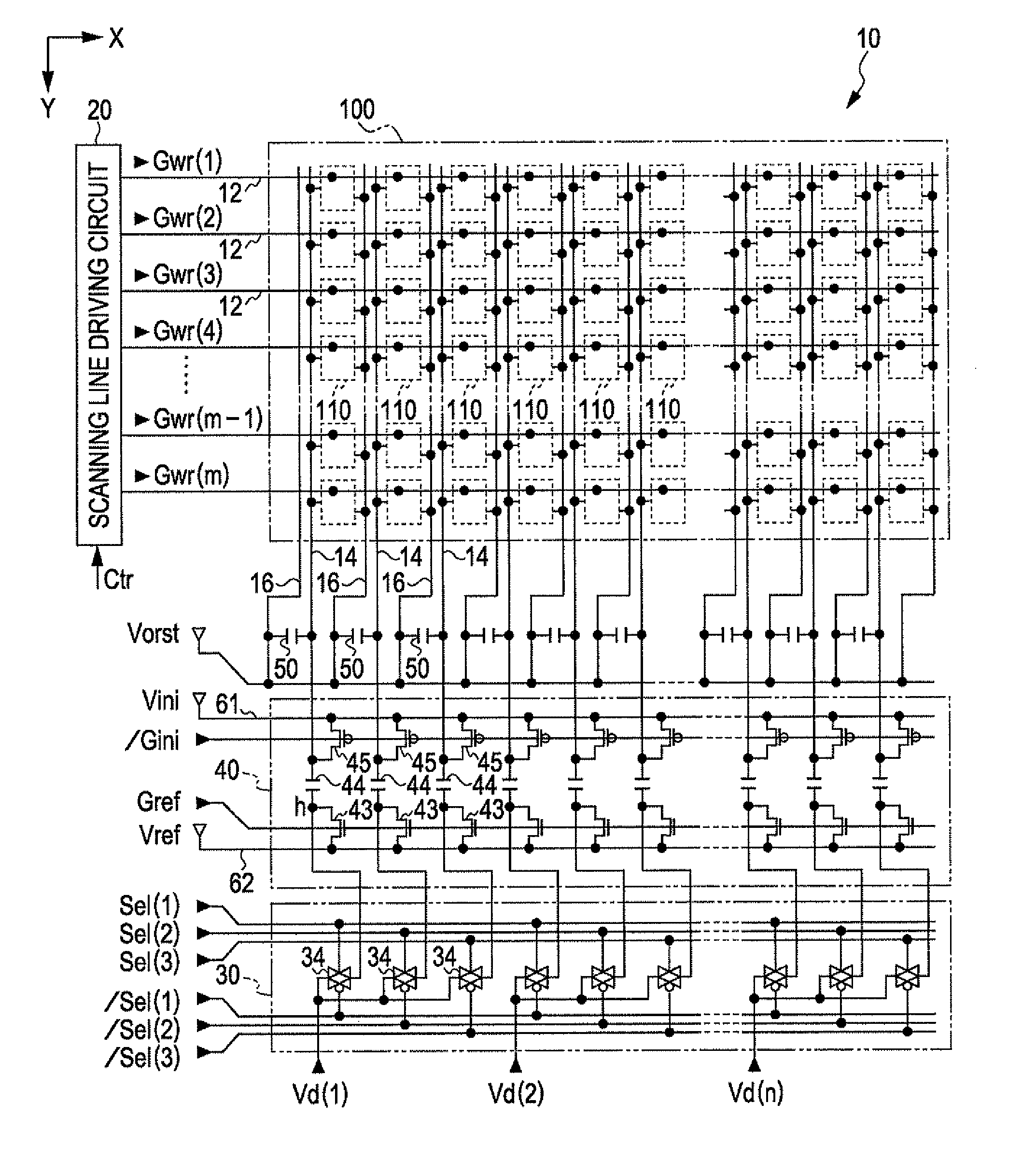

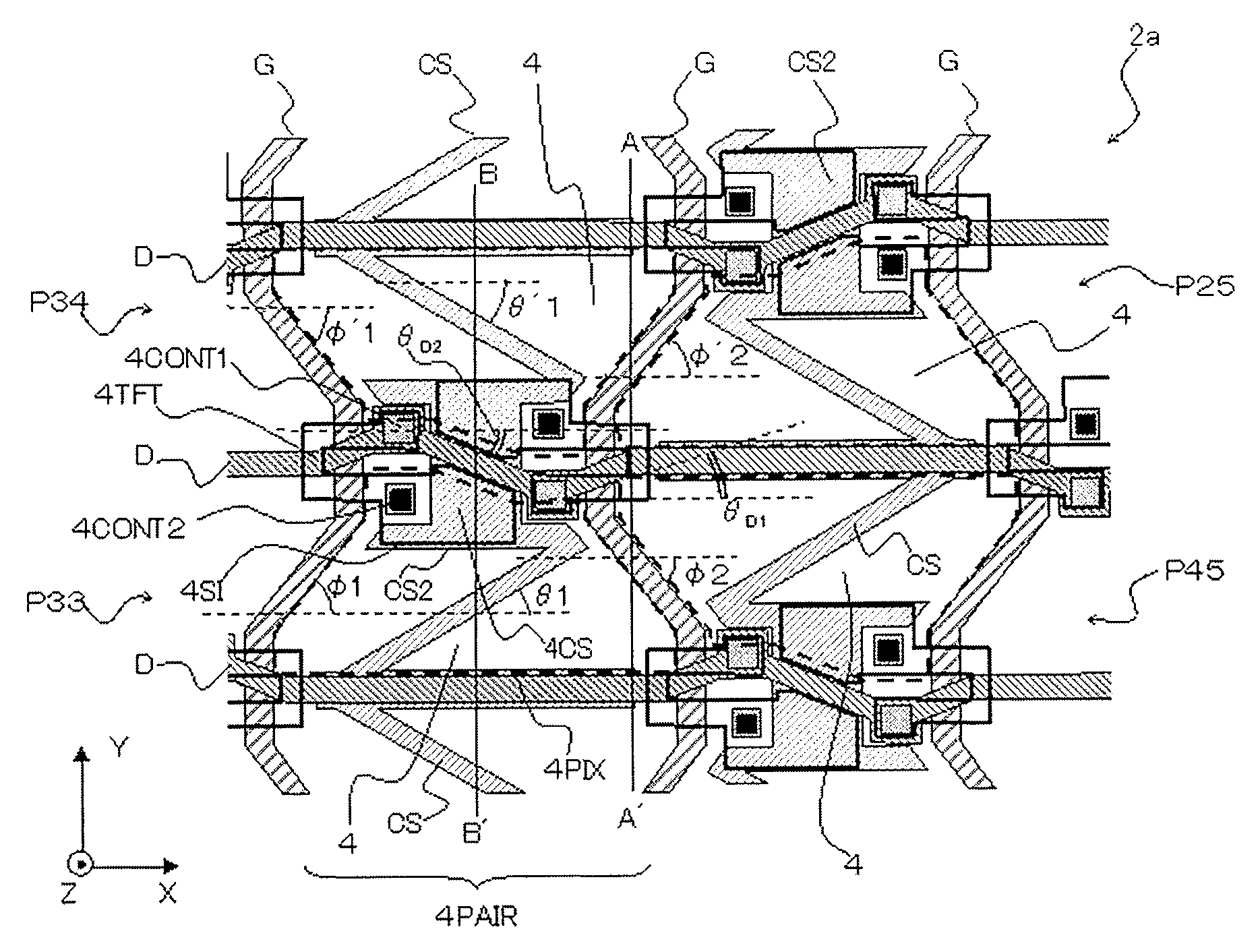

Image display device, driving method of image display device and terminal device

ActiveUS20110304601A1Improved aperture ratioPotential fluctuation be reduceCathode-ray tube indicatorsNon-linear opticsData linesComputer graphics (images)

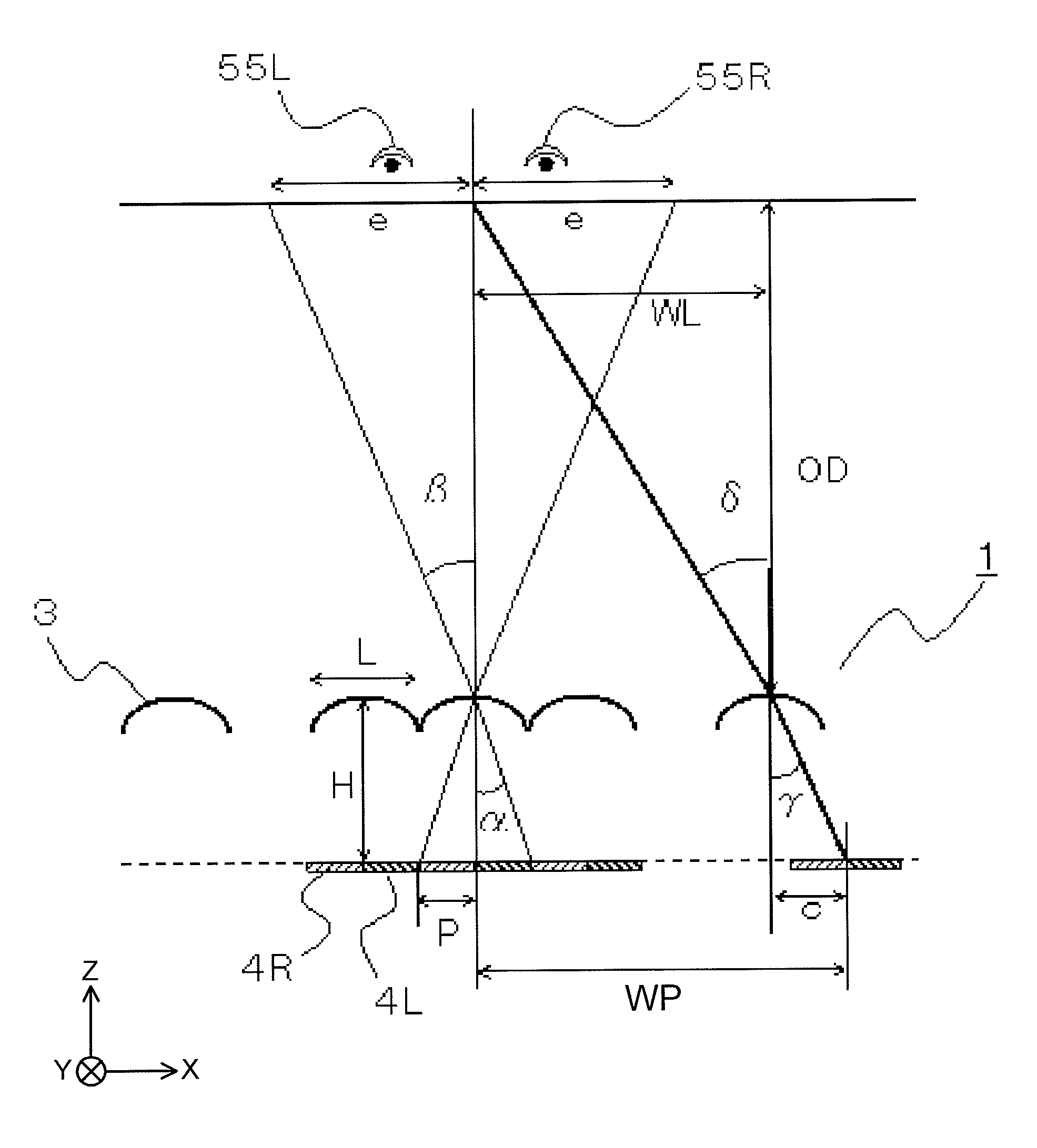

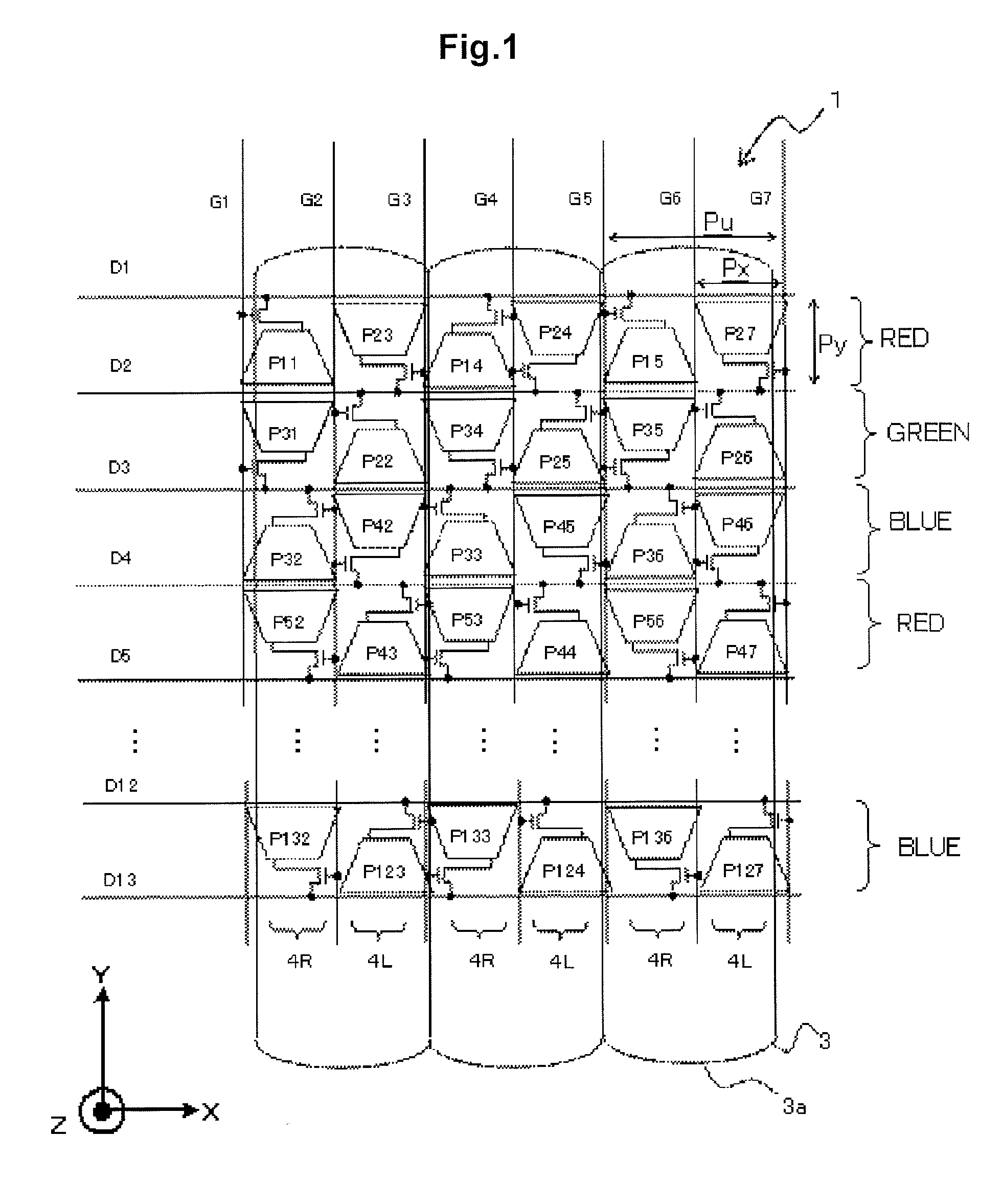

An image display device includes a display element having a unit of display comprising sub pixels displaying images for first and second view points, respectively, and an optical unit that distributes lights emitted from respective sub pixels into different directions. When a region surrounded by a data line, a gate line and a storage capacitor electrode in the sub pixel is defined as an aperture, the sub pixels form a base unit that is an adjoining pixel pair including two sub pixels arranged via a data line therebetween. The two sub pixels have switching elements connected to the data line between the two sub pixels and controlled by different gate lines. When virtual lines each evenly dividing a width of the sub pixel in the first direction into K+1 pieces are presumed, K number of storage capacitor lines are each arranged across at least one virtual line in the aperture.

Owner:NEC LCD TECH CORP

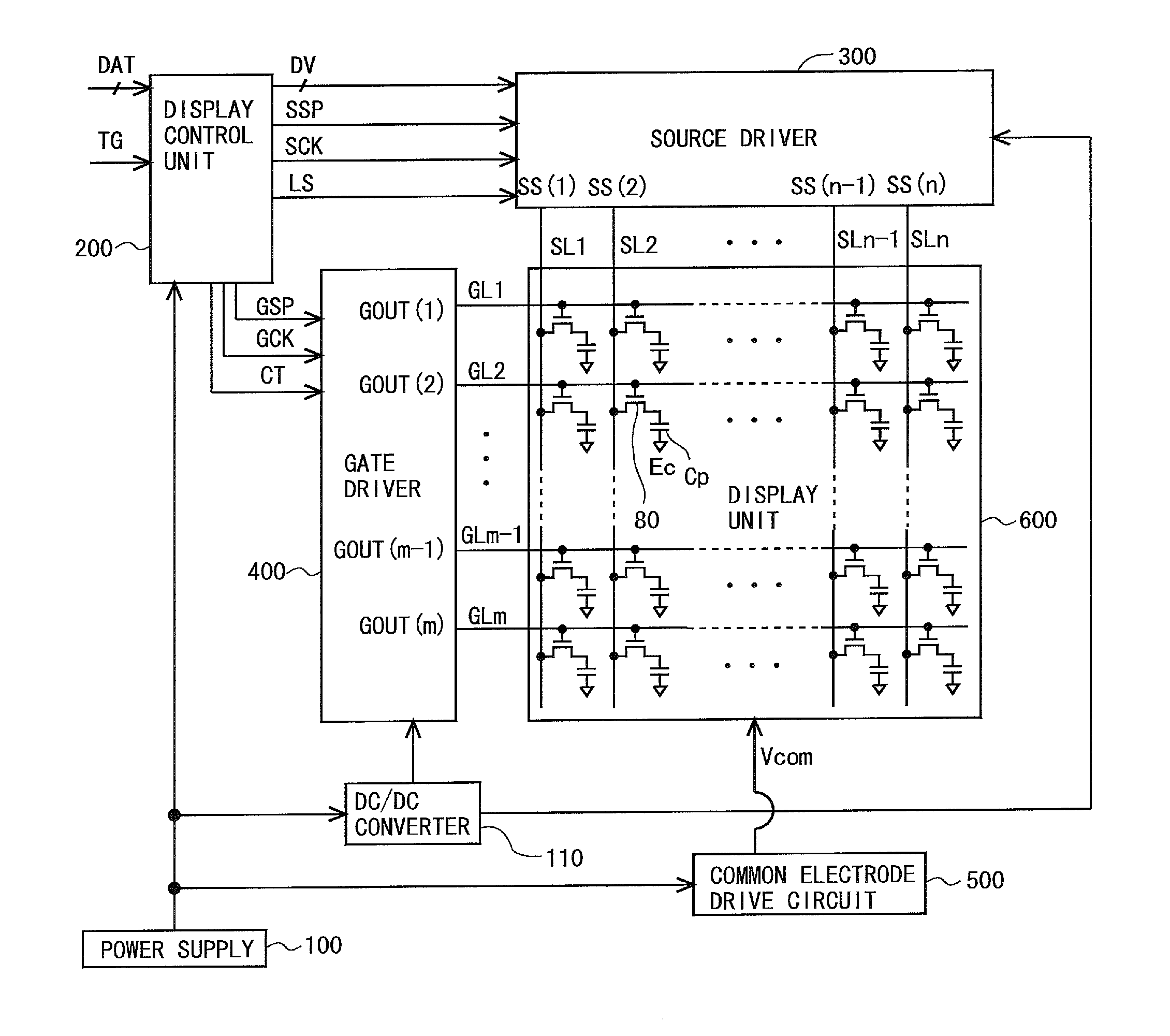

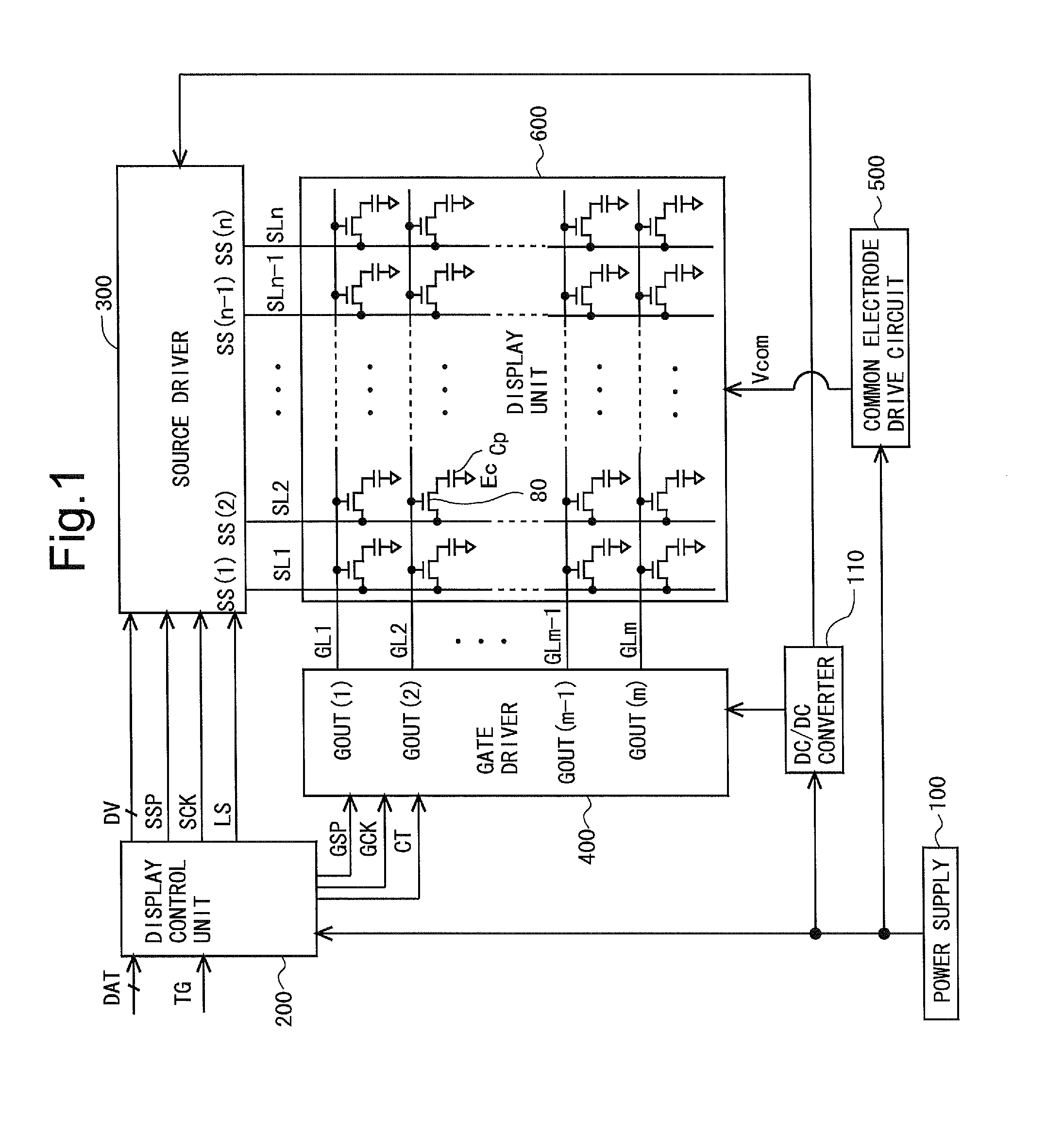

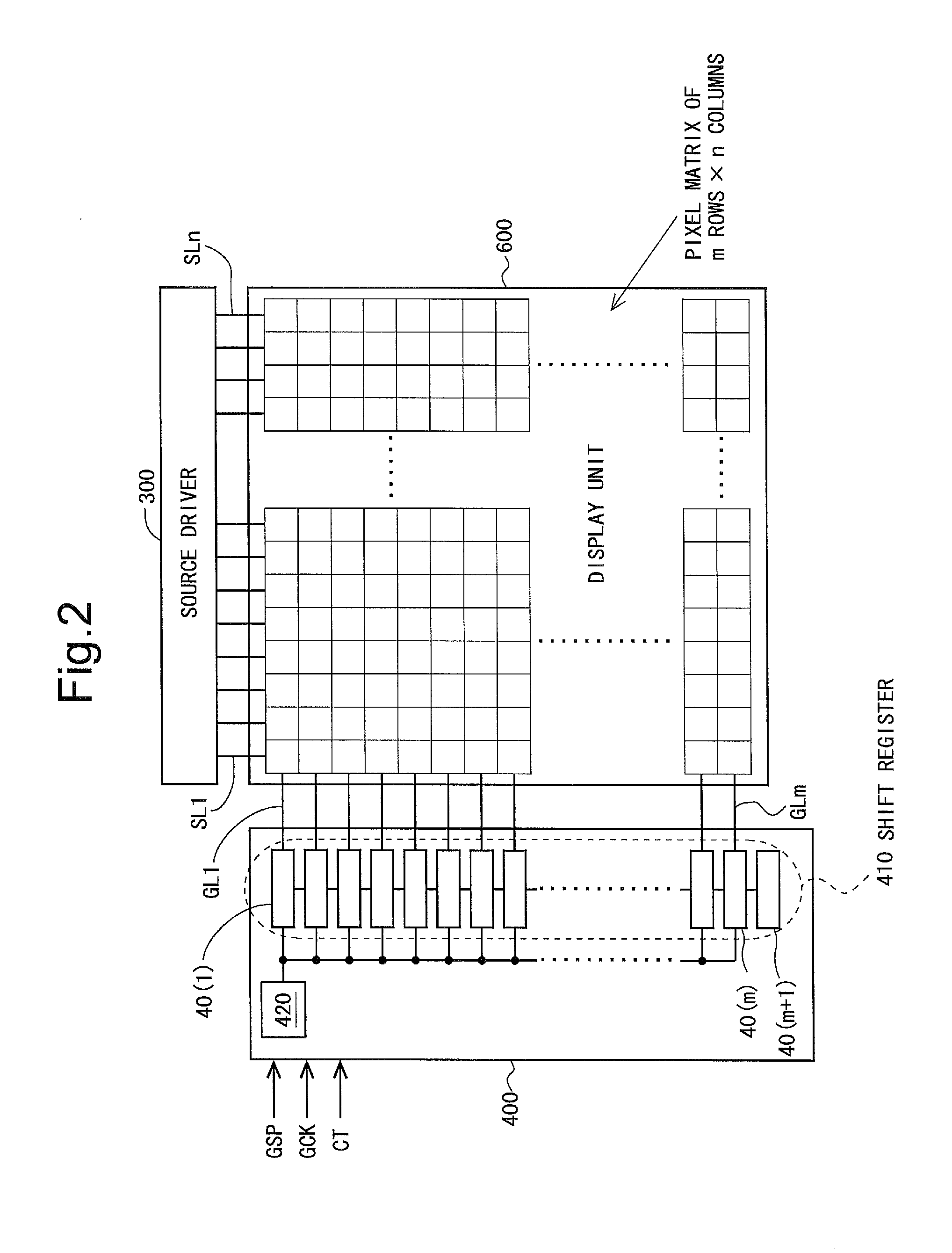

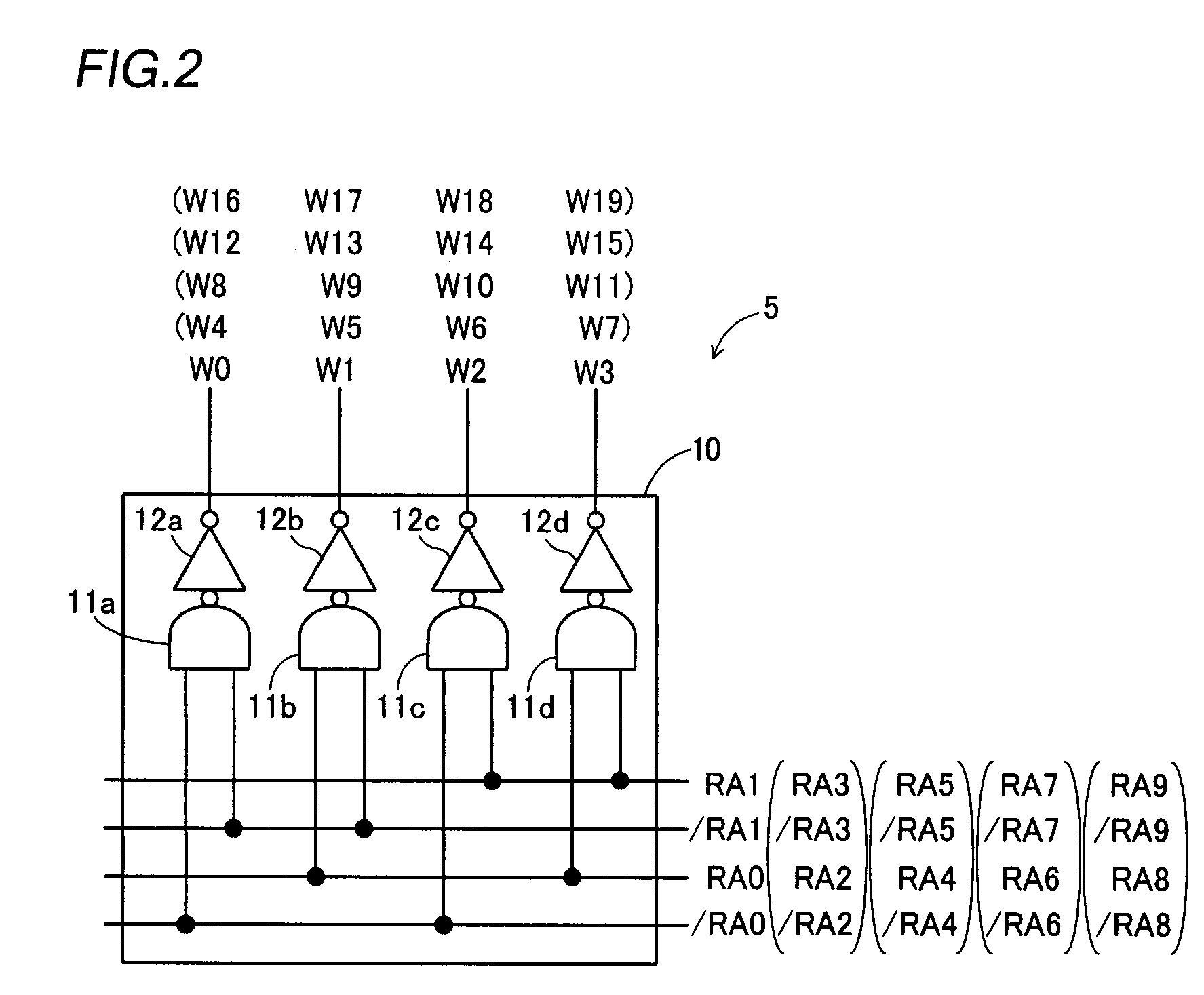

Scanning signal line drive circuit, display device having the same, and drive method for scanning signal line

ActiveUS20140035891A1Reduce controlGuaranteed uptimeCathode-ray tube indicatorsInput/output processes for data processingBistable circuitsControl signal

The present invention is directed to suppress dullness of a scanning signal in a scanning signal line drive circuit. A bistable circuit is provided with an input terminal (43) for receiving a first clock signal (CK), an input terminal (48) for receiving a control signal (CT), an input terminal (49) for receiving a level down signal (LD), an output terminal (51), a thin film transistor (T2), and a thin film transistor (TA). The thin film transistor (T2) has a gate terminal connected to a first node (N1), a drain terminal connected to the input terminal (43), and a source terminal connected to the output terminal (51). The thin film transistor (TA) has a gate terminal connected to the input terminal (48), a drain terminal connected to the first node (N1), and a source terminal connected to the input terminal (49). The potential of the control signal (CT) becomes the high level in a control period as a period except for the first one horizontal scanning period in a vertical blanking period. The level down signal (LD) is a potential lower than DC power supply potential (Vss).

Owner:SHARP KK

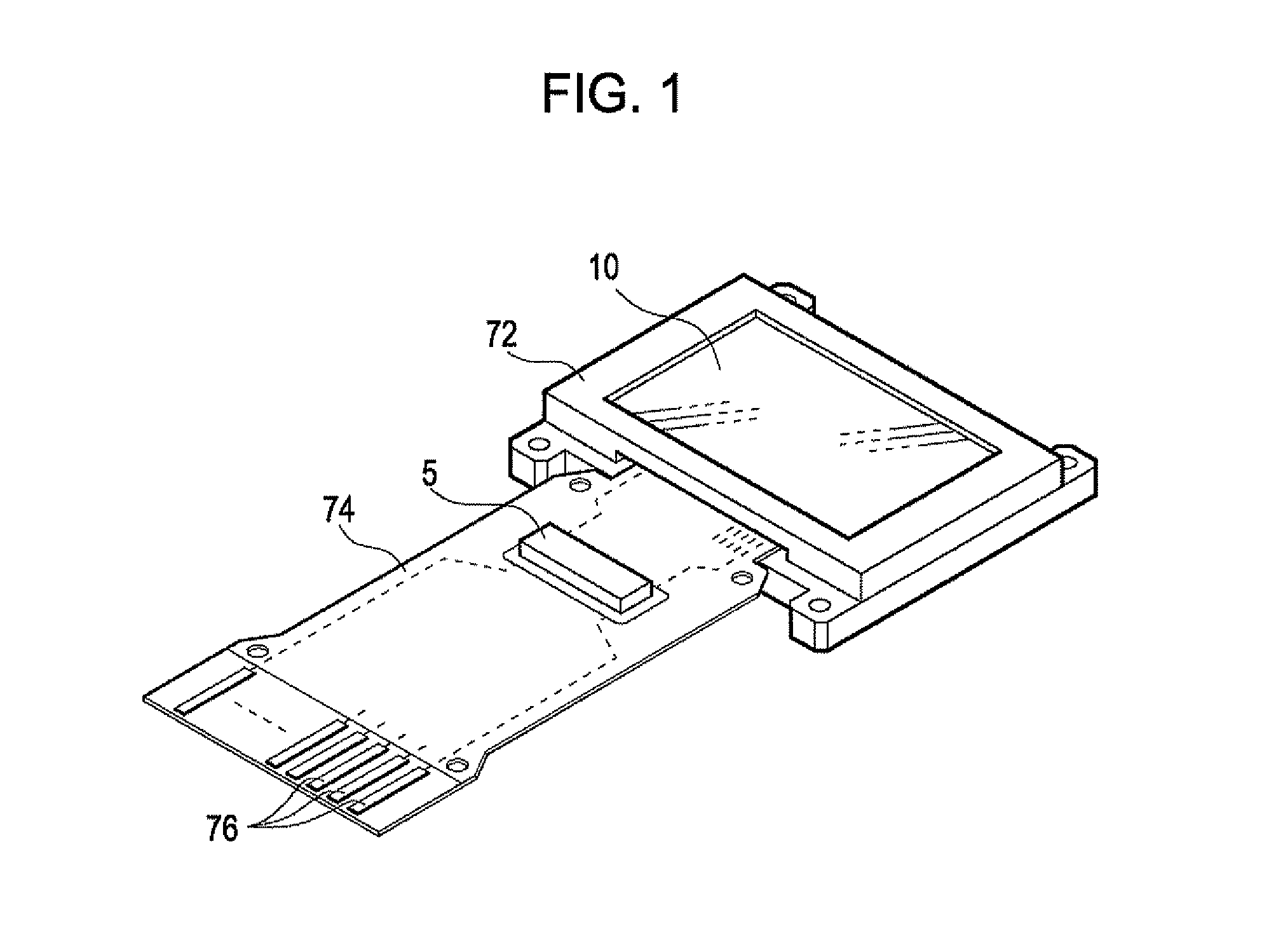

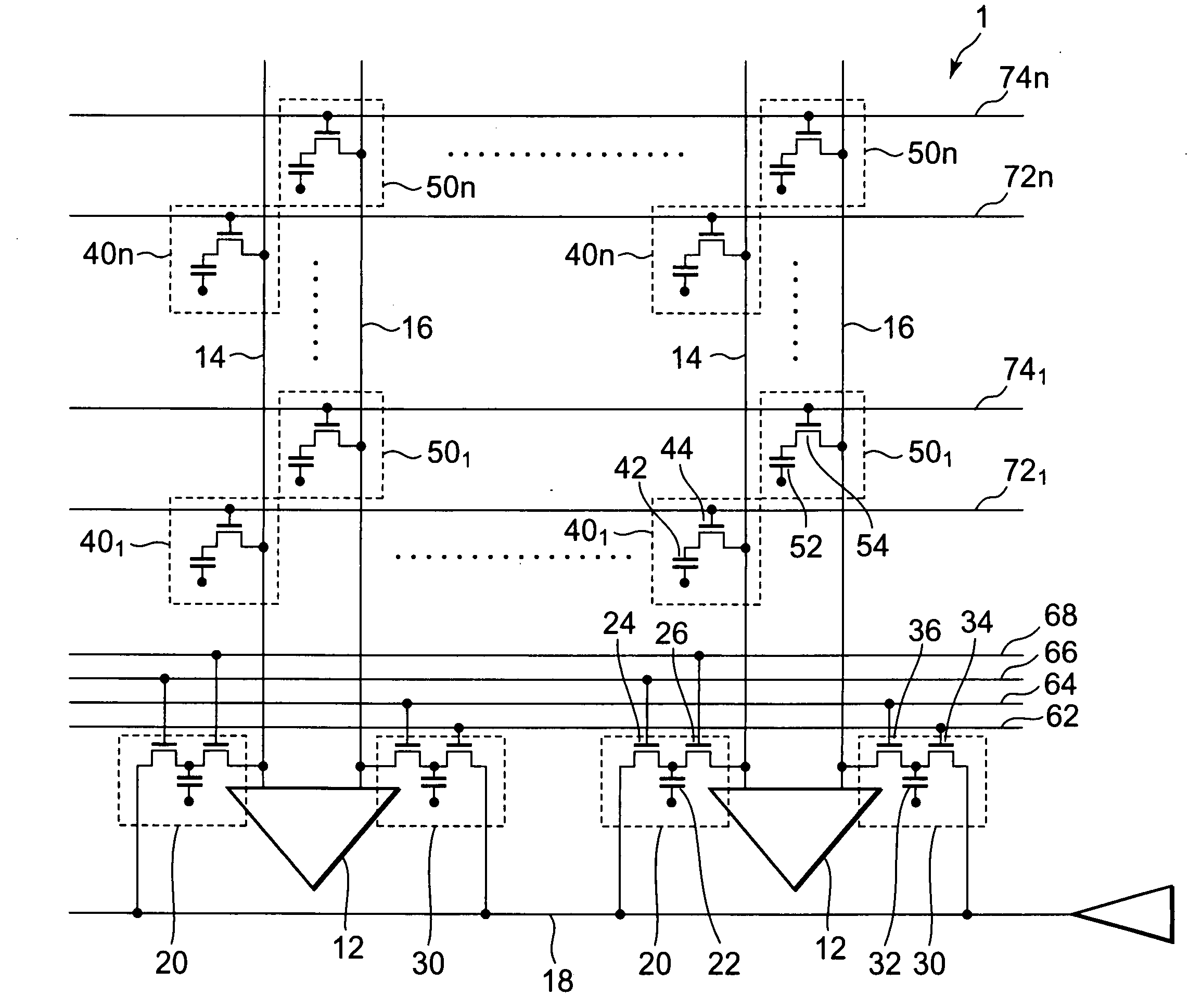

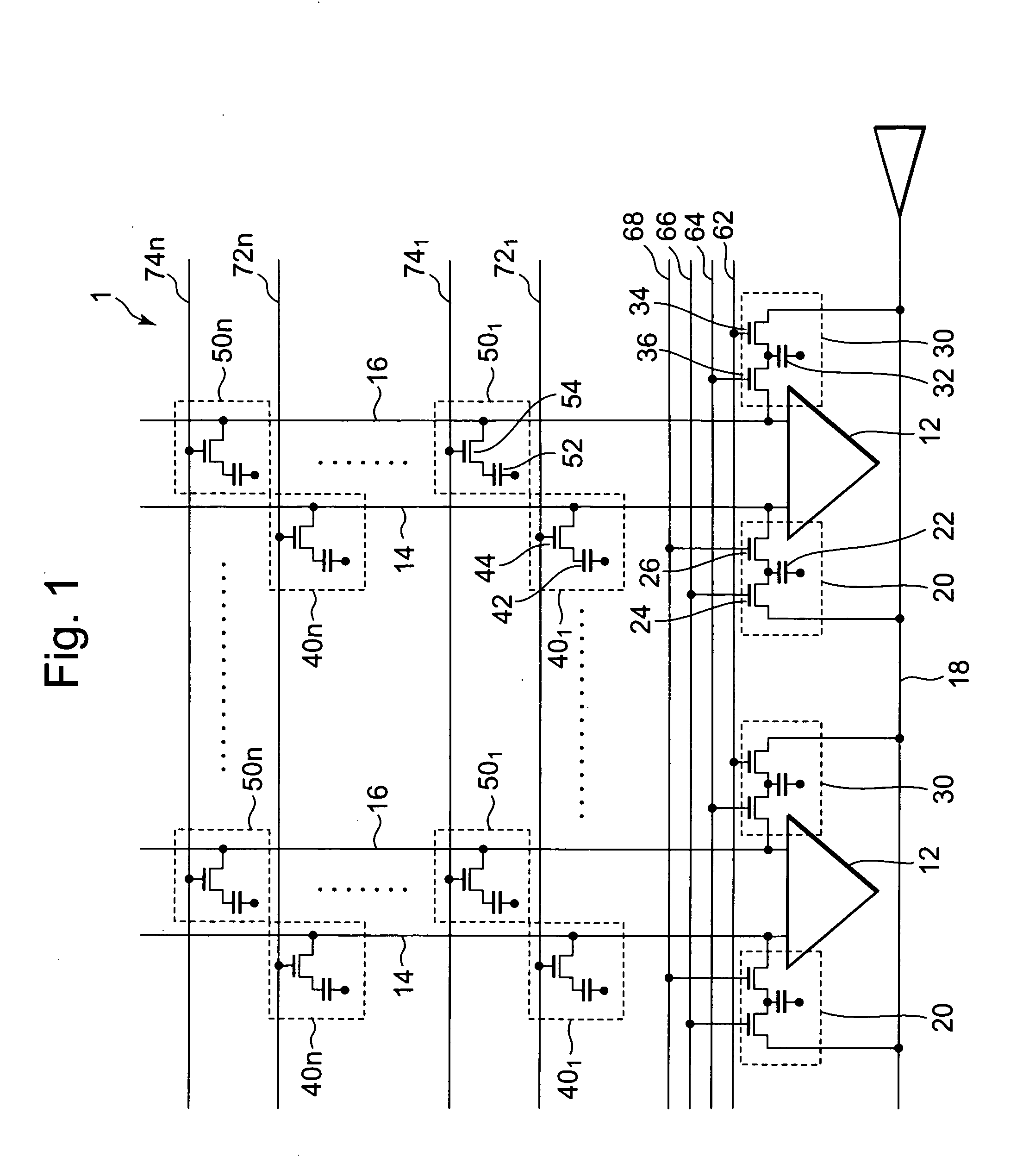

Electro-optical device, and electronic apparatus

ActiveUS20130120341A1Suppression of uneven brightnessPrecise data signalCathode-ray tube indicatorsInput/output processes for data processingPower flowVoltage control

An electro-optical device is provided with a plurality of data lines, a plurality of potential lines supplied with a predetermined potential, a driving transistor controlling a current level according to the voltage between the gate and the source, a first storage capacitor which holds the voltage between the gate and a source of the driving transistor, and a light-emitting element. One data line among the plurality of data lines and one potential line among the plurality of potential lines are arranged to be adjacent to each other, and a second storage capacitor holding the potential of the one data line is formed by the one data line and the one potential line.

Owner:SEIKO EPSON CORP

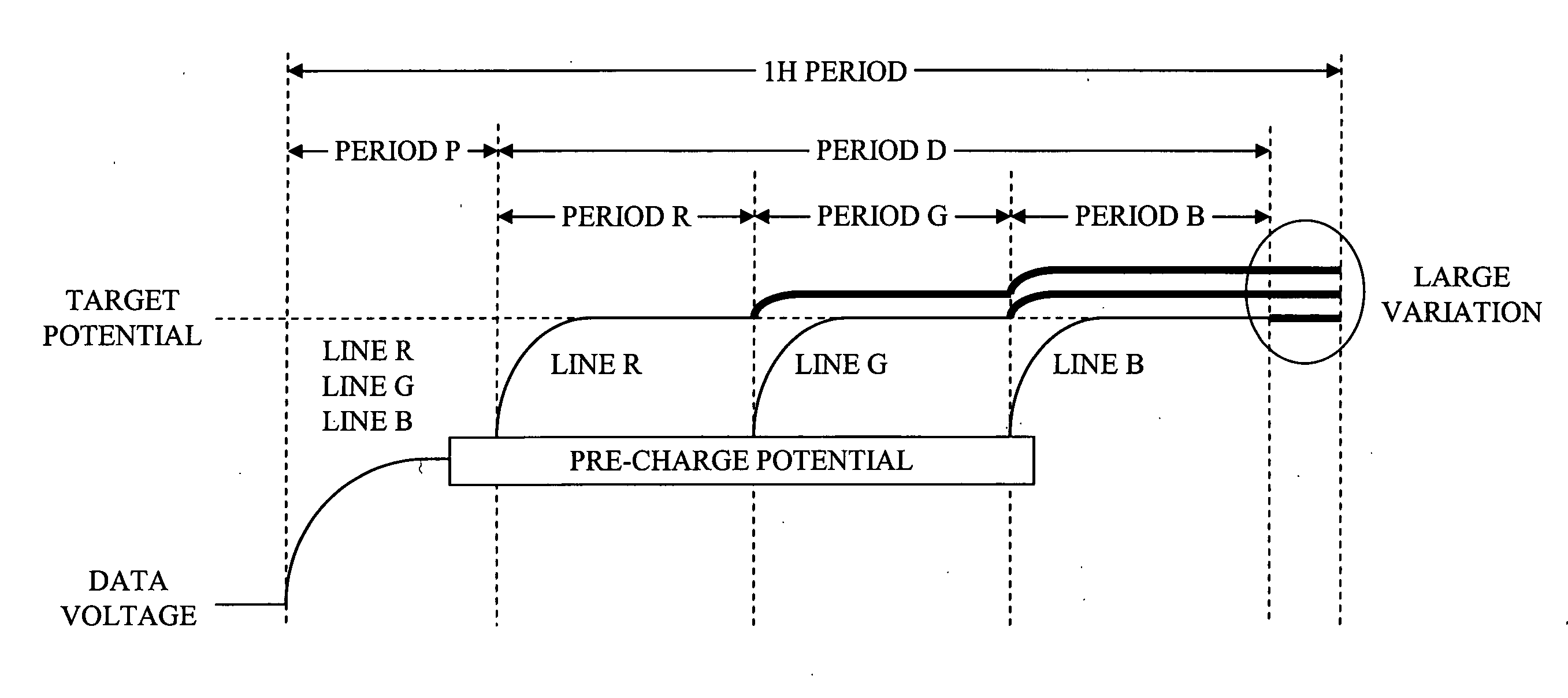

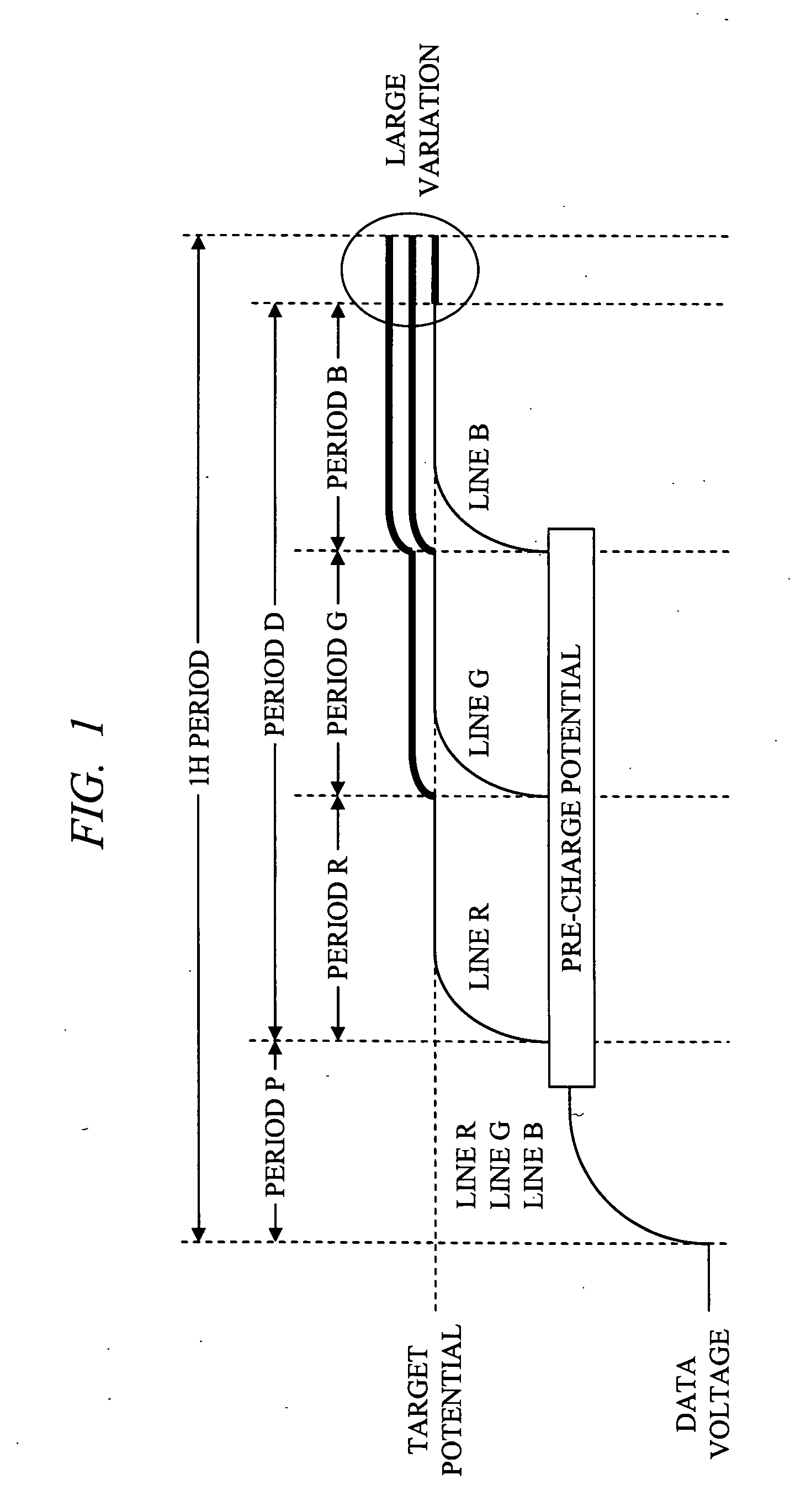

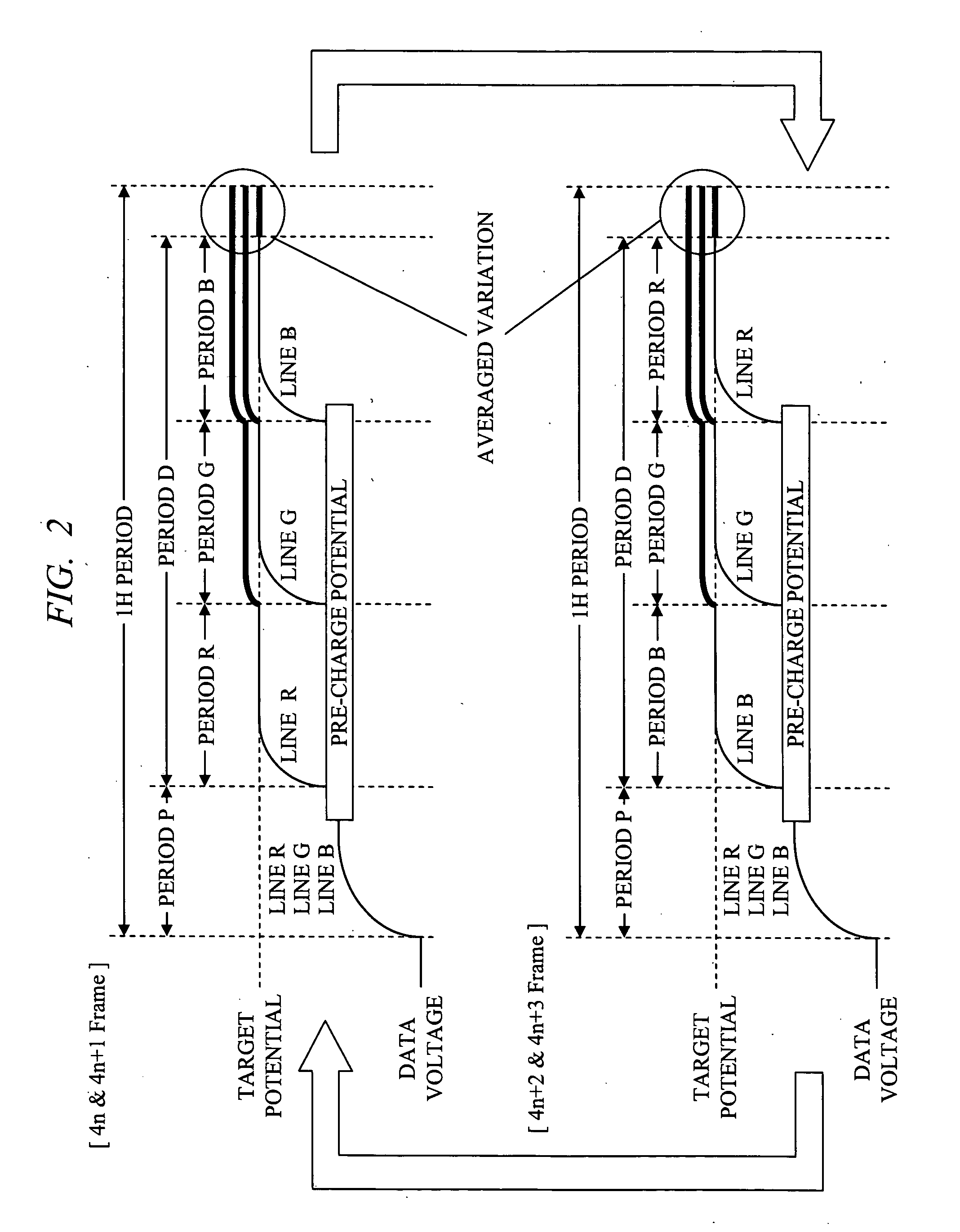

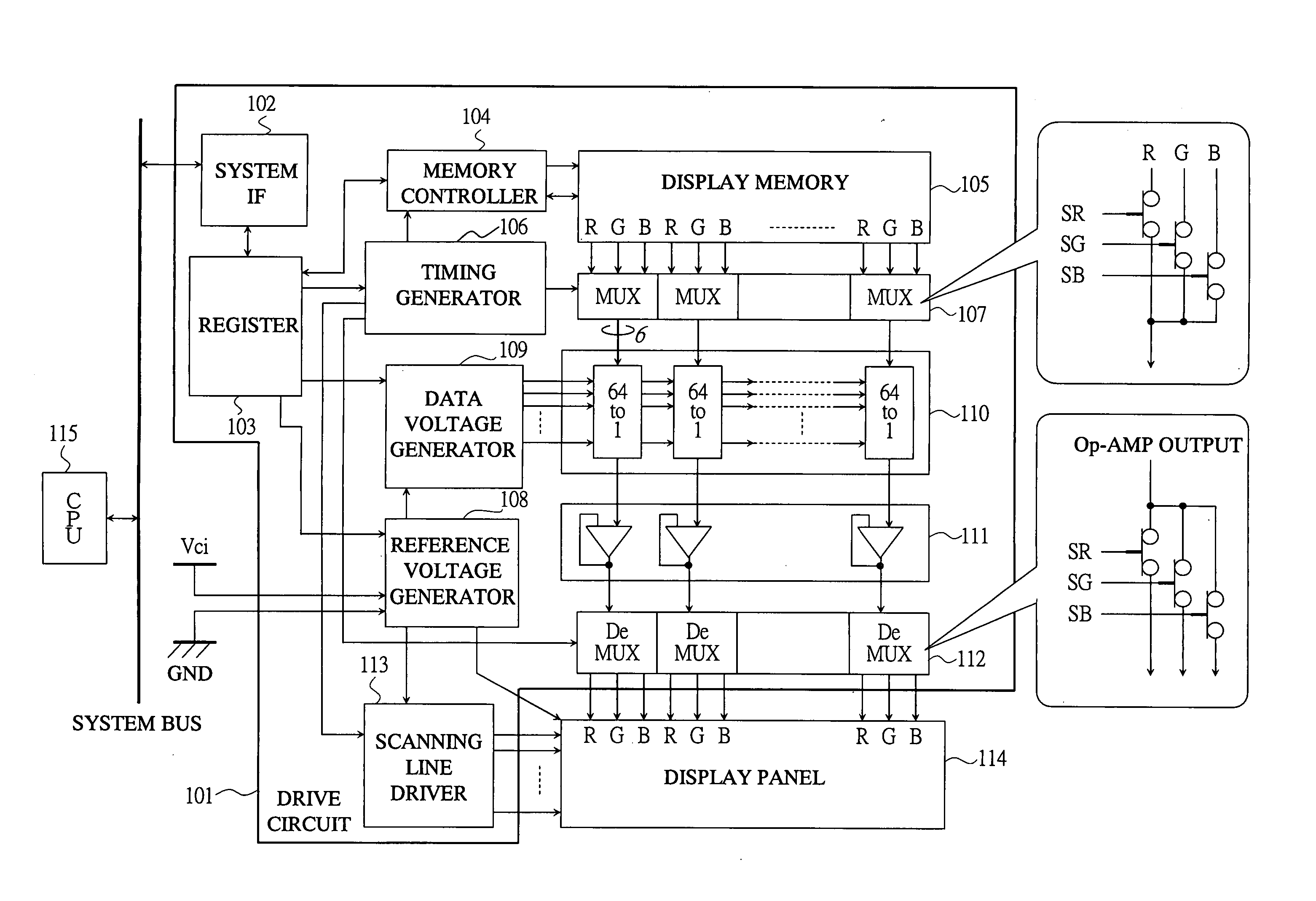

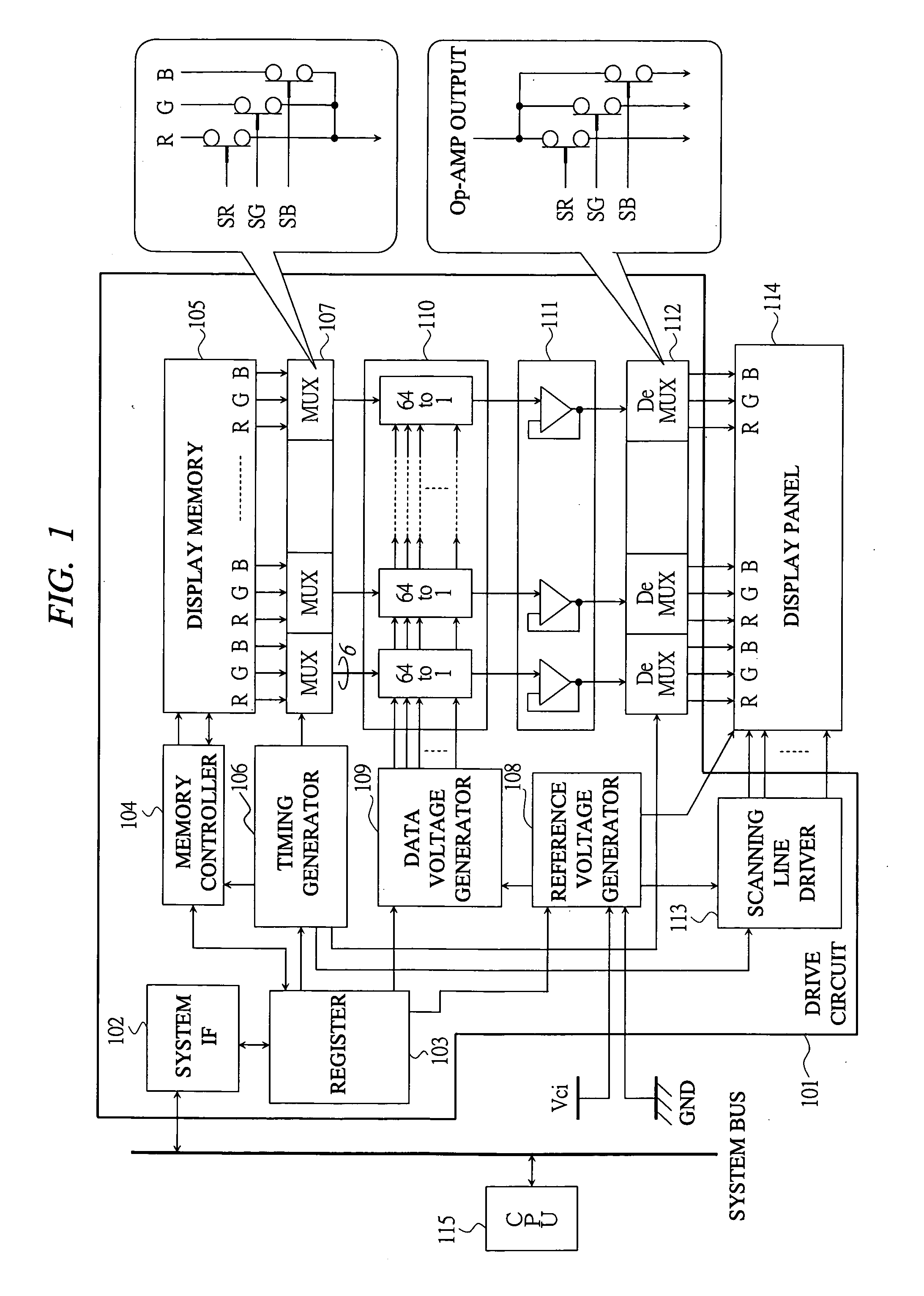

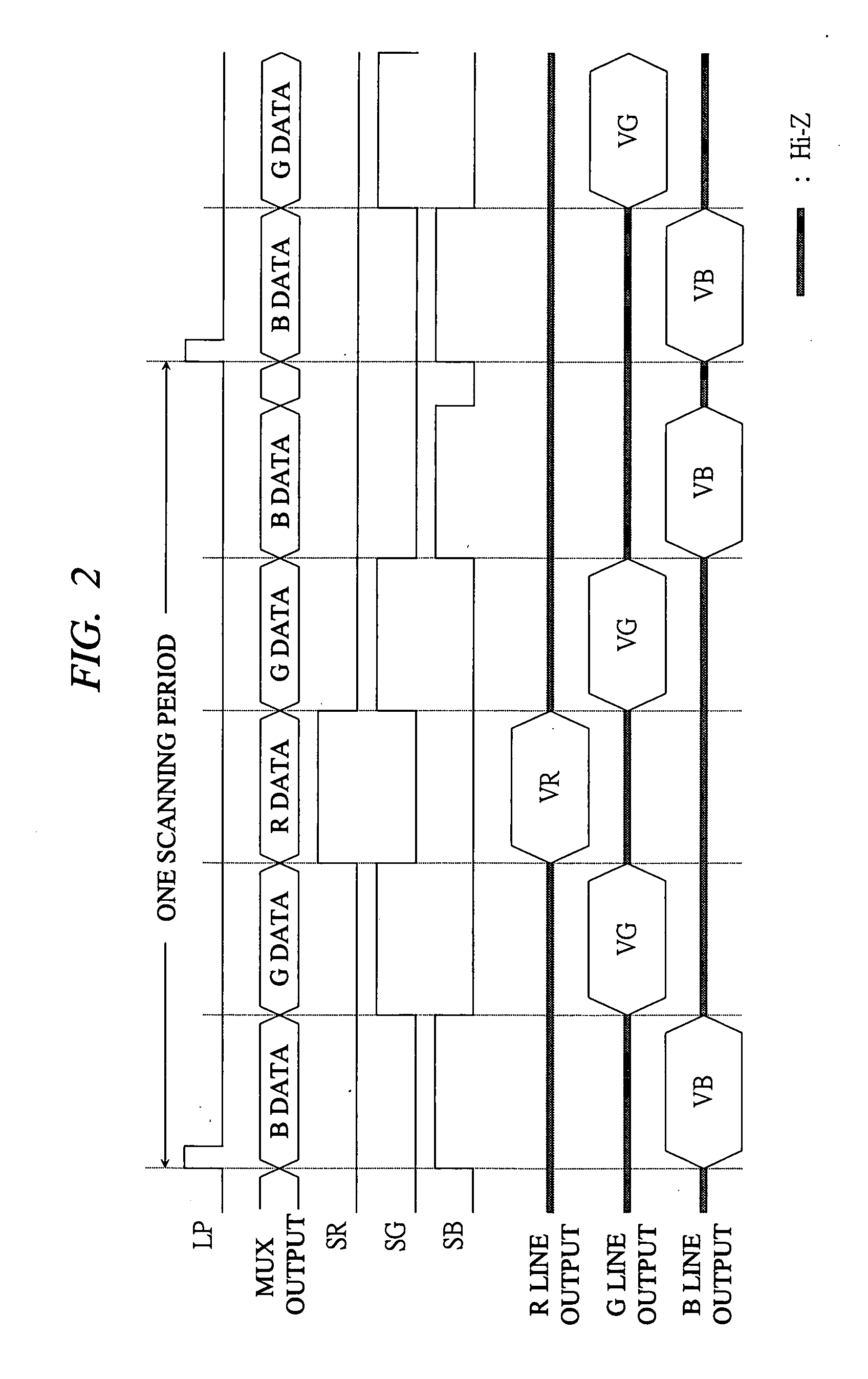

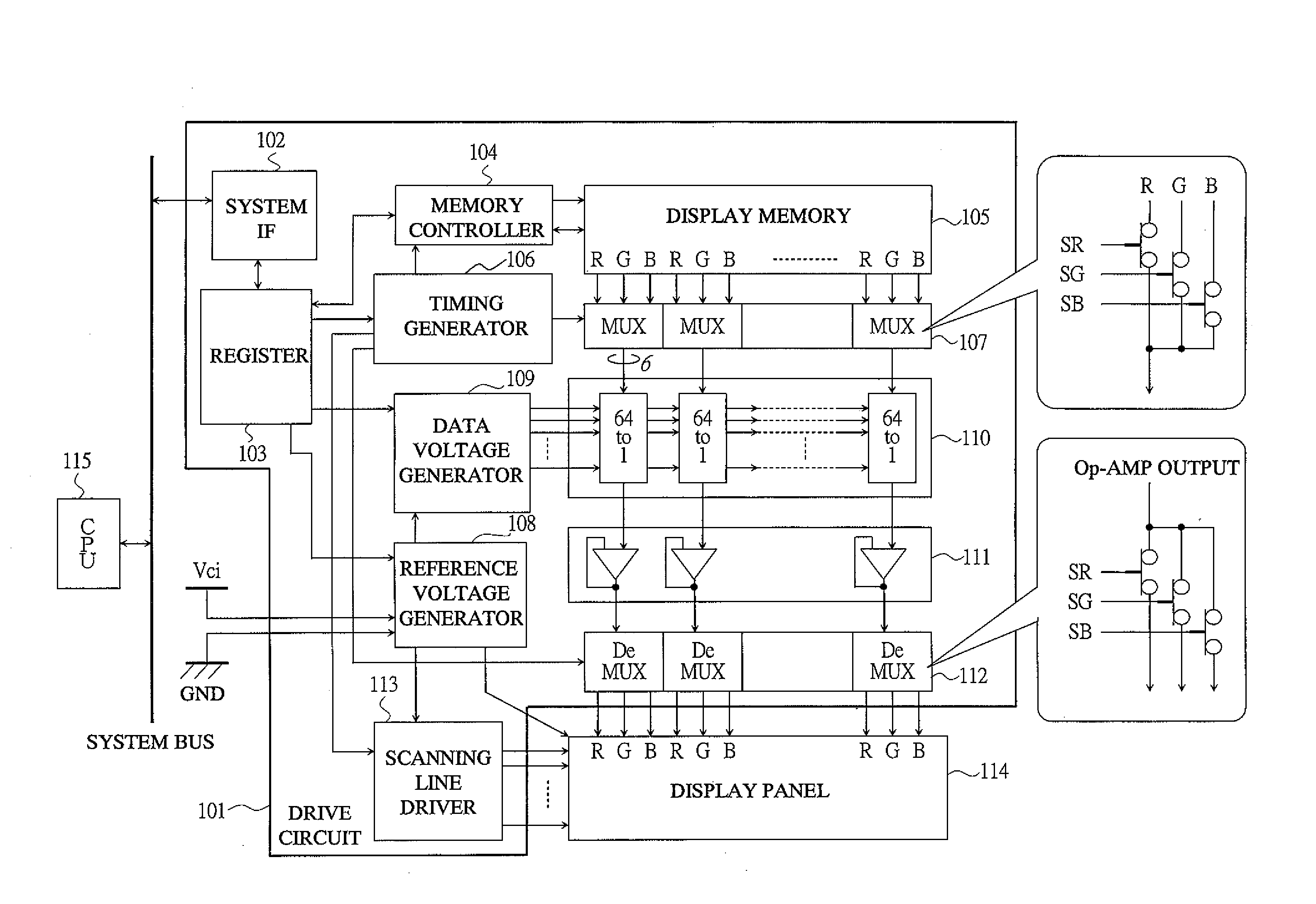

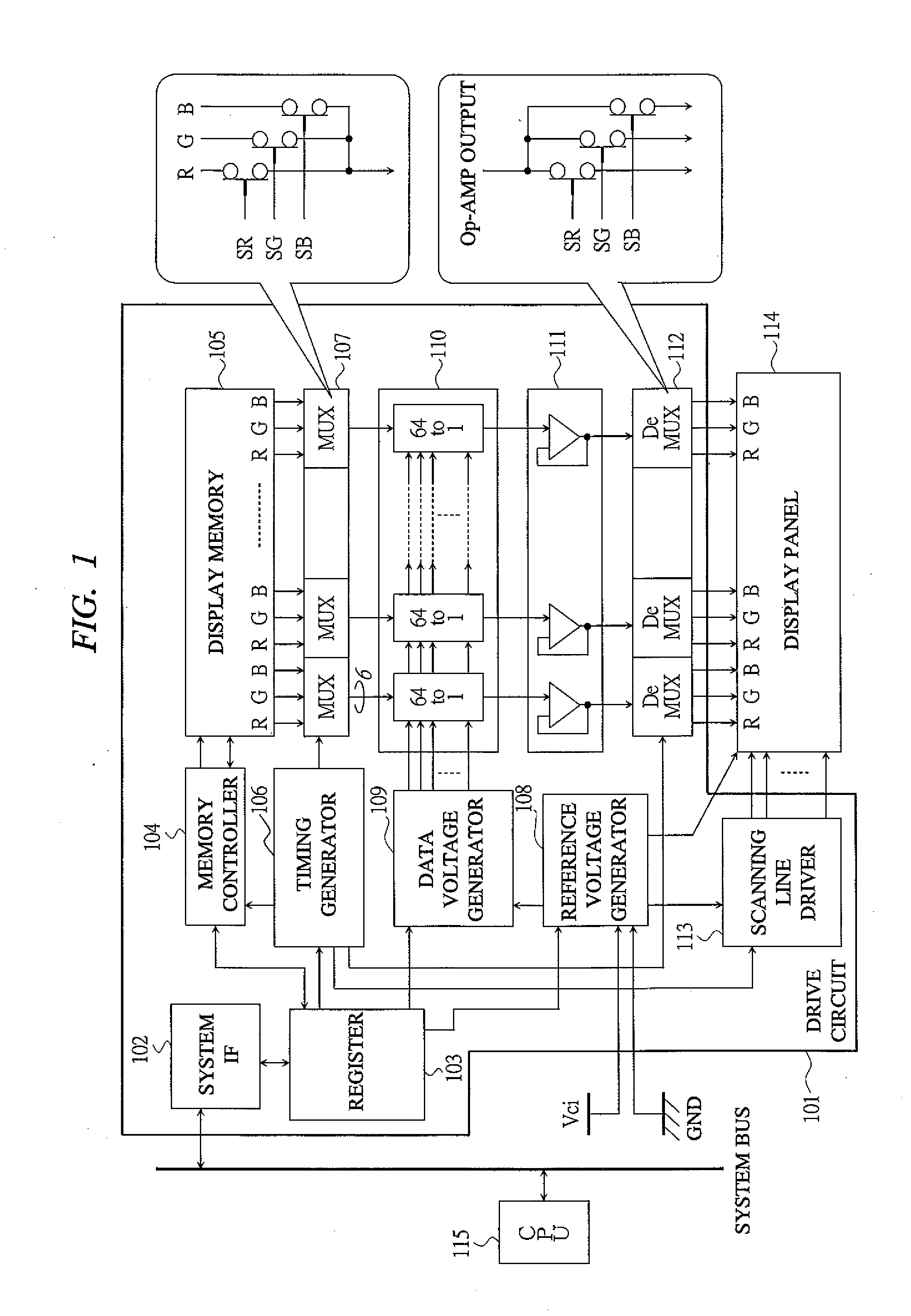

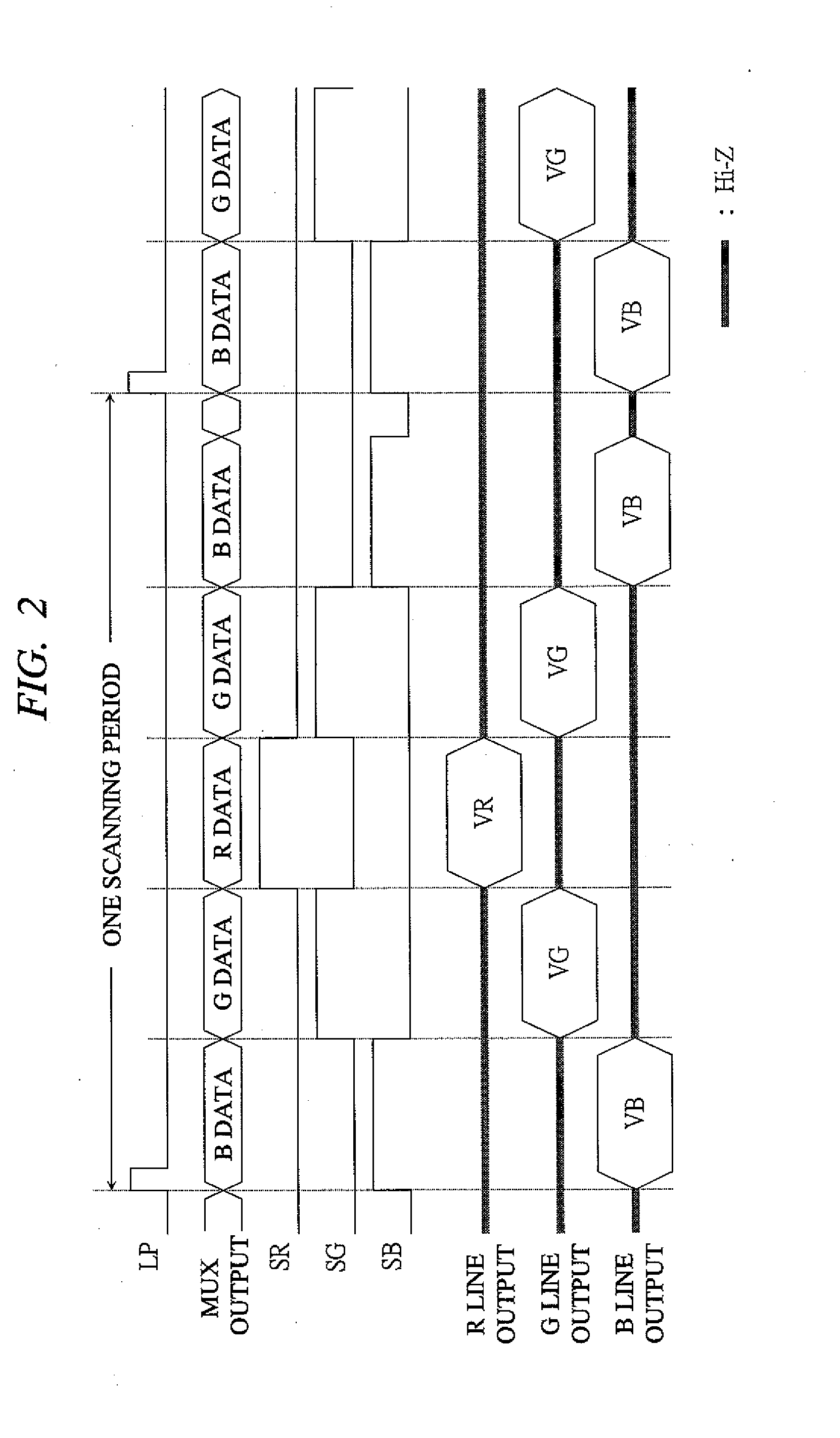

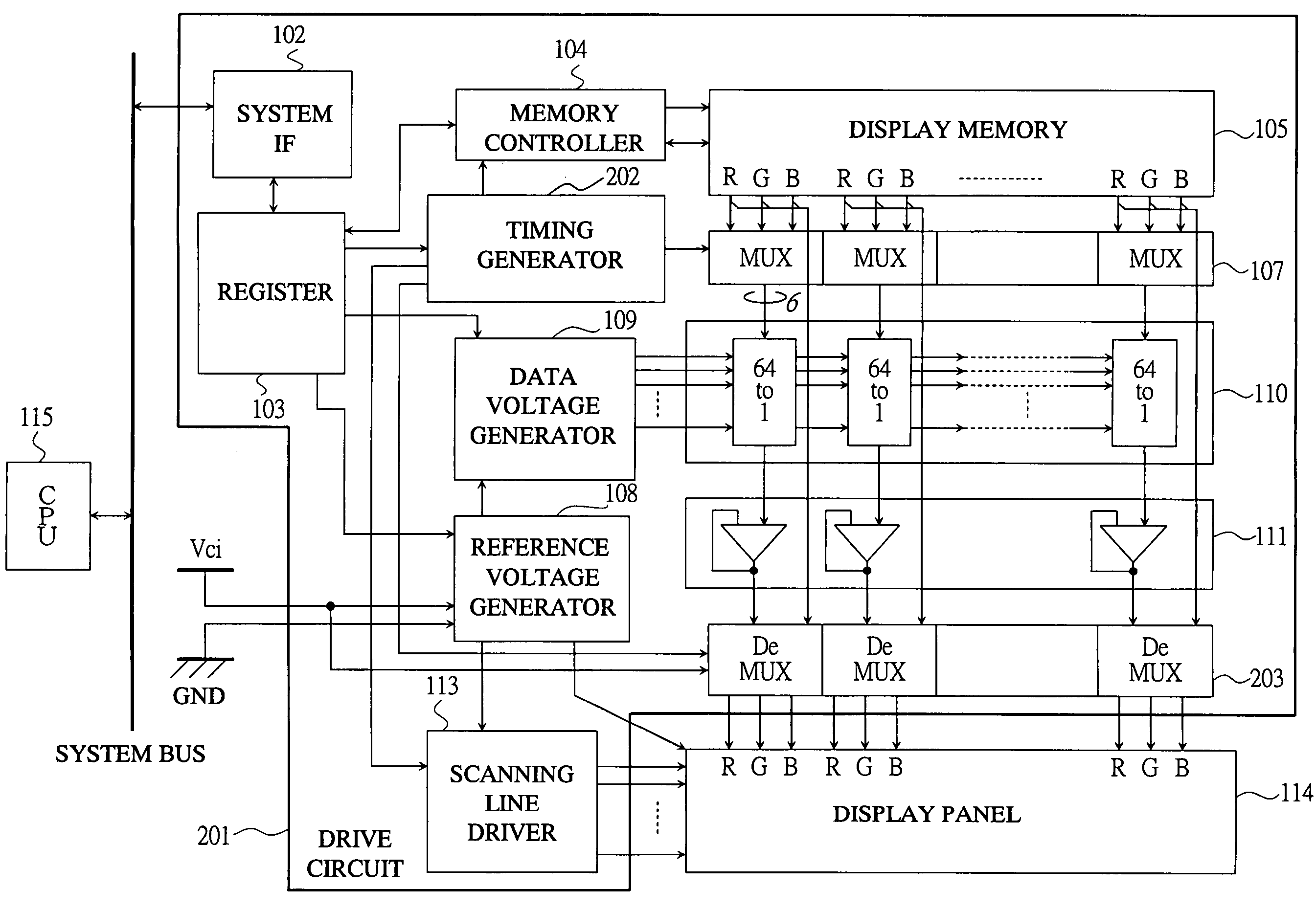

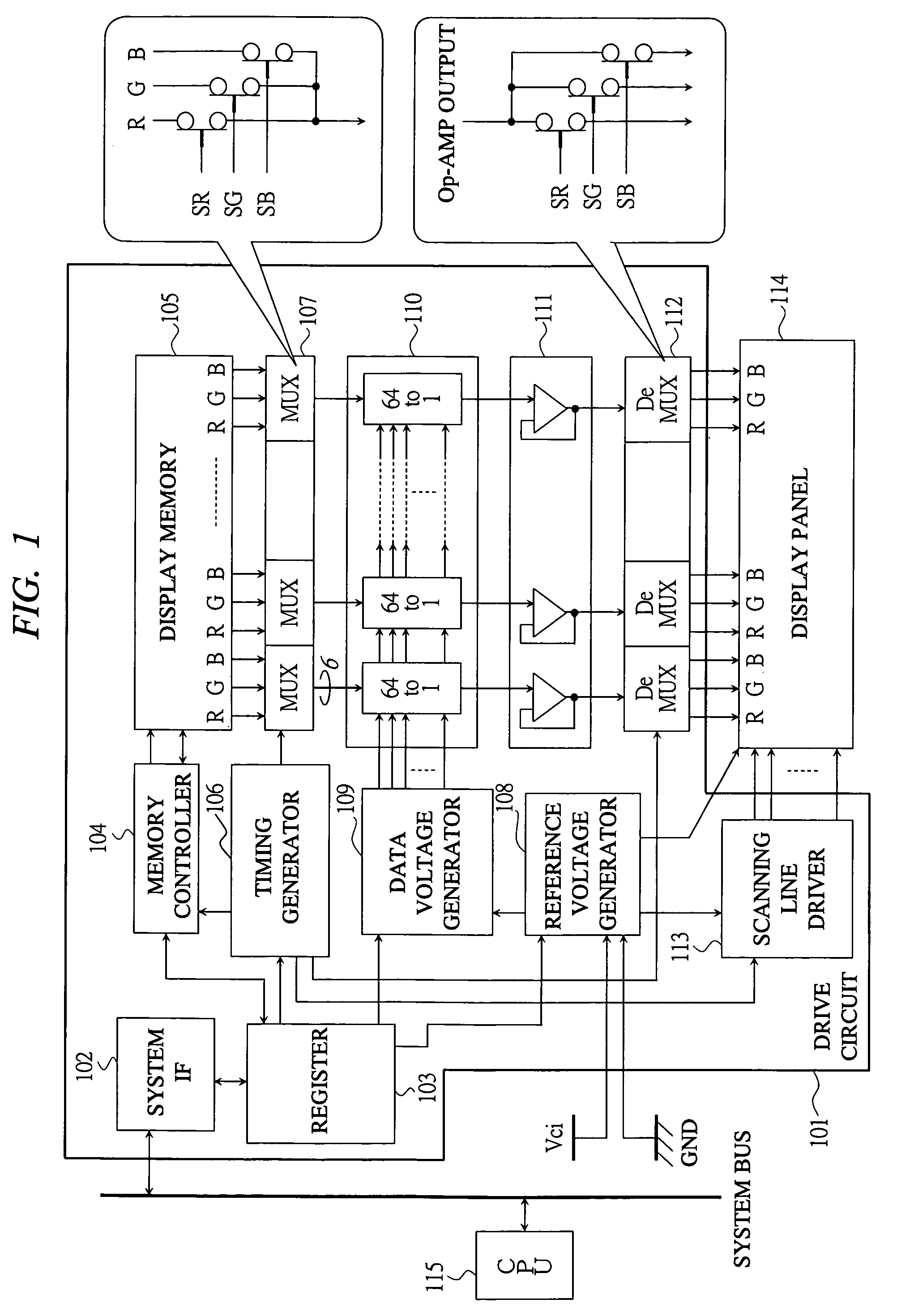

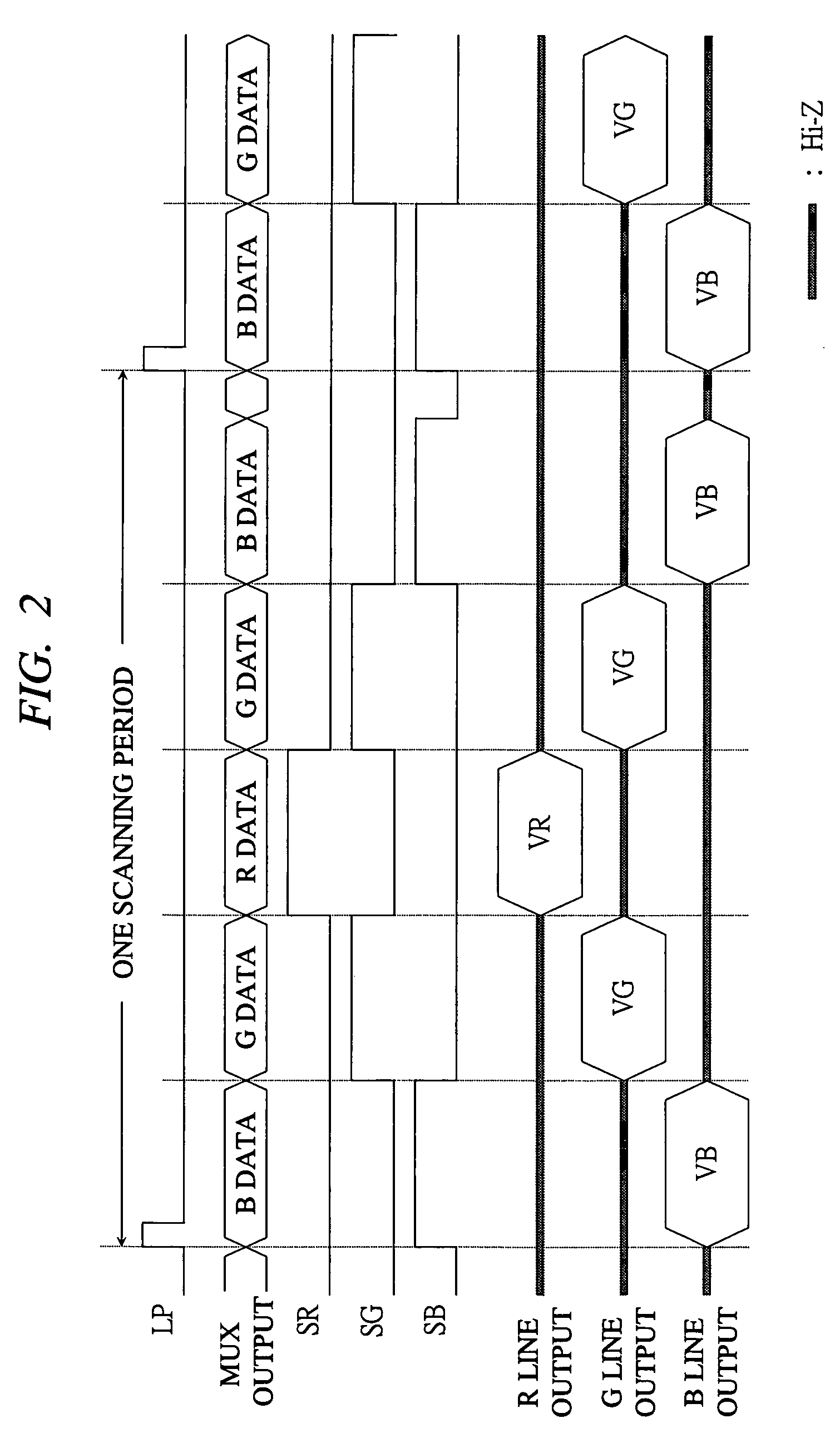

Display driver and display driving method

InactiveUS20060227628A1Easy to switchPotential fluctuationStatic indicating devicesDigital storageEngineeringVoltage

In a display driver, a period D following a period P in one scanning period is divided into periods R, G, and B in which data voltages are applied to data lines R, G, and B, and two output orders of the data voltage such as the period R→the period G→period B and the period B→the period G→period R are switched in each two frames.

Owner:RENESAS ELECTRONICS CORP

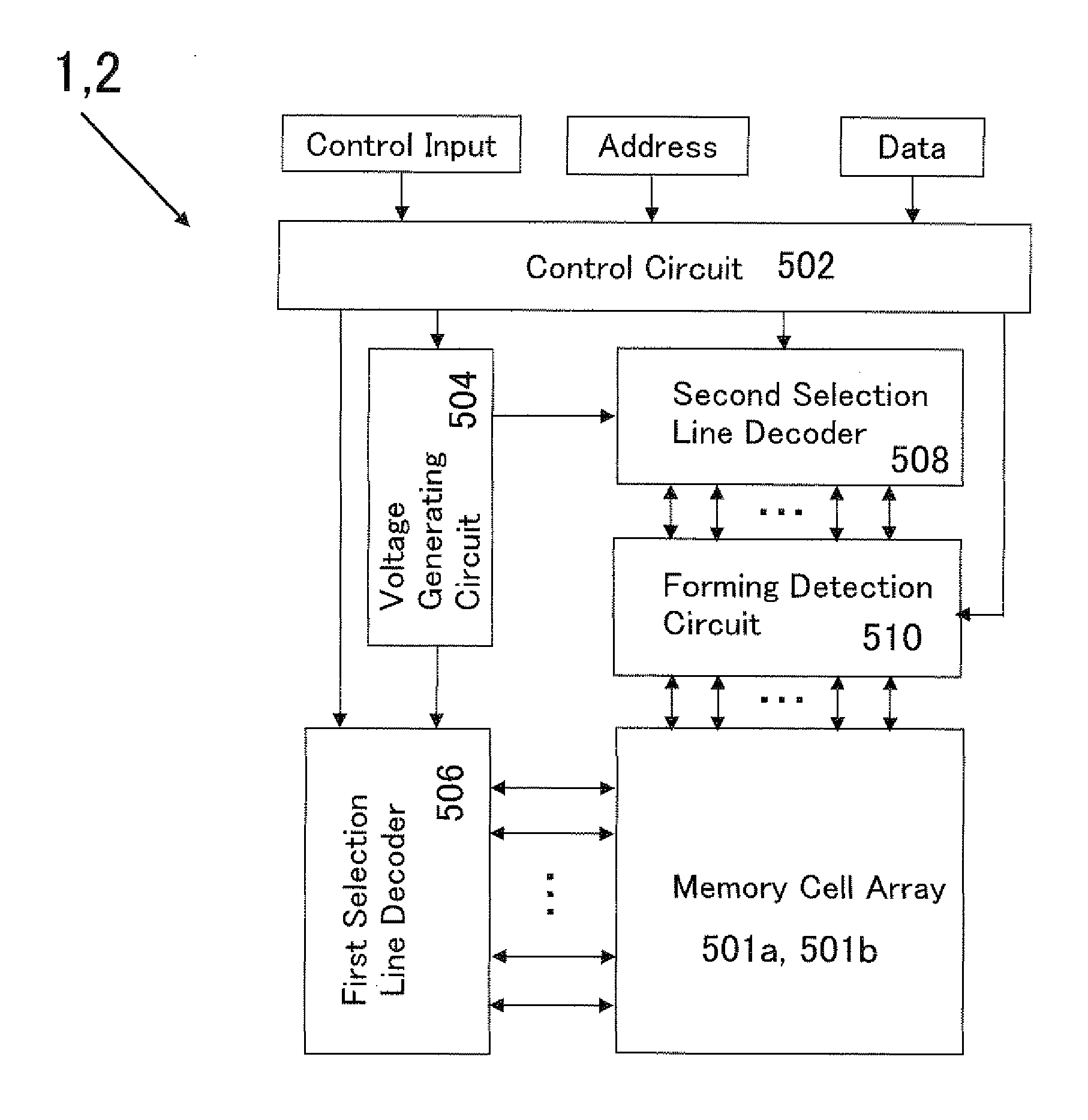

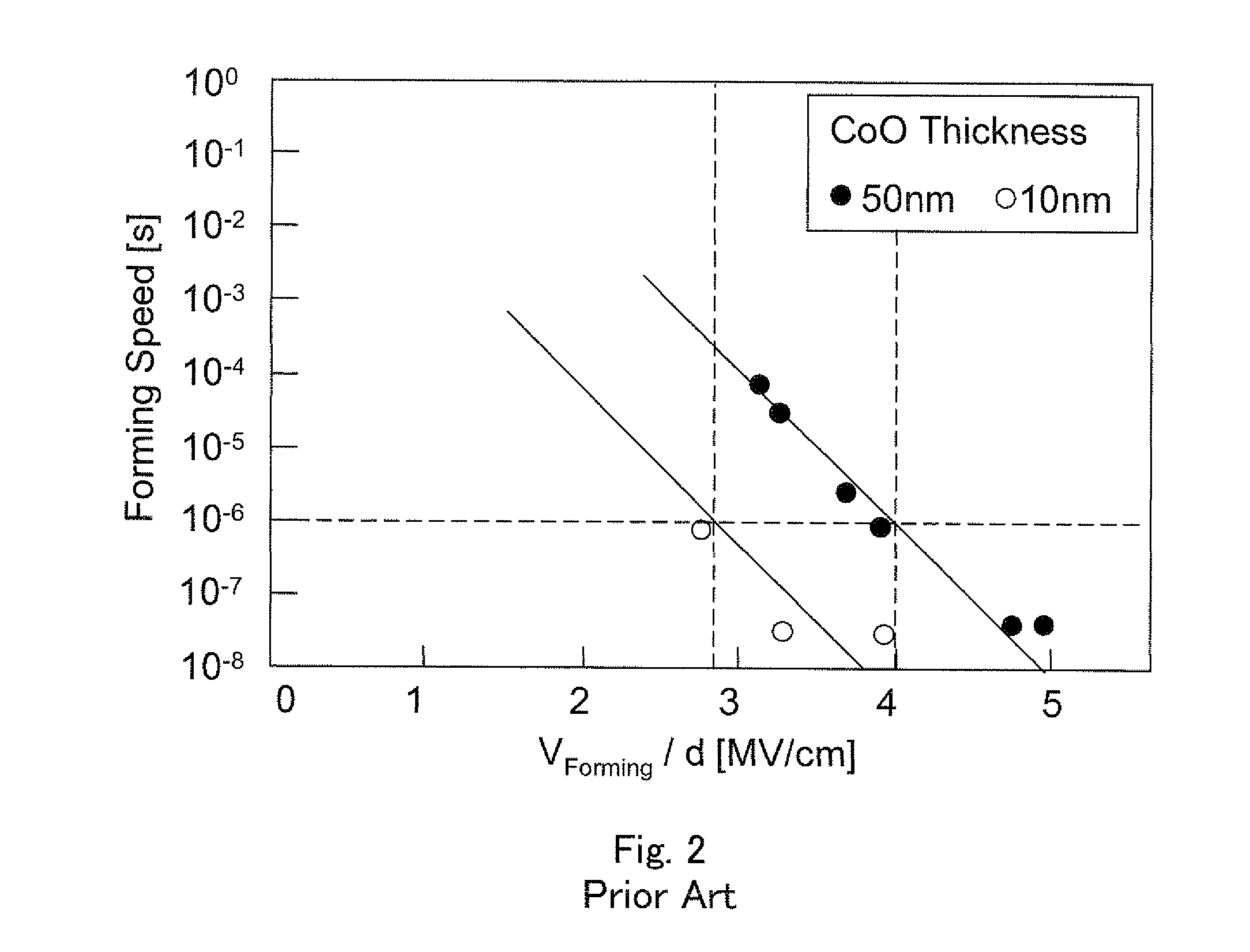

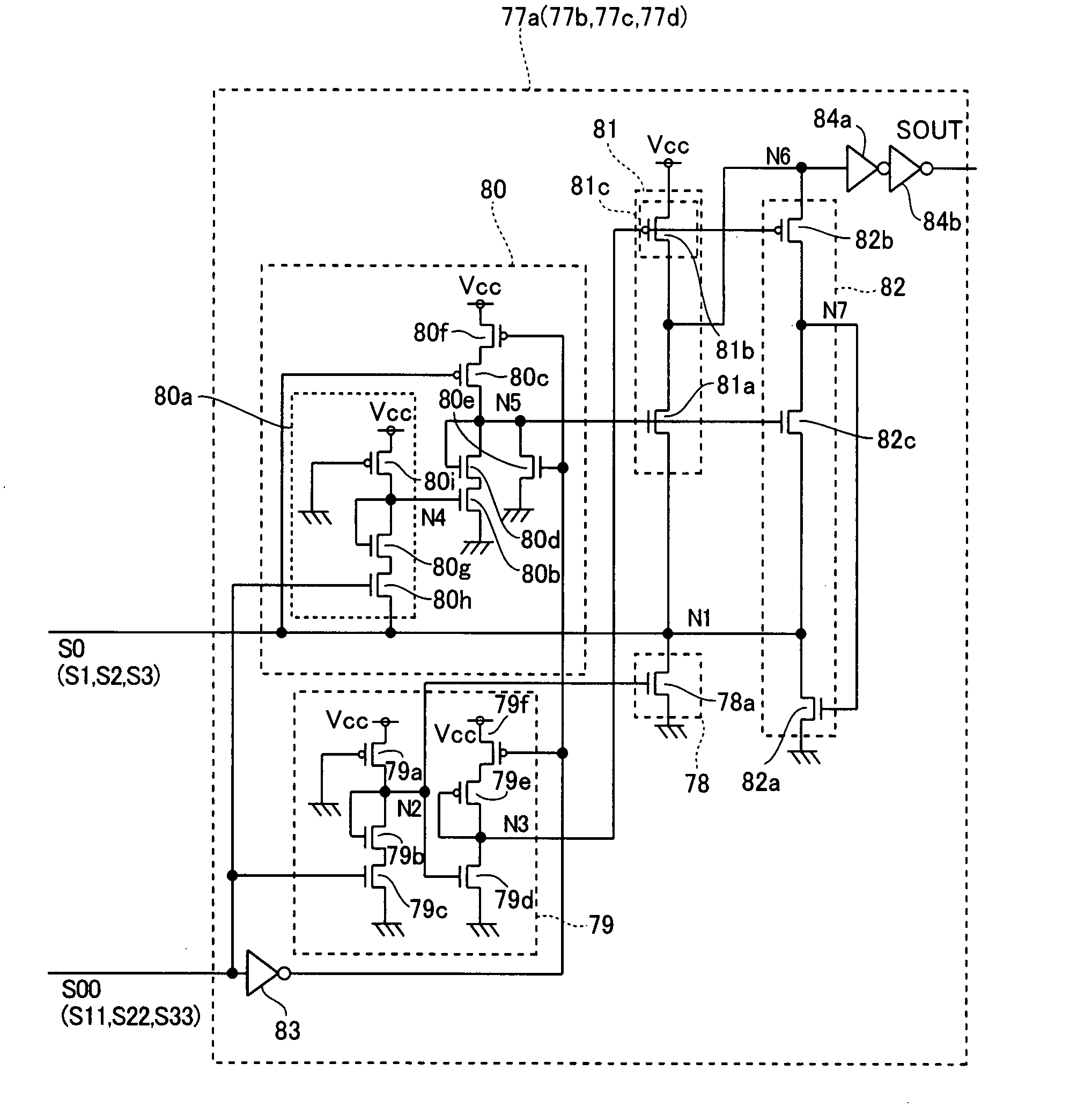

Control circuit for forming process on nonvolatile variable resistive element and control method for forming process

InactiveUS20100232209A1Shorten molding timePotential fluctuationSolid-state devicesDigital storageBit lineVoltage pulse

A nonvolatile semiconductor memory device can carry out a forming process simultaneously on the nonvolatile variable resistive elements of memory cells and make the forming time shorter. The nonvolatile semiconductor memory device has a forming detection circuit provided between the memory cell array and the second selection line (bit line) decoder. The forming detection circuit detects the completion of the forming process for memory cells by measuring the fluctuation in the potential of second selection lines or the current flowing through the second selection lines when applying a voltage pulse for a forming process through the second selection lines simultaneously to the memory cells on which a forming process is to be carried out connected to the same first selection line (word line), and prevents a voltage from being applied to the second selection lines connected to the memory cells where the completion of the forming process is detected.

Owner:SHARP KK

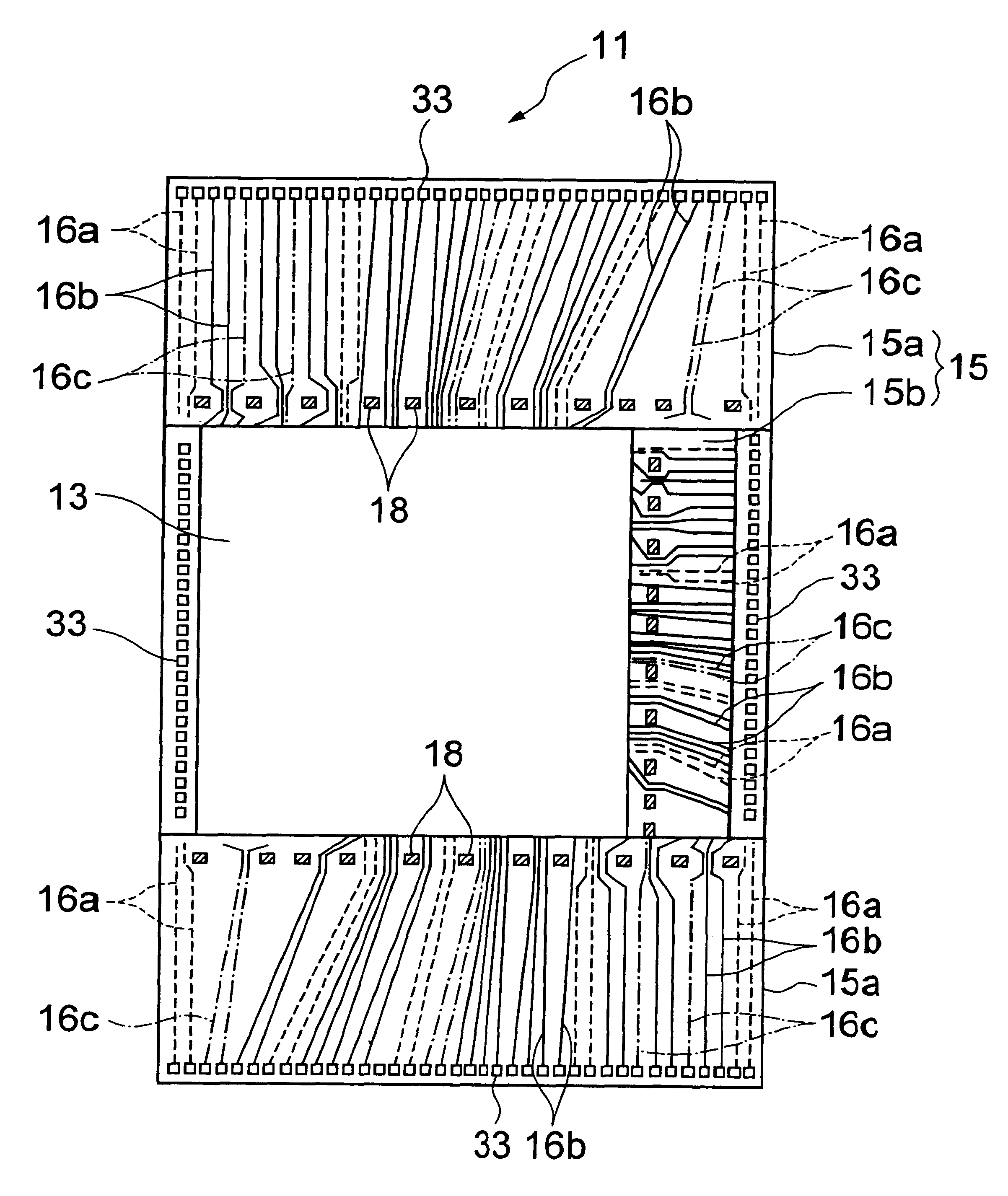

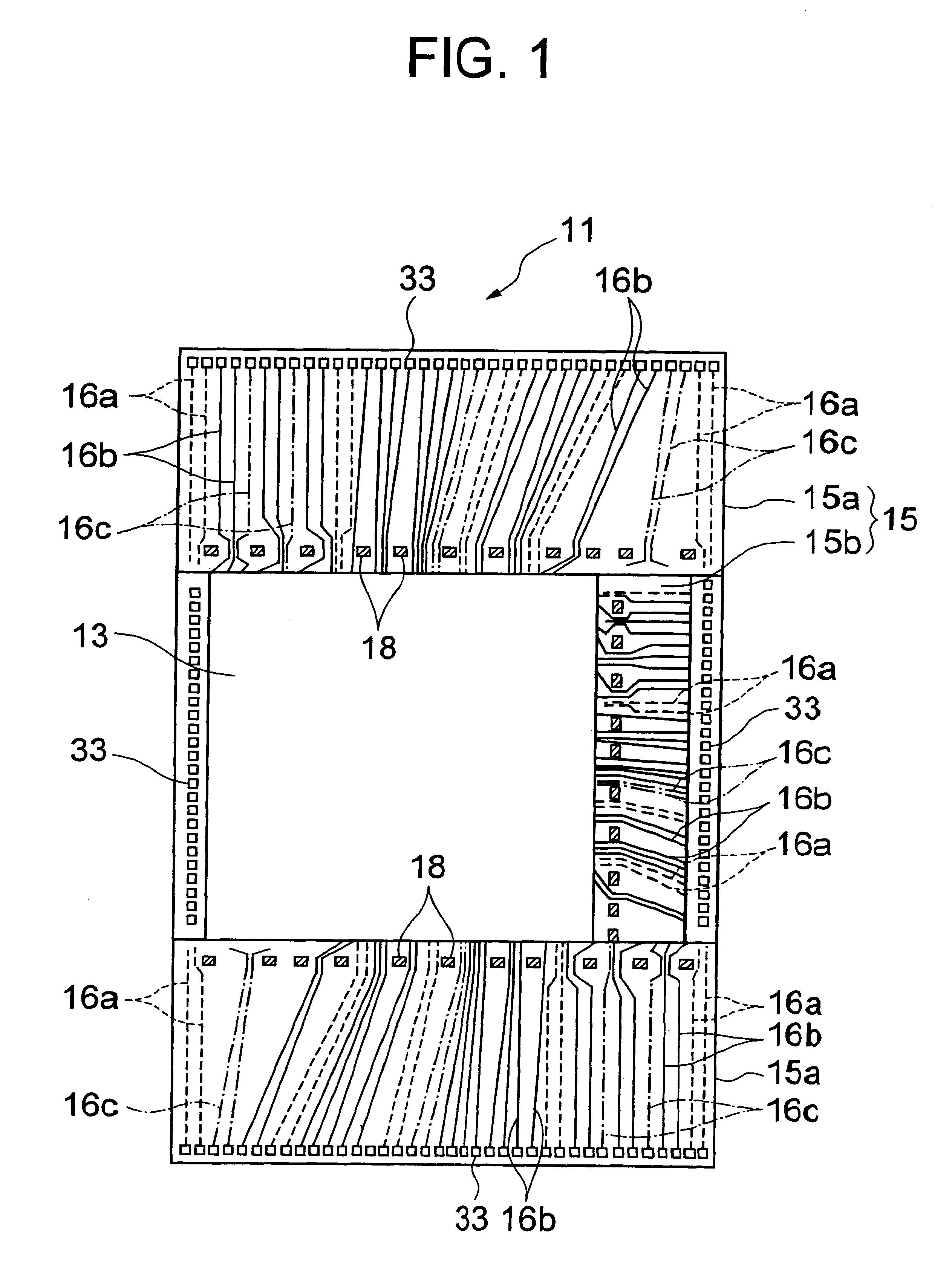

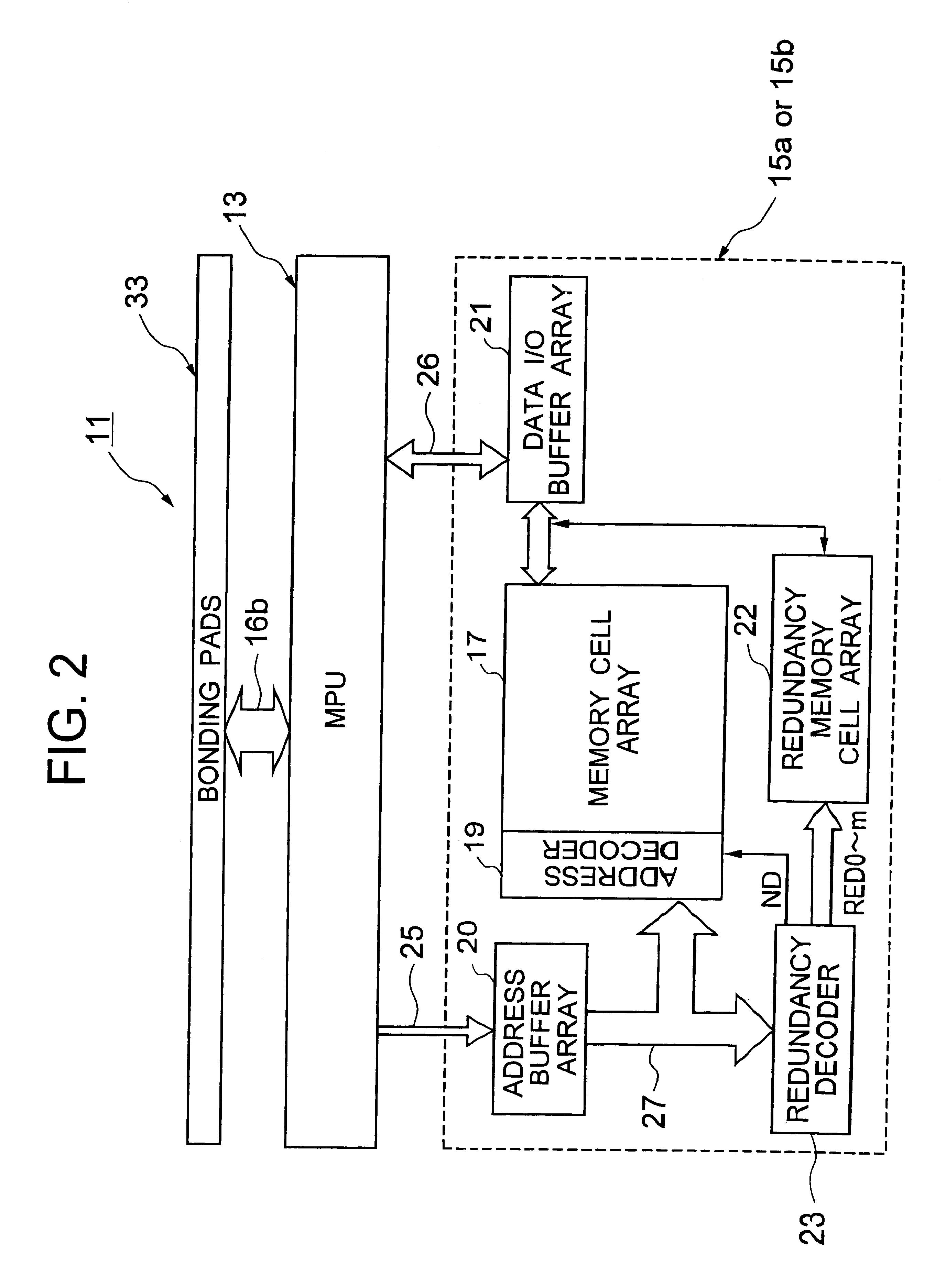

Semiconductor integrated circuit having a MPU and a DRAM cache memory

InactiveUS6378118B1Reduce noise transmissionPotential fluctuationTransistorSemiconductor/solid-state device detailsDram cacheComputer science

A large scale semiconductor integrated circuit, implemented on a chip, includes an MPU and a DRAM cache memory including a plurality of DRAM macro blocks located around the MPU. The DRAM macro block has a redundancy function for which a plurality of fuses are disposed for cut-out by laser beams. The lower metallic layers implement source lines for power and ground to the DRAM macro blocks, whereas a topmost metallic layer implements source lines for the MPU. The topmost metallic layer circumvents areas of the chip where portions of a metallic layer constituting fuses for implementing the redundancy function are located.

Owner:NEC ELECTRONICS CORP

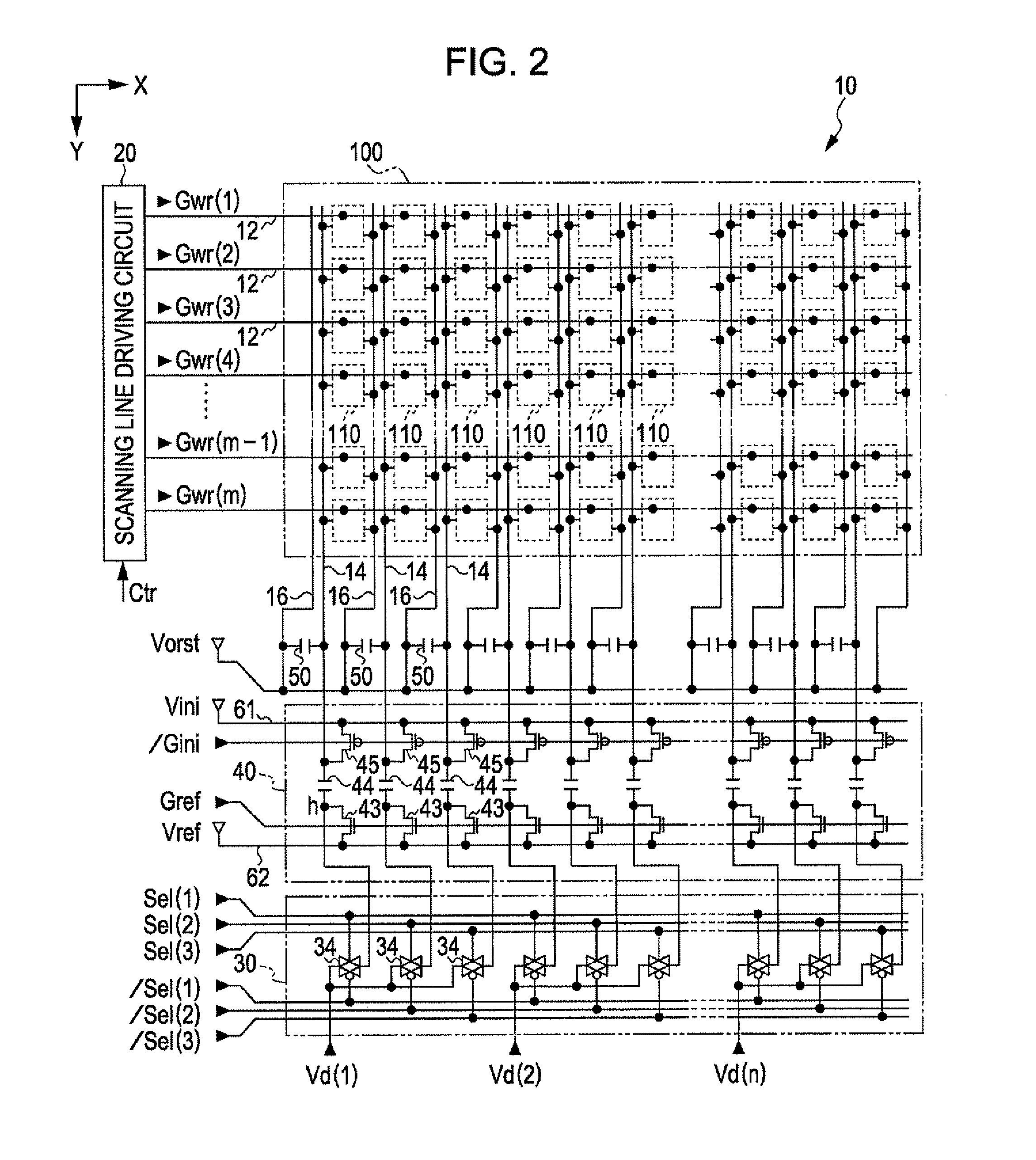

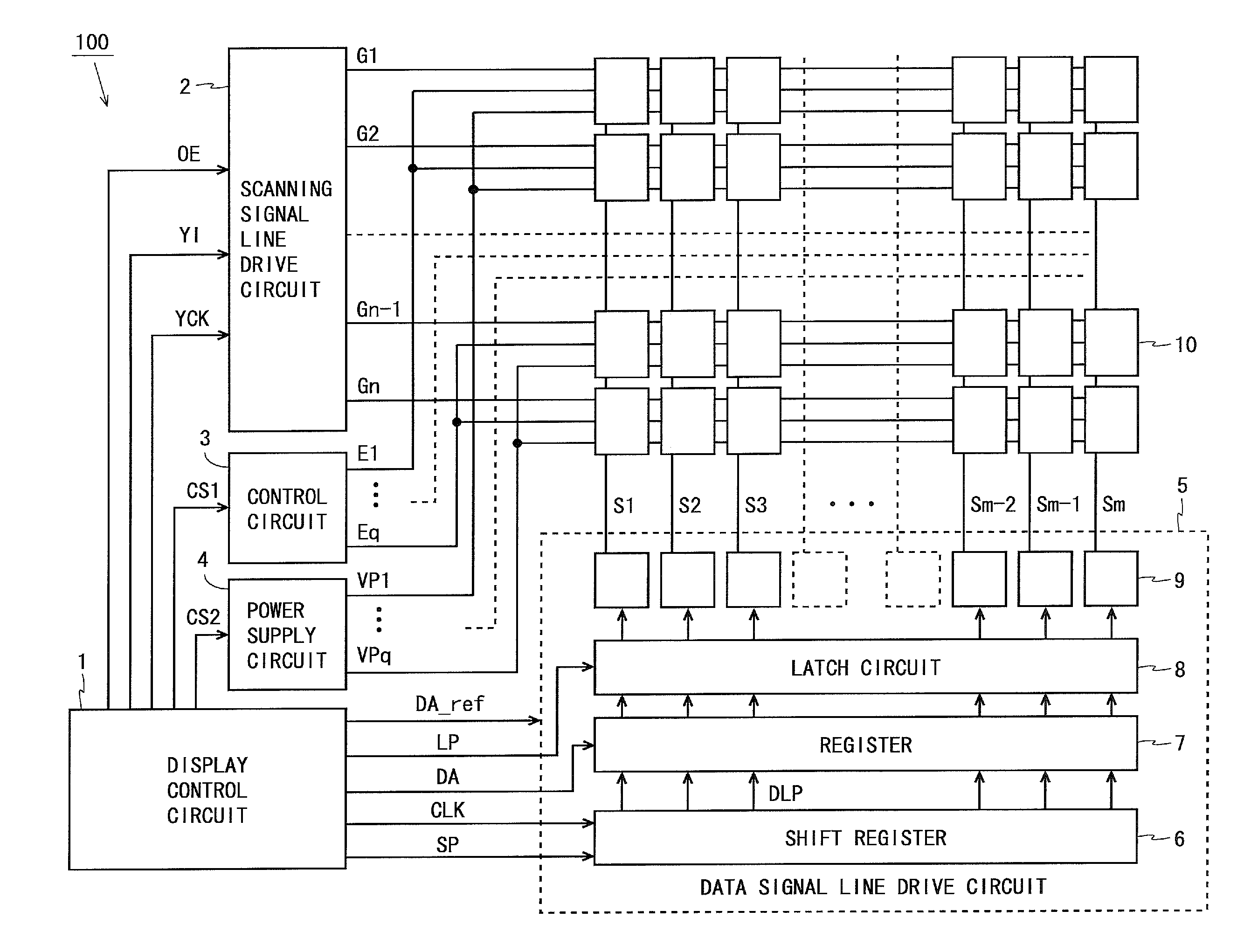

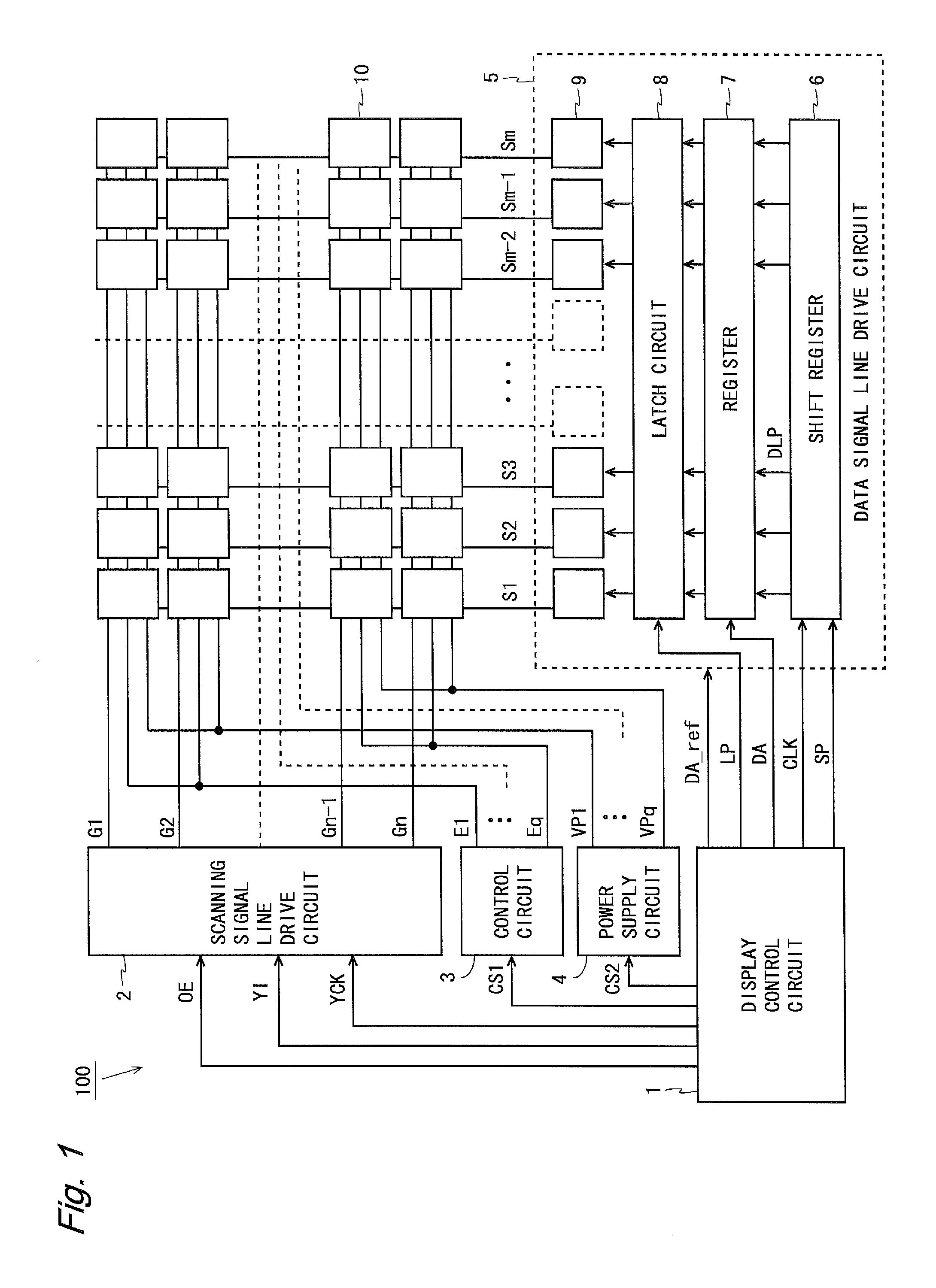

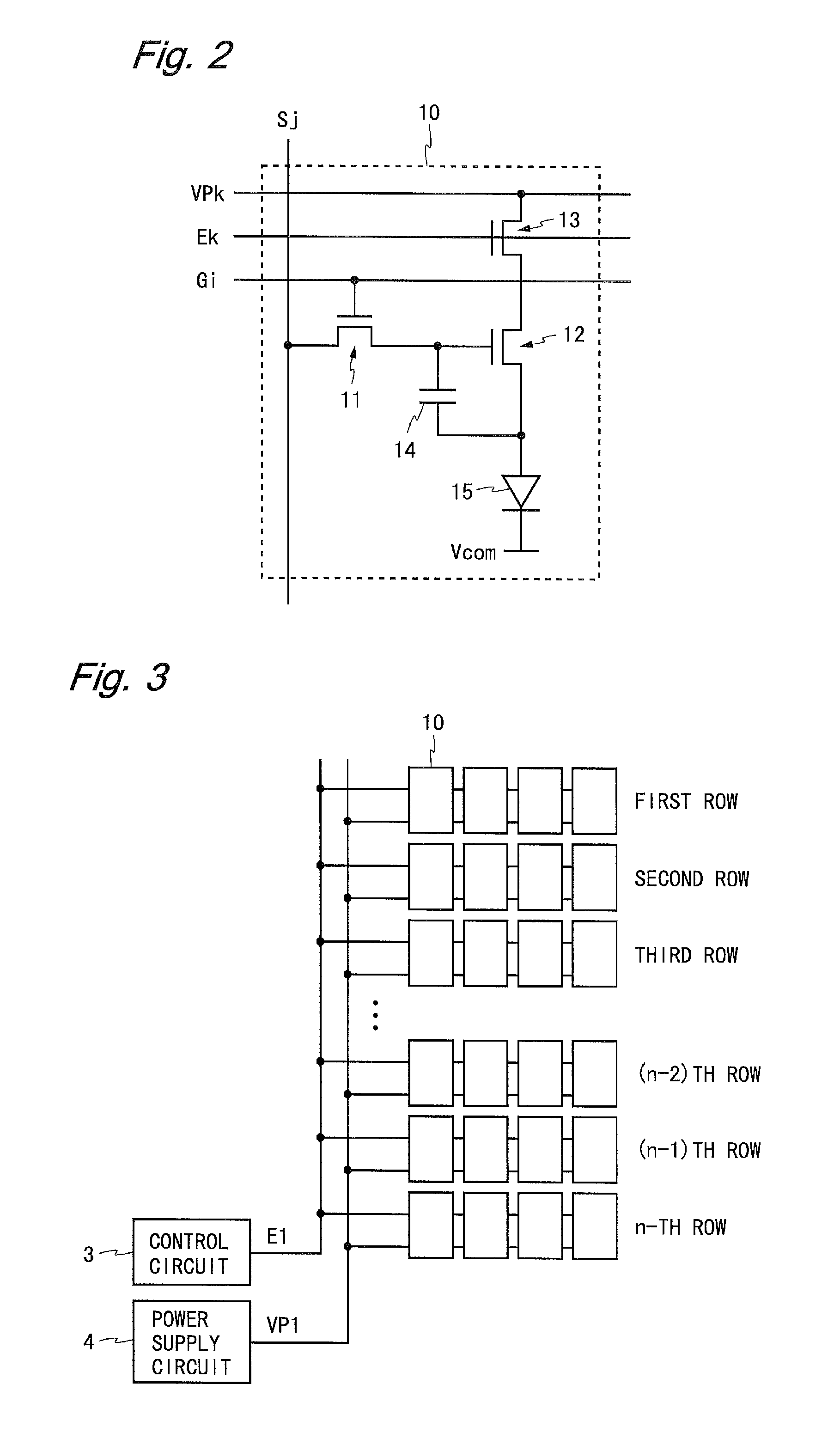

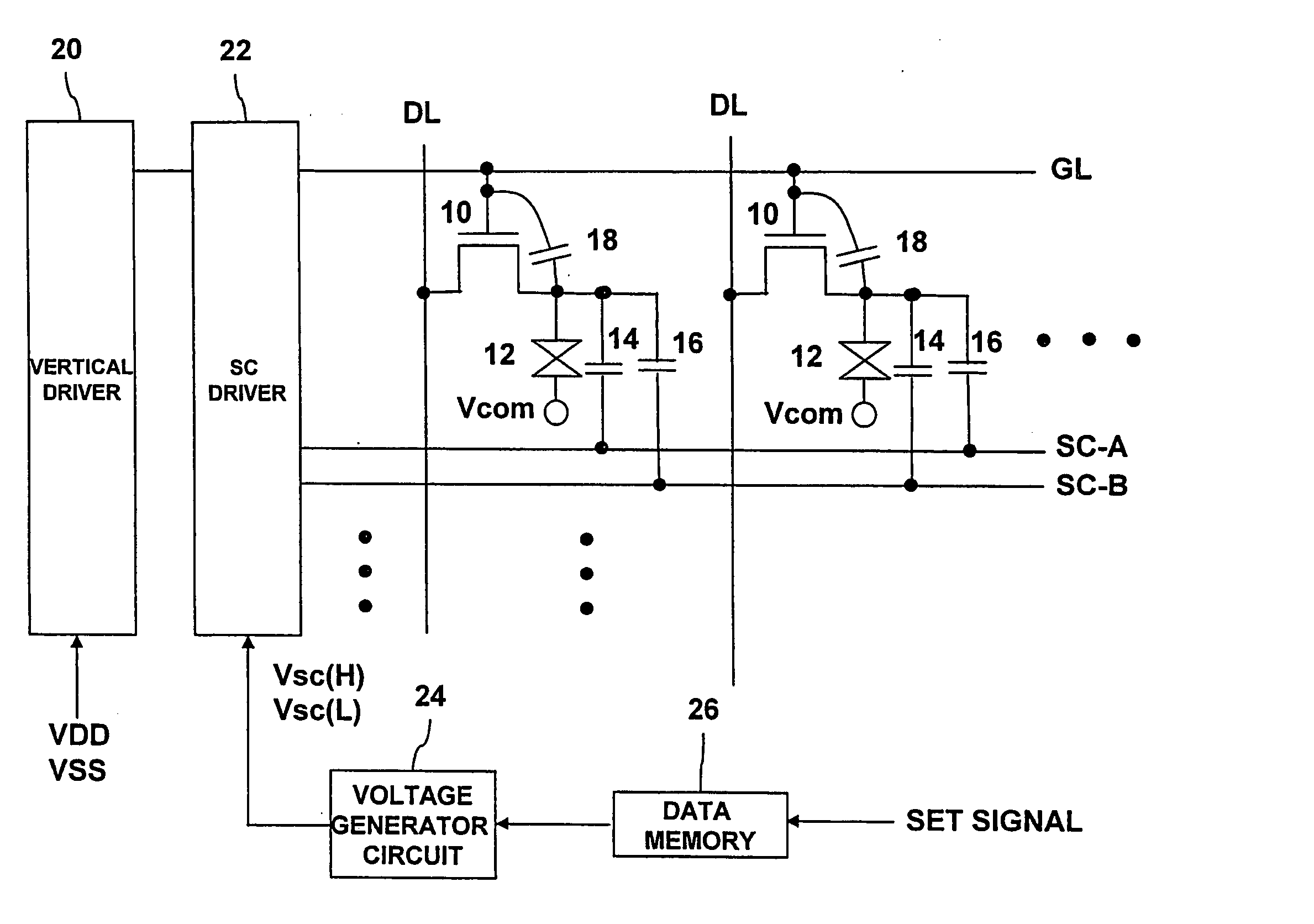

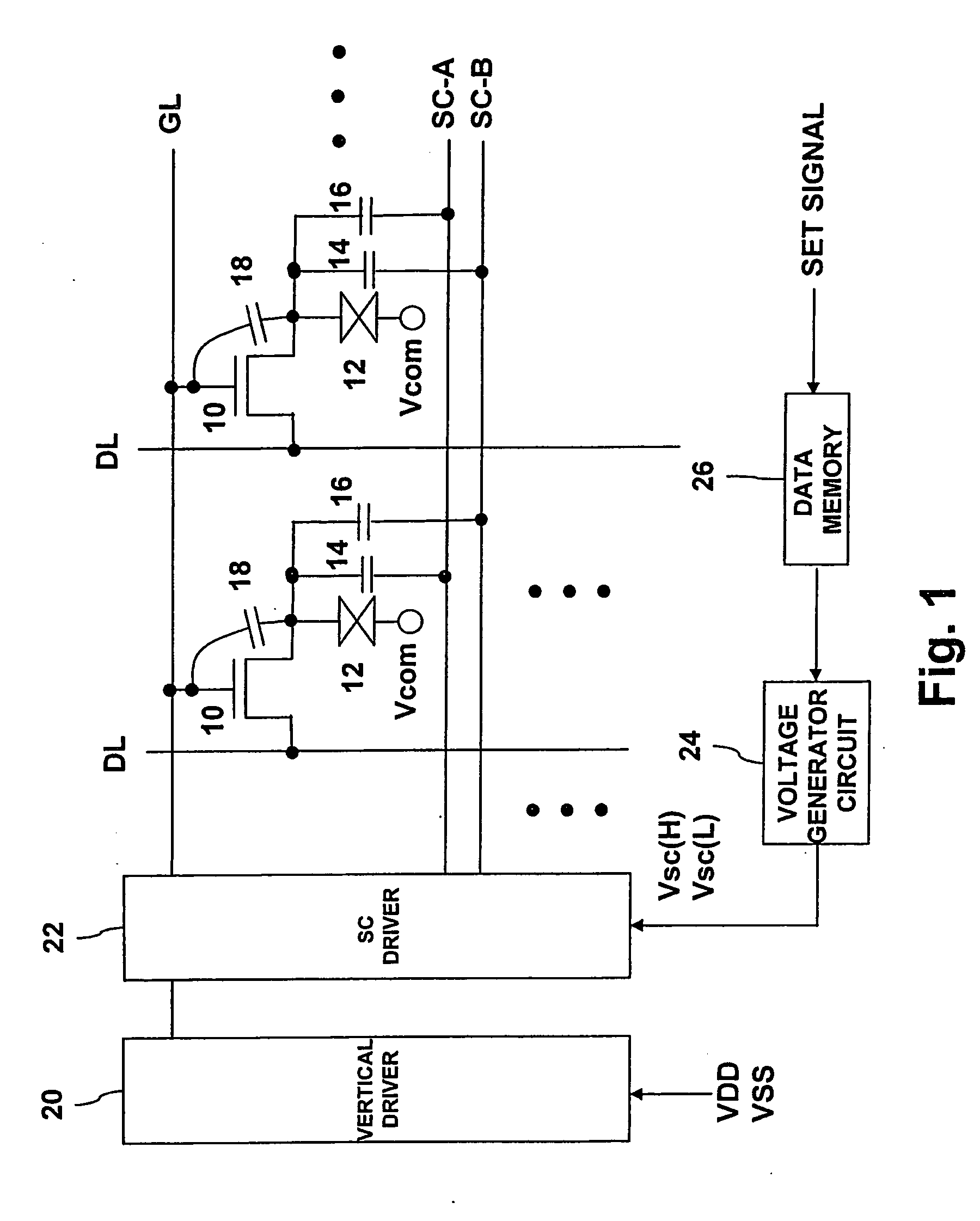

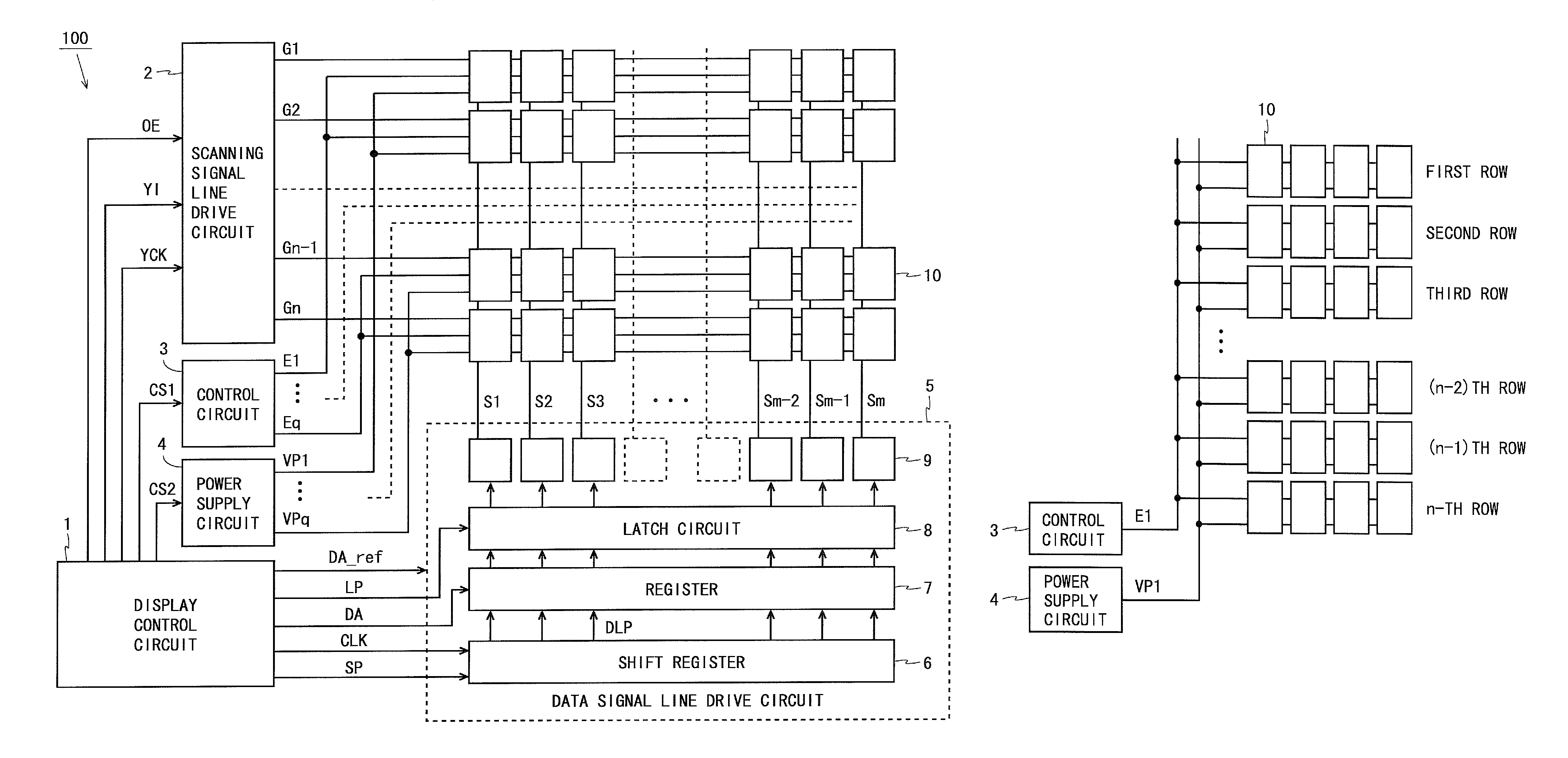

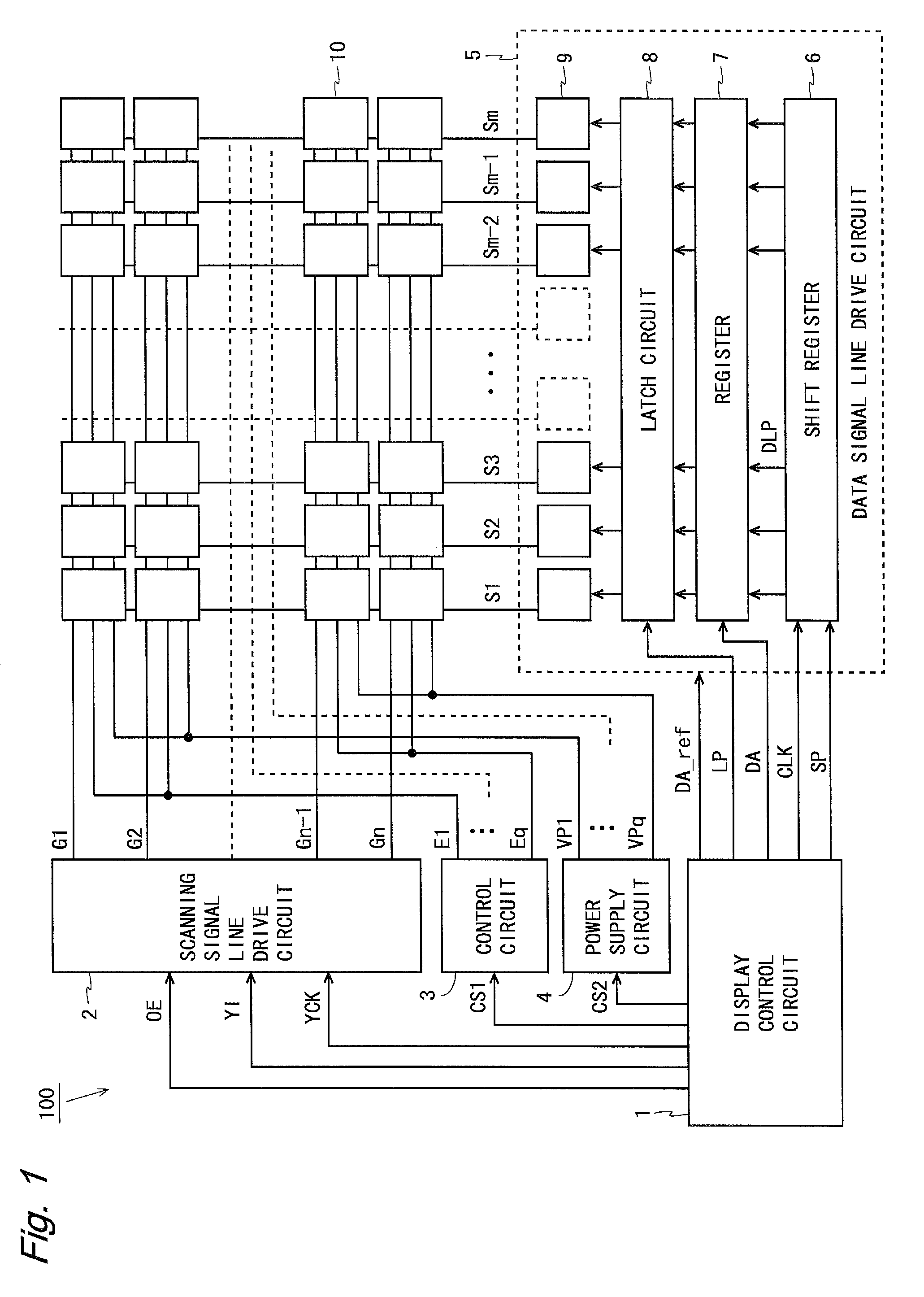

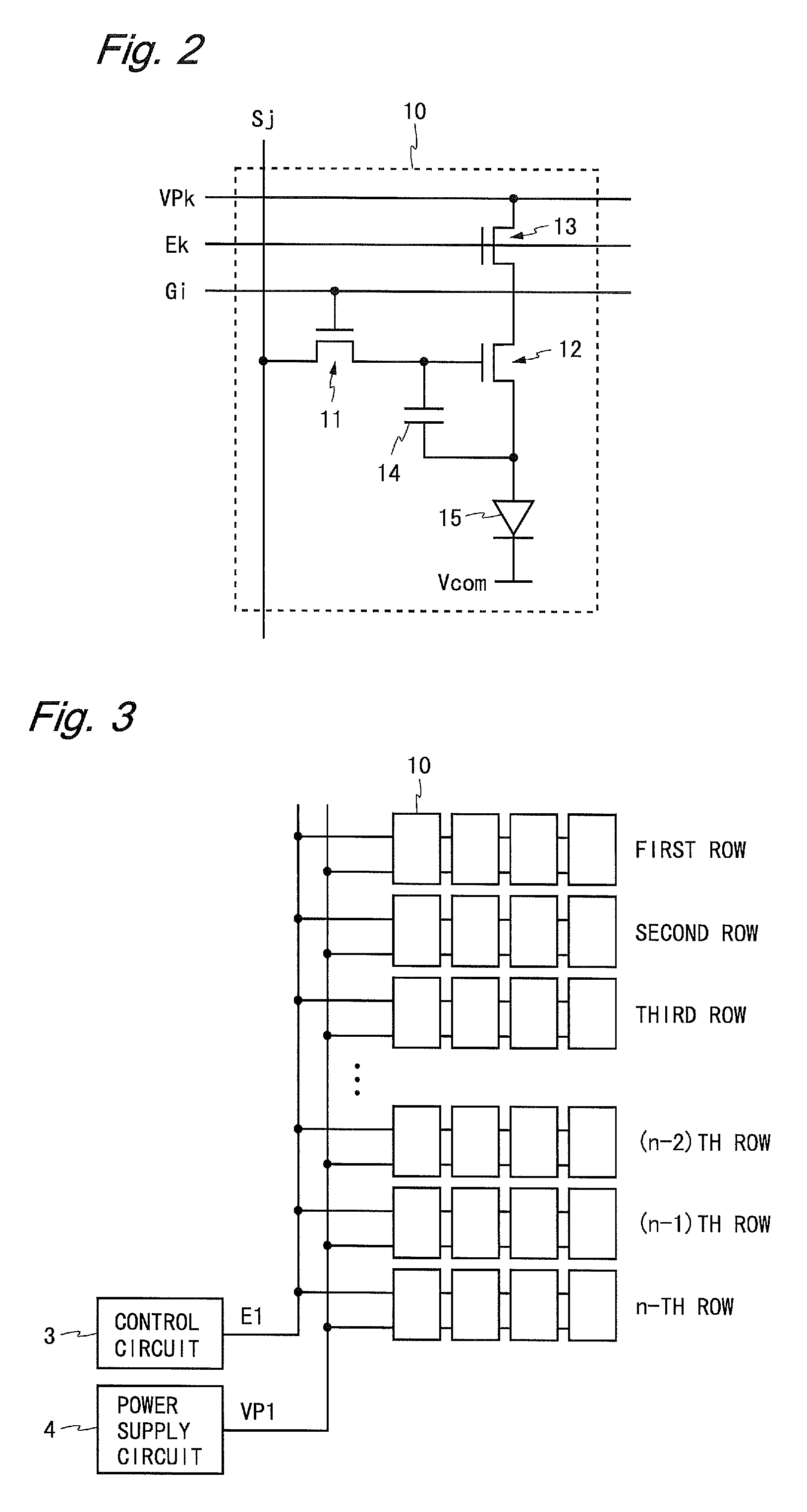

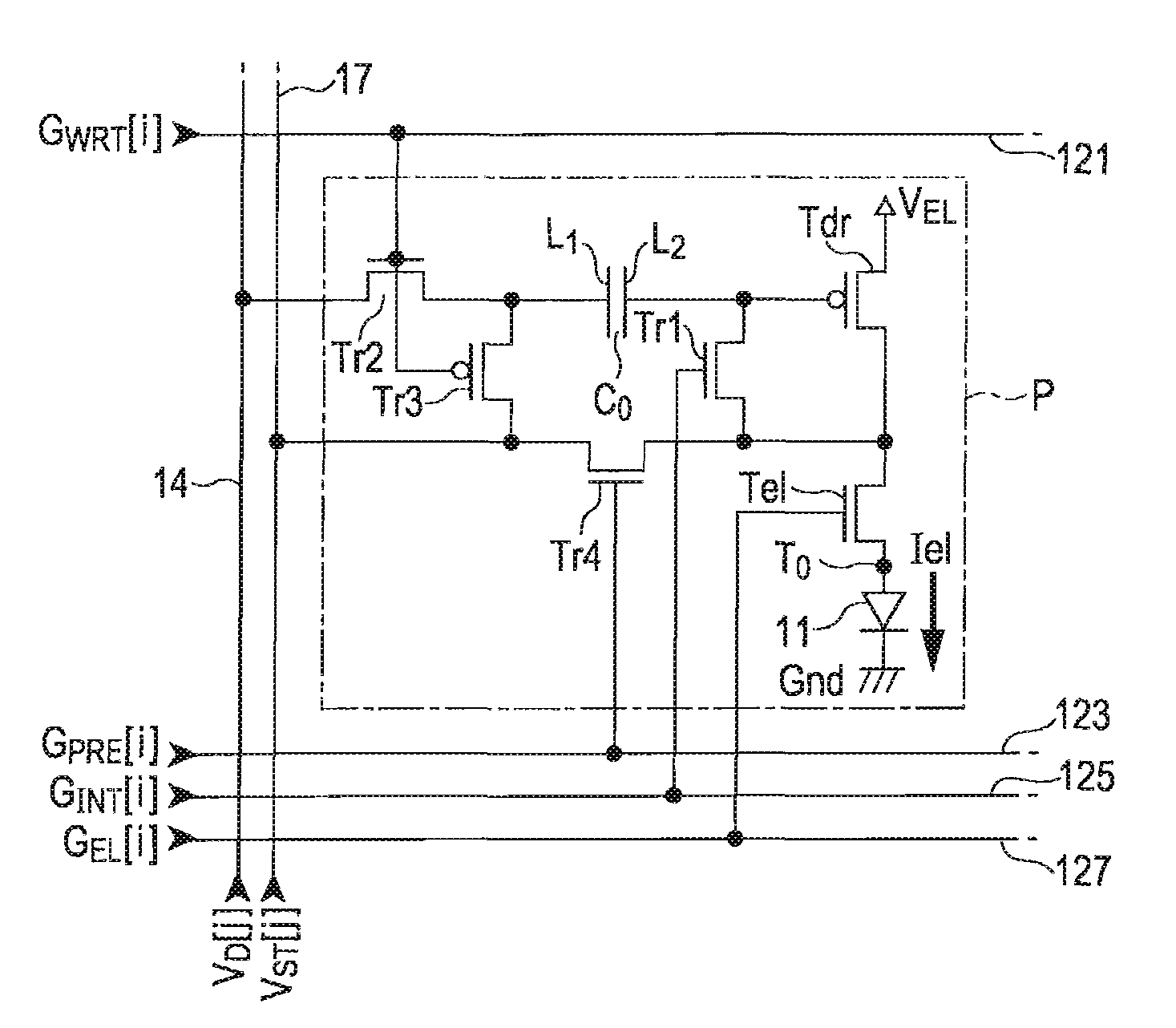

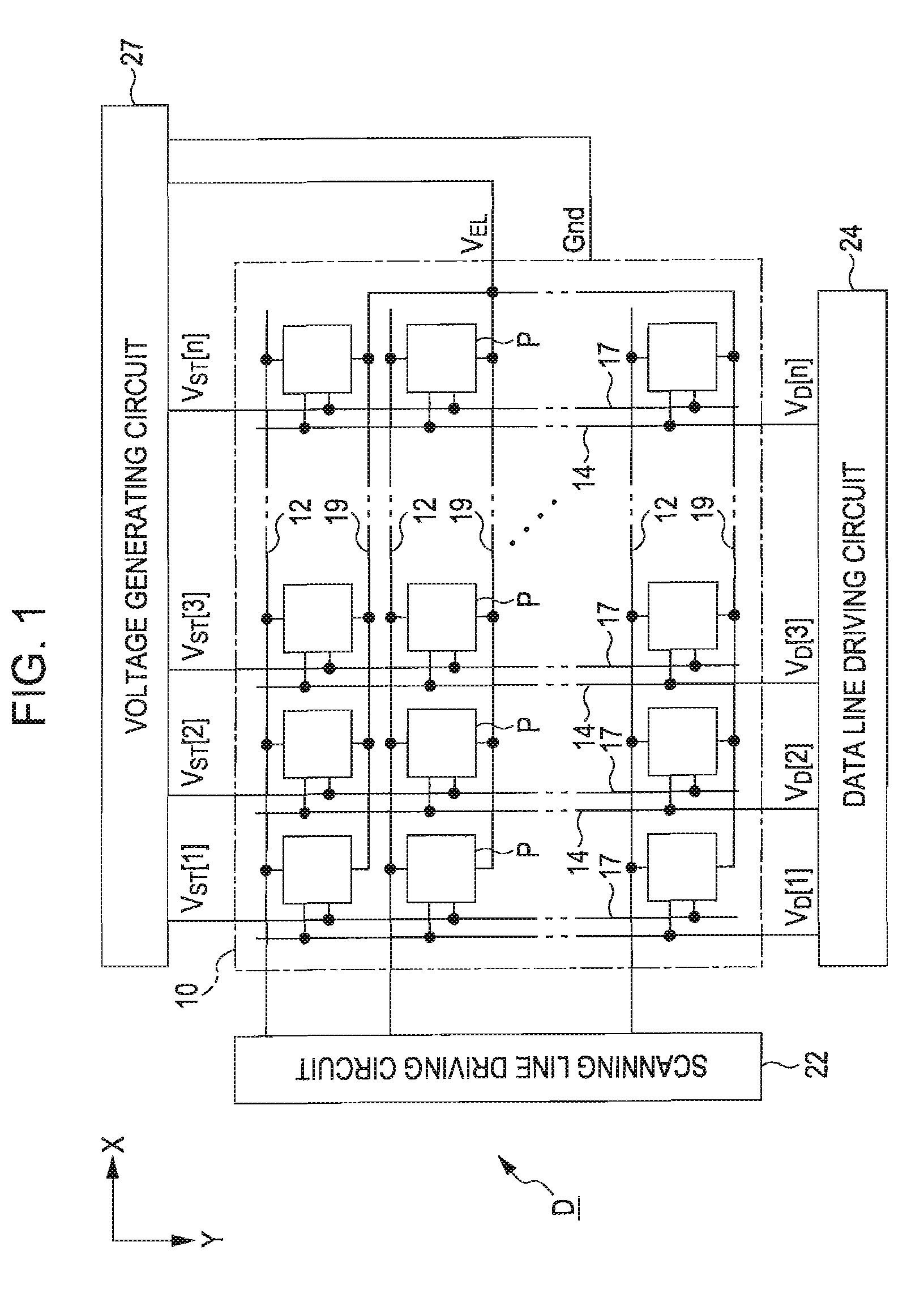

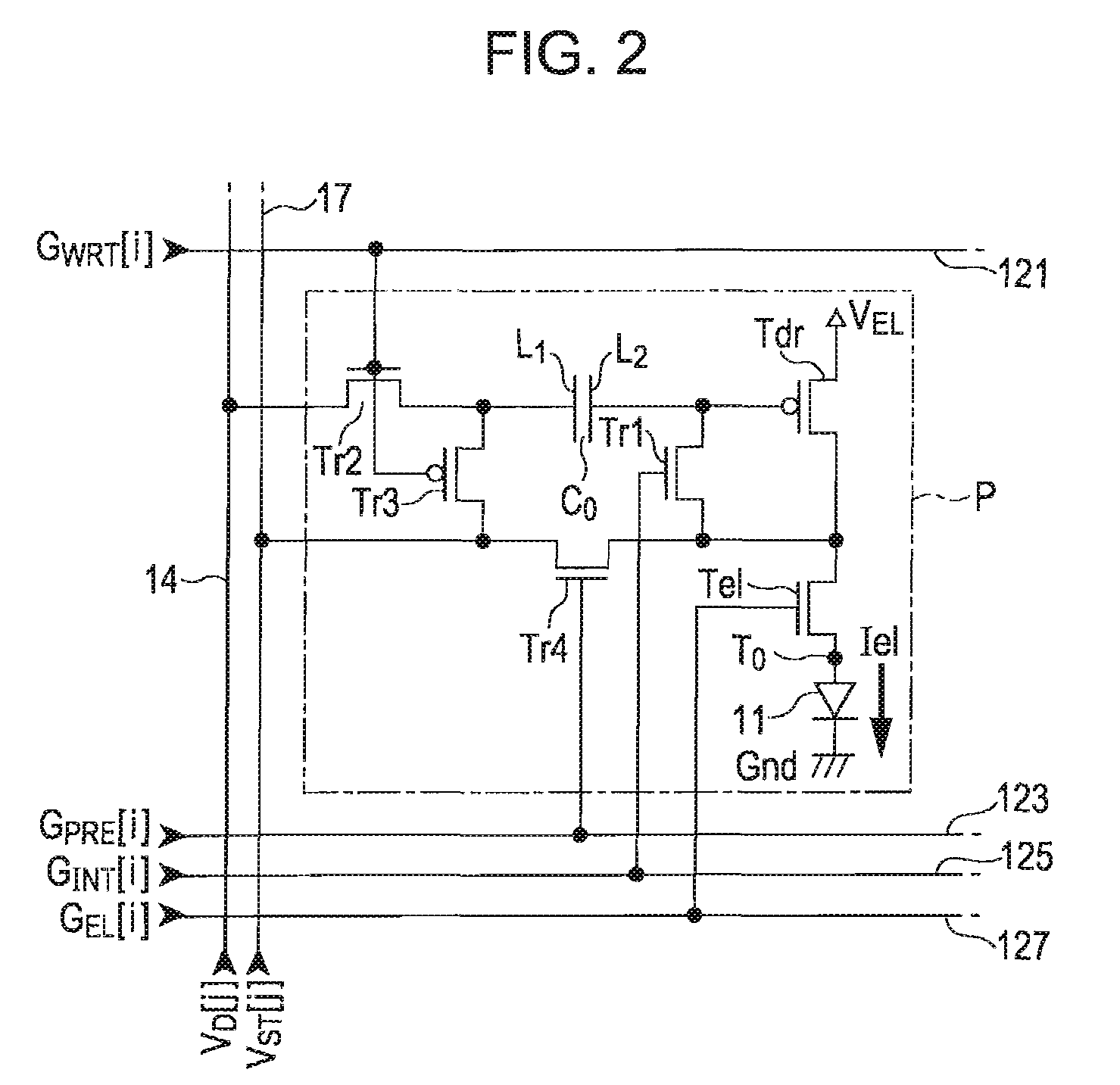

Display device and drive method thereof

ActiveUS20140307012A1Display brightness can be preventedSuppress brightnessCathode-ray tube indicatorsInput/output processes for data processingDisplay deviceHemt circuits

A pixel circuit 10 is provided with TFTs 12 and 13 and an organic EL element 15 on a current path connecting a power supply line VPk and an electrode having a common potential Vcom. A display device 100 simultaneously performs initialization to pixel circuits 10 in a plurality of rows, simultaneously perform threshold detection to the pixel circuits 10 in the plurality of rows, sequentially writes data to the pixel circuits 10 row by row, and makes the organic EL elements 15 included in the pixel circuits 10 in the plurality of rows emit light in the same period. In a period from completion of threshold detection to start of light emission, the TFTs 11 and 13 are controlled to an off state, and a potential VP_C which is substantially equal to the common potential Vcom is applied to the power supply line VPk. Consequently, leak current flowing through the TFTs 12 and 13 can be suppressed, and the fluctuation in the node potential in the pixel circuit 10 in a standby period can be prevented.

Owner:SHARP KK

Display driver and display driving method

ActiveUS20060227638A1Easily realizedPotential fluctuationCathode-ray tube indicatorsDigital storageOriginal dataPre-charge

In a display driver, one scanning period is divided into a period P and a subsequent period D. In the period P, a pre-charge voltage equal to an original data voltage is applied in a time-sharing manner to data lines in one block, and in the period D after the period P, the original data voltage is applied again.

Owner:RENESAS ELECTRONICS CORP

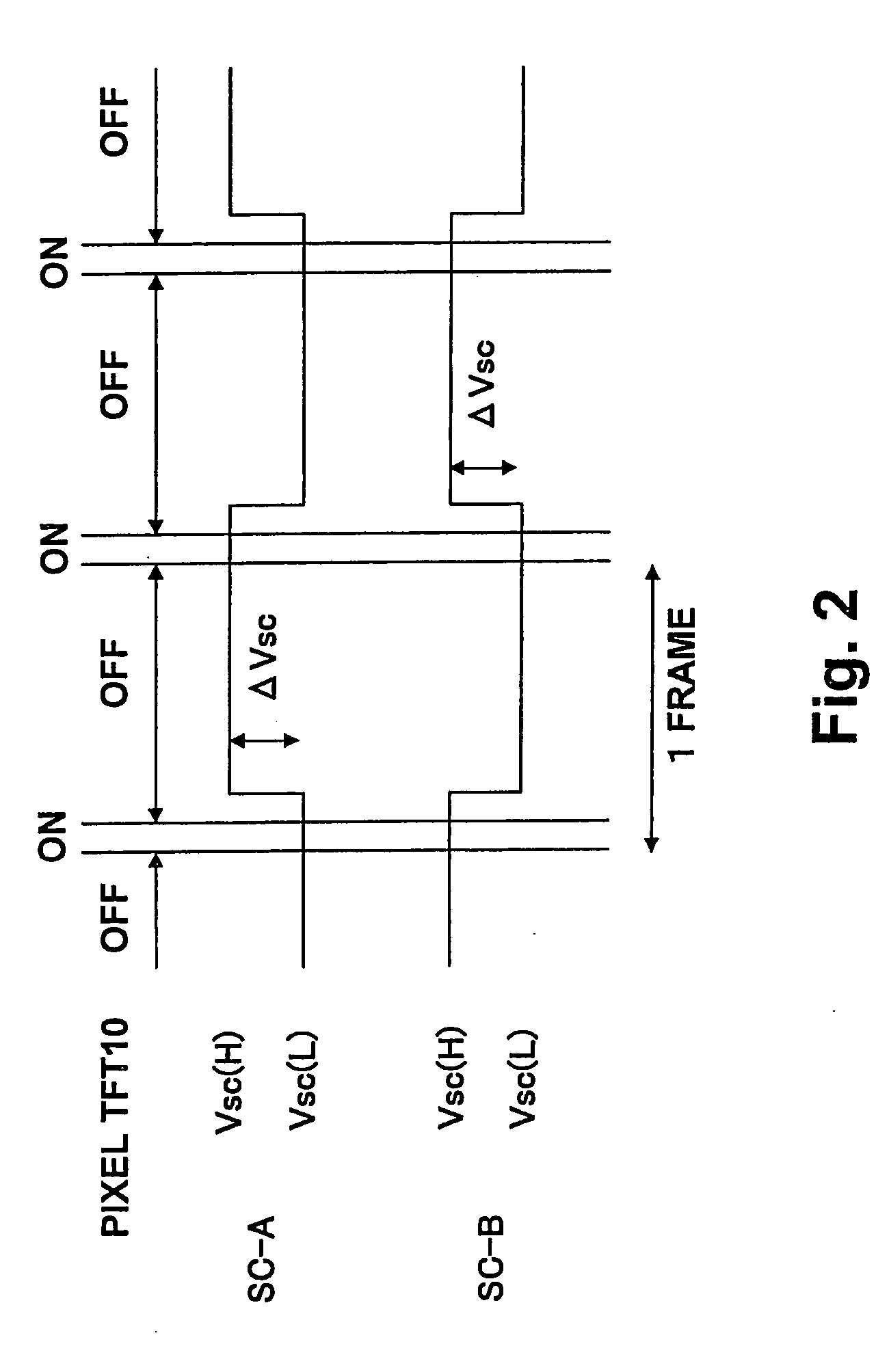

Display device

InactiveUS20050259062A1Reduce adverse effectsMinimizing dataStatic indicating devicesNon-linear opticsCapacitanceDisplay device

The level of a storage capacitor line changes between two types, an H level and an L level. As a result of this change, the voltage applied to a liquid crystal is shifted so that a sufficient voltage is applied to the liquid crystal to perform a display operation. Then, by changing the voltage value of the difference between a first level and a second level, the contrast and screen brightness are adjusted. Furthermore, the capacitances generated at the locations where the two storage capacitor lines and the data line intersect are set to be substantially the same.

Owner:SANYO ELECTRIC CO LTD

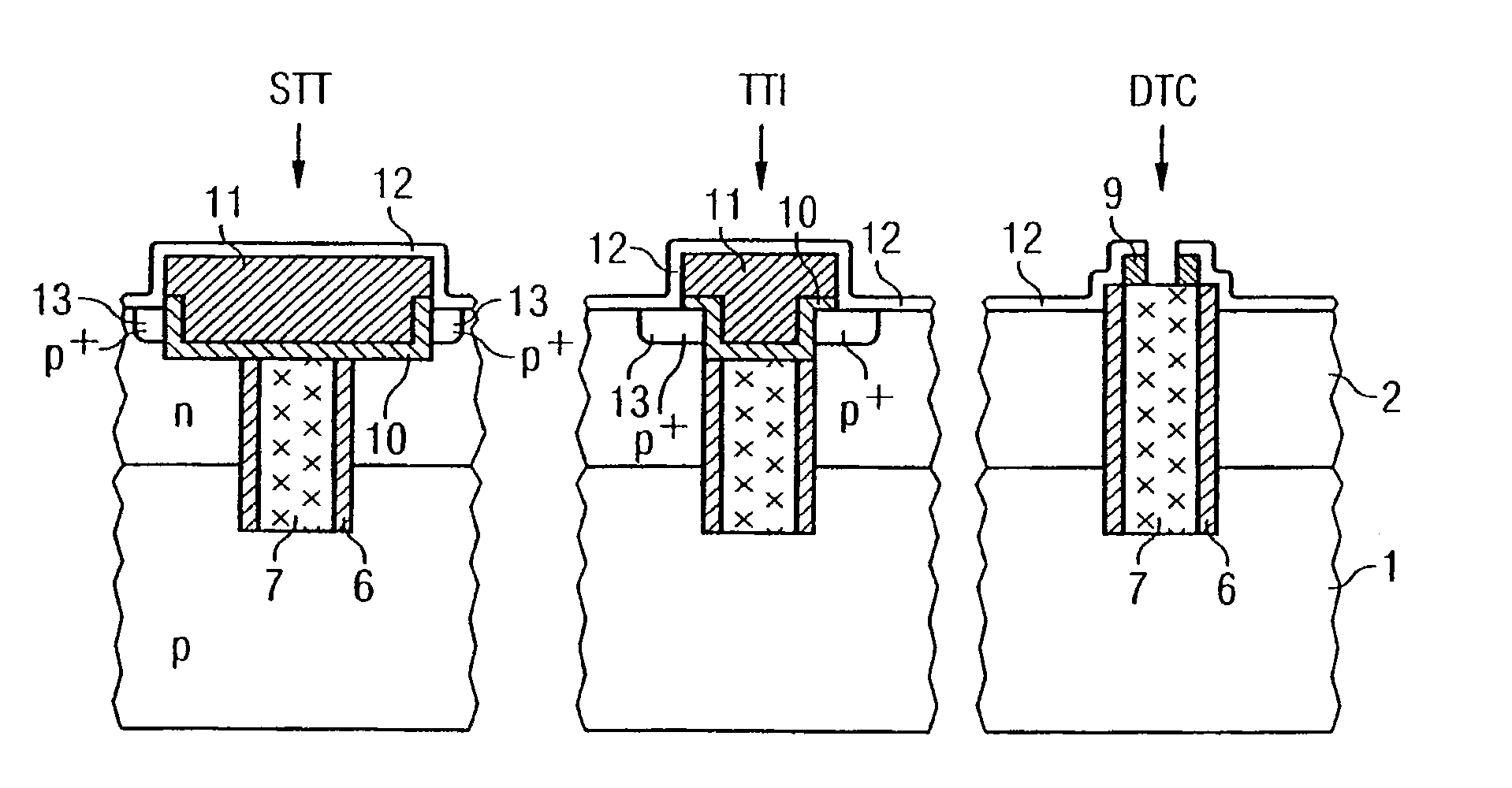

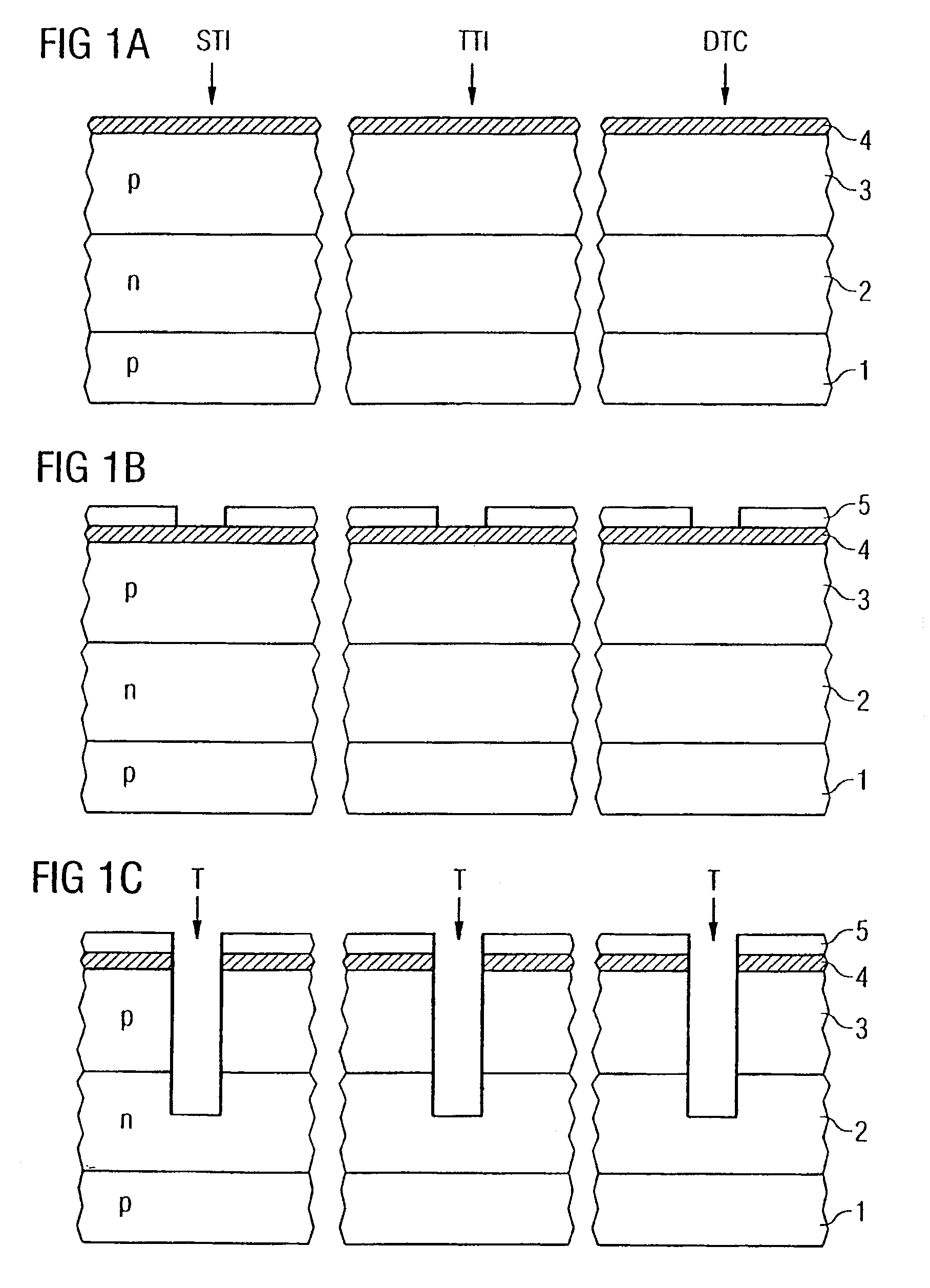

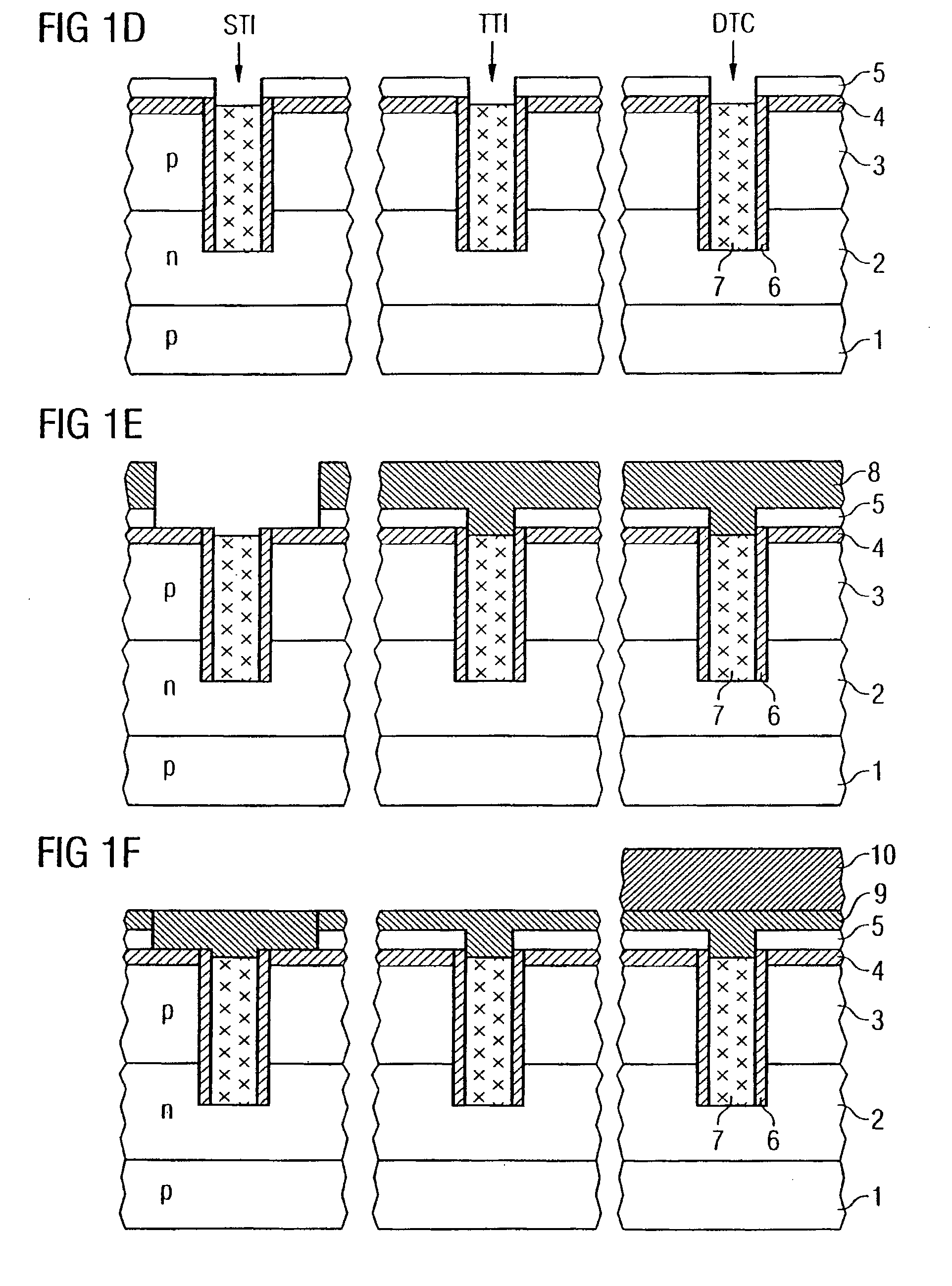

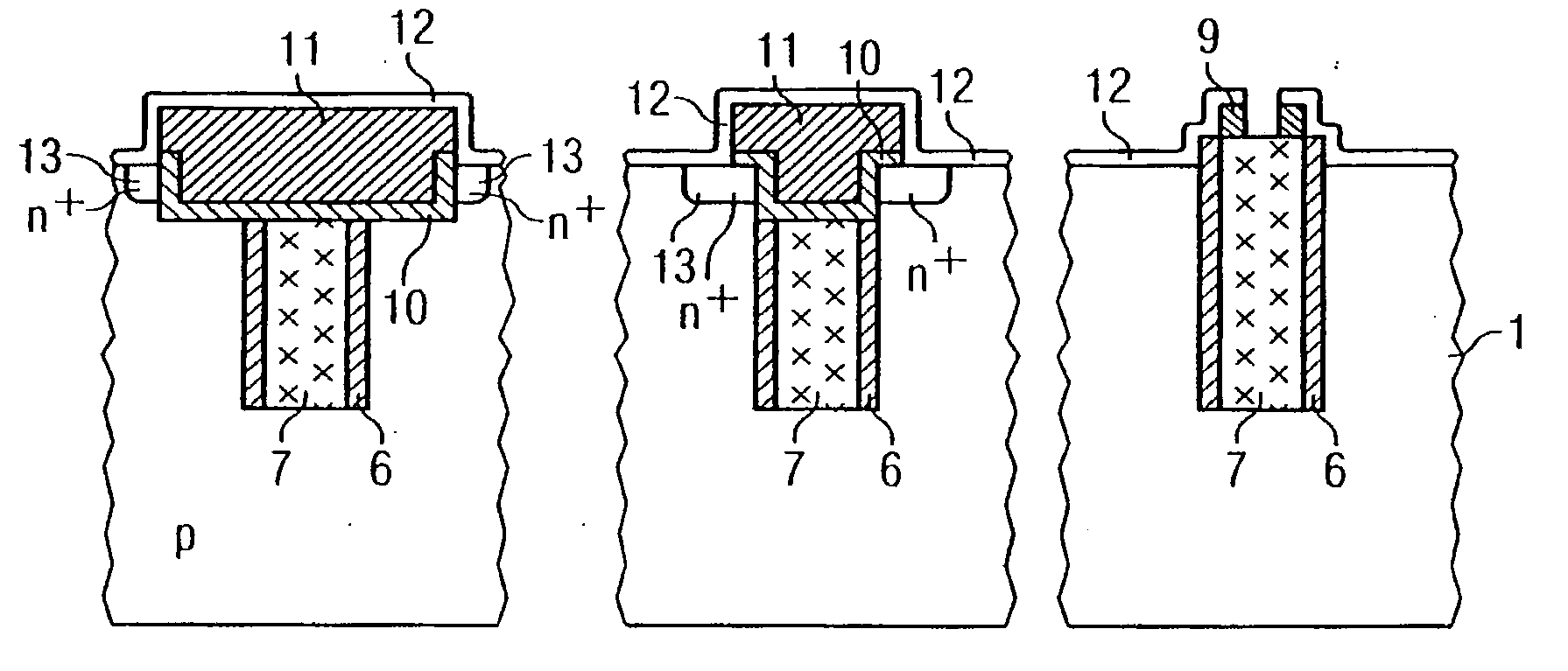

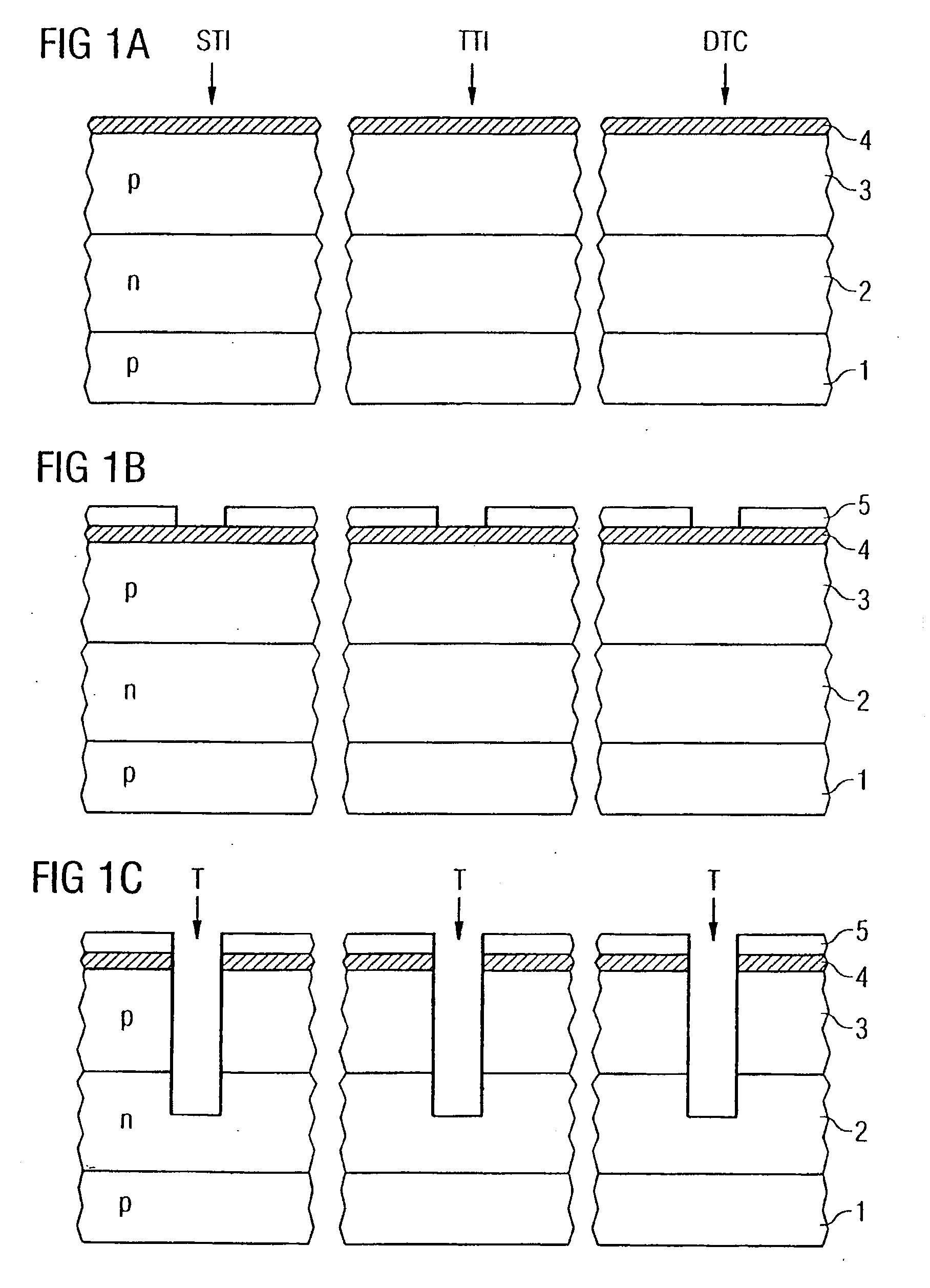

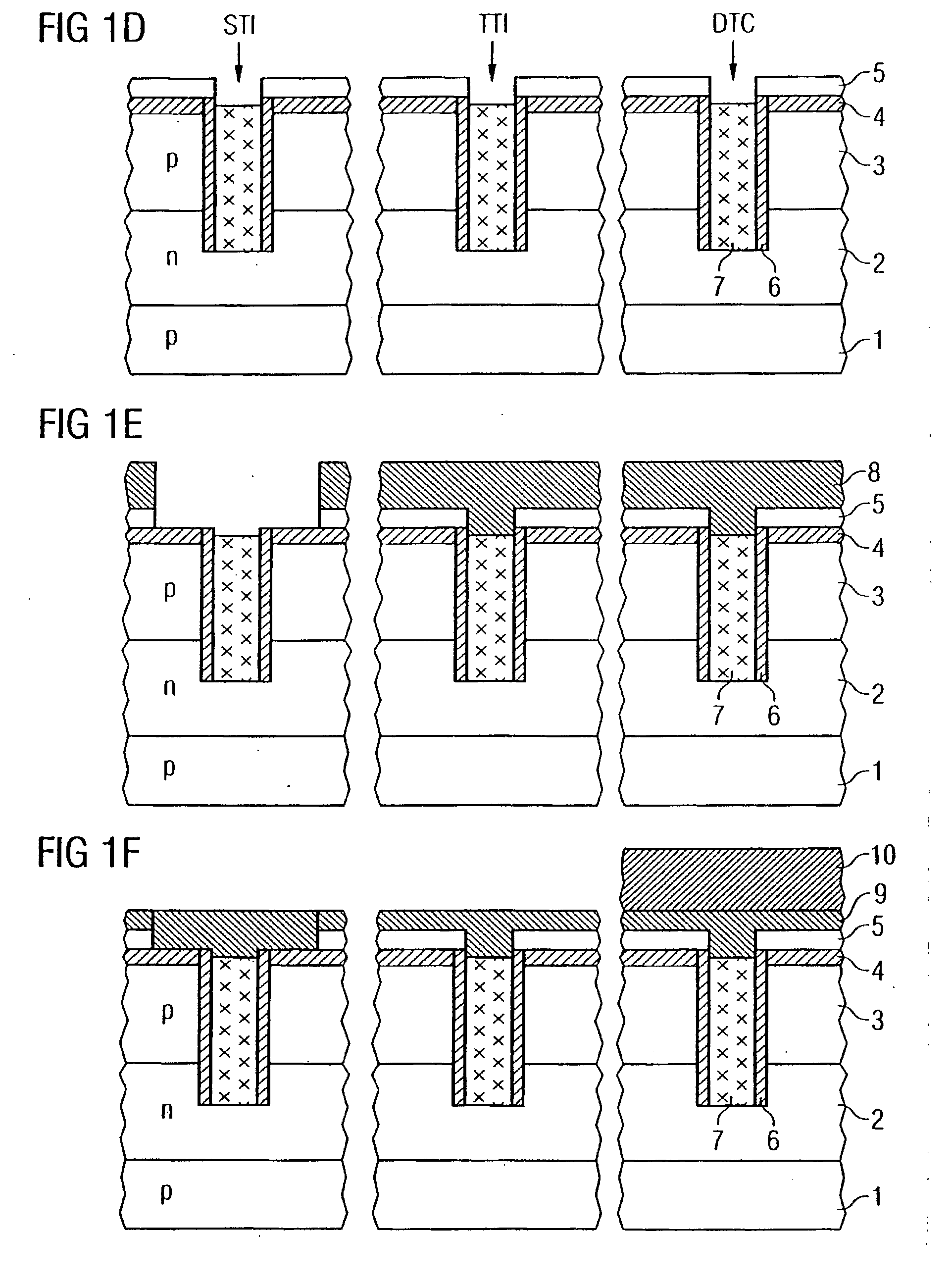

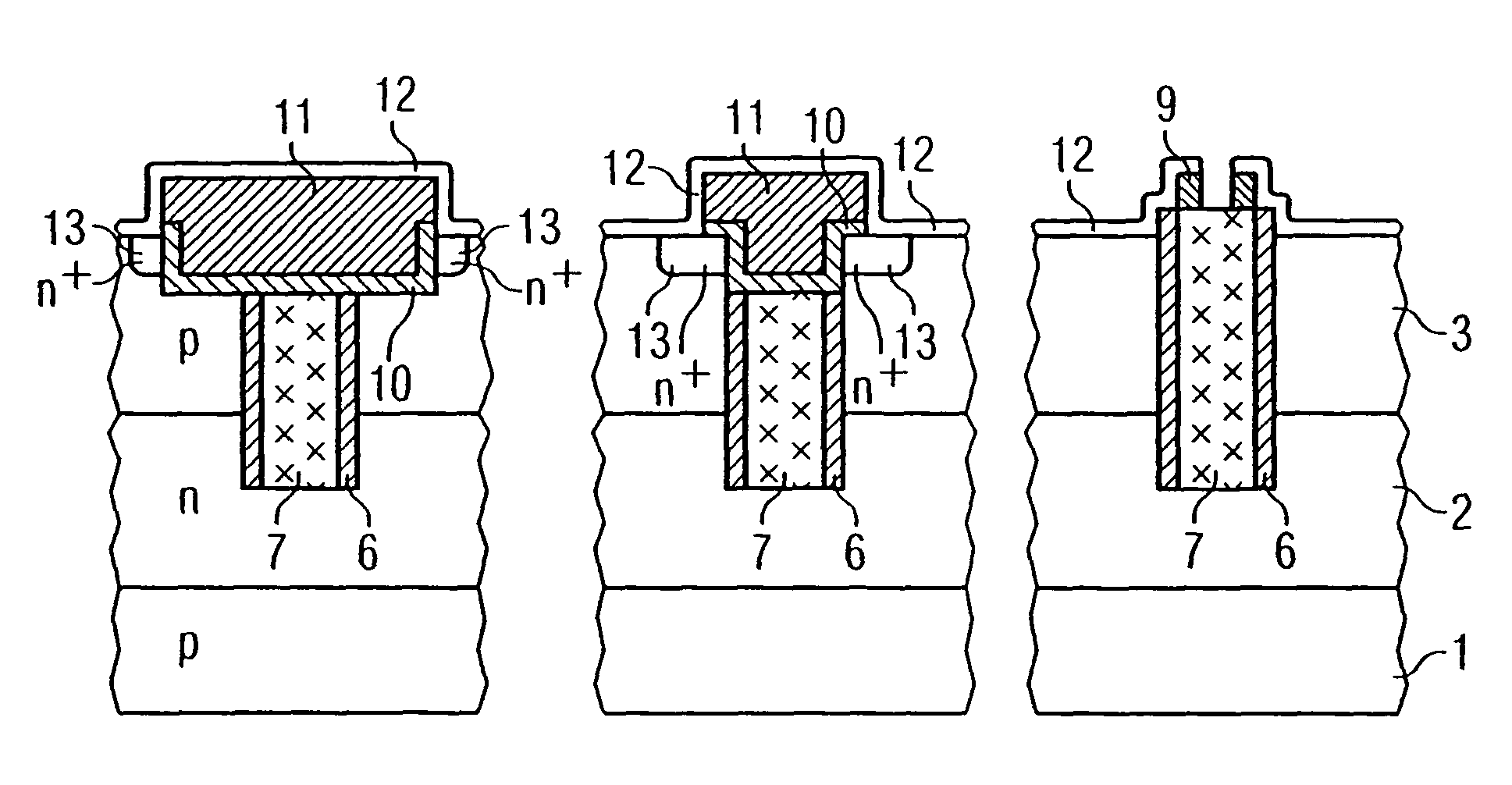

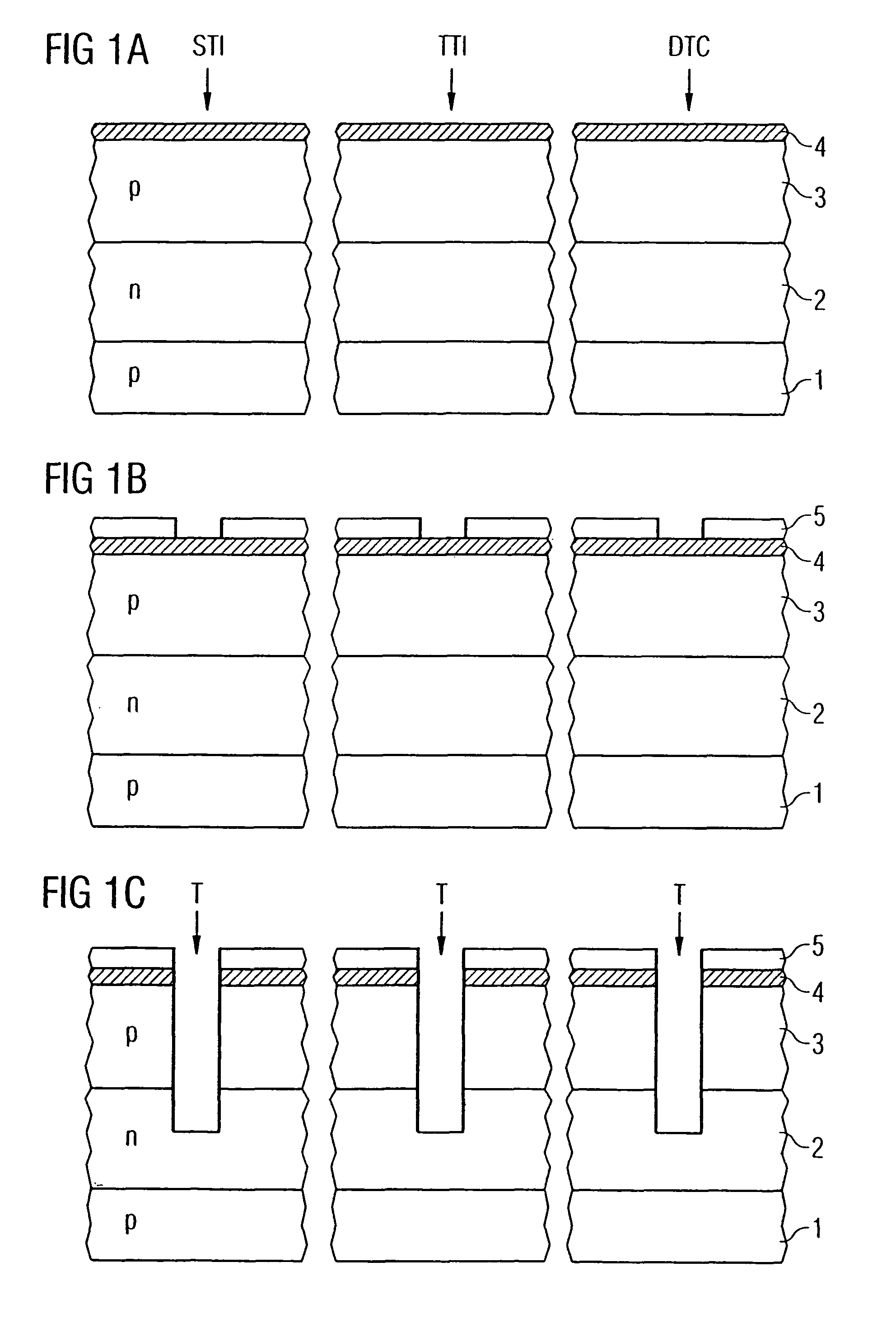

Semiconductor component with trench isolation and corresponding production method

InactiveUS8691660B2Reduce area requirementsImprove integration densitySolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

Owner:INFINEON TECH AG

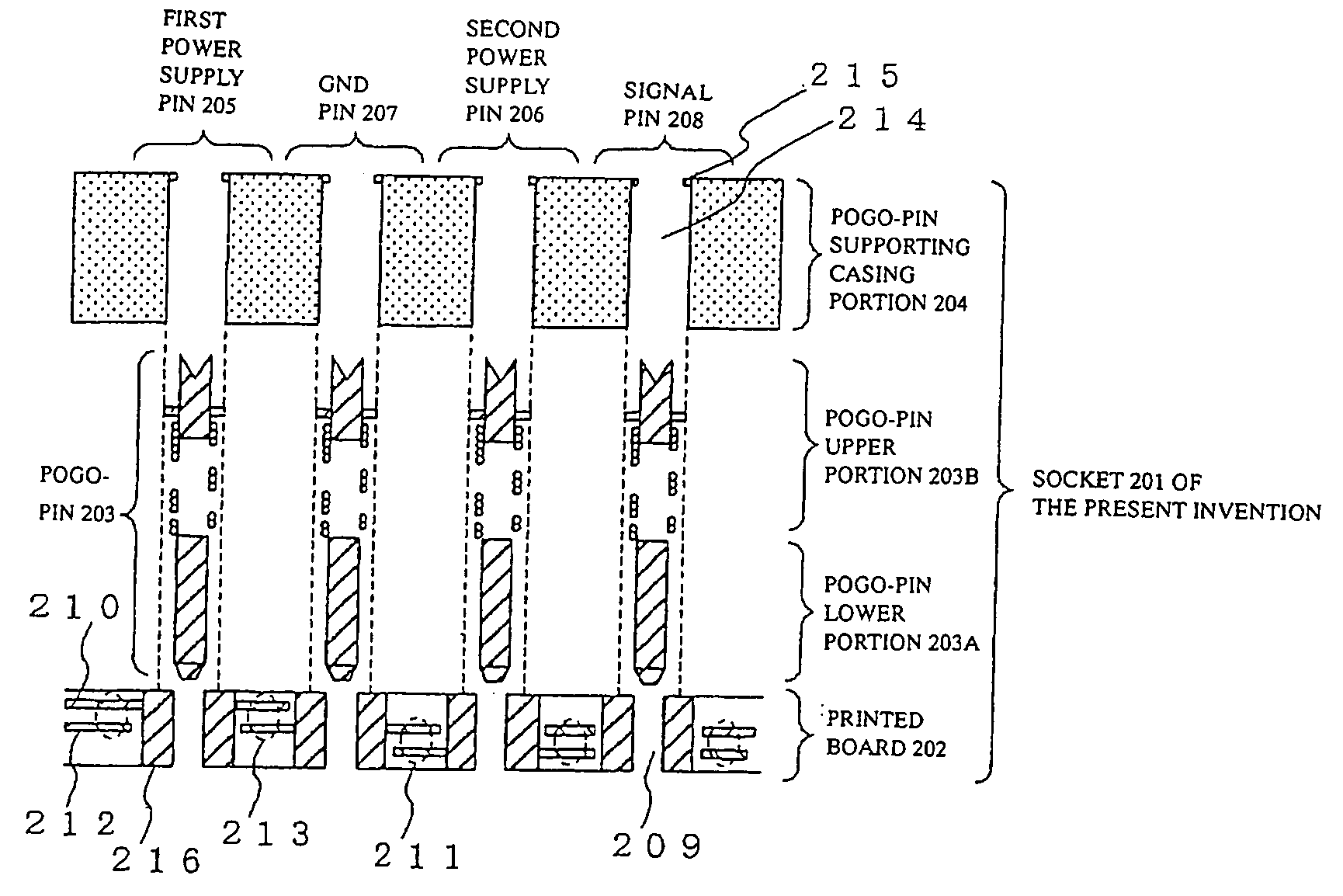

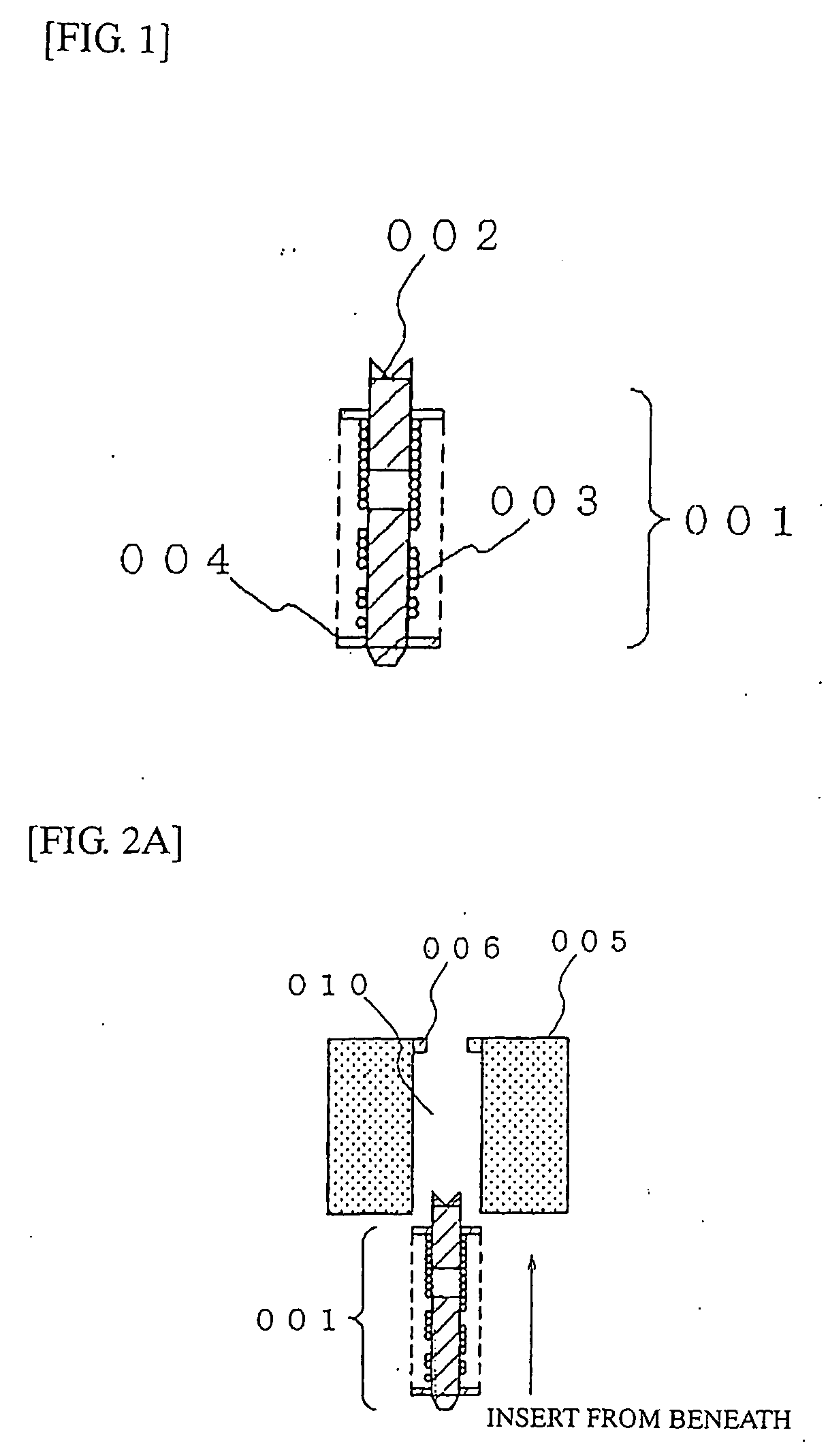

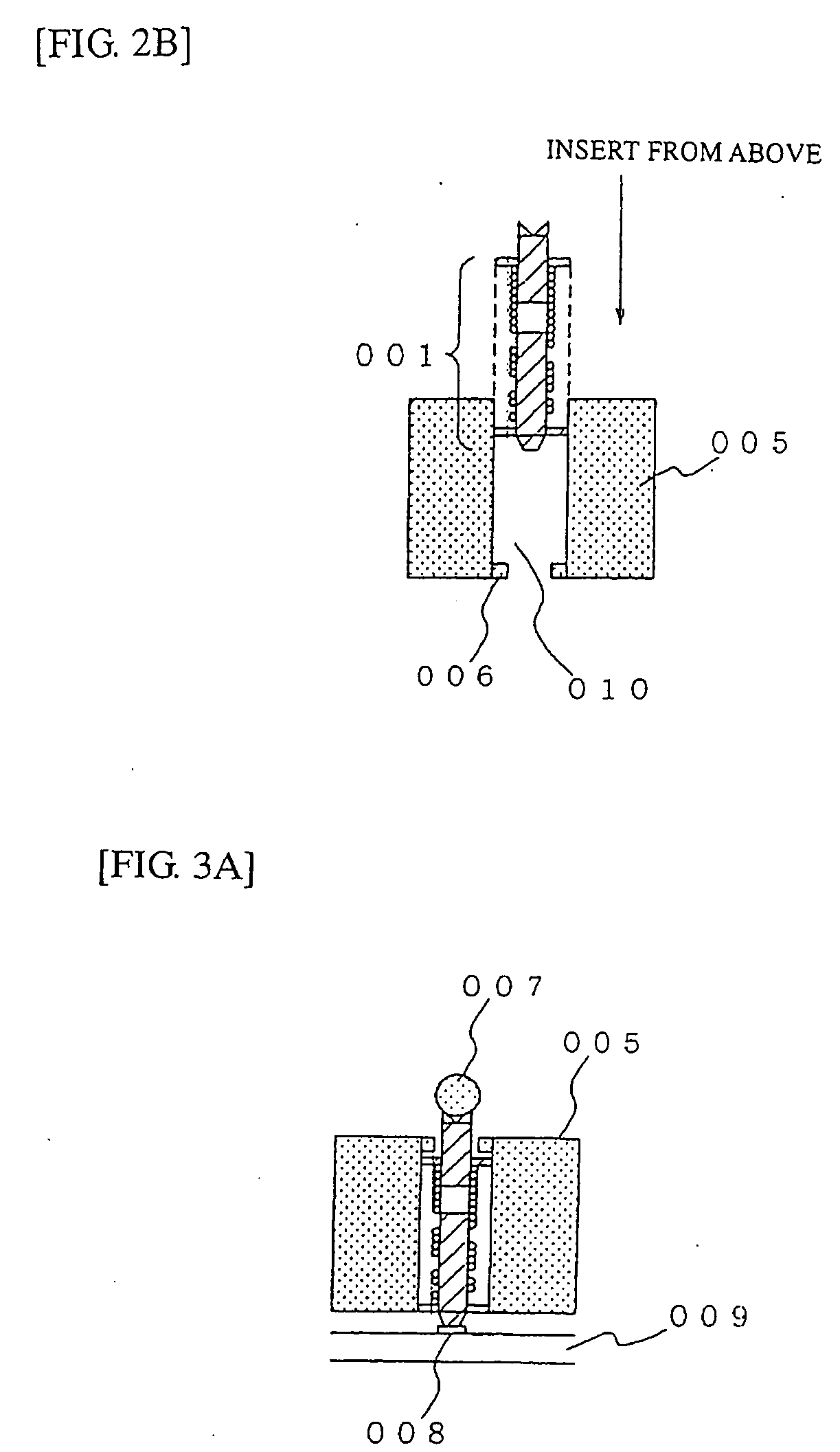

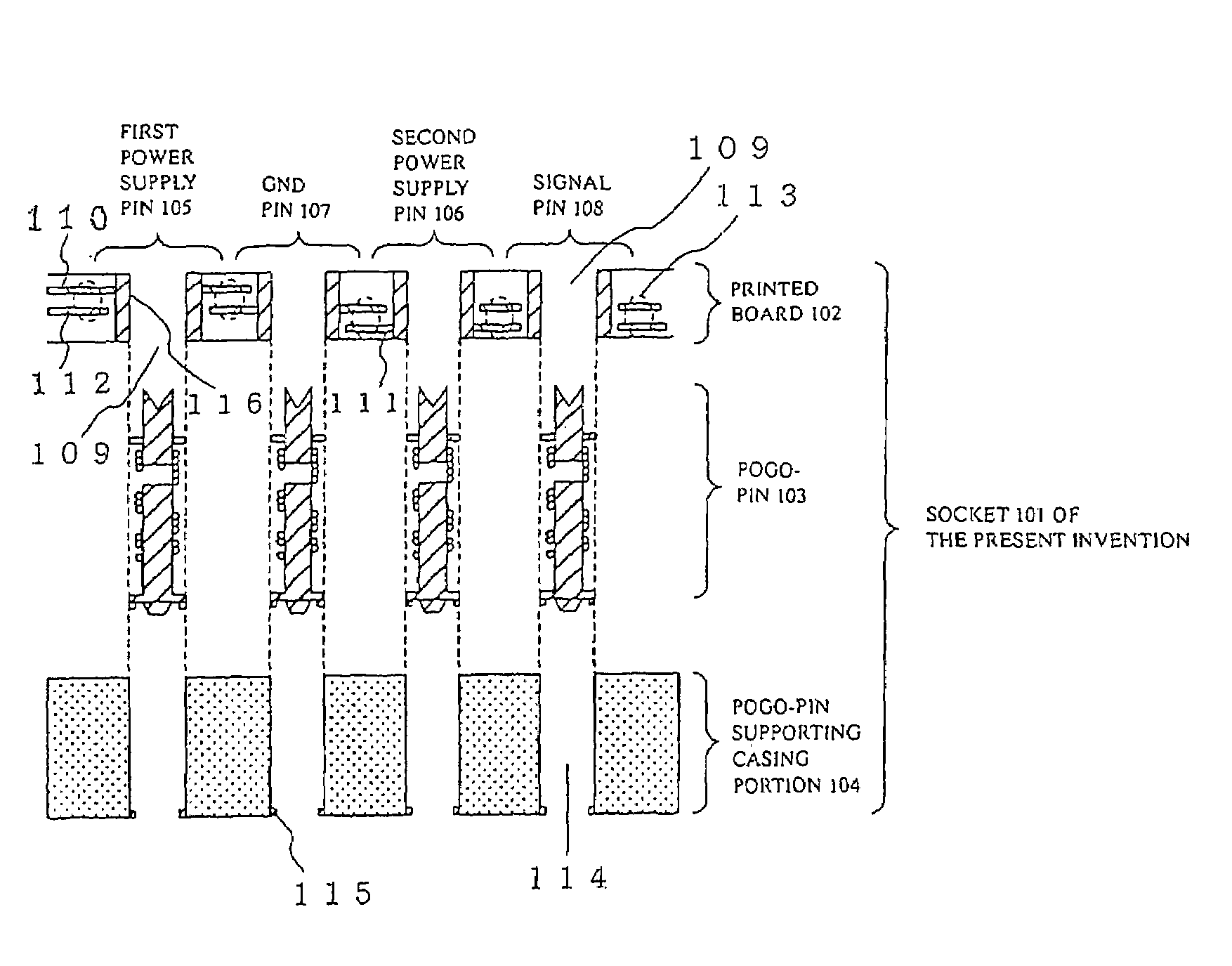

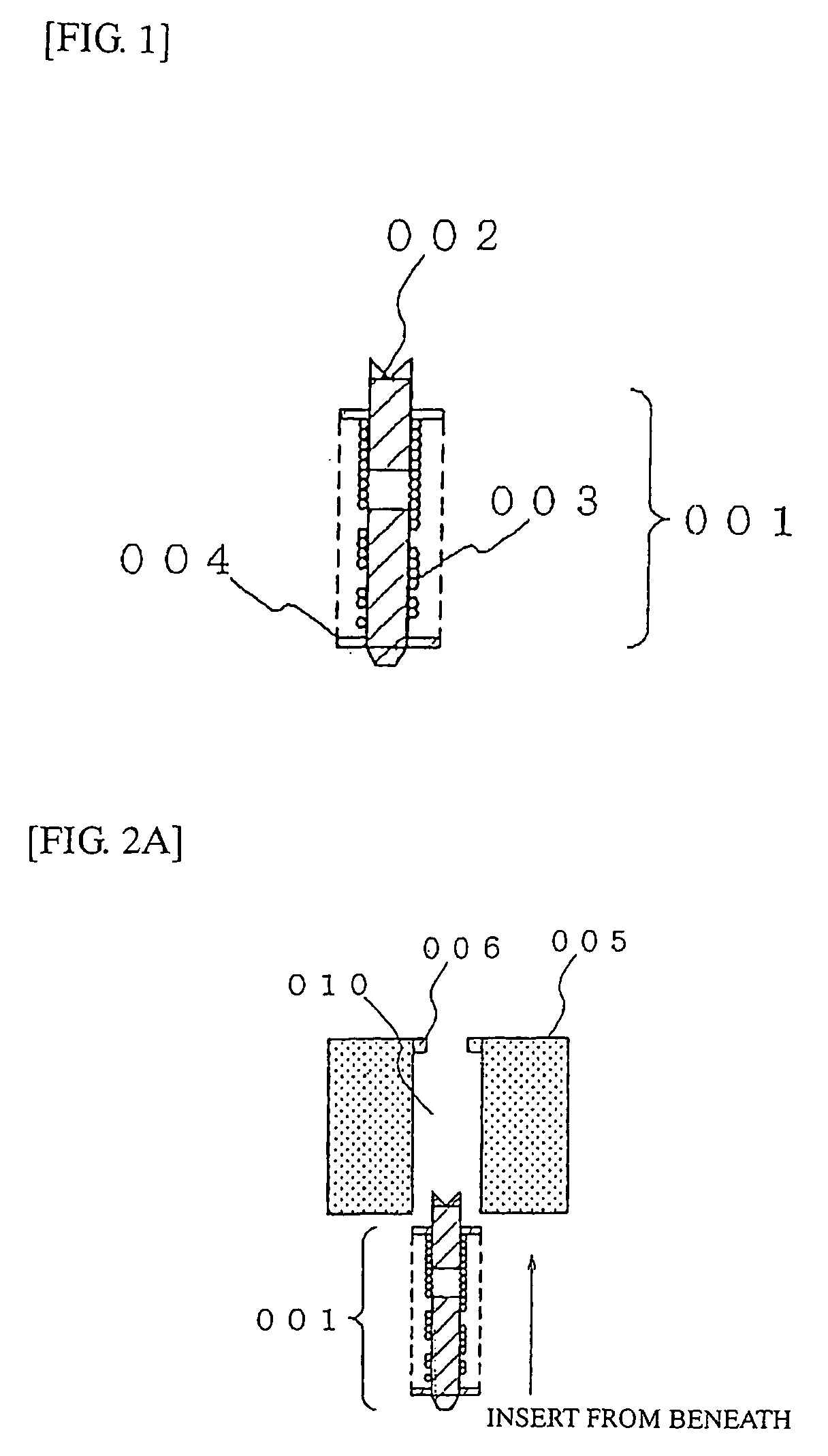

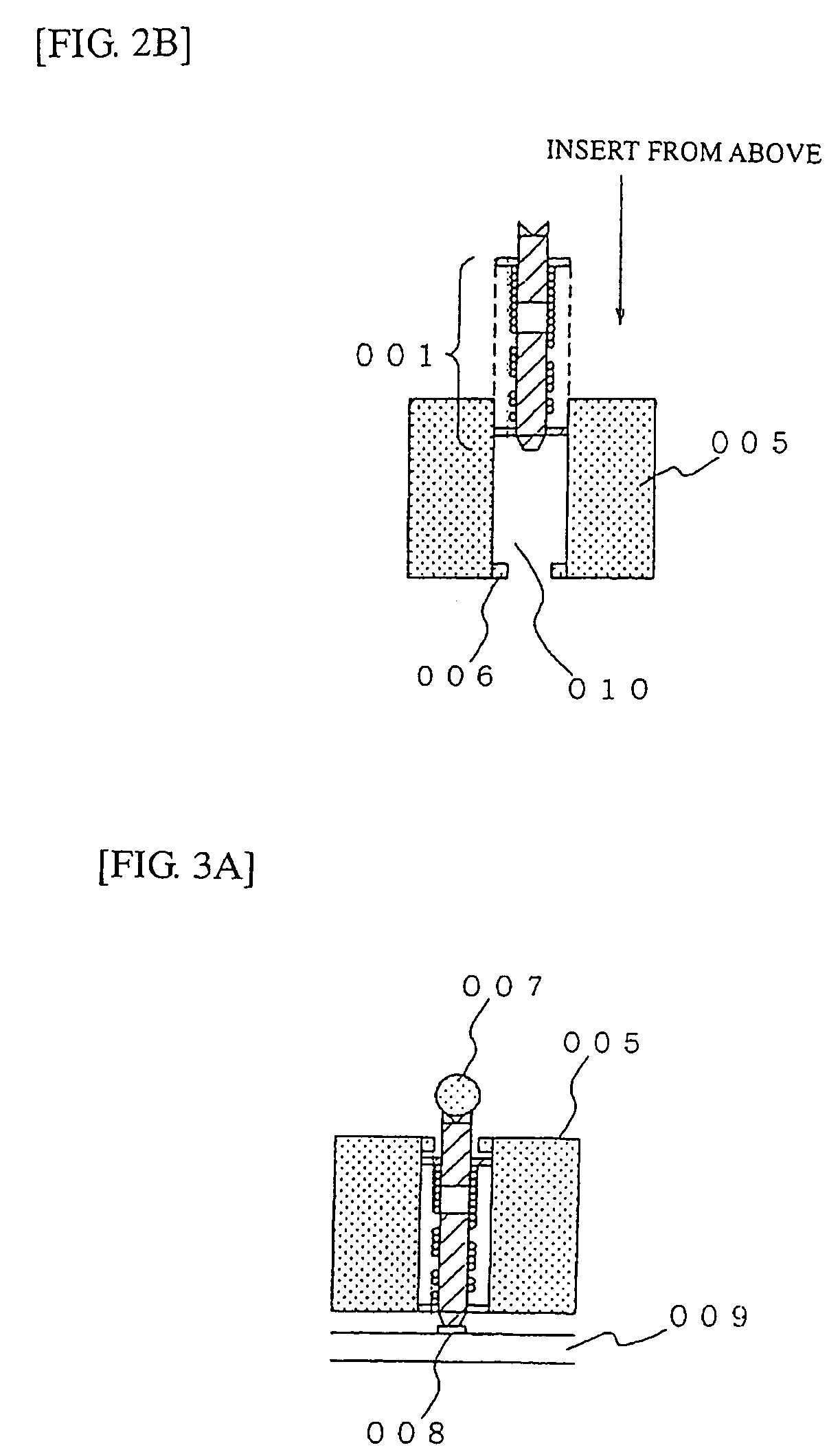

Lsi test socket for bga

InactiveUS20060132160A1Stable operation testExcellent manufacturing stabilityElectrical testingMeasurement instrument housingCapacitanceEngineering

There is provided an LSI socket containing a pogo-pin type decoupling capacitor for reducing the potential fluctuation of power supplies and GNDs at the time of testing LSI incorporated in a BGA package. The LSI socket comprises a printed board 102 containing decoupling capacitors 113 corresponding to one or more power supply voltages inside thereof, a pogo-pin supporting casing portion 104 on which the printed board 102 is overlapped into a single piece, and pogo-pins 103 inserted into penetrating holes in which hole positions of through holes 109 drilled in the printed board 102 and casing holes 114 drilled in the pogo-pin supporting casing portion 104 are allowed to be matched, wherein the printed board 102 is disposed on the upper surface side of the pogo-pin supporting casing portion 104 which faces the BGA package, or disposed on the lower surface side of the pogo-pin supporting casing portion 104, at the time of testing the LSI incorporated in the BGA package.

Owner:NEC CORP

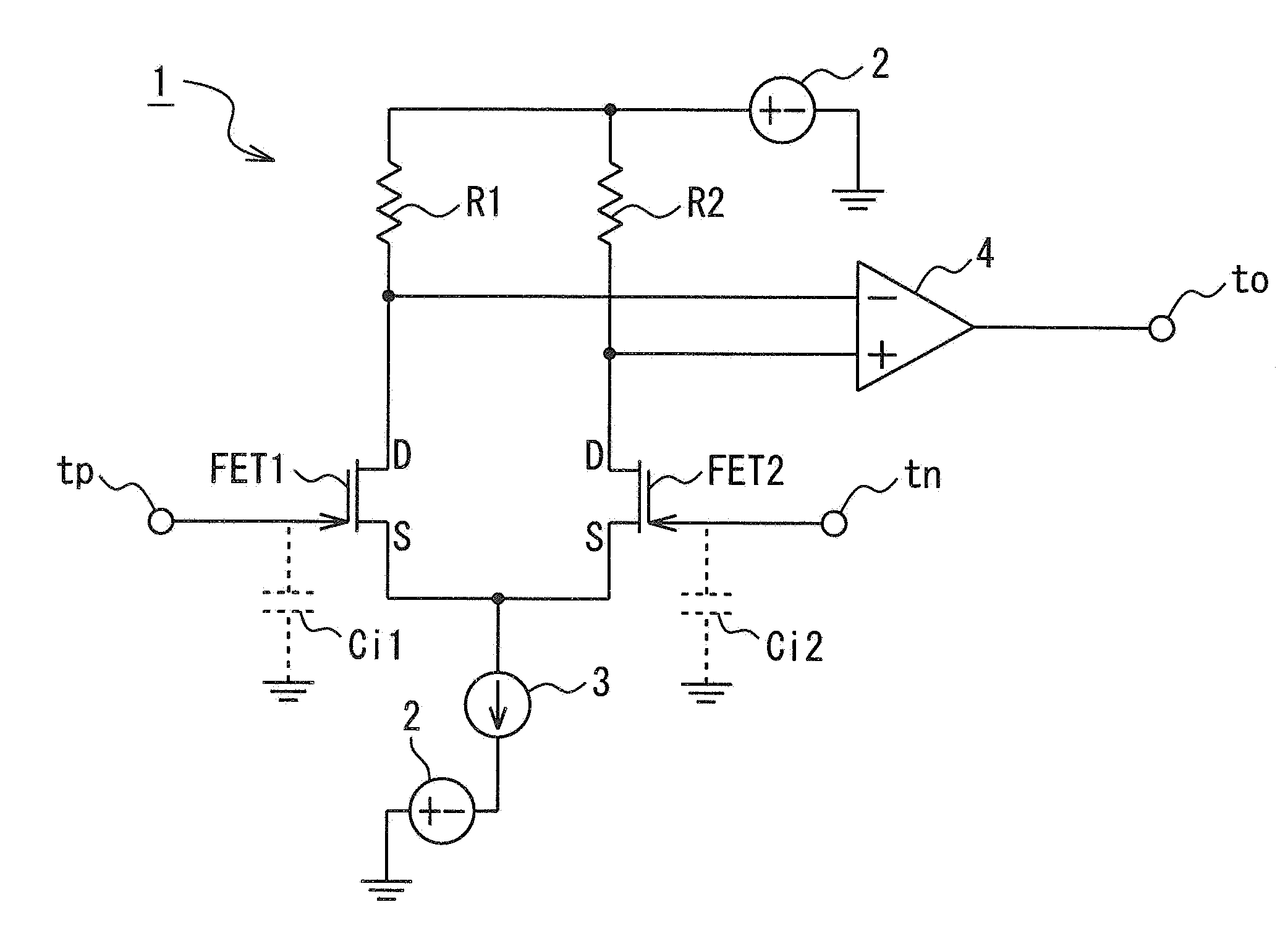

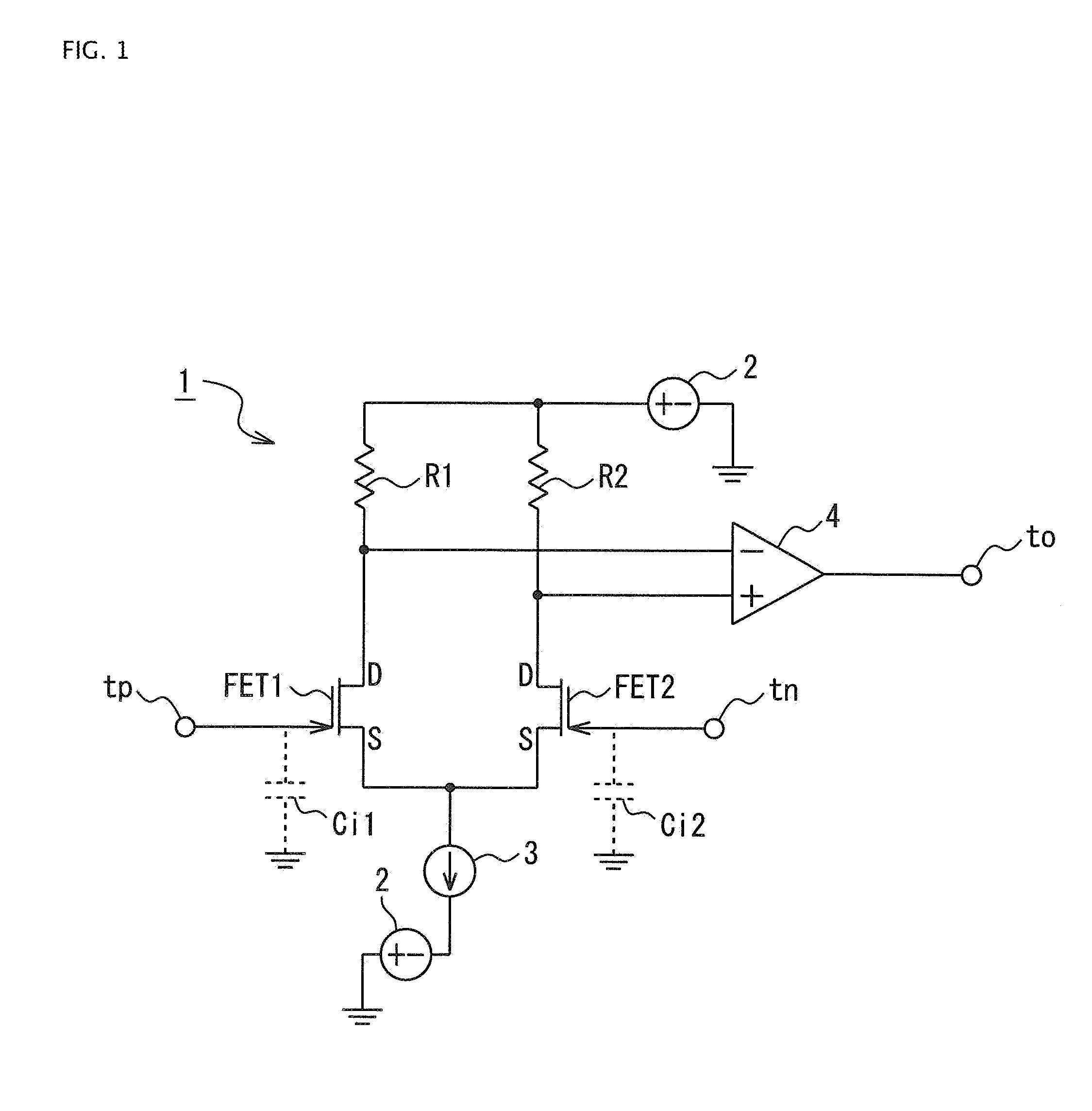

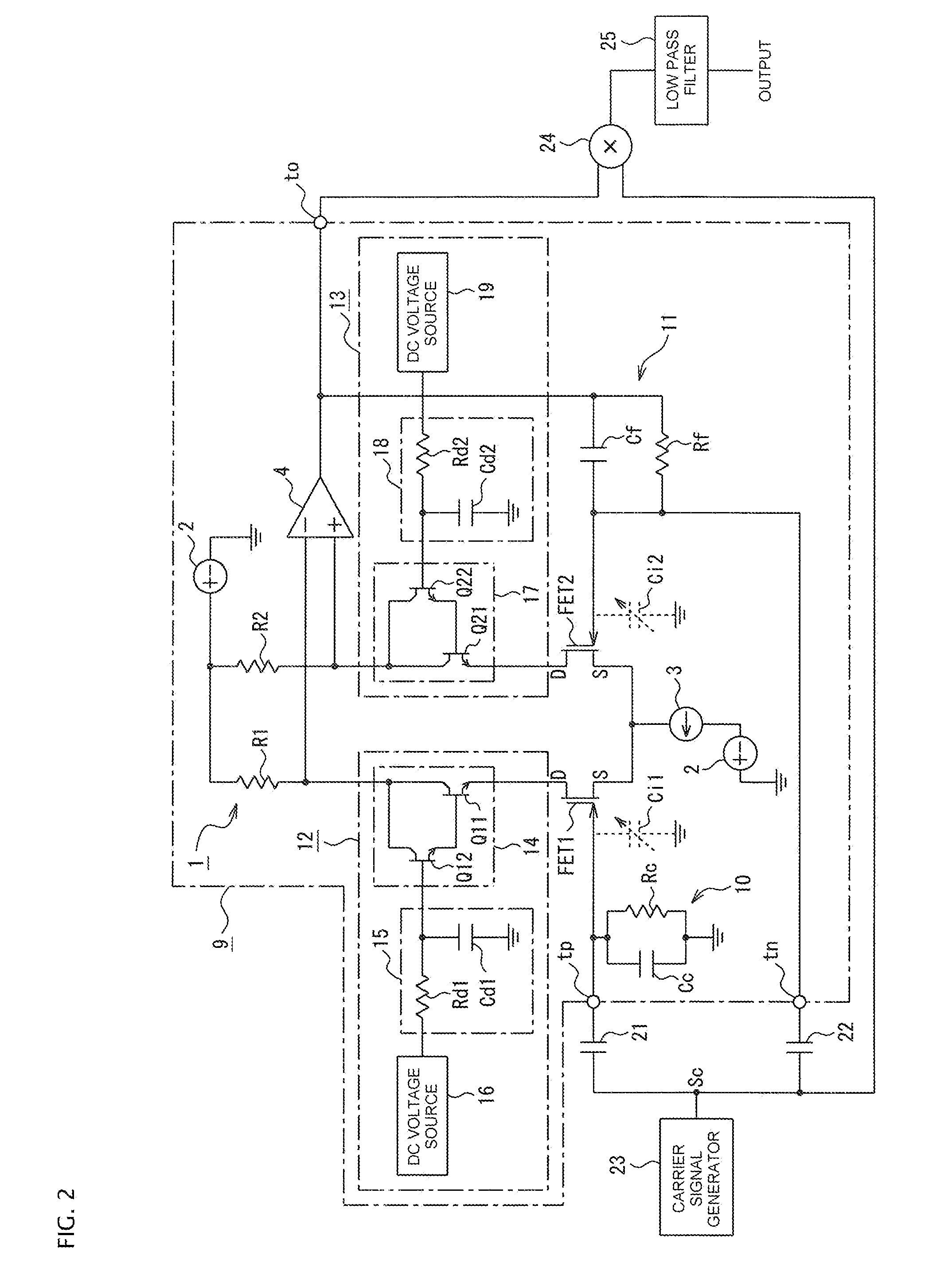

Electric charge detection circuit

InactiveUS20140062507A1Suppressing fluctuation of DC voltageSuppressing fluctuation of drain voltageCapacitance measurementsConverting sensor output electrically/magneticallyCapacitanceVoltage reference

Ends on one side of physical quantity detection sensors formed of any of an electric charge generation-type sensor and a capacitance change-type sensor can be connected to negative electrode input terminals of a differential amplifier circuit, and ends on the other side are connected to positive electrode input terminals of the differential amplifier circuit. A feedback resistor and a feedback capacitor are connected in parallel between the negative electrode input terminal and an output terminal of the differential amplifier circuit, and a cancel resistor and a cancel capacitor are connected in parallel between a reference voltage and the positive electrode input terminal of the differential amplifier circuit. Drain voltage adjustment circuits can be provided that adjust the drain voltage of at least one of two field effect transistors to which positive and negative differential inputs of the differential amplifier circuit are individually inputted.

Owner:FUJI ELECTRIC CO LTD

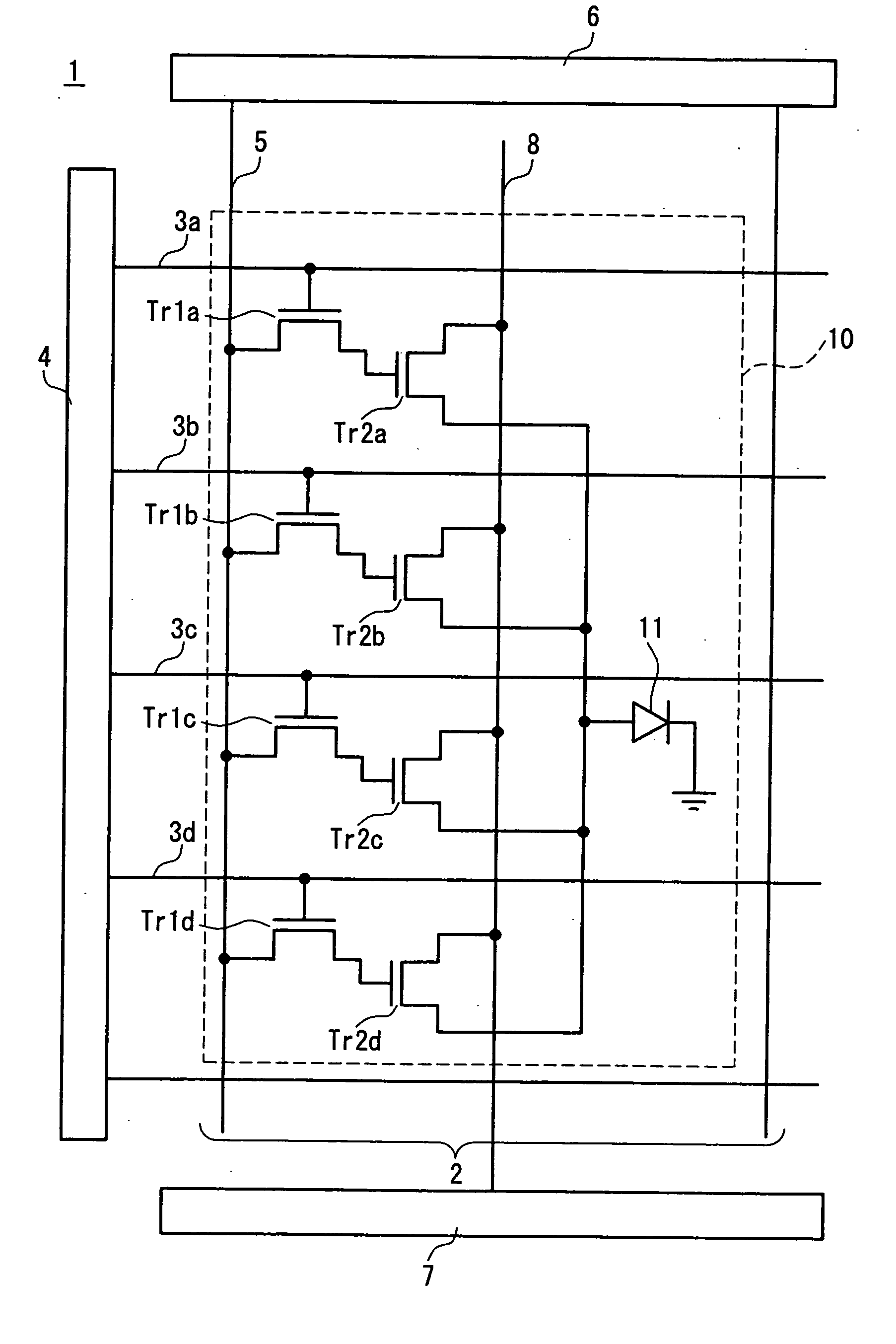

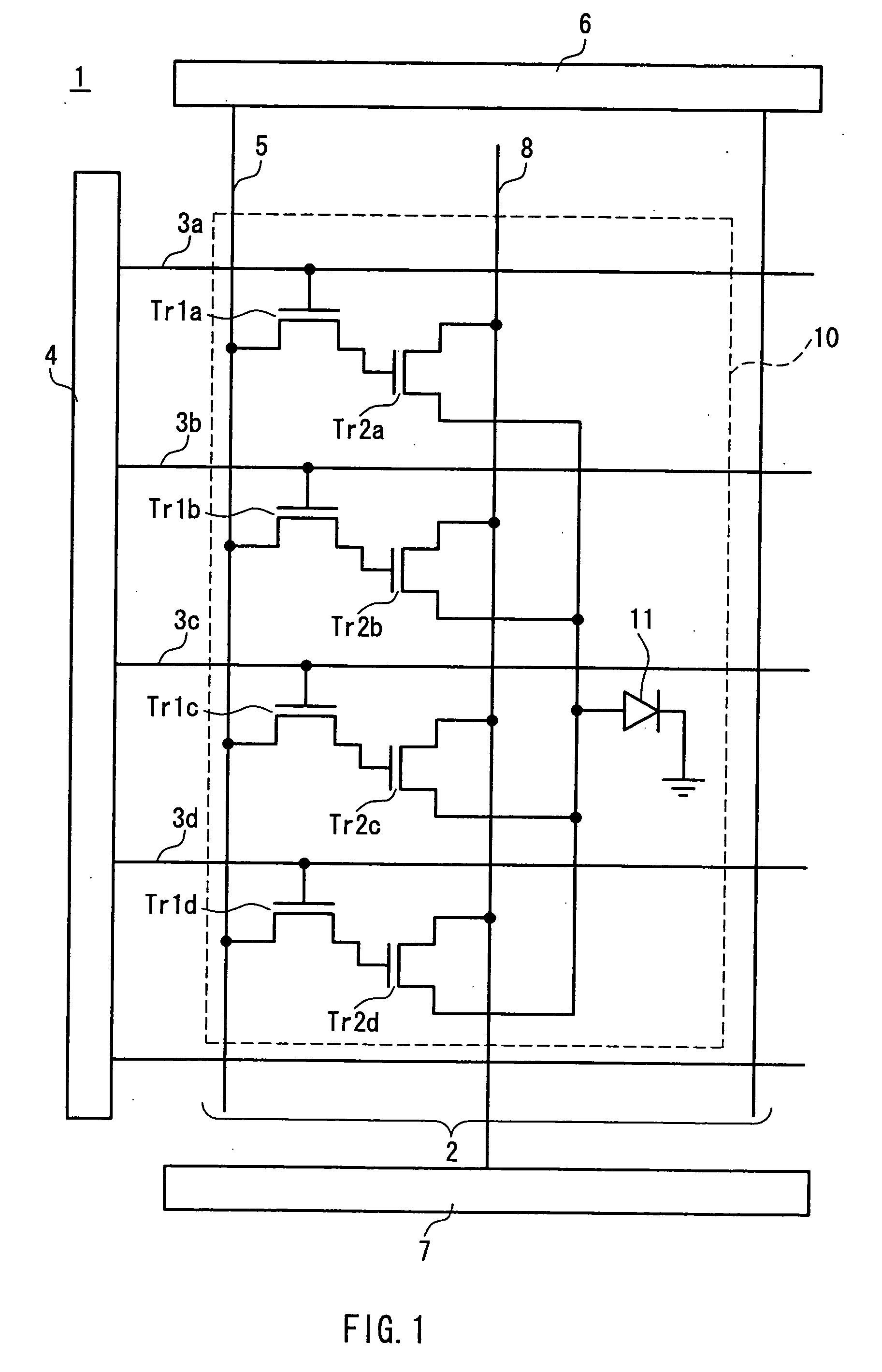

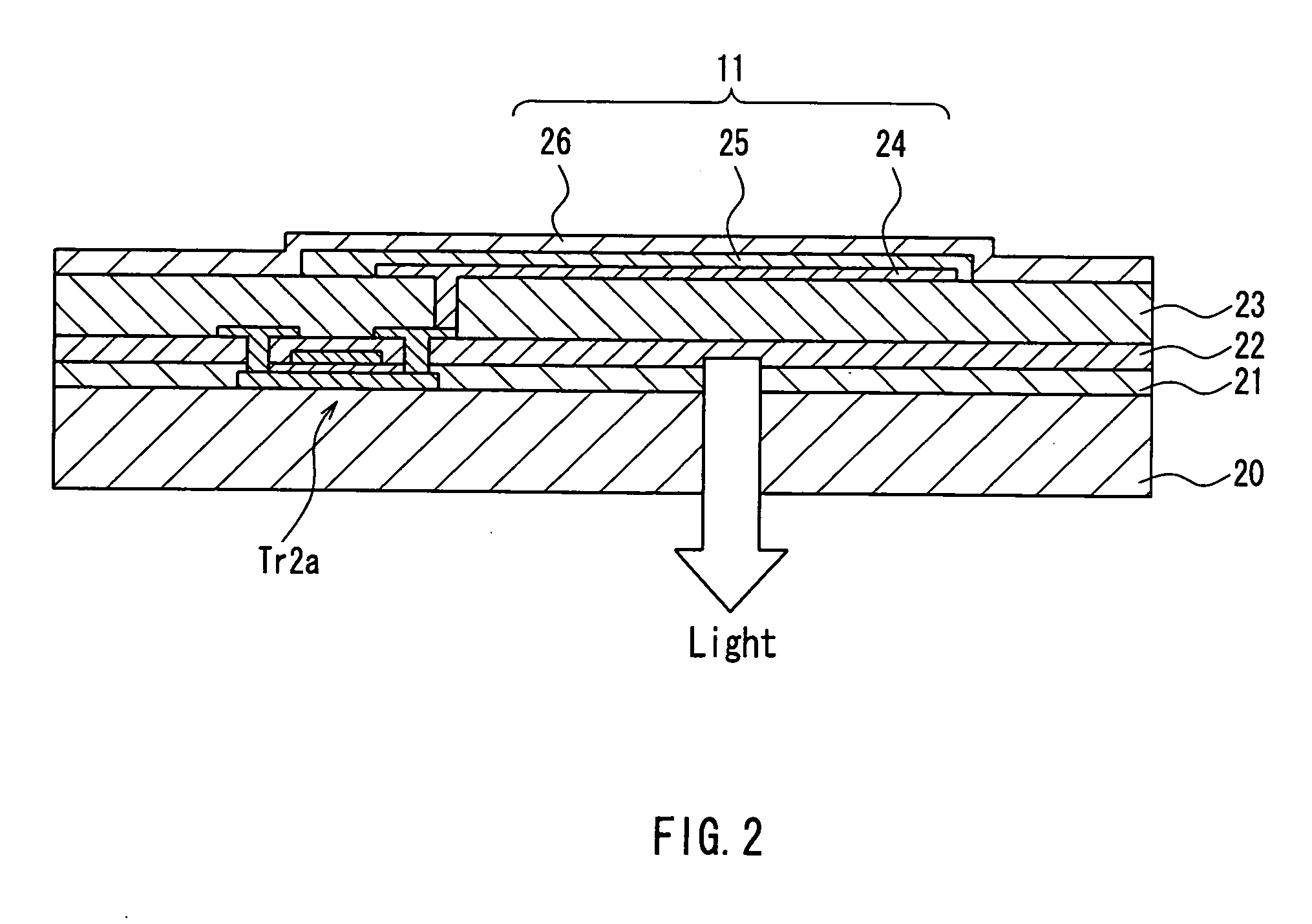

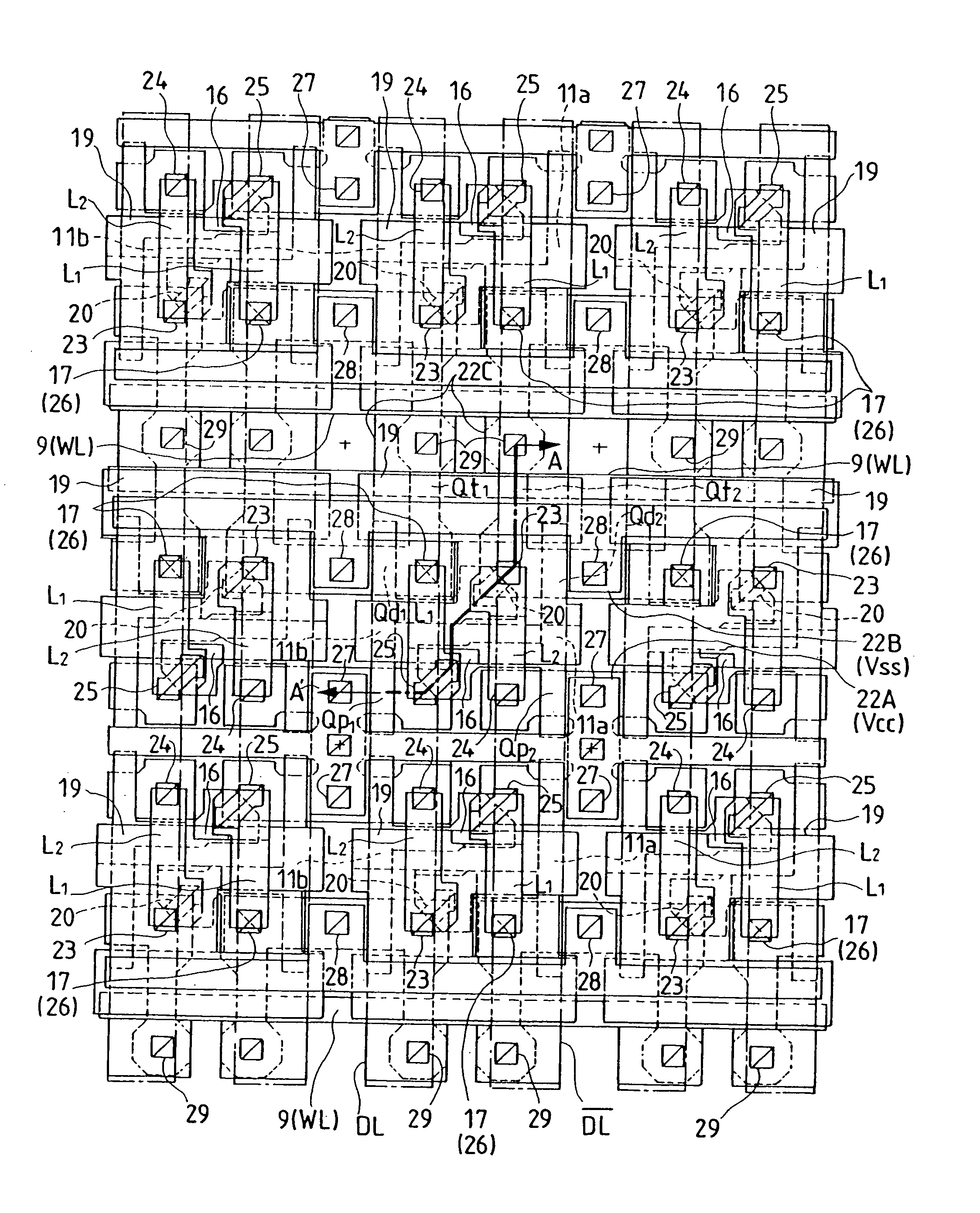

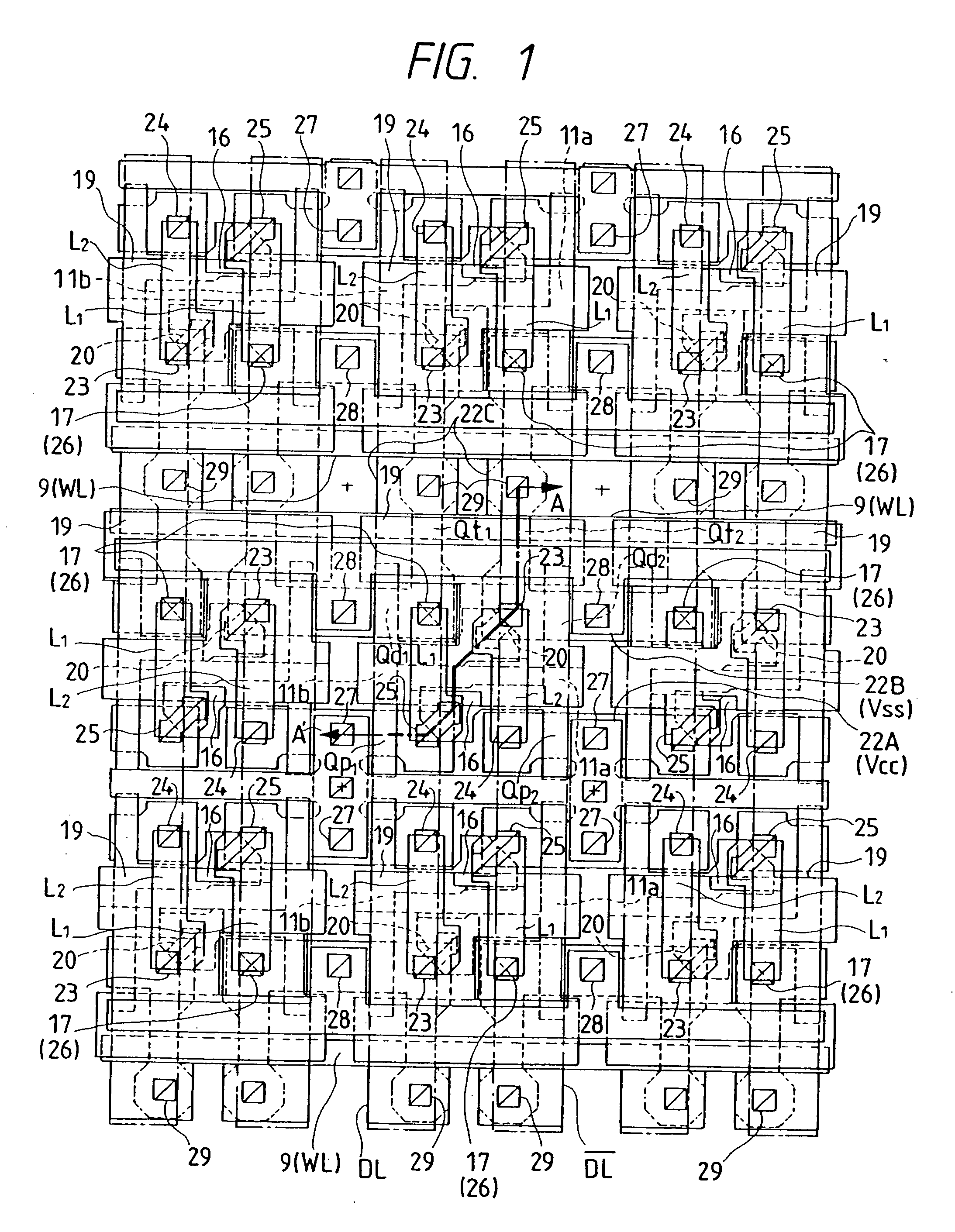

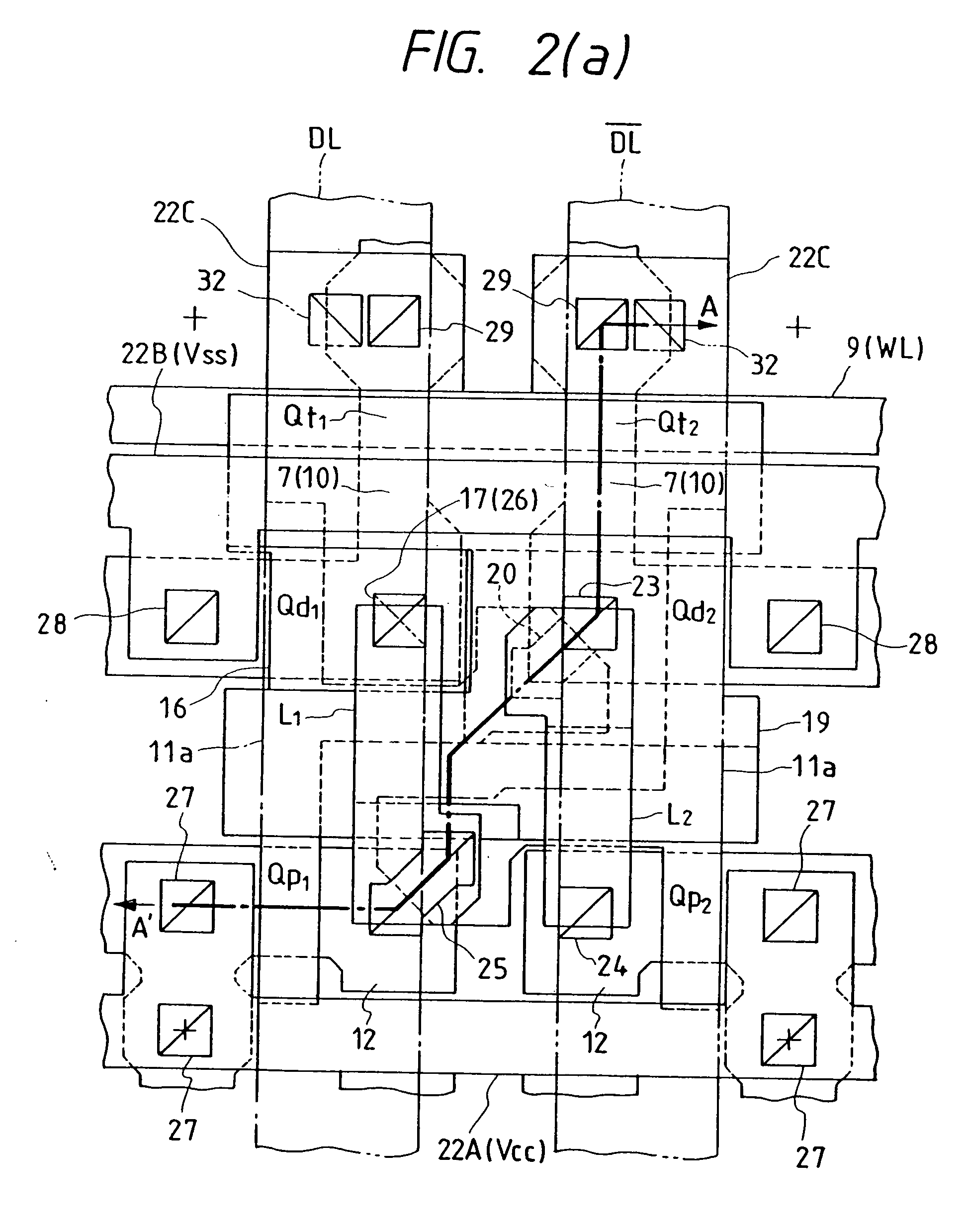

Active matrix el display and its driving method

InactiveUS20040196218A1Accurate gradation displayAccurate displayStatic indicating devicesSemiconductor/solid-state device manufacturingDriving currentActive matrix

A unit pixel (10) includes a plurality of current controlling elements (Tr2a-Tr2d) having controlling terminal and connected to a single EL element (11), and switching elements (Tr1a-Tr1d) provided to the respective current controlling elements in order to switch between application and cutoff of a digital image signal with respect to the controlling terminals in accordance with the condition of a scanning signal. Each of the current controlling elements is controlled by a voltage of the digital image signal so as to take an OFF state for cutting off a supply of a driving current to the EL element or an ON state for supplying the EL element with a driving current corresponding to the voltage of the digital image signal, and a value of the current flowing in the EL element is the sum value of currents supplied from the respective current controlling elements in the ON state. Based on a combination of the current controlling elements in the ON state, the current supplied to the EL element is controlled to be a value corresponding to the gradation.

Owner:JOLED INC

Method of manufacturing semiconductor integrated circuit device having capacitor element

InactiveUS20050242405A1Increase resistancePotential fluctuationTransistorSemiconductor/solid-state device detailsCapacitanceCMOS

In a complete CMOS SRAM having a memory cell composed of six MISFETs formed over a substrate, a capacitor element having a stack structure is formed of a lower electrode covering the memory cell, an upper electrode, and a capacitor insulating film (dielectric film) interposed between the lower electrode and the upper electrode. One electrode (the lower electrode) of the capacitor element is connected to one storage node of a flip-flop circuit, and the other electrode (the upper electrode) is connected to the other storage node. As a result, the storage node capacitance of the memory cell of the SRAM is increased to improve the soft error resistance.

Owner:ACACIA RES GROUP

Semiconductor component with trench insulation and corresponding production method

ActiveUS20110003457A1Reduce area requirementsImprove integration densitySolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerElectrically conductive

The invention relates to a semiconductor component with trench isolation and to an associated fabrication method, a trench isolation (STI, TTI) having a deep isolation trench with a covering insulation layer (10, 11), a side wall insulation layer (6) and an electrically conductive filling layer (7), which is electrically connected to a predetermined doping region (1) of the semiconductor substrate in a bottom region of the trench. The use of a trench contact (DTC), which has a deep contact trench with a side wall insulation layer (6) and an electrically conductive filling layer (7), which is likewise electrically connected to the predetermined doping region (1) of the semiconductor substrate in a bottom region of the contact trench, makes it possible to improve the electrical shielding properties with a reduced area requirement.

Owner:INFINEON TECH AG

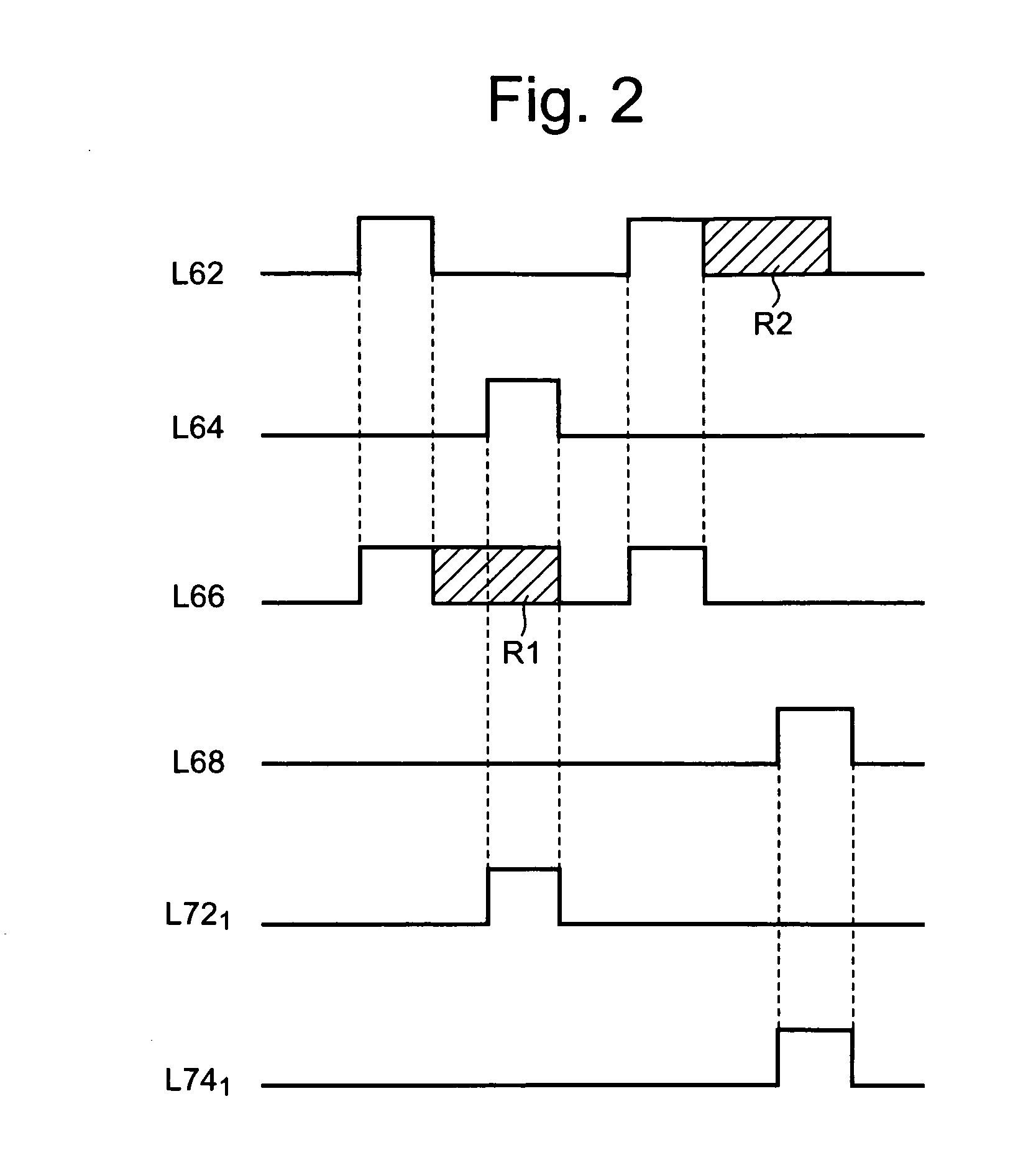

Display driver and display driving method

ActiveUS20100165011A1Potential fluctuationReduce volatilityCathode-ray tube indicatorsInput/output processes for data processingOriginal dataPre-charge

In a display driver, one scanning period is divided into a period P and a subsequent period D. In the period P, a pre-charge voltage equal to an original data voltage is applied in a time-sharing manner to data lines in one block, and in the period D after the period P, the original data voltage is applied again.

Owner:RENESAS ELECTRONICS CORP

LSI test socket for BGA

InactiveUS7129728B2Manufacturing stability and test stabilityPotential fluctuation of power supplies of LSI operating at high frequencies may be reducedElectrical testingMeasurement instrument housingEngineeringDecoupling capacitor

Owner:NEC CORP

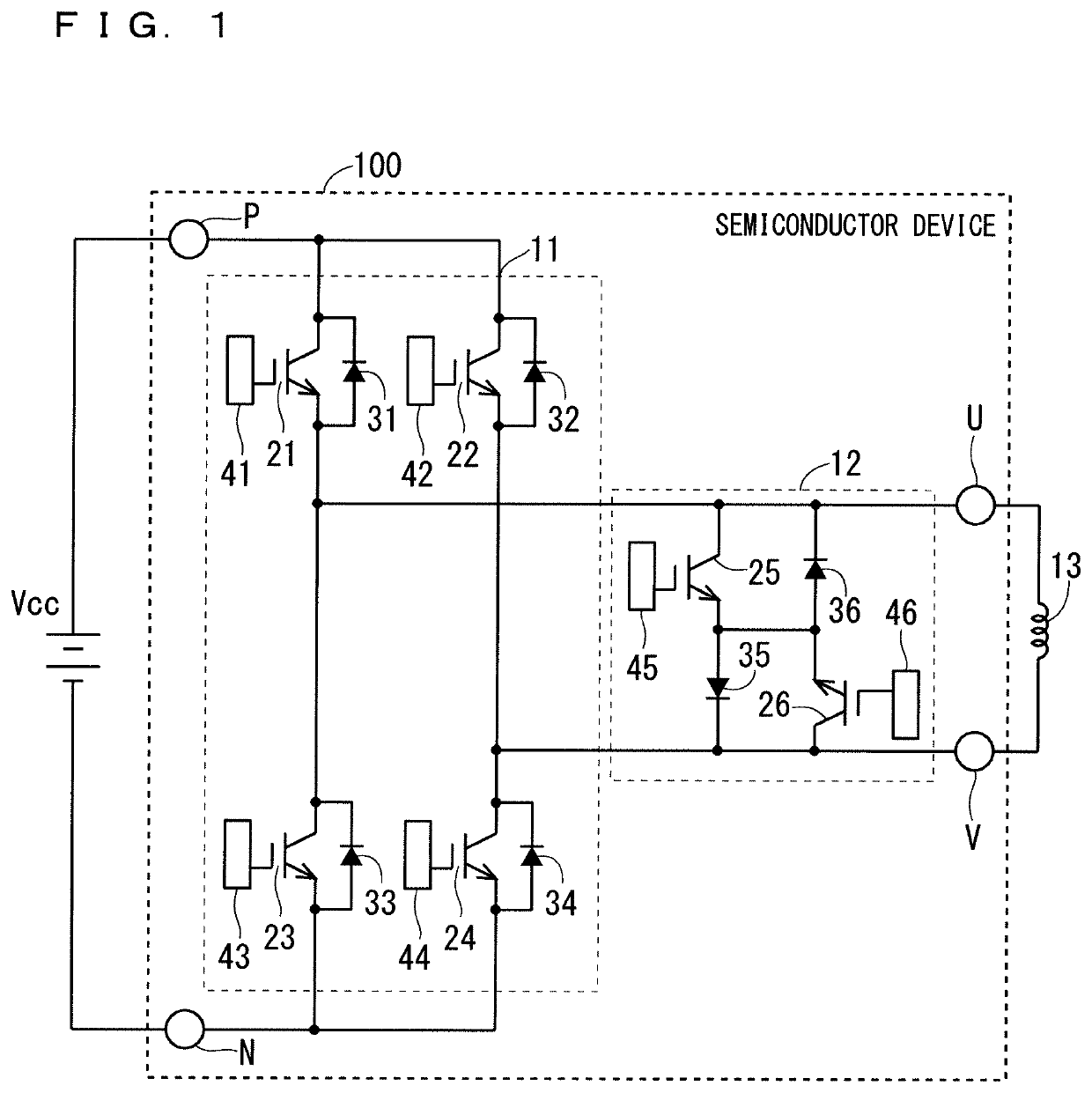

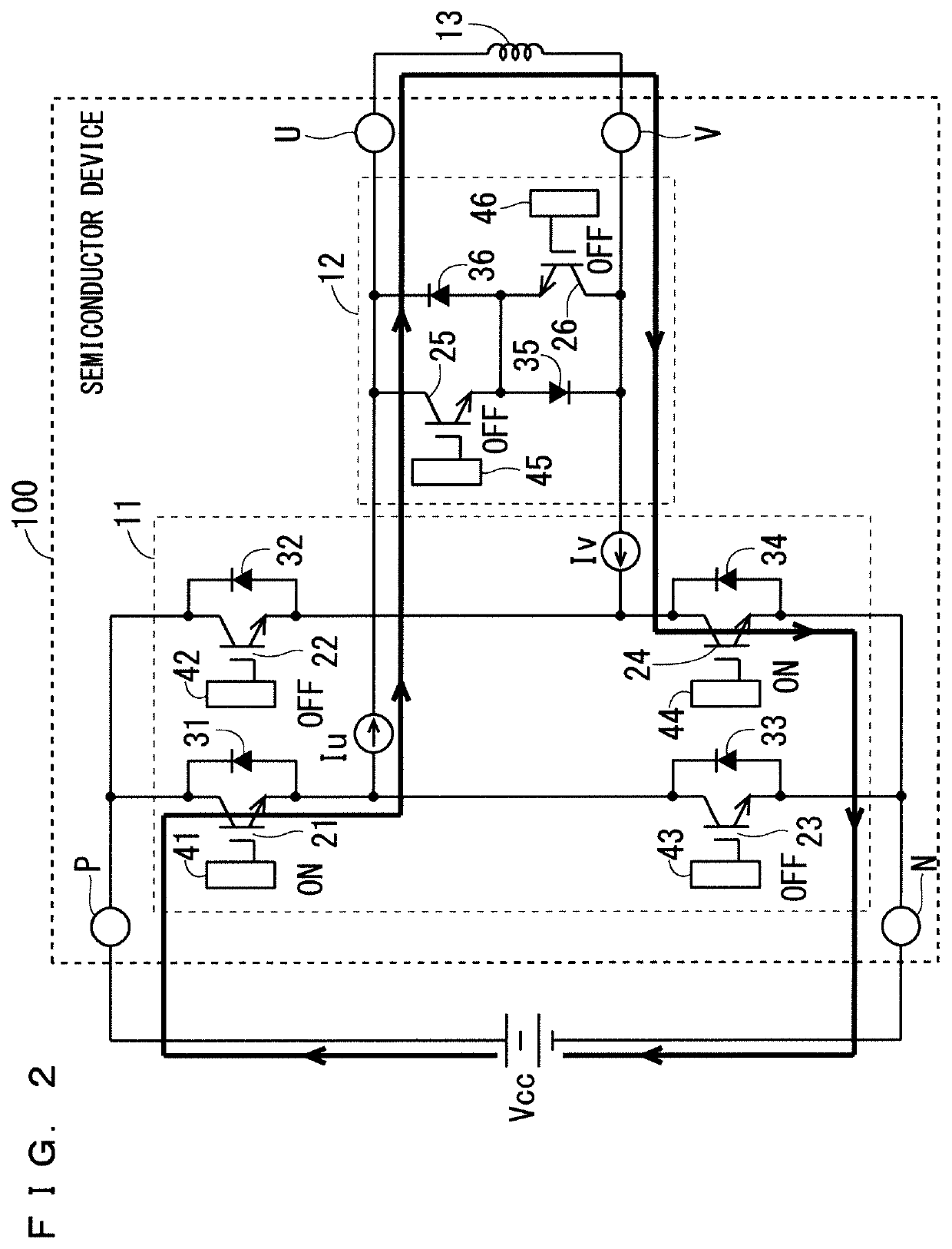

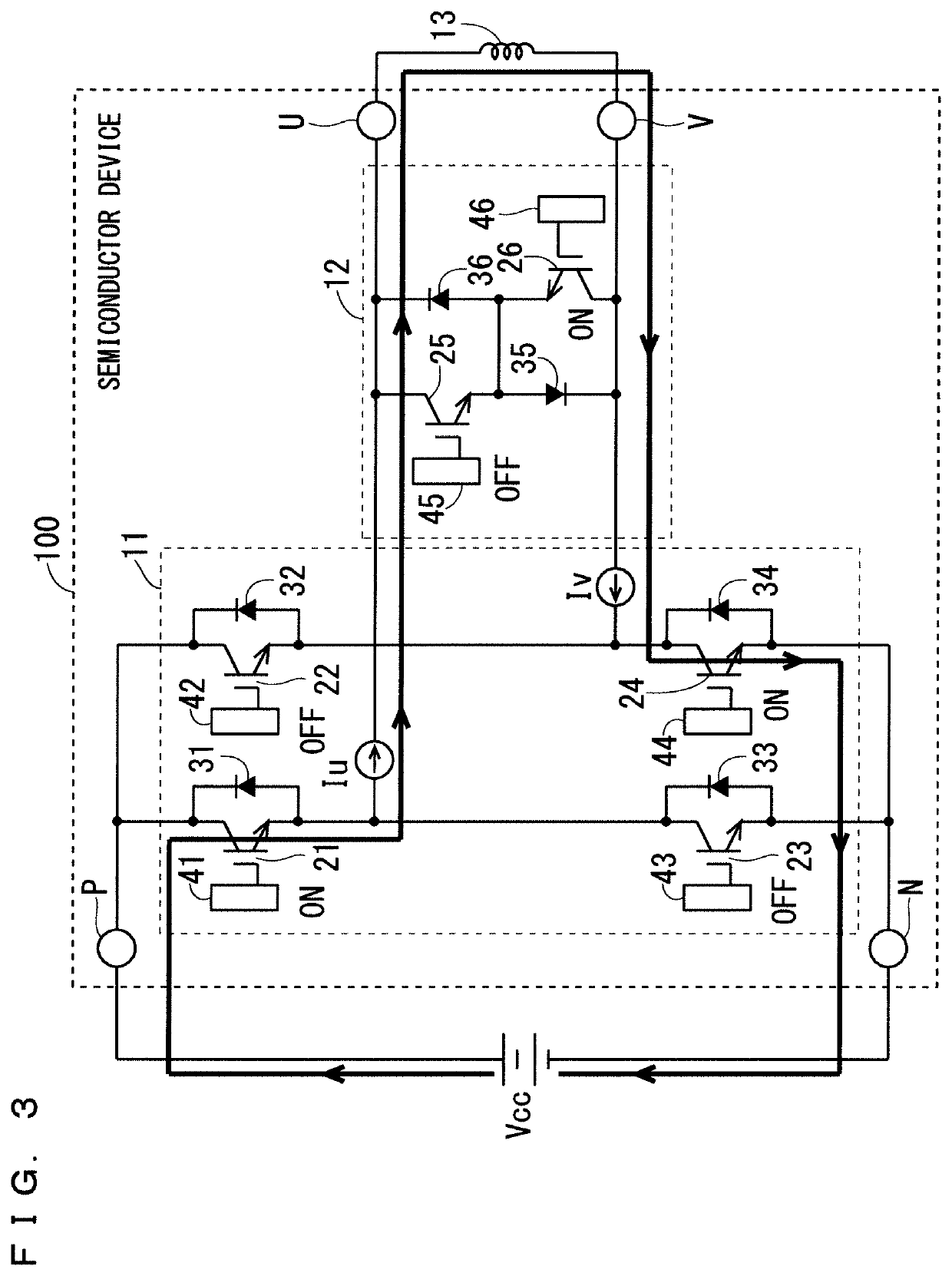

Semiconductor device

ActiveUS20210218328A1Suppress conduction noiseSuppress noiseConversion constructional detailsSolid-state devicesDevice materialFull bridge

The object of the present disclosure is to suppress the conduction noise in a semiconductor device. A semiconductor device includes an inverter section being a full-bridge inverter, and a reflux section that short-circuits between output terminals U and V of the inverter section, in which impedances and are provided between each of freewheel diodes and of the upper arm and the output terminals U and V, and impedances and are provided between the freewheel diodes and of the lower arm and the input terminal N of in the inverter section, and the impedances to are greater than parasitic impedance of wiring assuming that IGBTs to and the output terminals U and V or the IGBTs and the input terminal N are connected only by the wiring.

Owner:MITSUBISHI ELECTRIC CORP

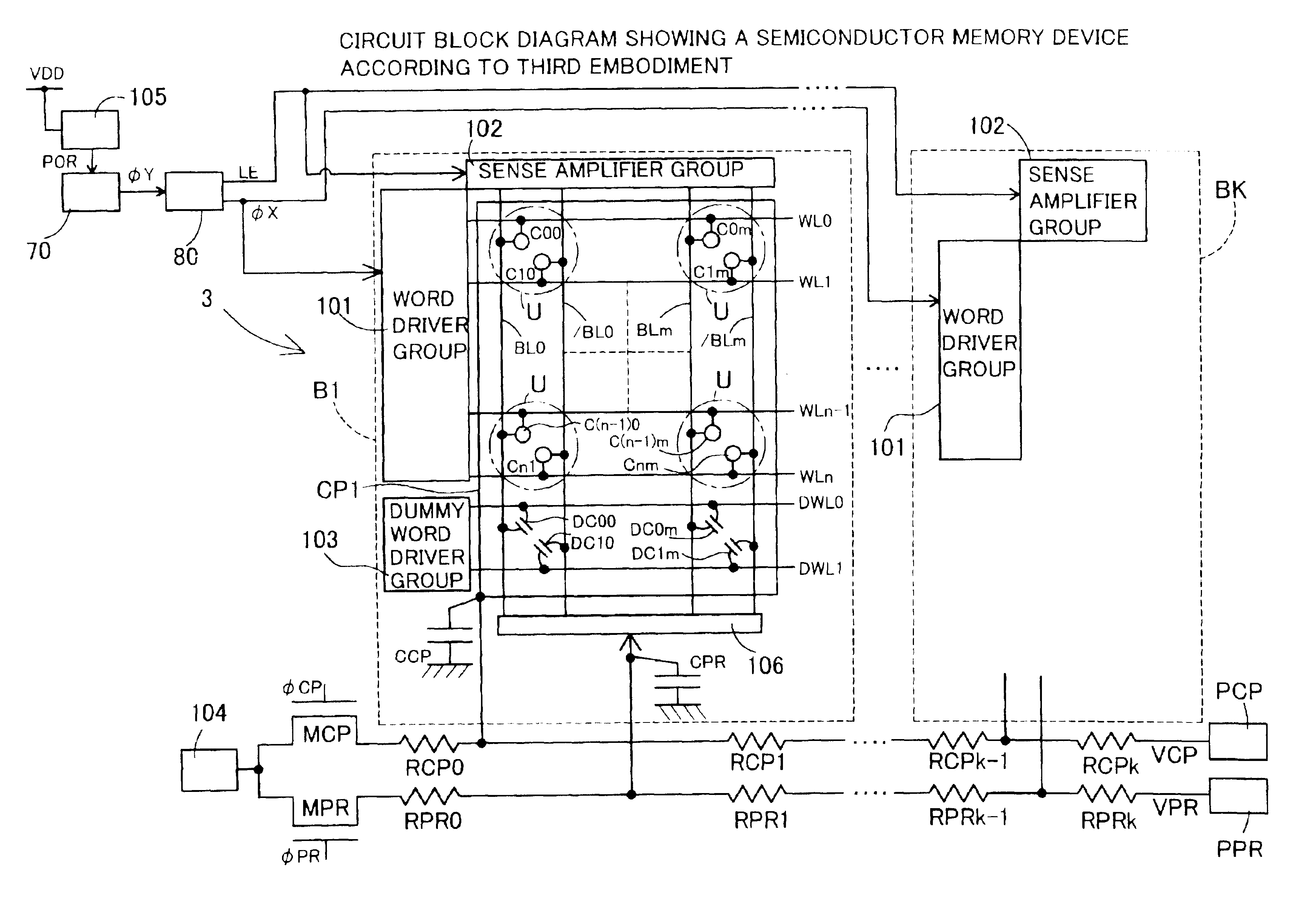

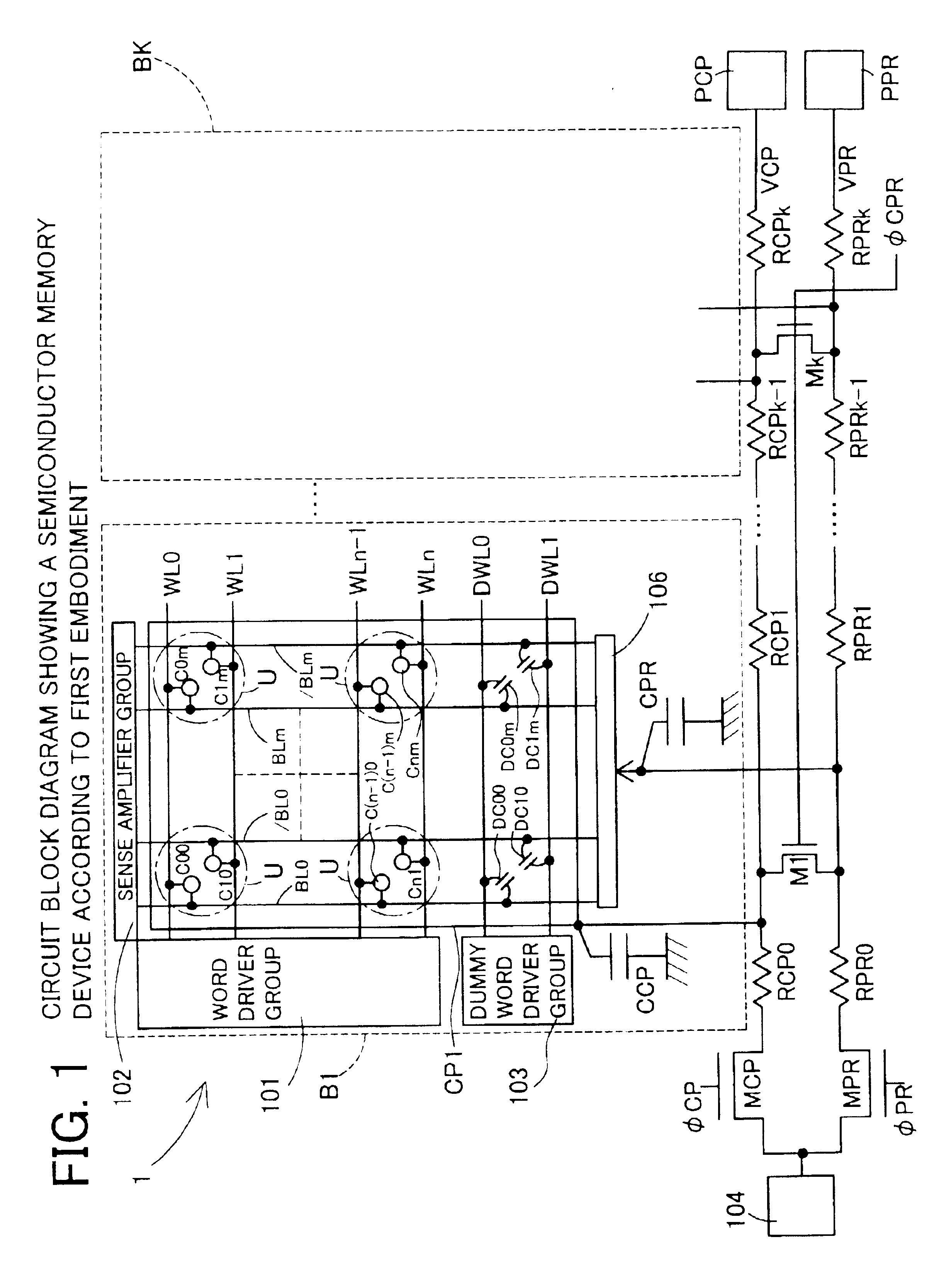

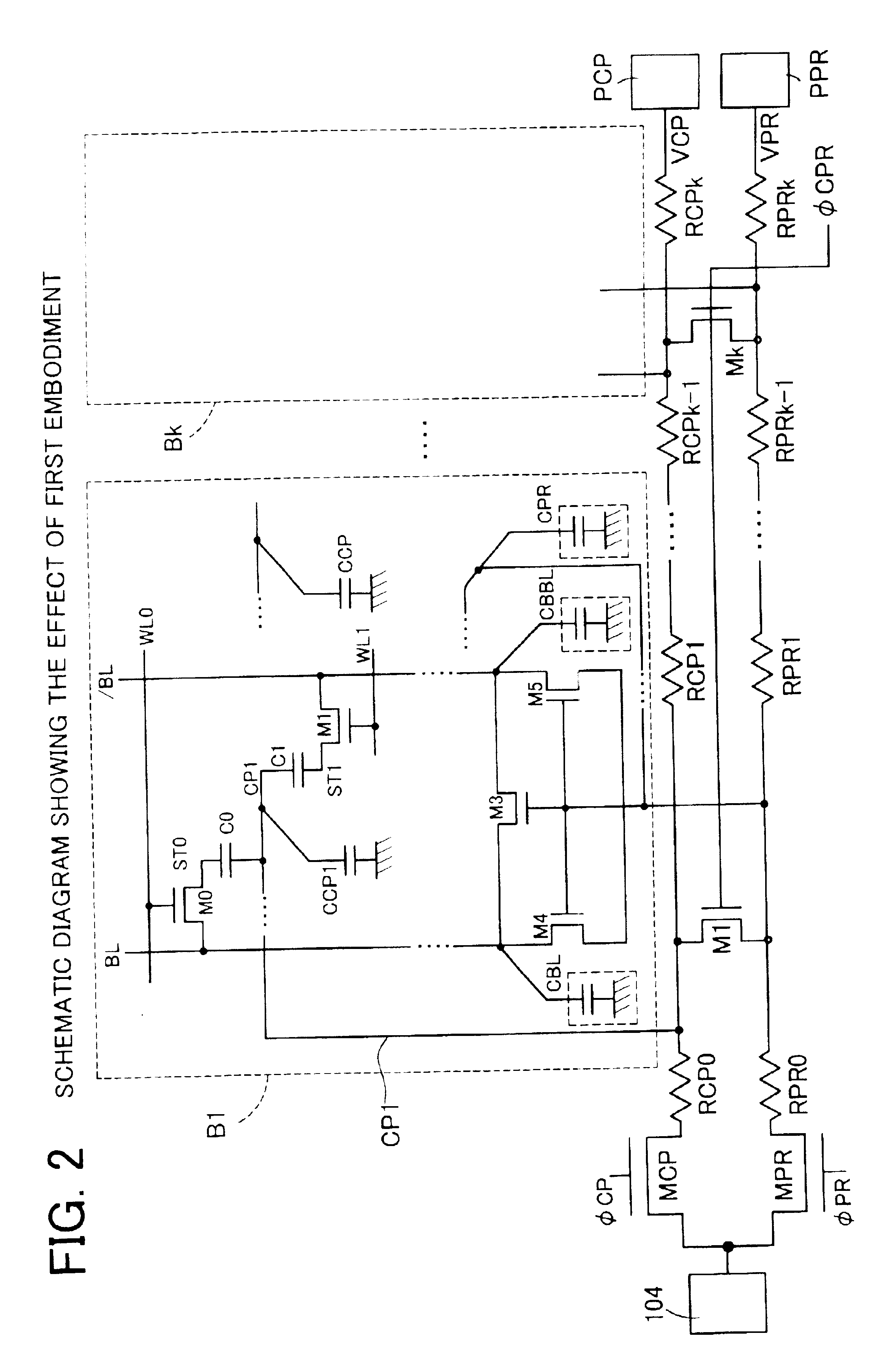

Semiconductor memory device and control method thereof

InactiveUS6847540B2Enough timeShort timeTransistorSemiconductor/solid-state device manufacturingElectricityVoltage reference

A semiconductor memory device, in which a cell plate potential does not fluctuate even when the device state is changed from a state without stored charge in all charge storage nodes of the cell capacitors at power-on to an access operation state, comprises NMOS transistors M1 to Mk for connecting a line VPR as a feeder for a reference voltage VPR from a reference voltage generation circuit with a line VCP as a feeder for a reference voltage VCP from the reference voltage generation circuit in each of cell blocks B1 to Bk. Gate terminals of the NMOS transistors M1 to Mk are connected to a common signal φCPR. The signal φCPR outputs a positive logical level at a predetermined time after power-on. By providing the NMOS transistors M1 to Mk for short-circuiting the line VPR with the line VCP in each of the cell blocks B1 to Bk, both lines are short-circuited in each of the cell blocks B1 to Bk.

Owner:SOCIONEXT INC

Display device and drive method thereof

ActiveUS9401111B2Fluctuation in the node potential in the pixel circuit in the standby period can be preventedSuppress brightnessStatic indicating devicesDisplay deviceEngineering

Owner:SHARP KK

Display driver and display driving method

ActiveUS7692641B2Potential fluctuationReduce volatilityCathode-ray tube indicatorsInput/output processes for data processingOriginal dataPre-charge

In a display driver, one scanning period is divided into a period P and a subsequent period D. In the period P, a pre-charge voltage equal to an original data voltage is applied in a time-sharing manner to data lines in one block, and in the period D after the period P, the original data voltage is applied again.

Owner:RENESAS ELECTRONICS CORP

Electro-optical device and electronic apparatus

InactiveUS7868854B2Simplifies the wiring processPotential fluctuationElectrical apparatusStatic indicating devicesCapacitanceElectron

An electro-optical device includes a plurality of data lines, a plurality of scanning lines, a plurality of unit circuits that are provided in correspondence with intersections of the data lines and the scanning lines. Each of the data lines is supplied with a data voltage in accordance with a gray-scale level. Each of the scanning lines is supplied with a scanning signal that specifies a writing period during which the data voltage is being written into the corresponding unit circuits. Each of the plurality of unit circuits includes a driving transistor, an electro-optical element, a capacitive element, a power feed line, a first switching element and a second switching element. The driving transistor generates a driving current in accordance with an electric potential of a gate thereof. The electro-optical element generates light with a gray-scale level in accordance with the driving current that is generated by the driving transistor. The capacitive element has a first electrode and a second electrode that is connected to the gate of the driving transistor. The power feed line is supplied with a constant electric potential and is, during an initialization period that is different from the writing period, electrically connected to the second electrode. The first switching element conducts the gate of the transistor with the drain thereof at least during the initialization period. The second switching element switches between conduction and non-conduction between the data line and the first electrode on the basis of the scanning signal. The power feed line is arranged in a direction that intersects with the scanning lines.

Owner:SEIKO EPSON CORP

Image display device capable of displaying images in a plurality of view points for suppressing a problem originating from a light blocking portion arranged in a pixel aperture or a structural object and accomplishing a high aperture ratio

ActiveUS9188823B2Increase opening ratioIncrease the aperture ratioStatic indicating devicesNon-linear opticsComputer graphics (images)Capacitor

Owner:NEC LCD TECH CORP

Semiconductor component with trench insulation and corresponding production method

ActiveUS8552524B2Reduce area requirementsSubstrate resistance and in particularSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

The invention relates to a semiconductor component with trench isolation and to an associated fabrication method, a trench isolation having a deep isolation trench with a covering insulation layer, a side wall insulation layer and an electrically conductive filling layer, which is electrically connected to a predetermined doping region of the semiconductor substrate in a bottom region of the trench. The use of a trench contact, which has a deep contact trench with a side wall insulation layer and an electrically conductive filling layer, which is likewise electrically connected to the predetermined doping region of the semiconductor substrate in a bottom region of the contact trench, makes it possible to improve the electrical shielding properties with a reduced area requirement.

Owner:INFINEON TECH AG

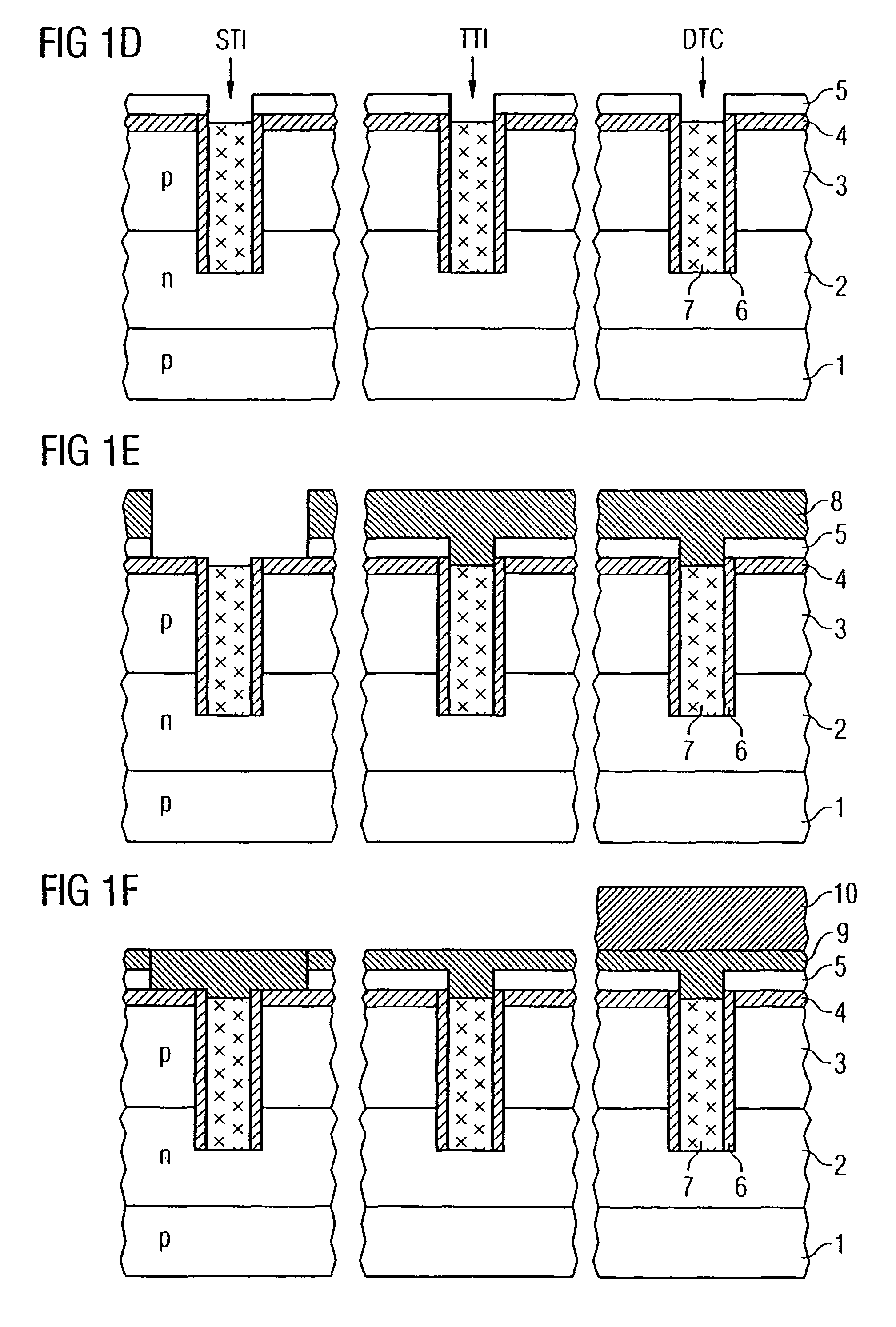

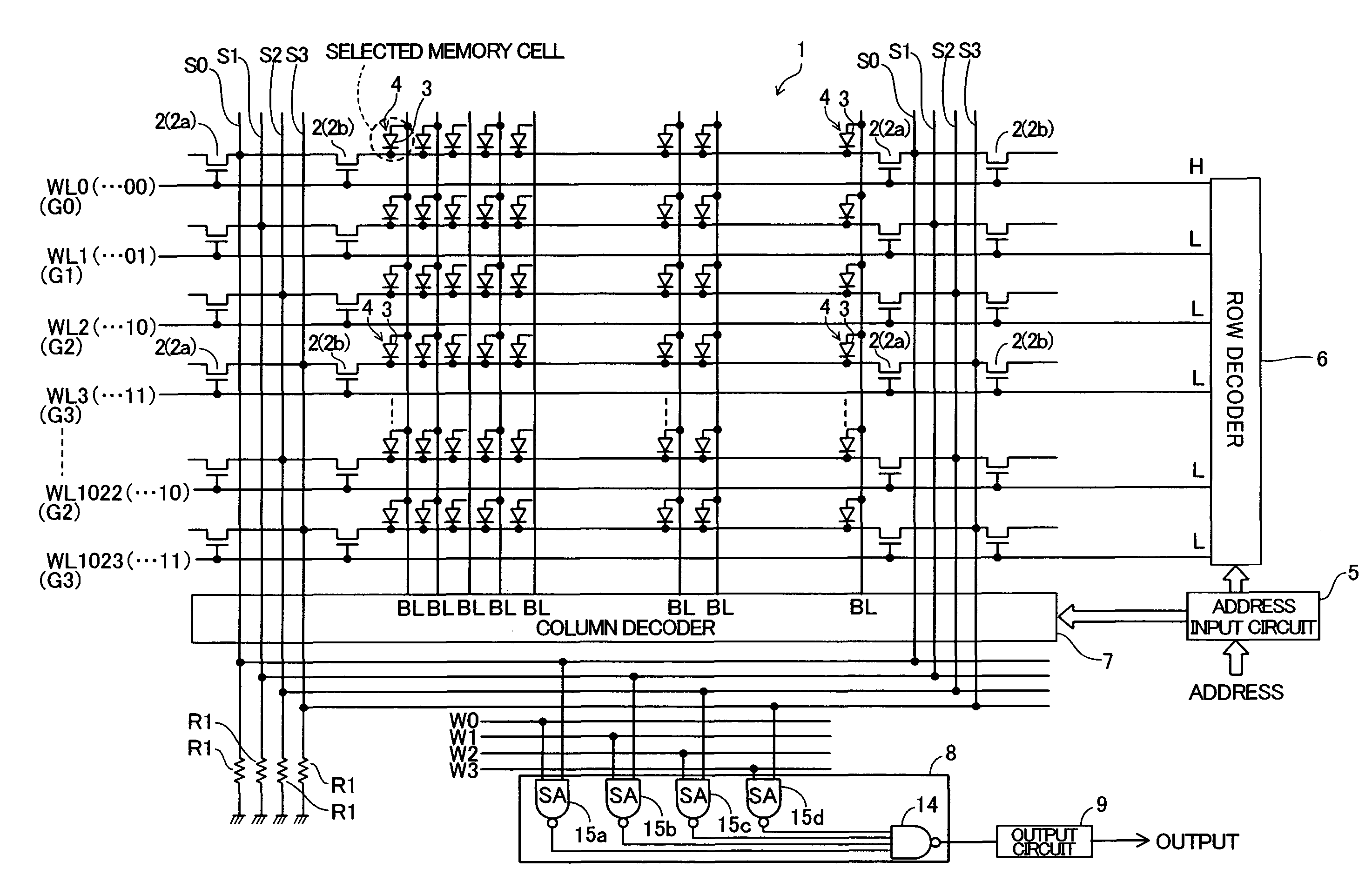

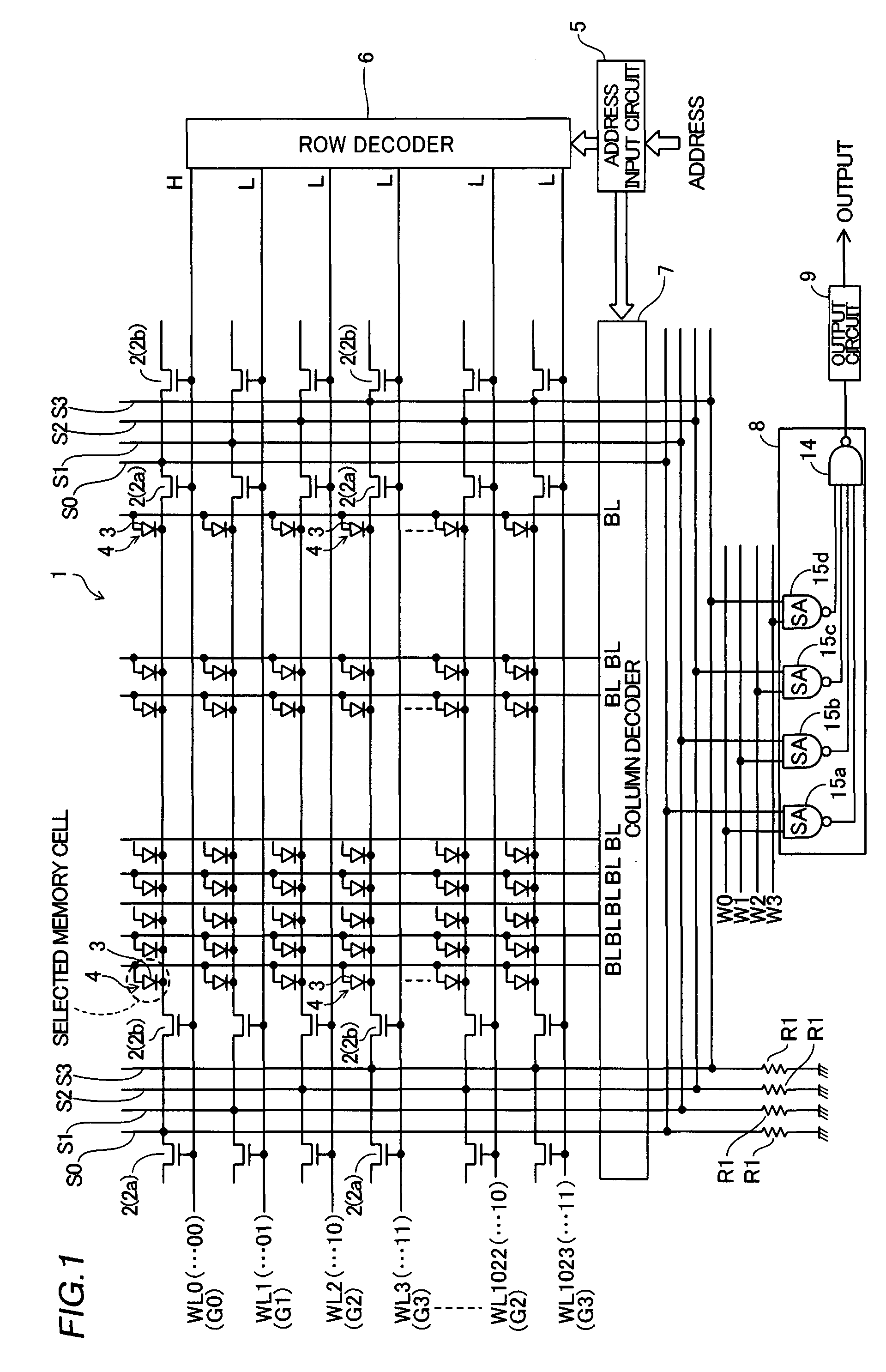

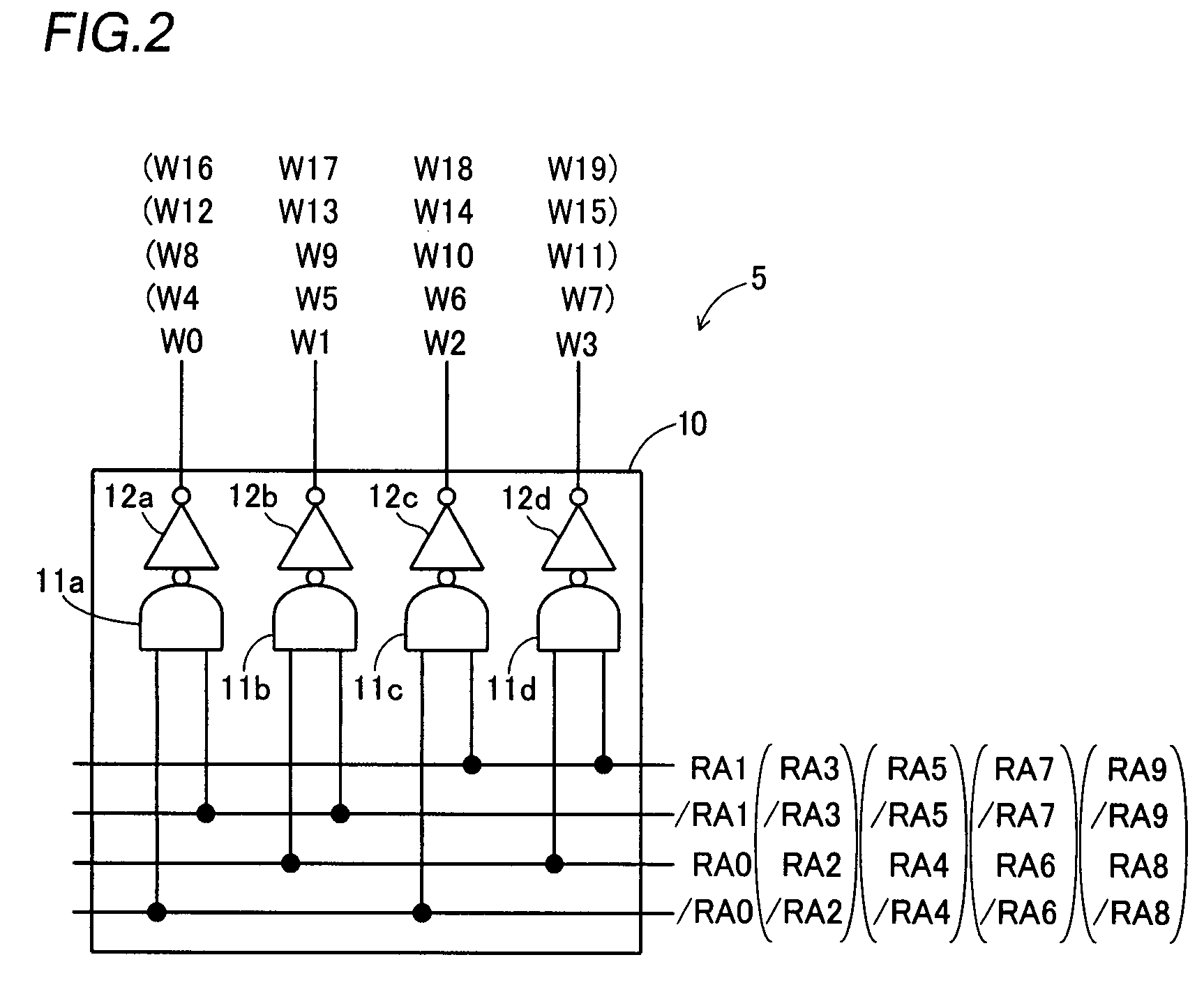

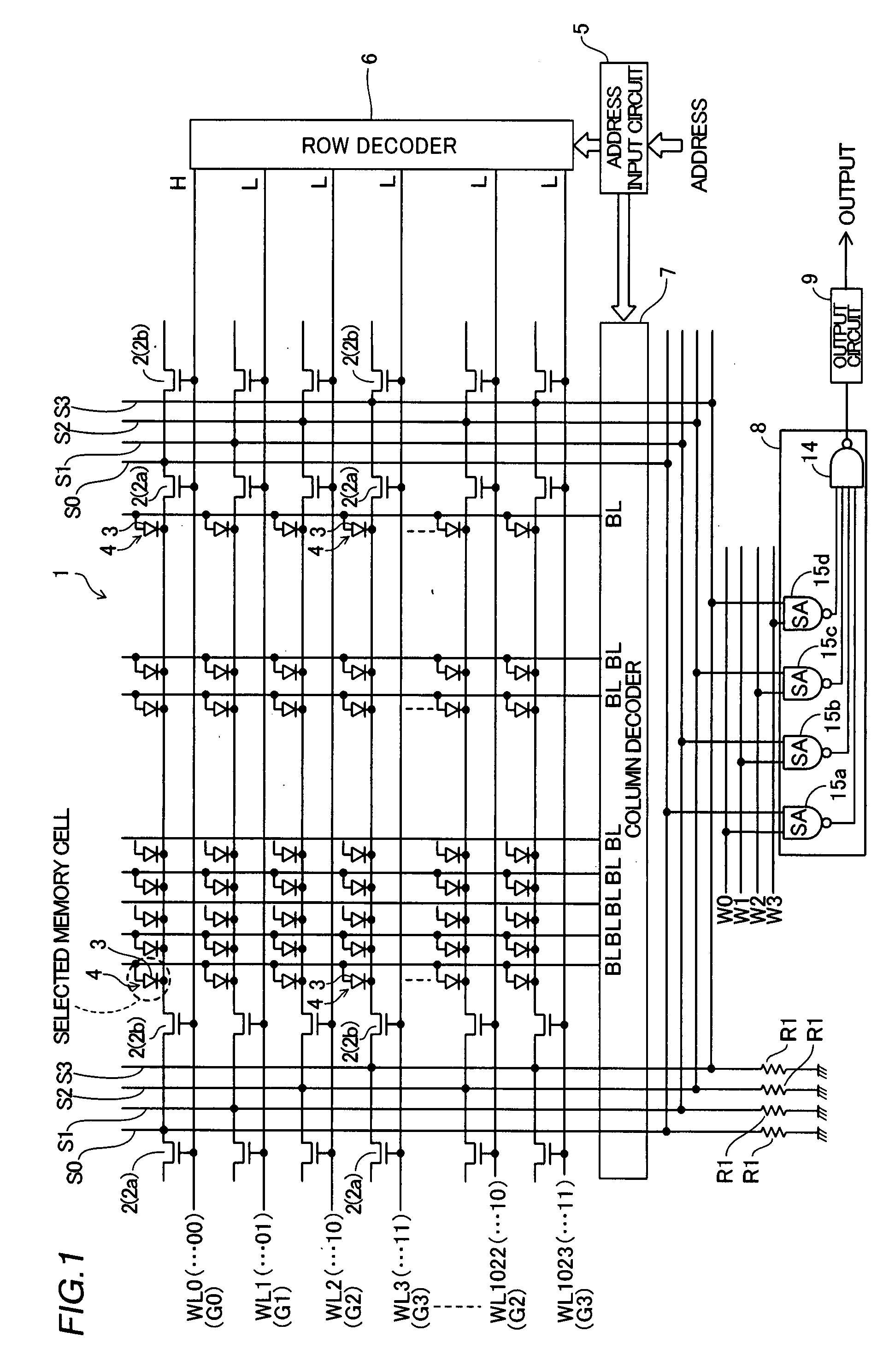

Memory comprising diode

InactiveUS7746690B2Avoid choiceIncrease speedRead-only memoriesDigital storageComputer scienceStorage cell

A memory operable at a high speed is obtained. This memory comprises a plurality of word lines, first transistors each connected to each the plurality of word lines for entering an ON-state through selection of the corresponding word line, a plurality of memory cells including diodes having cathodes connected to the source or drain regions of the first transistors respectively and a data determination portion connected to the drain or source regions of the first transistors for determining data read from a selected memory cell.

Owner:SEMICON COMPONENTS IND LLC

Semiconductor memory device having memory cell and reference cell connected to same sense amplifier and method of reading data thereof

InactiveUS20080310241A1Suppress potential fluctuation of potentialAvoid readingDigital storageBit lineAudio power amplifier

A semiconductor memory device includes a sense amplifier, first and second bit lines connected to the sense amplifier, a first reference cell connected to the first bit line, and a second reference cell connected to the second bit line. A reference potential is simultaneously written to the first and second reference cells. Further, a dummy cell may be provided to be simultaneously, with the reference cell, with the reference potential.

Owner:RENESAS ELECTRONICS CORP

Memory

InactiveUS20070242542A1Selective inhibitionHigh speedRead-only memoriesDigital storageDiodeTransistor

A memory operable at a high speed is obtained. This memory comprises a plurality of word lines, first transistors each connected to each the plurality of word lines for entering an ON-state through selection of the corresponding word line, a plurality of memory cells including diodes having cathodes connected to the source or drain regions of the first transistors respectively and a data determination portion connected to the drain or source regions of the first transistors for determining data read from a selected memory cell.

Owner:SEMICON COMPONENTS IND LLC

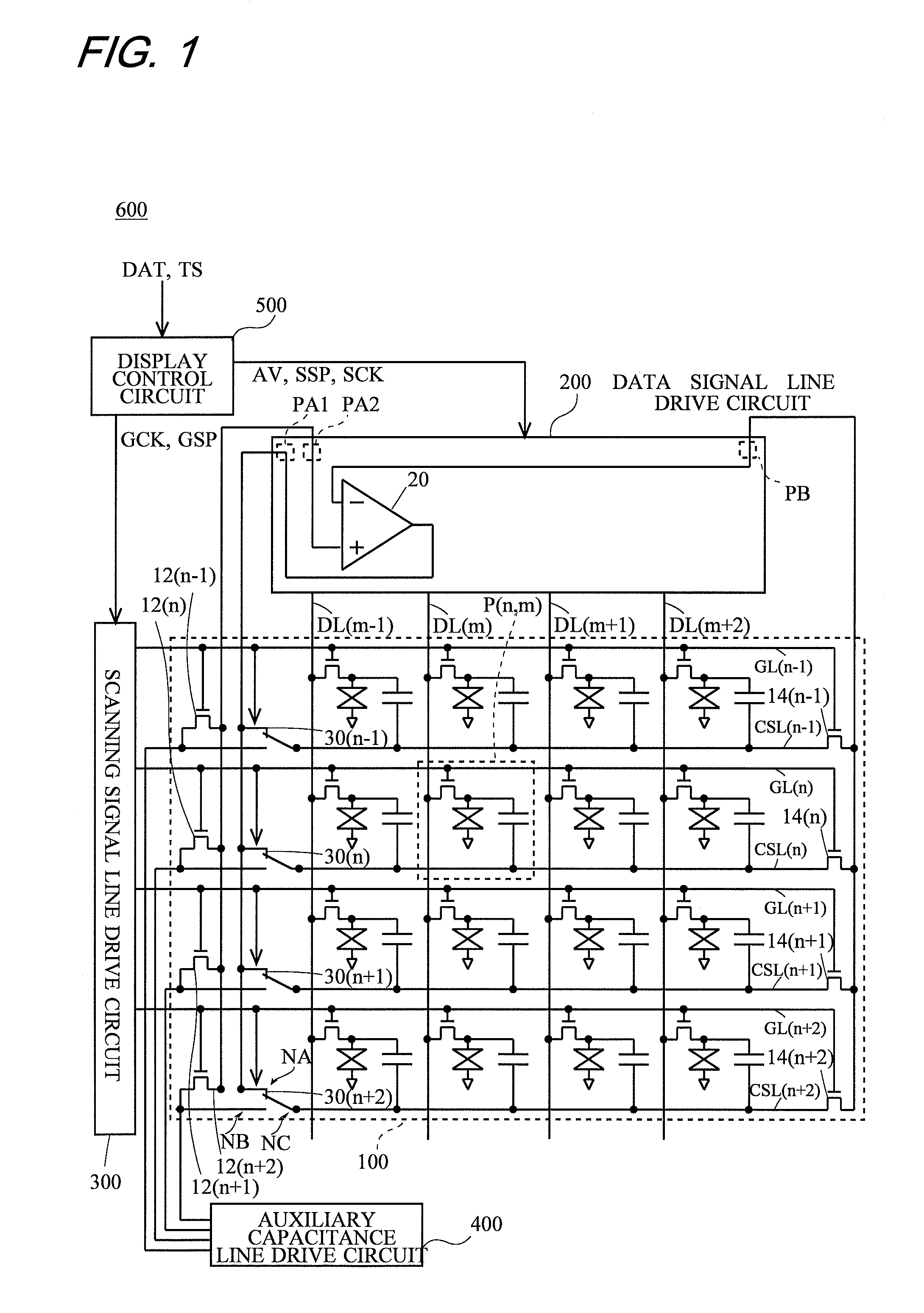

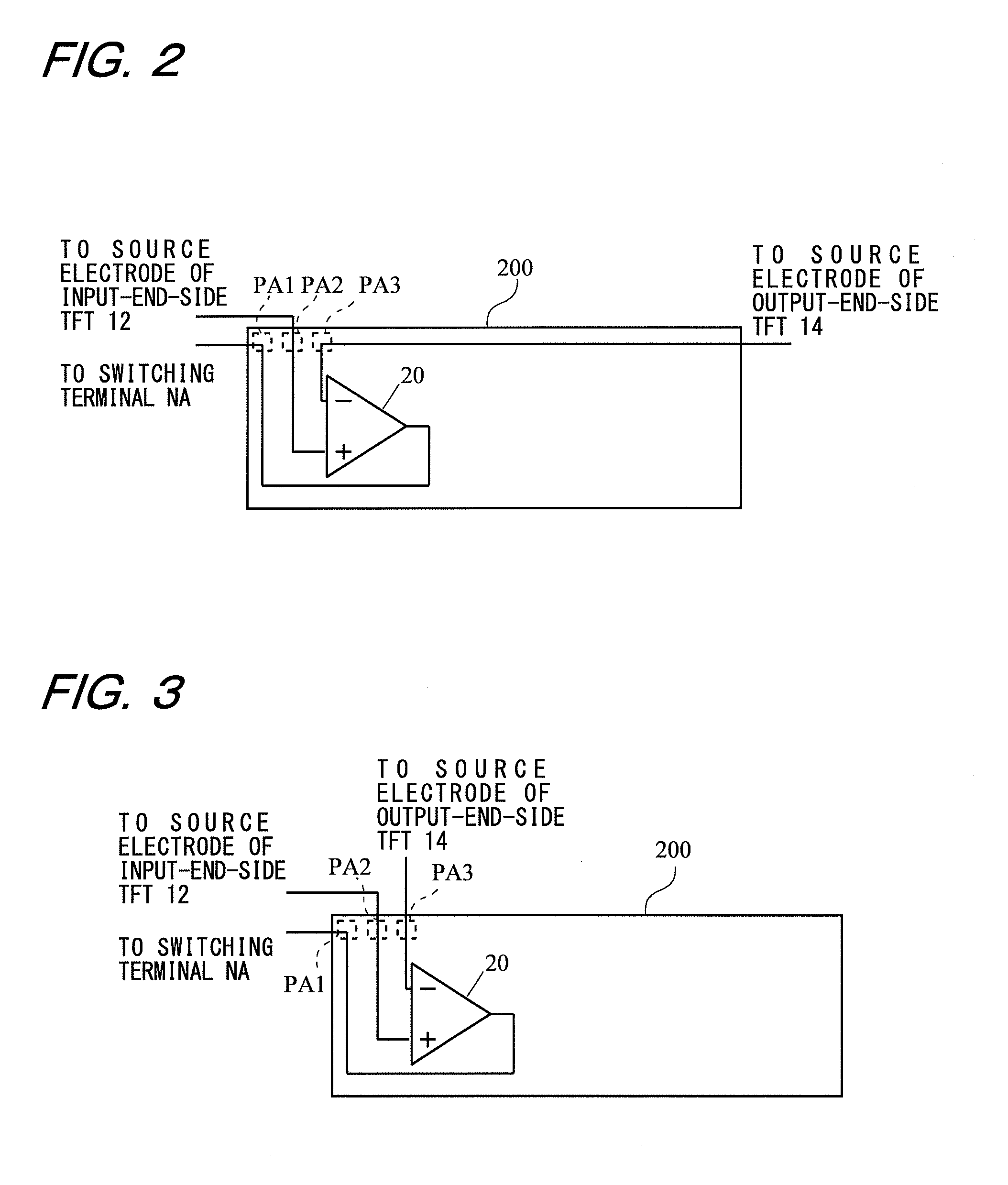

Display device

InactiveUS20130307841A1Simple configurationAccurate potentialCathode-ray tube indicatorsInput/output processes for data processingCapacitanceDisplay device

The present invention provides a display device in which a lateral crosstalk is suppressed with a simple configuration. A display panel includes a change-over switch, an input-end-side TFT, and an output-end-side TFT which are provided in correspondence with an auxiliary capacitance line CSL, and a data signal line drive circuit includes an operational amplifier. The operational amplifier receives a fluctuation auxiliary capacitance signal which is output from an output end of an auxiliary capacitance line via the output-end-side TFT, receives a reference auxiliary capacitance signal to be applied to the auxiliary capacitance line from an auxiliary capacitance line drive circuit via the input-end-side TFT and the change-over switch, generates an output signal to be output to make the voltage of the fluctuation auxiliary capacitance signal equal to the voltage of the reference auxiliary capacitance signal, and applies again the output signal to the auxiliary capacitance line.

Owner:SHARP KK