Patents

Literature

99results about How to "Reduce time difference" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

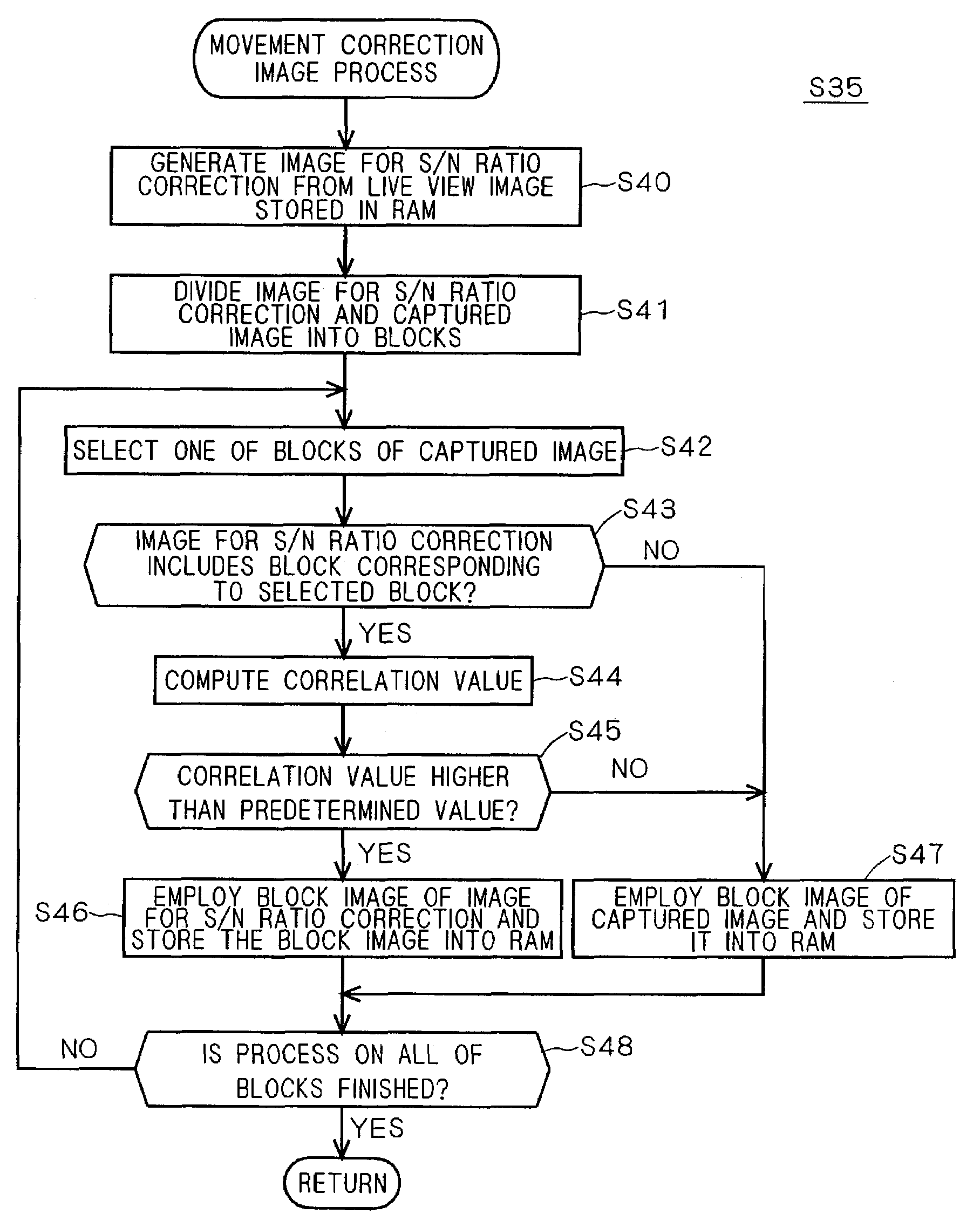

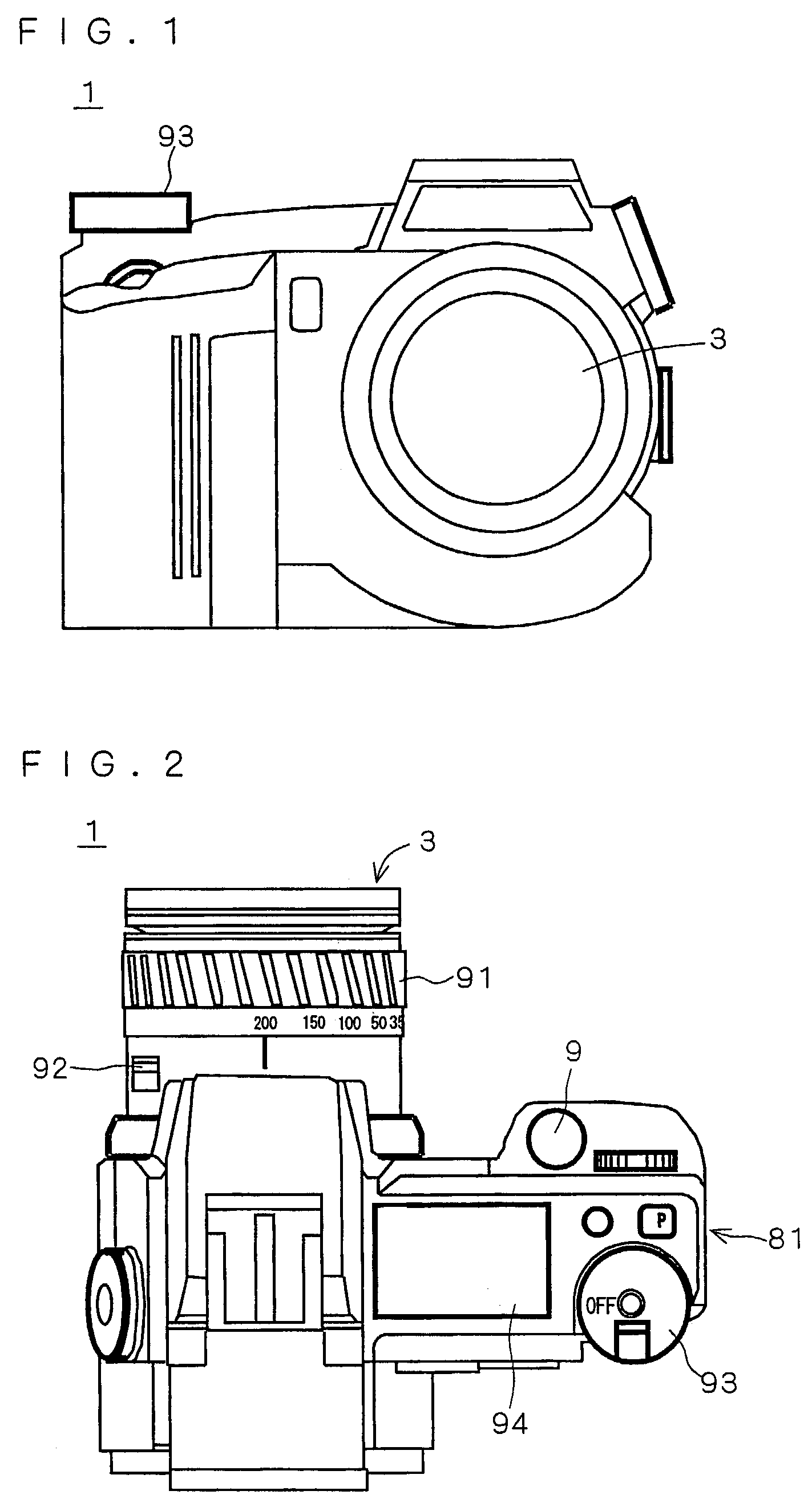

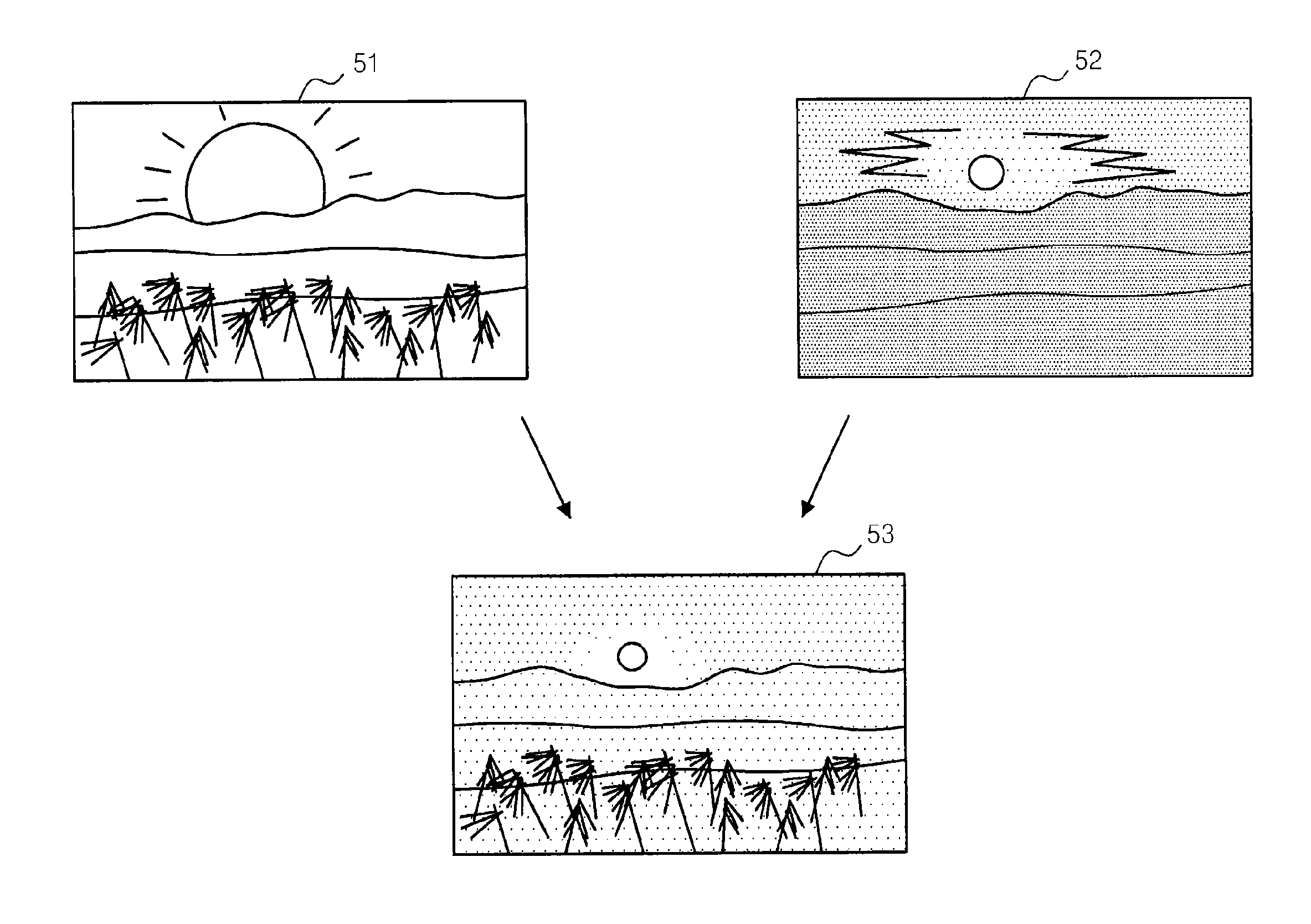

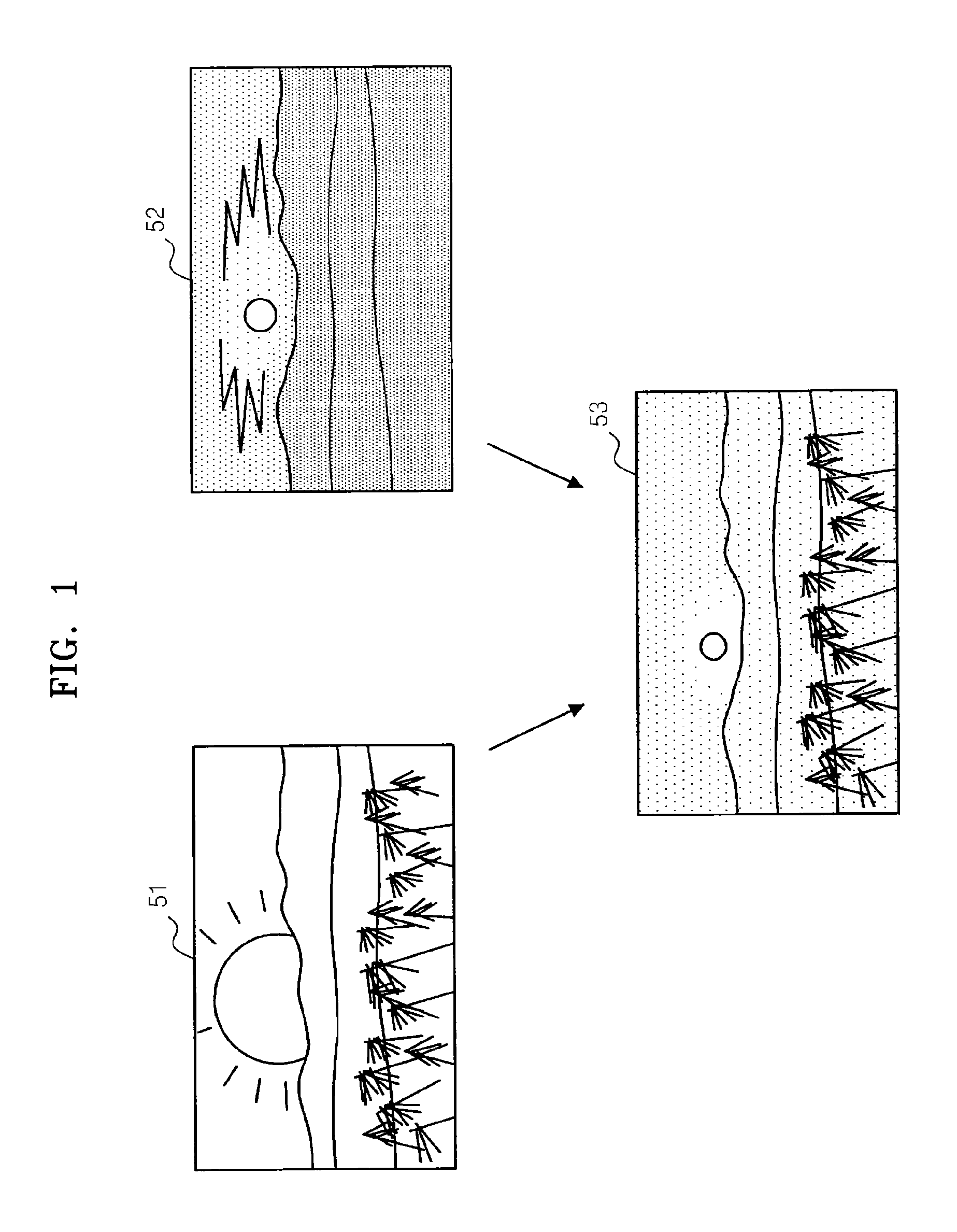

Image processing apparatus and method

InactiveUS7239342B2Solve the low matching degreeReduce time differenceTelevision system detailsPrintersImaging processingComputer science

An object of the present invention is to generate an image which is prevented from being influenced by a movement while suppressing increase in noise components. When a movement is detected during exposure of an image capturing device to light, an image capturing apparatus stops the exposure of the image capturing device and amplifies an image signal obtained with the exposure, thereby compensating exposure shortage. Luminance information is extracted from a captured image, and color information is extracted from a live view image obtained at a timing different from a timing at which the captured image is obtained. By synthesizing the luminance information of the captured image and the color information of the live view image, noise components included in color information are reduced.

Owner:MINOLTA CO LTD

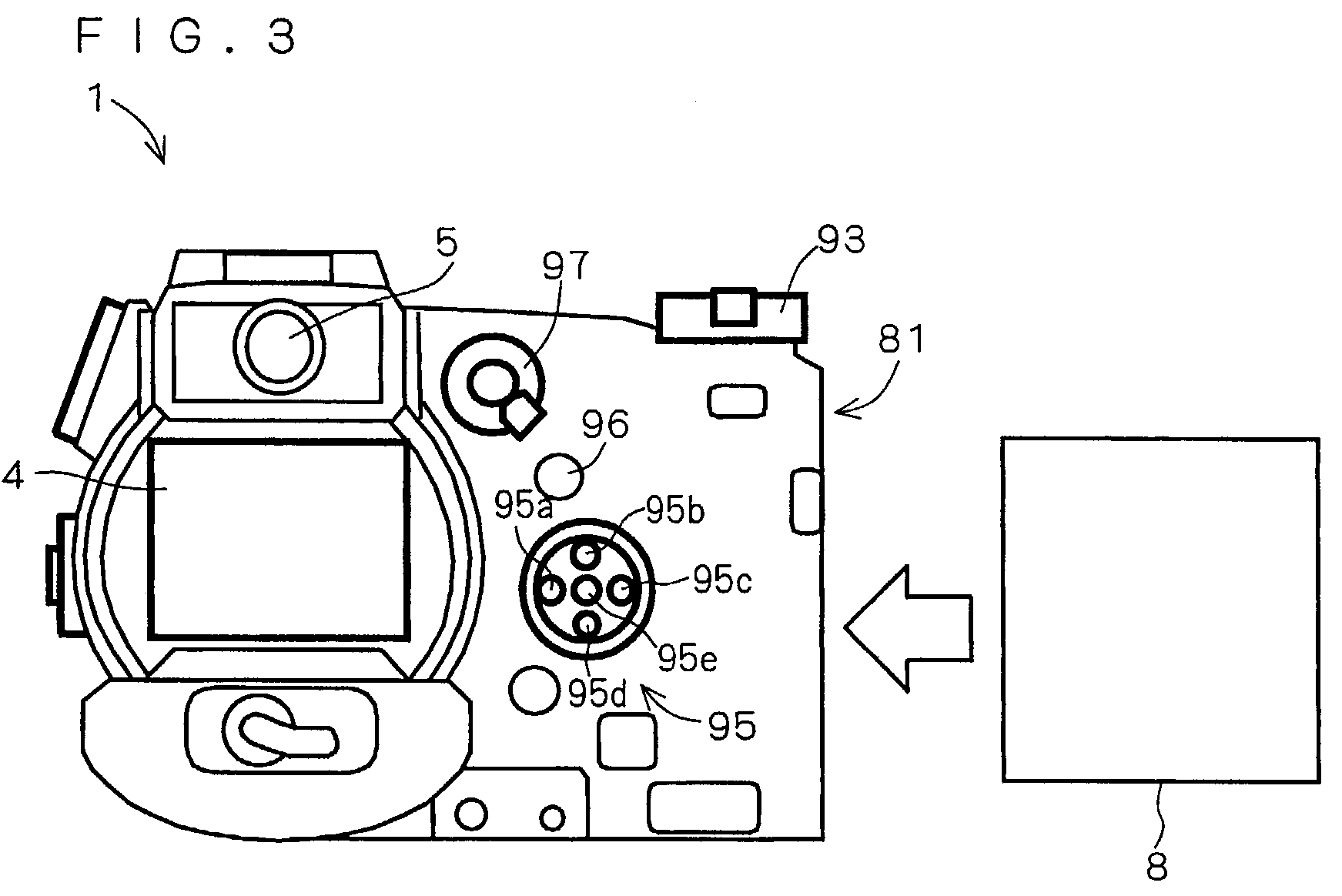

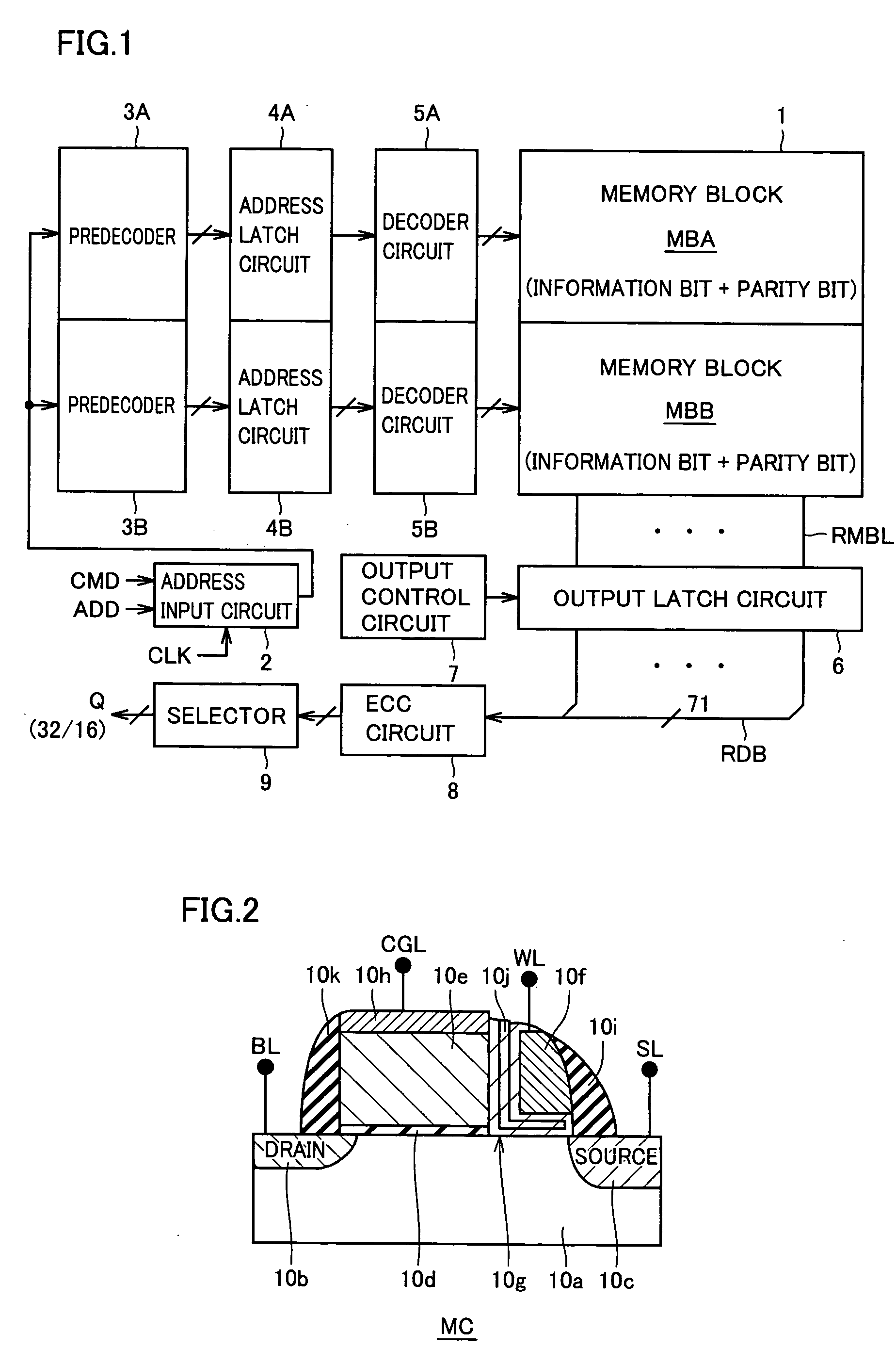

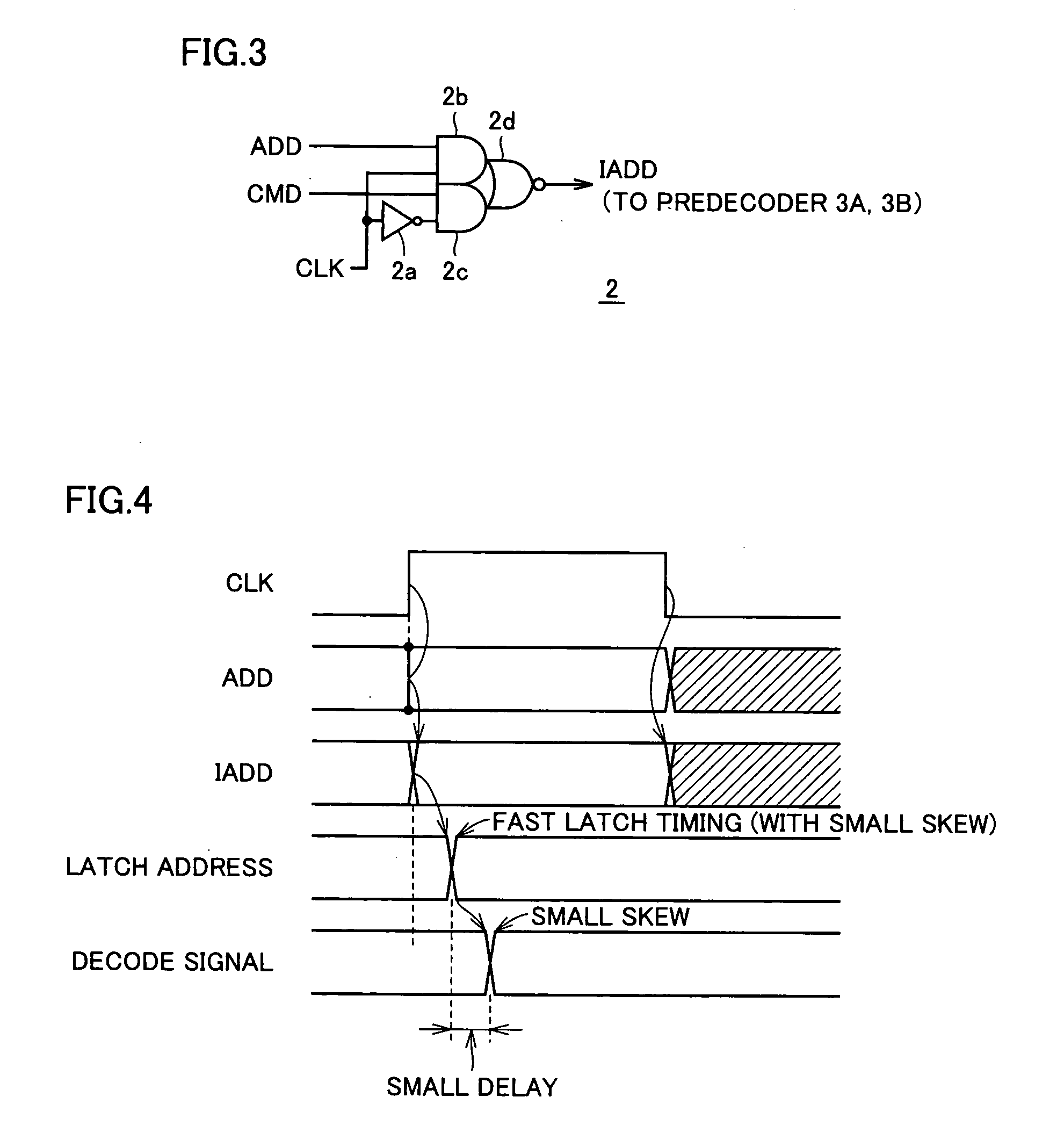

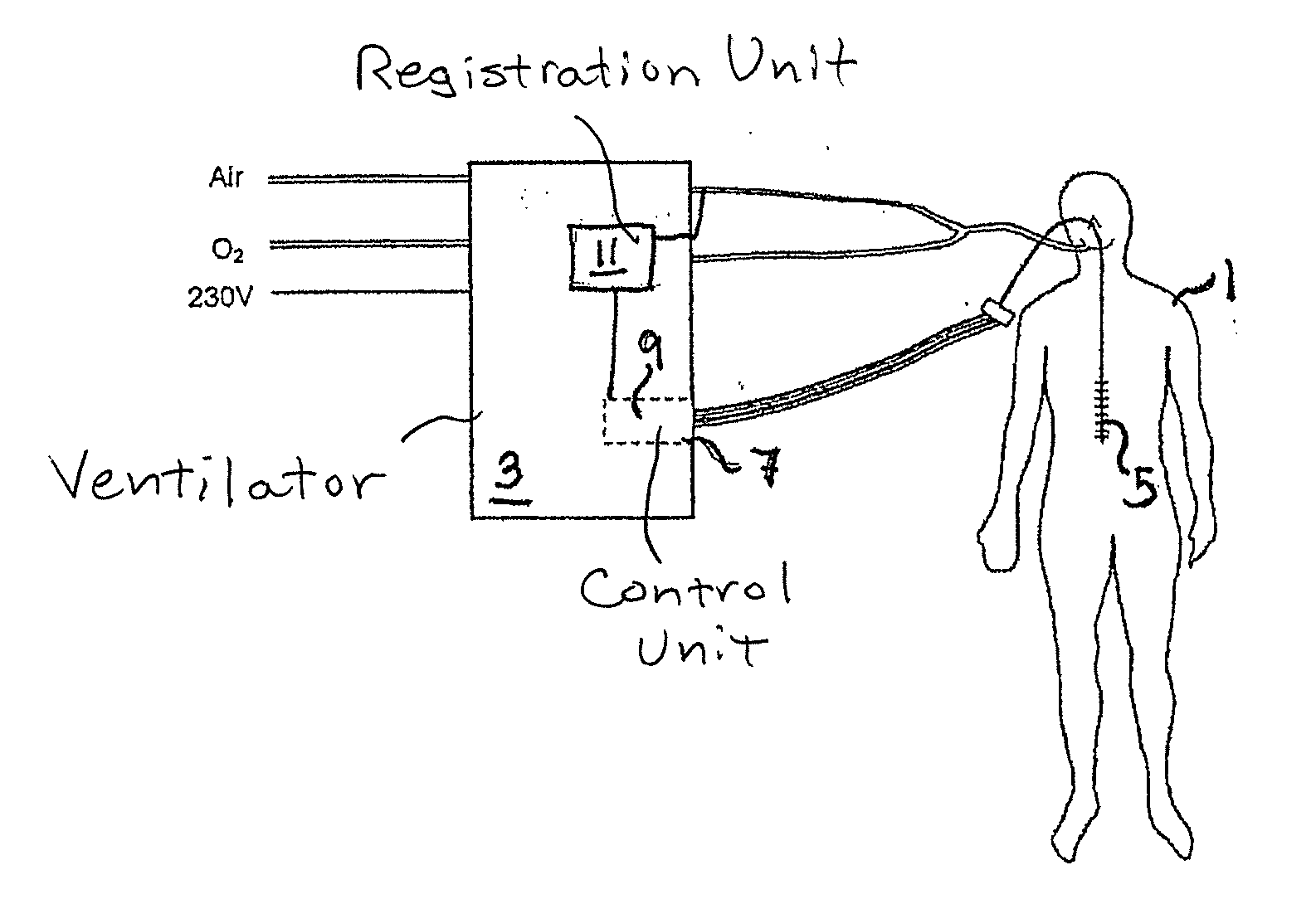

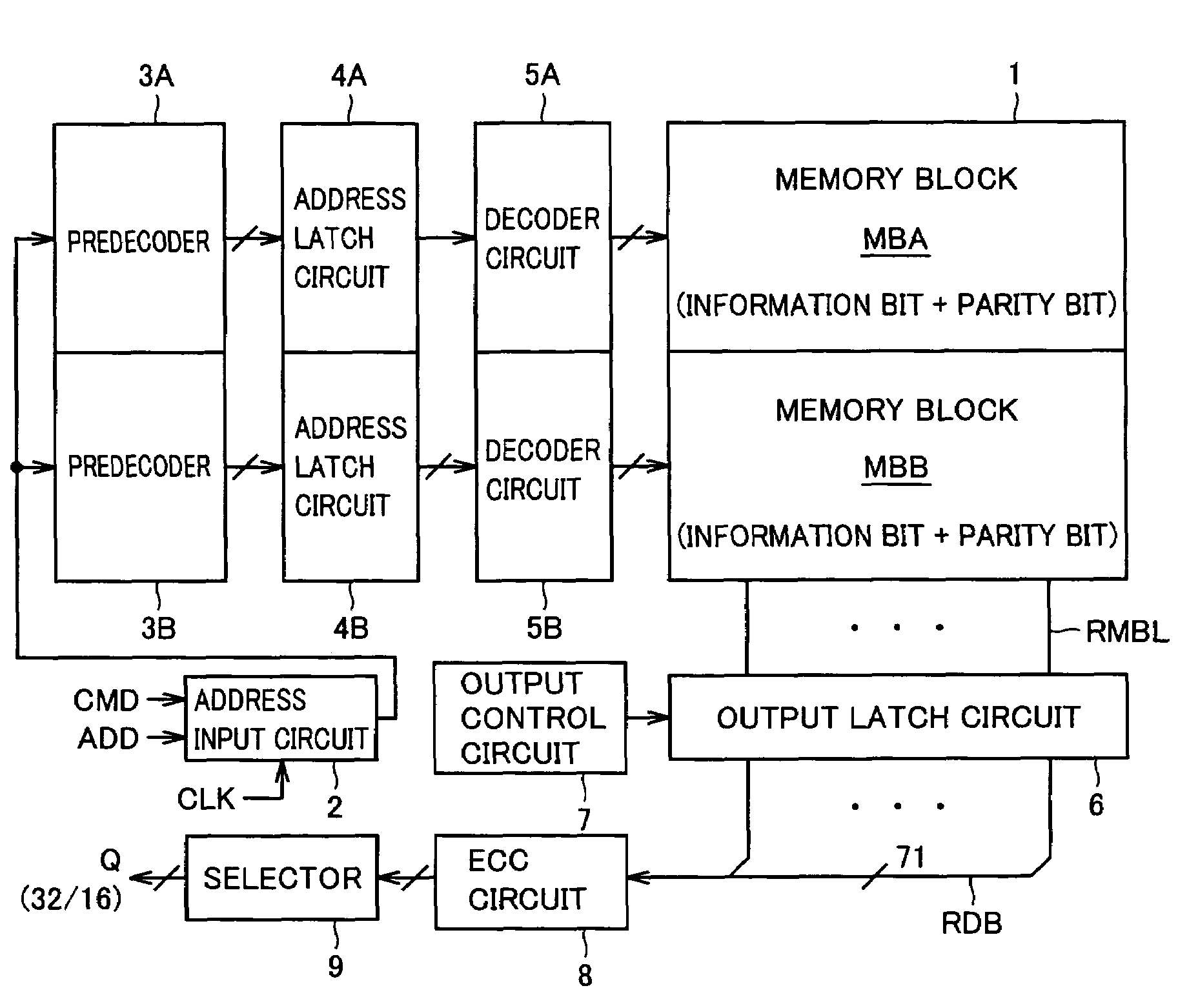

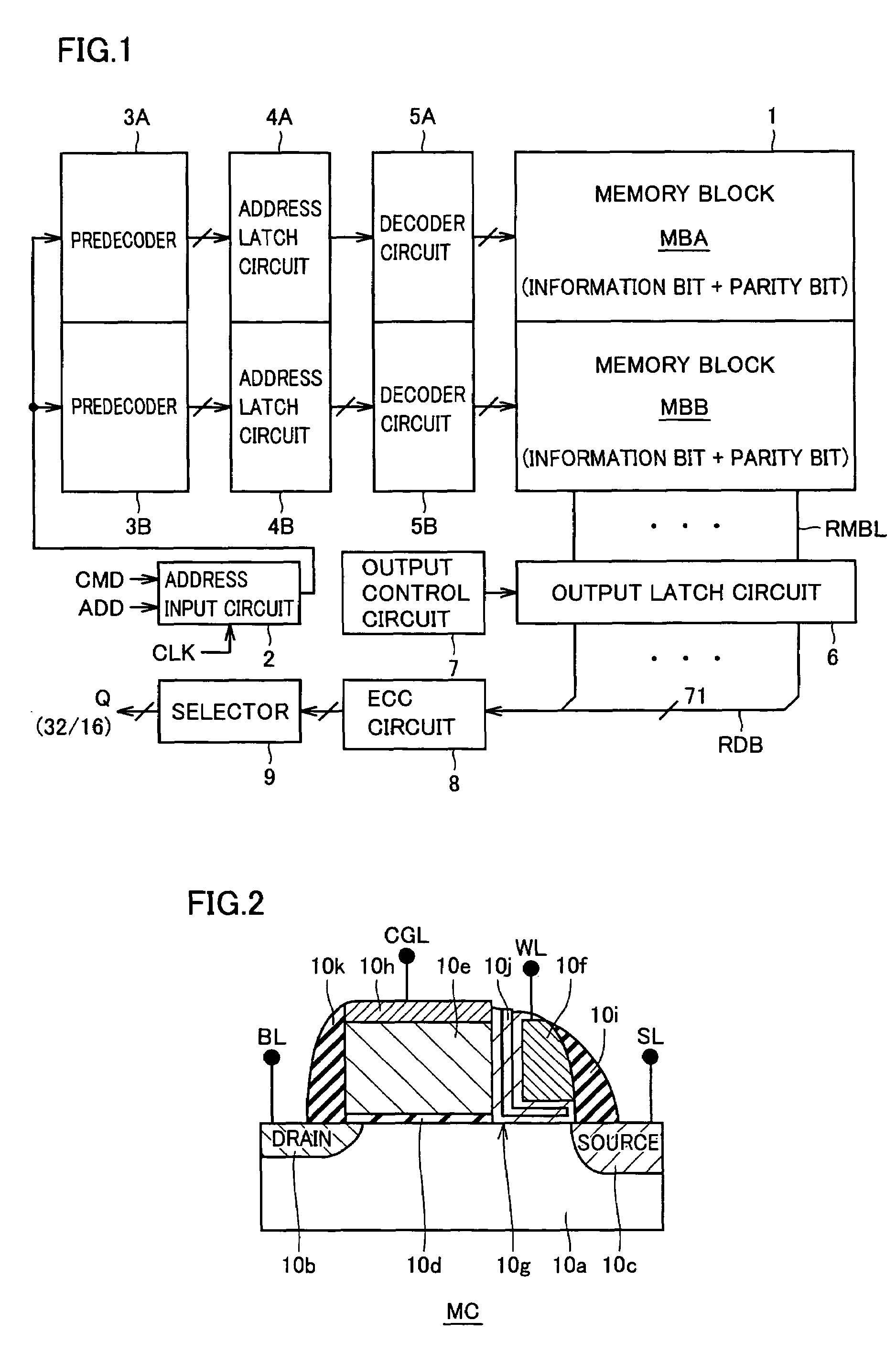

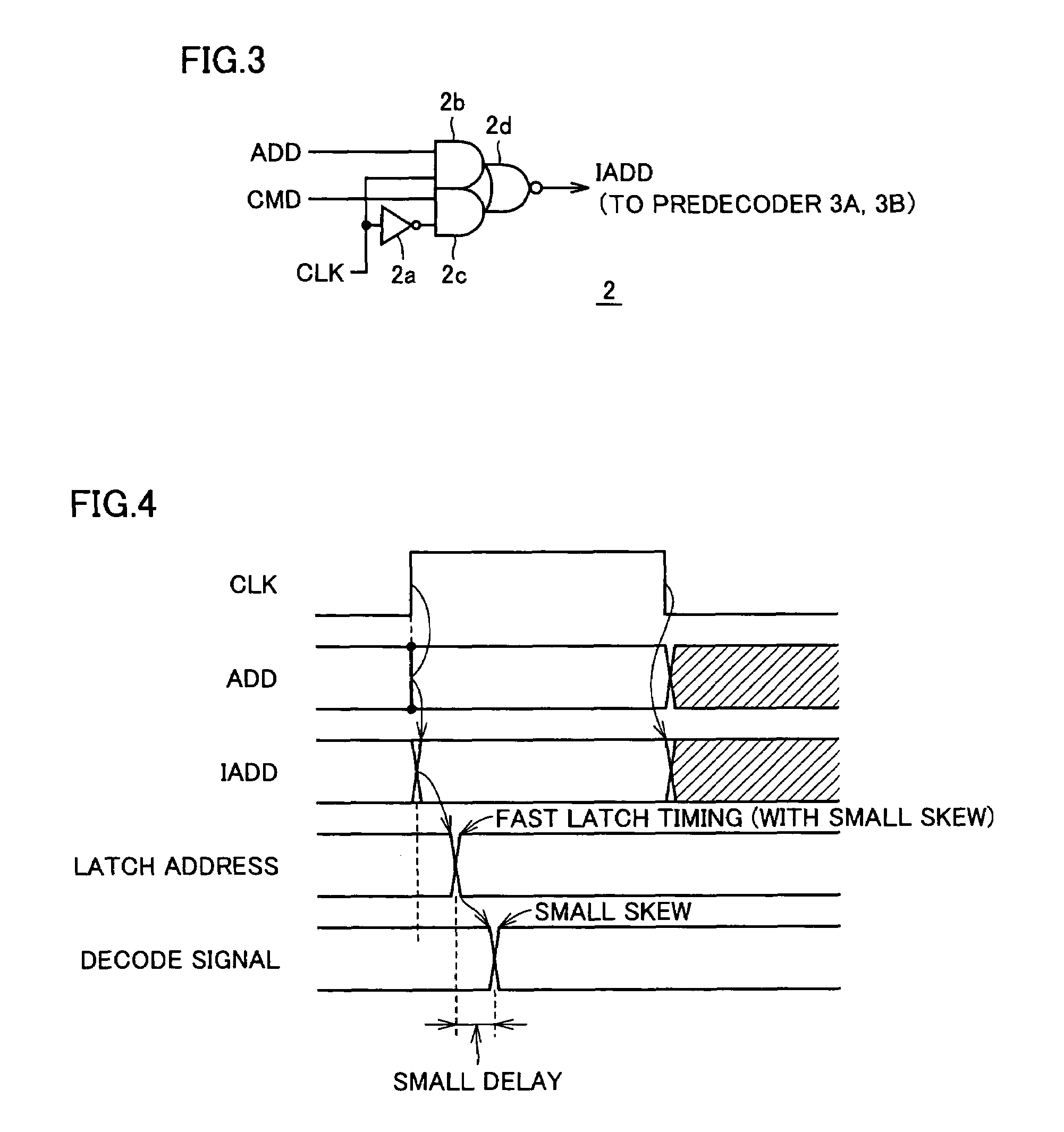

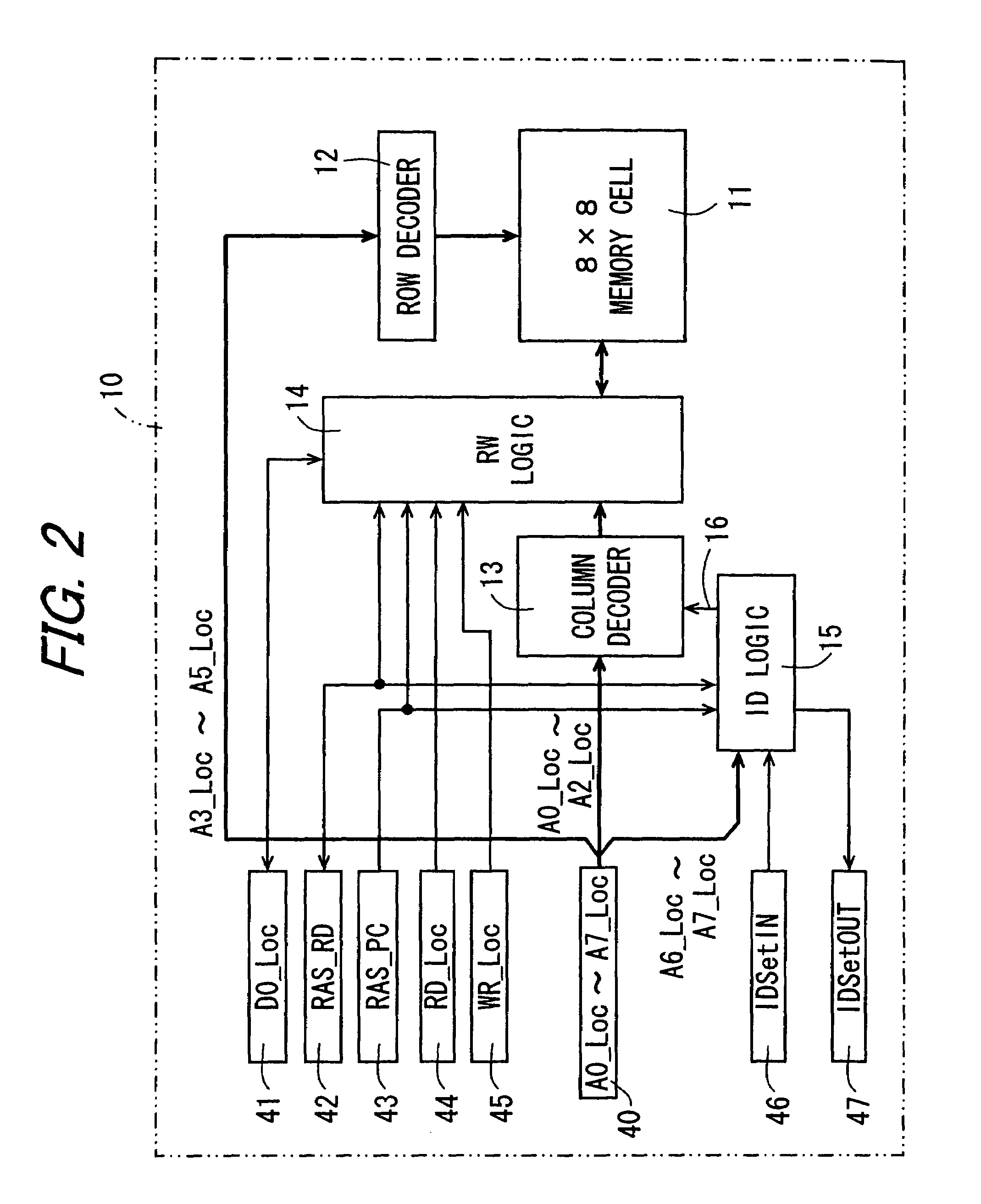

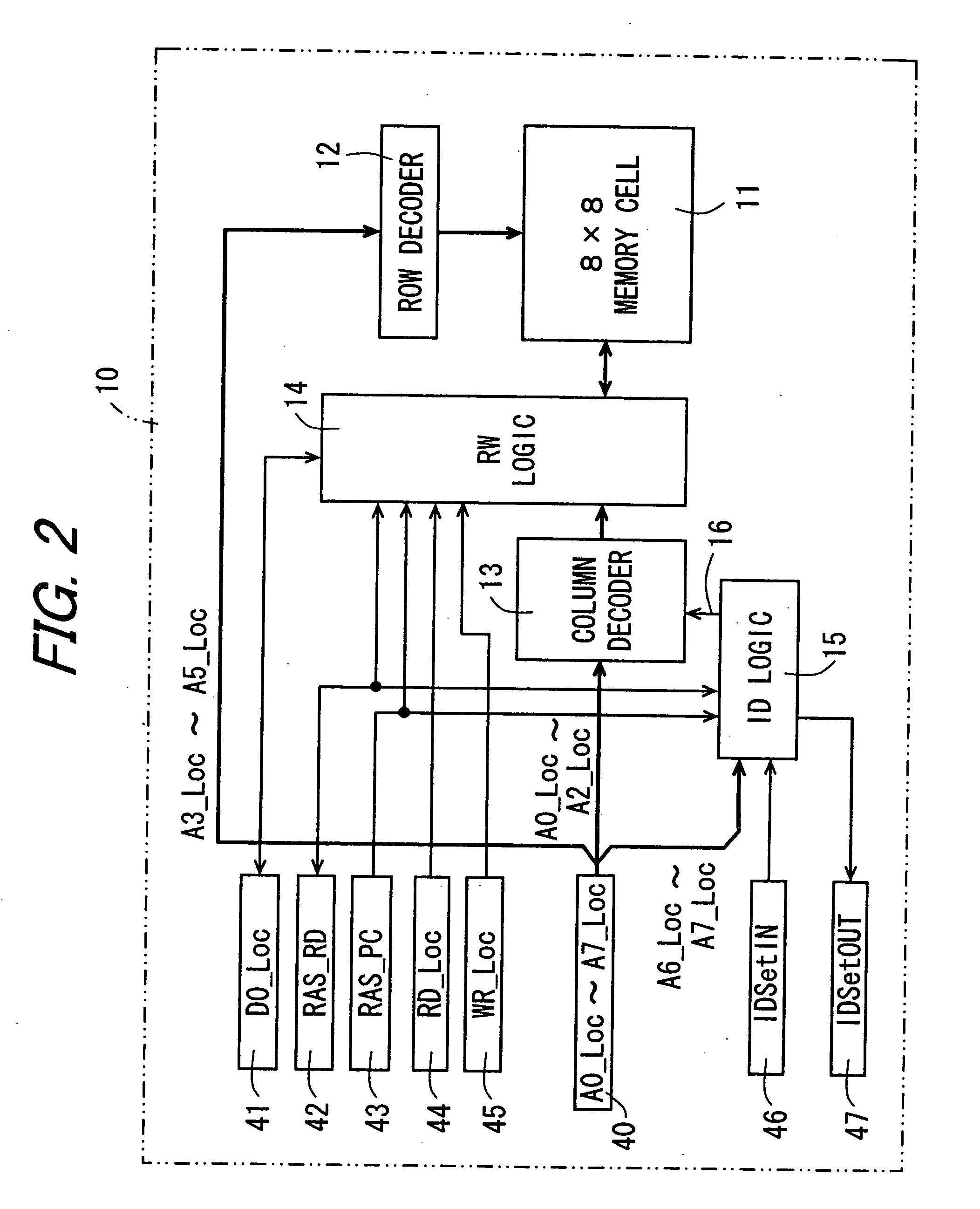

Non-volatile semiconductor memory device and semiconductor memory device

InactiveUS20060034142A1Reading data is accurateIncrease speedRead-only memoriesDigital storagePropagation delayHemt circuits

For each memory block, a predecoder for predecoding an applied address signal, an address latch circuit for latching the output signal of the predecoder, and a decode circuit for decoding an output signal of the address latch circuit and performing a memory cell selecting operation in a corresponding memory block are provided. Propagation delay of latch predecode signals can be made smaller and the margin for the internal read timing can be enlarged. In addition, the internal state of the decoder and memory cell selection circuitry are rest to an initial state when a memory cell is selected and the internal data output circuitry is reset to an initial state in accordance with a state of internal data reading. Thus, a non-volatile semiconductor memory device that can decrease address skew and realize an operation with sufficient margin is provided.

Owner:RENESAS ELECTRONICS CORP

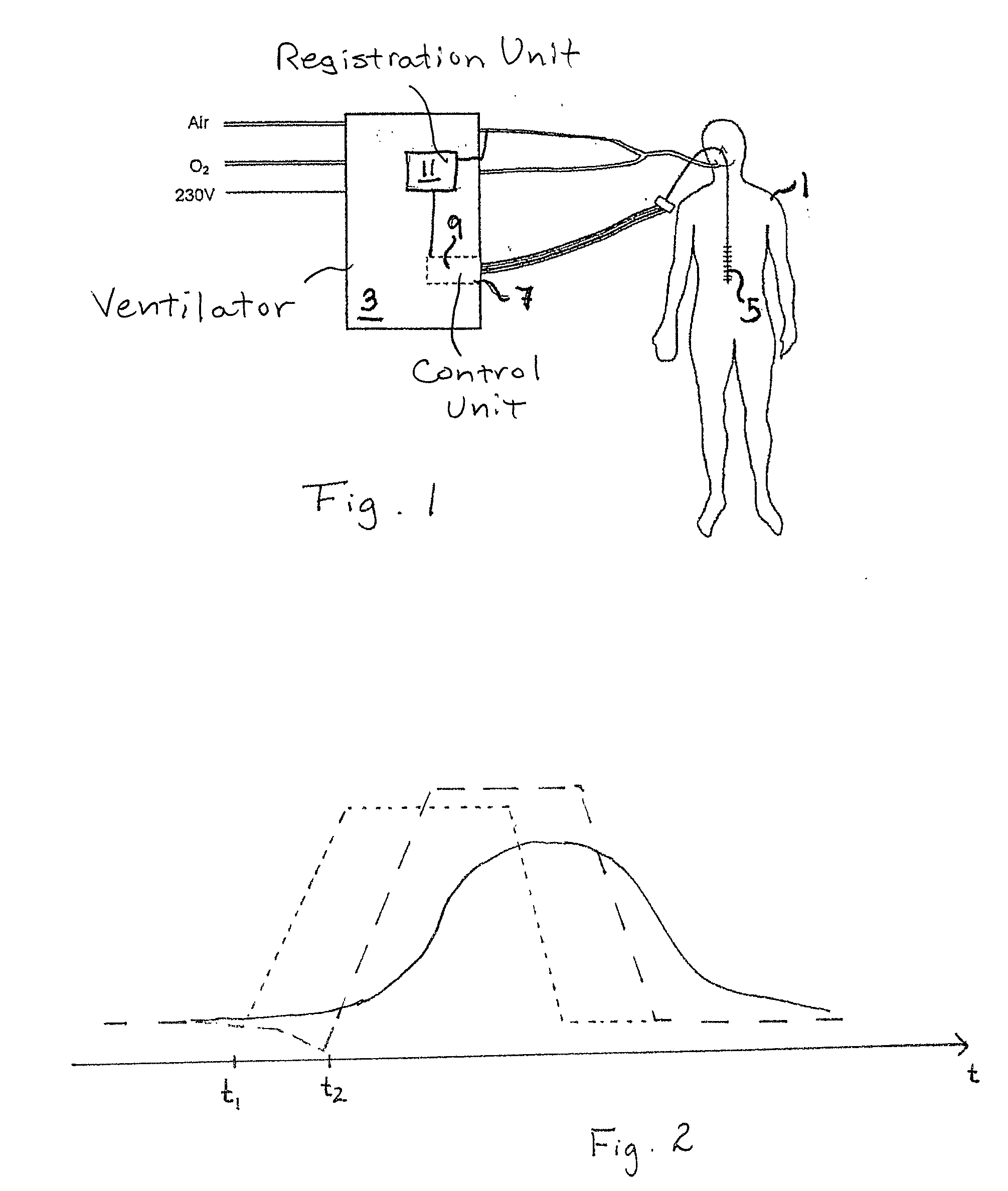

Control unit, method and computer-readable medium for operating a ventilator

InactiveUS20110000489A1Optimize trigger conditionsImprove ventilationRespiratorsOperating means/releasing devices for valvesInhalationEmergency medicine

To set trigger conditions correctly in pneumatic mode, a ventilator is controlled to obtain a measurement value of a bioelectric signal representative of the patient's breathing function, determine, based on the bioelectric signal, at least one point in time at which the patient starts inhalation, obtain a measurement value to be used for triggering an inspiration phase in the ventilator during the at least one point in time, determine a trigger condition for the inspiration phase on the basis of the measurement value, and use the trigger condition for initiating inspiration when ventilating the patient in support mode.

Owner:MAQUET CRITICAL CARE

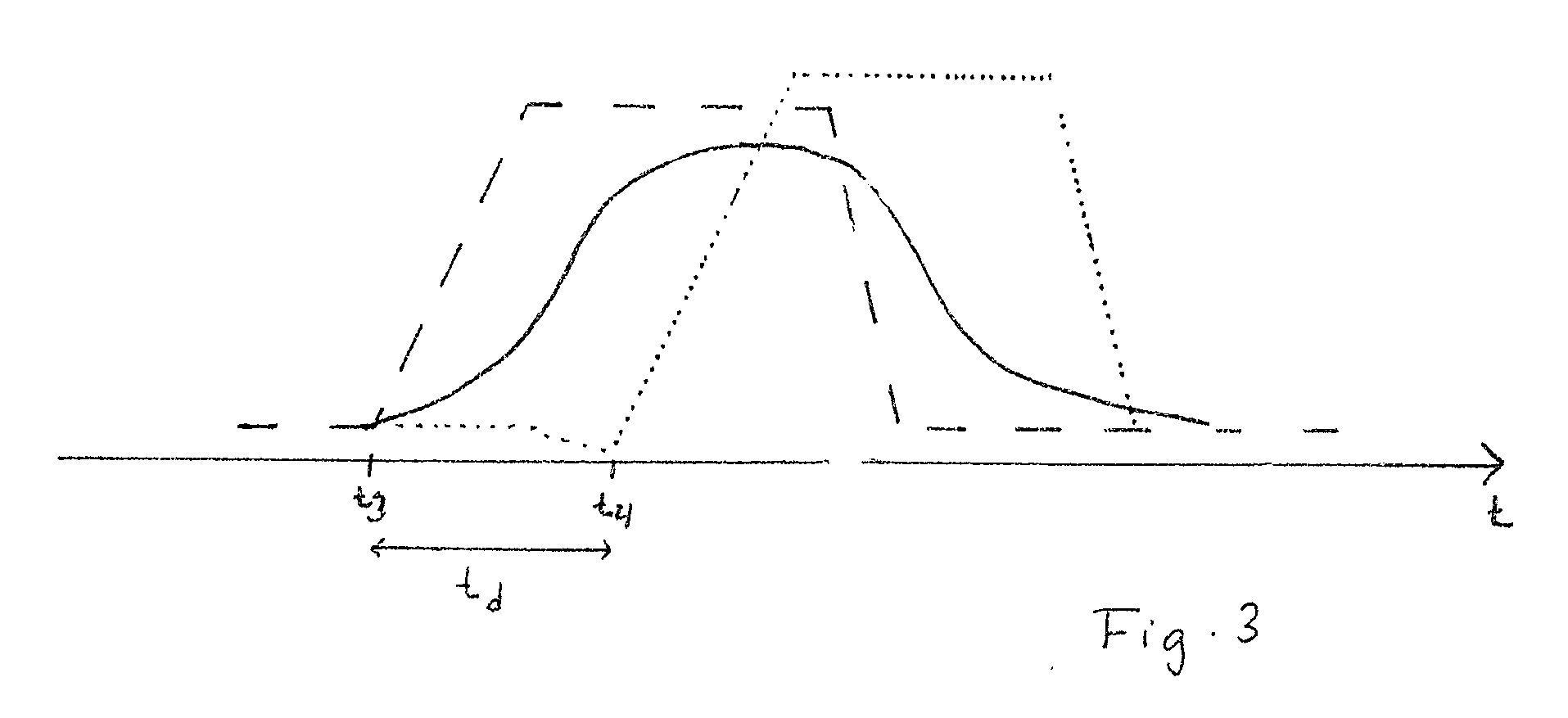

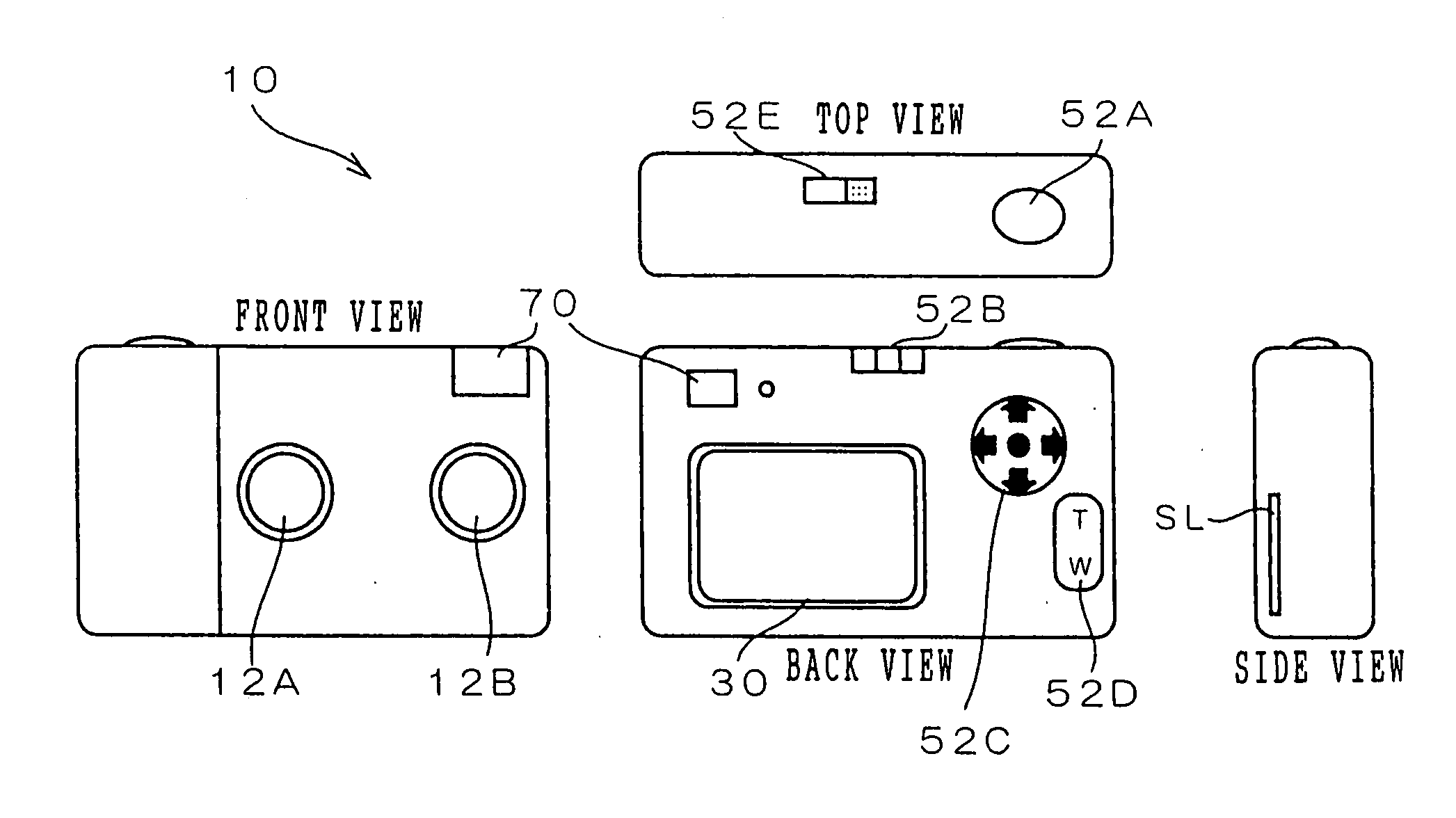

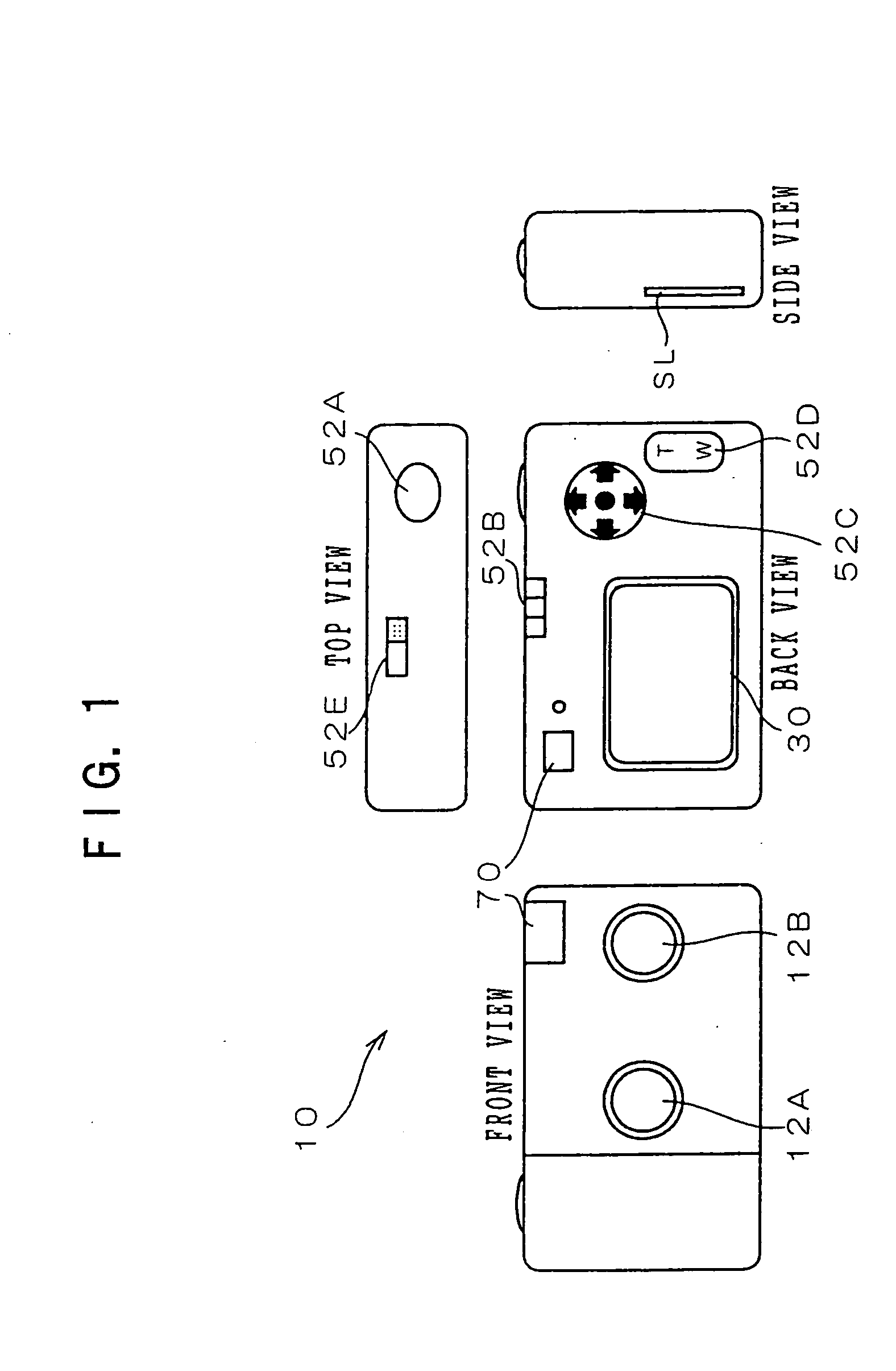

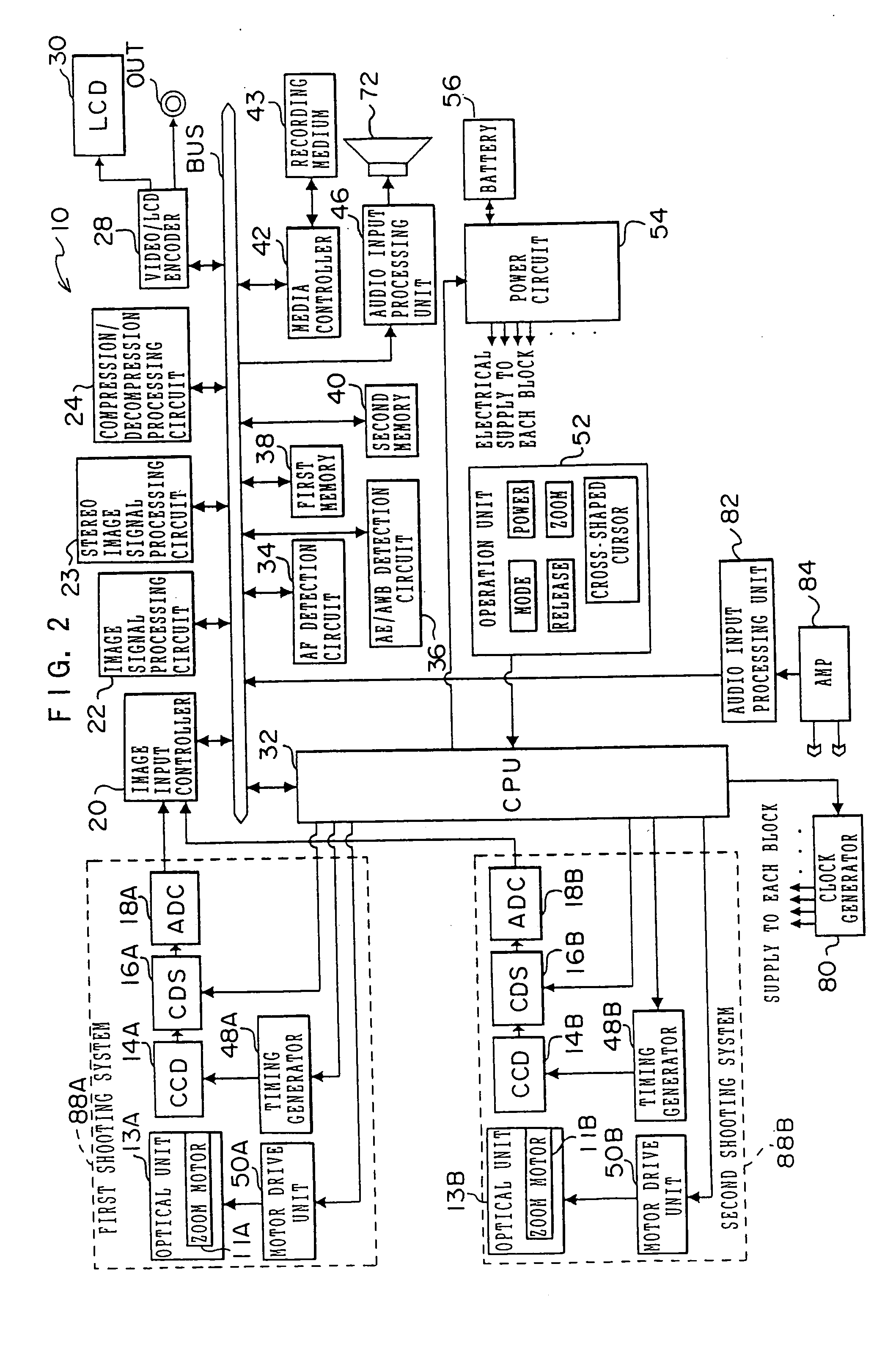

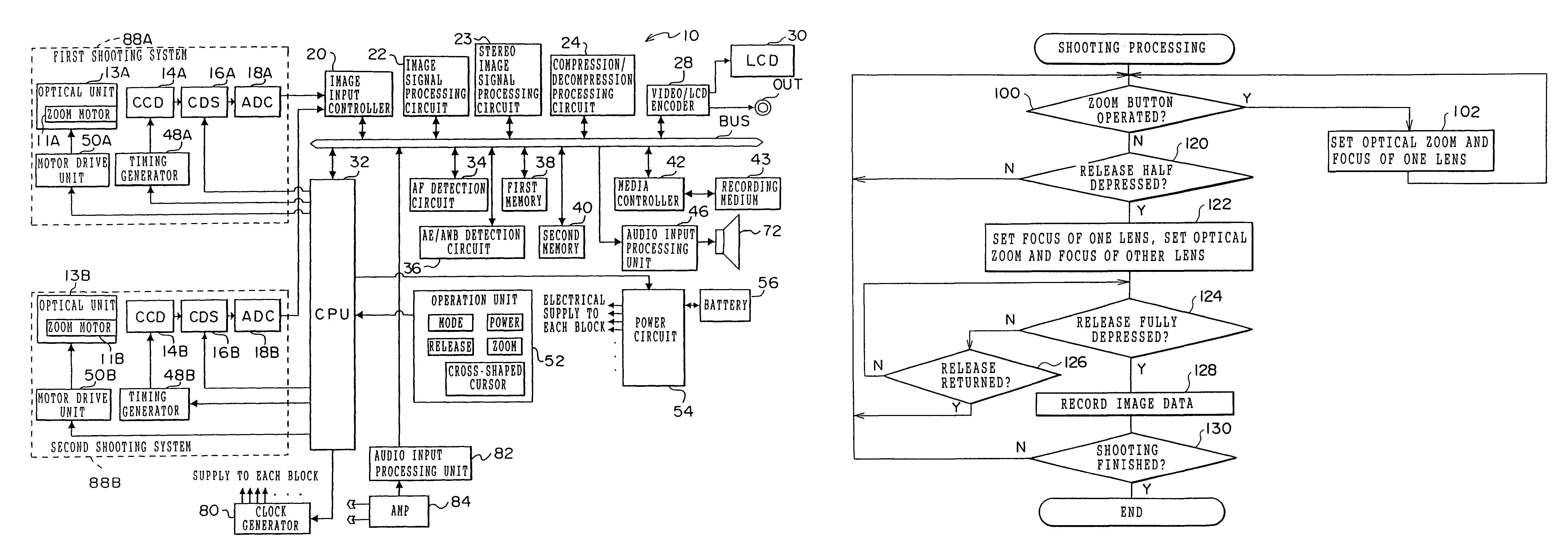

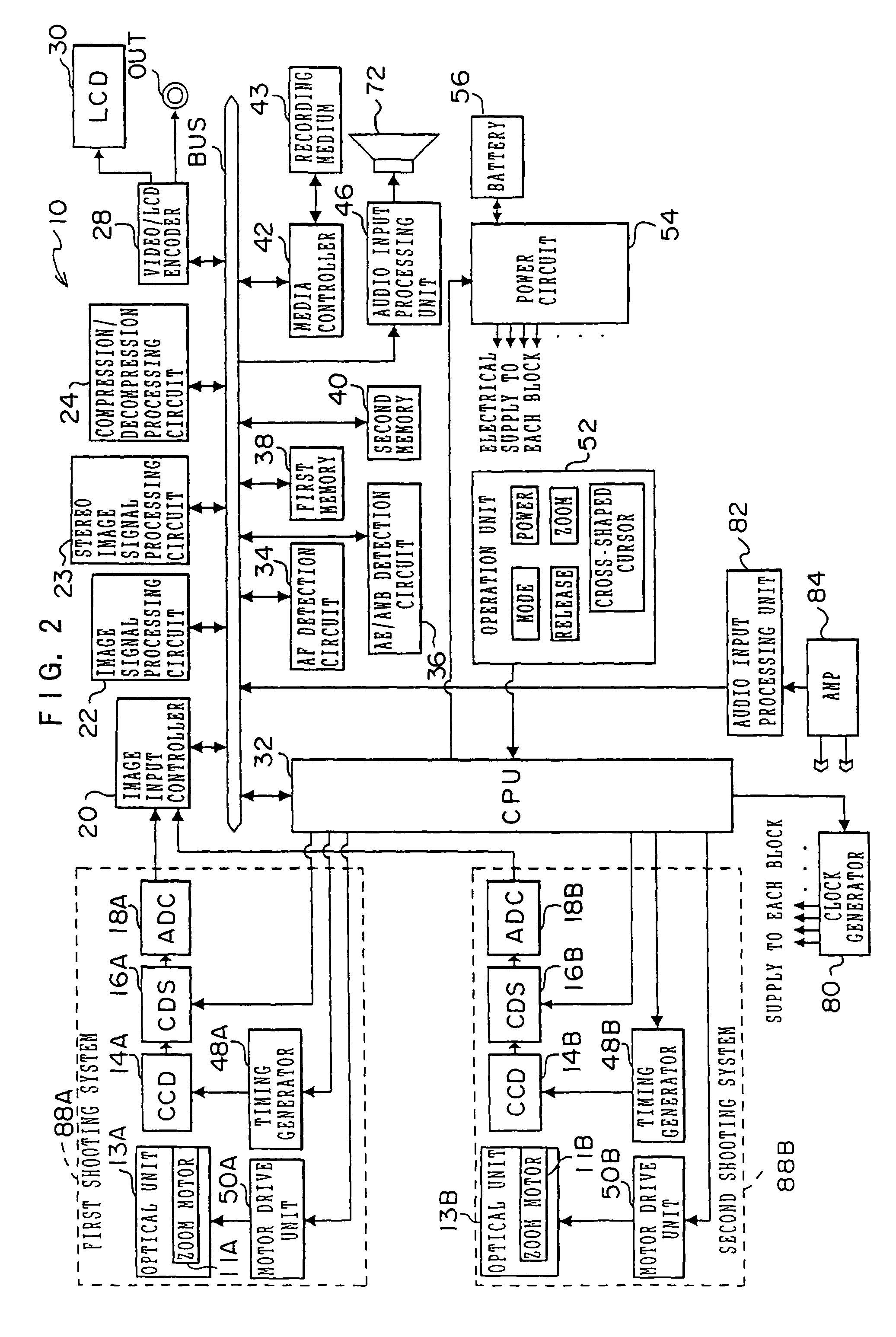

Camera and camera zoom control method

InactiveUS20050134709A1Reduce power consumptionTime differenceTelevision system detailsPrintersCamera lensTime difference

The present invention provides a camera and a camera zoom control method that can reduce power consumption at the time of zooming and shorten the time difference between the timing of a photographing instruction and the timing of actual photographing. Until a release button is operated, the optical zoom magnifying power of a lens is controlled to become a zoom magnifying power corresponding to an operation with respect to a zoom switch, and when the release button has been operated, the optical zoom magnifying power of the lens is controlled to become the zoom magnifying power corresponding to the operation with respect to the zoom switch.

Owner:FUJIFILM CORP

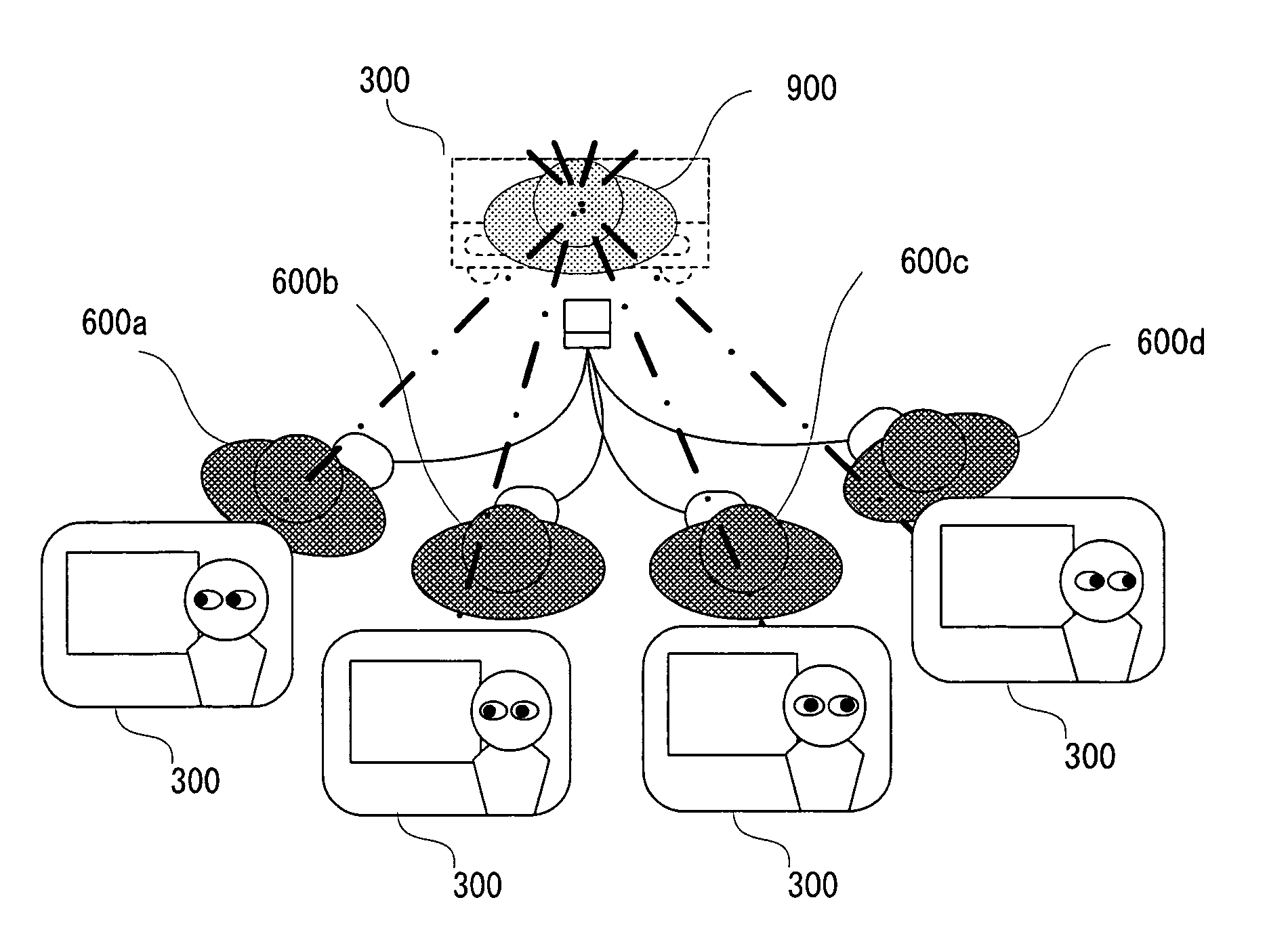

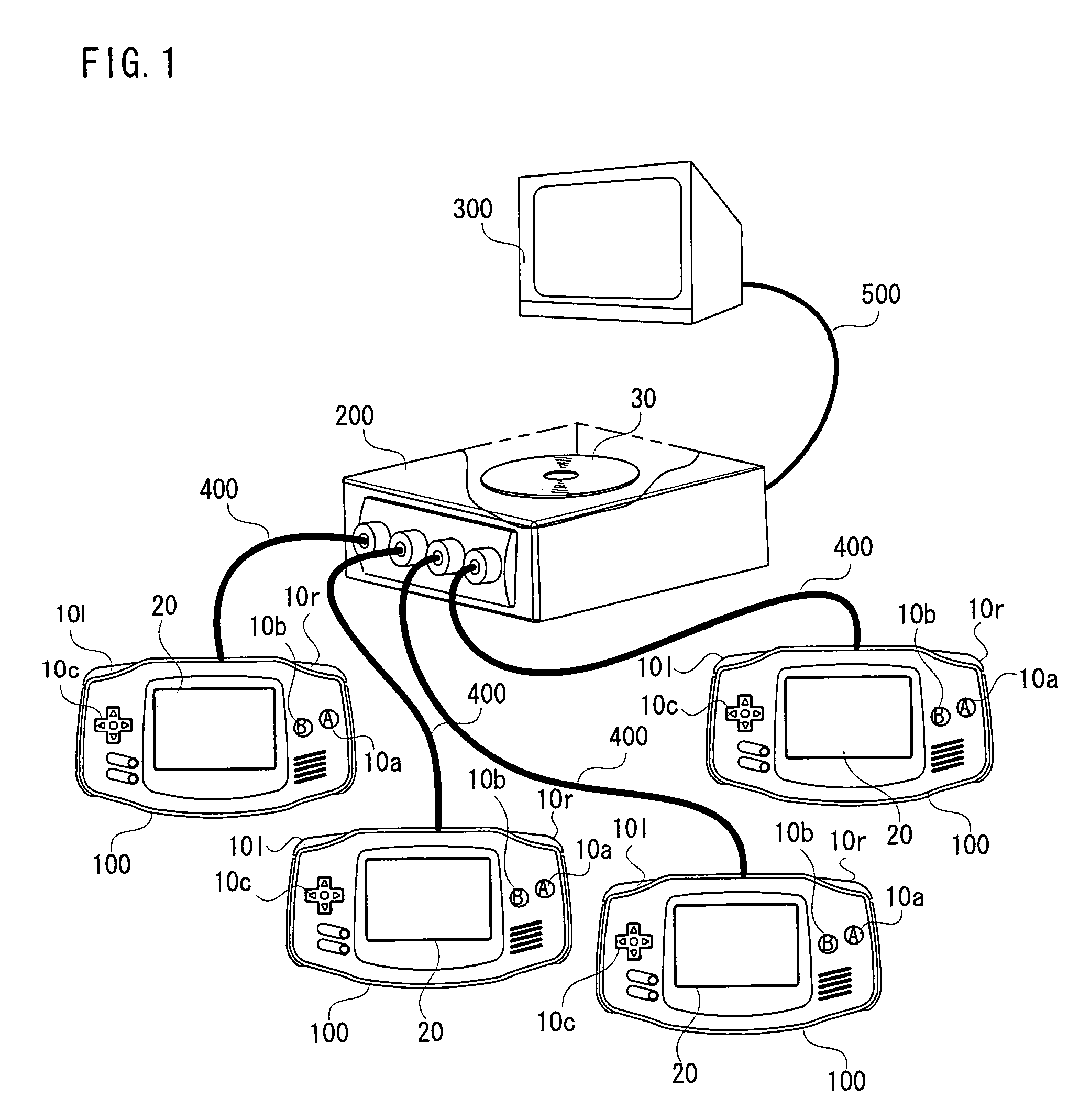

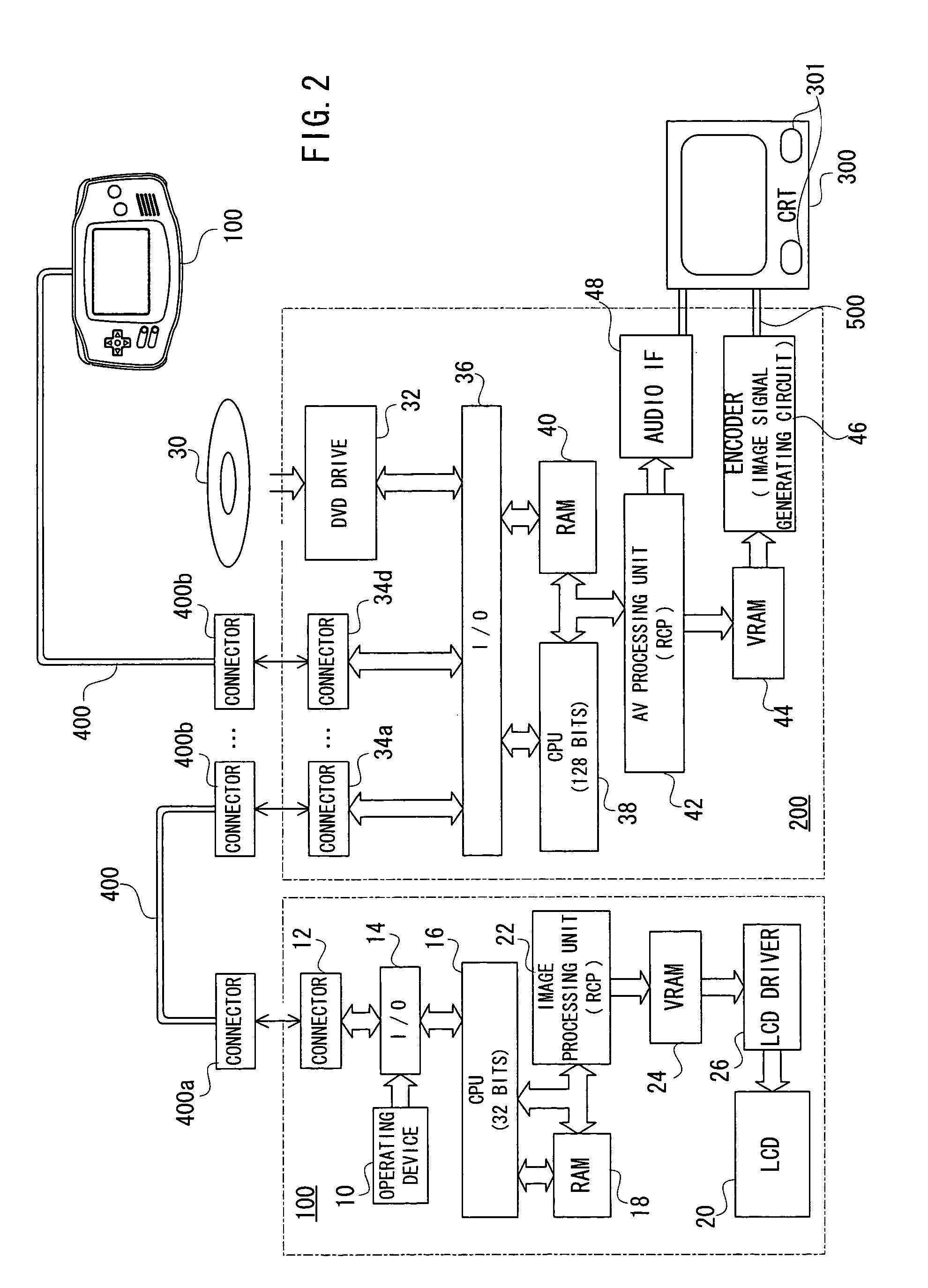

Game system using parent game machine and child game machine

InactiveUS8038533B2Reduce time differenceVideo gamesSpecial data processing applicationsEngineeringImaging data

A game system includes a parent game device and a plurality of child game devices connected thereto. The parent game device displays a common screen on a CRT, and each of the plurality of child game devices displays an individual screen on an LCD provided for each child device. The parent game device detects a degree of progress of a game of each child game device, selects for each child game device predetermined display information data out of a plurality of display information data on the basis of the detected degree of progress of the game, and creates different parent game device data for each child device on the basis of the display information data. Each child game device generates image data for displaying the individual screen on the LCD on the basis of the parent game device data received from the parent game device.

Owner:NINTENDO CO LTD

Non-volatile semiconductor memory device and semiconductor memory device

InactiveUS7286416B2Increase speedAccurate readingRead-only memoriesDigital storagePropagation delayHemt circuits

For each memory block, a predecoder for predecoding an applied address signal, an address latch circuit for latching the output signal of the predecoder, and a decode circuit for decoding an output signal of the address latch circuit and performing a memory cell selecting operation in a corresponding memory block are provided. Propagation delay of latch predecode signals can be made smaller and the margin for the internal read timing can be enlarged. In addition, the internal state of the decoder and memory cell selection circuitry are rest to an initial state when a memory cell is selected and the internal data output circuitry is reset to an initial state in accordance with a state of internal data reading. Thus, a non-volatile semiconductor memory device that can decrease address skew and realize an operation with sufficient margin is provided.

Owner:RENESAS ELECTRONICS CORP

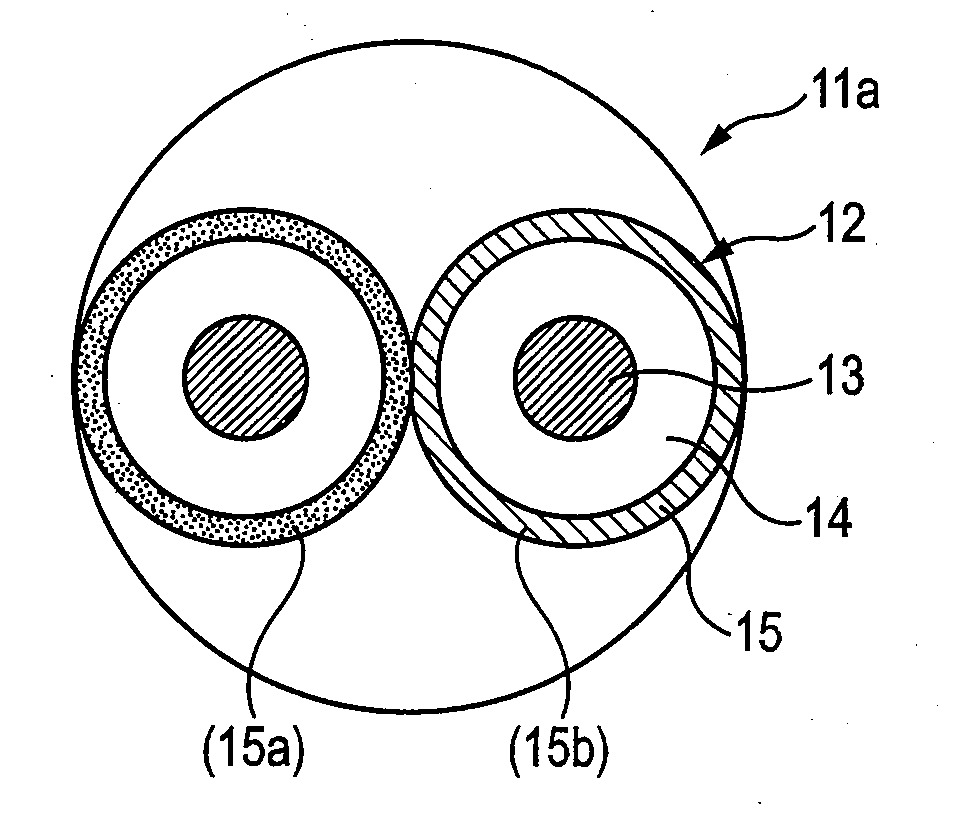

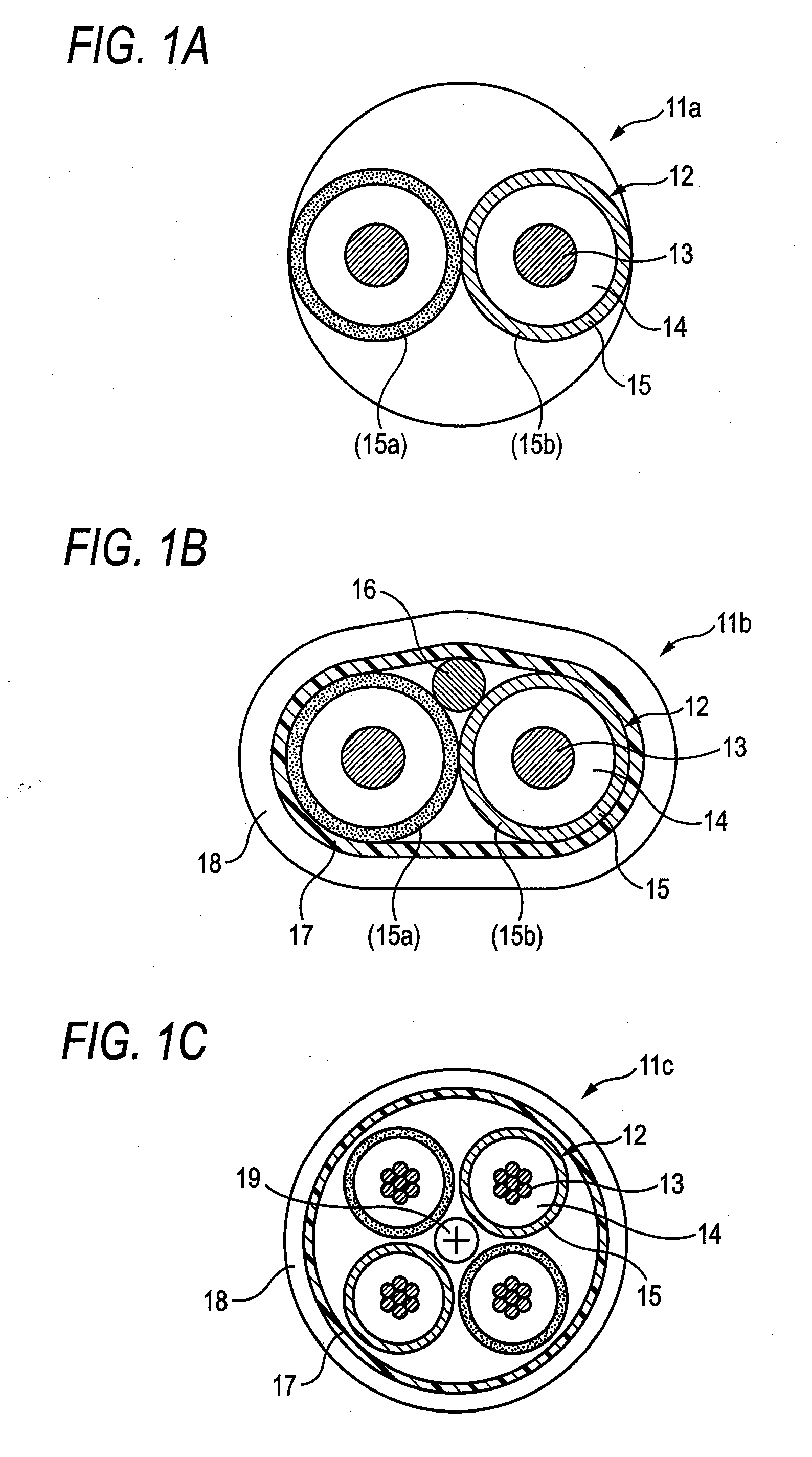

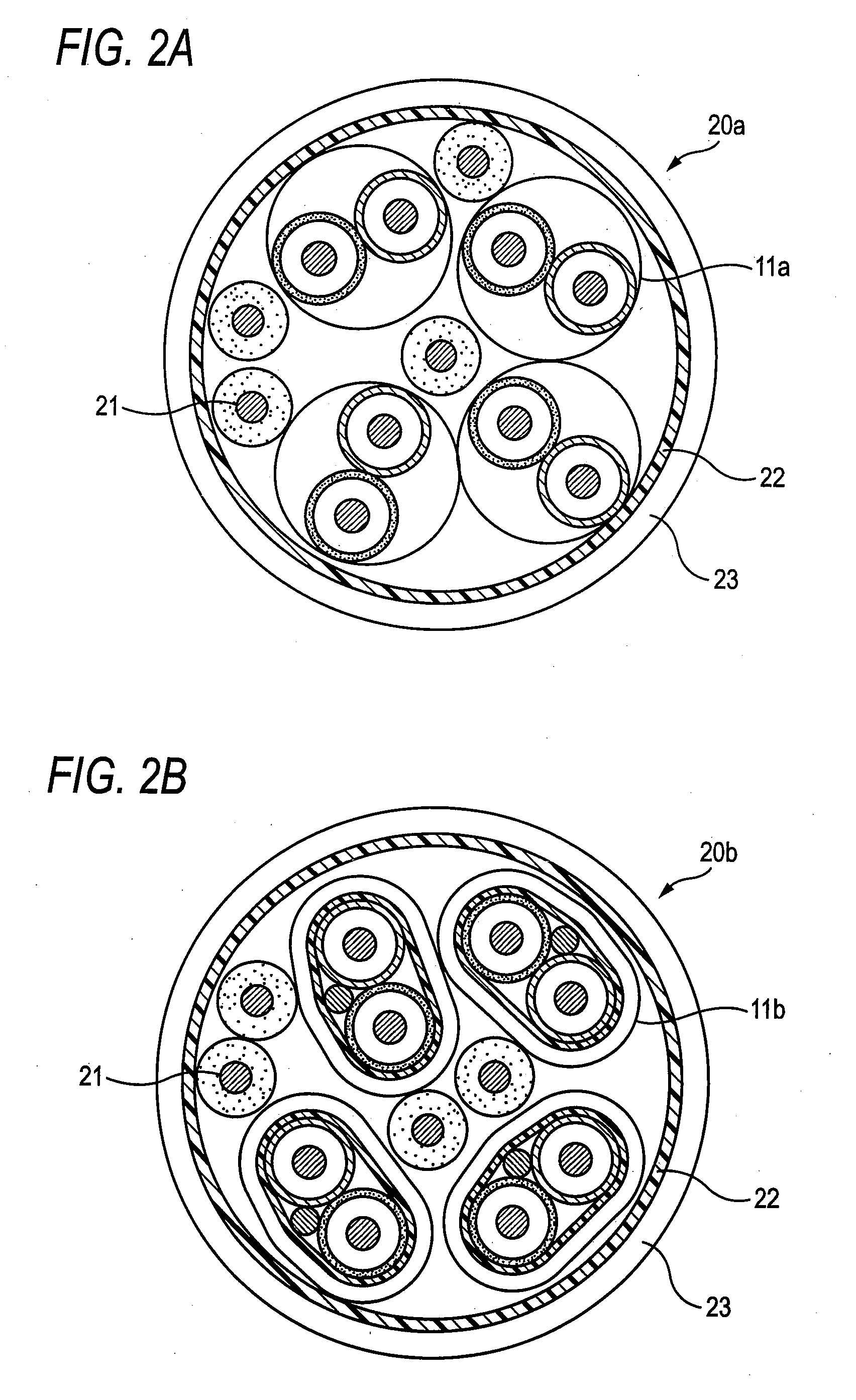

Twinax cable

InactiveUS20100307790A1High dielectric constantHigh mechanical strengthCoaxial cables/analogue cablesInsulated cablesEngineeringElectrical conductor

A twinax cable includes at least a pair of core wires, each of which includes a conductor and an insulator covering an outer periphery of the conductor. The insulator includes an inner insulator covering the outer periphery of the conductor and an outer insulator covering an outer periphery of the inner insulator. The inner insulator is formed by a non-colored compressed insulator. The outer insulator is formed by a colored compressed insulator. A thickness of the outer insulator is formed thinner than a thickness of the inner insulator. The outer insulators of the pair of core wires are formed to have hues that are set respectively differently.

Owner:SUMITOMO ELECTRIC IND LTD

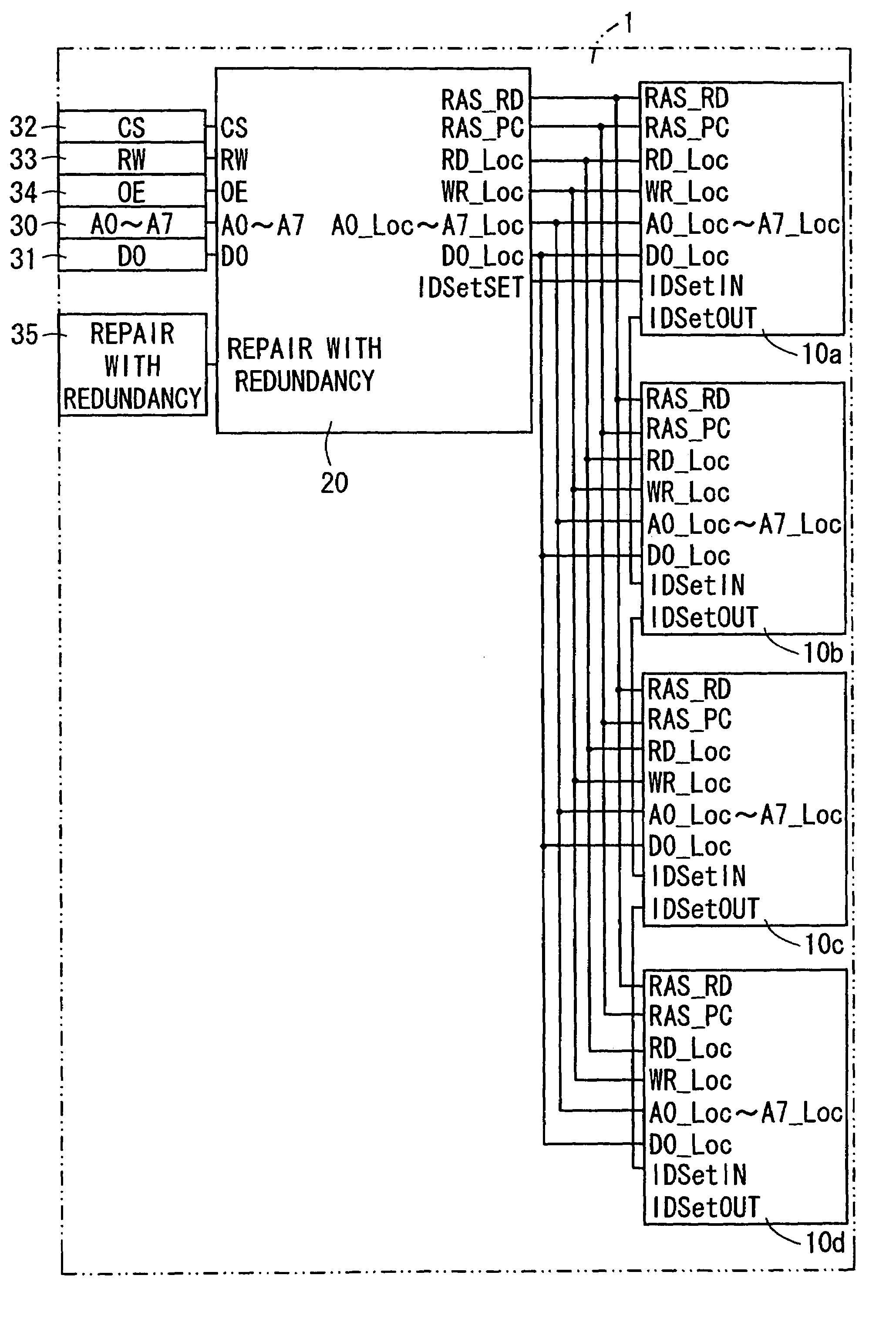

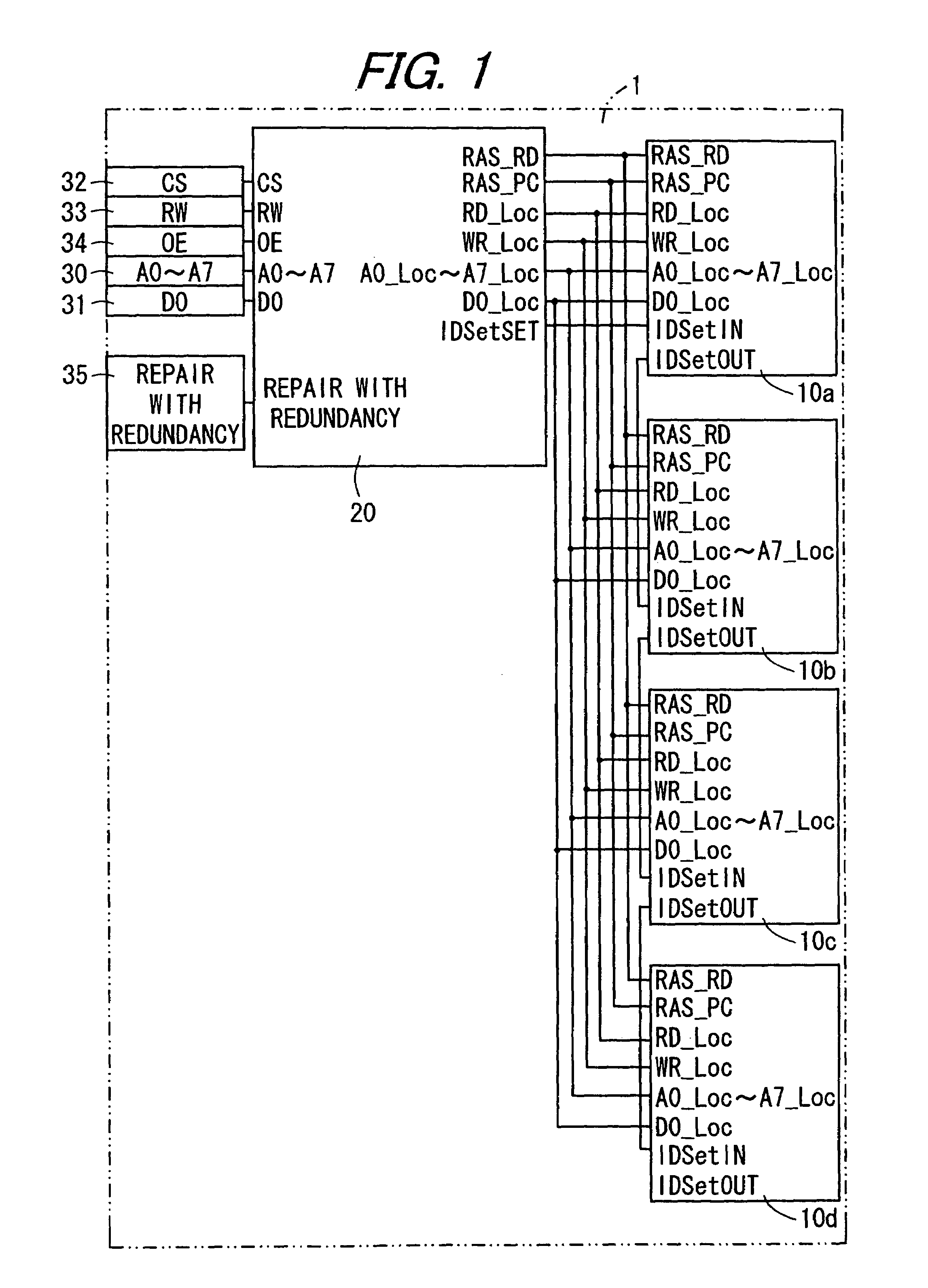

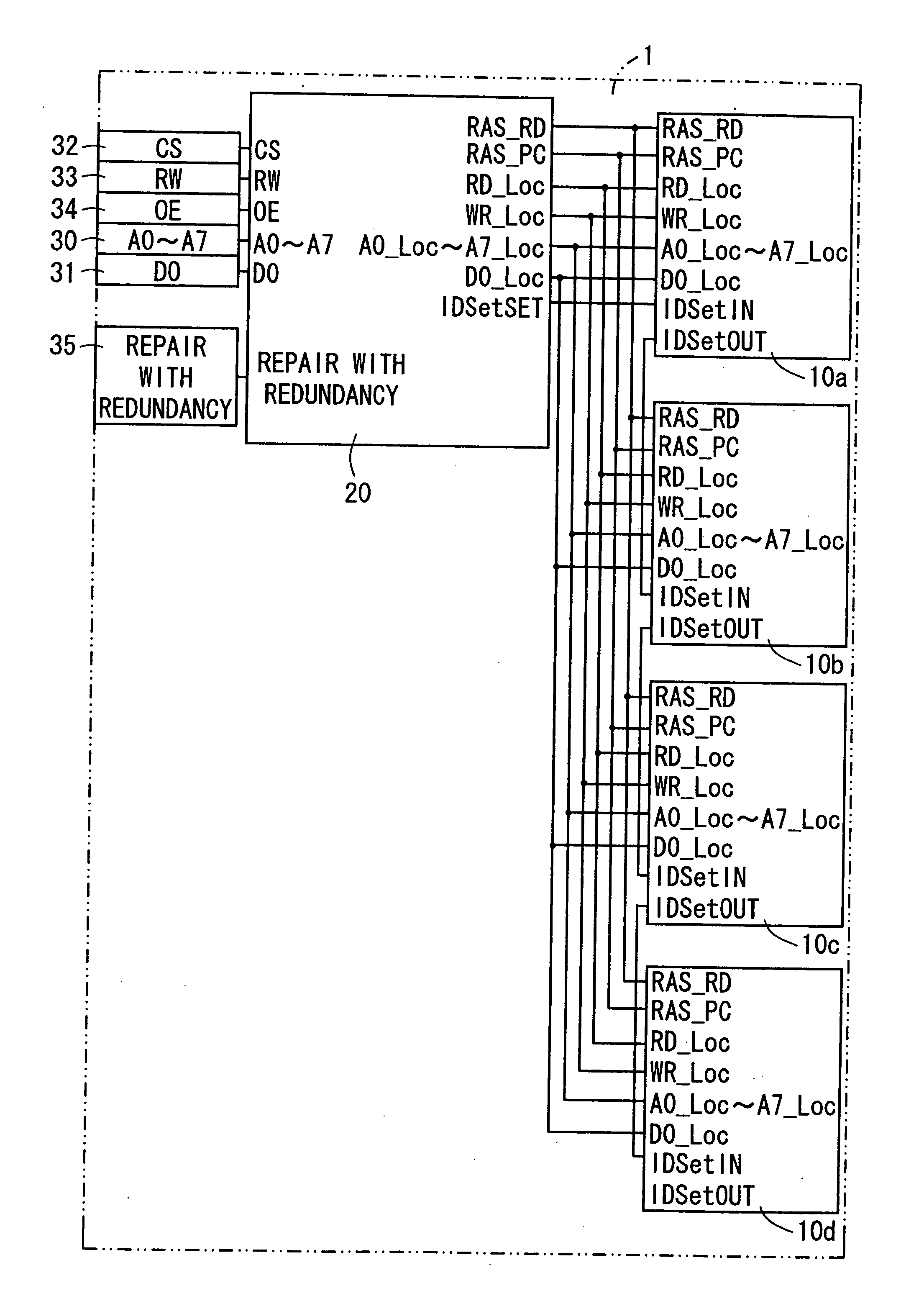

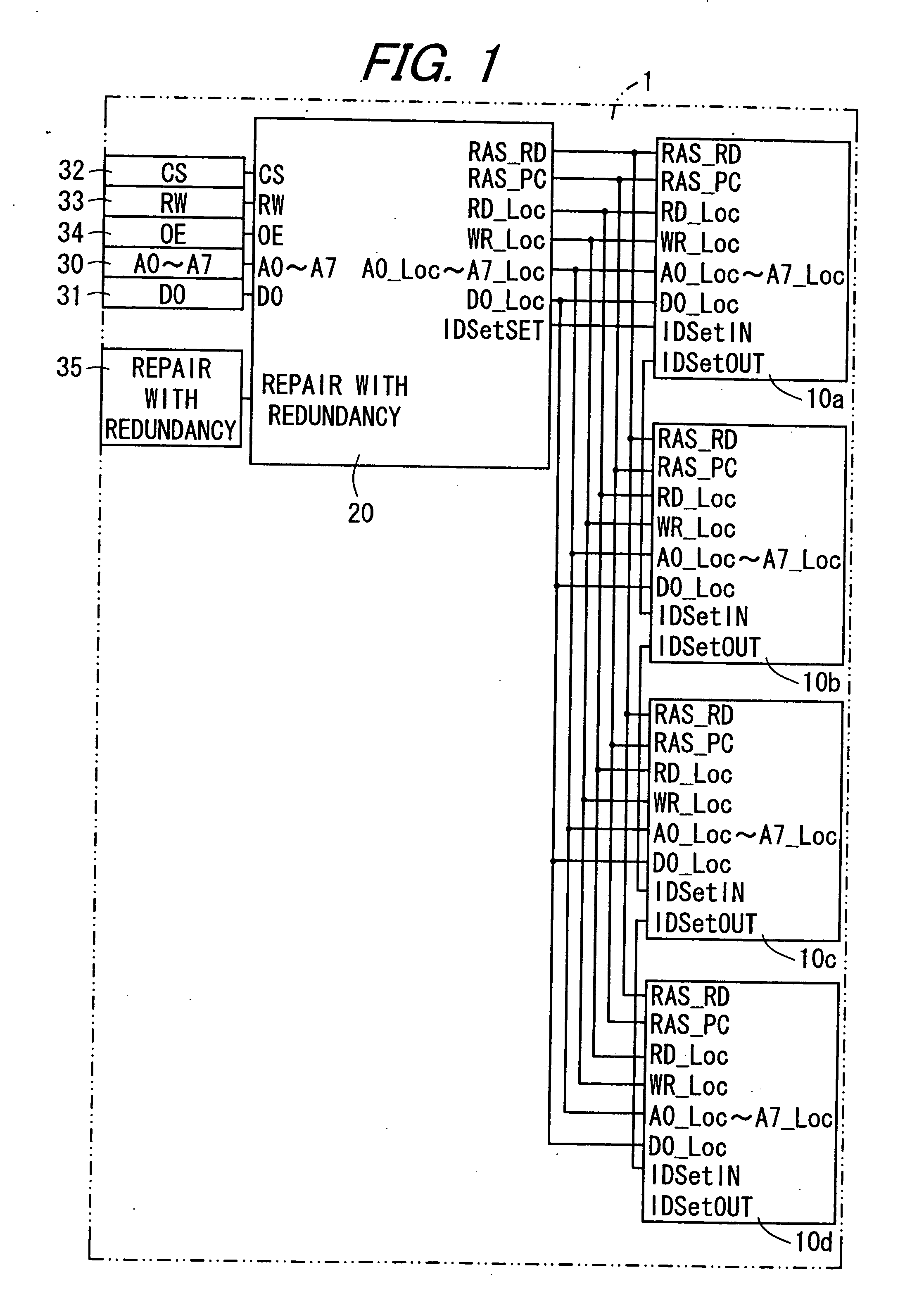

Memory device having redundant memory for repairing defects

First memory chips each have a memory cell as storage means for storing data and do not have a redundant memory cell as redundant storage means for repairing an erroneous bit in the memory cell. Furthermore, a logic minimal in degree is solely provided for operation on a control logic of a second memory chip. The second memory chip has a control logic for effecting memory control of the memory cells, the redundant memory cells, etc. and a redundant memory cell for repairing an error bit of the first memory chips. The memory device is structured by stacking the first and second memory chips.

Owner:SHARP KK

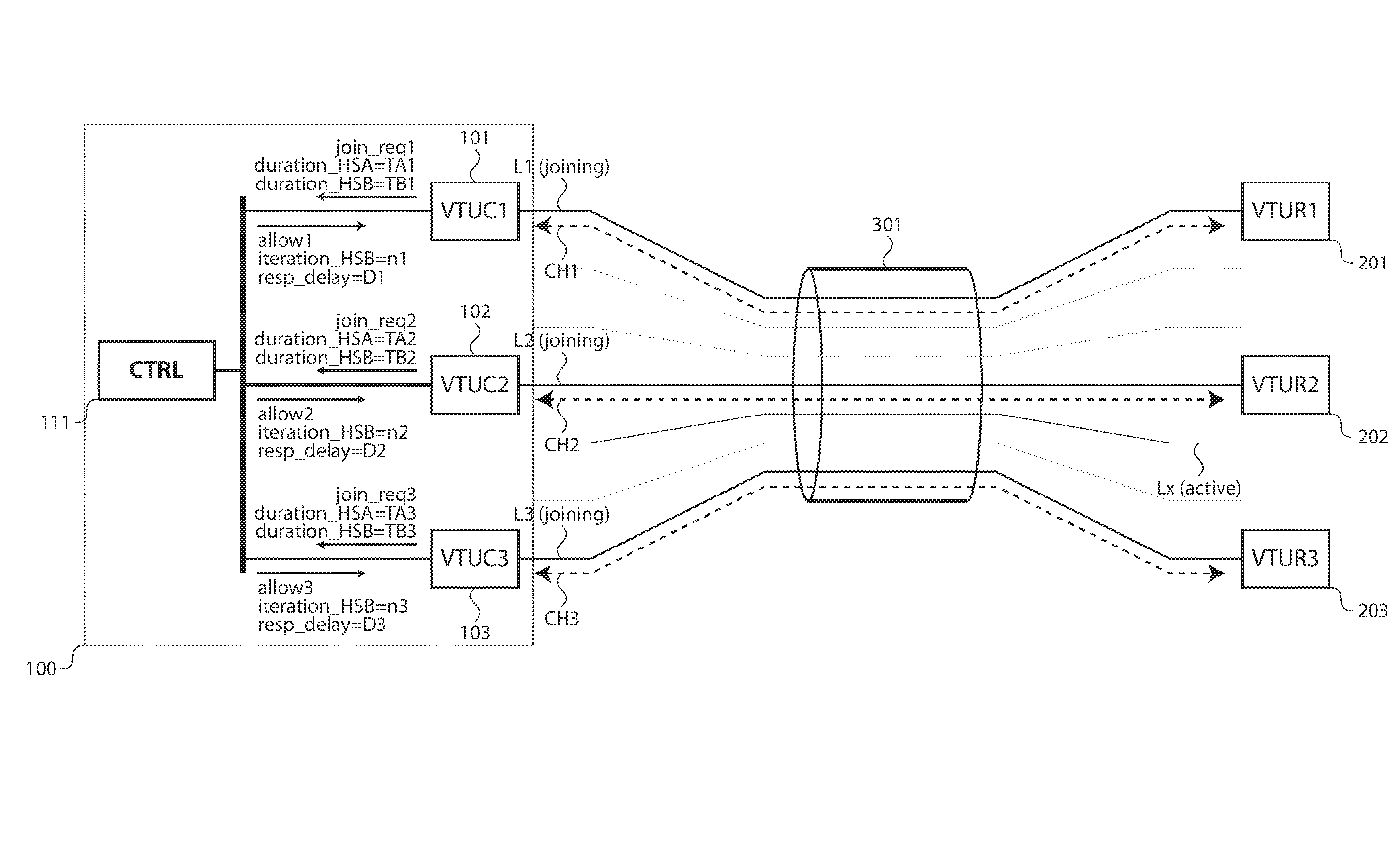

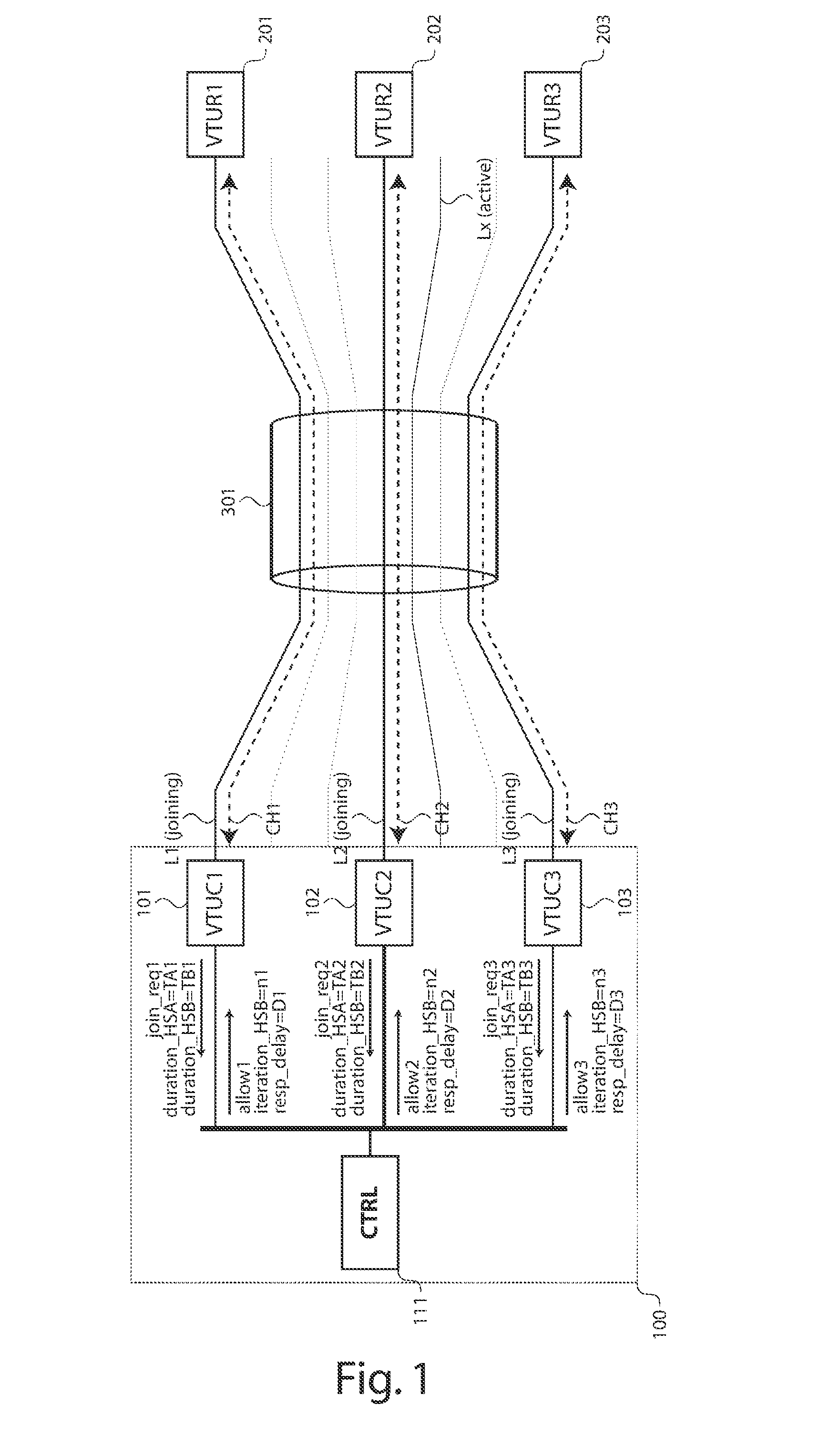

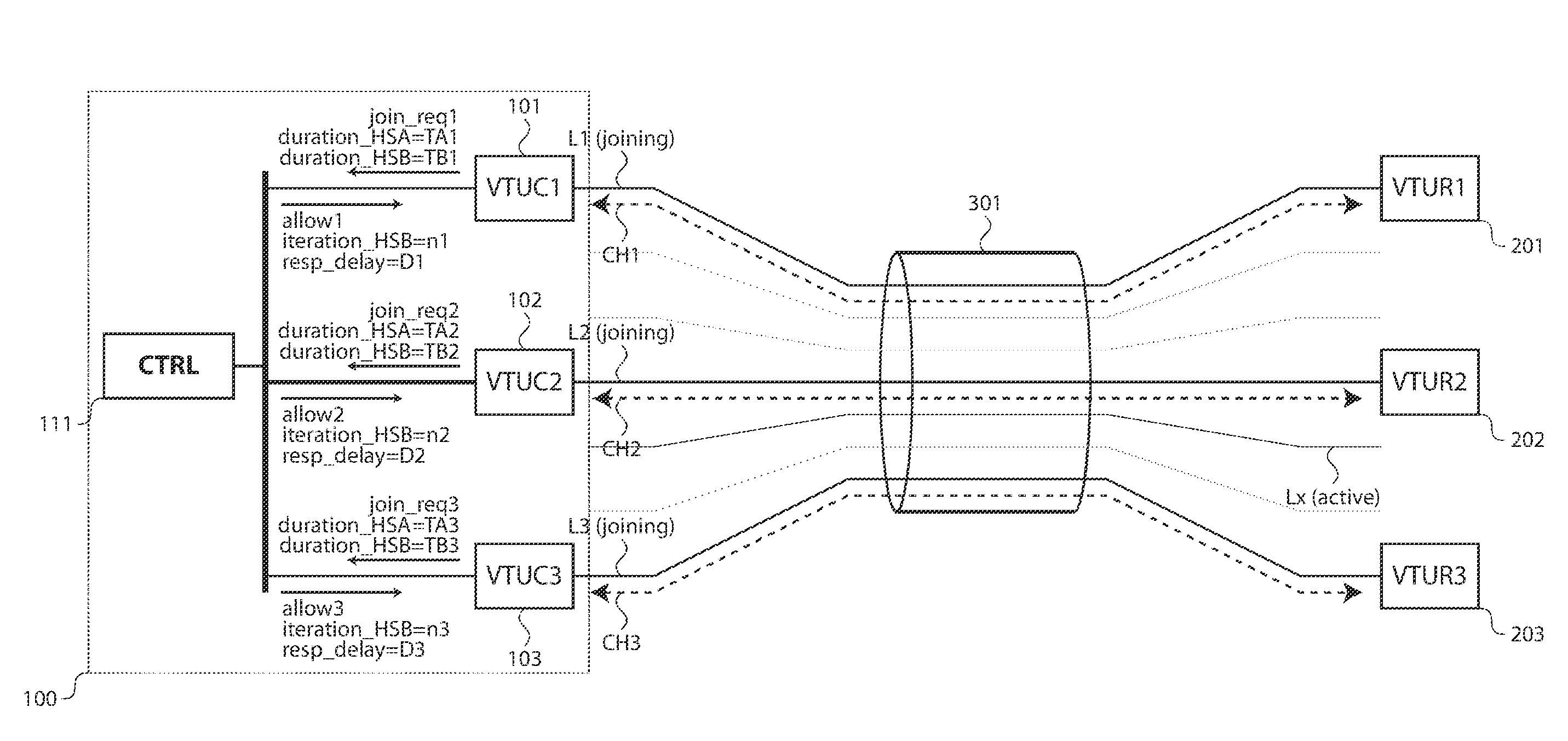

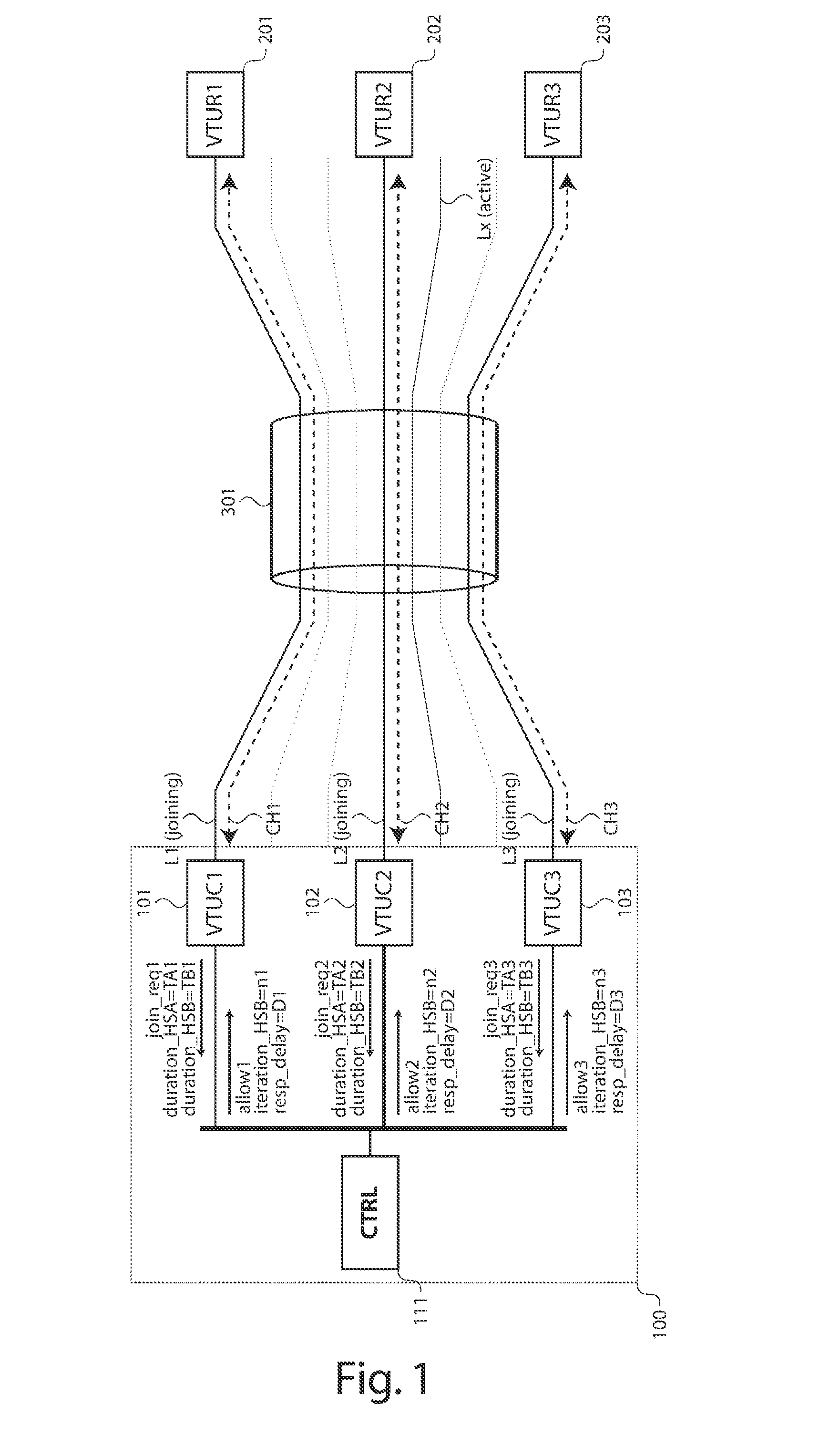

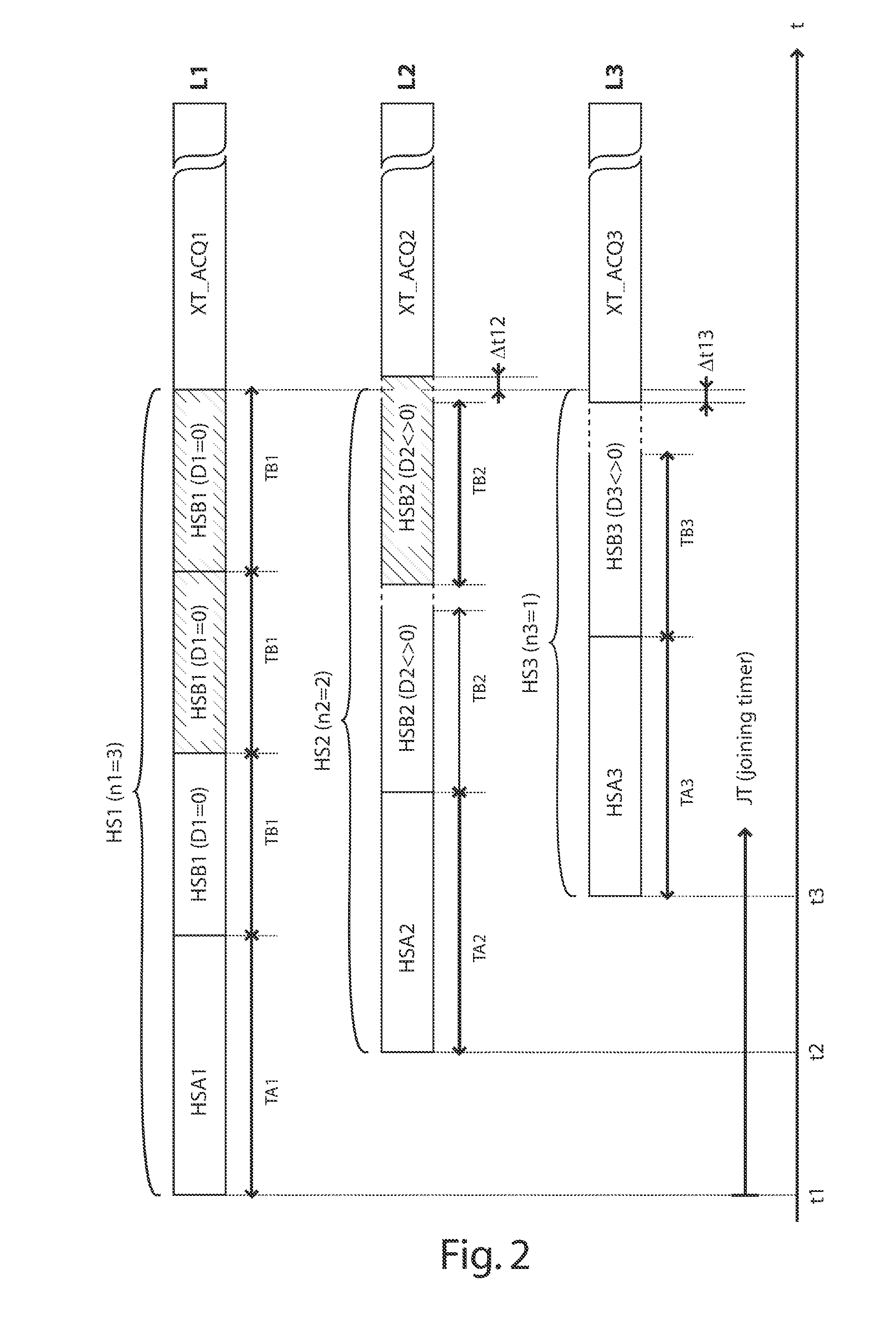

Time-alignment of crosstalk acquisition phases between multiple joining lines

ActiveUS20130251141A1Improve parallel joiningReduce time differenceTwo-way loud-speaking telephone systemsBaseband system detailsTransceiverTime alignment

In an embodiment, the access node includes first and second transceiver units for initializing first and second communication channels, respectively, over first and second communication lines, respectively. The initialization of the first and second communication channels respectively including first and second handshake phases wherein peer transceiver units exchange capabilities and select (i) a common mode of operation, (ii) first and second crosstalk channel acquisition phases from the first and second communication lines, and (iii) first and second generic initialization phases. The access node further includes a line initialization controller configured to stretch the execution of the first handshake phase with respect to the execution of the second handshake phase so as to shorten a time difference between respective entries into the first and second crosstalk channel acquisition phases.

Owner:META PLATFORMS INC

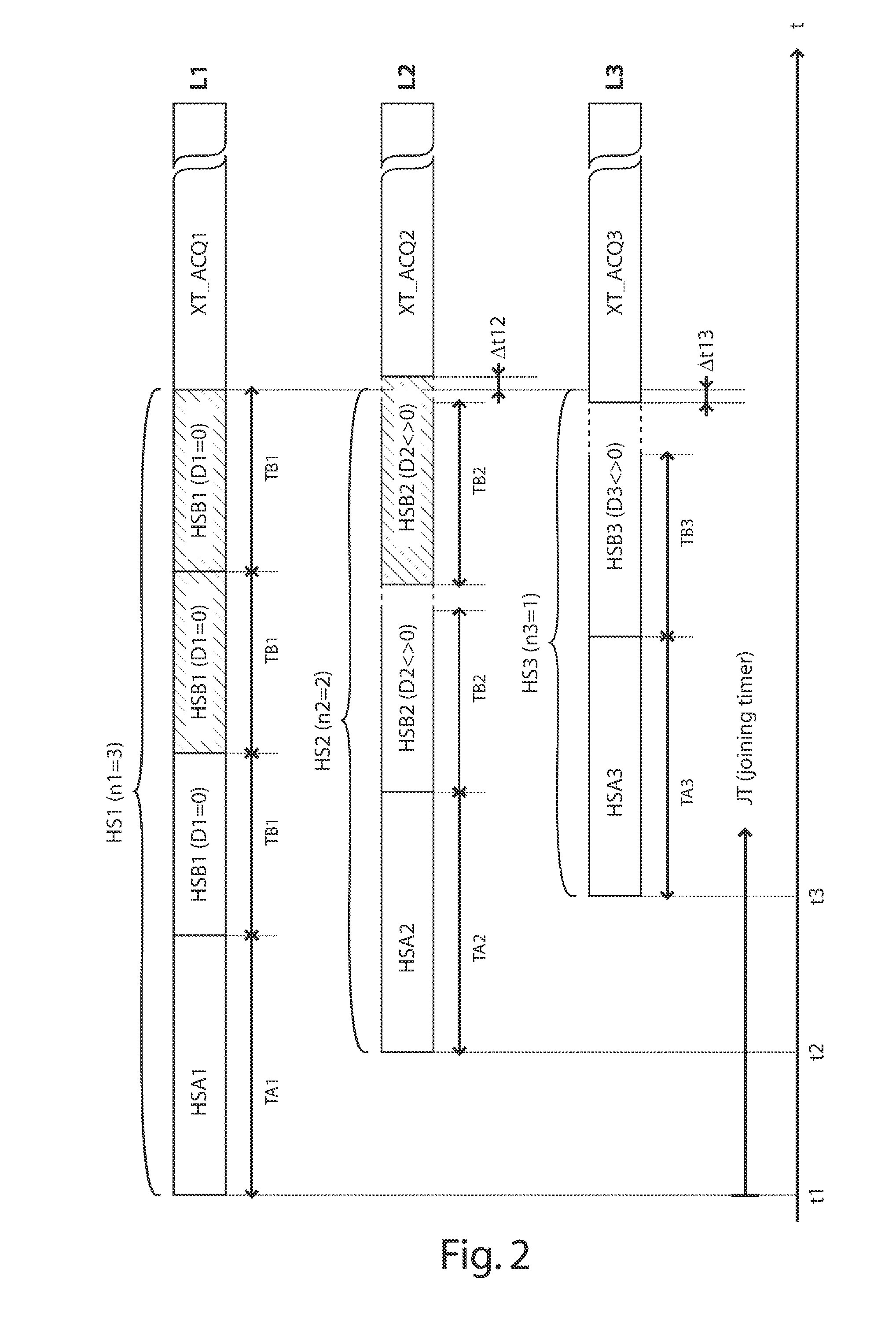

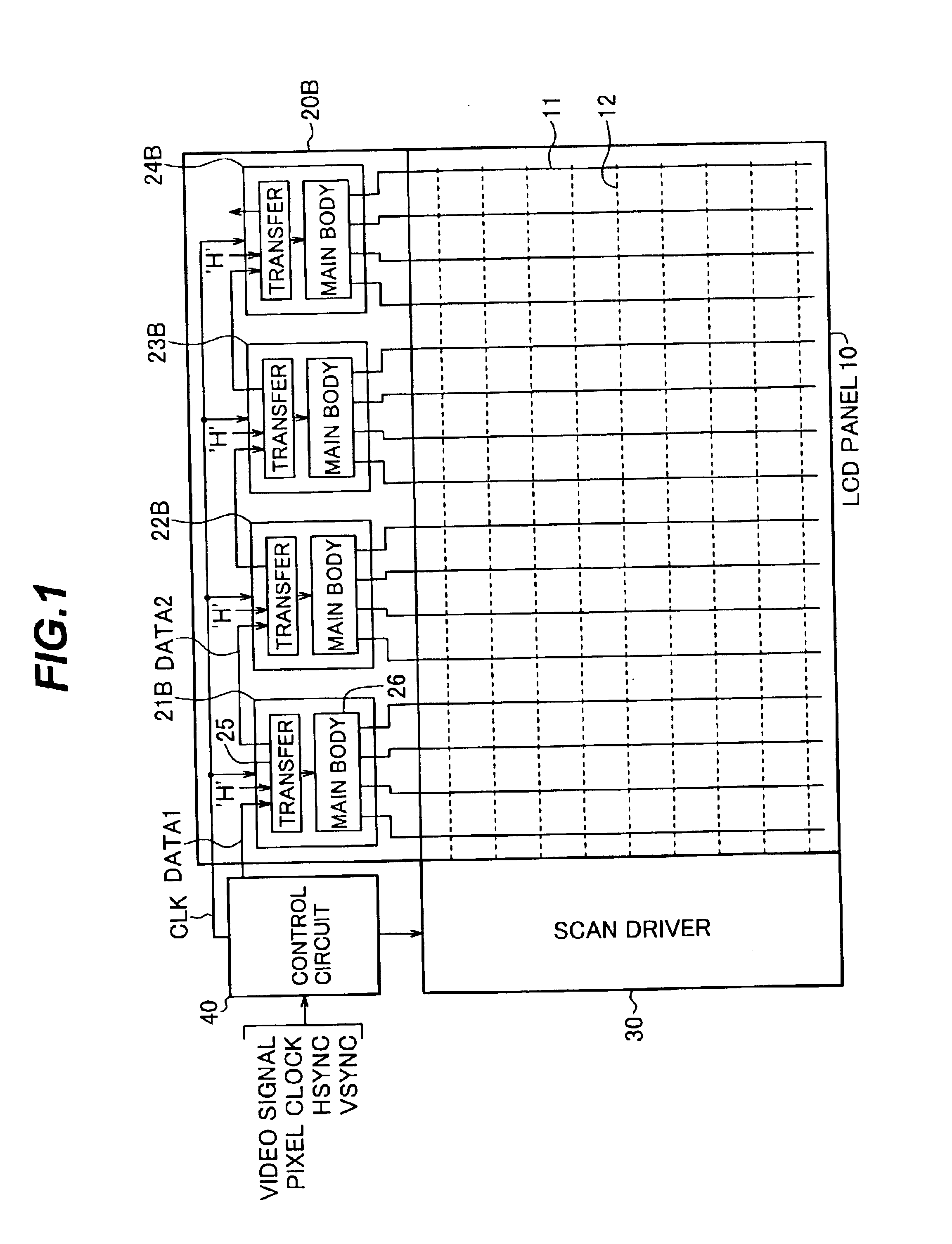

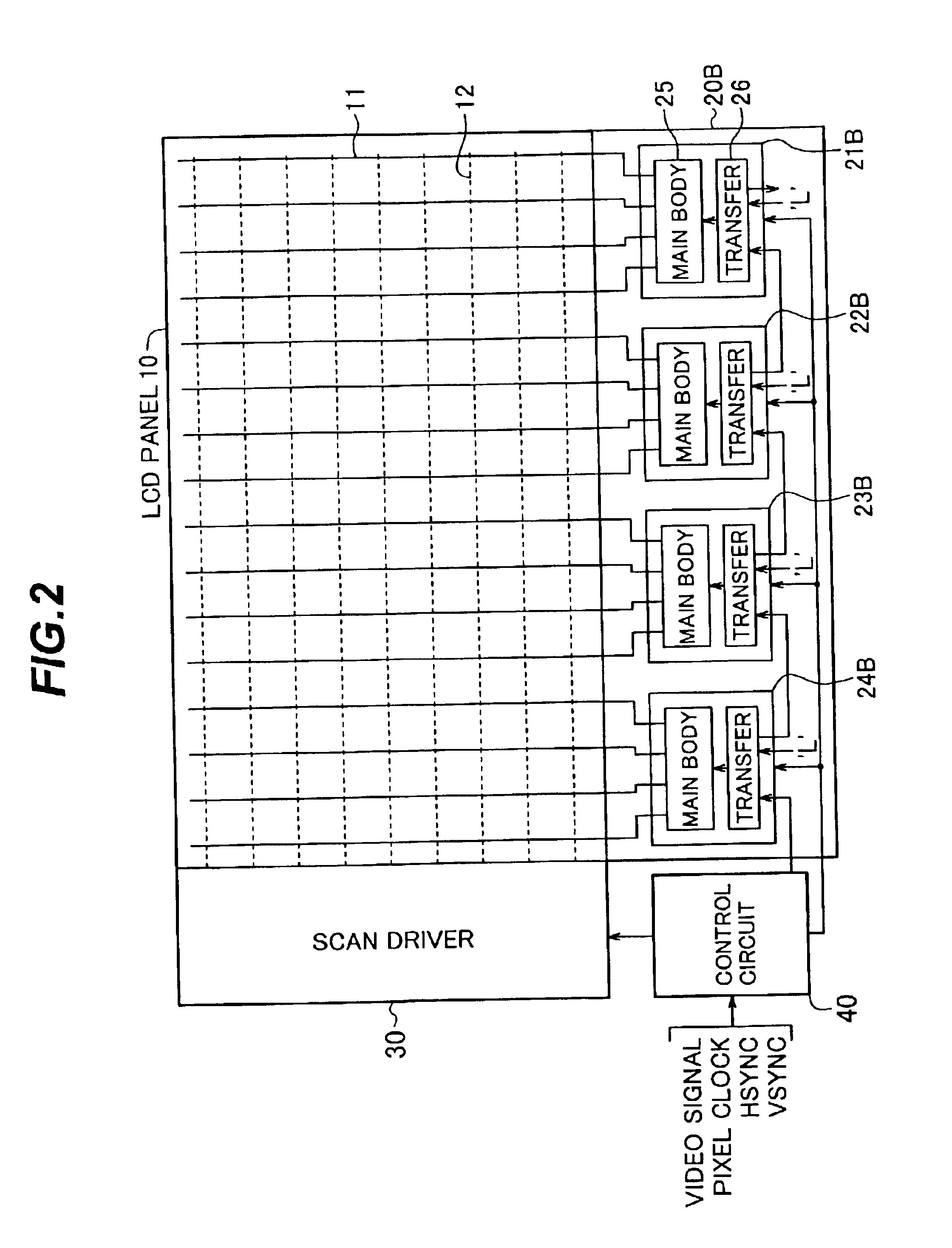

Semiconductor device equipped with transfer circuit for cascade connection

InactiveUS6847346B2Reduce crosstalk effectsReduce time differenceStatic indicating devicesGeneral purpose stored program computerMultiplexingMultiplexer

A transfer circuit 25 includes two sets of an input circuit 52A and an output circuit 53B, which allows bidirectional transfer. The input circuit 52A decomposes external input data signals DI11A and DI12A to signals on lines L11 to L14 in synchronism with a clock signal CLK in order to reduce the frequency thereof. The output circuit 53B composes the decomposed signals in synchronism with the clock signal CLK to regenerate the original signals and output them as external output data signals DO11B and DO12B. Signals on either the lines L11 to L14 or L21 to L24 are selected by a multiplexer 57 to provide to a main body circuit.

Owner:FUJITSU SEMICON LTD

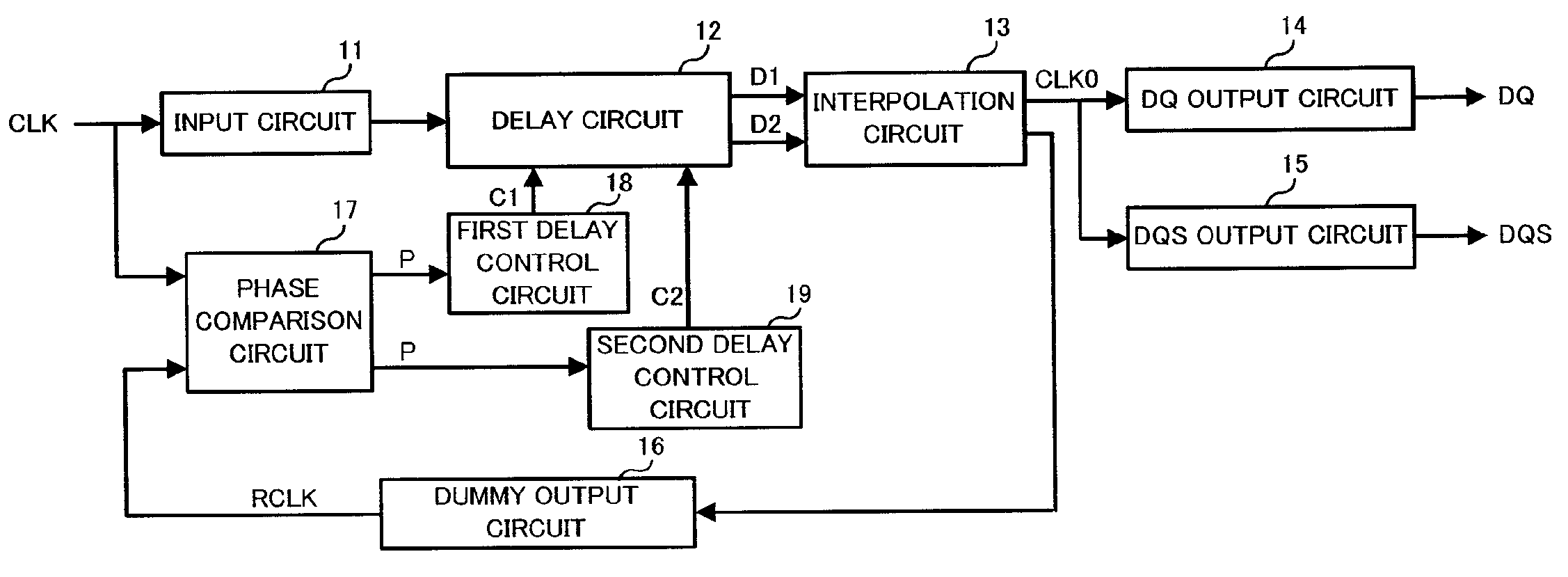

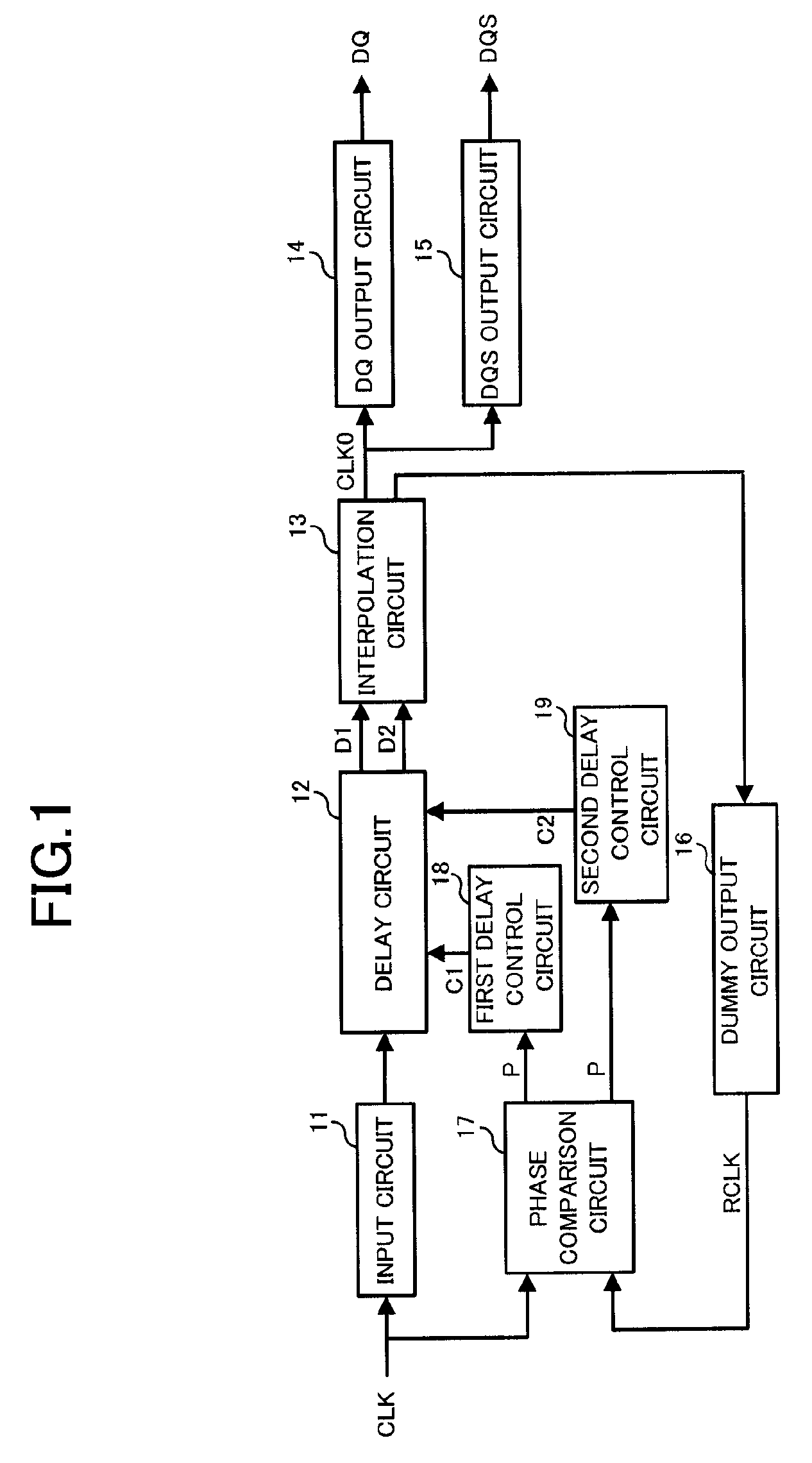

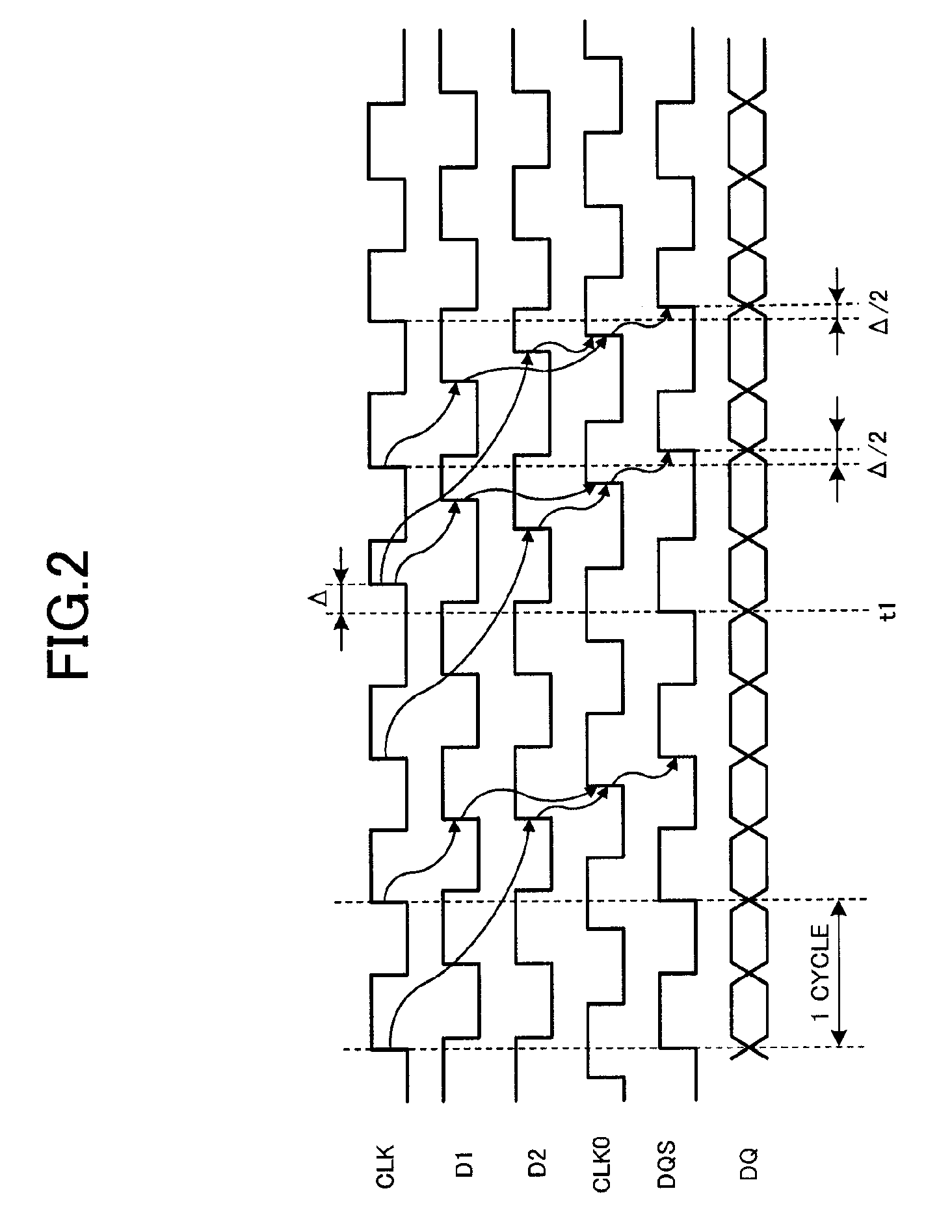

Dll circuit and semiconductor device having the same

InactiveUS20070210843A1Time differenceReduce the possibilityPulse automatic controlSingle output arrangementsControl signalPhase difference

A DLL circuit comprising: delay circuits which output first and second delayed clock signals obtained by delaying the reference clock signal by a delay times selected according to control signals; an interpolation circuit which interpolates a phase difference between the delayed clock signals to output an internal clock signal; an output circuit which generates a predetermined signal; a dummy output circuit which has the same transmission characteristics as the output circuit and outputs a feedback clock signal having the same phase as the predetermined signal; a phase comparison circuit which compares phases of the reference clock signal and the feedback clock signal; delay control circuits which controls the control signals in a direction where both phases are equal; wherein the delay time of the second delayed clock signal is larger than the first delayed clock signal by an amount equivalent to one cycle of the reference clock signal.

Owner:LONGITUDE SEMICON S A R L

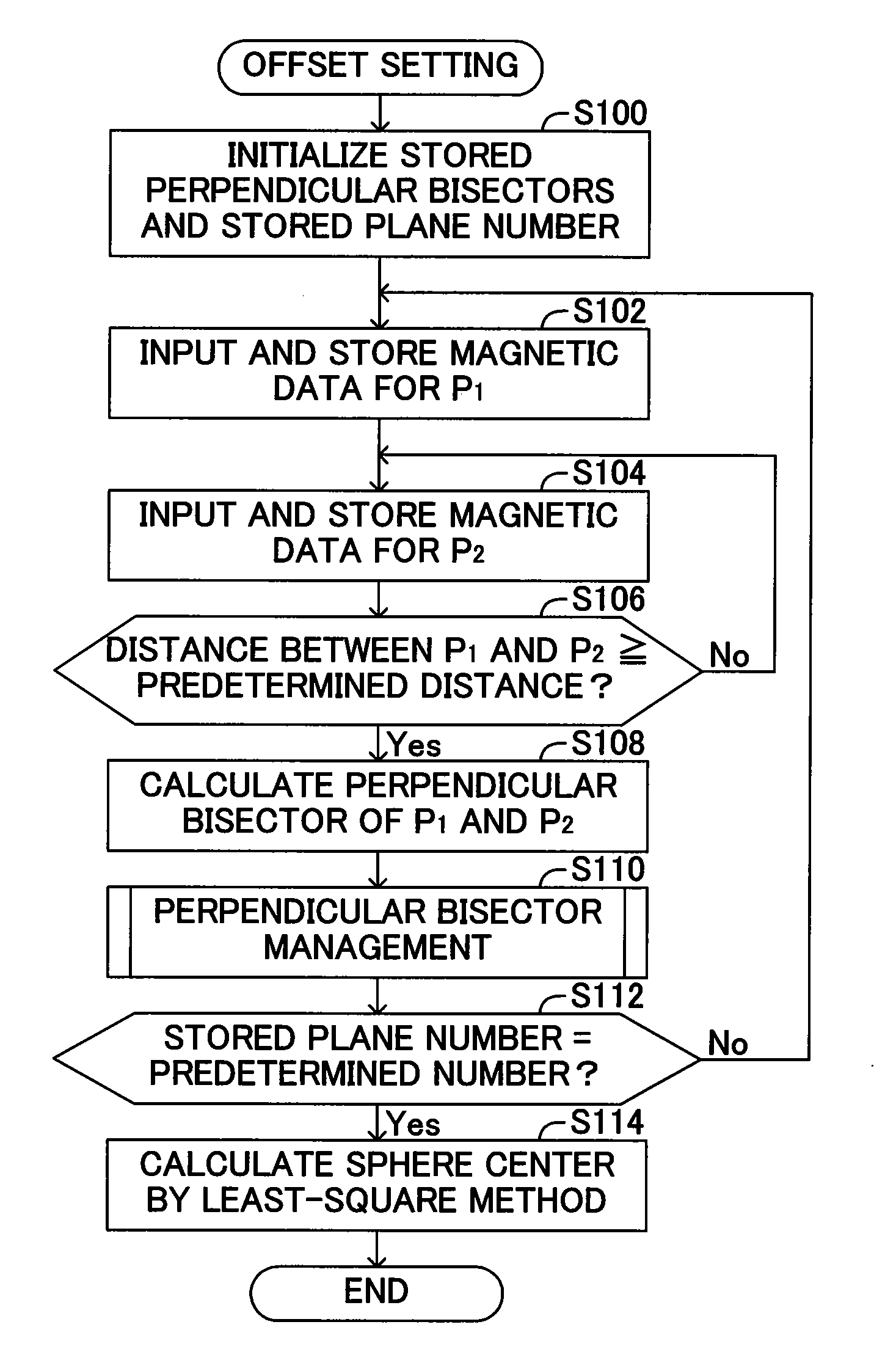

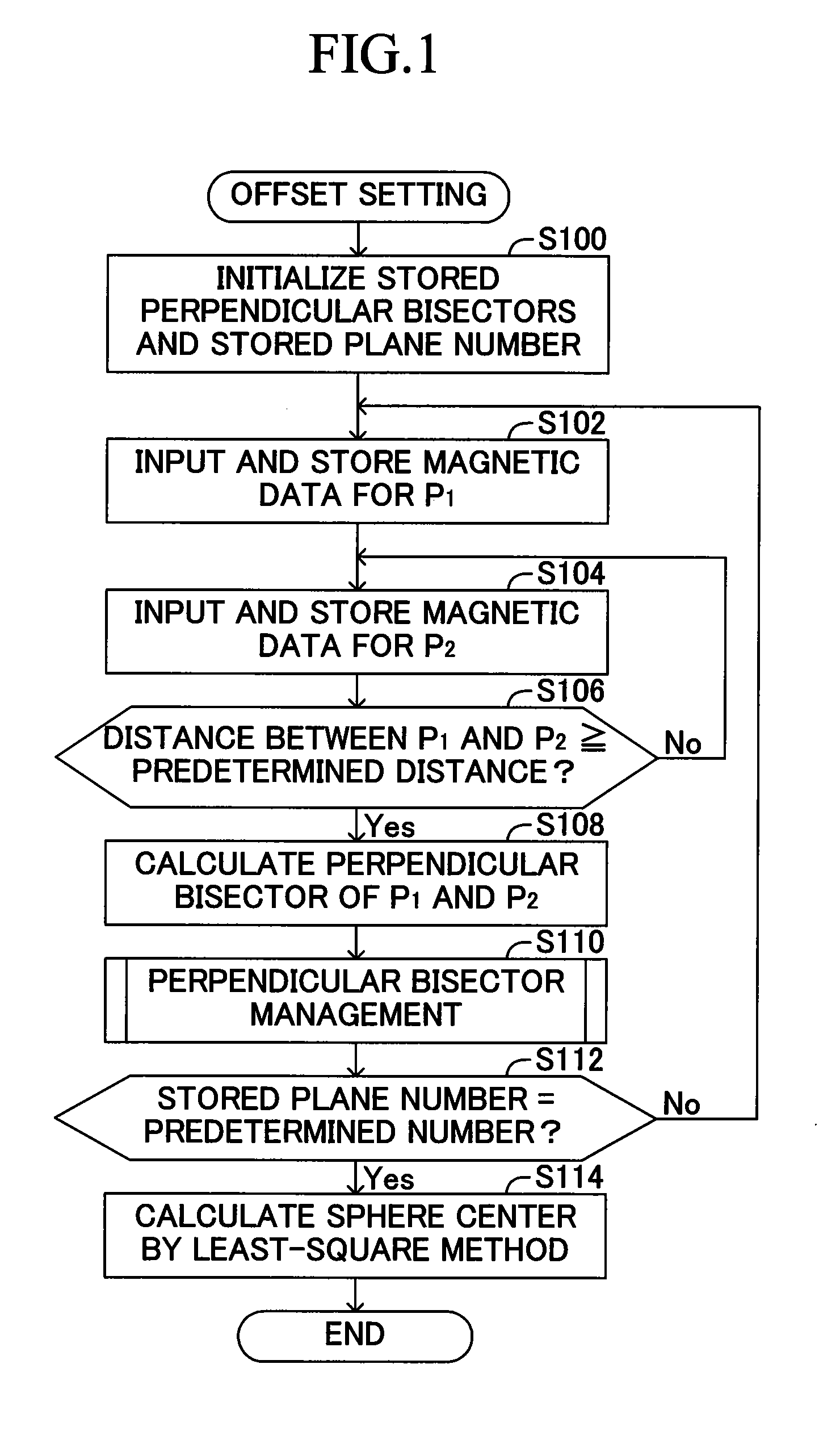

Magnetic-sensor controller, magnetism measurement apparatus, offset setting method, and computer-readable medium on which offset setting program is recorded

InactiveUS20070198209A1Accurate settingCorrection errorMeasurement arrangements for variableElectrical/magnetic diameter measurementsData setUltimate tensile strength

A magnetic-sensor controller includes an input section, a perpendicular-bisector calculation section, a storage section, and a setting section. The input section successively inputs a plurality of magnetic data sets successively output from a three-dimensional magnetic sensor. Each magnetic data includes three components. The perpendicular-bisector calculation section calculates, for each pair of two of the magnetic data sets, a perpendicular bisector of two points corresponding to the two magnetic data sets. The storage section stores a plurality of perpendicular bisectors. The setting section statistically approximates, by a single point, a region where the plurality of perpendicular bisectors stored in the storage section meet, and sets an offset of the magnetic data set on the basis of the single point. The magnetic-sensor controller enables accurate setting of an offset even when the magnetic field strength changes.

Owner:YAMAHA CORP

Memory device

First memory chips each have a memory cell as storage means for storing data and do not have a redundant memory cell as redundant storage means for repairing an erroneous bit in the memory cell. Furthermore, a logic minimal in degree is solely provided for operation on a control logic of a second memory chip. The second memory chip has a control logic for effecting memory control of the memory cells, the redundant memory cells, etc. and a redundant memory cell for repairing an error bit of the first memory chips. The memory device is structured by stacking the first and second memory chips.

Owner:SHARP KK

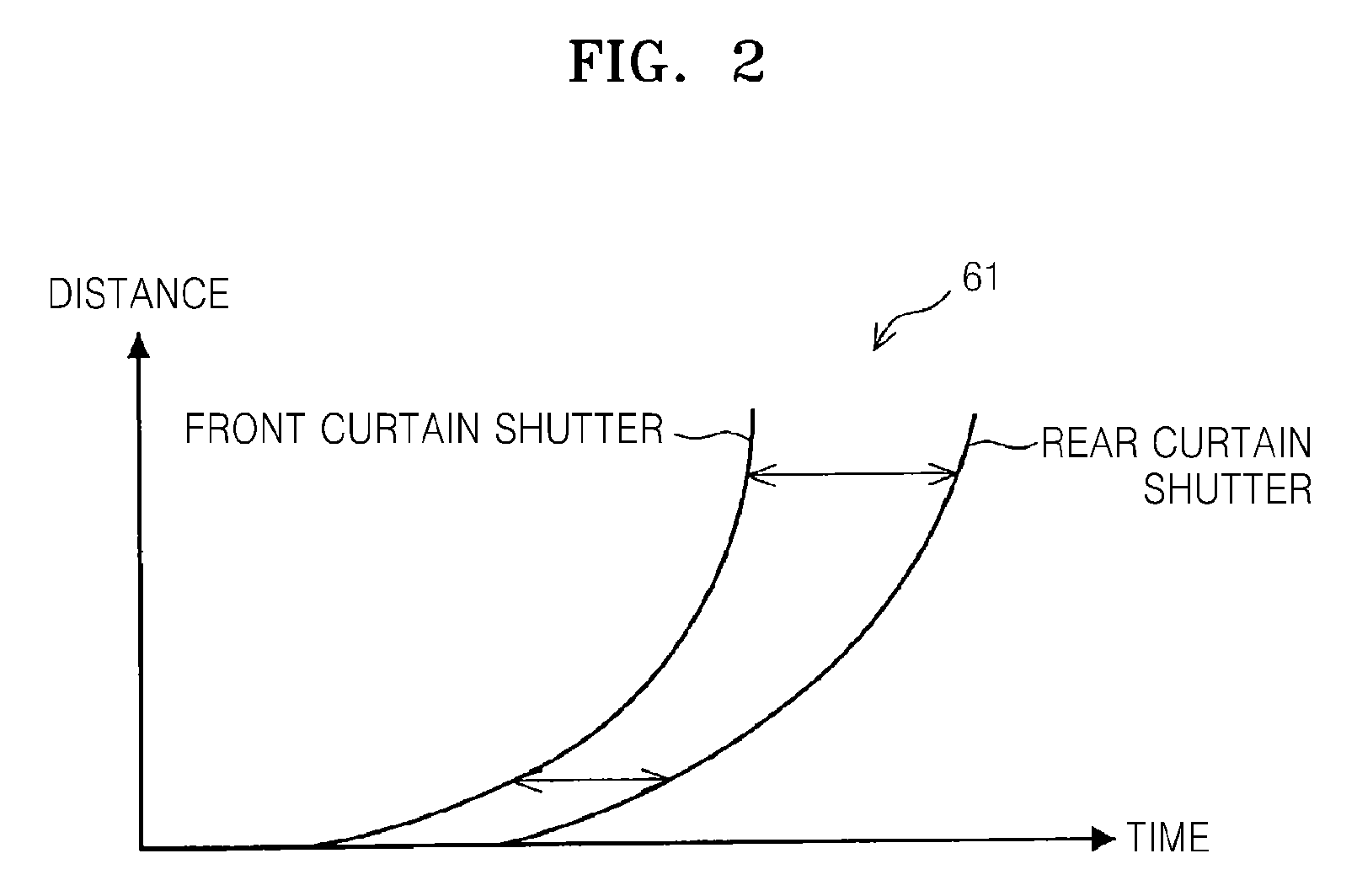

Photographing apparatus and method

InactiveUS20110043674A1Adjust in timeReduce time differenceTelevision system detailsTelevision system scanning detailsTime controlComputer science

A photographing apparatus includes an imaging unit having a plurality of pixels arranged in rows and columns and that captures an image of a subject; a detector that detects a photographing condition of the subject; a mechanical shutter that moves to shield the imaging unit; an operation controller that controls movement of the mechanical shutter; and a scan controller that controls an exposure start scan of the imaging unit by applying reset signals to the pixels at a time controlled based on the photographing condition of the subject before the mechanical shutter moves to shield the imaging unit.

Owner:SAMSUNG ELECTRONICS CO LTD

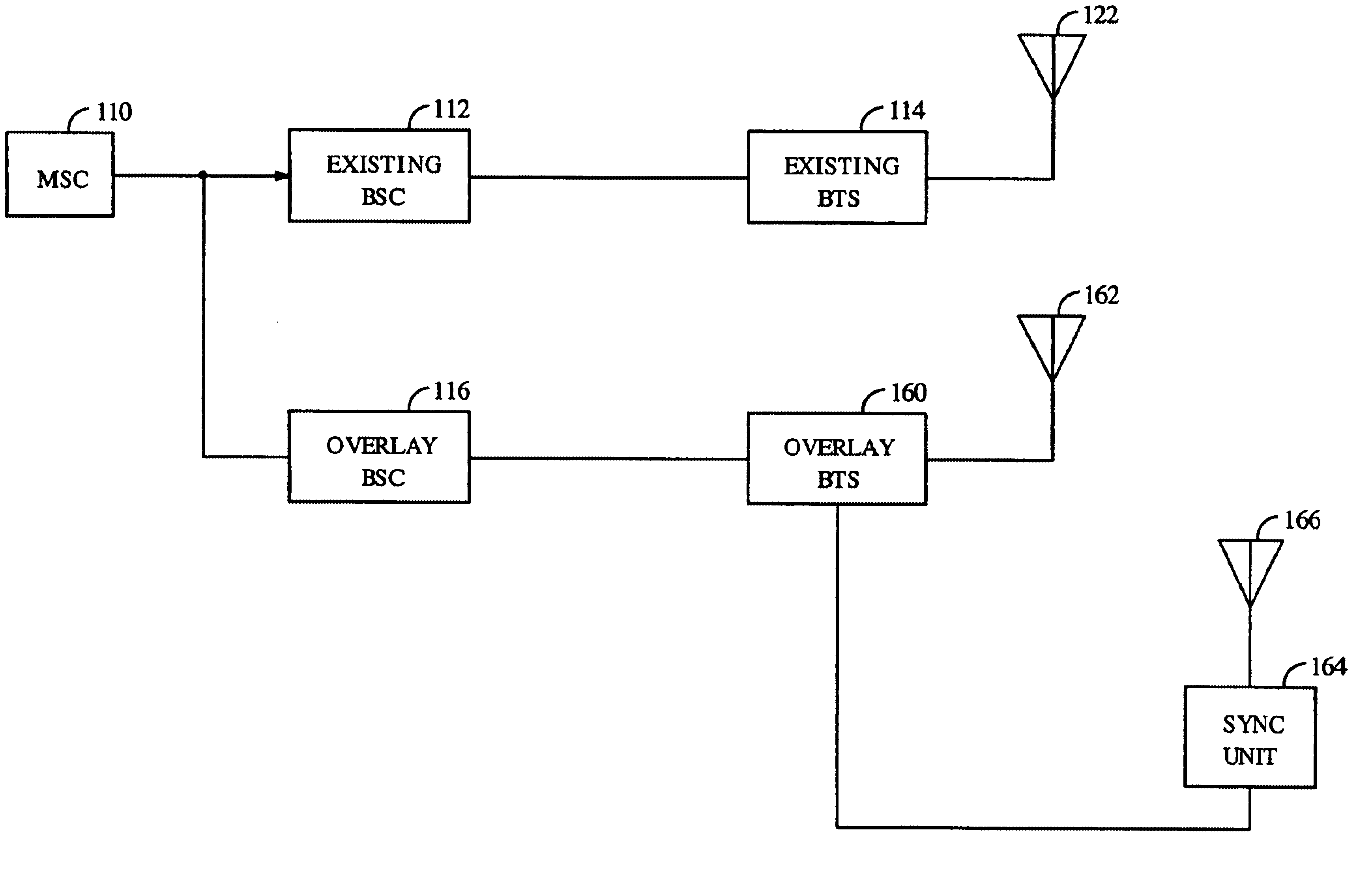

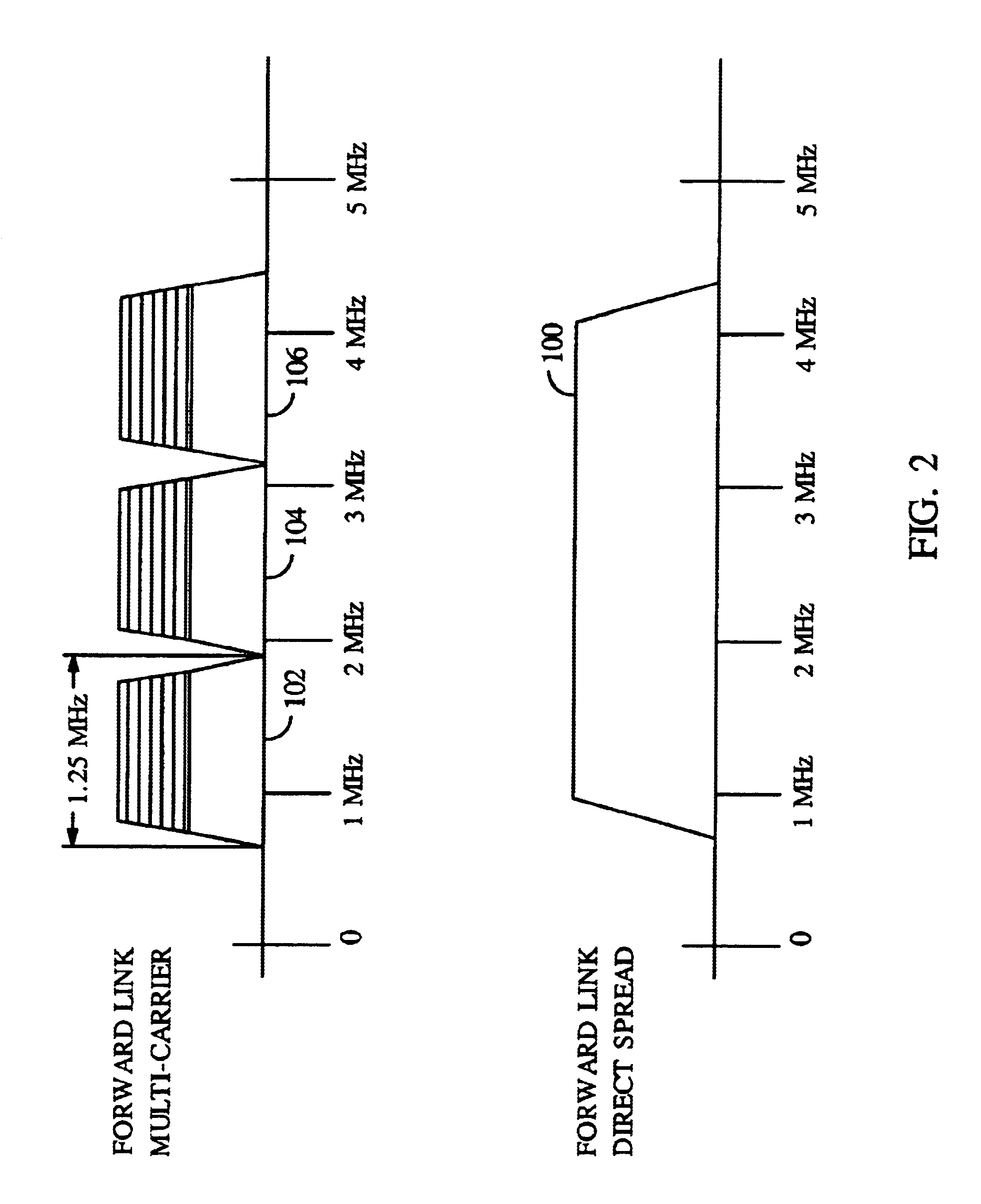

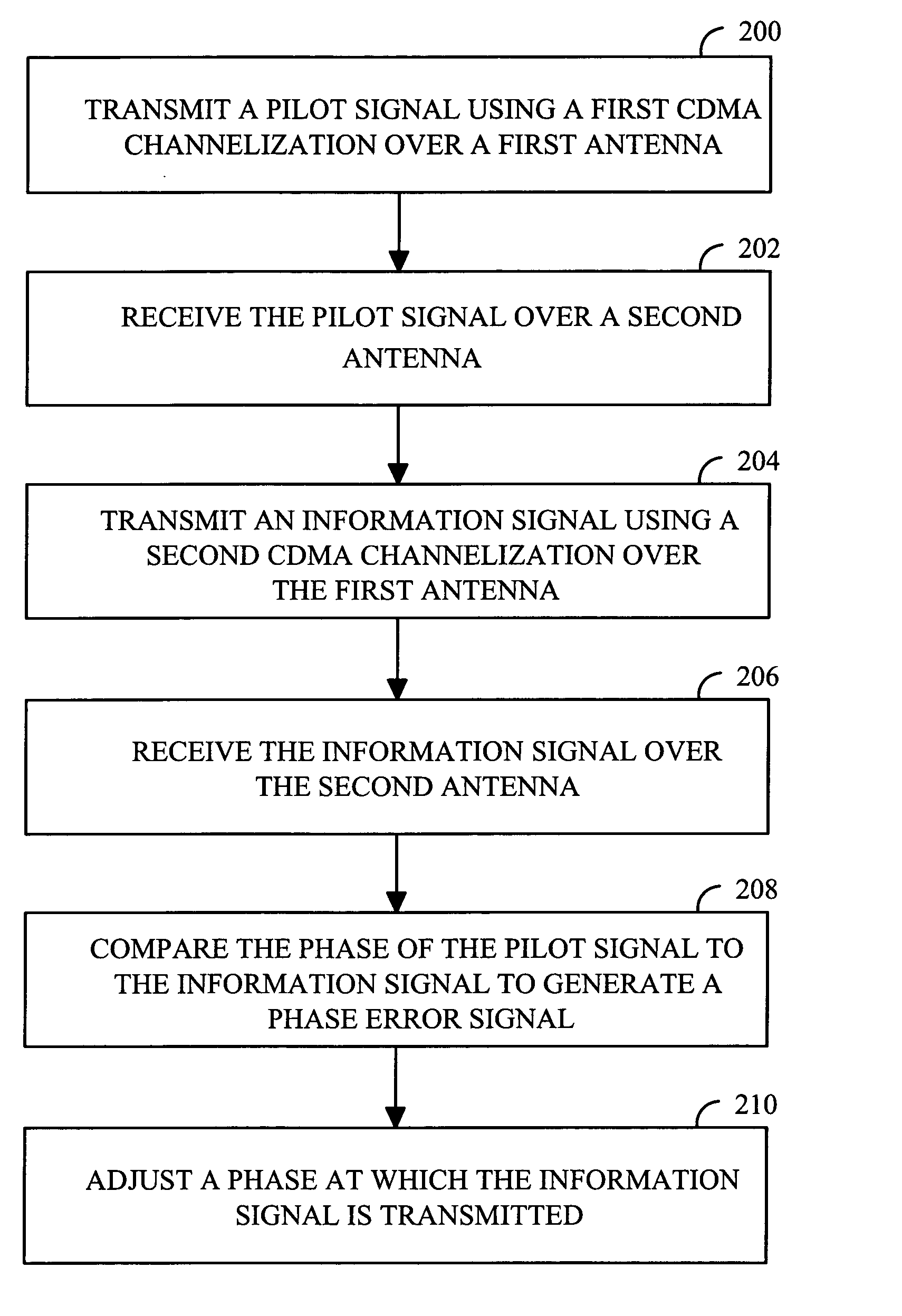

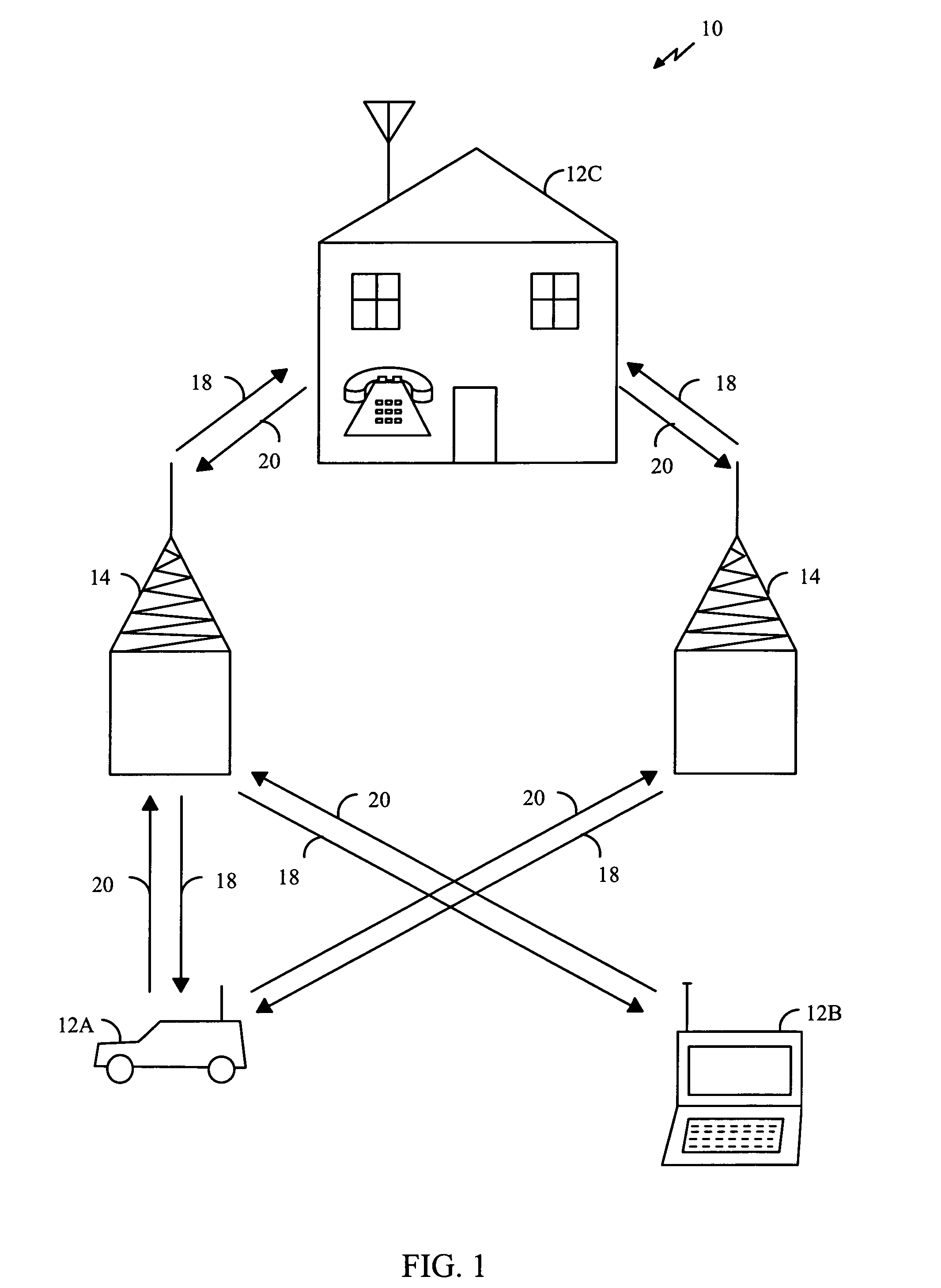

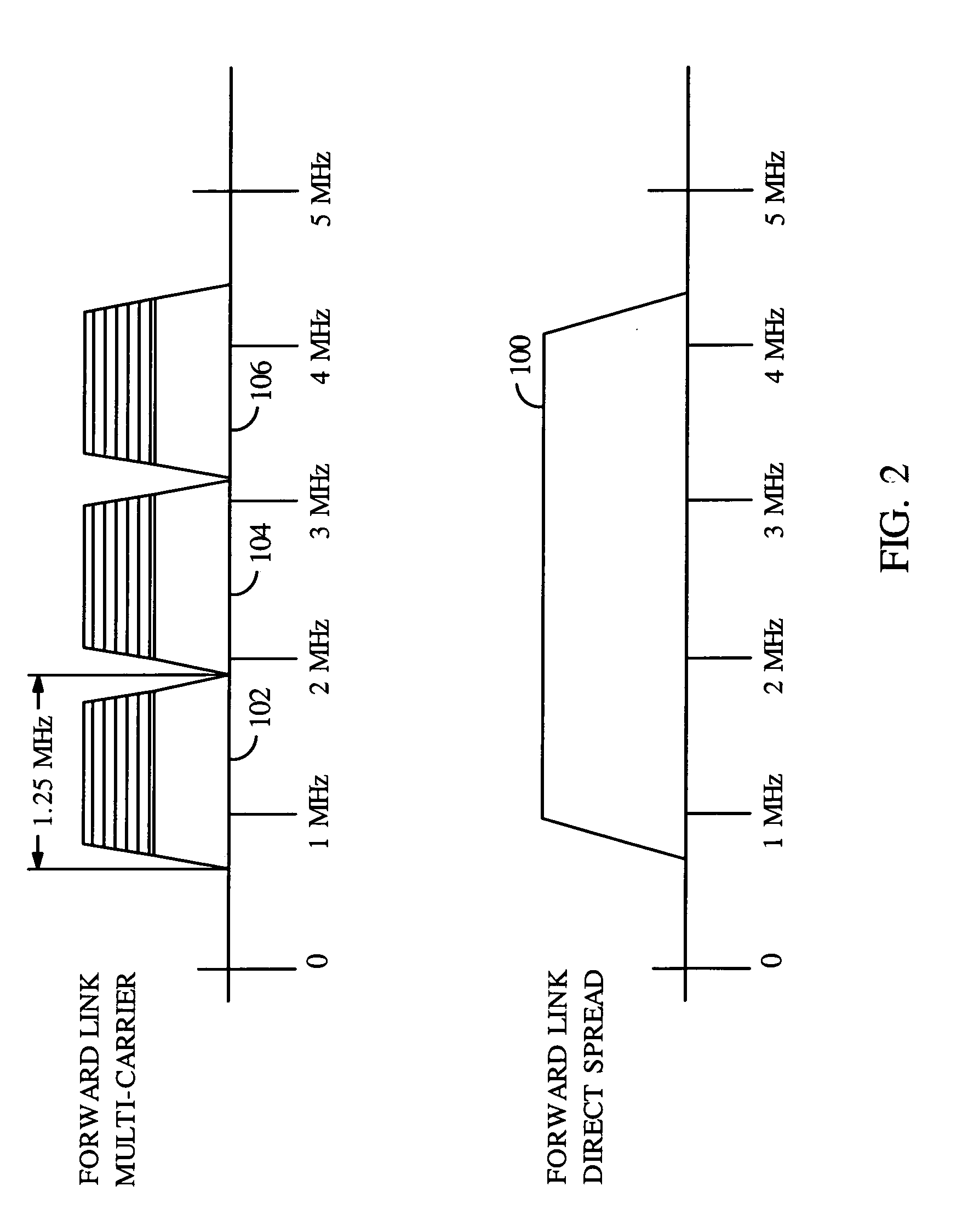

Method and apparatus for overlaying two CDMA systems on the same frequency bandwidth

InactiveUS6882631B1Reduce time differenceAvoid modificationTime-division multiplexCode division multiplexTime errorEngineering

In order to align the timing of an overlay base station to the timing of an existing base station, a sync unit is introduced into the system. The sync unit has a first receiver configured to receive a first signal, the first signal having a first CDMA channelization. The first receiver is configured to produce an indication of a timing of the first signal. The sync unit also has a second receiver configured to receive a second signal, the second signal having a second CDMA channelization. The second receiver is configured to produce an indication of a timing of the second signal. The sync unit also has a time error detection unit configured to compare the timing of the first signal and the timing of the second signal to determine a relative timing offset thereof.

Owner:QUALCOMM INC

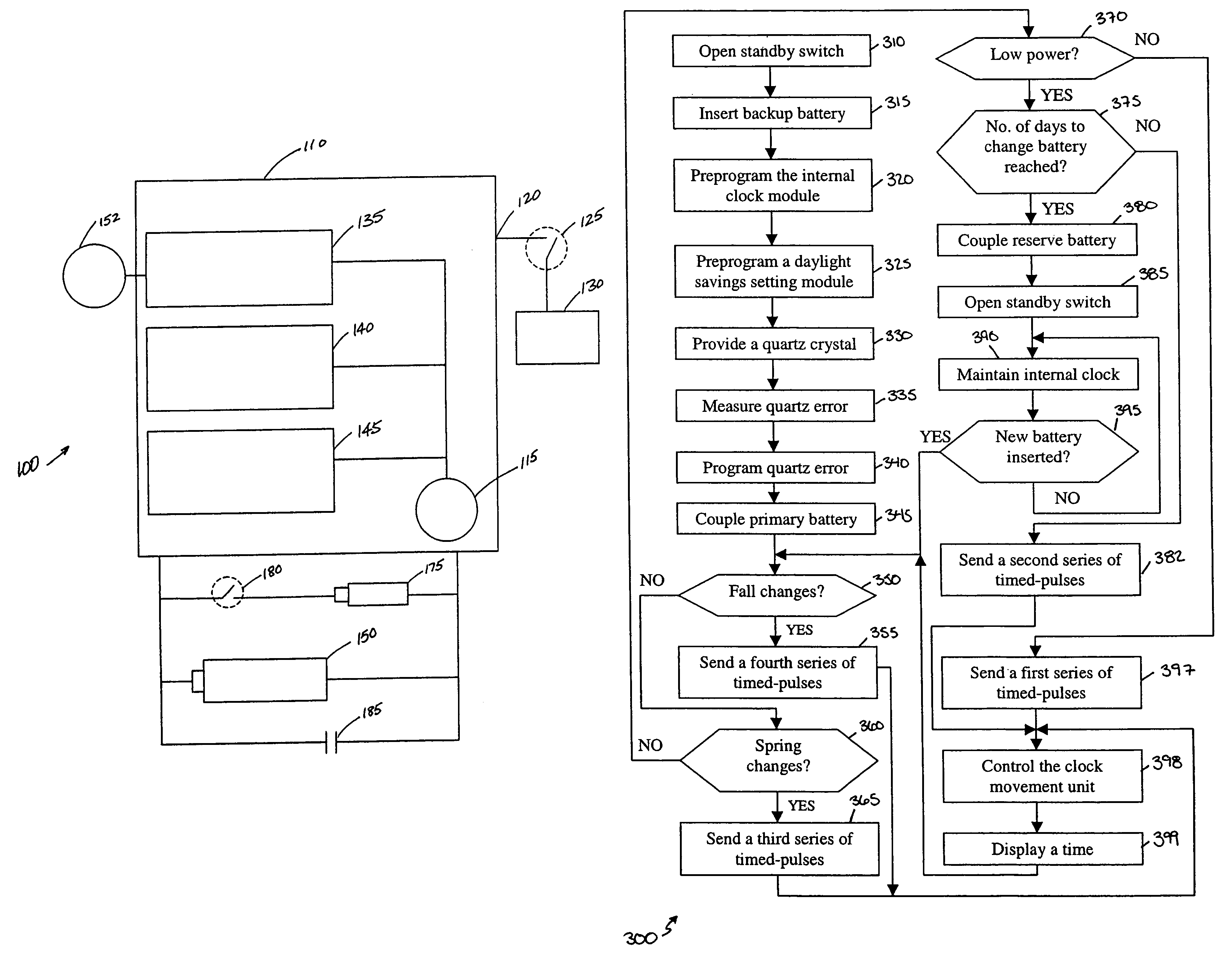

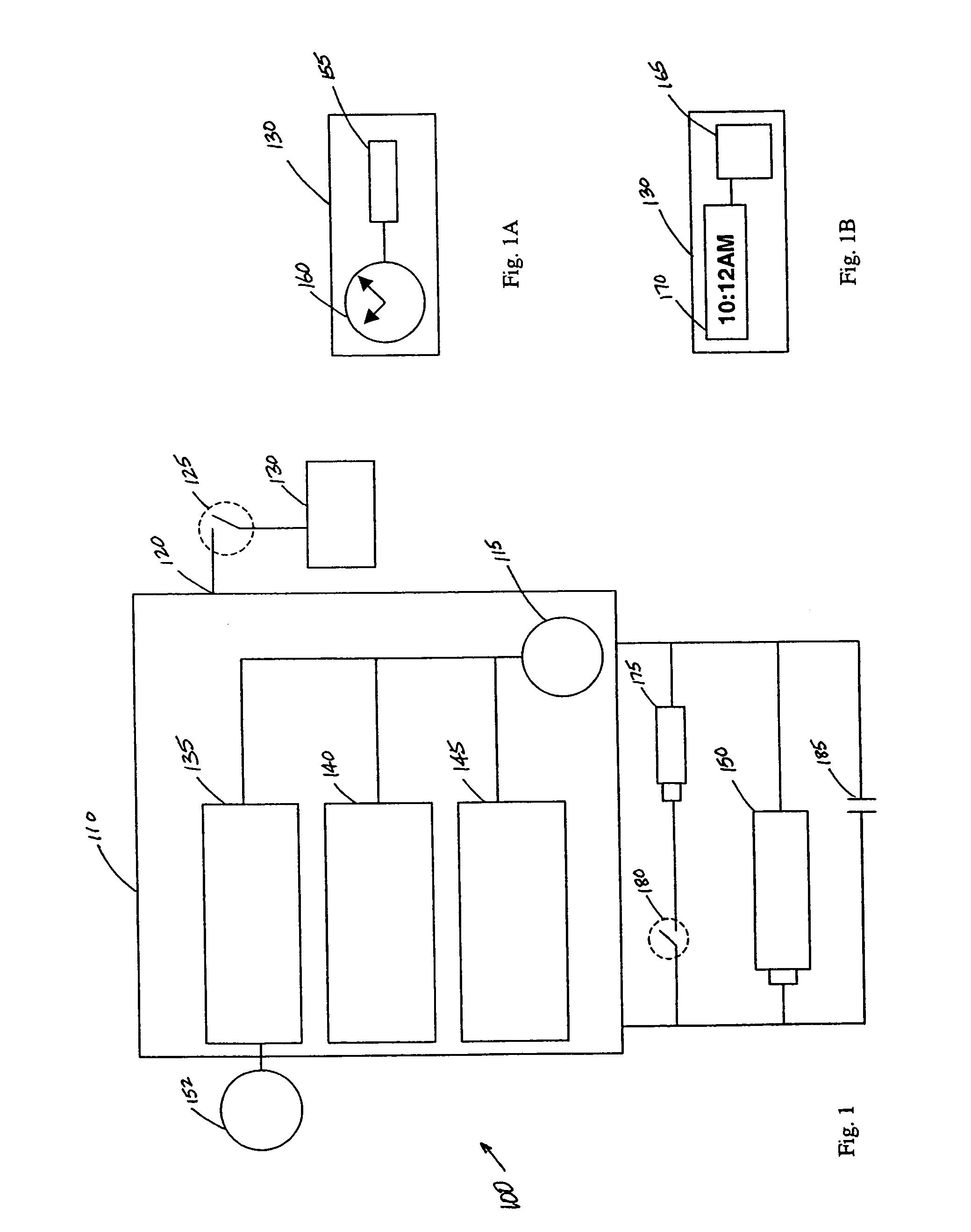

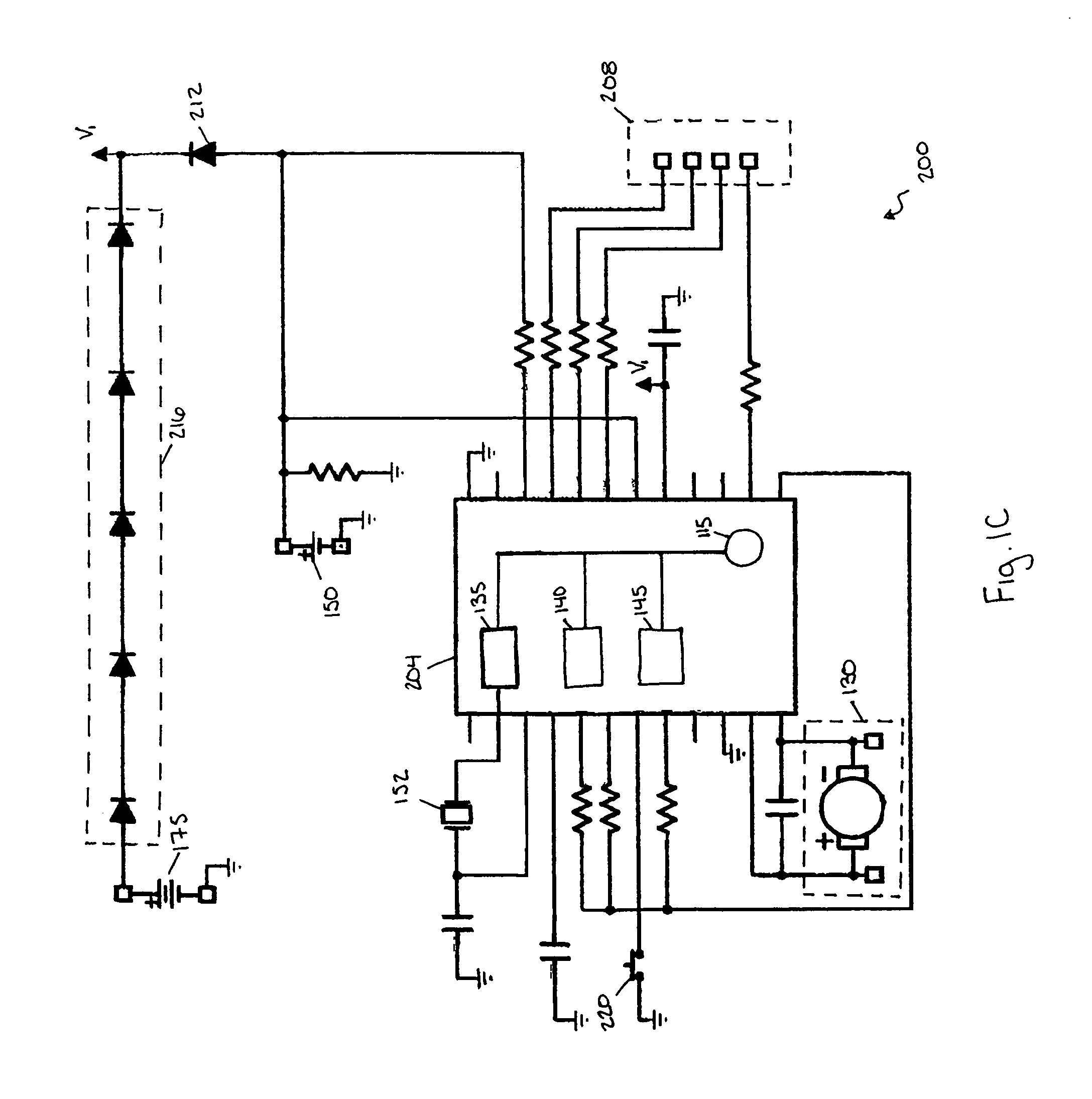

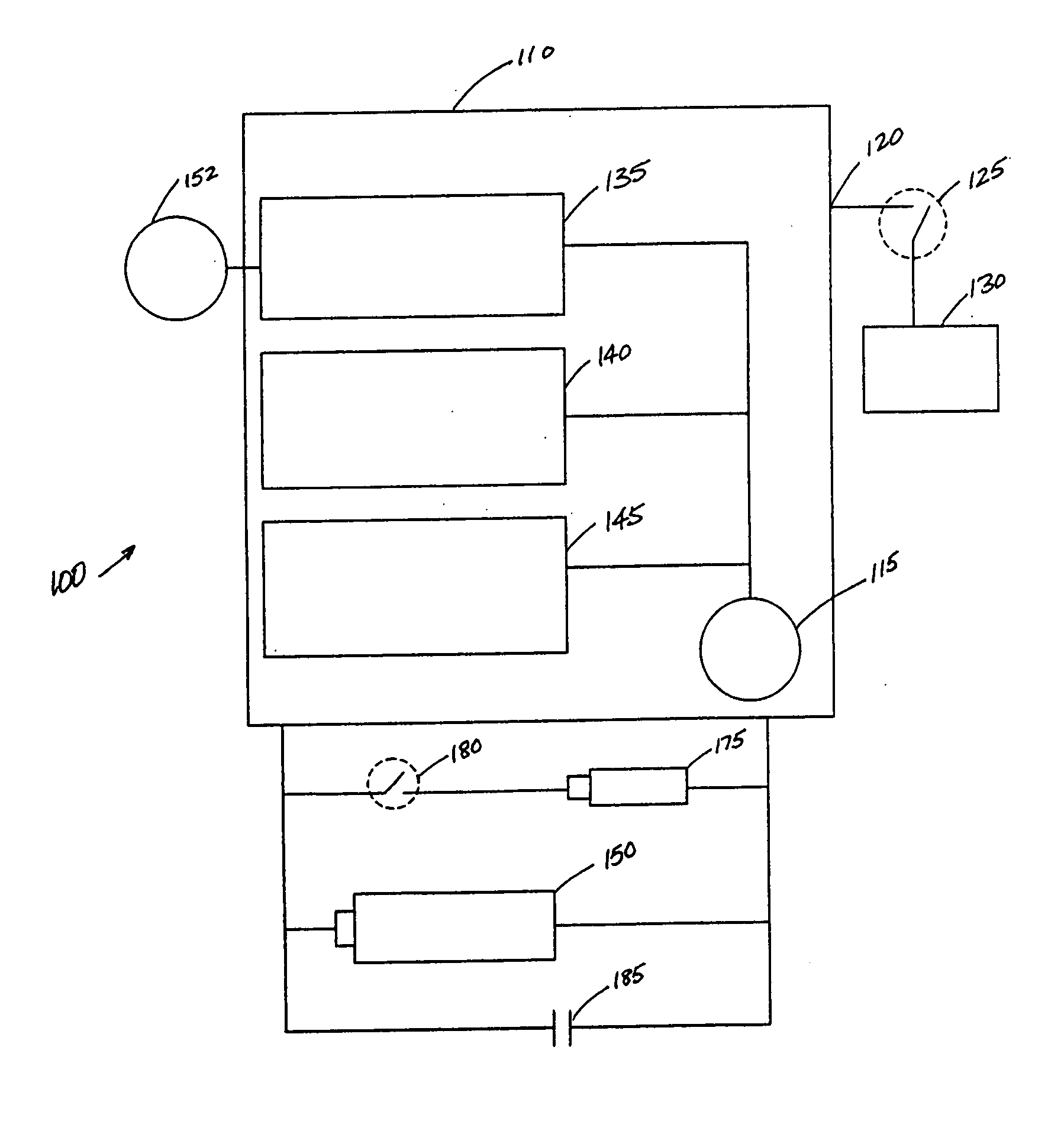

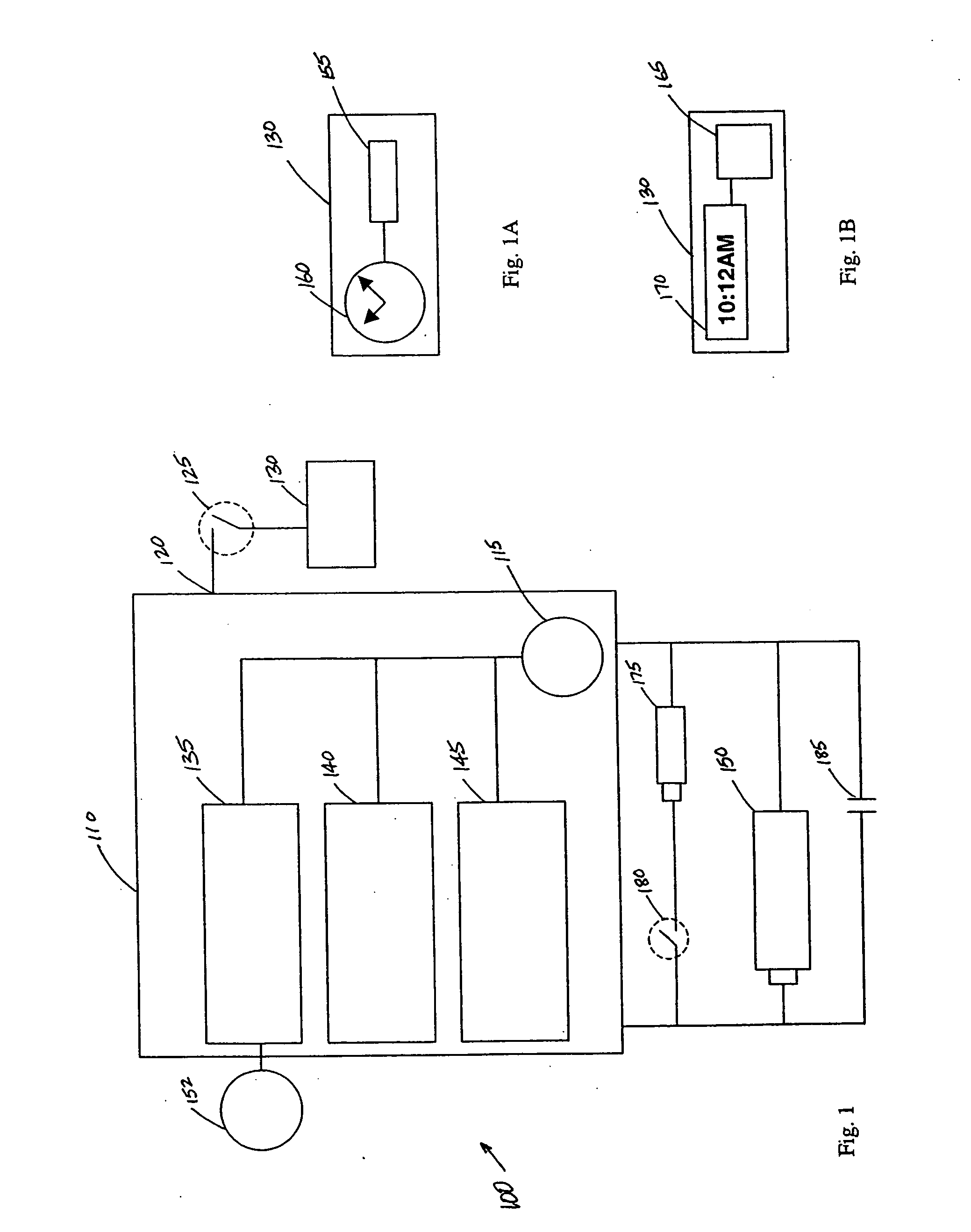

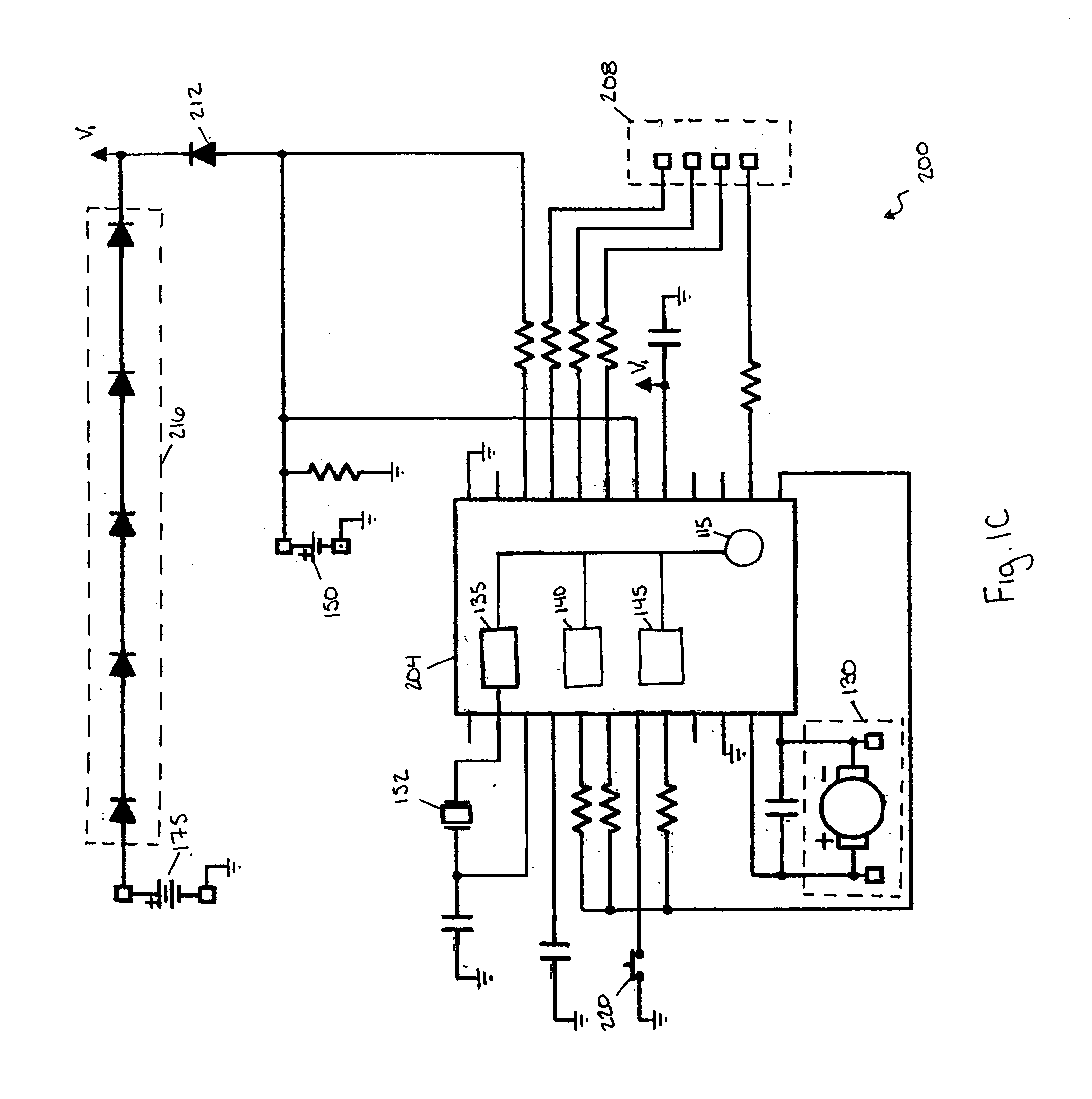

Time keeping system with automatic daylight savings time adjustment

InactiveUS7394726B2Reduce time differenceExtension of timeVisual indicationTime indicationEngineeringDaylight

A time keeping system having a first time module operable to keep a first time, a second time module operable to keep a second time, and a control module operatively coupled to the first time module and to the second time module. The control module adjusts the first time in response to information stored in the control module and adjusts the second time to reduce a time difference between the first time and the second time.

Owner:QUARTEX INC

Time keeping system with automatic daylight savings time adjustment

InactiveUS20060158963A1Reduce time differenceExtension of timeVisual indicationTime indicationEngineeringDaylight

A time keeping system having a first time module operable to keep a first time, a second time module operable to keep a second time, and a control module operatively coupled to the first time module and to the second time module. The control module adjusts the first time in response to information stored in the control module and adjusts the second time to reduce a time difference between the first time and the second time.

Owner:QUARTEX INC

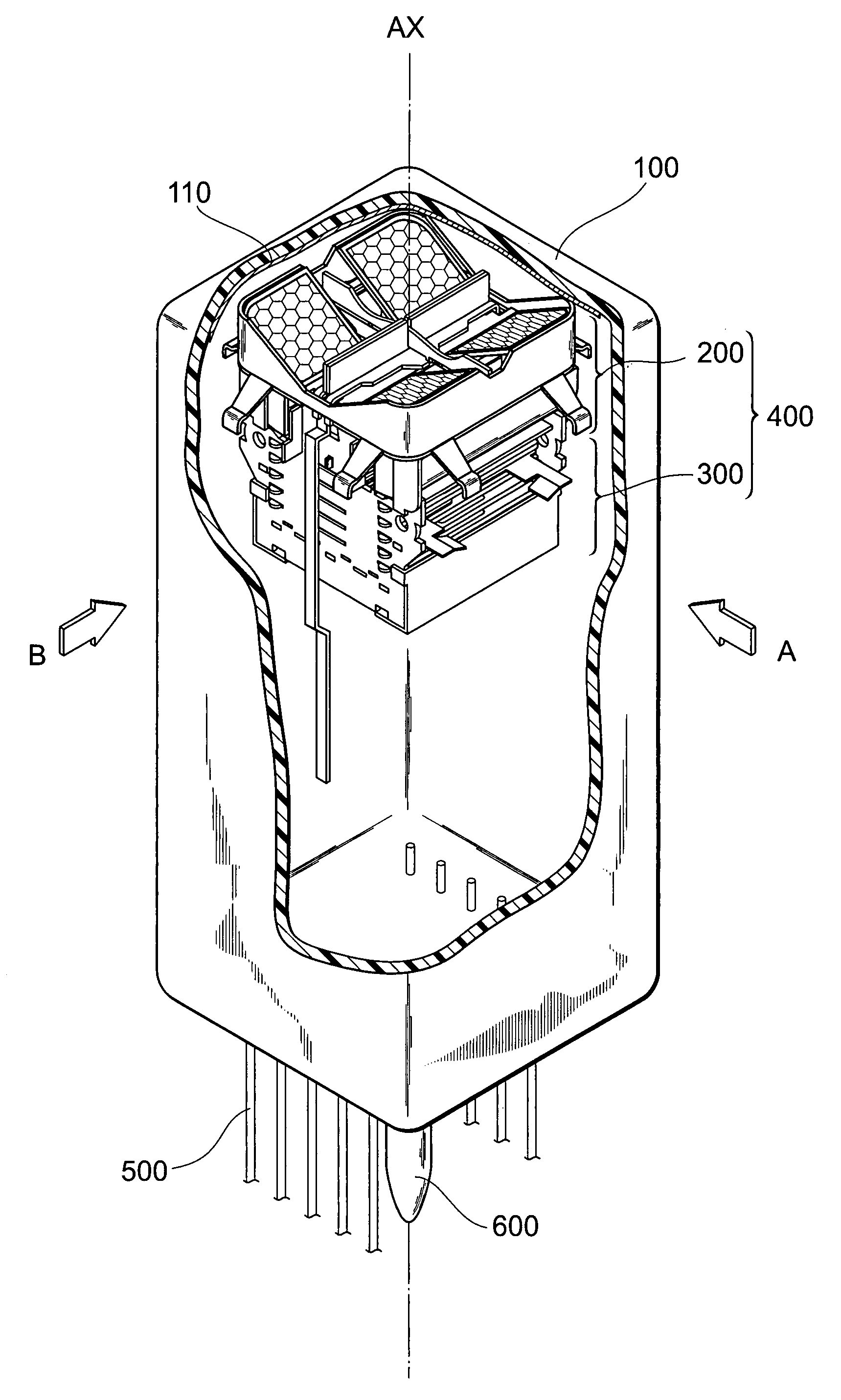

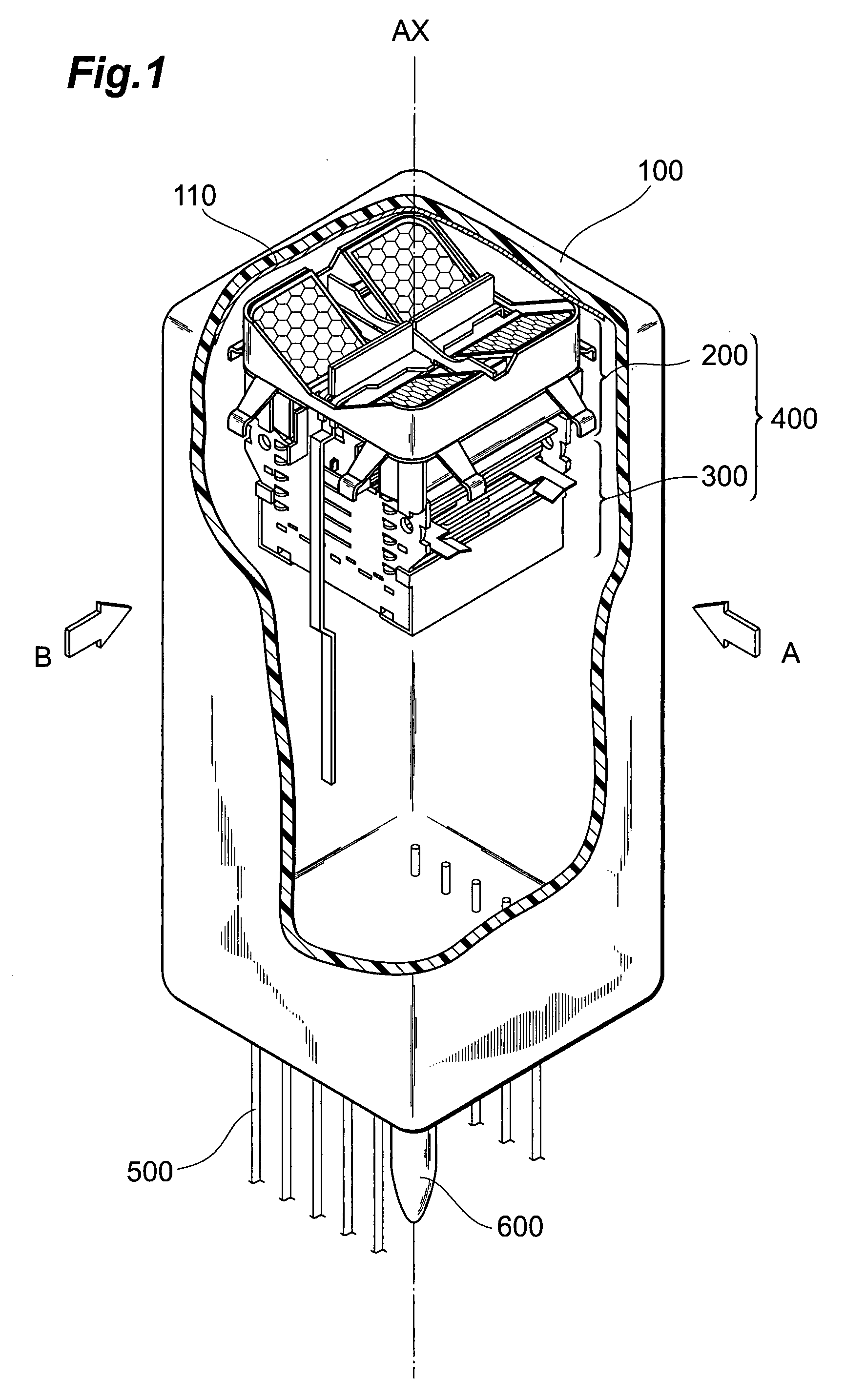

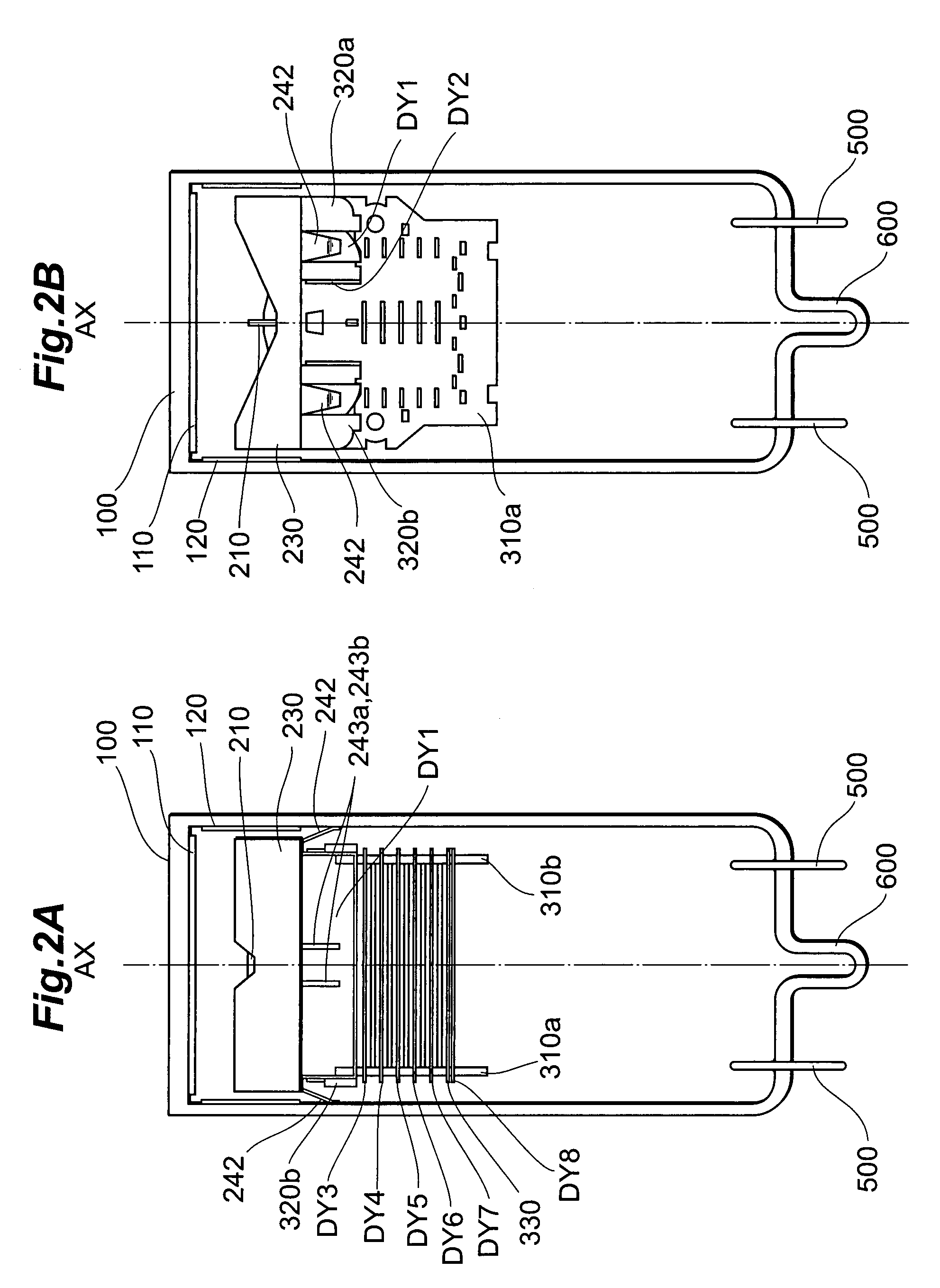

Photomultiplier

InactiveUS20070241680A1Reduce the differenceExtension of timeMutiple dynode arrangementsPhotocathodeDynode

The present invention relates to a photomultiplier having a configuration for improving response time characteristics. The photomultiplier comprises at least a sealed container, a photocathode, and an electron multiplier section. The electron multiplier section has an upper unit and a lower unit. The upper unit includes a focusing electrode, a mesh electrode, and a first dynode, among a multiple stages of dynodes, being a dynode at which the photoelectrons from the photocathode arrive. The lower unit includes the subsequent dynodes while excluding the first dynode from the multiple stages of dynodes, and a pair of insulating supporting members that clampingly hold the subsequent dynodes. The mesh electrode is positioned in an inclined state with respect to a tube axis.

Owner:HAMAMATSU PHOTONICS KK

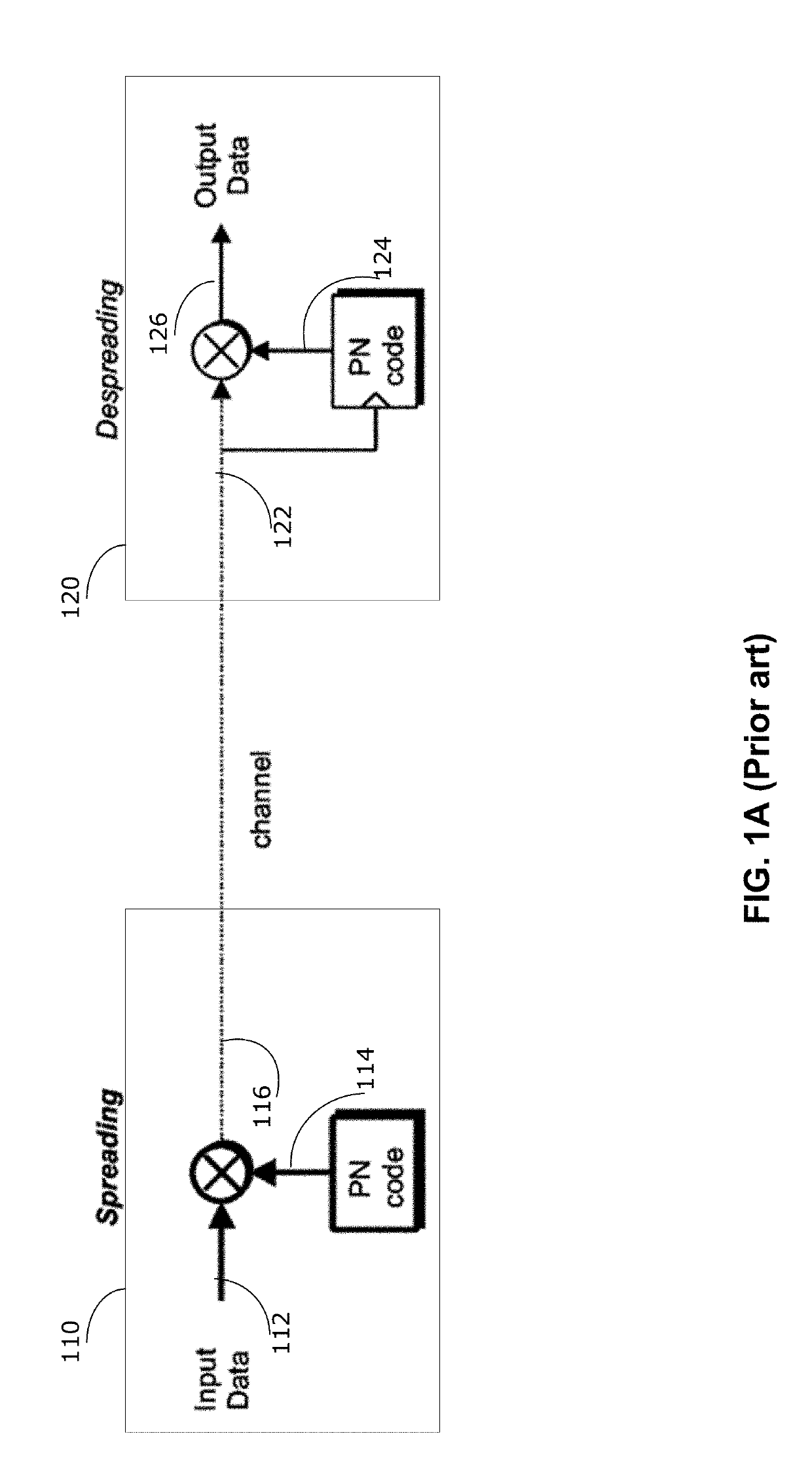

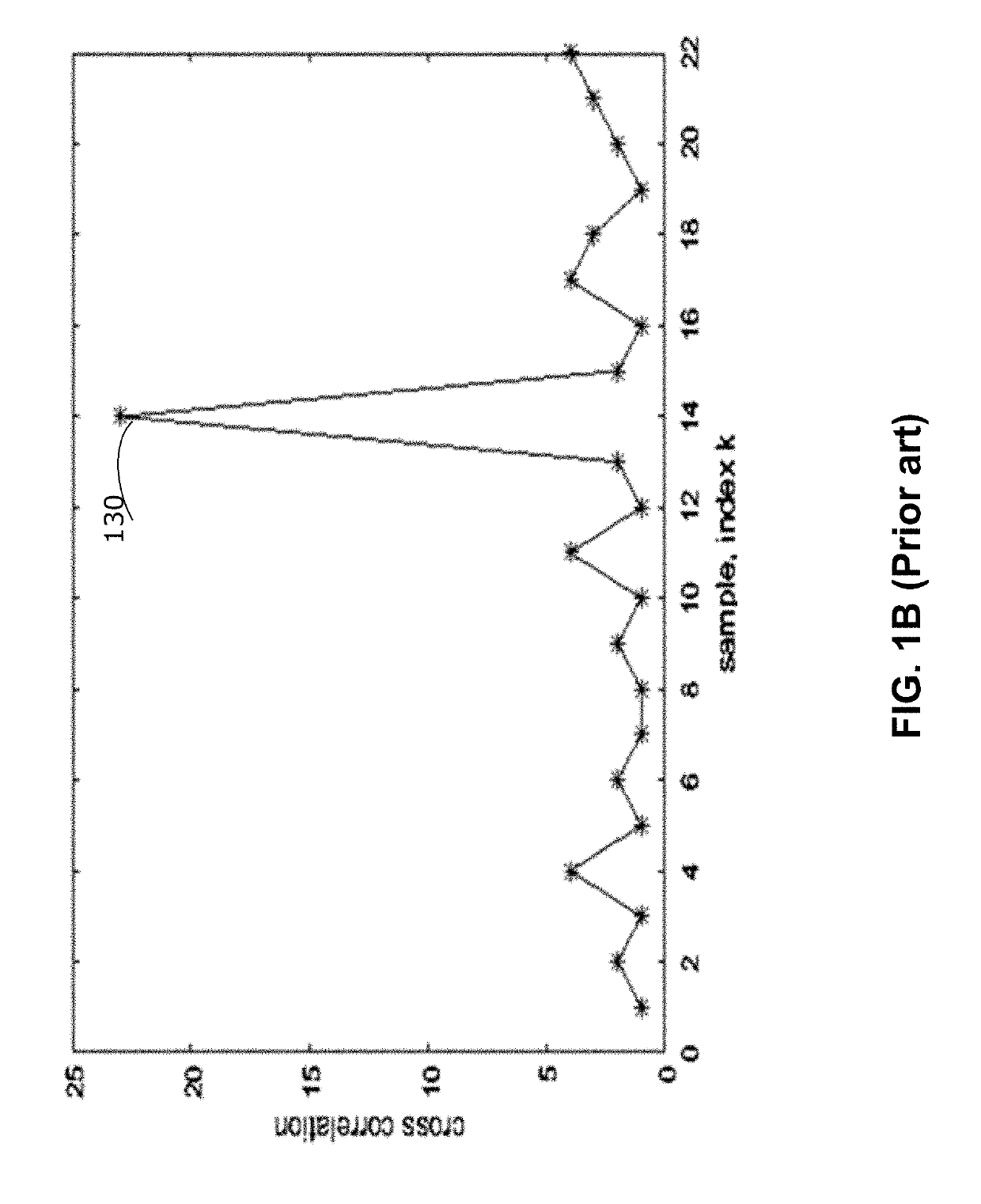

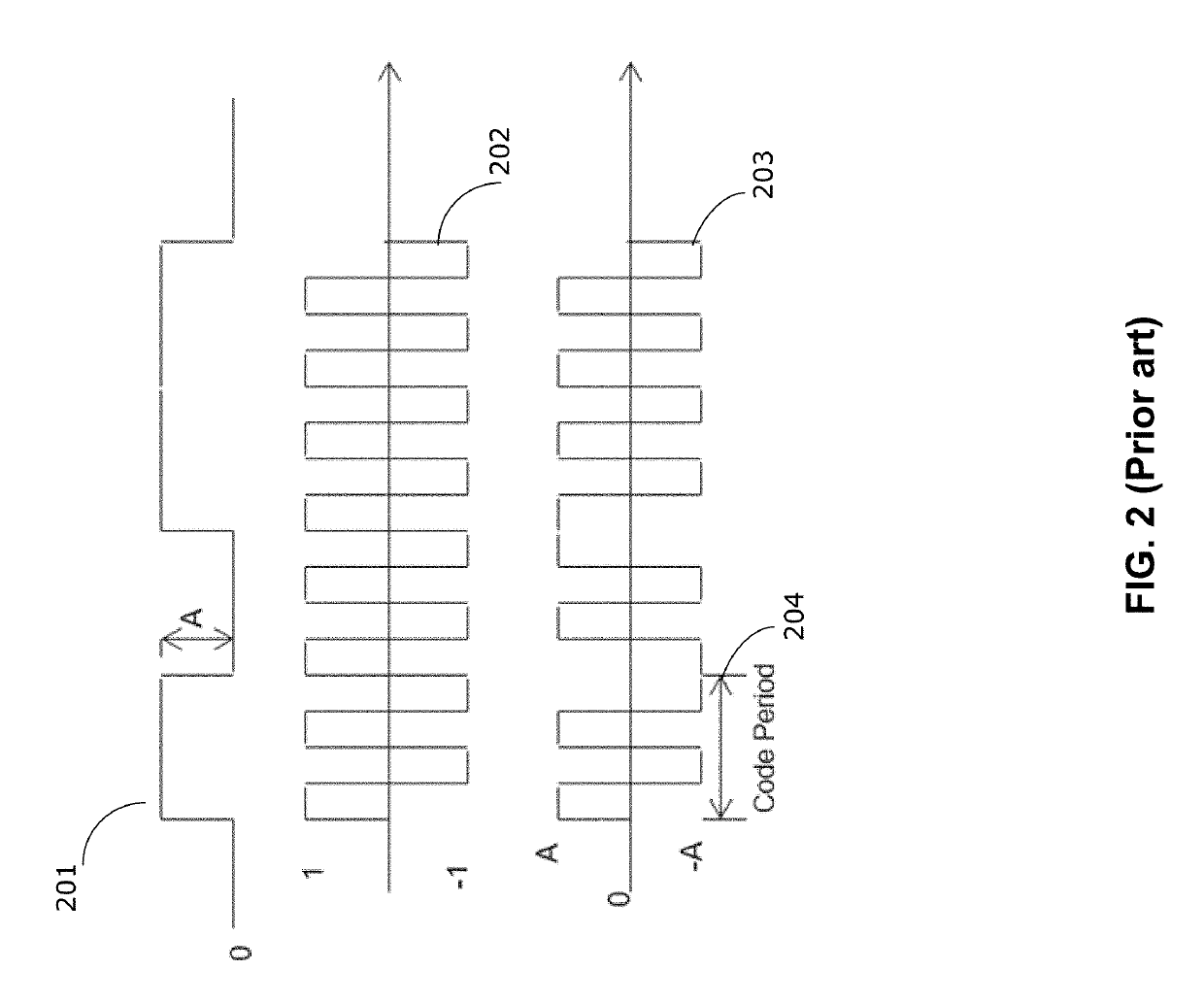

Apparatus and receiver for performing synchronization in analog spread spectrum systems

ActiveUS20190326948A1Reduce time differenceTransmissionCode shifting or hoppingTime delaysComputer science

Apparatuses and methods for decoding a spreading code-encoded signal. The decoder decodes a spreading code-encoded signal by performing a synchronization search to determine a synchronization point. The synchronization point defines a time delay for aligning a spreading code, which was used to generate the spreading code-encoded signal, with the spreading code-encoded signal. The synchronization search includes obtaining candidate results, where each candidate result is a decoding attempt that applies a time delay for aligning the spreading code with the spreading code-encoded signal. The synchronization search also includes determining the synchronization point by identifying the time delay corresponding to the candidate result that is associated with a power measurement that satisfies a synchronization search criterion. A decoder code synchronization is performed to align the spreading code with the spreading code-encoded signal, using the synchronization point. The spreading code-encoded signal is decoded using the aligned spreading code.

Owner:HUAWEI TECH CO LTD

Time-alignment of crosstalk acquisition phases between multiple joining lines

ActiveUS8958544B2Reduce time differenceTime available for crosstalk estimation is increasedTwo-way loud-speaking telephone systemsFrequency-division multiplex detailsTransceiverTime alignment

In an embodiment, the access node includes first and second transceiver units for initializing first and second communication channels, respectively, over first and second communication lines, respectively. The initialization of the first and second communication channels respectively including first and second handshake phases wherein peer transceiver units exchange capabilities and select (i) a common mode of operation, (ii) first and second crosstalk channel acquisition phases from the first and second communication lines, and (iii) first and second generic initialization phases. The access node further includes a line initialization controller configured to stretch the execution of the first handshake phase with respect to the execution of the second handshake phase so as to shorten a time difference between respective entries into the first and second crosstalk channel acquisition phases.

Owner:META PLATFORMS INC

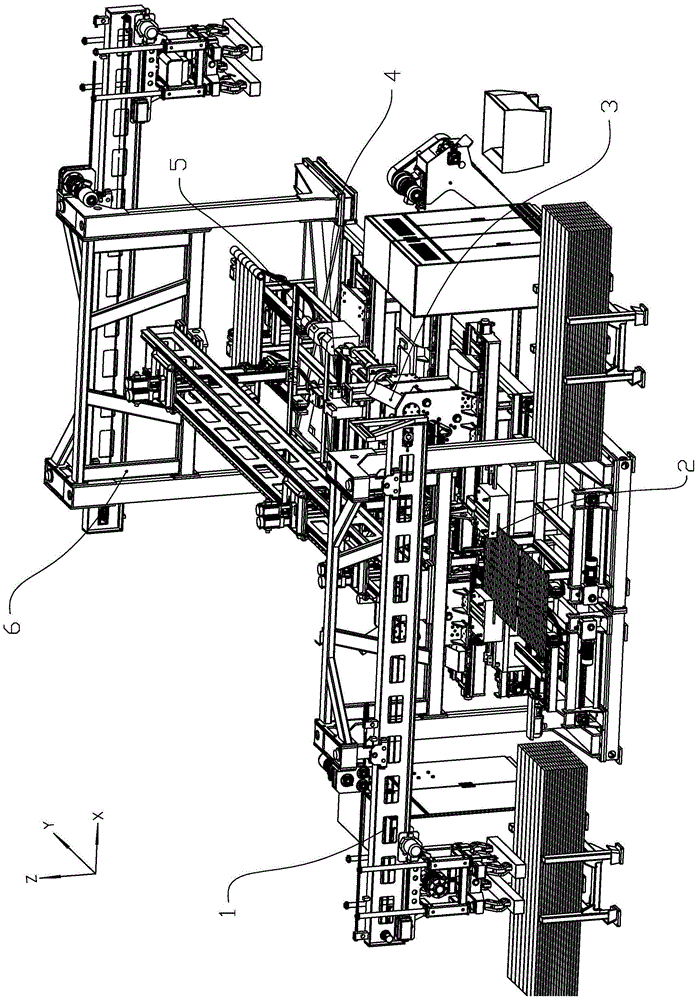

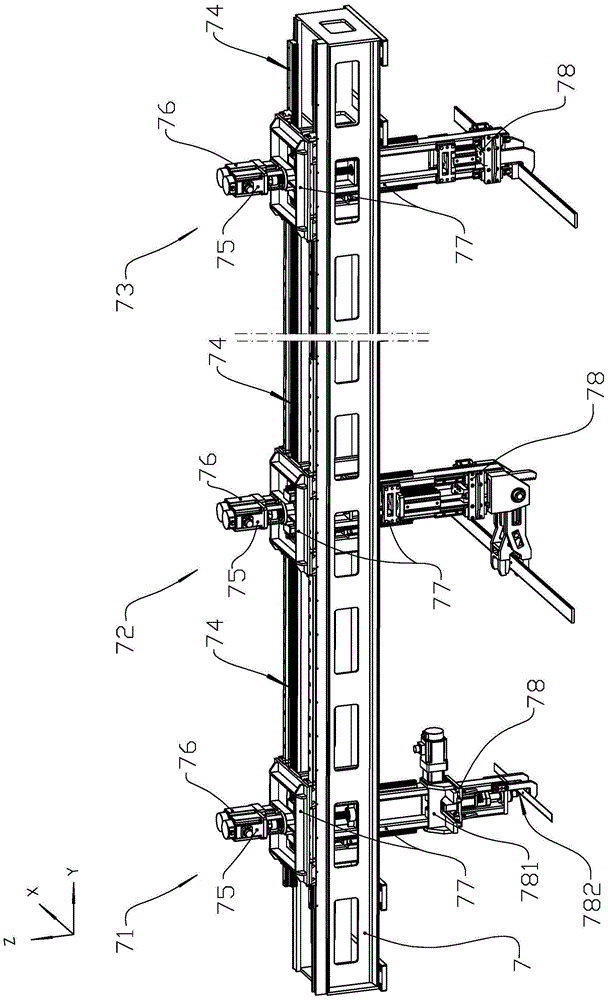

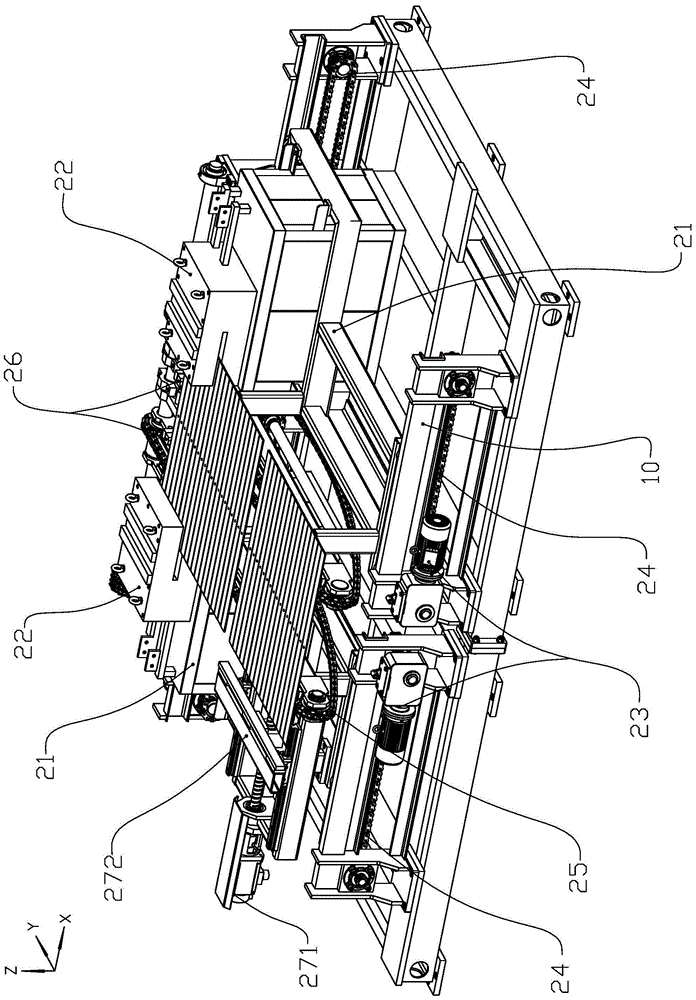

Plate spring double-headed synchronous eye coiling production line and head cutting, eye coiling and shaping units thereof

ActiveCN104923657AReduce operating intensityReduce the number of employeesMetal-working feeding devicesPositioning devicesProduction lineEngineering

The invention discloses a plate spring double-headed synchronous eye coiling production line and head cutting, eye coiling and shaping units thereof. The production line is sequentially provided with a feeding unit, a heating unit, the head cutting unit, the eye coiling unit, the shaping unit and a product integrated packaging unit from front to back. A mechanical arm guiding track bracket which extends front and back is arranged between the feeding unit and the product integrated packaging unit, and the mechanical arm guiding track bracket is provided with a mechanical arm so that a plate spring can be transferred between all the units. The number of electromagnetic heating furnaces, the number of head cutting machines, the number of eye coiling machines and the number of shapers are all two, and the electromagnetic heating furnaces, the head cutting machines, the eye coiling machines and the shapers are all symmetrically arranged relative to the left-right center base line of the production line. The plate spring can be positioned when the two ends of the plate spring are heated, the transferring time difference to the head cutting process is shortened, the thermoplasticity of the plate spring in the head cutting process is guaranteed, the two ends can be cut synchronously in the head cutting process, and thus efficiency is high. In the eye coiling process, the feed machining method of the eye coiling machines is adopted, double-headed synchronous eye coiling is realized, eye machining efficiency is greatly improved, and the quality of obtained coiled eyes is obviously improved as well. Double-headed synchronous shaping is conducted, and hence the depth of parallelism of the coiled eyes of the plate spring can be better improved.

Owner:山东森德数控机械有限公司

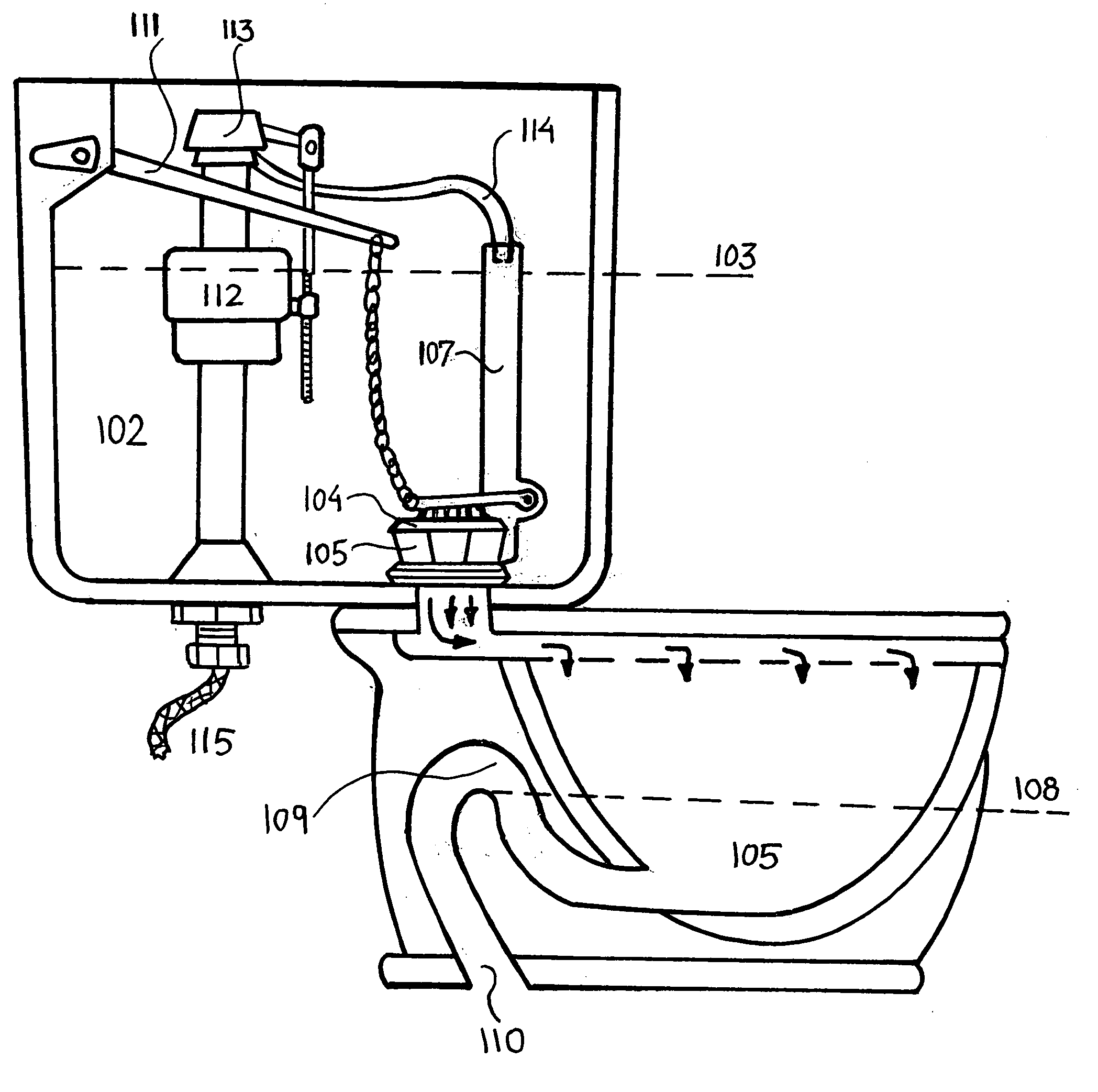

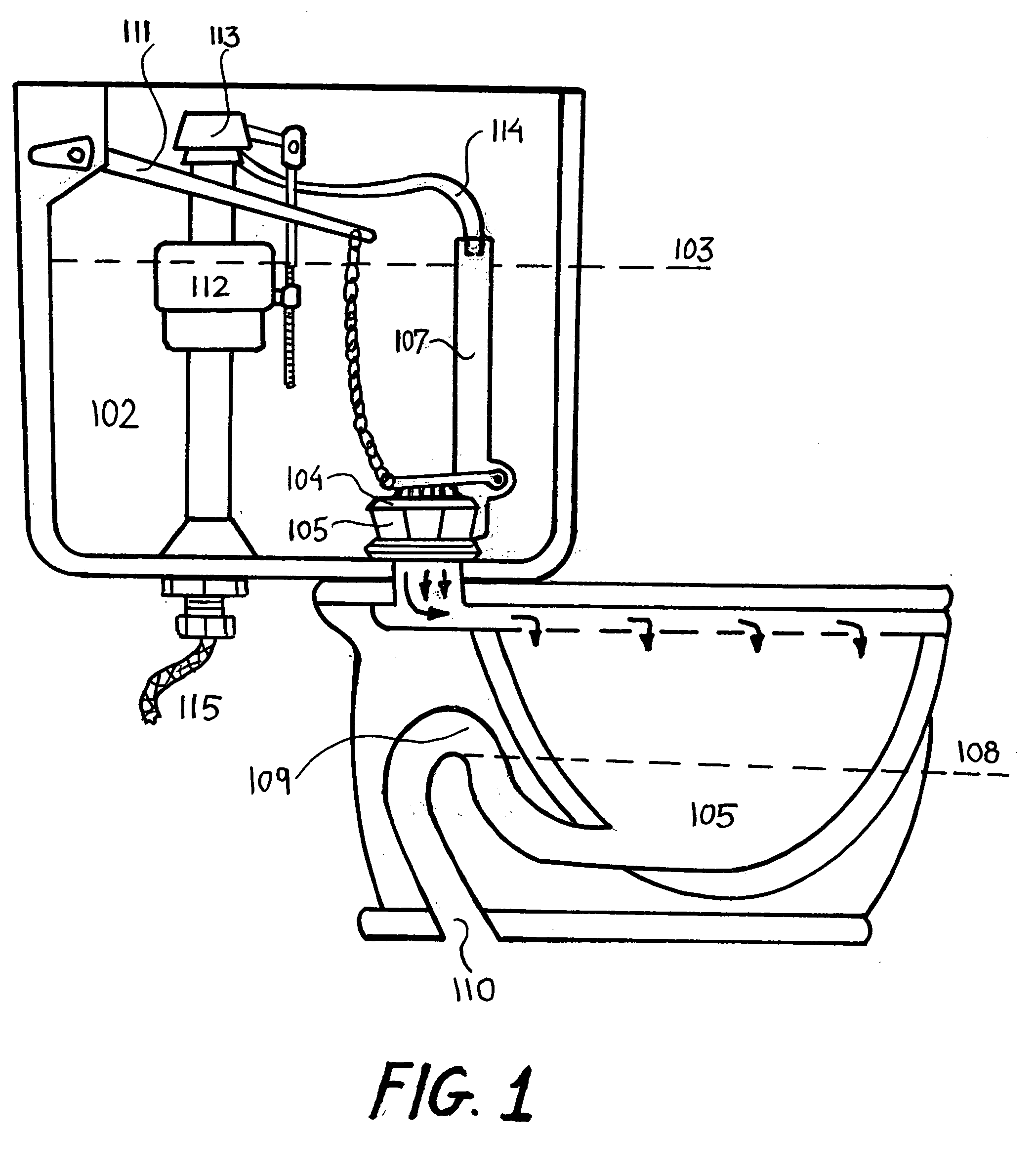

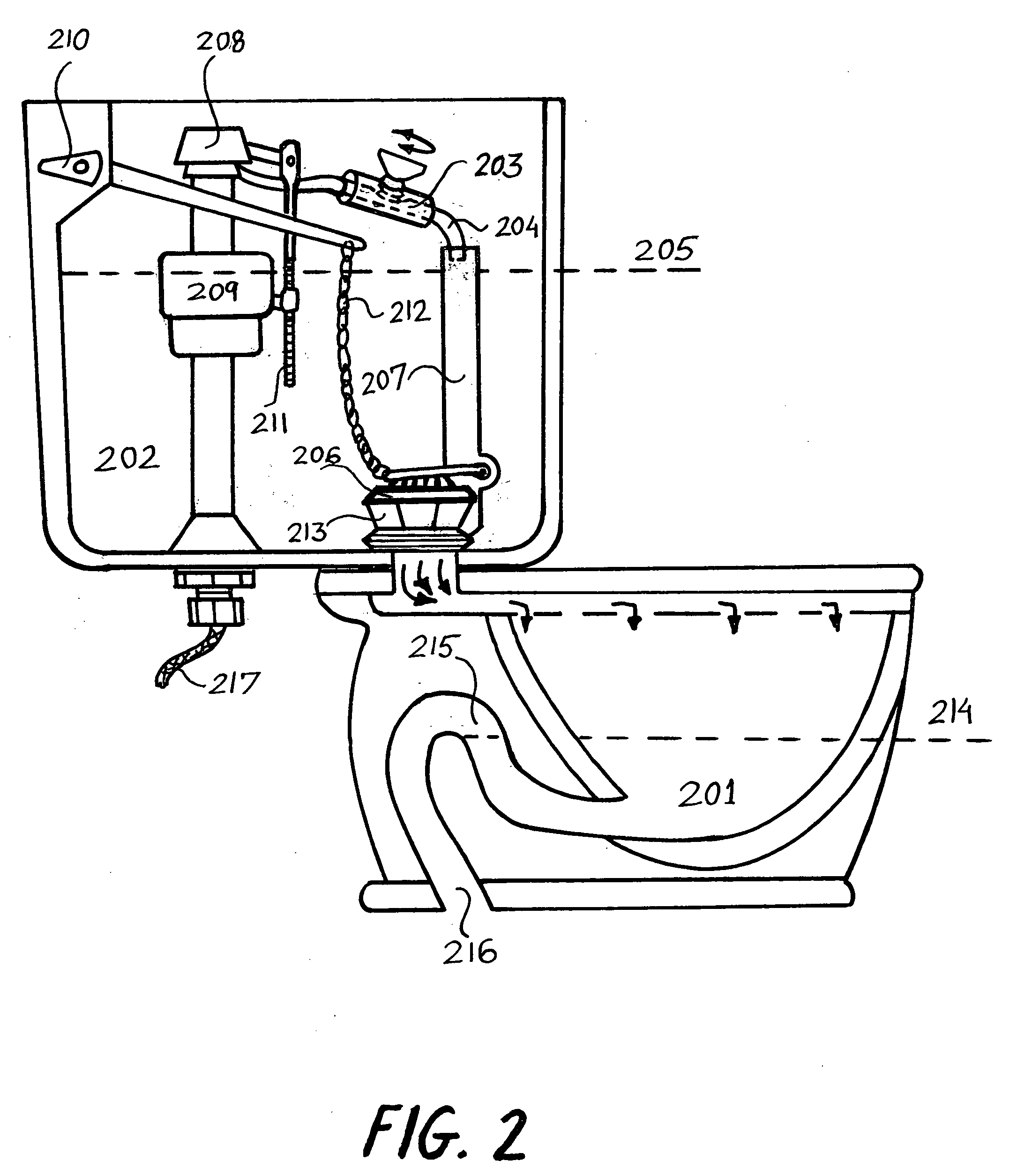

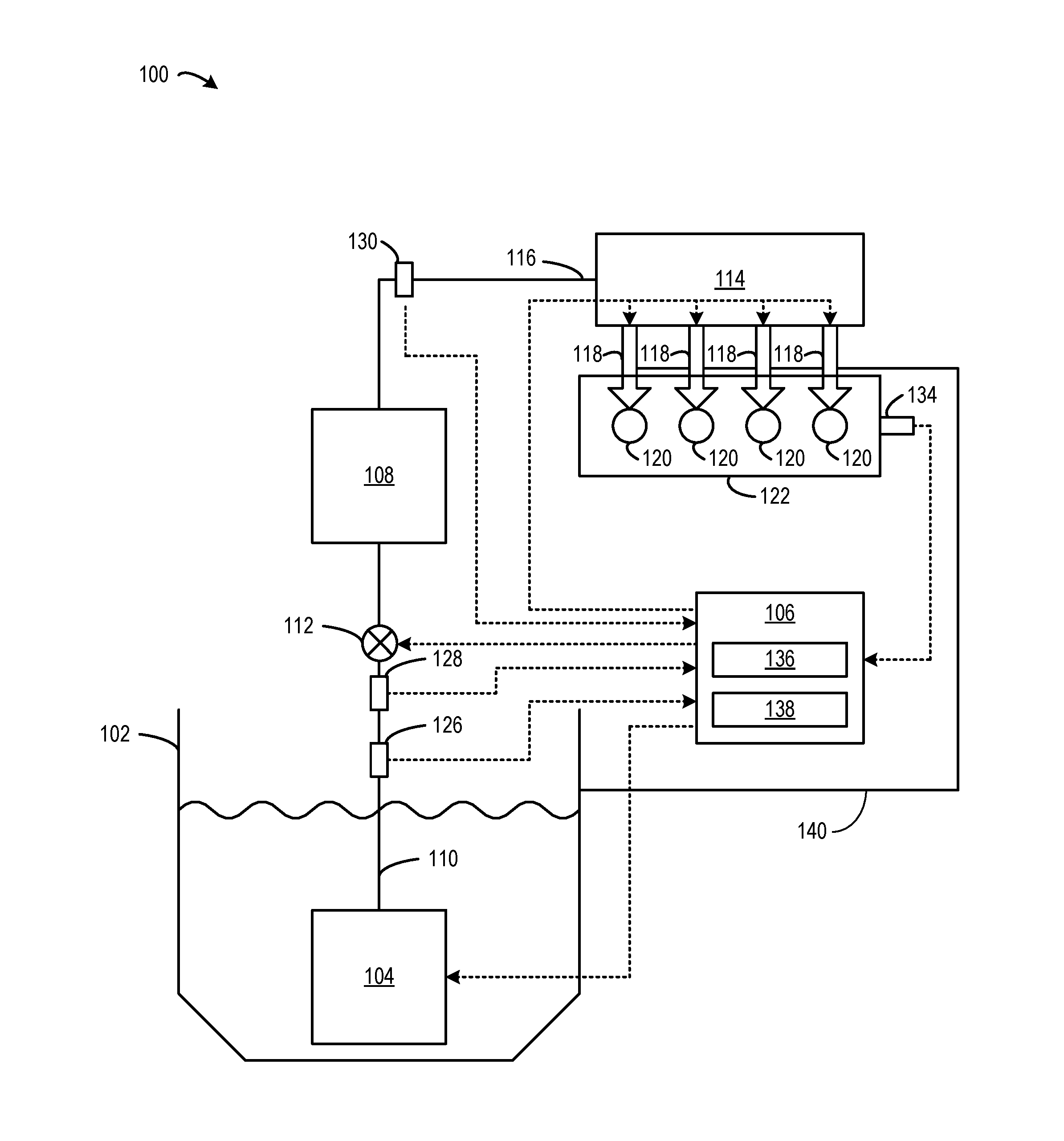

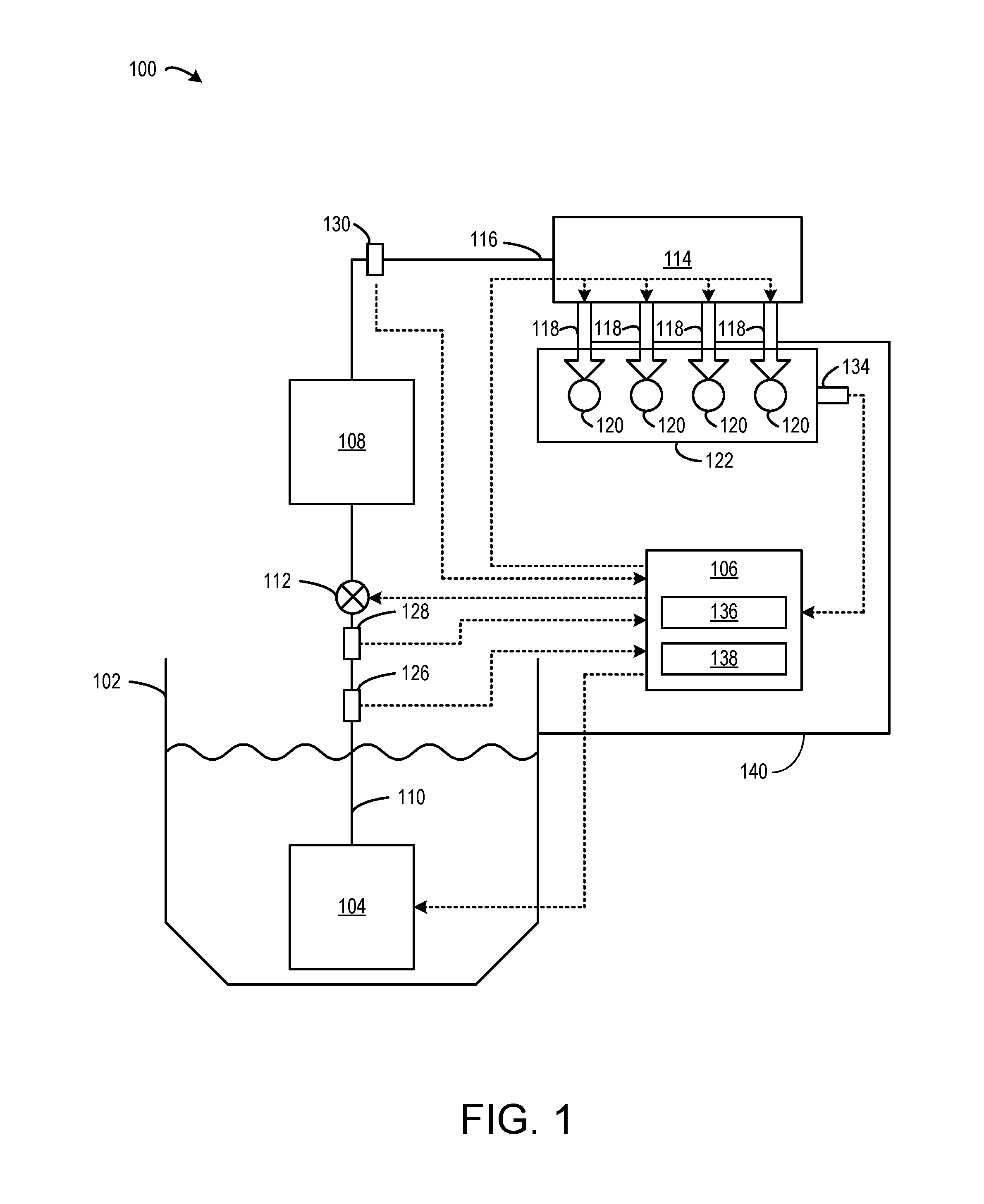

Apparatus and method to control and adjust water consumption by a toilet during refill of the bowl and reservior

InactiveUS20090165198A1Reduce water consumptionReduce time differenceDiaphragm valvesOperating means/releasing devices for valvesEngineeringStreamflow

This invention relates generally to an apparatus and a method for plumbing installations and more particularly to a mechanism and use of a mechanism contained within the water tank of a household toilet which improves the water consumption efficiency of the toilet by minimizing the amount of water consumed when refilling the toilet reservoir and bowl. The mechanism can be a constriction or water limiting device, such as an adjustable valve, pinching, squeezing or similar device, positioned in line with a refill tube, and between the fill valve and the overflow tube. By adjusting the flow-rate or maximum volume of water that can pass through the refill tube, the refill time for the toilet bowl and water reservoir can be synchronized, causing the reduction or elimination of water-wasting during refilling time.

Owner:SHALEV EFRAIM

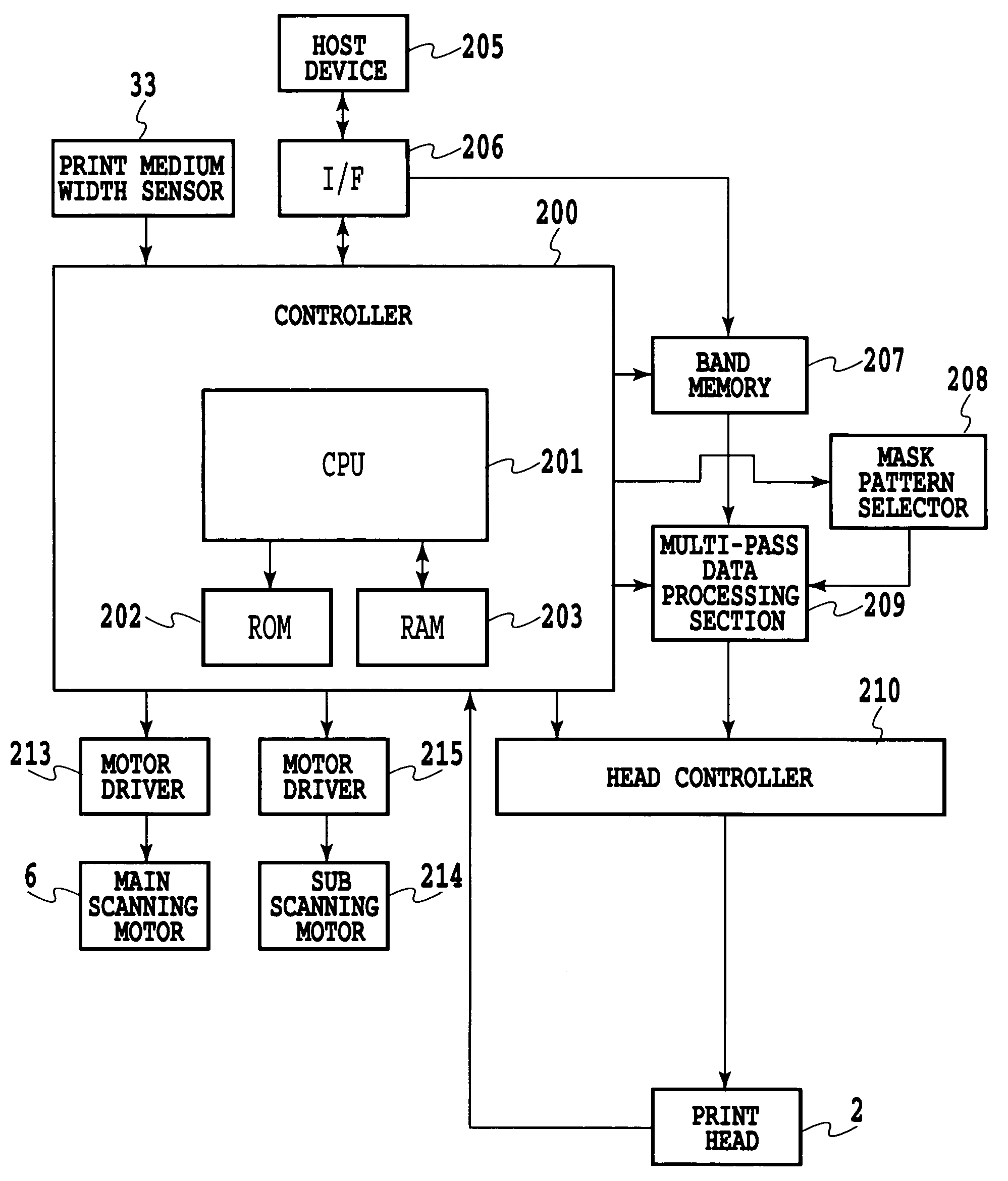

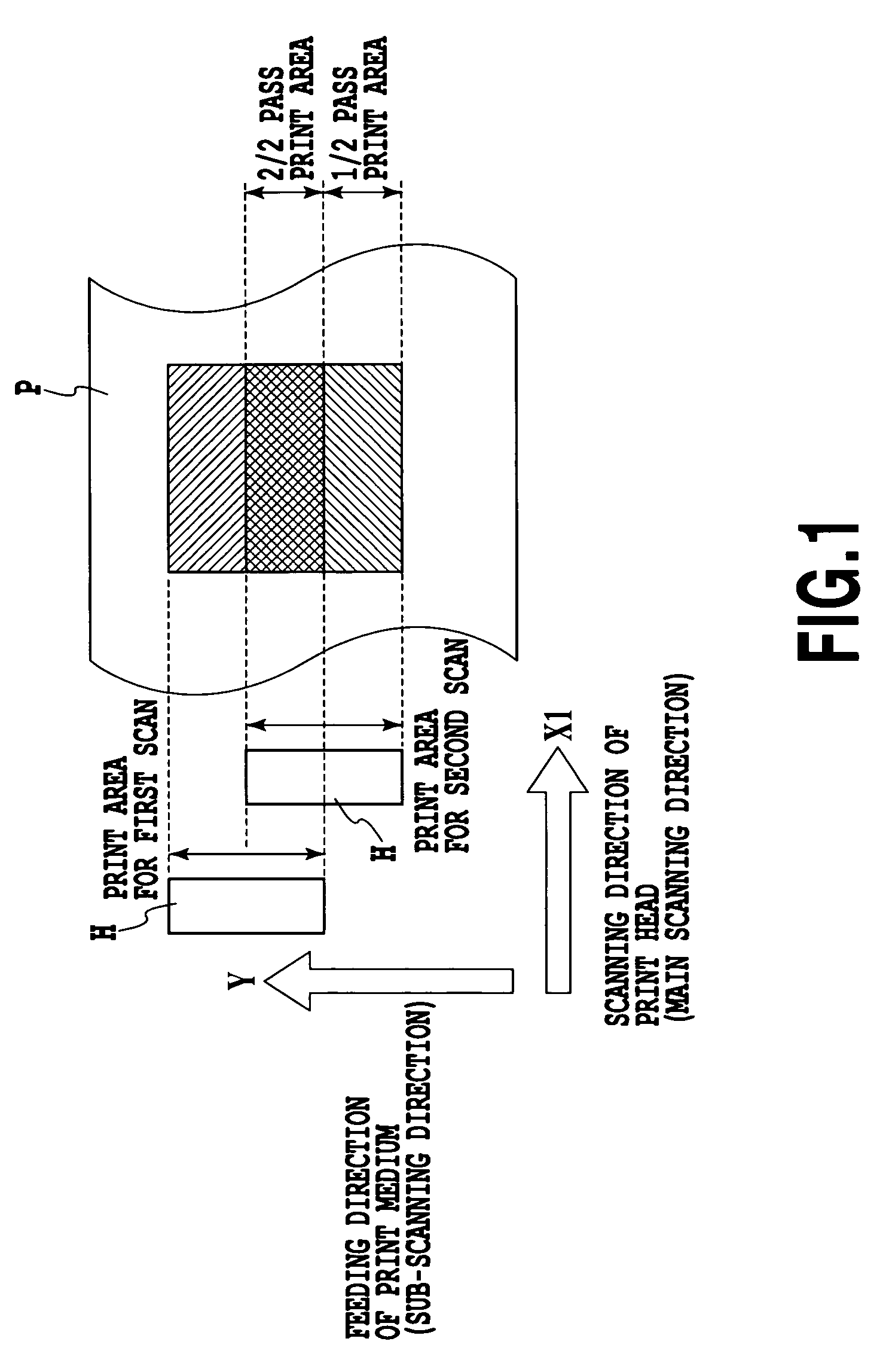

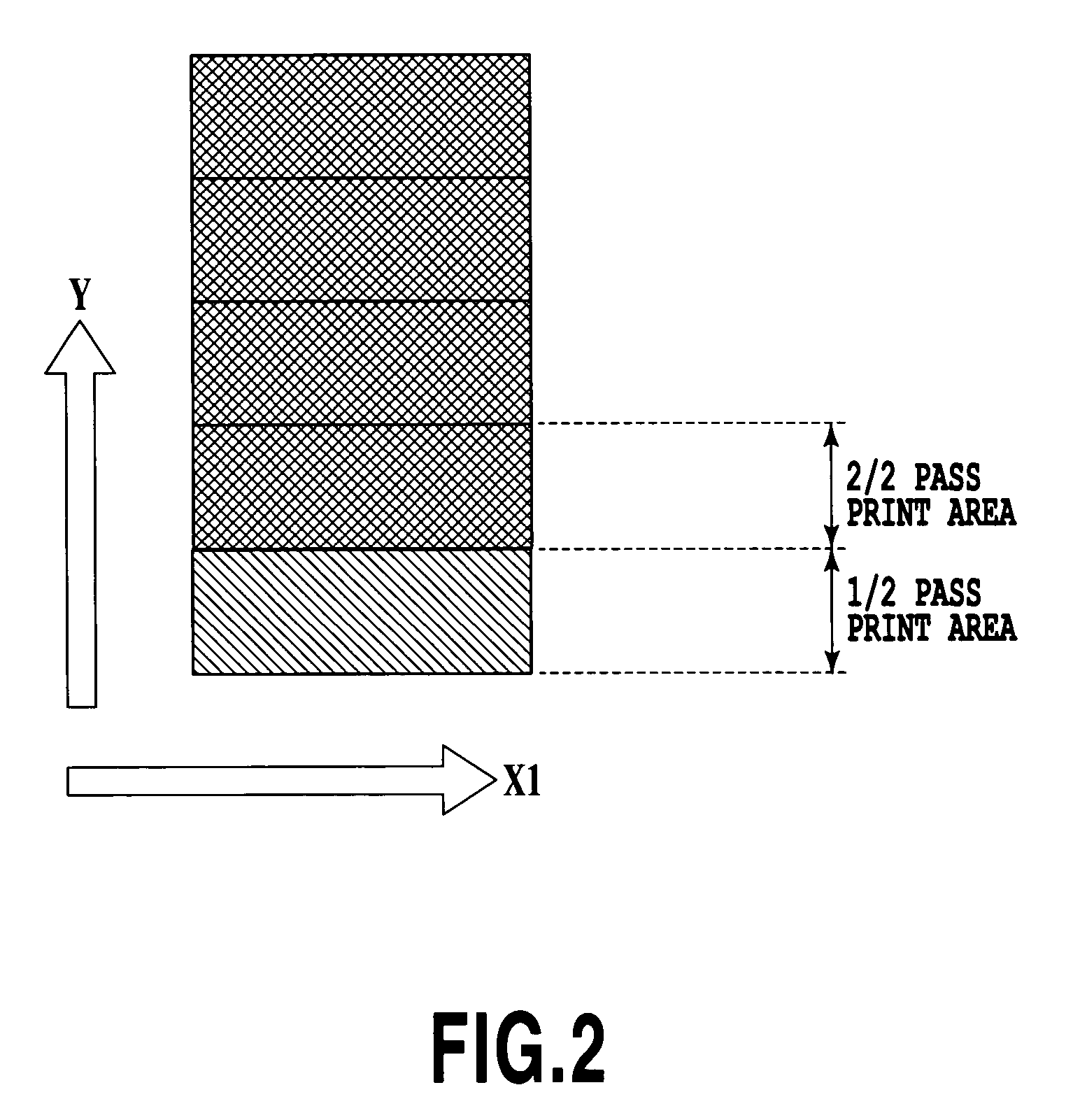

Ink jet printing apparatus and ink jet printing method

InactiveUS7396100B2Increasing loadIncreasing timeSpacing mechanismsTypewritersEngineeringLow density

There is provided an ink jet printing apparatus that suppresses density unevenness caused by a difference in print time resulting from printing based on a bidirectional multi-pass printing system. With a relatively small print medium width, the time difference unevenness does not occur even in 2 pass printing. Accordingly, the 2 pass printing is selected. With a relatively large print medium width, selection of the 2 pass printing may make the density unevenness significant. Accordingly, the density unevenness is suppressed by selecting 8 pass printing. That is, in the 8 pass printing, the same area is scanned eight times, which is four times as frequent as the twice in the 2 pass printing. This reduces the size of each area having different densities, while increasing a cycle frequency at which a high and low densities are alternately repeated. As a result, the time difference unevenness is not perceived easily.

Owner:CANON KK

Method and apparatus for overlaying two CDMA systems on the same frequency bandwidth

InactiveUS20050122917A1Reduce time differenceAvoid modificationBroadcast transmission systemsTime-division multiplexTime errorCdma systems

In order to align the timing of an overlay base station to the timing of an existing base station, a sync unit is introduced into the system. The sync unit has a first receiver configured to receive a first signal, the first signal having a first CDMA channelization. The first receiver is configured to produce an indication of a timing of the first signal. The sync unit also has a second receiver configured to receive a second signal, the second signal having a second CDMA channelization. The second receiver is configured to produce an indication of a timing of the second signal. The sync unit also has a time error detection unit configured to compare the timing of the first signal and the timing of the second signal to determine a relative timing offset thereof.

Owner:QUALCOMM INC

Camera and camera zoom control method

InactiveUS7884862B2Reduce power consumptionReduce time differenceTelevision system detailsPrintersCamera lensTime difference

Owner:FUJIFILM CORP

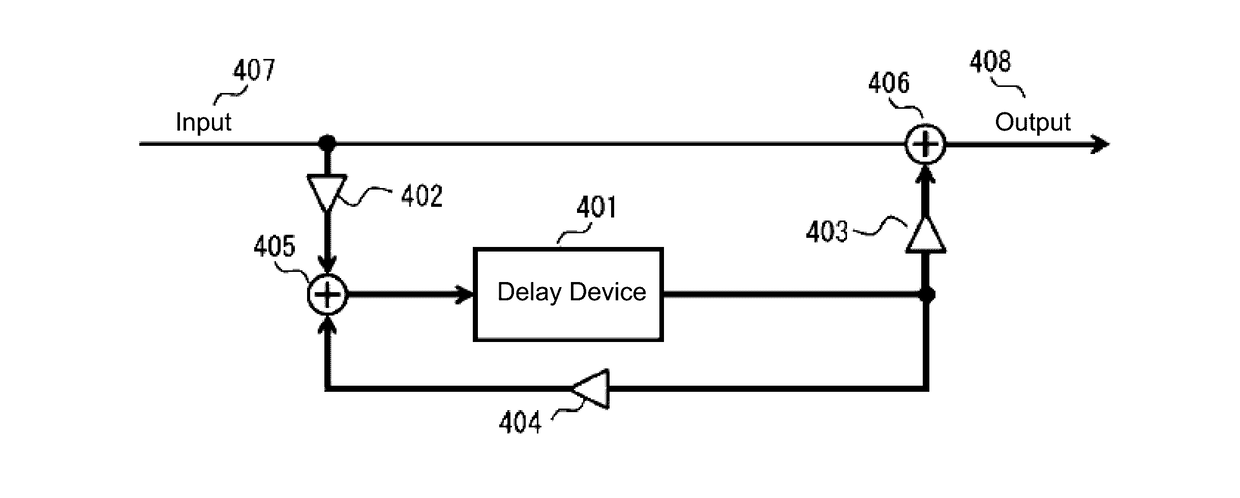

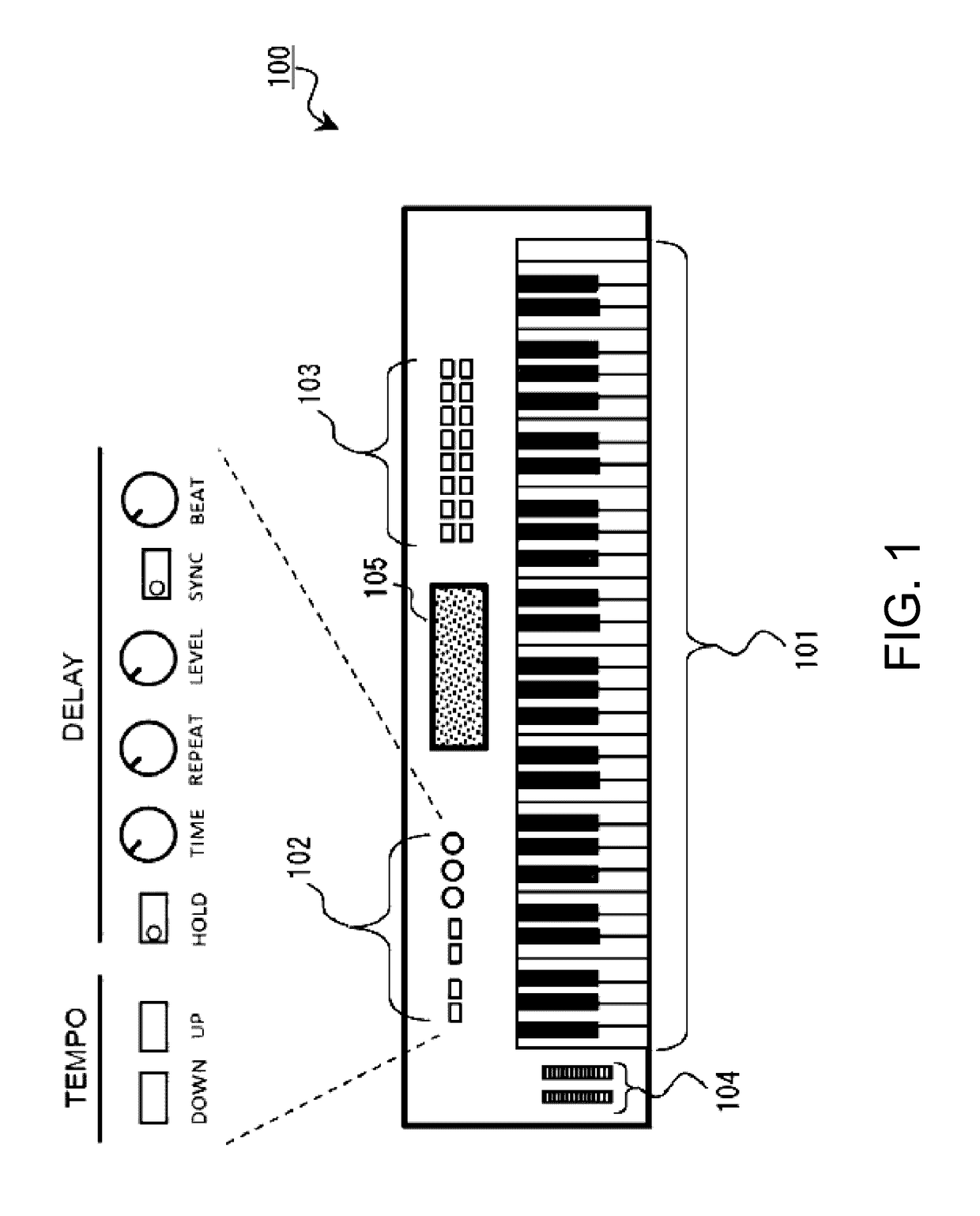

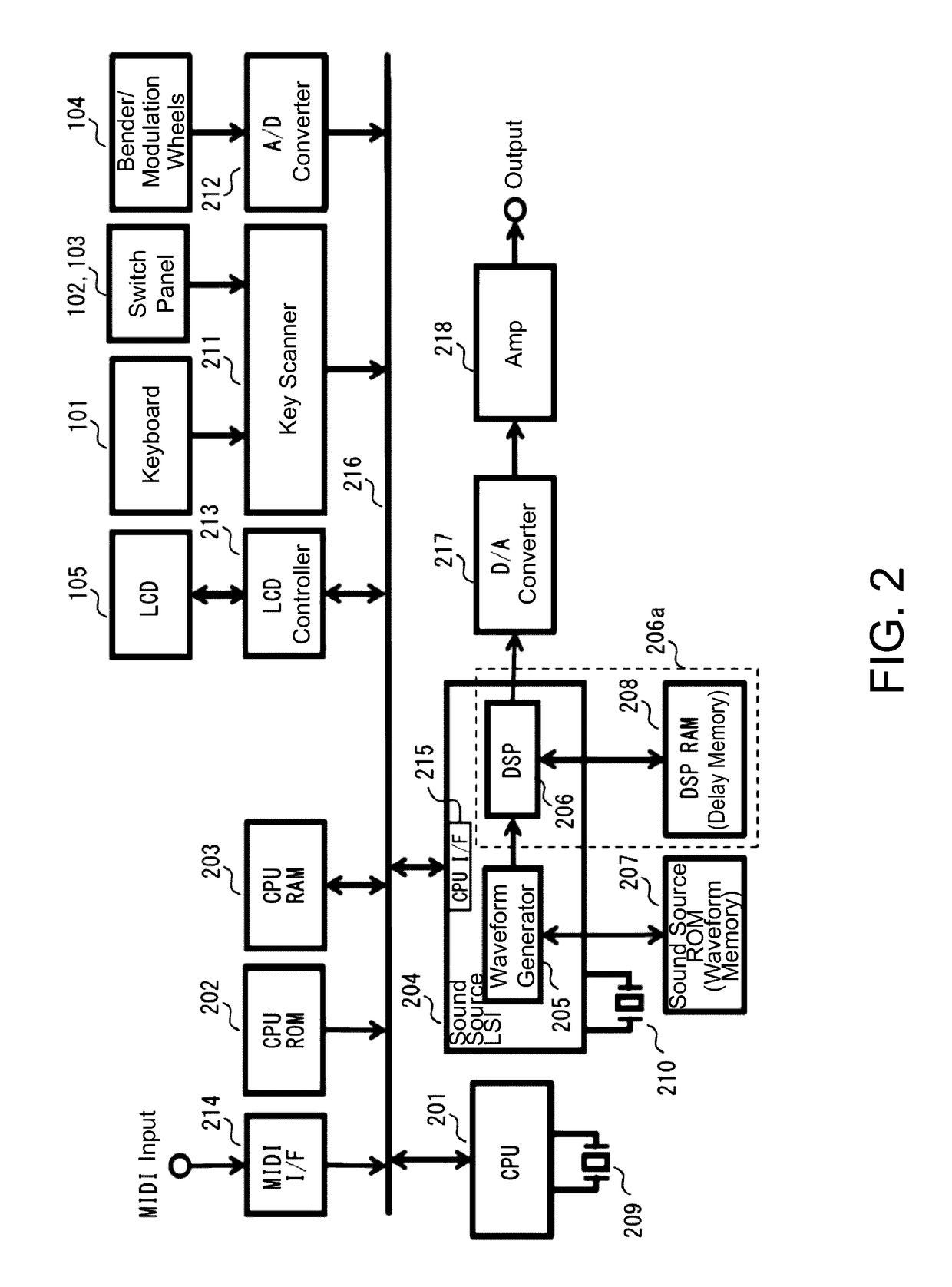

Audio processing device, method of audio processing, storage medium, and electronic musical instrument

ActiveUS20170169807A1Reduce time differenceElectrophonic musical instrumentsDelayed timeElectronic instrument

A delay time counter in a DSP cyclically counts a sampling clock from zero to a delay time sampling count and issues a delay time interrupt to a CPU each time the sampling clock count reaches the delay time sampling count. The CPU measures a time difference between each time the DSP issues the delay time interrupt and each time sequence clock interrupts occur a number of times corresponding to the delay time. Then, in order to reduce this time difference, the CPU increases or decreases a maximum count that is set to the sequence clock counter. Therefore, in the next delay process, the shift between the time by which the automatic performance is advanced by the CPU (which is equal to the delay time) and the timing of the delay process executed by the DSP (which is also equal in length to the delay time) will be corrected.

Owner:CASIO COMPUTER CO LTD

Engine system and method

ActiveUS20160319763A1Reduce time differenceElectrical controlMachines/enginesEngineeringElectrical current

Various methods and systems are provided for controlling and shaping the current waveform for a solenoid in a fuel injector that has variable impedance.

Owner:GE GLOBAL SOURCING LLC

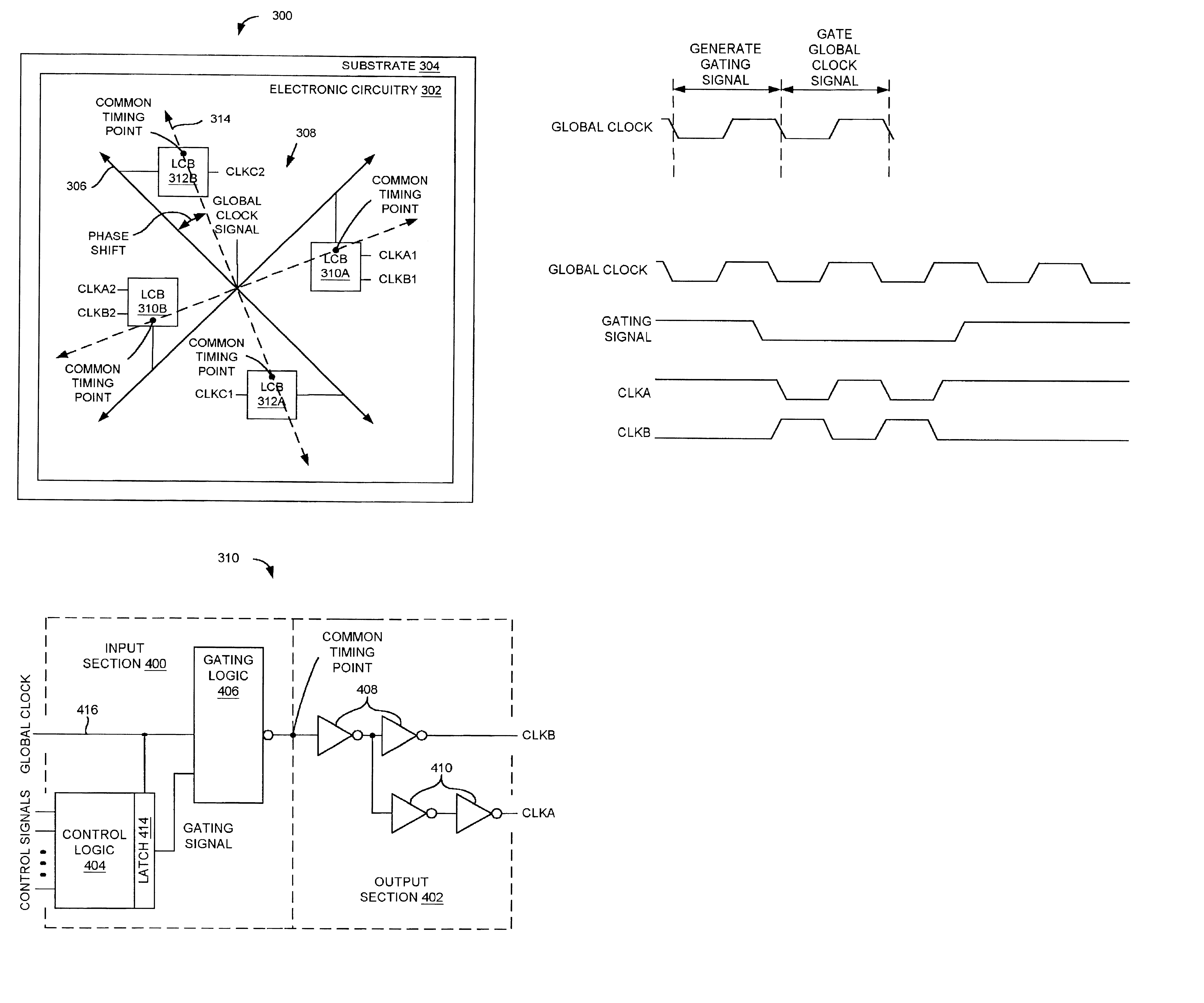

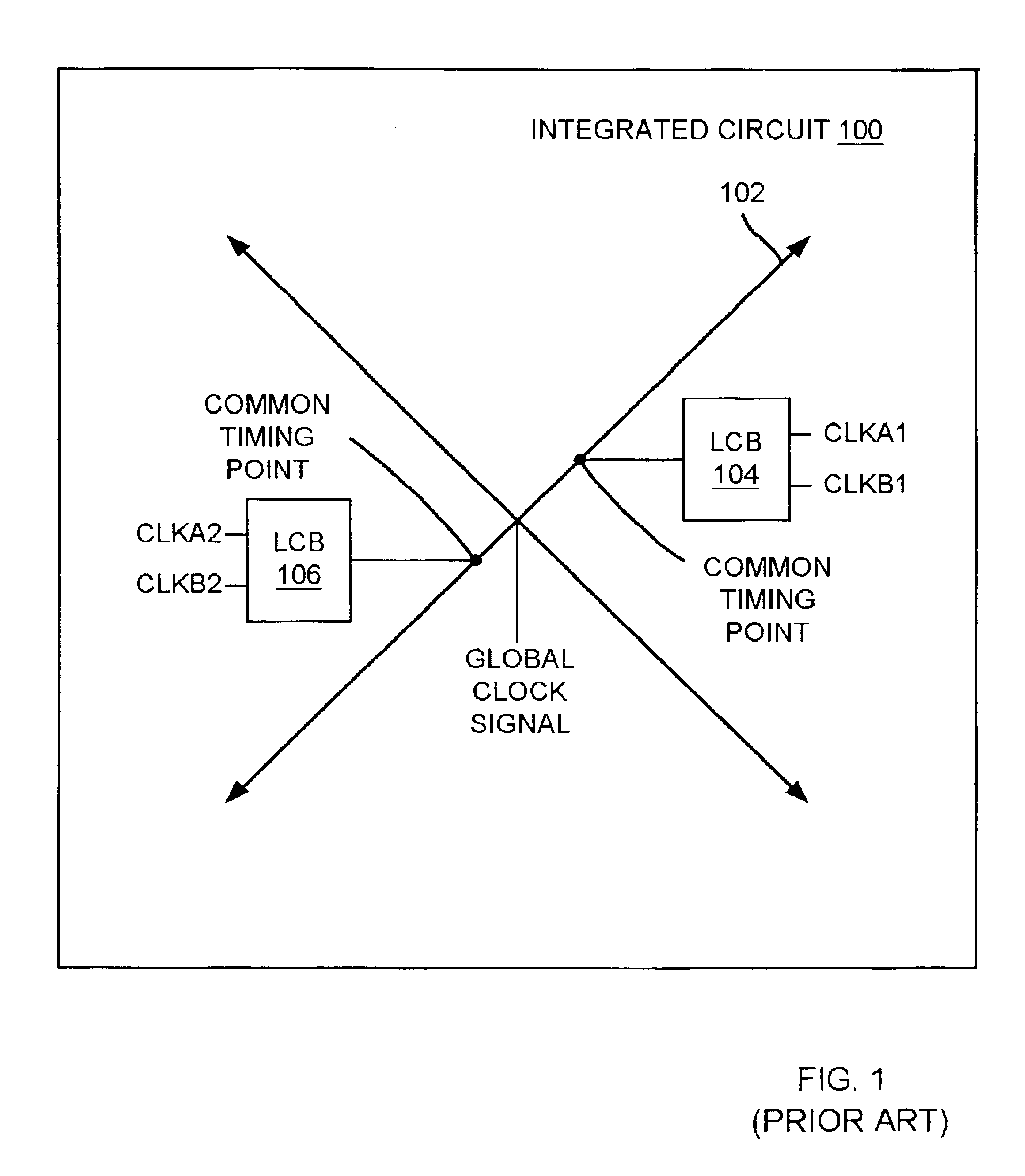

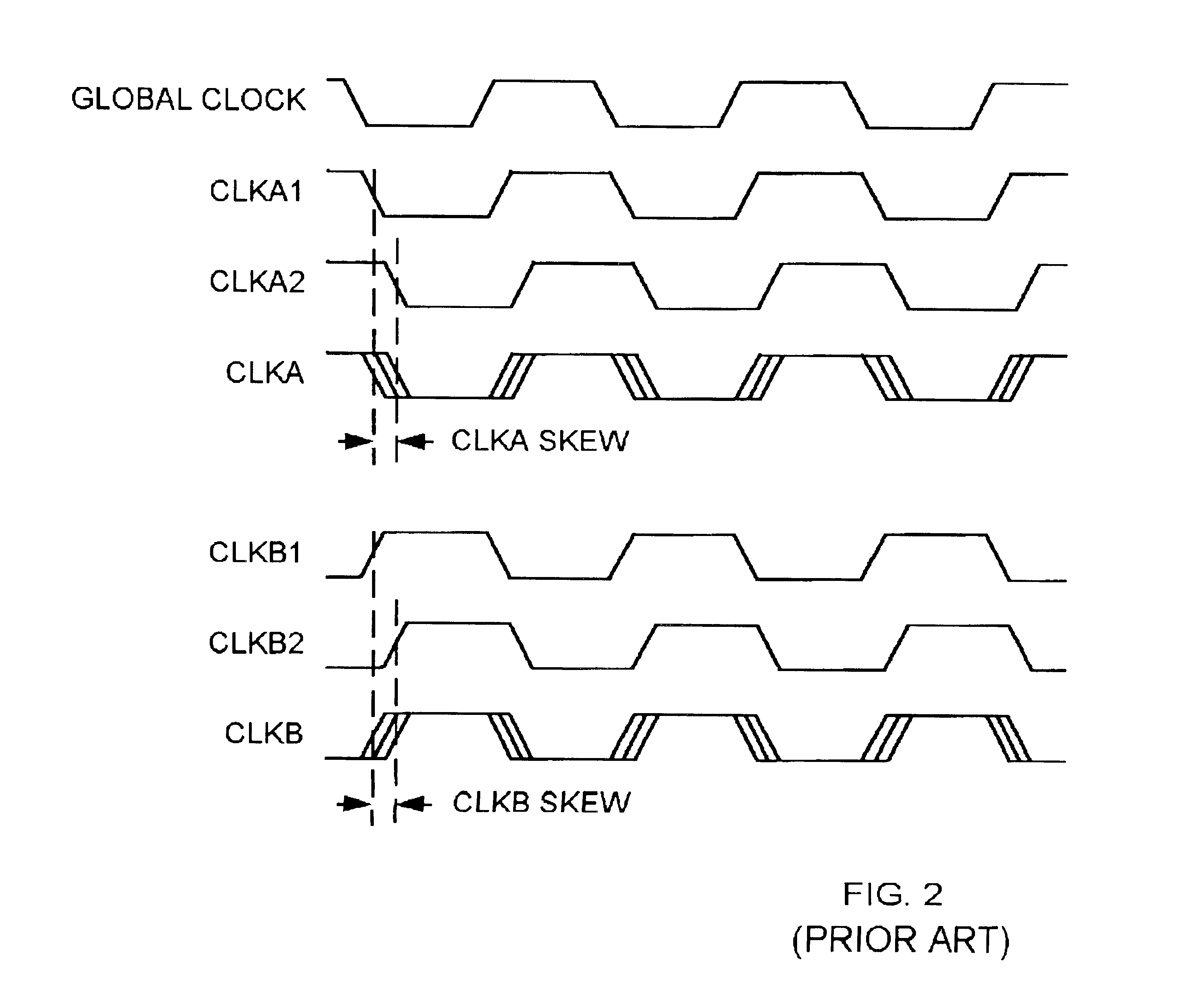

Low skew, power efficient local clock signal generation system

InactiveUS6927615B2Time differenceReduce time differenceElectric pulse generatorGenerating/distributing signalsPower efficientData signal

A local clock signal generation system is disclosed including multiple local clock buffers each receiving a global clock signal and producing a version of one or more local clock signals derived from the global clock signal. Each local clock buffer includes an input section and an output section. The input sections are substantially identical such that timing differences between the versions of the one or more local clock signals are reduced. An electronic circuit is described including the local clock signal generation system and a latch (e.g., a master latch of a flip-flop). A local clock buffer produces a gating signal and a local clock signal received by the latch. When the gating signal is a certain logic value, the local clock signal is a steady logic value, and the latch produces an input data signal as an output signal. An integrated circuit including the electronic circuit is disclosed.

Owner:IBM CORP

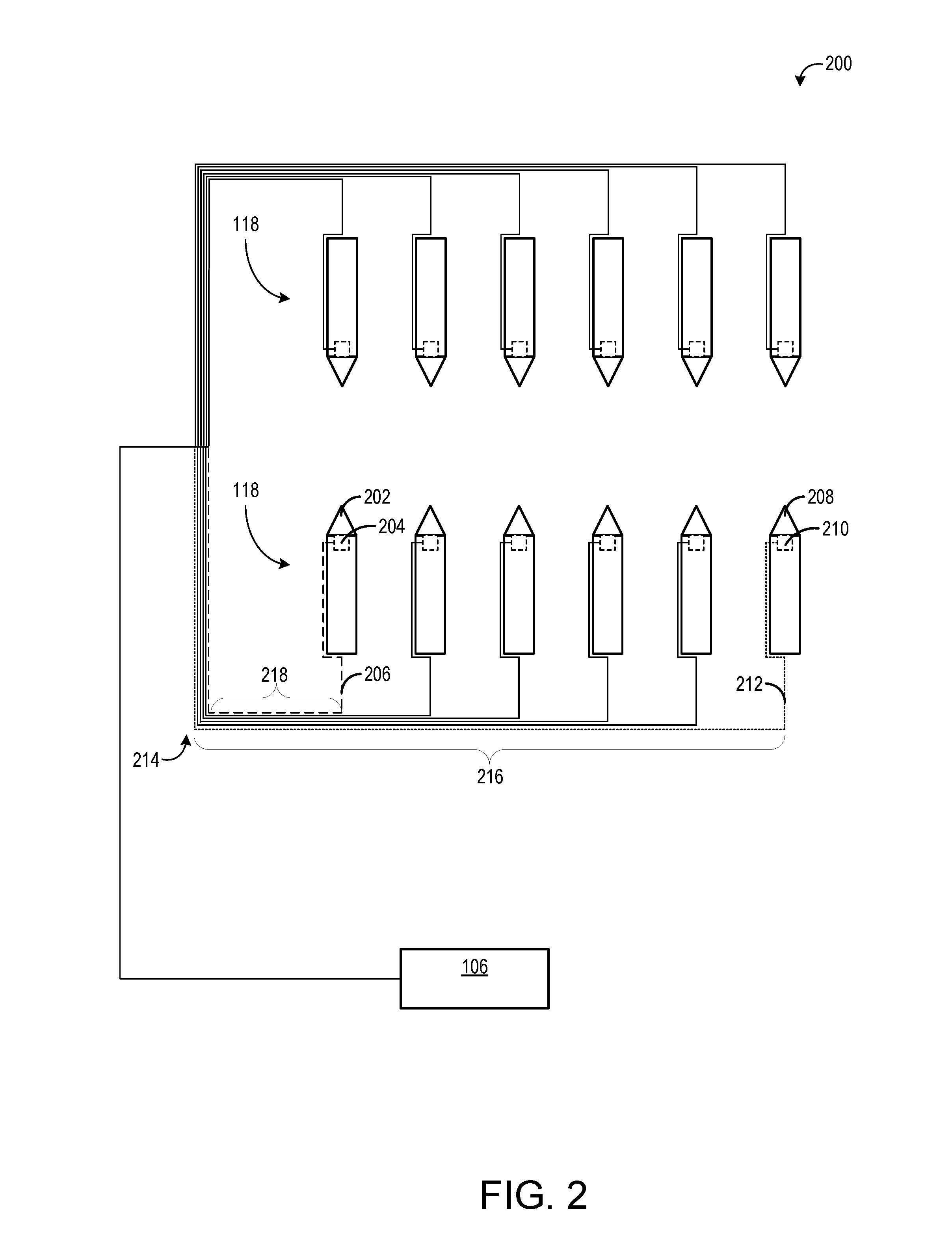

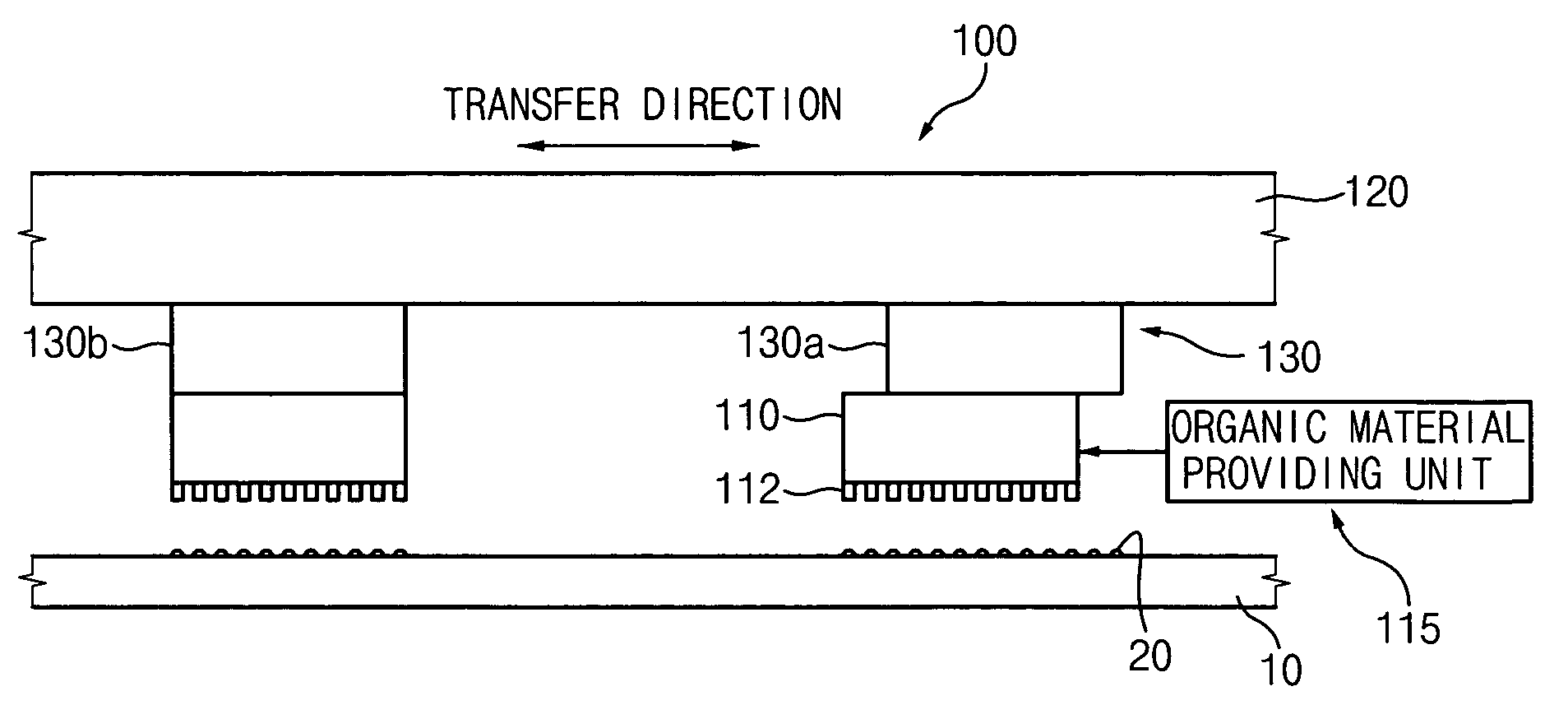

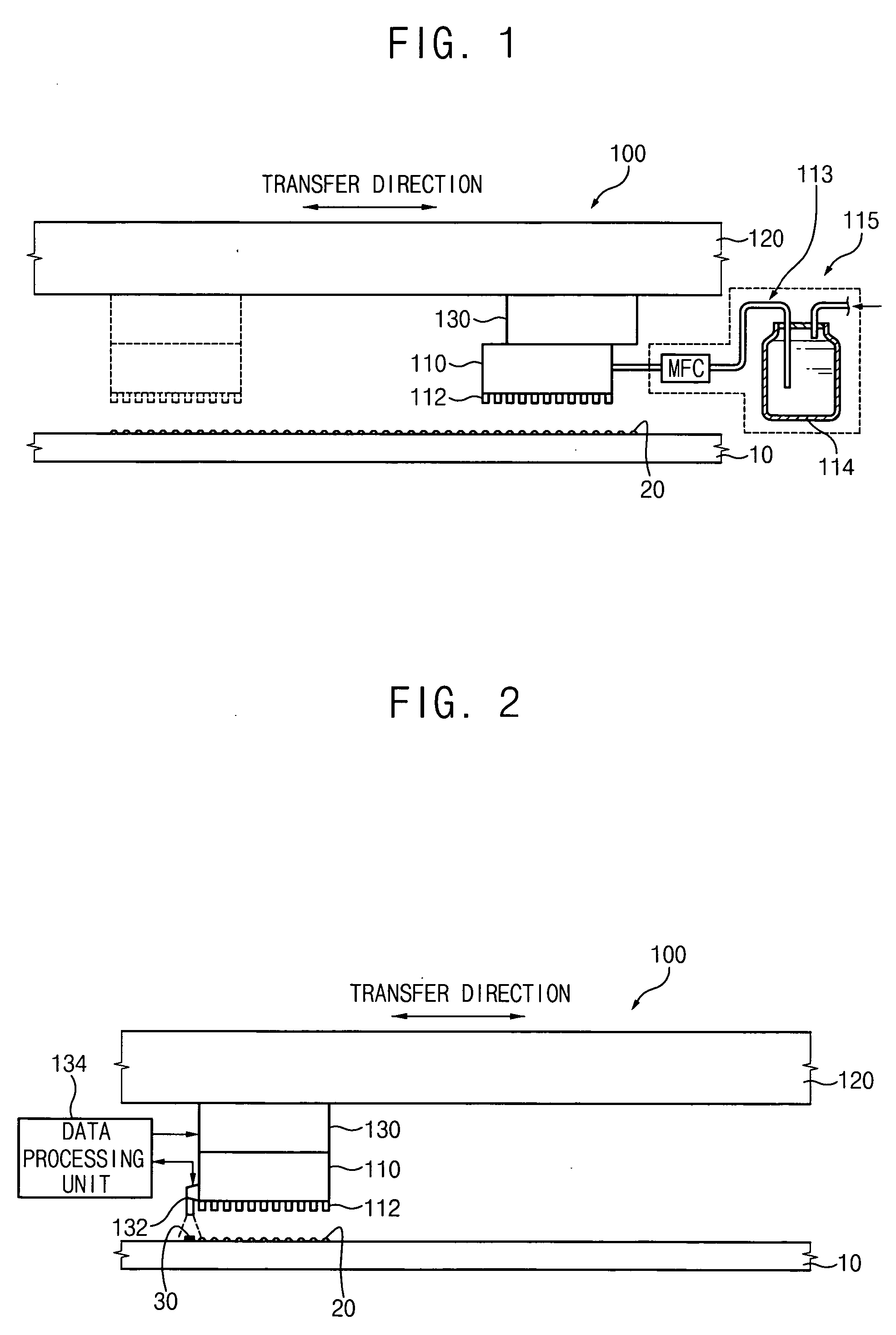

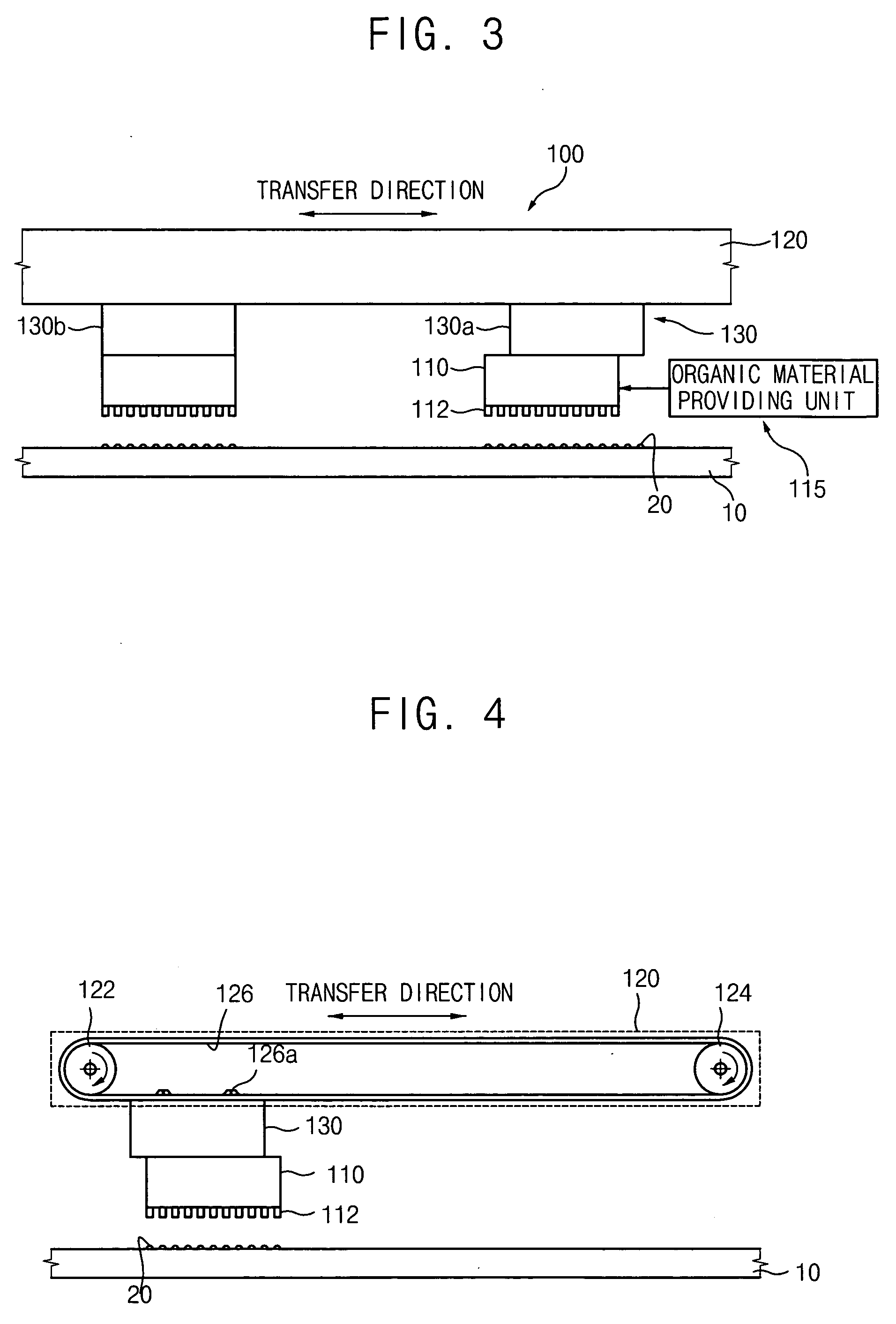

Apparatus for depositing an organic material on a substrate

ActiveUS20050183661A1Reduce time differenceEasy to adjustLiquid surface applicatorsElectroluminescent light sourcesTime differenceMechanical engineering

An apparatus includes a drop unit, a transfer unit and a position adjusting unit. The drop unit drops droplets of an organic material. The transfer unit transfers the drop unit along a first direction. The position adjusting unit is interposed between the drop unit and the transfer unit to adjust a position of the drop unit. Therefore, the apparatus of dropping the organic material has a small size and may drop droplets of the organic material onto an accurate position. Furthermore, the transfer unit moves the drop unit quickly, and the position adjusting unit adjusts the position of the drop unit accurately. Therefore, a time difference for drying the organic material injected into a cavity is reduced.

Owner:SAMSUNG DISPLAY CO LTD

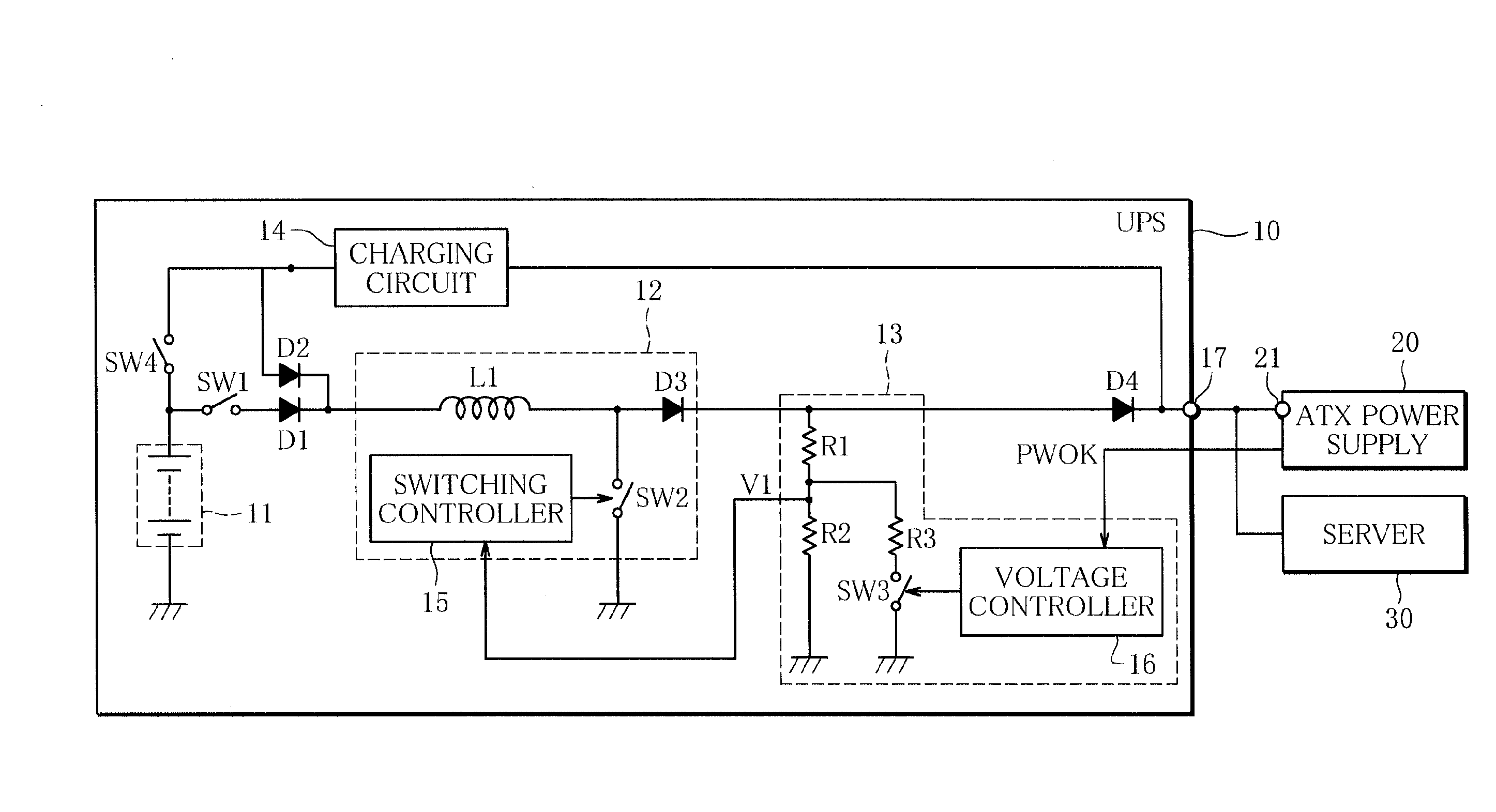

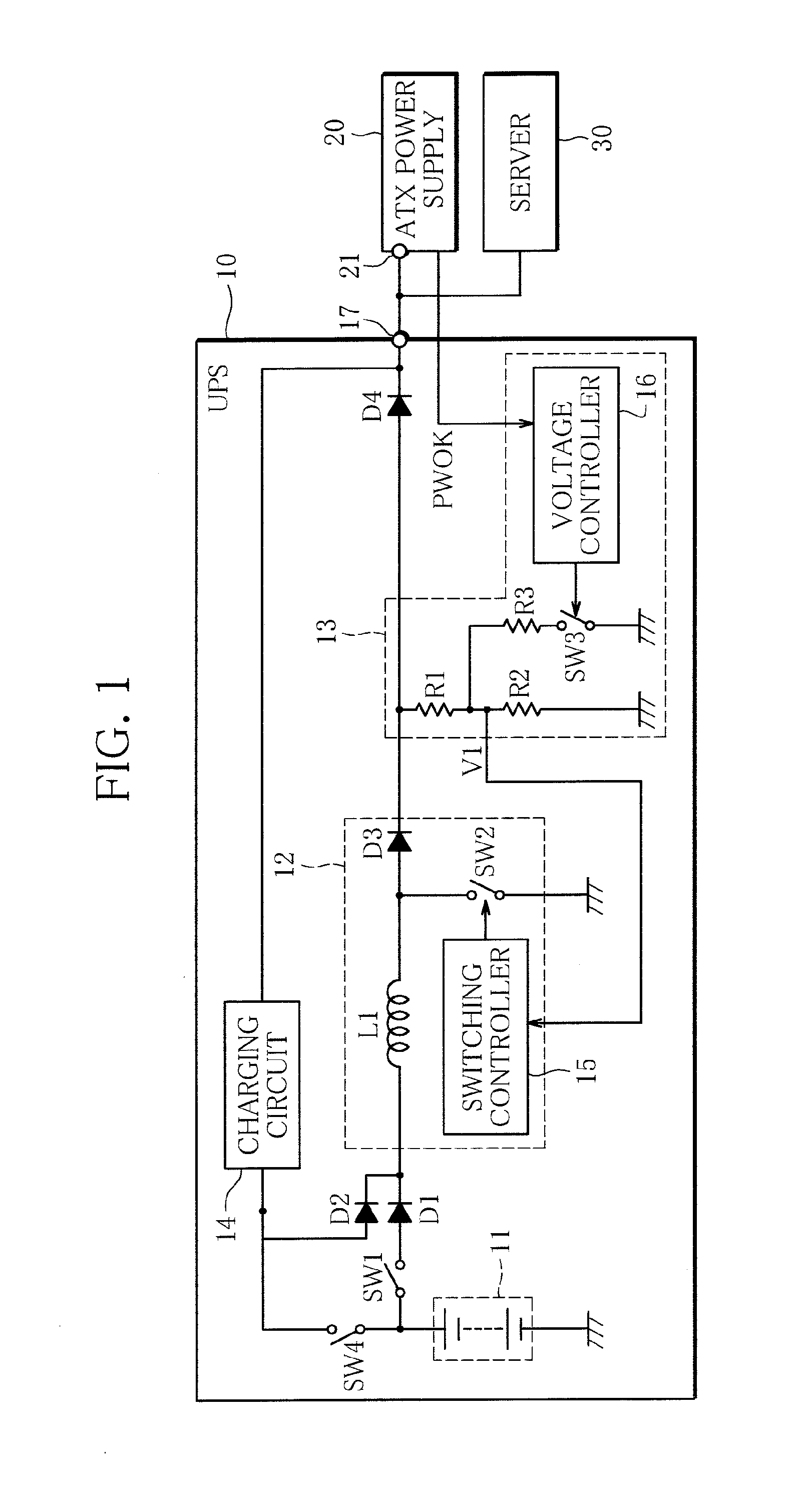

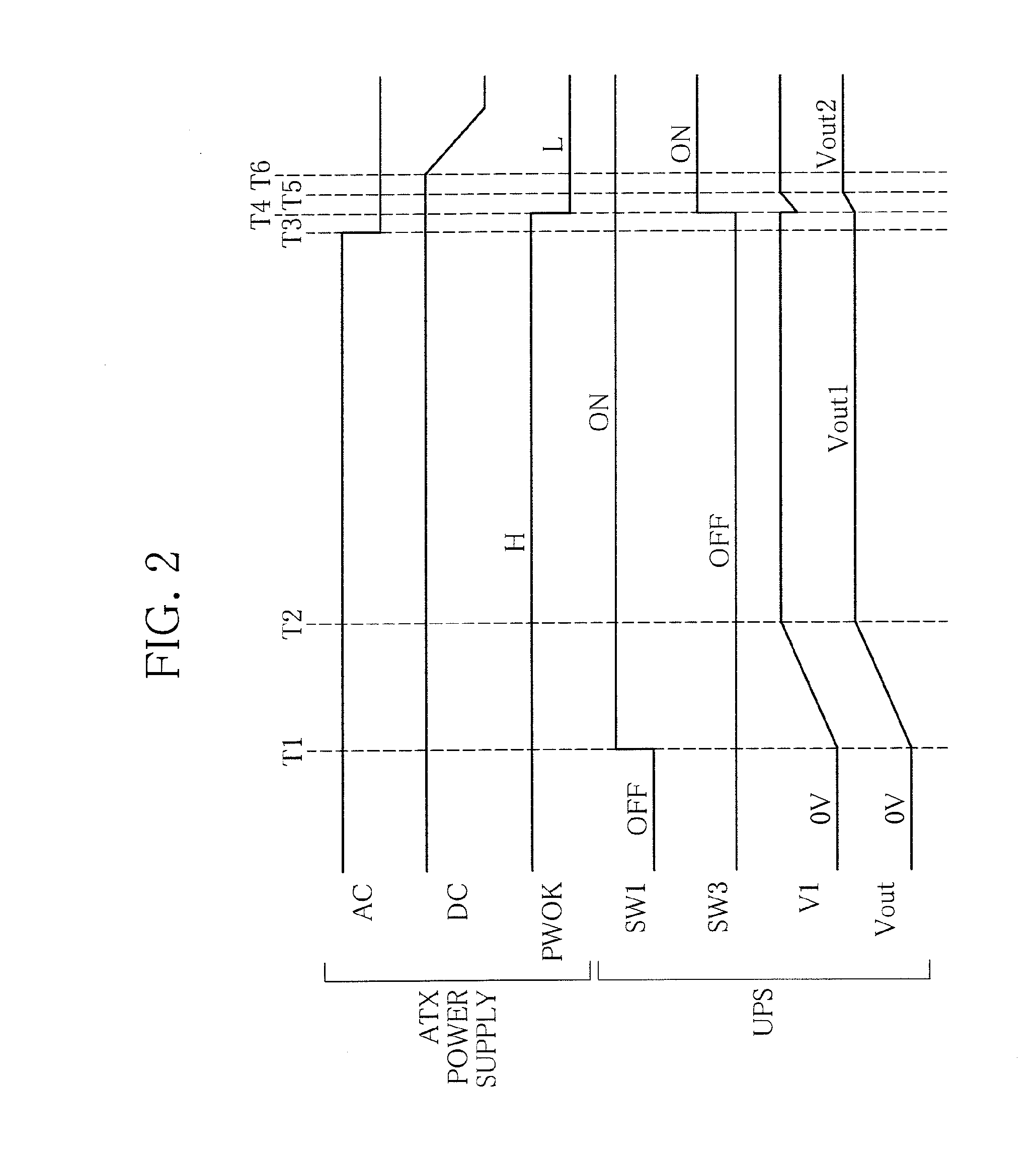

Uninterruptible power supply

ActiveUS20140183959A1Low costReduce time differenceBatteries circuit arrangementsEfficient power electronics conversionPower inverterControl circuit

An uninterruptible power supply is having a battery, a power inverter circuit for inverting the electrical power of the battery, and a voltage control circuit. The voltage control circuit controls the power inverter circuit, so that the output voltage of the power inverter circuit is maintained at a standby voltage lower than a rated voltage under the condition of a power failure detection signal being not output from an external power supply and the output voltage of the power inverter circuit equals the rated voltage under the condition of the power failure detection signal being output from the external power supply.

Owner:FDK CORP