Patents

Literature

37results about "Logic circuits using saturable magnetic devices" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

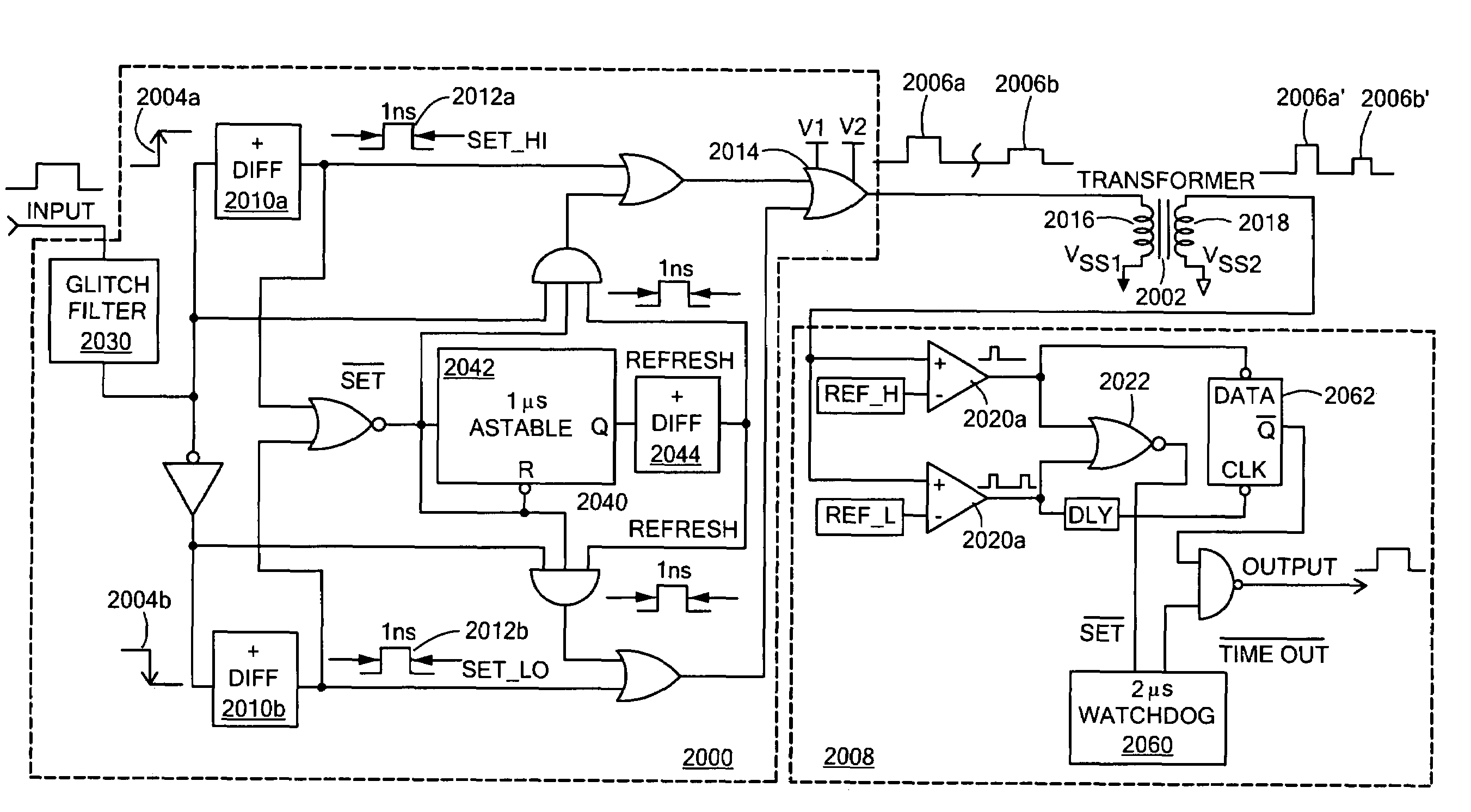

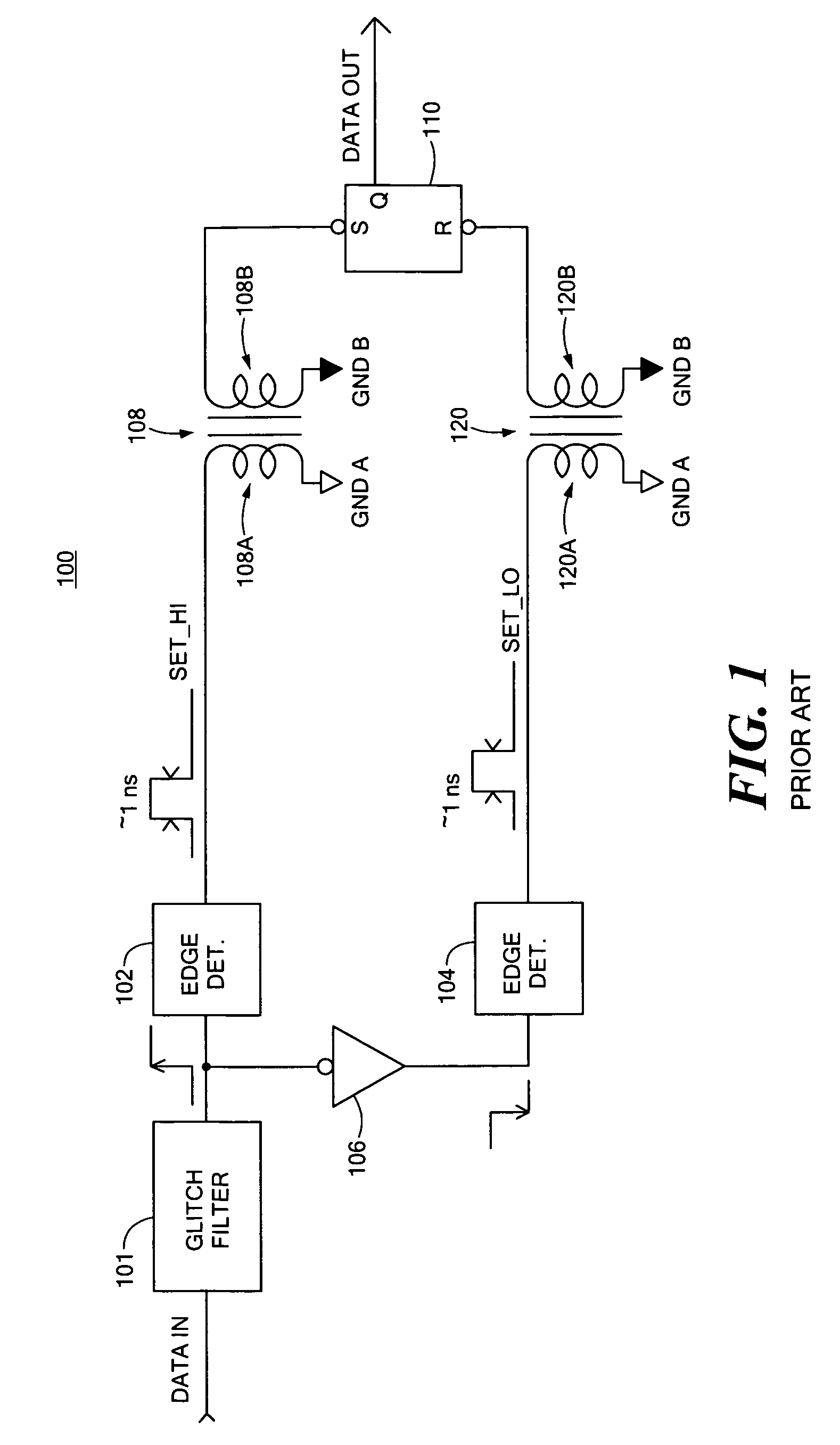

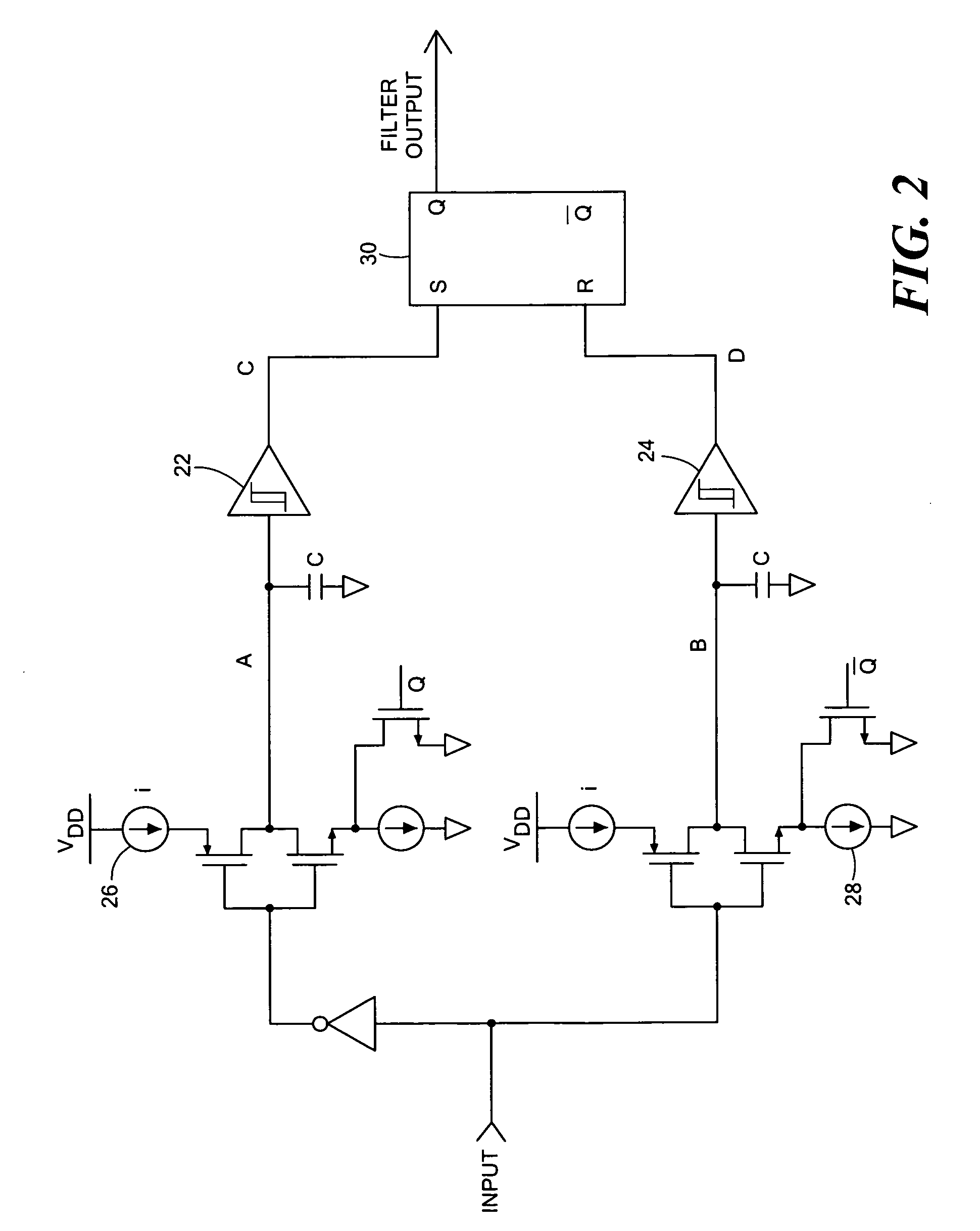

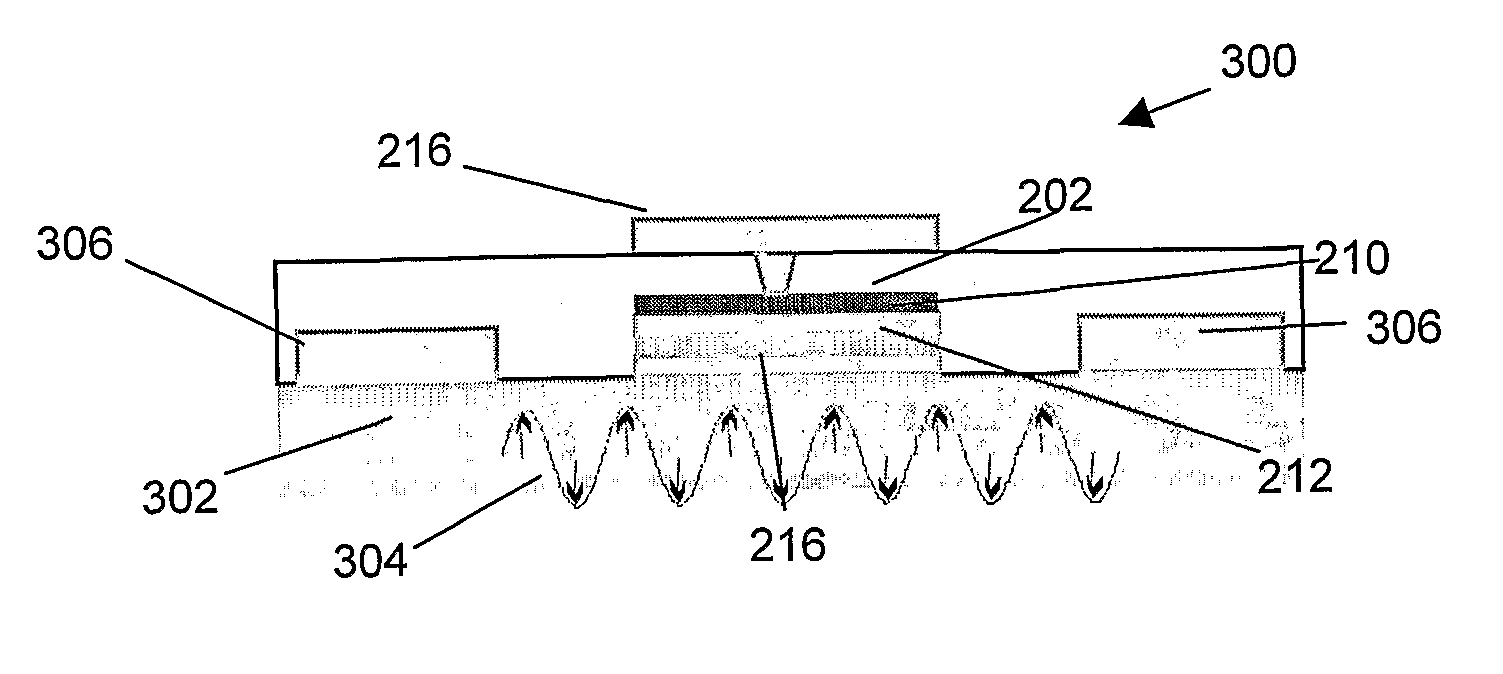

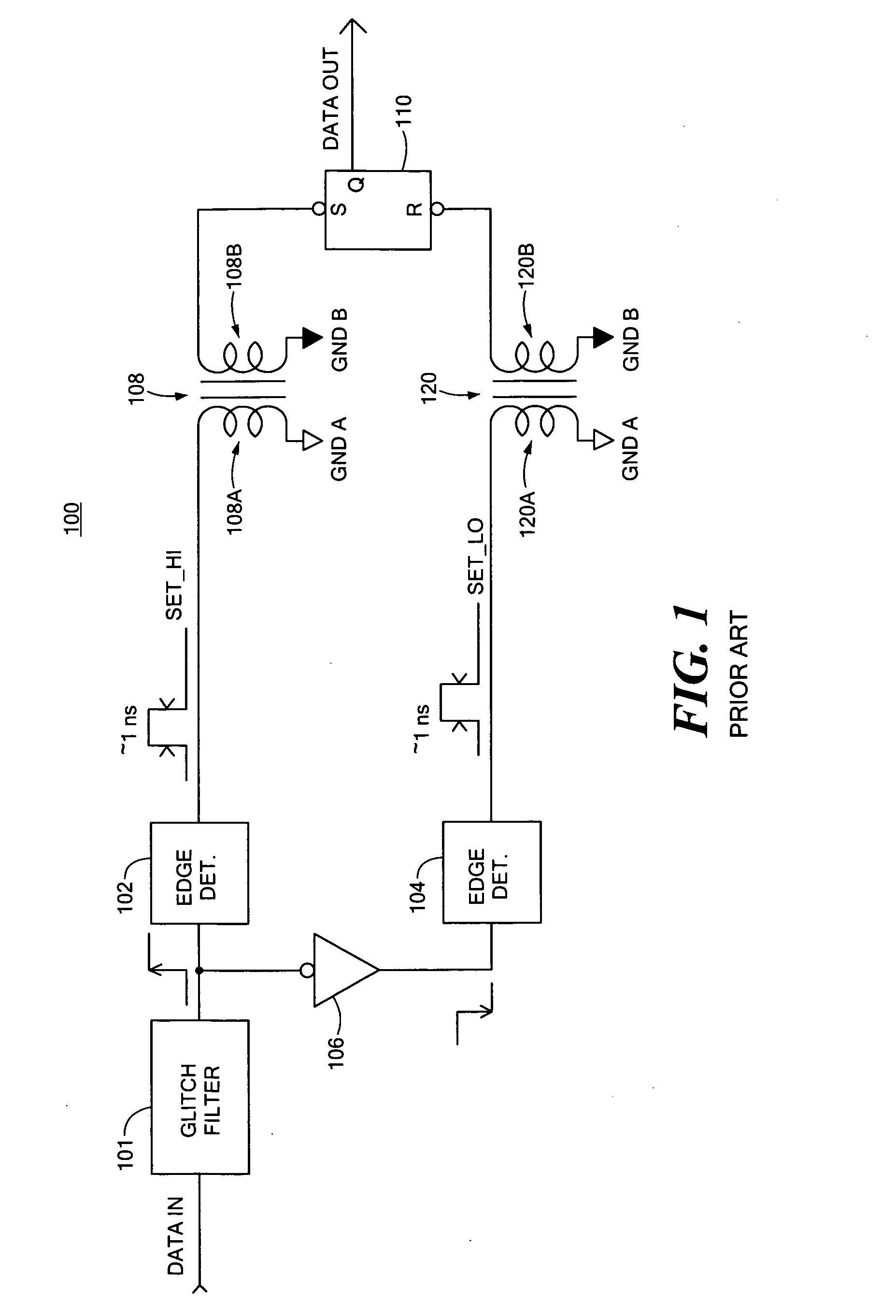

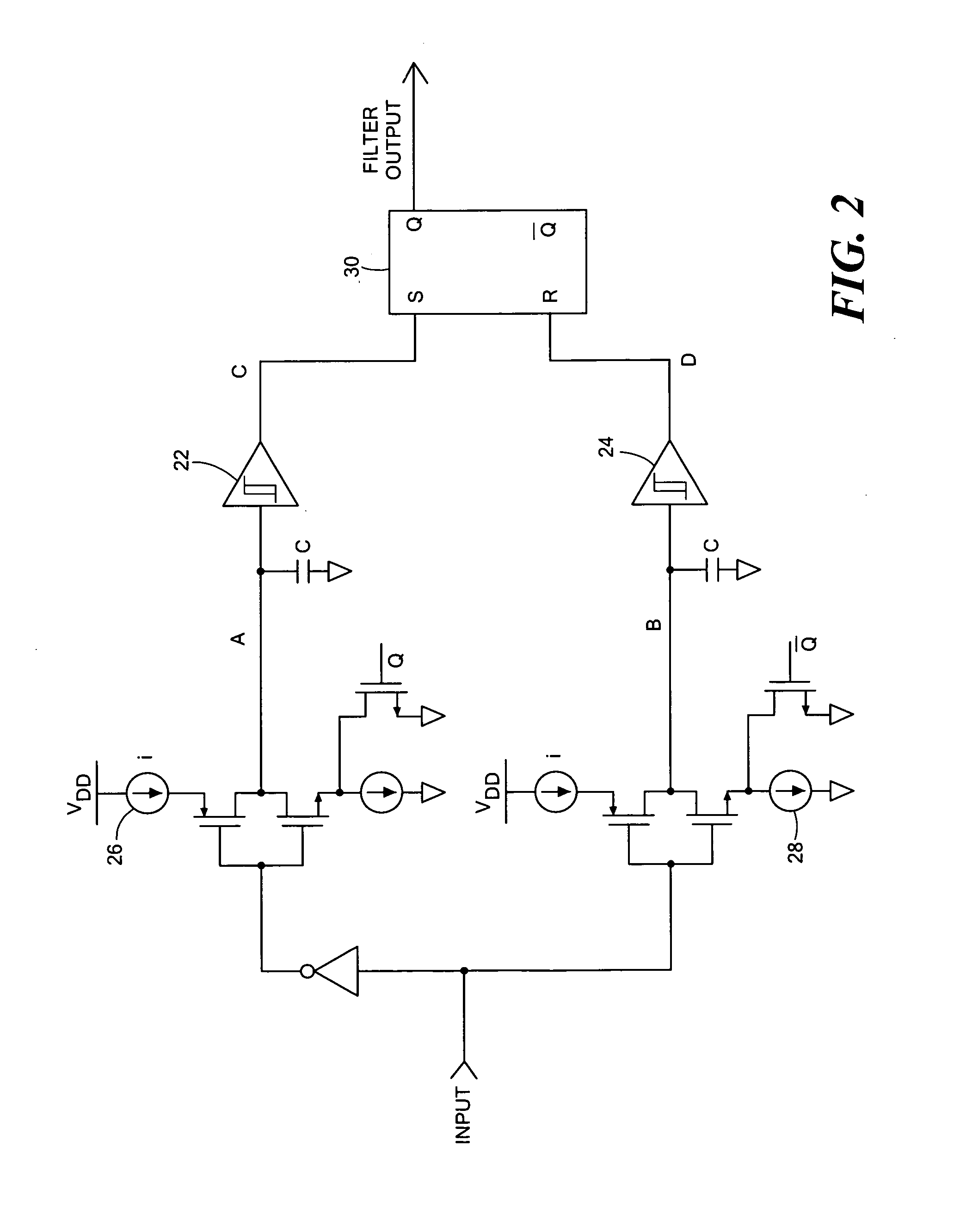

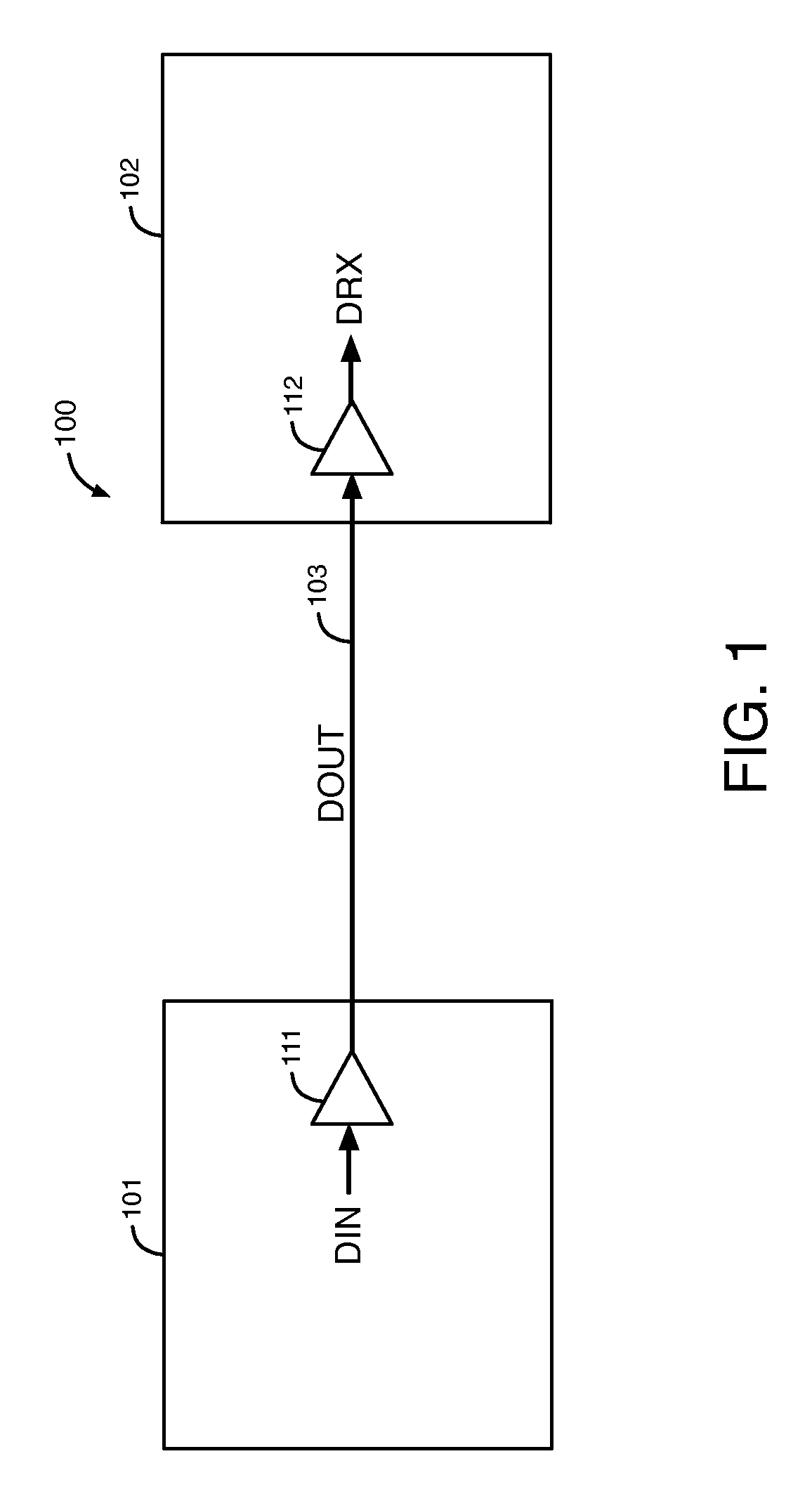

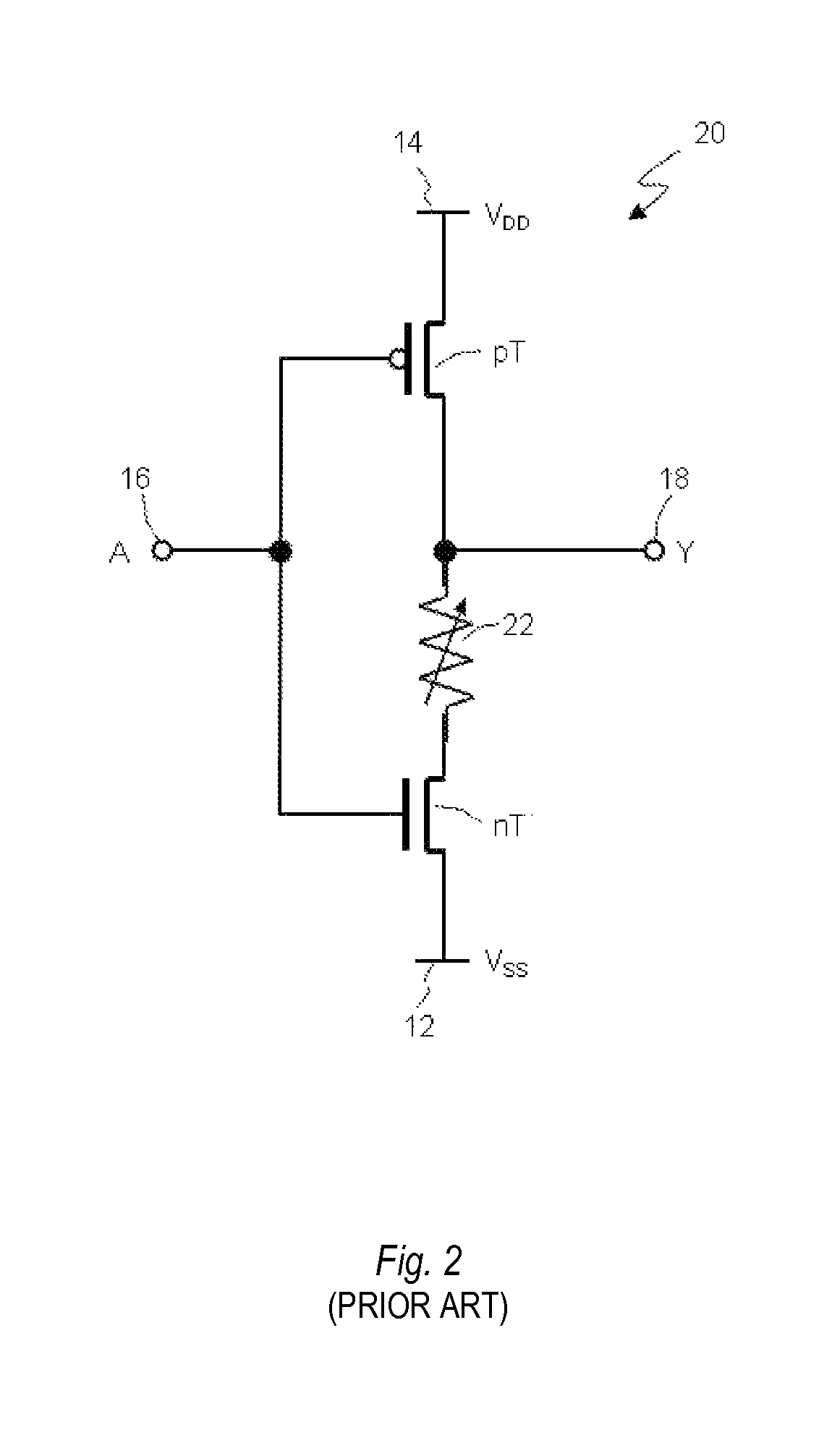

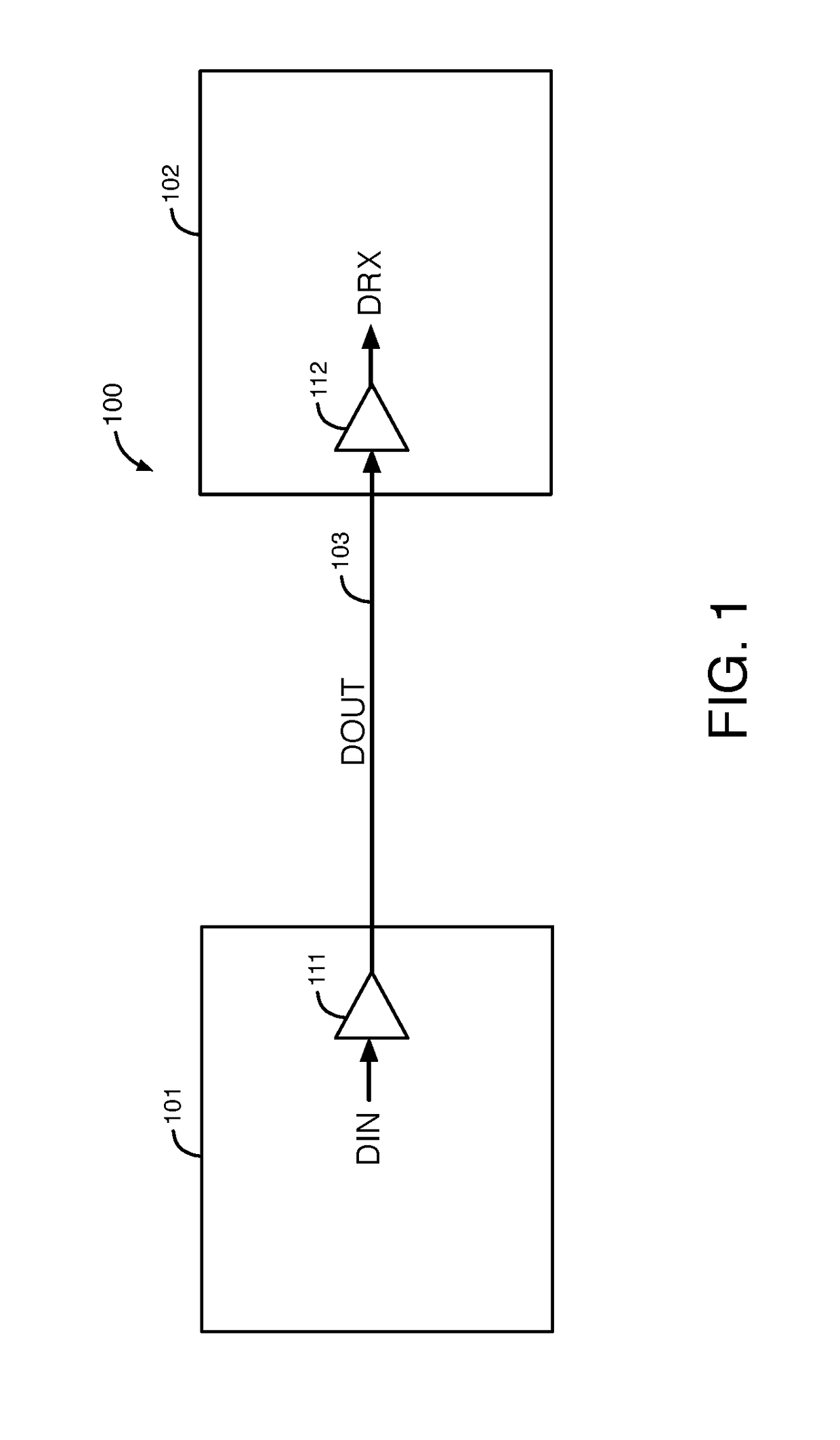

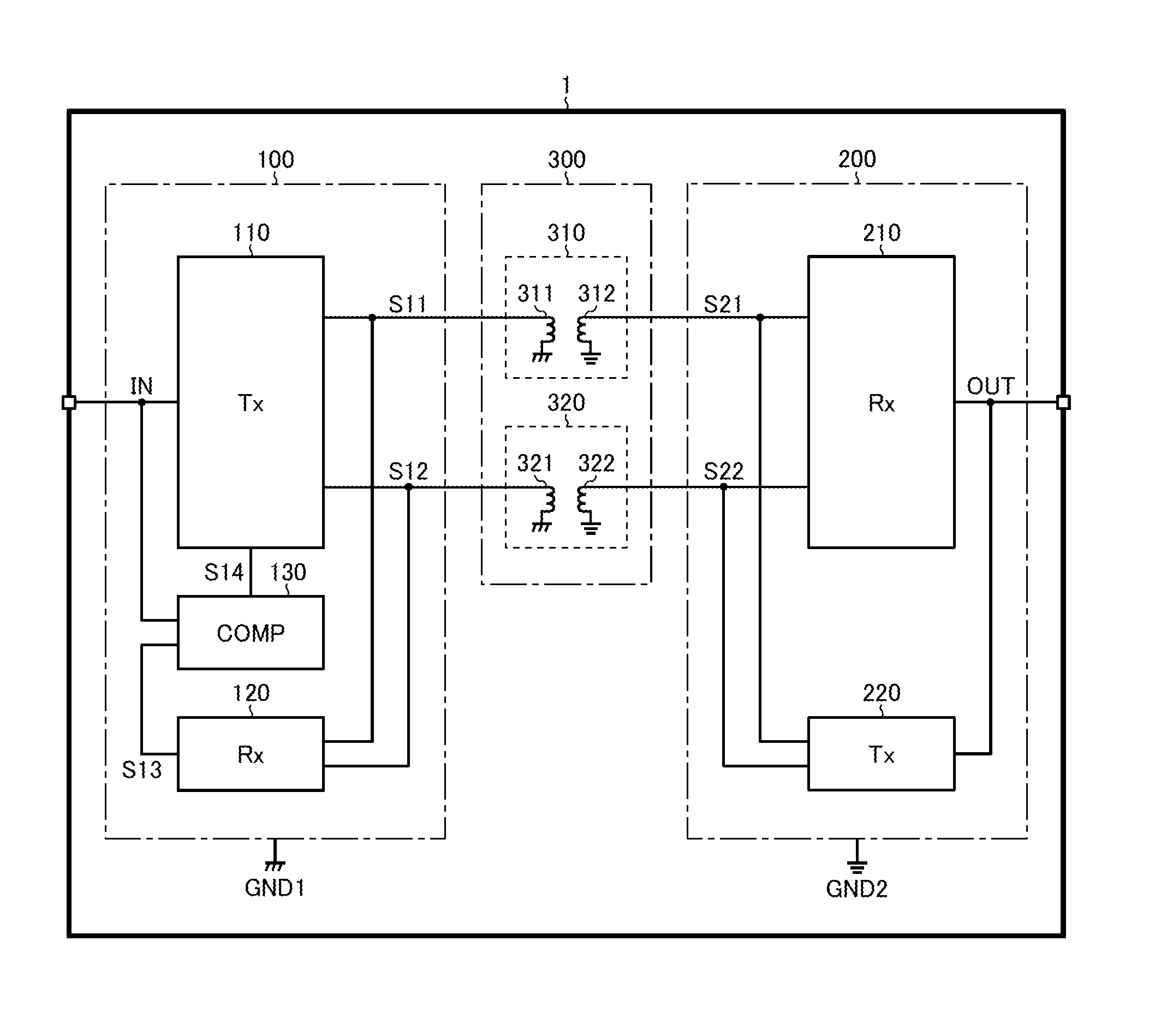

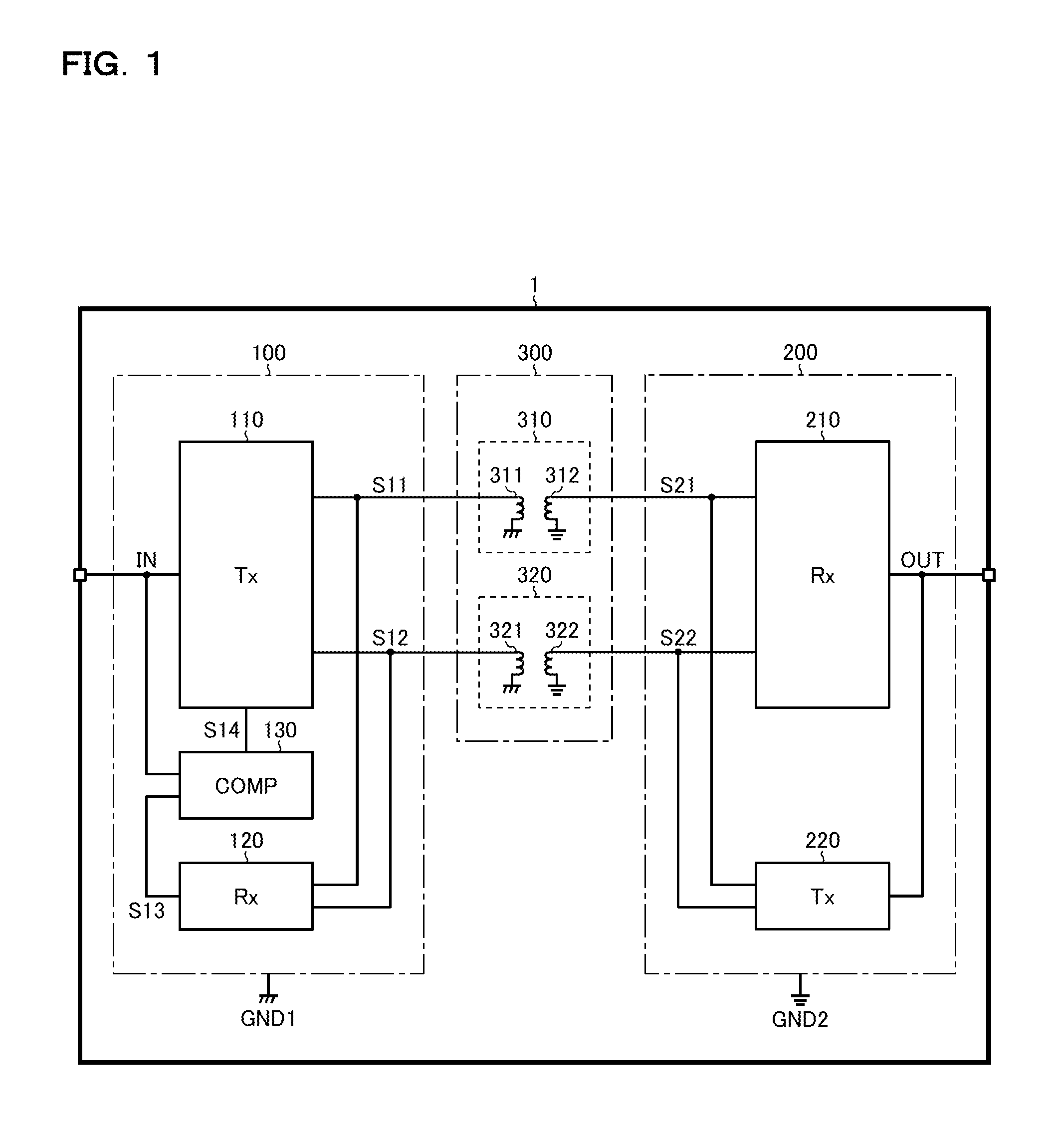

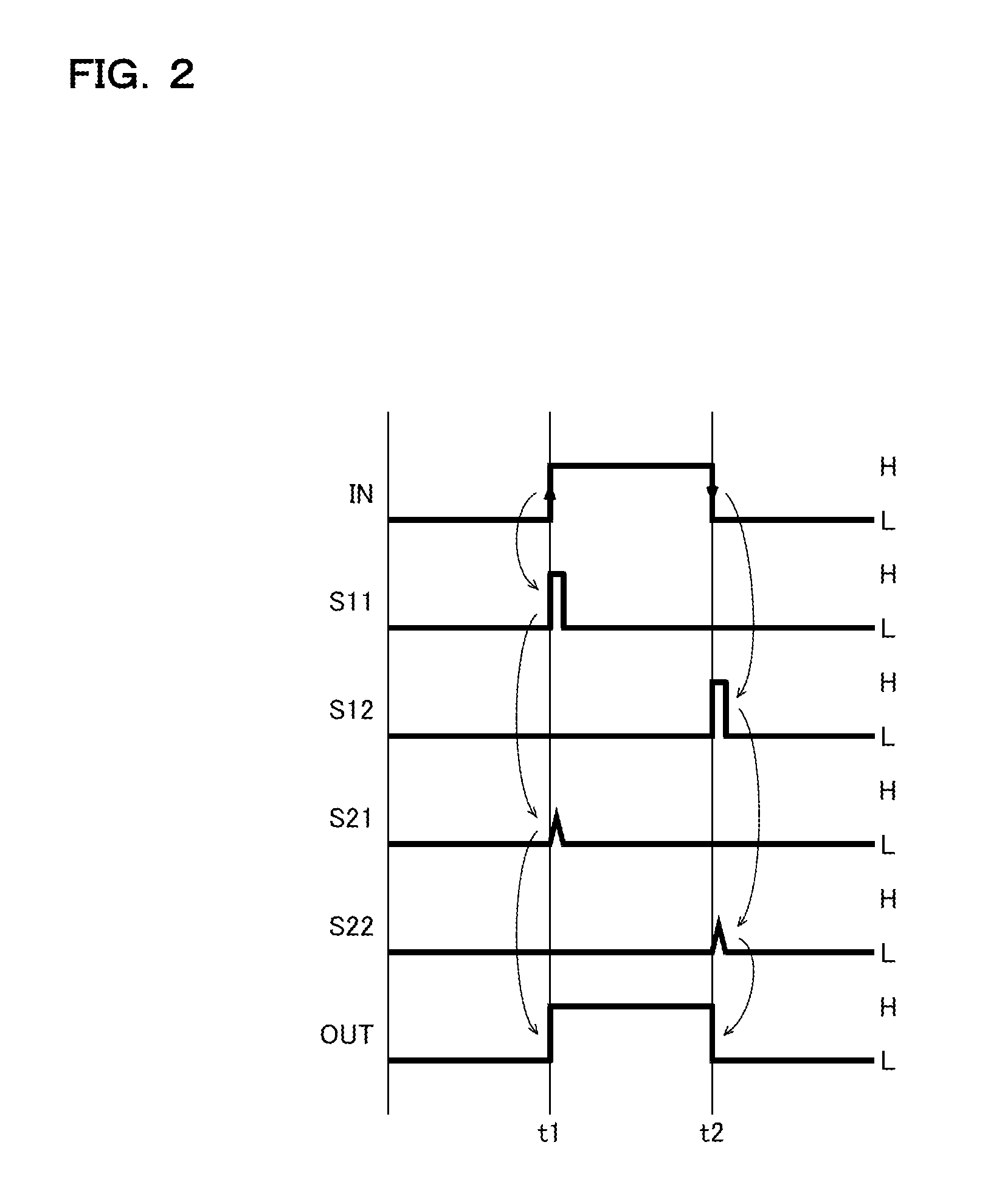

Signal isolator using micro-transformers

ActiveUS7719305B2Reliability increasing modificationsPulse generation by non-linear magnetic/dielectric devicesTransformerEngineering

A logic signal isolator including a micro-transformer with a primary winding and a secondary winding. A transmitter circuit drives the primary winding in response to a received input logic signal such that, in response to a first type of edge in the logic signal, at least a first amplitude signal is supplied to the primary winding and, in response to a second type of edge in the logic signal, a second different amplitude signal is supplied to the primary winding. A receiver circuit receives corresponding first amplitude and second amplitude signals from the secondary winding and reconstructs the received logic input signal from the received signals.

Owner:ANALOG DEVICES INC

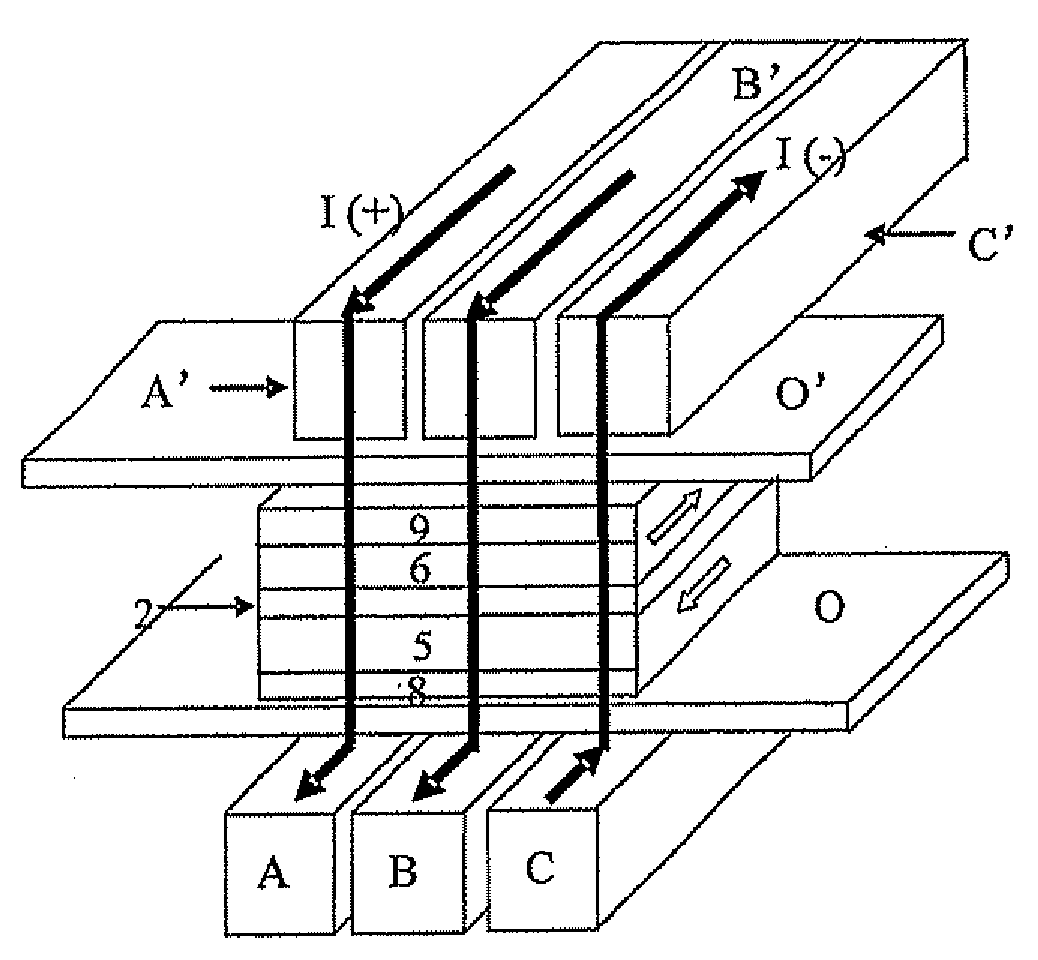

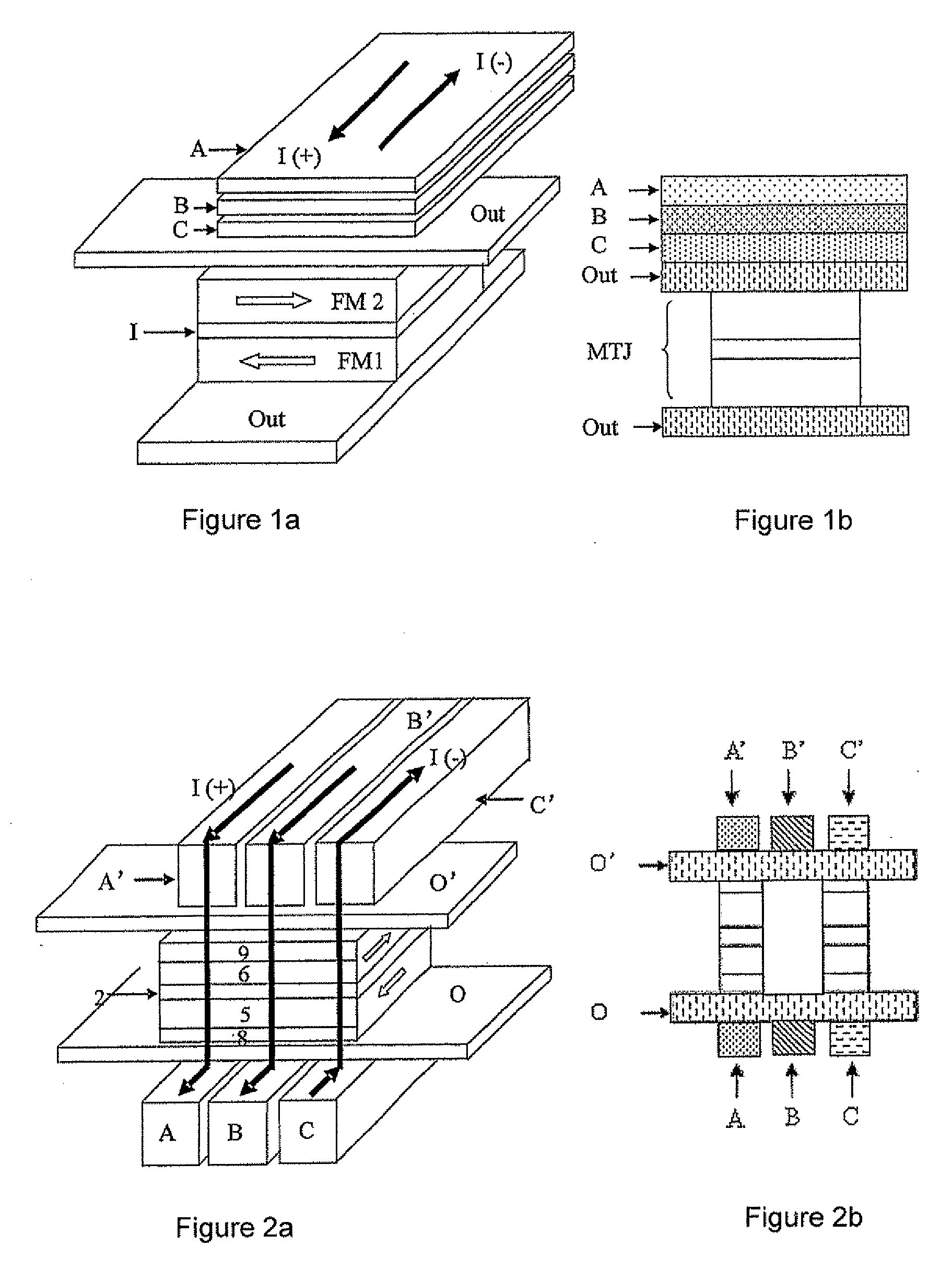

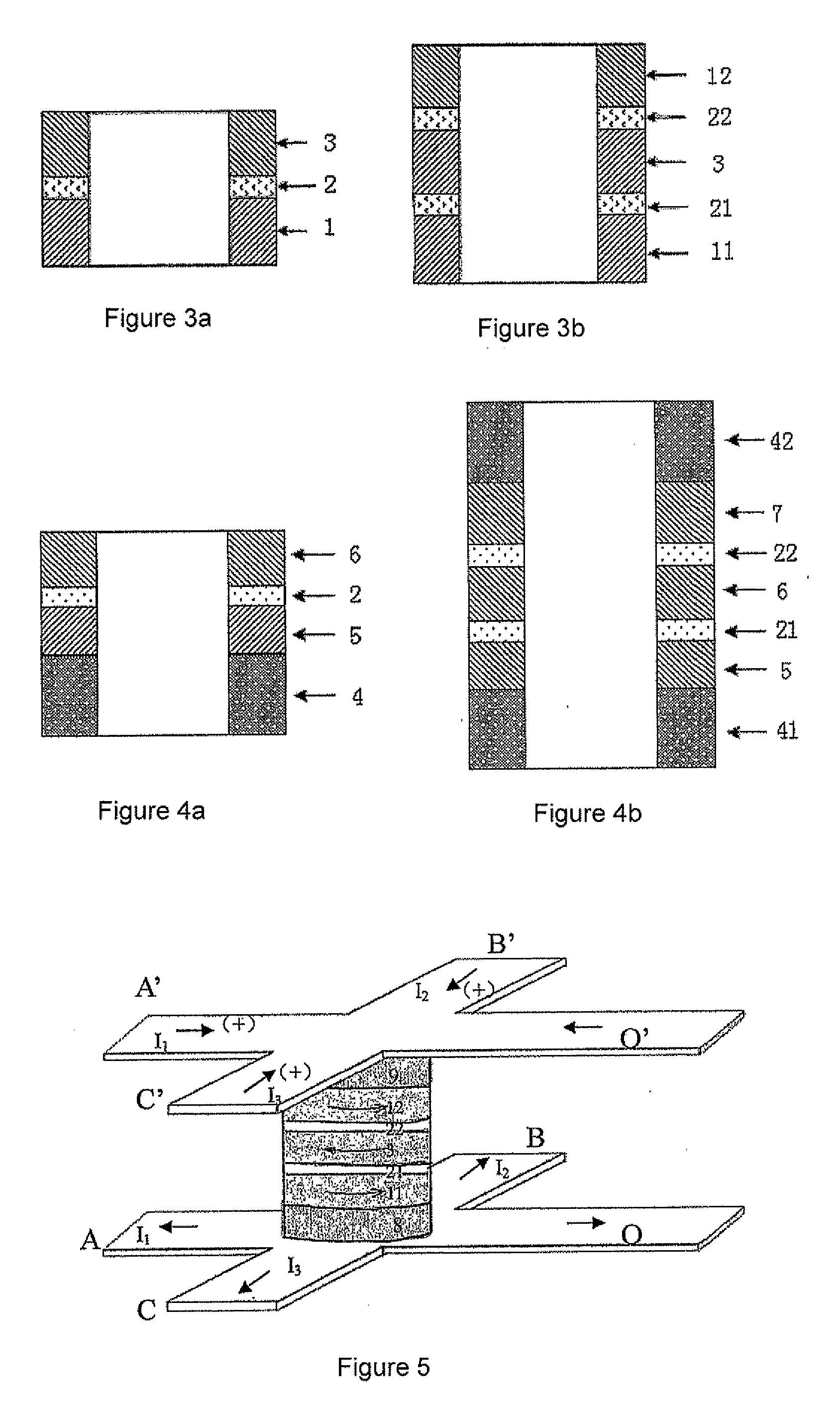

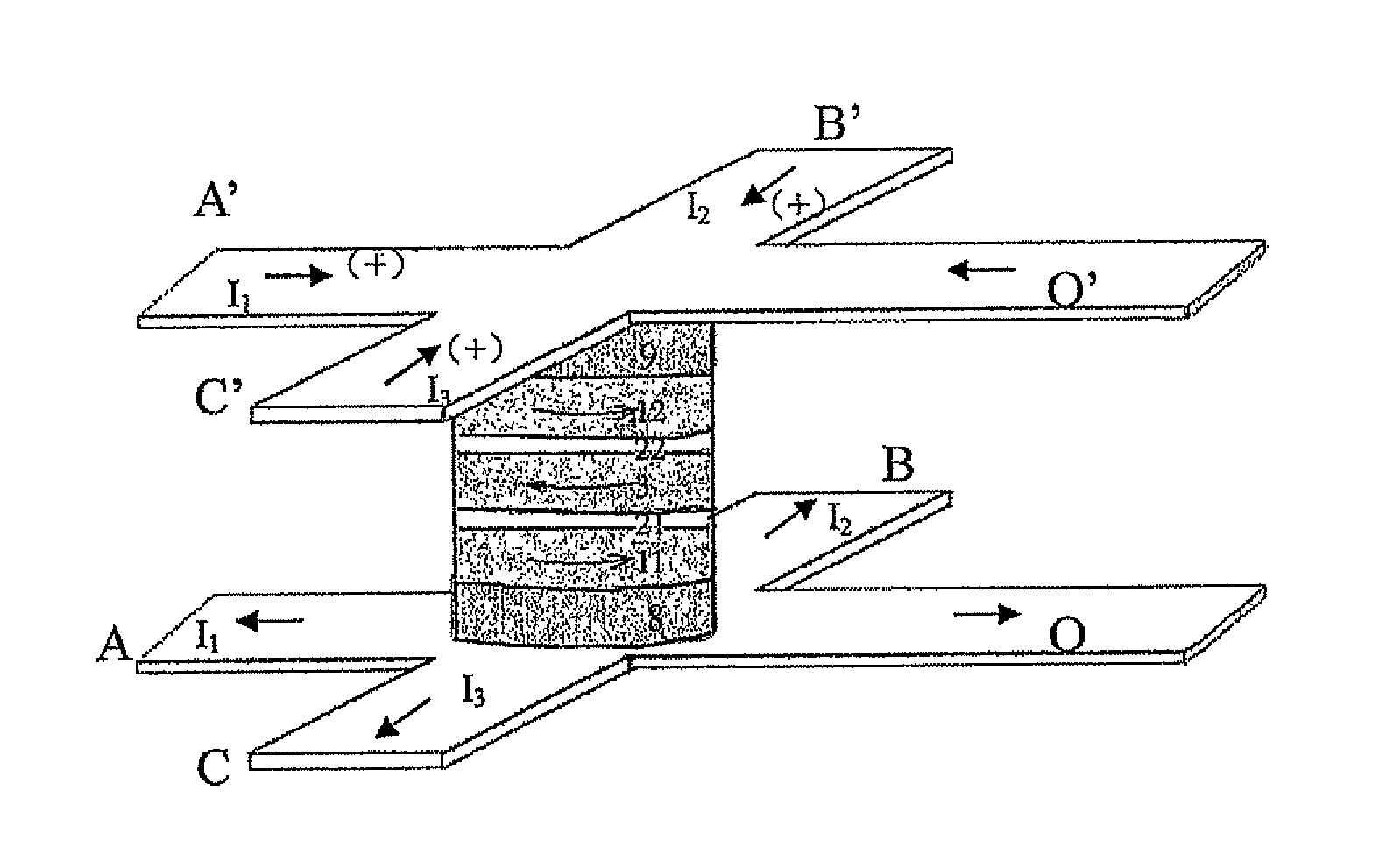

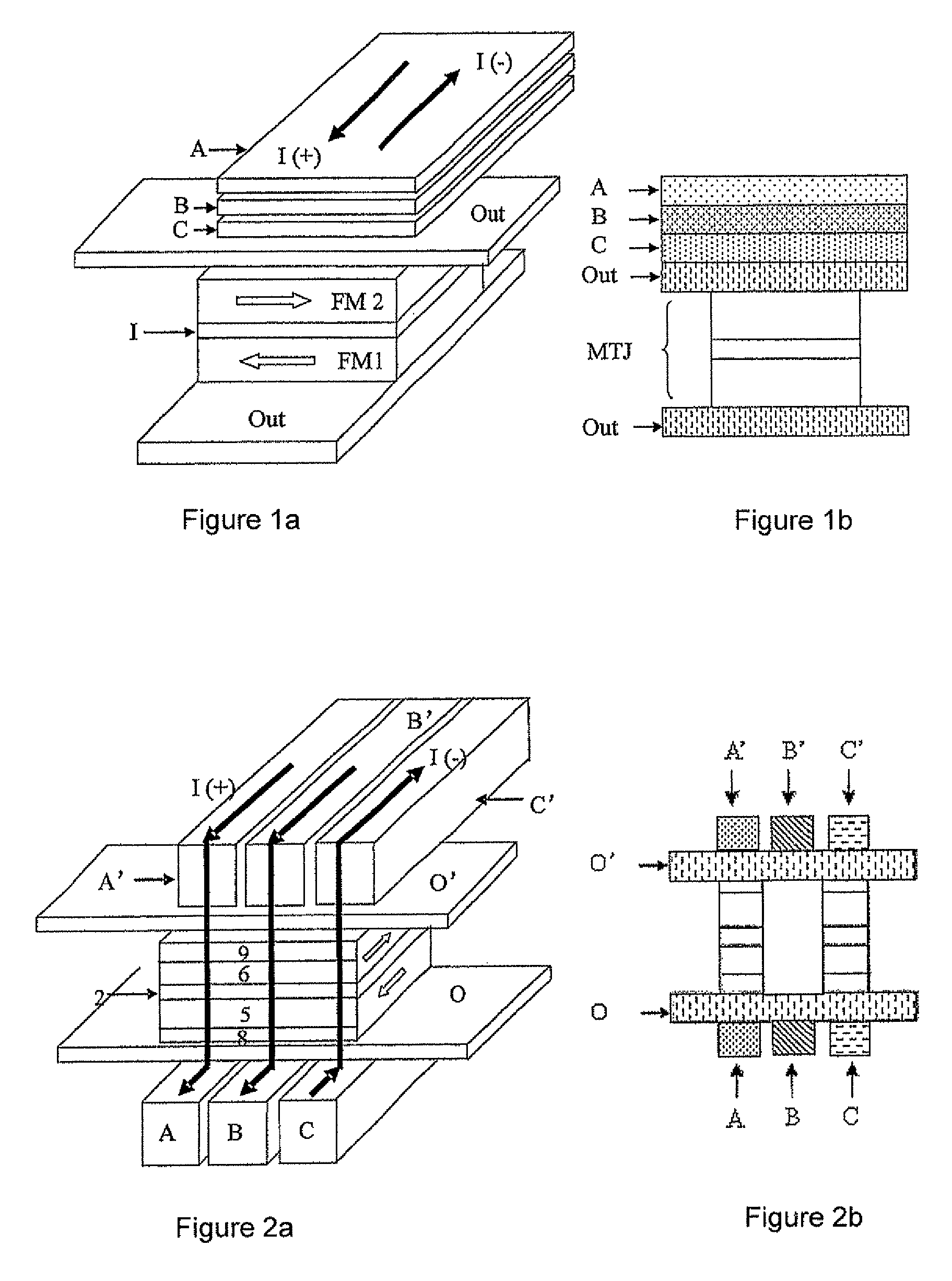

Magnetic logic element with toroidal multiple magnetic films and a method of logic treatment using the same

ActiveUS20090273972A1Small operating currentReduce shape anisotropyNanomagnetismMagnetic-field-controlled resistorsMagnetic logicMulti-level cell

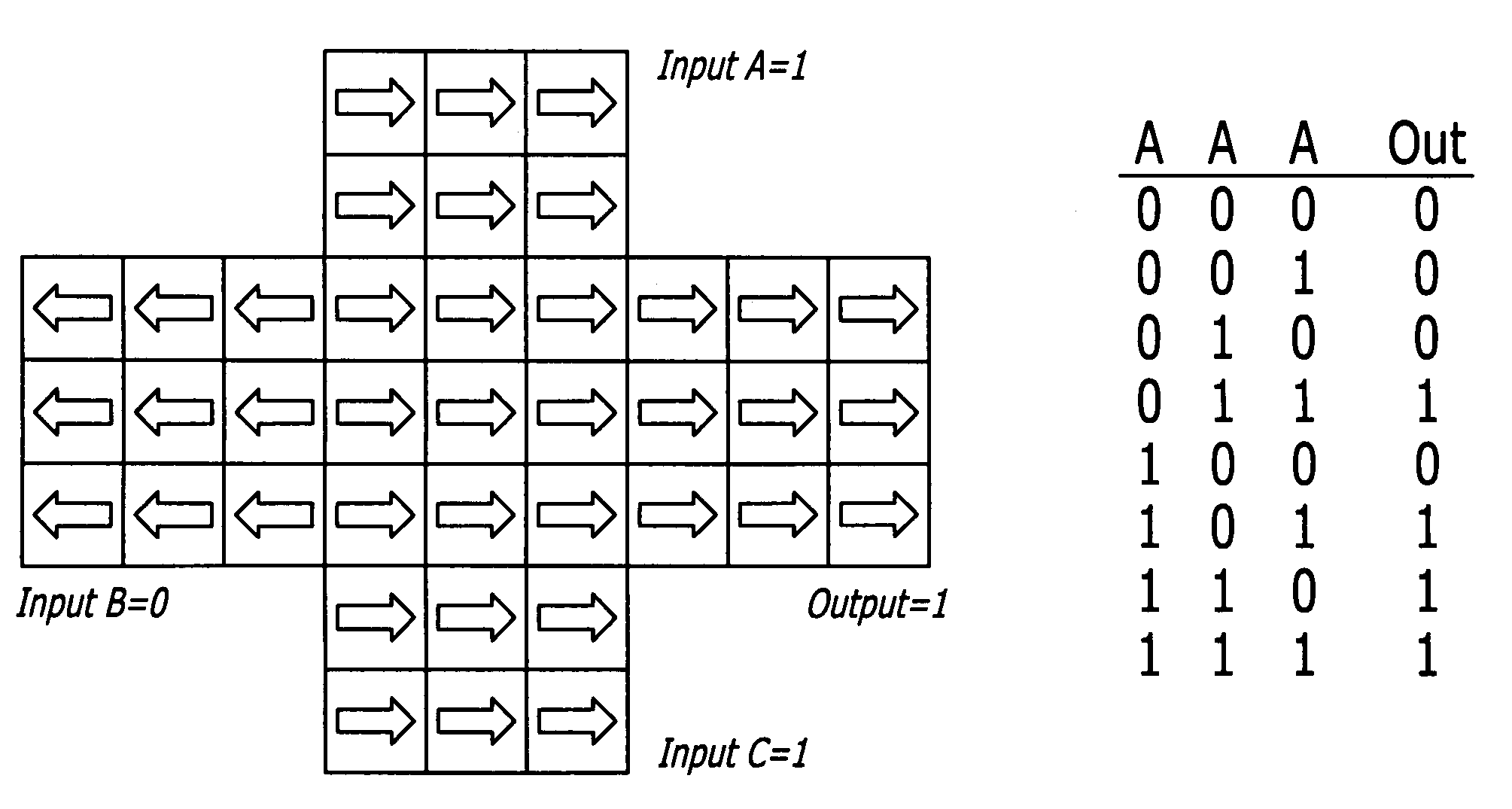

A magnetic logic element with toroidal magnetic multilayers (5,6,8,9). The magnetic logic element comprises a toroidal closed section which is fabricated by etching a unit of magnetic multilayers (5,6,8,9) deposited on a substrate. Optionally, the magnetic logic element may also comprise a metal core (10) in the closed toroidal section. Said magnetic multilayers (5,6,8,9) unit is arranged on the input signal lines A, B, C and an output signal line O, and then is made into a closed toroidal. Subsequently, on the toroidal magnetic multilayered unit (5,6,8,9), the input signal lines A′, B′, C′ and an output signal line O′ are fabricated by etching. This magnetic logic element can reduce the demagnetization field and the shape anisotropy effectively, leading to the decrease of the reversal field of magnetic free layer. Furthermore, this magnetic logic element has stable working performance and long operation life of the device.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

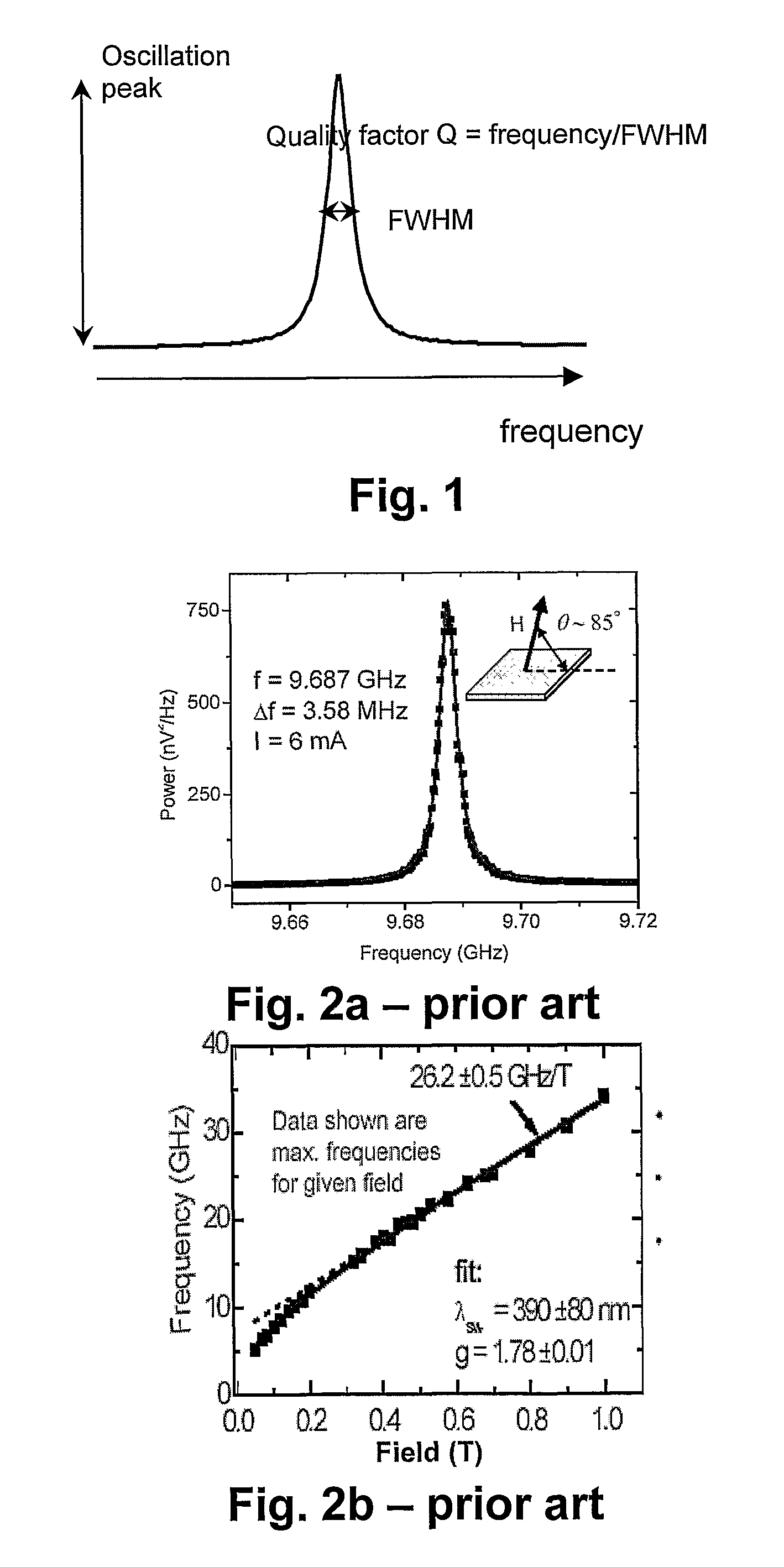

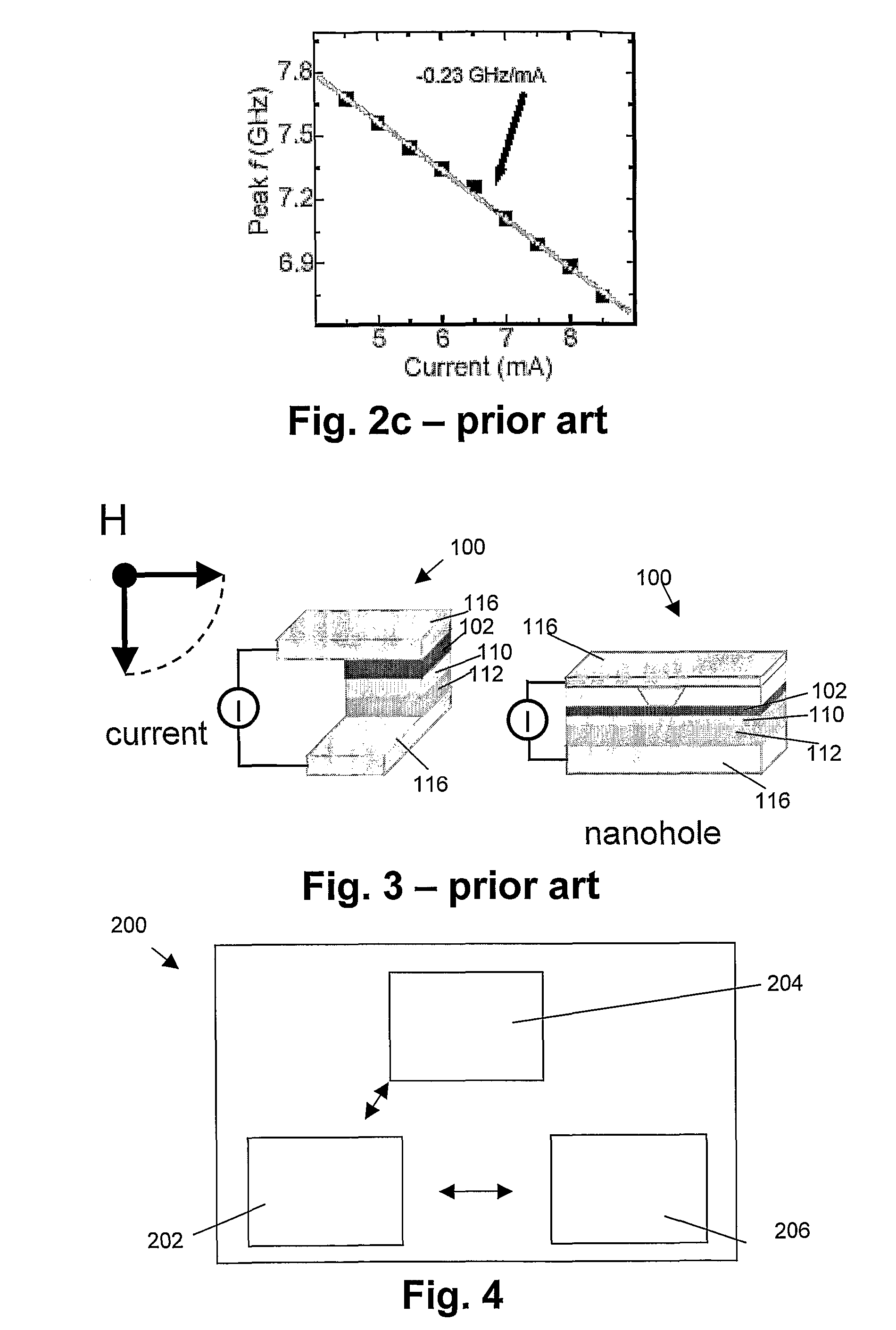

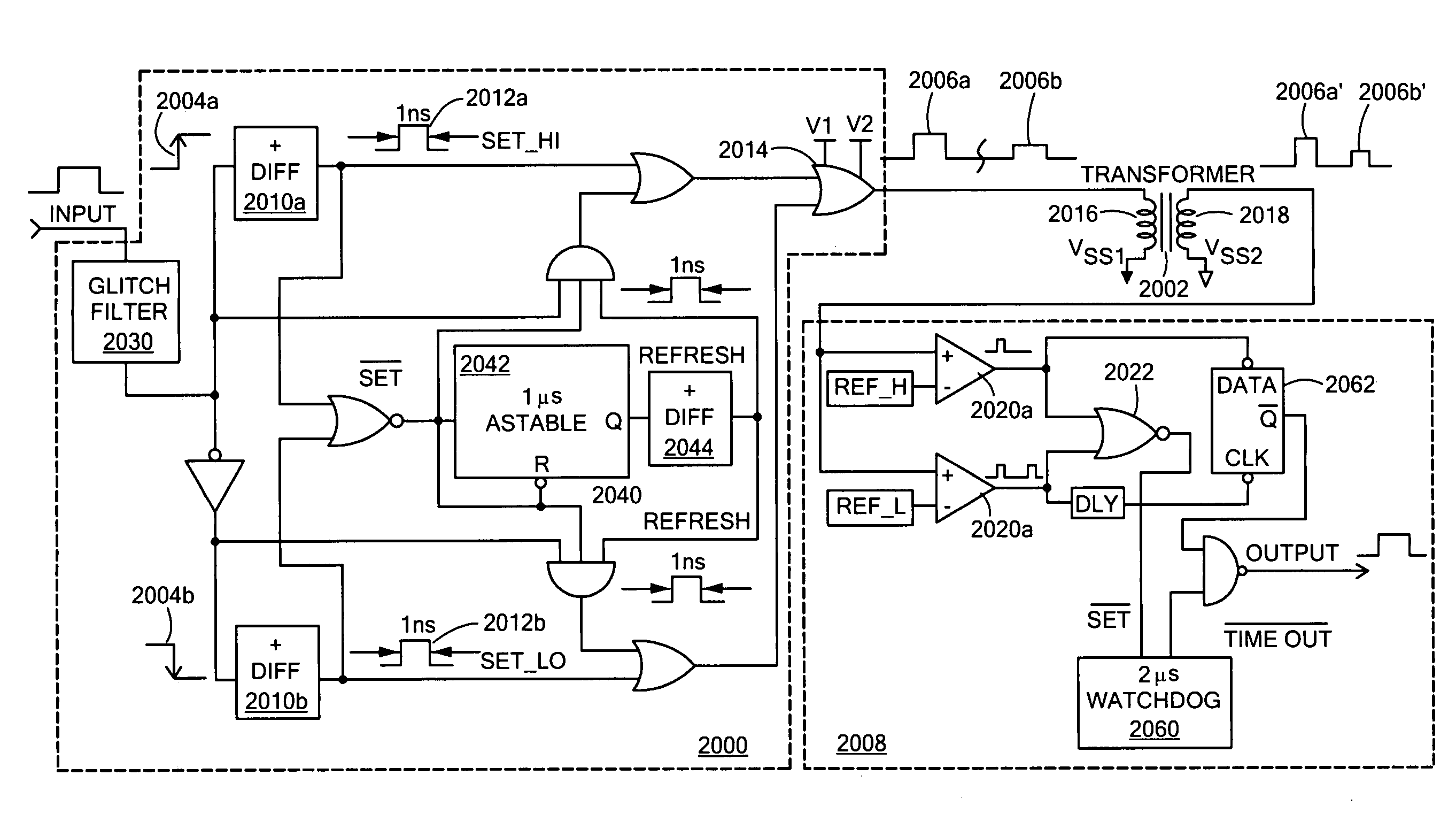

Fully Integrated Tuneable Spin Torque Device For Generating An Oscillating Signal And Method For Tuning Such Apparatus

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

Signal isolator using micro-transformers

A logic signal isolator including a micro-transformer with a primary winding and a secondary winding. A transmitter circuit drives the primary winding in response to a received input logic signal such that, in response to a first type of edge in the logic signal, at least a first amplitude signal is supplied to the primary winding and, in response to a second type of edge in the logic signal, a second different amplitude signal is supplied to the primary winding. A receiver circuit receives corresponding first amplitude and second amplitude signals from the secondary winding and reconstructs the received logic input signal from the received signals.

Owner:ANALOG DEVICES INC

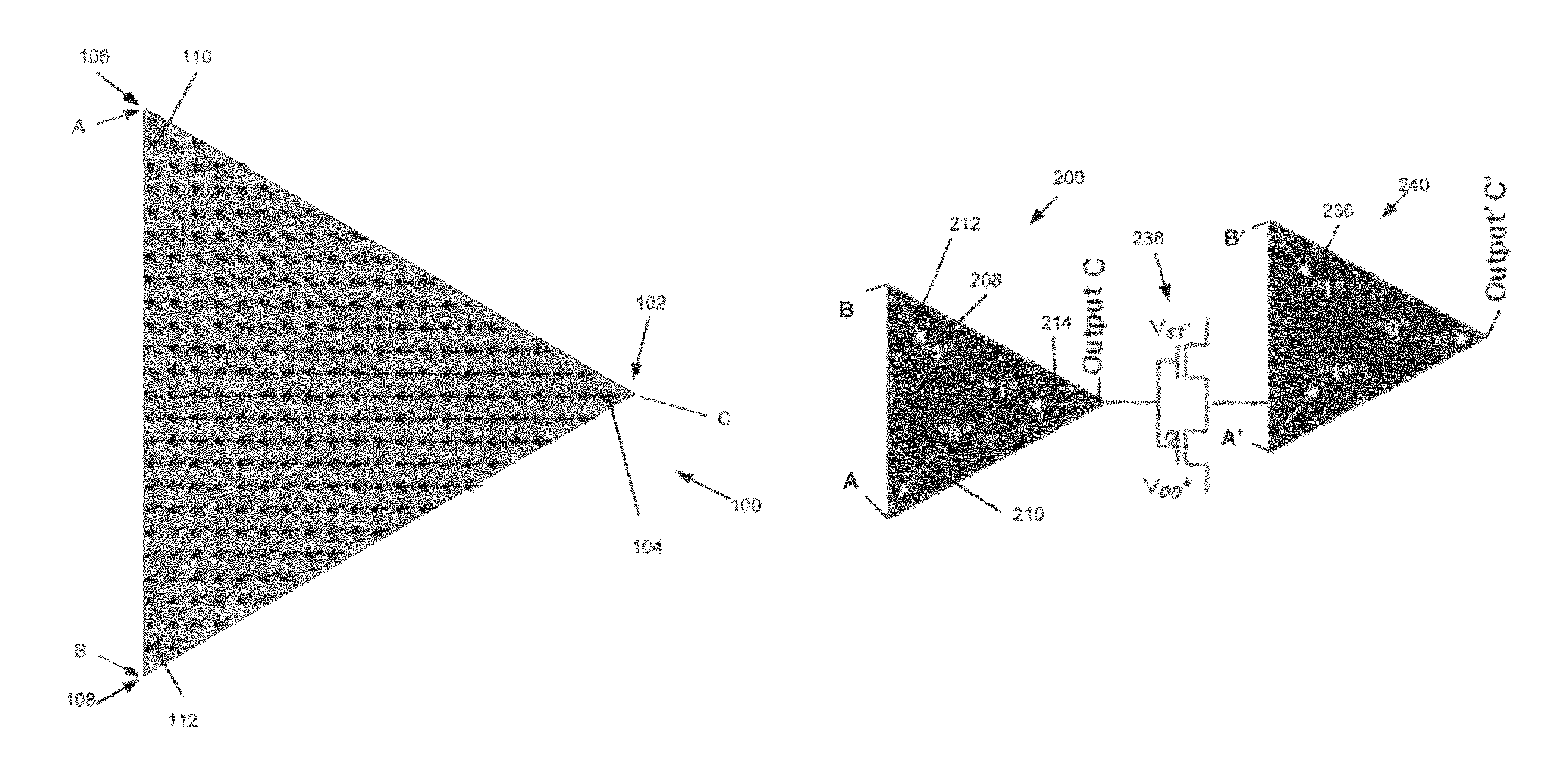

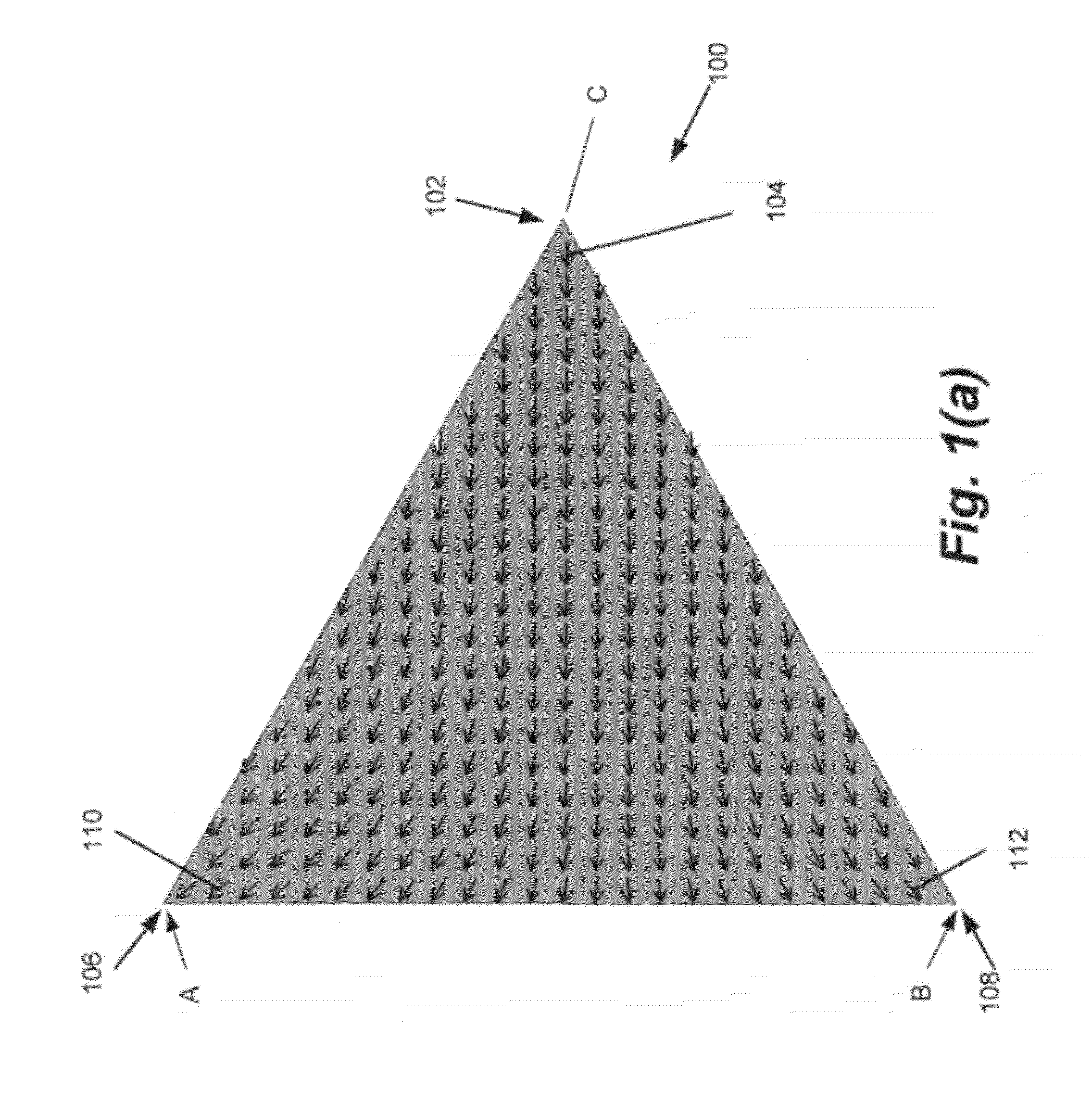

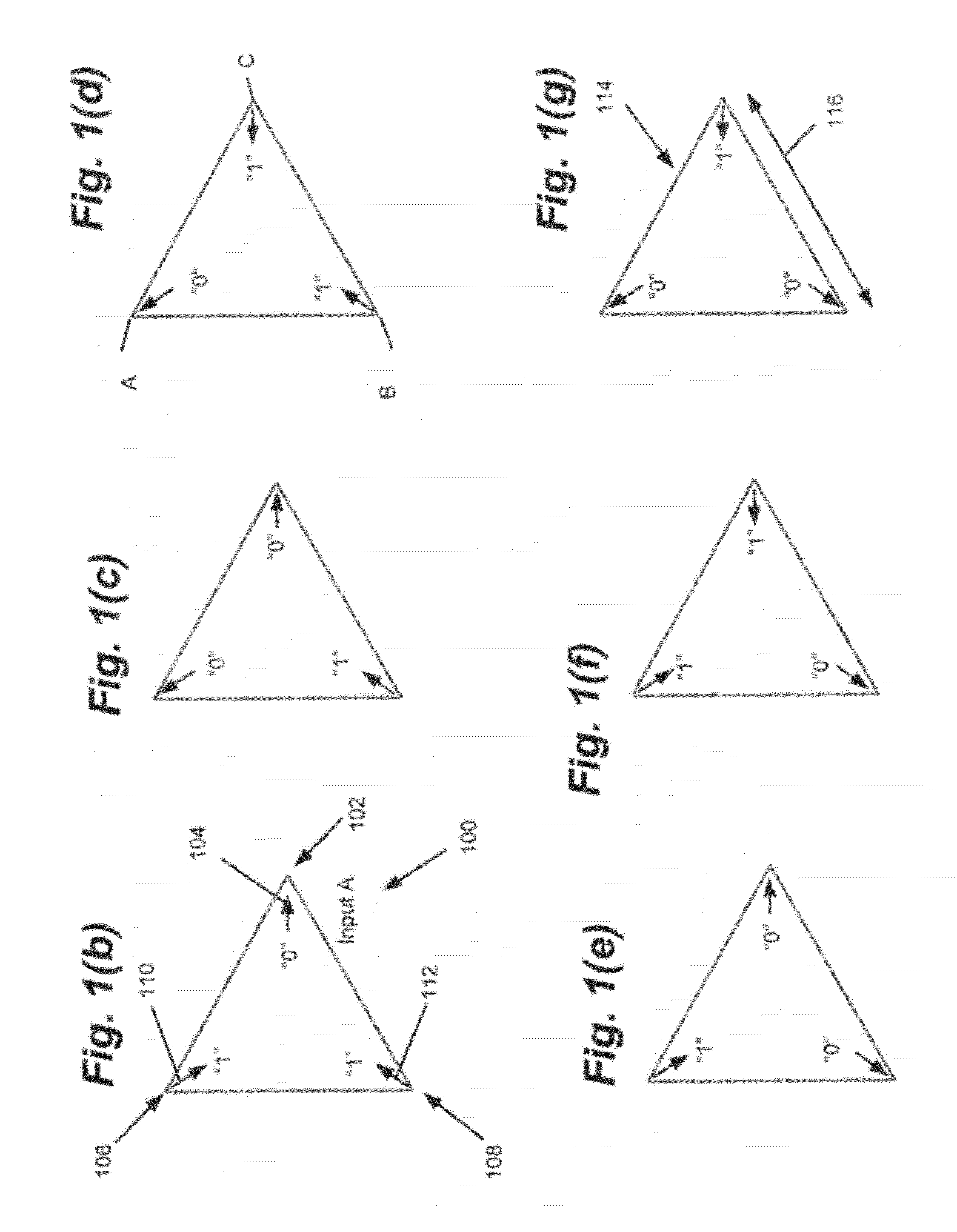

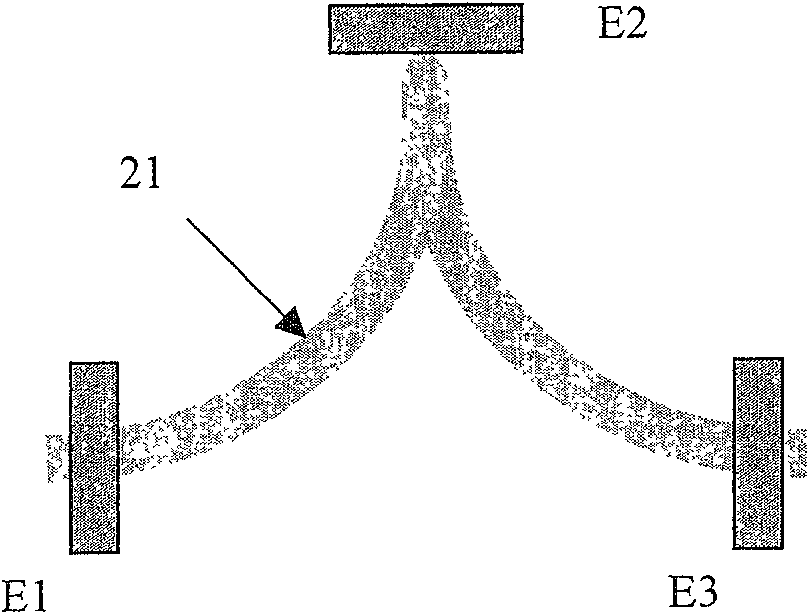

Spin transfer torque triad for non-volatile logic gates

InactiveUS8198919B1Exclusive-OR circuitsComputation using non-contact making devicesMagnetic anisotropySpin-transfer torque

A non-volatile logic gate, including a magnetic material having a shape induced magnetic anisotropy, wherein a shape of the magnetic material has a first vertex, a second vertex, and a third vertex and supports a single magnetic domain; regions of the magnetic material including a first input region adjacent the first vertex, a second input region adjacent the second vertex, and an output region adjacent a third vertex; the first input region for receiving a first logic input to the logic gate, the second input region for receiving a second logic input to the logic gate, and the output region for outputting at least one logic output of the logic gate; and the shape induced magnetic anisotropy determining at least part of a truth table for the logic gate, so that the logic gate produces the at least one logic output from the logic inputs using the shape.

Owner:RGT UNIV OF CALIFORNIA

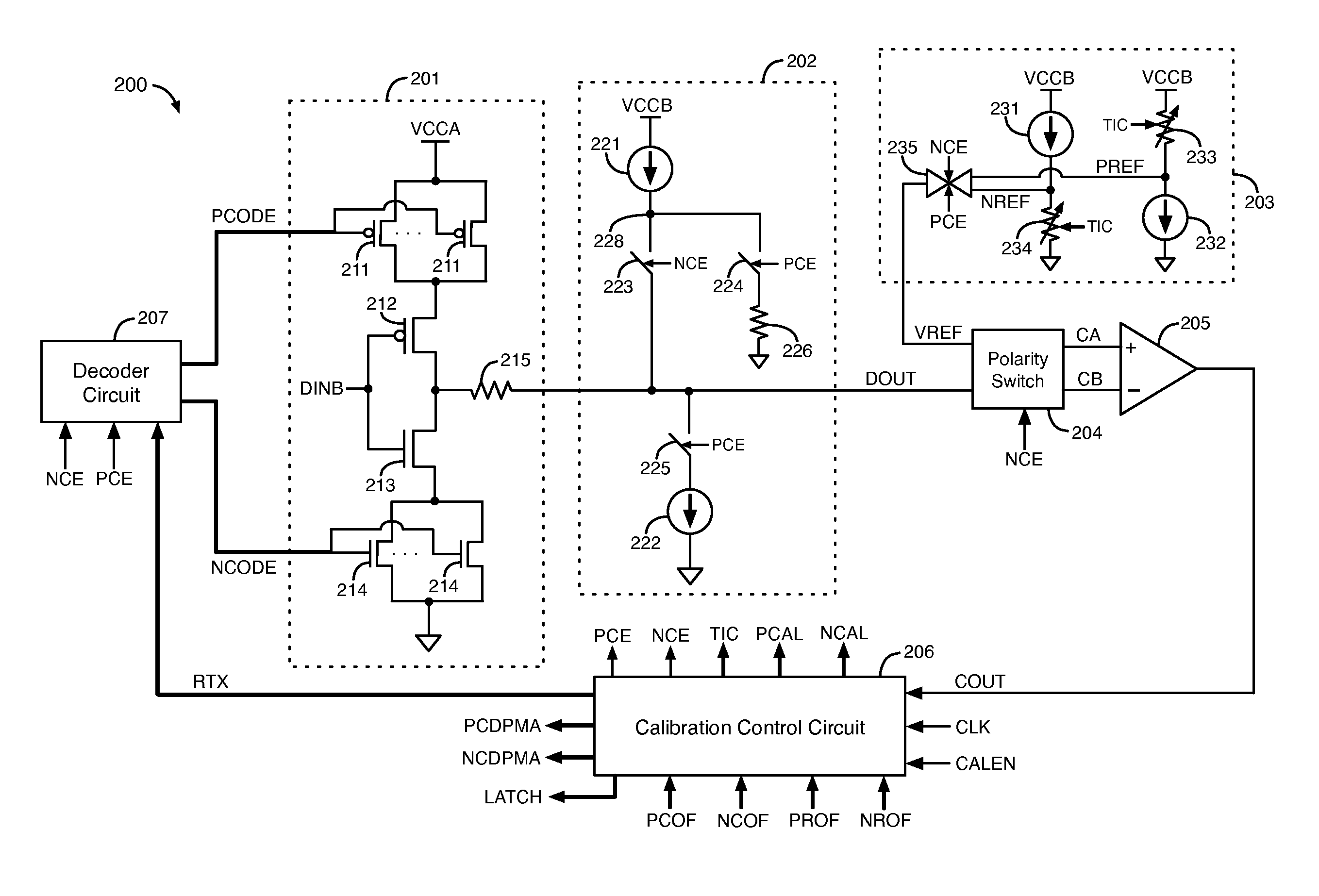

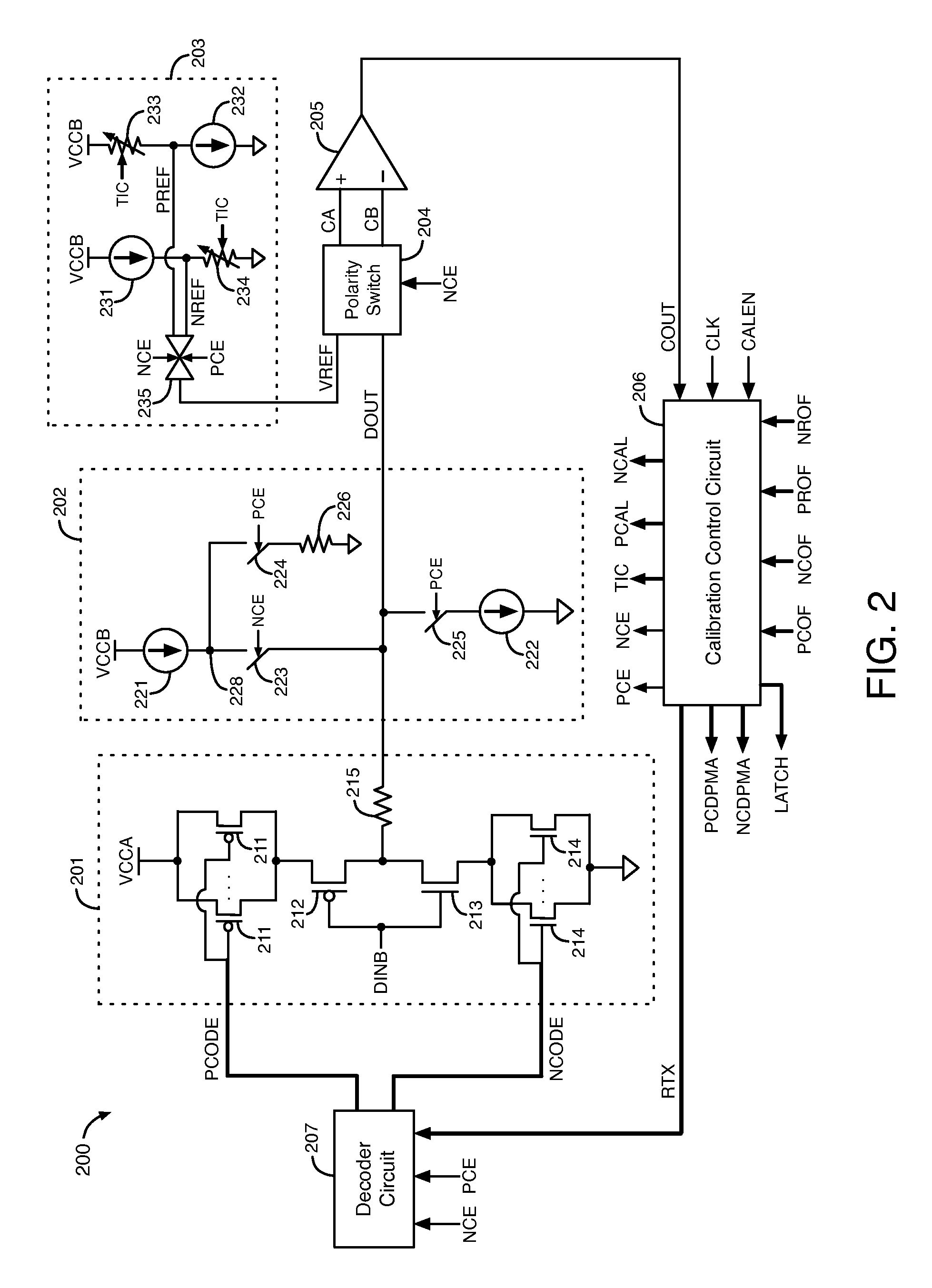

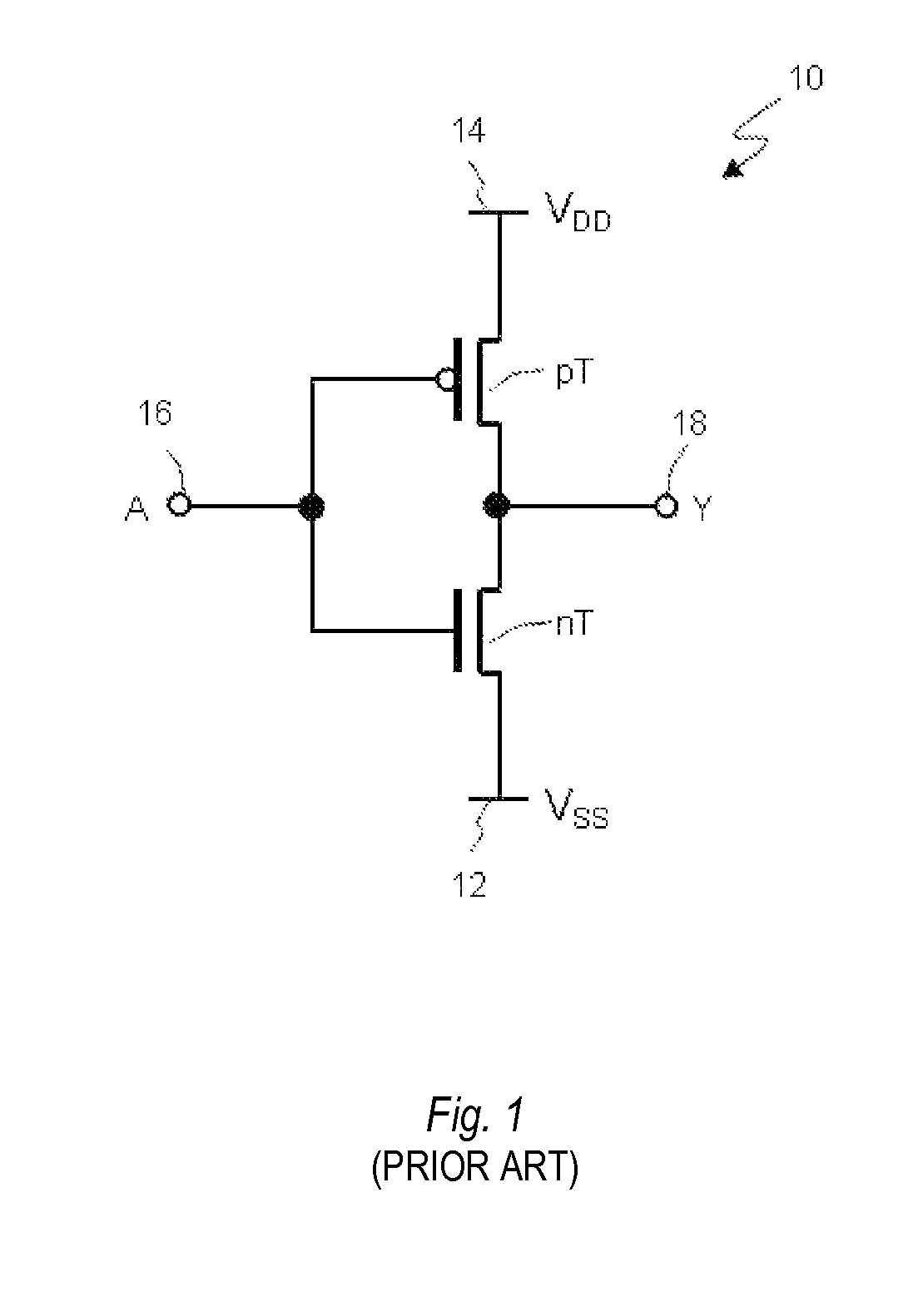

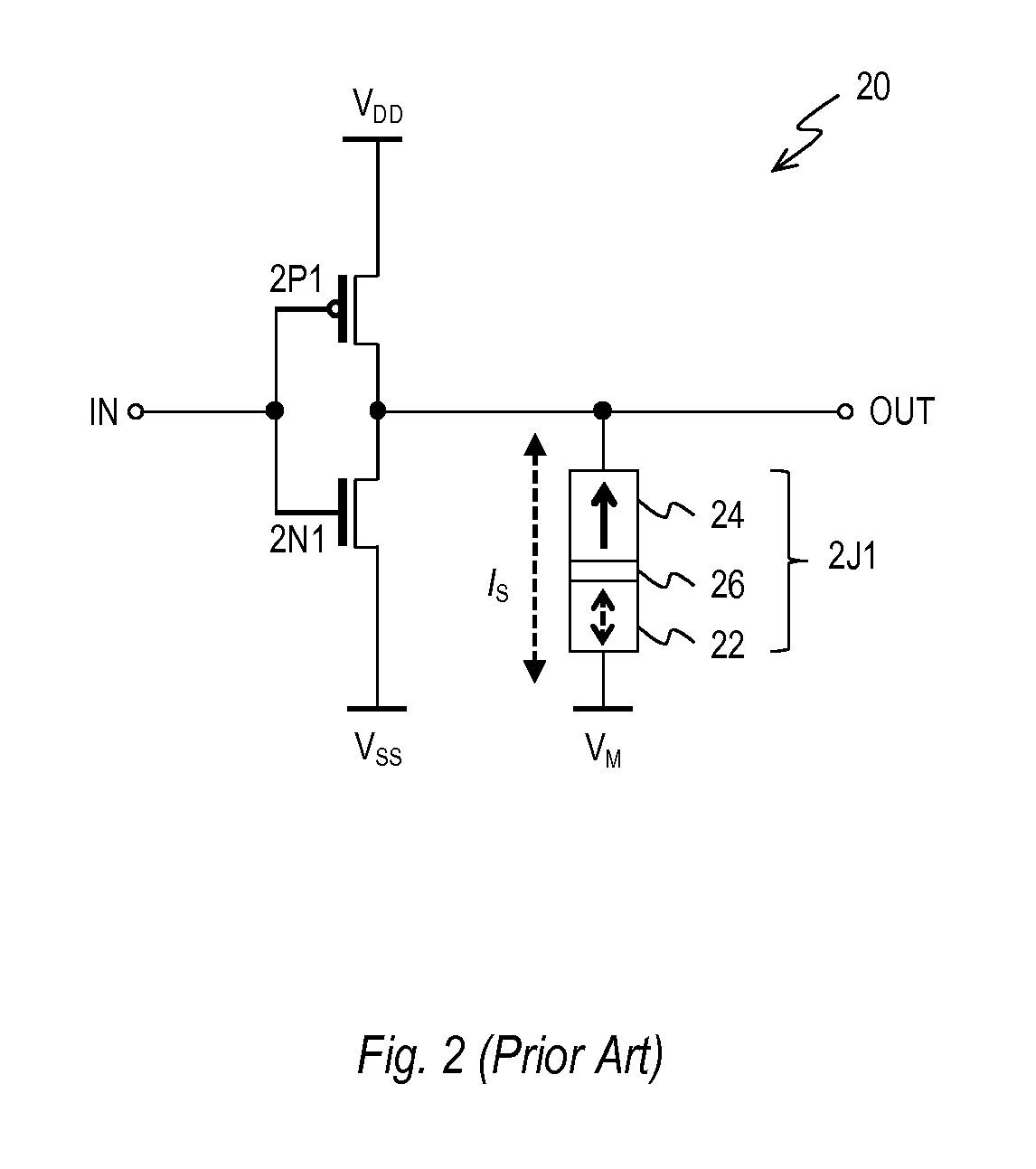

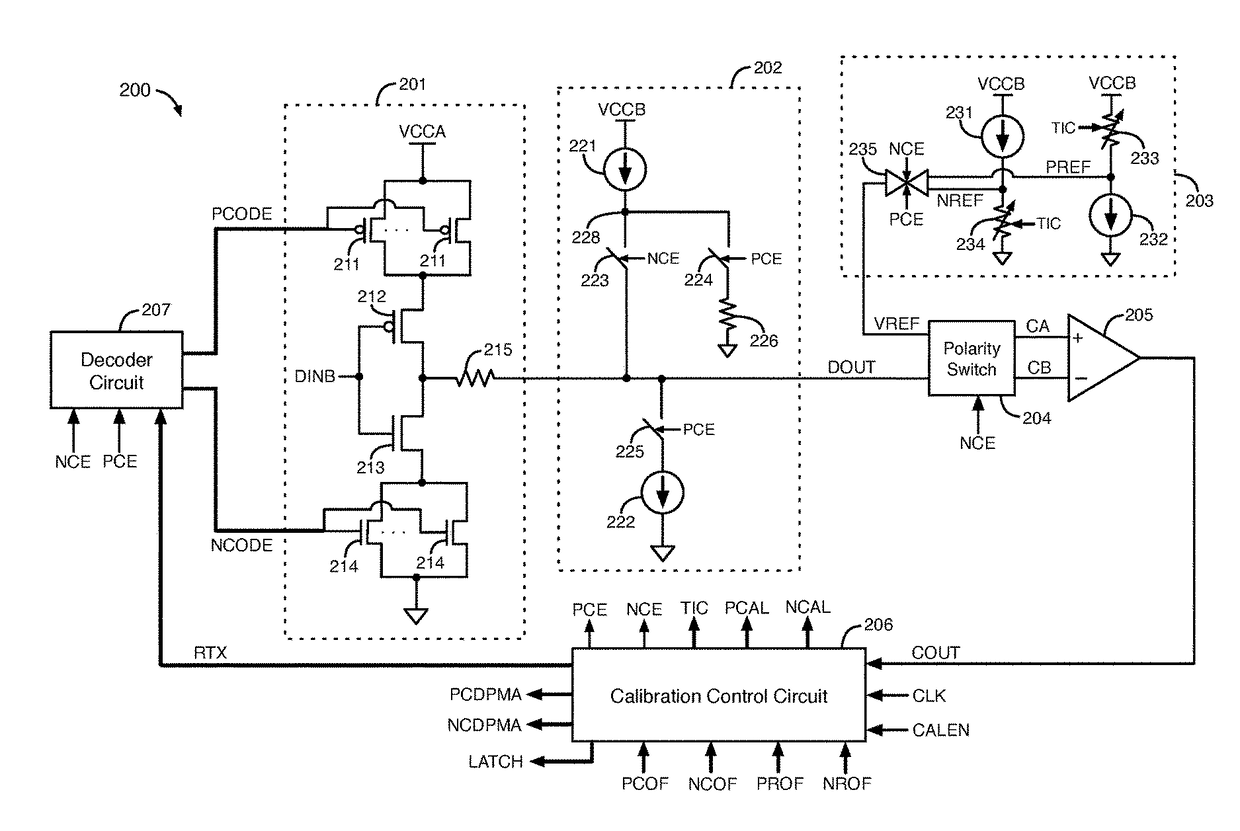

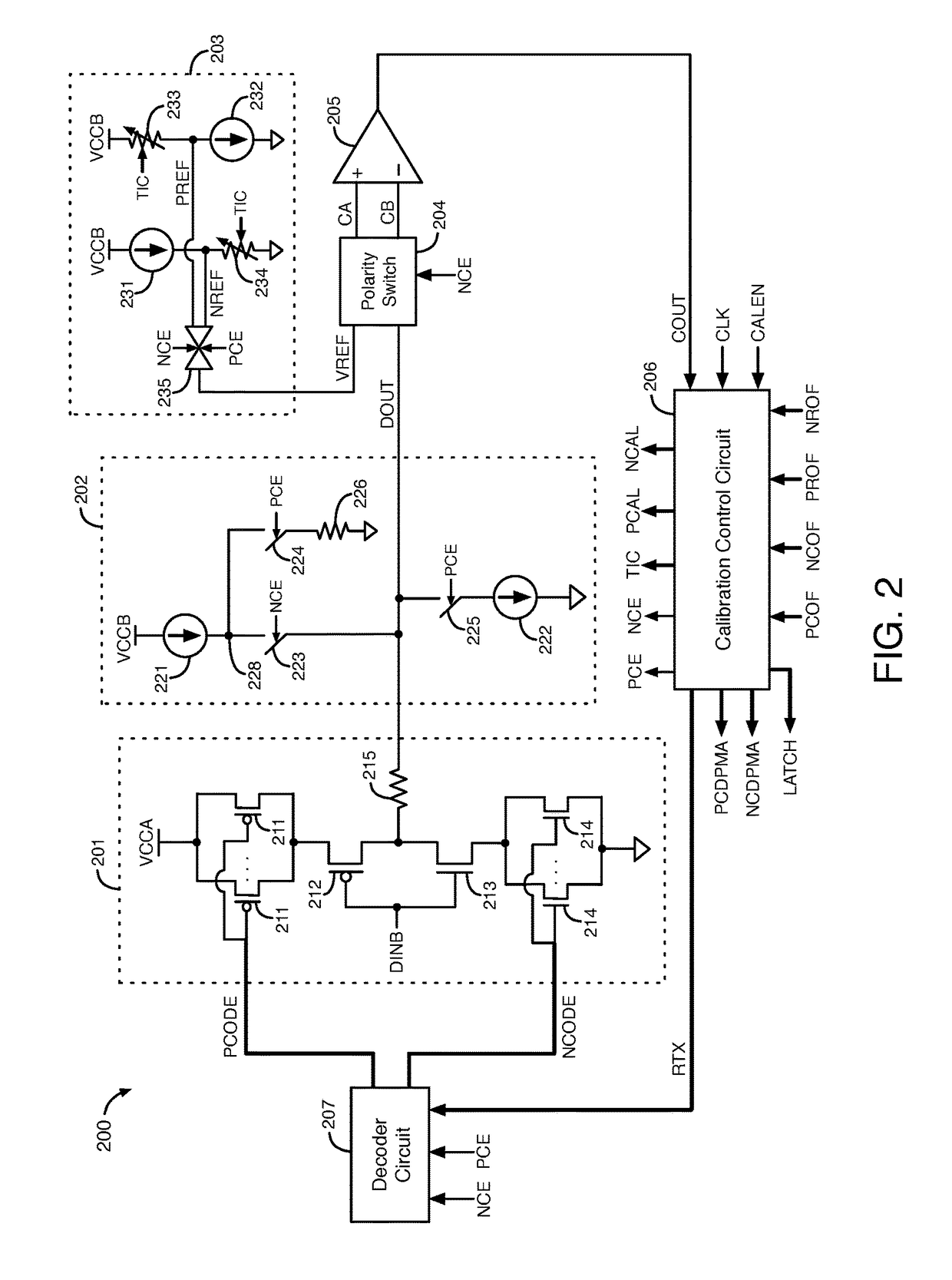

Circuits and methods for impedance calibration

ActiveUS9369128B1Input/output impedence modificationImpedence matching networksDriver circuitElectrical resistance and conductance

A driver circuit drives data to an output based on an input data signal in a transmission mode. The driver circuit includes transistors. A comparator generates a comparison output in a calibration mode based on a reference signal and a signal at the output of the driver circuit. A calibration control circuit adjusts an equivalent resistance of the transistors in the driver circuit based on the comparison output in the calibration mode. The equivalent resistance of the transistors in the driver circuit can be adjusted to support the transmission of data according to multiple different data transmission protocols using transmission links having different characteristic impedances. The equivalent resistance of the transistors in the driver circuit can also be adjusted to compensate for resistance in the package routing conductors and / or to compensate for parasitic resistance.

Owner:TAHOE RES LTD

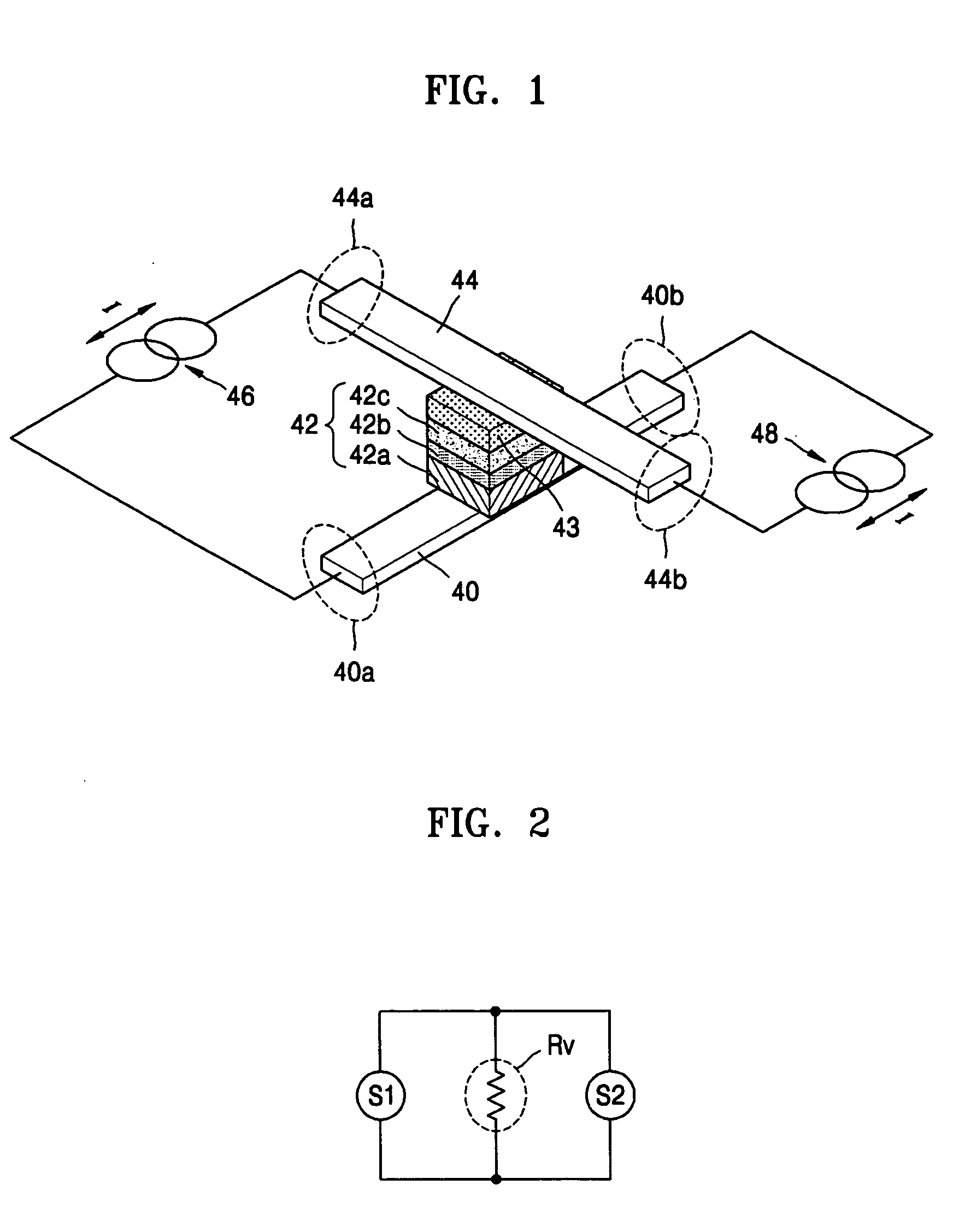

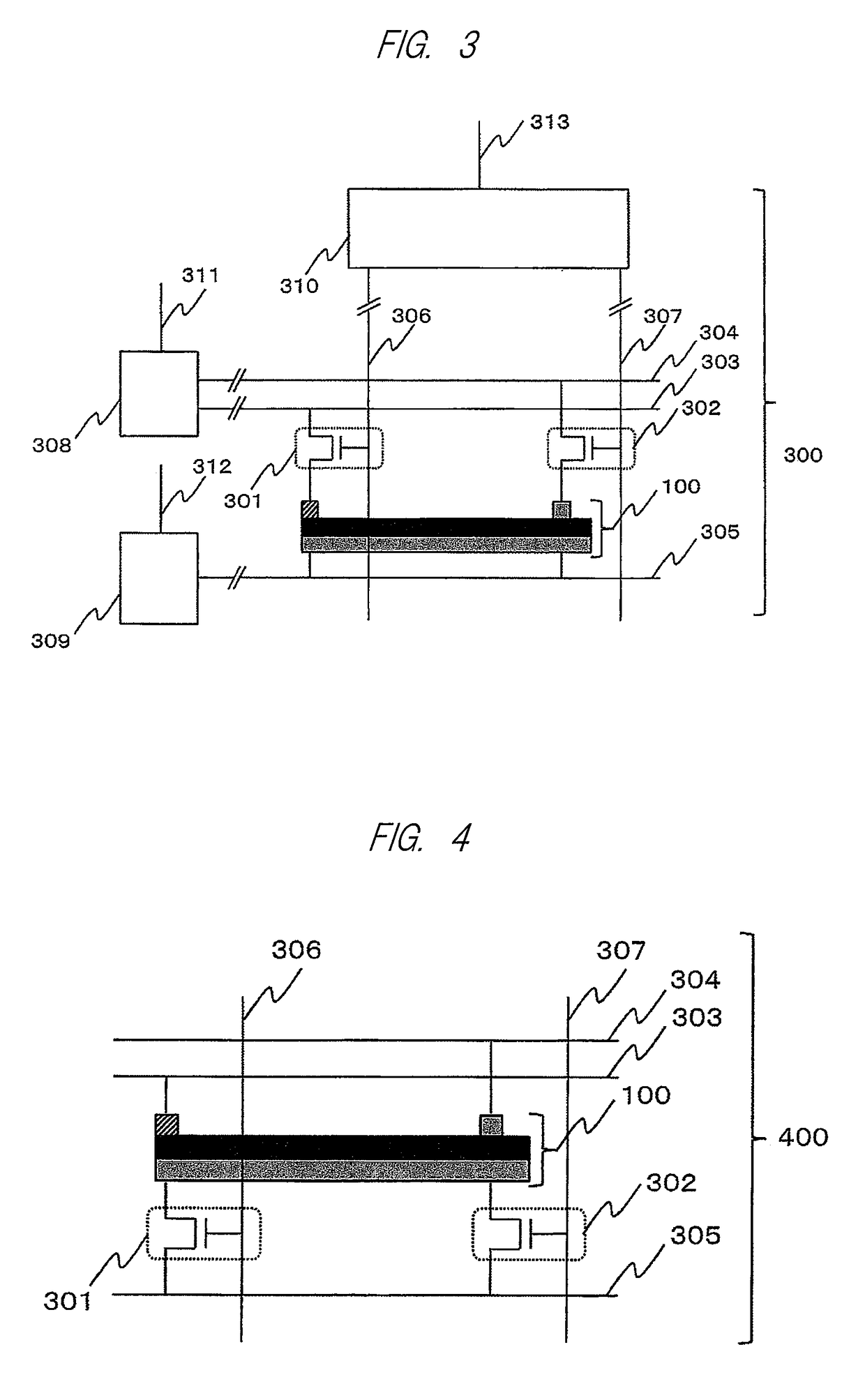

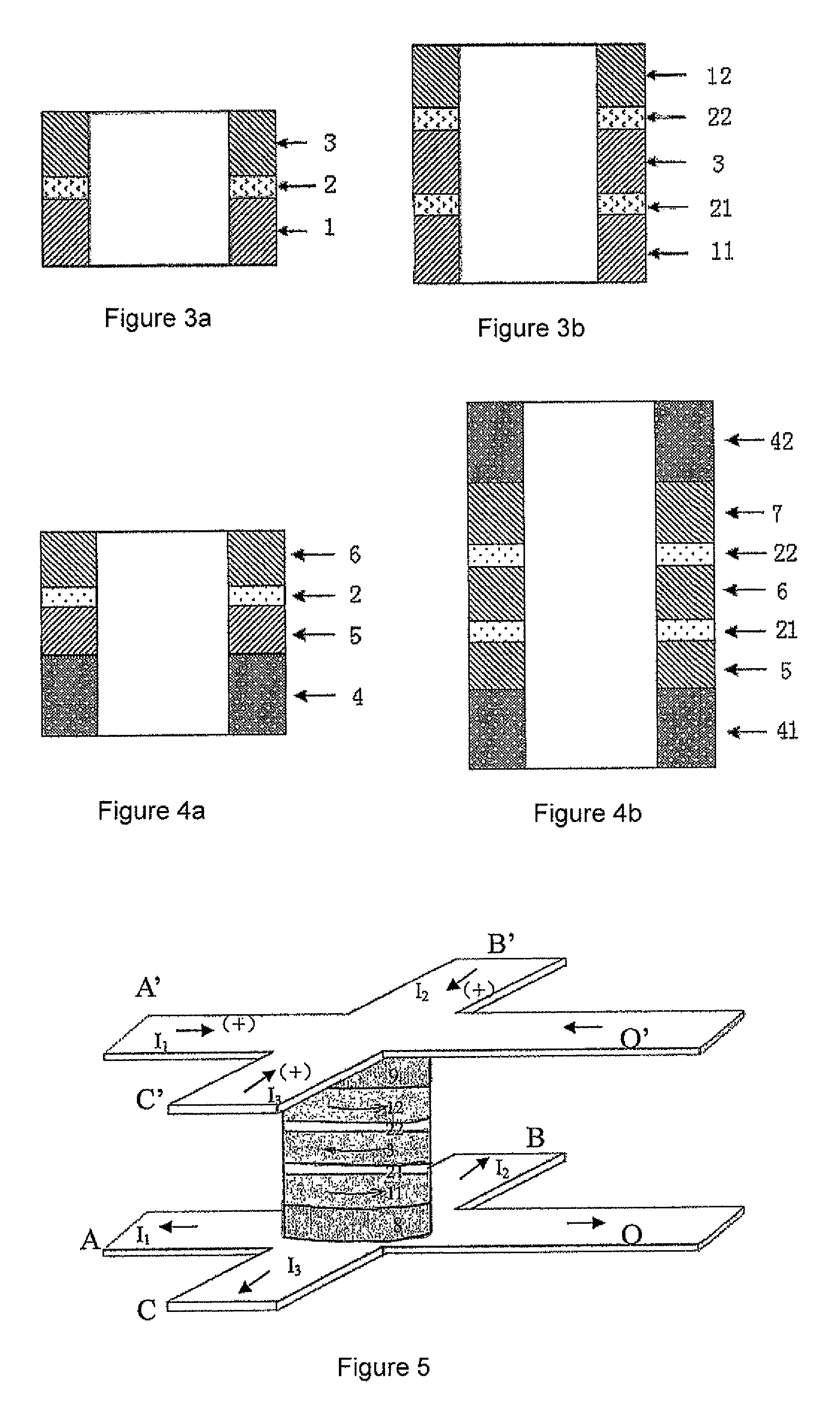

Magnetic logic device and methods of manufacturing and operating the same

ActiveUS20060145806A1Simple structureEasy to manufactureMagnetic-field-controlled resistorsLogic circuits using saturable magnetic devicesMagnetic logicInterconnection

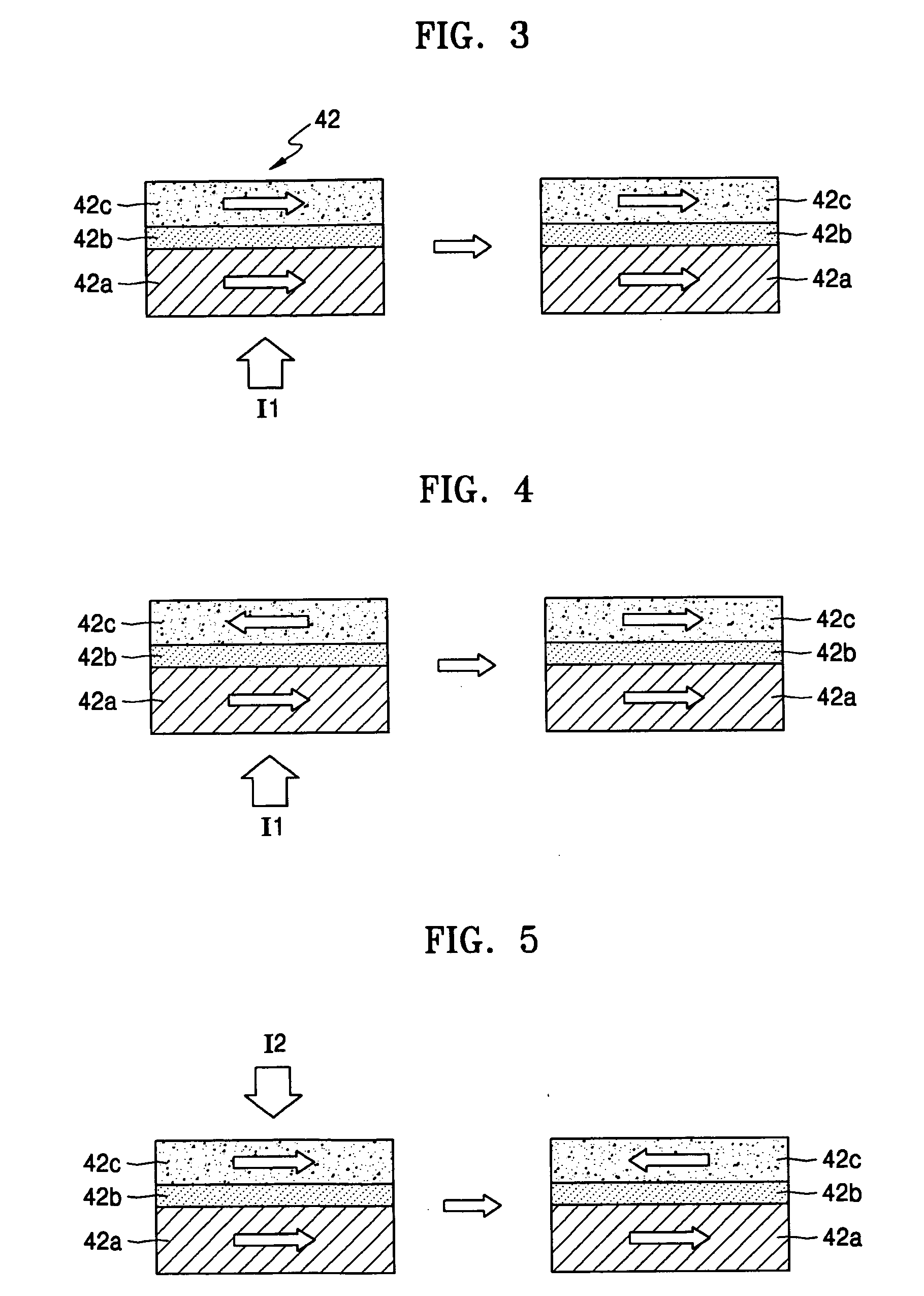

A magnetic logic device (MLD) and methods of manufacturing and operating an MLD are provided. The MLD includes: a first interconnection; a lower magnetic layer formed on the first interconnection, the lower magnetic layer having a magnetization direction fixed in a predetermined direction; a non-magnetic layer formed on the lower magnetic layer; an upper magnetic layer formed on the non-magnetic layer, the upper magnetic layer having a magnetization direction parallel or anti-parallel to the magnetization direction of the lower magnetic layer; and a second interconnection formed on the upper magnetic layer. A first current source is disposed between one end of the first interconnection and one end of the second interconnection and a second current source is disposed between the other end of the first interconnection and the other end of the second interconnection.

Owner:SAMSUNG ELECTRONICS CO LTD

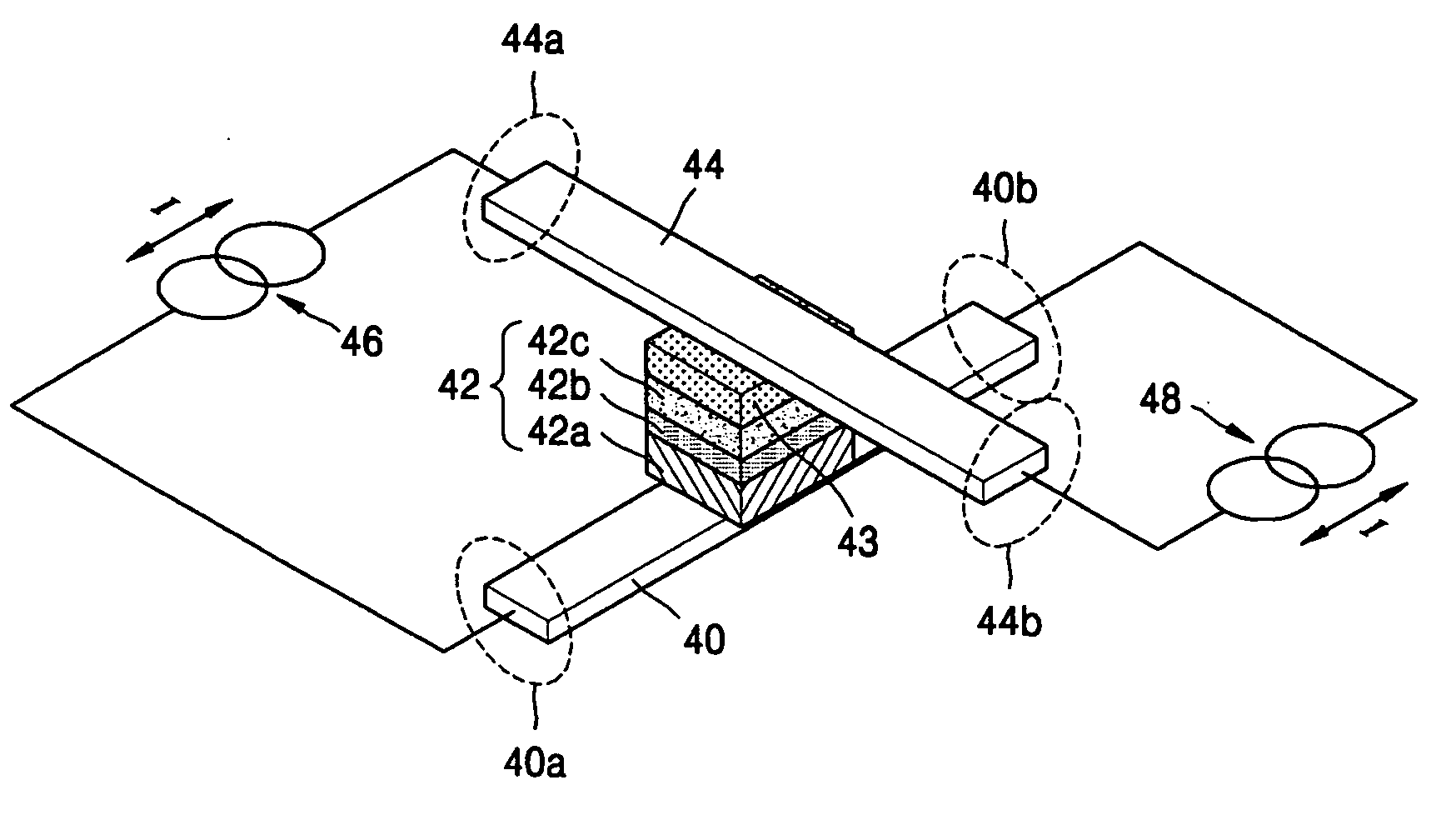

Spin-orbital quantum cellular automata logic devices and systems

InactiveUS7212026B2Logic circuits characterised by logic functionLogic circuits using saturable magnetic devicesMagnetic measurementsDirect coupling

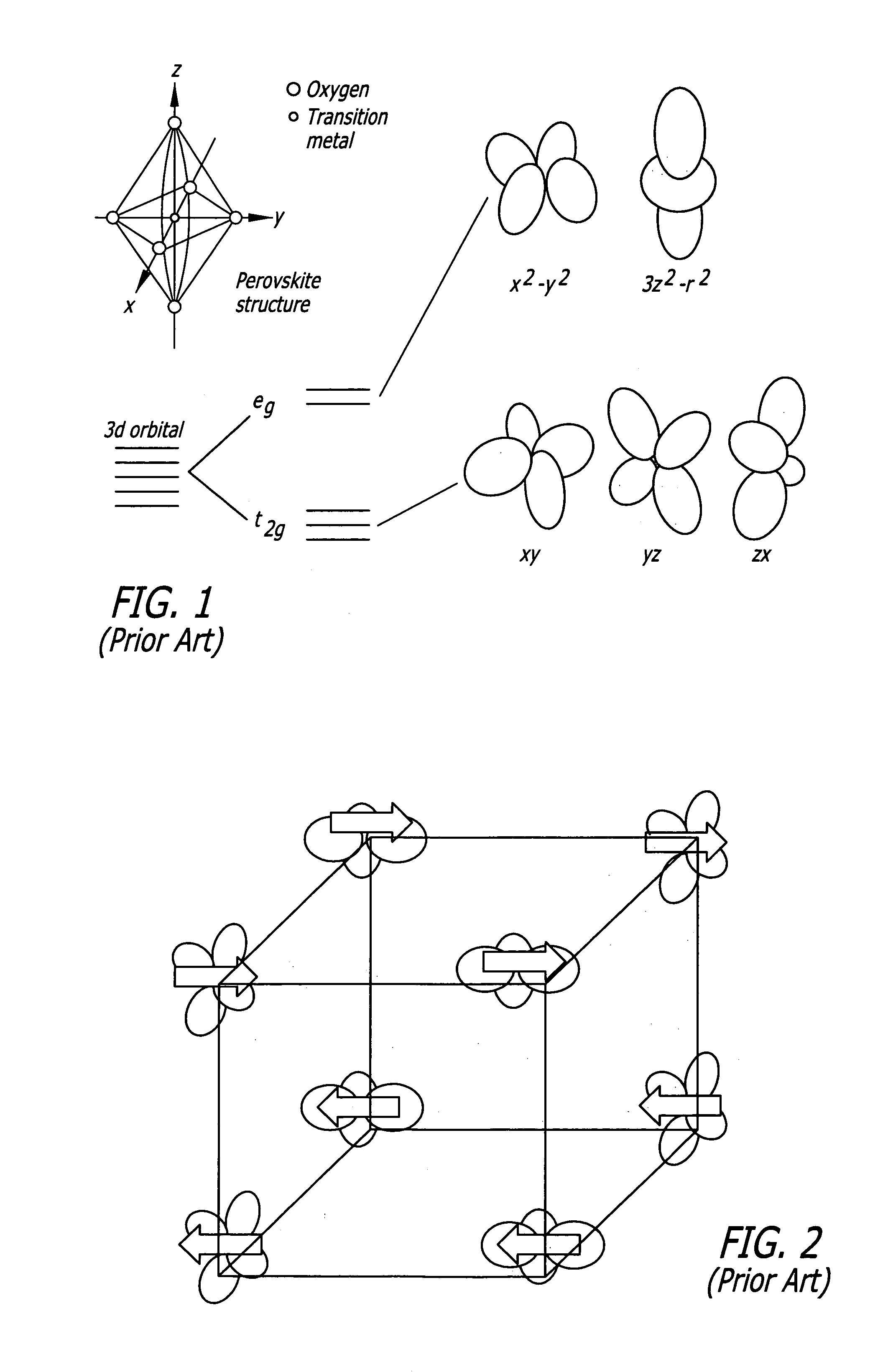

Spin-orbital quantum cellular automata logic devices and integrated circuits in the form of a substrate having a thin film of material on the substrate having strongly coupled spin-orbital states, the thin film being patterned to define at least one input and at least one output, and to perform at least one logic operation by associated arrangement of the spin-orbital states between the input and the output. The logic devices and integrated circuits further include an input device at each input to define the spin-orbital states at each input, and an output sensor at each output for sensing the spin-orbital states of the thin film at the output. In an integrated circuit, the output of one gate or circuit, in the form of the ferromagnetically aligned spins, can be directly coupled to the next gate or circuit, so that entire circuits can be fabricated and effectively interconnected, only requiring interfacing for overall. circuit input and output using the electromagnetic inputs and magnetic measurements for the outputs.

Owner:INTEL CORP

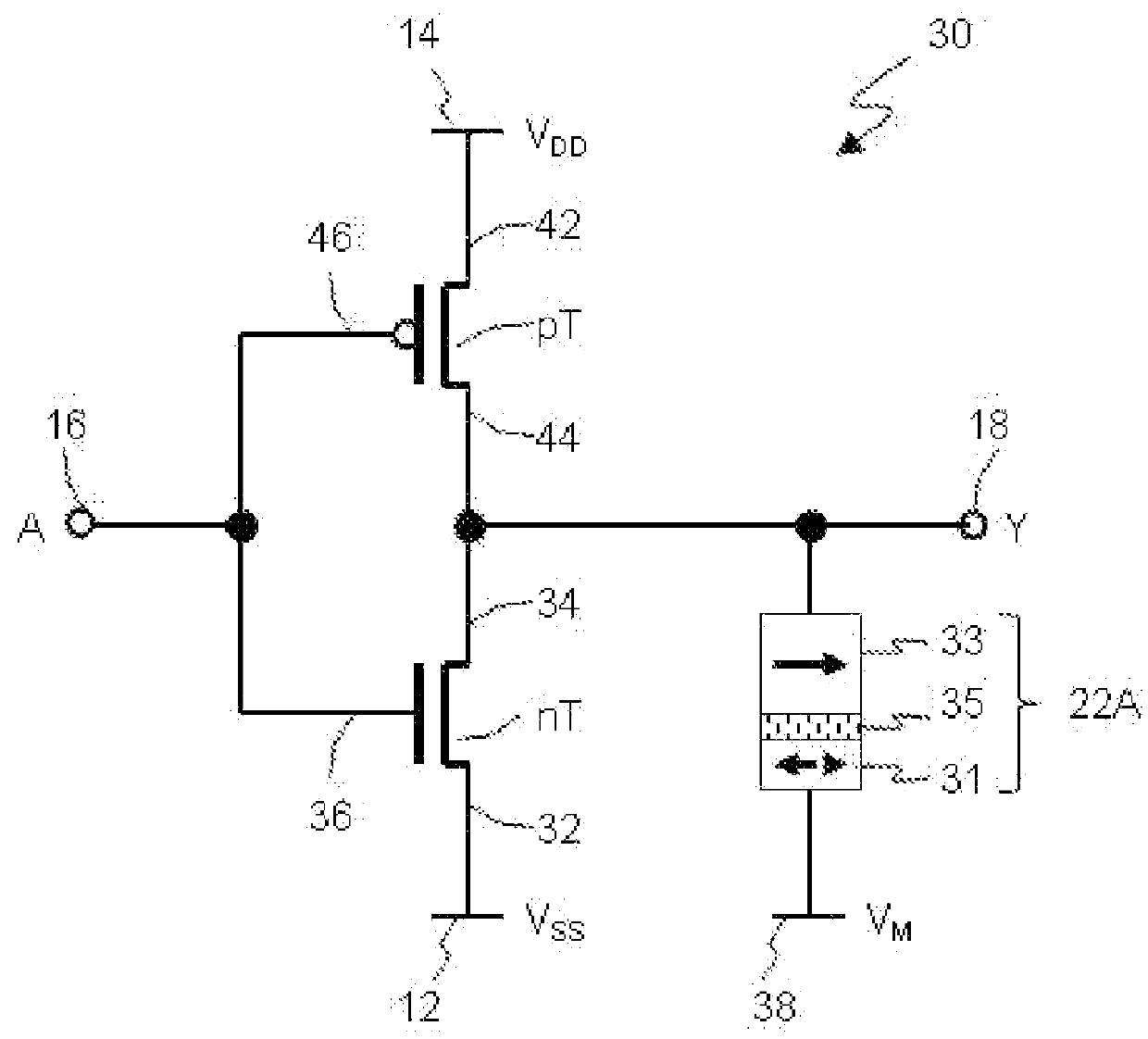

Nonvolatile Logic Circuit

InactiveUS20140159770A1Digital storageLogic circuits using saturable magnetic devicesLow voltageLogic state

Owner:SHUKH ALEXANDER MIKHAILOVICH

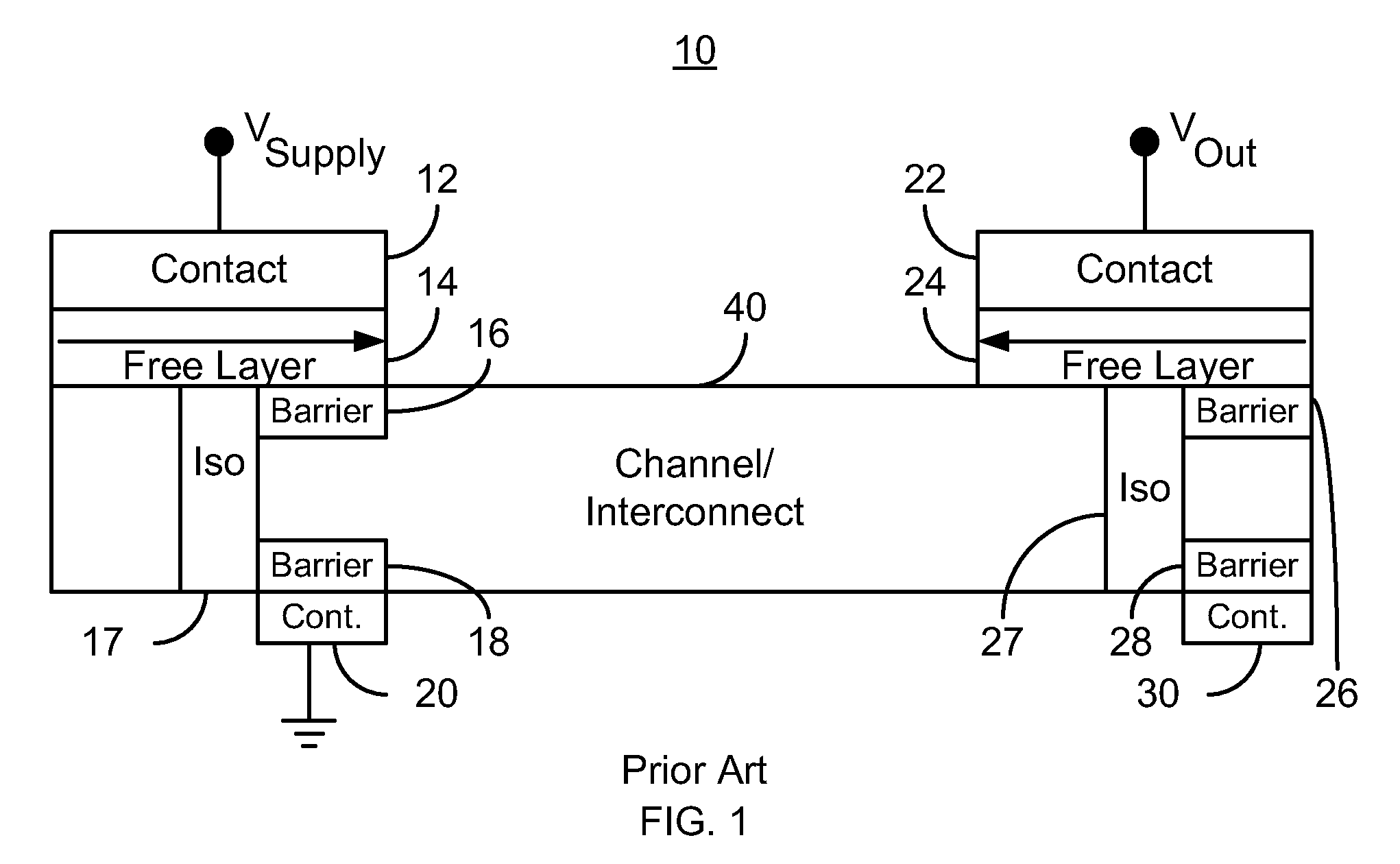

Nonvolatile logic circuit

ActiveUS8373438B2Logic circuits characterised by logic functionDigital storageEmbedded systemTunnel junction

Semiconductor industry seeks to replace traditional volatile logic and memory devices with the improved nonvolatile devices. The increased demand for a significantly advanced, efficient, and nonvolatile data retention technique has driven the development of magnetic tunnel junctions (MTJs) employing a giant magneto-resistance (GMR). The present application relates to nonvolatile logic circuits with integrated MTJs and, in particular, concerns a nonvolatile spin dependent logic device that may be integrated with conventional semiconductor-based logic devices to construct the nonvolatile logic circuits performing NOT, NOR, NAND and other logic functions.

Owner:SHUKH ALEXANDER MIKHAILOVICH

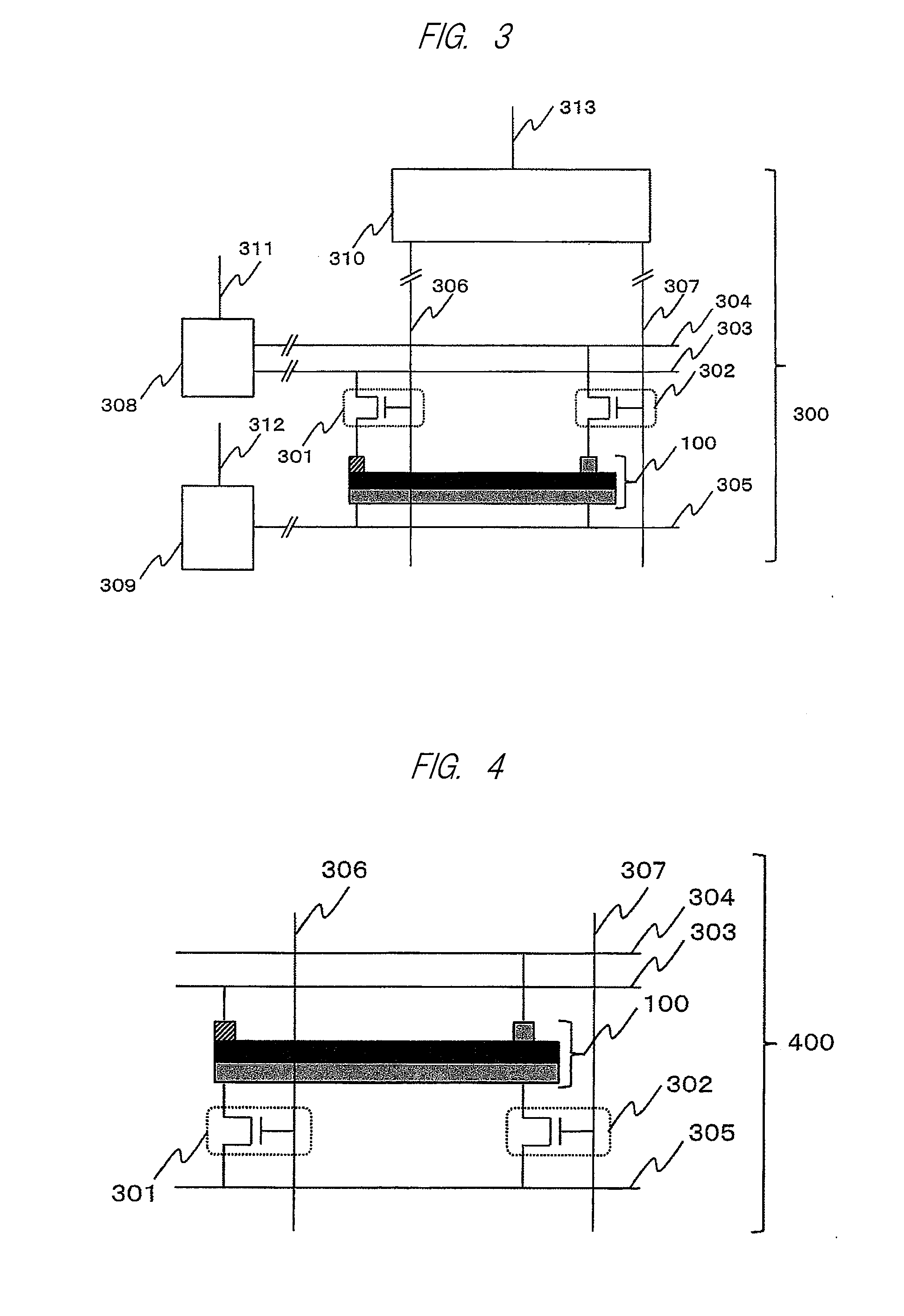

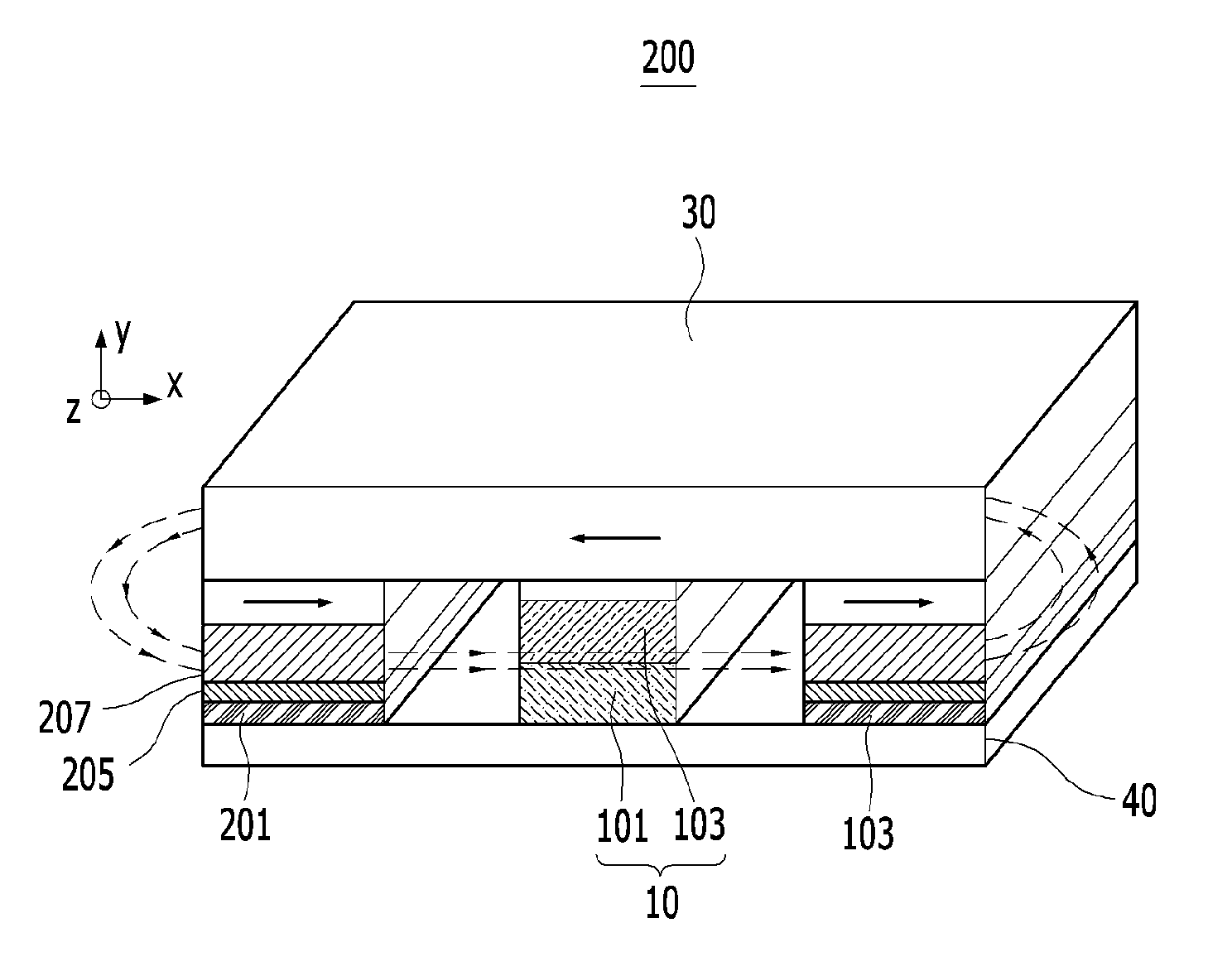

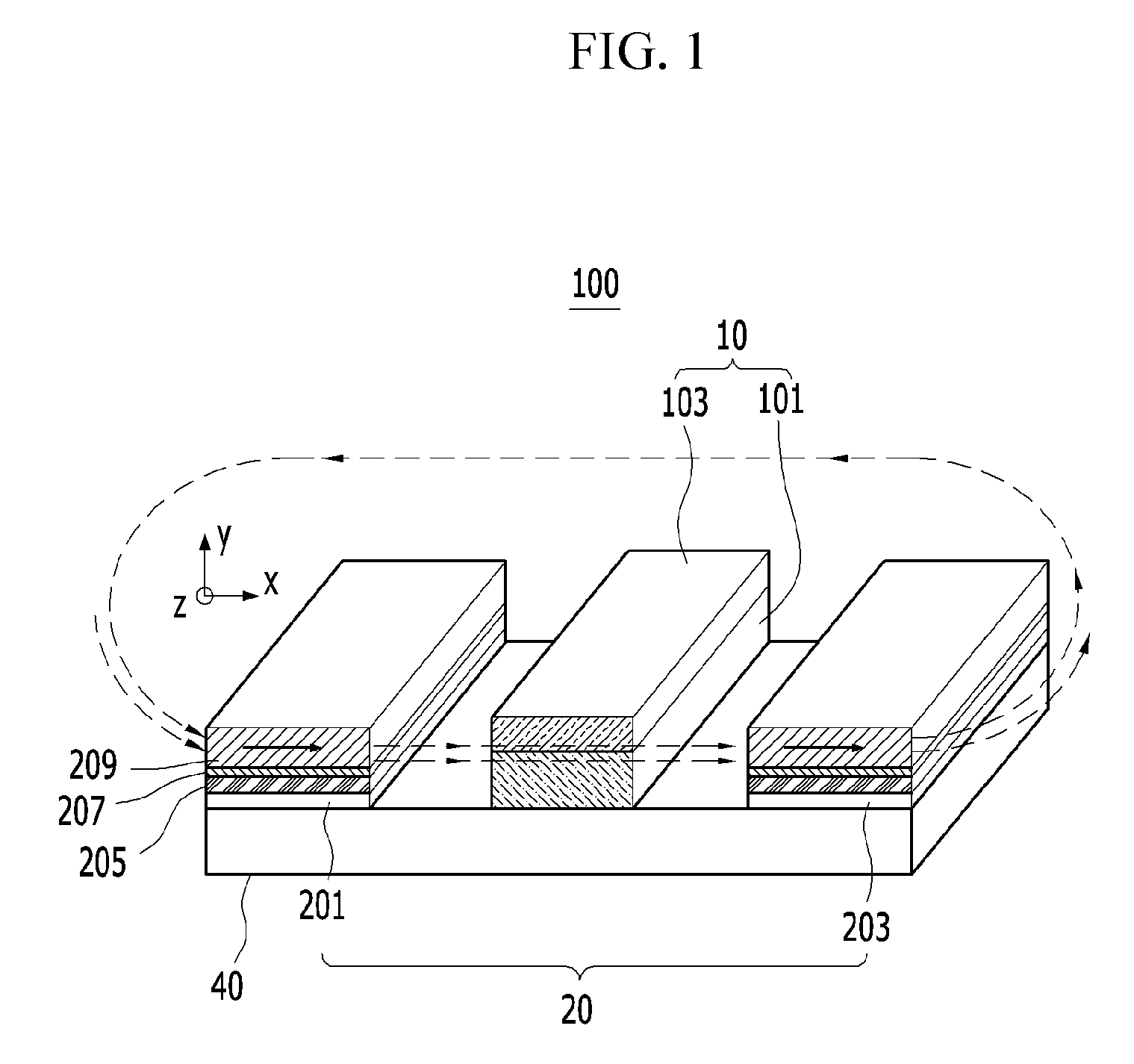

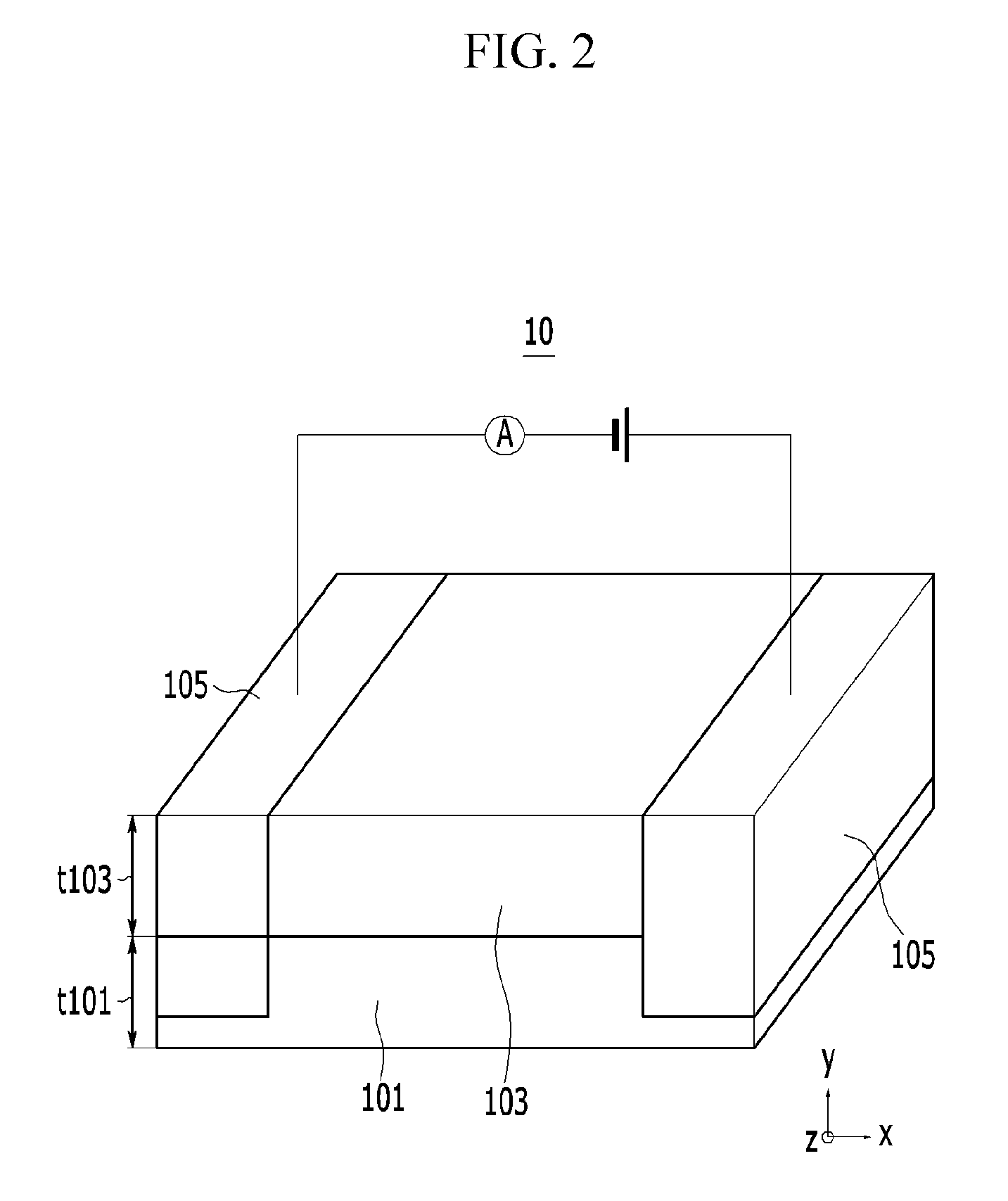

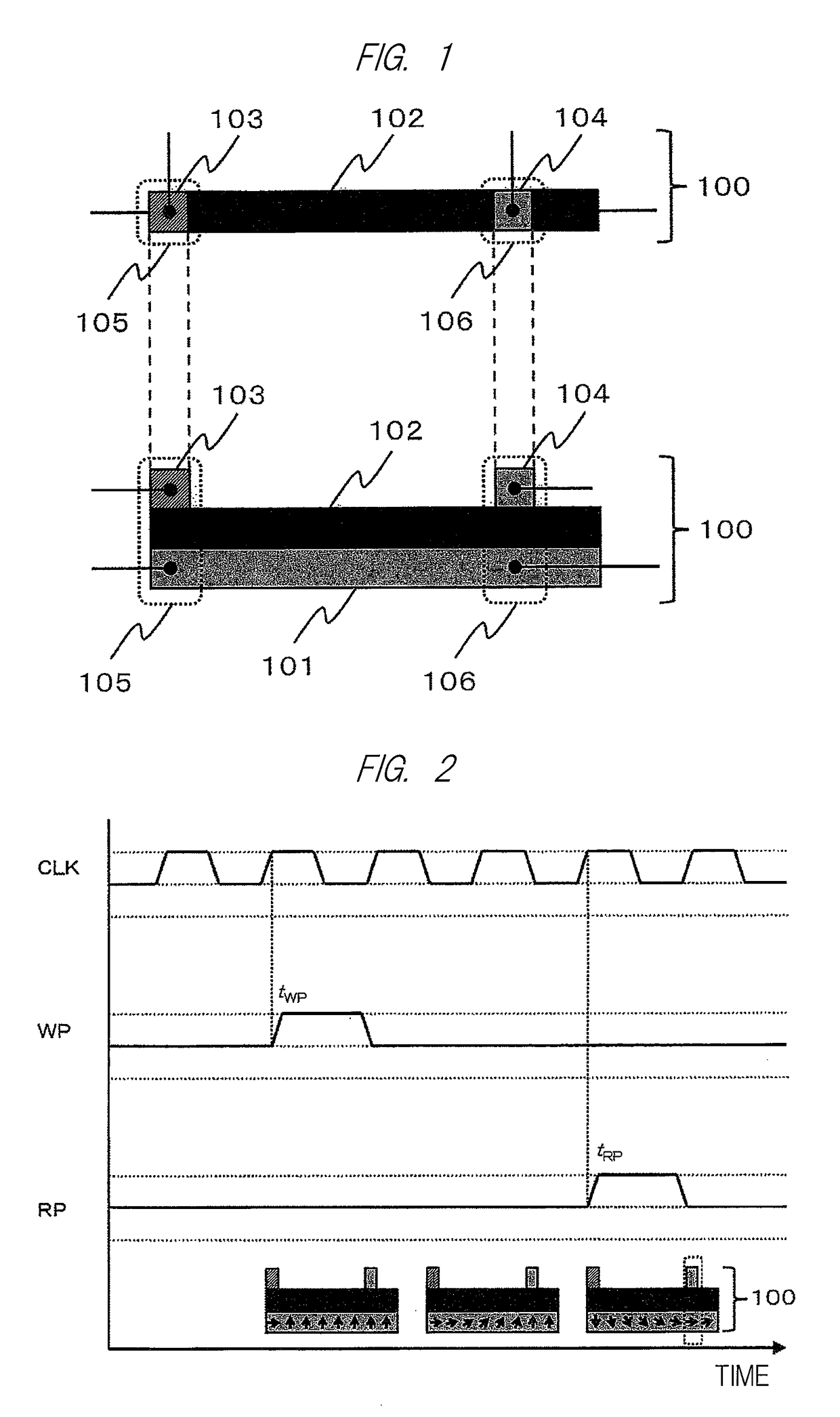

Spin wave device and logic circuit using spin wave device

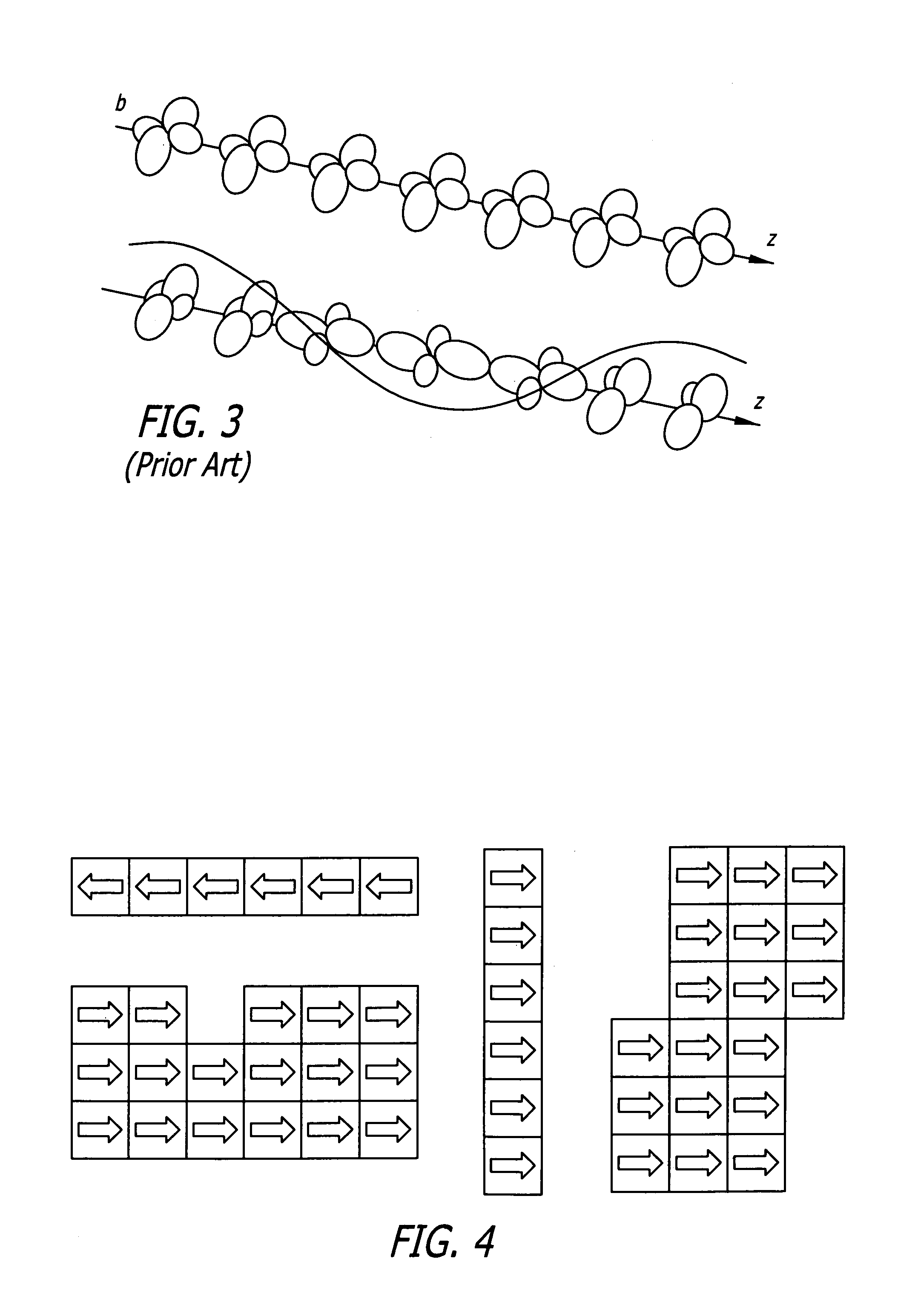

InactiveUS20160105176A1Increase speedTransistorPower reduction by control/clock signalSpin wavePhason

As a technique for attaining a reduction in power consumption, there is a technique for reducing power consumption using a spin wave. No specific proposal concerning spin wave generation, spin wave detection, and a latch technique for information has been made.A device applies an electric field to a first electrode of a nonmagnetic material using a thin line-shaped stacked body including a first ferromagnetic layer and a nonmagnetic layer to thereby generate a spin wave in the first ferromagnetic layer, and detects a phase or amplitude of the spin wave propagated in the first ferromagnetic layer using a second electrode of a ferromagnetic material with a magnetoresistance effect.

Owner:HITACHI LTD

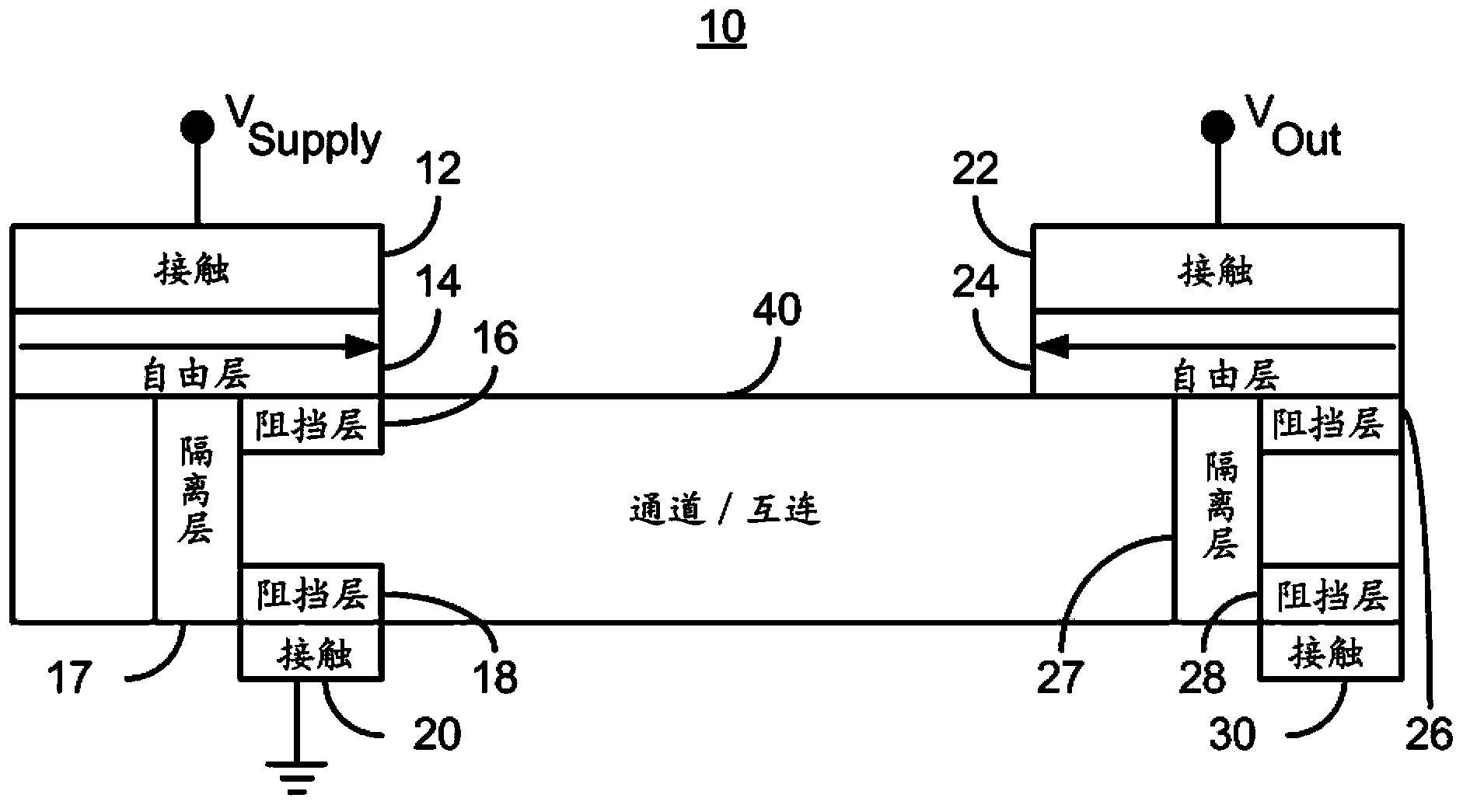

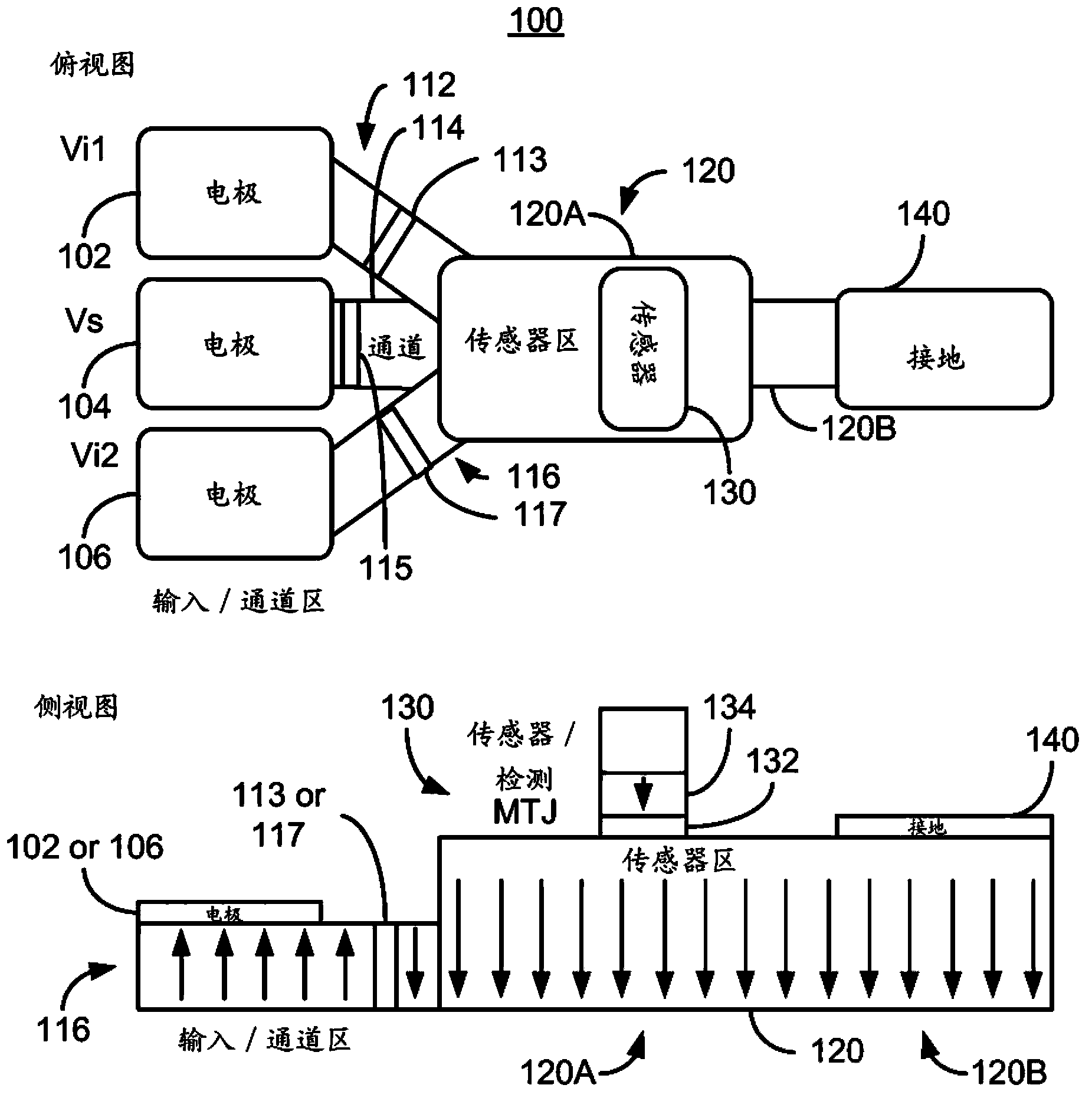

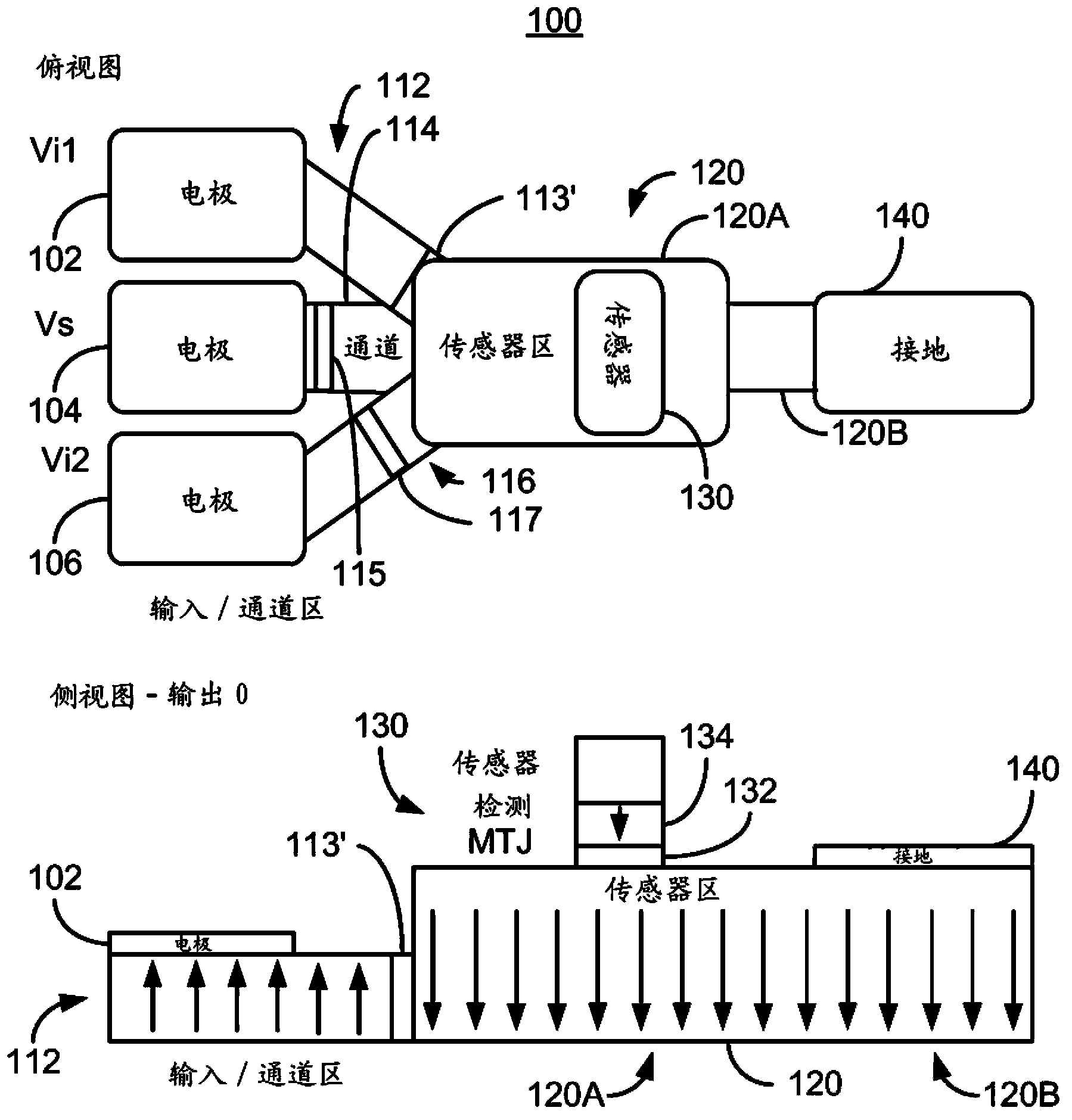

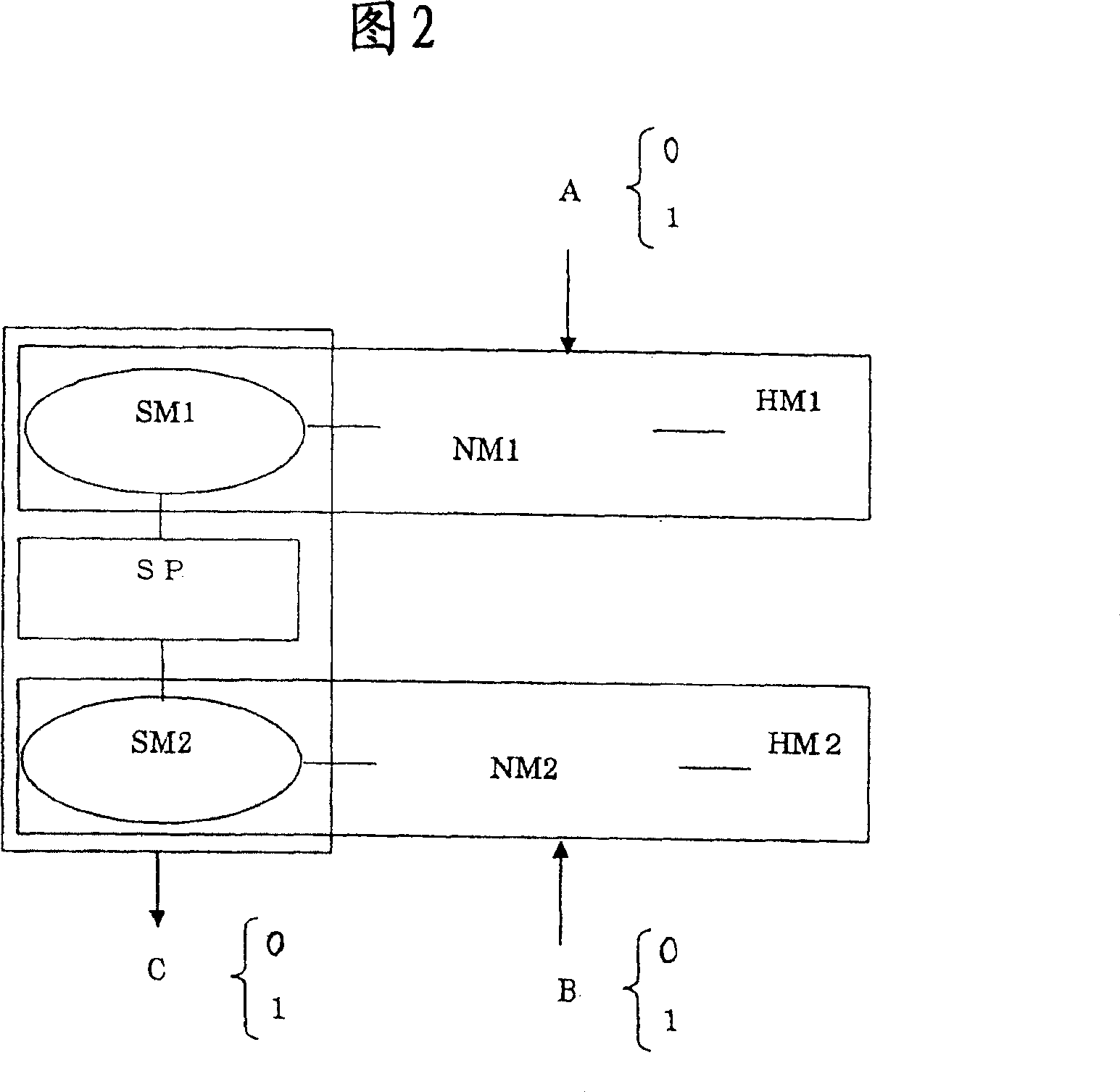

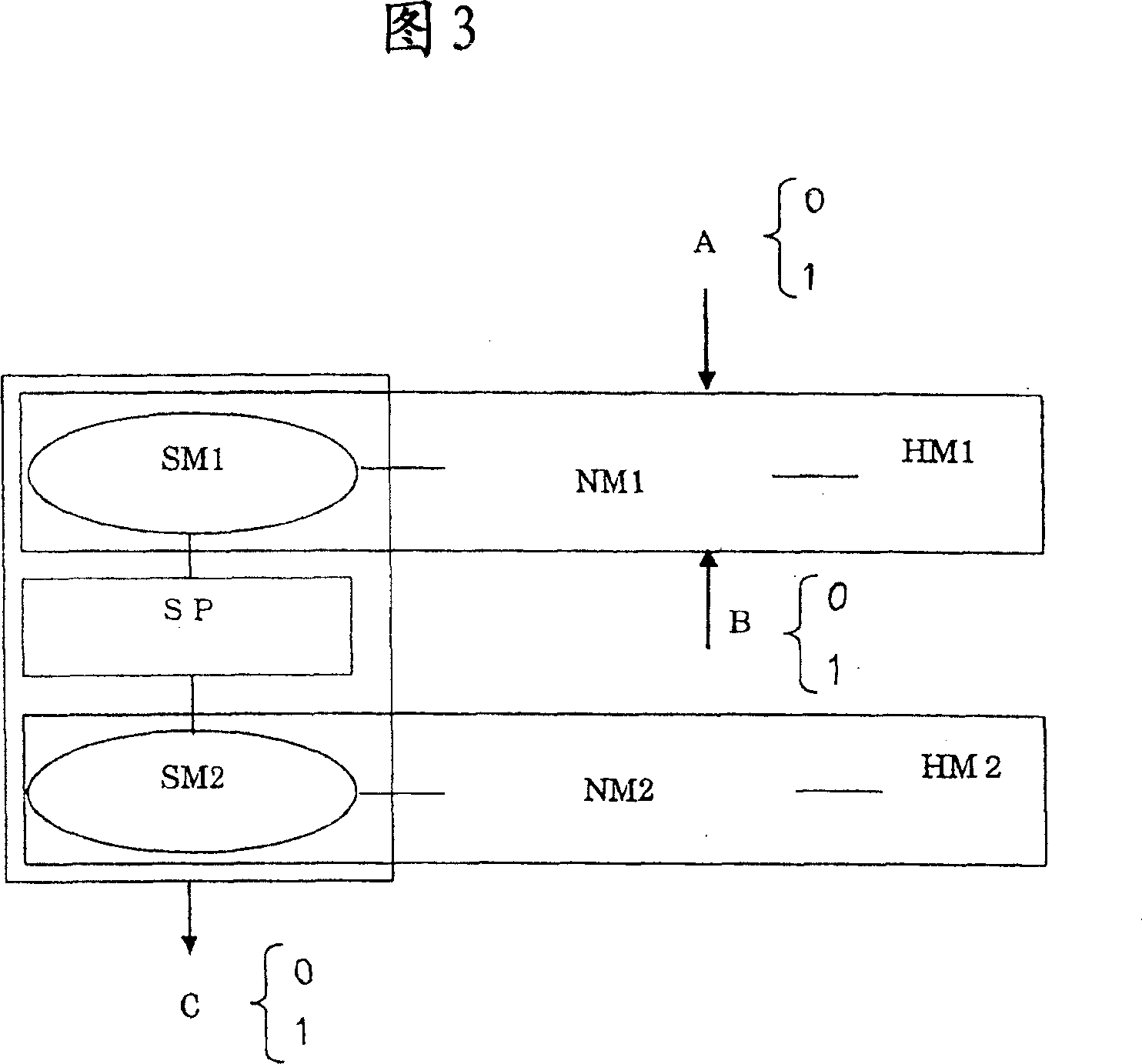

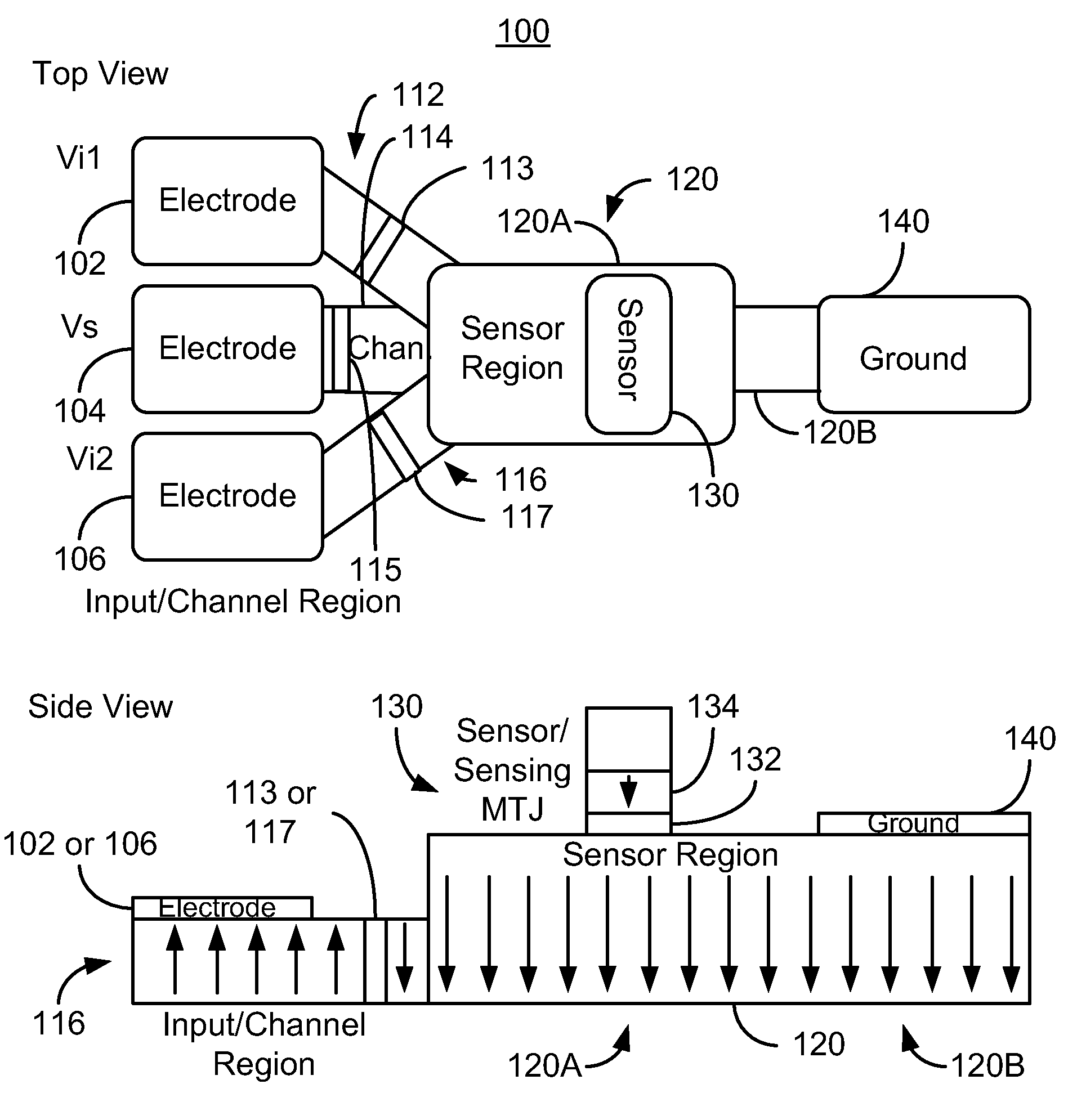

Method and system for providing spin transfer based logic devices

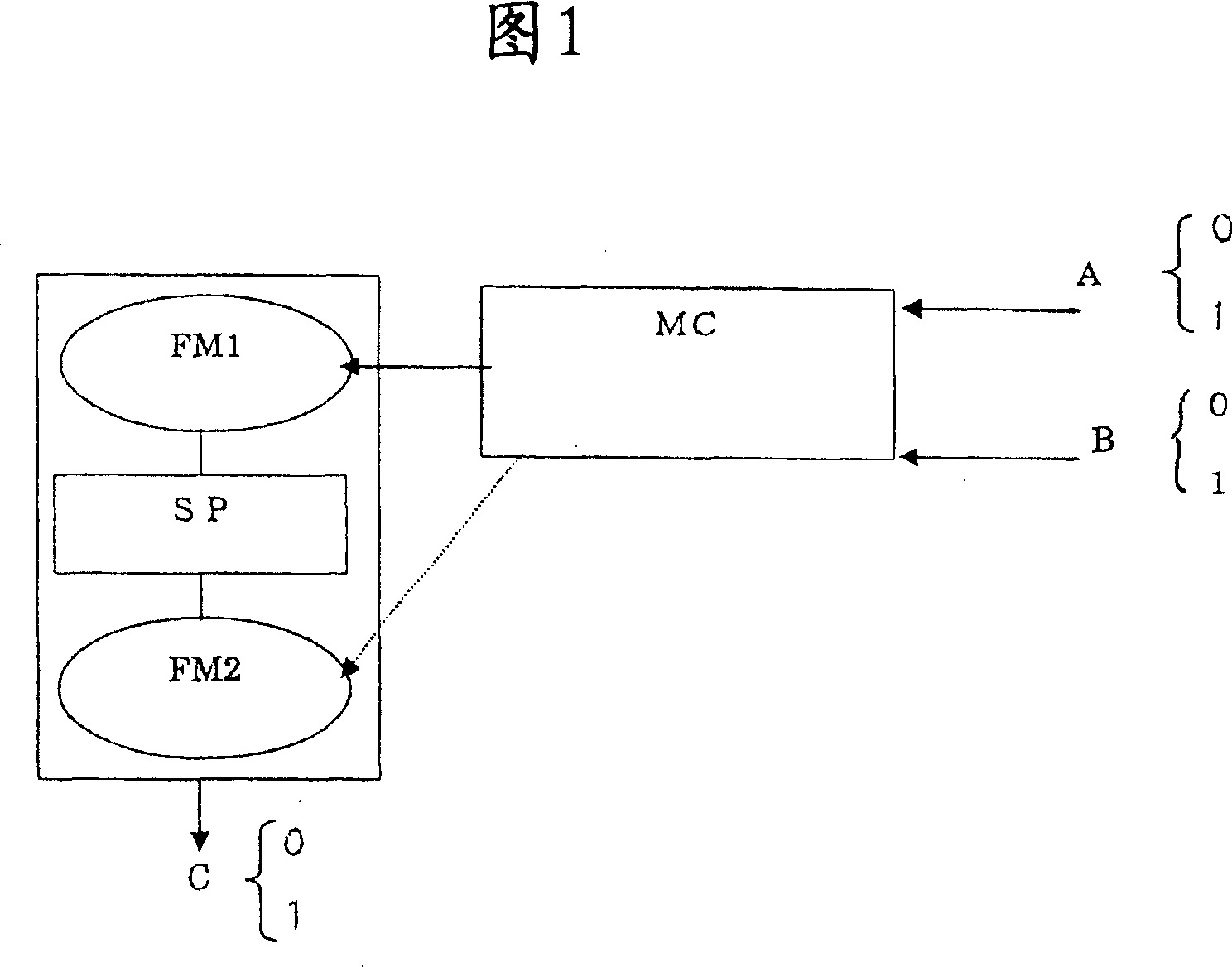

InactiveCN103580679ALogic circuits characterised by logic functionDigital storageEngineeringSpin transfer

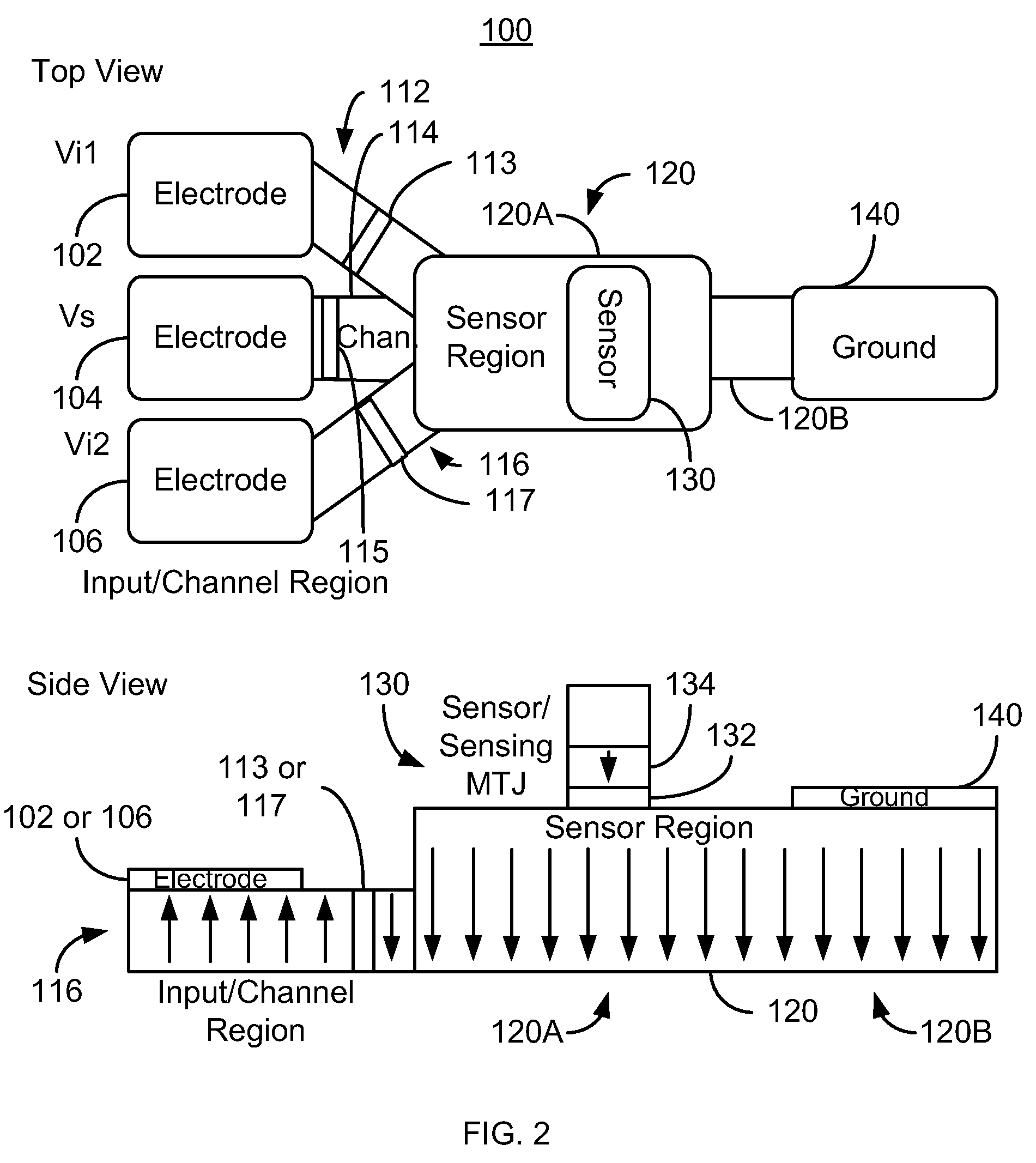

The invention provides a method and a system for providing a spin transfer based logic device. The logic device described includes a magnetic input / channel area, a magnetic sensor area, and a sensor coupled to the magnetic sensor area. Each magnetic input / channel area is magnetically biased in the first direction. The magnetic sensor area is magnetically biased in the second direction different from the first direction to make a domain wall in the magnetic input / channel area, if the logic device is in a static state. The sensor outputs signals based on the magnetic state of the magnetic sensor area. The magnetic input / channel area and the magnetic sensor area are configured to make the domain wall respond to the logic signals provided to the magnetic input area to move into the magnetic sensor area. The magnetic input / channel area includes FexCoyNizM1q1M2q2, wherein x+y+z+q1+q2=1, x, y, z, q1, q2 are at least zero, and M1 and M2 are non-magnetic.

Owner:SAMSUNG ELECTRONICS CO LTD

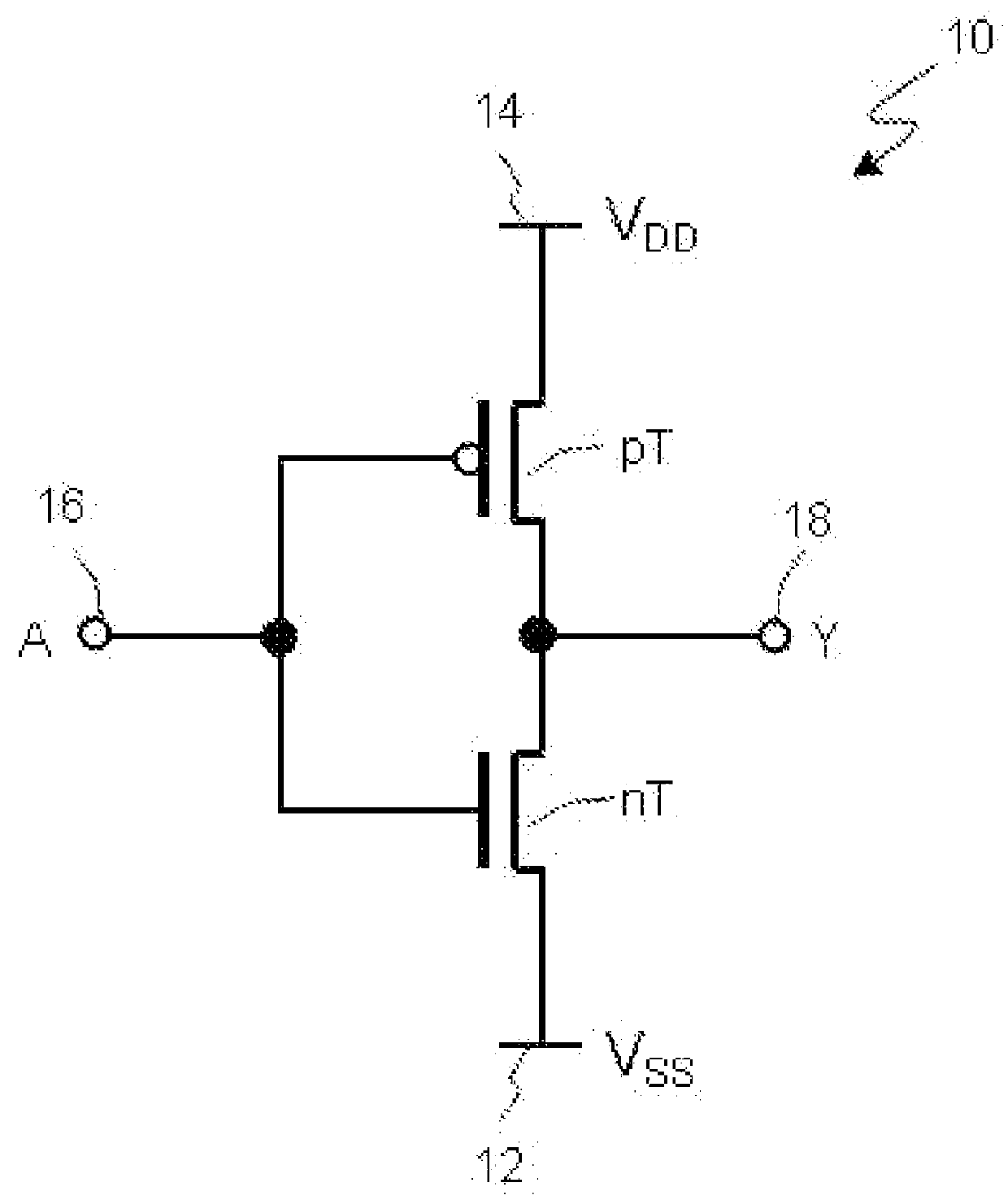

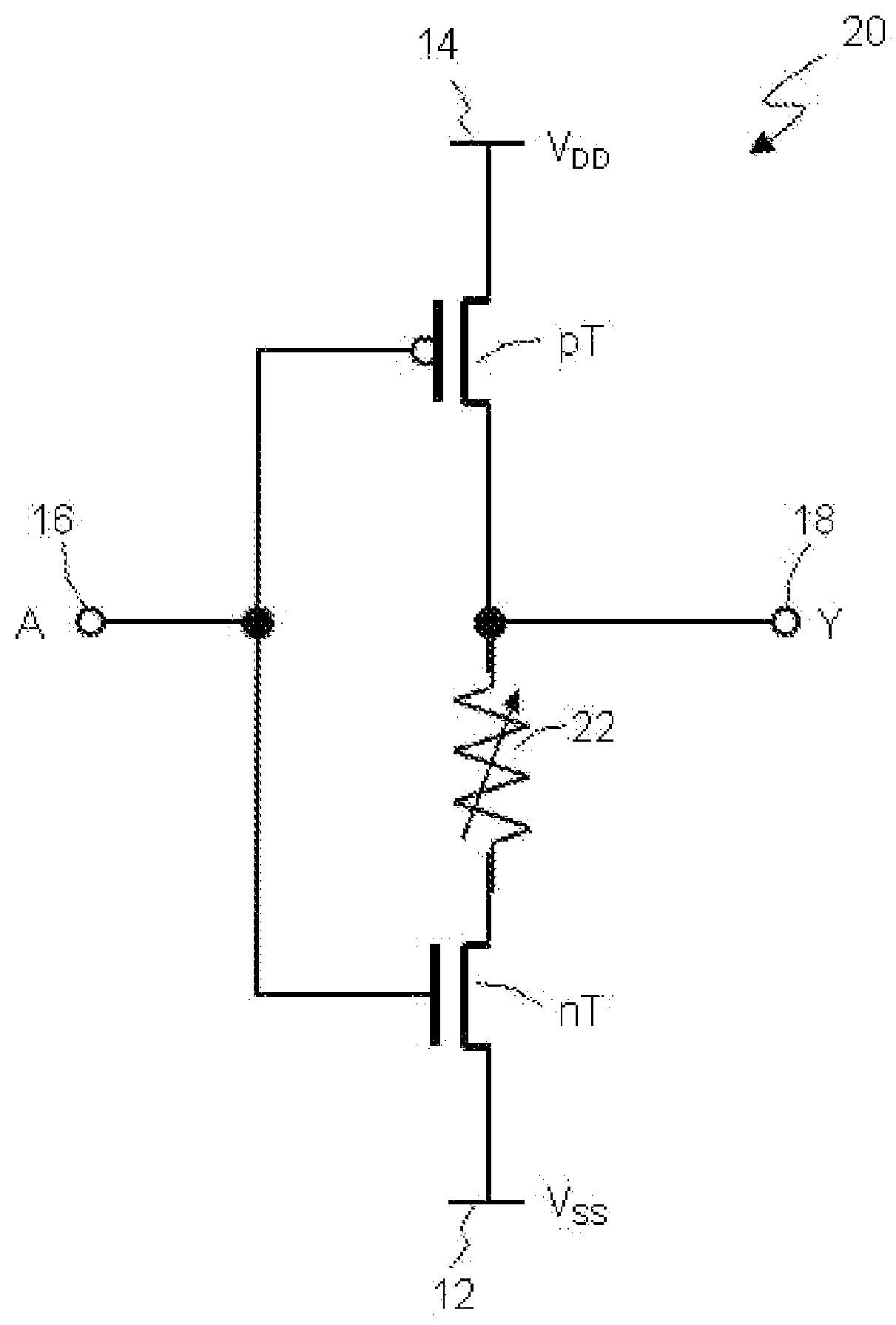

Nonvolatile Logic Circuit

ActiveUS20120105105A1Logic circuits characterised by logic functionDigital storageSpinsLogic circuitry

Semiconductor industry seeks to replace traditional volatile logic and memory devices with the improved nonvolatile devices. The increased demand for a significantly advanced, efficient, and nonvolatile data retention technique has driven the development of magnetic tunnel junctions (MTJs) employing a giant magneto-resistance (GMR). The present application relates to nonvolatile logic circuits with integrated MTJs and, in particular, concerns a nonvolatile spin dependent logic device that may be integrated with conventional semiconductor-based logic devices to construct the nonvolatile logic circuits performing NOT, NOR, NAND and other logic functions.

Owner:SHUKH ALEXANDER MIKHAILOVICH

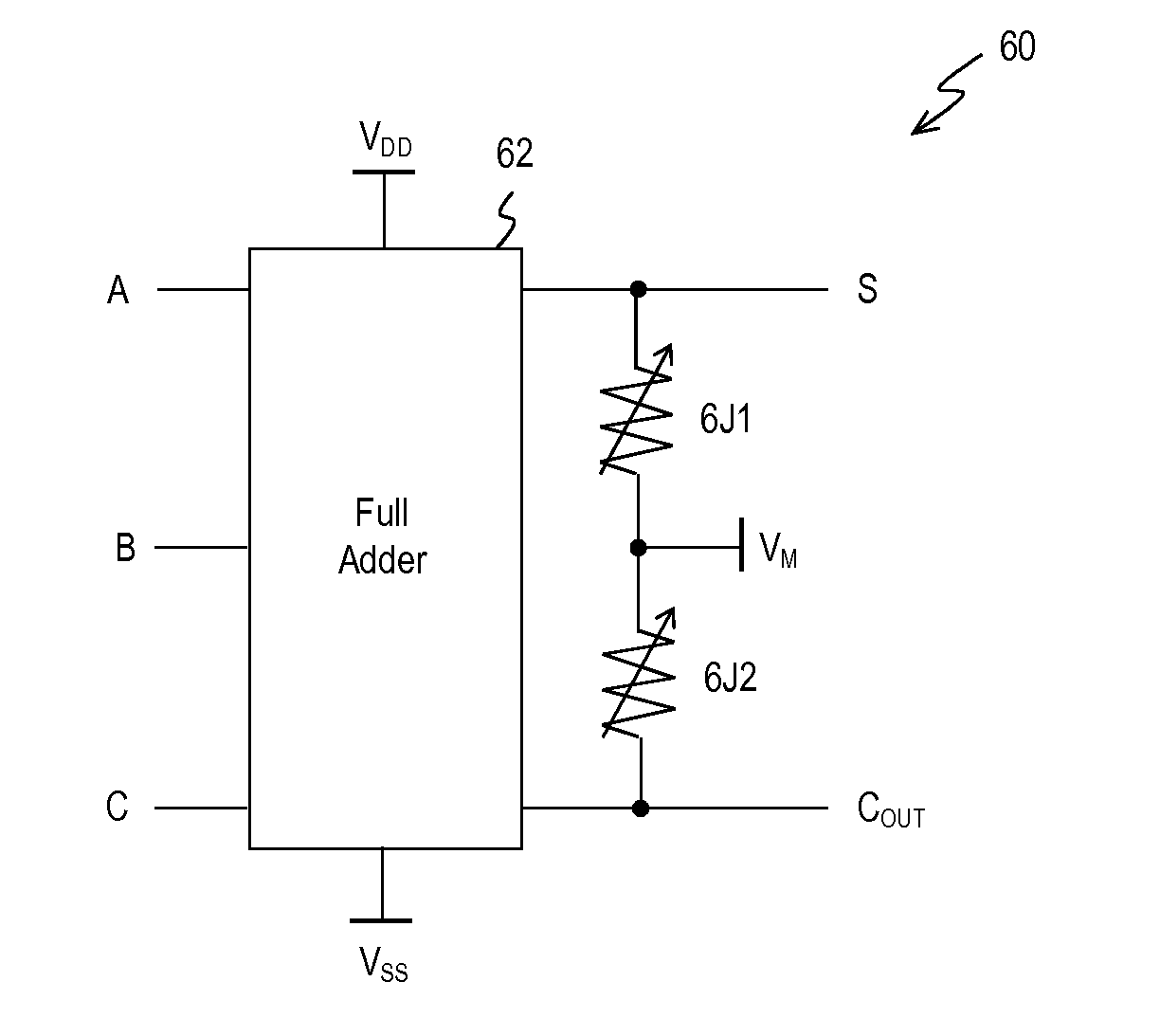

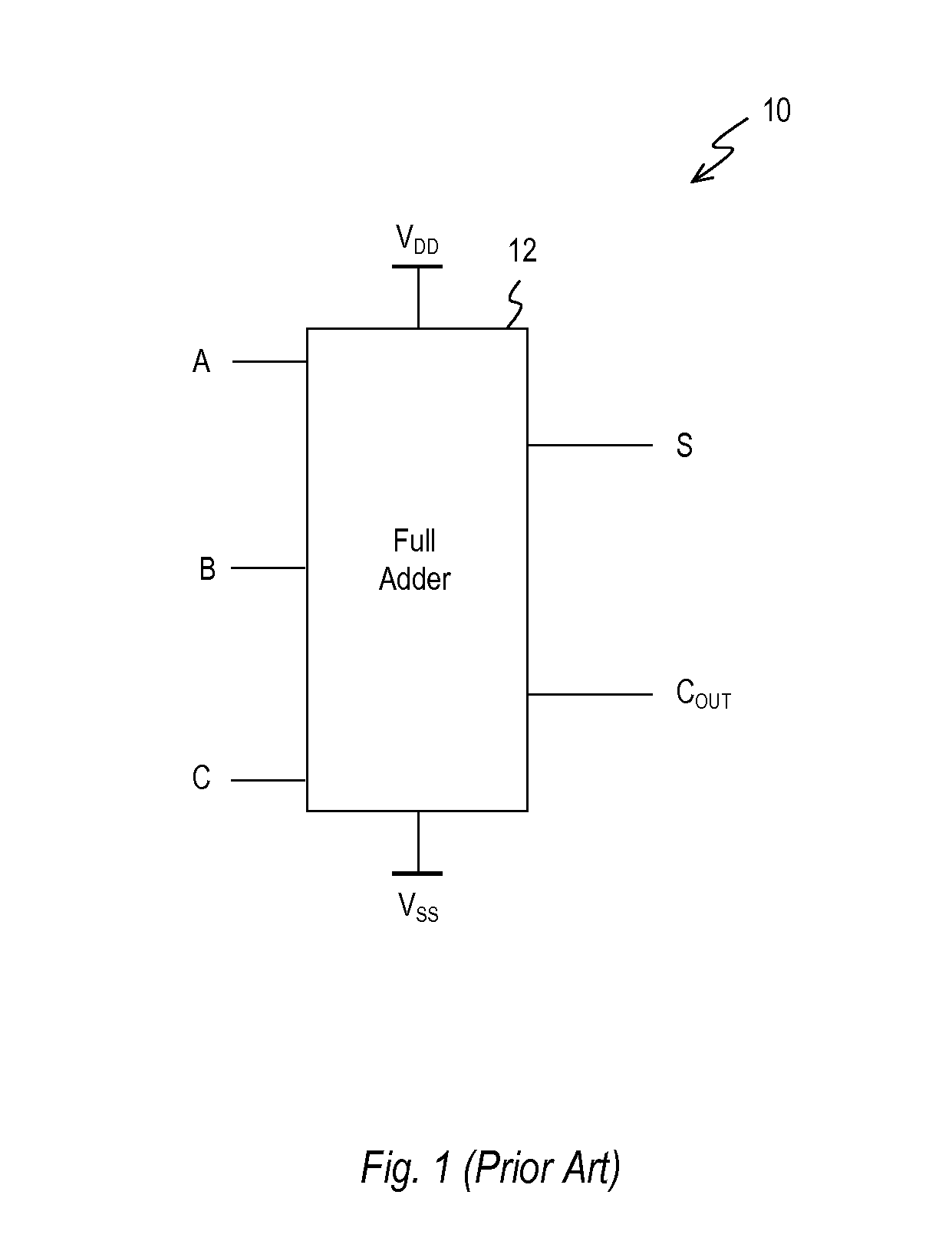

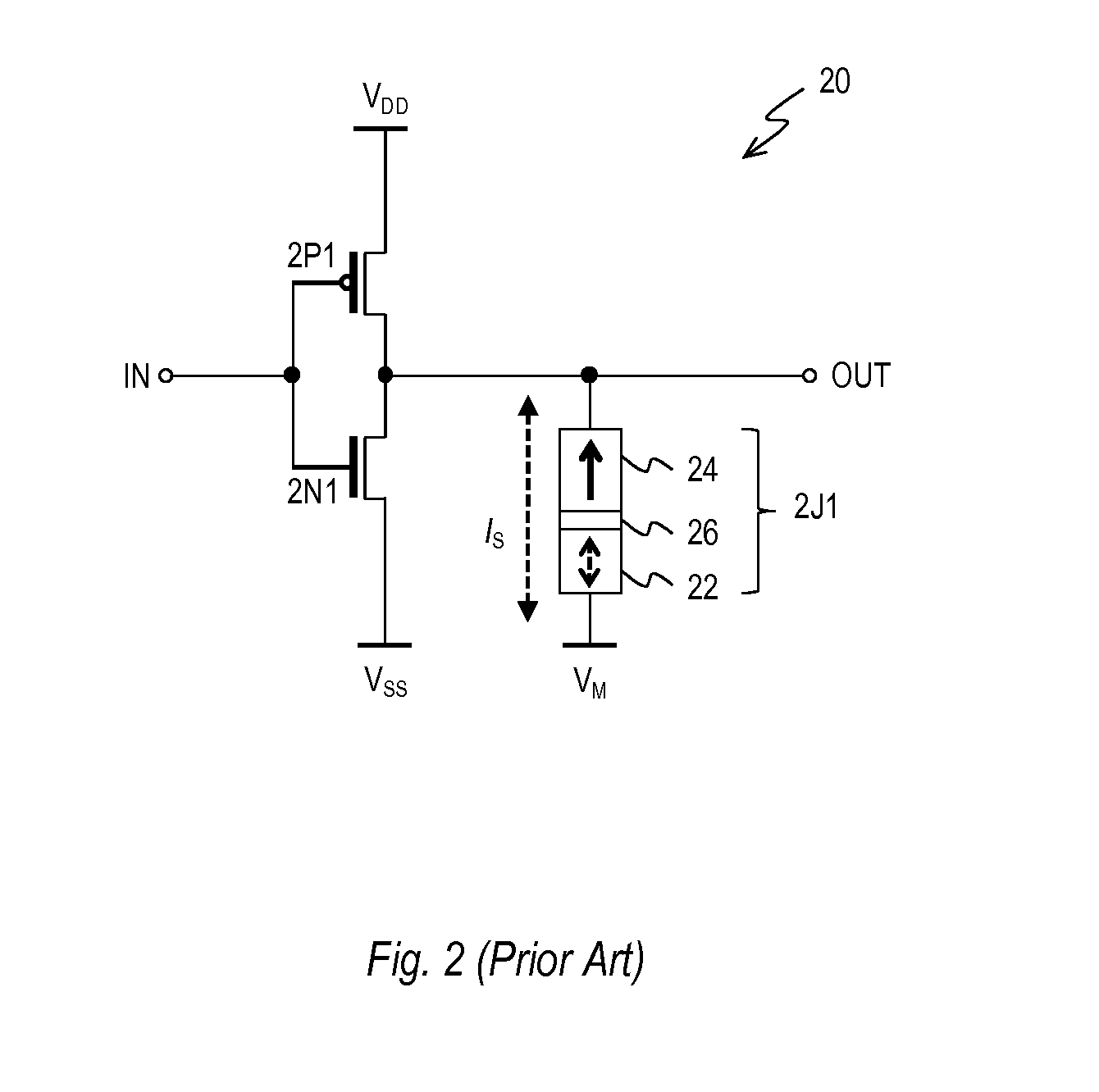

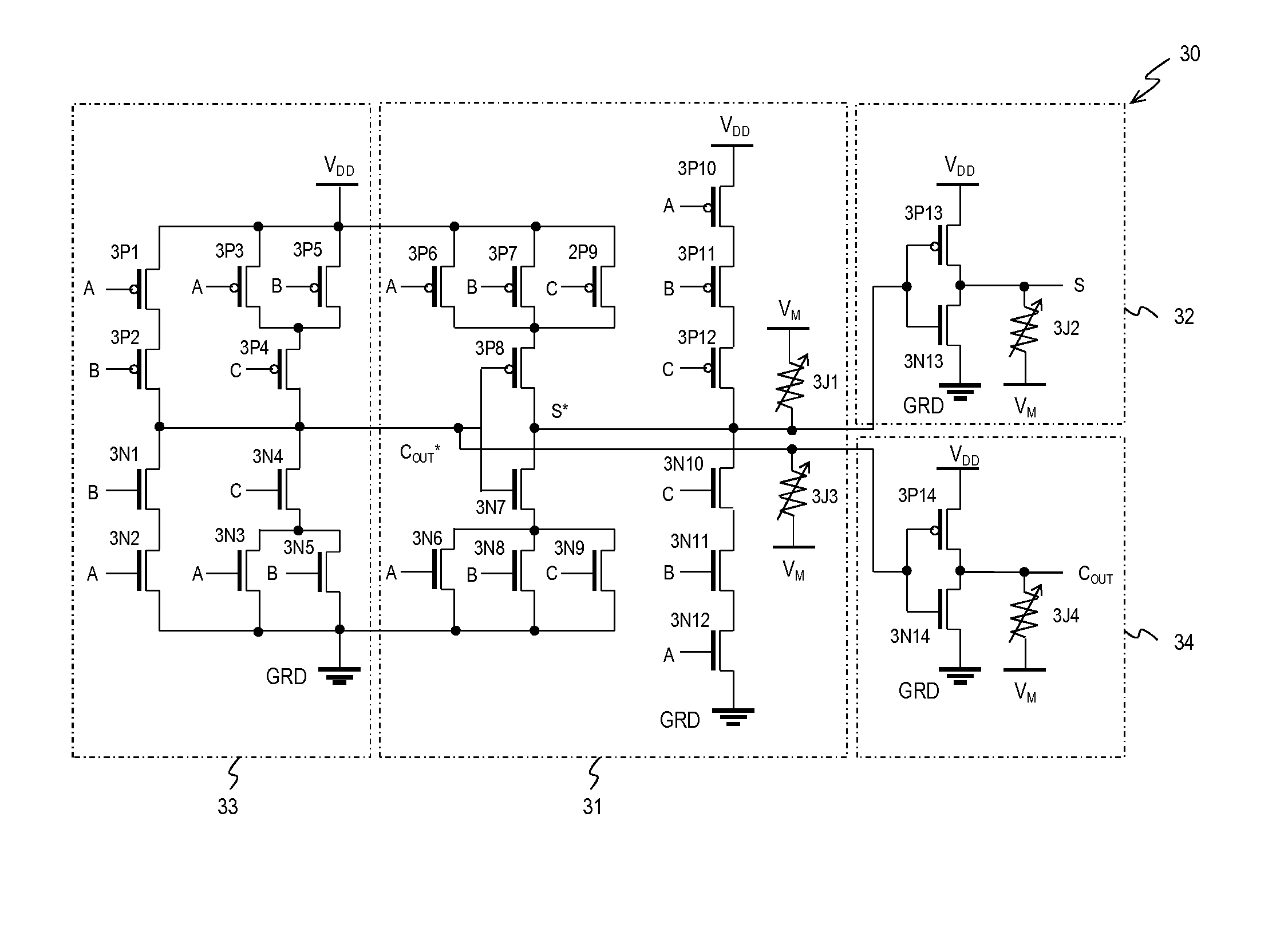

Nonvolatile Full Adder Circuit

InactiveUS20120306536A1Exclusive-OR circuitsComputation using non-contact making devicesElectricityPower flow

A nonvolatile full adder circuit comprising a full adder electrical circuitry comprising three input terminals for receiving two input and carry-in signals, a sum output terminal, and an carry-out output terminal; first and second nonvolatile memory elements electrically coupled to the first and second output terminal, respectively at their first ends and to an intermediate voltage source at their second ends. The nonvolatile memory elements comprise two stable logic states. A logic state each of the of the nonvolatile memory elements is controlled by a bidirectional electrical current running between its first and second ends. The full adder circuitry is electrically coupled to a high voltage source at its first source terminal and to a low voltage source at its second source terminal, wherein an electrical potential of the intermediate voltage source is lower than that of the high voltage source but higher than that of the low voltage source.

Owner:SHUKH ALEXANDER MIKHAILOVICH +1

Nonvolatile full adder circuit

InactiveUS8405421B2Exclusive-OR circuitsComputation using non-contact making devicesElectricityLow voltage

A nonvolatile full adder circuit comprising a full adder electrical circuitry comprising three input terminals for receiving two input and carry-in signals, a sum output terminal, and an carry-out output terminal; first and second nonvolatile memory elements electrically coupled to the first and second output terminal, respectively at their first ends and to an intermediate voltage source at their second ends. The nonvolatile memory elements comprise two stable logic states. A logic state each of the of the nonvolatile memory elements is controlled by a bidirectional electrical current running between its first and second ends. The full adder circuitry is electrically coupled to a high voltage source at its first source terminal and to a low voltage source at its second source terminal, wherein an electrical potential of the intermediate voltage source is lower than that of the high voltage source but higher than that of the low voltage source.

Owner:SHUKH ALEXANDER MIKHAILOVICH +1

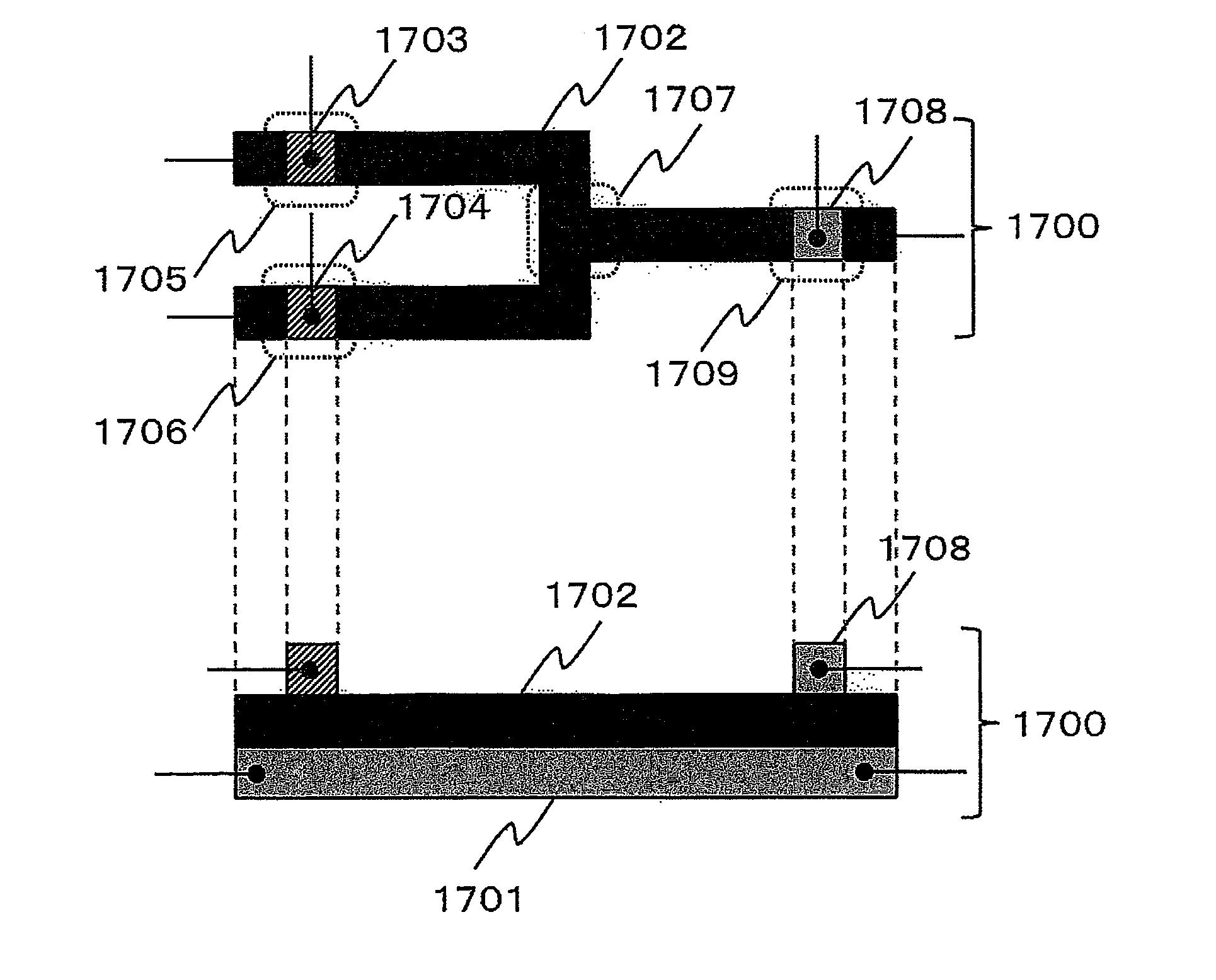

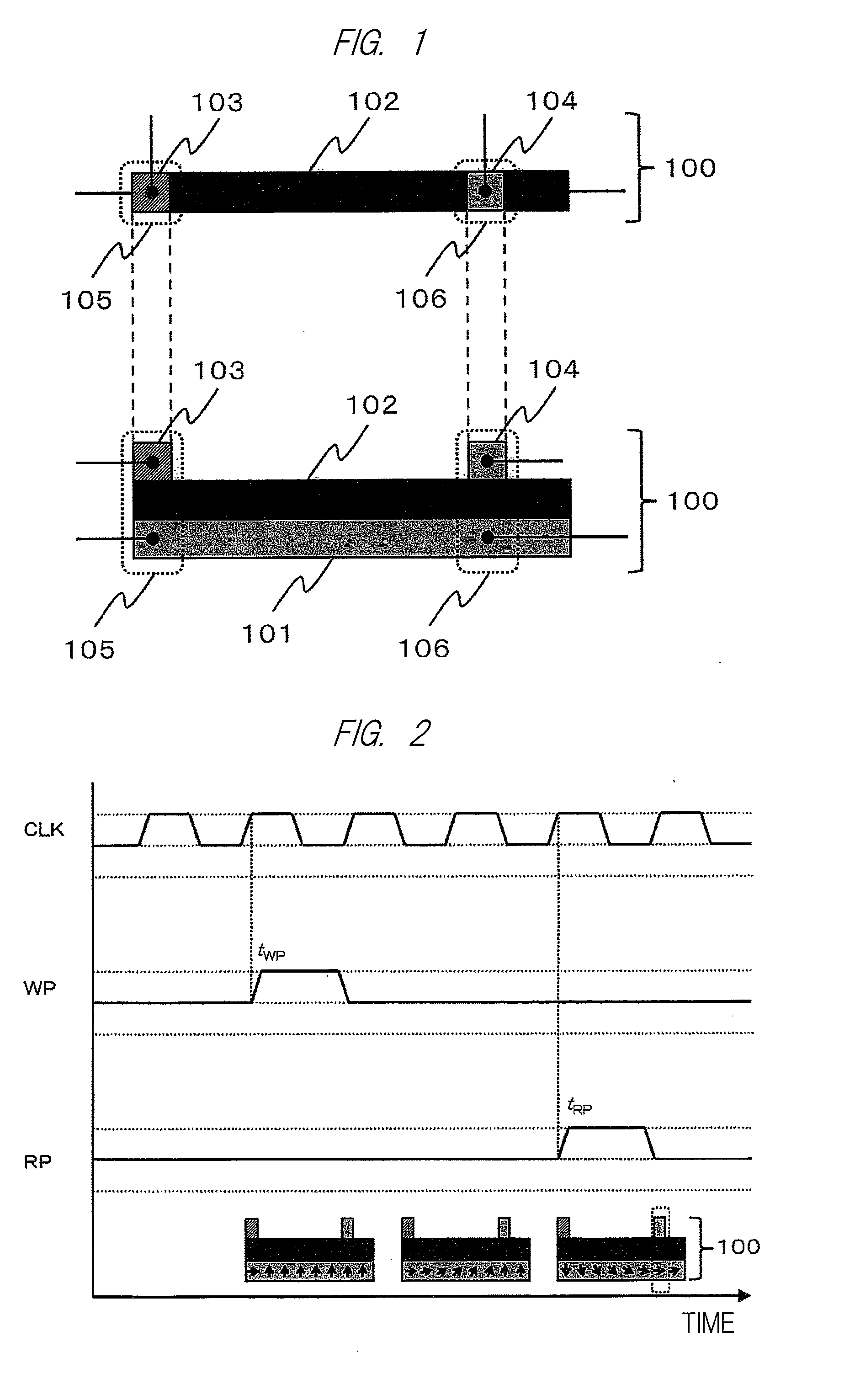

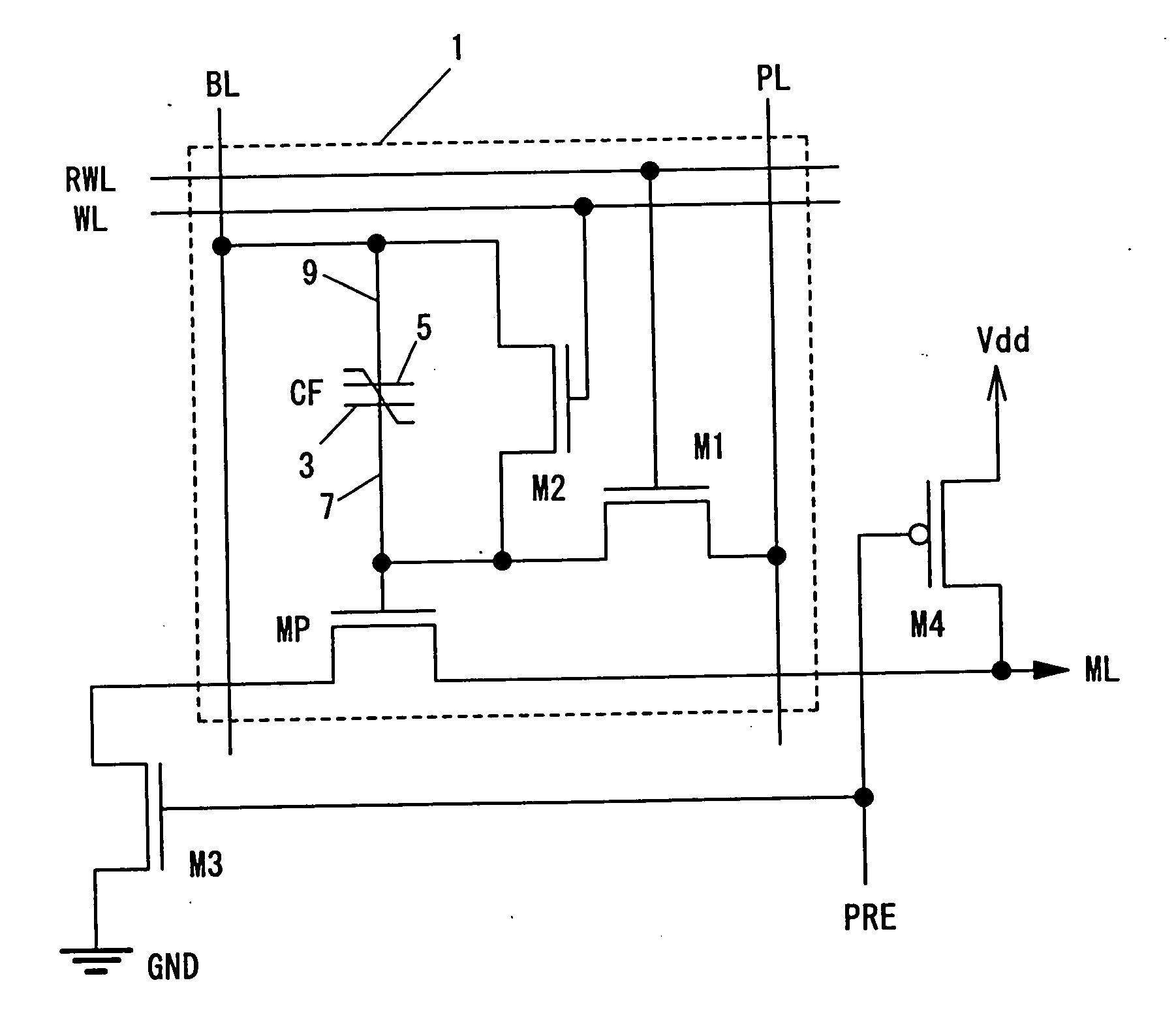

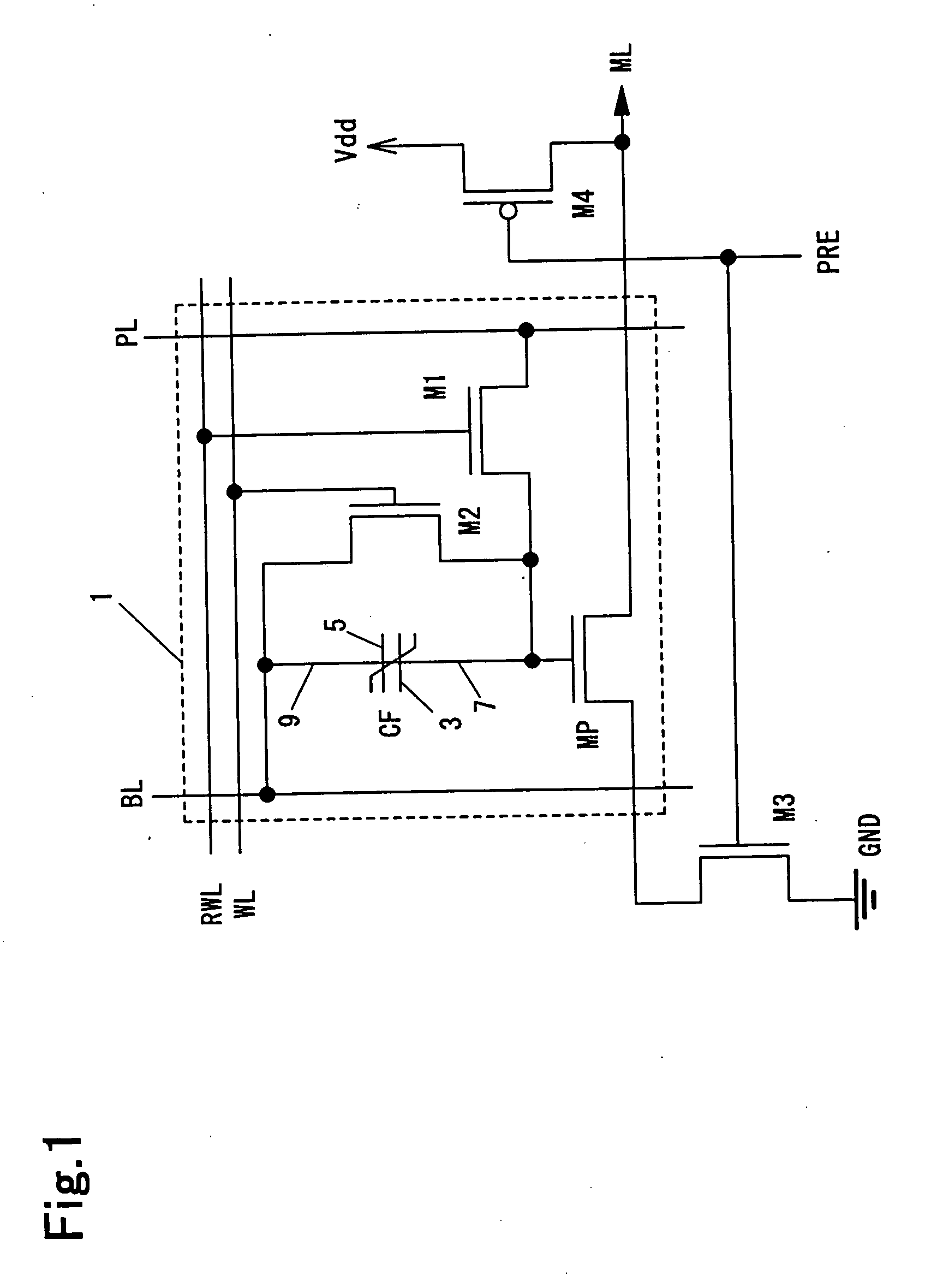

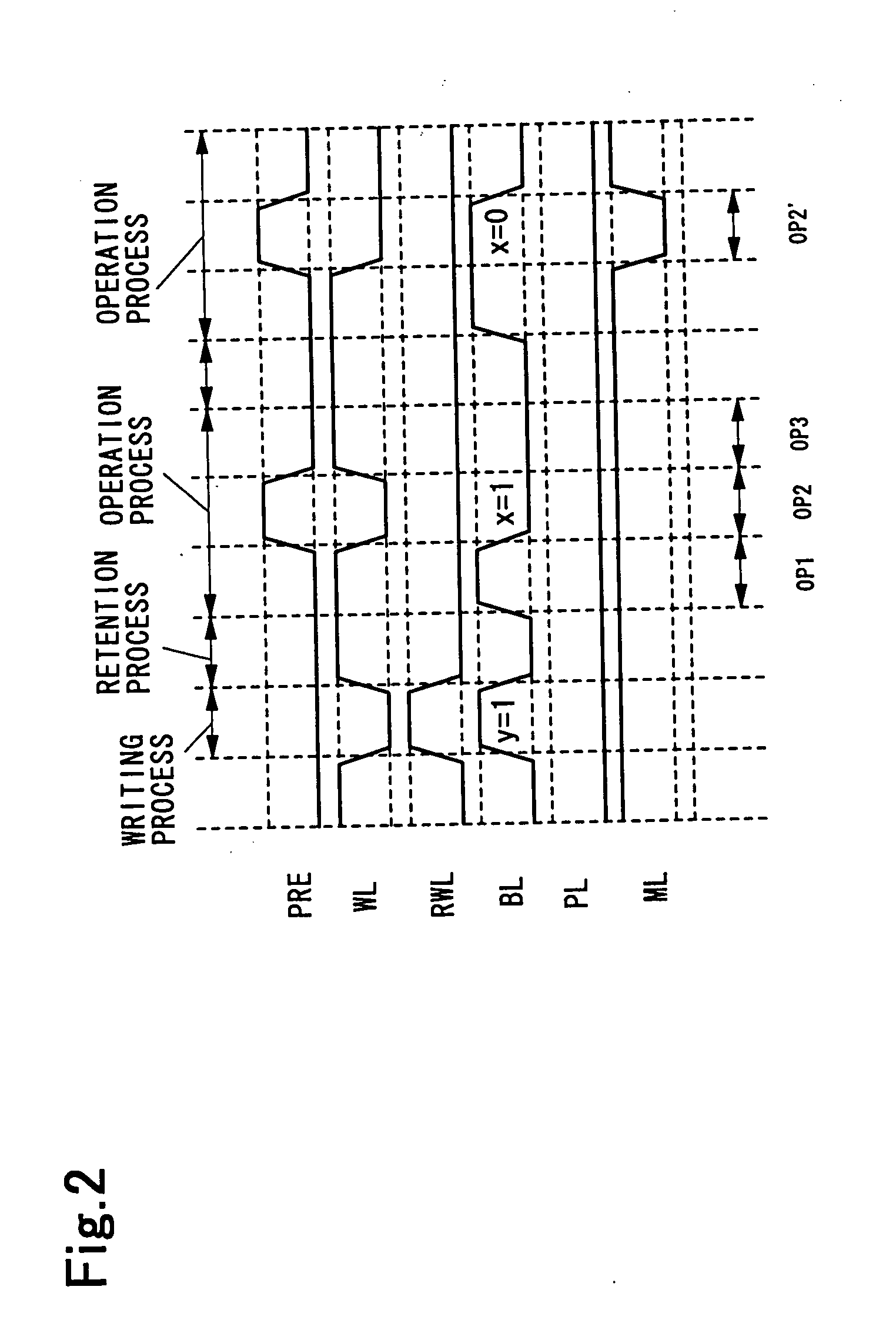

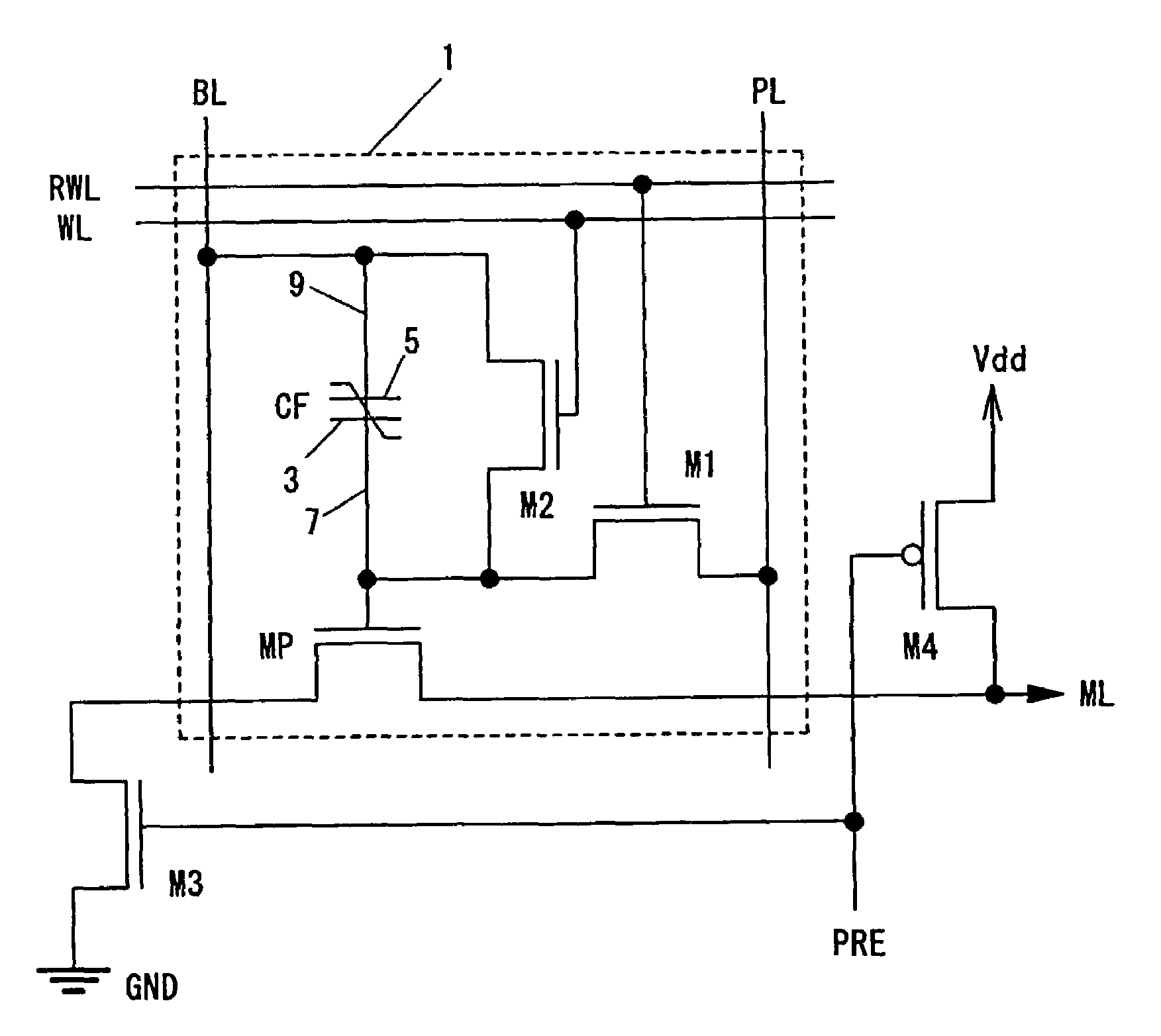

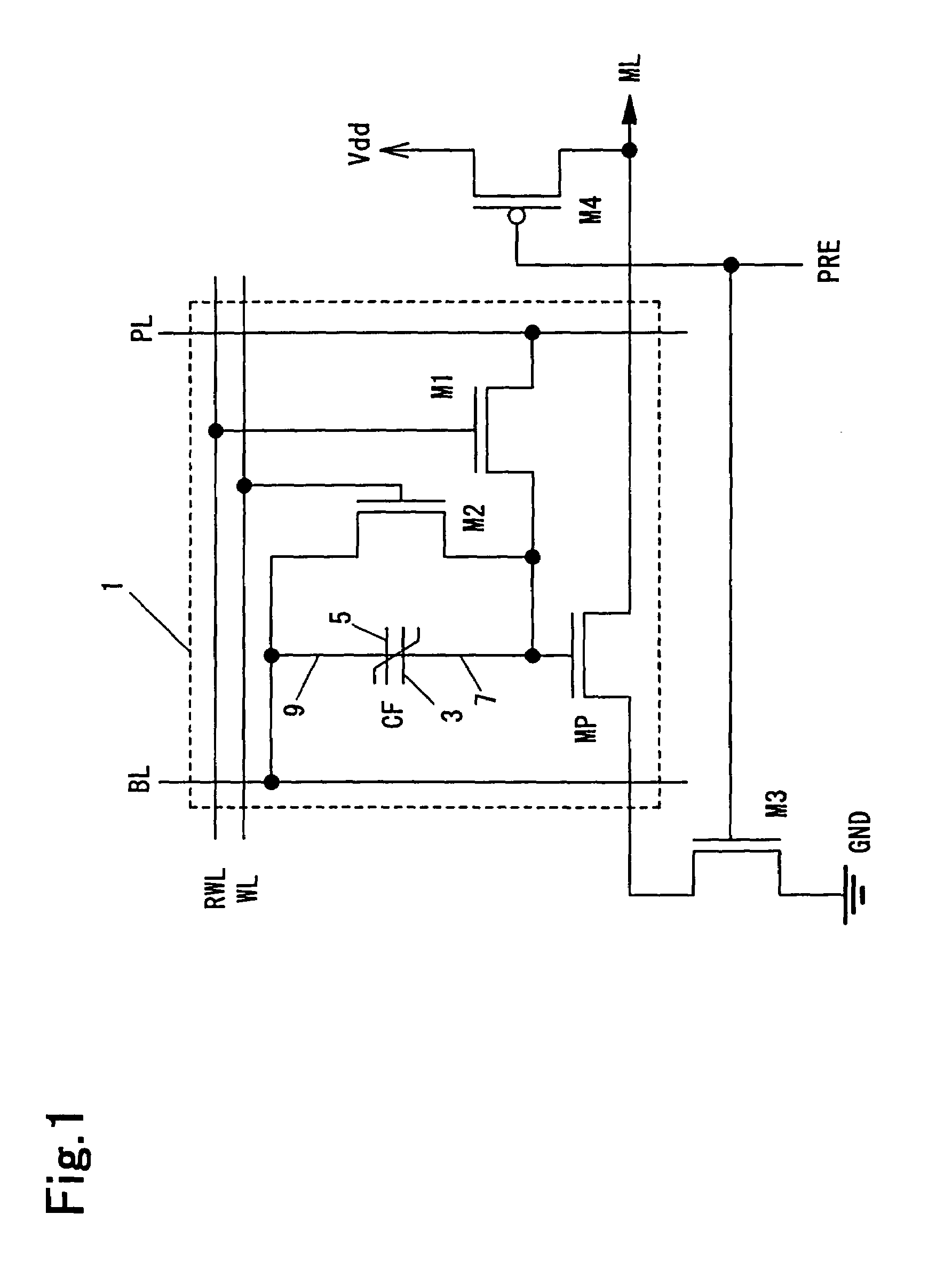

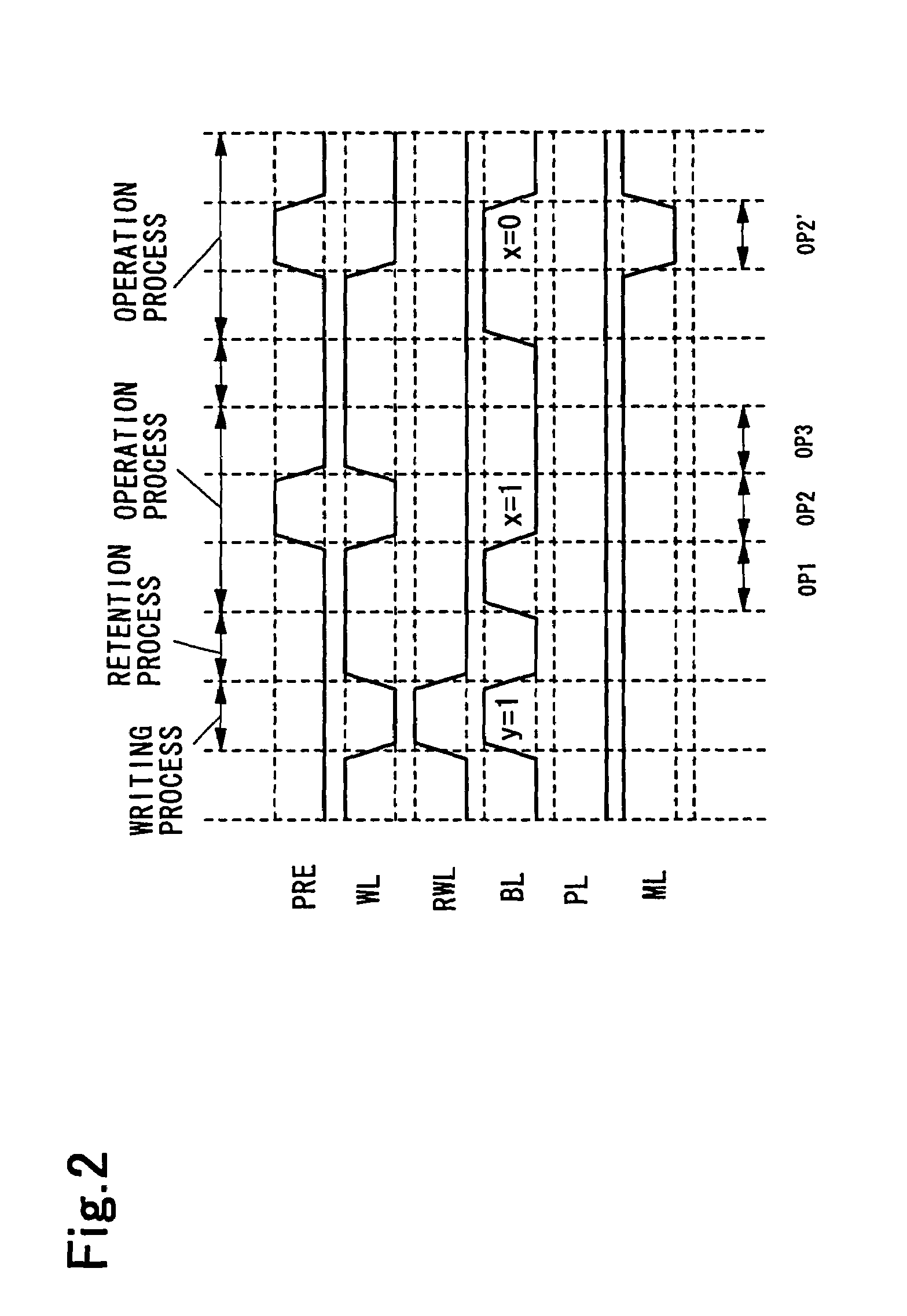

Logical operation circuit and logical operation method

InactiveUS20050146922A1Logic circuits characterised by logic functionDigital storageBit lineLogical operations

To provide a logical operation circuit which can perform a logical operation using a ferroelectric capacitor and a logical operation method. A logical operation circuit 1 has a ferroelectric capacitors CF and a transistor MP. The ferroelectric capacitor CF can retain a polarization state P1 (y=1) or P2 (y=0) corresponding to first operation target data y. In an operation process, a first terminal 3 of the ferroelectric capacitor 1 is precharged to a source potential Vdd, and a potential corresponding to second operation target data x, that is, a ground potential GND (x=1) or the source potential Vdd (x=0), is given to a second terminal 5 of the ferroelectric capacitor via a bit line BL. When the threshold voltage Vth of the transistor MP is set properly, the transistor MP becomes on or off (on, on, on, off) depending on the combination of x and y (0-0, 0-1, 1-0, 1-1).

Owner:ROHM CO LTD

Frequency generator and method for generating frequency

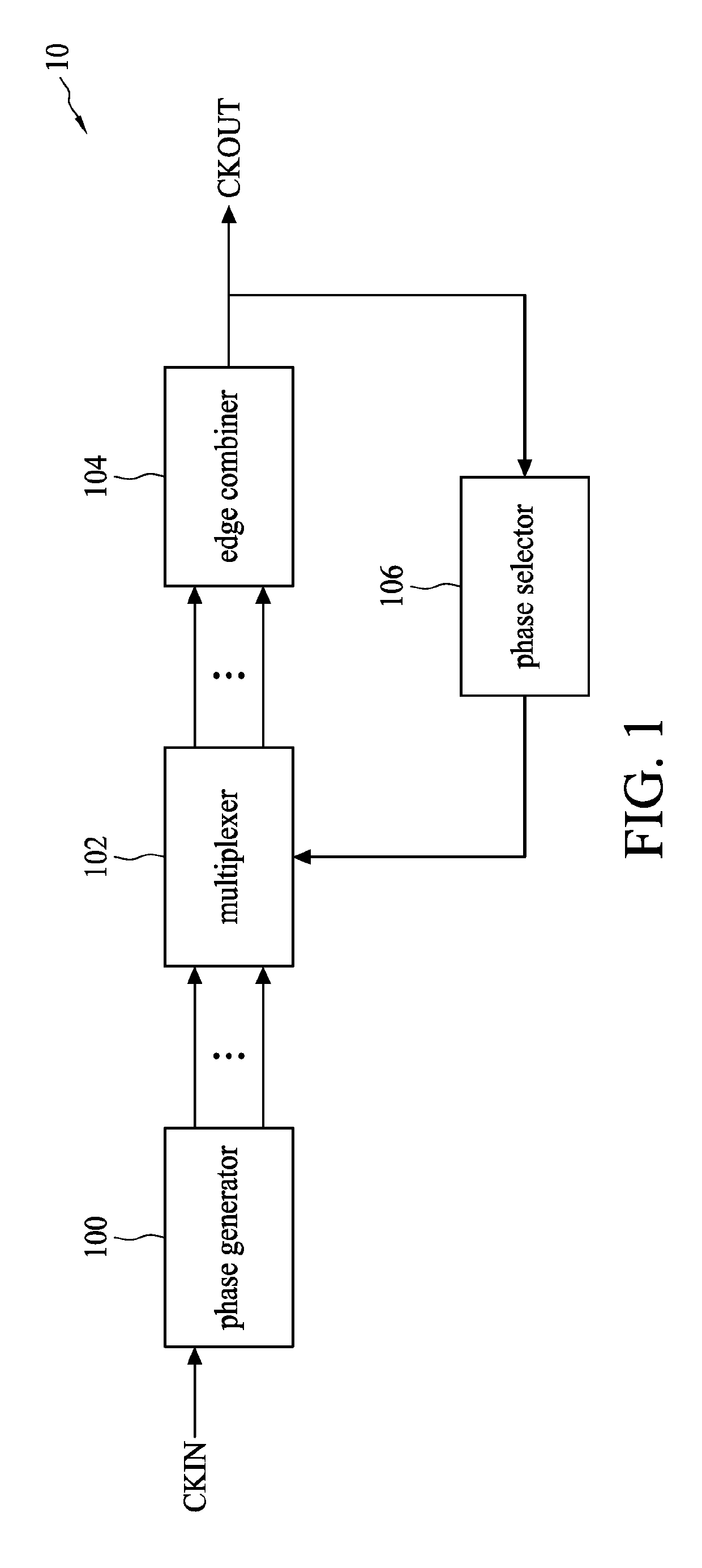

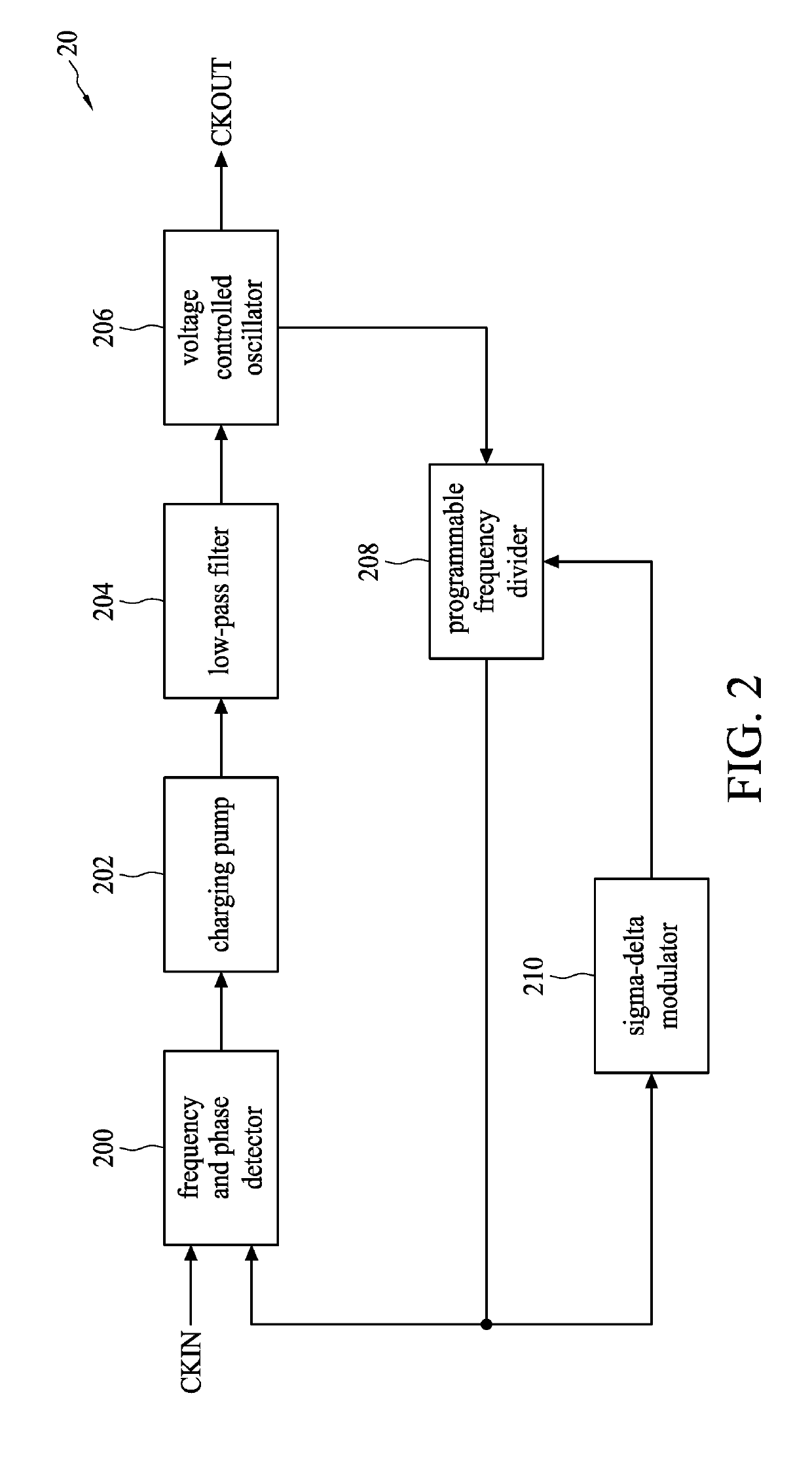

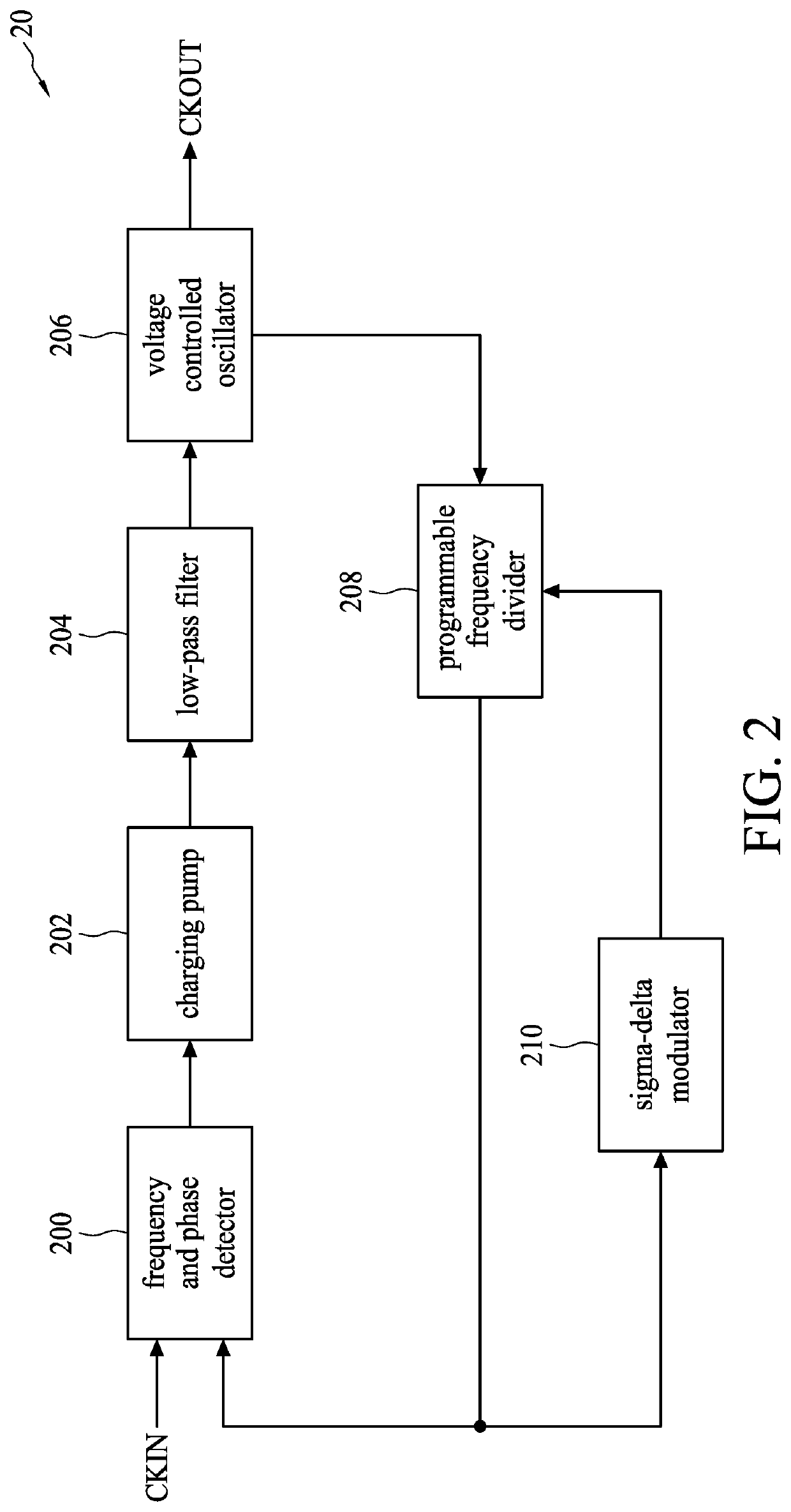

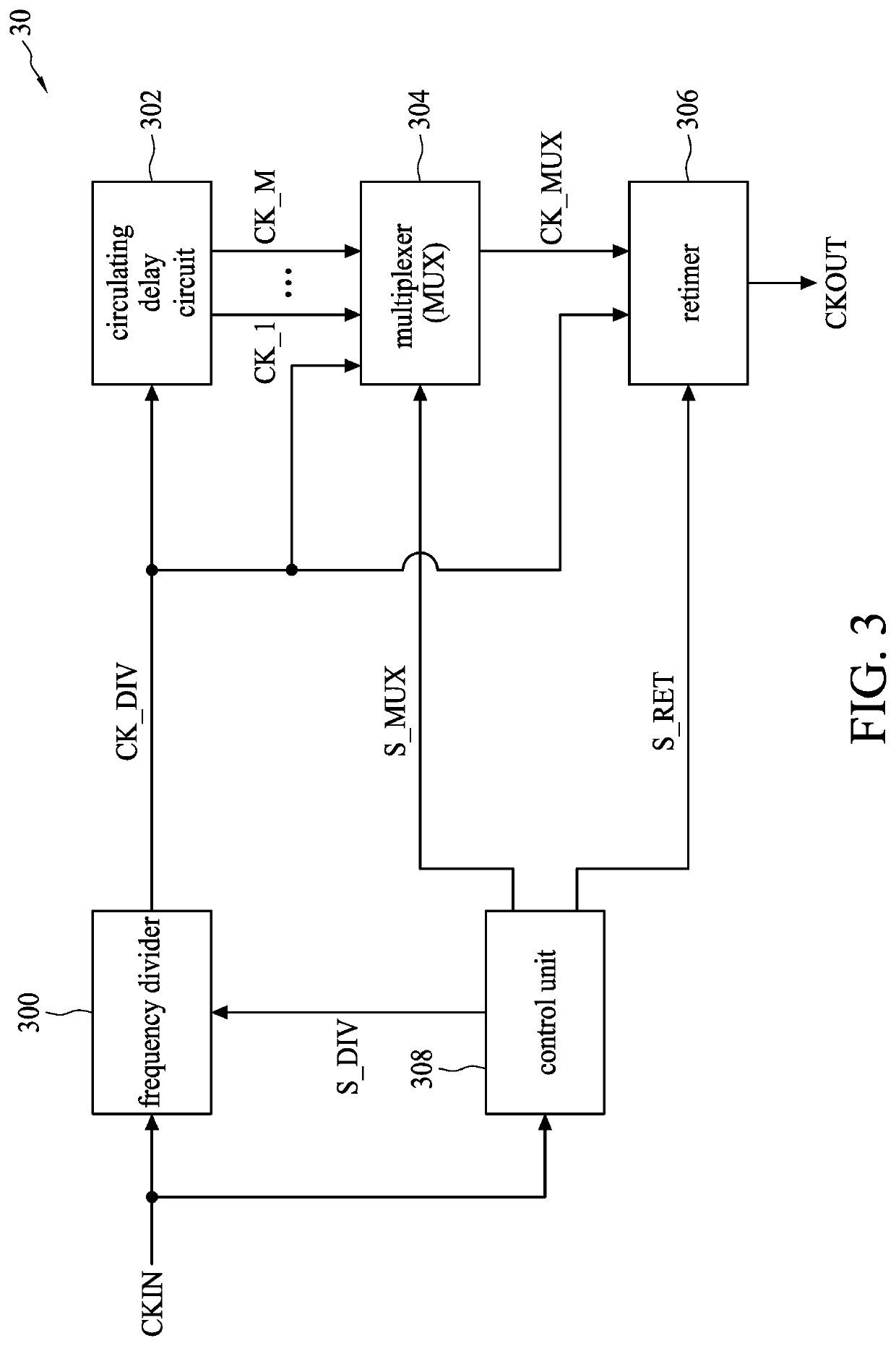

ActiveUS20190334529A1Make up for deficienciesPulse automatic controlGenerating/distributing signalsMultiplexingMultiplexer

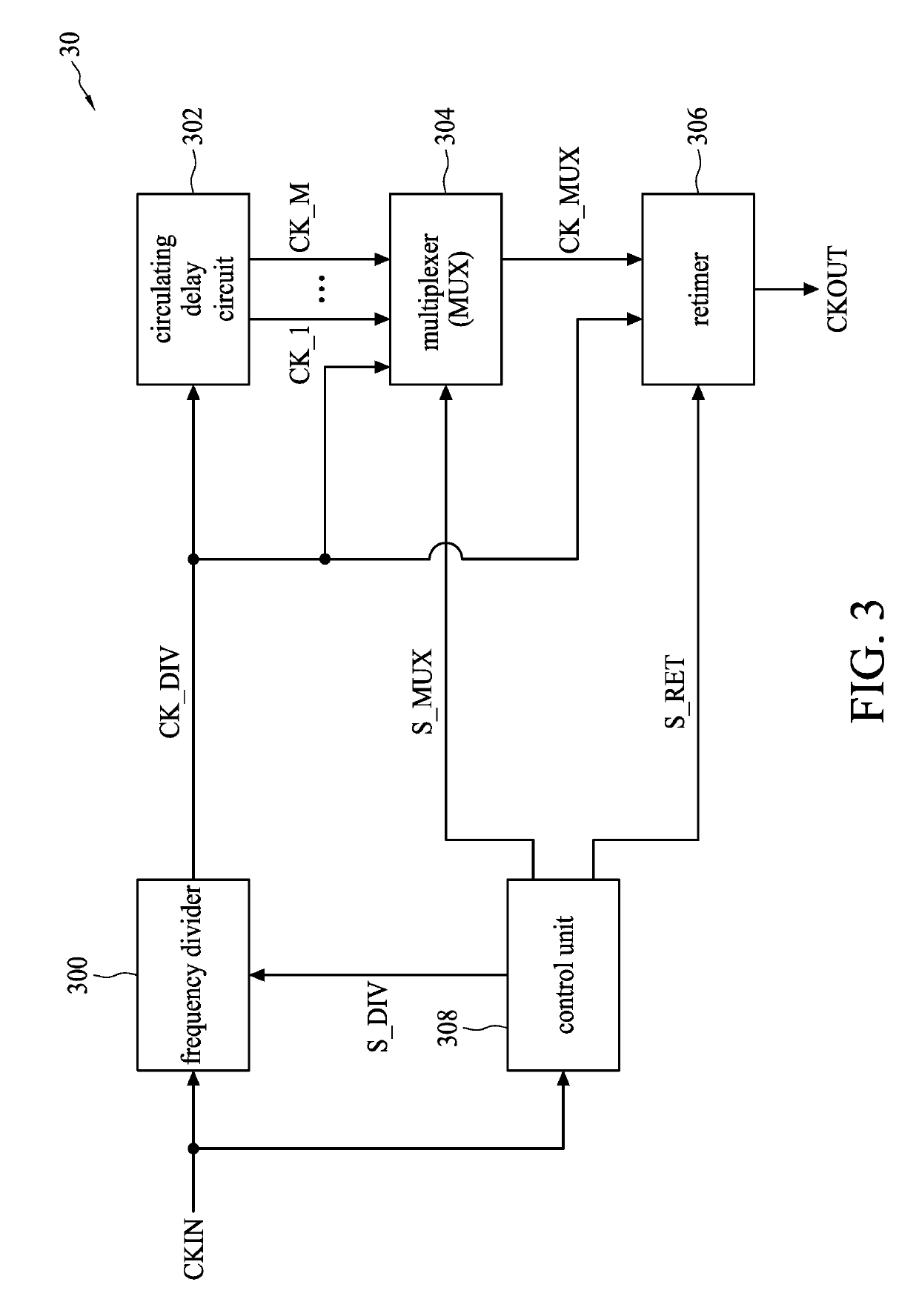

A frequency generator, includes a control unit, configured to receive an input signal to generate a divisor signal, a phase signal and a circulation signal; a frequency divider, configured to receive the input signal and perform an integer division to the input signal according to the divisor signal, so as to generate a frequency division signal; a circulating delay circuit, coupled to the frequency divider and configured to perform at least one circulating operation to the frequency division signal, and for each circulating operation, generate at least one phase delay signal; a first multiplexer, coupled to the circulating delay circuit and configured to select one signal from the frequency division signal and the at least one phase delay signal according to the phase signal, so as to generate a multiplexed signal; and a retimer, coupled to the first multiplexer and configured to generate an output signal.

Owner:SHENZHEN GOODIX TECH CO LTD

Frequency generator and method for generating frequency

ActiveUS10680620B2Make up for deficienciesPulse automatic controlGenerating/distributing signalsMultiplexingMultiplexer

A frequency generator, includes a control unit, configured to receive an input signal to generate a divisor signal, a phase signal and a circulation signal; a frequency divider, configured to receive the input signal and perform an integer division to the input signal according to the divisor signal, so as to generate a frequency division signal; a circulating delay circuit, coupled to the frequency divider and configured to perform at least one circulating operation to the frequency division signal, and for each circulating operation, generate at least one phase delay signal; a first multiplexer, coupled to the circulating delay circuit and configured to select one signal from the frequency division signal and the at least one phase delay signal according to the phase signal, so as to generate a multiplexed signal; and a retimer, coupled to the first multiplexer and configured to generate an output signal.

Owner:SHENZHEN GOODIX TECH CO LTD

Logical operation circuit and logical operation method

InactiveUS7450412B2Logic circuits characterised by logic functionDigital storageBit lineLogical operations

To provide a logical operation circuit which can perform a logical operation using a ferroelectric capacitor and a logical operation method. A logical operation circuit 1 has a ferroelectric capacitors CF and a transistor MP. The ferroelectric capacitor CF can retain a polarization state P1 (y=1) or P2 (y=0) corresponding to first operation target data y. In an operation process, a first terminal 3 of the ferroelectric capacitor 1 is precharged to a source potential Vdd, and a potential corresponding to second operation target data x, that is, a ground potential GND (x=1) or the source potential Vdd (x=0), is given to a second terminal 5 of the ferroelectric capacitor via a bit line BL. When the threshold voltage Vth of the transistor MP is set properly, the transistor MP becomes on or off (on, on, on, off) depending on the combination of x and y (0-0, 0-1, 1-0, 1-1).

Owner:ROHM CO LTD

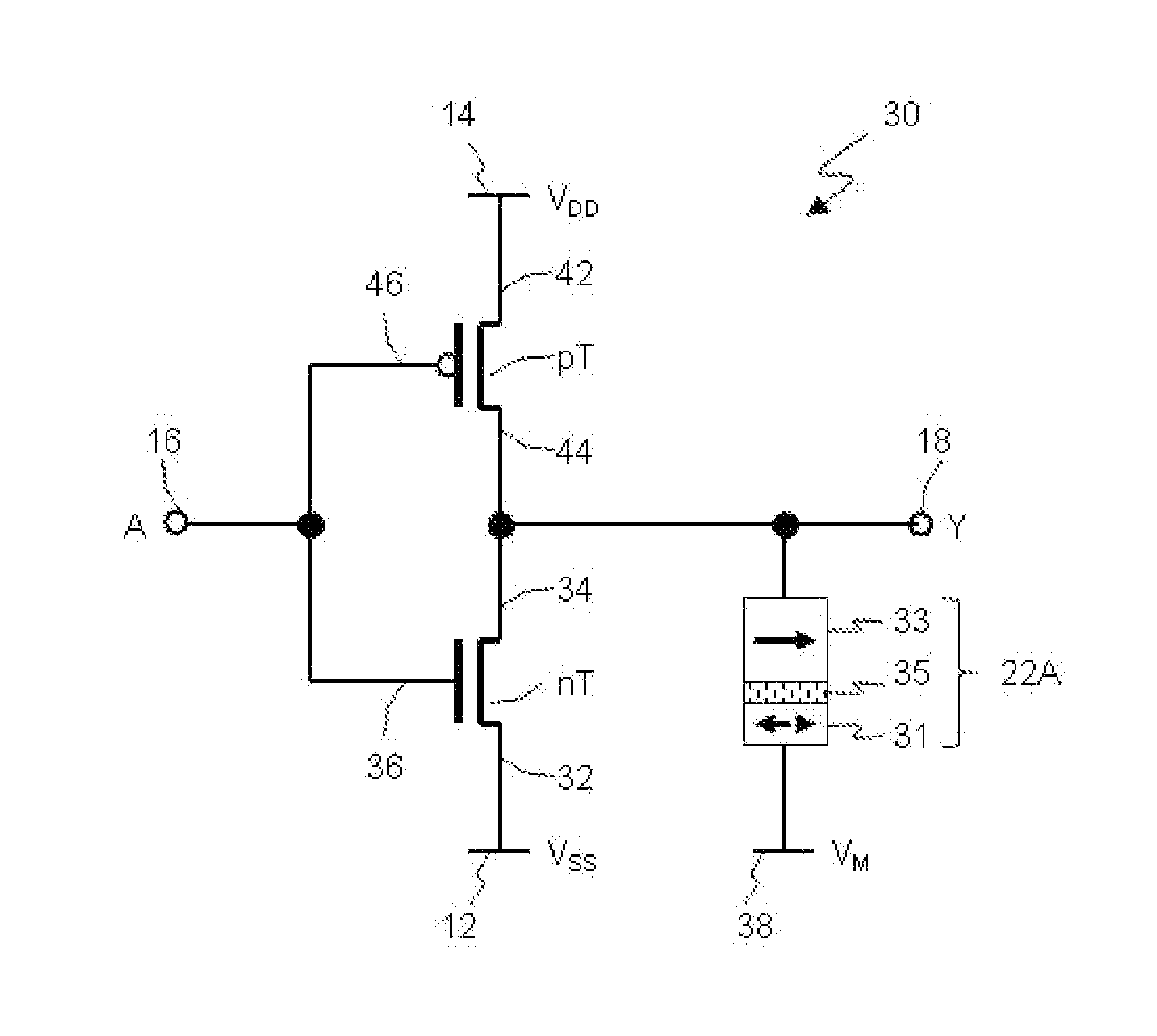

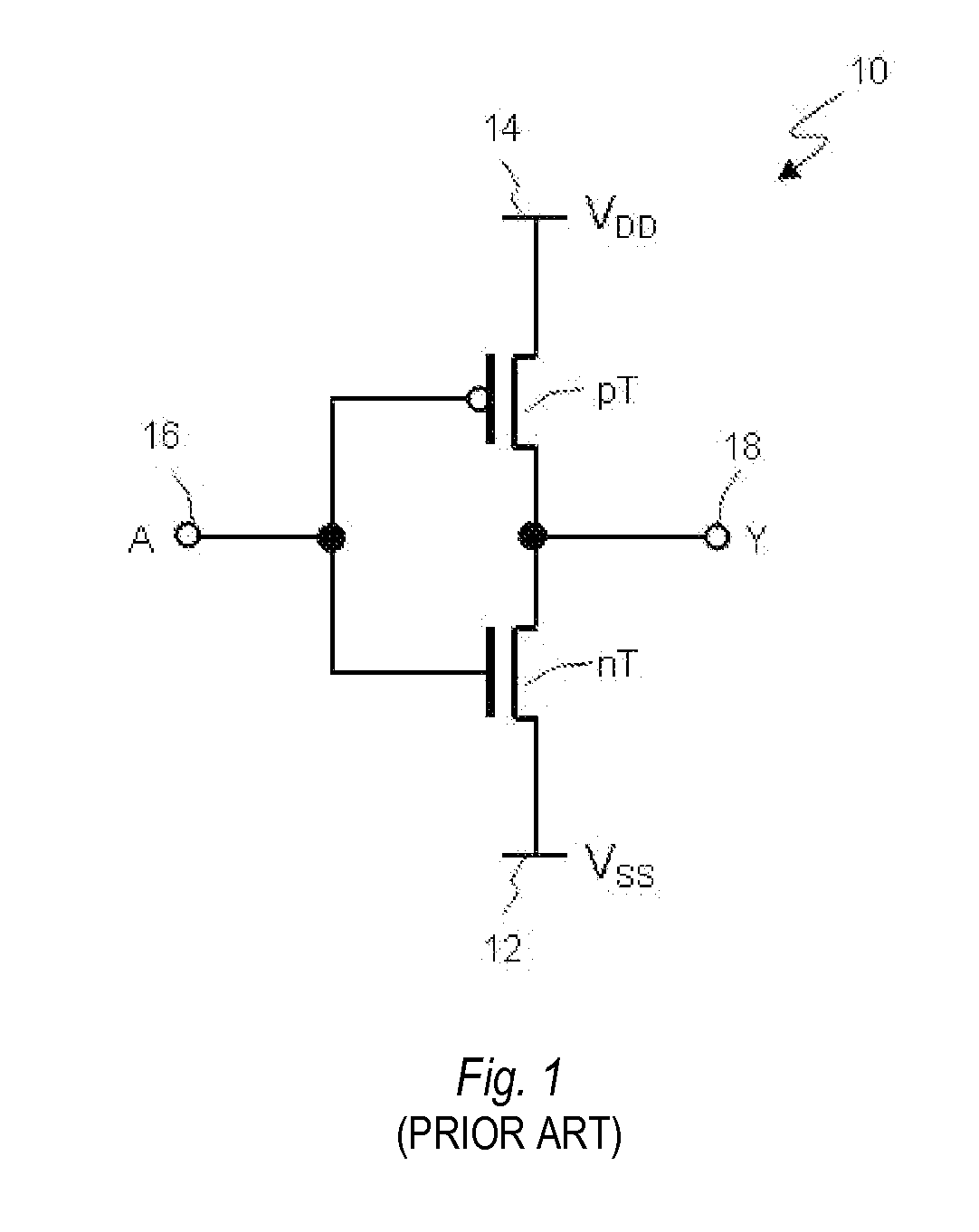

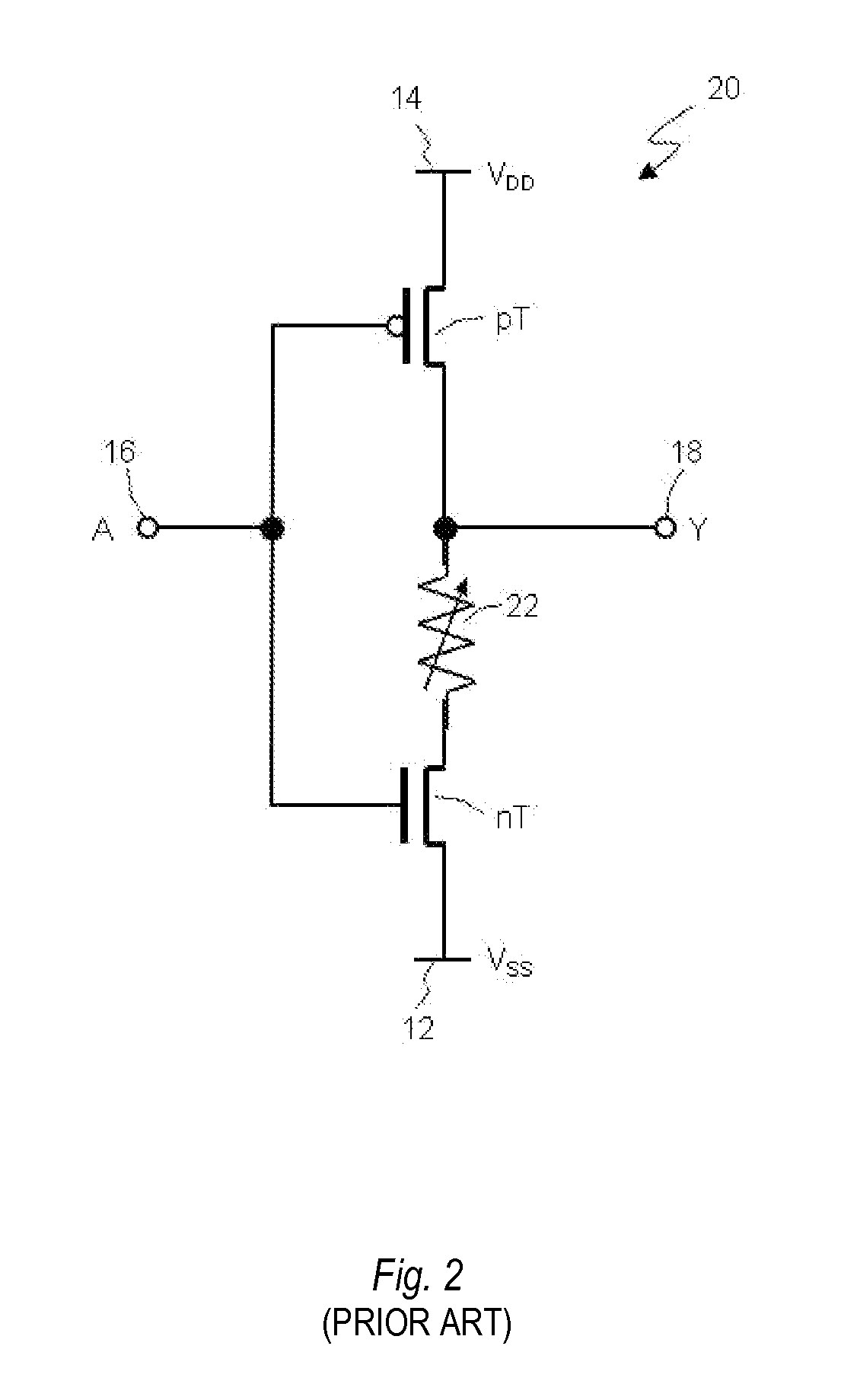

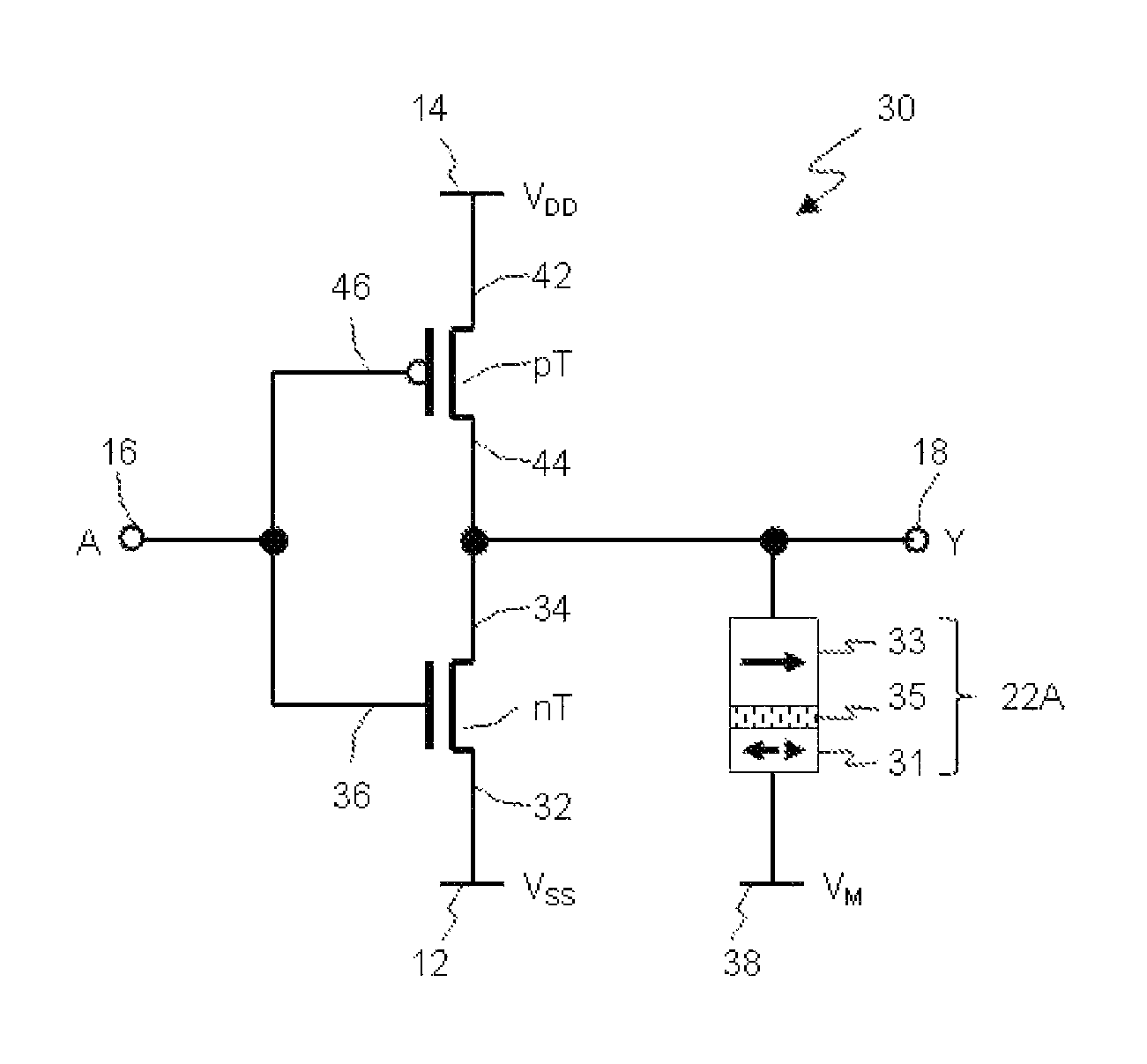

Magnetic field controlled reconfigurable semiconductor logic device and method for controlling the same

ActiveUS9331266B2Programmable logic circuit arrangementsMagnetic-field-controlled resistorsElectrical conductorLogical operations

A non-volatile reconfigurable logic device executing logical operations and a memory function and controlled by a magnetic field is provided. The reconfigurable logic device includes i) at least one semiconductor device; and ii) a pair of magnetic field controlled devices respectively spaced apart from both sides of the semiconductor device and that are adapted to generate magnetic field leakage to control the semiconductor device. The semiconductor device includes i) a first semiconductor layer; and ii) a second semiconductor layer located on the first semiconductor layer. One of the first semiconductor layer and the second semiconductor layer is a p-type semiconductor layer and the other is an n-type semiconductor layer.

Owner:UNITED STATES OF AMERICA +1

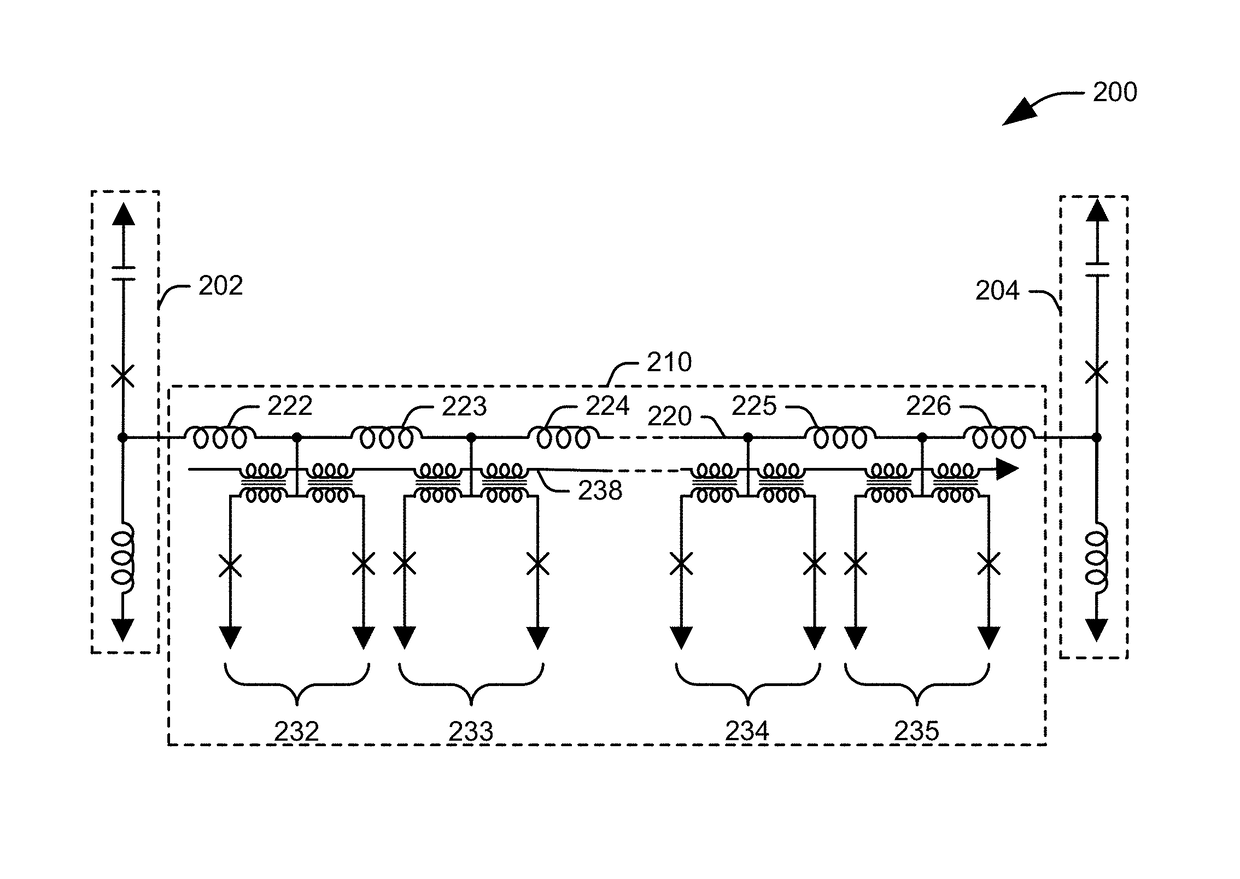

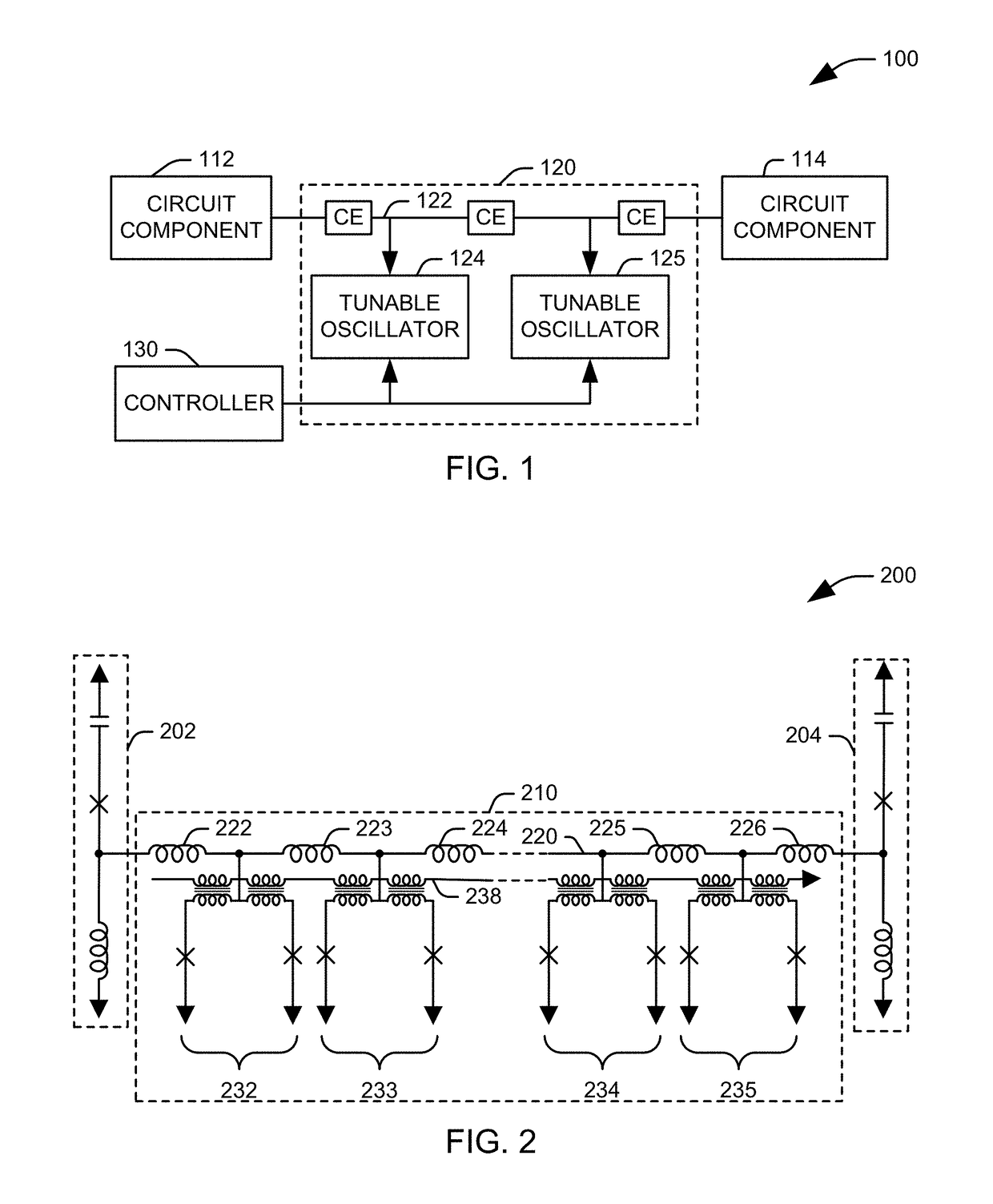

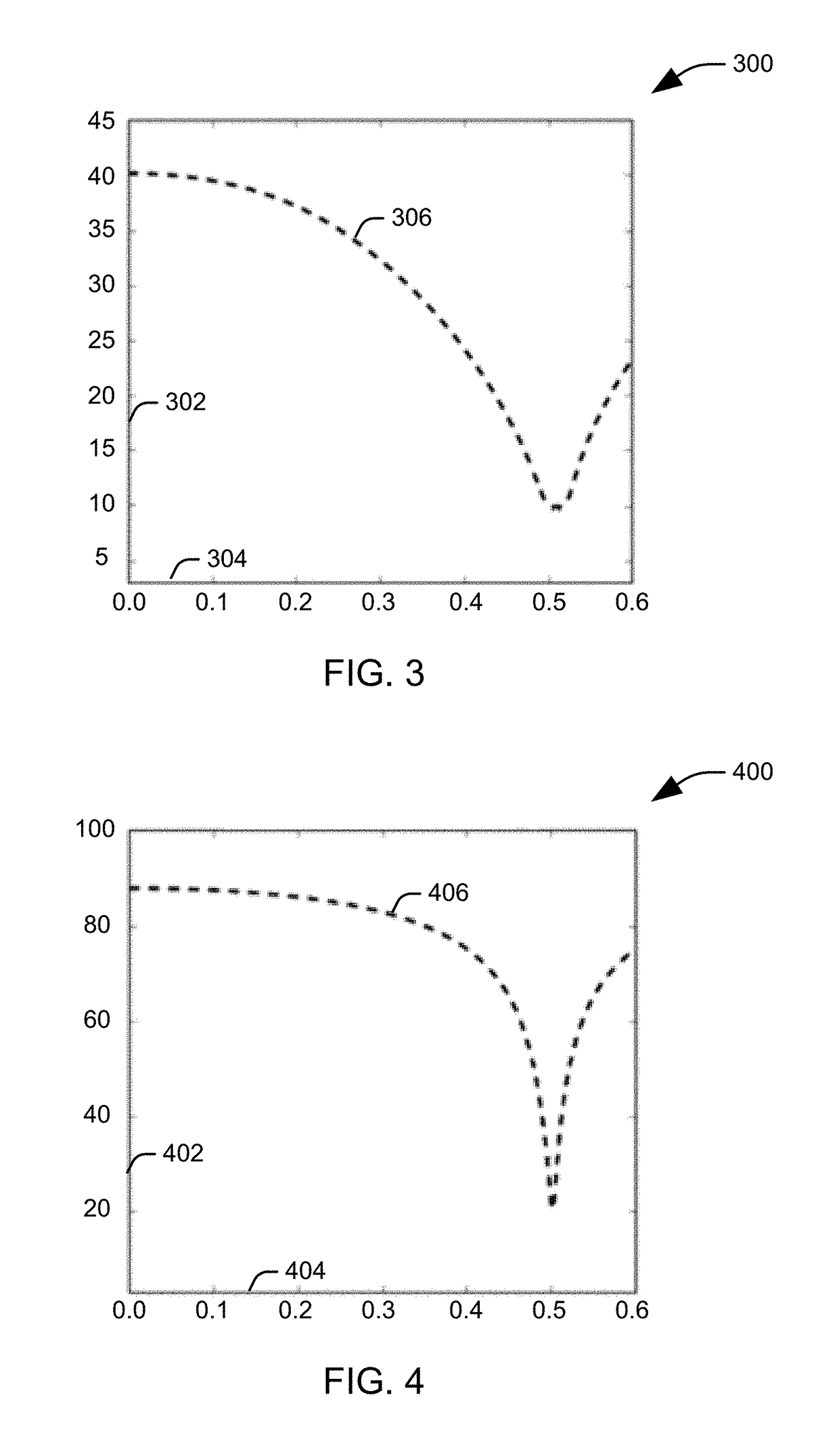

Robust tunable coupling between superconductive circuits

ActiveUS10097186B1Tune frequencyQuantum computersPulse generation by super conductive devicesResonanceCoupling

Systems and methods are provided for linking two components in a superconducting circuit. A plurality of circuit elements, each comprising one of an inductor, a capacitor, and a Josephson junction, are connected in series on a path connecting the two components. A plurality of tunable oscillators are connected from the path connecting the two components. Each tunable oscillator is responsive to a control signal to tune an associated resonance frequency of the tunable oscillator within a first frequency range, within which the two components are coupled, and within a second frequency range, within which the two components are isolated.

Owner:NORTHROP GRUMMAN SYST CORP

Circuits and methods for impedance calibration

ActiveUS9680469B1Input/output impedence modificationImpedence matching networksDriver circuitElectrical resistance and conductance

A driver circuit drives data to an output based on an input data signal in a transmission mode. The driver circuit includes transistors. A comparator generates a comparison output in a calibration mode based on a reference signal and a signal at the output of the driver circuit. A calibration control circuit adjusts an equivalent resistance of the transistors in the driver circuit based on the comparison output in the calibration mode. The equivalent resistance of the transistors in the driver circuit can be adjusted to support the transmission of data according to multiple different data transmission protocols using transmission links having different characteristic impedances. The equivalent resistance of the transistors in the driver circuit can also be adjusted to compensate for resistance in the package routing conductors and / or to compensate for parasitic resistance.

Owner:TAHOE RES LTD

Spin wave device and logic circuit using spin wave device

InactiveUS9602103B2Increase speedTransistorPower reduction by control/clock signalSpin waveNon magnetic

As a technique for attaining a reduction in power consumption, there is a technique for reducing power consumption using a spin wave. No specific proposal concerning spin wave generation, spin wave detection, and a latch technique for information has been made.A device applies an electric field to a first electrode of a nonmagnetic material using a thin line-shaped stacked body including a first ferromagnetic layer and a nonmagnetic layer to thereby generate a spin wave in the first ferromagnetic layer, and detects a phase or amplitude of the spin wave propagated in the first ferromagnetic layer using a second electrode of a ferromagnetic material with a magnetoresistance effect.

Owner:HITACHI LTD

Magnetic logic element with toroidal multiple magnetic films and a method of logic treatment using the same

ActiveUS8236576B2Facilitate conductionSmall resistivityNanomagnetismMagnetic-field-controlled resistorsMagnetic logicMulti-level cell

A magnetic logic element with toroidal magnetic multilayers (5,6,8,9). The magnetic logic element comprises a toroidal closed section which is fabricated by etching a unit of magnetic multilayers (5,6,8,9) deposited on a substrate. Optionally, the magnetic logic element may also comprise a metal core (10) in the closed toroidal section. Said magnetic multilayers (5,6,8,9) unit is arranged on the input signal lines A, B, C and an output signal line O, and then is made into a closed toroidal. Subsequently, on the toroidal magnetic multilayered unit (5,6,8,9), the input signal lines A′, B′, C′ and an output signal line O′ are fabricated by etching. This magnetic logic element can reduce the demagnetization field and the shape anisotropy effectively, leading to the decrease of the reversal field of magnetic free layer. Furthermore, this magnetic logic element has stable working performance and long operation life of the device.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

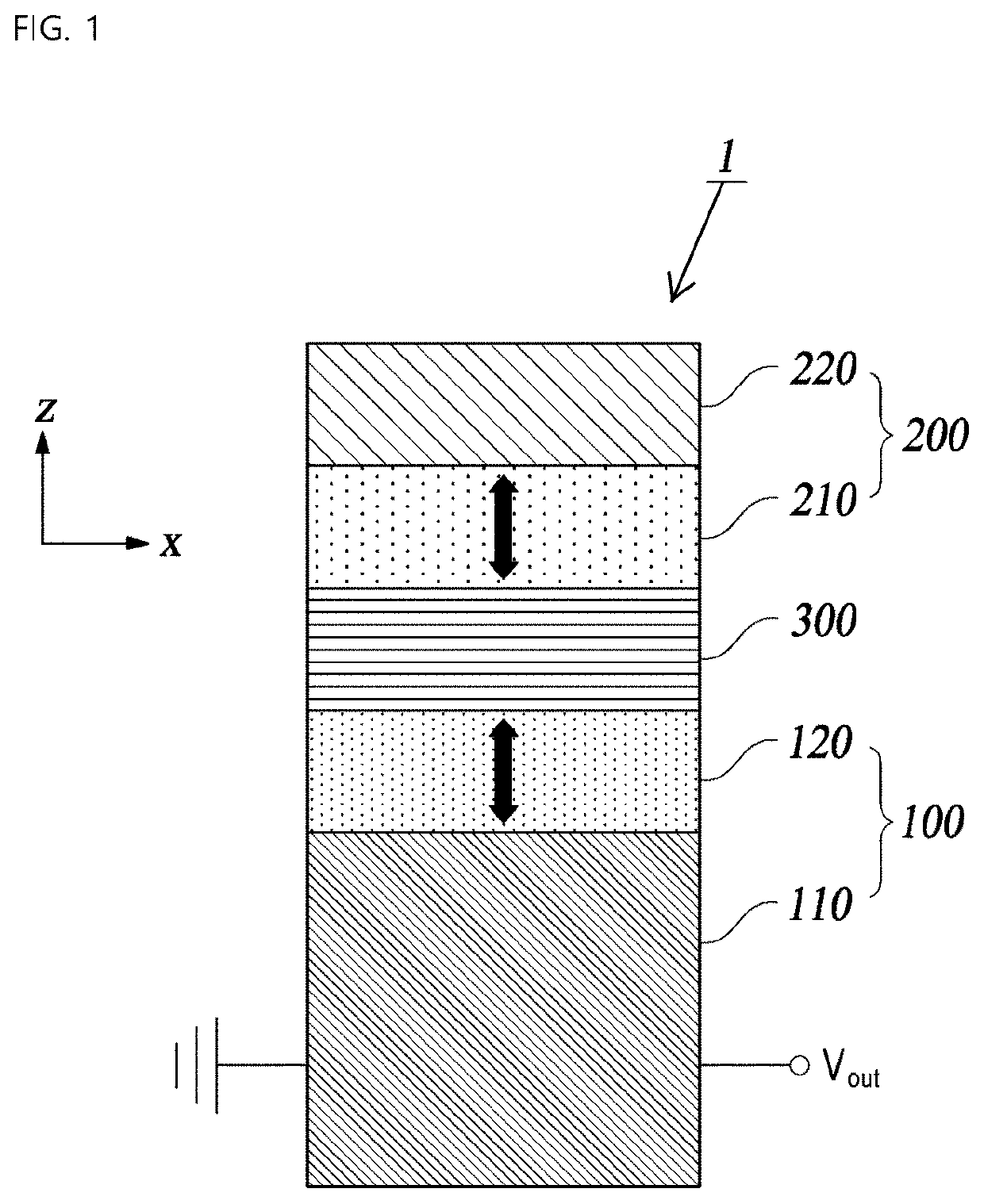

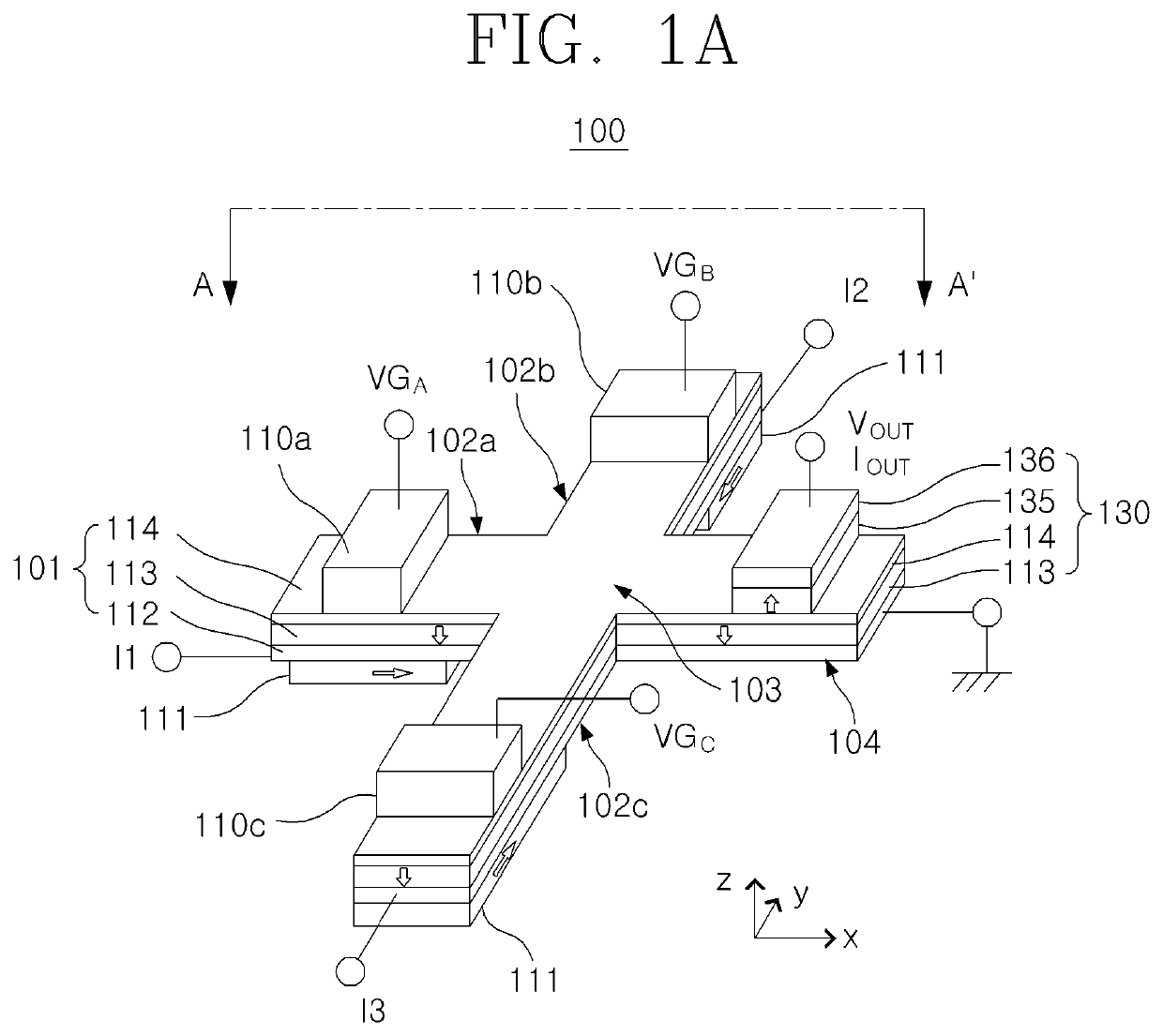

Logic device using spin torque

ActiveUS20210126639A1Overcome limitationsLogic circuits characterised by logic functionDigital storageSoftware engineeringMechanical engineering

A logic function device according to an embodiment of the present invention includes one or more function reconfiguring units having magnetization in one direction set by spin torque caused due to an function reconfiguring current, and an output terminal formed at an end thereof; and one or more input units formed on the function reconfiguring unit and having magnetization in the one direction set by spin torque caused due to an input current, wherein an output voltage of the output terminal is determined on the basis of whether a magnetization direction of the function reconfiguring unit and a magnetization direction of the input unit are parallel or anti-parallel.

Owner:KOREA INST OF SCI & TECH

Magnet logic element and magnet logic element array

InactiveCN100351946CWith arithmetic processing functionGalvano-magnetic devicesNanomagnetismMagnetic logicEngineering

Owner:KK TOSHIBA

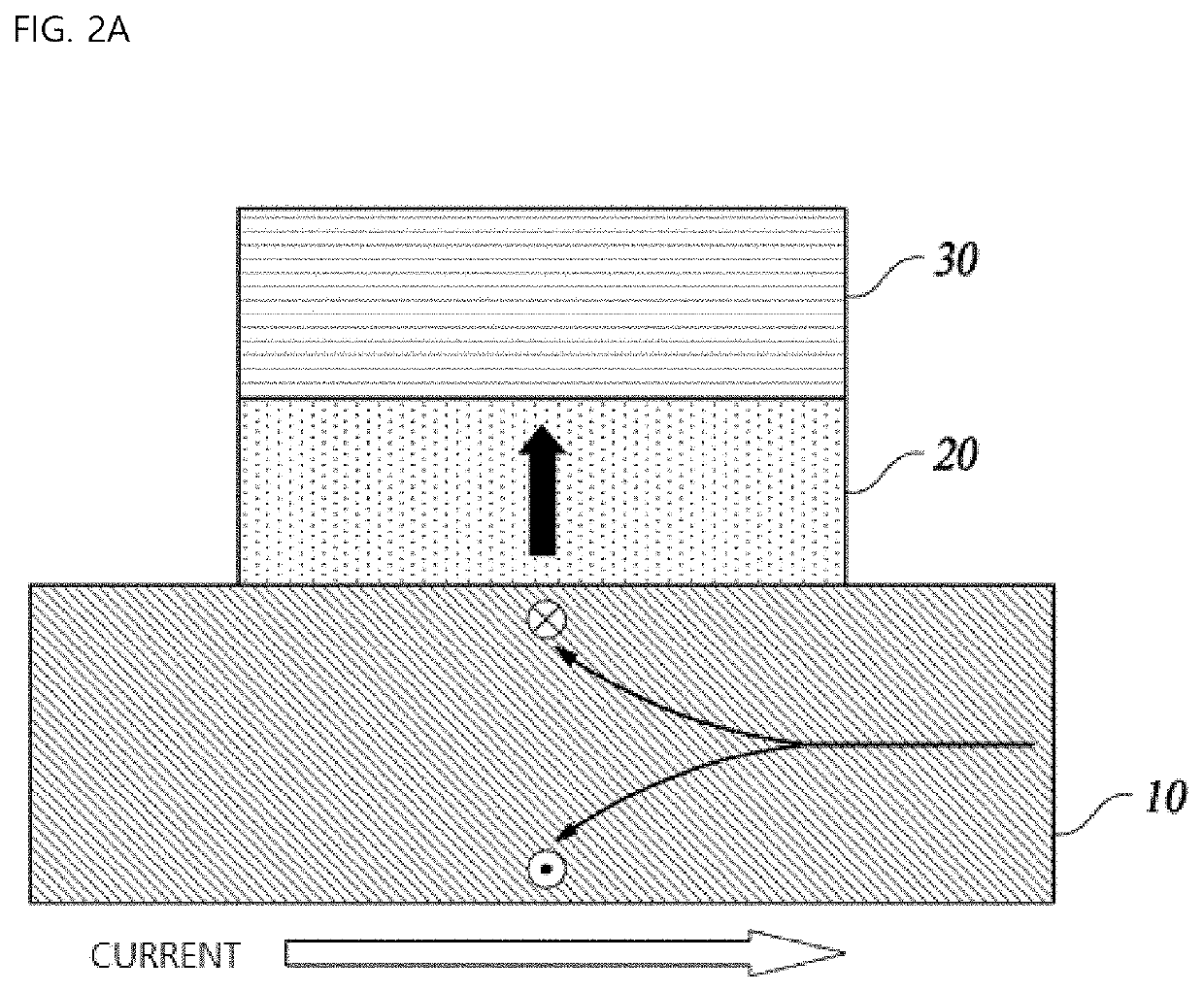

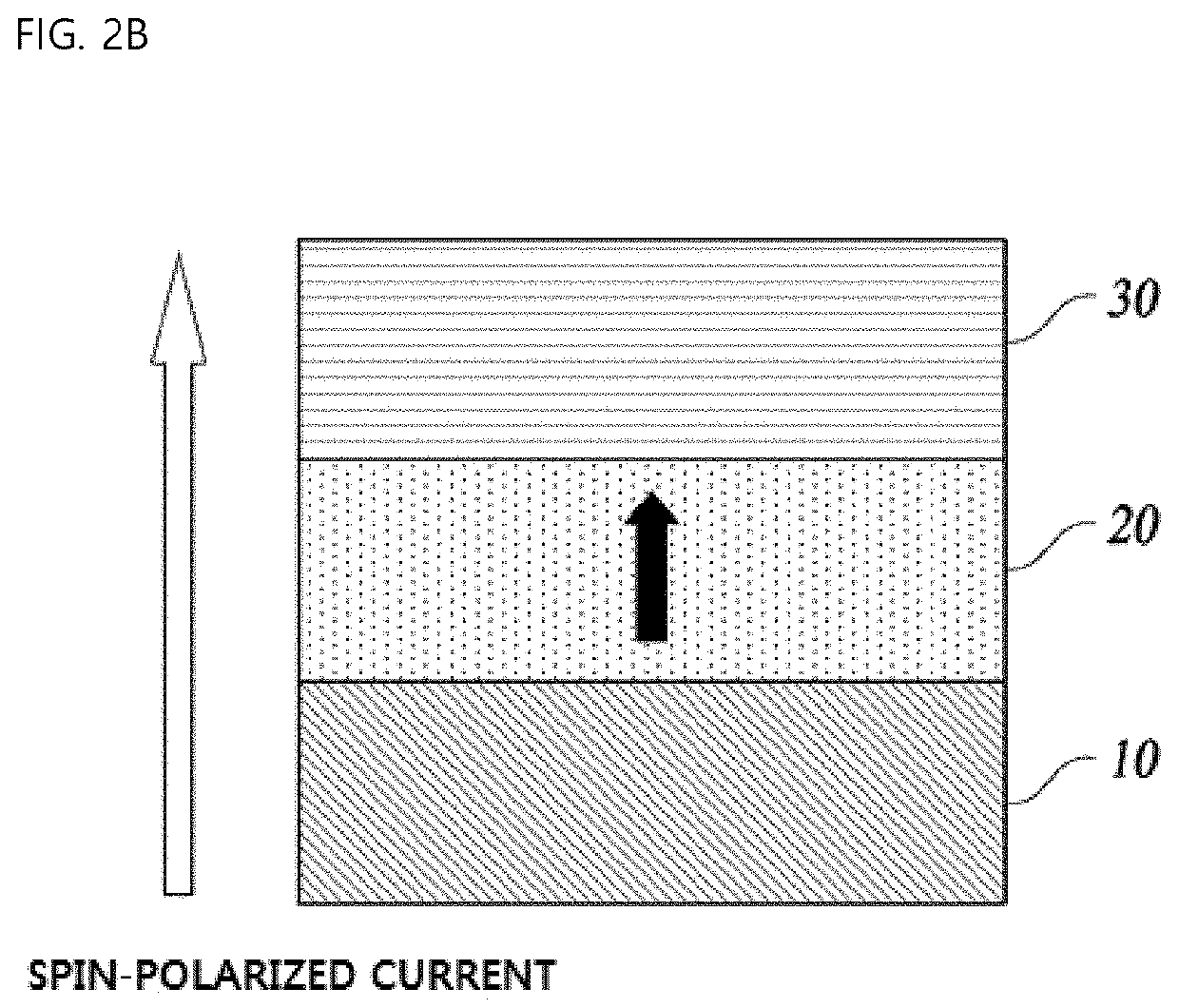

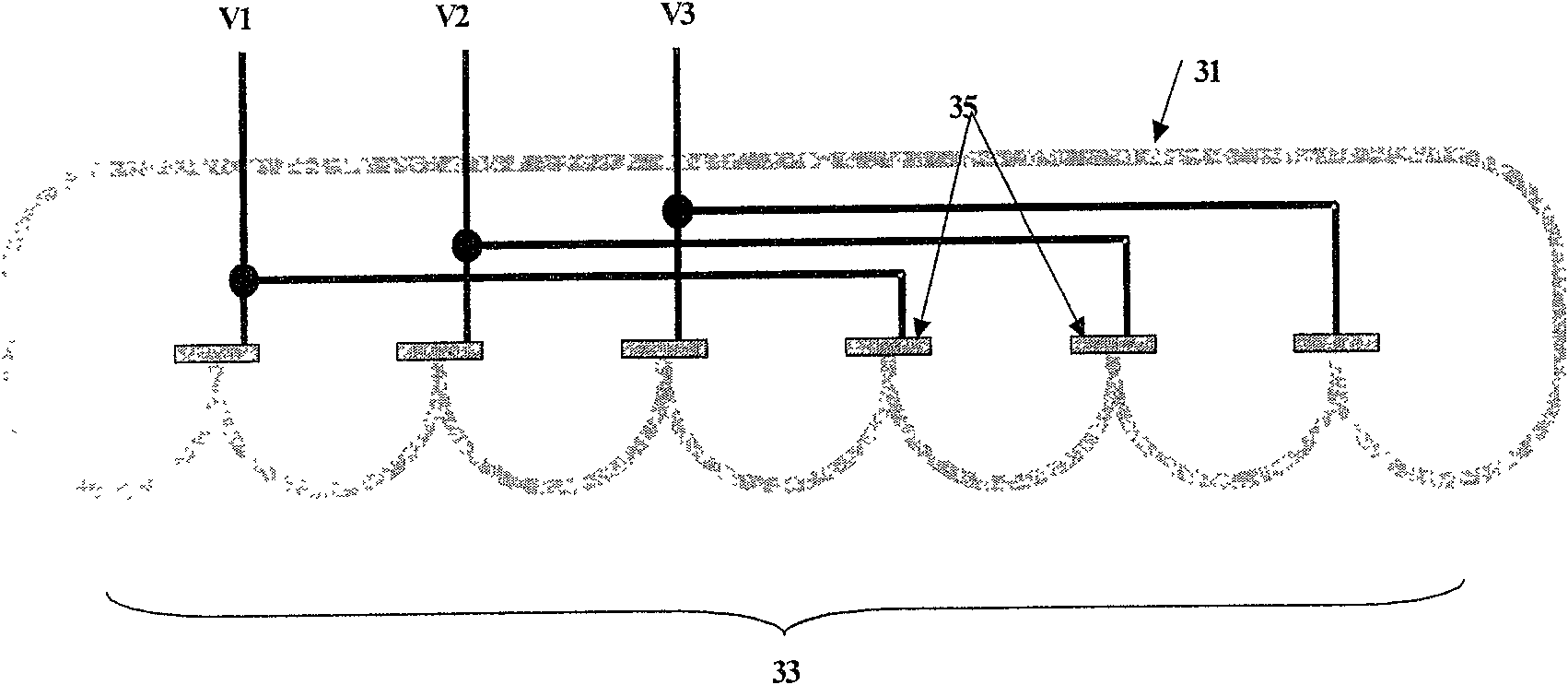

Method and system for providing spin transfer based logic devices

A method and system for providing a logic device are described. The logic device includes a plurality of magnetic input / channel regions, at least one magnetic sensor region, and at least one sensor coupled with the at least one magnetic sensor region. Each of the magnetic input / channel regions is magnetically biased in a first direction. The magnetic sensor region(s) are magnetically biased in a second direction different from the first direction such that at least one domain wall resides in the magnetic input / channel regions if the logic device is in a quiescent state. The sensor(s) output a signal based on a magnetic state of the magnetic sensor region(s). The input / channel regions and the magnetic sensor region(s) are configured such that the domain wall(s) may move into the magnetic sensor region(s) in response to a logic signal being provided to at least a portion of the magnetic input regions.

Owner:SAMSUNG SEMICON

Signal transfer device

ActiveUS9088444B2Quick fixBaseband system detailsLogic circuits using saturable magnetic devicesElectrical and Electronics engineeringLogic level

Owner:ROHM CO LTD

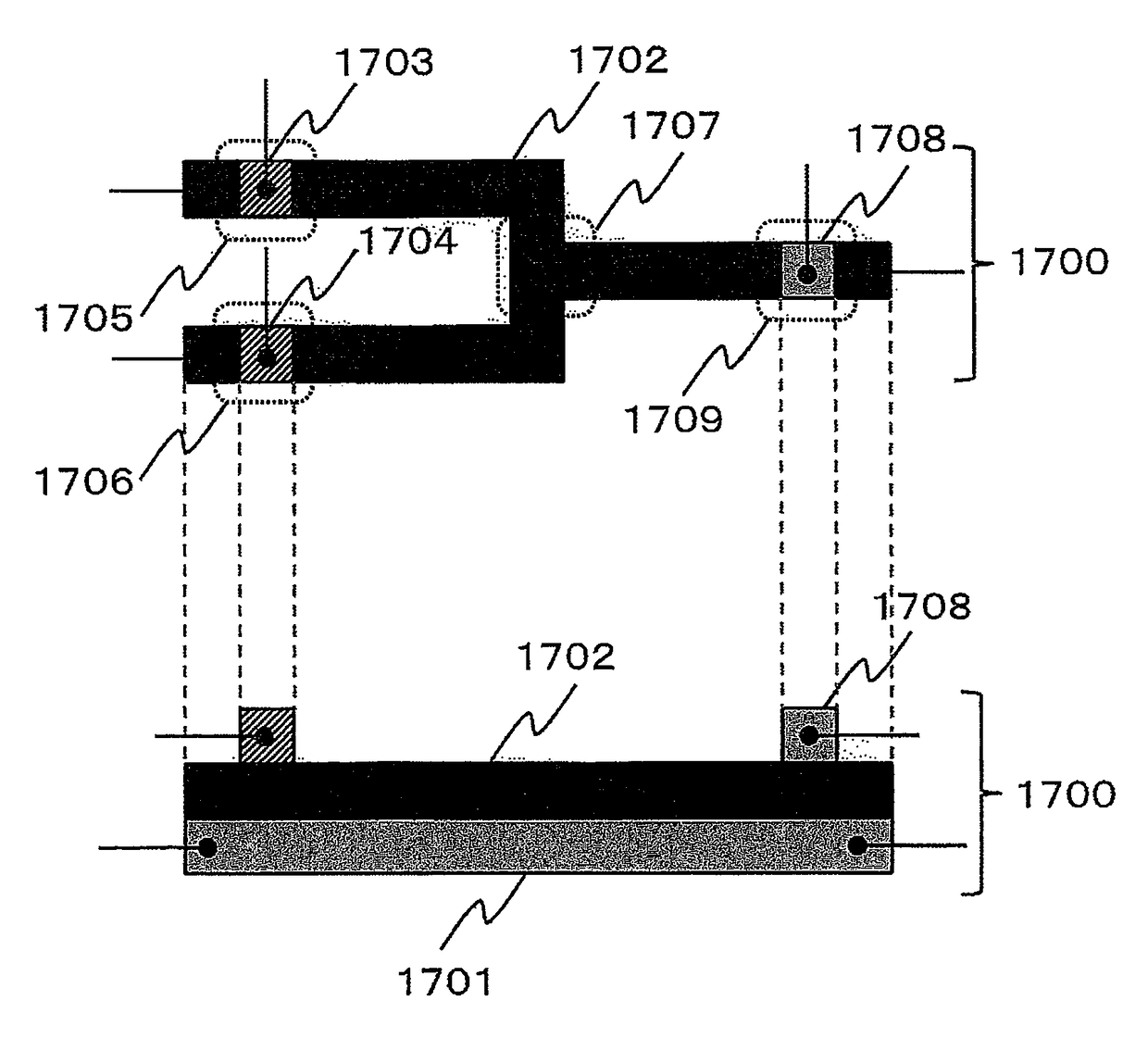

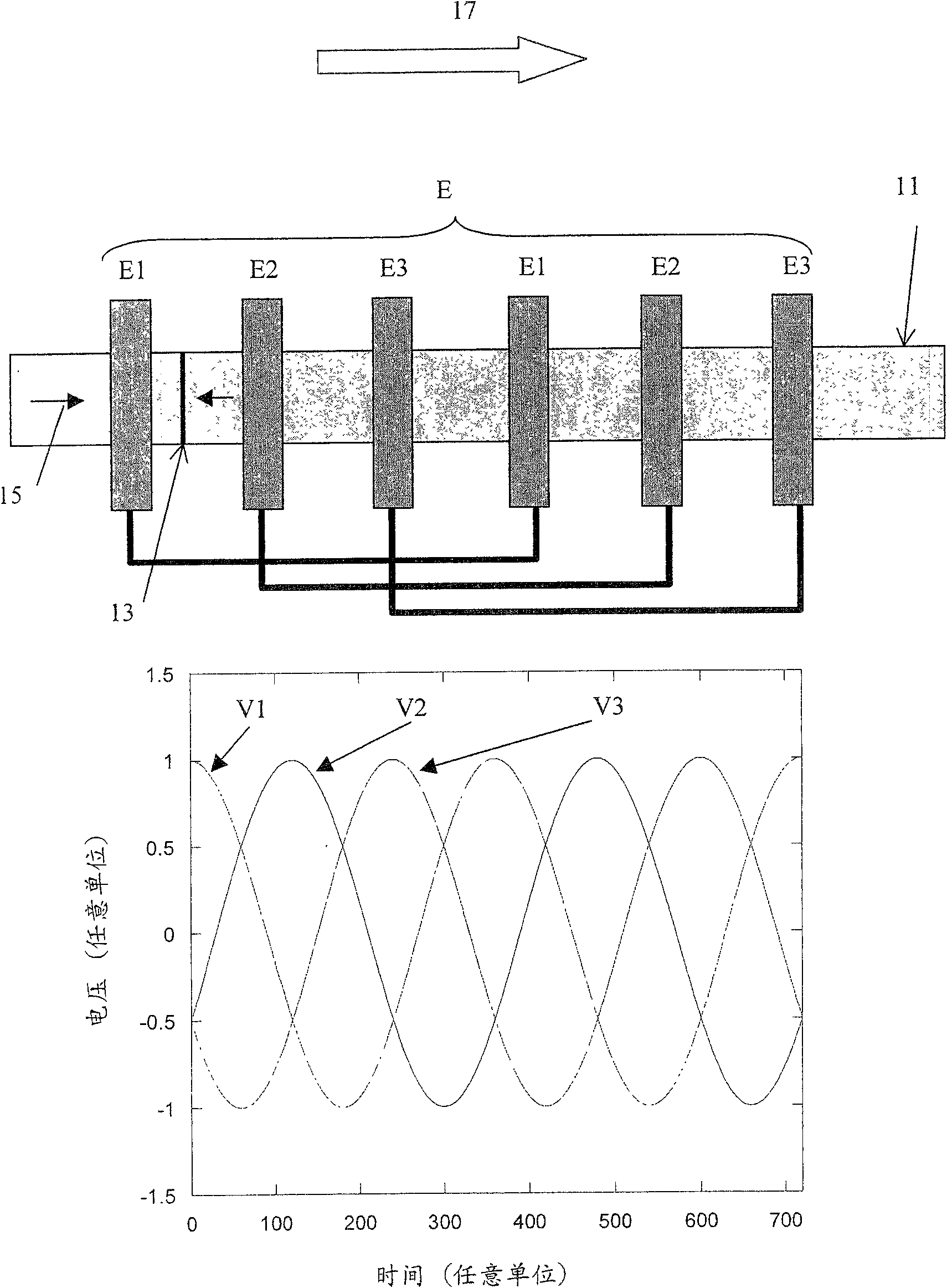

Drive system and method for moving domain wall of ferromagnetic conduit

InactiveCN100585741CDigital storageLogic circuits using saturable magnetic devicesElectricityElectrical connection

A driving system and method to effect propagation of a magnetic domain wall through a ferromagnetic conduit are described, wherein oscillating electrical current is passed through the conduit from an oscillating current supply source via at least two electrical contacts adapted to make electrical connection with at least two spaced points on the conduit. A ferromagnetic conduit is described comprising an elongate ferromagnetic element formed as a continuous track of magnetic material capable of sustaining and propagating a domain wall, and such a driving system in serial array, preferably being further adapted to serve as a magnetic logic element by the provision of nodes and / or directional changes as a result of which logical functions may be processed.

Owner:INGENIA TECH LTD (GB)

Magnetic logic device

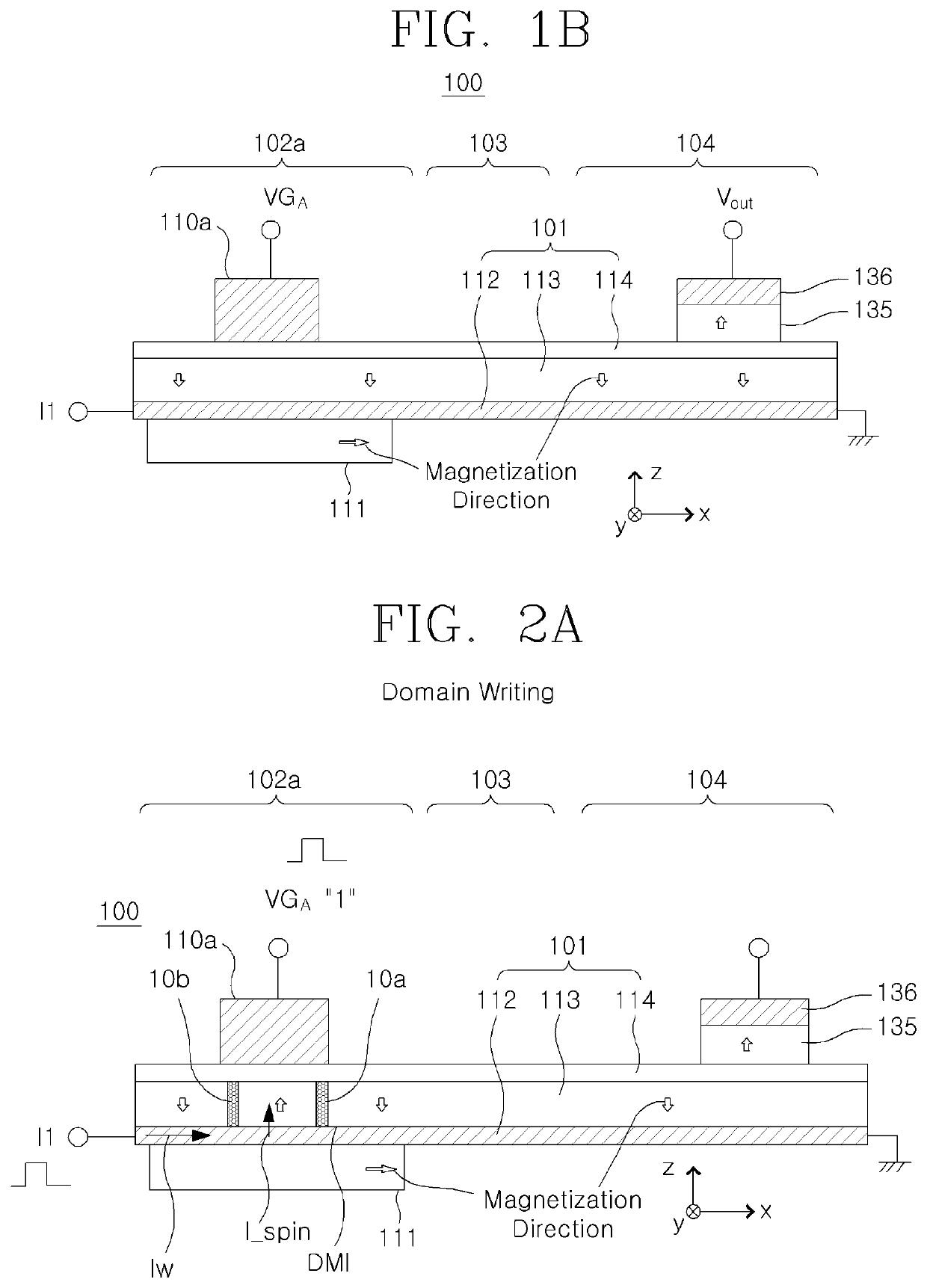

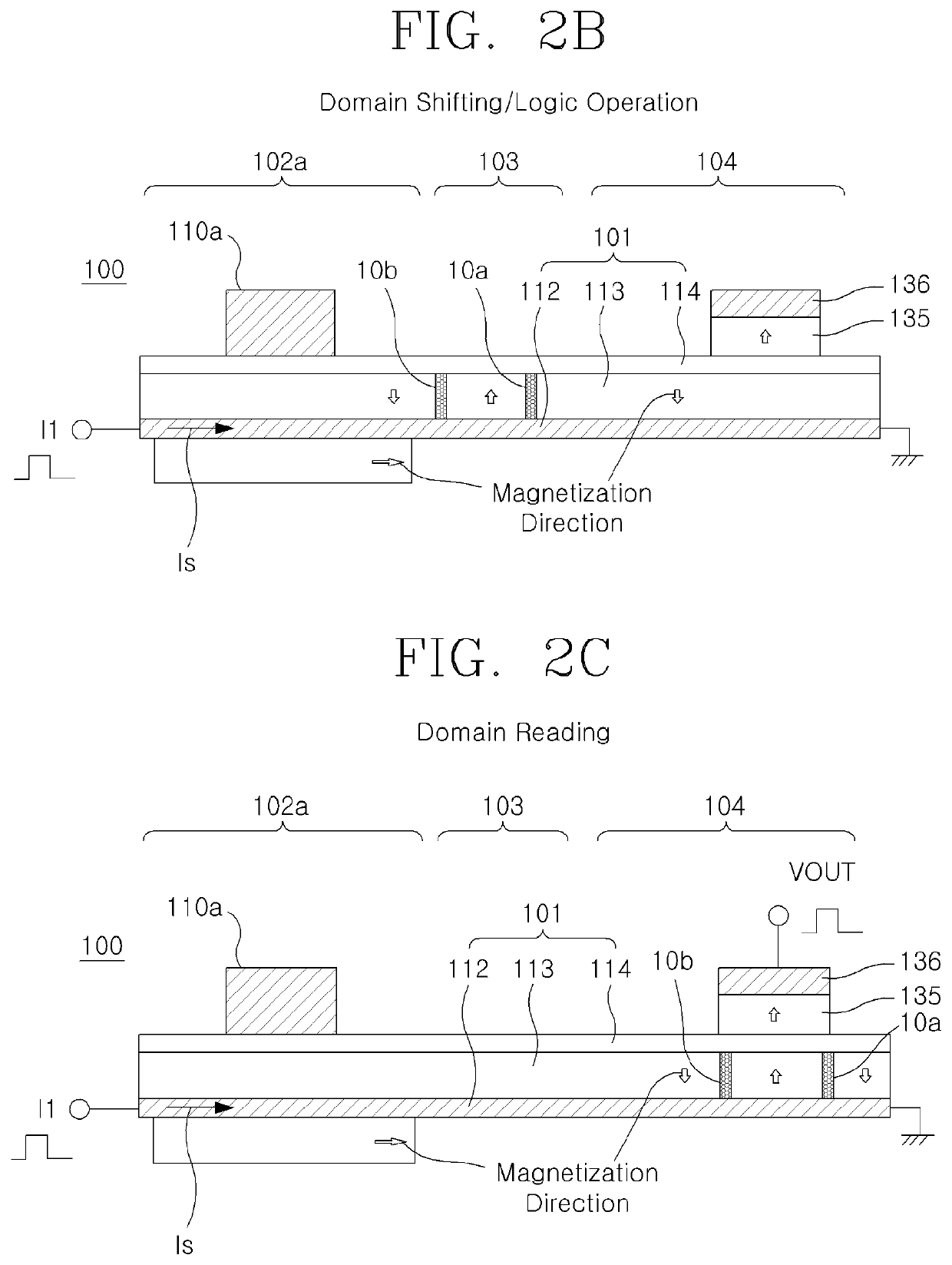

ActiveUS11362661B2Low write in-plane currentEasy to operateLogic circuits characterised by logic functionSubstrate/intermediate layersNanowireSoftware engineering

Disclosed is a magnetic logic device including: a plurality of input branches configured by a magnetic nanowire including a non-magnetic metallic layer, a free layer, and an insulating layer sequentially stacked; an output branch configured by the magnetic nanowire; a coupling portion configured by the magnetic nanowire and where the input branches and the output branch meet; gate electrodes arranged adjacent to the insulating layer in each of the plurality of input branches; and in-plane anisotropic ferromagnetic layers arranged adjacent to the non-magnetic metallic layer in each of the plurality of input branches.

Owner:KOREA ADVANCED INST OF SCI & TECH