Patents

Literature

34 results about "Test graph" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Graphing Test. In mathematics, a graph is an abstract representation of the set of objects where some pairs of the objects are connected by links. The interconnected objects are the represented by mathematical abstractions called vertices, and the links that connect some pairs of vertices are called edges.

Method for optimizing exposure auxiliary graph

ActiveCN104090468AOptimize adding rulesReduce computationOriginals for photomechanical treatmentGraphicsTest graph

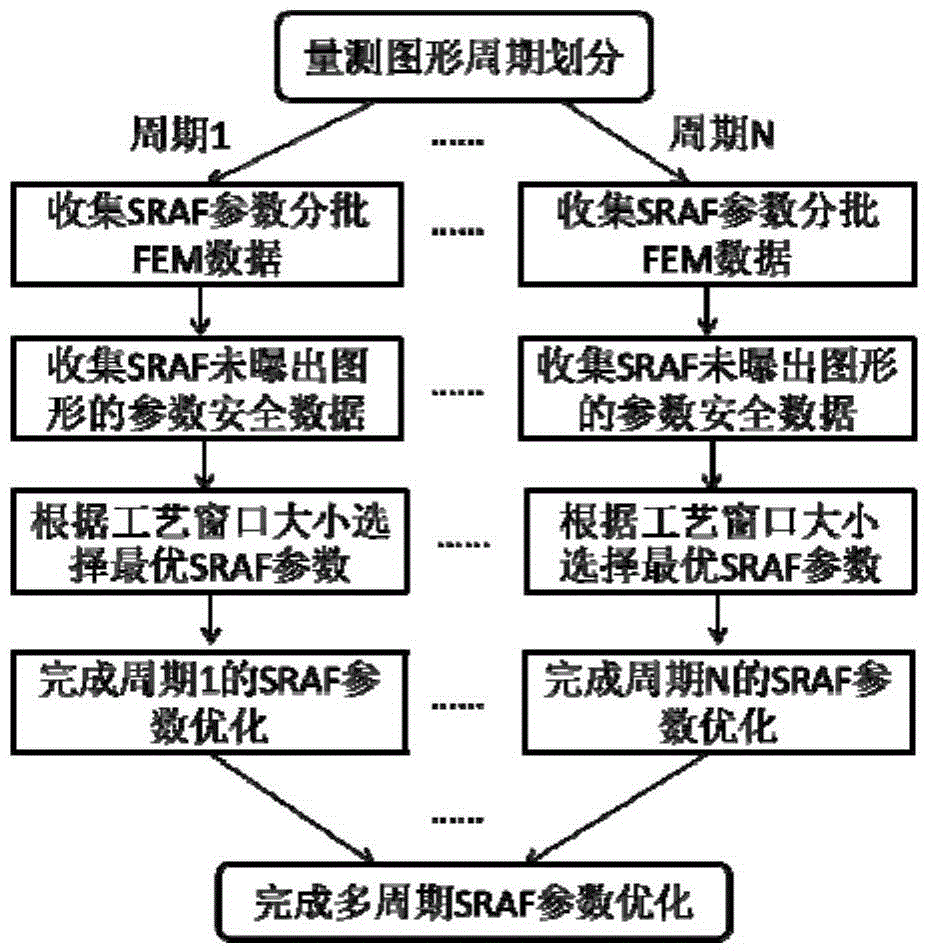

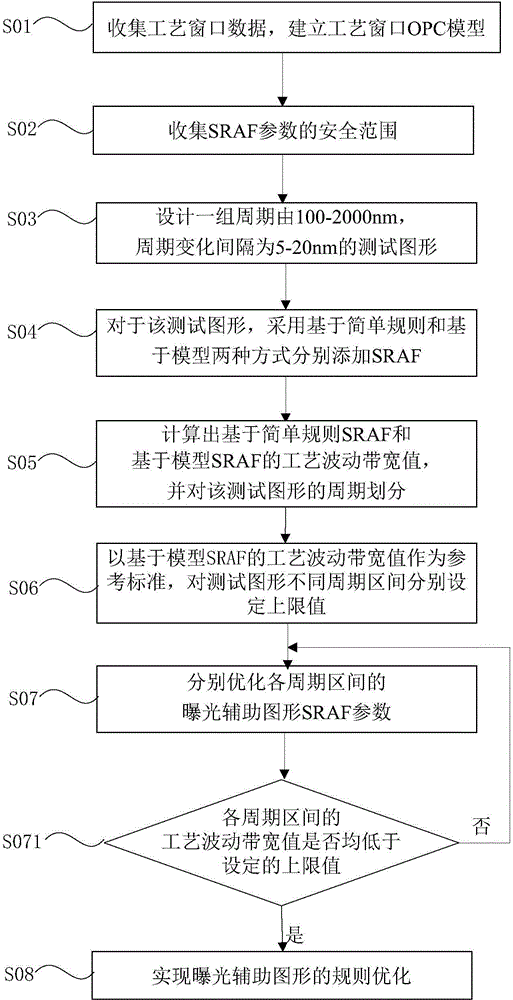

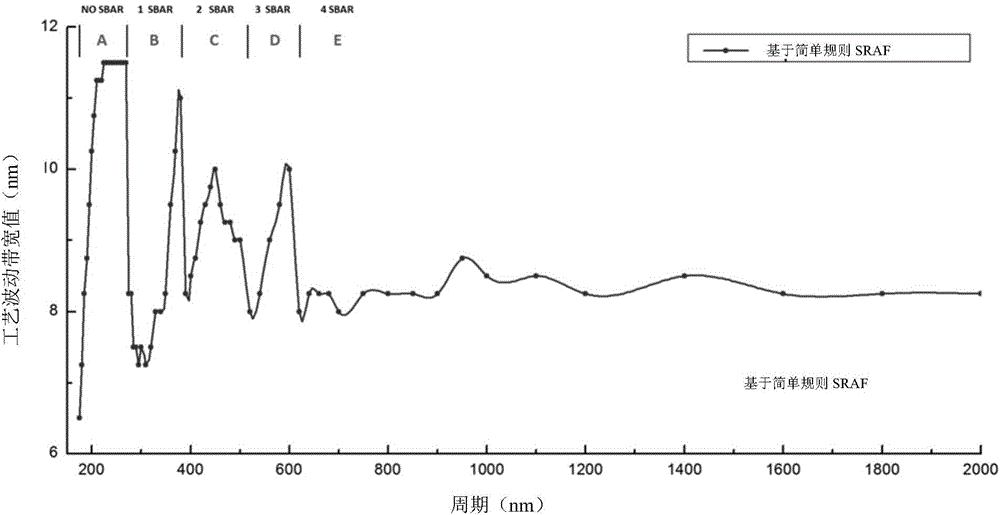

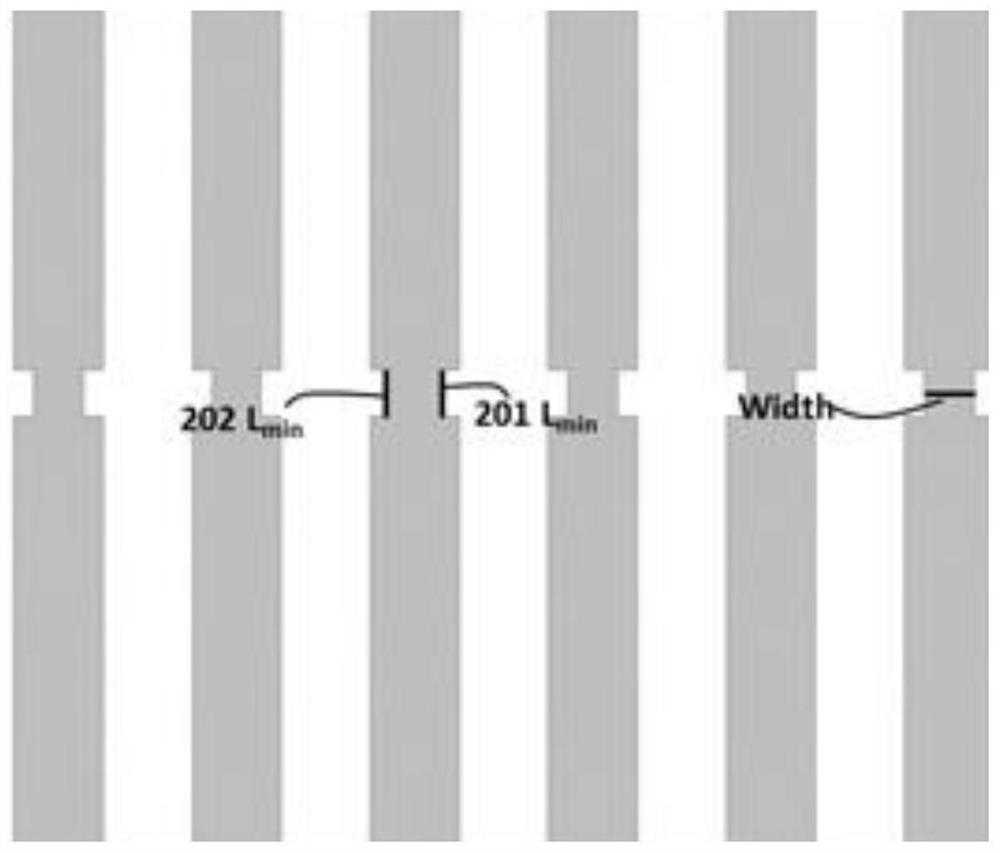

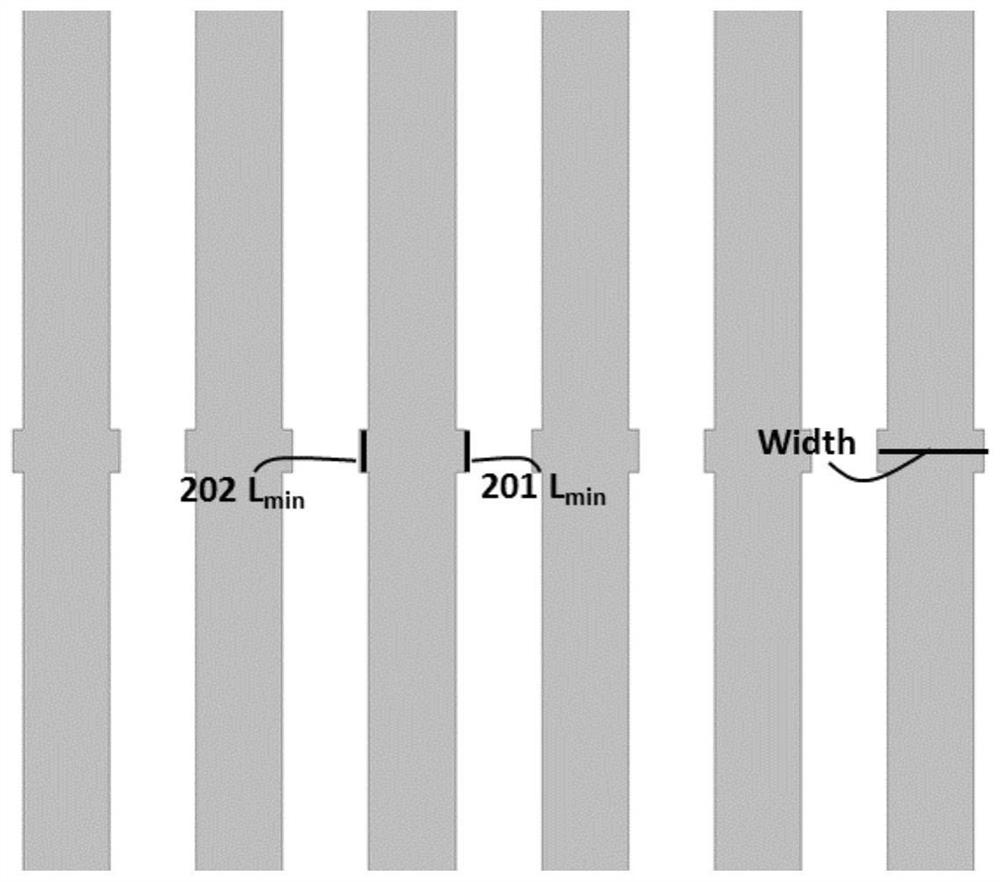

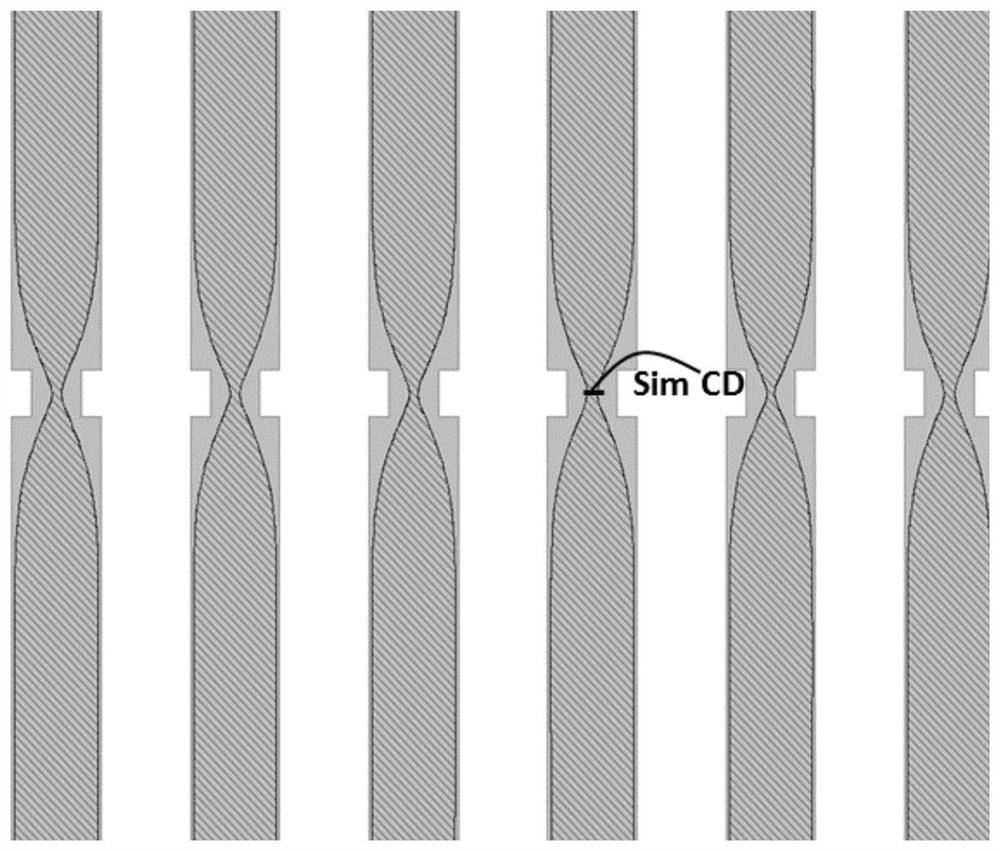

The invention discloses a method for optimizing an exposure auxiliary graph. The method comprises the following steps: collecting process window data and establishing an OPC (Optical Proximity Correction) model of a process window; collecting a safe range of SRAF (Sub Resolution Assist Feature) parameters; designing a periodic gradient test graph; adding SRAF based on simple rules and the model; obtaining a process fluctuation bandwidth value and dividing the test graph into periods; setting process fluctuation bandwidth upper limit values for period zones of the test graph; respectively optimizing the SRAF parameters of the exposure auxiliary graph of the period zones; and optimizing the rules of the exposure auxiliary graph. The method for optimizing the exposure auxiliary graph is capable of efficiently and quickly optimizing the addition rules of the exposure auxiliary graph and reducing the operation quantity; compared with that by adopting a method based on the model, the operation time can be reduced by about 60%.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Method for measuring quality of dynamic image of liquid crystal display

InactiveCN102682684AHigh precisionMeet measurement needsStatic indicating devicesTest graphData acquisition

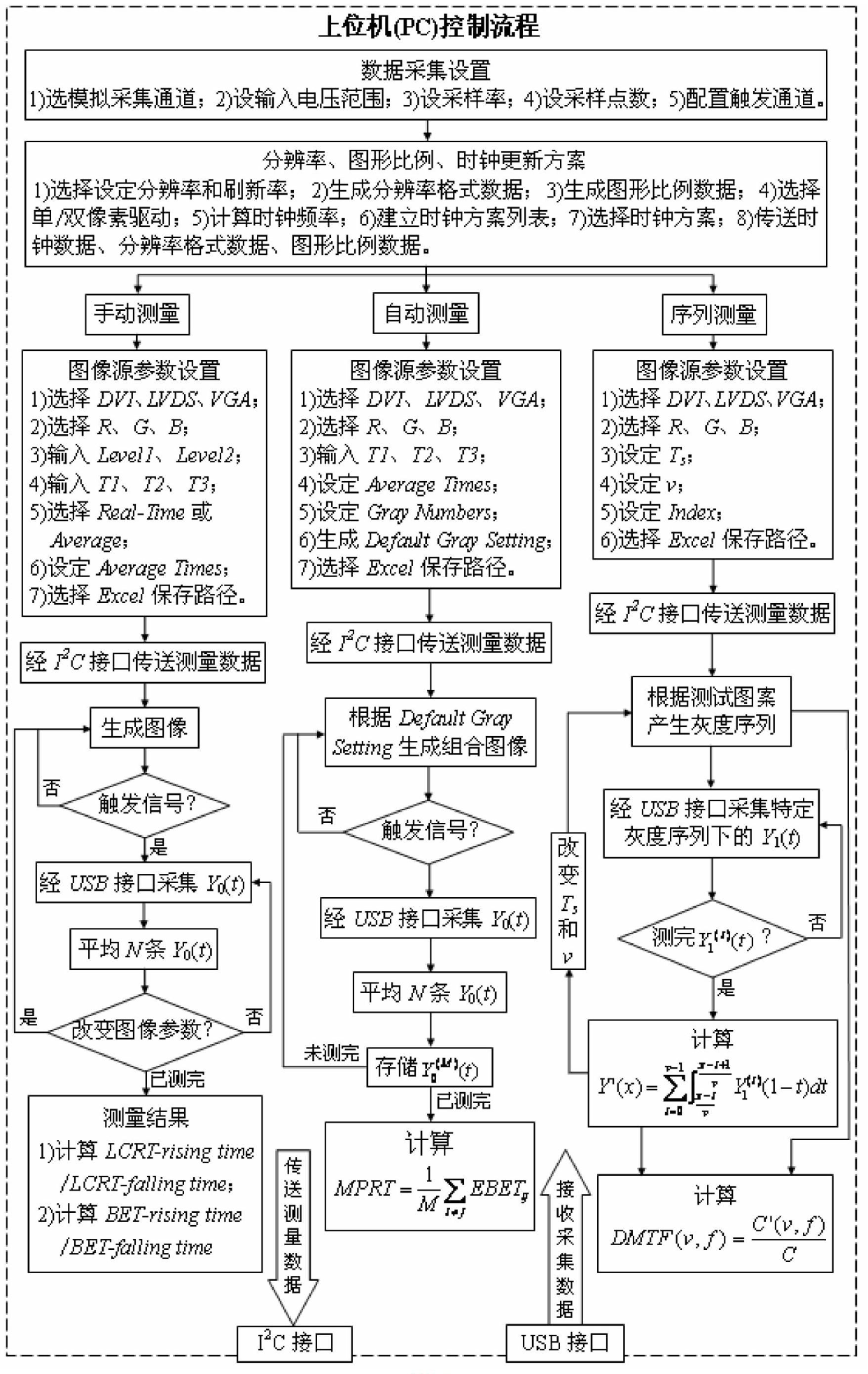

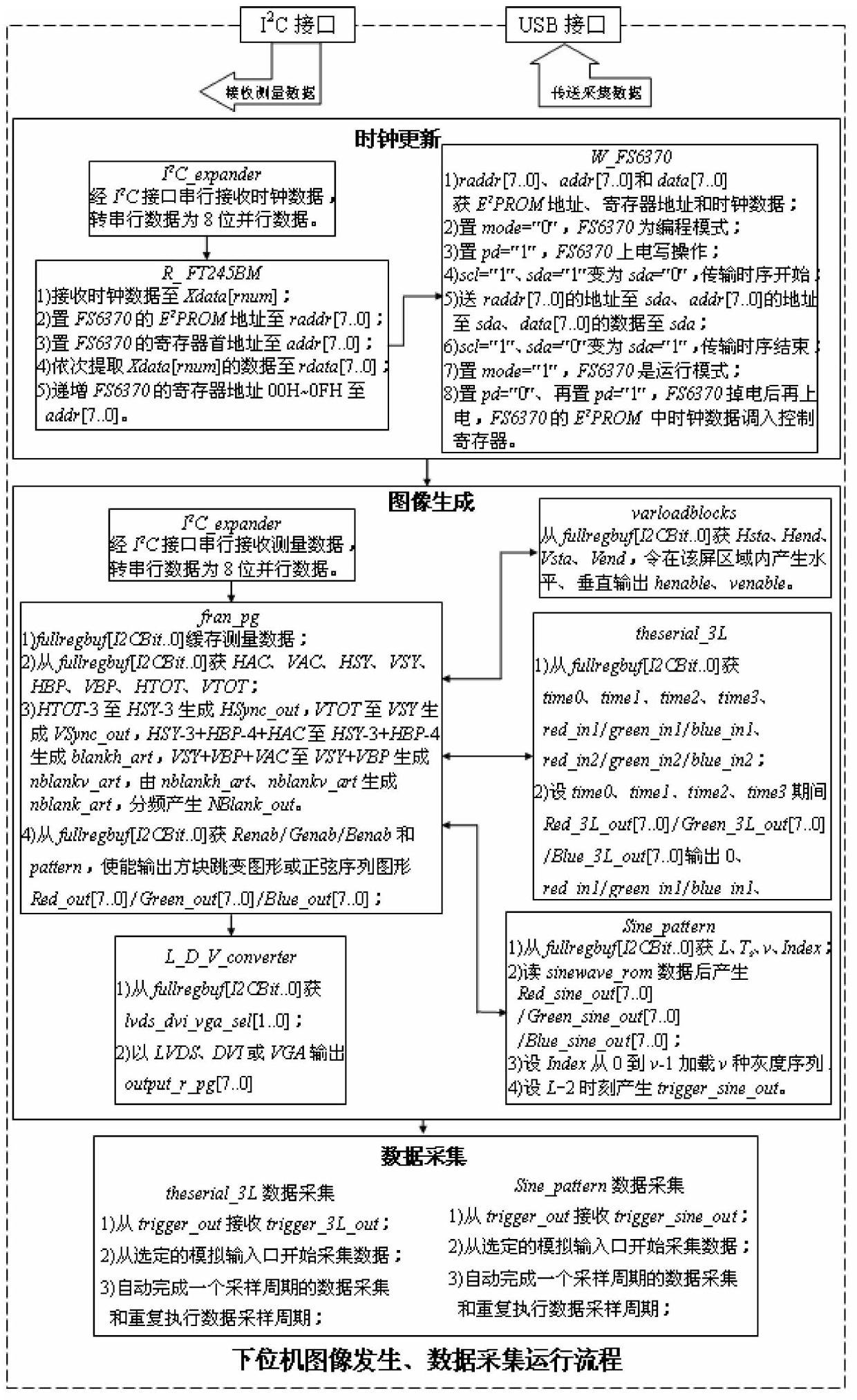

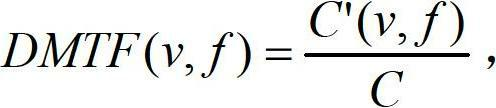

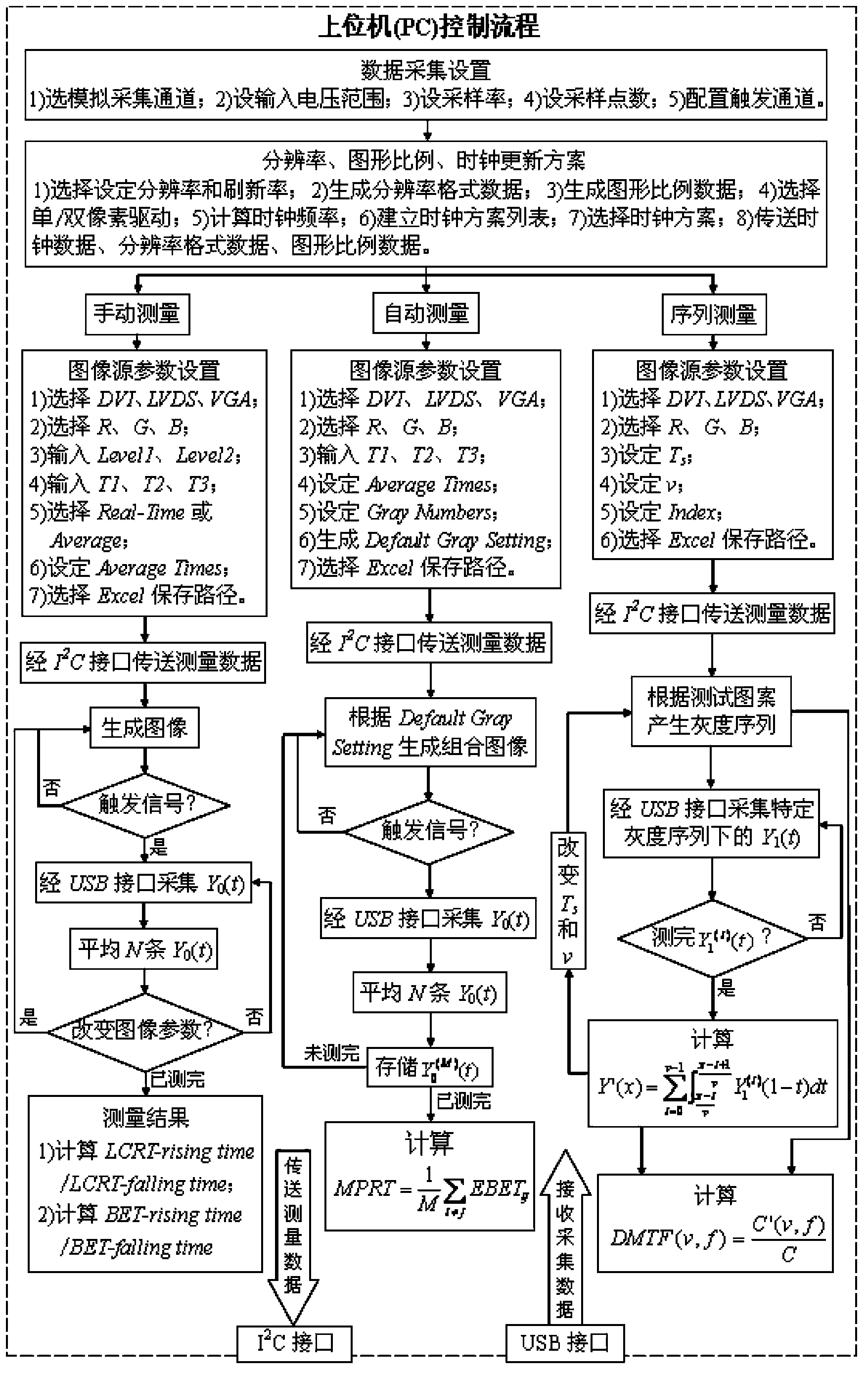

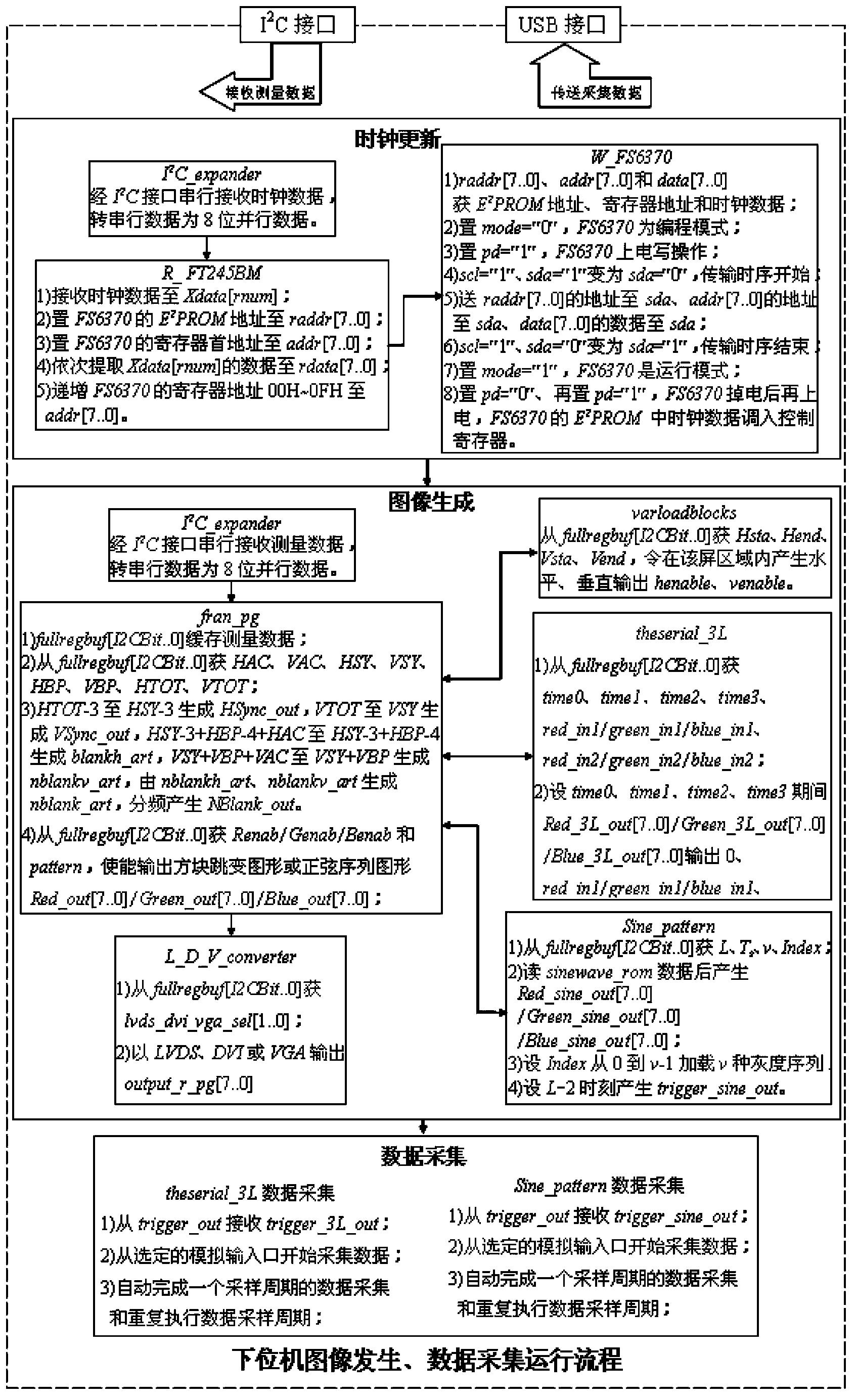

The invention discloses a method for measuring the quality of a dynamic image of a liquid crystal display. The method comprises an upper machine control flow and a lower machine image generation and data acquisition operating flow, wherein the upper machine control flow is used for defining a display image format, selecting a clock updating scheme, setting graph driving configuration, determining a data acquisition mode and computing the quality parameters of the dynamic image; the lower machine image generation and data acquisition operating flow is used for receiving and converting operating data, generating and controlling a synchronizing signal, generating and configuring a test graph, selecting and setting display drive, and acquiring and transmitting characteristic data; and transmission of measuring data in an inter-integrated circuit (I2C) bus mode and transmission of transient response characteristic data through a universal serial bus (USB) interface are performed between the upper machine control flow and the lower machine image generation and data acquisition operating flow. The method provided by the invention is used for comprehensively identifying the dynamic characteristic of the liquid crystal display and can meet measuring requirements of different types of liquid crystal displays.

Owner:南京东晖光电有限公司

Anti-shake effect test method and device, electronic equipment and medium

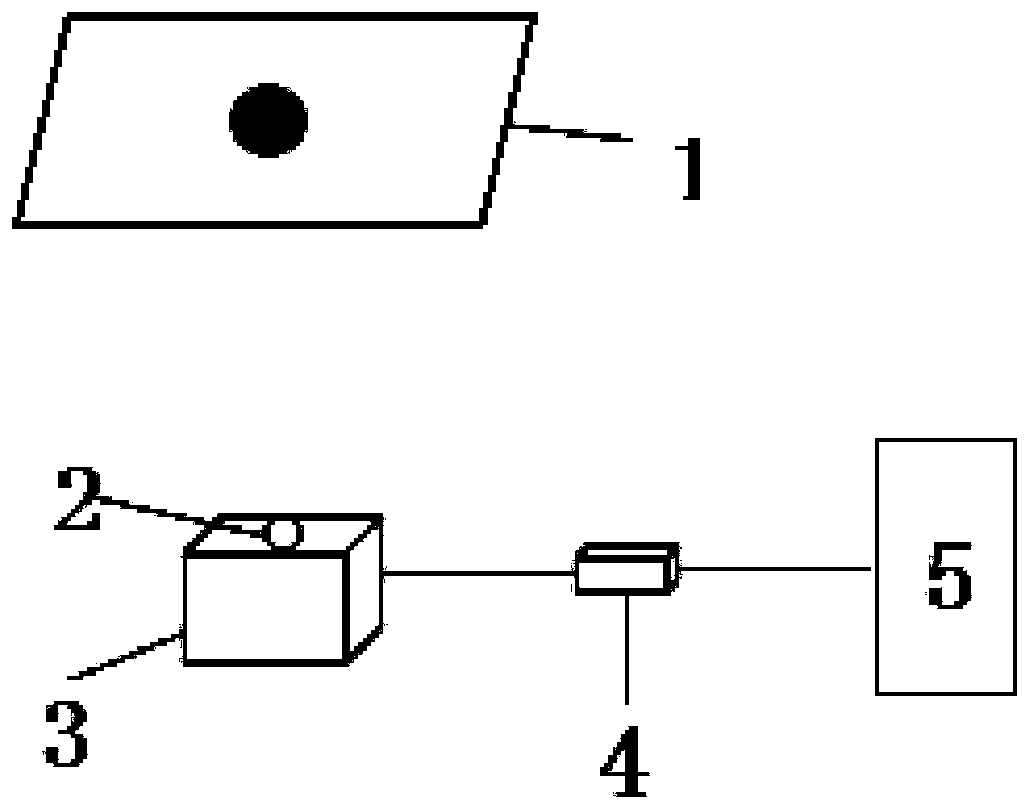

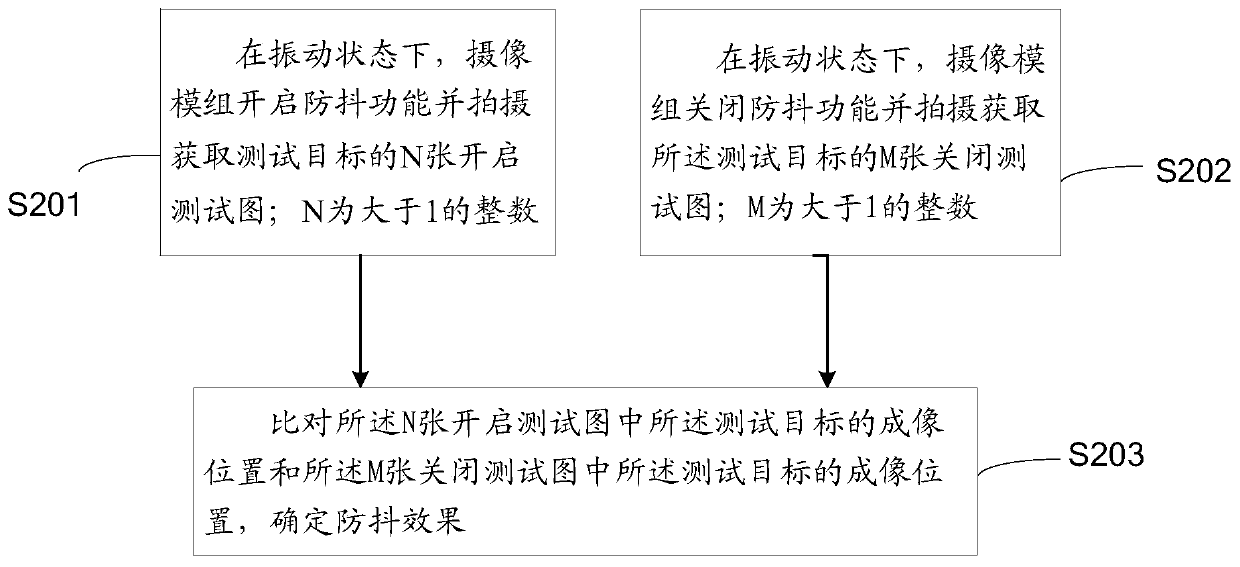

ActiveCN110572638AAvoid inaccuraciesGuaranteed detection accuracyTelevision system detailsColor television detailsTest graphCamera module

The invention discloses an anti-shake effect test method and device, electronic equipment and a medium, and the method comprises the steps: enabling a camera module to start an anti-shake function ina vibration state, and carrying out the photographing of N start test graphs of a test target, wherein N is an integer greater than 1; in the vibration state, enabling the camera module to close the anti-shake function and shoots to obtain M closing test pictures of the test target, wherein M is an integer greater than 1; and comparing the imaging positions of the test targets in the N opening test images with the imaging positions of the test targets in the M closing test images to determine an anti-shake effect. The method, the device, the electronic equipment and the medium provided by theinvention are used for solving the technical problem of inaccurate anti-shake effect of a long exposure test in the prior art, and realize the technical effect of improving the anti-shake effect testaccuracy.

Owner:KUNSHAN Q TECH CO LTD

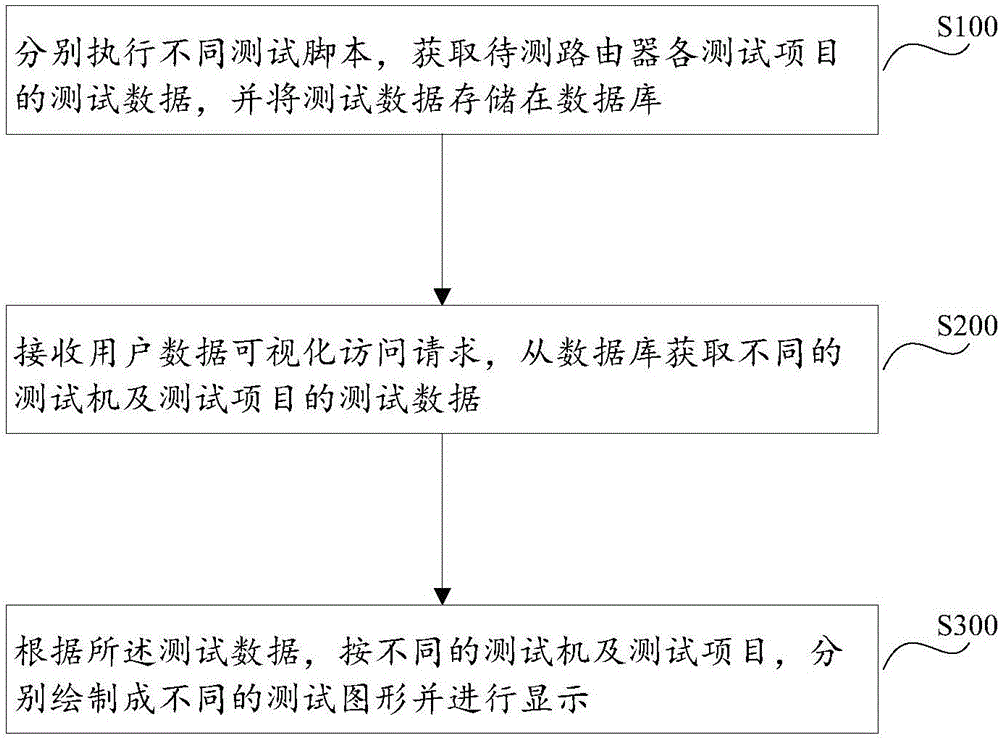

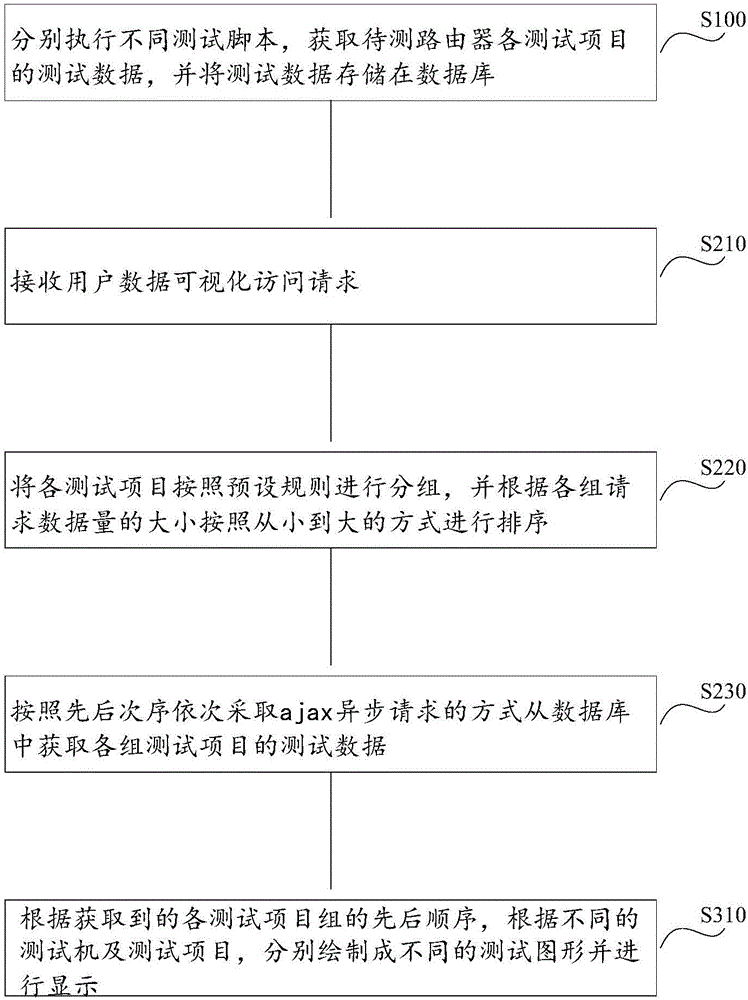

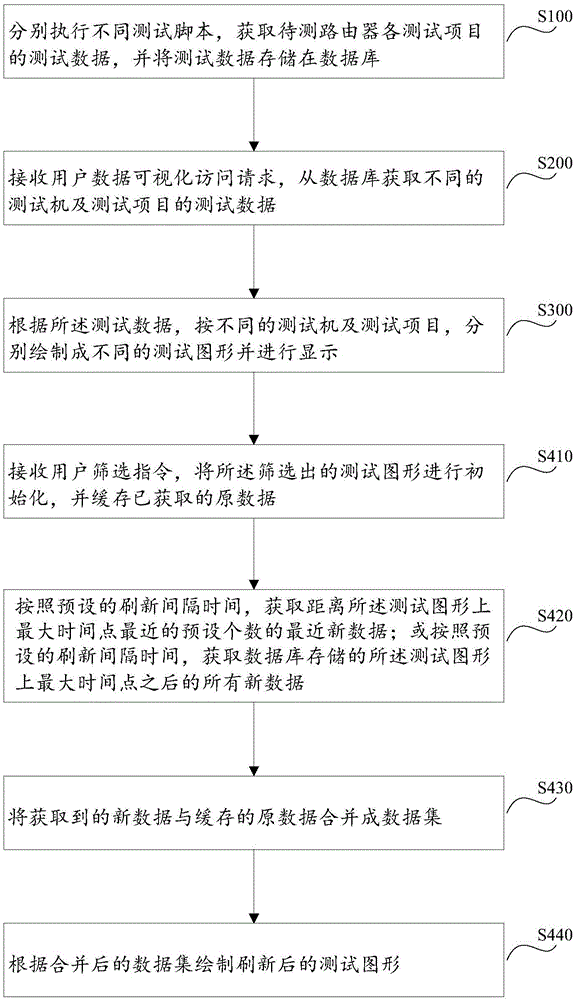

Router test data visualization method and system

ActiveCN106604312ARealize visualizationImprove legibilityData switching networksWireless communicationGraphicsTest graph

The invention discloses a router test data visualization method, and the method comprises the following steps: respectively executing different testing scripts, obtaining the test data of all test projects of a to-be-tested router, and storing the test data in a database; receiving a data visualization access data of a user, and obtaining the test data of different testers and test projects from the database; respectively drawing different test graphs according to the test data and different testers and test projects, and displaying the test graphs. The invention also discloses a router test data visualization system, and the system comprises at least two testers, a storage module, a management module, and a drawing module. The storage module is connected with the testers, and the management module is connected with the storage module and the drawing module. From the aspect of testing and monitoring of the router, the method and system elaborate the specific implementation and detailed functions, achieve the visualization of test data, and improve the testing efficiency.

Owner:王蕴卓

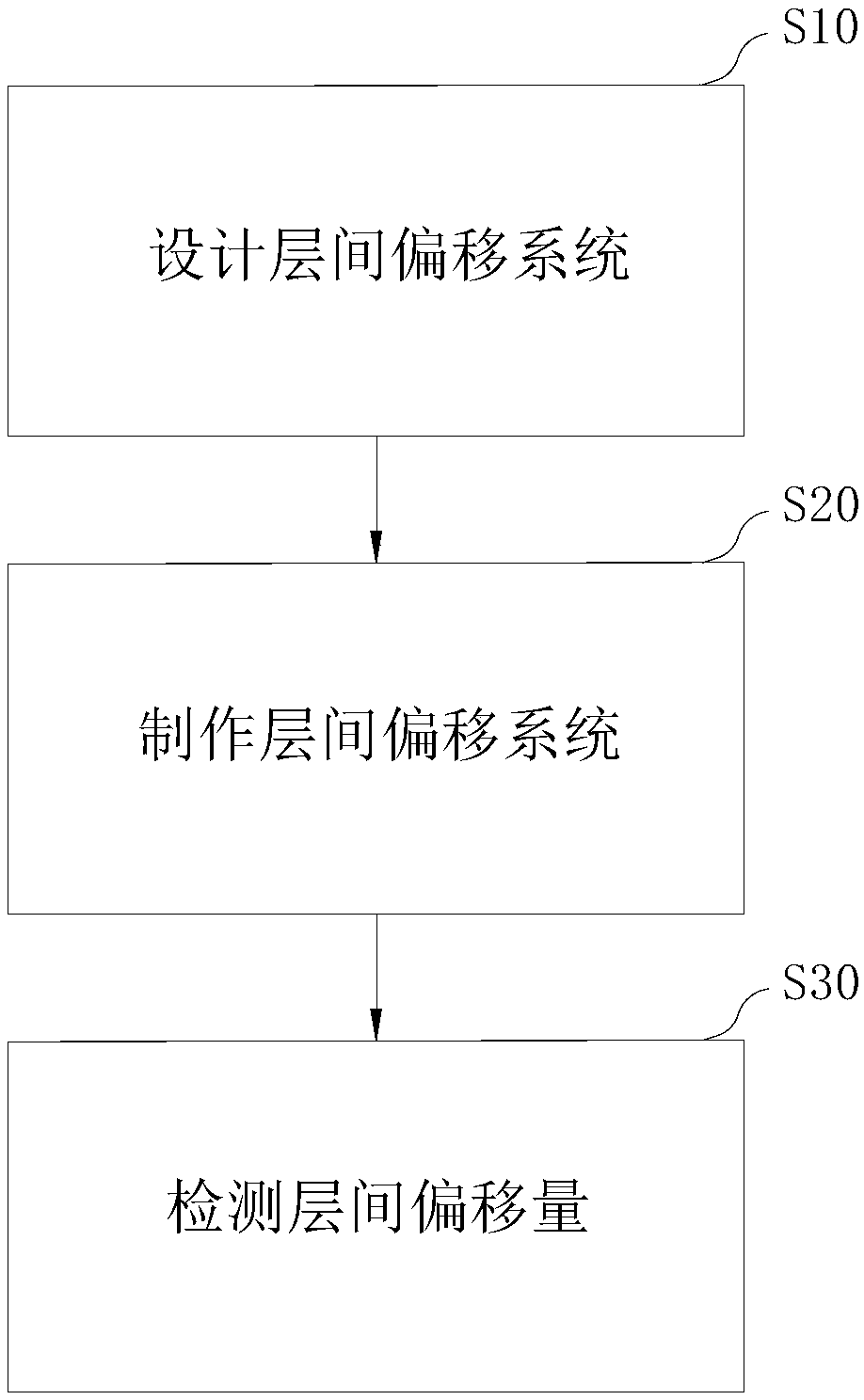

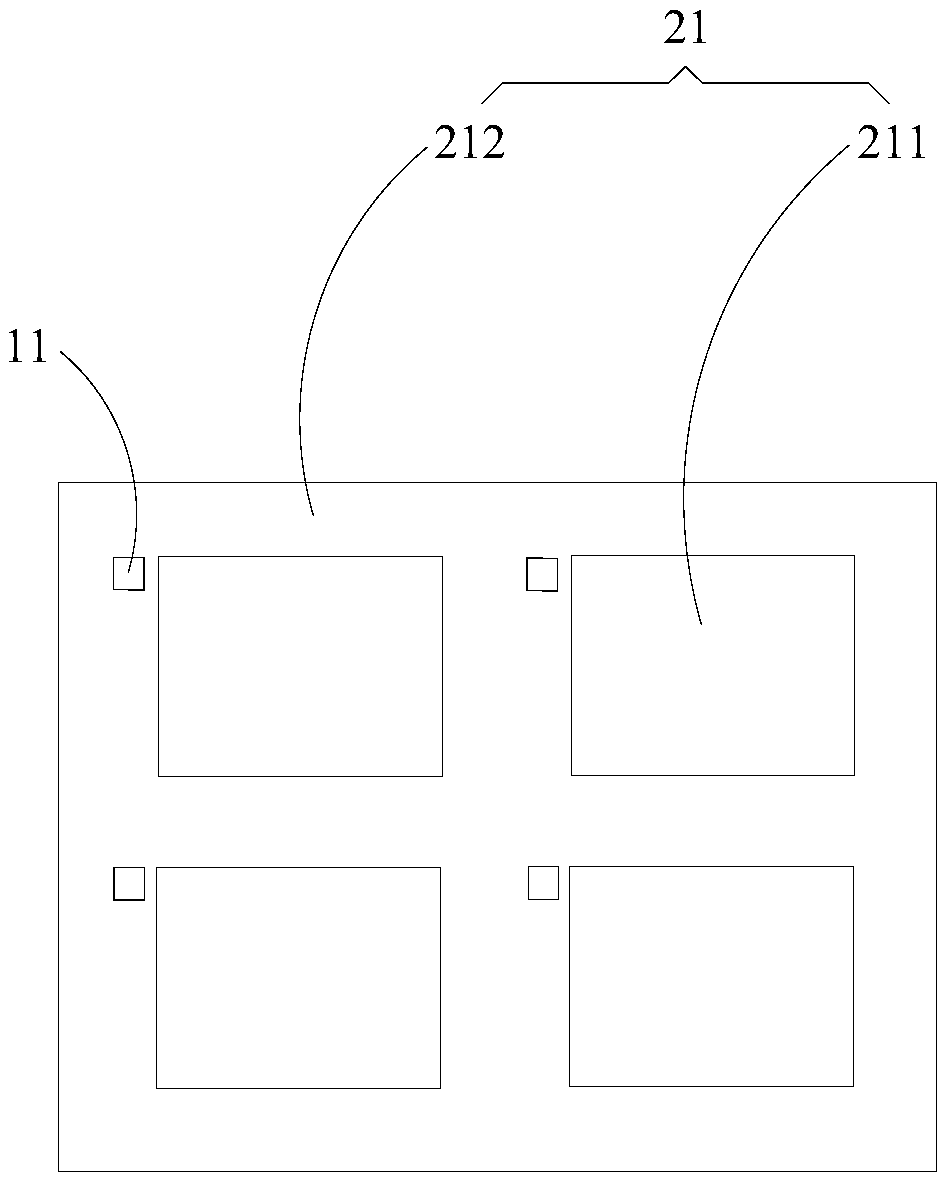

Multi-layer board interlayer offset detection method and detection system

ActiveCN108925066AGuaranteed measurement accuracyHigh measurement accuracyMultilayer circuit manufacturePrinted circuit boardTest graph

The invention relates to the technical field of printed circuit board manufacturing, and provides a multi-layer board interlayer offset detection method and detection system. The multi-layer board interlayer offset detection method comprises the steps that an interlayer offset system is designed, specifically, one layer of a multi-layer circuit board is selected as a datum layer, other layers of the multi-layer circuit board are used as test layers, a datum graph is arranged on a preset position of a datum layer work board provided with the datum layer, test graphs are arranged on preset positions of test layer work boards provided with the test layers, and the test graphs of the test layers are mutually staggered; an interlayer offset system is made, specifically, the datum layer and thetest layers in the multi-layer circuit board are made, the datum graph is made on the datum layer work board, and the test graphs are made on the test layer work boards; and interlayer offsets are detected, specifically, the position of the finished datum graph of the multi-layer circuit board is obtained, the distance between each test graph on each corresponding test layer and the datum graph ismeasured, the distances are compared with designed distance, and the interlayer offset of each test layer is obtained. The higher measurement accuracy is achieved.

Owner:SHENZHEN KINWONG ELECTRONICS

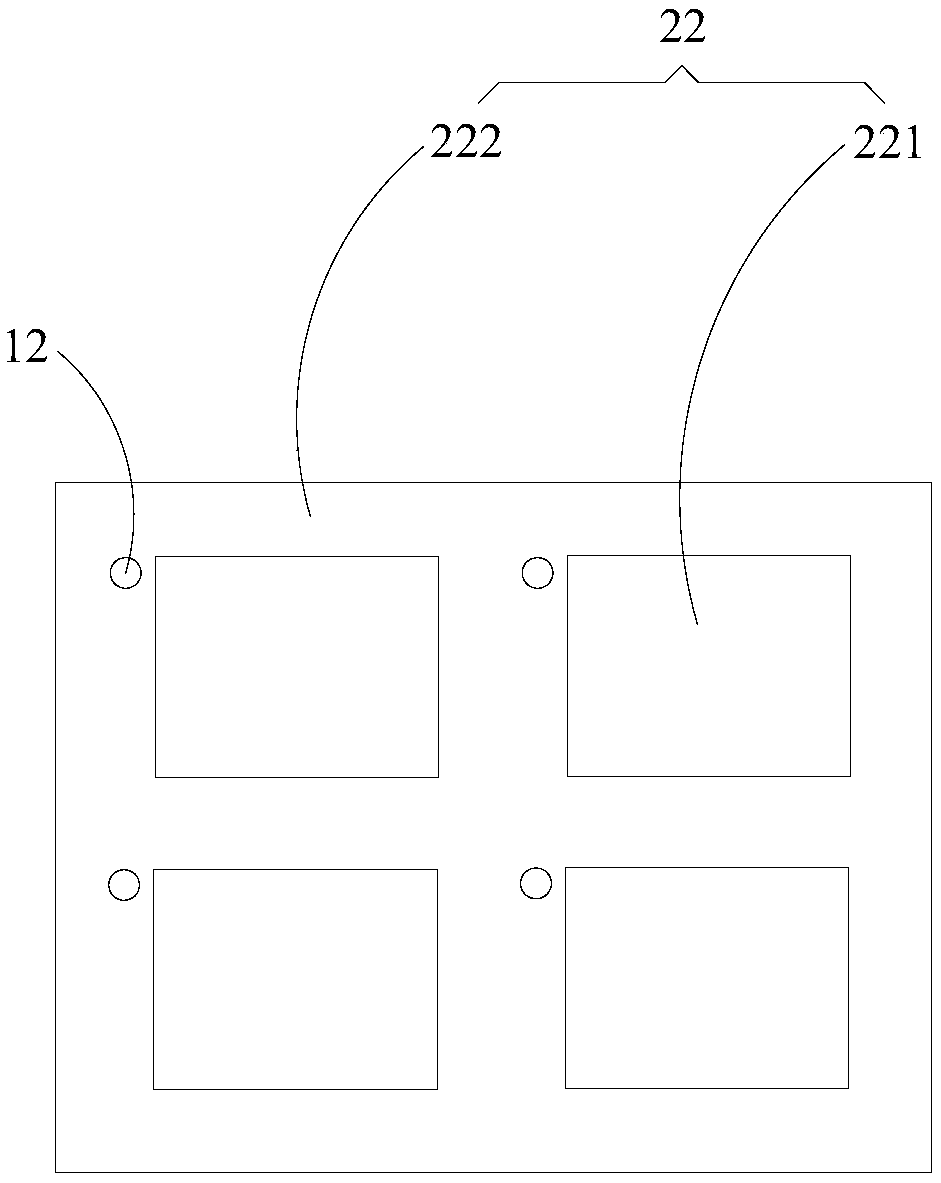

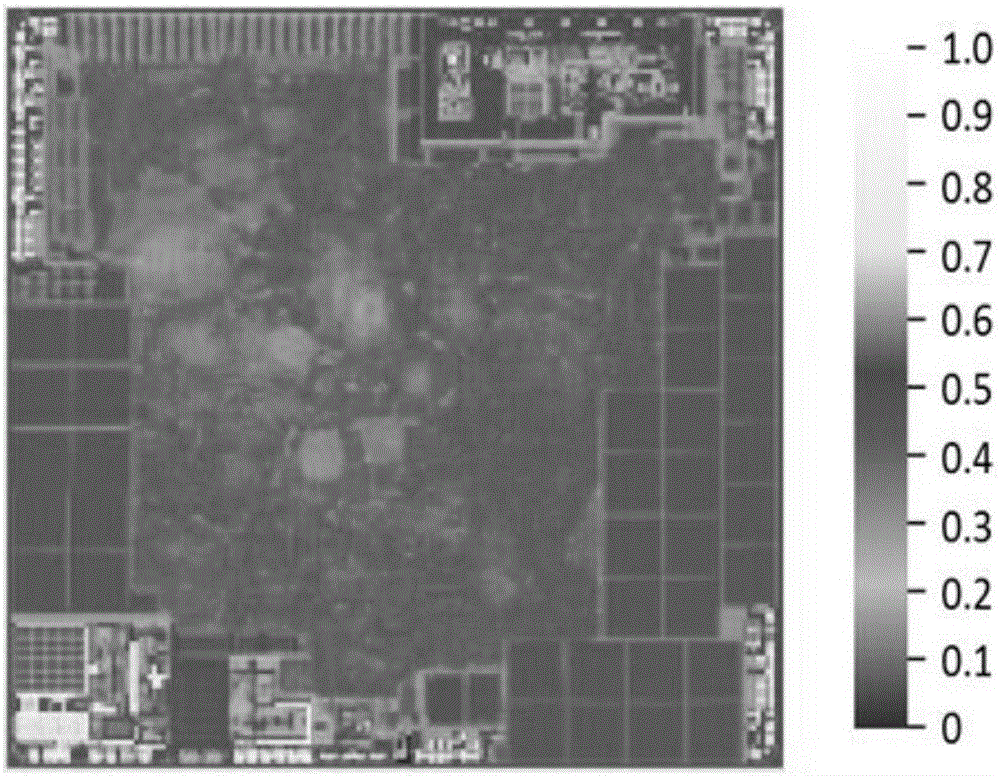

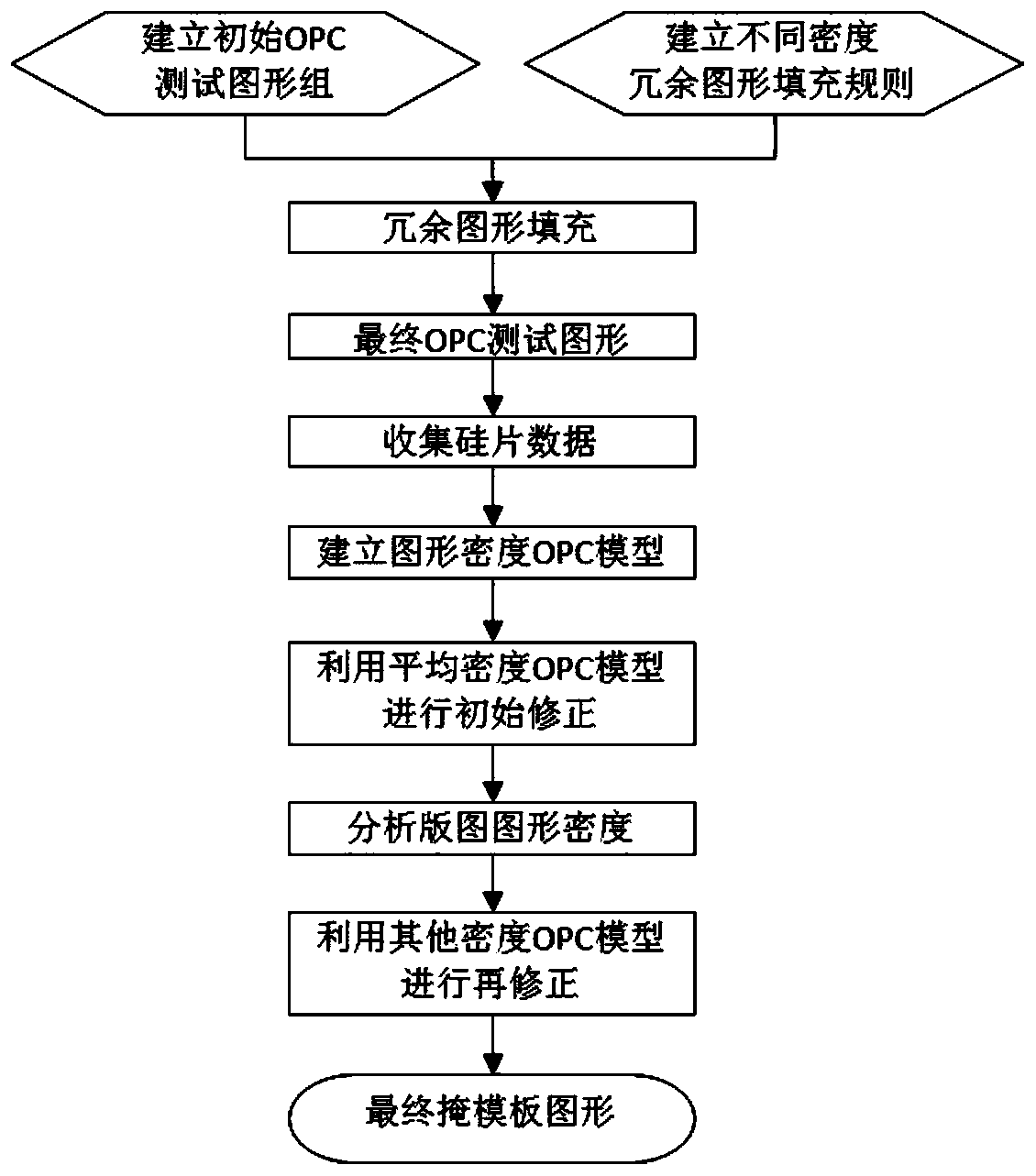

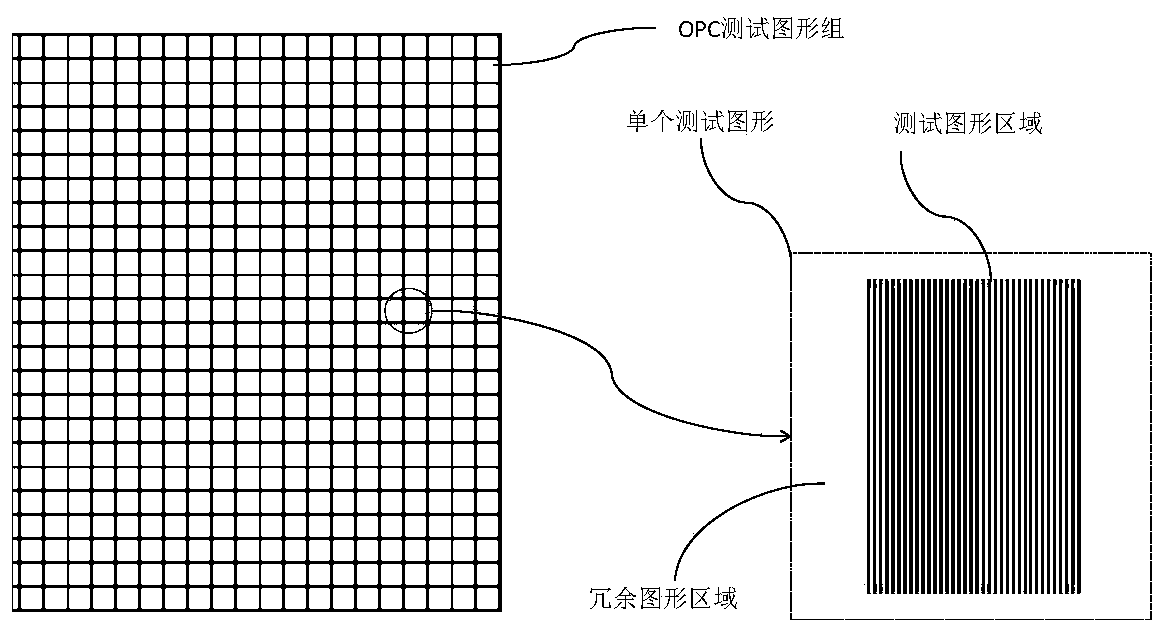

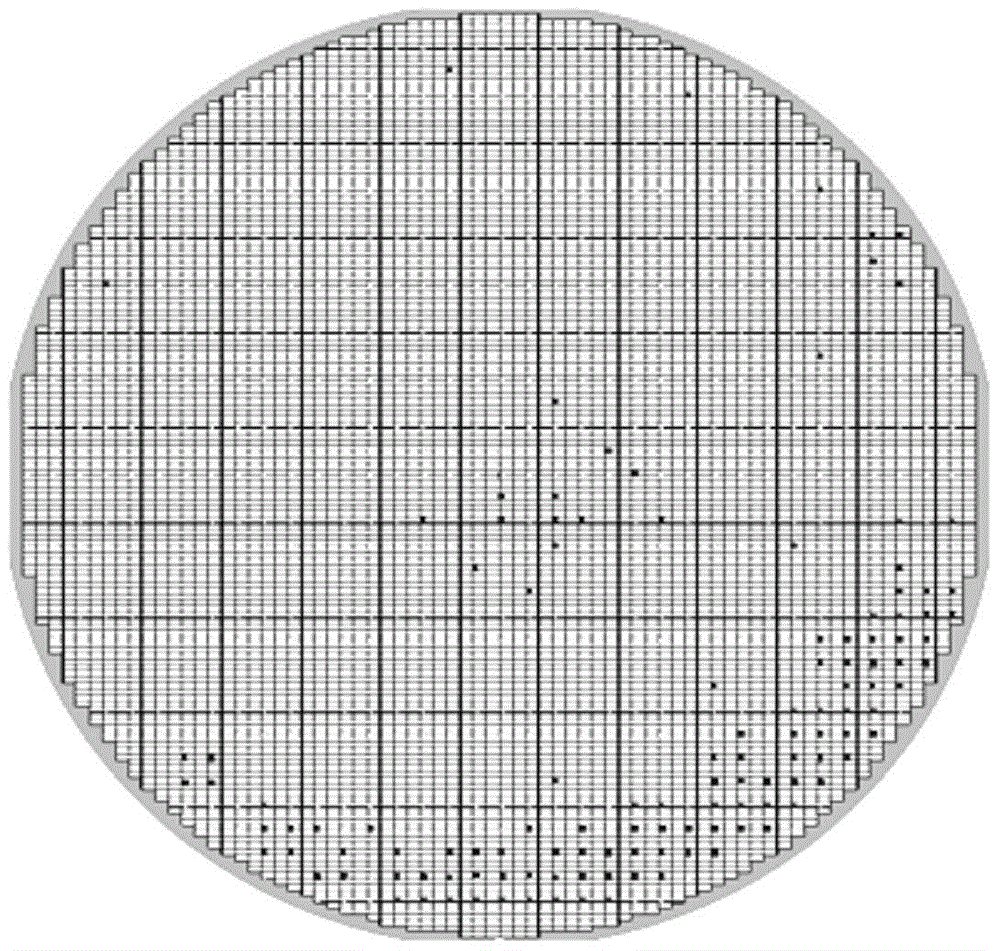

Process model modeling and correcting method based on graph density

ActiveCN106294935AAddressing Accuracy ImpactsImprove accuracyComputer aided designSpecial data processing applicationsGraphicsTest graph

The invention provides a process model molding and correcting method based on a graph density. The method comprises the steps that by adding redundant graphs with different graph densities and adjusting the OPC test graph region area, a test graph of a target graph density is obtained; according to silicon wafer data calibration models collected by the test graphs with different graph density ranges, OPC models under different graph density ranges are obtained; in the OPC processing process, a model representing the average density is used for correcting the whole layout data, layout density distribution is analyzed, graph areas with low density and high density are selected and subjected to correction with corresponding models respectively, and a mask graph is obtained finally.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

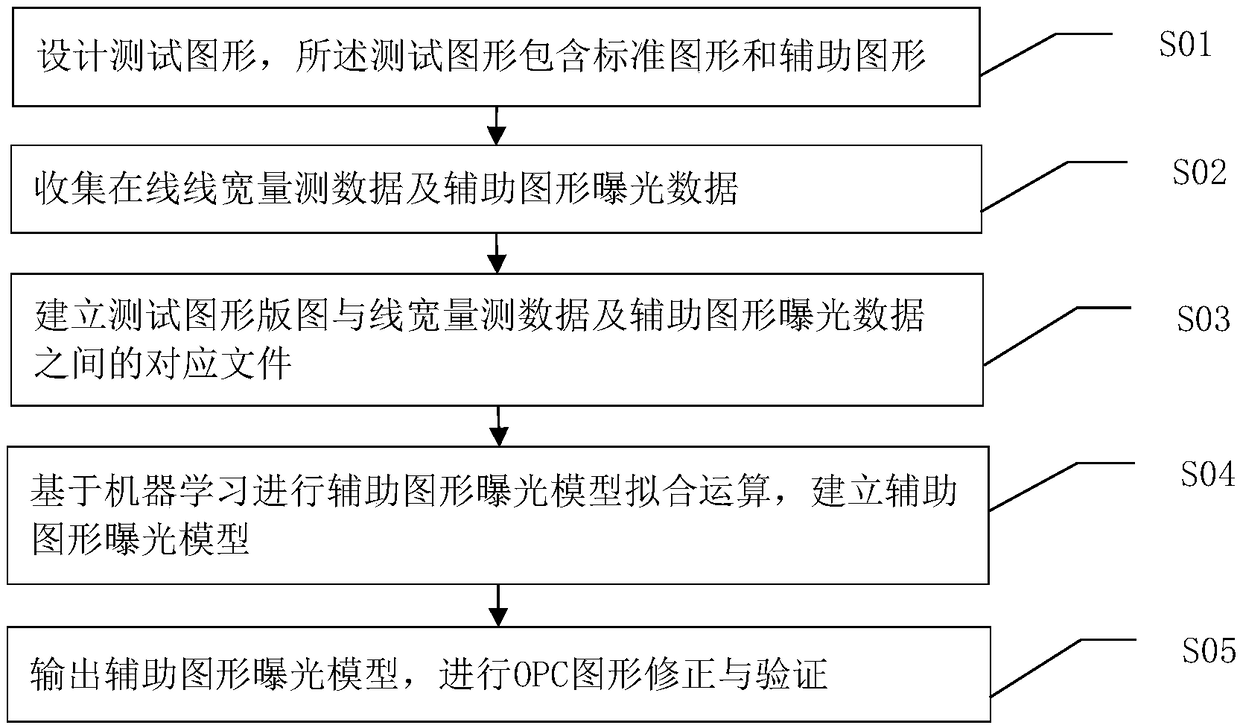

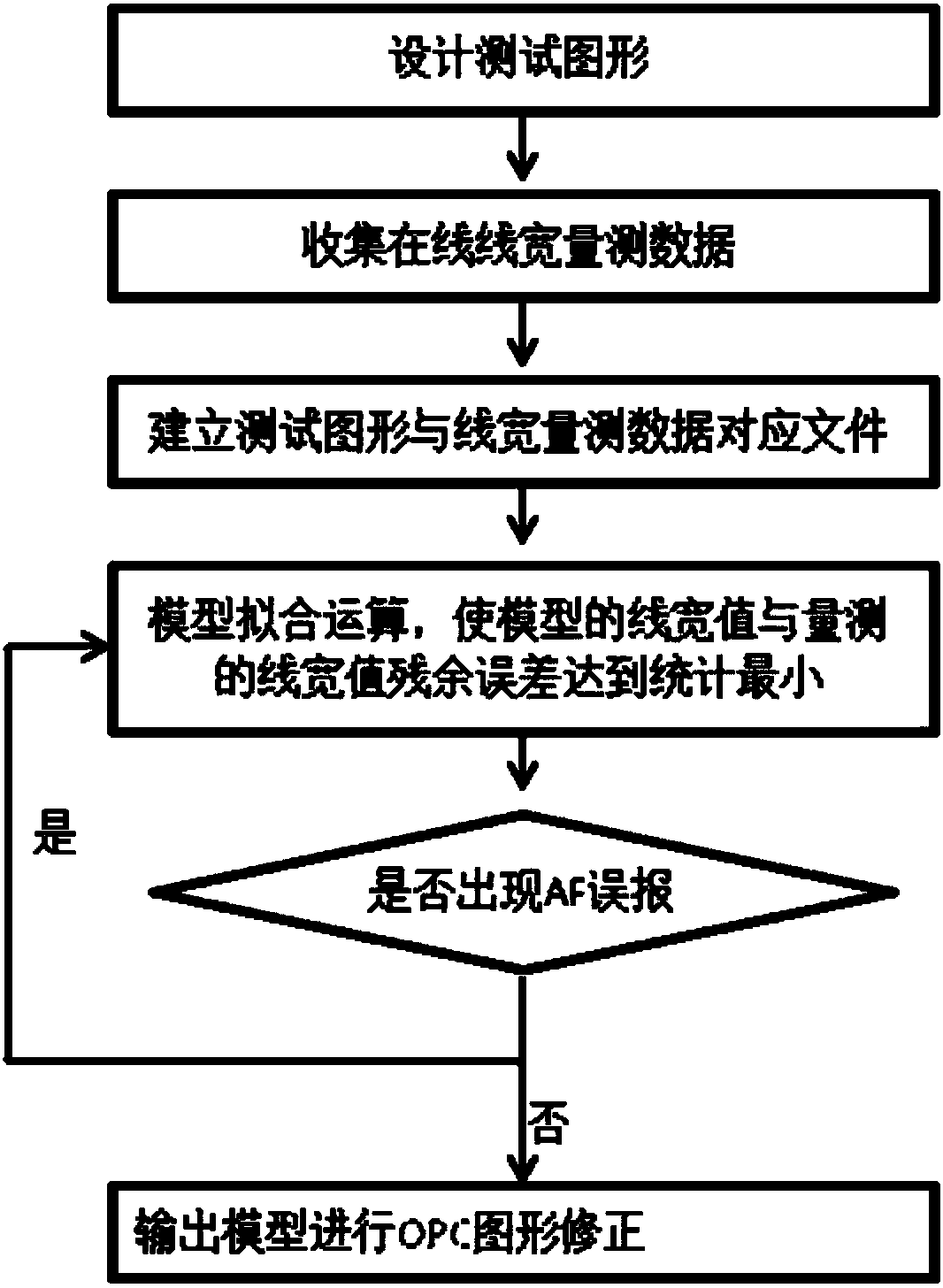

Method for establishing auxiliary graph exposure model

The invention discloses a method for establishing an auxiliary graph exposure model. The method comprises the following steps: S01, designing a test graph, including standard graphs and auxiliary graphs; S02, collecting online line width measurement data and auxiliary graph exposure data; S03, establishing a testing graph layout and a corresponding file between the line width measurement data andthe auxiliary graph exposure data; S04, performing auxiliary graph exposure model fitting operation based on machine learning to establish an auxiliary graph exposure model; and S05, outputting the auxiliary graph exposure model, and performing OPC graph correction and verification. By adopting the method, an auxiliary graph exposure model with higher accuracy can be obtained.

Owner:上海微阱电子科技有限公司

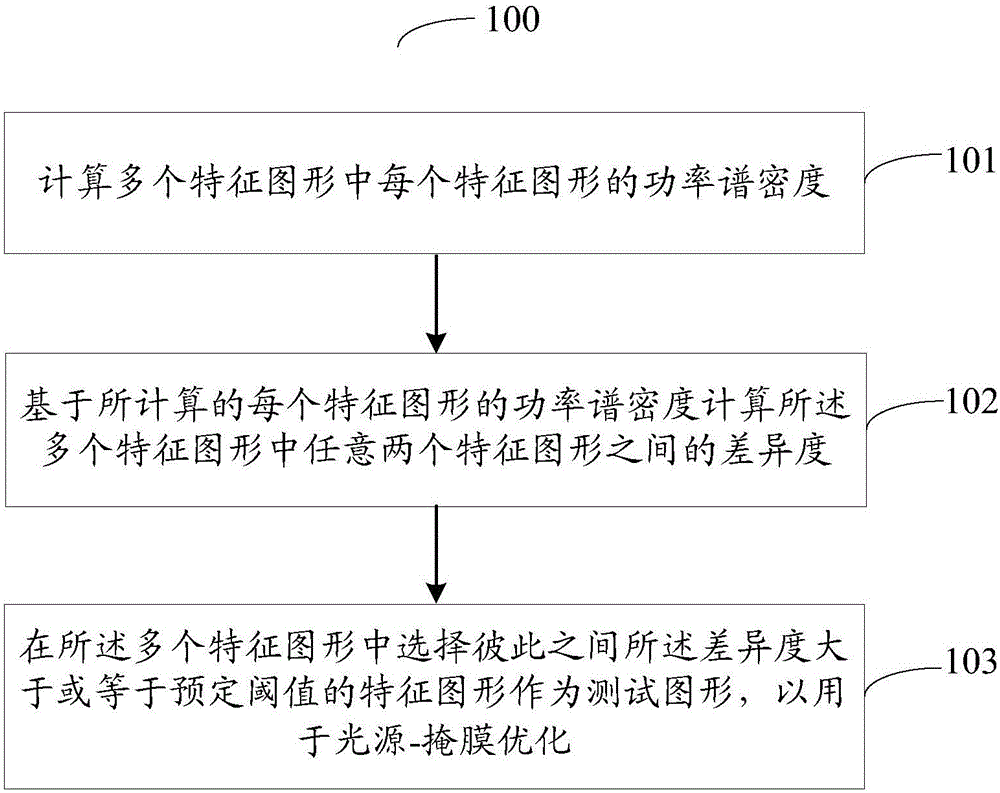

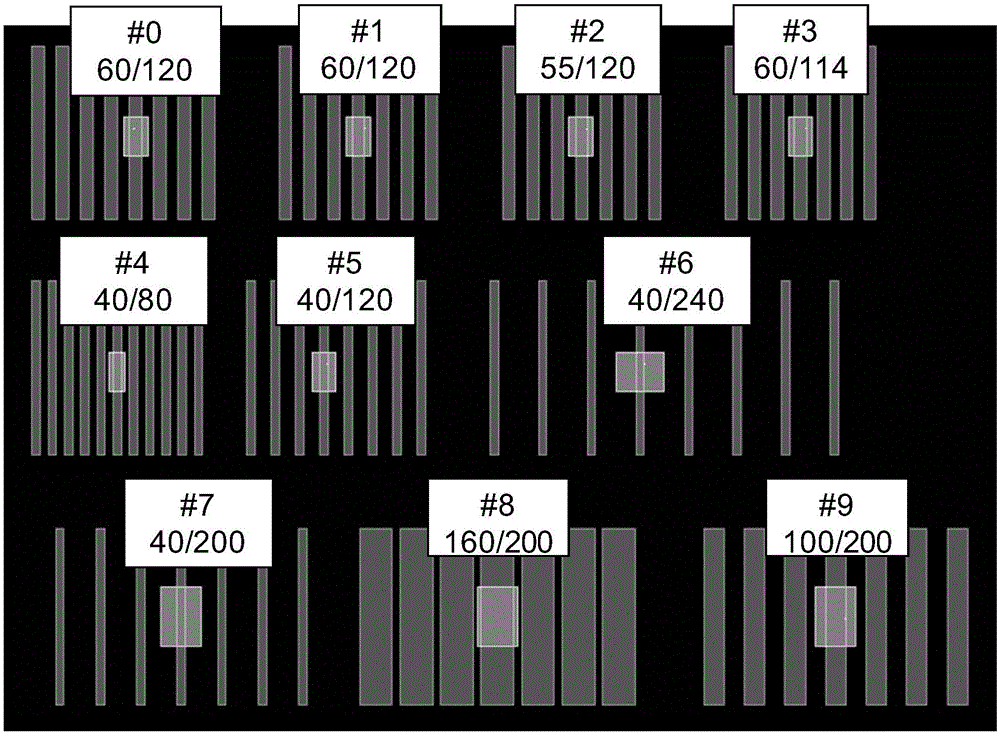

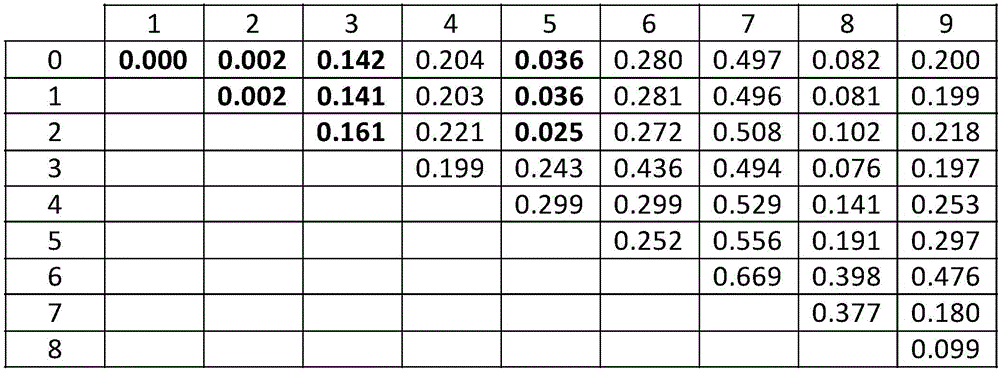

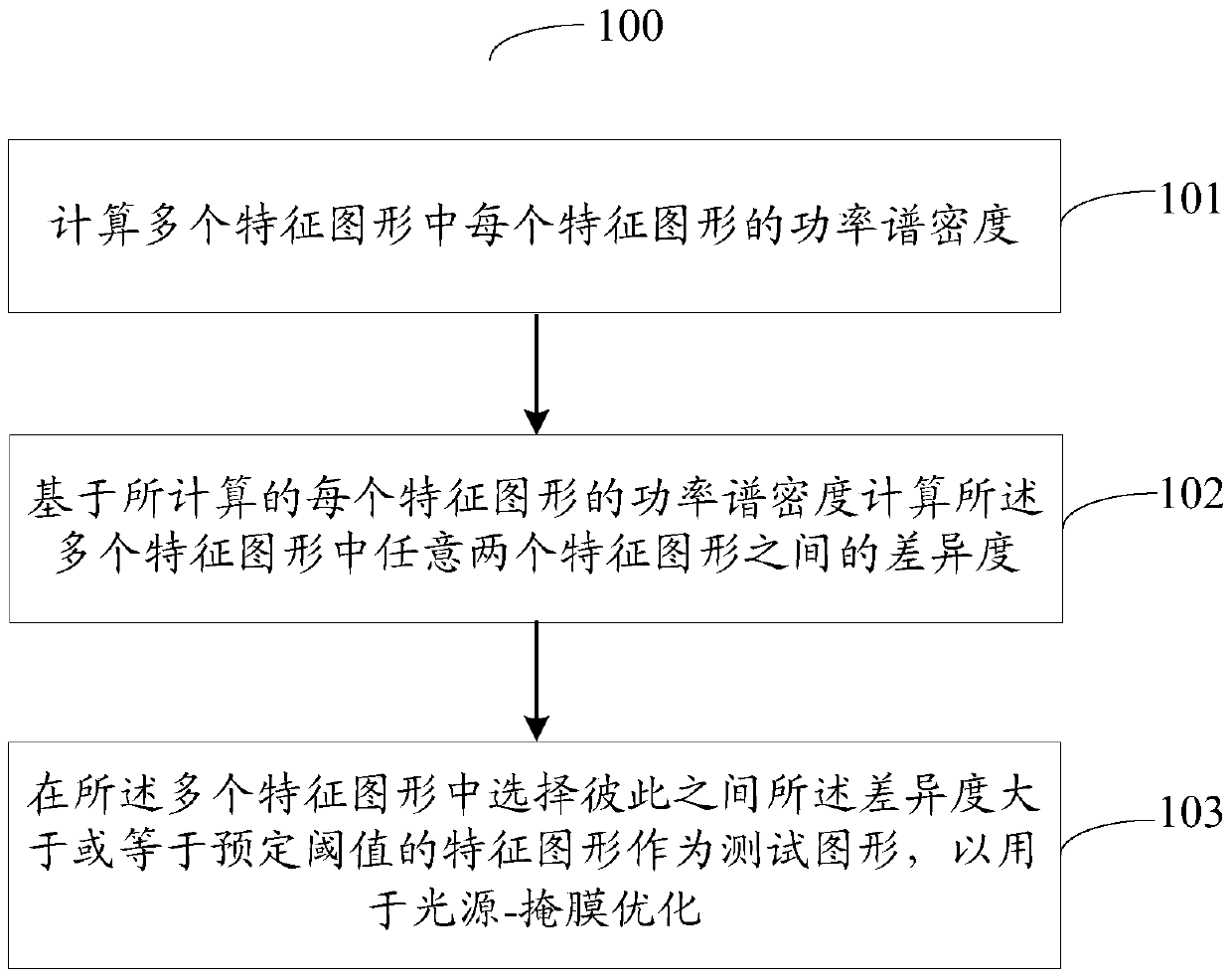

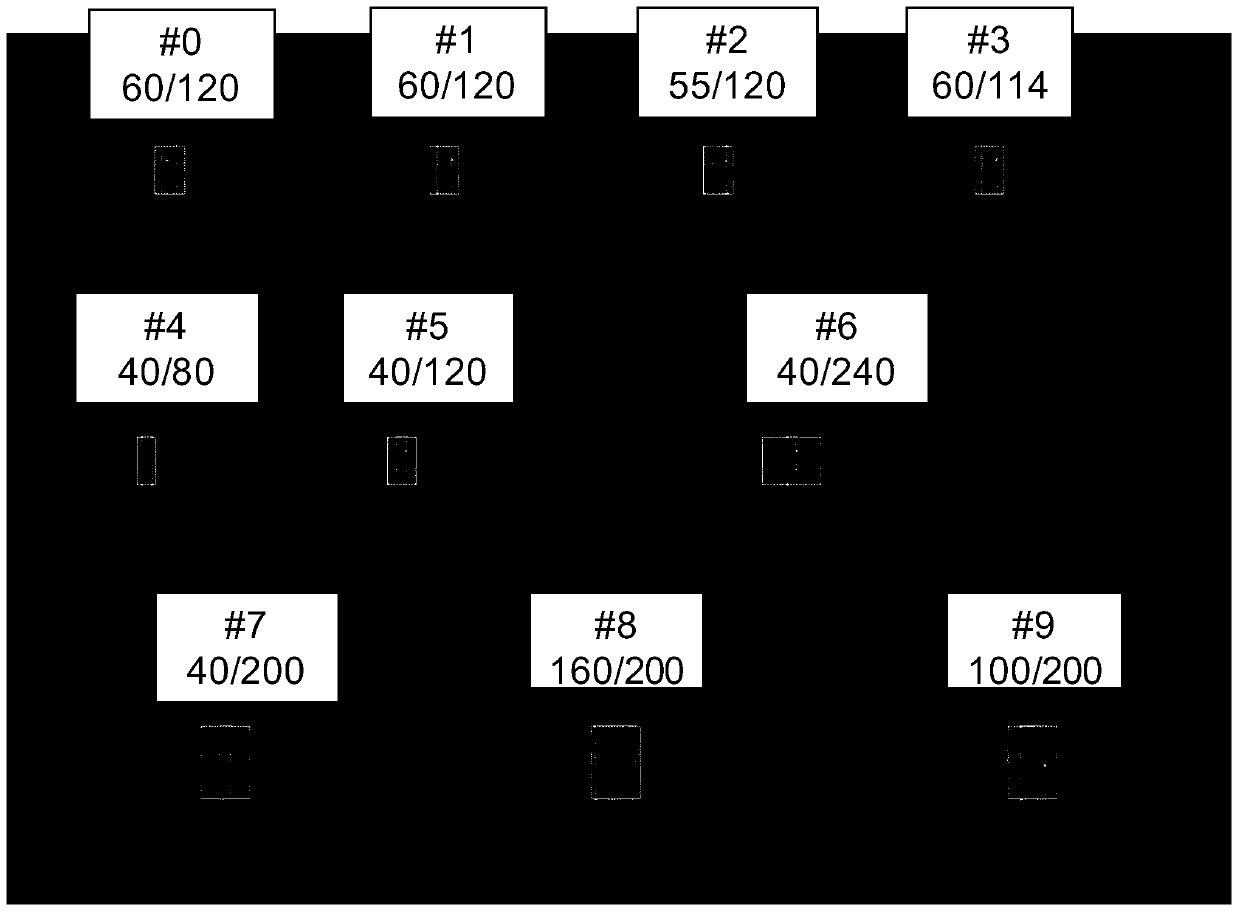

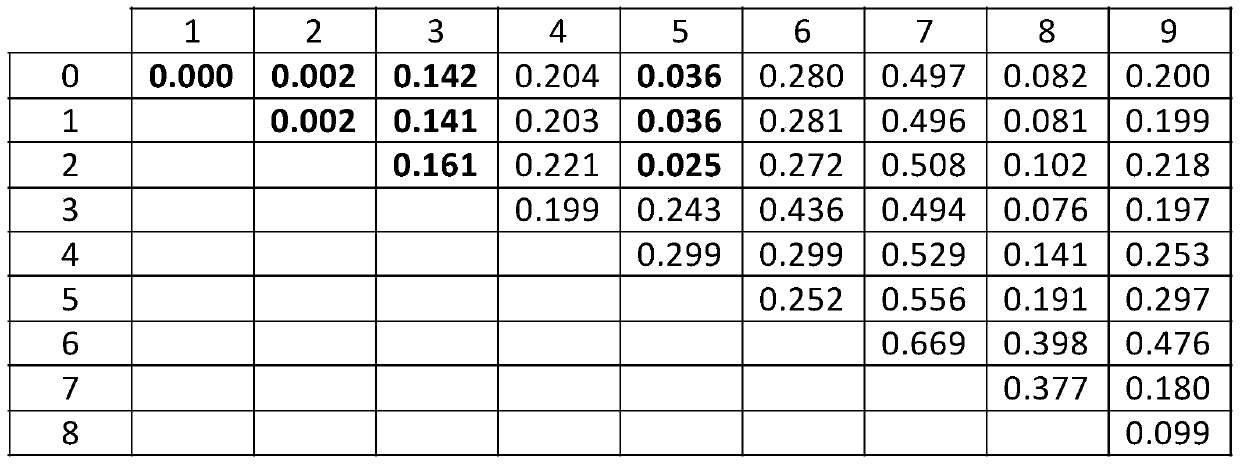

Graph selection method used for light source-mask optimization

The invention provides a graph selection method used for light source-mask optimization. The graph selection method comprises the steps of calculating power spectrum density of each feature graph in a plurality of feature graphs; calculating a difference degree between any two feature graphs in the feature graphs based on the calculated power spectrum density of each feature graph; and selecting the feature graphs with the difference degree greater than or equal to a predetermined threshold in the feature graphs as test graphs used for the light source-mask optimization. According to the graph selection method used for the light source-mask optimization, provided by the invention, the test graphs used for the light source-mask optimization can be efficiently and quickly selected, and any key graph is not omitted, so that efficient and high-accuracy light source-mask optimization is realized.

Owner:SEMICON MFG INT (SHANGHAI) CORP

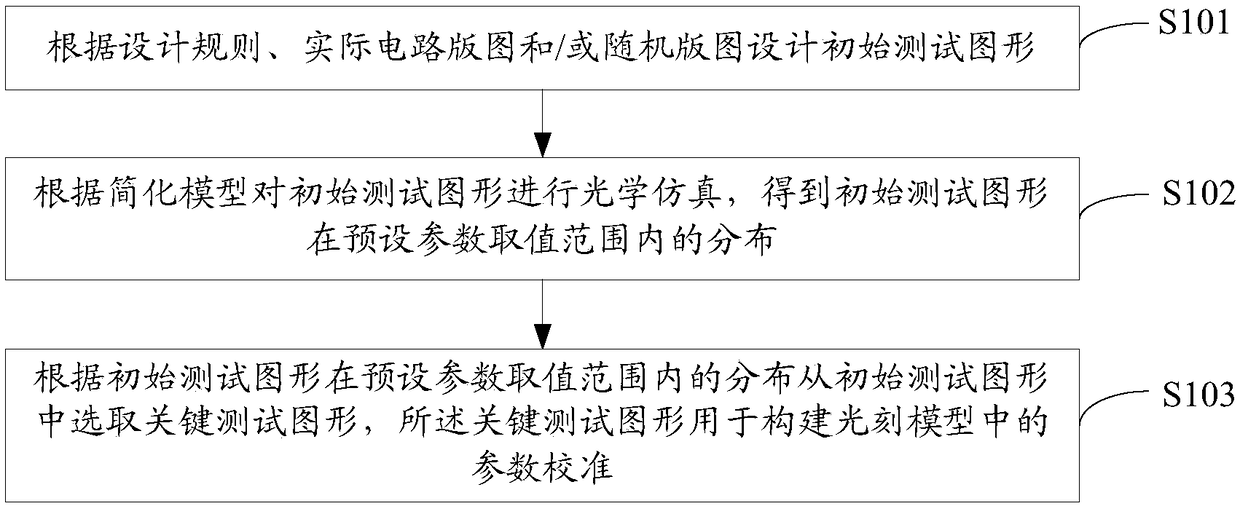

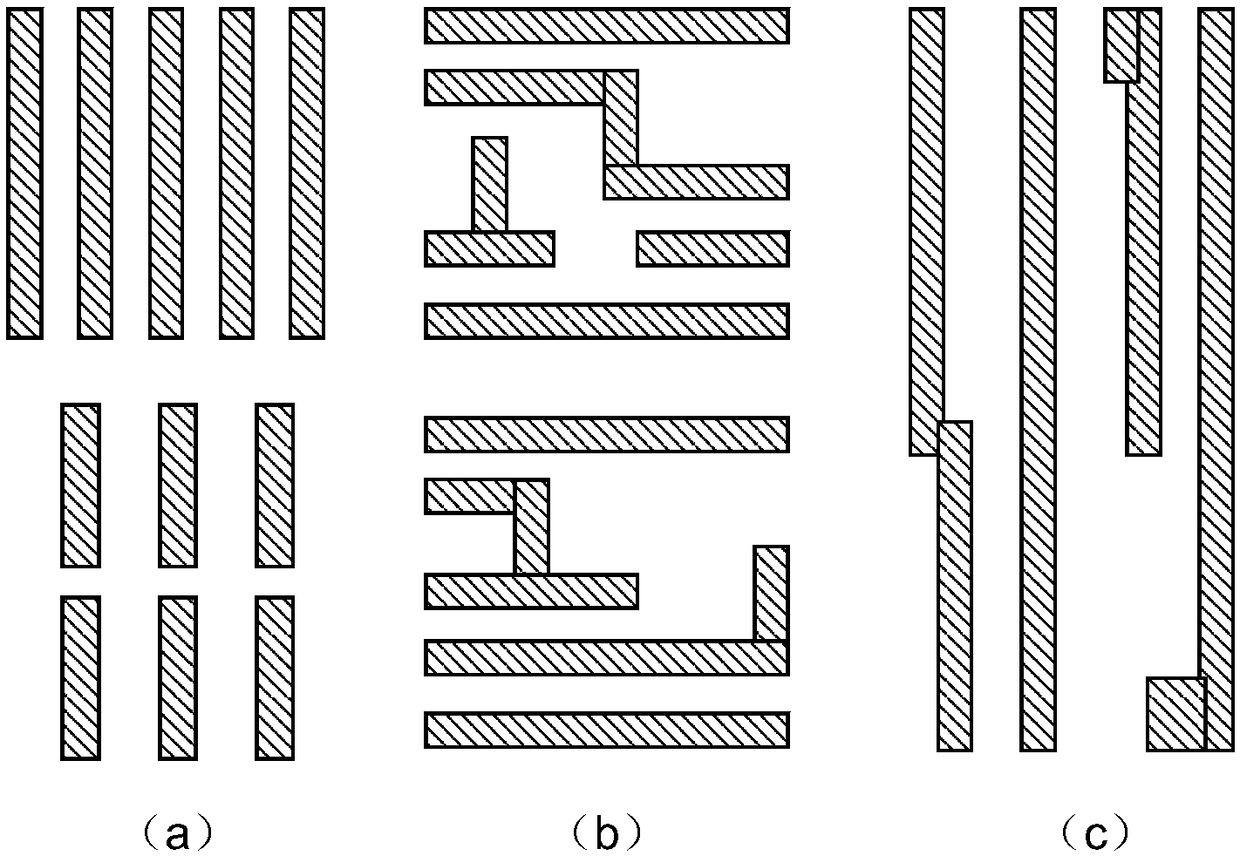

Method and device for selecting test graphs and method and device for building photolithography models

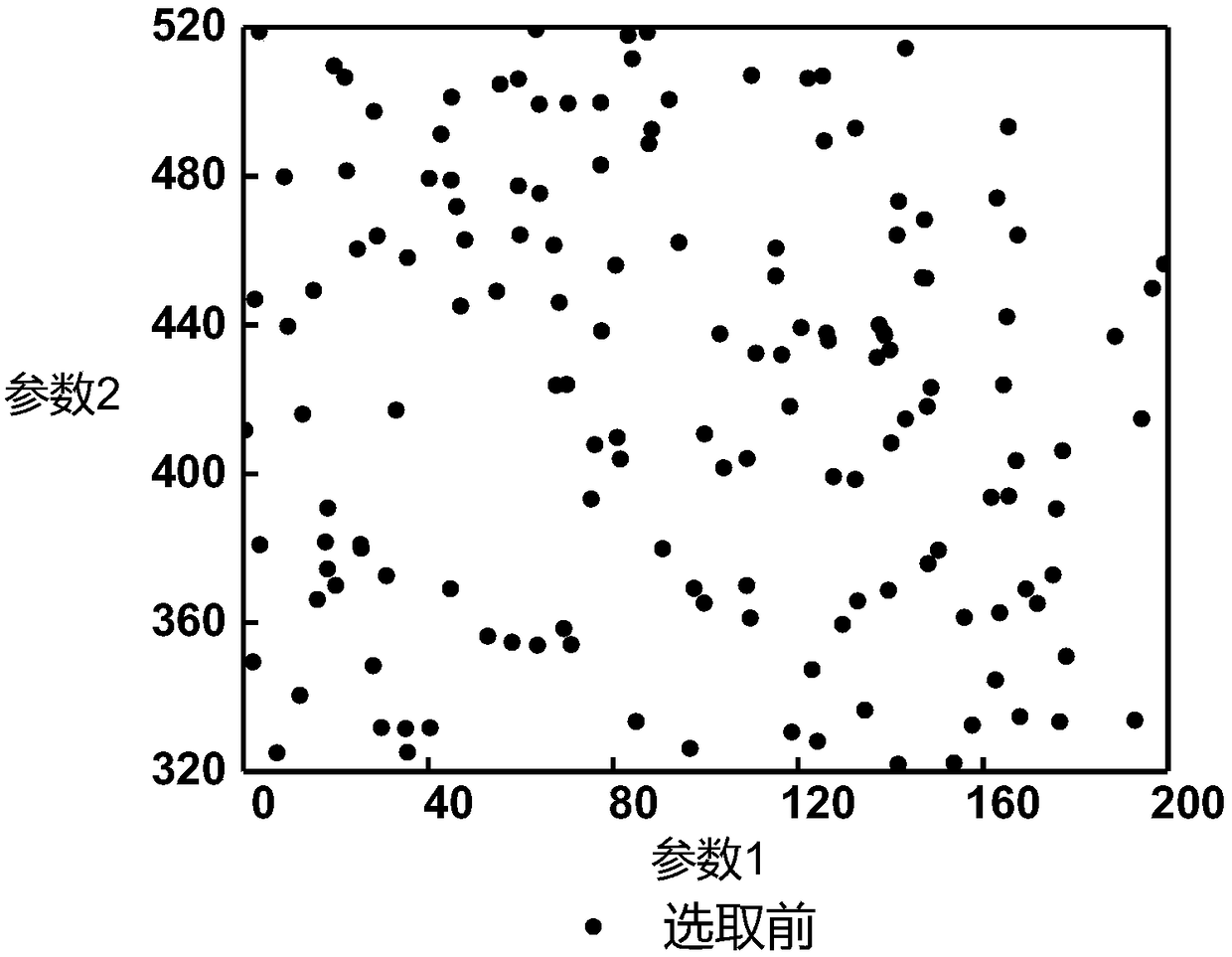

ActiveCN108153995ASimulation is accurateImprove accuracyDesign optimisation/simulationCAD circuit designReduced modelGraphics

An embodiment of the invention discloses a method and a device for selecting test graphs. The method includes designing initial test graphs according to design rules, actual circuit layout and / or random layout; optically simulating the initial test graphs according to simplified models to obtain distribution of the initial test graphs in preset parameter value ranges; selecting key test graphs from the initial test graphs according to the distribution of the initial test graphs in the preset parameter value ranges. The key test graphs are used for calibrating parameters during photolithographymodel building. The method and the device have the advantages that the test graphs selected by the aid of the method can be used for building photolithography models, and accordingly the model building efficiency and the accuracy of the photolithography models can be improved. The invention further relates to a method and a device for building the photolithography models.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Method of establishing optical data correction model

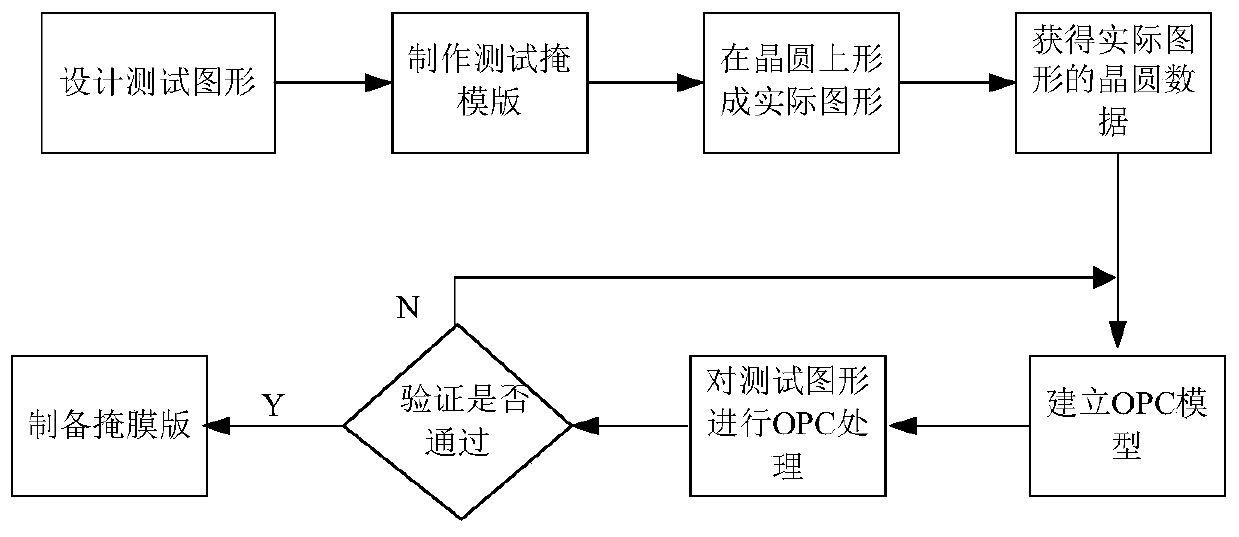

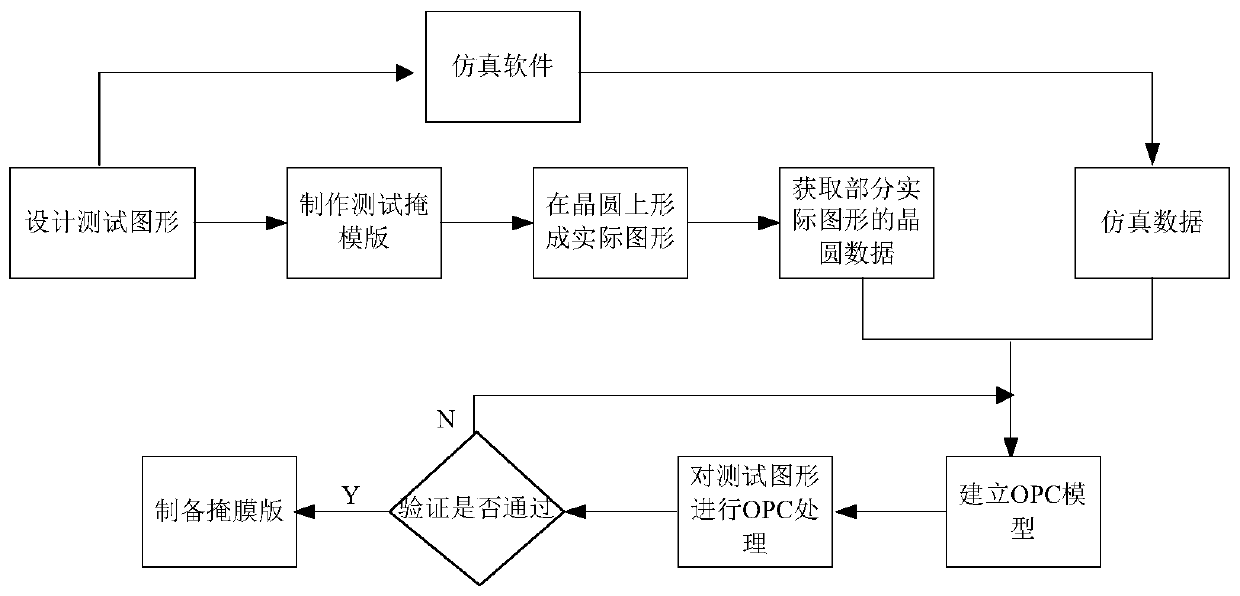

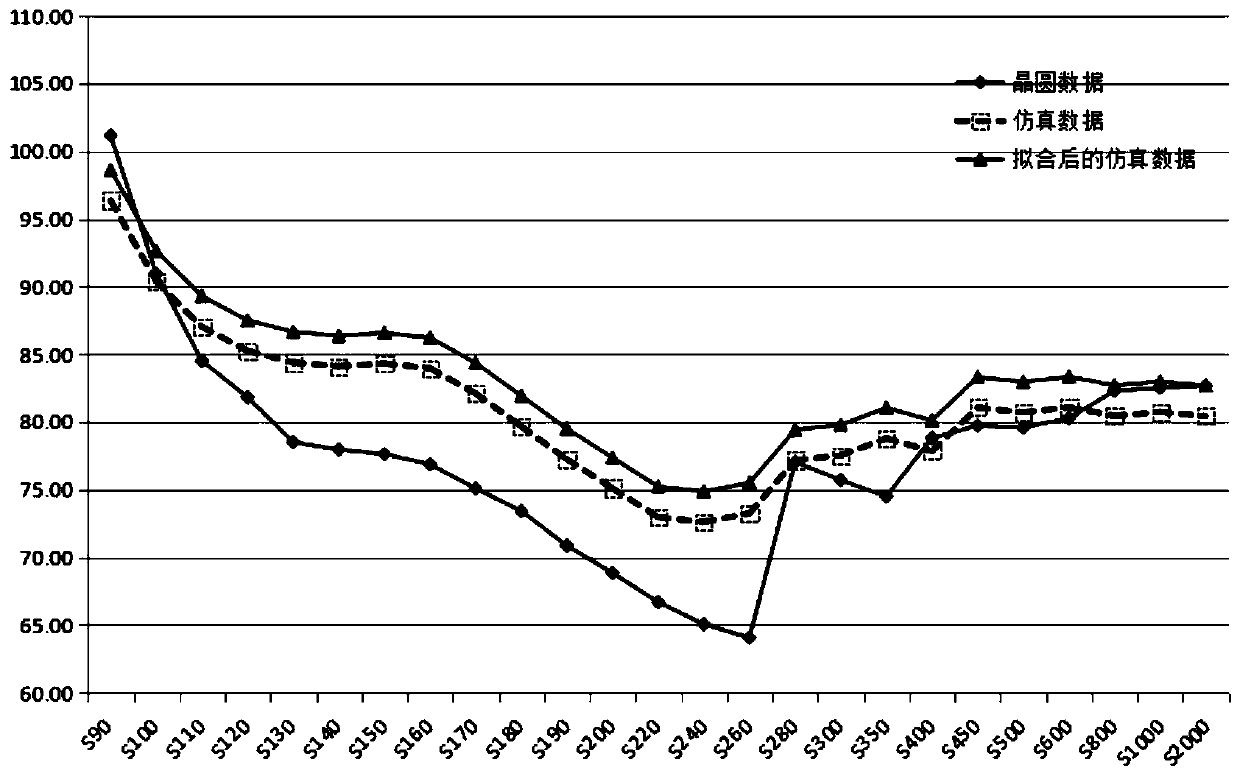

ActiveCN111427240AGuaranteed accuracyAvoid gettingDesign optimisation/simulationPhotomechanical exposure apparatusTest graphAlgorithm

The invention provides a method for establishing an OPC model. The method comprises the following steps of transferring a test graph to a wafer by using a test mask plate; forming an actual graph on awafer, obtaining the wafer data obtained by testing part of the actual graph, simulating the test graph through a simulation software to obtain the simulation data of the test graph, fitting the simulation data with the wafer data, and establishing an OPC model by adopting the fitted simulation data. According to the method for establishing the OPC model provided by the invention, the wafer dataof part of the actual graph is fitted with the overall simulation data of the test graph, and the OPC model is established through the fitted data, so that the situation of spending a lot of time to obtain the large amount of wafer data is avoided, the modeling time is shortened, and the research and development efficiency is improved.

Owner:NEXCHIP SEMICON CO LTD

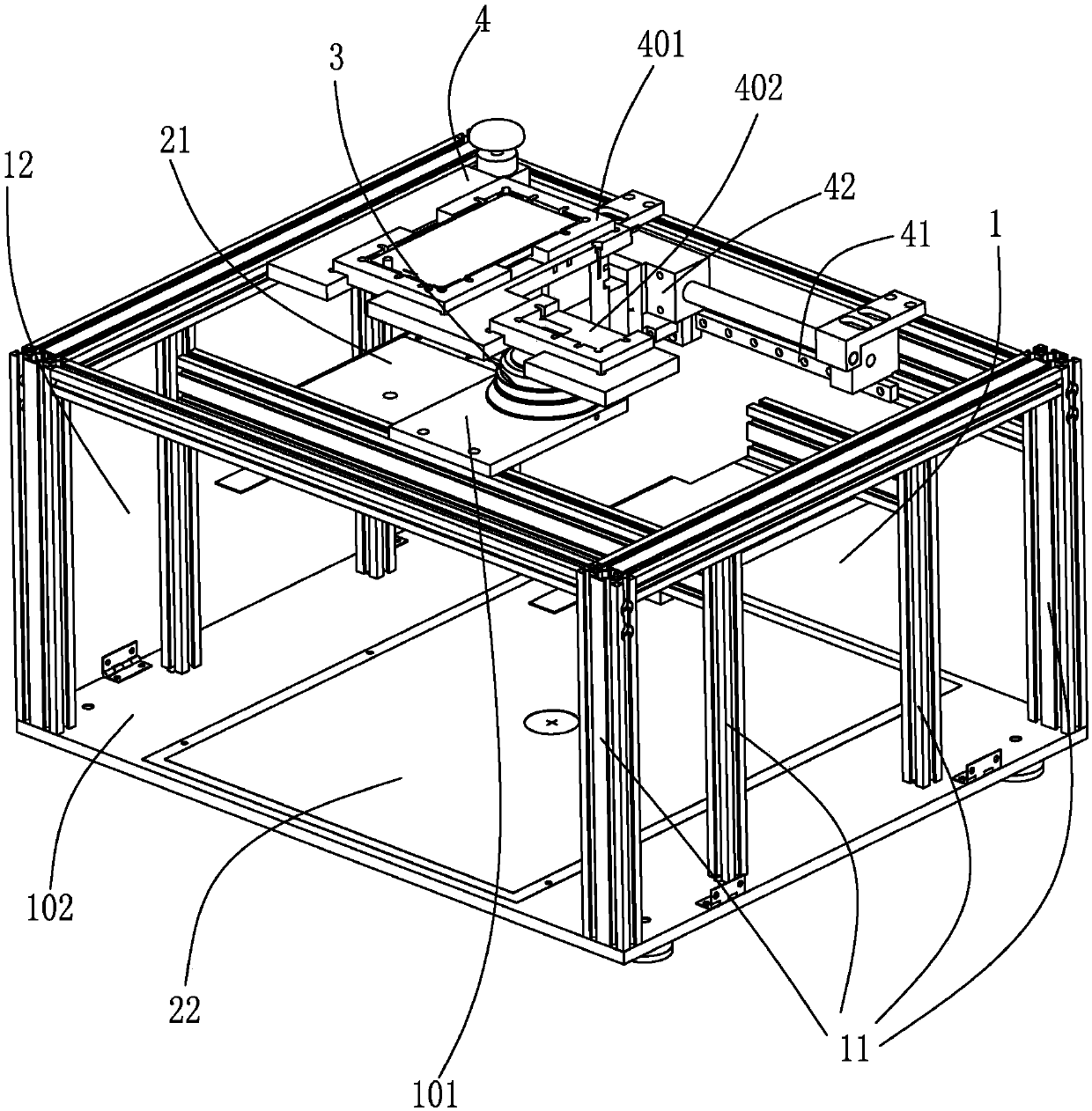

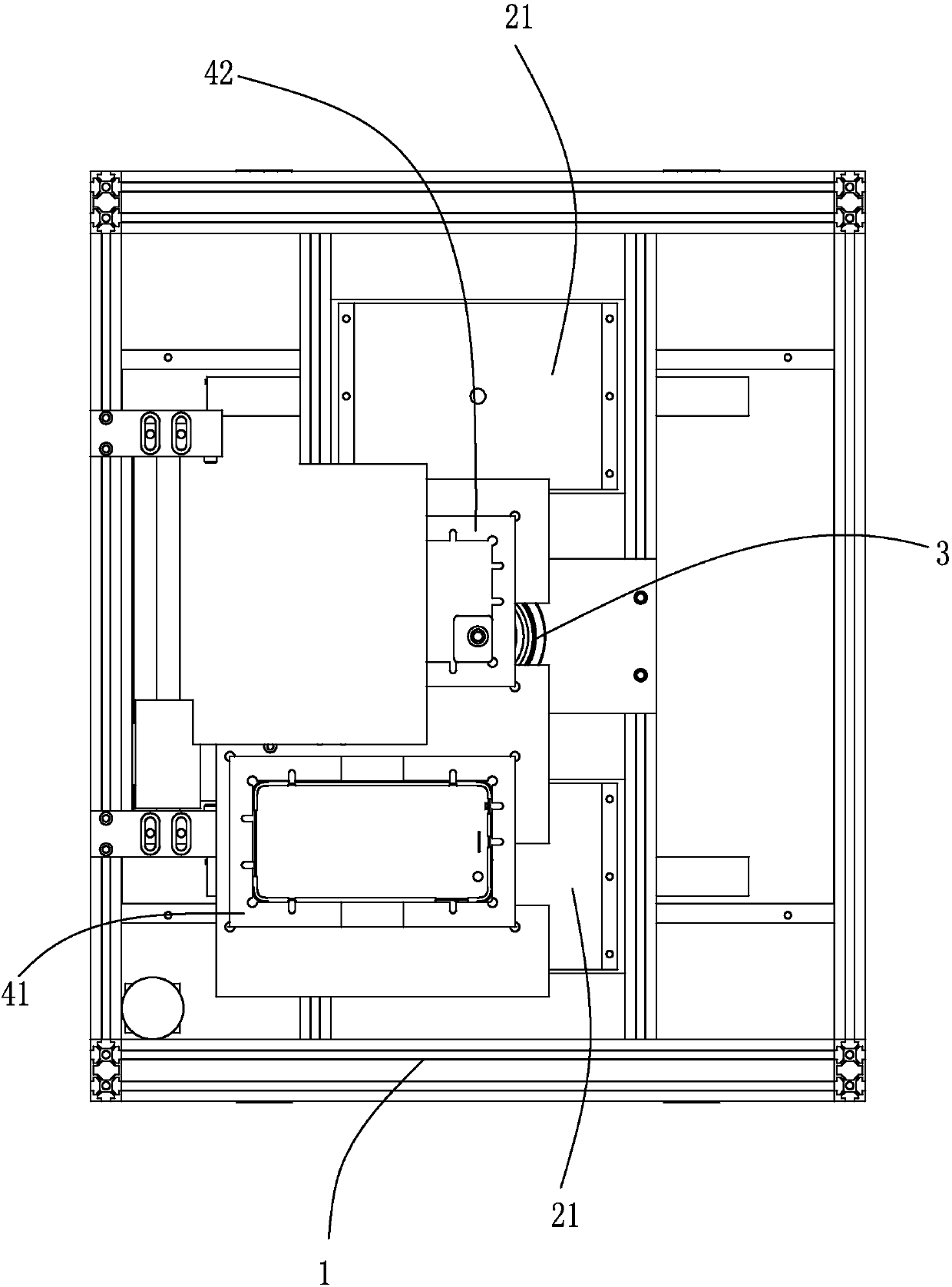

Mobile phone focus-fixed image quality detector

InactiveCN107806984AReduce volumeImprove detection efficiencyTesting optical propertiesFar distanceComputer hardware

The invention relates to a detecting instrument of a mobile phone lens, in particular to a mobile phone focus-fixed image quality detector. The mobile phone focus-fixed image quality detector comprises a rack and also comprises a testing graph card group including a near-focus testing graph card and a far-focus testing graph card located on the rack, a teleconverter lens group, an illumination light source for emitting and irradiating uniform light to the testing graph card group, and a mobile carrier capable of driving a mobile phone to be detected to move on the rack, wherein the testing graph card group, the teleconverter lens group is opposite to the far-focus testing graph card, the near-focus testing graph card and the far-focus testing graph card are installed on the rack, and the mobile phone to be detected moves on the two graph cards through the mobile carrier to achieve switching of near-focus and far-focus tests. In addition, the teleconverter lens group is added on the rack and is utilized to make the imaging distance of the far-focus testing graph card greater than the actual distance from the mobile phone to be detected to the far-focus testing graph card so as to simulate far-distance shooting, the size of the detecting instrument can be greatly decreased, and accordingly the detecting efficiency is effectively improved.

Owner:ZHONGSHAN UVATA OPTICAL

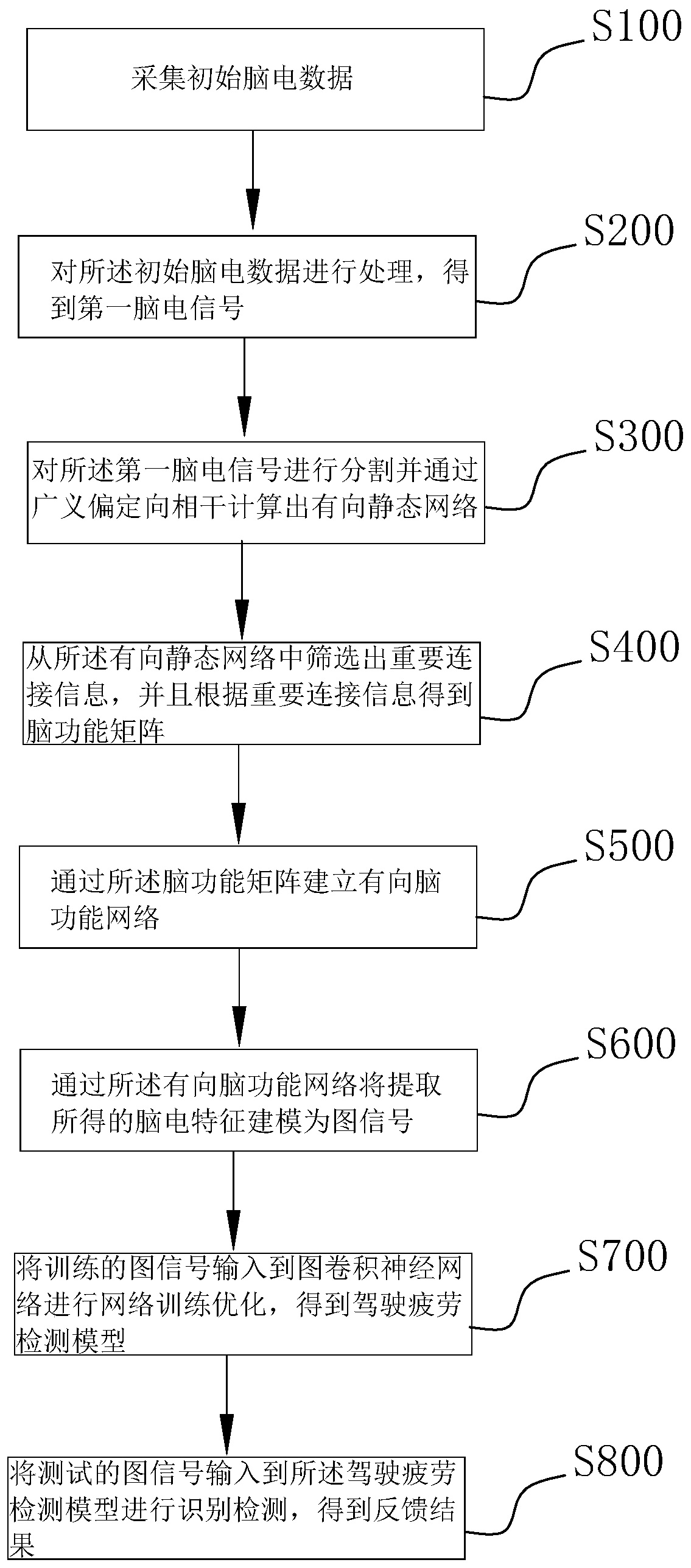

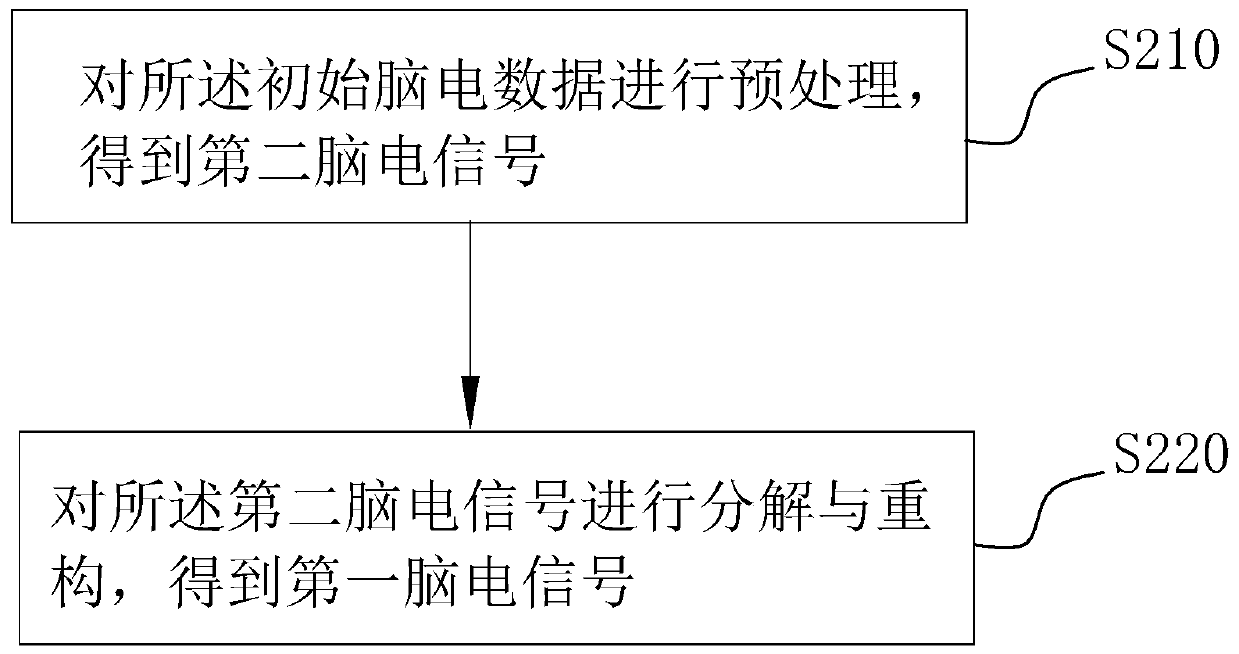

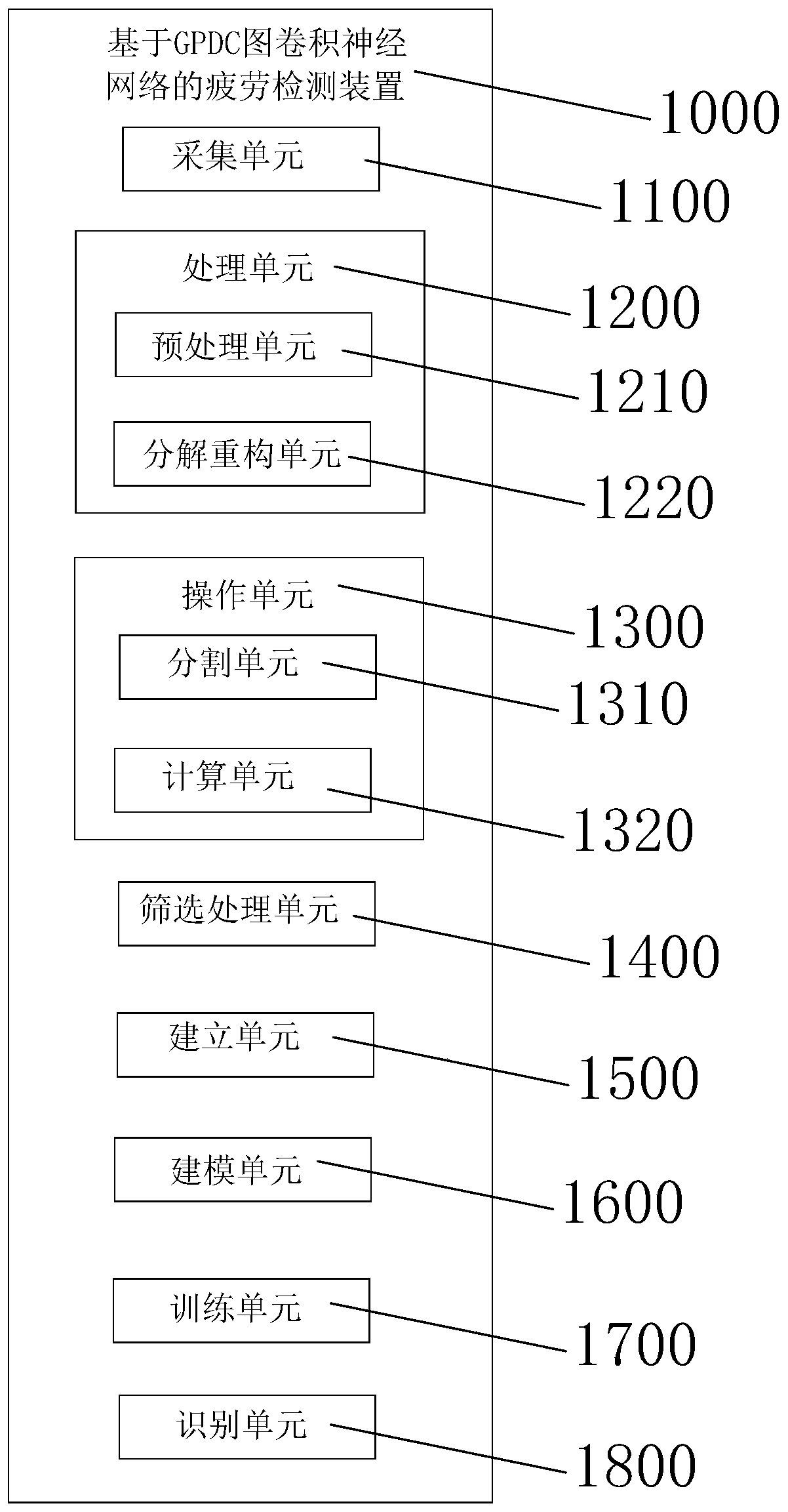

Fatigue detection method and device based on GPDC graph convolutional neural network and storage medium

InactiveCN111544017AEasy to detectDiagnostic recording/measuringSensorsElectroencephalogram featureTest graph

The invention discloses a fatigue detection method and device based on a GPDC graph convolutional neural network and a storage medium. The fatigue detection method comprises the steps of collecting initial electroencephalogram data, processing the initial electroencephalogram data to obtain a first electroencephalogram signal, segmenting the first electroencephalogram signal, calculating a directed static network through generalized partial directional coherence, screening important connection information from the directed static network, performing binarization processing on the important connection information to obtain a brain function matrix, establishing a directed brain function network through a brain function matrix, modeling the extracted electroencephalogram features into a graphsignal through the directed brain function network, inputting the trained graph signal into a graph convolutional neural network, carrying out network training optimization to obtain a driving fatigue detection model, inputting the tested graph signal into the driving fatigue detection model, and carrying out identification and detection to obtain a feedback result, thereby improving the detection performance in a driving fatigue state.

Owner:WUYI UNIV

Adding method and adding device for auxiliary graphs, storage medium and processor

ActiveCN110221516AHigh precisionAccurately add rulesOriginals for photomechanical treatmentSpecial data processing applicationsGraphicsTest graph

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

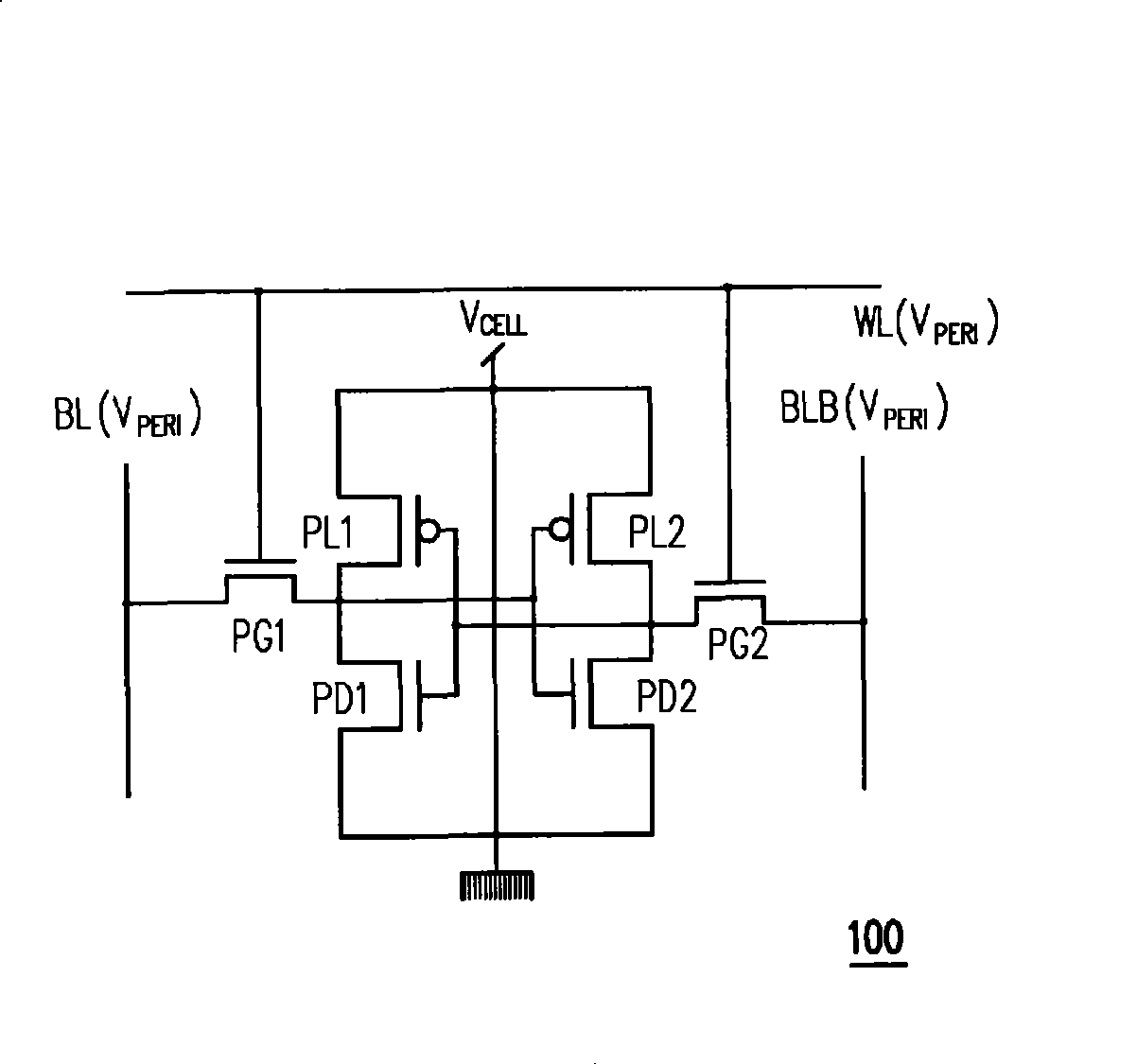

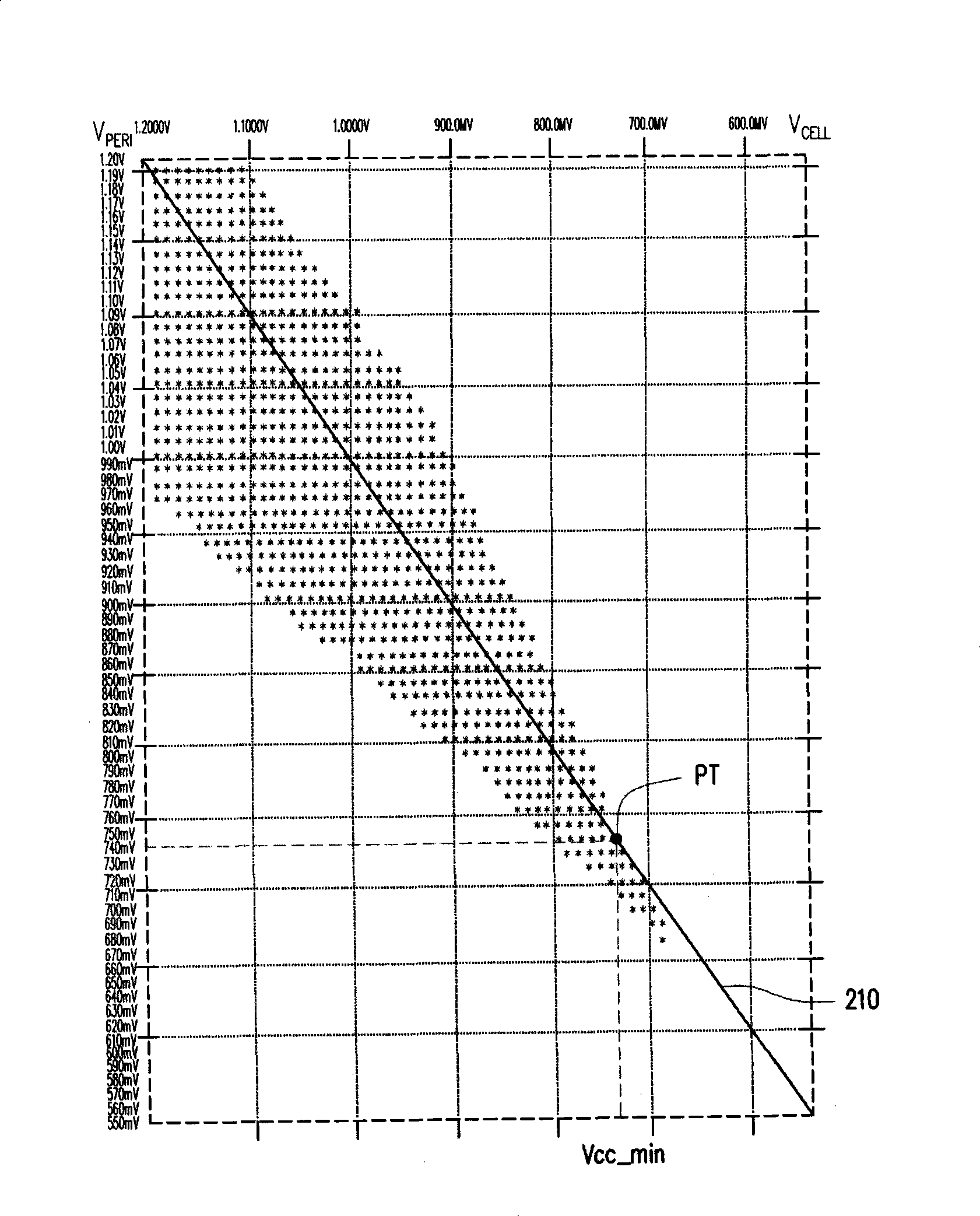

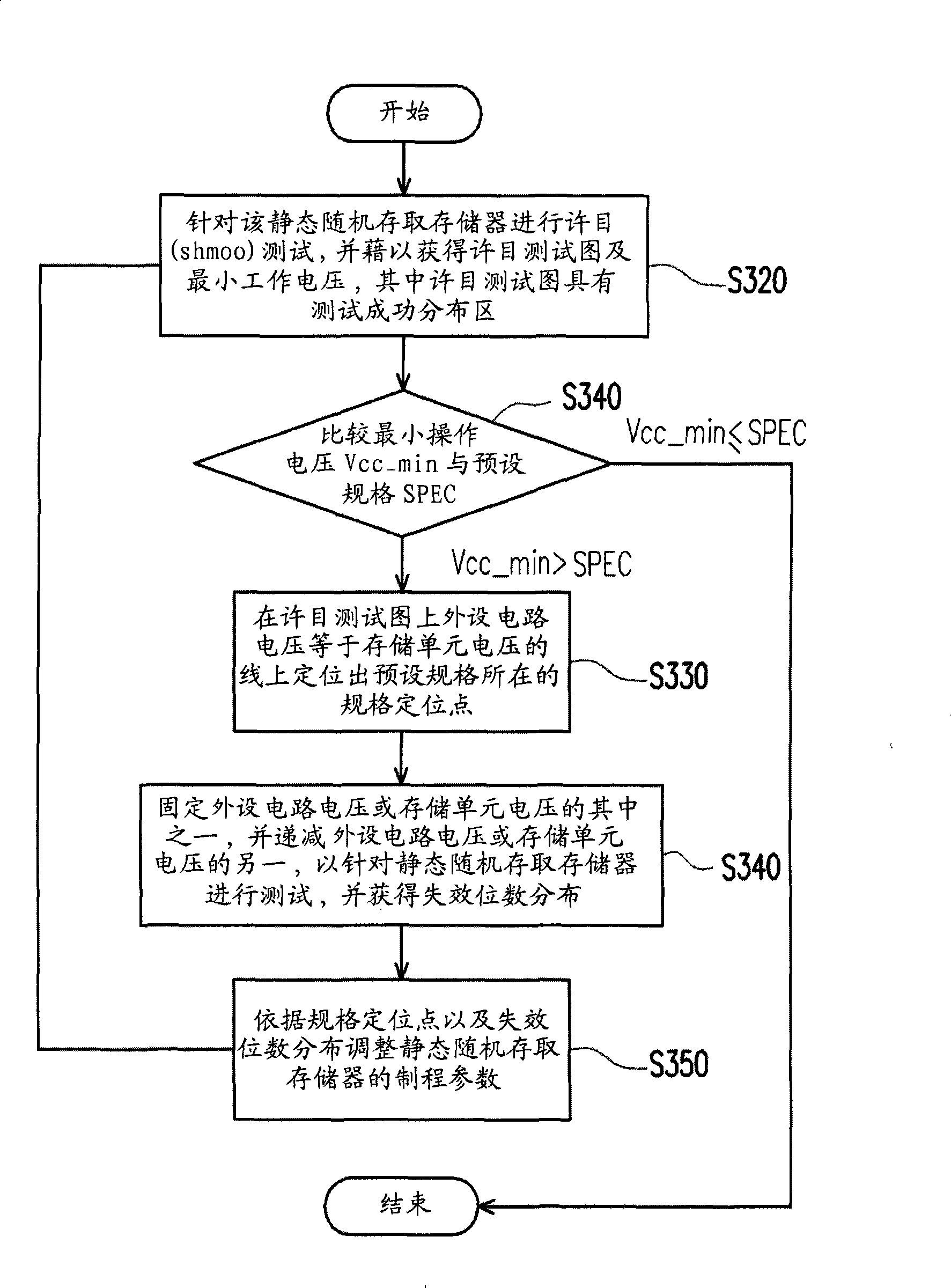

Adjusting method for operating voltage of SRAM (static random access memory)

ActiveCN101752009BAdjust the minimum operating voltageThe minimum operating voltage effectively resolvesStatic storageTest graphStatic random-access memory

The invention provides an adjusting method for minimum operating voltage of an SRAM (static random access memory), which can reach the optimal state. The SRAM receives voltage of a peripheral circuit and a memory unit. The adjusting method includes the following steps: first, a shmoo test is carried out on the SRAM to obtain a shmoo test graph and the minimum operating voltage; second, comparisonis carried out between the minimum operating voltage and a preset specification, and a specification positioning point of the preset specification is positioned on the line on the test graph that thevoltage of the peripheral circuit is equal to that of the memory unit; third, one of the voltage of the peripheral circuit or the memory unit is fixed, and the other voltage of the peripheral circuitor the memory unit is gradually lowered, so as to carry out the test on the SRAM and obtain the failure digit distribution; finally, processing parameters of the SRAM are adjusted according to the specification positioning point and the failure digit distribution.

Owner:UNITED MICROELECTRONICS CORP

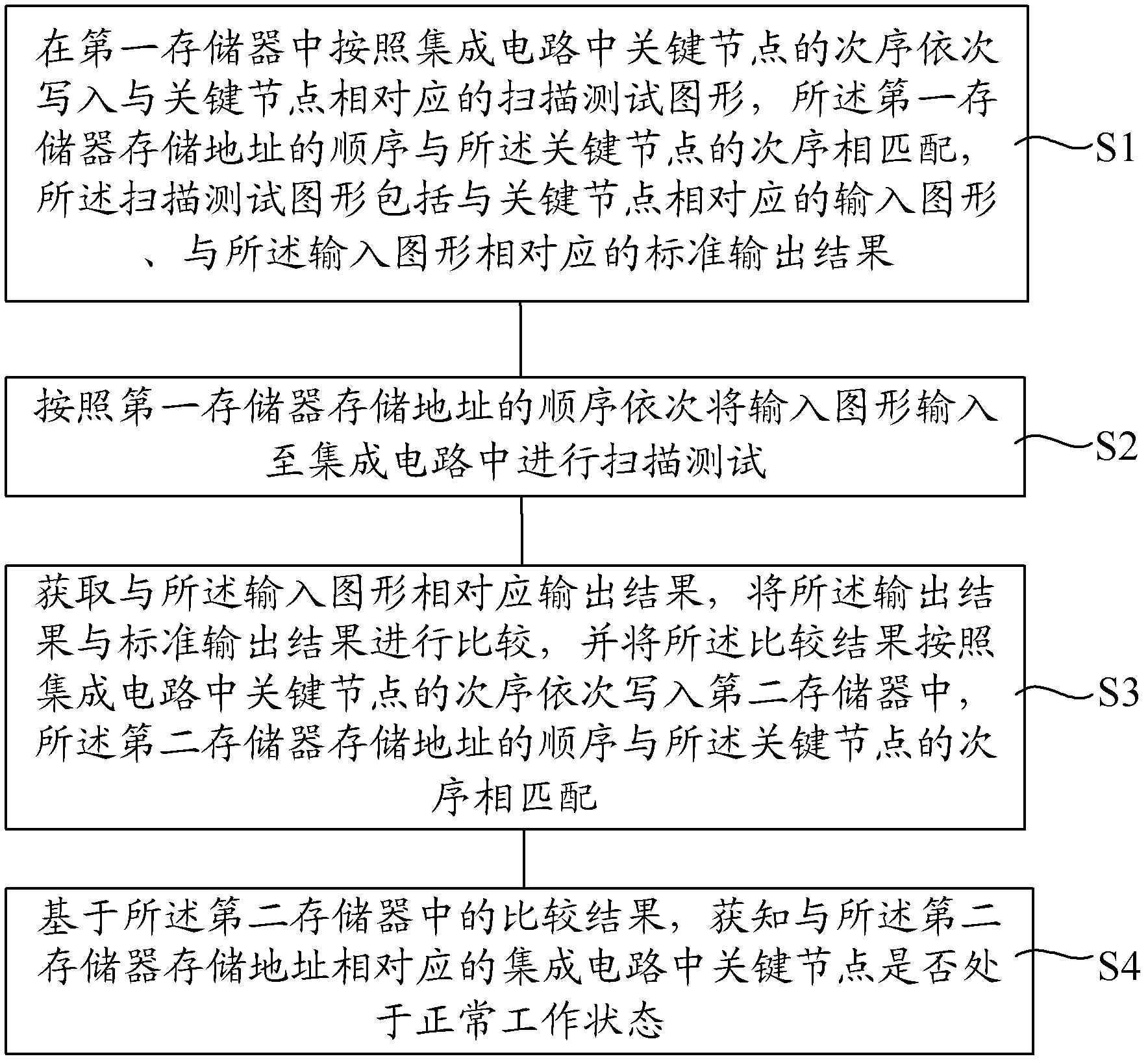

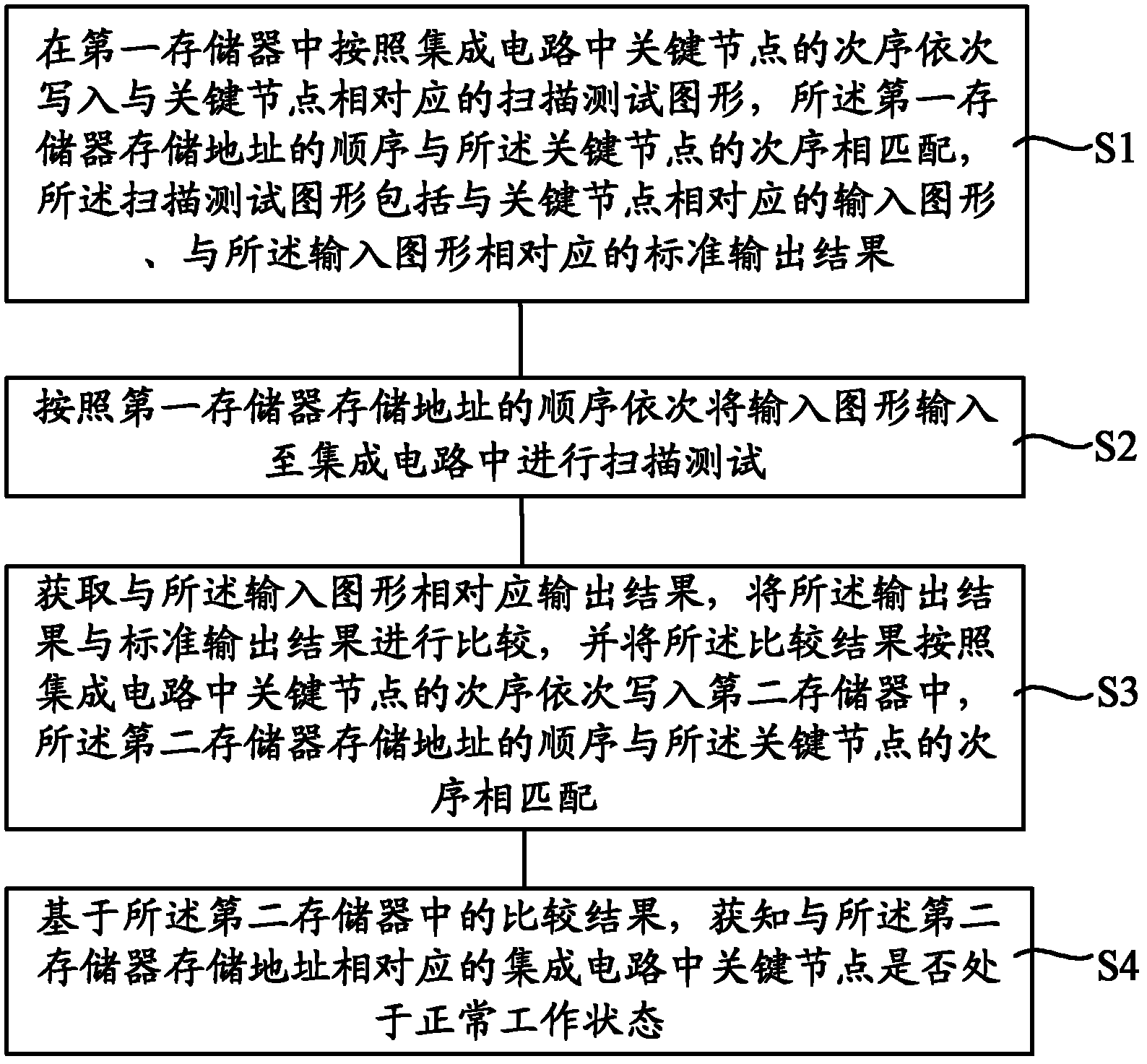

Scanning test method

ActiveCN102435935ALow storage depth requirementsReduce Scan Test CostsDigital circuit testingGraphicsComputer hardware

A scanning test method comprises the following steps: successively writing a scanning test graph corresponding to key nodes in a first memory according to an sequence of the key nodes in an integrated circuit (IC), wherein the sequence of a first memory storage address is matched with the sequence of the key nodes, and the scanning test graph comprises: an input graphs corresponding to the key nodes and a standard output result corresponding to the input graphs; inputting the input graphs successively into the IC according to the sequence of the first memory storage address and performing scanning test; acquiring an output result corresponding to the input graphs, comparing the output result with a standard output result and successively writing a comparison result in a second memory according to the sequence of the key nodes, wherein the sequence of a second memory storage address is matched with the sequence of key nodes; based on the comparison result in the second memory, knowing whether the key nodes corresponding to the second memory storage address in the IC are in a normal working state. By using the method of the invention, scanning test costs can be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Pattern selection method for light source-mask optimization

The invention provides a graph selection method used for light source-mask optimization. The graph selection method comprises the steps of calculating power spectrum density of each feature graph in a plurality of feature graphs; calculating a difference degree between any two feature graphs in the feature graphs based on the calculated power spectrum density of each feature graph; and selecting the feature graphs with the difference degree greater than or equal to a predetermined threshold in the feature graphs as test graphs used for the light source-mask optimization. According to the graph selection method used for the light source-mask optimization, provided by the invention, the test graphs used for the light source-mask optimization can be efficiently and quickly selected, and any key graph is not omitted, so that efficient and high-accuracy light source-mask optimization is realized.

Owner:SEMICON MFG INT (SHANGHAI) CORP

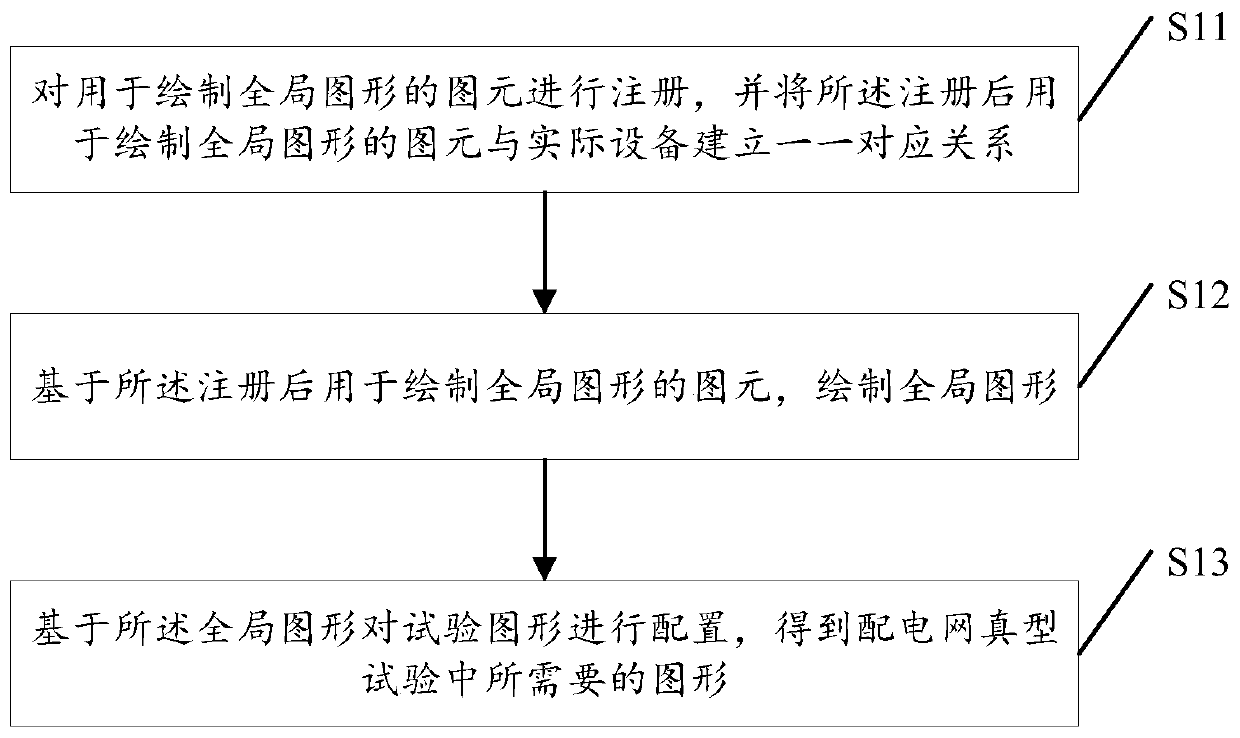

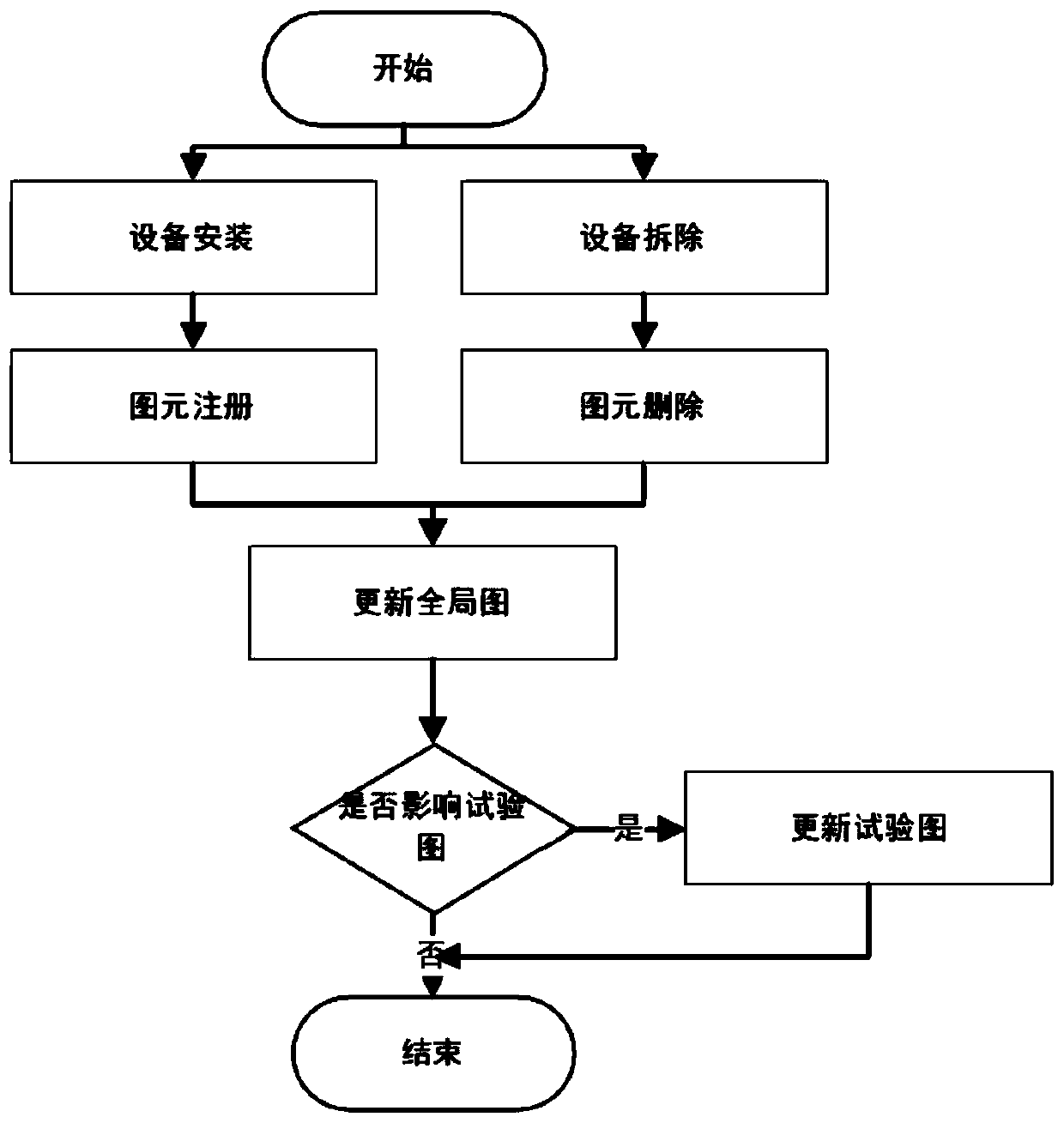

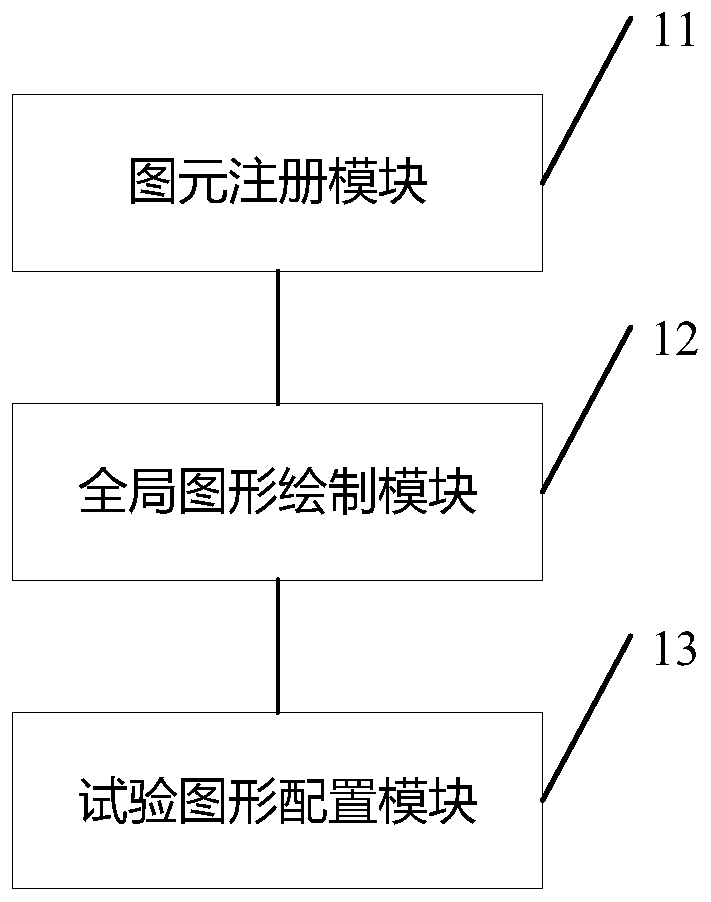

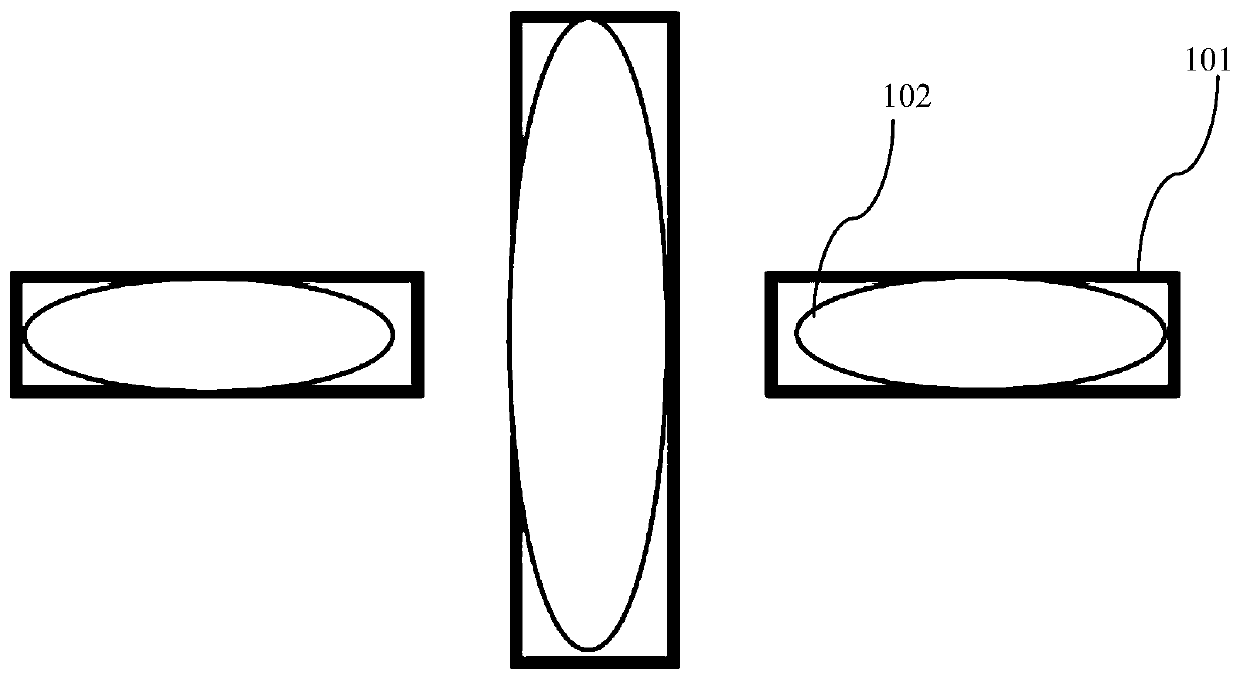

Graph maintenance method and device in power distribution network true form test system

PendingCN111460595AReduce errorsReduce error rateGeometric CADCAD network environmentFull life cycleTest graph

The invention discloses a graph maintenance method in a power distribution network true model test system, which comprises the following steps: registering primitives for drawing a global graph, and establishing a one-to-one correspondence relationship between the registered primitives for drawing the global graph and actual equipment; drawing a global graph based on the registered primitives usedfor drawing the global graph; configuring a test pattern based on the global pattern to obtain a pattern required in a power distribution network true test, wherein the device comprises a primitive registration module, a global graph drawing module and a test graph configuration module. In the embodiment of the invention, the method and the device maintain the full life cycle of the test patternin a mode of matching the global pattern with the primitives and tightly coupling the primitives with the equipment, so that the workload of workers can be reduced to a great extent, and the error probability of the test pattern is reduced.

Owner:ELECTRIC POWER RES INST OF GUANGXI POWER GRID CO LTD

Quantitative analysis method of verification graph for OPC verification

ActiveCN109857881AImprove OPC processDigital data information retrievalOriginals for photomechanical treatmentGraphicsTest graph

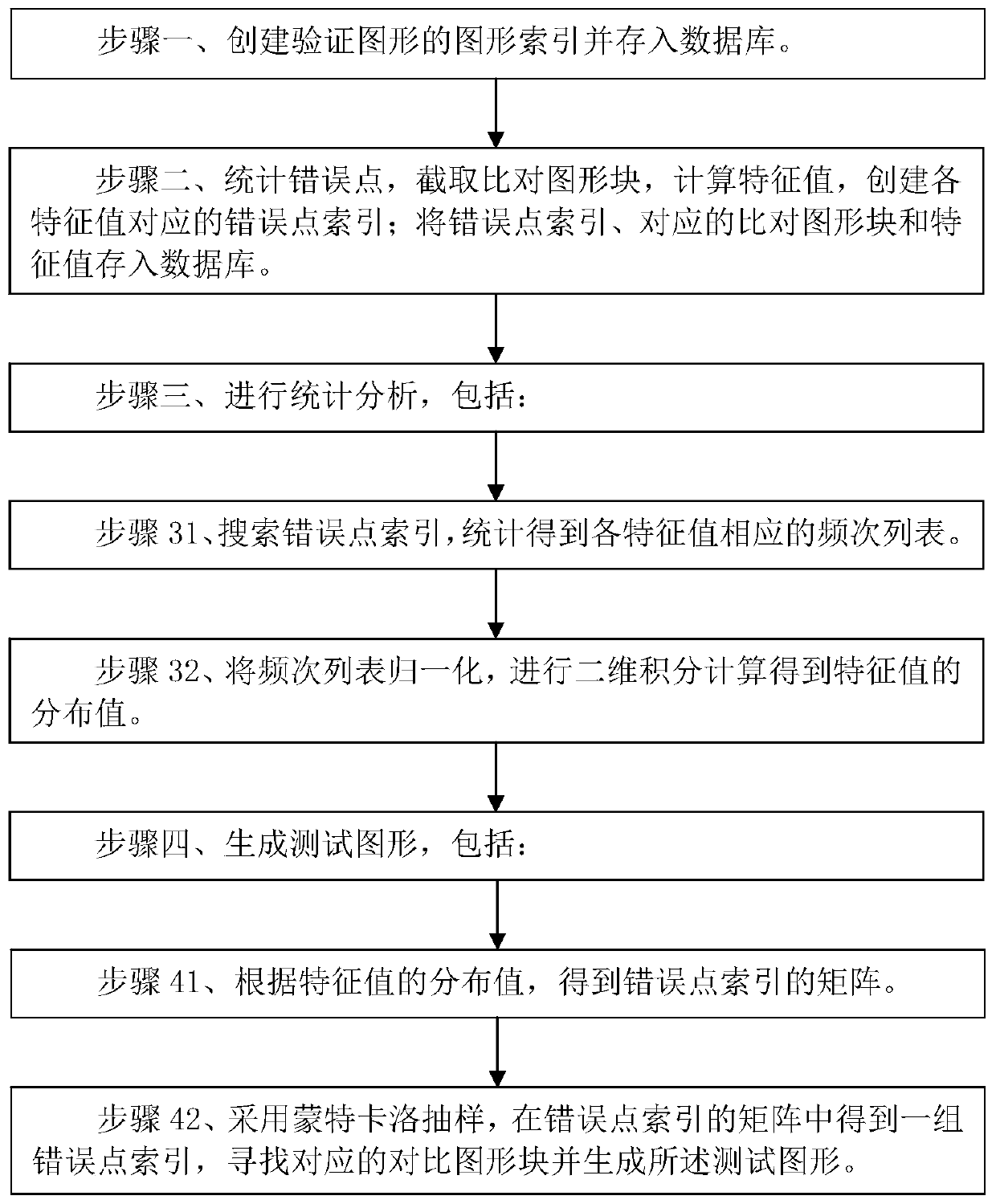

The invention discloses a quantitative analysis method of a verification graph for OPC verification. The quantitative analysis method comprises the following steps: step 1, creating a graph index of the verification graph and storing the graph index into a database; step 2, counting error points, intercepting and comparing graphic blocks, calculating characteristic values, and creating error pointindexes corresponding to the characteristic values; storing the error point index, the corresponding comparison graphic block and the feature value into a database; step 3, performing statistical analysis, including: step 31, searching an error point index, and performing statistics to obtain a frequency list corresponding to each characteristic value; step 32, normalizing the frequency list, andcarrying out two-dimensional integral calculation to obtain a distribution value of a characteristic value; step 4, generating a test pattern, including: step 41, obtaining an error point index matrix according to the distribution value of the feature value; and step 42, obtaining a group of error point indexes by adopting Monte Carlo sampling, searching corresponding comparison graph blocks, andgenerating the test graph. According to the invention, time and labor can be saved, and the OPC process can be improved more accurately.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Measurement method of dynamic image quality of liquid crystal display

InactiveCN102682684BHigh precisionMeet measurement needsStatic indicating devicesTest graphImaging quality

The invention discloses a method for measuring the quality of a dynamic image of a liquid crystal display. The method comprises an upper machine control flow and a lower machine image generation and data acquisition operating flow, wherein the upper machine control flow is used for defining a display image format, selecting a clock updating scheme, setting graph driving configuration, determining a data acquisition mode and computing the quality parameters of the dynamic image; the lower machine image generation and data acquisition operating flow is used for receiving and converting operating data, generating and controlling a synchronizing signal, generating and configuring a test graph, selecting and setting display drive, and acquiring and transmitting characteristic data; and transmission of measuring data in an inter-integrated circuit (I2C) bus mode and transmission of transient response characteristic data through a universal serial bus (USB) interface are performed between the upper machine control flow and the lower machine image generation and data acquisition operating flow. The method provided by the invention is used for comprehensively identifying the dynamic characteristic of the liquid crystal display and can meet measuring requirements of different types of liquid crystal displays.

Owner:南京东晖光电有限公司

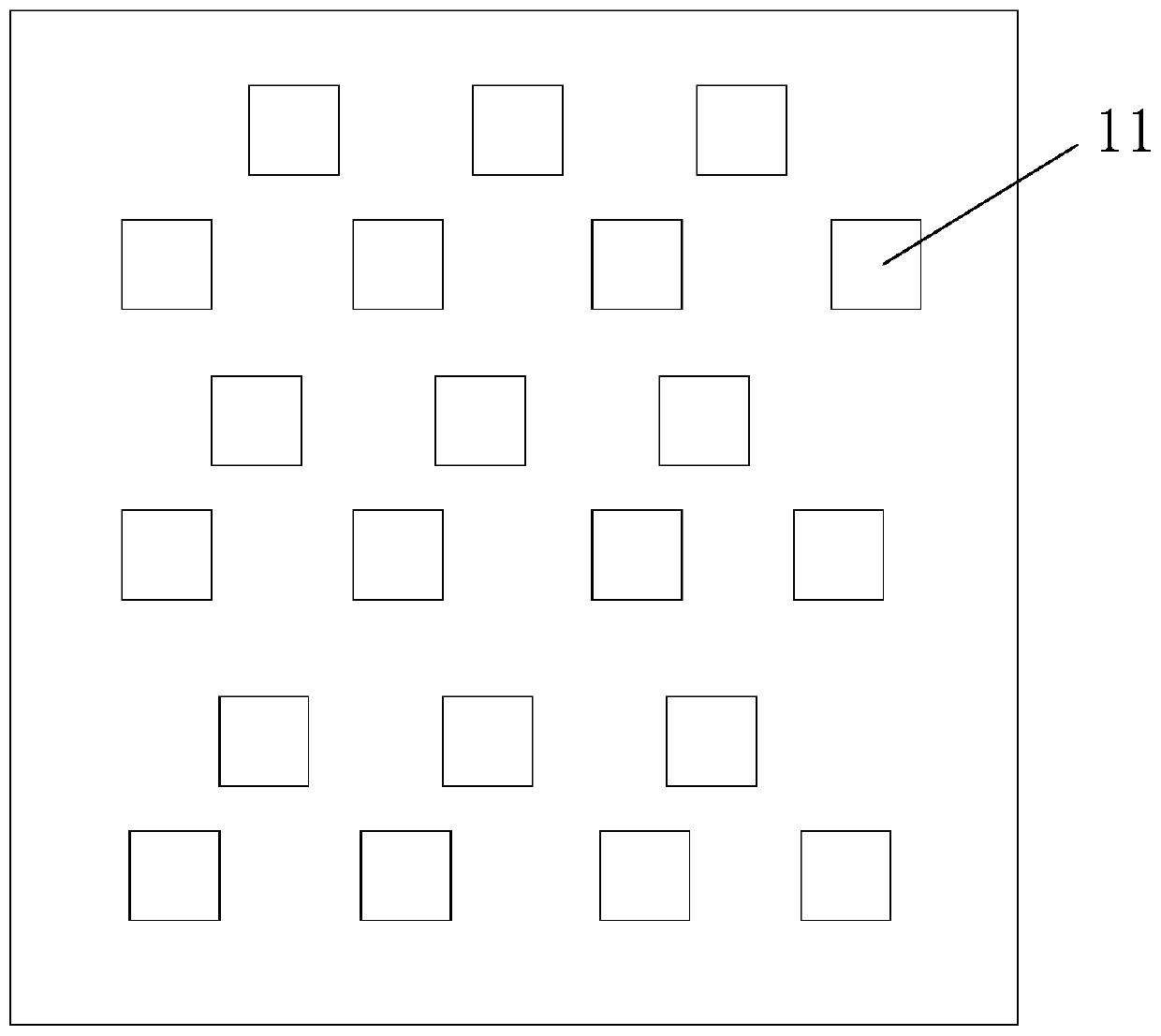

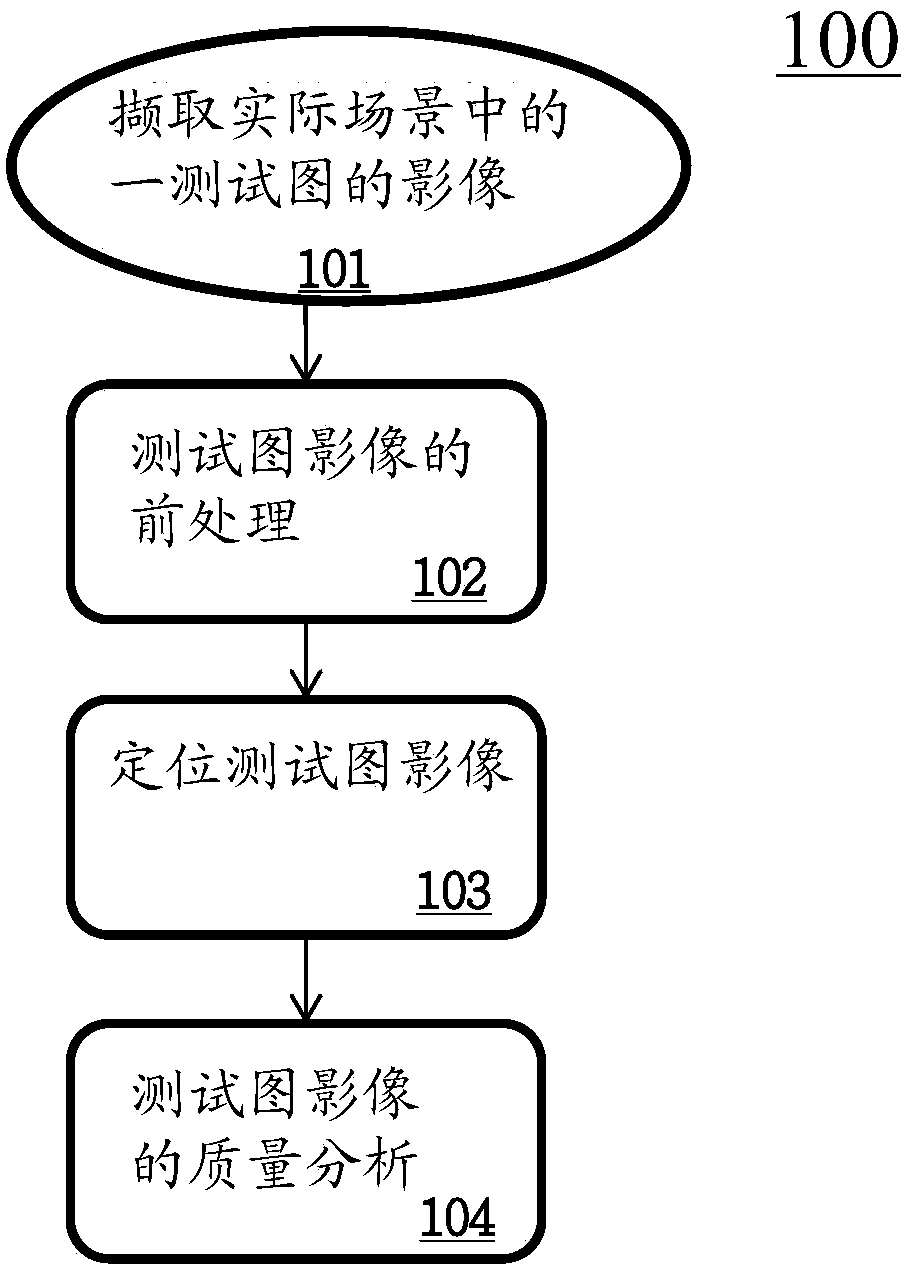

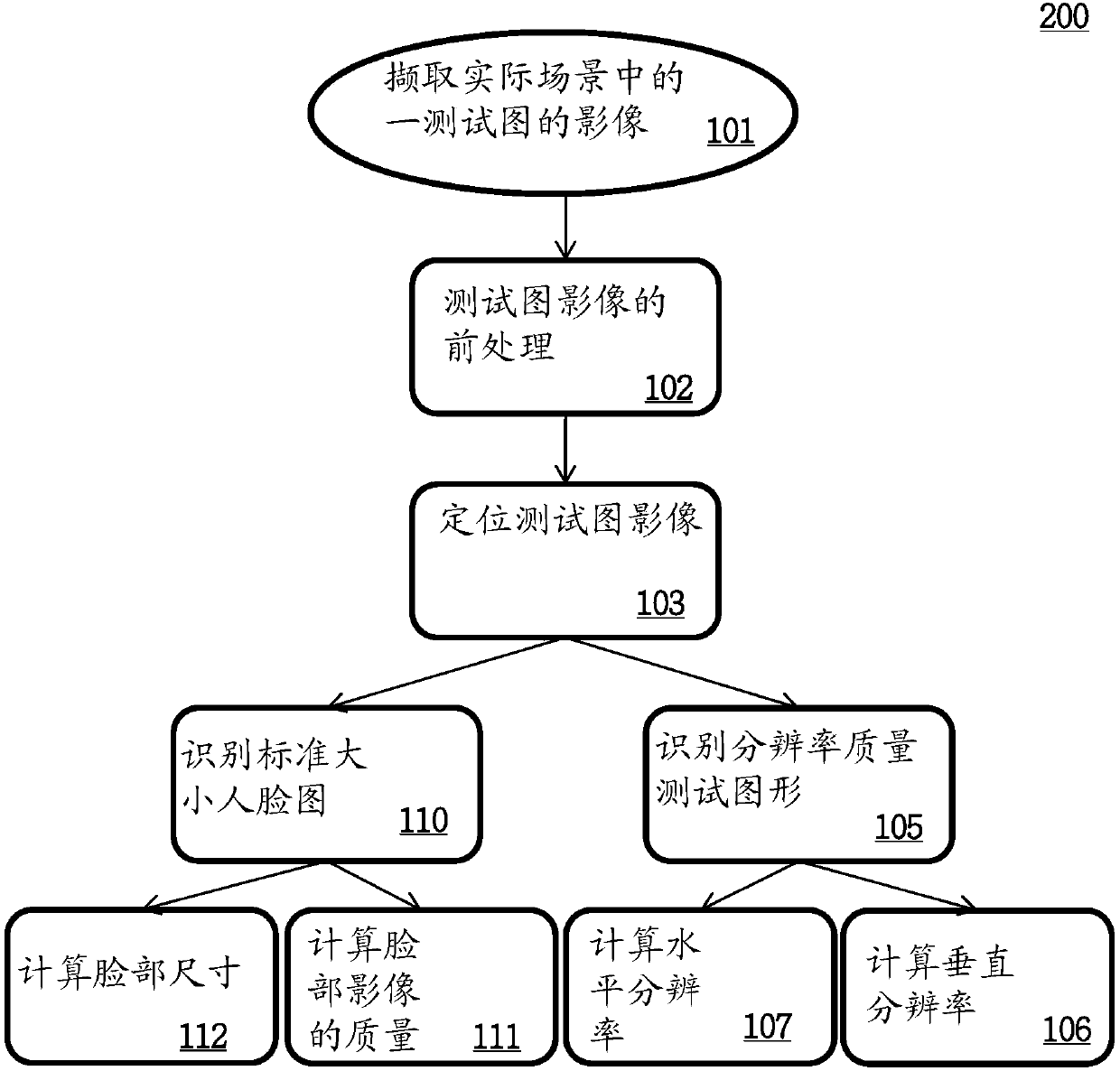

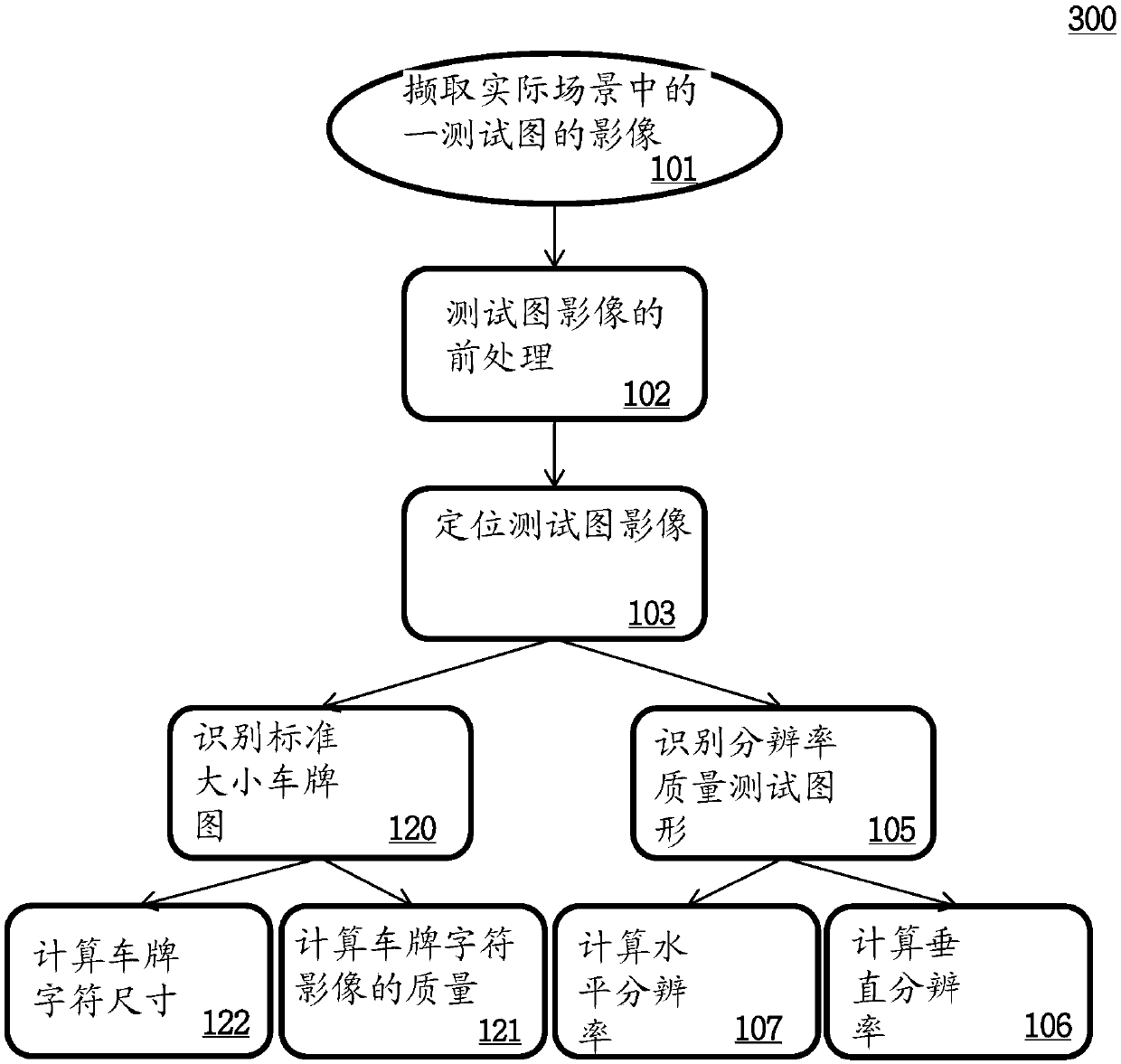

Method of evaluating image quality

The invention discloses a method of evaluating image quality and a test graph used for evaluating the image quality. The method comprises the steps of: providing the test graph, wherein the test graphis placed in an actual scene and comprises a plurality of positioning graphics and a plurality of quality test graphics; picking an image of the test graph in the actual scene; finding the pluralityof positioning graphics in the image of the test graph to determine an orientation of the image of the test graph; and identifying images of the plurality of quality test graphics in the image of thetest graph, and evaluating quality of the images of the plurality of quality test graphics.

Owner:GORILLA TECH

Method of determining OPC minimum segmentation length

ActiveCN112415864ASolve the problem of low correction accuracyImprove yieldPhotomechanical exposure apparatusMicrolithography exposure apparatusGraphicsTest graph

The invention provides a method for determining an OPC minimum segmentation length. The method comprises the steps: setting different graph edge segmentation lengths for a series of test graphs, calculating a difference between an OPC simulation value of the test graphs based on a model and light resistance CD data on a wafer, solving a root mean square, and determining the corresponding graph segmentation length to be the minimum segmentation length of the edge of each test graph when the root mean square has the minimum value. A problem that the OPC correction precision is not high due to afact that a target layout graph cannot be reasonably segmented in OPC based on the model is solved, and a product yield is increased.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

A Process Model Modeling and Correction Method Based on Pattern Density

ActiveCN106294935BAddressing Accuracy ImpactsImprove accuracyComputer aided designSpecial data processing applicationsGraphicsTest graph

The invention provides a process model molding and correcting method based on a graph density. The method comprises the steps that by adding redundant graphs with different graph densities and adjusting the OPC test graph region area, a test graph of a target graph density is obtained; according to silicon wafer data calibration models collected by the test graphs with different graph density ranges, OPC models under different graph density ranges are obtained; in the OPC processing process, a model representing the average density is used for correcting the whole layout data, layout density distribution is analyzed, graph areas with low density and high density are selected and subjected to correction with corresponding models respectively, and a mask graph is obtained finally.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

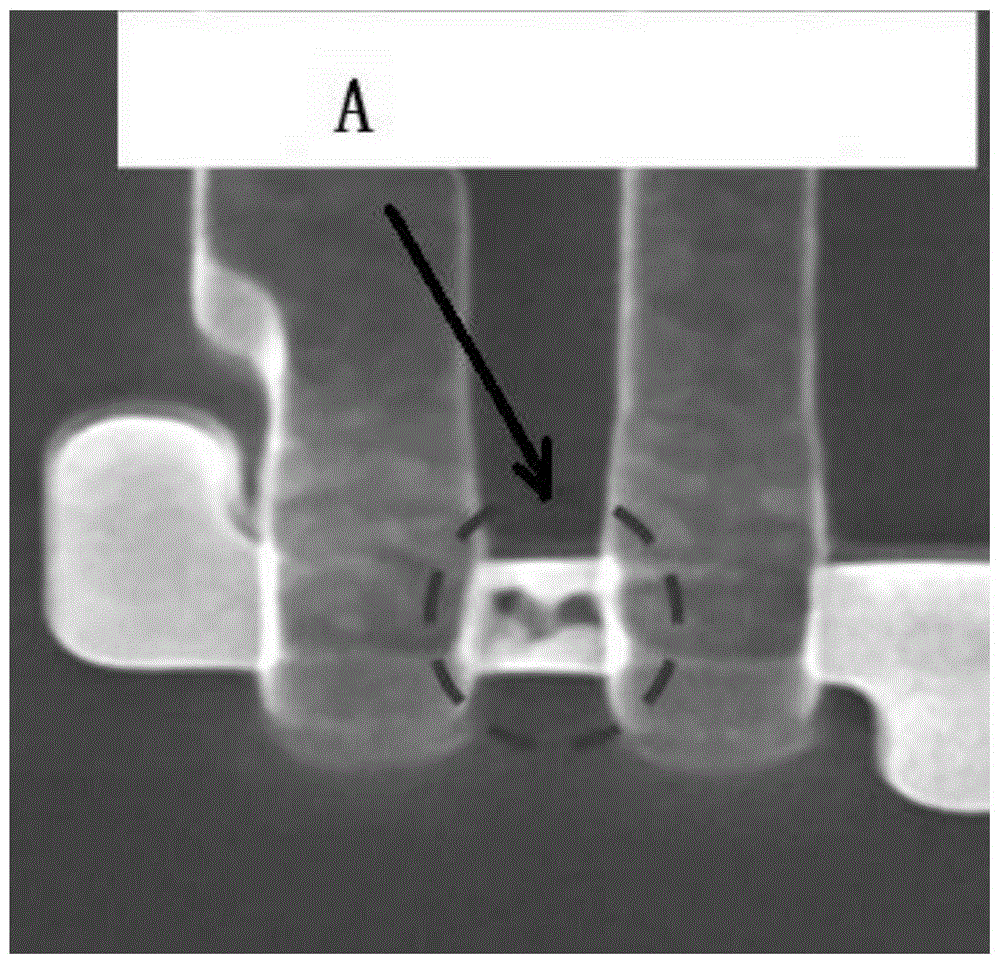

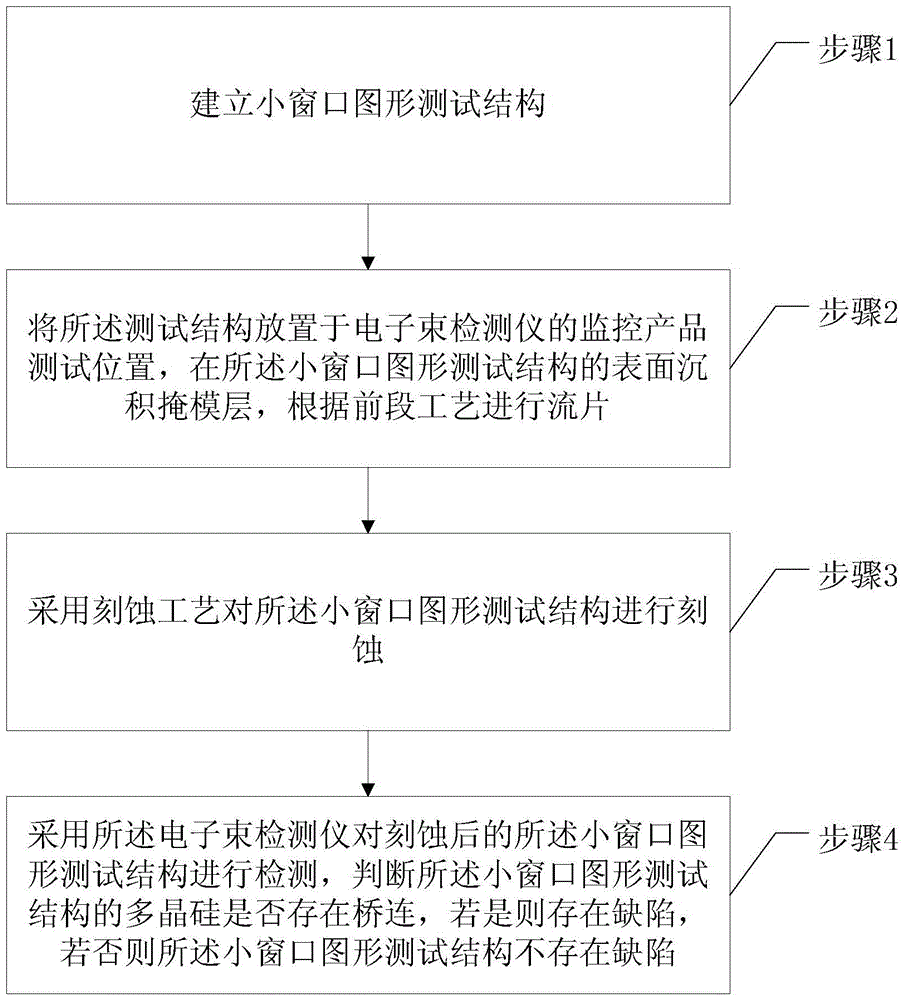

Method for Detecting Bridge Defects at the Bottom of Polysilicon Using Small Window Pattern Test Structure

ActiveCN103887196BIncreased sensitivityTimely detection of online defectsMaterial analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementTest graphManufacturing technology

The invention discloses a method for detecting a bridging defect on a polysilicon bottom by using a small window graph detection structure, relating to the circuit manufacture technology field. The method comprising steps of establishing a small window graph test structure, placing the test structure on a monitor product test position of an electron beam detection instrument, depositing a mask layer on the surface of the small window test graph structure and tapping out according to the previous technology, utilizing the etching technology to etch on the small window graph test structure, utilizing the electron beam detection instrument to detect the etched small window graph test structure, determining that whether the polysilicon of the small window graph test structure has bridging, if yes, the defect of the small window graph test structure exists, if not , the defect of the small window graph test structure does not exist. The method provided by the invention can discover the defect promptly, can provide data reference for improving yield during the process of research and development, can shorten the research and development cycle, can provide monitor means for products, can shorten influence interval and can provide guarantee for the yield of products.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

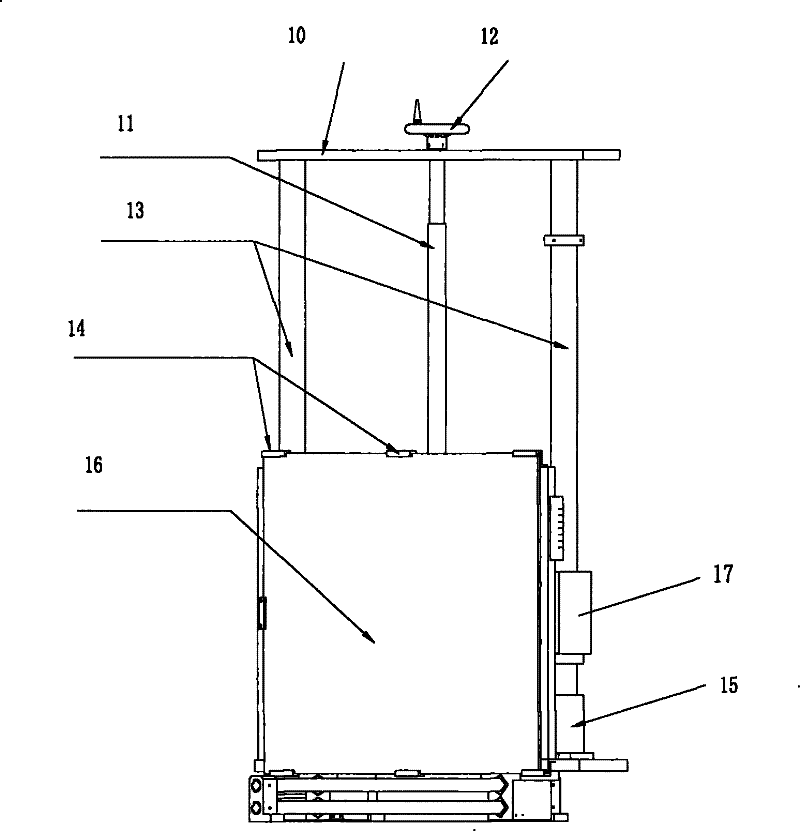

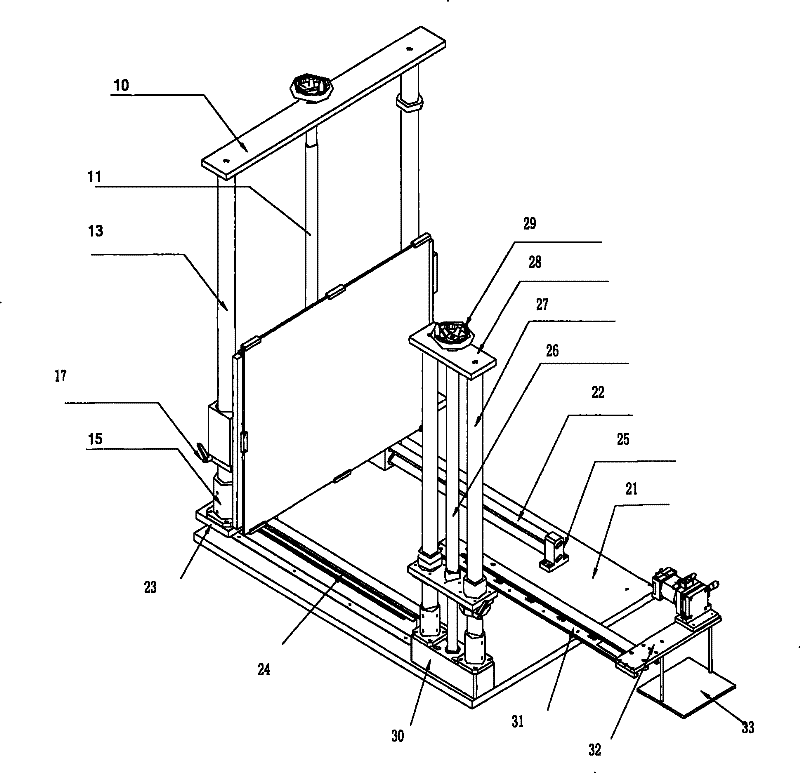

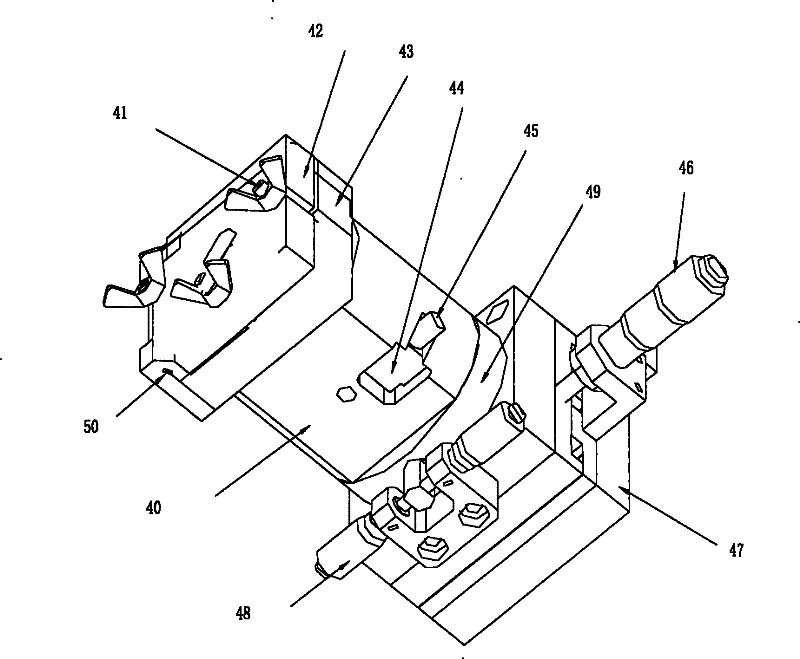

Camera detecting equipment and system

ActiveCN101625519BFeel free to adjust spacingMeet the test requirementsPhotographyTest graphImage quality

The invention discloses camera detecting equipment, which comprises a base, a support, a test graph fixing frame and a camera fixing bracket, wherein the support is arranged on the base and can move on the base along the Y-axis direction; the test graph fixing frame is used for fixing a test graph, arranged on the support and can move on the support in the Z-axis direction; the camera fixing bracket is arranged on the base; and a camera to be detected is arranged on the camera fixing bracket, so that the camera is opposite to the test graph arranged on the test graph fixing frame. The invention also discloses a camera detecting system. The equipment provided by the invention can be fixed on a worktable, and related test parts can be adjusted along a screw rod and are stable so as to assist a computer to detect and calculate the central offset and rotation angle of an image shot by the camera and meet the higher level requirement on the quality of the shot image.

Owner:BYD SEMICON CO LTD

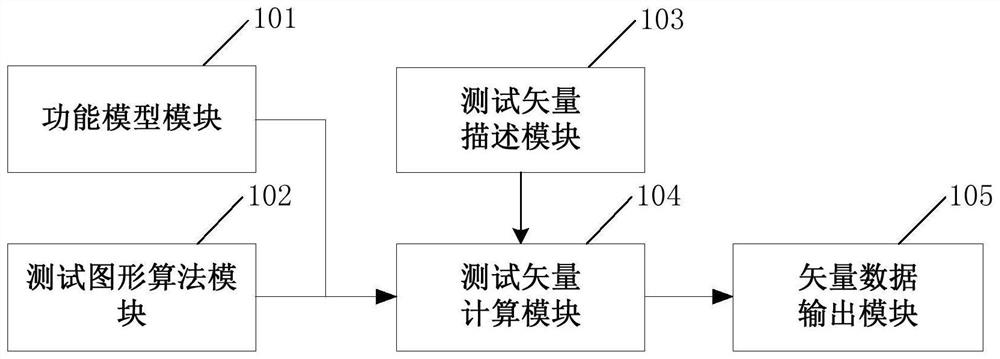

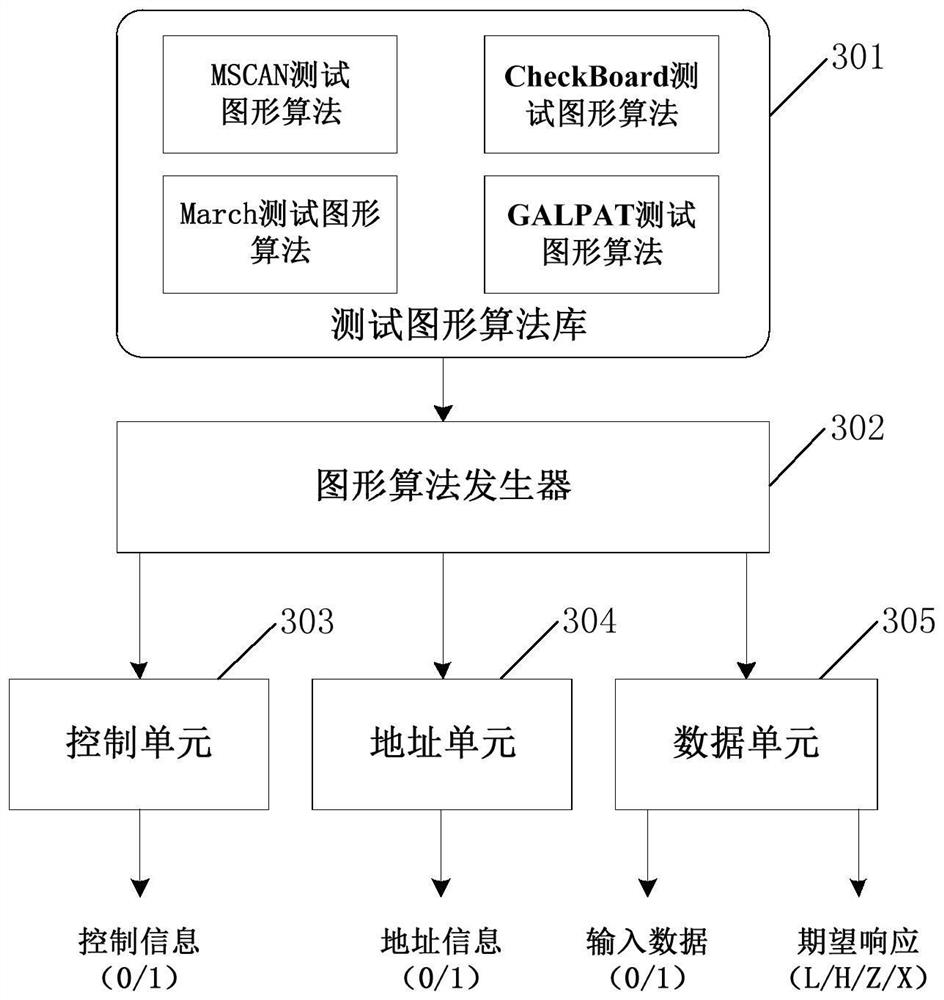

Test vector generation device and method

PendingCN114283872AFix technical issue with long build process timeImprove test efficiencyStatic storageTest graphModel testing

The invention relates to a test vector generation device and method, and belongs to the technical field of integrated circuit testing. The test vector generation device comprises a function model module, a test graph algorithm module, a test vector description module, a test vector calculation module and a vector data output module. The function model module is used for establishing a test function model according to interface information acquired from the to-be-tested memory; the test graph algorithm module is used for providing test graph calculation logic; the test vector description module is used for providing vector data information of a storage address and providing pin definition; the test vector calculation module is used for calculating test vector data of each storage address of the to-be-tested memory; and the vector data output module is used for outputting test vector data. According to the device, the test vector data applied to the memory function test can be conveniently and quickly generated, the technical problem that the time of the test vector generation process is relatively long is solved, and the test efficiency of the memory is improved.

Owner:BEIJING AEROSPACE MEASUREMENT & CONTROL TECH

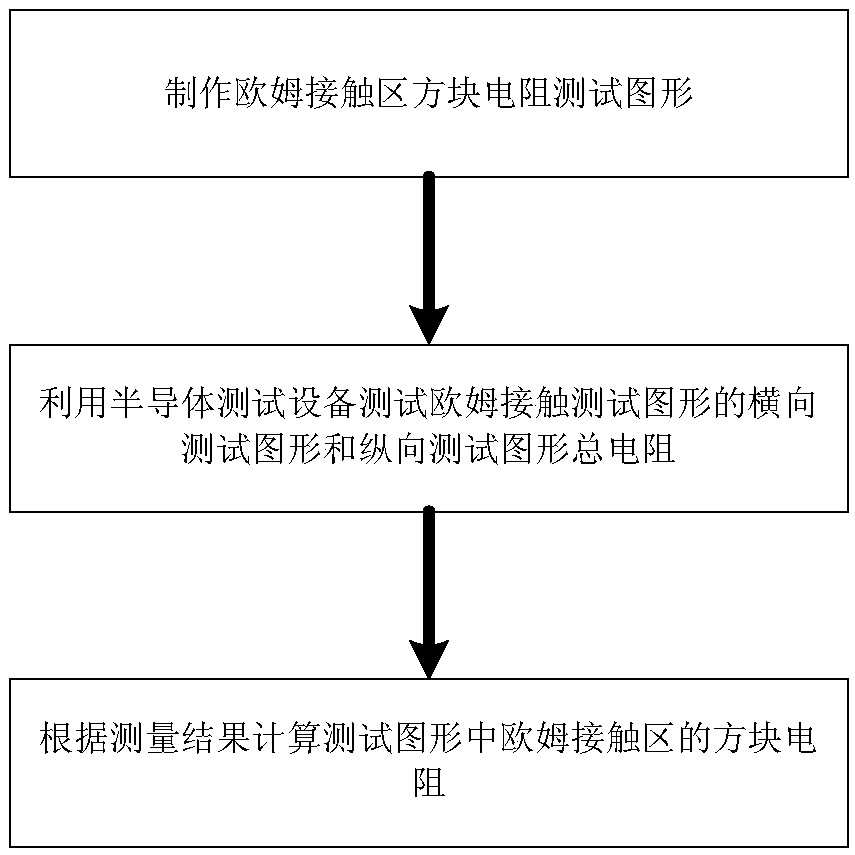

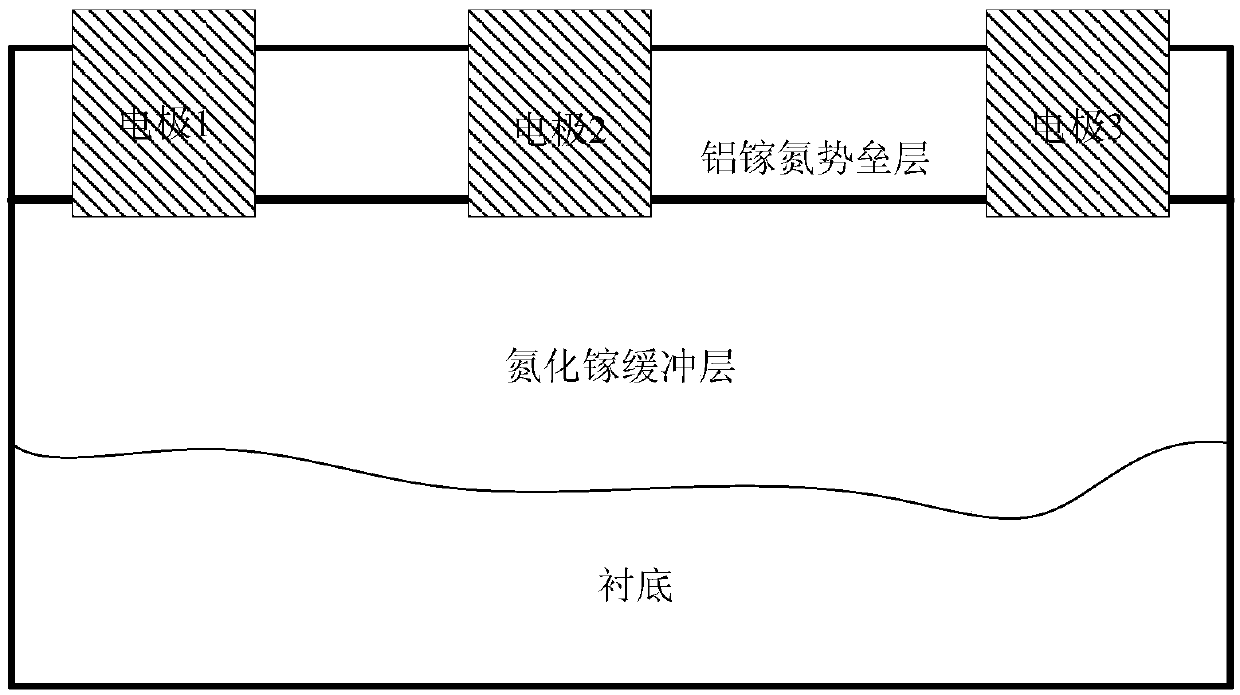

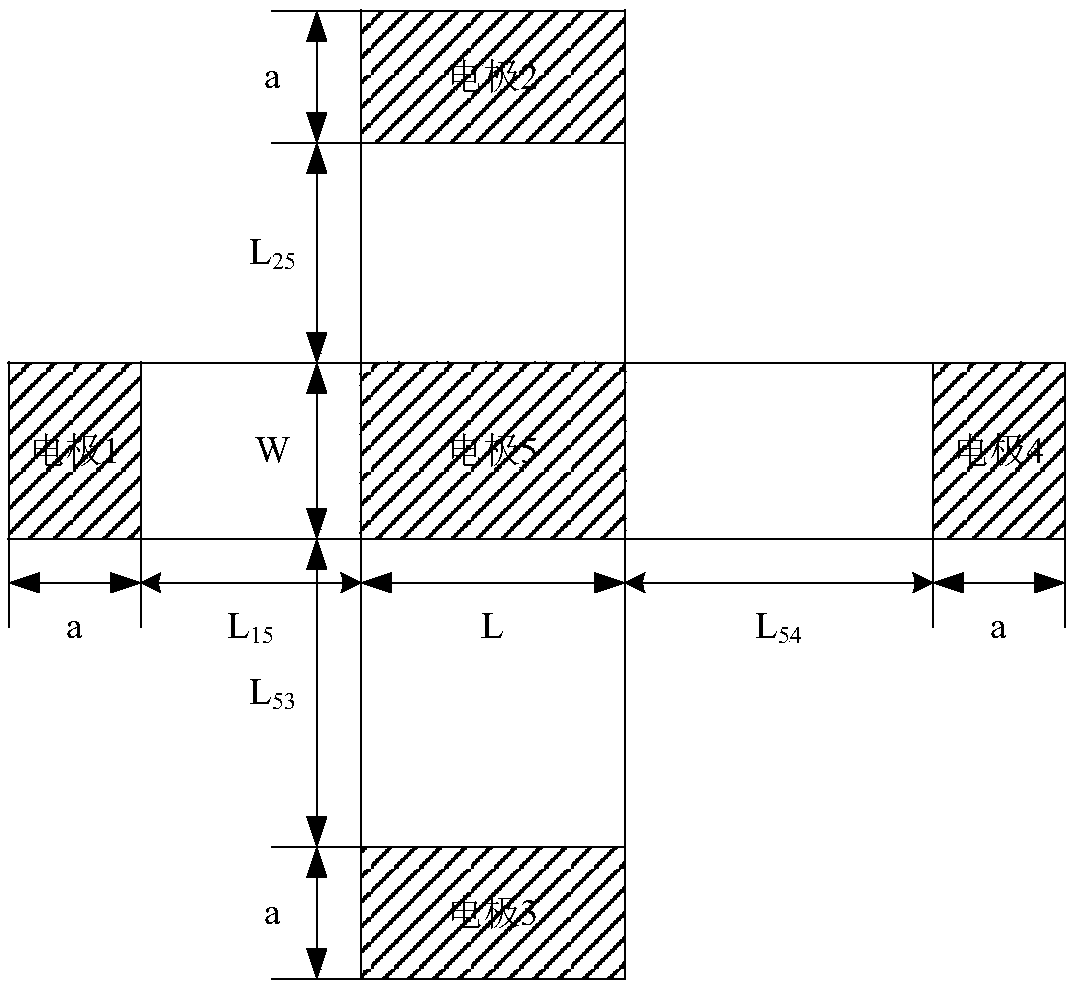

Measuring Method of Sheet Resistance in Ohmic Contact Area Based on Vertical Test Pattern

ActiveCN106783661BEasy to prepareSimple test methodSemiconductor/solid-state device testing/measurementHeterojunctionContact test

The invention discloses a method for testing square resistance in an ohm contact area based on vertical test graphs. According to the implementation scheme, the method comprises the following steps: preparing a group of transverse and longitudinal vertically crossed ohm contact test graphs, wherein the transverse test graph comprises a first electrode, a fifth electrode and a fourth electrode, and the longitudinal test graph comprises a second electrode, a fifth electrode and a third electrode; 2, testing a resistance value between the first electrode and the fourth electrode as well as a resistance value between the second electrode and the third electrode in the transverse and longitudinal test graphs separately; and 3, multiplying the obtained resistance value of the longitudinal test graph by a coefficient L / W, performing subtraction with the obtained resistance value of the transverse test graph, and dividing a coefficient 1-L / W by the difference value to obtain the square resistance of the ohm contact area in the test graphs, wherein L and W are lengths of the fifth electrodes in the transverse and longitudinal test graphs. The test graphs are simple and easy to manufacture, the test speed is high, the result is accurate and reliable, and the method can be applied to manufacturing of high-electro-mobility heterojunction transistors.

Owner:XIDIAN UNIV

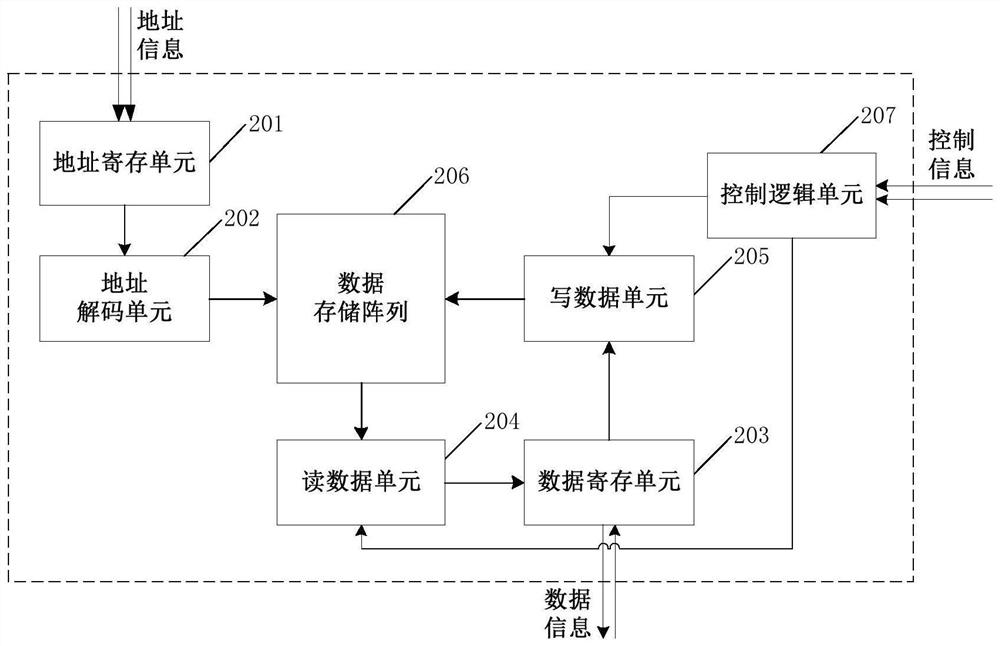

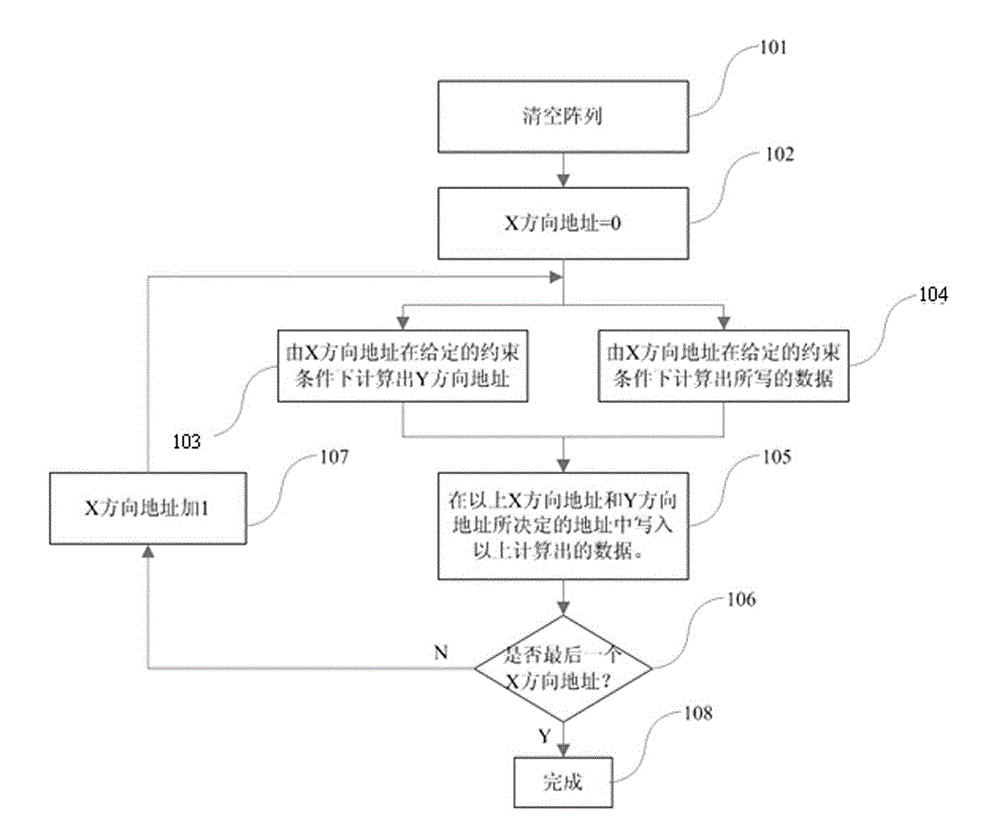

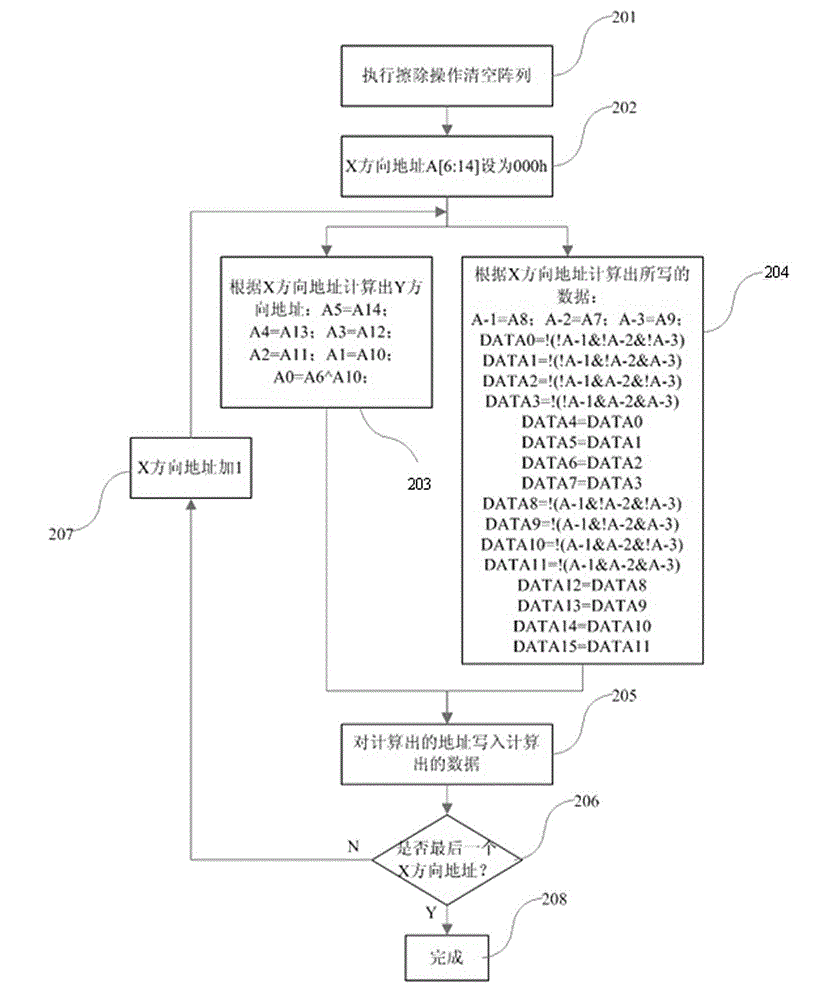

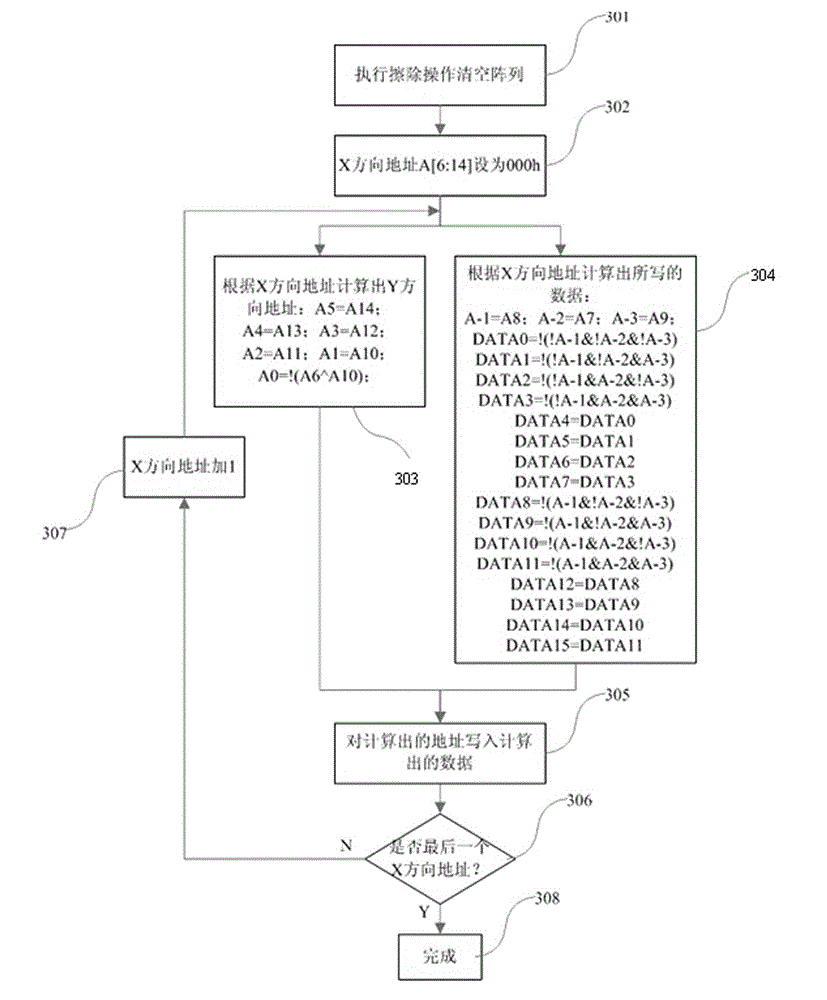

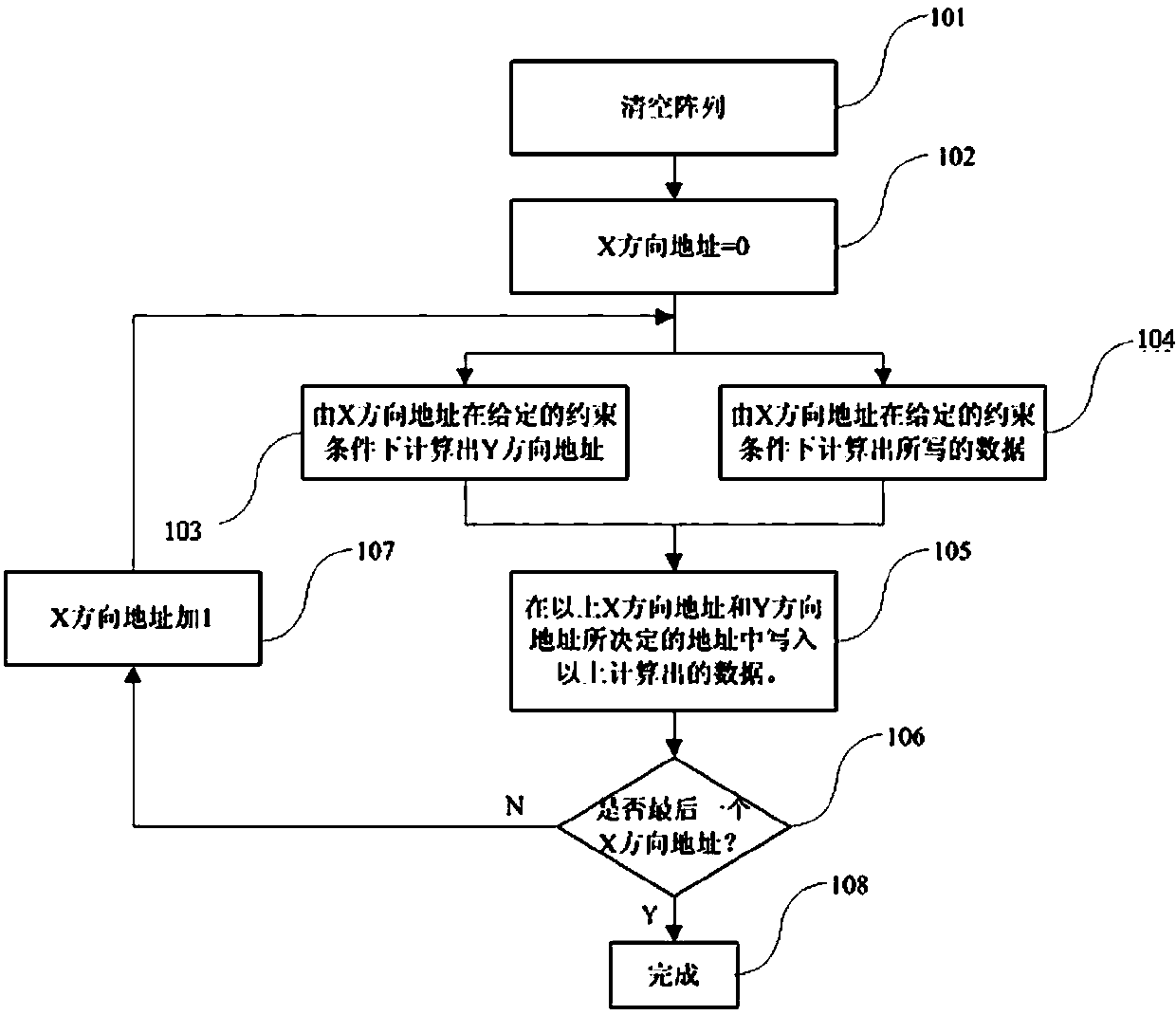

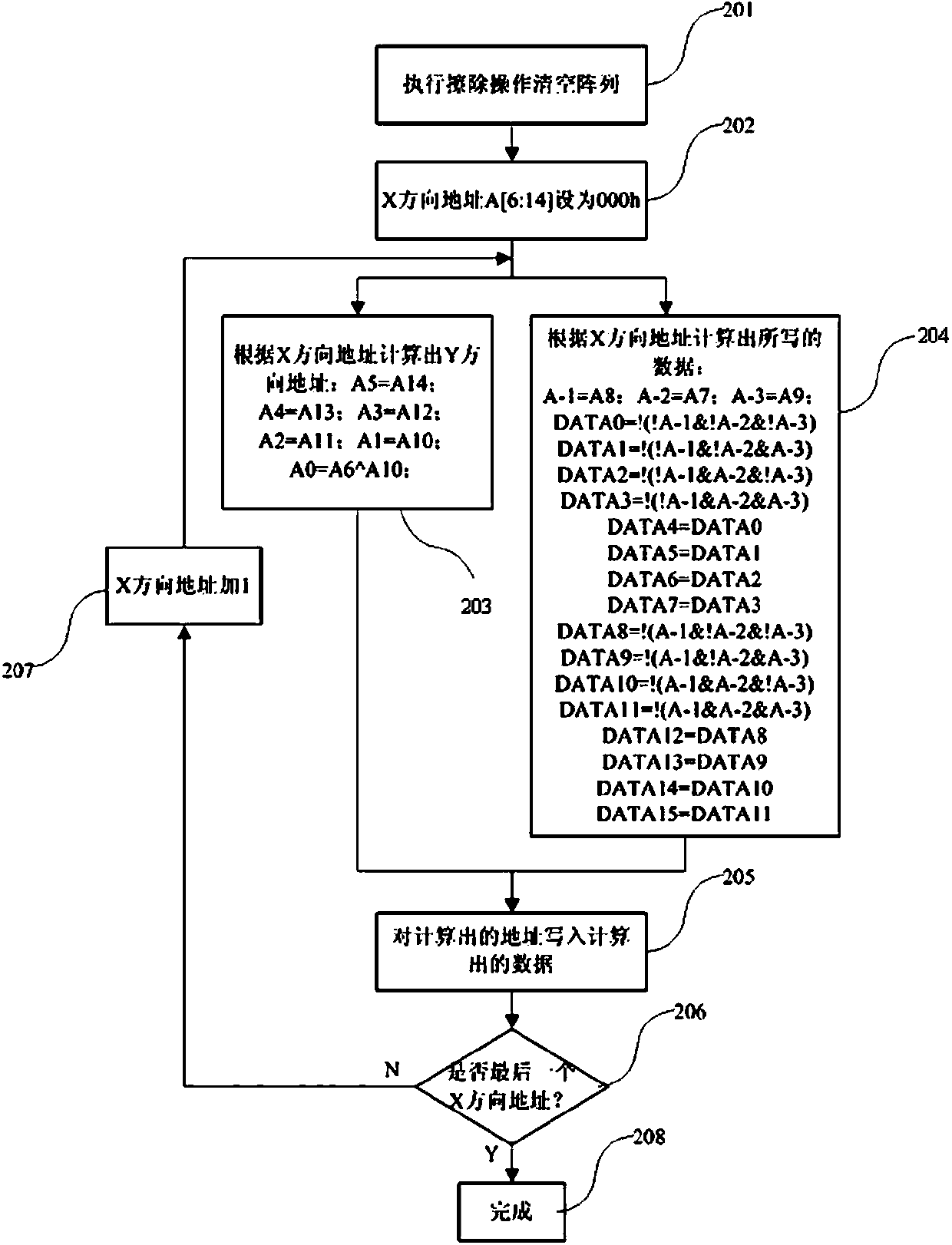

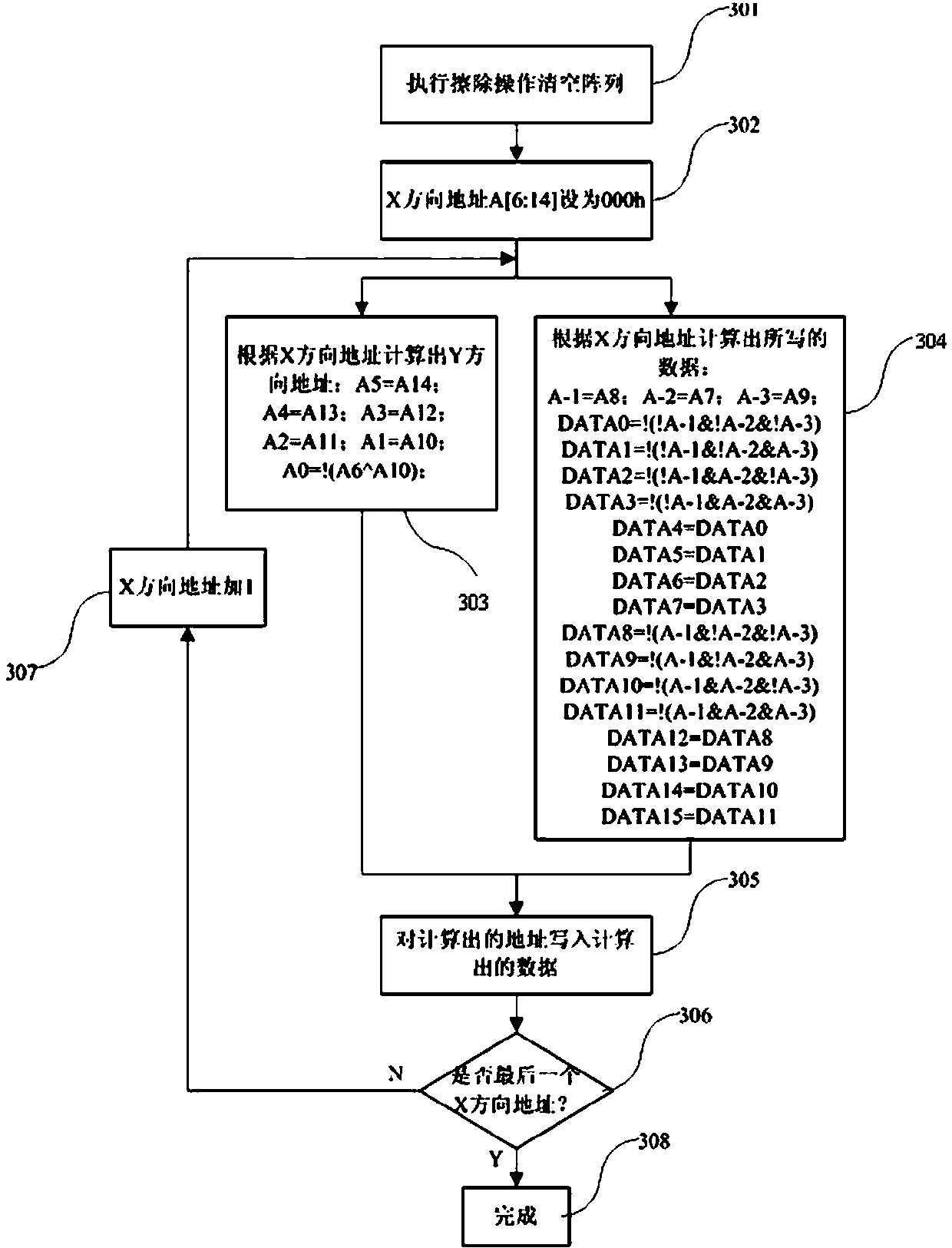

Method for generating test graph for detecting decoding circuit of memory

The invention discloses a method for generating a test graph for detecting a decoding circuit of a memory. The method comprises the following steps of: emptying an array; initializing an X direction address; under a given constraint condition, calculating a Y direction address according to the X direction address, and calculating data to be written; and finally, writing the obtained data into an address determined by the X direction address and the Y direction address obtained in the step 103, and traversing the X direction address, and repeating the operation. The method is used for detecting whether the decoding circuit in the memory is normal and is universal, so that the test graph for detecting the decoding circuit can be generated by the method according to different memories, and the test graph of the decoding circuit can be compatible with other test graphs; and an array emptying operation for writing between two test graphs is eliminated, so that the test cost is saved.

Owner:SHANGHAI FUDAN MICROELECTRONICS GROUP

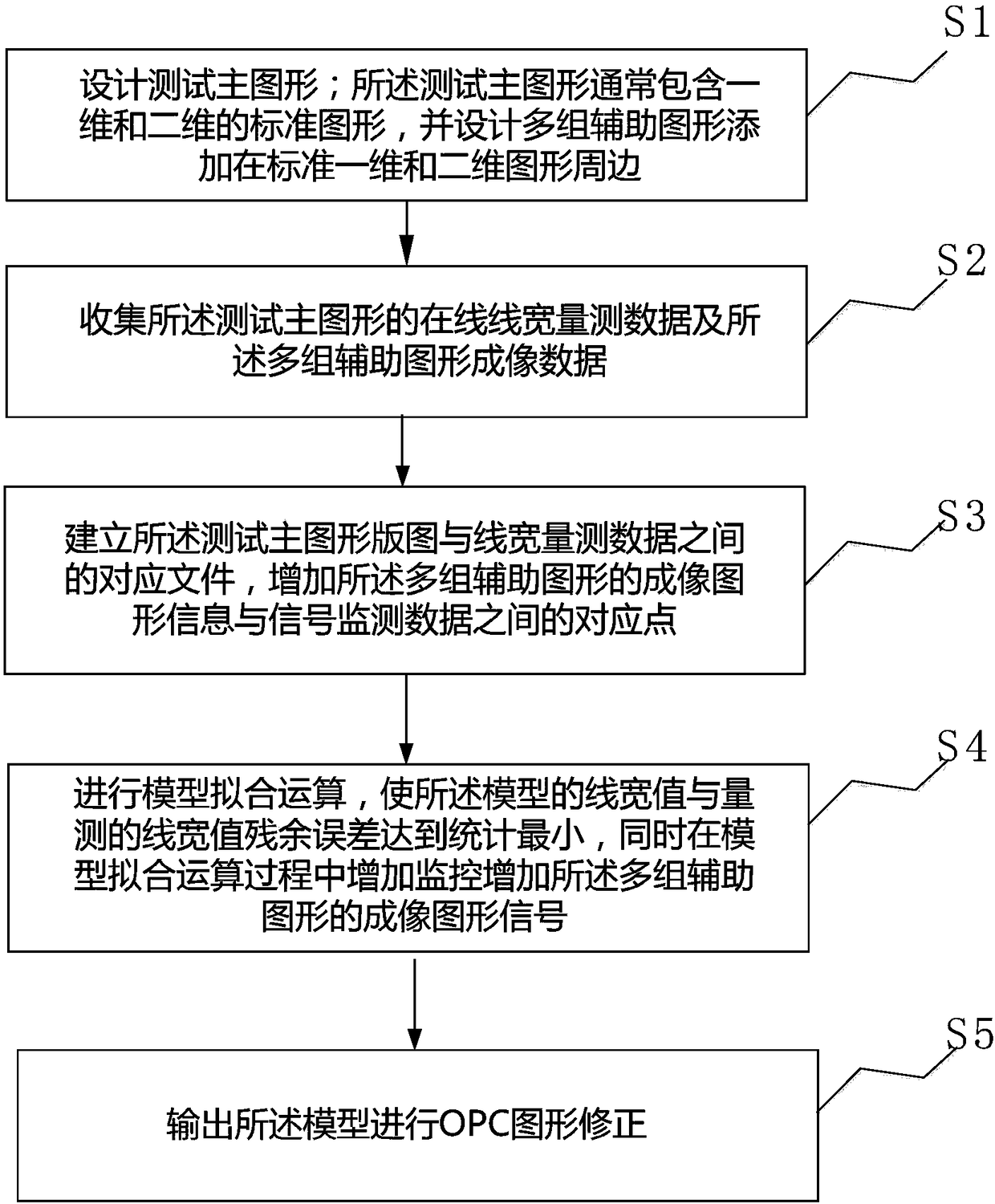

An OPC Modeling Method for Controlling the False Alarm Rate of Auxiliary Graphic Signals

ActiveCN106773544BSave computing resourcesImprove work efficiencyDesign optimisation/simulationPhotomechanical exposure apparatusGraphicsTest graph

An OPC (optical proximity correction) modeling method controlling a false alarm rate of an auxiliary graph signal comprises the steps of designing a main test graph, designing a plurality of groups of auxiliary graphs to be added to the peripheries of a one-dimensional standard graph and a two-dimensional standard graph, collecting on-line line width measurement data of the main test graph and imaging data of the groups of auxiliary graphs, establishing a corresponding document between a layout and the line width measurement data of the main test graph, adding a corresponding point between imaging graphic information and signal monitoring data of the groups of auxiliary graphs, performing model fitting operation, allowing a residual error between a line width value of a model and a measured line width value to be statistically minimum, adding an imaging graphic signal for monitoring the groups of auxiliary graphs in the model fitting operation process, and outputting the model for graph OPC.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

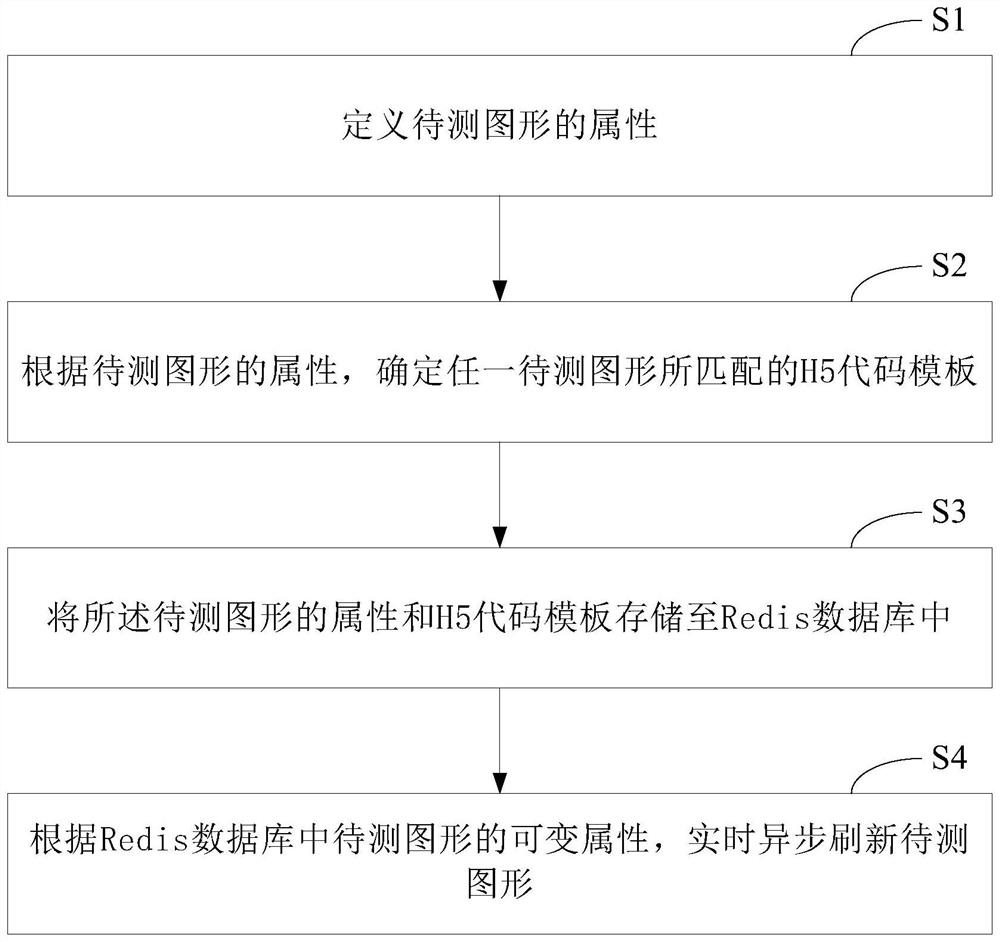

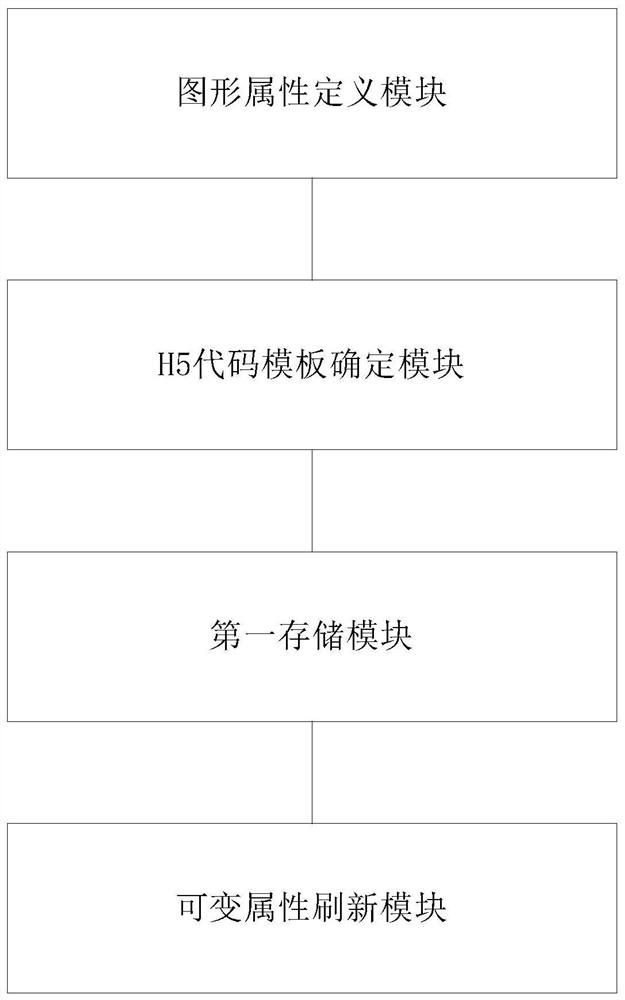

Visual view method and system based on Redis

PendingCN112380472AImprove reading speedIncrease refresh rateVisual data miningStructured data browsingGraphicsTest graph

The invention discloses a visual view method and system based on Redis, and the method comprises the steps: defining the attribute of a to-be-detected graph, determining an H5 code template matched with any to-be-detected graph according to the attribute of the to-be-detected graph, and storing the attribute of the to-be-detected graph and the H5 code template in a Redis database, and finally, asynchronously refreshing the to-be-tested graph in real time according to the variable attribute of the to-be-tested graph in the Redis database. The system comprises a graphic attribute definition module, an H5 code template determination module, a first storage module and a variable attribute refreshing module. Through the data refreshing method and device, the data refreshing efficiency and the data visual display accuracy can be improved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

Method for generating test graph for detecting decoding circuit of memory

The invention discloses a method for generating a test graph for detecting a decoding circuit of a memory. The method comprises the following steps of: emptying an array; initializing an X direction address; under a given constraint condition, calculating a Y direction address according to the X direction address, and calculating data to be written; and finally, writing the obtained data into an address determined by the X direction address and the Y direction address obtained in the step 103, and traversing the X direction address, and repeating the operation. The method is used for detecting whether the decoding circuit in the memory is normal and is universal, so that the test graph for detecting the decoding circuit can be generated by the method according to different memories, and the test graph of the decoding circuit can be compatible with other test graphs; and an array emptying operation for writing between two test graphs is eliminated, so that the test cost is saved.

Owner:SHANGHAI FUDAN MICROELECTRONICS GROUP