Patents

Literature

64results about "Measurment by measuring phase" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

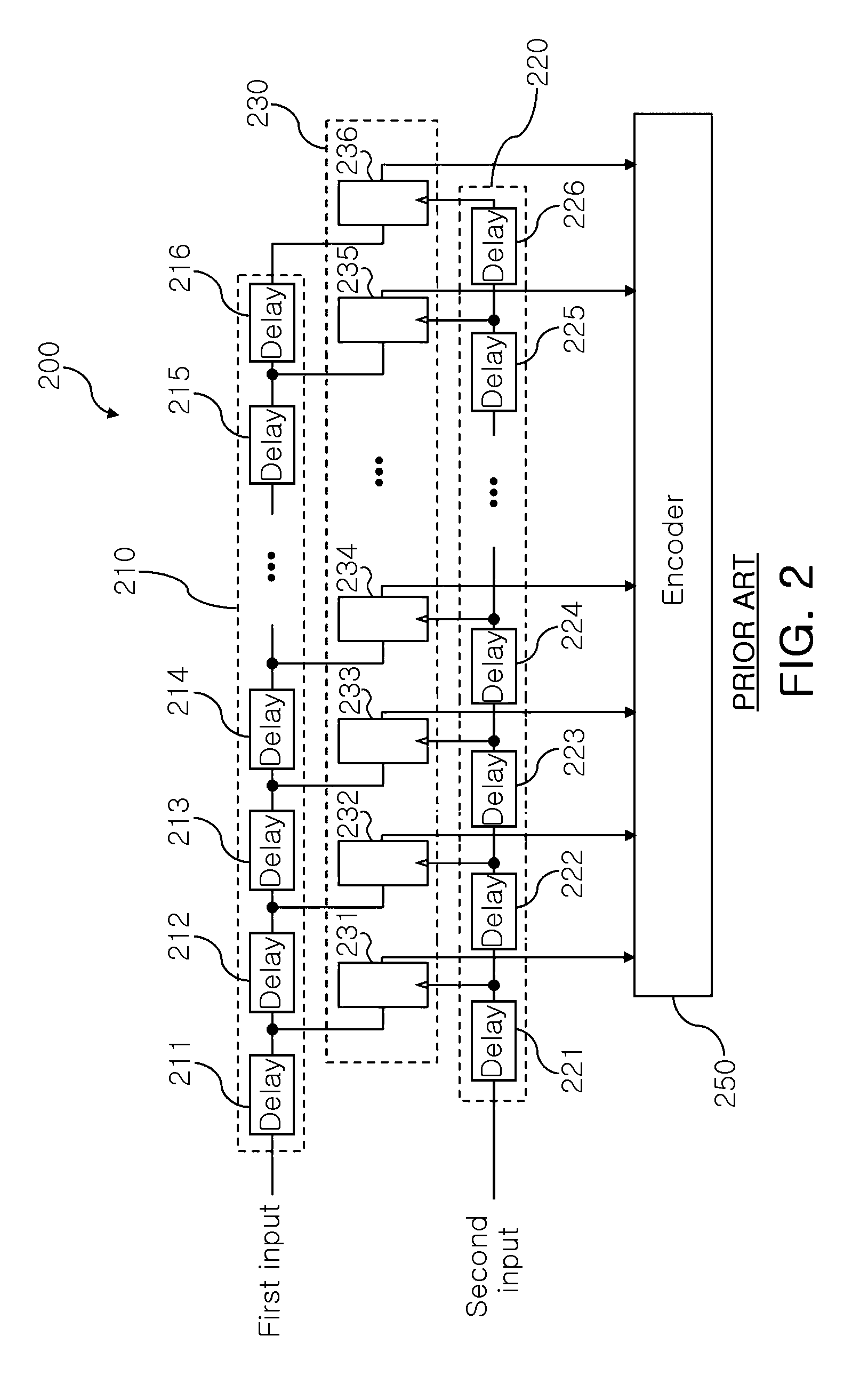

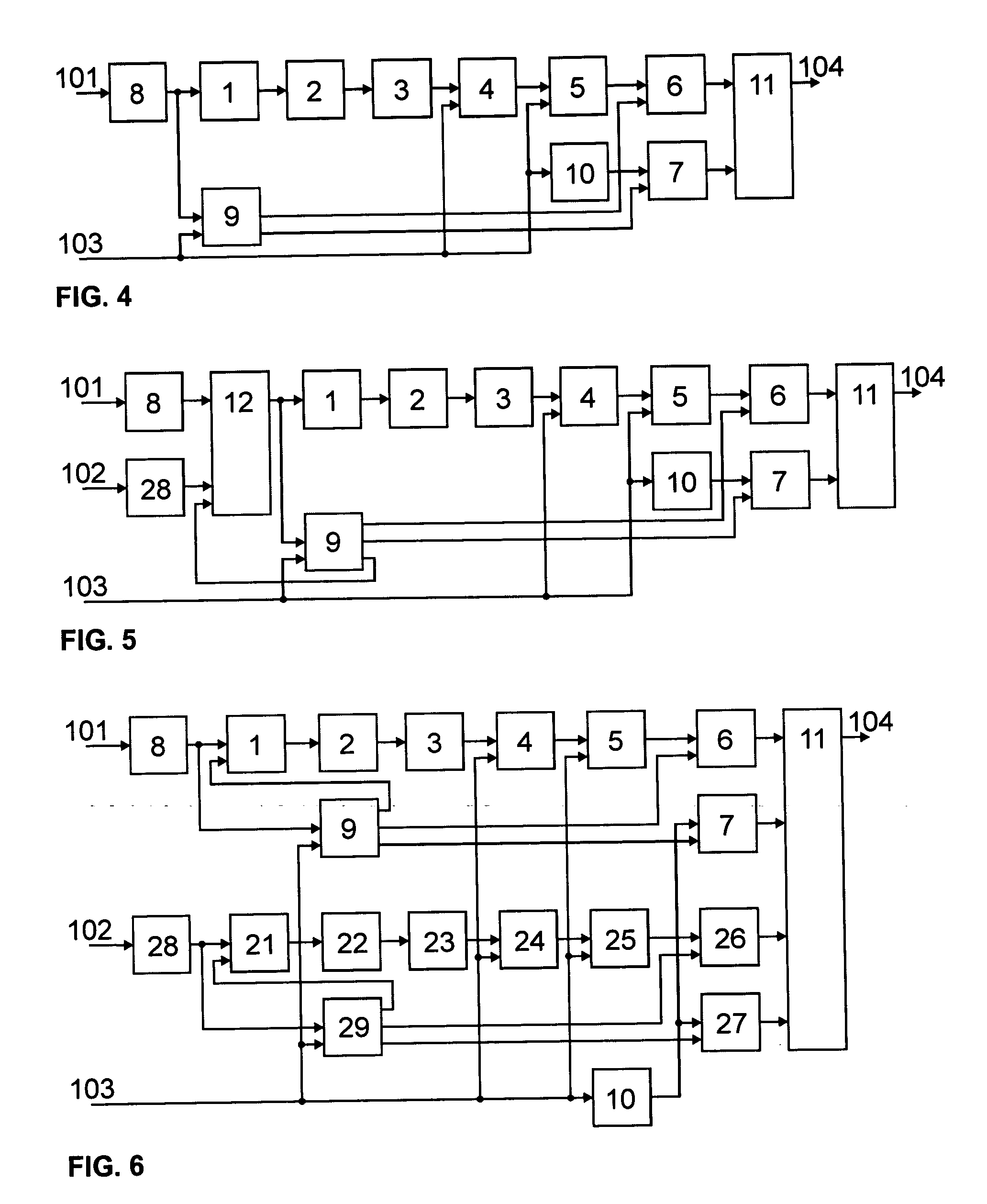

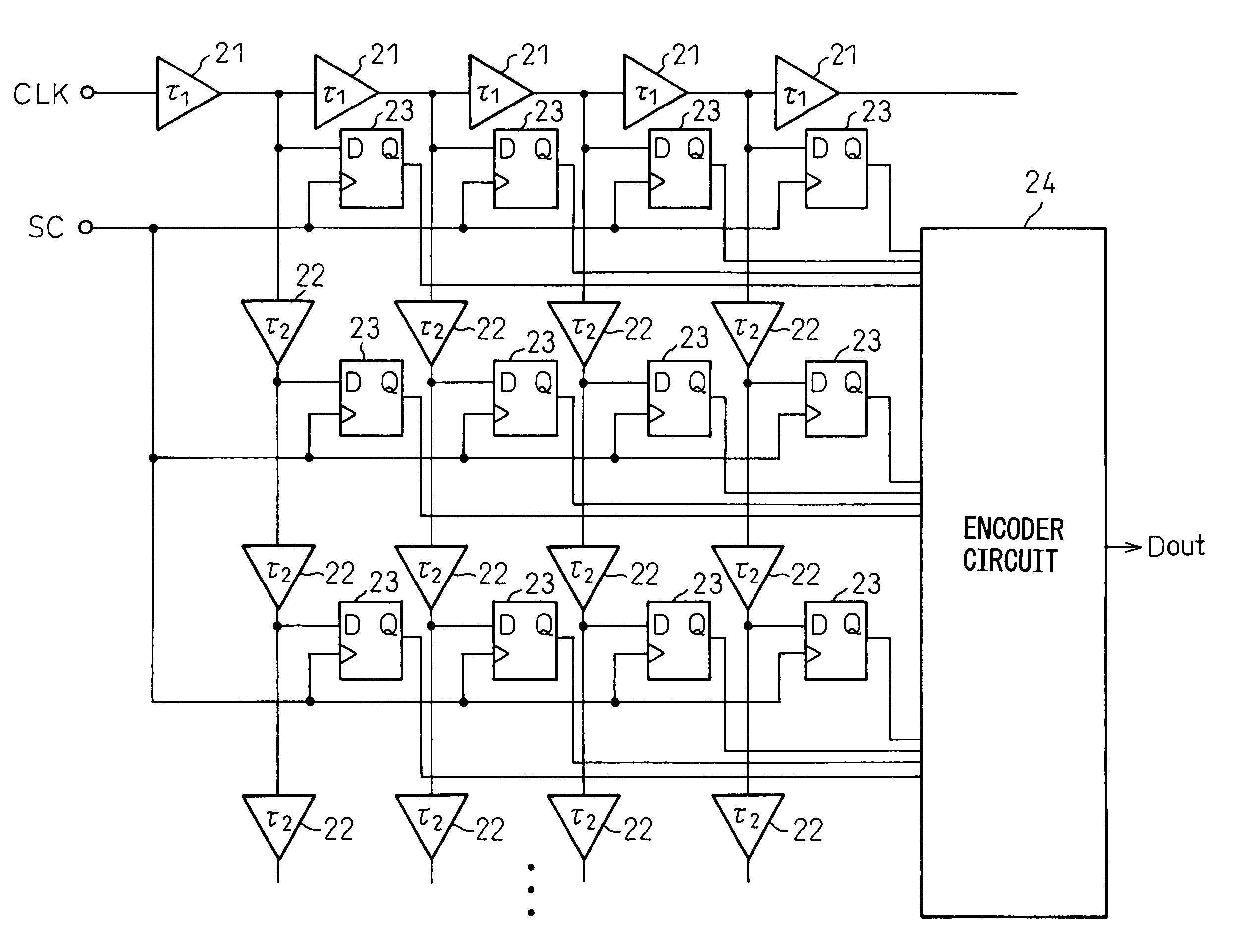

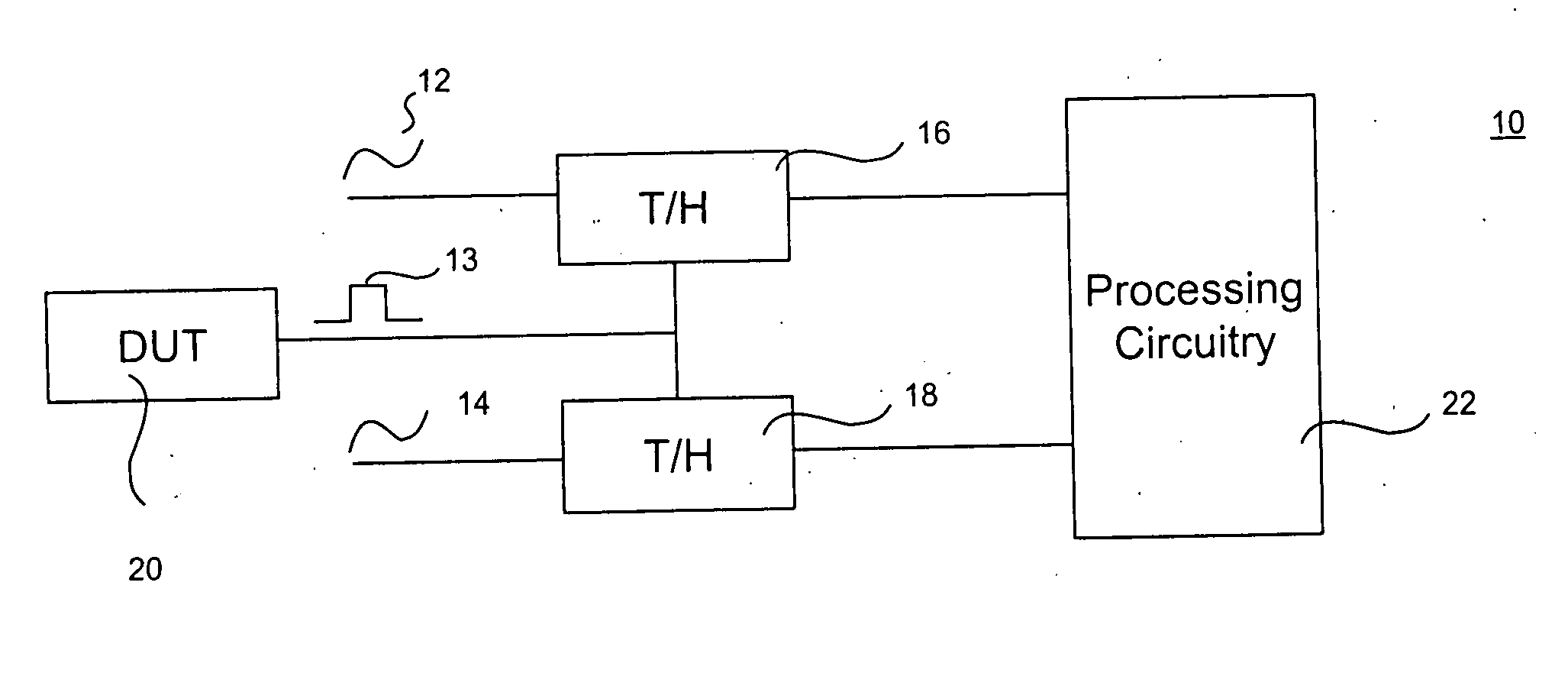

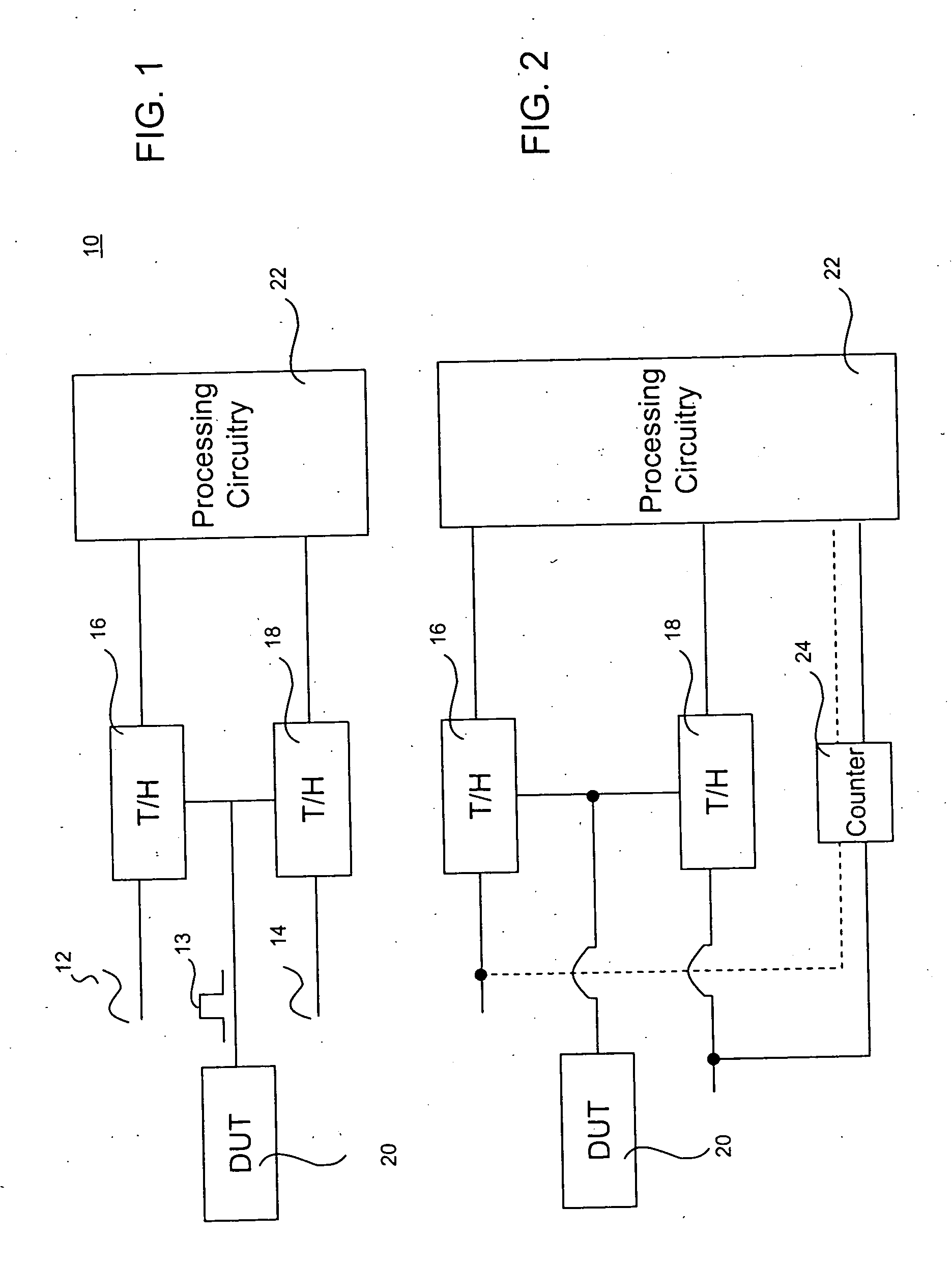

Timing measurement device using a component-invariant vernier delay line

InactiveUS6850051B2Reduced measurement timeAvoid matching problemsPulse characteristics measurementsFrequency to phase shift conversionSingle stageMeasurement device

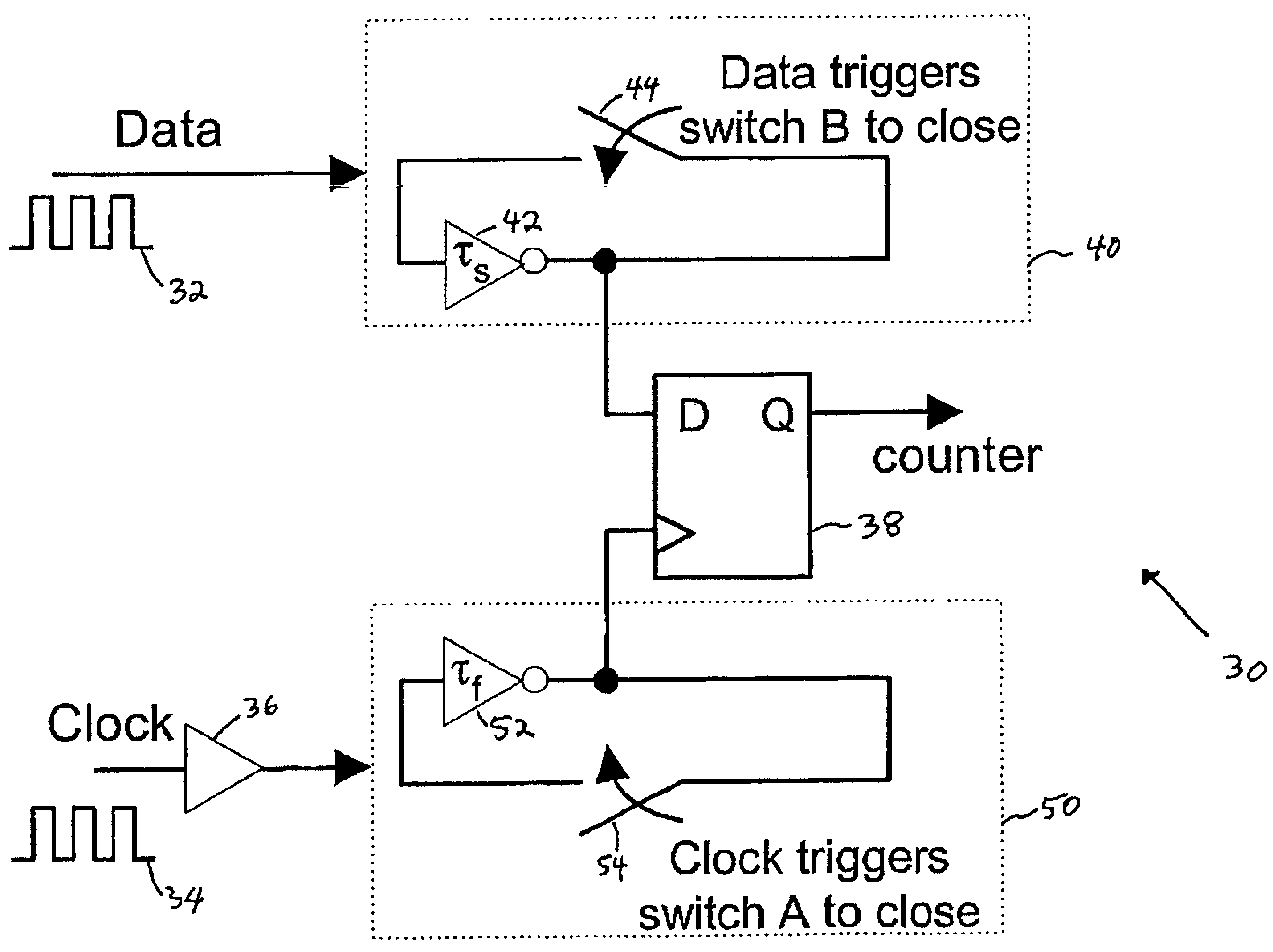

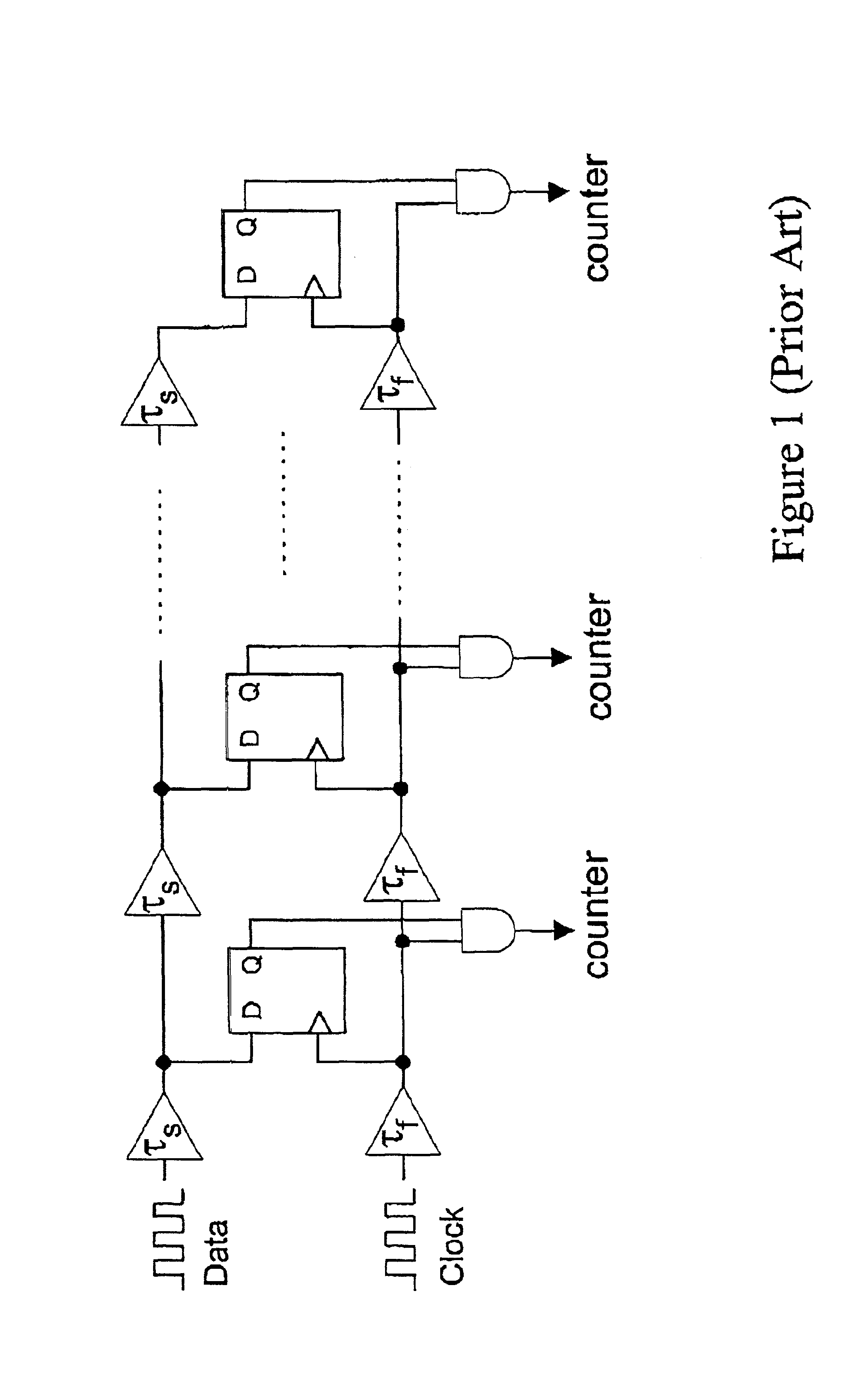

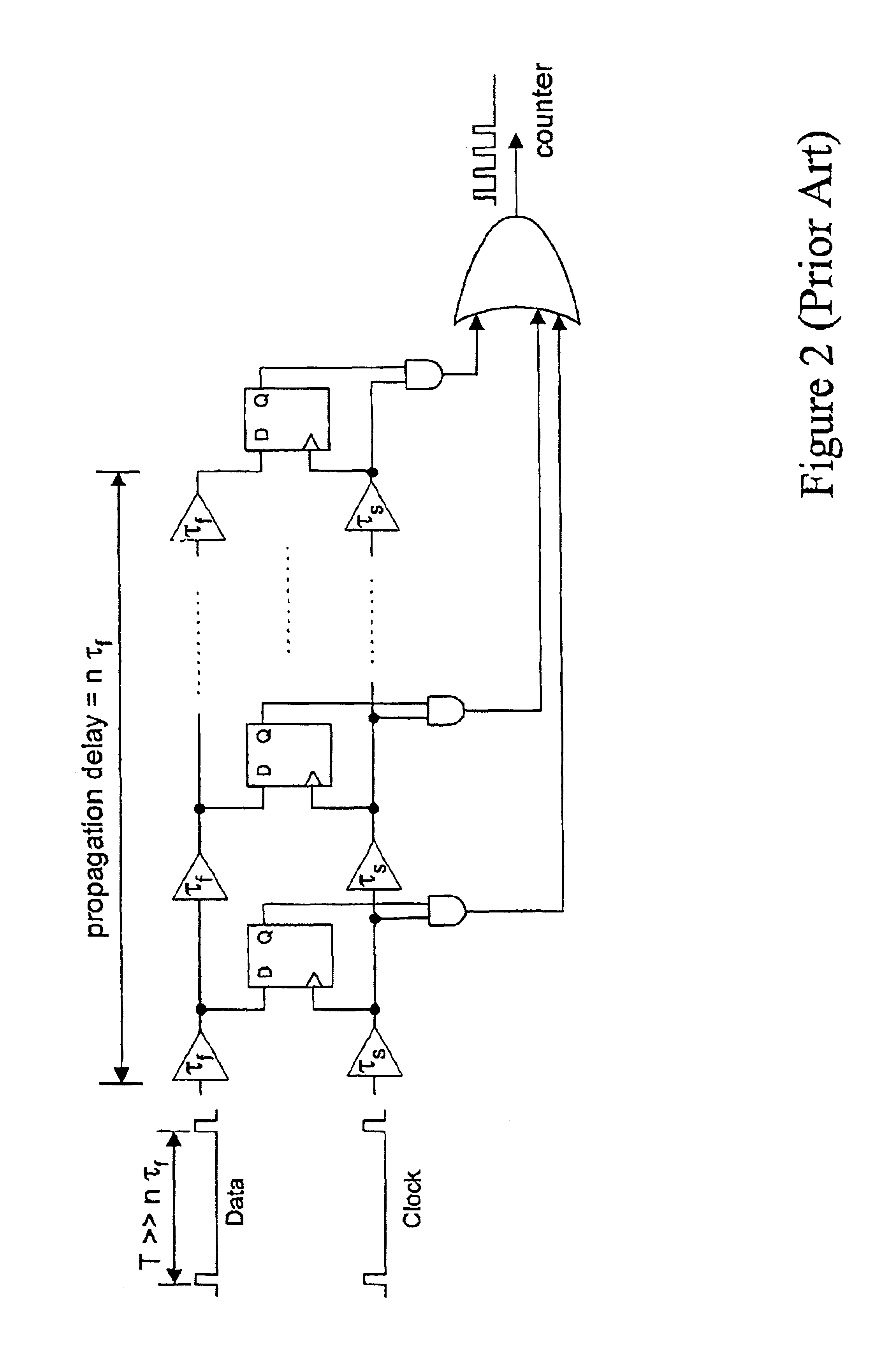

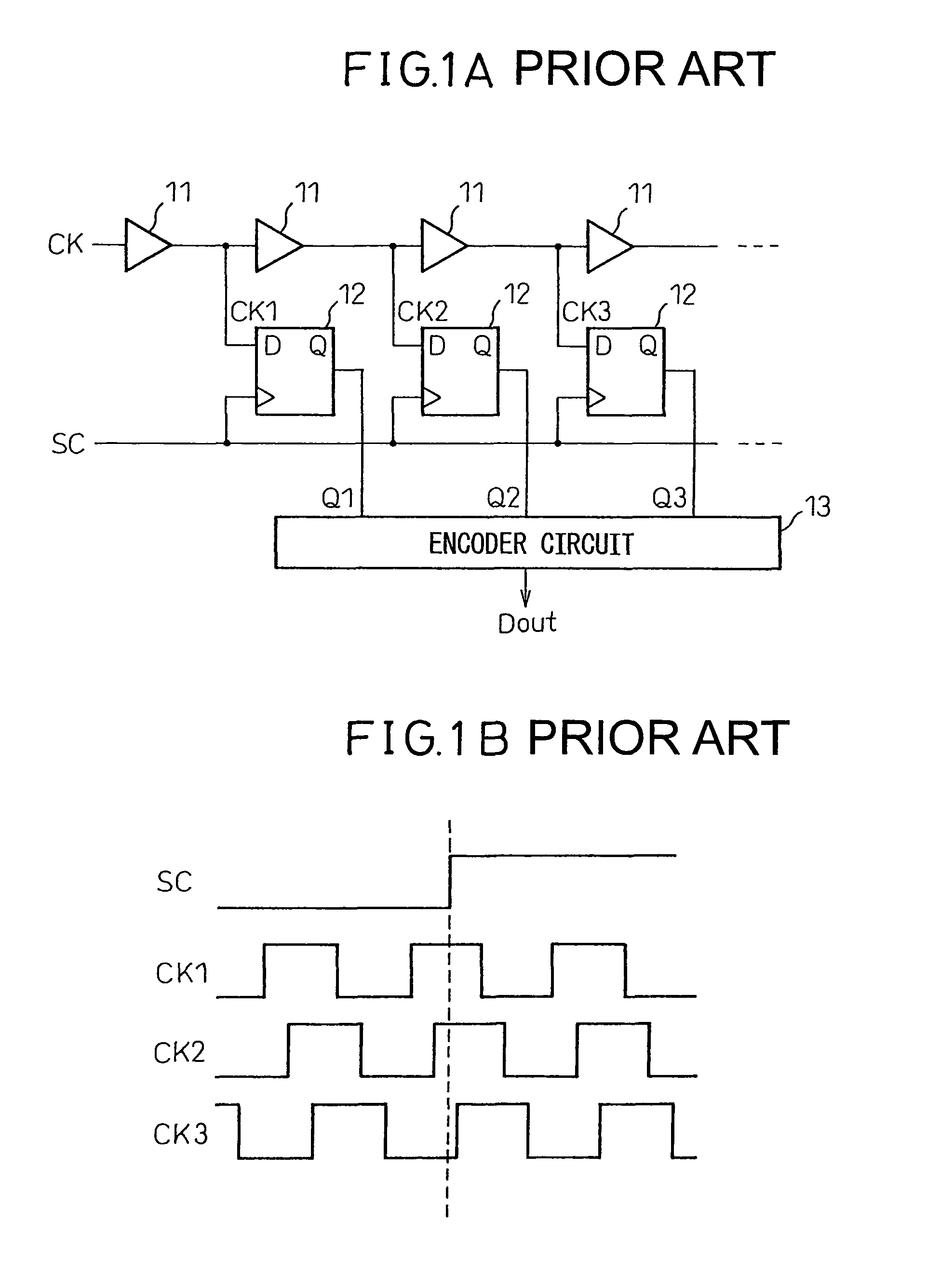

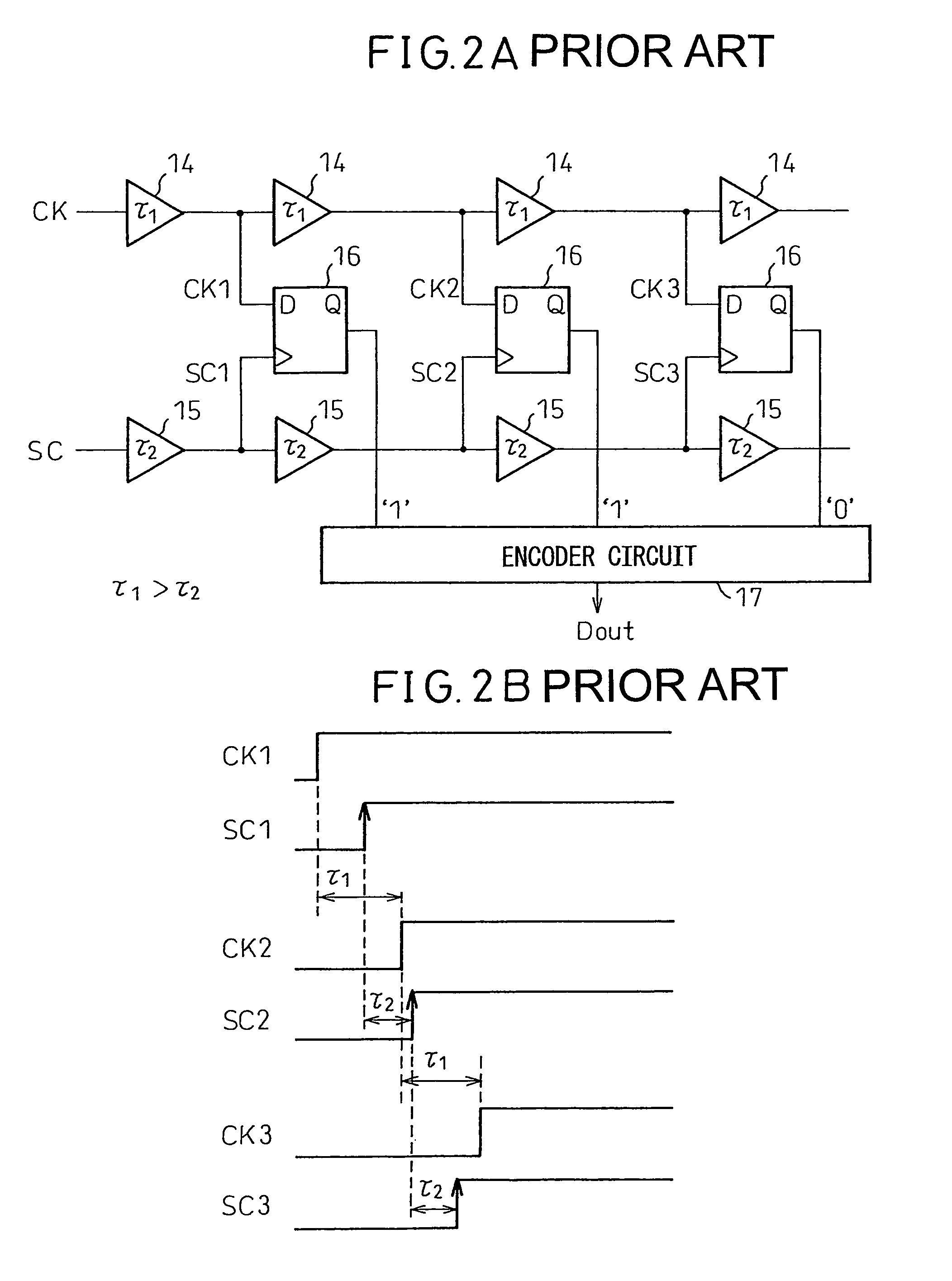

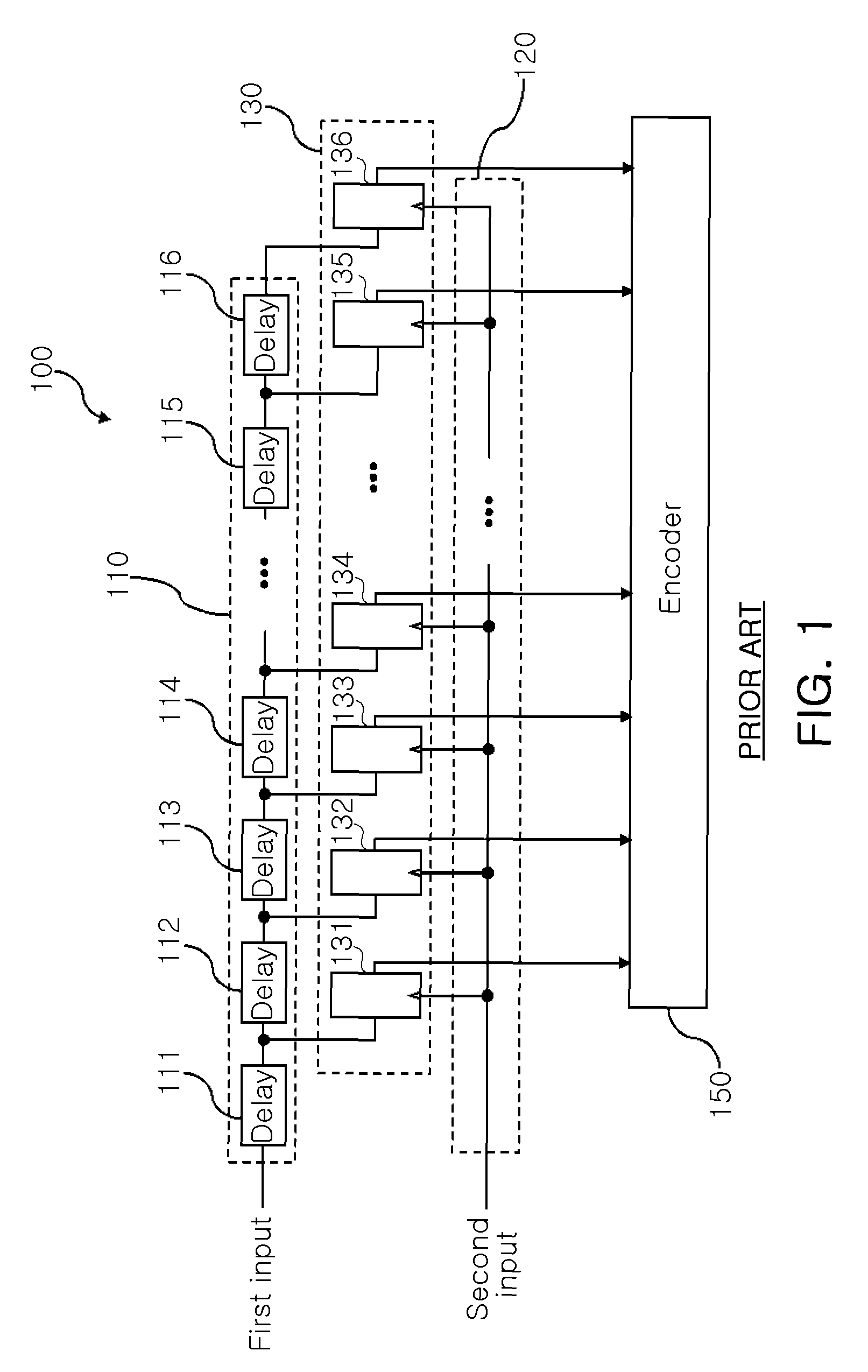

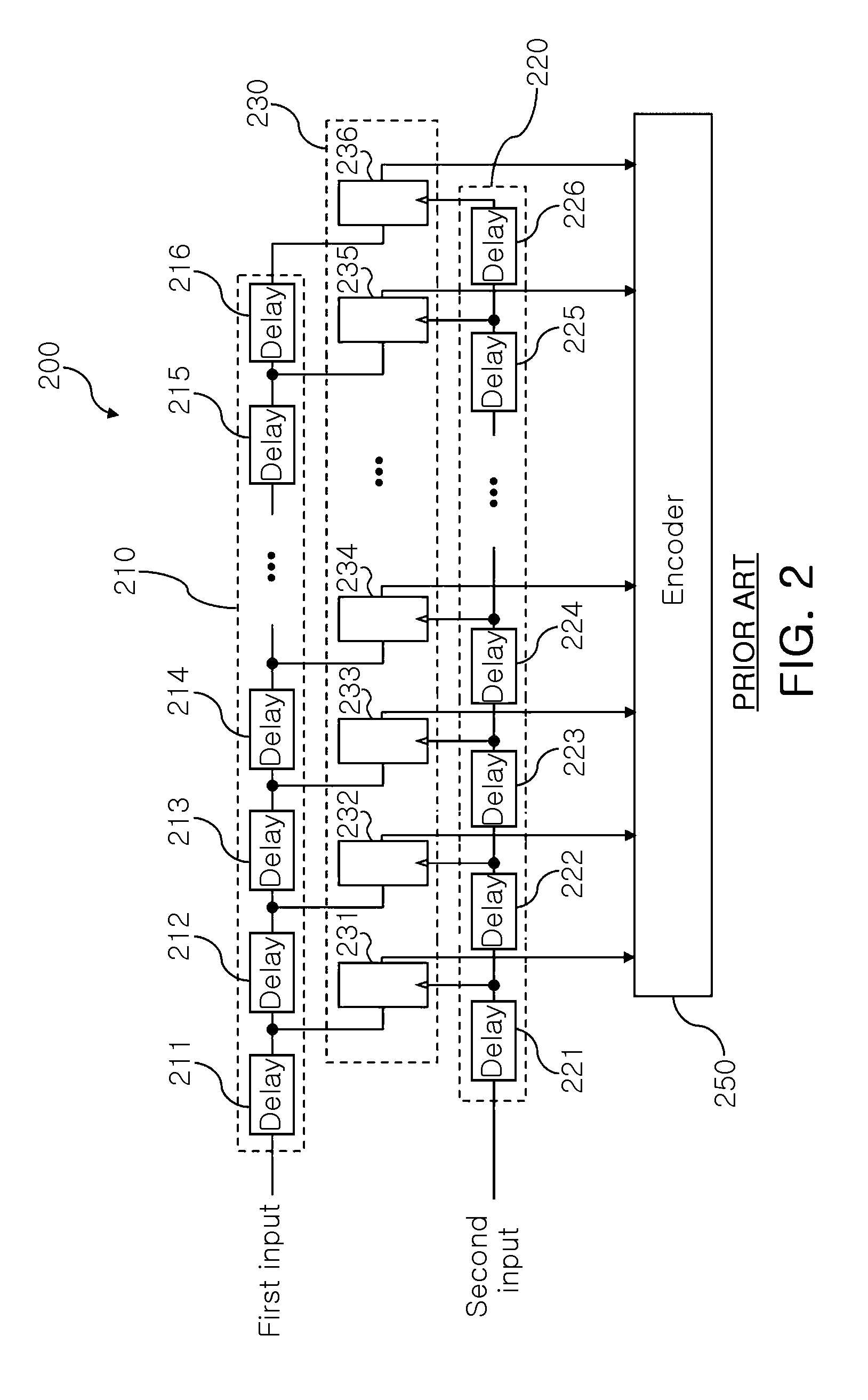

In recent years, much effort has been placed on improving the performance of timing and jitter measurement devices using Delay Locked Loop (DLL) and Vernier Delay Line (VDL) techniques. However, these approaches require highly matched elements in order to reduce differential non-linearity timing errors. In an attempt to reduce the requirement on element matching, a component-invariant VDL technique is disclosed that enables the measurement device to be synthesized from an RTL description. The present invention is based on a single-stage VDL structure, which is used to mimic the behavior of a complete VDL. Furthermore, as test time is an important consideration during a production test, a method and system is provided that reduces test time at the expense of additional hardware.

Owner:MCGILL UNIV

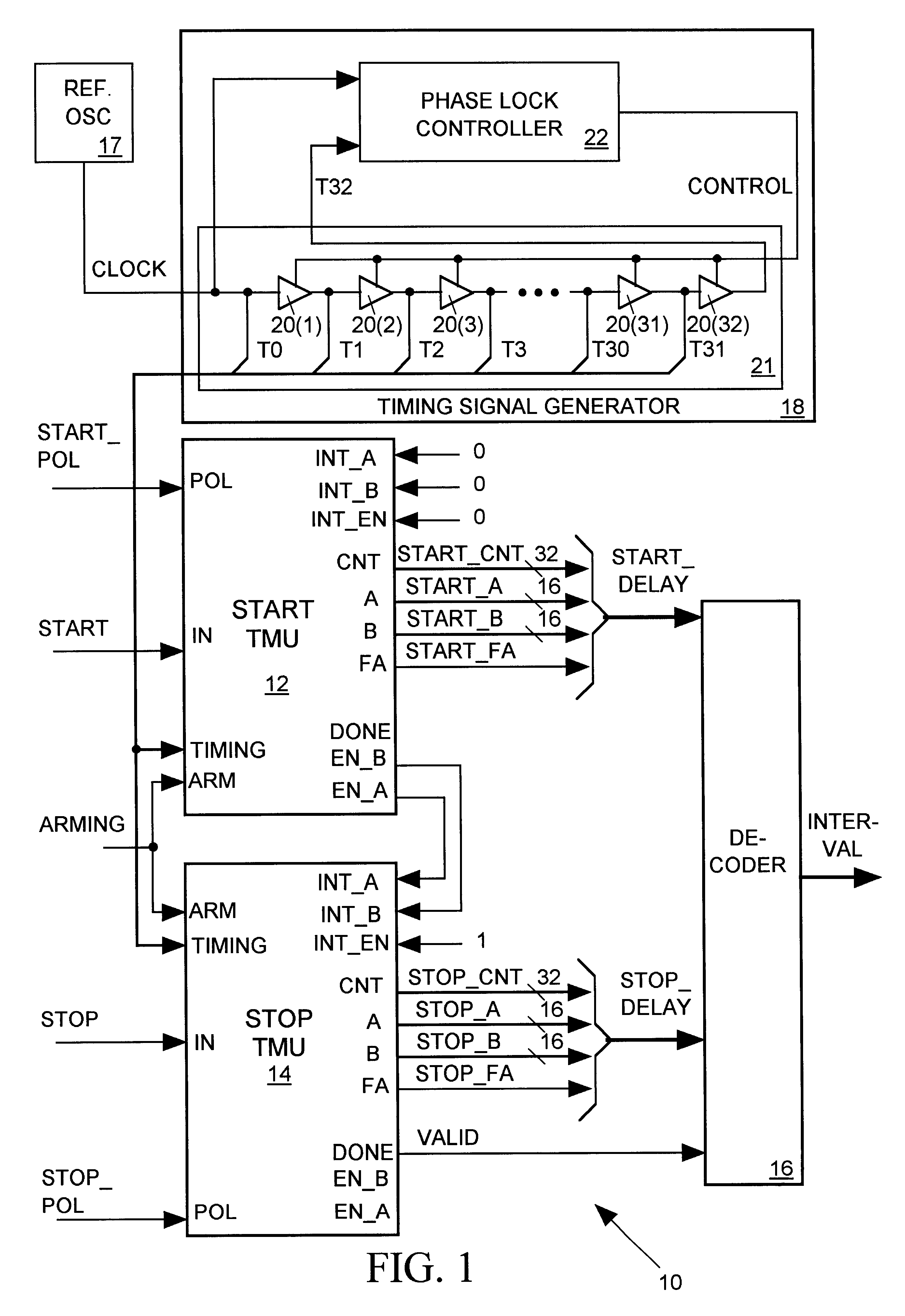

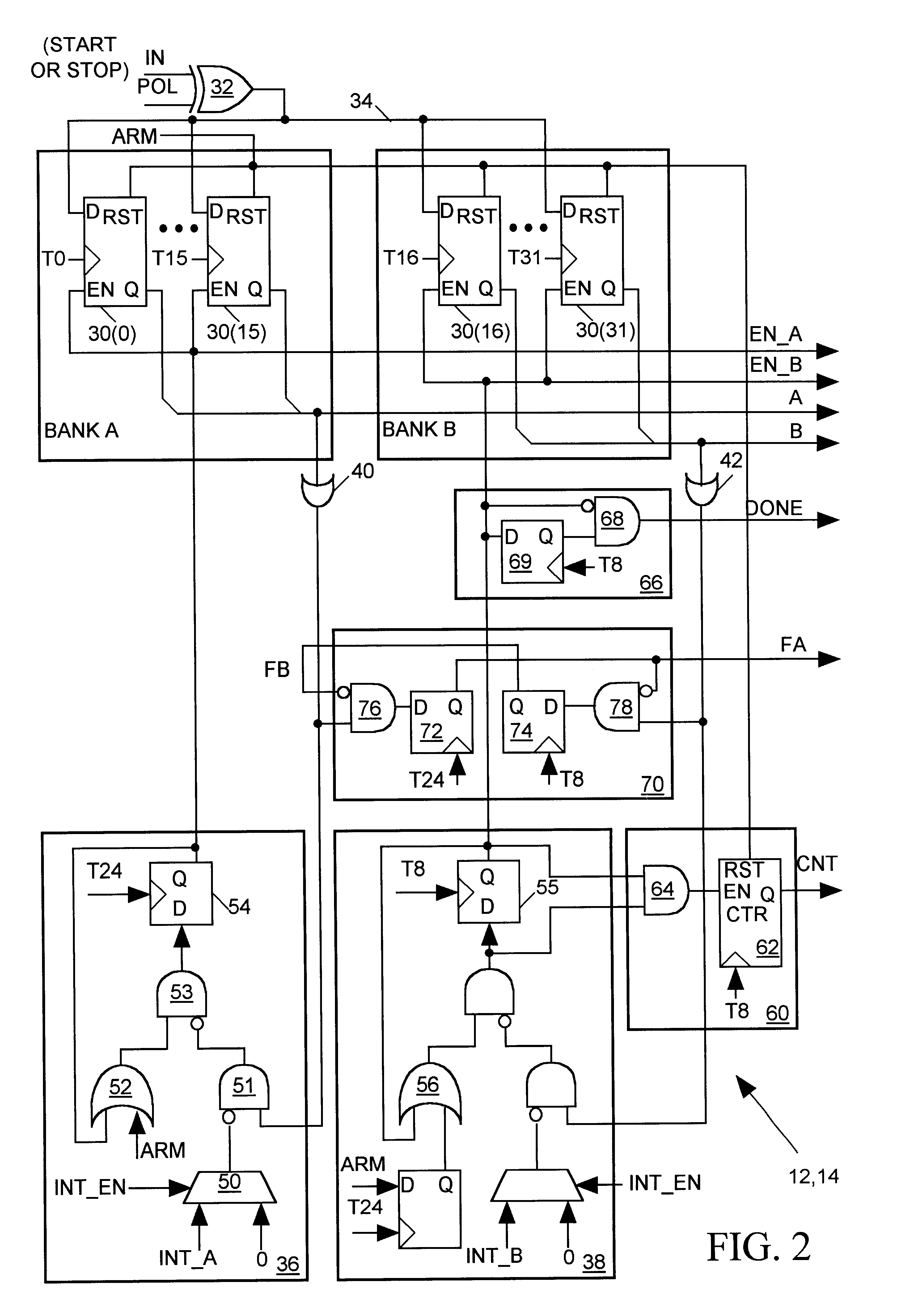

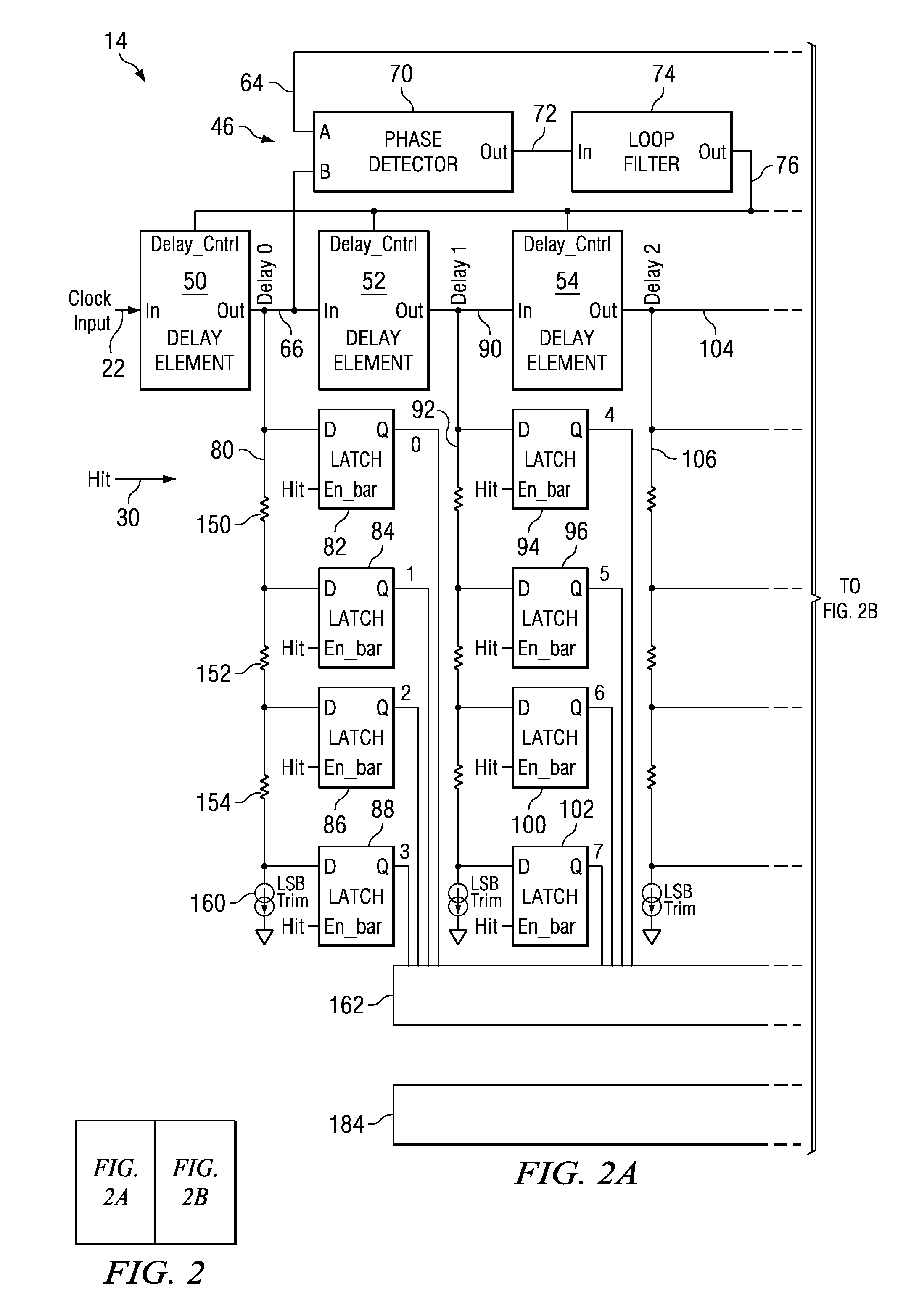

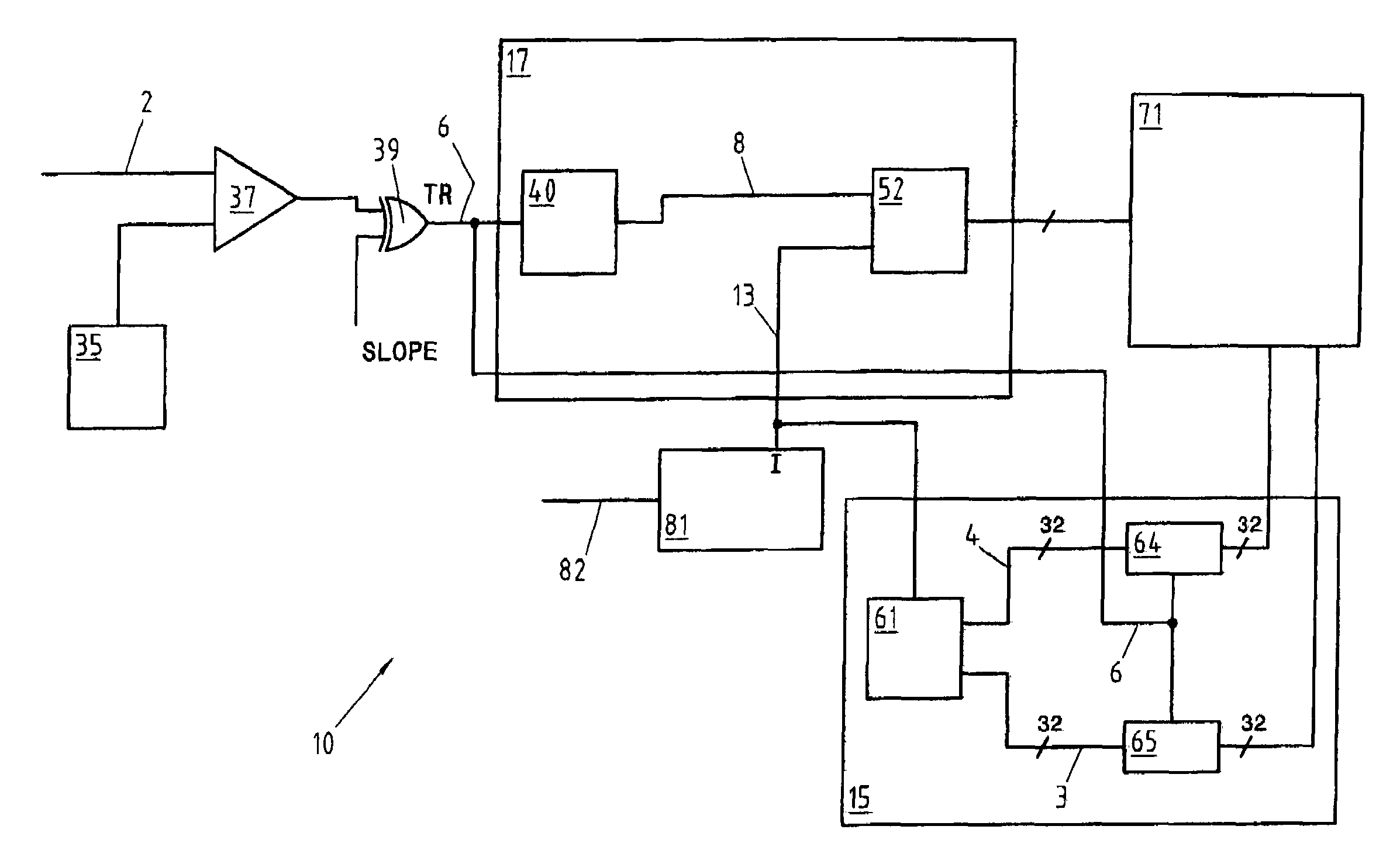

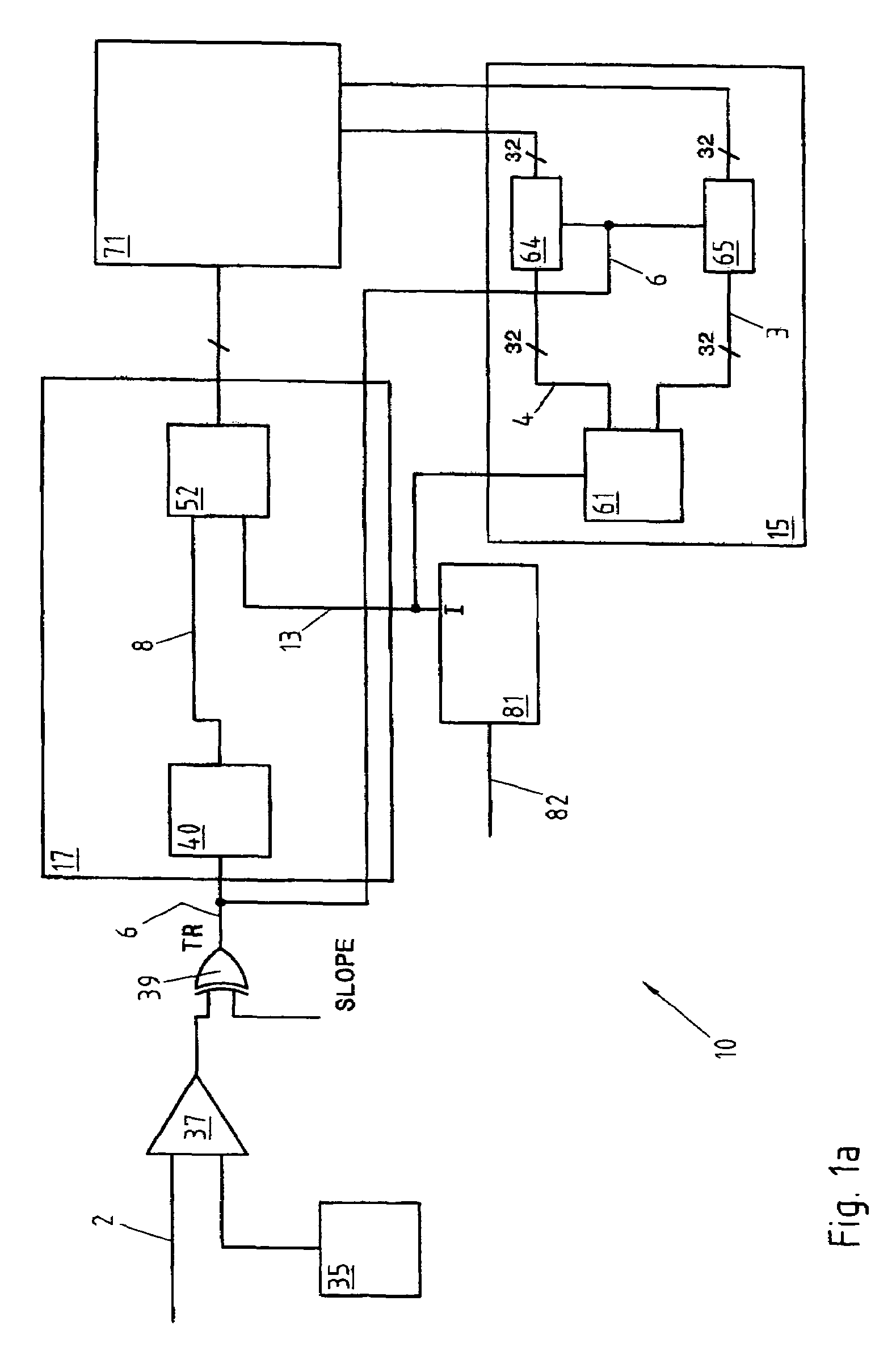

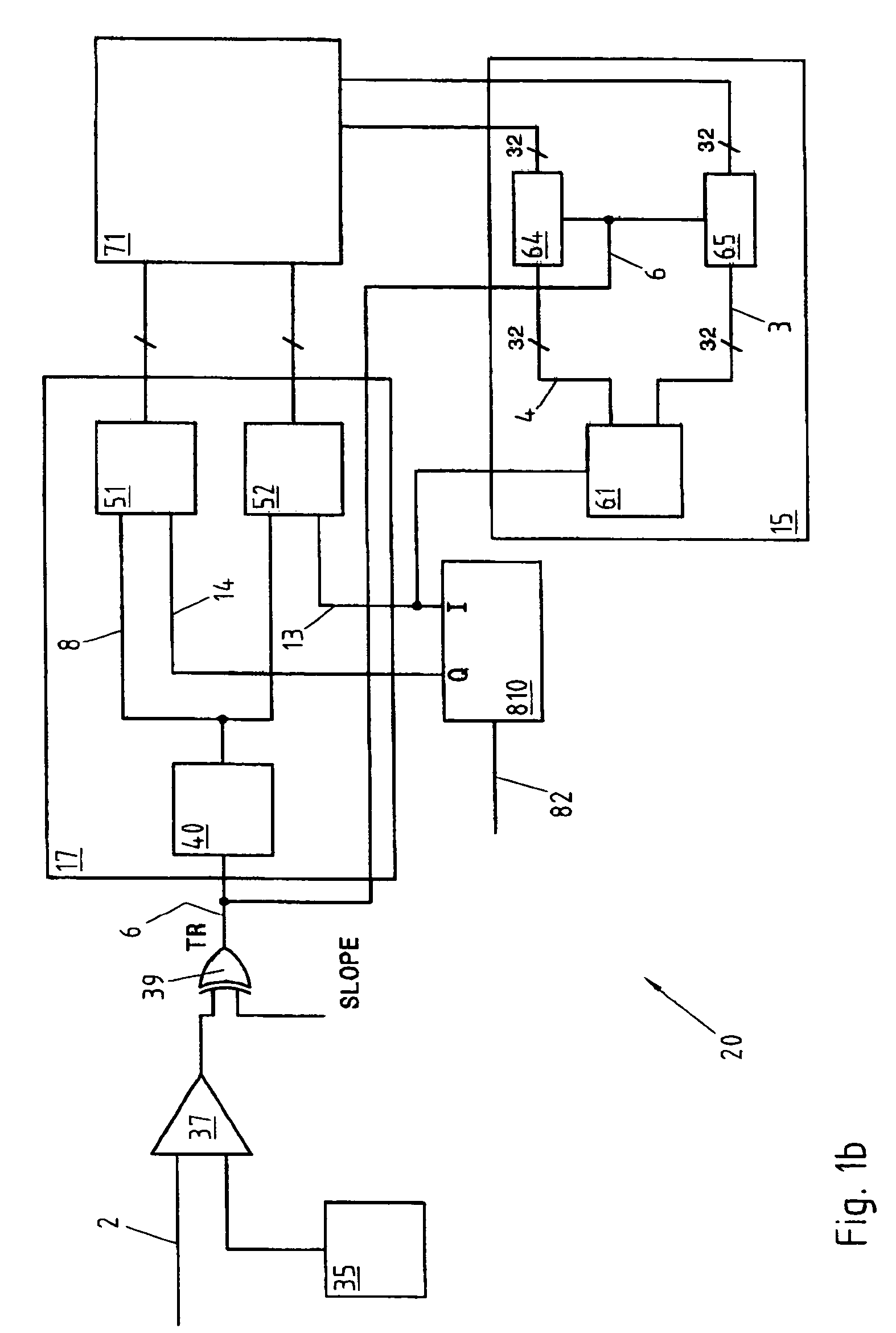

Apparatus for measuring intervals between signal edges

InactiveUS6246737B1Pulse automatic controlElectromechanical unknown time interval measurementStart timeTime delays

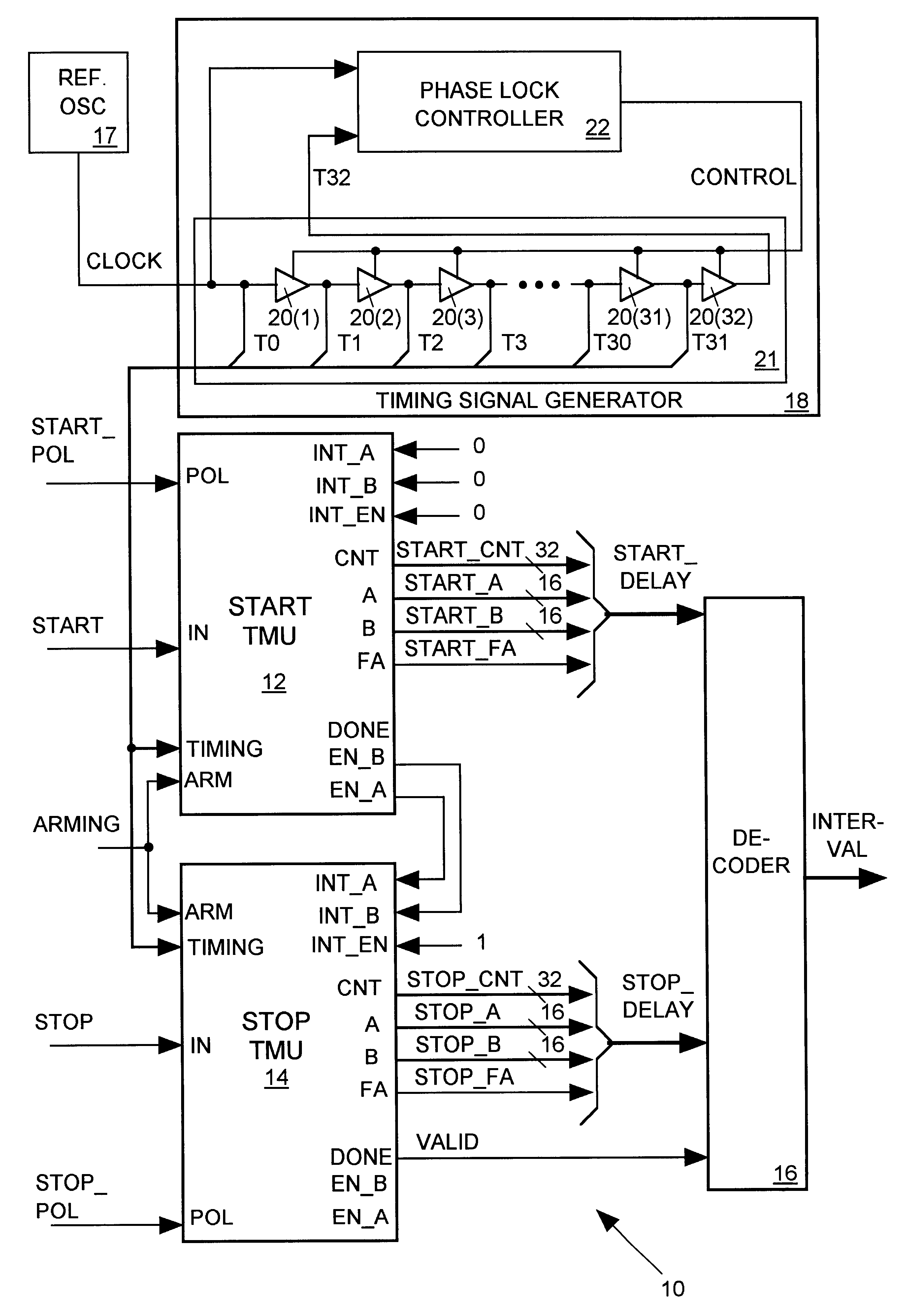

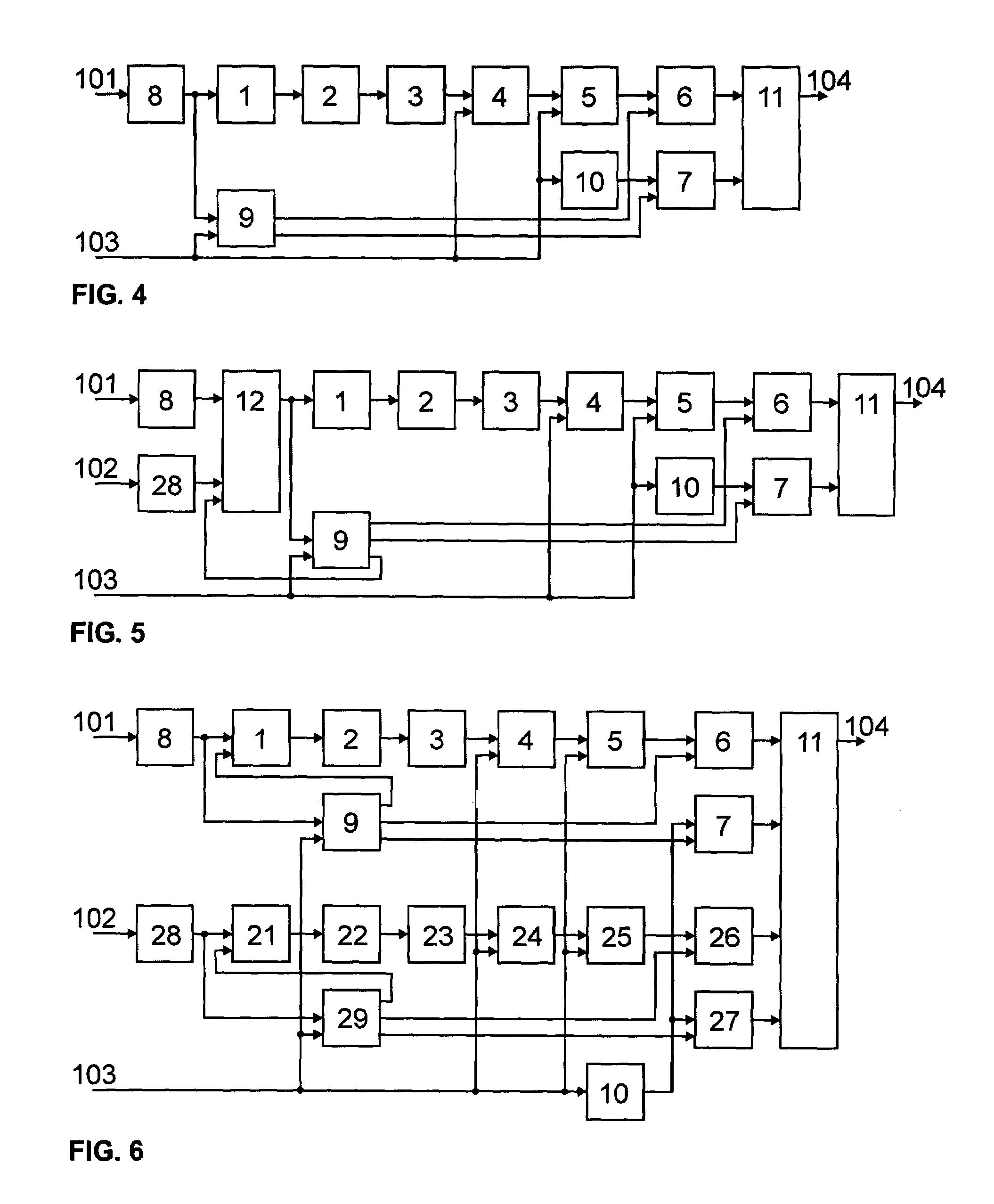

An apparatus for measuring a time interval between a start signal edge and a stop signal edge provides a stable clock signal as input to a delay line formed by a series of similar logic gates. The output signal of the last gate of the series is phase locked to the clock signal by adjusting a bias signal controlling the switching speed of all gates. The clock signal and the output signal of each gate form a set of phase distributed periodic timing signals applied to a start time measurement unit (TMU) and a similar stop TMU. The start TMU counts edges of one of the timing signals occurring between an edge of an arming signal and the start signal edge and generates output data representing a time delay between the arming signal and the start signal edge. The data represents the start delay as a whole and fractional number of clock signal periods by conveying the counter output and by indicating which of the timing signals had an edge most closely following the start signal edge. The stop TMU similarly produces output data indicating a whole an fractional number of clock cycles occurring between the arming signal and the stop signal edge. The delay represented by the start TMU output data is subtracted from the delay represented by the stop TMU output data to determine the interval between the start and stop signal edges.

Owner:CREDENCE SYSTEMS

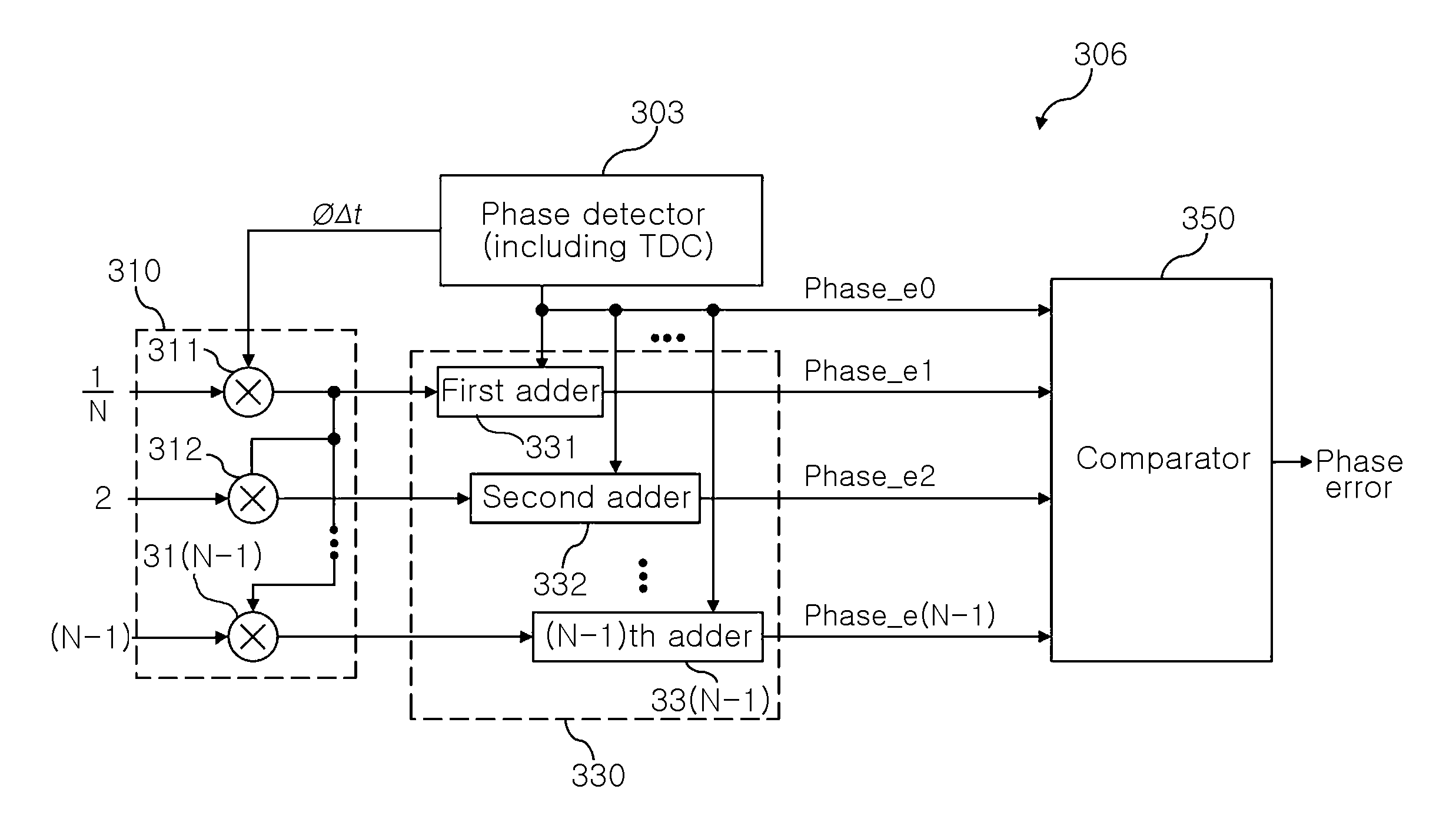

Apparatus for compensating for error of time-to-digital converter

InactiveUS20100134335A1Improve time resolutionReduce delaysElectric signal transmission systemsPulse automatic controlPhase detectorImage resolution

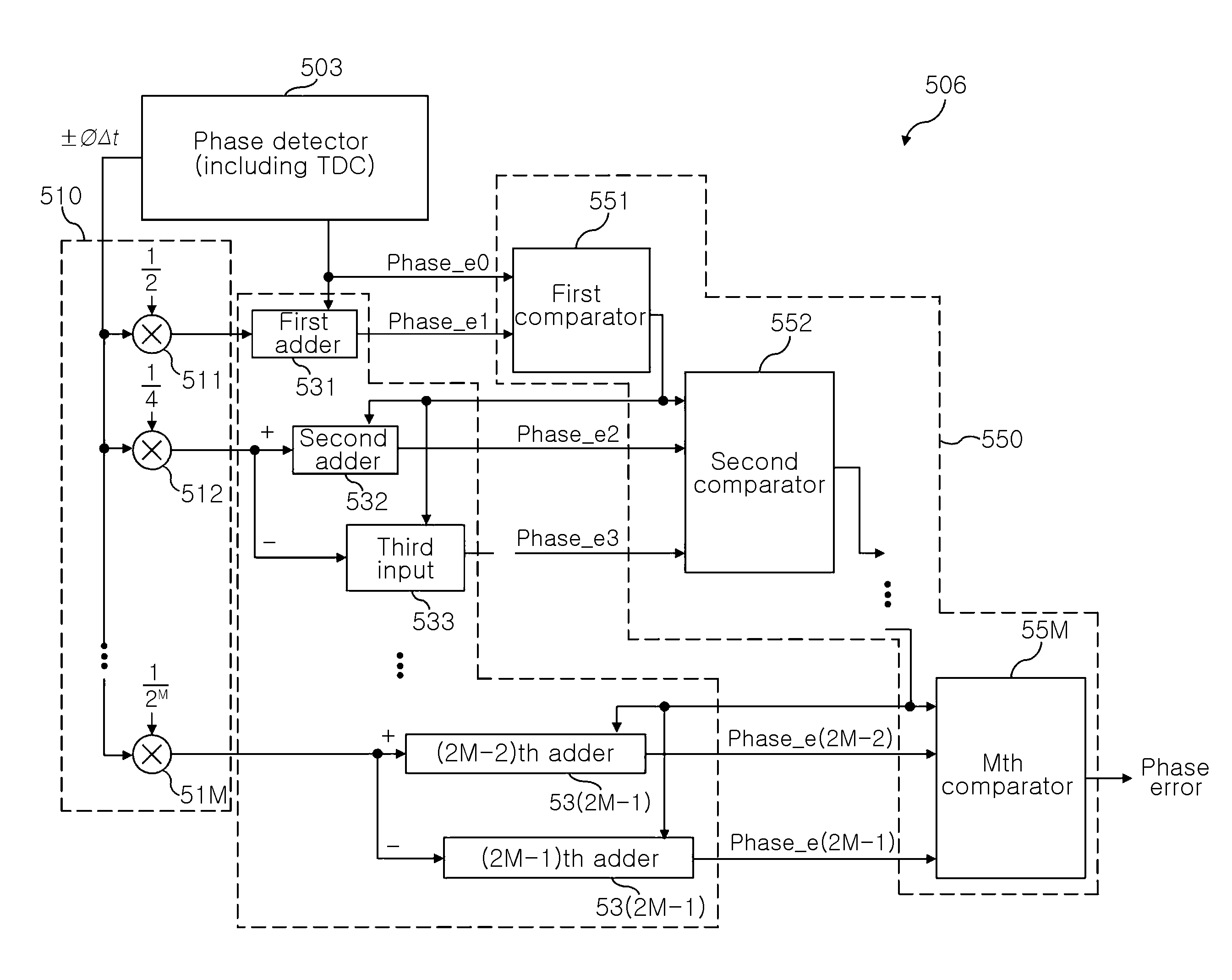

An apparatus for compensating for an error of a time-to-digital converter (TDC) is disclosed to receive a delay phase from a phase detector including the TDC and a phase error including a TDC error and compensate for the TDC error to have a time resolution higher by N times (N is a natural number). The apparatus includes: a fragmenting and multiplying unit fragmenting the delay phase by N times (N is a natural number) to generate first to (N−1)th fragmented delay phases; an adding unit adding each of the first to the (N−1)th fragmented delay phases to the phase error to generate first to (N−1)th phase errors; and a comparison unit acquiring a phase error compensation value nearest to an actual phase error from the phase error and the first to (N−1)th phase errors.

Owner:ELECTRONICS & TELECOMM RES INST

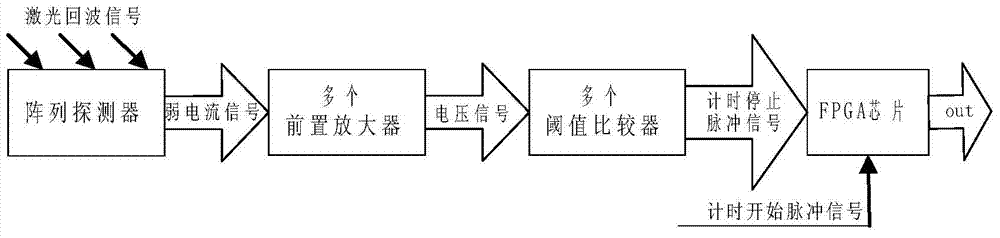

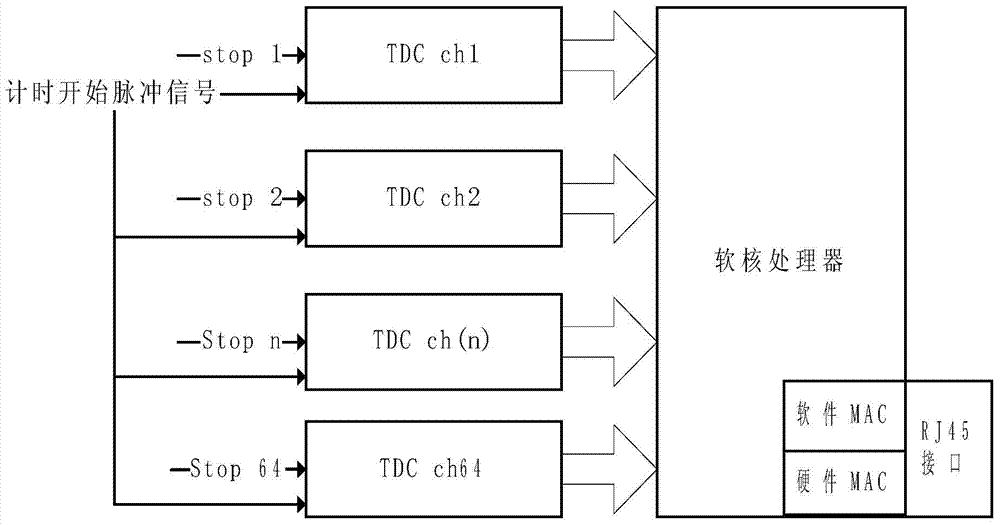

Multi-channel laser echo time measurement system based on FPGA (Field Programmable Gate Array) chip

InactiveCN103698770AReduce resource usageNo subsequent calibration requiredElectromagnetic wave reradiationMeasurment by measuring phaseVoltage referenceWeak current

The invention discloses a multi-channel laser echo time measurement system based on an FPGA (Field Programmable Gate Array) chip, and relates to the field of photoelectric measurement. The system solves the problems that the existing single-point detector cannot meet requirements of multiple channels, high accuracy, wide measurement range, rapid measurement and the like. The system comprises an array detector used for converting a received laser echo signal into a weak current signal, a plurality of preamplifiers with the same quantity as array detector pixels, a plurality of threshold comparators with the same quantity as the preamplifiers, and the FPGA chip of a plurality of channels with the same quantity as the threshold comparators, wherein the preamplifiers are used for amplifying the weak current signal to a voltage signal; the threshold comparators are used for comparing the voltage signal with reference voltage, and generating a timing stop pulse signal used for marking the laser echo signal; and the FPGA chip is used for measuring a time difference between the received timing stop pulse signal and a timing start pulse signal, and obtaining the pulse flight time. The system realizes high-accuracy, wide-range and high-speed array signal measurement through multi-channel signal processing.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

Time-to-digital converter

InactiveUS20090225631A1Reduce circuit sizeHigh resolutionAnalogue/digital conversionElectric signal transmission systemsDigital down converterEngineering

A TDC circuit having a small scale circuit and high resolution is disclosed, which is a time-to-digital converter that detects a phase with respect to a reference clock of a signal to be measured, comprising a first delay line in which a plurality of first delay elements with a first delay amount is connected in series, a second delay line group that is connected to a plurality of connection nodes of the first delay line or an input node in the first stage and in which at least one or more second delay elements with a second delay amount different from the first delay amount are connected in series, a plurality of judgment circuits that judge whether the changing edge of the signal to be measured is advanced or delayed with respect to the changing edges of a delayed clock output from the first delay element and the second delay element, and an operation circuit that calculates a phase with respect to the reference clock of the changing edge of the signal to be measured from the judgment results, wherein a difference between the first delay amount and the second delay amount is smaller than the first delay amount and the second delay amount.

Owner:SEMICON TECH ACADEMIC RES CENT

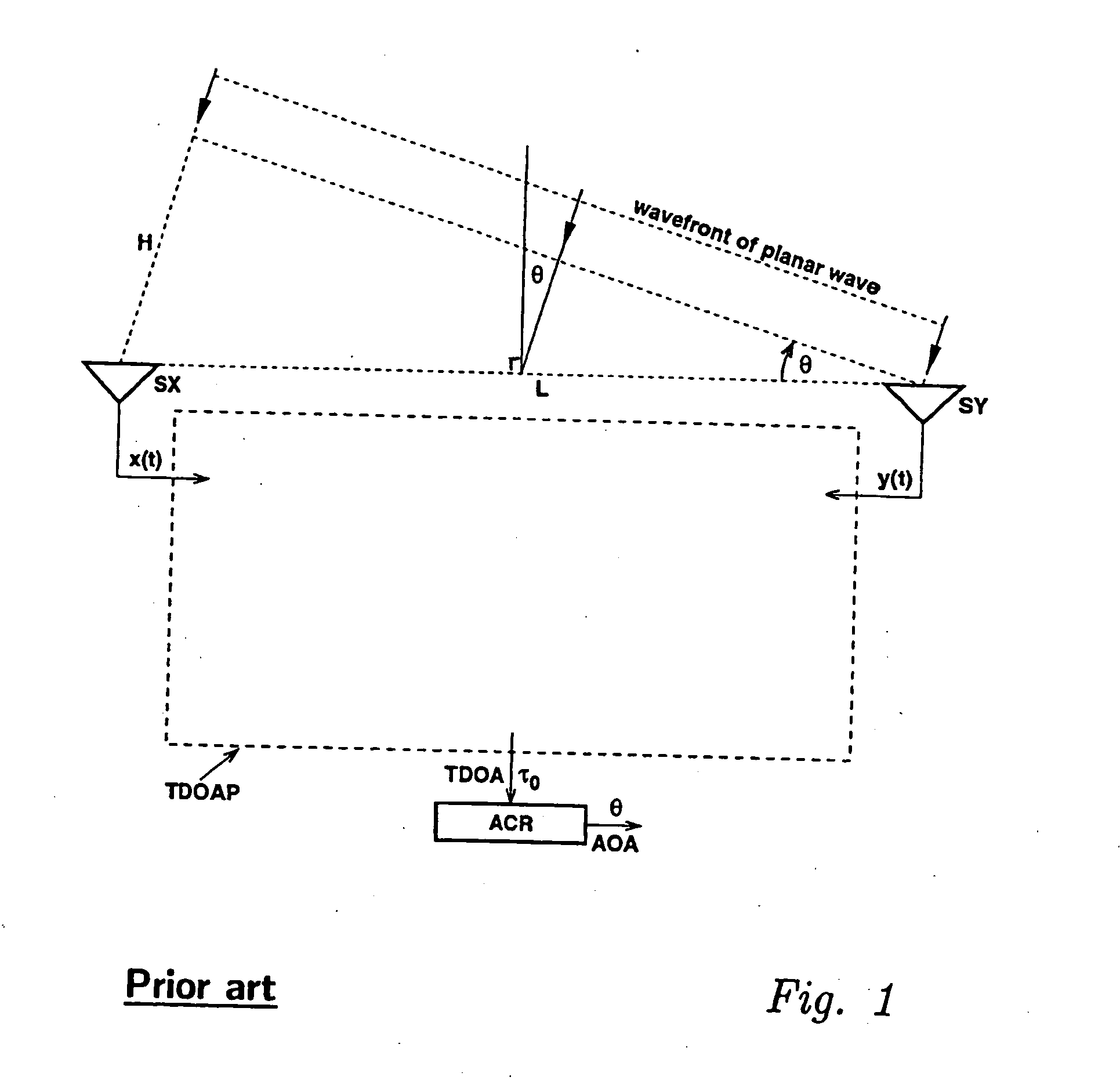

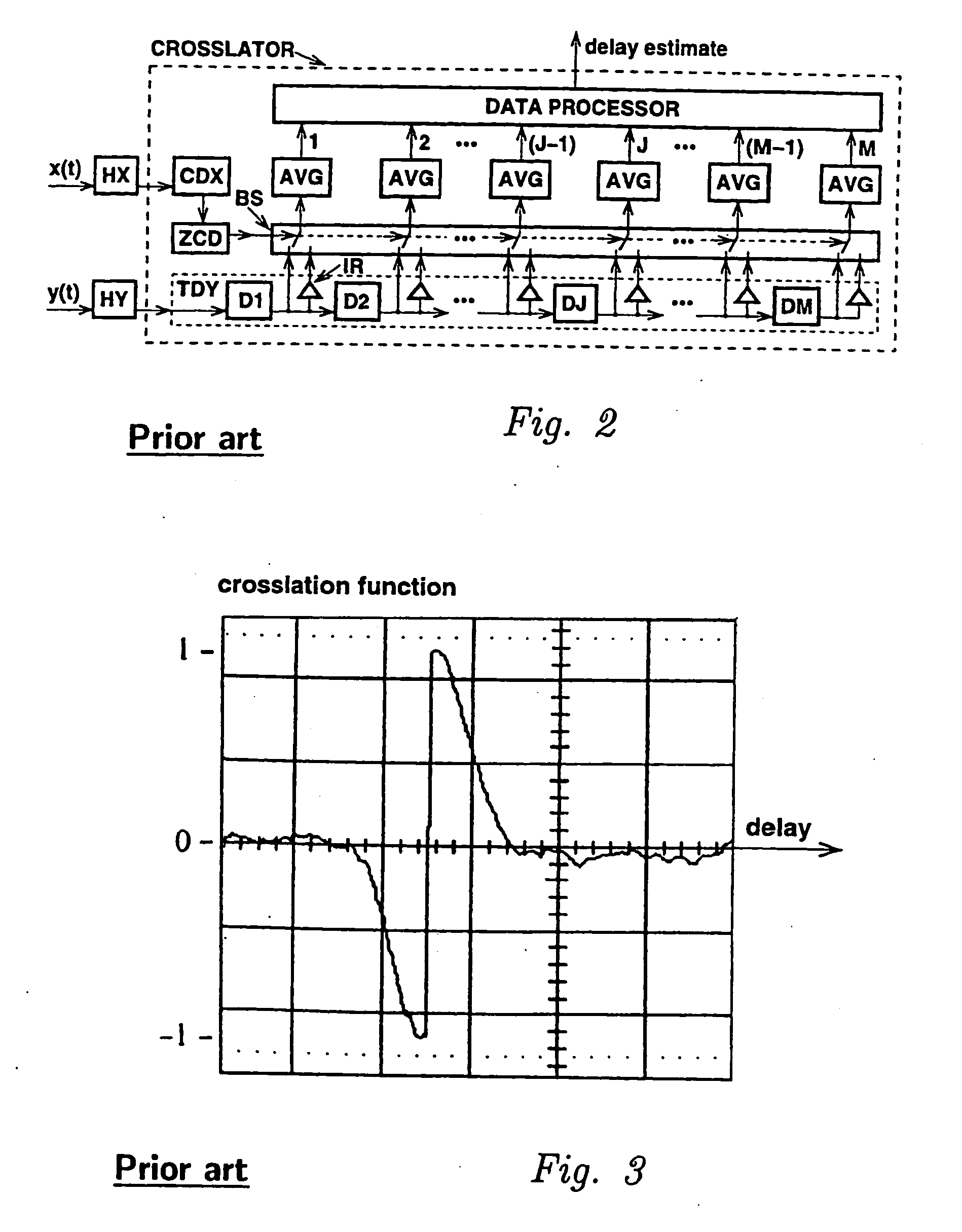

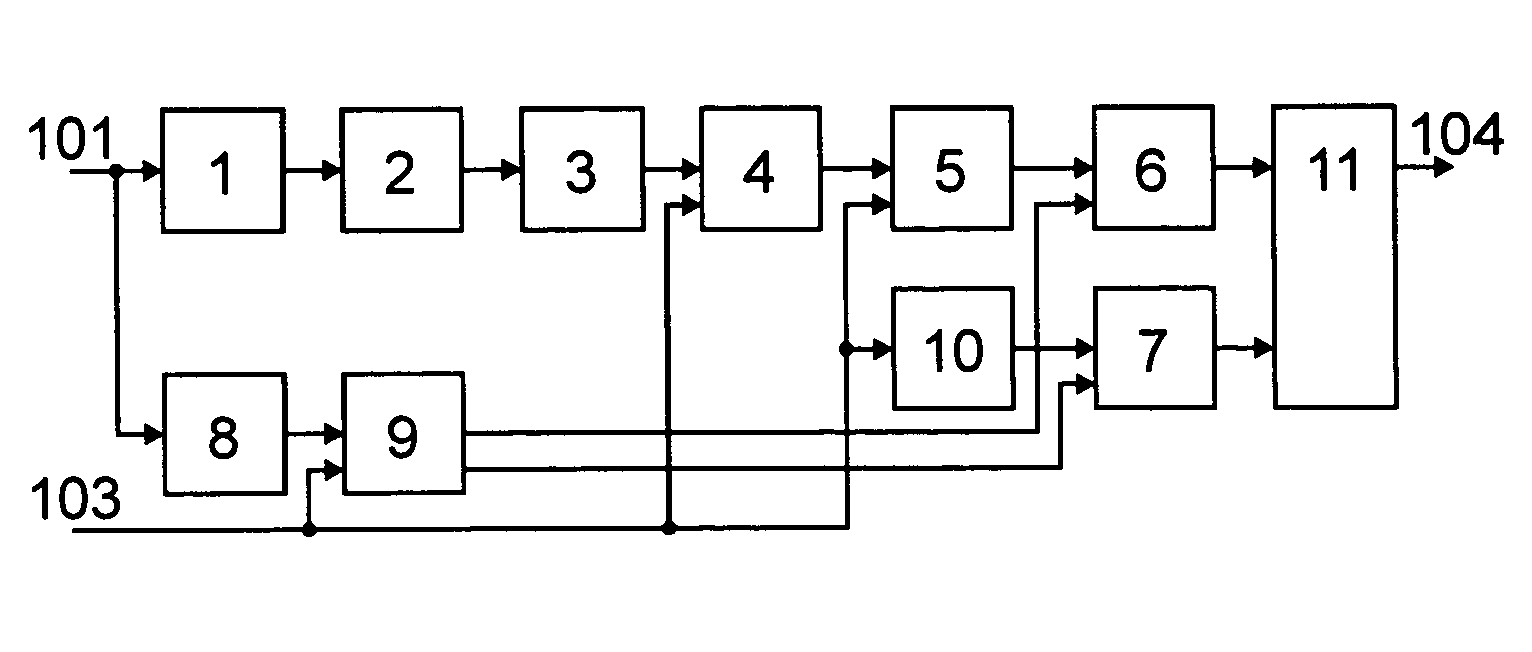

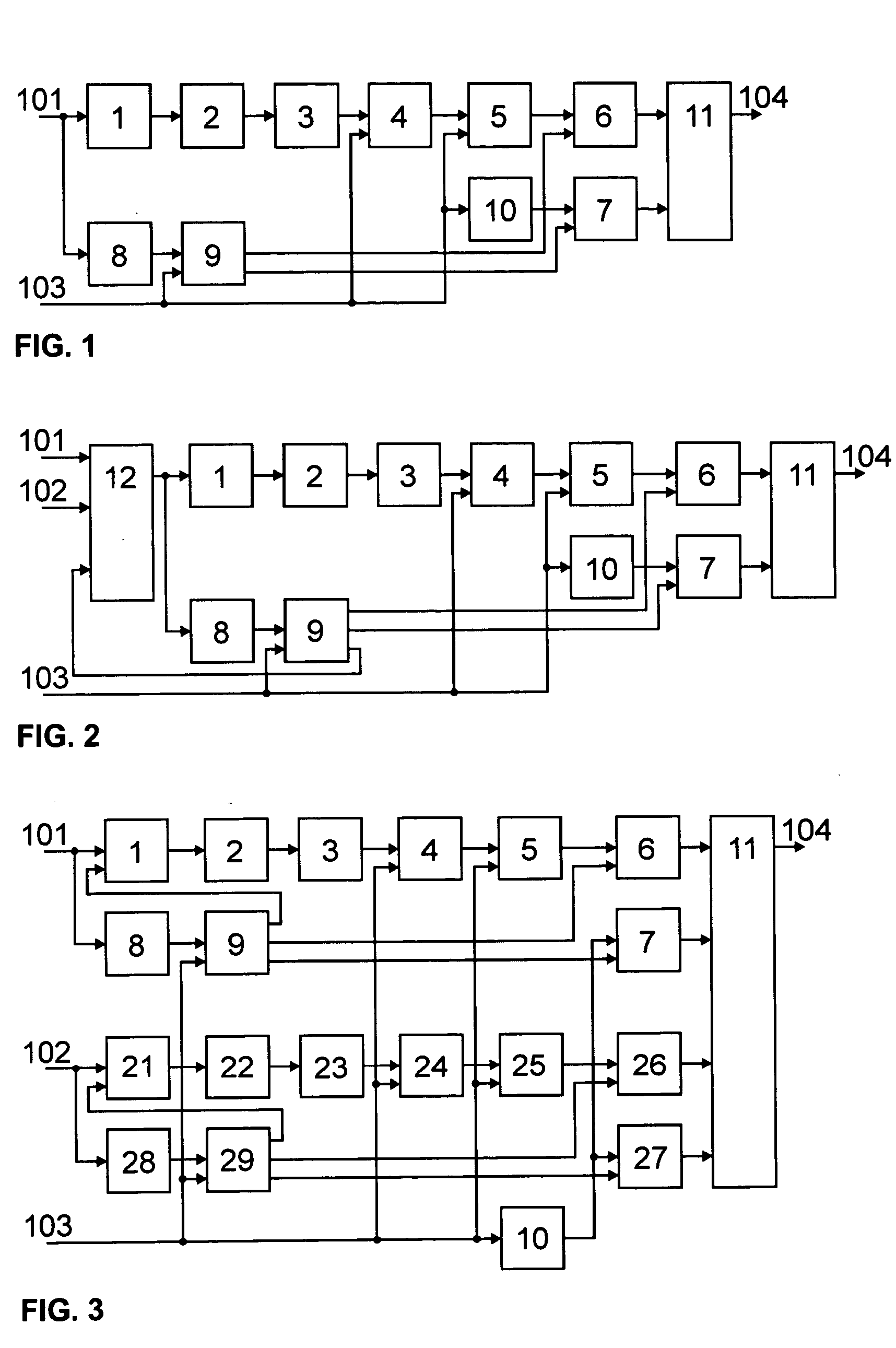

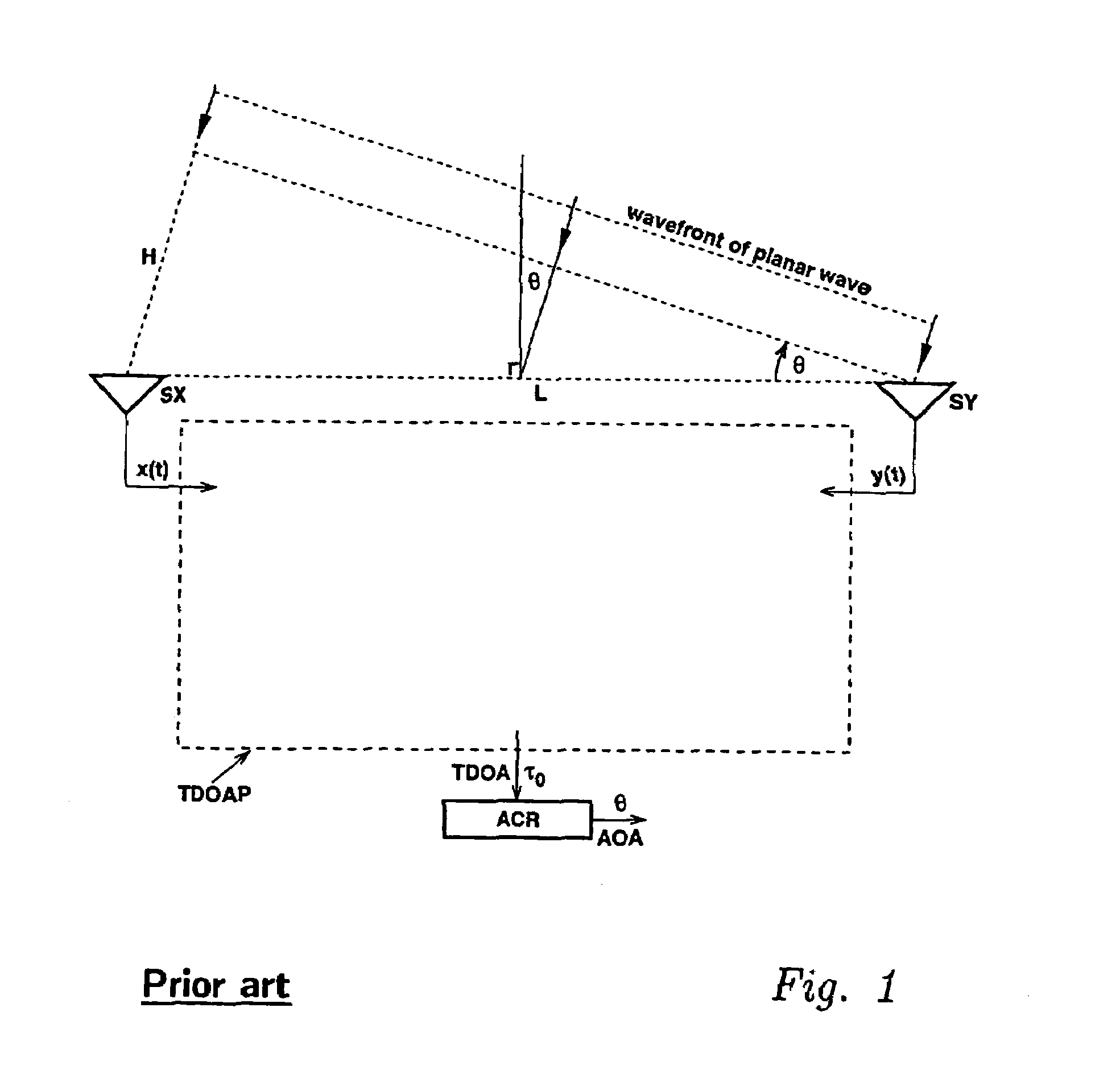

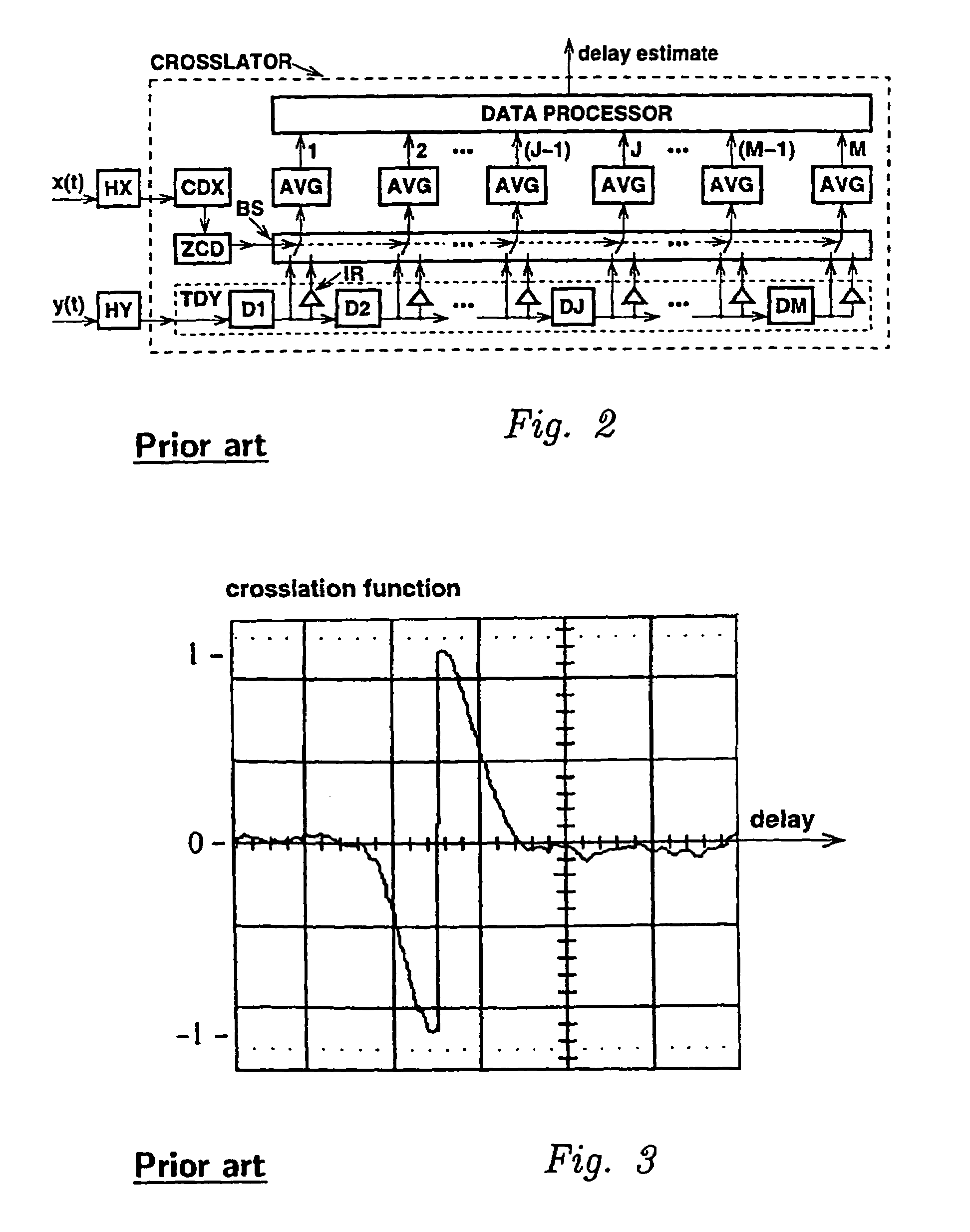

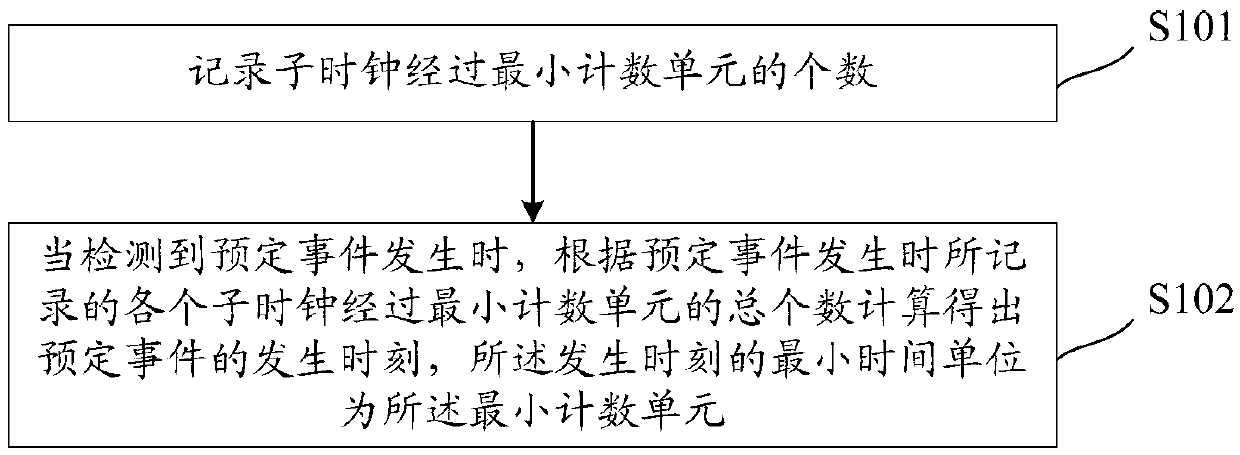

Determination of time-difference of arrival and angle of arrival

InactiveUS20060280032A1Reduce the impact of noisePosition fixationDirection/deviation determination systemsTime differenceCoincidence

The delay between two signals is determined by obtaining zero crossings from each signal, and using each crossing to trigger the sampling of the other signal. Two samples are taken in response to each zero crossing, and the difference between those two samples is calculated. This difference is summed for each event and both signals to derive a value. The process is repeated for different delays between the first and second signals. The values are examined to determine the delay which corresponds to the greatest coincidence between the signals.

Owner:MITSUBISHI ELECTRIC CORP

Time interval measurement device

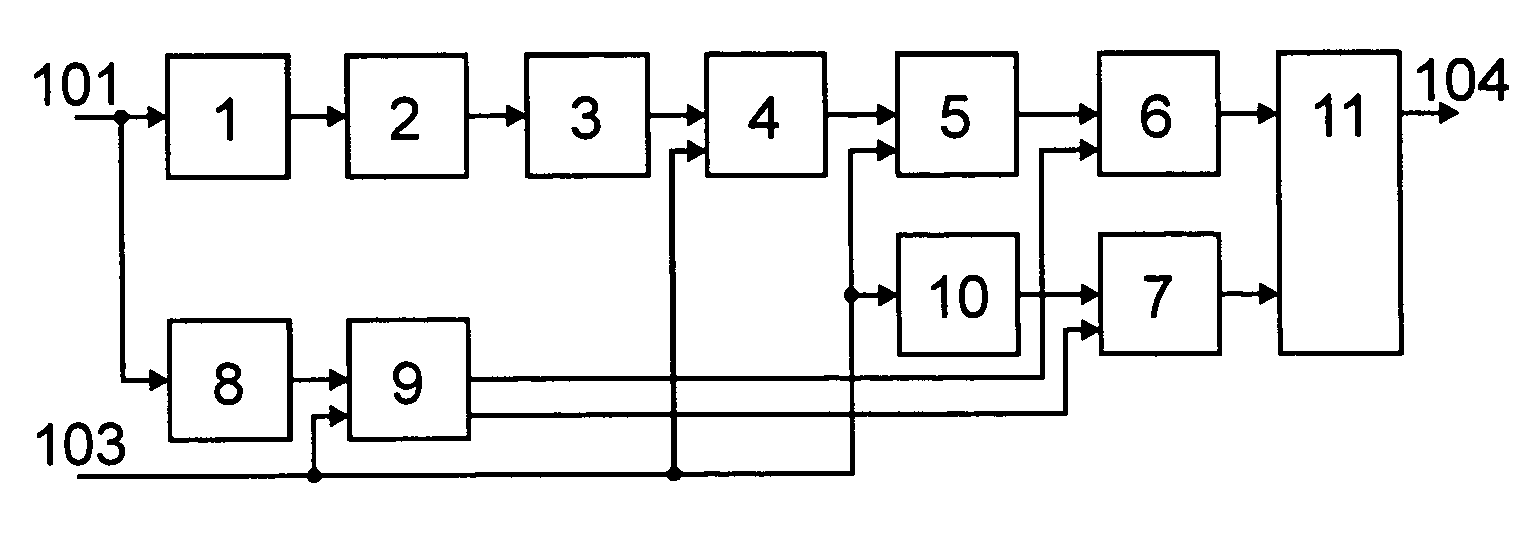

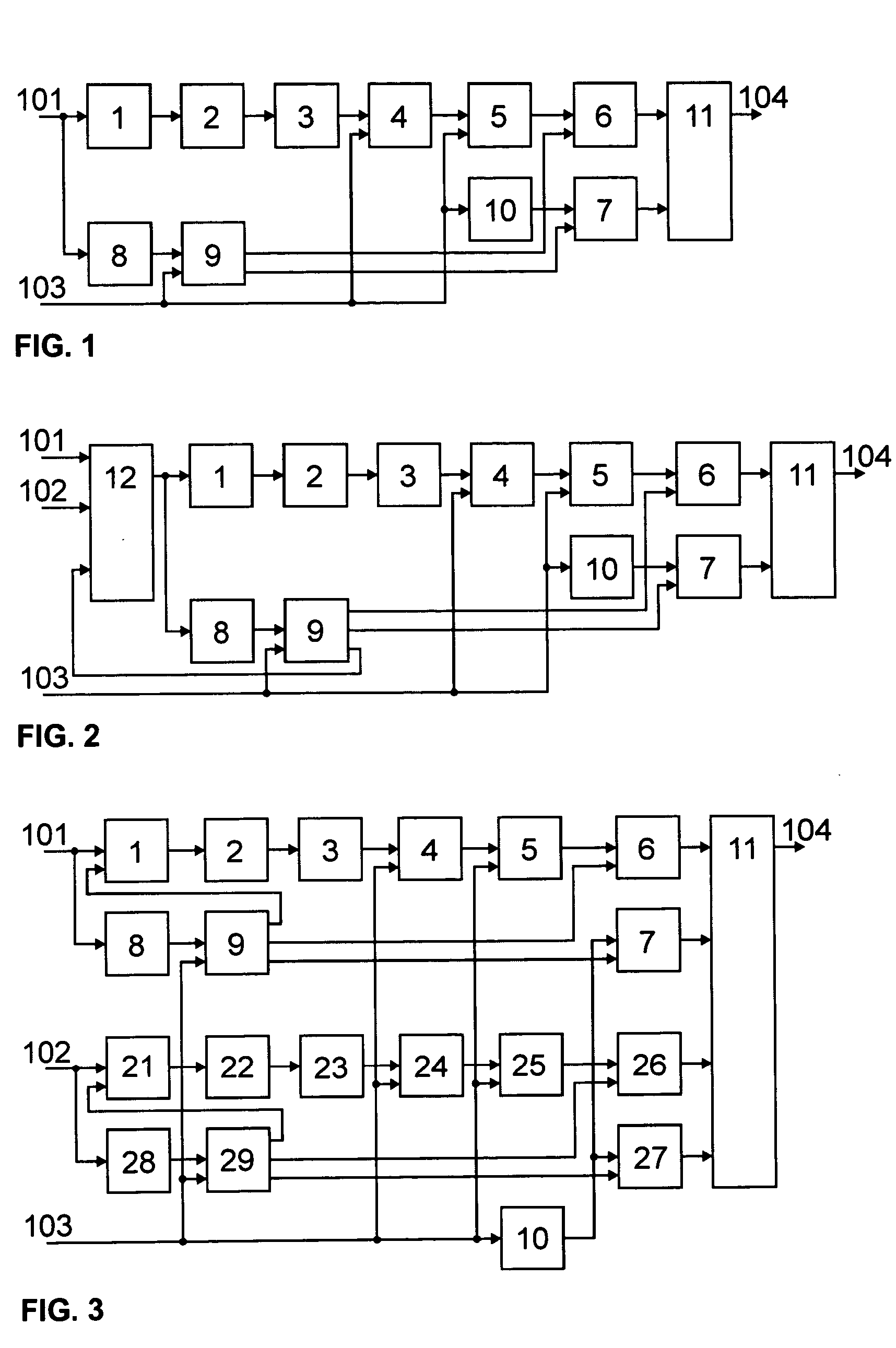

InactiveUS20050052952A1Improve accuracyUnlimited dynamic rangeMultiple input and output pulse circuitsMechanical clocksMeasurement deviceA d converter

A device for high accurate measurement of time intervals is based on the conversion of the time interval to a sequence of samples of the response of a surface acoustic wave filter excited at the beginning and at the end of the measured interval. In one of its configurations, the time interval measurement device includes the input of the pulse signal, the filter exciter, the surface acoustic wave filter, the amplifier, the sampler, the analog-to-digital converter, the sample registers, the register of sample numbers, the voltage comparator, the control circuits, the sample counter, the computer, the output of the reference clock signal source, and the output of the measured time intervals.

Owner:PANEK PETR +1

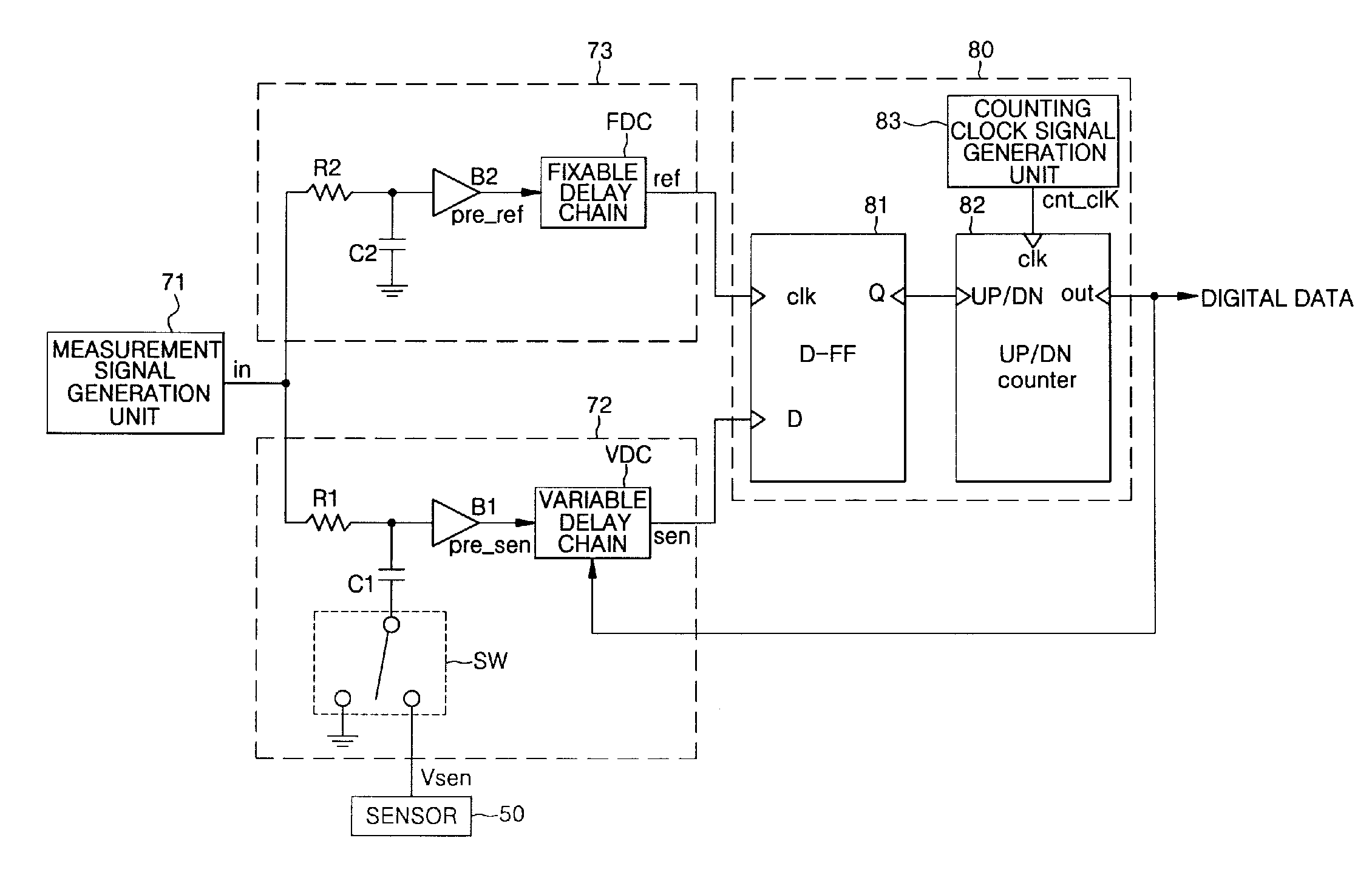

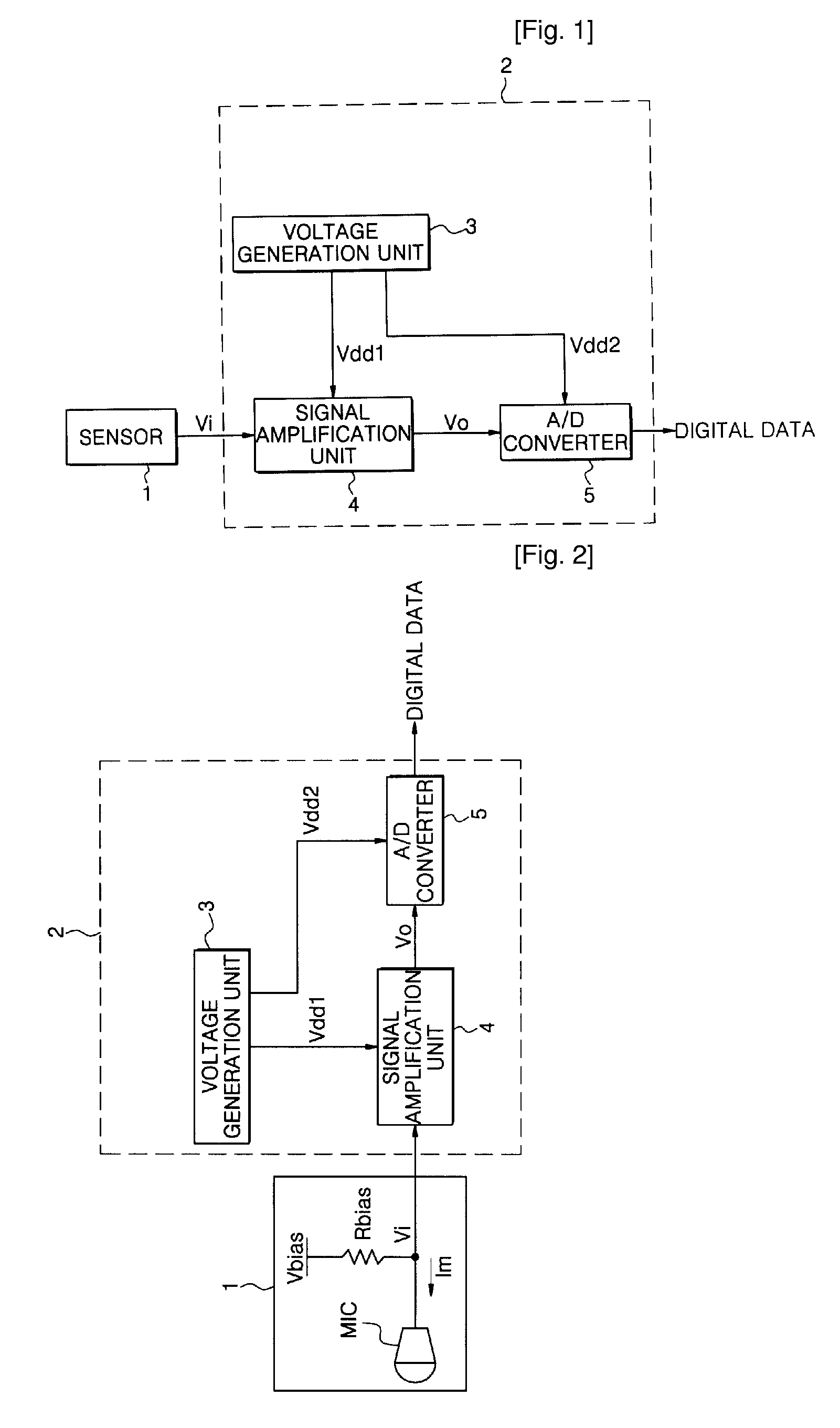

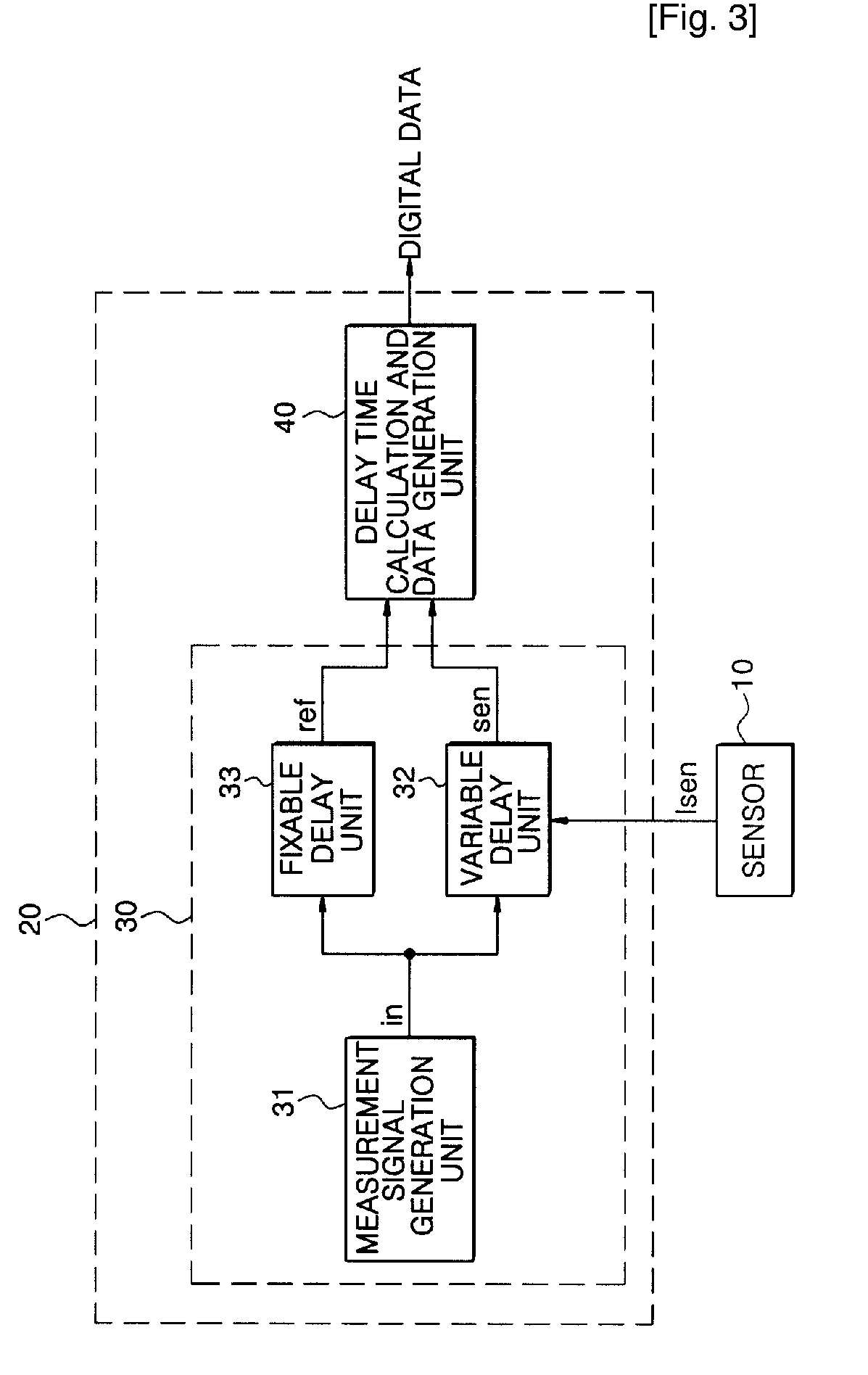

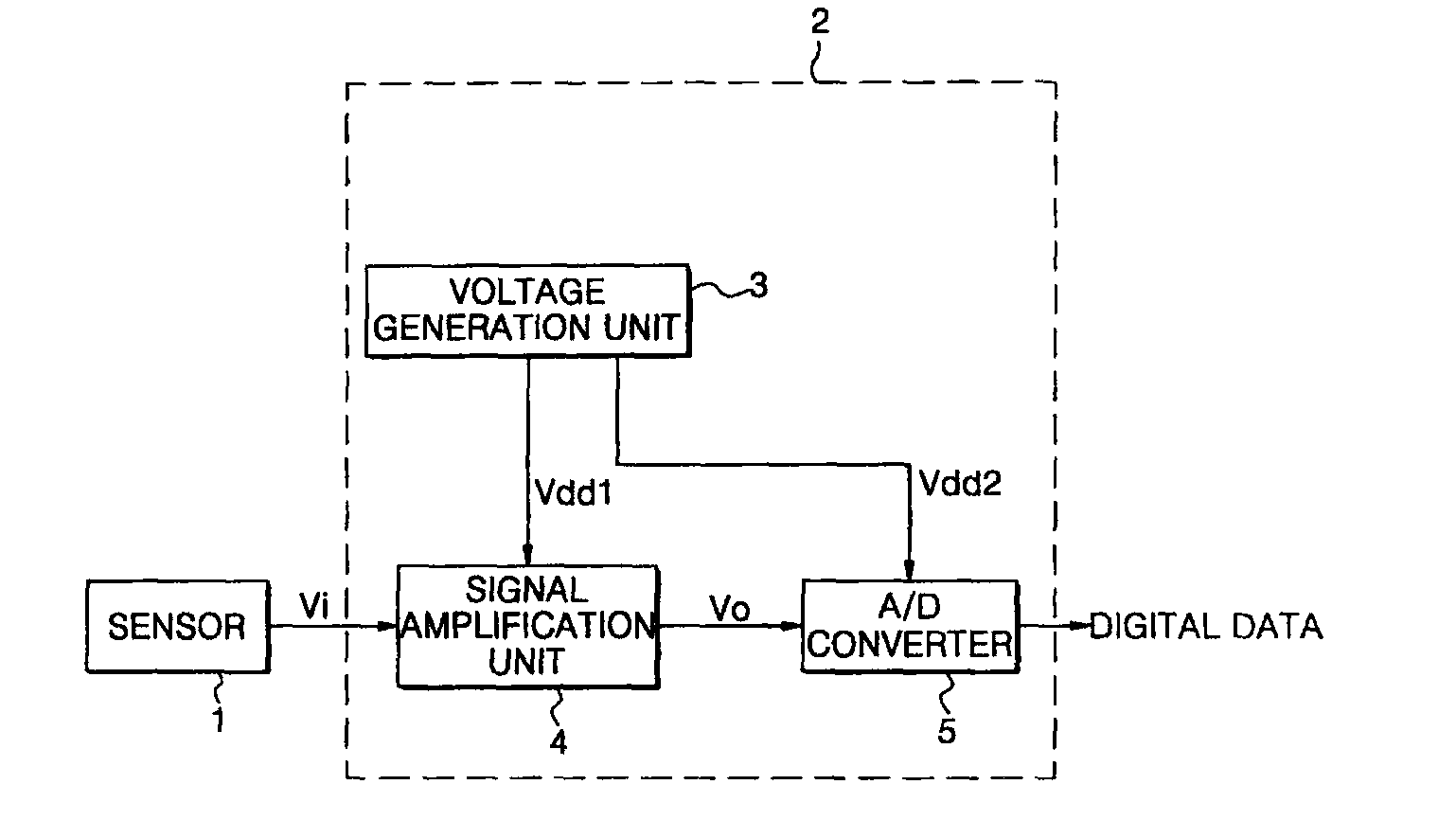

Time to Digital Converting Circuit and Pressure Sensing Device Using the Same

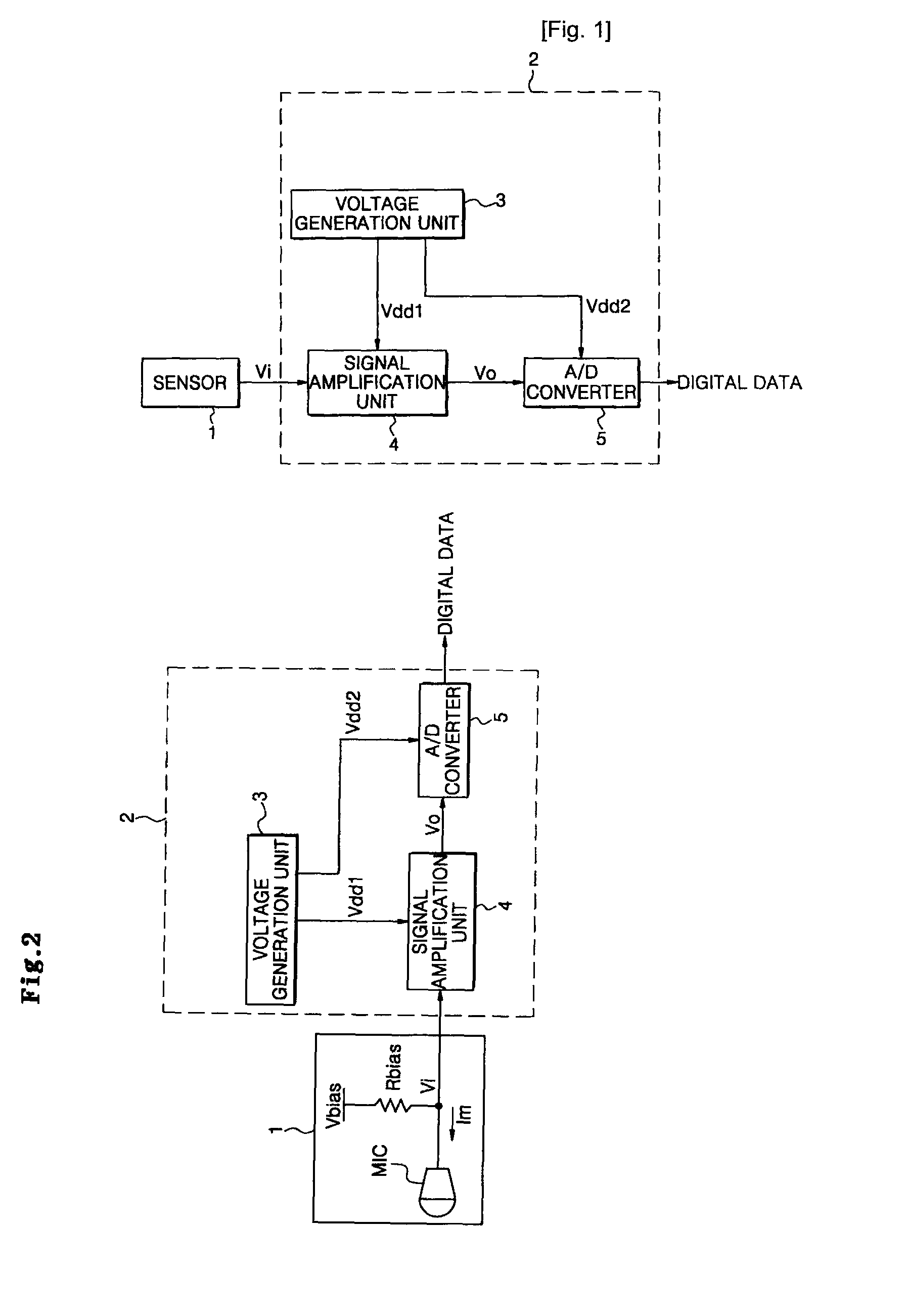

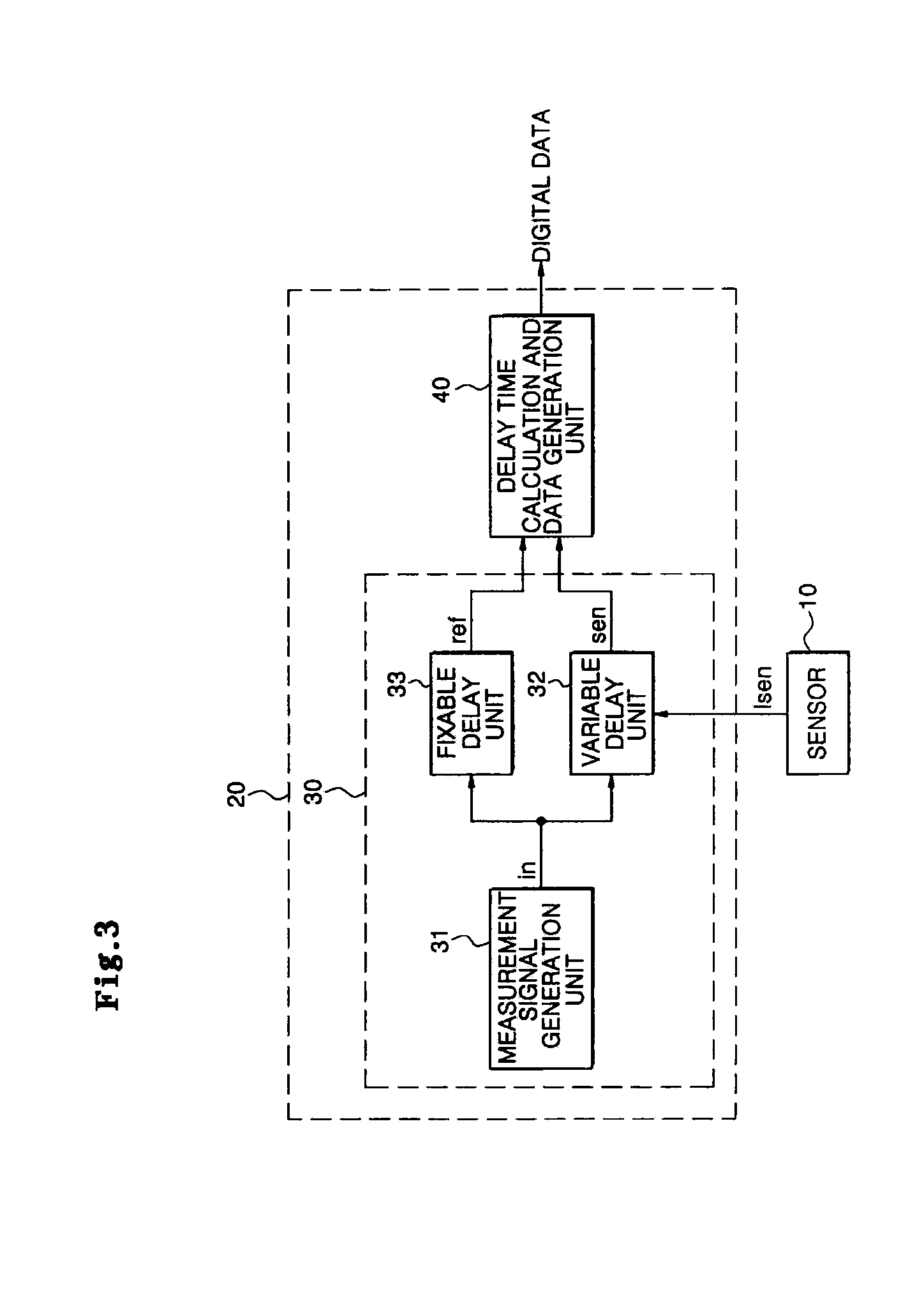

ActiveUS20080295603A1Small sizeMinimizing affectionElectric signal transmission systemsFluid pressure measurement by mechanical elementsDigital dataPressure sense

A time-to-digital converting circuit and a pressure sensing device using the same are provided. The circuit includes: a delay time-varying unit generating a reference signal having a fixed delay time, and a sensing signal having a variable delay time in response to an impedance of an externally applied signal; and a delay time calculation and data generation unit calculating a delay time difference between the reference signal and the sensing signal, and generating digital data having a value corresponding to the calculated delay time difference. Accordingly, the digital data are generated using the delay time varied in response to the externally applied signal, so that the size of the time-to-digital circuit is significantly reduced. In addition, an affect due to external noises is minimized.

Owner:ATLAB INC

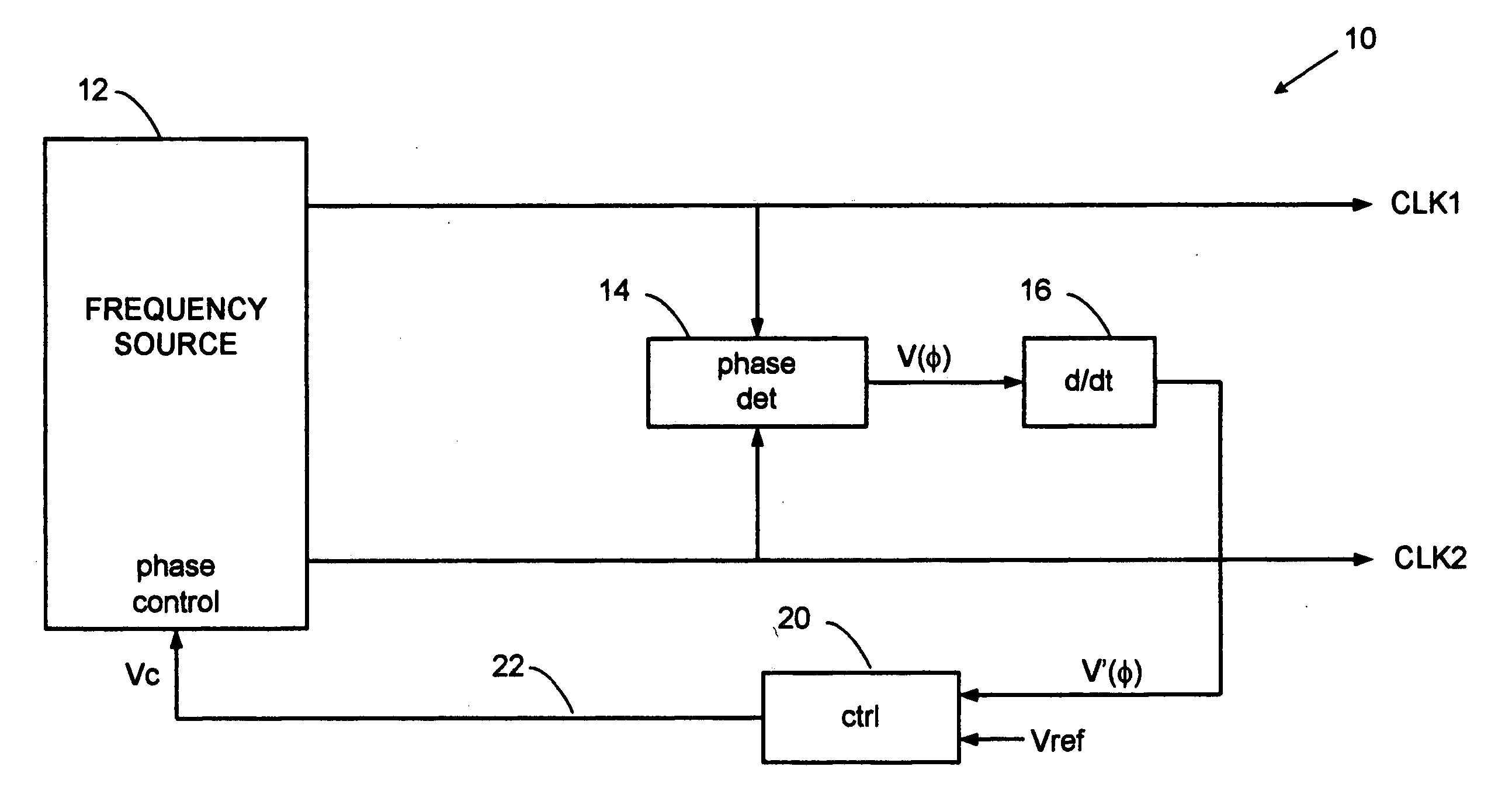

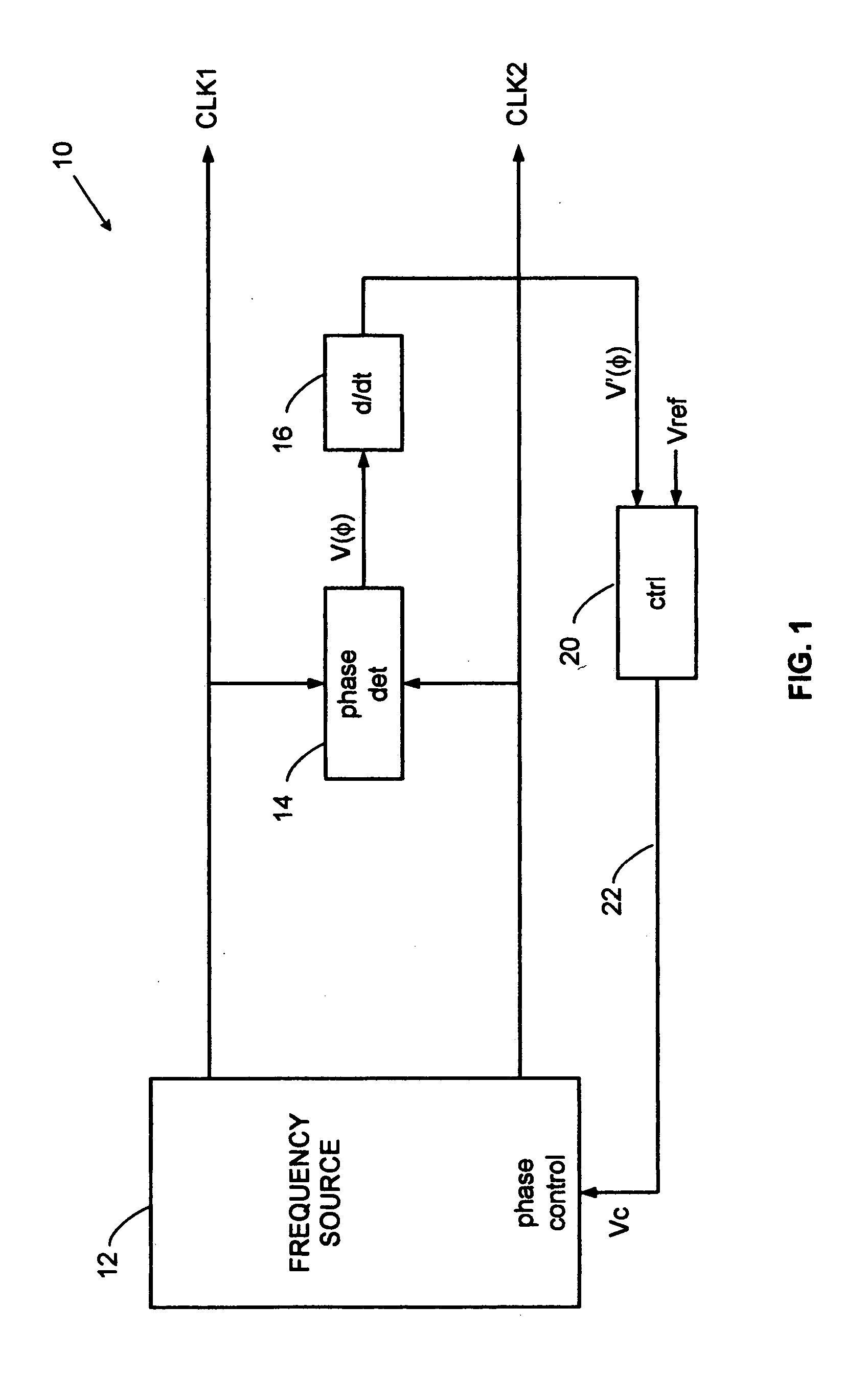

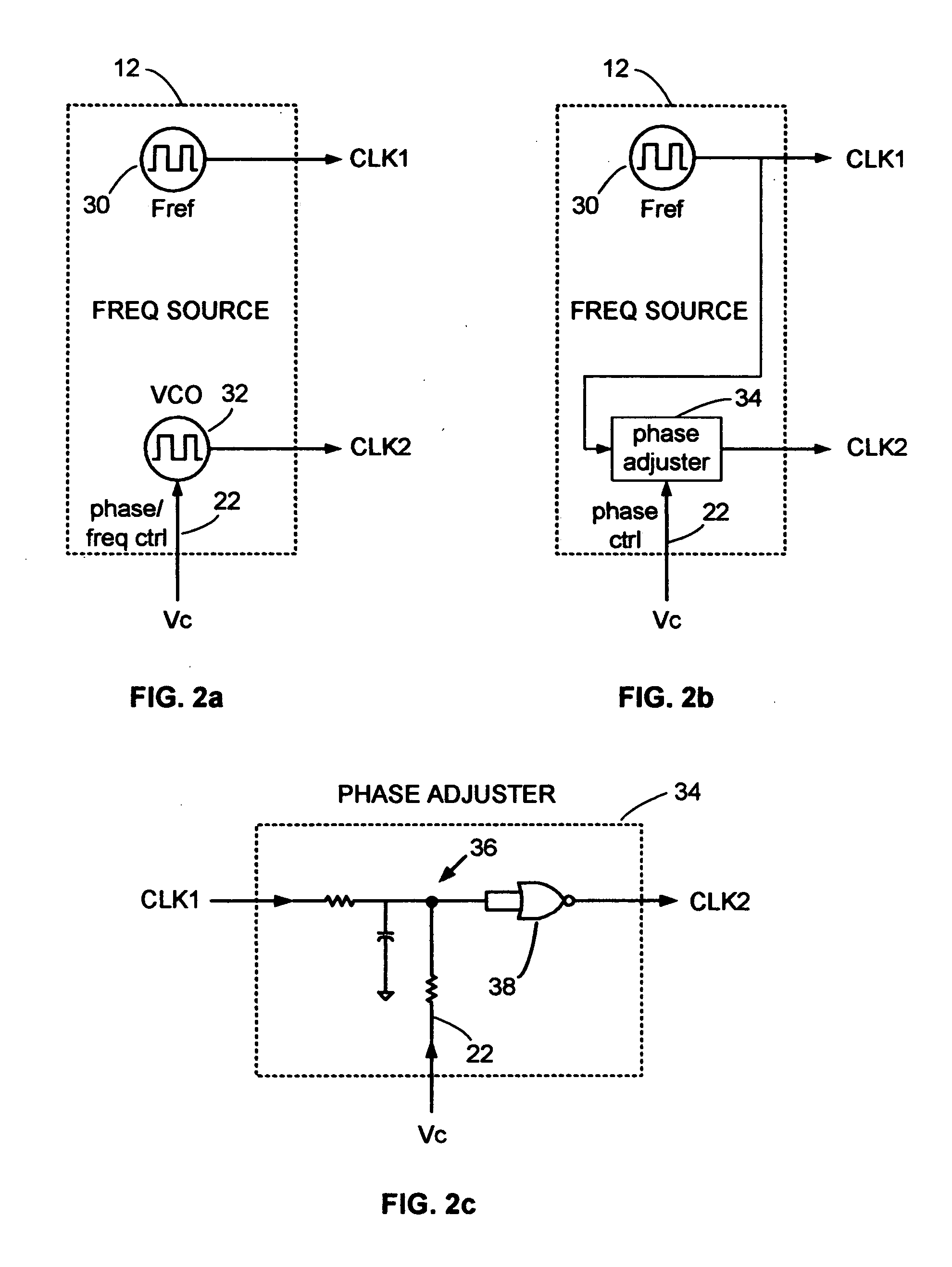

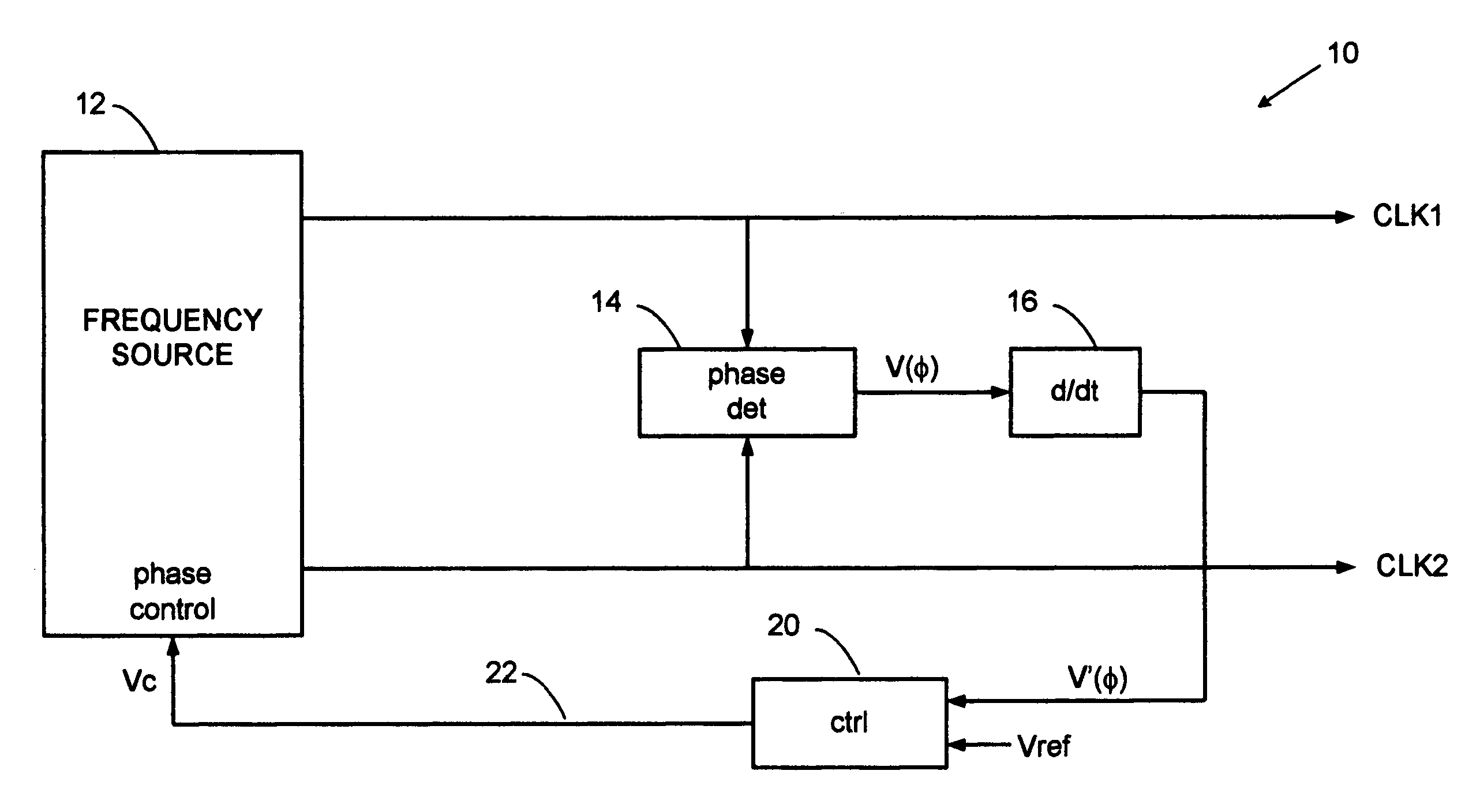

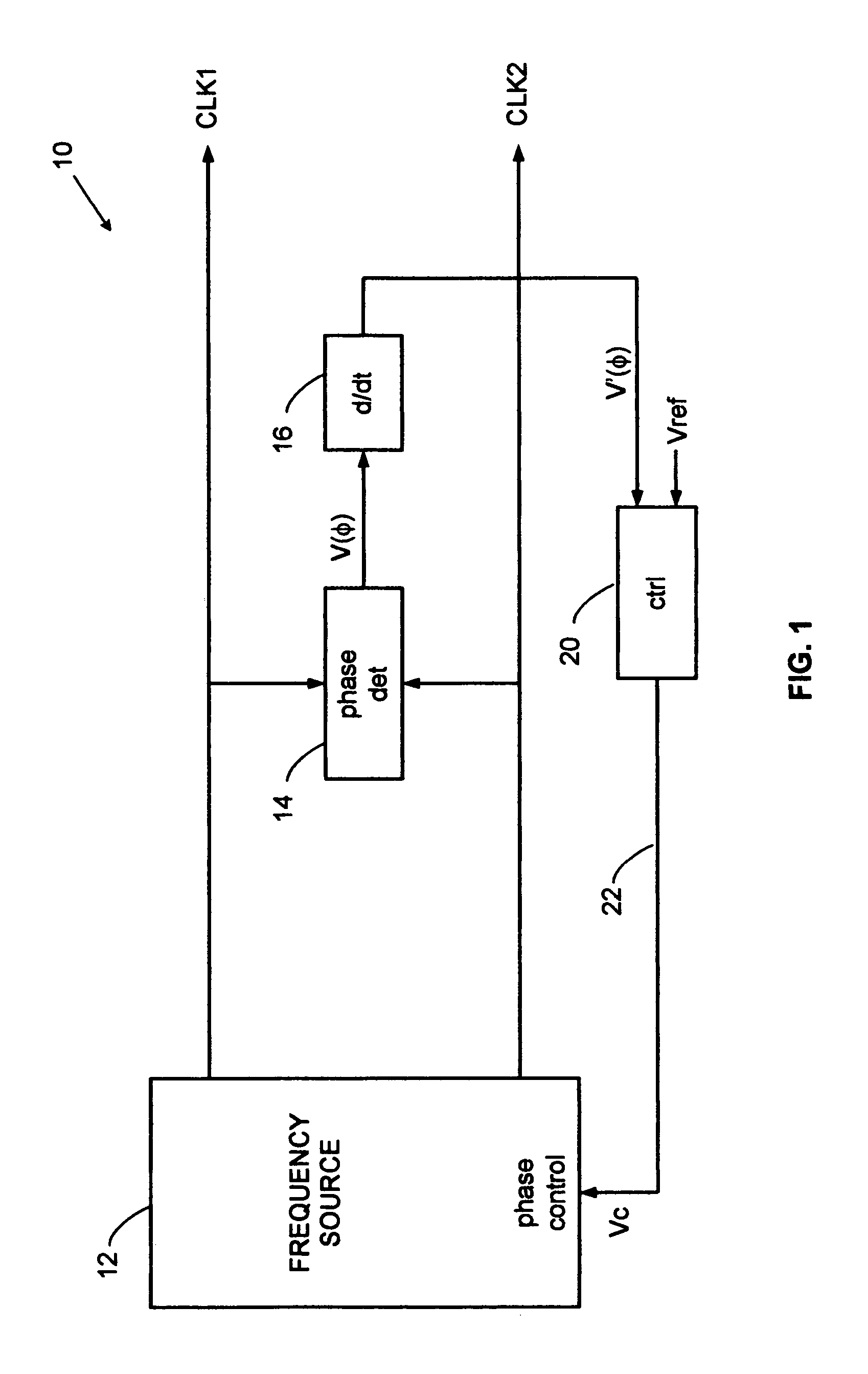

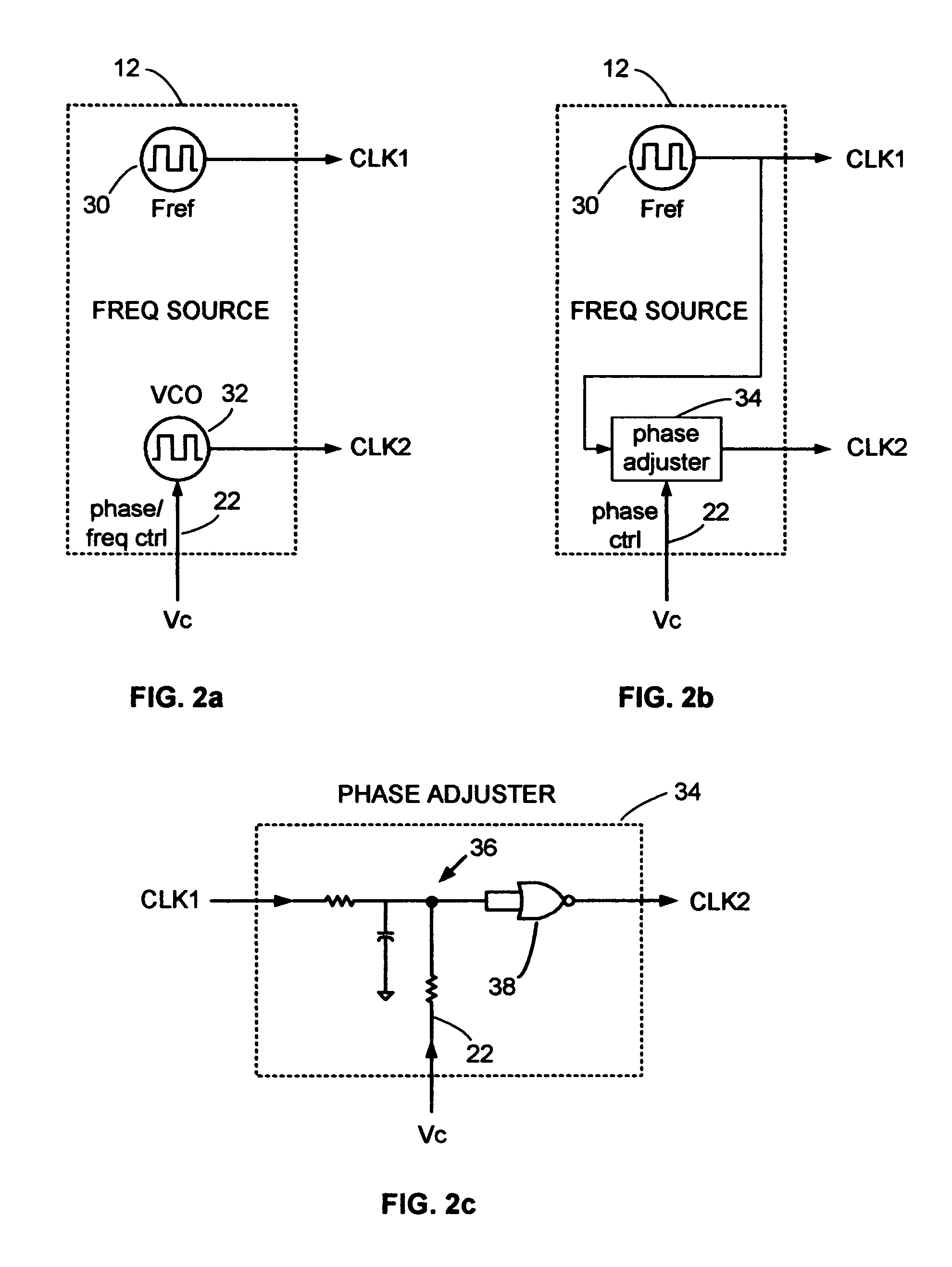

Rate locked loop radar timing system

A rate locked loop (RLL) regulates phase slip between two clock signals to provide precision timing for radar, TDR and laser ranging systems. Two clocks having a small mutual frequency offset exhibit a slowing changing relative phase, or phase slip, that produces a stroboscopic time expansion effect in a ranging system. A phase detector converts clock phase to voltage and the voltage is differentiated to provide a rate-of-change signal to a loop controller that precisely regulates the rate-of-phase change. The RLL controls a VCO to produce a constant, linear phase slip having phase errors below the time equivalent of 1-picosecond.

Owner:MCEWAN TECH

Time-to-digital converter

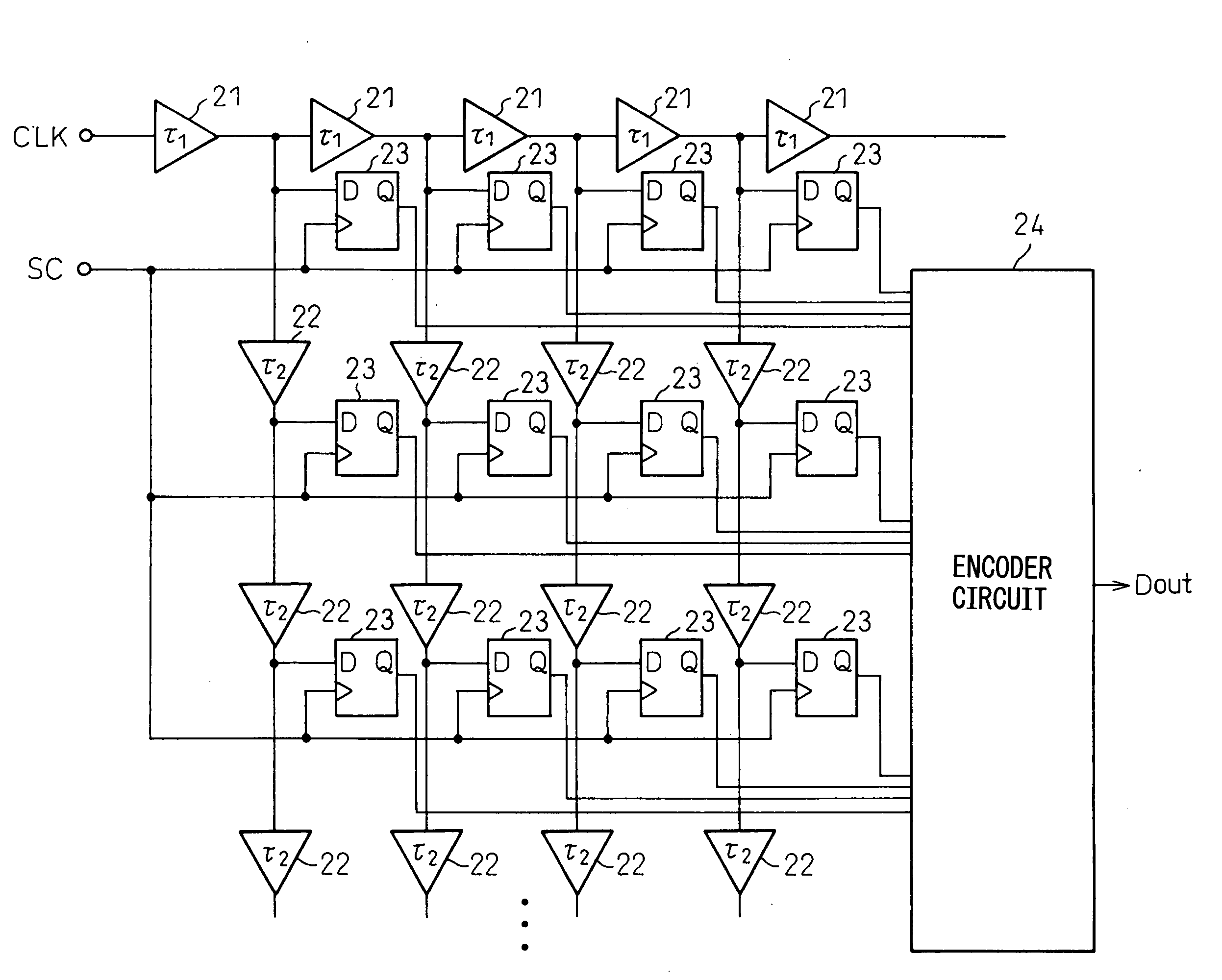

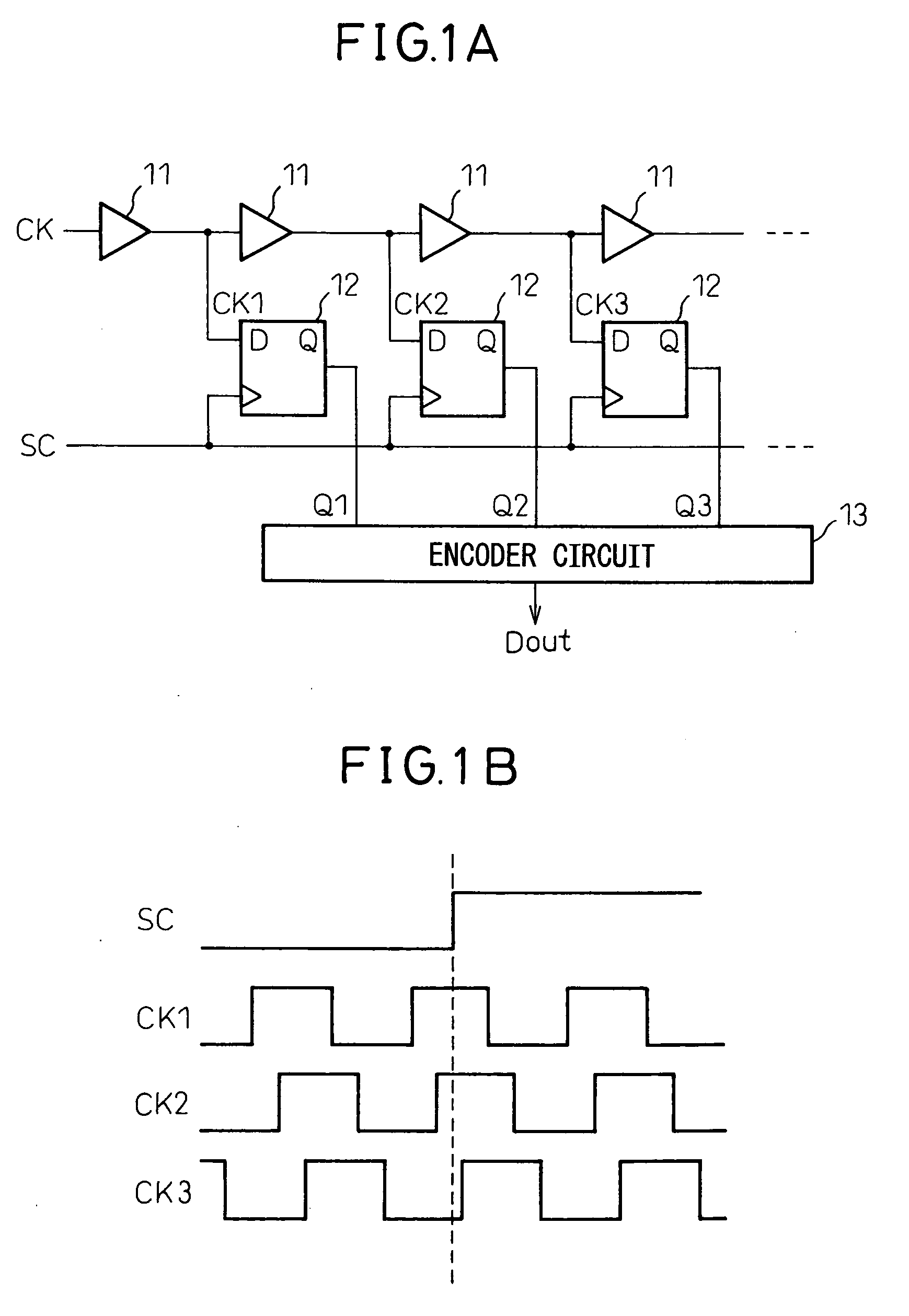

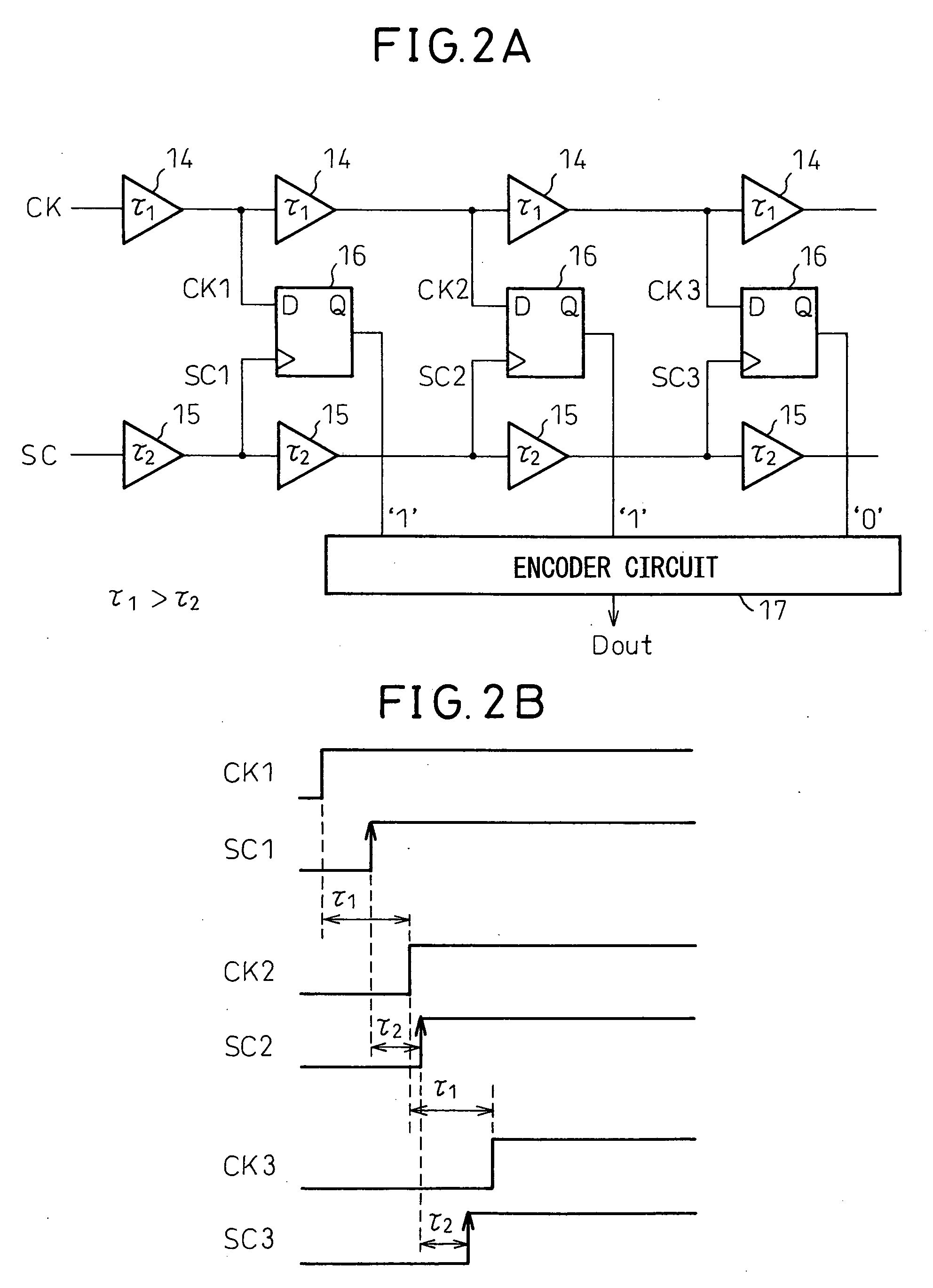

InactiveUS7884751B2Reduce circuit sizeHigh resolutionAnalogue/digital conversionElectric signal transmission systemsDigital down converterEngineering

A TDC circuit having a small scale circuit and high resolution is disclosed, which is a time-to-digital converter that detects a phase with respect to a reference clock of a signal to be measured, comprising a first delay line in which a plurality of first delay elements with a first delay amount is connected in series, a second delay line group that is connected to a plurality of connection nodes of the first delay line or an input node in the first stage and in which at least one or more second delay elements with a second delay amount different from the first delay amount are connected in series, a plurality of judgment circuits that judge whether the changing edge of the signal to be measured is advanced or delayed with respect to the changing edges of a delayed clock output from the first delay element and the second delay element, and an operation circuit that calculates a phase with respect to the reference clock of the changing edge of the signal to be measured from the judgment results, wherein a difference between the first delay amount and the second delay amount is smaller than the first delay amount and the second delay amount.

Owner:SEMICON TECH ACADEMIC RES CENT

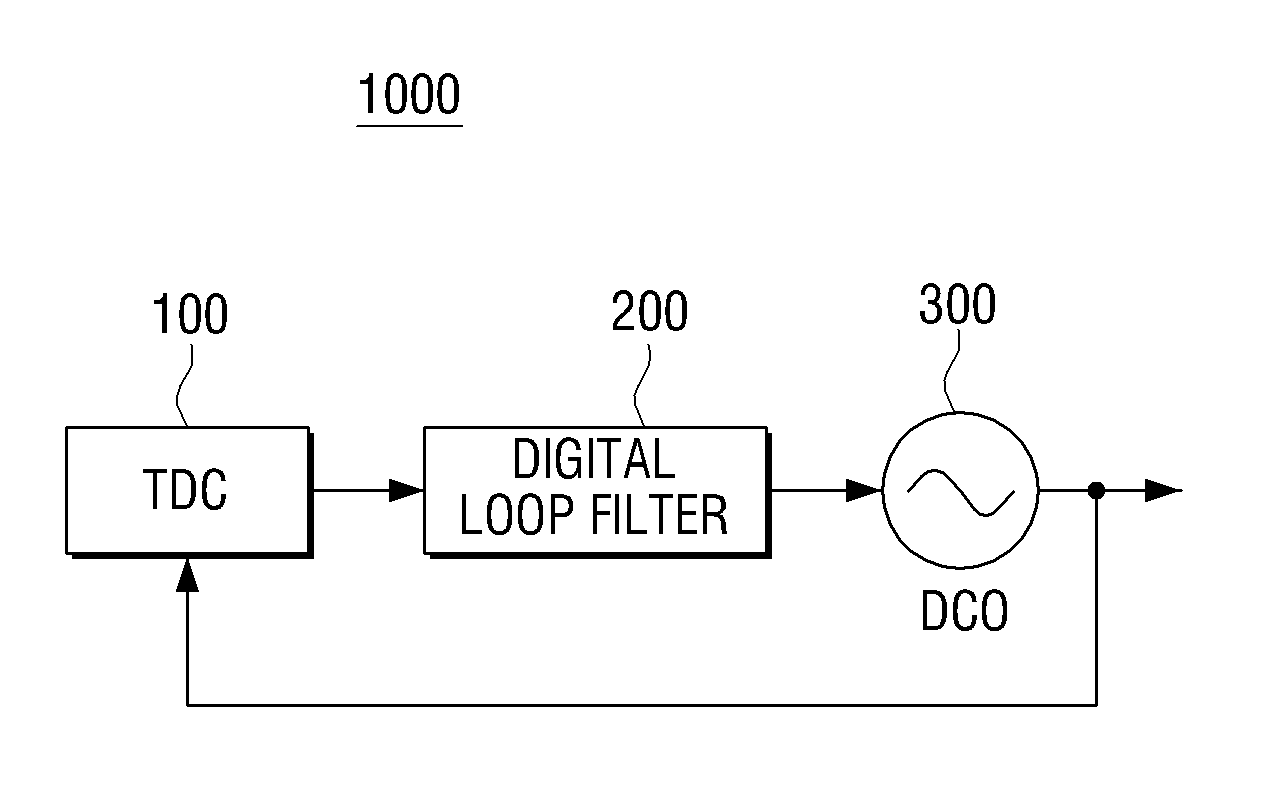

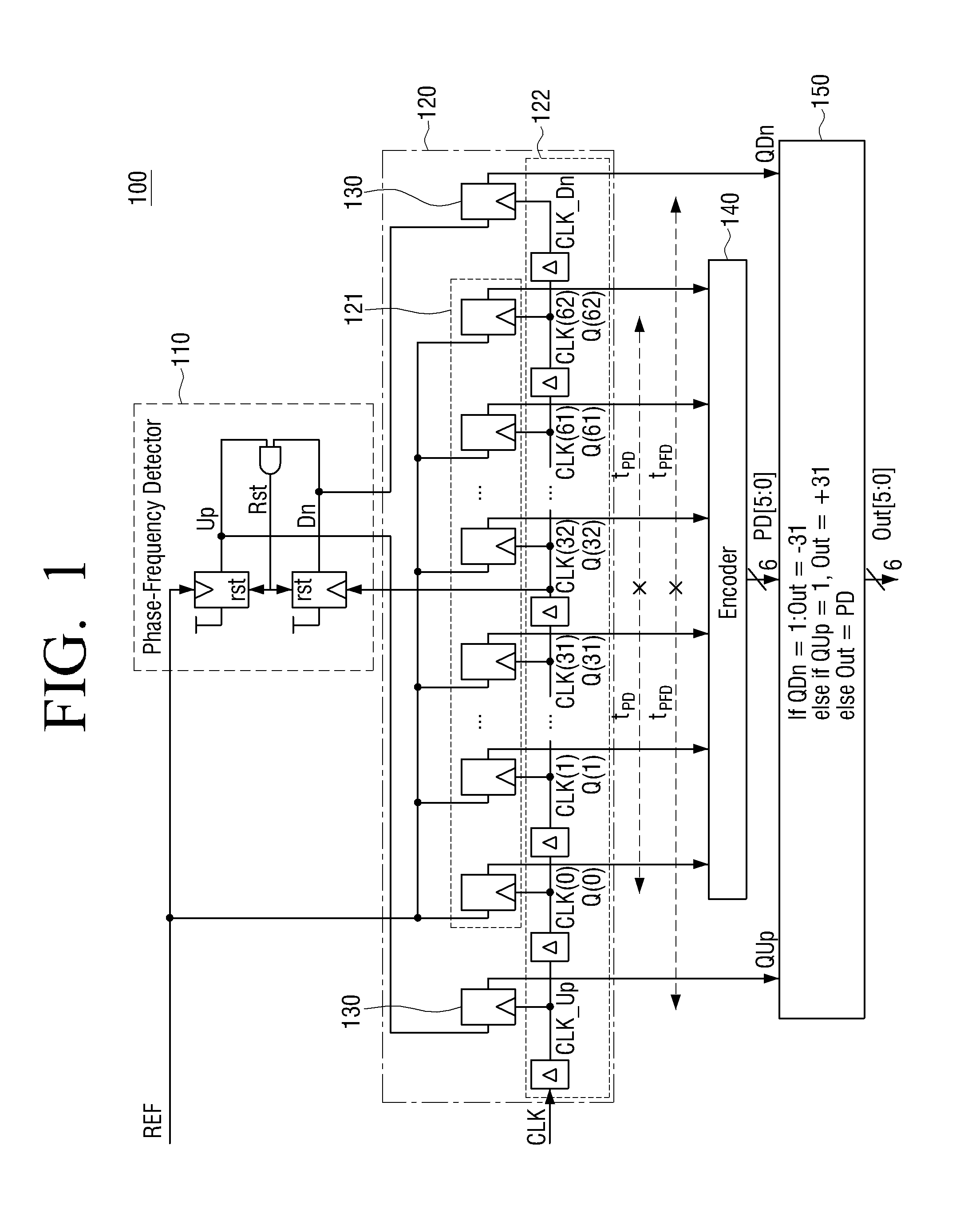

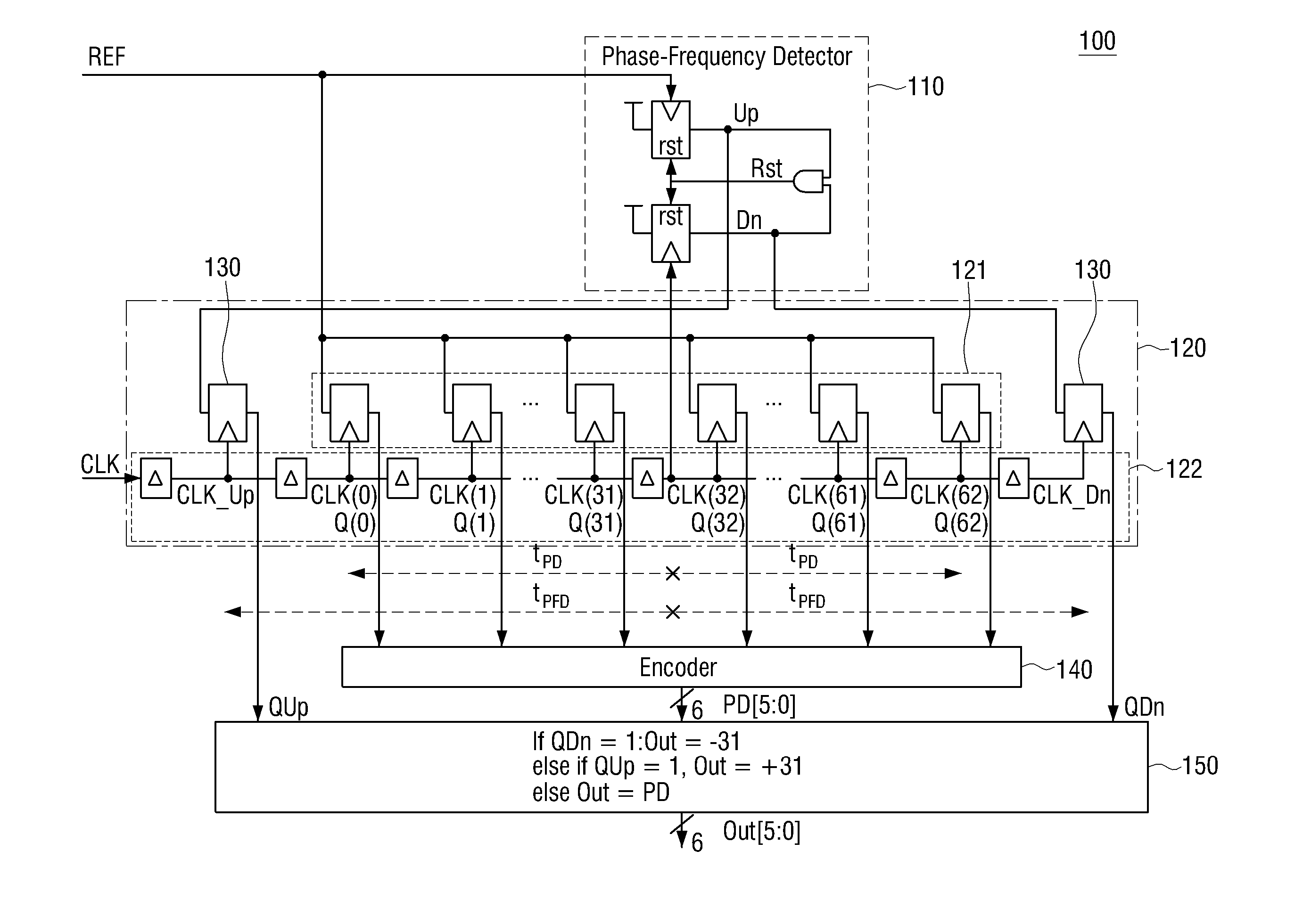

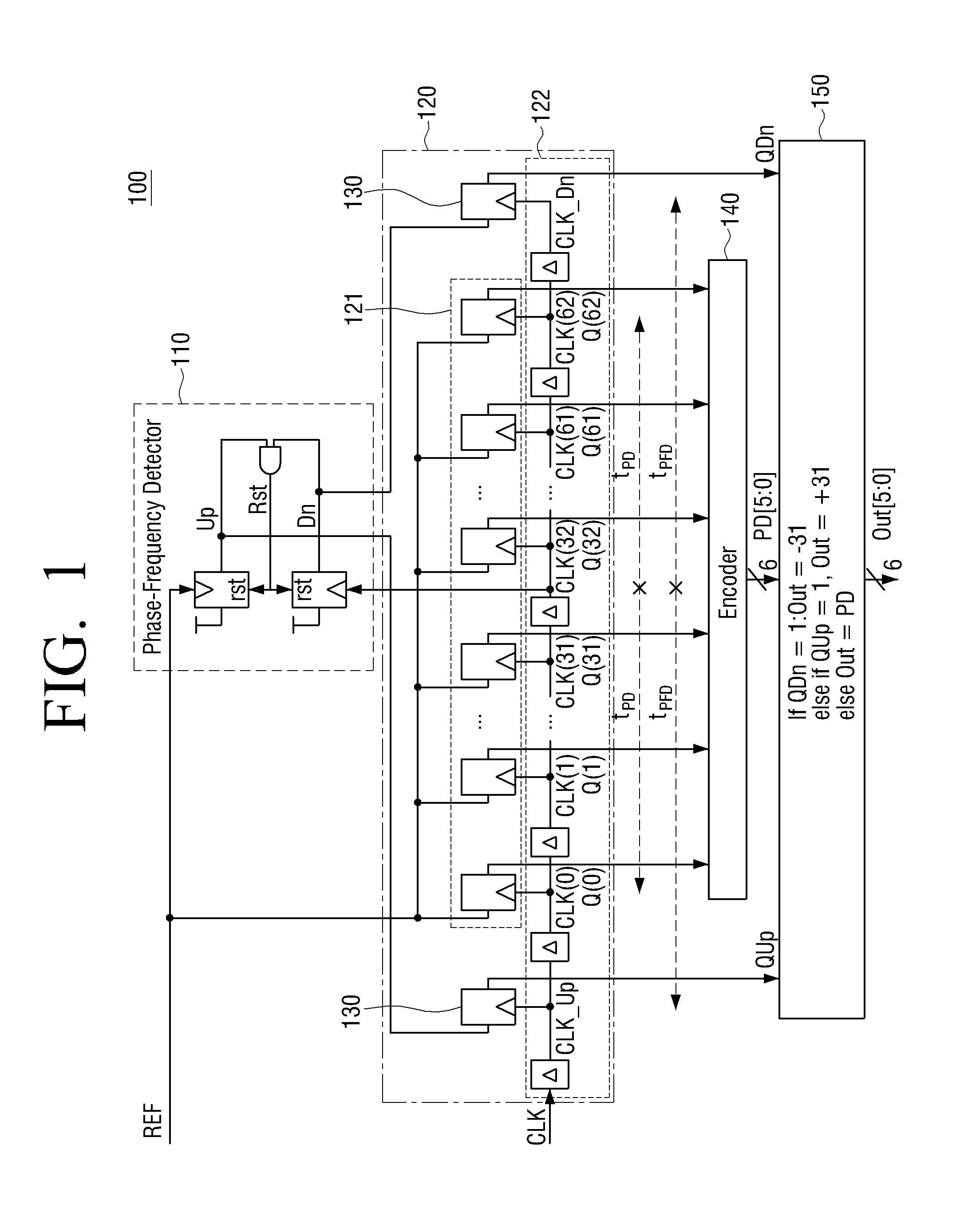

Time-to-digital converter and all-digital phase-locked loop

ActiveUS20100134165A1Multiple input and output pulse circuitsPulse automatic controlPhase differencePhase frequency detector

A time-to-digital converter (TDC) includes a converter which receives a first signal and a second signal, delays the second signal in phases using a plurality of delay elements which are coupled in series, compares the delayed second signal with the first signal, and outputs a phase error of the second signal with respect to the first signal, a phase frequency detector which receives the first signal, and a third signal from one of the nodes in the plurality of delay elements, and outputs a phase difference between the first signal and the third signal, and a frequency detector which outputs a frequency error of the second signal with respect to the first signal as a digital code using an output signal of the phase frequency detector and the second signal.

Owner:SAMSUNG ELECTRONICS CO LTD +1

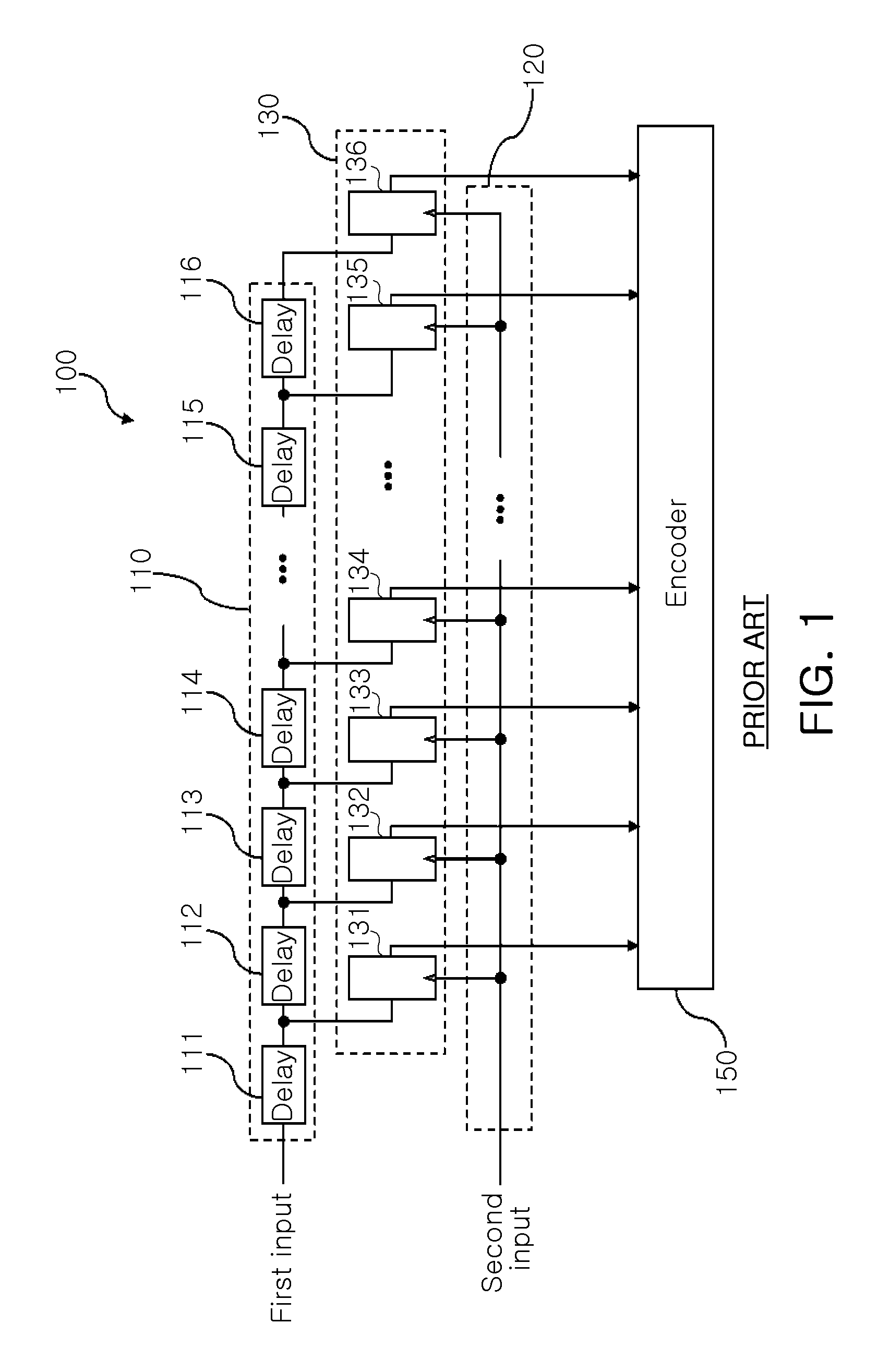

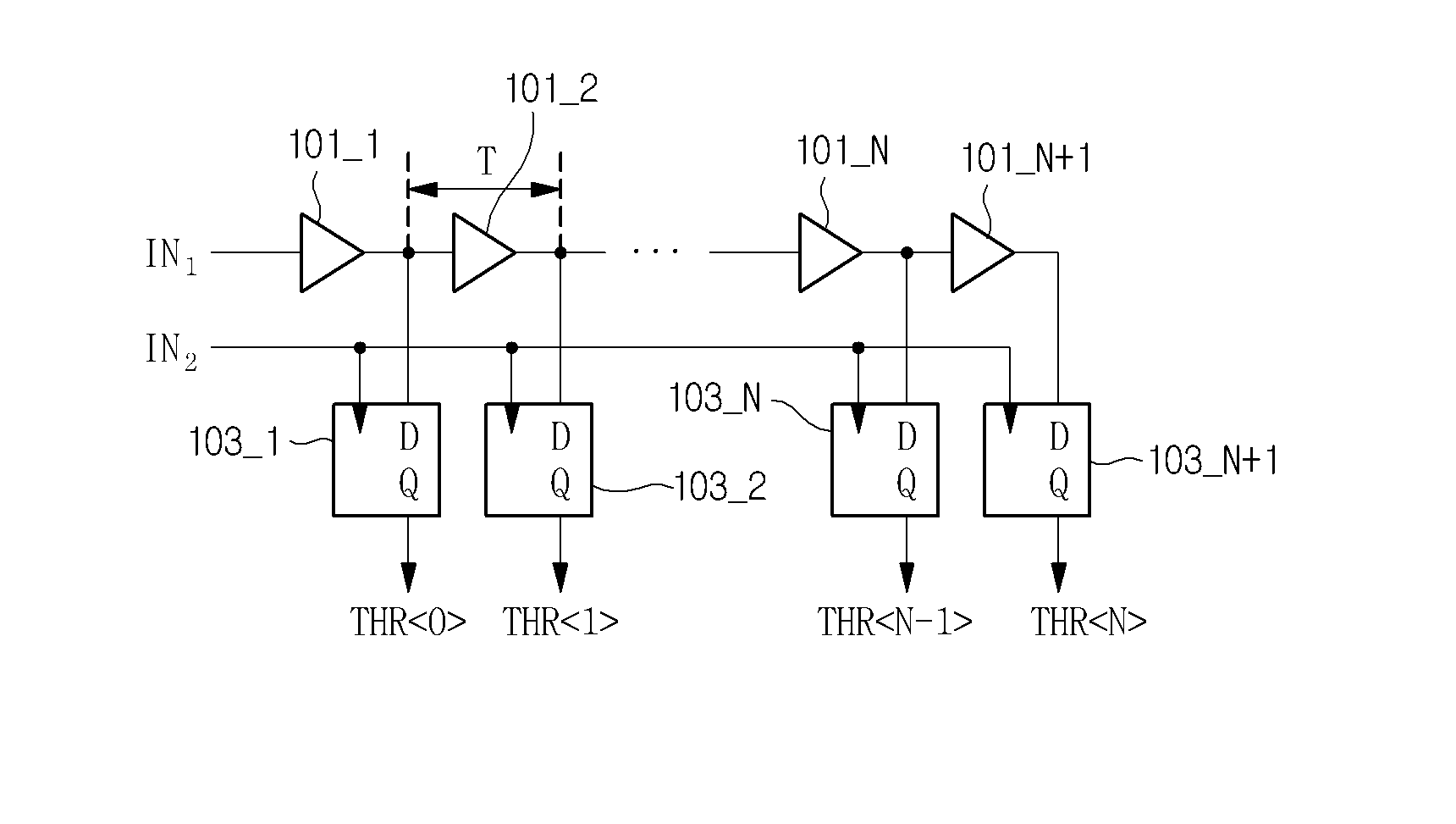

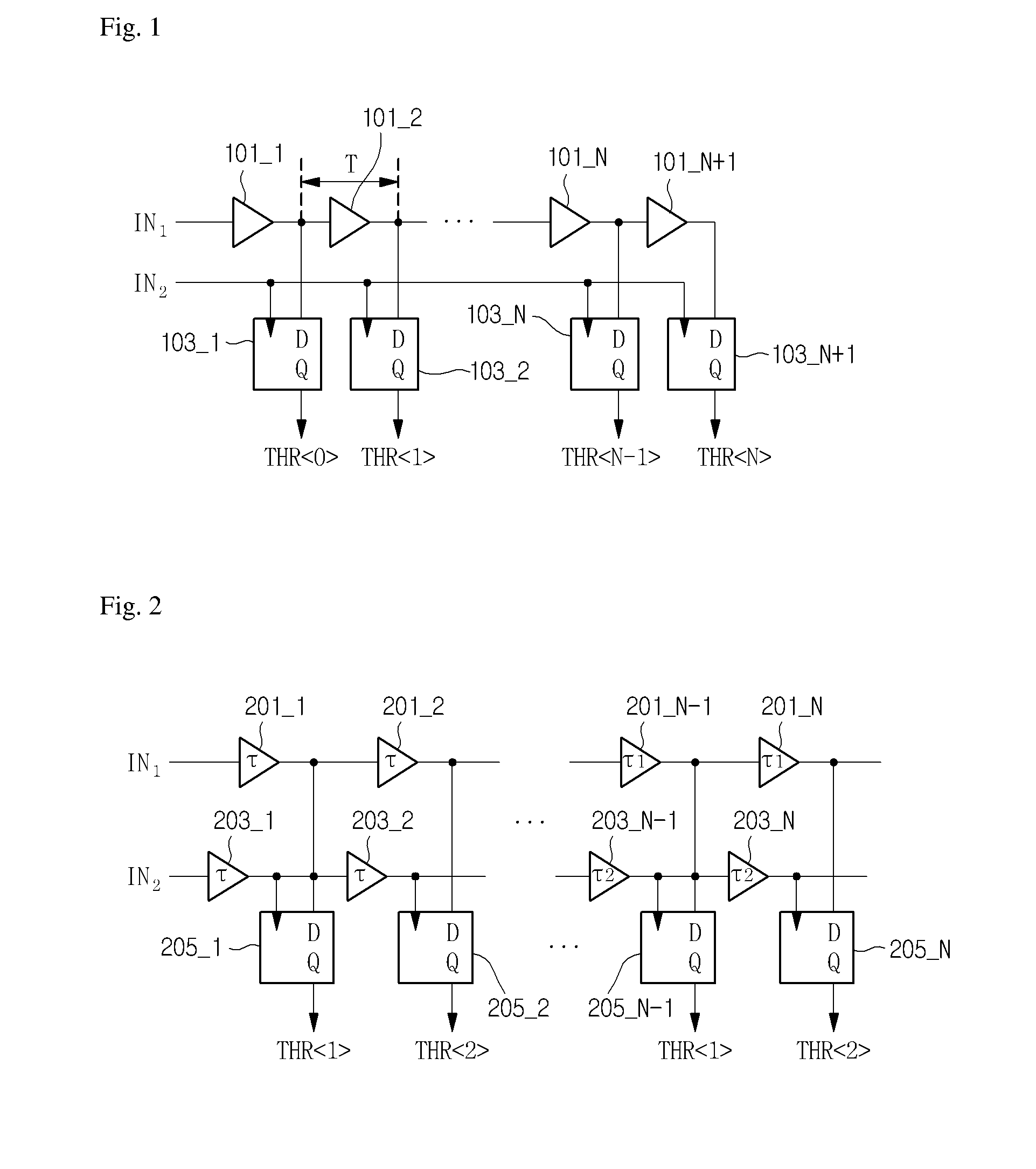

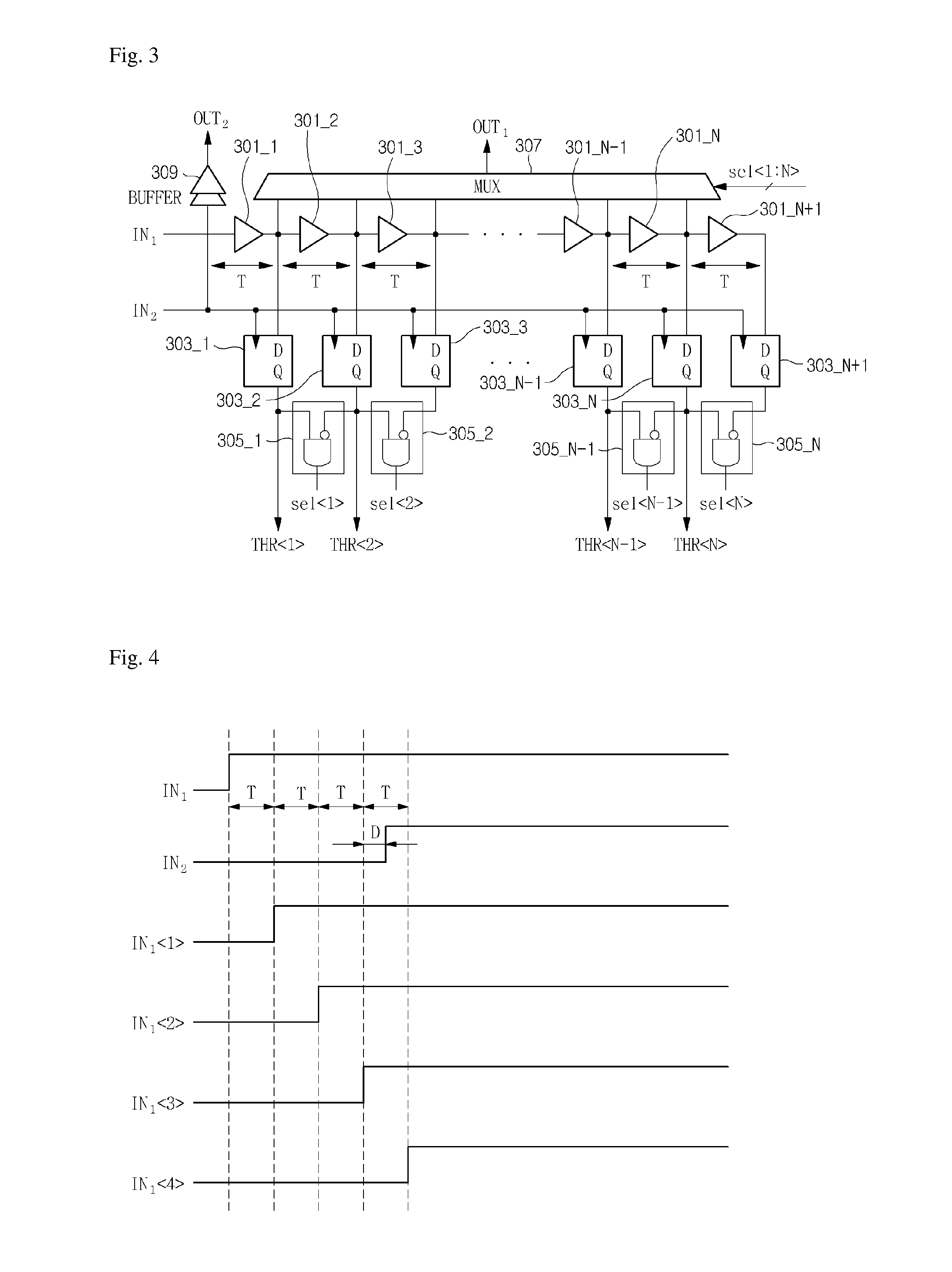

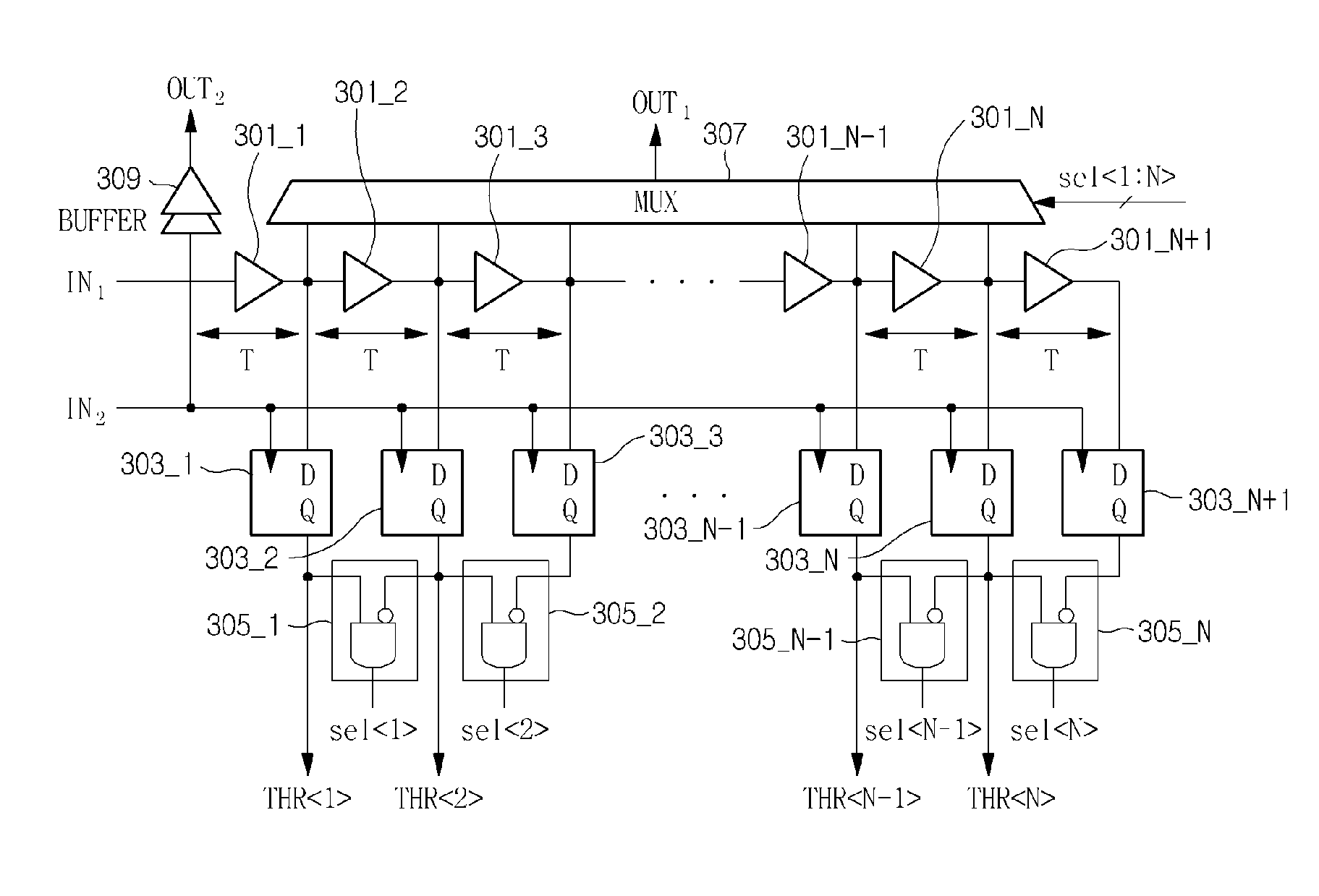

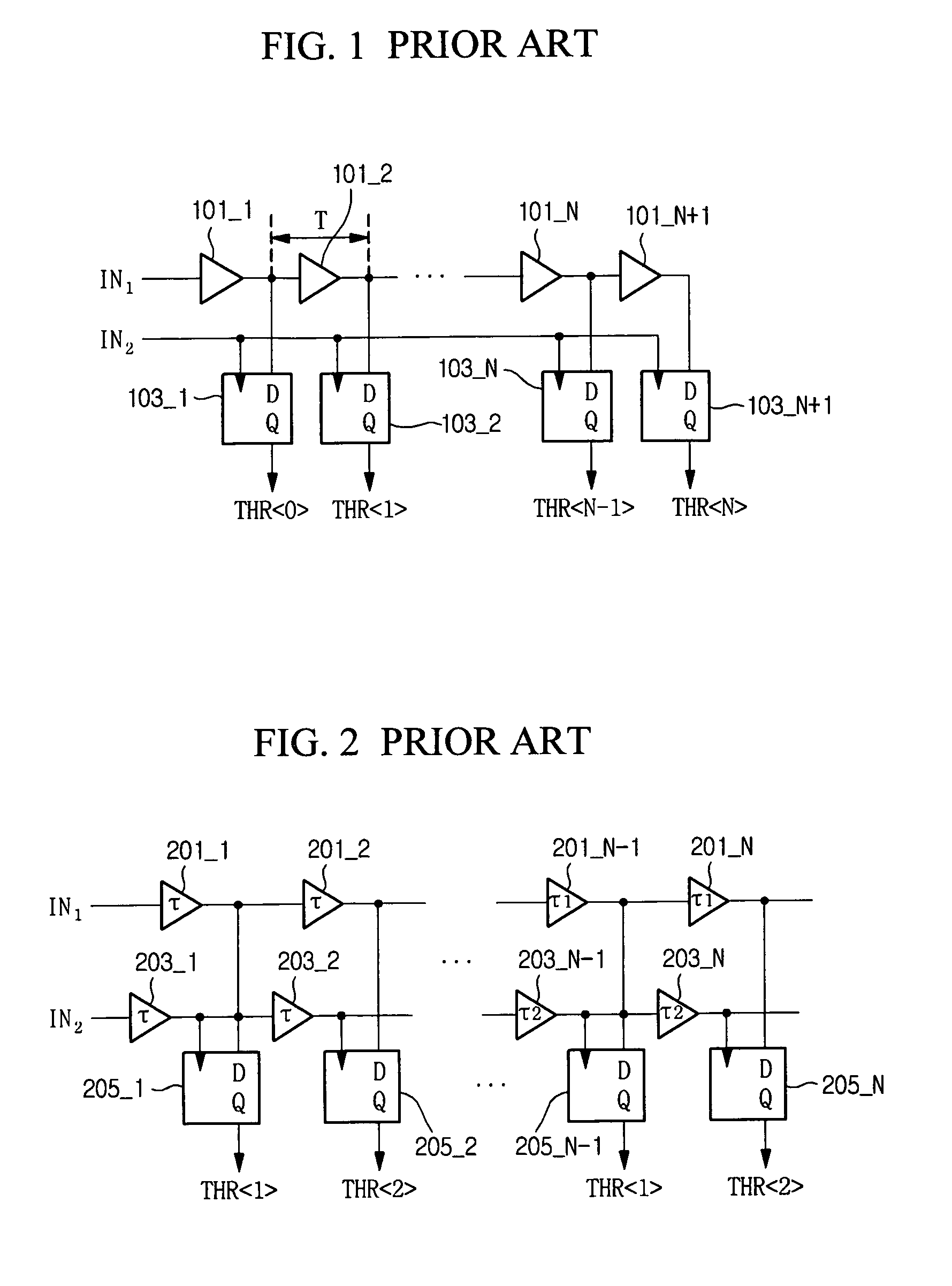

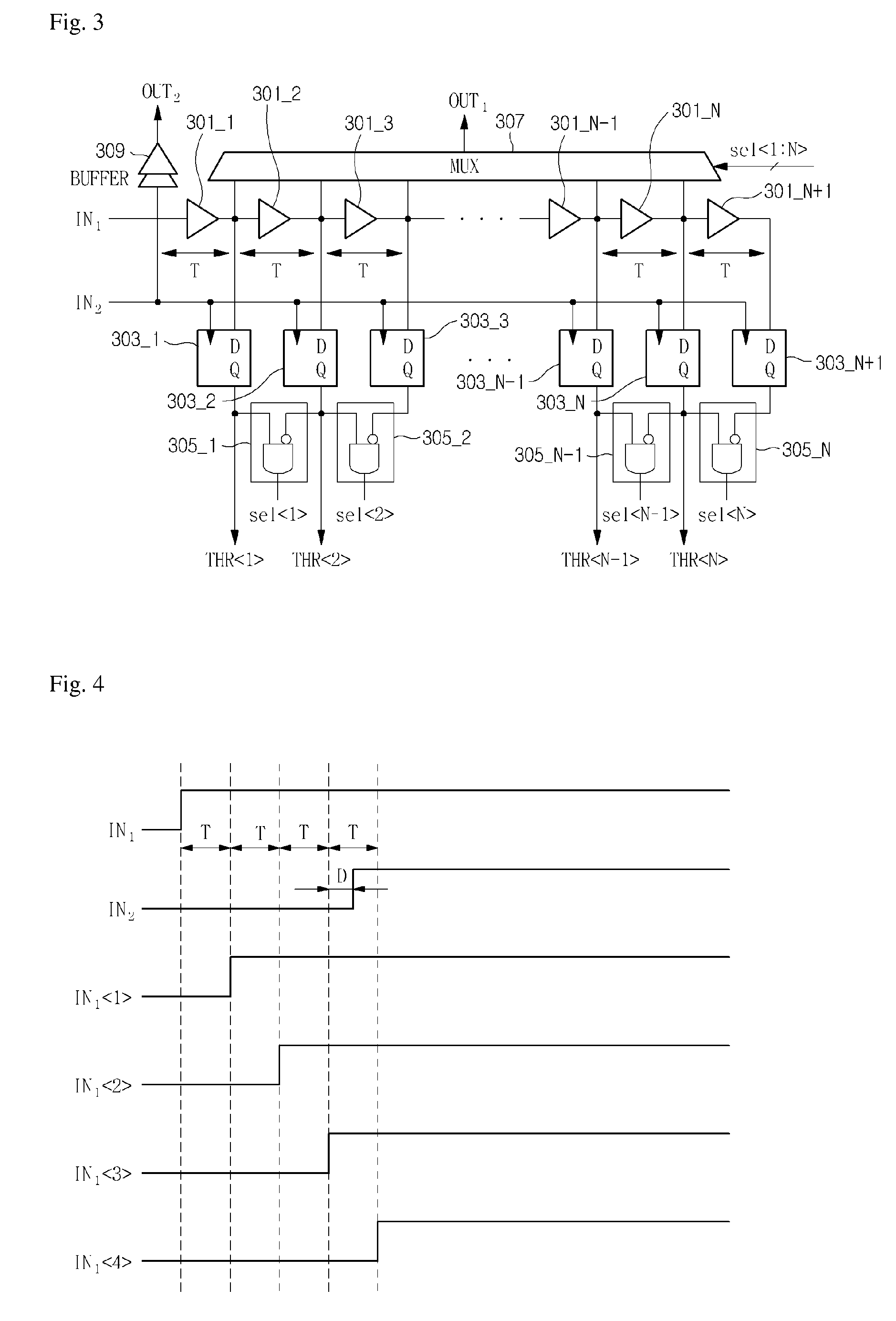

Phase-digital converter having hierarchical structure

InactiveUS20090028274A1Small sizeHigh resolutionAnalogue/digital conversionMultiple-port networksDigital down converterPhase difference

A time to digital converter having a hierarchical structure is provided. The time to digital converter includes: a plurality of delay stages for sequentially delaying a first signal for a specific delay time; a plurality of flip-flops for comparing delay signals of the first signal delayed by the delay stages with a second signal, and generating different outputs before and after a phase difference between the delay signals of the first signal and the second signal becomes smaller than a resolution of the phase detector; a selection signal generator for generating a selection signal for selecting a signal most similar to the second signal among the delay signals of the first signal from the outputs of the flip-flops; and a Multiplexer (MUX) for receiving the delay signals of the first signal and the selection signal, and outputting the signal most similar to the second signal among the delay signals of the first signal.

Owner:KOREA UNIV IND & ACADEMIC CALLABORATION FOUND

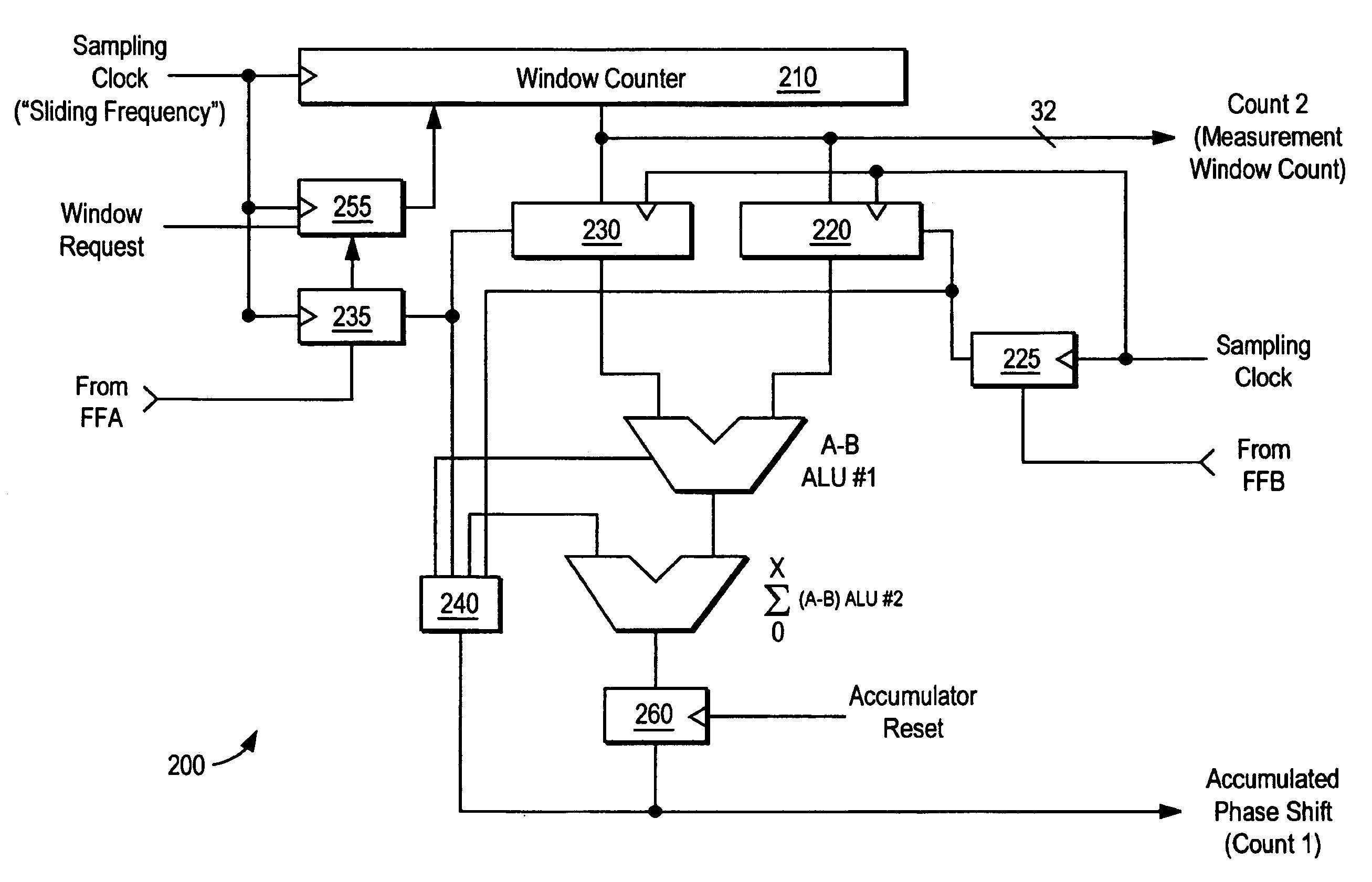

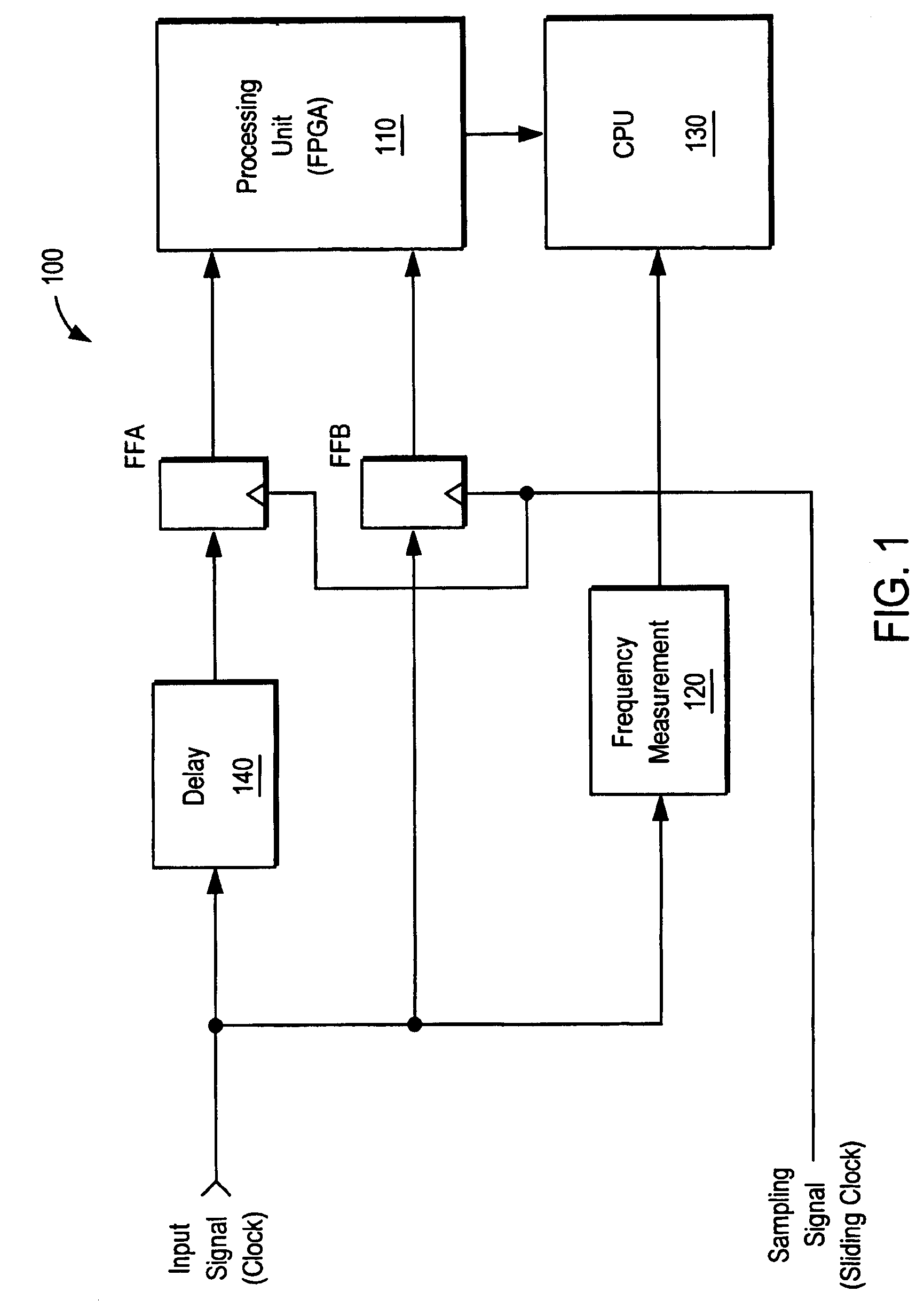

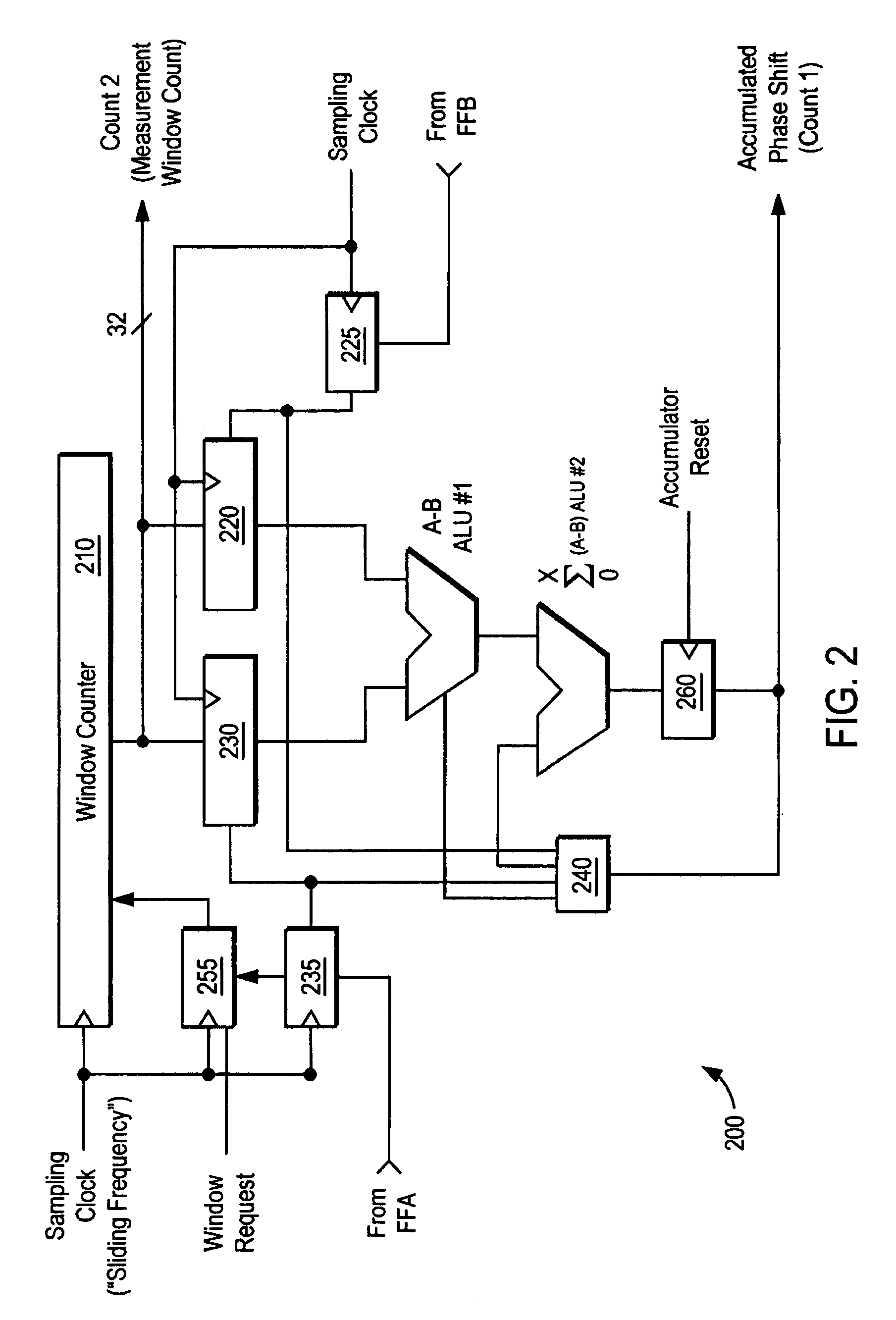

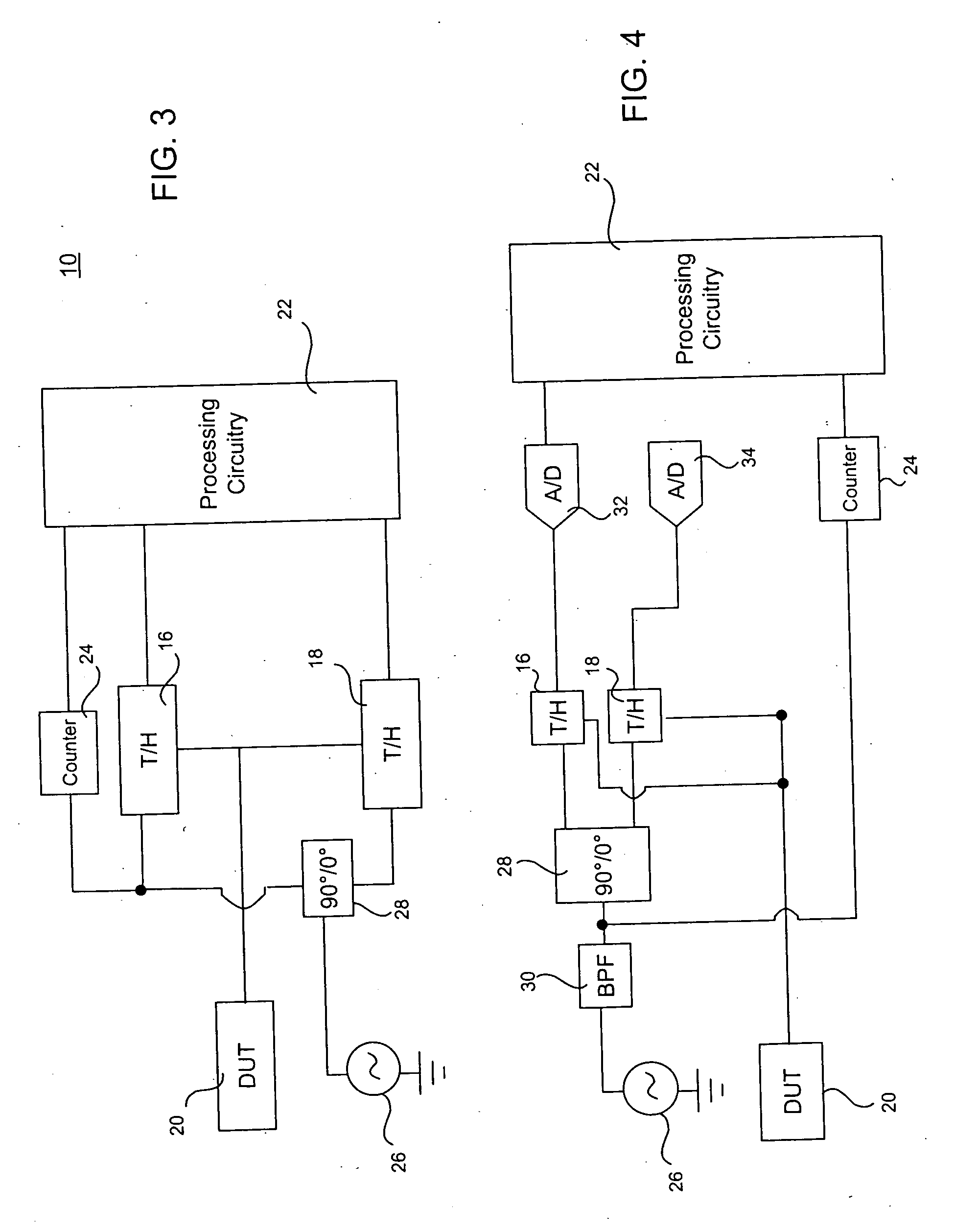

Method and apparatus for delay line calibration

InactiveUS7062733B1Conveniently implementedSoftware simulation/interpretation/emulationSpecial data processing applicationsTime domainMeasurement device

Sub-sampled signals are compared to determine time delay, calibration of delay elements, and other precise time domain measurements, based on properties of aliased signals produced by the sub-sampling. In one embodiment, flip-flops sub-sample an input signal and a delayed signal. A counter measures time delay between edges in the sub-sampled input and sub-sampled delayed signal. The time delay is determined and averaged over a measurement window, and then scaled to determine an amount of delay of the delayed signal. Means to calibrate a delay element inside a measurement device (e.g., Bit Error Ratio Tester), utilizing sub-sampling techniques to achieve precise measurements very quickly and without the need for factory calibration.

Owner:TEKTRONIX INC

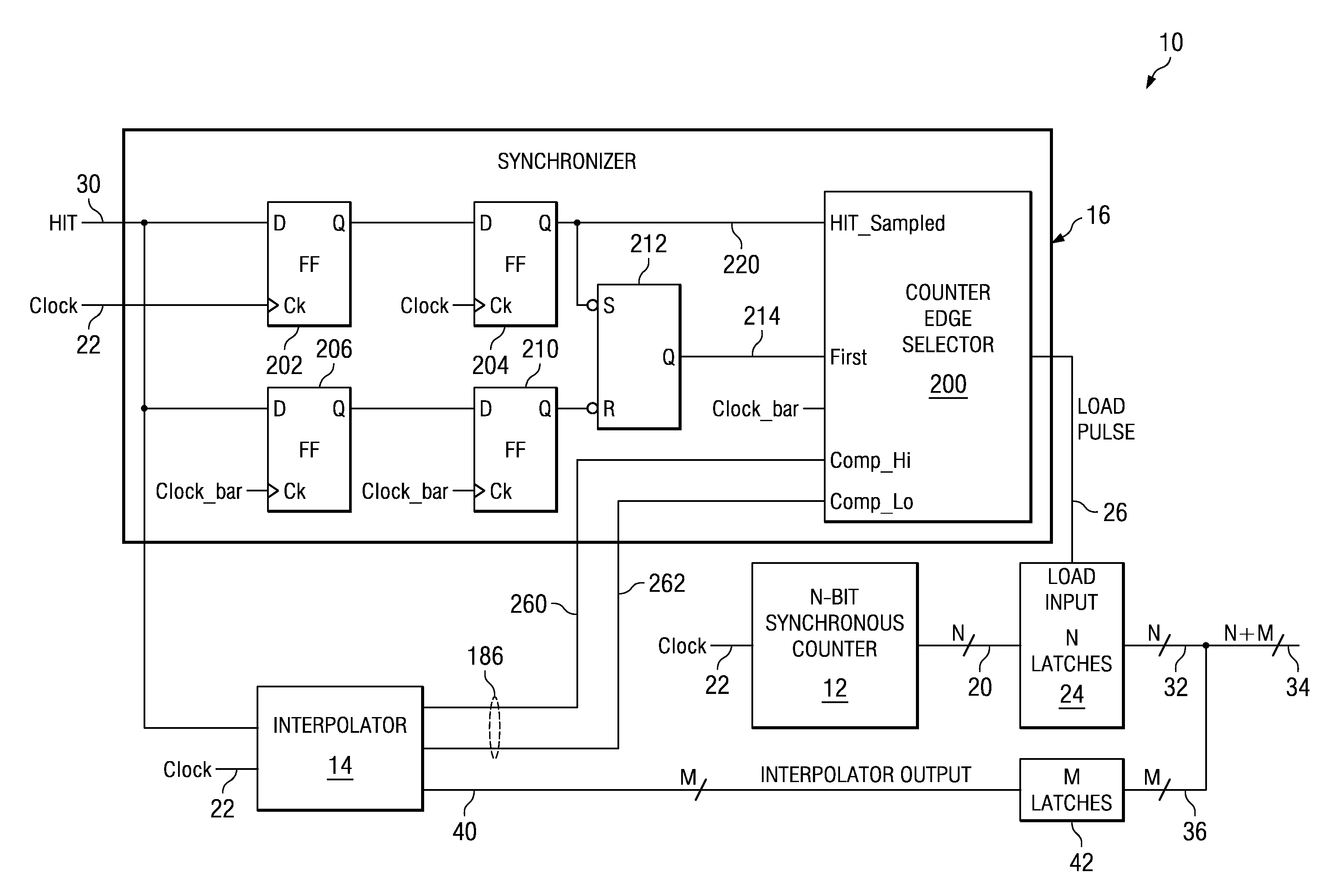

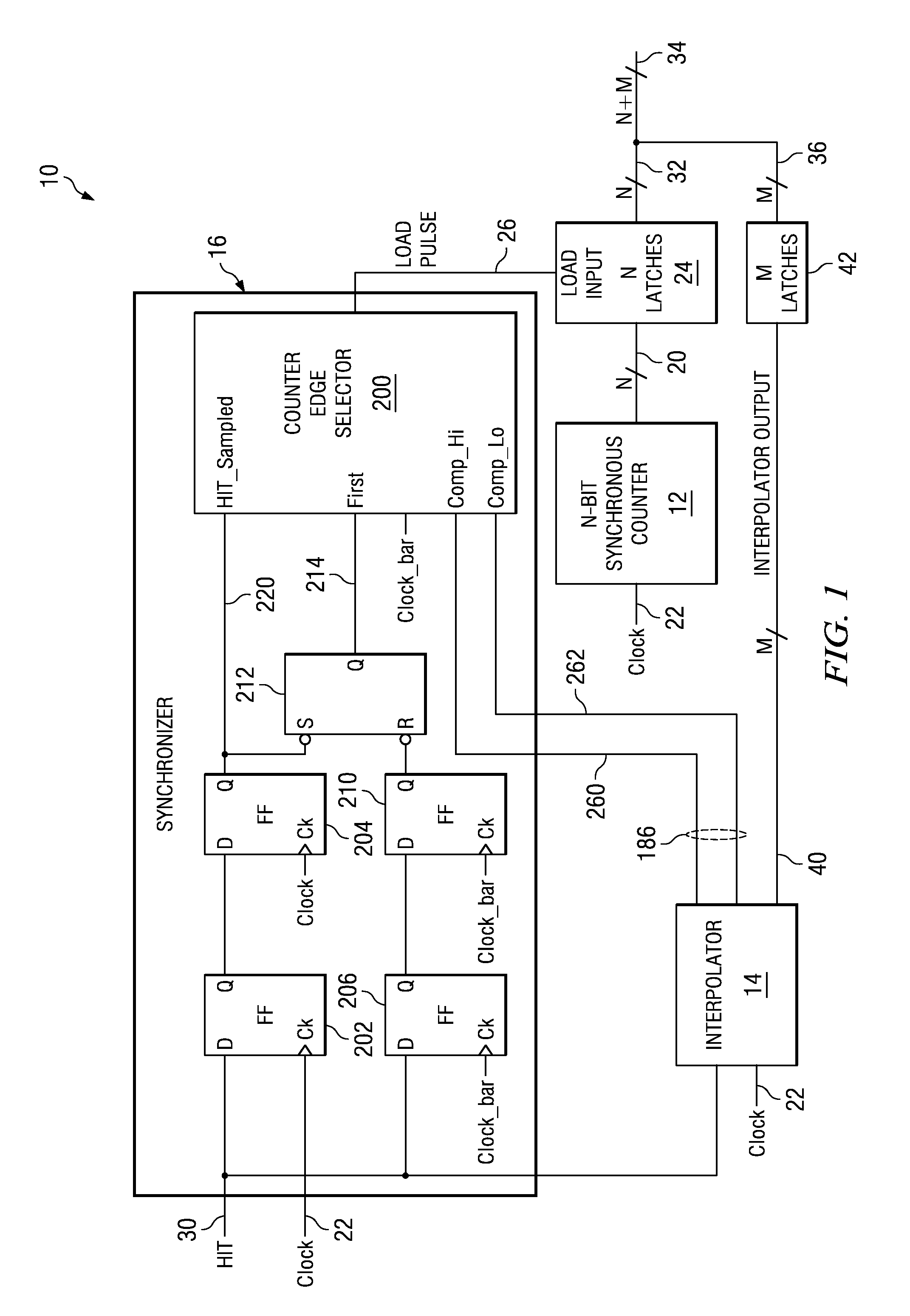

Method and Apparatus for Synchronizing Time Stamps

ActiveUS20100001769A1Pulse automatic controlVoltage-current phase angleSignal transitionReal-time computing

Various apparatuses and methods for synchronizing time stamps are disclosed herein. For example, some embodiments of the present invention provide apparatuses for synchronizing a coarse time stamp with a fine time stamp. Such apparatuses include an event signal input, a clock input, a coarse time stamp generator having an input connected to the clock input, and a fine time stamp generator having a first input connected to the clock input, a second input connected to the event signal input, and a synchronization signal output. The apparatuses also include a synchronizer having a first input connected to the clock input, a second input connected to the event signal input, a third input connected to the synchronization signal output and an output connected to the coarse time stamp generator. The synchronizer is adapted to synchronize the coarse time stamp generator to the fine time stamp generator based at least in part on the synchronization signal output. The apparatuses are adapted to combine a synchronized coarse time stamp from the coarse time stamp generator with a fine time stamp from the fine time stamp generator to form a time stamp indicating when an event signal transitioned on the event signal input.

Owner:TEXAS INSTR INC

Time-to-digital converter and all-digital phase-locked loop

ActiveUS7973578B2Multiple input and output pulse circuitsPulse automatic controlPhase differencePhase frequency detector

A time-to-digital converter (TDC) includes a converter which receives a first signal and a second signal, delays the second signal in phases using a plurality of delay elements which are coupled in series, compares the delayed second signal with the first signal, and outputs a phase error of the second signal with respect to the first signal, a phase frequency detector which receives the first signal, and a third signal from one of the nodes in the plurality of delay elements, and outputs a phase difference between the first signal and the third signal, and a frequency detector which outputs a frequency error of the second signal with respect to the first signal as a digital code using an output signal of the phase frequency detector and the second signal.

Owner:SAMSUNG ELECTRONICS CO LTD +1

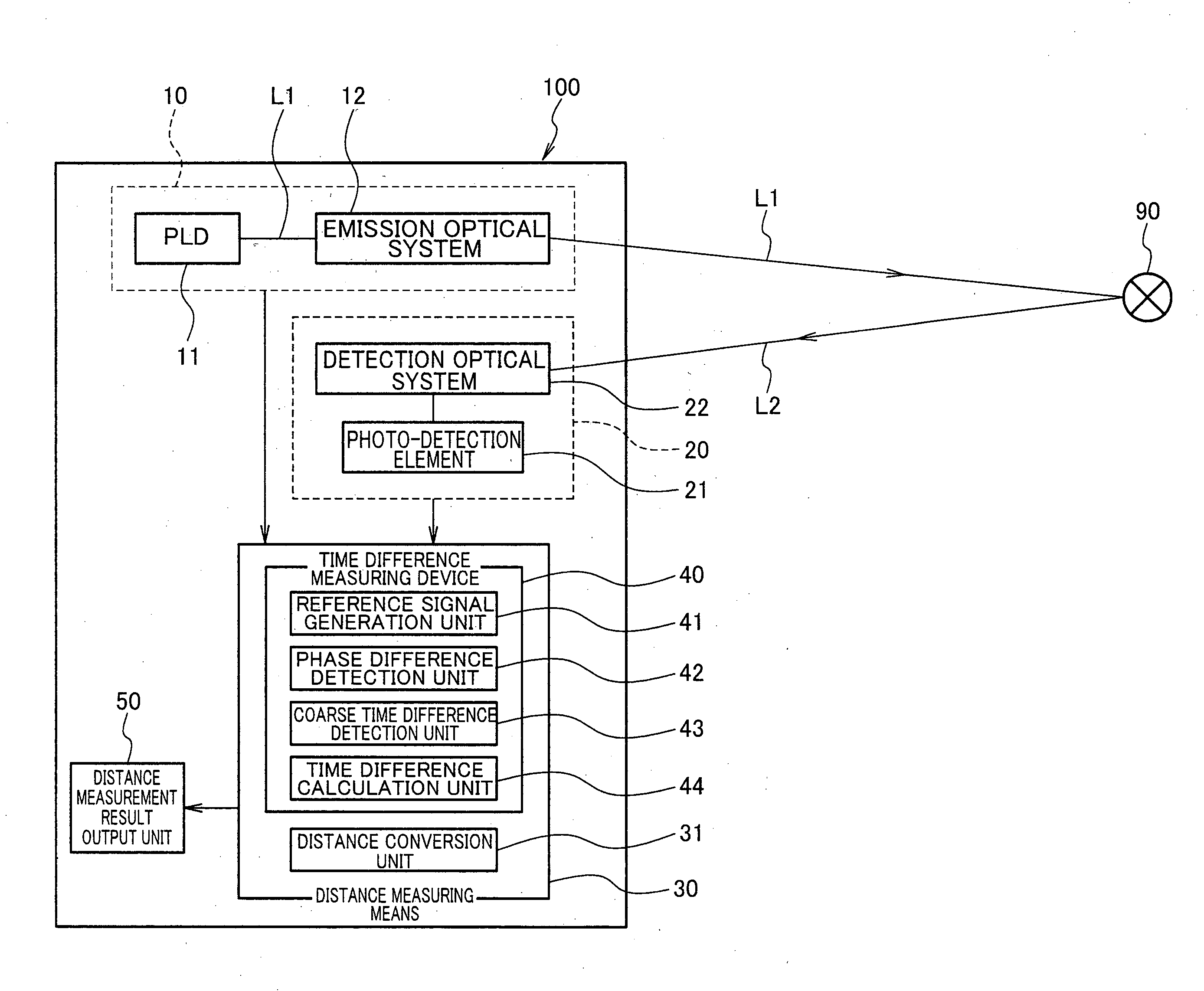

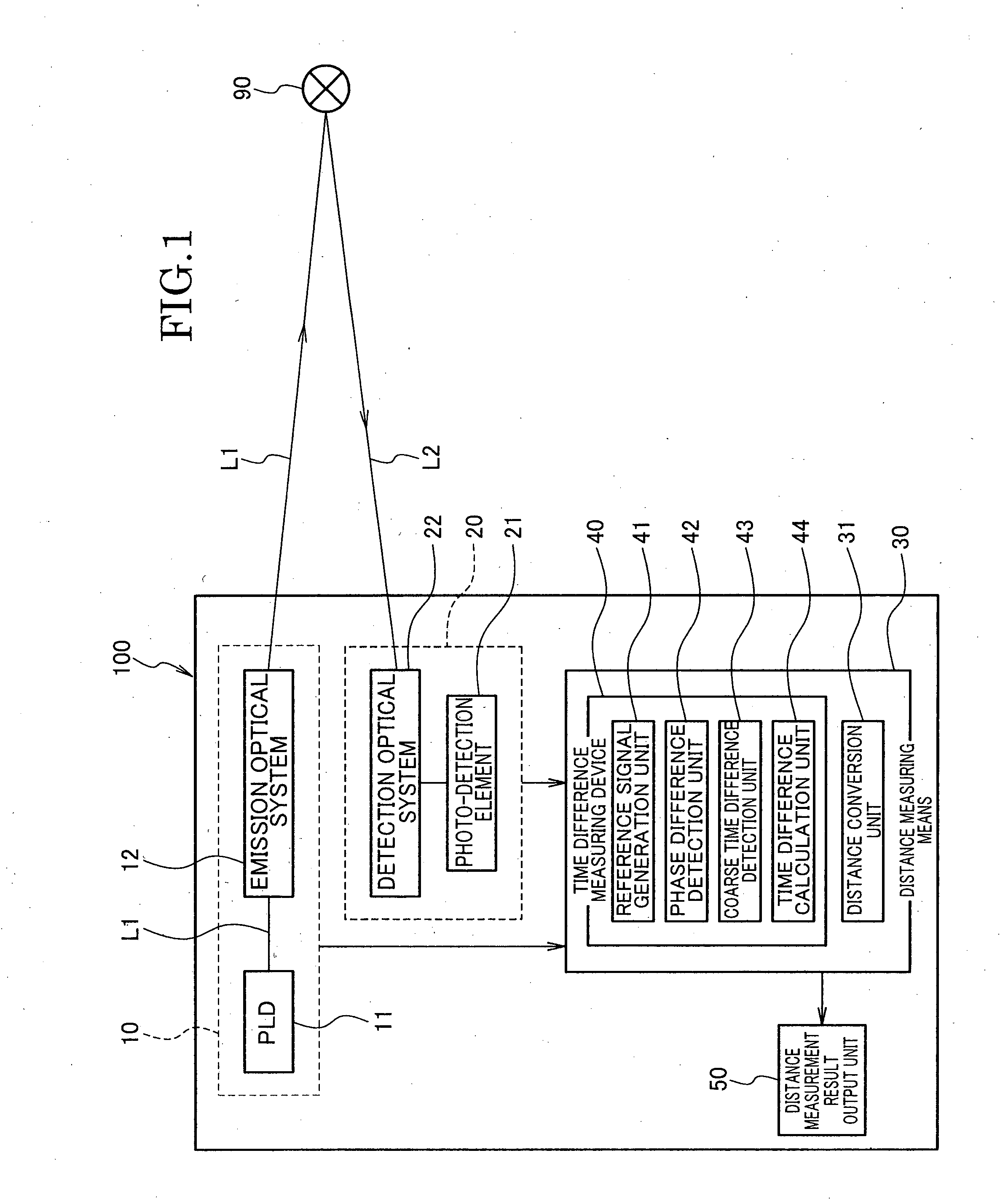

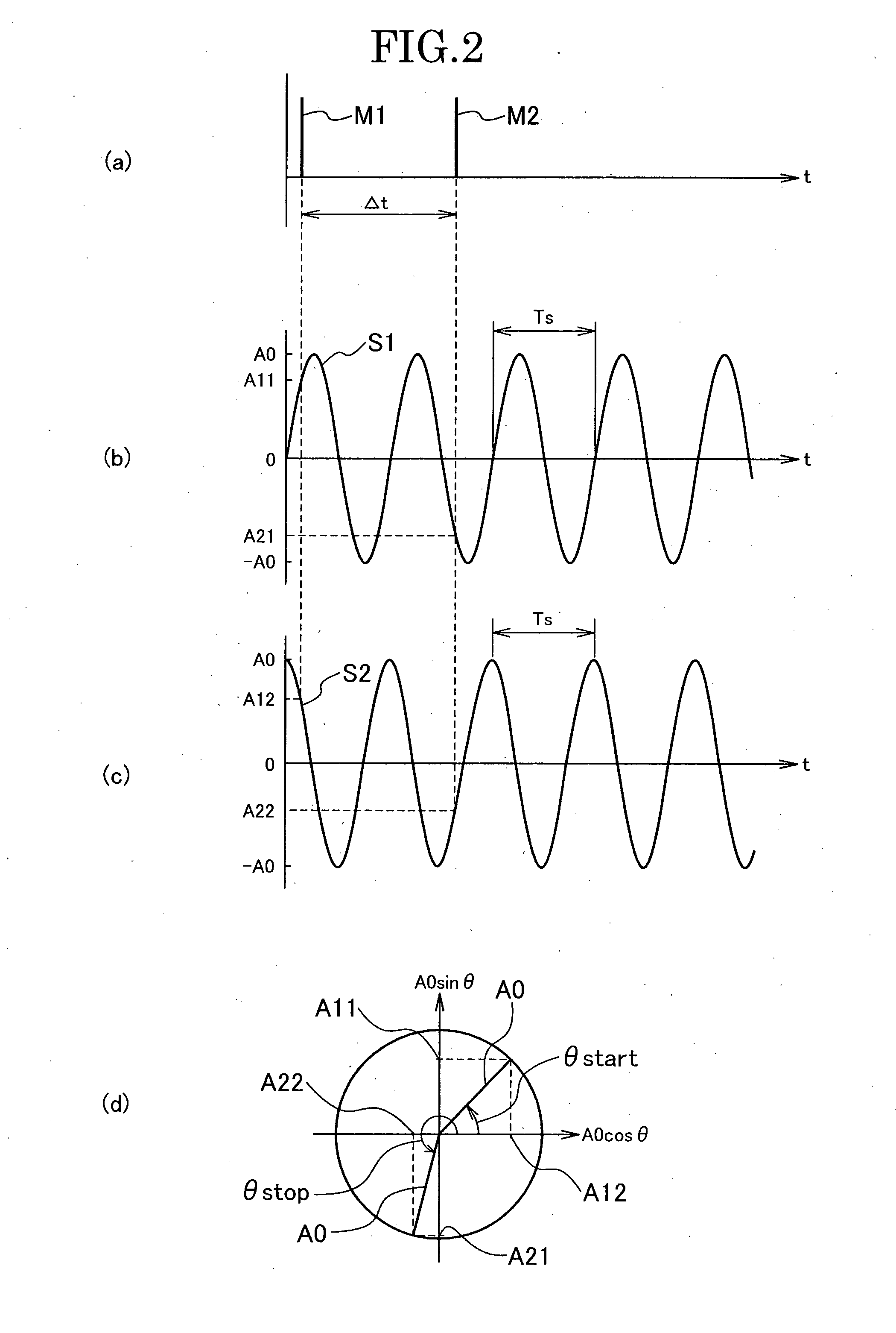

Time Difference Measuring Device, Measuring Method, Distance Measuring Device, and Distance Measuring Method

ActiveUS20090122296A1Quick measurementDistance measuring performance can be quickenedTime indicationOptical rangefindersMeasurement devicePhase difference

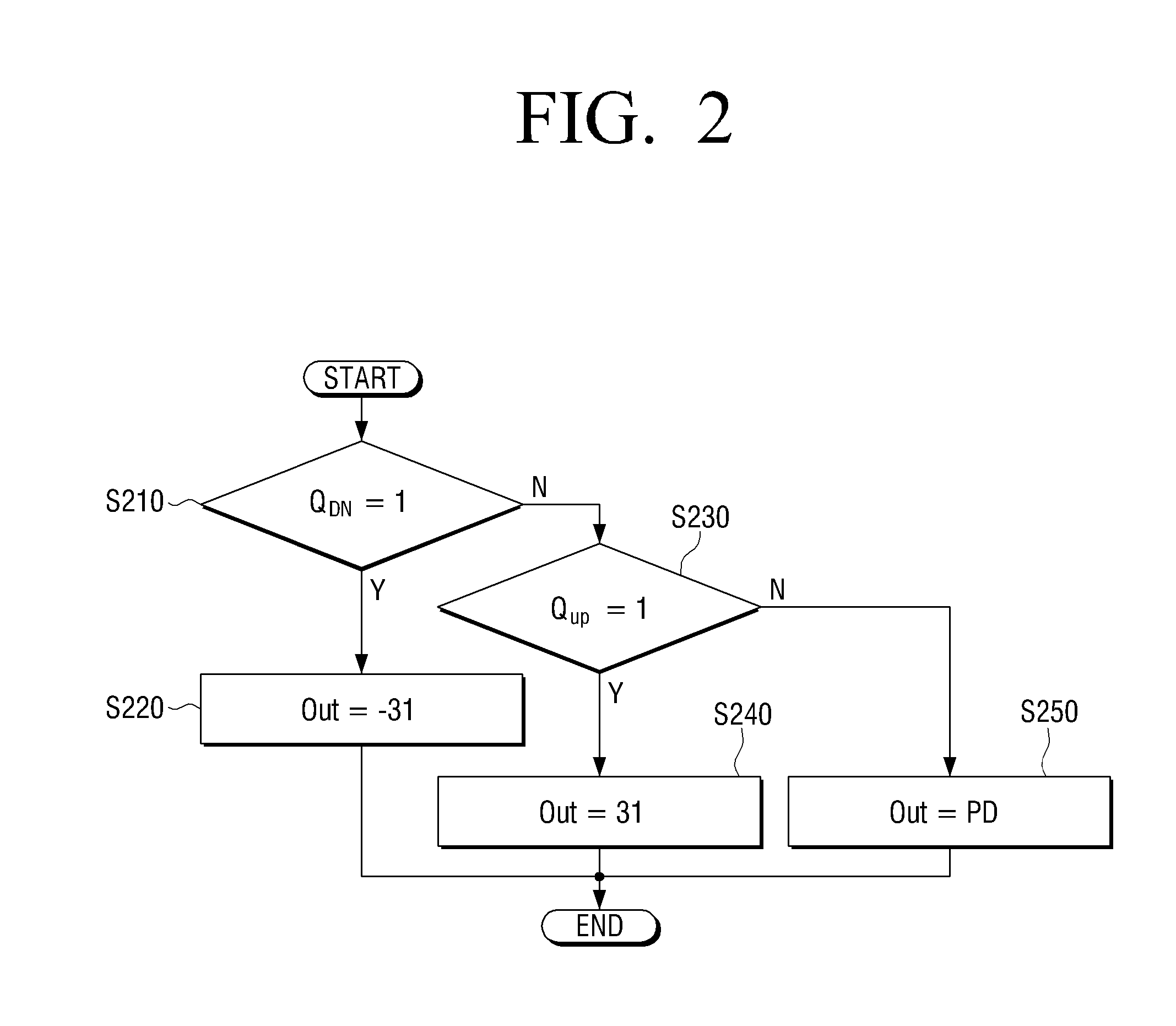

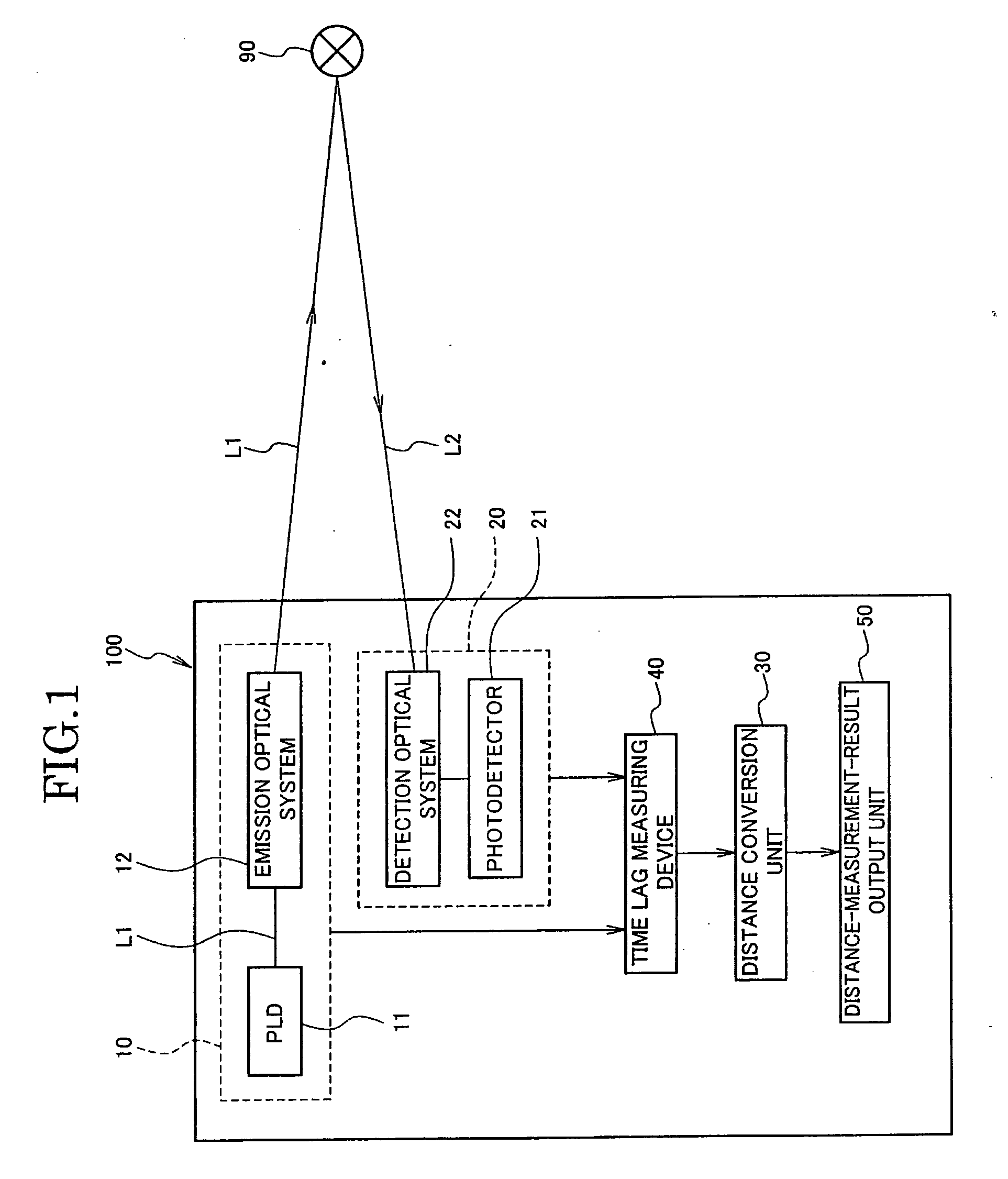

A time difference measuring device can accurately measure a time difference between two pulse signals generated with a predetermined time difference by measuring the two pulse signals by one measurement. The time difference measuring device measures a time difference between a start signal (M1) and a stop signal (M2). The device has a reference signal generation unit (41) for generating two reference signals (S1, S2) having a π / 2 phase difference. According to corresponding amplitude values (A11, A12) and (A21, A22) of the reference signals (S1, S2) at each generation timing of the start signal (M1) and the stop signal (M2), a phase difference detection unit (42) calculates a phase difference Δθ (=θstop−θstart) between the generation timings of the pulse signals (M1, M2). According to the detected phase difference Δθ and the cycle (Ts) of the reference signals (S1; S2), a time difference calculation unit (44) calculates the generation time difference Δt between the pulse signals (m1, M2).

Owner:KK TOPCON

Rate locked loop radar timing system

A rate locked loop (RLL) regulates phase slip between two clock signals to provide precision timing for radar, TDR and laser ranging systems. Two clocks having a small mutual frequency offset exhibit a slowing changing relative phase, or phase slip, that produces a stroboscopic time expansion effect in a ranging system. A phase detector converts clock phase to voltage and the voltage is differentiated to provide a rate-of-change signal to a loop controller that precisely regulates the rate-of-phase change. The RLL controls a VCO to produce a constant, linear phase slip having phase errors below the time equivalent of 1-picosecond.

Owner:MCEWAN TECH

Hierarchical time to digital converter

InactiveUS7791377B2Small sizeHigh resolutionAnalogue/digital conversionMultiple-port networksDigital down converterPhase difference

A time to digital converter having a hierarchical structure is provided. The time to digital converter includes: a plurality of delay stages for sequentially delaying a first signal for a specific delay time; a plurality of flip-flops for comparing delay signals of the first signal delayed by the delay stages with a second signal, and generating different outputs before and after a phase difference between the delay signals of the first signal and the second signal becomes smaller than a resolution of the phase detector; a selection signal generator for generating a selection signal for selecting a signal most similar to the second signal among the delay signals of the first signal from the outputs of the flip-flops; and a Multiplexer (MUX) for receiving the delay signals of the first signal and the selection signal, and outputting the signal most similar to the second signal among the delay signals of the first signal.

Owner:KOREA UNIV IND & ACADEMIC CALLABORATION FOUND

Dual sine-wave time stamp method and apparatus

ActiveUS20070100570A1Resistance/reactance/impedenceUser identity/authority verificationReal-time computingSine wave

A time of an event can be determined by acquiring an amplitude, at the time of the event, of at least two periodic timing signals that are out of phase with each other. The time of the event within a cycle of at least one of the timing signals can be determined as a function of the amplitudes of the timing signals. The phase angle and complex coordinates of at least one of the timing signals can be determined as a function of the amplitudes. The time of the event within a cycle of a timing signal can be determined as a function of the phase angle or complex coordinates of the timing signal at the time of the event.

Owner:TERADYNE

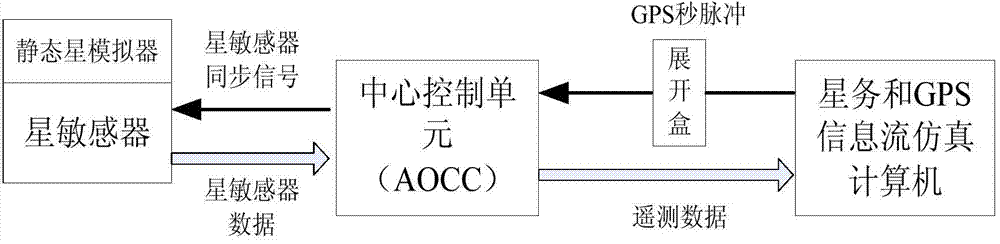

Method for satellite control system to obtain star sensor data generation time

ActiveCN103487051ATruly reflect the actual working situationRaise the ratioNavigation by astronomical meansRadio-controlled time-piecesControl systemObservation data

A method for a satellite control system to obtain a star sensor data generation time comprises the following steps: expanding GPS second pulse signals emitted by a satellite and a GPS information flow simulation computer in the ground equipment of the satellite control system by using an expansion box, carrying out static satellite model power-up of a star sensor for obtaining the data generation time, accessing to the central control unit of the control system, and powering up the central control unit; sending GPS second pulses to the star sensor through the central control unit as a synchronous signal; observing the remote measurement to obtain the exposure time and attitude quaternion output by the star sensor; slowly moving the GPS second pulses, and observing that whether the data change or not; recording the present phase of the GPS second pulses if the data change; and recording the change between the GPS second pulses and seven recorded phases if the data do not change. The method allows the star sensor exposure time to be obtained through ground tests.

Owner:BEIJING INST OF CONTROL ENG

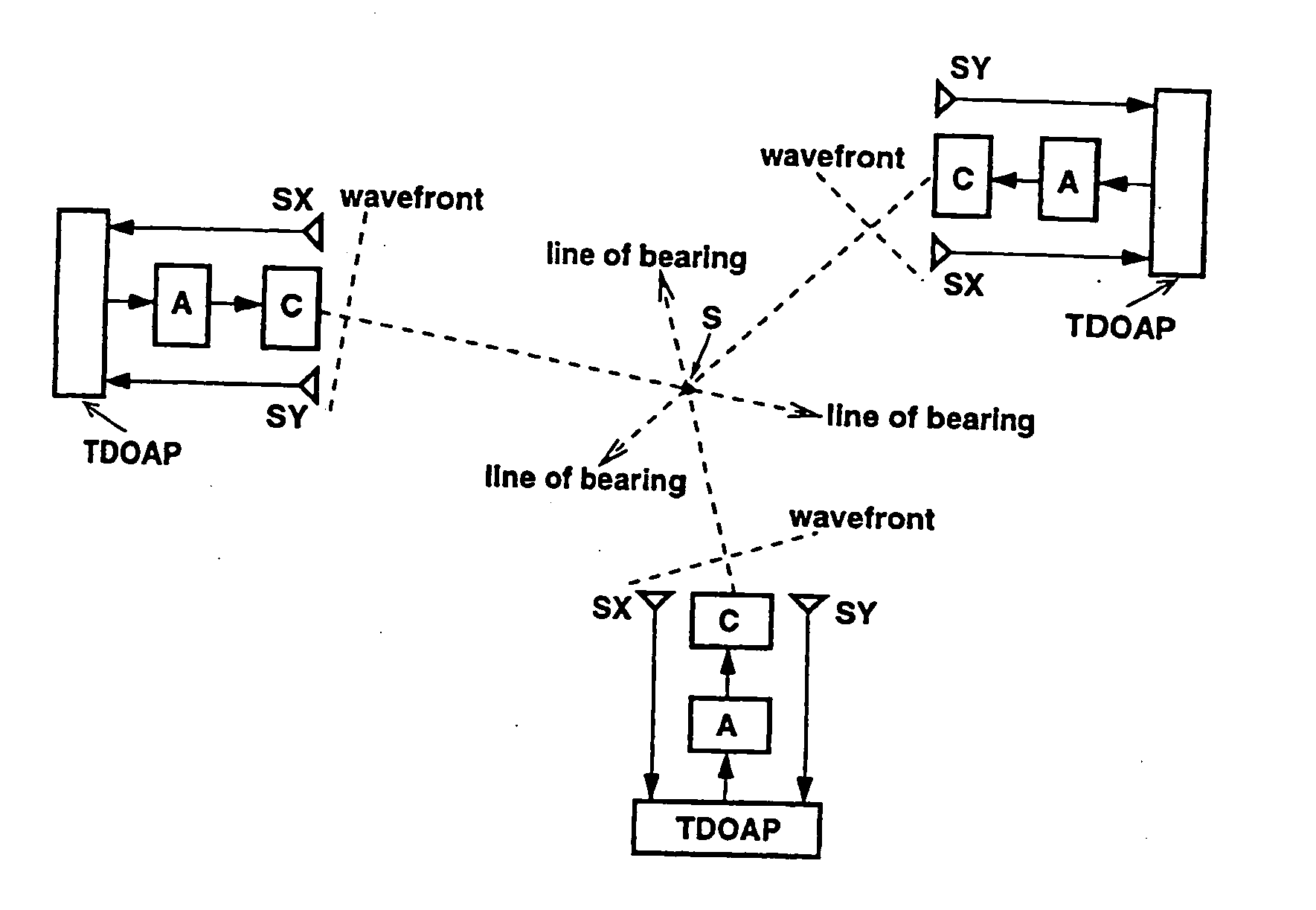

Determination of time-difference of arrival and angle of arrival

InactiveUS7515506B2Reduce the impact of noisePosition fixationDirection/deviation determination systemsEngineeringTime difference

The delay between two signals is determined by obtaining zero crossings from each signal, and using each crossing to trigger the sampling of the other signal. Two samples are taken in response to each zero crossing, and the difference between those two samples is calculated. This difference is summed for each event and both signals to derive a value. The process is repeated for different delays between the first and second signals. The values are examined to determine the delay which corresponds to the greatest coincidence between the signals.

Owner:MITSUBISHI ELECTRIC CORP

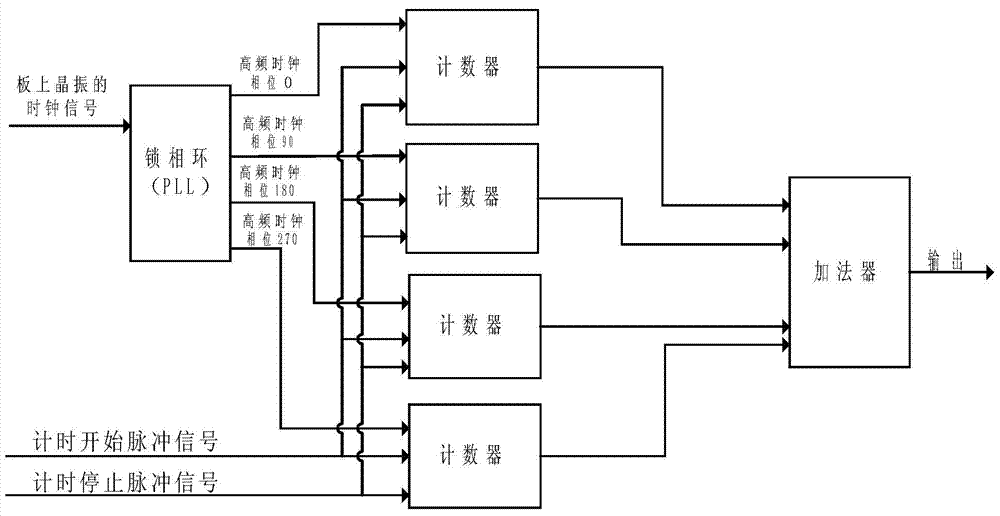

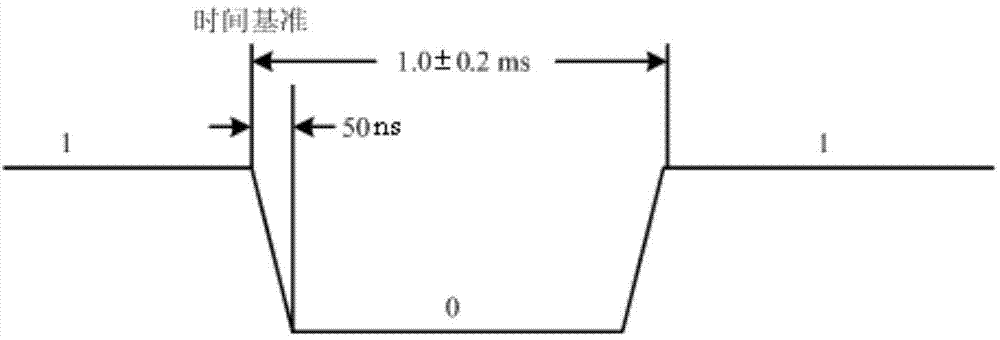

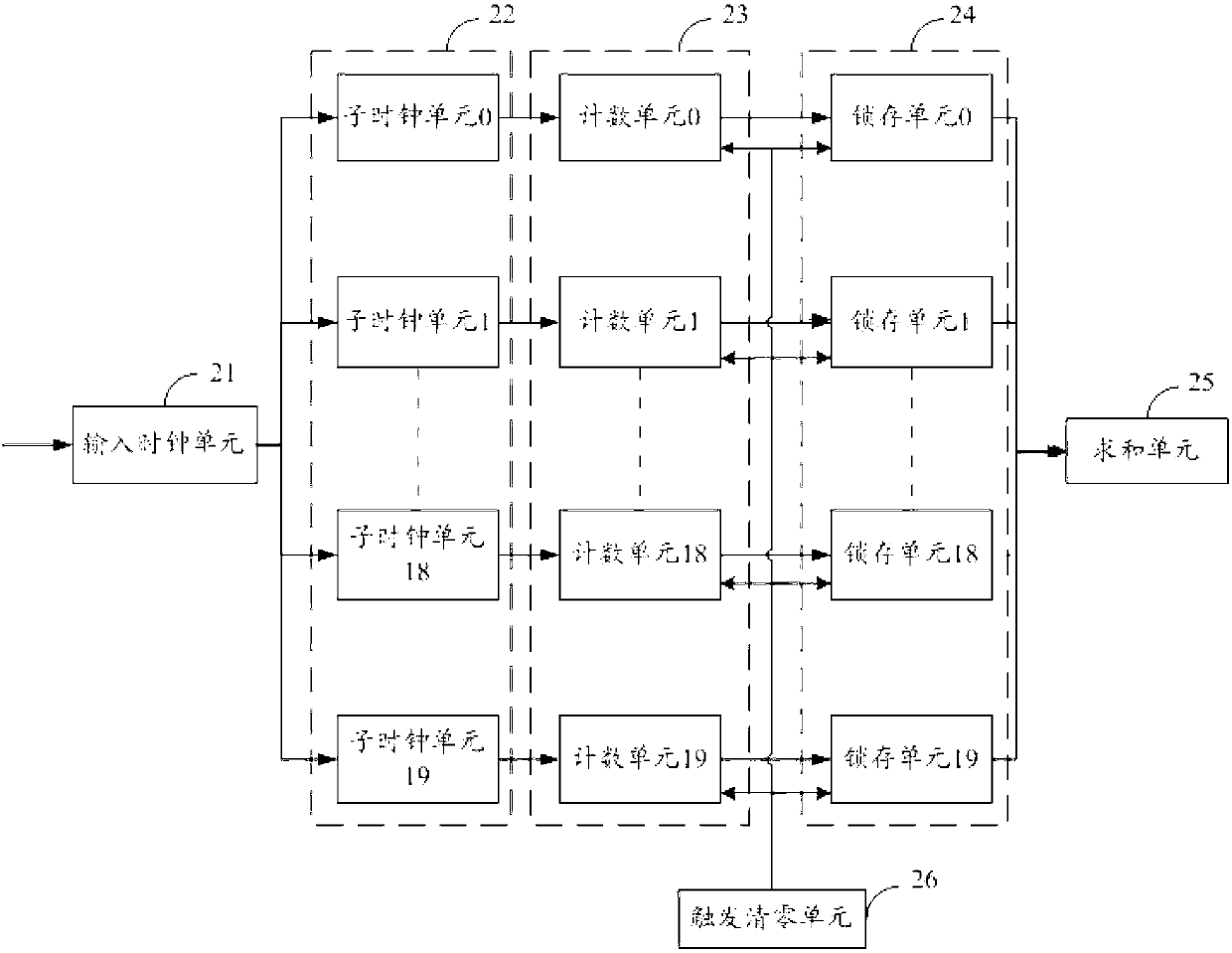

Time measurement method and device

InactiveCN103345144AIncrease the minimum counting unitImprove measurement time accuracyMeasurment by measuring phasePhase differenceFpga chip

The invention discloses a time measurement method and device which are applied to an FPGA. An input clock is converted to N sub clocks, and the period of each sub clock is M, wherein the quotient obtained by dividing M with N is the smallest counting unit for time measurement; the phase difference between every two adjacent sub clocks is adjusted to be L, wherein L is the quotient obtained by dividing 360 degrees with N; when timing is started, the number of the smallest counting units which the sub clocks pass through is recorded; when occurrence of a preset event is detected the total number of the smallest counting units which the sub clocks pass through is recorded to calculate the occur moment of the preset event, and the smallest time unit of the occur moment is the smallest counting unit. Therefore, through the method that the input clock of an FPGA chip is adjusted to form a plurality of sub clocks with the same period and the phase difference between every two adjacent sub clocks is correspondingly adjusted, the smallest counting unit of the FPGA can be increased, and the technical effect that the time measurement precision of a PET system is improved is achieved.

Owner:NEUSOFT MEDICAL SYST CO LTD

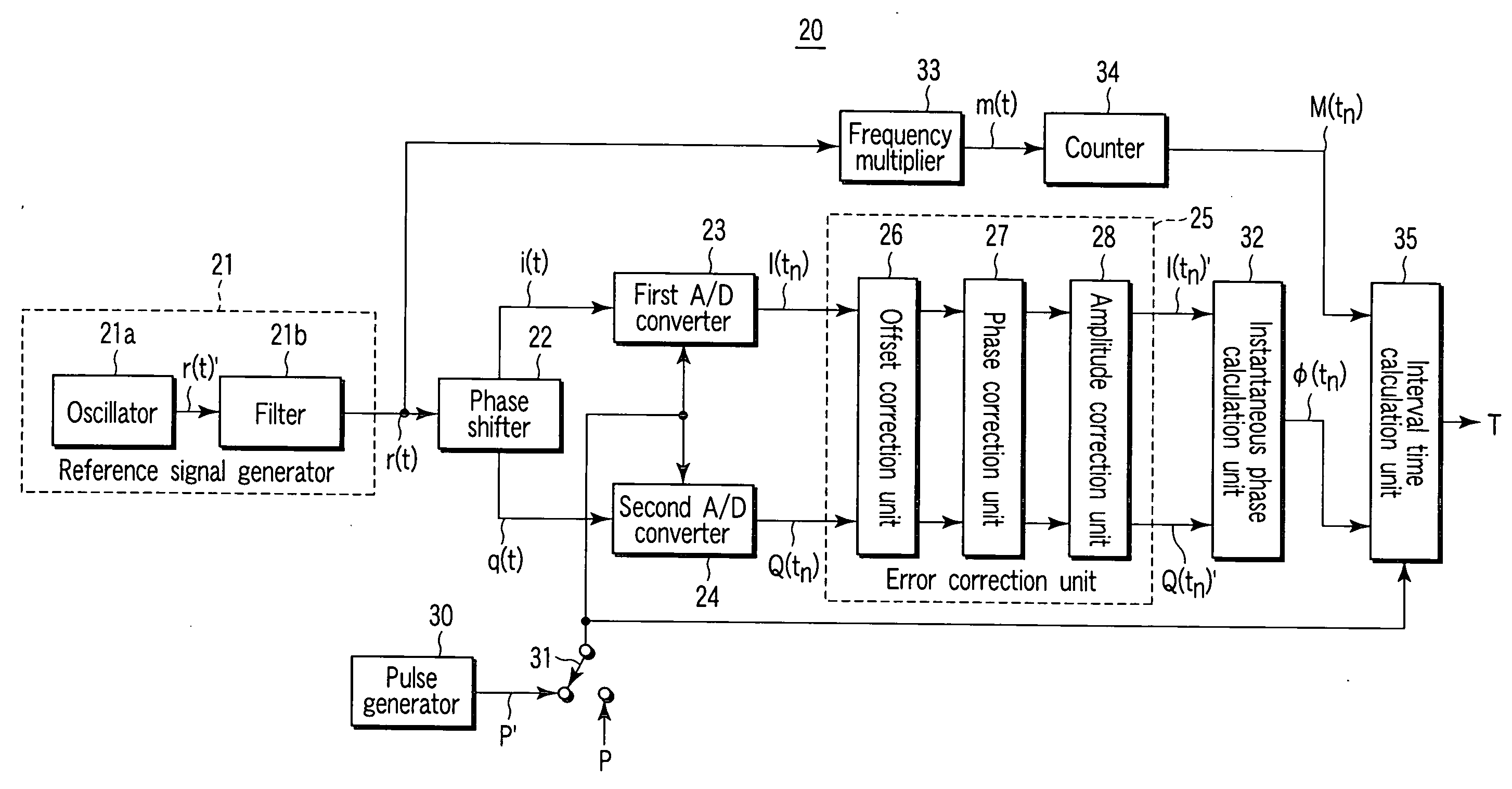

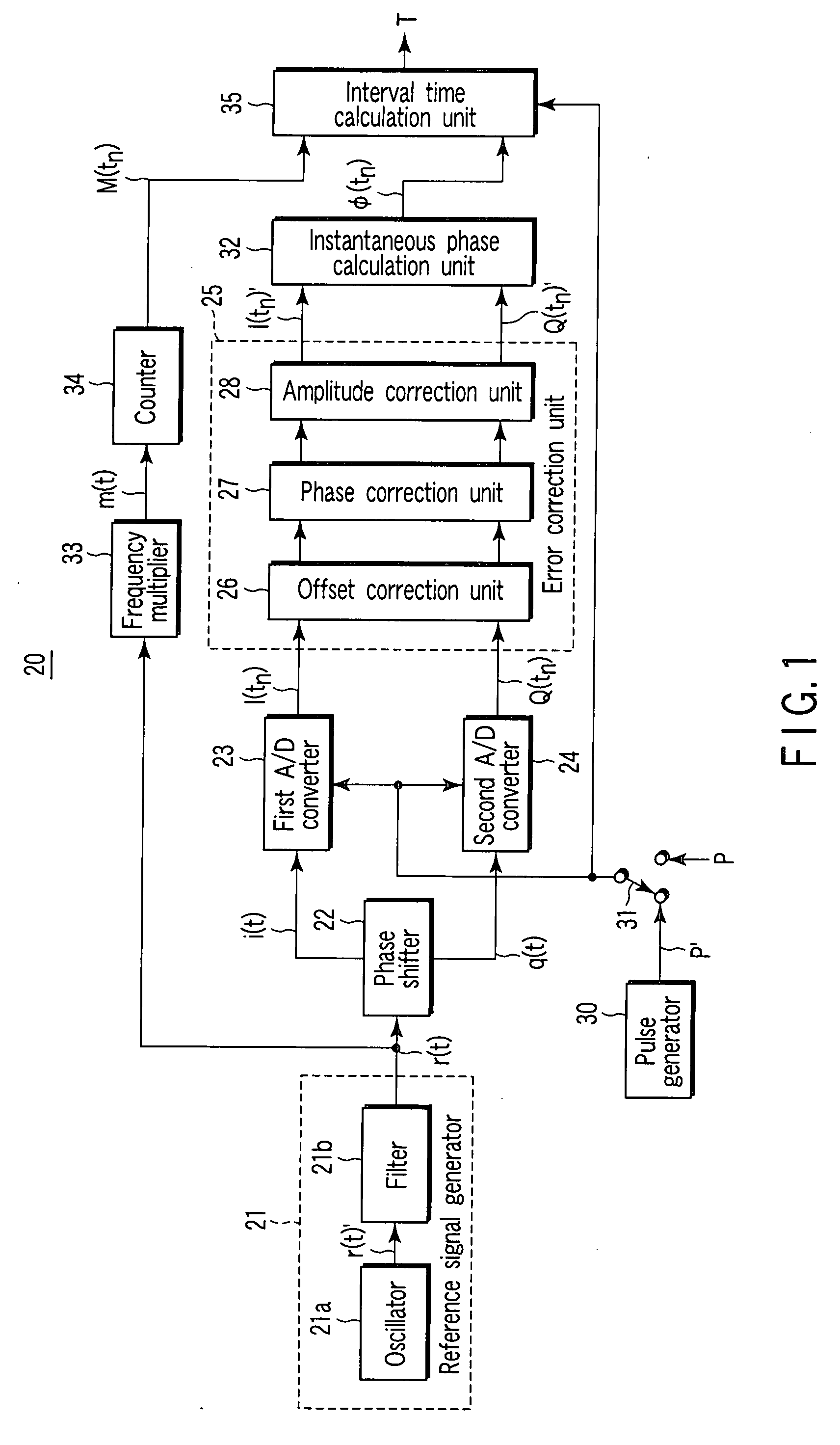

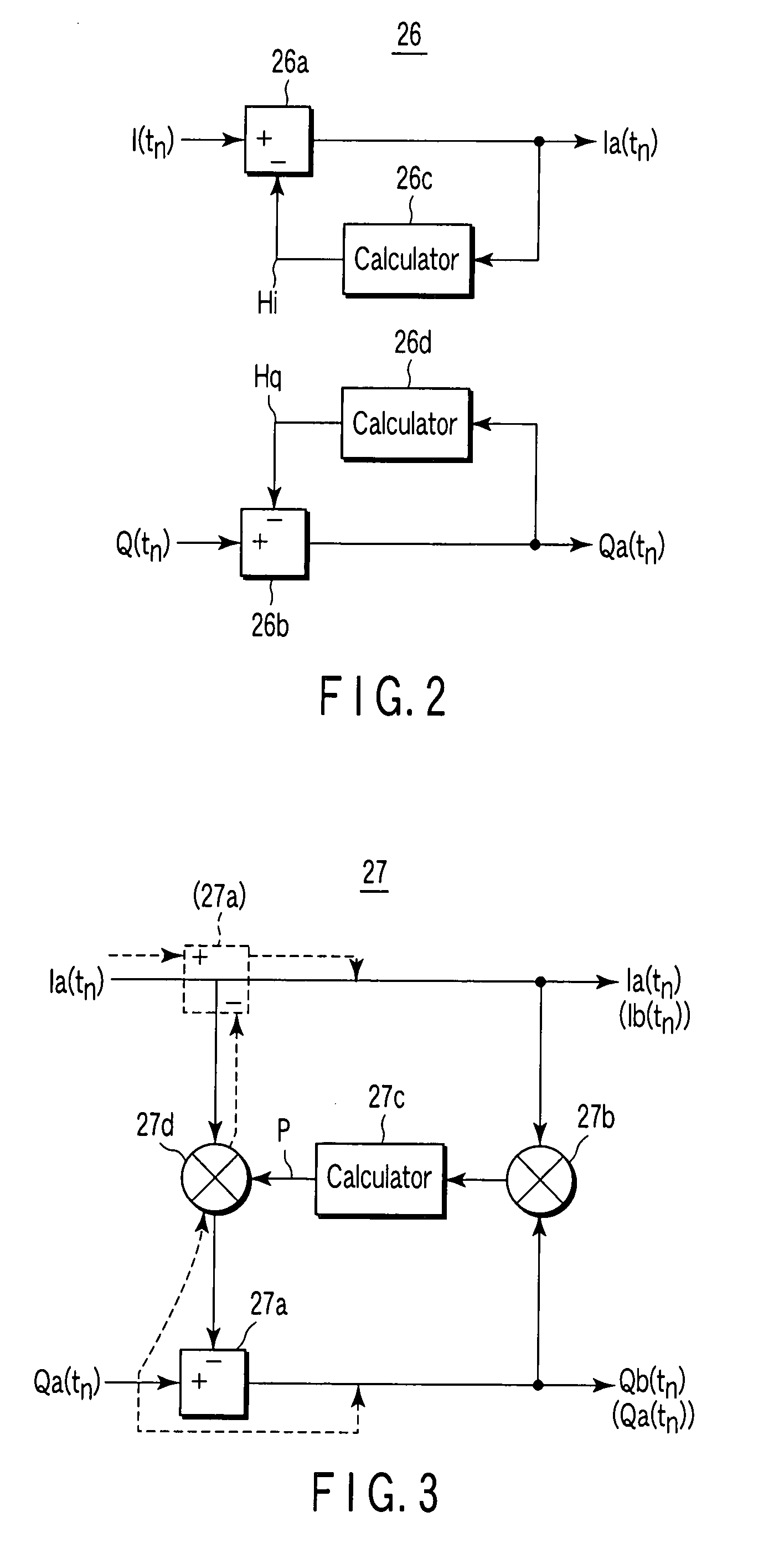

Time Interval Measuring Apparatus and Jitter Measuring Apparatus Using the Same

InactiveUS20080172194A1Accurate and stable measurementImprove accuracyNoise figure or signal-to-noise ratio measurementVoltage-current phase anglePhase shiftedMeasurement device

In order to stably measure an input interval time of a pulse signal with high precision, a time interval measuring apparatus includes a reference signal generator, a phase shifter, first and second A / D converters, an error correction unit, an instantaneous phase calculation unit, and an interval time calculation unit. The phase shifter divides a reference signal of a sine wave having a predetermined frequency from the reference signal generator into a first analog signal and a second analog signal having phases shifted to each other. The first and second A / D converters perform sampling of the first analog signal and the second analog signal from the phase shifter, respectively, at an input timing of a pulse signal to be measured, and output a first and second digital sample values. The error correction unit corrects direct current offset errors generated in, respectively, the first and second digital sample values output from the first and second A / D converters, a phase error with respect to 90°, and an amplitude error. The instantaneous phase calculation unit calculates an instantaneous phase of the reference signal based on the corrected first and second digital sample values. The interval time calculation unit determines an input interval time of the pulse signal based on a variation of instantaneous phases.

Owner:ANRITSU CORP

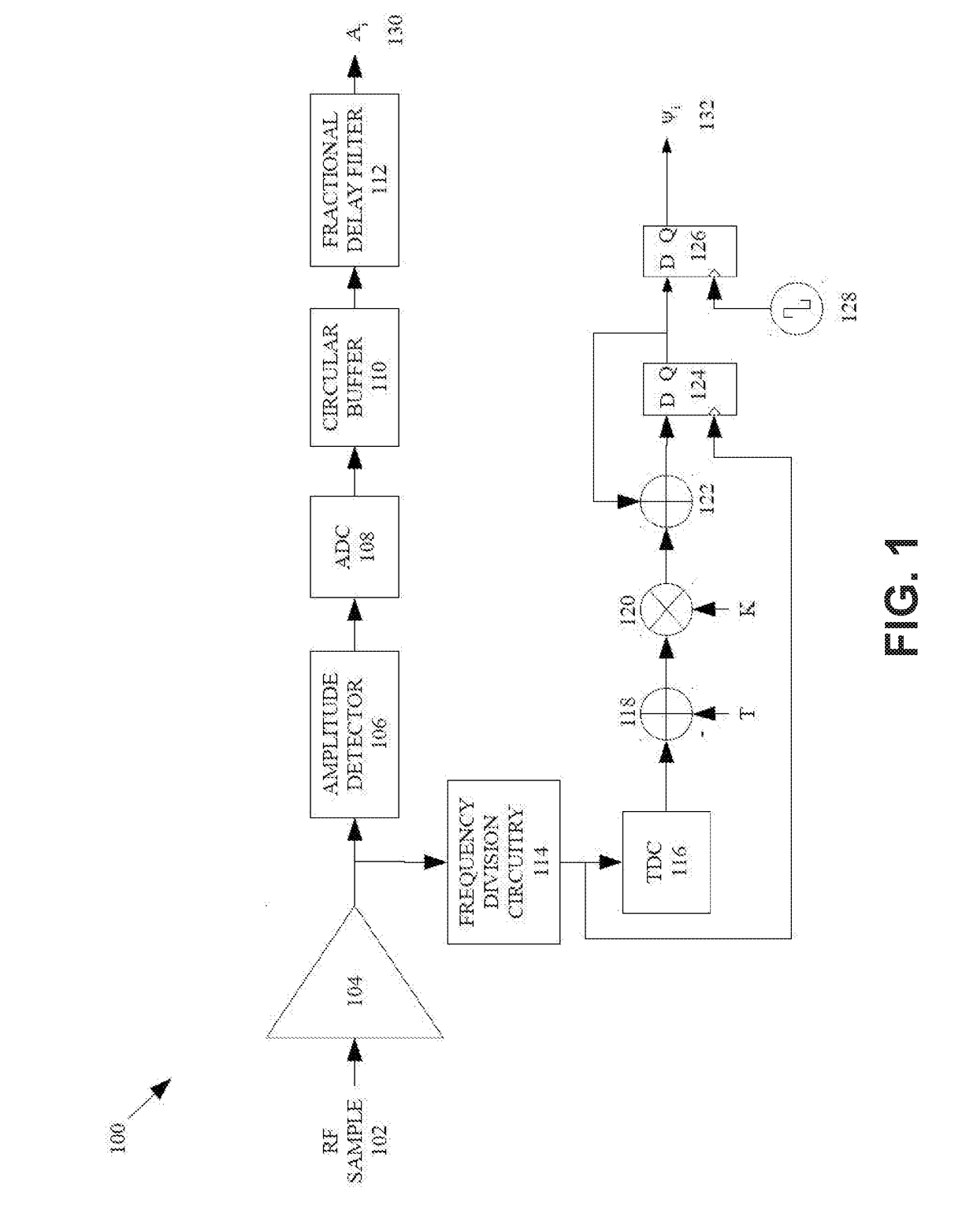

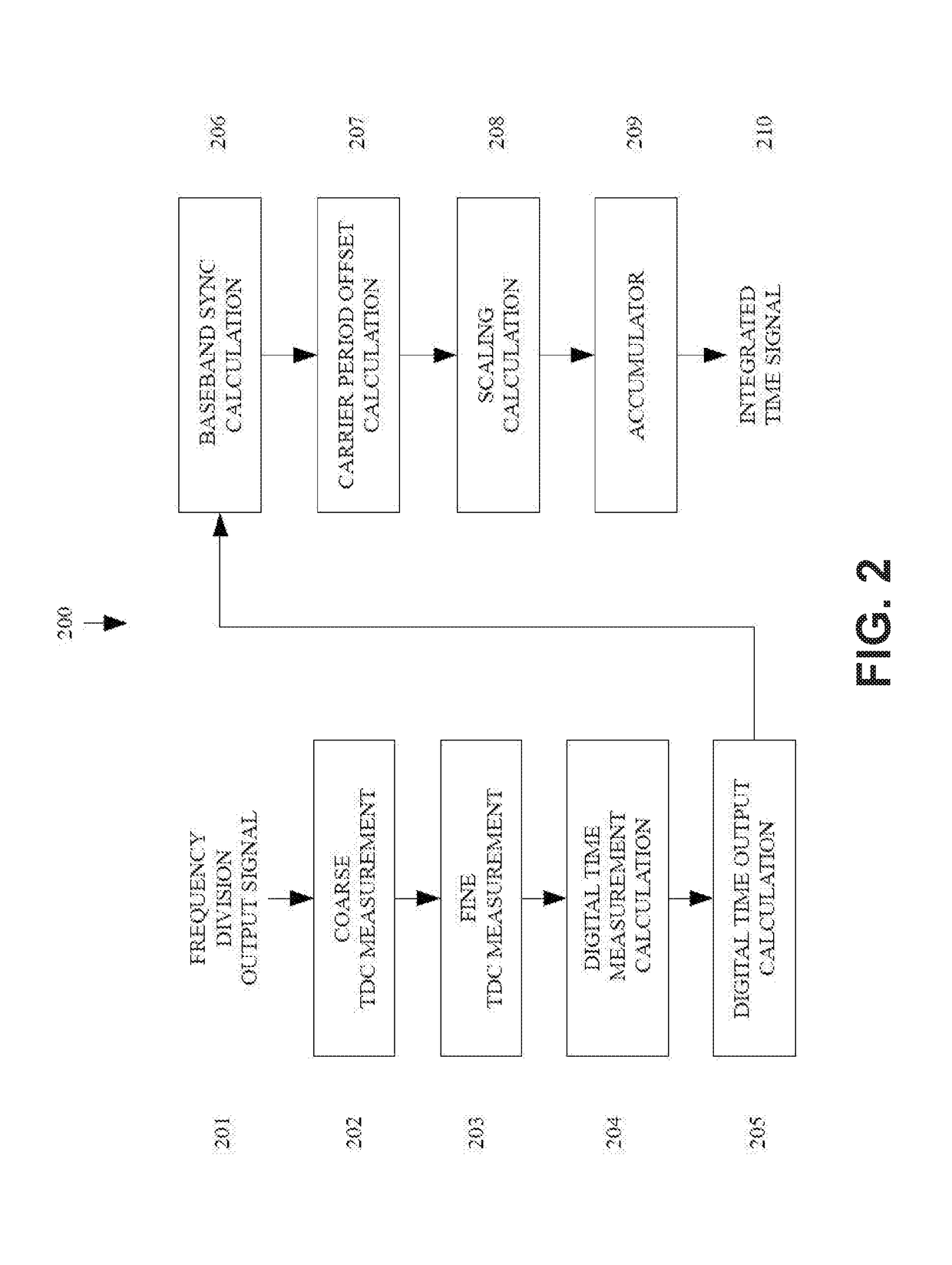

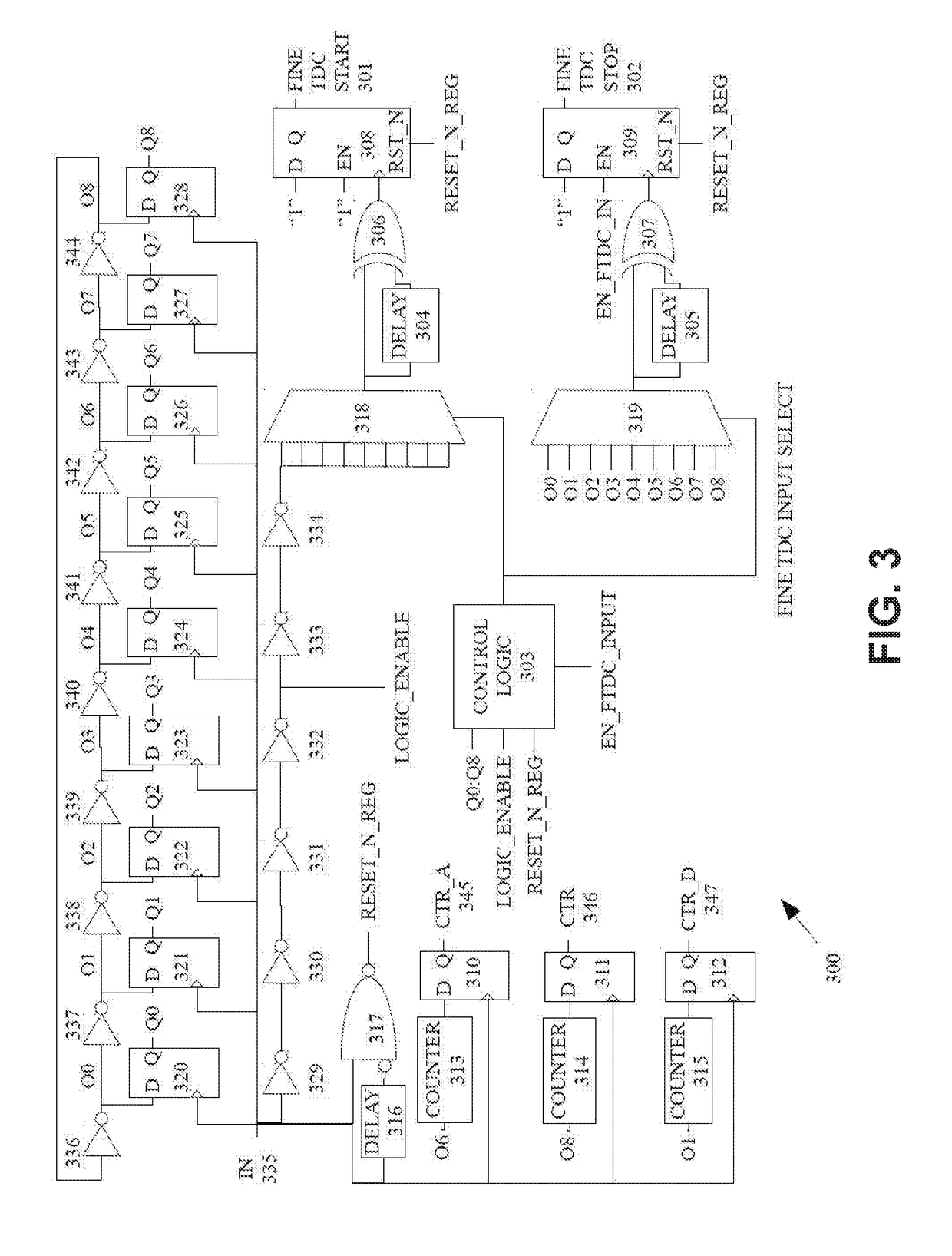

Time to digital converter with increased range and sensitivity

ActiveUS20190056698A1Optimize analog/RF performanceImprove performanceModulated-carrier systemsPulse automatic controlPhase correctionDigital down converter

Systems and methods are described for determining a phase measurement difference between a received modulated signal and a local clock signal. An adjusted local clock phase measurement may be determined by subtracting, from the phase measurement difference, a phase correction that is based on the frequency difference between the modulator signal's carrier frequency and the local clock's frequency. A phase modulation value may be generated by scaling the adjusted local clock phase measurement. The scaling may be based on a ratio of the modulated signal's carrier frequency and the local clock's frequency. The phase correction may be based on (i) a count of periods of the modulated signal occurring between each corrected phase measurement and (ii) a difference between the carrier frequency and the local clock frequency.

Owner:INNOPHASE

Time to digital converting circuit and pressure sensing device using the same

ActiveUS8261619B2Small sizeAffect due to external noises may also be minimizedAnalogue/digital conversionElectric signal transmission systemsDigital dataPressure sense

A time-to-digital converting circuit and a pressure sensing device using the same are provided. The circuit includes: a delay time-varying unit generating a reference signal having a fixed delay time, and a sensing signal having a variable delay time in response to an impedance of an externally applied signal; and a delay time calculation and data generation unit calculating a delay time difference between the reference signal and the sensing signal, and generating digital data having a value corresponding to the calculated delay time difference. Accordingly, the digital data are generated using the delay time varied in response to the externally applied signal, so that the size of the time-to-digital circuit is significantly reduced. In addition, an affect due to external noises is minimized.

Owner:ATLAB INC

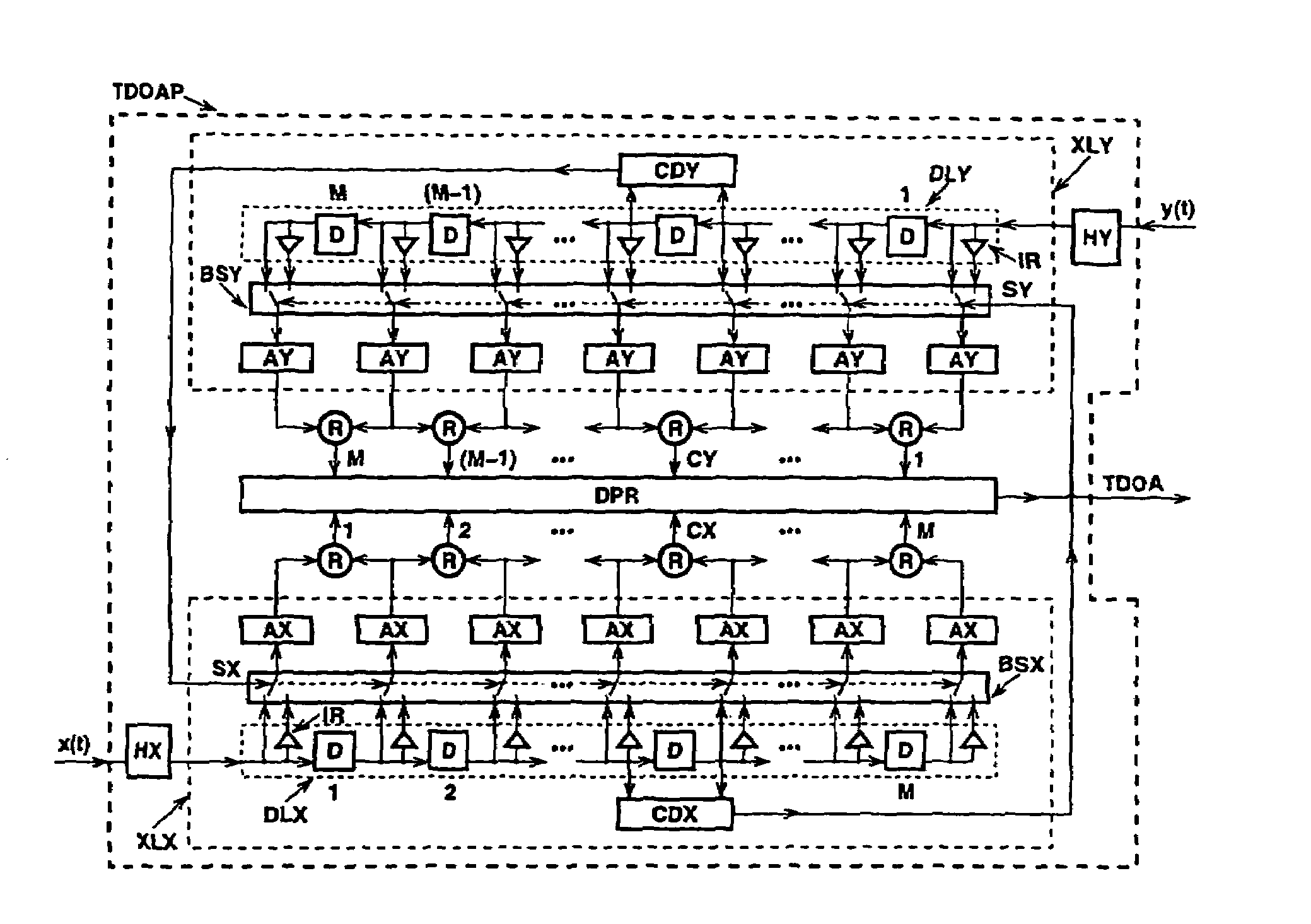

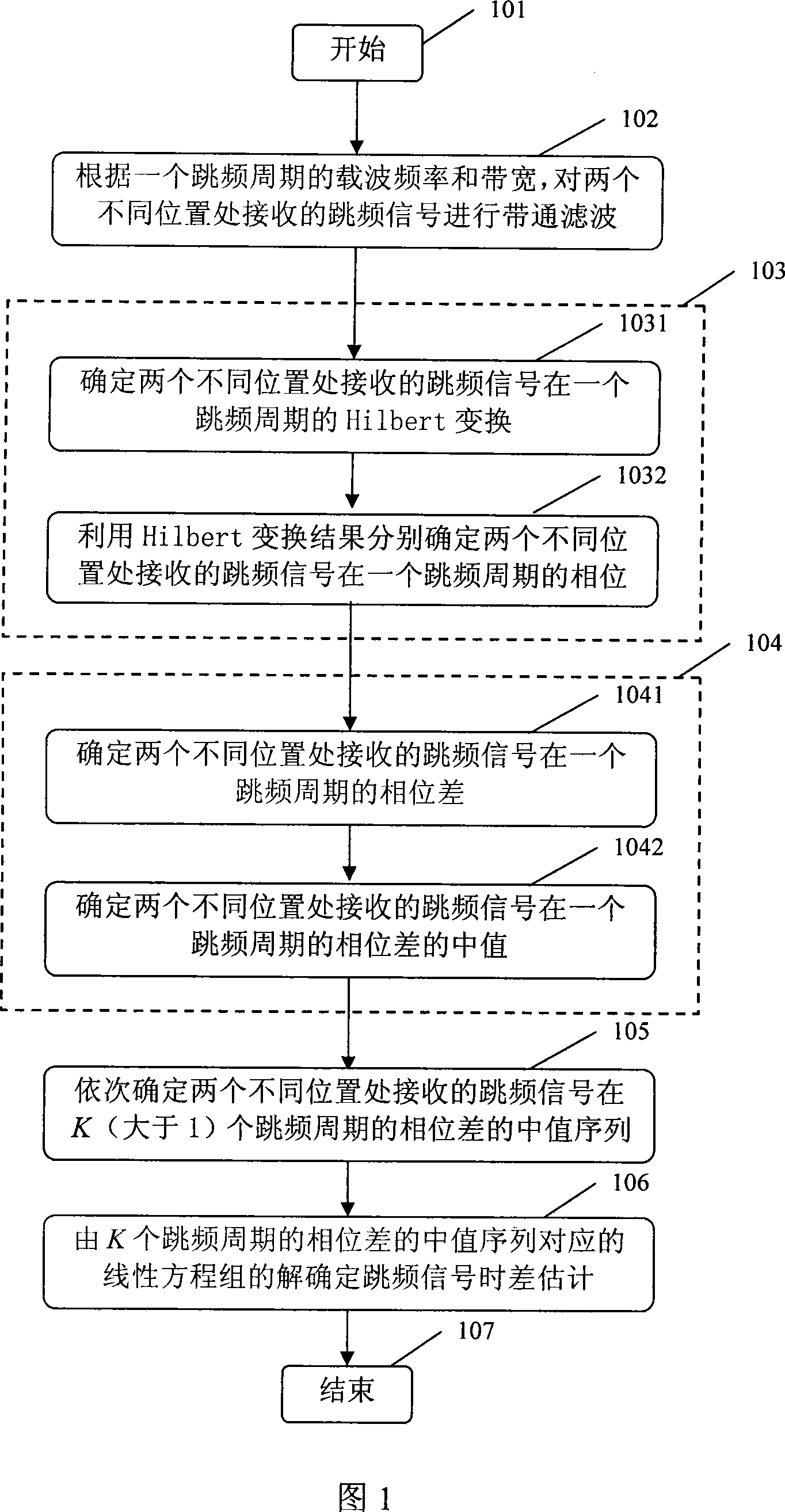

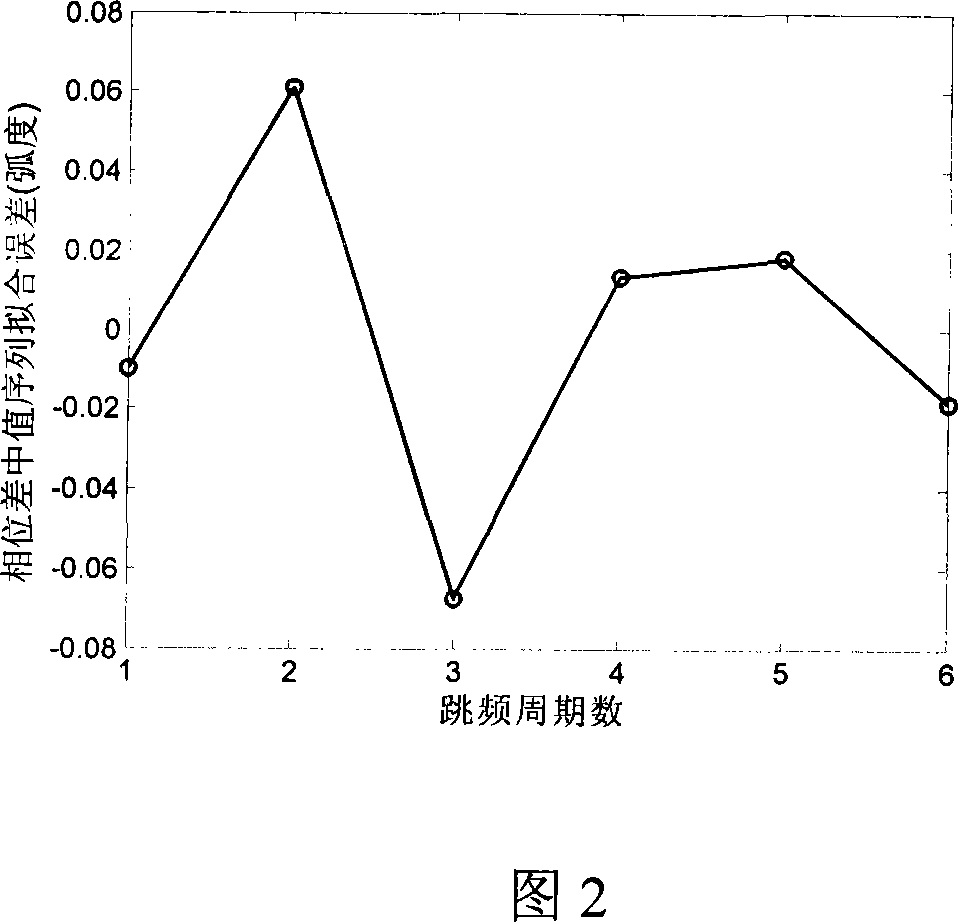

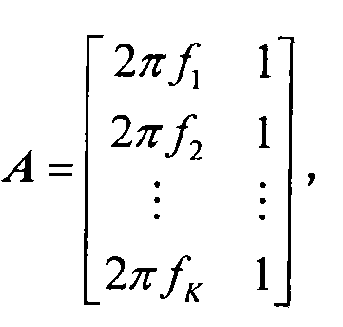

Frequency hopping signal time difference estimation method

InactiveCN101247141APrecise positioningRapid positioningTransmissionMeasurment by measuring phaseBandpass filteringPhase difference

A frequency hopping signal time difference estimating method belongs to the signal processing category. With the linear corresponding relationship of the phase difference between the time difference of the frequency of the hopping signals which are received in two different positions and the carrier waves of the frequency hopping signals that are received at two positions, and through measuring the phase difference which is between the frequency hopping carrier waves received at two different positions in a plurality of frequency hopping periods, the time difference between the frequency hopping signals which are received at two different positions is estimated. The method comprises the steps of executing band pass filtering to the frequency hopping signal received at two different positions; Hilbert converting in a frequency hopping period and calculating the phase; confirming the phase difference between the frequency hopping signals in two different positions in one frequency hopping period and the middle value of the phase difference; and in the phase difference middle value sequence in K frequency hopping periods, calculating the least square solution of the linear equation set corresponding to the middle value sequence for confirming the time difference estimation of the frequency hopping signal and the like steps. The method of the invention can rapidly estimate time difference to the frequency hopping signal with high frequency, and is widely applied in the frequency hopping radiating signal source positioning system.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Time converter

ActiveUS7423937B2Time indicationSynchronous motors for clocksEngineeringElectrical and Electronics engineering

Owner:KEYSIGHT TECH

Time lag measuring device, distance measuring apparatus and distance measuring method

InactiveUS20090235127A1Accurate measurementAccurate acquisitionFault responseRecord information storageTime lagMeasurement device

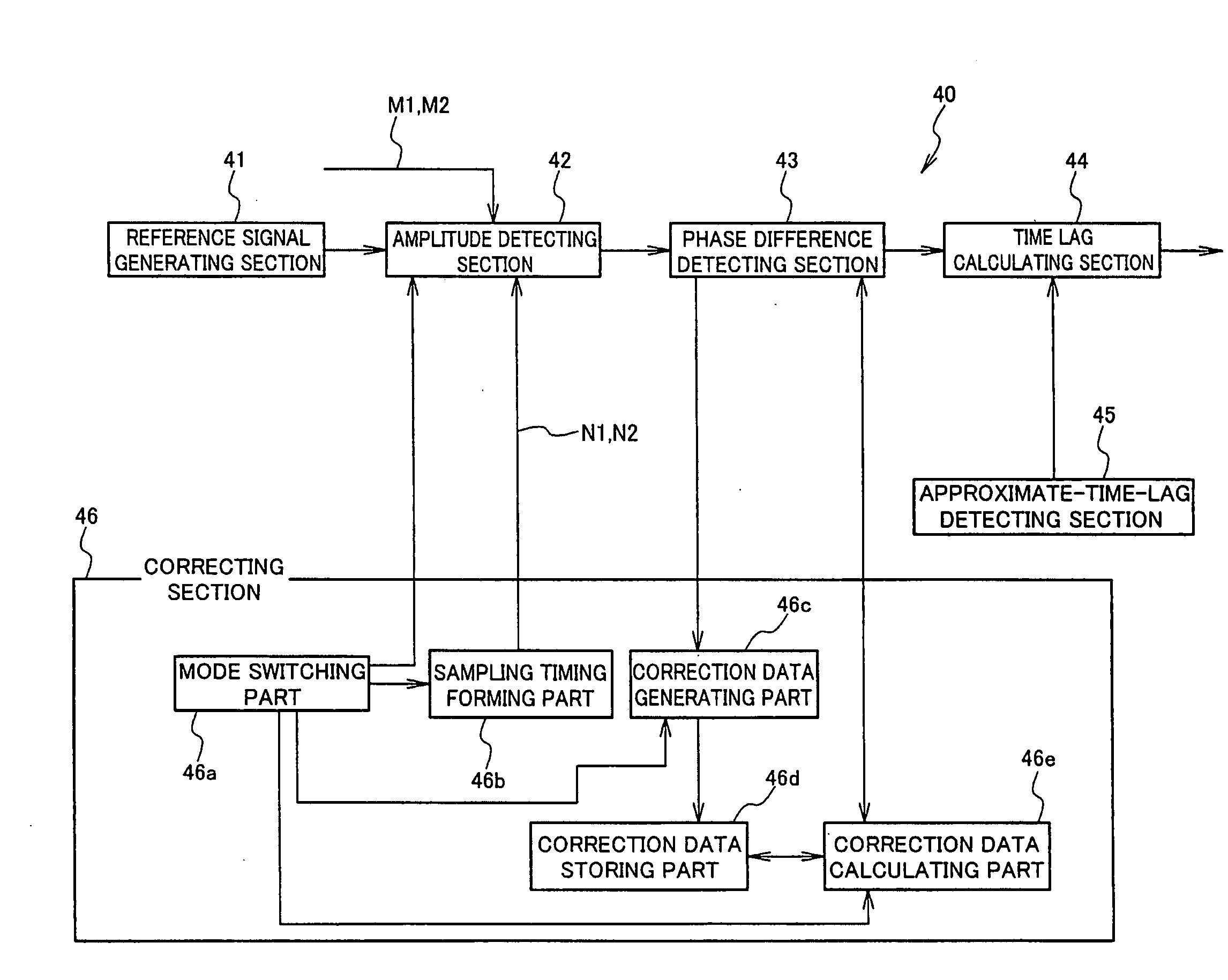

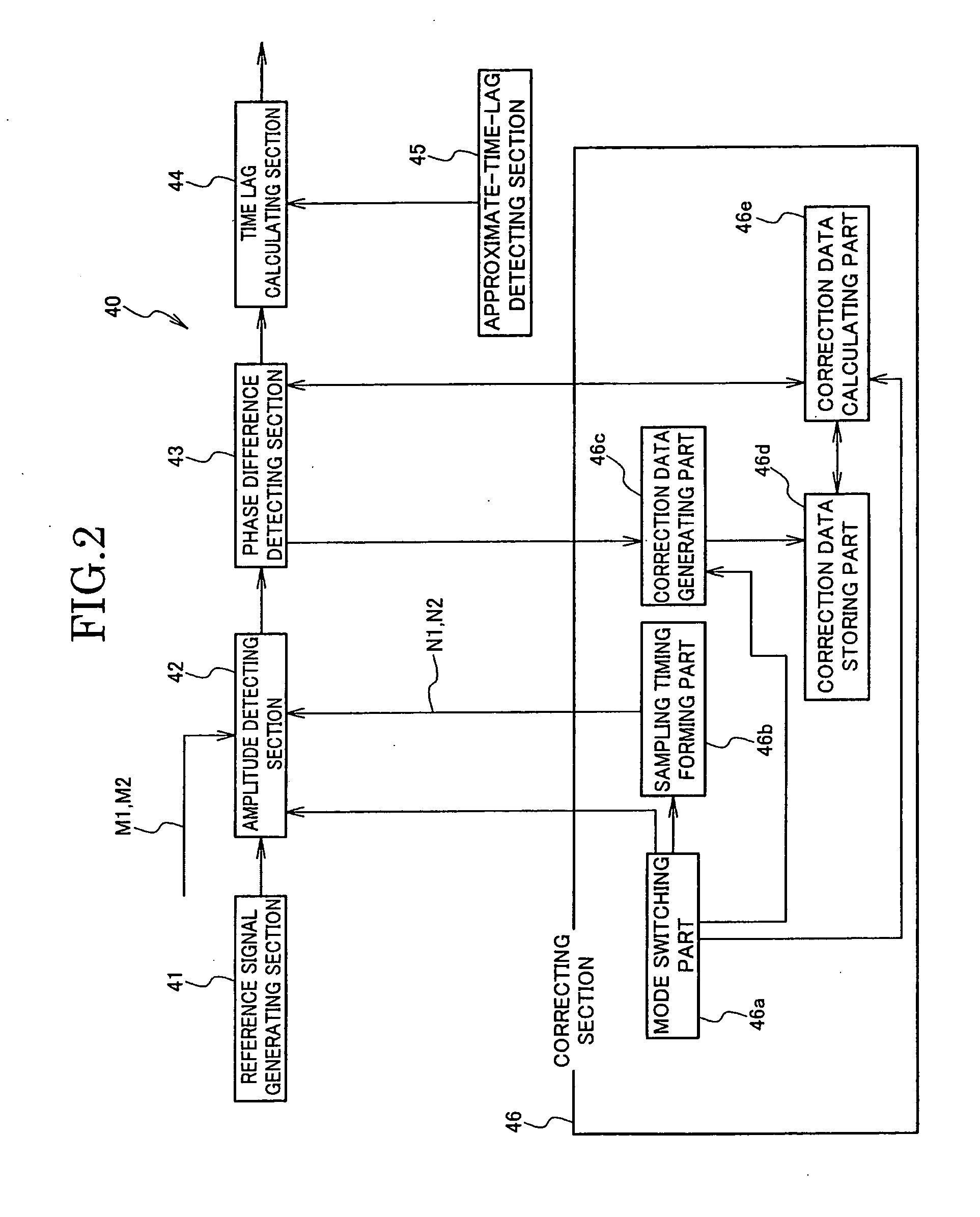

In measuring a certain time lag between generations of two pulse signals, a time lag measuring device prevents errors in measurement results even with an error in two reference signals for measuring the time lag. The device measures a time lag between a start signal M1 and a stop signal M2 and includes a reference signal generating section 41 generating two reference signals S1, S2 having a phase difference π / 2, and an amplitude detecting section 42 detects amplitudes A11, A12 and A21, A22 of the reference signals S1, S2 at generation timings for the start signal M1 and the stop signal M2, a phase difference detecting section 43 calculating a phase _ of the reference signals S according to each set of the amplitudes (A11, A12) and (A21, A22), and a correcting section 46 correcting the calculated phase using correction data for error correction in the reference signals S1, S2.

Owner:KK TOPCON

Apparatus for compensating for error of time-to-digital converter

InactiveUS7999707B2Improve time resolutionReduce delaysElectric signal transmission systemsPulse automatic controlPhase detectorImage resolution

An apparatus for compensating for an error of a time-to-digital converter (TDC) is disclosed to receive a delay phase from a phase detector including the TDC and a phase error including a TDC error and compensate for the TDC error to have a time resolution higher by N times (N is a natural number). The apparatus includes: a fragmenting and multiplying unit fragmenting the delay phase by N times (N is a natural number) to generate first to (N−1)th fragmented delay phases; an adding unit adding each of the first to the (N−1)th fragmented delay phases to the phase error to generate first to (N−1)th phase errors; and a comparison unit acquiring a phase error compensation value nearest to an actual phase error from the phase error and the first to (N−1)th phase errors.

Owner:ELECTRONICS & TELECOMM RES INST

Time interval measurement device

InactiveUS7057978B2Improve accuracyUnlimited rangeMultiple input and output pulse circuitsMechanical clocksMeasurement deviceSurface acoustic wave sensor

A device for high accurate measurement of time intervals is based on the conversion of the time interval to a sequence of samples of the response of a surface acoustic wave filter excited at the beginning and at the end of the measured interval. In one of its configurations, the time interval measurement device includes the input of the pulse signal, the filter exciter, the surface acoustic wave filter, the amplifier, the sampler, the analog-to-digital converter, the sample register, the register of sample numbers, the voltage comparator, the control circuit, the sample counter, the computer, the output of the reference clock signal source, and the output of the measured time intervals.

Owner:PANEK PETR +1

Popular searches

Pulse generation by logic circuits Synchronisation signal speed/phase control Radio transmission Generating/distributing signals Angle demodulation by phase difference detection Synchronous/start-stop systems Analogue-digital converters Physical parameters compensation/prevention Analogue/digital conversion calibration/testing Time-delay networks