Patents

Literature

32results about How to "Easy Design Changes" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

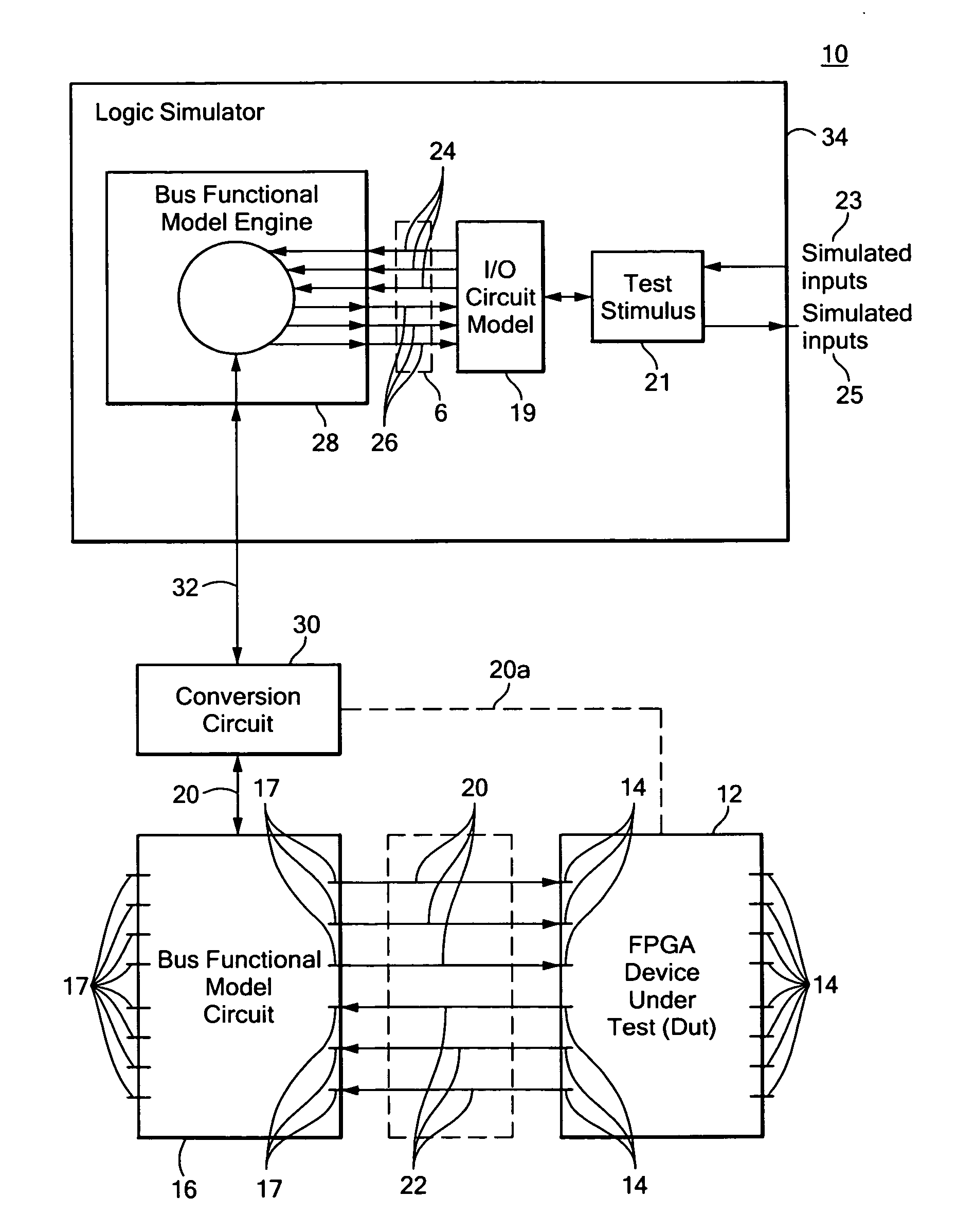

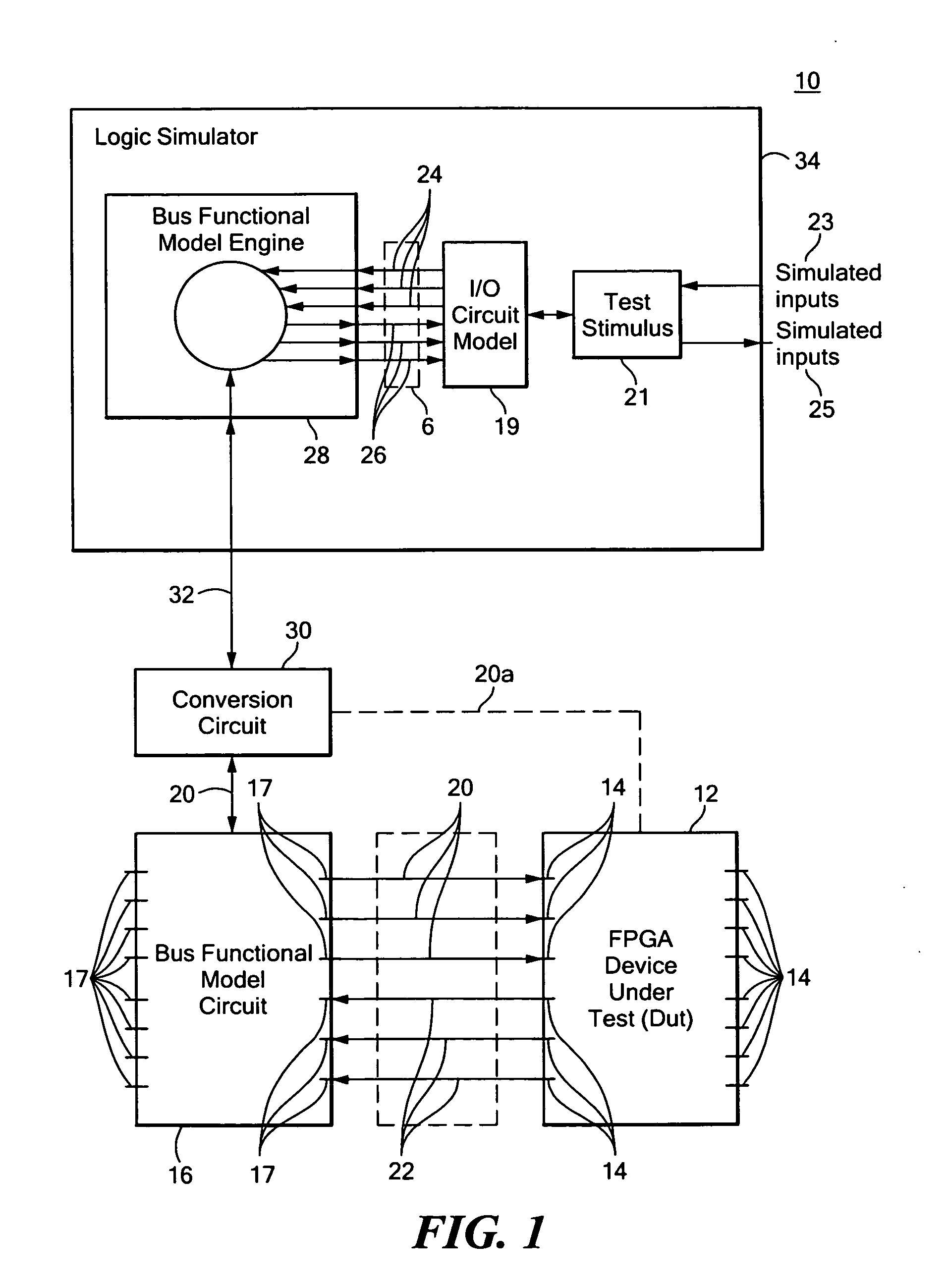

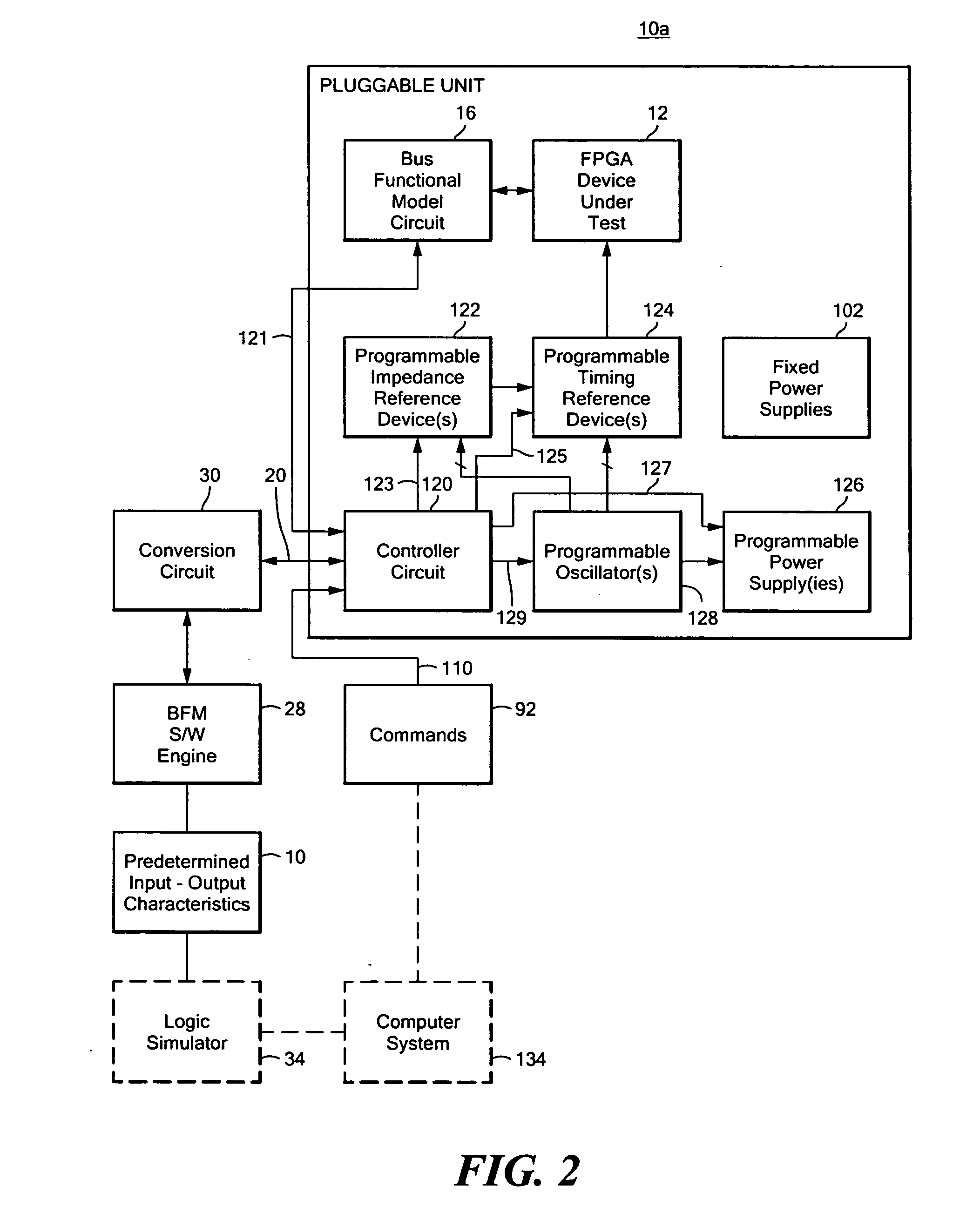

FPGA emulation system

InactiveUS20060253762A1Fast formingEasy Design ChangesElectronic circuit testingError detection/correctionFpga emulationOperating environment

This invention features an FPGA emulation system including an FPGA device under test having a plurality of pins. A bus functional model circuit responsive to signals representing predetermined input characteristics of the FPGA device under test and configured to apply one or more signals to the FPGA device under test corresponding to the predetermined input characteristics and configured to receive one or more signals representing output characteristics of the FPGA device under test to emulate the operation of the FPGA device under test in a predefined selectable and flexible electrical operating environment. This invention also features an FPGA emulation system including an FPGA device under test having at least one component and a plurality of pins operating in a predetermined native target environment, a bus functional model engine for simulating and capturing output characteristics of the at least one component of the FPGA device under test and simulating and releasing input characteristics of the at least one component of the FPGA device under test, and a bus functional model circuit embedded in the FPGA device under test configured to receive one or more signals representing the input characteristics of the at least one component and configured to release one or more signals representing the output characteristics of the at least one component such that the bus functional model engine emulates the operation of the at least one component of the FPGA device under test in the predetermined native target environment.

Owner:ALTERA CORP

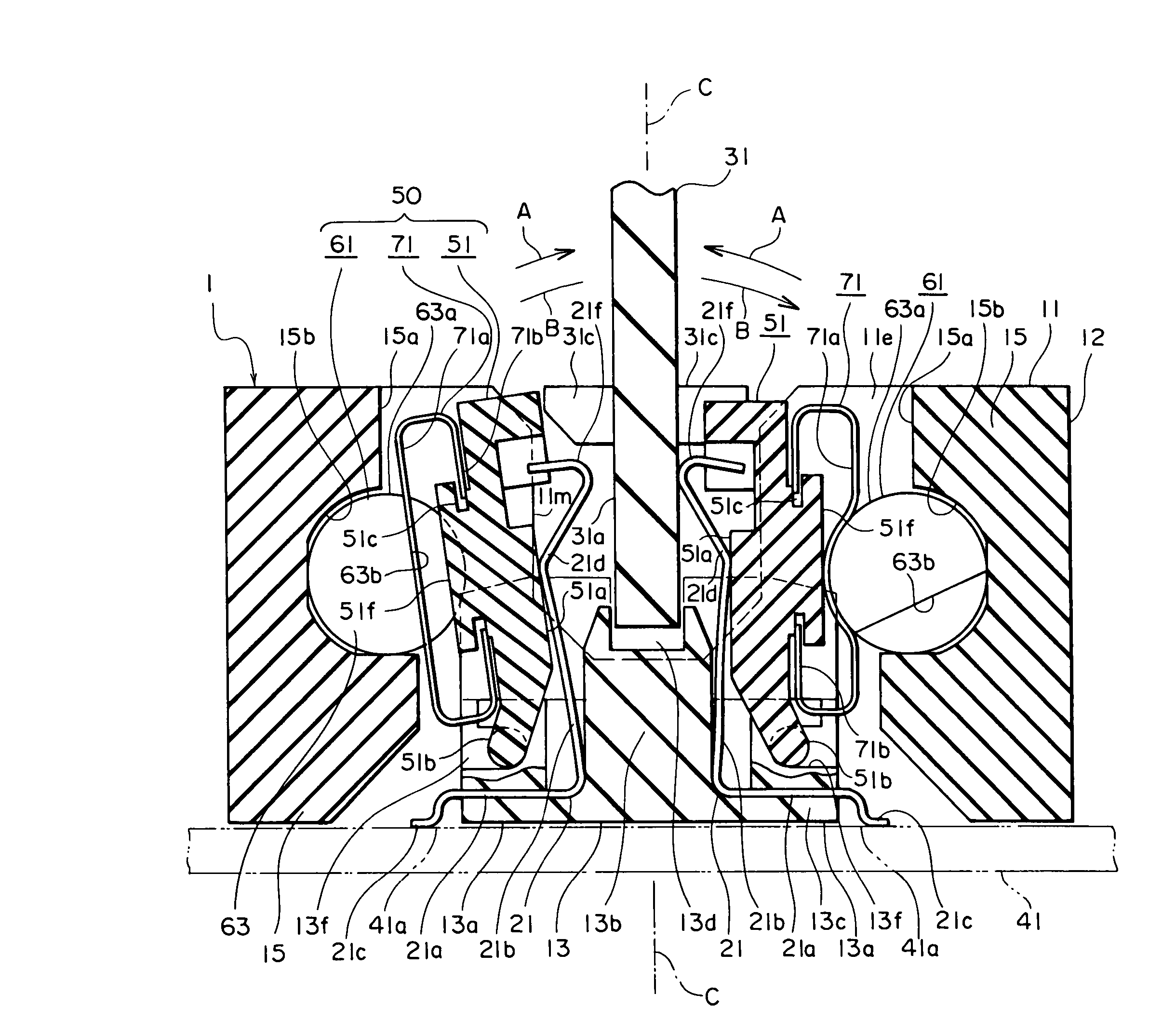

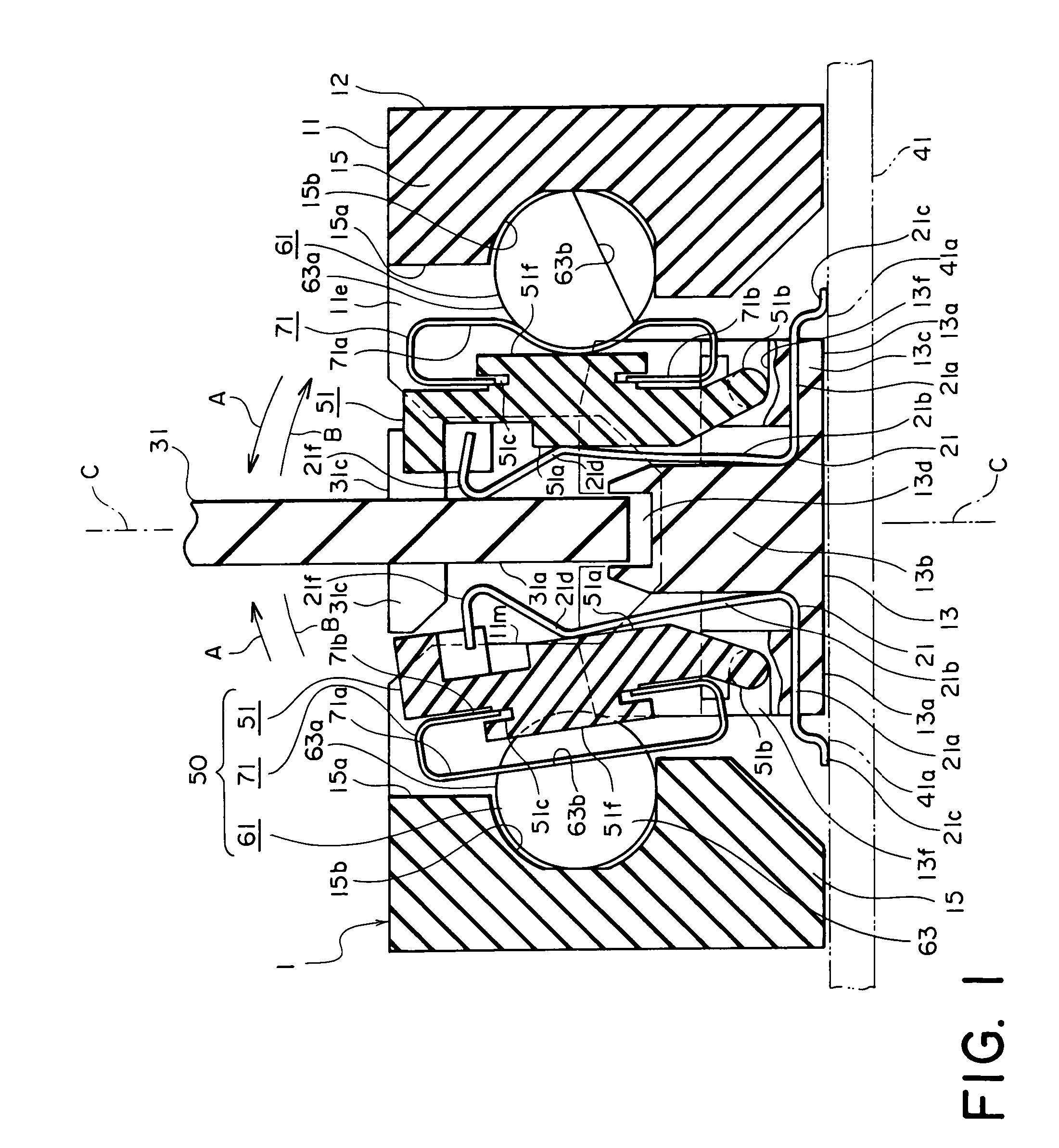

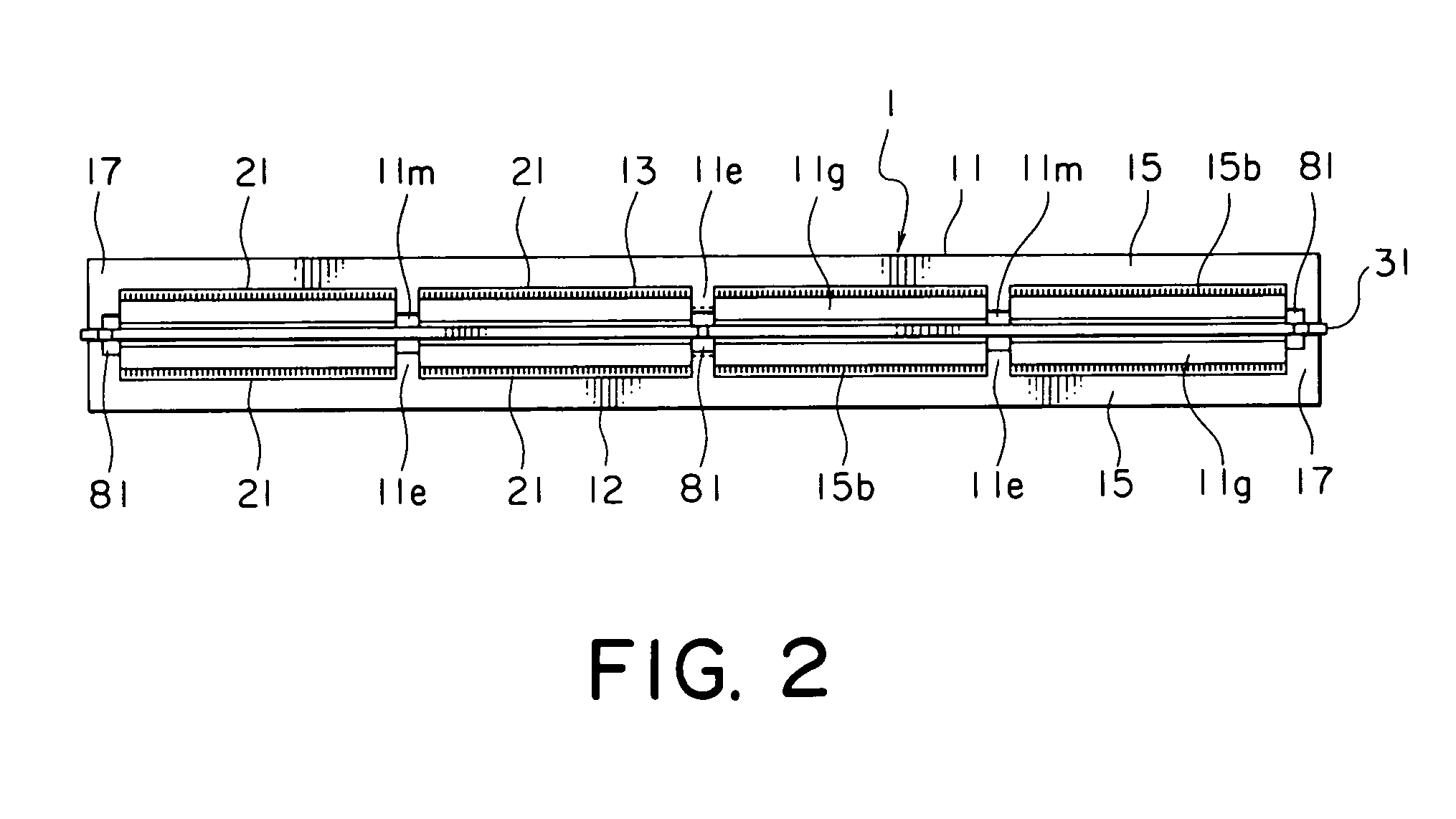

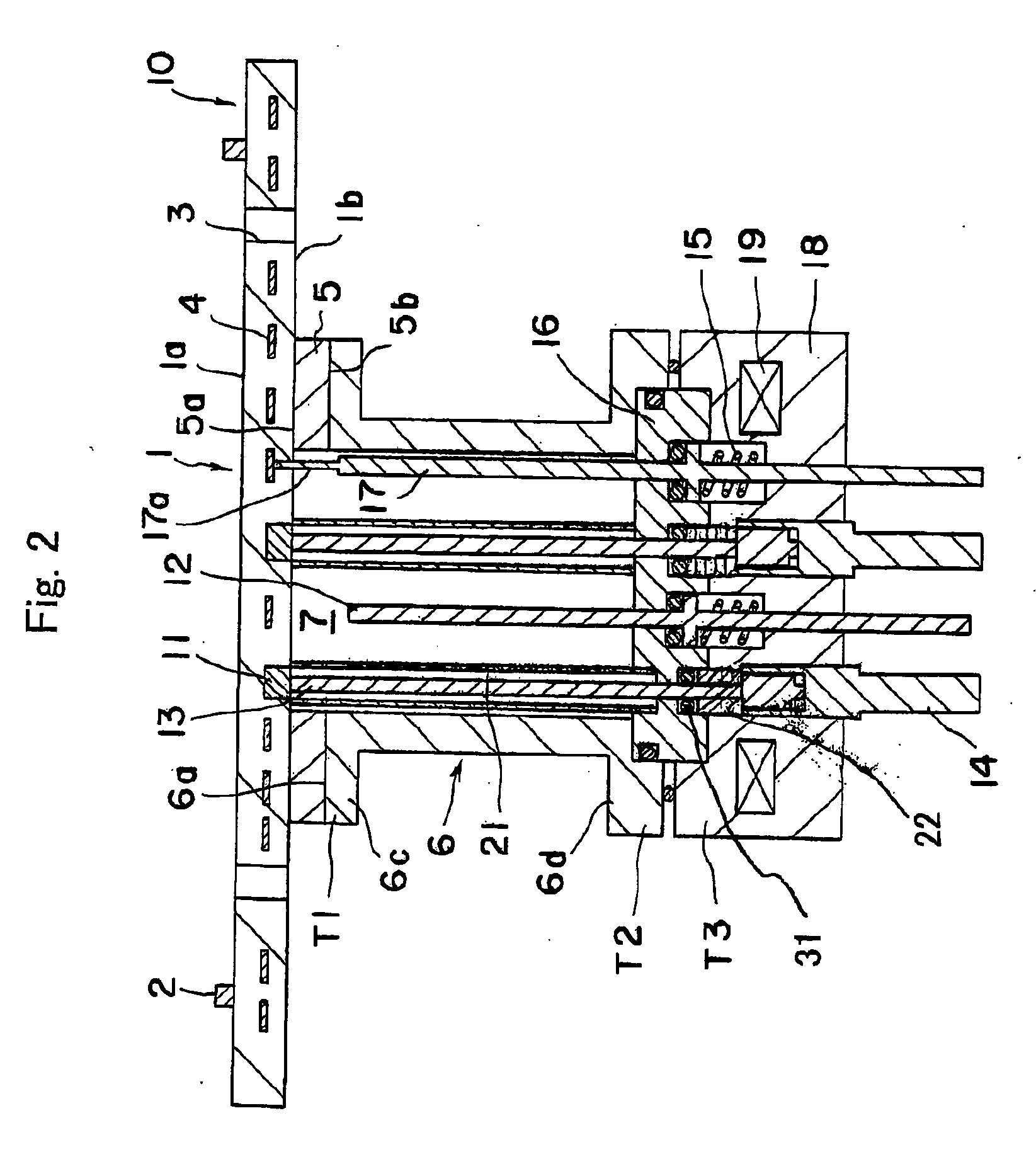

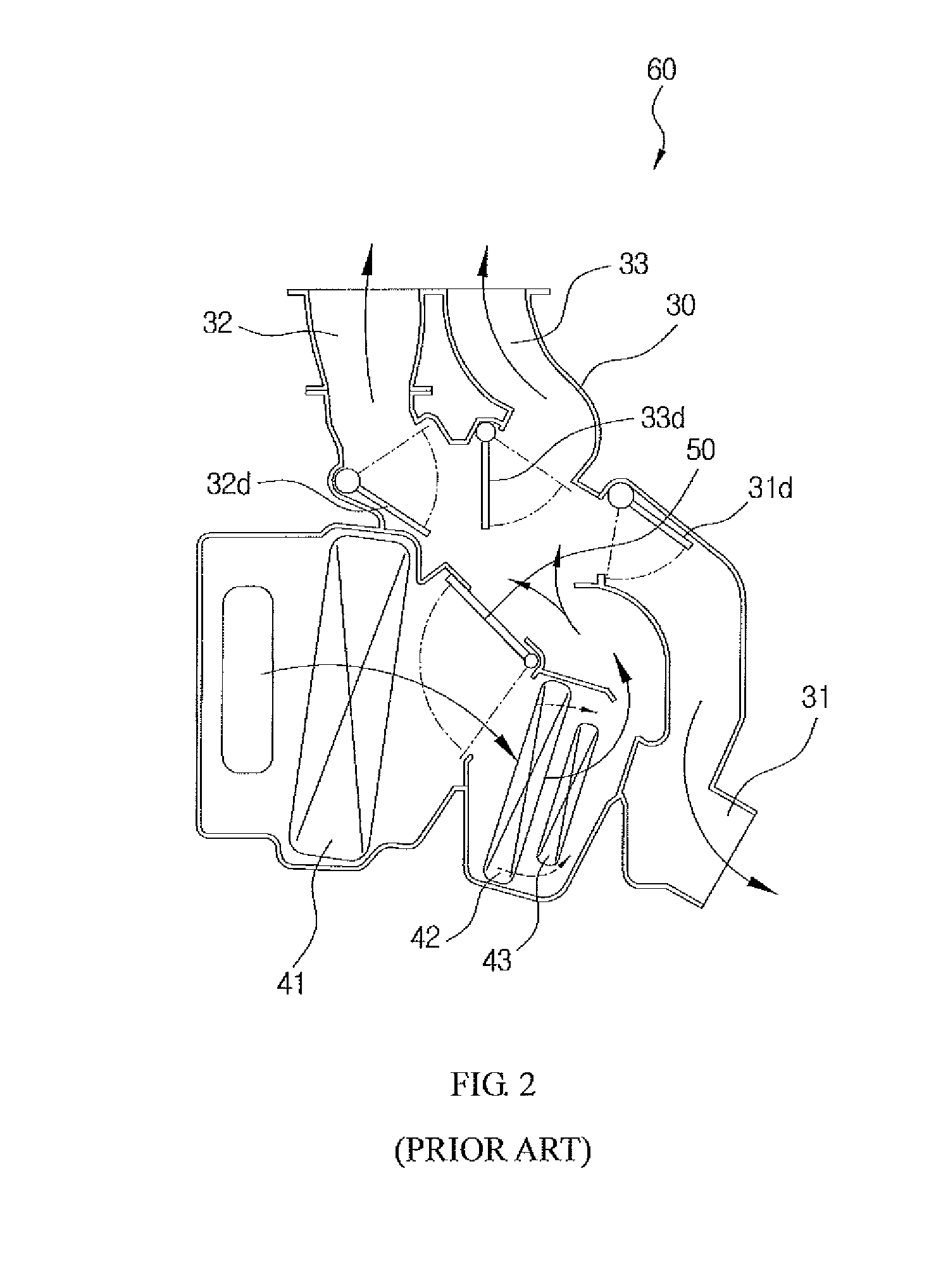

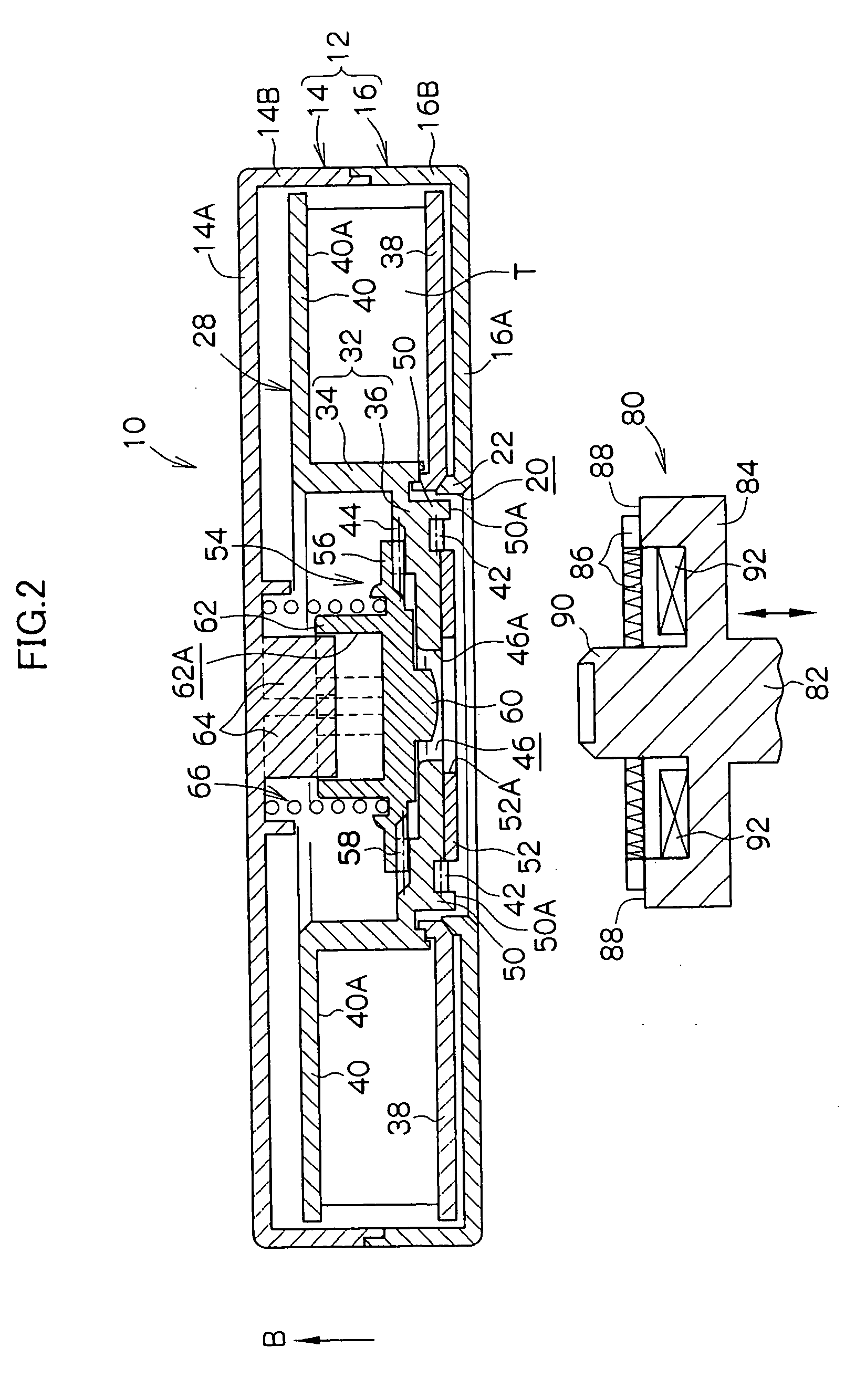

Electrical connector having a mechanism for supplementing spring characteristics of a contact

InactiveUS6979216B2Improve contact reliabilityEasy Design ChangesEngagement/disengagement of coupling partsCoupling contact membersElectrical connectorCam

In a connector comprising a housing (11) and a contact (21) held by the housing, the contact is brought into contact with a connection object under a pressing force obtained by operating an operating member (61). An elastic member (71) elastically deformable is interposed between the contact and the operating member. The operating member has a first cam surface (63a) for applying the pressing force to the contact with elastic deformation of the elastic member and a second cam surface (63b) for releasing the pressing force. An insulating actuator (51) cooperating with the contact may be interposed between the contact and the elastic member. The elastic member may be a leaf spring member held by the actuator.

Owner:JAPAN AVIATION ELECTRONICS IND LTD +1

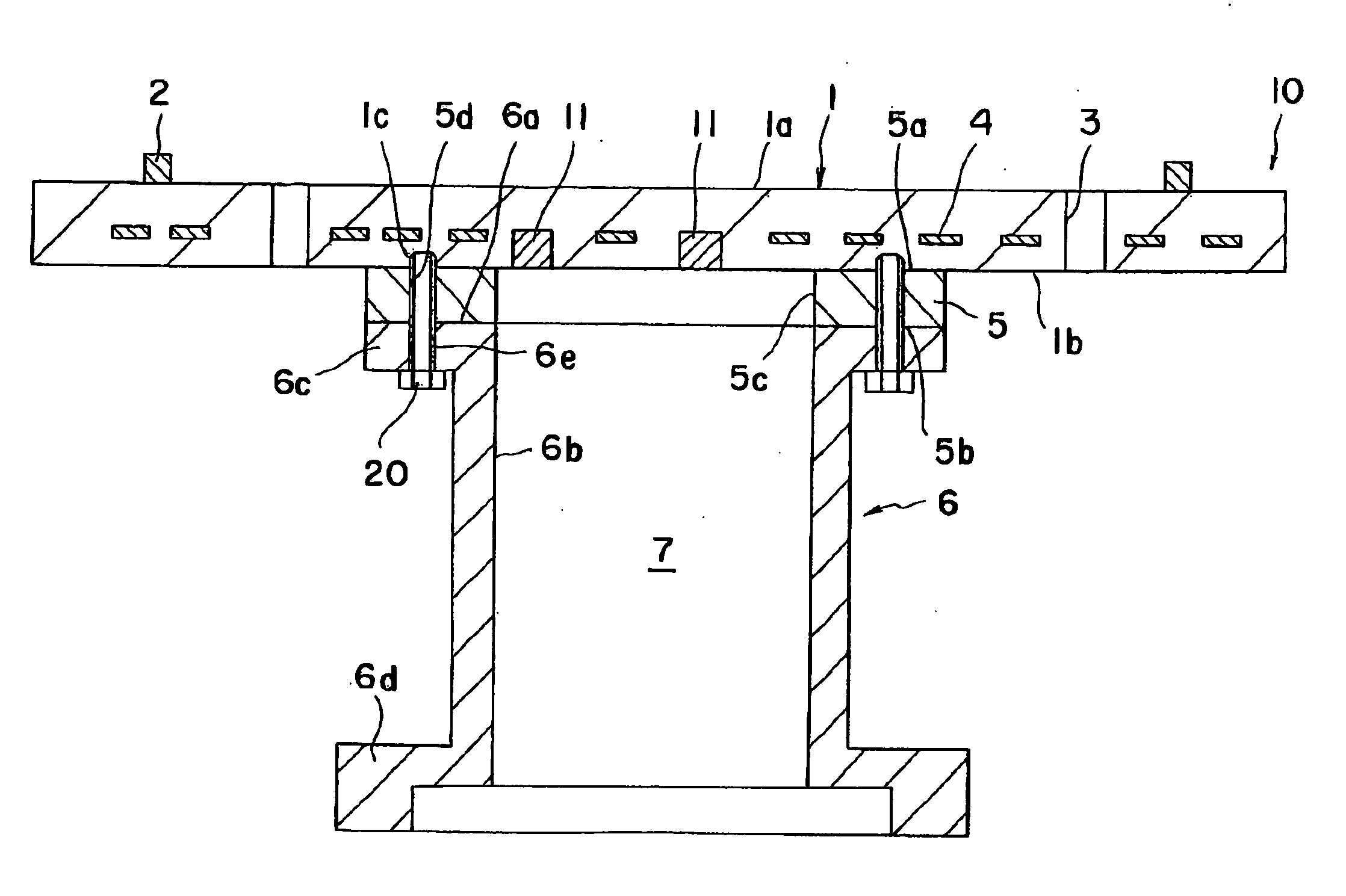

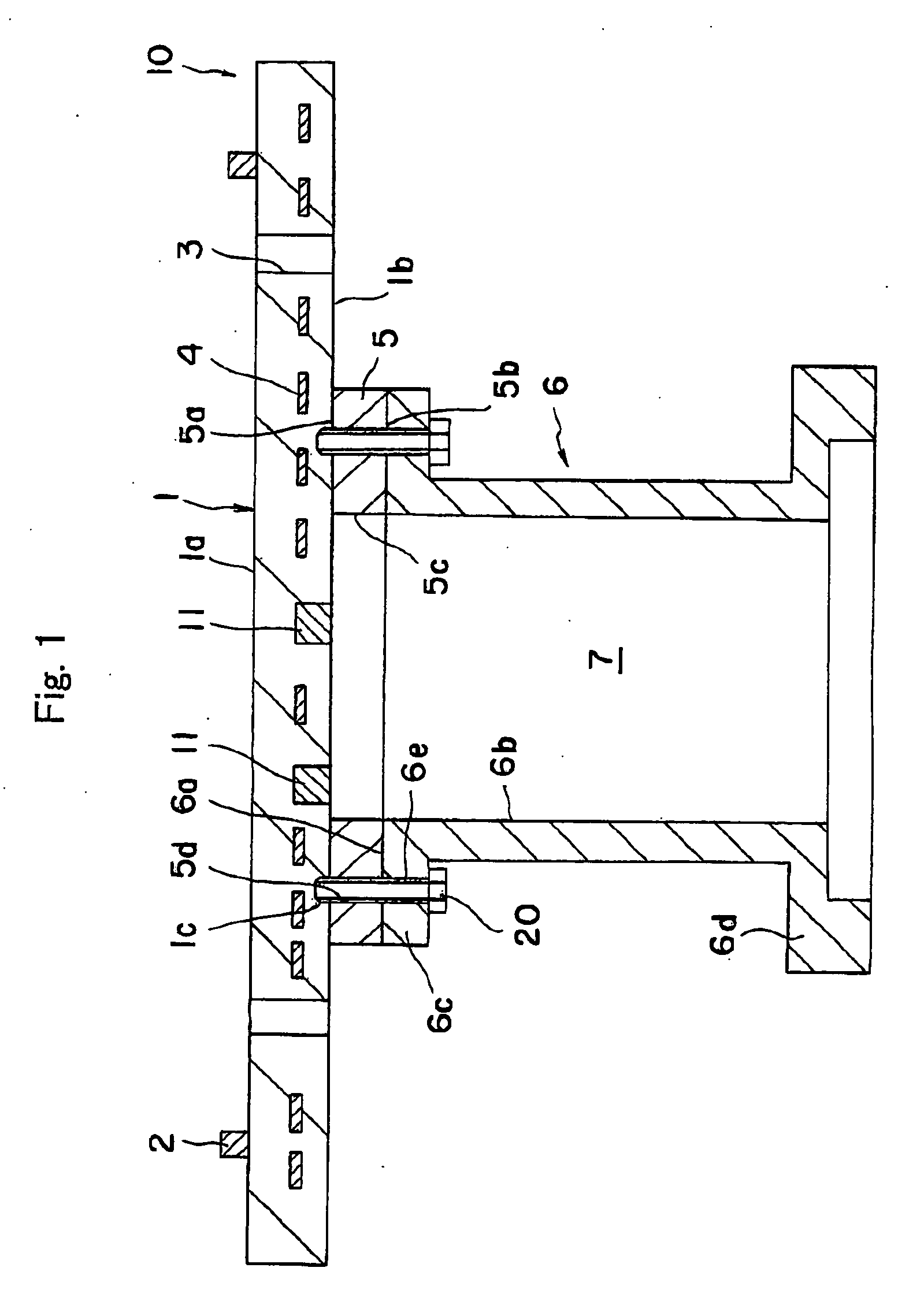

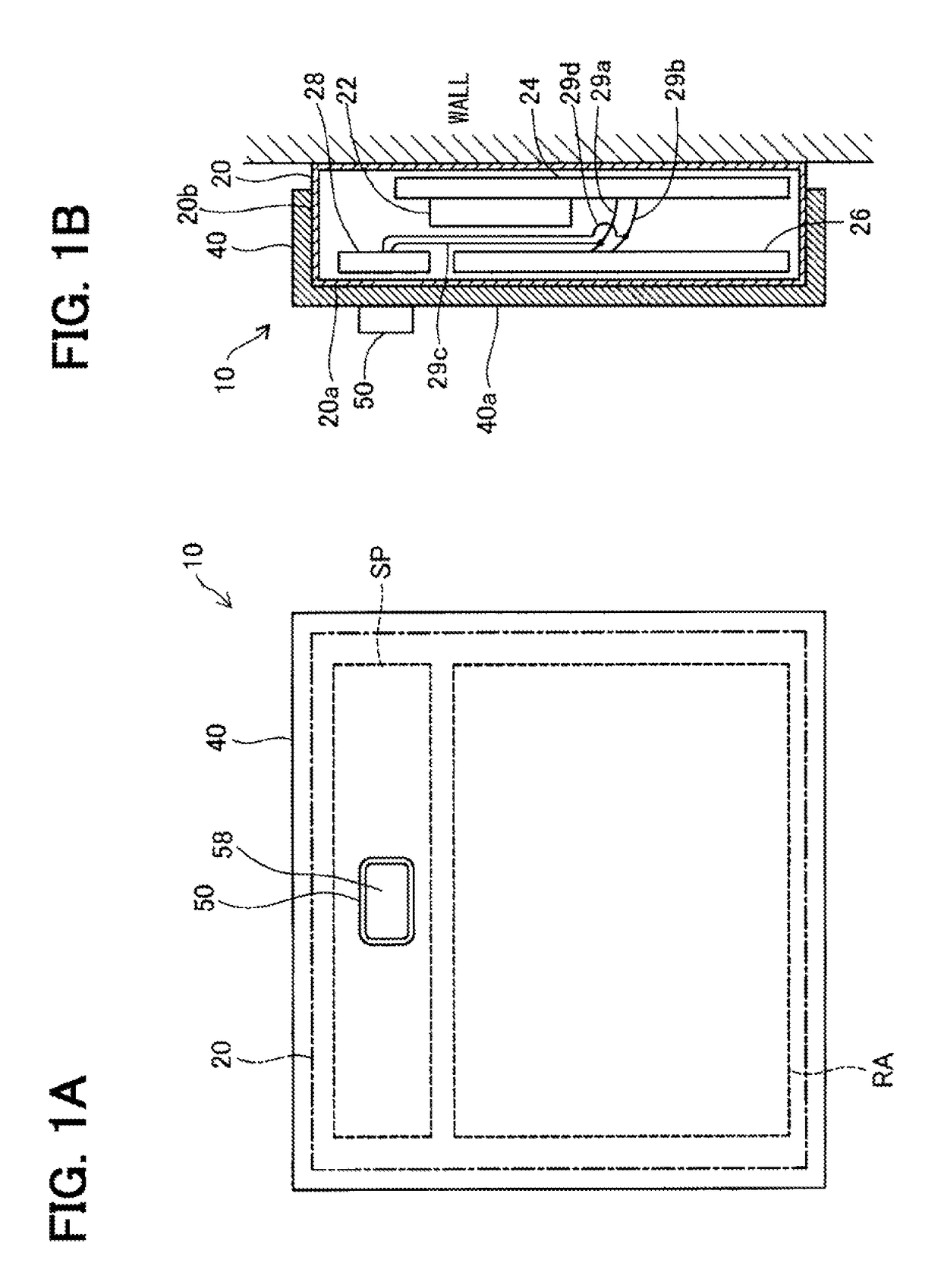

Heating systems

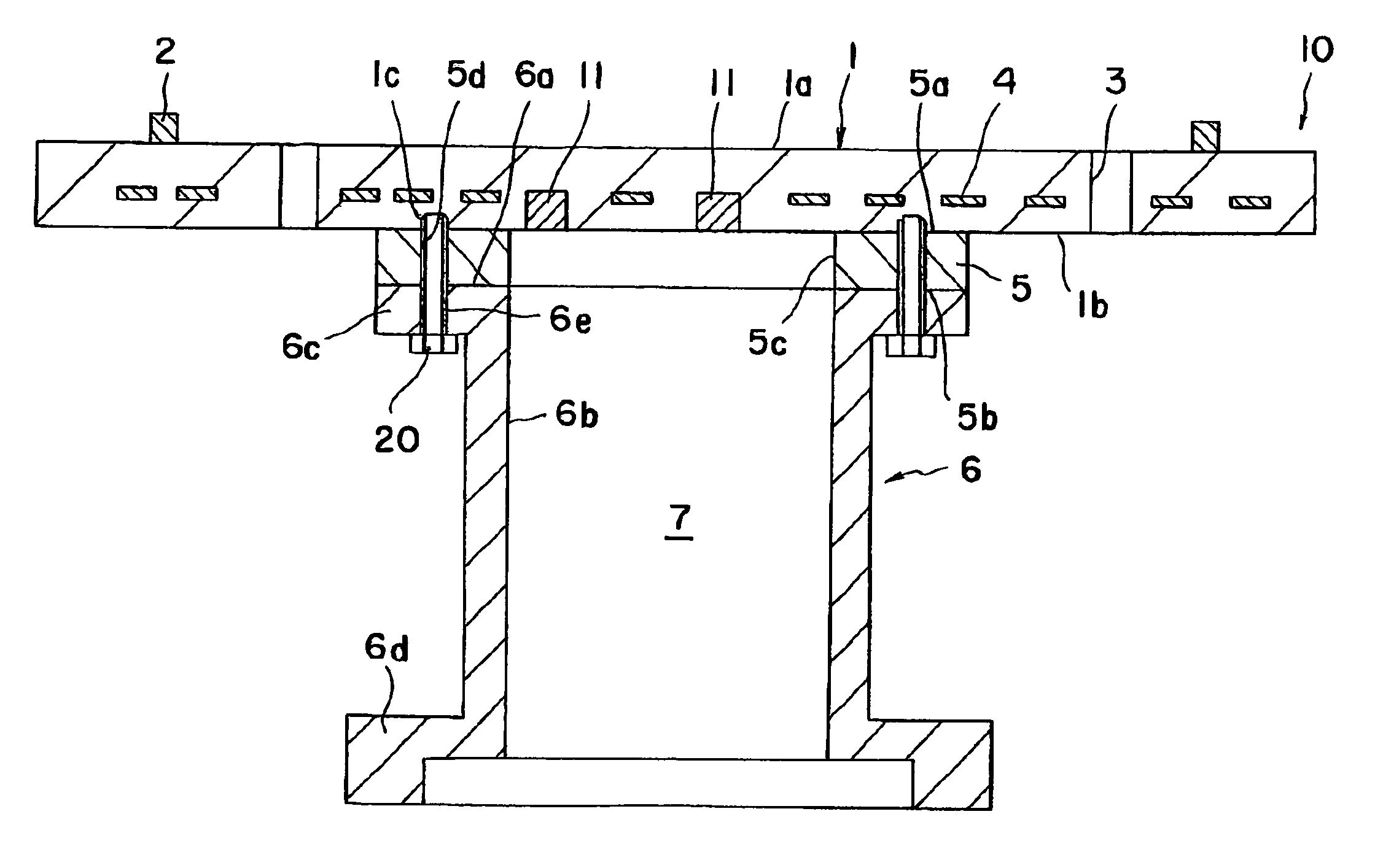

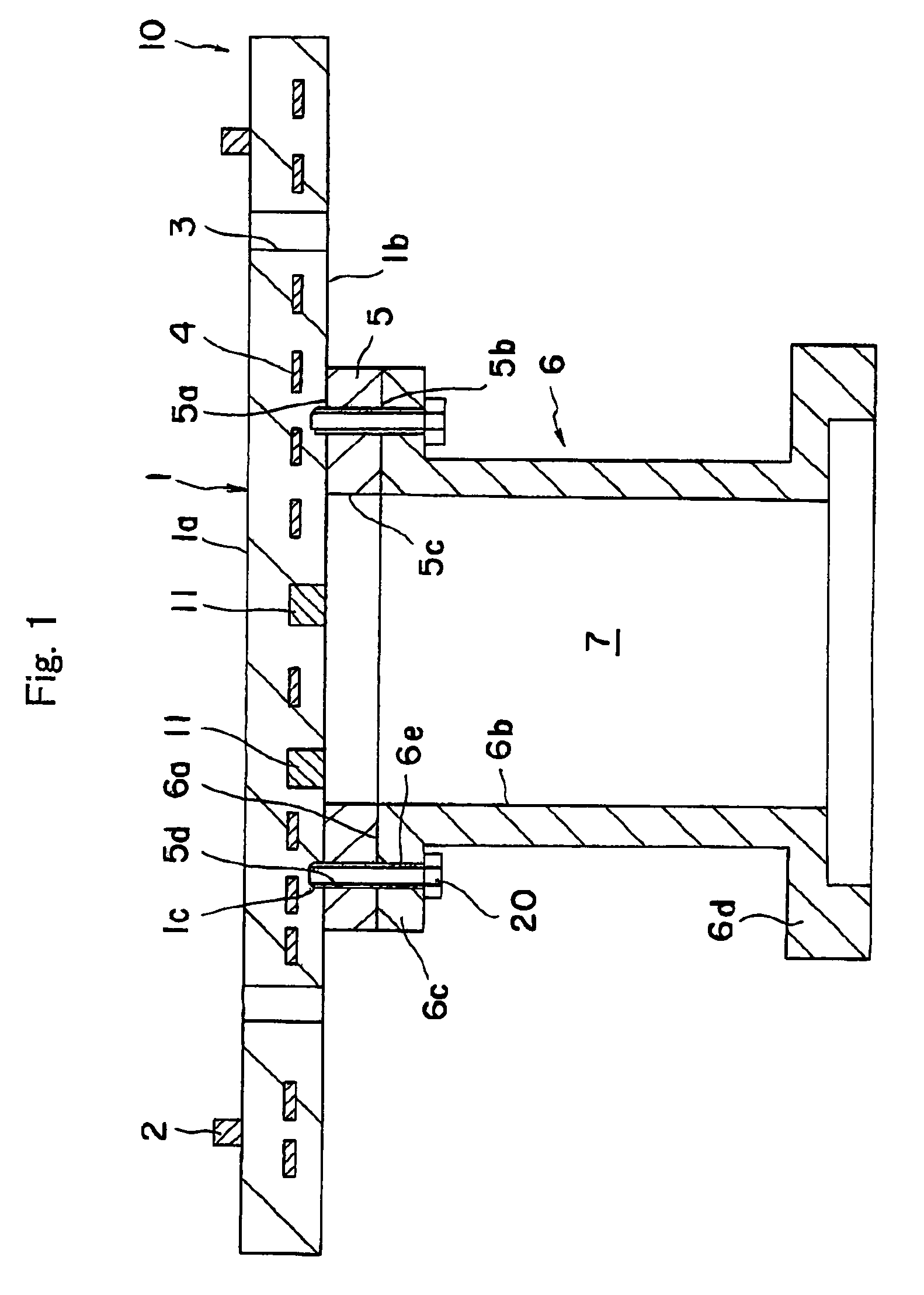

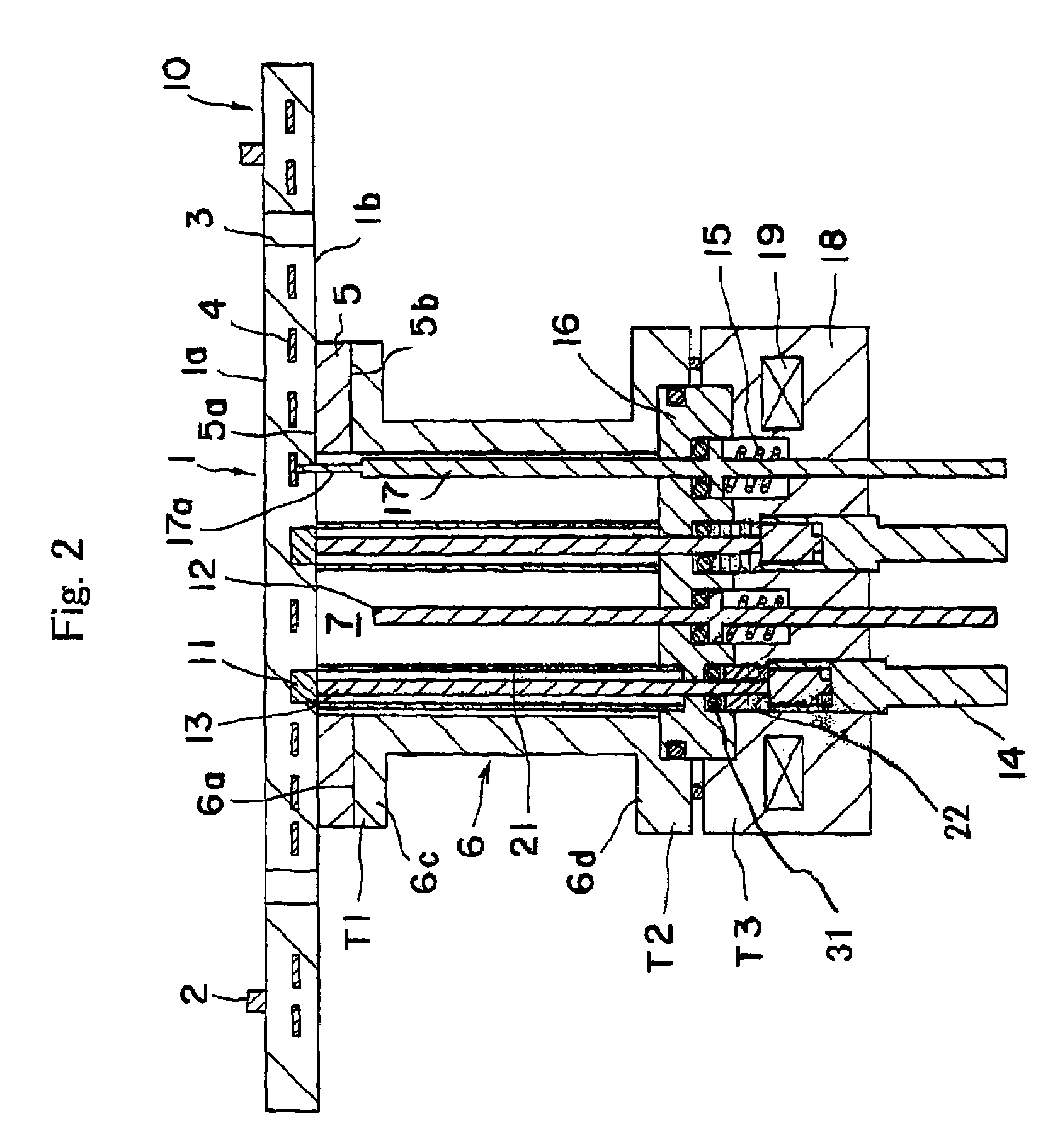

ActiveUS20060186109A1Deterioration flatness and inclination can be preventedEasy to carrySemiconductor/solid-state device manufacturingHot plates heating arrangementsHeating systemEngineering

An object of the present invention is to provide a heating system having a ceramic heater and a supporting member supporting the back face of the heater, so that the cost of the supporting member can be reduced, the design change of the heater is made easier and excellent flatness of the heating face on use can be maintained. The heating system has a ceramic substrate 1 having a heating face 1a and a back face 1b, a heating means 4 for generating heat from the heating face 1a of the substrate 1, a metal supporting member 6 supporting The back face 1b of the substrate 1, and a heat insulating plate 5 provided between the back face 1b of the substrate 1 and the supporting member 6.

Owner:NGK INSULATORS LTD

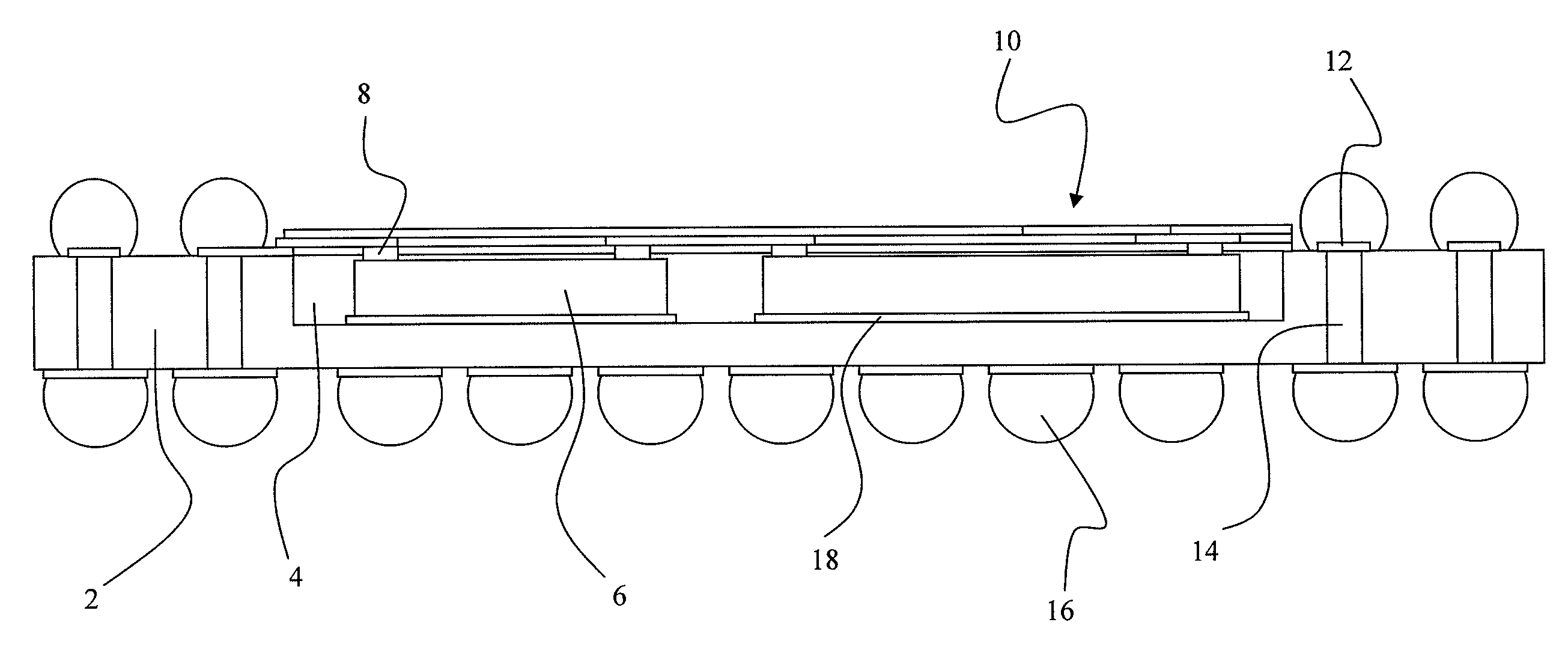

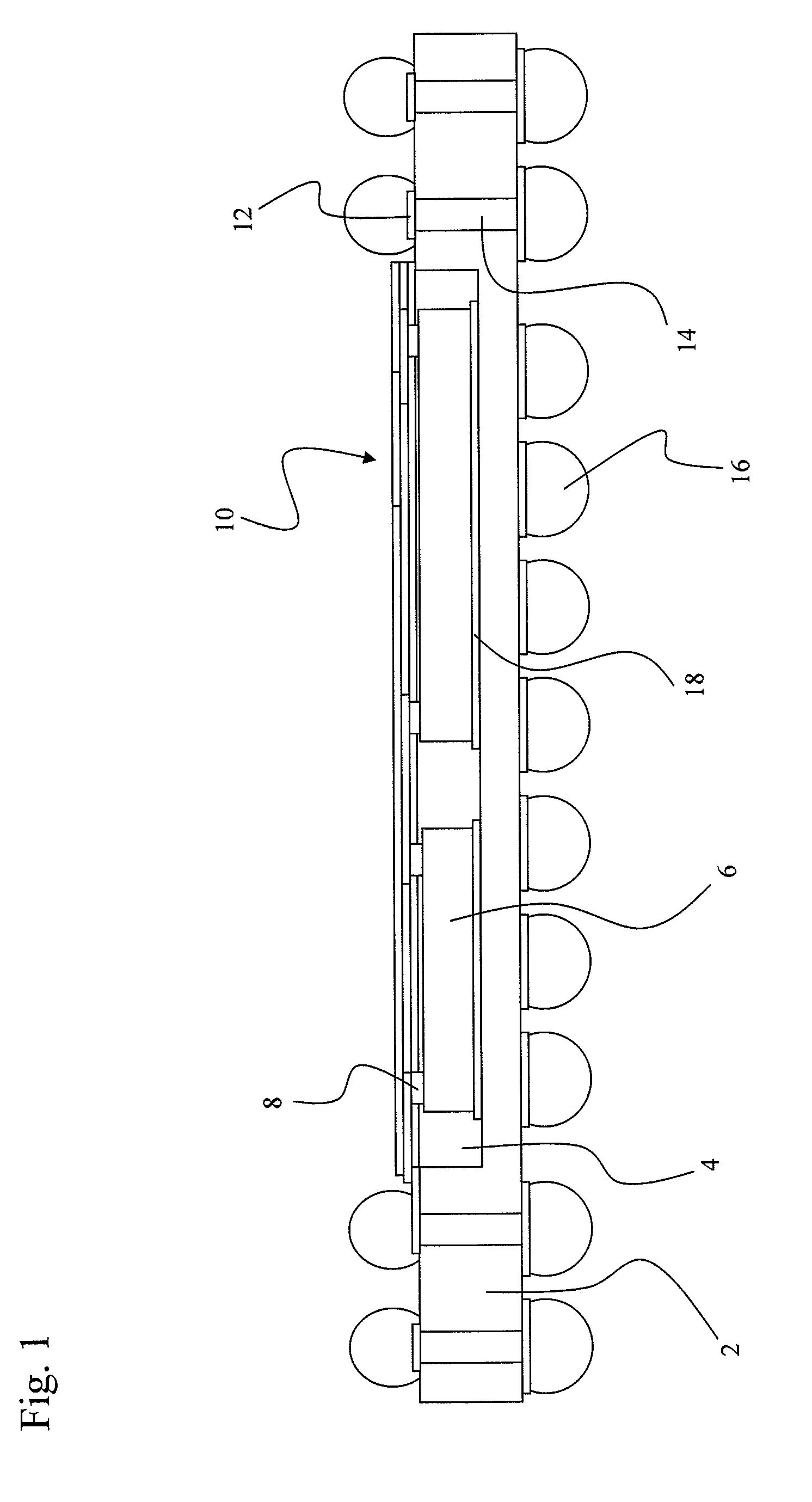

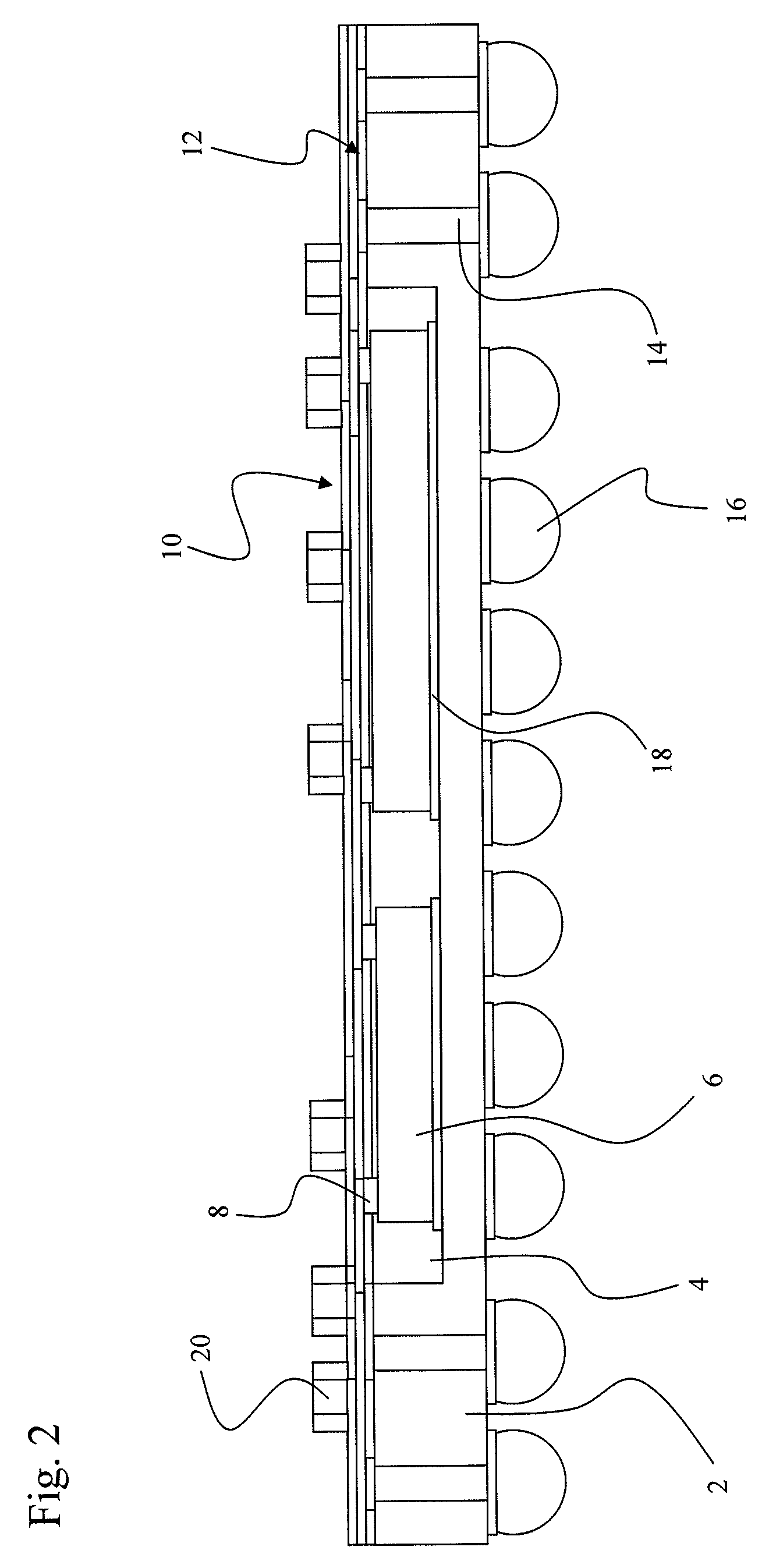

Electronics Package And Manufacturing Method Thereof

InactiveUS20080186690A1Lose weightSmall sizePrinted circuit assemblingSemiconductor/solid-state device detailsShell moldingEngineering

A method for manufacturing an electronics package is provided that comprises forming at least one module block by providing a carrier substrate having a recess, placing at least one electronic component die in said recess, filling said recess with a molding material, and depositing a circuit layer connected with said at least one component die. It further provides an electronics package, comprising a carrier substrate having a recess, at least one electronic component die placed in said recess, a molding material filling said recess, and a circuit layer connected with said at least one component die.

Owner:NOKIA CORP

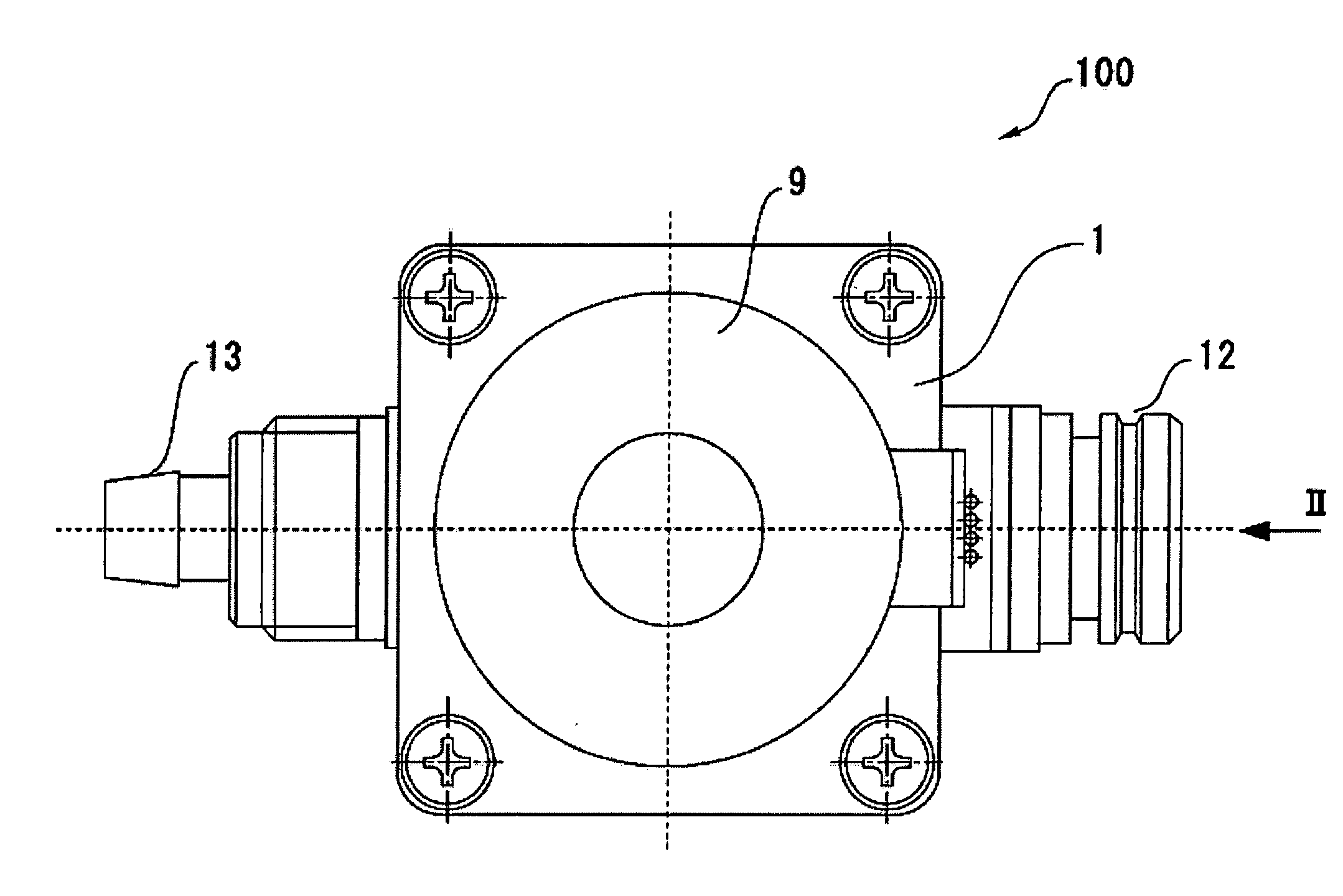

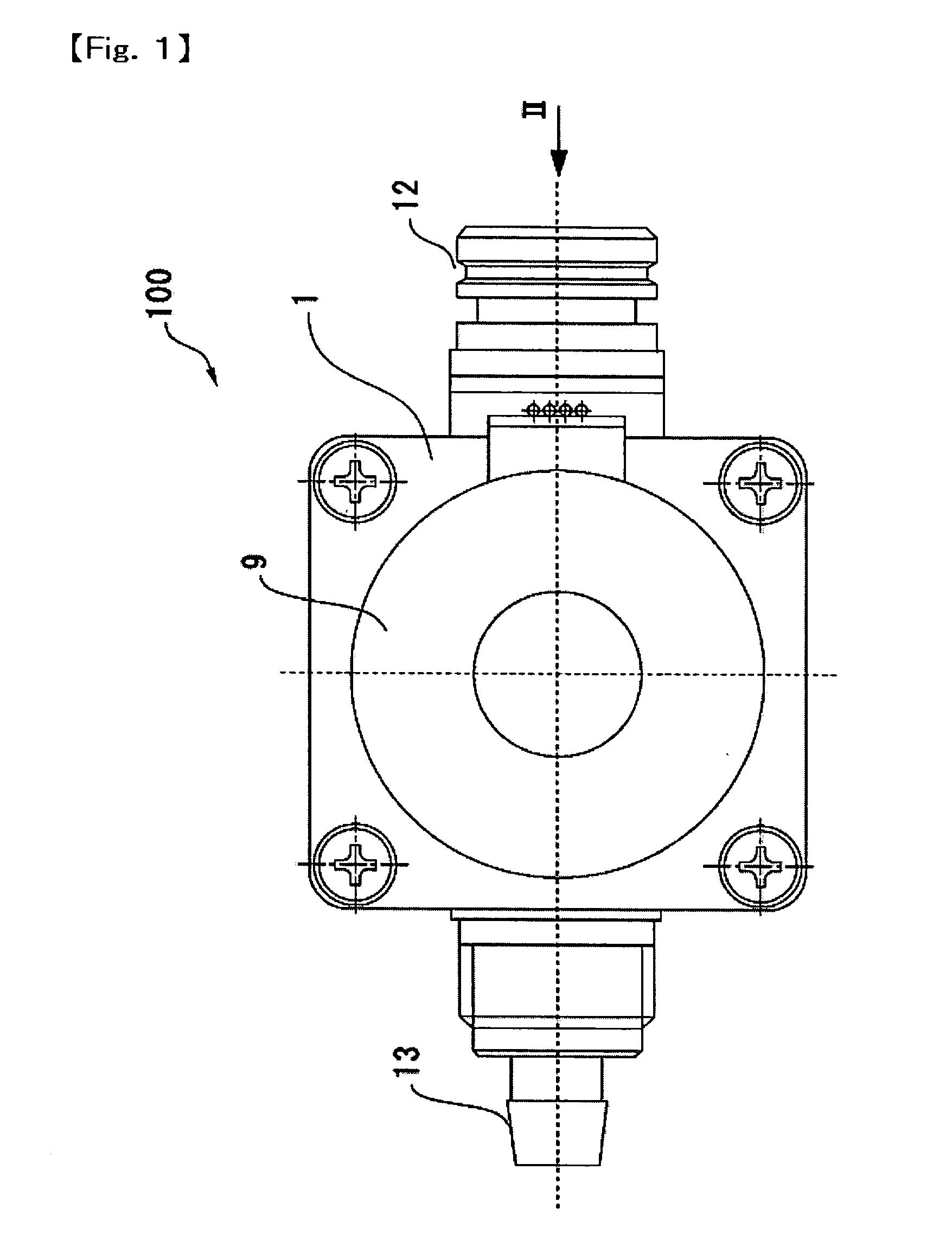

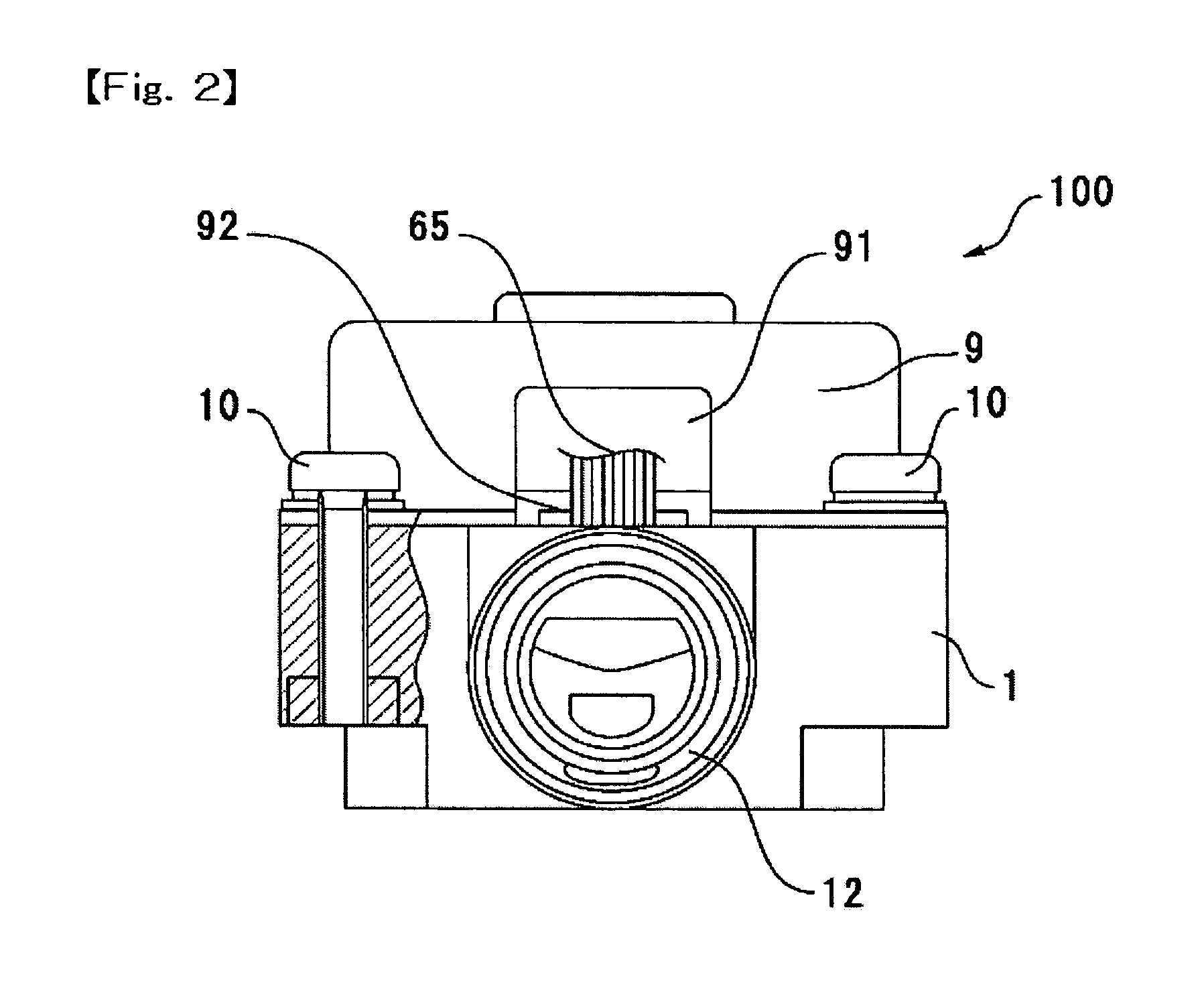

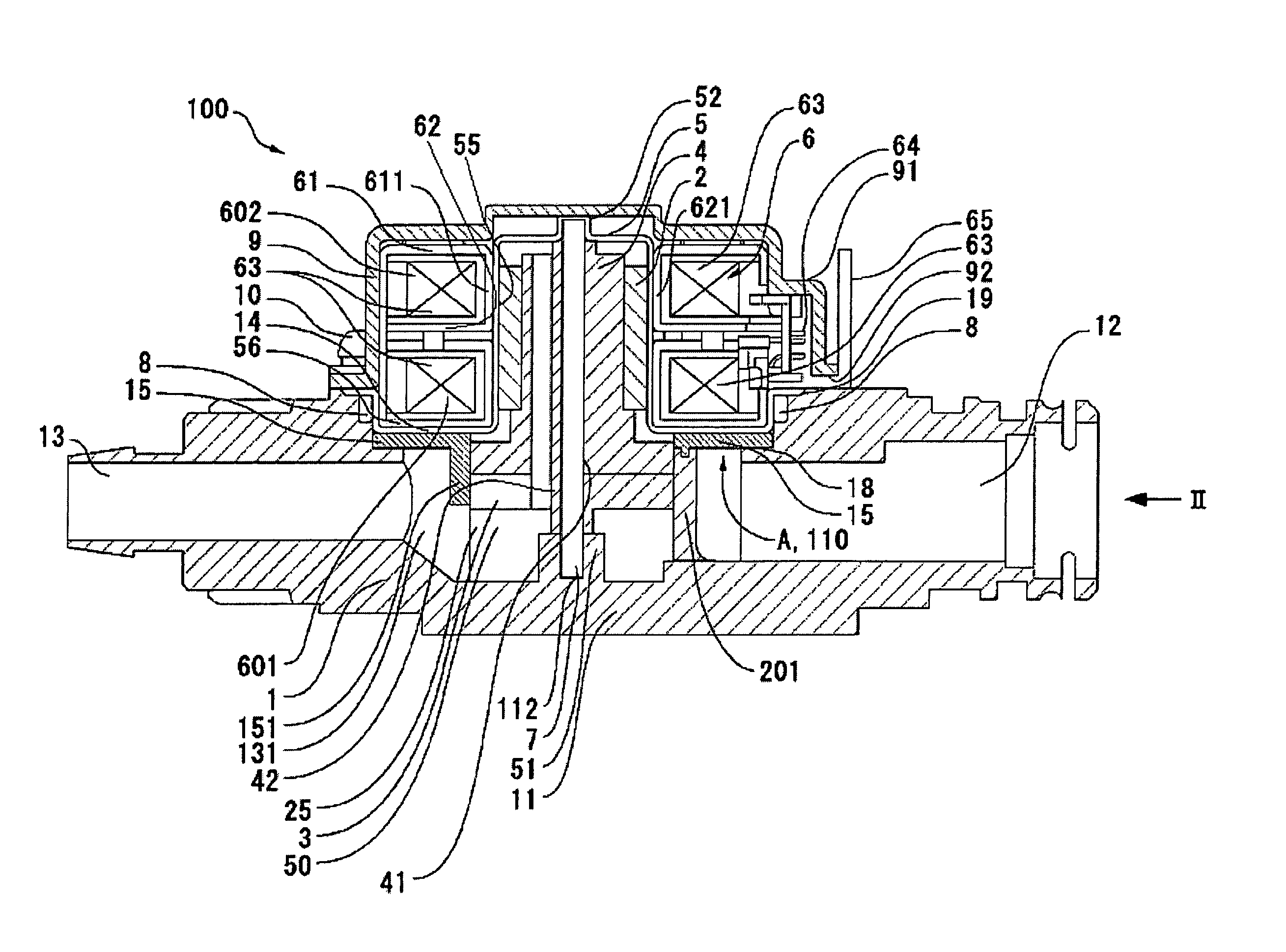

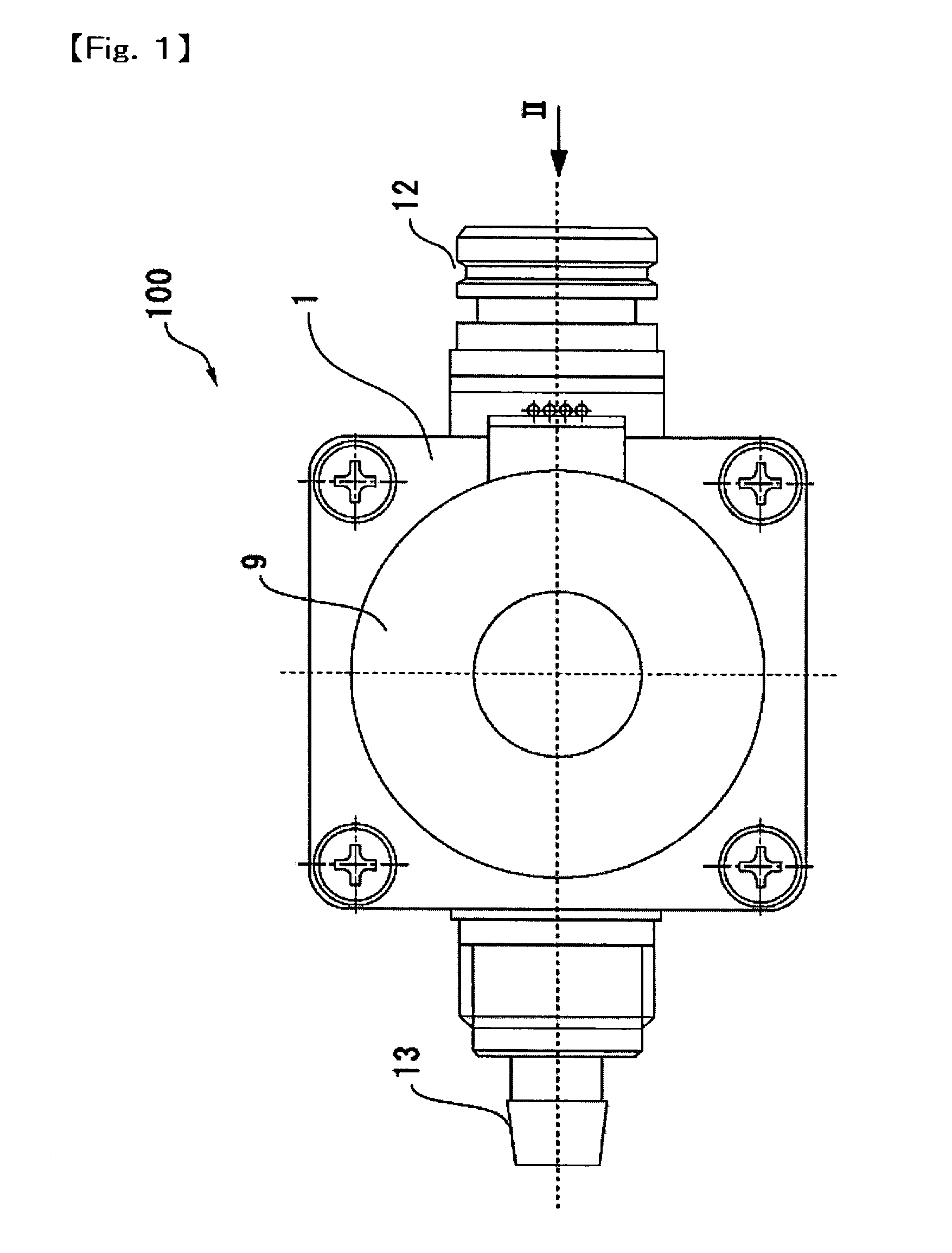

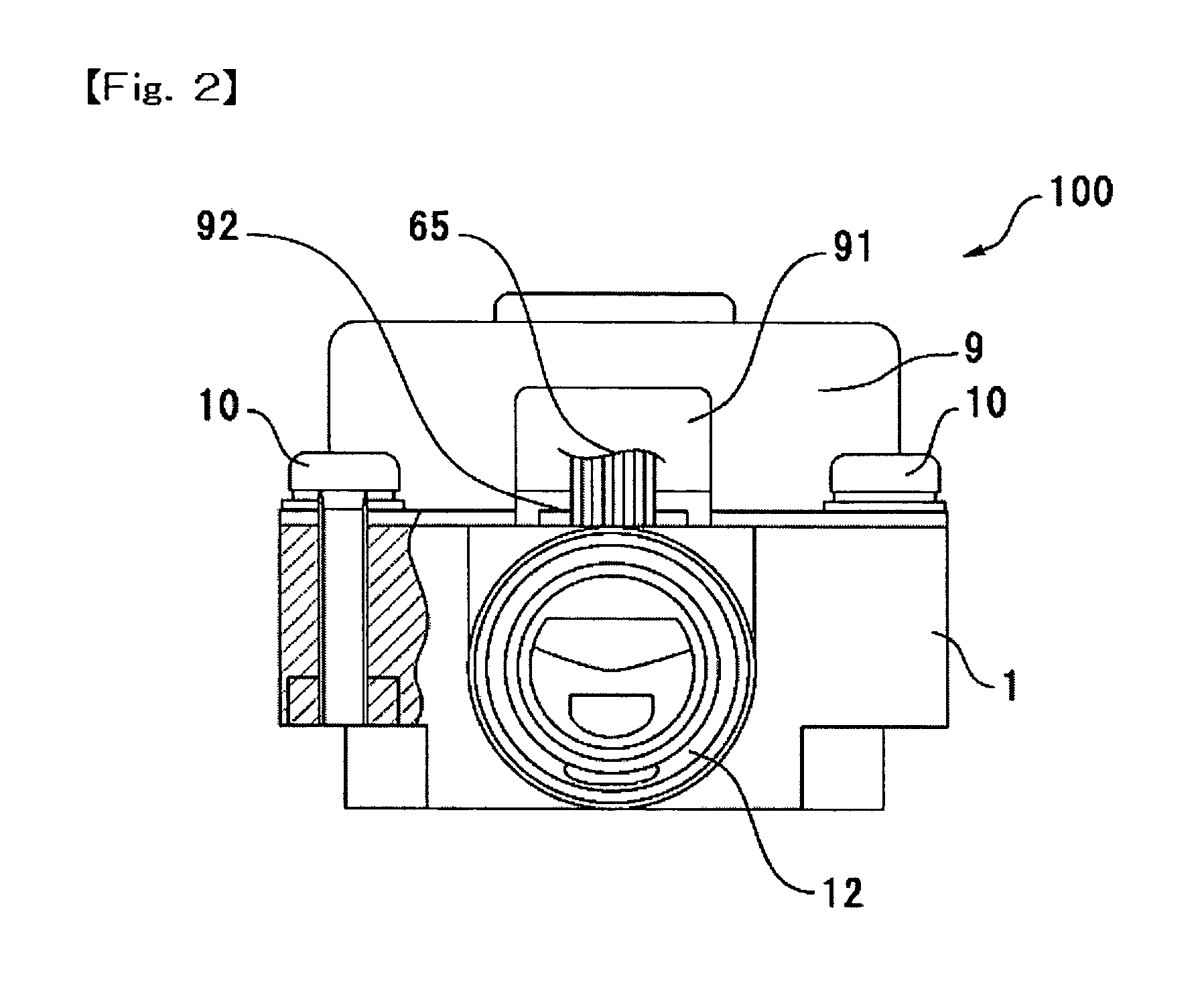

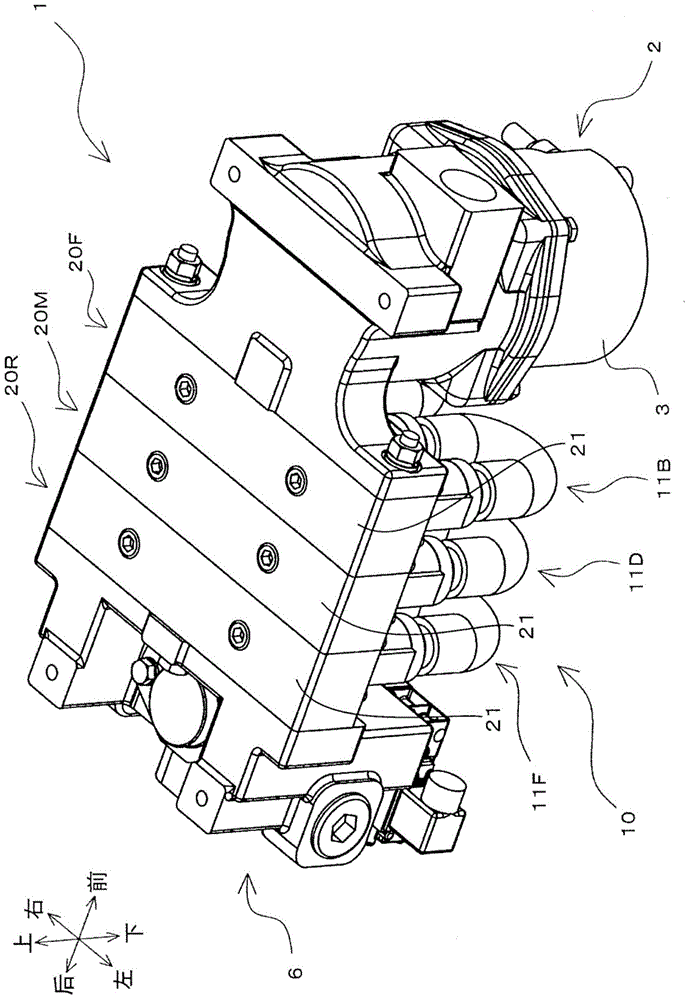

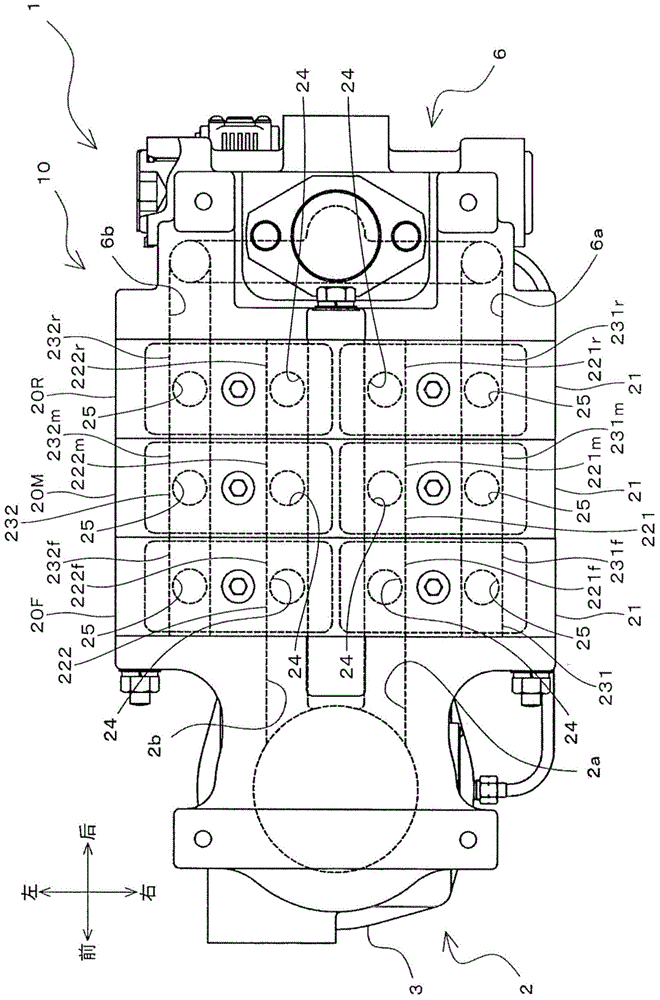

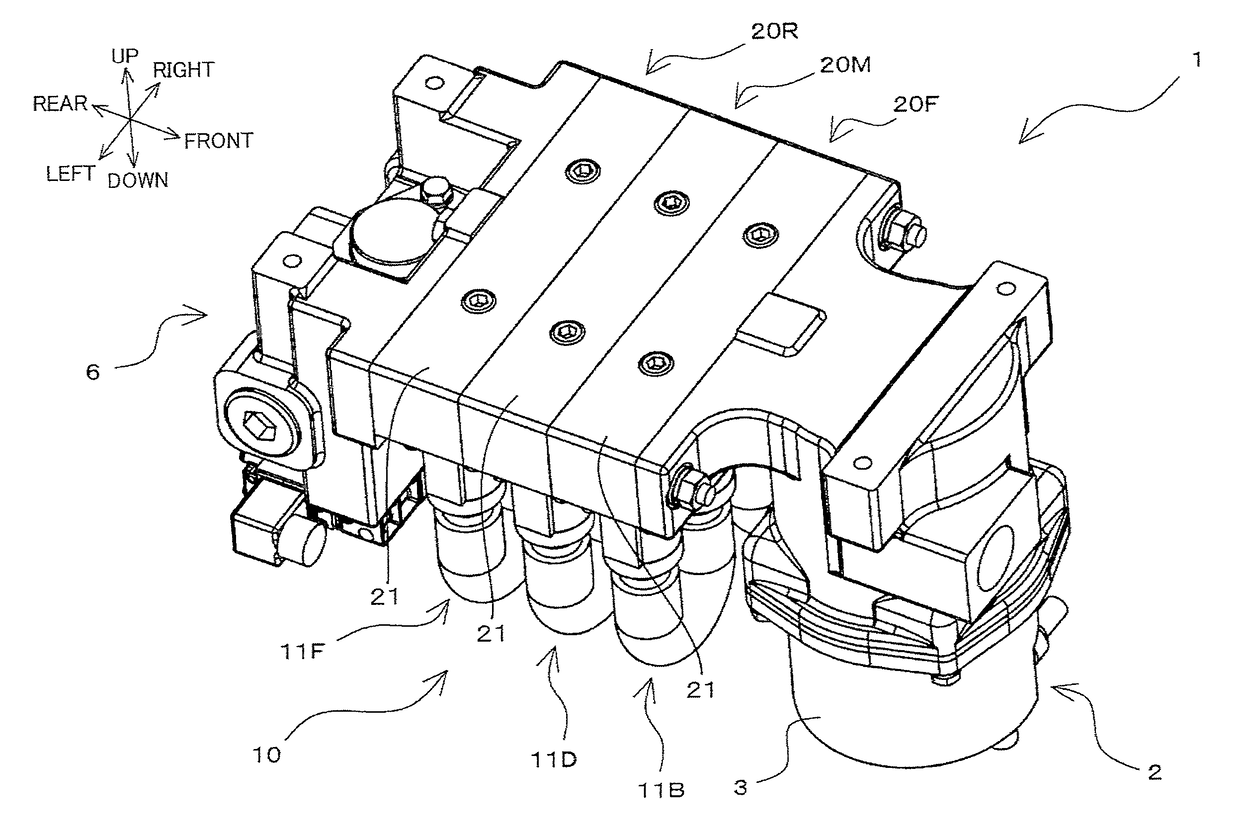

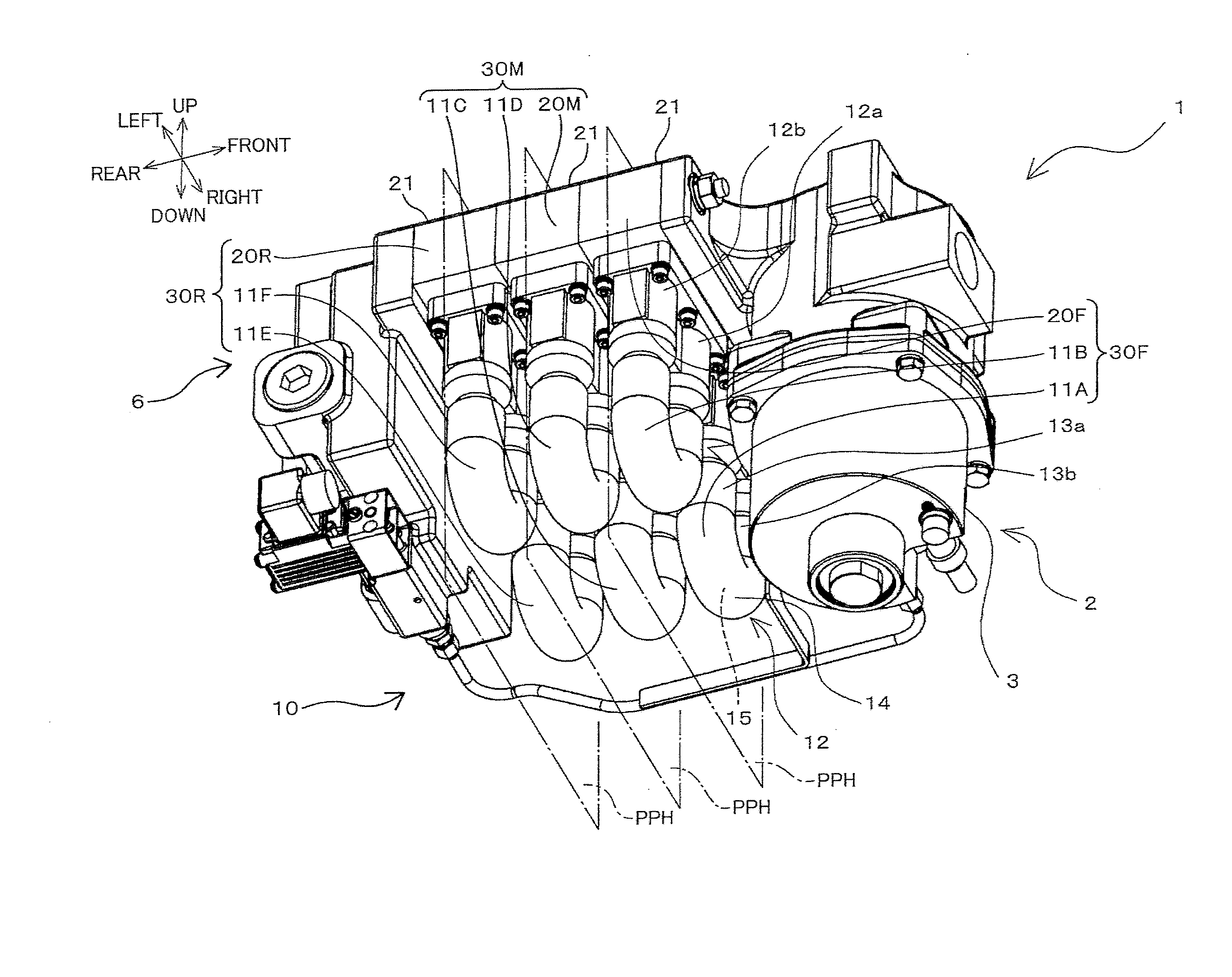

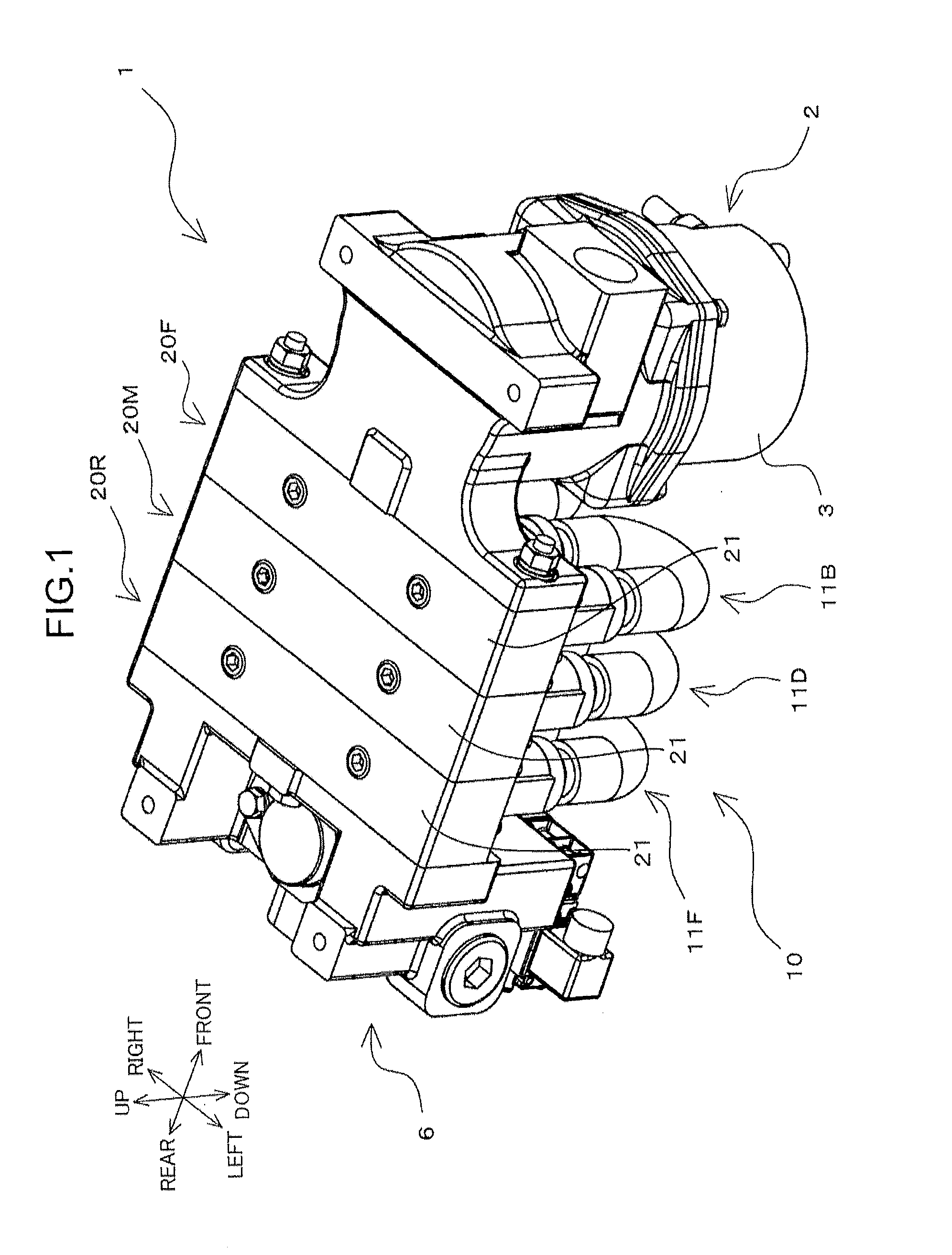

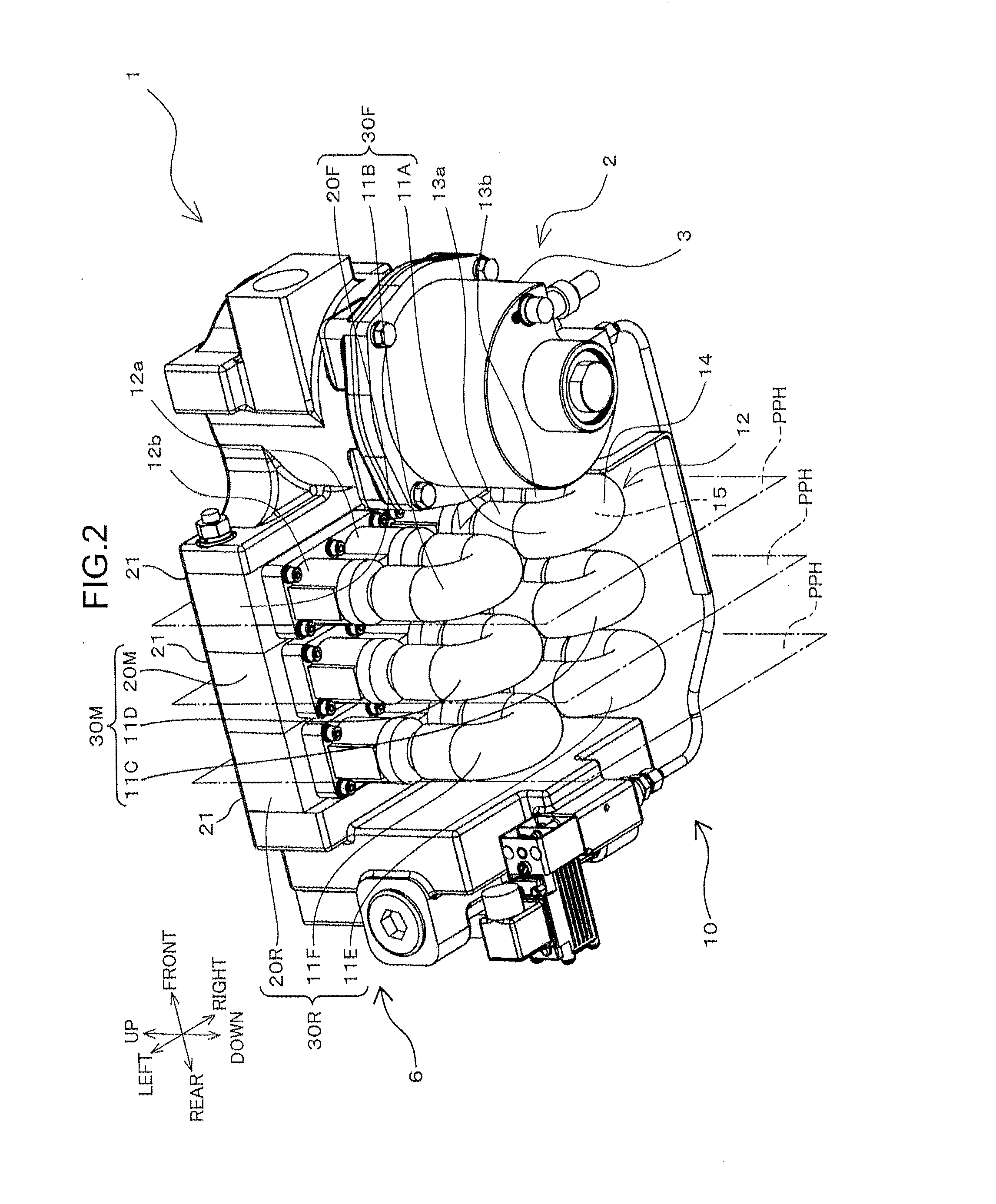

Hydraulic power generating device

A hydraulic power generating device includes a main body case forming a flow passage provided with a water wheel chamber between a fluid inlet port and a fluid outlet port, a cover covering the main body case, a water wheel for power generation disposed in the water wheel chamber, a rotor magnet for rotating in cooperation with the water wheel. An ejection port including a groove is formed on the main body case for ejecting fluid toward the blades of the water wheel at a high speed and an protrusion part is formed on the cover for adjusting the aperture area of the ejection port by entering into the groove. Further, a discharge space is formed at a downstream position of the water wheel chamber so as to be in communication with the fluid outlet port, to which fluid after having rotated the water wheel is ejected and a stagnation preventing protrusion part is formed in the discharge space to facilitate flow of air bubbles to the fluid outlet port.

Owner:SANKYO SEIKI MFG CO LTD

Hydraulic power generating device

A hydraulic power generating device includes a main body case forming a flow passage provided with a water wheel chamber between a fluid inlet port and a fluid outlet port, a cover covering the main body case, a water wheel for power generation disposed in the water wheel chamber, a rotor magnet for rotating in cooperation with the water wheel. An ejection port including a groove is formed on the main body case for ejecting fluid toward the blades of the water wheel at a high speed and an protrusion part is formed on the cover for adjusting the aperture area of the ejection port by entering into the groove. Further, a discharge space is formed at a downstream position of the water wheel chamber so as to be in communication with the fluid outlet port, to which fluid after having rotated the water wheel is ejected and a stagnation preventing protrusion part is formed in the discharge space to facilitate flow of air bubbles to the fluid outlet port.

Owner:SANKYO SEIKI MFG CO LTD

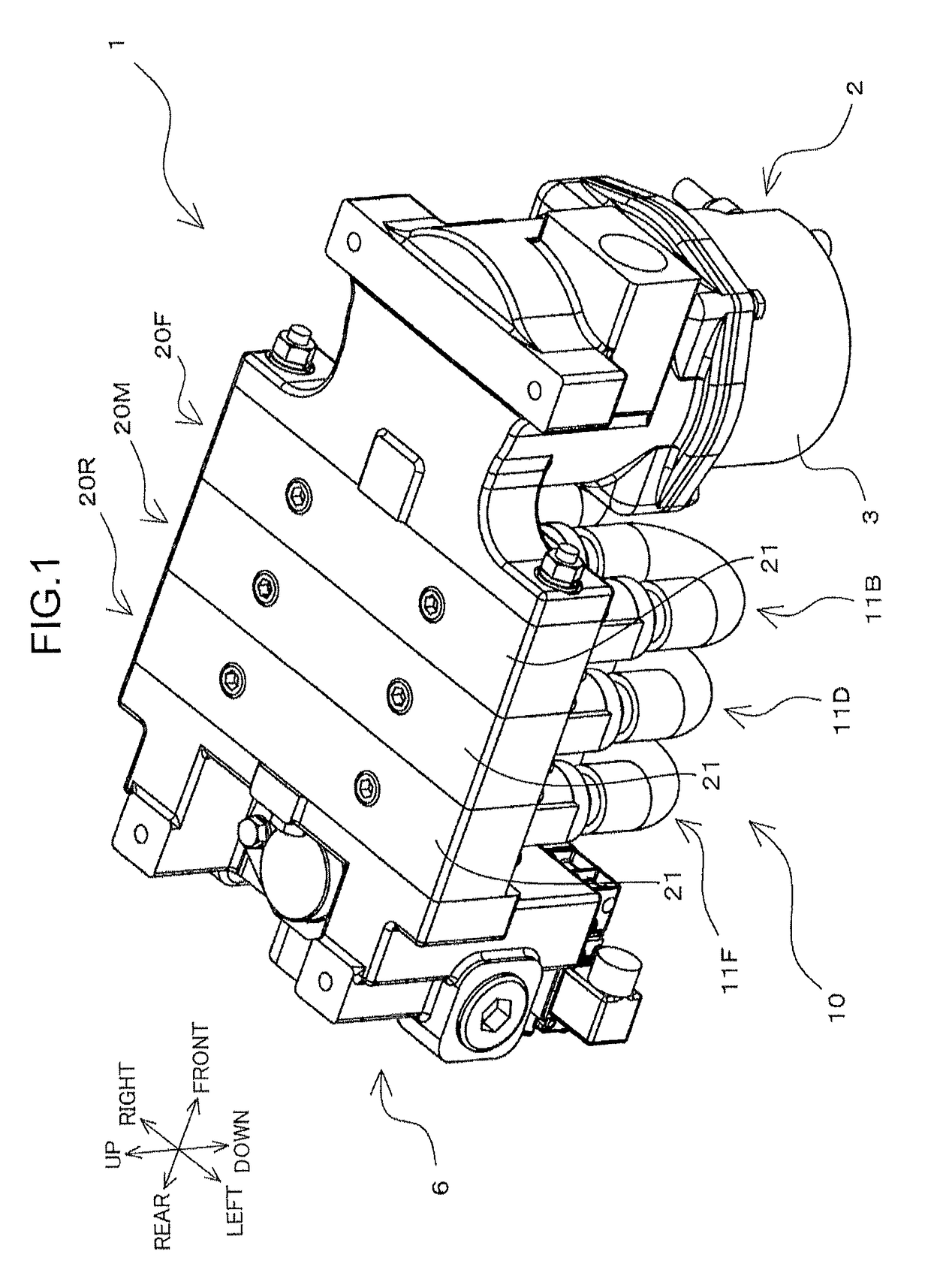

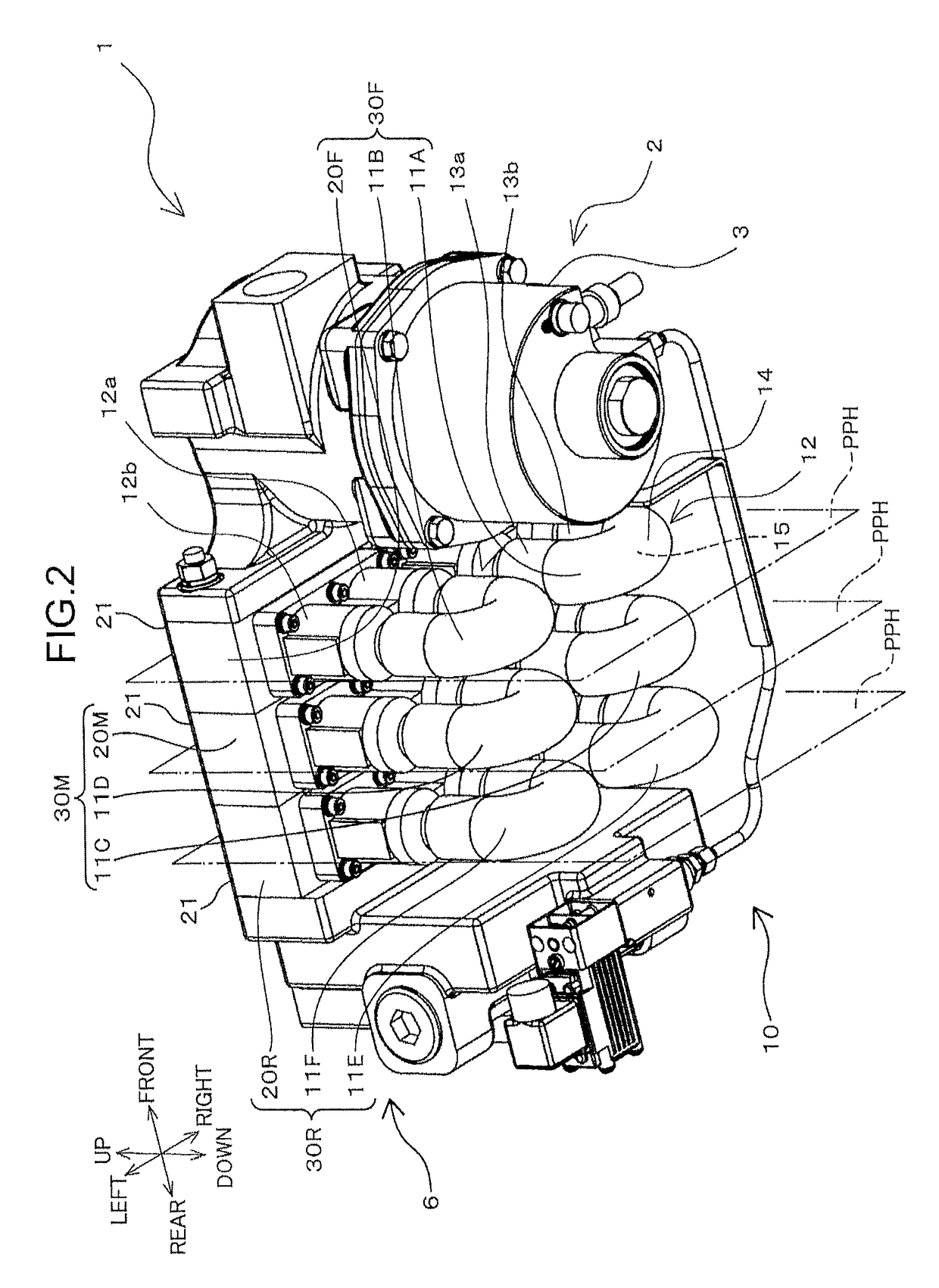

Vehicle heater

ActiveUS20150043898A1Easy to manufactureImprove the heating effectAir-treating devicesAir heatersEngineeringMechanical engineering

Owner:HANON SYST

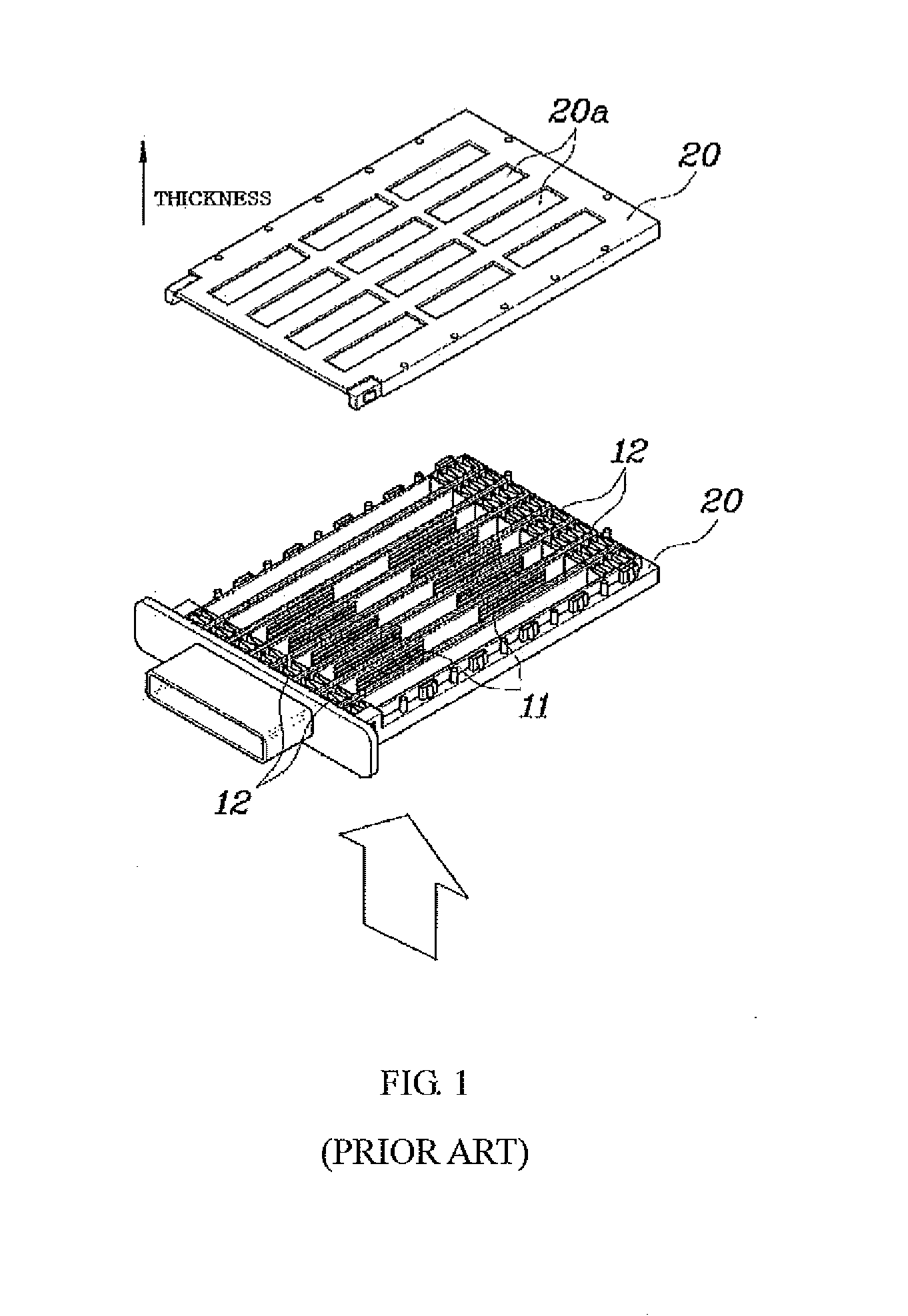

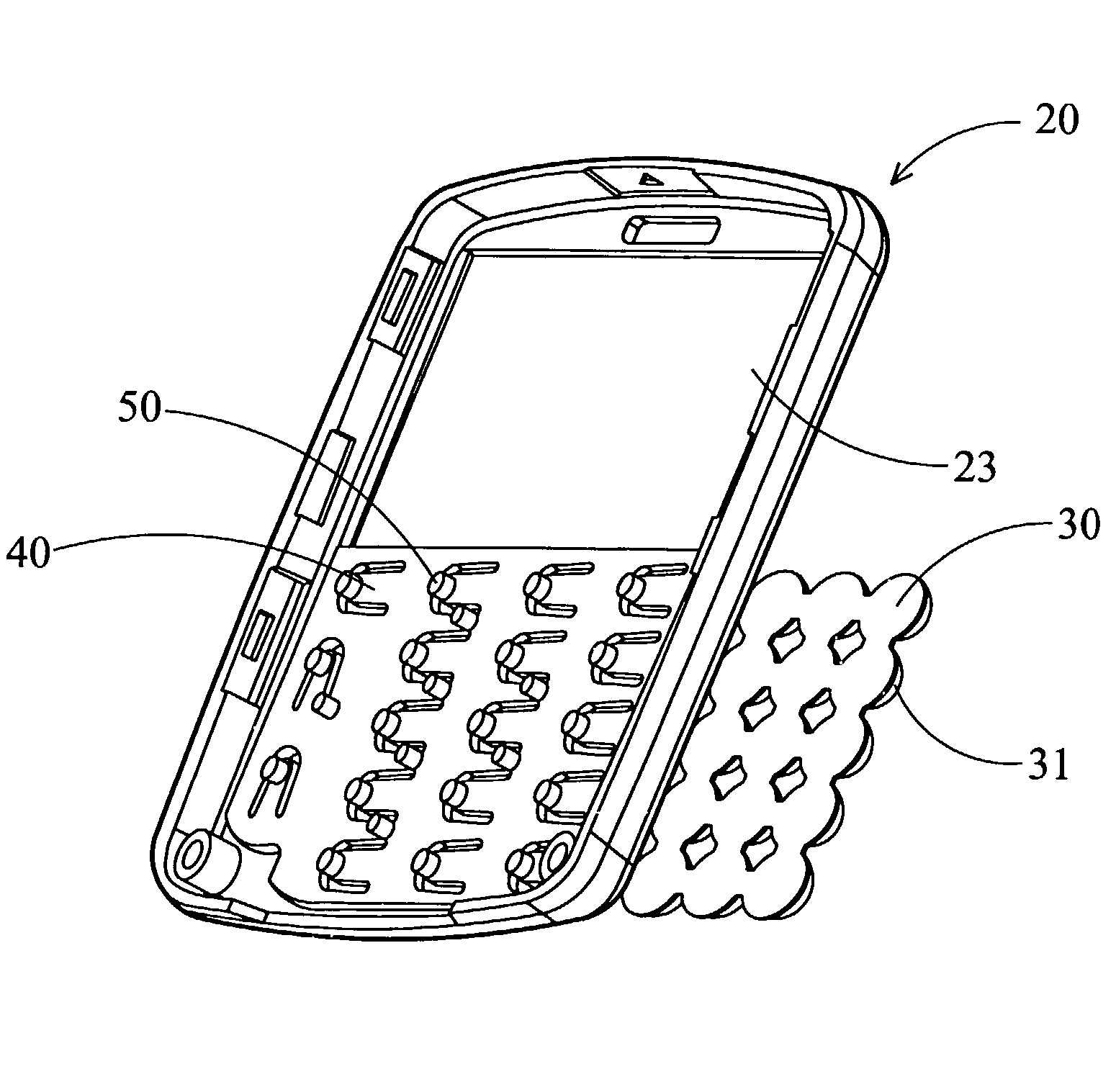

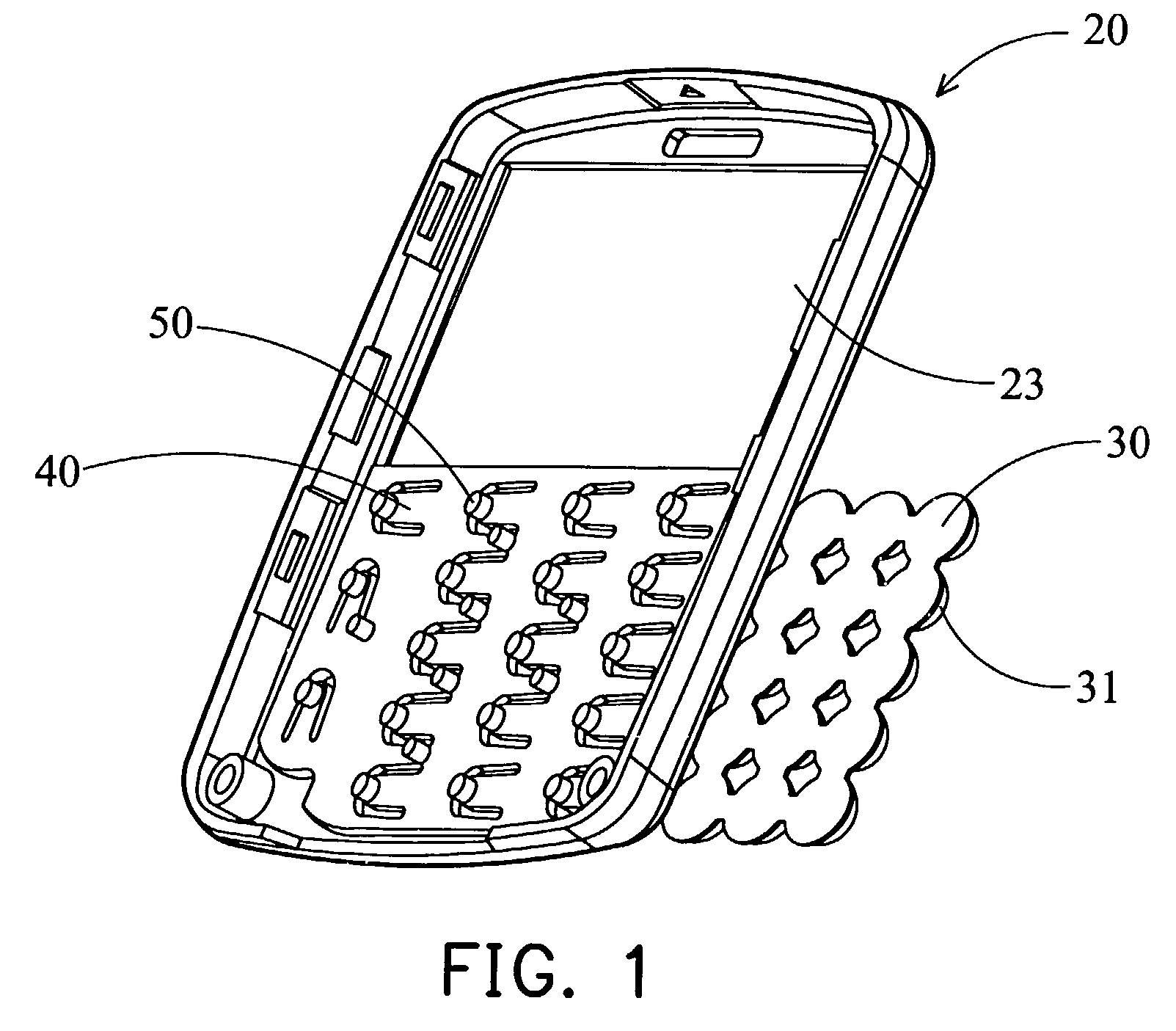

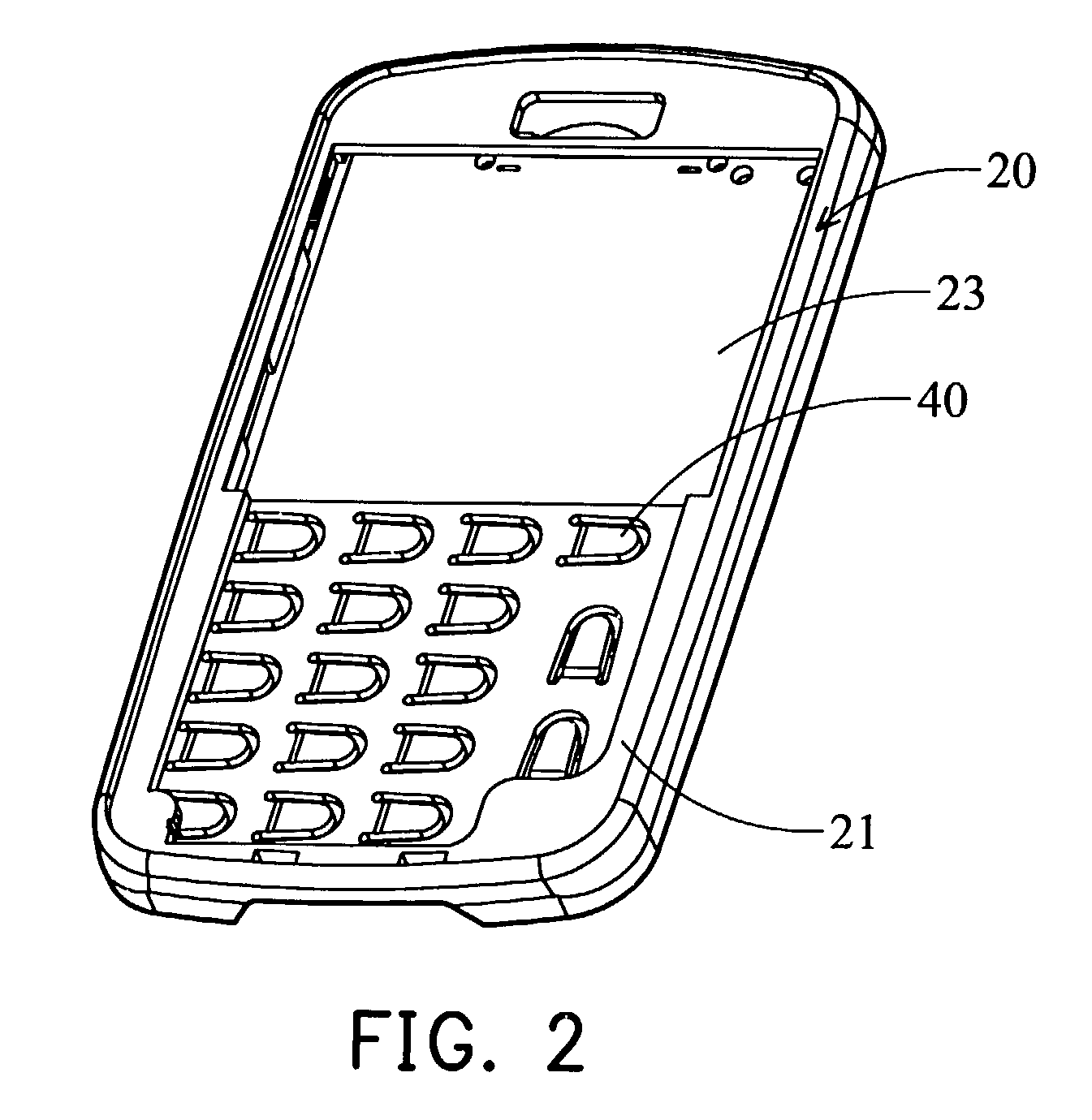

Keypad structure

InactiveUS7228111B2Simple structureReduce manufacturing costEmergency actuatorsInterconnection arrangementsCantileverMobile phone

A keypad structure. A mobile phone has a casing and an elastic sheet. The casing includes a plurality of resilient cantilever arms and a plurality of protrusions formed on the plurality of resilient cantilever arms. The elastic sheet includes a plurality of keypad buttons to press the plurality of resilient cantilever arms.

Owner:QUANTA COMPUTER INC

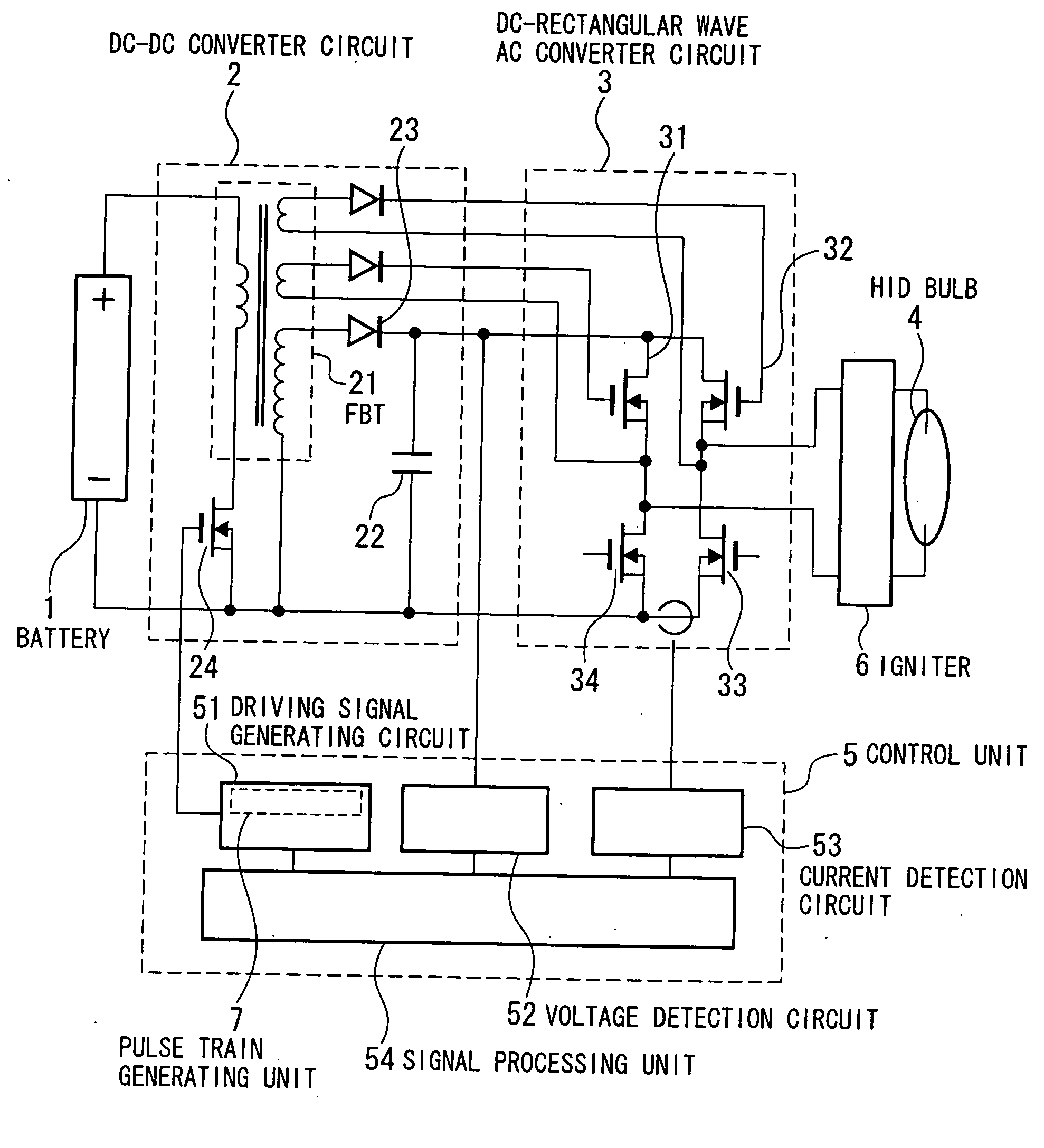

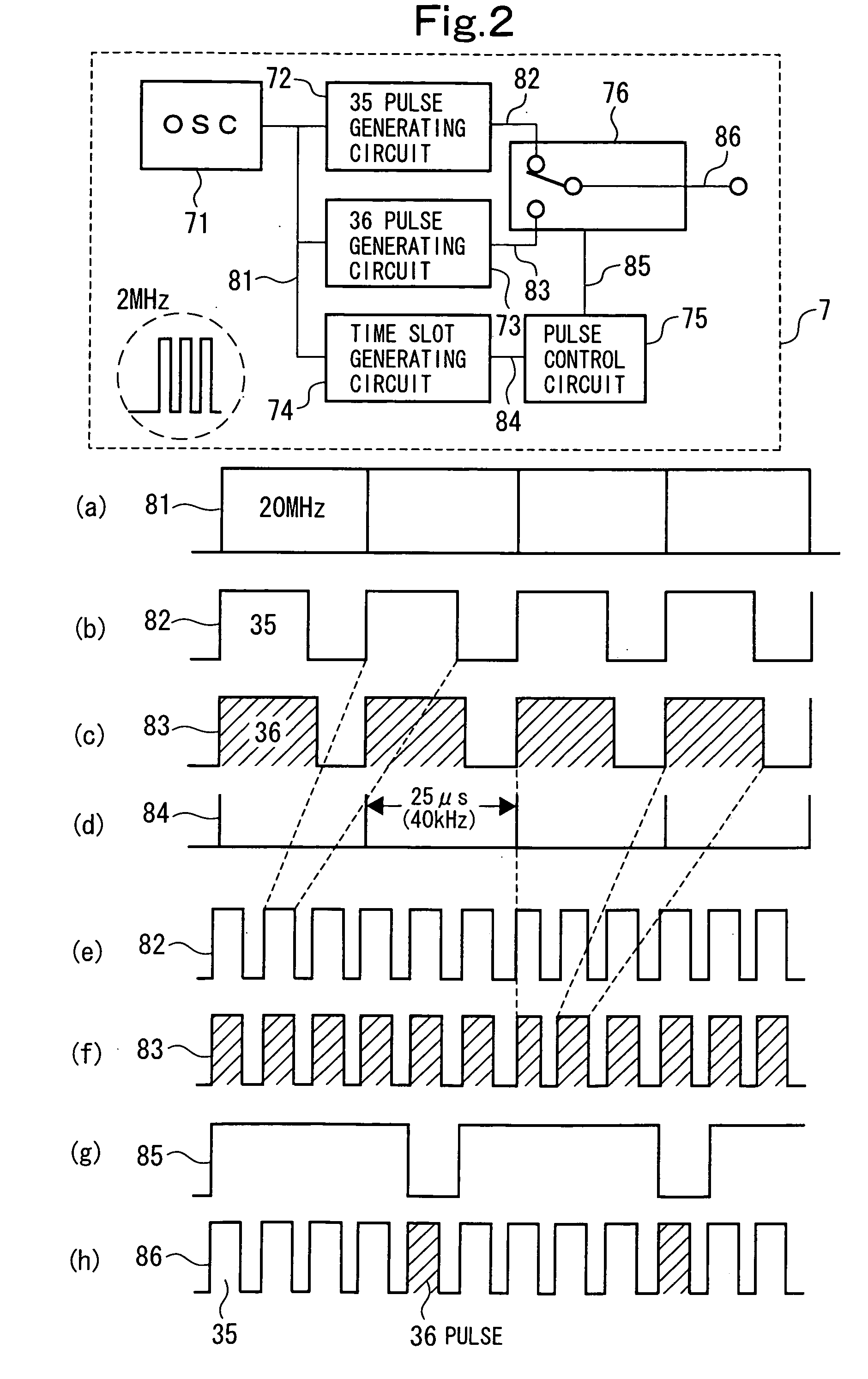

Control device for high intensity discharge bulb and method of controlling high intensity discharge bulb

InactiveUS20060208664A1Error minimizationGuaranteed uptimeElectrical apparatusElectric light circuit arrangementEngineeringHigh intensity

Two types of rectangular waves having different numbers of driving pulses are applied to the HID bulb. By changing the combination of these two different types of rectangular waves to be supplied , the driving energy of the HID bulb is increased or decreased, thereby supply electric energy to the HID bulb is controlled accurately.

Owner:SANYO TECNICA

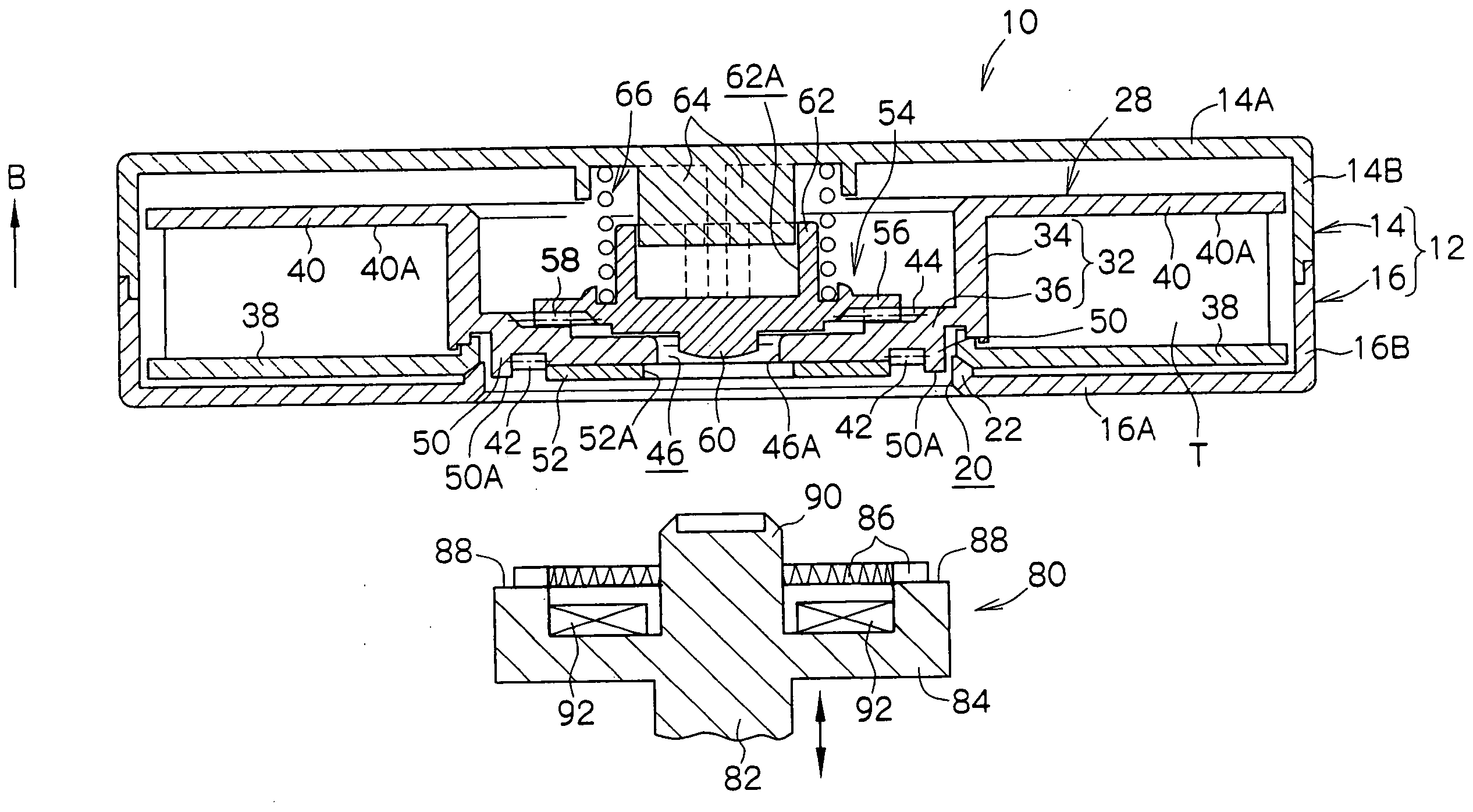

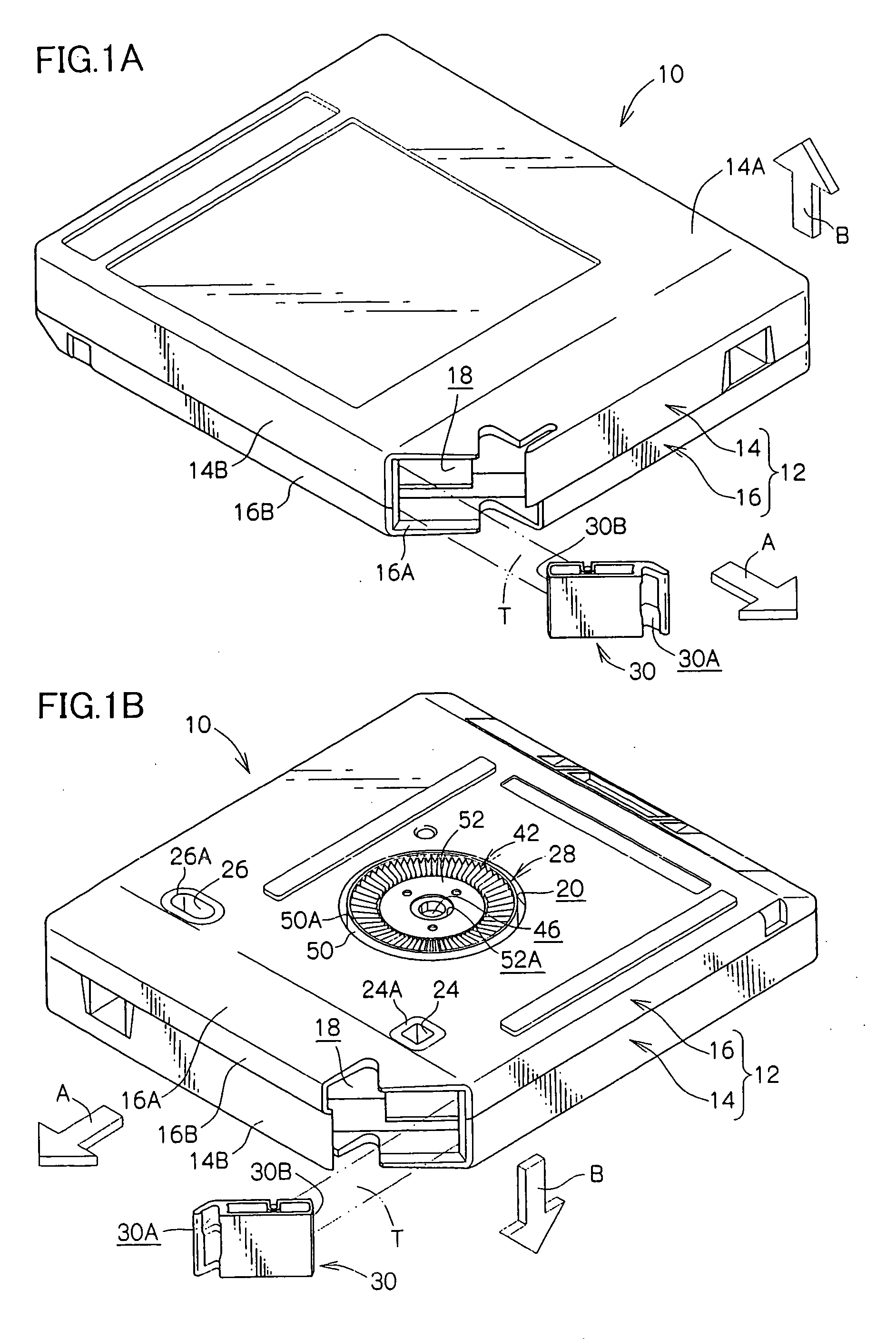

Reel, recording tape cartridge and method of manufacturing the reel

InactiveUS20050023397A1Simple designEasy Design ChangesPicture changing apparatusRecord information storageEngineeringMechanical engineering

A reel of a recording tape cartridge includes a reel hub formed in a bottomed cylindrical shape, an annular reel gear coaxially disposed at an outer surface of a bottom portion of the reel hub, and a through-hole the penetrates the axial center of the bottom portion and opens to an outer surface side of the bottom portion. The reel is resin-molded using a mold comprising a fixed mold, a movable mold and an insert. The reel gear and the through-hole are formed by a reel gear forming portion and a hole portion forming portion disposed in a single insert. As a result, the axial centers thereof are aligned with high precision.

Owner:FUJIFILM HLDG CORP +1

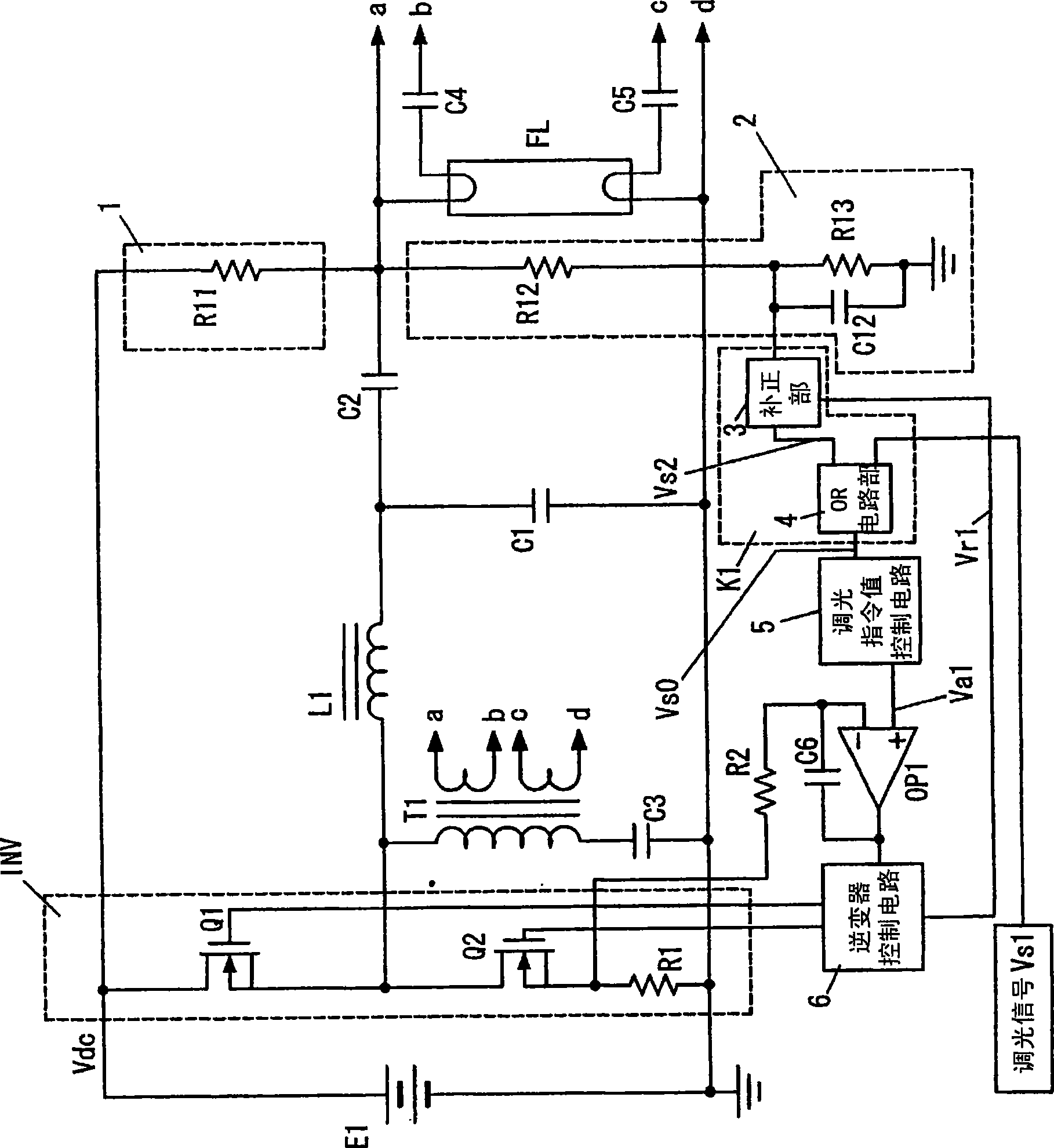

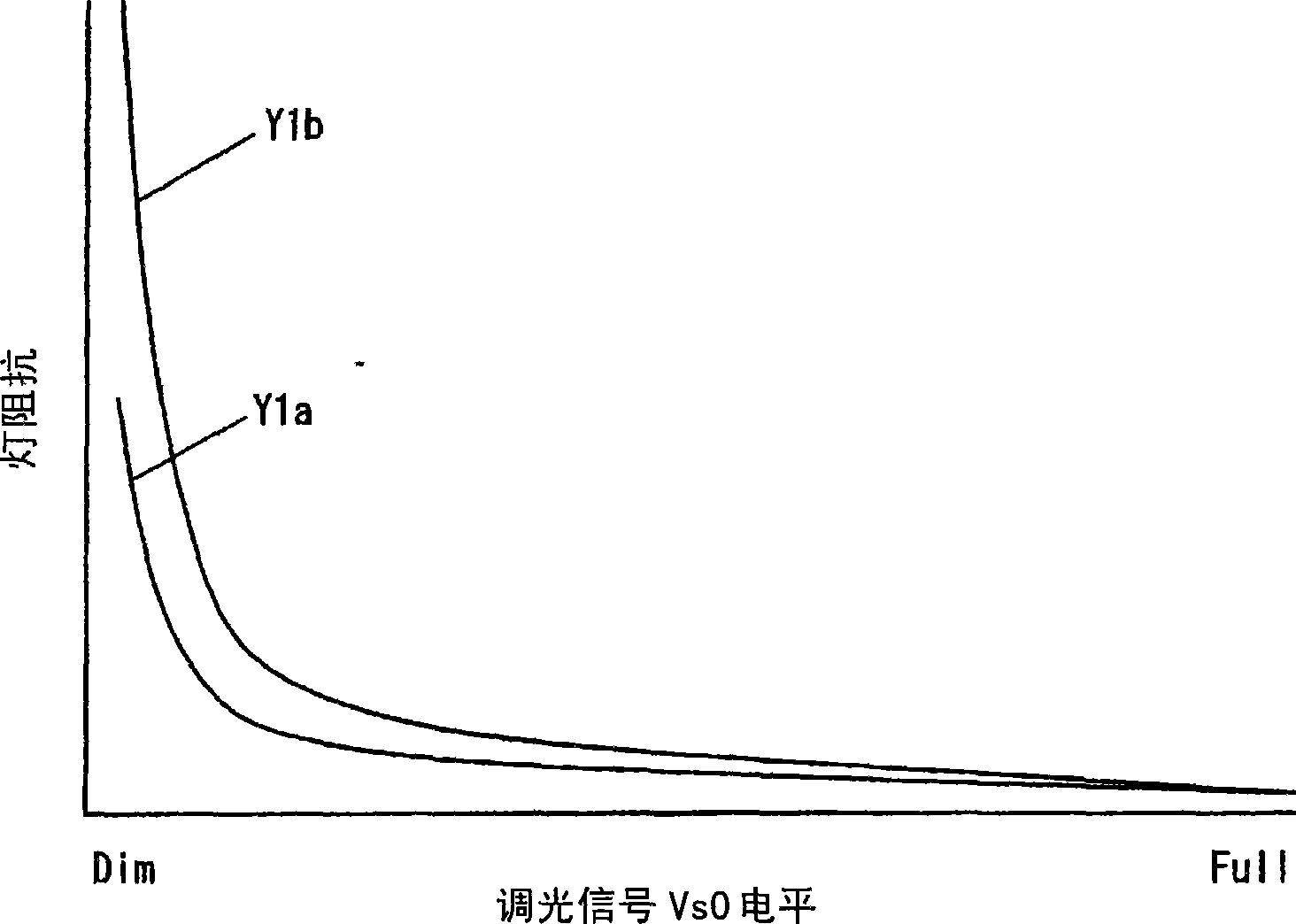

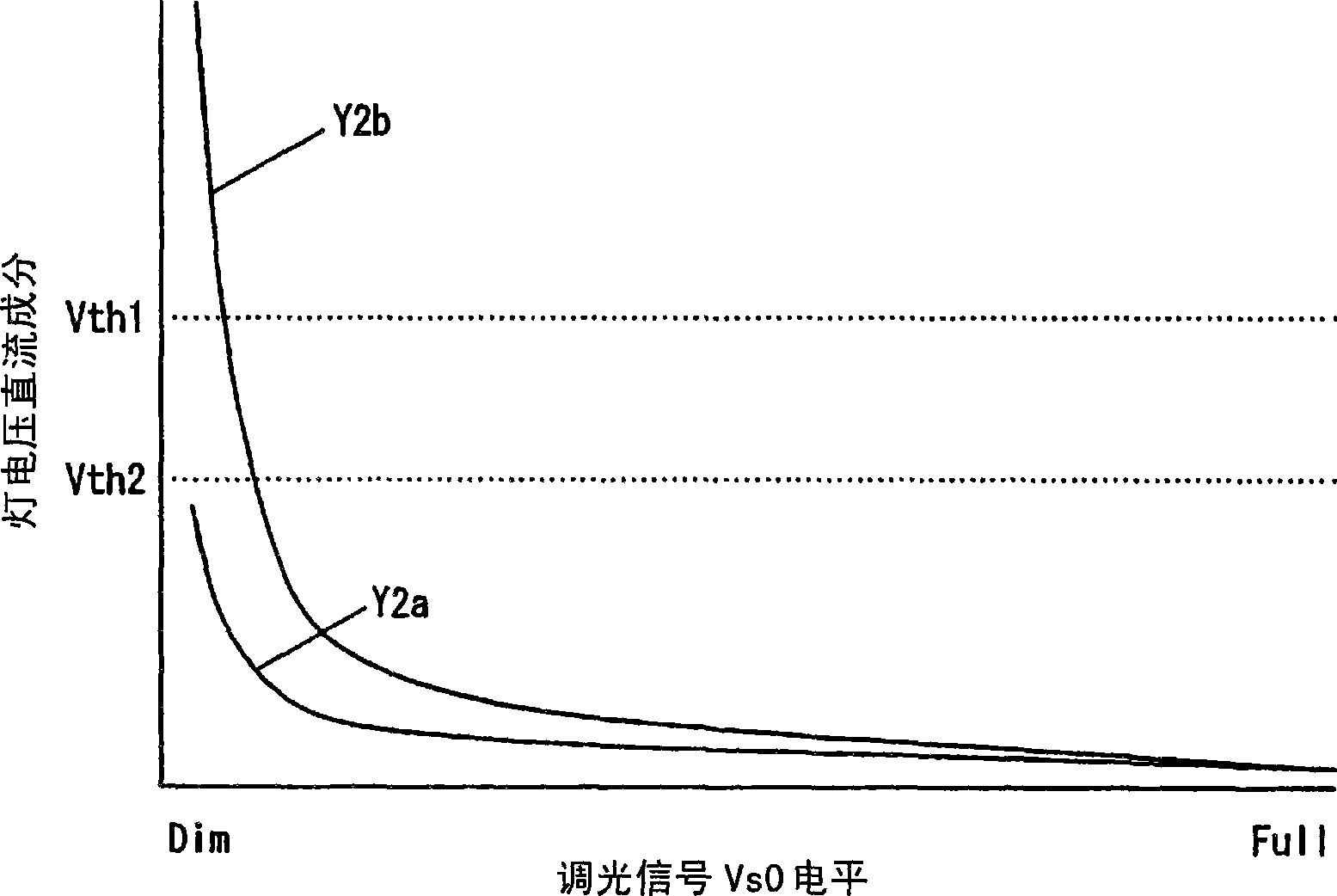

Discharge lamp operation device and illumination device

InactiveCN101513129ALow costSave installation spaceElectric lighting sourcesDc-ac conversion without reversalSignal correctionEffect light

In order to enhance stability of a discharge lamp at the time of dimming lighting even in the case where a light output is lowered, a direct current superimposing circuit 1 superimposes a direct current voltage on an alternating current voltage applied to a fluorescent lamp FL, and a dimming signal correction circuit K1 receives a detection value of a direct current voltage detection circuit 2 and a dimming signal Vs1 that is from an outside, outputs a dimming signal Vs0 higher in level than the dimming signal Vs1 in the case where the detection value of the direct current voltage detection circuit 2 exceeds a first threshold value Vth1, and decreases the level of the outputted dimming signal Vs0 to the level of the inputted dimming signal Vs1 in the case where the detection value of the direct current voltage detection circuit 2 falls down below a second threshold value Vth2 that is equal to or less than the first threshold value Vth1. Then, an amount of alternating current power supplied to the fluorescent lamp FL by an inverter circuit INV is increased and decreased in response to fluctuations of the level of the dimming signal Vs0 outputted by the dimming signal correction circuit K1, whereby the fluorescent lamp FL is dimmed.

Owner:PANASONIC CORP +1

Heating systems

ActiveUS7126093B2Easy to carryReduce manufacturing costSemiconductor/solid-state device manufacturingHot plates heating arrangementsEngineeringHeating system

An object of the present invention is to provide a heating system having a ceramic heater and a supporting member supporting the back face of the heater, so that the cost of the supporting member can be reduced, the design change of the heater is made easier and excellent flatness of the heating face on use can be maintained. The heating system has a ceramic substrate 1 having a heating face 1a and a back face 1b, a heating means 4 for generating heat from the heating face 1a of the substrate 1, a metal supporting member 6 supporting the back face 1b of the substrate 1, and a heat insulating plate 5 provided between the back face 1b of the substrate 1 and the supporting member 6.

Owner:NGK INSULATORS LTD

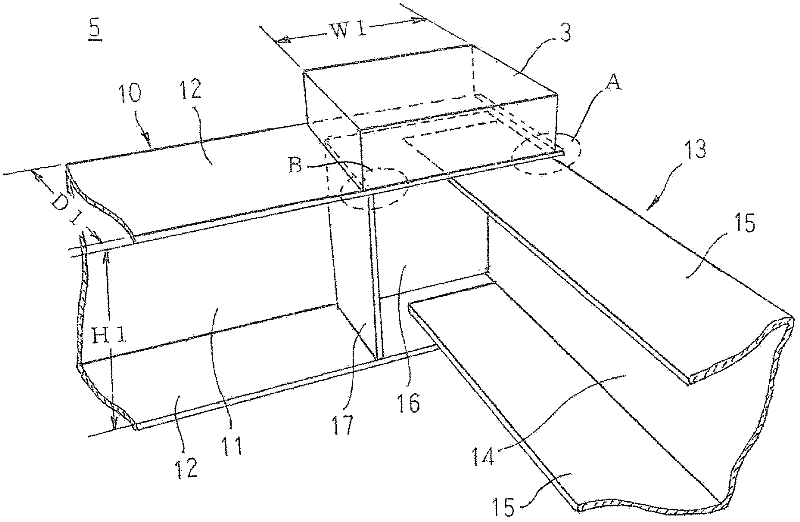

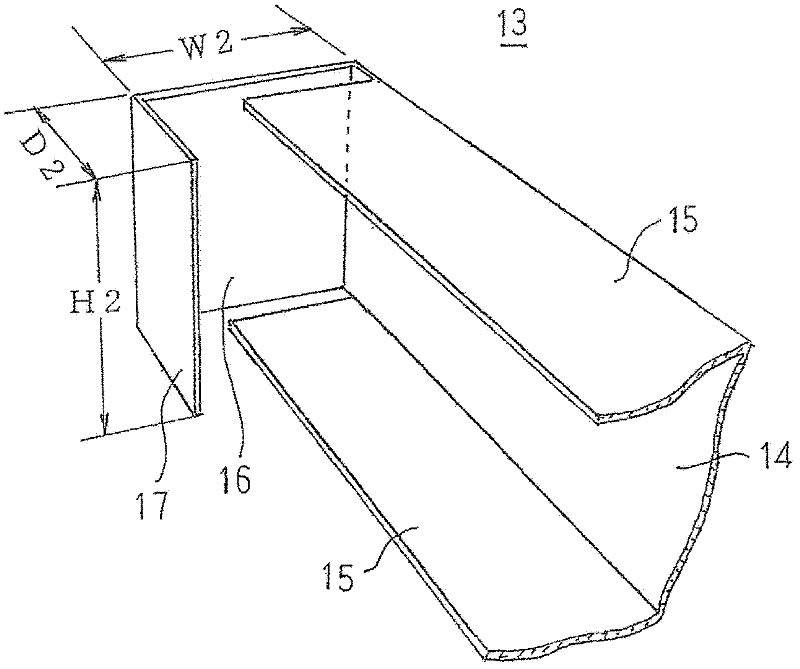

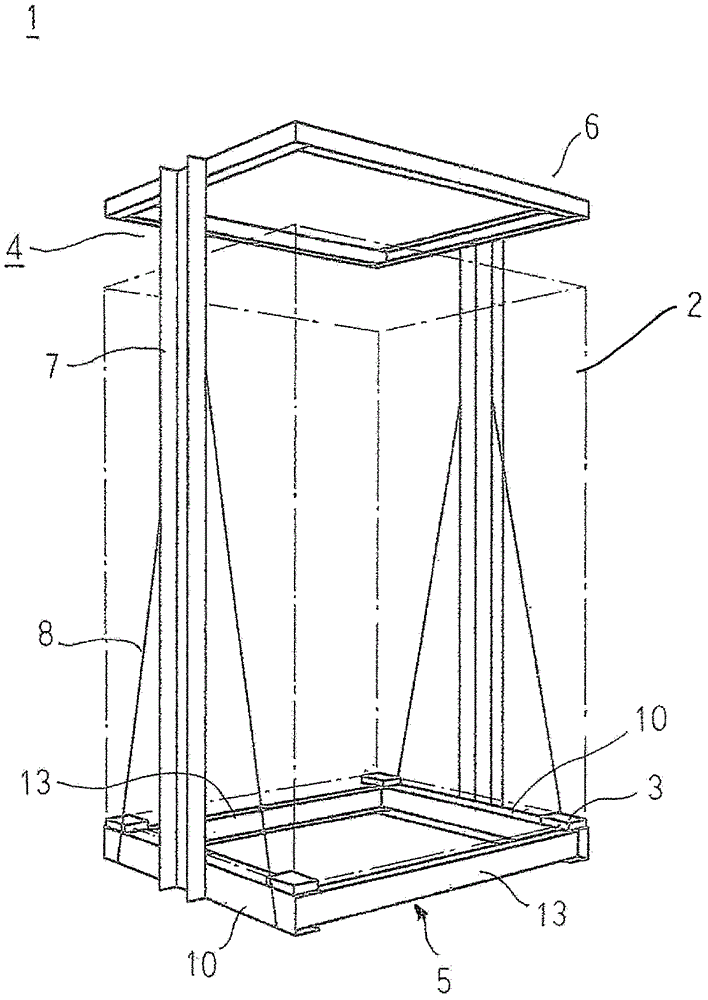

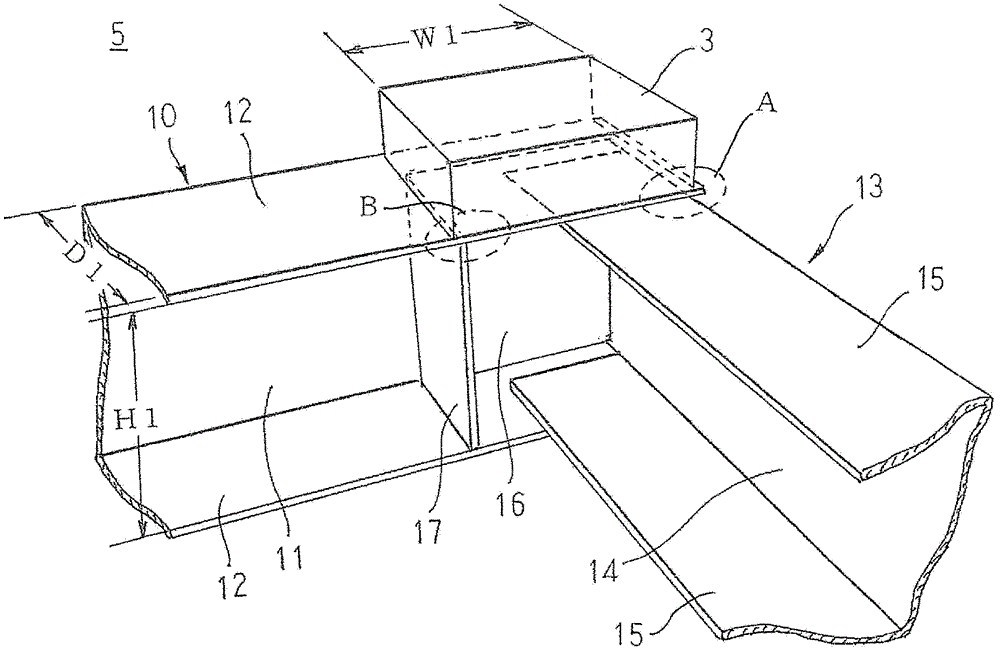

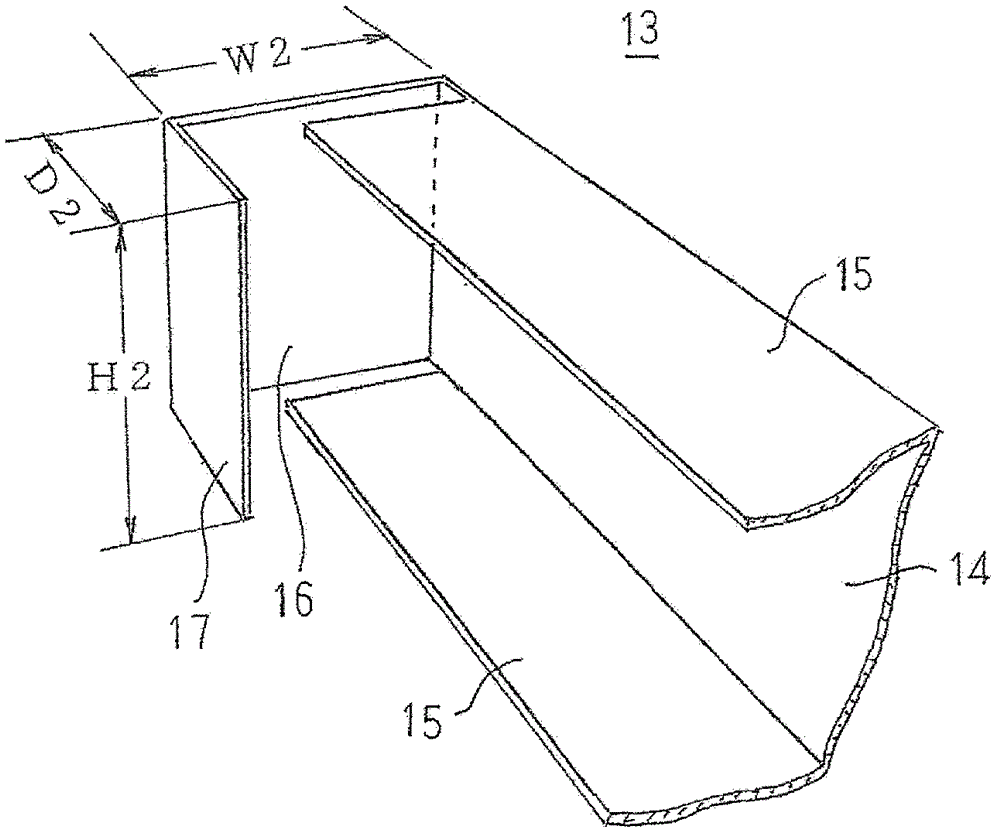

Elevator car frame

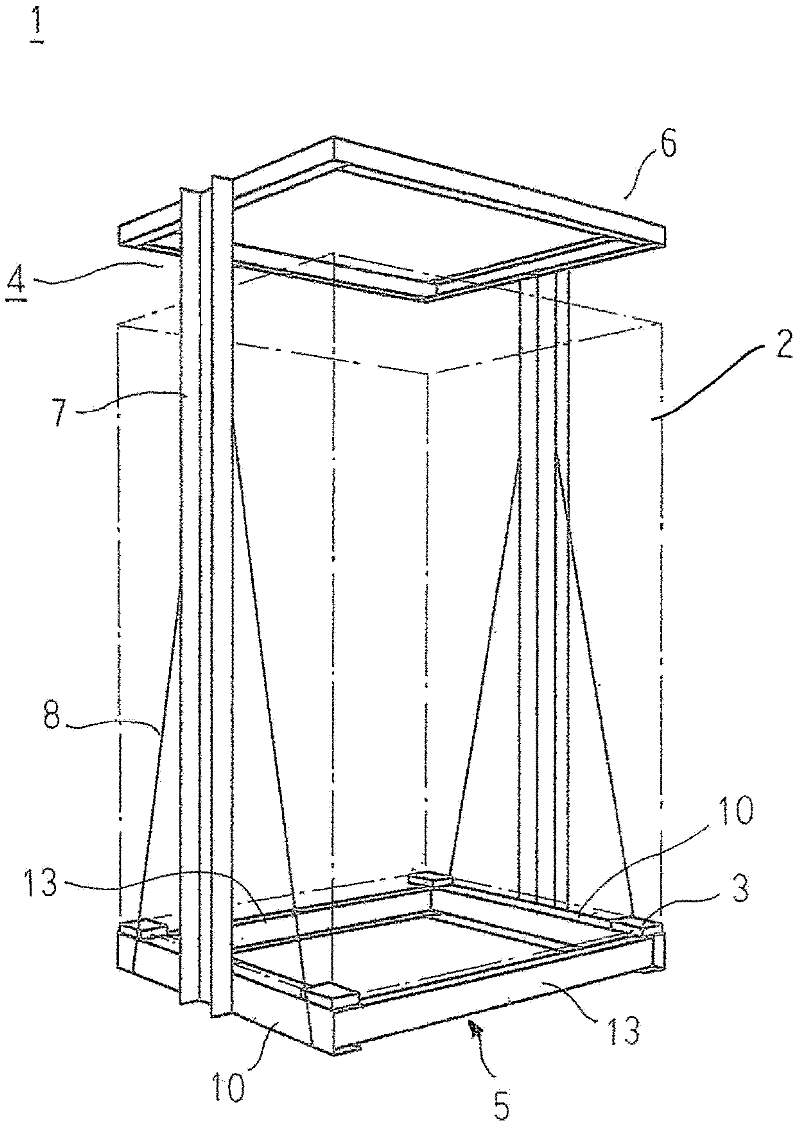

InactiveCN102642755AEasy Design ChangesAvoid deformationBuilding liftsManufacturing cost reductionEngineering

The invention provides an elevator car frame, which can restrain distortion of flange parts for a front beam and a rear beam on the upper side due to loading inside the car without increasing the plate thickness, lower the manufacturing cost, easily adapt to the design change of vibration part materials and achieve lightness. A cross beam (13) comprises a web part (14); a pair of flange parts (15) formed by bending towards the two ends of the web part (14) along the width direcction into a right angle; a second folding part (17) bending from the end of the web part (14) and formed in a way to be opposed to the web part (14). The ends of the cross beam (13) are inserted into the openings of the front beam and the rear beam (10). The second folding part (17) is configured on the position right below a vibration-proof rubber (3) in a way to be face to face to the web part (14) on the length direction of the front and rear beams (10) and orthogonal to the inner surface of a flange part (12).

Owner:MITSUBISHI ELECTRIC CORP

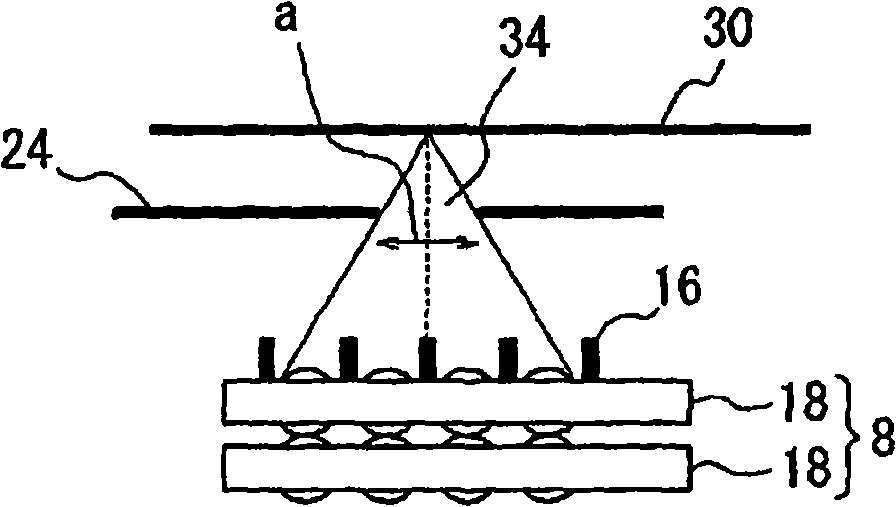

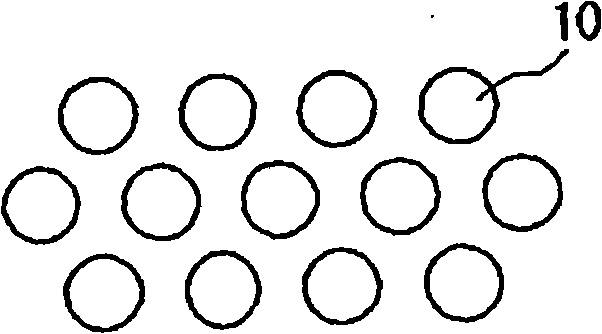

Image forming optical system, image reader using image forming optical system, and image writer

InactiveCN101273297AIncrease brightnessEasy Design ChangesLensPictoral communicationOptoelectronicsOcular straylight

An image forming optical system for forming a high-quality image by determining a most suitable design condition while ensuring a uniform and adequate amount of light and preventing ghost. In this image forming optical system having a slit, the factors to remove the stray light include the inclination of the direction of a lens array, the slit width, the lens pitch, the angle of view, and height of the light-shielding wall. The position of the slit, the thickness of the lens, and width of the lens line do not affect the stray light removal but affect the brightness. If the system has no slit, the essential factors to remove the stray light include the height of the light-shielding wall and the lens pitch. The thickness of the lens and width of the lens line do not affect the stray light removal but affects the brightness.

Owner:NIPPON SHEET GLASS CO LTD

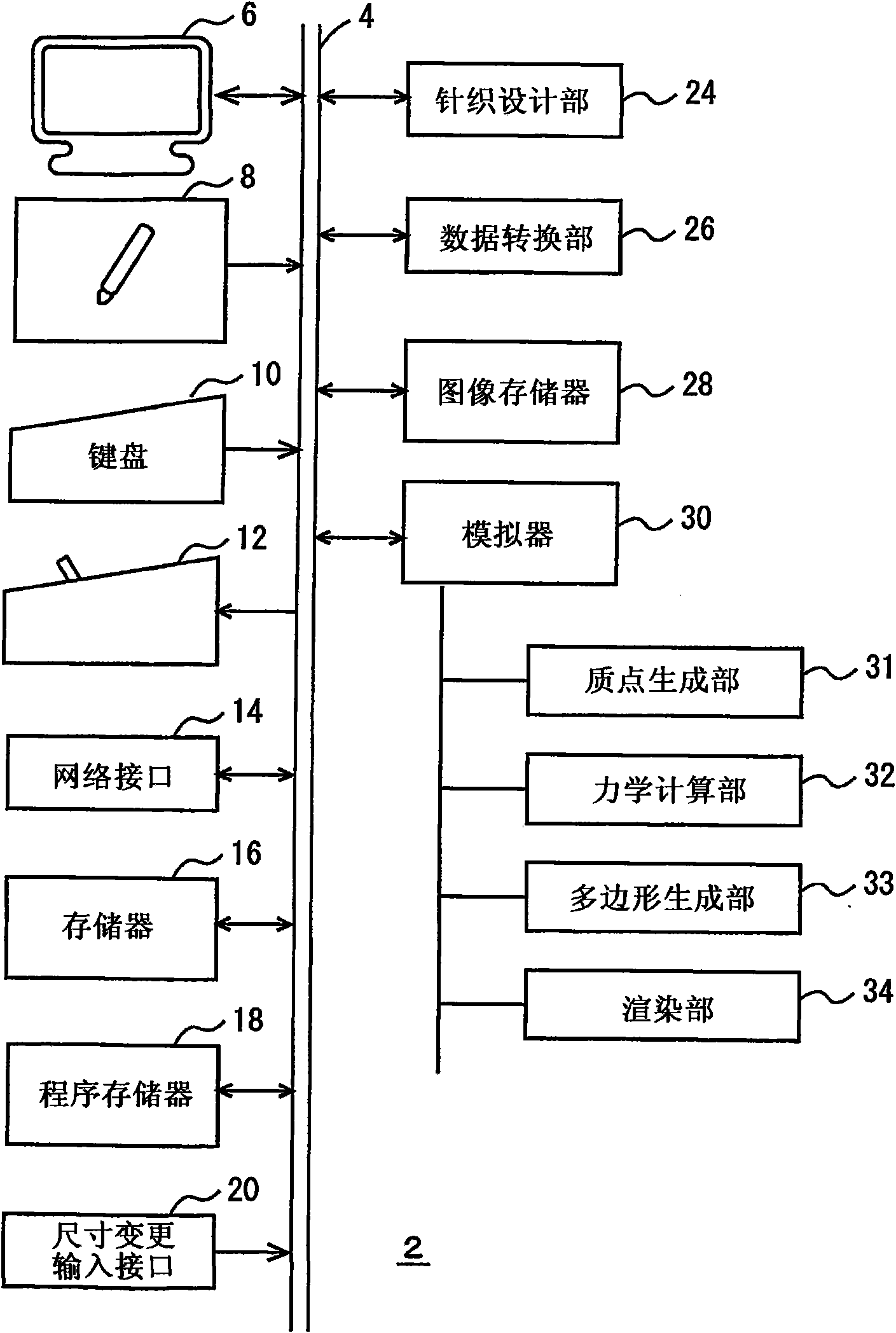

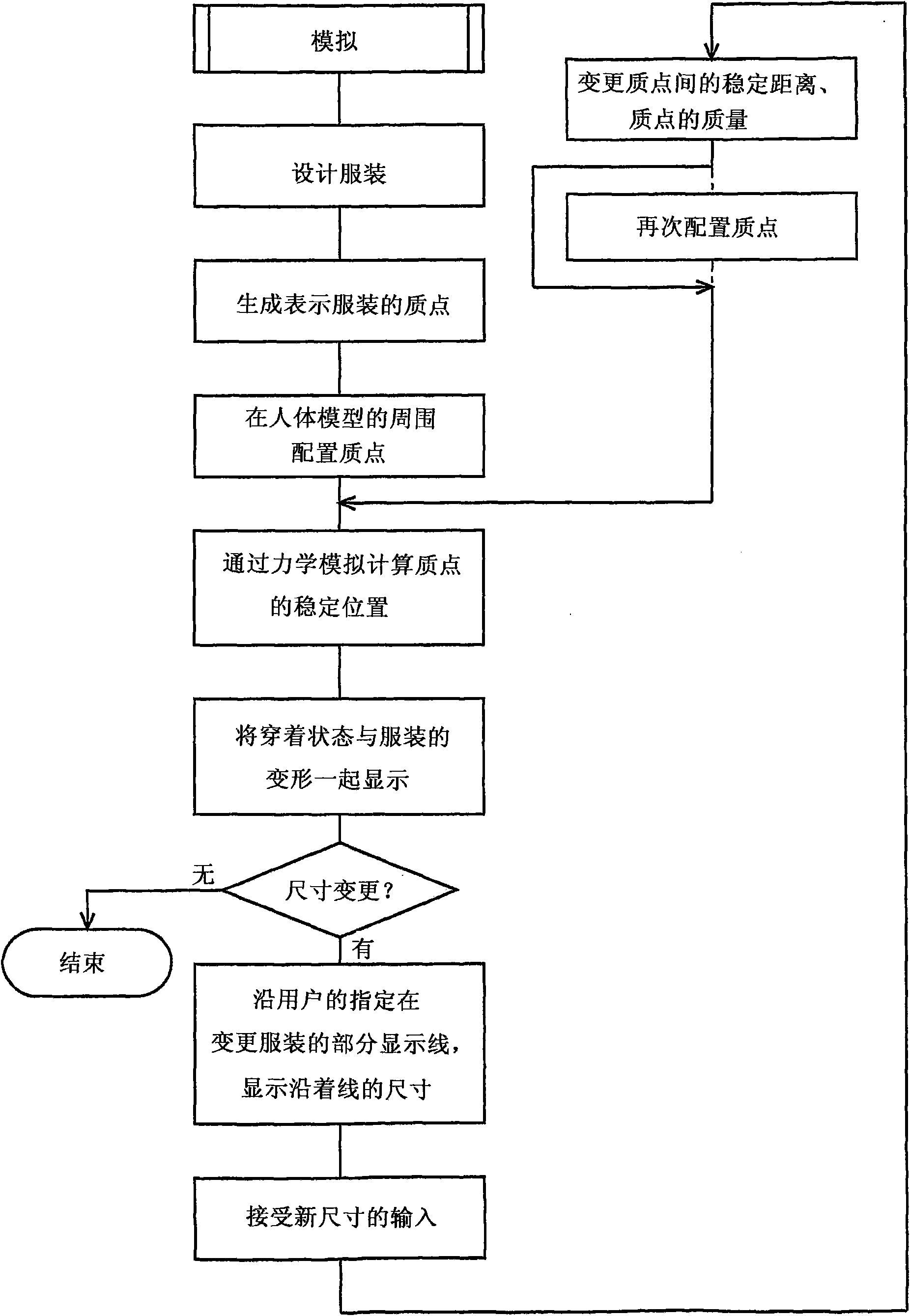

Dressing simulation device, simulation program and method for simulation

InactiveCN101933021ASimulate fast and accurateThe simulation results are re-simulated at high speed and correctlyDesign optimisation/simulationSpecial data processing applicationsStable stateDisplay device

Multiple mass points are generated on a designed virtual garment and stable conditions of the multiple mass points are simulated by elastic force between the mass points and force exerted between a human body model and the mass point. A result of the simulation is displayed on a display device and, when the design is changed, a distance at which the elastic force becomes zero is changed so that a simulation of the stable conditions of the mass points is carried out again. Thus, even if the design of a garment is changed, a real time and precise simulation can be carried out.

Owner:SHIMA SEIKI MFG LTD

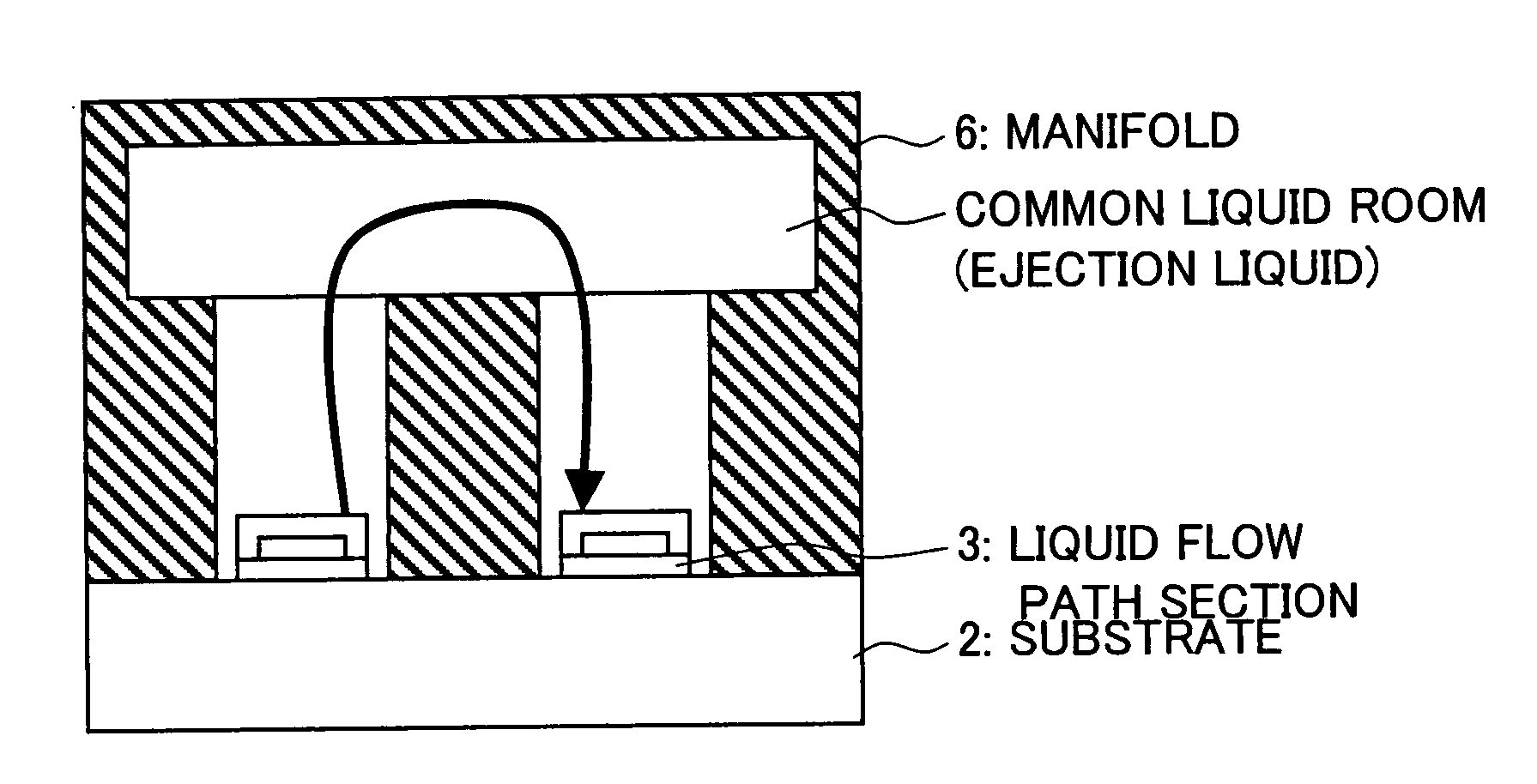

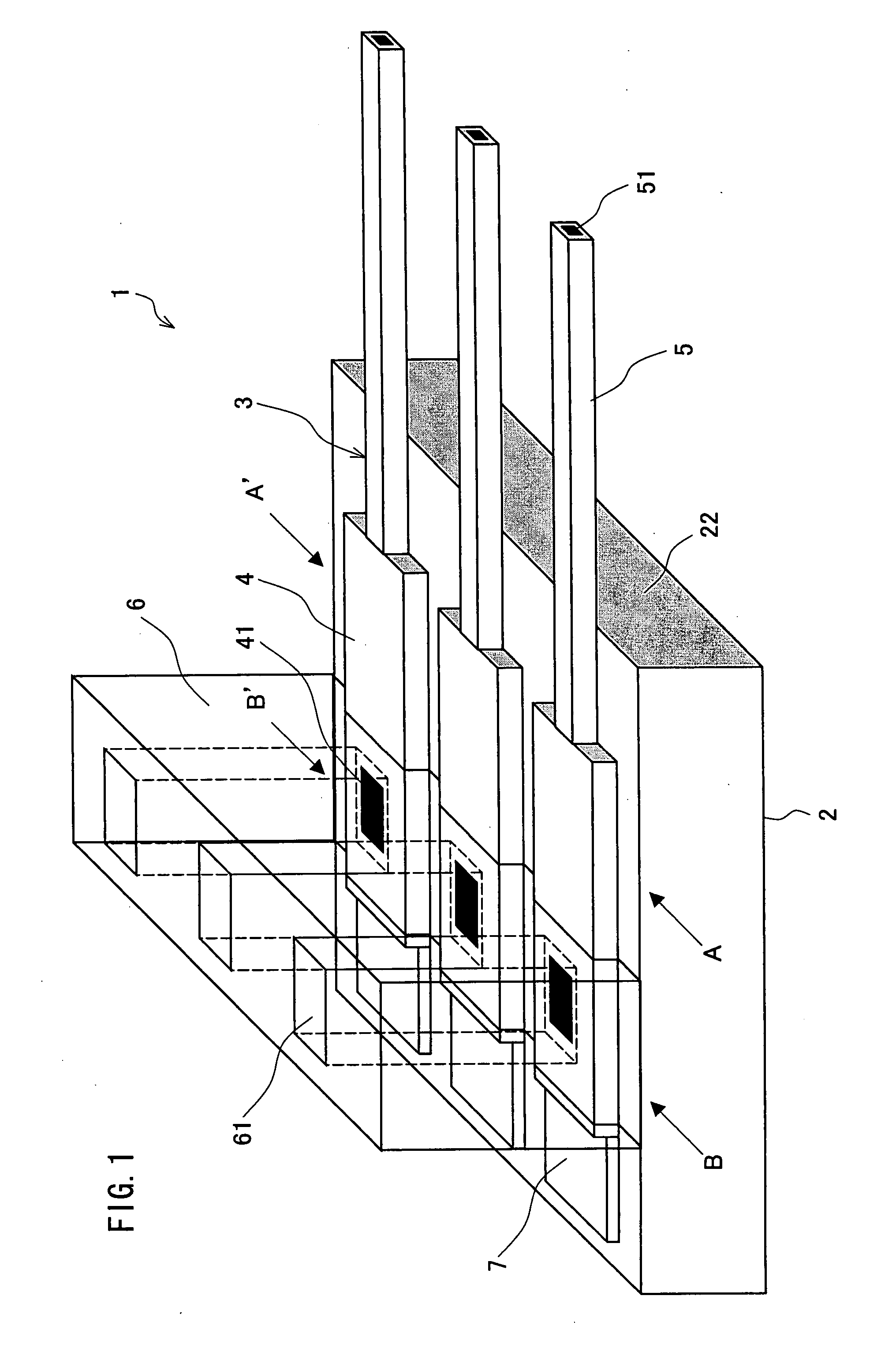

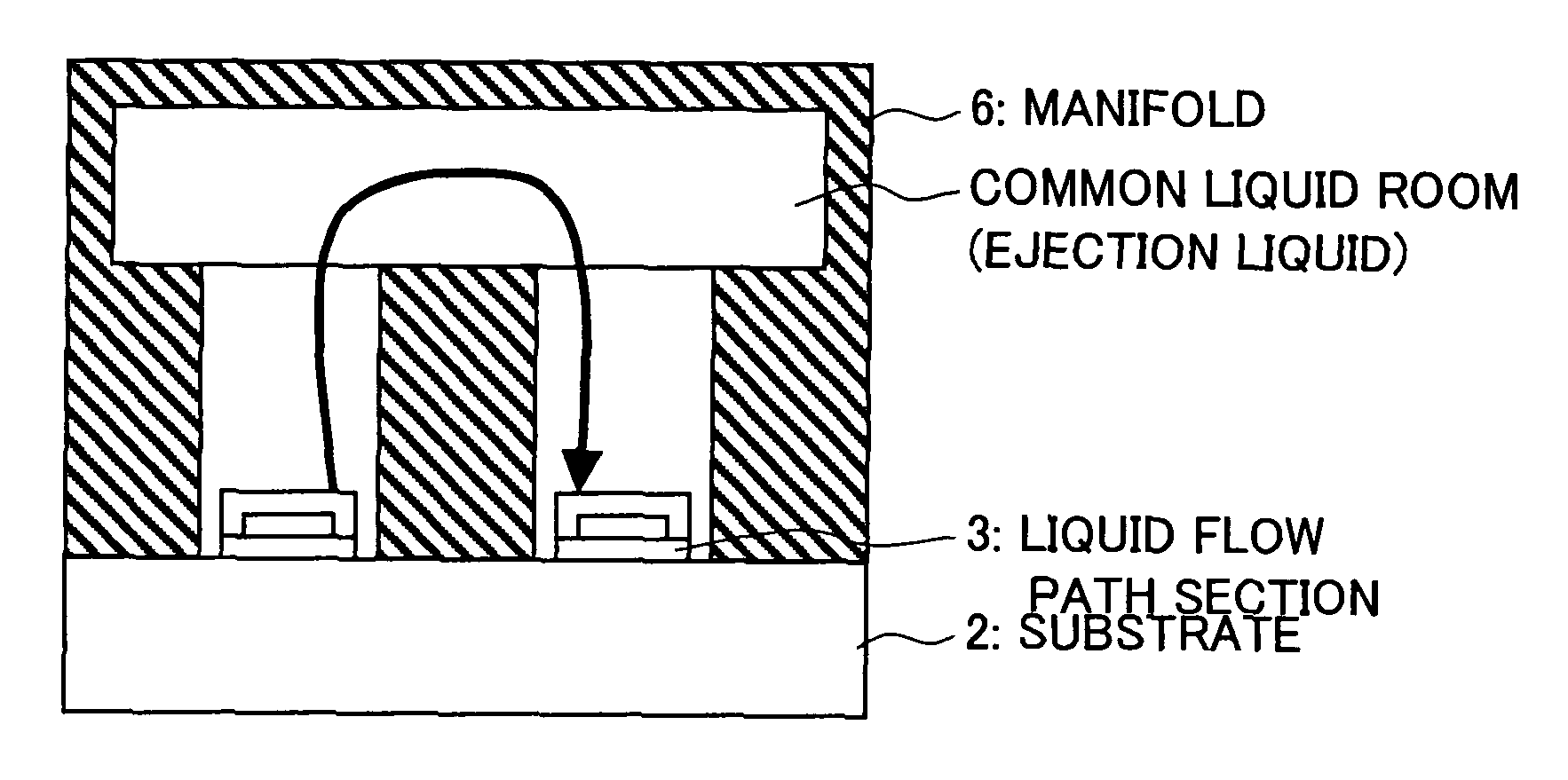

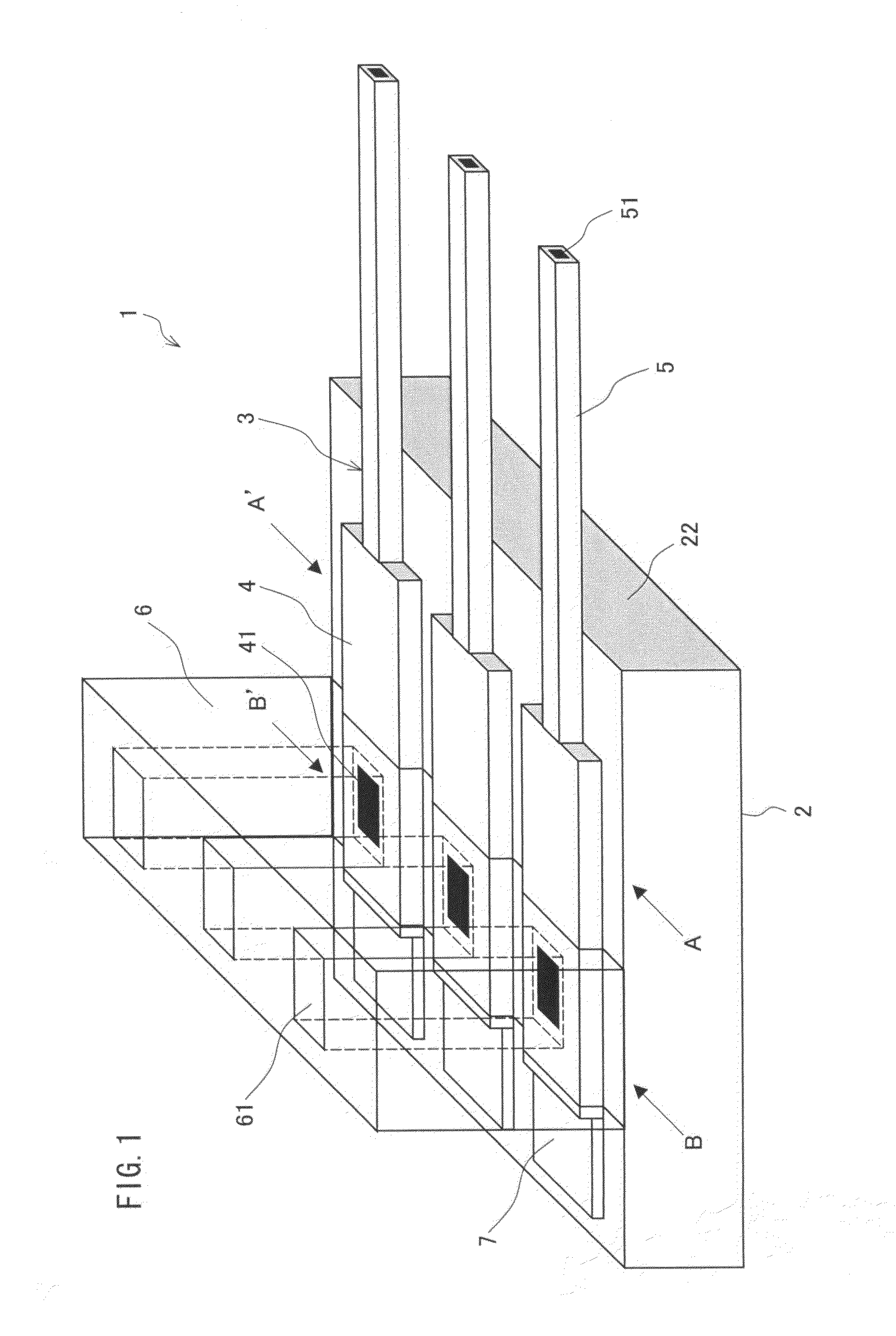

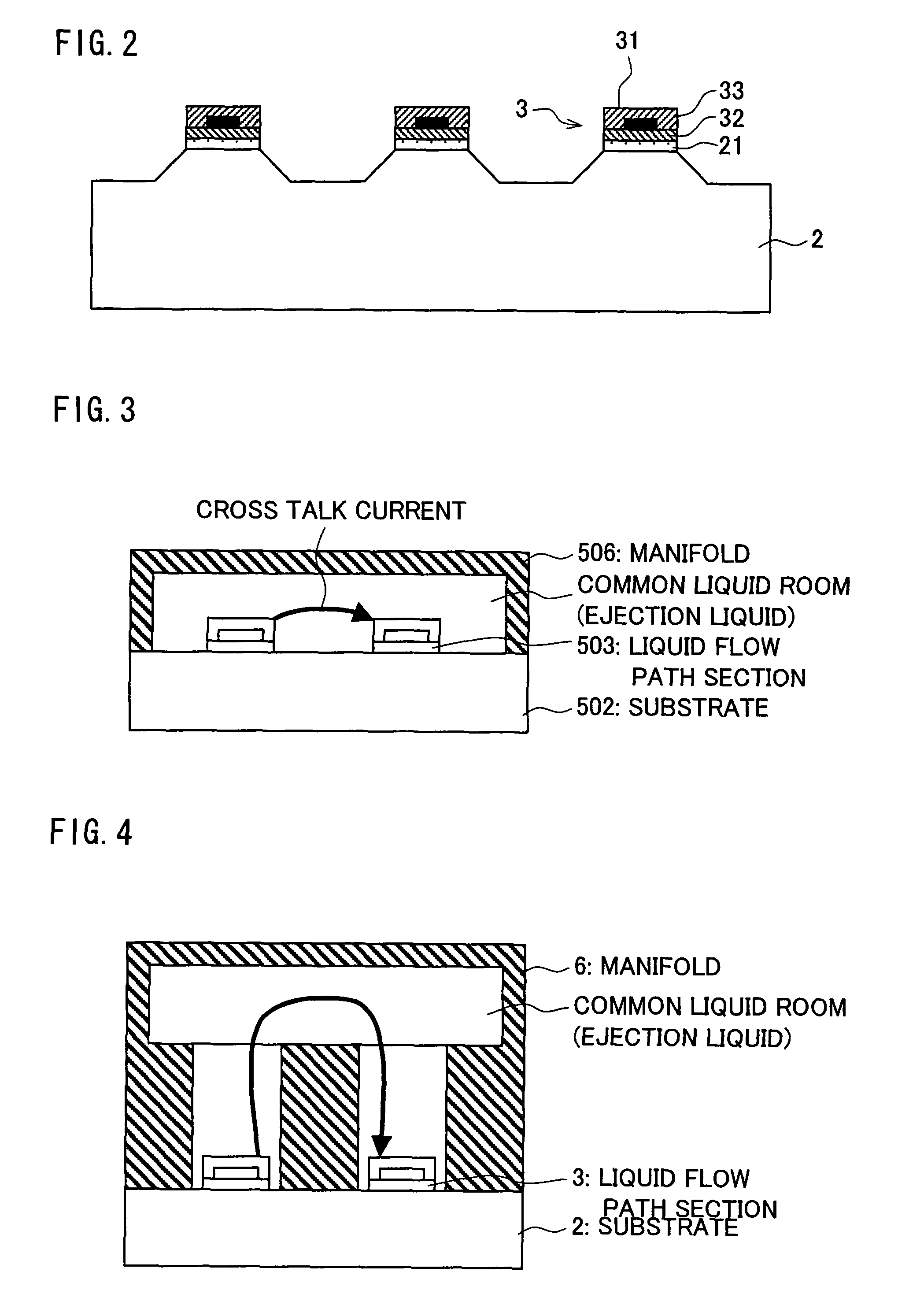

Inkjet Head And Method For Manufacturing The Same

InactiveUS20080049074A1Increase production costDifficult to stably producePrintingEngineeringMechanical engineering

An inkjet head (1) has a liquid flow path section (3) for receiving liquid and, in response to application of a voltage, ejecting the liquid to an object on which a drawing is to be made. The degree of design freedom of the shape of the liquid channel section (3) or the shape of a liquid channel in the liquid channel section (3) can be improved because the liquid channel section (3) is formed on the upper surface of a substrate. Furthermore, the inkjet head can have a structure corresponding to the properties of liquid to be ejected or to an object to which the liquid is to be ejected.

Owner:SHARP KK

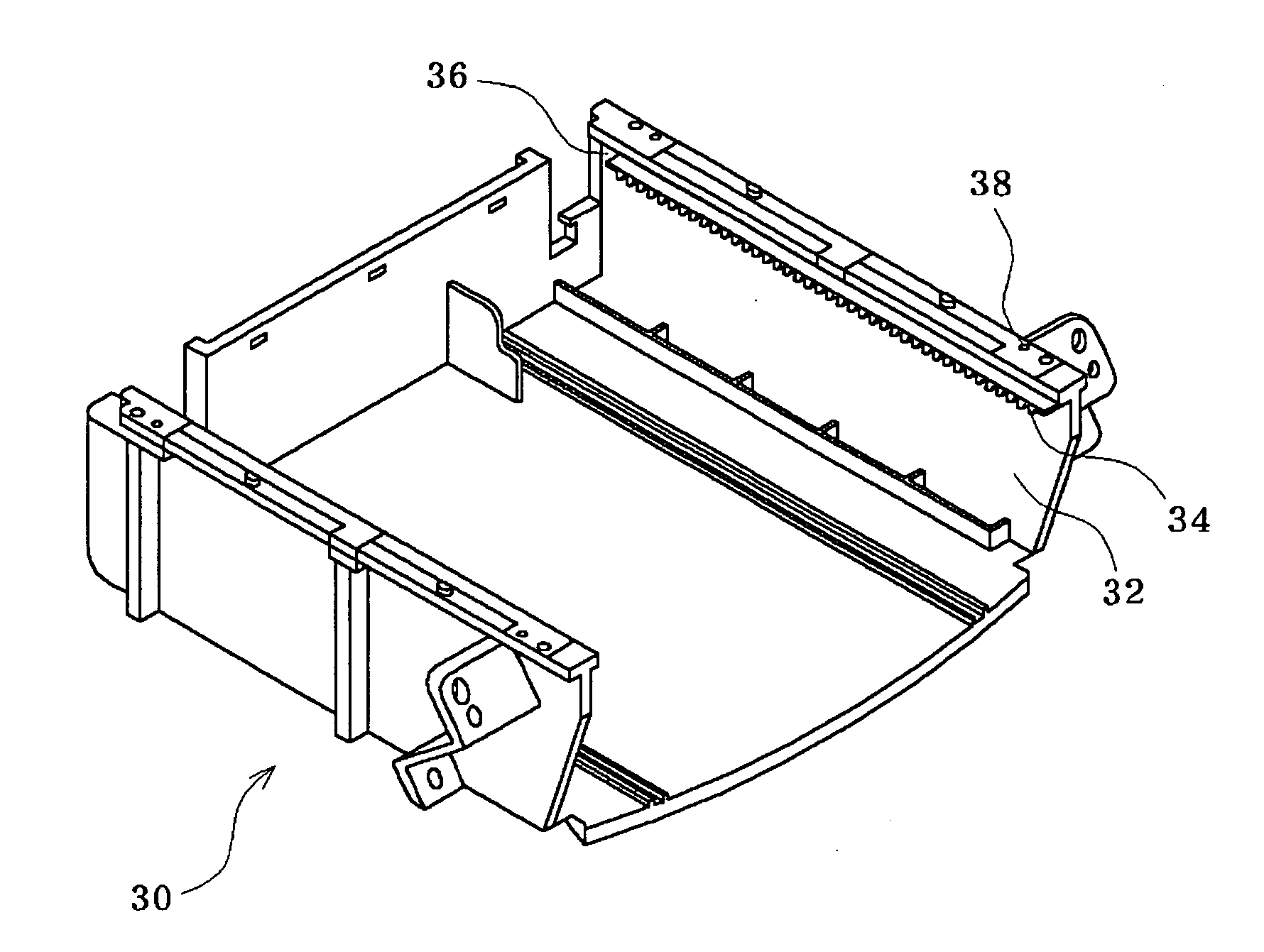

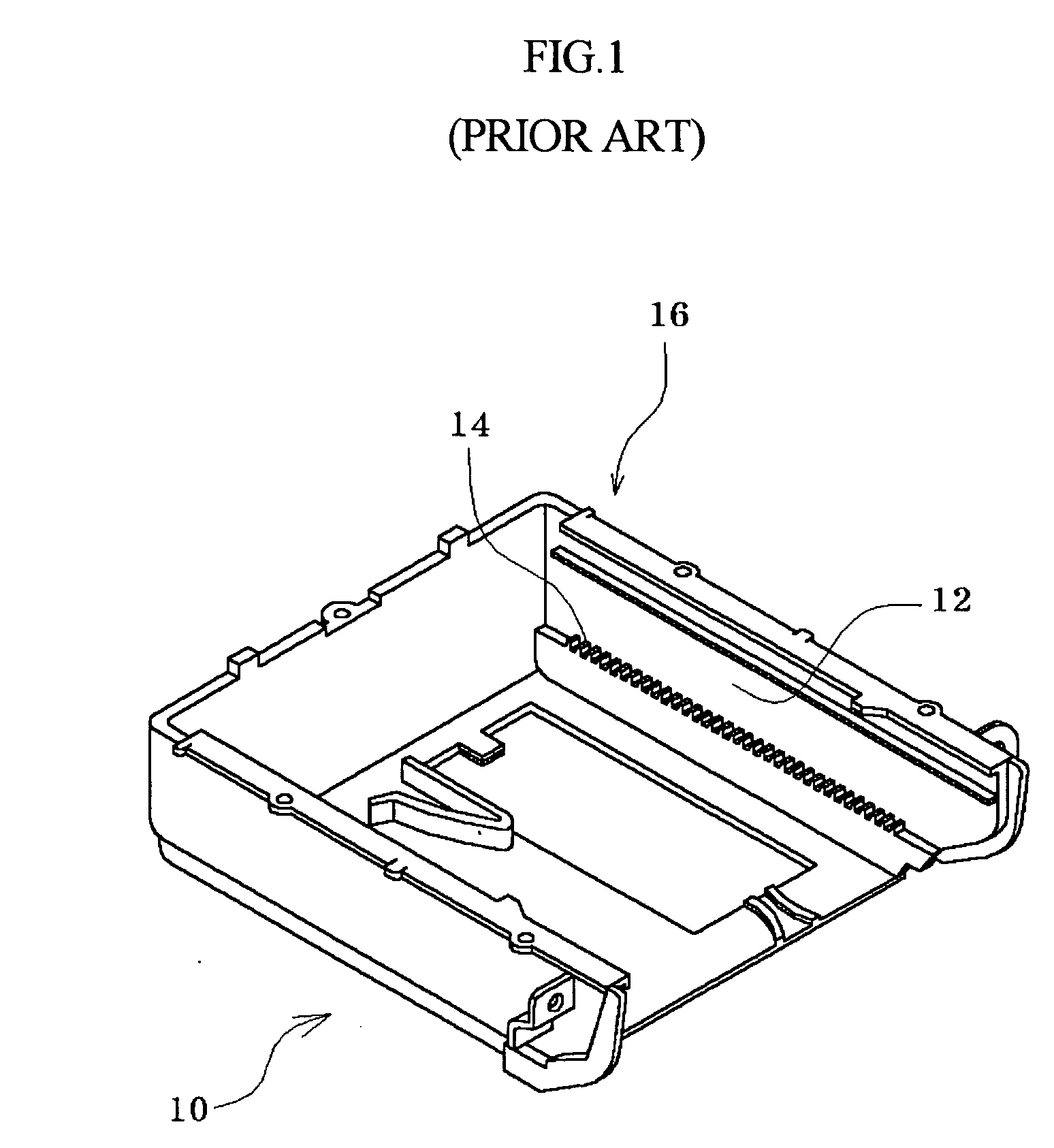

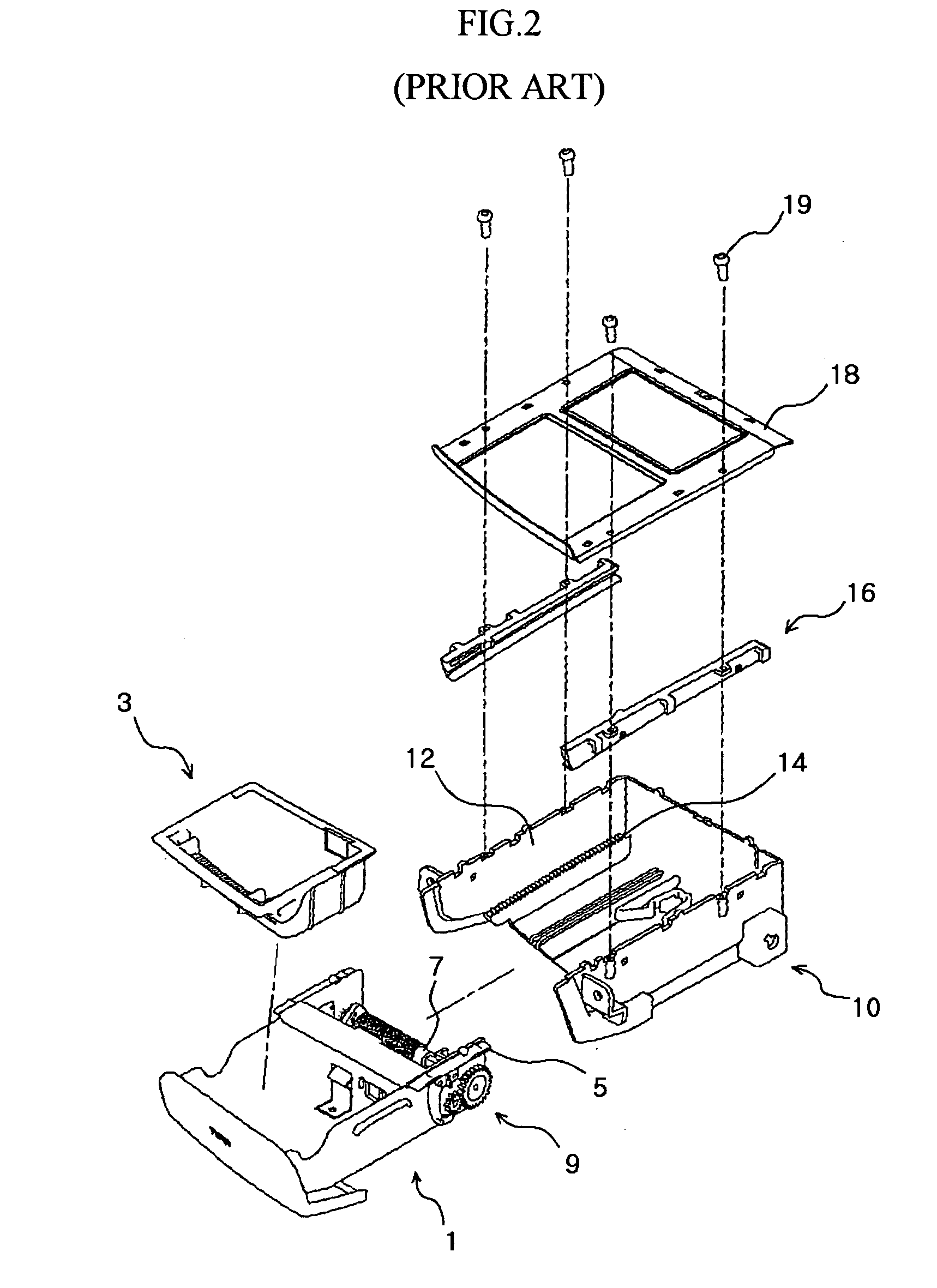

Guide structure for vehicular tray

InactiveUS20050275236A1Smooth operationOperational reliability is increasedPassenger spaceVehicle arrangementsEngineeringConstant speed

A guide structure for a vehicular tray includes a plurality of slides formed at opposite lateral outer surfaces of the tray, the slides guiding the tray in the movement direction, a plurality of guides formed at opposite lateral inner surfaces of a housing configured to receive the tray, the guides guiding the slides, a plurality of toothed rails installed at lower sides of the guides and formed with teeth in the movement direction of the tray, and toothed gears connected to opposite ends of a damper member and configured to protrude outward from opposite lateral outer surfaces of the tray, the toothed gears being rotated and moved at a constant speed in an engaged state with the toothed rails.

Owner:HYUNDAI MOBIS CO LTD

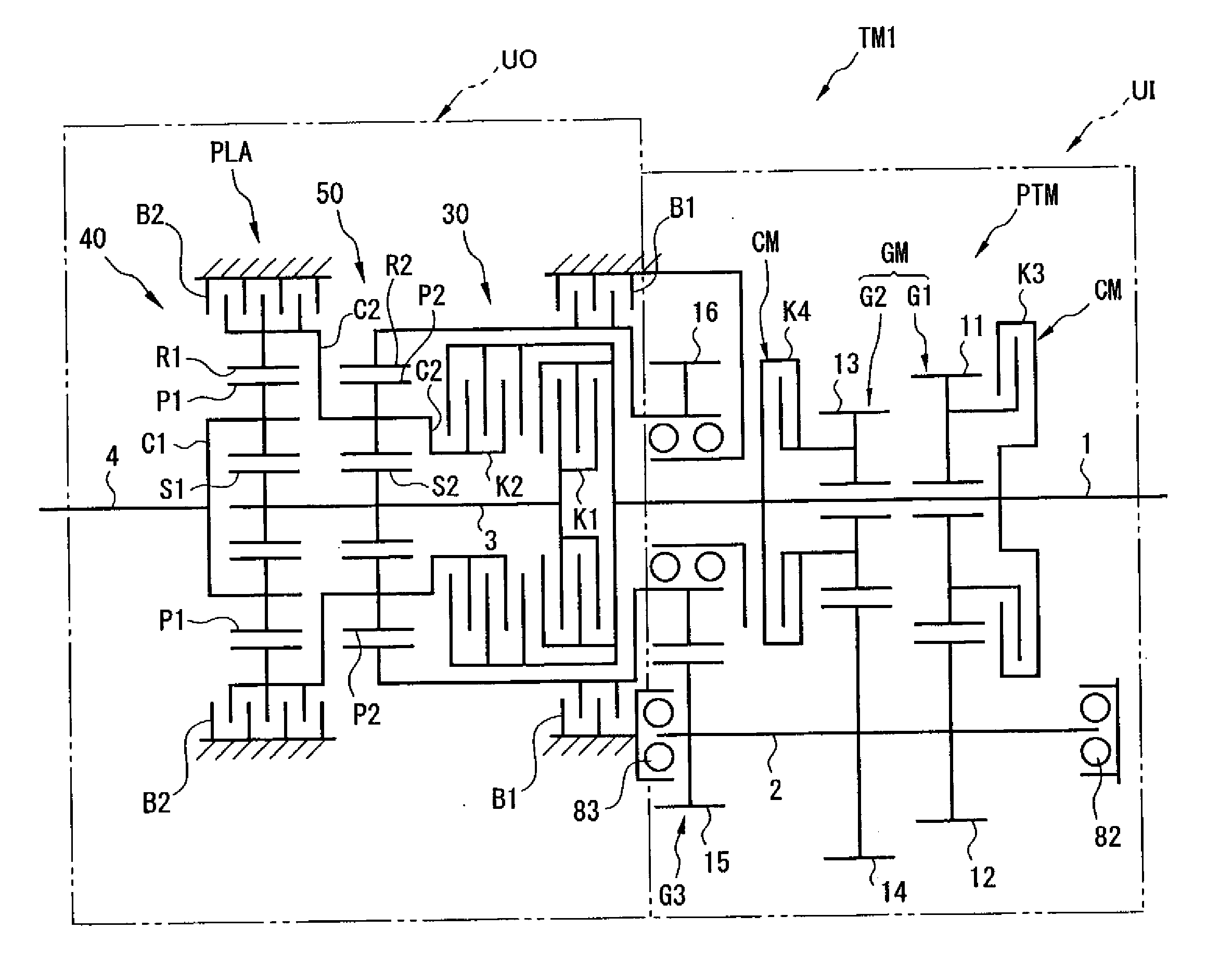

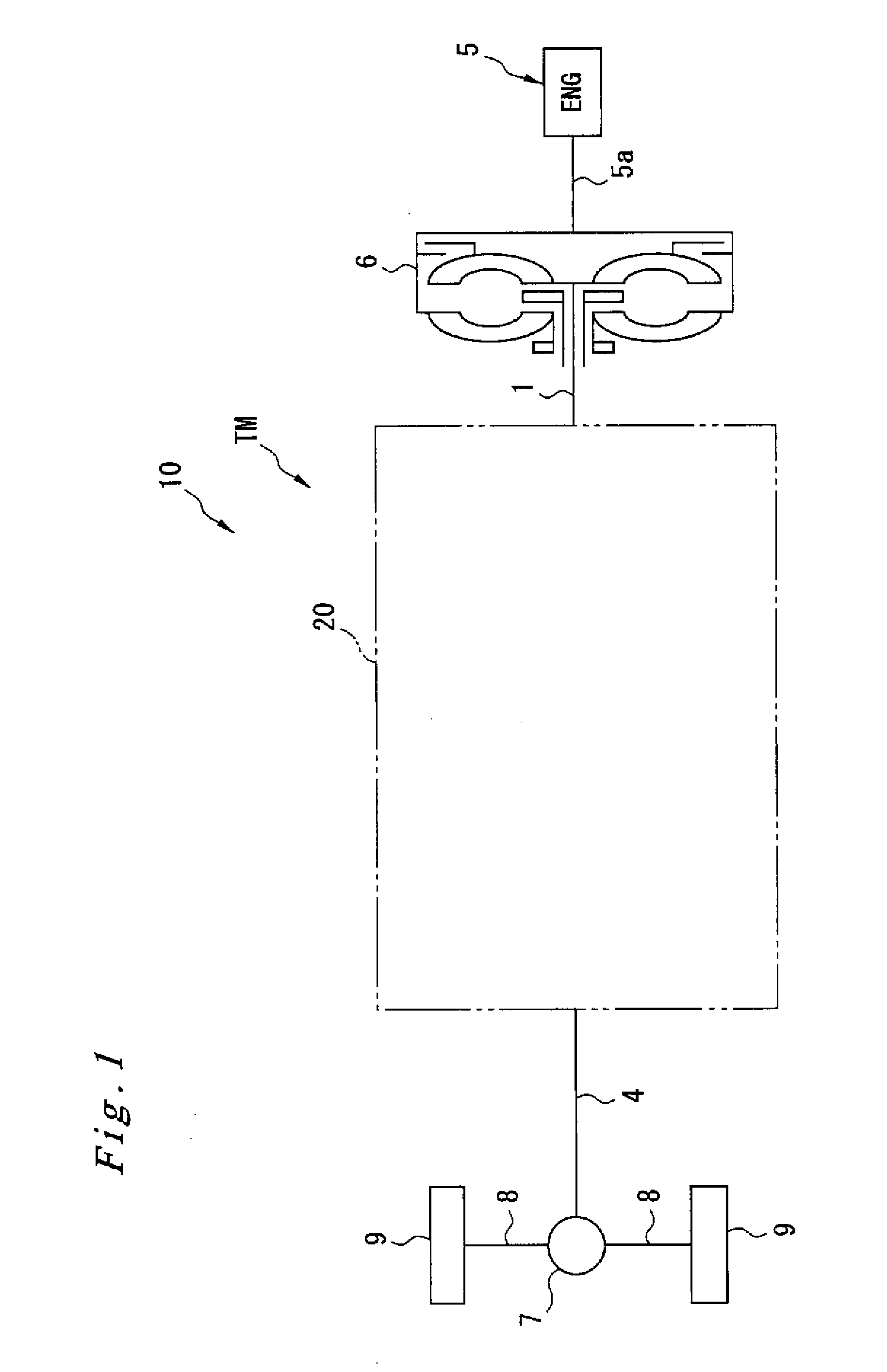

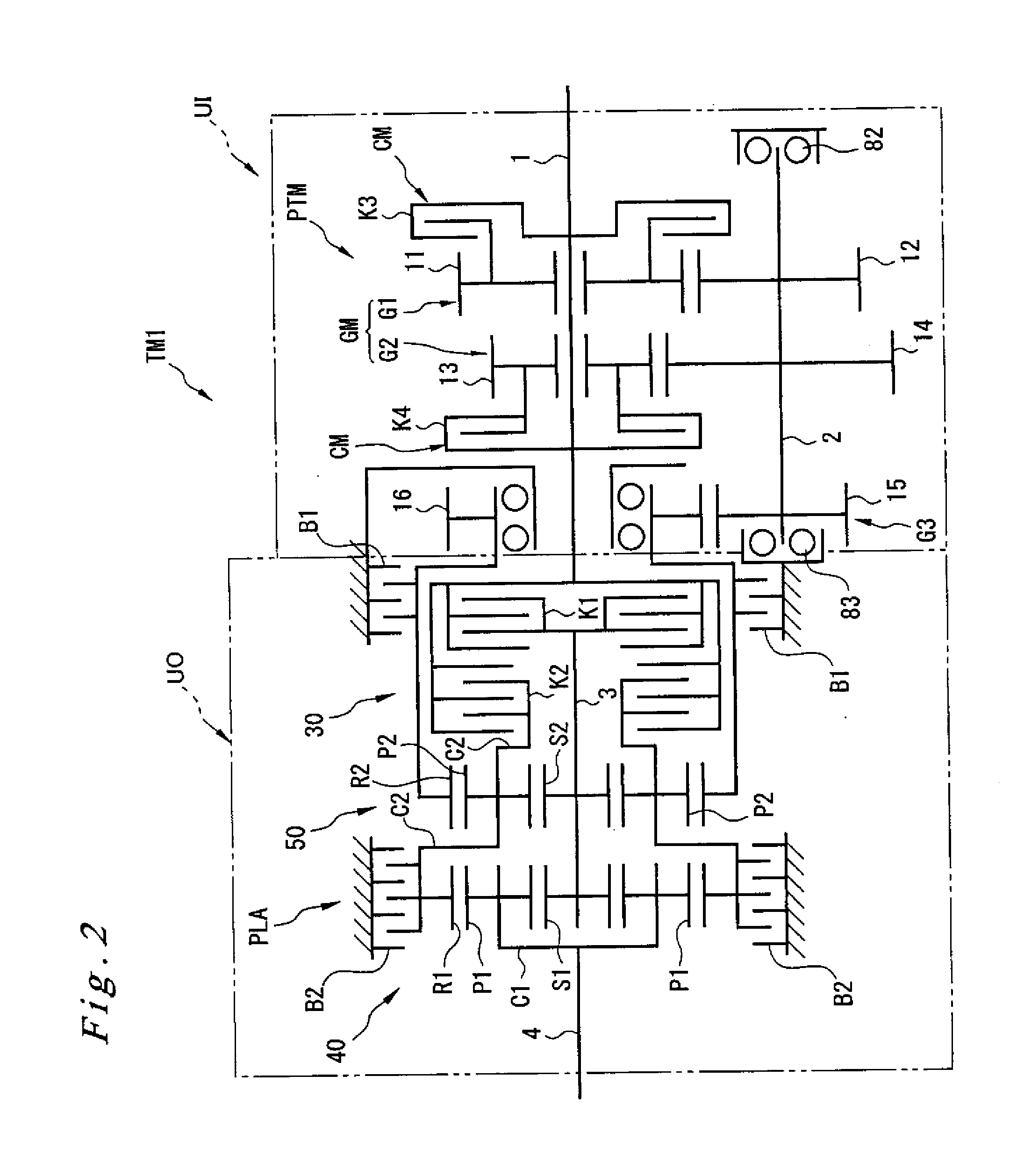

Transmission

InactiveUS20070287567A1Easy to changeReduce manufacturing costToothed gearingsTransmission elementsGear wheelGear train

The present invention includes an input side transmission unit that transforms the rotation of the input shaft that rotates by receiving input rotation into N steps, and transmits the transformed rotation to the counter shaft; and an output side transmission unit that includes a first planet gear train and a second planet gear train, and that transforms the rotation of the counter shaft and outputs the transformed rotation to the output shaft. Of the first through fourth rotating elements constituting the output side transmission unit, the first and second sun gears are connected so that they can be freely engaged with or disengaged from the input shaft via the first clutch; the first carrier is connected to the output shaft; the second carrier and the first ring gear are connected so that they can be freely engaged with or disengaged from the input shaft via the second clutch and can be held fixed by the second brake; and the second ring gear can be held fixed by the first brake, and is connected to the upstream side output member.

Owner:HONDA MOTOR CO LTD

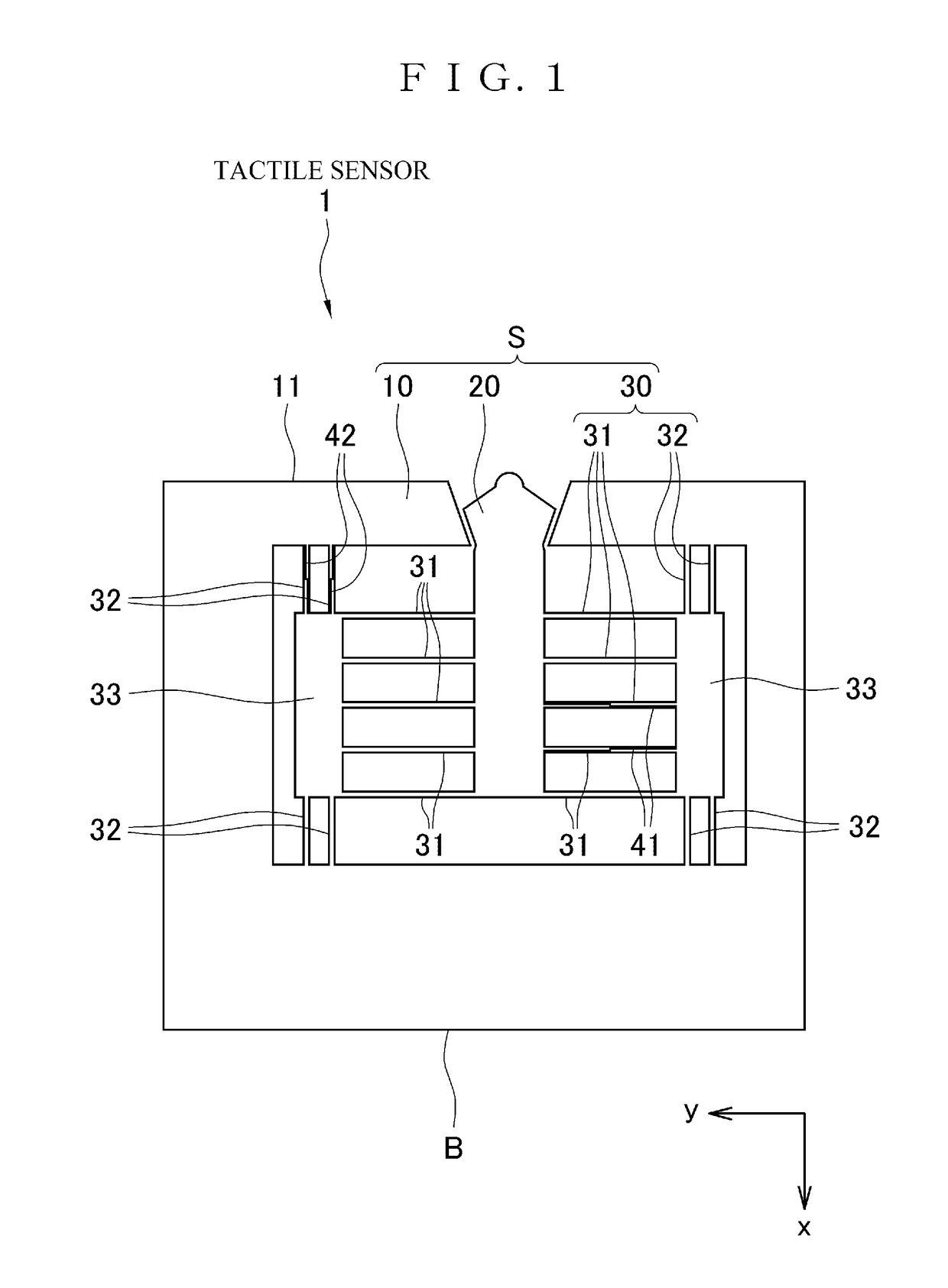

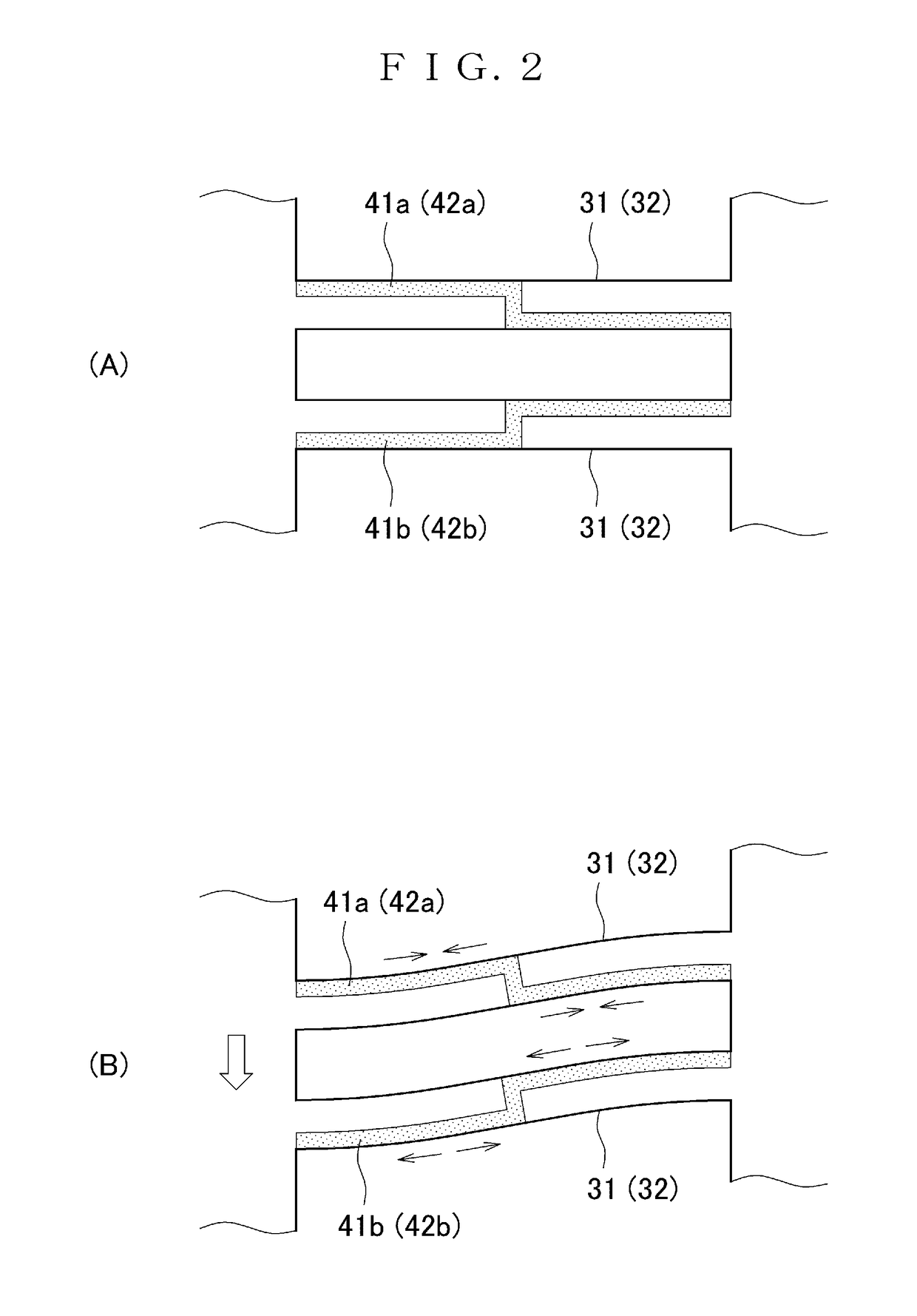

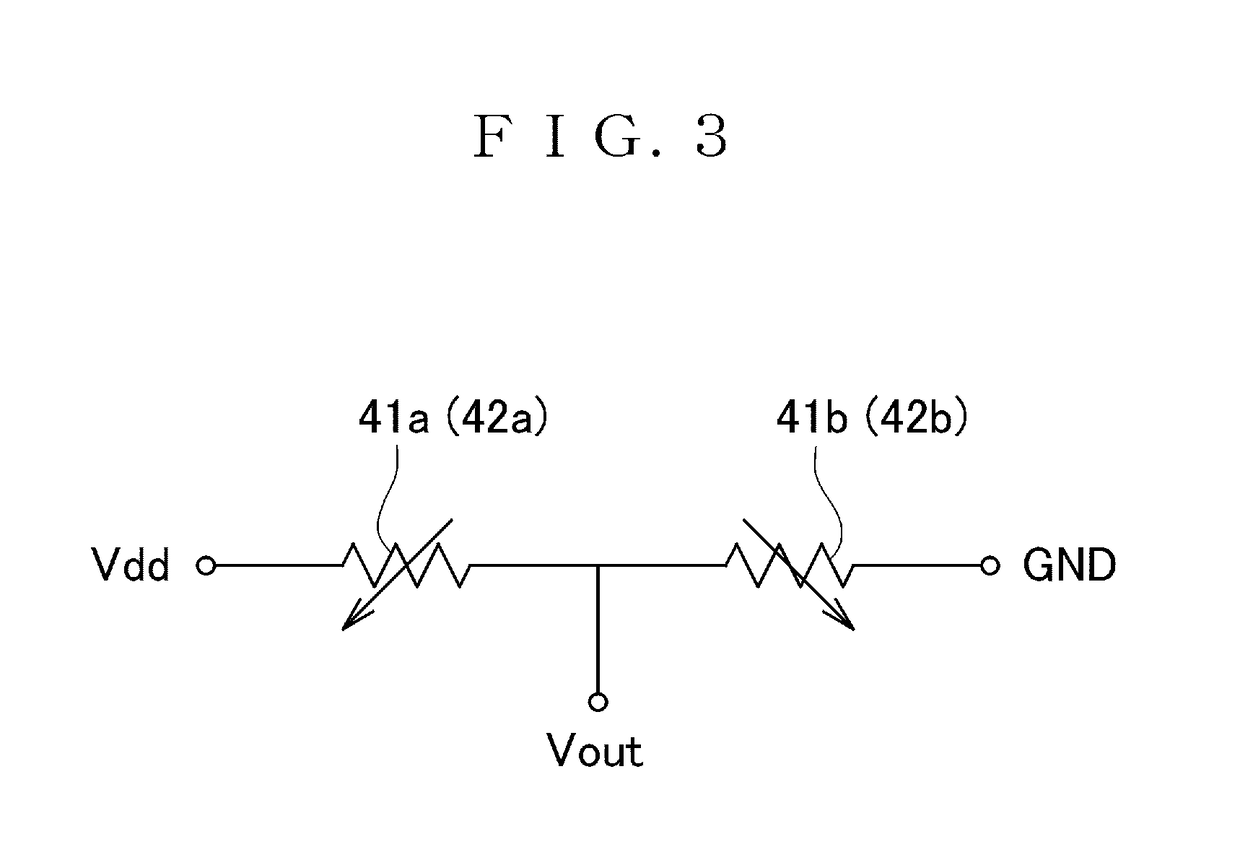

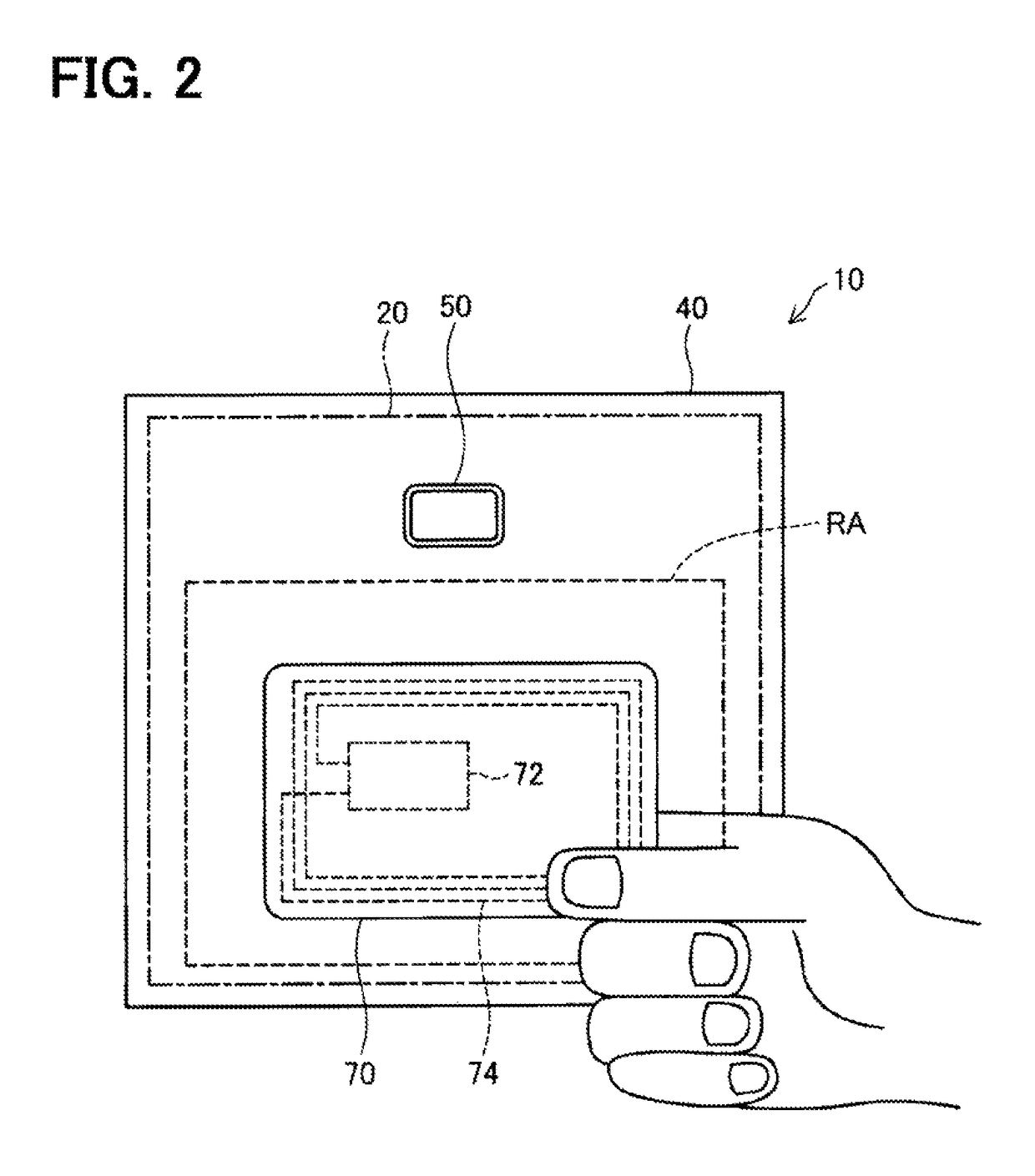

Tactile sensor and method for evaluating touch feeling

ActiveUS10190927B2Improve design flexibilityEasy Design ChangesError detection/correctionForce measurement using piezo-resistive materialsEngineeringTactile sensor

To provide a tactile sensor that allows a contact to be displaced largely and can detect fine ruggedness, flexibility, and other features of a surface of a measuring object.A sensor part S includes a frame 10 that includes a side part of a substrate B, a contact 20 that is disposed in parallel to the substrate B so that a tip of the contact 20 projects from a side face of the substrate B, a suspension 30 that supports the contact 20 to the frame 10, and displacement detectors 41 and 42 each of which detects displacement of the contact 20. The side face of the substrate B functions as a sensing surface. The contact 20 coming in contact with a measuring object O is displaced on a level parallel to the substrate B. Since the sensor part S can be configured widely in a planar manner along the substrate B, the structure has higher flexibility of design. As a result, the sensor part S allows the contact 20 to be displaced largely, and can detect fine ruggedness, flexibility and other features of the surface of the measuring object O.

Owner:KAGAWA UNIVERSITY

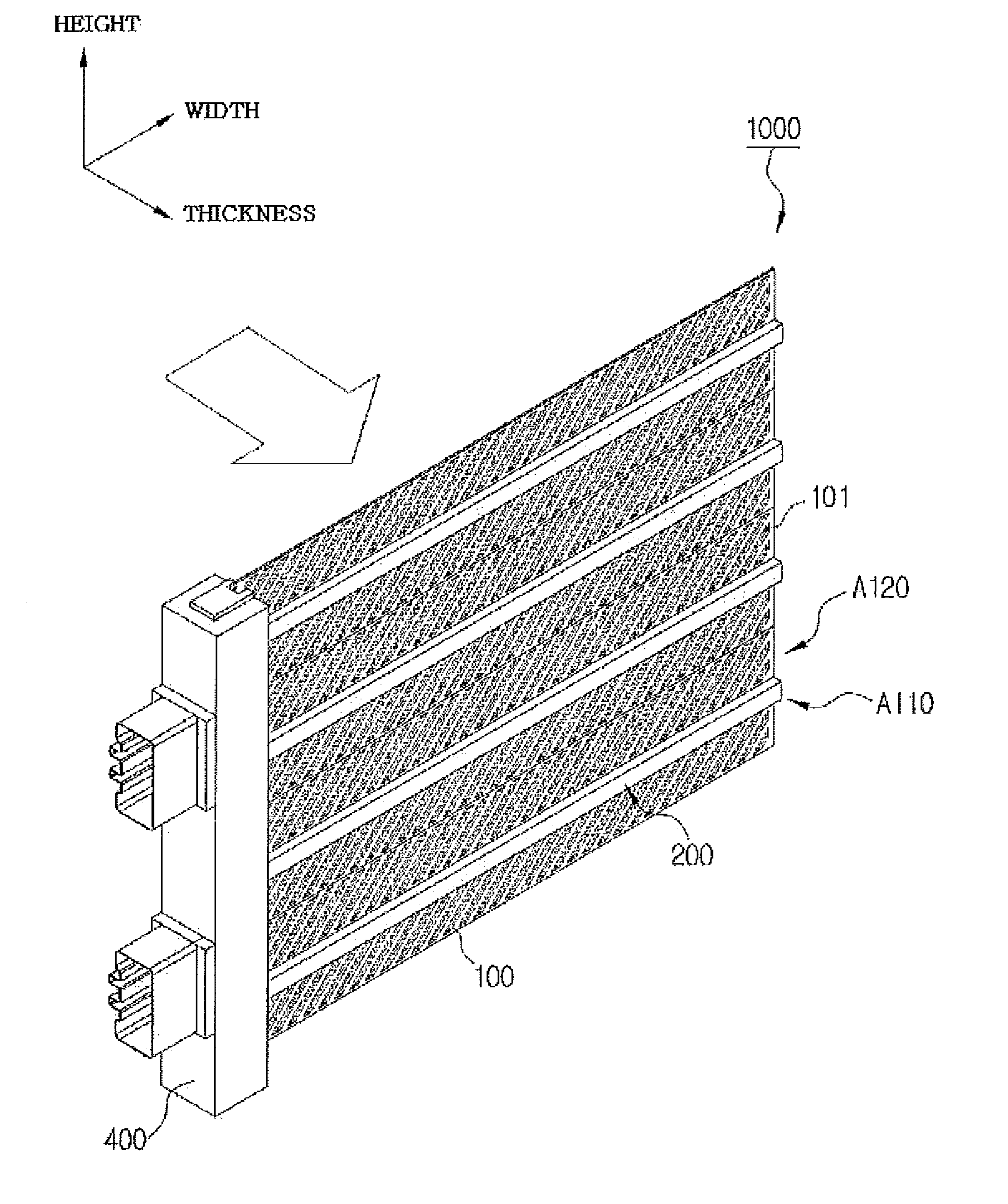

Dehumidifying device and dehumidifying module

ActiveCN105214453AEasy Design ChangesSemi-permeable membranesLighting and heating apparatusInlet channelEngineering

The present application discloses a dehumidifying device including a base configured to define an inlet channel for first air flow, and an outlet channel for second air flow less humid than the first; and a first dehumidifier including a first inlet and outlet in communication with the inlet and outlet channel, and configured to dehumidify the first air between the first inlet and the first outlet to generate the second air. The base includes a first base portion configured to define first inlet and outlet regions for the first and second air flows; and a second base portion configured to define second inlet and outlet regions in communication with the first inlet and outlet regions. The first and second inlet regions form at least a part of the inlet channel. The first and second outlet regions form at least a part of the outlet channel.

Owner:NABLESCO CORP

Inkjet head and method for manufacturing the same

Owner:SHARP KK

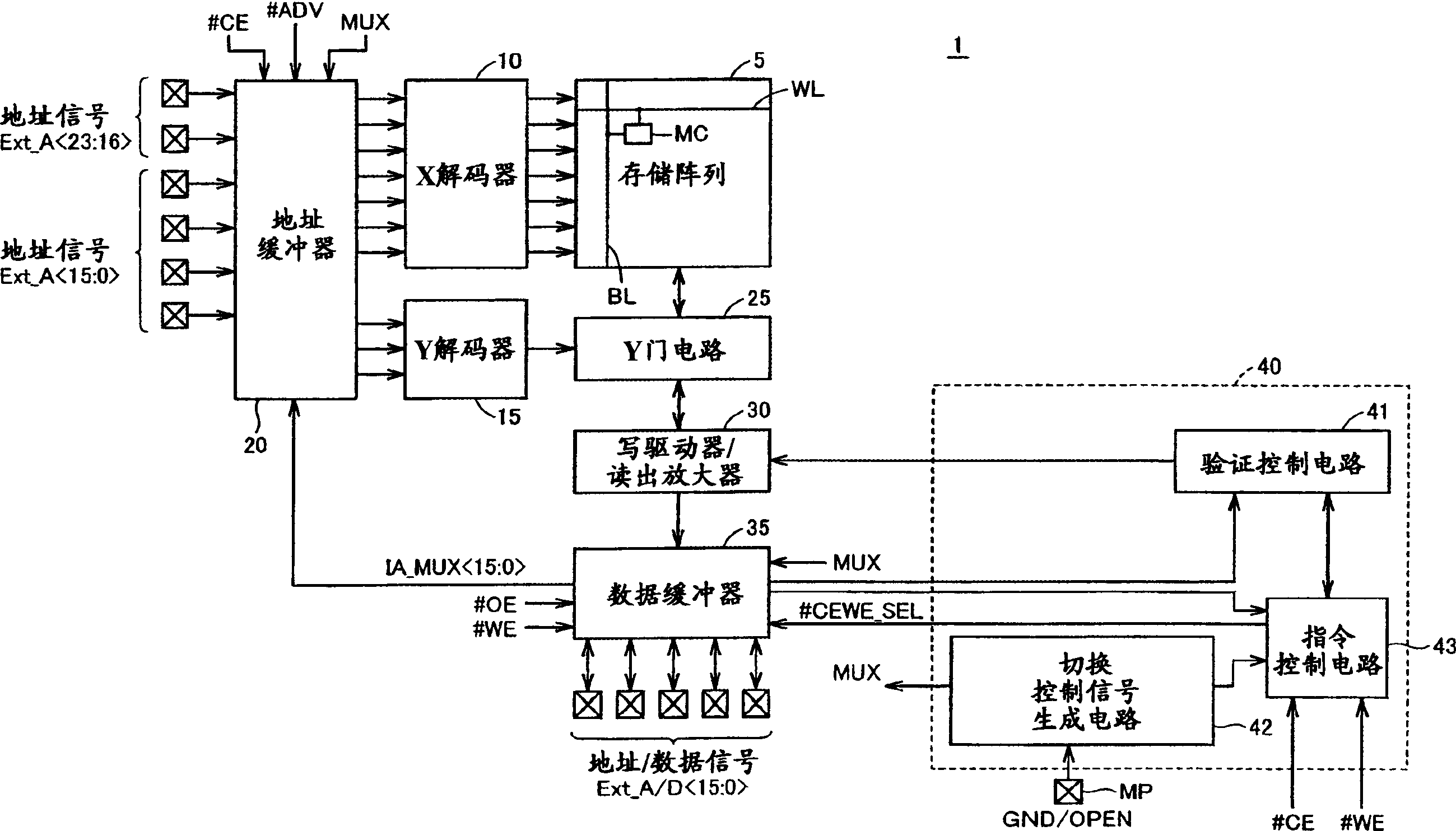

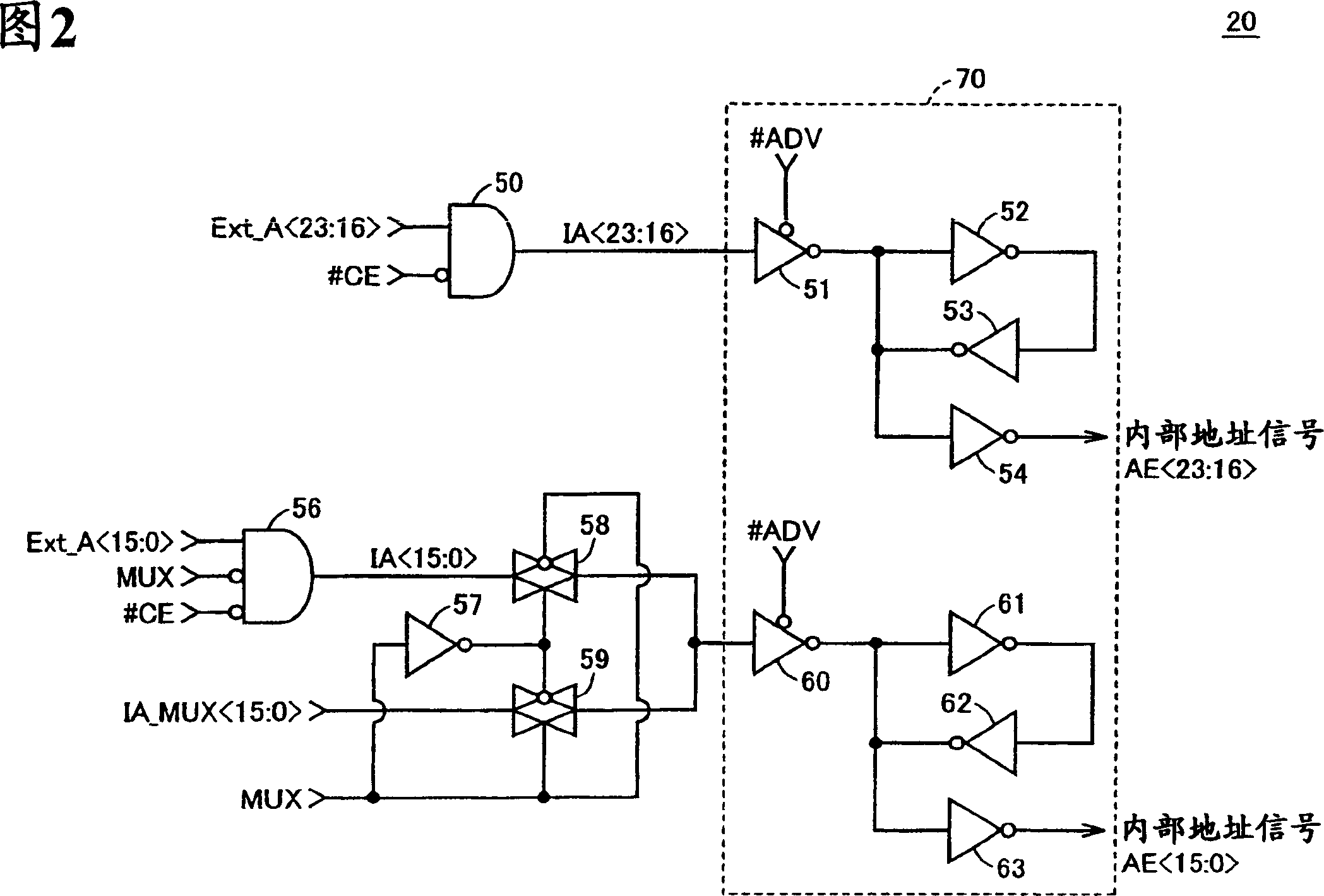

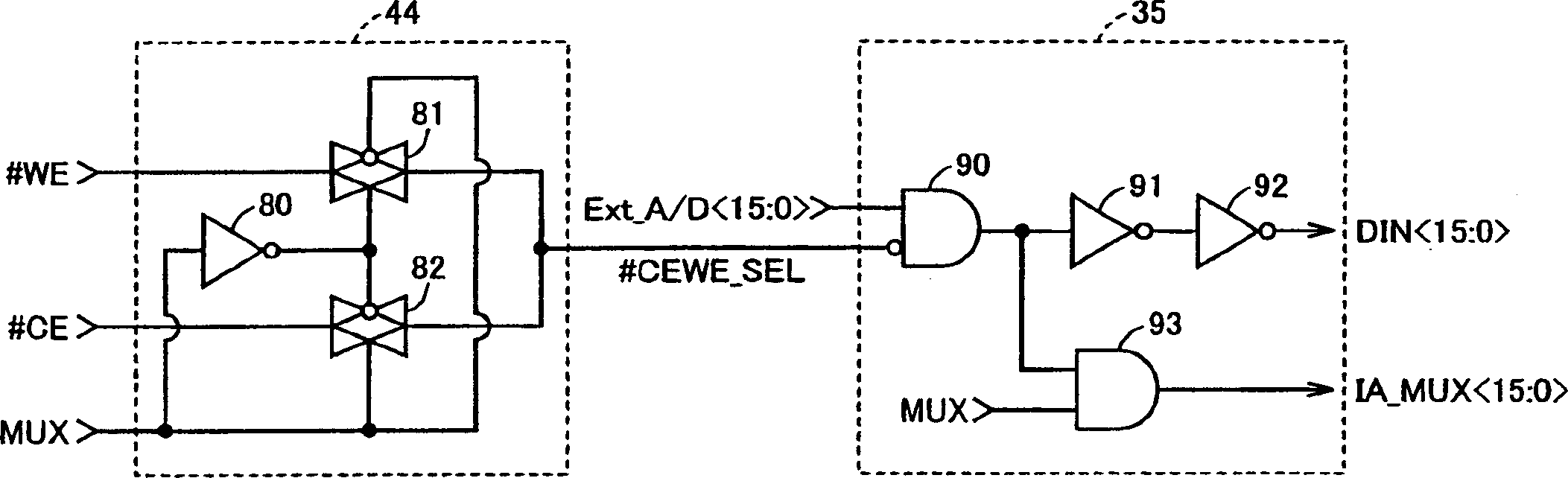

Semiconductor memory device capable of switching from multiplex method to non-multiplex method

An address pad is independently provided to receive only the address signals independently from an address data multi-pad into which the address signals and the data signals are inputted. The path of the address signals to be inputted to an address buffer is switched by a switching control signal generated in the multiplex system / non-multiplex system. Thus, the address signals and the data signals can respectively be inputted to the address buffer and a data buffer 35 in parallel.

Owner:RENESAS TECH CORP

Dehumidifying device and dehumidifying module

ActiveUS9751048B2Easy Design ChangesSemi-permeable membranesLighting and heating apparatusInlet channelEngineering

The present application discloses a dehumidifying device including a base configured to define an inlet channel for first air flow, and an outlet channel for second air flow less humid than the first; and a first dehumidifier including a first inlet and outlet in communication with the inlet and outlet channel, and configured to dehumidify the first air between the first inlet and the first outlet to generate the second air. The base includes a first base portion configured to define first inlet and outlet regions for the first and second air flows; and a second base portion configured to define second inlet and outlet regions in communication with the first inlet and outlet regions. The first and second inlet regions form at least a part of the inlet channel. The first and second outlet regions form at least a part of the outlet channel.

Owner:NABLESCO CORP

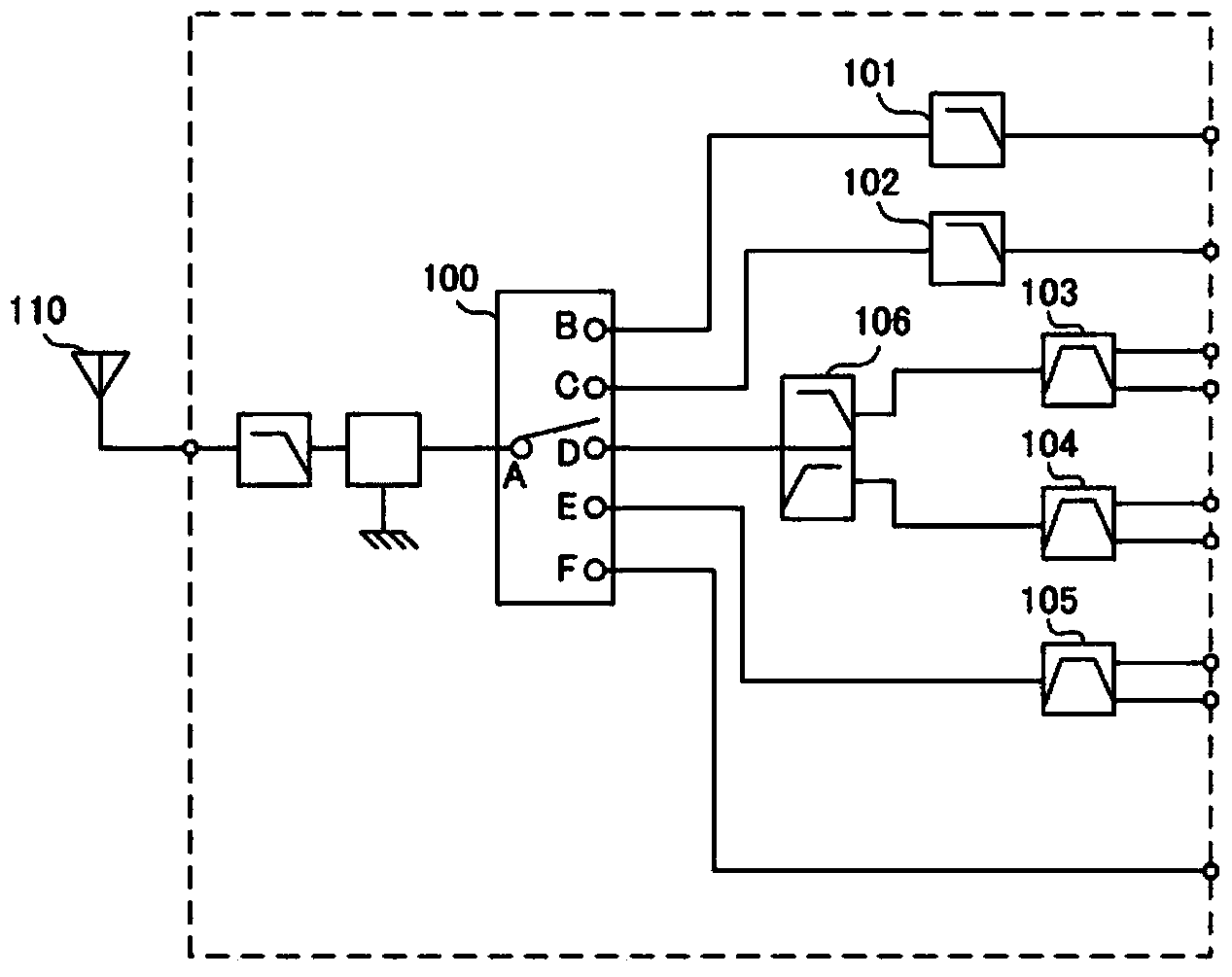

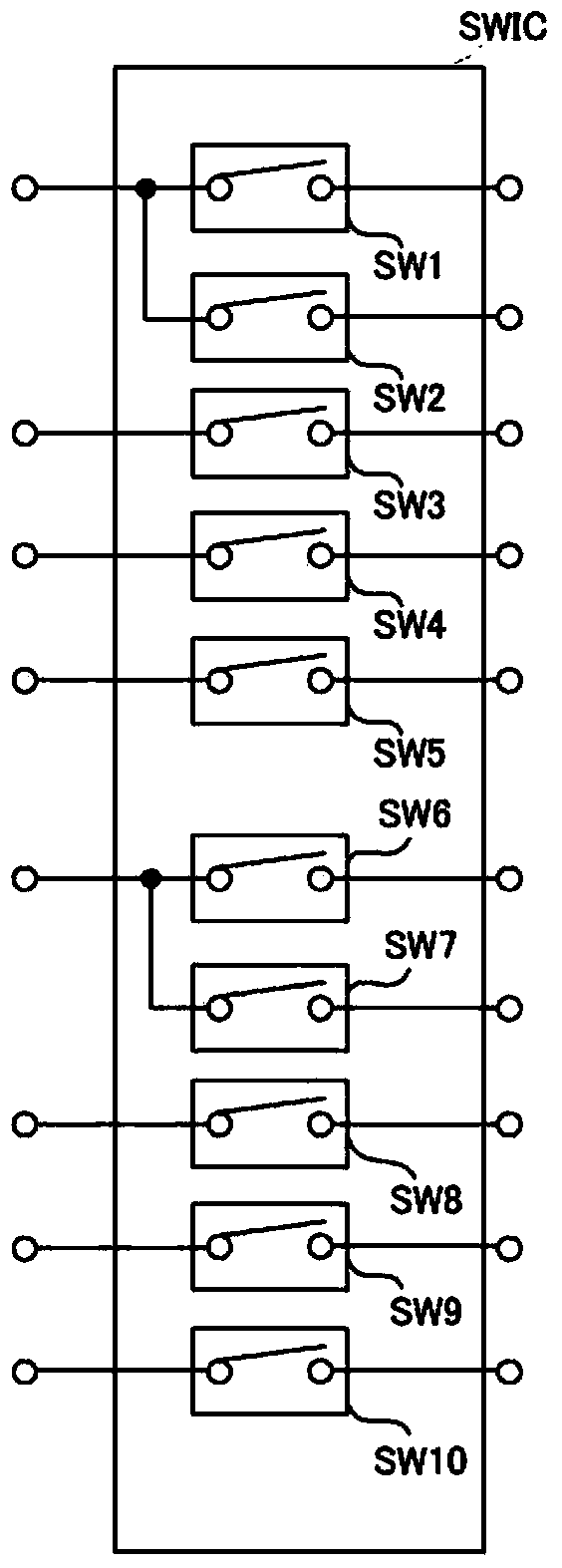

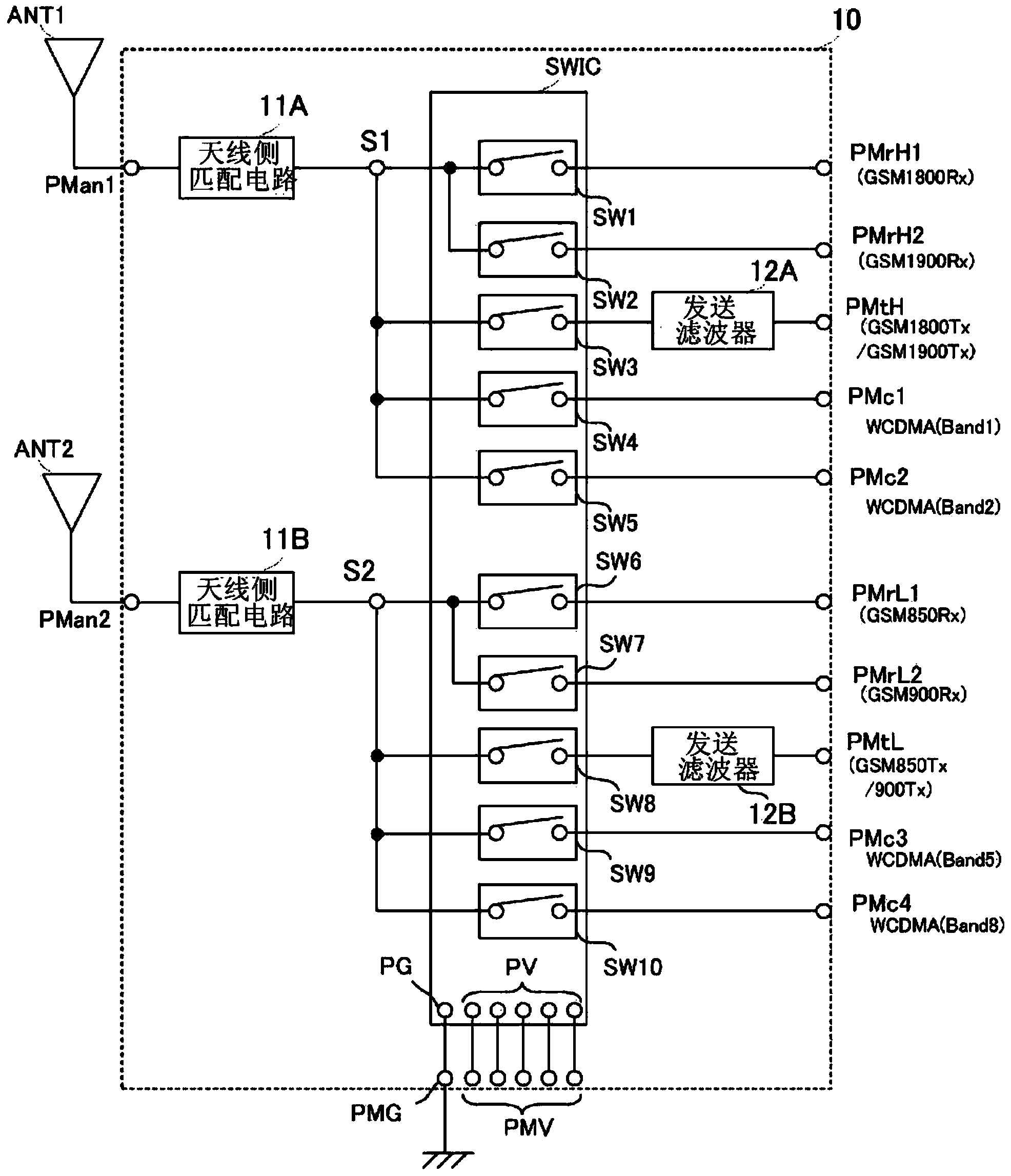

High-frequency module

ActiveCN103620971AEasy Design ChangesThere will be no problems such as cost surgesParticular array feeding systemsAntennas earthing switches associationElectricityCommunications system

This high-frequency module has port electrodes (PMan1, PMrH1, PMrH2, PMtH, PMc1, PMc2) which serve as external connection terminals provided on a laminated body of dielectric layers. Port electrode (PMan1) is connected to an antenna (ANT1). Port electrodes (PMrH1, PMrH2, PMtH, PMc1, PMc2) are respectively connected to communication systems having corresponding frequency bands. Port electrode (PMan1) is connected, by means of switch elements (SW1-SW5), to port electrodes (PMrH1, PMrH2, PMtH, PMc1, PMc2). Switch elements (SW1, SW2) and switch elements (SW3-SW5) are unconnected with each other inside a switch circuit (SWIC), and the switch elements can be connected by means of a common terminal (S1) provided outside the switch circuit (SWIC). Thus, the resulting high-frequency module can accommodate a design change using the same switch circuit without modifying the switch circuit.

Owner:MURATA MFG CO LTD

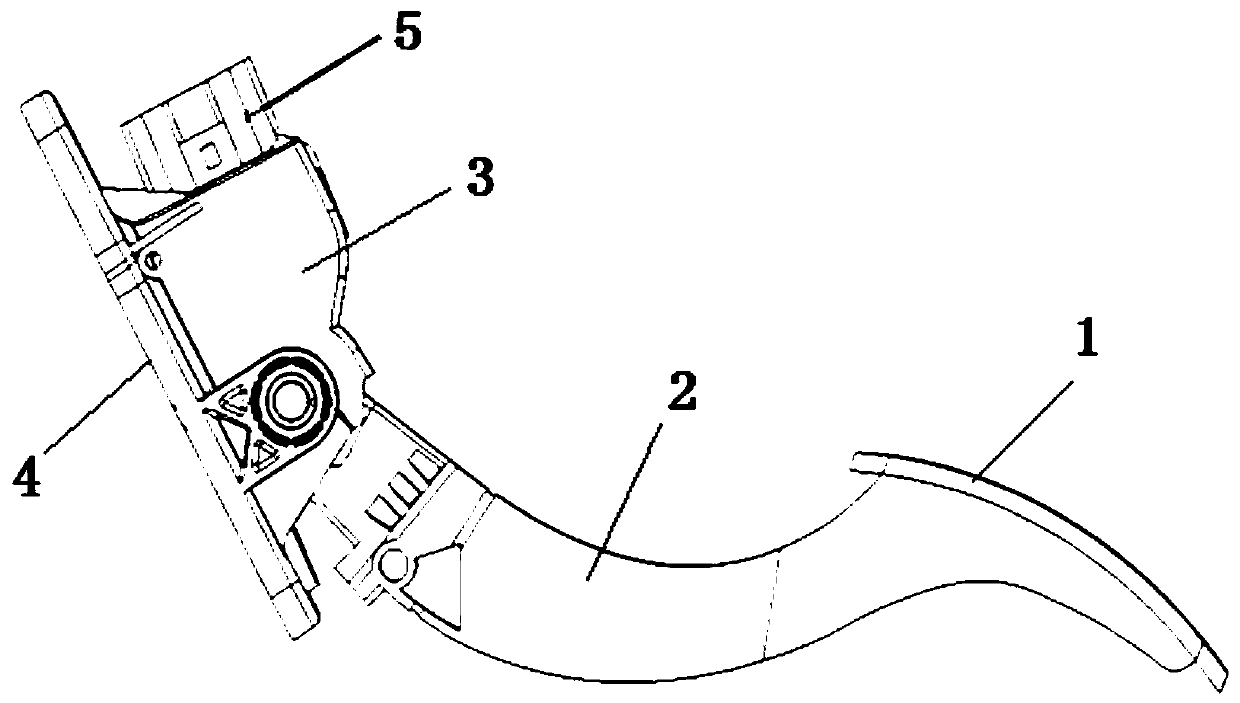

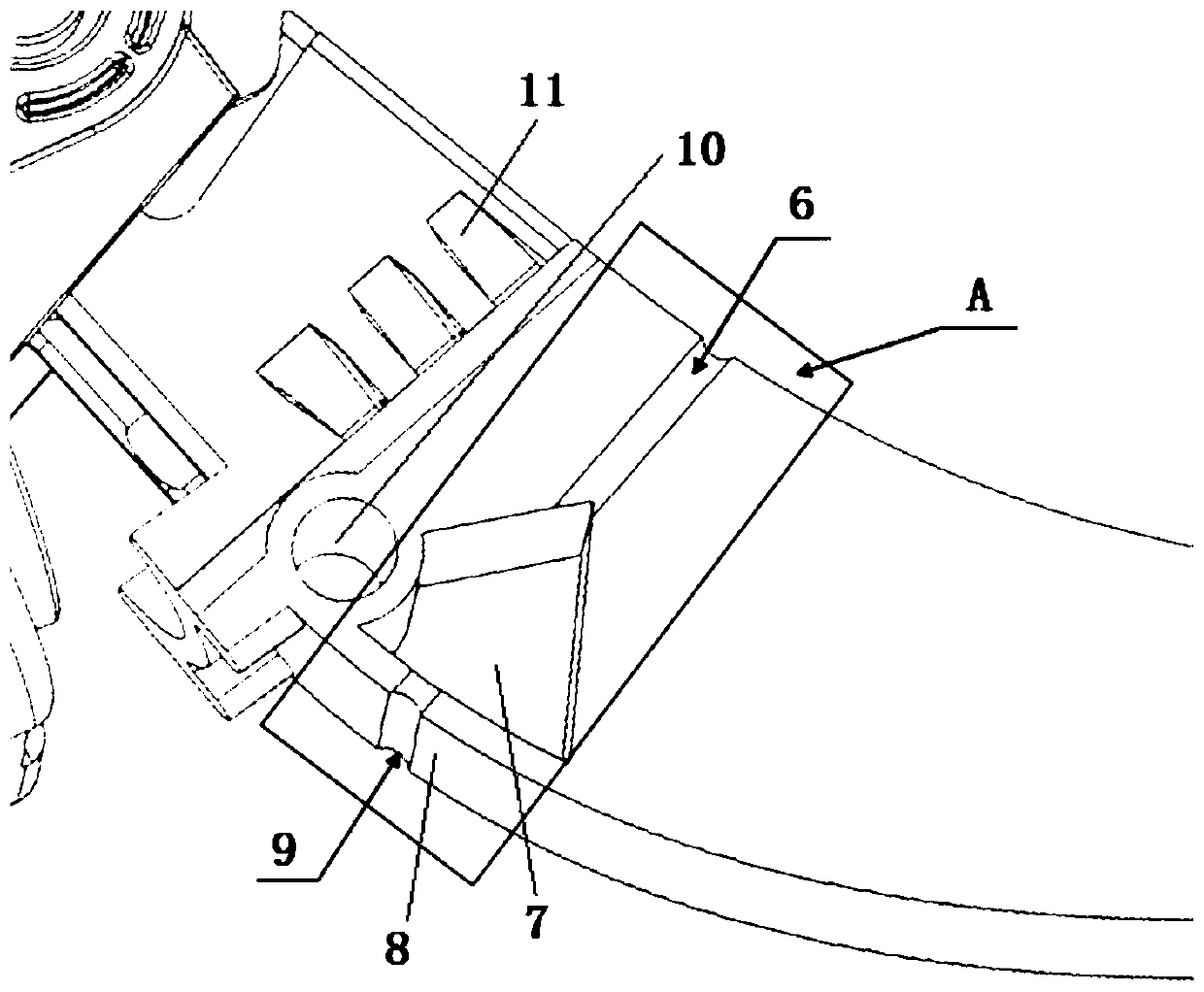

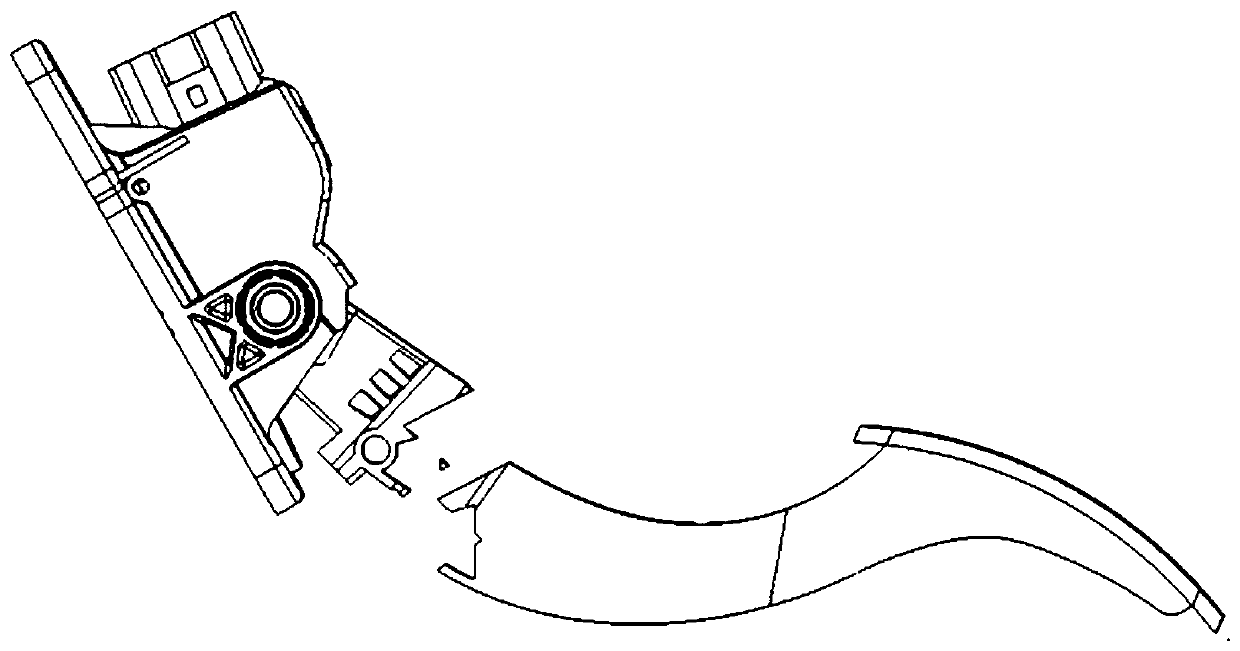

An energy-absorbing electronic accelerator pedal

ActiveCN106240360BReduce weightReduce procurement costsPropulsion unit arrangementsGlass fiberElectronic throttle

The invention discloses an energy-absorbing electronic throttle pedal comprising a pedal surface, a pedal arm and a pedal connecting support which are connected; the throttle pedal is made of composite glass fiber material; the pedal arm is provided with an energy-absorbing fracture zone which can be fractured under impact force. The energy-absorbing electronic throttle pedal has the advantages of simple structure, light weight, low cost and good safety performance, and can prevent drivers from being injured in the legs during collision; the energy-absorbing electronic throttle pedal has good application prospect.

Owner:CHERY COMML VEHICLE ANHUI

Elevator car frame

InactiveCN102642755BEasy Design ChangesAvoid deformationBuilding liftsManufacturing cost reductionEngineering

Owner:MITSUBISHI ELECTRIC CORP

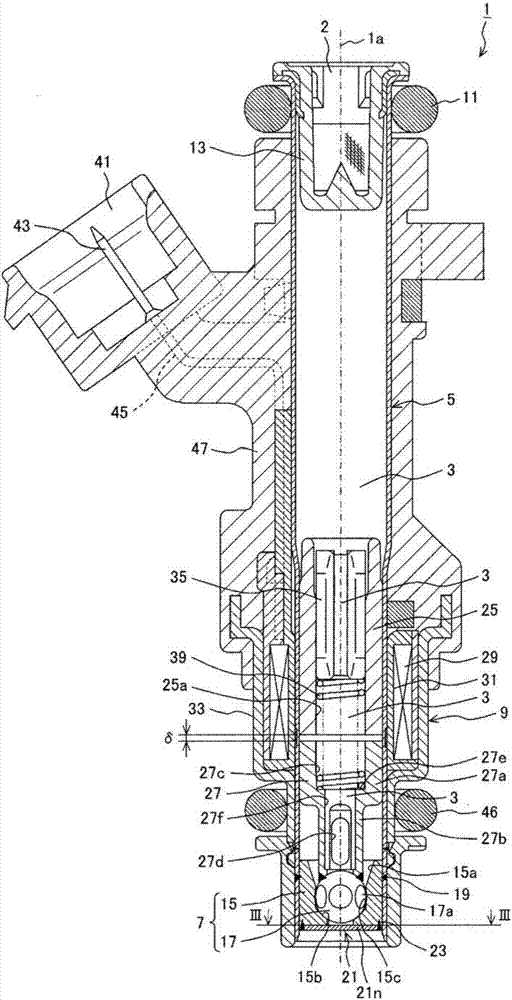

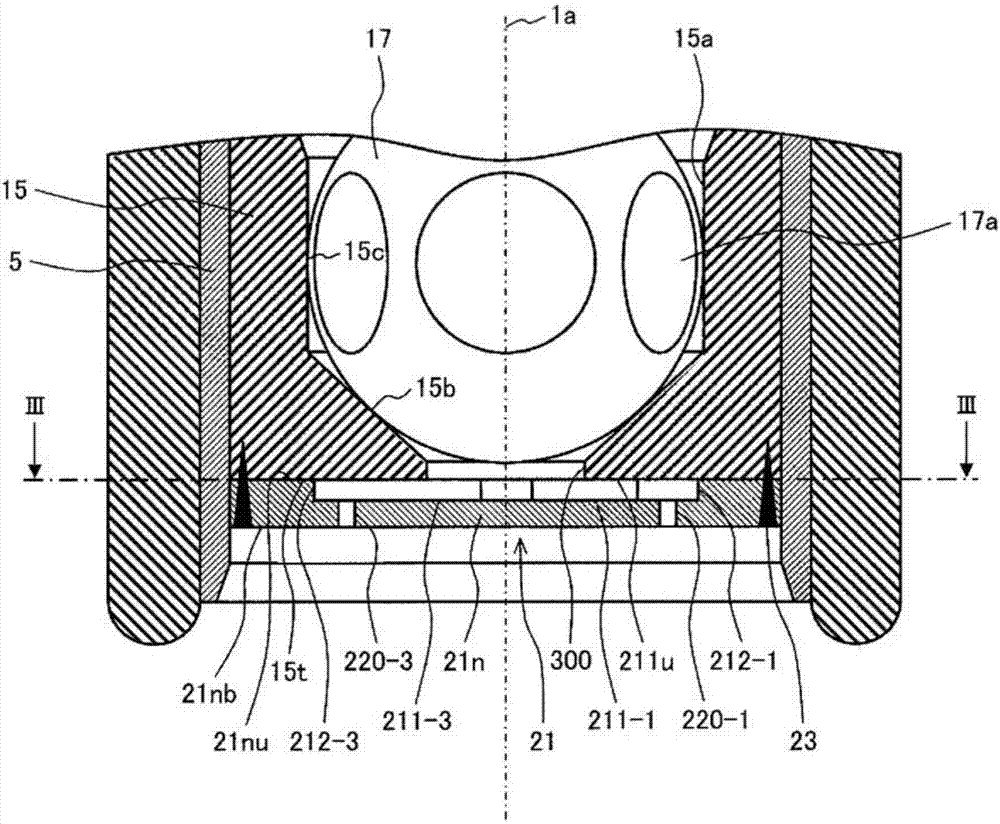

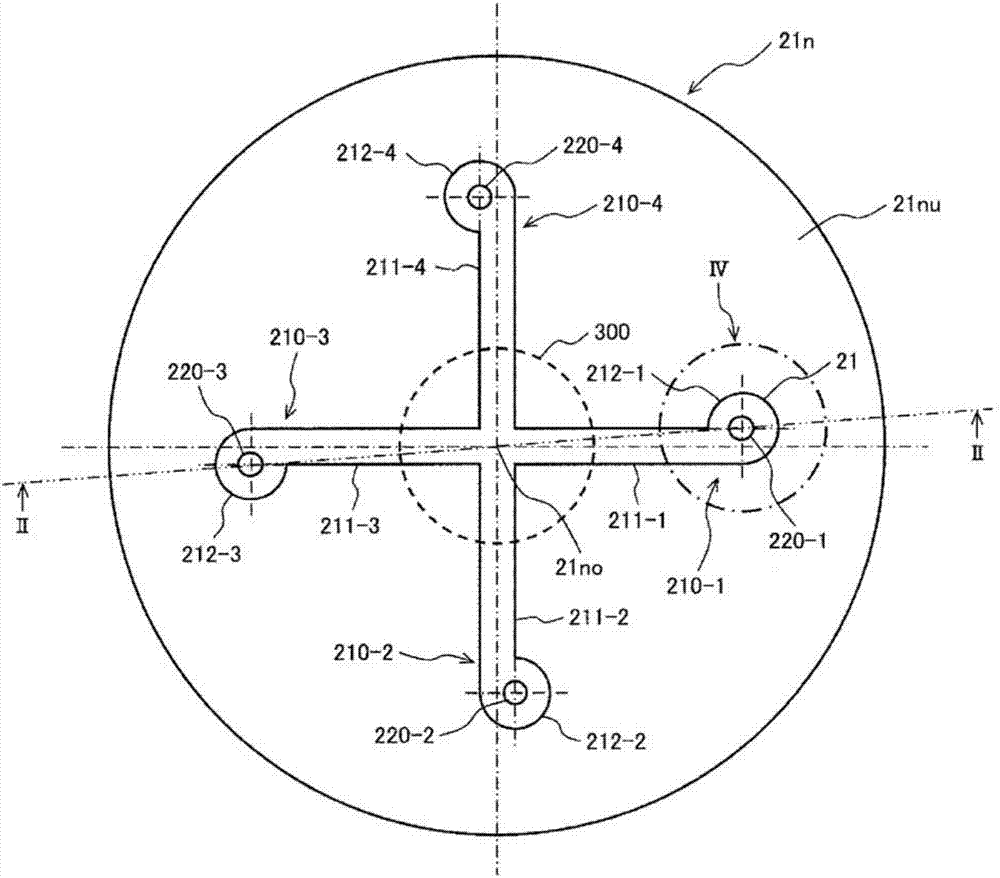

Fuel injection valve

ActiveCN107110086AEasy Design ChangesIncrease changeFuel injection apparatusMachines/enginesEngineeringFuel injection

This fuel injection valve comprises: a fuel injection hole 220 provided on a downstream side of a valve seat which a valve body comes into contact with and separates from; a swirl chamber 212 in which a fuel swirl flow path 212d is formed around an inlet opening 220i of the fuel injection hole 220; and a lateral passage 211 which opens in an inner circumferential wall 212c and supplies fuel to the swirl chamber 212. A center O2 of the inlet opening 220i of the fuel injection hole 220 is disposed displaced from a first position O1 in which the swirl-direction velocity component of the fuel flowing into the fuel injection hole 220 is maximal, to a second position O2 in which the swirl-direction velocity component is reduced, and a velocity component in the central axial direction of the fuel injection hole 220 is increased. By this means it is possible for the fuel injection quantity and the spray angle to be easily adjusted.

Owner:HITACHI ASTEMO LTD

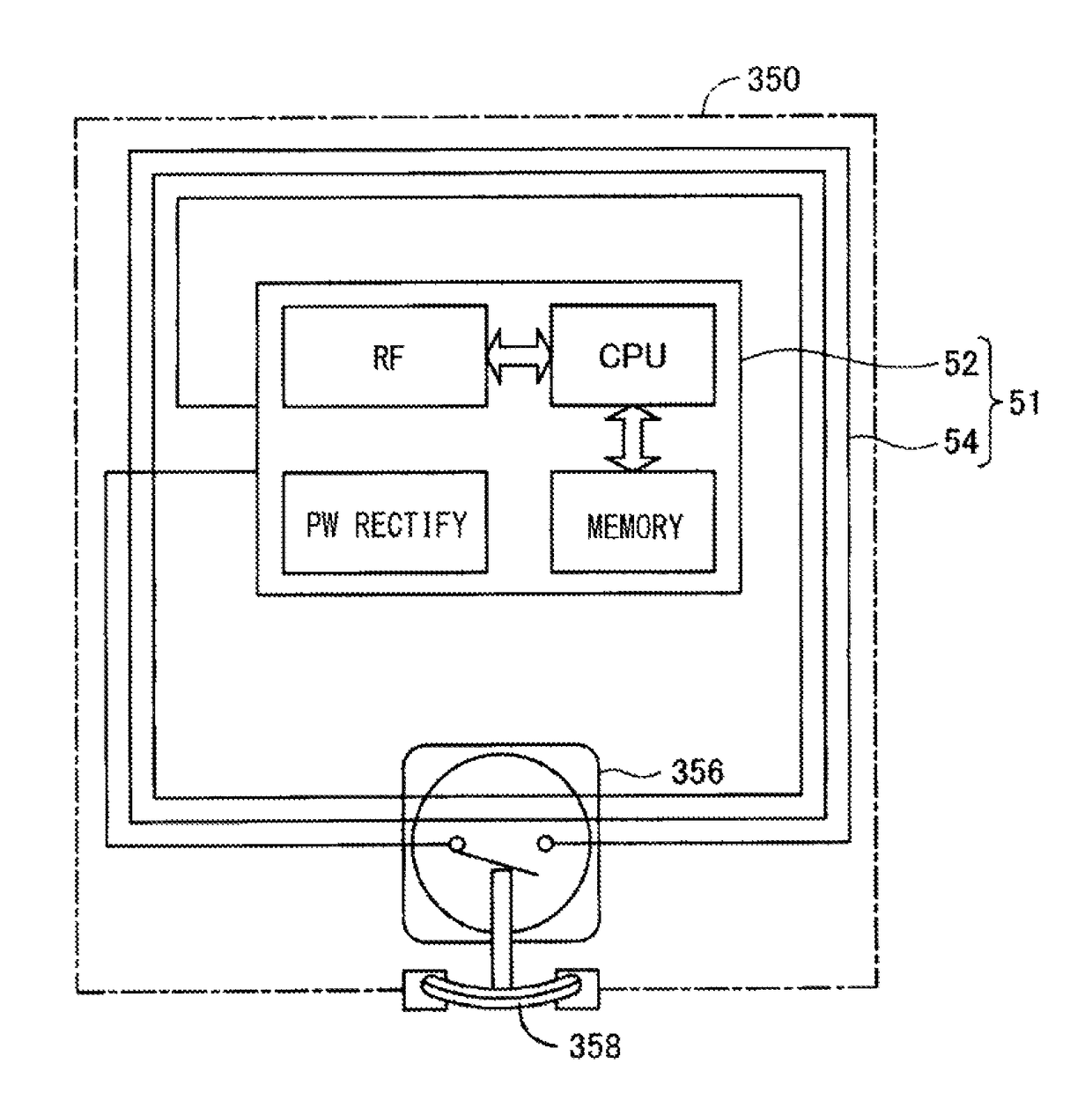

Card reader

ActiveUS9703999B2Reliable wireless communicationReduce areaSensing by electromagnetic radiationCard readerControl circuit

A card reader to read information in an integrated circuit (IC) card includes a housing, a first antenna, a control circuit, a switch unit, and a third antenna. The first antenna is disposed inside of the housing. The control circuit is to communicate with the IC card within a communication range of the first antenna and perform at least a process that acquires data from a memory in the IC card. The switch unit is provided to the housing and includes a radio frequency (RF) tag that includes a second antenna. The third antenna is disposed inside of the housing. The switch unit functions as a switch that performs a predetermined function by causing the RF tag to communicate with the control circuit via the second antenna and the third antenna when a predetermined condition is satisfied.

Owner:DENSO WAVE INC

Dehumidifying device and dehumidifying module

ActiveUS20150375171A1Easy Design ChangesSemi-permeable membranesLighting and heating apparatusInlet channelEngineering

The present application discloses a dehumidifying device including a base configured to define an inlet channel for first air flow, and an outlet channel for second air flow less humid than the first; and a first dehumidifier including a first inlet and outlet in communication with the inlet and outlet channel, and configured to dehumidify the first air between the first inlet and the first outlet to generate the second air. The base includes a first base portion configured to define first inlet and outlet regions for the first and second air flows; and a second base portion configured to define second inlet and outlet regions in communication with the first inlet and outlet regions. The first and second inlet regions form at least a part of the inlet channel. The first and second outlet regions form at least a part of the outlet channel.

Owner:NABLESCO CORP

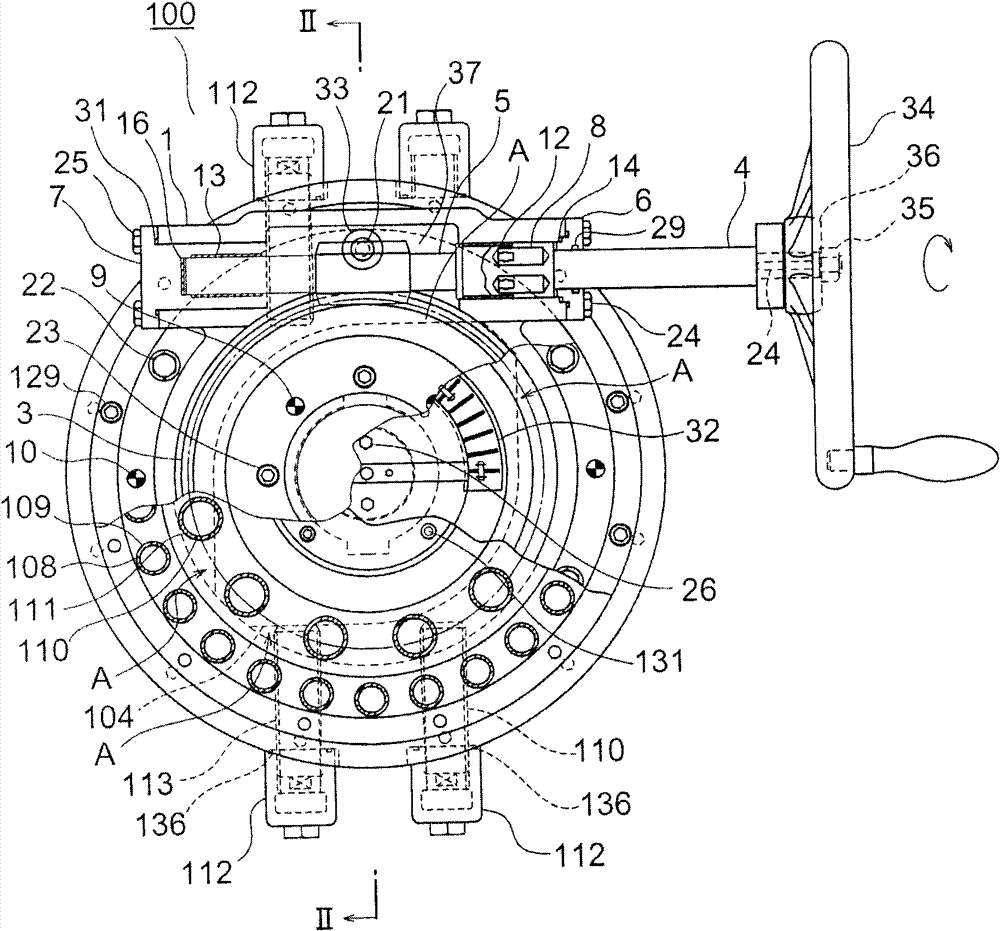

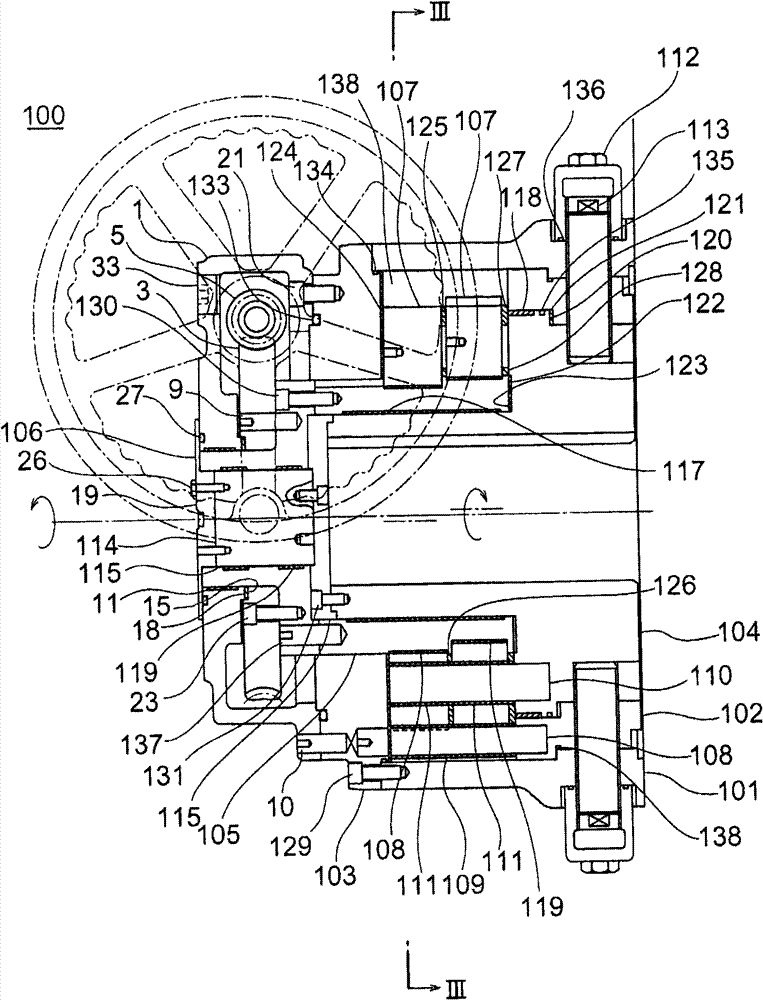

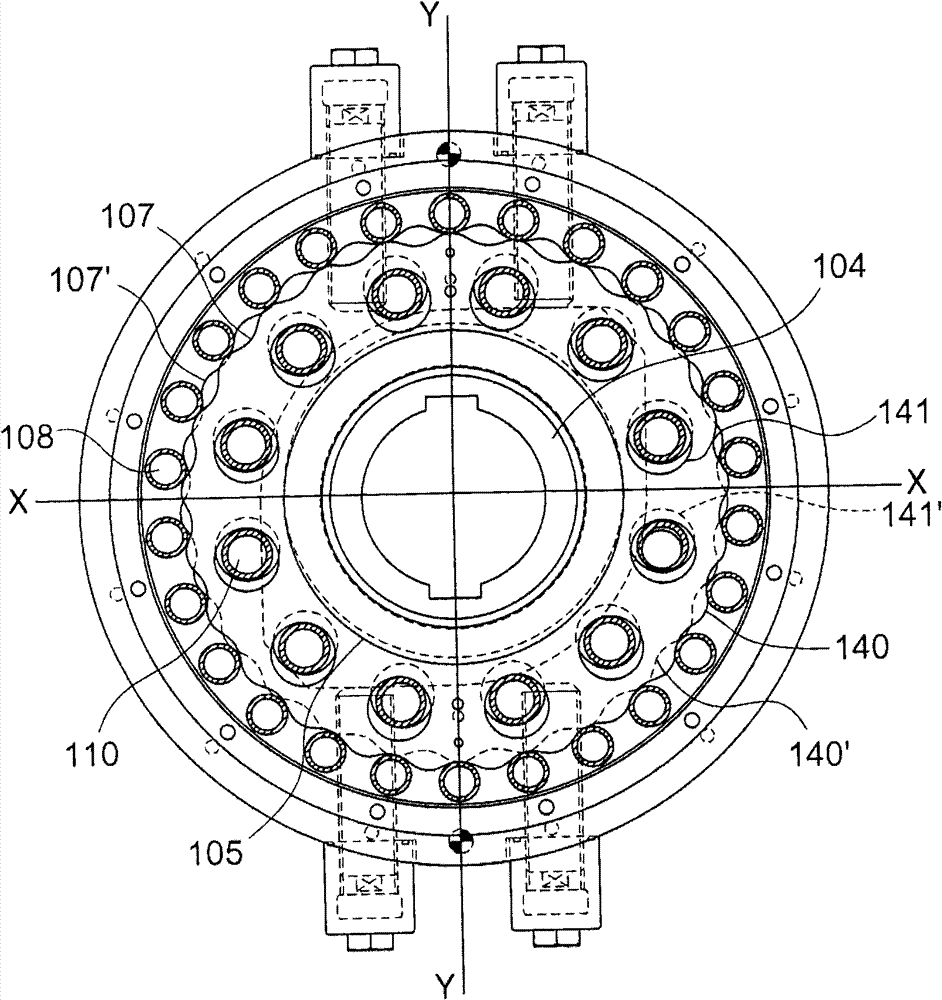

Valve operating device

InactiveCN102620044BCompact structureReduce output efficiencyOperating means/releasing devices for valvesRotational axisLine tubing

The invention provides a valve operating device. By adopting the valve operating device, assigned torque at an input side is reduced, the characteristics of a normal-inverse rotation prevention function can be played, an output torque can be high efficiently acquired at an output side, more assigned torque on the operation can be loaded, and a compact structure can be achieved. In order to open and close a valve by rotating a valve rod of the valve which is arranged on a pipeline and the like, the valve operating device comprises a worm gear mechanism, a whirlwind-type reducer and a valve rod embedded shaft, wherein the worm gear mechanism is provided with a mechanism for inputting the rotation, a rotating shaft which rotates through the mechanism and is provided with a worm gear and a worm wheel which is engaged onto the worm gear; the whirlwind-type reducer is used for implementing the rotation input and reduction output of an input shaft for supporting the worm gear; and the valve rod embedded shaft is used for transferring the rotation output from the whirlwind-type reducer to the valve rod of the valve, so that the normal-inverse rotation prevention function achieved through the engagement between the rotating shaft and the worm wheel can be acquired, the output torque can be high efficiently acquired through the whirlwind-type reducer, and the compact structure can be realized through the combination of the worm gear mechanism and the whirlwind-type reducer.

Owner:株式会社蒂克斯IKS