Patents

Literature

74results about How to "Efficient programming" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

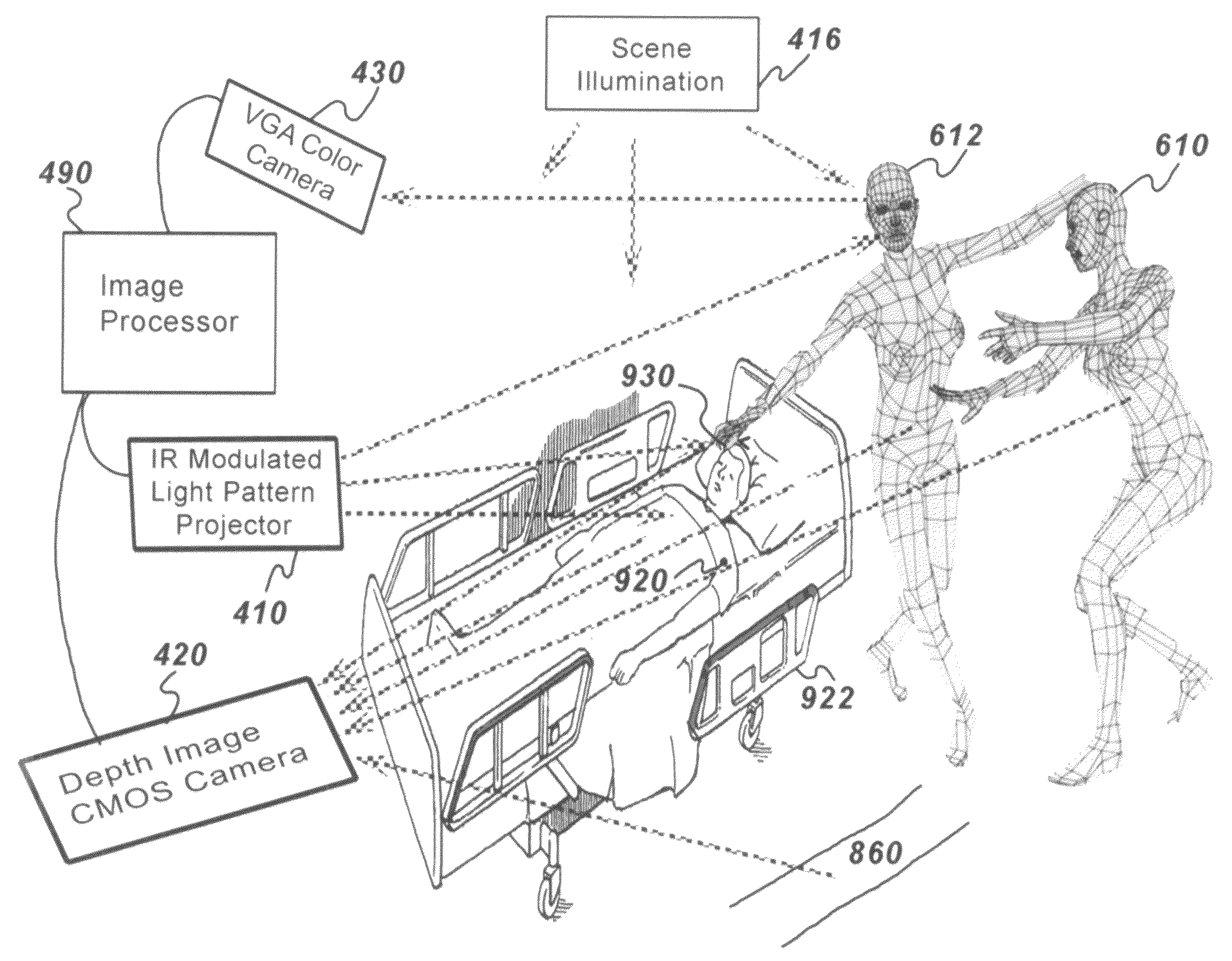

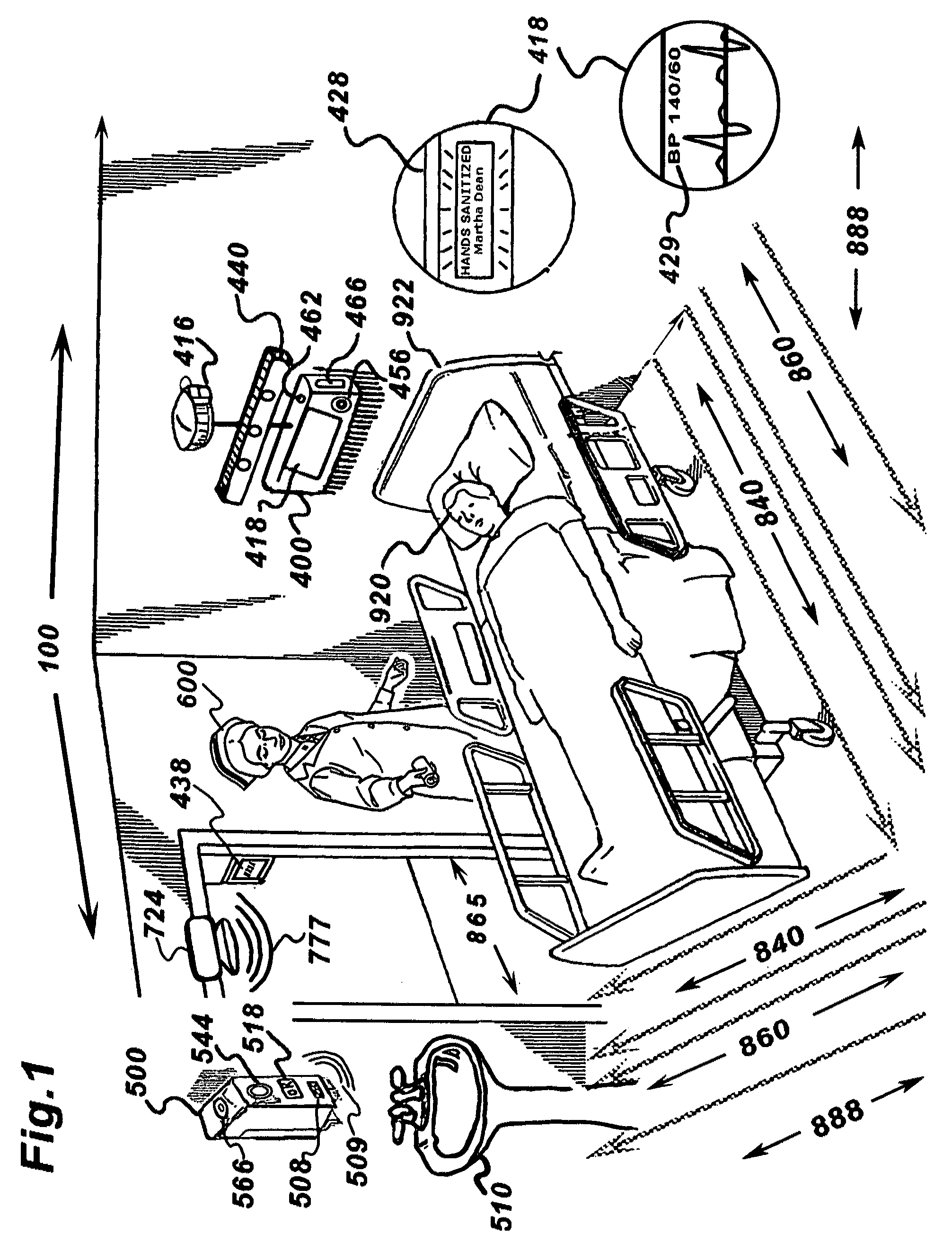

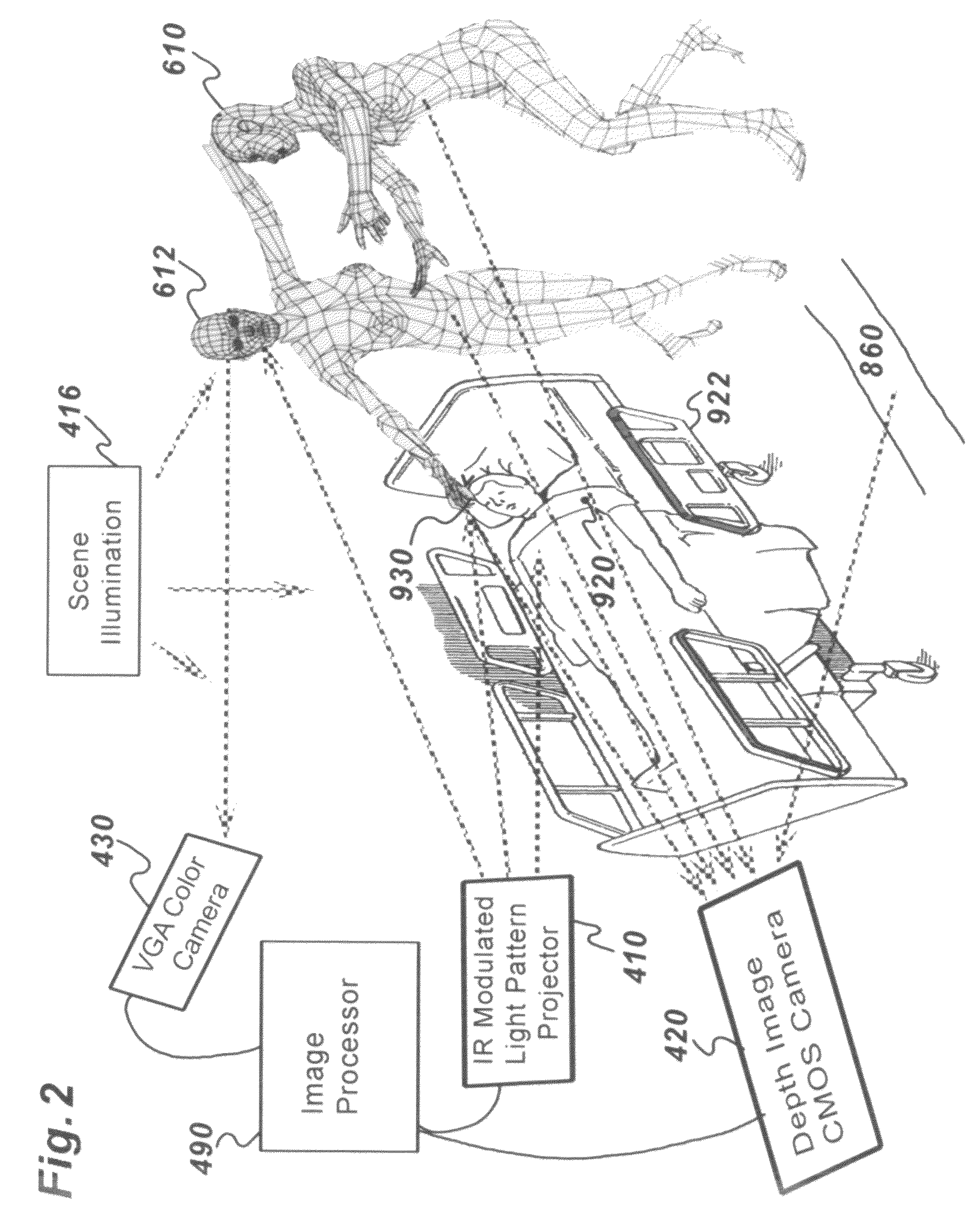

Systems and methods for monitoring caregiver and patient protocol compliance

ActiveUS20120212582A1Improve abilitiesSimple processAlarmsHealthcare resources and facilitiesCaregiver personPatient compliance

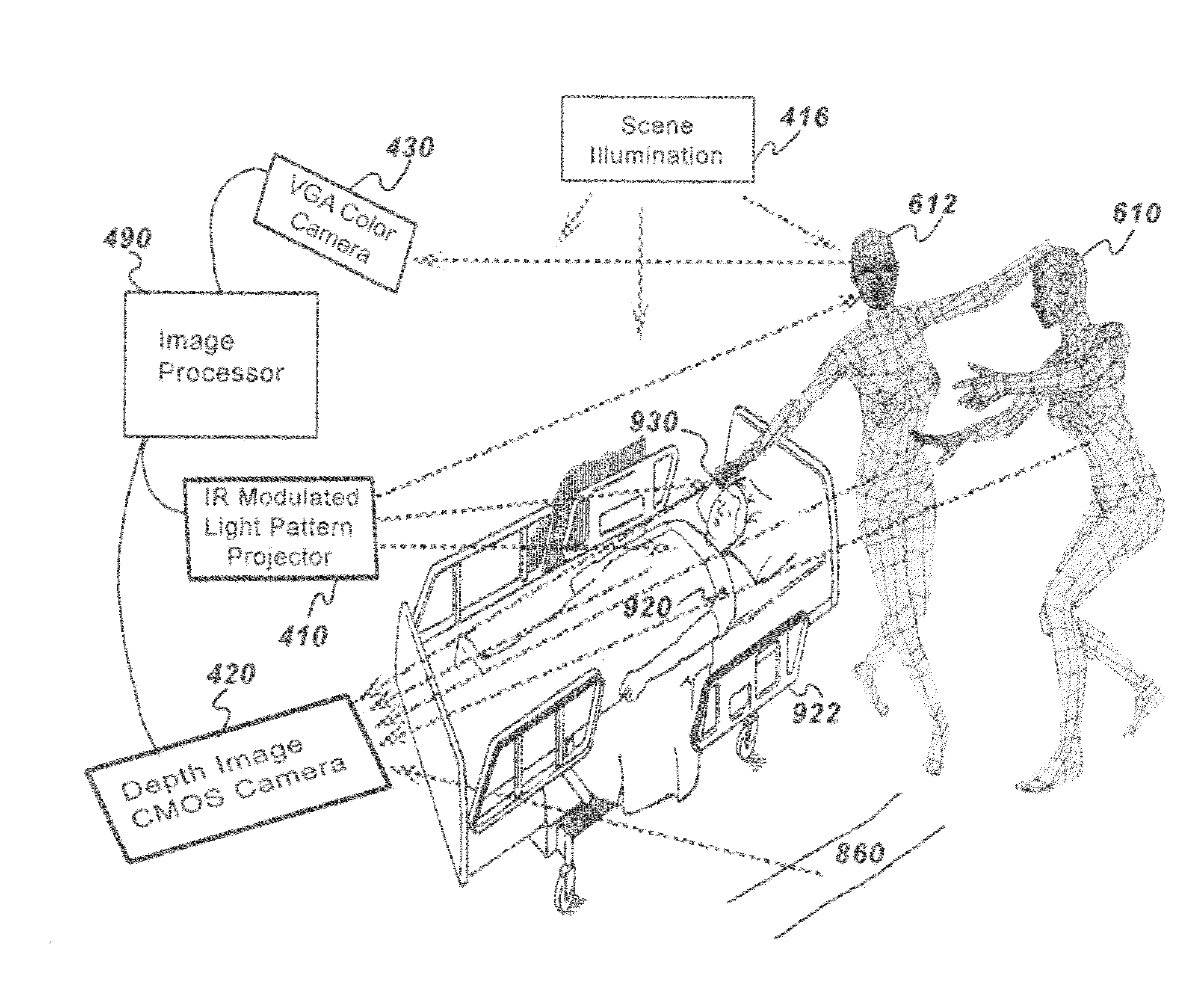

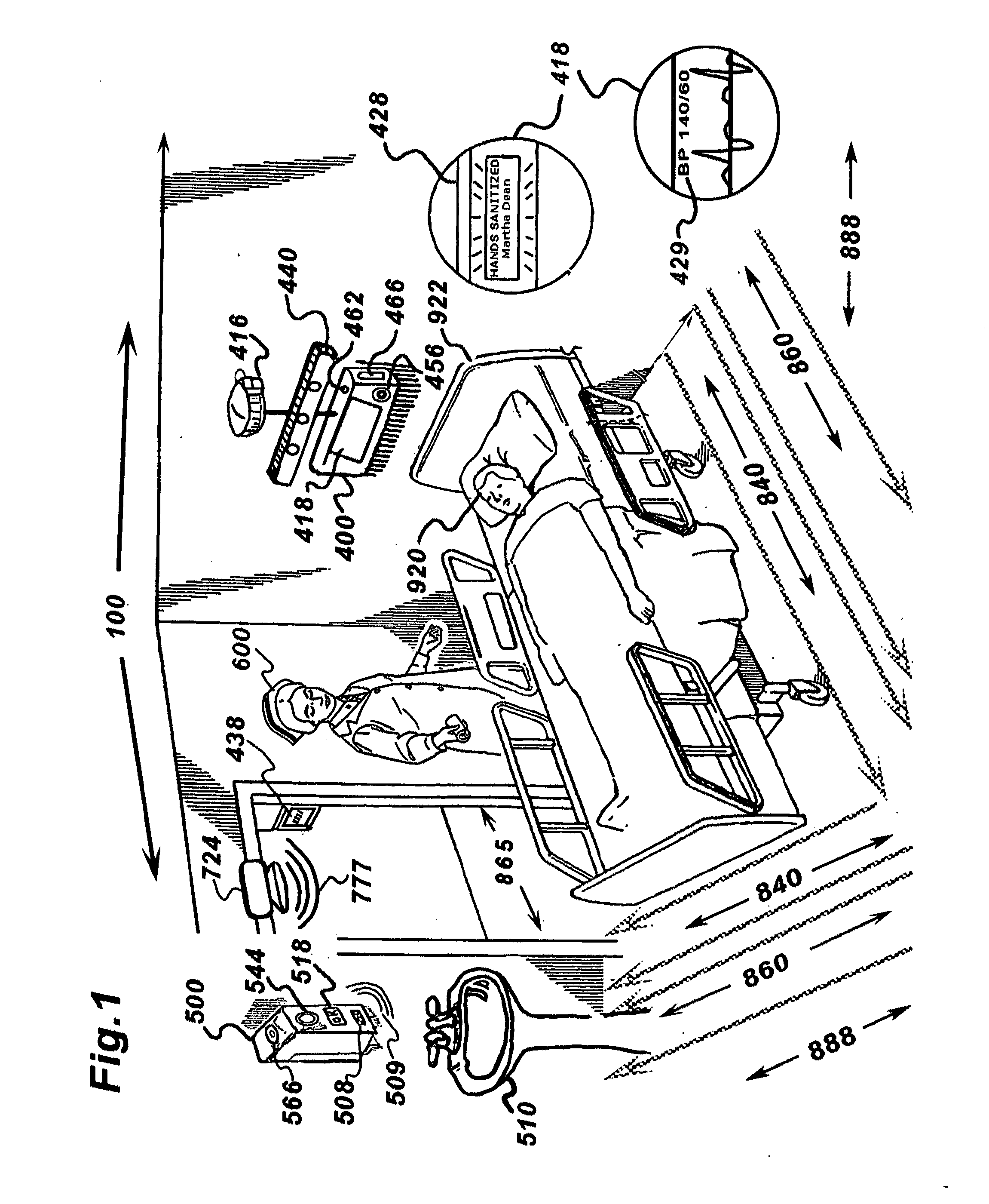

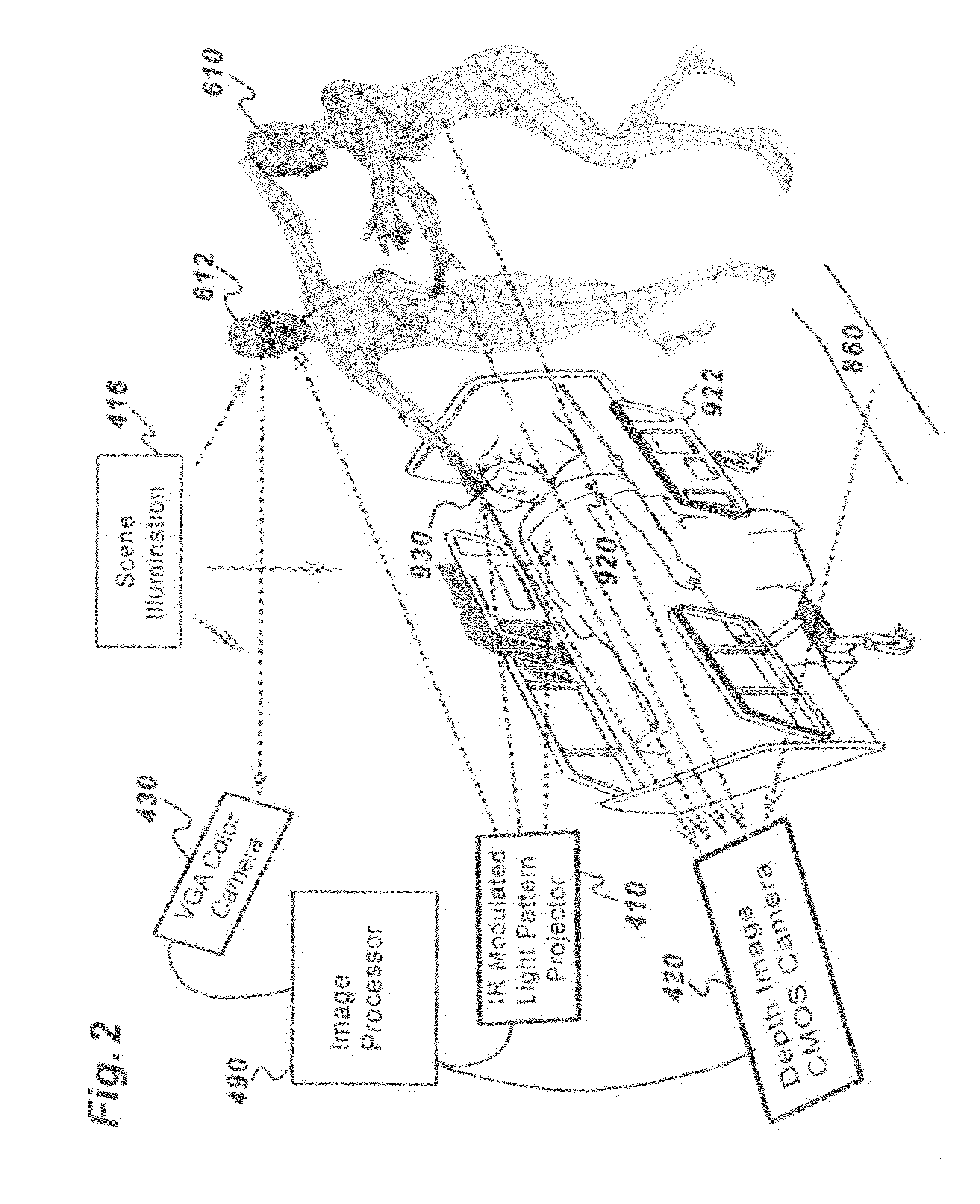

A system and methods is provided for facilitating, monitoring and recording caregiver and patient compliance with established hospital hand hygiene protocols. The system comprises a 3-D imaging and monitoring assembly and an optional intelligent programmable monitor / sanitizer. Three dimensional imagery tracks a caregiver's movements and location while generating a representative image value. Information acquired by the imaging system determines the proximity of a caregiver to the patient and / or contamination source and determines if the sanitizers provided have been utilized and if so, at an appropriate time and distance from the patient per hospital protocol. While being monitored, a representative Avatar based on physical characteristics derived from three dimensional images of the caregiver and patient may be generated so as to maintain anonymity of both unless a violation of institutional protocol occurs which may be forensically recorded in real-time for analysis.

Owner:DEUT RICHARD

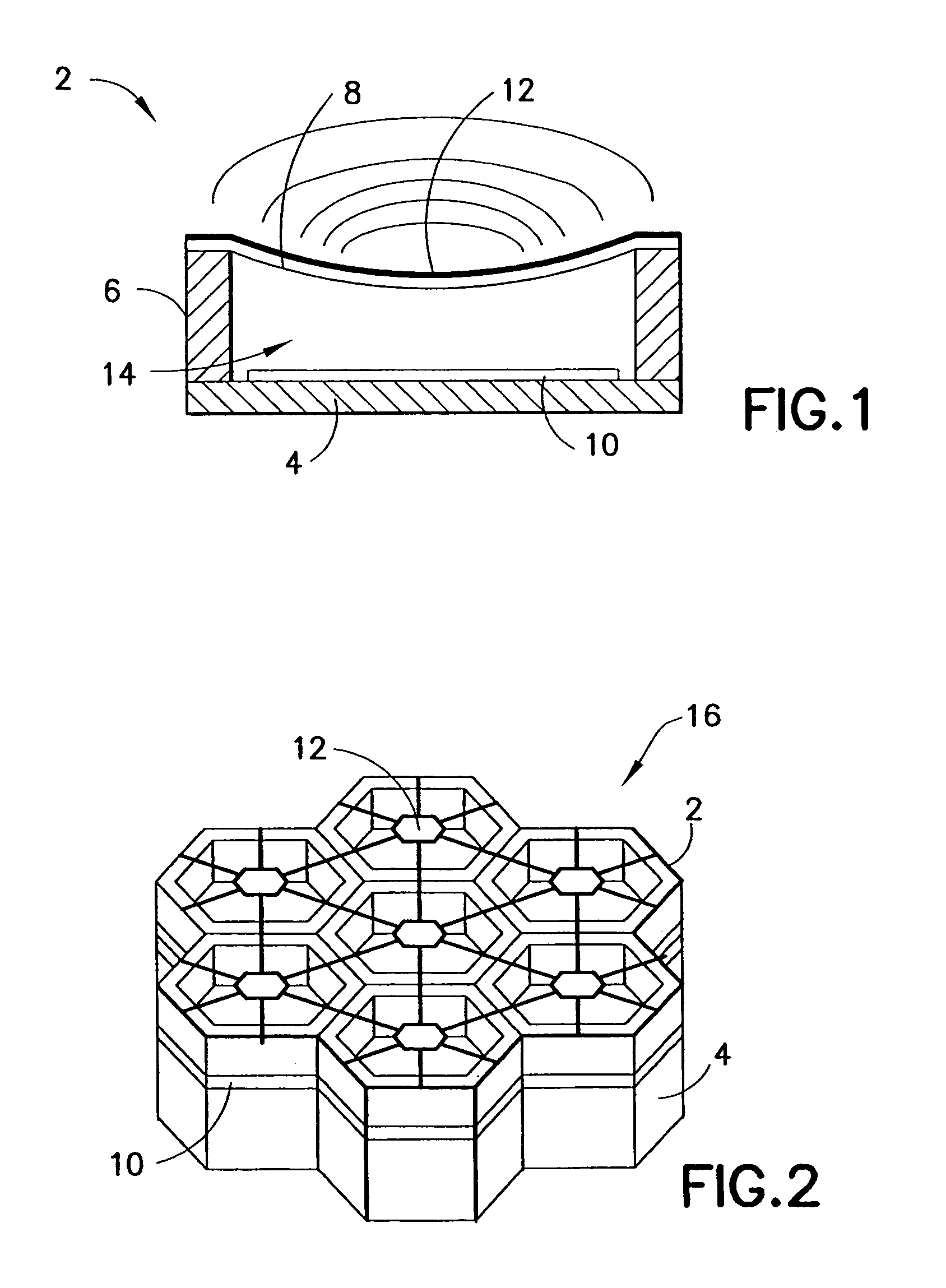

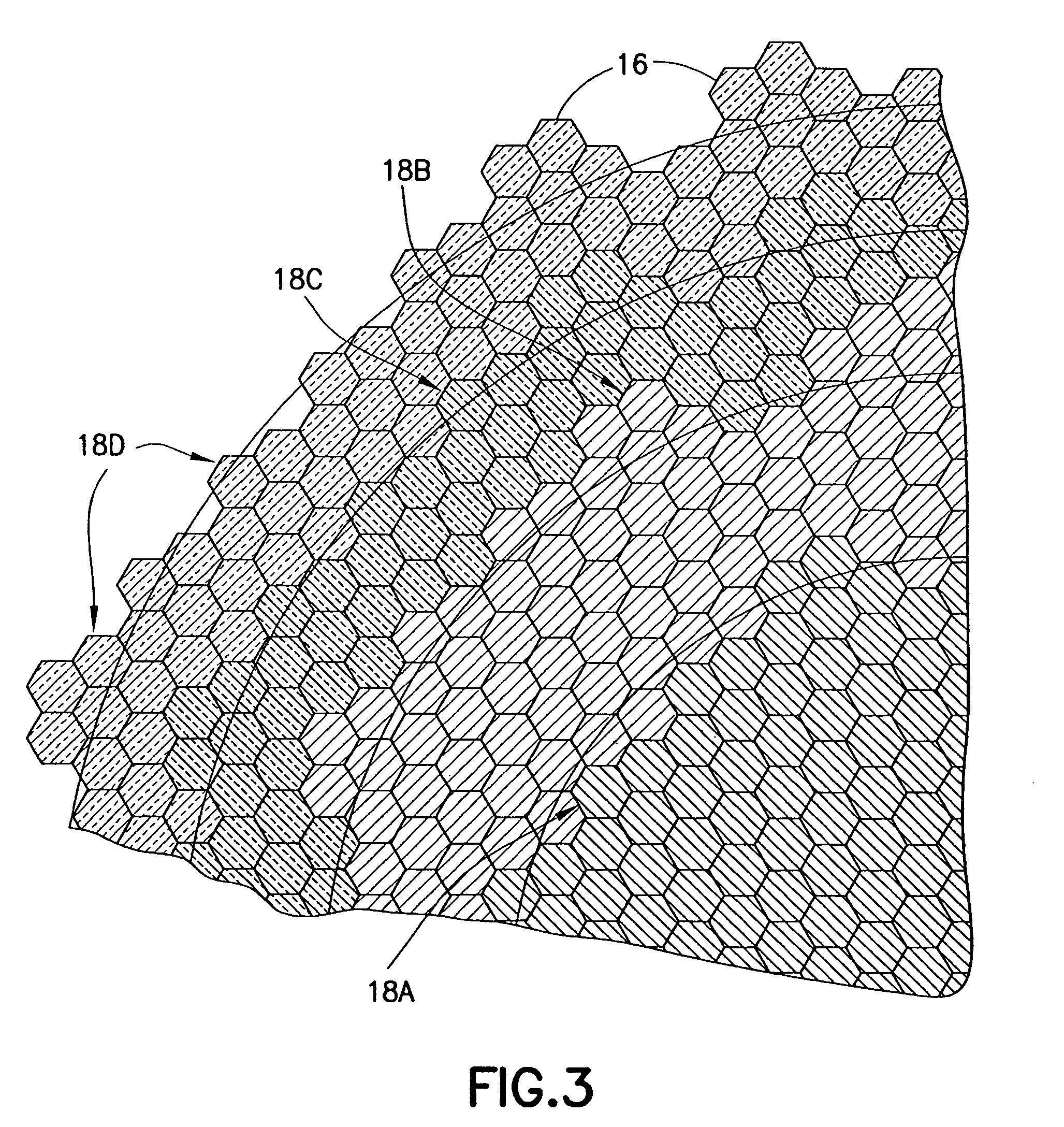

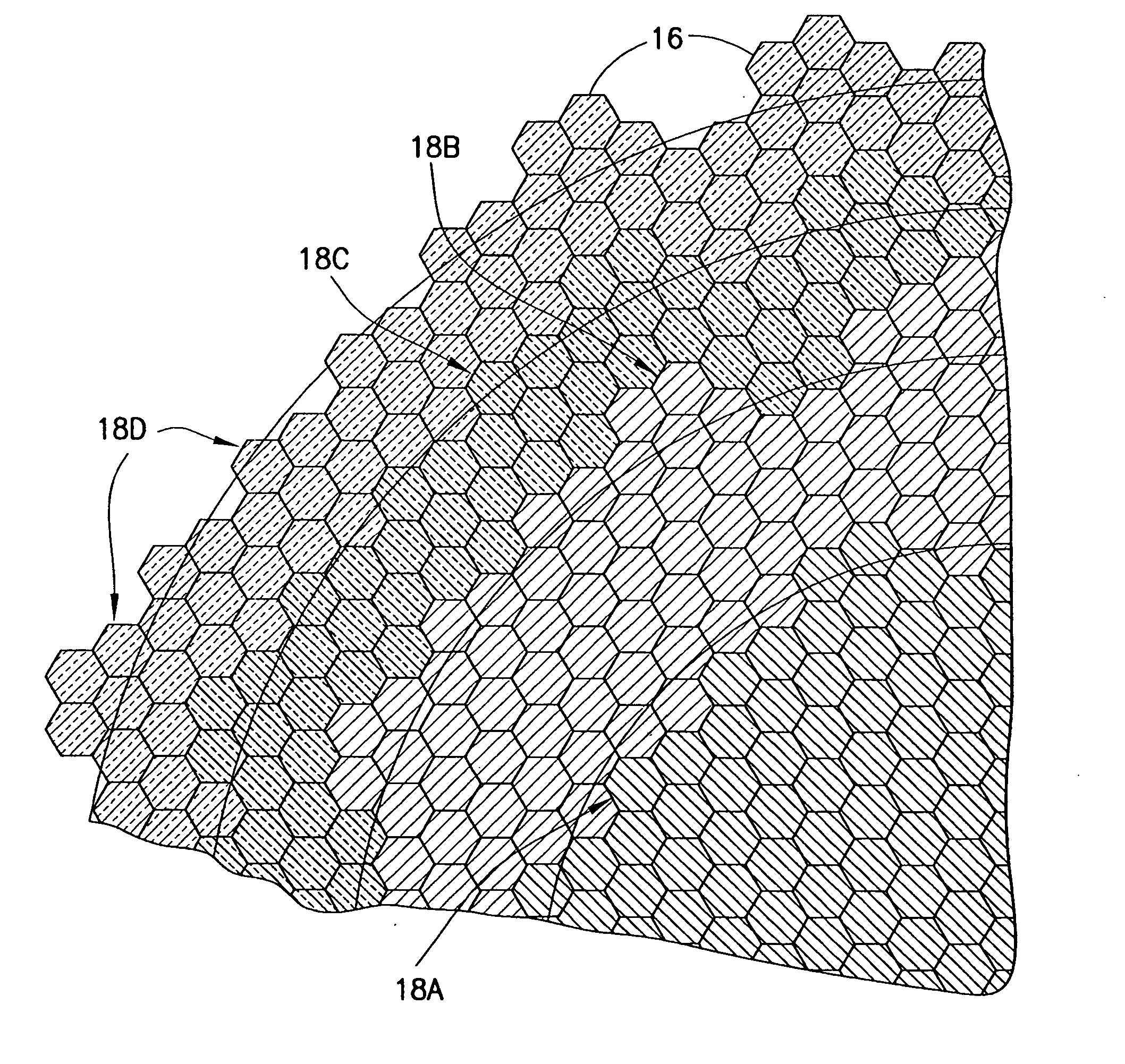

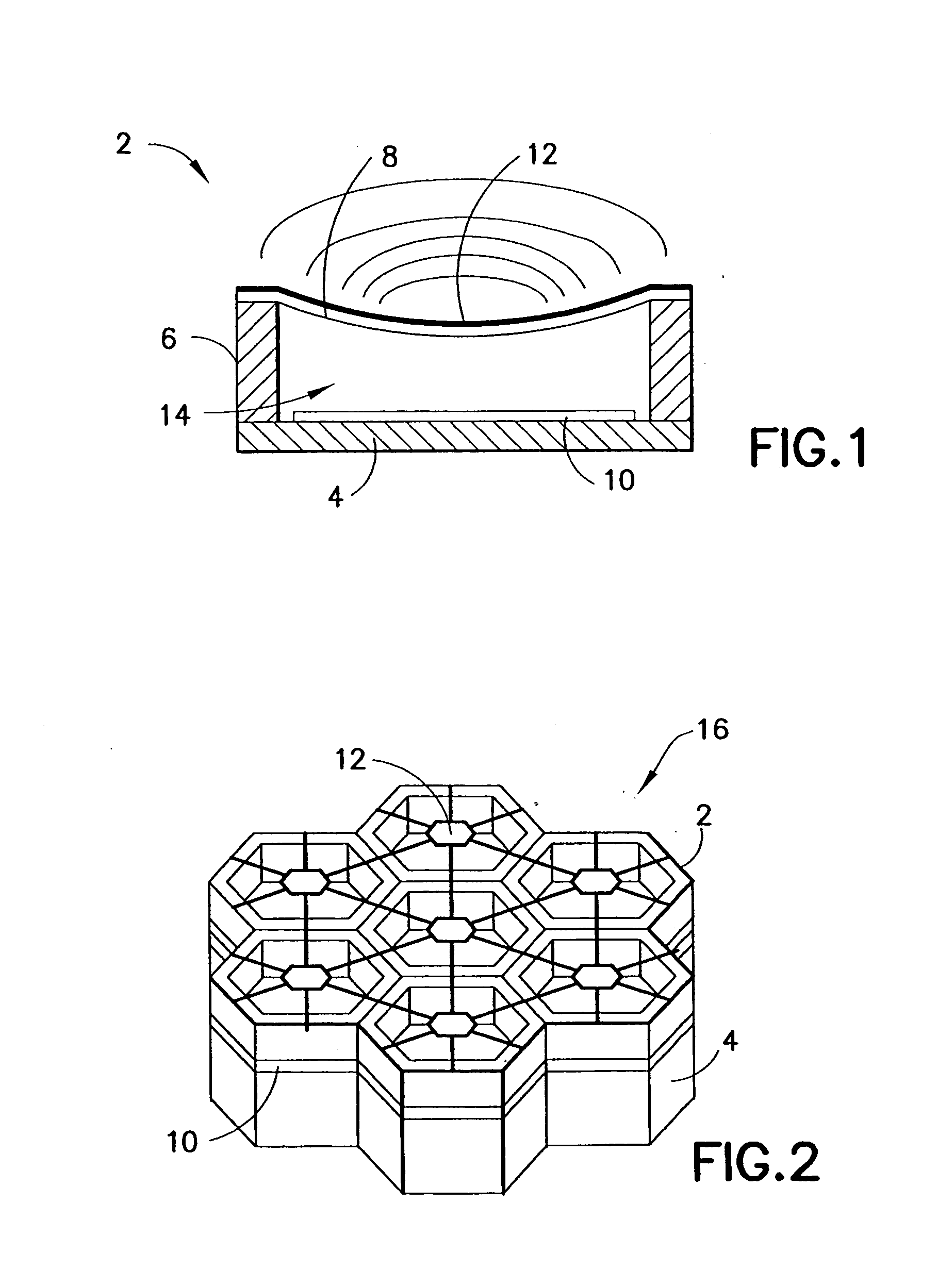

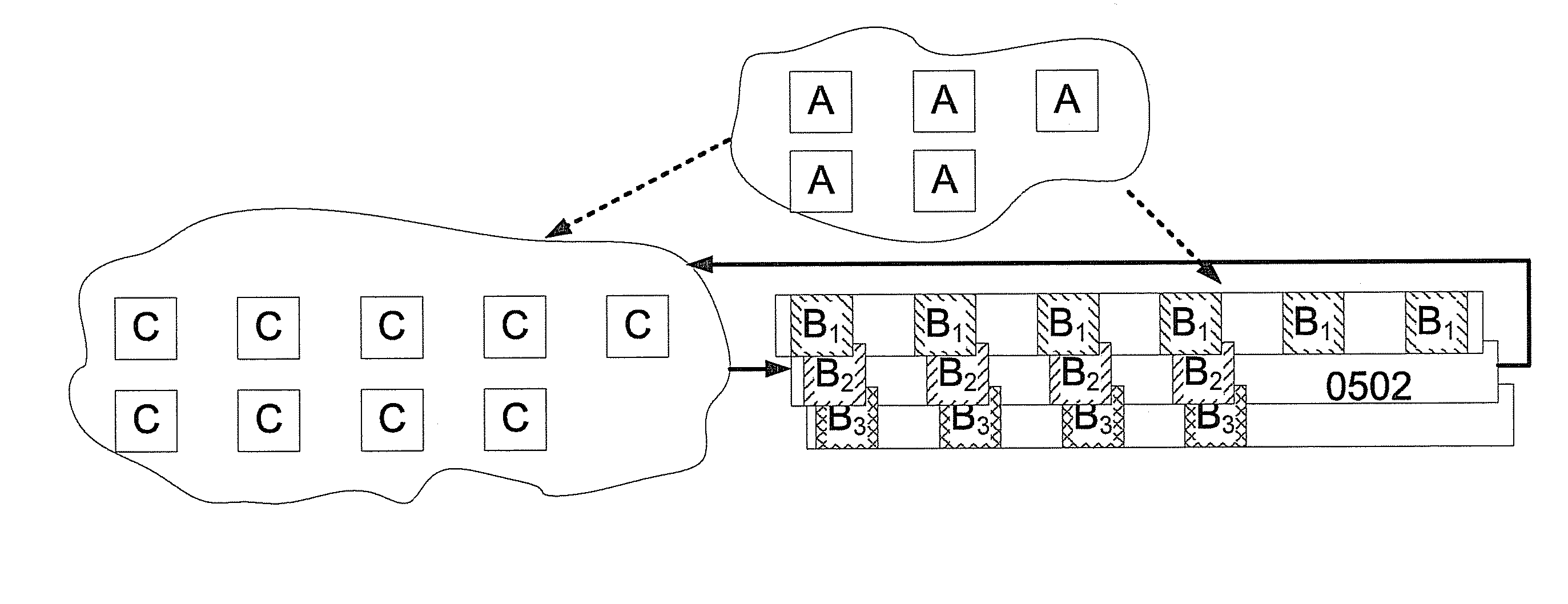

Method and apparatus for controlling scanning of mosaic sensor array

InactiveUS7313053B2Quick configurationMinimize powerUltrasonic/sonic/infrasonic diagnosticsWave based measurement systemsComputer hardwareSensor array

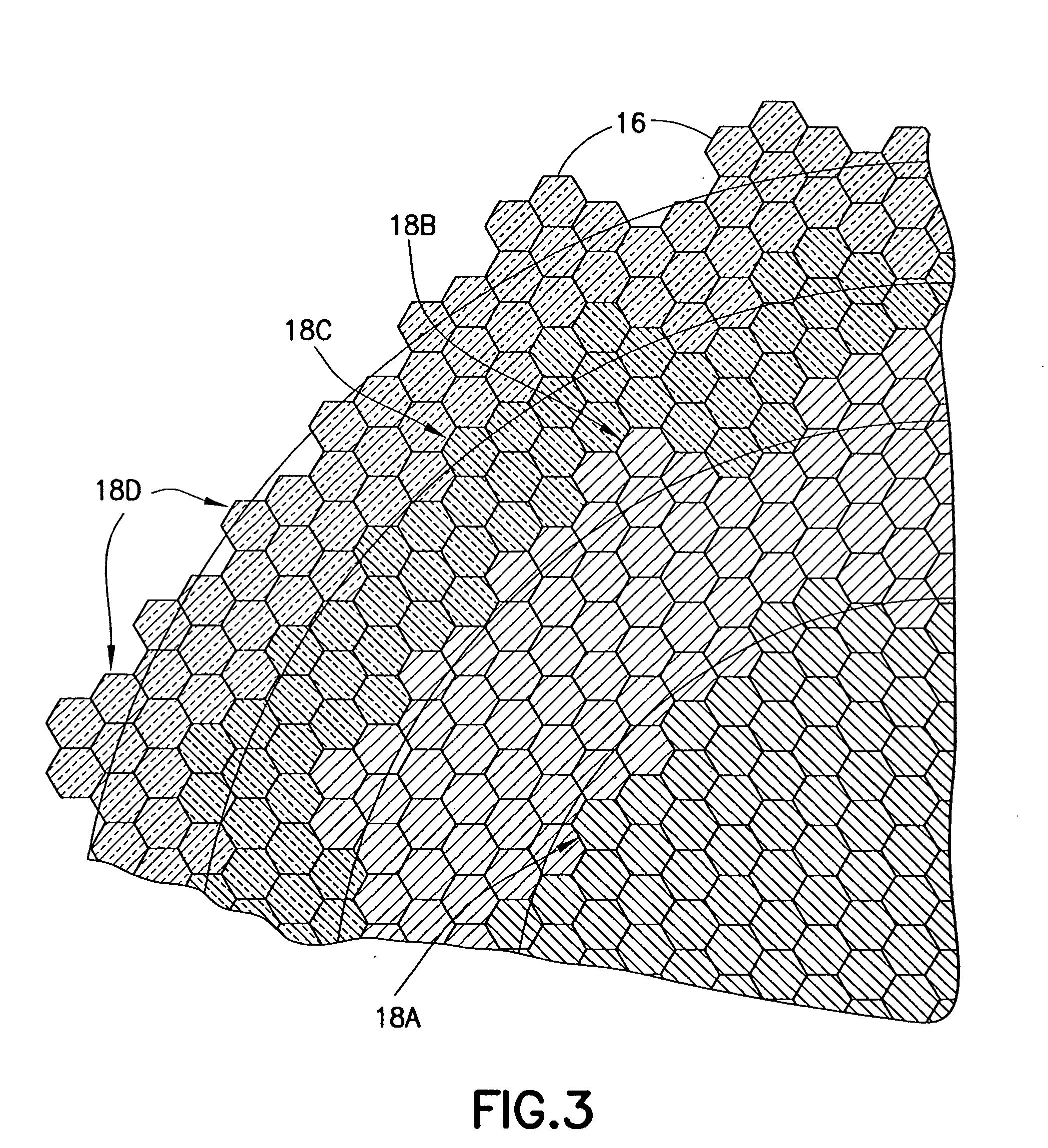

A scanning architecture that makes it possible to update only those ultrasonic transducer subelements of a mosaic transducer array that change from view to view. The configuration of the switch matrix is fully programmable. The switch matrix includes access switches that connect subelements to bus lines and matrix switches that connect subelements to subelements. Each subelement has a unit switch cell associated therewith, each unit switch cell comprising at least one access switch, at least one matrix switch, and addressing and control logic. Optionally, each unit switch cell also includes latches for storing the future switch states of the switches to be programmed. The switches themselves have memory for storing their current switch states.

Owner:GENERAL ELECTRIC CO

Method and apparatus for controlling scanning of mosaic sensor array

InactiveUS20050057284A1Quick configurationMinimize powerUltrasonic/sonic/infrasonic diagnosticsElectronic switchingSensor arrayUltrasonic sensor

A scanning architecture that makes it possible to update only those ultrasonic transducer subelements of a mosaic transducer array that change from view to view. The configuration of the switch matrix is fully programmable. The switch matrix includes access switches that connect subelements to bus lines and matrix switches that connect subelements to subelements. Each subelement has a unit switch cell associated therewith, each unit switch cell comprising at least one access switch, at least one matrix switch, and addressing and control logic. Optionally, each unit switch cell also includes latches for storing the future switch states of the switches to be programmed. The switches themselves have memory for storing their current switch states.

Owner:GENERAL ELECTRIC CO

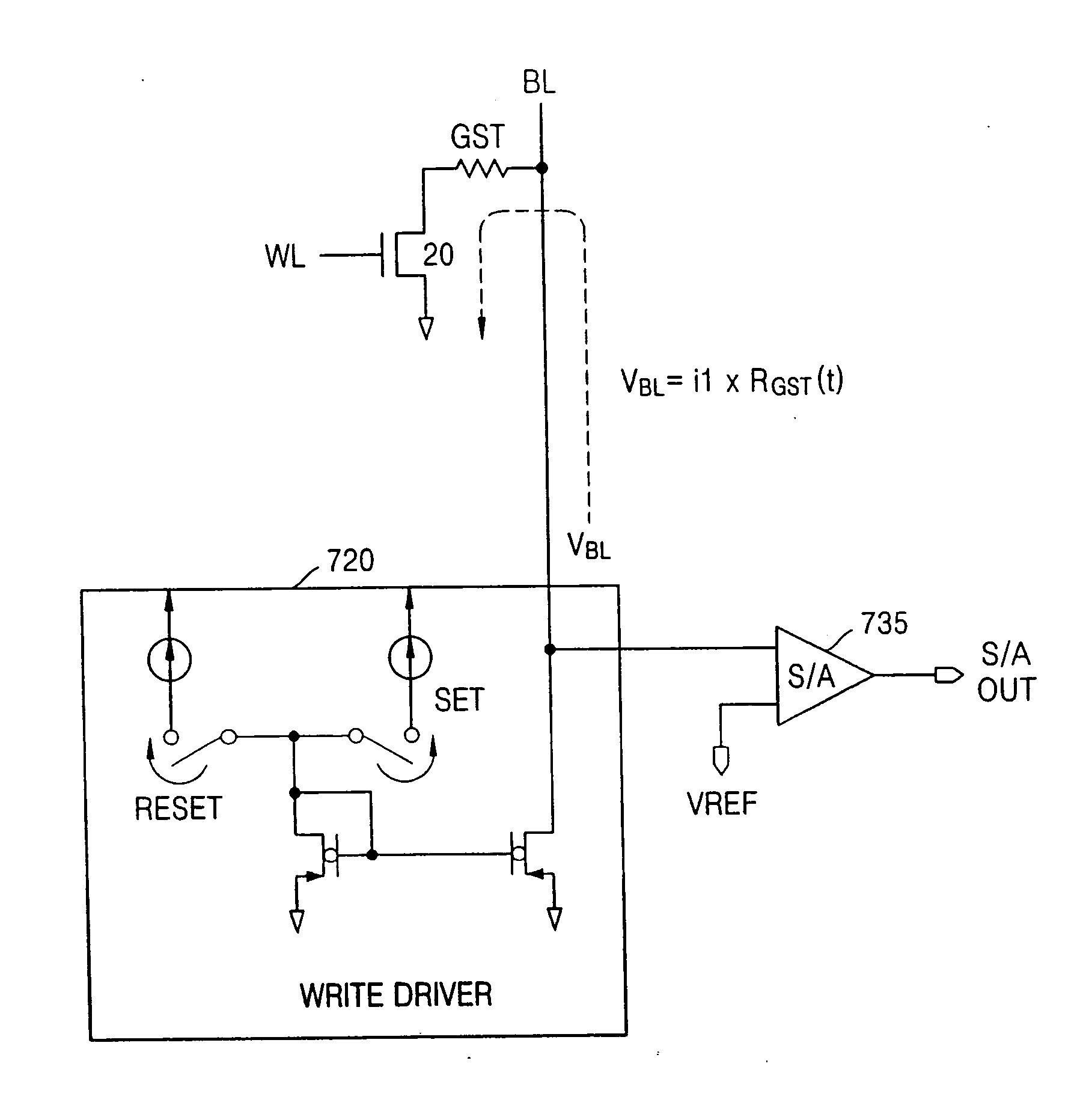

Device and method for pulse width control in a phase change memory device

ActiveUS7085154B2Reduced programming errorReduce power consumptionSolid-state devicesRead-only memoriesBit lineComputer hardware

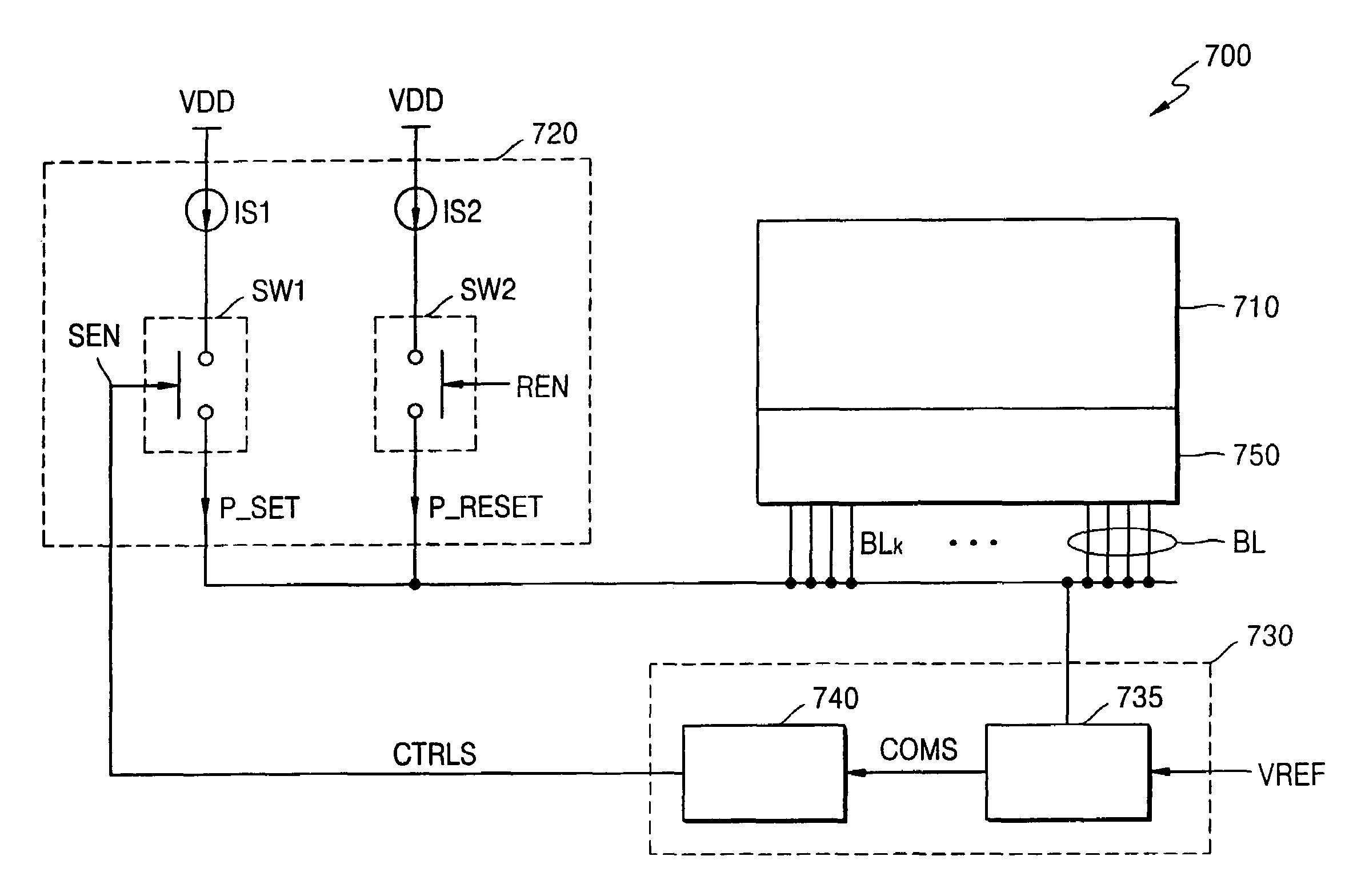

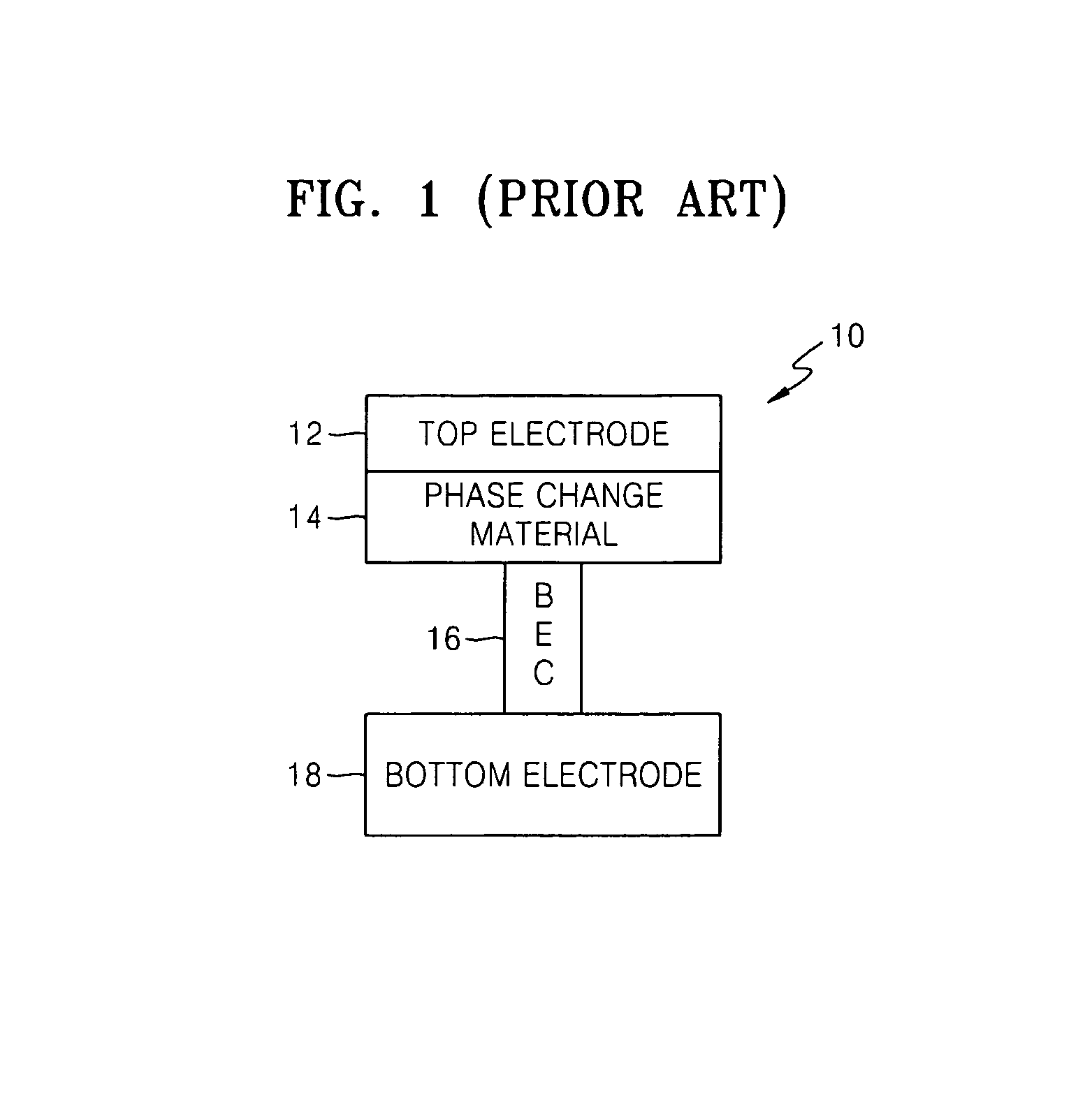

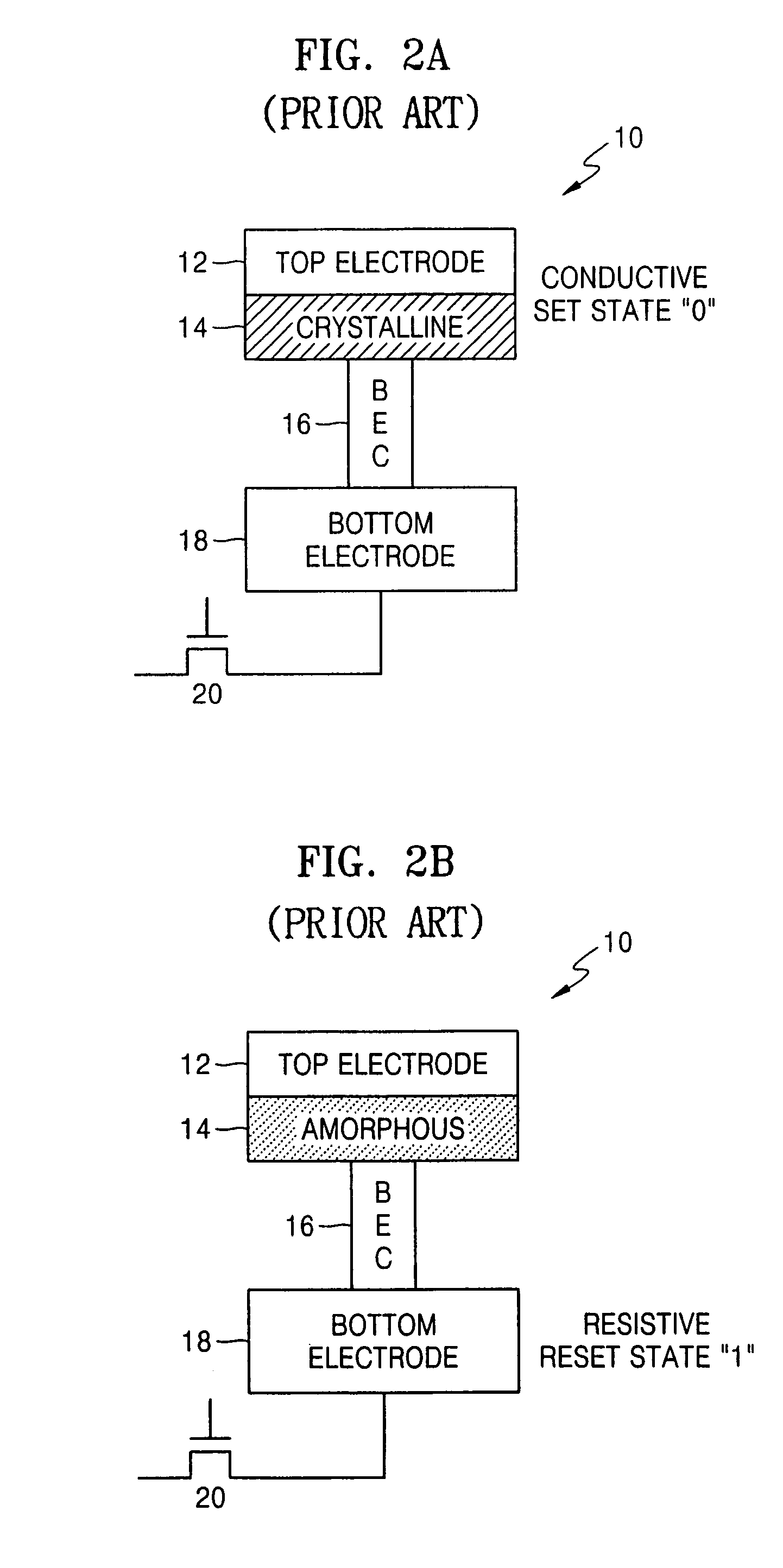

A circuit and method for programming phase-change memory devices, such as chalcogenide memory (PRAM), are described. The invention is directed to an approach to programming PRAM elements from a reset state to a set state or from a set state to the set state. The invention provides a novel and nonobvious PRAM device and method in which a set pulse duration time is controlled by monitoring the state of the memory element during programming such as by comparing the voltage of a bit line with a reference voltage or comparing the cell resistance with a set state cell resistance. The duration of the set pulse is controlled in response to the detected state of the memory element. The result of the approach of the invention is the significant reduction in PRAM programming errors, such as those caused by a constant-duration set pulse, as well as reduction in programming time duration and power consumption.

Owner:SAMSUNG ELECTRONICS CO LTD

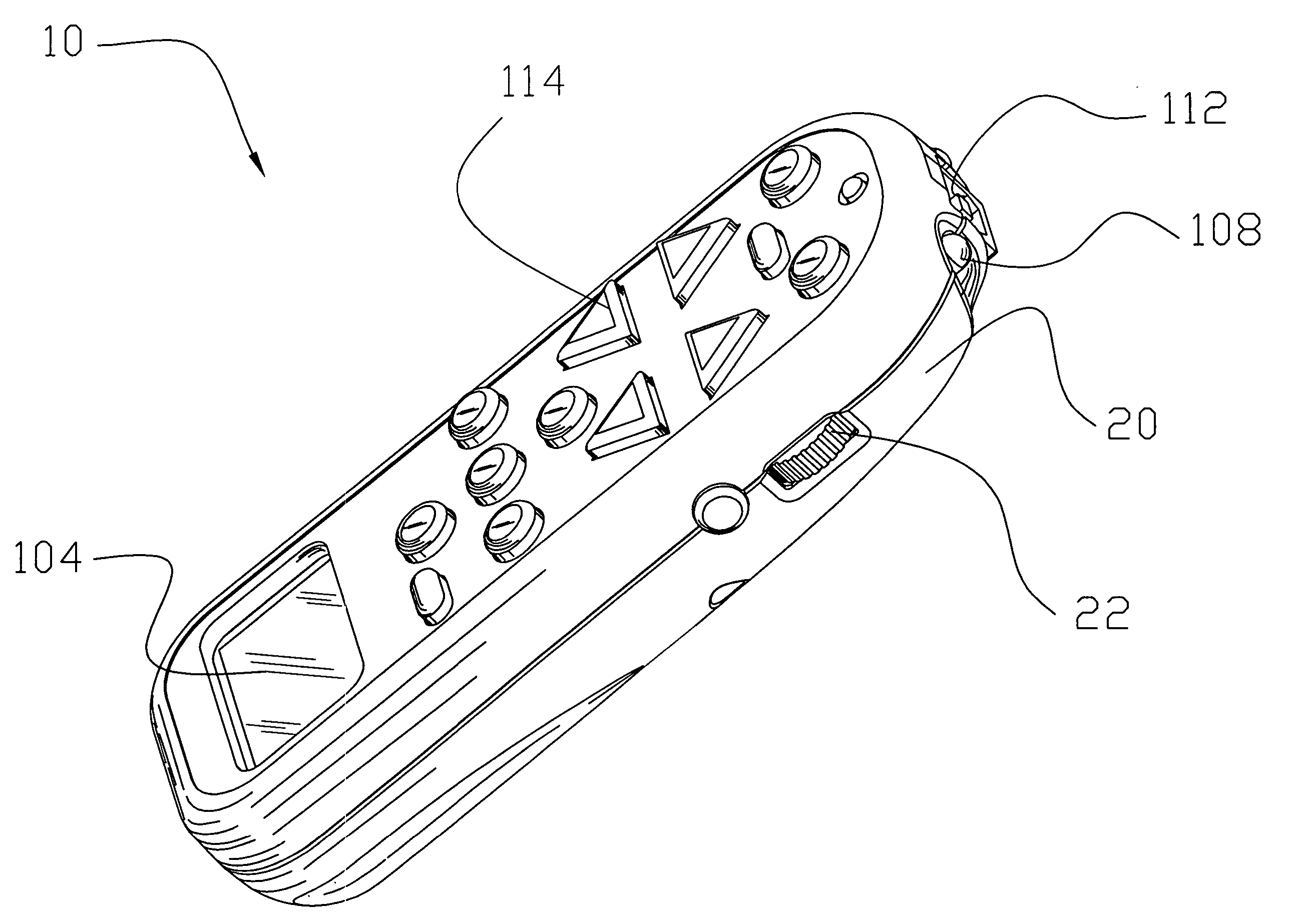

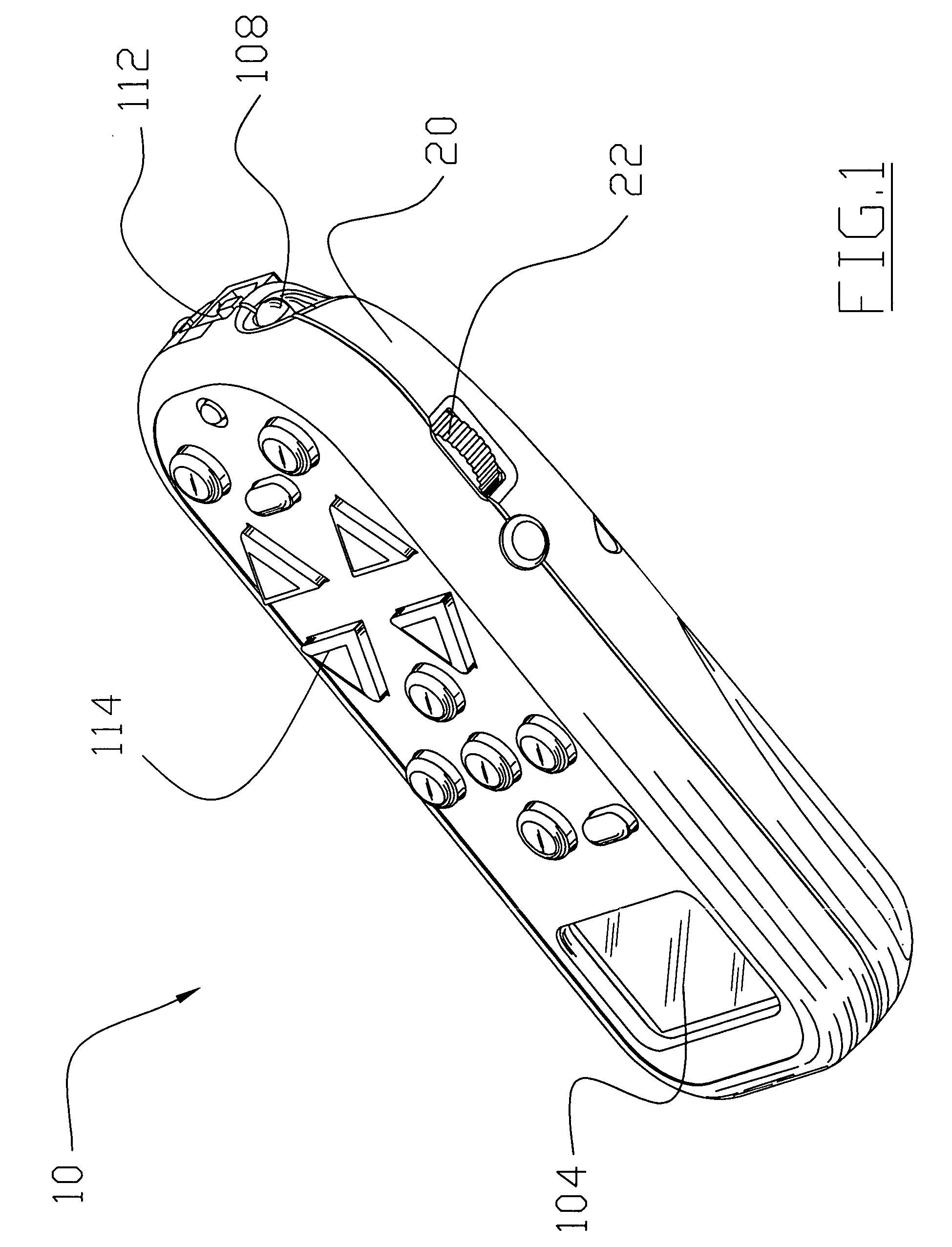

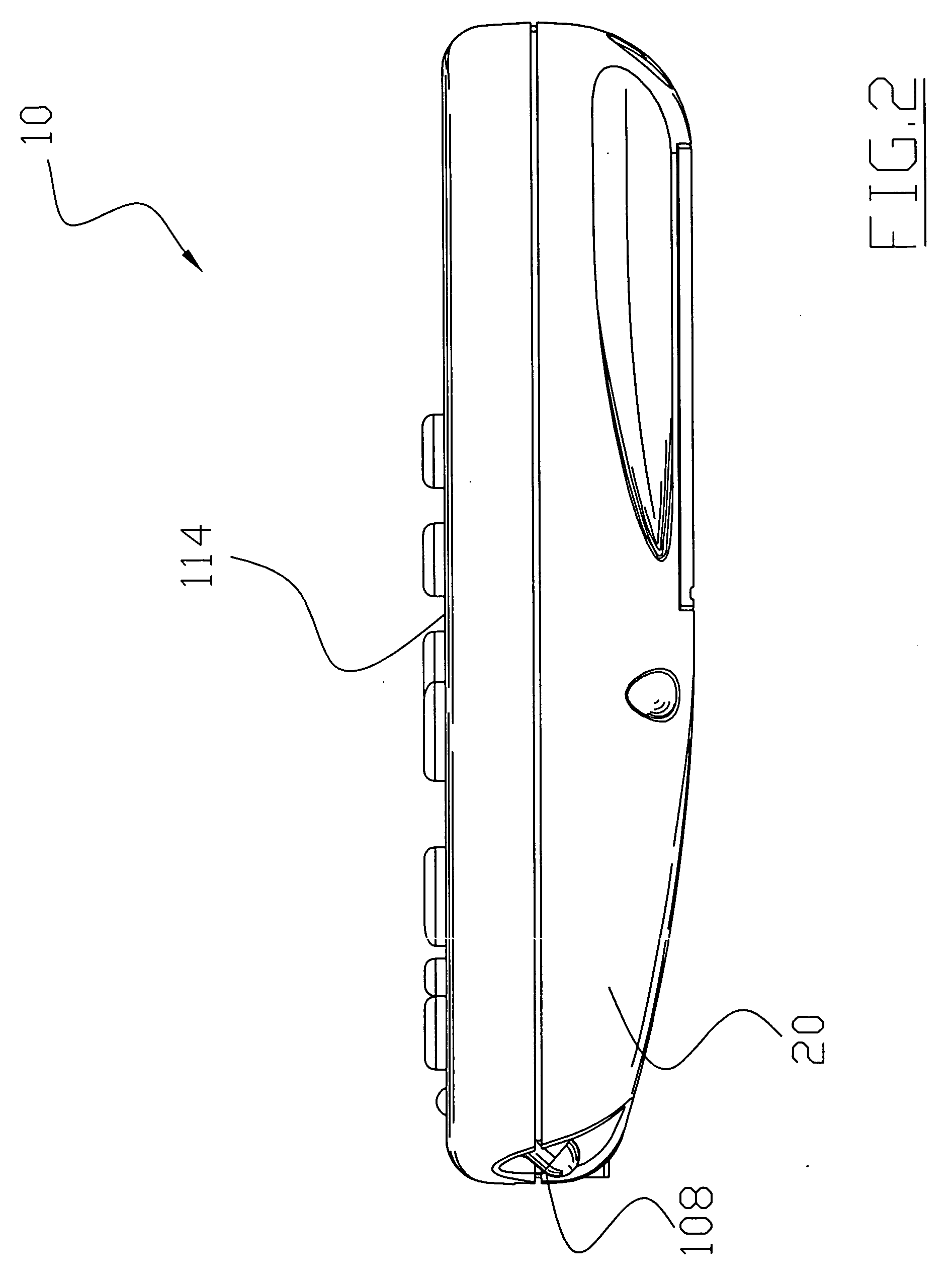

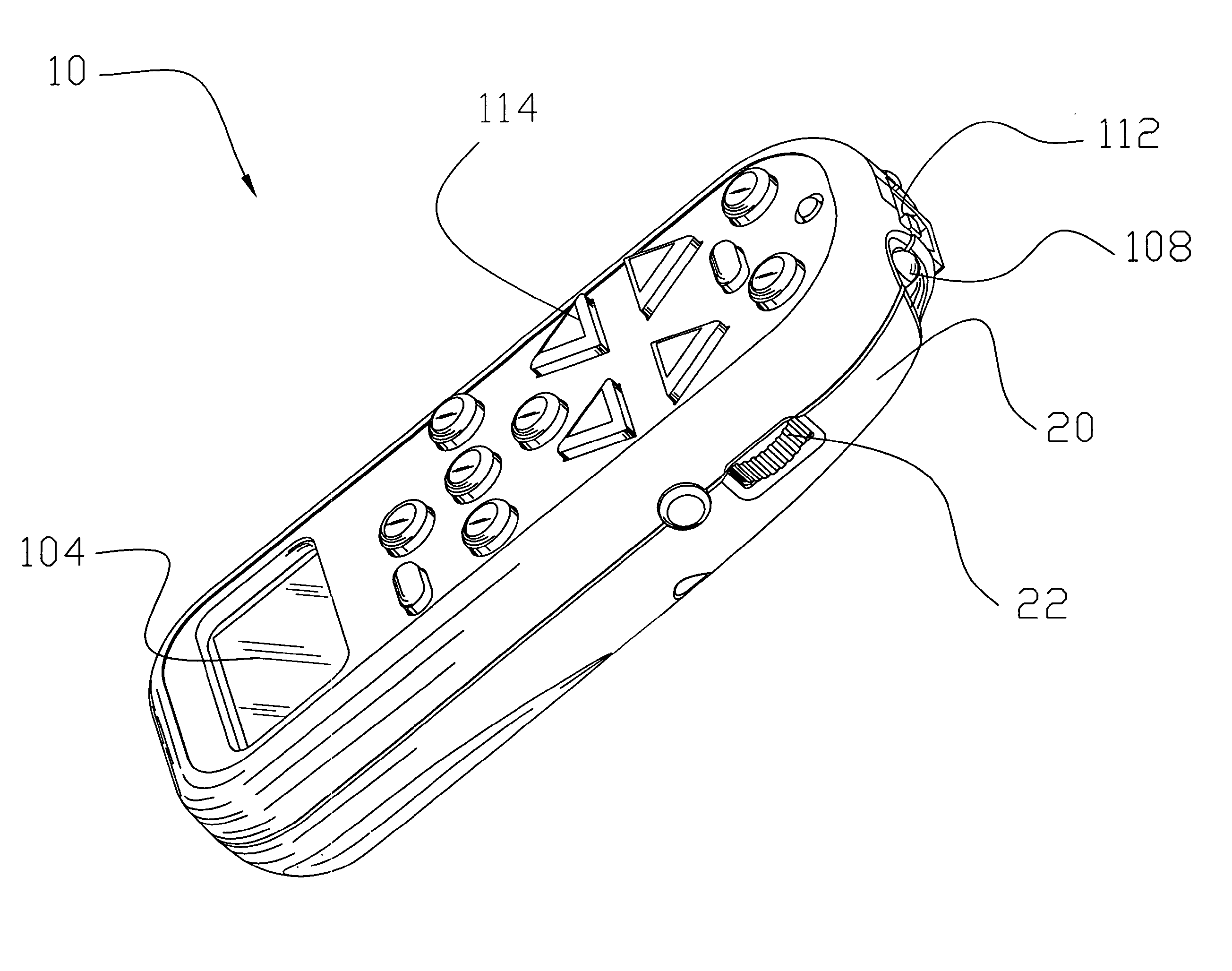

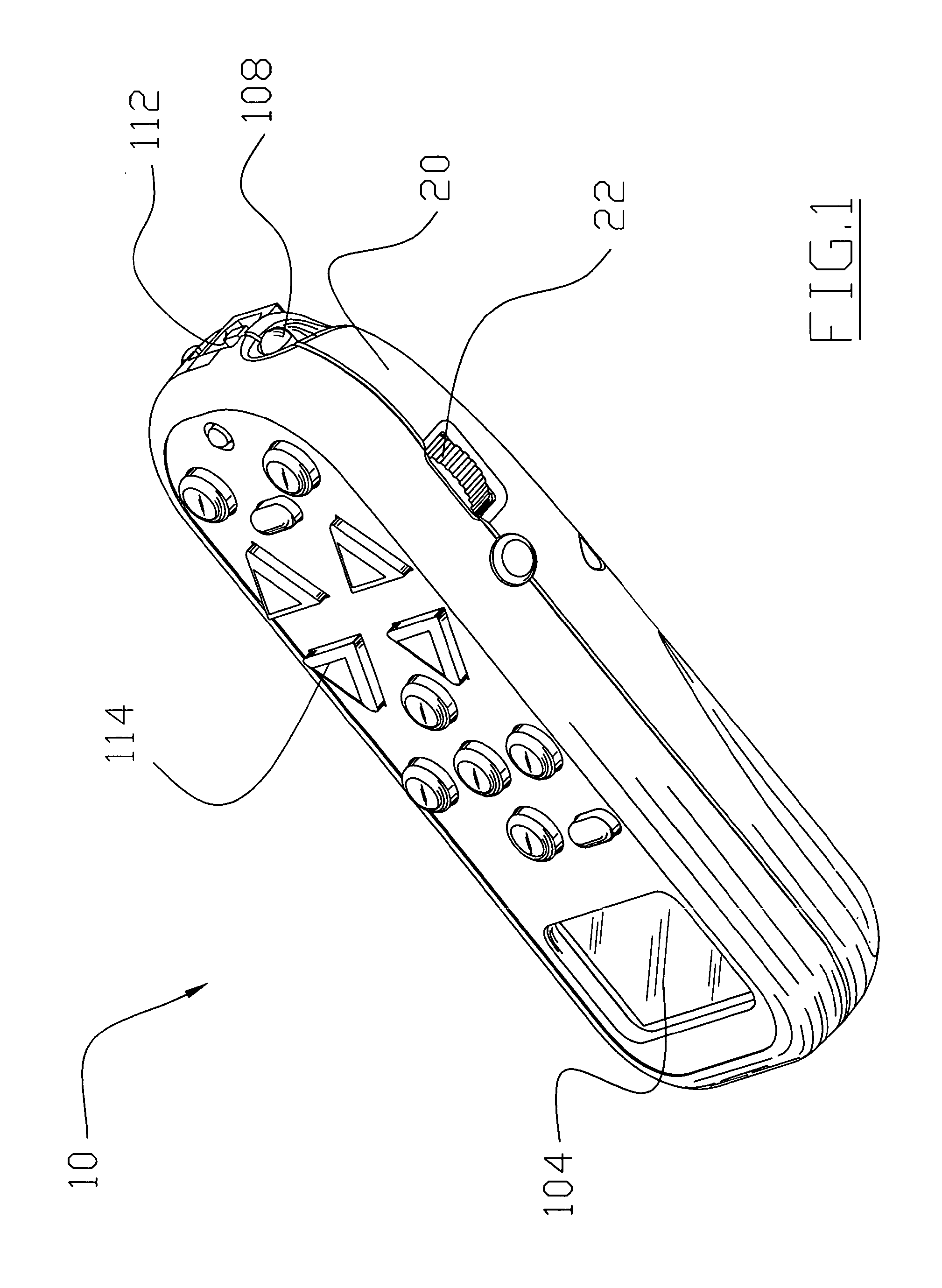

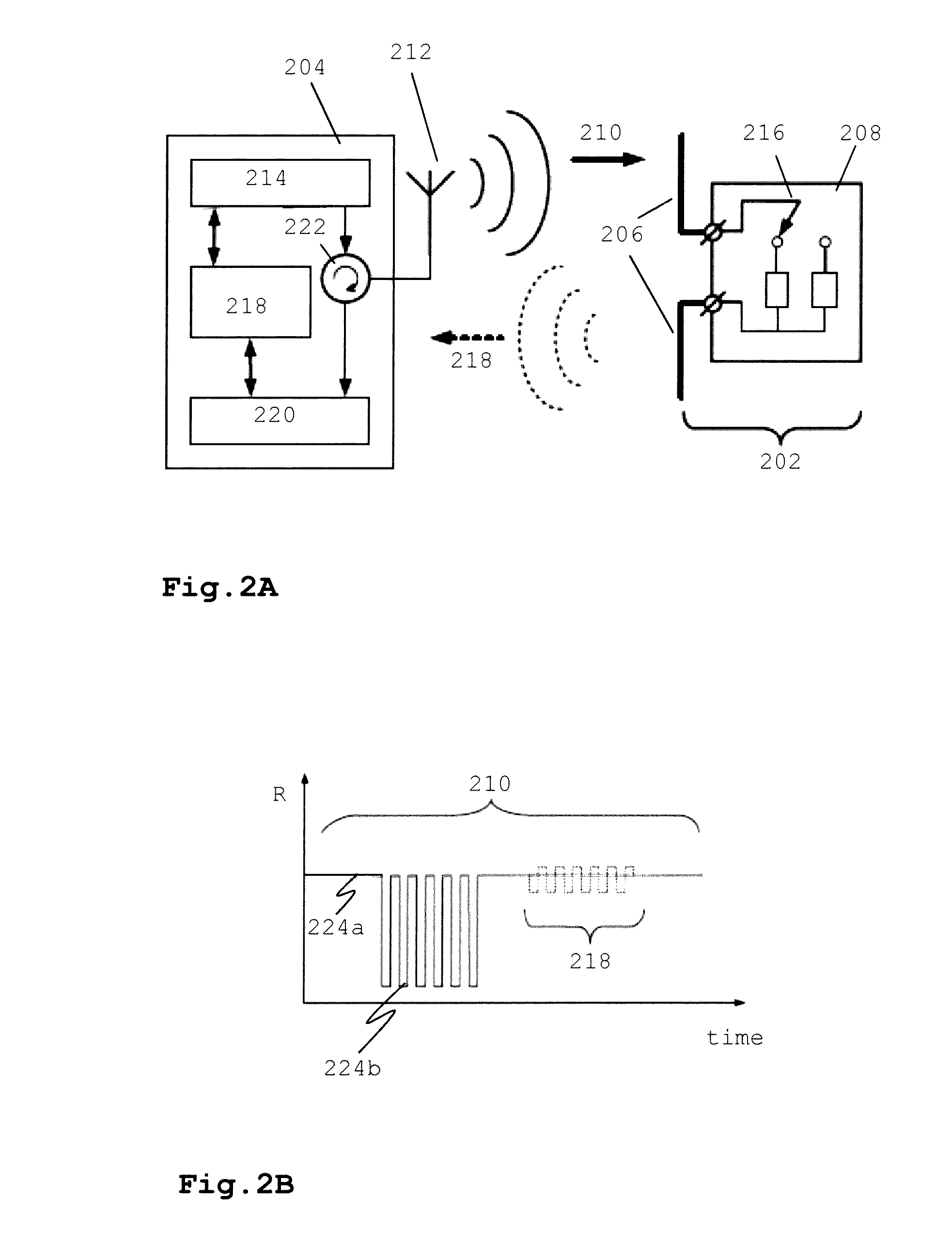

Online remote control configuration system

InactiveUS20050052423A1Efficient programmingQuick configurationInput/output for user-computer interactionElectric signal transmission systemsWeb siteElectronic systems

An online remote control configuration system for efficiently programming a remote control to recognize a plurality of external electronic devices. The online remote control configuration system includes a remote control having a housing, a keypad, and an electronic system for receiving configuration data from a control station via a global computer network (e.g. Internet). The user preferably “samples” one or more signals from a remote control into the electronic system and then uploads the samples to the control station. The control station analyzes the uploaded samples and transmits the appropriate configuration data to properly configure the electronic system. The user may also access a web site of the control station and manually select each of the external electronic devices that the remote control is to operate after which the control station sends the appropriate configuration data to the electronic system.

Owner:LOGITECH EURO SA

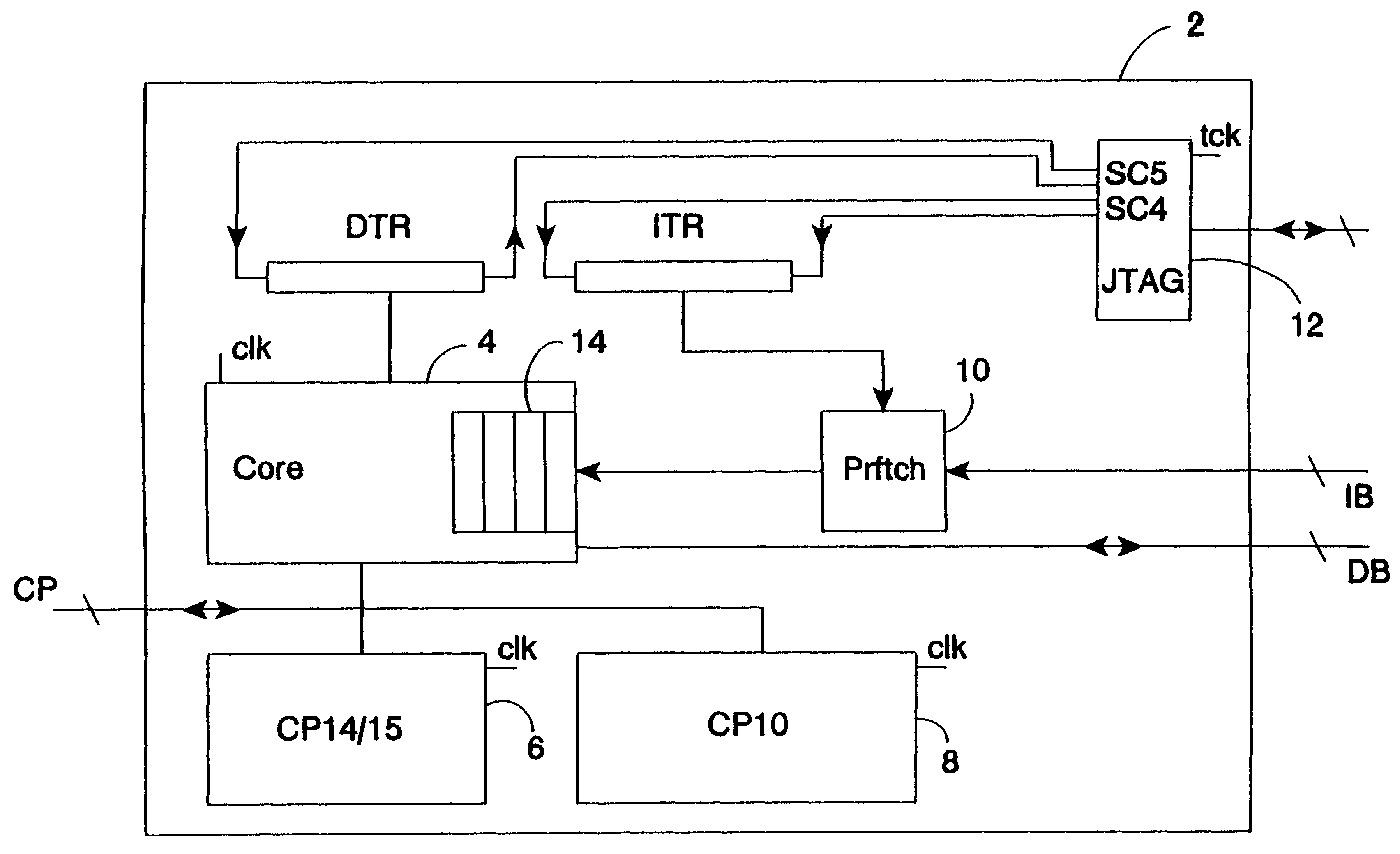

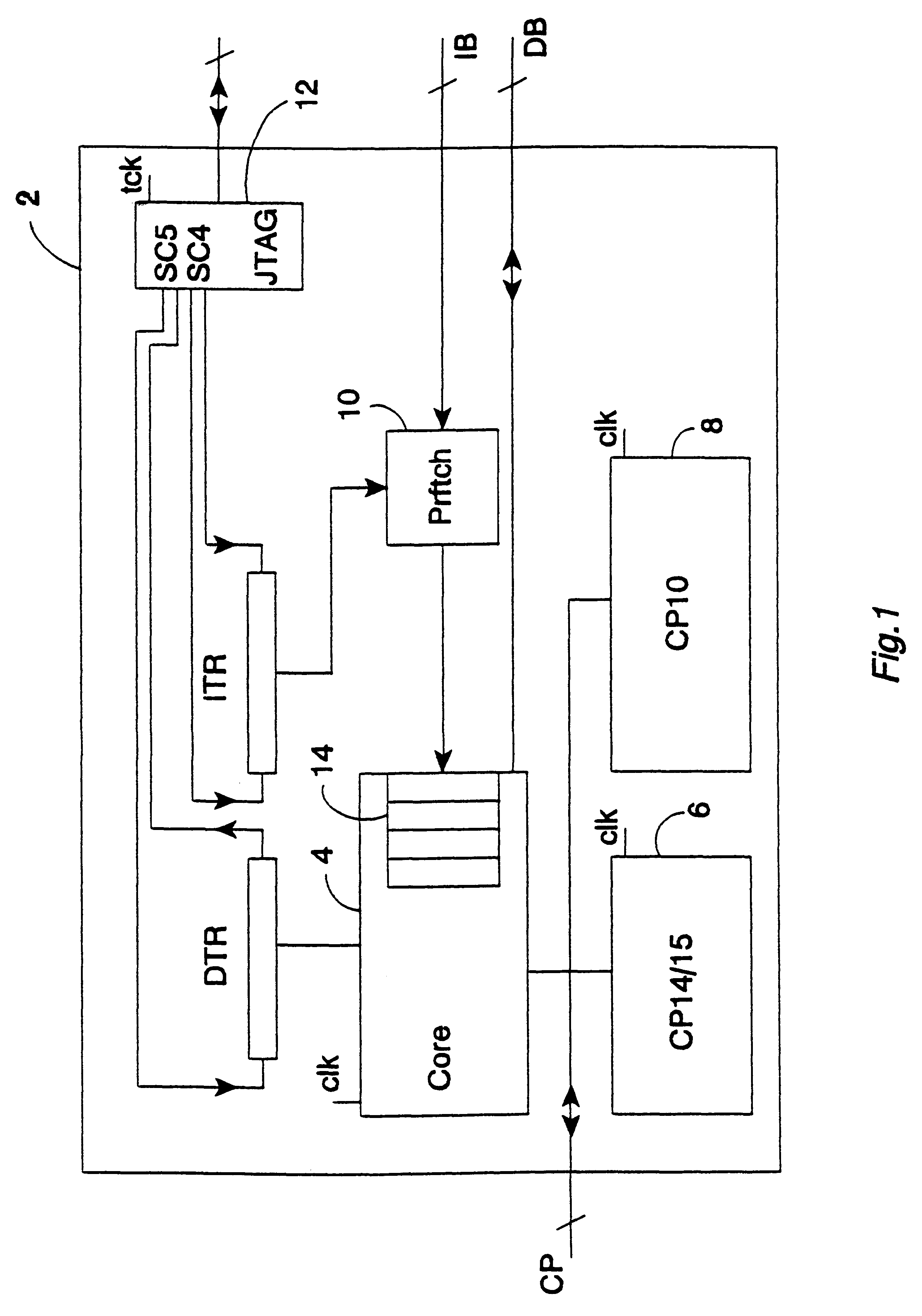

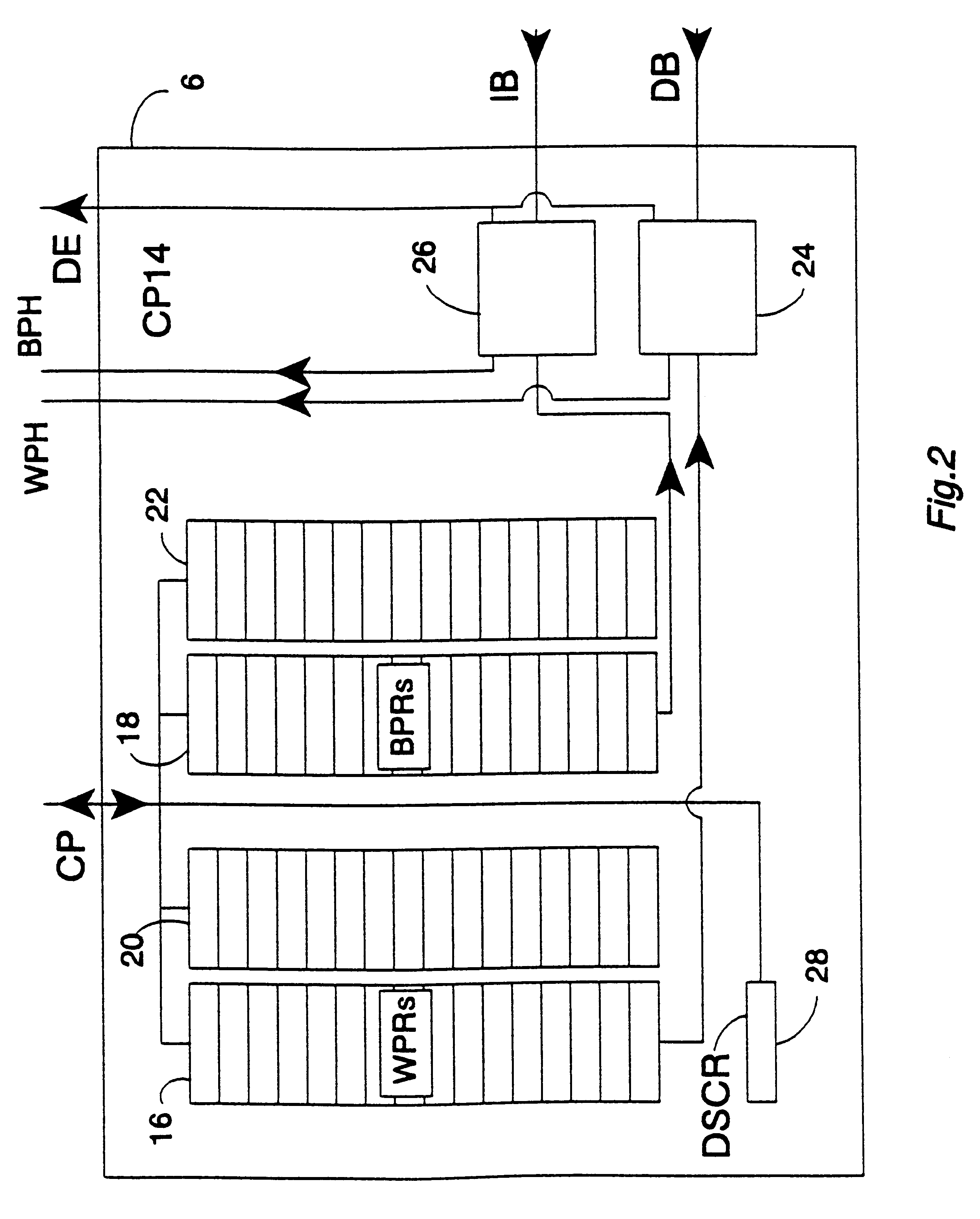

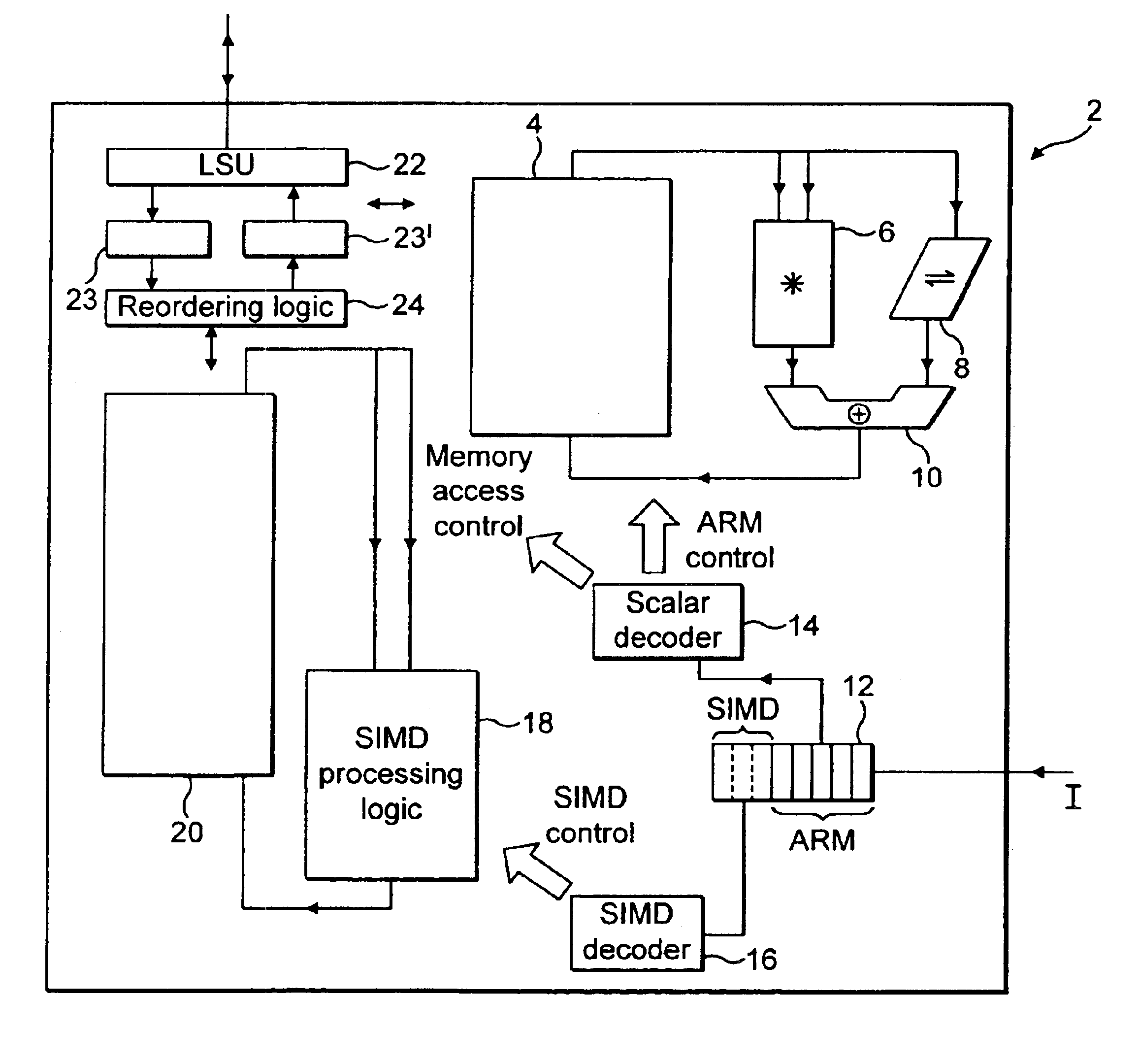

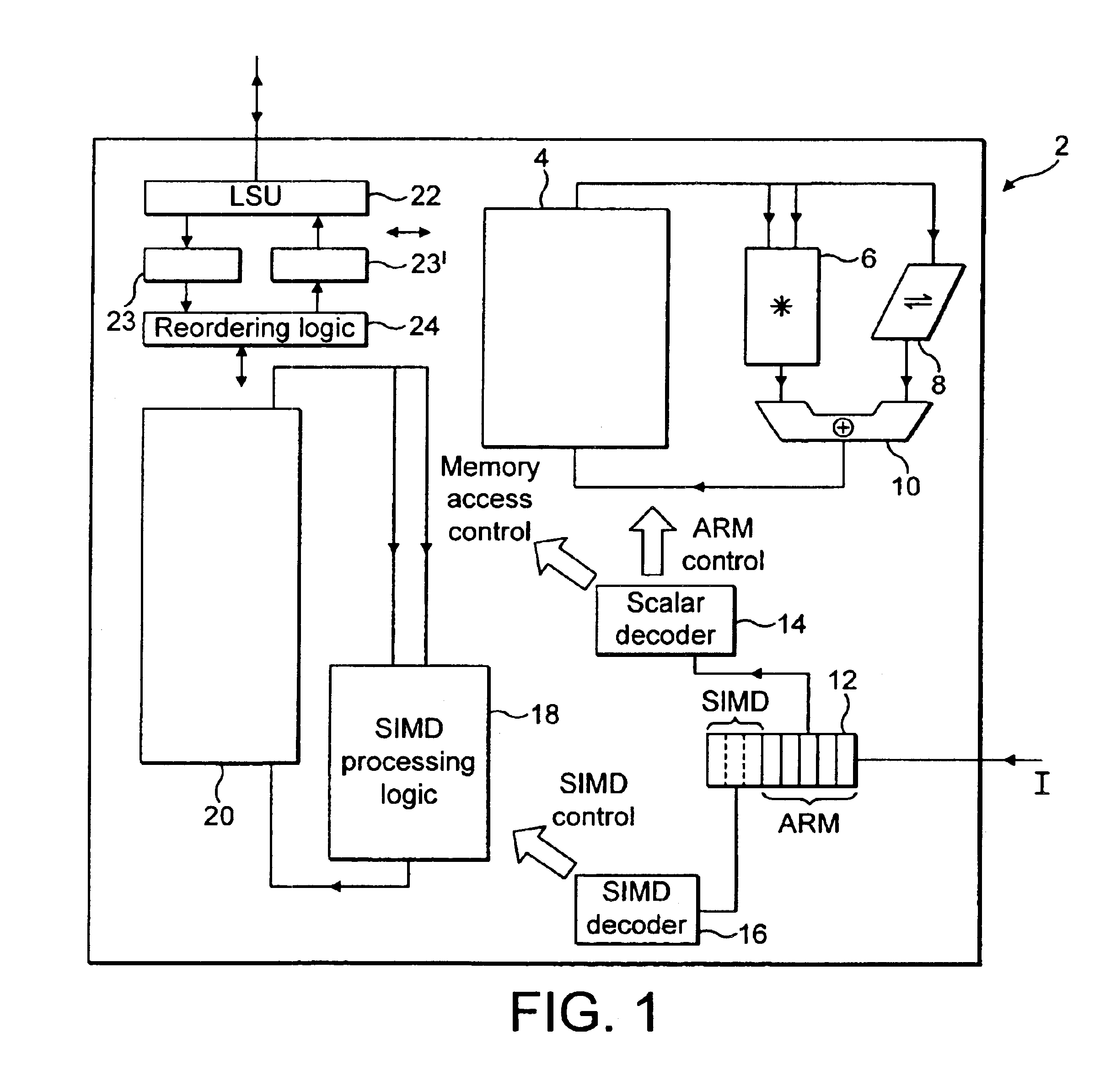

Debug mechanism for data processing systems

InactiveUS6446221B1Efficient programmingAvoid Data ConflictsProgram synchronisationDetecting faulty computer hardwareDiagnostic dataData processing system

Apparatus for processing data is provided, said apparatus comprising: a main processor 4 responsive to main processor instructions within a stream of instructions input to said main processor 4 to perform main processor operations; a coprocessor 6 coupled to said main processor 4 via a coprocessor interface CP and responsive to coprocessor instructions MCR, MRC within said stream of instructions to perform coprocessor operations; wherein said coprocessor 6 is a debug coprocessor operable to at least partially control generation of diagnostic data for debugging said apparatus for processing data and said coprocessor instructions are debug coprocessor instructions that control operation of said debug coprocessor. Using a debug mechanism in the form of a debug coprocessor reduces the impact of the debug mechanism upon normal operation.

Owner:ARM LTD

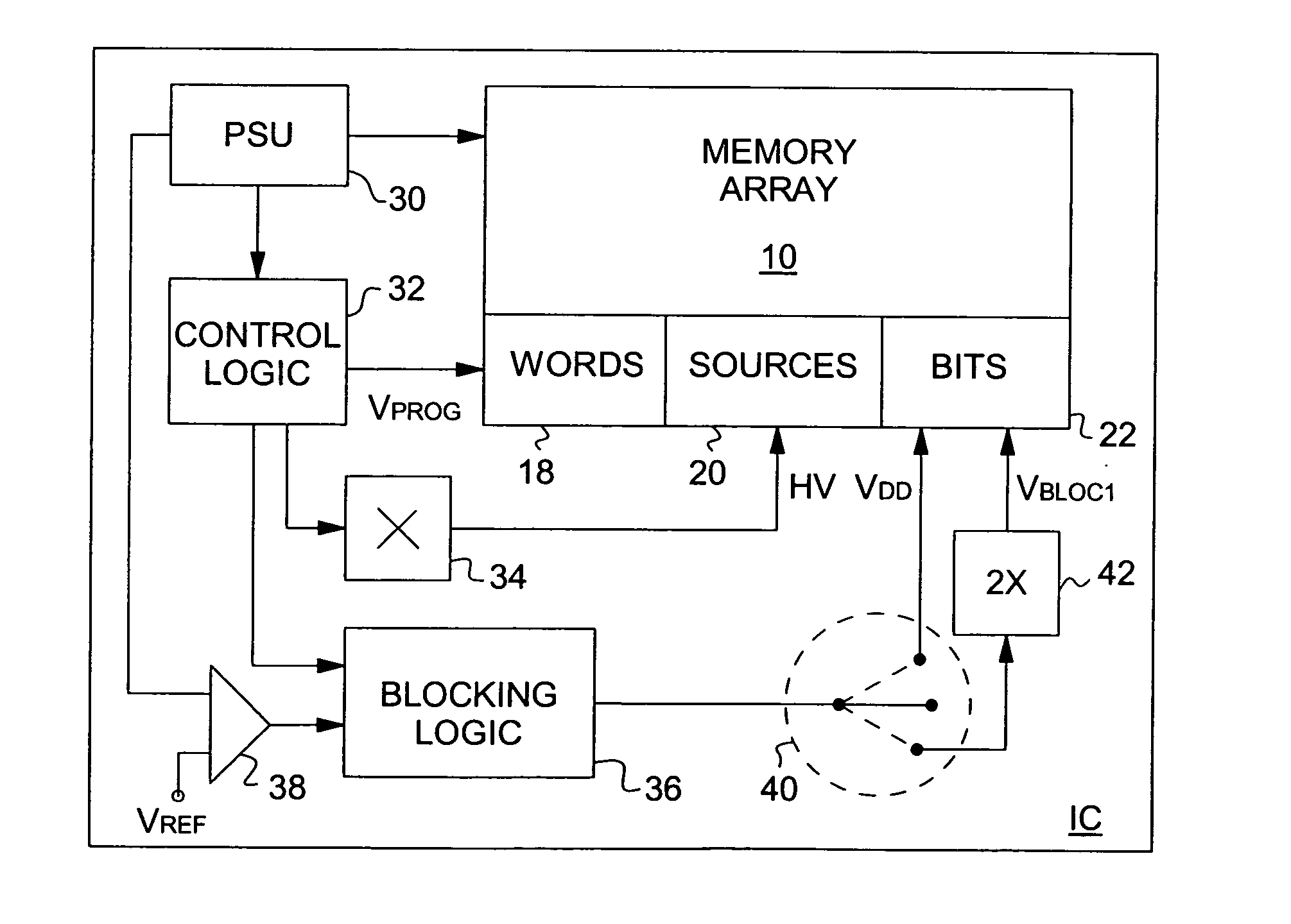

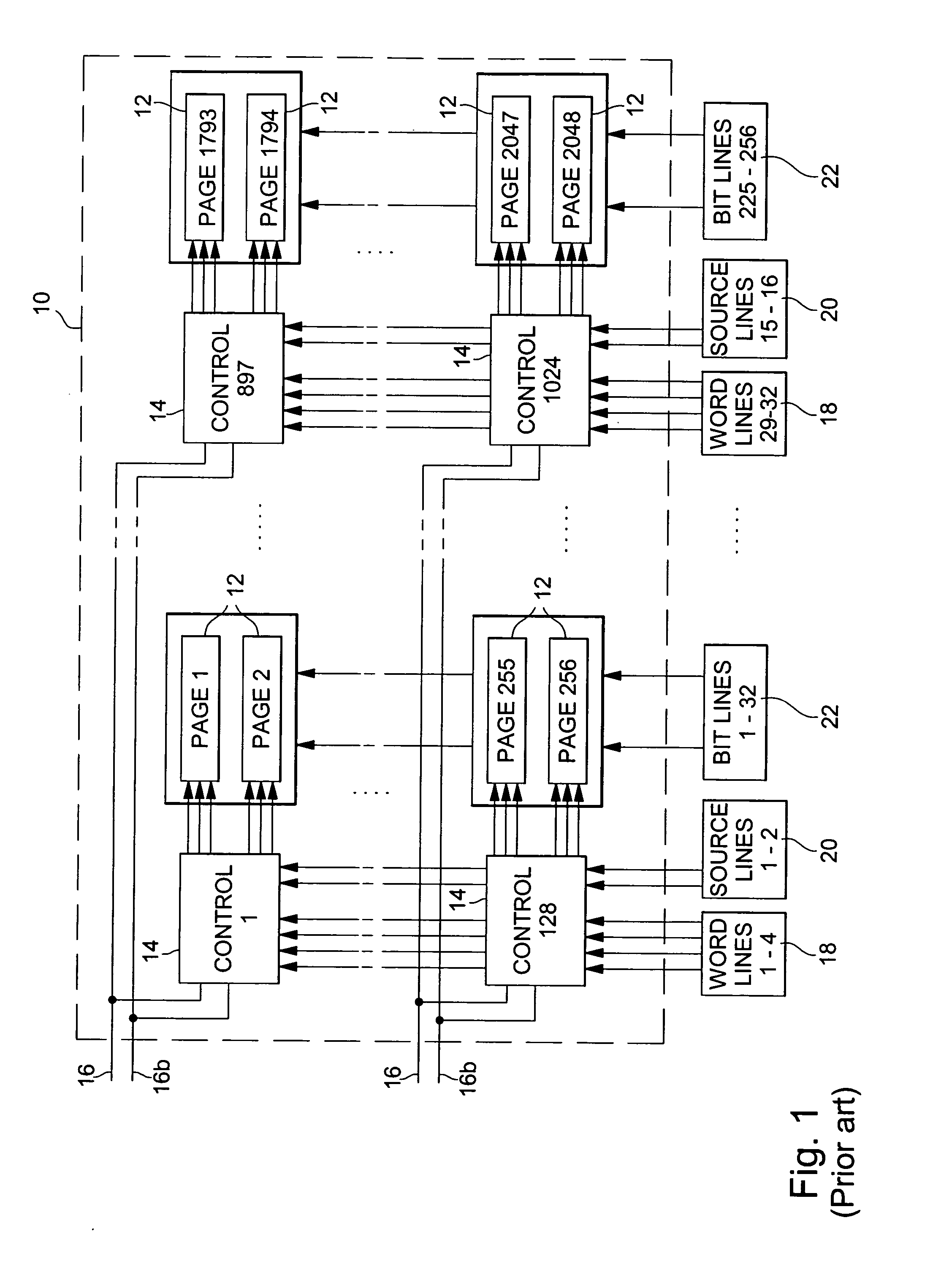

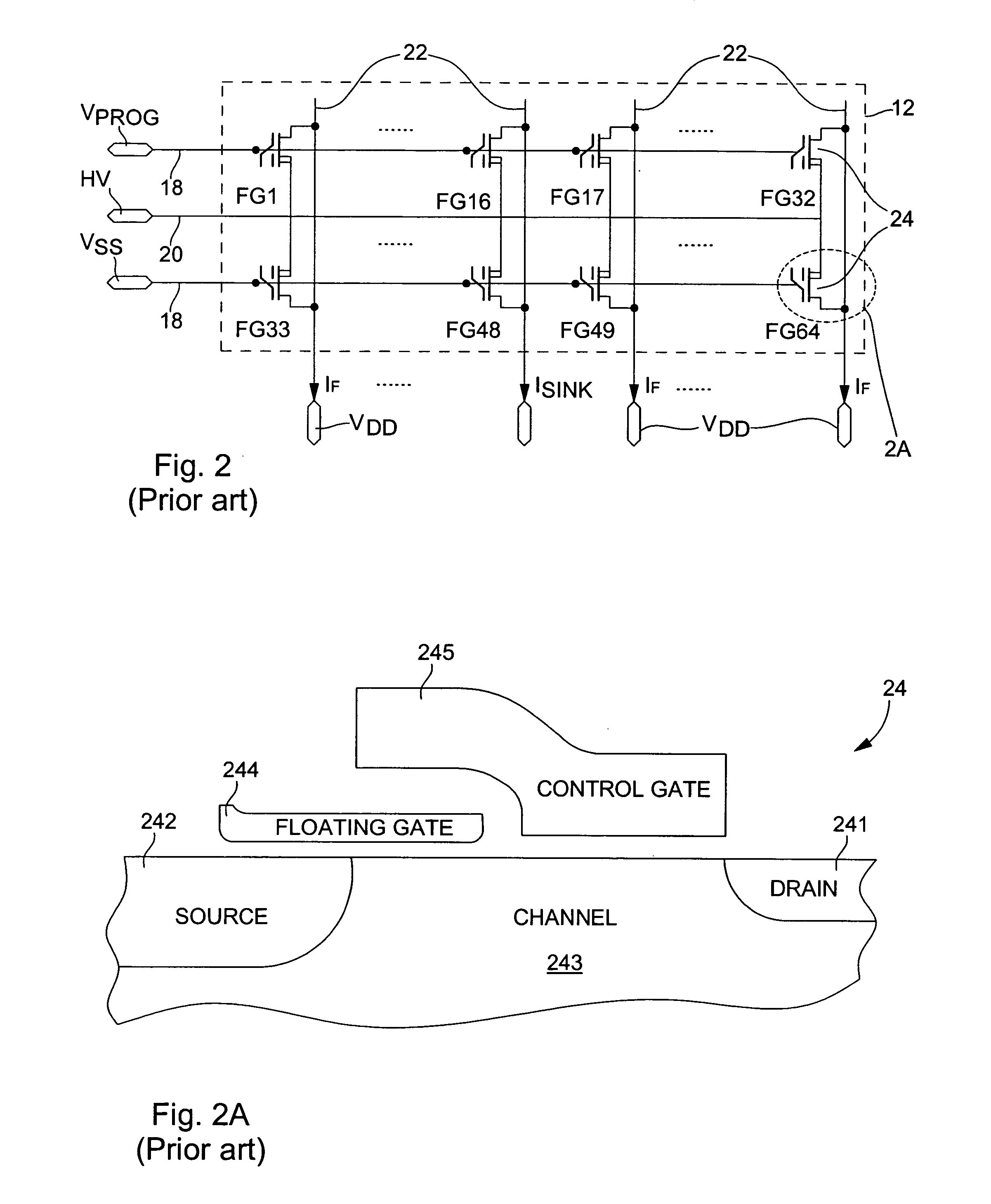

Array of non volatile split-gate memory cells for avoiding parasitic programming and programming method thereof

InactiveUS20050018504A1Efficient programmingHigh riskRead-only memoriesDigital storageElectricityControl line

There is disclosed an array (10) of split-gate non-volatile memory cells (24) supplied with power at a low voltage (VDD) by a power supply (30), said cells being arranged in one or more rows and columns and electrically interconnected in groups to form one or more pages (12). The array comprises control logic (32) delivering a defined programming voltage (VPROG) that is close or or substantially equal to the low power supply voltage that is applied to a control gate (245) of at least one cell (24A) that is to be programmed via a word control line (18) corresponding to that cell and blocking logic (36) delivering a first blocking voltage (VBLOC1) that is greater than said low power supply voltage and is applied to the first regions (241) of the cells (24B) sharing the same word control line (18) as said cell that is to be programmed via a bit control line (22) corresponding to those cells.

Owner:EM MICROELECTRONIC-MARIN

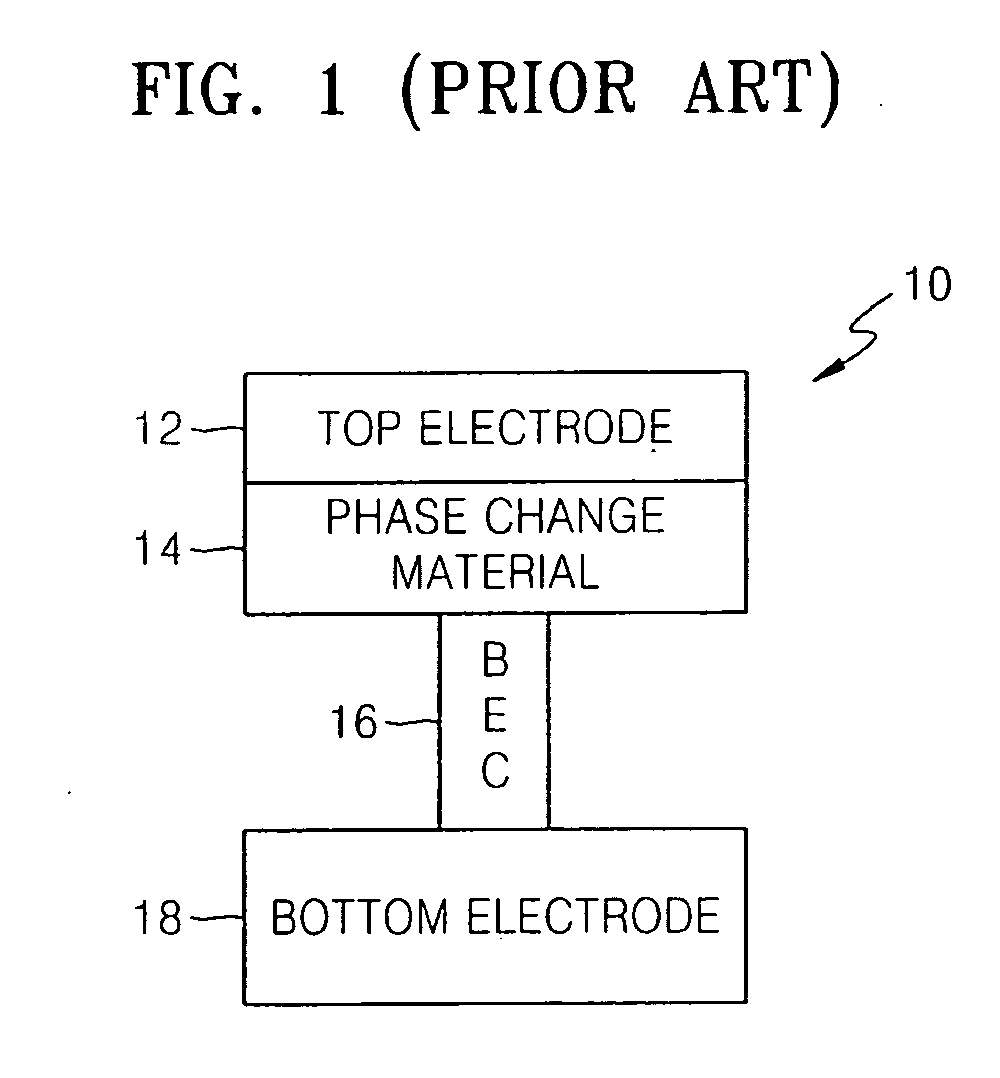

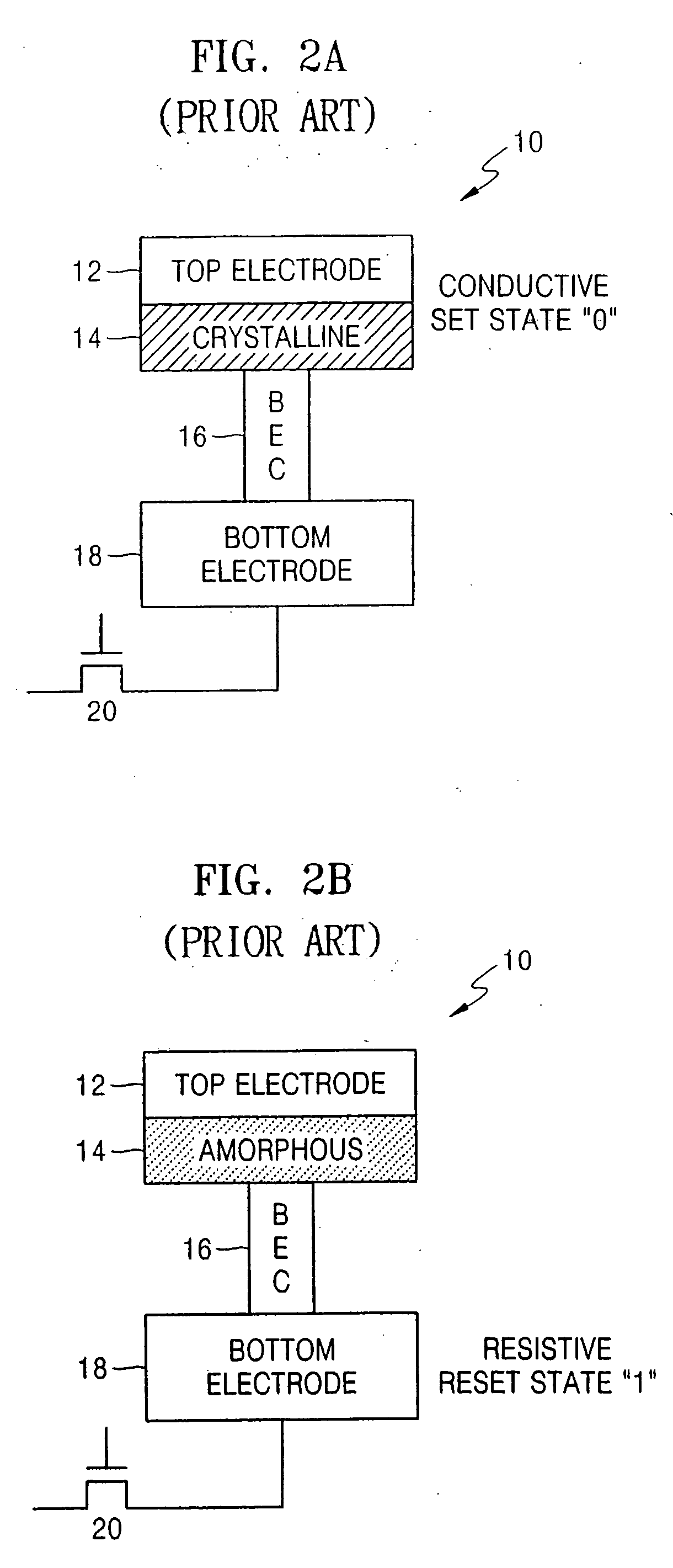

Integrated circuit memory devices having memory cells therein that utilize phase-change materials to support non-volatile data retention

InactiveUS7038261B2Efficient executionAvoid pollutionTransistorSolid-state devicesPhase changePhase-change material

An integrated circuit memory device includes a semiconductor substrate and a first electrically insulating layer that extends on the semiconductor substrate and has a first contact hole extending therethrough. An electrically conductive plug is provided in the first contact hole. A phase-change material layer pattern is provided as a non-volatile storage medium. The phase-change material layer pattern has a bottom surface that is electrically connected to the electrically conductive plug. A second electrically insulating layer is provided on the phase-change material layer pattern. The second electrically insulating layer has a second contact hole therein. This contact hole exposes a portion of an upper surface of the phase-change material layer pattern. To improve data writing efficiency, the area of the exposed portion of the upper surface of the phase-change material layer pattern is less than a maximum cross-sectional area of the electrically conductive plug. A plate electrode is also provided. This plate electrode is electrically connected to the phase-change material layer pattern. Barrier layers may also be provided directly on the plug and directly on the exposed portion of the upper surface.

Owner:SAMSUNG ELECTRONICS CO LTD

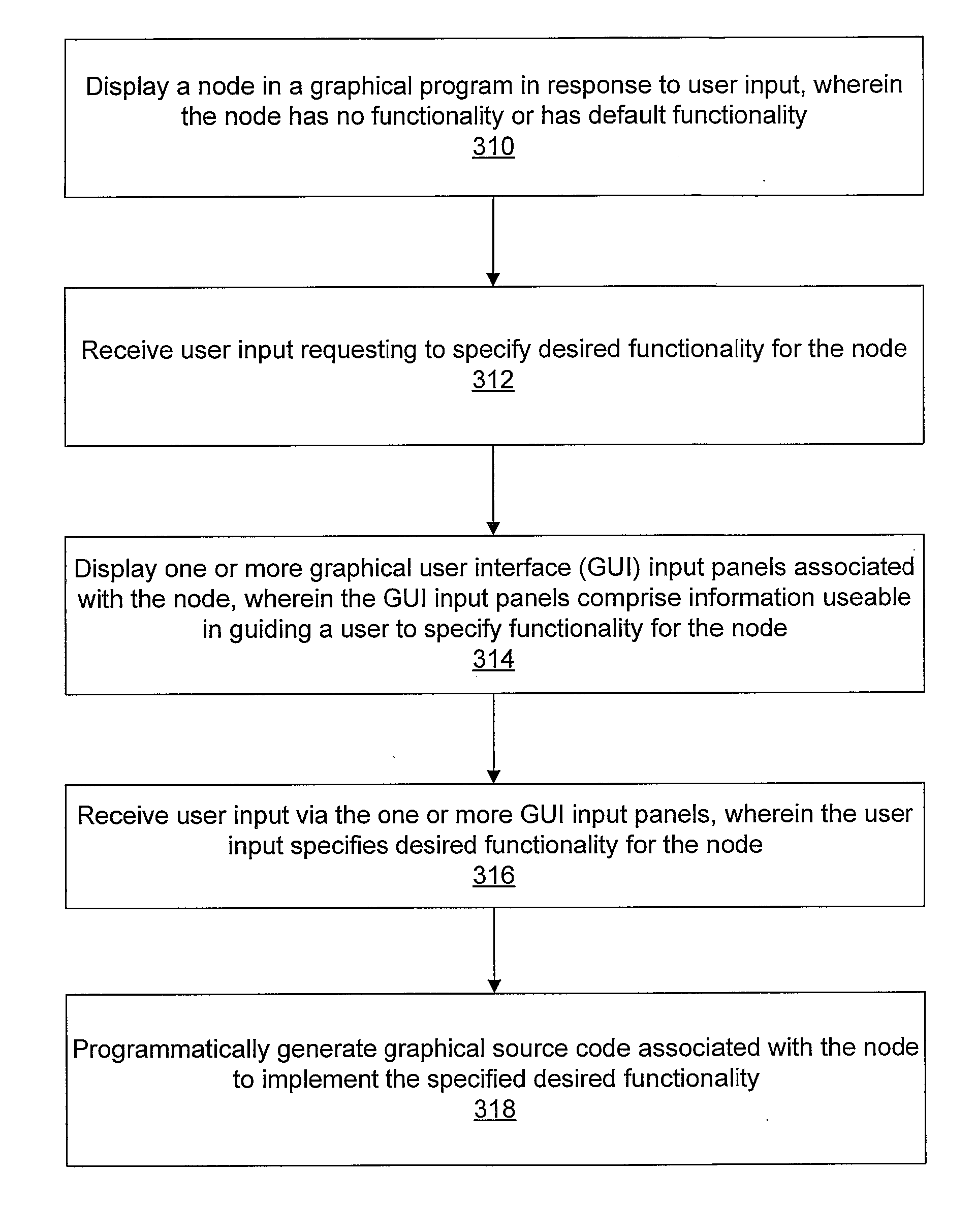

Programmatically Generating a Graphical Program in Response to User Input

InactiveUS20060259871A1Simple taskEasy to specifyVisual/graphical programmingSpecific program execution arrangementsGraphicsUser input

A system and method for programmatically generating a graphical program or a portion of a graphical program in response to receiving user input. The user input may specify functionality of the graphical program or graphical program portion to be generated. In response to the user input, a graphical program (or graphical program portion) that implements the specified functionality may be programmatically generated. Thus, different graphical programs may be generated, depending on the user input received.

Owner:NATIONAL INSTRUMENTS

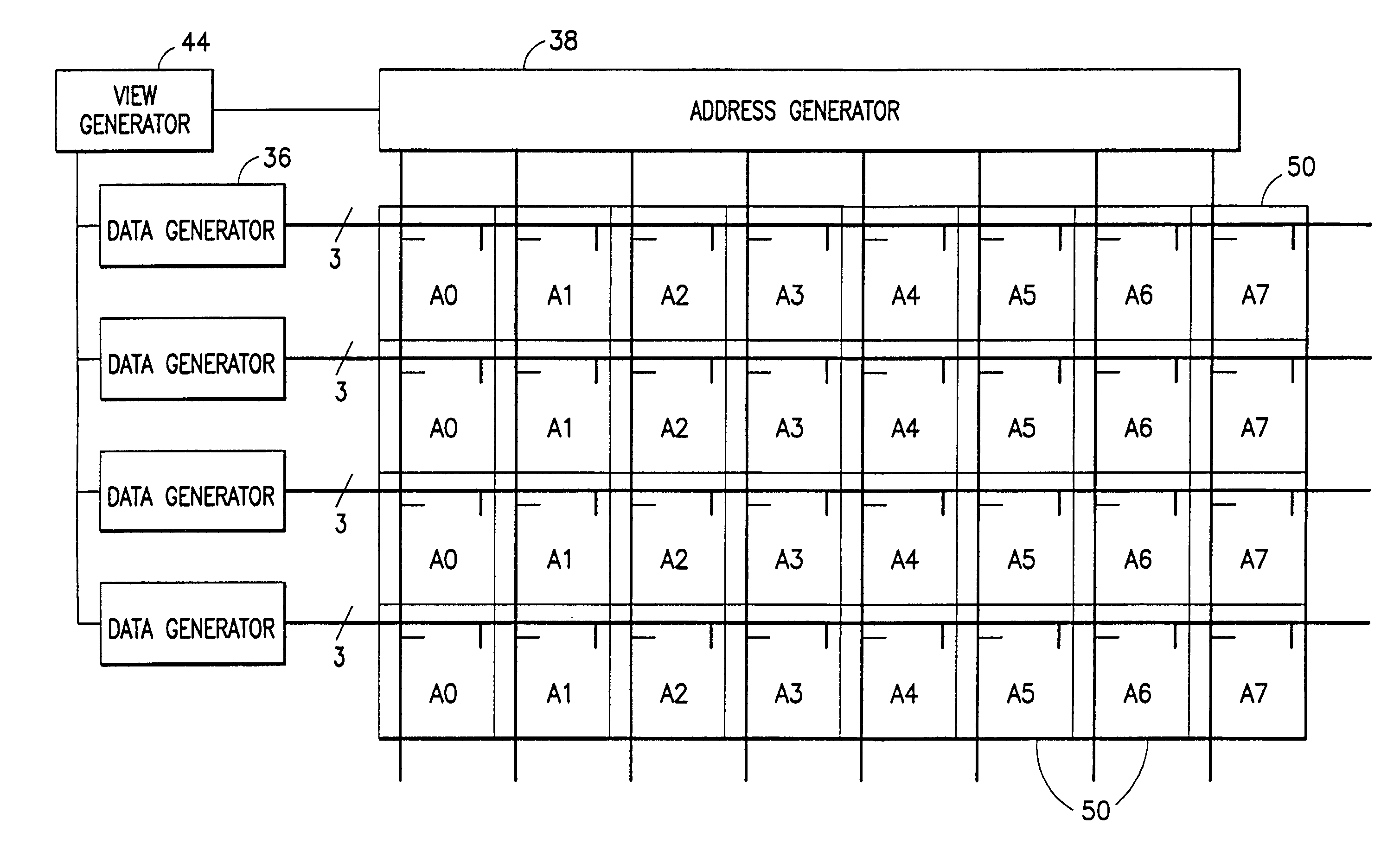

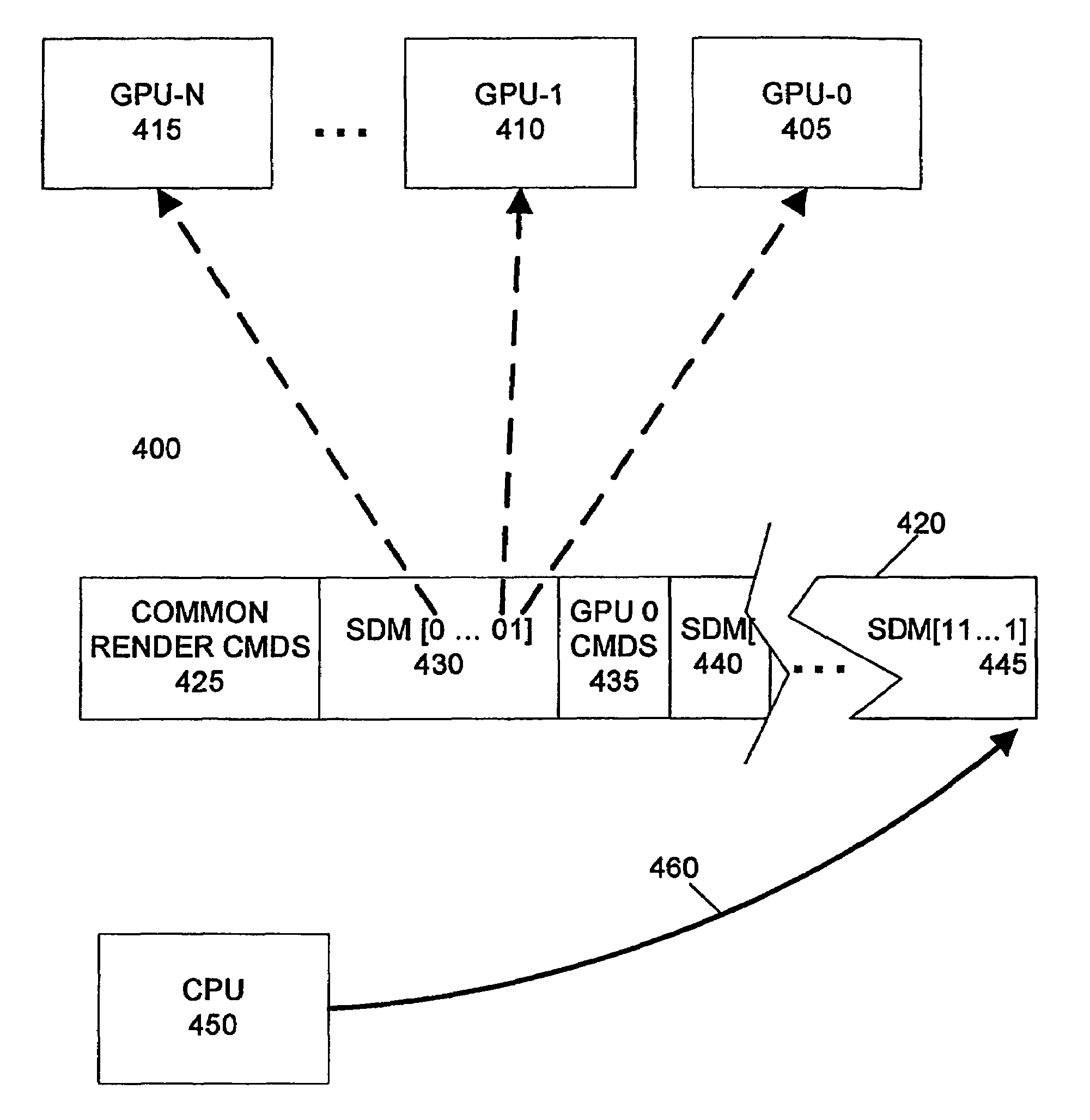

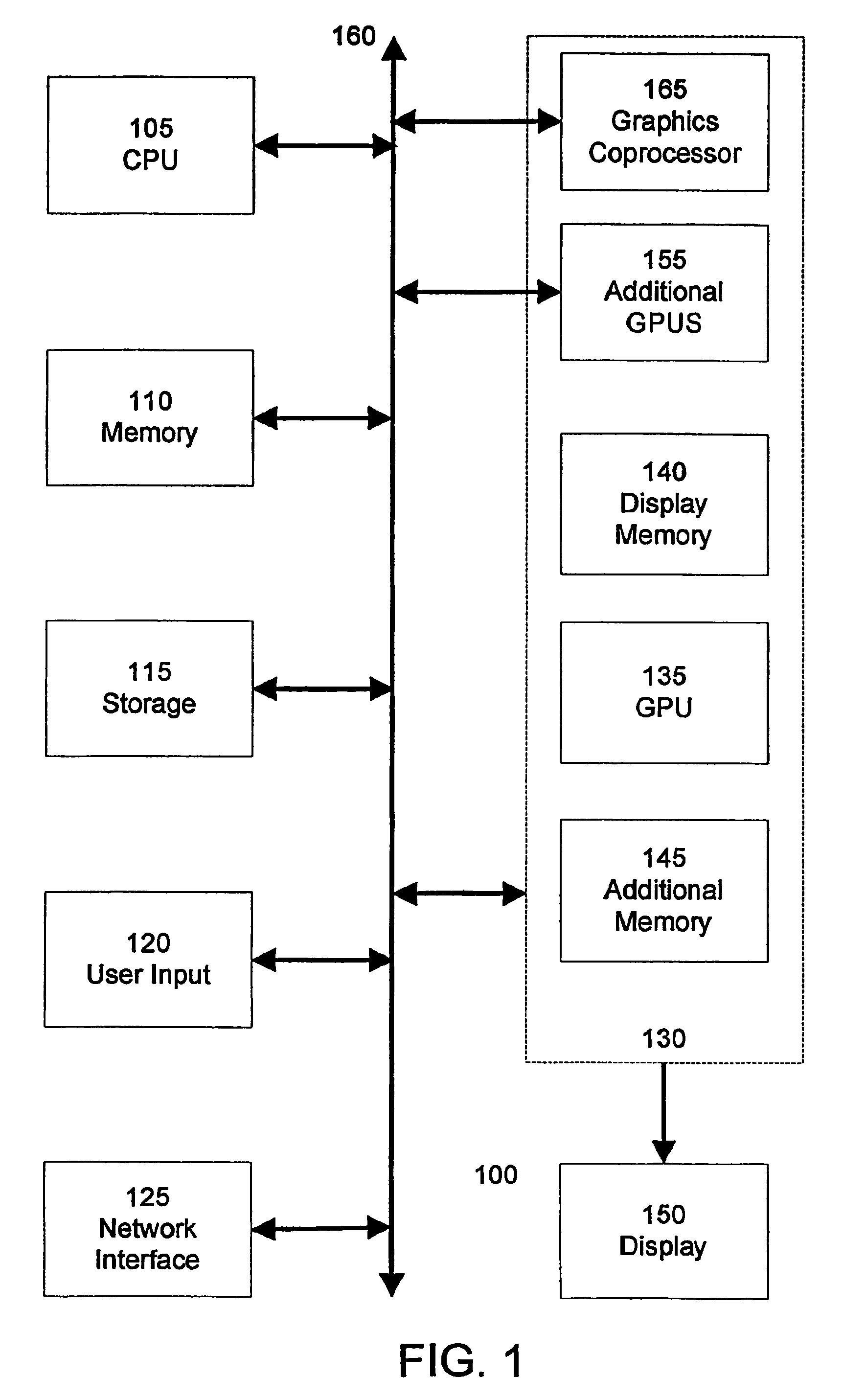

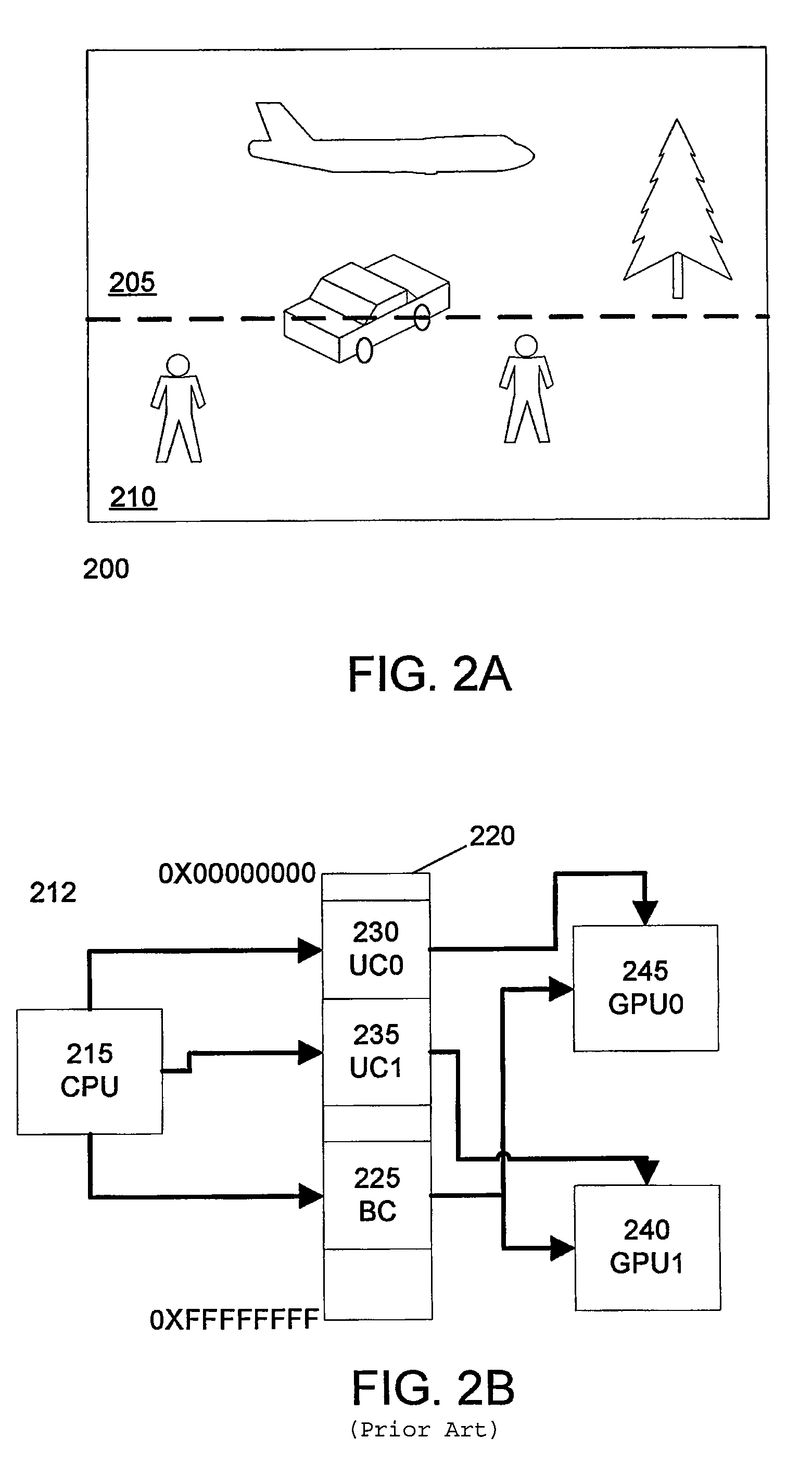

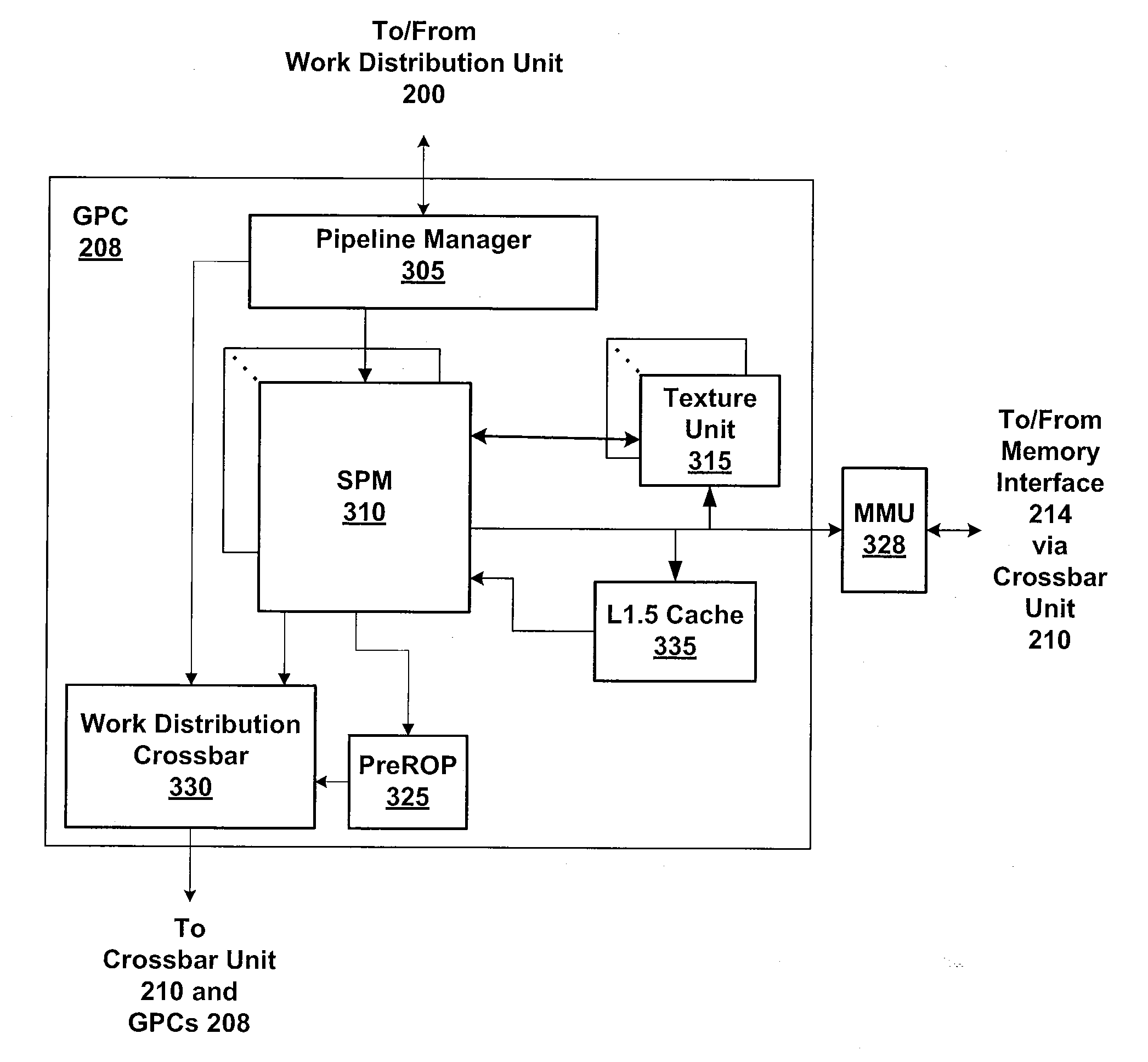

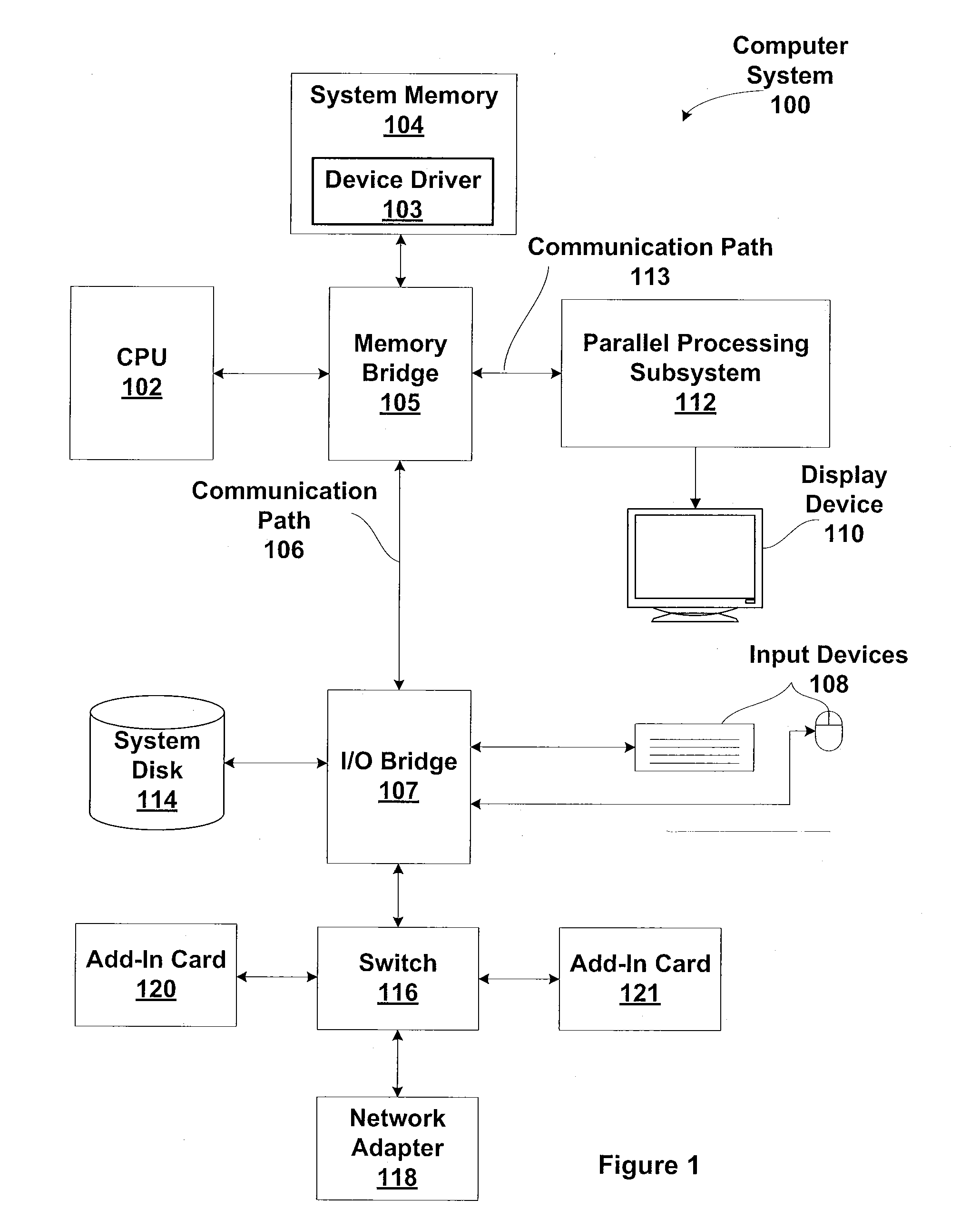

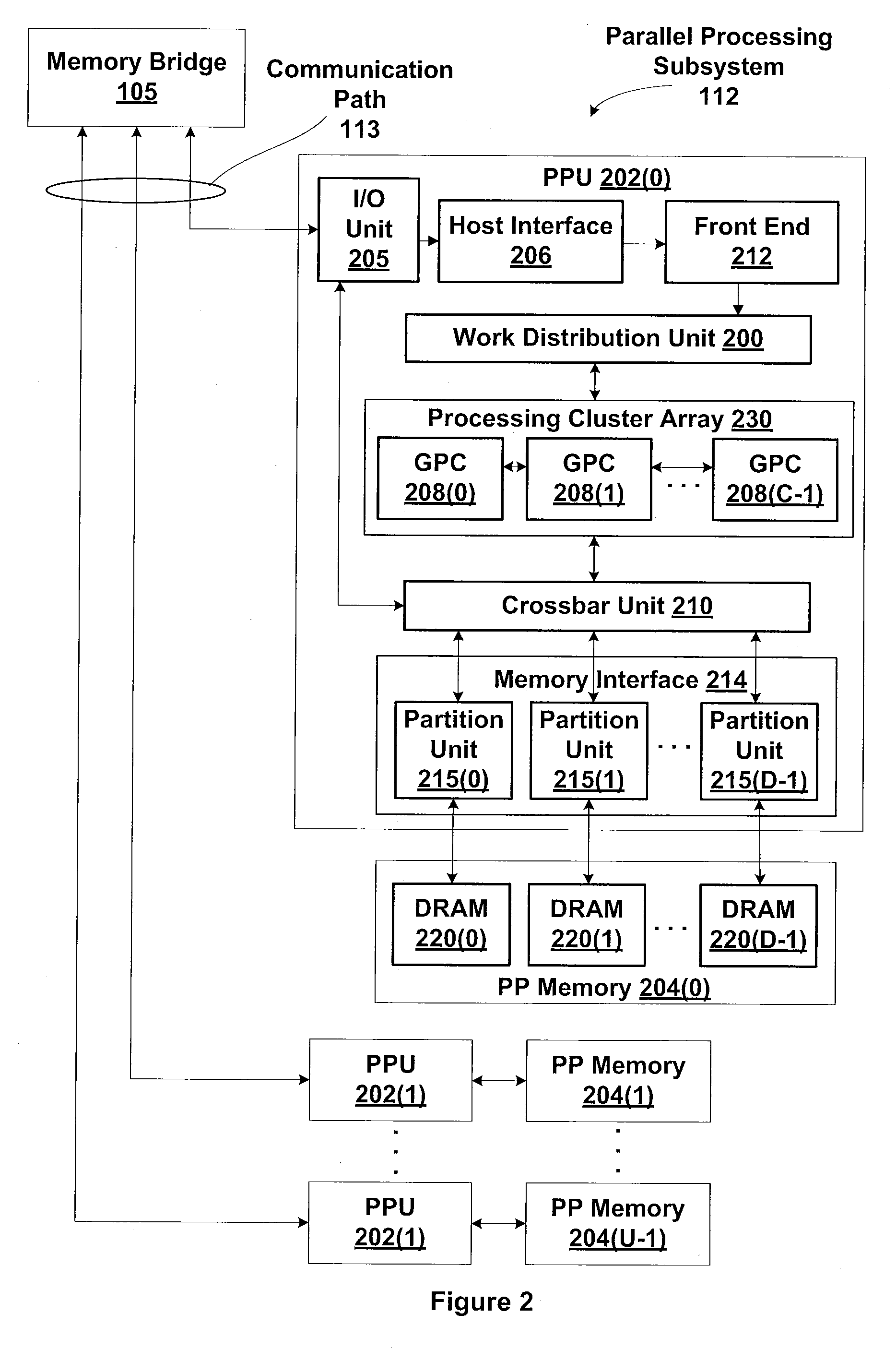

Programming multiple chips from a command buffer for stereo image generation

ActiveUS7602395B1Efficient programmingReduce deliveryMultiple digital computer combinationsProcessor architectures/configurationGraphicsViewpoints

Multiple graphics devices are operable in parallel to render stereo images using efficient programming techniques. The same command stream is delivered to each graphics device, and device masks are used to control the execution of commands by different graphics devices. A viewing transform command corresponding to a left-eye transform is executed by one device while a viewing transform command corresponding to a right-eye transform is executed another device. Other rendering commands are executed by both devices to render the same image from somewhat different viewpoints.

Owner:NVIDIA CORP

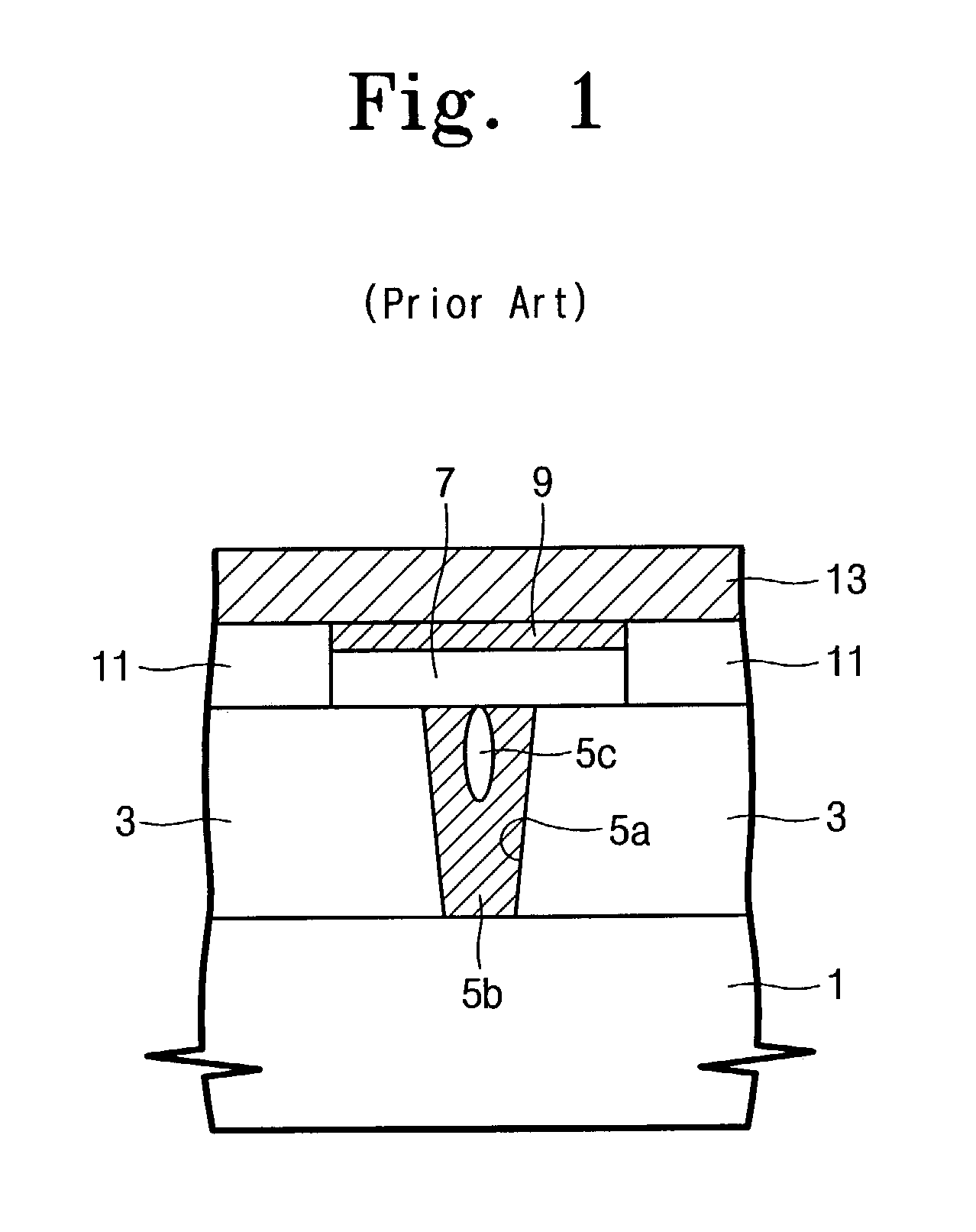

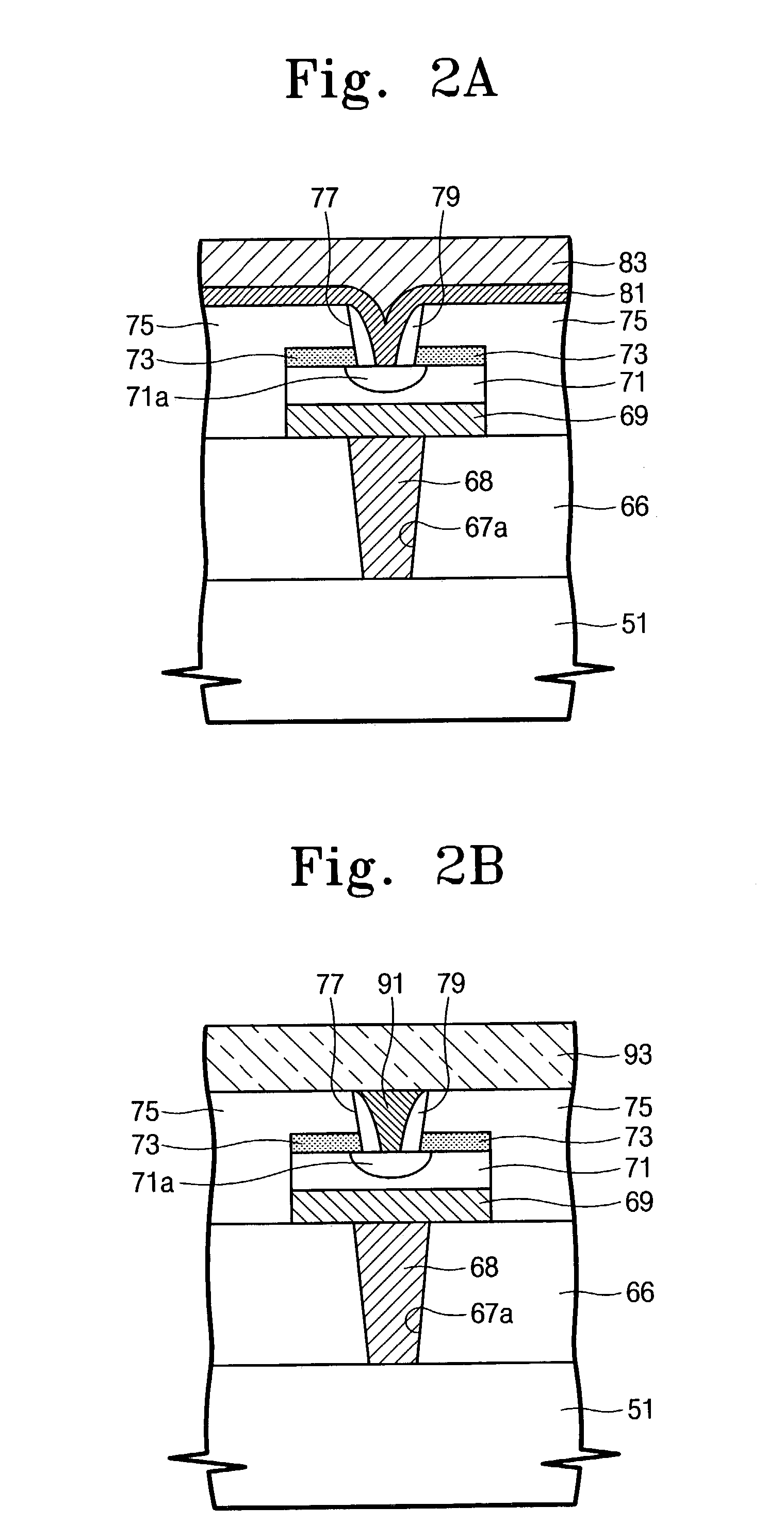

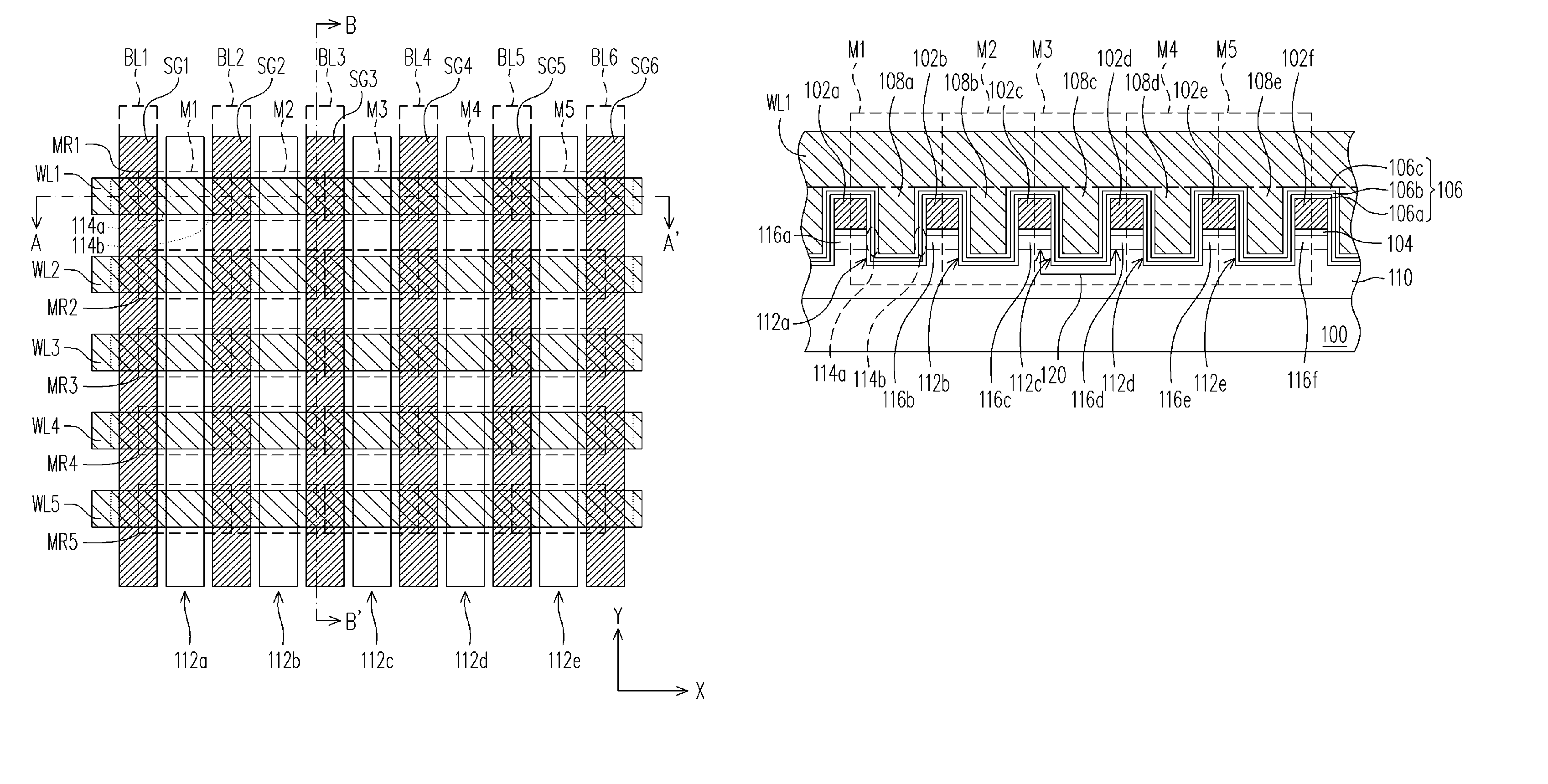

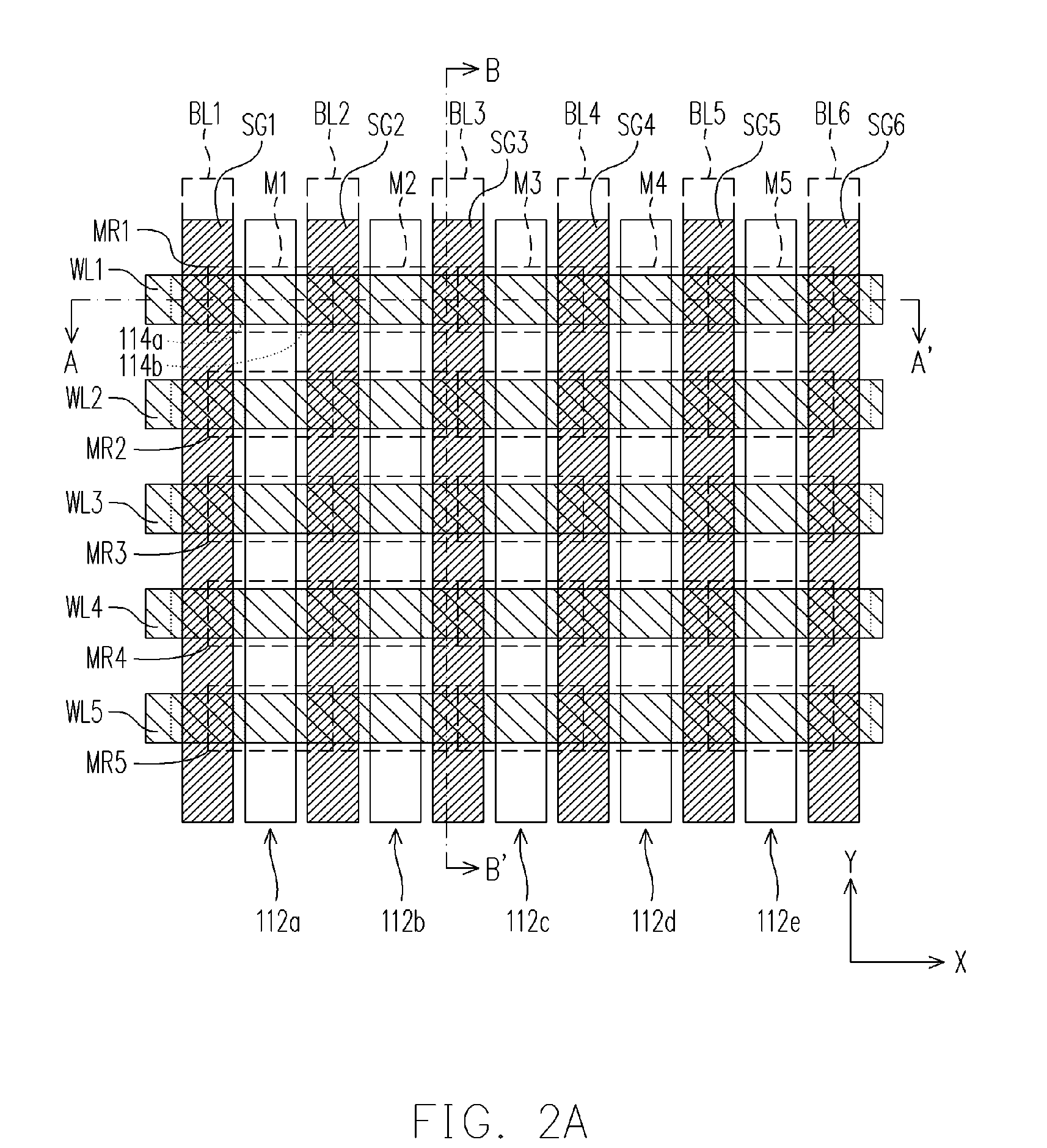

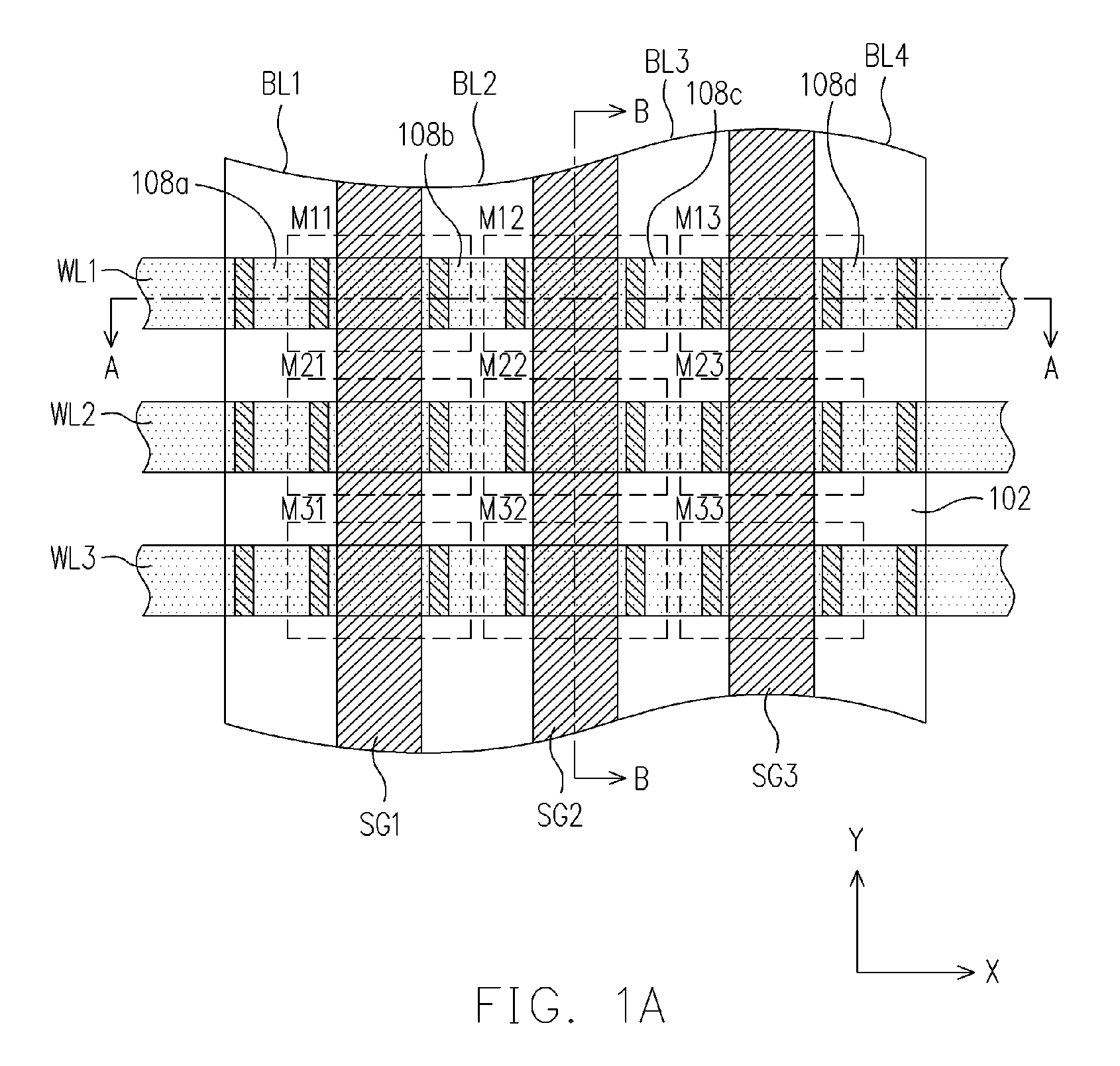

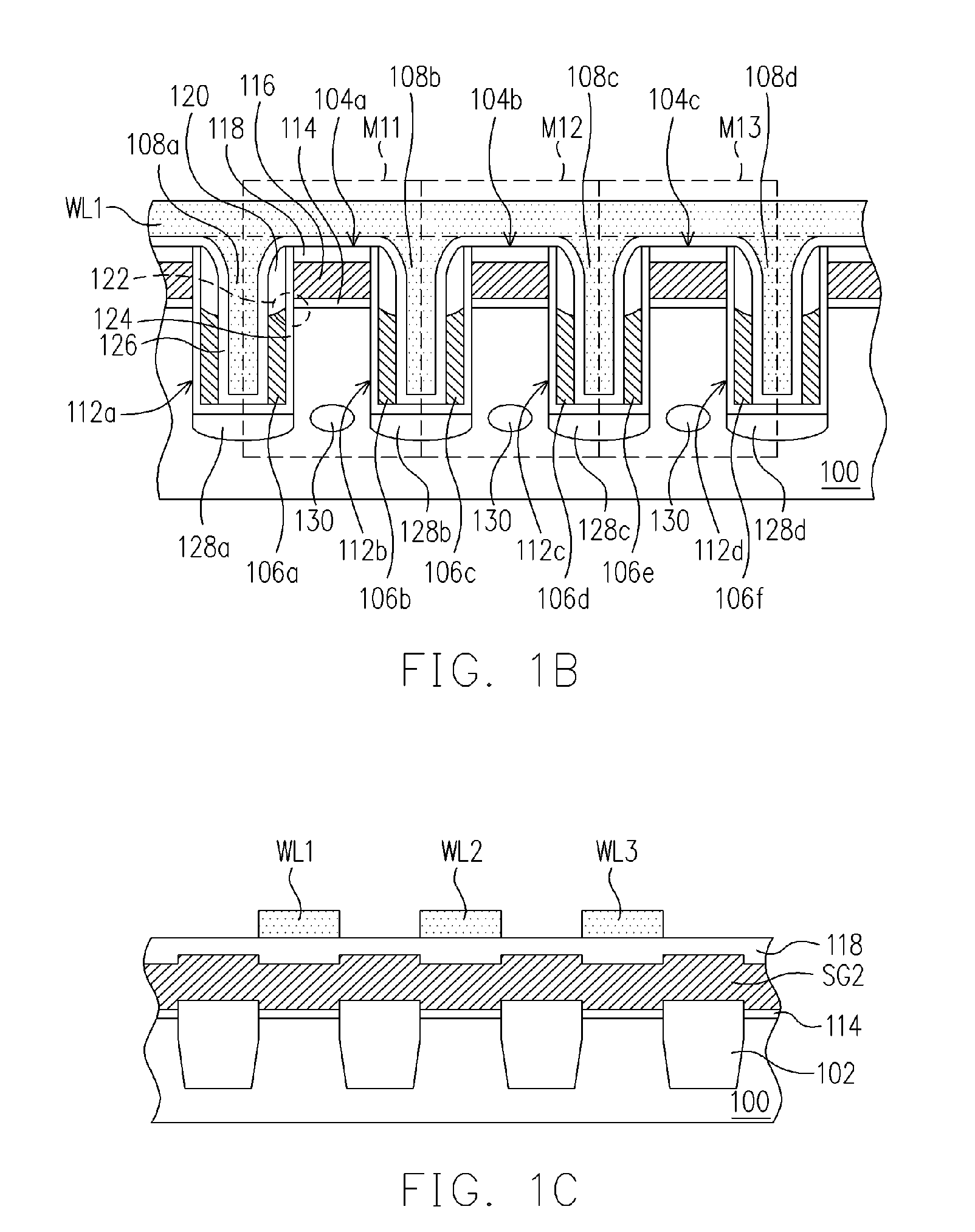

Non-volatile memory and manufacturing and operating method thereof

ActiveUS20060170038A1Highly integratedHigh speedSolid-state devicesSemiconductor devicesGate dielectricTrapping

A non-volatile memory is provided. A substrate having a plurality of trenches and a plurality of select gates is provided. The trenches are arranged in parallel and extend in a first direction. Each of the select gates is disposed on the substrate between two adjacent trenches respectively. A plurality of select gate dielectric layers are disposed between the select gates and the substrate. A plurality of composite layers are disposed over the surface of the trenches and each composite layer has a charge trapping layer. A plurality of word lines are arranged in parallel in a second direction, wherein each of the word lines fills the trenches between adjacent select gates and is disposed over the composite layers.

Owner:POWERCHIP SEMICON MFG CORP

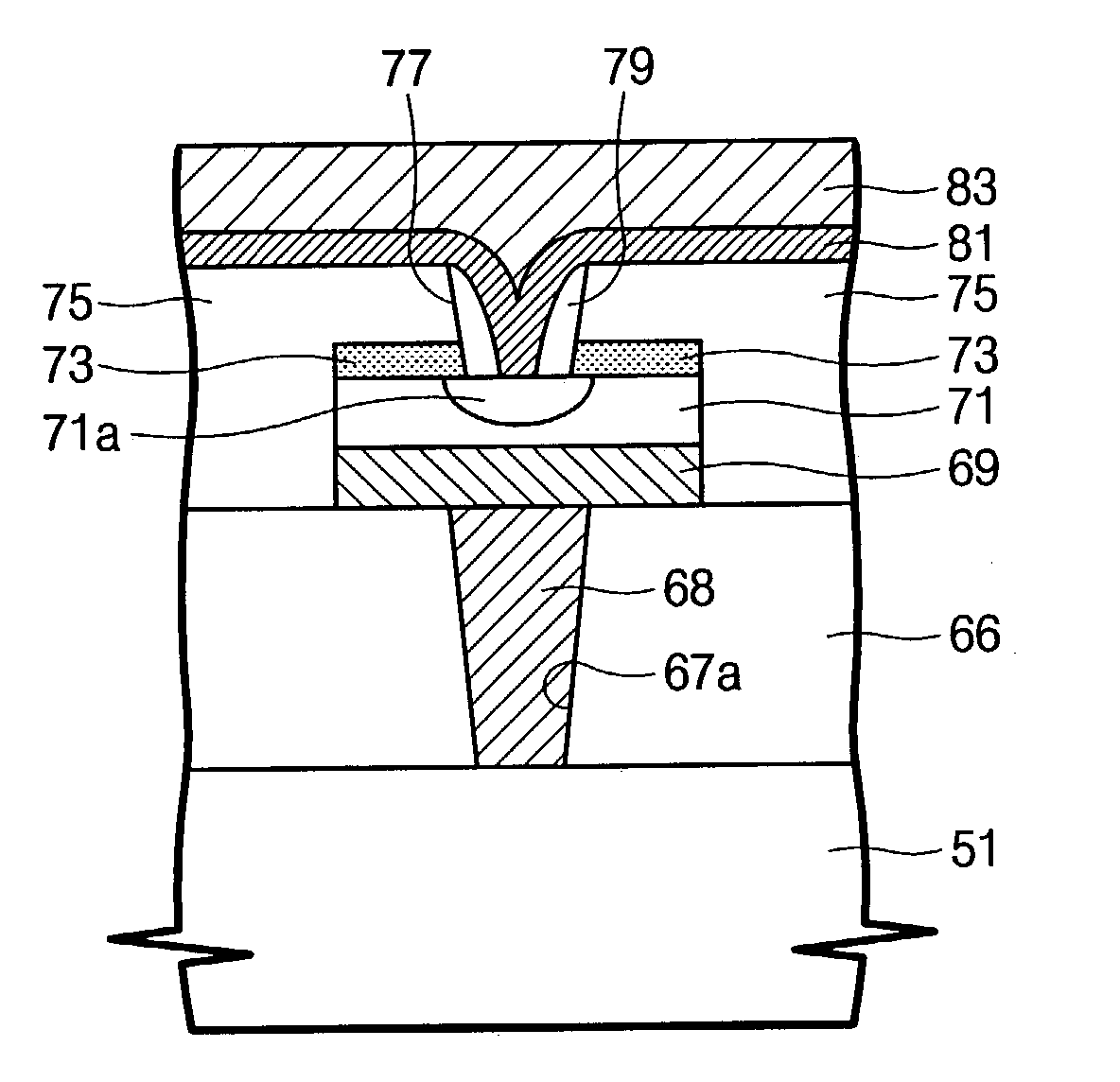

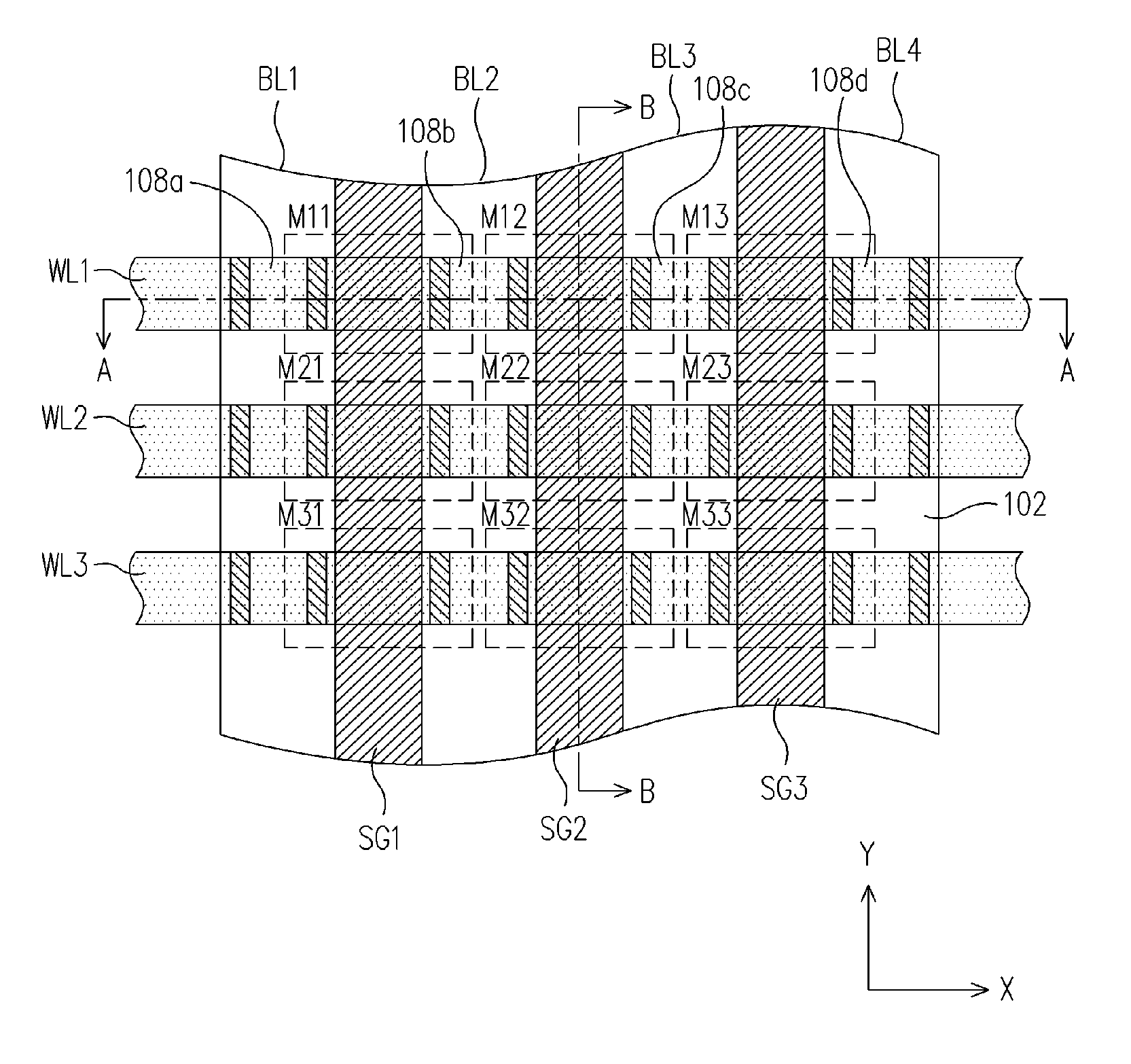

Non-volatile memory, manufacturing and operating method thereof

InactiveUS20060291281A1Total current dropHigh speedSolid-state devicesRead-only memoriesEngineeringNon-volatile memory

A non-volatile memory having a substrate, a select gate, a pair of charge storage layers, a pair of source / drain regions and a control gate is provided. At least a pair of trenches are formed in the substrate. The select gate is formed on the substrate between the pair of trenches. A pair of charge storage layers is formed on the sidewalls of the trenches next to the select gate. A pair of source / drain regions is formed in the substrate at the bottom of the trenches. The control gate is formed on the substrate to fill the trenches completely.

Owner:POWERCHIP SEMICON CORP

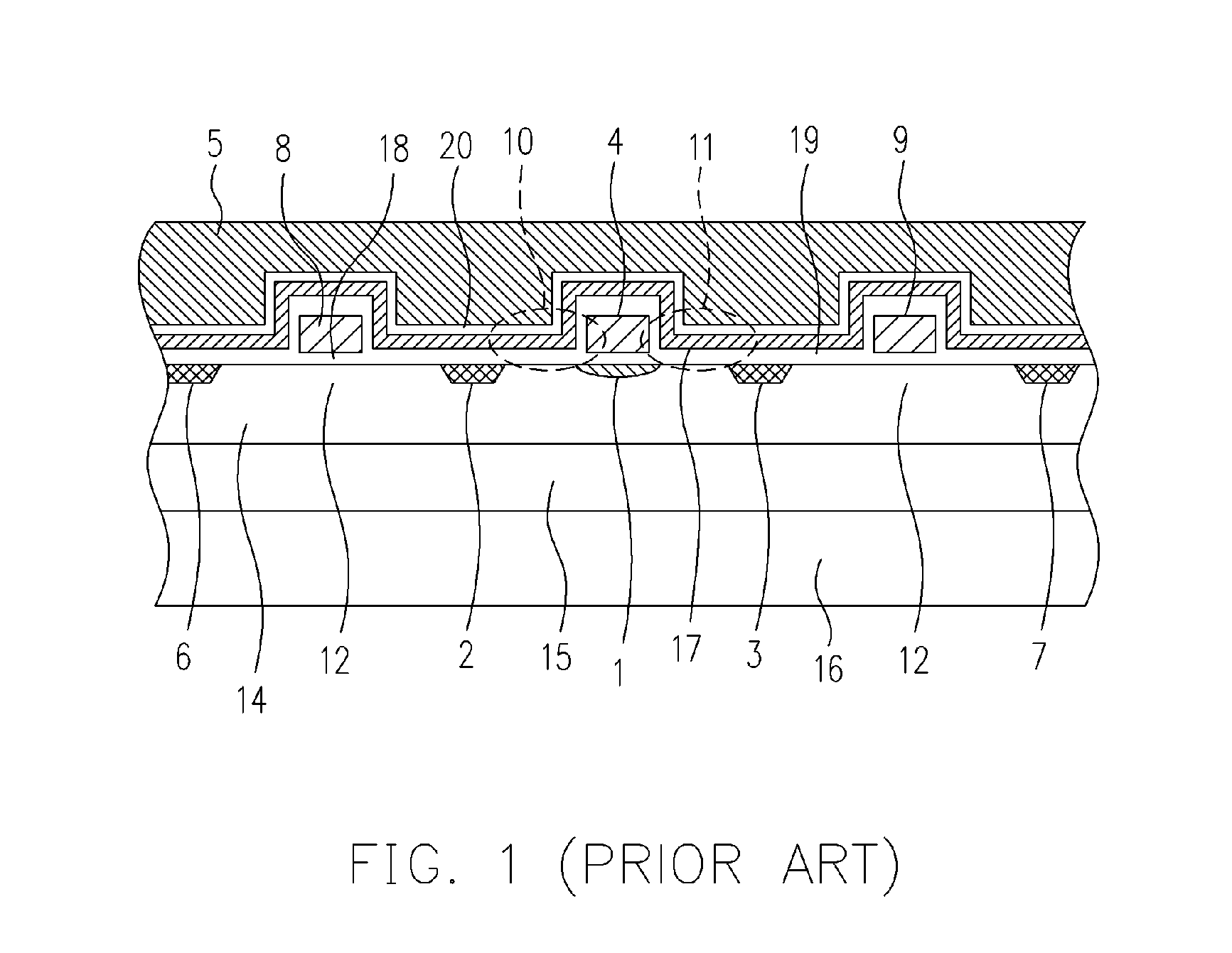

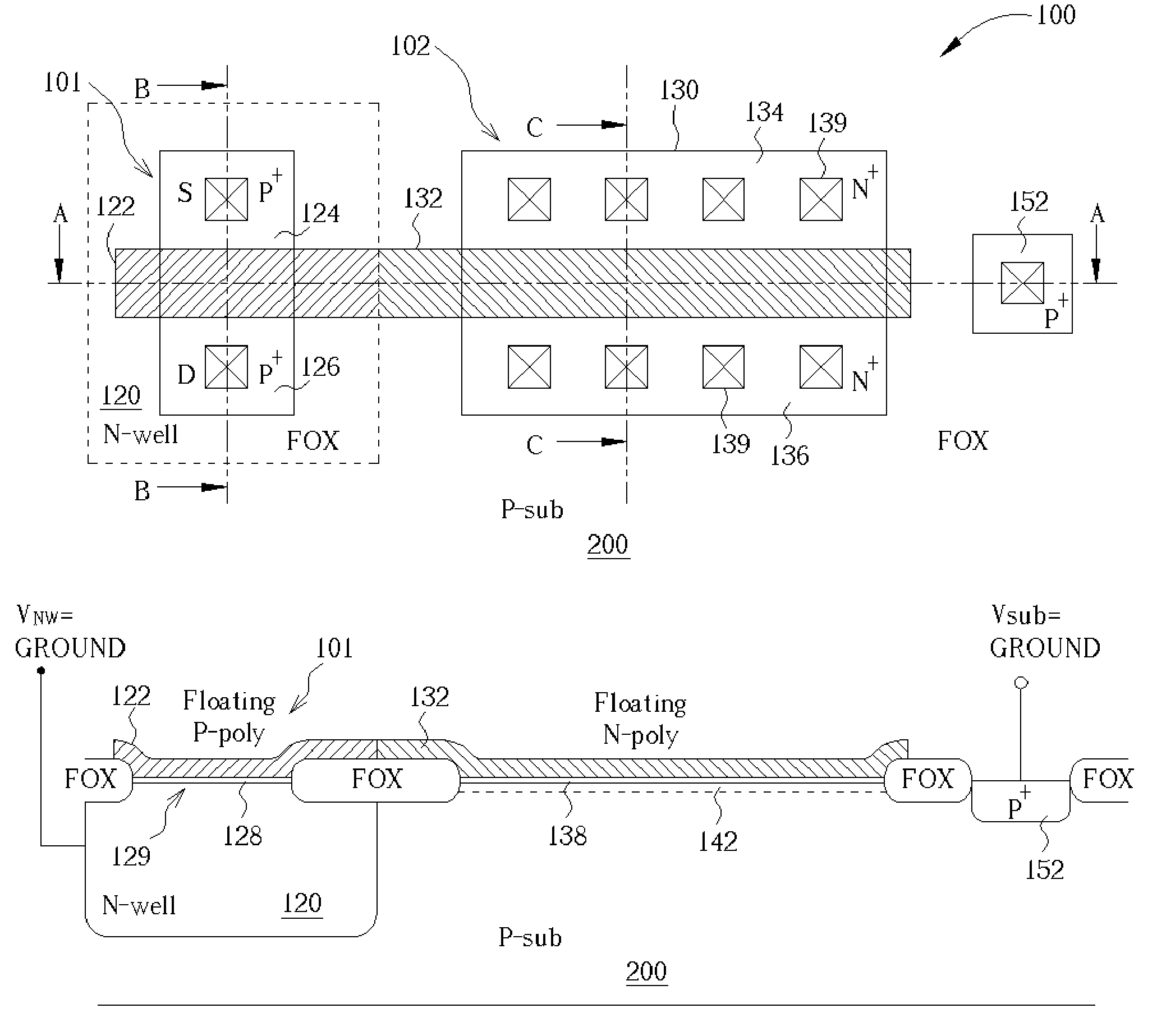

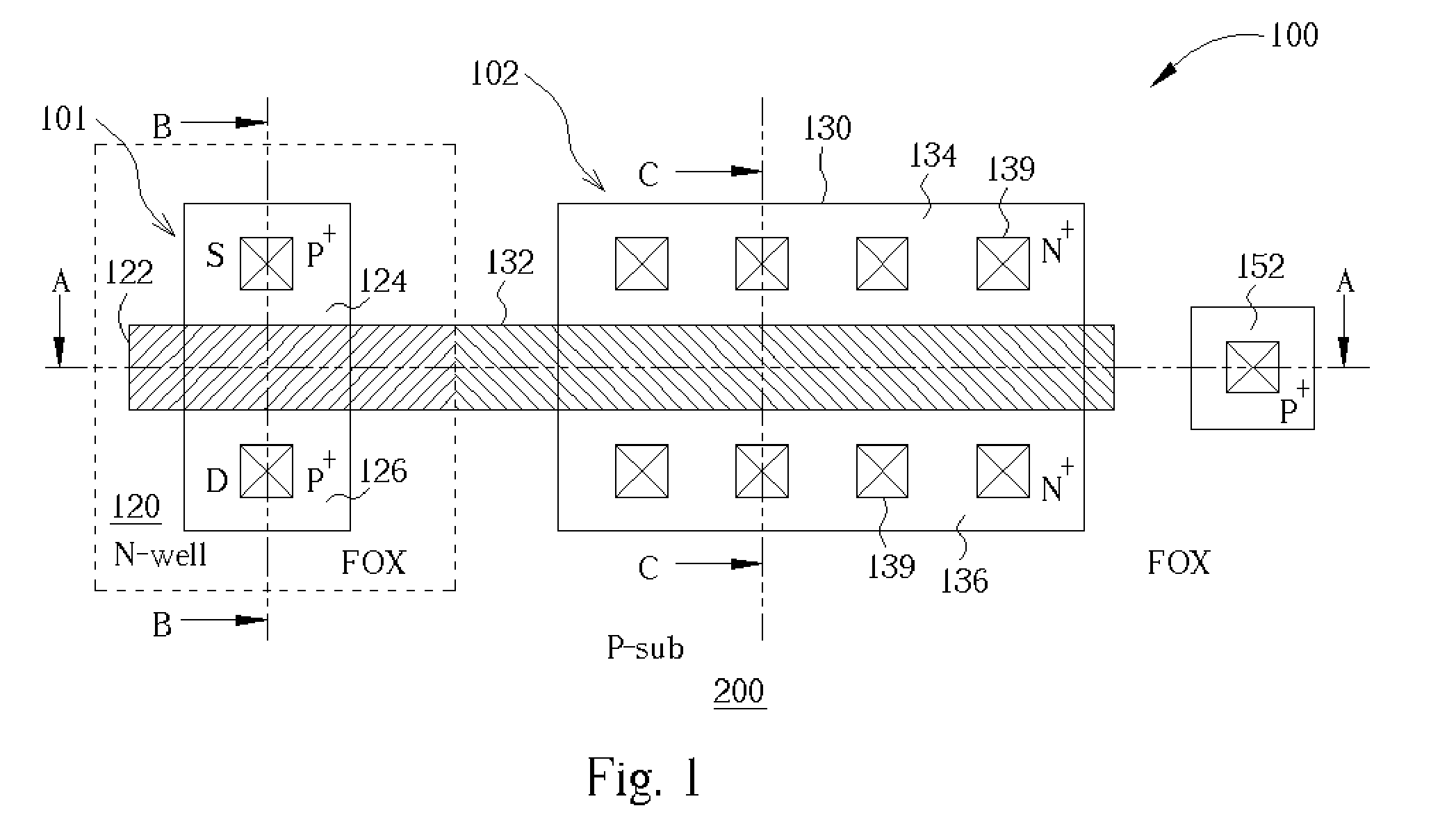

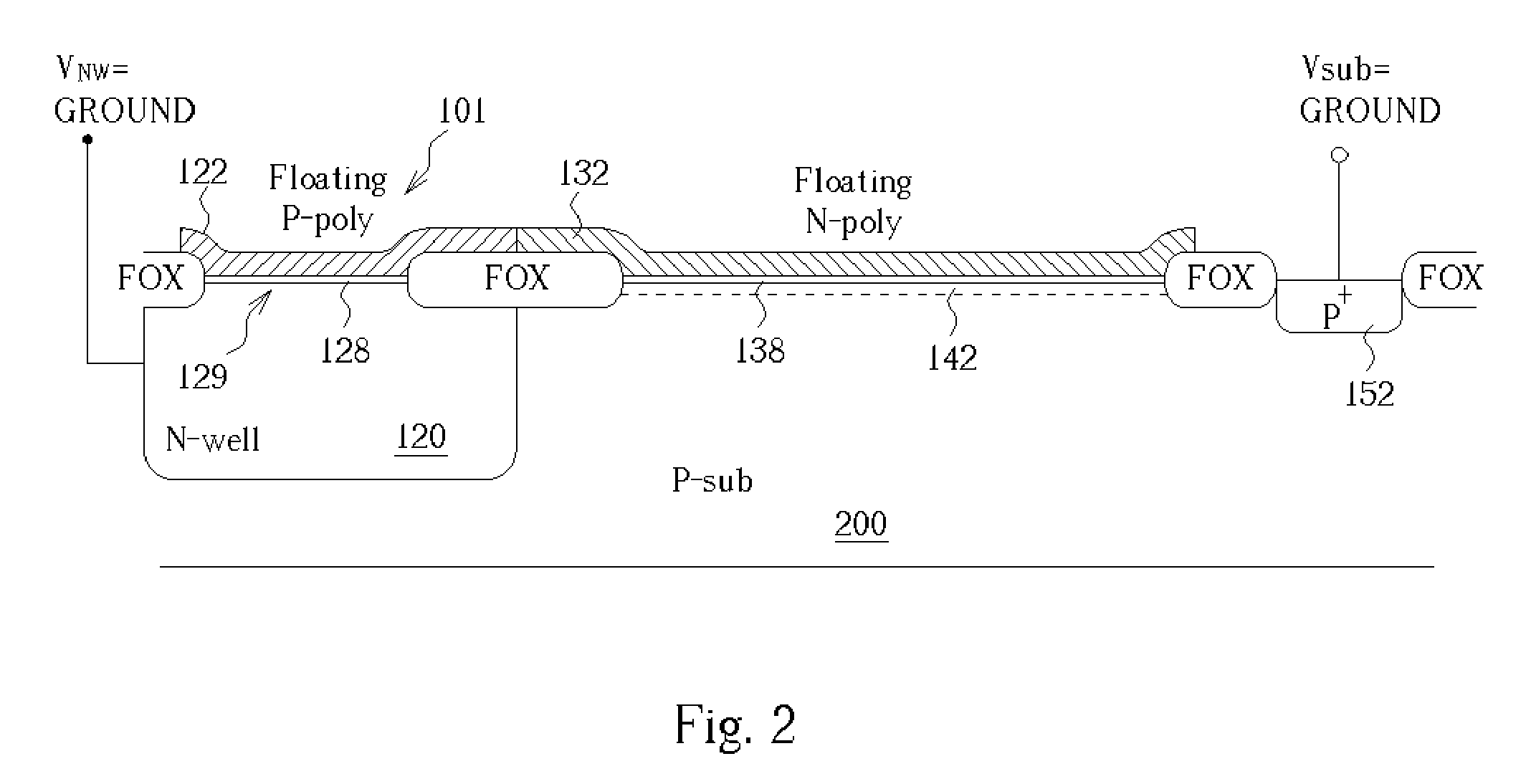

Method for programming single-poly EPROM at low operation voltages

A method for programming a single-poly EPROM cell at relatively low operation voltages (±Vcc) is disclosed. According to this invention, the single-poly EPROM cell includes a P-channel floating-gate transistor formed on an N well of a P type substrate, and an N-channel coupling device. The P-channel floating-gate transistor has a P+ doped drain, P+ doped source, a P channel defined between the P+ doped drain and P+ doped source, a tunnel oxide layer on the P channel, and a floating doped poly gate disposed on the tunnel oxide layer. The N-channel coupling device includes a floating poly electrode, which is electrically connected to the floating doped poly gate of the P-channel floating-gate transistor, and is capacitively coupled to a control region doped in the P type substrate.

Owner:UNITED MICROELECTRONICS CORP

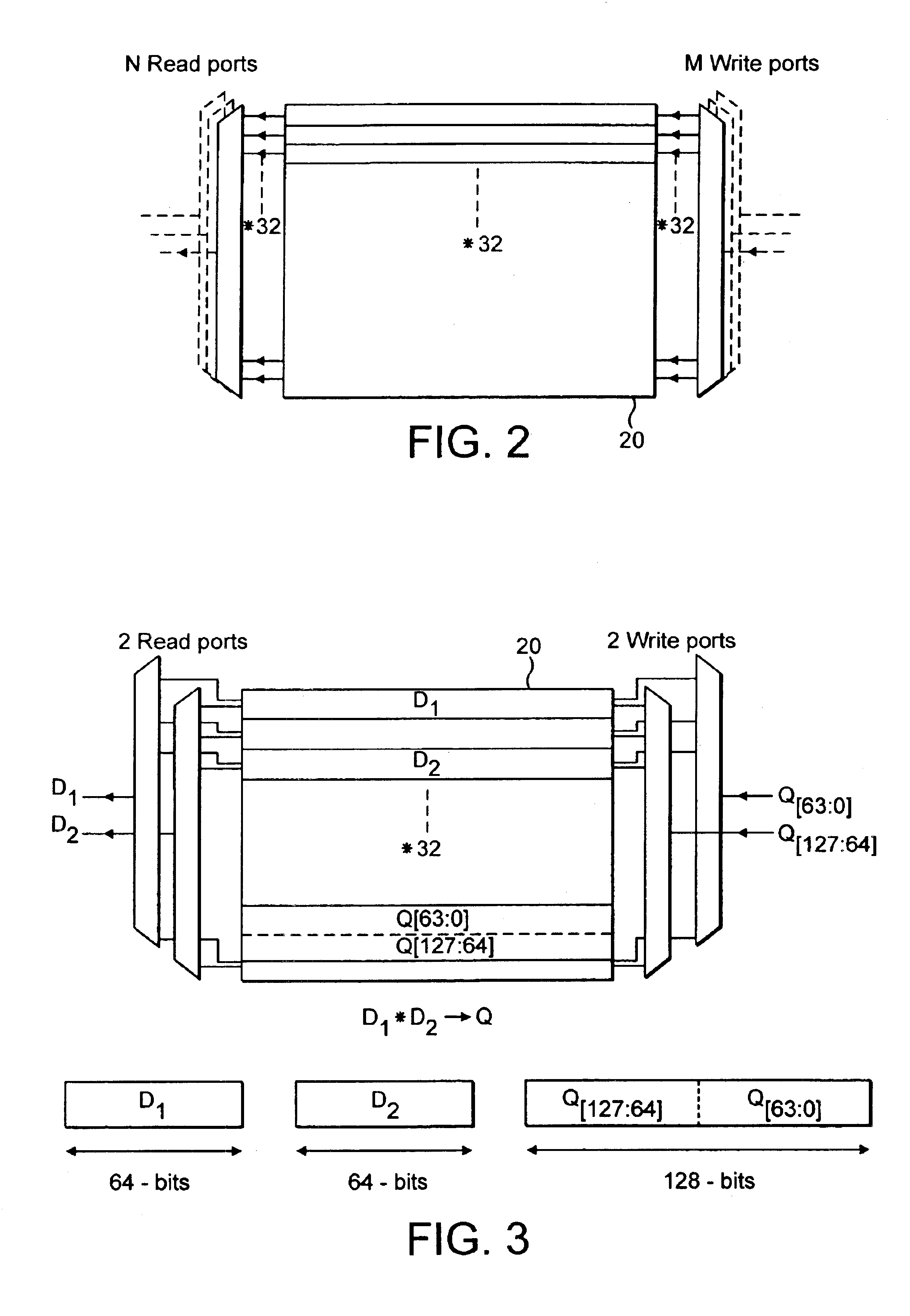

Table lookup operation within a data processing system

ActiveUS6958718B2Efficient programmingCode conversionGeneral purpose stored program computerData processing systemIndex register

A table lookup extension instruction is provided in which index values stored within an index register D2 are used to select data elements stored within one or more table registers D0, D1 for storage into corresponding positions within a result register D3. Out-of-range index values result in the corresponding locations within the result register being left unchanged U. In this way, an offset can be applied to index values held and then those index values reused with the table registers D0, D1 being reloaded with a different portion of a table so as to give the effect of a larger table than can be directly supported by the number of table registers available.

Owner:ARM LTD

Online remote control configuration system

InactiveUS20080062034A1Efficient programmingQuick configurationElectric signal transmission systemsNon-electrical signal transmission systemsWeb siteElectronic systems

An online remote control configuration system for efficiently programming a remote control to recognize a plurality of external electronic devices. The online remote control configuration system includes a remote control having a housing, a keypad, and an electronic system for receiving configuration data from a control station via a global computer network (e.g. Internet). The user preferably “samples” one or more signals from a remote control into the electronic system and then uploads the samples to the control station. The control station analyzes the uploaded samples and transmits the appropriate configuration data to properly configure the electronic system. The user may also access a web site of the control station and manually select each of the external electronic devices that the remote control is to operate after which the control station sends the appropriate configuration data to the electronic system.

Owner:LOGITECH EURO SA

Device and method for pulse width control in a phase change memory device

InactiveUS20060181932A1Shorten the durationReduce power consumptionSolid-state devicesRead-only memoriesComputer hardwareBit line

A circuit and method for programming phase-change memory devices, such as chalcogenide memory (PRAM), are described. The invention is directed to an approach to programming PRAM elements from a reset state to a set state or from a set state to the set state. The invention provides a novel and nonobvious PRAM device and method in which a set pulse duration time is controlled by monitoring the state of the memory element during programming such as by comparing the voltage of a bit line with a reference voltage or comparing the cell resistance with a set state cell resistance. The duration of the set pulse is controlled in response to the detected state of the memory element. The result of the approach of the invention is the significant reduction in PRAM programming errors, such as those caused by a constant-duration set pulse, as well as reduction in programming time duration and power consumption.

Owner:SAMSUNG ELECTRONICS CO LTD

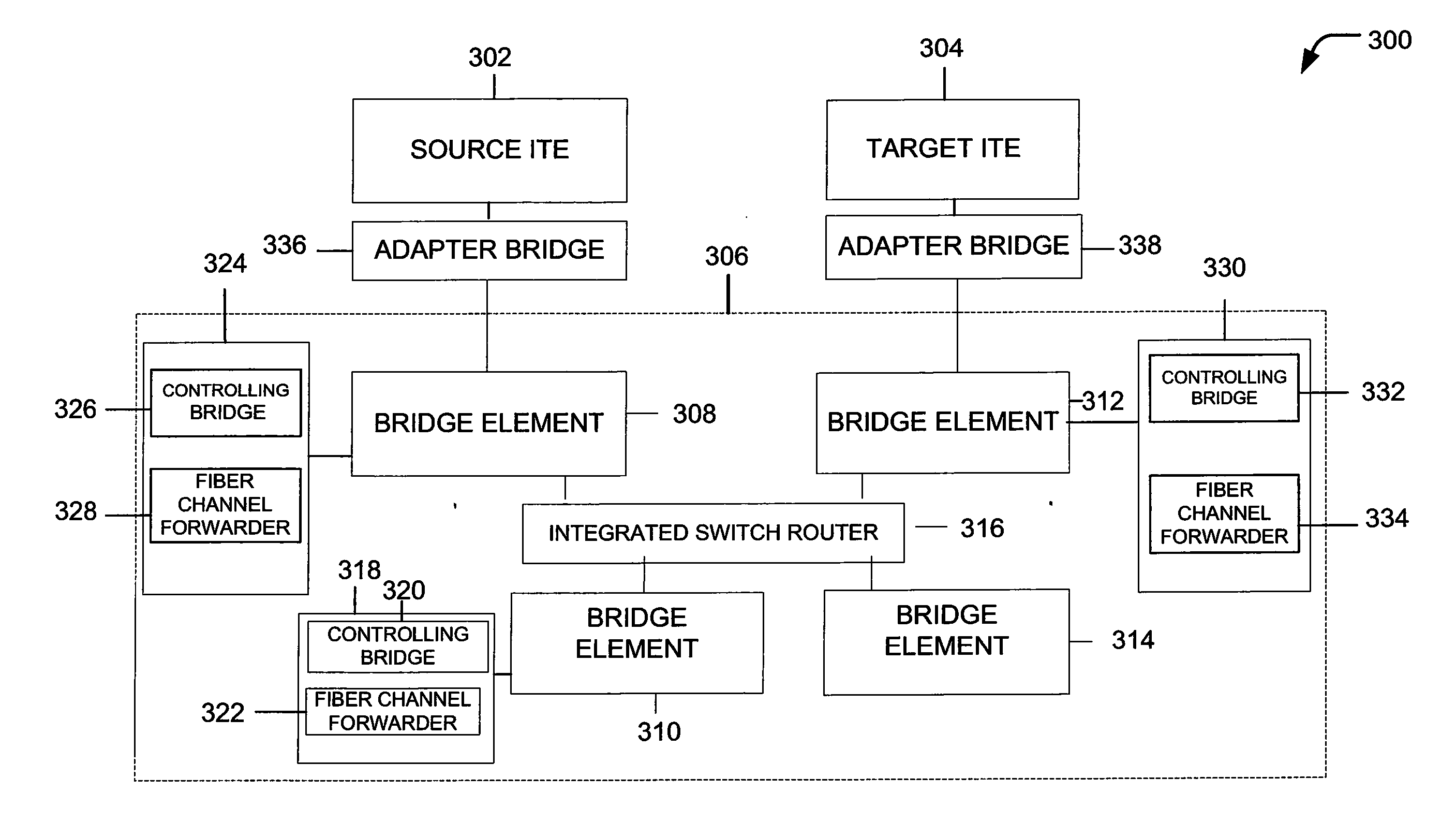

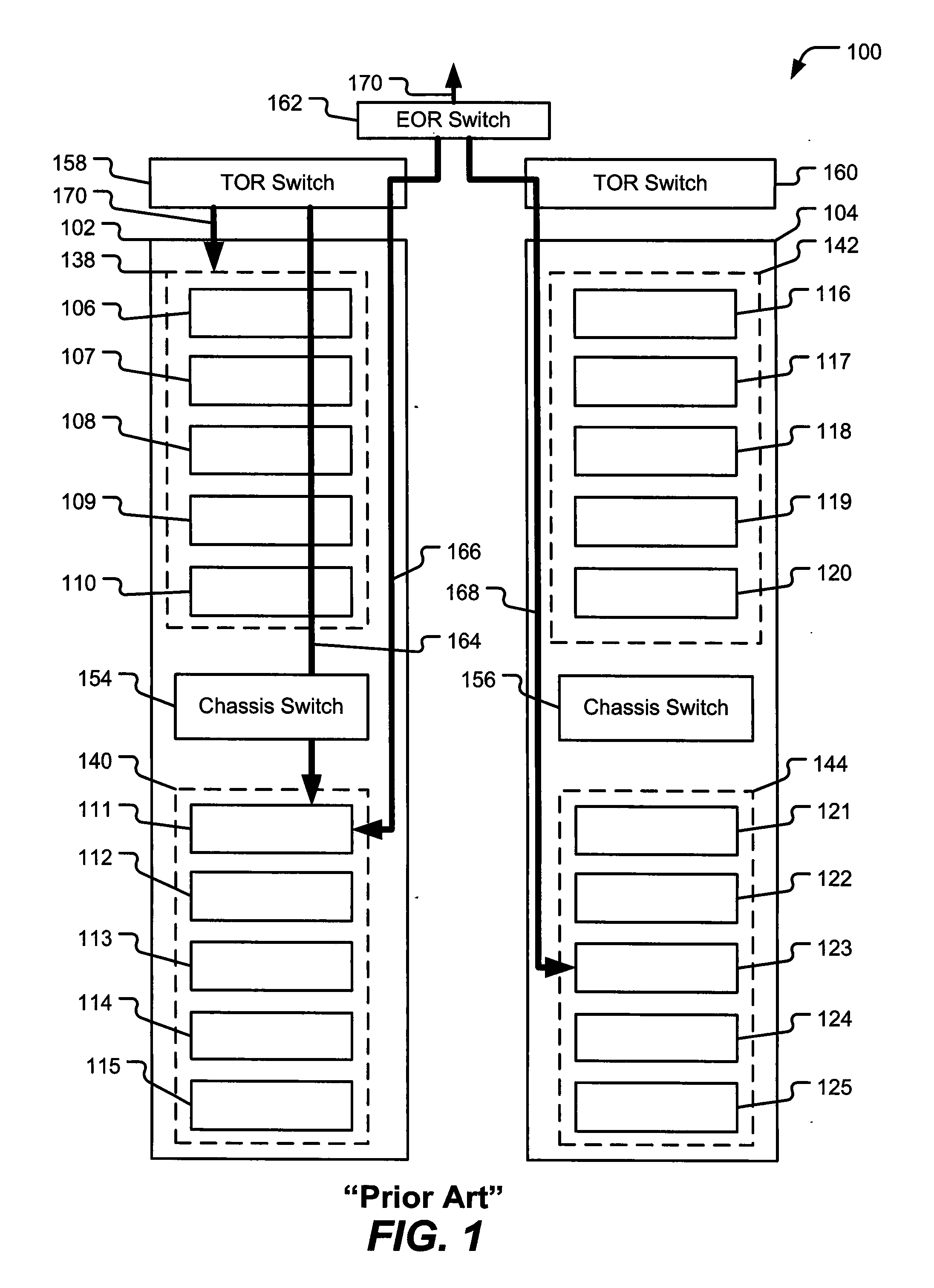

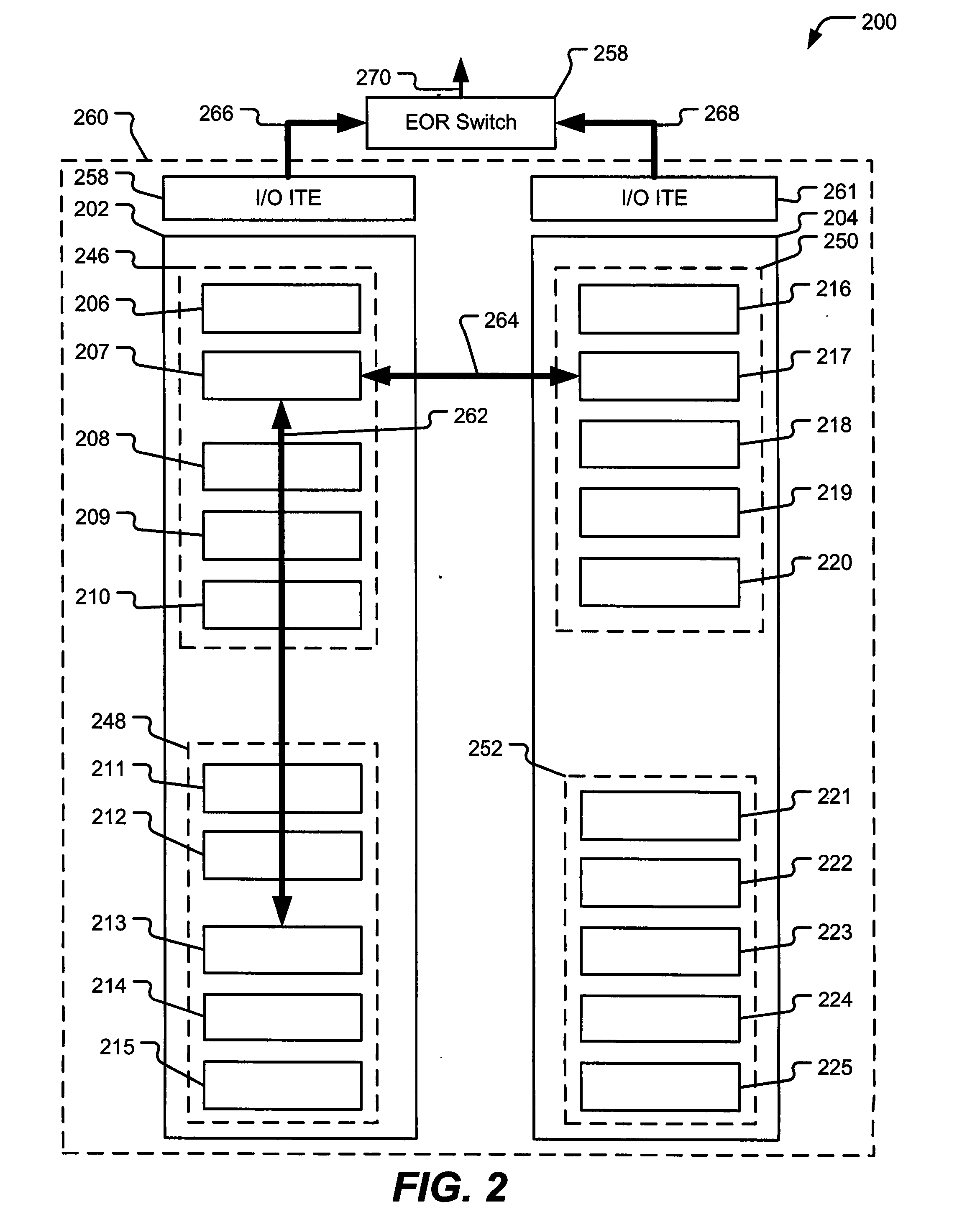

Distributed Virtual Bridge Management

ActiveUS20110258340A1Efficient programmingReduce potential bottleneckDigital computer detailsData switching networksManagement systemServer

Systems and methods to forward data frames are described. A particular method may include receiving a data frame at a switch of a plurality of networked switches coupled to a plurality of server computers. The data frame may be forwarded from a controlling bridge coupled to the plurality of networked switches. The data frame may be determined to include management data, and an operating parameter of the switch may be modified.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

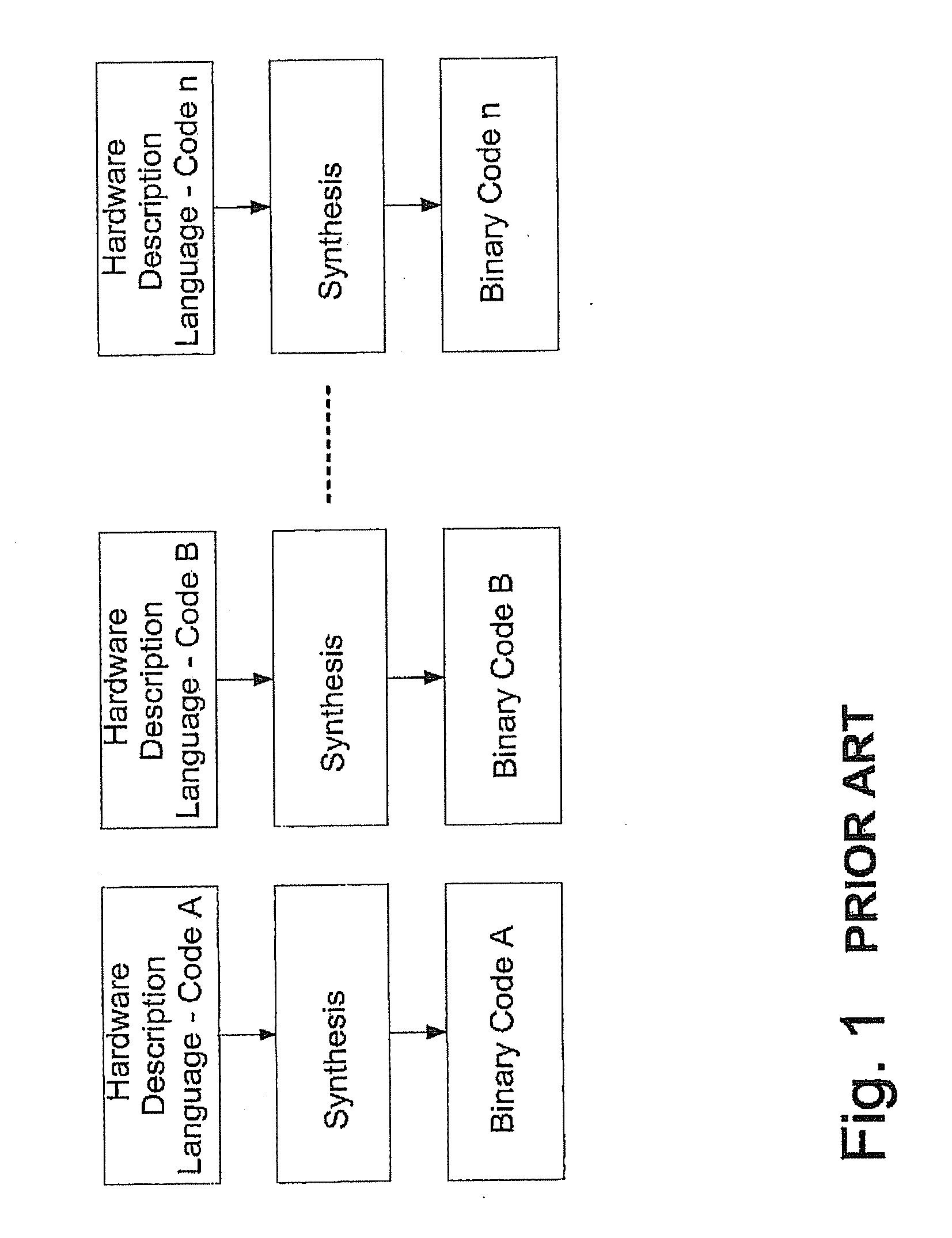

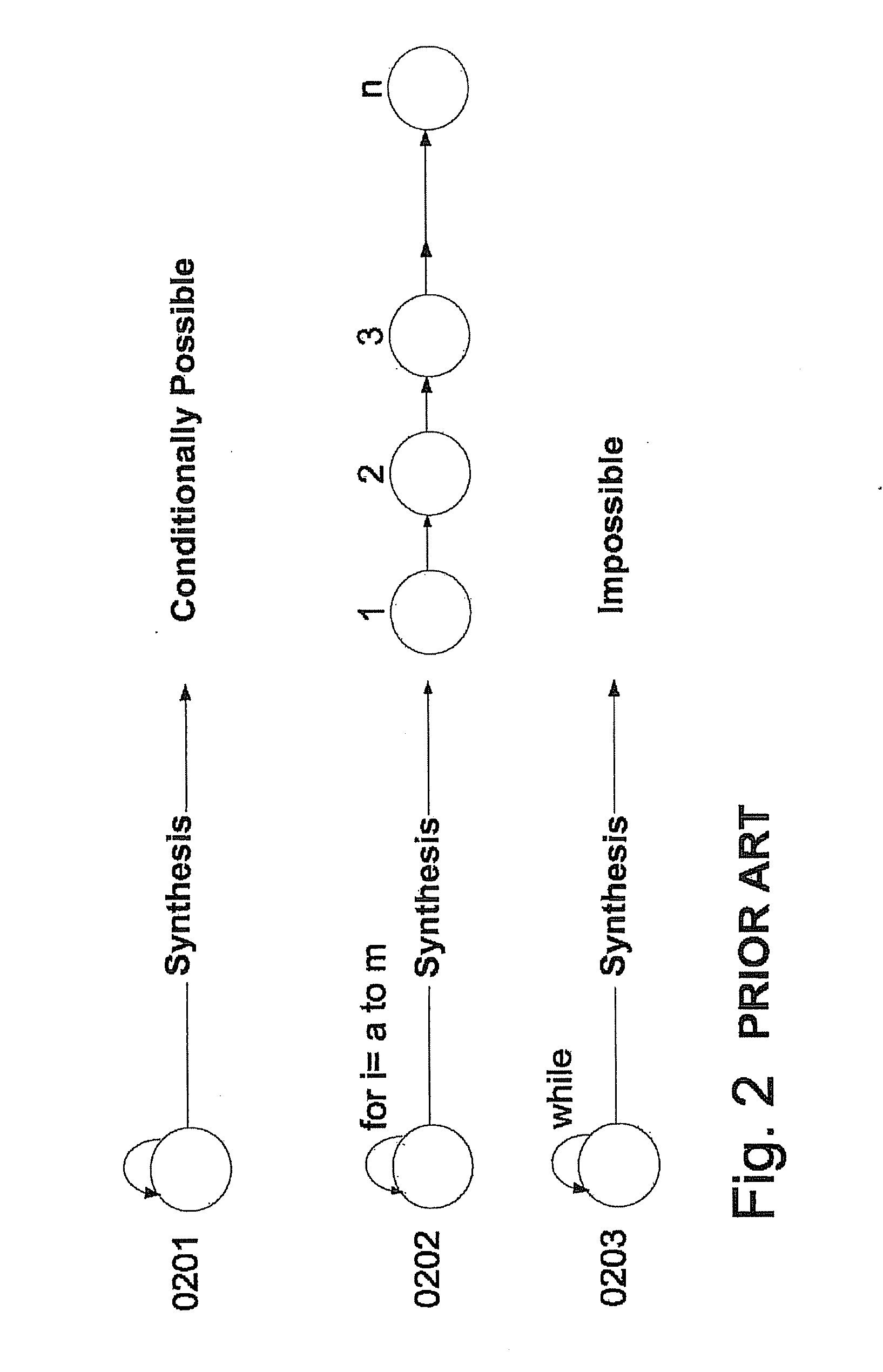

Configurable logic integrated circuit having a multidimensional structure of configurable elements

InactiveUS20100228918A1Efficient programmingProgram control using stored programsError detection/correctionComputer architectureIntegrated circuit

Programming of modules which can be reprogrammed during operation is described. Partitioning of code sequences is also described.

Owner:SCIENTIA SOL MENTIS AG

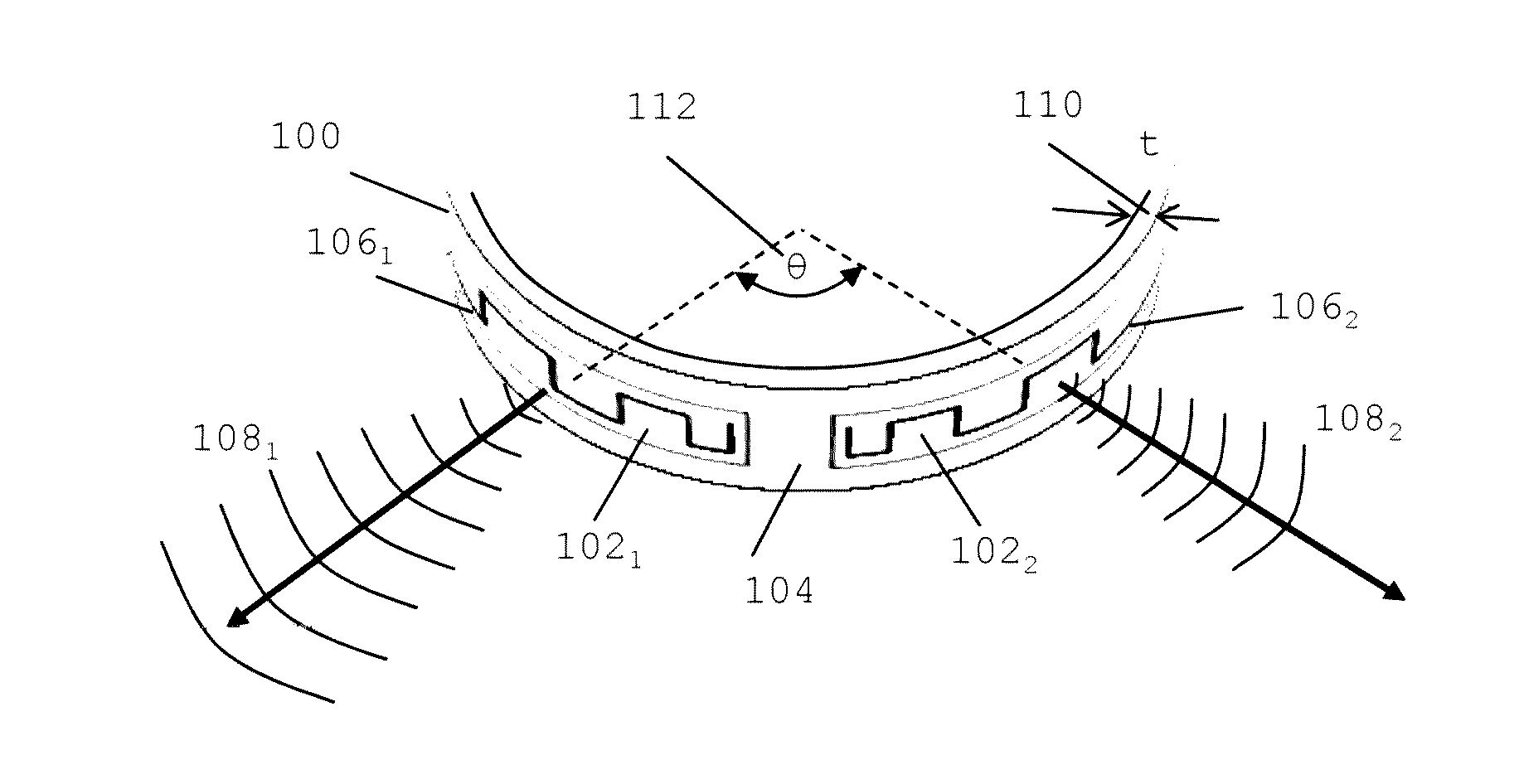

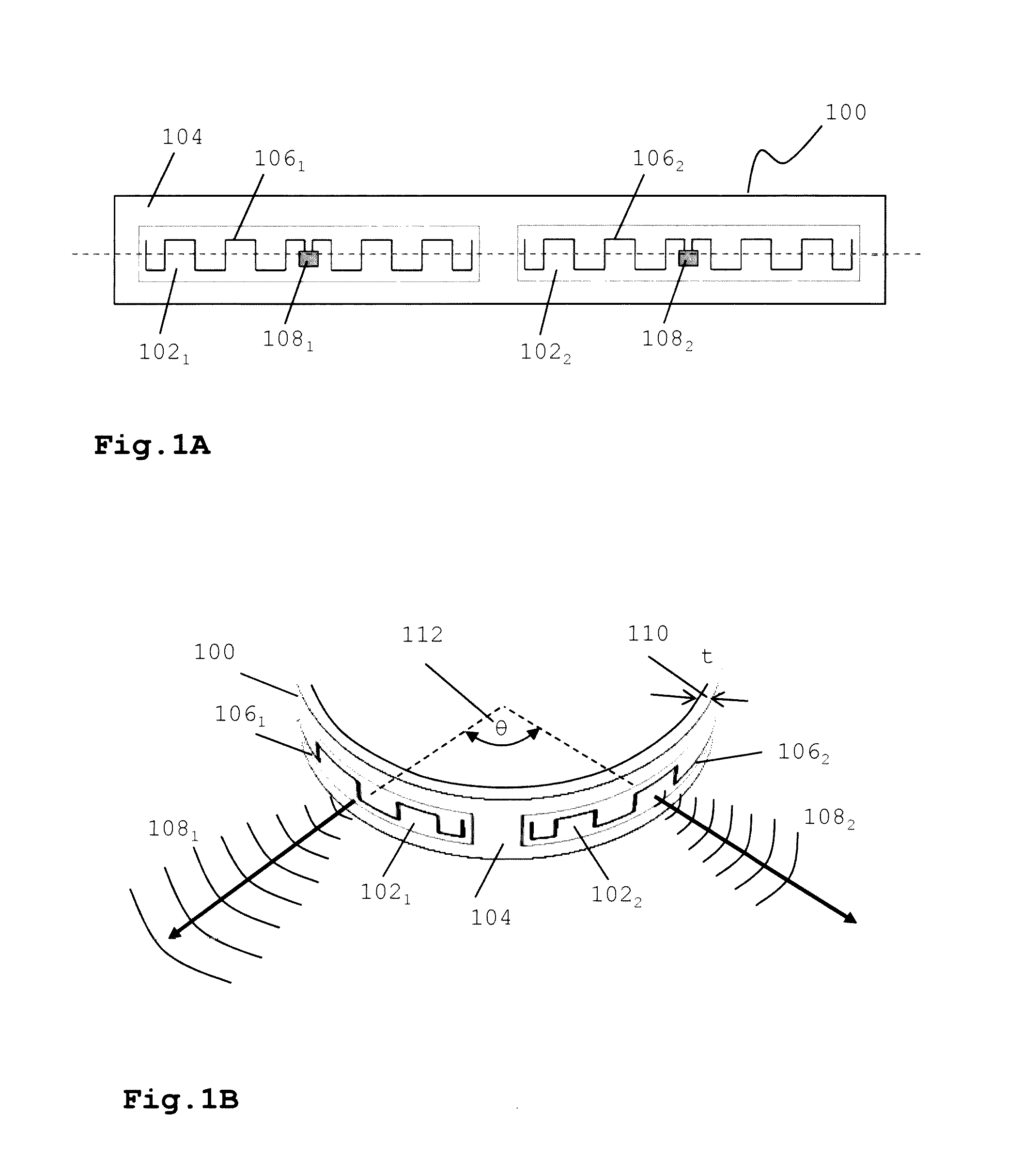

A Wearable sports timing tag assembly

ActiveUS20160259952A1Interference and coupling effectAvoiding and at least minimizing detuningRegistering/indicating time of eventsRecord carriers used with machinesEngineering

A wearable sport timing tag assembly comprising at least a first and second tag is described for transmitting data associated with the wearer of the tag assembly to at least one detection antenna, wherein the tag assembly comprises means for attaching the tag assembly to at least a body part or clothing of the wearer, wherein when attached to said body or clothing the main signal transmission direction of said first tag being in a first direction; and, the main signal transmission direction of said second tag being in a second direction which is different from said first direction.

Owner:MYLAPS BV

Systems and methods for monitoring caregiver and patient protocol compliance

A system and methods is provided for facilitating, monitoring and recording caregiver and patient compliance with established hospital hand hygiene protocols. The system comprises a 3-D imaging and monitoring assembly and an optional intelligent programmable monitor / sanitizer. Three dimensional imagery tracks a caregiver's movements and location while generating a representative image value. Information acquired by the imaging system determines the proximity of a caregiver to the patient and / or contamination source and determines if the sanitizers provided have been utilized and if so, at an appropriate time and distance from the patient per hospital protocol. While being monitored, a representative Avatar based on physical characteristics derived from three dimensional images of the caregiver and patient may be generated so as to maintain anonymity of both unless a violation of institutional protocol occurs which may be forensically recorded in real-time for analysis.

Owner:DEUT RICHARD

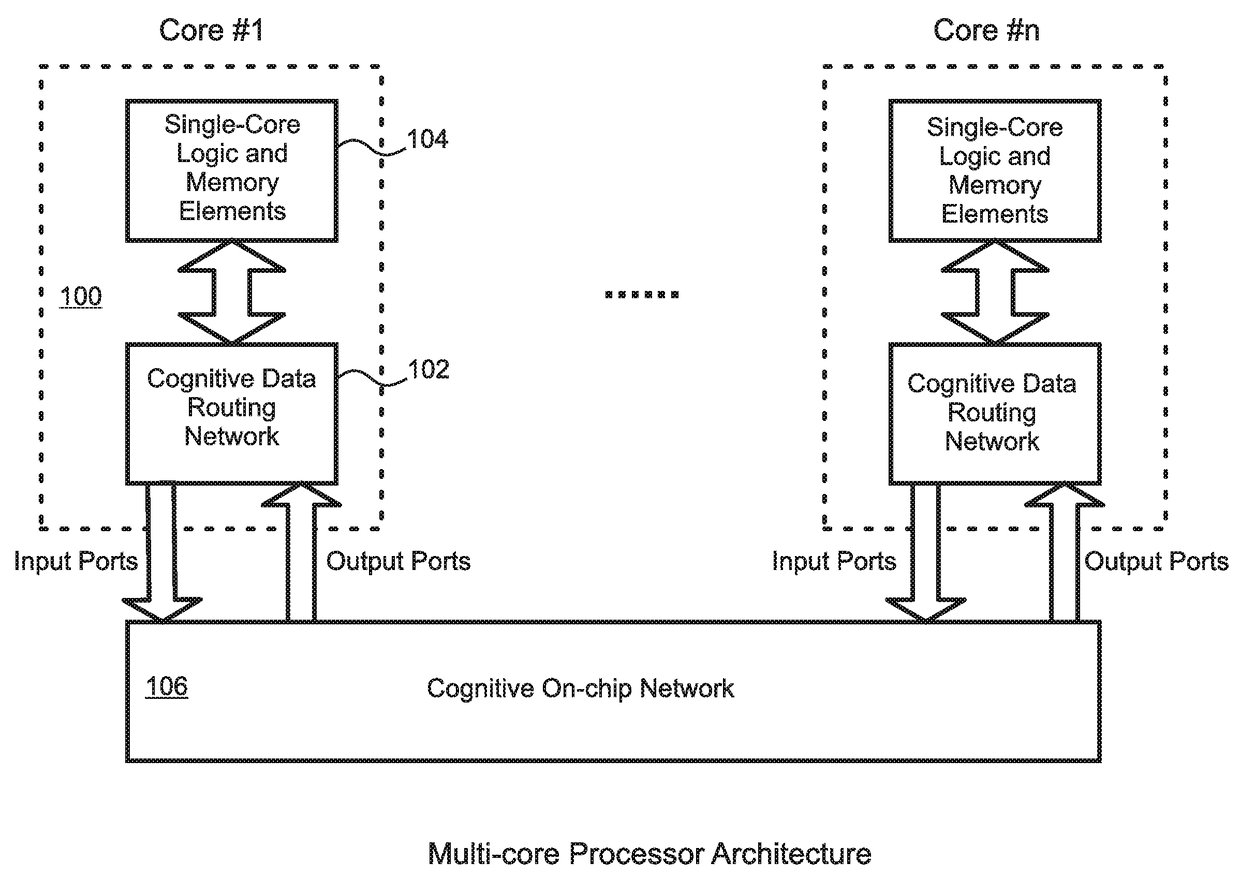

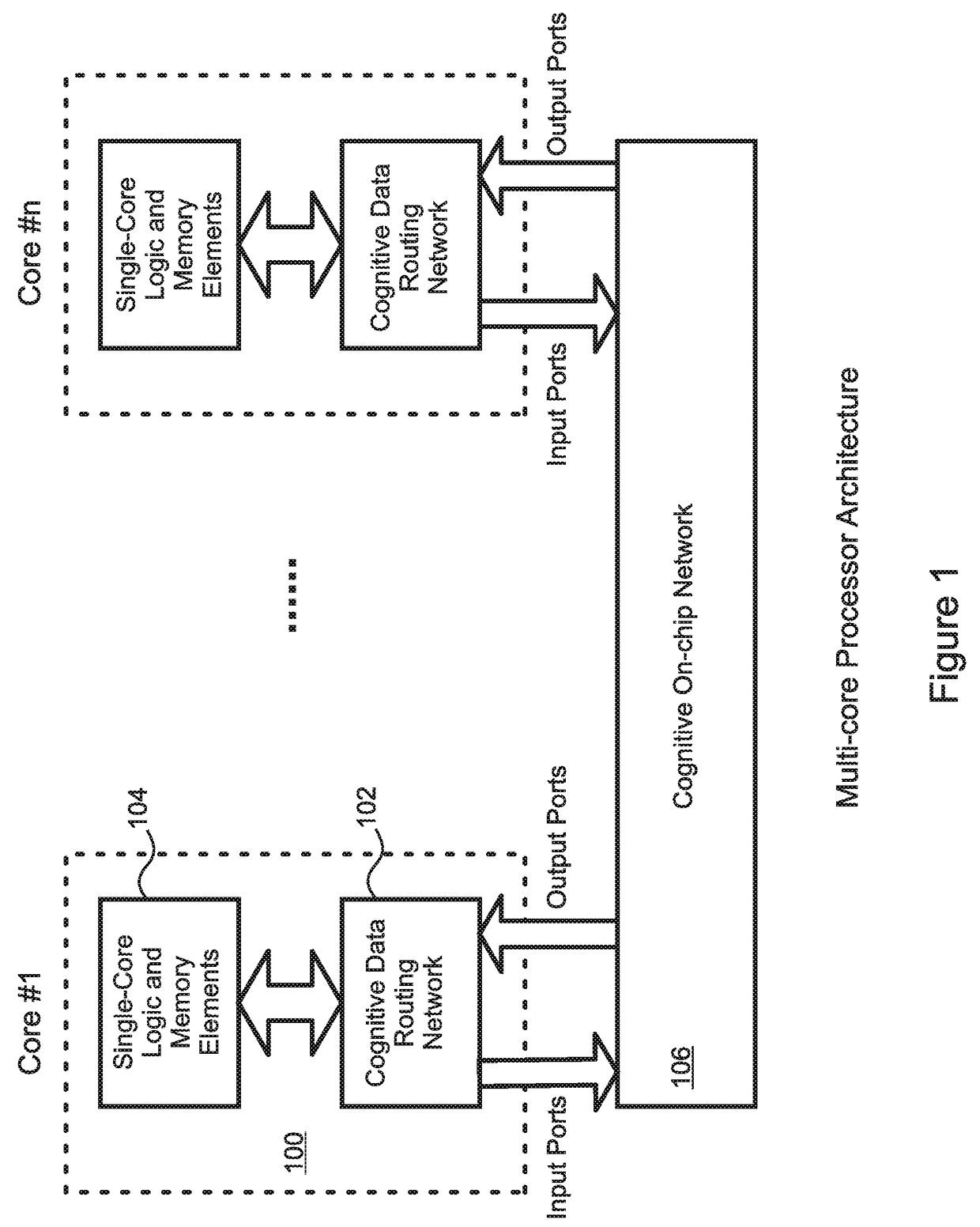

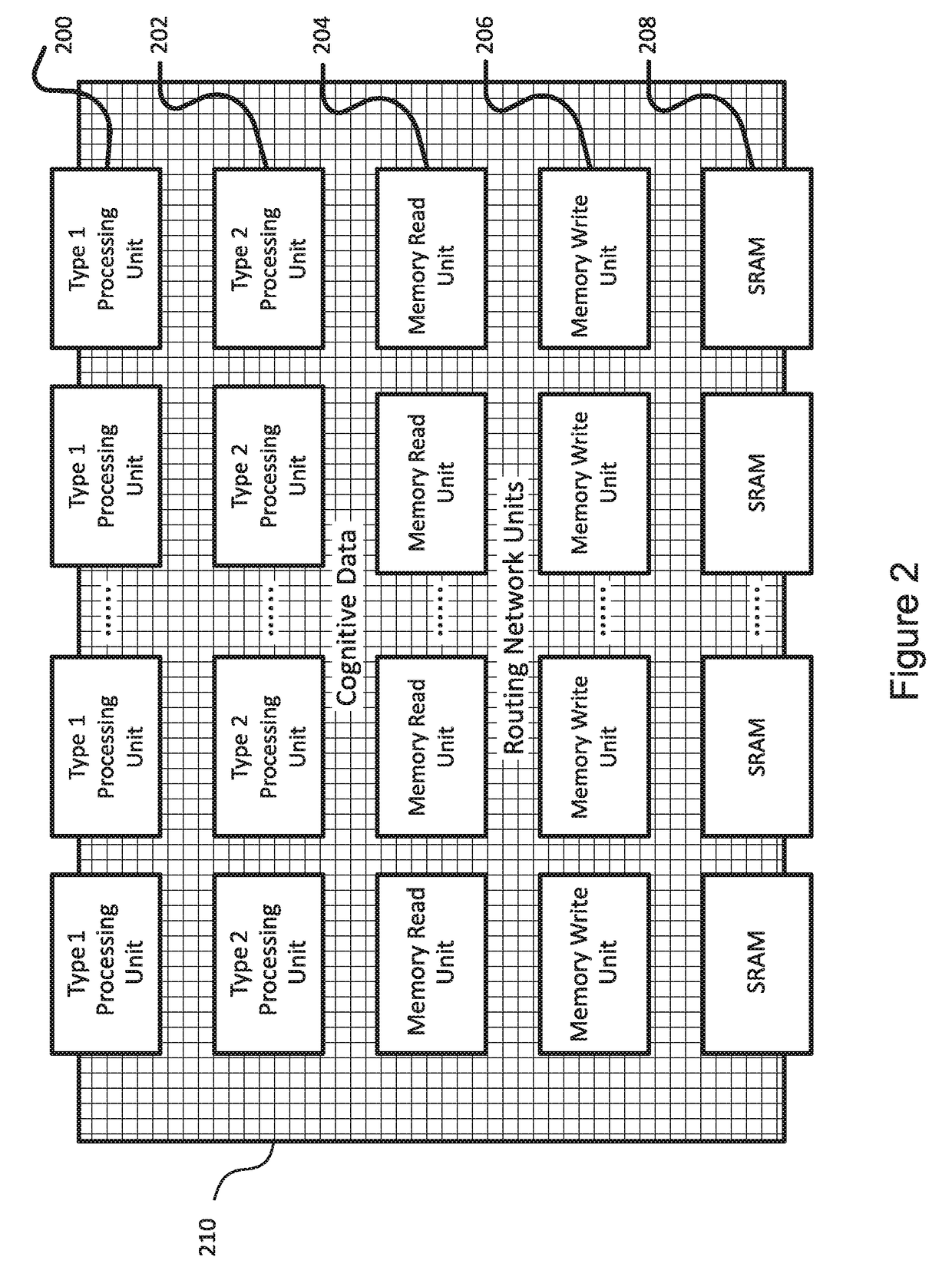

Reconfigurable microprocessor hardware architecture

ActiveUS20170300333A1Reduce delayReduce operational latencyCAD circuit designTransmissionMulti-core processorMemory interface

A reconfigurable, multi-core processor includes a plurality of memory blocks and programmable elements, including units for processing, memory interface, and on-chip cognitive data routing, all interconnected by a self-routing cognitive on-chip network. In embodiments, the processing units perform intrinsic operations in any order, and the self-routing network forms interconnections that allow the sequence of operations to be varied and both synchronous and asynchronous data to be transmitted as needed. A method for programming the processor includes partitioning an application into modules, determining whether the modules execute in series, program-driven parallel, or data-driven parallel, determining the data flow required between the modules, assigning hardware resources as needed, and automatically generating machine code for each module. In embodiments, a Time Field is added to the instruction format for all programming units that specifies the number of clock cycles for which only one instruction fetch and decode will be performed.

Owner:WANG XIAOLIN +1

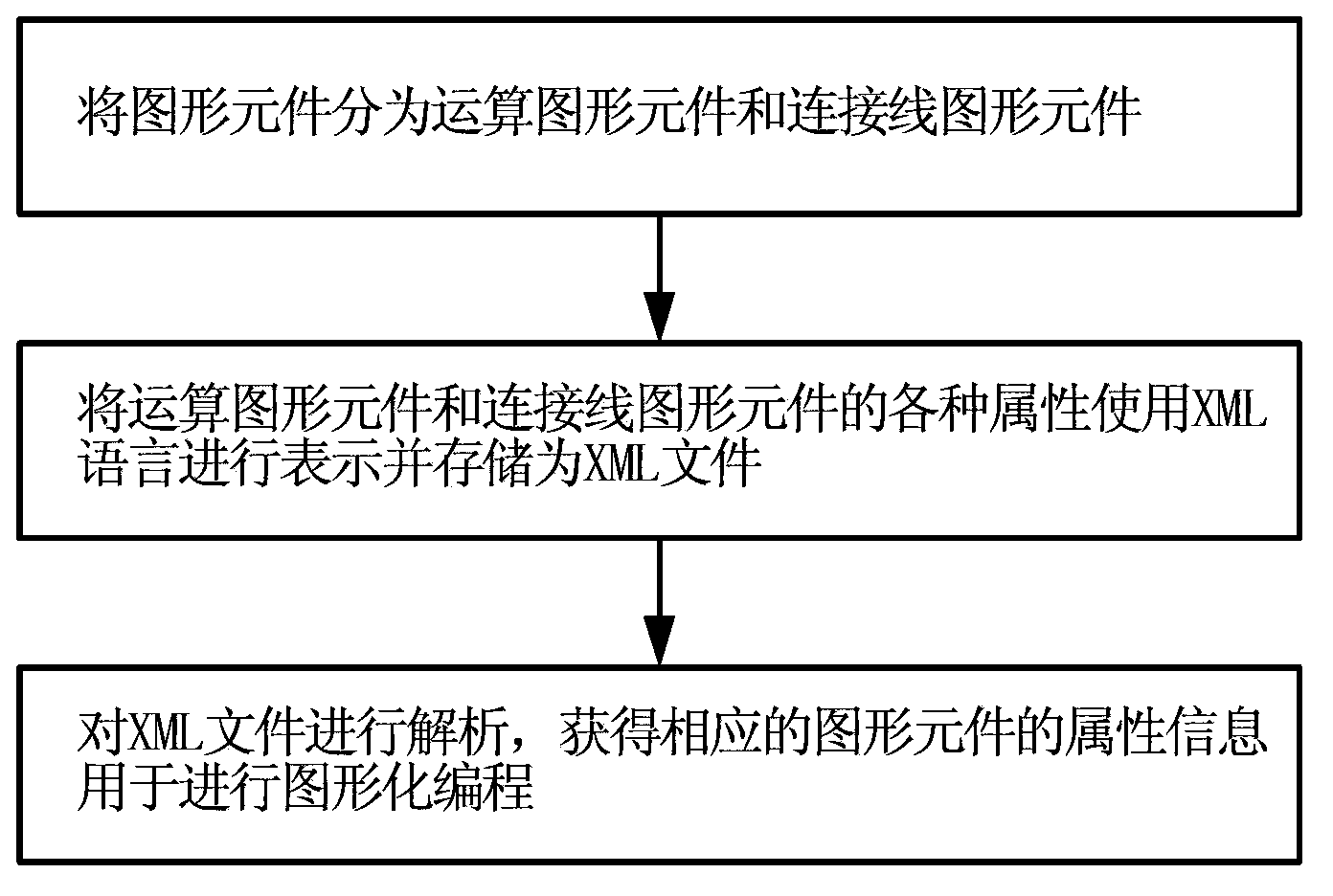

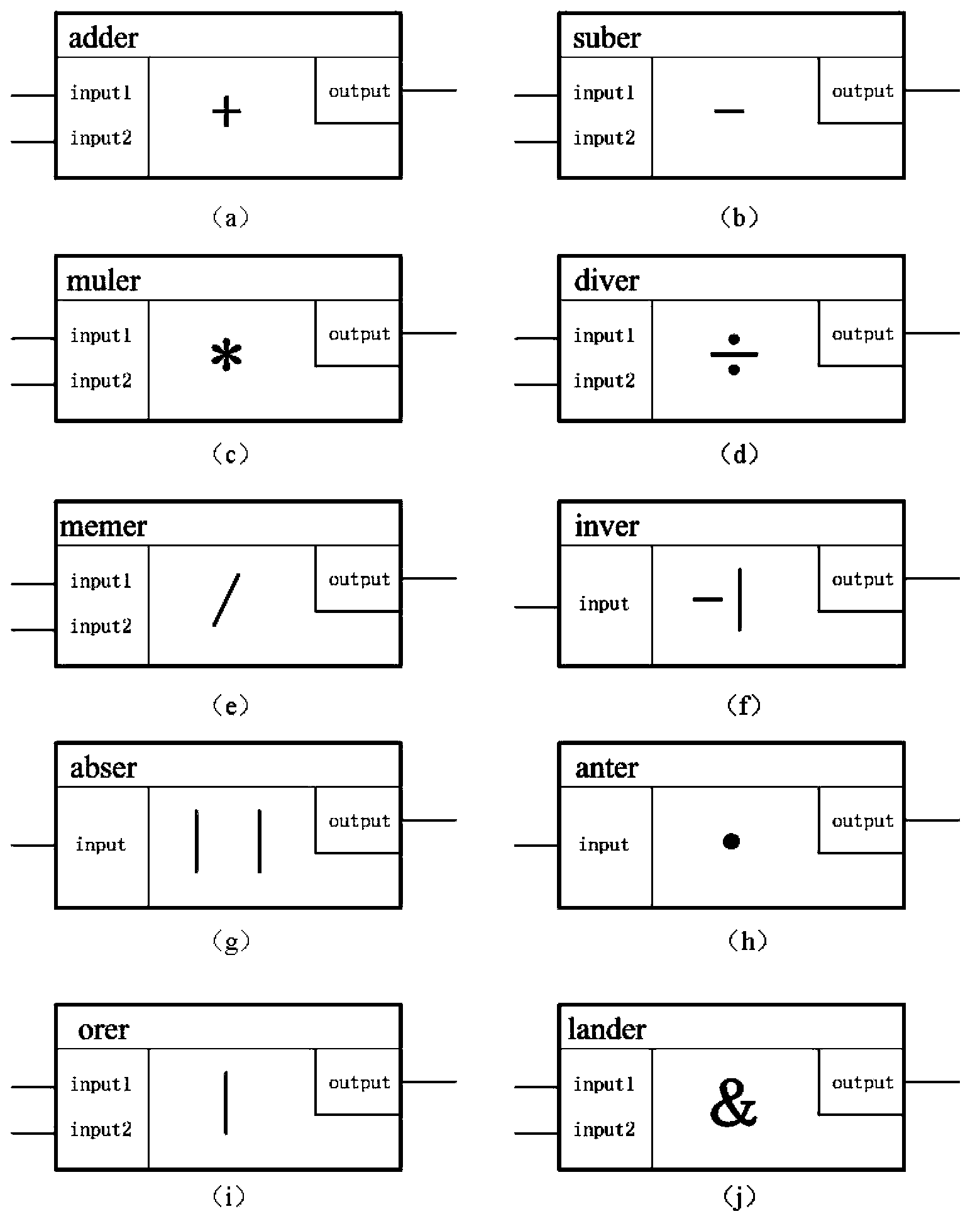

Graphical programming source file storage and analytic method

The invention provides a graphical programming source file storage and analytic method. The method includes the steps that graphic elements needed by graphical programming are divided into operation graphic elements and connecting line graphic elements; various attributes of the operation graphic elements and various attributes of the connecting line graphic elements are expressed by XMLs, and each type of the graphic elements is stored as an XML file; the XML files are analyzed, and attribute information of the corresponding graphic elements is obtained and used for graphical programming. The XML technology is used in graphical programming source file storage and conversion processes, interconversion between graphical programs and XML descriptions can be conveniently achieved, programming work is more efficient and convenient, and development cycles of products are shortened.

Owner:INST OF SOFTWARE - CHINESE ACAD OF SCI

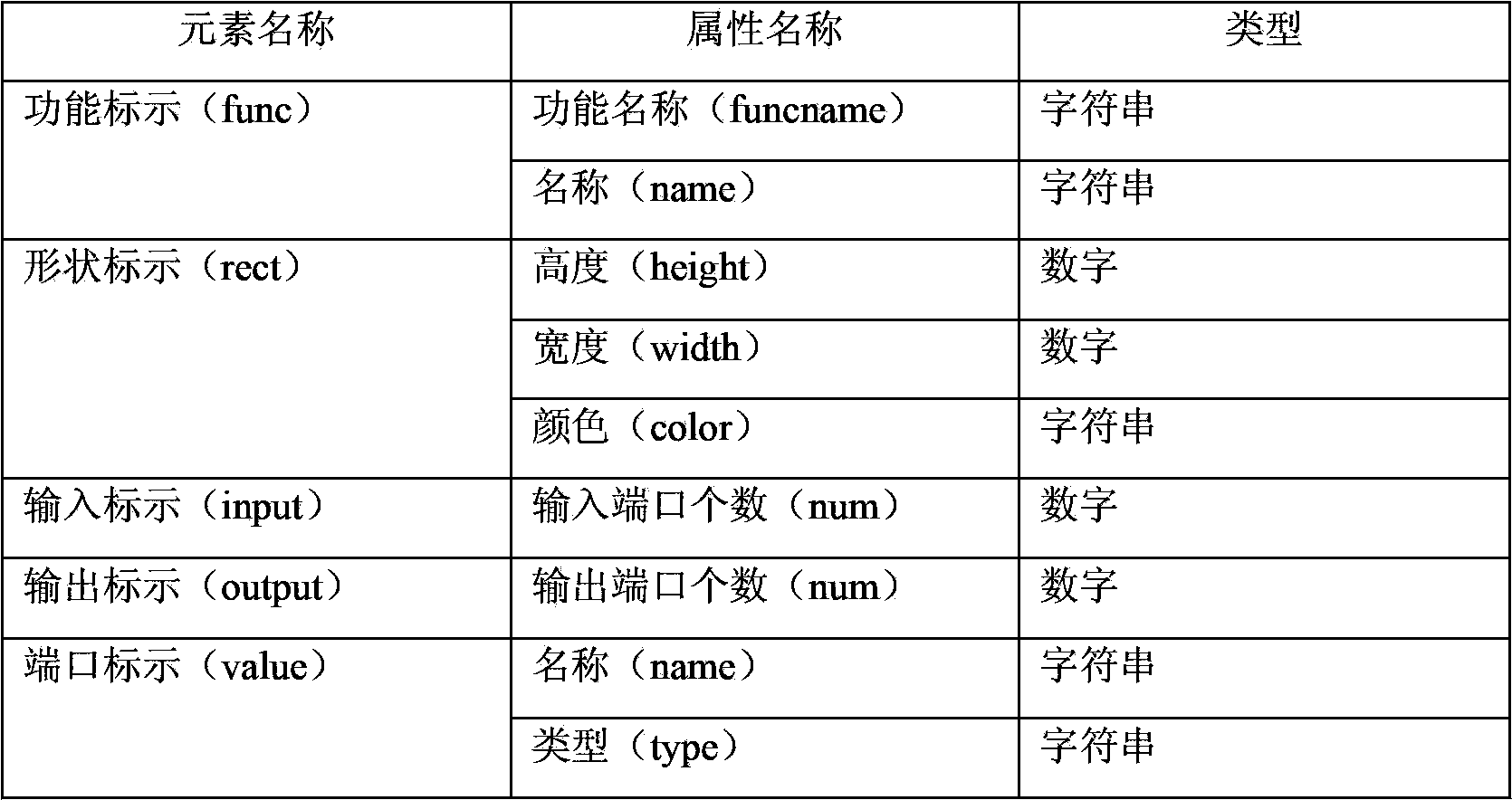

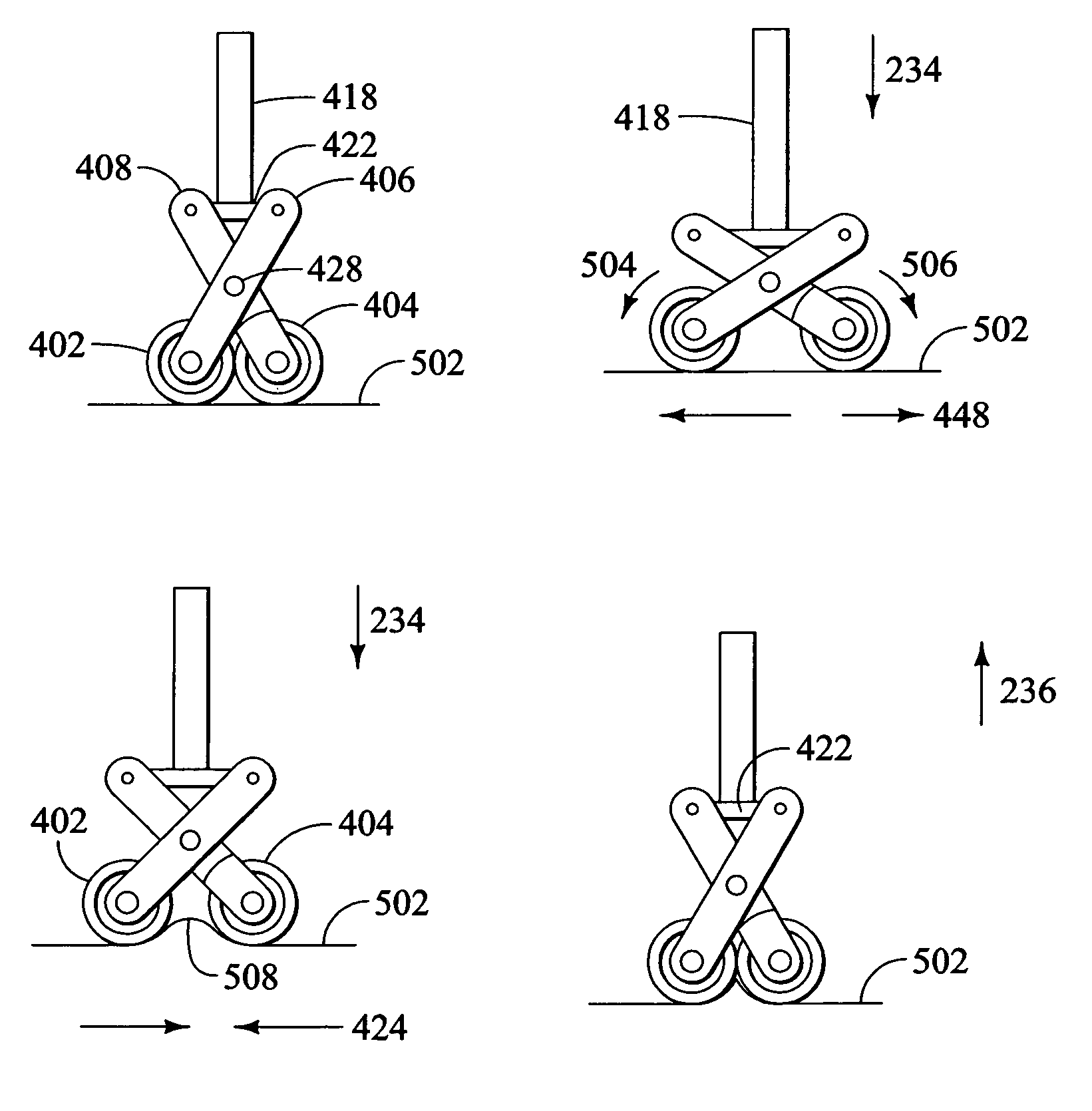

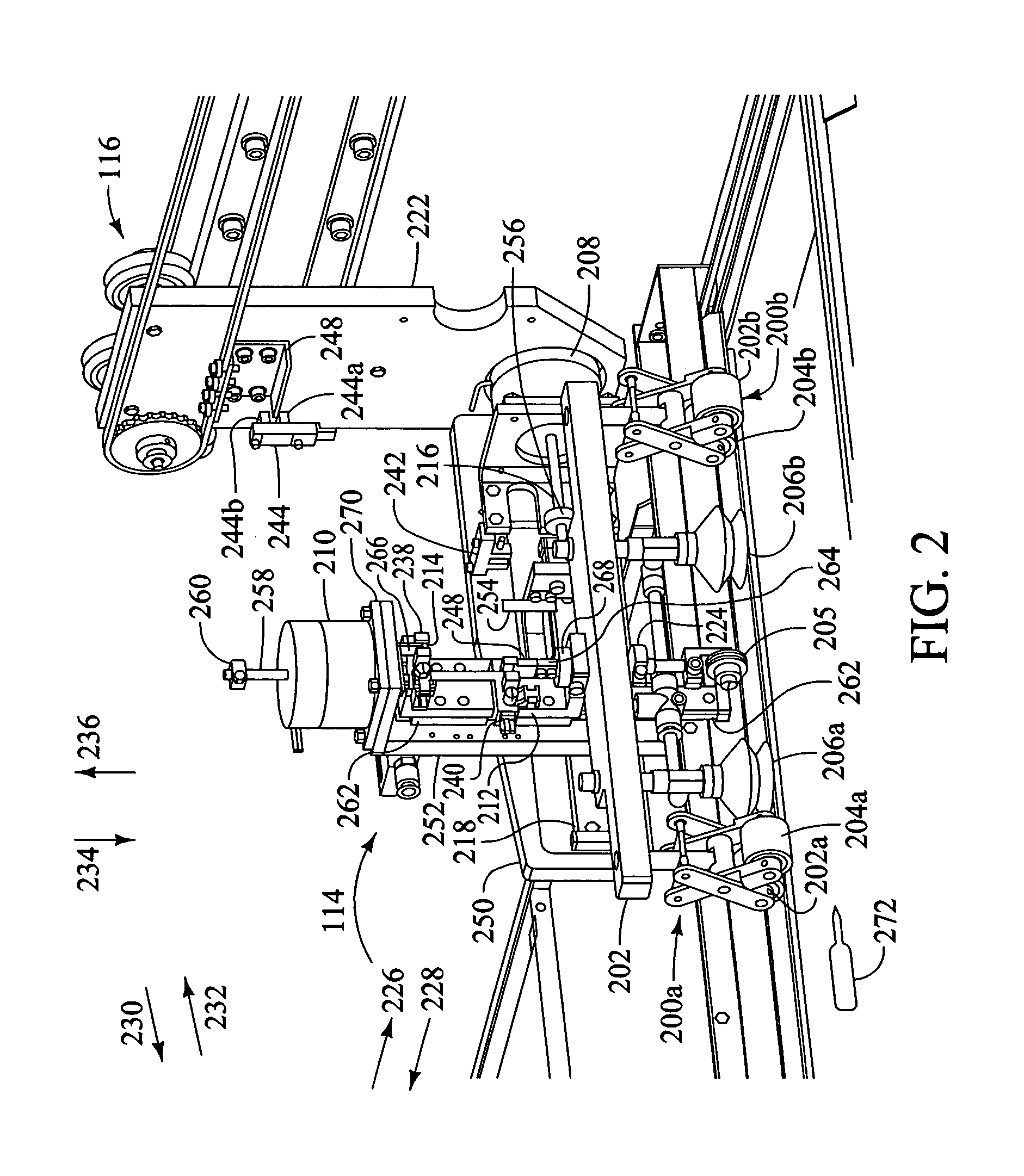

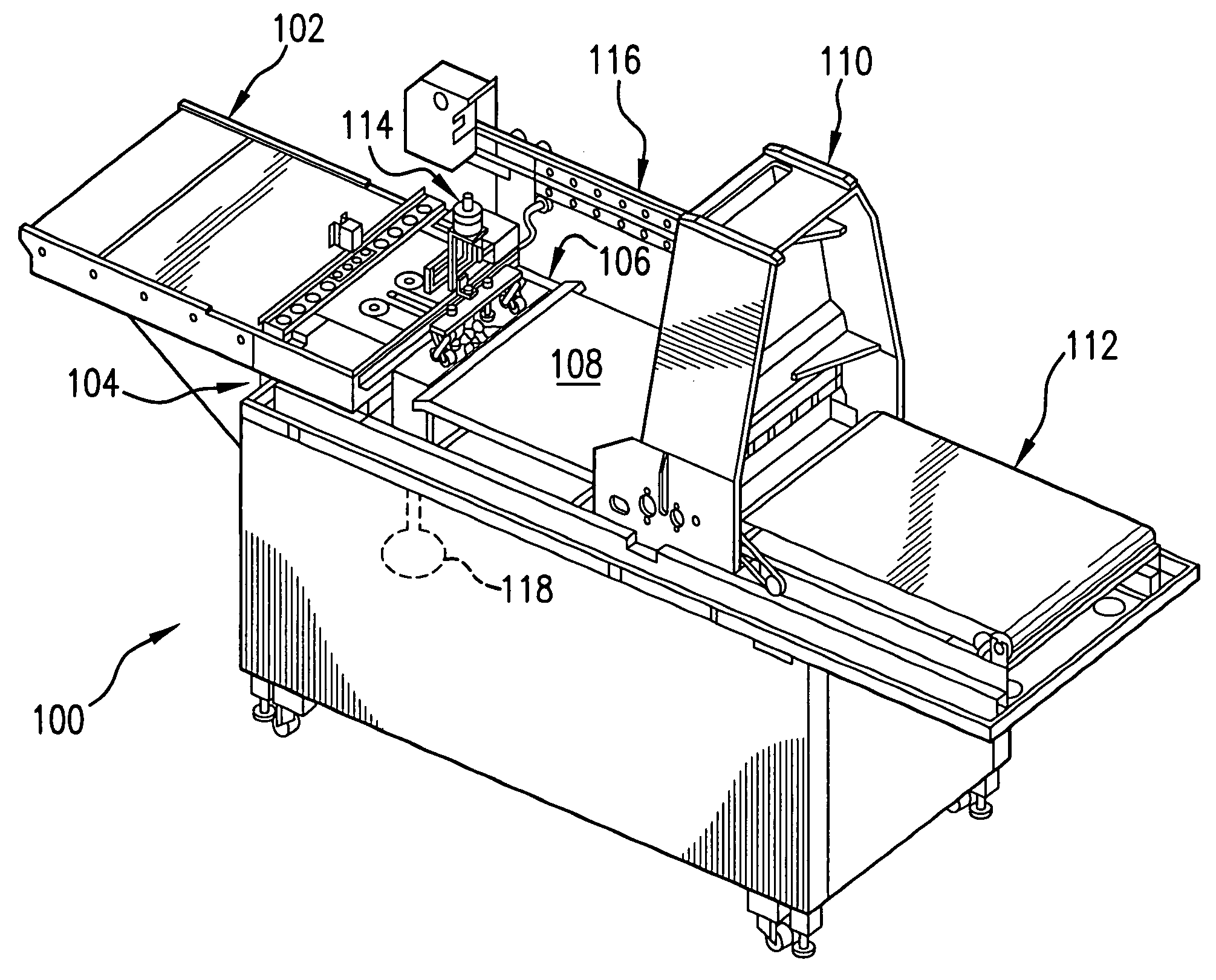

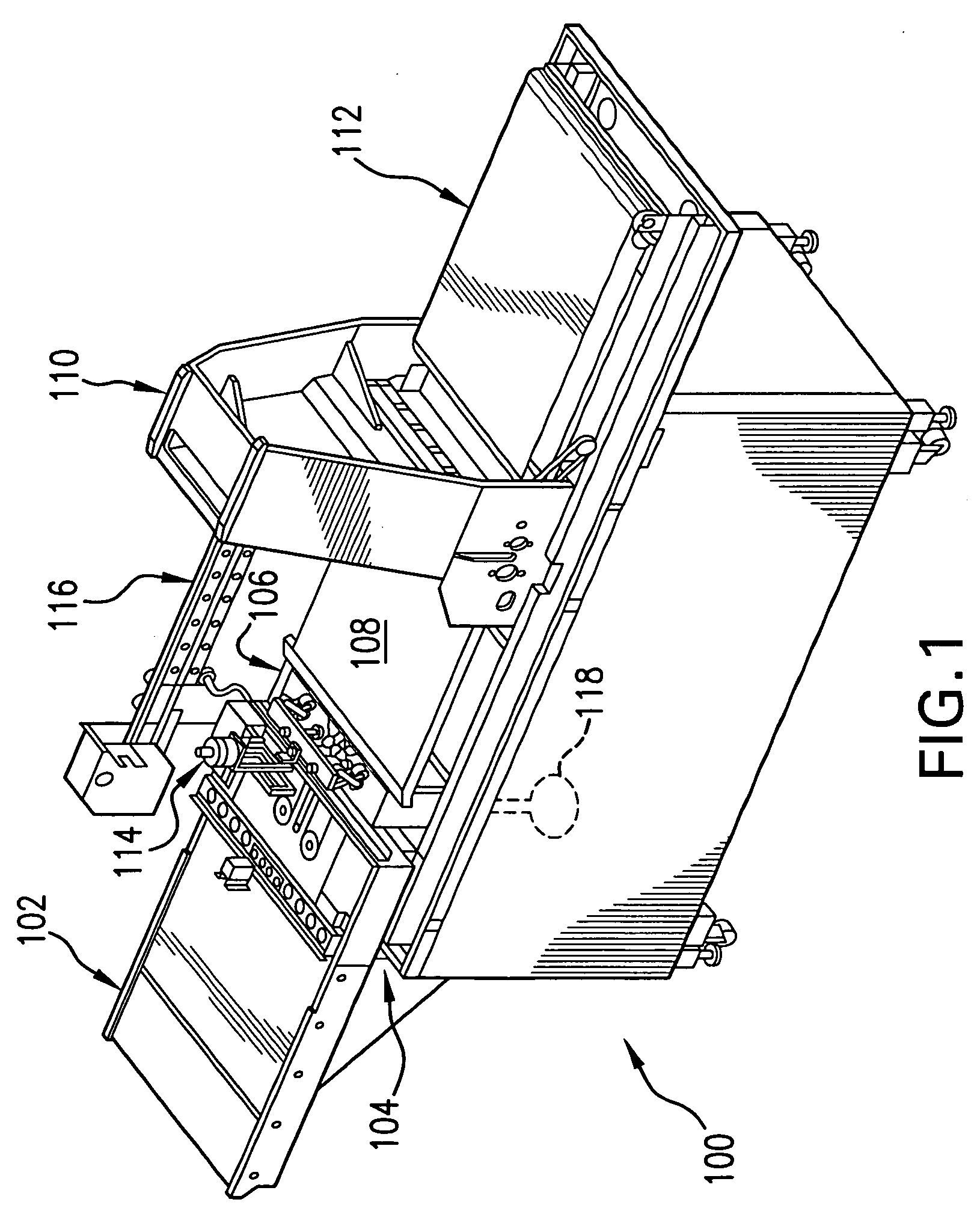

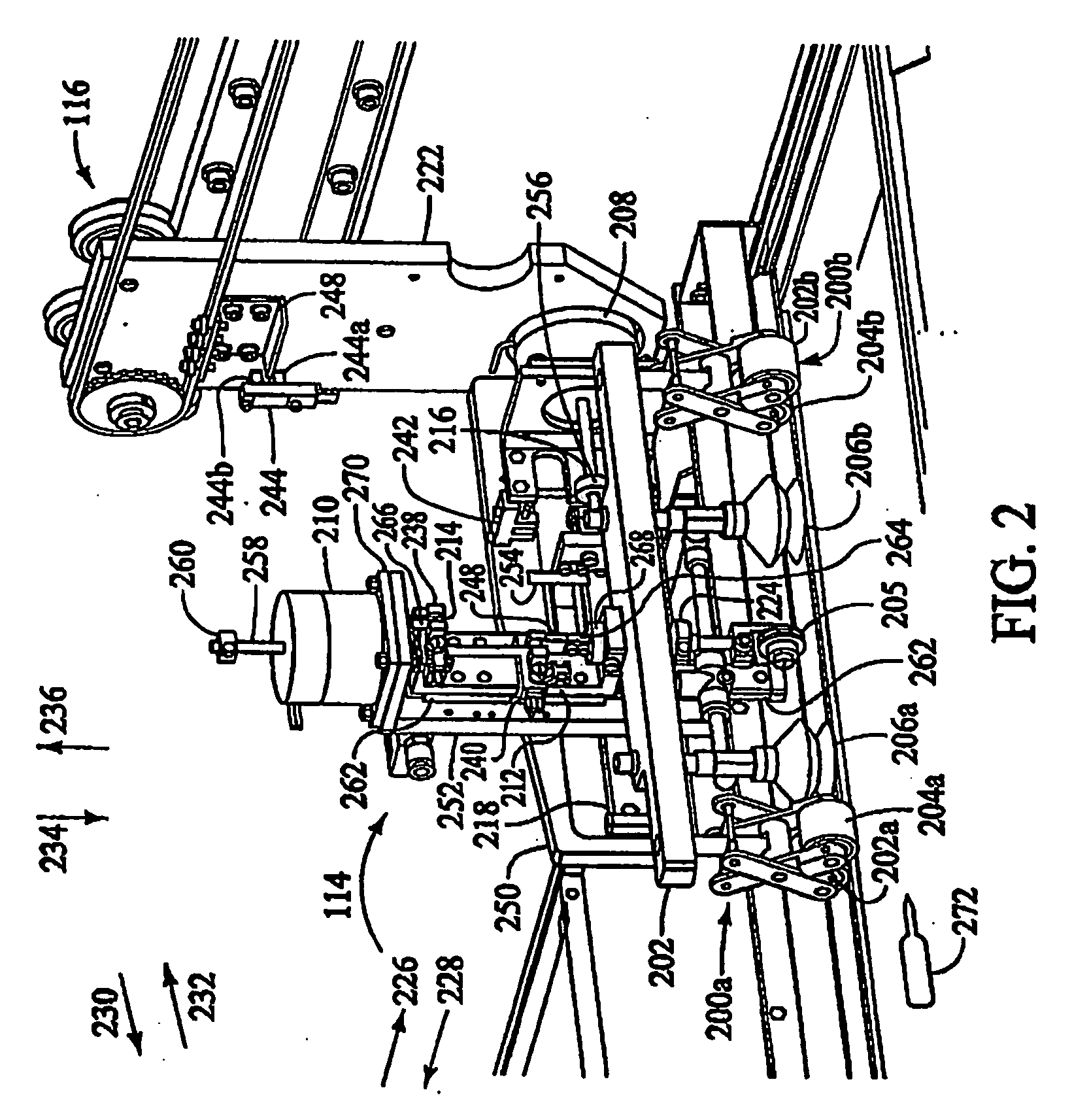

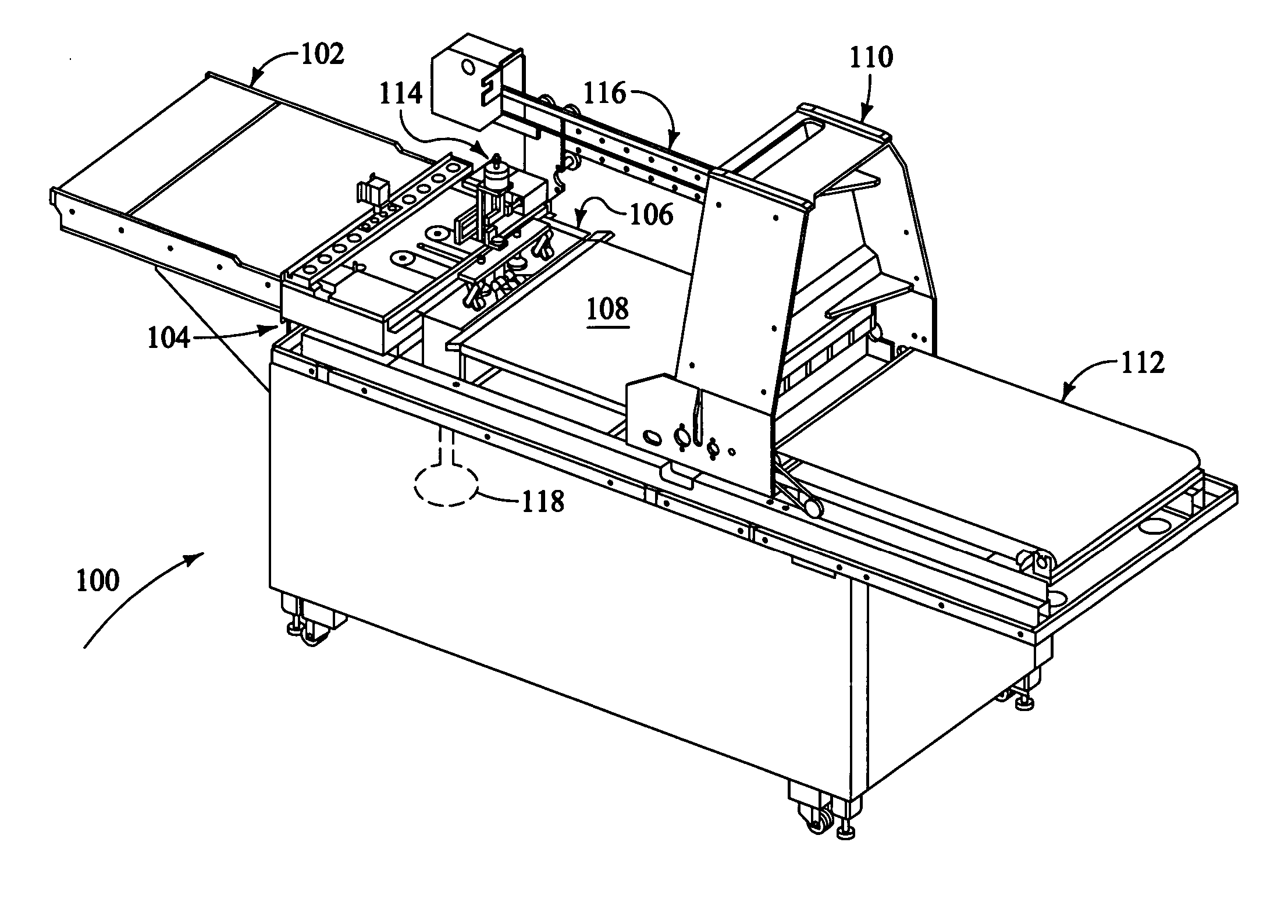

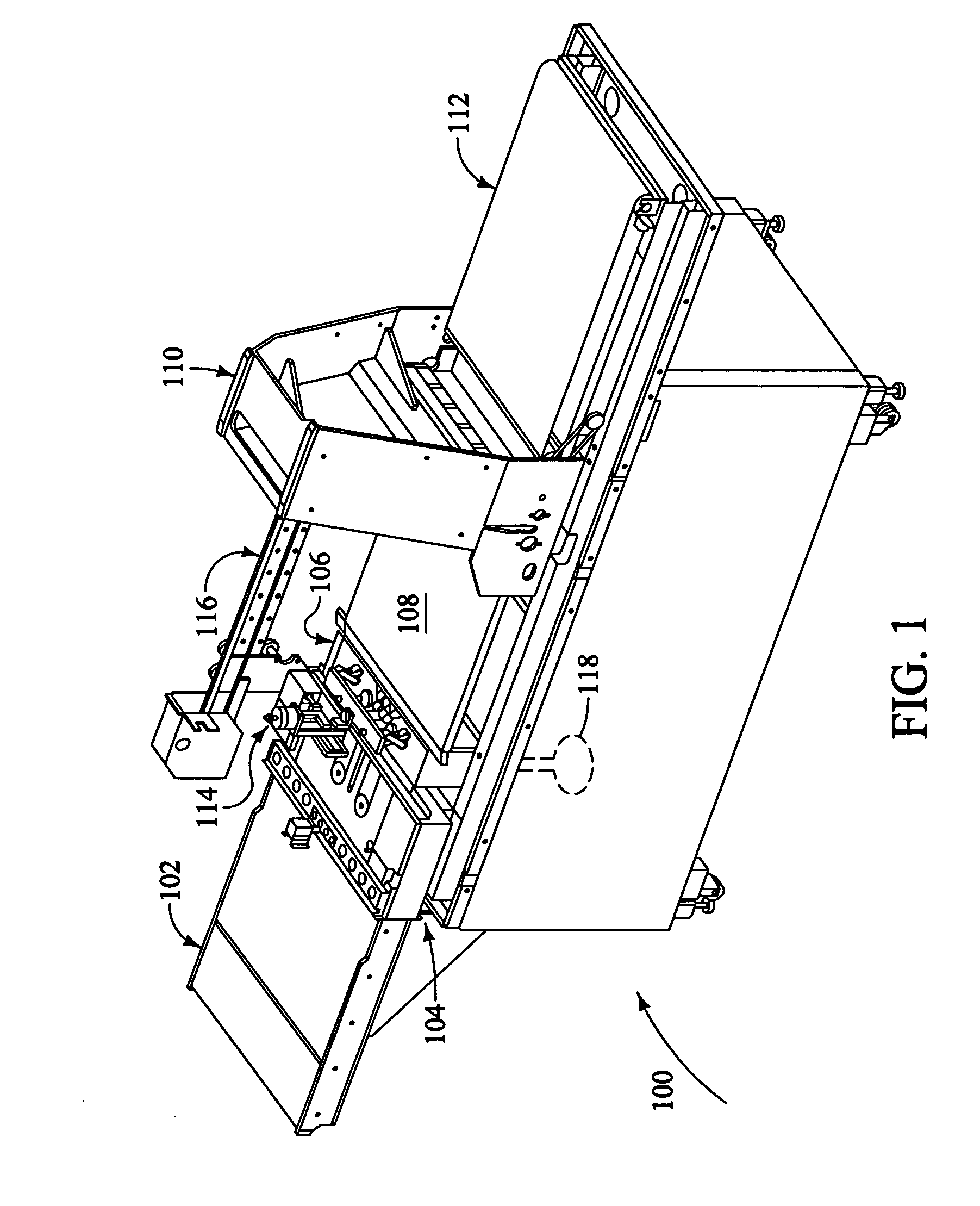

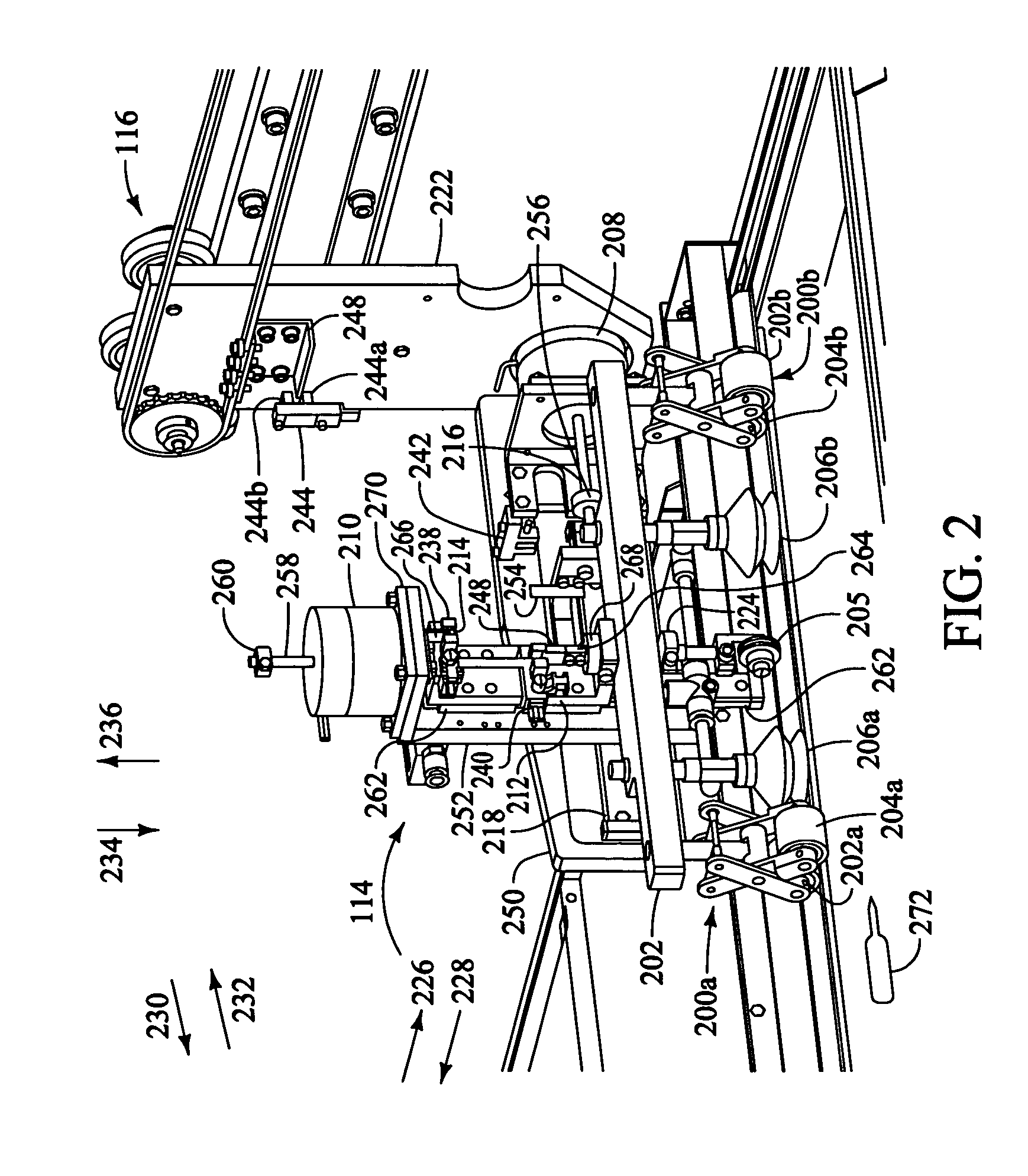

System and method for interleaf sheet and/or plate sheet removal and/or transport for use with a printing apparatus

InactiveUS7000541B2Minimize the numberSimple and low solutionAddressographsLetterpress printingComputer to plateImage system

The present invention relates generally to systems and methods that remove an interleaf sheet interposed between plate sheets from a material stack used, for example, in a computer-to-plate imaging system and / or environment. Embodiments of the system and method can also remove plate sheets from an interleaf sheet, and transport the plate sheet for subsequent imaging.

Owner:ECRM

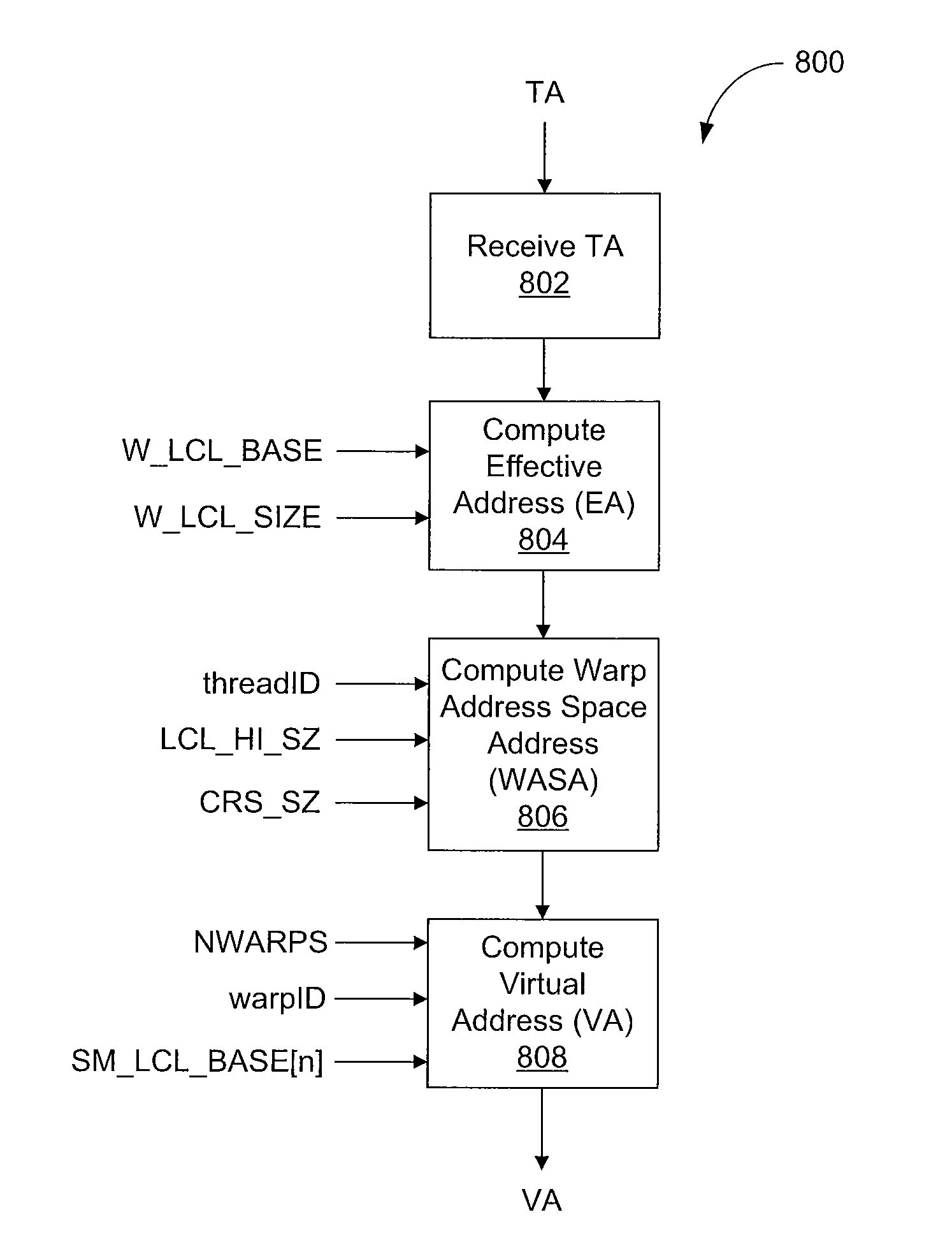

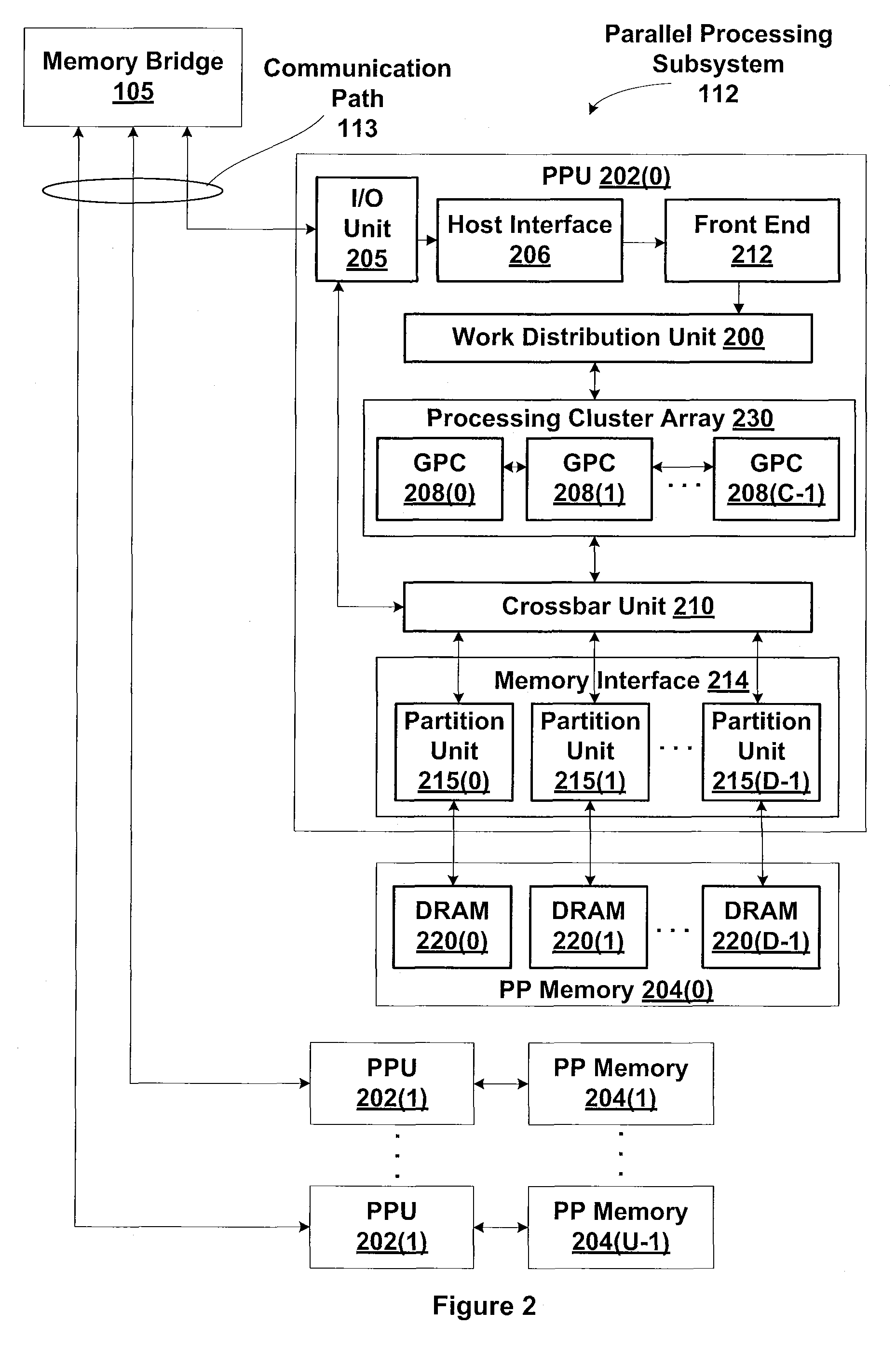

Address Mapping for a Parallel Thread Processor

ActiveUS20110078689A1Efficient programmingMultiprogramming arrangementsMemory systemsParallel computingAddress mapping

A method for thread address mapping in a parallel thread processor. The method includes receiving a thread address associated with a first thread in a thread group; computing an effective address based on a location of the thread address within a local window of a thread address space; computing a thread group address in an address space associated with the thread group based on the effective address and a thread identifier associated with a first thread; and computing a virtual address associated with the first thread based on the thread group address and a thread group identifier, where the virtual address is used to access a location in a memory associated with the thread address to load or store data.

Owner:NVIDIA CORP

System and method for interleaf sheet and/or plate sheet removal and/or transport for use with a printing apparatus

InactiveUS20060174790A1Easy to separateSimple actionAddressographsLetterpress printingComputer to plateEngineering

One or more embodiments of the present invention relate generally to systems and methods that remove an interleaf sheet interposed between plate sheets from a material stack used, for example, in a computer-to-plate imaging system and / or environment.

Owner:ECRM

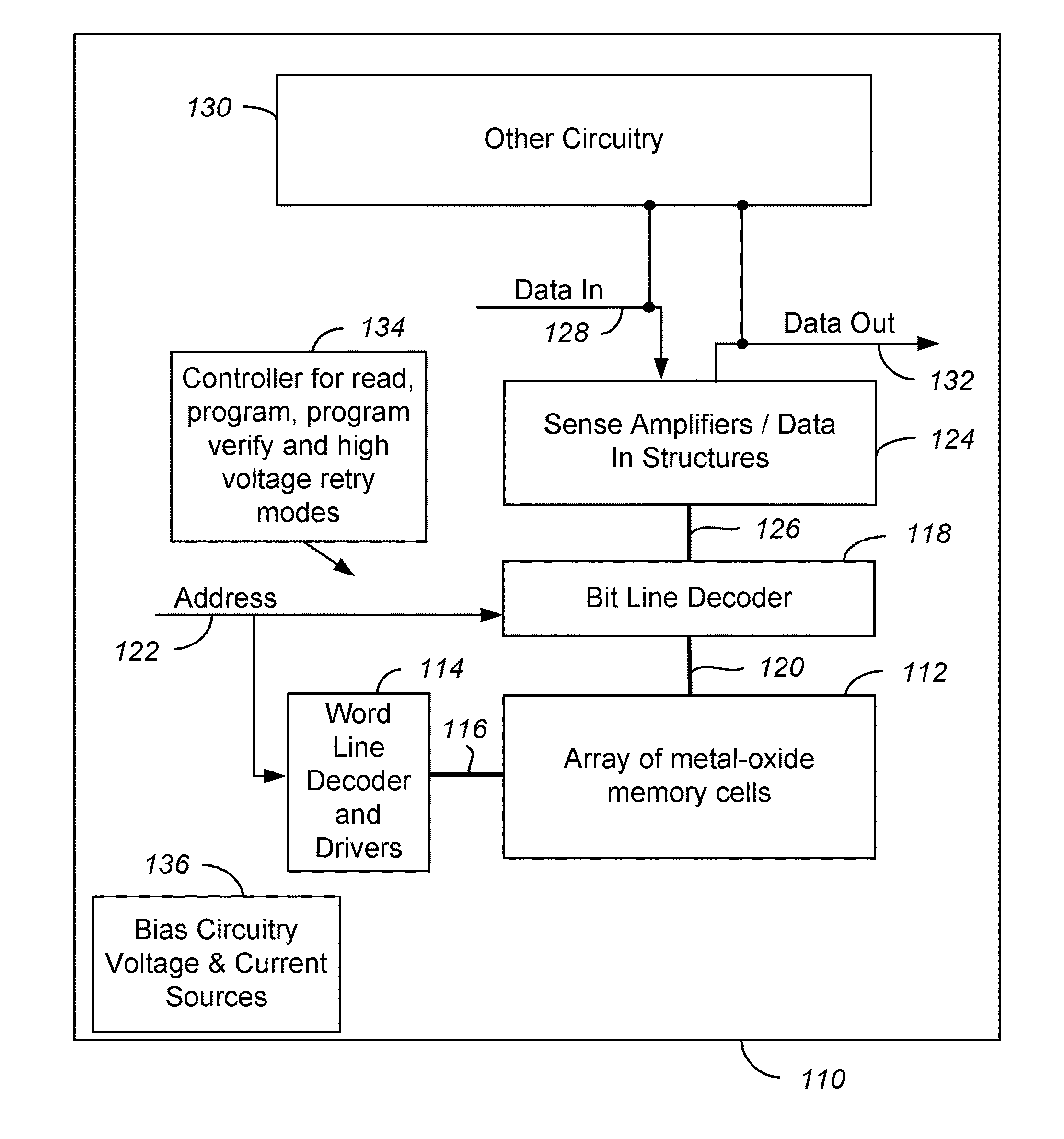

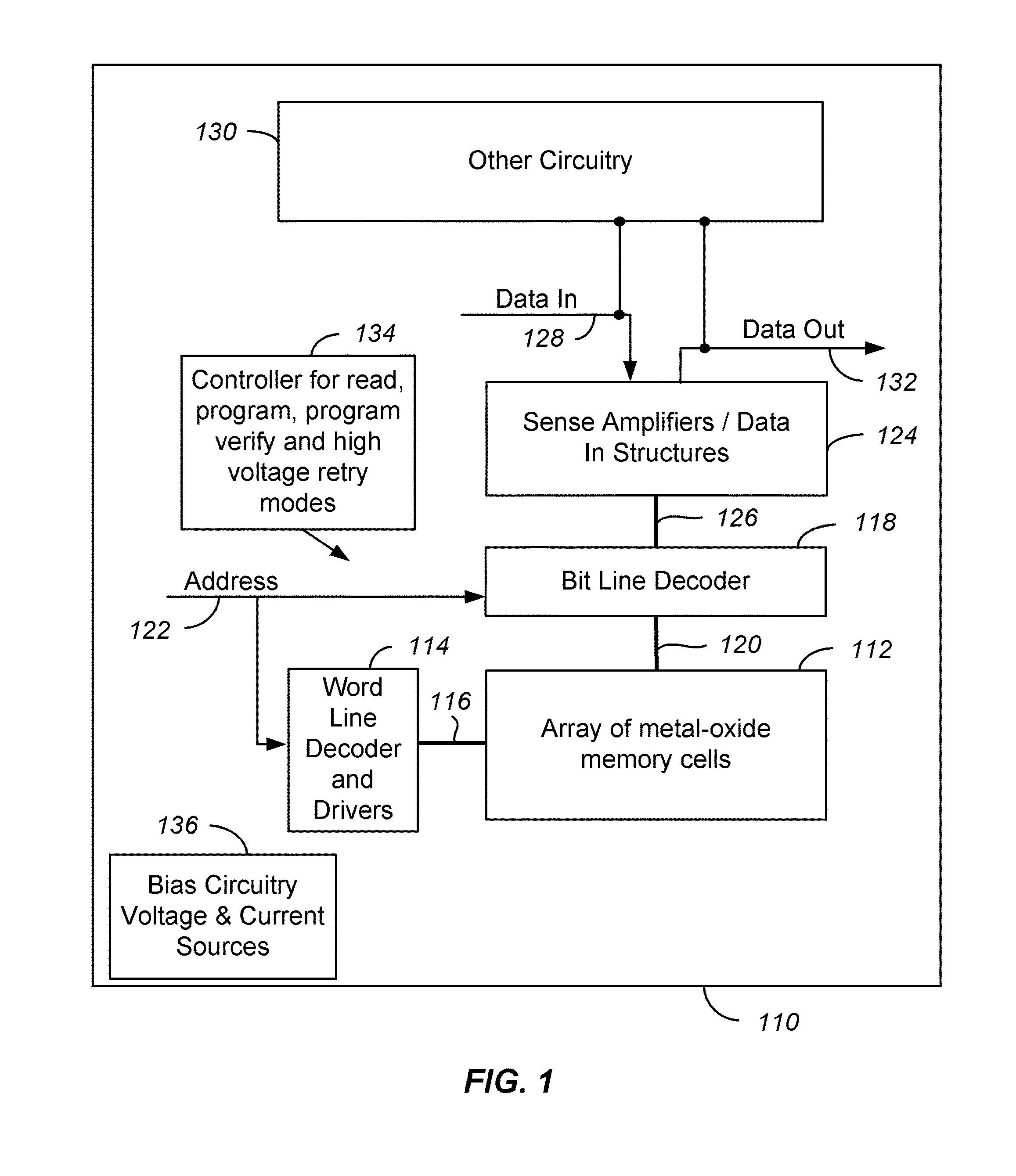

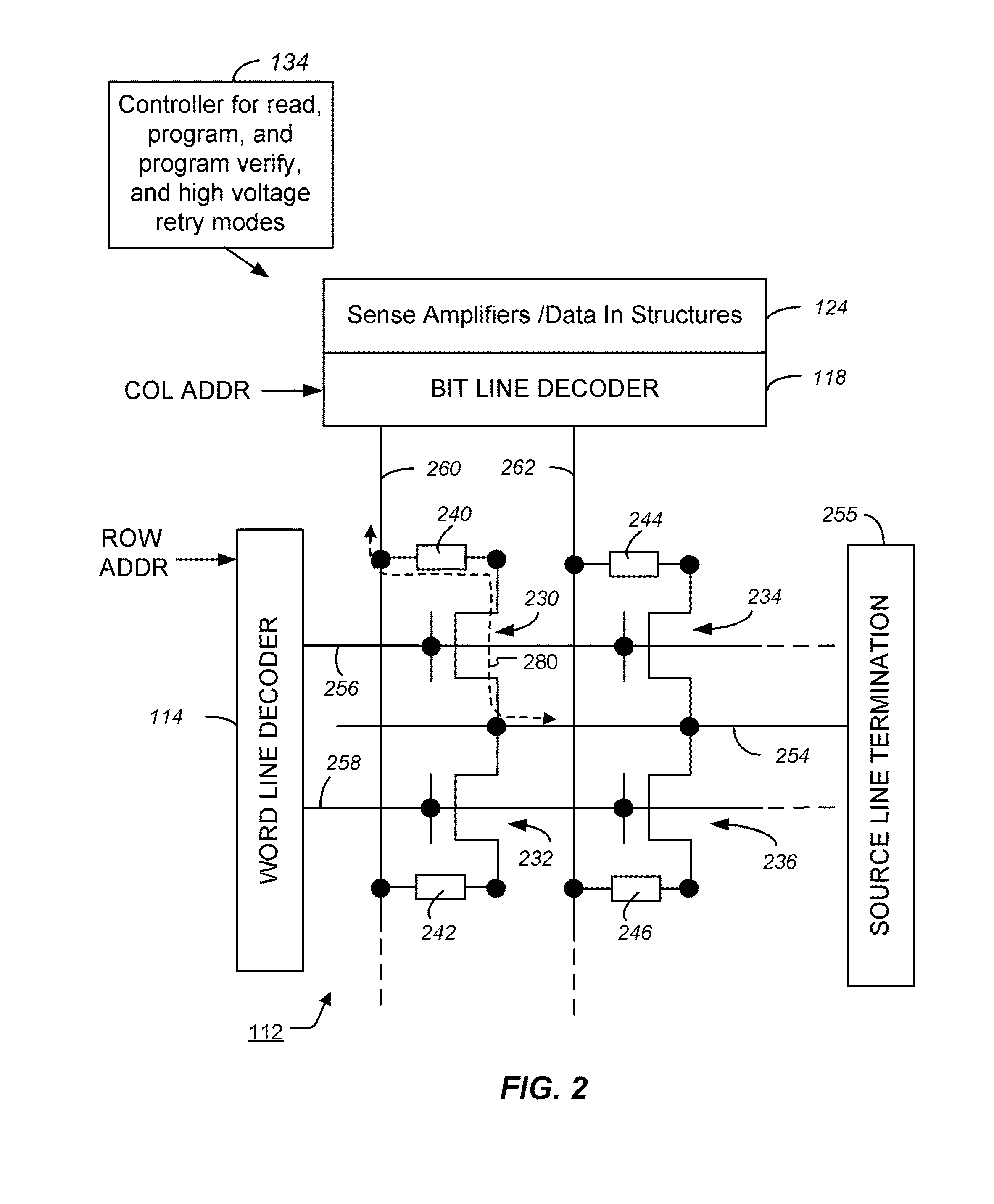

Verification algorithm for metal-oxide resistive memory

ActiveUS8699258B2Efficient programmingHigh voltageDigital storageElectrical resistance and conductanceVoltage pulse

Memory devices and methods for operating such devices are described which can effectively program the metal-oxide memory elements in an array, while also avoiding applying unnecessarily high voltage pulses. Programming operations described herein include applying a lower voltage pulse across a metal-oxide memory element to establish a desired resistance state, and only applying a higher voltage pulse when the lower voltage pulse is insufficient to program the memory element. In doing so, issues associated with applying unnecessarily high voltages across the memory element can be avoided.

Owner:MACRONIX INT CO LTD

System and method for interleaf sheet and/or plate sheet removal and/or transport for use with a printing apparatus

InactiveUS20060117975A1Minimize the numberSimple and low solutionPlaten pressesFunction indicatorsComputer to plateImage system

The present invention relates generally to systems and methods that remove an interleaf sheet interposed between plate sheets from a material stack used, for example, in a computer-to-plate imaging system and / or environment. Embodiments of the system and method can also remove plate sheets from an interleaf sheet, and transport the plate sheet for subsequent imaging.

Owner:ECRM

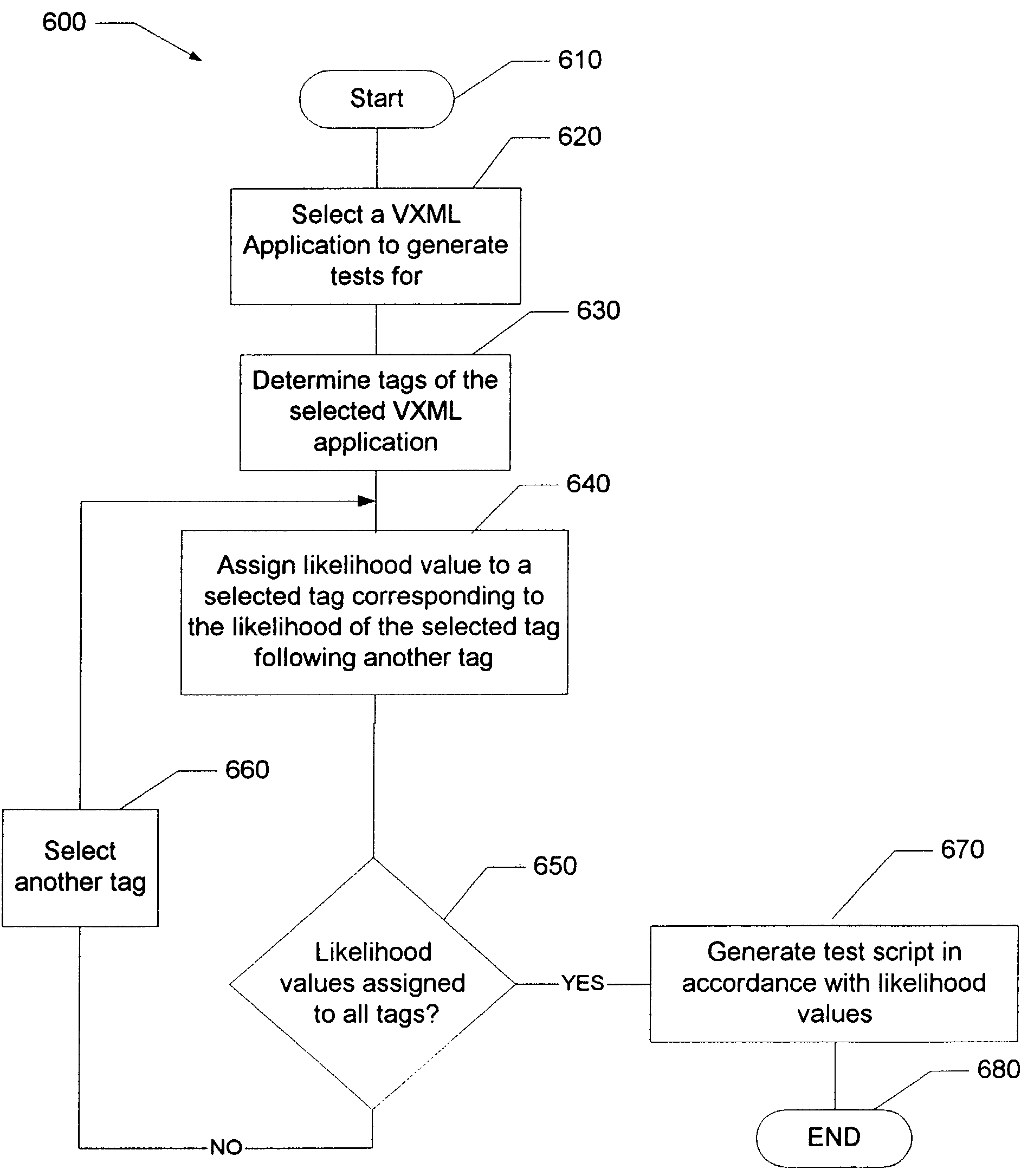

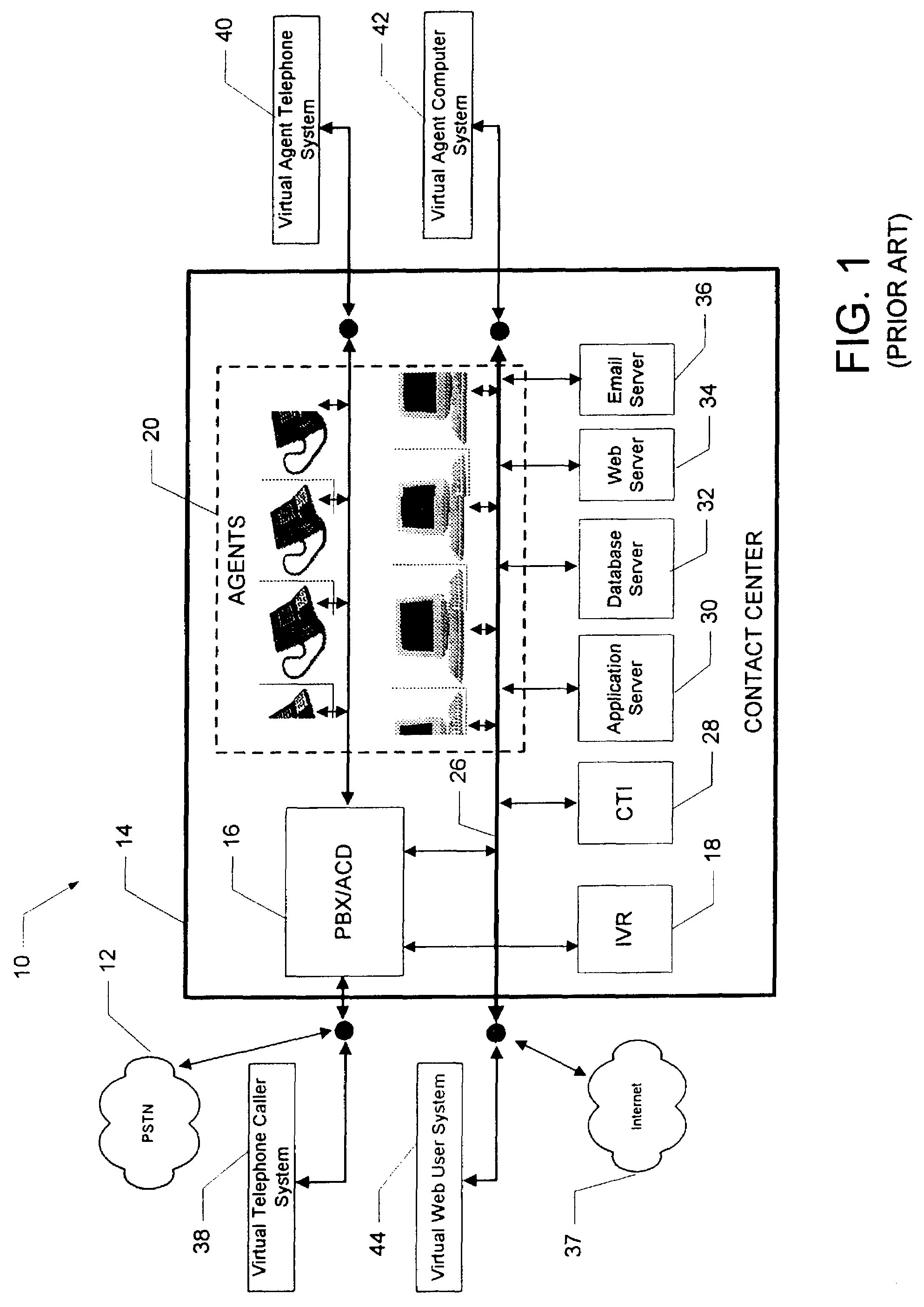

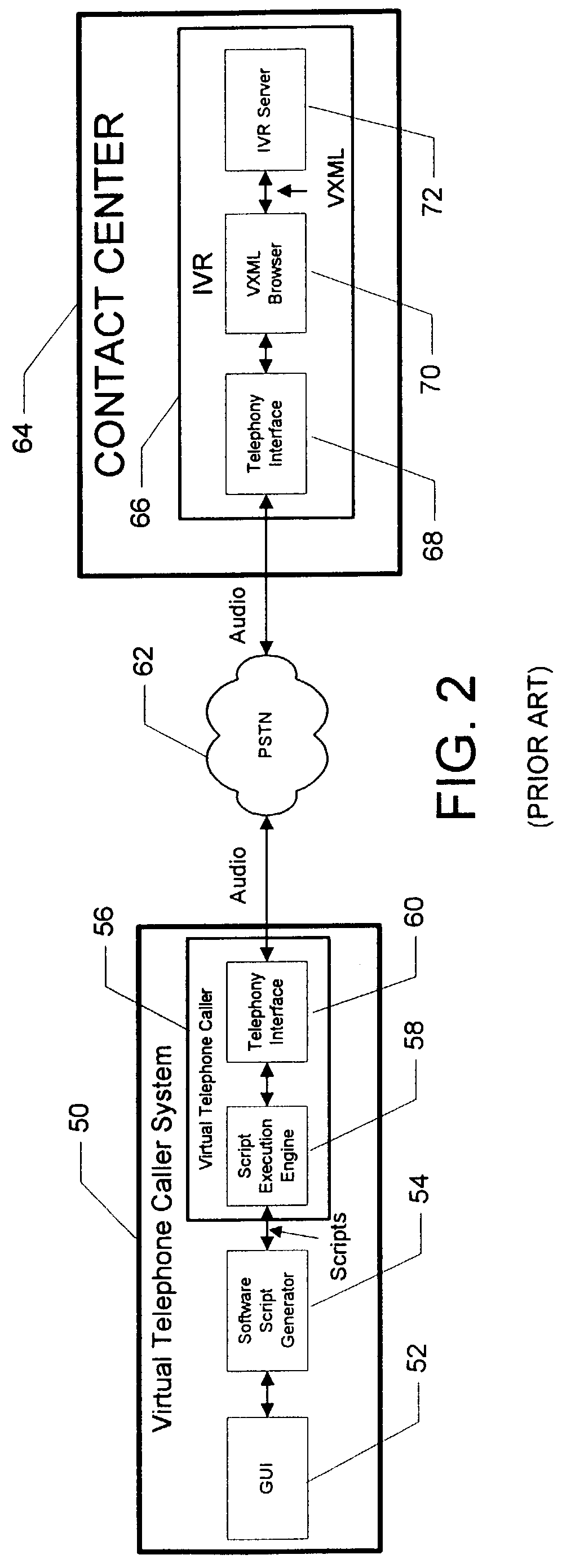

Method of generating test scripts using a voice-capable markup language

InactiveUS7590542B2Efficient programmingSpecial service for subscribersSupervisory/monitoring/testing arrangementsGraphicsTest script

A method is disclosed for generating test scripts for testing an IVR from an IVR's voice-capable markup language application. The test scripts can be generated directly from the voice-capable markup language application, from a product which provides a graphical representation of the IVR from the IVR's voice-capable markup language application, or a grid can be used to represent the tags within the voice-capable markup language application and a test script generated from the grid. Additionally, a virtual telephone caller system is provided to test the IVR of a contact center, wherein the virtual telephone caller system operates with voice-capable markup language software scripts.

Owner:EMPIRIX

Address mapping for a parallel thread processor

ActiveUS8700877B2Efficient programmingMultiprogramming arrangementsMemory systemsAddress mappingAddress space

A method for thread address mapping in a parallel thread processor. The method includes receiving a thread address associated with a first thread in a thread group; computing an effective address based on a location of the thread address within a local window of a thread address space; computing a thread group address in an address space associated with the thread group based on the effective address and a thread identifier associated with a first thread; and computing a virtual address associated with the first thread based on the thread group address and a thread group identifier, where the virtual address is used to access a location in a memory associated with the thread address to load or store data.

Owner:NVIDIA CORP

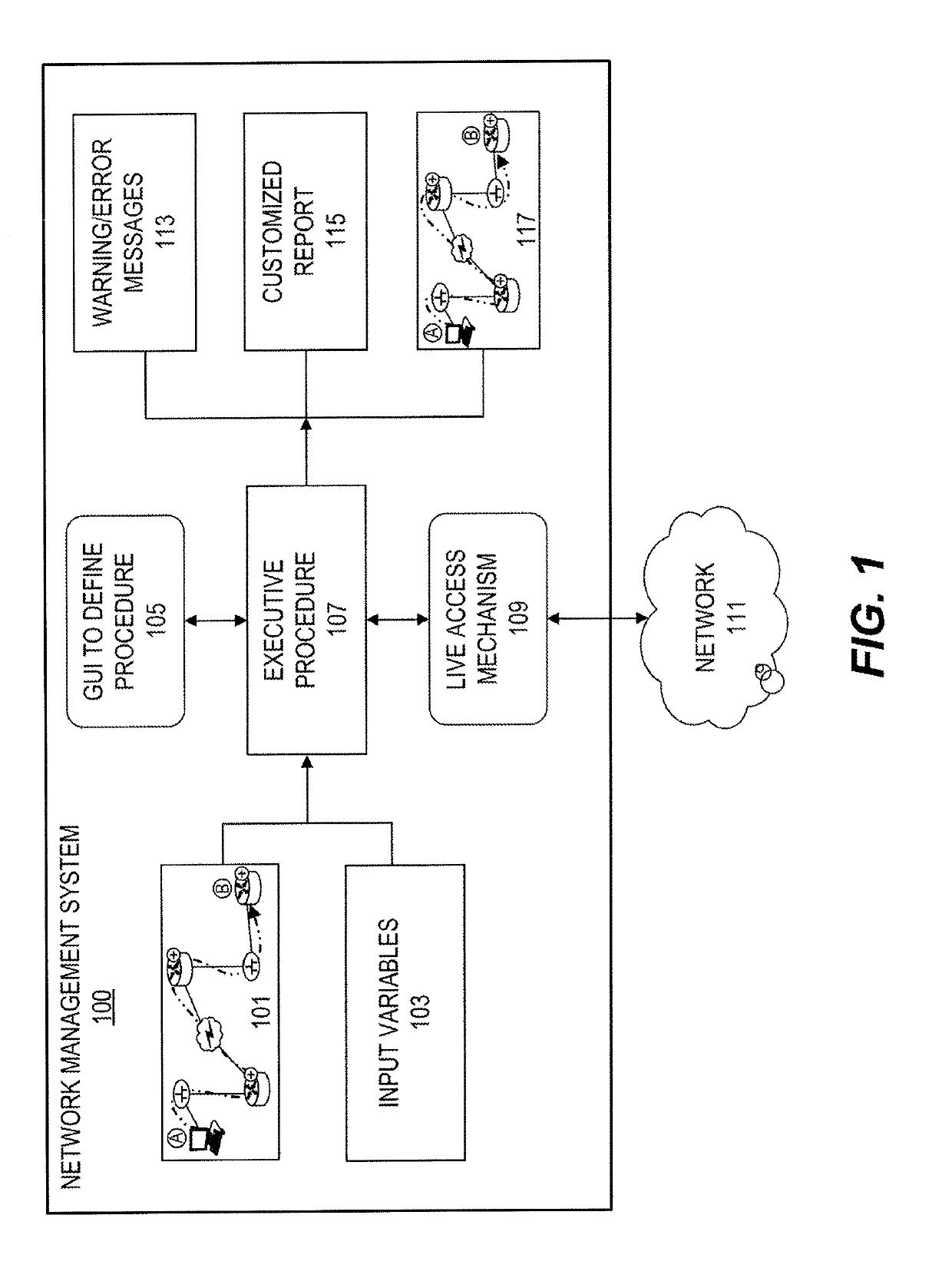

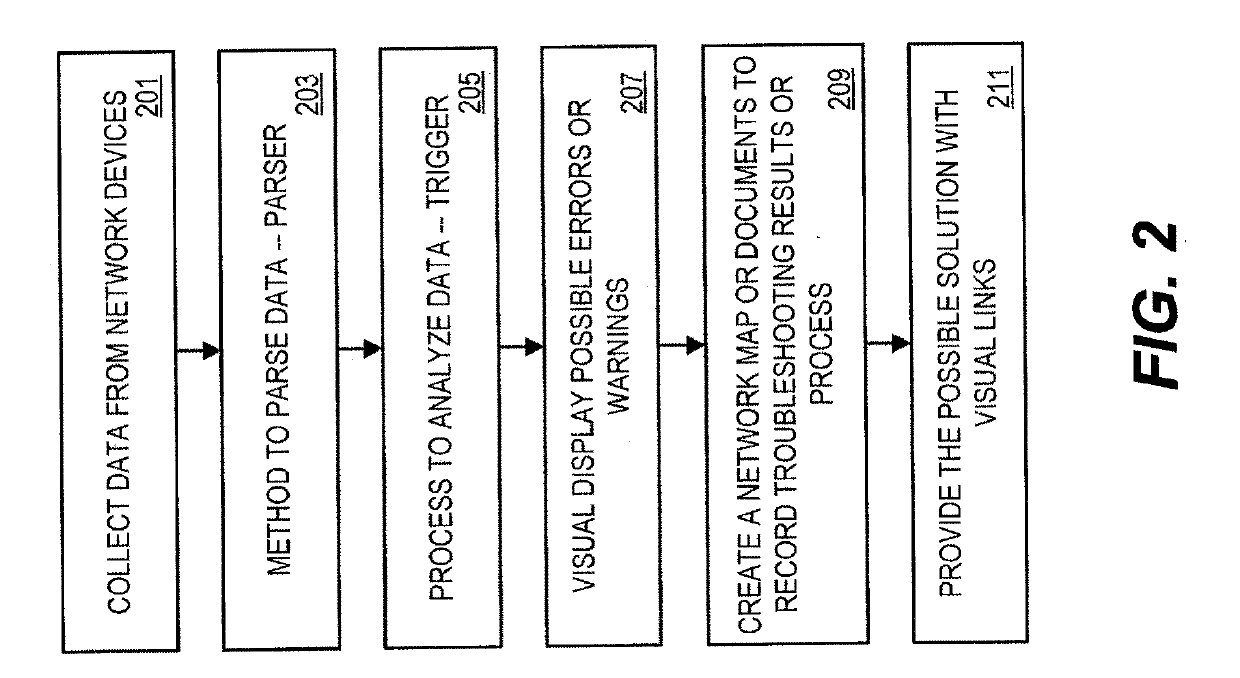

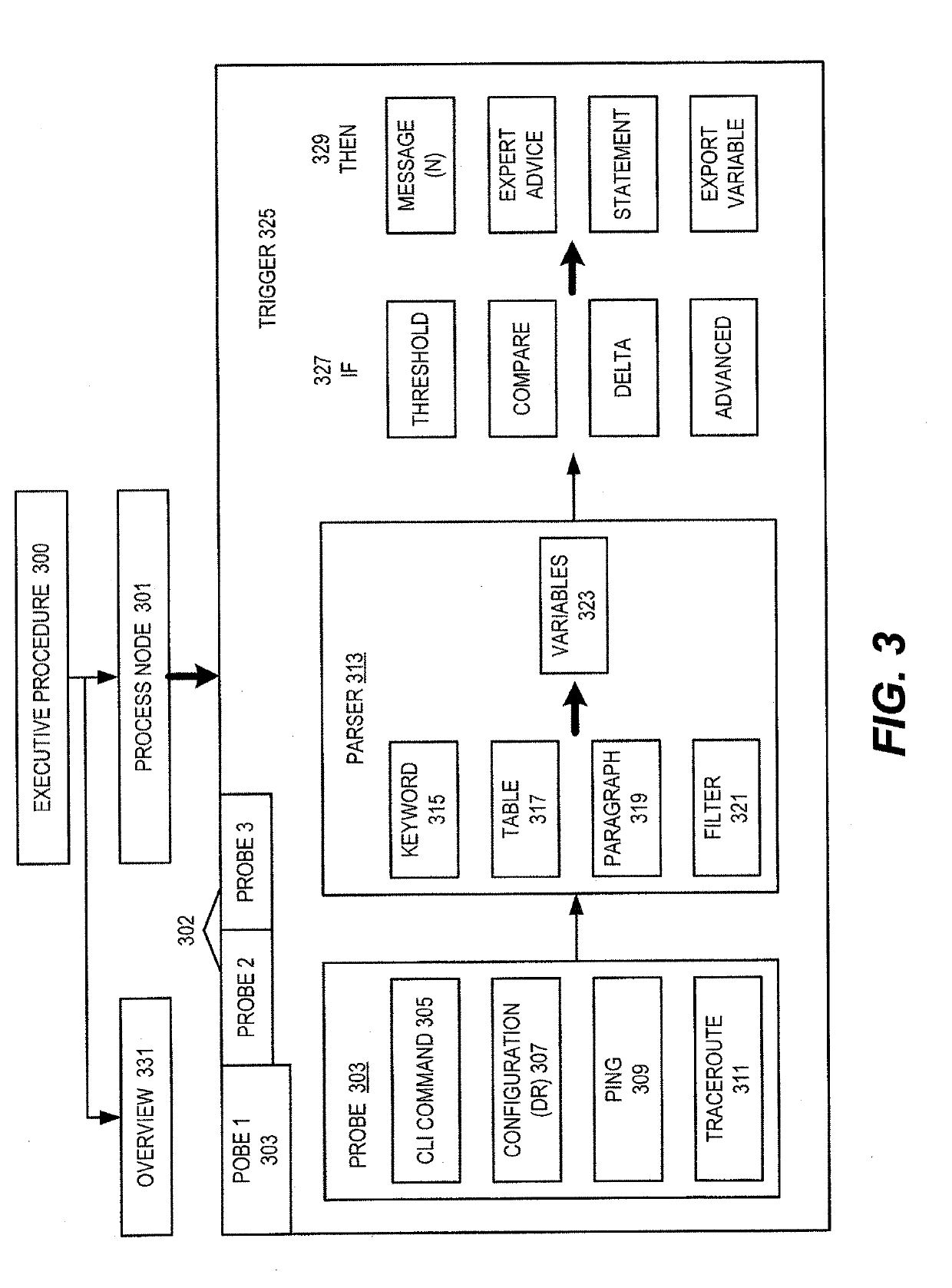

System for creating network troubleshooting procedure

ActiveUS20190230003A1Efficient programmingBe consistentData switching networksDiagnostic programDistributed computing

A system for constructing and storing procedures for troubleshooting computer networks. A user can design and add troubleshooting steps, via a GUI, to define the procedure including annotations. Each step is configured to take an action on the network. The order of the steps can be re-arranged via the GUI. The procedure can be stored and re-executed by another user.

Owner:NETBRAIN TECH