Patents

Literature

62results about How to "Avoid initialization" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

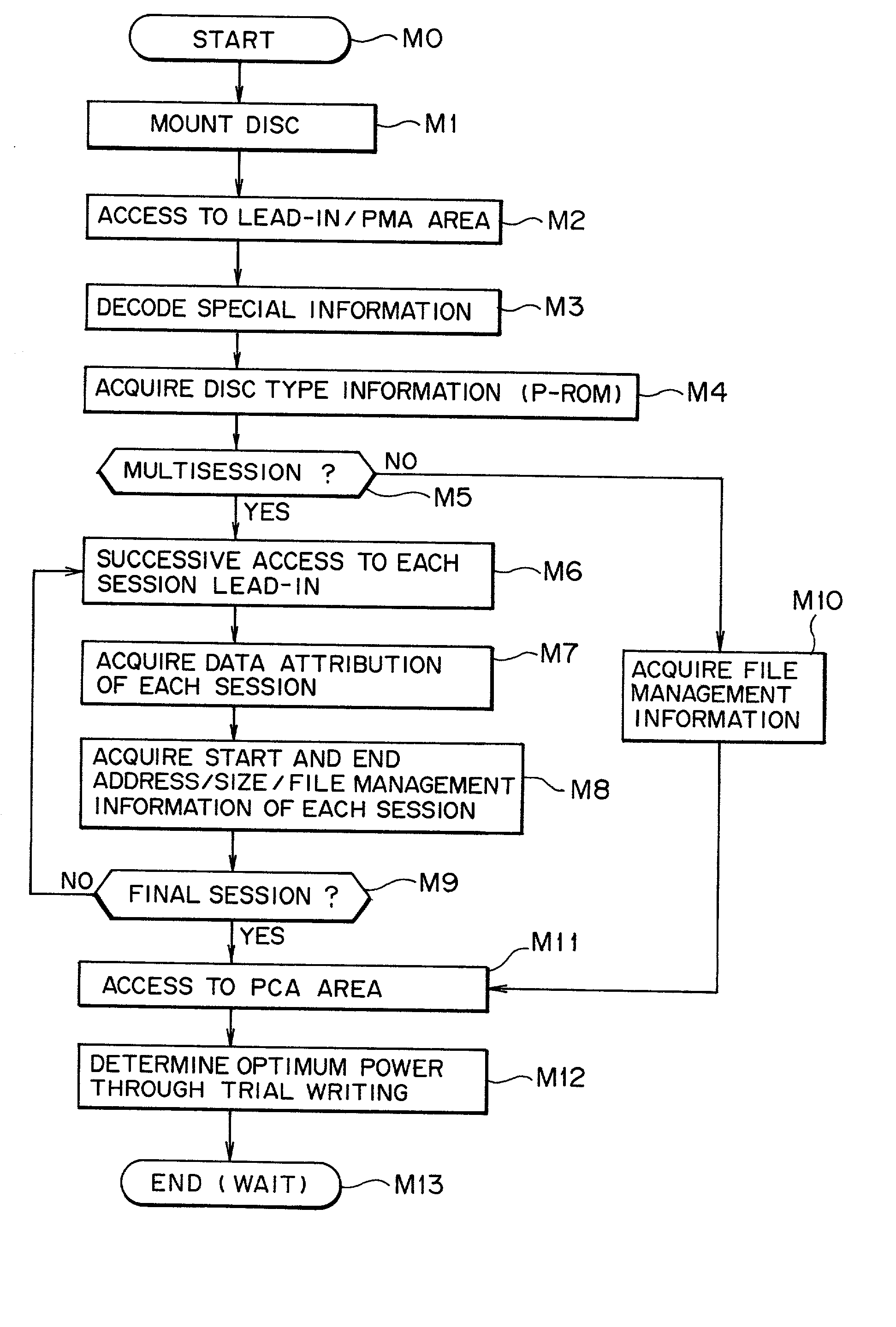

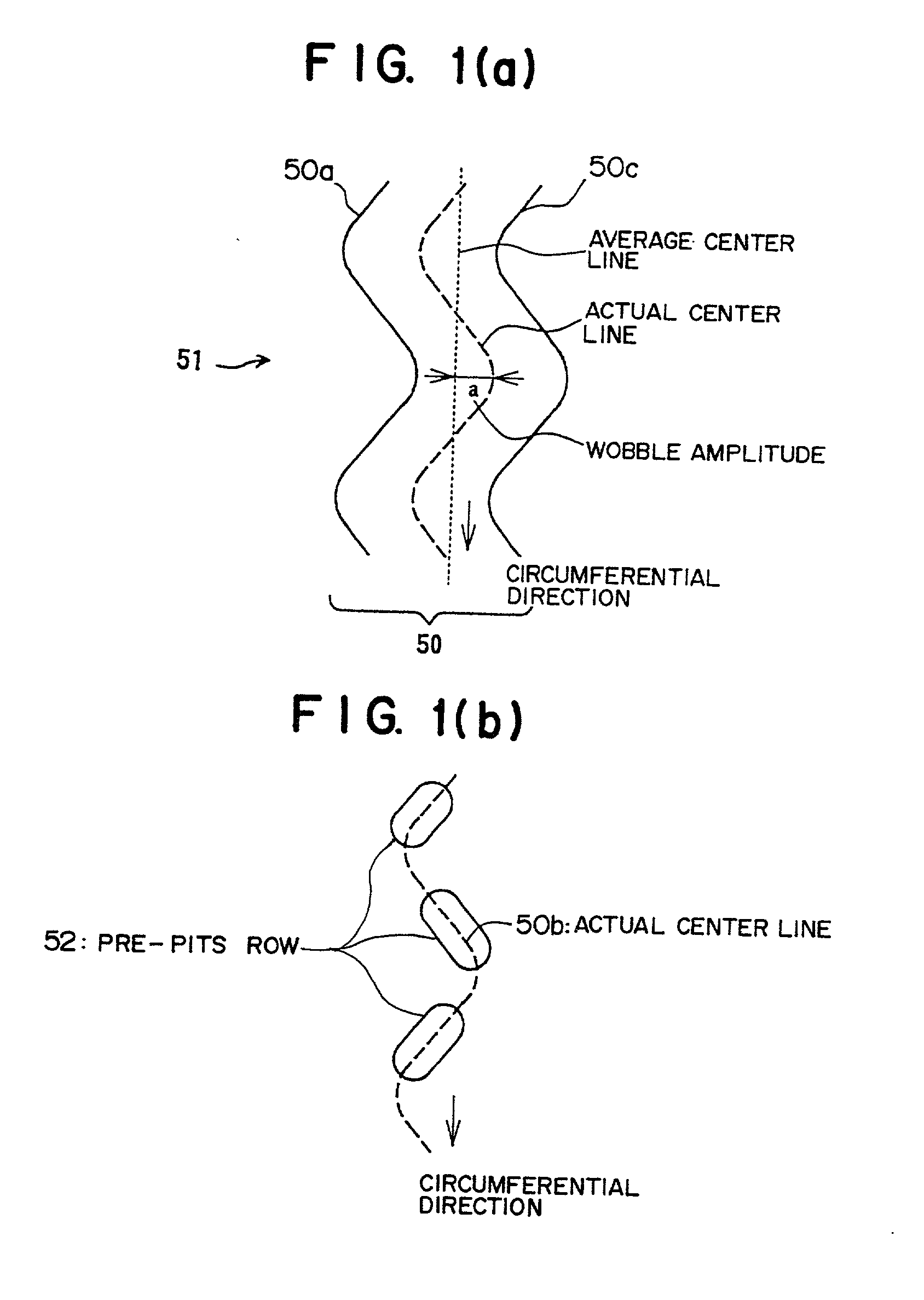

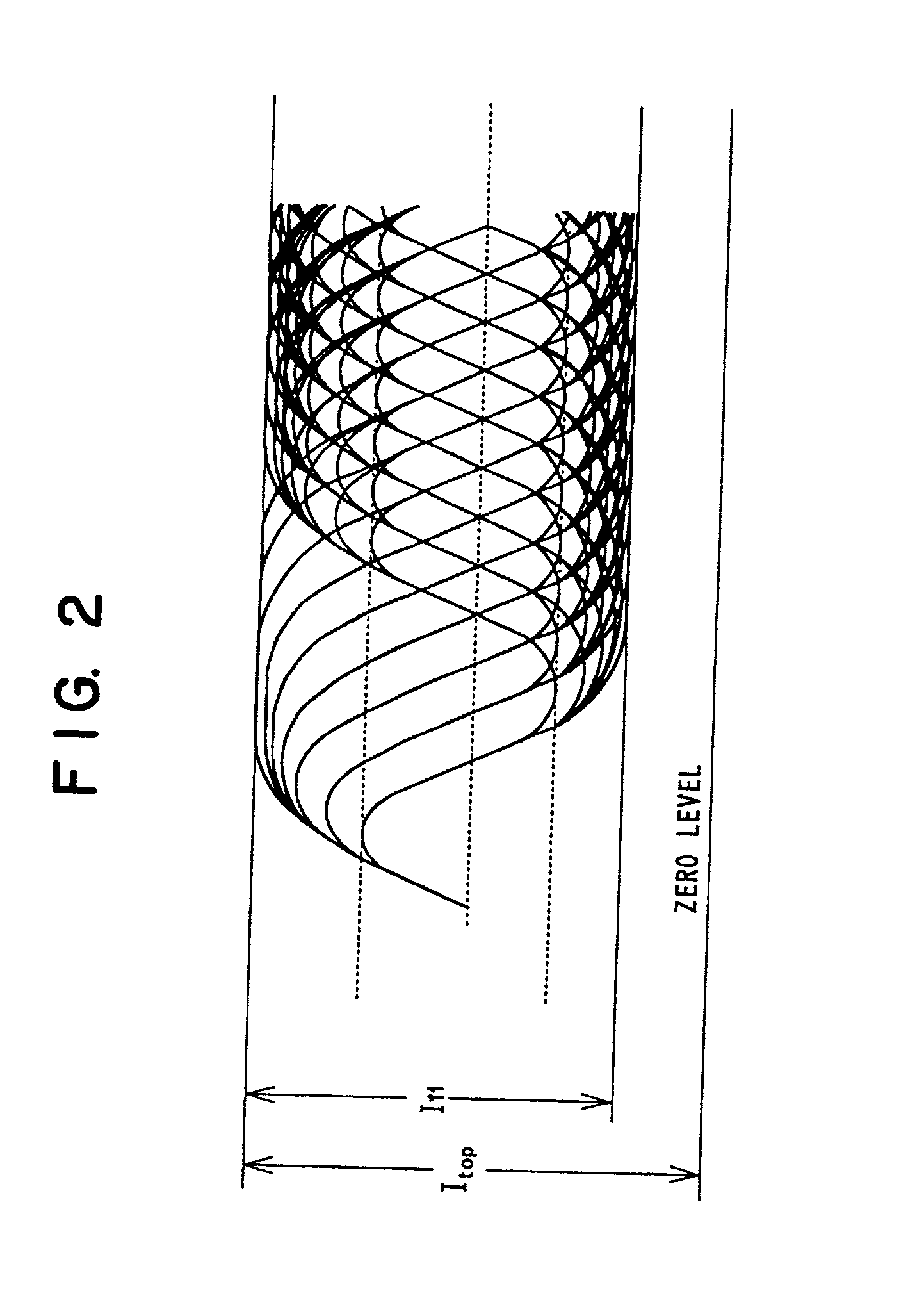

Optical recording medium, data recording method for rewritable-type phase change type optical disc. data erase method for rewritable compact disc. data erase method for rewritable phase change type recording medium, read only data erase method, and recording/readout apparatus

InactiveUS20020064111A1Avoid initializationReduce the possibilityCombination recordingRecording carrier detailsRewritable compact discPhase change

For an optical recording medium having a phase change type recording layer on its a substrate and having as read only area and a writable area in a recording area, a data recording method is provided which records data in the writable area. This data recording method comprises a transfer step of transferring program data recorded in the read only area in a practical form to an external computer, and an execution step (step A10) of automatically executing the program data in the external computer to record data in the writable area, which can facilitate manufacturing and reduce the possible of destruction or falsification of ROM data.

Owner:CMC MAGNETICS CORPORATION

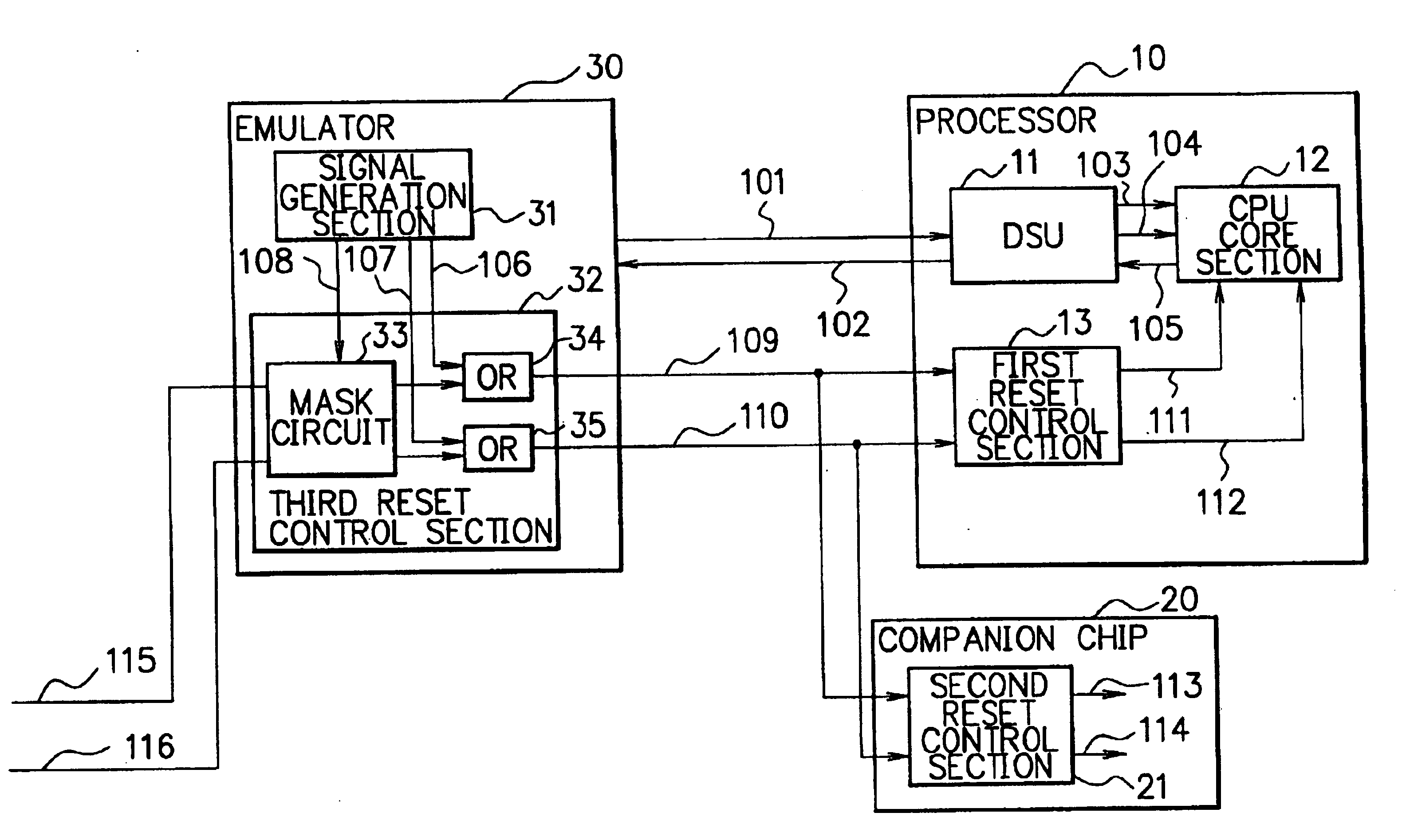

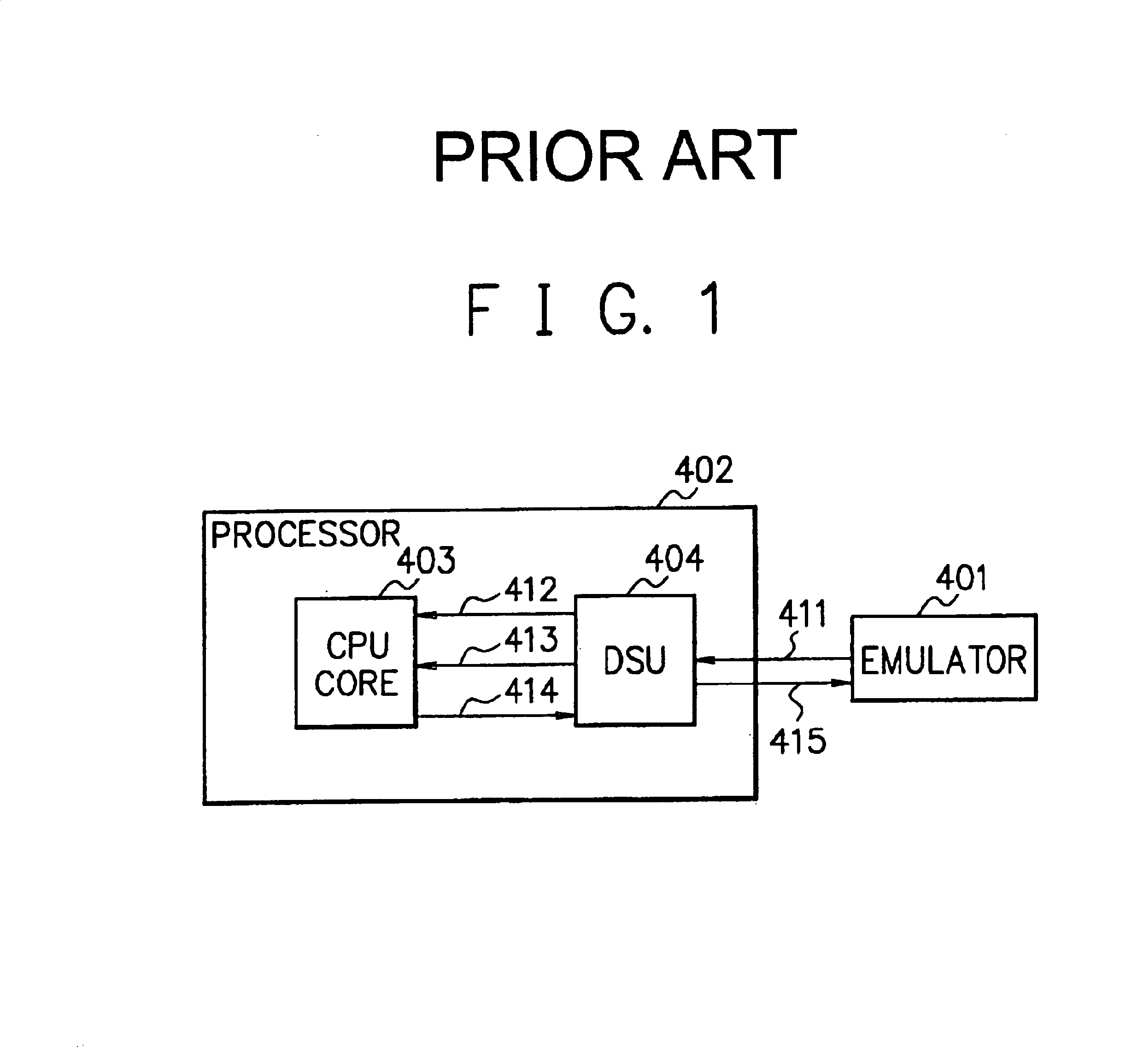

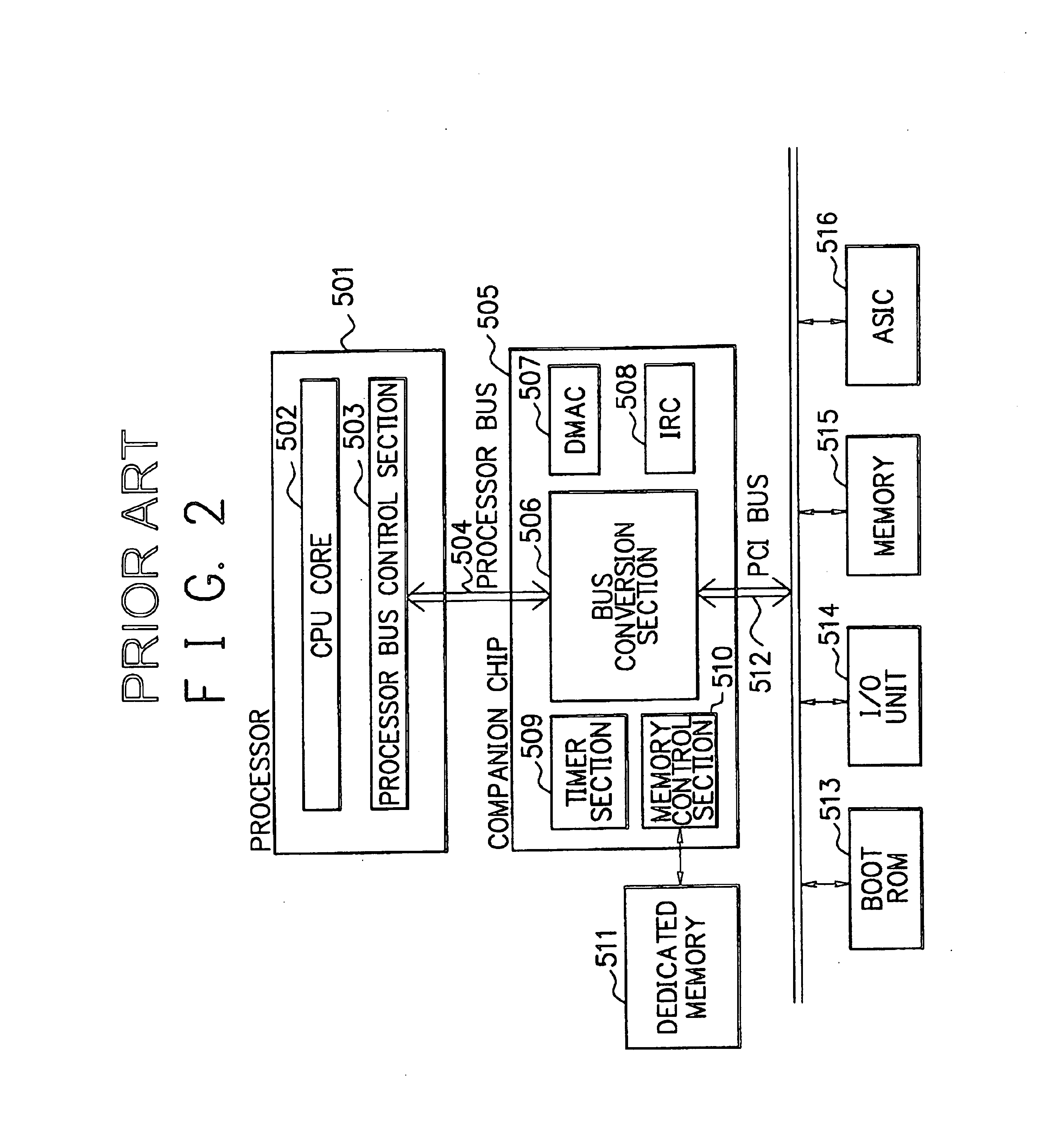

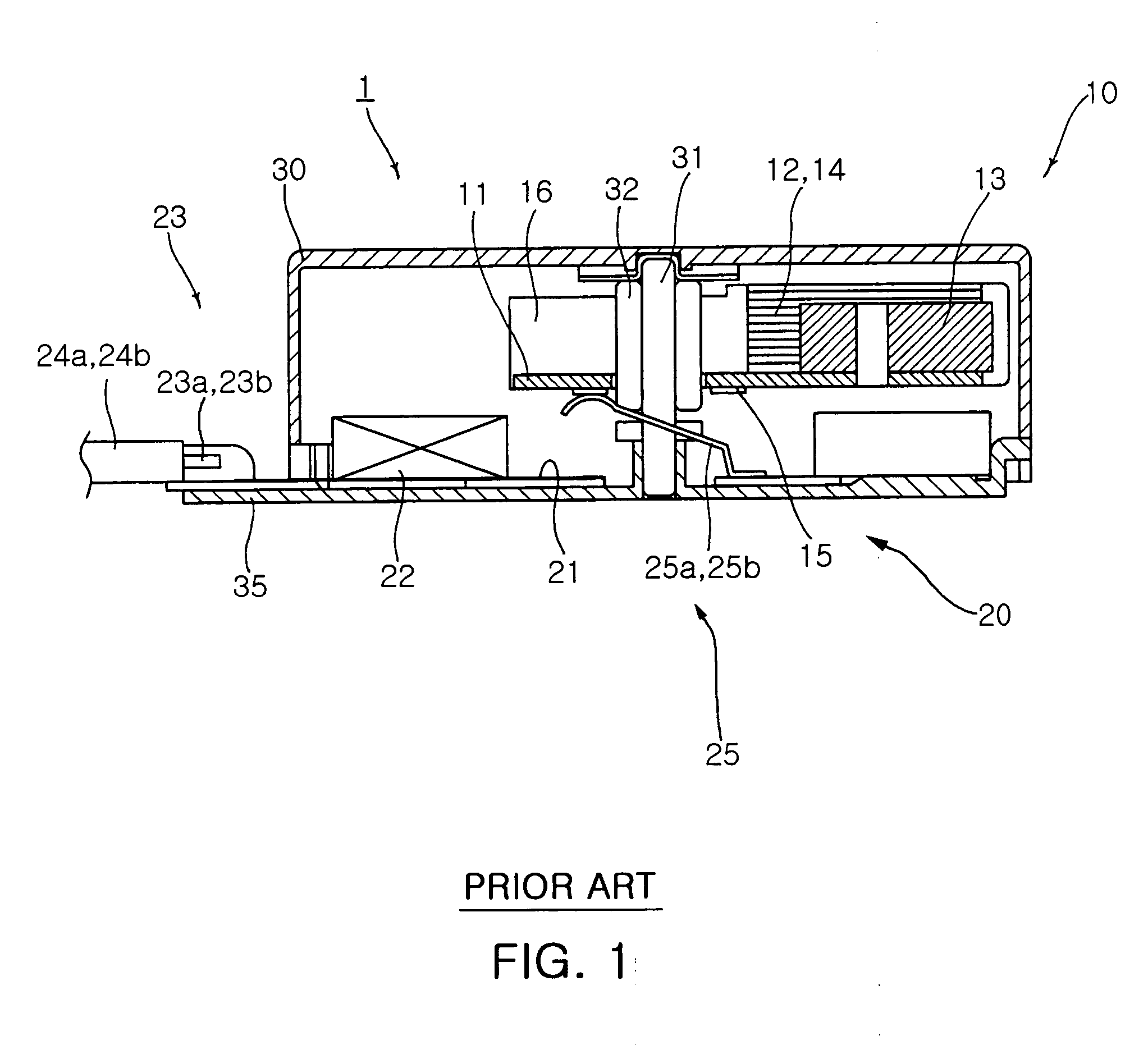

Reset control system and method

InactiveUS6877112B1Avoid signalingAvoid accessDetecting faulty computer hardwareData resettingControl systemEmbedded system

An OR circuit (34, 35) OR-operates an emulator reset signal (106, 107) based on a reset instruction from an emulator (30) and an external reset signal (115, 116) supplied from an external reset generation circuit. The OR operation result is distributed and supplied to a processor (10) and a companion chip (20) as a system reset signal (109, 110), thereby initializing both chips of the processor (10) and the companion chip (20) in accordance with the reset the emulator (30).

Owner:FUJITSU LTD

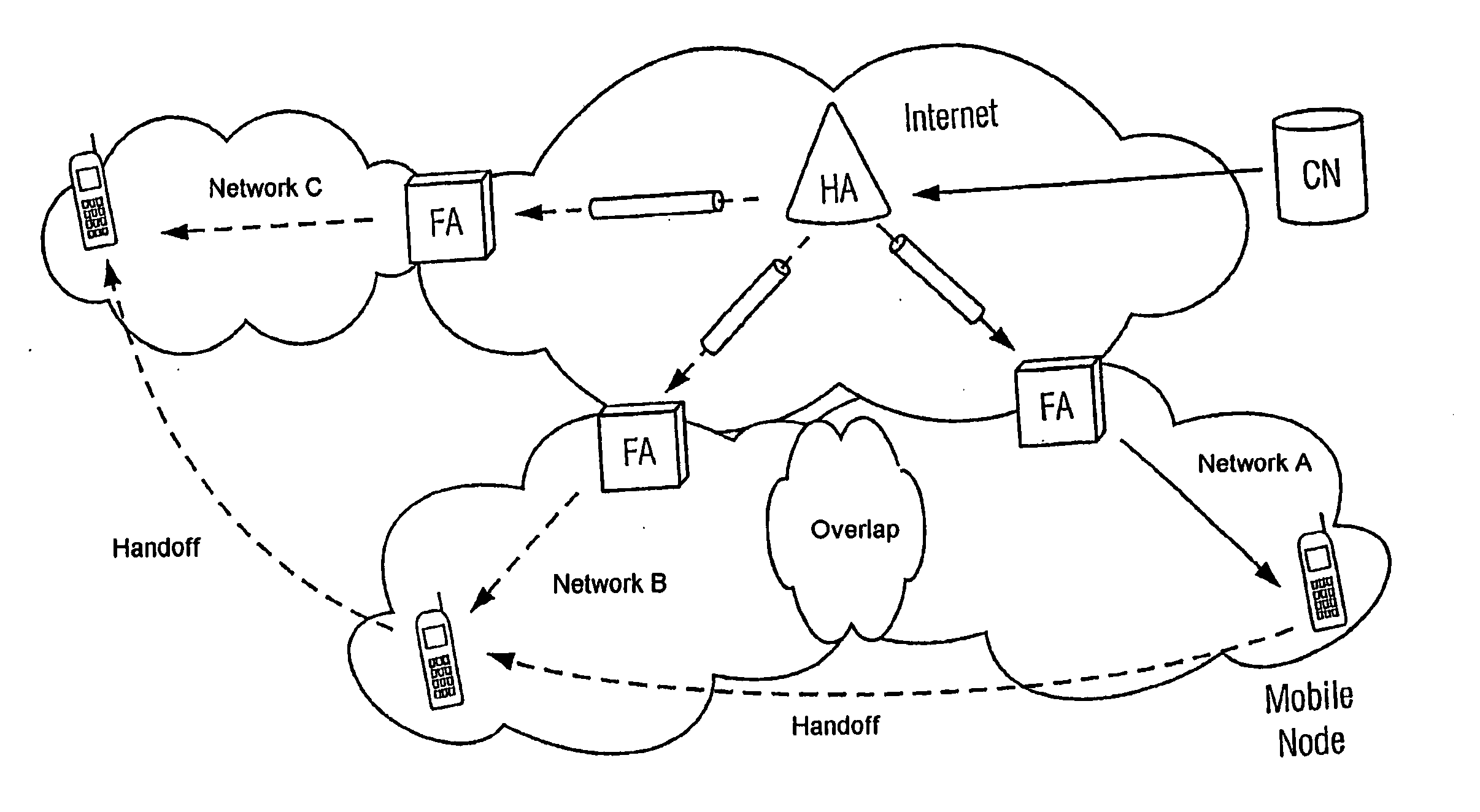

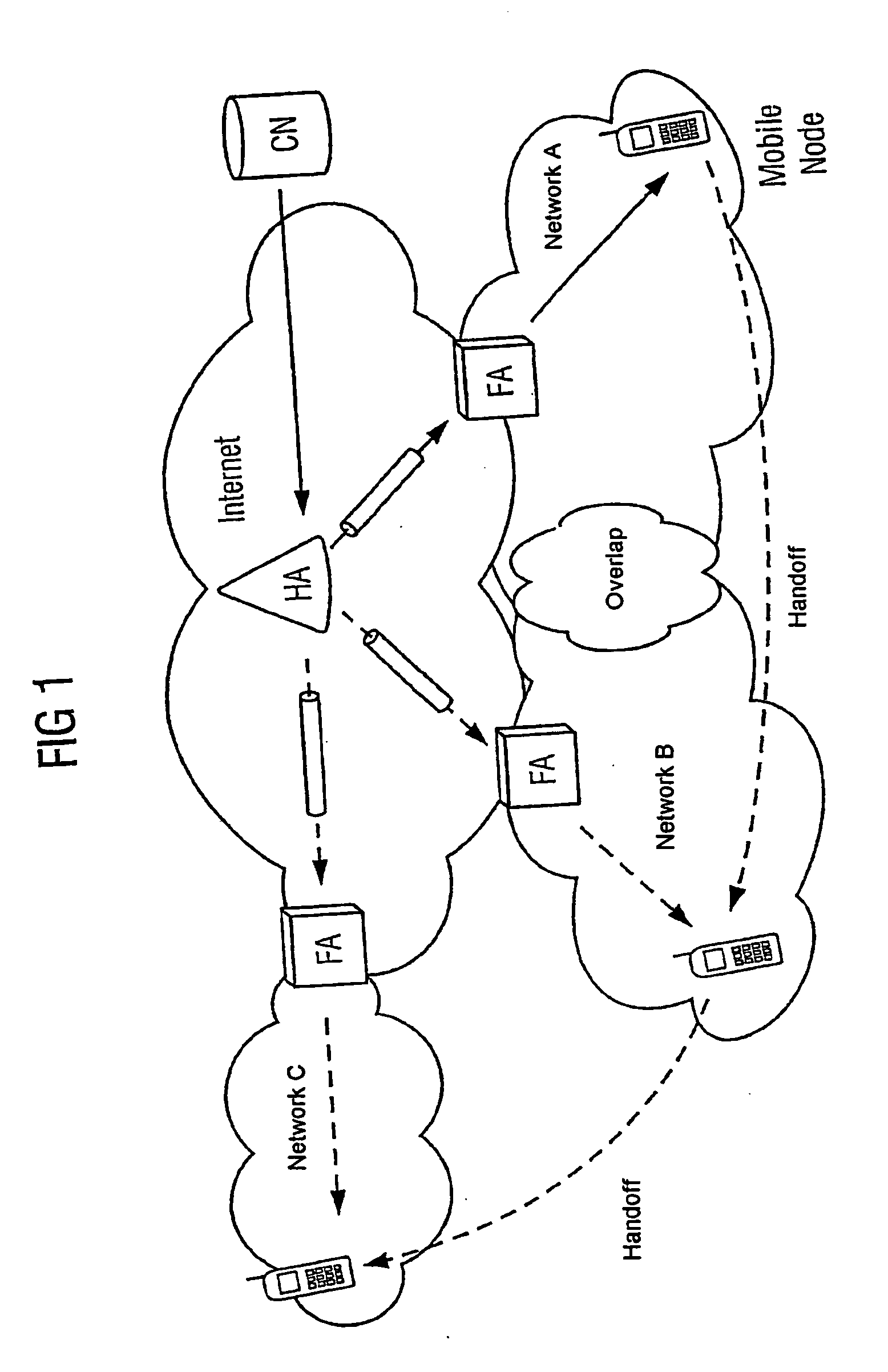

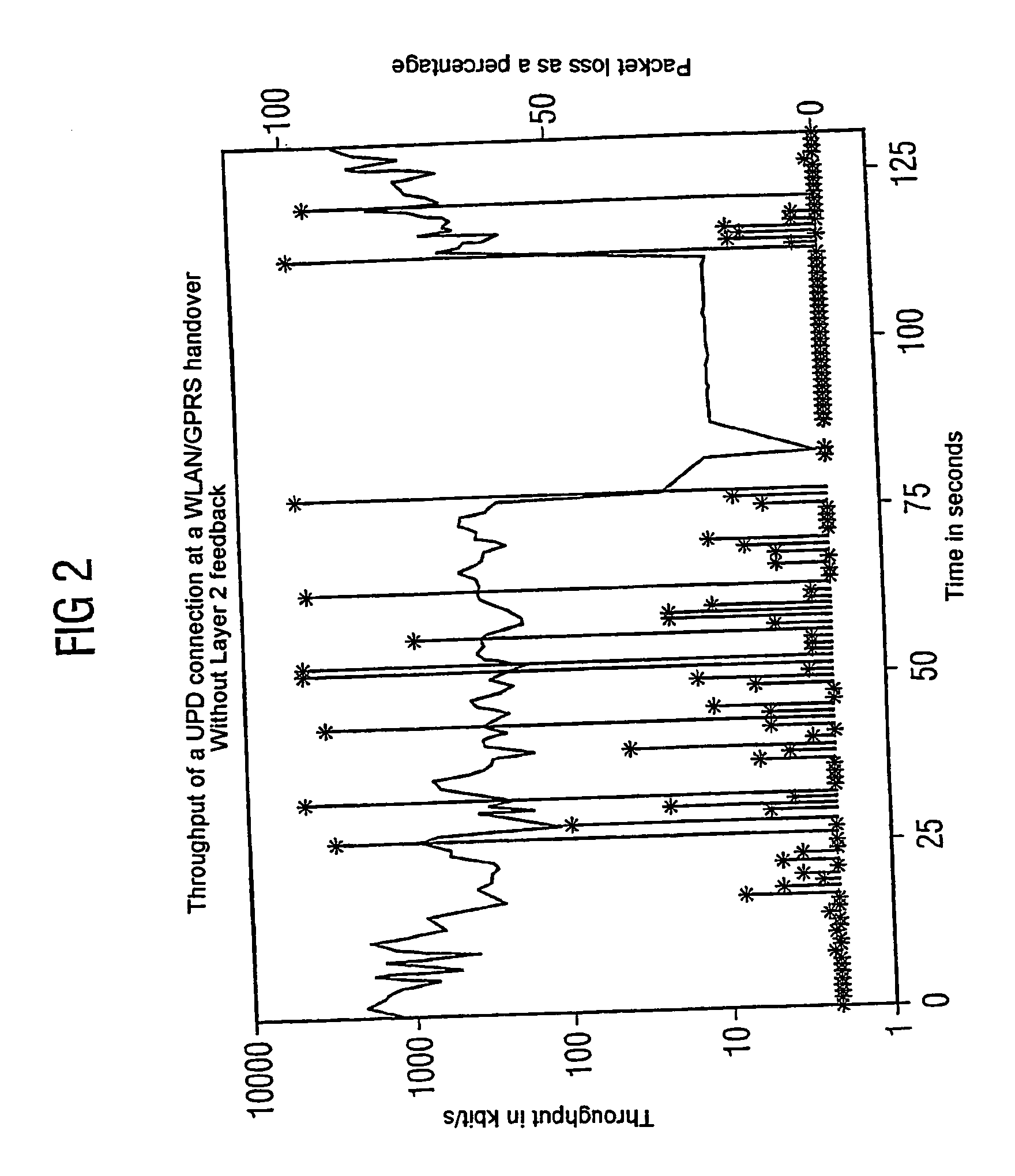

Method for controlling a handover between two network access devices

InactiveUS20060291417A1Accelerates Mobile-IP-basedAccelerates a Mobile-IP-based handoverTime-division multiplexRadio/inductive link selection arrangementsPhysical layerMass parameter

At least one quality parameter determined in a link layer based on signal transmission to a physical layer mobility-controlling mechanisms of a network layer is used to decide on the transfer in handover between two network access devices. At least one message received by a currently supplying network access device is relayed from the physical layer to the network layer or suppressed according to the at least one quality parameter.

Owner:NOKIA SIEMENS NETWORKS GMBH & CO KG

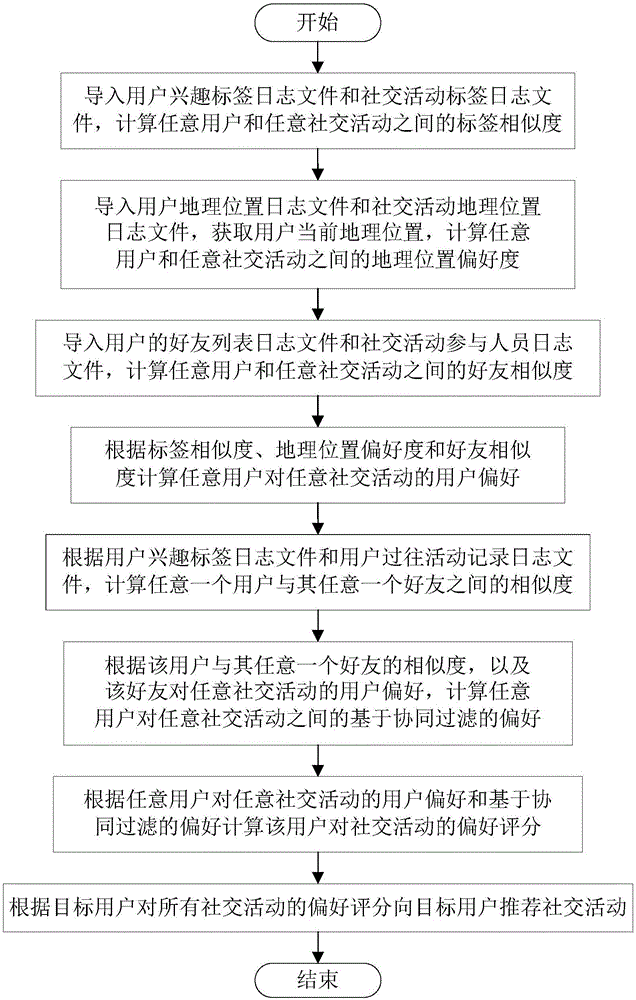

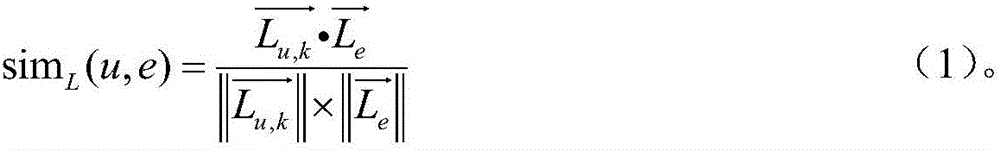

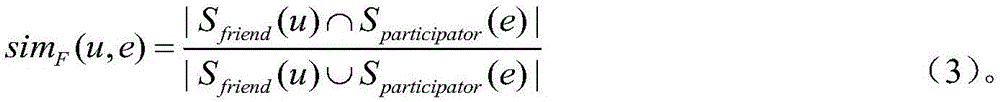

Social activity recommendation algorithm in mobile social network

ActiveCN106339483ASolve problems that do not satisfy usersOvercome the limitations of mechanizationData processing applicationsSpecial data processing applicationsGeographic siteGeolocation

The invention discloses a social activity recommendation algorithm in a mobile social network, comprising the following steps: S1, calculating label similarity between any user and any social activity; S2, calculating geographical position preference degree between any user and any social activity; S3, calculating friend similarity between any user and any social activity; S4, calculating user preference of any user on any social activity; S5, calculating similarity between any user and any friend of the user; S6, calculating collaborative-filtering-based preference between any user and any social activity; S7, calculating preference scores of users on social activities; S8, recommending one social activity to a target user according to the preference scores of the target user on all the social activities. By adopting the social activity recommendation algorithm disclosed by the invention, the limitation of mechanized recommendation results caused by content-based recommendation is eliminated, so that the recommended social activity has more pertinence and accuracy.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

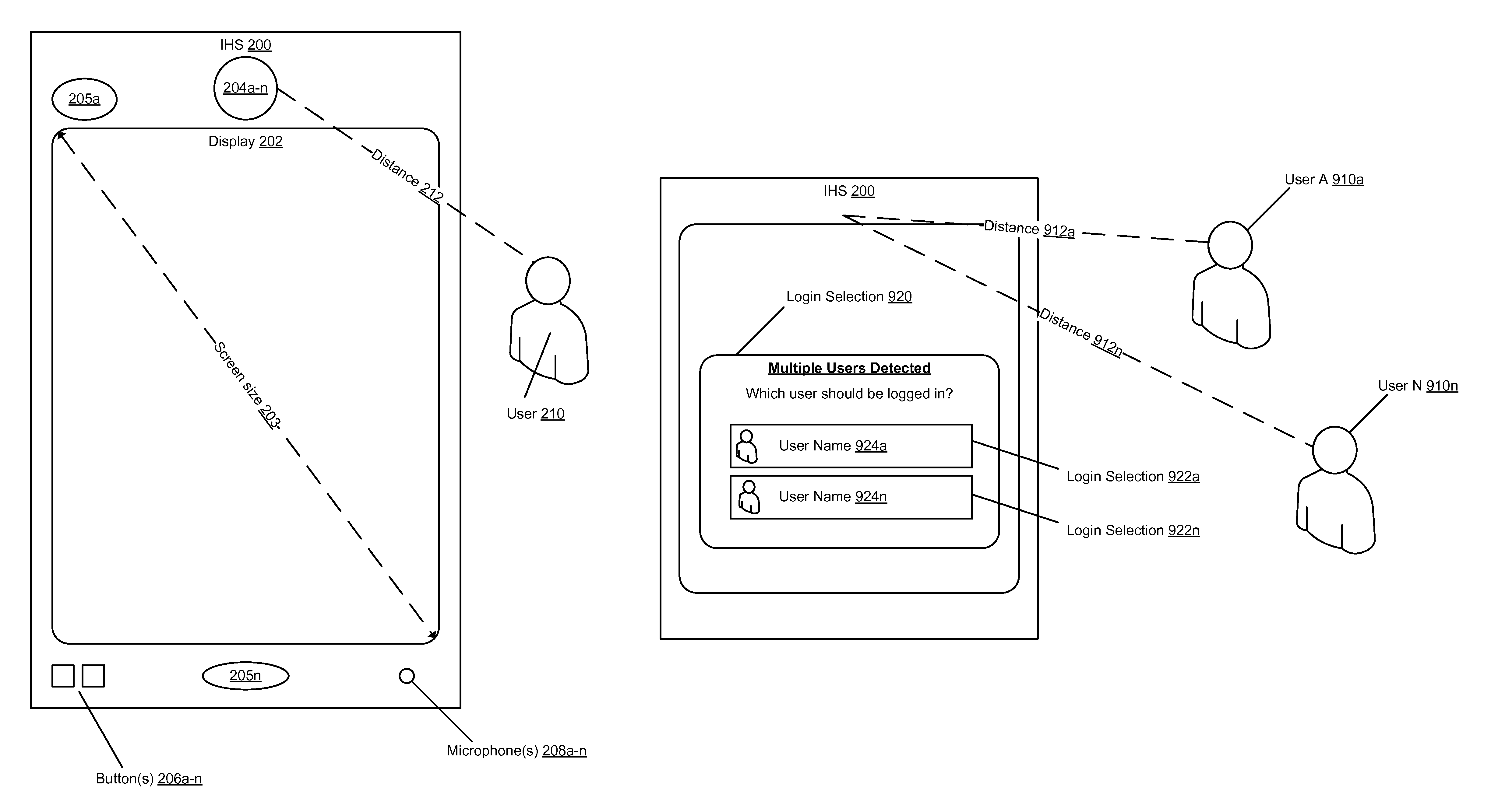

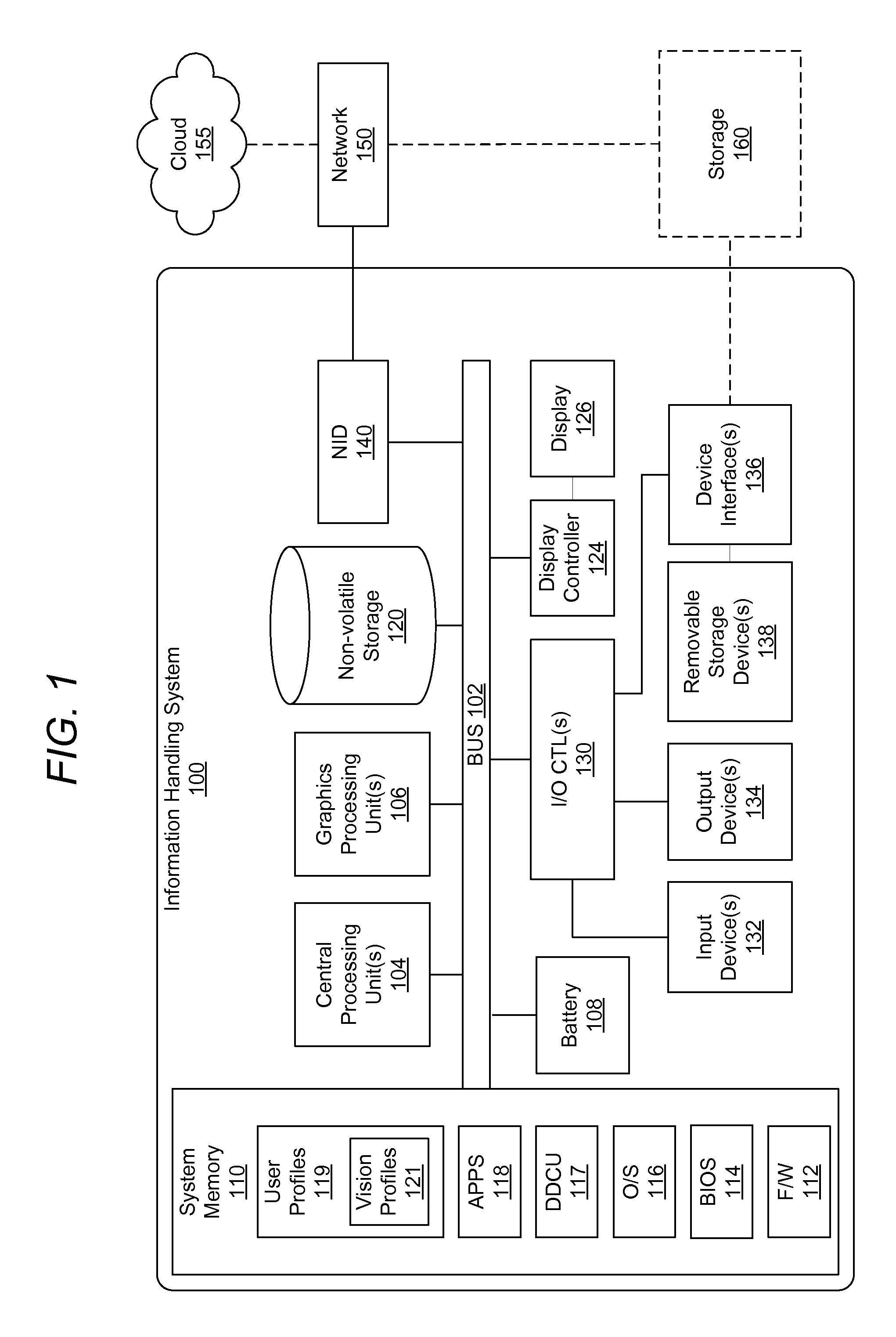

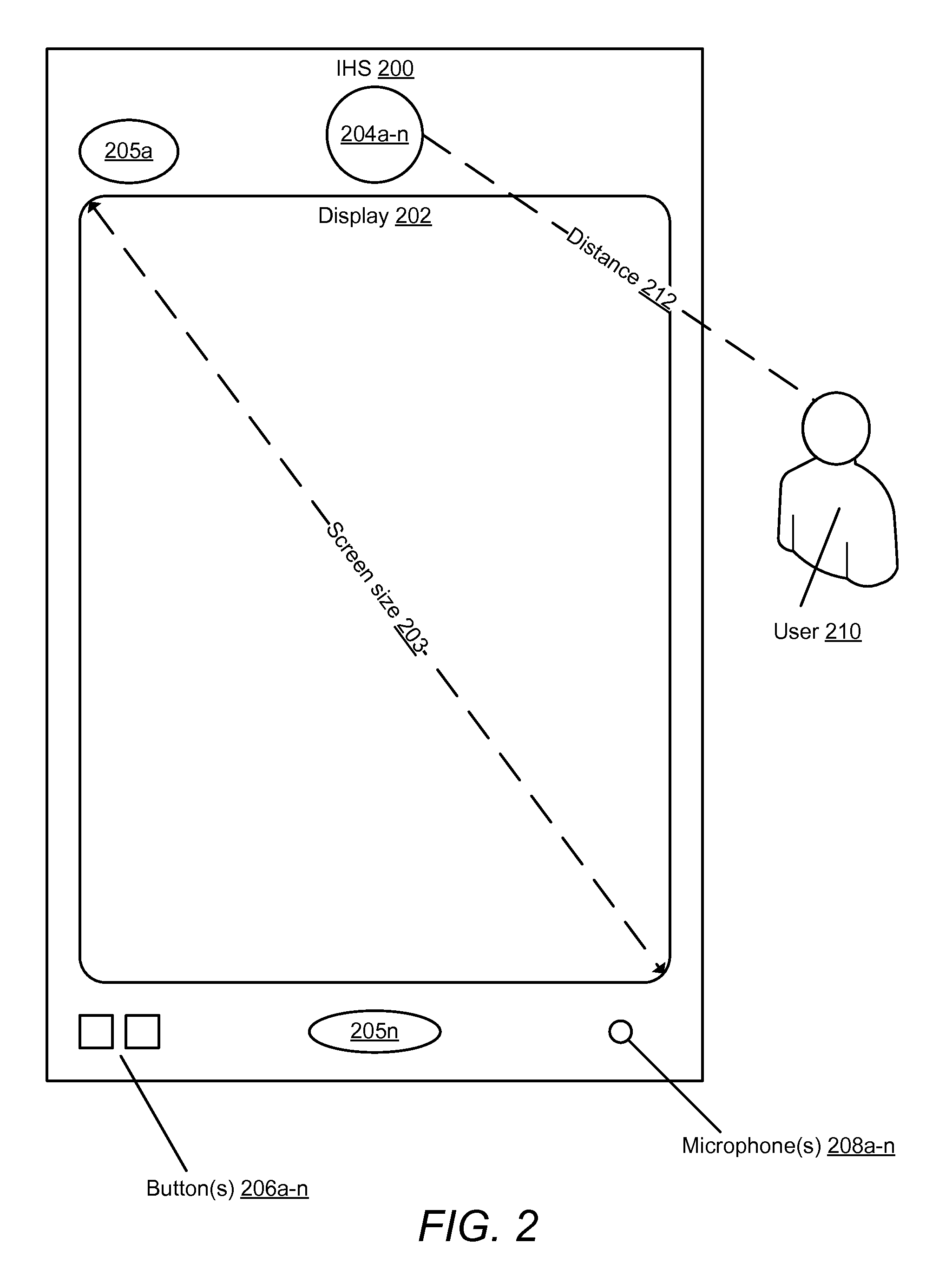

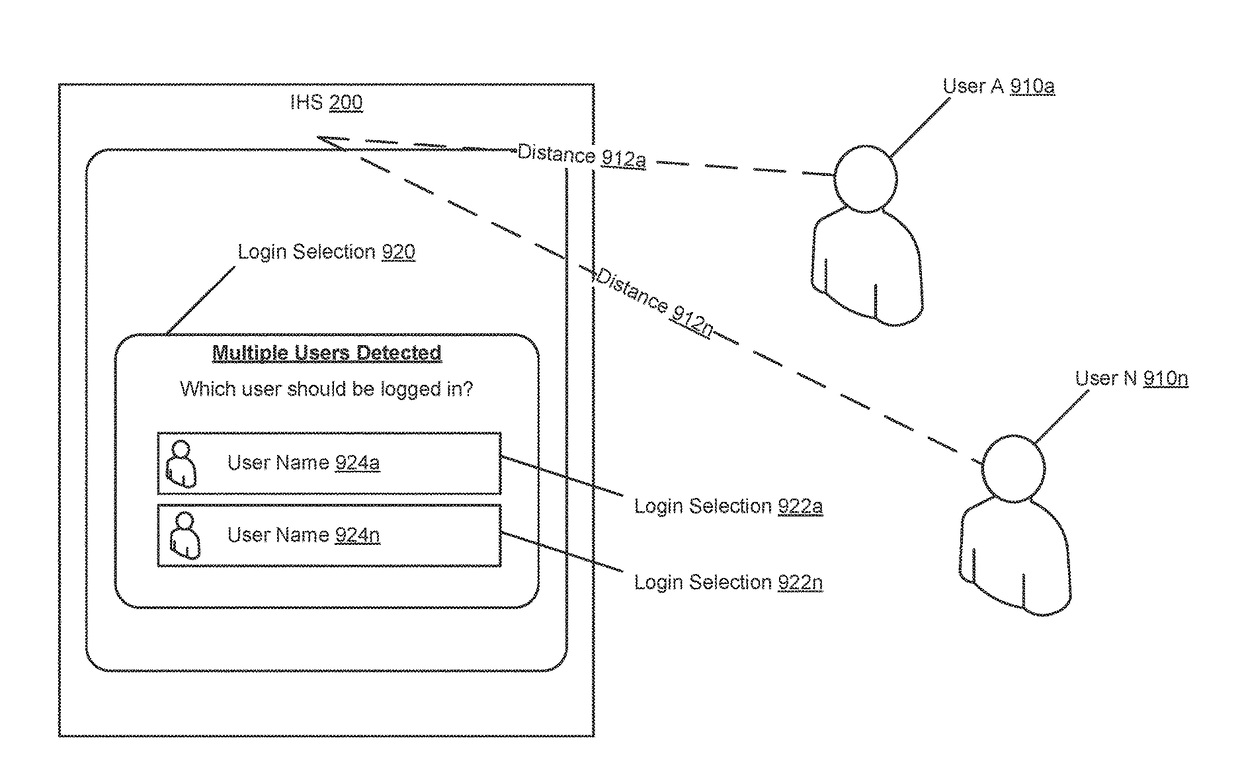

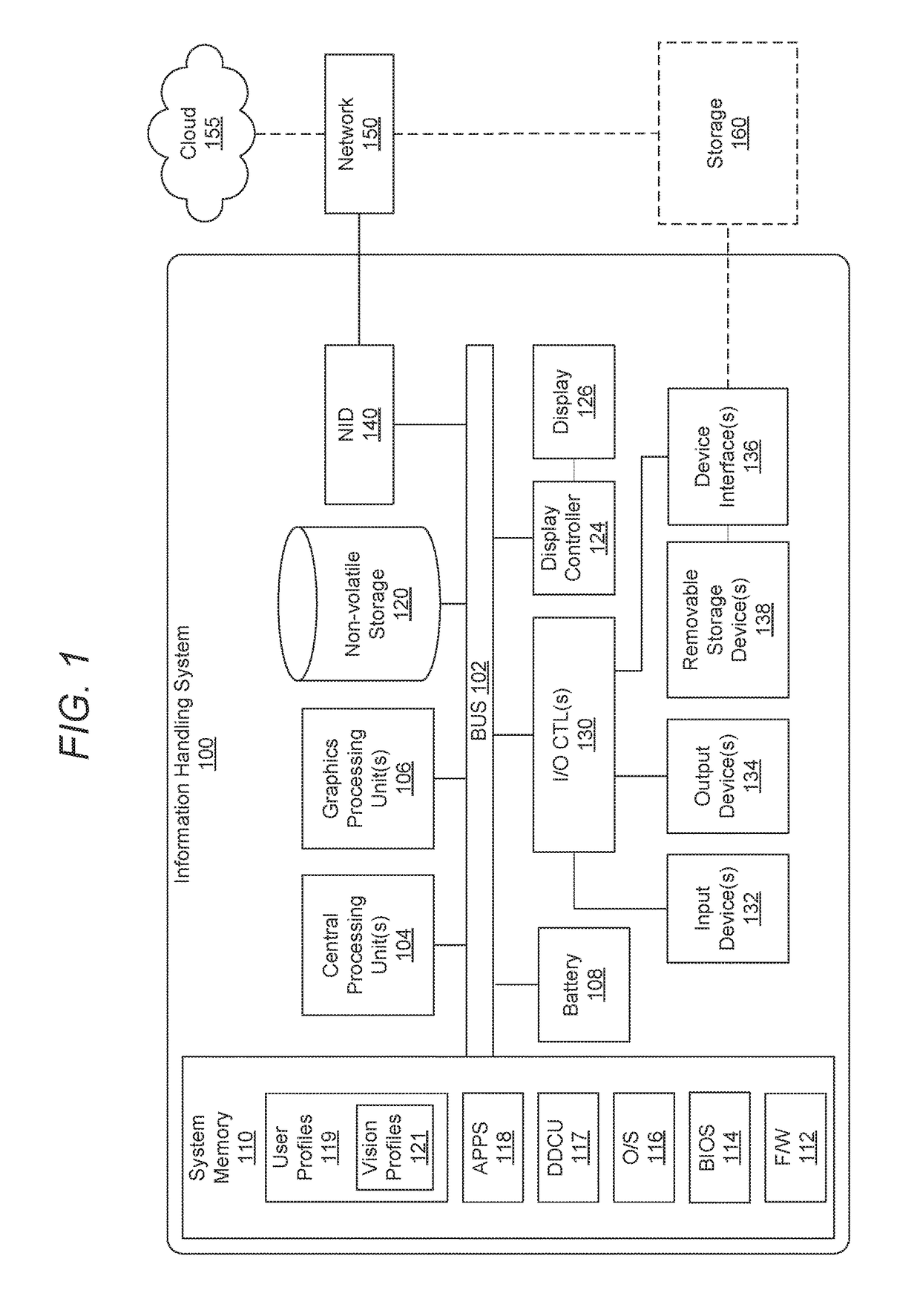

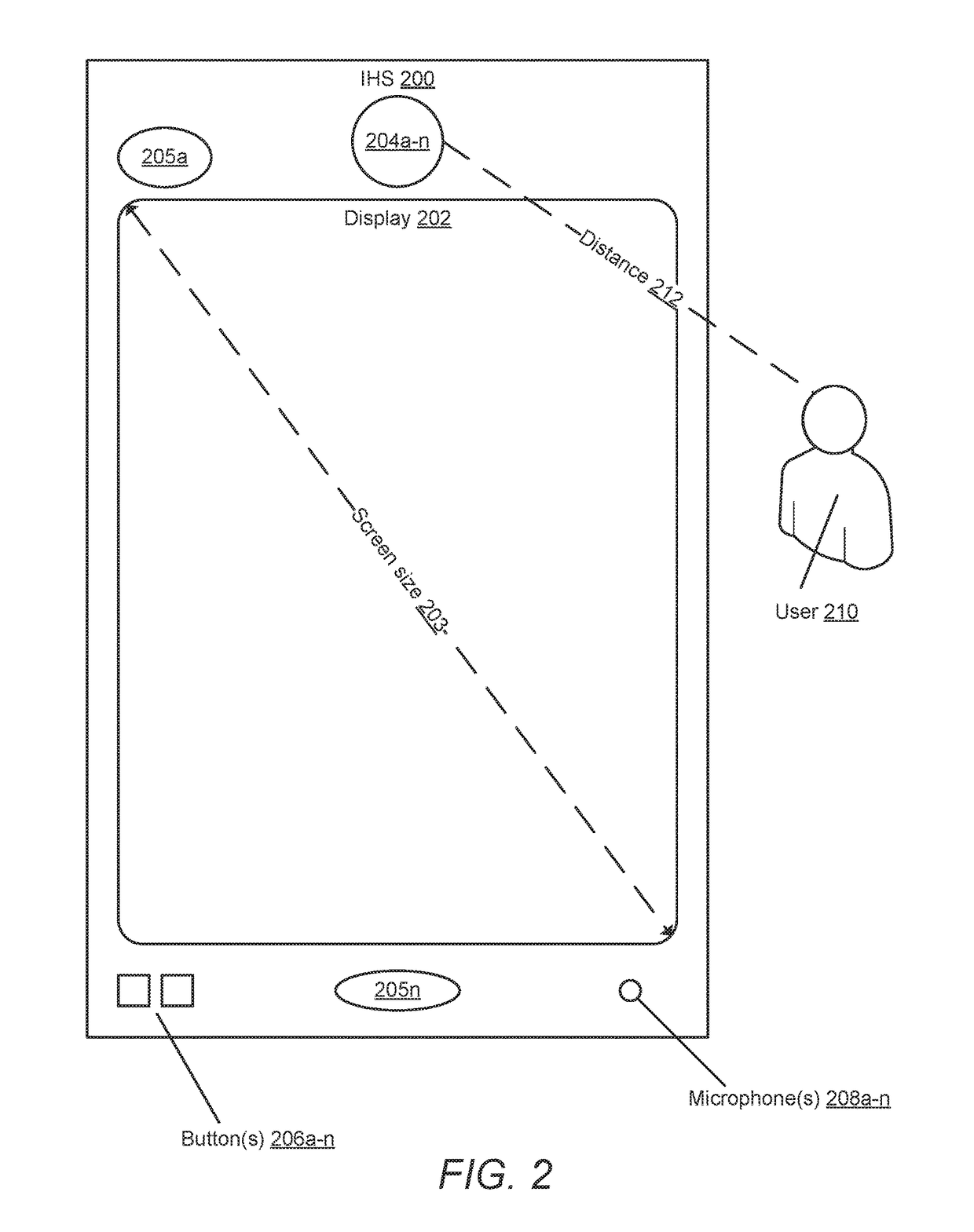

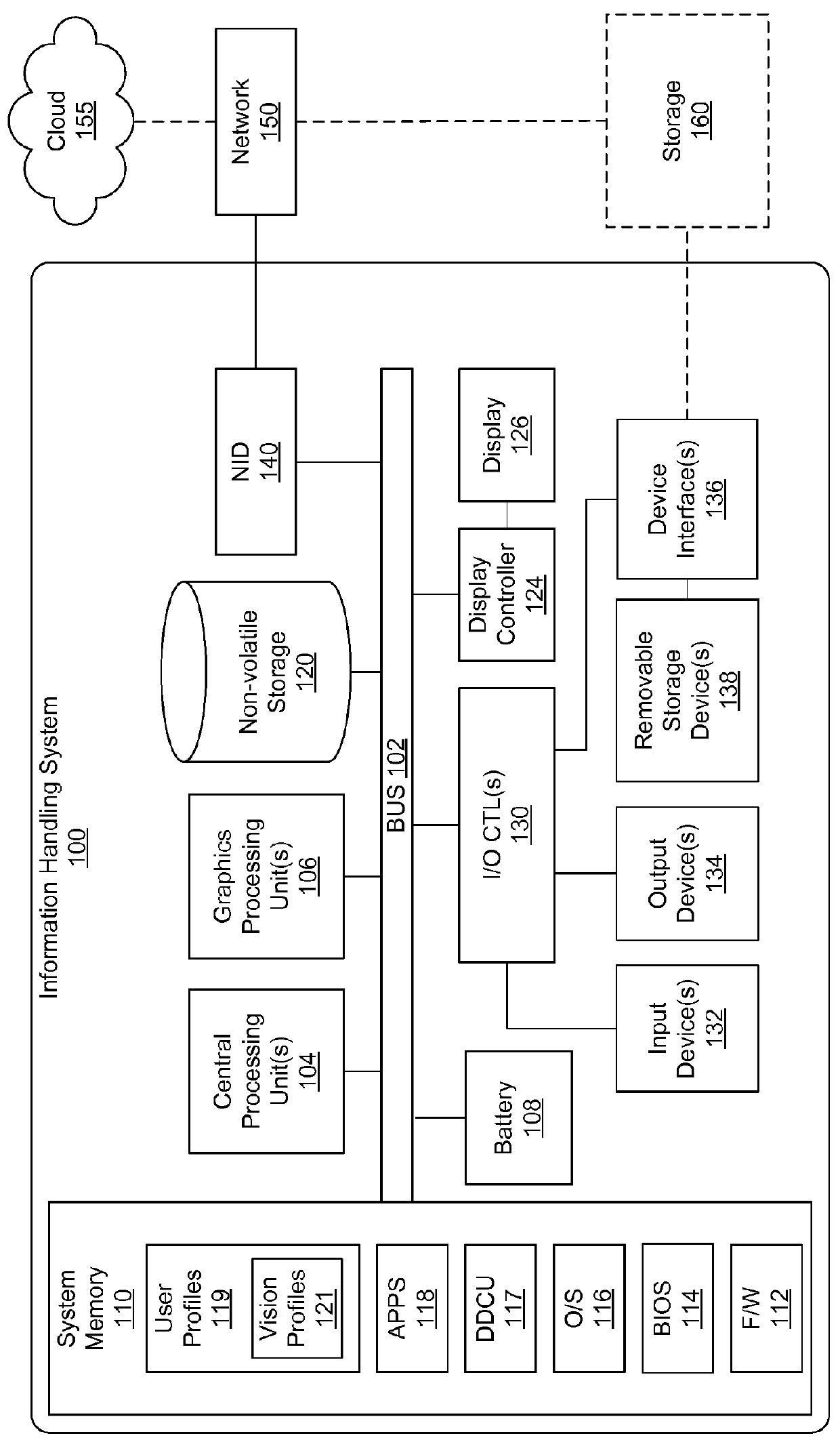

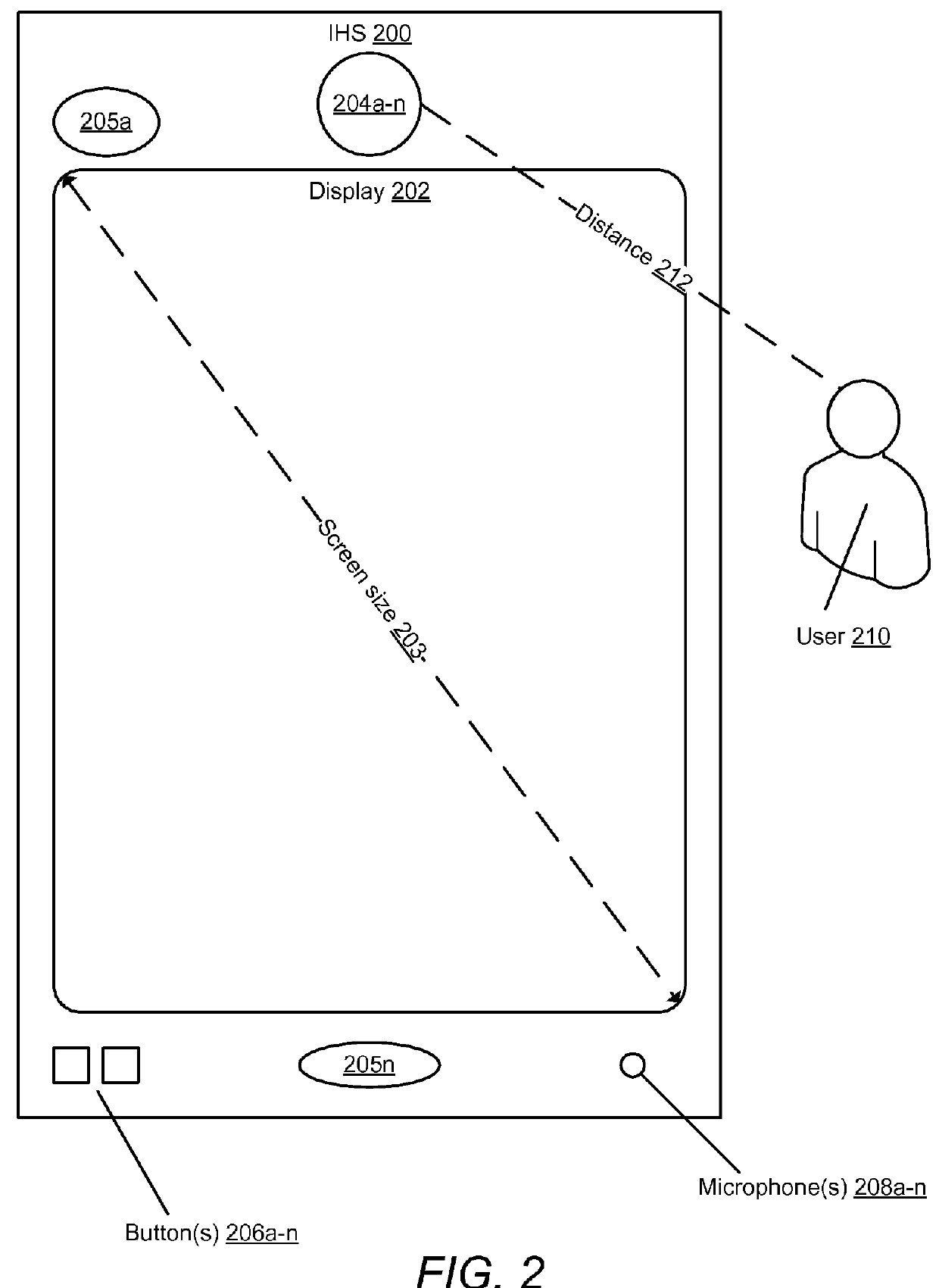

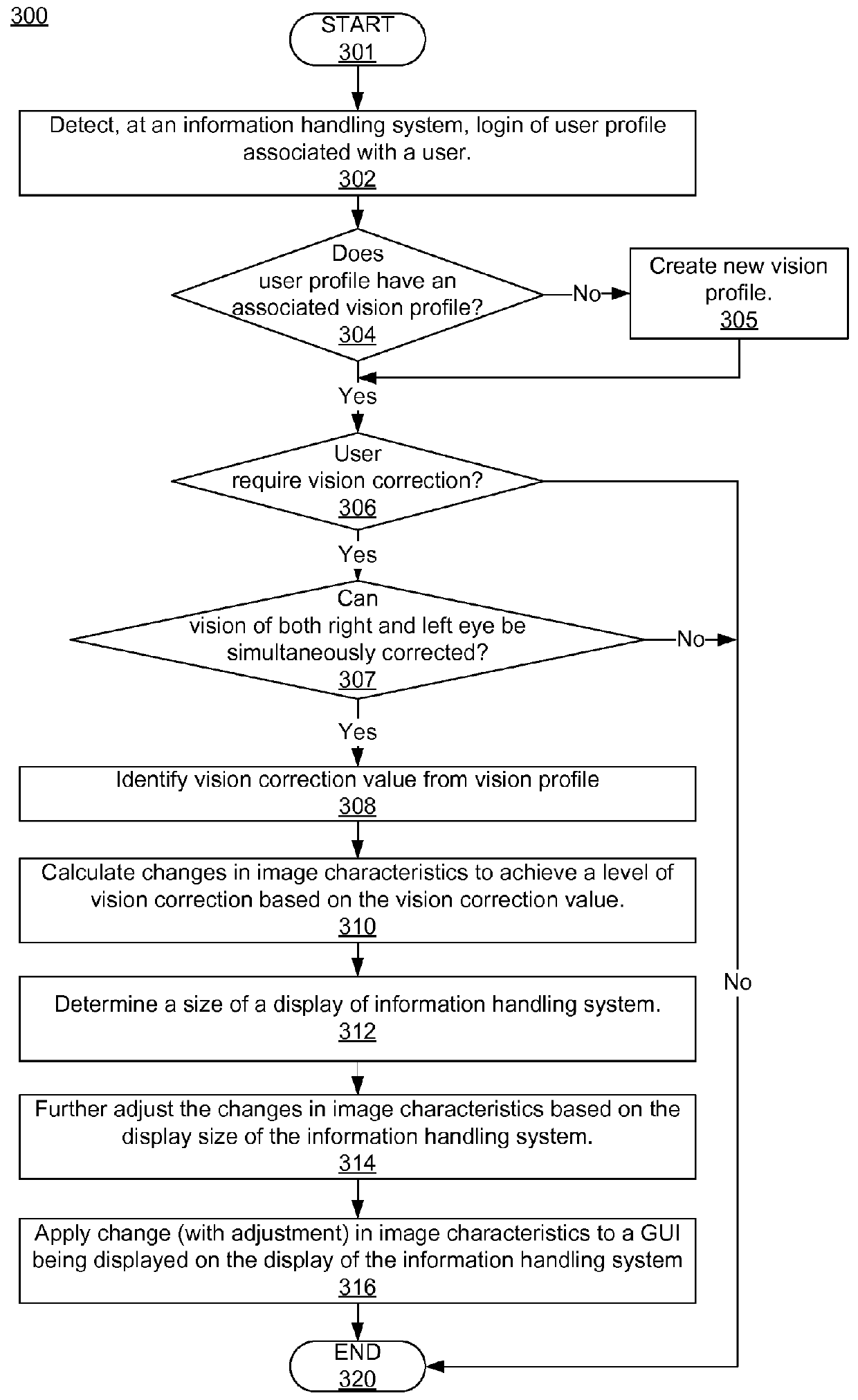

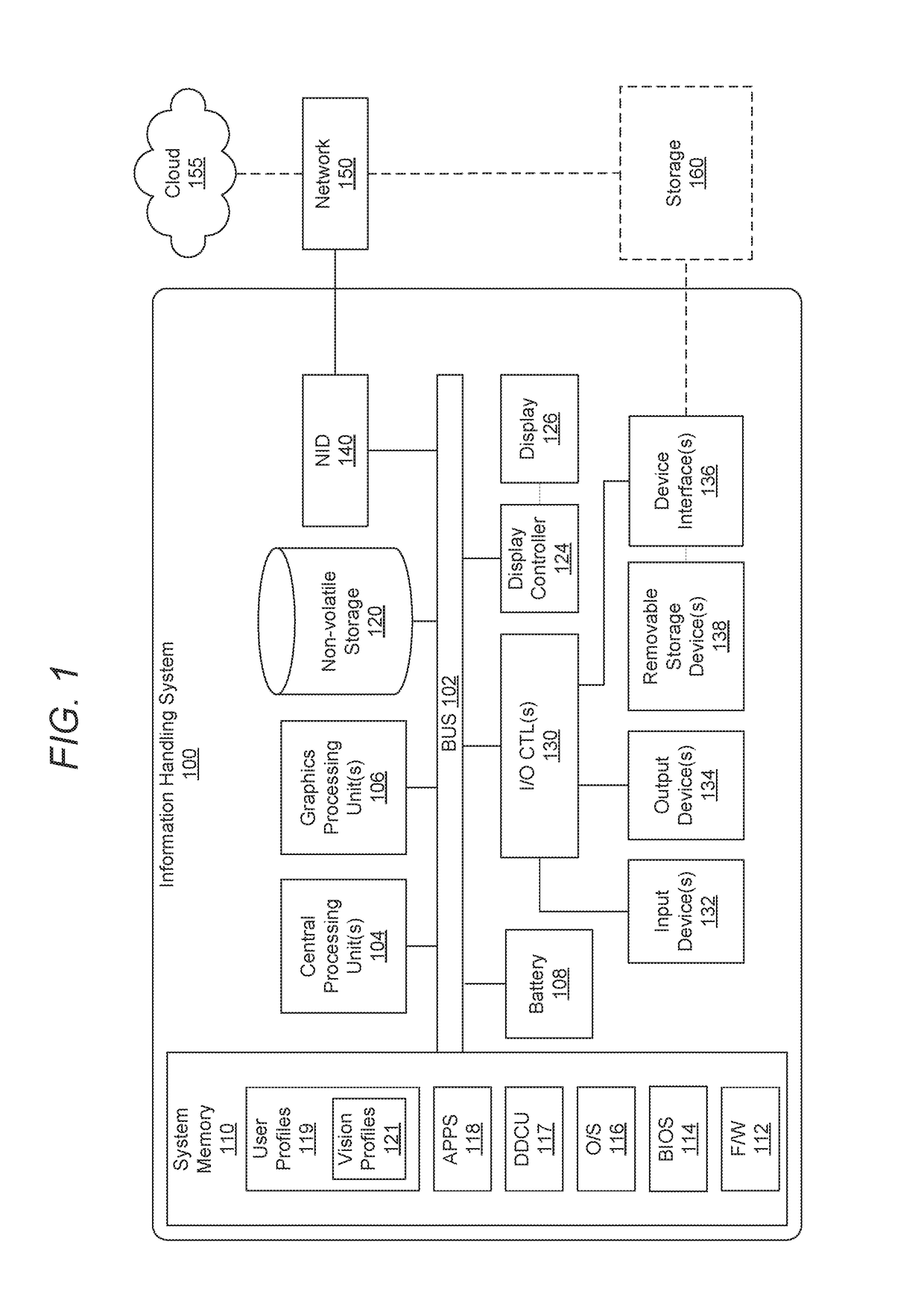

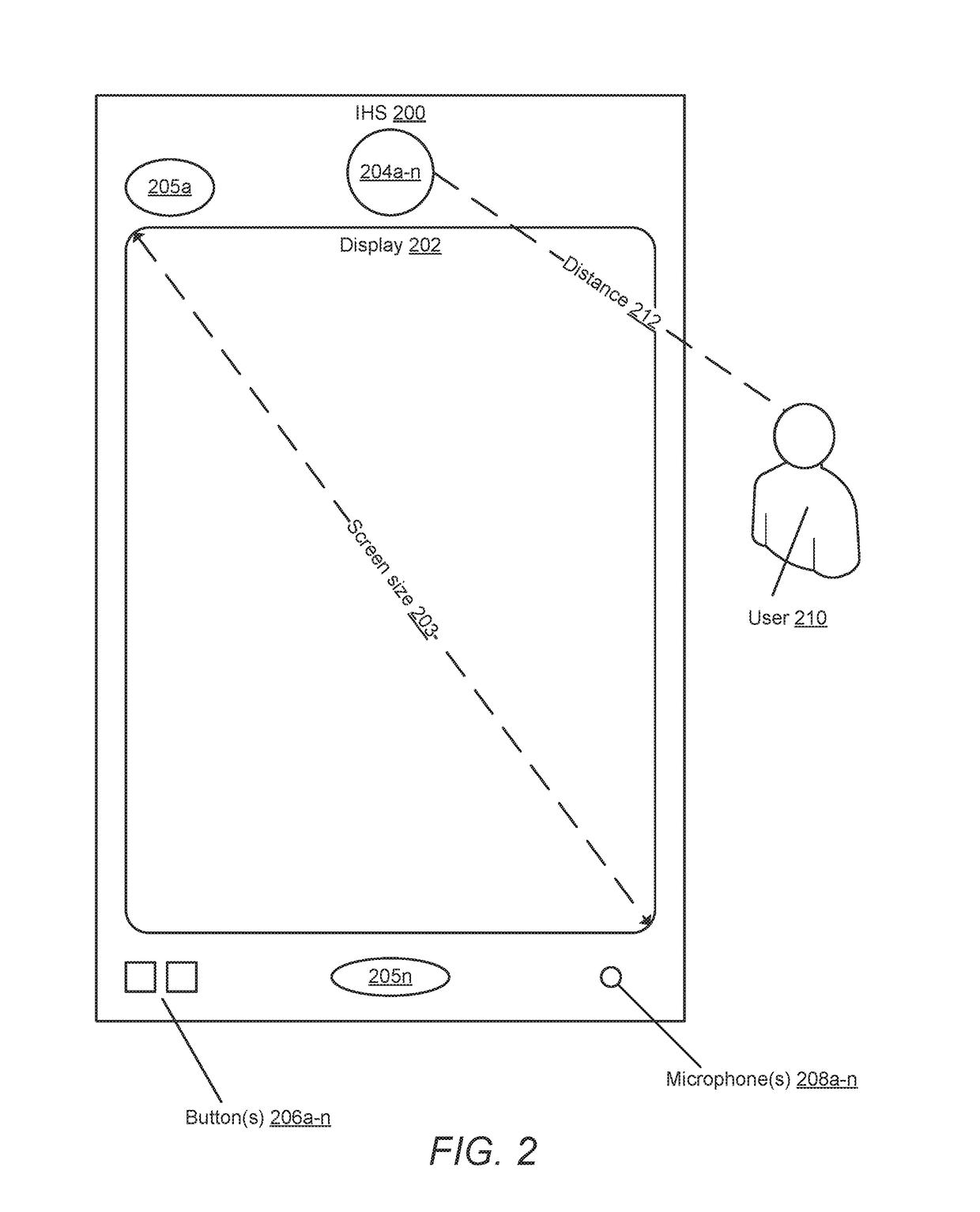

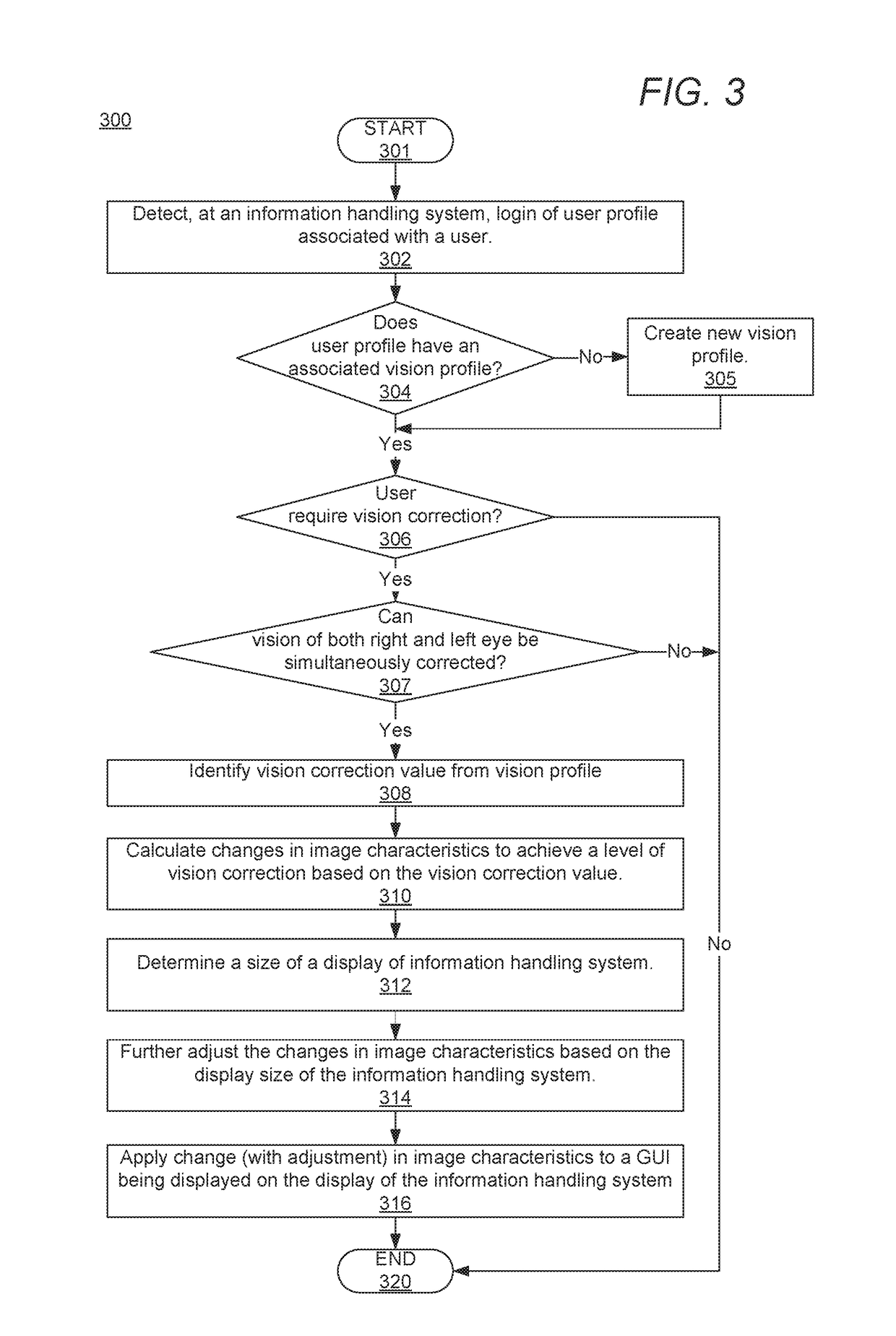

User aware digital vision correction

ActiveUS9241620B1Avoid eyesightAvoid initializationCharacter and pattern recognitionCathode-ray tube indicatorsGraphicsPersonalization

A method, a system, and an information handling system dynamically provide individualized dynamic digital display correction for users of an electronic device. An information handling system detects a login of a first user profile that is associated with a first user. The information handling system then determines whether the first user profile has an associated first vision profile. In response to the first user profile having an associated first vision profile, a vision correction value associated with the first user is identified and a first change in image characteristics which may be applied to a graphical user interface (GUI) in order to achieve the vision correction value is calculated. A size of the display of the information handling system is detected and the first change in image characteristics is further adjusted based on this size before the adjusted image characteristic in image characteristics is applied.

Owner:DELL PROD LP

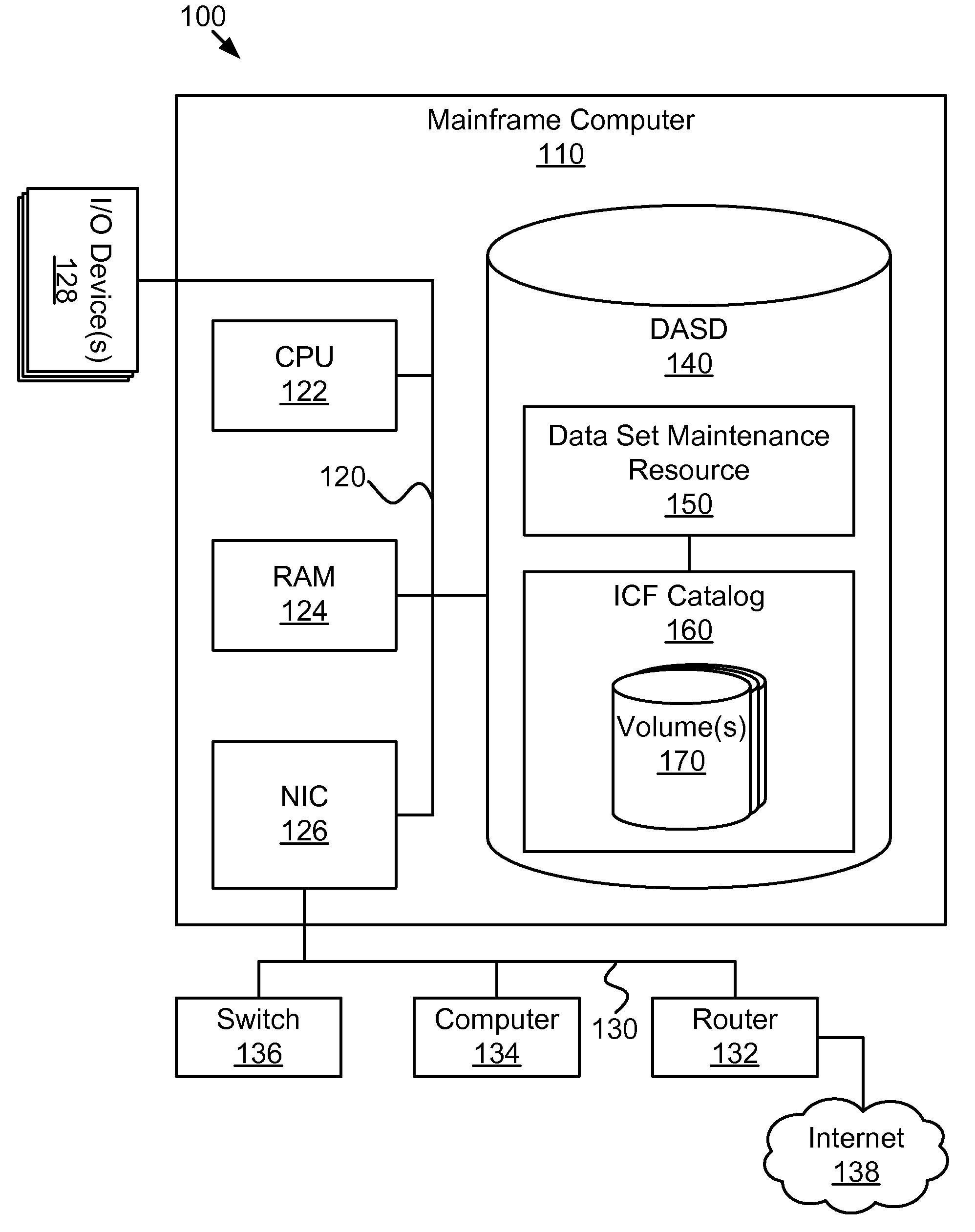

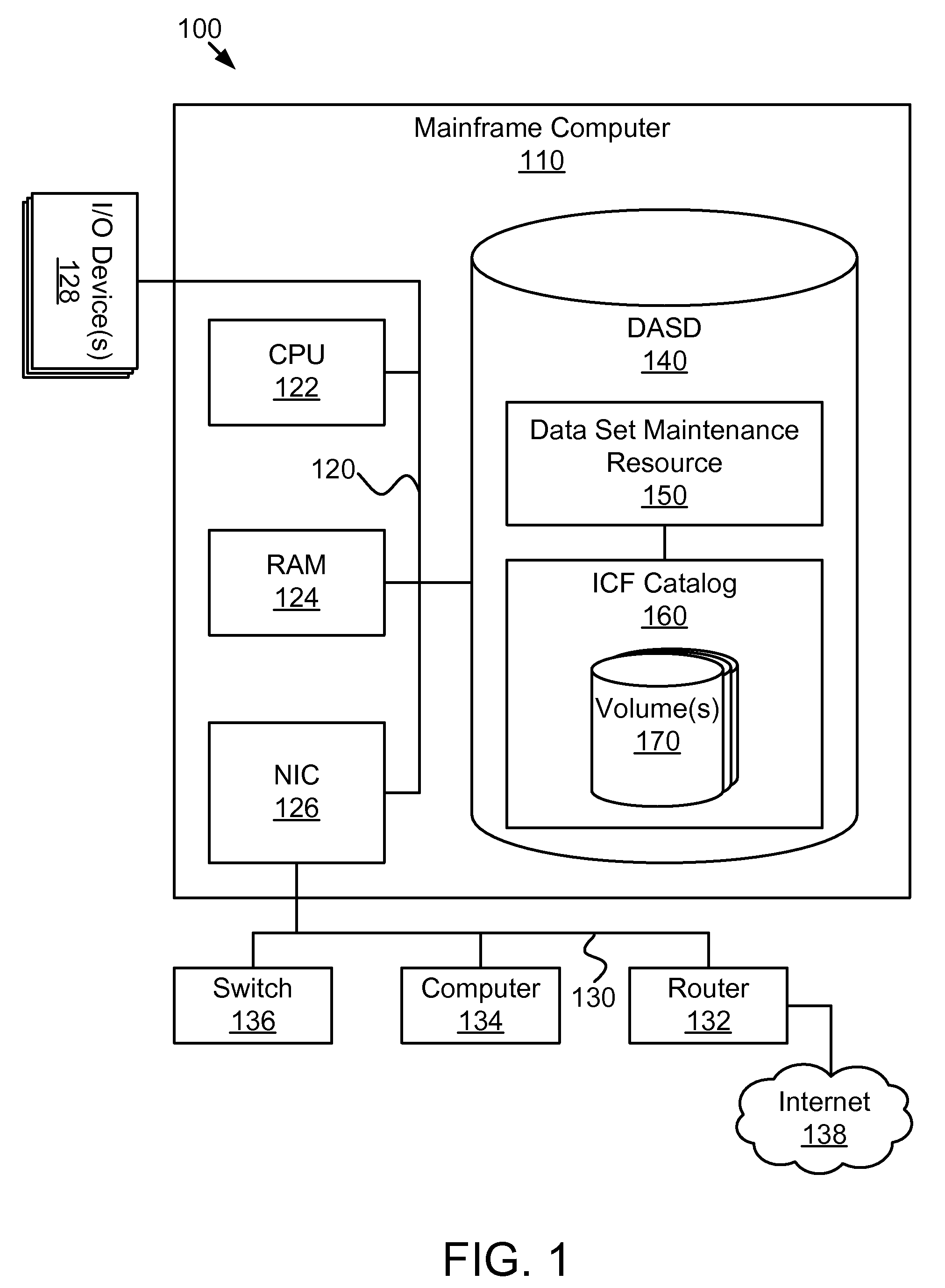

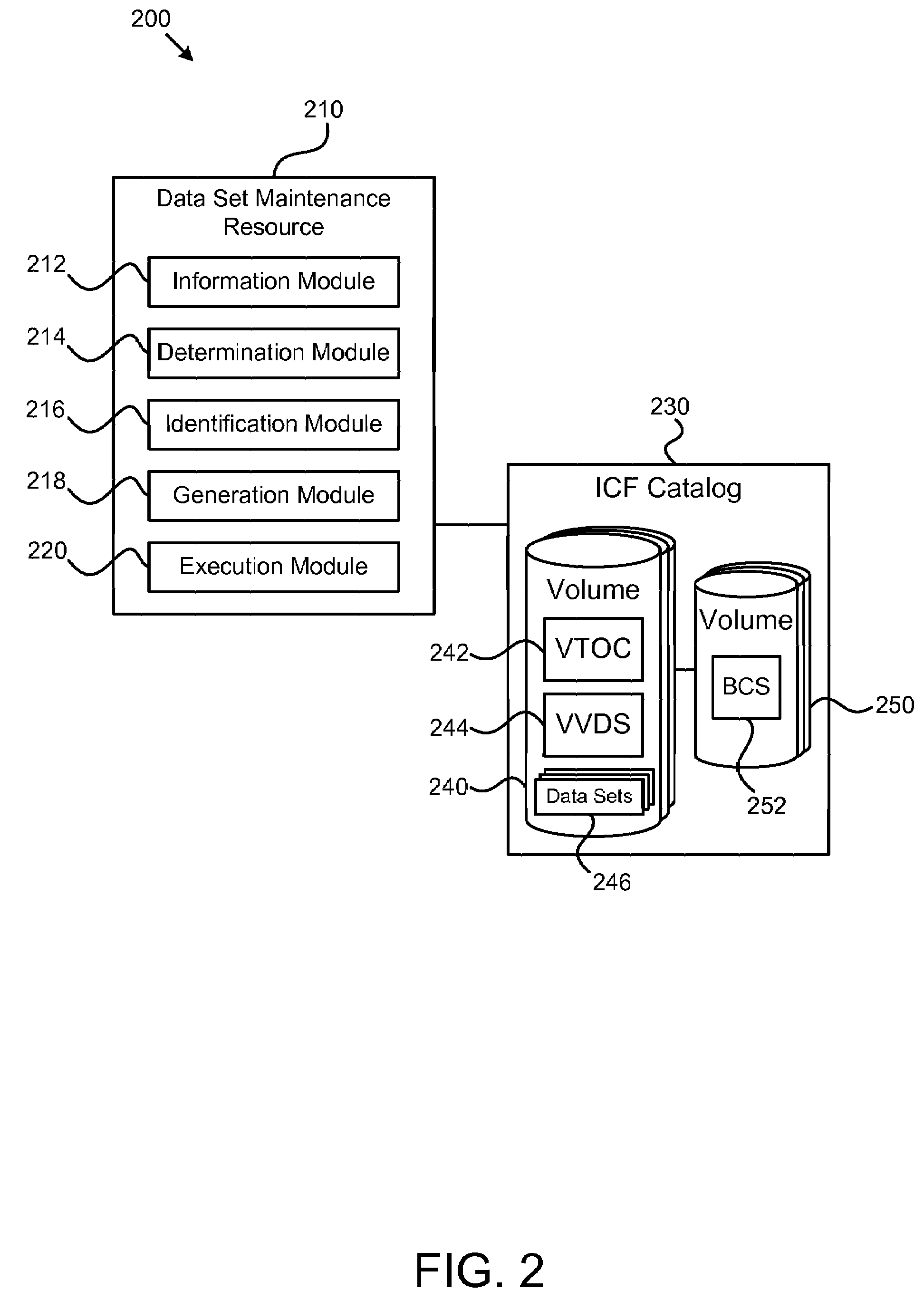

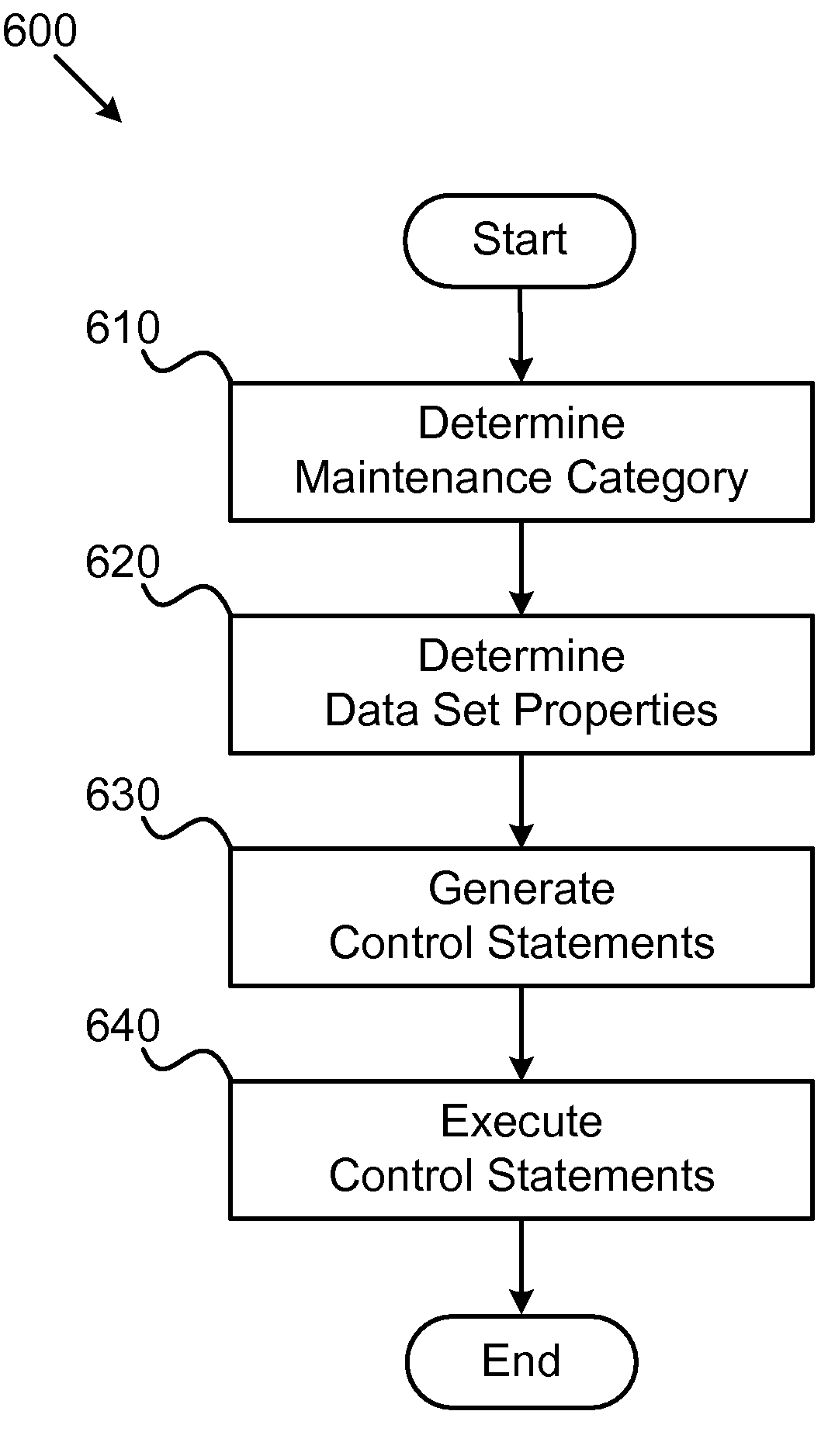

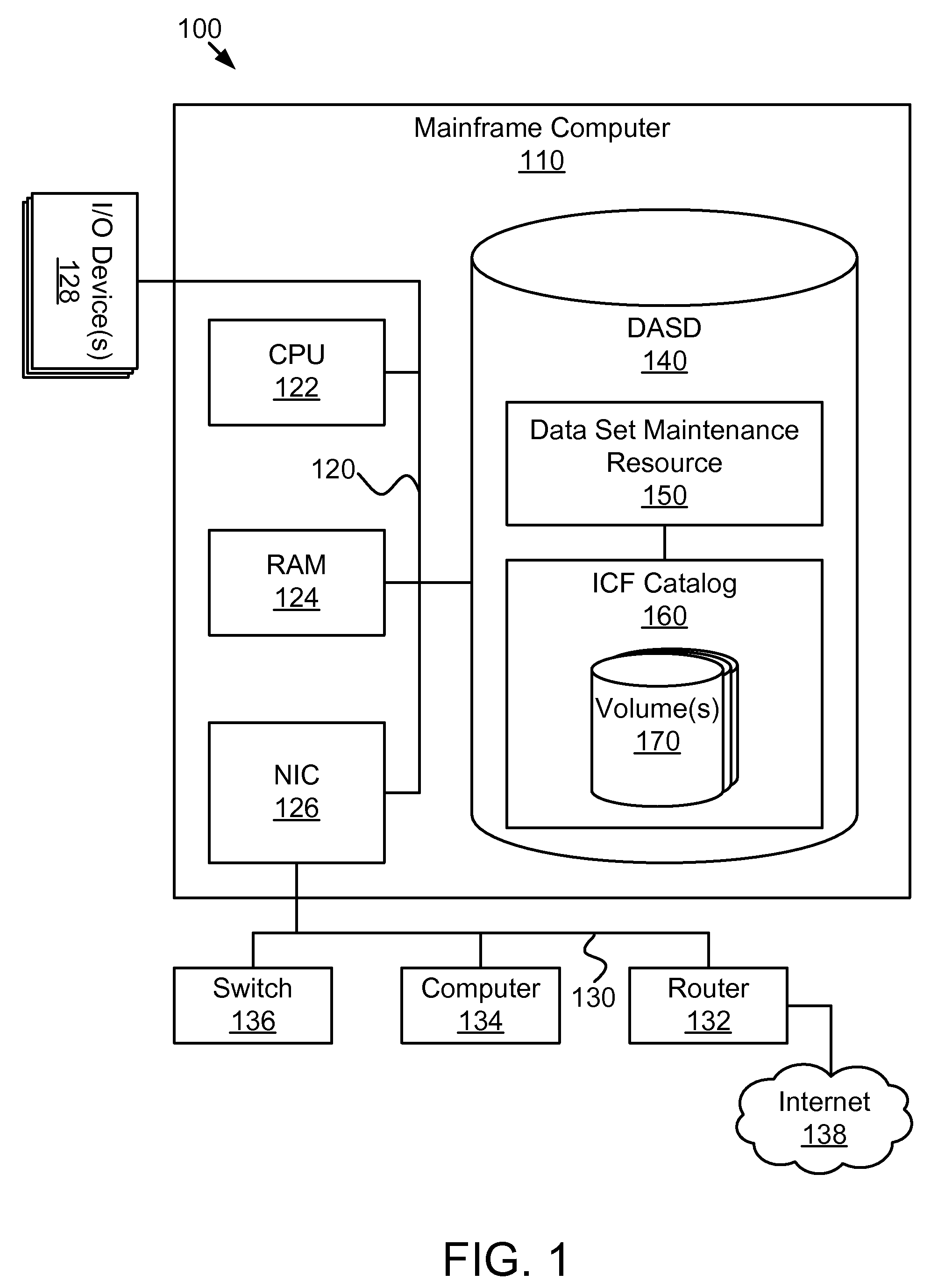

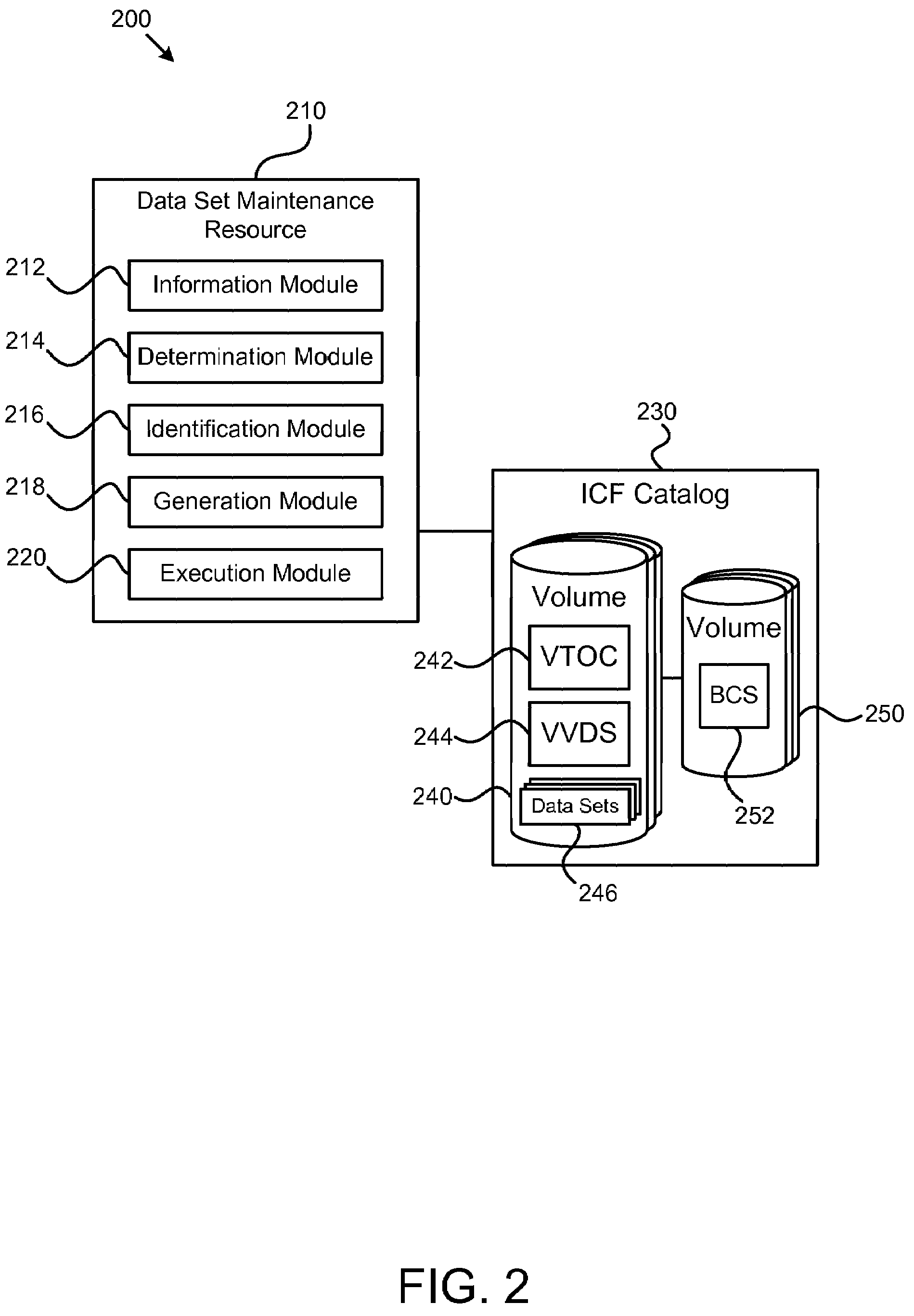

Apparatus, system, and method for automating vtoc driven data set maintenance

InactiveUS20080109599A1Facilitates maintenance completionEliminationData processing applicationsSpecial data processing applicationsData setTime efficient

The present invention increases the efficiency of dynamically, reusable computer environments by first retrieving data set information from a volume table of contents (VTOC) to ensure its consistency with the catalog. After obtaining the necessary information about the data sets, control statements are generated and appropriate programs invoked to perform the desired maintenance operations. Reinitializing and reconfiguring the reusable computer environment by starting with the VTOC prevents post-maintenance issues such as a data set with an entry in an integrated catalog facility (ICF) catalog while the data set no longer exists on a volume, a cataloged virtual storage access method (VSAM) cluster with disassociated DATA or INDEX data sets, and a data set catalog entry that has been scratched while the data set still exists on a volume. The present invention saves time and money by preventing such problems up-front instead of correcting them after-the-fact.

Owner:IBM CORP

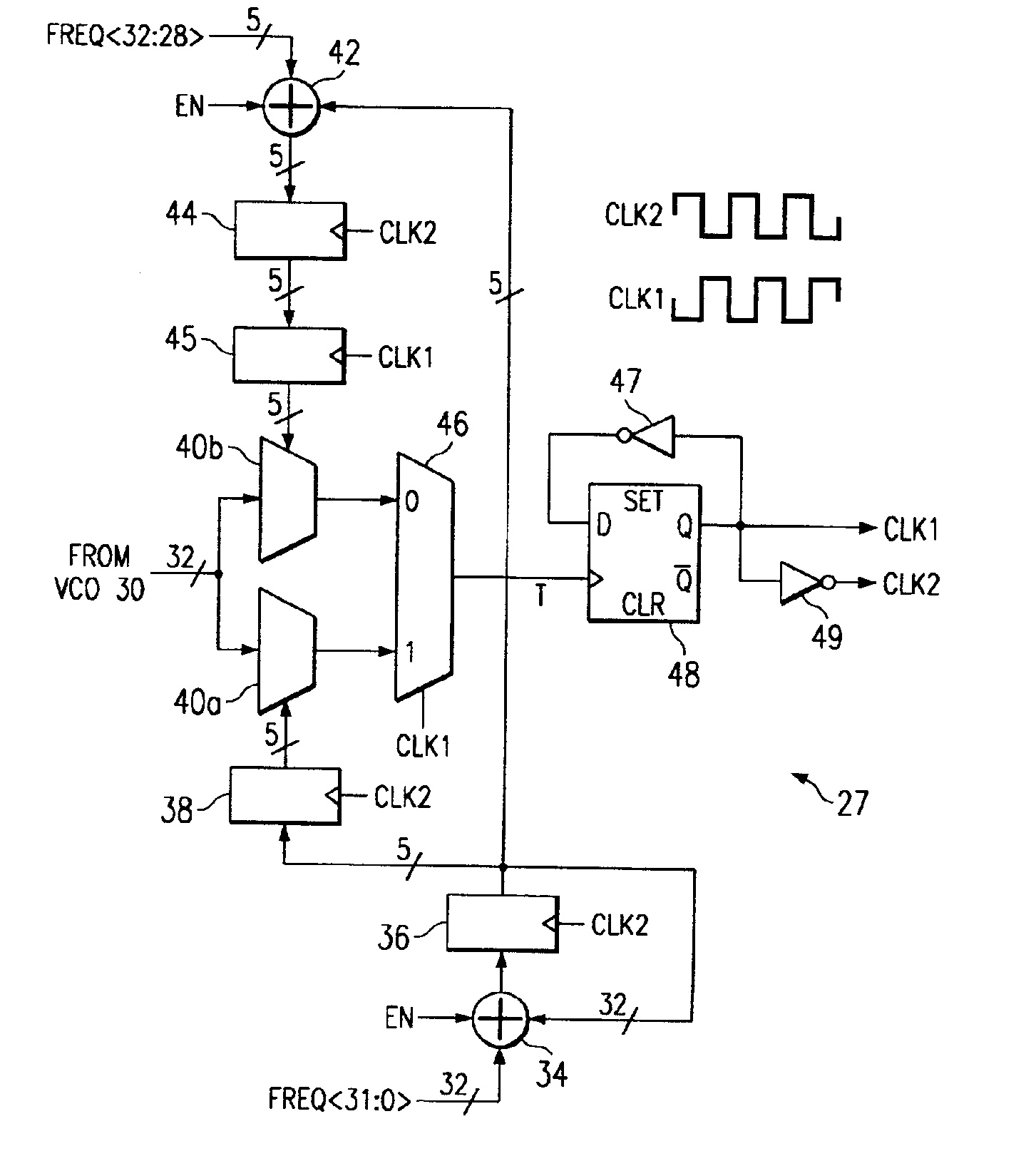

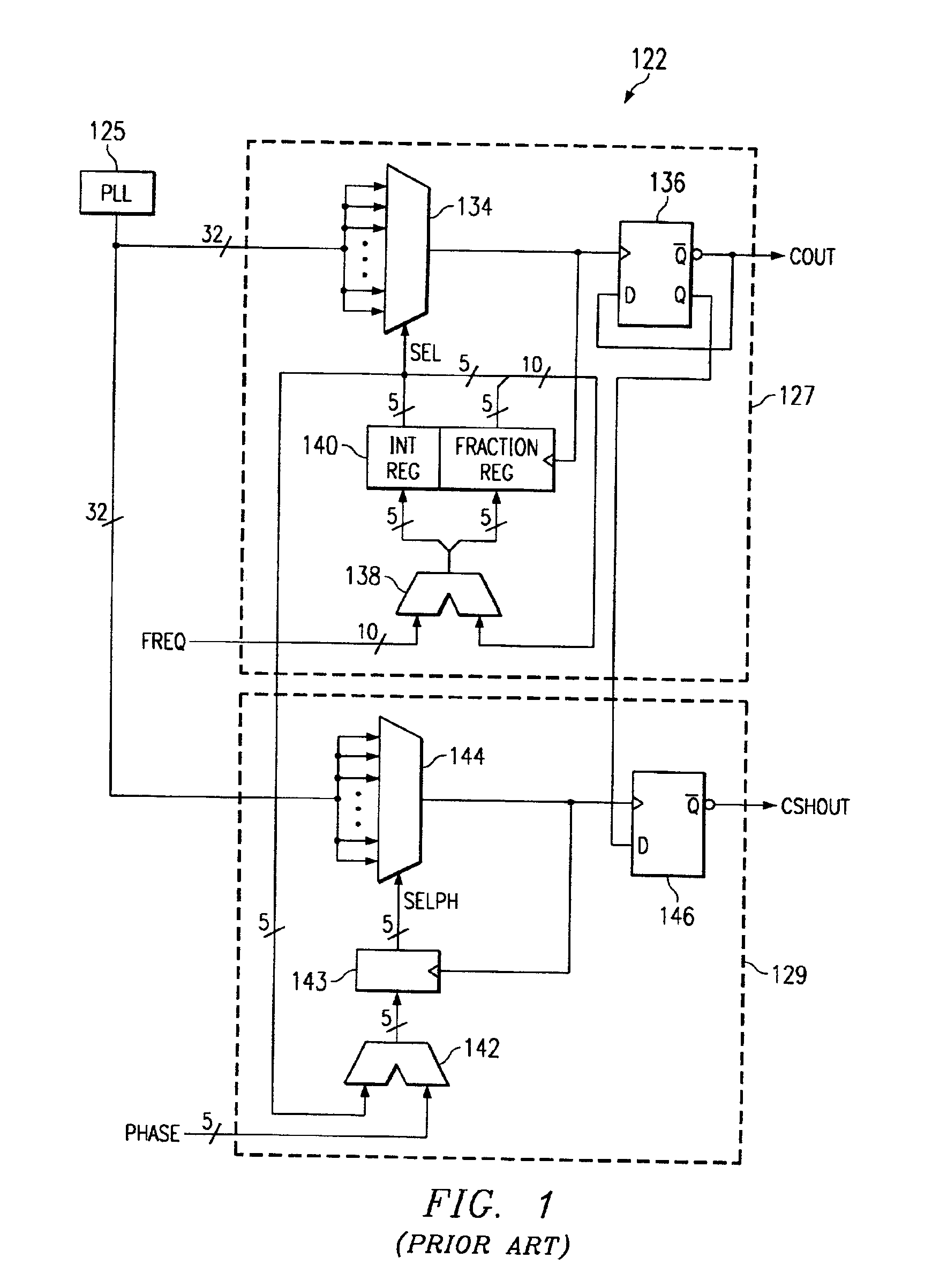

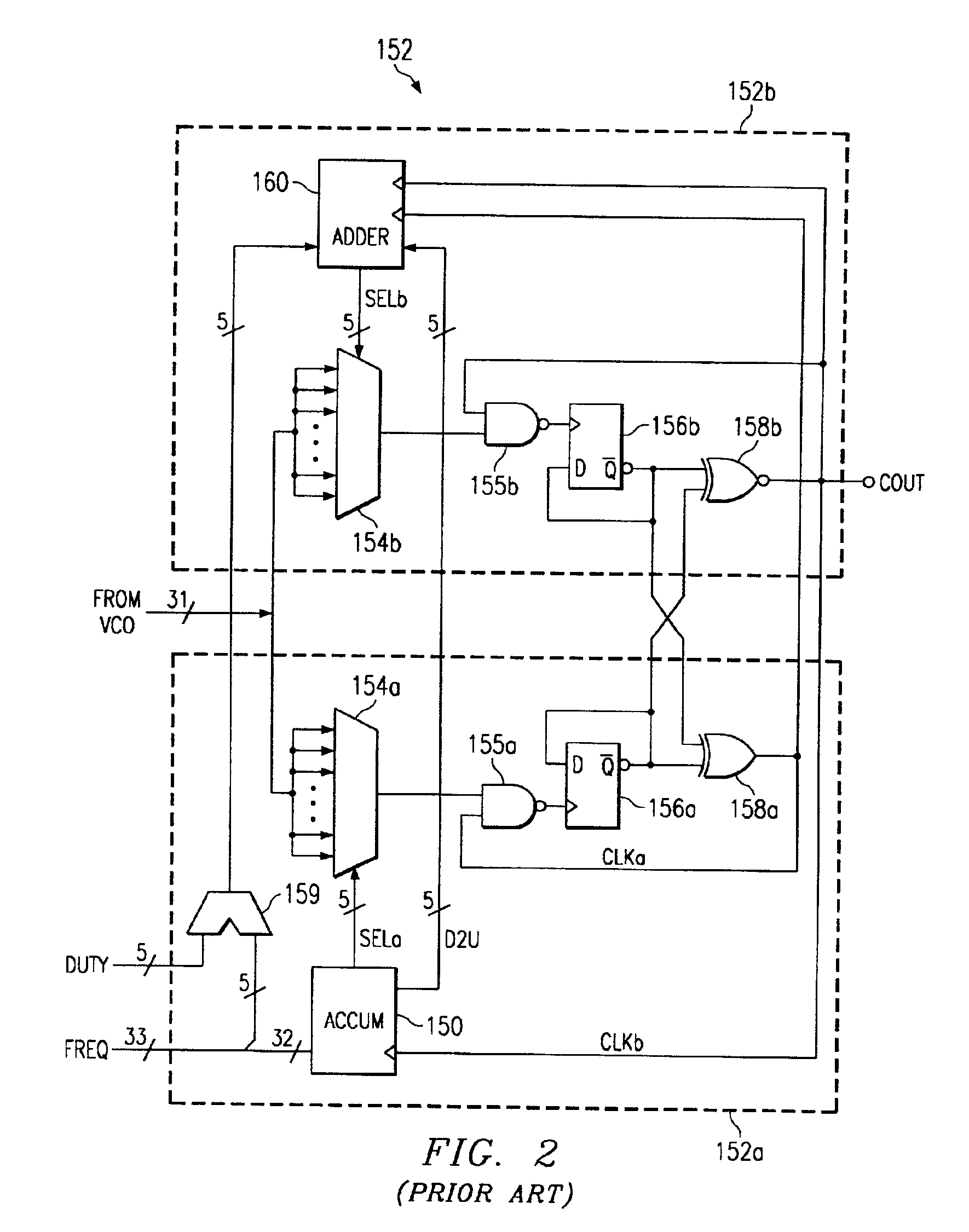

Scalable high-speed precision frequency and phase synthesis

ActiveUS6940937B2Increase the output frequencyIncrease the number ofPulse automatic controlAngle demodulation by phase difference detectionPhase shiftedPhase difference

A clock synthesis circuit (22) including a phase-locked loop (25) and one or more frequency synthesis circuits (27; 77; 227; 237) is disclosed. A disclosed implementation of the phase-locked loop (25) includes a voltage-controlled oscillator (30) having an even number of differential stages (31) to produce an even number of equally spaced clock phases. In one arrangement, the frequency synthesis circuit (27) includes two adder legs that generate select signals applied to first and second multiplexers (40a, 40b), for selecting among the clock phases from the voltage-controlled oscillator (30). The outputs of the first and second multiplexers (40a, 40b) are applied to a two-to-one multiplexer (46) which is controlled by the output clock signal (CLK1), to drive clock edges to a T flip-flop (48) to produce the output clock signals (CLK1, CLK2). In another embodiment, more than two adder and register units (55) control corresponding multiplexers (56) for selecting clock phases from the voltage-controlled oscillator (30) for application to an output multiplexer (58), which is controlled by a clock control circuit (60) to apply the selected clock phases to the T flip-flop (62). In another embodiment, primary and phase-shifted frequency synthesis circuits (227, 327) receive initialization values (INIT1, INIT2) that establish the phase differential and ensure proper initialization.

Owner:TEXAS INSTR INC

User aware digital vision correction

ActiveUS20170177166A1Avoid eyesightAvoid initializationCharacter and pattern recognitionCathode-ray tube indicatorsGraphicsPersonalization

A method, a system, and an information handling system dynamically provide individualized dynamic digital display correction for users of an electronic device. An information handling system detects a login of a first user profile that is associated with a first user. The information handling system then determines whether the first user profile has an associated first vision profile. In response to the first user profile having an associated first vision profile, a vision correction value associated with the first user is identified. A first change in image characteristics that may be applied to a graphical user interface (GUI) in order to achieve the vision correction value is calculated and applied to one or more content displayed on the GUI.

Owner:DELL PROD LP

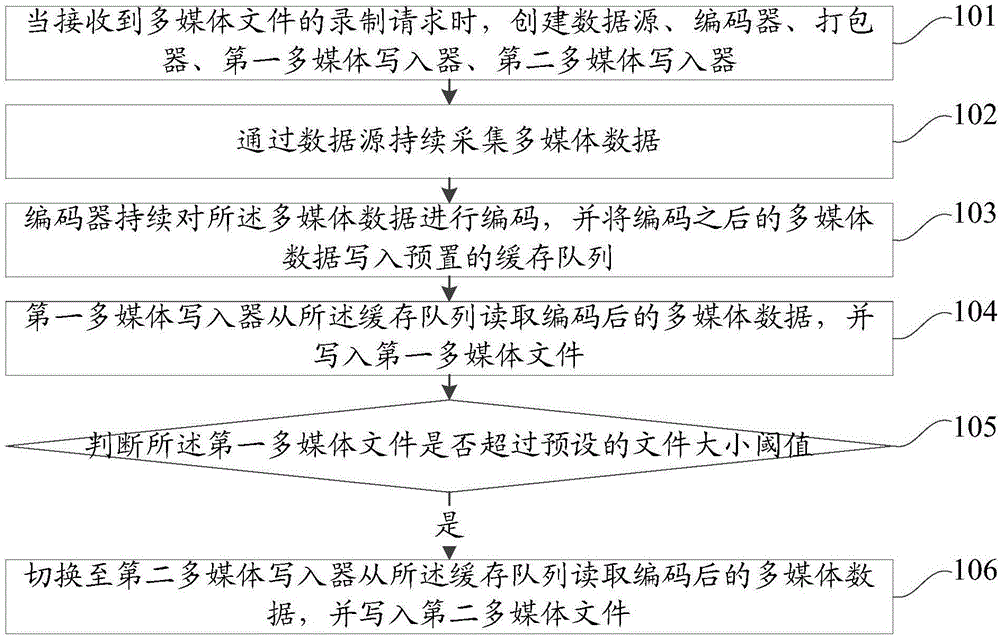

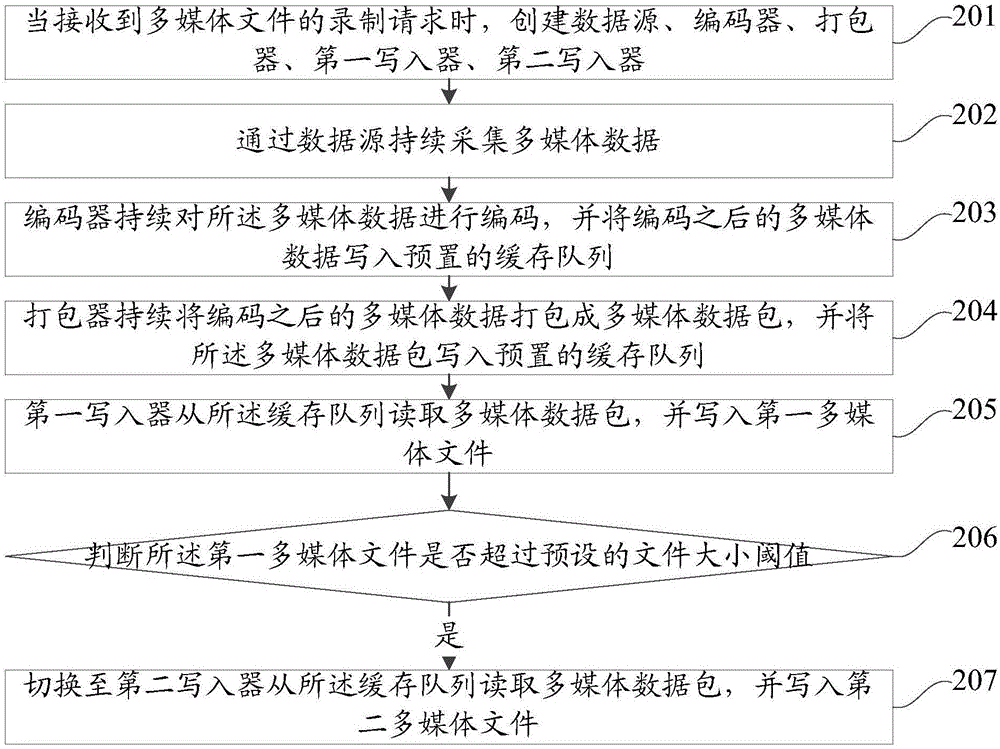

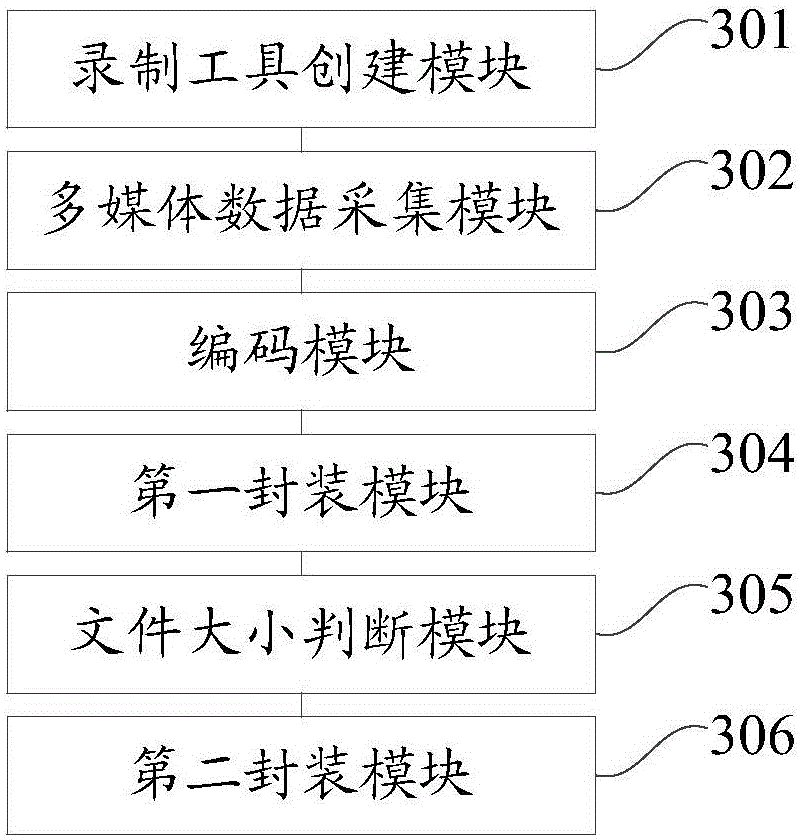

Method and device for recording multimedia file

ActiveCN105049919AAvoid initializationAvoid closingSelective content distributionComputer hardwareData source

The embodiment of the invention provides a method and device for recording a multimedia file. The method comprises the following steps: when a recording request of the multimedia file is received, creating a data source, an encoder, a packer, a first multimedia writer and a second multimedia writer; continuously acquiring multimedia data through the data source; continuously encoding the multimedia data by the encoder, and writing the encoded multimedia data into a preset buffer queue; reading the encoded multimedia data from the buffer queue, and writing the encoded multimedia data into a first multimedia file by the first multimedia writer; judging whether the first multimedia file exceeds a preset file size threshold or not; and if so, switching to the second multimedia writer, reading the encoded multimedia data from the buffer queue, and writing the encoded multimedia data into a second multimedia file by the second multimedia writer. Through the embodiment of the invention, ceaseless work during switching is ensured; the condition that part of content of the recorded file is blank is avoided; and seamless continuous recording is realized.

Owner:QINGDAO HISENSE MOBILE COMM TECH CO LTD

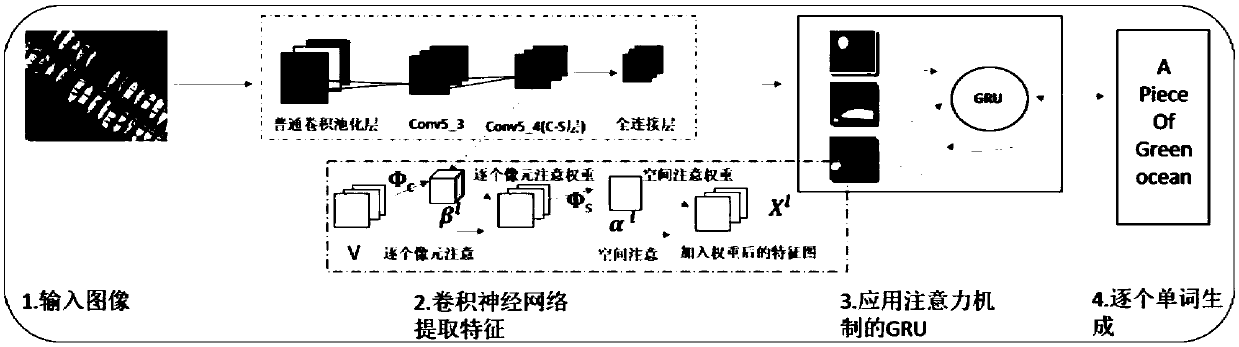

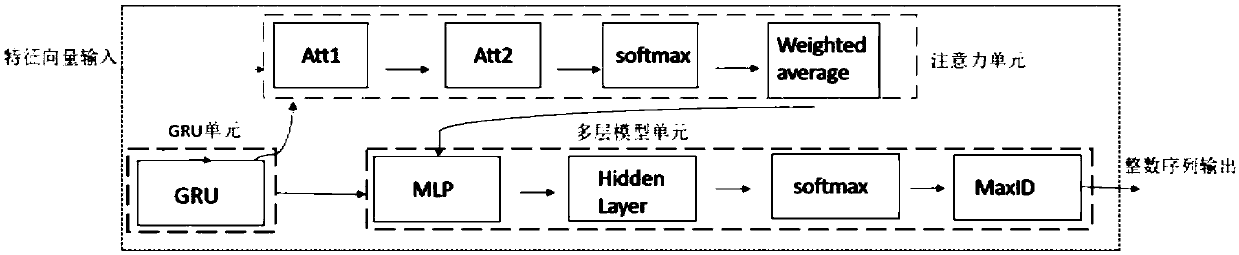

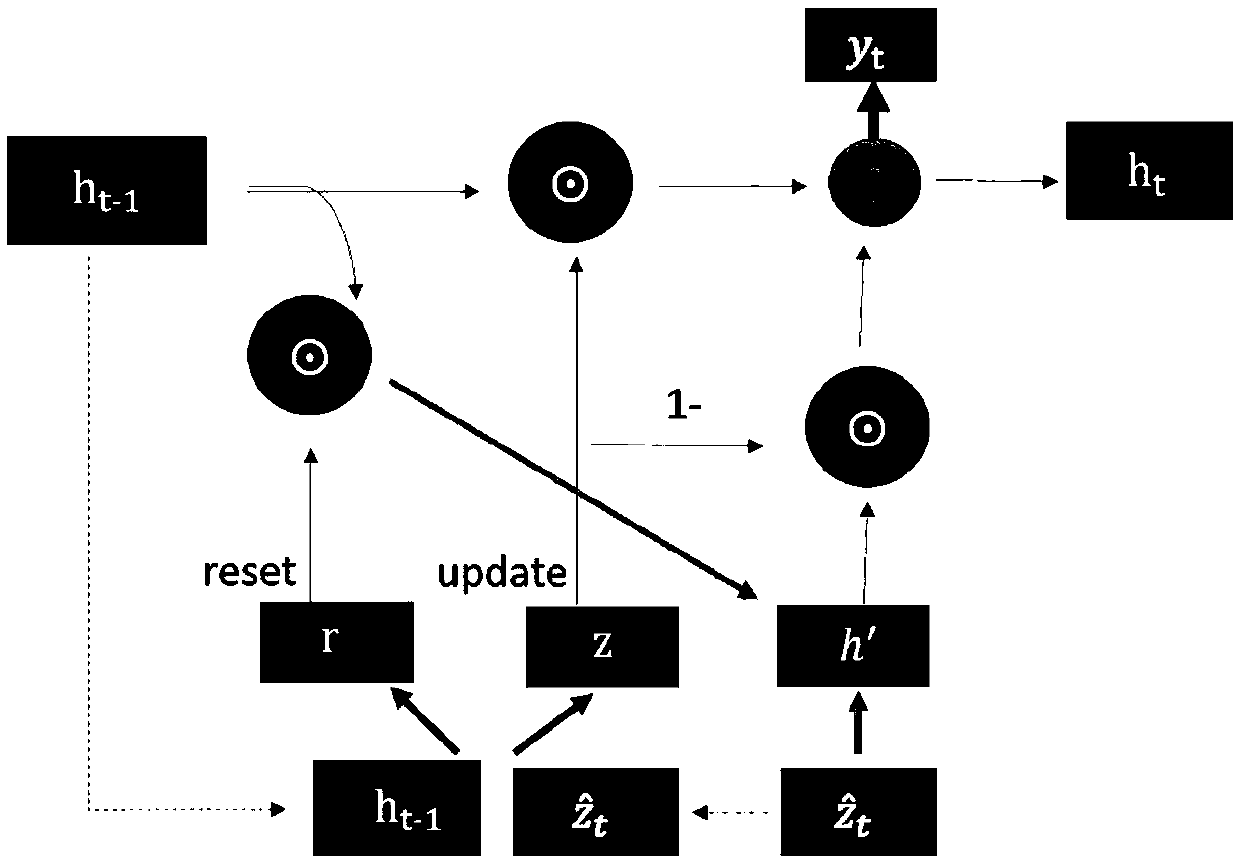

Attention mechanism-based natural language generating method for remote sensing images

InactiveCN108764303APrecise and flexible language descriptionReduce performanceCharacter and pattern recognitionNeural architecturesFeature vectorHidden layer

The invention discloses an attention mechanism-based natural language generating method for remote sensing images, and belongs to the technical field of computer vision. A CNN part comprises a commonconvolutional pooling layer, a C-S layer and a full connection layer; an RNN part structurally comprises a multi-layer model unit, a GRU unit and an attention unit; the remote sensing images at different moments in the same area are input into the initialized CNN part to obtain eigenvectors; the eigenvectors are input into the GRU unit and the attention unit, the attention unit also receives hidden layer states from the GRU unit, and the attention unit maps the eigenvectors and the hidden layer states to low dimension for further compression and normalization to obtain eigenvectors subjected to weighted average; and the eigenvectors subjected to the weighted average and the hidden layer states of the GRU unit are integrated through the multi-layer model unit, and then maximum likelihood isperformed through a hidden layer and a normalization layer to obtain an integer sequence. The problem that a result of generating a natural language by the remote sensing images at present is not ideal is solved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

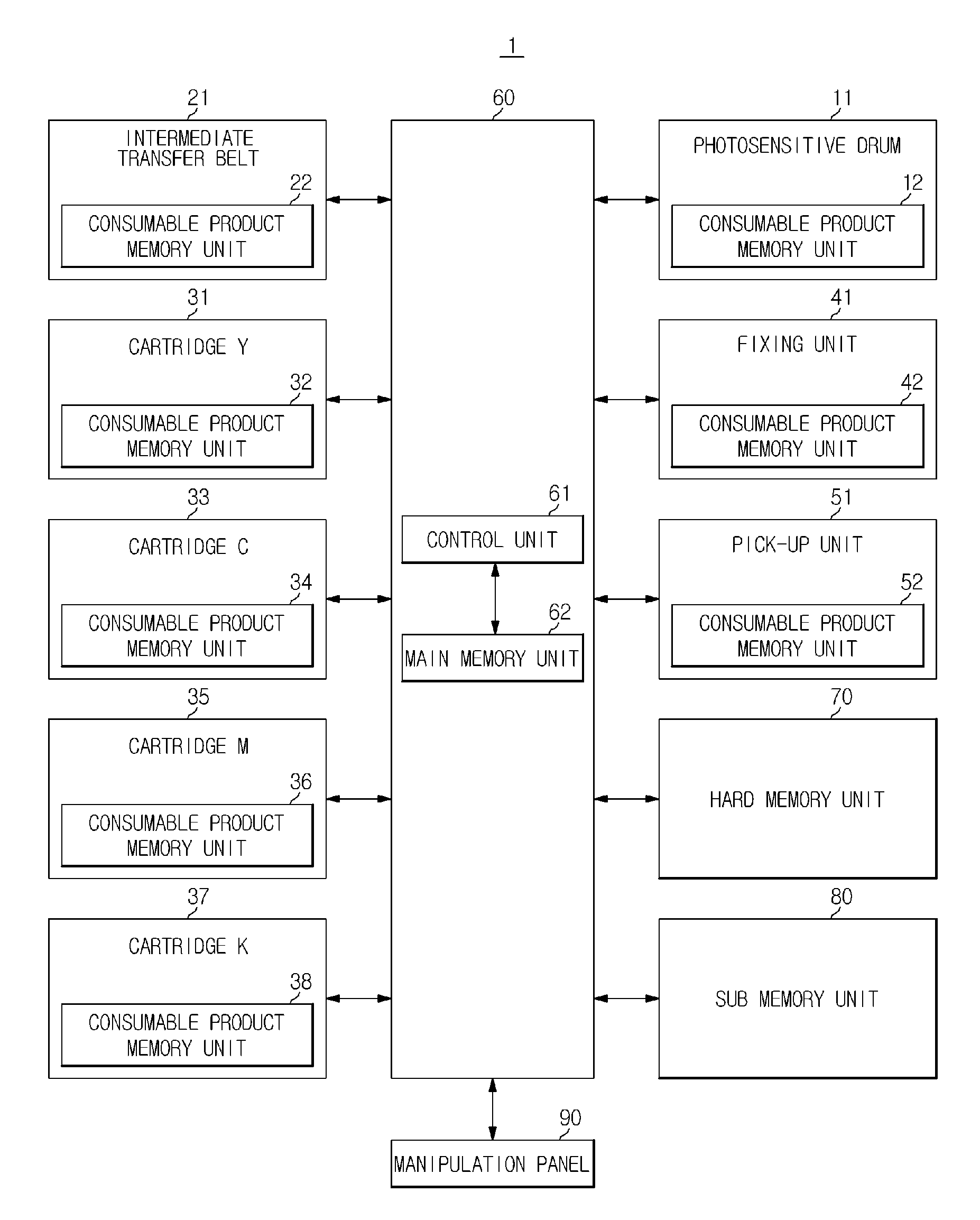

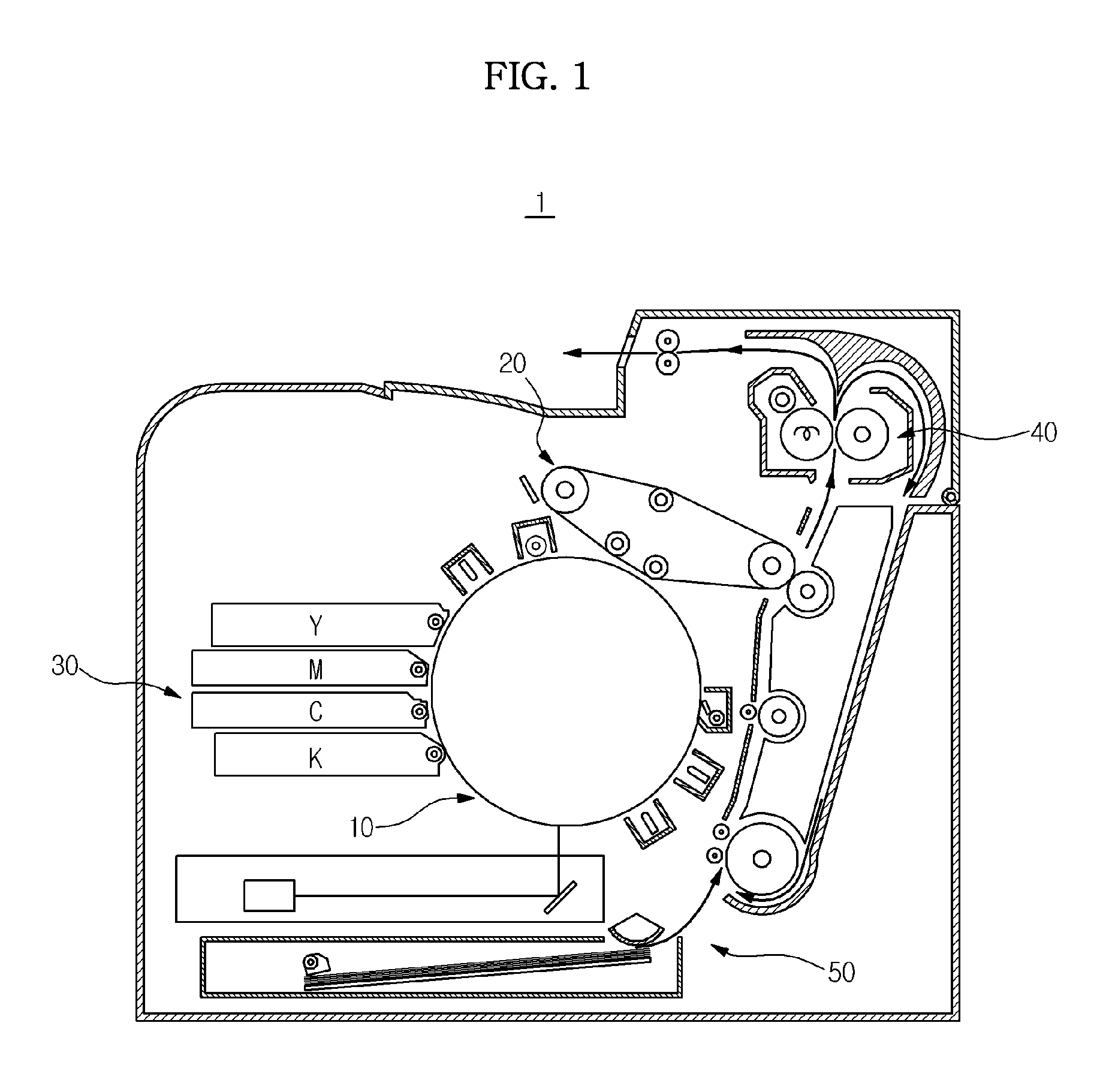

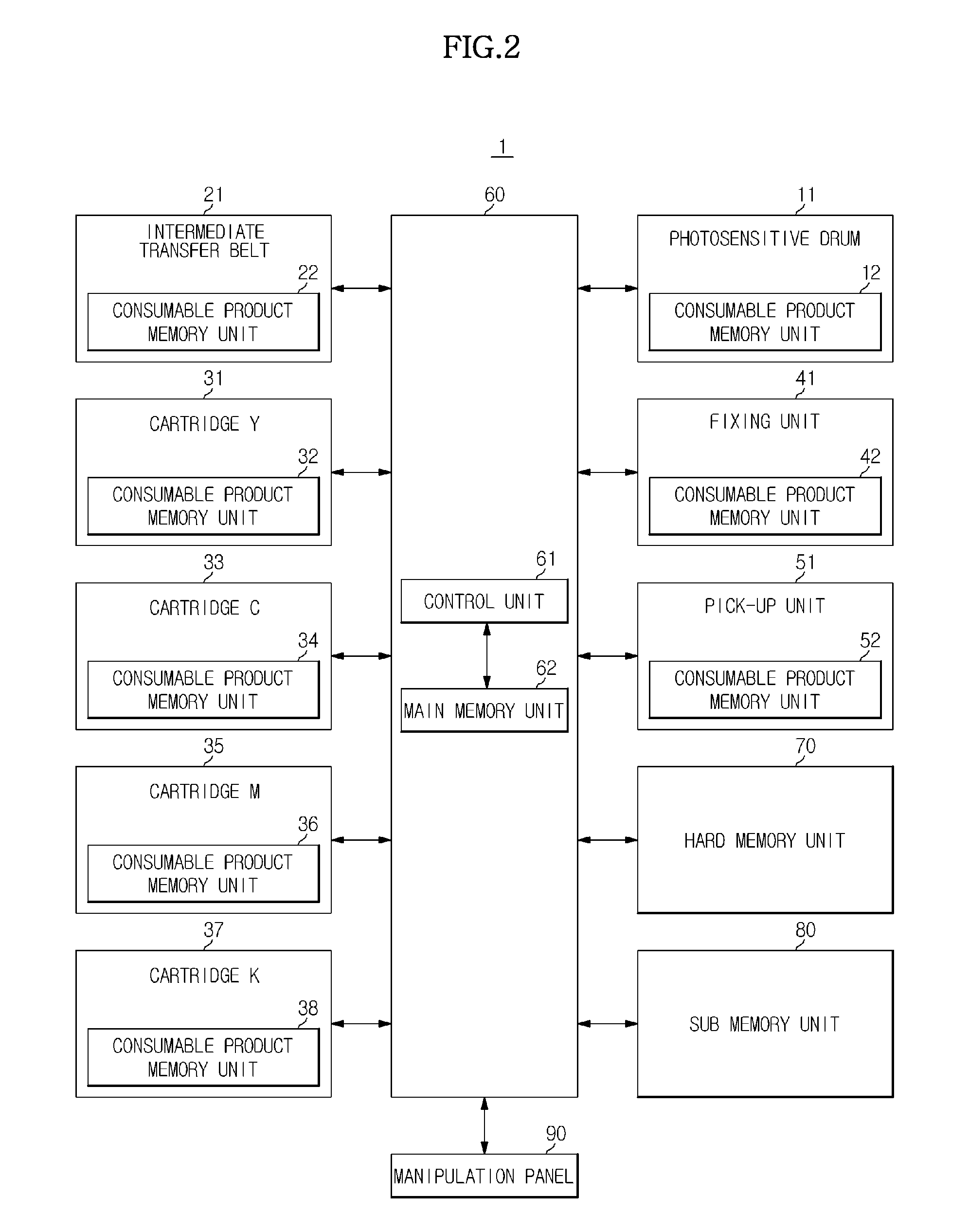

Image forming apparatus and control method thereof

ActiveUS20130183048A1Avoid initializationEffective informationElectrographic process apparatusColor imageImage formation

An image forming apparatus configured to form a color image by having at least one consumable product, the image forming apparatus including a main board, a first memory unit detachably coupled to the main body, a consumable product memory unit installed at the consumable product, and configured to store information on a lifespan of the consumable product, and a control unit configured to read the information on the lifespan of the consumable product from the consumable product memory unit, and to store the information on the lifespan of the consumable product at the first memory unit in the form of a backup.

Owner:HEWLETT PACKARD DEV CO LP

User aware digital vision correction

ActiveUS20160029884A1Avoid eyesightAvoid initializationCharacter and pattern recognitionCathode-ray tube indicatorsPersonalizationUser perception

Owner:DELL PROD LP

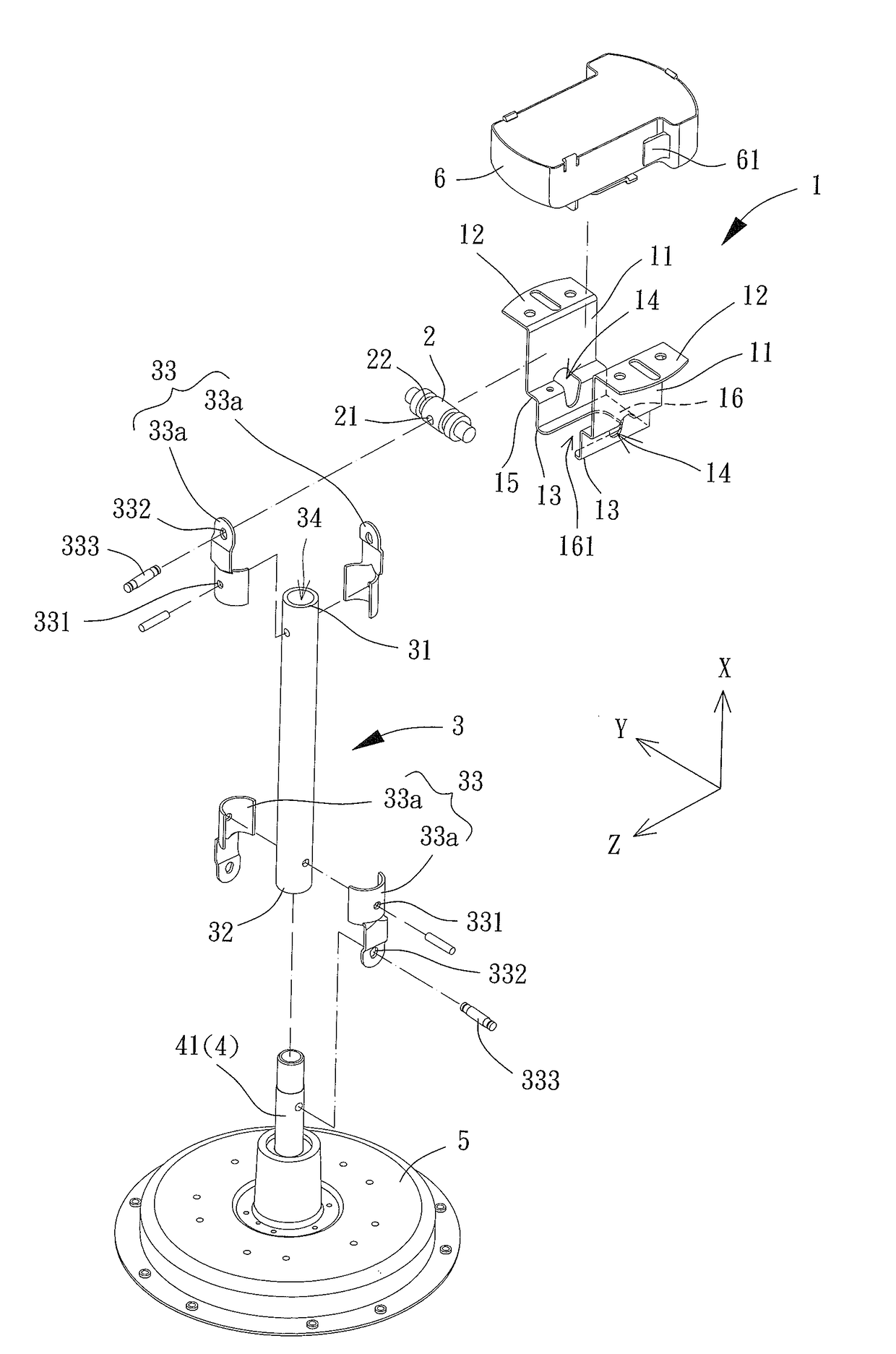

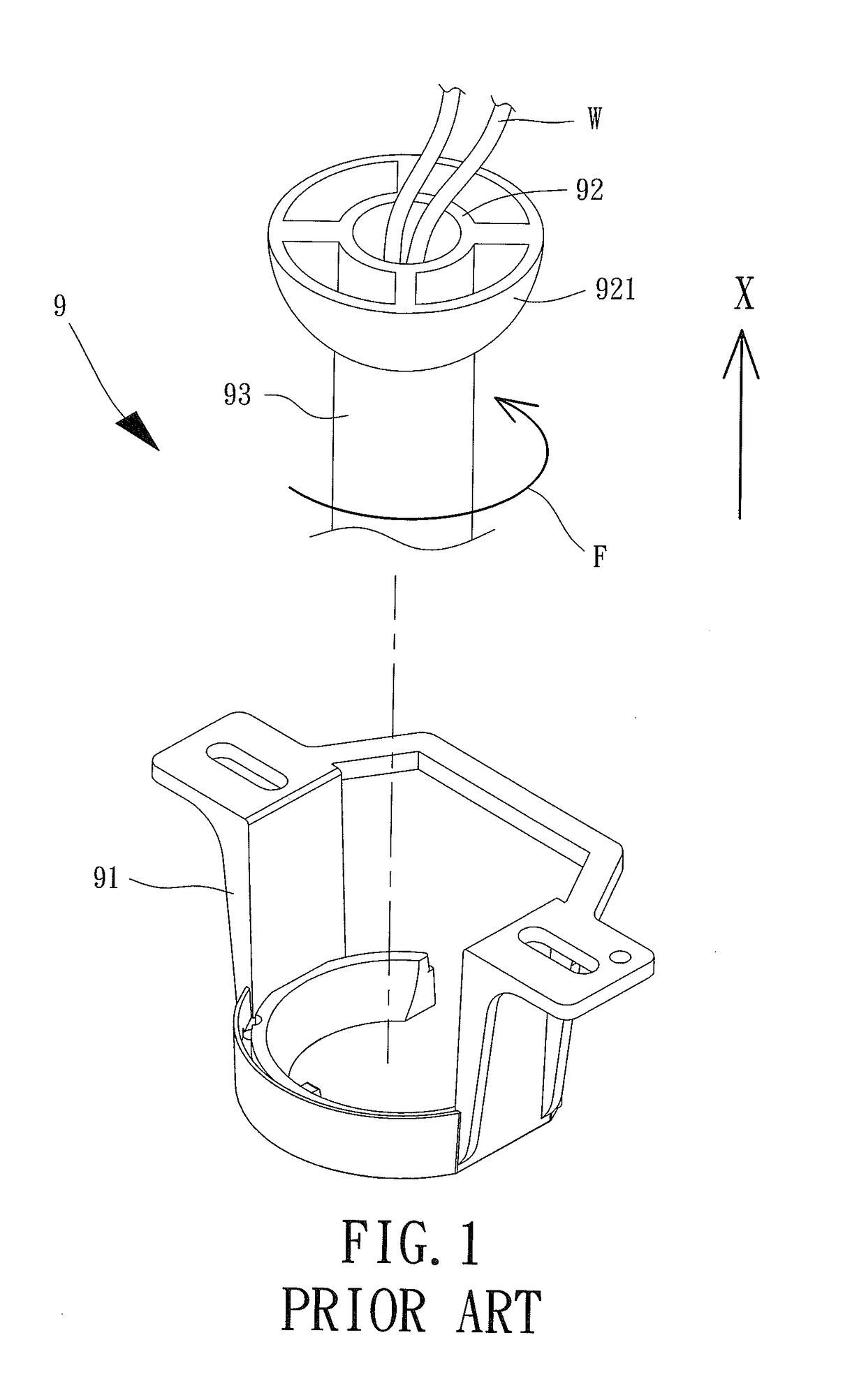

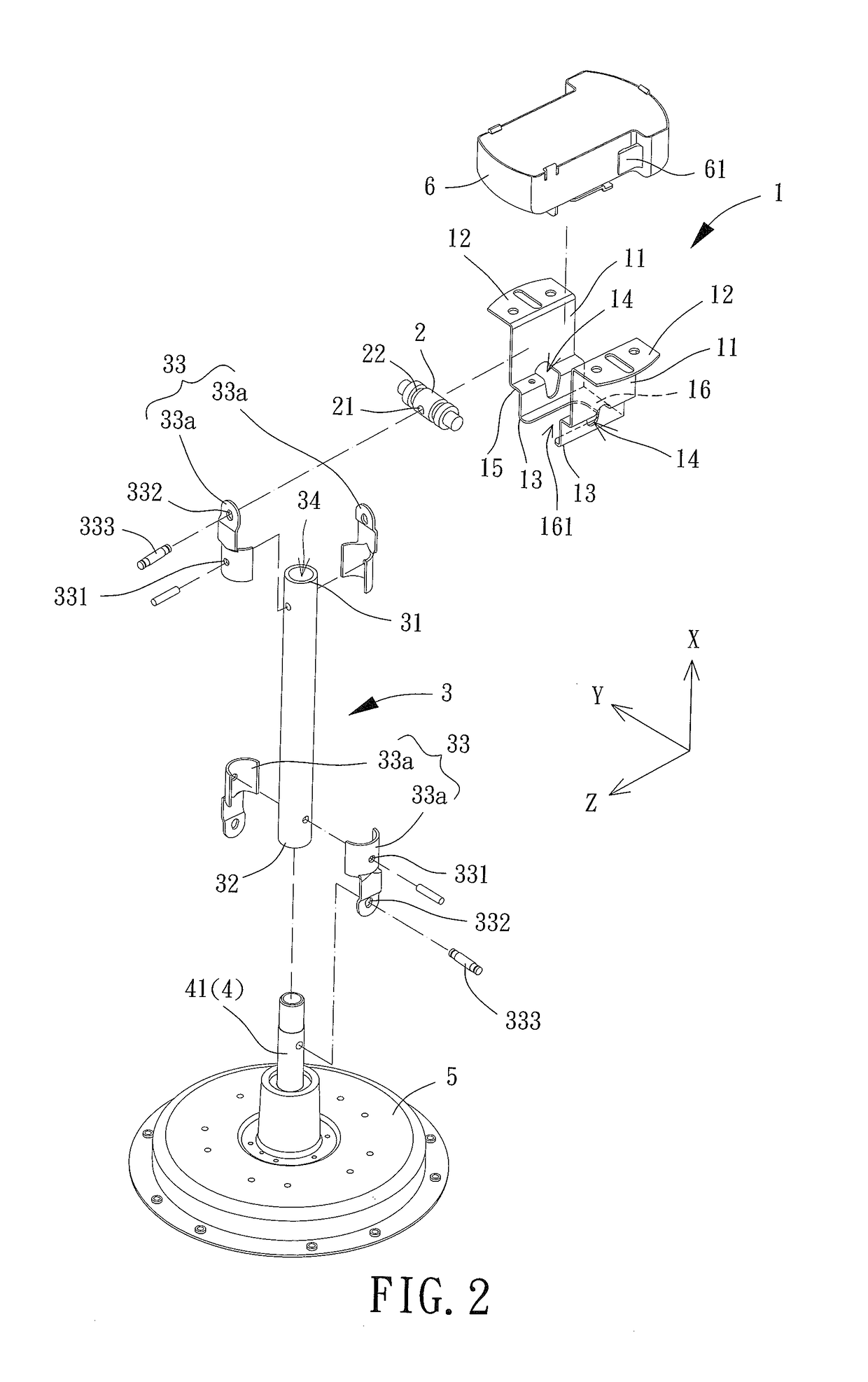

Ceiling Fan, Hanger Assembly of the Ceiling Fan, and Mounting Bracket of the Hanger Assembly

ActiveUS20170204869A1Extended service lifeLow failure ratePump componentsPump installationsCeiling fanCoupling

A ceiling fan, a hanger assembly of the ceiling fan, and a mounting bracket of the hanger assembly are designed with a lower failure rate. The hanger assembly of the ceiling fan includes a coupling rod and a fan rod. The mounting bracket has two lateral walls opposing to each other. Each of the two lateral walls includes a mounting end, a hanger end and a receiving portion. The coupling rod has two ends respectively received in the receiving portions of the two lateral walls. The fan rod has a first end coupled with the coupling rod, as well as a second end coupled with a stator of a motor of the ceiling fan.

Owner:SUNONWEALTH ELECTRIC MACHINE IND

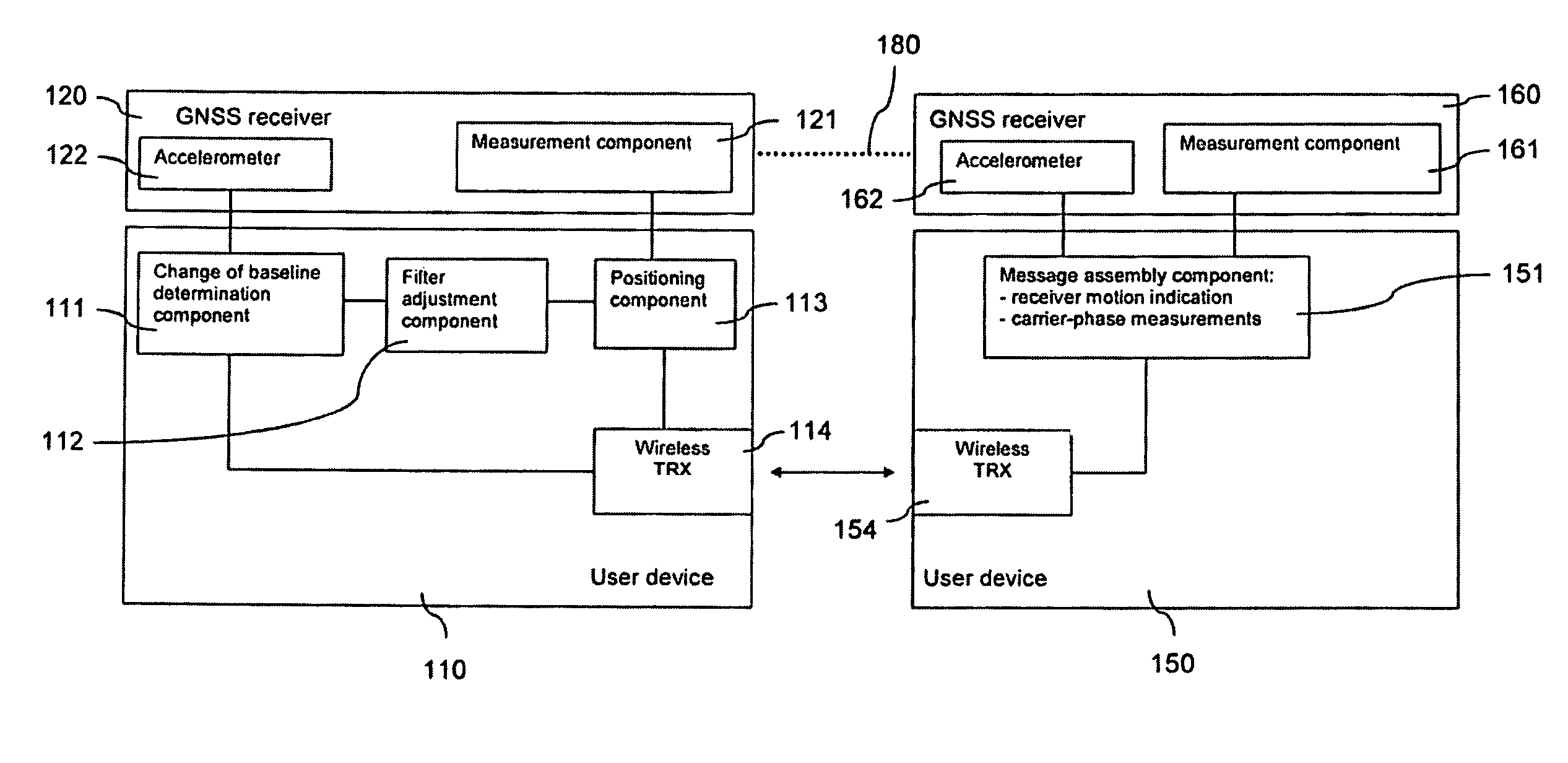

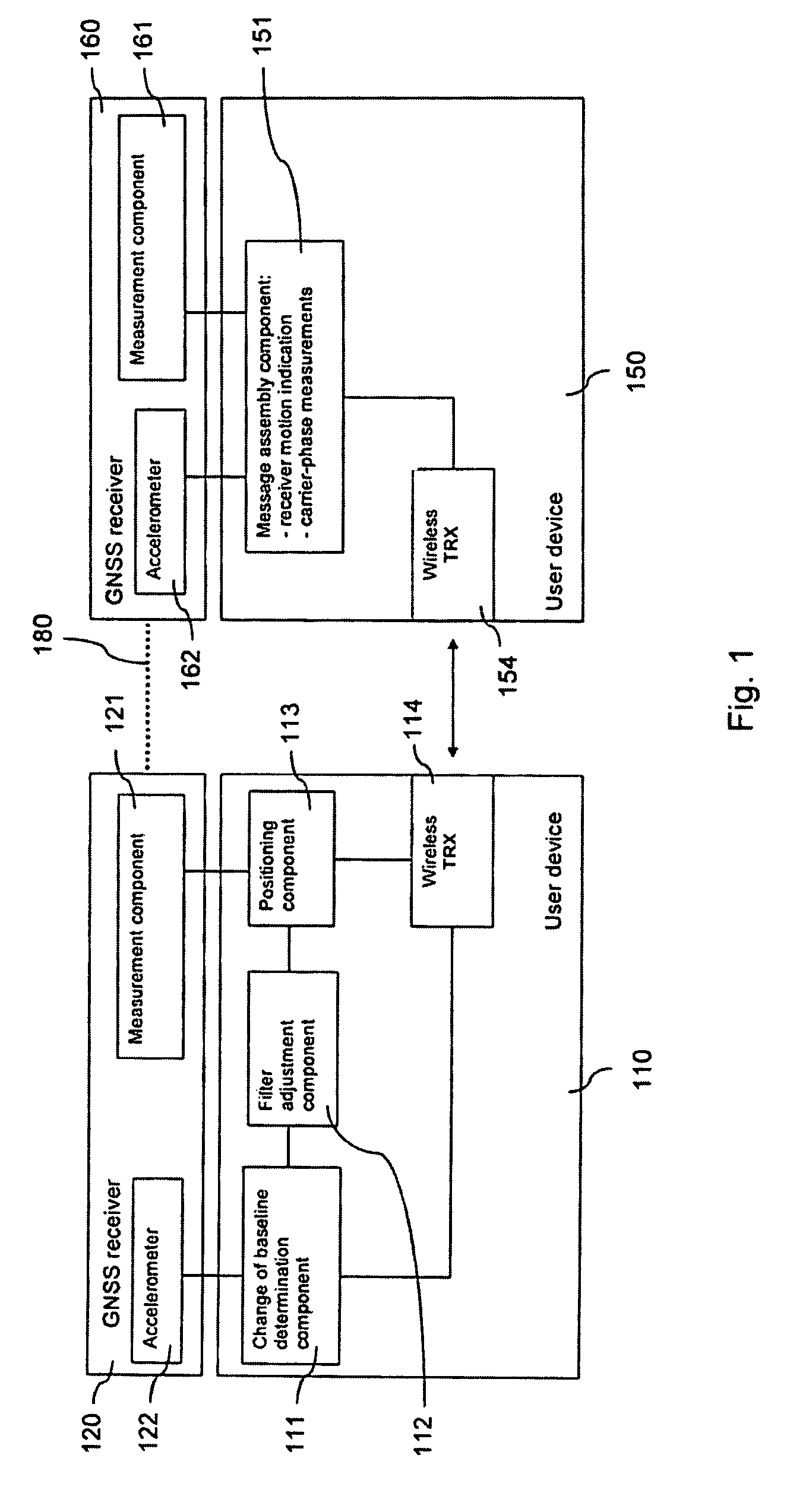

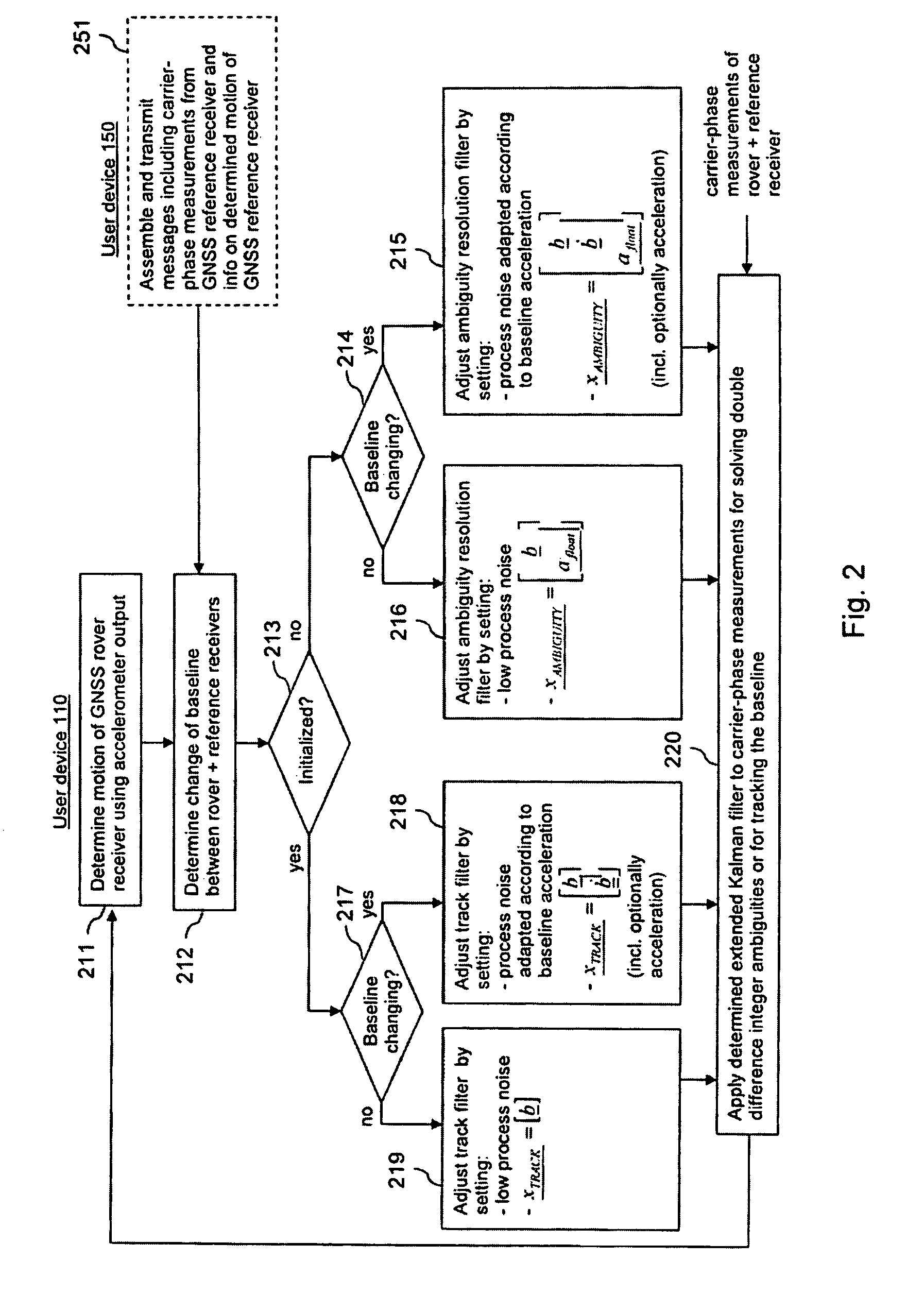

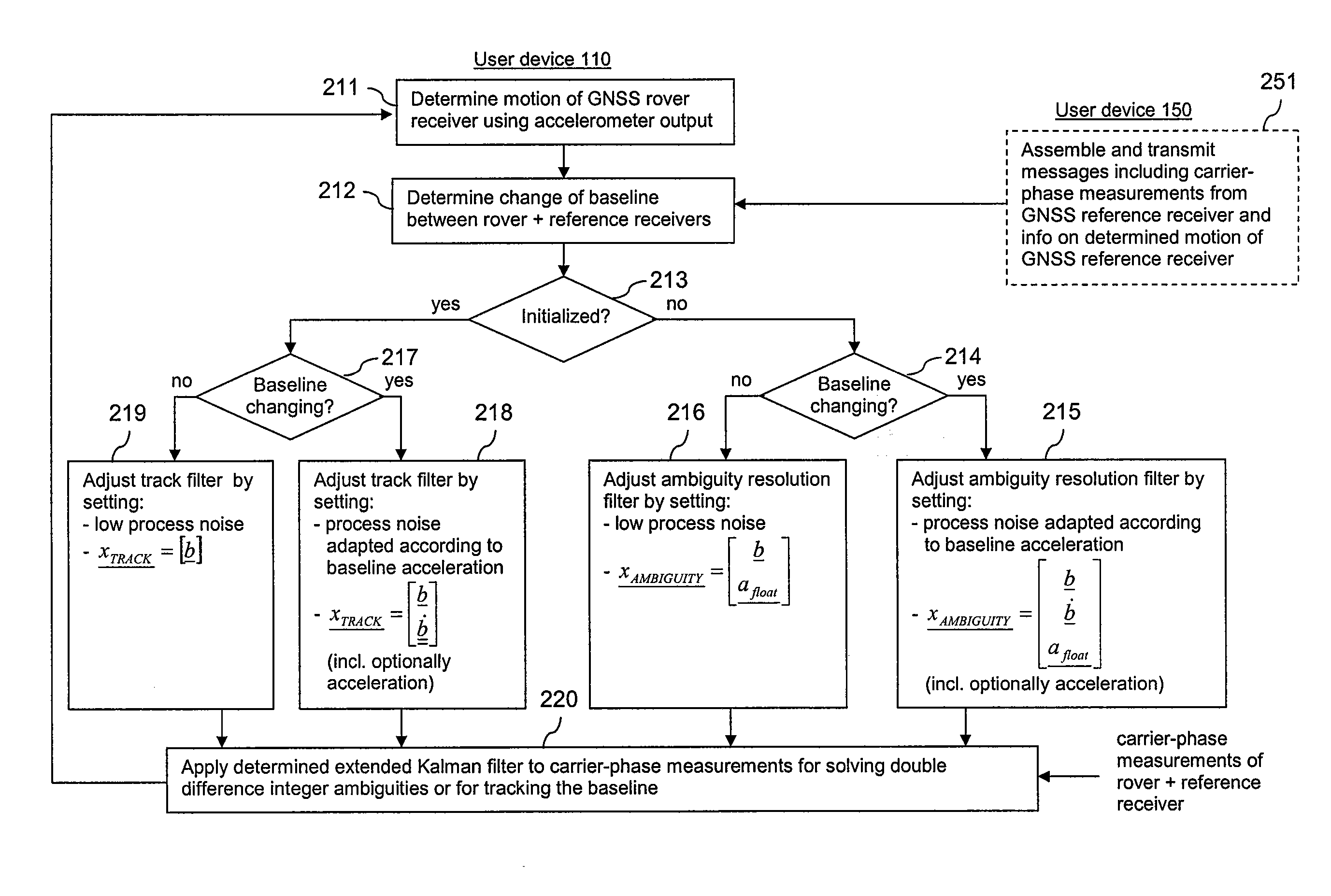

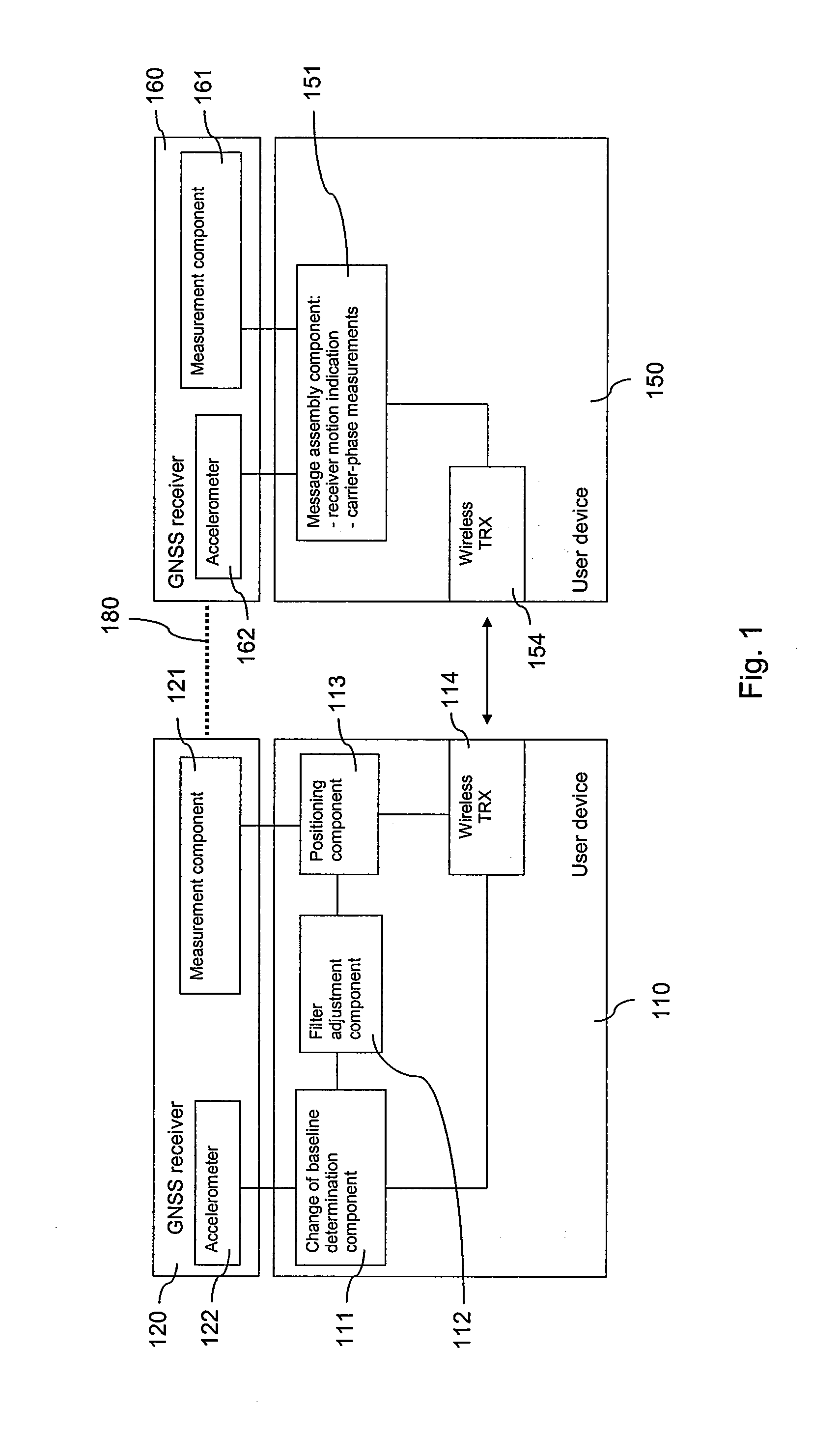

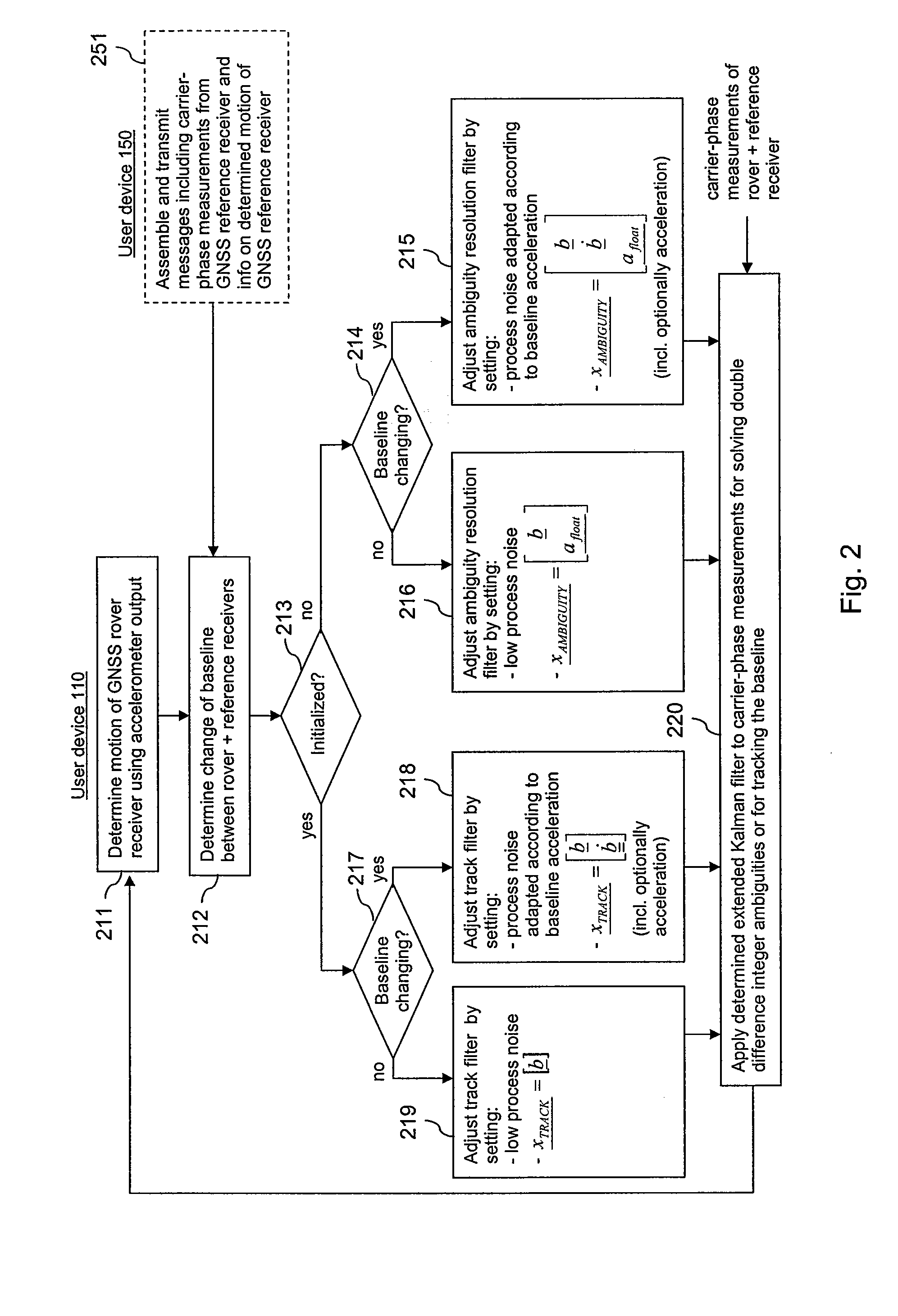

Determination of a relative position of a satellite signal receiver

InactiveUS7869811B2Enabling useImprove positioning qualityPosition fixationSatellite radio beaconingVIT signalsSatellite

For enhancing the quality of a relative positioning, a filter is adjusted depending on information on a movement of a satellite signal receiver. A position of the satellite signal receiver is determined relative to a reference station using the filter, wherein measurements on satellite signals received by the satellite signal receiver and measurements on satellite signals provided for the reference station are used as input to the filter. The measurements for the reference station may be received in messages which are assembled and provided for transmission and which may include in addition an indication of a current movement of the reference station.

Owner:NOKIA TECHNOLOGLES OY

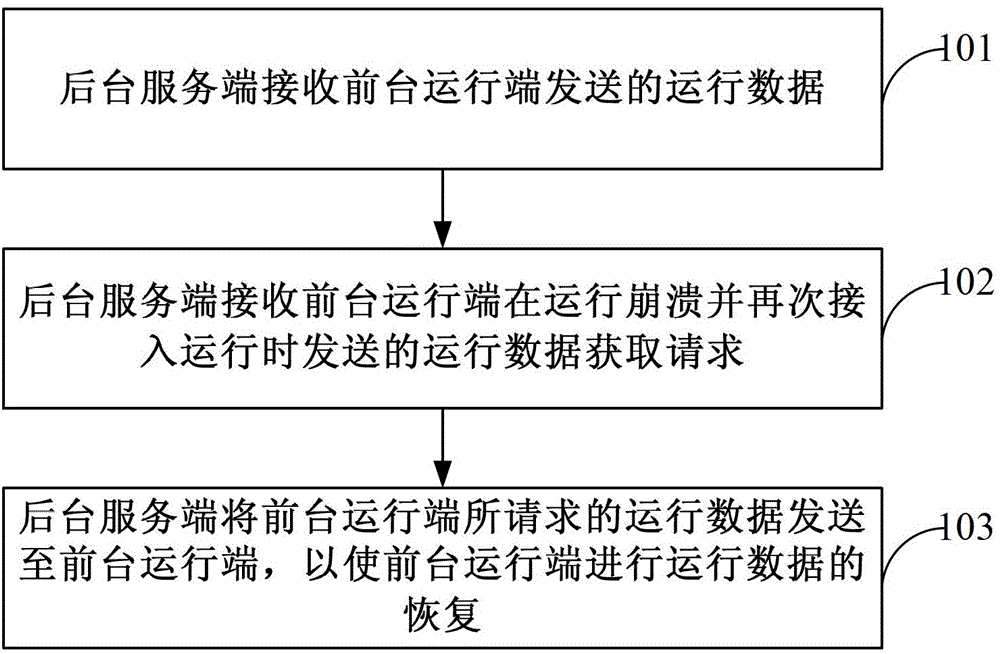

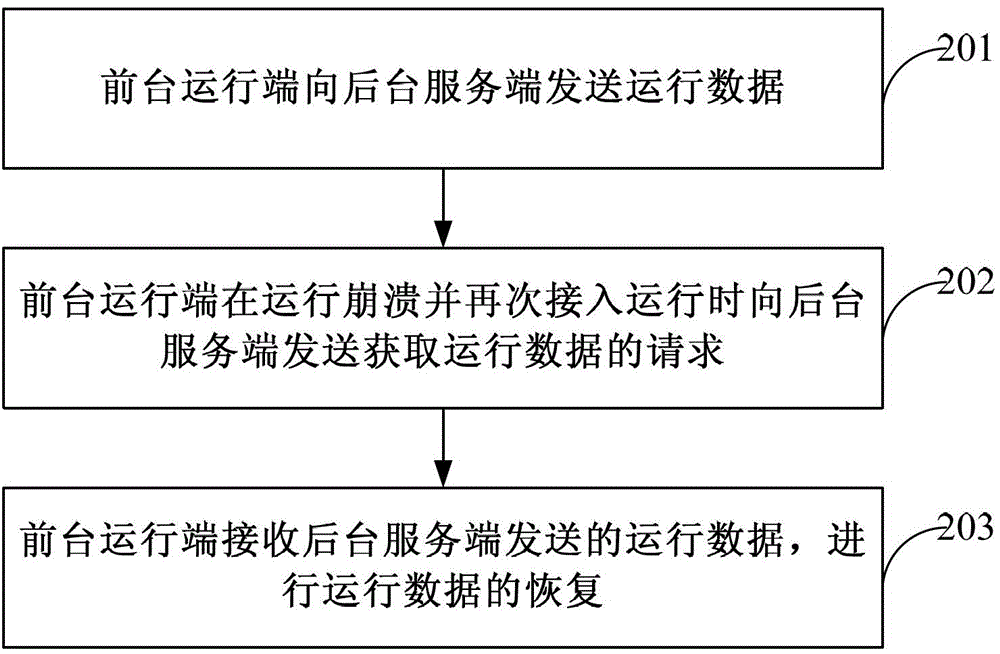

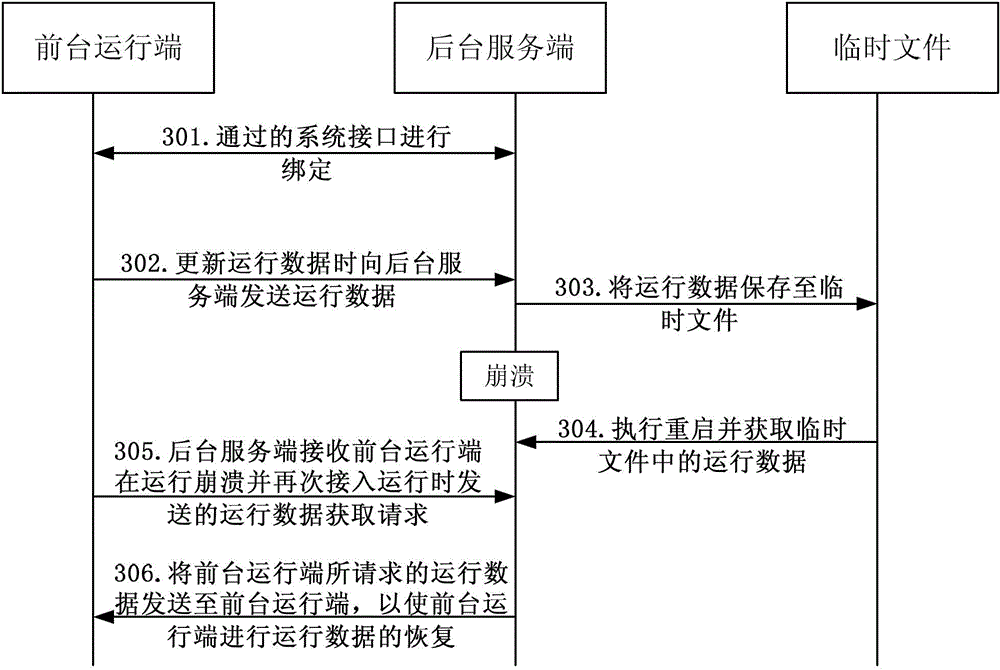

Recovery method of running data, and electronic device

ActiveCN102945193AAvoid initializationImprove user experienceInterprogram communicationRedundant operation error correctionComputer securityInput/output

The invention discloses a recovery method of running data, and an electronic device, wherein the recovery method of the running data comprises the following steps: a backend server receives the running data sent from a foreground running end; the backend server receives a running data acquisition request sent from the foreground running end when the foreground running end collapses the running and accesses to the running again; and the backend server sends the running data requested by the foreground running end to the foreground running end, so that the foreground running end recovers the running data, wherein the backend server is interacts with the foreground running end through inter-process communication. The method disclosed by the invention realizes quick recovery of the running data on the foreground running end and overleaps an initialization process. The inter-process communication is an internal storage operation, compared with file and network input / output in the initialization process, the inter-process communication has a qualitative leap, therefore, procedures of the foreground running end can be restarted very quickly, and the user experience is greatly improved.

Owner:ALIBABA (CHINA) CO LTD

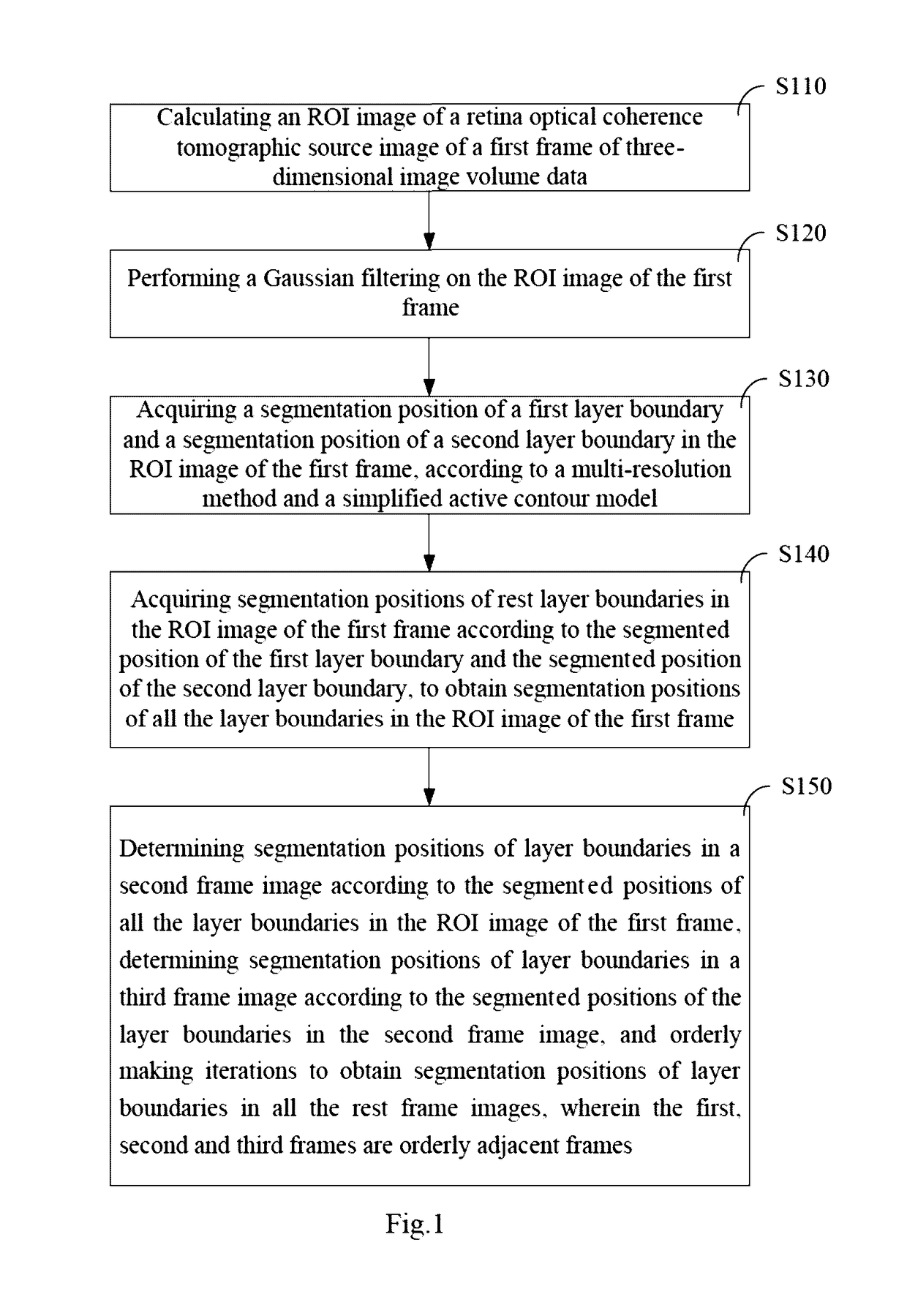

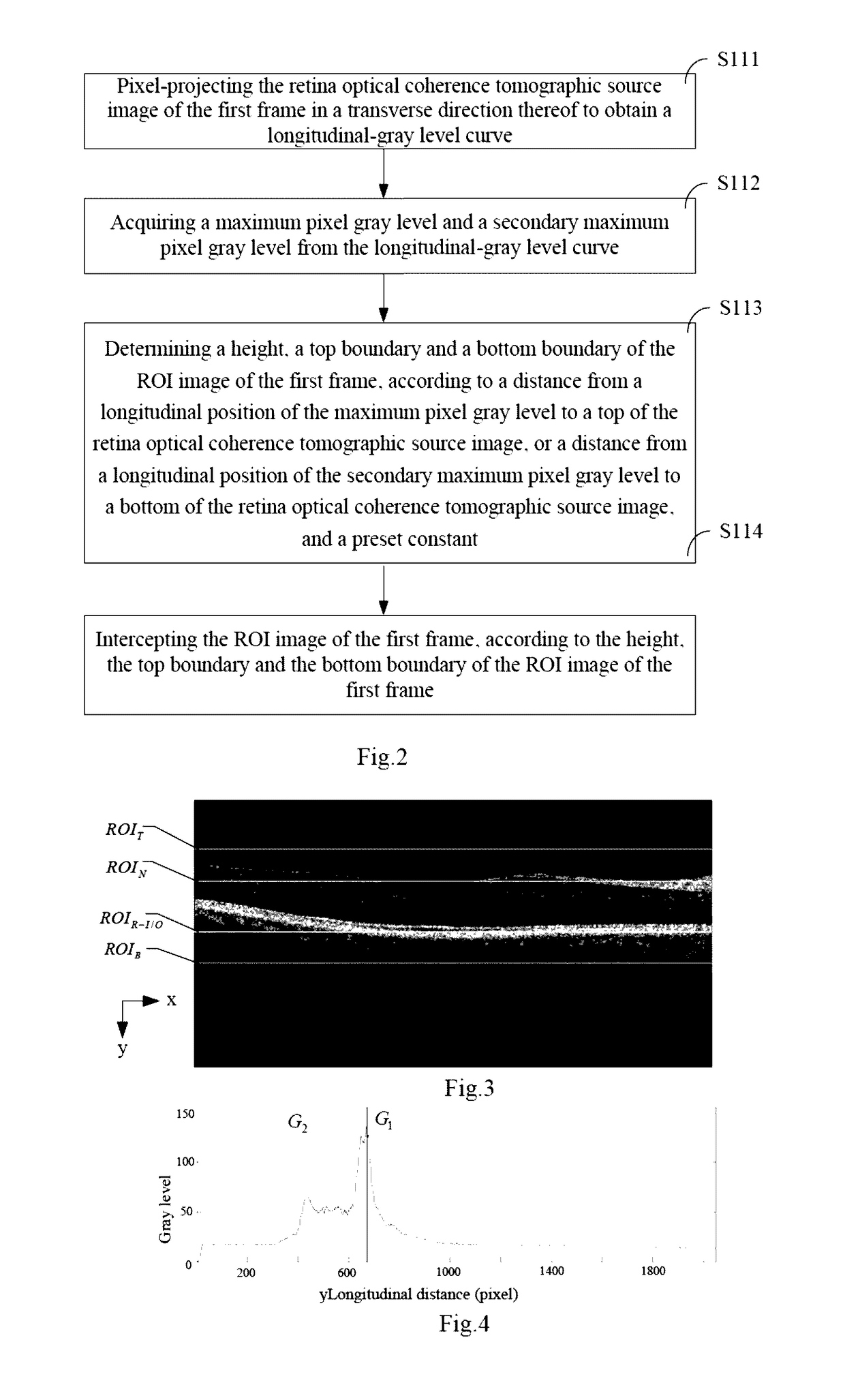

Method for acquiring retina structure from optical coherence tomographic image and system thereof

ActiveUS20170132793A1Simple calculationCalculation complexity is reducedImage enhancementImage analysisComputation complexityRetinal structure

The present disclosure provides a method for acquiring a retina structure from an optical coherence tomographic image and a system thereof. The method comprises: calculating a region of interest (ROI) image of a source image; performing a Gaussian filtering of the ROI image; calculating a first estimated boundary position of a first layer boundary and a second estimated boundary position of a second layer boundary using a multi-resolution method; refining the first layer boundary and the second layer boundary respectively using a simplified active contour model according to the first estimated boundary position and the second estimated boundary position, to obtain a first initial boundary position of the first layer boundary and a second initial boundary position of the second layer boundary; smoothing the first initial boundary position and the second initial boundary position using a filtering method; acquiring segmentation positions of rest layer boundaries in the ROI image according to a segmented position of the first layer boundary and a segmented position of the second layer boundary. The present disclosure can improve the calculation speed and reduce the calculation complexity while maintaining high location accuracy.

Owner:SHENZHEN INST OF ADVANCED TECH

Determination of a Relative Position of a Satellite Signal Receiver

InactiveUS20110074625A1Improve positioning qualityQuality improvementPosition fixationSatellite radio beaconingVIT signalsSatellite

For enhancing the quality of a relative positioning, a filter is adjusted depending on information on a movement of a satellite signal receiver. A position of the satellite signal receiver is determined relative to a reference station using the filter, wherein measurements on satellite signals received by the satellite signal receiver and measurements on satellite signals provided for the reference station are used as input to the filter. The measurements for the reference station may be received in messages which are assembled and provided for transmission and which may include in addition an indication of a current movement of the reference station.

Owner:NOKIA CORP

Apparatus, system, and method for automating VTOC driven data set maintenance

InactiveUS7624127B2Easy to determineAvoid initializationData processing applicationsSpecial data processing applicationsAccess methodTime efficient

The present invention increases the efficiency of dynamically, reusable computer environments by first retrieving data set information from a volume table of contents (VTOC) to ensure its consistency with the catalog. After obtaining the necessary information about the data sets, control statements are generated and appropriate programs invoked to perform the desired maintenance operations. Reinitializing and reconfiguring the reusable computer environment by starting with the VTOC prevents post-maintenance issues such as a data set with an entry in an integrated catalog facility (ICF) catalog while the data set no longer exists on a volume, a cataloged virtual storage access method (VSAM) cluster with disassociated DATA or INDEX data sets, and a data set catalog entry that has been scratched while the data set still exists on a volume. The present invention saves time and money by preventing such problems up-front instead of correcting them after-the-fact.

Owner:INT BUSINESS MASCH CORP

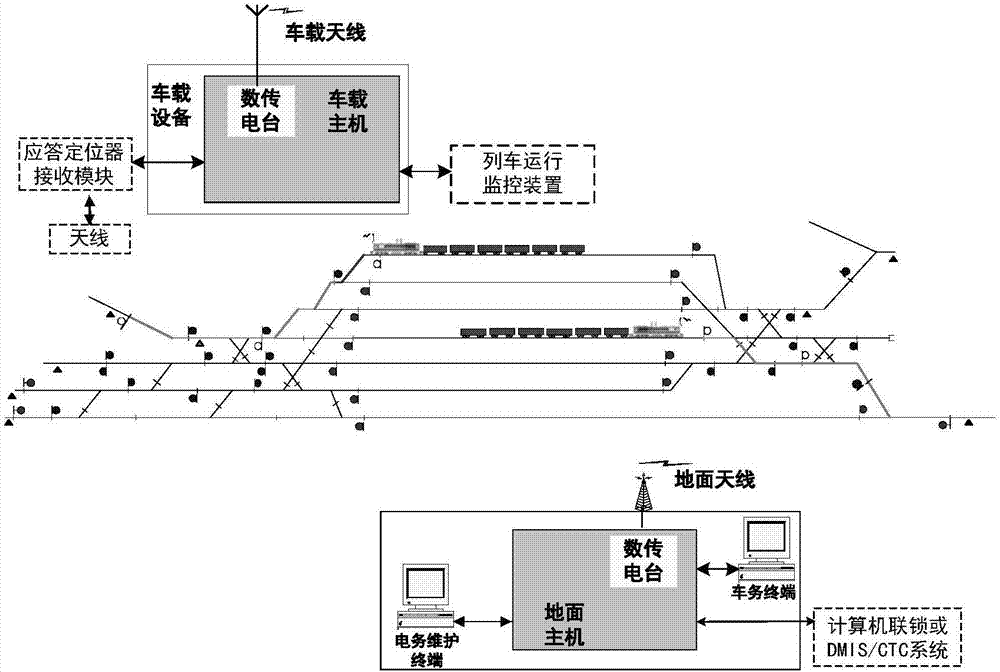

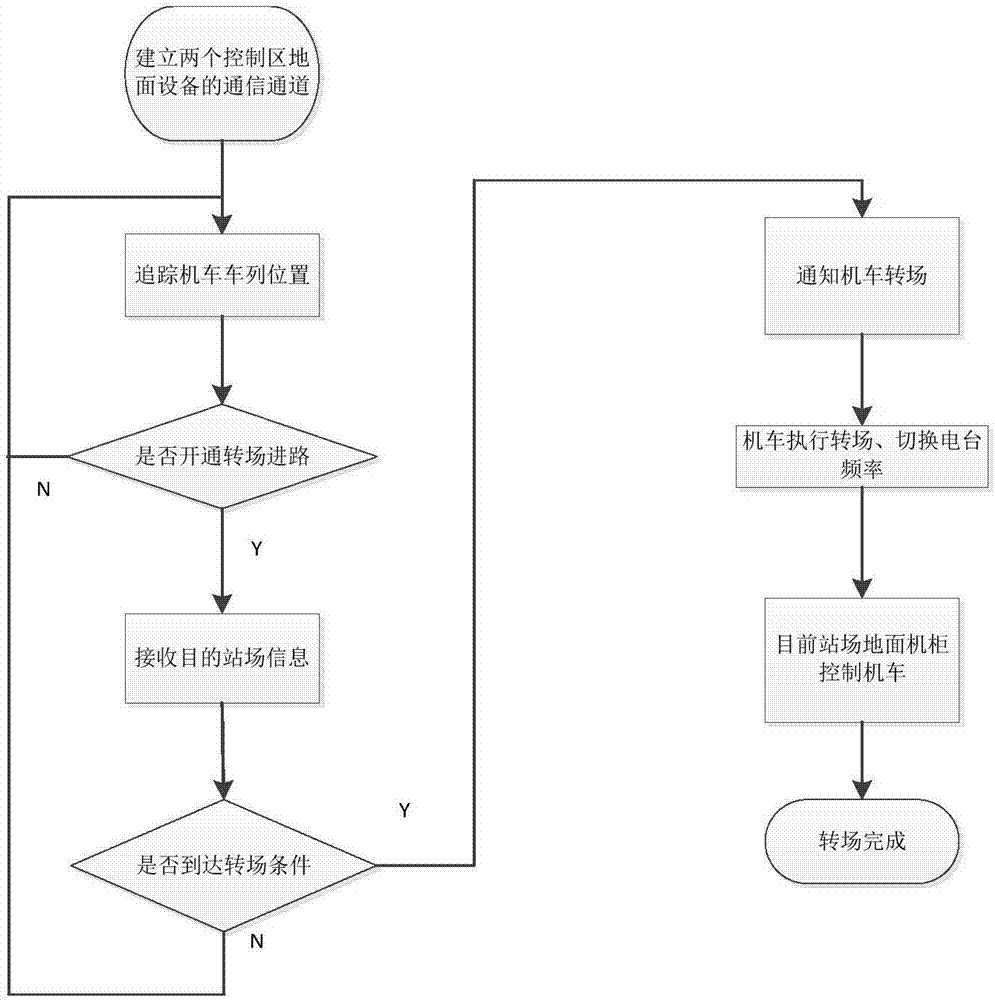

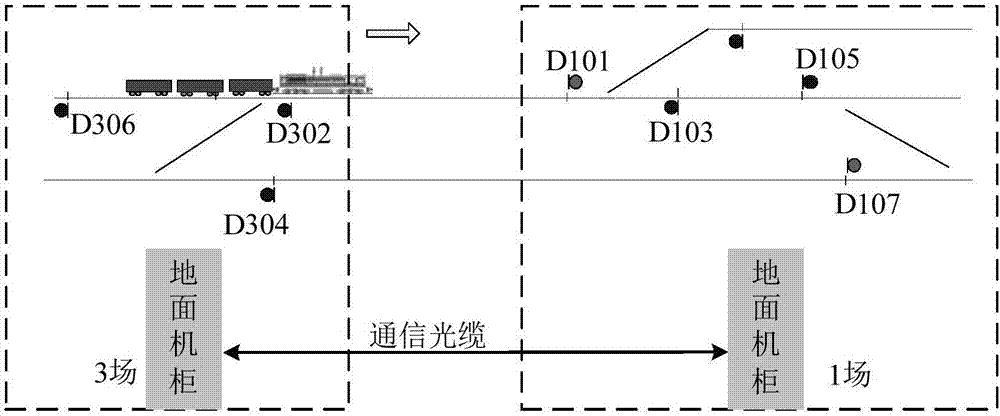

Station-yard switching method of shunting train protection (STP) system

ActiveCN107089250ASolve the display effectSolve the speed limitRailway traffic control systemsEngineeringControl zone

The invention discloses a station-yard switching method of a shunting train protection (STP) system. The method comprises: establishing a communication channel between ground equipment of every two adjacent control zones, exchanging the adjoined part signal condition and the approach road condition of the two control zones, the ground cabinet of the control zone where a registered locomotive is located transmitting the signal condition of the adjoined areas of the two control zones to the locomotive when a transfer approach road is opened in front of the registered locomotive and informing the locomotive of performing station-yard switching in real time, switching to the control zone which the locomotive is about to enter, meanwhile, transmitting train set information of the locomotive to the corresponding ground cabinet through the communication channel, and the corresponding ground equipment directly taking over the control of the locomotive, without carrying out the process of registration, network access, and re-initialization of the train set information of the locomotive. The purpose of continuous control over the transfer operation of the locomotive is realized. The station-yard switching method of the STP system is of great significance in improving the control performance of STP systems.

Owner:SIGNAL & COMM RES INST OF CHINA ACAD OF RAILWAY SCI +3

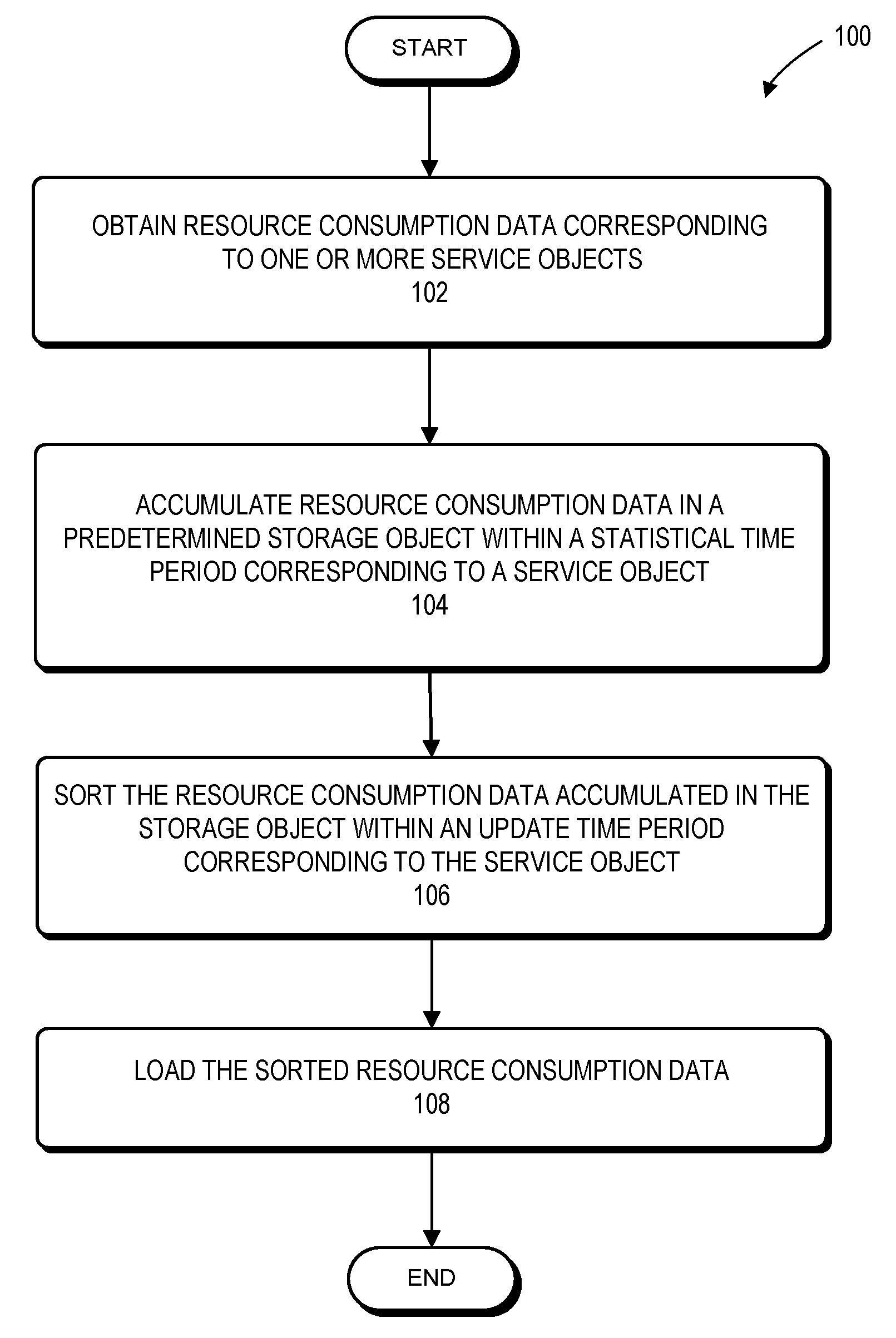

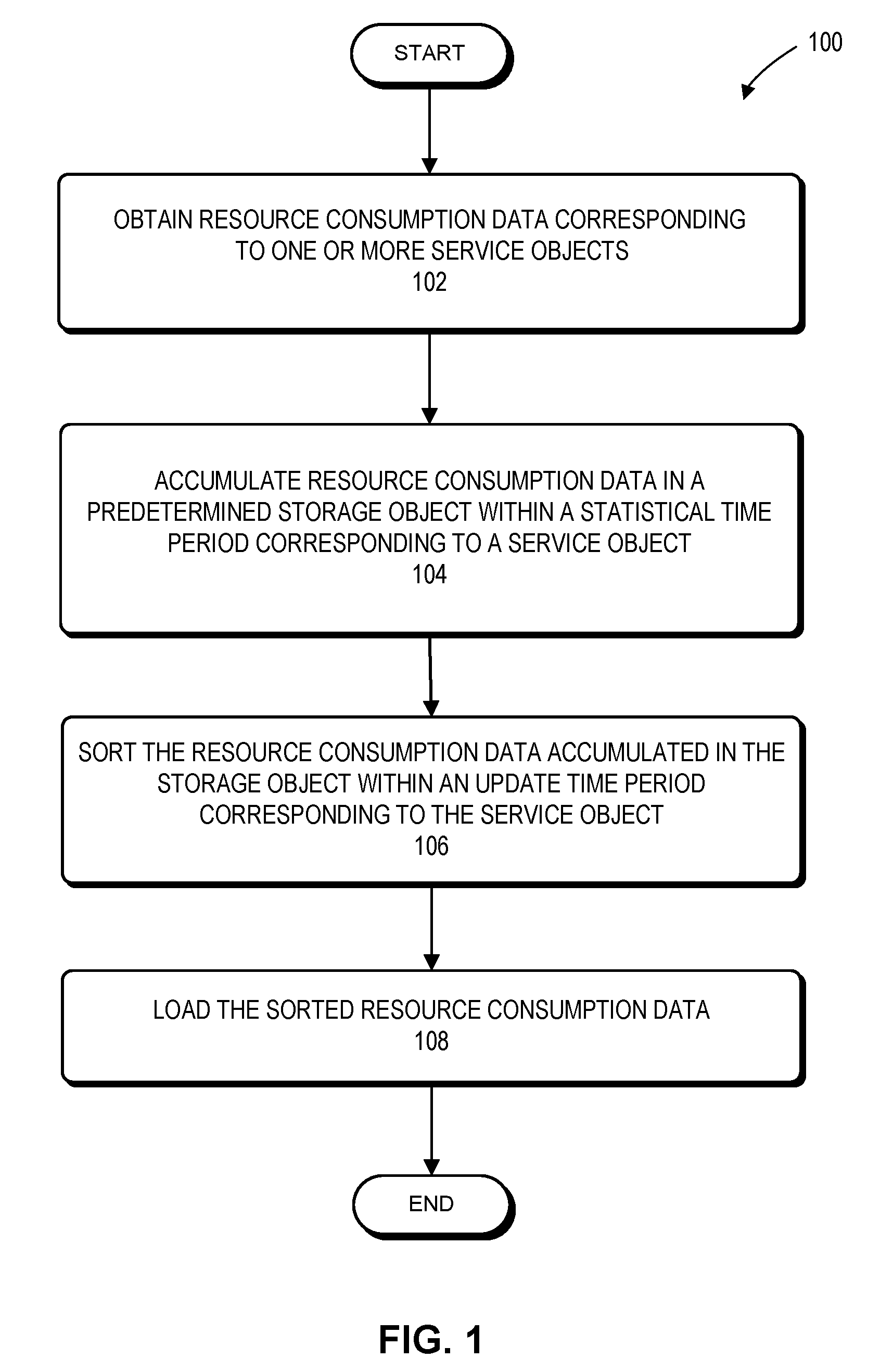

Method and system of monitoring a service object

ActiveUS20160323169A1Lower performance requirementsEfficient collectionHardware monitoringData switching networksResource consumptionOperating system

Embodiments of the present application provide a method and system for monitoring a service object. During operation, the system obtains resource consumption data corresponding to one or more service objects. The resource consumption data may include data indicating device resource usage. The system may then accumulate the resource consumption data in a predetermined storage object within a statistical time period corresponding to a service object. The system may sort the resource consumption data accumulated in the predetermined storage object within an update time period corresponding to the service object. The system may then load the sorted resource consumption data.

Owner:ALIBABA GRP HLDG LTD

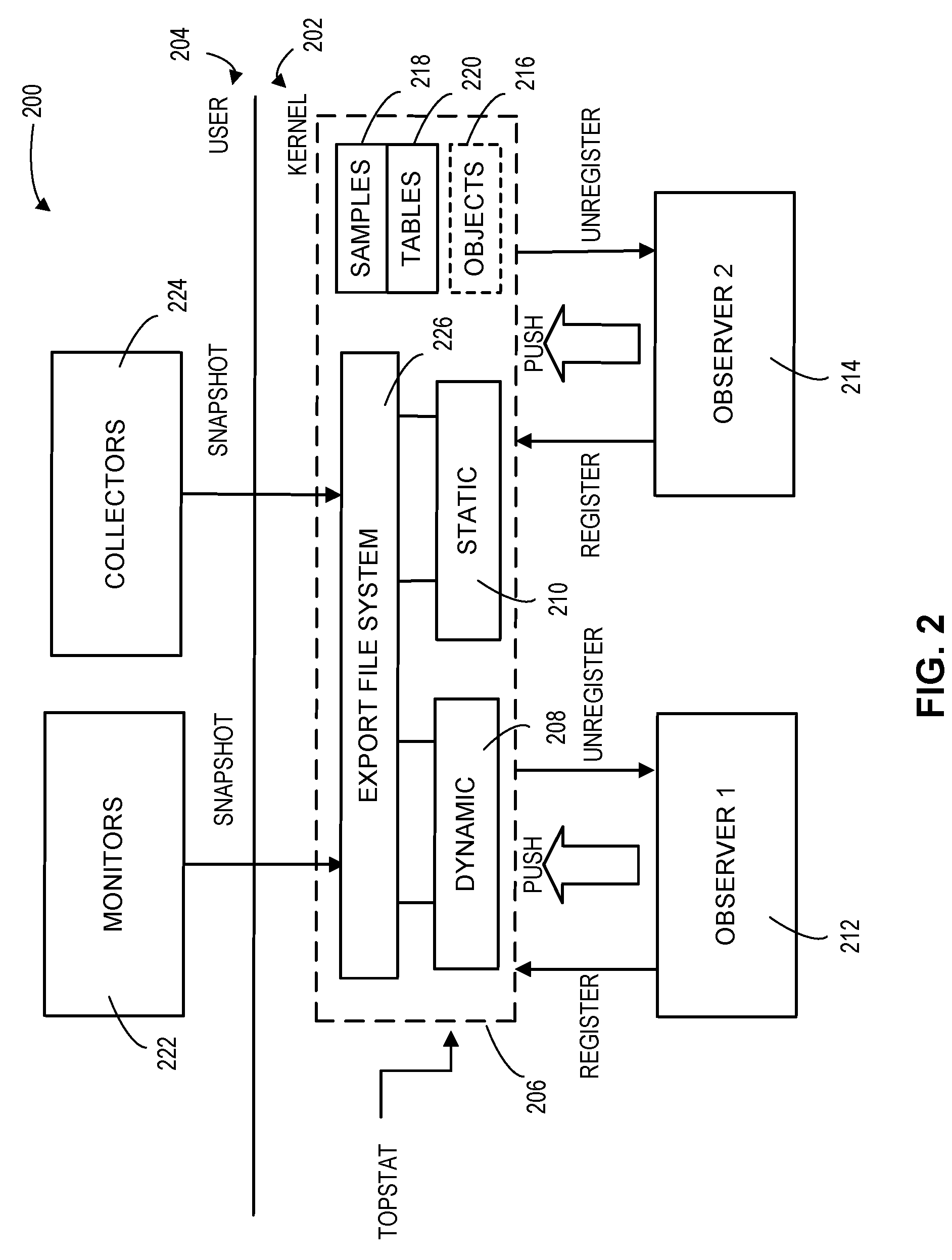

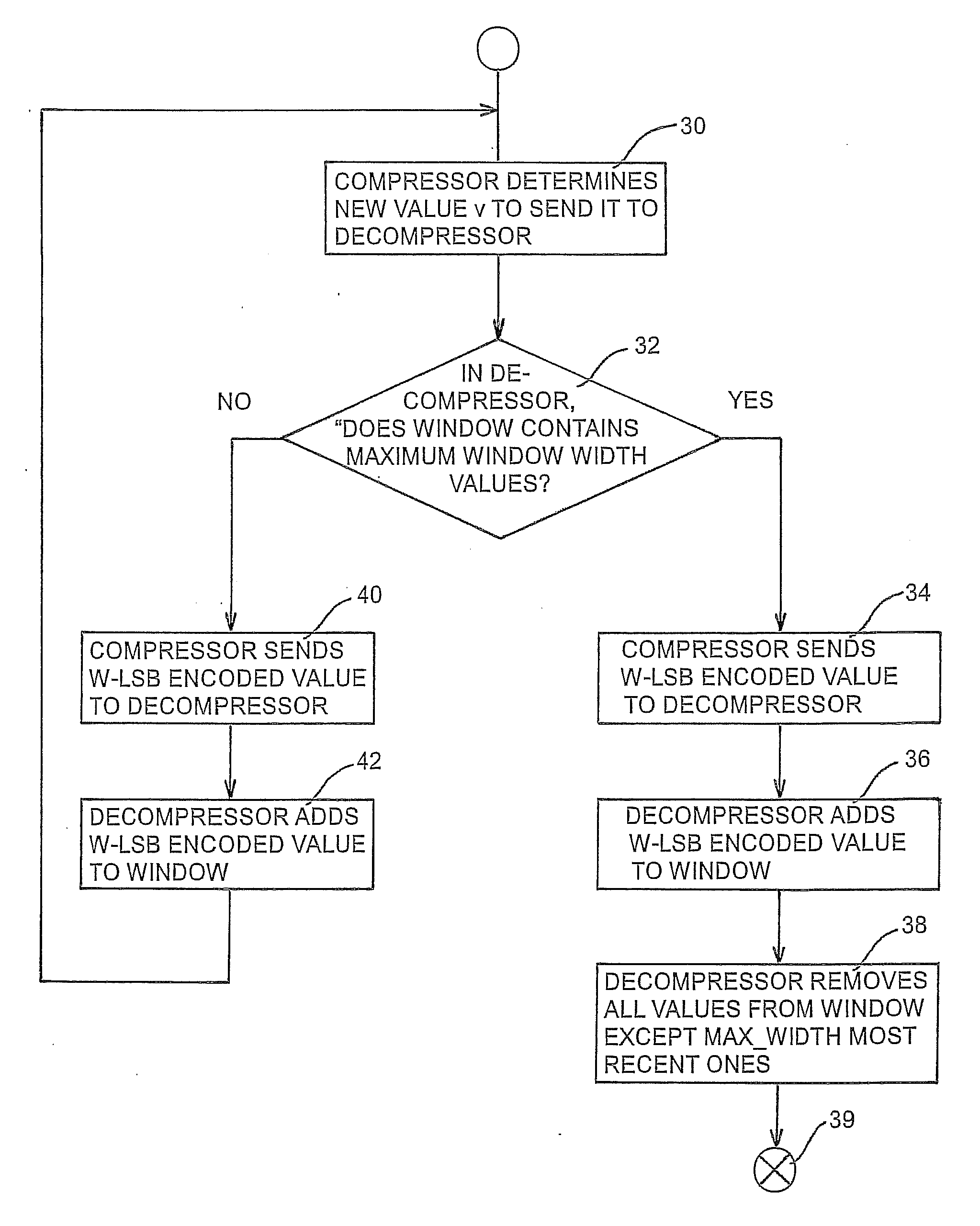

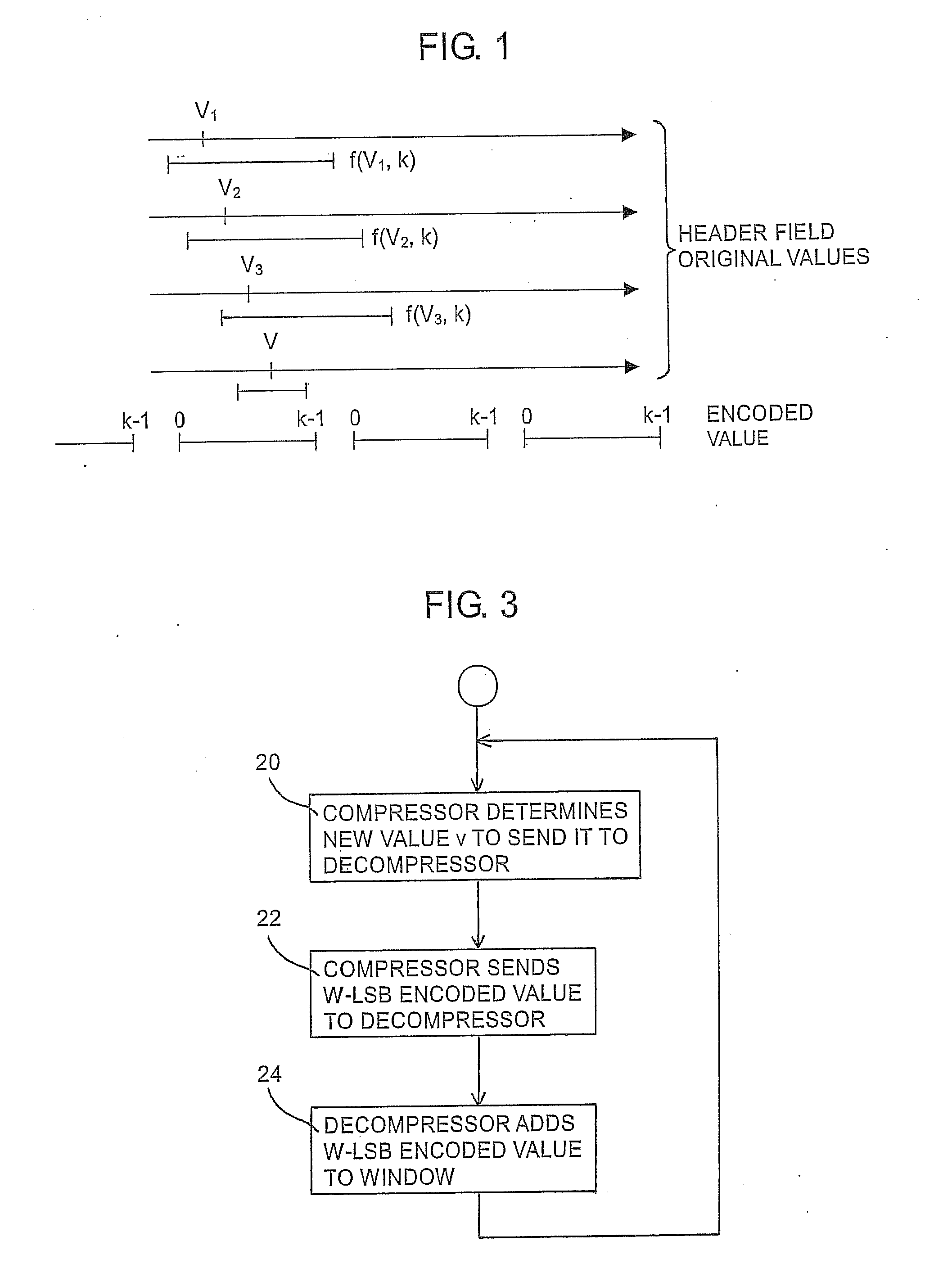

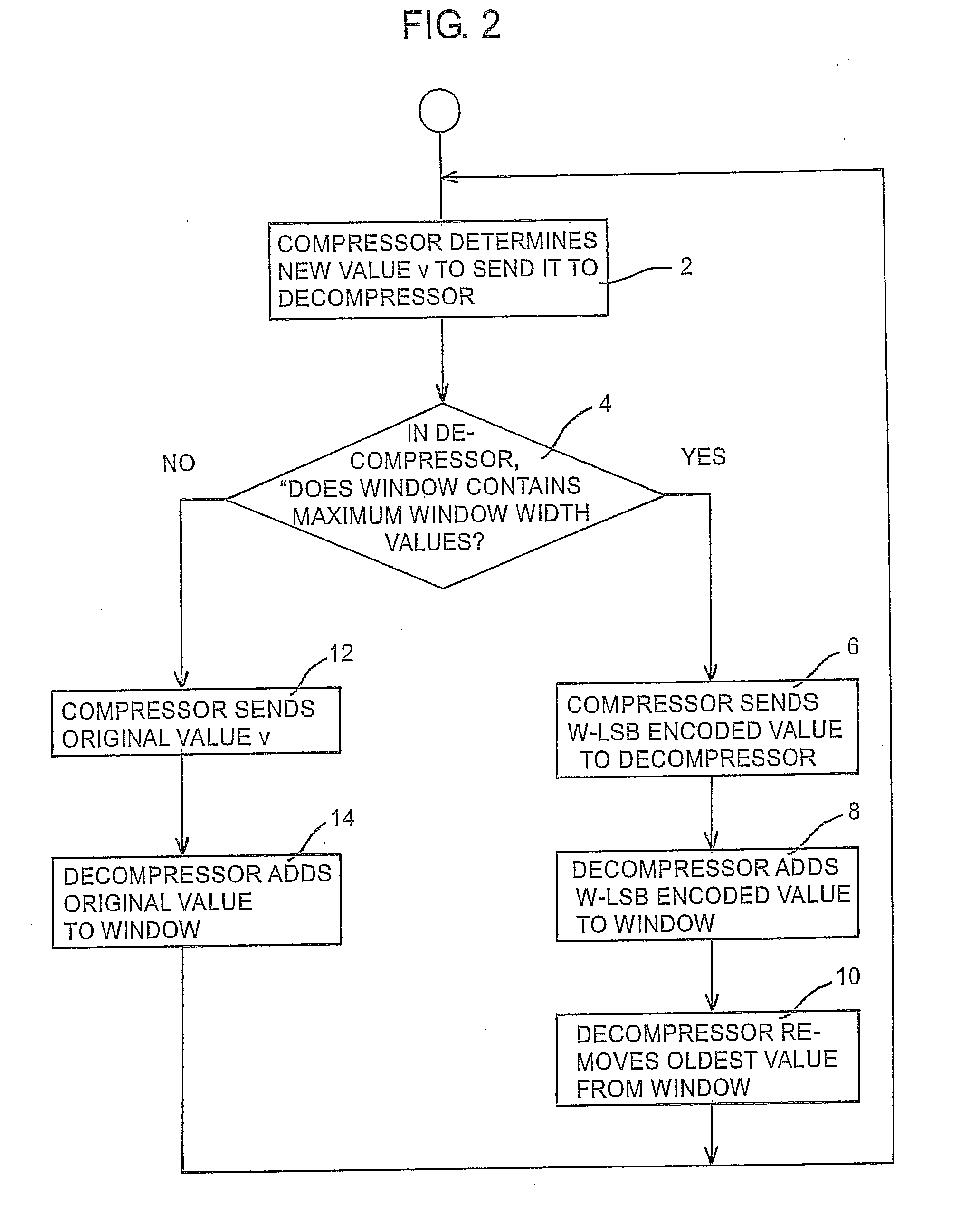

Header compression optimization method during and after handovers in cellular communication network

ActiveUS20090232093A1Improve techniqueSave resourcesNetwork traffic/resource managementNetwork topologiesNo referenceTime Protocol

The present invention concerns a method for optimizing ROHC RTP (Robust Header Compression Real Time Protocol) compression applied to IP header of data packets stream so as to use more compact formats enable to remain in a steady state, to never discard received packet, and to serve radio resources without requiring to modify ROHC specification. In the method, when handover or mobility procedure is started, new reference values are normally added to a sliding compression window, but no reference value is removed from the window as long as the handover or mobility procedure is on going. After the handover or mobility procedure is complete, when the number of values transmitted on the new radio link are appropriate to cope against the error properties on the new link, all older values can be removed at once from the compression window, thereby reverting to normal window operation.

Owner:NEC CORP

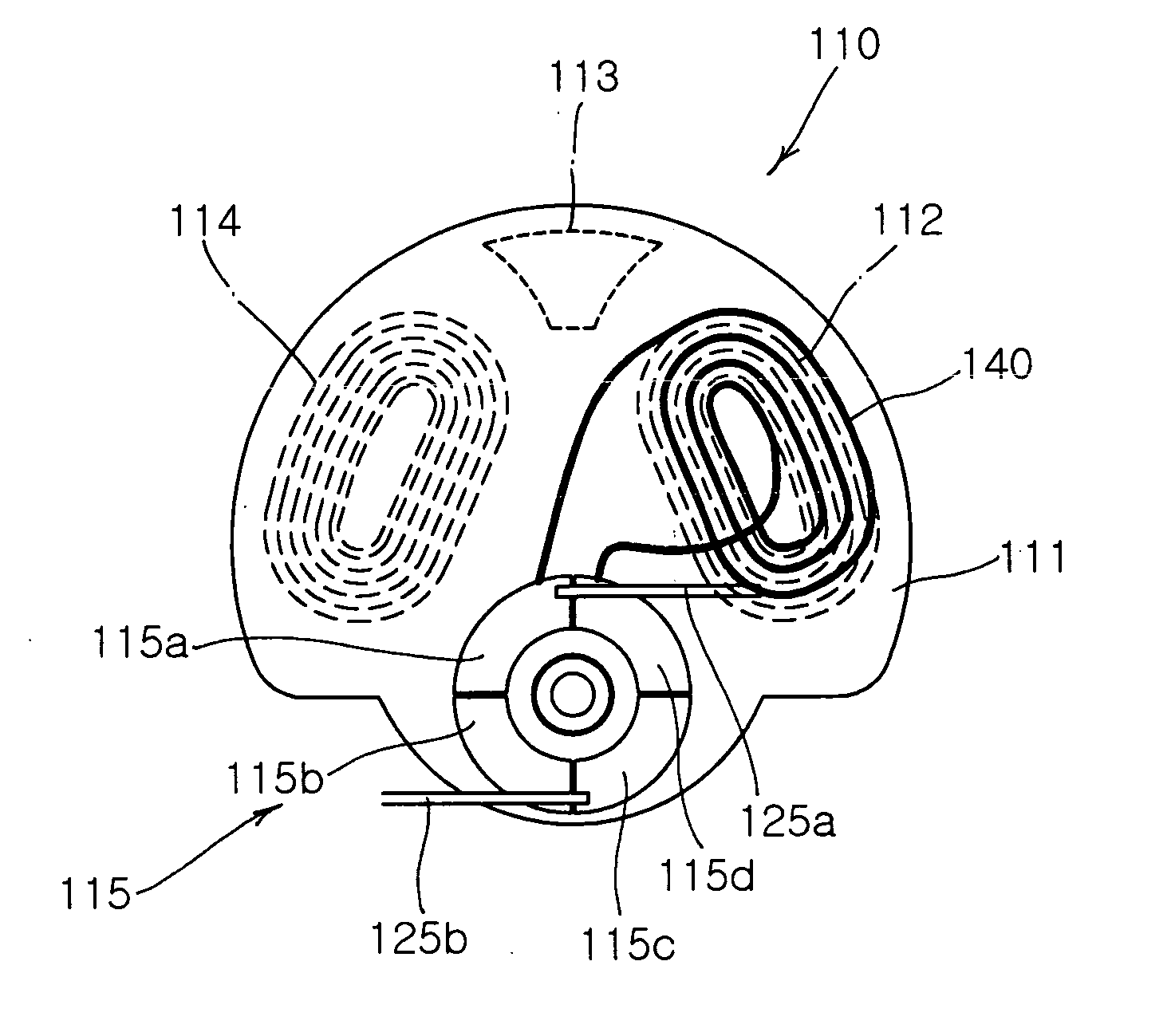

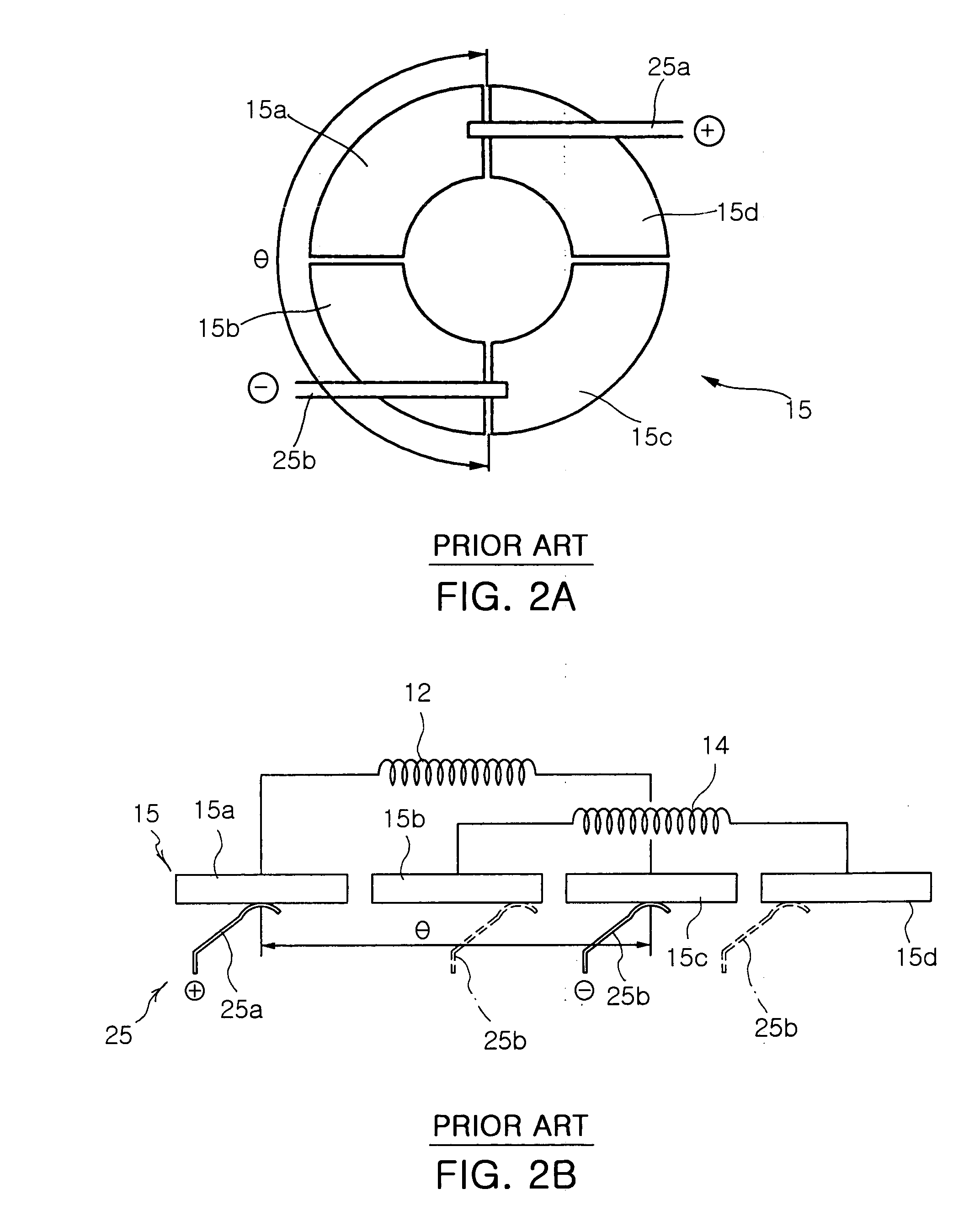

Flat type vibration motor

InactiveUS20050184602A1Efficient and stable initializationGuaranteed uptimeUsing liquid separation agentLiquid spraying apparatusConductor CoilRectifier

Disclosed is a flat type vibration motor, in which a shaft is supported between a housing and a bracket. A rotor includes an upper board, A and B phase winding coils, an eccentric weight and a rectifier. The rectifier has a plurality of segments electrically connected to first and second ends of the A and B phase winding coils. A stator includes a lower board, a magnet and a pair of brush fingers electrically connected to a power supply and in contact with the segments. A pattern coil on the upper board electrically connects between a segment connected to a first end of the A phase winding coil and another segment connected to a second end of the B phase winding coil to generate electromagnetic force for rotating the rotor from an electrically disconnected section to an electrically connected section.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

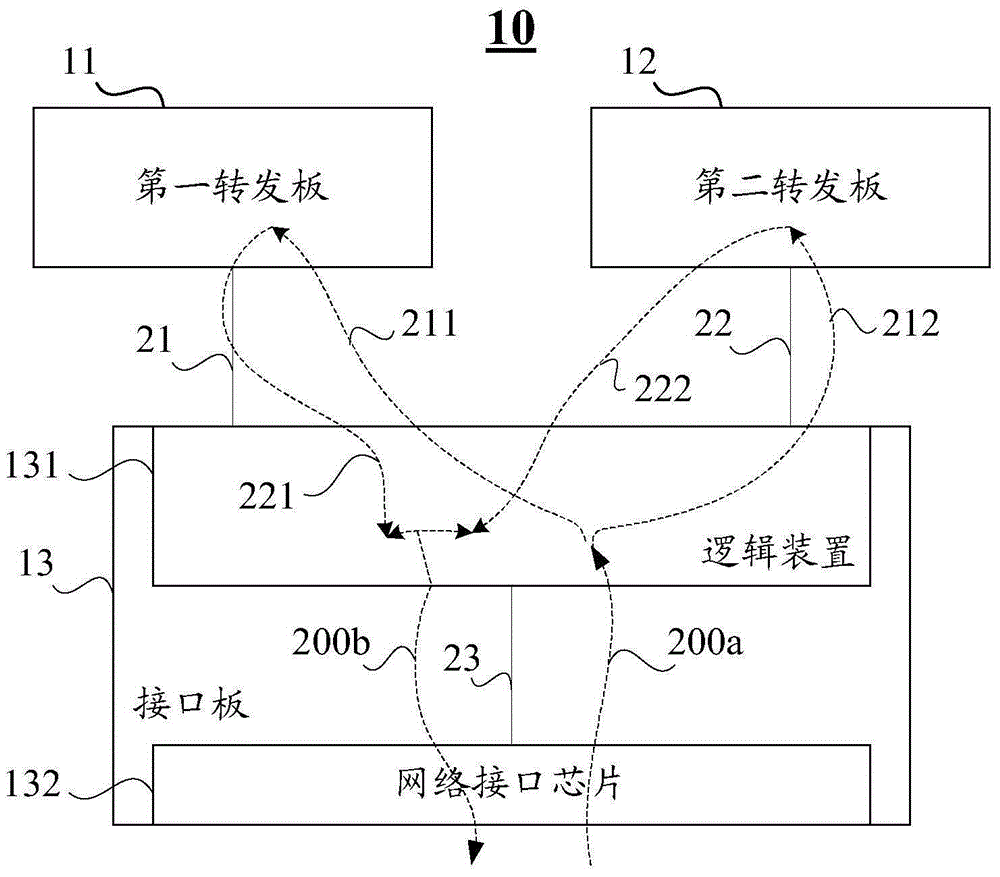

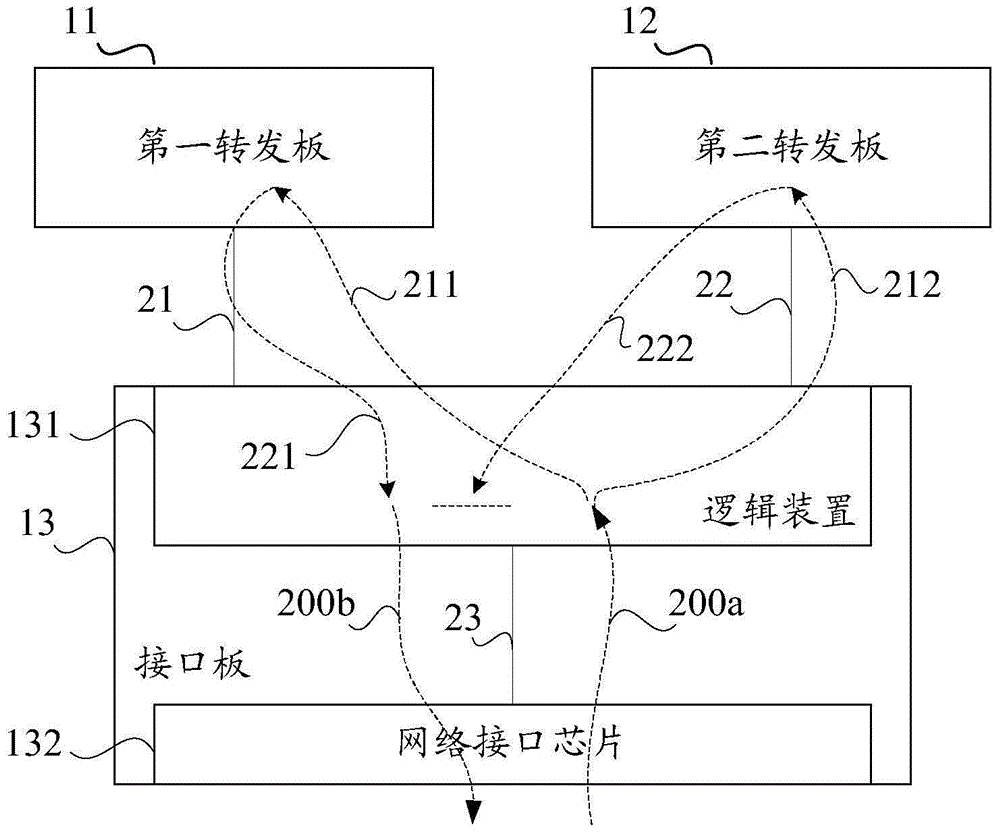

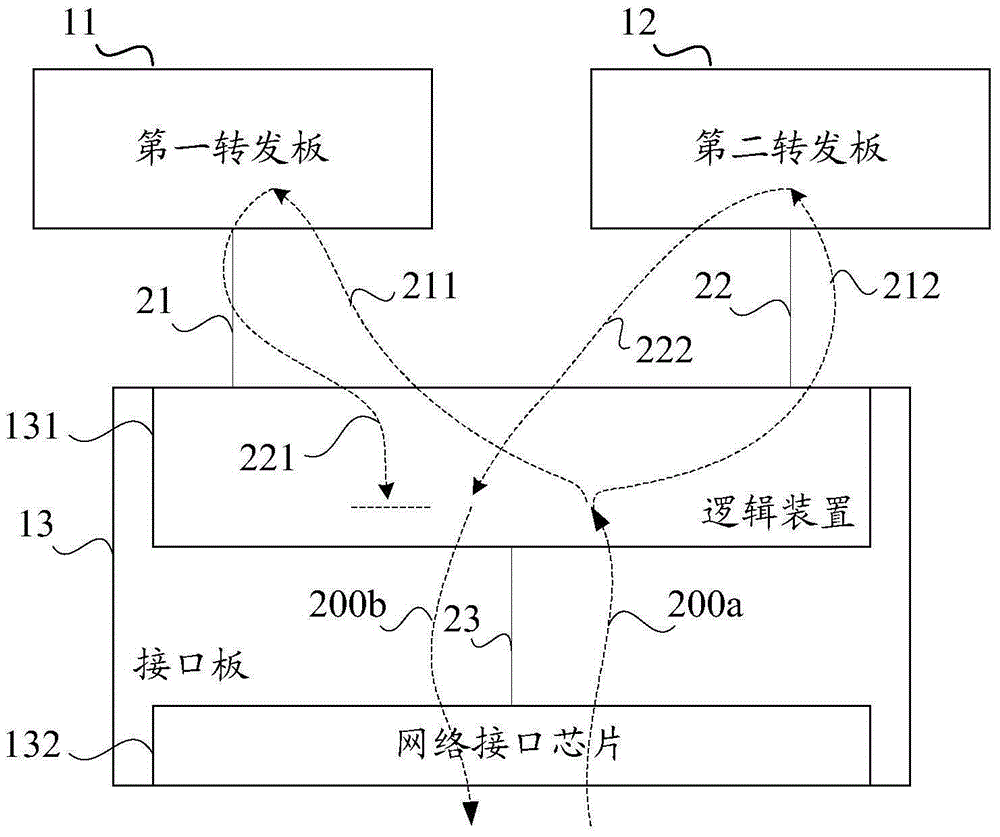

Network device and message forwarding method applied to the network device

ActiveCN106487721AAvoid Physical Switching OperationsShorten the timeError detection/correctionData switching networksNetwork interfaceNetwork Access Device

The invention discloses a network device and a message forwarding method applied to the network device. Through application of the device and the method, data messages received by a network interface chip of an interface board from the exterior of the network device can form first uplink data message stream which is sent to a first forwarding board through a first I / O bus, and second uplink data message stream which is sent to a second forwarding board through a second I / O bus. Therefore, when the first forwarding board and the second forwarding board can realize normal forwarding, the first uplink data message stream and the second uplink data message stream can be transmitted through the first I / O bus and the second I / O bus independently at the same time, and the first uplink data message stream and the second uplink data message stream are connected with the network interface chip alternatively.

Owner:NEW H3C TECH CO LTD

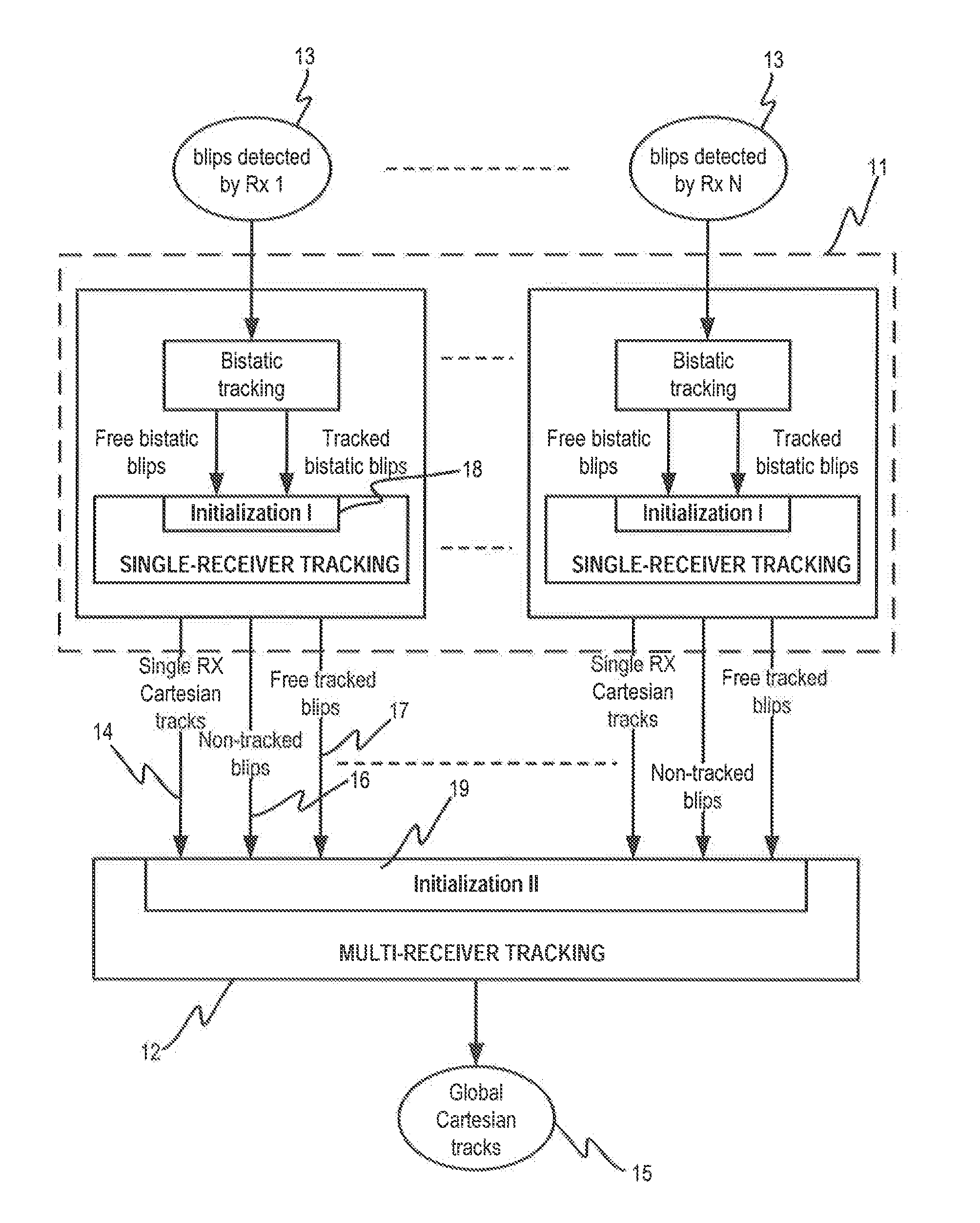

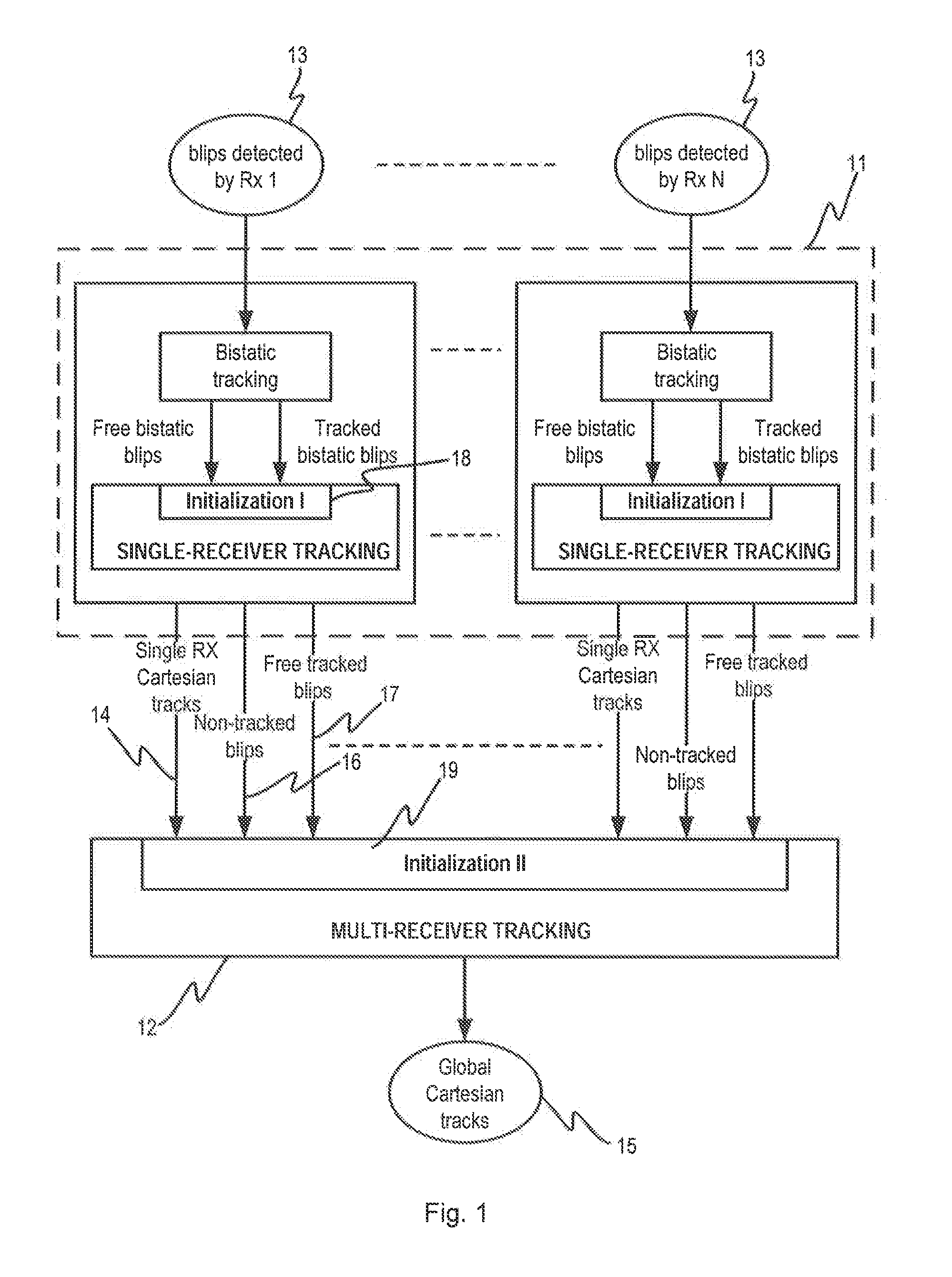

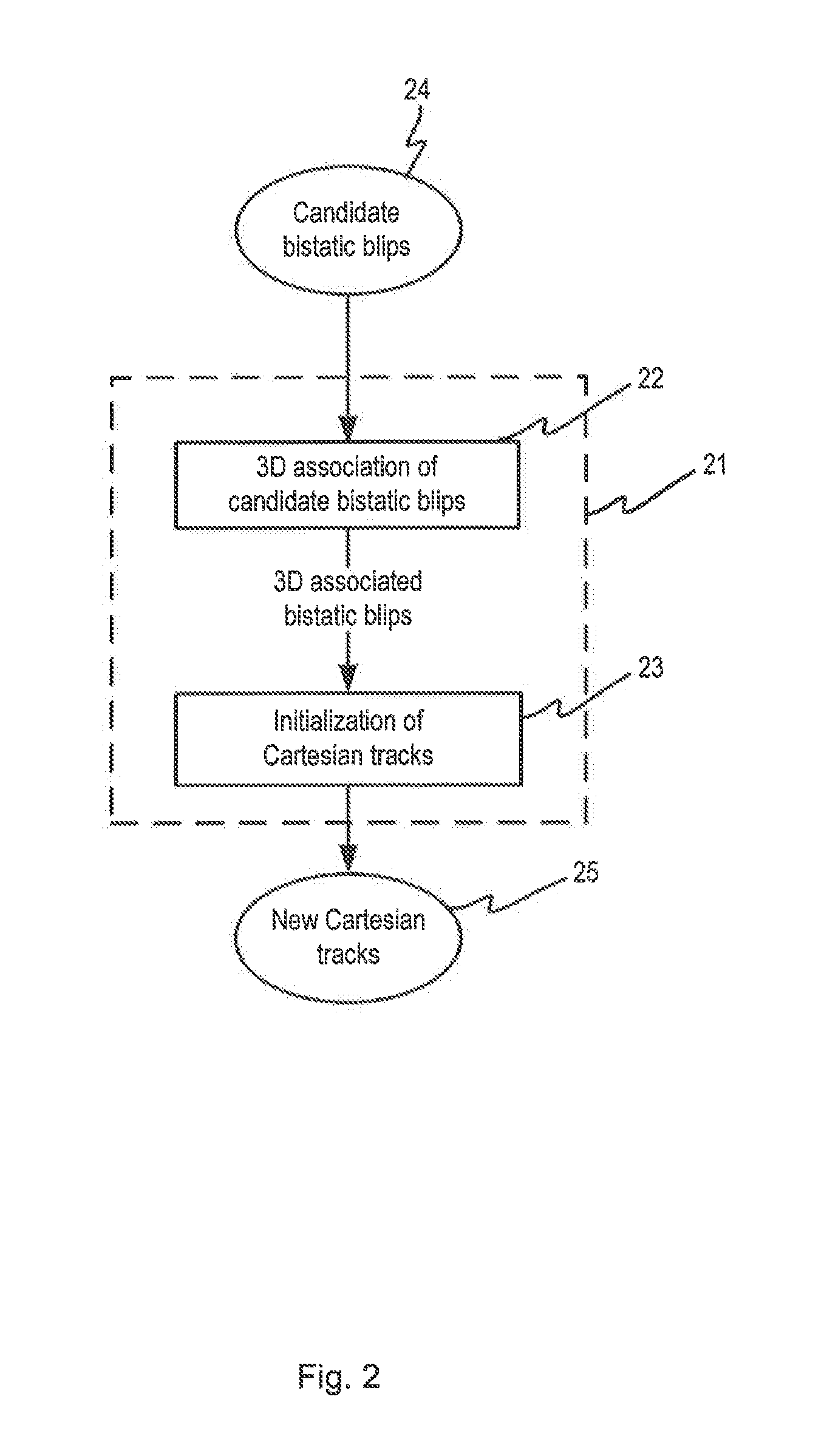

Method for initializing cartesian tracks based on bistatic measurements performed by one or more receivers of a multistatic radar system

ActiveUS20130099958A1Easy to analyzeAvoid initializationRadio wave reradiation/reflectionRadarMultistatic radar

The invention consists of a method that makes it possible to produce an association of bistatic blips, formed by the different bistatic bases of a multistatic radar system comprising a plurality of transmitters and receivers remote from one another, this association making it possible to transmit to the tracking means only bistatic blips that probably correspond to one and the same target so as to facilitate the work of the tracking means. The association of blips that is produced takes into account the parameters defining, in three dimensions, the bistatic measurements (distance and speed), as well as the azimuth measurement, relating to the corresponding target.

Owner:THALES SA

User aware digital vision correction

ActiveUS10168854B2Avoid eyesightAvoid initializationCharacter and pattern recognitionCathode-ray tube indicatorsGraphicsPersonalization

A method, a system, and an information handling system dynamically provide individualized dynamic digital display correction for users of an electronic device. An information handling system detects a login of a first user profile that is associated with a first user. The information handling system then determines whether the first user profile has an associated first vision profile. In response to the first user profile having an associated first vision profile, a vision correction value associated with the first user is identified. A first change in image characteristics that may be applied to a graphical user interface (GUI) in order to achieve the vision correction value is calculated and applied to one or more content displayed on the GUI.

Owner:DELL PROD LP

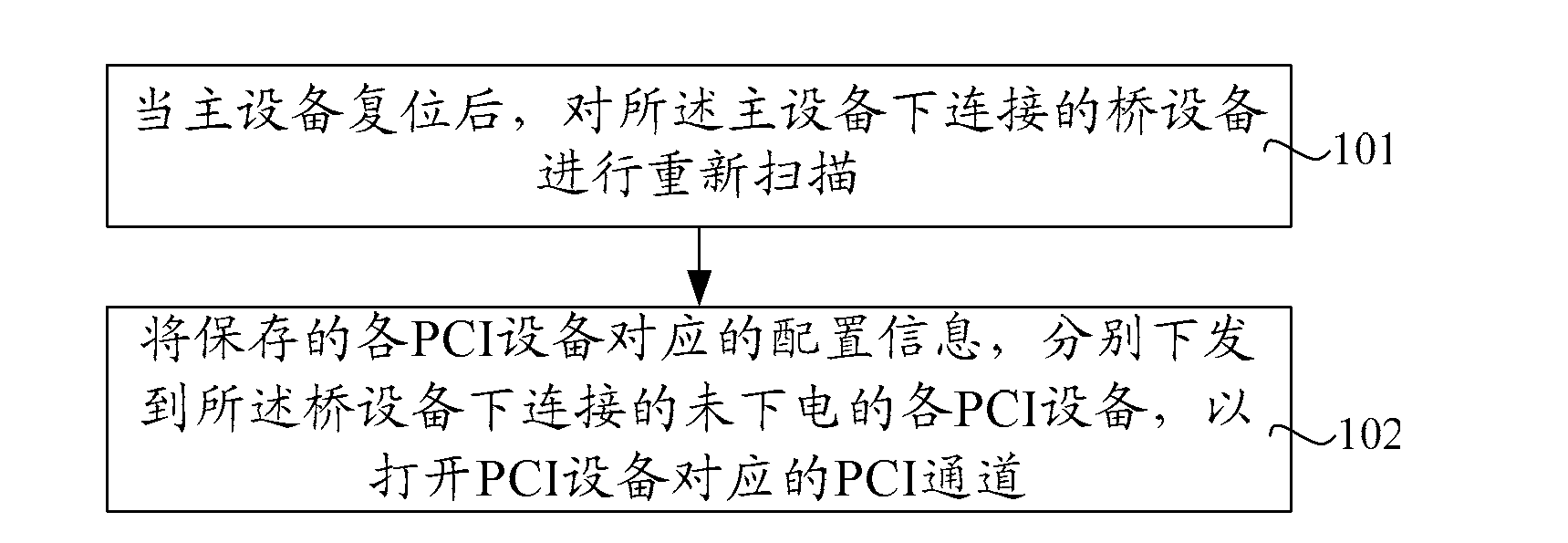

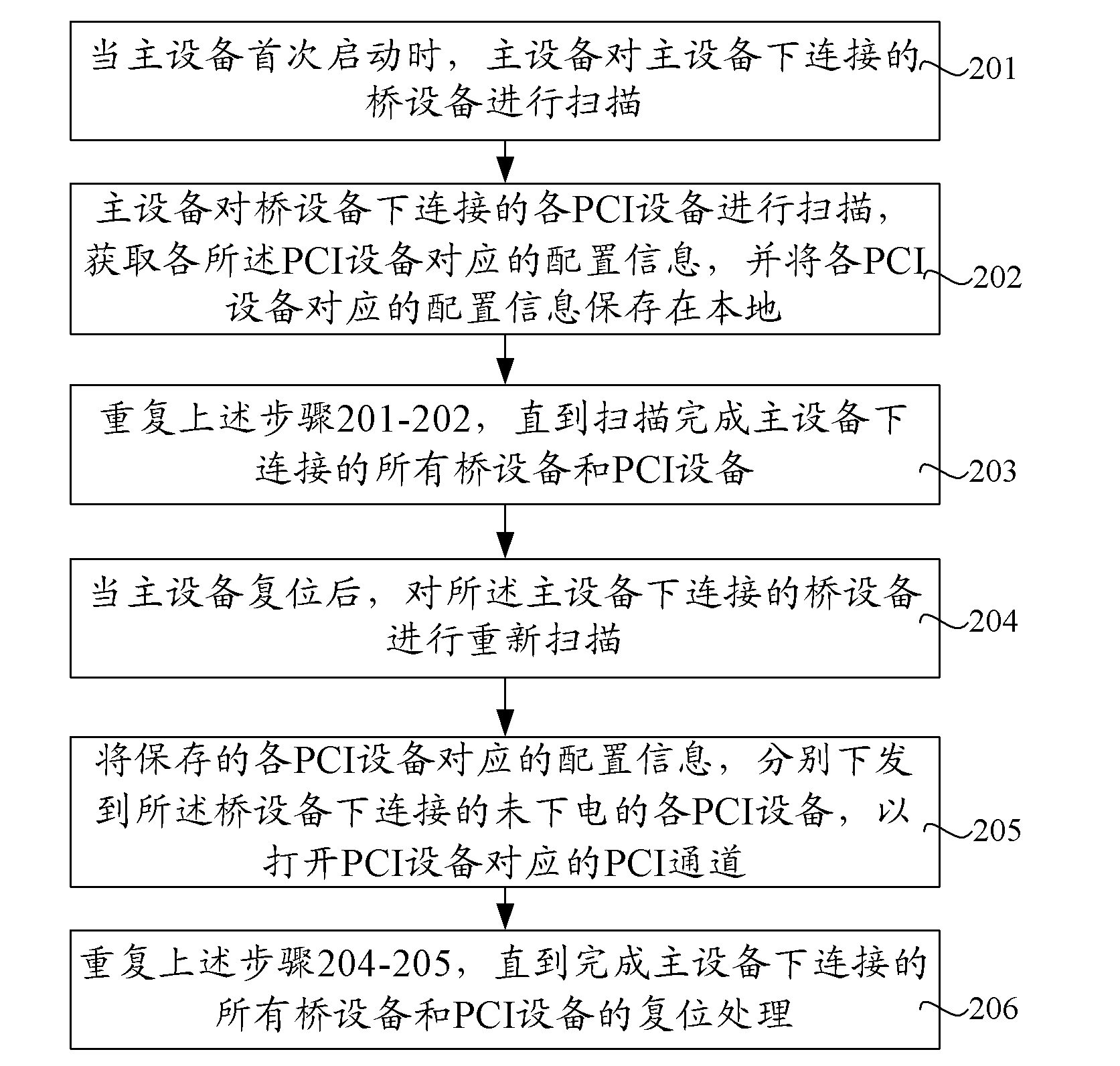

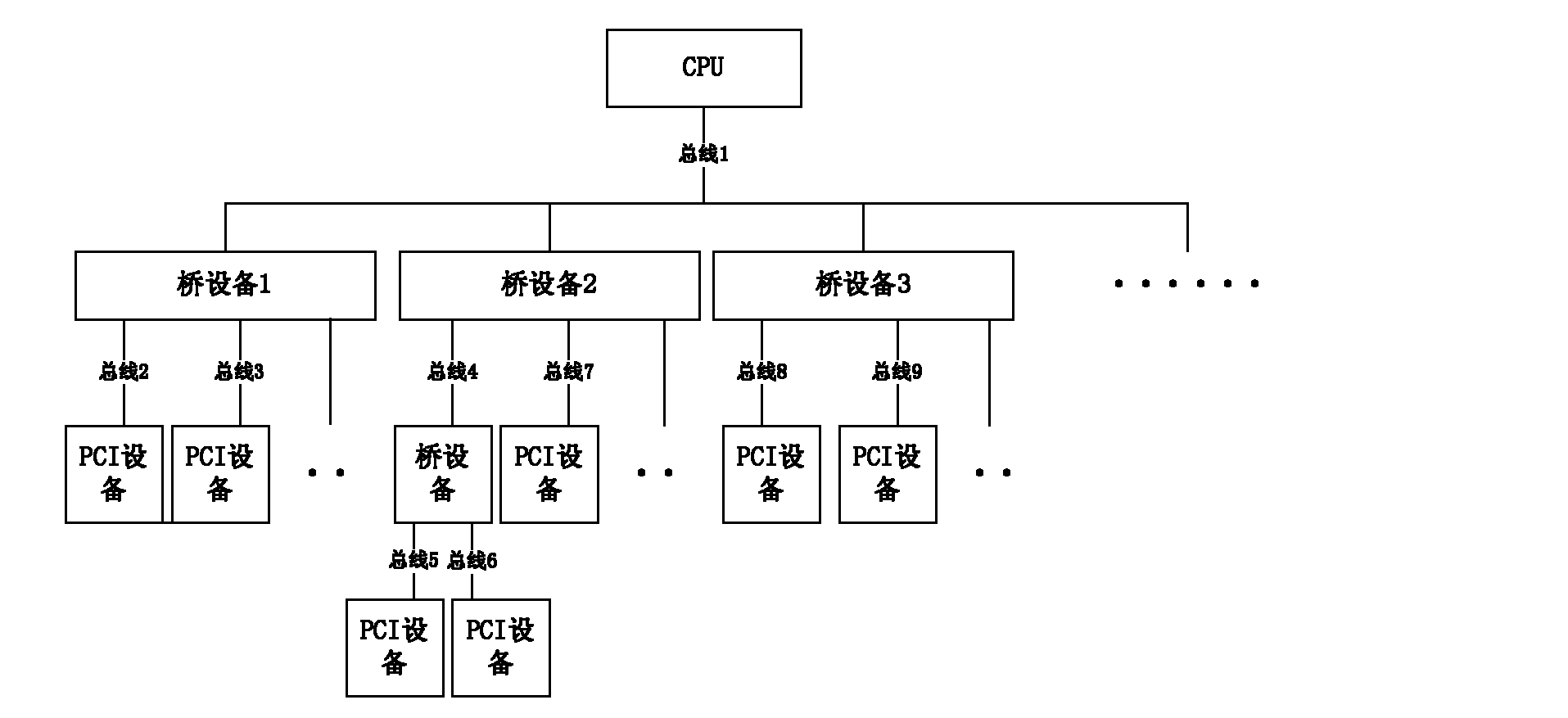

Reset processing method, device and system of equipment

InactiveCN102360241AAvoid repeated scans and initializationsImprove efficiencyData resettingElectricitySystem recovery

The invention provides a reset processing method, device and system of equipment. The method comprises the following steps: rescanning bridge equipment connected below main equipment after the main equipment is reset; and sending the stored configuration information corresponding to each PCI (peripheral component interconnect) equipment down to the PCI equipment which is not powered off and is connected below the bridge equipment respectively so as to open PCI channels corresponding to the PCI equipment. The device comprises a scanning module and a sending down module. The system comprises the main equipment, a plurality of bridge equipment connected below the main equipment and a plurality of PCI equipment connected below the bridge equipment, wherein the main equipment comprises the reset processing device of the equipment. By adopting the method, the device and the system, the efficiency of system recovery after abnormal reset of the main equipment is improved.

Owner:RUIJIE NETWORKS CO LTD

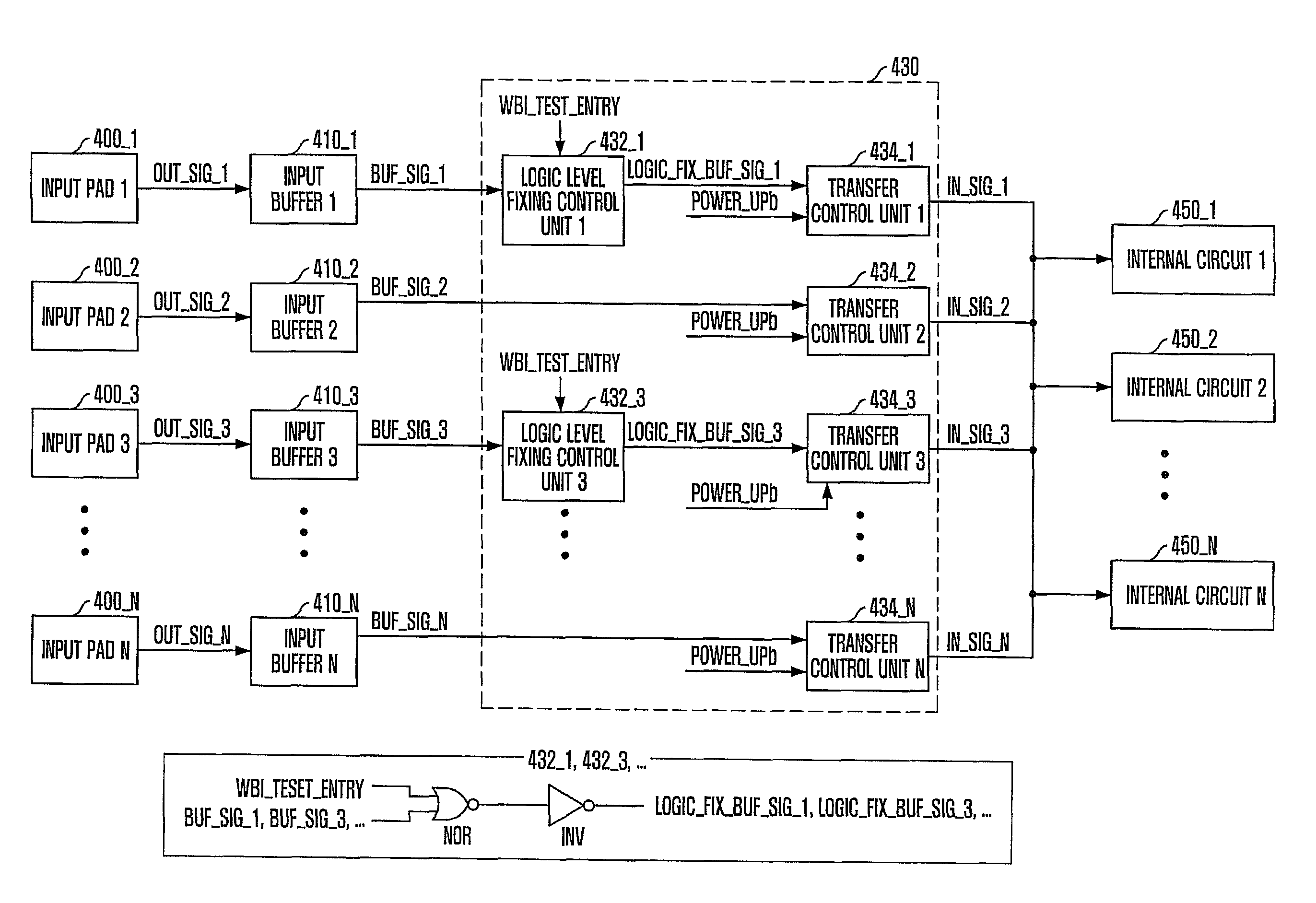

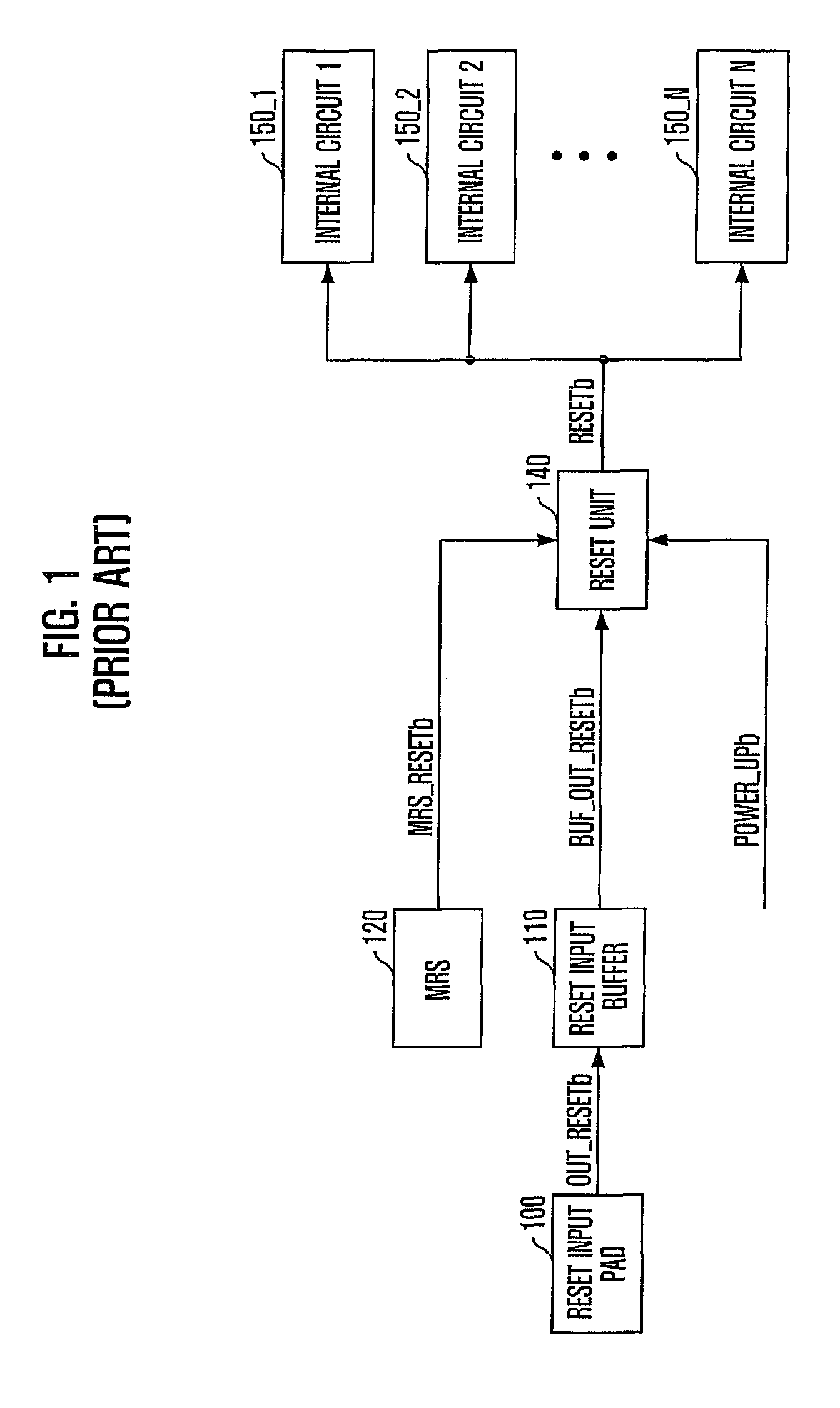

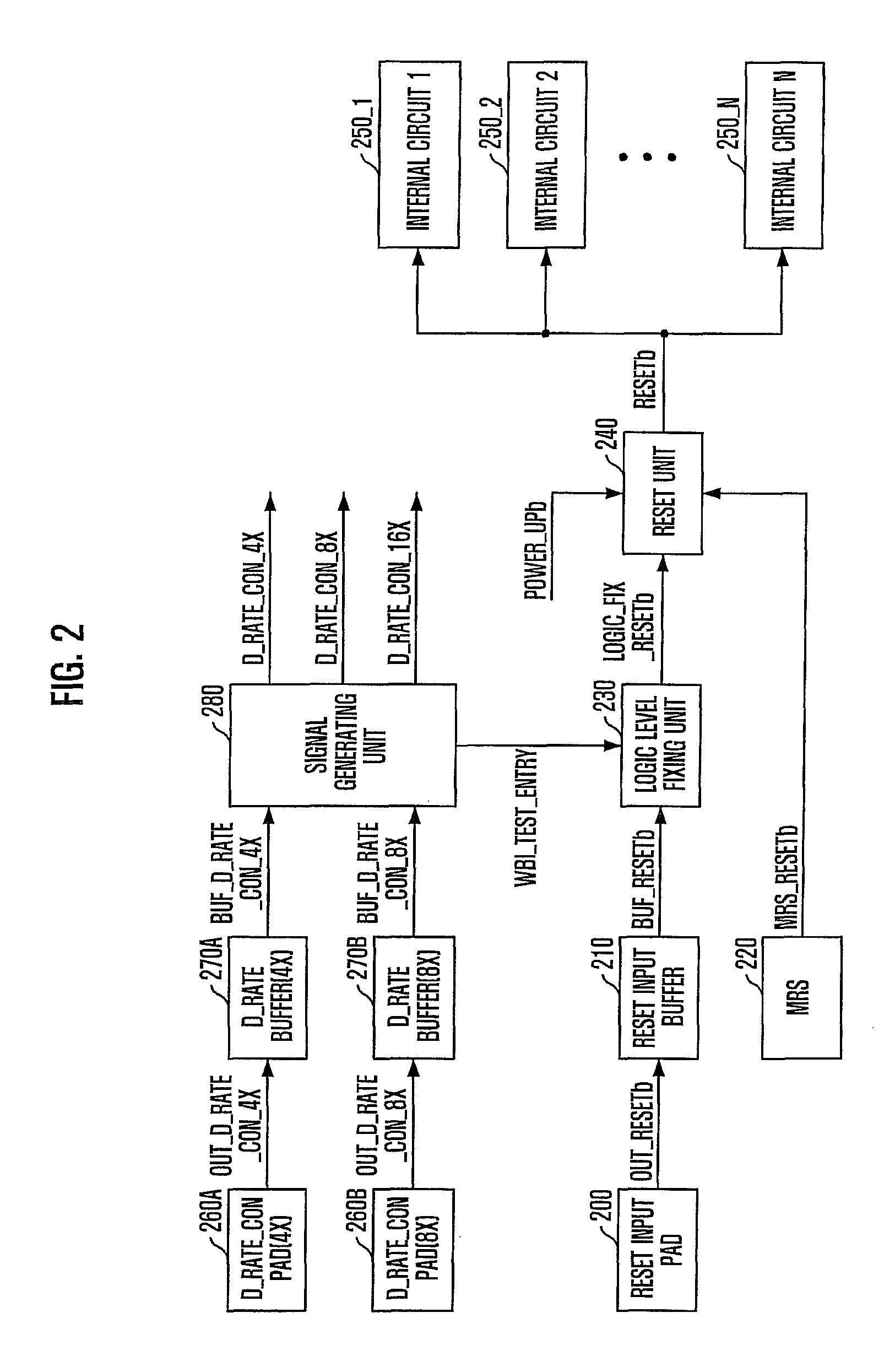

Semiconductor device

ActiveUS7868647B2Avoid initializationElectrical testingLogic circuits using specific componentsPower semiconductor deviceNormal mode

Owner:SK HYNIX INC

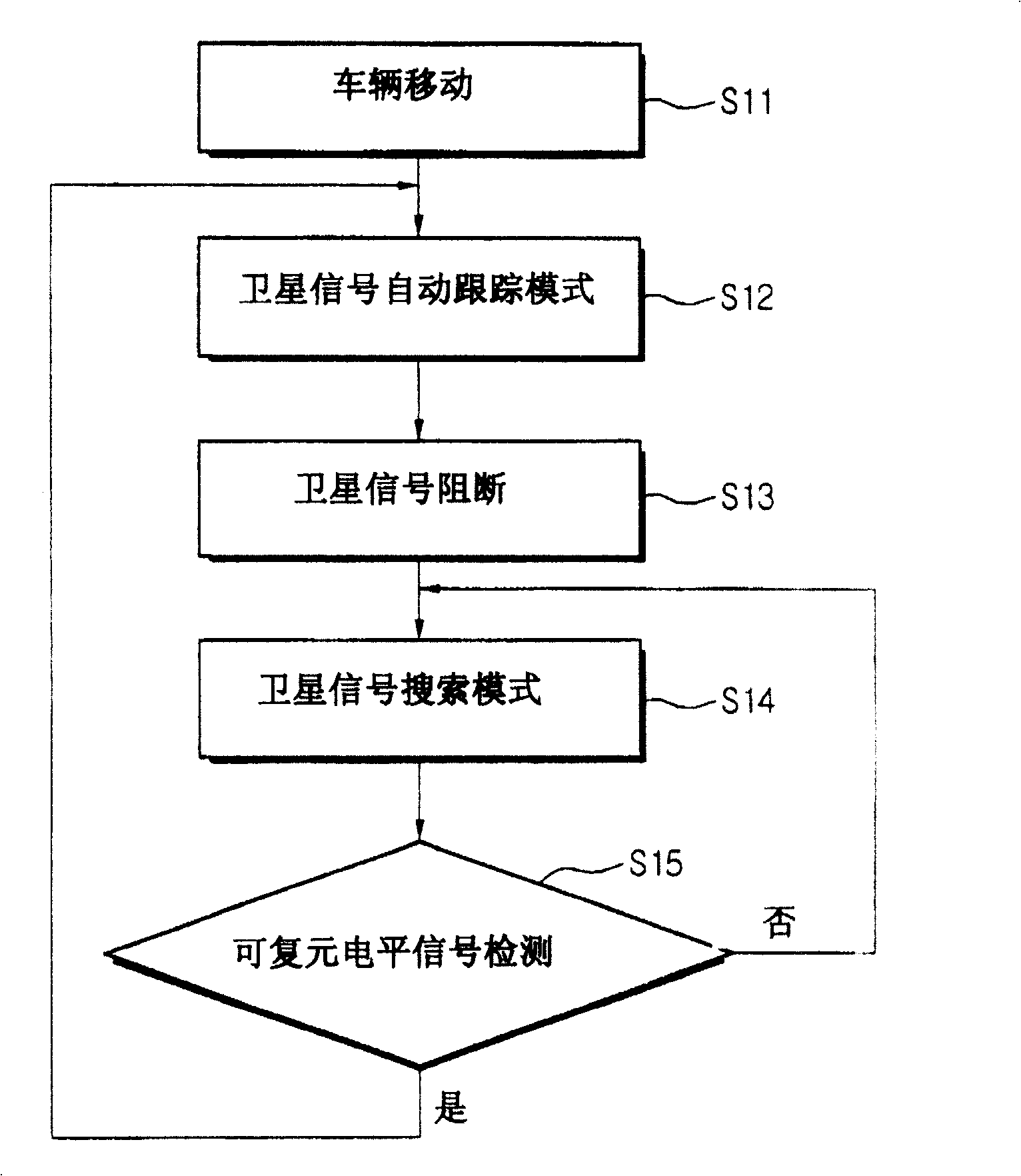

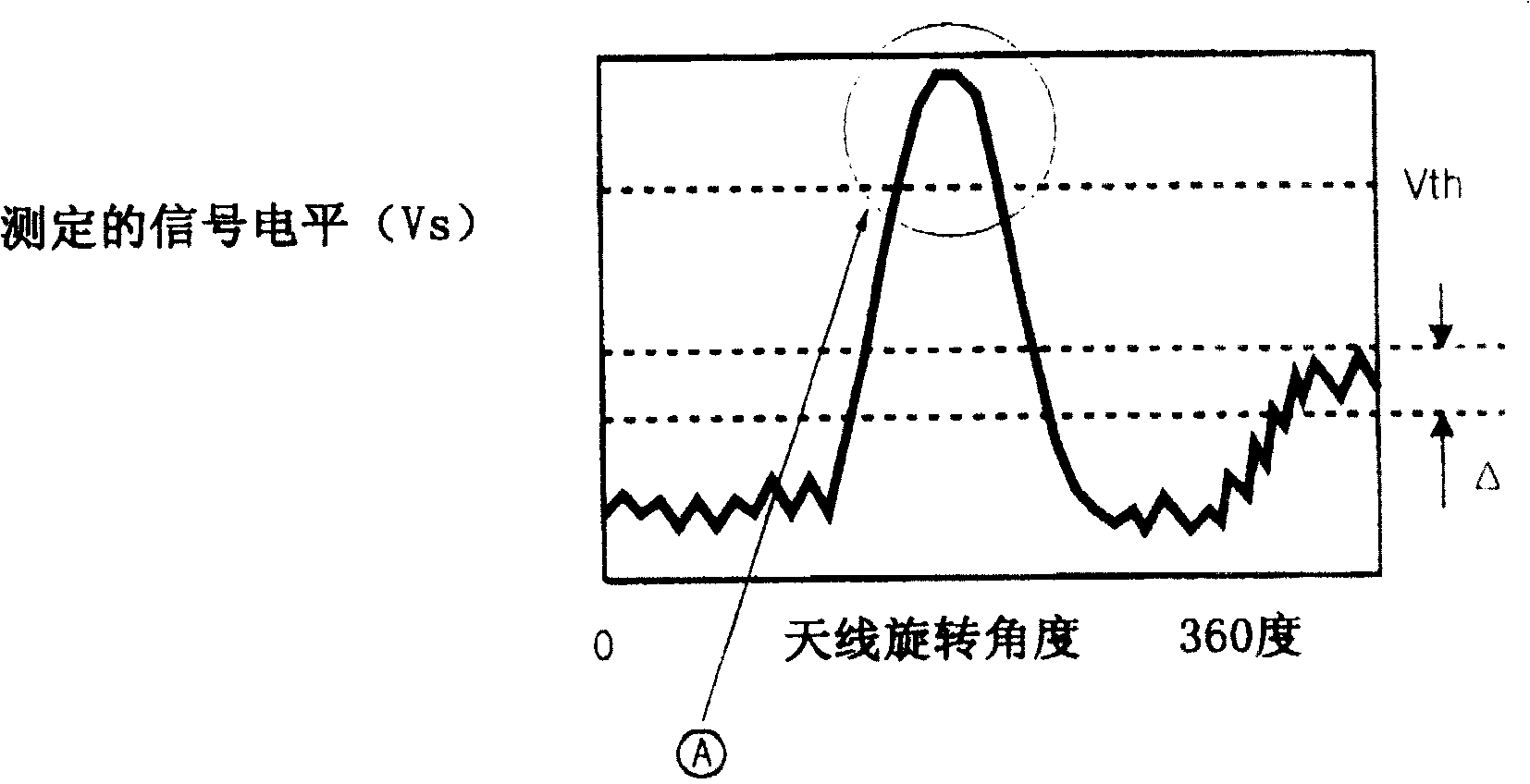

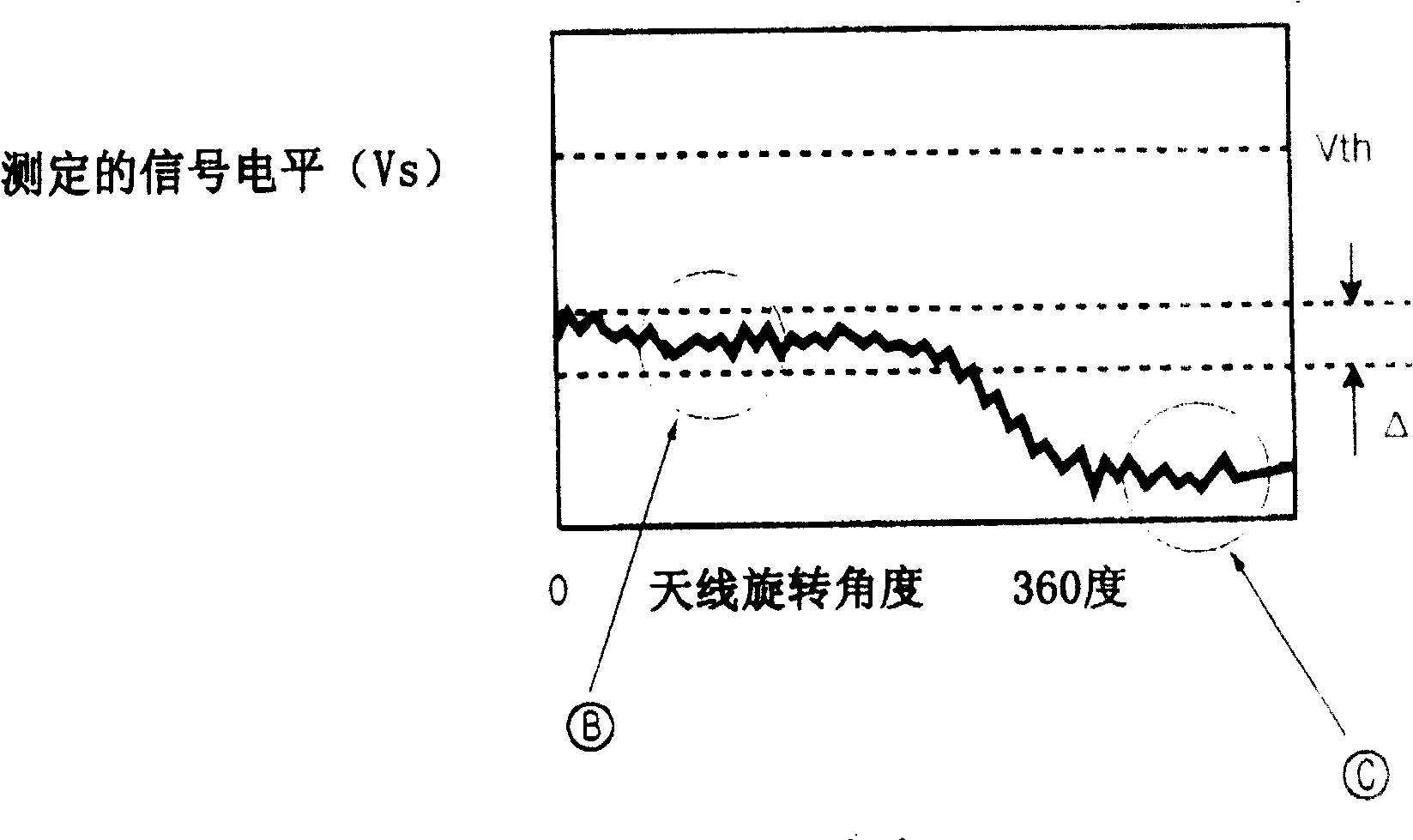

Method for controlling mobile satellite tracking antenna system

InactiveCN100423362CIncreased durabilityAvoid initializationAntenna supports/mountingsAntenna adaptation in movable bodiesSatellite trackingVIT signals

The invention provides a control method for portable satellite tracking antenna system, comprising a plurality of procedures: receiving and detecting the satellite signal if the signal is blocked; automatic tracking mode of the satellite signal is carried out if size of a level for receiving the signal is recoverable when the antenna is rotated 360 degrees; the maximal variation of the signal level measured by the antenna after rotated 360 degrees and a normal temperature noise signal level are compared if the size of the level for receiving signal is unrecoverable; the satellite searching mode is carried out when the maximal variation of the signal level exceeds range of the normal temperature noise signal level; and drive of a rotary motor of the antenna is stopped when the maximal variation of the signal level is in the range of the normal temperature noise signal level.

Owner:KIA MOTORS CORP

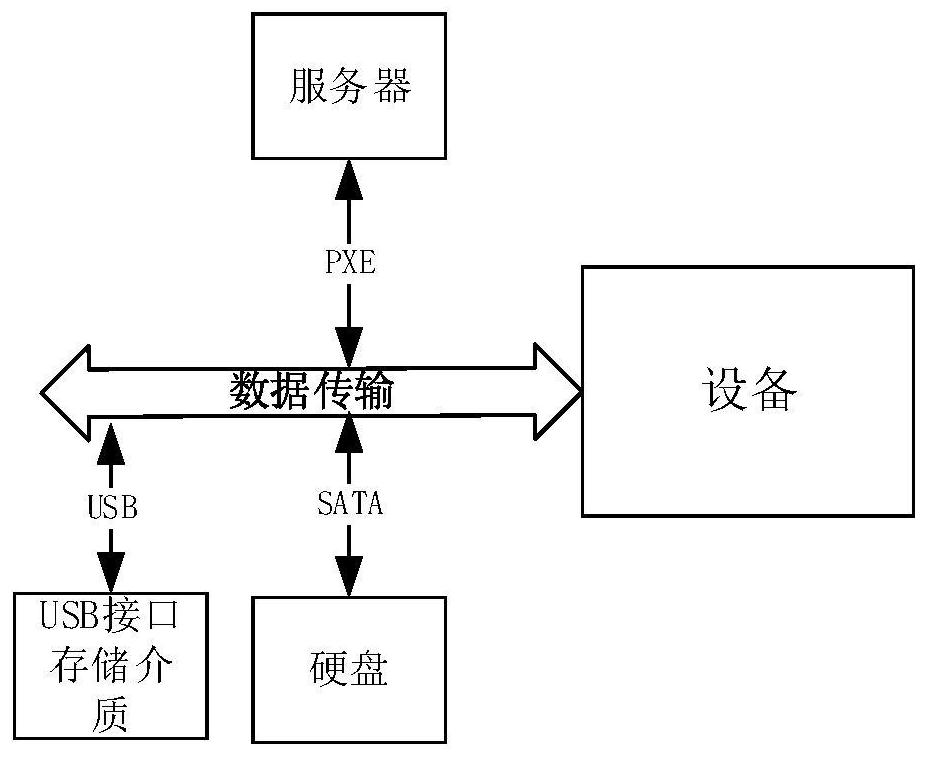

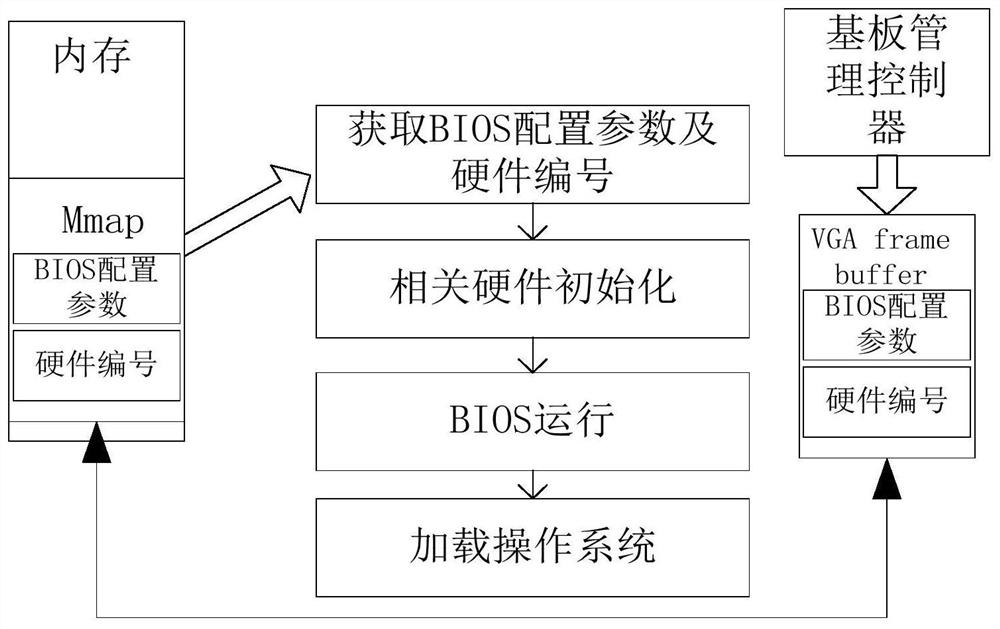

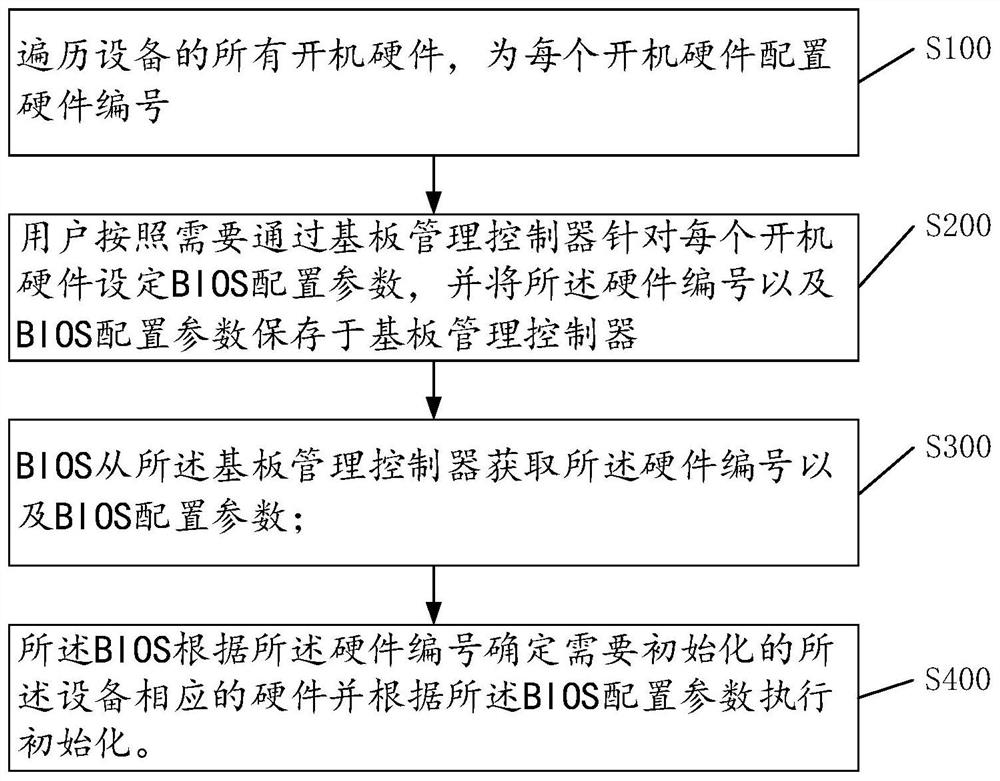

Method for managing BIOS configuration by baseboard management controller and medium

ActiveCN112306581ALow costAvoid initializationVersion controlProgram loading/initiatingBIOSUser interface

The invention discloses a method for managing BIOS (Basic Input Output System) configuration by a baseboard management controller and a medium, and the method comprises the following steps that: traversing of all startup hardware of equipment is carried out, and a hardware number is configured for each startup hardware; a user sets BIOS configuration parameters for each piece of startup hardware as required, and stores the hardware number and the BIOS configuration parameters in a baseboard management controller; and during startup, the BIOS acquires the hardware number and the BIOS configuration parameters from the baseboard management controller, and the BIOS determines hardware corresponding to the equipment to be initialized according to the hardware number and executes initializationaccording to the BIOS configuration parameters. The user sets and modifies BIOS configuration parameters and selects startup hardware through a user interface provided by the baseboard management controller, the BIOS configuration parameters and the hardware number of the startup hardware are directly provided for the BIOS through the baseboard management controller, and the BIOS executes startupinitialization according to the BIOS configuration parameters and the hardware number. The BIOS configuration parameter synchronization conflict in the prior art is eliminated, and the startup speed is increased.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

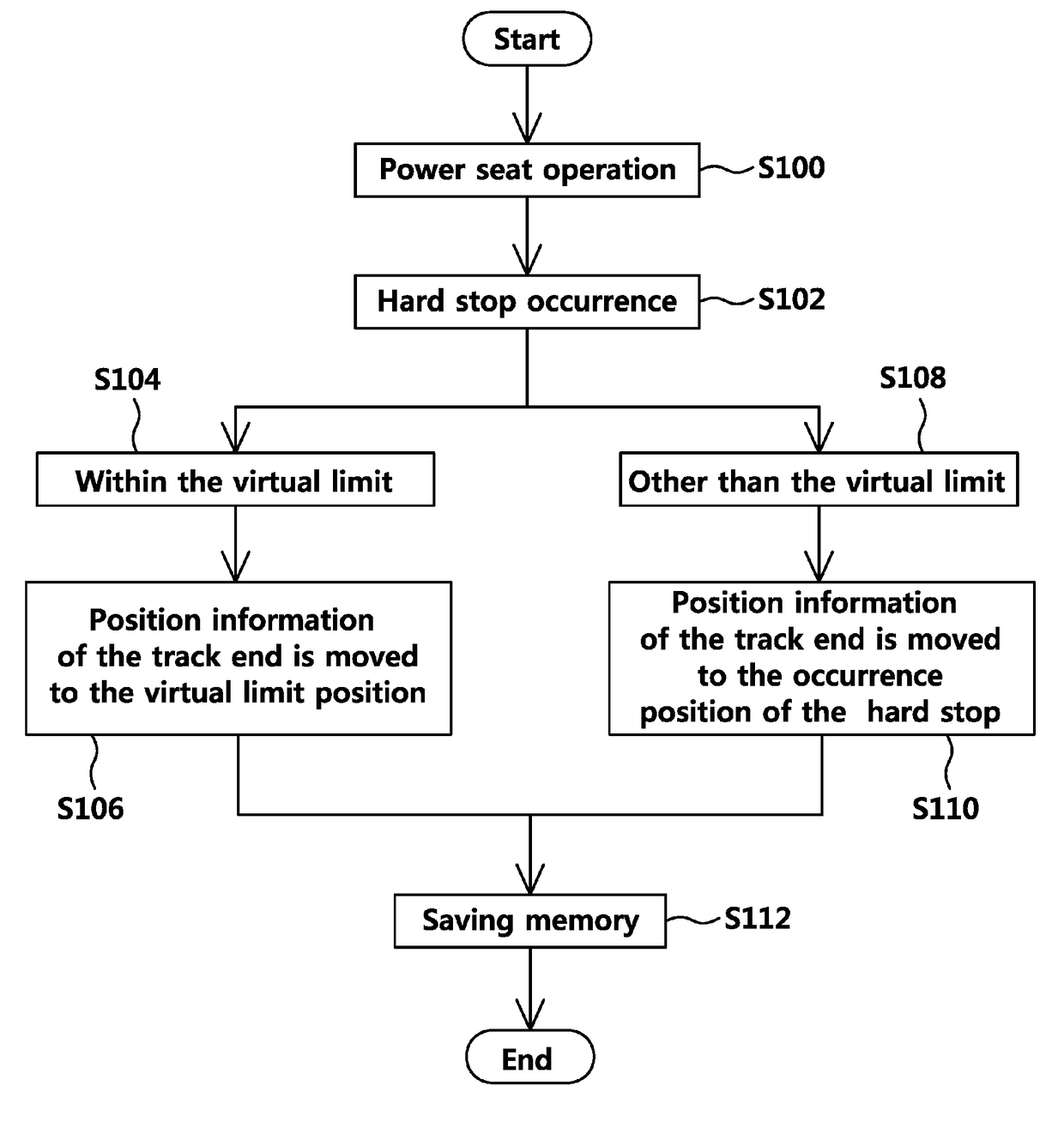

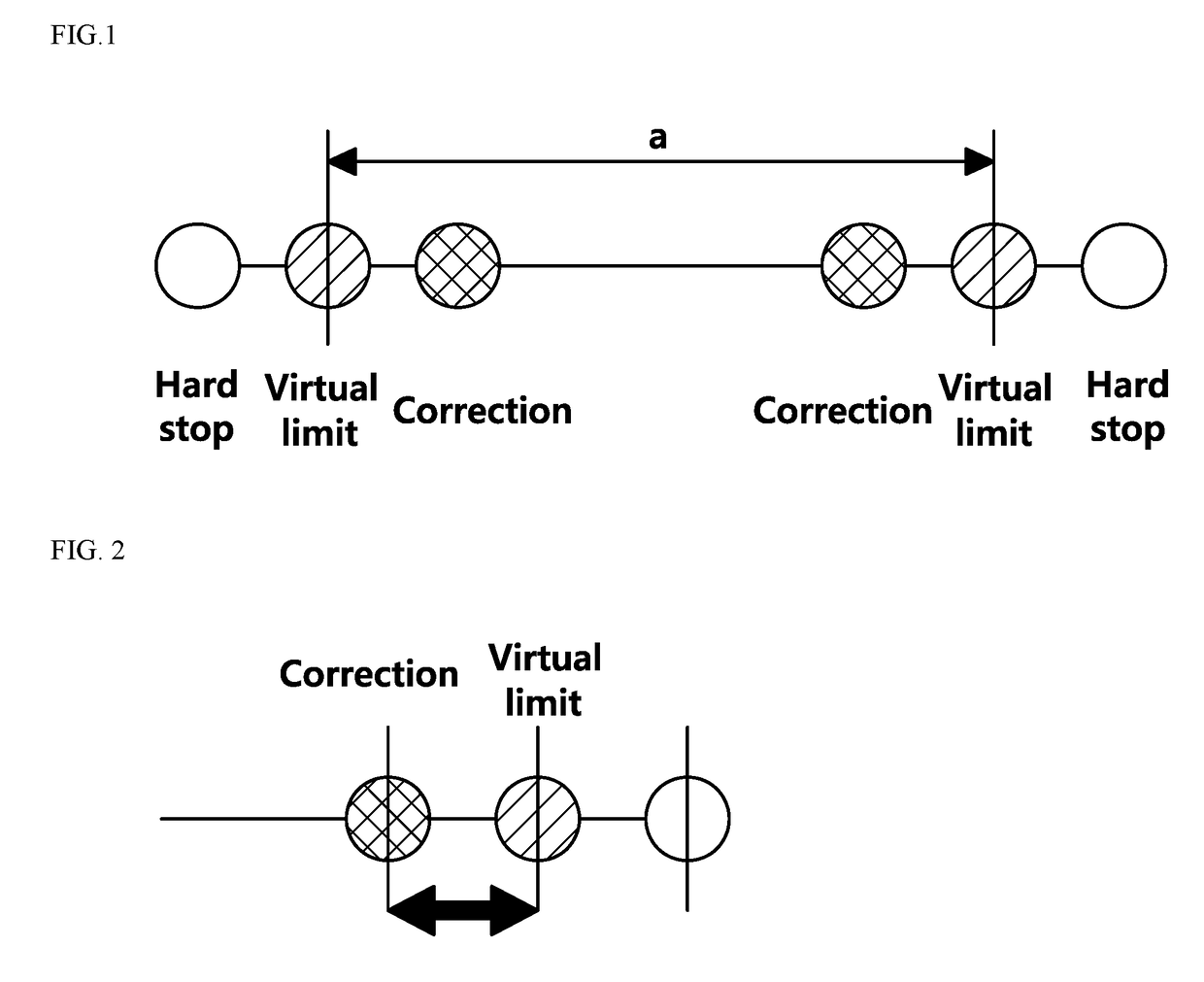

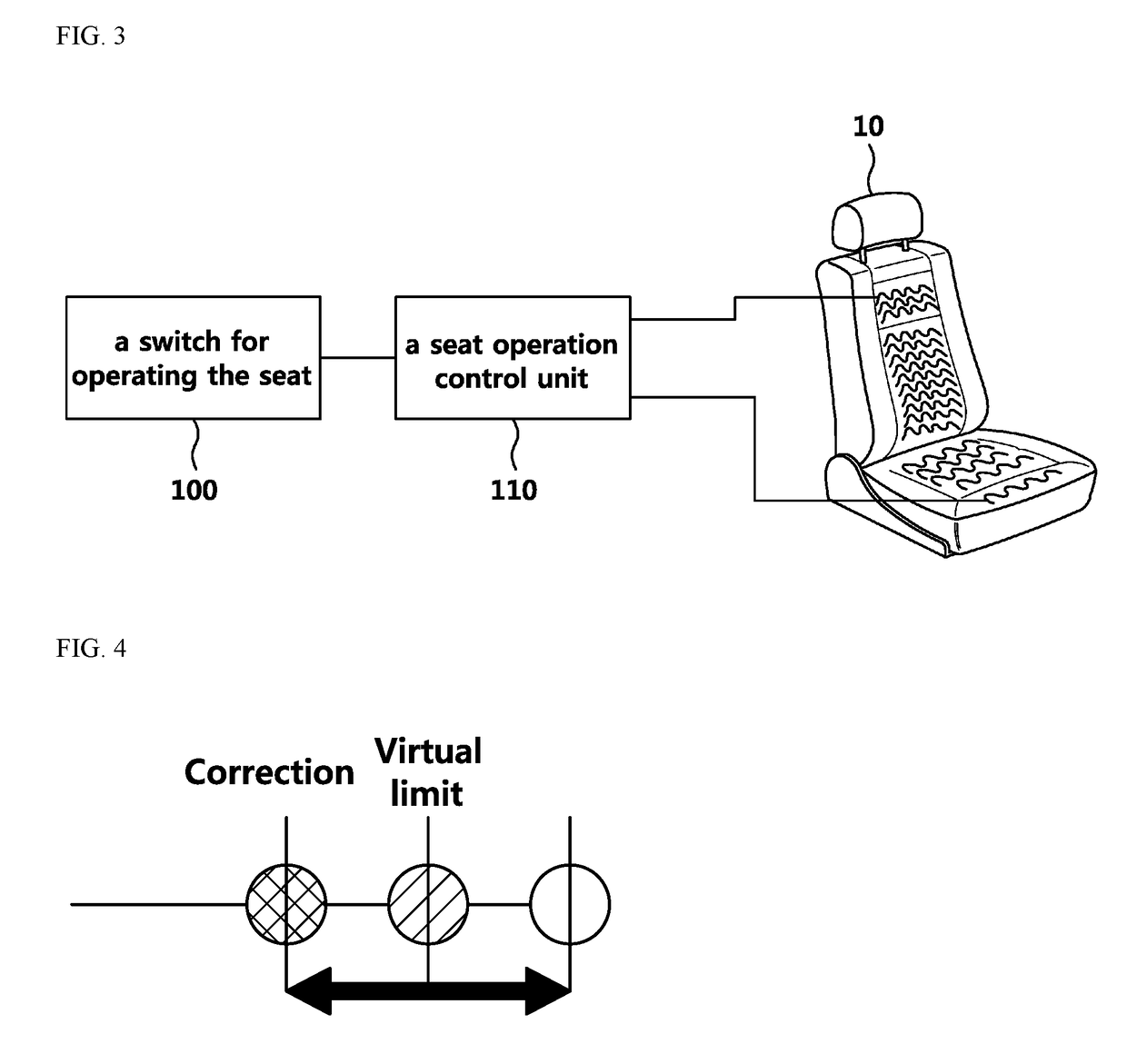

Virtual limit correction device of power seat for vehicle, and correction method therefor

The present invention prevents the virtual limit setting information from being initialized by expanding the position of the virtual limit to a wider range than the conventional one when the hard stop situation occurs in the before / after section of the virtual limit. For the purpose, the present invention provides a virtual limit correction device of power seat for vehicle comprising a switch for seat operation; and a seat operation control unit for correcting the virtual limit position by moving the end position of the track by using the track end position and the compensation position as compensation regions if a hard stop situation occurs in the front / rear direction based on the initially set virtual limit point during the movement of the power seat according to the switch operation.

Owner:HYUNDAI DYMOS