Patents

Literature

49results about How to "Variation in threshold voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

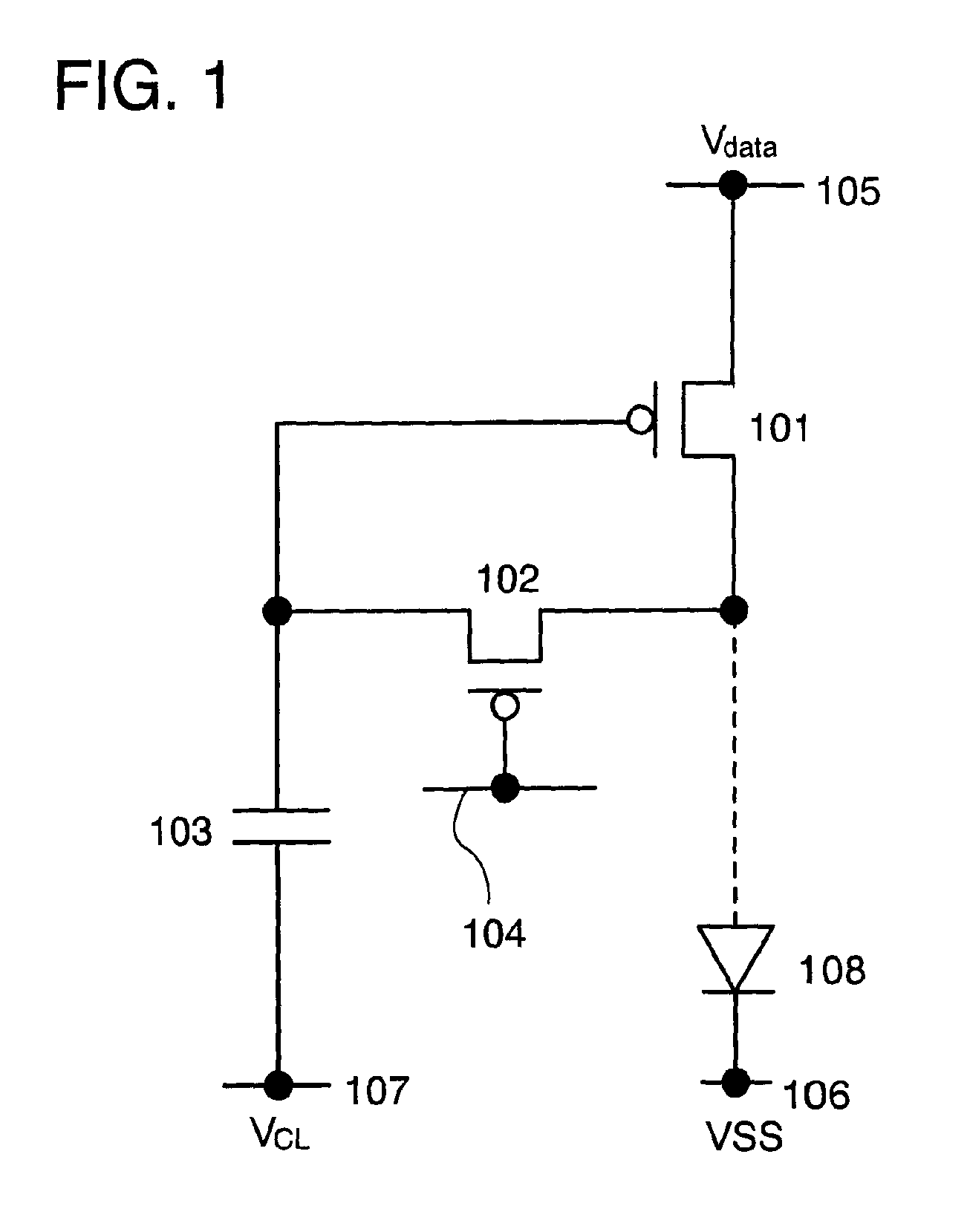

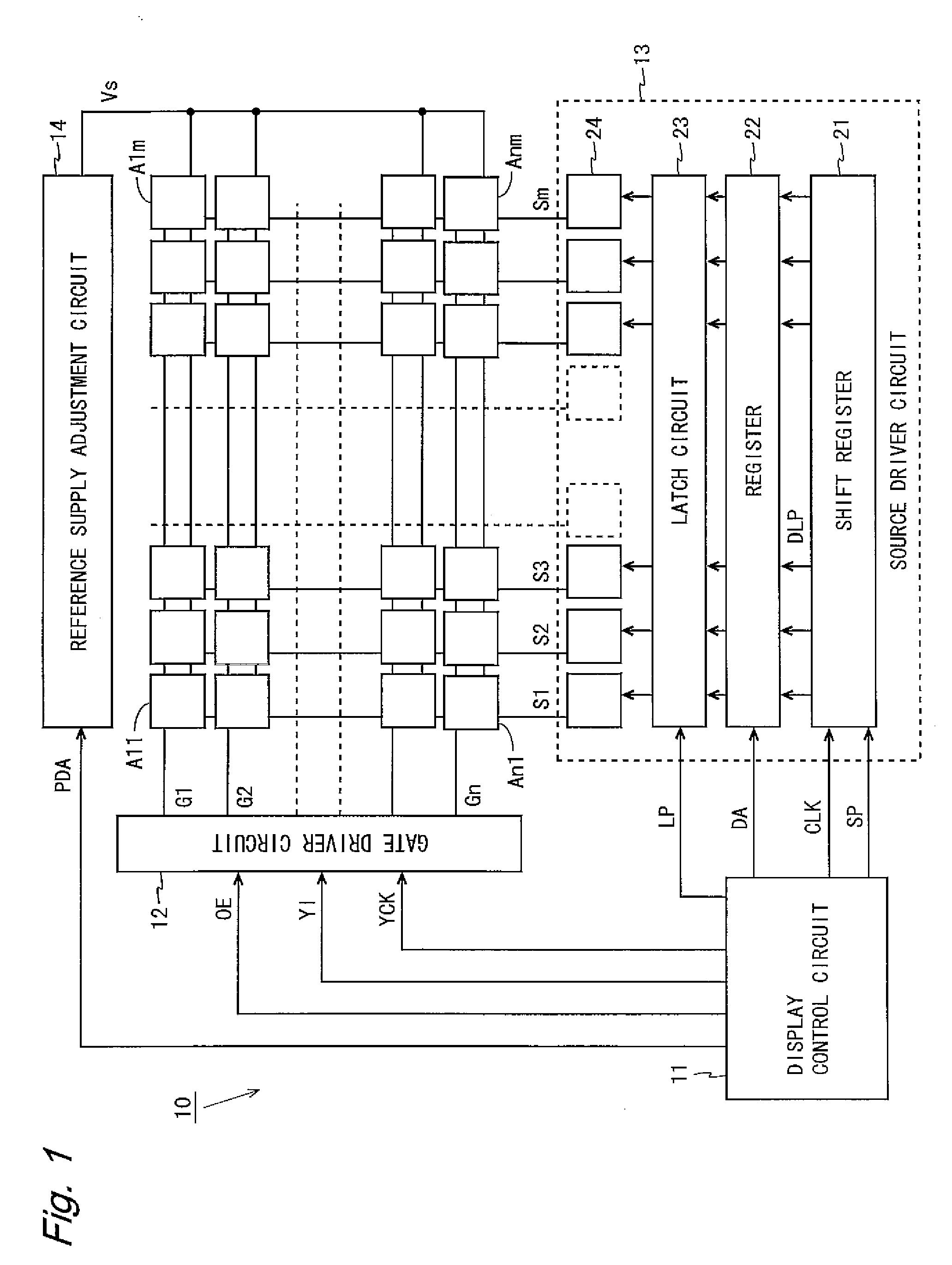

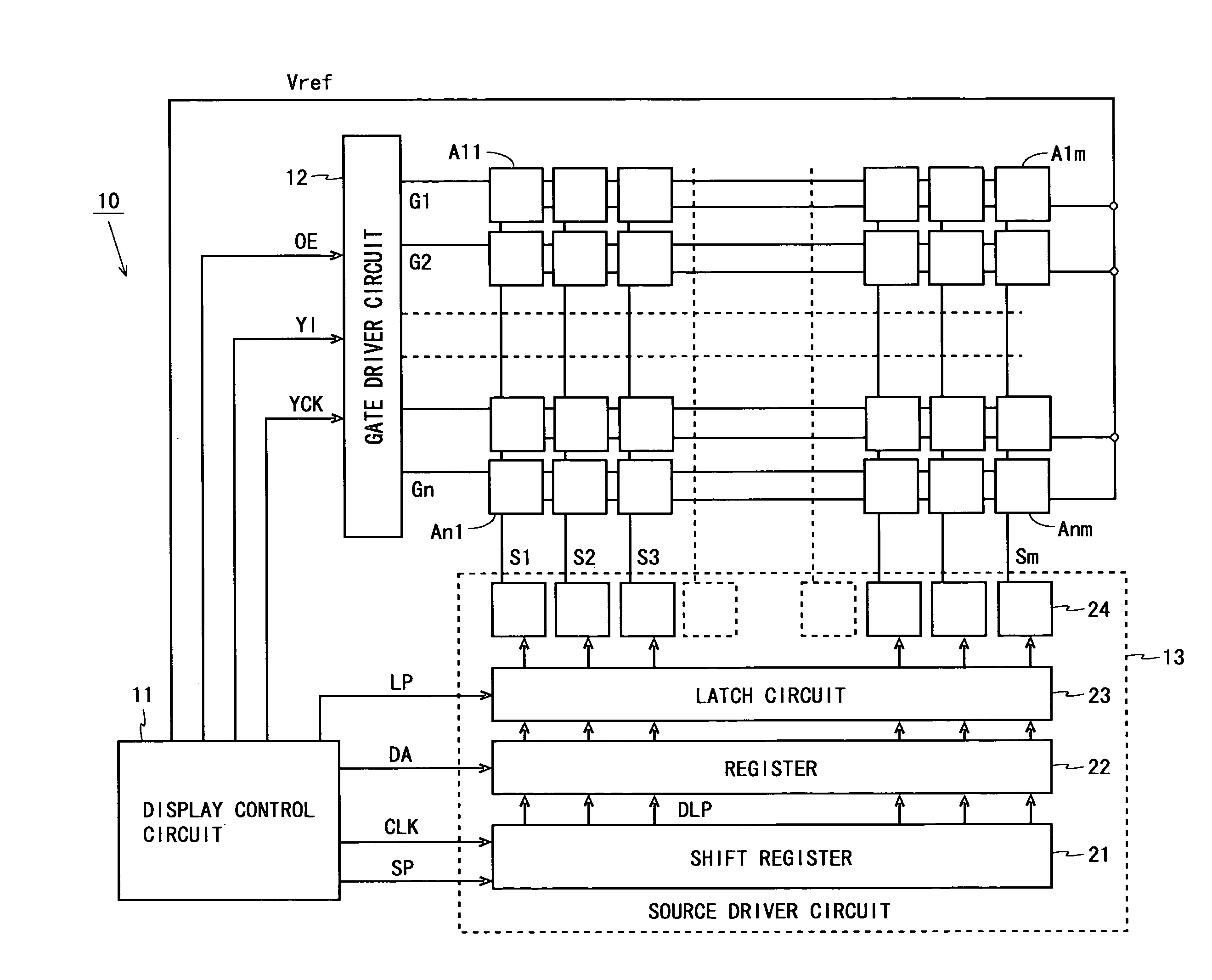

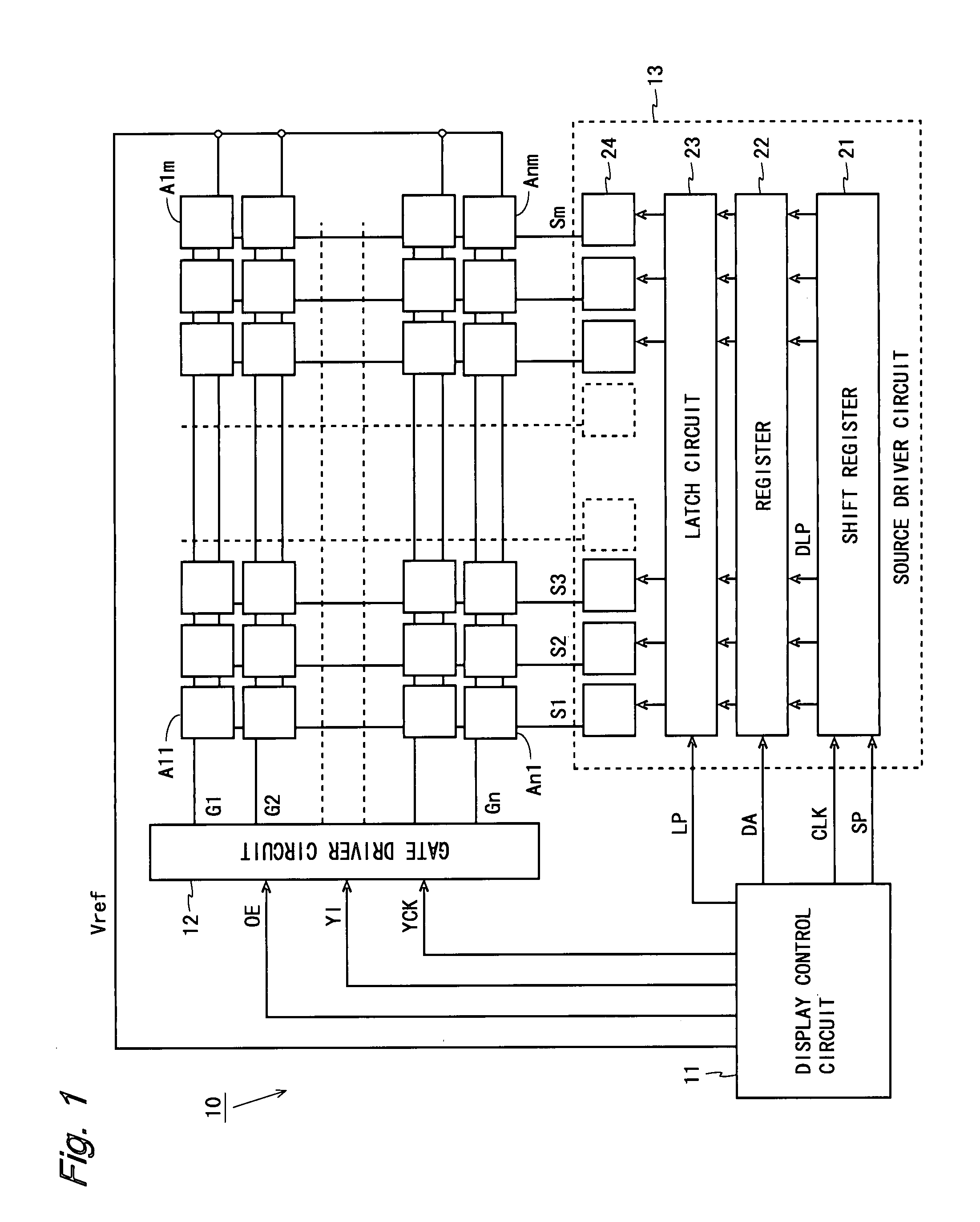

Display device and its driving method

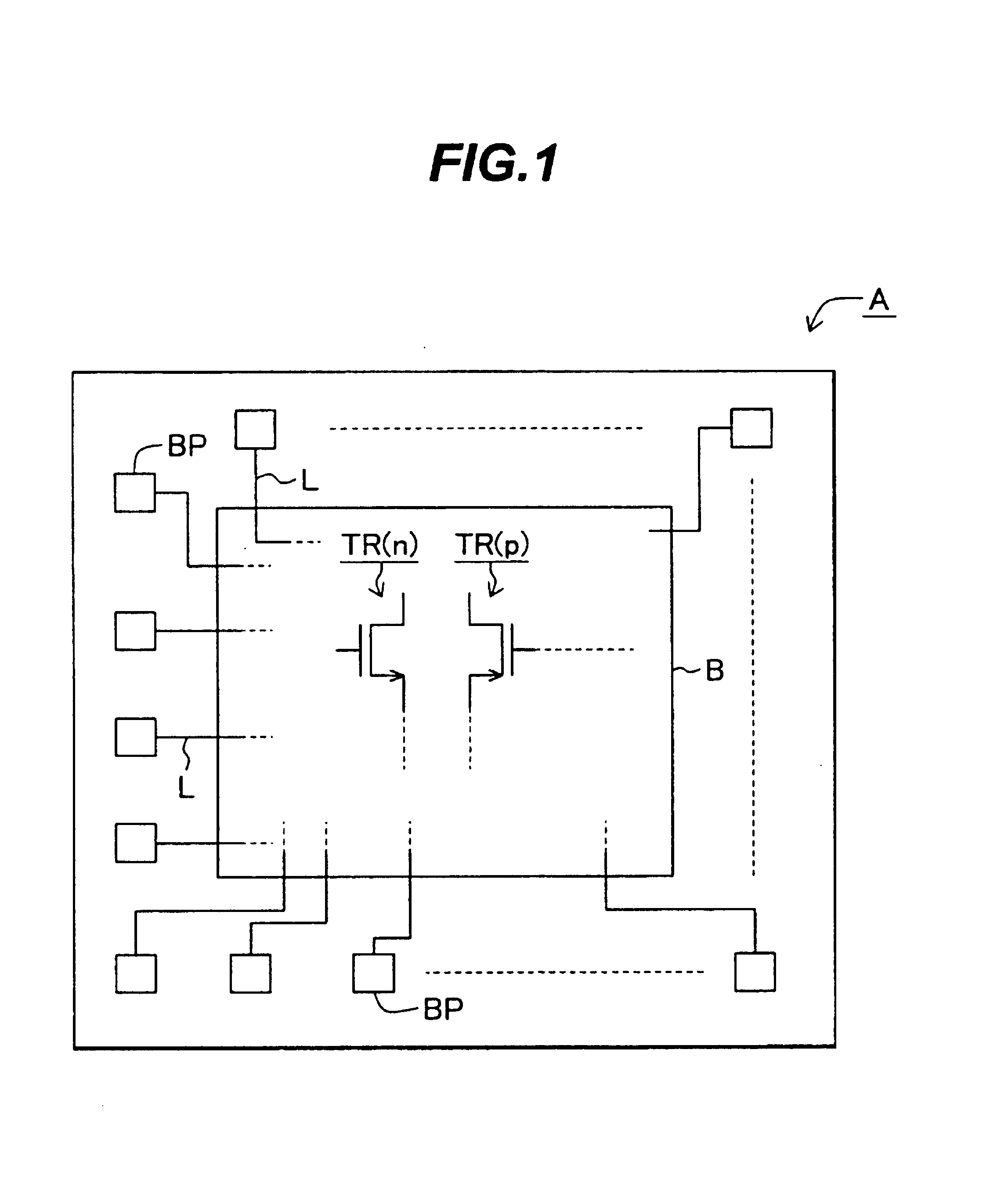

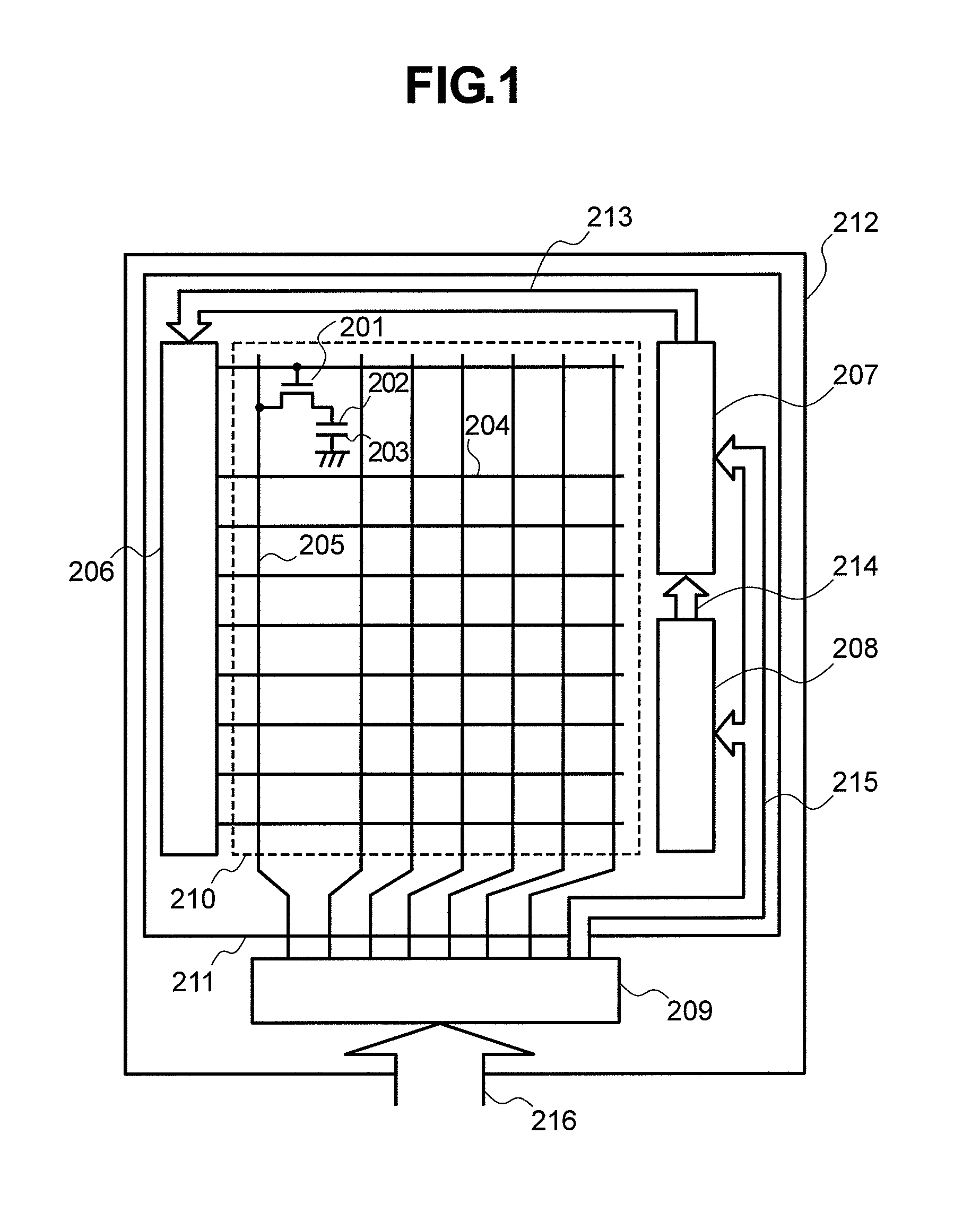

ActiveUS20100045646A1Reduce scaleReduce areaCathode-ray tube indicatorsInput/output processes for data processingDriver circuitDisplay device

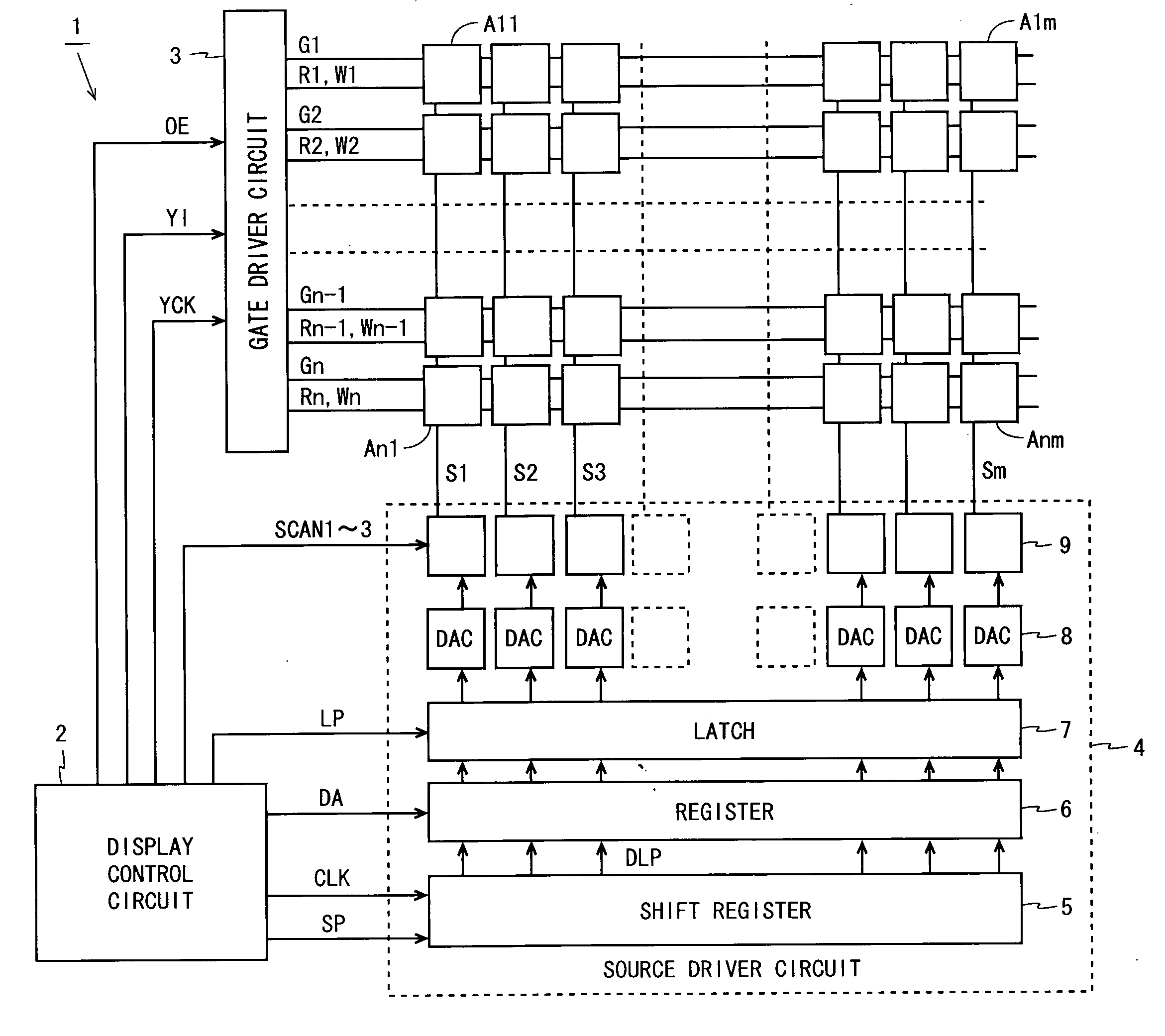

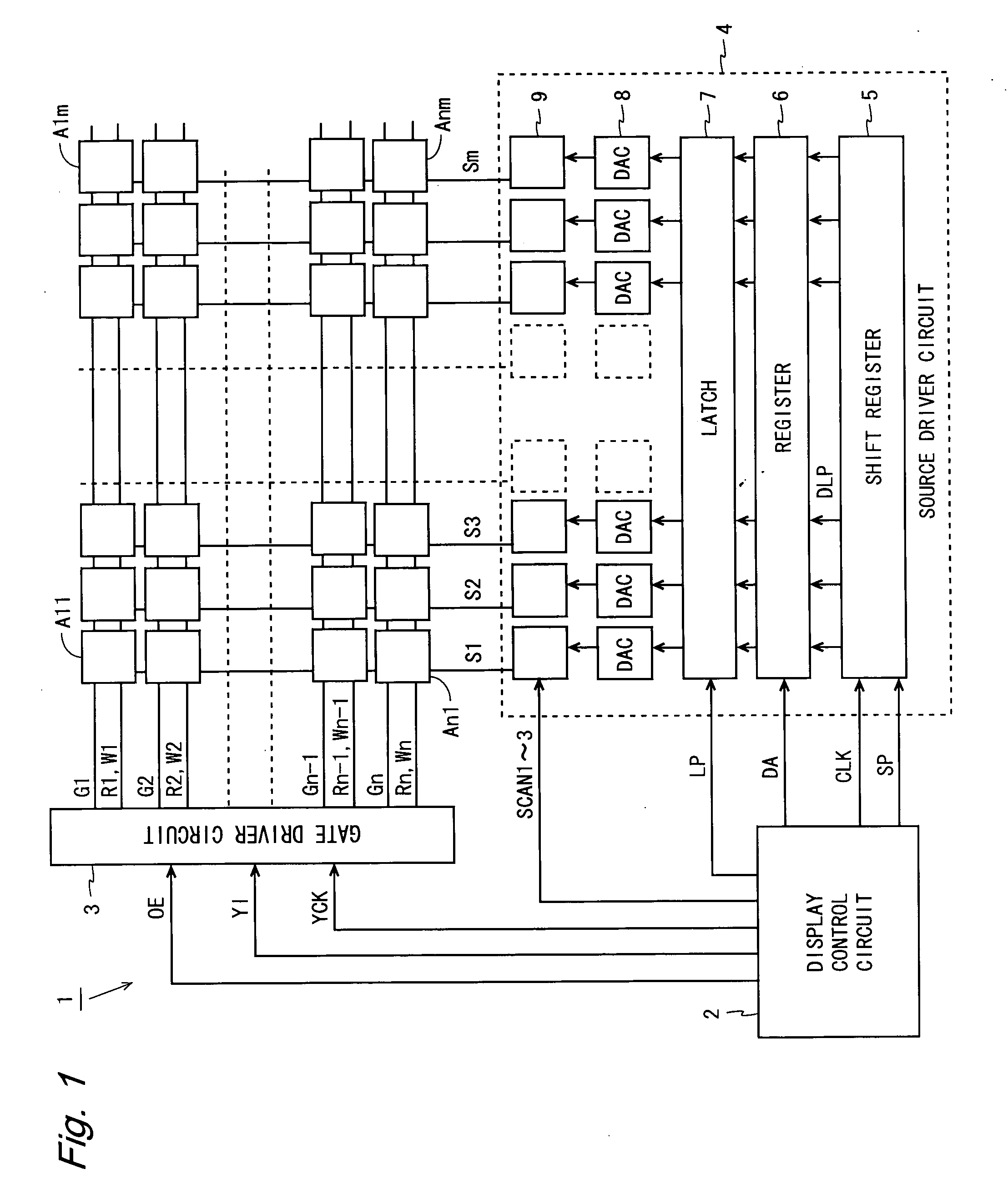

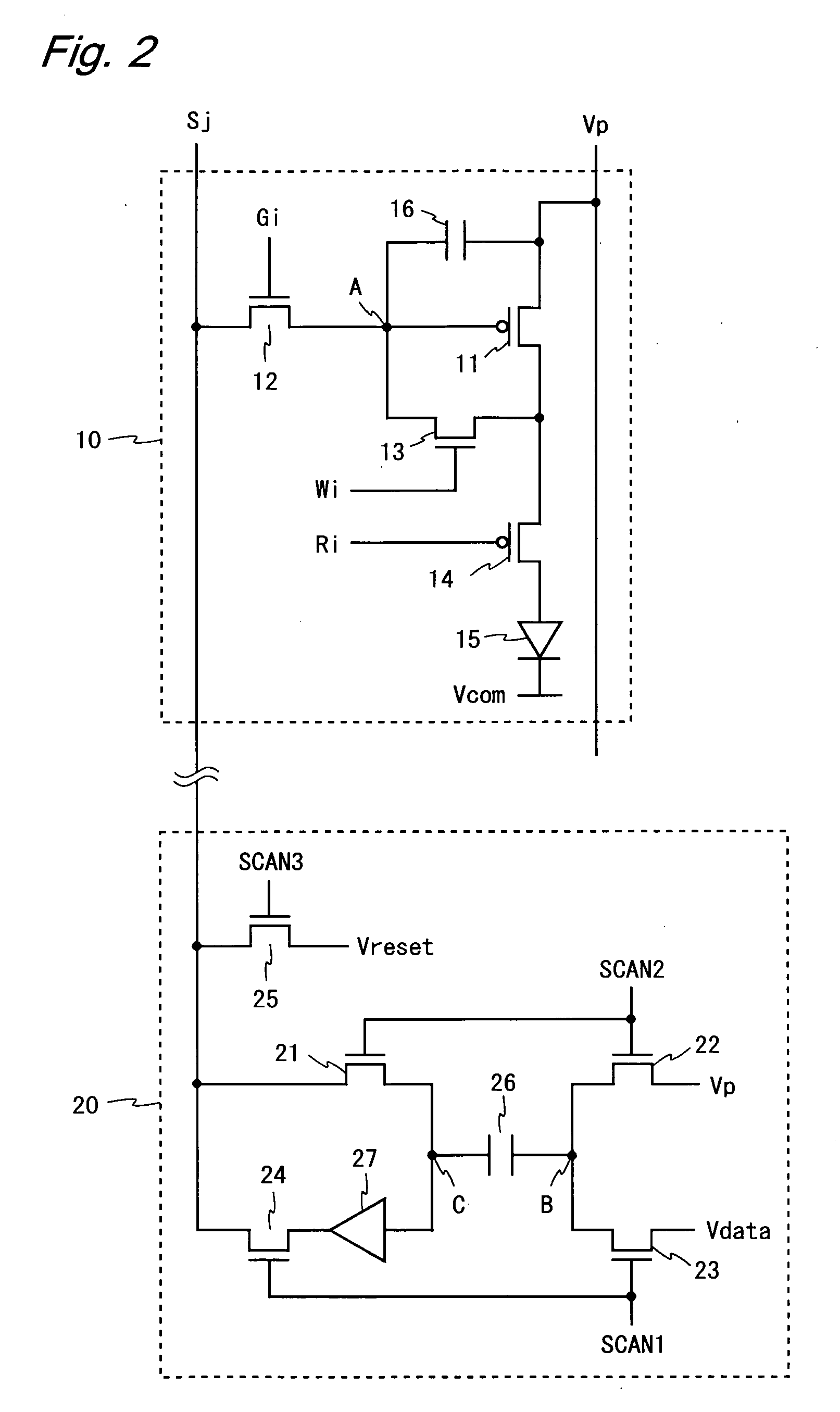

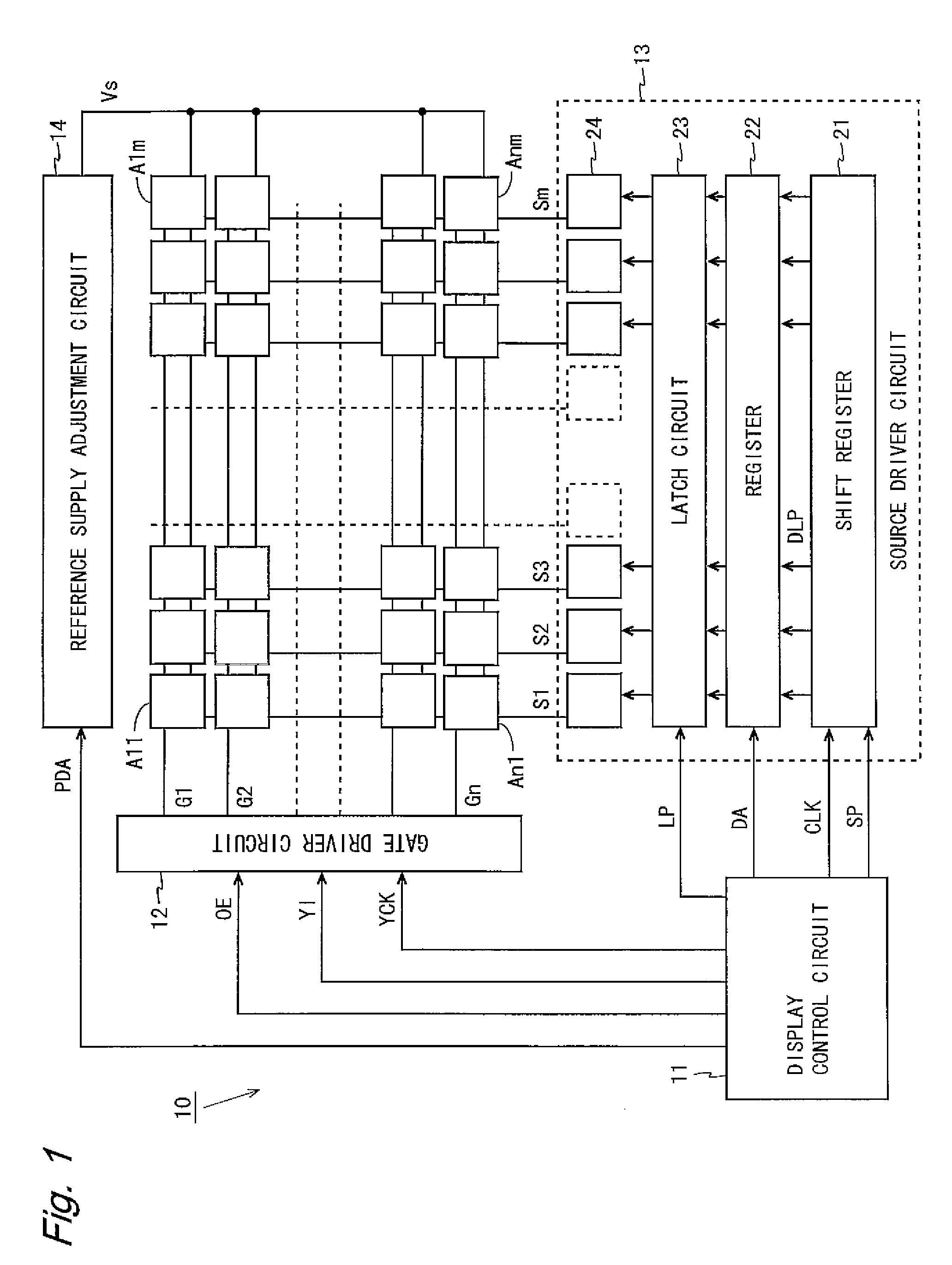

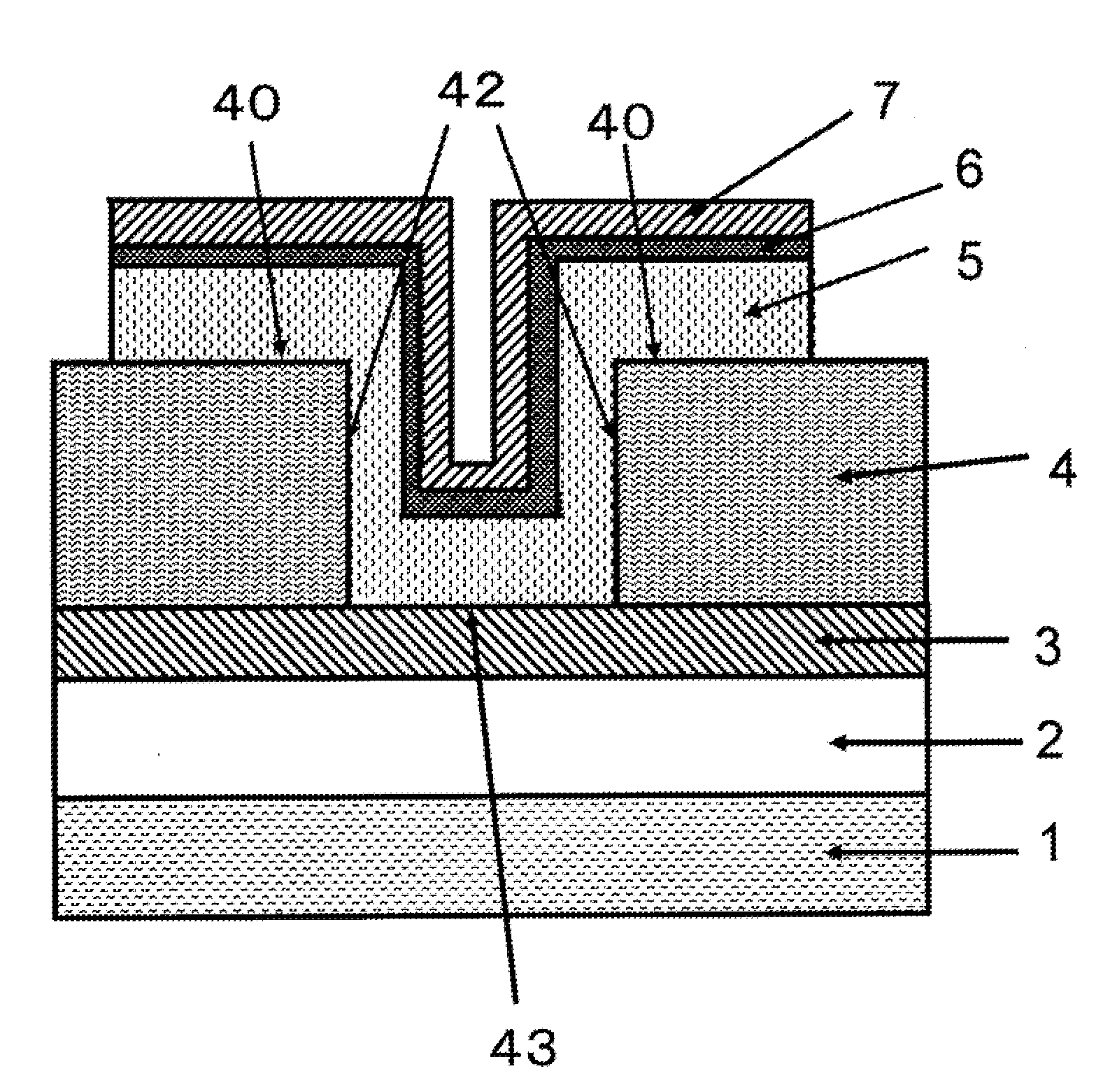

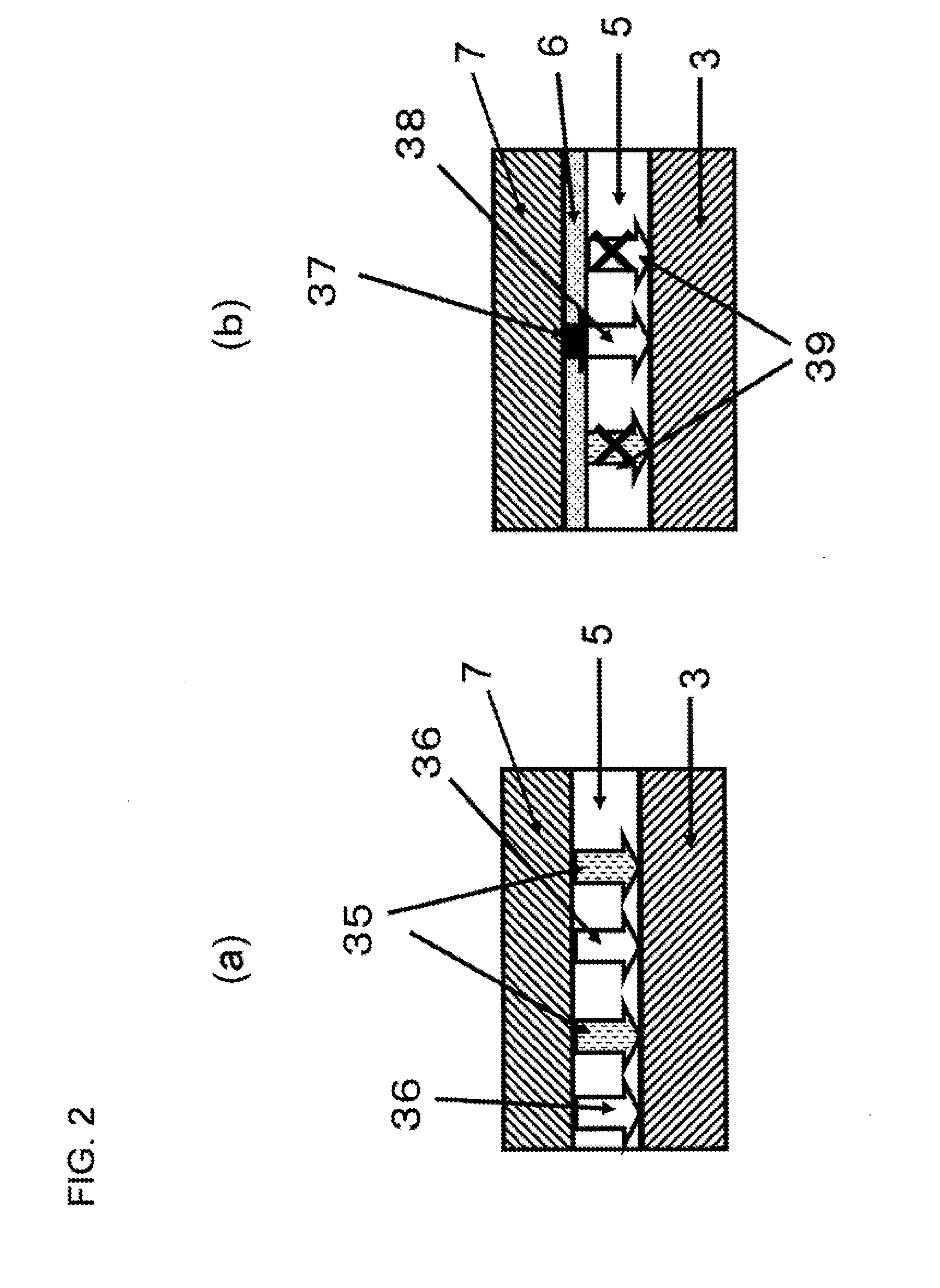

In a pixel circuit 10, TFTs 12 and 13 are turned on while a TFT 14 is turned off, and a voltage (VDD+Vx) which depends on a threshold voltage Vth of a driving TFT 11 is read onto a data line Sj. Moreover, switches 21 and 22 in a source driver circuit are turned on, and a voltage Vx is held at a capacitor 26. Next, the TFT 13 is turned off, states of switches 21 to 24 are switched, and a voltage (Vdata+Vx) is applied to the data line Sj. Further, the TFT 12 is turned off while the TFT 14 is turned on. An amount of an electric current flowing through an organic EL element 15 after the turn-on of the TFT 14 is determined from the voltage (Vdata+Vx) of a gate terminal of the driving TFT 11. Thus, it is possible to efficiently utilize an amplitude of a data voltage and compensate variations in threshold voltage of the driving TFT 11 with high accuracy, without increasing a scale of the pixel circuit 10.

Owner:SHARP KK

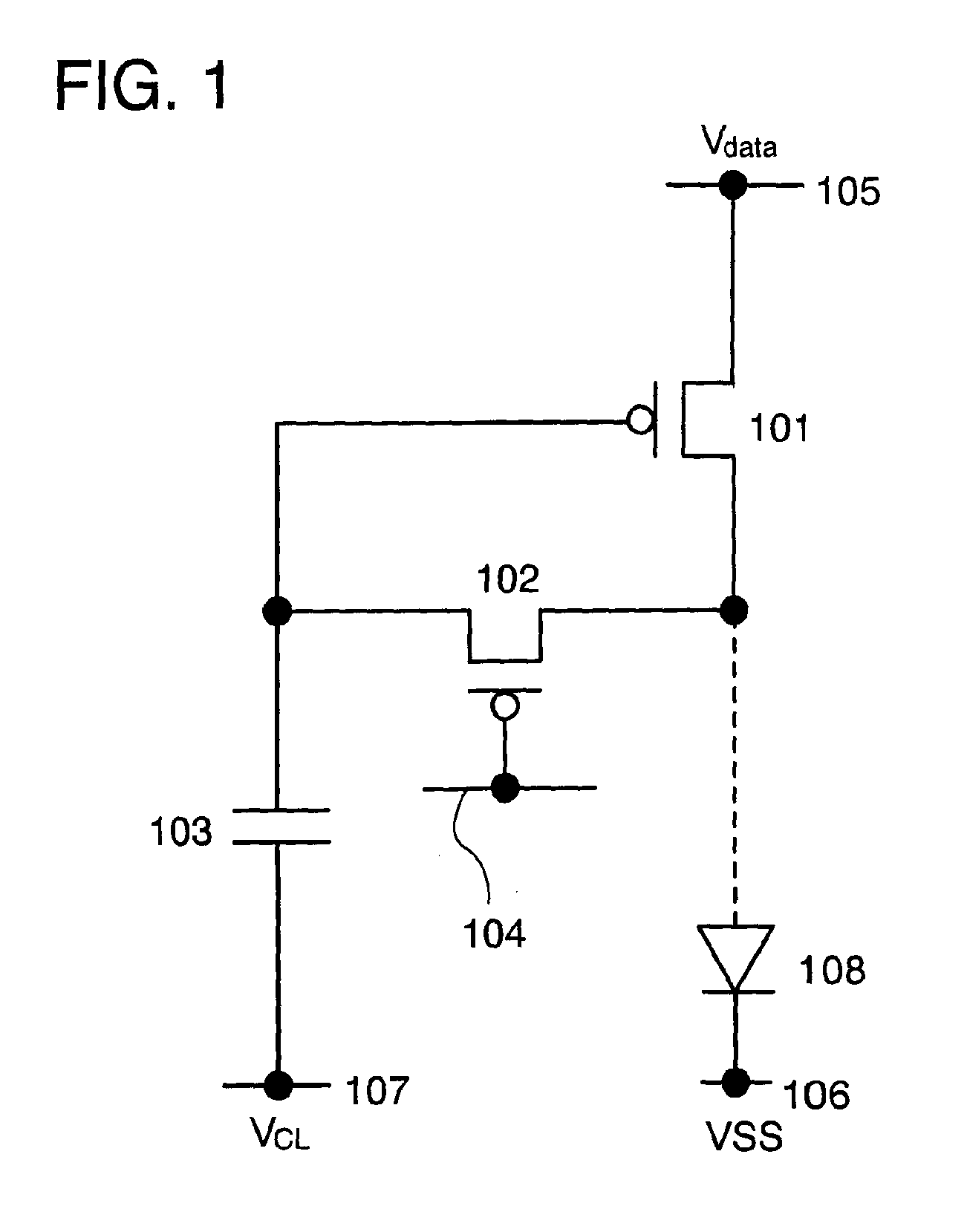

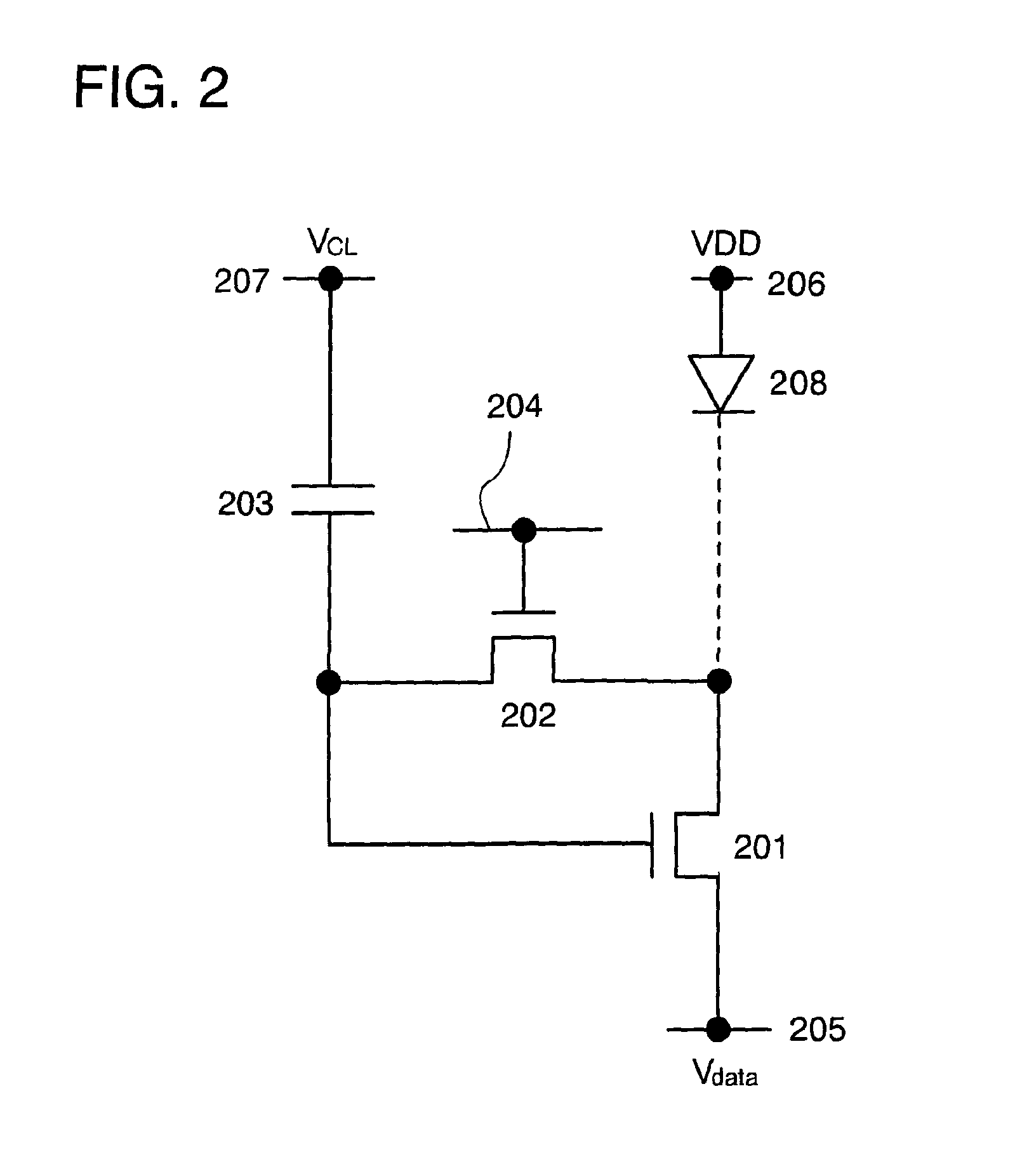

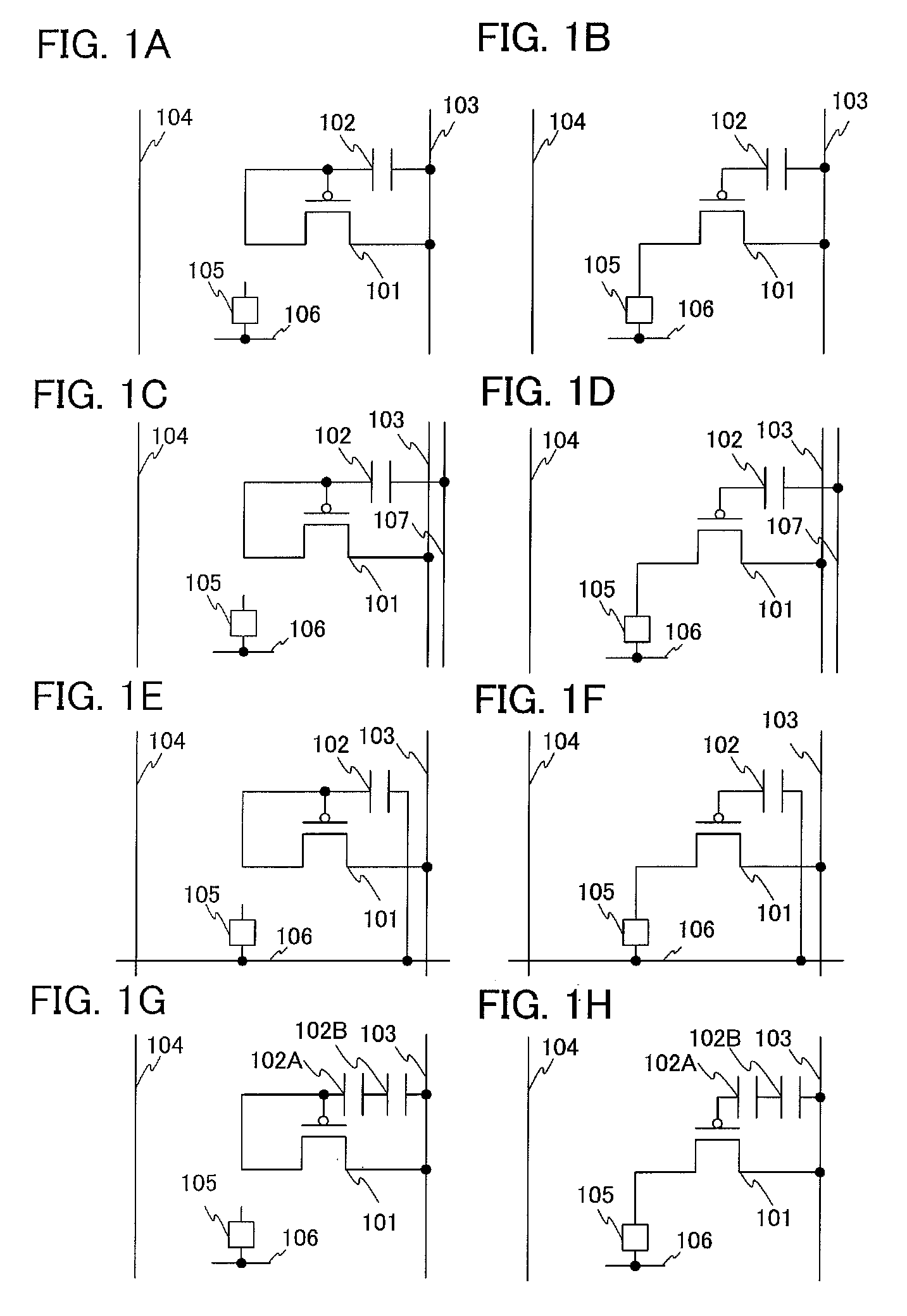

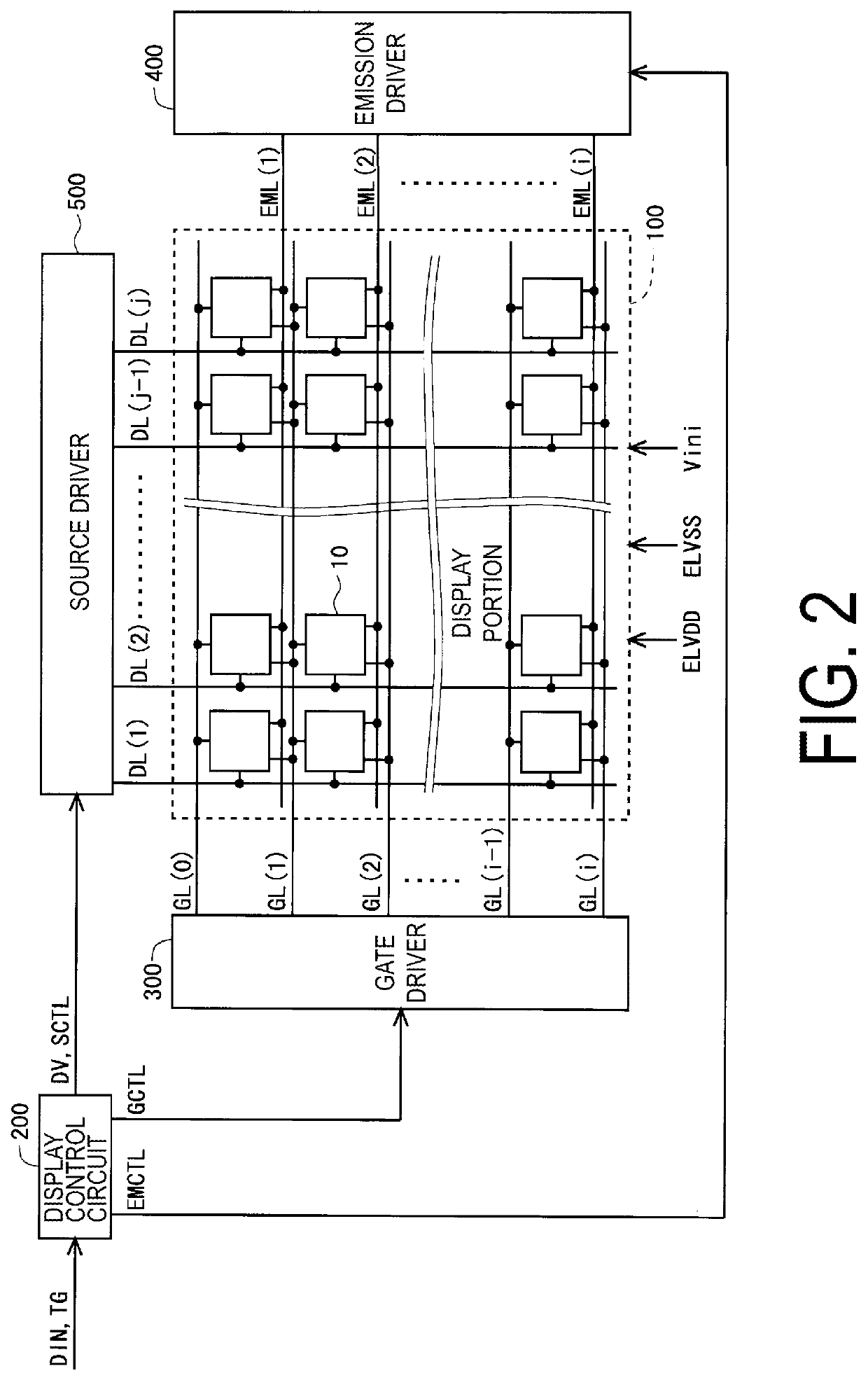

Semiconductor device and driving method thereof

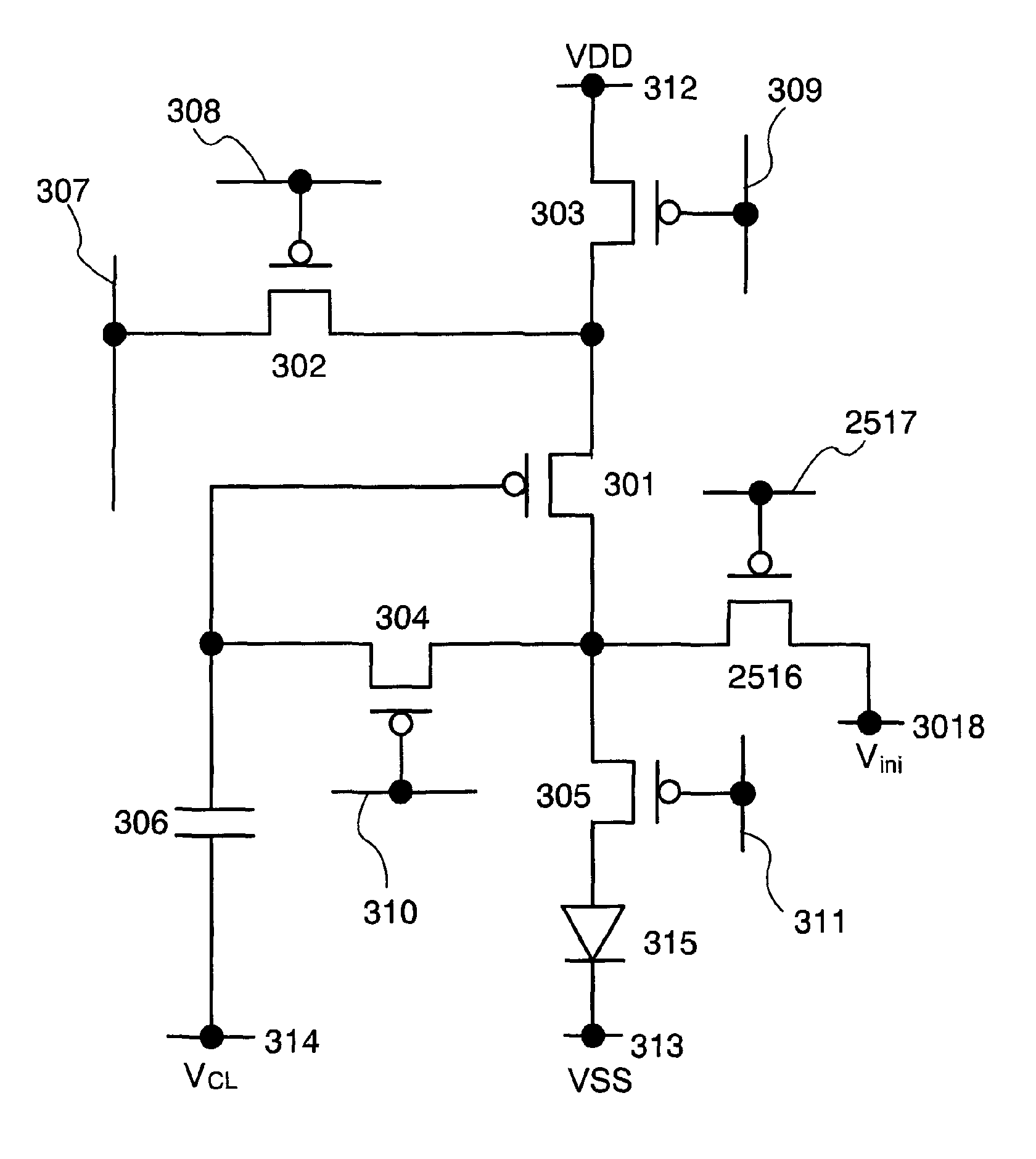

InactiveUS20080143653A1Reduce variationImprove image qualityStatic indicating devicesElectroluminescent light sourcesDisplay deviceEngineering

A display device which can compensate for variations of the threshold voltage of transistors and suppress variations in luminance, and a driving method thereof are provided. Current is supplied to a light emitting element and light is emitted from the light emitting element by following steps: in the first period initial voltage is stored in a storage capacitor; in the second period, voltage based on video signal voltage and the threshold voltage of the transistor is stored in the storage capacitor; and in the third period, the voltage stored in the storage capacitor in the second period is applied to a gate electrode of the transistor. By these operation processes, the current which compensates the effect of the variations of the threshold voltage of the transistor can be supplied to the light emitting element. Therefore, variations in luminance are suppressed.

Owner:SEMICON ENERGY LAB CO LTD

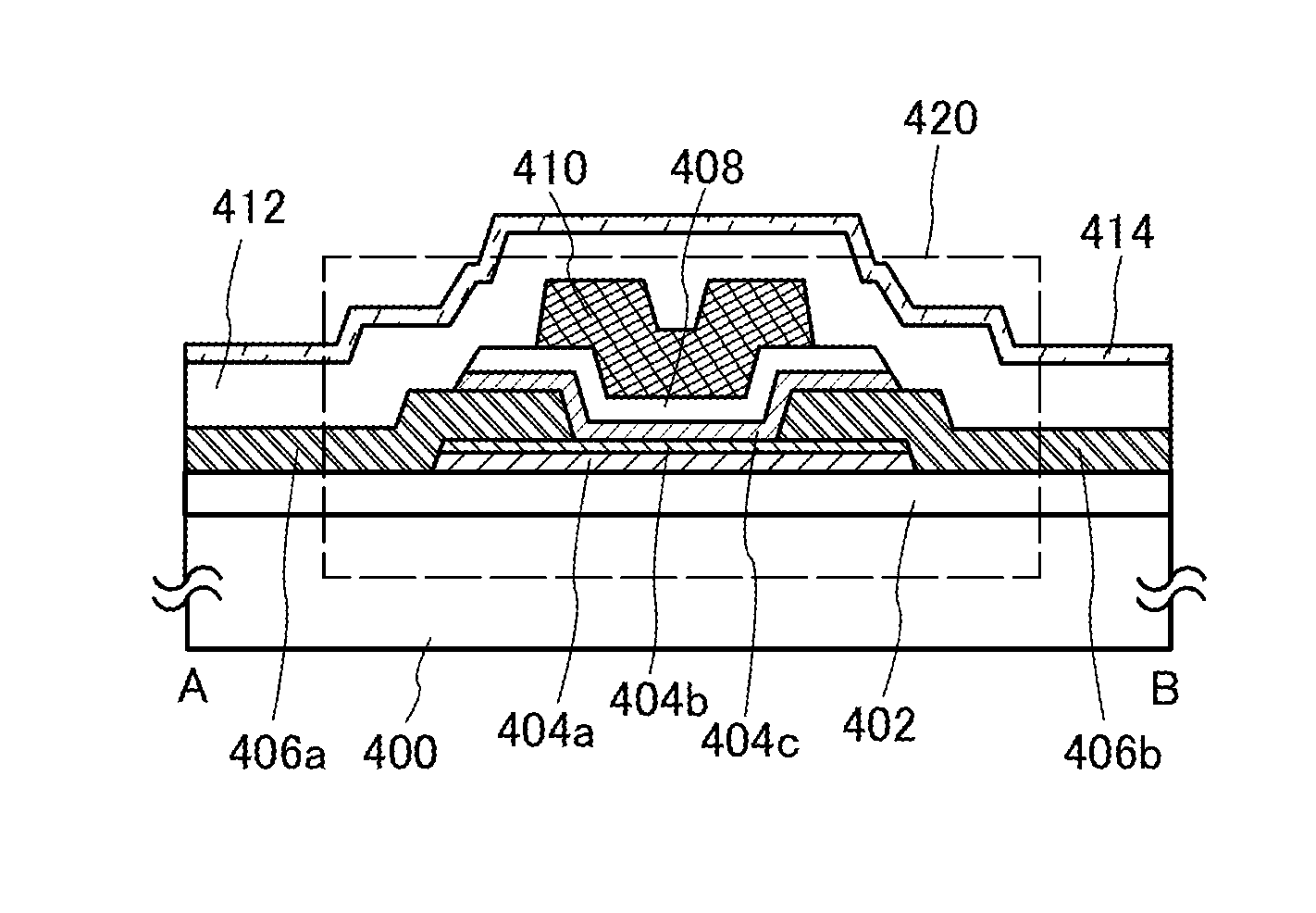

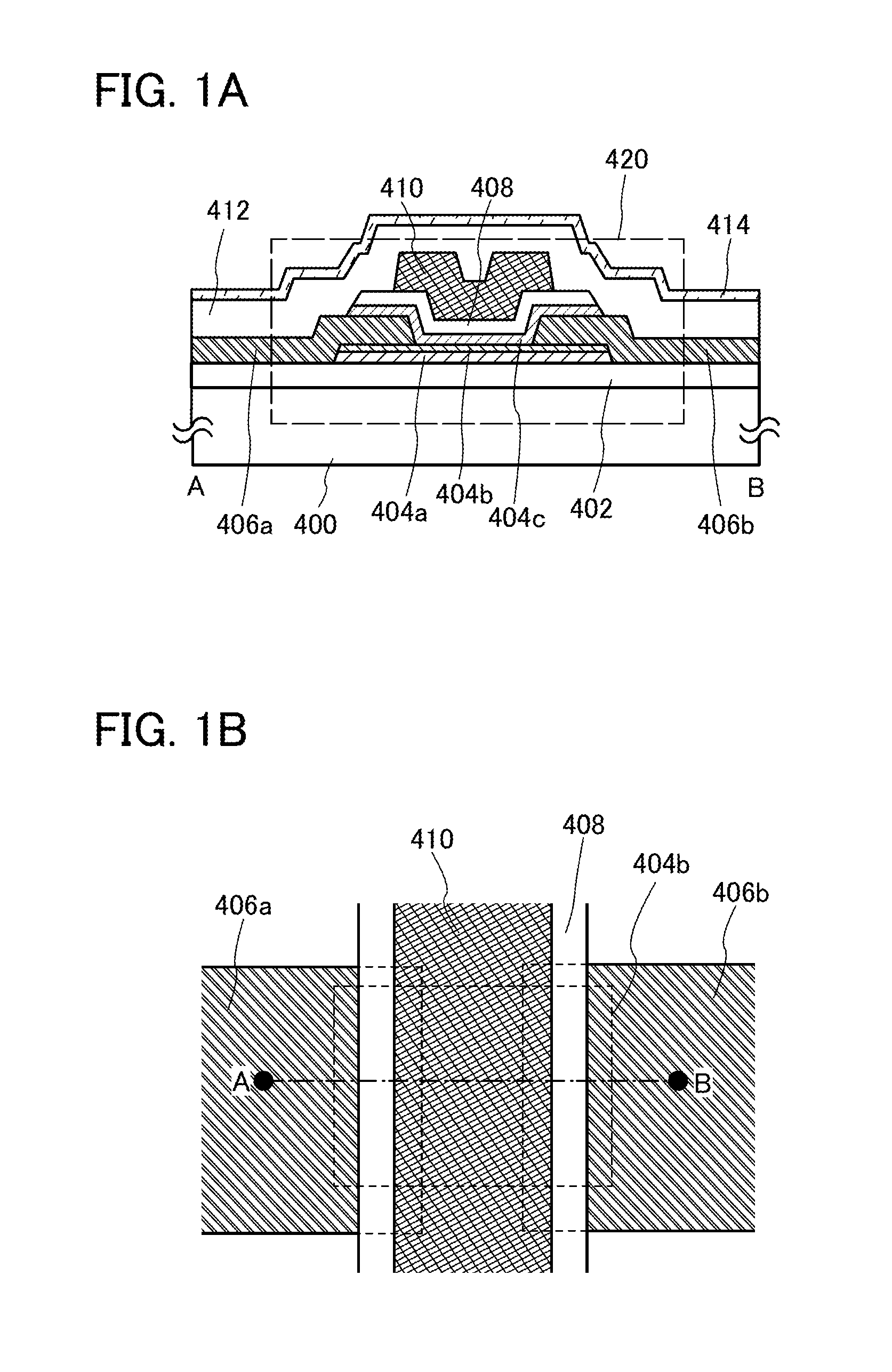

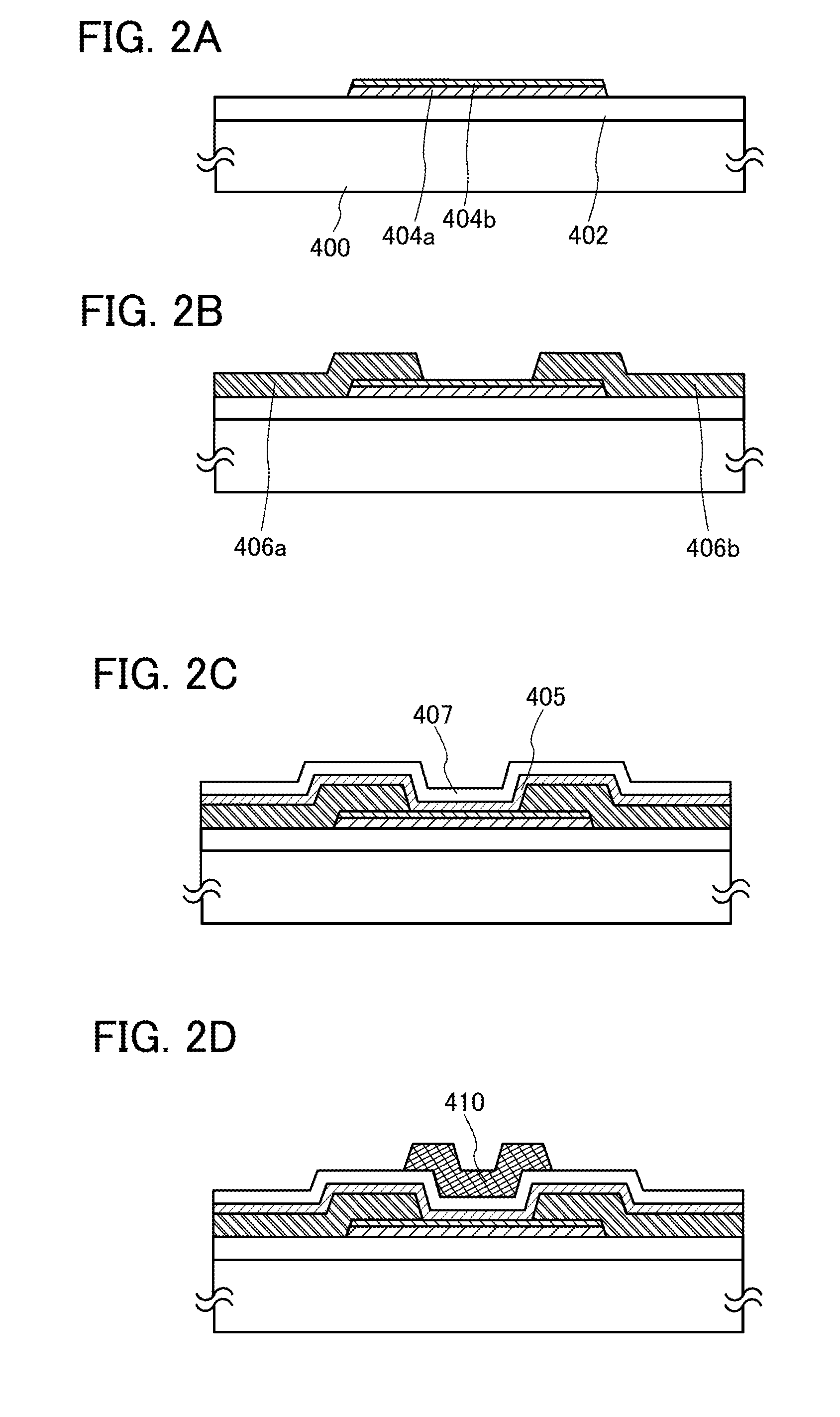

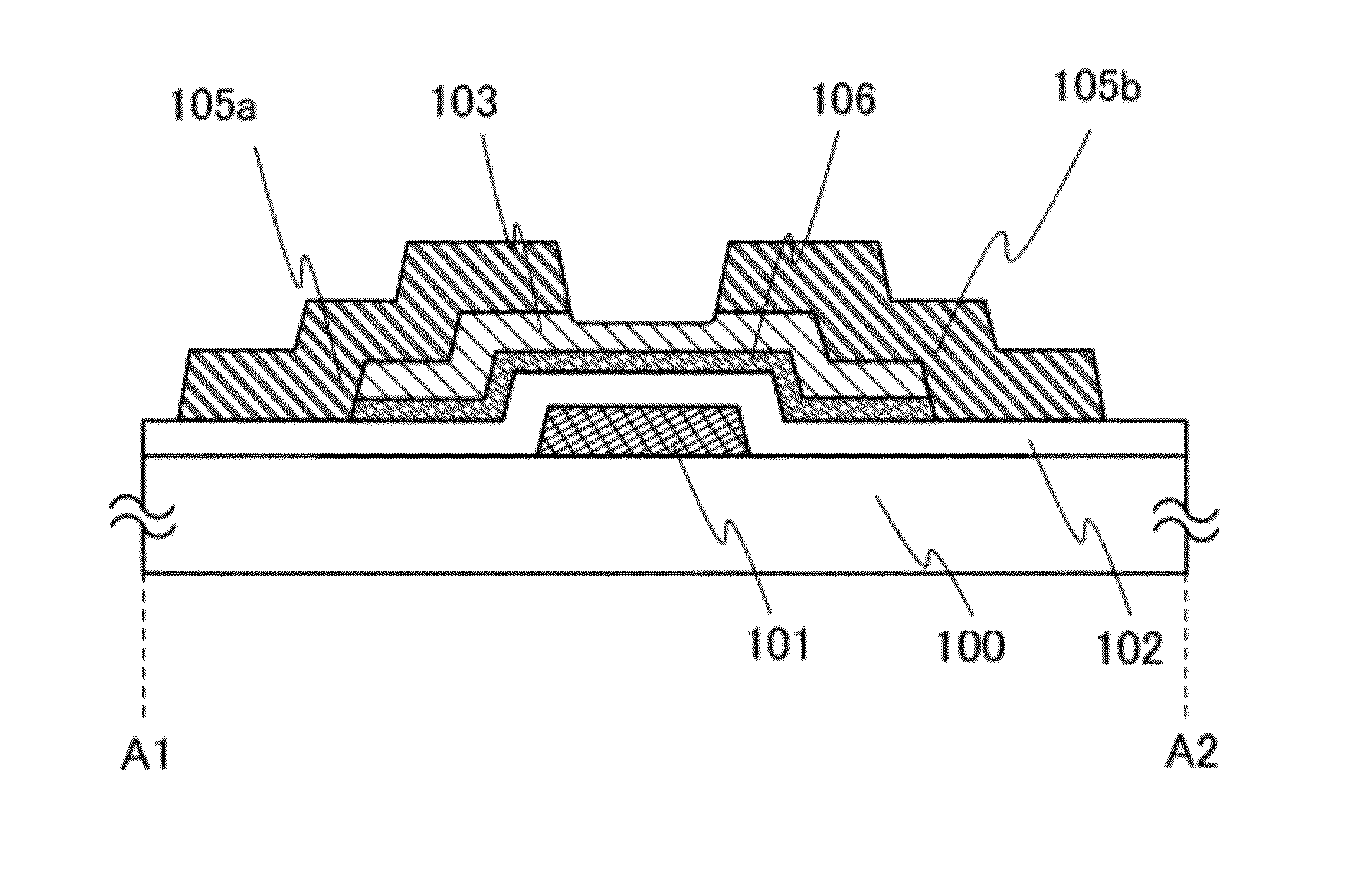

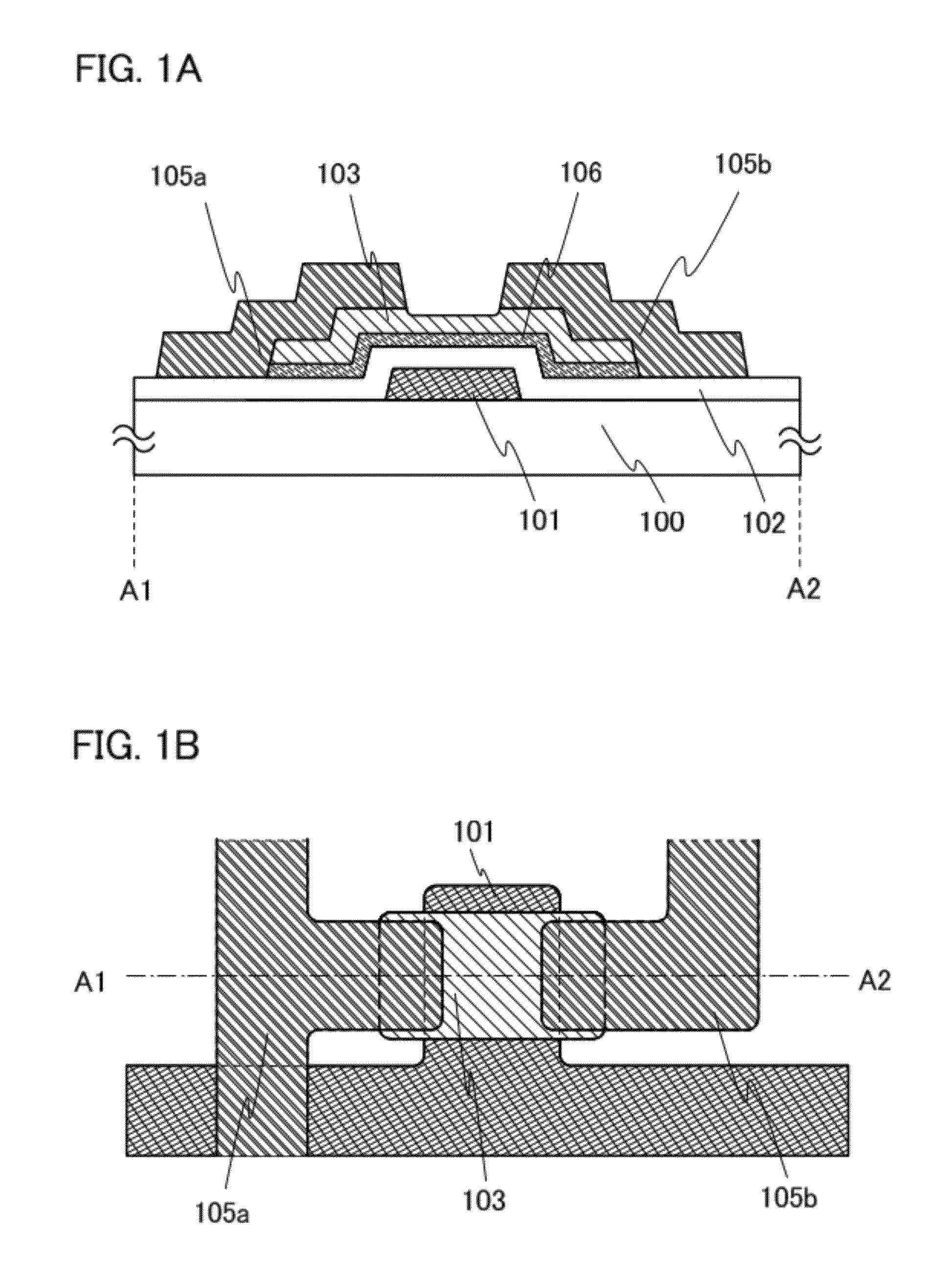

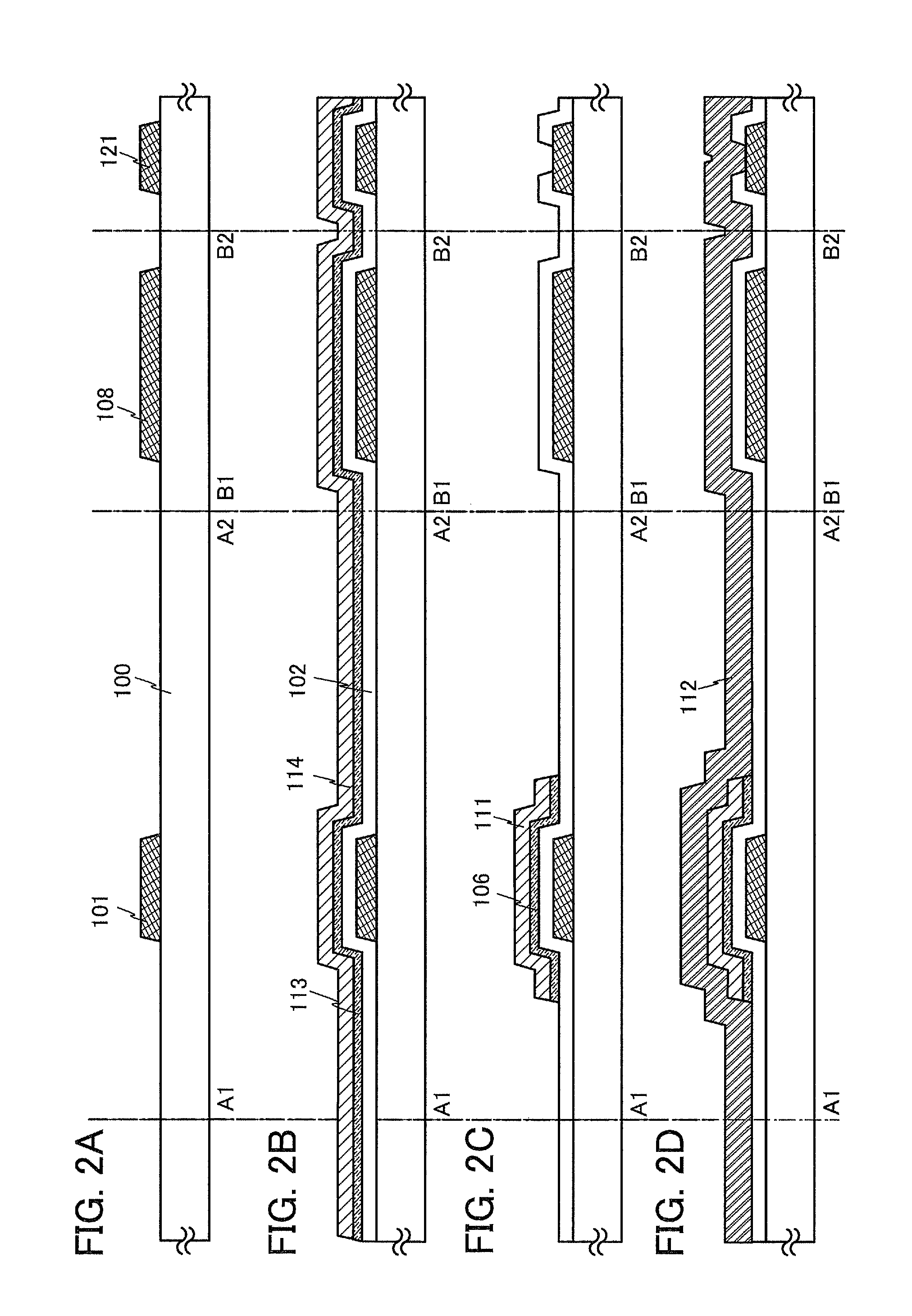

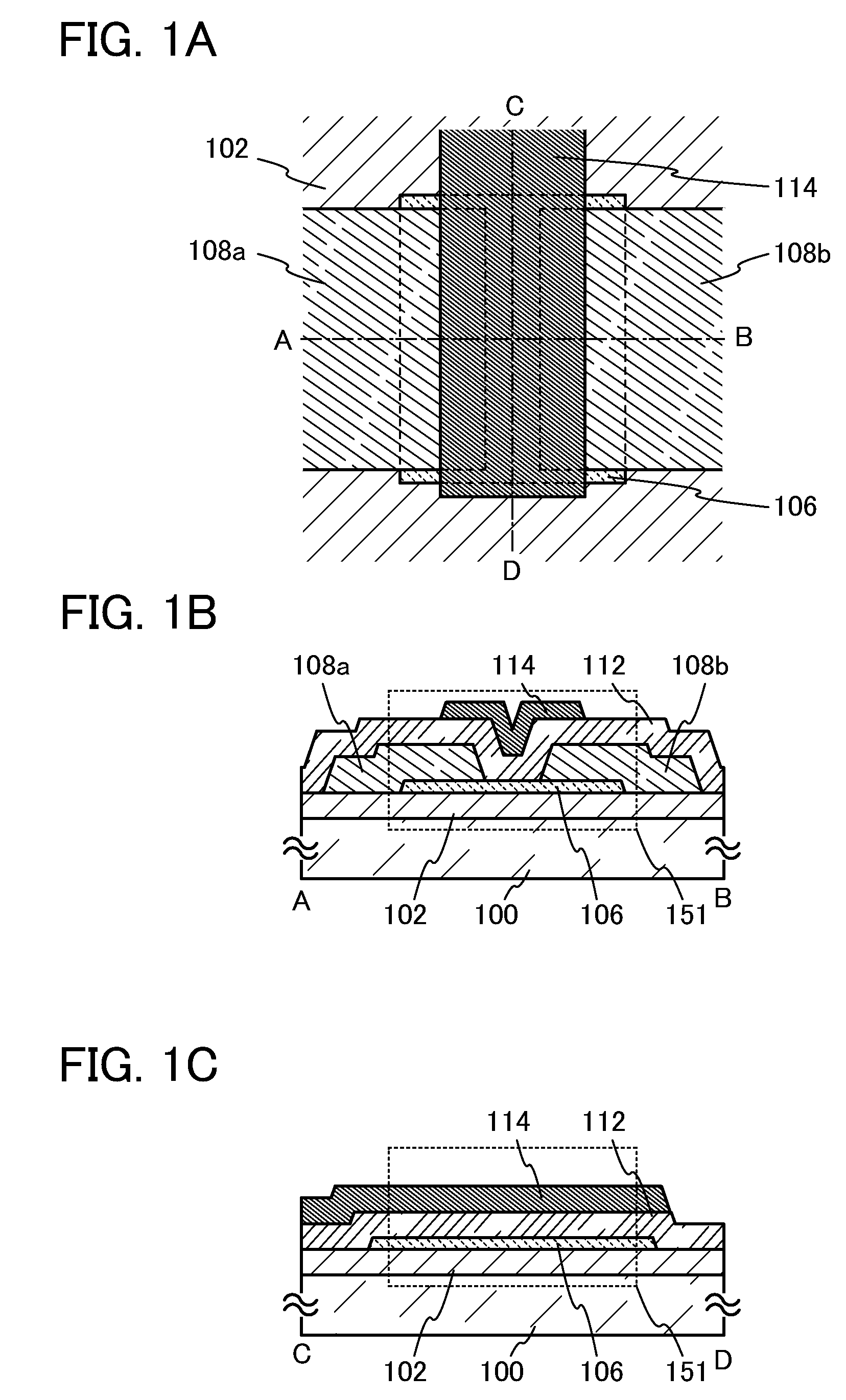

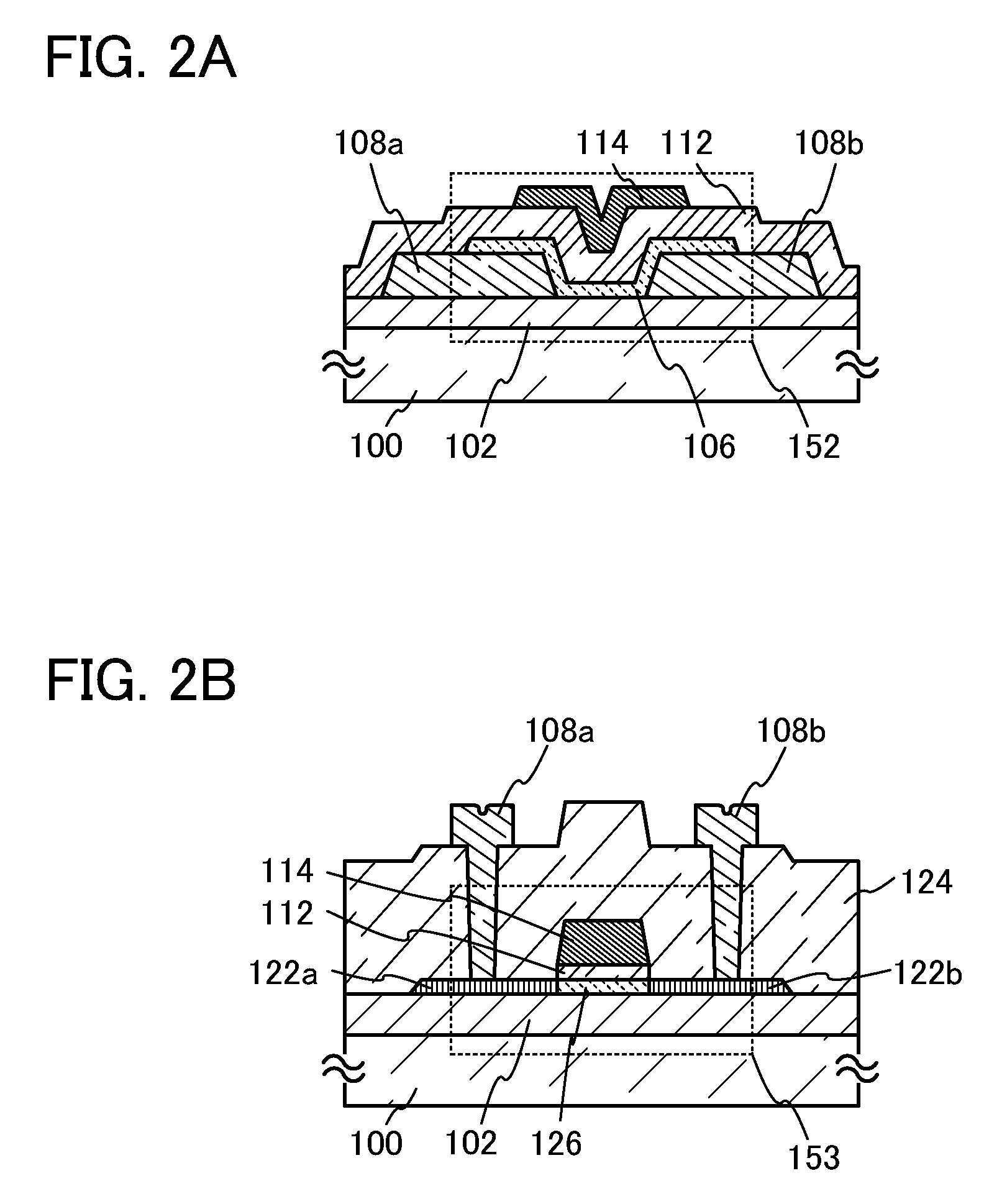

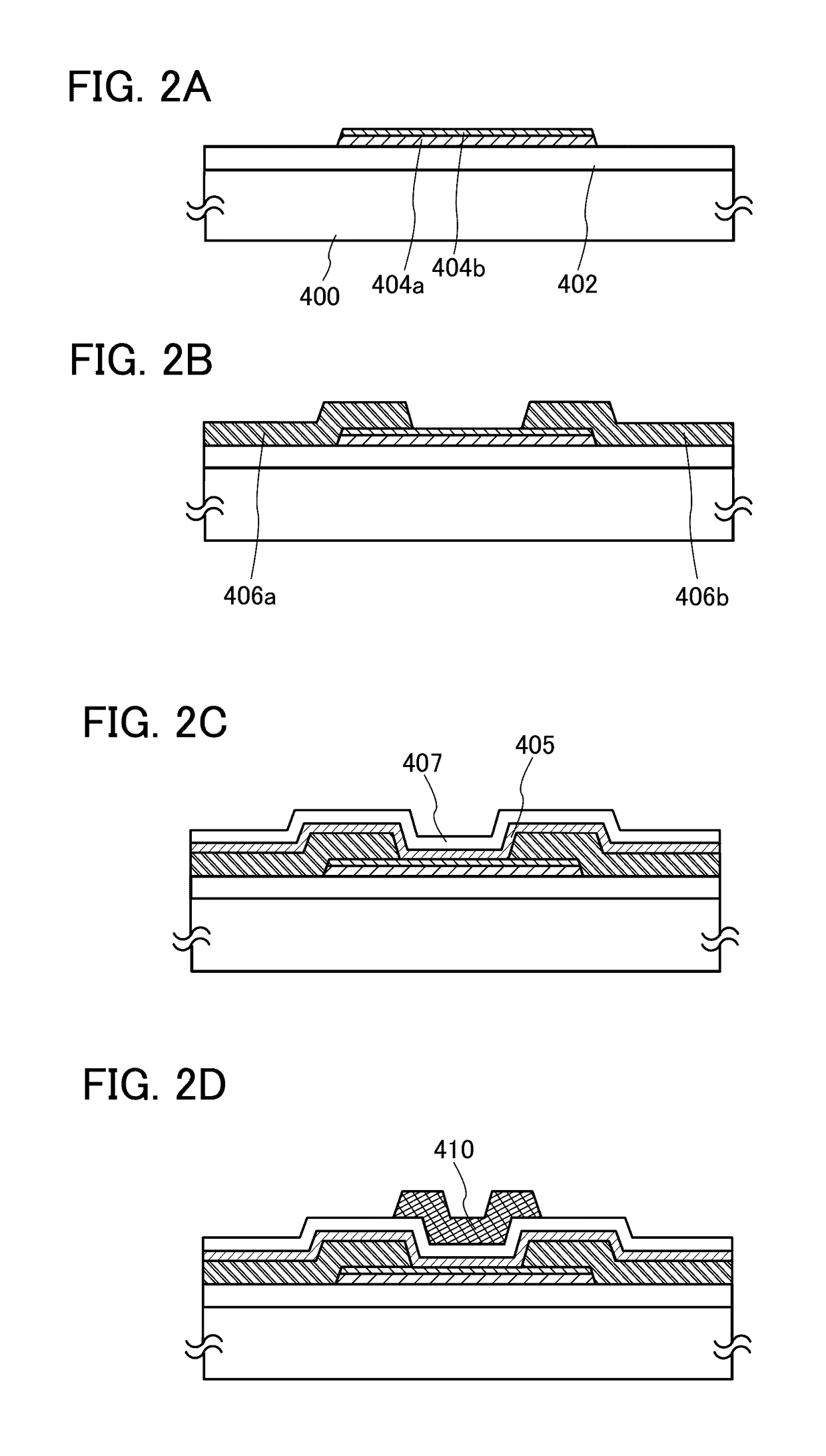

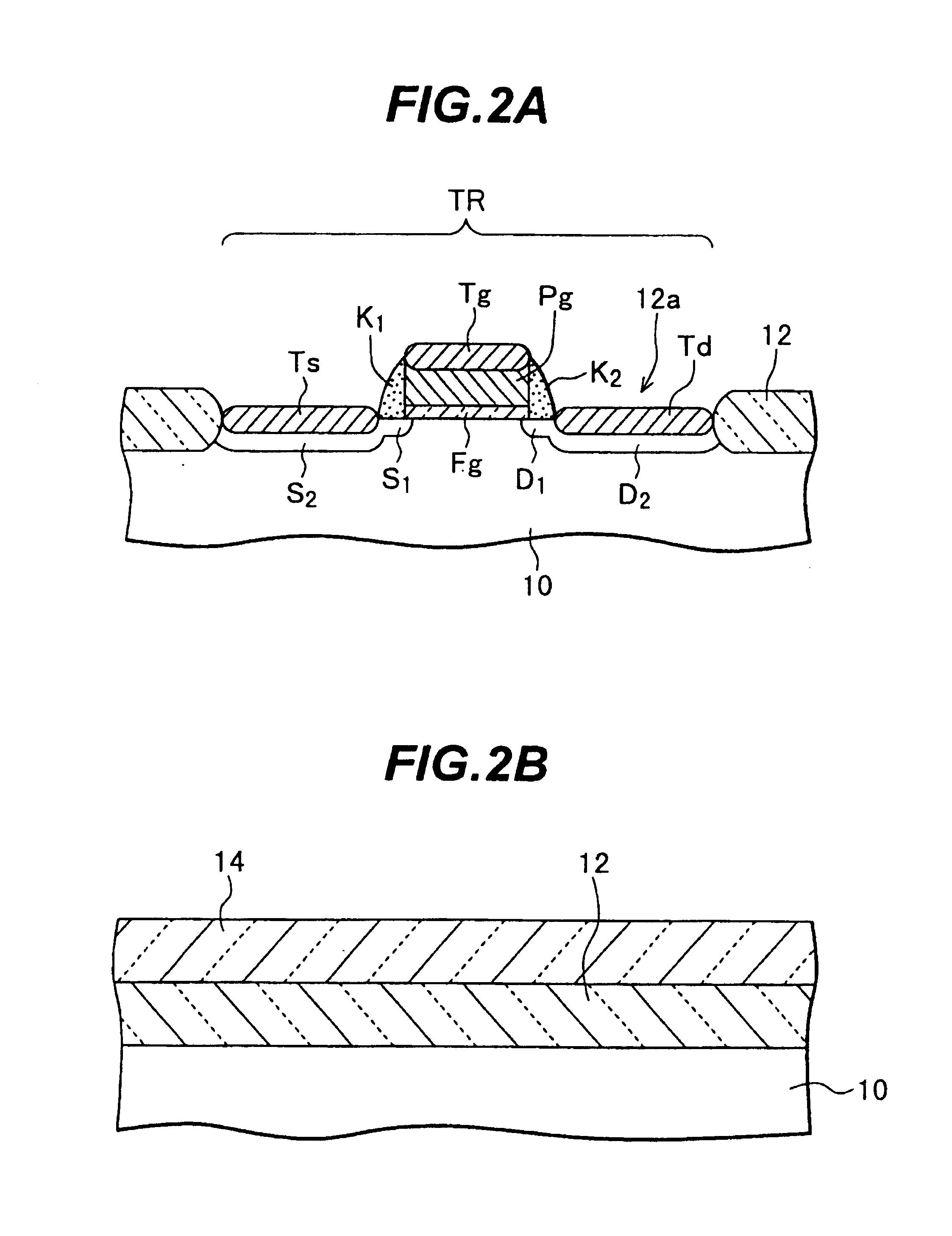

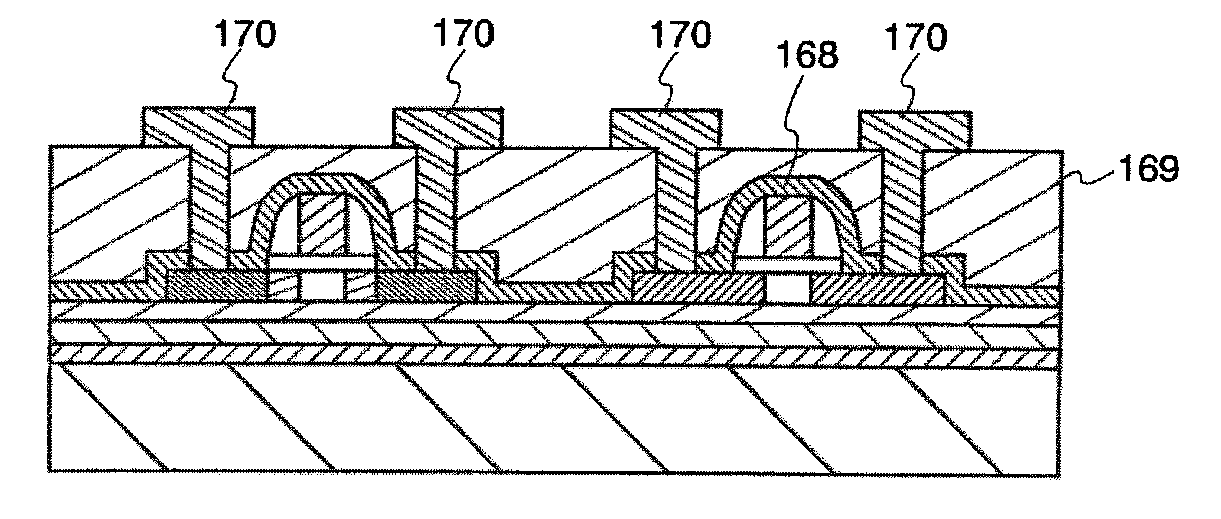

Semiconductor device and method for fabricating the same

ActiveUS20140077205A1Stable electric characteristicHigh-speed response and high-speed operationTransistorSolid-state devicesOxide semiconductorOxide

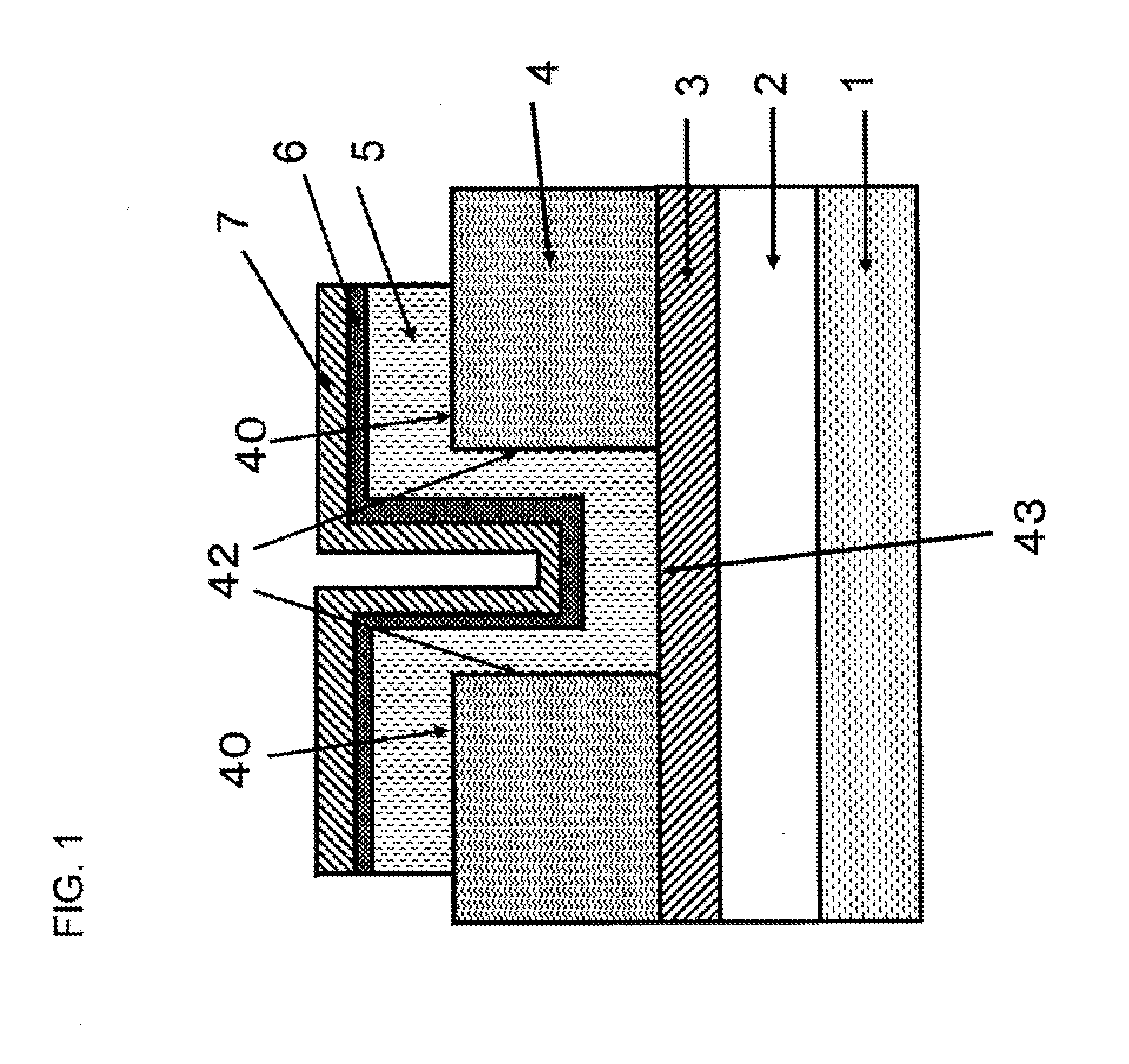

The on-state characteristics of a transistor are improved and thus, a semiconductor device capable of high-speed response and high-speed operation is provided. A highly reliable semiconductor device showing stable electric characteristics is made. The semiconductor device includes a transistor including a first oxide layer; an oxide semiconductor layer over the first oxide layer; a source electrode layer and a drain electrode layer in contact with the oxide semiconductor layer; a second oxide layer over the oxide semiconductor layer; a gate insulating layer over the second oxide layer; and a gate electrode layer over the gate insulating layer. An end portion of the second oxide layer and an end portion of the gate insulating layer overlap with the source electrode layer and the drain electrode layer.

Owner:SEMICON ENERGY LAB CO LTD

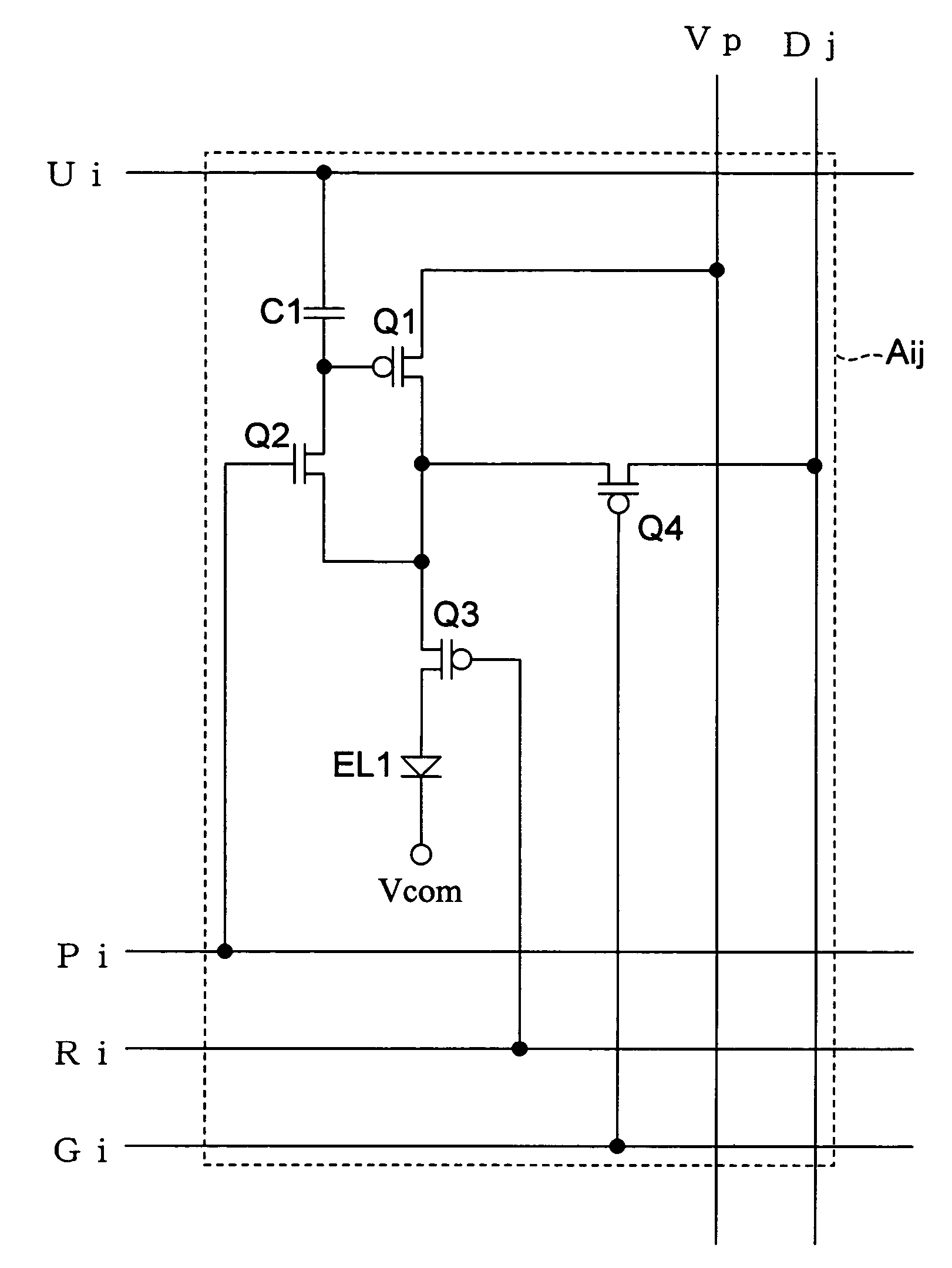

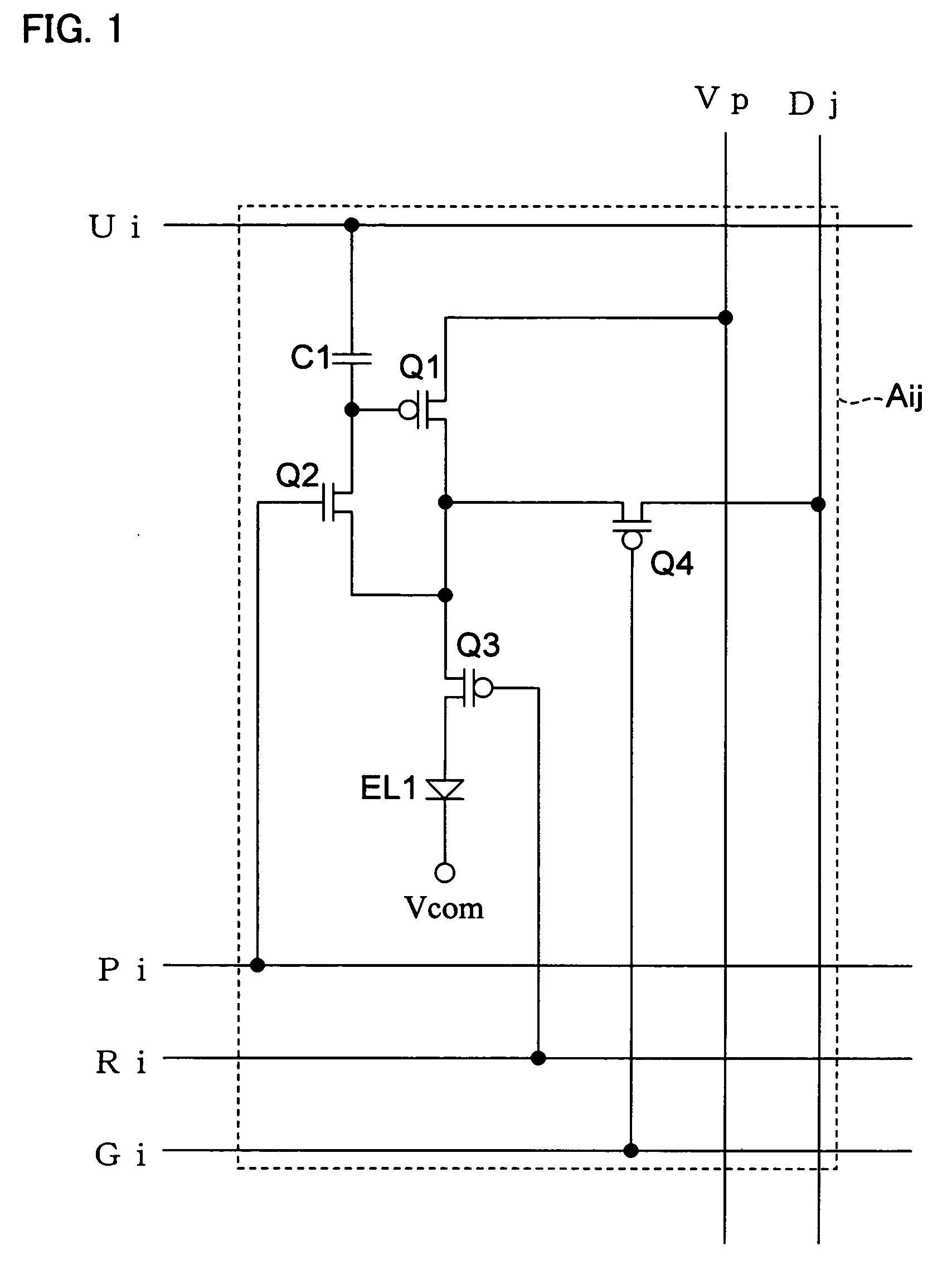

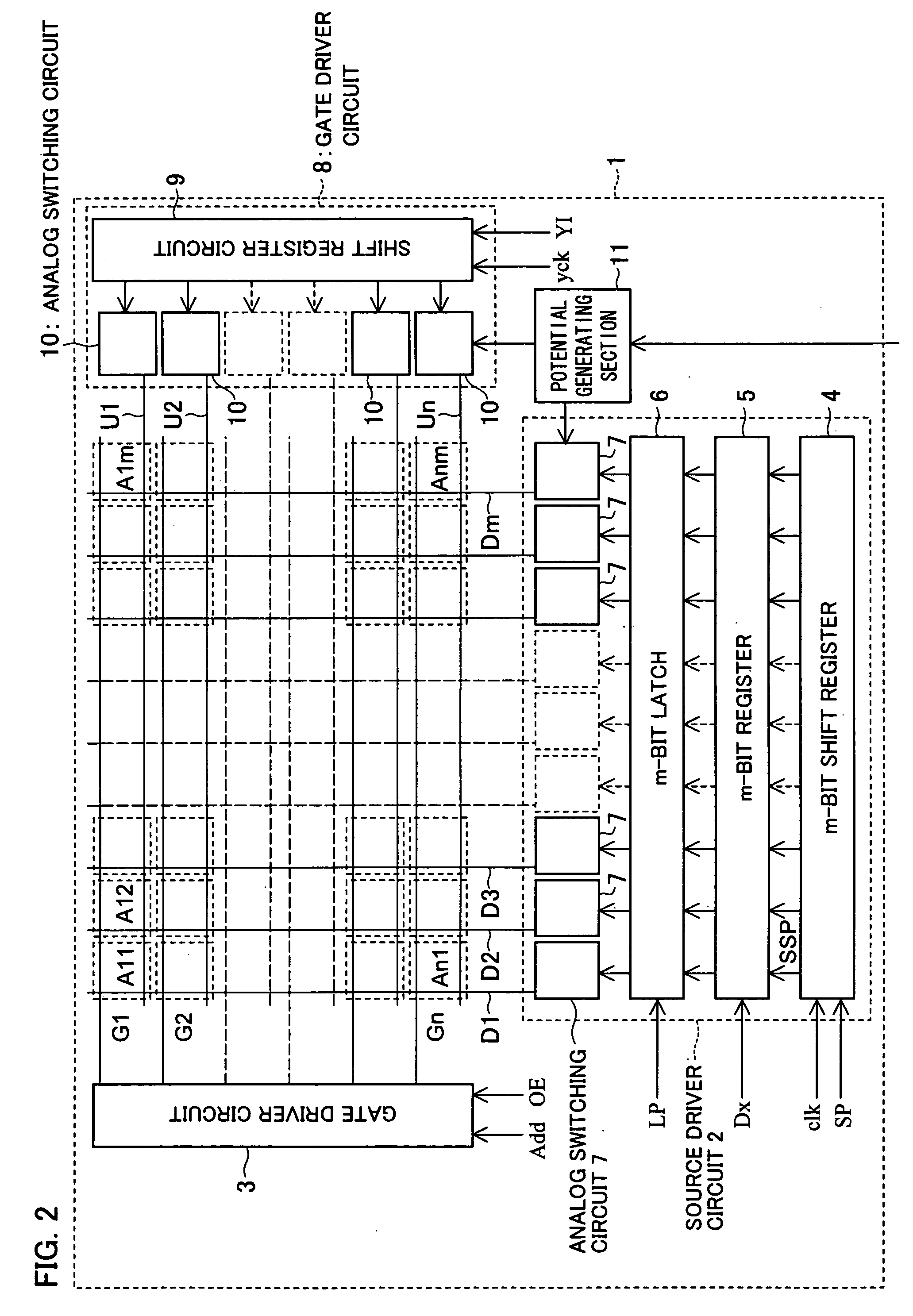

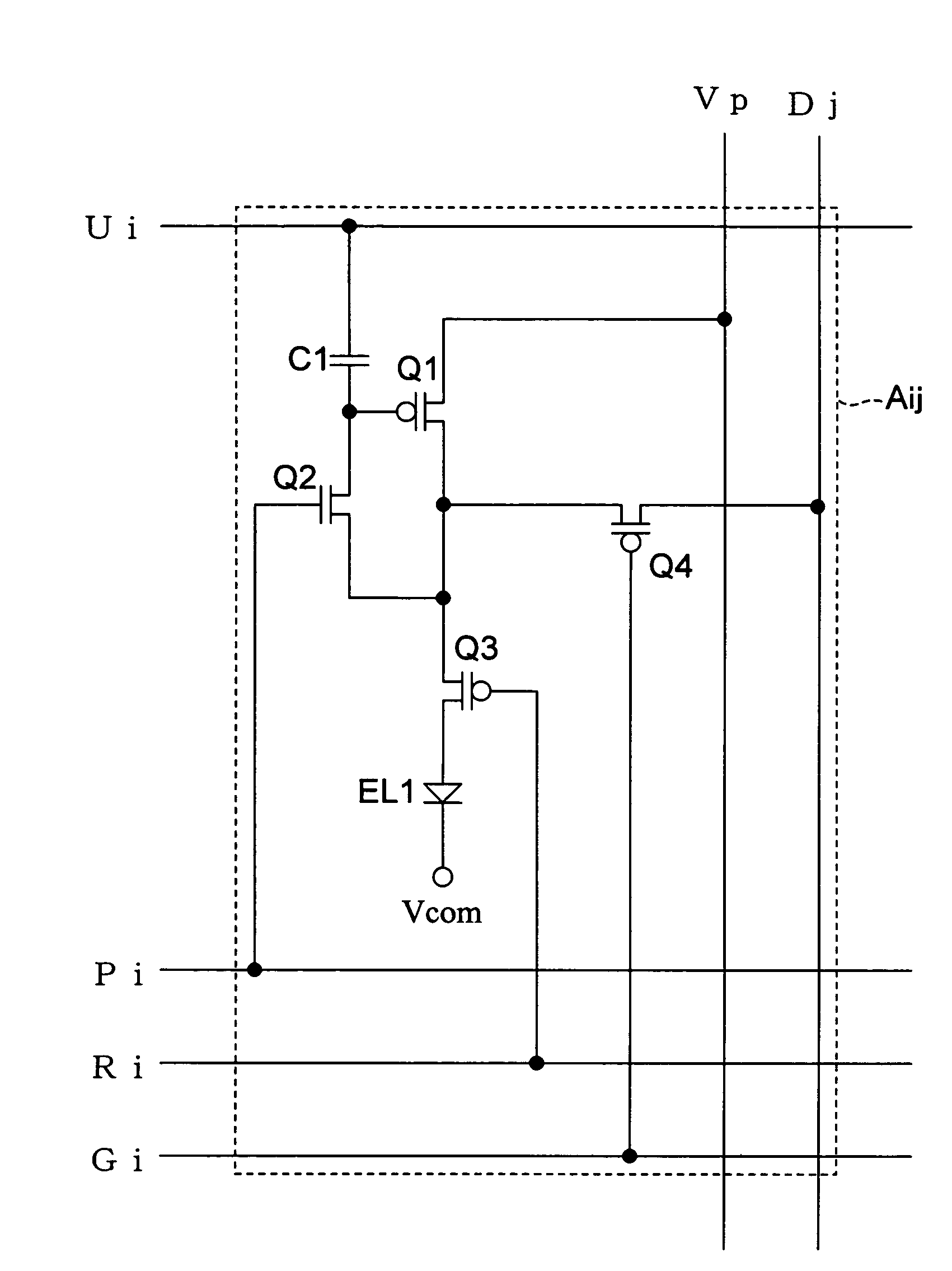

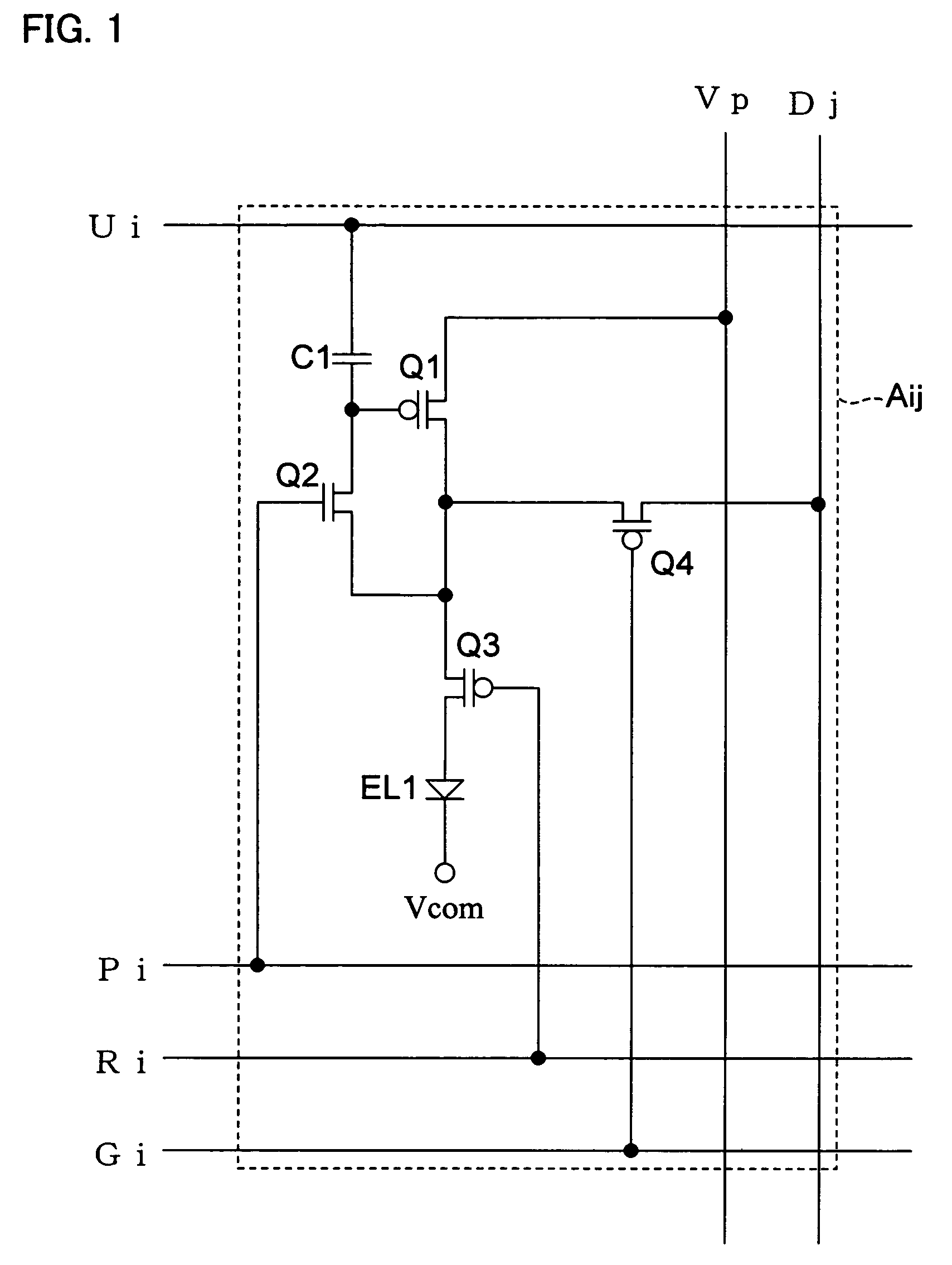

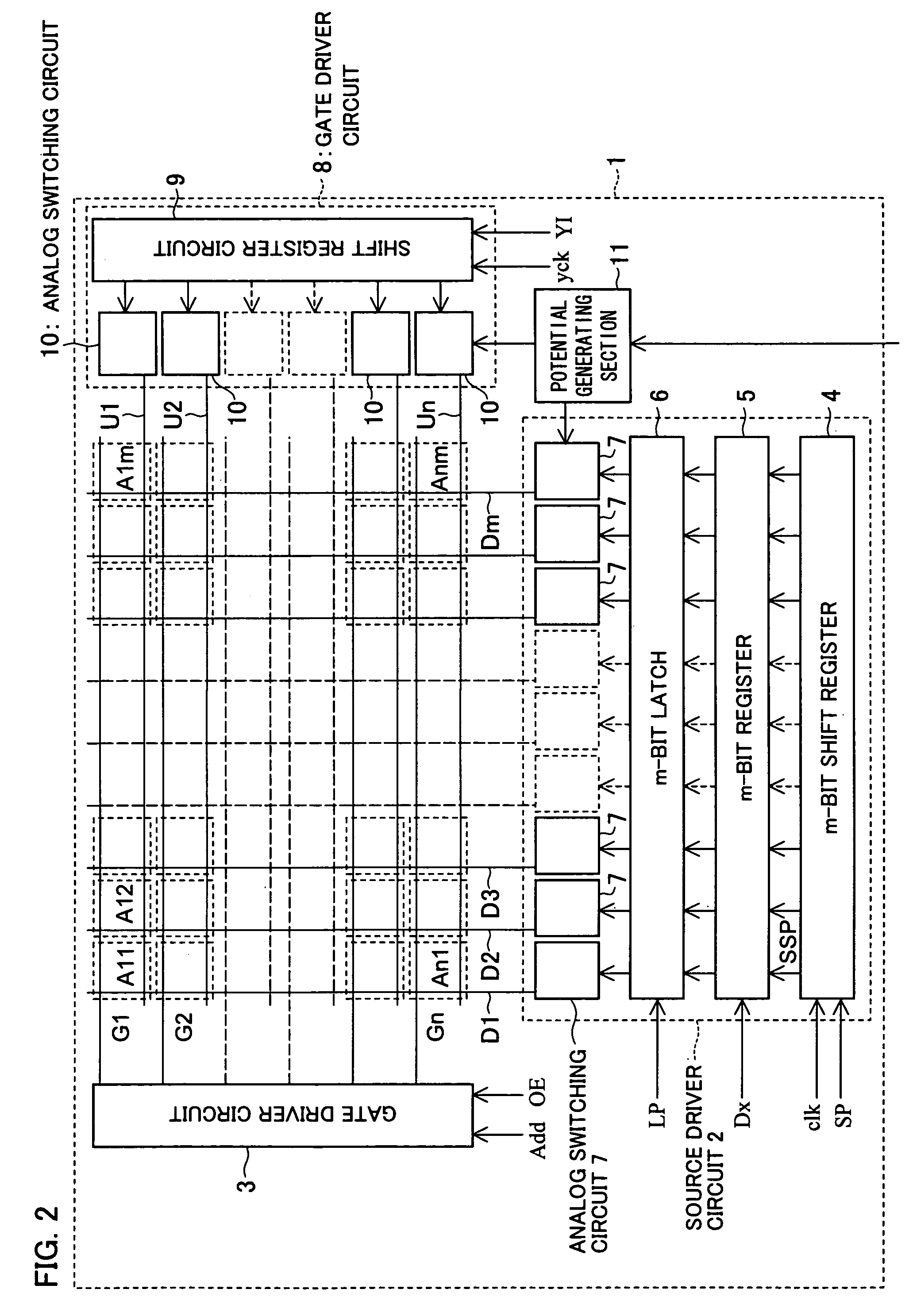

Display device and method for driving the same

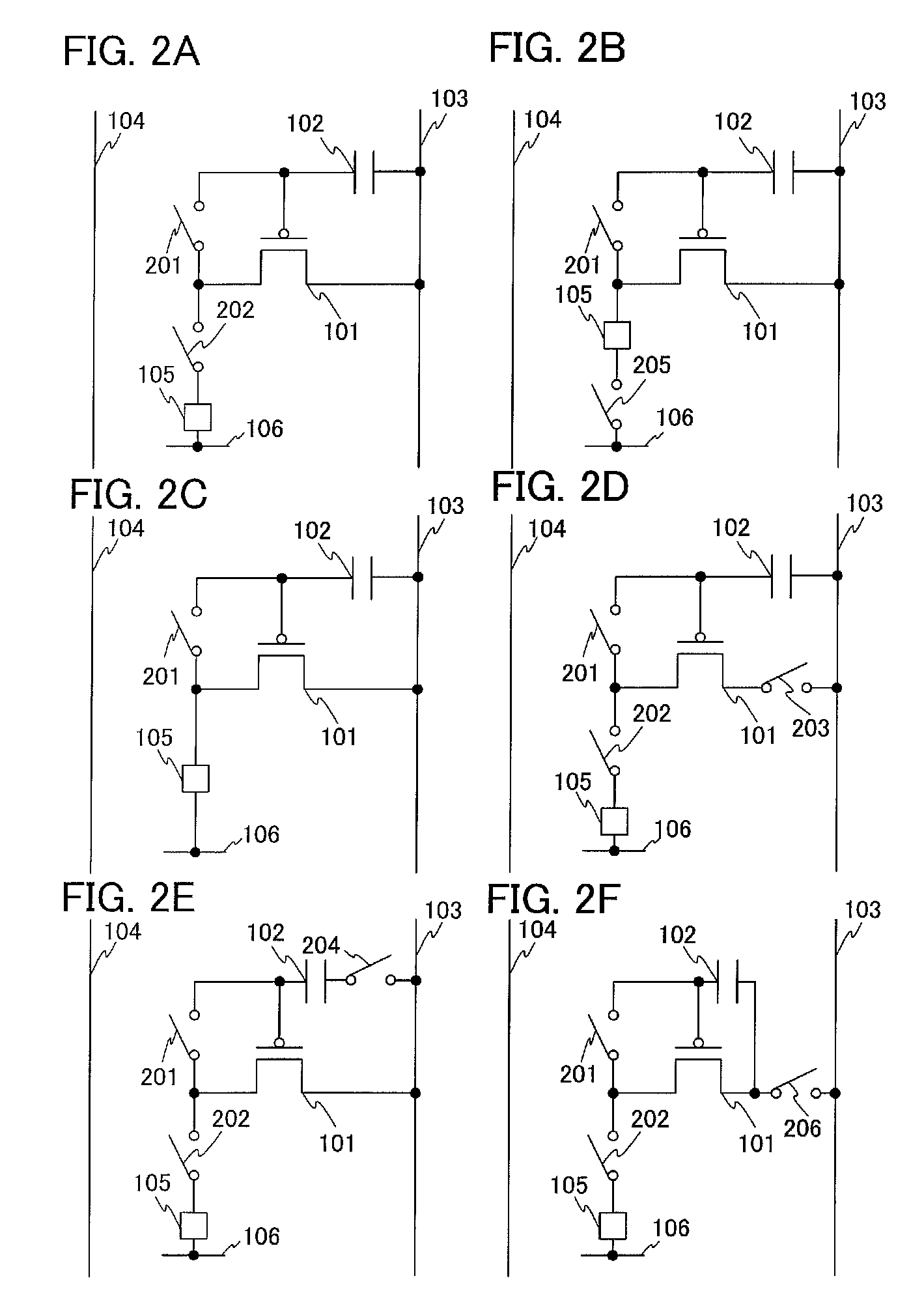

ActiveUS20060044244A1Shorten the overall cycleGreat potentialStatic indicating devicesDriving currentDisplay device

A display device which makes it possible to shorten a selection period per pixel while compensating variations in a threshold voltage of the driving transistor, and a method for driving the same are achieved. In a pixel circuit Aij, a potential wire Ui is set to a potential Vcc, a voltage of a gate wire Gi becomes Low, a voltage of a control wire Ri becomes High, and a voltage of a control wire Pi becomes High, so that a gate terminal of a driving TFT: Q1 has a potential of a data wire Dj. Moreover, a voltage of the gate wire Gi becomes High so as to compensate a threshold voltage of the driving TFT: Q1. Thereafter, a voltage of the control wire Pi becomes Low, and the potential wire Ui is set to a potential Vc, so that a voltage of a capacitor C1, i.e., a gate-source voltage of the driving TFT is changed. This causes a voltage of the control wire Ri to be Low, so that a driving current is flown into an organic EL: EL1.

Owner:SHARP KK

Semiconductor device and manufacturing method thereof

ActiveUS8362478B2Reduce variationStable characteristicsTransistorElectroluminescent light sourcesSemiconductorMetal

An object is to provide a transistor including an oxide layer which includes Zn and does not include a rare metal such as In or Ga. Another object is to reduce an off current and stabilize electric characteristics in the transistor including an oxide layer which includes Zn. A transistor including an oxide layer including Zn is formed by stacking an oxide semiconductor layer including insulating oxide over an oxide layer so that the oxide layer is in contact with a source electrode layer or a drain electrode layer with the oxide semiconductor layer including insulating oxide interposed therebetween, whereby variation in the threshold voltage of the transistor can be reduced and electric characteristics can be stabilized.

Owner:SEMICON ENERGY LAB CO LTD

Display device and method for driving the same

ActiveUS7443367B2Shorten the overall cycleGreat potentialStatic indicating devicesDriving currentDisplay device

A display device which makes it possible to shorten a selection period per pixel while compensating variations in a threshold voltage of the driving transistor, and a method for driving the same are achieved. In a pixel circuit Aij, a potential wire Ui is set to a potential Vcc, a voltage of a gate wire Gi becomes Low, a voltage of a control wire Ri becomes High, and a voltage of a control wire Pi becomes High, so that a gate terminal of a driving TFT: Q1 has a potential of a data wire Dj. Moreover, a voltage of the gate wire Gi becomes High so as to compensate a threshold voltage of the driving TFT: Q1. Thereafter, a voltage of the control wire Pi becomes Low, and the potential wire Ui is set to a potential Vc, so that a voltage of a capacitor C1, i.e., a gate-source voltage of the driving TFT is changed. This causes a voltage of the control wire Ri to be Low, so that a driving current is flown into an organic EL: EL1.

Owner:SHARP KK

Driving method of semiconductor device

ActiveUS20090225010A1Long input periodReduce the impactElectrical apparatusElectroluminescent light sourcesImage signalCapacitor

The semiconductor device includes a transistor and a capacitor element which is electrically connected to a gate of the transistor. Charge held in the capacitor element according to total voltage of voltage corresponding to the threshold voltage of the transistor and image signal voltage is once discharged through the transistor, so that variation in current flowing in the transistor or mobility of the transistor can be reduced.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and driving method thereof

InactiveUS8477085B2Reduce variationDecrease in luminanceStatic indicating devicesElectroluminescent light sourcesDisplay deviceEngineering

A display device which can compensate for variations of the threshold voltage of transistors and suppress variations in luminance, and a driving method thereof are provided. Current is supplied to a light emitting element and light is emitted from the light emitting element by following steps: in the first period initial voltage is stored in a storage capacitor; in the second period, voltage based on video signal voltage and the threshold voltage of the transistor is stored in the storage capacitor; and in the third period, the voltage stored in the storage capacitor in the second period is applied to a gate electrode of the transistor. By these operation processes, the current which compensates the effect of the variations of the threshold voltage of the transistor can be supplied to the light emitting element. Therefore, variations in luminance are suppressed.

Owner:SEMICON ENERGY LAB CO LTD

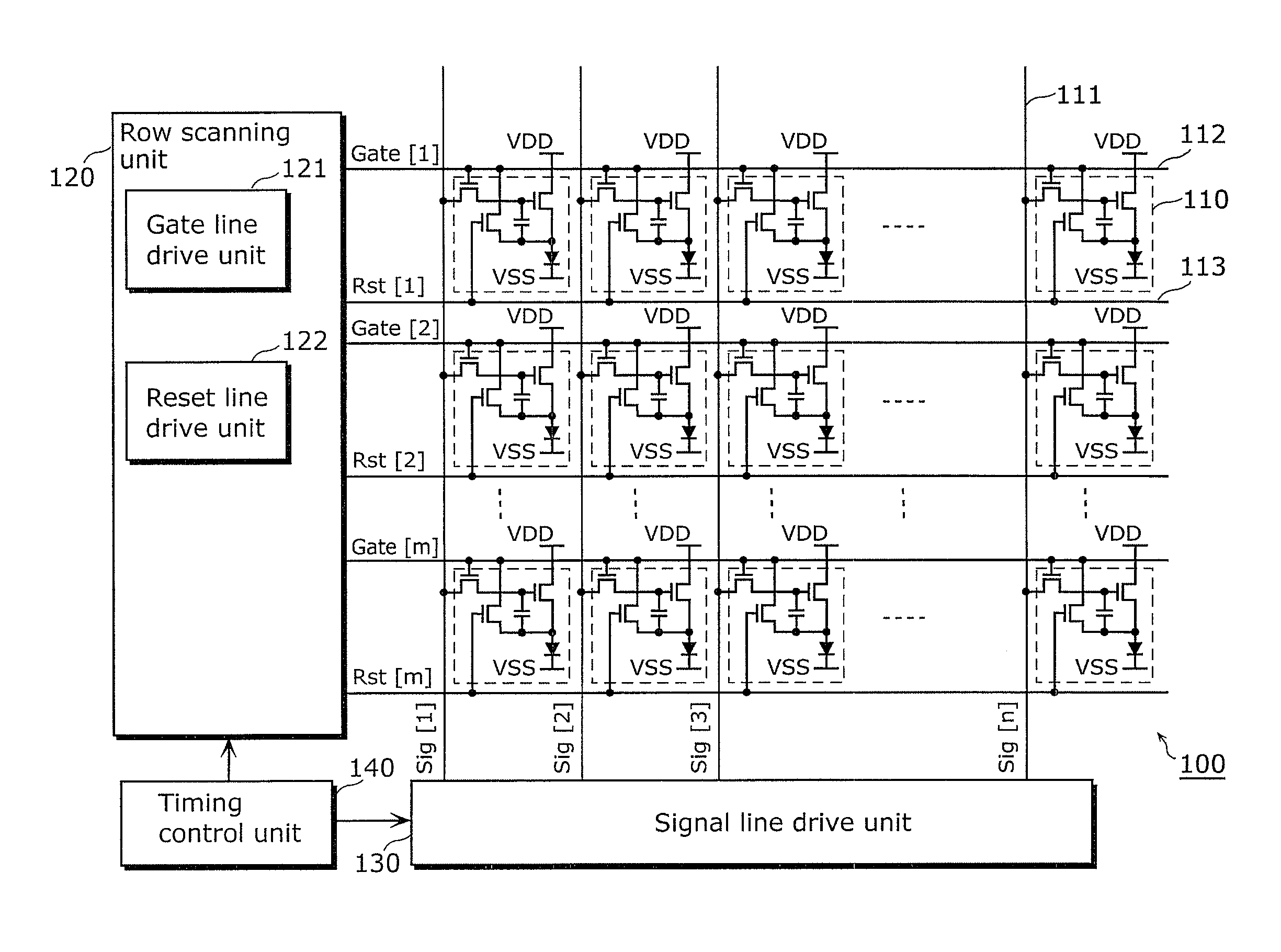

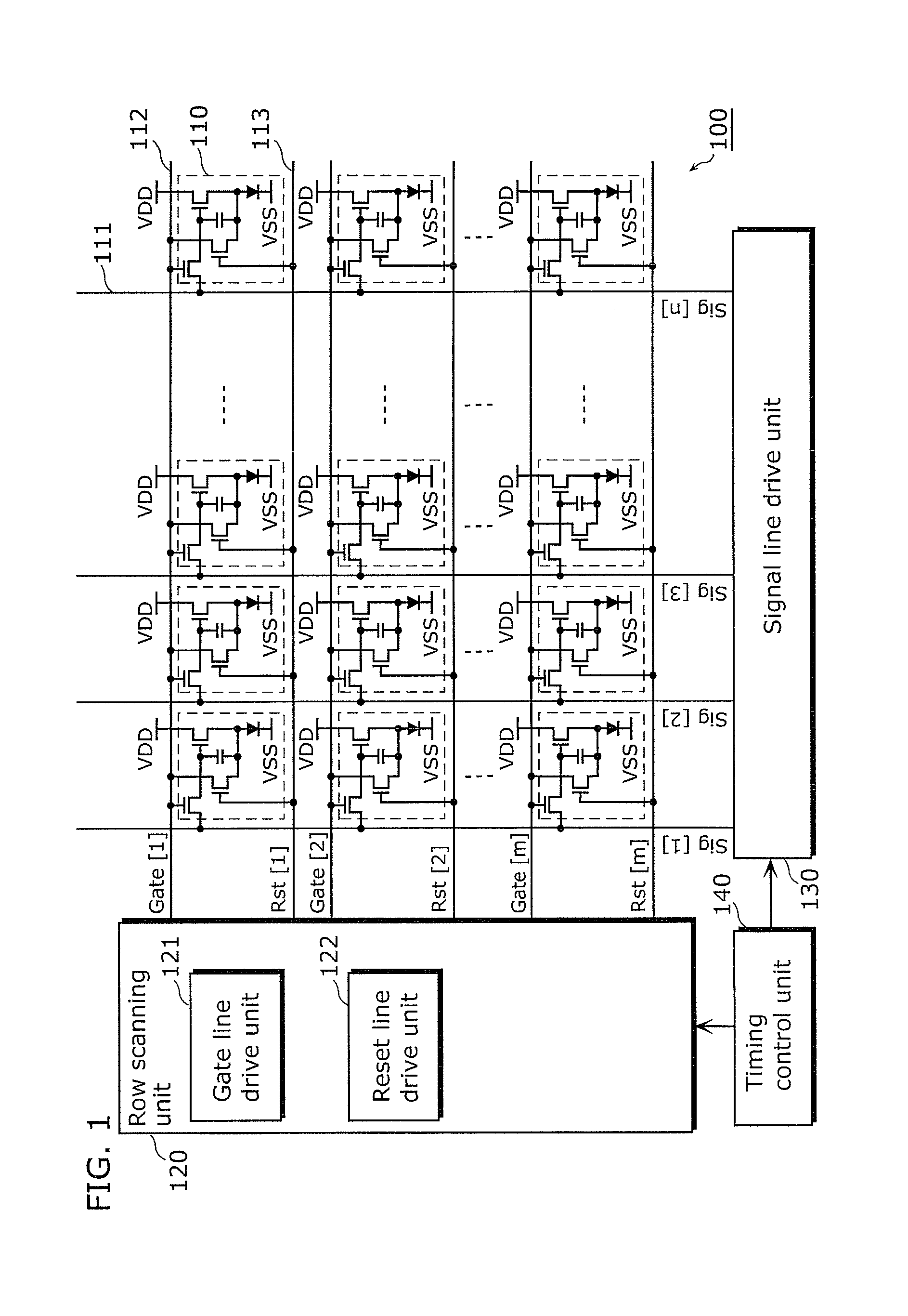

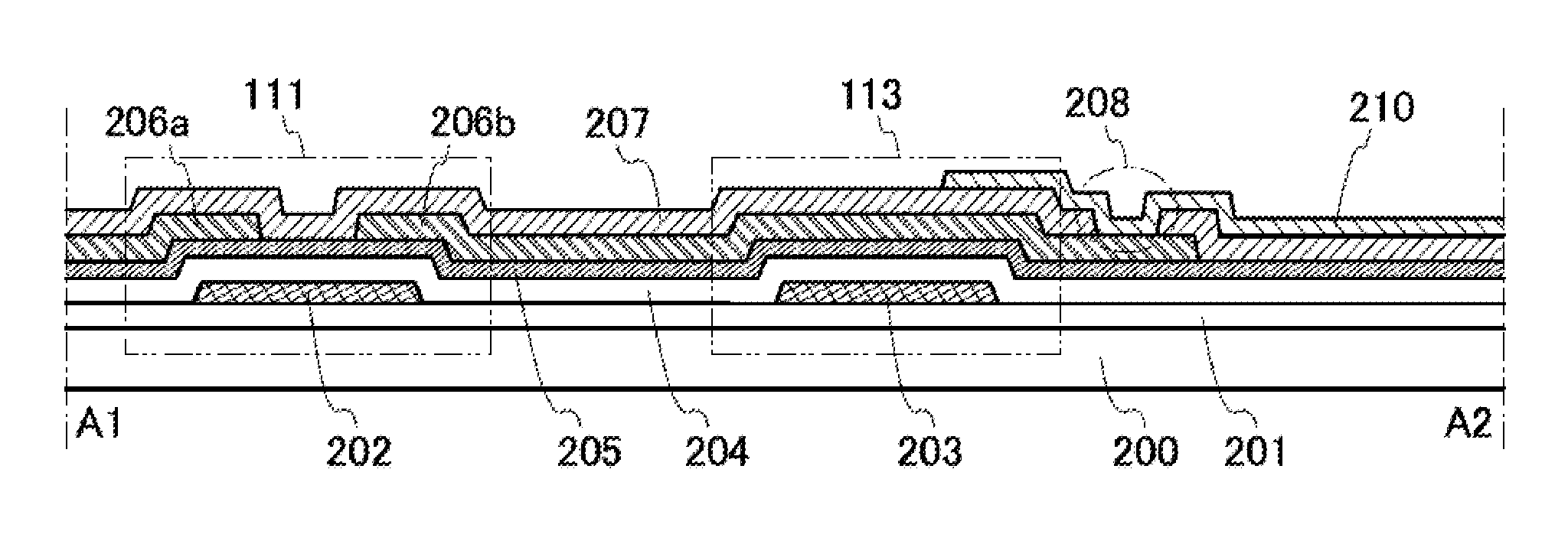

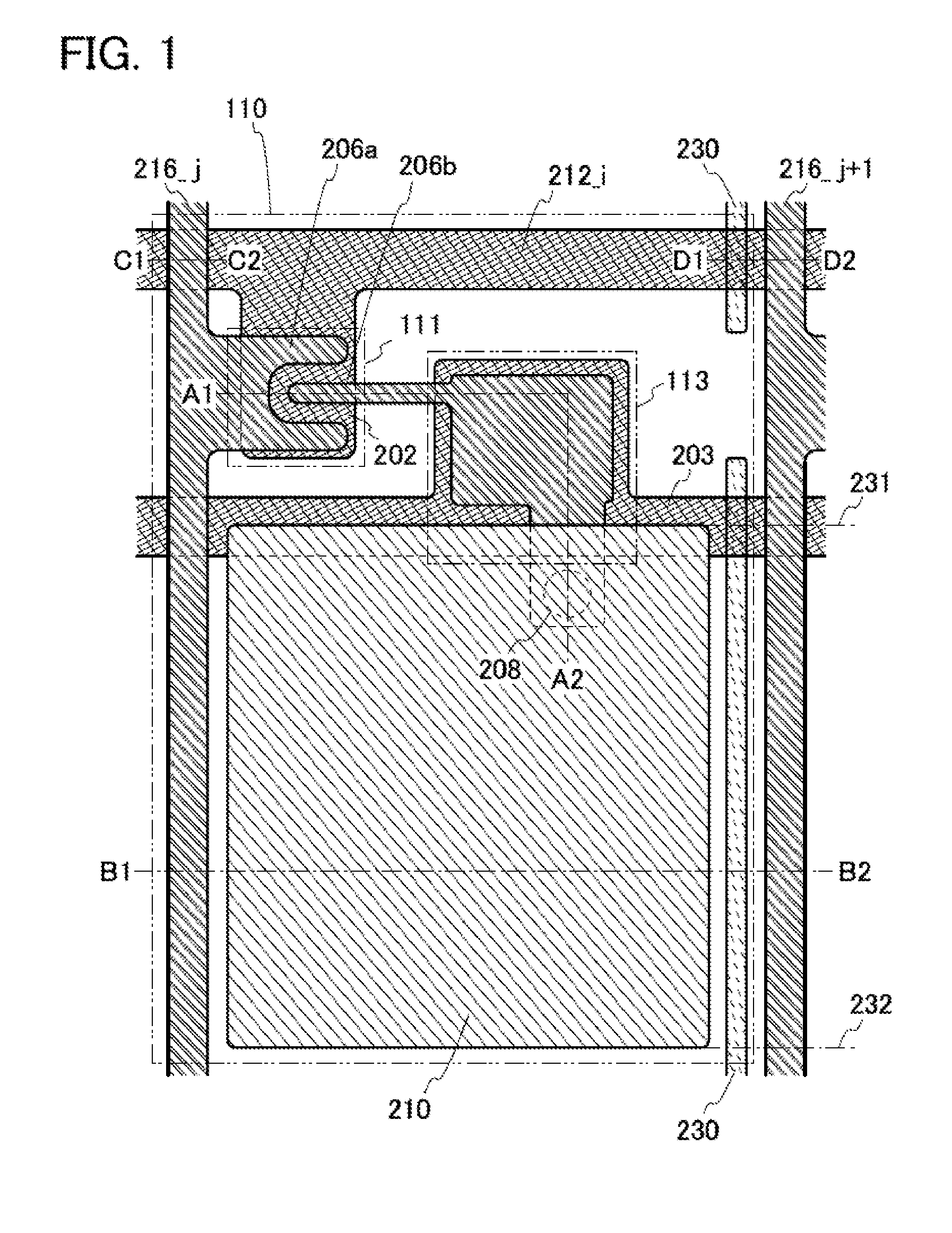

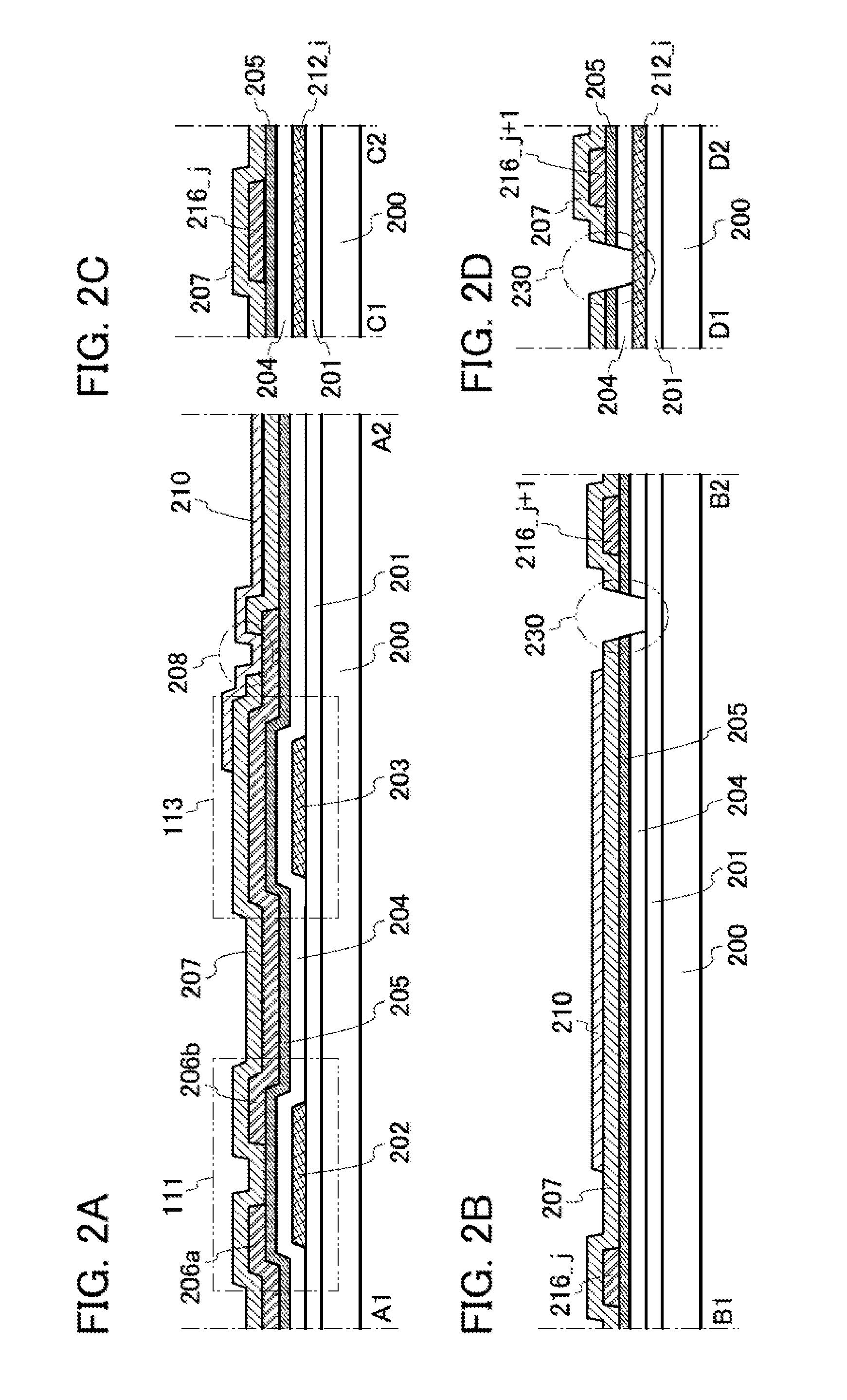

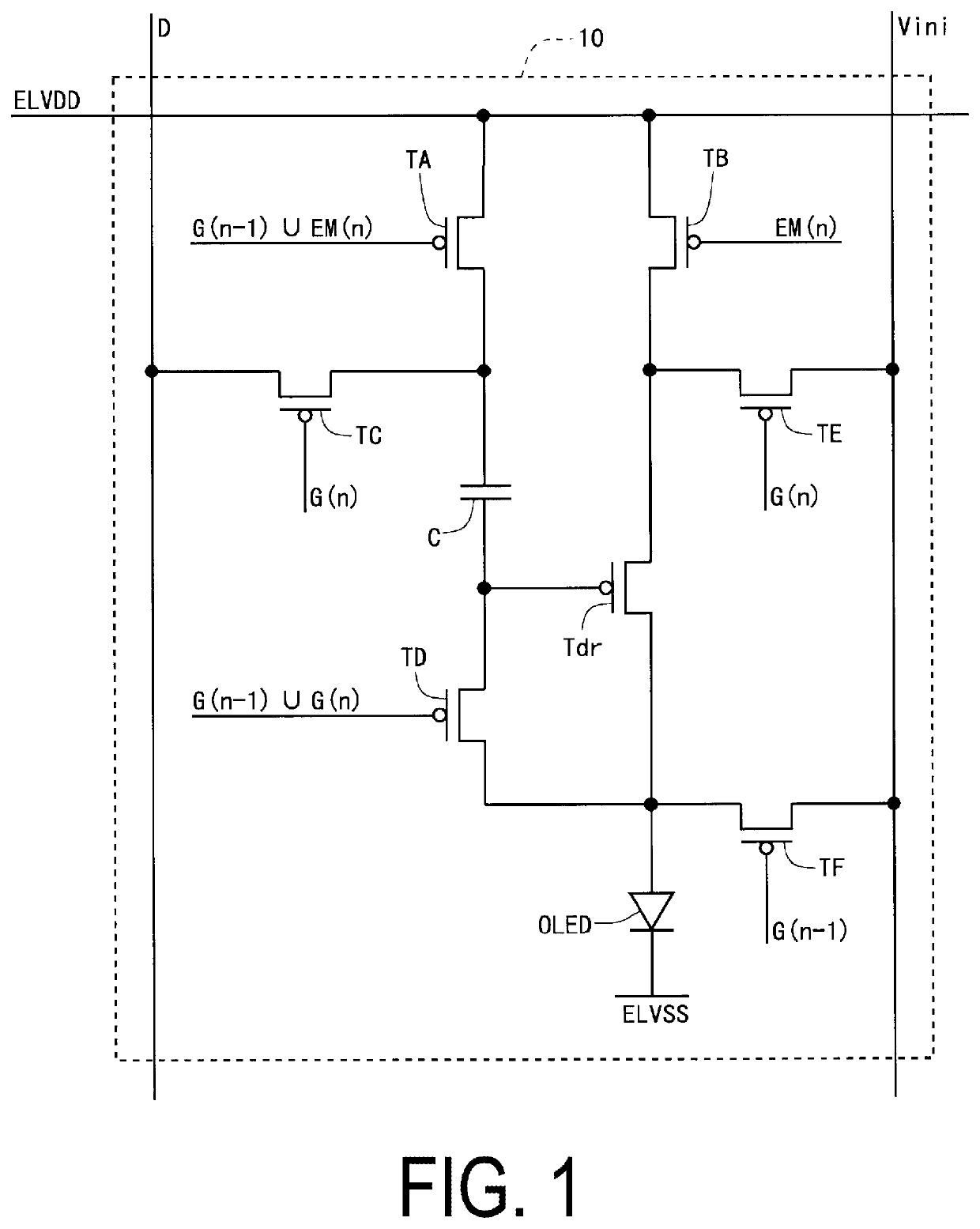

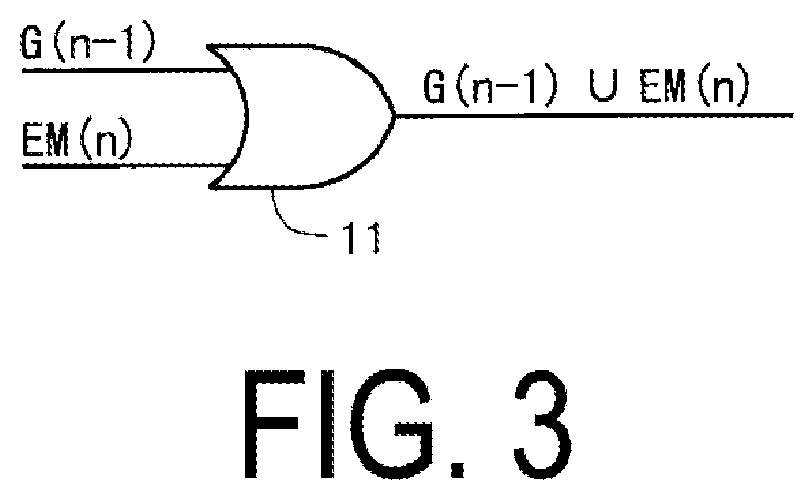

Display device and method of driving the same

ActiveUS20120050350A1Compensation Threshold VoltageOvercome unevennessCathode-ray tube indicatorsInput/output processes for data processingPower flowDisplay device

A display device includes luminescence pixels arranged in rows and columns. Each of gate lines and reset lines correspond to one of the rows, and signals lines each correspond to one of the columns. Each luminescence pixels includes a luminescence element, a switching transistor, a drive transistor which supplies current to the luminescence element, and a reset transistor. The reset transistor includes a gate terminal connected to a corresponding reset line, one of a source and drain terminal connected to a source or drain terminal of the drive transistor, and the other of the source and drain terminal connected to a corresponding gate line. A capacitor is connected between the gate terminal and the source terminal of the drive transistor.

Owner:JOLED INC

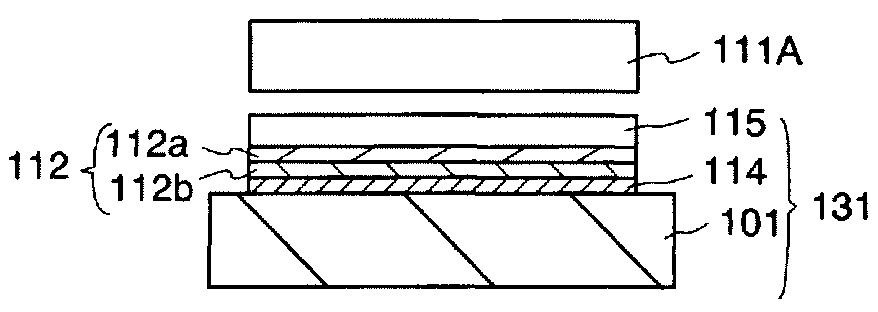

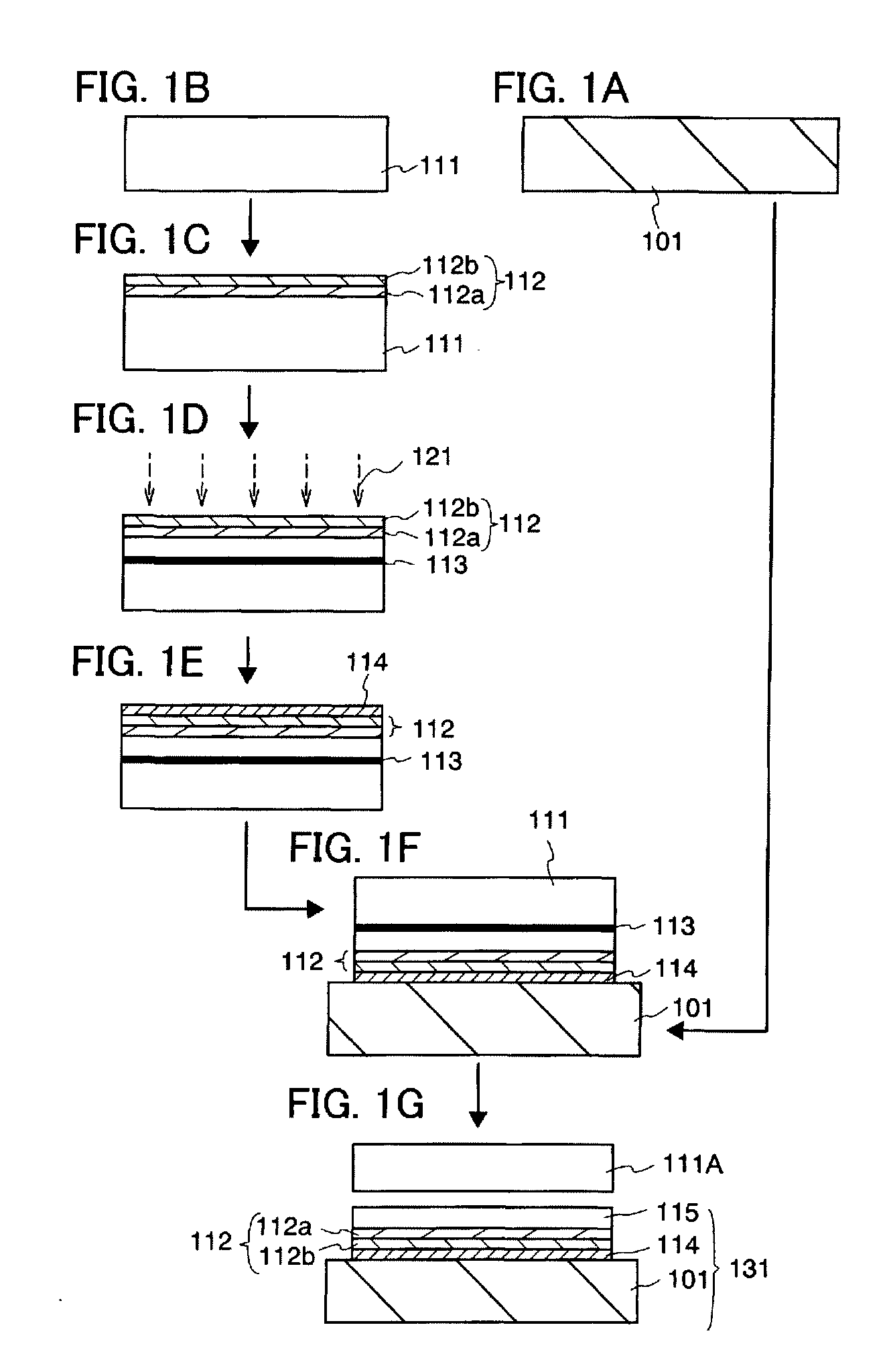

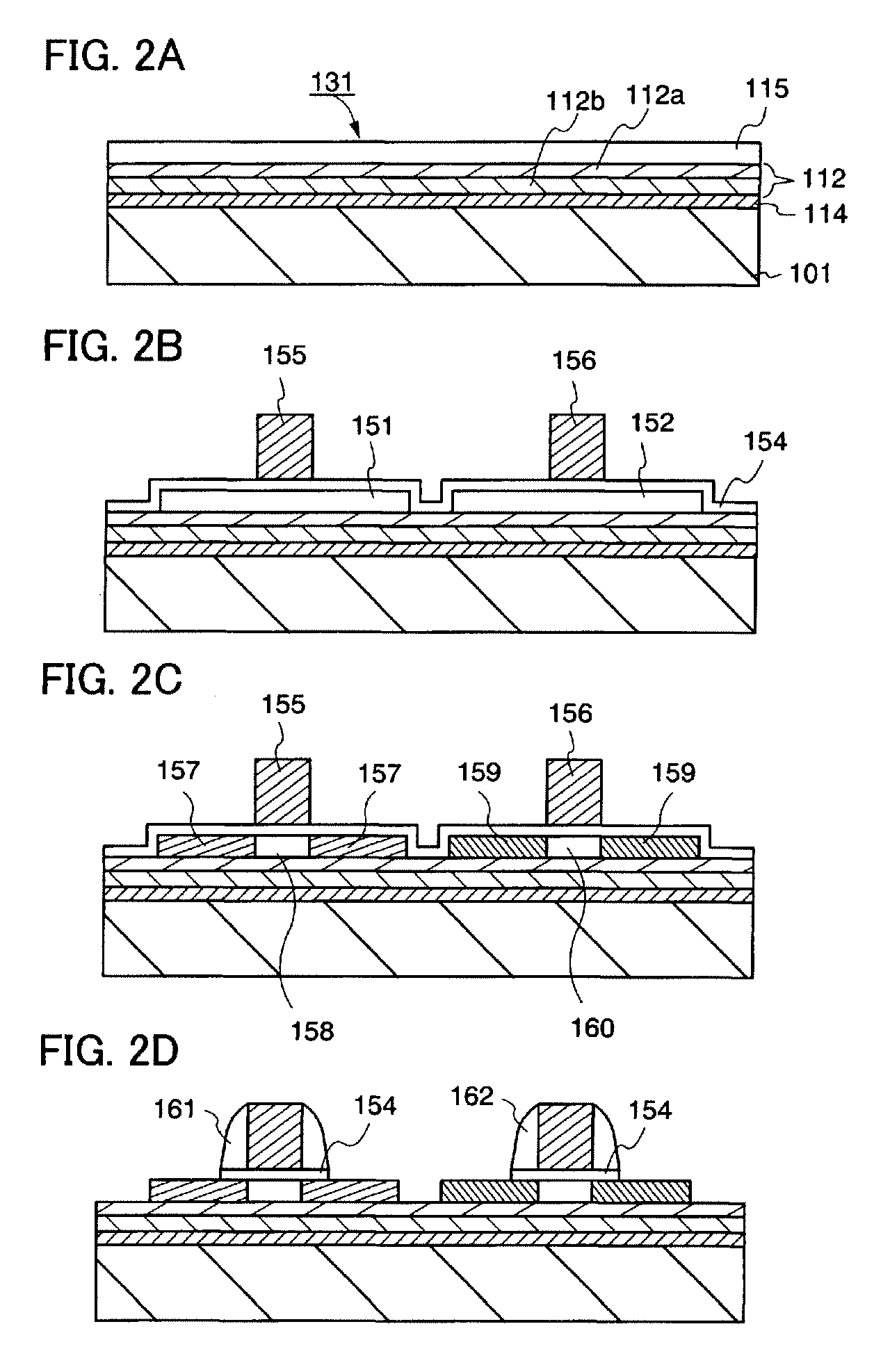

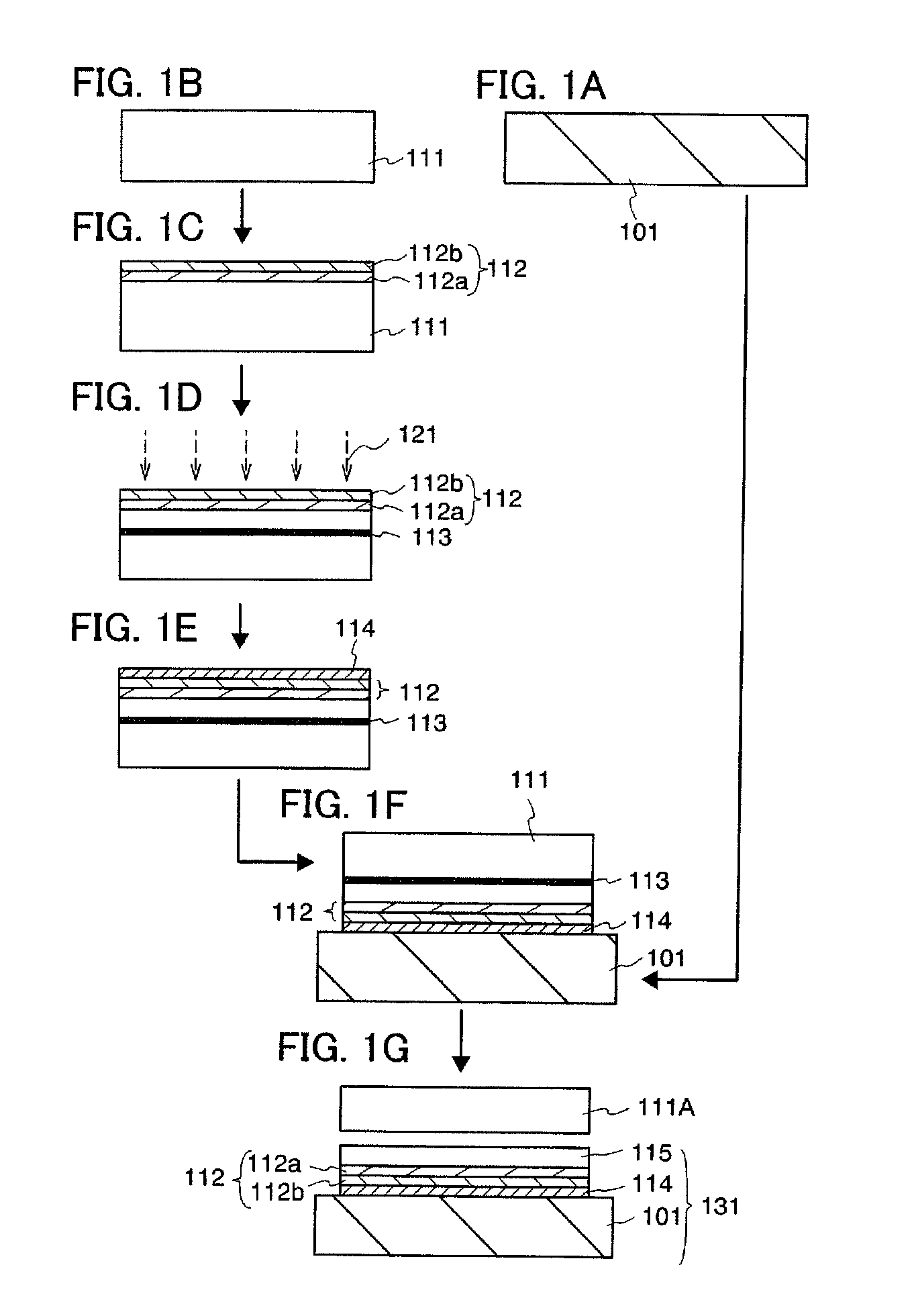

Method of manufacturing semiconductor device

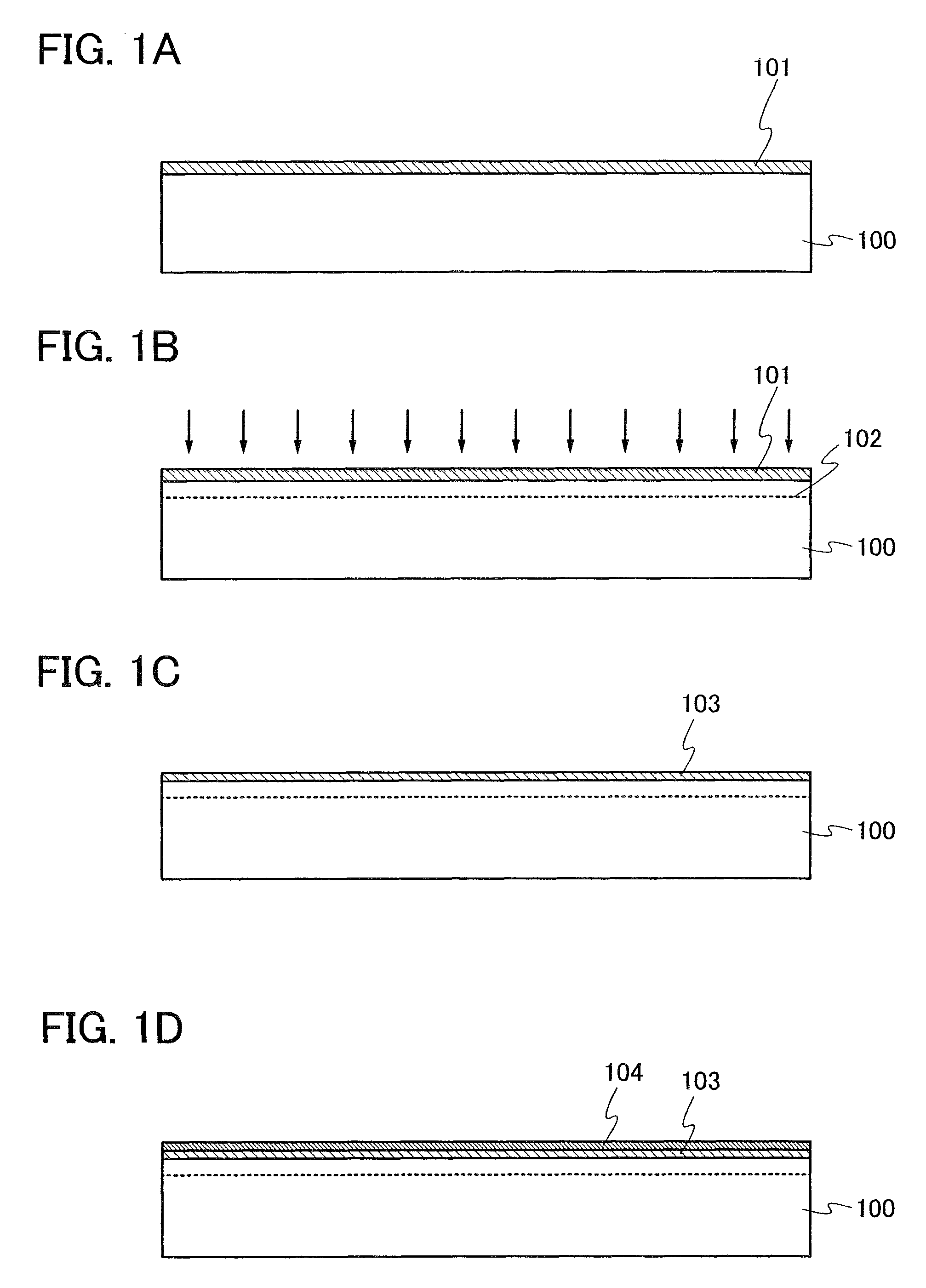

InactiveUS20080318367A1Dampening effectImprove reliability and electrical characteristicSemiconductor/solid-state device manufacturingMetal contaminationIon doping

To suppress an effect of metal contamination caused in manufacturing an SOI substrate. After forming a damaged region by irradiating a semiconductor substrate with hydrogen ions, the semiconductor substrate is bonded to a base substrate. Heat treatment is performed to cleave the semiconductor substrate; thus an SOI substrate is manufactured. Even if metal ions enter the semiconductor substrate together with the hydrogen ions in the step of hydrogen ion irradiation, the effect of metal contamination can be suppressed by the gettering process. Accordingly, the irradiation with hydrogen ions can be performed positively by an ion doping method.

Owner:SEMICON ENERGY LAB CO LTD

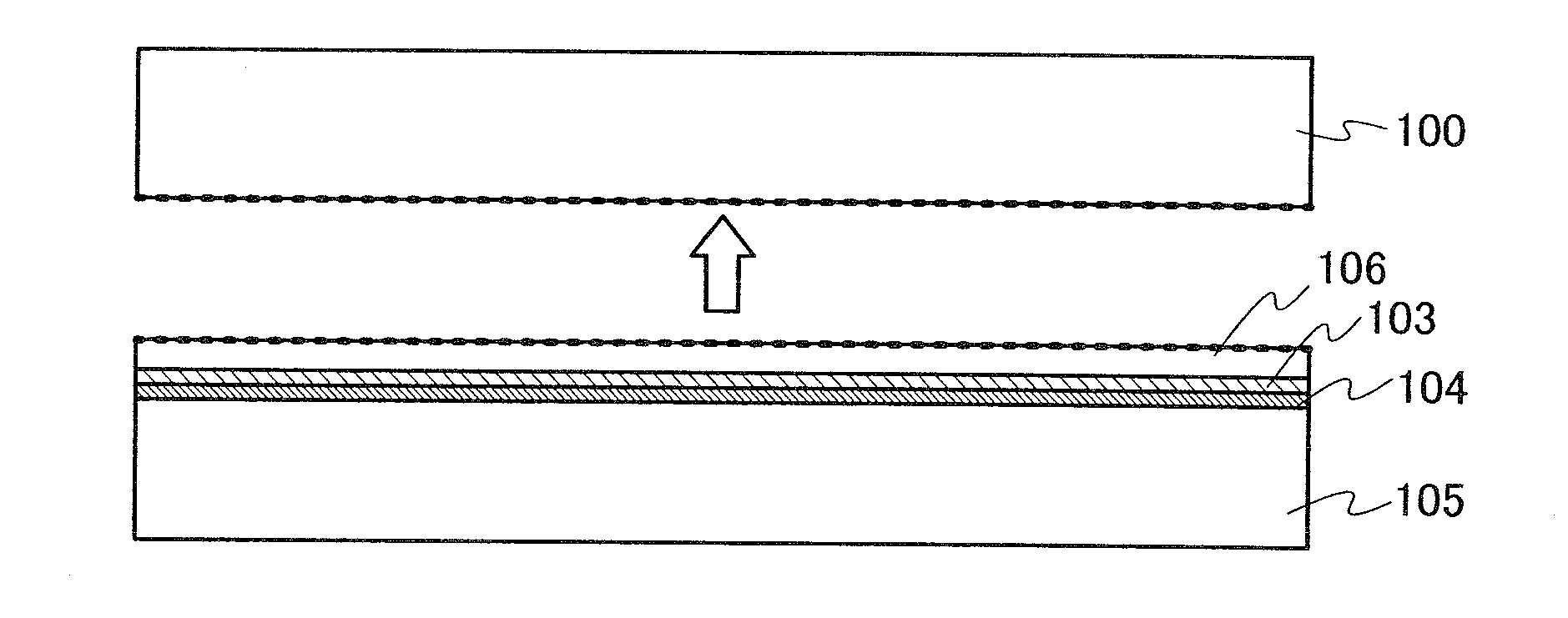

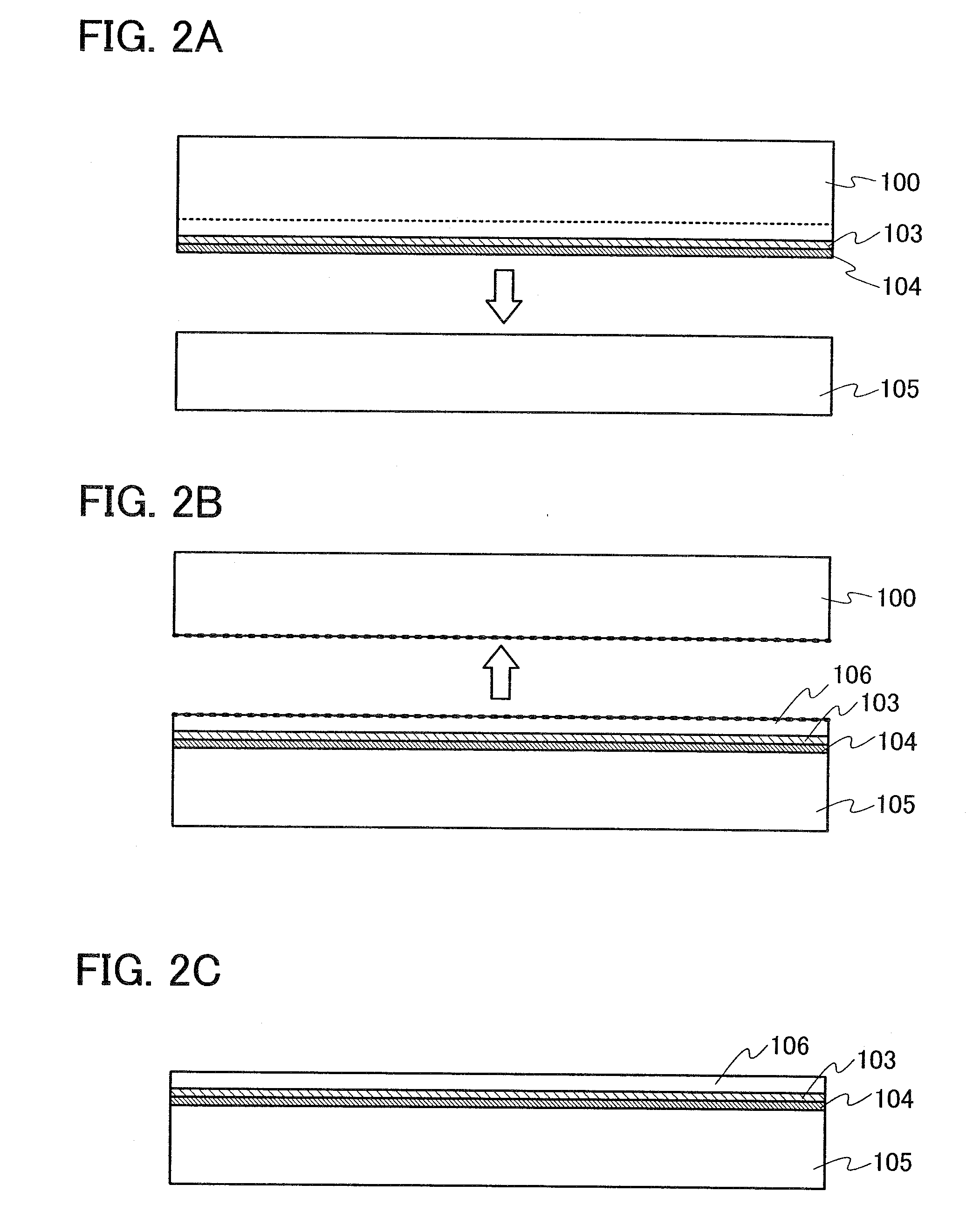

Method of manufacturing semiconductor device

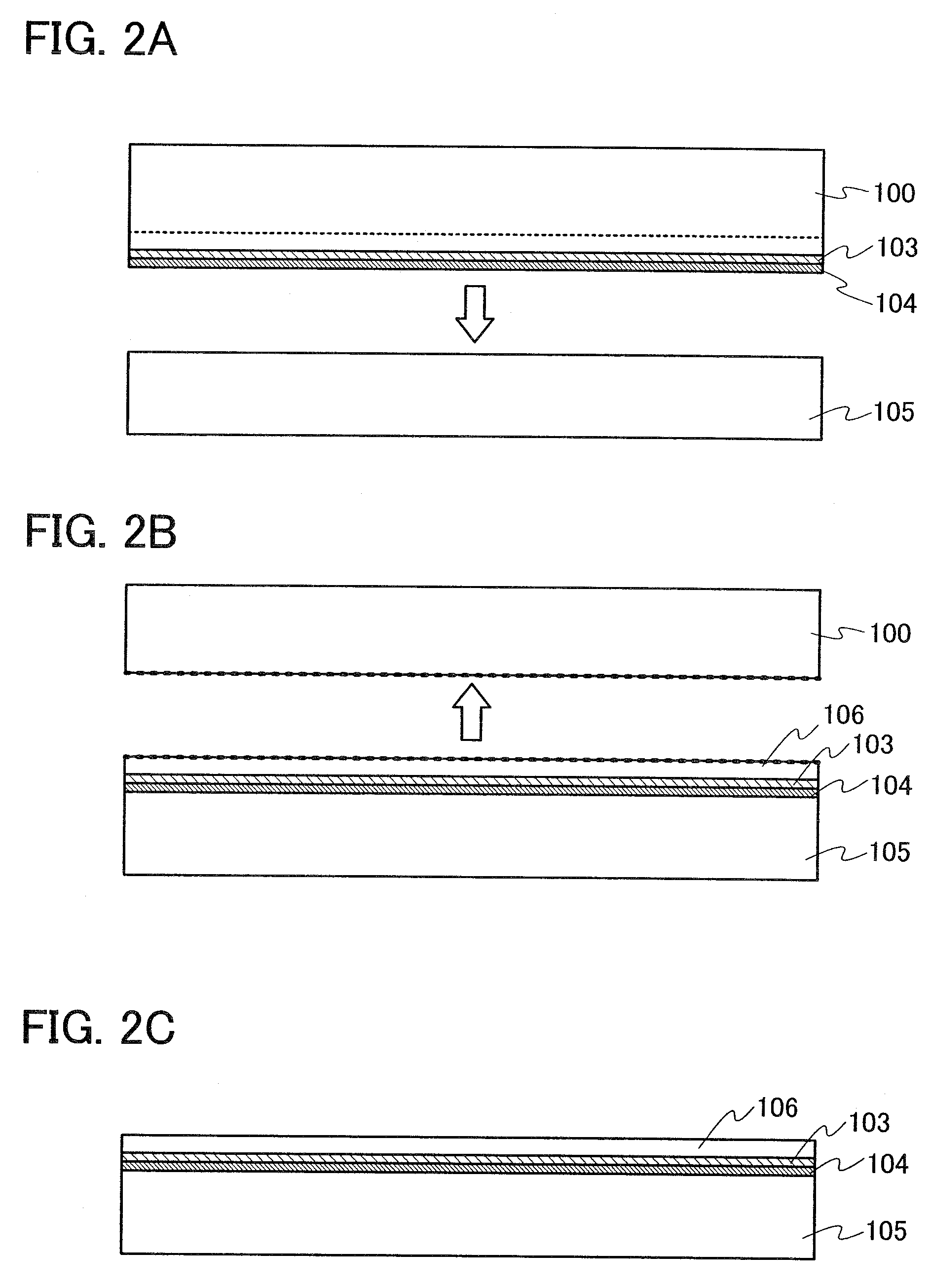

InactiveUS20090098709A1Low reliabilitySuppression amountSolid-state devicesSemiconductor/solid-state device manufacturingHydrogenSoi substrate

To provide a method of manufacturing a semiconductor device, which prevents impurities from entering an SOI substrate. A source gas including one or plural kinds selected from a hydrogen gas, a helium gas, or halogen gas are excited to generate ions, and the ions are added to a bonding substrate to thereby form a fragile layer in the bonding substrate. Then, a region of the bonding substrate that is on and near the surface thereof, i.e., a region ranging from a shallower position than the fragile layer to the surface is removed by etching, polishing, or the like. Next, after attaching the bonding substrate to a base substrate, the bonding substrate is separated at the fragile layer to thereby form a semiconductor film over the base substrate. After forming the semiconductor film over the base substrate, a semiconductor element is formed using the semiconductor film.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

ActiveUS9263589B2Low reliabilityImprove reliabilityTransistorSemiconductor/solid-state device manufacturingElectricitySemiconductor

An object of the present invention is to manufacture a semiconductor device where fluctuation in electrical characteristics is small and reliability is high in a transistor in which an oxide semiconductor is used. An insulating layer from which oxygen is released by heating is used as a base insulating layer of an oxide semiconductor layer which forms a channel. Oxygen is released from the base insulating layer, whereby oxygen deficiency in the oxide semiconductor layer and an interface state between the base insulating layer and the oxide semiconductor layer can be reduced. Thus, a semiconductor device where fluctuation in electrical characteristics is small and reliability is high can be manufactured.

Owner:SEMICON ENERGY LAB CO LTD

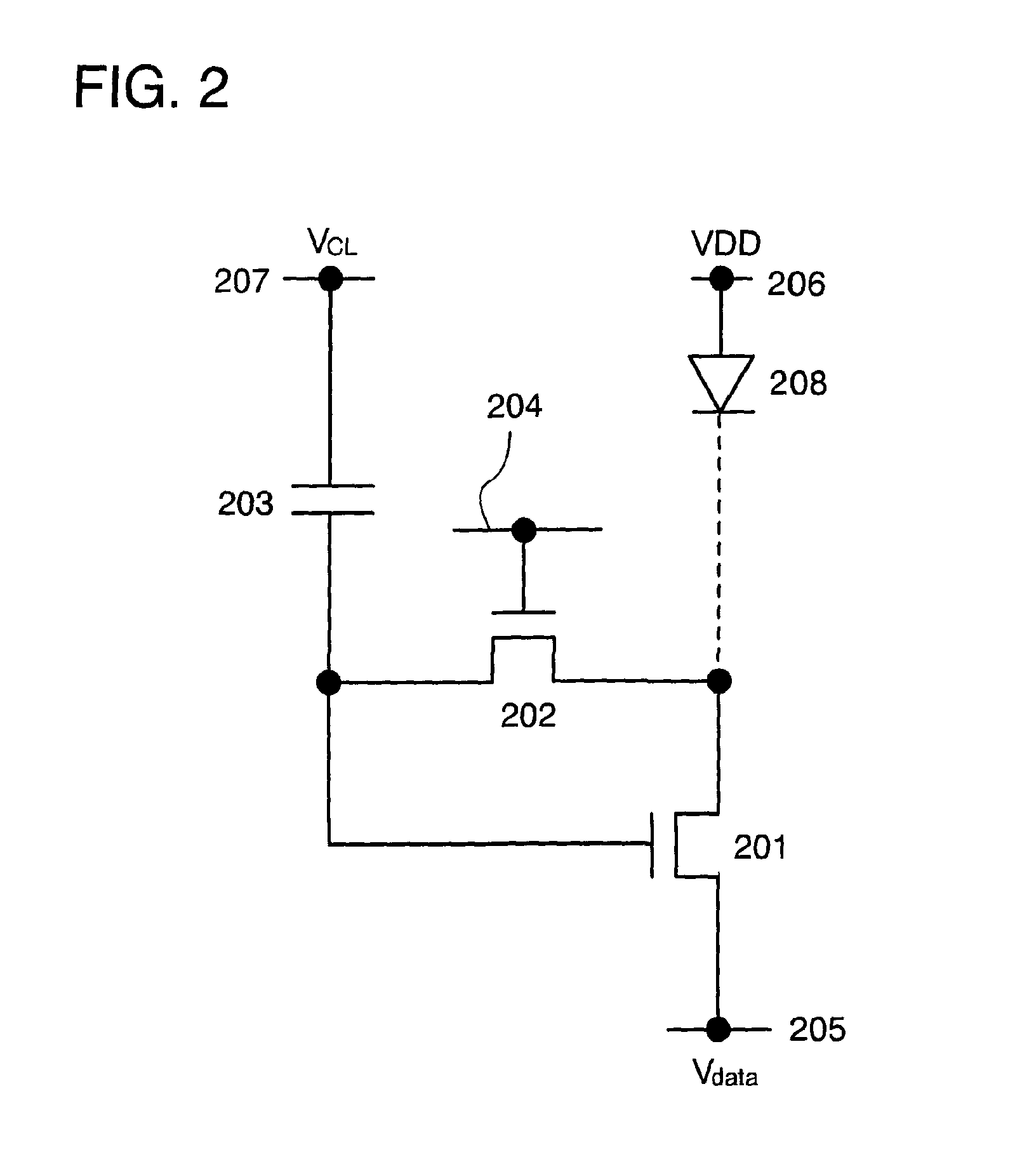

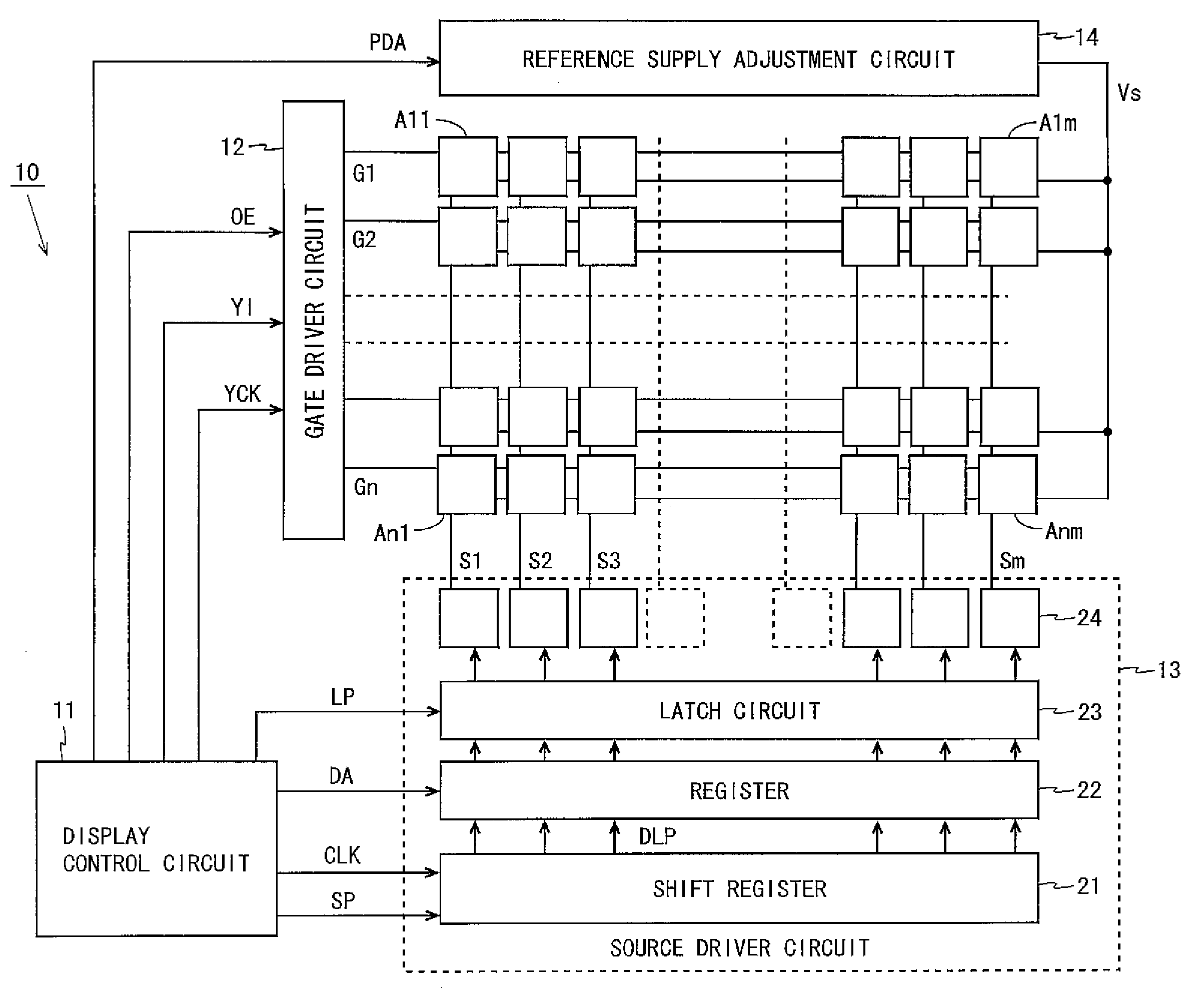

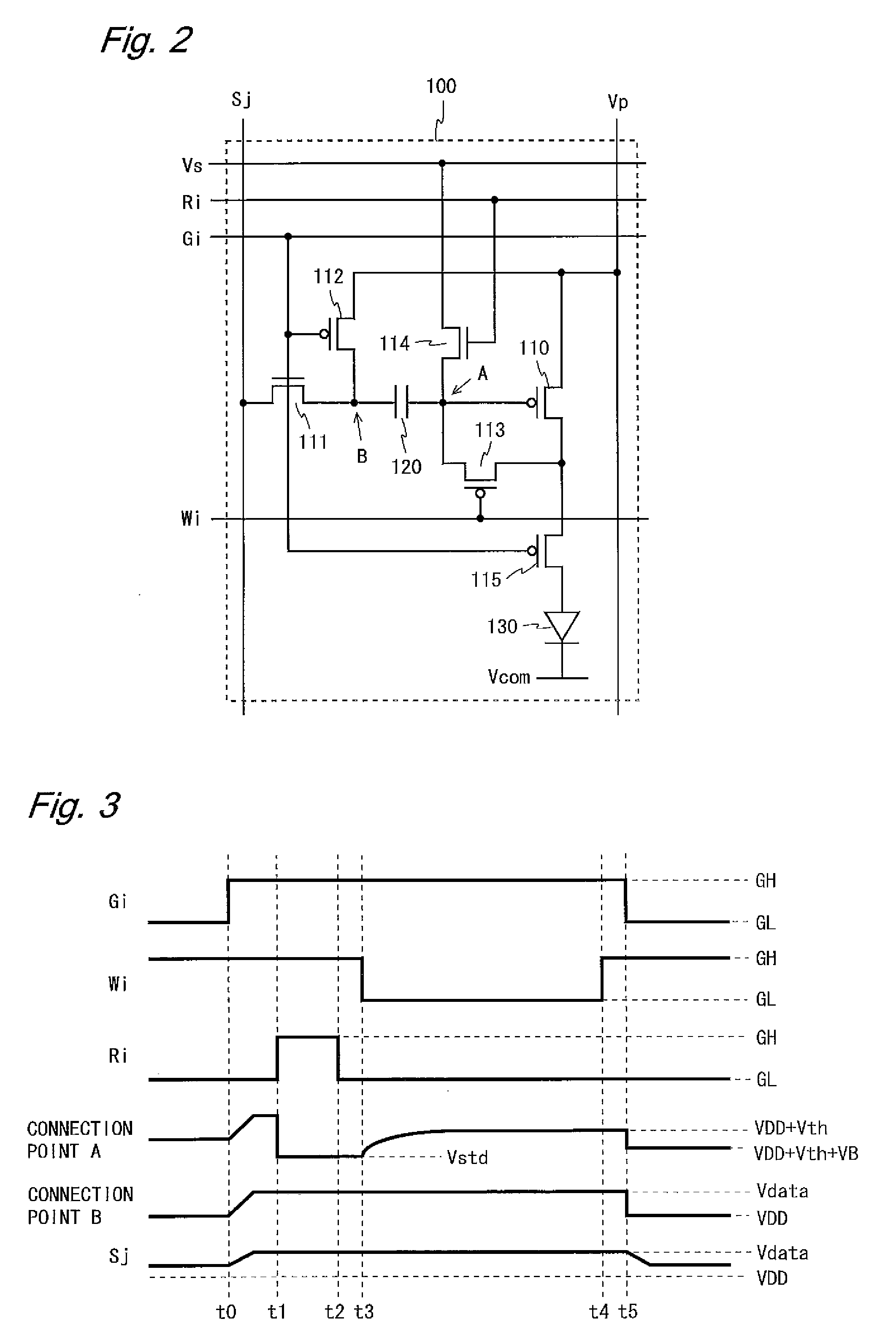

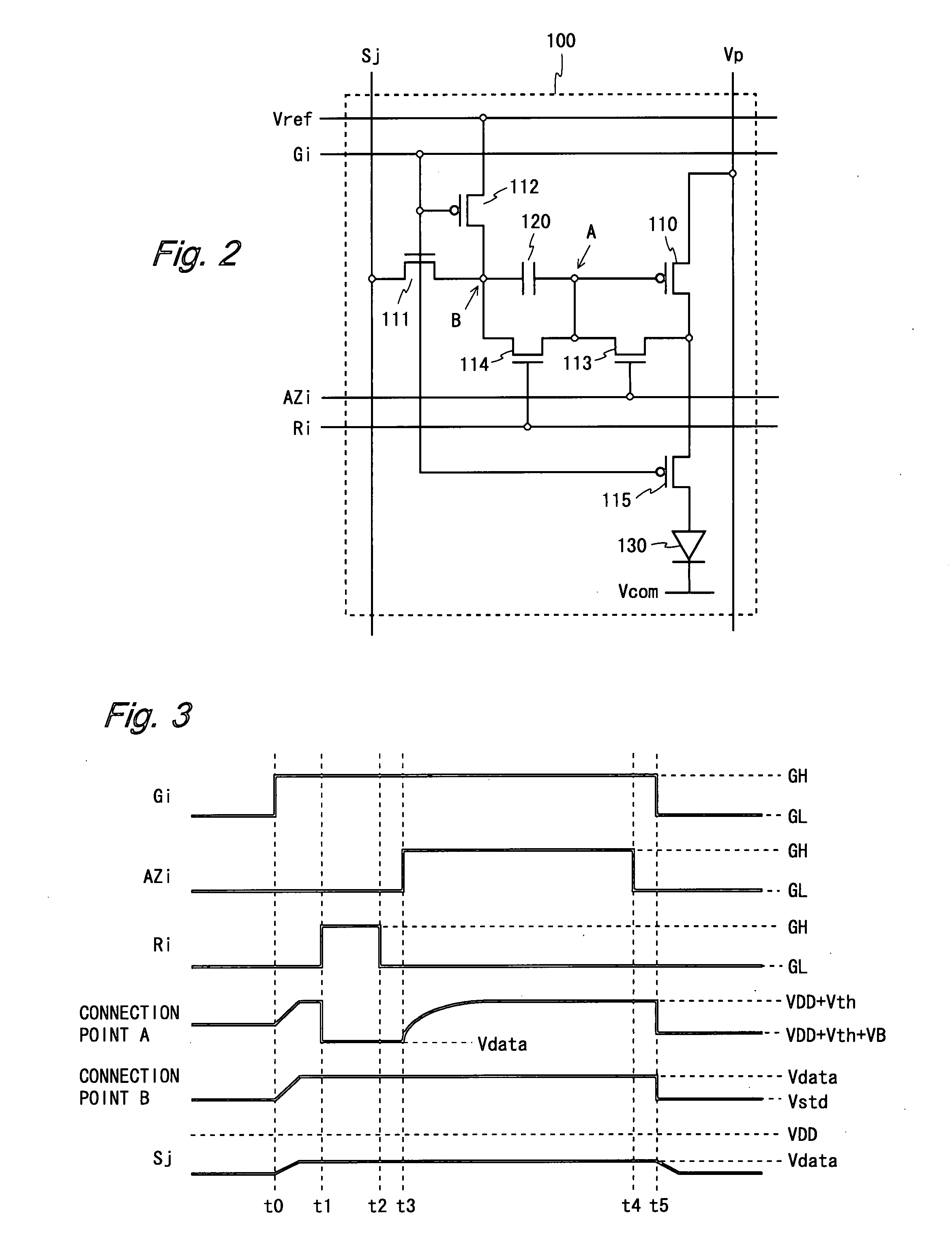

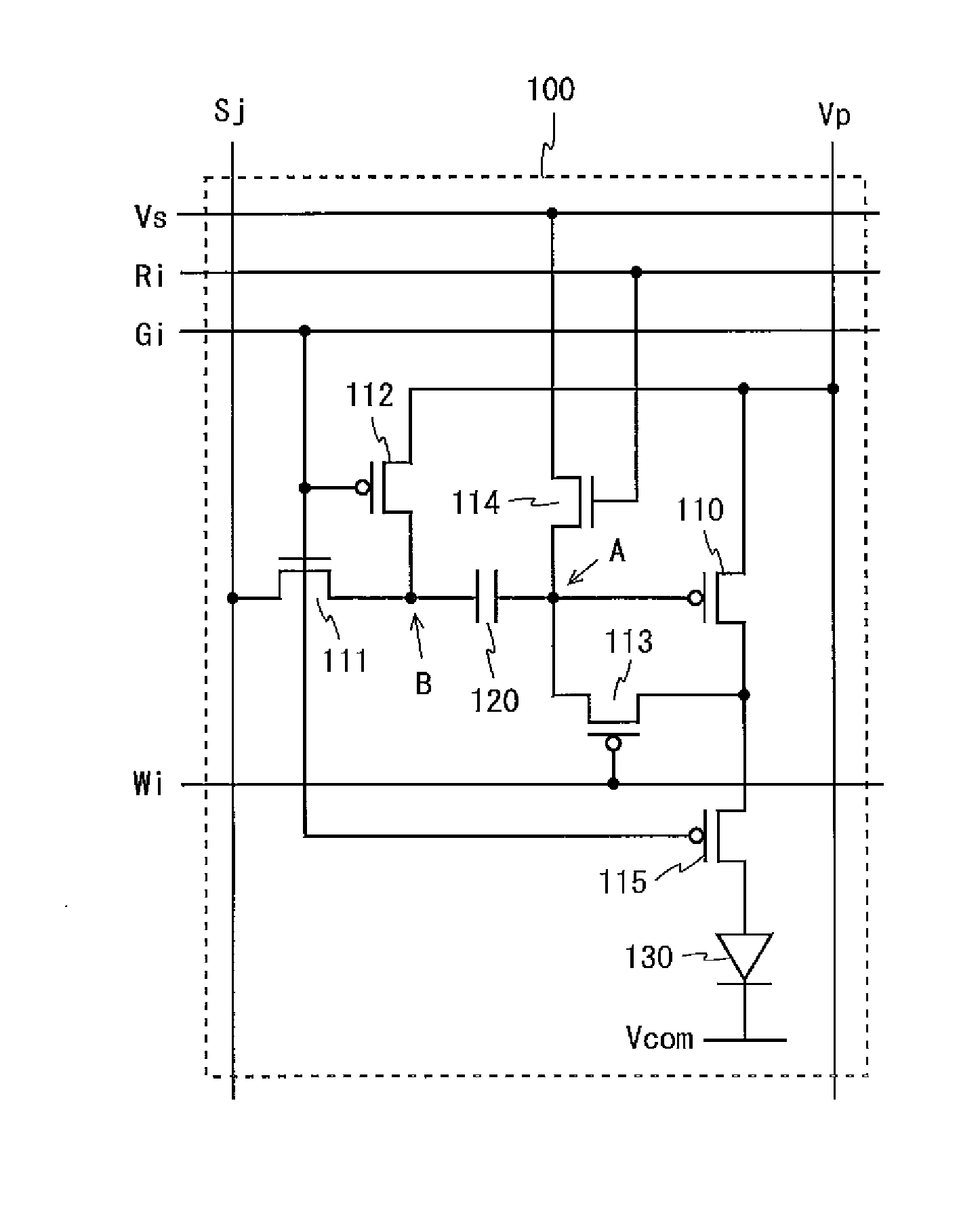

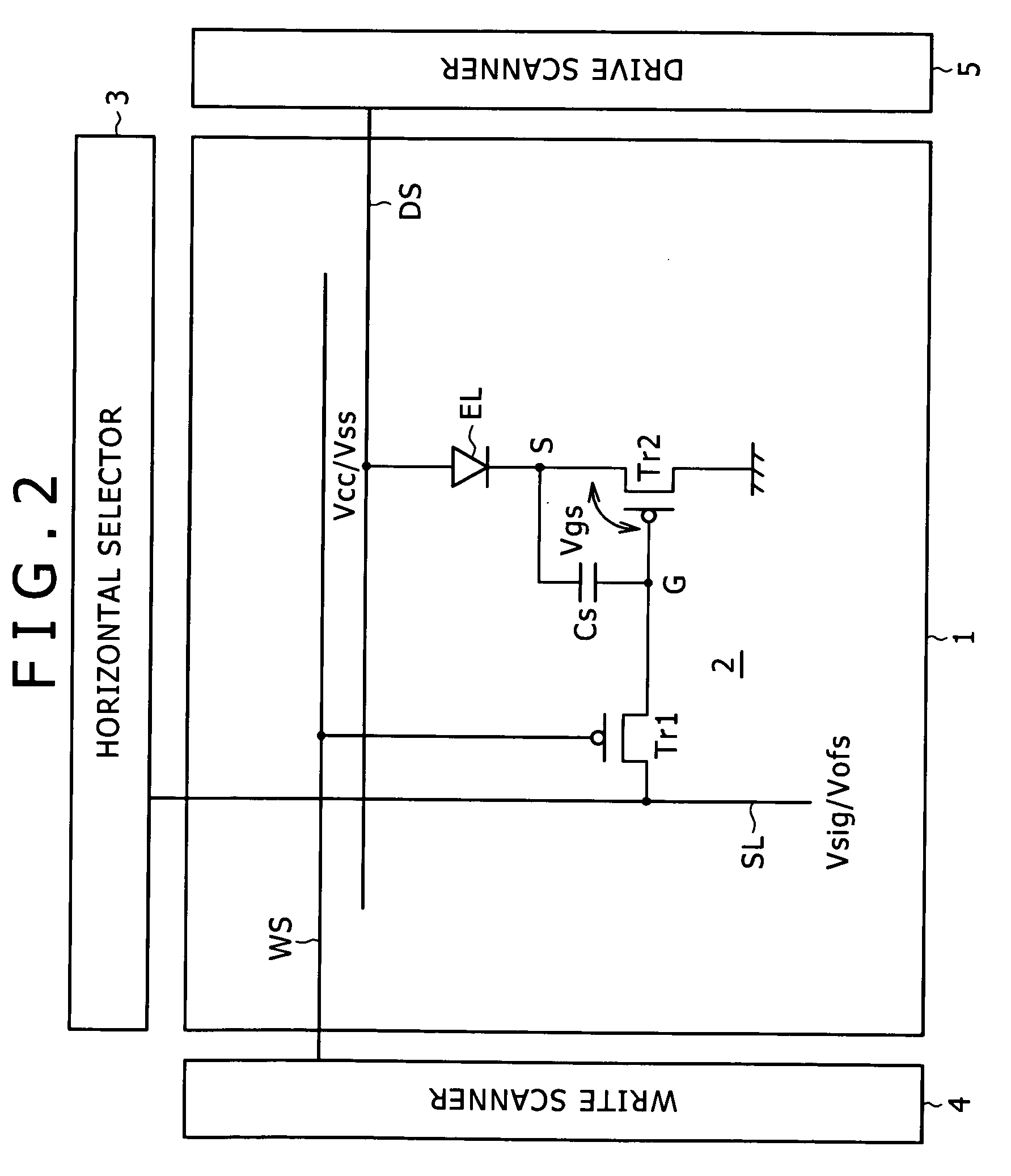

Electric current driving type display device

ActiveUS20090040150A1Enhance display qualityNumber be smallStatic indicating devicesSolid-state devicesDriven elementEngineering

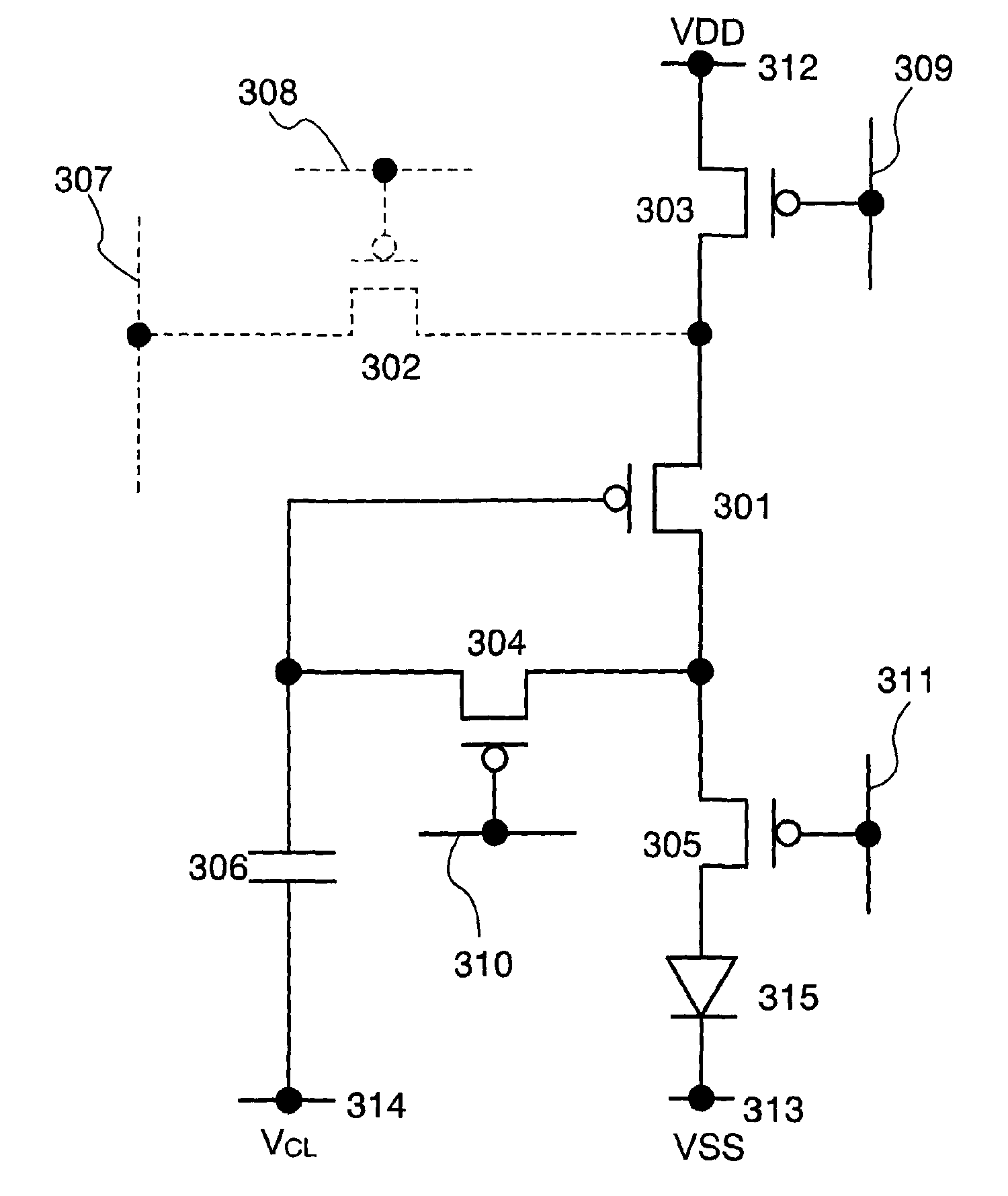

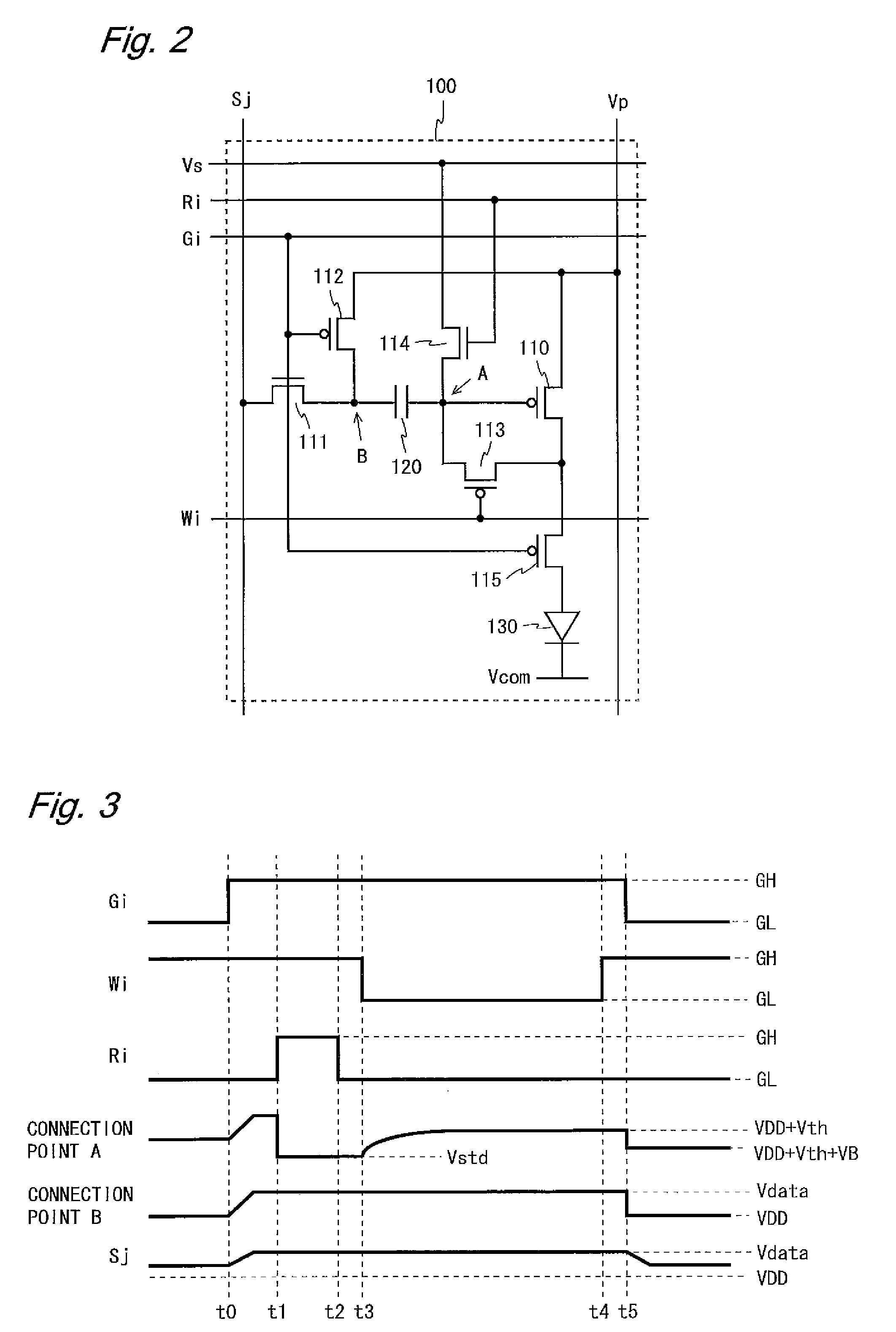

In a pixel circuit 100, a driving TFT 110, a switching TFT 115, and an organic EL element 130 are provided between a power supply wiring line Vp and a common cathode Vcom and a capacitor 120 and a switching TFT 111 are provided between a gate terminal of the driving TFT 110 and a data line Sj. A switching TFT 112 is provided between a connection point B between the capacitor 120 and the switching TFT 111 and the power supply wiring line Vp, a switching TFT 113 is provided between the gate and drain terminals of the driving TFT 110, and a switching TFT 114 is provided between the gate terminal of the driving TFT 110 and a reference supply wiring line Vs. A potential that brings the driving TFT 110 into a conduction state is applied to the reference supply wiring line Vs. Thus, variations in the threshold voltage of a drive element can be properly compensated for and unwanted light emission from an electro-optical element can be prevented.

Owner:SHARP KK

Driving method of semiconductor device

ActiveUS8305304B2Reduce impactReduce power consumptionElectrical apparatusElectroluminescent light sourcesDevice materialEngineering

The semiconductor device includes a transistor and a capacitor element which is electrically connected to a gate of the transistor. Charge held in the capacitor element according to total voltage of voltage corresponding to the threshold voltage of the transistor and image signal voltage is once discharged through the transistor, so that variation in current flowing in the transistor or mobility of the transistor can be reduced.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device for radiation detection

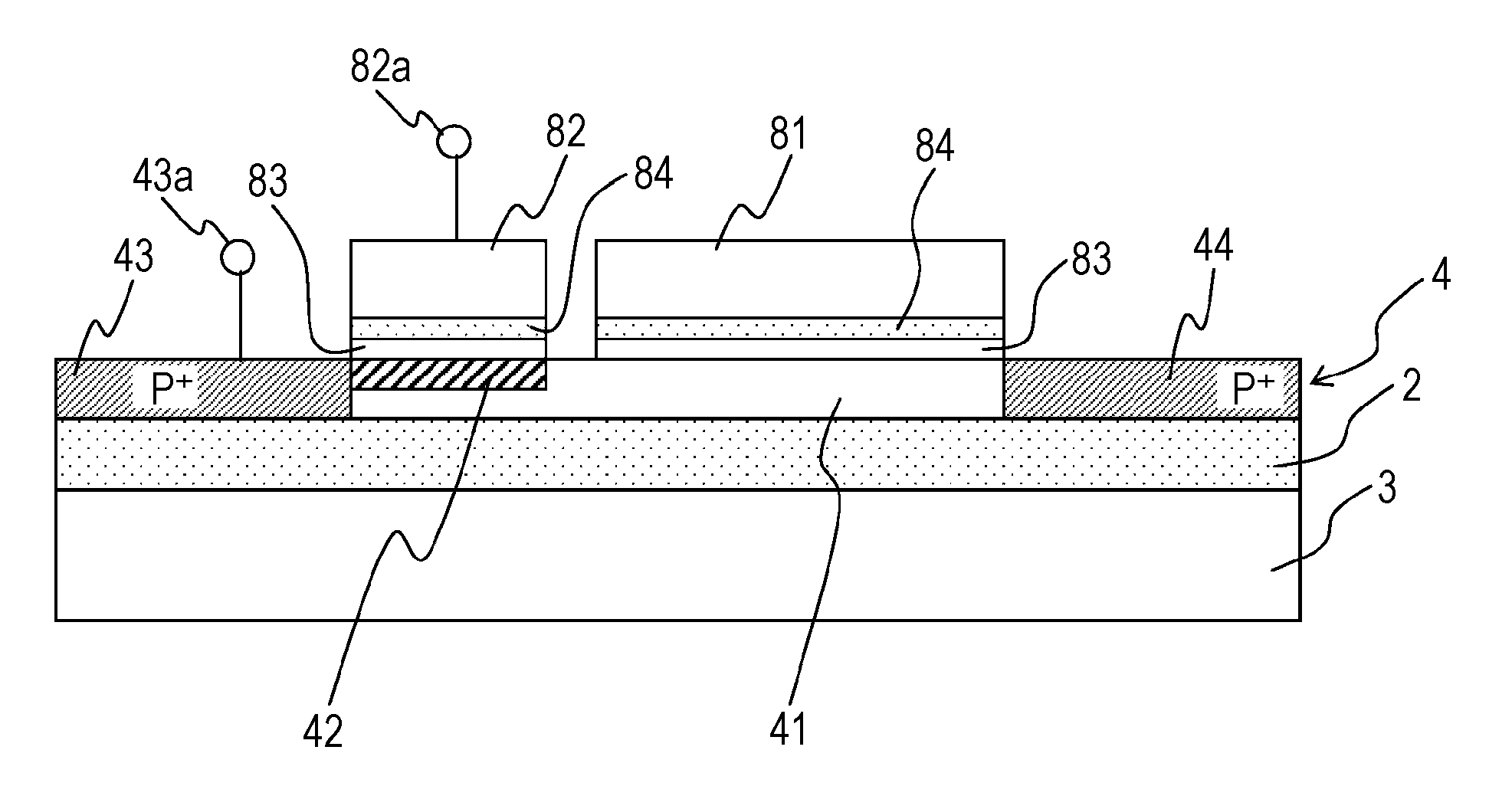

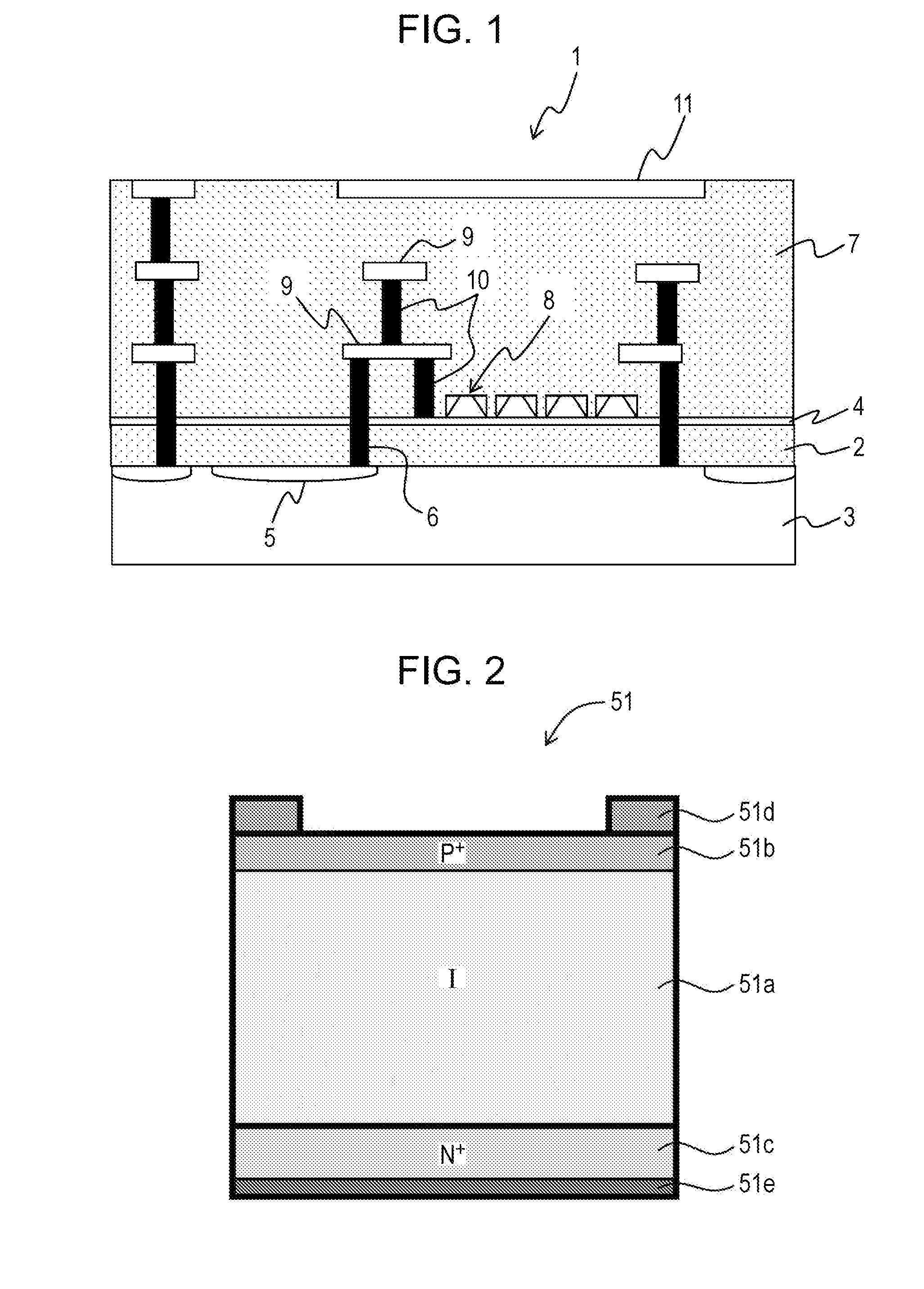

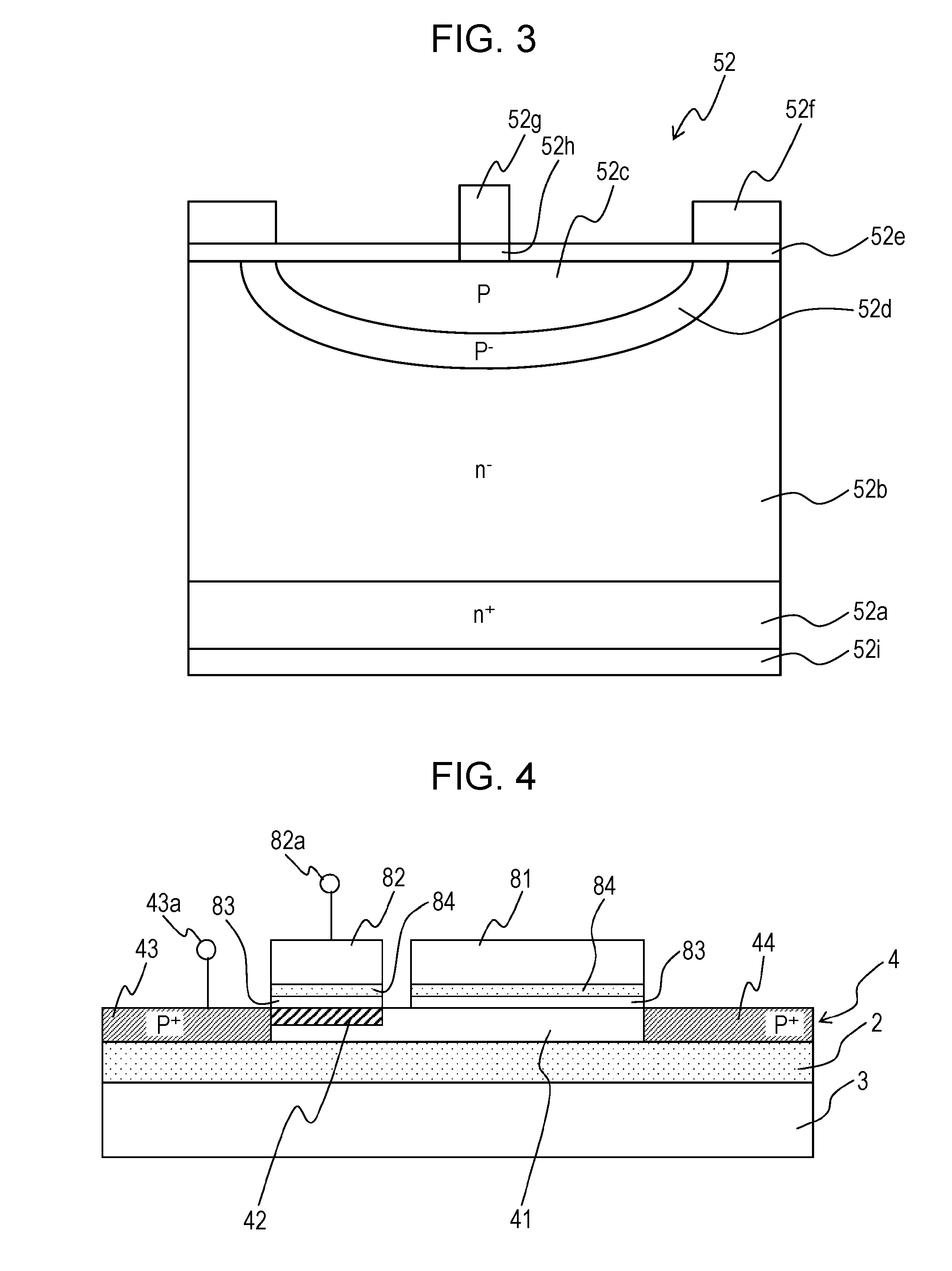

ActiveUS20160172396A1Reduce threshold voltageReduce variationTransistorSolid-state devicesSilicon nitridePower semiconductor device

Variation in threshold voltages in a device operation is reduced.An insulator layer which is disposed to be opposed to a channel region 41 of a MOS transistor and is formed to have a laminated structure of a silicon nitride film 83 and a silicon oxide film 83 and an inverted signal input unit which inputs a signal obtained by inverting an input signal inputted into a source region 43 of a MOS transistor into a channel region 41 are provided and the inverted signal input unit includes another gate electrode 82 which is formed on an extended portion of the channel region 41 of the gate electrode 81 in a manner to be adjacent to the gate electrode 81 of the MOS transistor and a CMOS circuit 80 which inverts an input signal inputted into the source region 43 of the MOS transistor in accordance with an input value of the input signal and inputs a signal obtained through inversion in the CMOS circuit 80 into another gate electrode 82.

Owner:SHARP KK

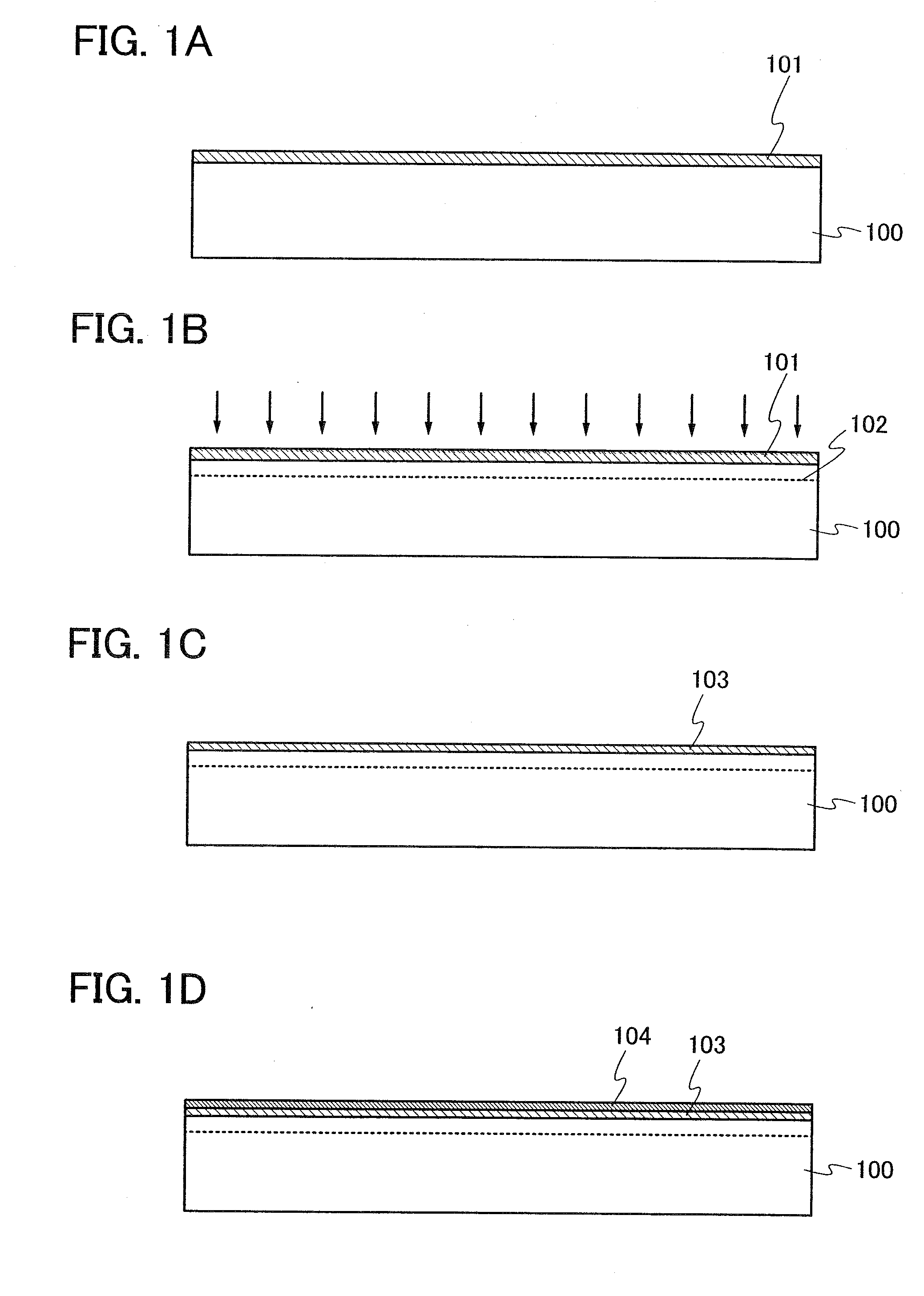

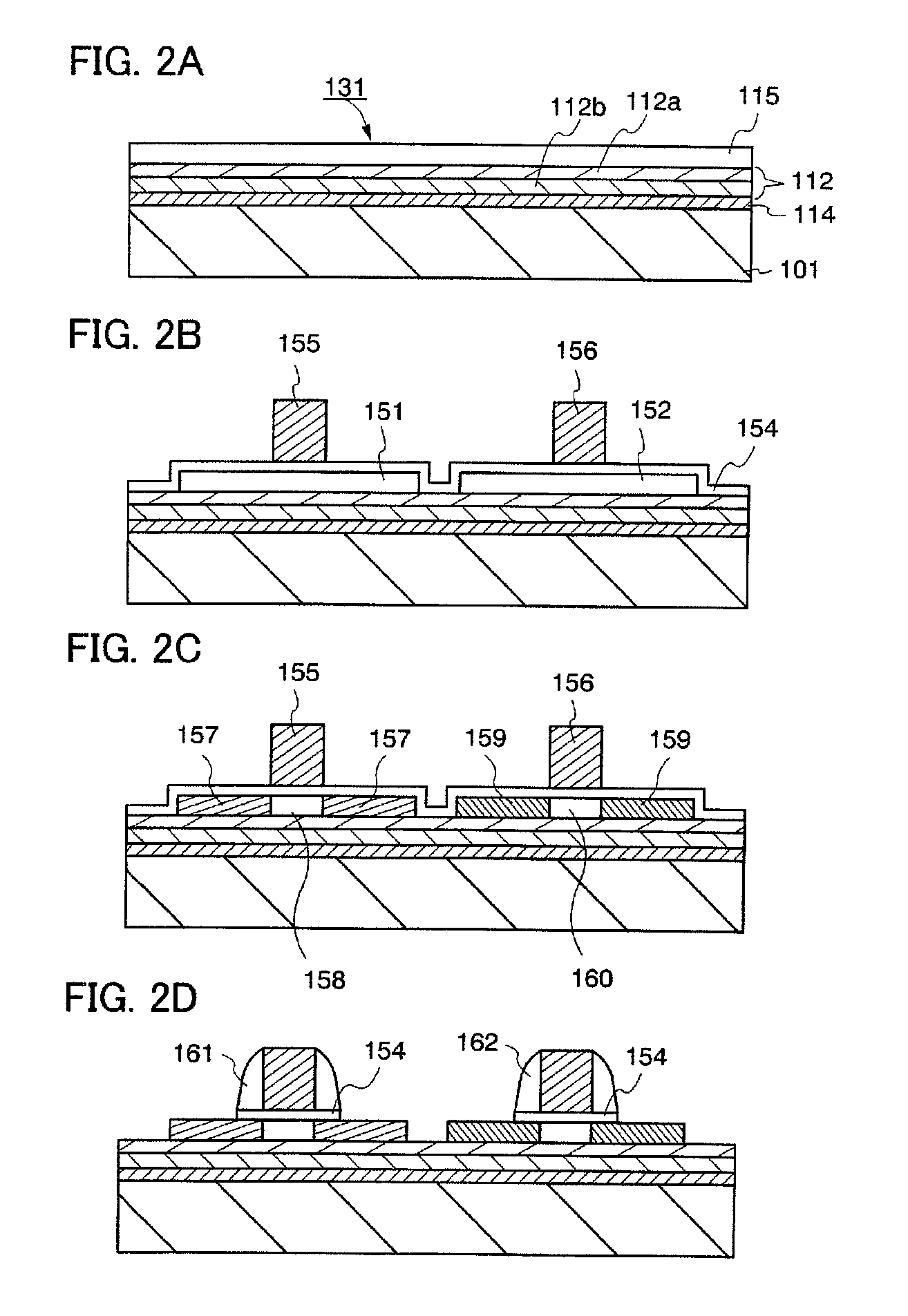

Semiconductor device and manufacturing method thereof

InactiveUS20130134414A1Improve productivityLow costTransistorElectroluminescent light sourcesProduction rateDisplay device

A step for forming an island-shaped semiconductor layer of a semiconductor device used in a display device is omitted in order to manufacture the semiconductor device with high productivity and low cost. The semiconductor device is manufactured through four photolithography processes: four steps for forming a gate electrode, for forming a source electrode and a drain electrode, for forming a contact hole, and for forming a pixel electrode. In the step for forming the contact hole, a groove portion in which a semiconductor layer is removed is formed, whereby formation of a parasitic transistor is prevented. An oxide semiconductor is used as a material of the semiconductor layer in which a channel is formed, and an oxide semiconductor having a higher insulating property than the semiconductor layer is provided over the semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

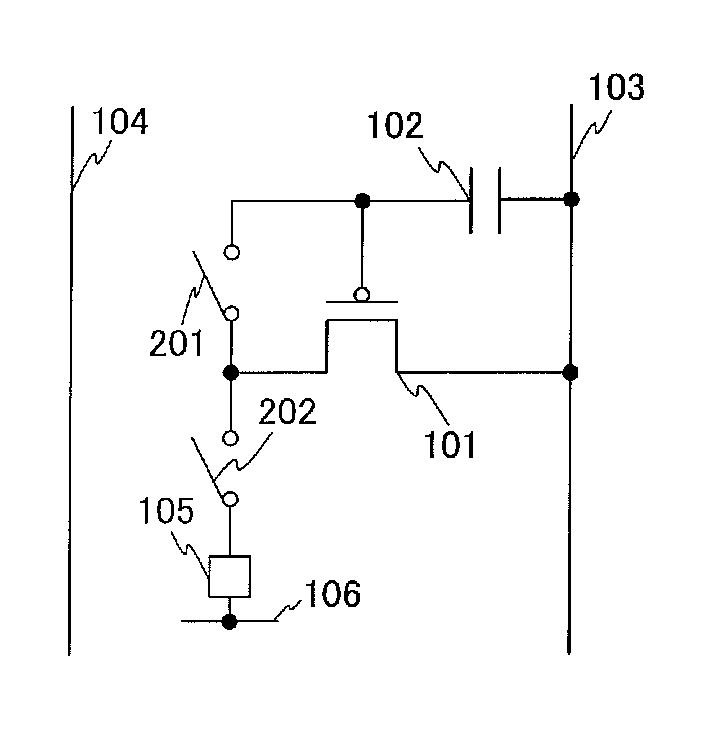

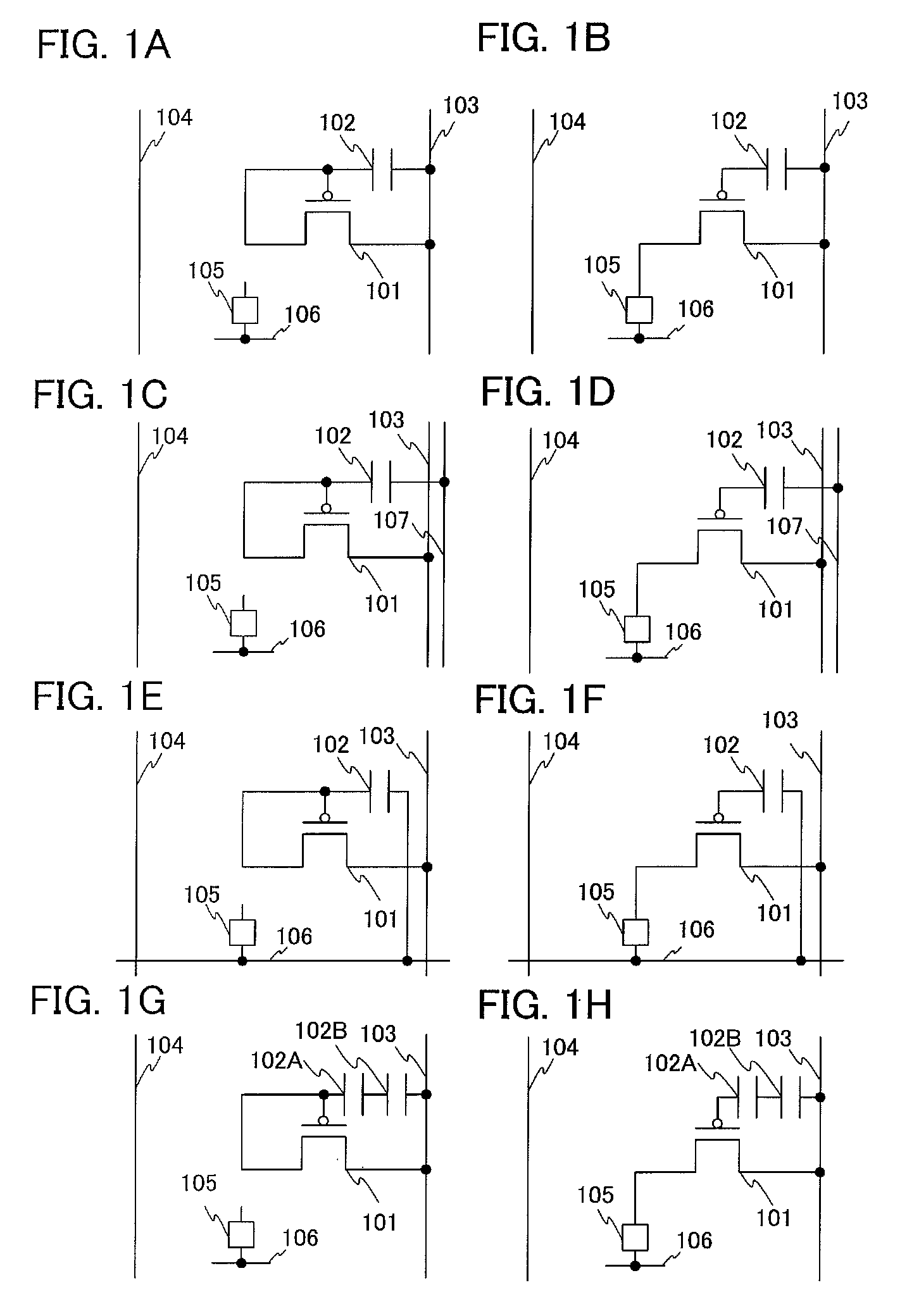

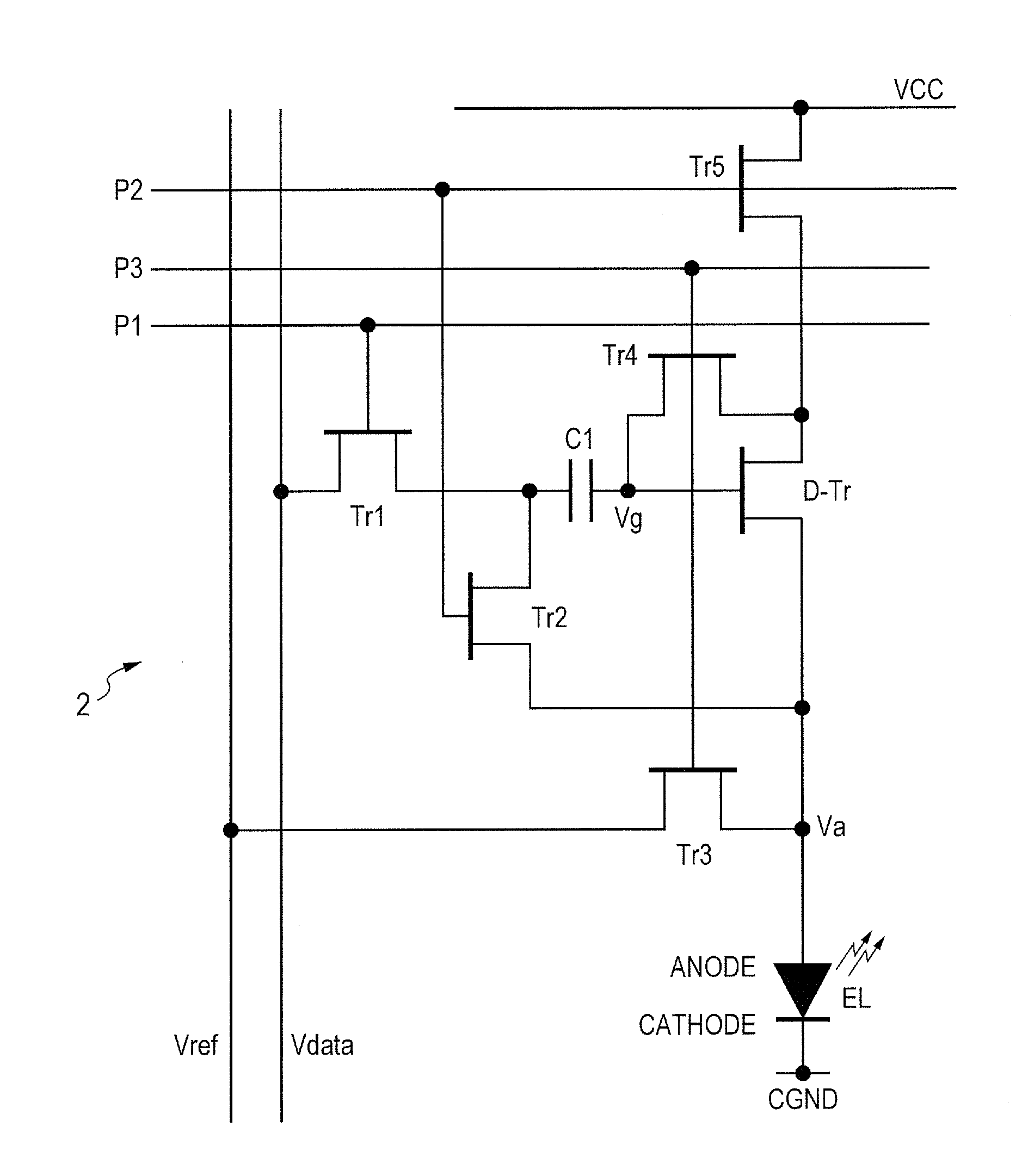

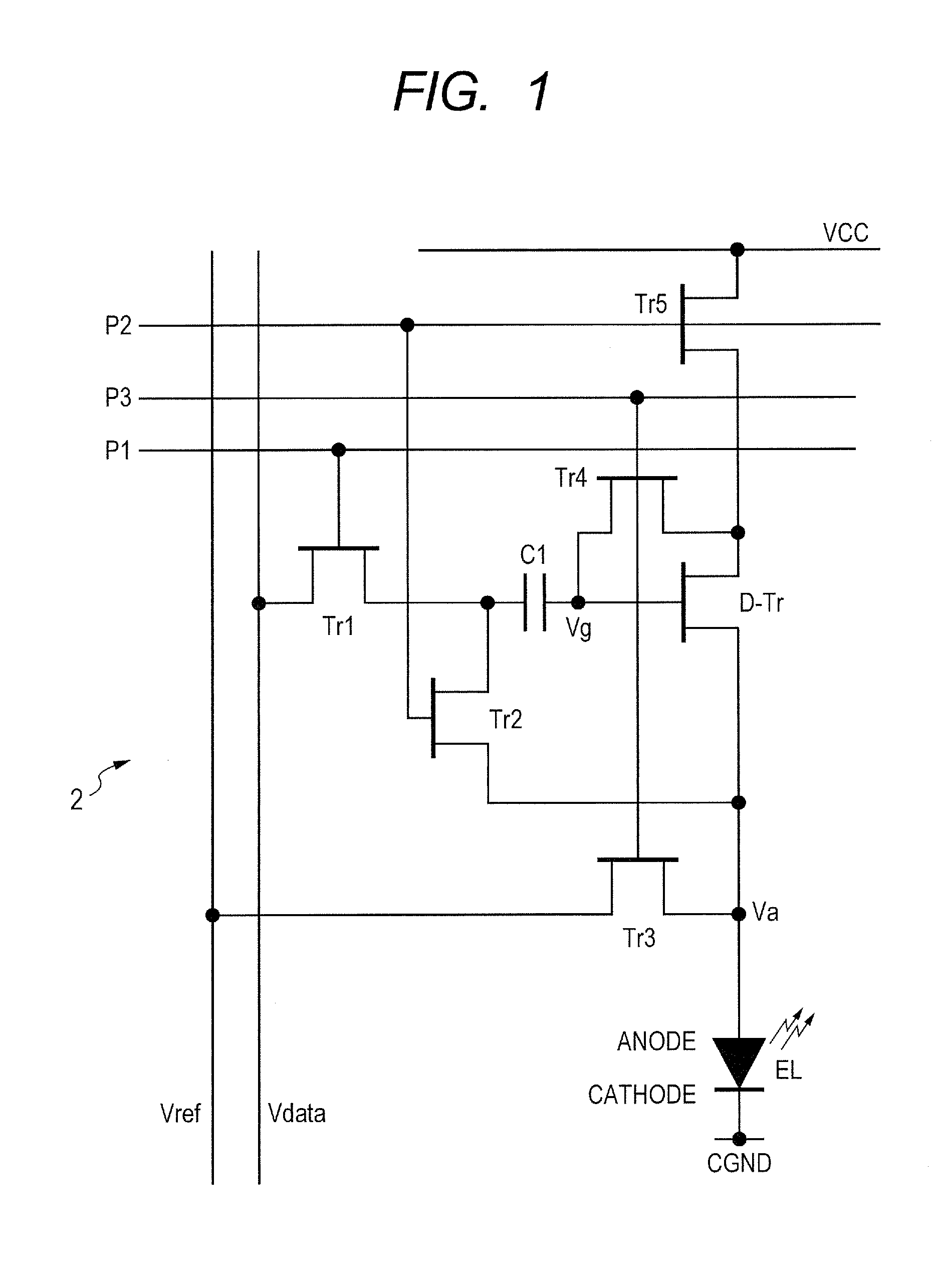

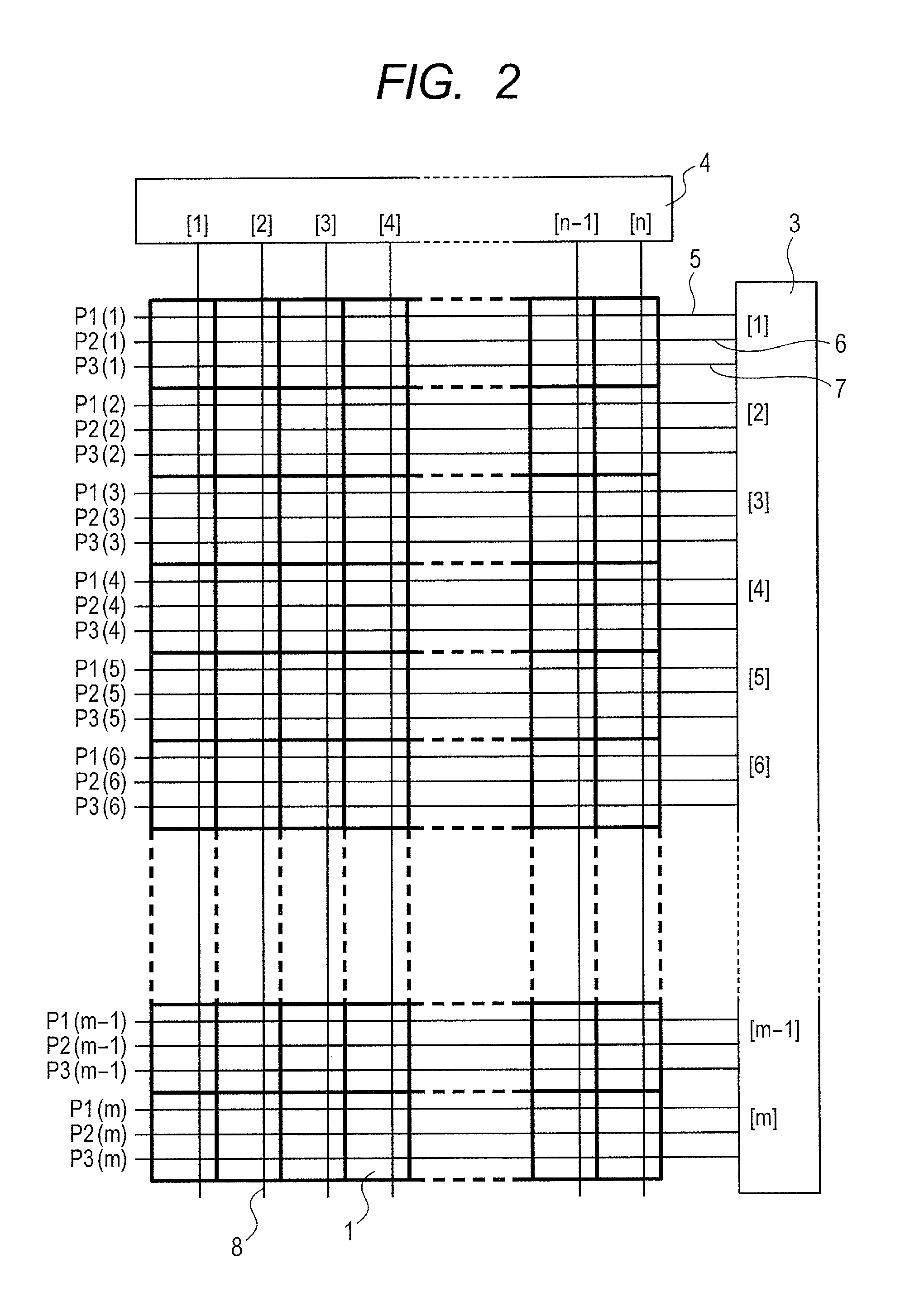

Pixel circuit and driving method thereof

ActiveUS20130222440A1Reduce power consumptionHigh resolutionElectrical apparatusElectroluminescent light sourcesControl signalVoltage reference

A pixel circuit with a source follower type connection is provided that corrects variation in threshold voltage of a driving transistor, reduces power consumption and realizes high resolution. The pixel circuit includes: a data line for supplying a data voltage; a power source line for supplying a power source voltage; a reference voltage line for supplying a reference voltage lower than the power source voltage; a plurality of control signal lines for supplying control signals; a light emitting element; a driving transistor; a capacitor; and a plurality of switching transistors. The circuit writes the data voltage through one end of the capacitor and subsequently connects the one end of the capacitor to the anode electrode of the light emitting element.

Owner:CANON KK

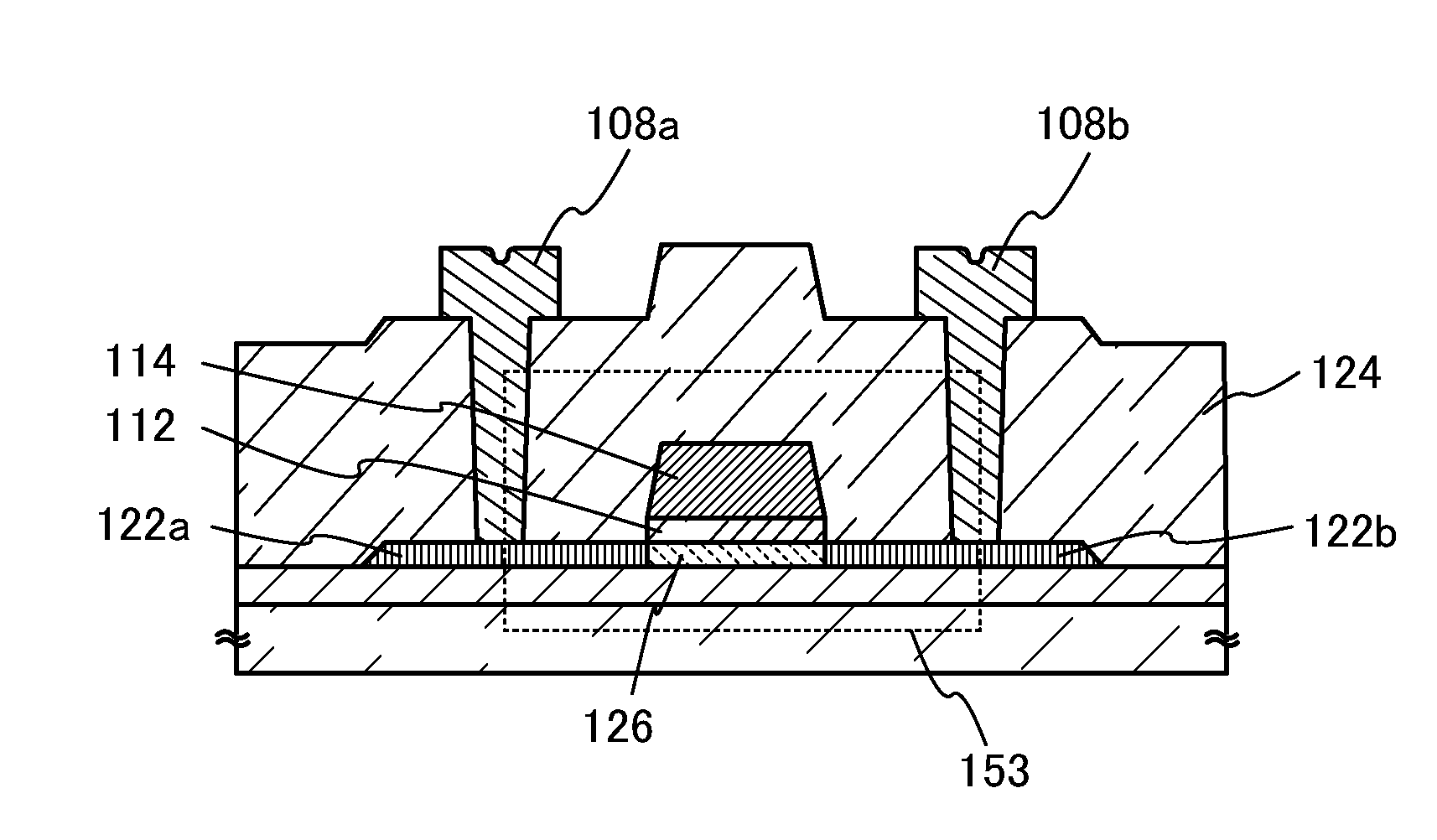

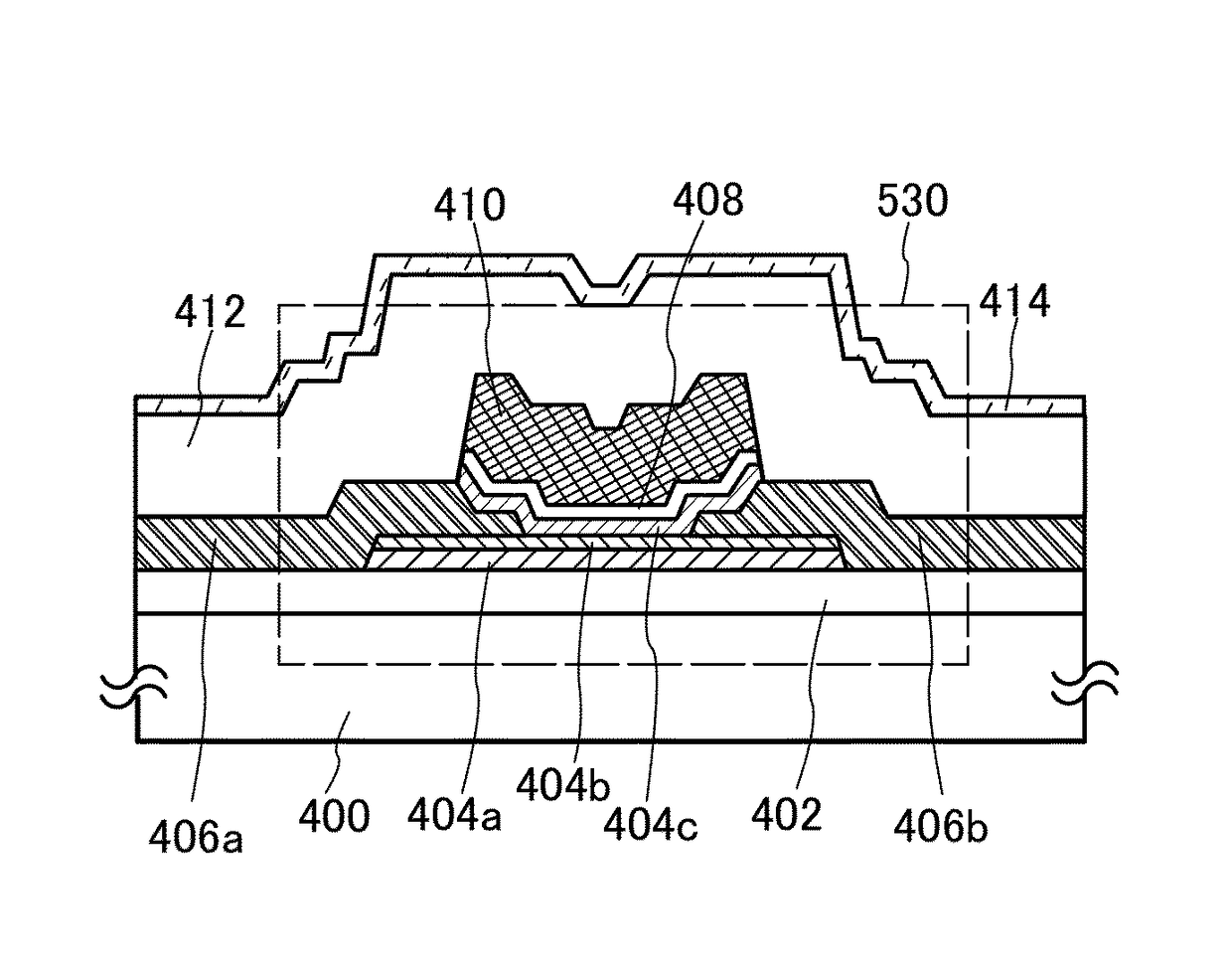

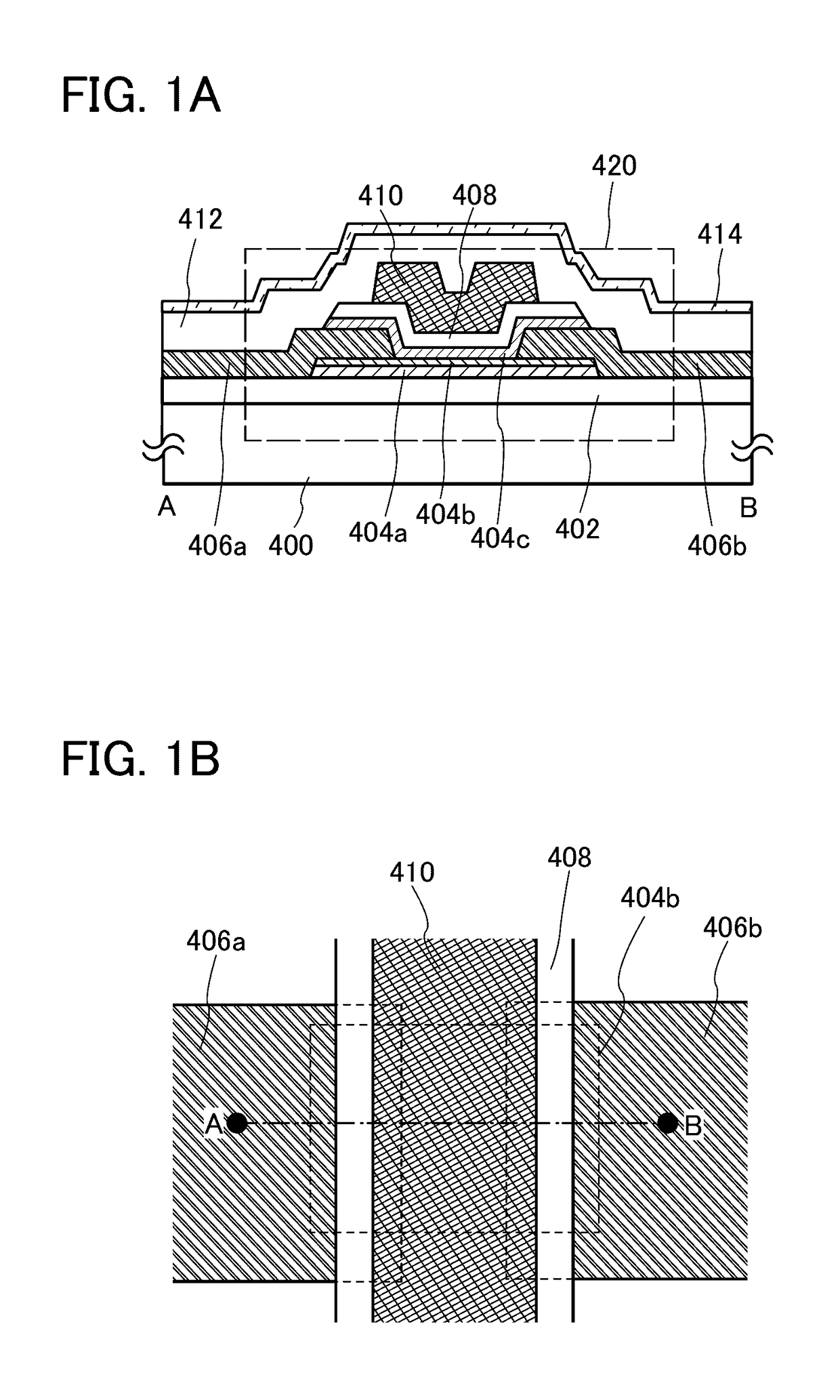

Semiconductor device and method for fabricating the same

ActiveUS9601632B2Improve performanceHigh-speed high-speed operationTransistorSolid-state devicesPower semiconductor deviceSemiconductor

Owner:SEMICON ENERGY LAB CO LTD

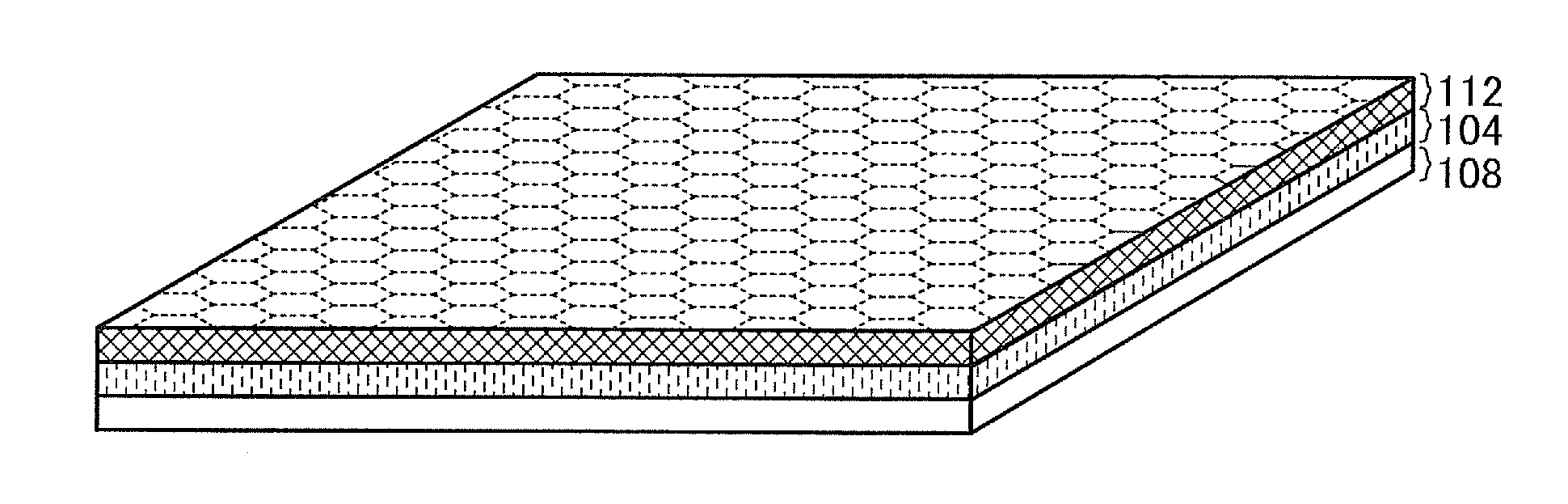

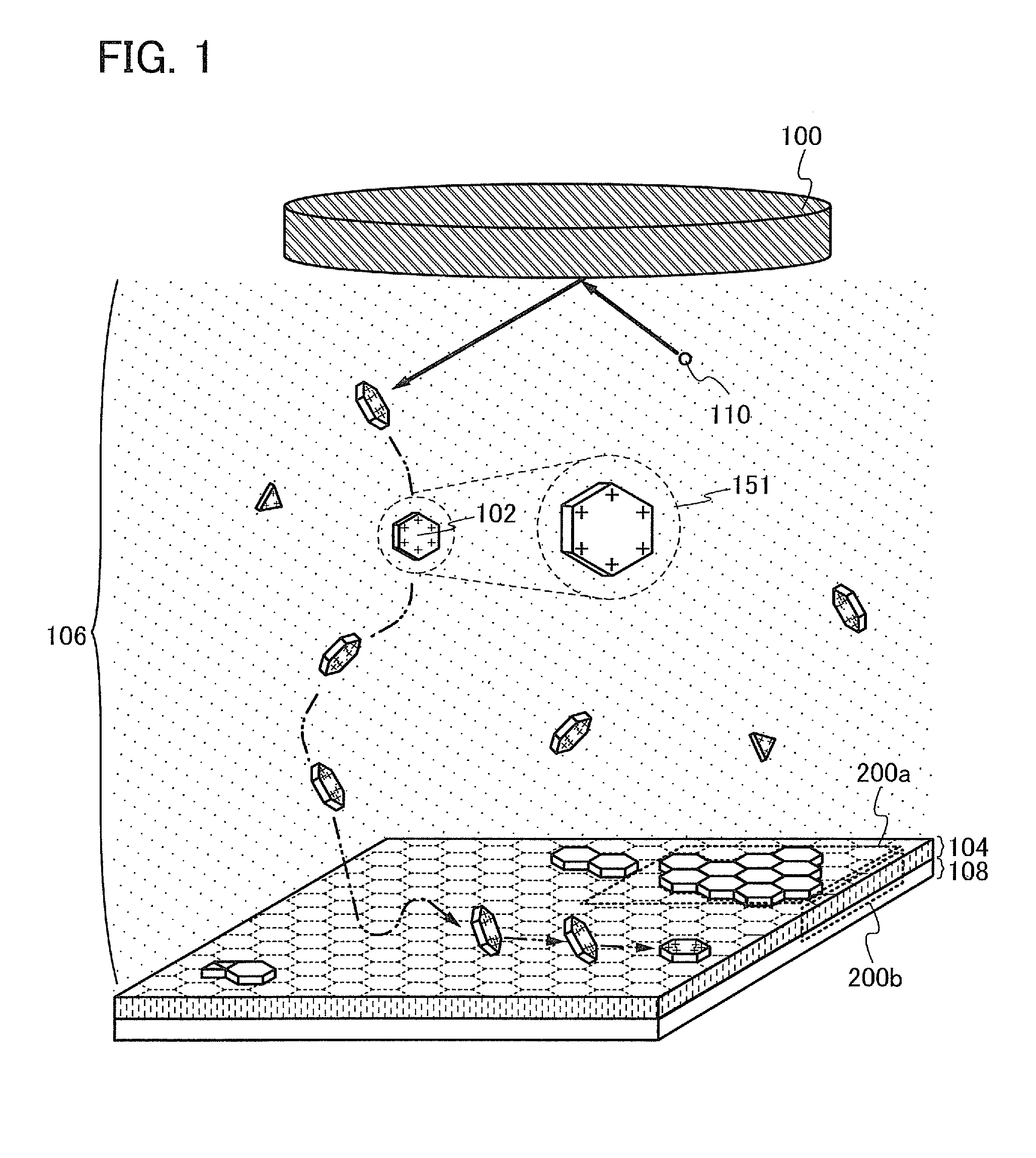

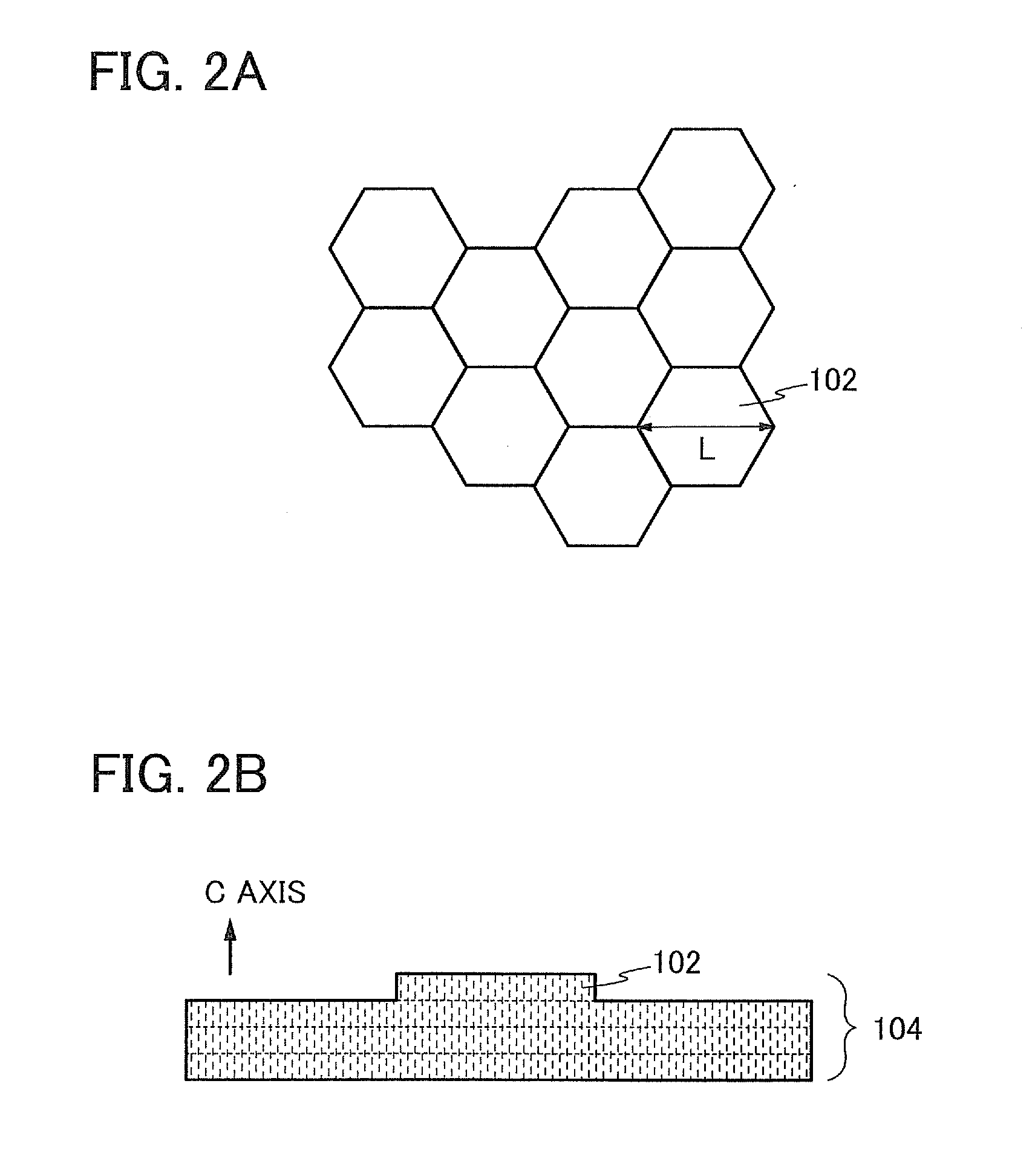

Oxide semiconductor film, film formation method thereof, and semiconductor device

ActiveUS20140145183A1High crystallinityImprove reliabilityVacuum evaporation coatingSputtering coatingDevice materialSingle crystal

An oxide semiconductor film with high crystallinity is formed. An oxide semiconductor film having a single crystal region, which is formed by a sputtering method using a sputtering target including a polycrystalline oxide containing a plurality of crystal grains, is provided. The plurality of crystal grains contained in the sputtering target has a plane that is cleaved or is likely to be cleaved because of a weak crystal bond; therefore, the cleavage planes in the plurality of crystal grains are cleaved when an ion collides with the sputtering target, whereby flat plate-like sputtered particles can be obtained. The obtained flat plate-like sputtered particles are deposited on a deposition surface; accordingly, an oxide semiconductor film is formed. The flat plate-like sputtered particle is formed by separation of part of the crystal grain and therefore the oxide semiconductor film can have high crystallinity.

Owner:SEMICON ENERGY LAB CO LTD

Current-driven display device

ActiveUS20100118059A1Accurate operationSimple processCathode-ray tube indicatorsInput/output processes for data processingHemt circuitsDisplay device

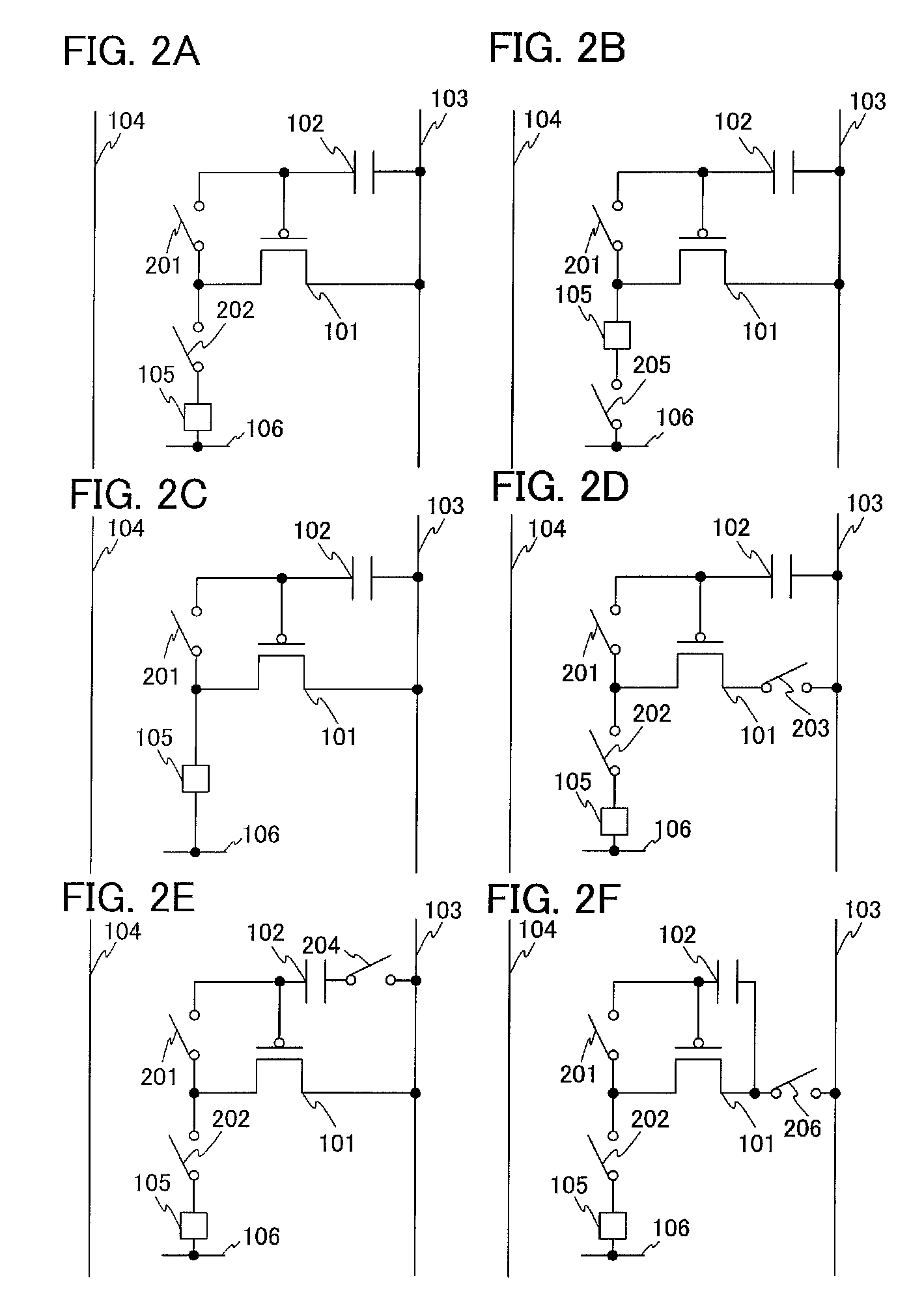

In one embodiment of the present invention, to allow a circuit that compensates for variations in a threshold voltage of a drive element to operate properly and prevent luminances of other pixel circuits from fluctuating due to a compensation operation, a pixel circuit is disclosed. A driving TFT, a switching TFT, and an organic EL element are provided between a power supply wiring line and a common cathode, and a capacitor and a switching TFT are provided between a gate terminal of the driving TFT and a data line. A switching TFT is provided between a connection point B between the capacitor and the switching TFT and a reference supply wiring line, a switching TFT is provided between the gate terminal and a drain terminal of the driving TFT, and a switching TFT is provided between the gate terminal of the driving TFT and the connection point B.

Owner:SHARP KK

Electric current driving type display device

ActiveUS8325118B2Variation in threshold voltageLuminance can be correctedCathode ray tubes/electron beam tubesStatic indicating devicesDisplay deviceEngineering

Owner:SHARP KK

Nonvolatile storage device

InactiveUS20100038615A1Variation in threshold voltageStable storageSolid-state devicesDigital storageElectrical resistance and conductanceOperating voltage

An element structure for a resistance variable type nonvolatile storage device is provided in which enables a reduction in variation in operating voltage and in a leakage current in an off state of an element. The nonvolatile storage device is characterized by including a lower electrode, an upper electrode, and a laminated structure in which at least one amorphous insulating layer and at least one resistance variation layer are laminated between the lower electrode and the upper electrode.

Owner:NEC CORP

Method of fabricating semiconductor device

InactiveUS20050037579A1Lower Reliability RequirementsLow reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialOptoelectronics

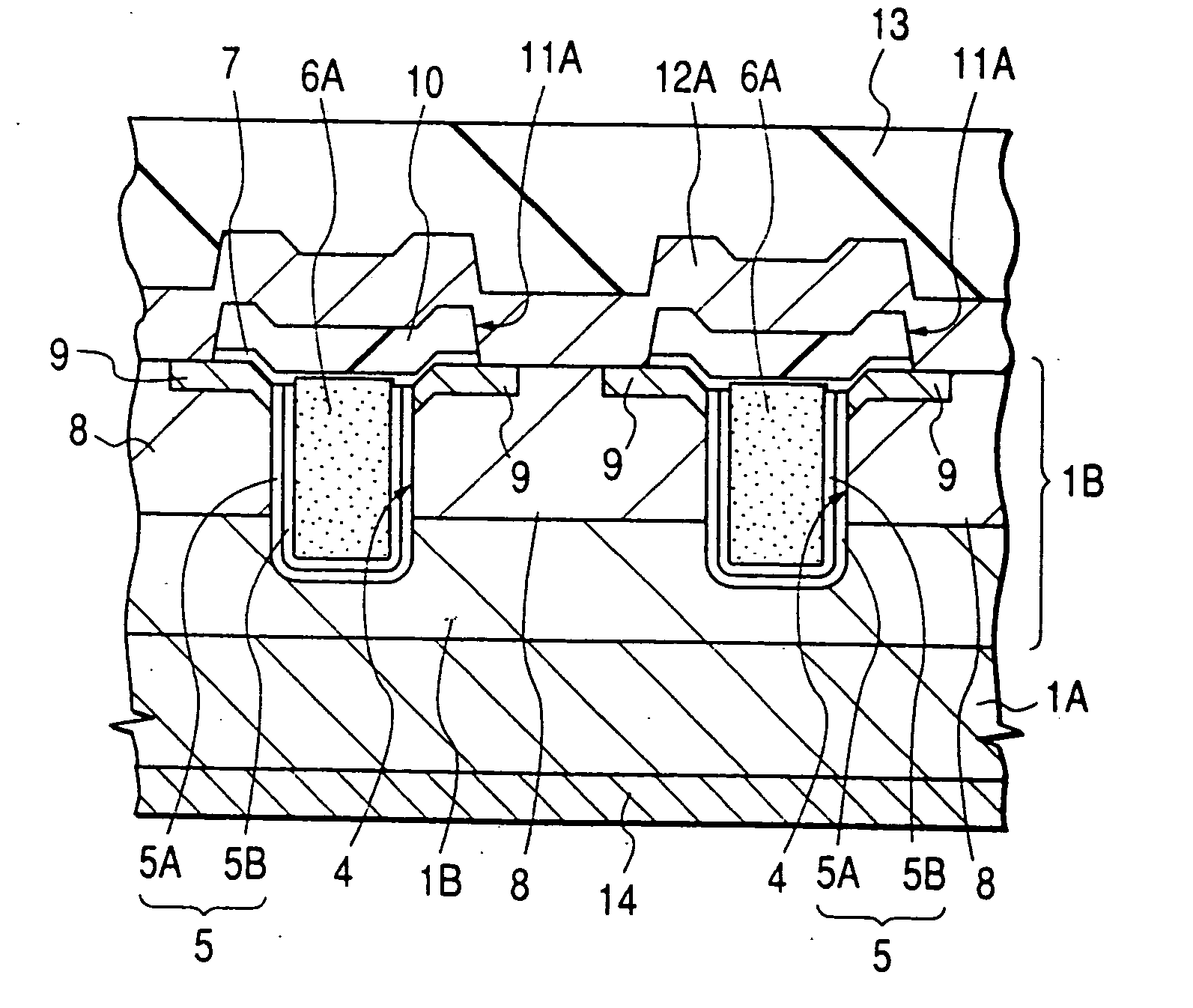

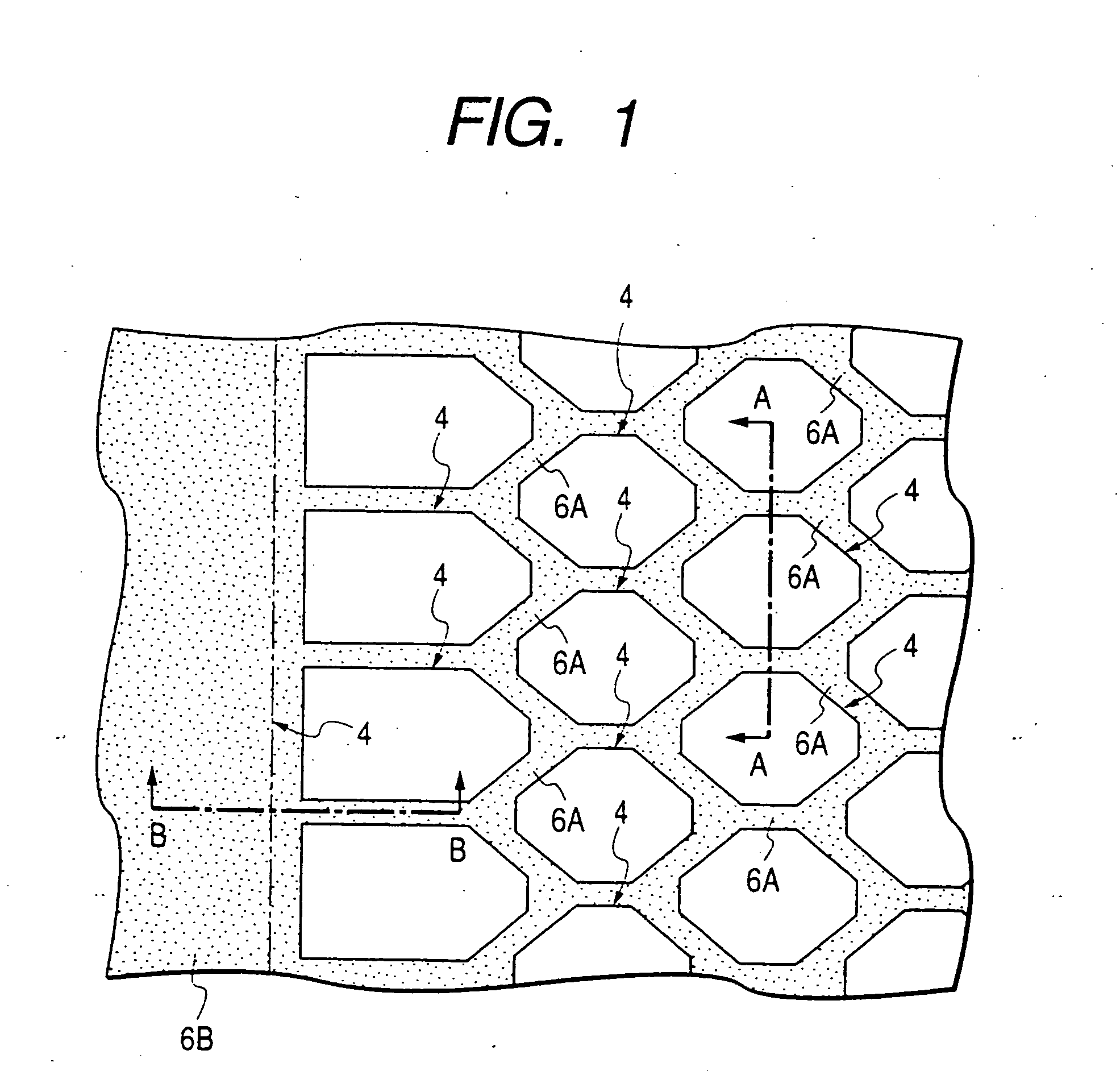

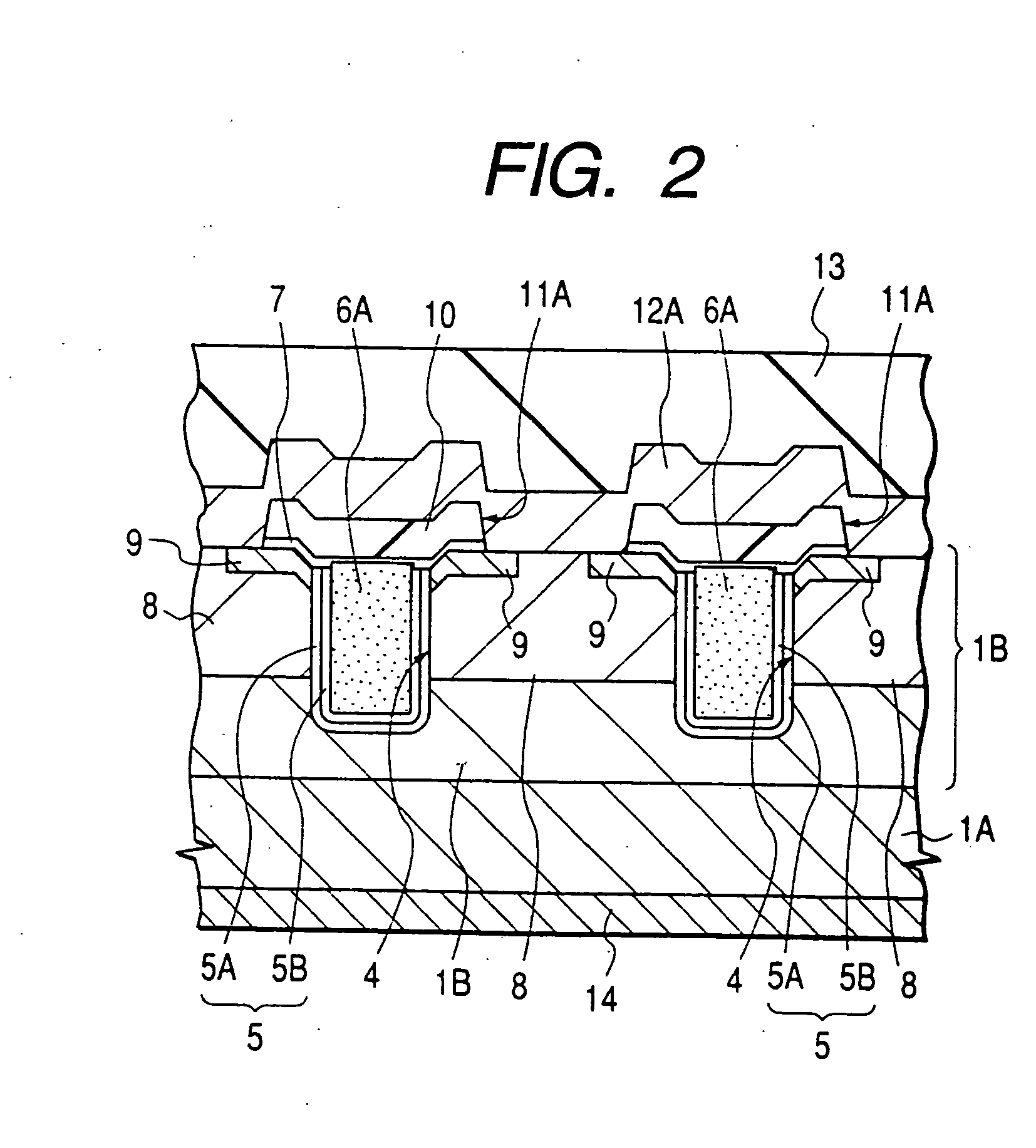

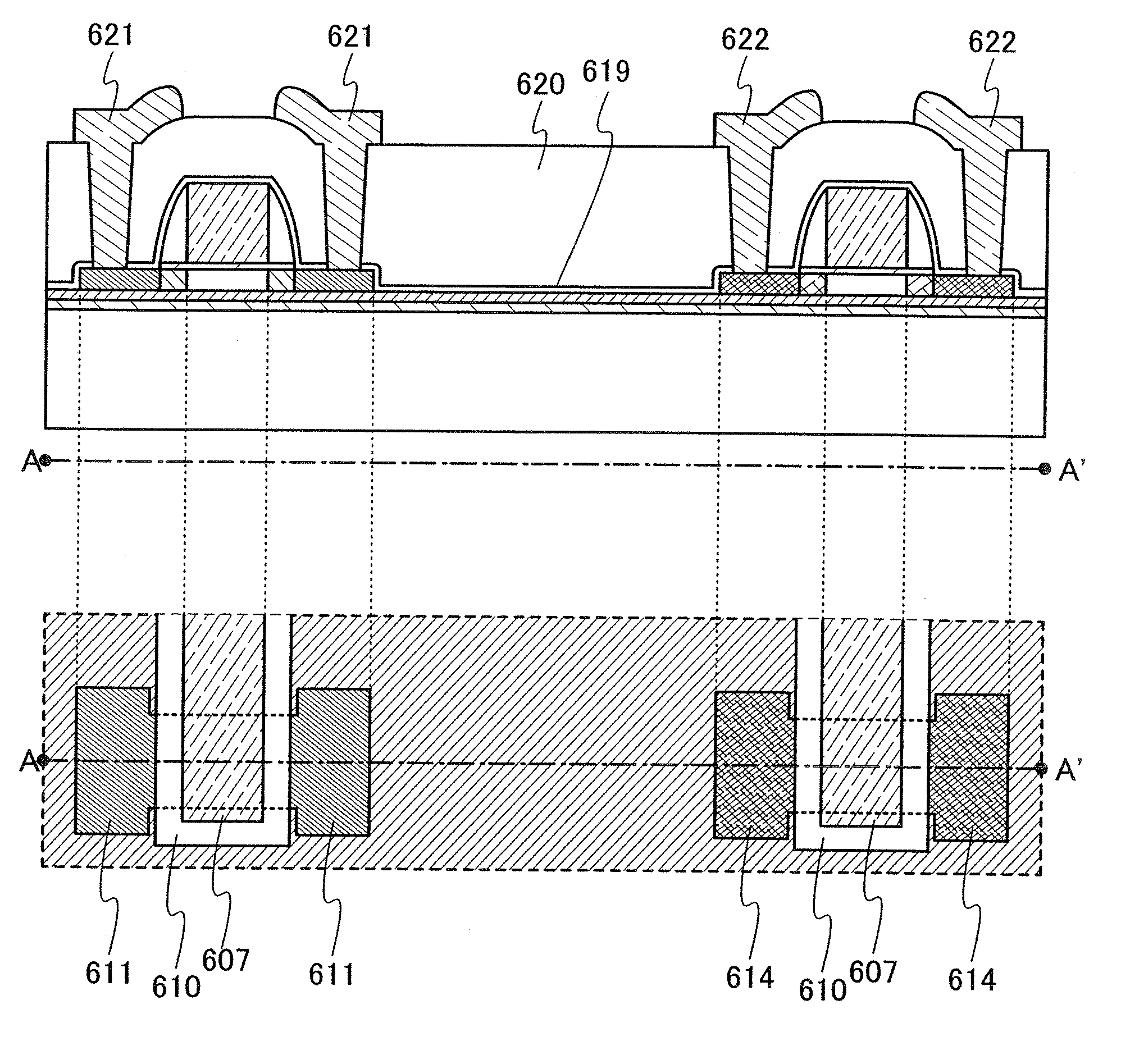

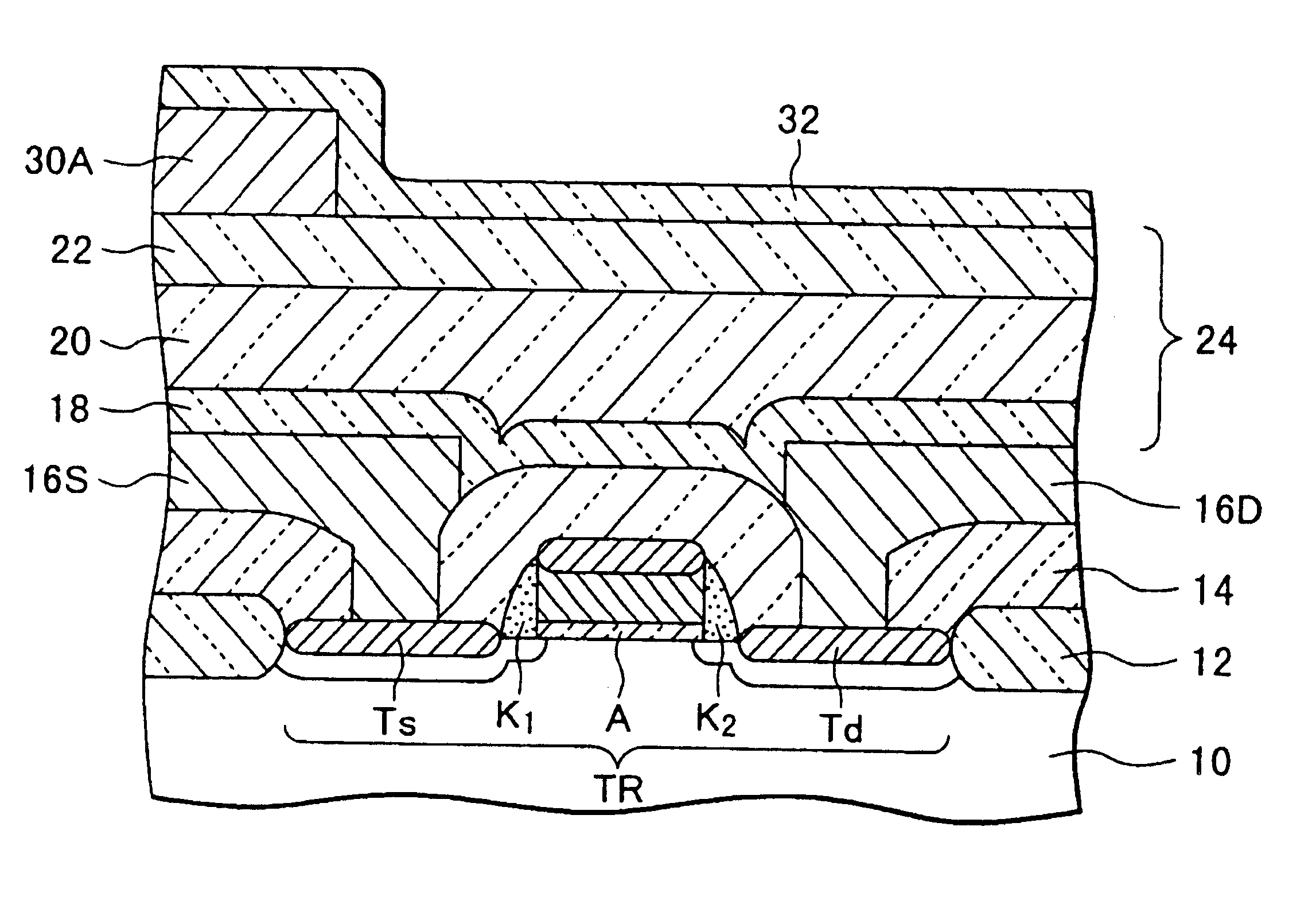

In a method of fabricating a semiconductor device having a MISFET of trench gate structure, a trench is formed from a major surface of a semiconductor layer of first conductivity type which serves as a drain region, in a depth direction of the semiconductor layer, a gate insulating film including a thermal oxide film and a deposited film is formed over the internal surface of the trench, and after a gate electrode has been formed in the trench, impurities are introduced into the semiconductor substrate of first conductivity type to form a semiconductor region of second conductivity type which serves as a channel forming region, and impurities are introduced into the semiconductor region of second conductivity type to form the semiconductor region of first conductivity type which serves as a source region.

Owner:RENESAS ELECTRONICS CORP

Method of manufacturing semiconductor device

InactiveUS8101501B2Short cycle timeLow reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingHydrogenSoi substrate

To provide a method of manufacturing a semiconductor device, which prevents impurities from entering an SOI substrate. A source gas including one or plural kinds selected from a hydrogen gas, a helium gas, or halogen gas are excited to generate ions, and the ions are added to a bonding substrate to thereby form a fragile layer in the bonding substrate. Then, a region of the bonding substrate that is on and near the surface thereof, i.e., a region ranging from a shallower position than the fragile layer to the surface is removed by etching, polishing, or the like. Next, after attaching the bonding substrate to a base substrate, the bonding substrate is separated at the fragile layer to thereby form a semiconductor film over the base substrate. After forming the semiconductor film over the base substrate, a semiconductor element is formed using the semiconductor film.

Owner:SEMICON ENERGY LAB CO LTD

Manufacture method for semiconductor device with small variation in MOS threshold voltage

InactiveUS6888183B1Easy to fallReduce interface state densityTransistorSemiconductor/solid-state device detailsSilicon oxideEngineering

After a MOS type transistor is formed on the surface of a semiconductor substrate, an interlayer insulating film covering the transistor is formed. The insulating film includes a silicon oxide film made of hydrogen silsesquioxane resin in a ceramic state. After a wiring layer is formed on the insulating film, a silicon oxide film as a surface protection film is formed on the insulating film, covering the wiring layer. In order to reduce process damages, heat treatment is performed 30 minutes at 400° C. in a nitrogen gas atmosphere. With this heat treatment, hydrogen in the silicon oxide film is released and diffuses into the channel region of the transistor to lower interfacial energy levels. Since the silicon nitride film does not transmit hydrogen, it is not necessary for the heat treatment atmosphere to contain hydrogen. A variation in threshold voltages of MOS type transistors can be easily lowered.

Owner:YAMAHA CORP

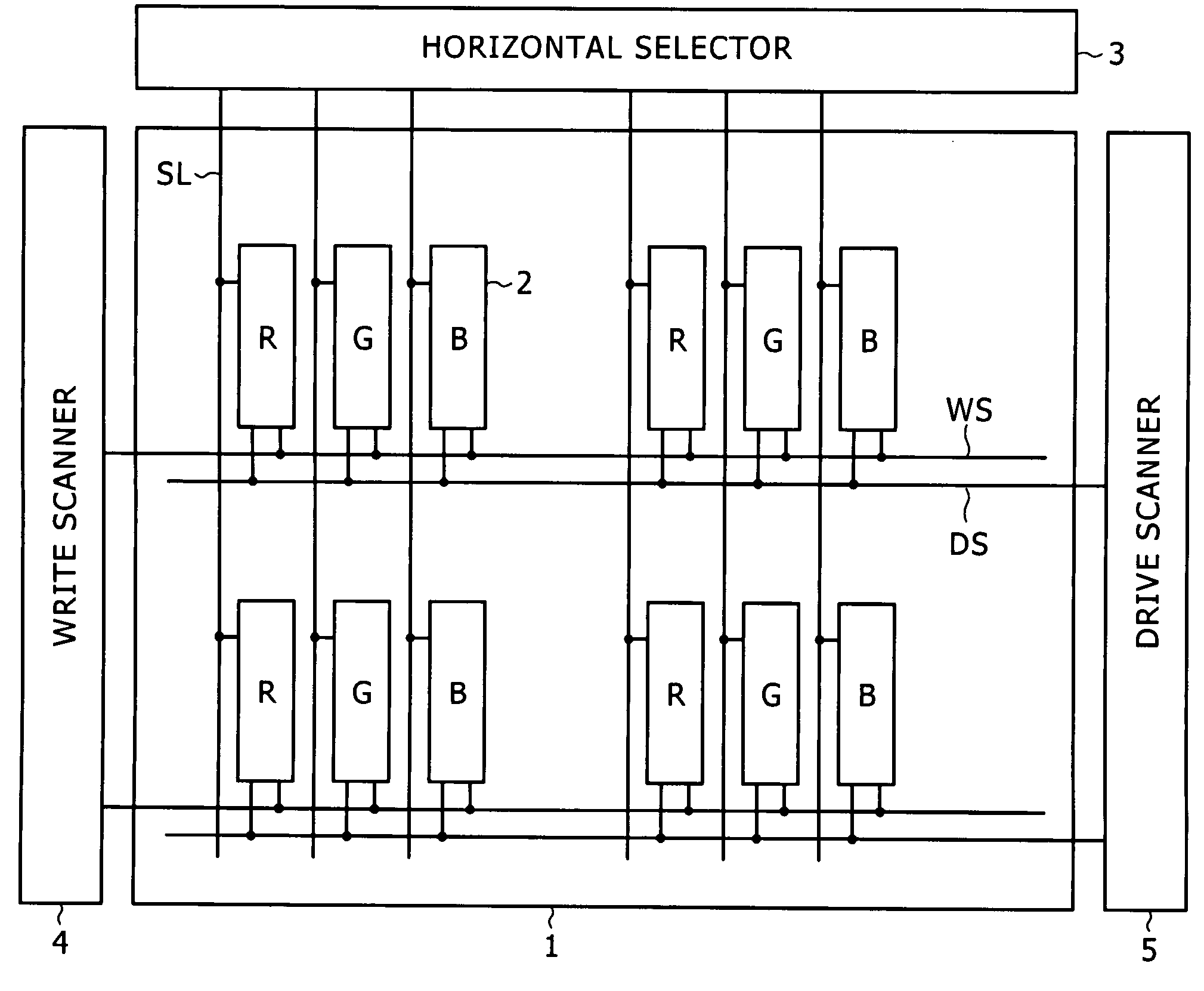

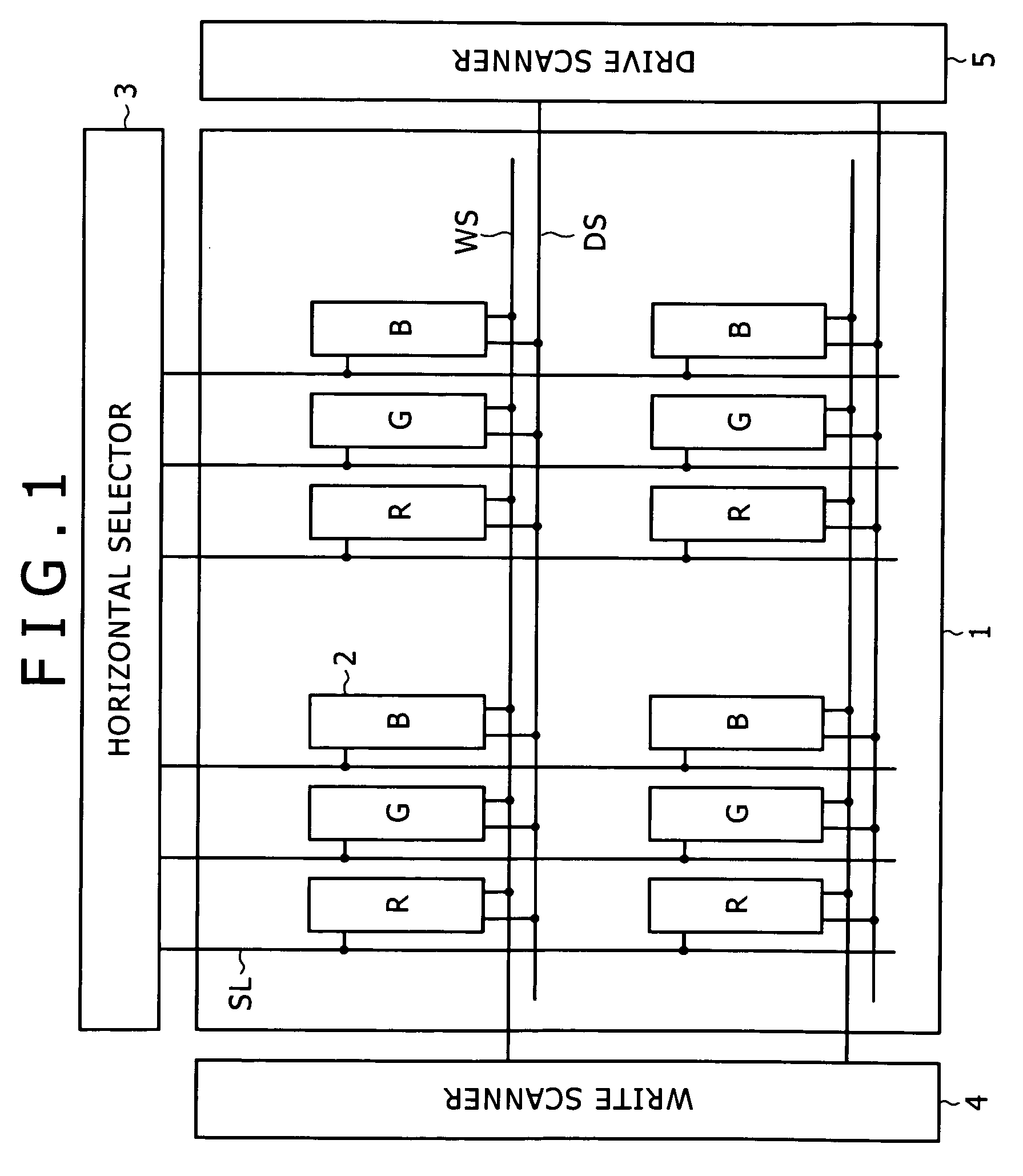

Display device and electronic equipment

ActiveUS20090179888A1Variation in threshold voltageReduction of pixel sizeSemiconductor/solid-state device manufacturingCathode-ray tube indicatorsPixel arraySignal lines

A display device includes: a pixel array section; and a drive section, the pixel array section including scan lines, signal lines, pixels, and power lines, the drive section including a main scanner, a drive scanner, and a signal selector, wherein each of the pixels includes a light-emitting element, sampling transistor, drive transistor, and holding capacitor.

Owner:JOLED INC

Display device and driving method for same

ActiveUS20200402457A1Small variationStable data writeStatic indicating devicesSolid-state devicesPhysicsCapacitance

An object of the disclosure is to achieve a current-driven display device able to compensate for a variation in threshold voltage of a drive transistor without causing a variation in luminance.A pixel circuit includes a light-emitting element, a drive transistor, a power supply control transistor, a light emission control transistor, a first writing control transistor, a threshold voltage compensation transistor, a second writing control transistor, an initialization transistor, and a data-holding capacitor. During a data writing period, a scanning signal is active, an initialization voltage is supplied to a first electrode of the data-holding capacitor via the drive transistor, and a data voltage is supplied to a second electrode of the data-holding capacitor.

Owner:SHARP KK

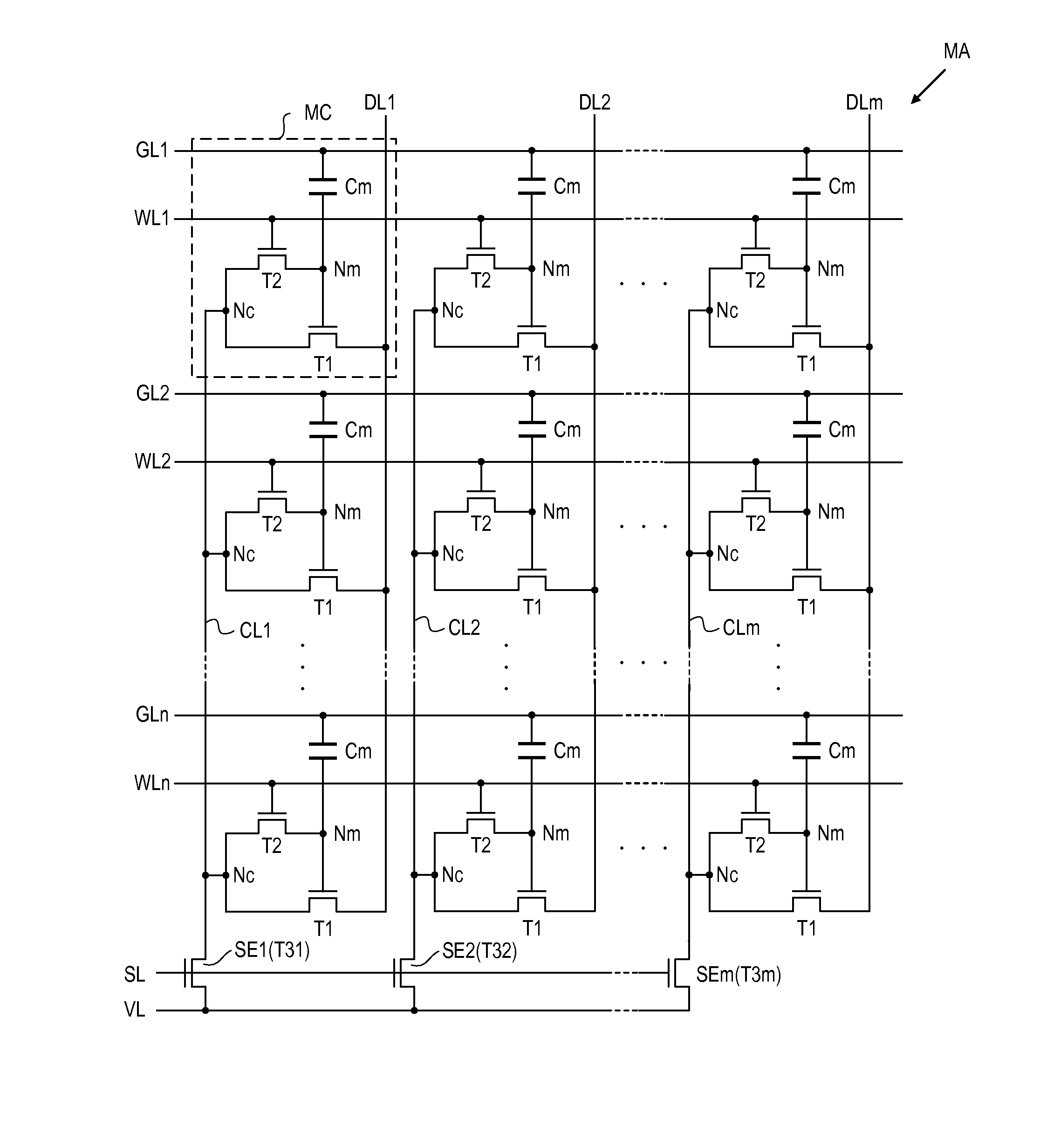

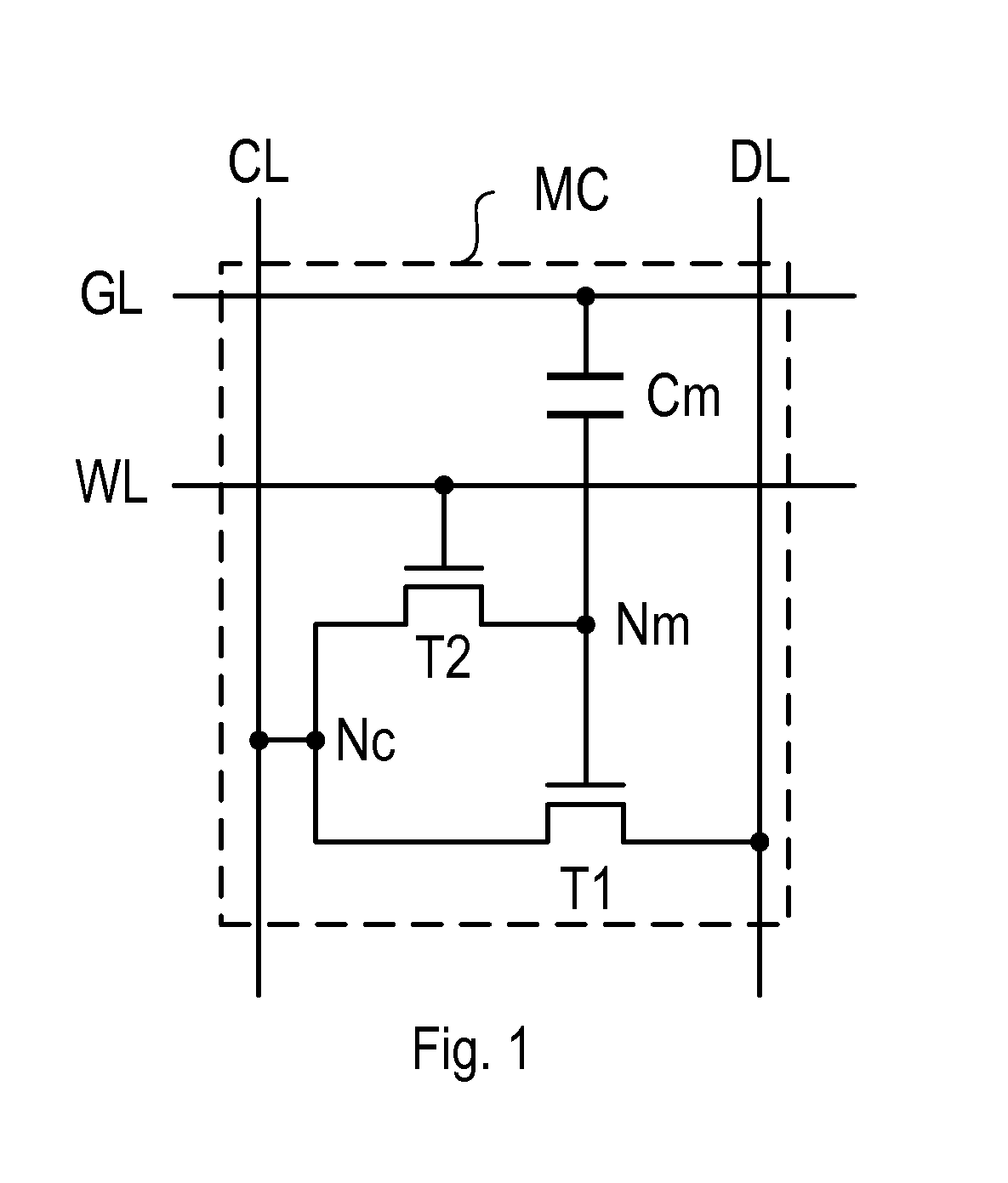

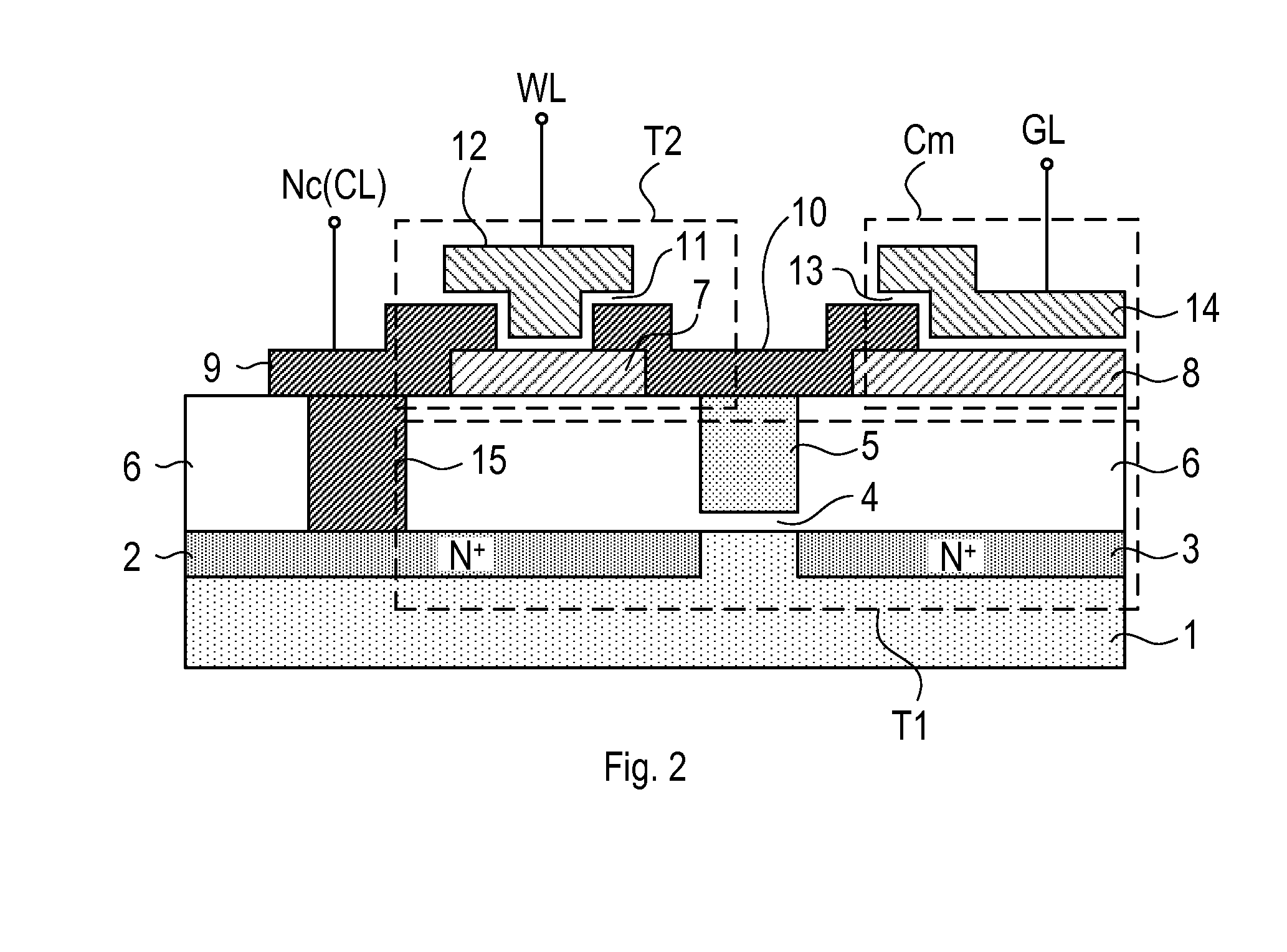

Semiconductor memory device

Provided is a semiconductor memory device including an oxide semiconductor insulated gate FET and having a capability to implement advanced performance without being affected by a variation in threshold voltage. A memory cell MC includes a memory node Nm formed at a connection point of a gate of a first transistor element T1, a source of a second transistor element T2, and one end of a capacitive element Cm, and a control node Nc formed at a connection point of a drain of the first transistor element T1 and a drain of the second transistor element T2. Each memory cell MC arranged in the same column includes the control node Nc connected to a shared first control line CL extending in a column direction, the first transistor element T1 having a source connected to a shared data signal line DL extending in the column direction, the second transistor element T2 having a gate connected to an individual first selection line WL, and the capacitive element Cm having the other end connected to an individual second selection line GL, and a switching element SE having one end connected to the first control line CL, and the other end connected to a voltage supply line VL is provided with respect to each first control line CL.

Owner:SHARP KK

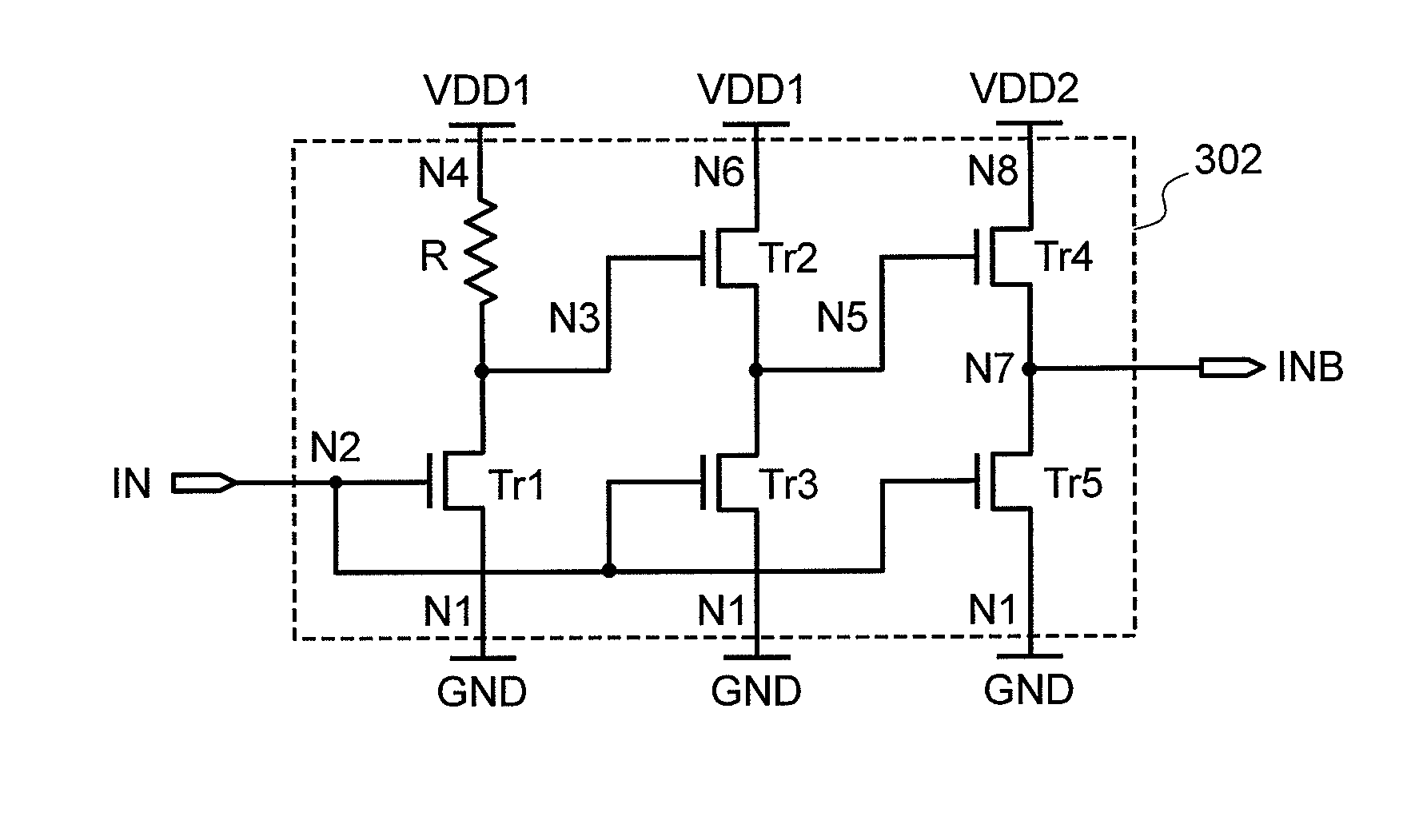

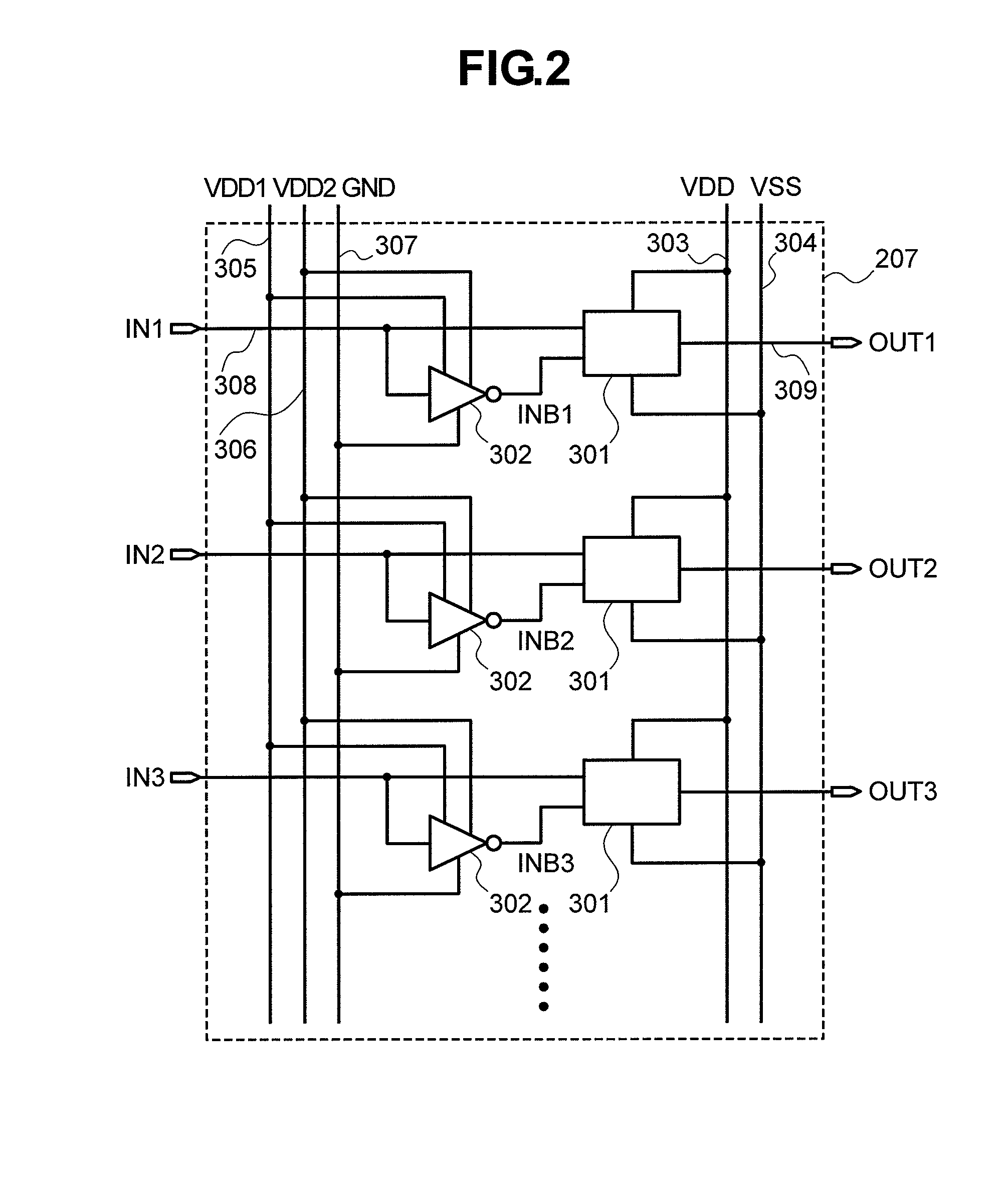

Display device

ActiveUS8102357B2Fall fastQuickly riseCathode-ray tube indicatorsNon-linear opticsHigh resistancePower flow

An inverter includes an input inverter having a high-resistance load and a first transistor and an output buffer including second and third transistors coupled in series. A power supply voltage is provided to satisfy an inequality VDD1>VDD2+Vth where VDD1 is the power supply voltage of the input inverter, VDD2 is the power supply voltage of the output buffer, and Vth is the threshold voltage of the transistors. Use of the high-resistance load allows an output waveform to rise and fall quickly, as well as reduces current consumption.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

Method of manufacturing semiconductor device

InactiveUS20110117708A1High suppression characteristicsVariation in threshold voltageSemiconductor/solid-state device manufacturingHydrogenSoi substrate

To suppress an effect of metal contamination caused in manufacturing an SOI substrate. After forming a damaged region by irradiating a semiconductor substrate with hydrogen ions, the semiconductor substrate is bonded to a base substrate. Heat treatment is performed to cleave the semiconductor substrate; thus an SOI substrate is manufactured. Even if metal ions enter the semiconductor substrate together with the hydrogen ions in the step of hydrogen ion irradiation, the effect of metal contamination can be suppressed by the gettering process. Accordingly, the irradiation with hydrogen ions can be performed positively by an ion doping method.

Owner:SEMICON ENERGY LAB CO LTD