Patents

Literature

133 results about "Half Rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

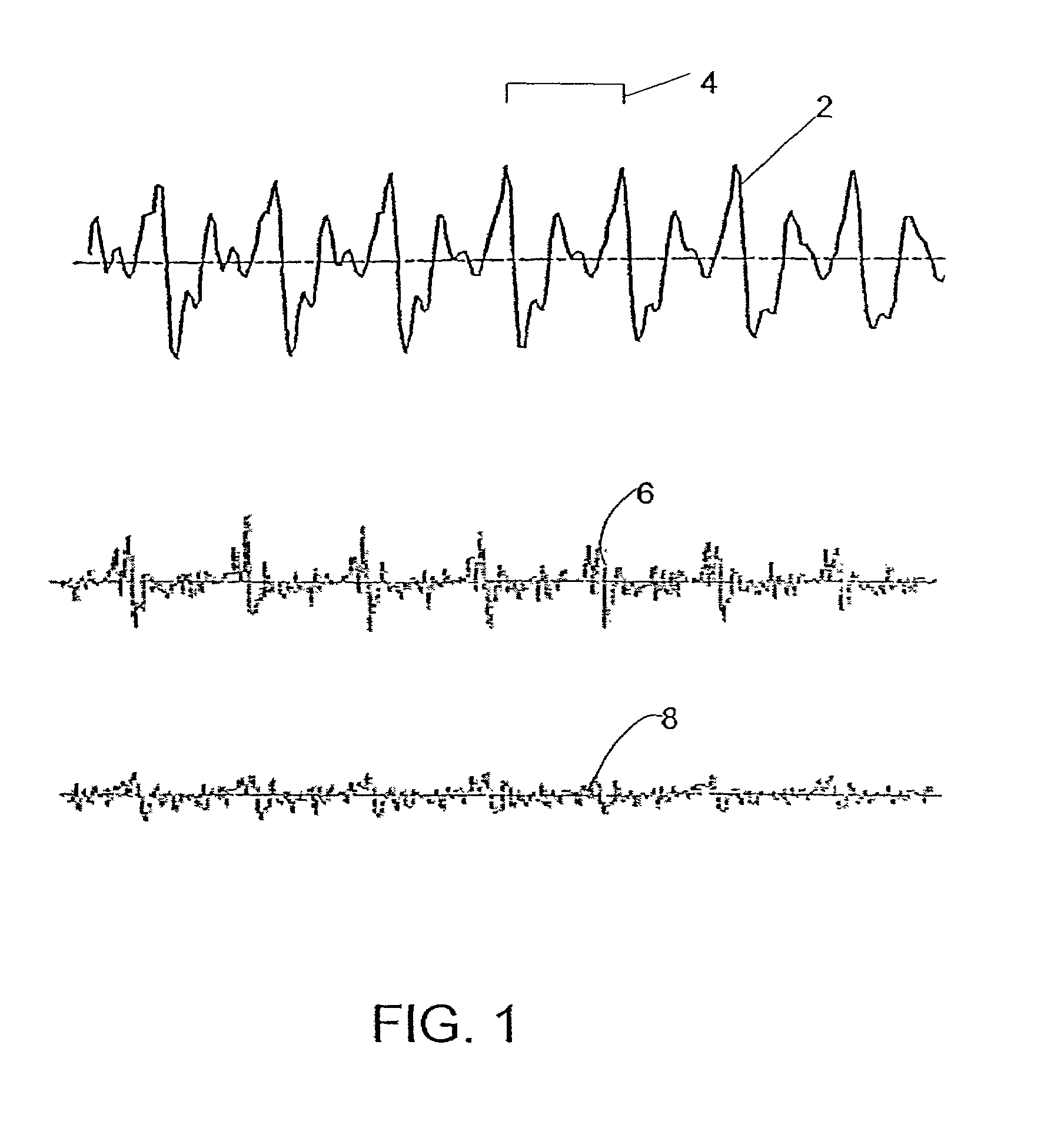

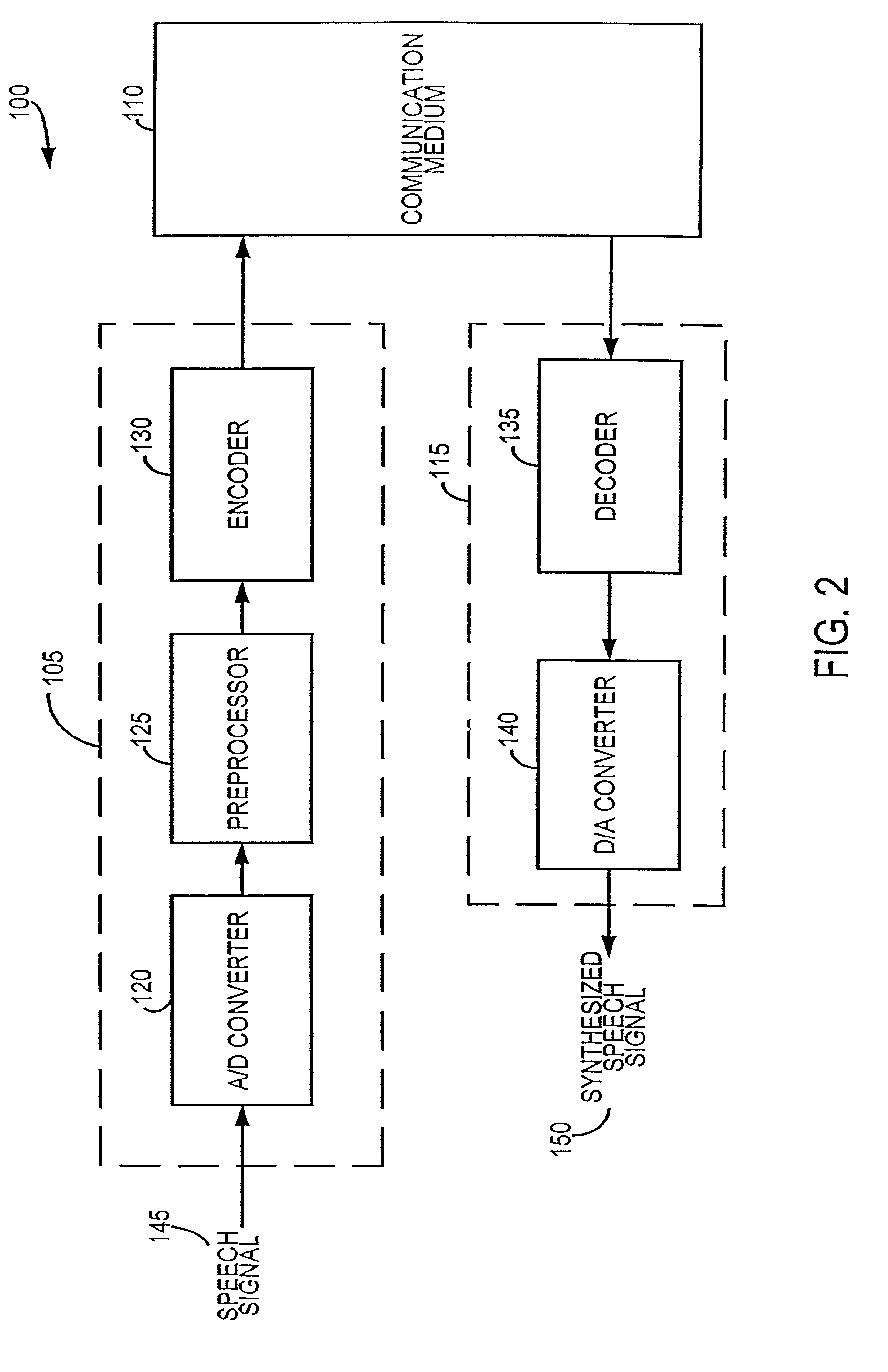

Half Rate (HR or GSM-HR or GSM 06.20) is a speech coding system for GSM, developed in the early 1990s. Since the codec, operating at 5.6 kbit/s, requires half the bandwidth of the Full Rate codec, network capacity for voice traffic is doubled, at the expense of audio quality. It is recommended to use this codec when the battery is low as it may consume up to 30% less energy. The sampling rate is 8 kHz with resolution 13 bit, frame length 160 samples (20 ms) and subframe length 40 samples (5 ms).

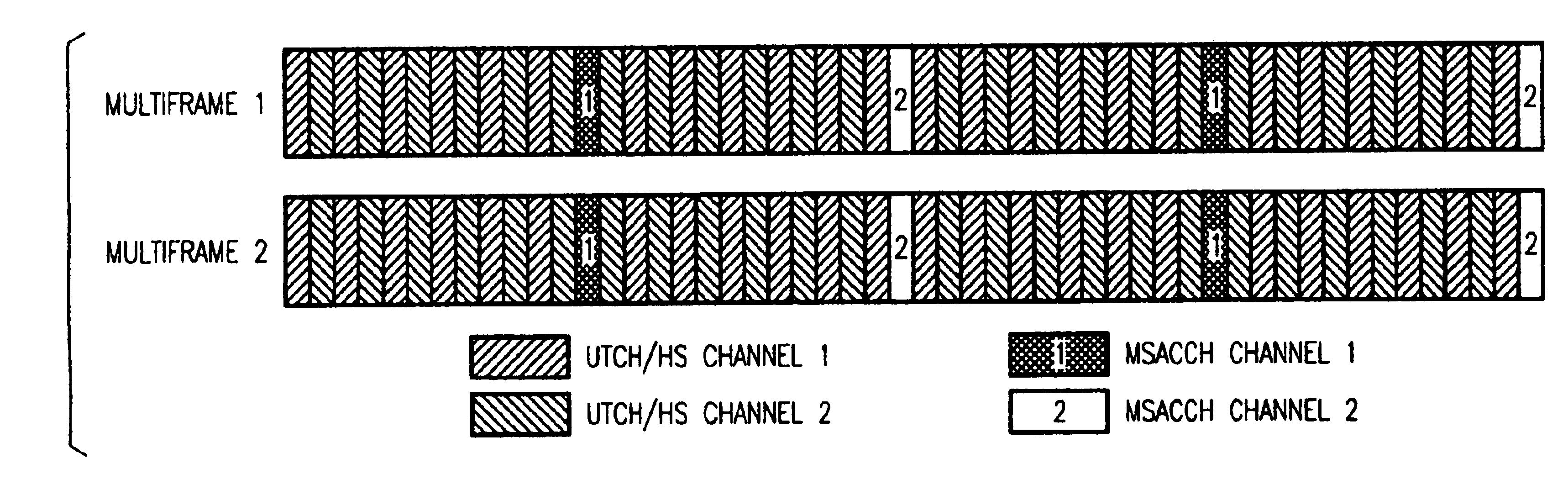

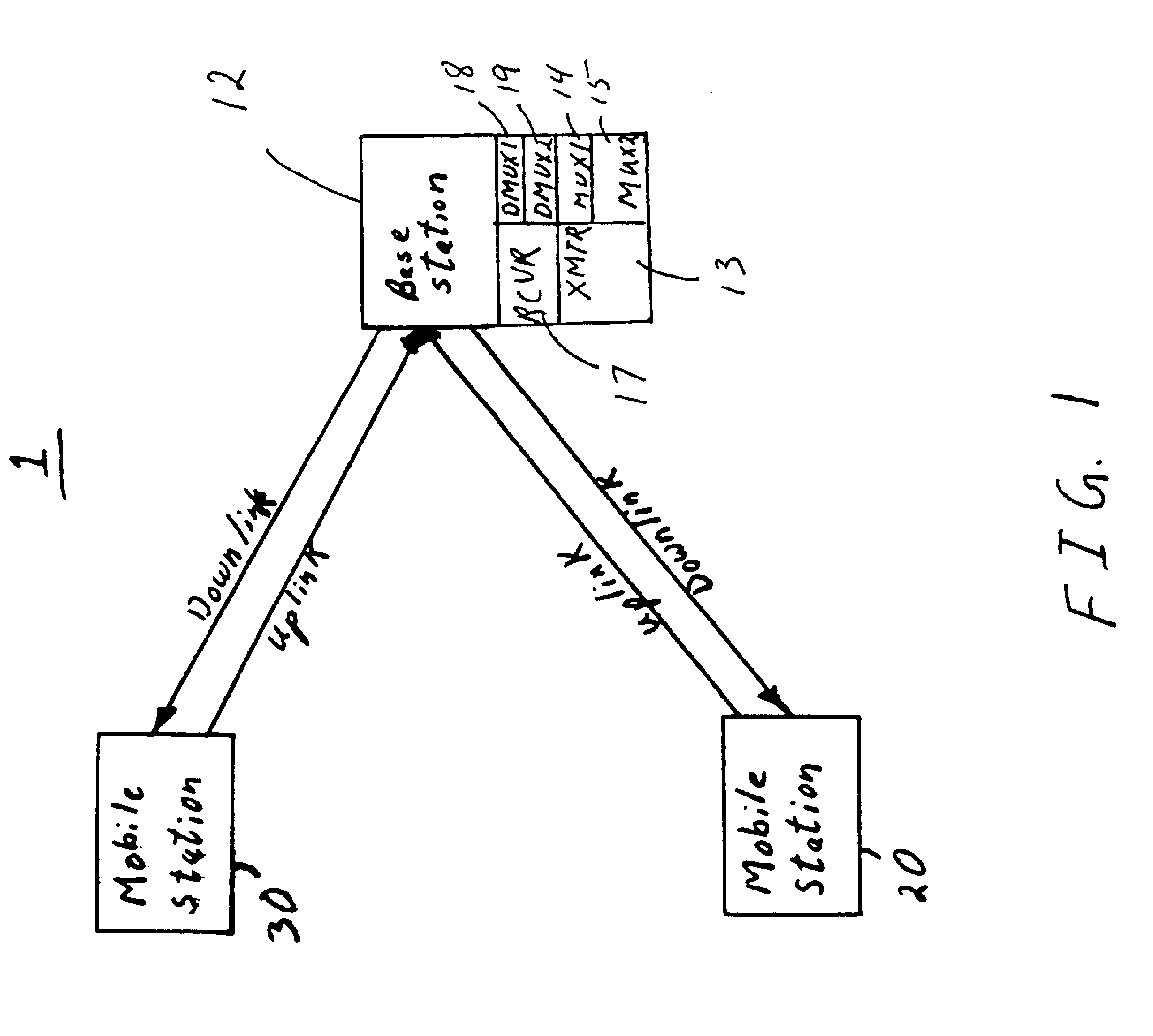

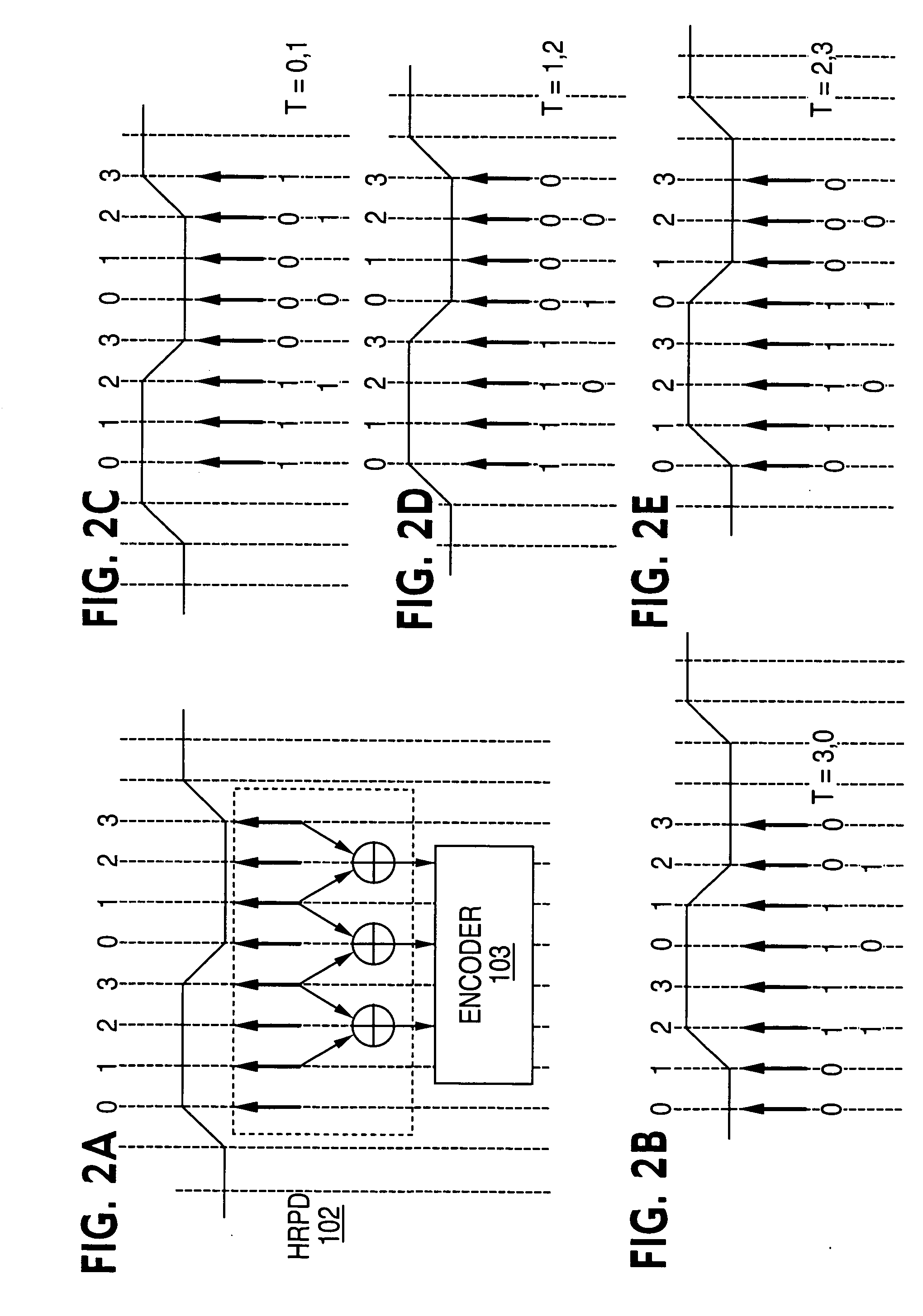

Method for interleaving of half rate channels suitable for half duplex operation and statistical multiplexing

InactiveUS7006477B1Effective movementTime-division multiplexRadio transmission for post communicationMultiplexerHalf Rate

A system and method for providing wireless time division multiplexed communications in which time is divided into a plurality of frames and each frame is divided into N data bursts, which has a first multiplexer defining a channel as a series of bursts that occur periodically every N bursts once per frame; a second multiplexer defining a sub-channel as every Mth burst of said channel; and a transmitter transmitting said channel and sub-channel from a first station to a second station. A new interleaving 0246 / 1357 method is used by the system which is just as good as the known 0123 / 4567 method when ideal frequency hopping is used, and 0246 / 1357 has better performance when non-ideal frequency hopping or no frequency hopping is used.

Owner:ALCATEL-LUCENT USA INC +1

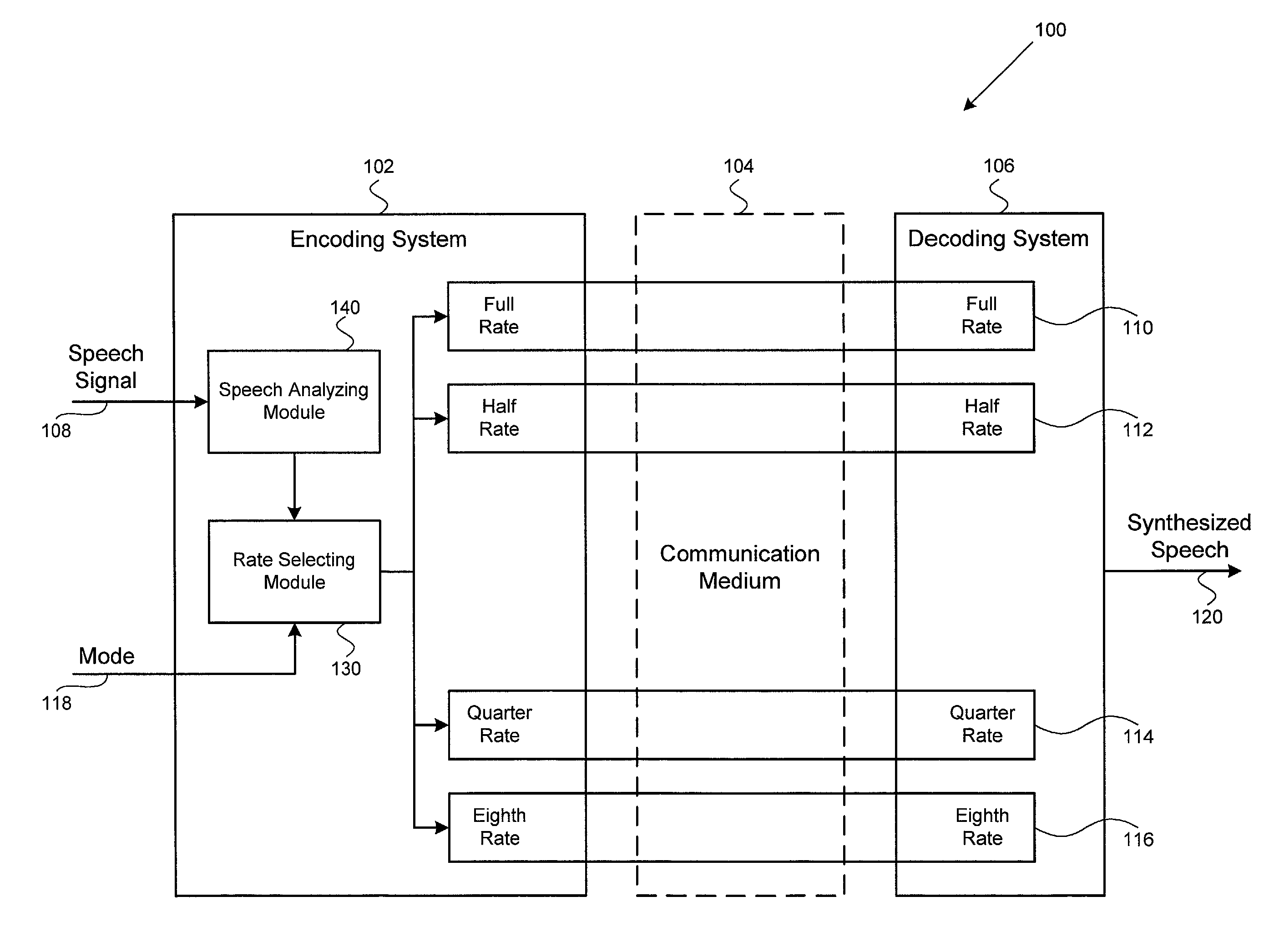

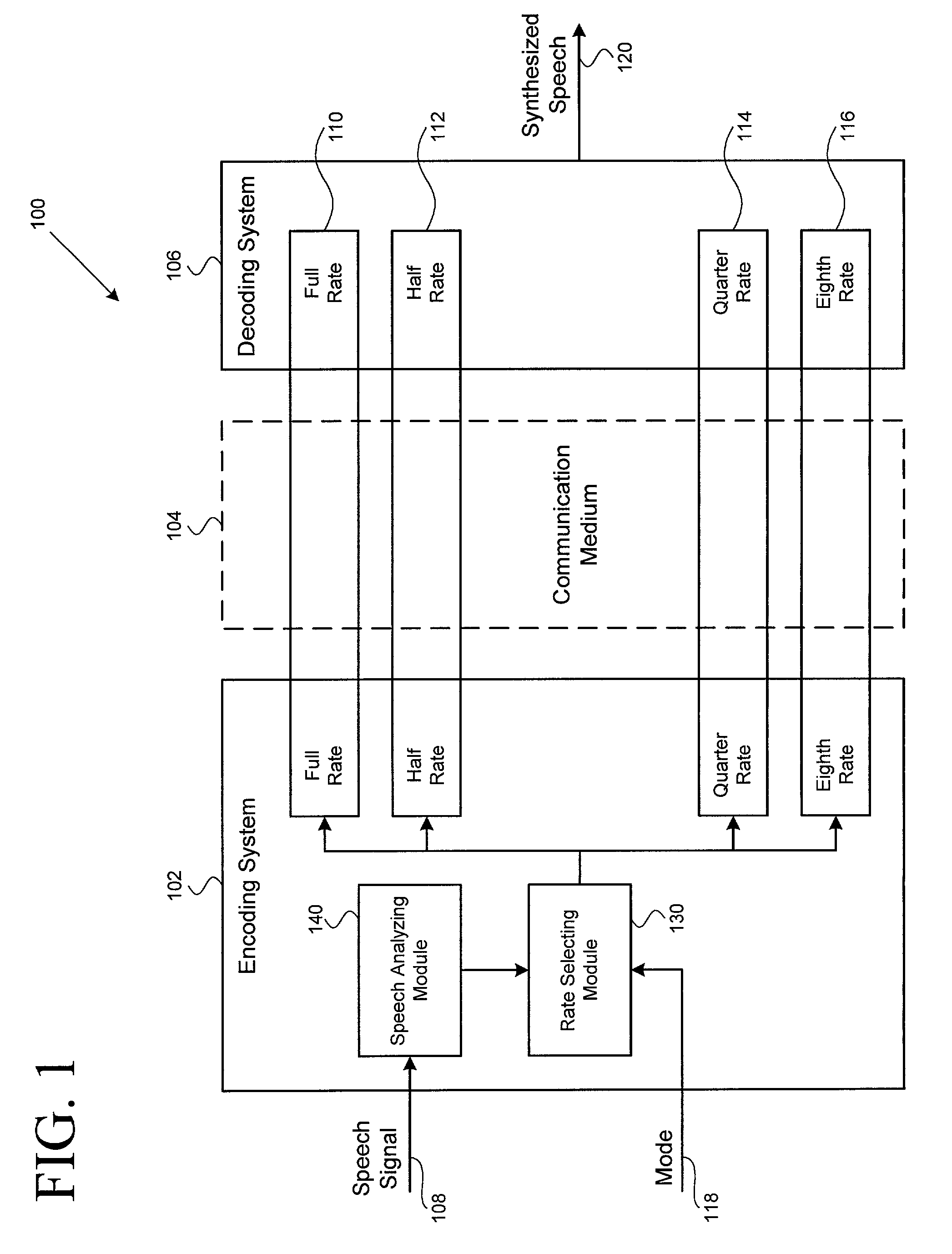

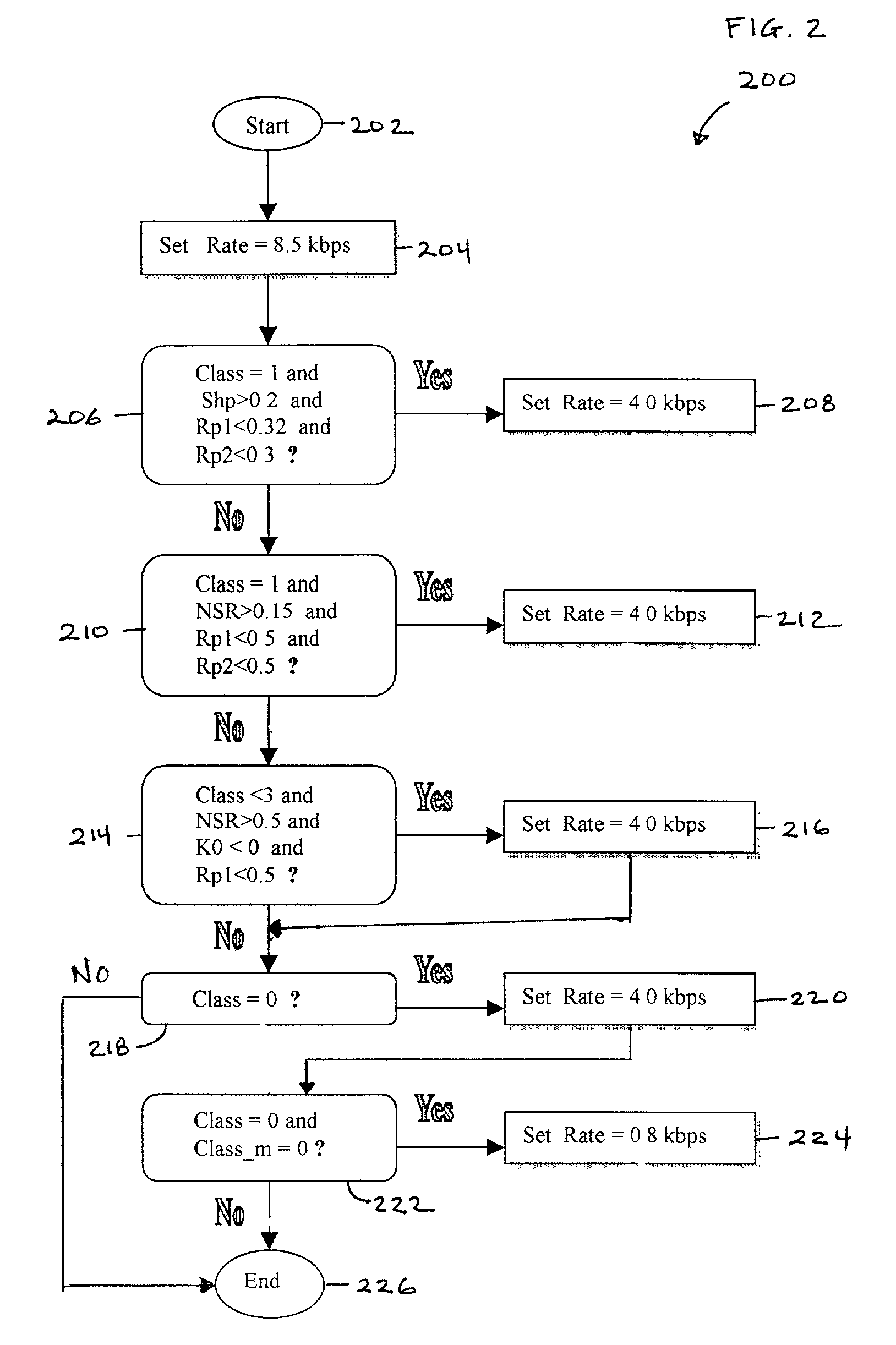

Rate selection method for selectable mode vocoder

InactiveUS7054809B1Reduce bandwidth requirementsQuality improvementSpeech analysisHalf RateFull Rate

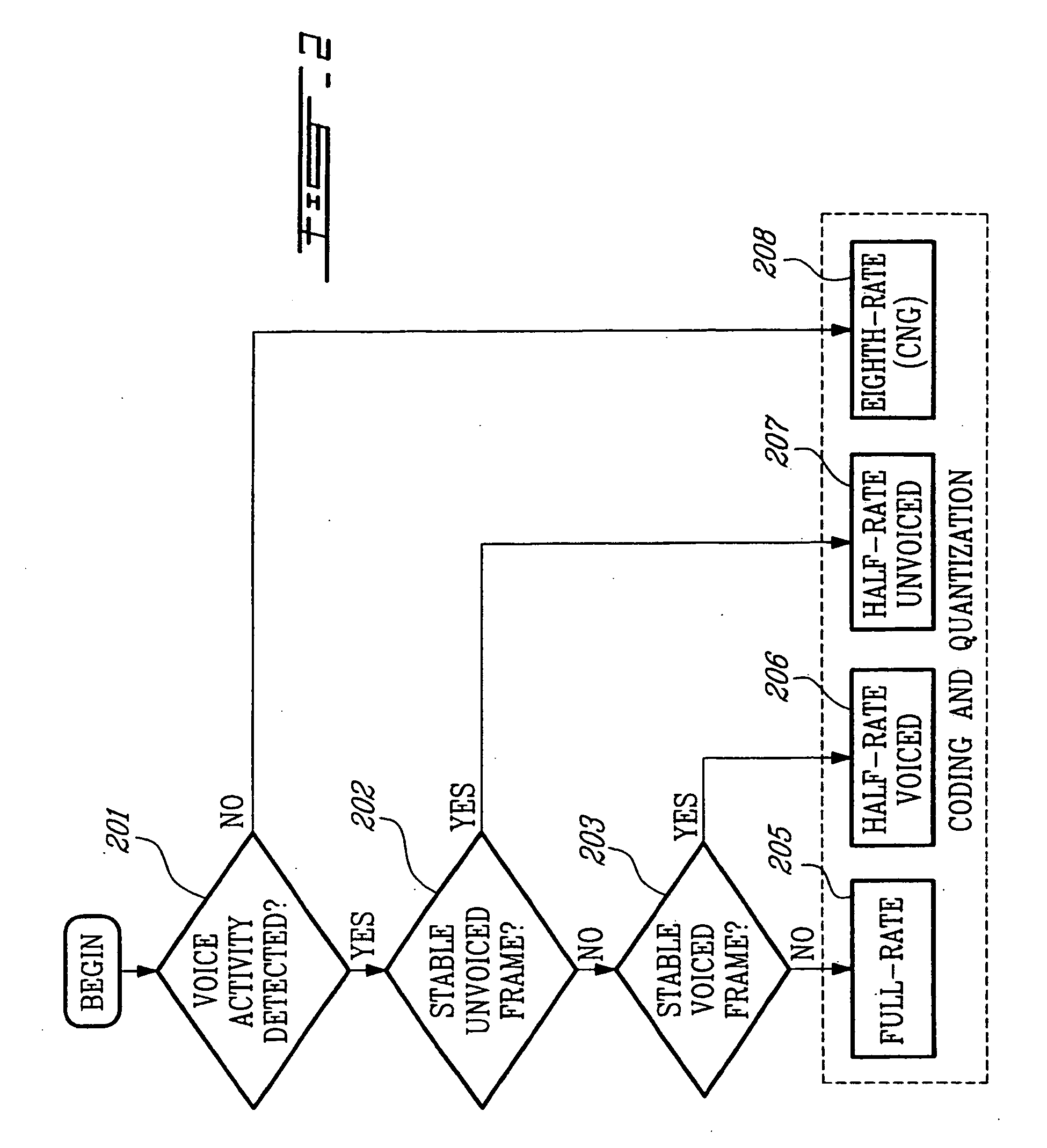

There is provided rate selection methods and systems for selecting coding rates for coding frames of a speech signal to realize an average bit rate indicated by a mode. For example, a mode 0, mode 1, and a mode 2 may be defined, with each mode requiring a different average bit rate. To achieve the average bit rate of a particular mode, a coding rate is selected for each frame of the speech signal, based on the characteristics of a frame. A frame can be categorized in a class, such as noise or silence, noise-like unvoiced speech, pulse-like unvoiced speech, transition into voiced speech, unstable voiced speech, stable voiced speech. Other parameters may also be used, such as the sharpness, noise-to-signal ratio, pitch correlation, energy, and reflection coefficient. A frame may then be coded at a full-rate, a half-rate, a quarter-rate, or an eighth-rate.

Owner:DIGIMEDIA TECH LLC

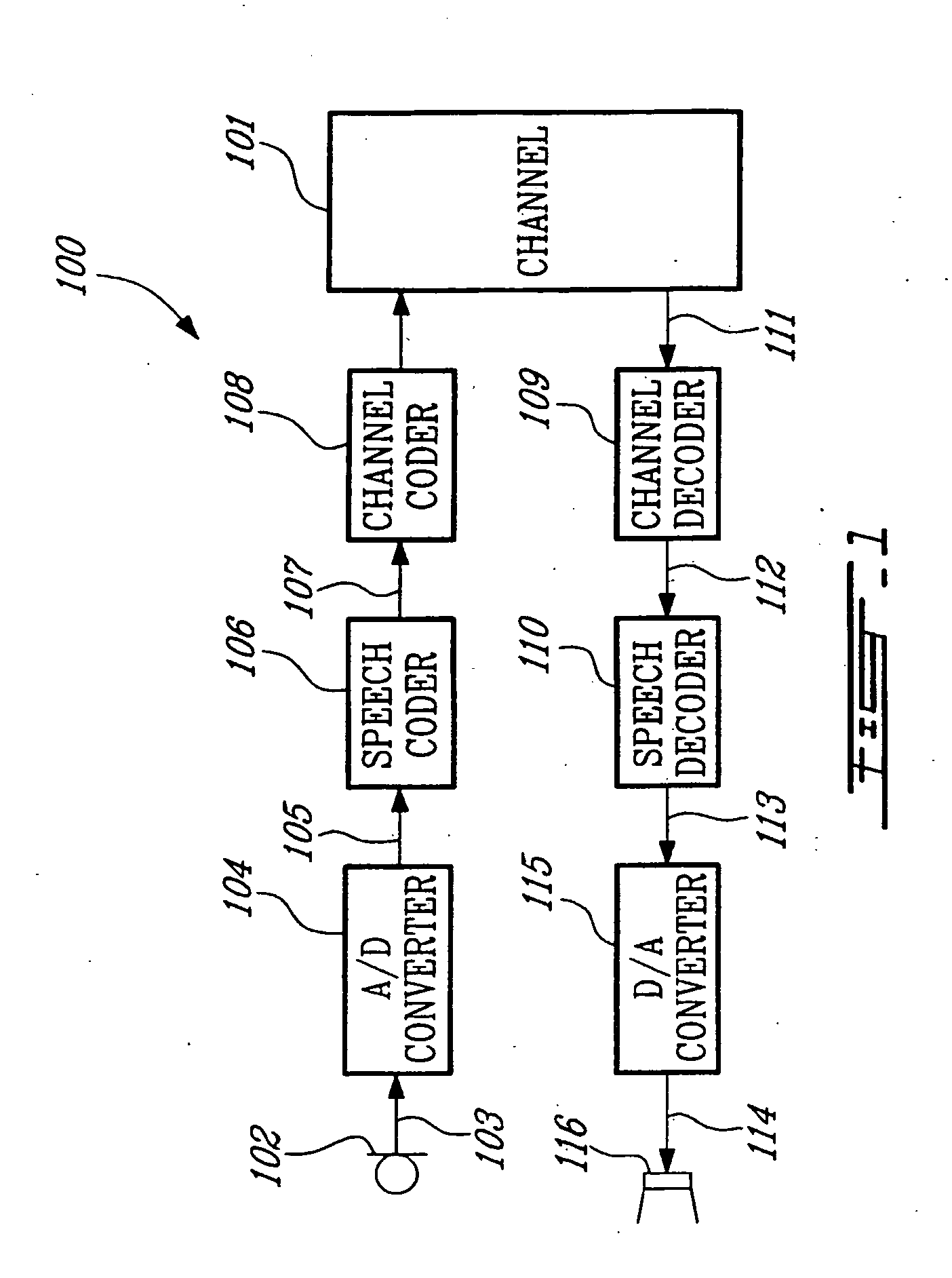

Method and device for efficient in-band dim-and-burst signaling and half-rate max operation in variable bit-rate wideband speech coding for cdma wireless systems

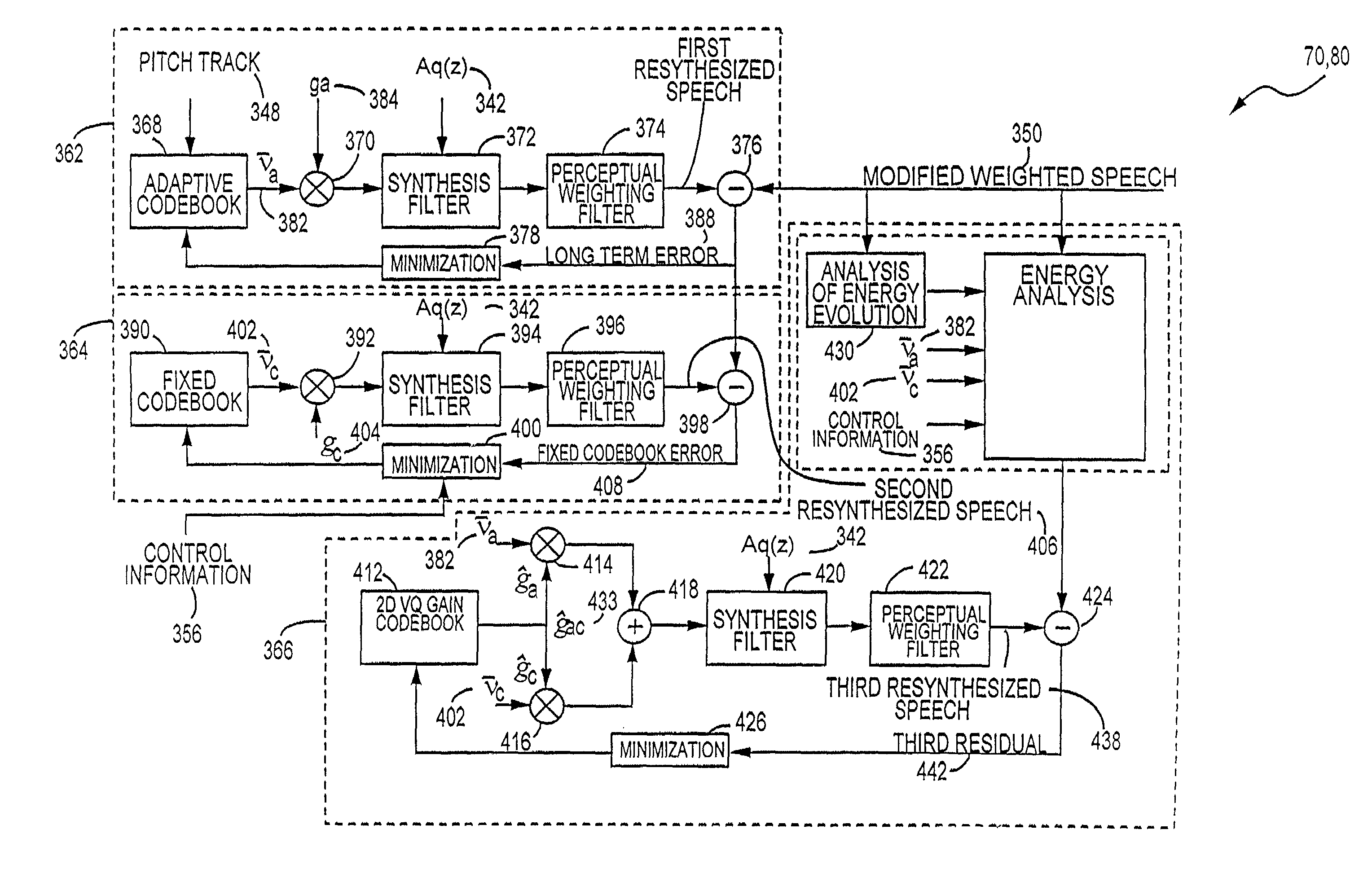

In the method and device for interoperating a first station using a first communication scheme and comprising a first coder and a first decoder with a second station using a second communication scheme and comprising a second coder and a second decoder, communication between the first and second stations is conducted by transmitting signal-coding parameters related to a sound signal from the coder of one of the first and second stations to the decoder of the other station. The sound signal is classified to determine whether the signal-coding parameters should be transmitted from the coder of one station to the decoder of the other station using a first communication mode in which full bit rate is used for transmission of the signal-coding parameters. When classification of the sound signal determines that the signal-coding parameters should be transmitted using the first communication mode and when a request to transmit the signal-coding parameters from the coder of one station to the decoder of the other station using a second communication mode designed to reduce bit rate during transmission of the signal-coding parameters is received, a portion of the signal-coding parameters from the coder one station is dropped and the remaining signal-coding parameters are transmitting to the decoder of the other station using the second communication mode. The dropped portion of the signal-coding parameters are regenerated before the decoder of the other station decodes the signal-coding parameters.

Owner:NOKIA TECHNOLOGLES OY

Half-rate DFE with duplicate path for high data-rate operation

InactiveUS7782935B1Improve performanceReduce loadMultiple-port networksDelay line applicationsMultiplexerData rate

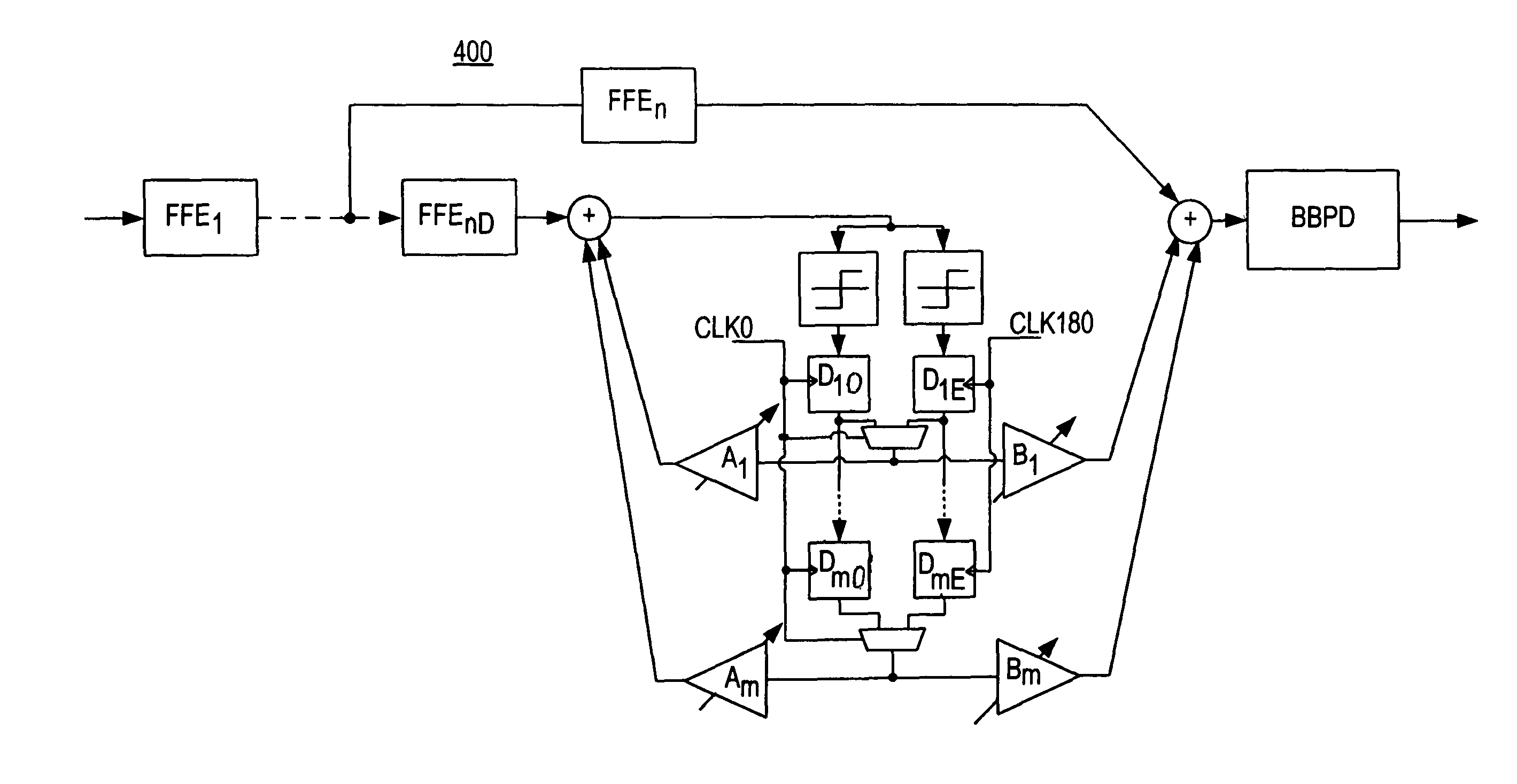

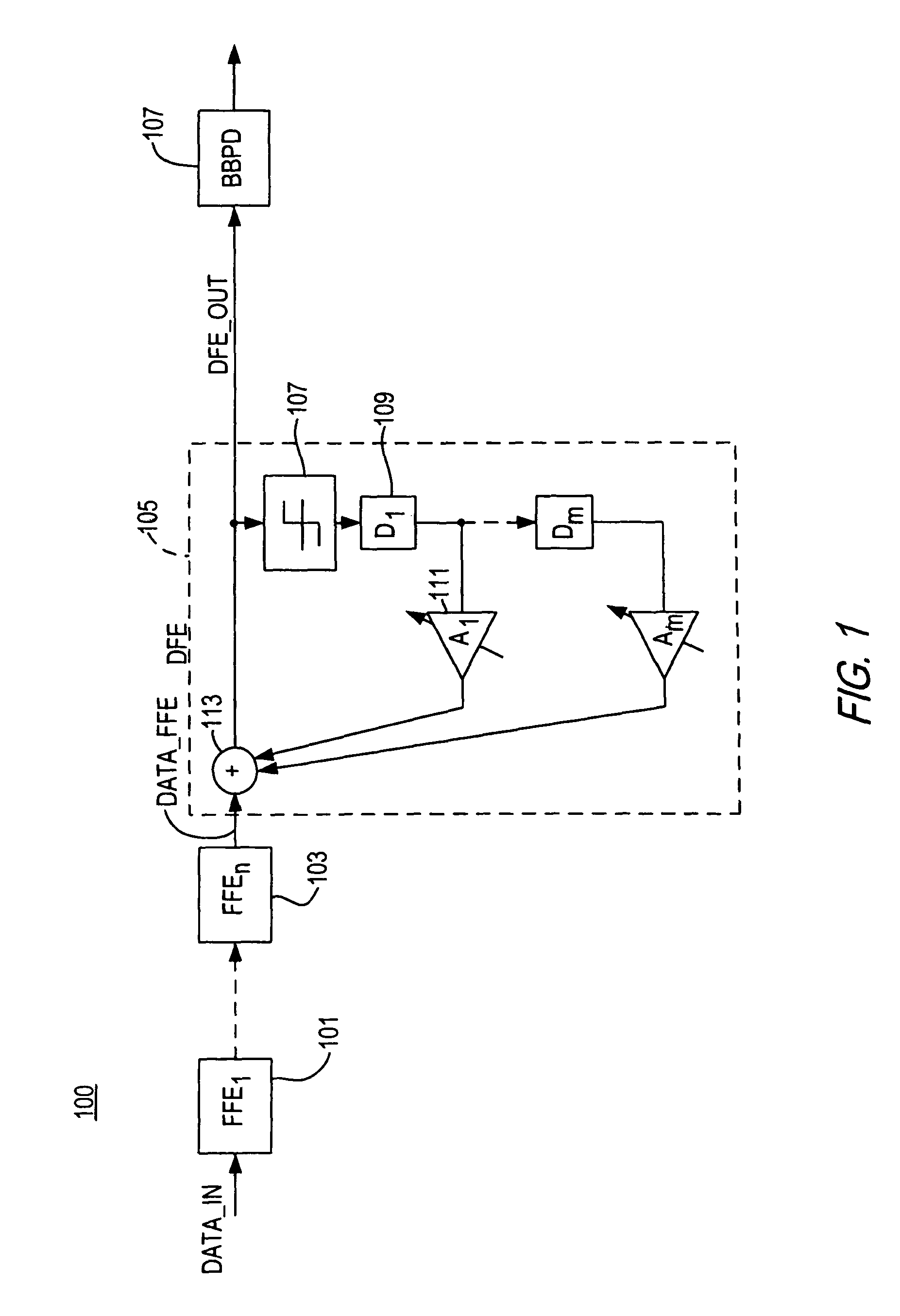

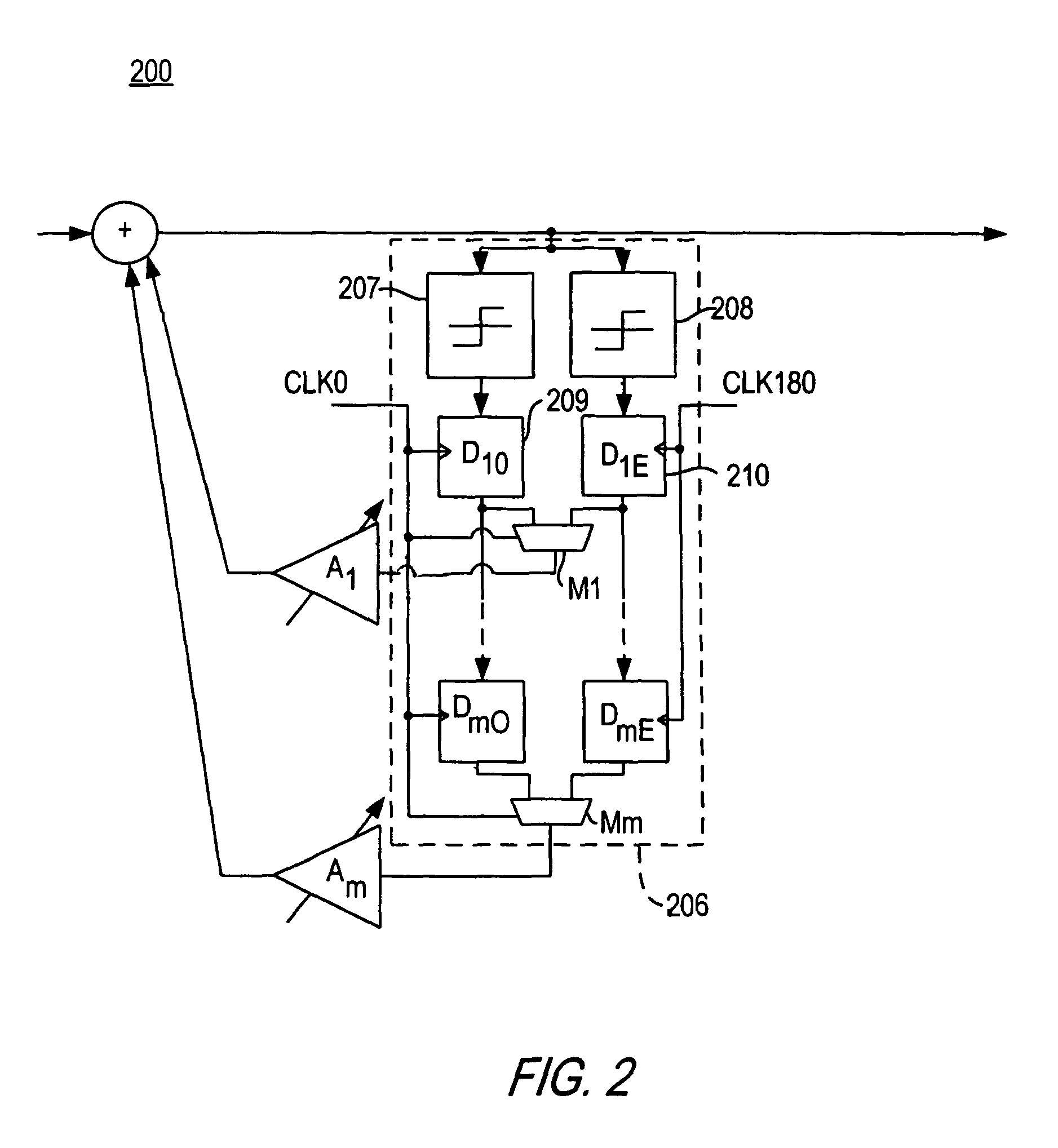

Methods and circuits are presented for providing equalization, including decision feedback equalization (DFE), to high data-rate signals. Half-rate delay-chain circuitry produces delayed samples of an input signal using two or more delay-chain circuits operating at a fraction of the input signal data-rate. Two delay-chain circuits operating at one-half the input signal data-rate may be used. More generally, n delay-chain circuits operating at 1 / n the input signal data-rate may be used. Multiplexer circuitry combines the outputs of the delay-chain circuits to produce an output signal including samples of the input signal at the input signal data-rate. Duplicate path DFE circuitry includes two paths used to provide DFE equalization while reducing the load of the DFE circuitry on the circuitry that precedes it. A first path produces delayed samples of a DFE signal, while a second path produces the DFE output signal from the delayed samples.

Owner:ALTERA CORP

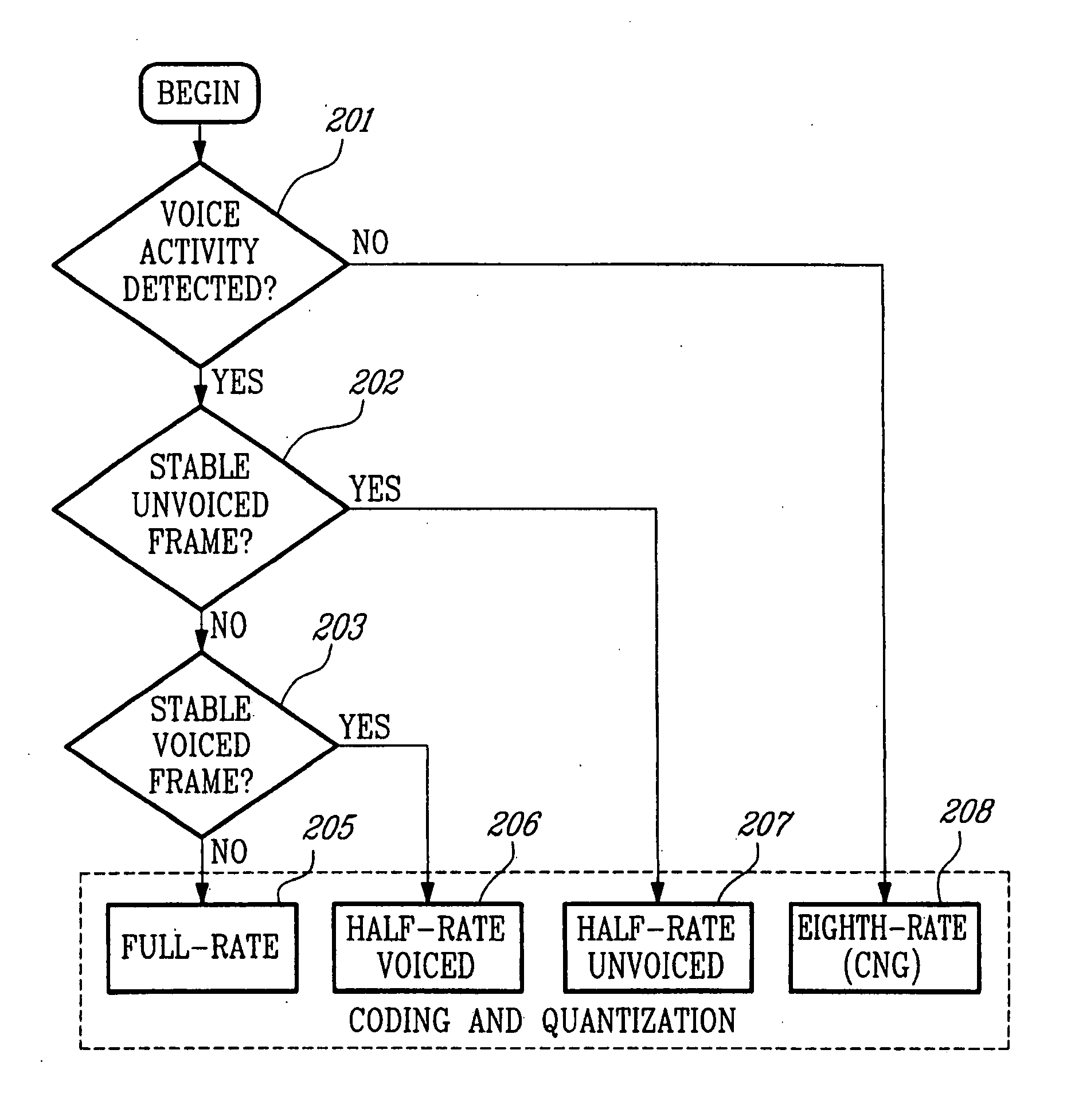

System for improved use of pitch enhancement with subcodebooks

ActiveUS7117146B2Easy to useCapture redundancySpeech analysisFluid pressure measurement by acoustic meansTyping ClassificationHalf Rate

A speech compression system capable of encoding a speech signal into a bitstream for subsequent decoding to generate synthesized speech is disclosed. The speech compression system optimizes the bandwidth consumed by the bitstream by balancing the desired average bit rate with the perceptual quality of the reconstructed speech. The speech compression system comprises a full-rate codec, a half-rate codec, a quarter-rate codec and an eighth-rate codec. The codecs are selectively activated based on a rate selection. In addition, the full and half-rate codec are selectively activated based on a type classification. Each codec is selectively activated to encode and decode the speech signals at different bit rates emphasizing different aspects of the speech signal to enhance overall quality of the synthesized speech. The overall quality of the system is strongly related to the excitation. In order to enhance the excitation, the system contains a fixed codebook comprising several subcodebooks. The invention reveals a way to apply a pitch enhancement efficiently and differently for different subcodebooks without using additional bits. The technique is particularly applicable to selectable mode vocoder (SMV) systems.

Owner:SAMSUNG ELECTRONICS CO LTD

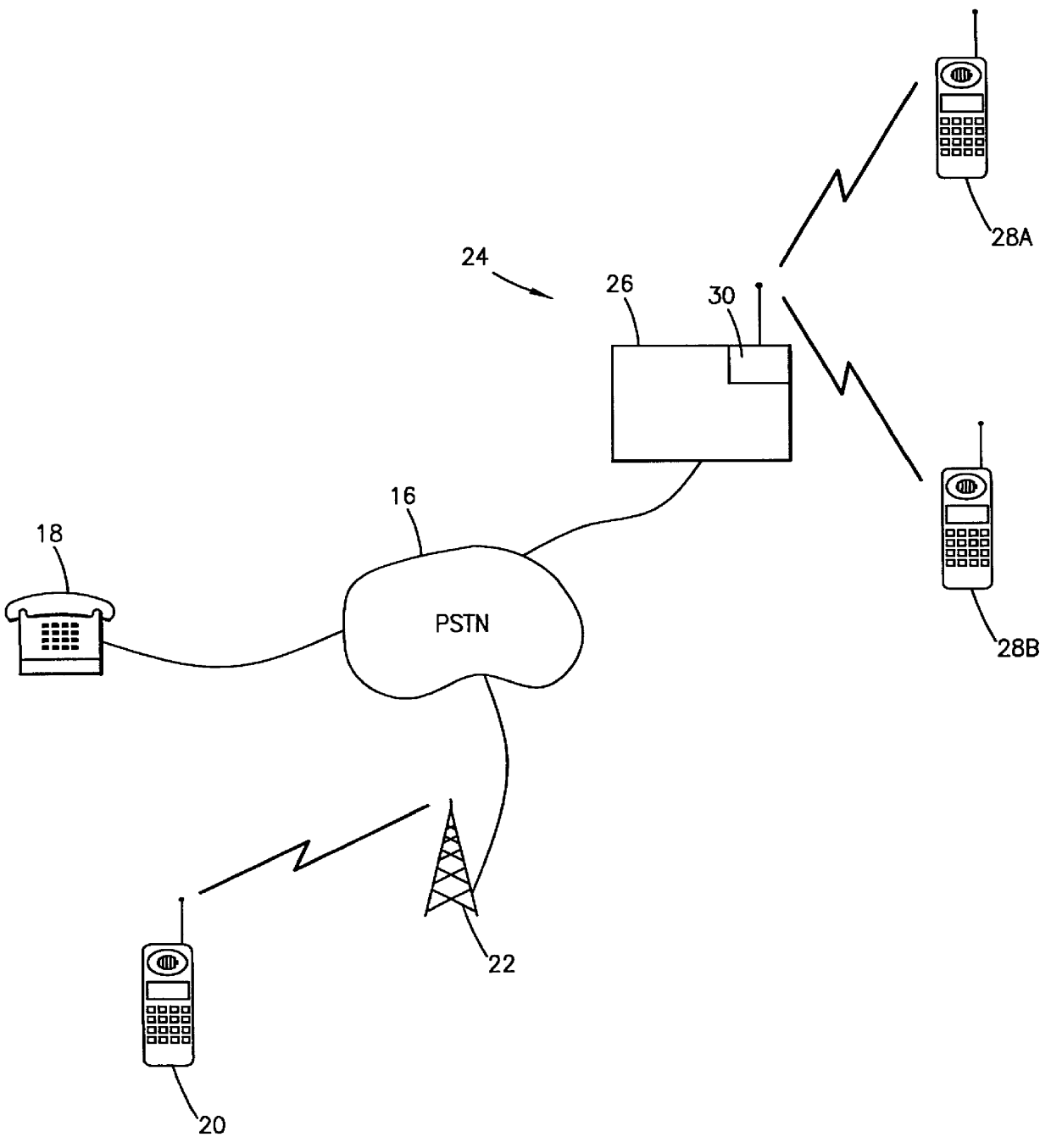

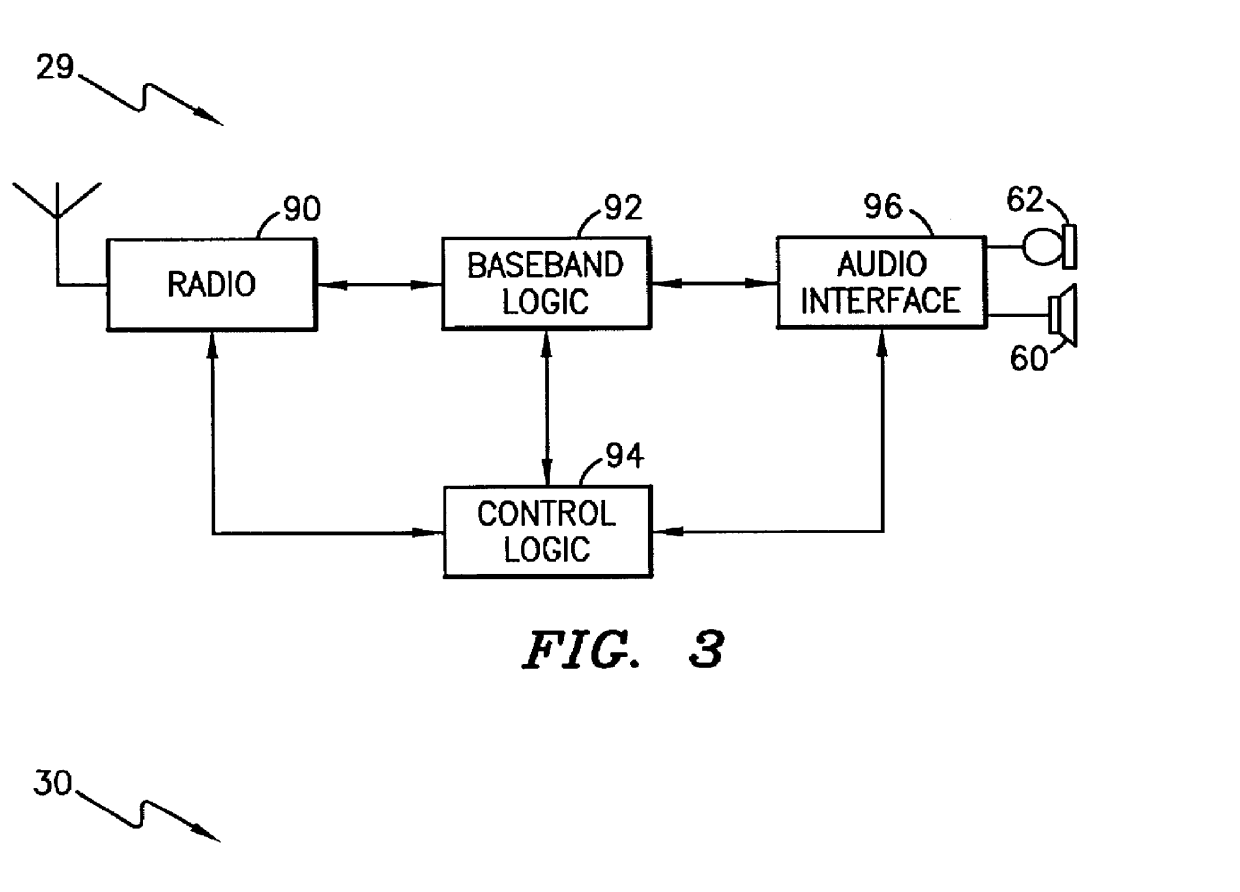

System and method for providing intercom and multiple voice channels in a private telephone system

InactiveUS6044268AEliminate needTechnology moreCordless telephonesNetwork topologiesTransceiverHalf Rate

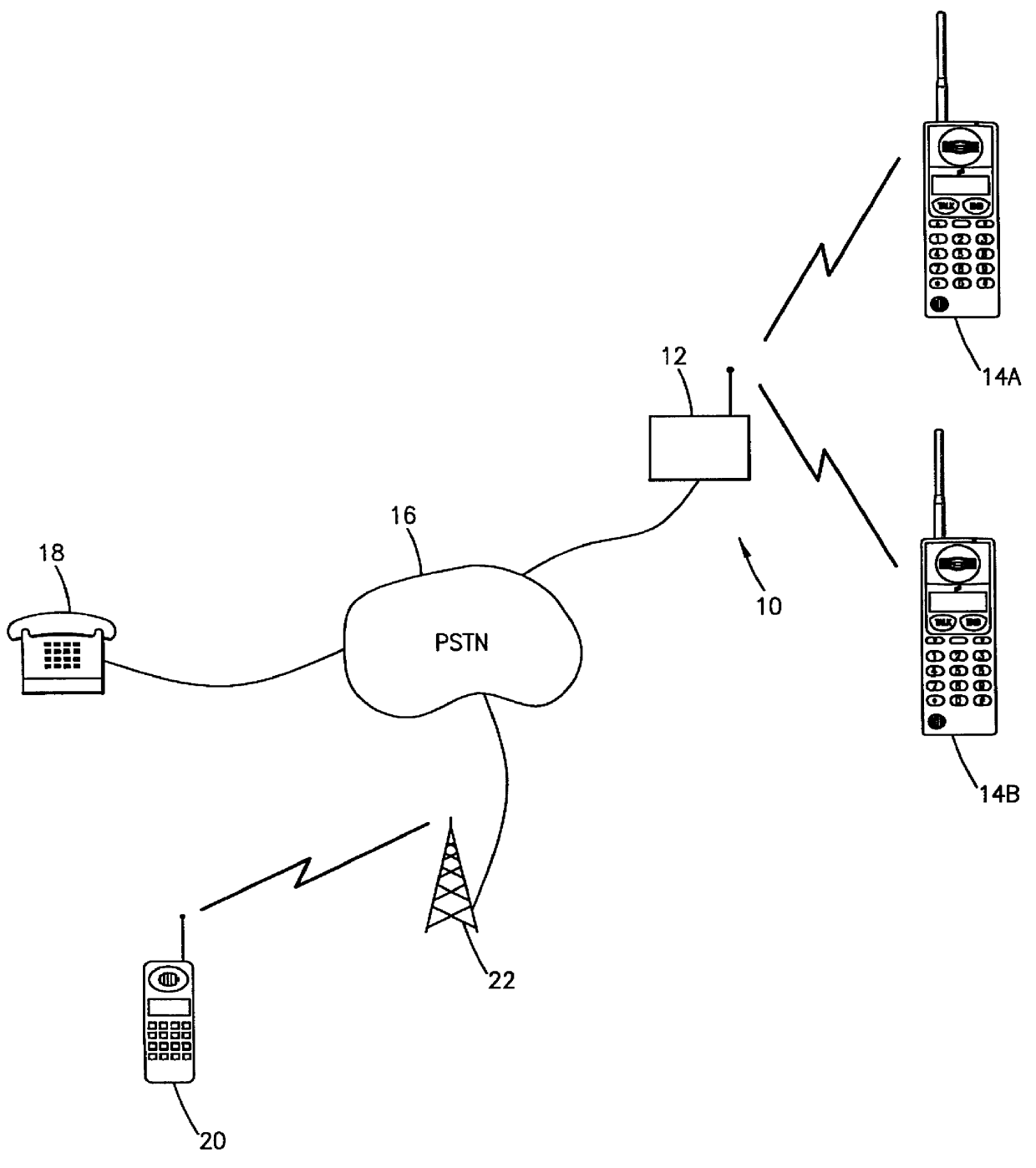

A system and method for allowing intercom and multiple voice channel communication within a private telephone system employing a private base station and a multiplicity of standard cellular terminals is disclosed. Full duplex intercom communications between two users within the private telephone system may be facilitated by use of two half-rate channels, one channel transceiver on even-numbered TDMA transmission frames and another channel transceiver on odd-numbered transmission frames, both from respective terminals to a private base station, which mediates the communication therebetween. Multiple voice channels are also provided within the private telephone system, allowing two users on two separate channels to communicate with respective remote wireline users simultaneously.

Owner:TELEFON AB LM ERICSSON (PUBL)

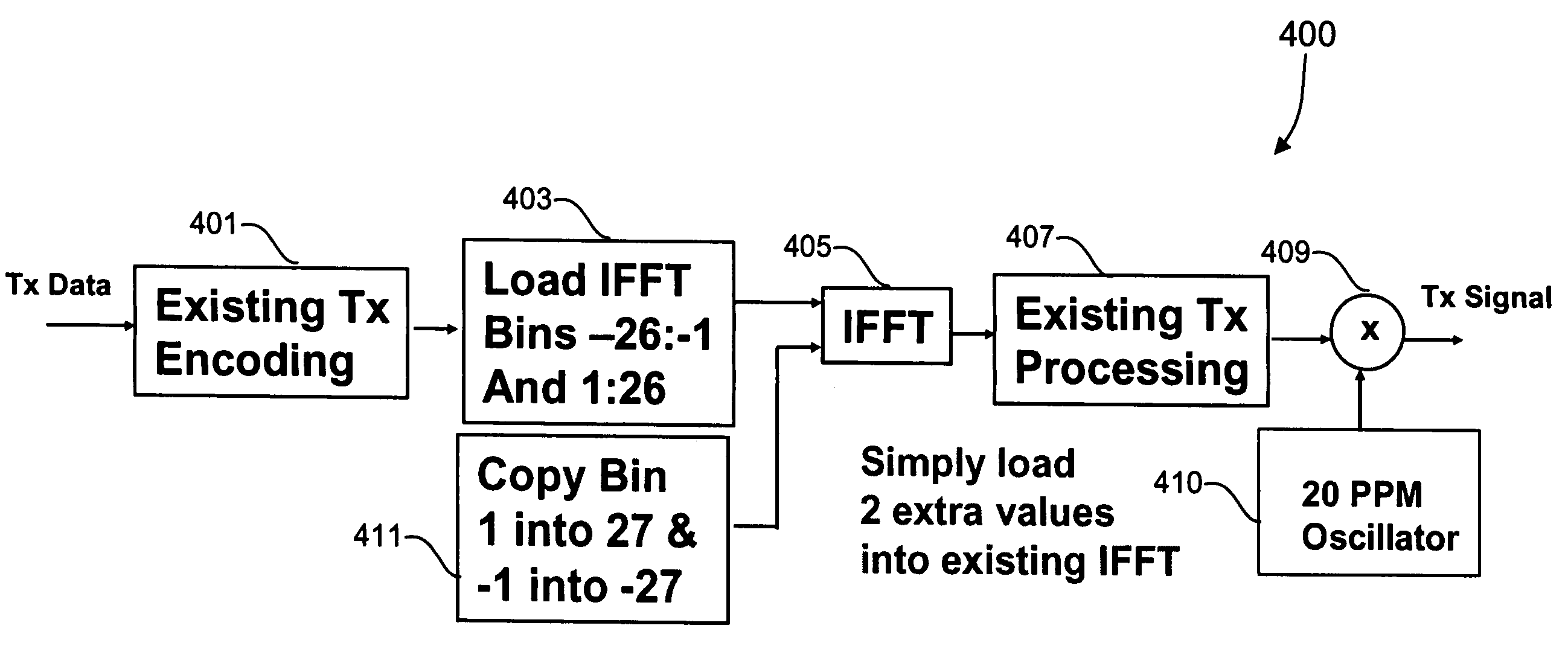

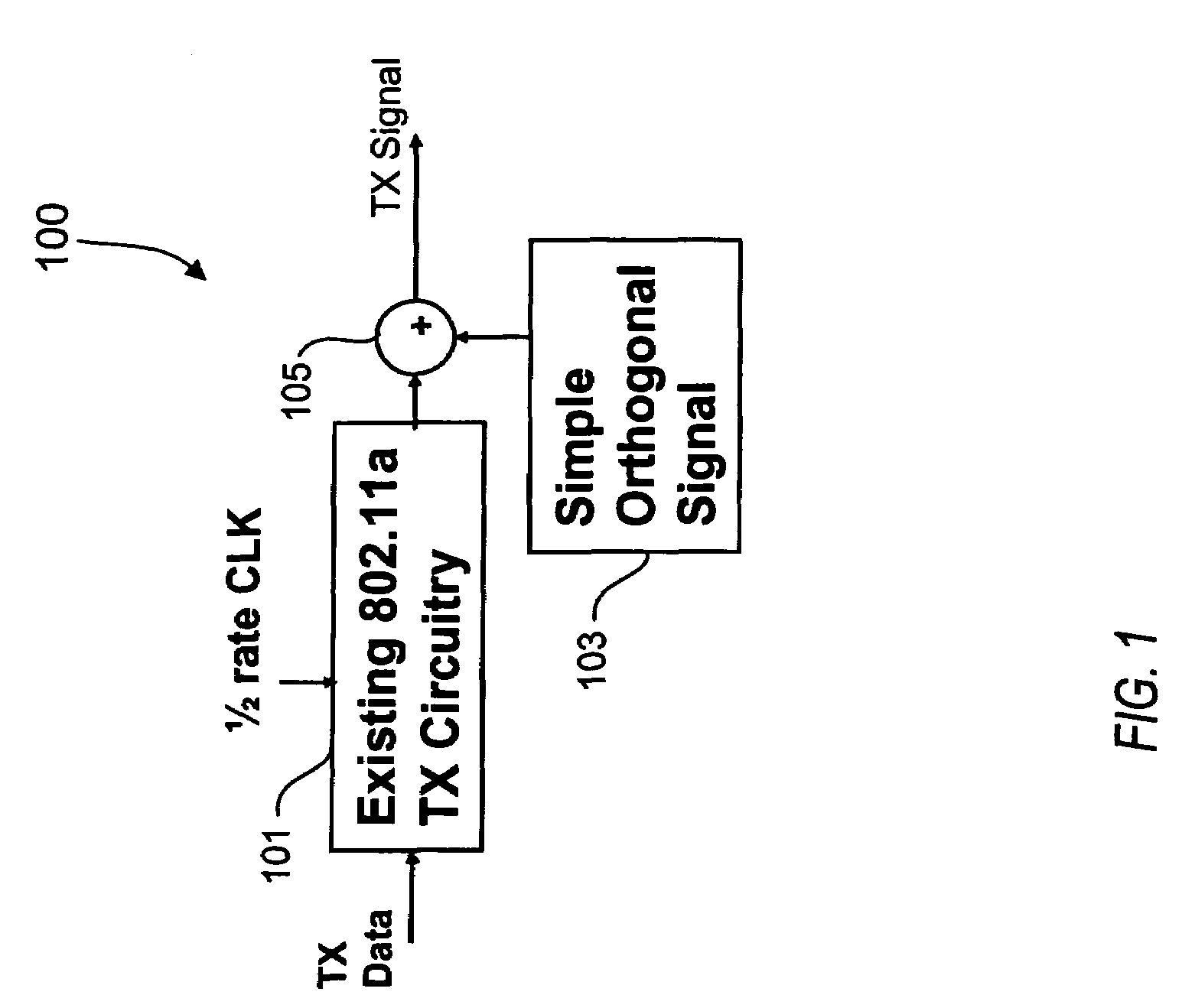

Modified OFDM subcarrier profile

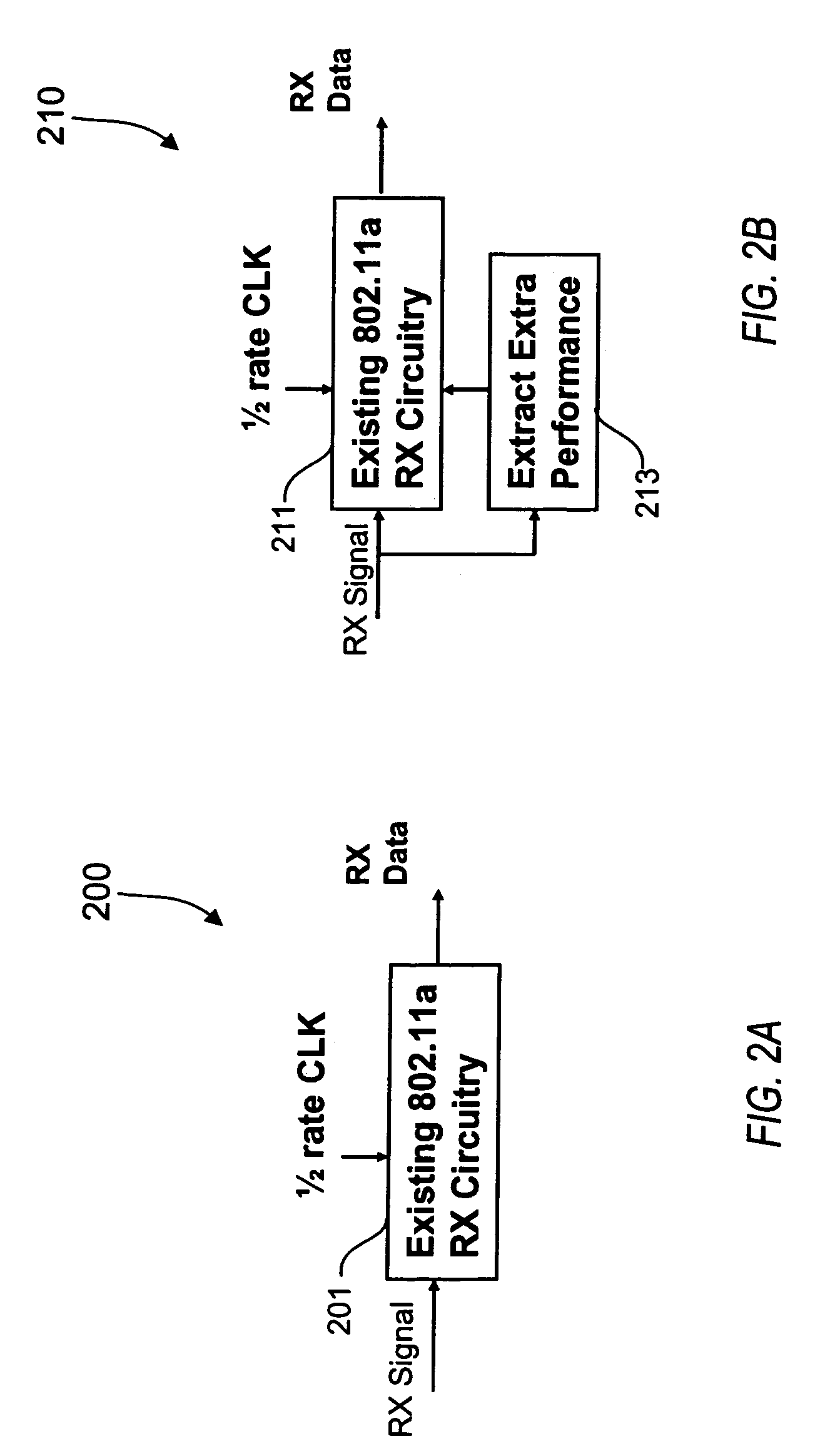

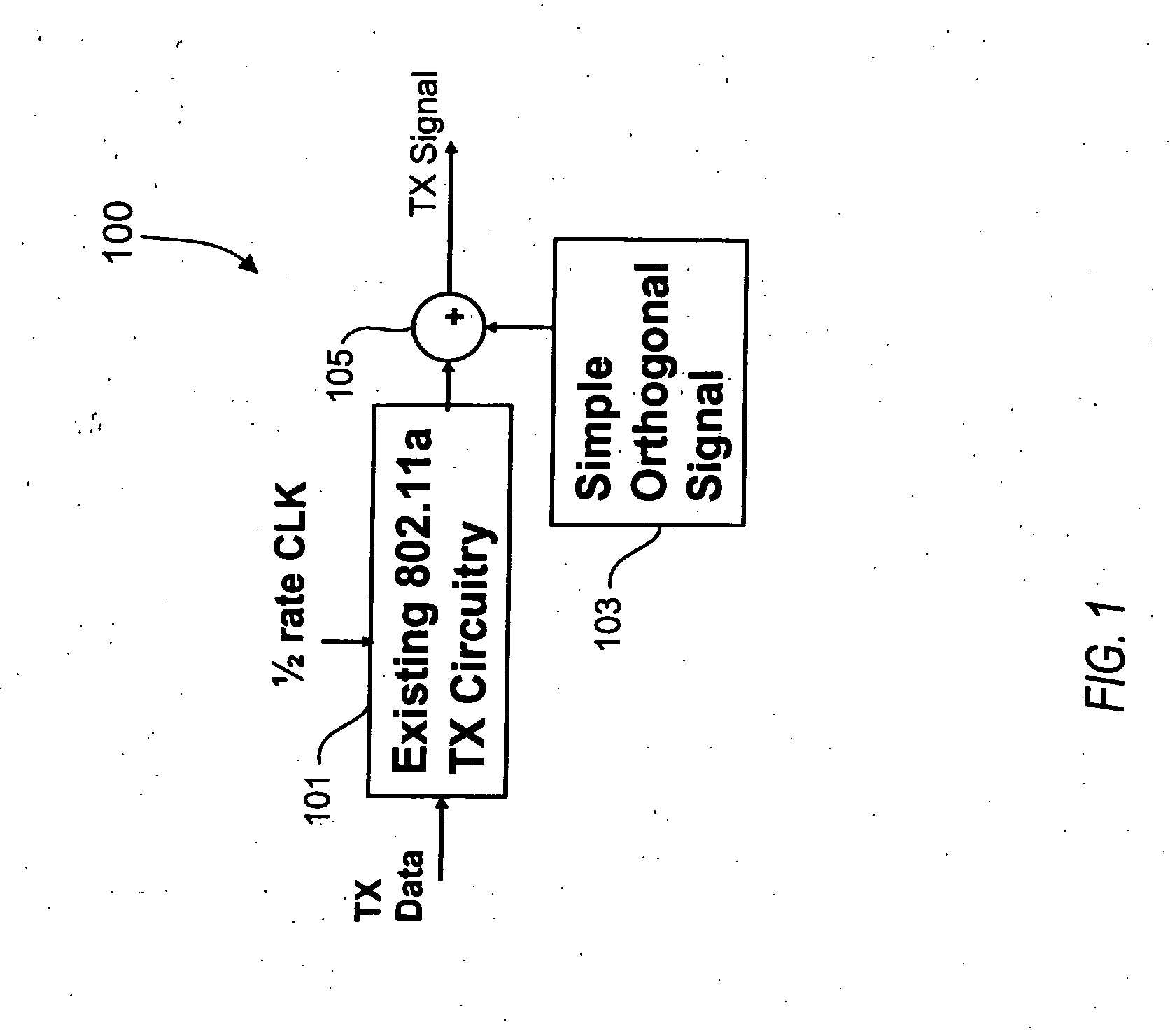

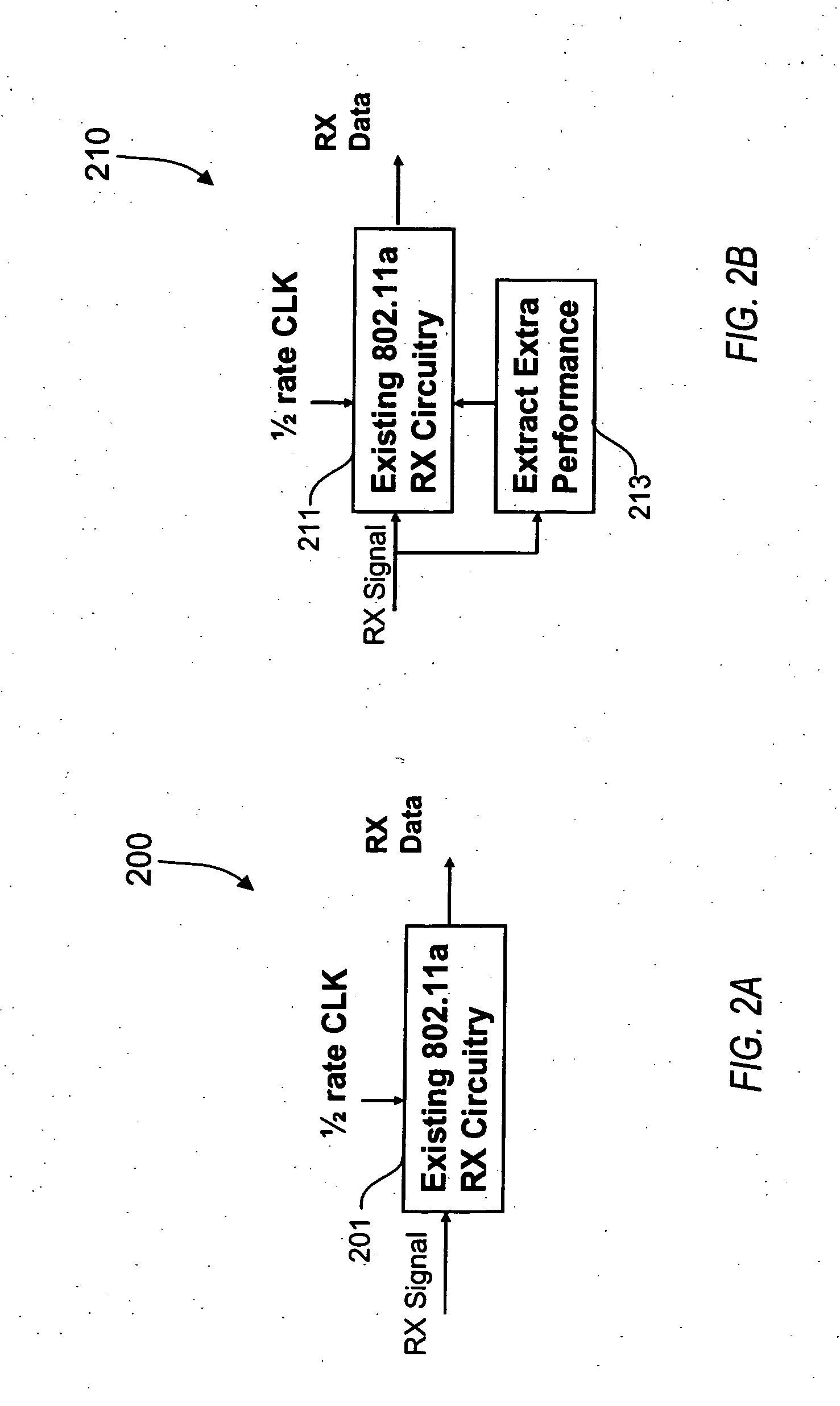

ActiveUS7272109B2Tracking performanceLower performance requirementsFrequency-division multiplexSecret communicationPhase shiftedCarrier signal

A 10 MHz channelized orthogonal frequency division multiplexing (OFDM) transmitter is provided that communicates using a modified OFDM packet structure with a half-rate oscillator having standard accuracy. The transmitter has an inverse fast fourier transform (IFFT) data processor that appends an outer pair of data subcarriers on either end of an OFDM subcarrier profile. An IFFT long sync processor appends an outer pair of binary phase shift key (BPSK) subcarriers on either end of an OFDM long sync subcarrier profile. By copying or appending the information of the data subcarriers closest to zero Hz. to more robust locations, 10 MHz channelized OFDM can be achieved with half-rate clocks and 20 PPM oscillators.

Owner:INTELLECTUAL VENTURES I LLC

Modified OFDM subcarrier profile

ActiveUS20050117670A1Improve performanceReduce complexityFrequency-division multiplexSecret communicationFast Fourier transformPhase shifted

A 10 MHz channelized orthogonal frequency division multiplexing (OFDM) transmitter is provided that communicates using a modified OFDM packet structure with a half-rate oscillator having standard accuracy. The transmitter has an inverse fast fourier transform (IFFT) data processor that appends an outer pair of data subcarriers on either end of an OFDM subcarrier profile. An IFFT long sync processor appends an outer pair of binary phase shift key (BPSK) subcarriers on either end of an OFDM long sync subcarrier profile. By copying or appending the information of the data subcarriers closest to zero Hz. to more robust locations, 10 MHz channelized OFDM can be achieved with half-rate clocks and 20 PPM oscillators.

Owner:INTELLECTUAL VENTURES I LLC

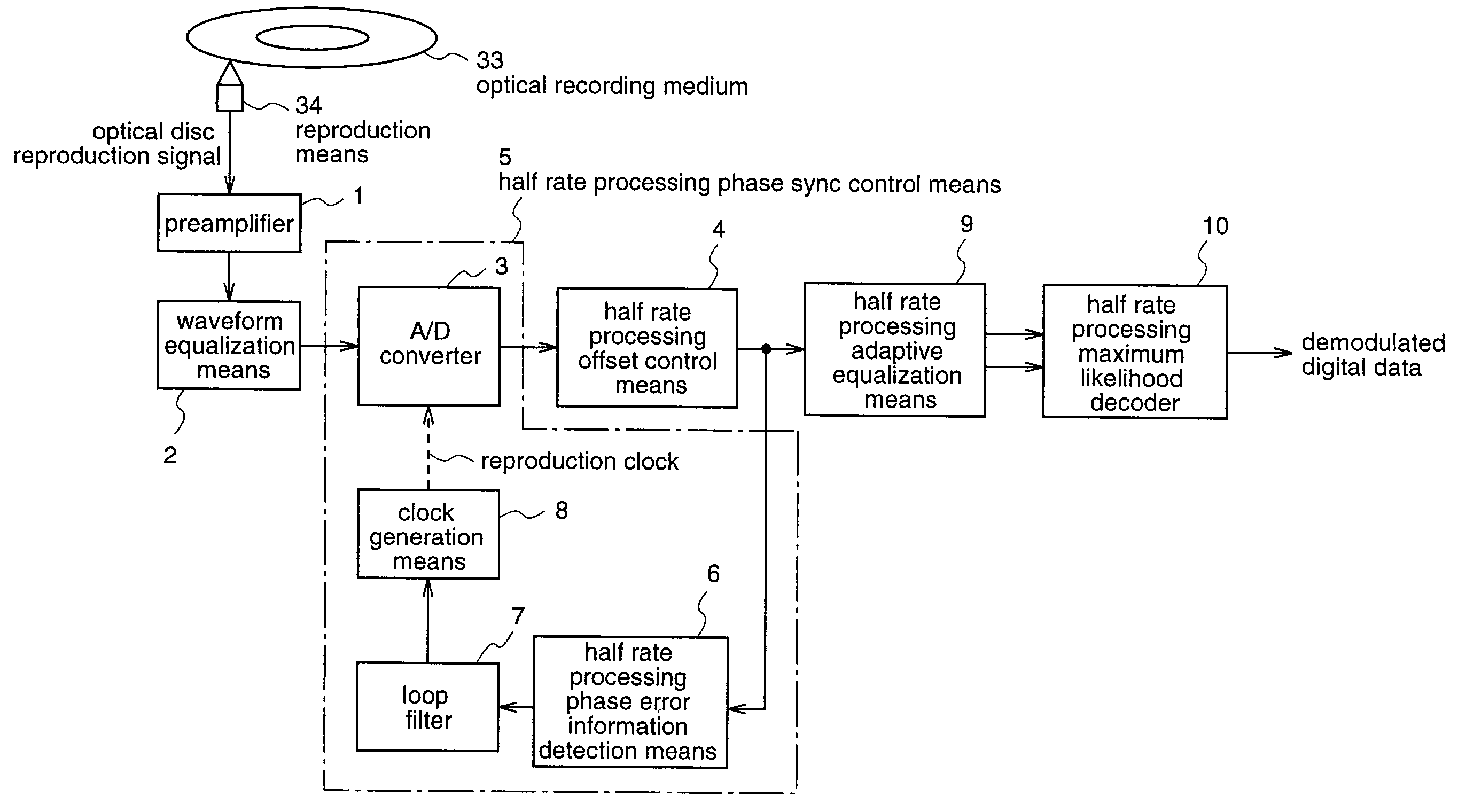

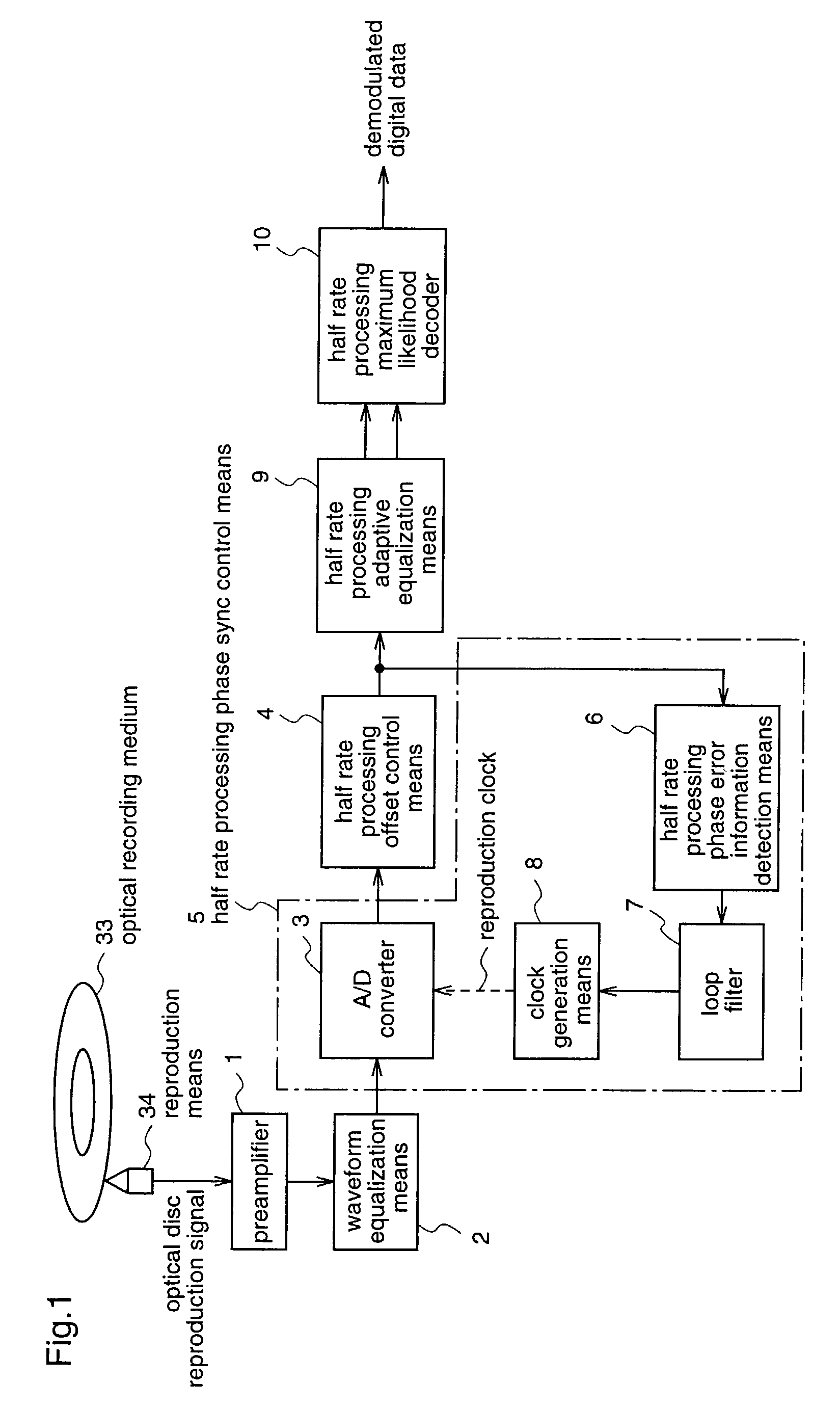

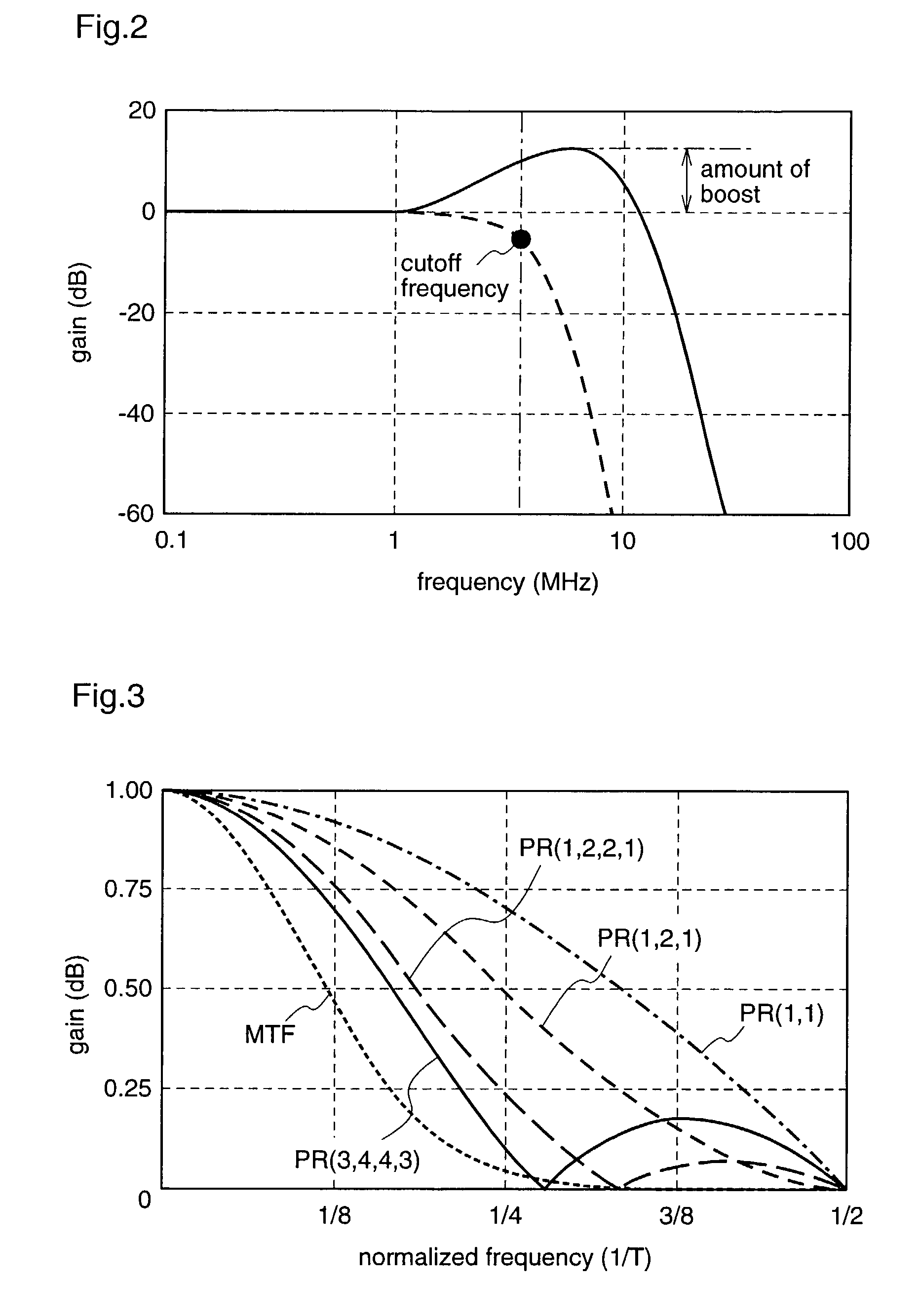

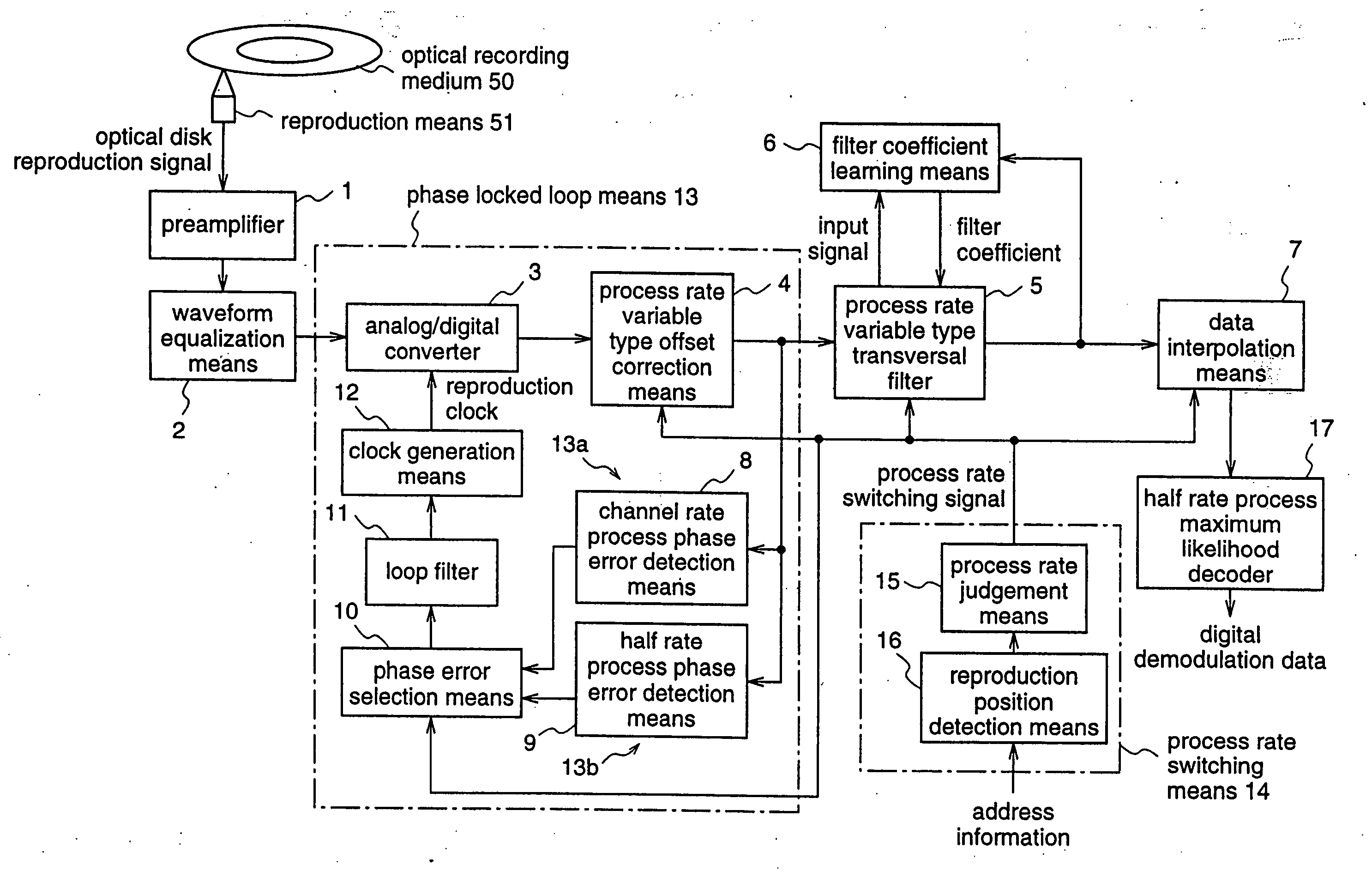

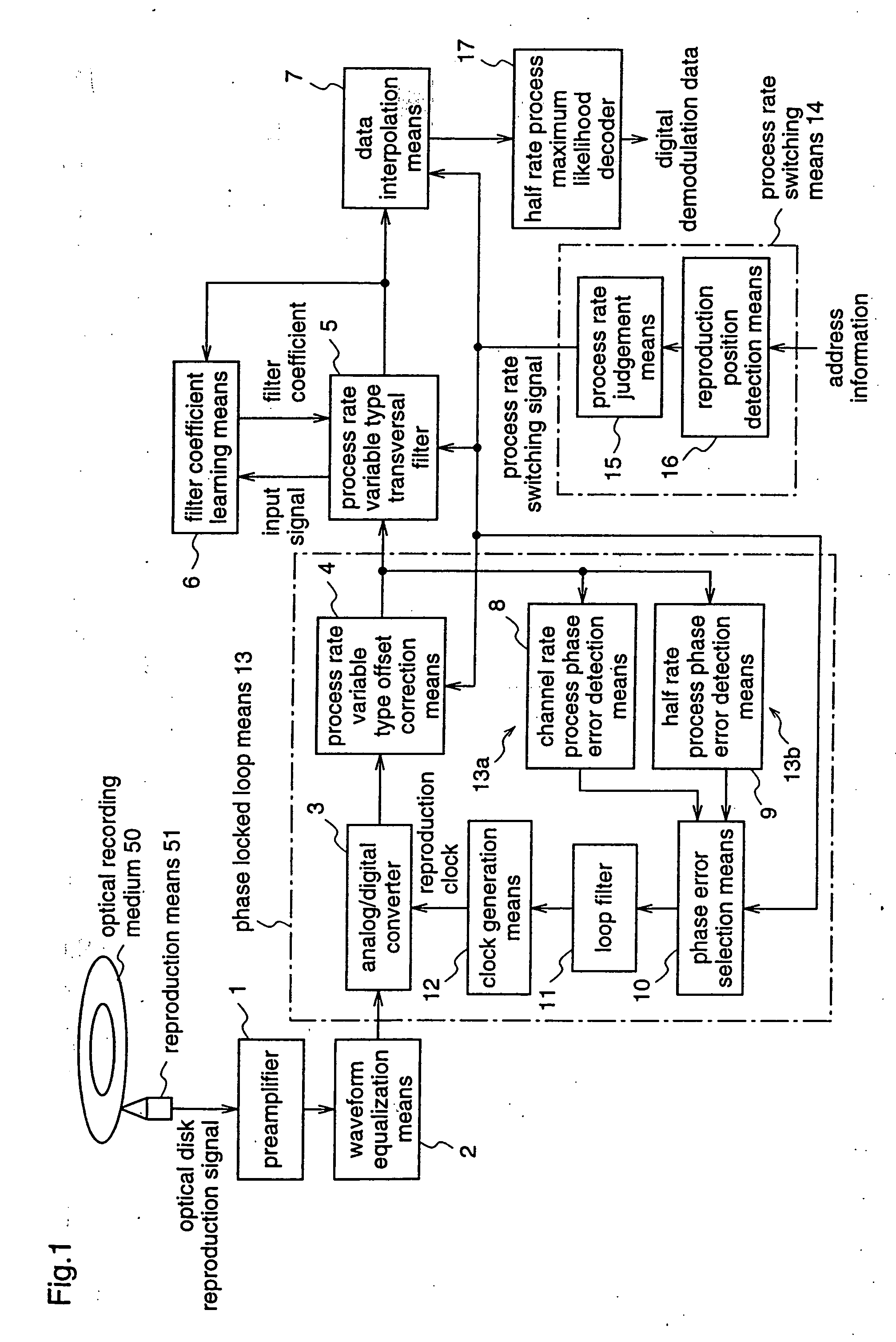

Digital data reproduction apparatus

InactiveUS6963528B2Reliable controlImprove reliabilityTelevision system detailsModification of read/write signalsDigital dataHigh density

In a digital data reproduction apparatus for demodulating digital data from an optical recording medium, PRML (Partial Response Maximum Likelihood) signal processing effective to high-density recording / reproduction is carried out by using a half rate processing offset control means which performs data demodulation using half of the channel bit frequency, a half rate processing phase sync control means, a half rate processing adaptive equalization means, and a half rate processing maximum likelihood decoder, and the digital data recorded on the optical recording medium are reproduced while restoring signal components which are missing in the time direction, by linear interpolation or Nyquist interpolation. Therefore, digital data reproduction performance is improved, and power consumption is reduced.

Owner:PANASONIC CORP

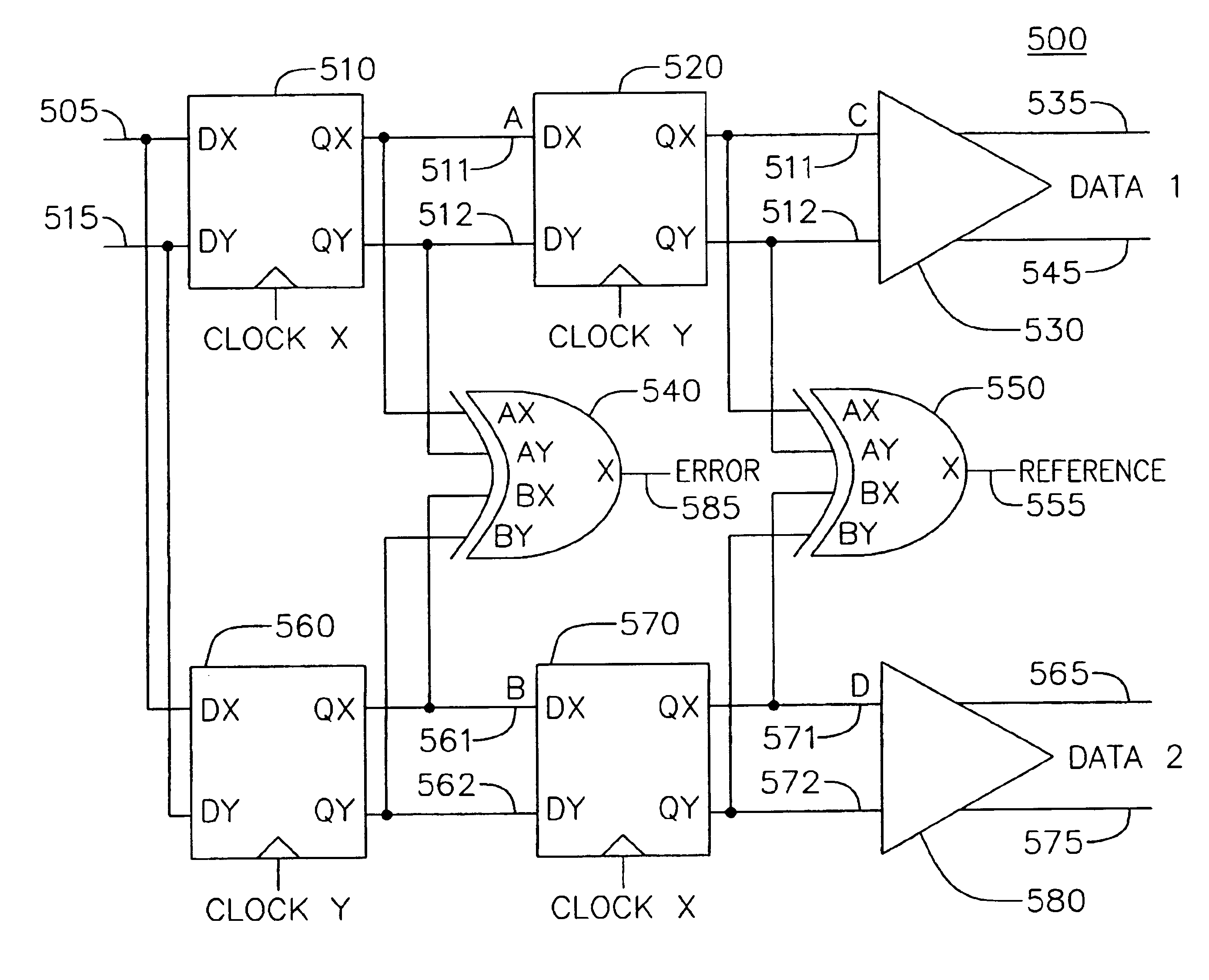

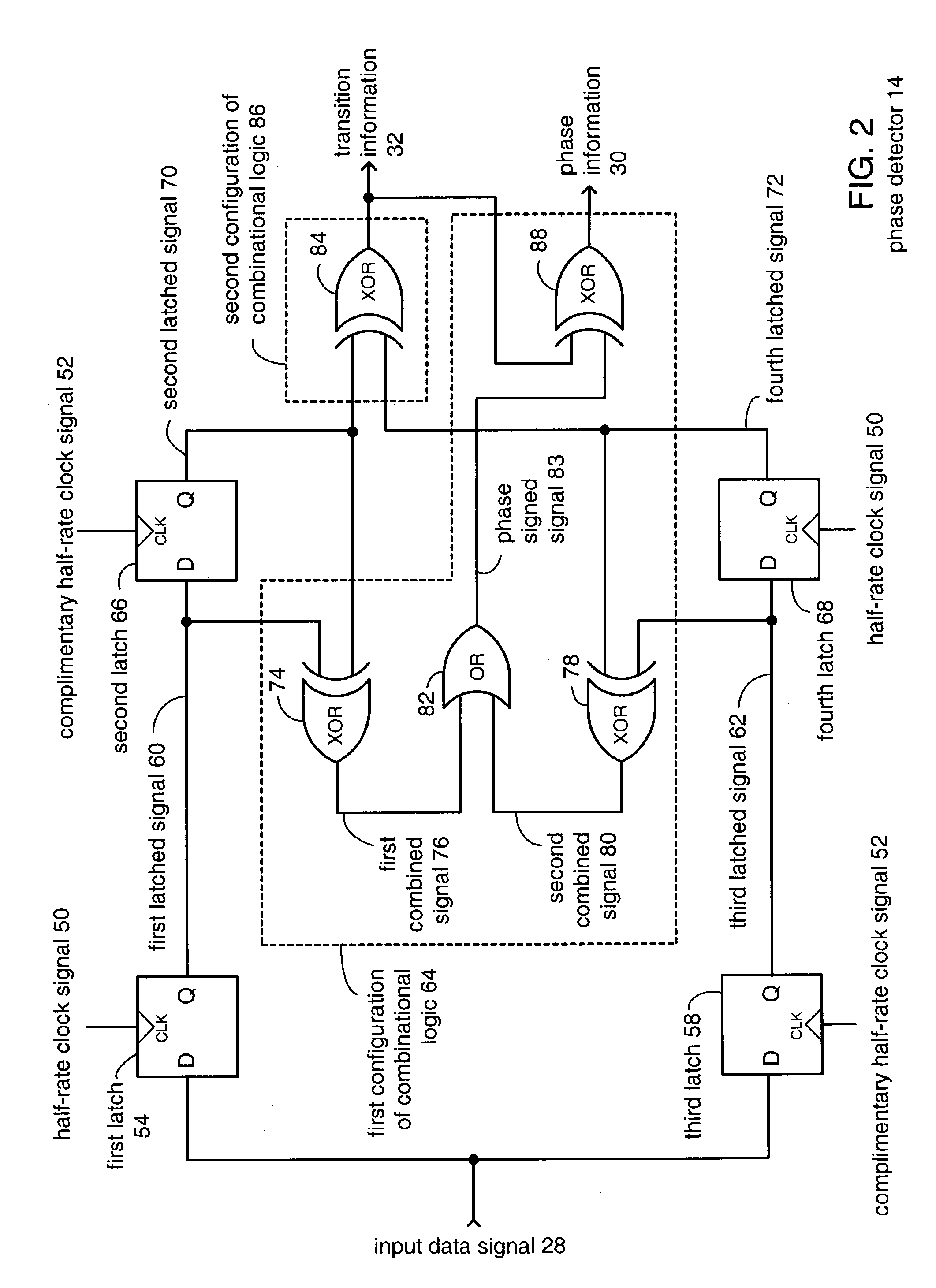

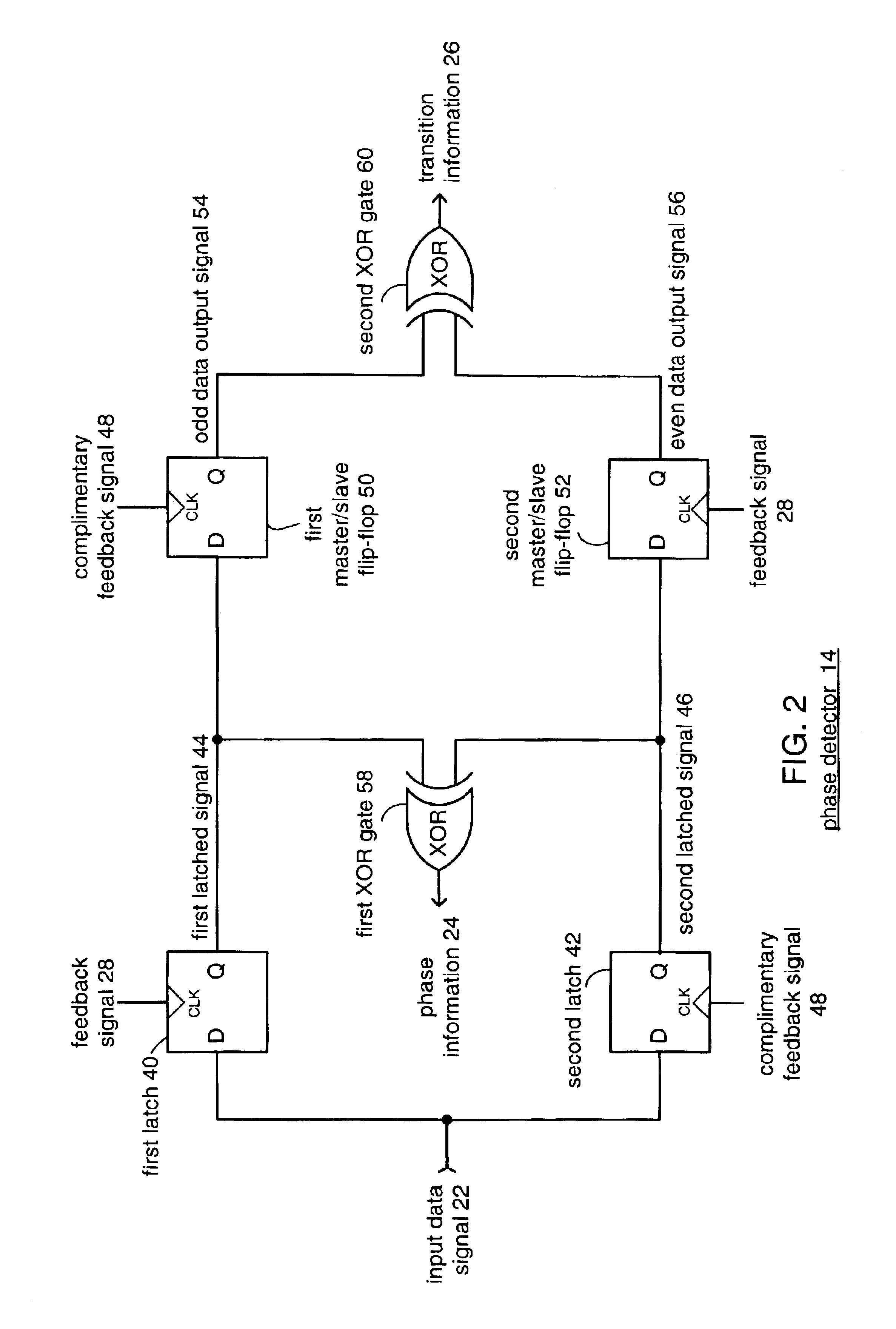

Linear half-rate phase detector and clock and data recovery circuit

InactiveUS6847789B2Less expensiveReduce noisePulse automatic controlVoltage-current phase anglePhase detectorClock rate

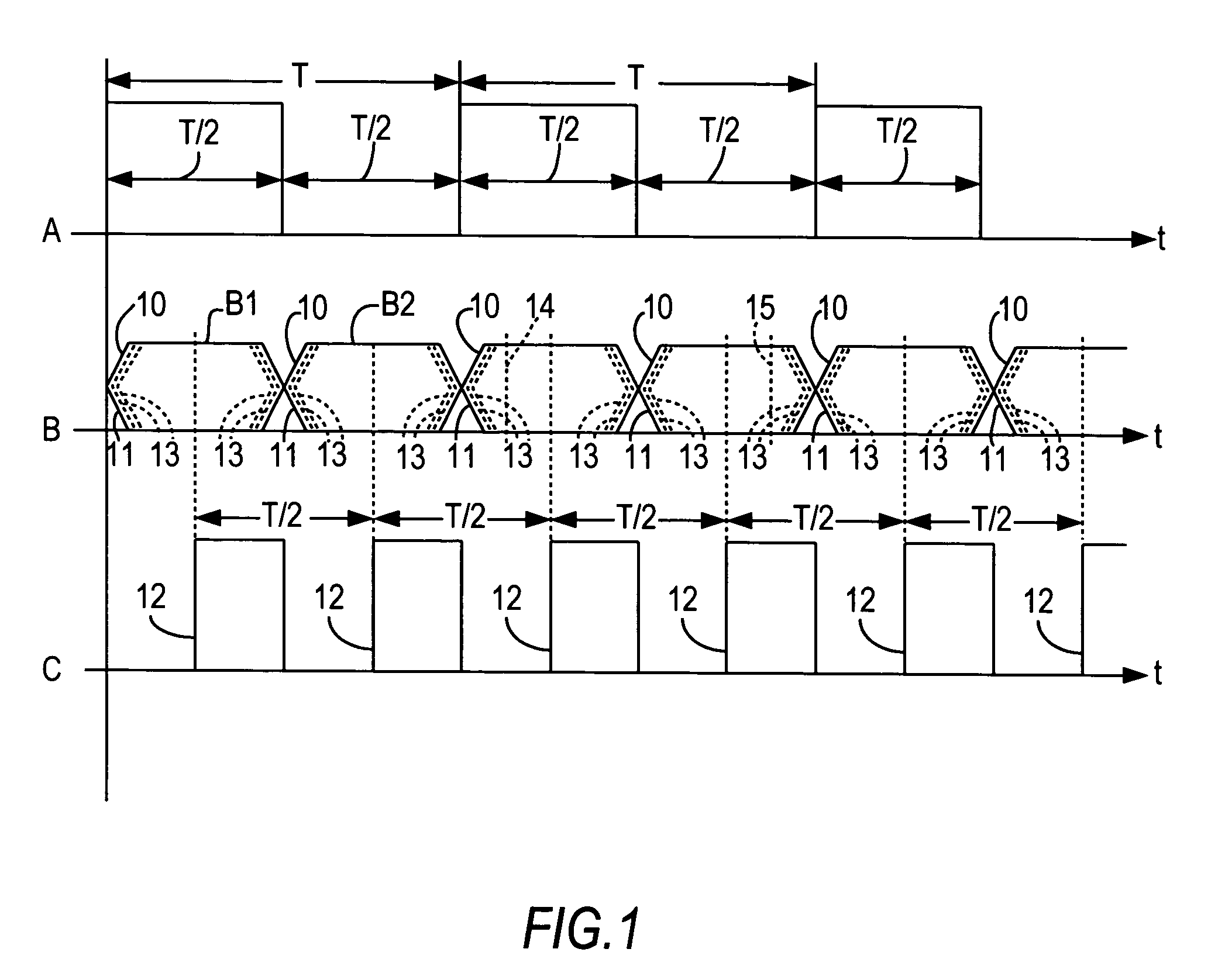

Method and apparatus for recovering a clock and data from a data signal. One method of the invention includes receiving the data signal having a first data rate, receiving the clock signal having a first clock frequency, alternating between a first level and a second level, wherein the first data rate is twice the first clock frequency. A first signal is generated by passing the data signal when the clock signal is at the first level, and storing the data signal when the clock signal is at the second level. A second signal is generated by passing the data signal when the clock signal is at the second level, and storing the data signal when the clock signal is at the first level. A third signal is generated by passing the first signal when the clock signal is at the second level, and storing the first signal when the clock signal is at the first level. A fourth signal is generated by passing the second signal when the clock signal is at the first level, and storing the second signal when the clock signal is at the second level. An error signal is generated by taking the exclusive-OR of the first signal and the second signal, and a reference signal is generated by taking the exclusive-OR of the third signal and the fourth signal.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

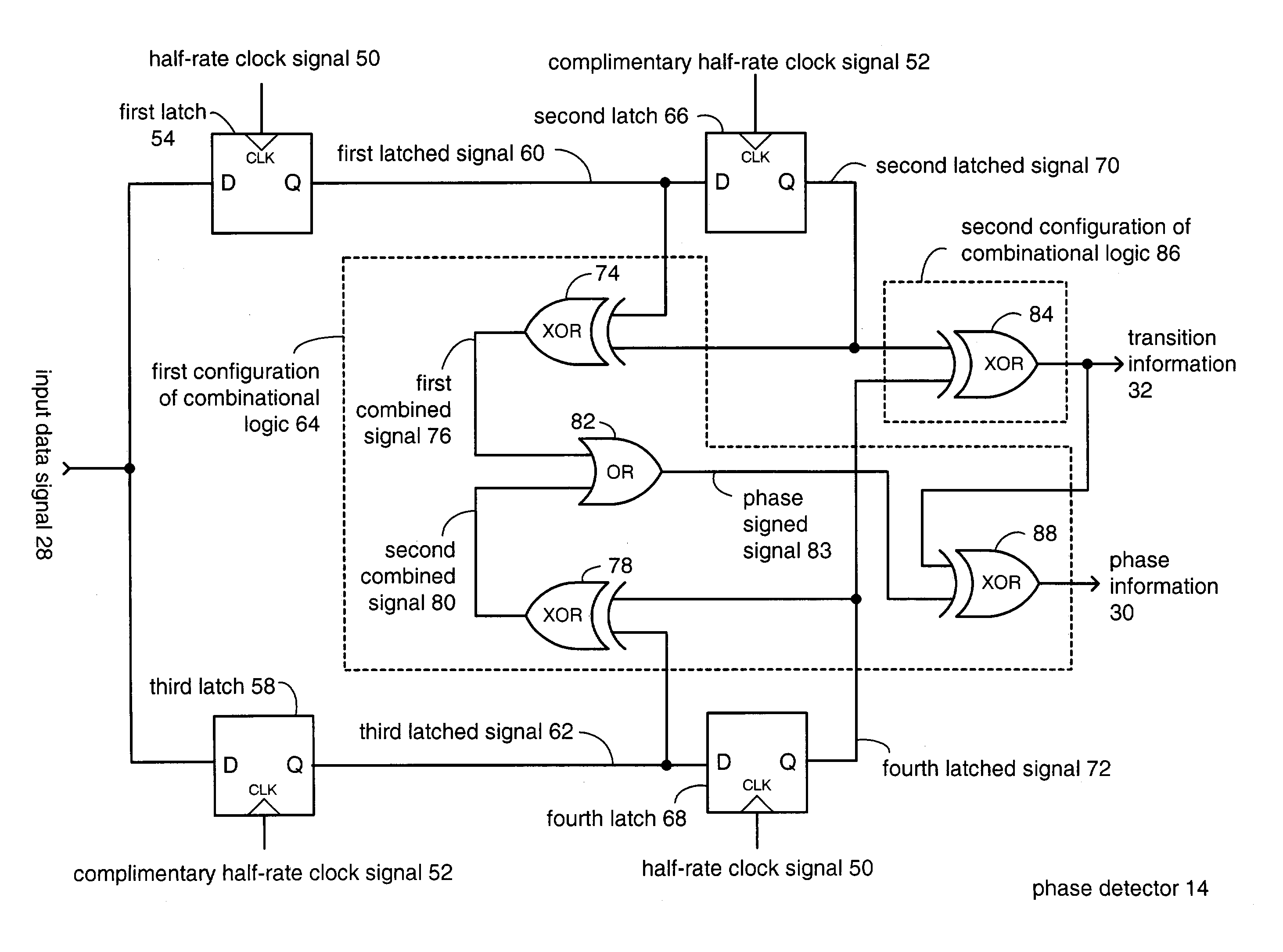

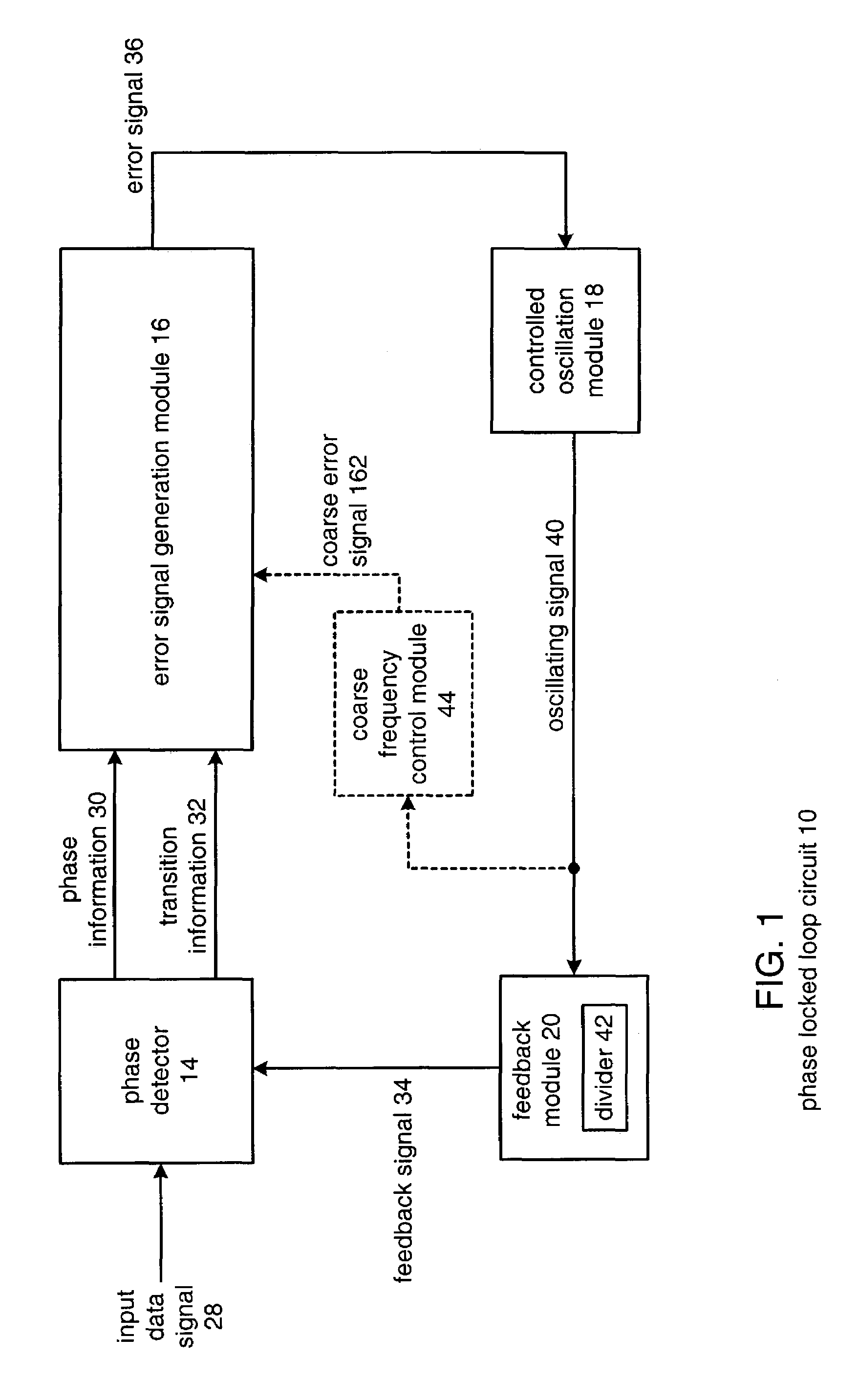

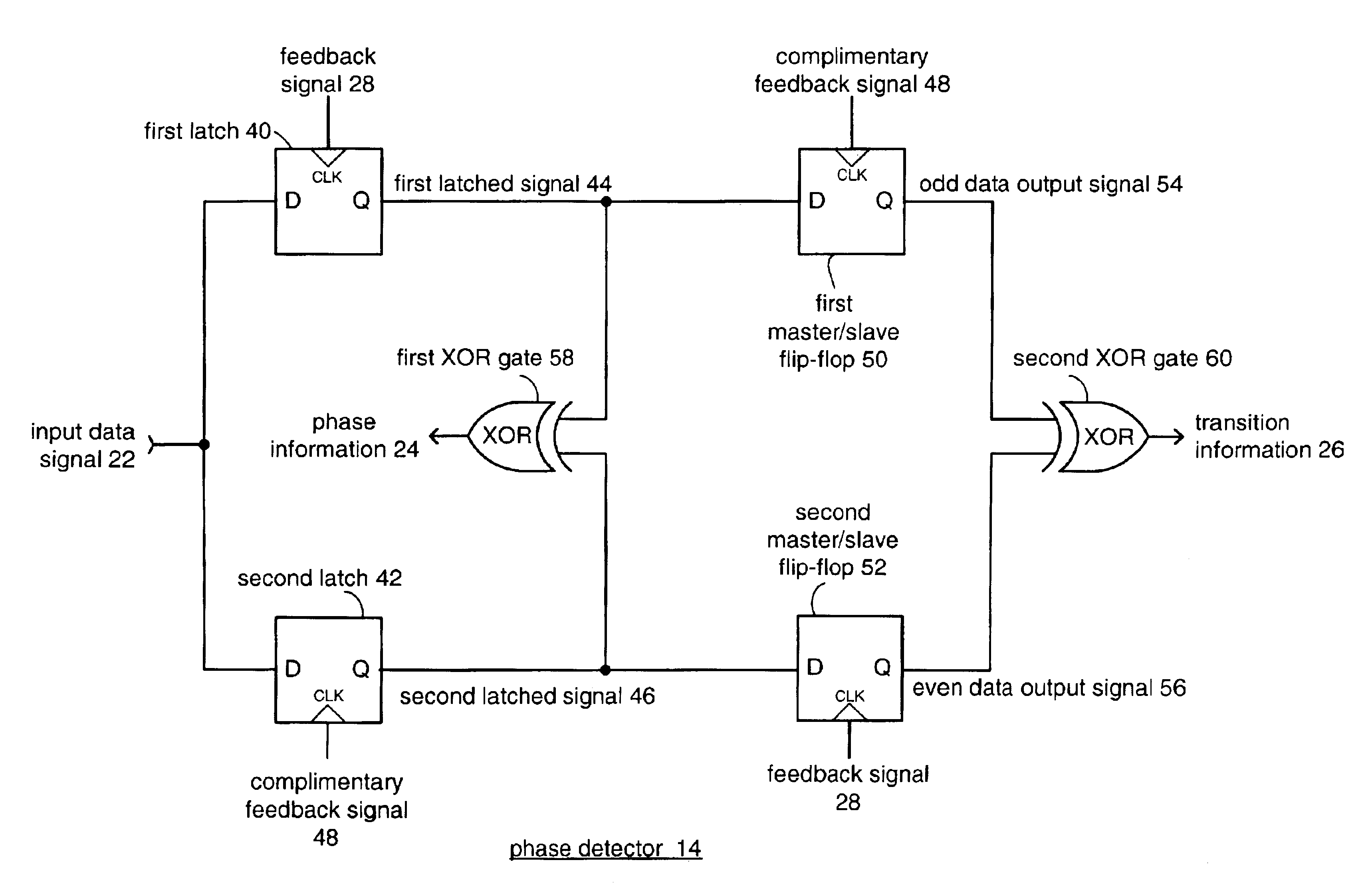

High speed phase detector architecture

InactiveUS6956923B1Pulse automatic controlOscillations comparator circuitsPhase detectorDetector circuits

A high speed phase detector circuit operating at a clock speed equal to one-half an input data rate (i.e. a half-rate clock) provides phase information and transition information from incoming serial data. The high speed phase detector circuit samples the incoming serial data on both the rising edge and falling edge of the half-rate clock to provide equivalent full high speed data rate sampling. The high speed phase detector circuit generates a delay between the phase information and the transition information. The phase information is produced in a first bit period and the transition information is produced in a second bit period relative to the first bit period.

Owner:XILINX INC

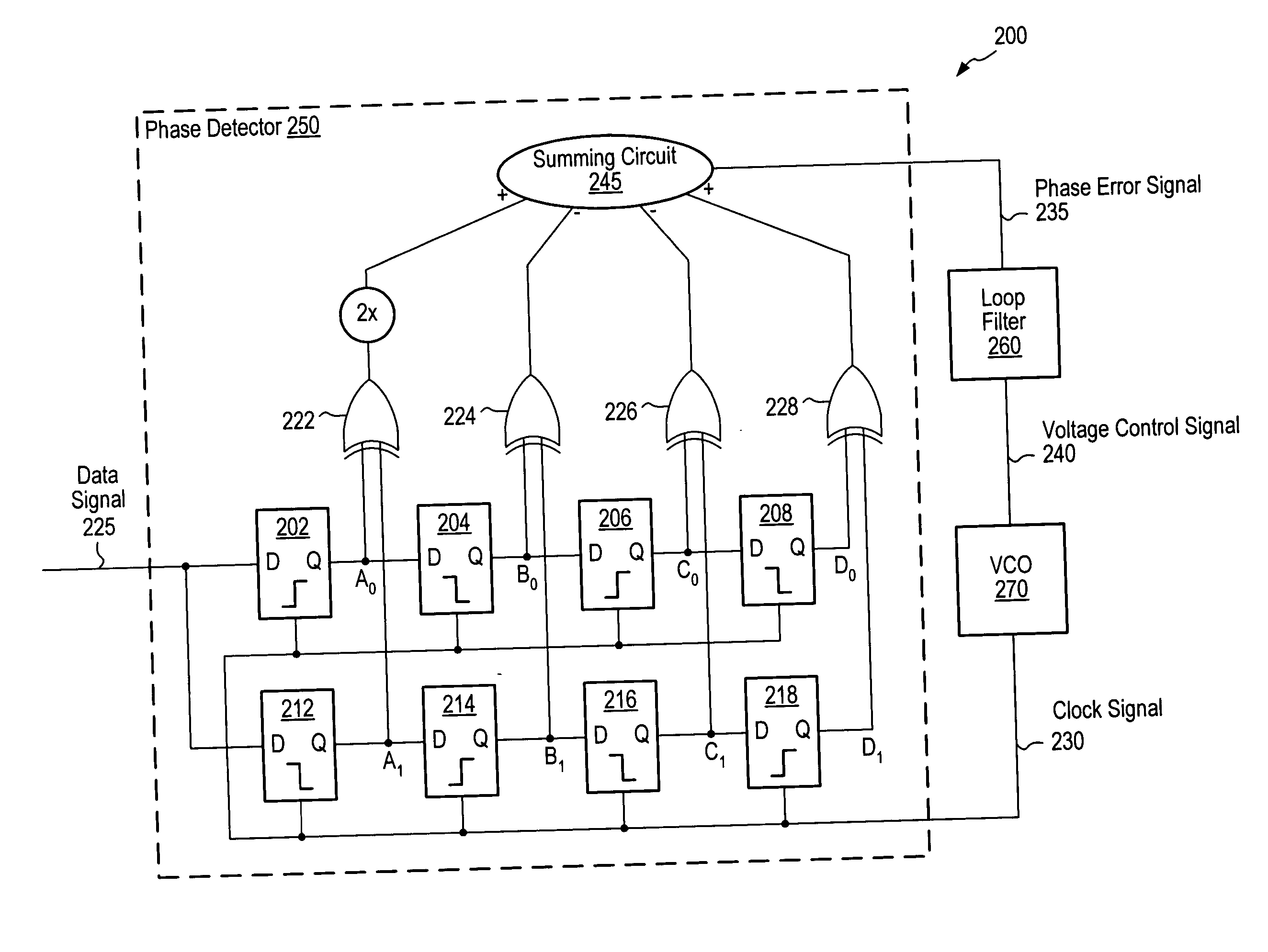

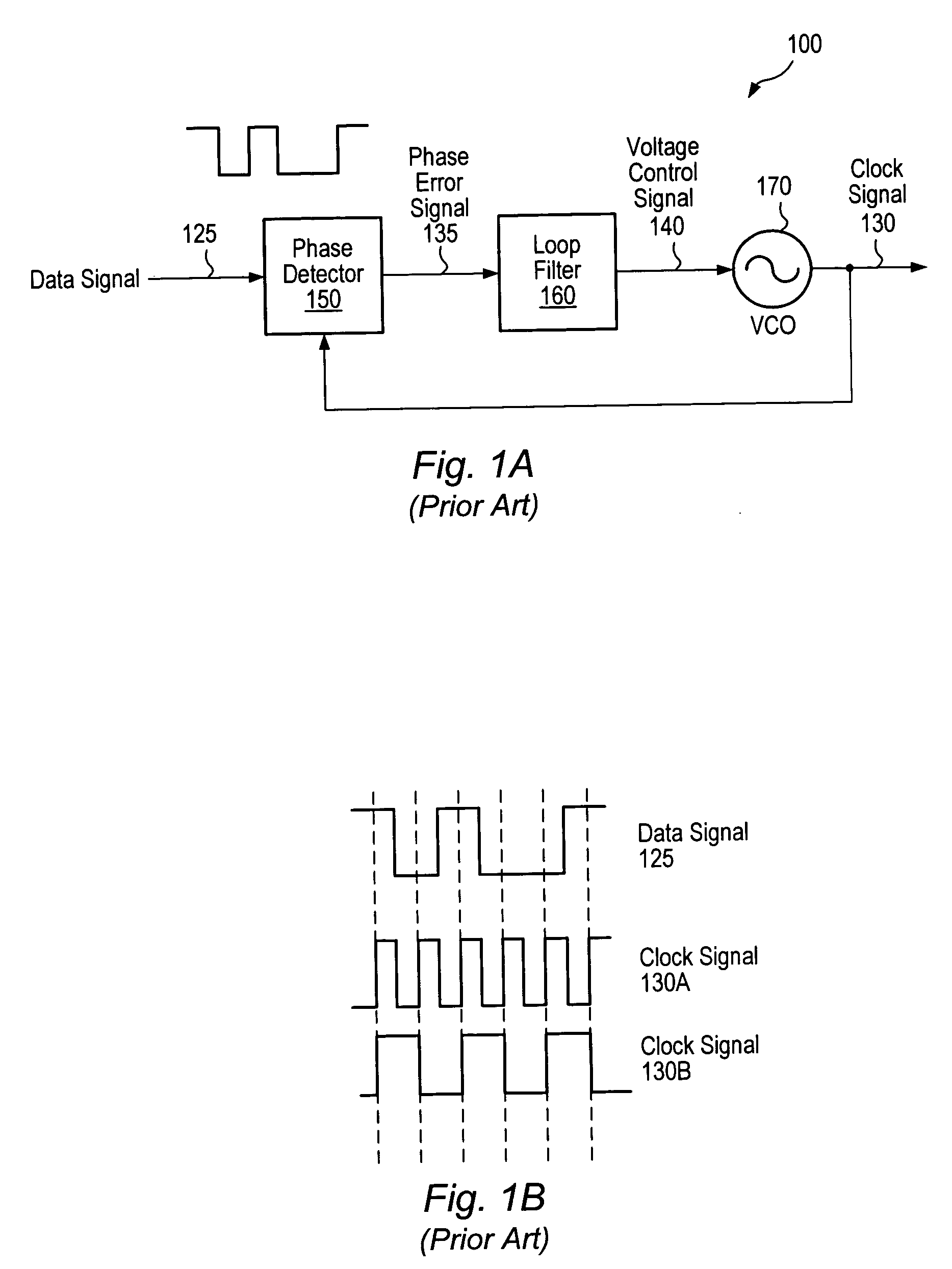

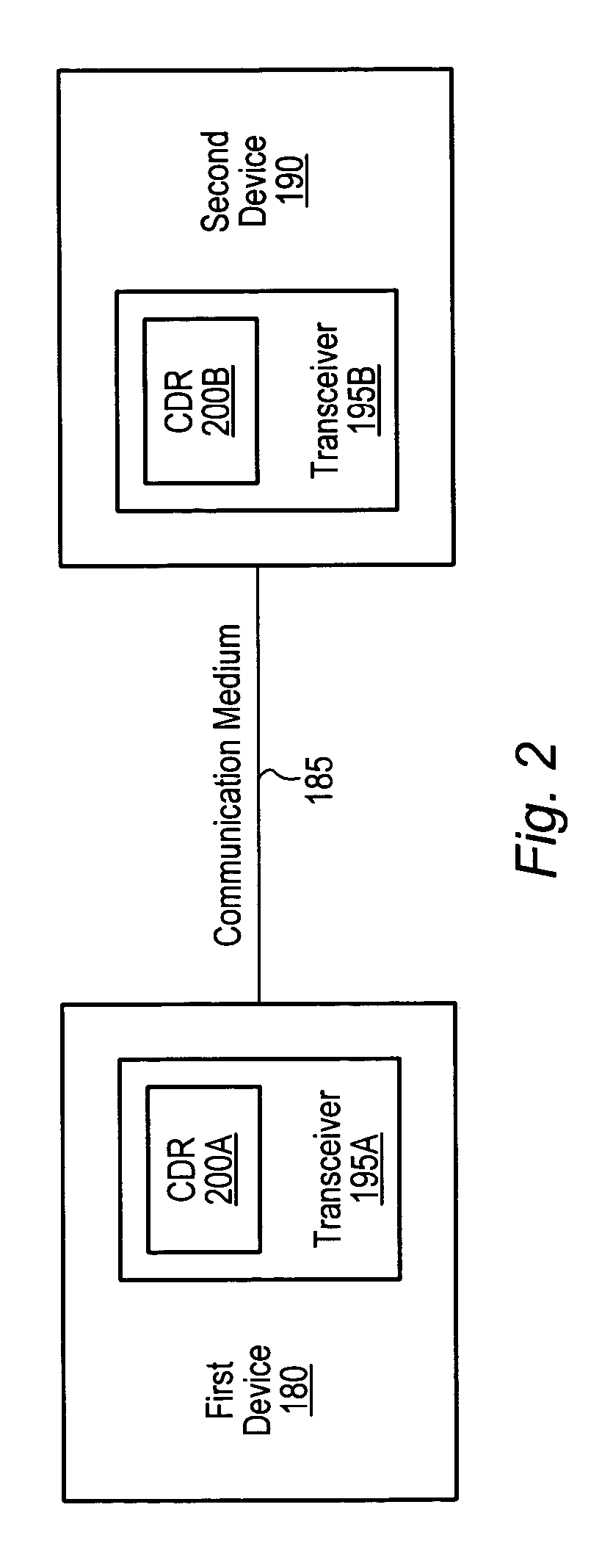

Linear half-rate clock and data recovery (CDR) circuit

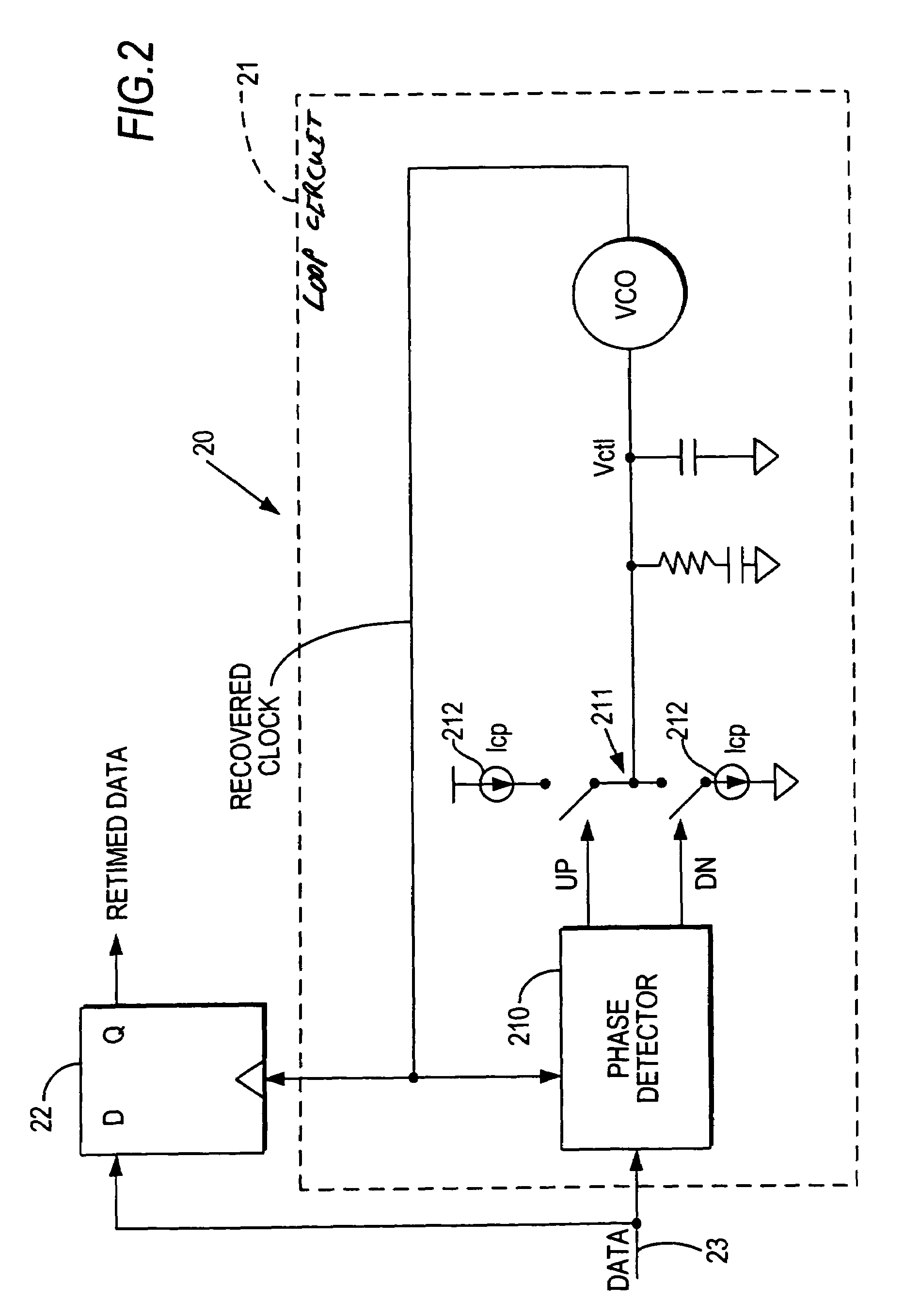

A linear, half-rate clock and data recovery (CDR) circuit for recovering clock information embedded in a received data signal. The half-rate CDR circuit comprises a phase detector that may receive the data signal and generate a phase error signal representative of the phase difference between the received data signal and a clock signal produced by a voltage-controlled oscillator (VCO) of the CDR circuit. The half-rate CDR typically changes the frequency of the clock signal and generates a clock signal that is aligned with the baud center of the received data signal. More specifically, when the half-rate CDR circuit is in a locked condition, both the rising and falling edges of the clock signal are aligned with the baud center of the received data signal. The half-rate CDR preferably generates a clock signal with an average frequency that is half the data rate of a received data signal.

Owner:MICROCHIP TECH INC

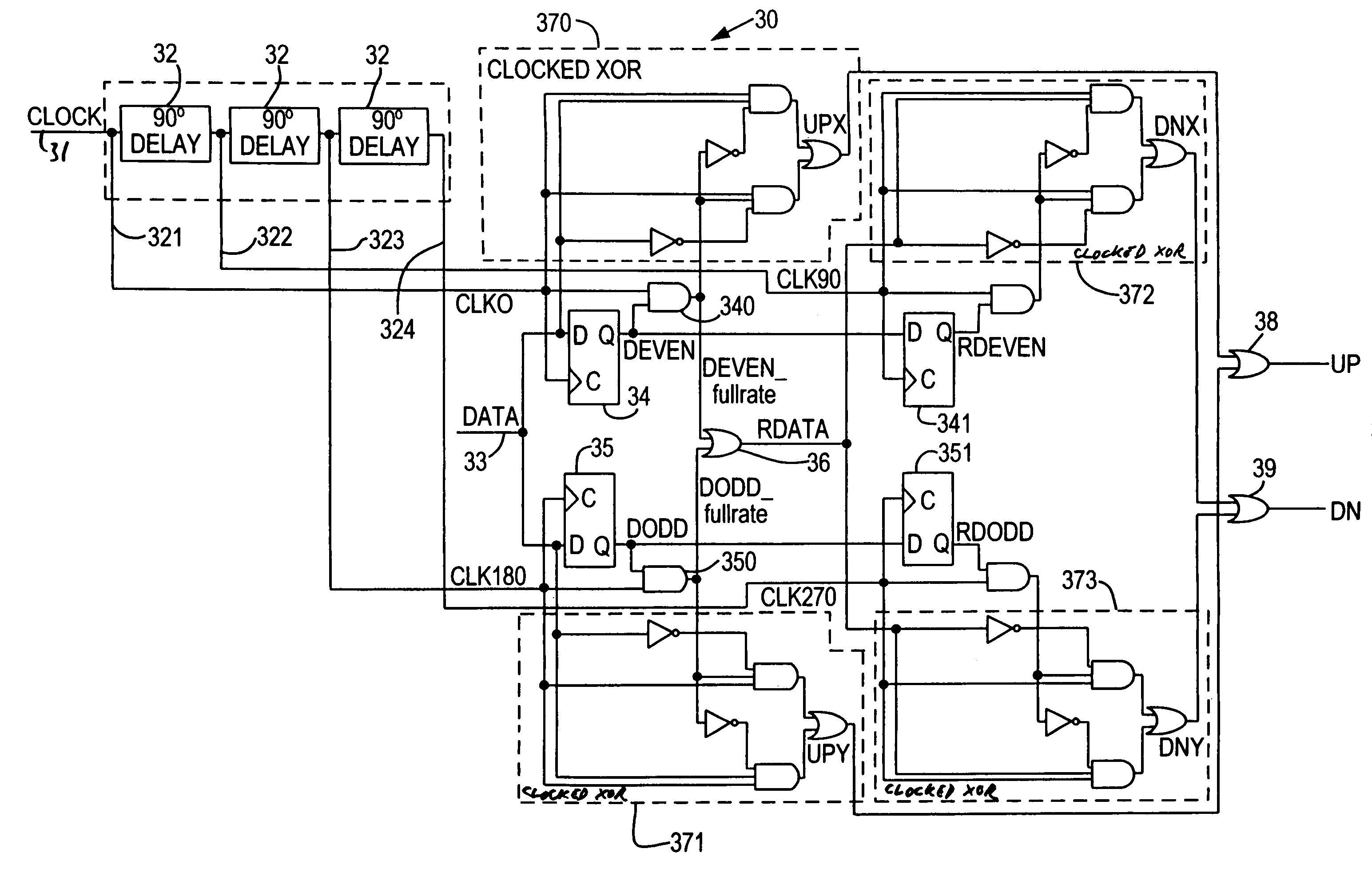

Half-rate linear quardrature phase detector for clock recovery

InactiveUS6970020B1Minimize jitterMinimizing control signalVoltage-current phase angleSingle output arrangementsPhase detectorControl signal

A half-rate linear phase detector is particularly well-suited to clock data recovery in a serial data interface. The phase detector uses a quadrature clock to process different portions of the incoming data with different phases of the clock. The resulting component signals can be combined to provide the expected UP and DOWN phase detector output control signals. The phase detector output signals are balanced and of uniform width, minimizing oscillator control signal ripple in the clock data recovery circuit, while the linearity of the phase detector makes its output predictable.

Owner:ALTERA CORP

High-speed serial link clock and data recovery

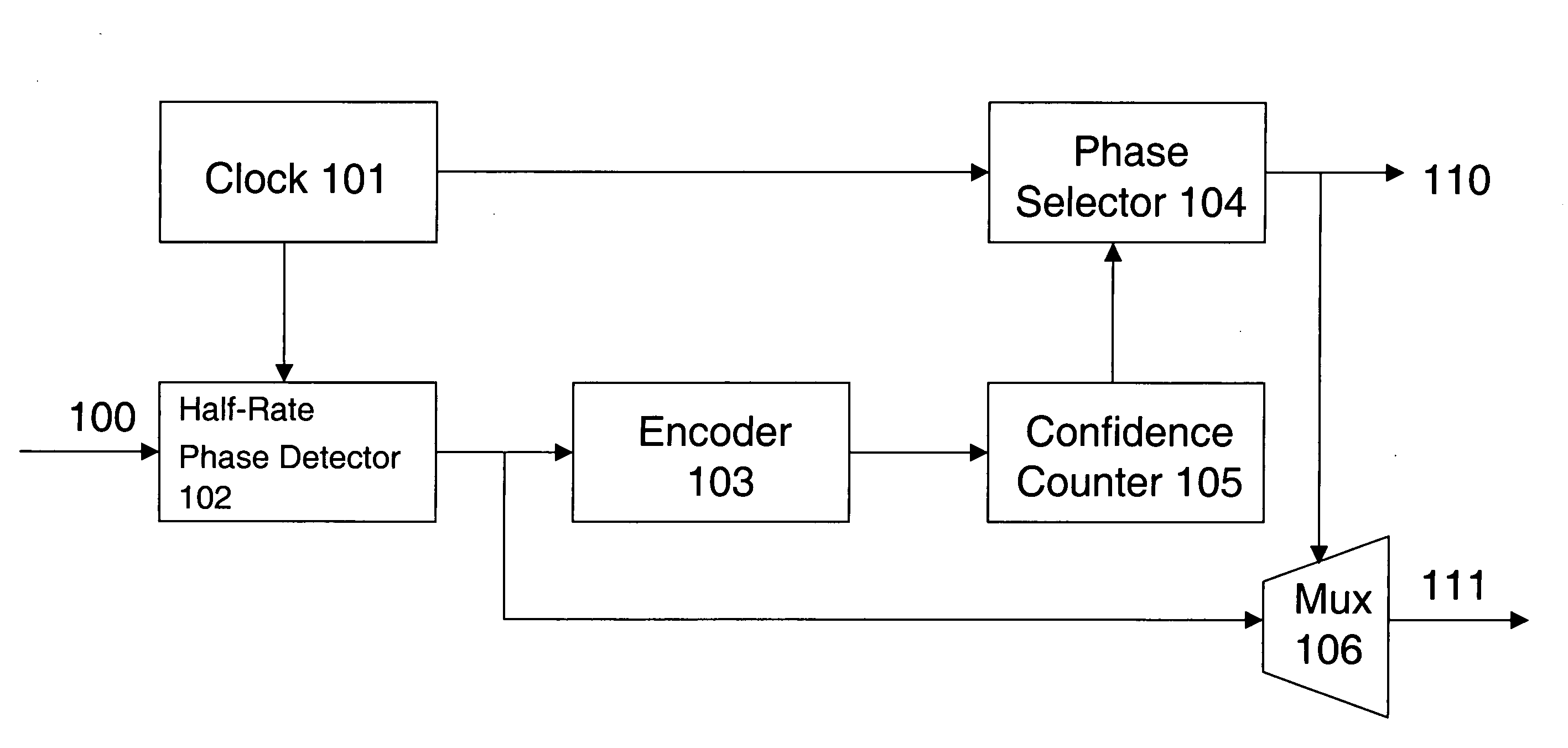

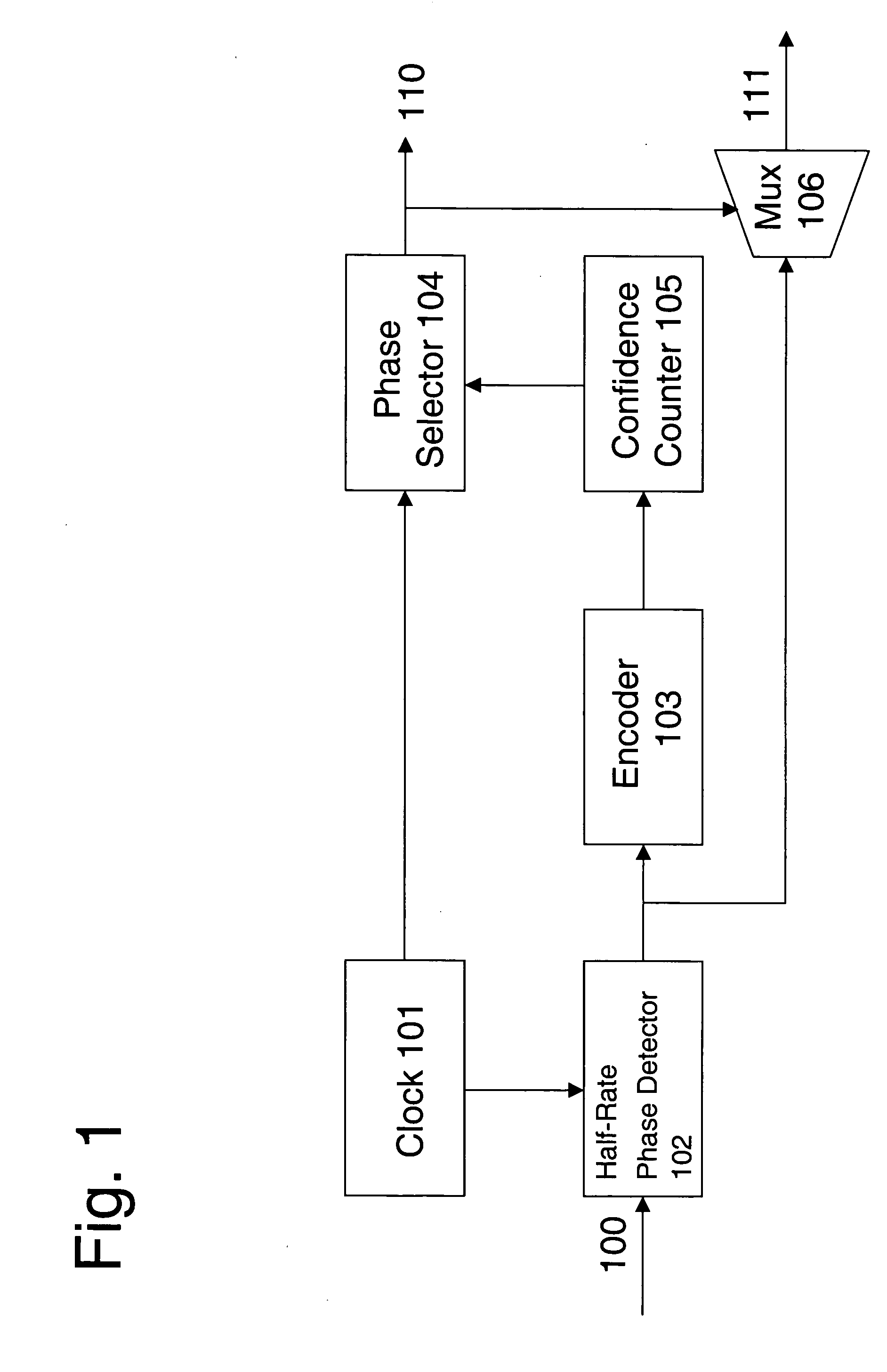

A system for clock and data recovery (“CDR”) includes a clock generator, a half-rate phase detector for receiving the input data, an encoder, a phase selector outputting recovered clock, a confidence counter, and a multiplexer outputting recovered data. The clock generator generates an 8-phase clock signal at half a rate of the transmitted serial data. The phase detector samples input data at four times the standard sampling rate, takes the oversampled data and detects phase transitions therein, i.e., phase lead and lag. The encoder encodes the phase transition data. The confidence counter receives the phase transition data and generates a signal representing the accumulated net effect of the phase transitions. The phase selector receives the confidence counter signal and the 8-phase clock from the clock generator, and determines the optimum phase for data sampling.

Owner:IND TECH RES INST

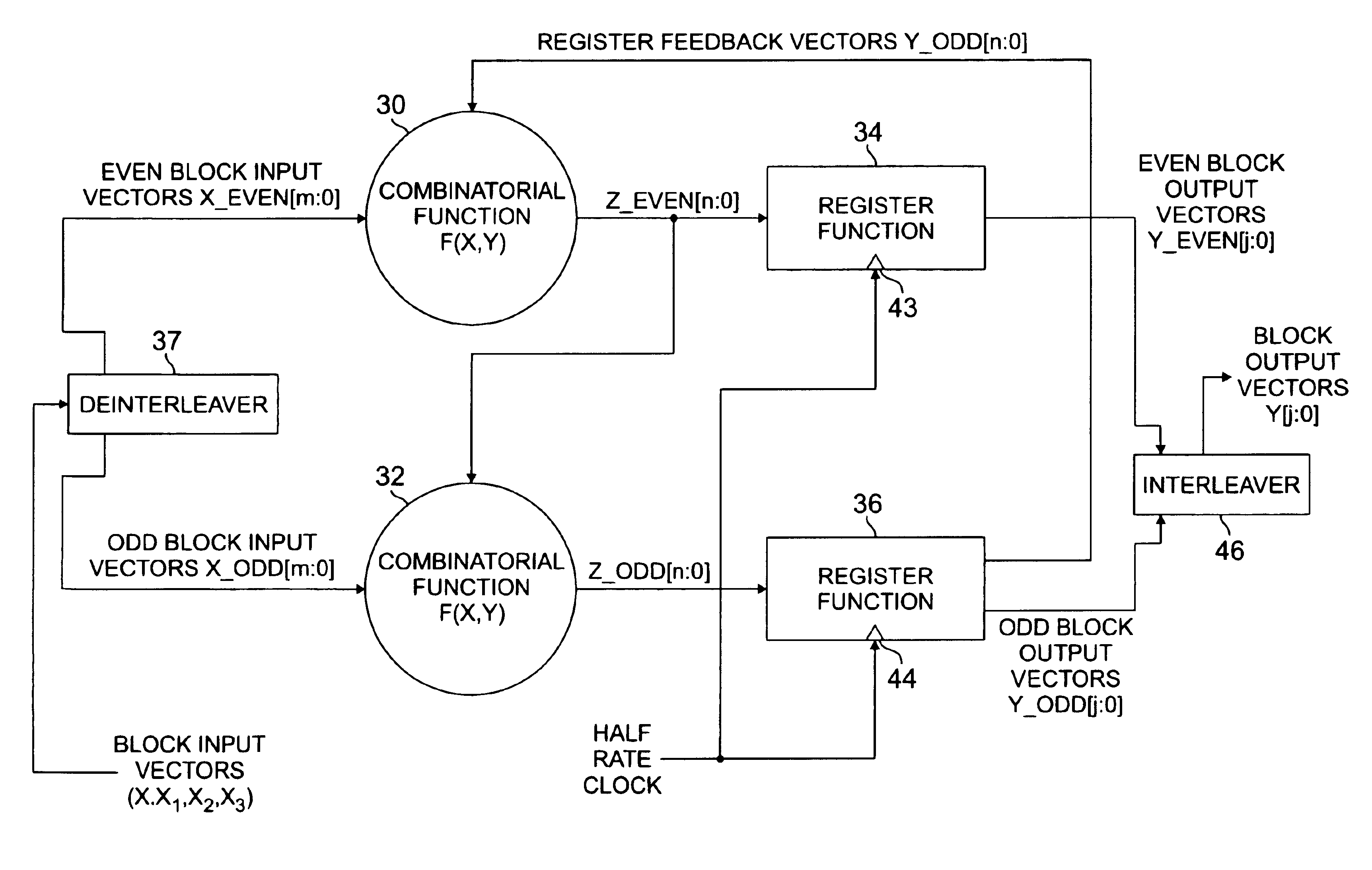

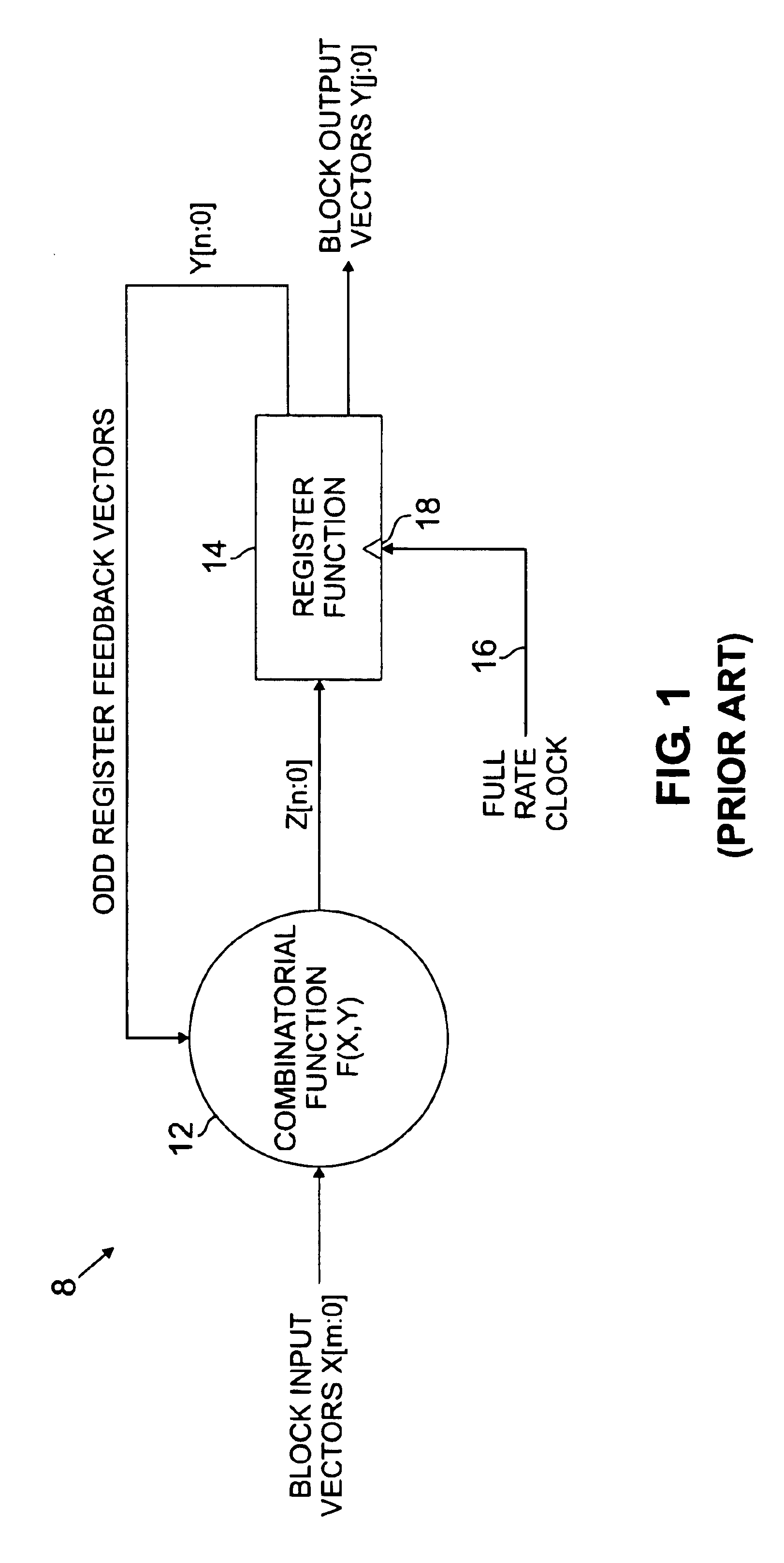

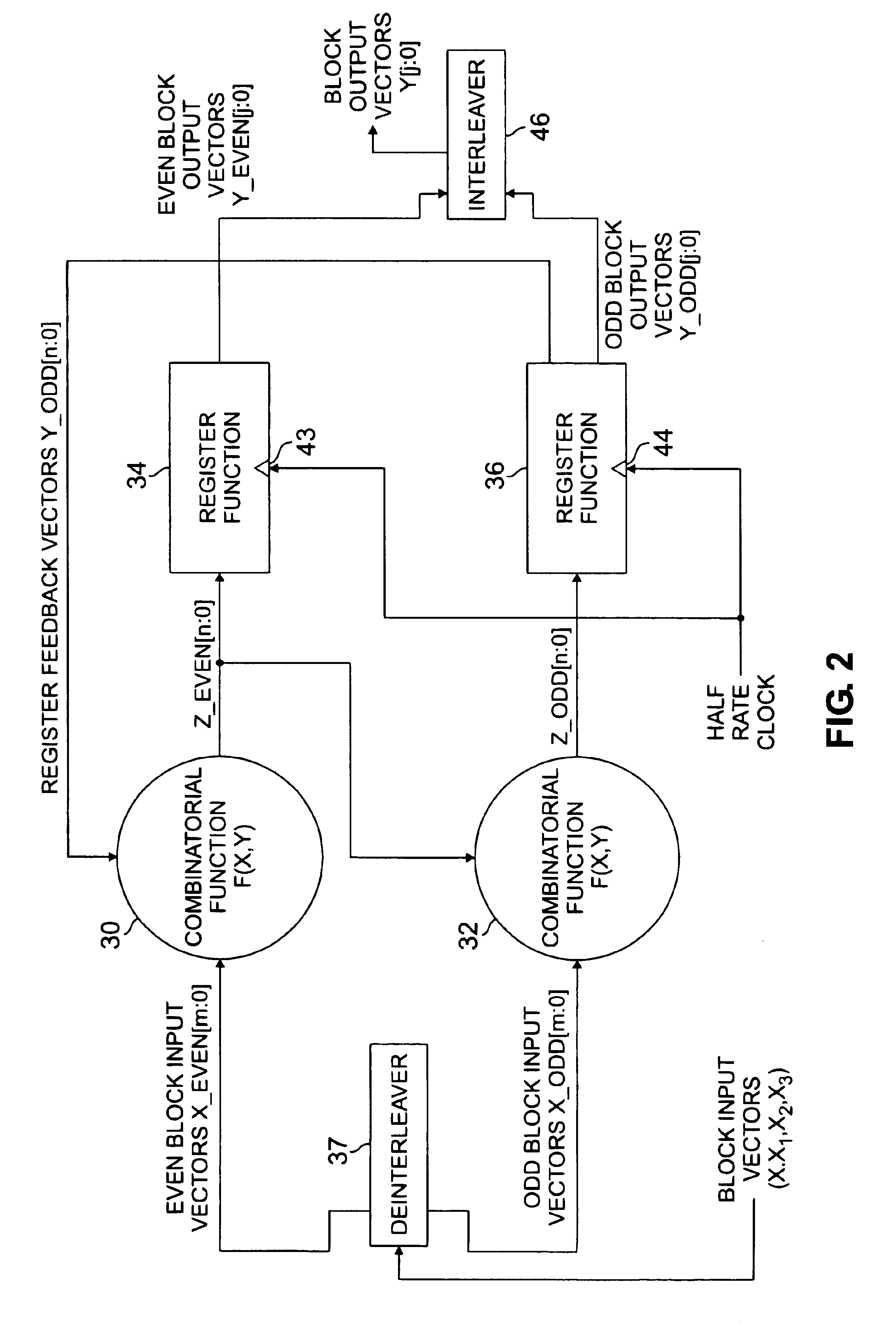

Half-rate clock logic block and method for forming same

InactiveUS6867617B2Concurrent instruction executionLogic circuits using elementary logic circuit componentsDigital clockClock rate

A method and apparatus for converting a full-rate digital clock circuit to a fractional-rate clock circuit. The combinatorial and sequential functions of the full rate design are duplicated, with a first combinatorial function responsive to even input logic vectors and a second combinatorial function responsive to odd input logic vectors. Output vectors from the first and the second combinatorial function are provided as input vectors to the respective first and second sequential function, which operate at a fractional clock rate and provide the output block vectors.

Owner:AVAGO TECH INT SALES PTE LTD

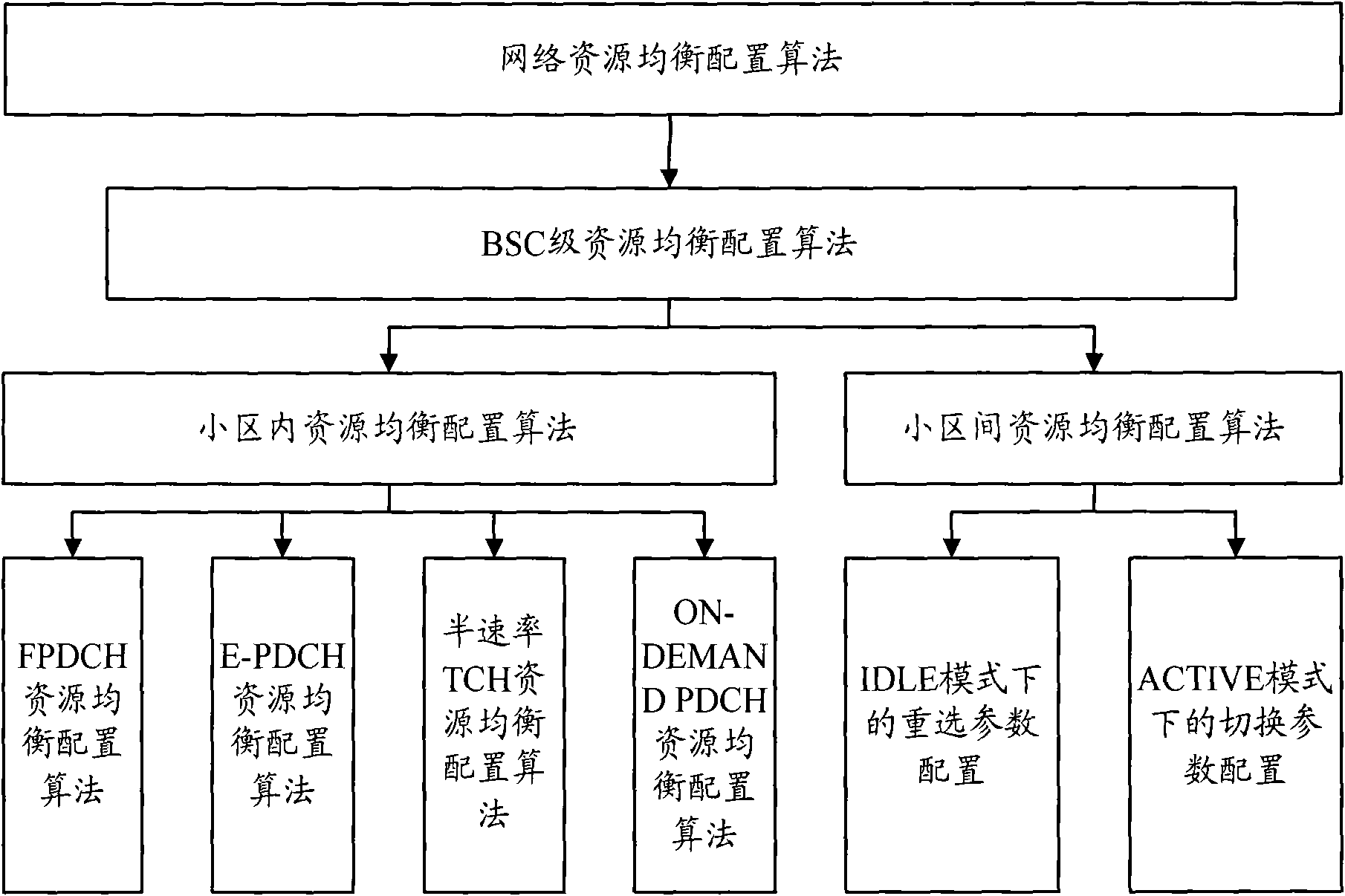

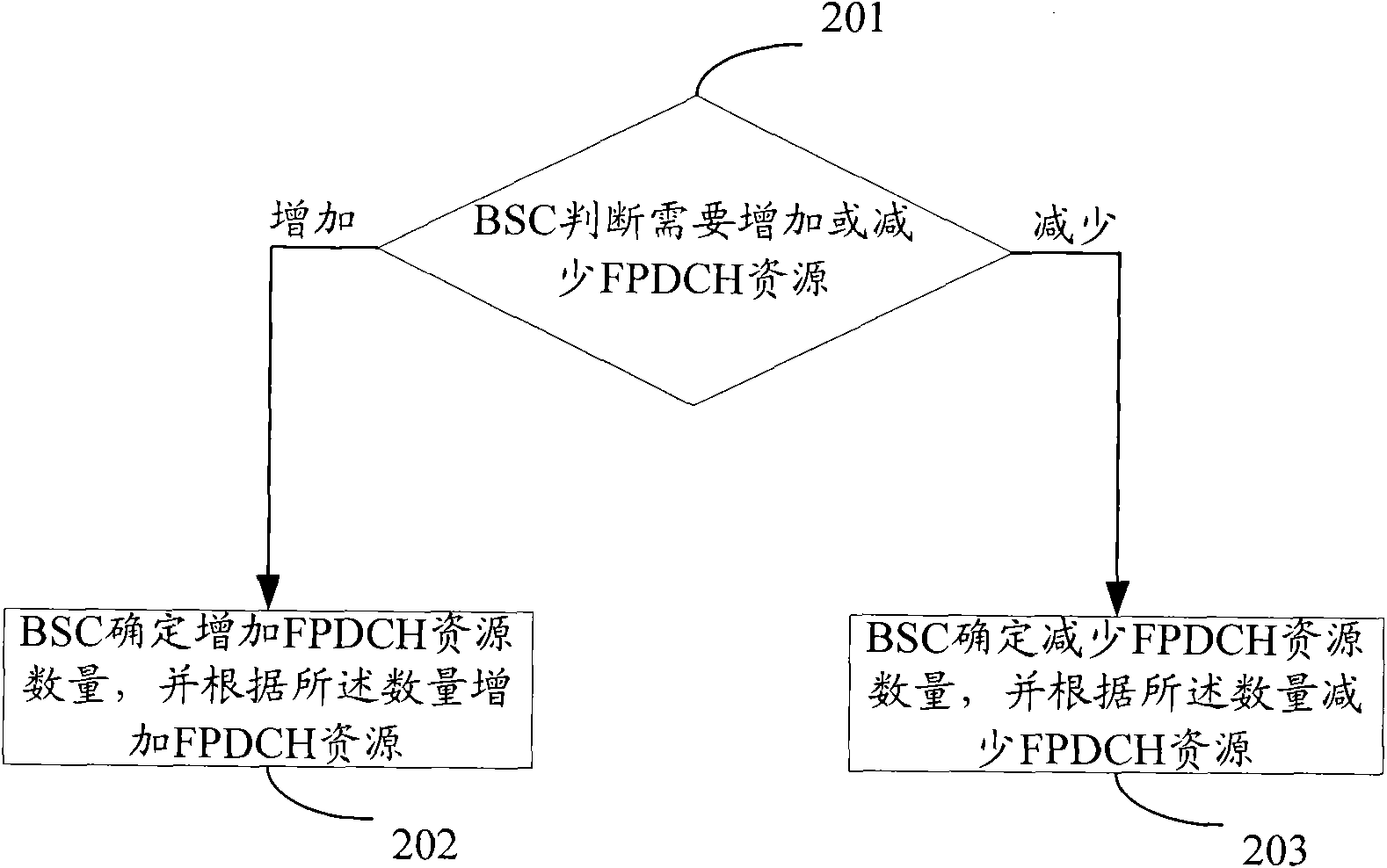

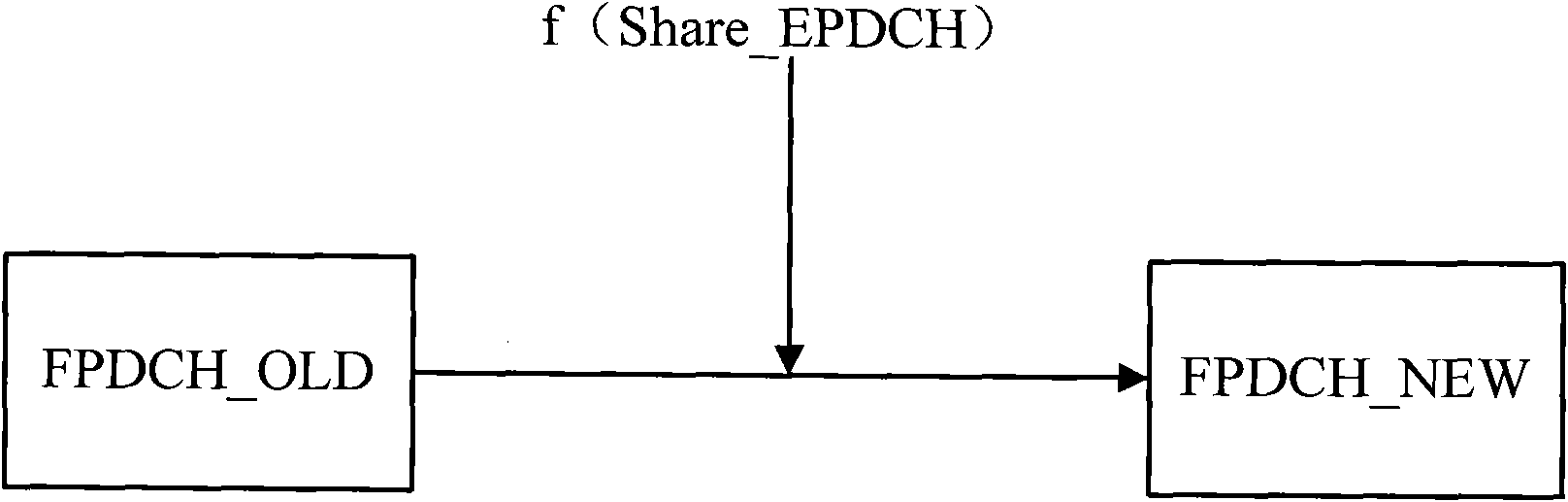

Method and device for balanced configuration of wireless channel

The embodiment of the invention discloses a method for balanced configuration of a wireless channel, comprising the following steps of: judging whether TCH (TrafficCHannel) resource balanced configuration is necessary to be performed in a cell or between cells; and performing balanced configuration on corresponding TCH resource according to the judging result. In the method, a new computing method for cell resource estimation and resource configuration is provided under a condition of comprehensively considering data service traffic and half rate traffic, so that an index can reflect service condition of network practical resource more accurately.

Owner:CHINA MOBILE GROUP JIANGSU

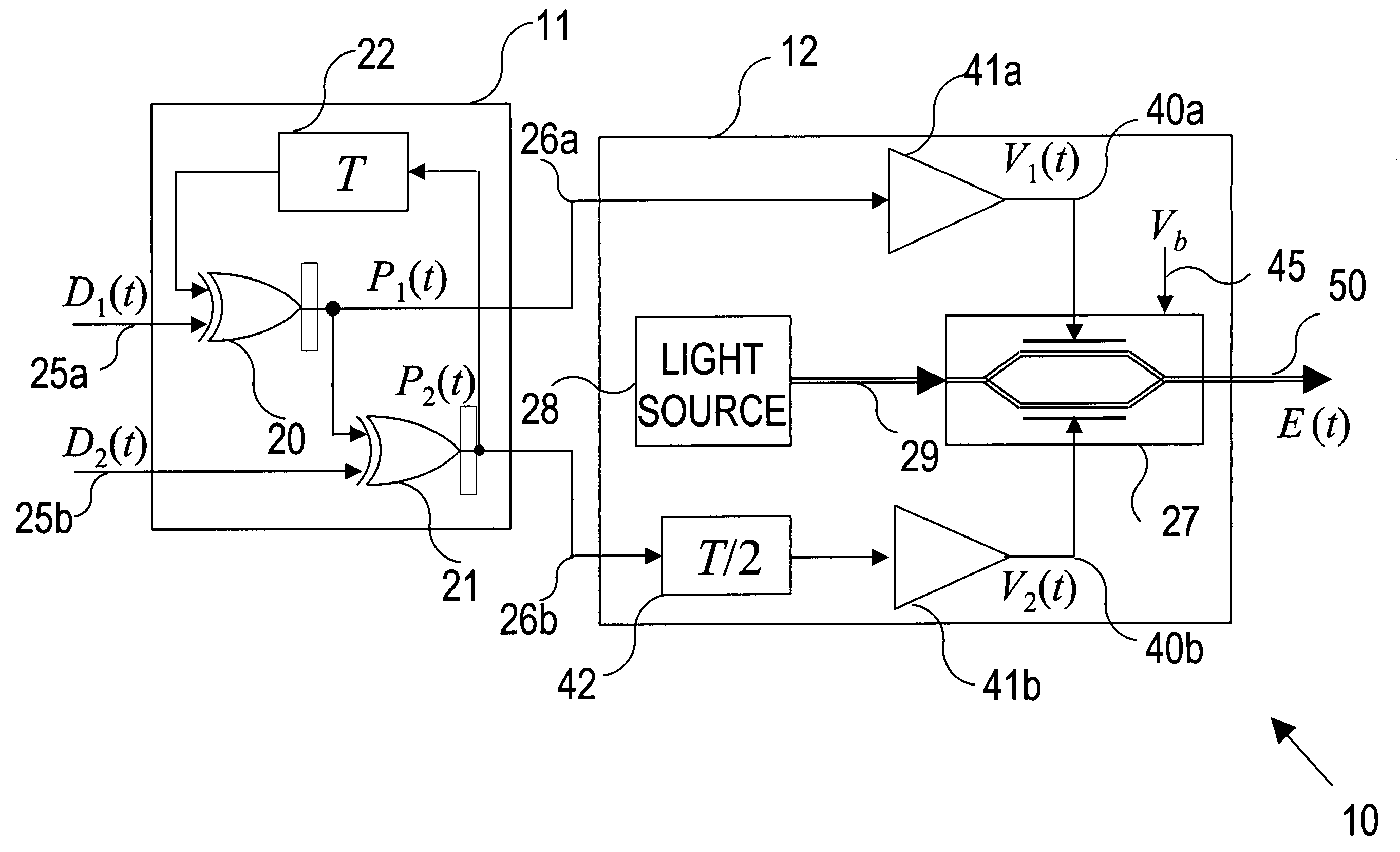

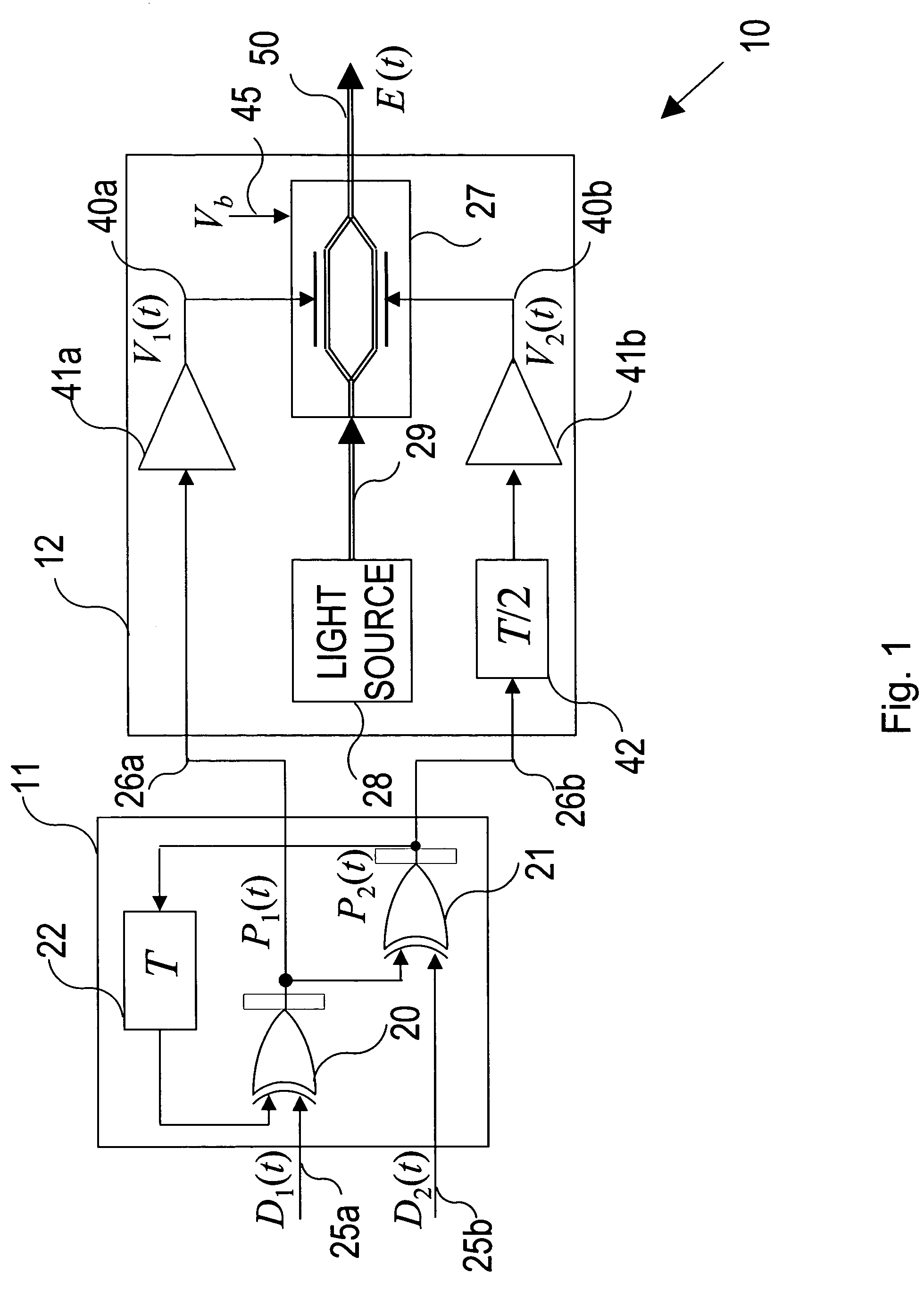

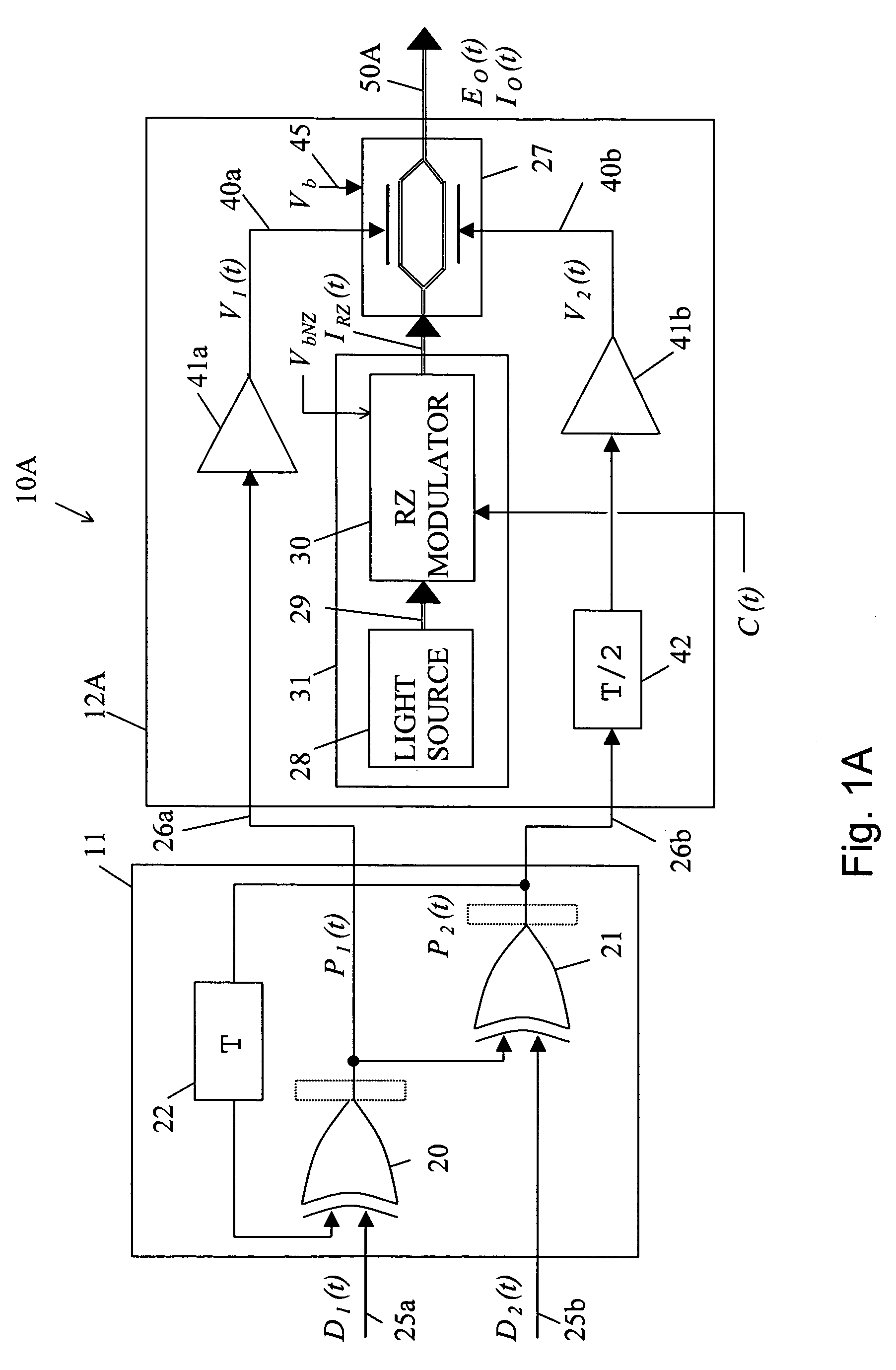

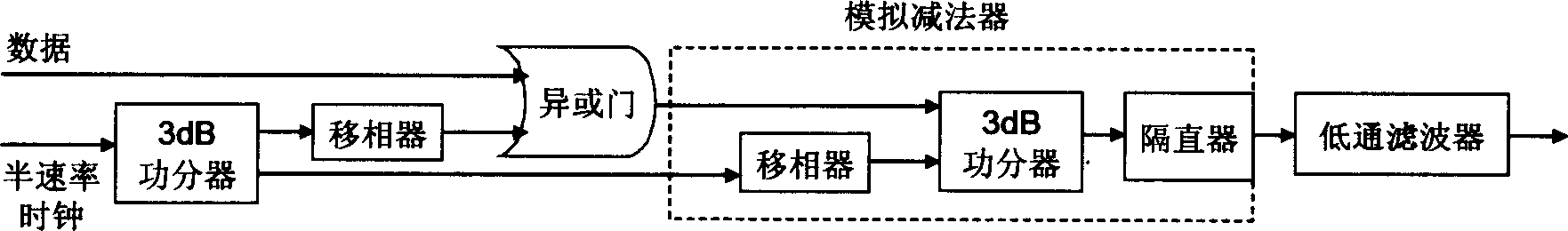

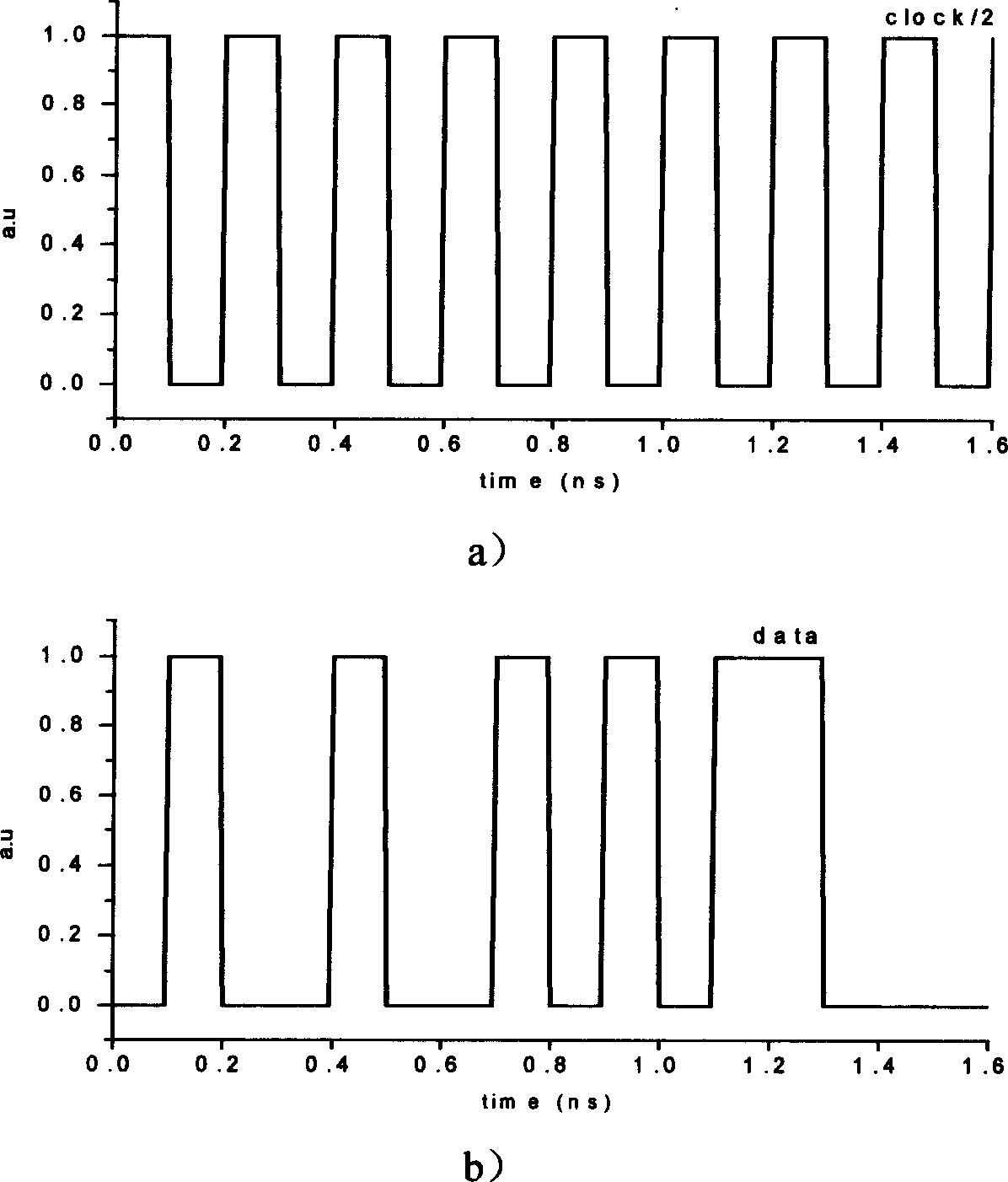

Half rate precoded data RZ transmitter

An optical duobinary transmitter. The transmitter uses a half-rate precoder, half-rate non-linear modulation drive circuits and a multiplex modulator for generating duobinary modulation on an optical signal from which full-rate data can be detected without decoding. The intensity of the optical signal is modulated to be zero between data symbols.

Owner:OPNEXT SUBSYST

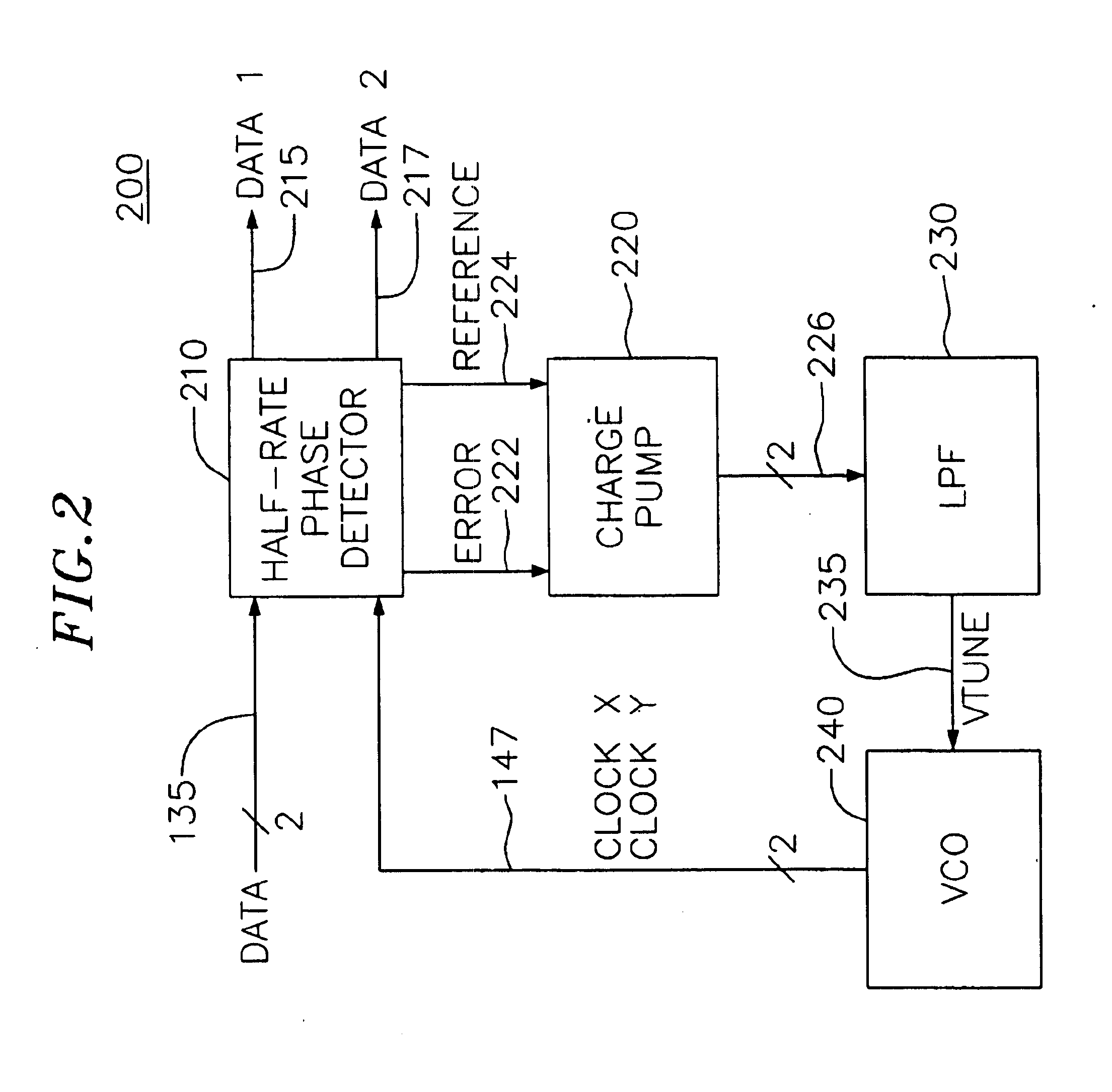

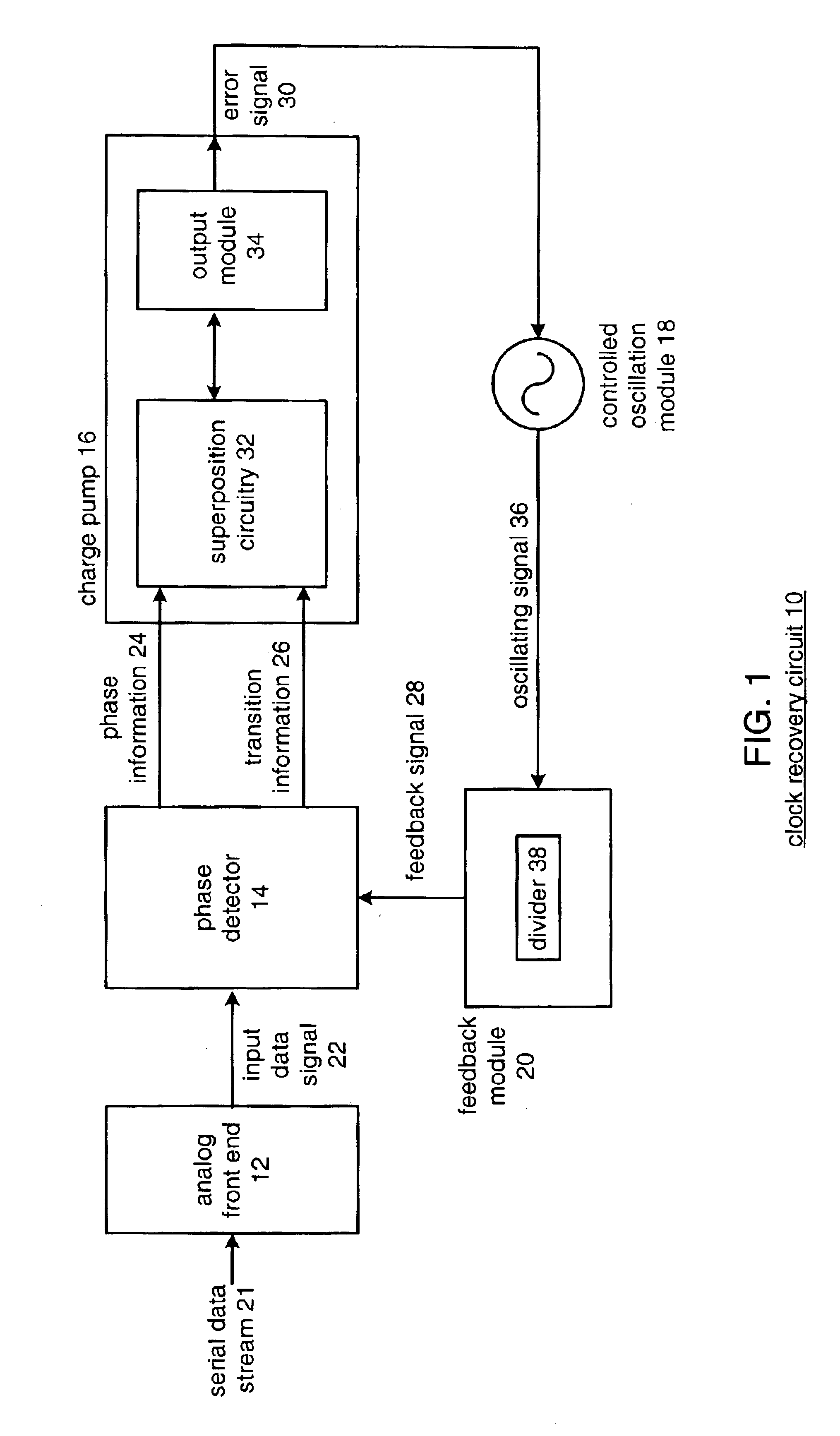

Clock and data recovery phase-locked loop

A clock recovery circuit that operates at a clock speed equal to one-half the input data rate is presented. The clock recovery circuit uses dual input latches to sample the incoming serial data on both the rising edge and falling edge of a half-rate clock signal to provide equivalent full data rate clock recovery. The clock recovery circuit functions to maintain the half-rate clock transitions in the center of the incoming serial data bits. The clock recovery circuit includes a phase detector, charge pump, controlled oscillation module and a feedback module. The phase detector produces information on the phase and data transitions in the incoming data signal to the charge pump. Generally, the circuit is delay insensitive and receives phase and transition information staggered relative to each other.

Owner:XILINX INC

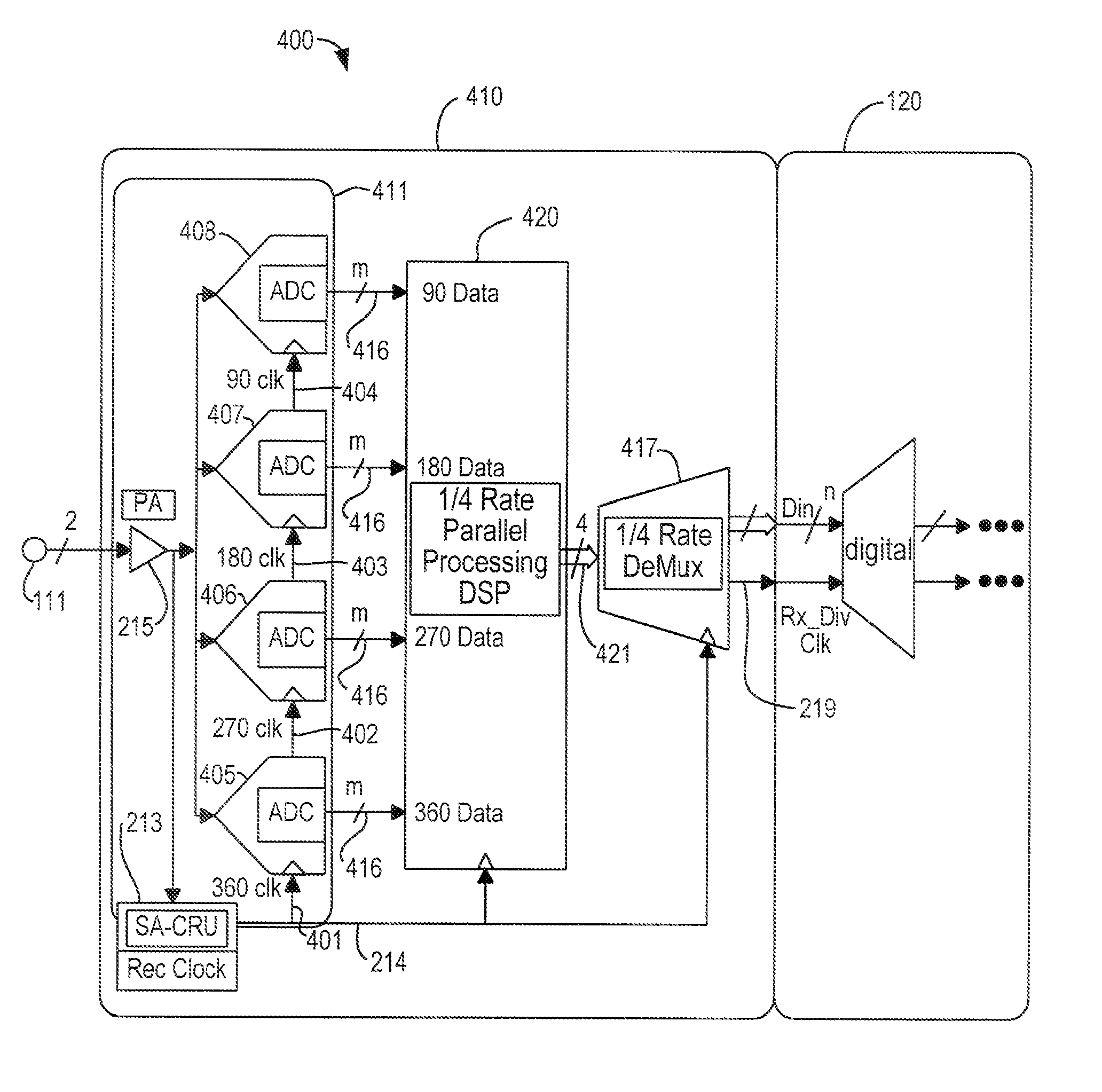

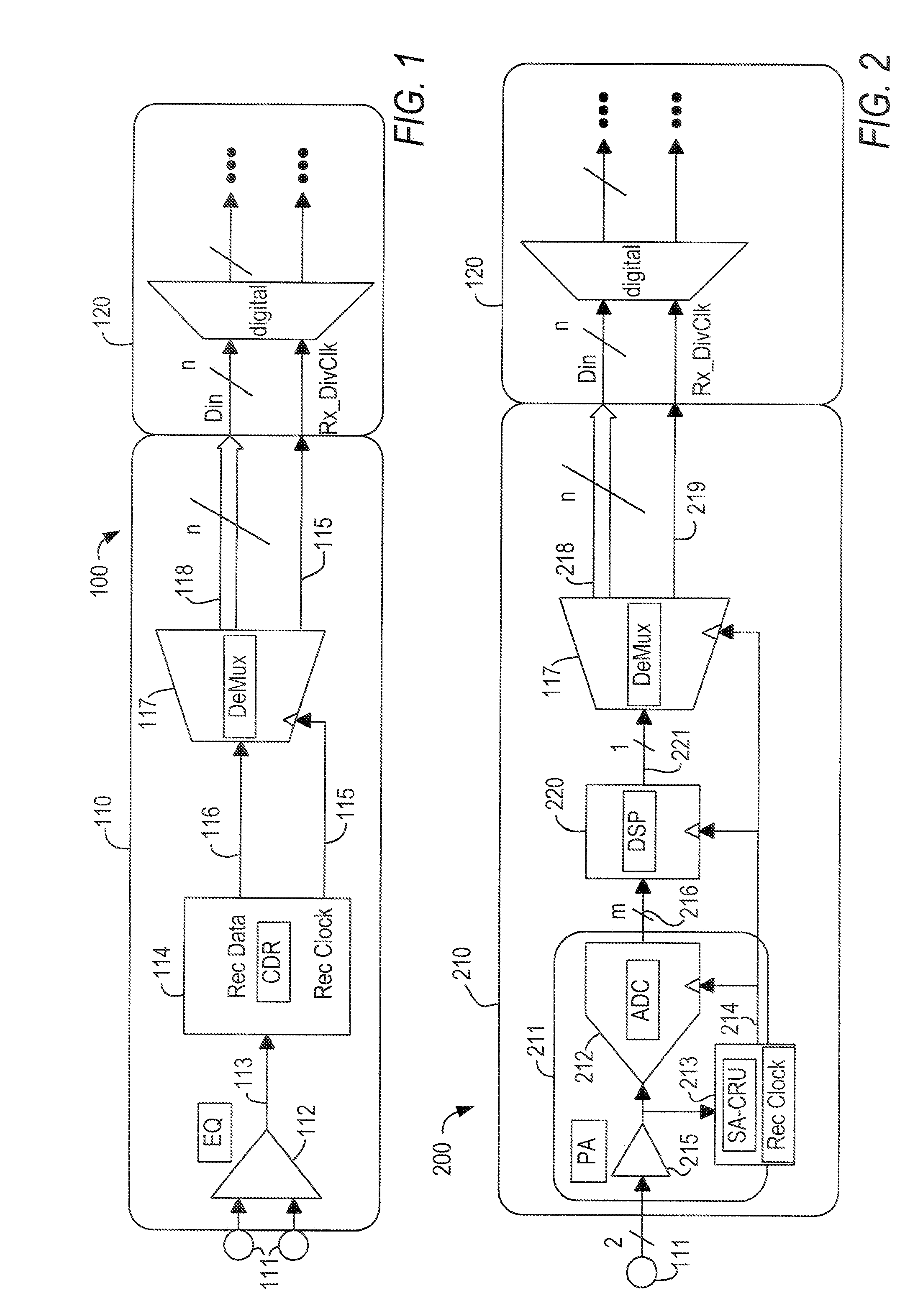

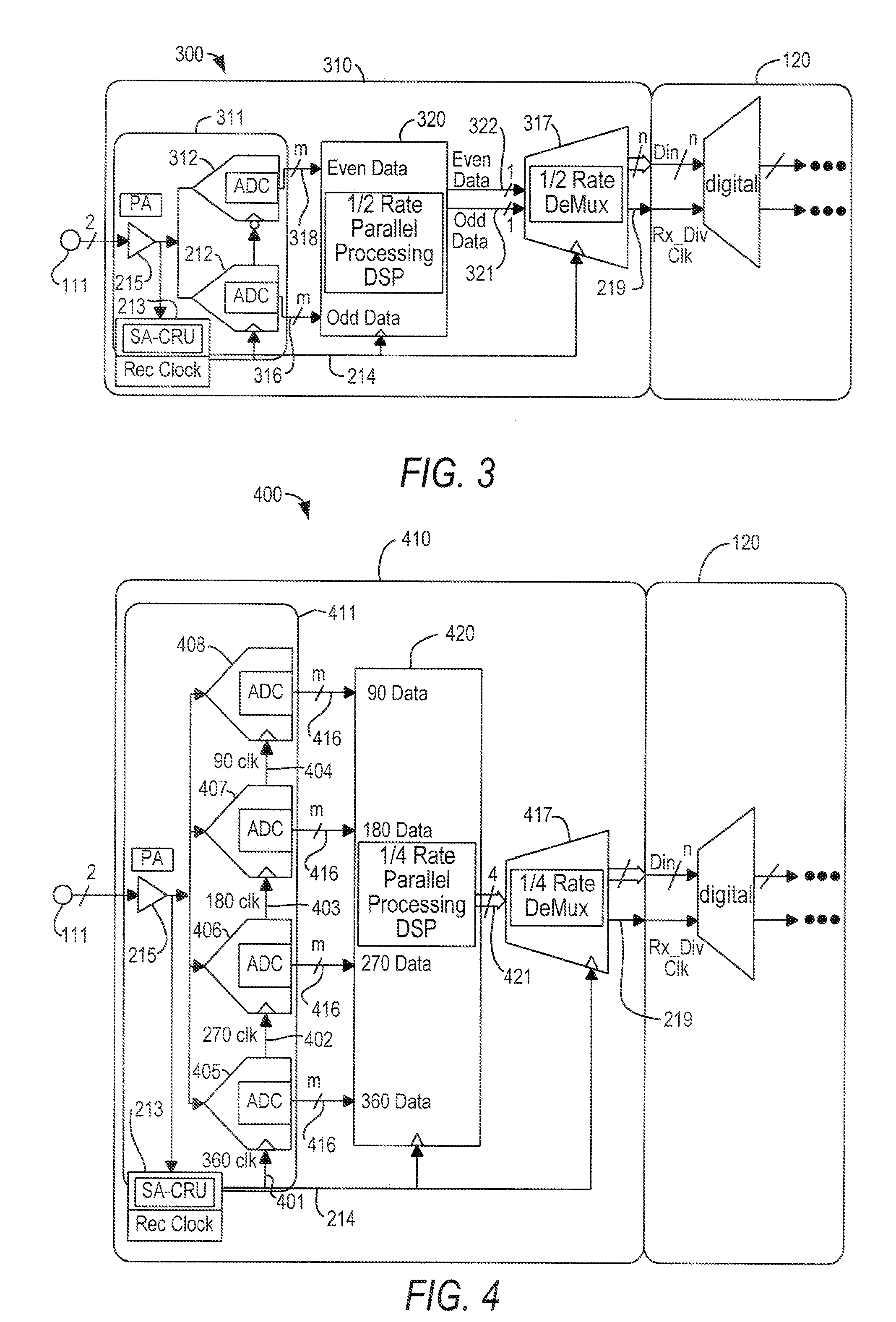

Digital equalizer for high-speed serial communications

InactiveUS8654898B2Multiple-port networksDelay line applicationsDigital signal processingChannel geometry

Incoming data at a high-speed serial receiver is digitized and then digital signal processing (DSP) techniques may be used to perform digital equalization. Such digital techniques may be used to correct various data anomalies. In particular, in a multi-channel system, where crosstalk may be of concern, knowledge of the characteristics of the other channels, or even the data on those channels, may allow crosstalk to be subtracted out. Knowledge of data channel geometries, particularly in the context of backplane transmissions, may allow echoes and reflections caused by connectors to be subtracted out. As data rates increase, fractional rate processing can be employed. For example, the analog-to-digital conversion can be performed at half-rate and then two DSPs can be used in parallel to maintain throughput at the higher initial clock rate. At even higher rates, quadrature techniques can allow analog-to-digital conversion at quarter-rate, with four DSPs used in parallel.

Owner:ALTERA CORP

Method for assigning time slots and base station apparatus utilizing the same

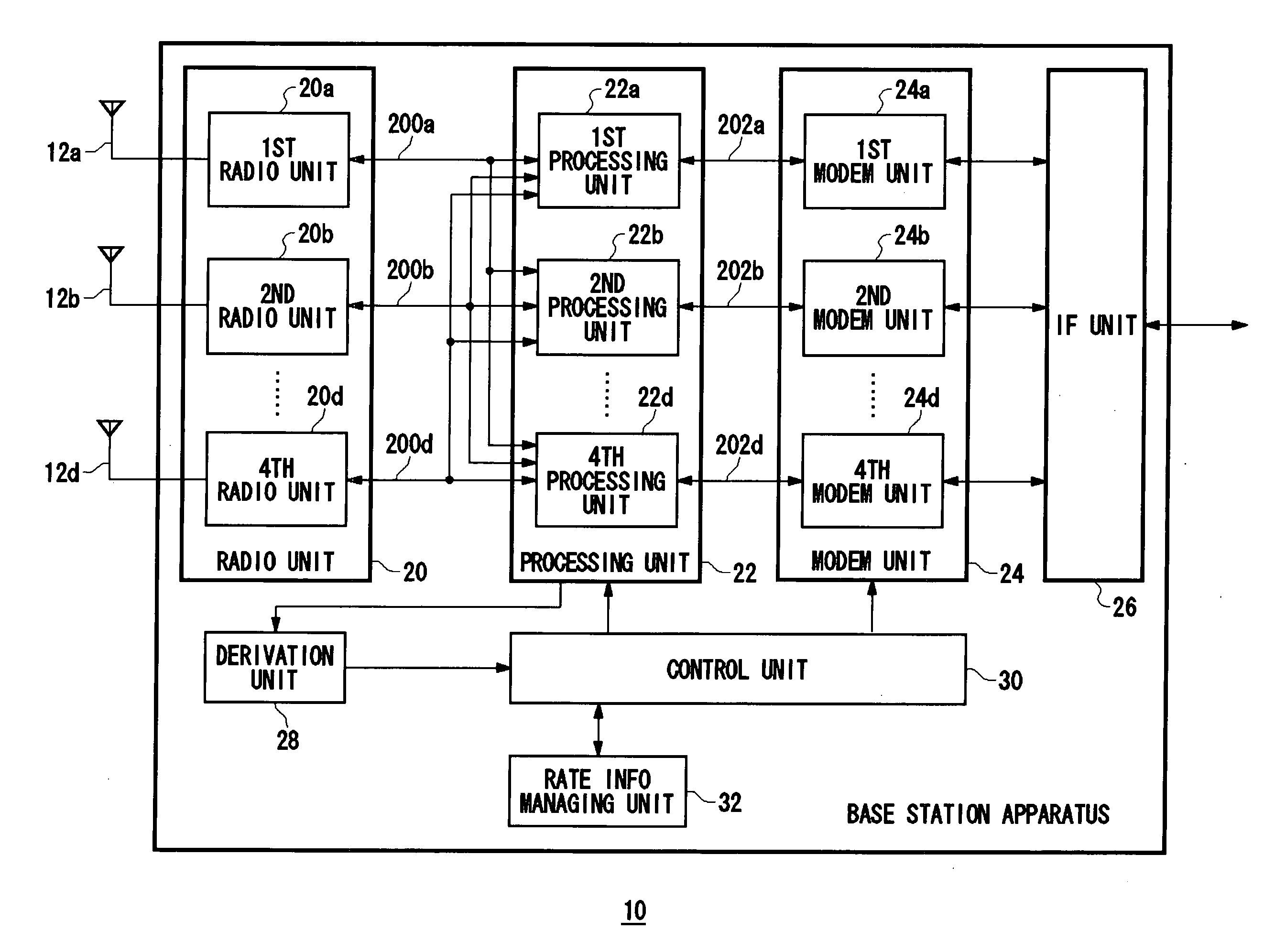

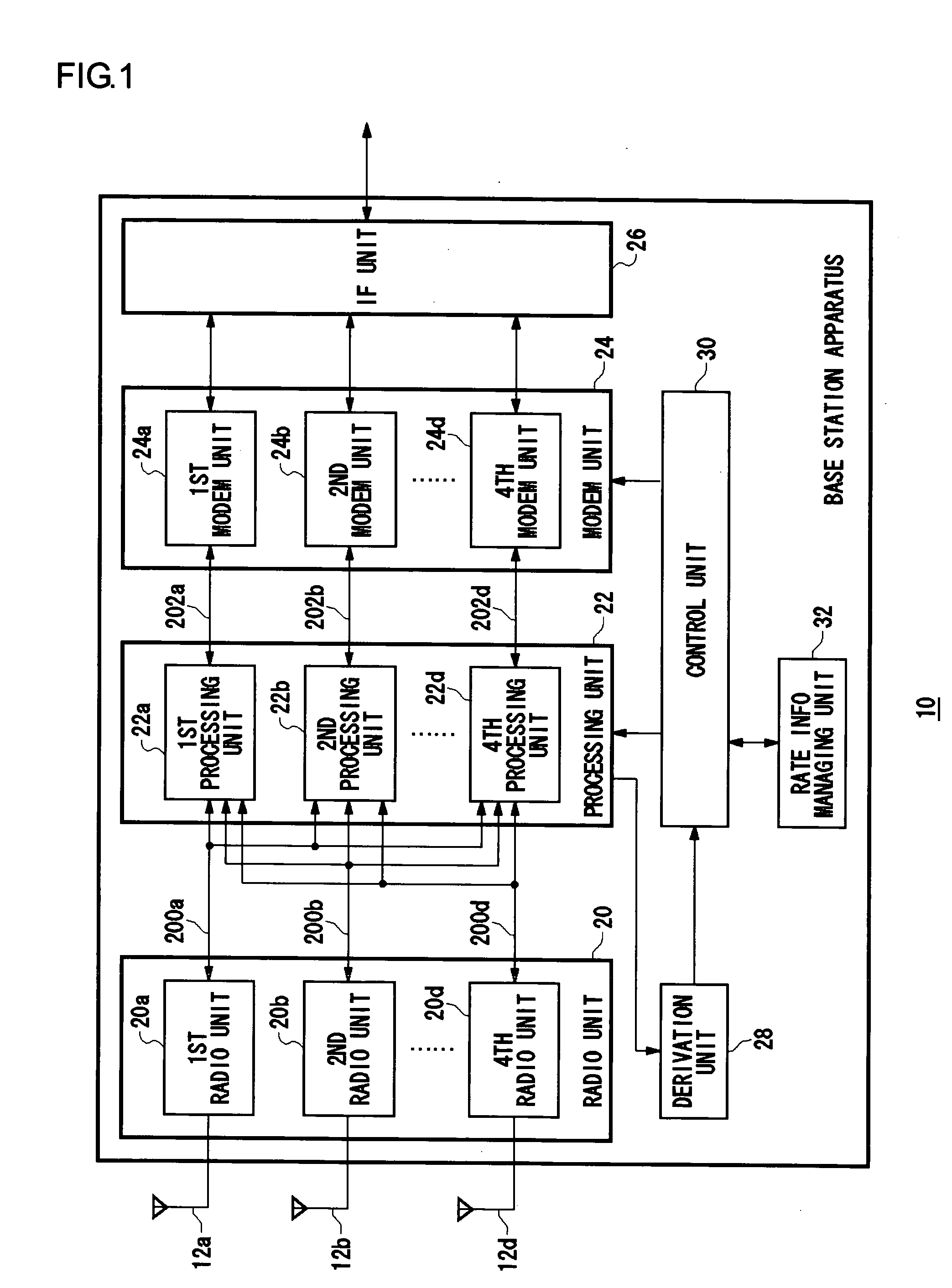

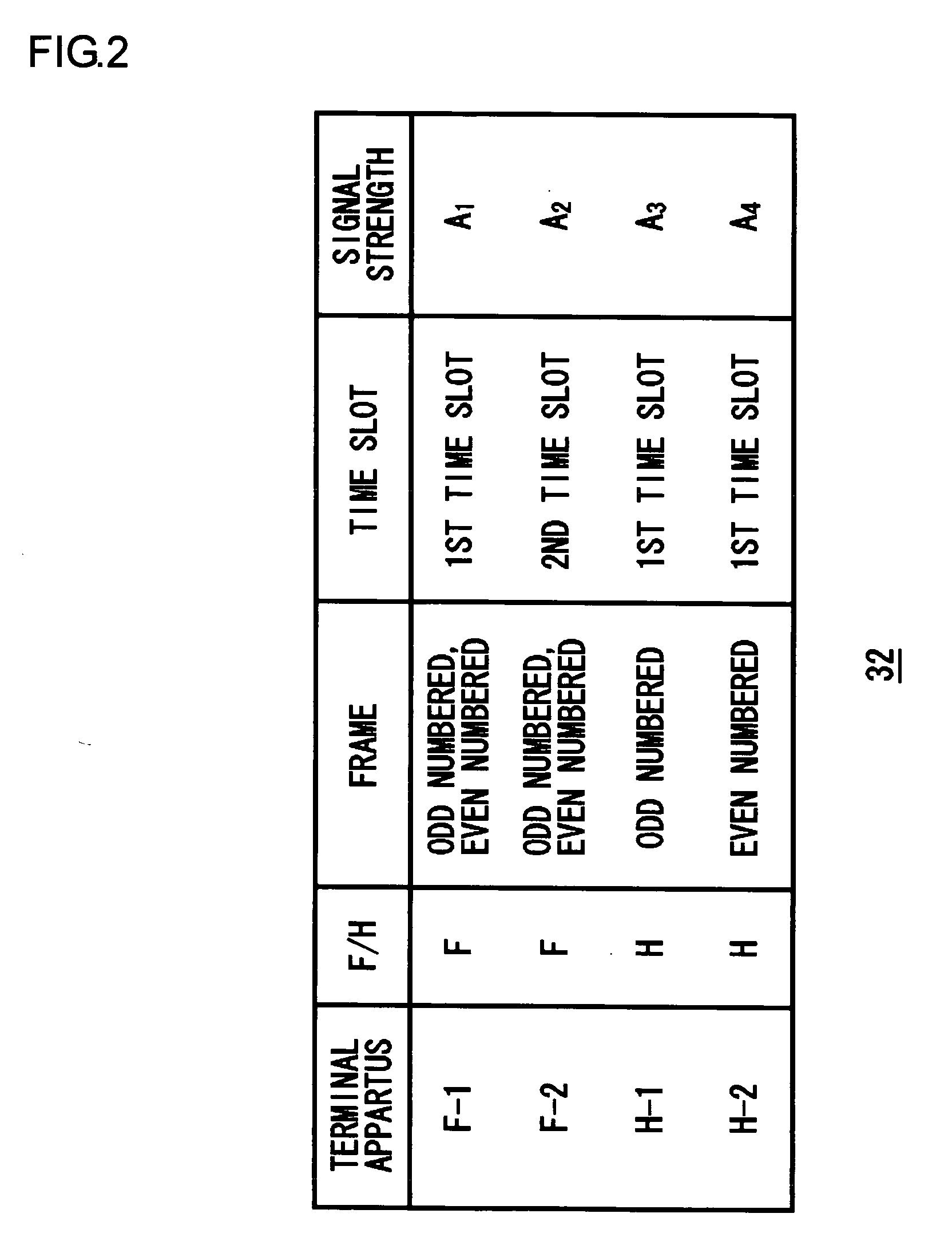

InactiveUS20060126578A1Reduce adverse effectsTime-division multiplexRadio transmissionModem deviceCommunication quality

A processing unit performs adaptive array signal processing. A modem unit performs modulation and demodulation processing. A derivation unit derives signal strength as radio communication qualities among a plurality of terminal apparatuses of half rate format. A control unit assigns time slots in a plurality of terminal apparatuses of half rate format to be communicated with a base station apparatus. The control unit selects two terminal apparatuses whose difference between signal strengths is smaller, from among the plurality of terminal apparatuses of half rate, and then assigns time slots, having predetermined relationships, in these selected terminal apparatuses.

Owner:PANASONIC INTELLECTUAL PROPERTY CORP OF AMERICA

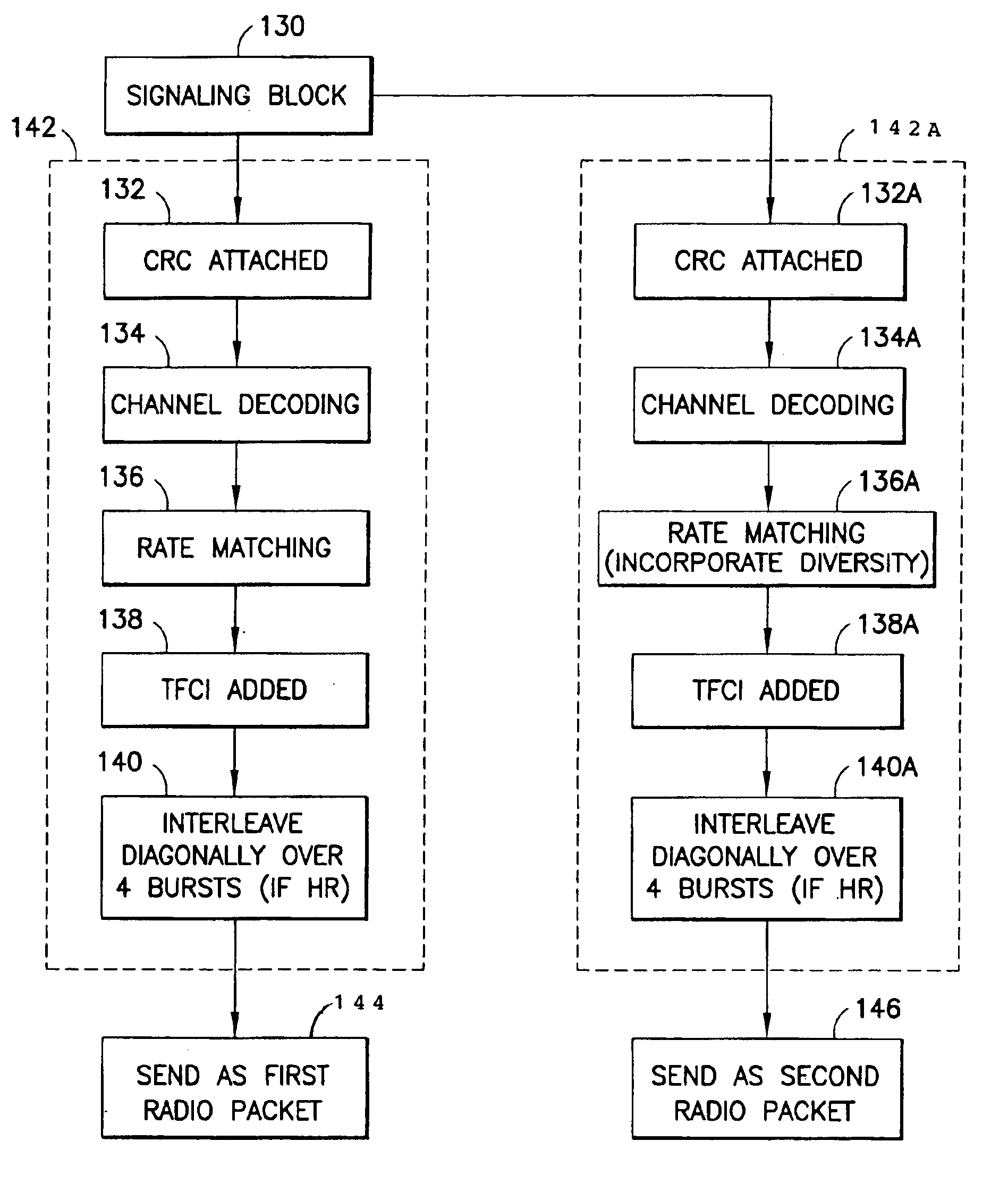

Flexible layer overlay for seamless handovers between full rate and half rate channels

InactiveUS6870821B2Network traffic/resource managementRadio/inductive link selection arrangementsHalf RateFull Rate

A Method and system for transmitting a signaling message between a base station and a mobile station over a half rate channel are shown. Traffic data is interleaved over k bursts diagonally (4 bursts diagonally in GERAN) and a signaling message is interleaved over m bursts diagonally, where m>k. The method includes transmitting the same encoded signaling message in two consecutive radio packets, where each radio packet is interleaved over k bursts diagonally (the consecutive radio packets have an interleaving depth of 6 in GERAN). By doing so the coded bits of the signaling message are effectively interleaved over two radio packets, and m>k. The receive side of the communication reads the first packet, stores the soft values for decoding, and soft combines them when the second radio packet is received. Diversity may be added by the transmit side. The re-transmission of the second radio packet is preferably mandatory at call set-up.

Owner:NOKIA TECHNOLOGLES OY

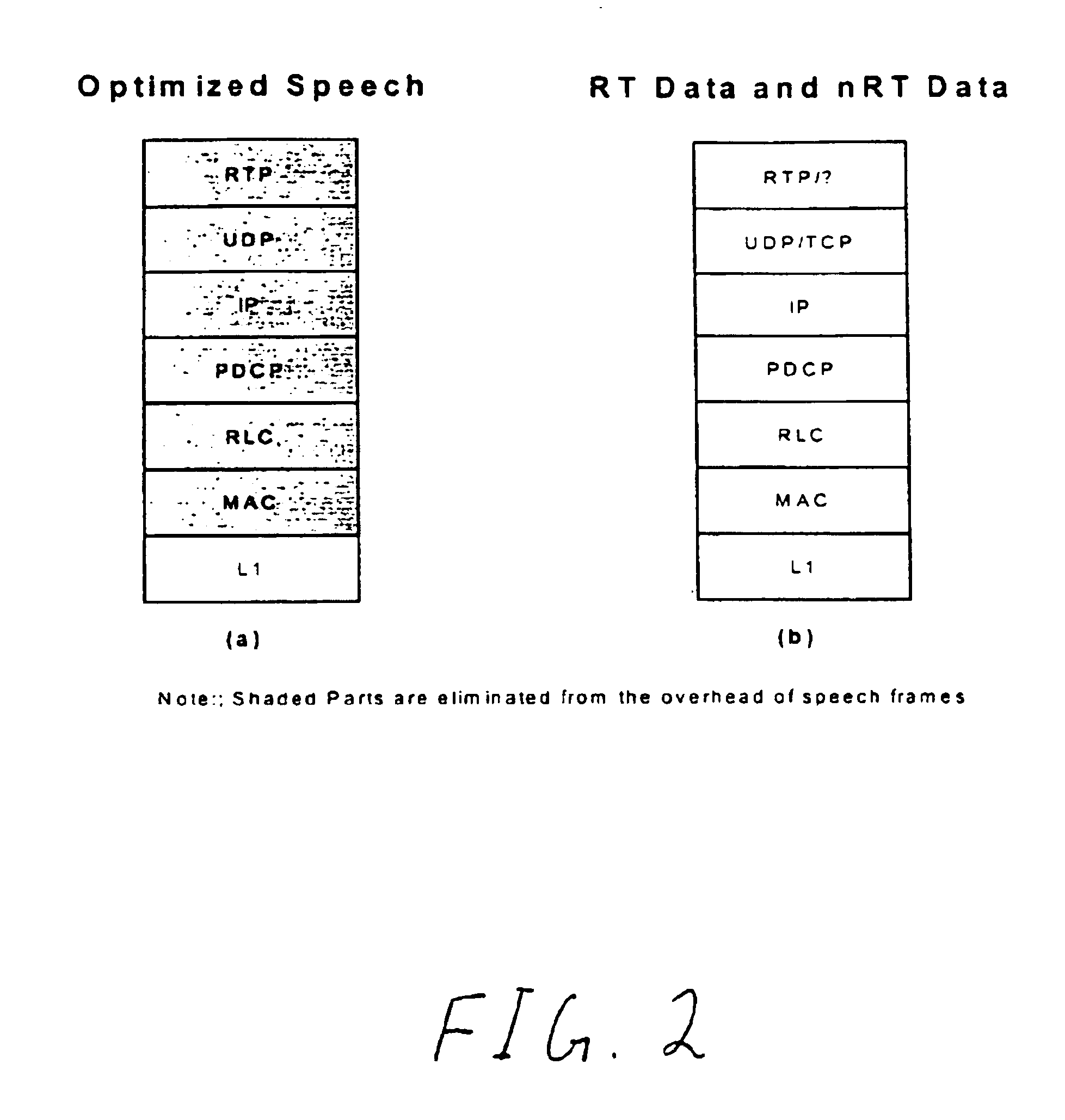

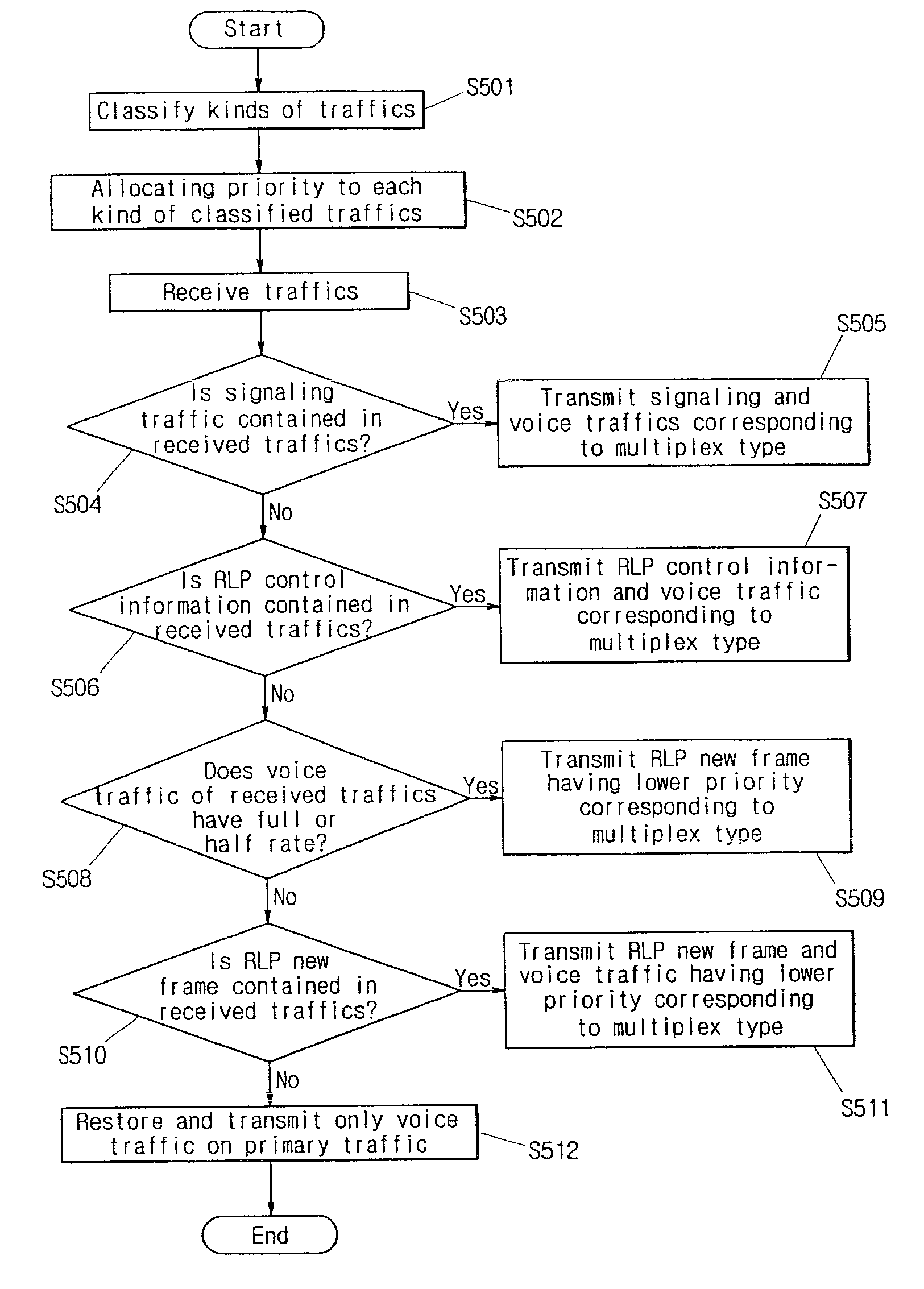

Method of processing traffic in a mobile communication system

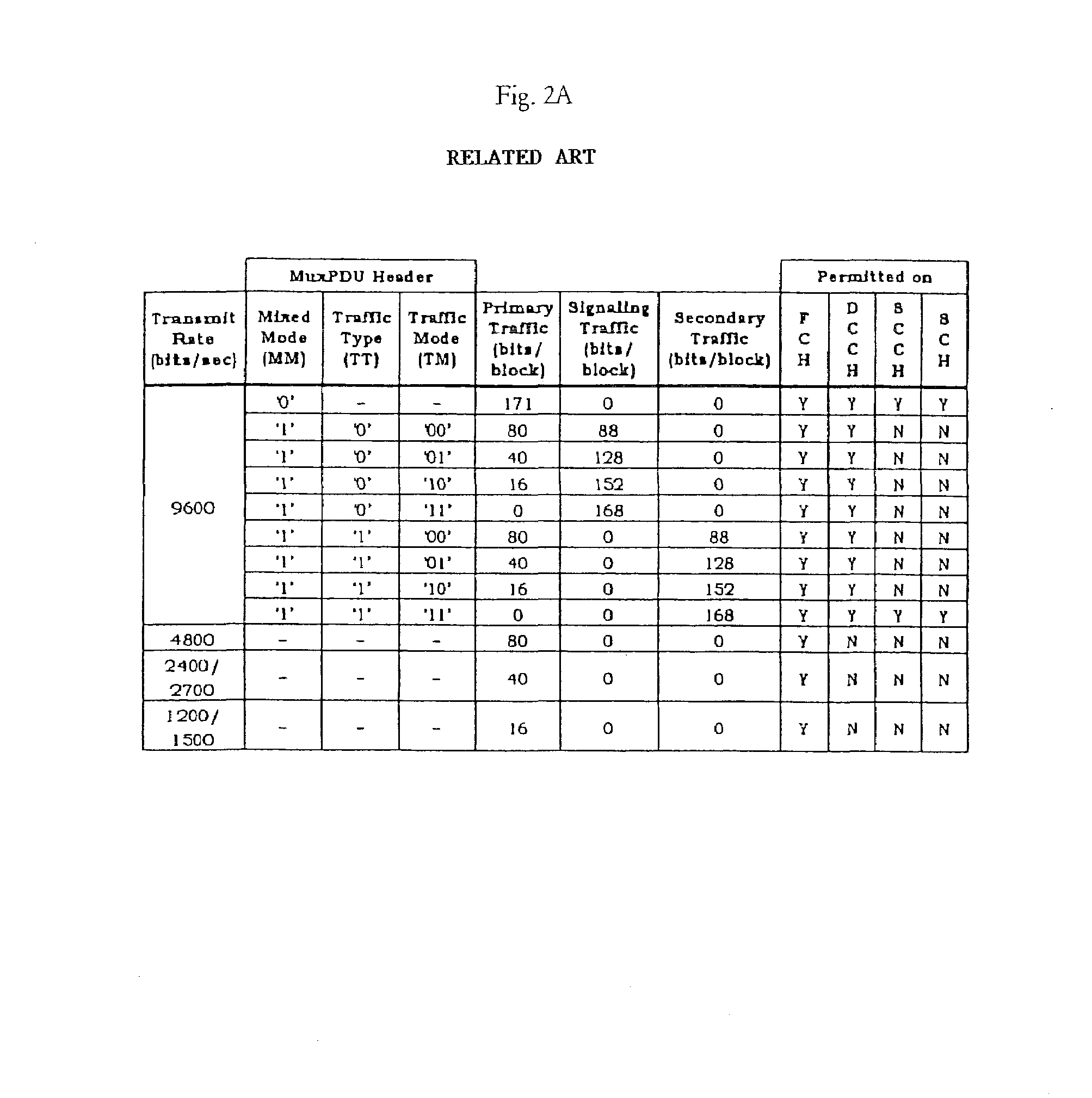

InactiveUS7346029B2Quality improvementSmooth voice serviceError prevention/detection by using return channelNetwork traffic/resource managementMultiplexingTraffic capacity

A system and method for communicating data assigns priorities to different types of traffic based on one or more system conditions. The method includes classifying different kinds of traffic, allocating a priority to each kind of classified traffic, and when data received including different kinds of traffic multiplexing the traffic and the received data and transmitting the data according to the allocated priority. The traffic may be classified into signaling traffic, data traffic, and voice traffic. The data traffic may further be classified as follows: an RLP control frame, an RLP new frame, as well as other RLP frames. The voice traffic may be classified as full-rate voice traffic, half-rate voice traffic, quarter-rate voice traffic, and eighth-rate voice traffic. The method may be further controlled based on the type of multiplexing to be performed. Through this system and method, it is possible to provide good quality SVD (service simultaneous voice and data) by avoiding interruptions in transmissions.

Owner:ERICSSON-LG

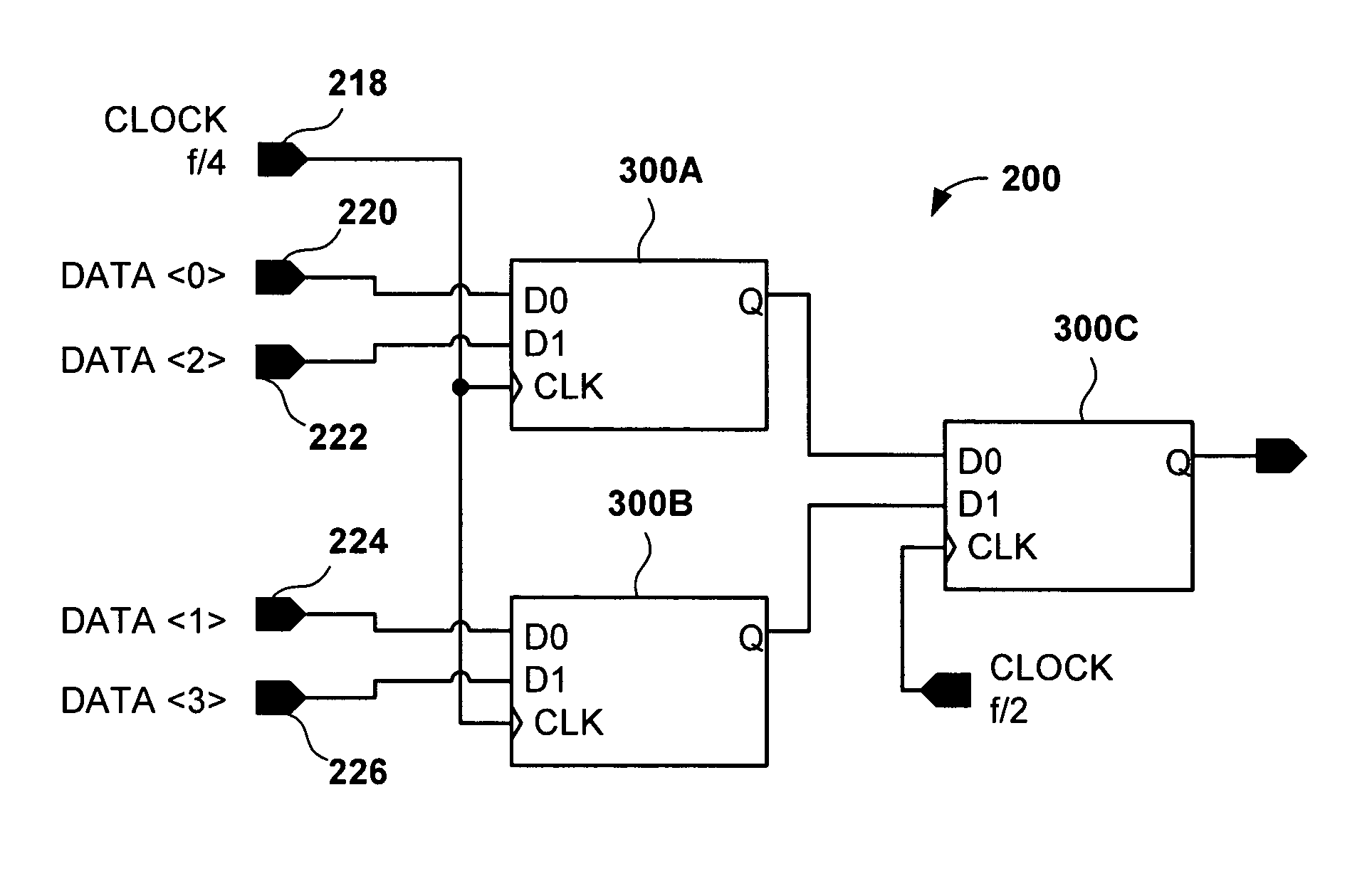

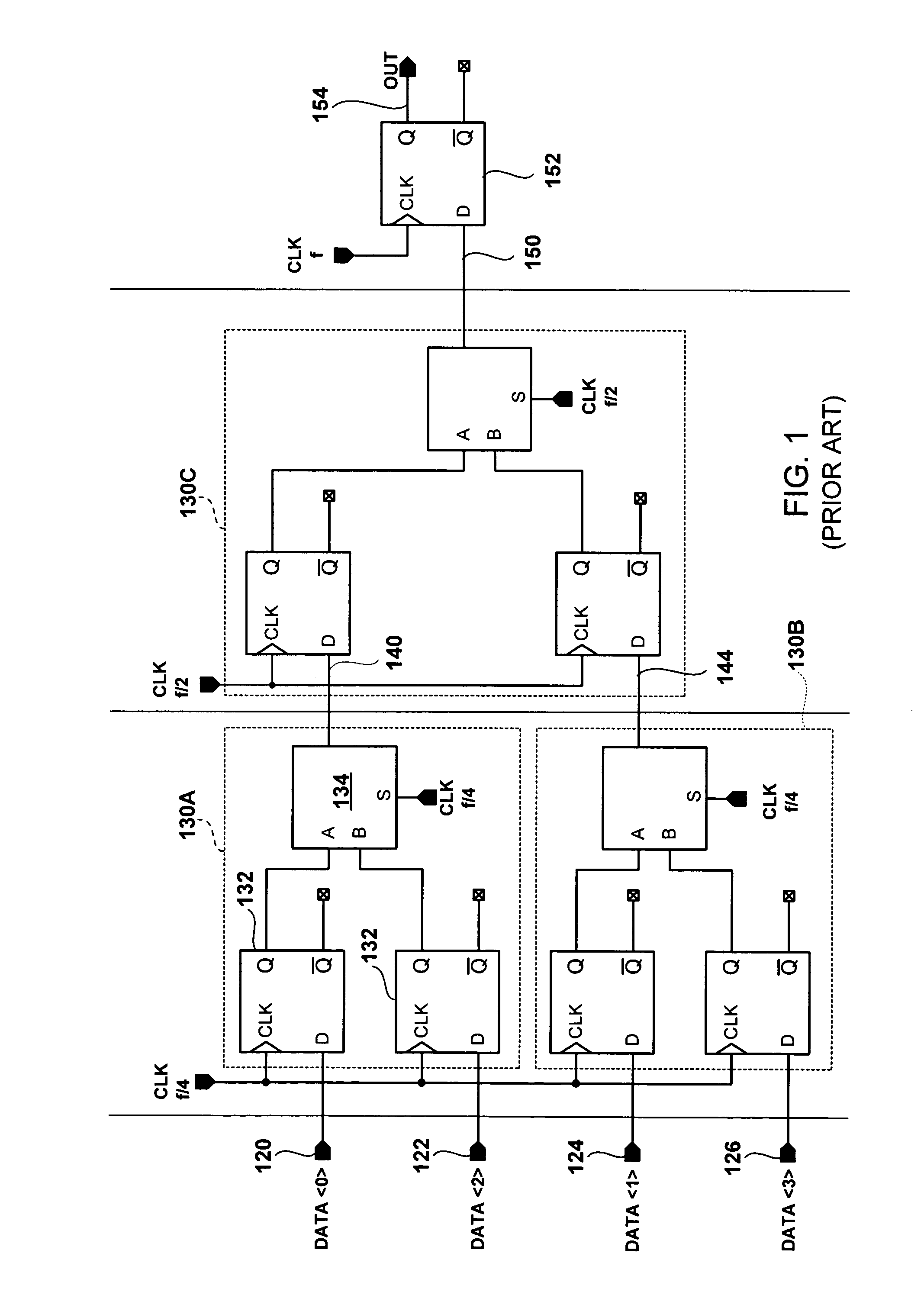

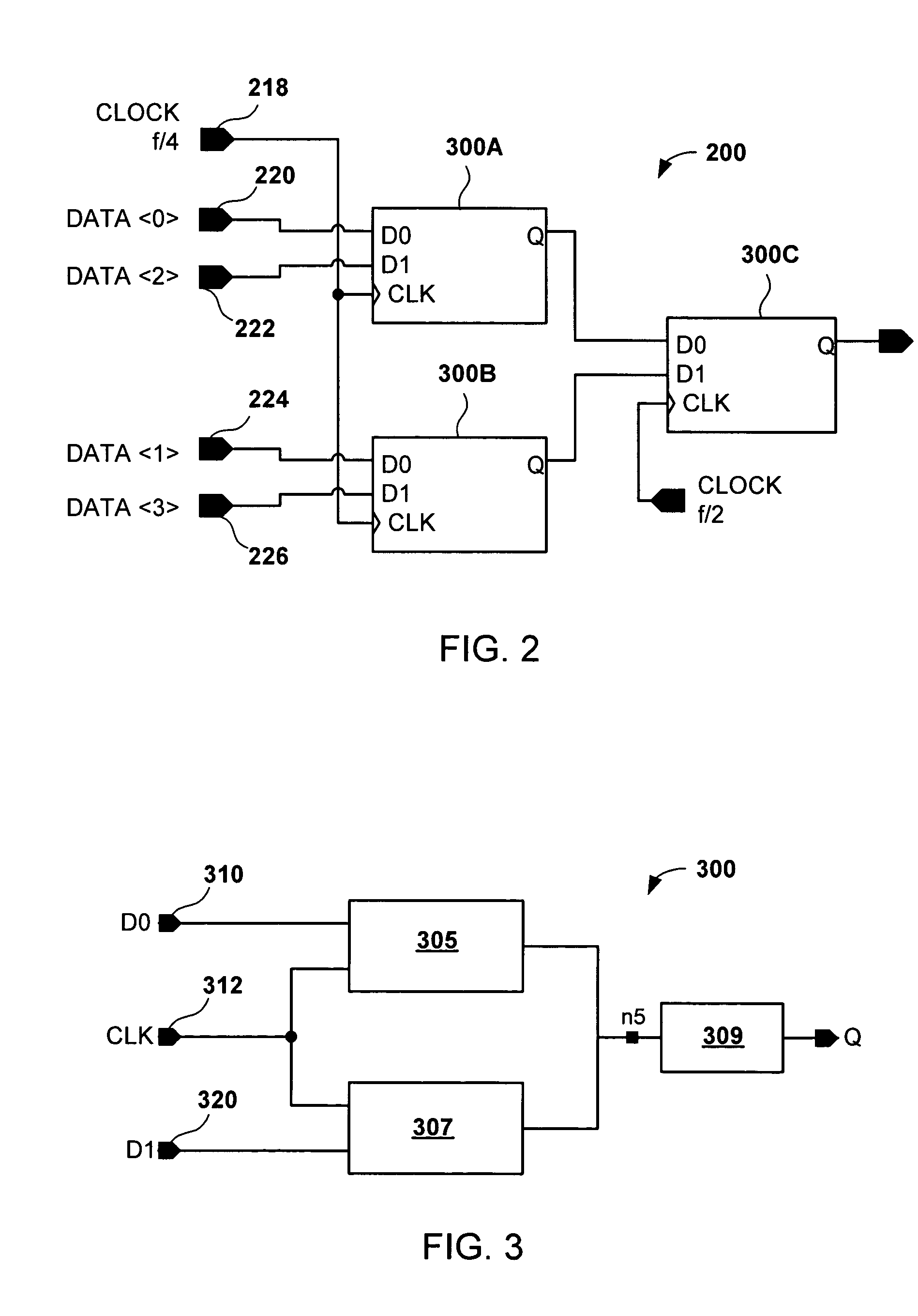

Low-power serializer with half-rate clocking and method

Owner:SEIKO EPSON CORP

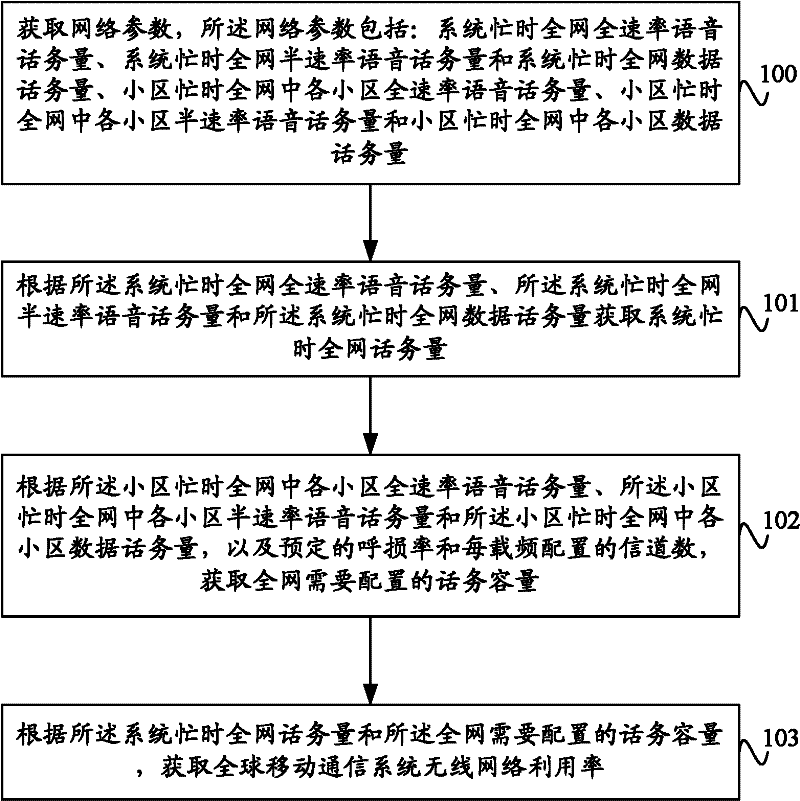

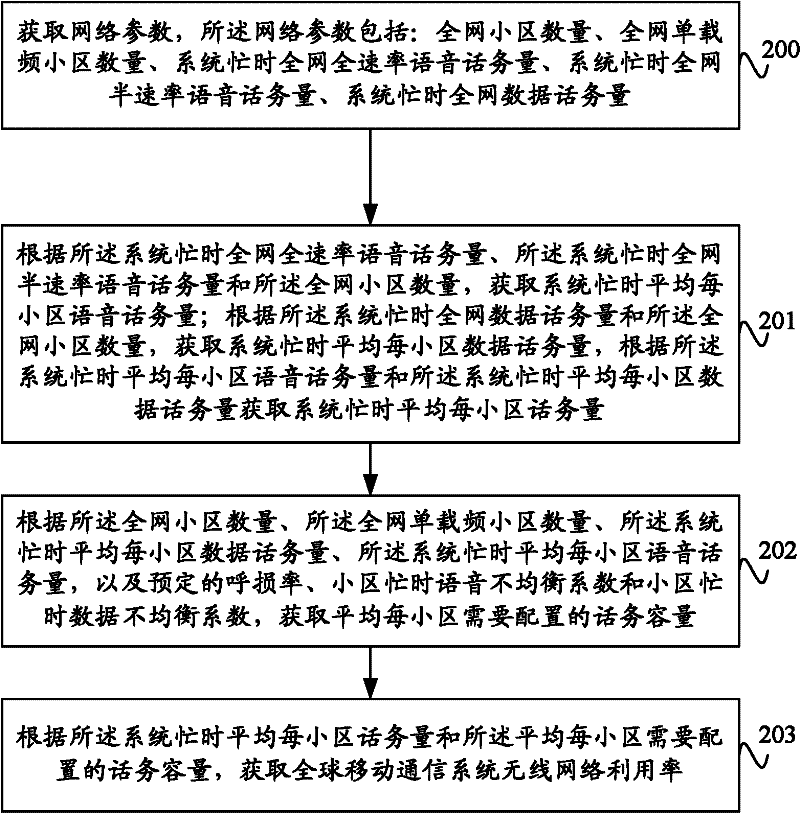

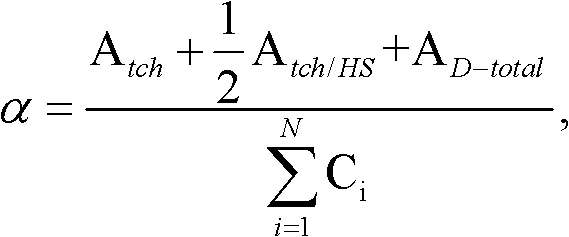

Acquisition method of wireless network utilization of global system for mobile communication

ActiveCN102202329AImprove resource utilizationTelephonic communicationWireless communicationTraffic capacityResource utilization

The invention provides an acquisition method of wireless network utilization of a global system for mobile communication (GSM). The method comprises the following steps: acquiring network parameters comprising whole network full rate voice telephone traffic when a system is busy, whole network half rate voice telephone traffic and whole network data telephone traffic when the system is busy, fullrate voice telephone traffic when each cell is busy in the whole network, half rate voice telephone traffic when each cell is busy in the whole network, and data telephone traffic when each cell is busy in the whole network; acquiring the whole network telephone traffic and the telephone traffic capacity needs to be configured in the whole network when the system is busy according to the network parameters, the preset percent of call lost and the number of channels of each carrier frequency, so as to acquire the wireless network utilization of the global system for mobile communication, thus realizing the acquisition of the matched wireless capacity aiming to the telephone traffic in some time, and acquiring the corresponding best wireless network resource utilization of the GSM.

Owner:CHINA UNITED NETWORK COMM GRP CO LTD

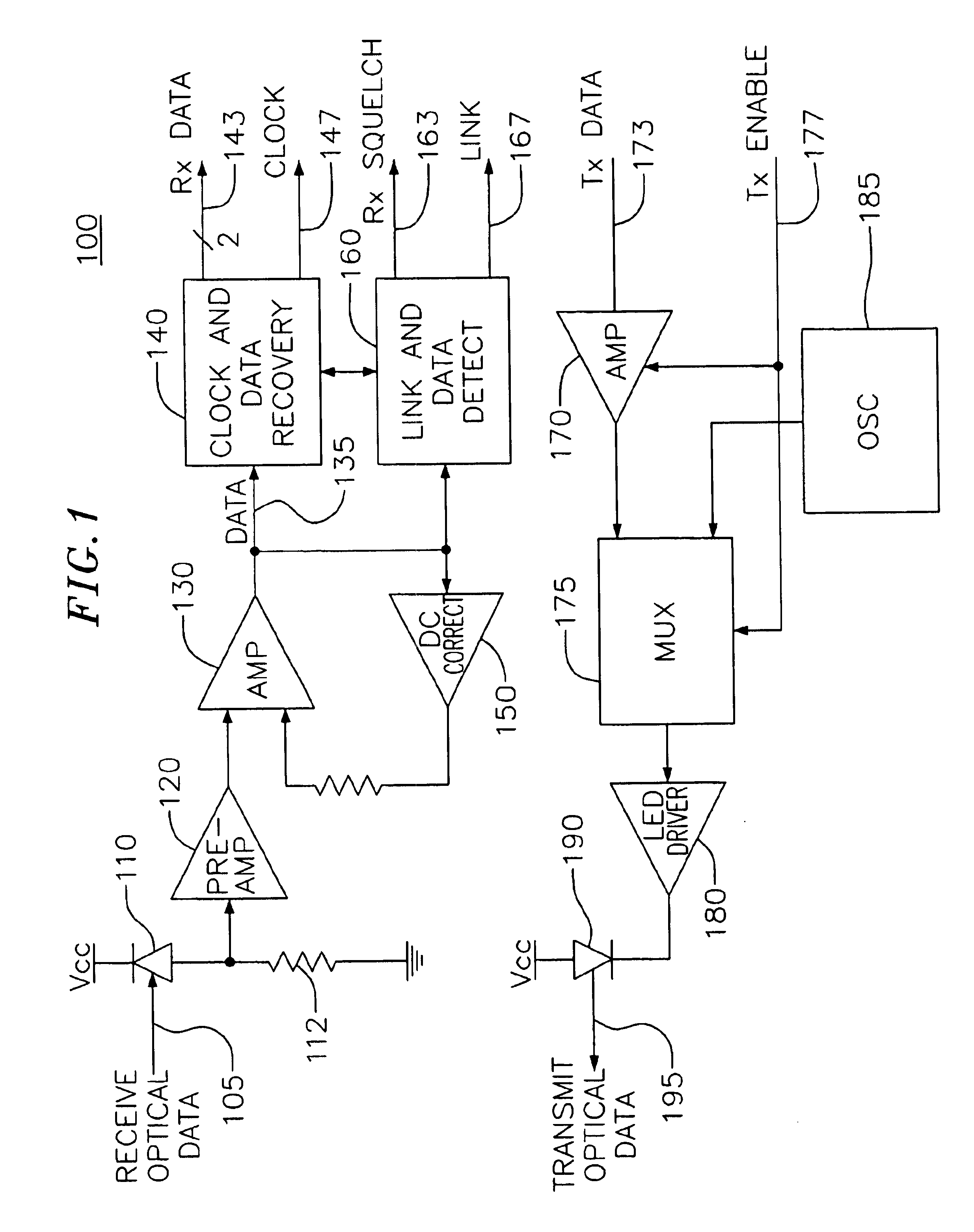

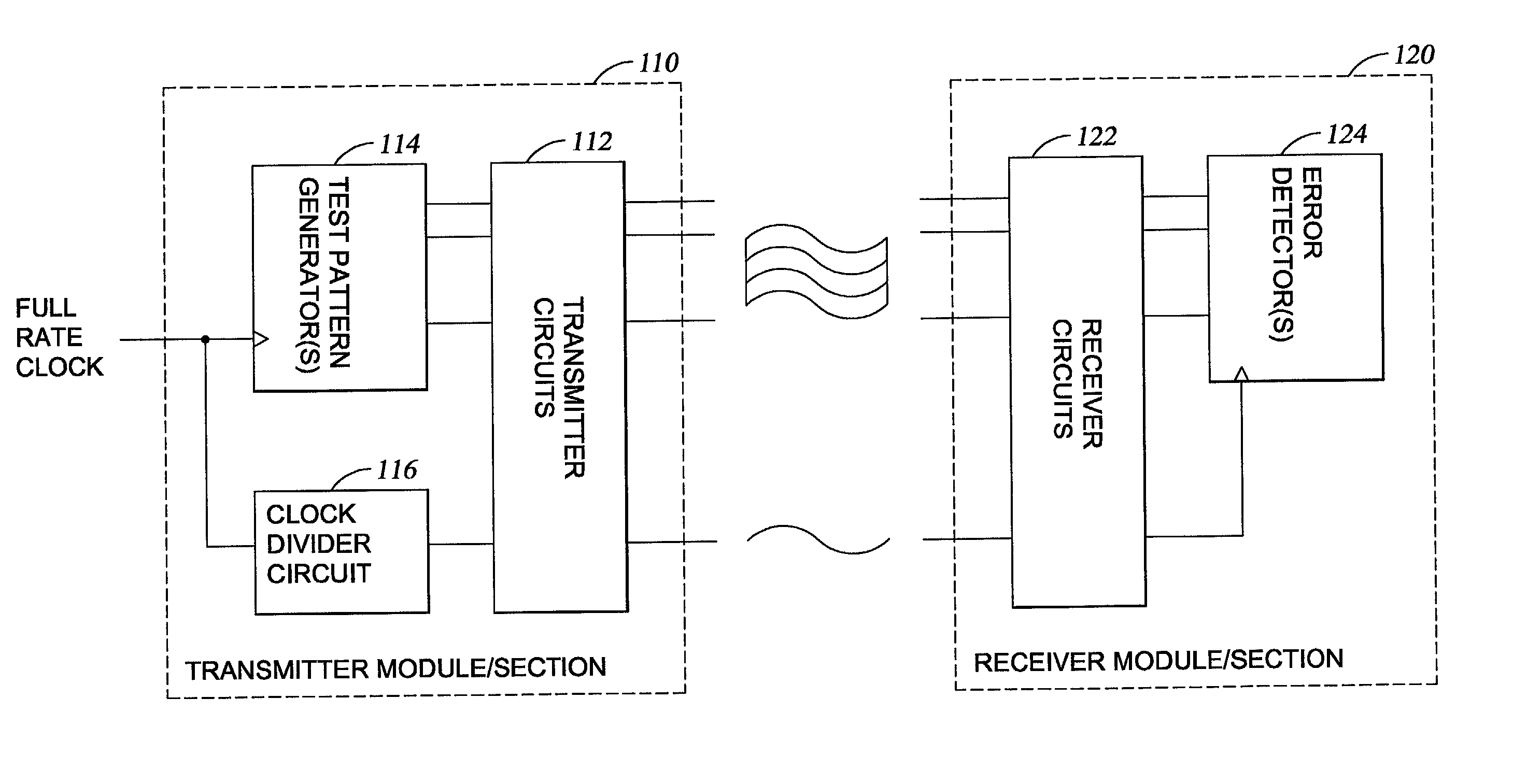

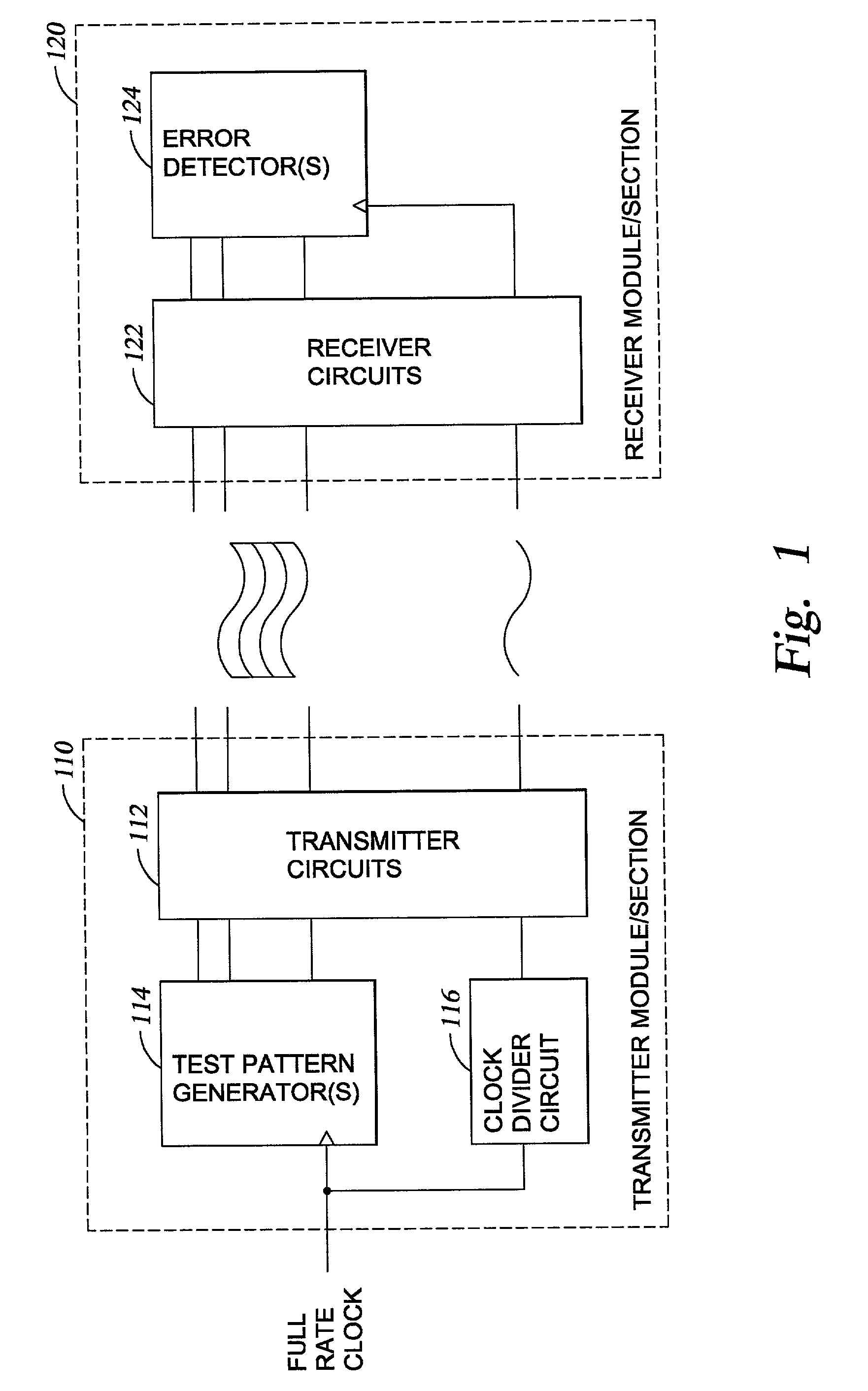

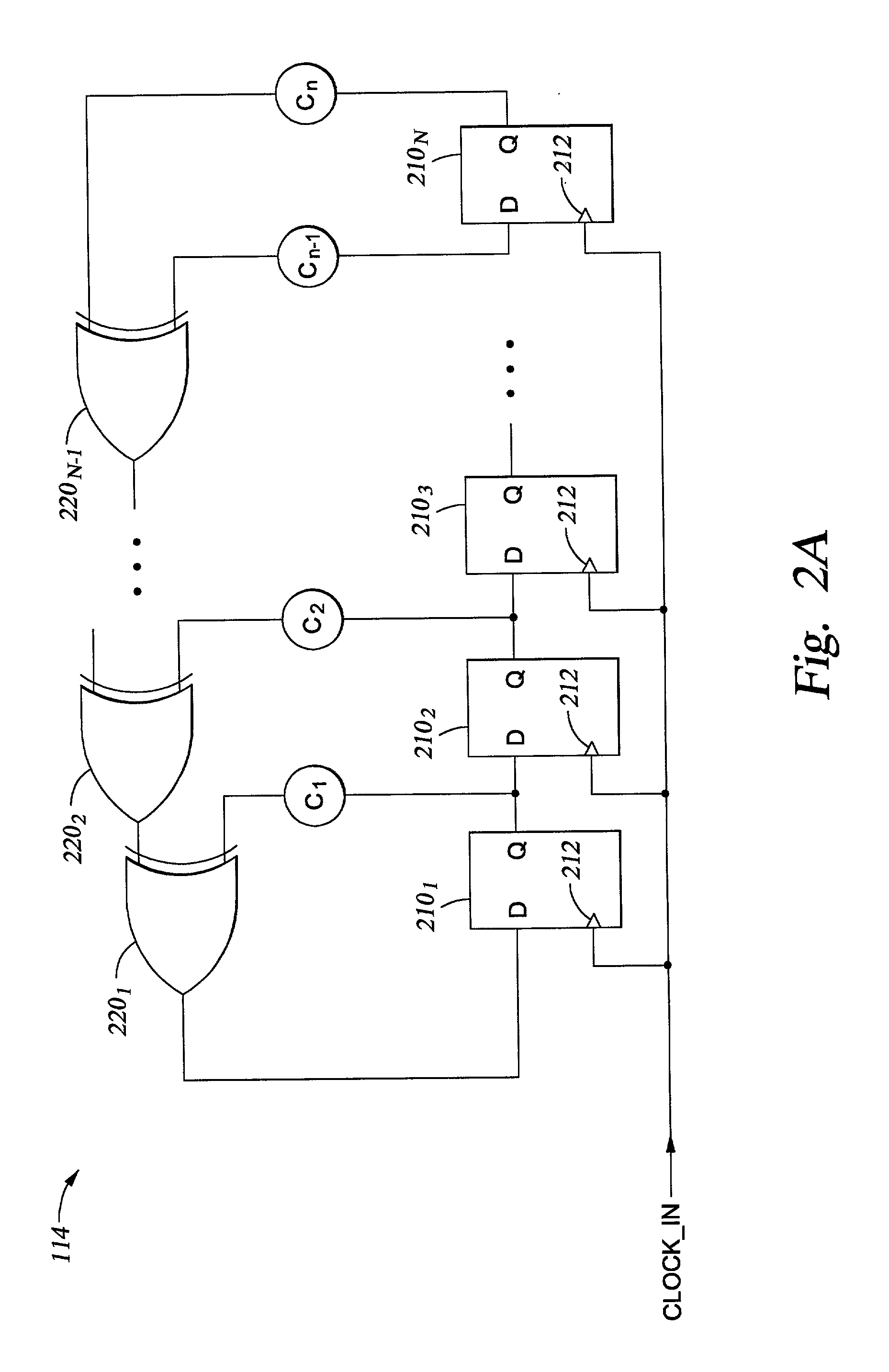

Architecture for built-in self-test of parallel optical transceivers

Method and apparatus for testing a parallel optical transceiver are provided. One embodiment provides a built-in self-testing (BIST) parallel optical transceiver comprising a full-rate clock test pattern generator and a clock divider circuit connected to provide a half-rate clock signal to one of the one or more transmitter channels, and an error detector comprising one or more error detection circuits connected to one or more receiver channels and configured to receive the half-rate clock signal. Another embodiment provides a method for testing a parallel optical transceiver, comprising: generating a full-rate clock test pattern to one or more transmitter channels; providing a half-rate clock signal to one of the one or more transmitter channels utilizing a clock divider circuit; transmitting test pattern and half-rate clock signals to one or more corresponding receiver channels; and detecting error utilizing one or more error detection circuits connected to receive the half-rate clock signal.

Owner:IBM CORP

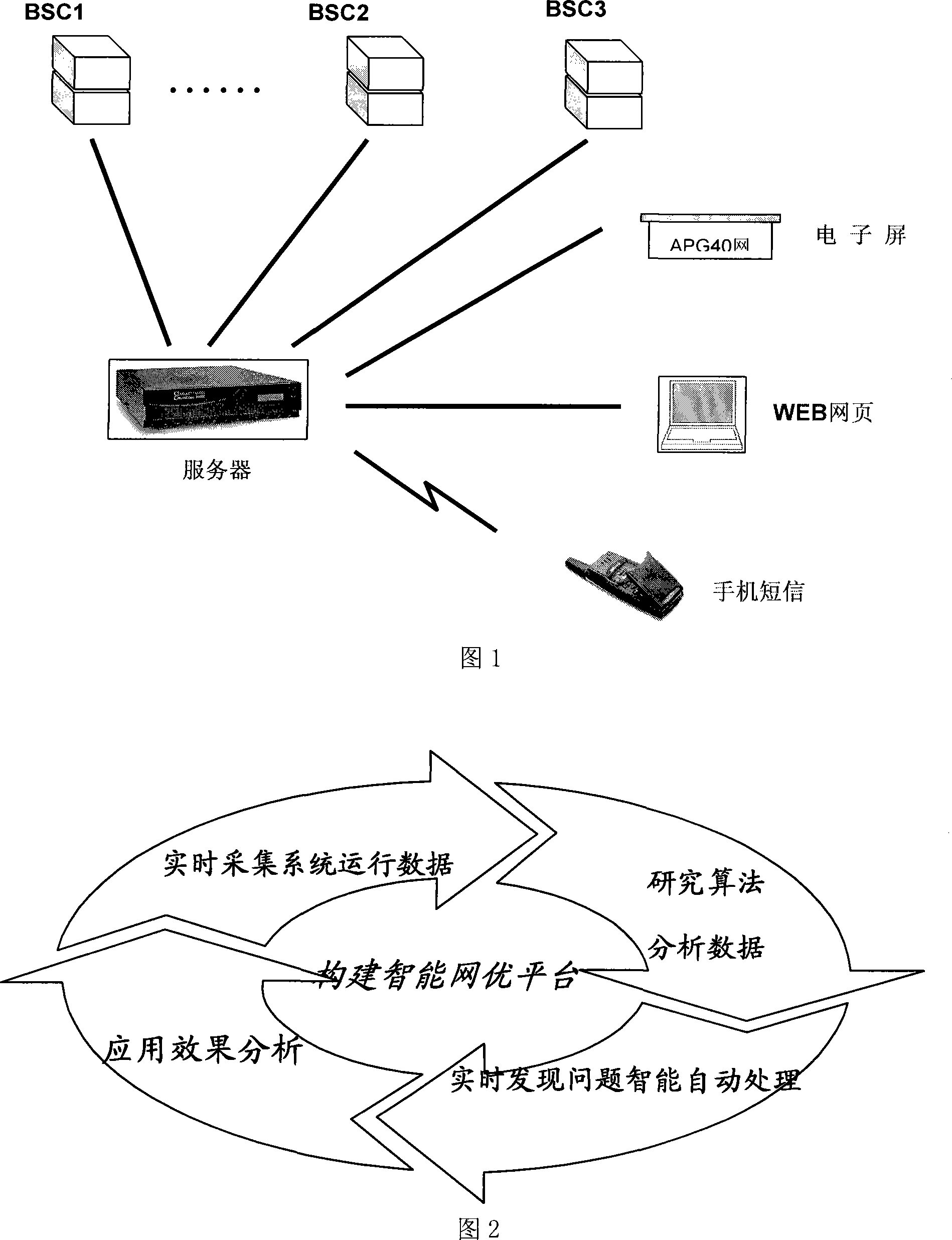

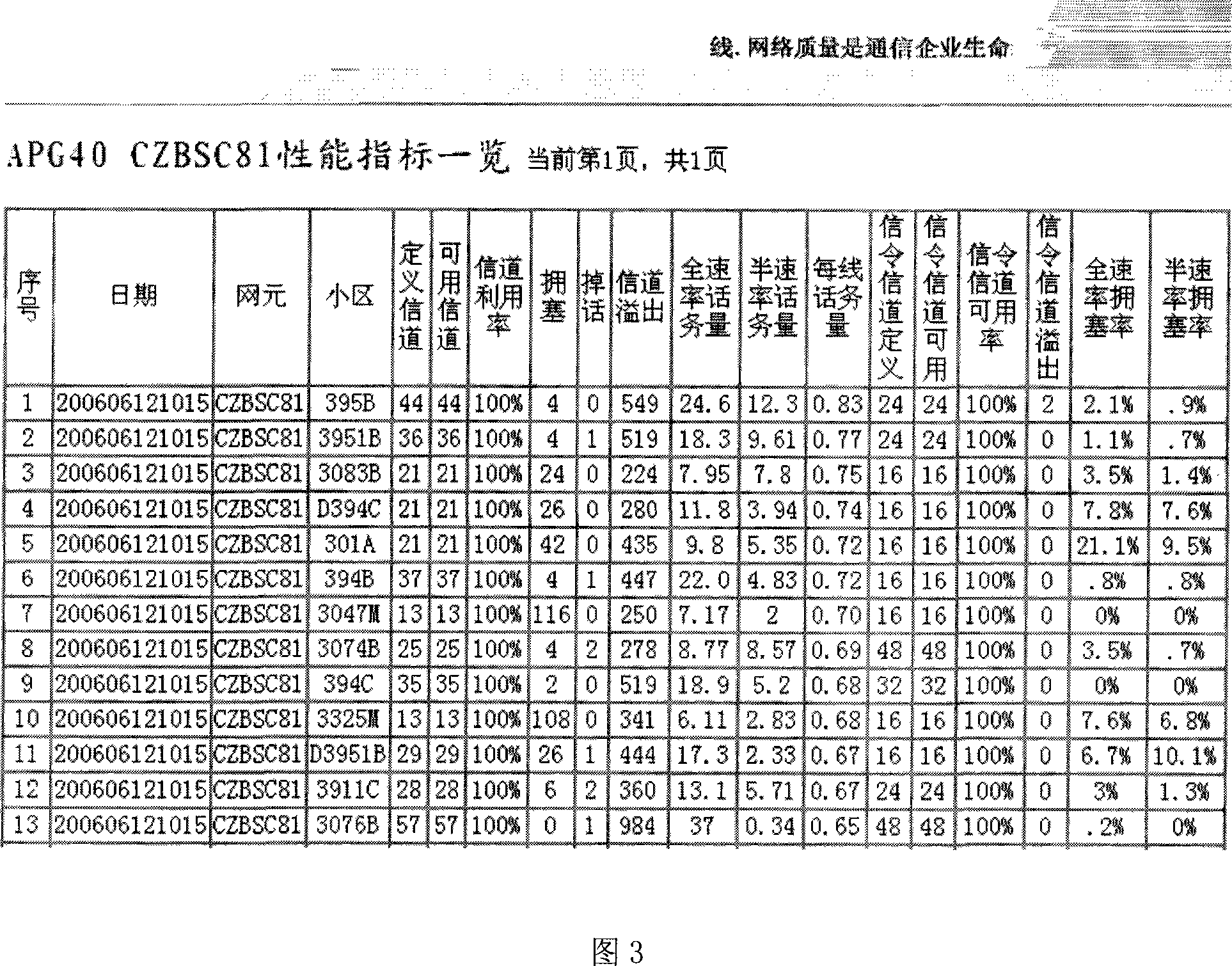

Self-adapted adjustment system and its method for GSM network intelligent cell

InactiveCN101106789ARealize intelligenceReal-time detection of load exceeding the threshold operationRadio/inductive link selection arrangementsData switching networksQuality of serviceHalf Rate

The invention provides a system capable of realizing intelligent self-adapting regulation on GSM network parameters via software according to change of mobile communication network business. By establishing the system, parameters switching between cells, ratio of half rates of different cells, configuration of cell signaling channel, and configuration of GPRS signaling channel can be automatically regulated the make the GSM network have 'breath effect' when cell load (sound, signaling, and data) is increased. If failure occurs in a cell, the system can automatically find and processing the failure and all the regulations provide WEB enquiry and correlation analysis, therefore intelligent and automatic management of the cells is realized to achieve win-win of network capacity and service quality to more effectively support management of the network. With the system, economic effectiveness increased by more than ten millions can be achieved.

Owner:CHINA MOBILE GROUP JIANGSU

Optical disk reproducing device selectively using a channel bit frequency or a frequency that is half of the channel bit frequency

InactiveUS20060187800A1Reduce the number of timesReduce power consumptionTelevision system detailsModification of read/write signalsDigital dataHalf Rate

A data demodulation process rate is varied according to a reproduction state, thereby reducing power consumption while maintaining a reading performance in a favorable state. A channel rate process data demodulation device performs a data demodulation process by employing channel bit frequency. Further, a half rate process data demodulation device performs a data demodulation process by employing frequency half as high as the channel bit frequency. These devices demodulate digital data from an optical recording medium. A process rate switching device switches a process rate at data demodulation, whereby demodulation is performed by switching between the data demodulation devices according to a quality of a reproduction signal, so as to reproduce the digital data recorded on the optical recording medium.

Owner:PANASONIC HEALTHCARE HLDG CO LTD

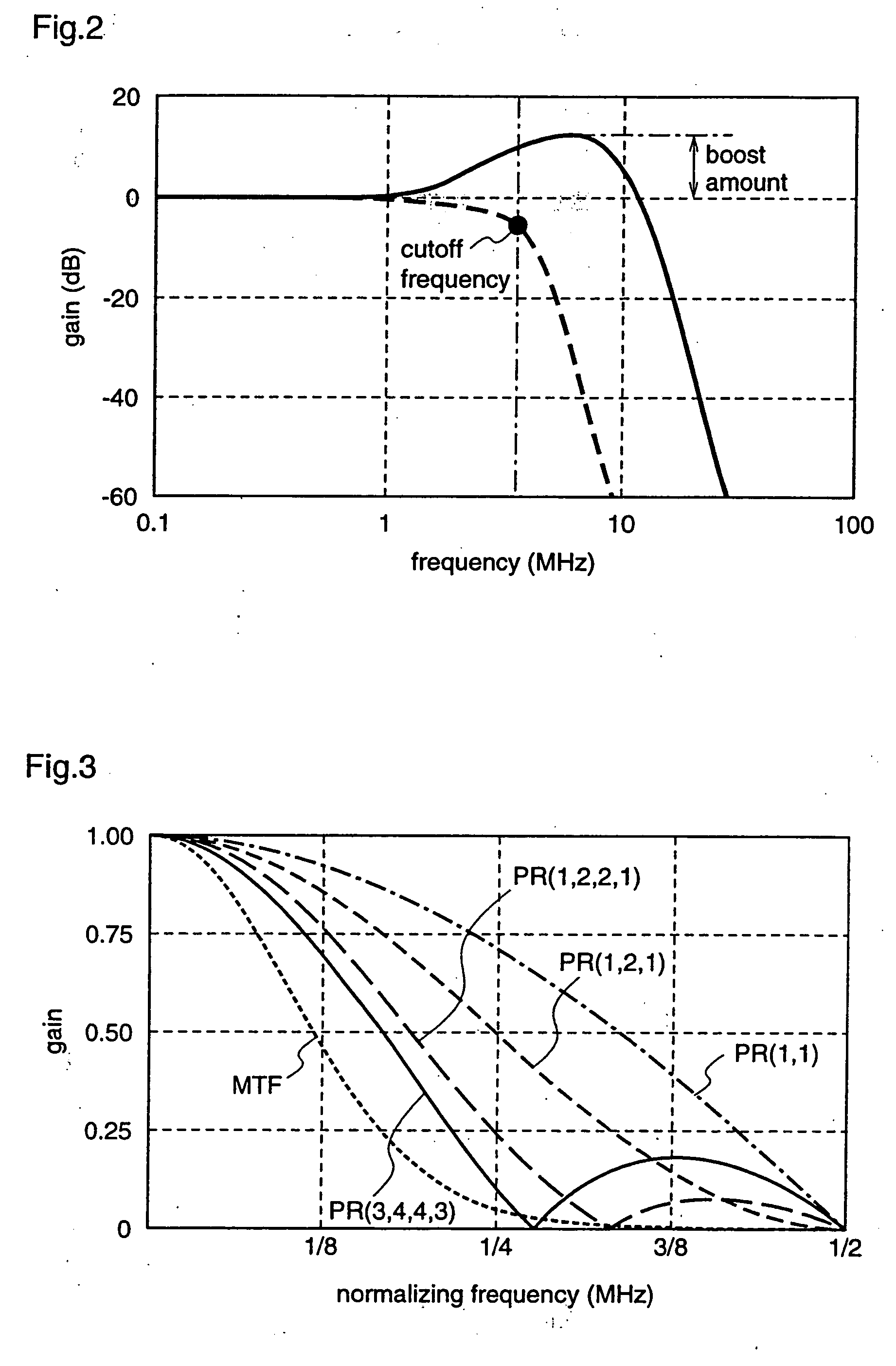

Method of implementing precoding based modulator for carrier suppression return-to-zero optical signals

This invention relates to single modulator realization method based on pre-coding load wave suppression zero in fiber communication technique field, which comprises the following steps: A, forming impulse weighted three-level signals through pre-coding processing by input data and simultaneous semi-time signal; b, pre-compiling to generate three level signal through amplifying and driving to enlarge the signal to peak to peak value as two times of modulator TV voltage; c, modulating the three-level signal to light load wave through light modulation relative to three-level signal zero and the light signal zero phase on and relative to one or -1 to realize the load suppression zero modulation signals.

Owner:SHANGHAI JIAO TONG UNIV

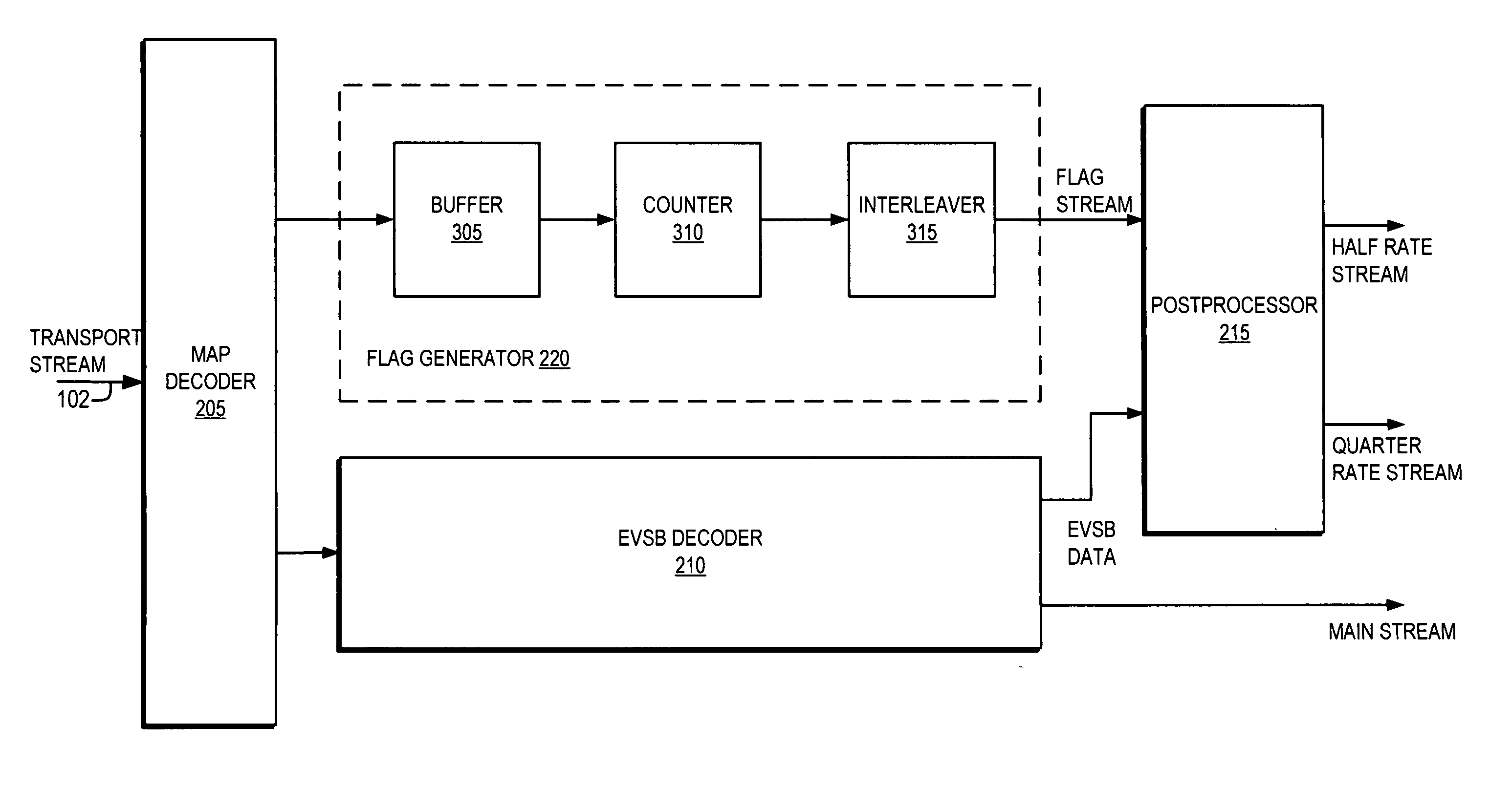

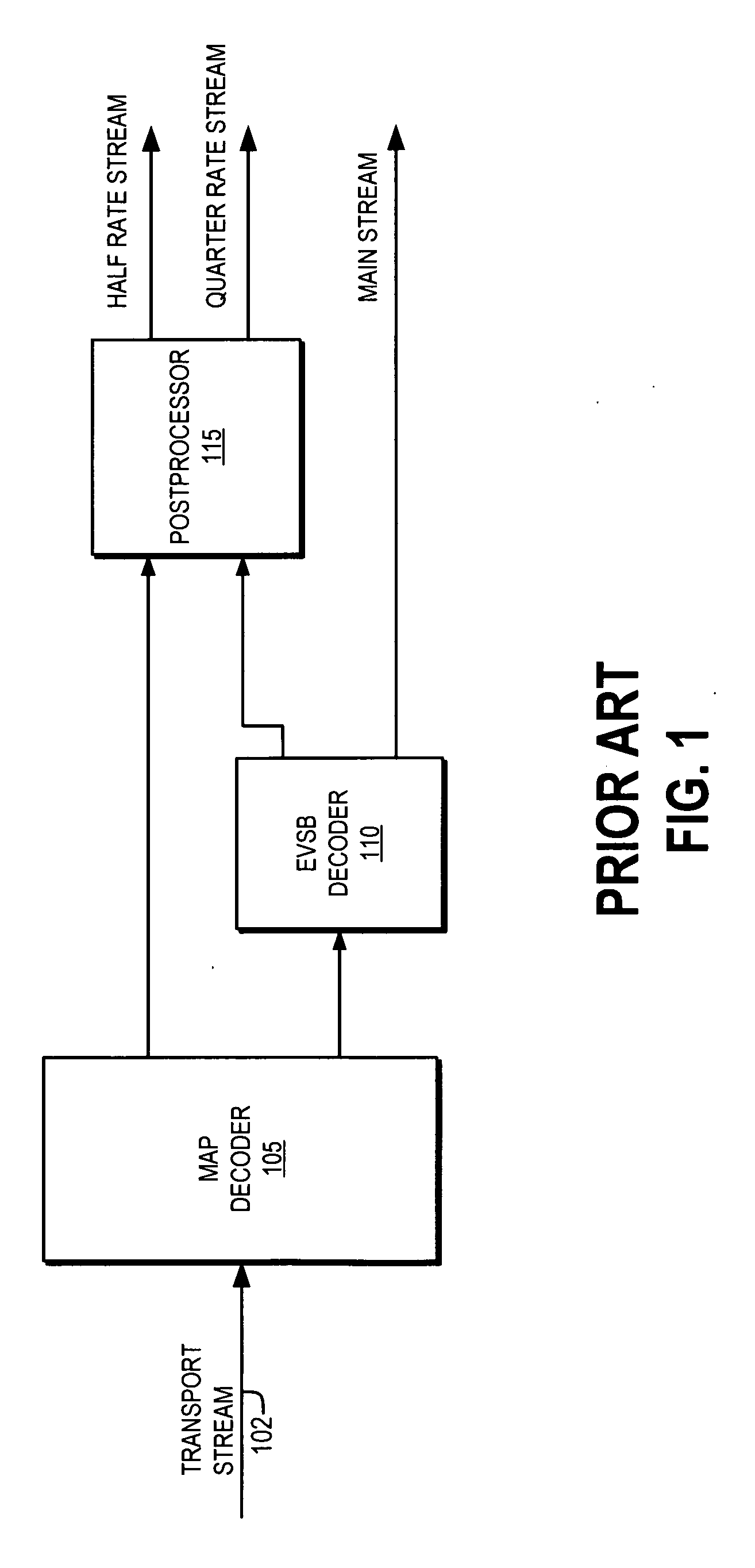

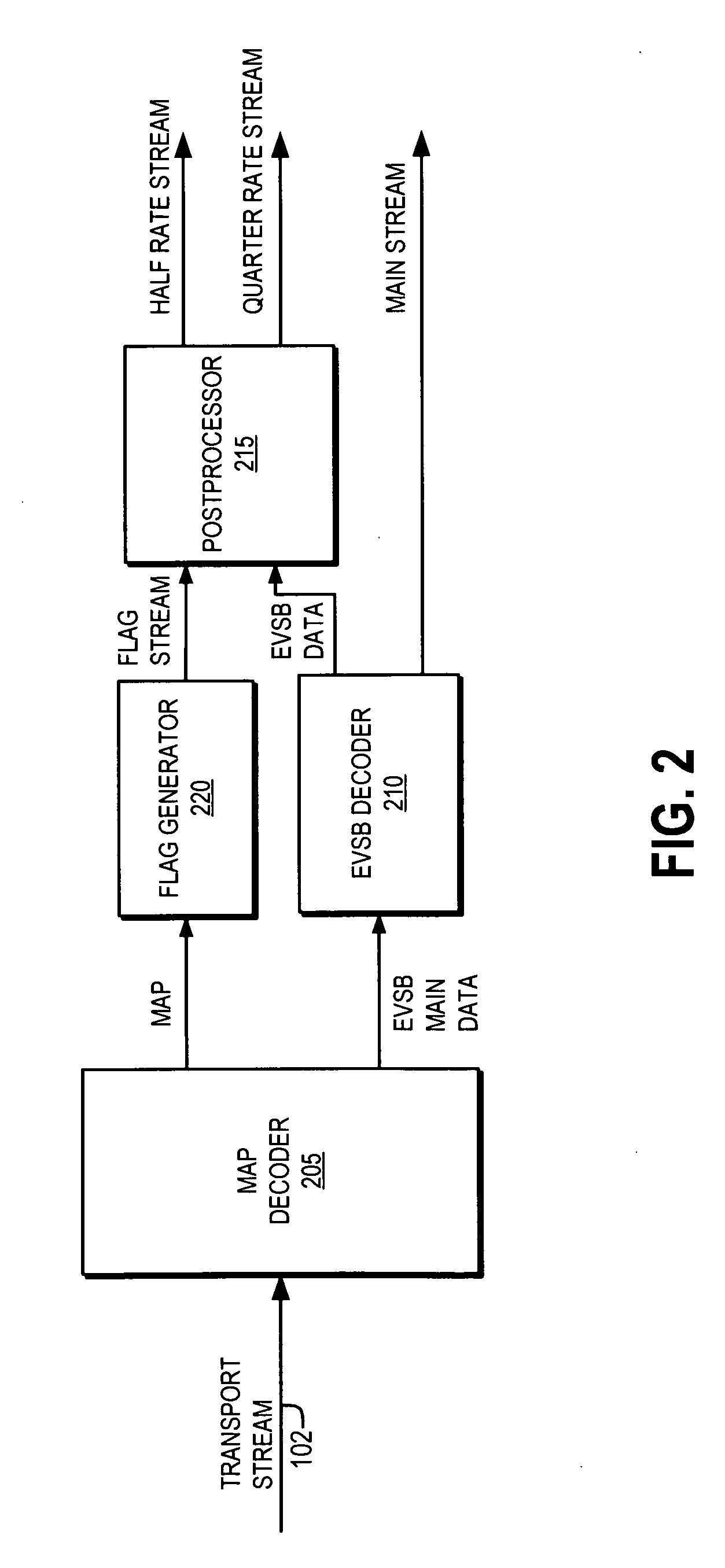

Generating a half rate/quarter rate flag stream for enhanced VSB decoder

InactiveUS20060140224A1Time-division multiplexDigital video signal modificationMultiplexingData stream

A system and method are provided for generating a flag stream that is used to mark the half rate and quarter rate bytes in an enhanced vestigial sideband (eVSB) data stream. The flag generator includes a buffer, a counter, and an interleaver. The buffer receives map data from a map decoder. The map data indicates the number of half rate and quarter rate packets that are present in a given eVSB data frame. The map data also includes a multiplexer option bit that indicates how the half rate and quarter rate packets are multiplexed in the eVSB data frame. The flag generator uses the map data to generate a flag stream that marks the bytes of the eVSB data frame for accurately separating the half rate data and the quarter rate data.

Owner:PANASONIC CORP

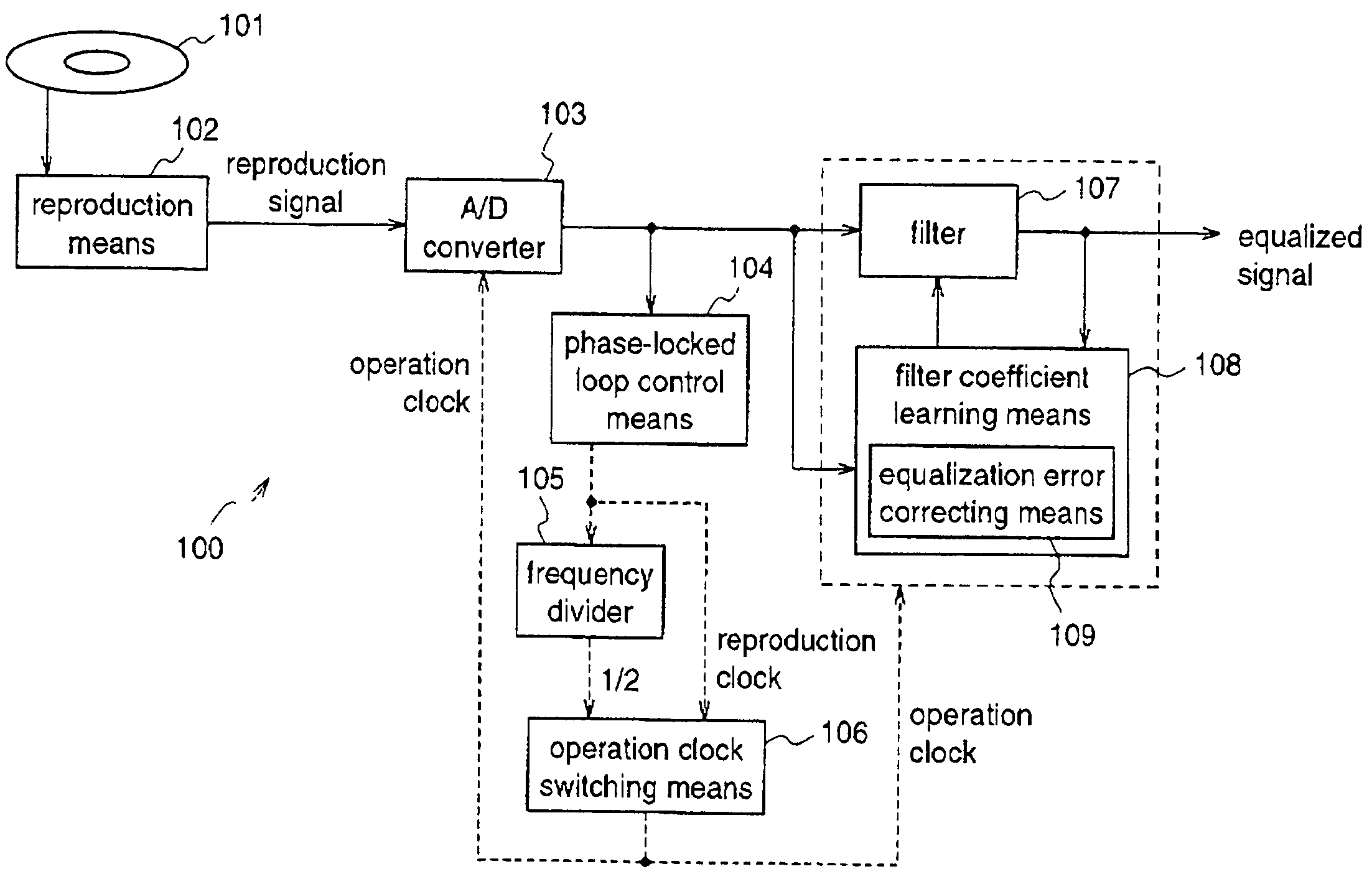

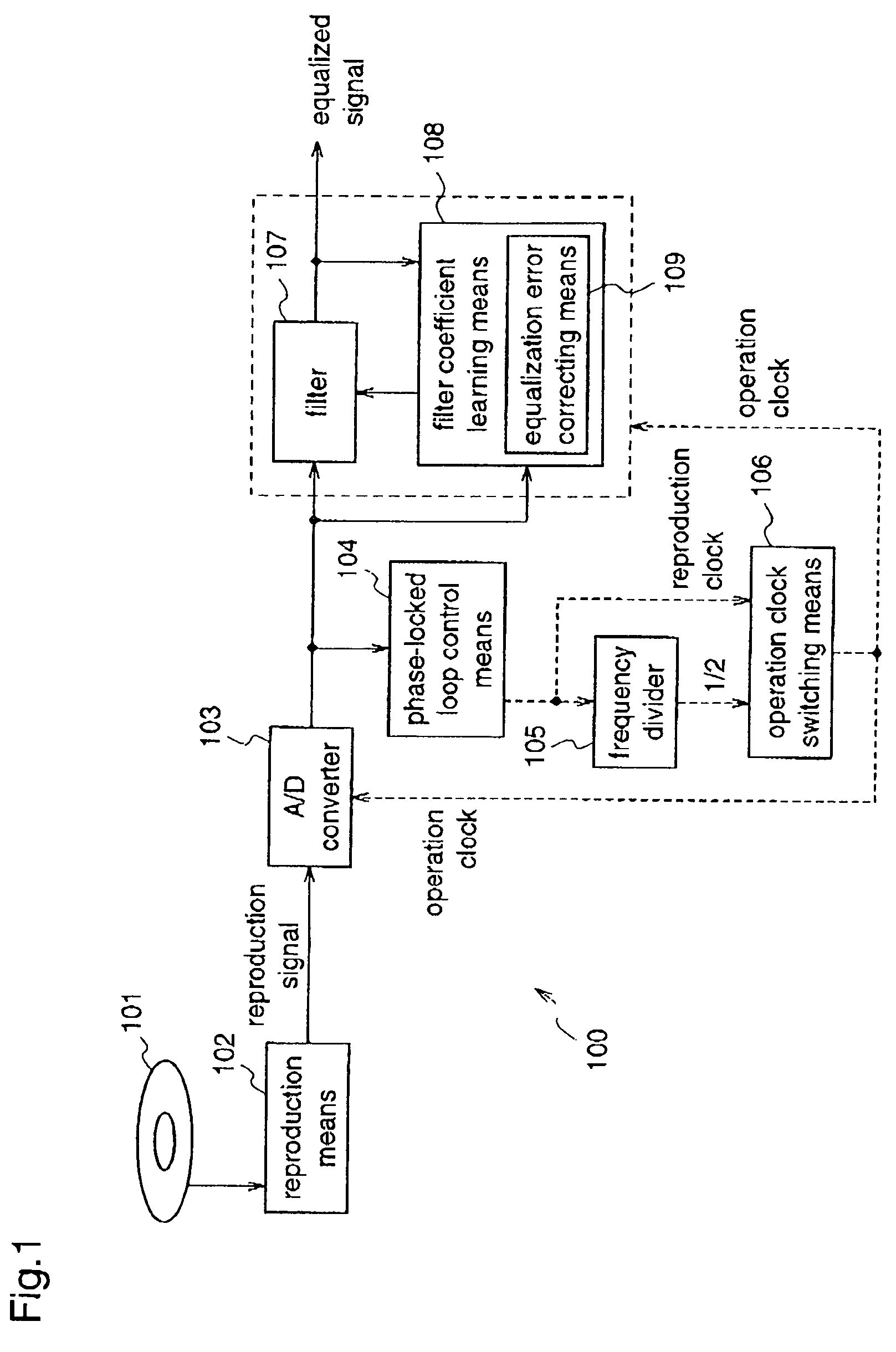

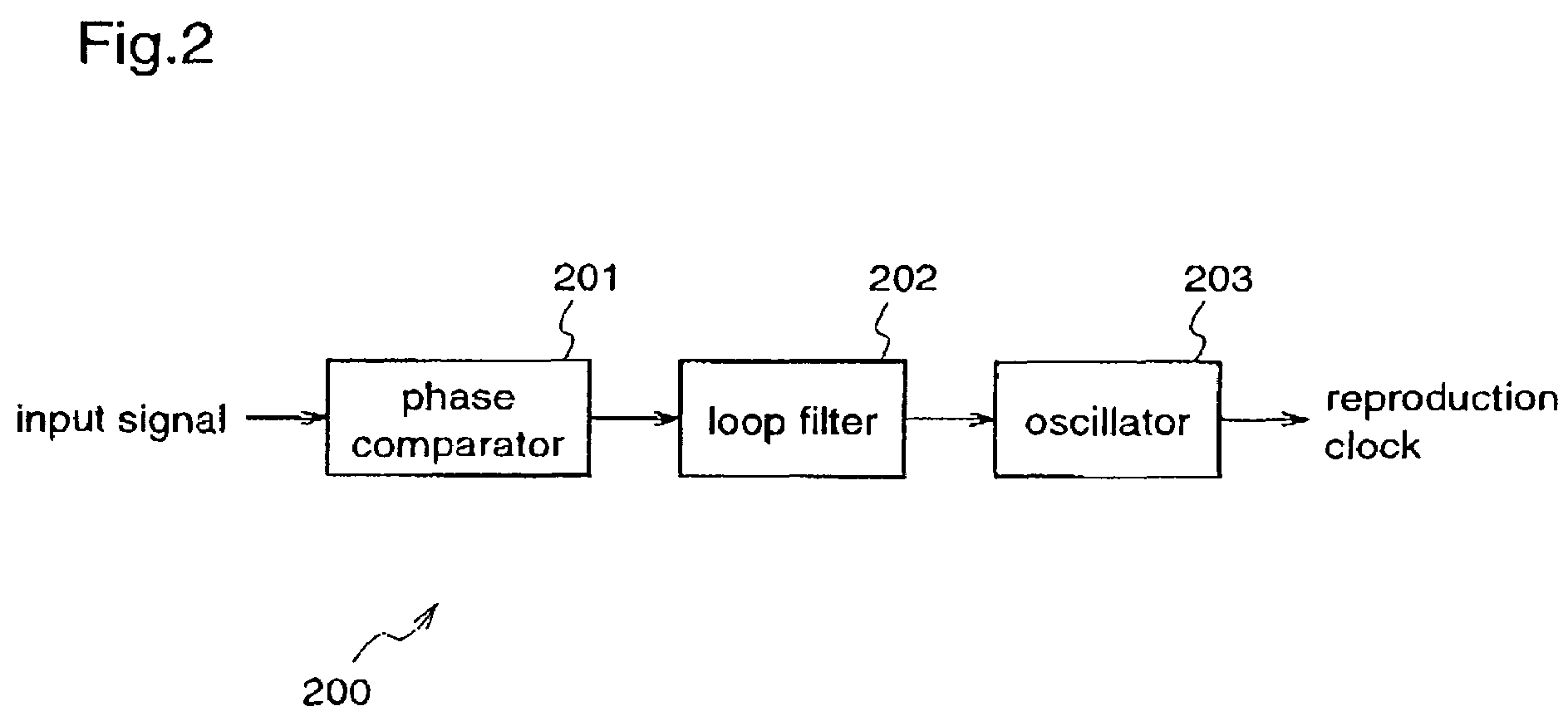

Reproduction signal processing apparatus and optical disc player including the same

InactiveUS7274645B2Satisfactory adaptiveSuppress power consumptionCombination recordingTelevision system detailsLearning unitHalf Rate

A reproduction signal processing apparatus includes: a reproduction unit, an A / D converter for sampling a reproduction signal to obtain a multi-bit digital signal, a phase-locked loop controller for outputting a reproduction clock that is in phase with clock components included in the reproduction signal from an oscillator, a frequency divider for frequency-dividing the reproduction clock, an operation clock switching unit for selecting an operation clock, a filter for performing digital equalization, a filter coefficient learning unit for adaptively controlling the filter coefficients to minimize an equalization error, and an equalization error correcting unit for performing correction so as not to output an abnormal equalization error, thereby performing the adaptive equalization control with stability not only in the channel rate mode but also in the half rate mode that is introduced to suppress the power consumption.

Owner:PANASONIC HEALTHCARE HLDG CO LTD