Patents

Literature

40 results about "Low voltage swing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

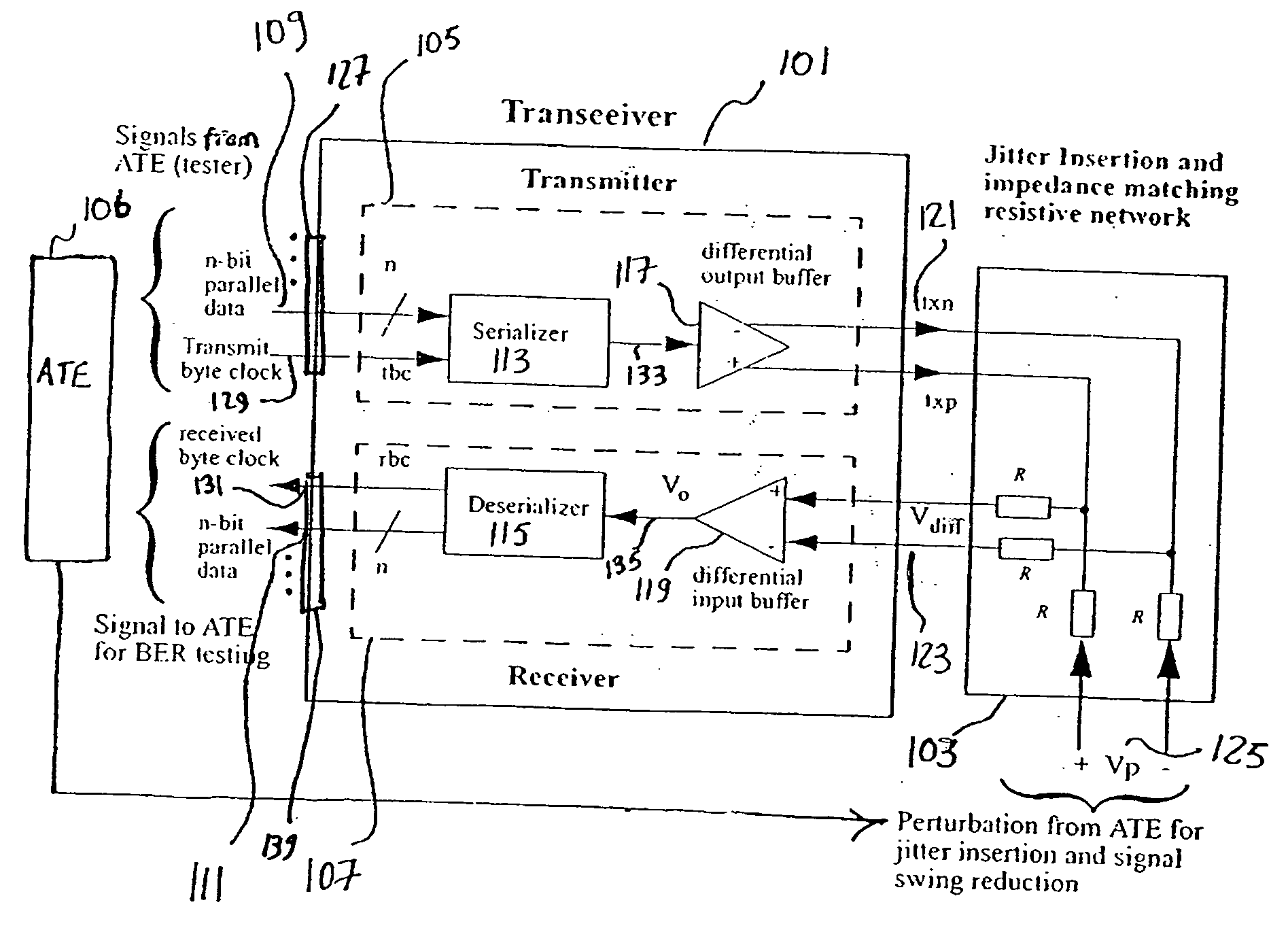

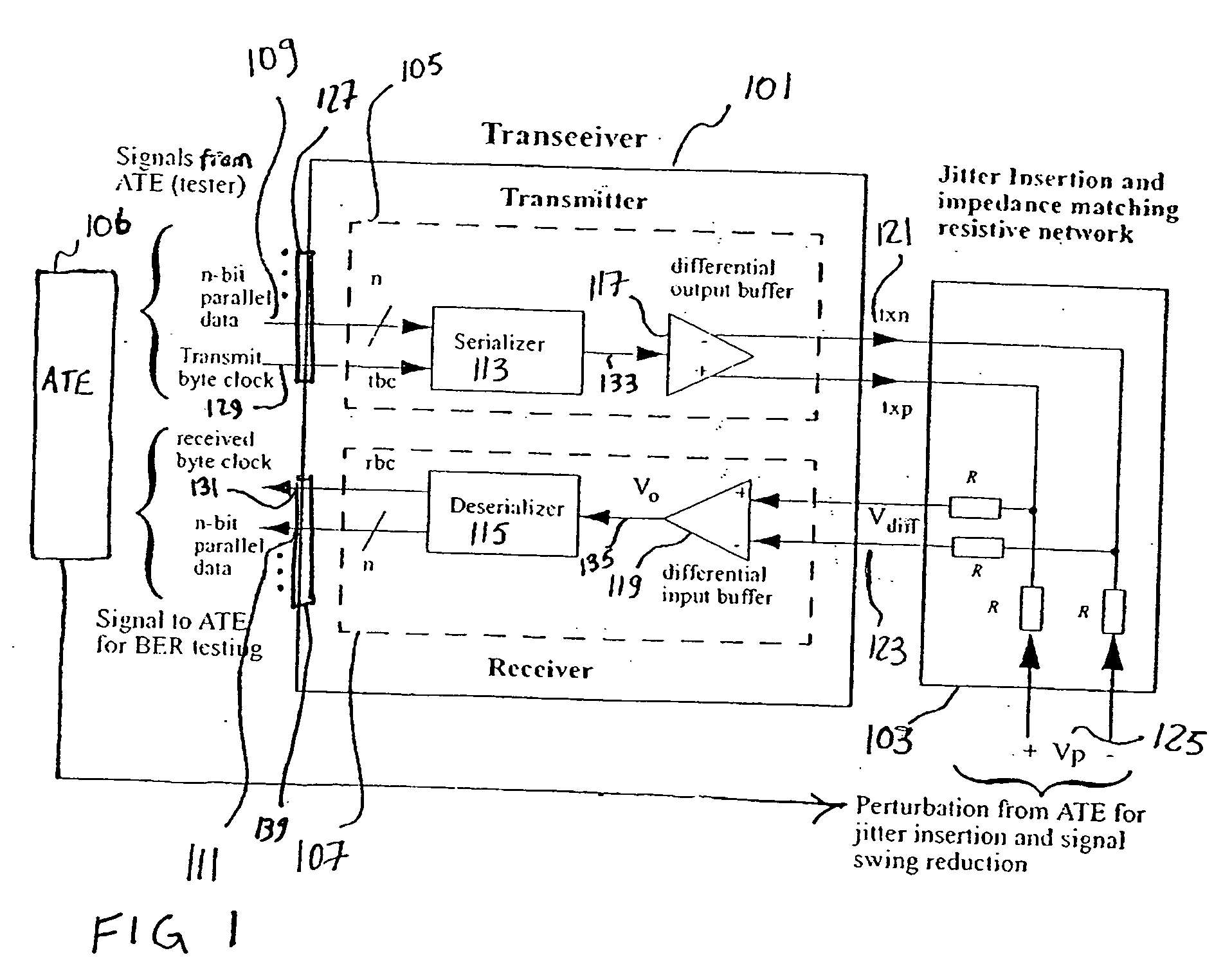

System and method for production testing of high speed communications receivers

InactiveUS20050172181A1Digital circuit testingElectrical measurement instrument detailsTransceiverLow voltage

A method for testing a semiconductor device with a multi-gigabit communications receiver includes combining a data output from a high-speed communications transmitter with a perturbation signal generated by automatic test equipment. The combined signal data signal including jitter and low voltage swings is input to the communications receiver port under test. The automatic test equipment determines the bit error rate of the parallel data output from the receiver port under test. This test method is appropriate for semiconductor devices with multiple transceiver ports.

Owner:MELLANOX TECHNOLOGIES LTD

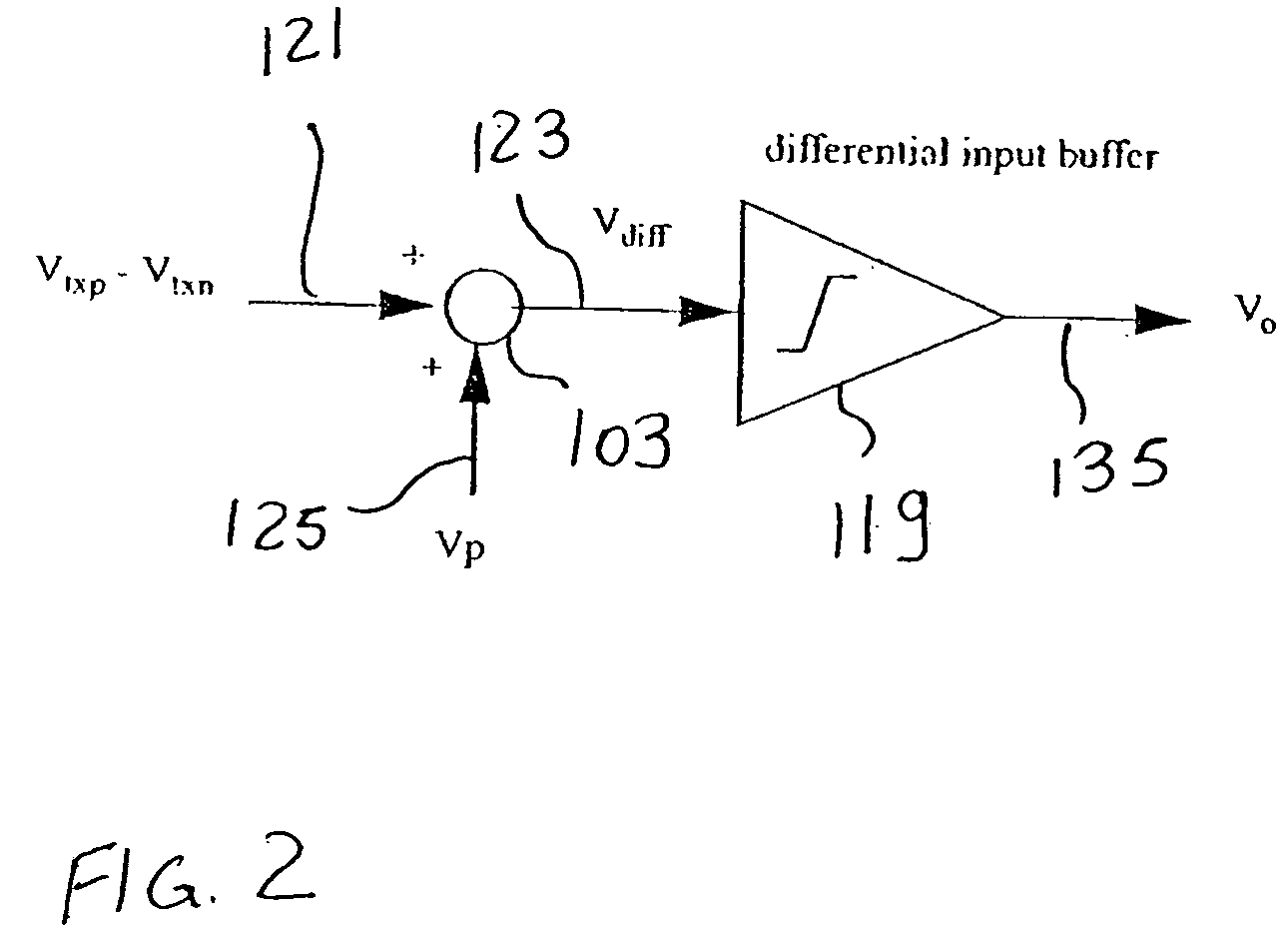

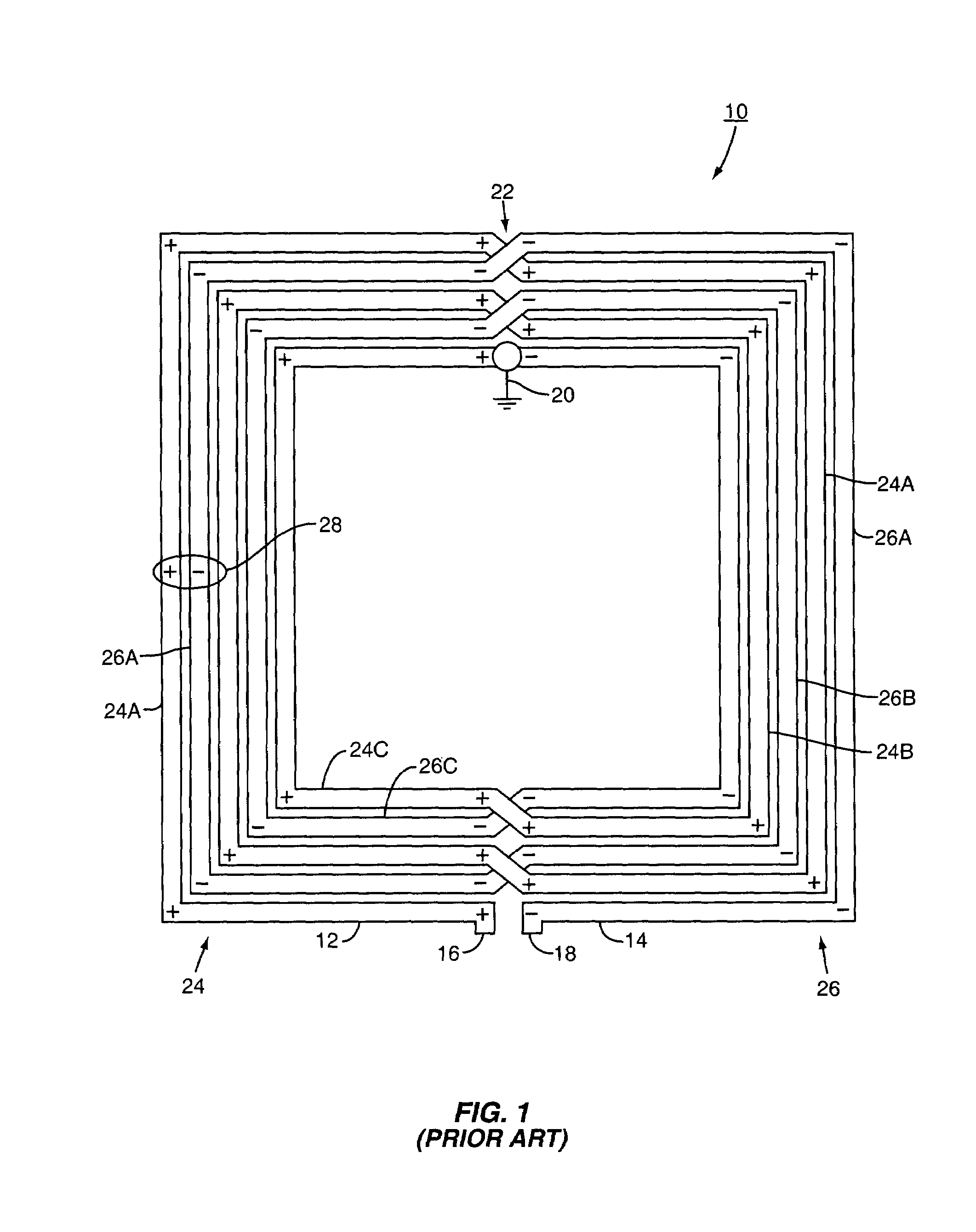

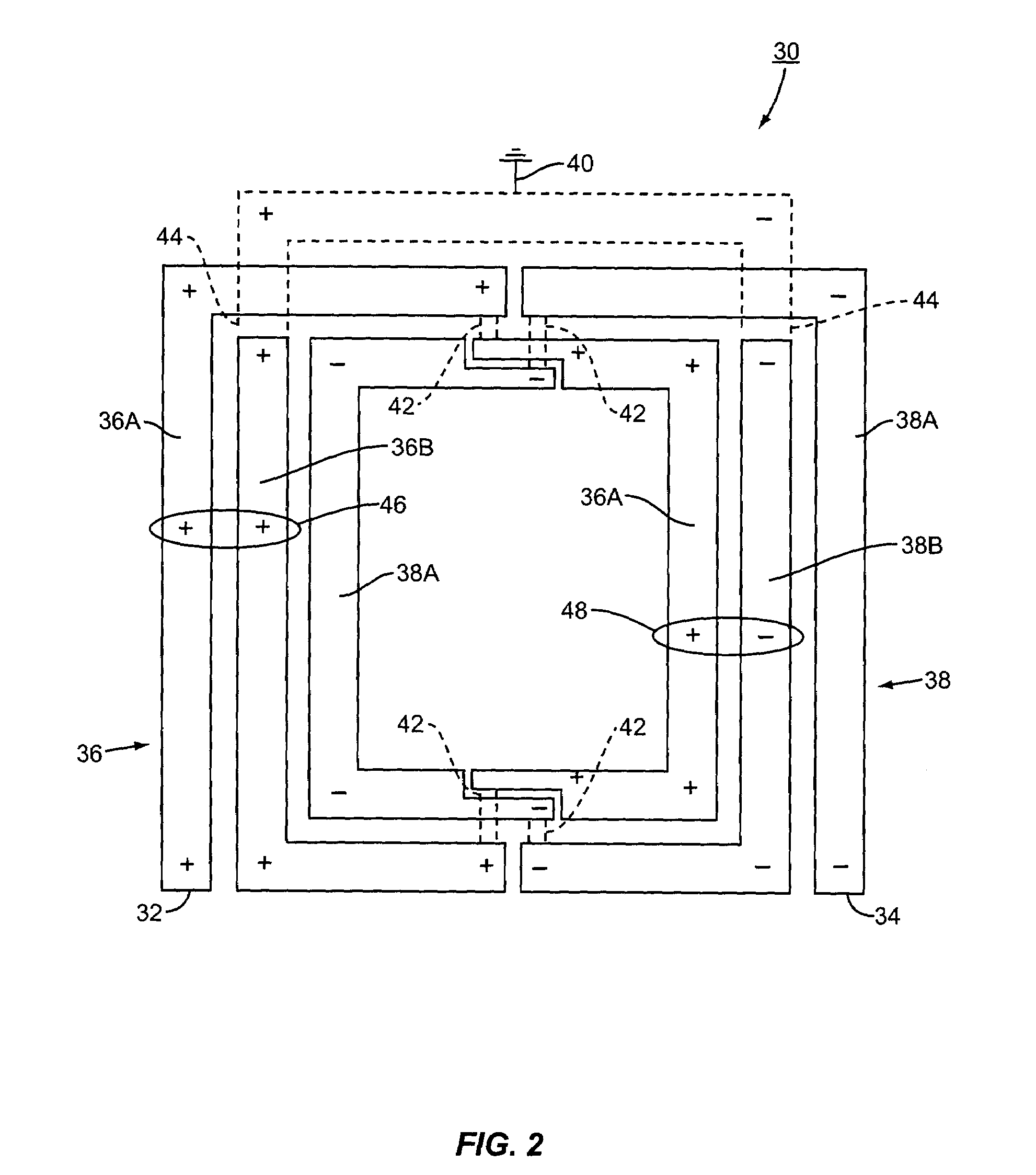

Differential inductor design for high self-resonance frequency

ActiveUS6972658B1Low effective capacitanceRaise the self-resonant frequencySemiconductor/solid-state device detailsSolid-state devicesCapacitanceEngineering

A differential inductor is formed from branch coils that are staggered with respect to one another rather than concentrically coiled within one another. Each coil is formed from conductive strips. The conductive strips with the largest voltage swings thereon are shielded from one another by conductive strips with lower voltage swings thereon. This shielding allows the effective capacitance of the differential inductor to be lowered, which in turn raises the range of frequencies at which the differential inductor can operate.

Owner:QORVO US INC

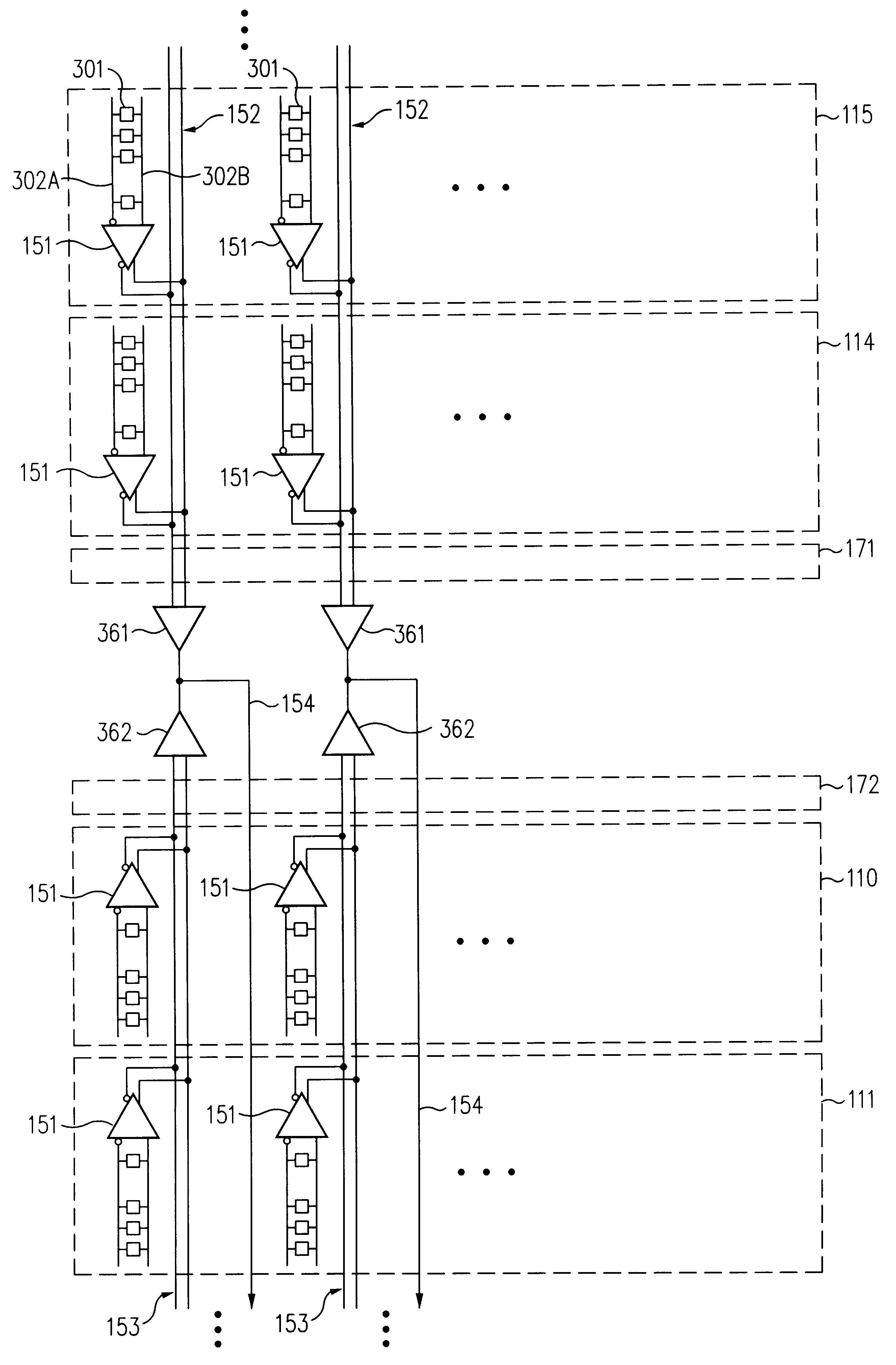

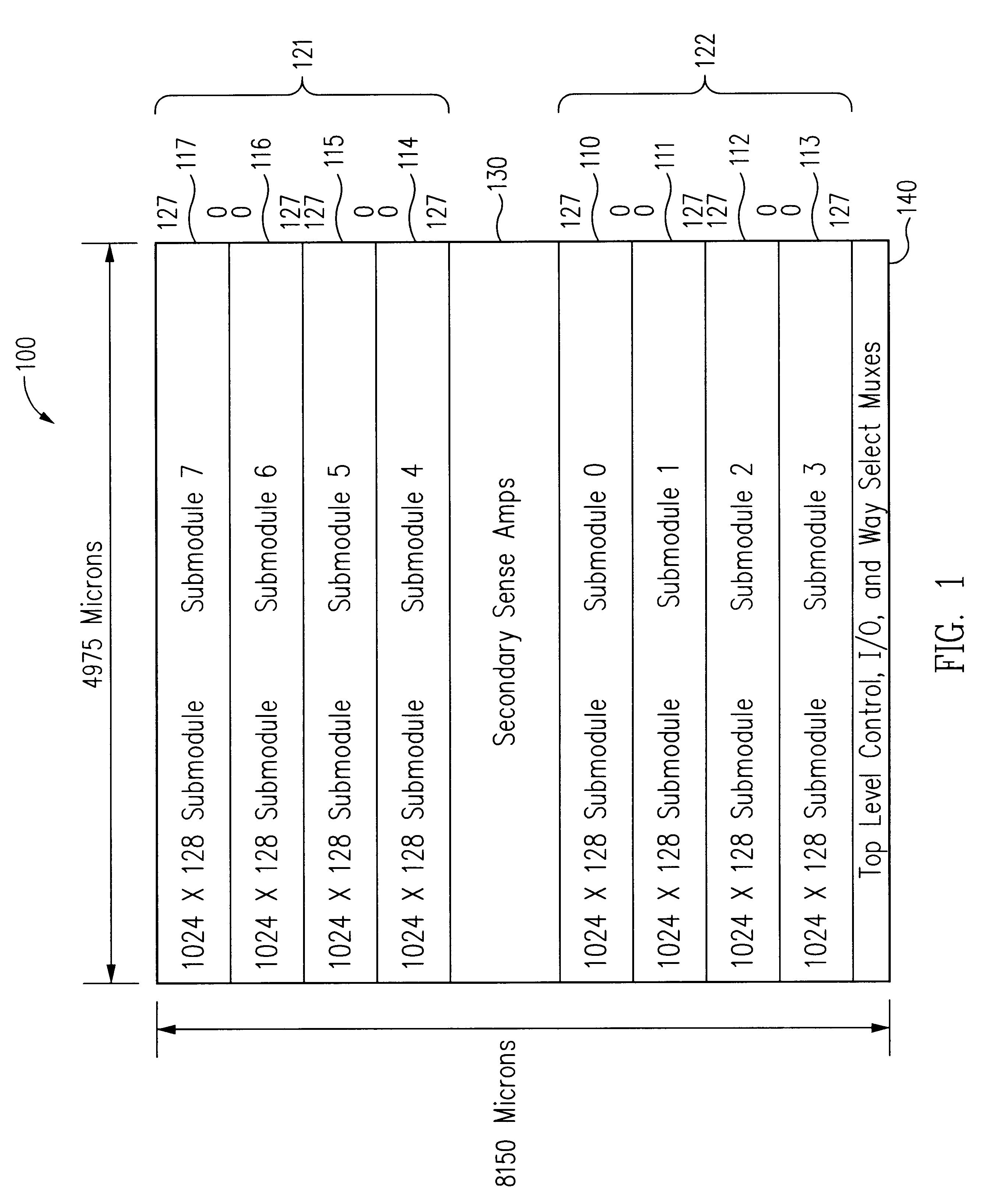

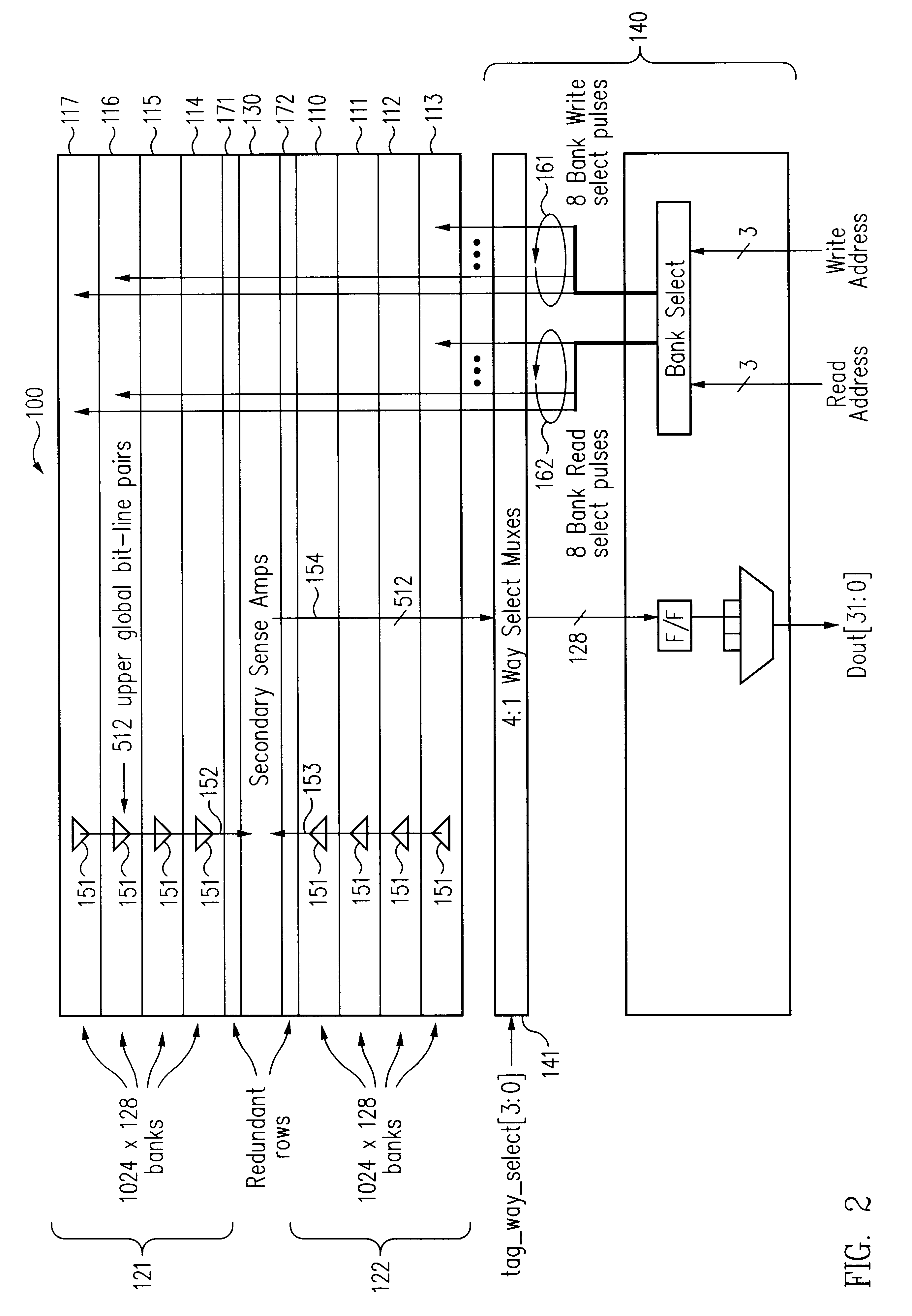

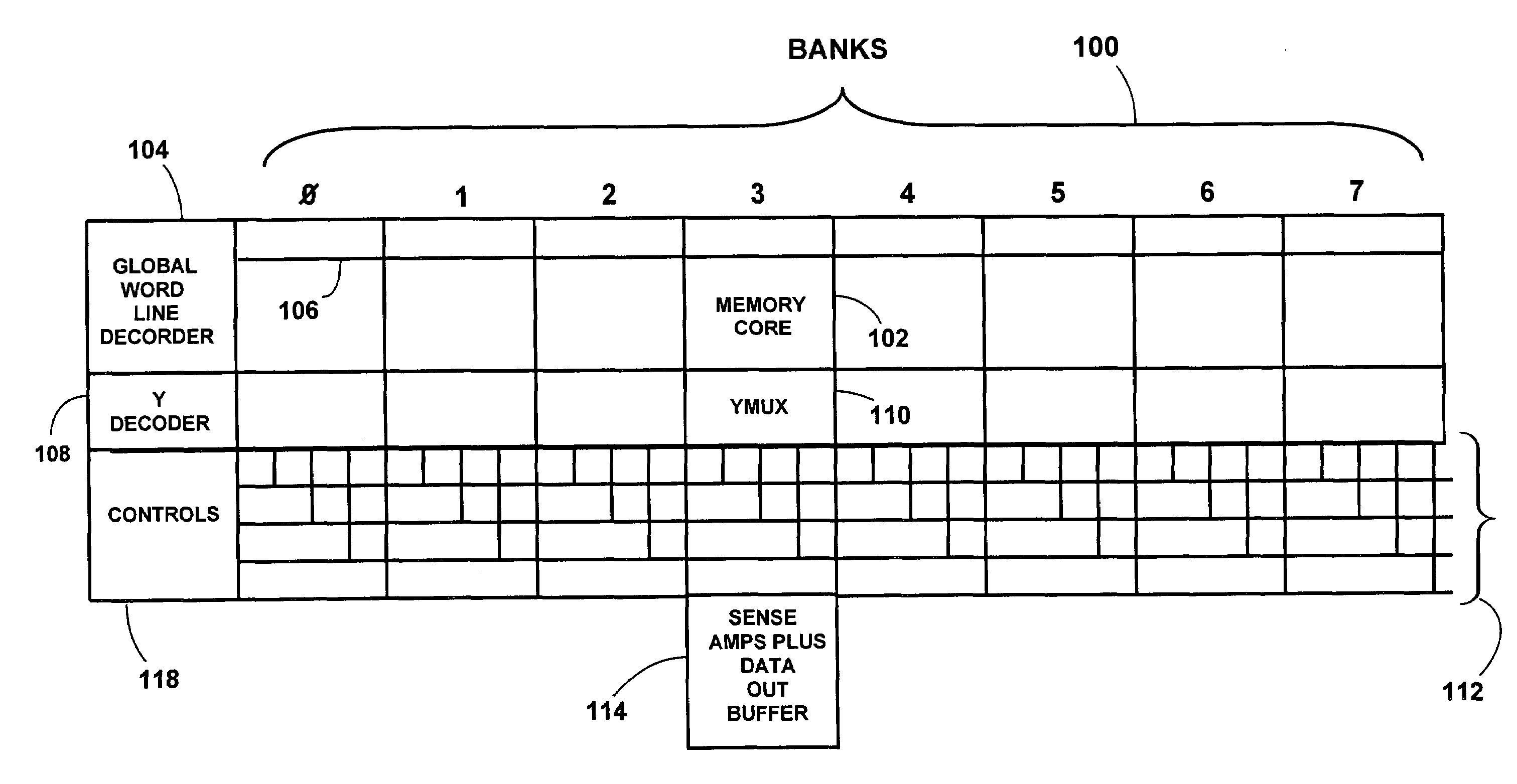

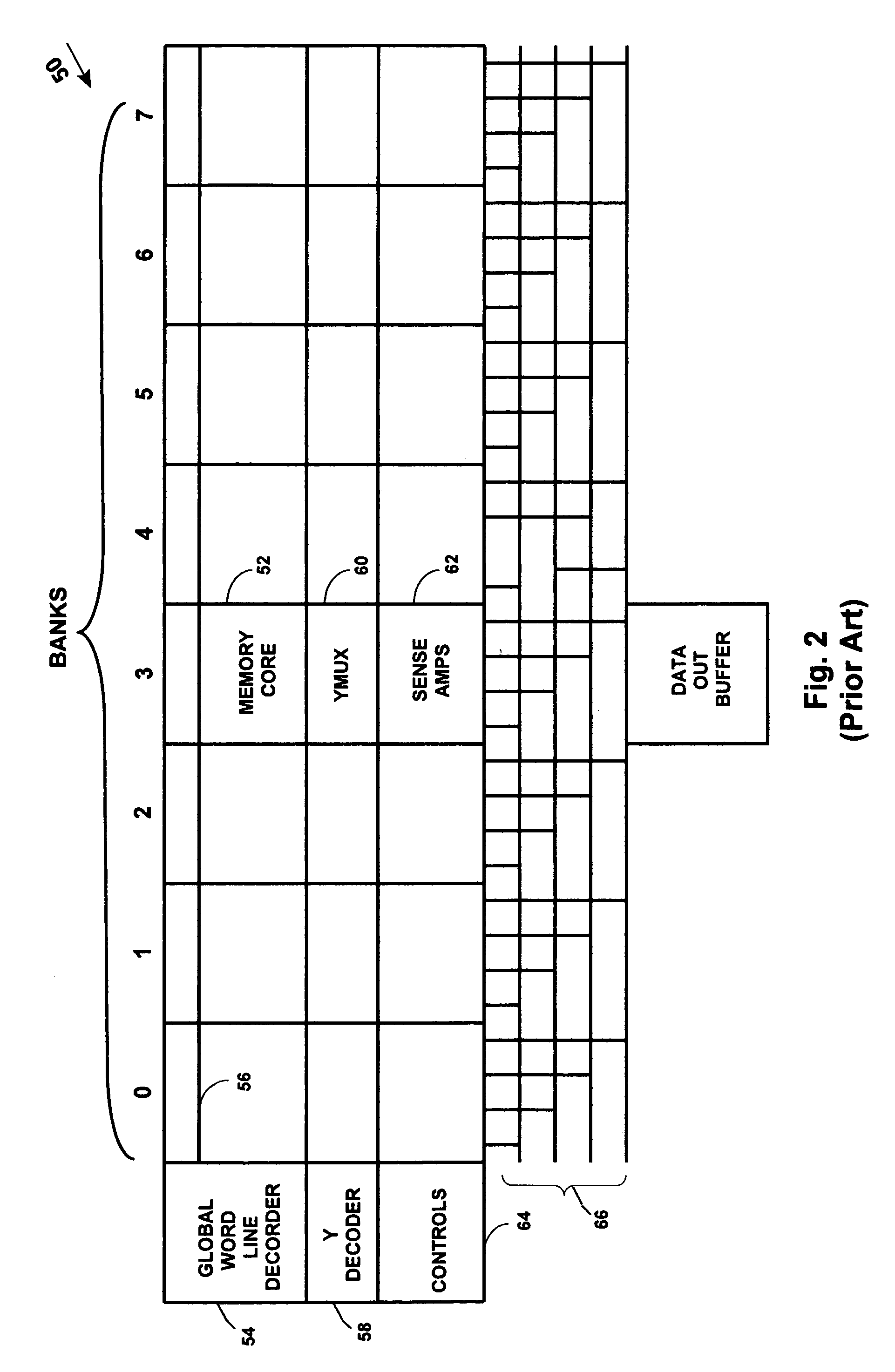

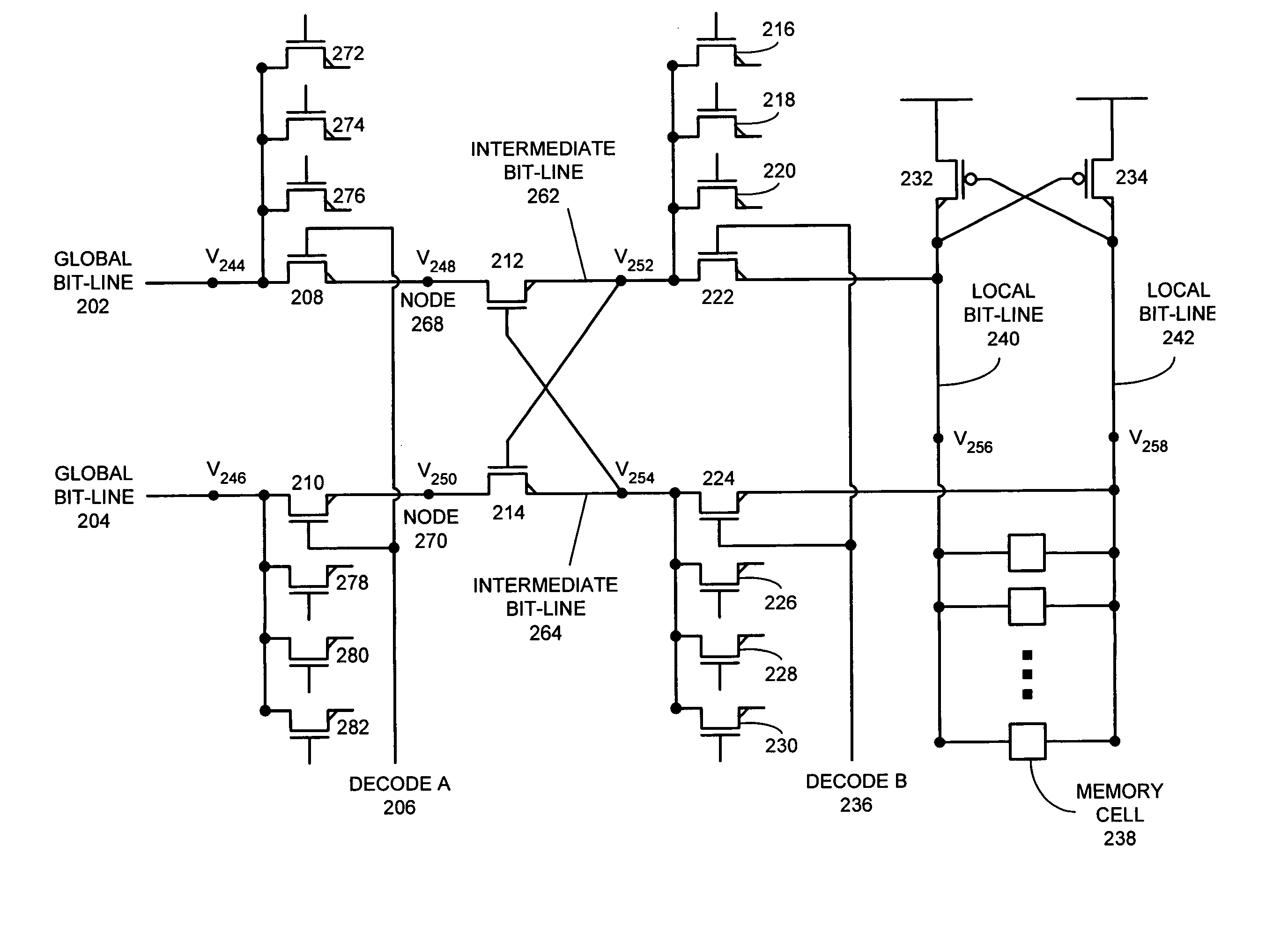

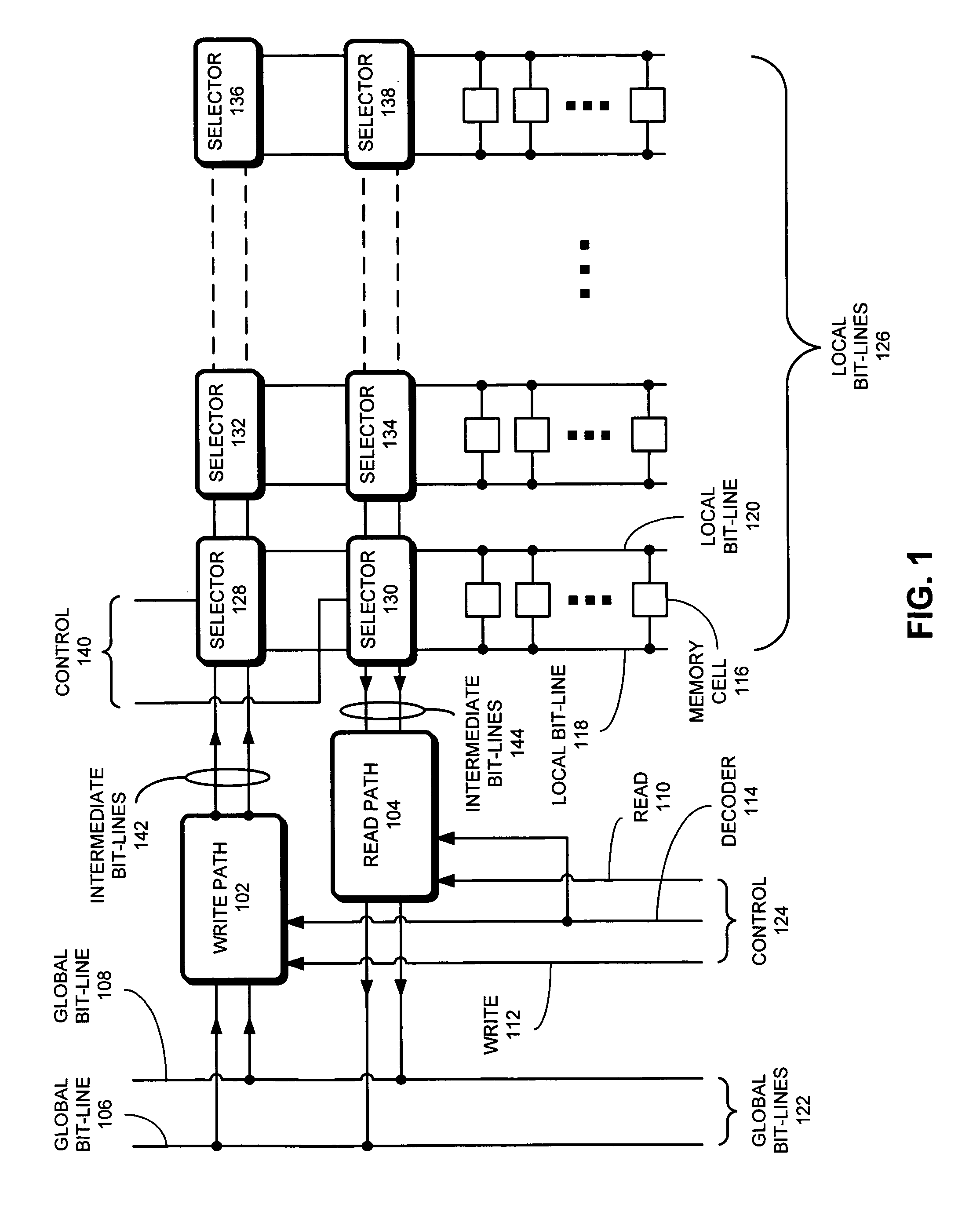

Layout for semiconductor memory including multi-level sensing

InactiveUS6188596B1Reduce the differenceReduce power consumptionDigital storageBit lineAudio power amplifier

A memory module configuration has been developed, which employs multi-level sensing, low-voltage-swing differential signal paths, and array layout techniques to better optimize area / speed / power tradeoffs. In some configurations two-level sensing is employed with secondary sense amplifiers positioned toward a middle of the memory module with memory banks or submodules positioned therearound. Primary sense-amplifiers in the submodules or banks sense differential signals on local bit-lines spanning the corresponding submodule or bank and drive a low-voltage-swing differential signal onto global bit-lines that span a subset of the submodules or banks. The global bit-lines are sensed by secondary sense amplifiers that drive data outputs across a subset of the submodules or banks toward output circuits. In some configurations the memory module is divided into upper and lower portions with upper global bit-lines spanning the upper portion and lower global bit-lines spanning the lower portion. Corresponding upper and lower global bit-lines are disjoint and are sensed by corresponding upper and lower secondary sense amplifiers. By this arrangement, the minimum to maximum variation in access time between the different rows of the memory module is reduced. Moreover, smaller drivers and lower power is achieved by use of such a two-level arrangement. In particular, area reductions and power reductions are achieved for submodule- or bank-resident primary sense amplifiers.

Owner:GLOBALFOUNDRIES INC

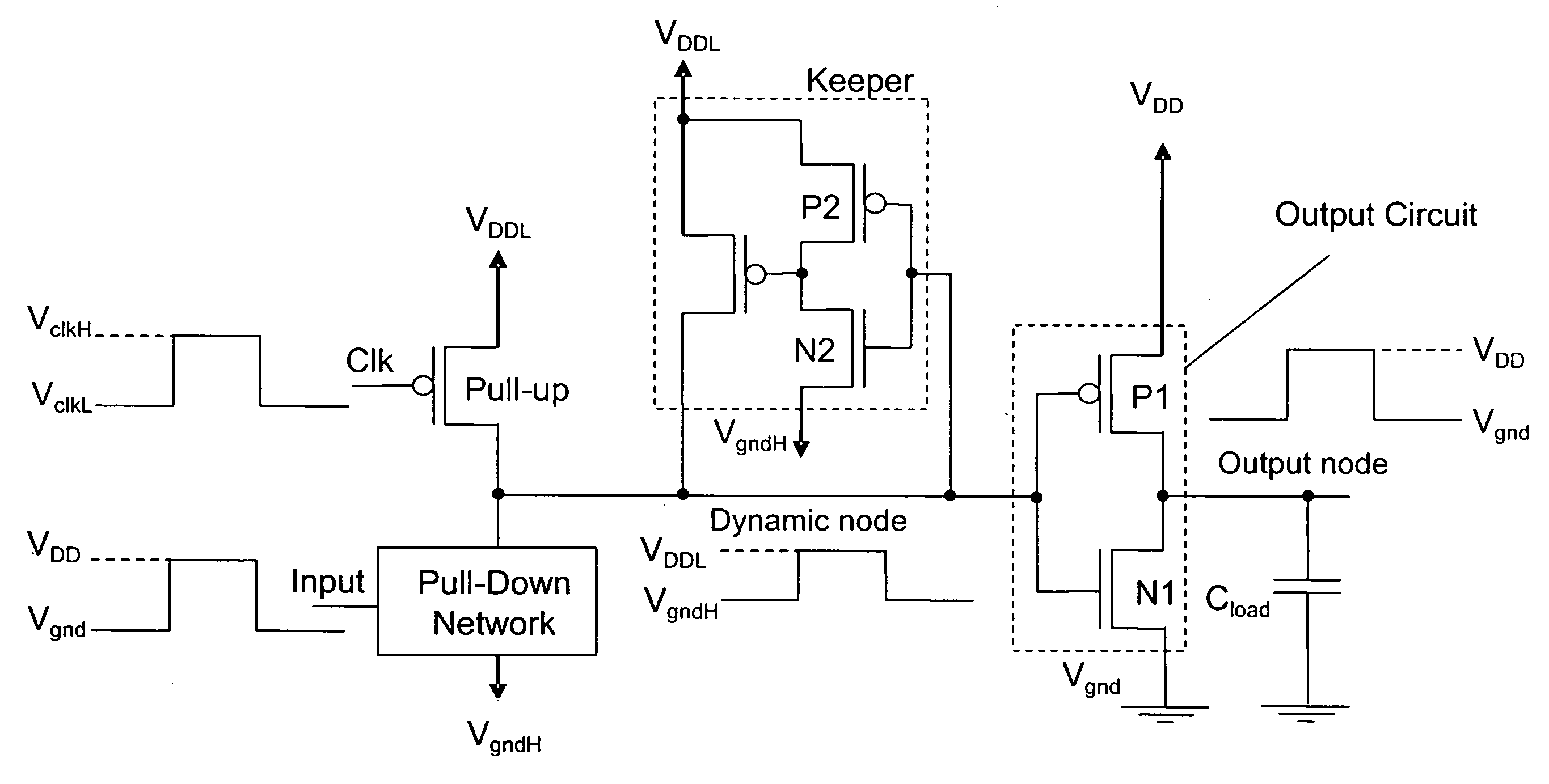

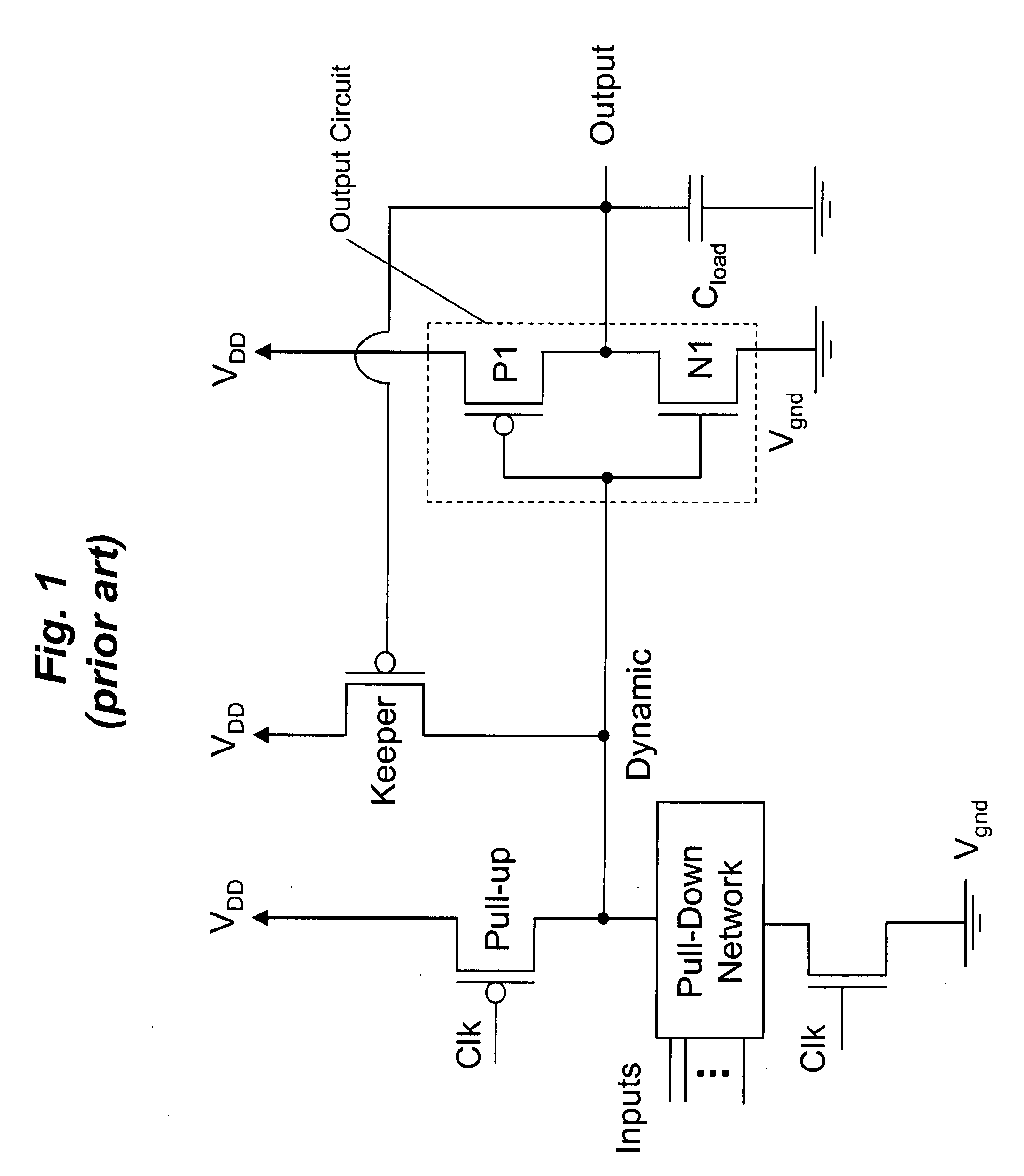

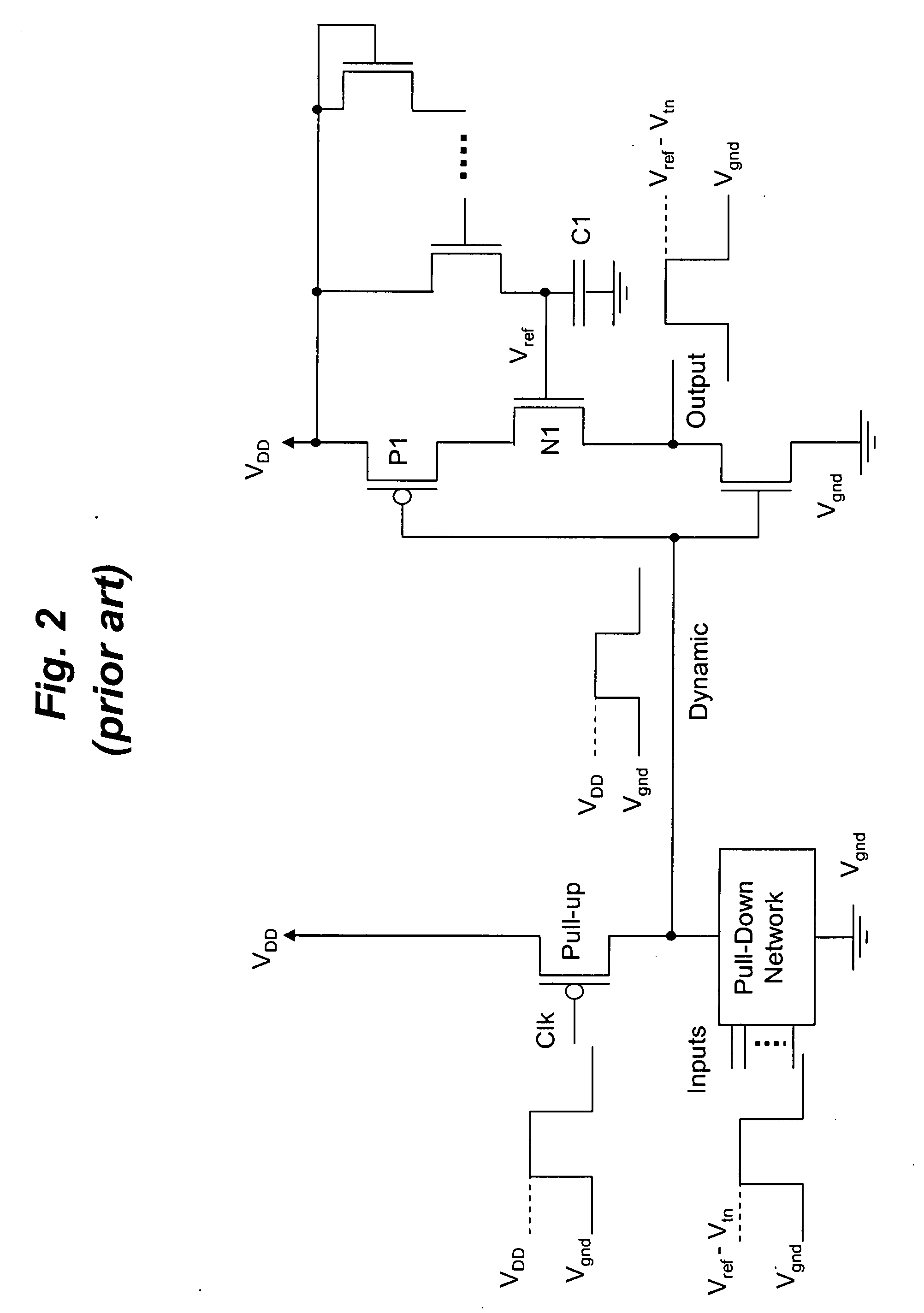

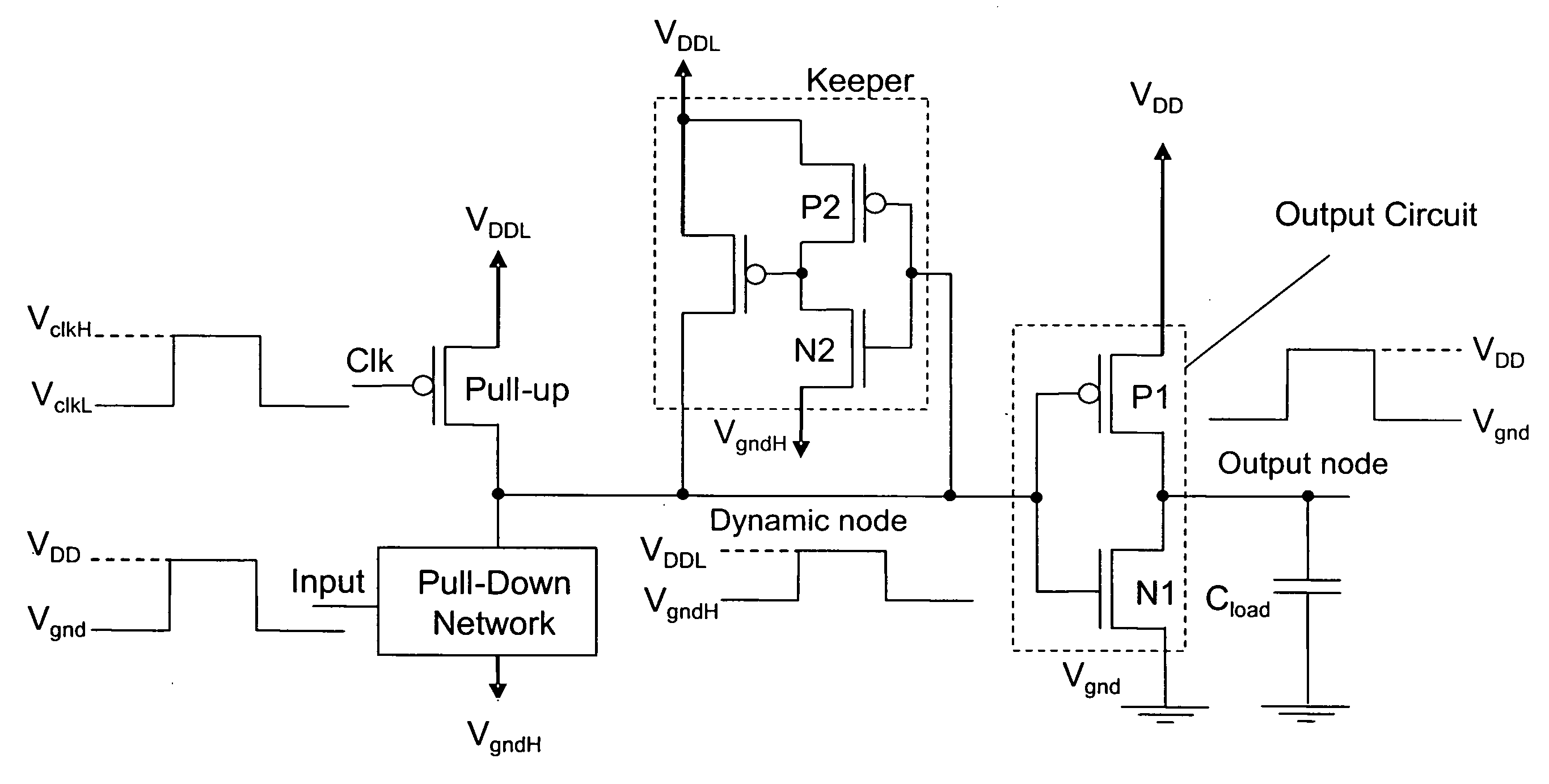

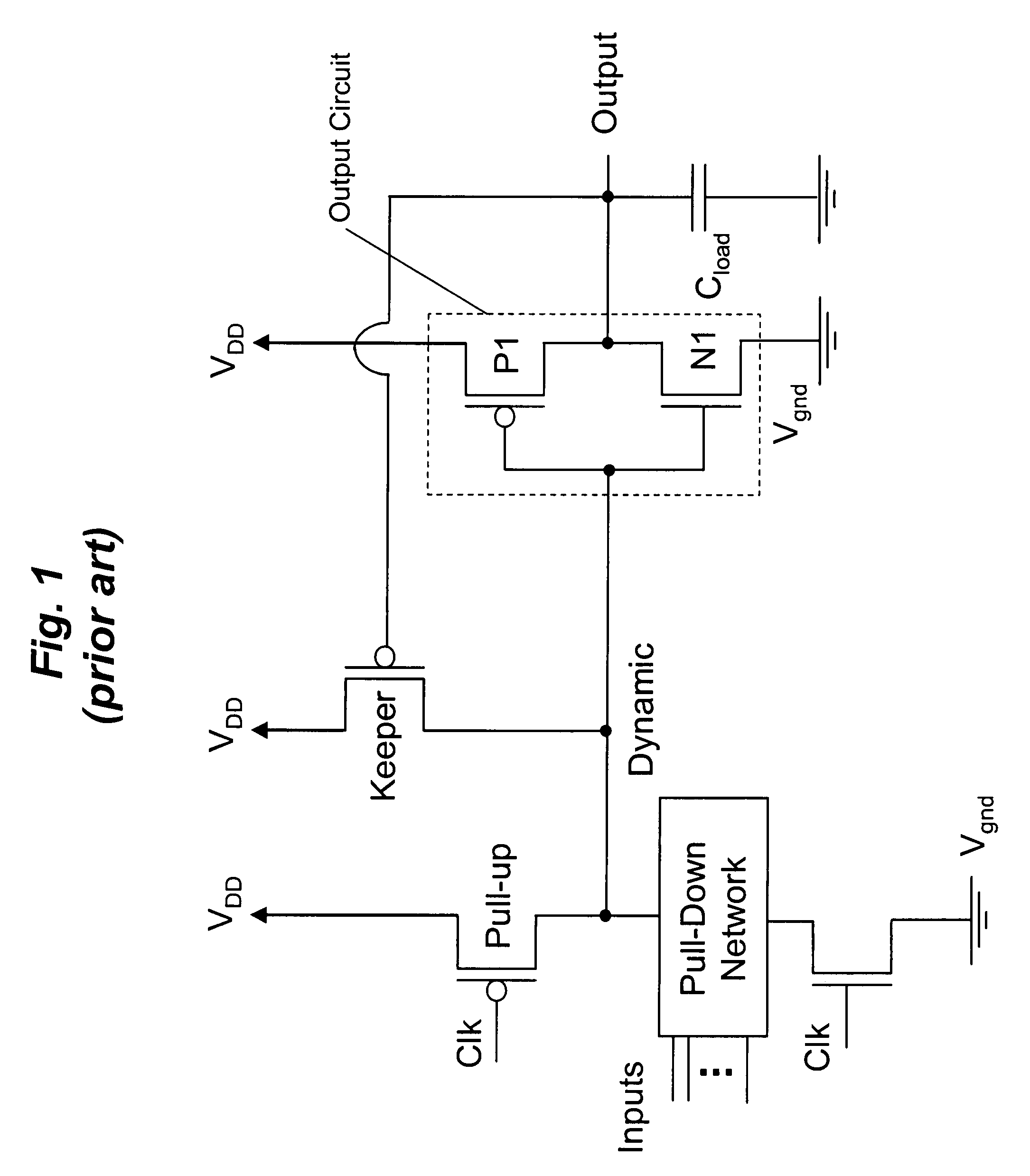

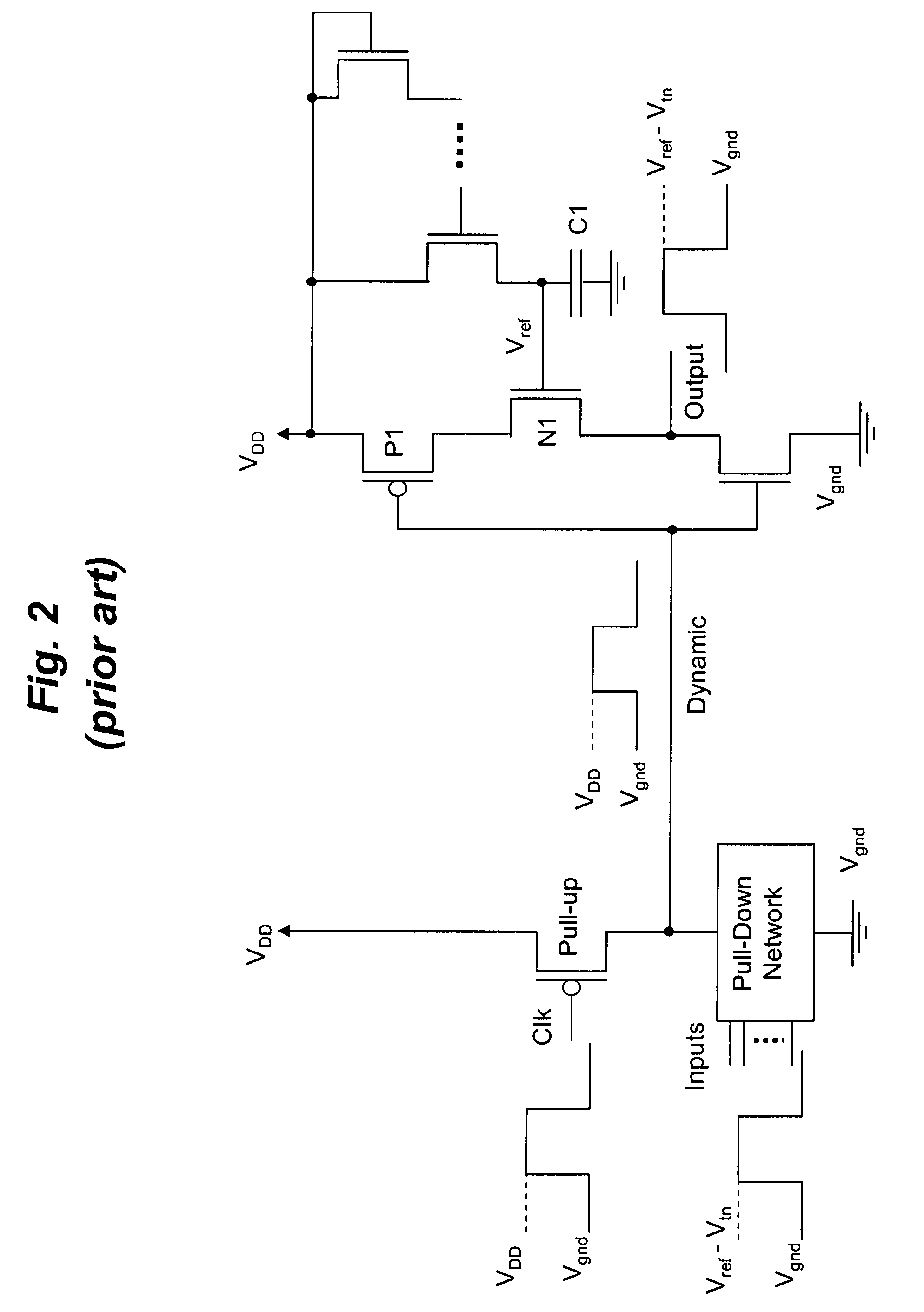

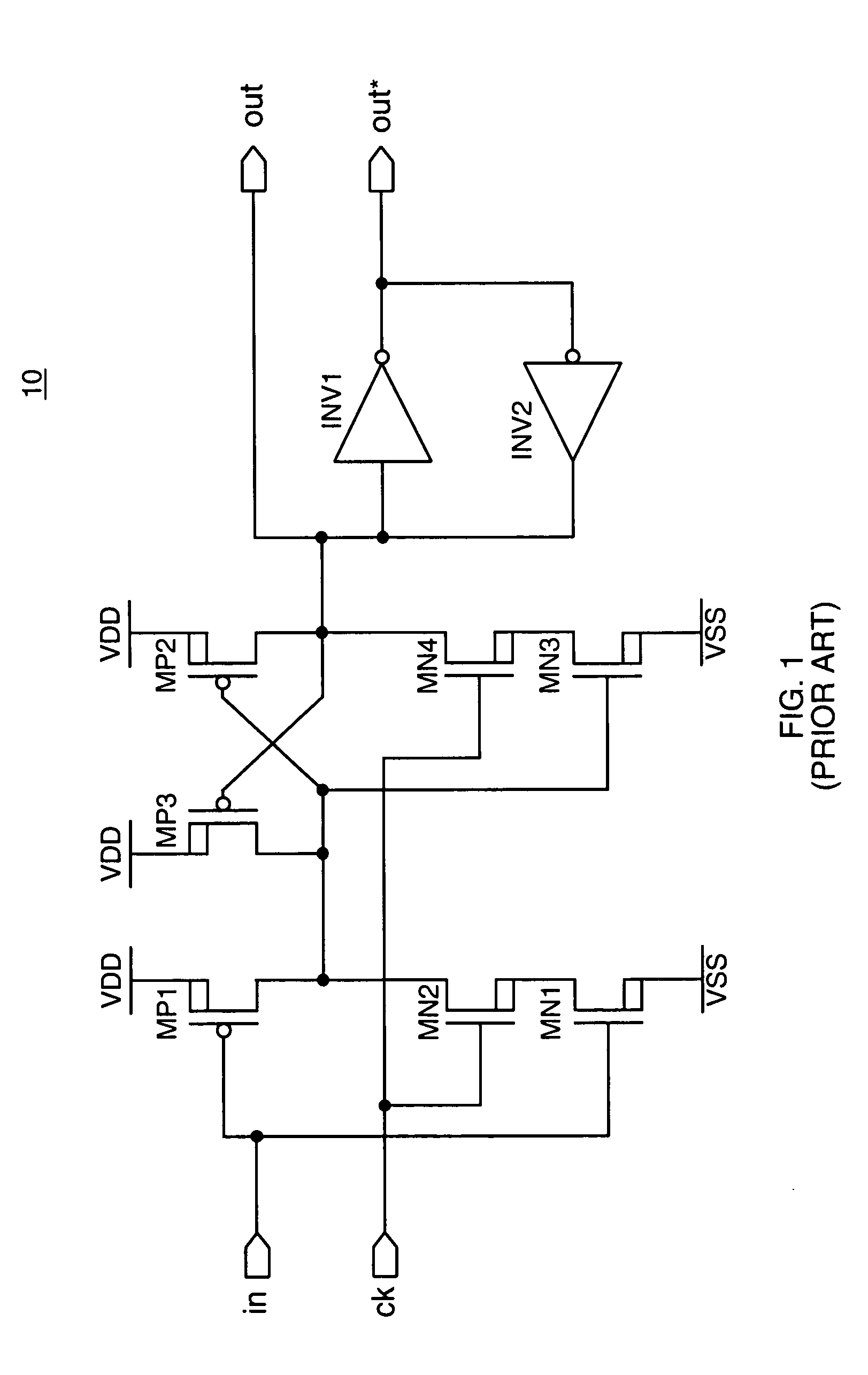

Low swing domino logic circuits

ActiveUS20070176641A1Reduce upper boundary of voltage swingMinimizing PDPLogic circuits characterised by logic functionLogic circuitsDomino logicLogic circuitry

Low voltage swing techniques are provided for simultaneously reducing the active and standby mode power consumption and enhancing the noise immunity in domino logic circuits. One or both the upper and lower boundaries of the voltage swing at the dynamic node may be different from the upper and lower boundaries of the voltage swing at the output node. For example, the voltage swing at the dynamic node may be less than the voltage swing at the output node, optimized for speed or power consumption. As another example, the voltage swing at the dynamic node may be greater than the voltage swing at the output node, optimized for speed or power consumption. Further, the domino logic circuit may use dual Vt thereby reducing the short-circuit current during operation.Meanwhile, full voltage swing signals may be maintained at the inputs and outputs for high speed operation. The low swing circuit techniques are provided that modify the output voltage swing of a domino gate, thereby reducing the active mode power consumption.

Owner:WISCONSIN ALUMNI RES FOUND

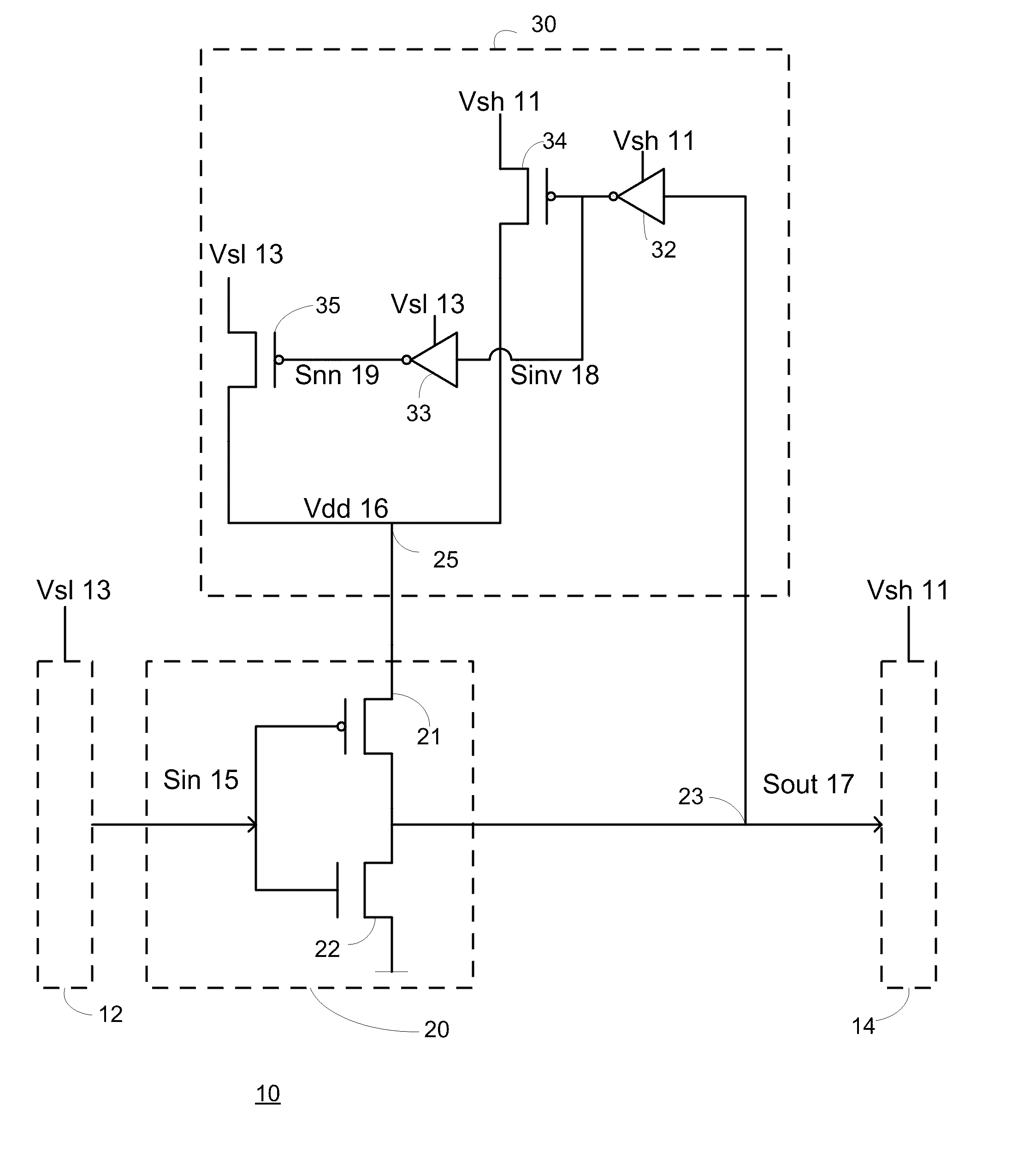

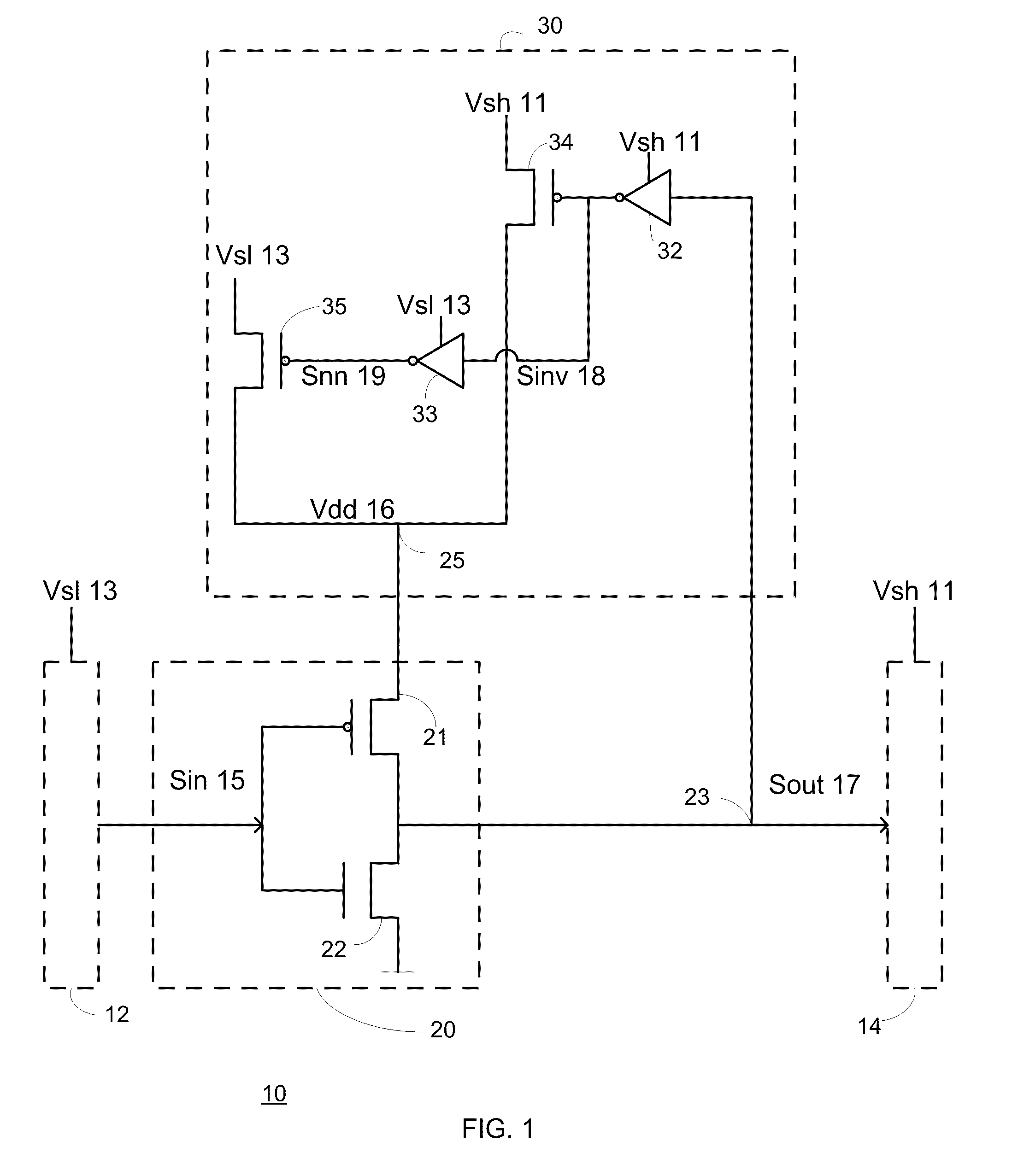

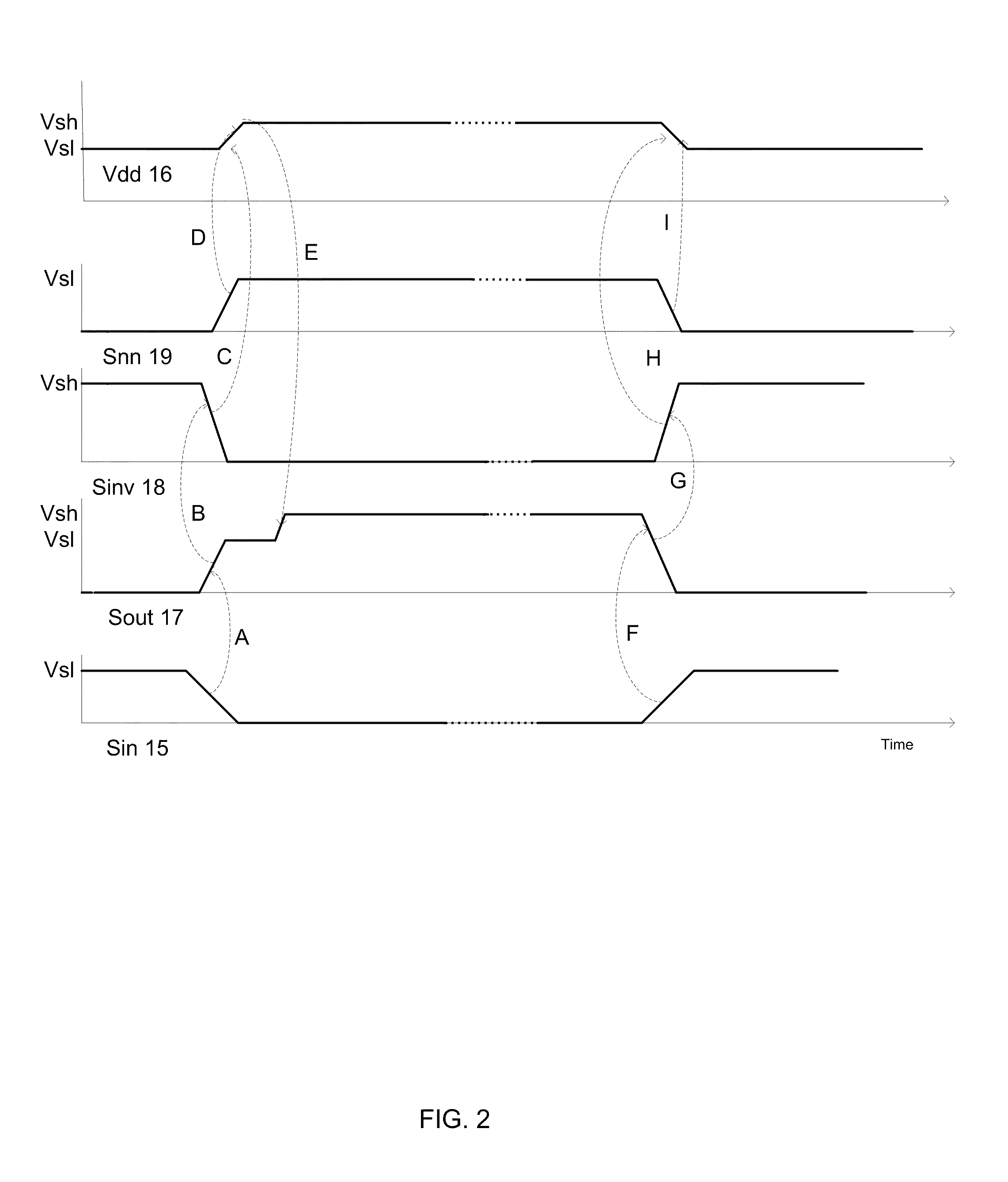

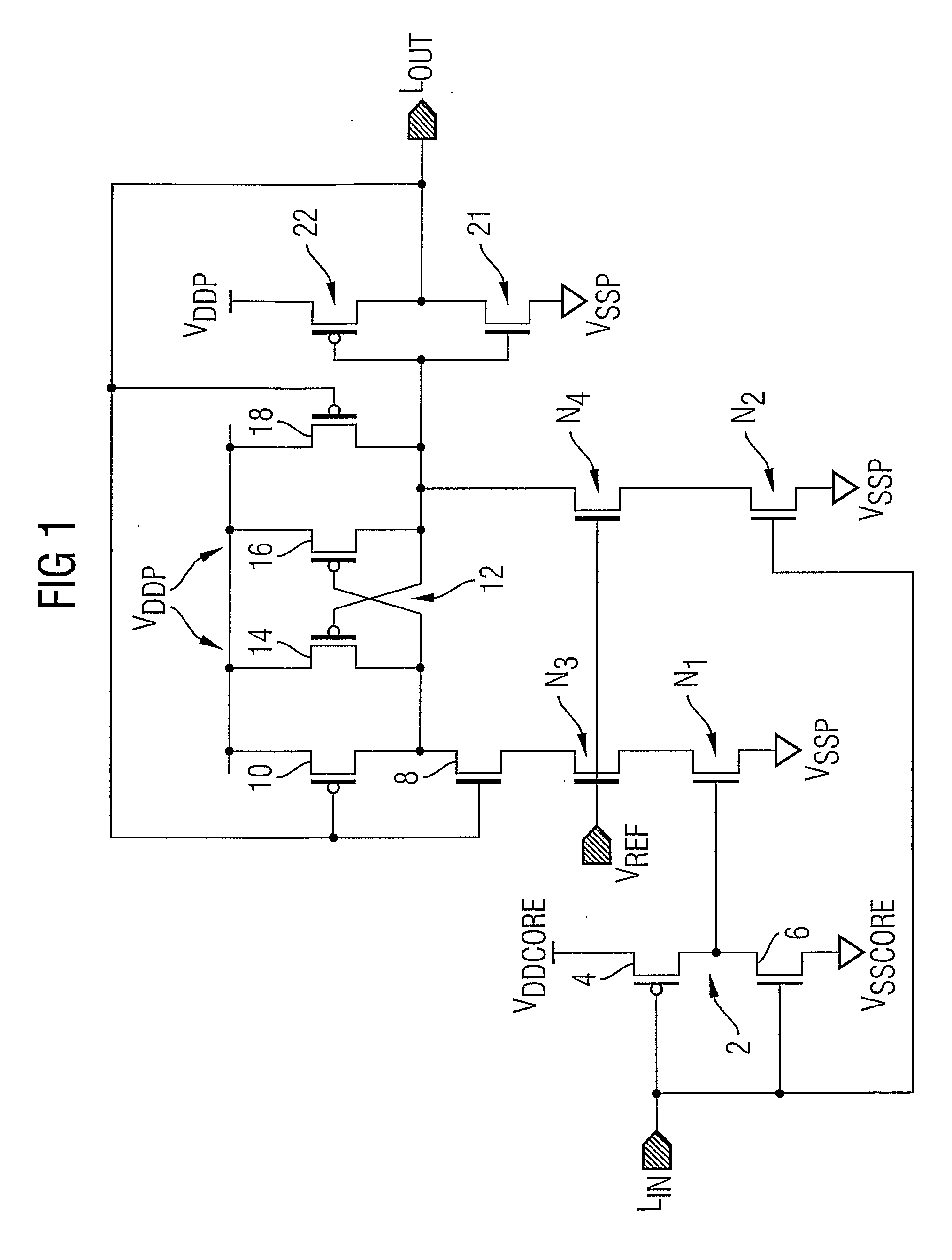

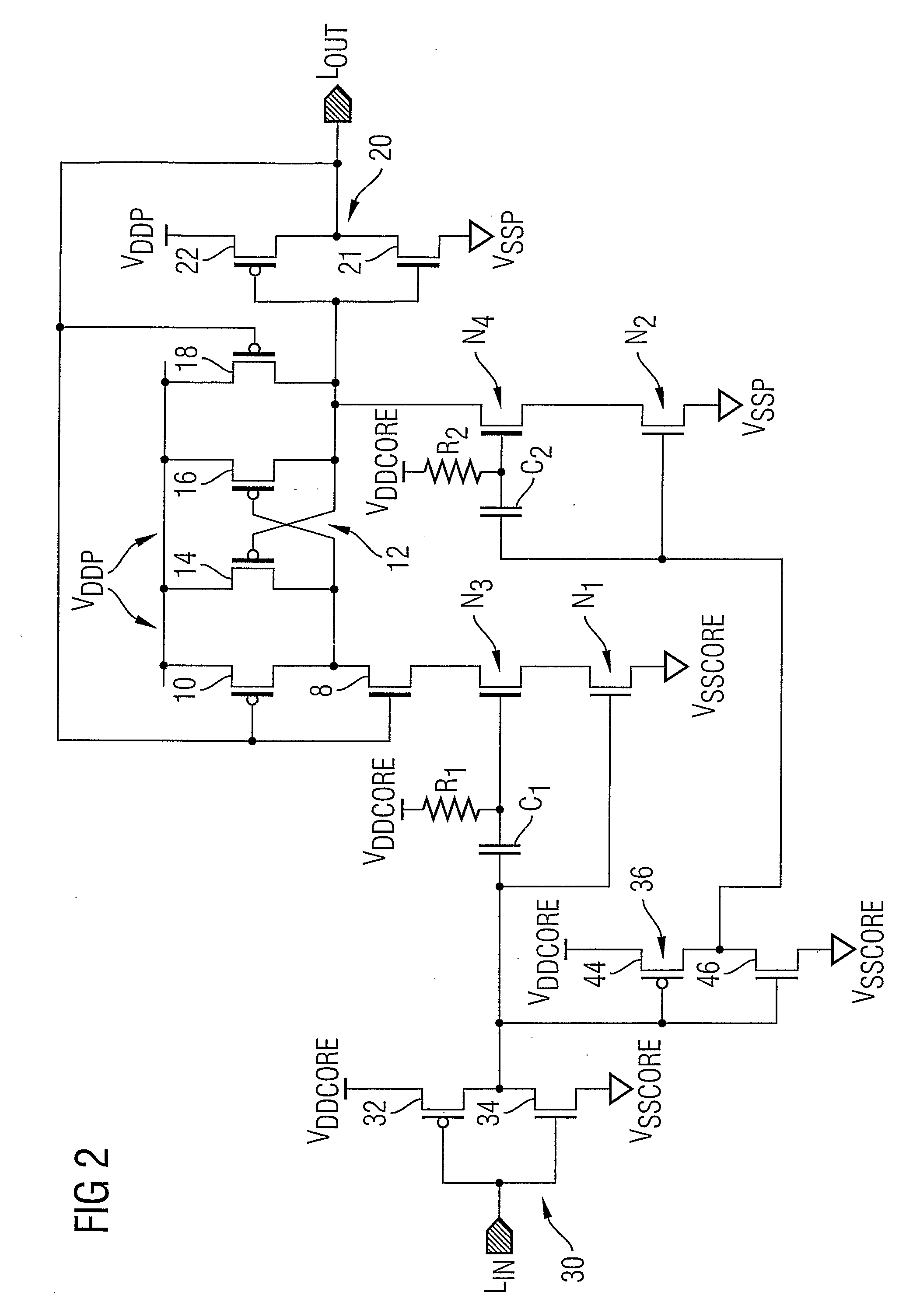

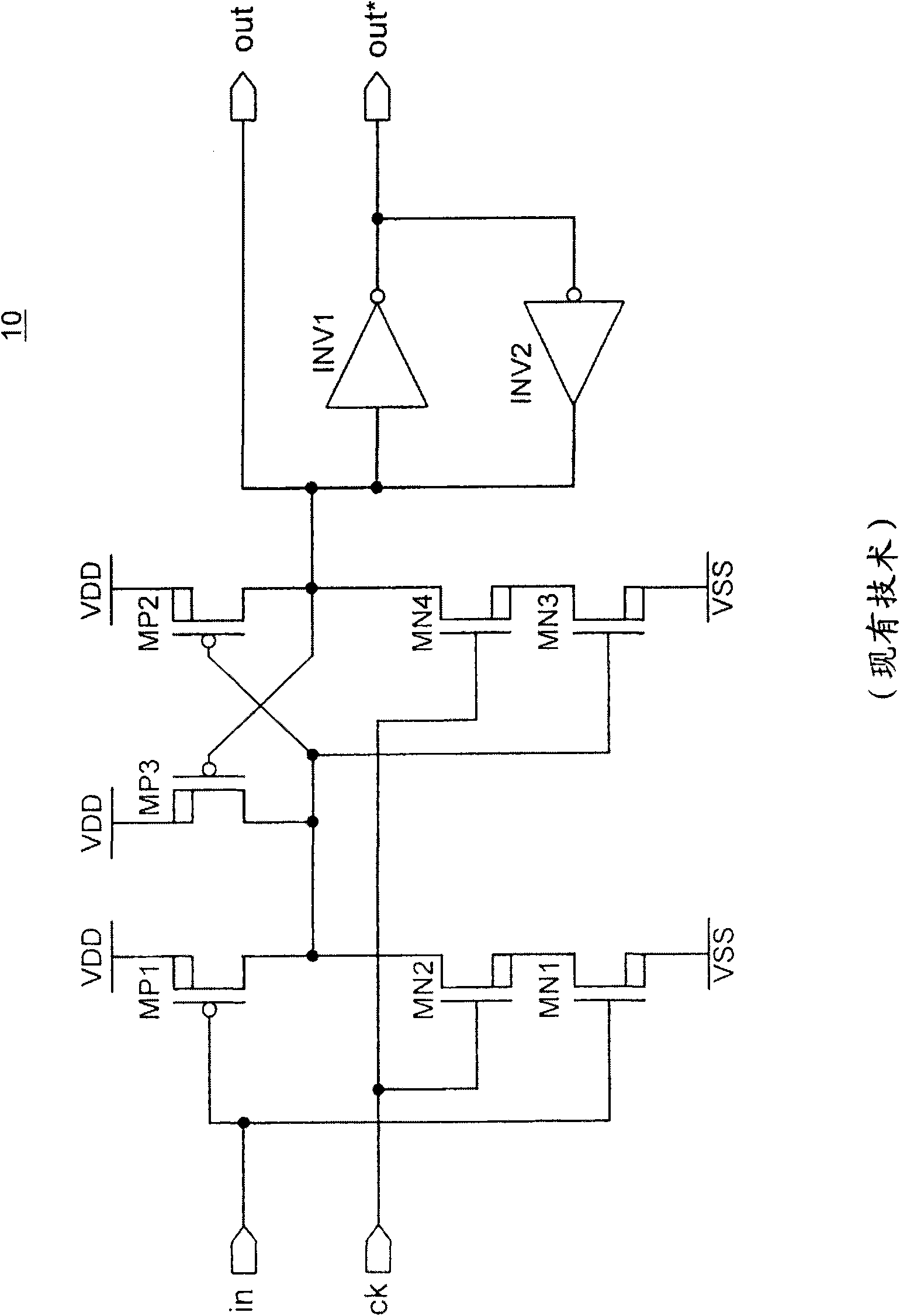

Scheme of level shifter cell

A system having voltage level shifting capabilities, the system includes a logic circuit and a multiple level voltage supply circuit; wherein the logic circuit comprises at least one PMOS transistor and at least one NMOS transistor; wherein the logic circuit receives an input signal, receives a voltage supply signal from the multiple level voltage supply circuit, and outputs an output signal via a first node; wherein the input signal has a low voltage swing between a low level supply voltage and a rail voltage; wherein the output signal has a high voltage swing between a high level supply voltage and the rail voltage; and wherein the multiple level voltage supply circuit selects, in response to a level of the output signal, whether to provide to the supply node of the logic circuit a high level supply voltage or a low level supply voltage.

Owner:NORTH STAR INNOVATIONS

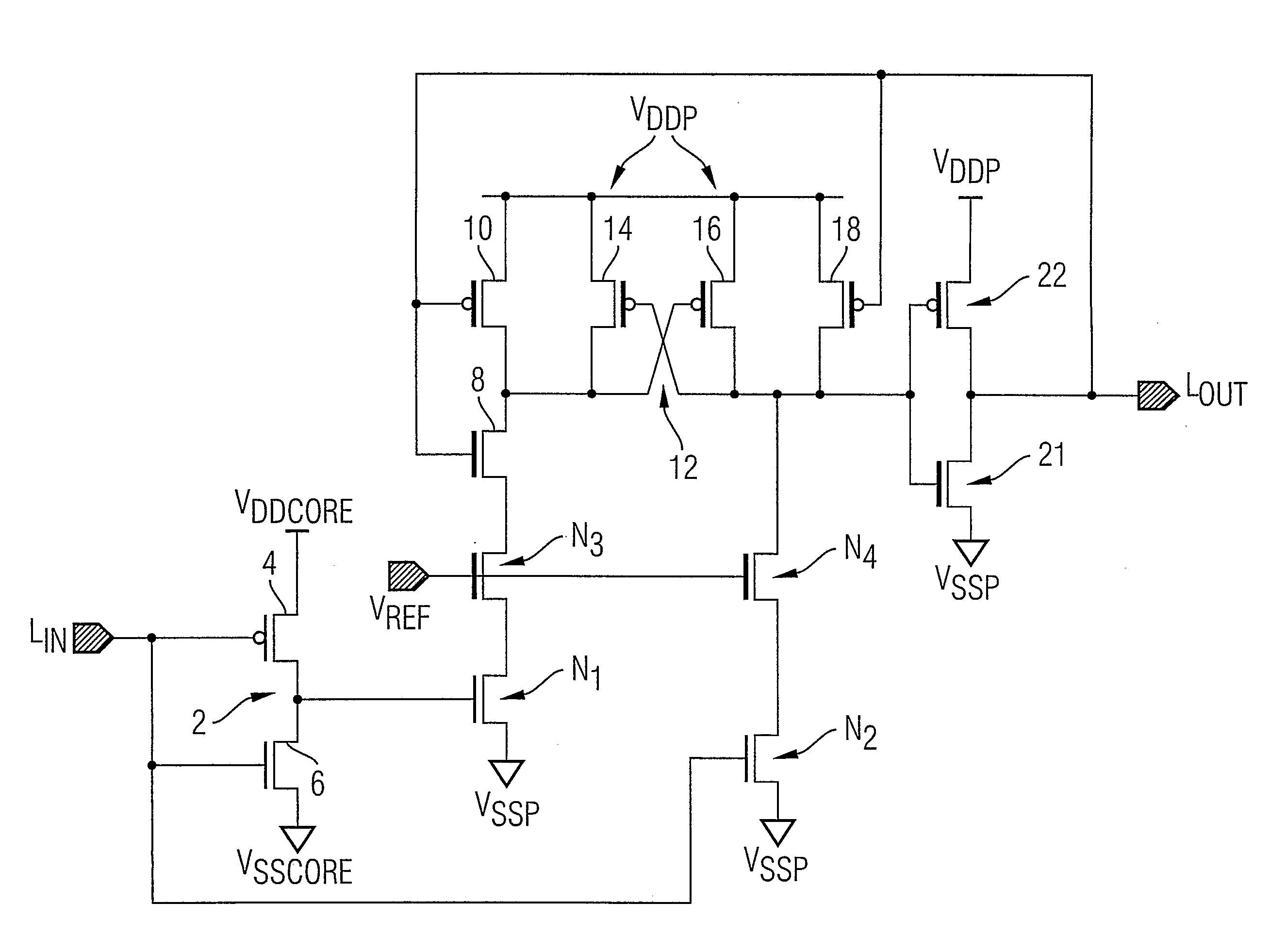

Digital Voltage Level Shifter

A digital voltage level shifter for converting an input signal with a low voltage swing to an output signal with a high voltage swing comprises a first inverter stage for generating an inverted signal from an input signal, the inverted signal having a voltage swing between a core voltage and ground, and a second inverter stage for producing an anti-phase signal from the inverted input signal, the anti-phase signal having a voltage swing between the core voltage and ground. The first and second inverters each drive a respective thin gate NMOS transistor connected in cascode with a respective NMOS transistor. The sources of the first and second thin gate NMOS transistors are connected to ground. The gates of the NMOS transistors are connected to the output of the respective inverters through a respective capacitor and are referenced to the core voltage through a respective resistor. The drains of the NMOS transistors are connected to an output circuit to provide an output signal having a voltage higher than the core voltage.

Owner:INFINEON TECH AG

Low swing domino logic circuits

ActiveUS7764087B2Reduce upper boundary of voltage swingMinimizing PDPLogic circuits characterised by logic functionDomino logicLogic circuitry

Low voltage swing techniques are provided for simultaneously reducing the active and standby mode power consumption and enhancing the noise immunity in domino logic circuits. One or both the upper and lower boundaries of the voltage swing at the dynamic node may be different from the upper and lower boundaries of the voltage swing at the output node. Further, the domino logic circuit may use dual Vt thereby reducing the short-circuit current during operation. Meanwhile, full voltage swing signals may be maintained at the inputs and outputs for high speed operation. The low swing circuit techniques are provided that modify the output voltage swing of a domino gate, thereby reducing the active mode power consumption.

Owner:WISCONSIN ALUMNI RES FOUND

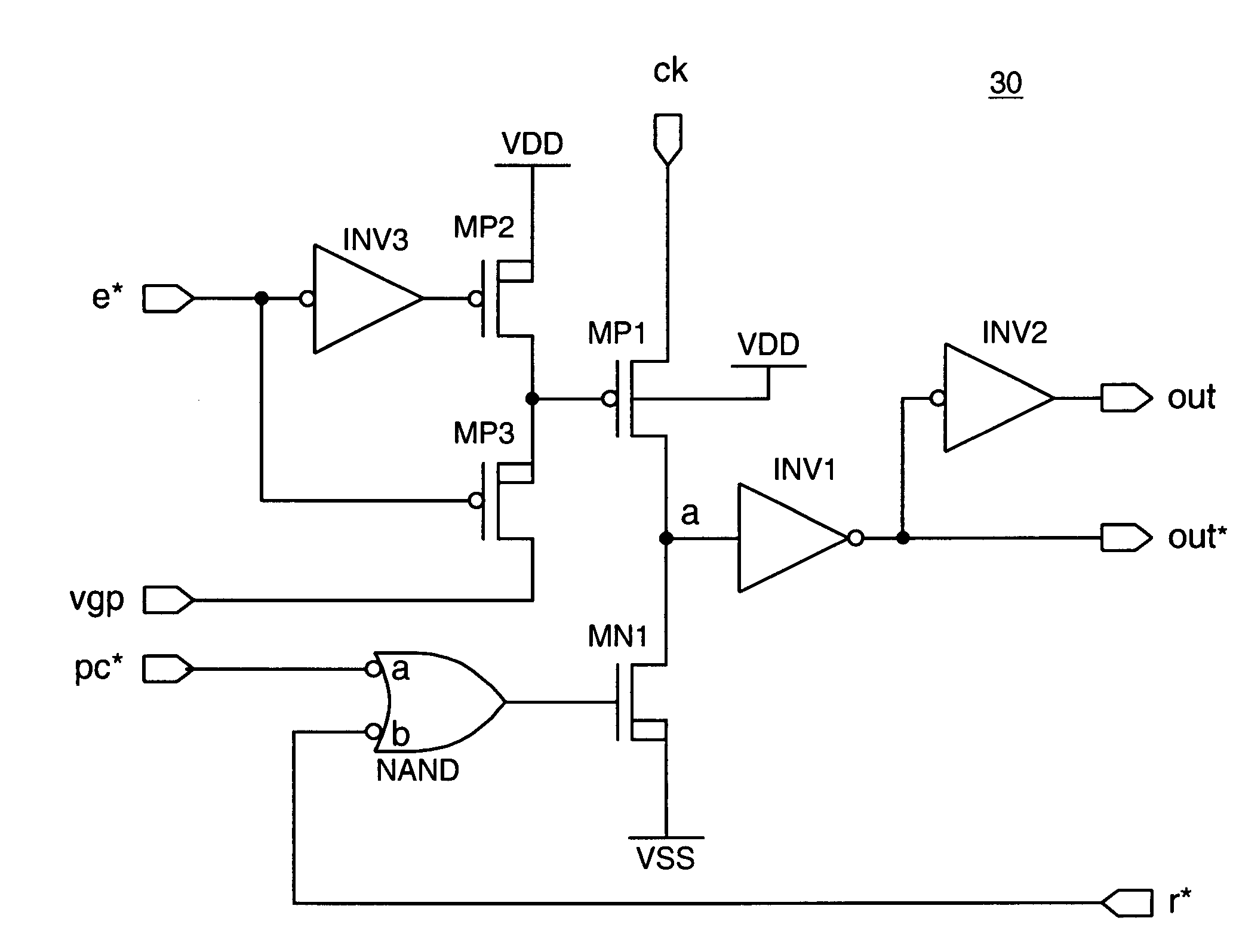

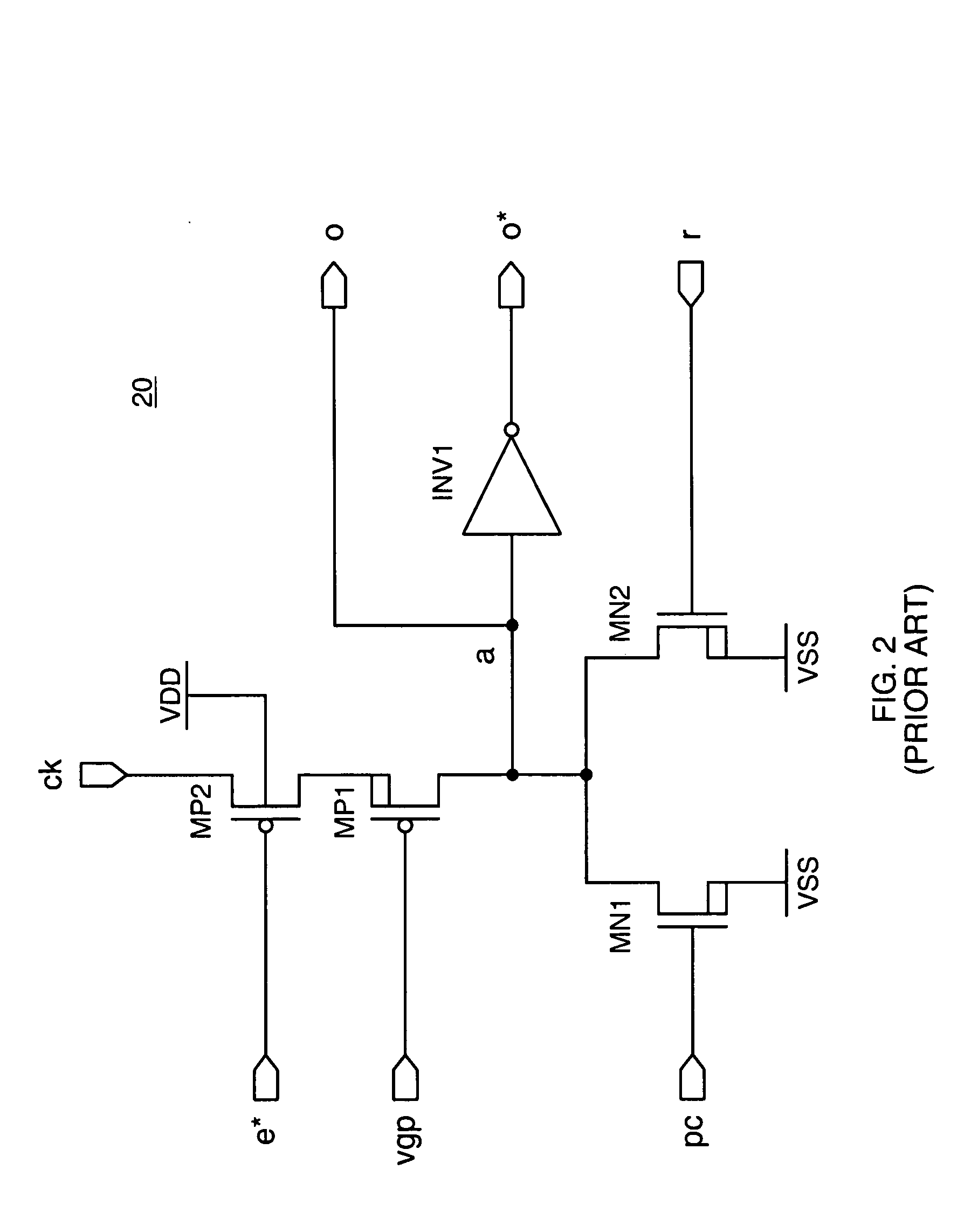

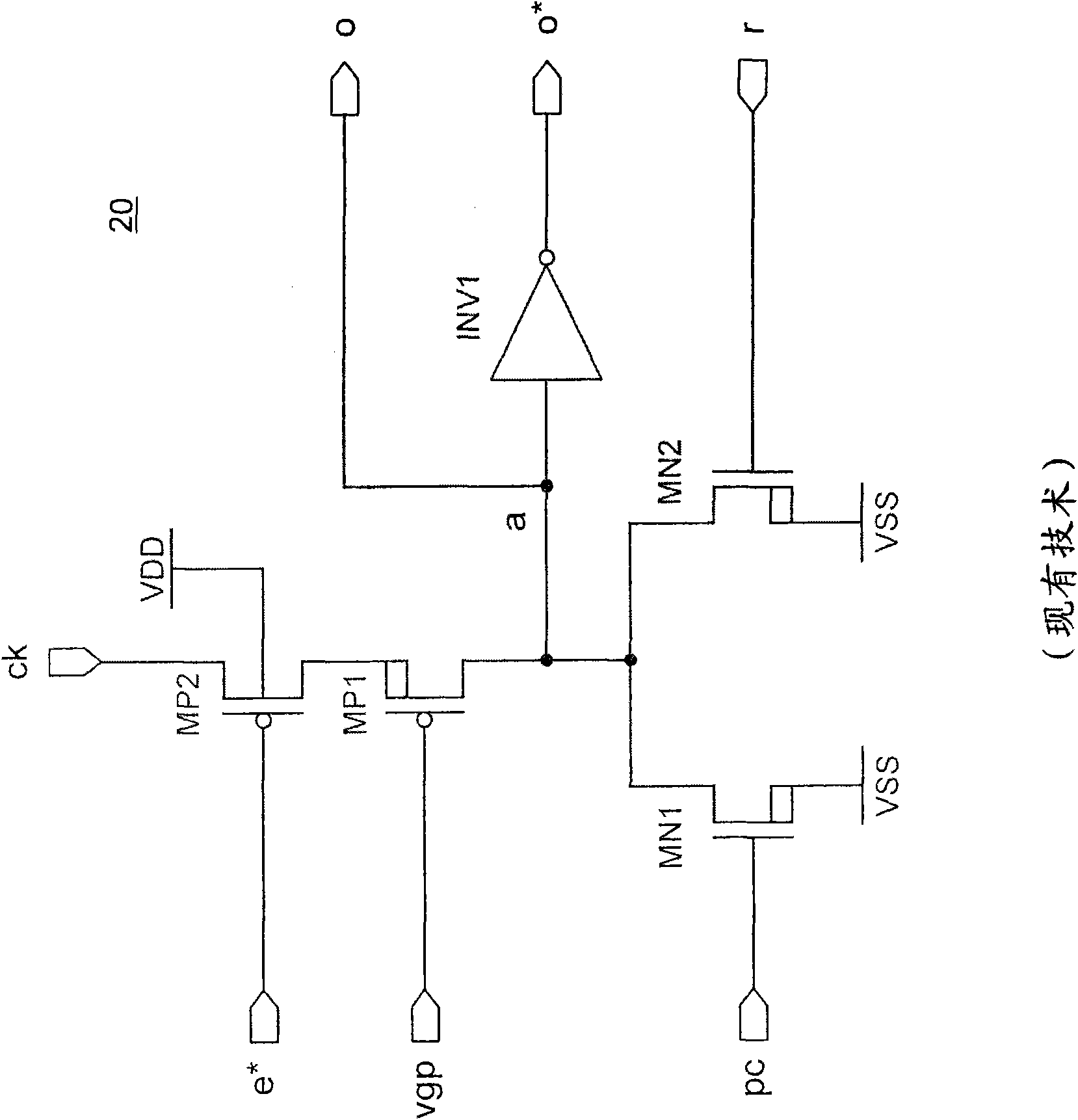

Shifter register for low power consumption application

A high voltage shift register stage which directly accepts low voltage clock signal inputs without using clock buffers. In particular, a shift register stage circuit is adapted to operate with a low voltage swing clock signal, with the stage circuit having a single state node, a, driven directly. This arrangement allows for reduced power consumption and higher operating speeds.

Owner:KOPIN CORPORATION

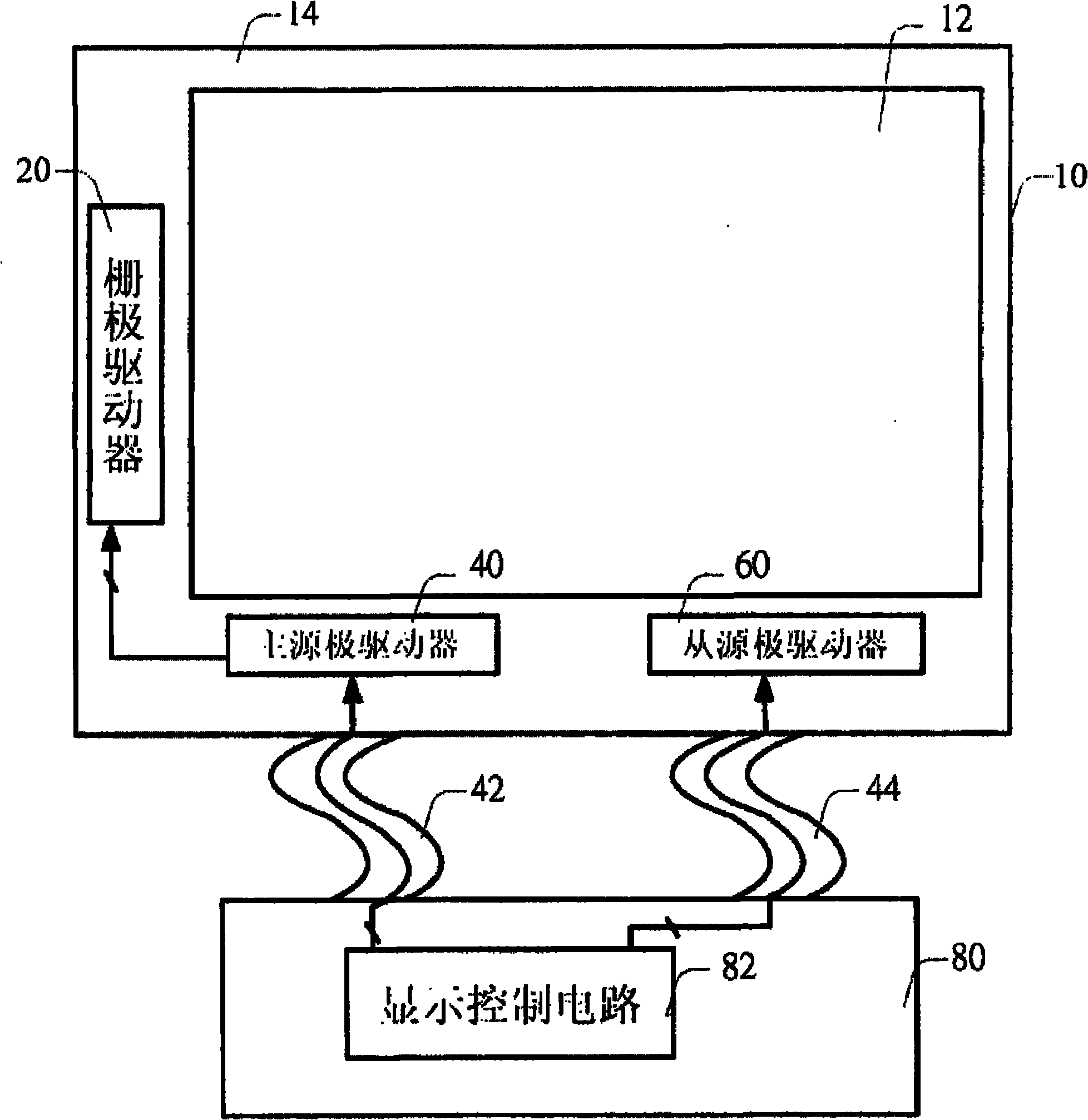

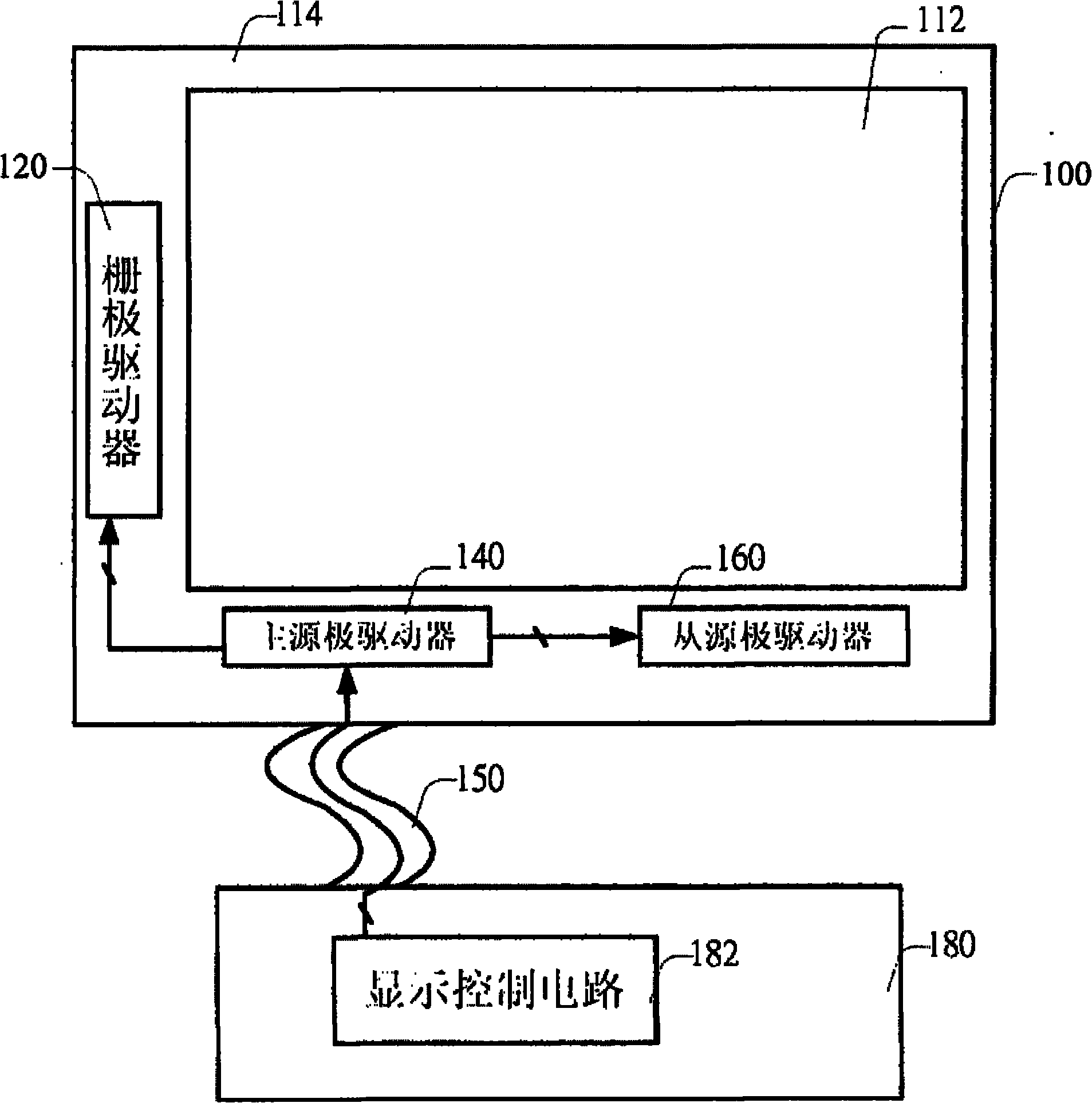

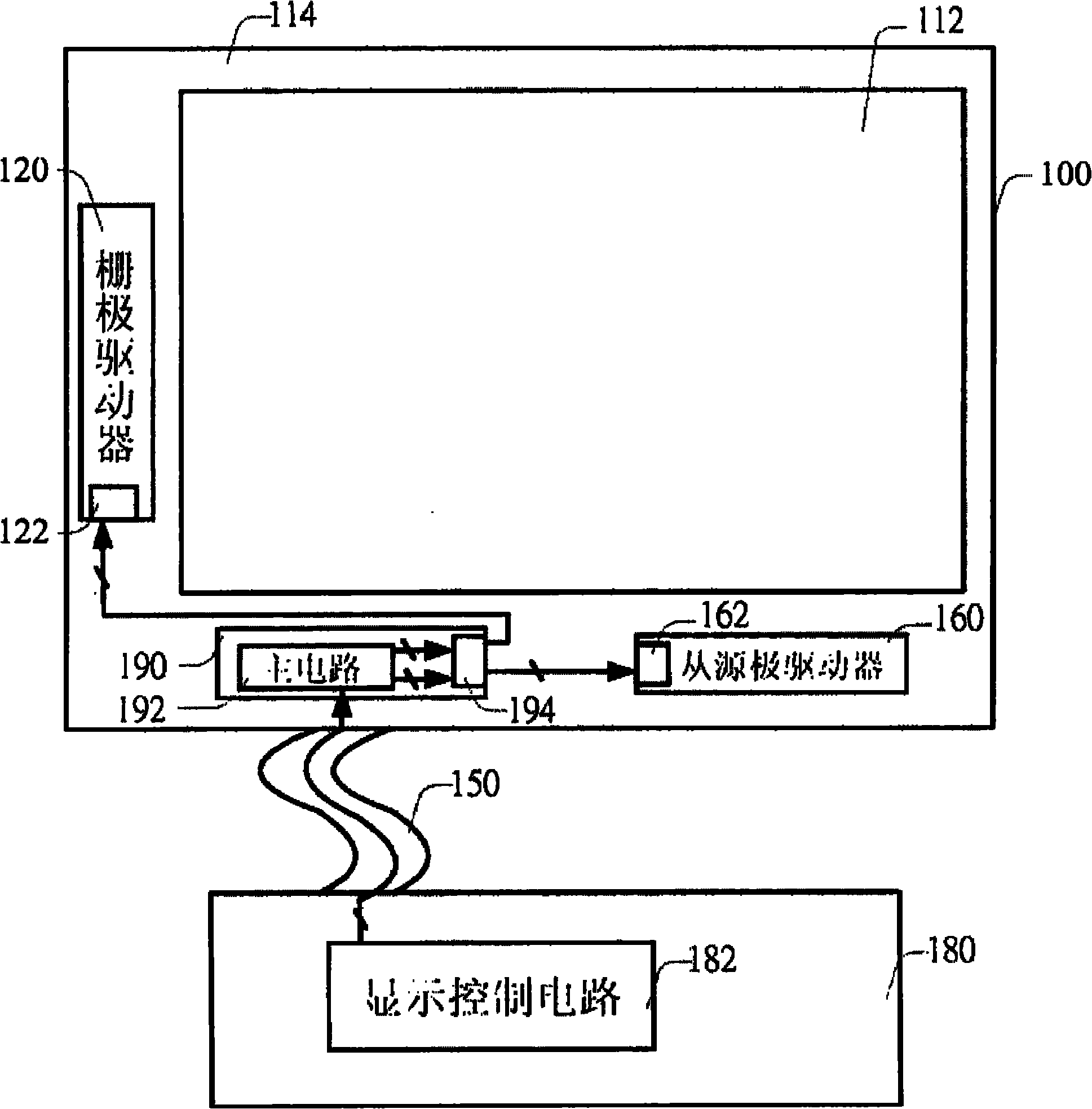

Driver on liquid crystal display panel and related control method

InactiveCN101894526AReduce electromagnetic interferenceReduced voltage swingStatic indicating devicesNon-linear opticsLiquid-crystal displayEngineering

The invention discloses a driver on a liquid crystal display panel and a related control method, which can effectively make a signal transferred through a line on the liquid crystal display panel have low-voltage swing amplitude and an adjustable low rotating speed. The liquid crystal display panel is connected to a display control circuit through a soft plate and comprises a master source driver, a gate driver and a slave source driver, wherein the master source driver receives a digital image signal of a first electrical specification output by the display control circuit through the soft plate and converts the digital image signal into a gate driving signal and a slave source driving signal of a second electrical specification; the gate driver can receive the gate driving signal of the second electrical specification; the slave driver can receive the slave source driving signal of the second electrical specification; and the master source driver, the slave source driver and the gate driver drive a thin film transistor array of the liquid crystal display panel.

Owner:MSTAR SOFTWARE R&D (SHENZHEN) LTD +1

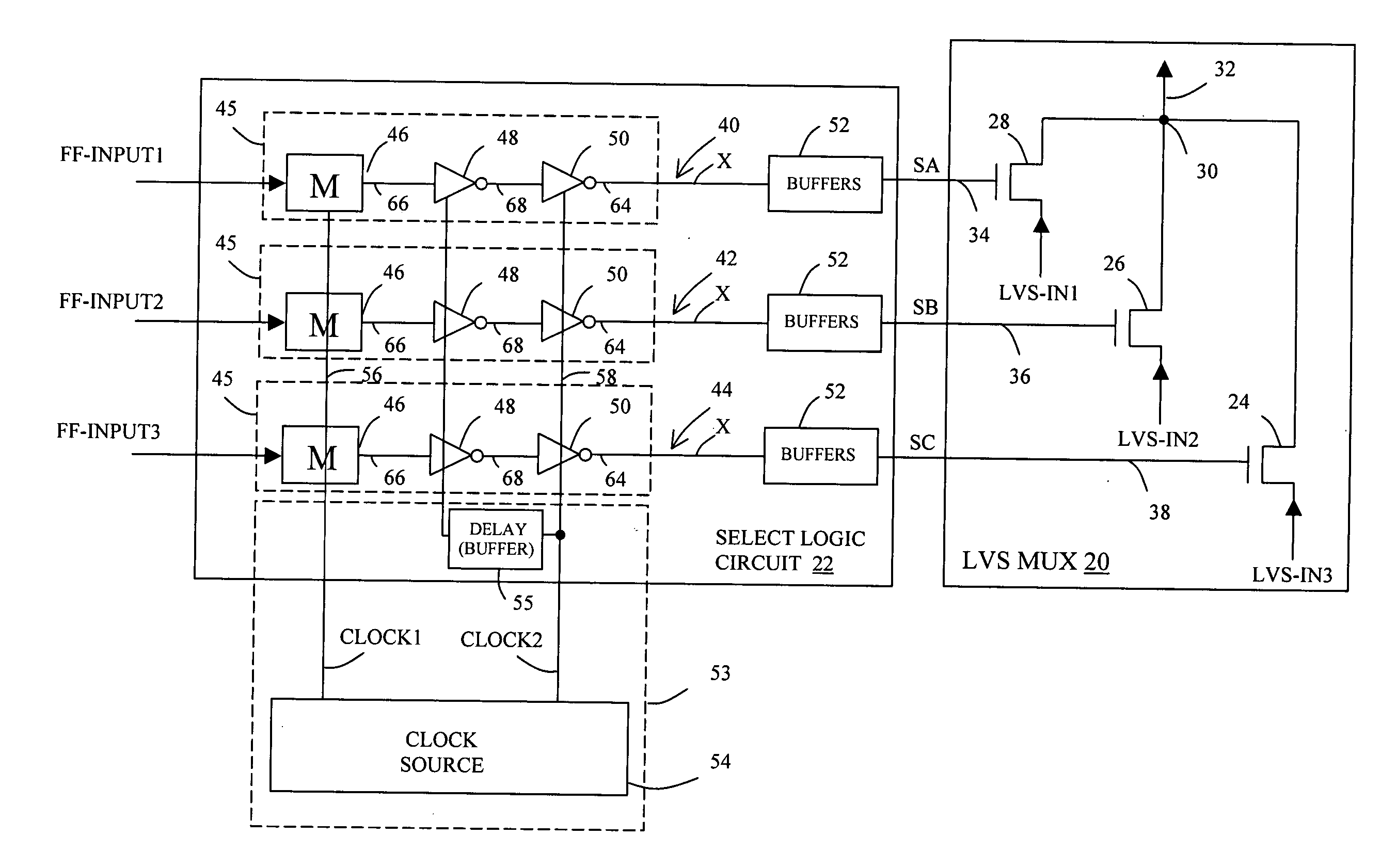

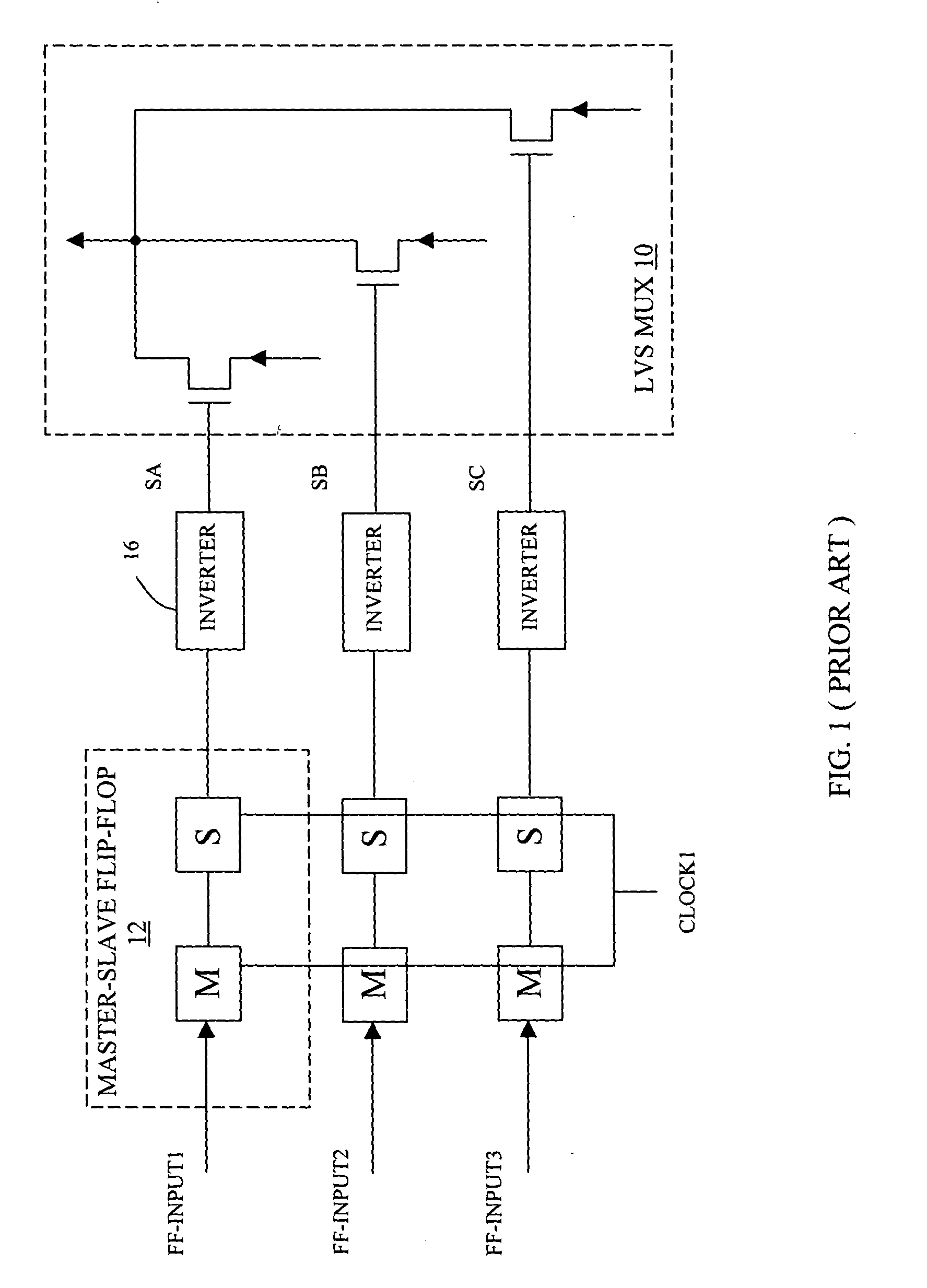

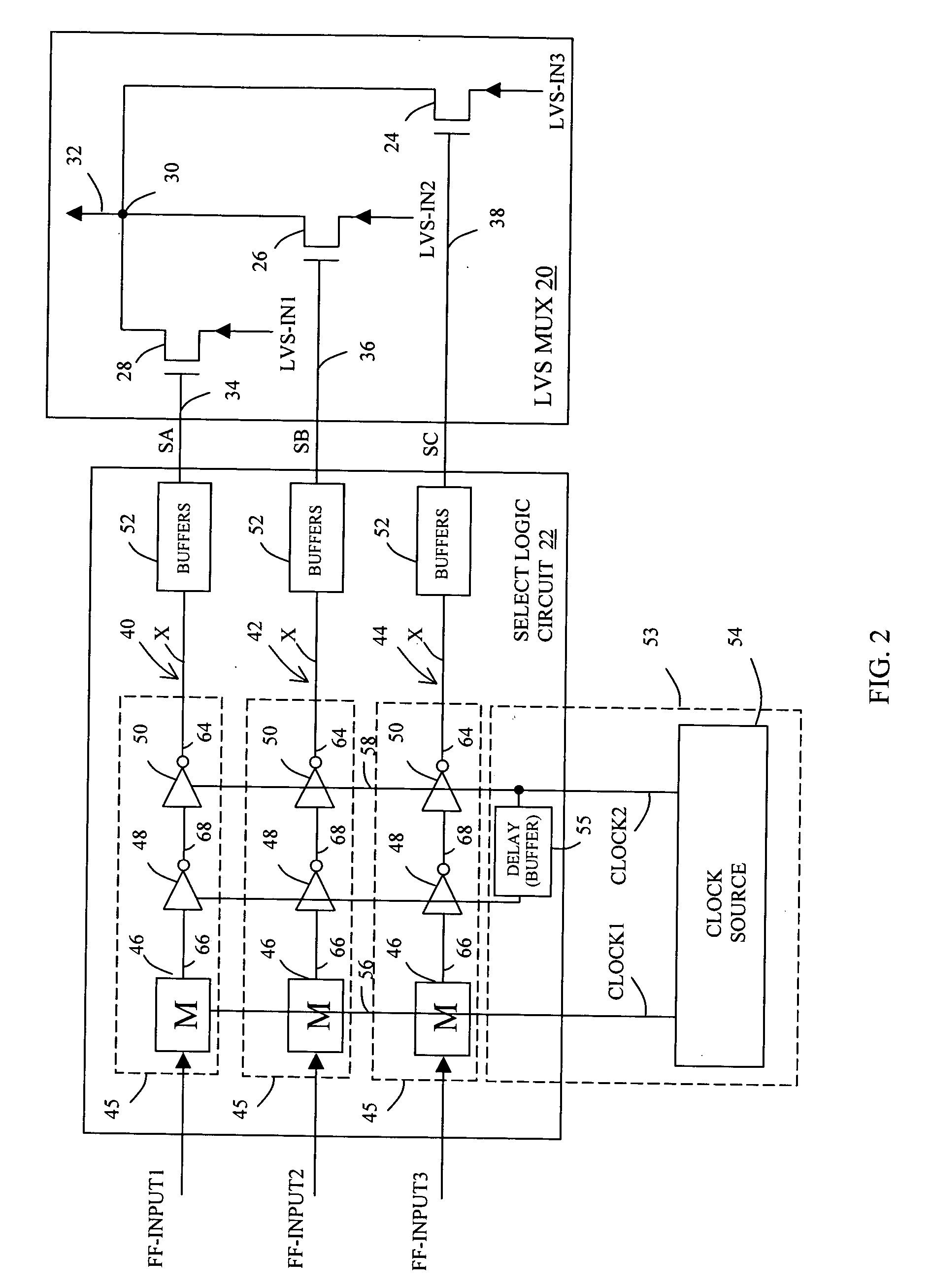

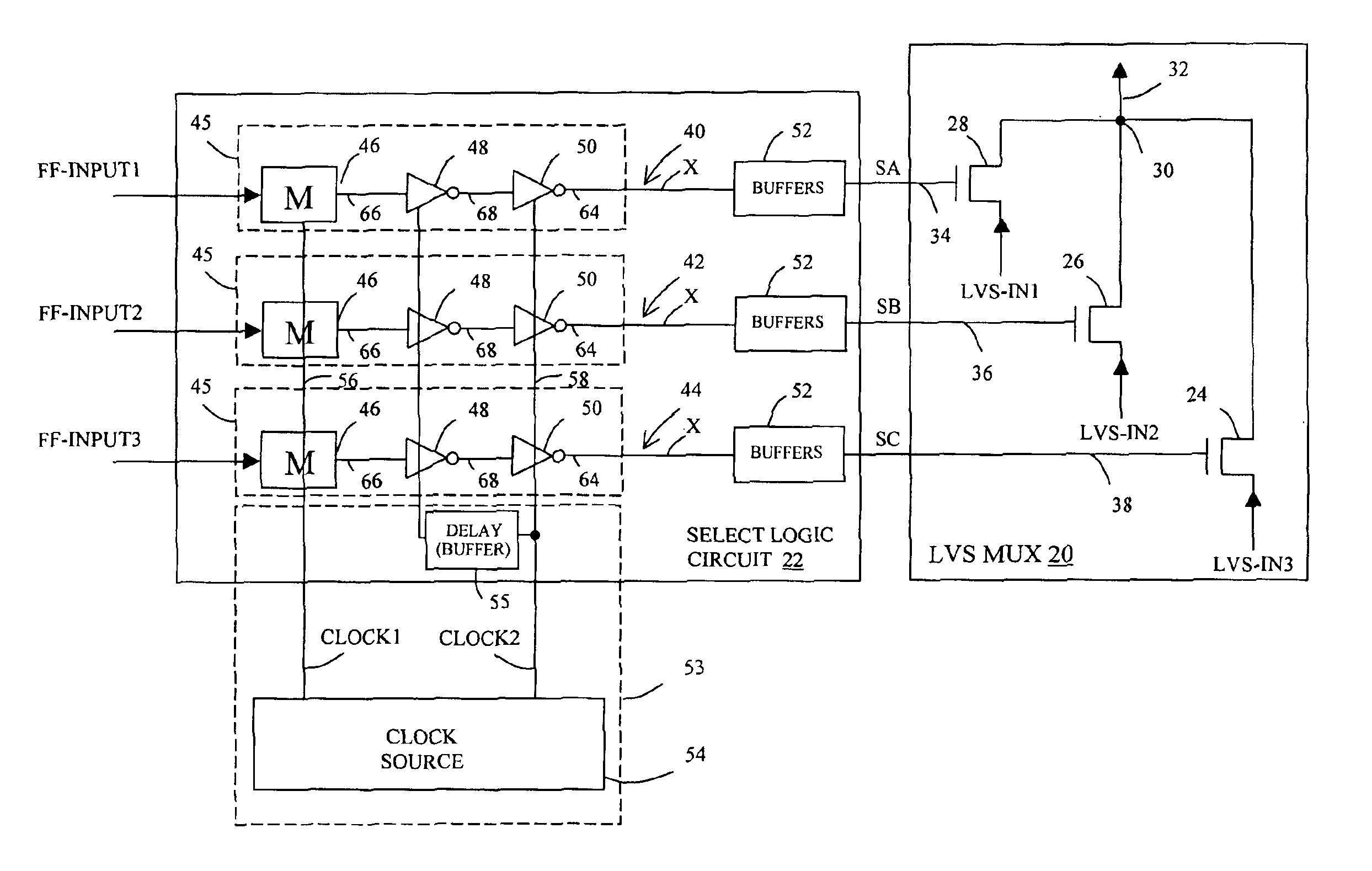

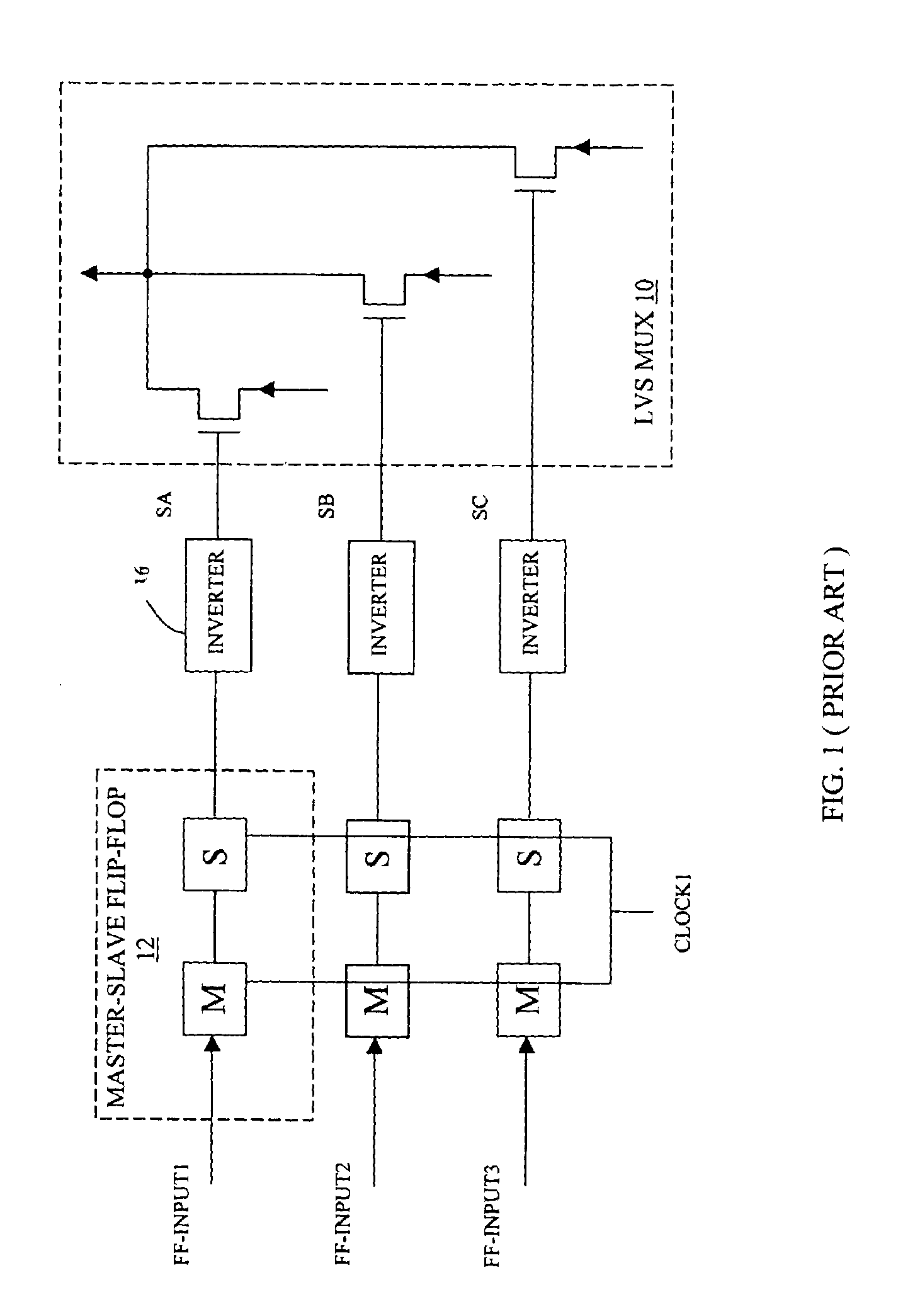

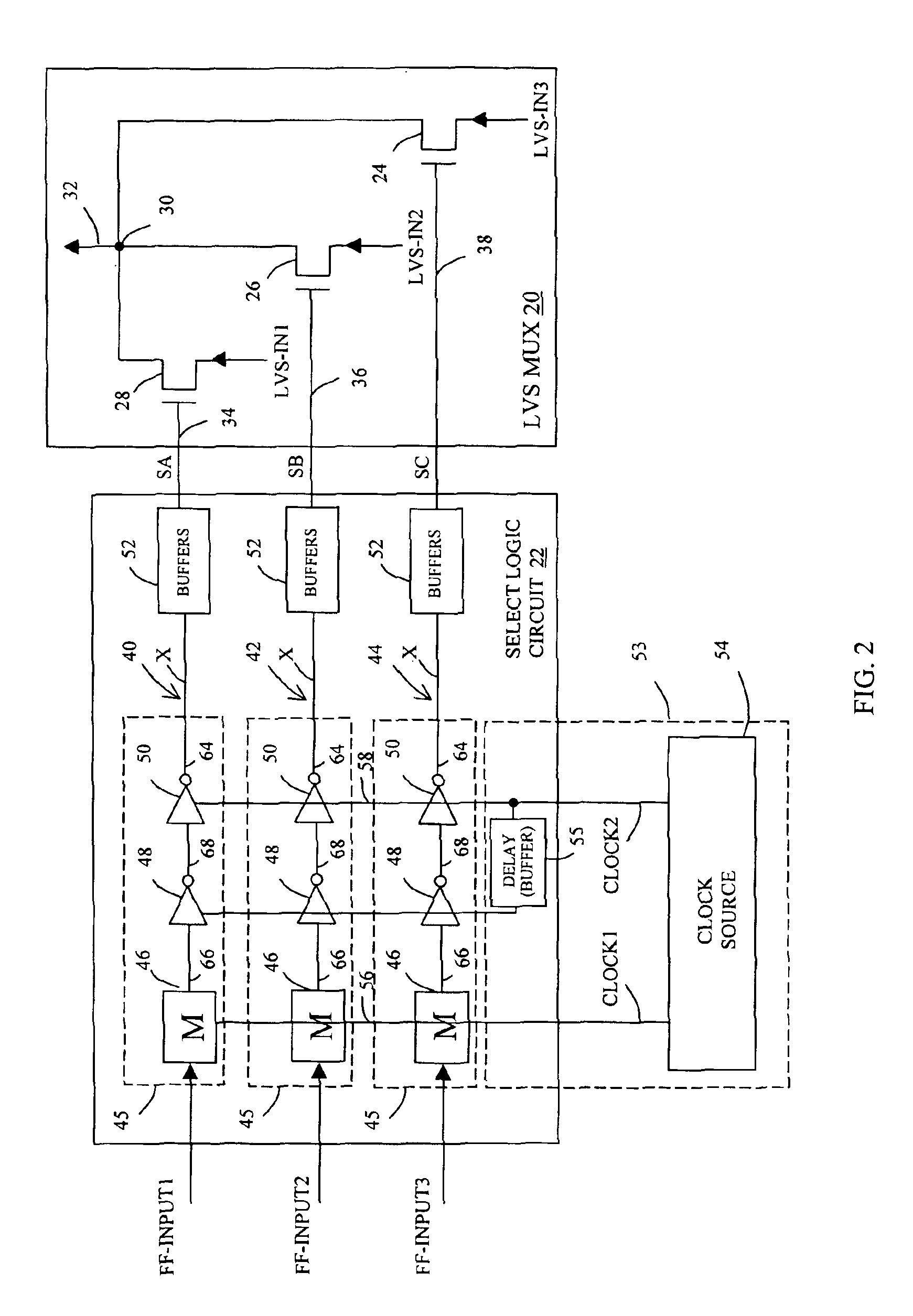

Select logic for low voltage swing circuits

InactiveUS20050068065A1Digital storageElectric pulse generatorEngineeringElectrical and Electronics engineering

An apparatus comprising a low voltage swing (LVS) circuit having a plurality of alternating LVS pre-charging and evaluation phases and a select logic circuit coupled to the LVS circuit and responsive to a plurality of input data signals to generate a plurality of select signals for the LVS circuit. Each of the select signals occurs during one of the LVS evaluation phases and has a turning-on edge and a turning-off edge. The turning-off edge of each of the select signals is generated independent of the input data signals.

Owner:INTEL CORP

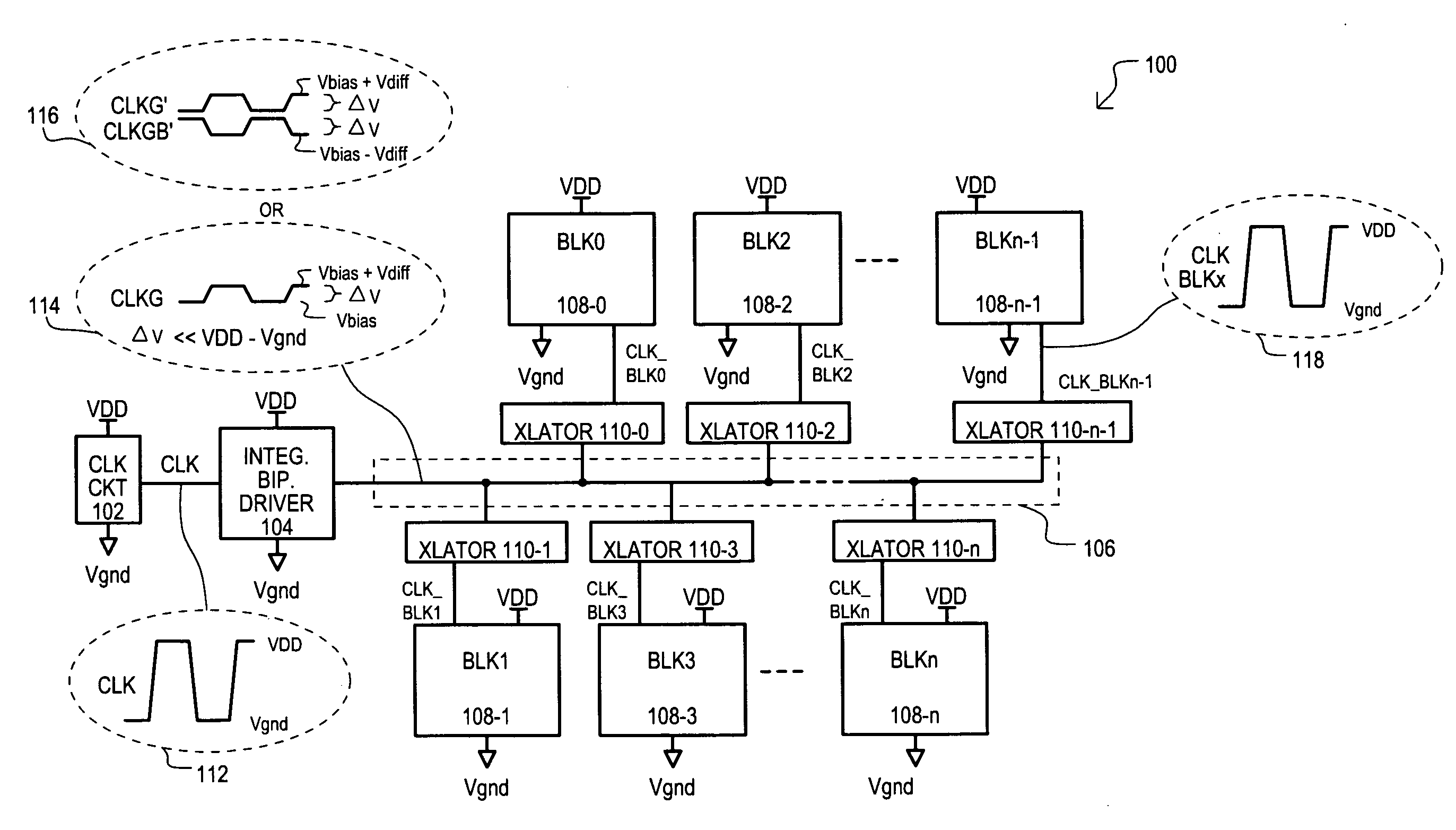

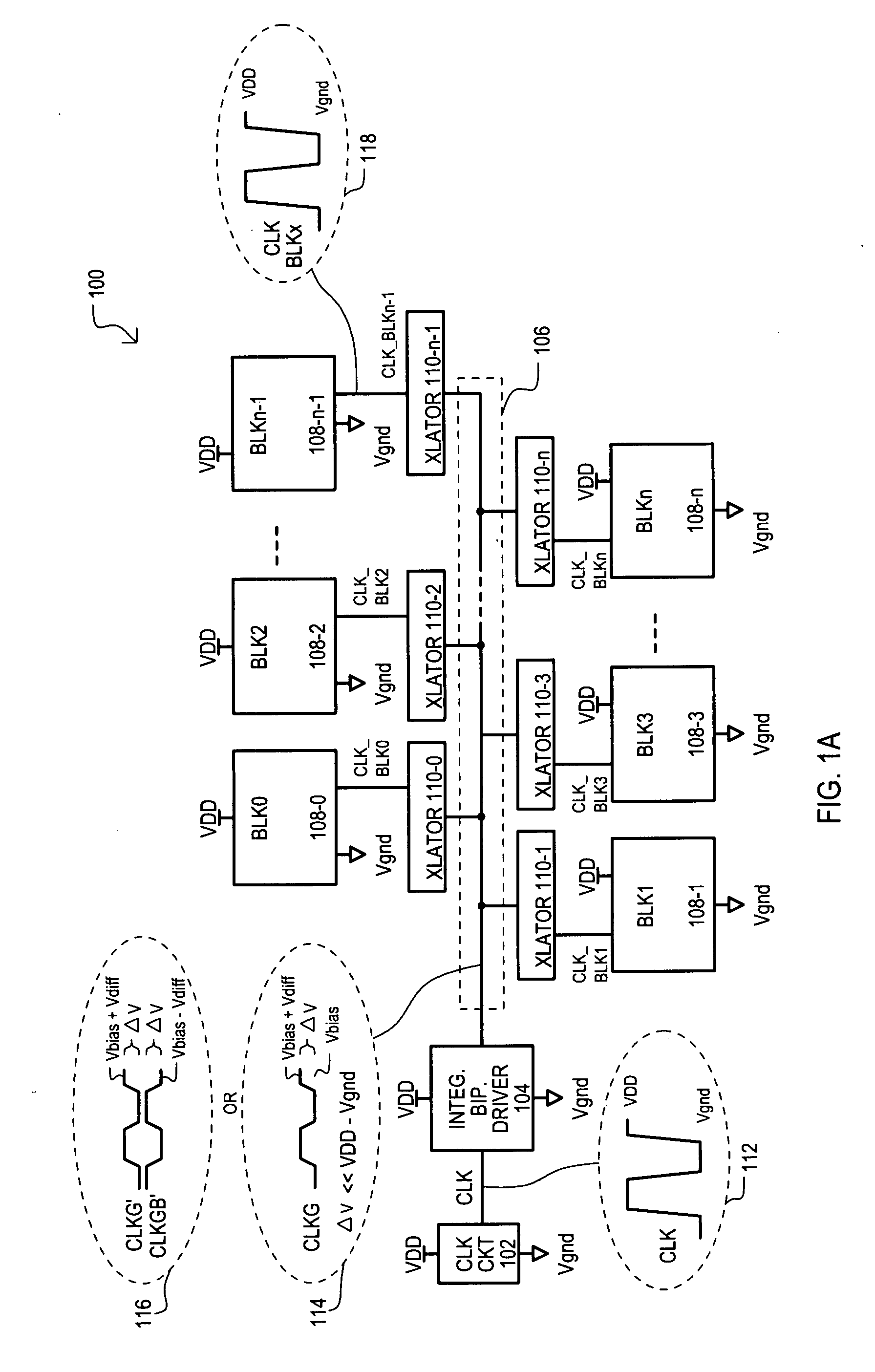

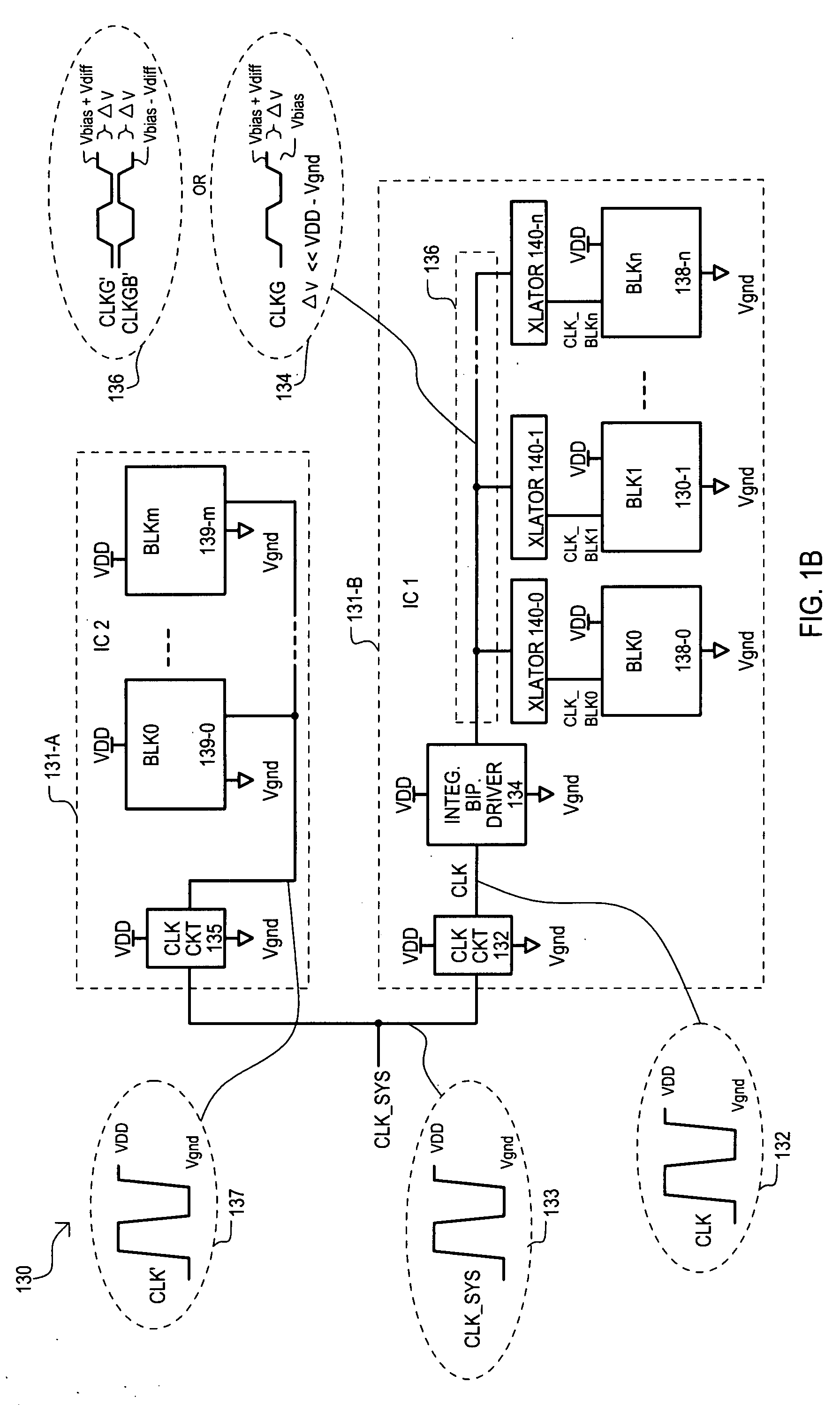

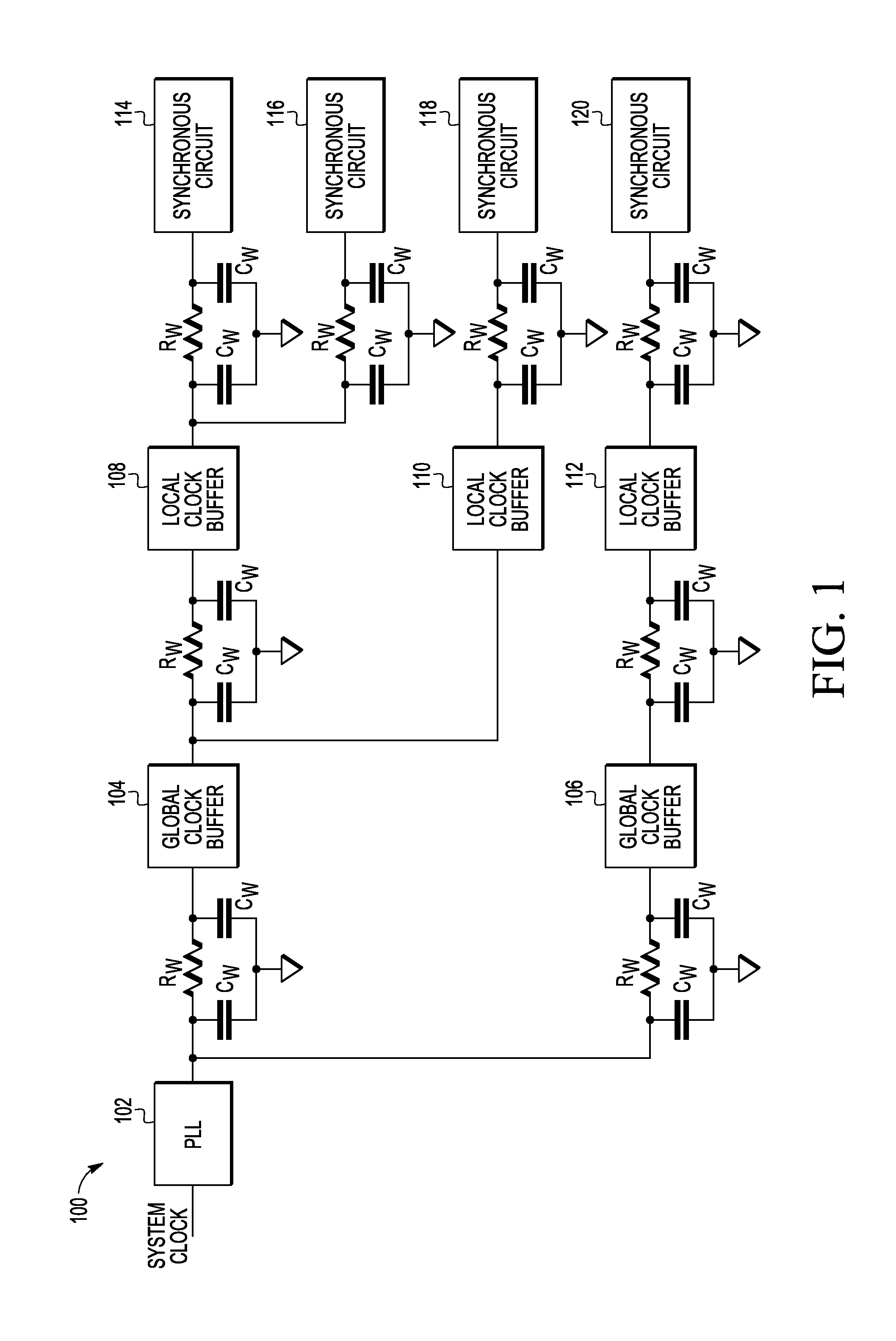

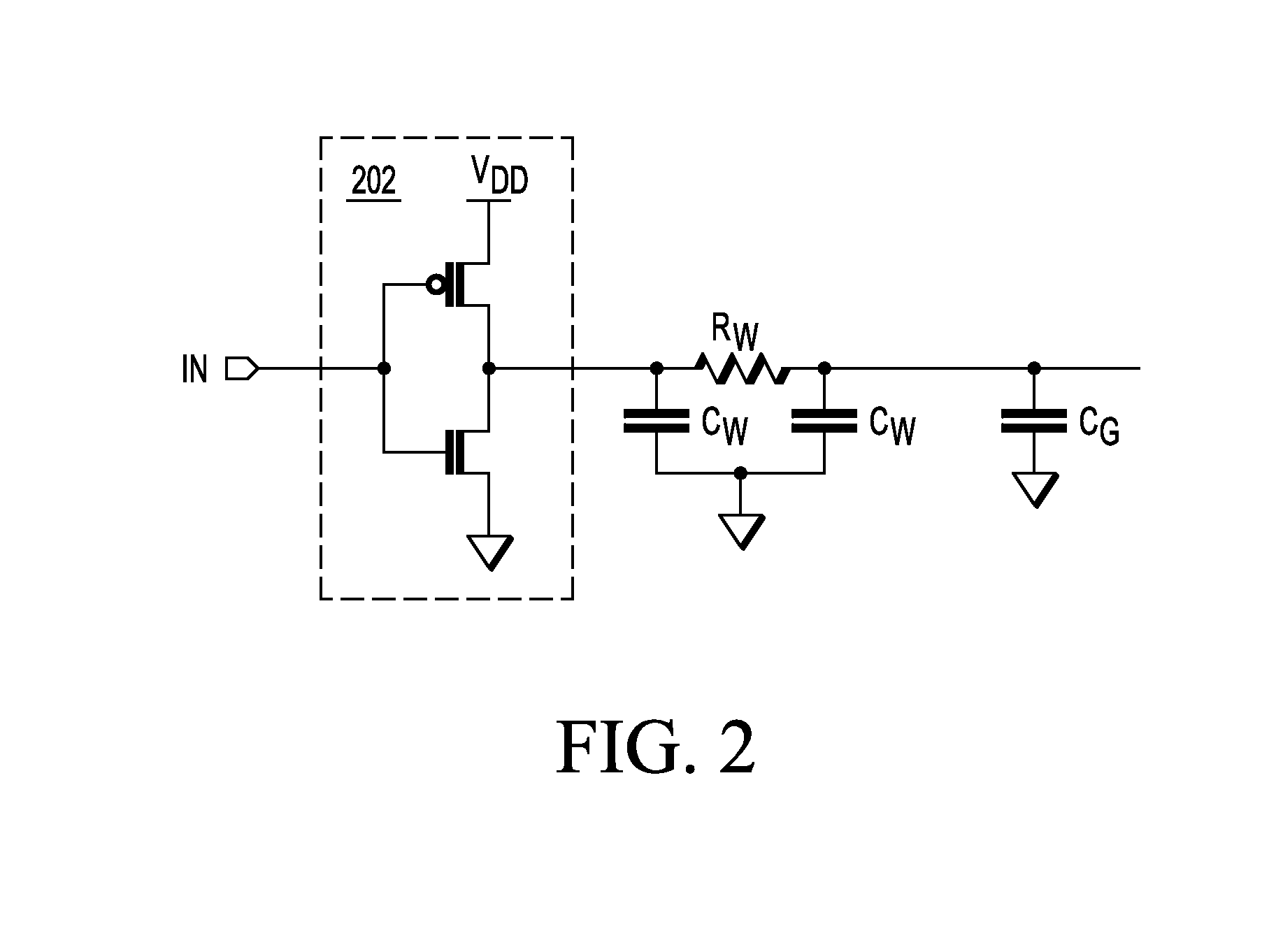

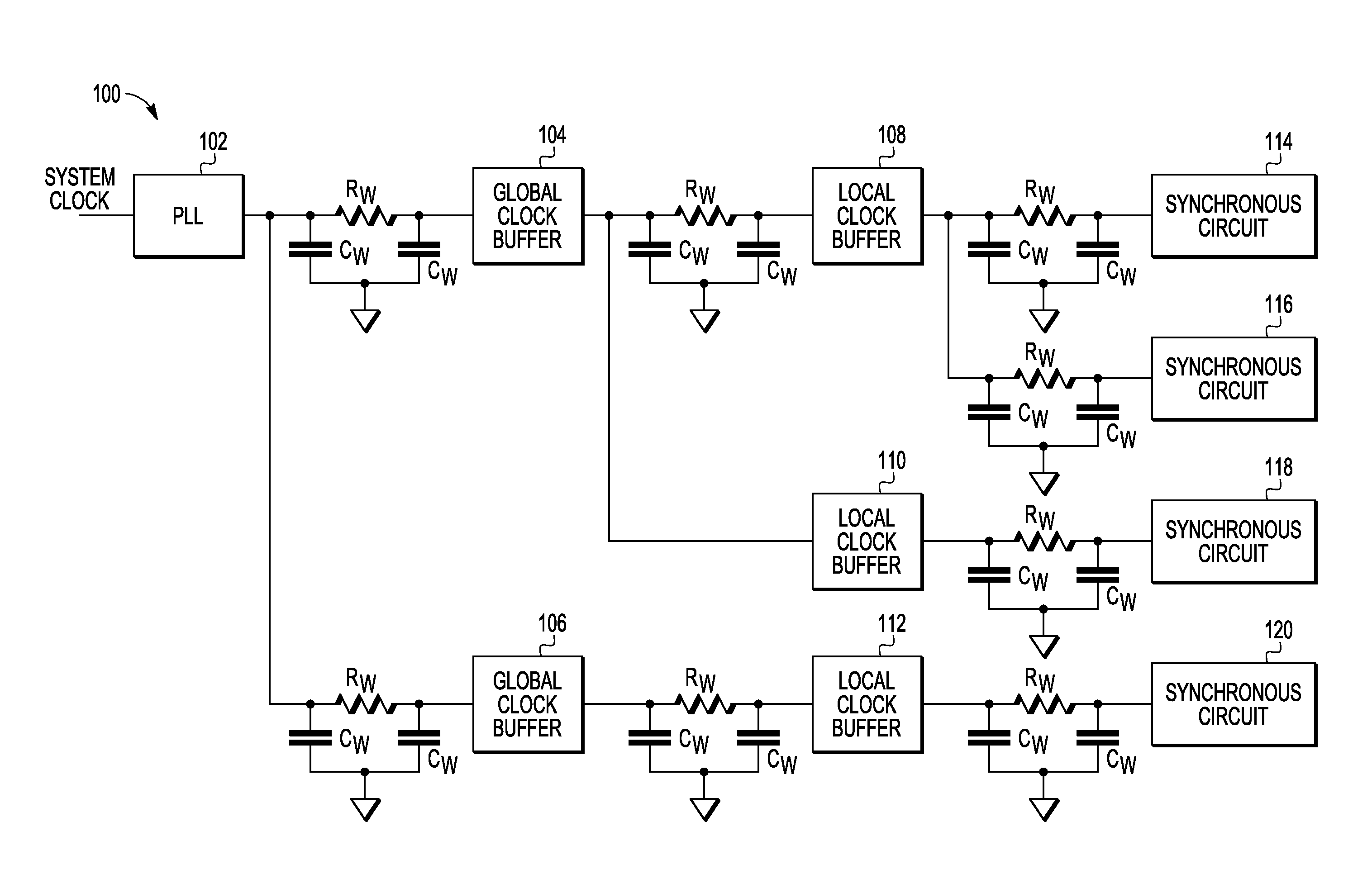

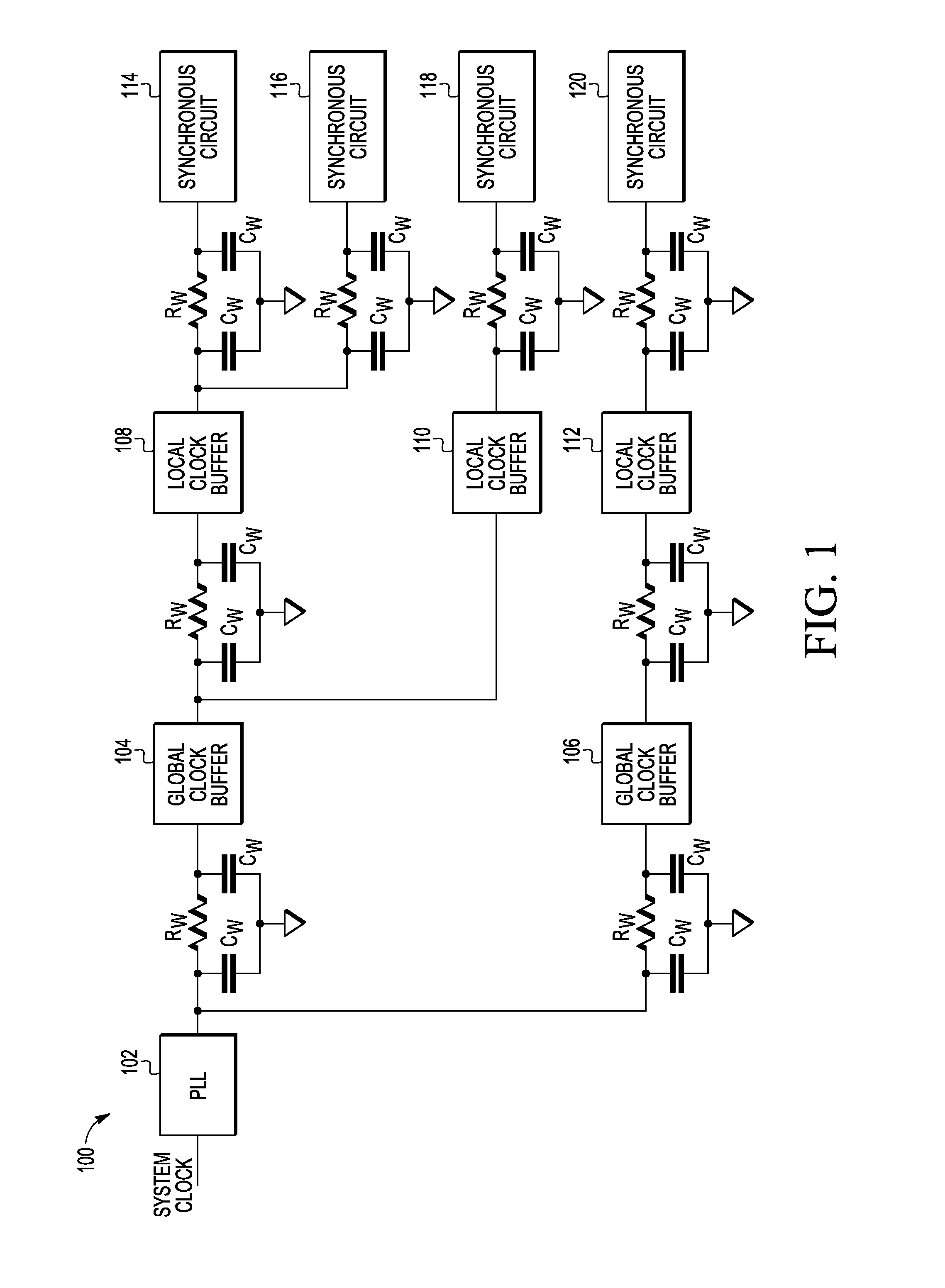

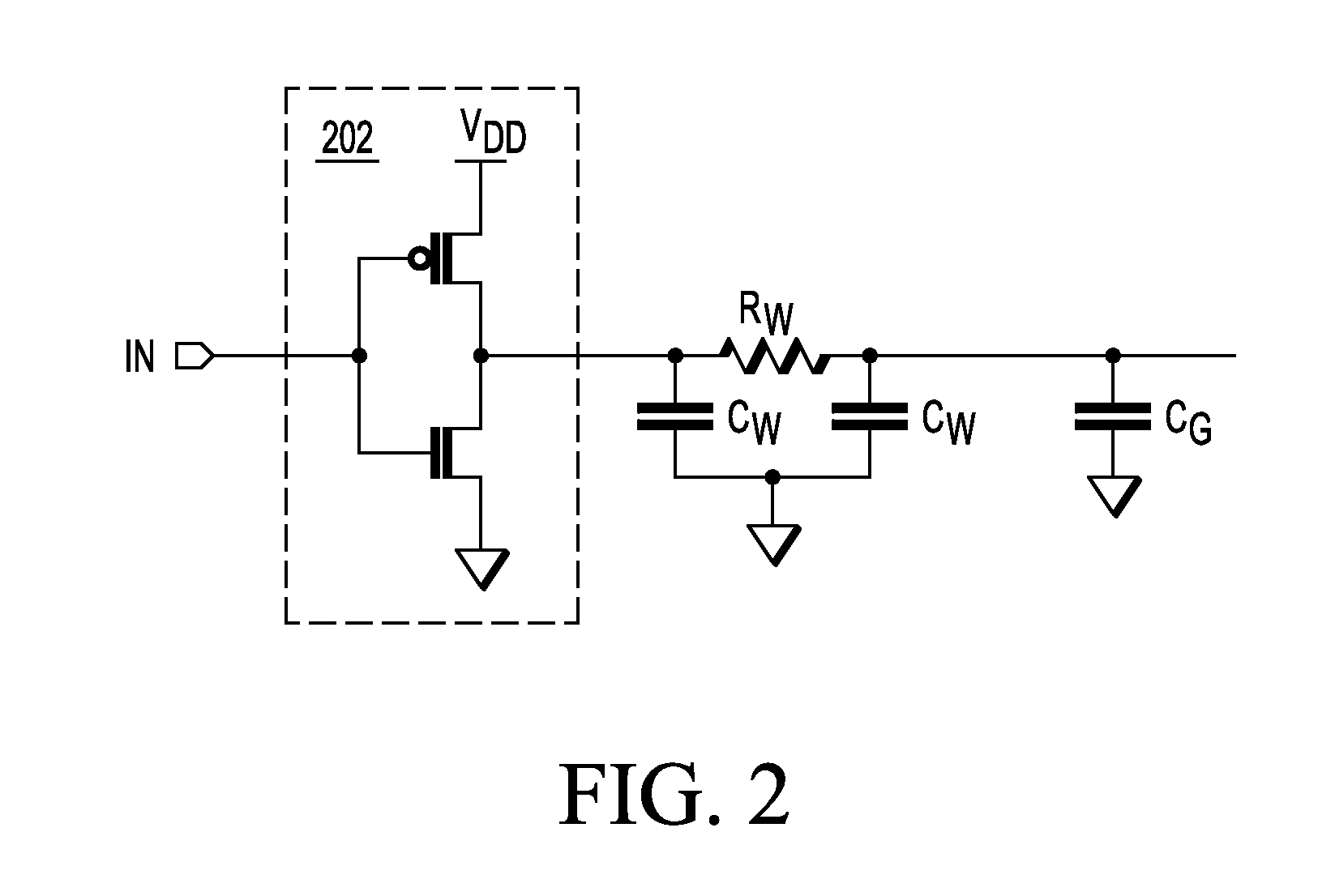

Signaling circuit and method for integrated circuit devices and systems

InactiveUS20080238519A1Pulse generation by bipolar transistorsPower supply for data processingDriver circuitDevice material

Integrate circuit systems and semiconductor devices for generating, transmitting, receiving, and manipulating clock and / or data signals. A semiconductor device including a clock circuit having field effect transistors and a clock driver circuit having bipolar junction transistors is disclosed. The clock circuit may provide a first clock output having a first voltage swing. The clock driver circuit may receive the first clock output and provide a second clock output having a second voltage swing substantially less than the first voltage swing. The field effect transistors can be junction field effect transistors or insulated gate field effect transistors, or the like. The system / devices further including a translator circuit, for translating signals with a lower voltage swing into signals with a higher voltage swing, and a circuit block, for operating at such higher voltage swing. Further included are global and local wiring networks for communicating the signals between and among the individual circuits or system components.

Owner:DSM SOLUTIONS

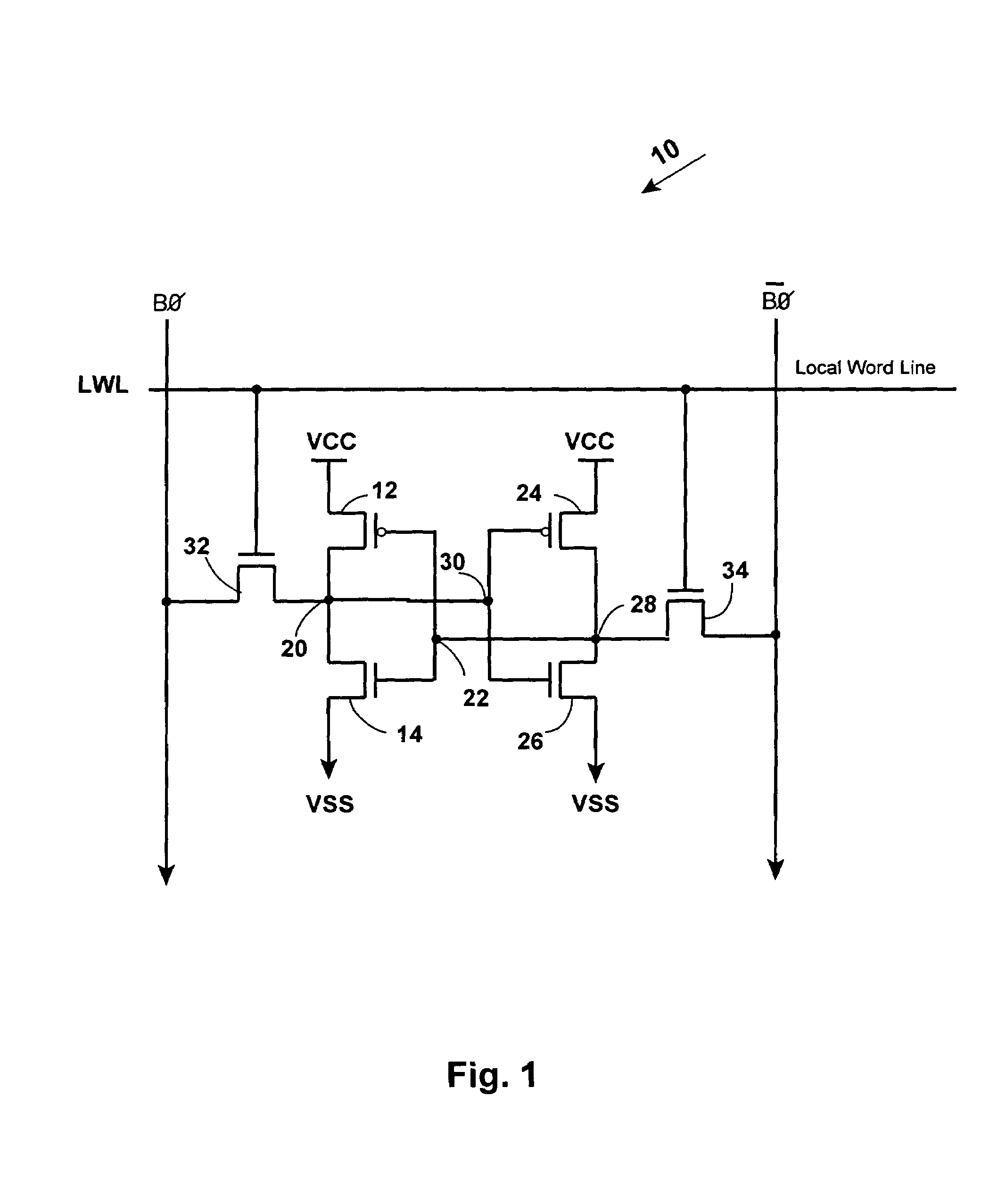

SRAM power reduction

A SRAM uses a number of memory banks in a configuration that uses lower voltage swings on a differential internal data bus so that the internal data bus no longer uses single-ended VDD / VSS, HIGH-to-LOW, rail-to-rail voltage swing for a read mode of operation. This consumes less power for a read operation. Senseamps for finally converting low-level signals to full logic output voltage levels are located right next to output buffers and data output pads for the SRAM. The bit lines for a memory CORE are formed in lower metal layers that are closer to the core memory cells and, thus, have higher capacitance. The present invention uses lower-capacitance top layers 4–6 of a 6 metal layer scheme for the signal lines of the differential internal data bus. An optimum configuration has the capacitance of a bitline equal to the capacitance of the differential internal data bus bit-line.

Owner:VIRTUAL SILICON TECH

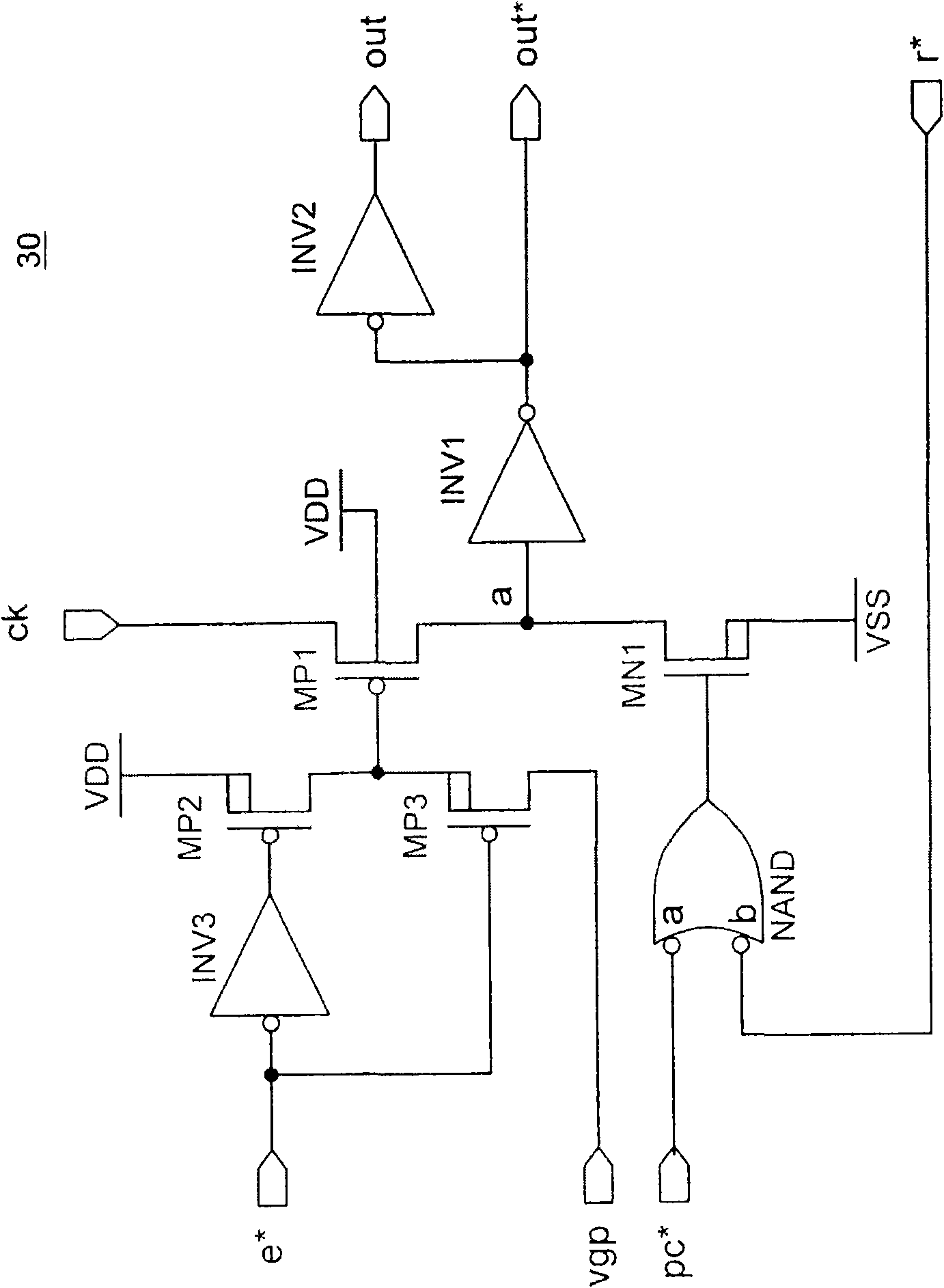

Shifter register for low power consumption application

A high voltage shift register stage which directly accepts low voltage clock signal inputs without using clock buffers. In particular, a shift register stage circuit is adapted to operate with a low voltage swing clock signal, with the stage circuit having a single state node, a, driven directly. This arrangement allows for reduced power consumption and higher operating speeds.

Owner:KOPIN CORPORATION

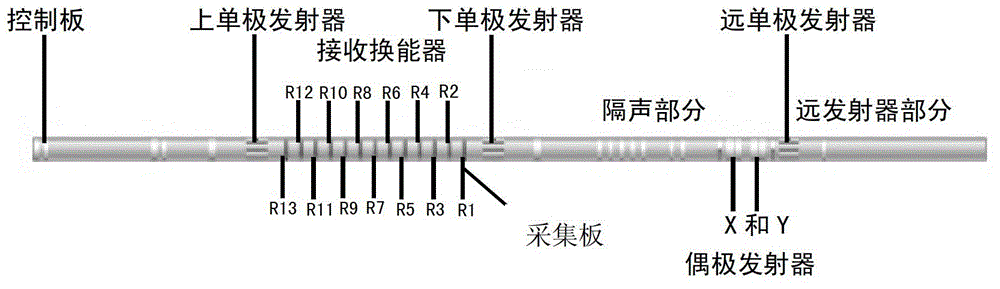

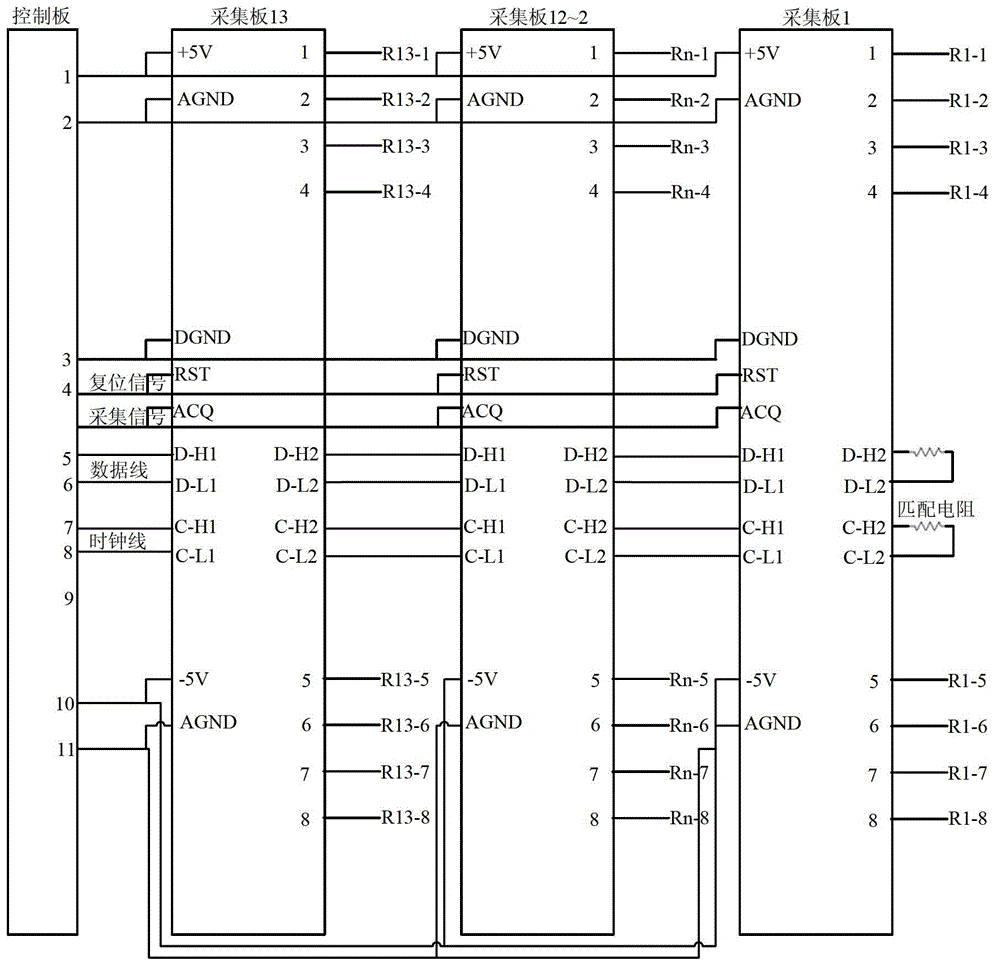

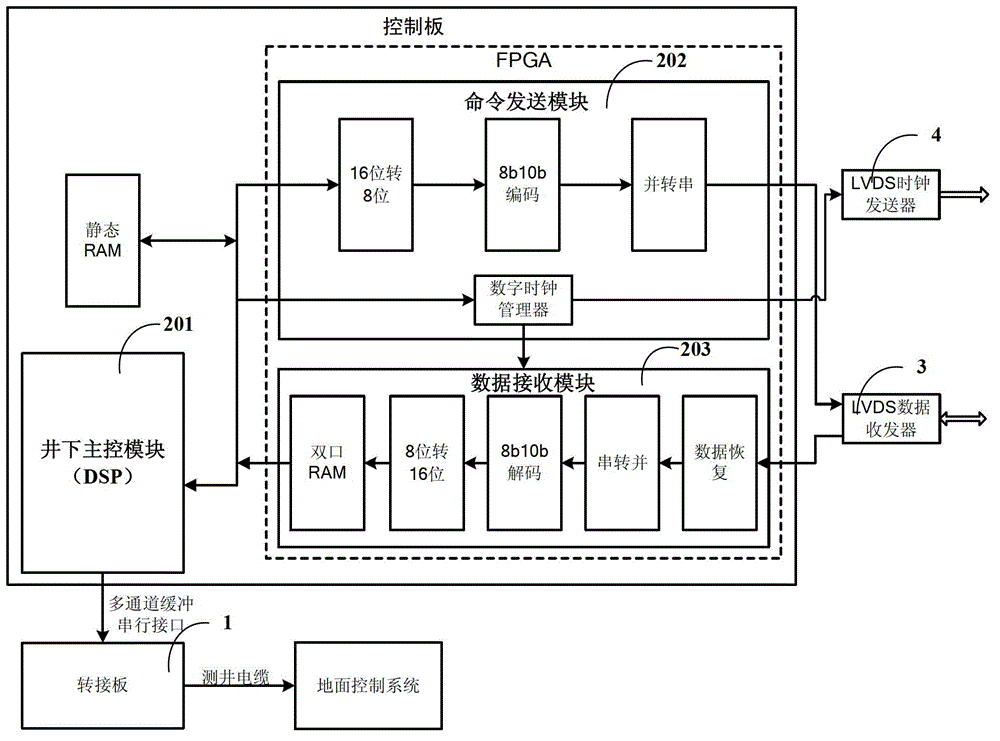

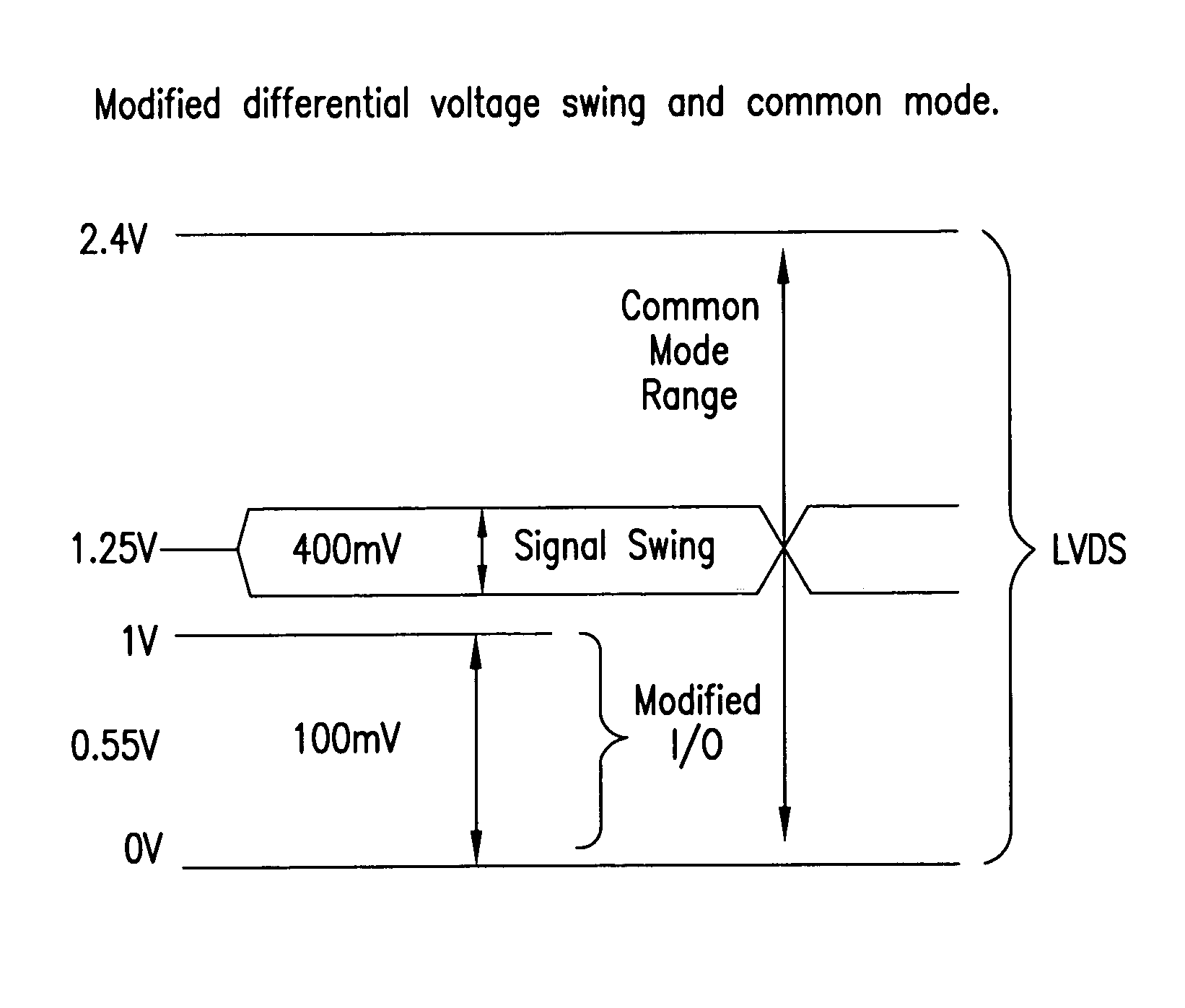

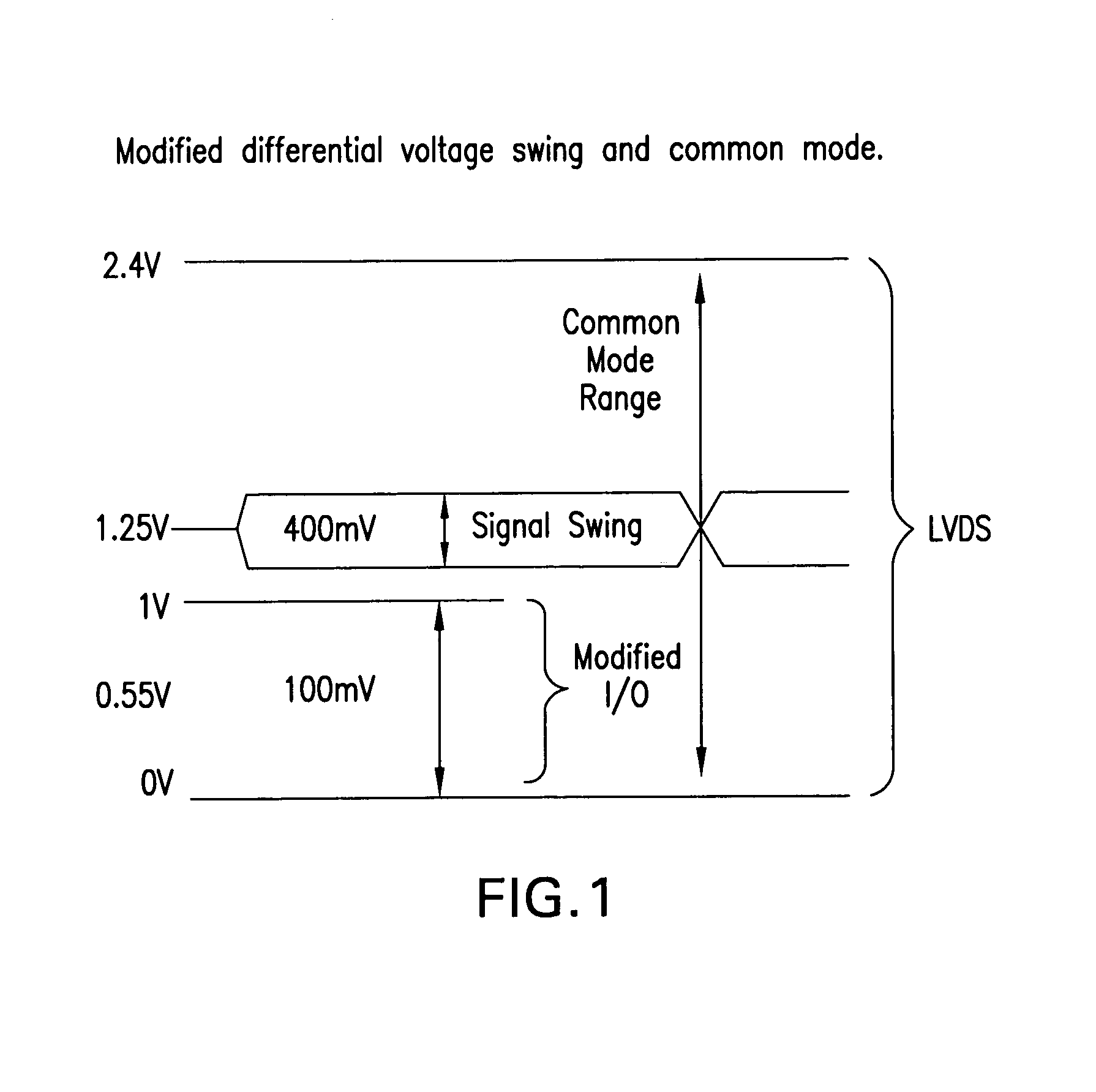

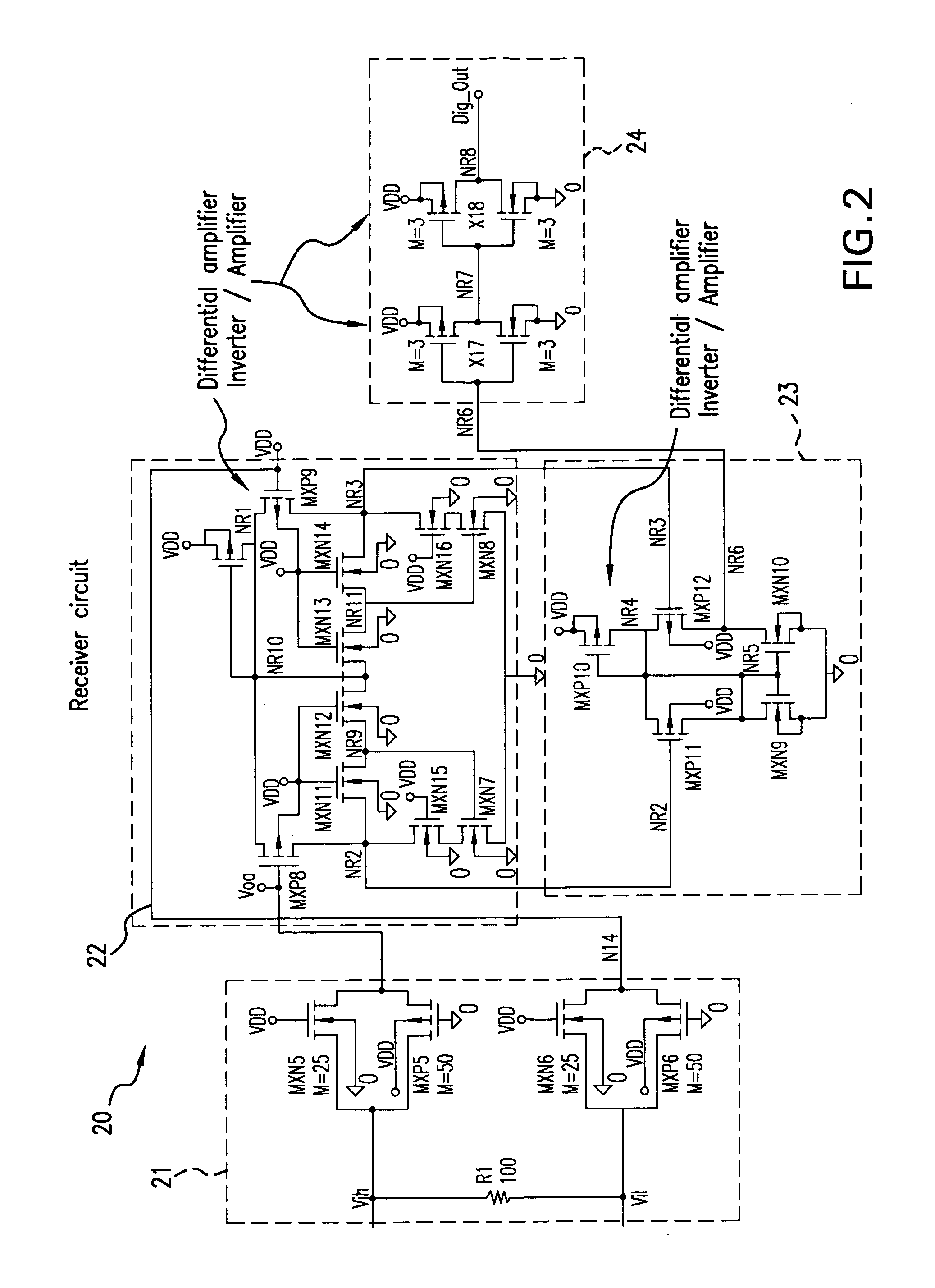

Three dimensional sonic logging data high-speed transmission device based on LVDS technology

The invention discloses a three dimensional sonic logging data high-speed transmission device based on an LVDS (Low Voltage Differential Signaling) technology. Firstly, a ground control system issues control commands, a pinboard receives commands through an LAN (local area network) port and downloads the commands to a control panel through an Mcbsp (Multichannel Buffercd Scrial Port) interface, and command control and high-speed serial transmission of three dimensional logging sound wave data can be achieved by using an LVDS (Low Voltage Differential Signaling) interface. The LVDS communication interface technology refers that data transmission is performed by using extremely low voltage swing in a high-speed differential manner, has the advantages of low noise, excellent common mode inhibiting capability and low power consumption, and can integrate a circuit into a systematical IC (integrated circuit), thereby overcoming problems of far distance sonic logging data transmission, complex circuit working environment and high possibility of external interferences to three dimensional sonic logging signal, and high-speed date transmission between the control panel and the collection board can be accurately achieved in a real time manner.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

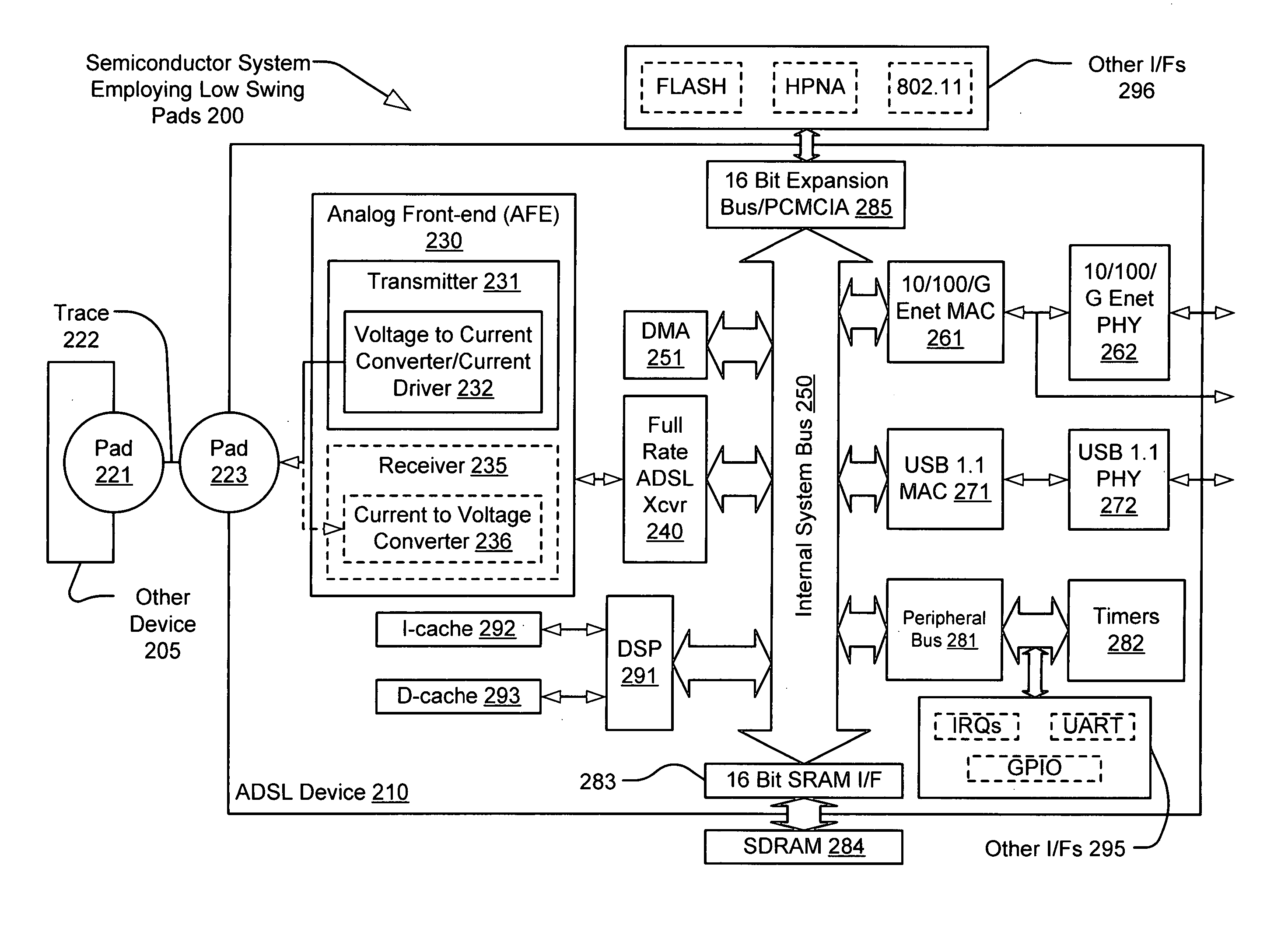

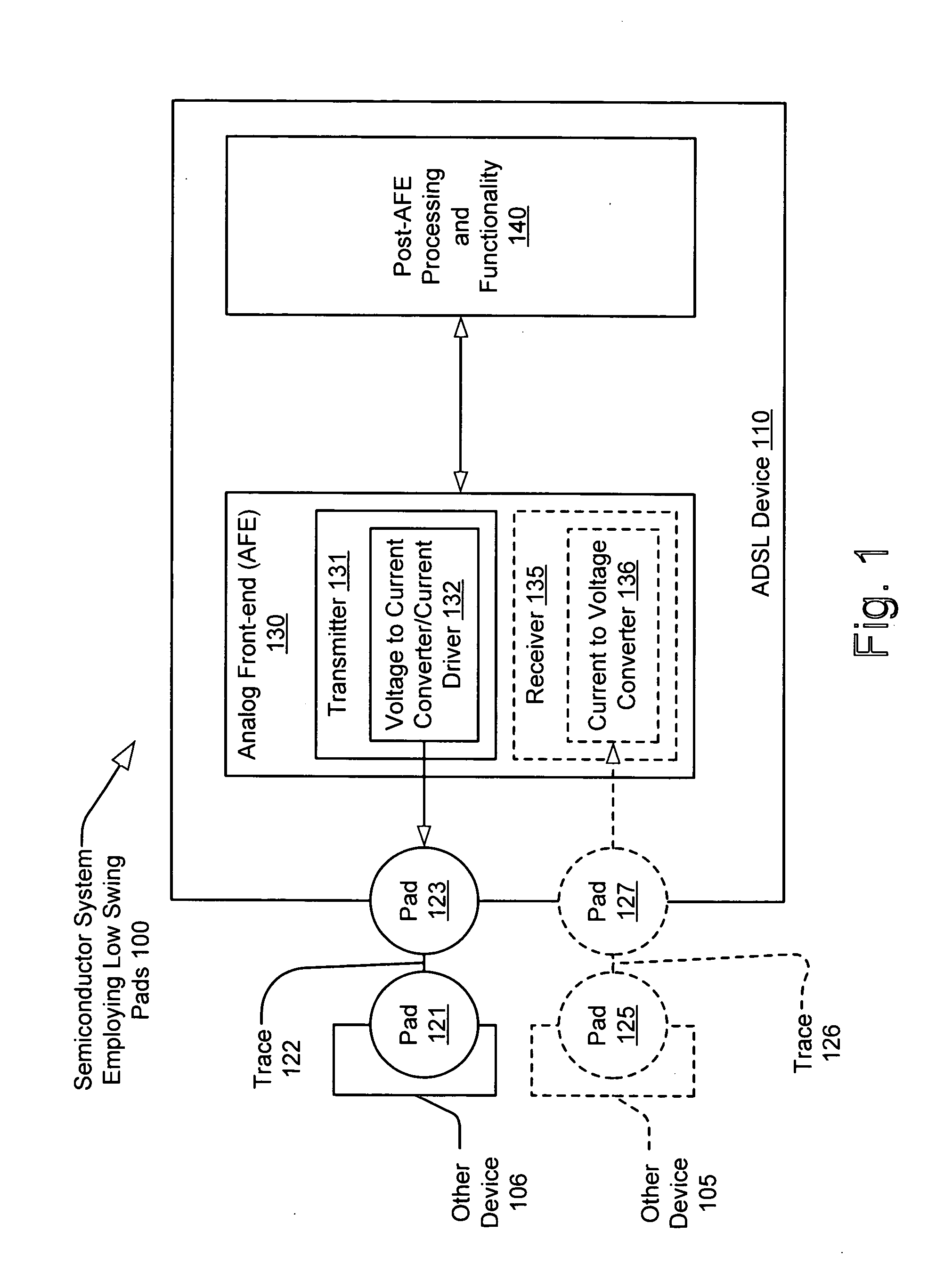

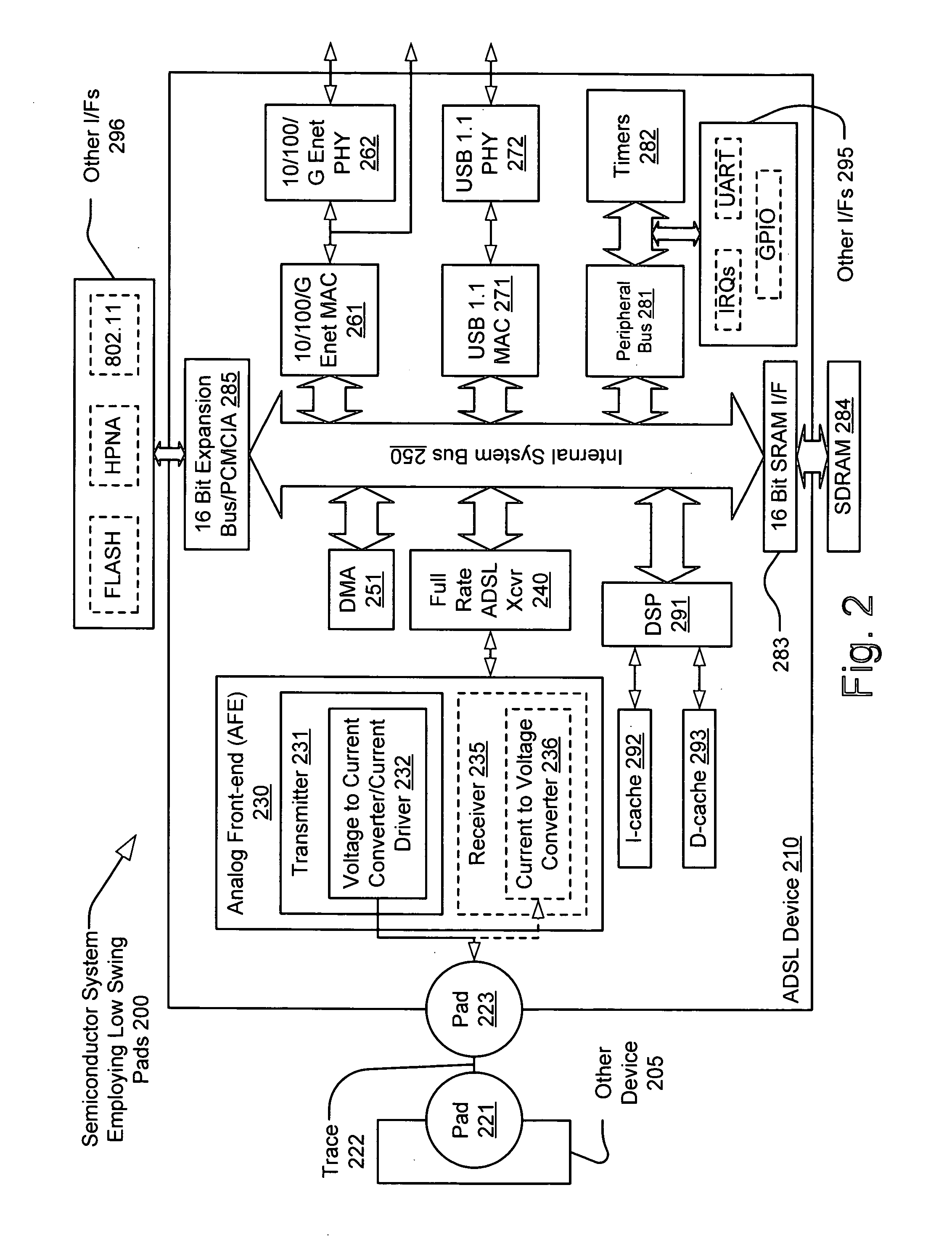

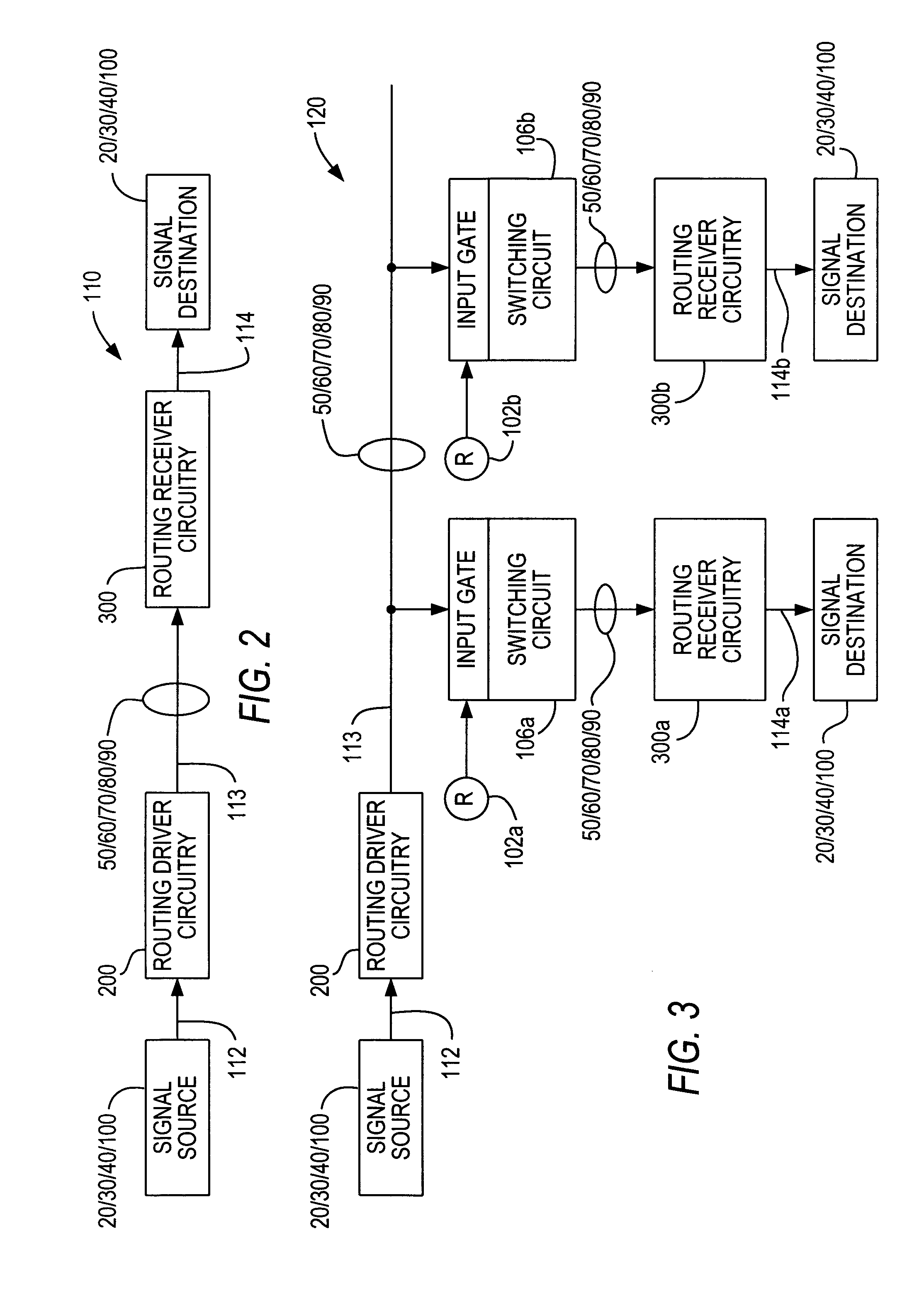

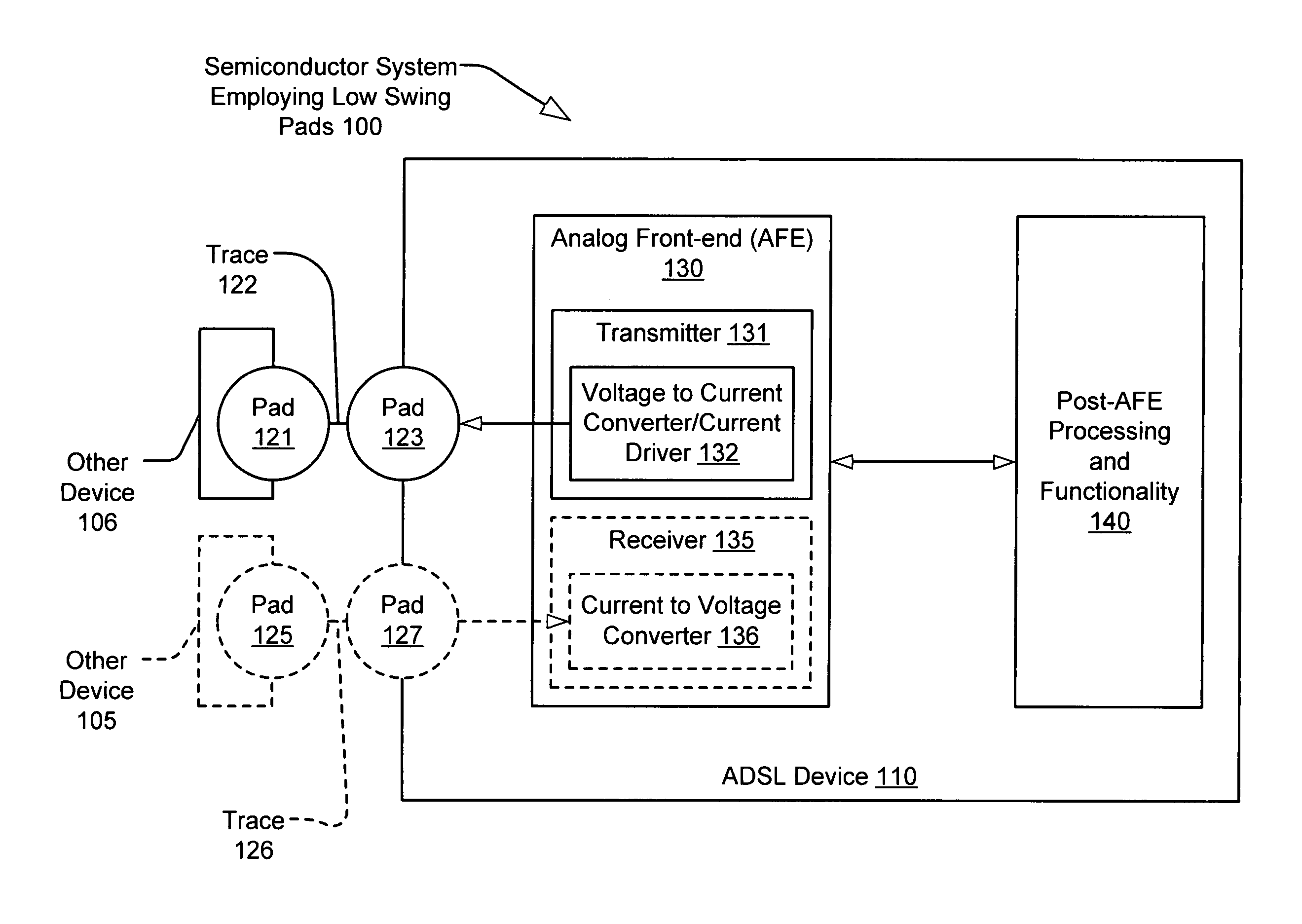

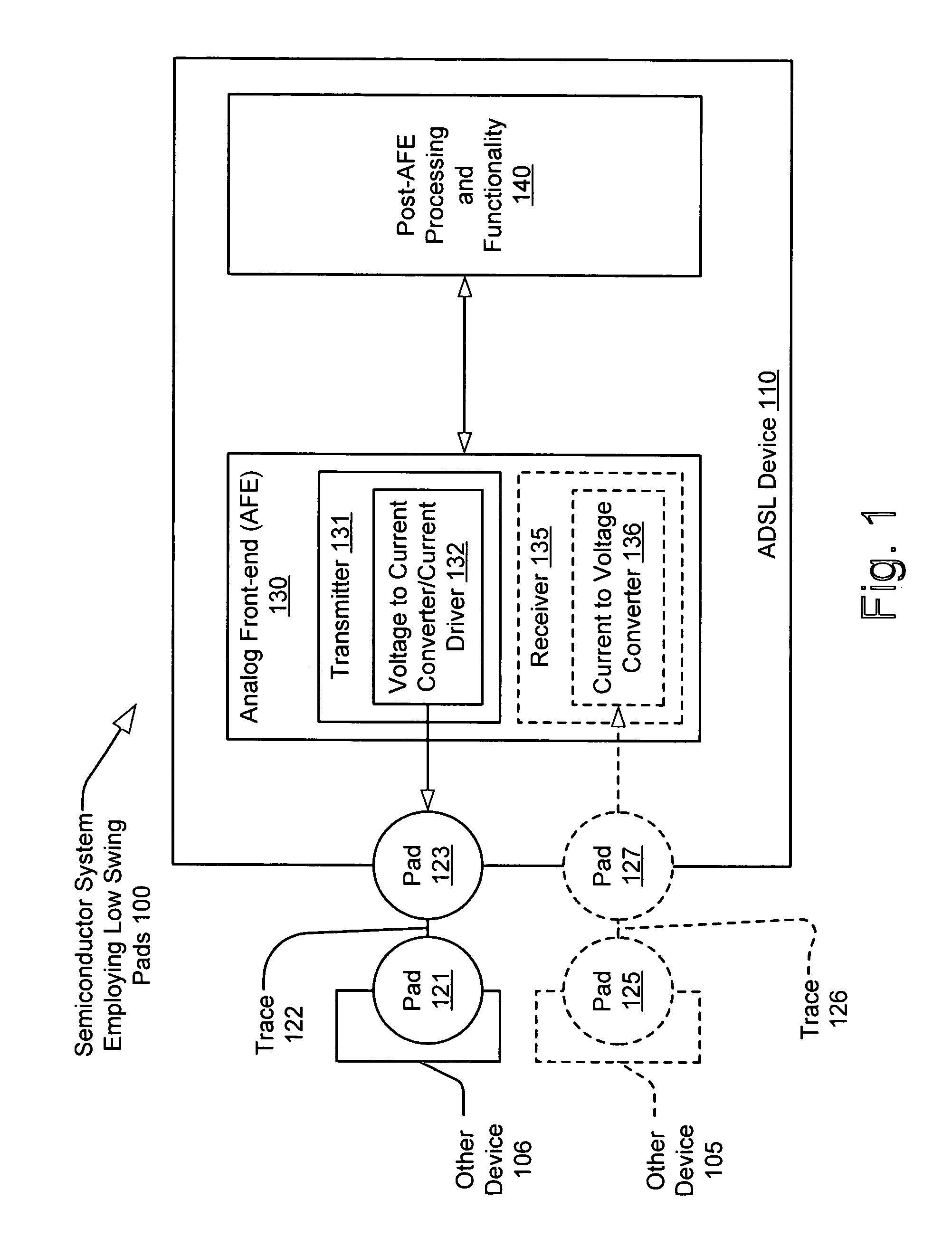

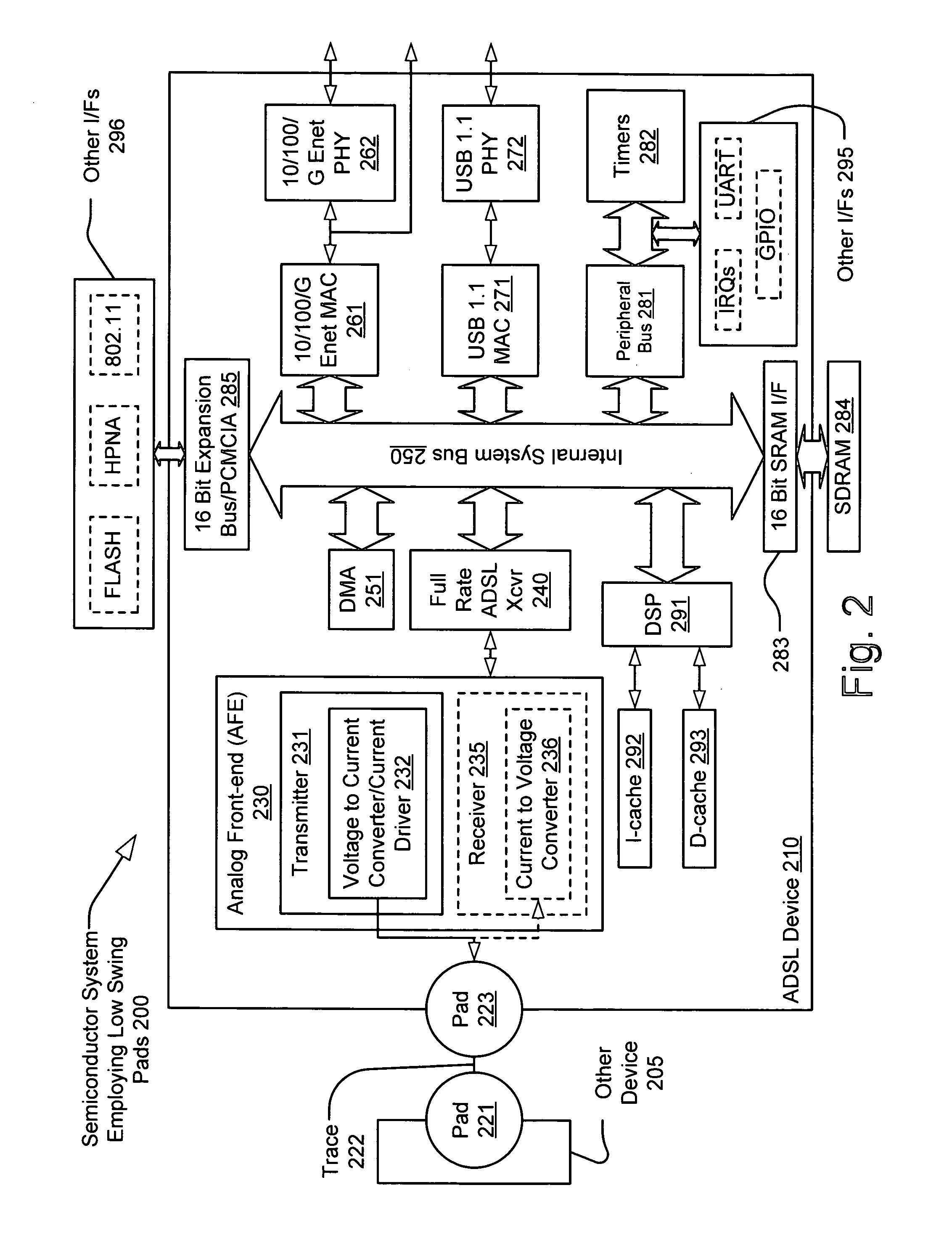

Low voltage swing pad driver and receiver

InactiveUS20050036562A1Reduce distortion problemsMinimize distortionModulation with suppressed carrierAmplitude-modulated carrier systemsEngineeringTransimpedance amplifier

Low voltage swing pad driver and receiver. A transmitter portion and a receiver portion are implemented within various devices that communicate using low voltage swing pads communicatively coupled via a trace. The transmitter portion of one device generates a current signal that is pushed / pulled to a low voltage swing pad and is then passed across the trace to another low voltage swing pad. The transmitter portion includes a current driver that outputs the current signal to the low voltage swing pads, and the receiver portion includes a trans-impedance amplifier that transforms the received current signal into a voltage signal. The low voltage swing pad driver and receiver generates a relatively low voltage swing when compared to CMOS full-scale voltage swings thereby significantly reducing the possibility of introducing any noise and / or distortion of data that is communicated via the interface.

Owner:AVAGO TECH INT SALES PTE LTD

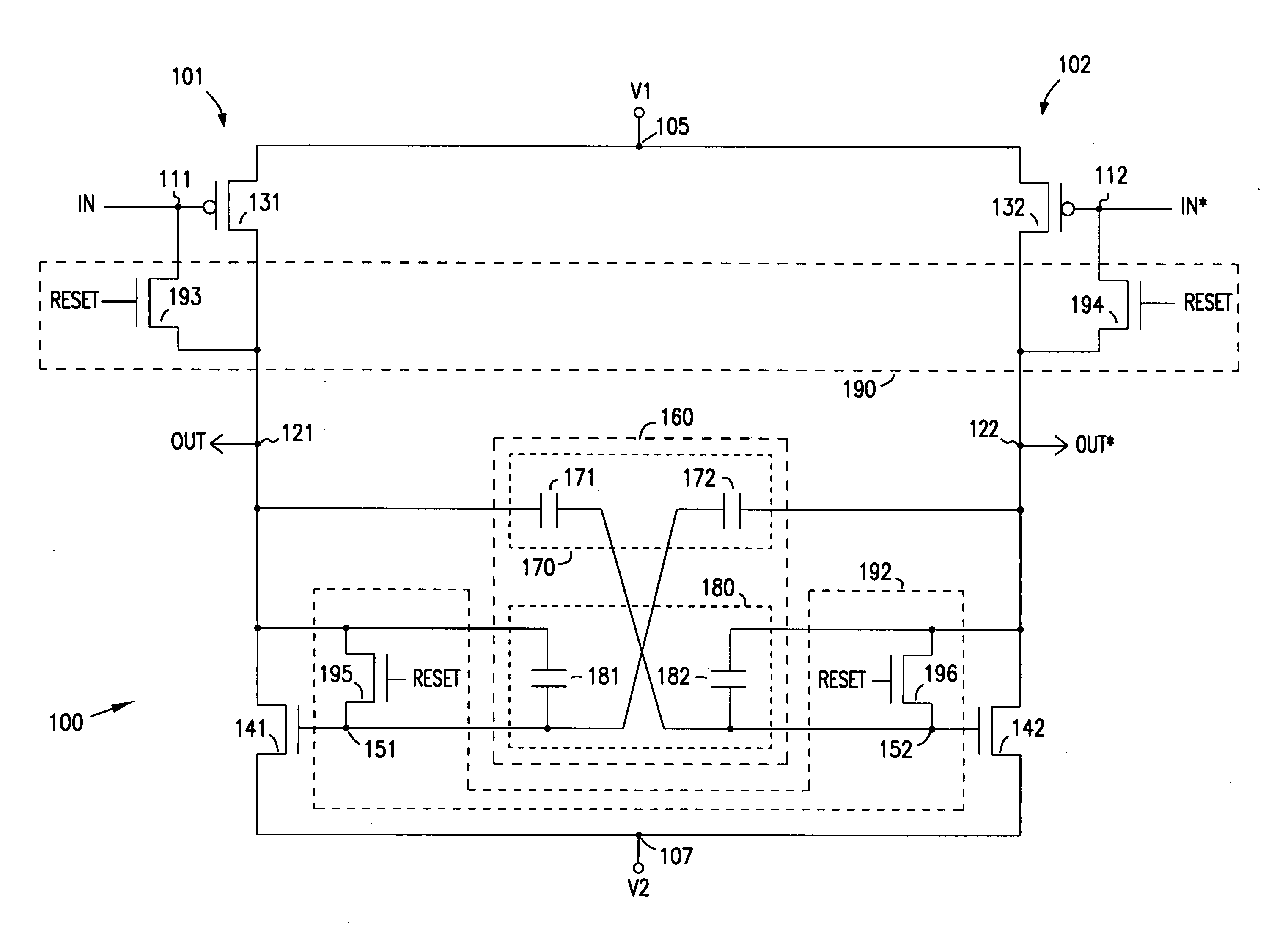

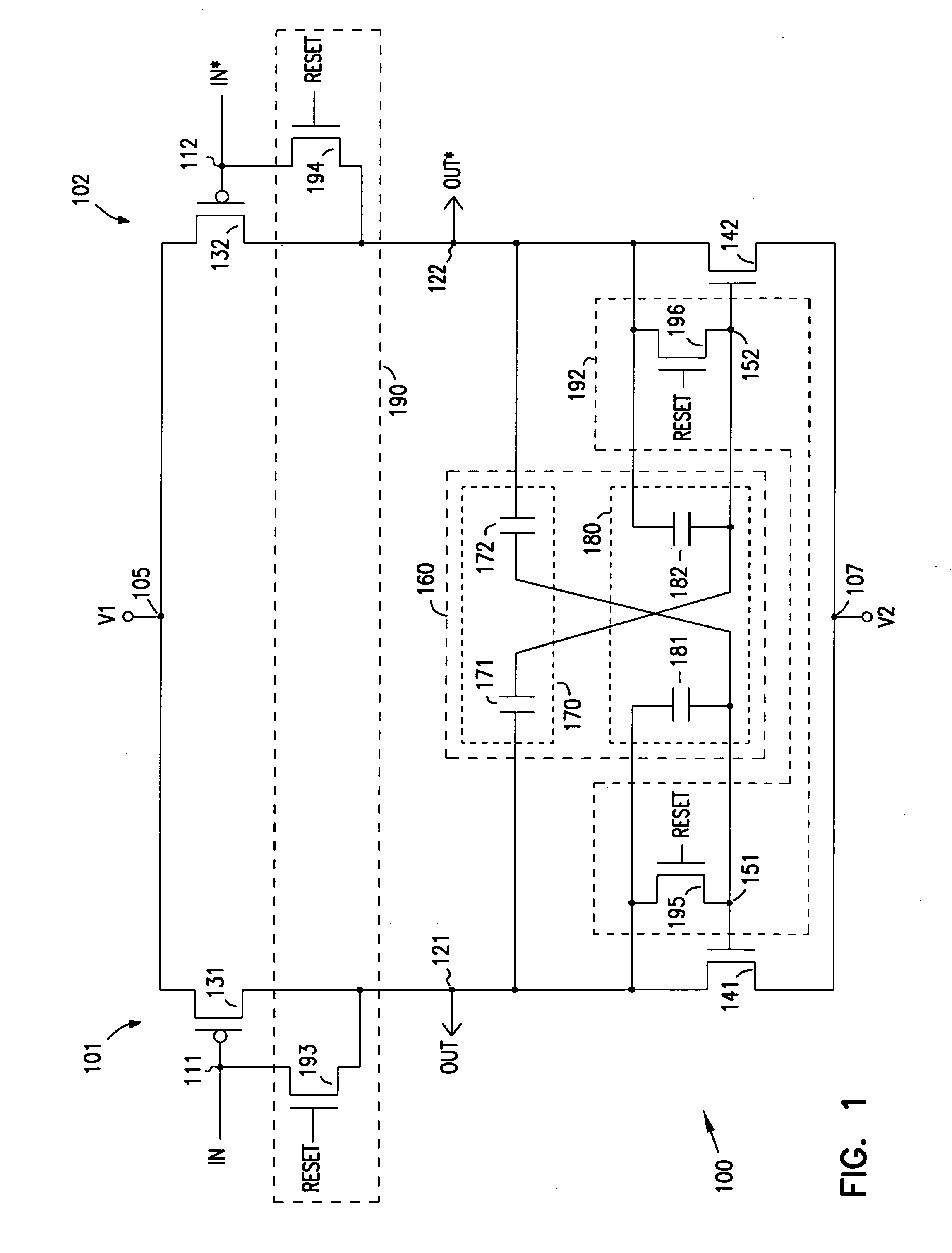

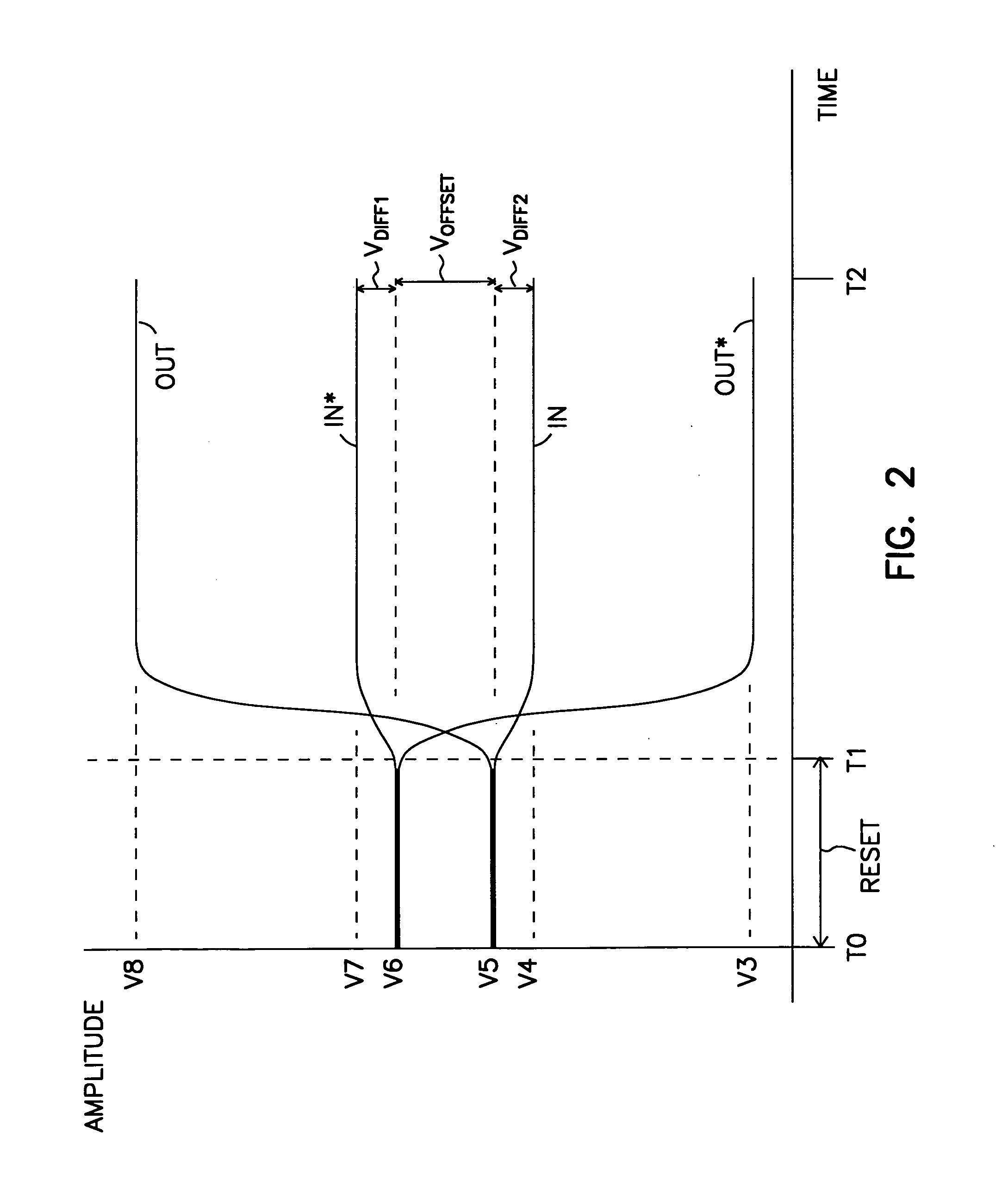

Capacitively-coupled level restore circuits for low voltage swing logic circuits

ActiveUS20060261850A1Electric pulse generatorLogic circuit coupling/interface arrangementsCapacitanceCapacitive coupling

Some embodiments of the disclosure include a circuit having differential sides and a capacitive network coupled to differential sides. The circuit further includes a reset network for resetting the first differential side to a first voltage and for resetting the second differential side to a second voltage. Other embodiments are described and claimed.

Owner:MICRON TECH INC

High speed chip-to-chip communication links

ActiveUS7176724B1Increase data rateReduce power consumptionReliability increasing modificationsElectronic switchingDouble data rateDifferential signaling

A very low voltage swing is used to achieve very high data rates (up to 4 Gbps double data rate) at very low power consumption. A differential signaling approach is used for noise rejection, and a constant current approach also is used to minimize switching noise.

Owner:NORTHROP GRUMMAN SYST CORP

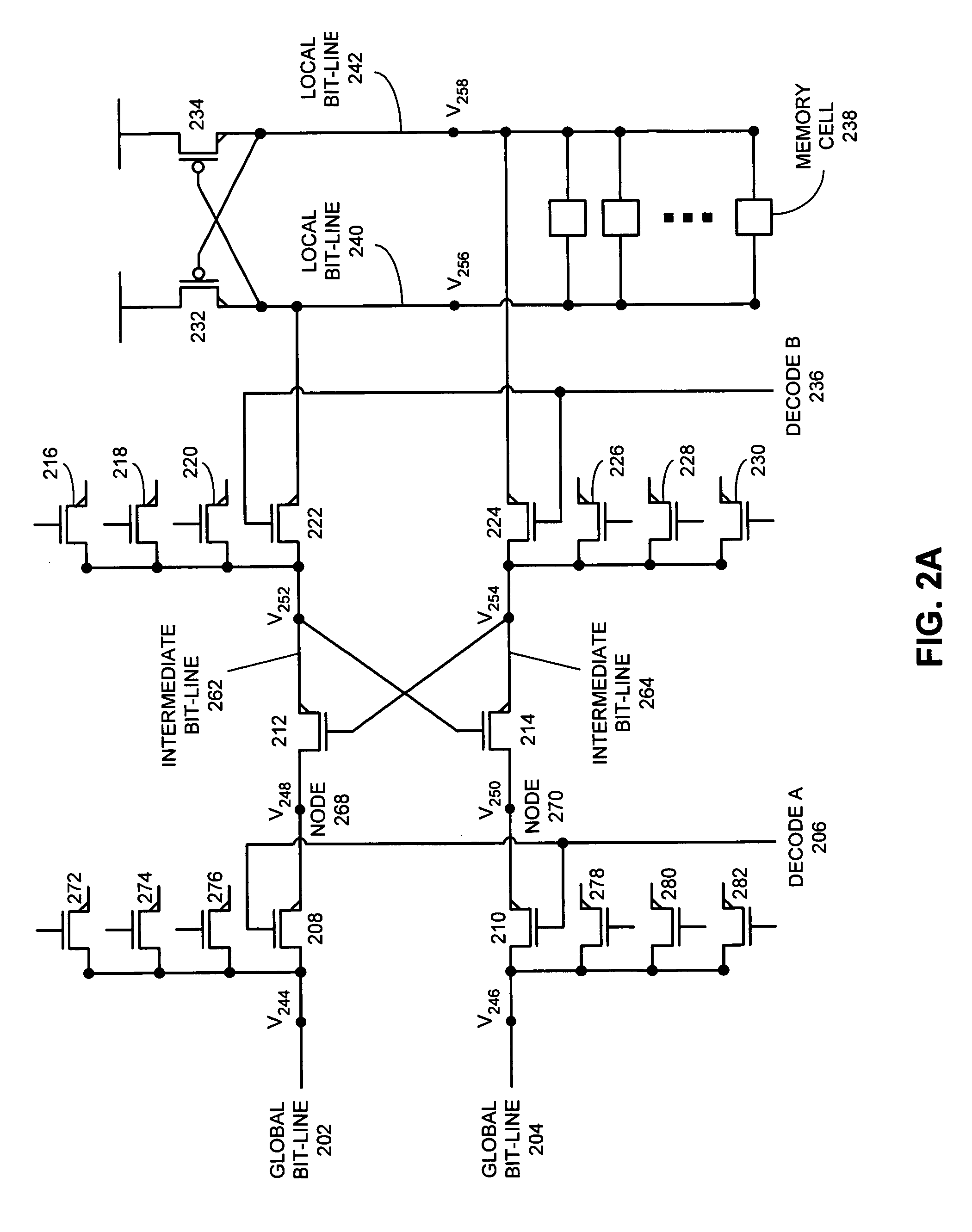

Low-power memory write circuits

One embodiment of the present invention provides a system that writes to a cell in a memory using a low-voltage-swing signal across a pair of global bit-lines. During operation, the system receives a low-voltage-swing signal across a pair of global bit-lines, which is too low to reliably write the memory cell. Next, the system converts the low-voltage-swing signal to a high-voltage-swing signal, which is adequate to reliably write the memory cell. The system then writes to the memory cell by applying the high-voltage-swing signal across a pair of local bit-lines that are coupled to the memory cell. The use of low-voltage-swing signals on the global bit-lines reduces overall power consumption. Furthermore, in one embodiment of the present invention, the voltage conversion is achieved using a pair of cross-coupled NMOS transistors whose sources are directly or indirectly coupled with the global bit-lines, and whose drains are directly or indirectly coupled with the local bit-lines.

Owner:ORACLE INT CORP

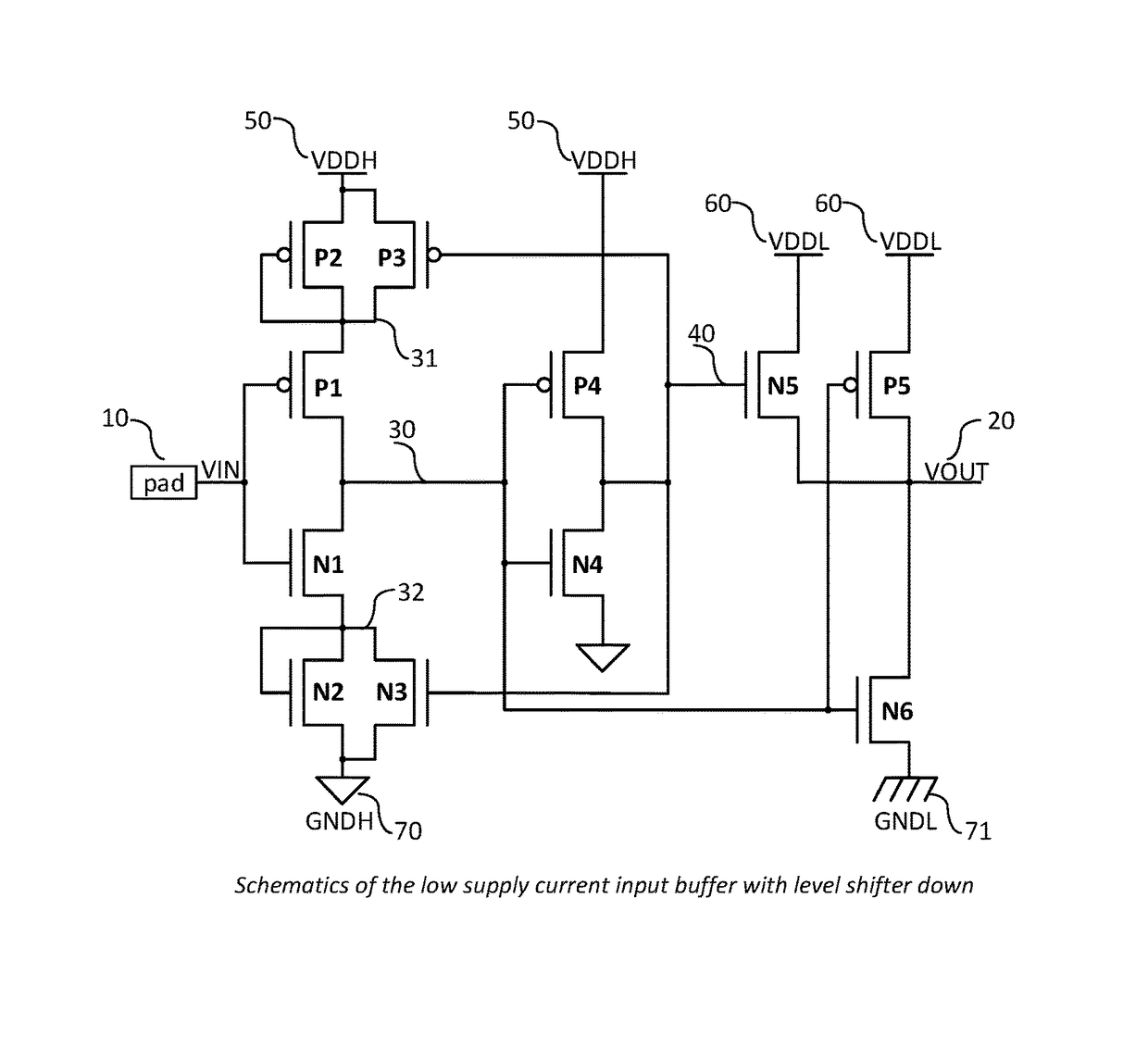

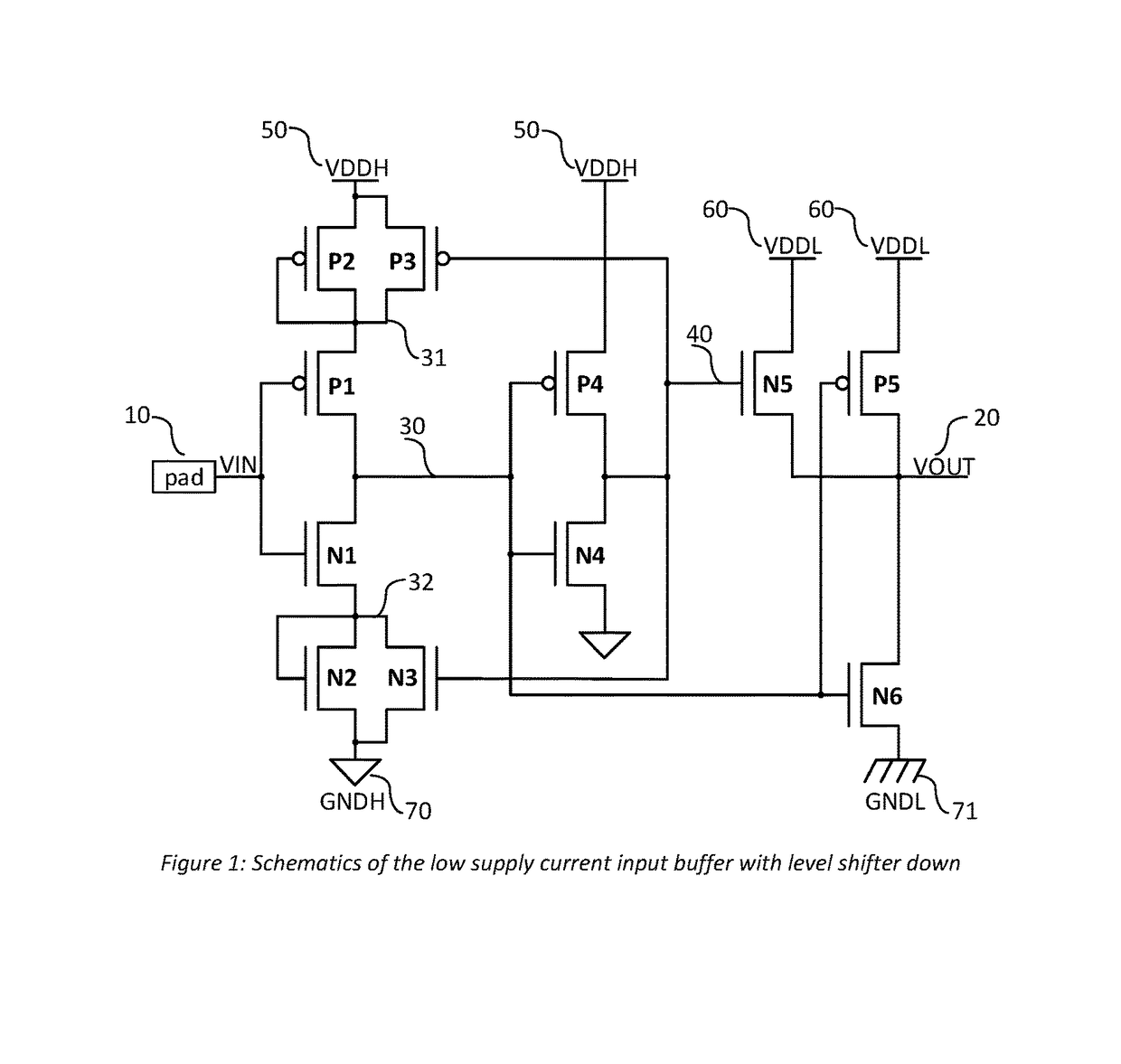

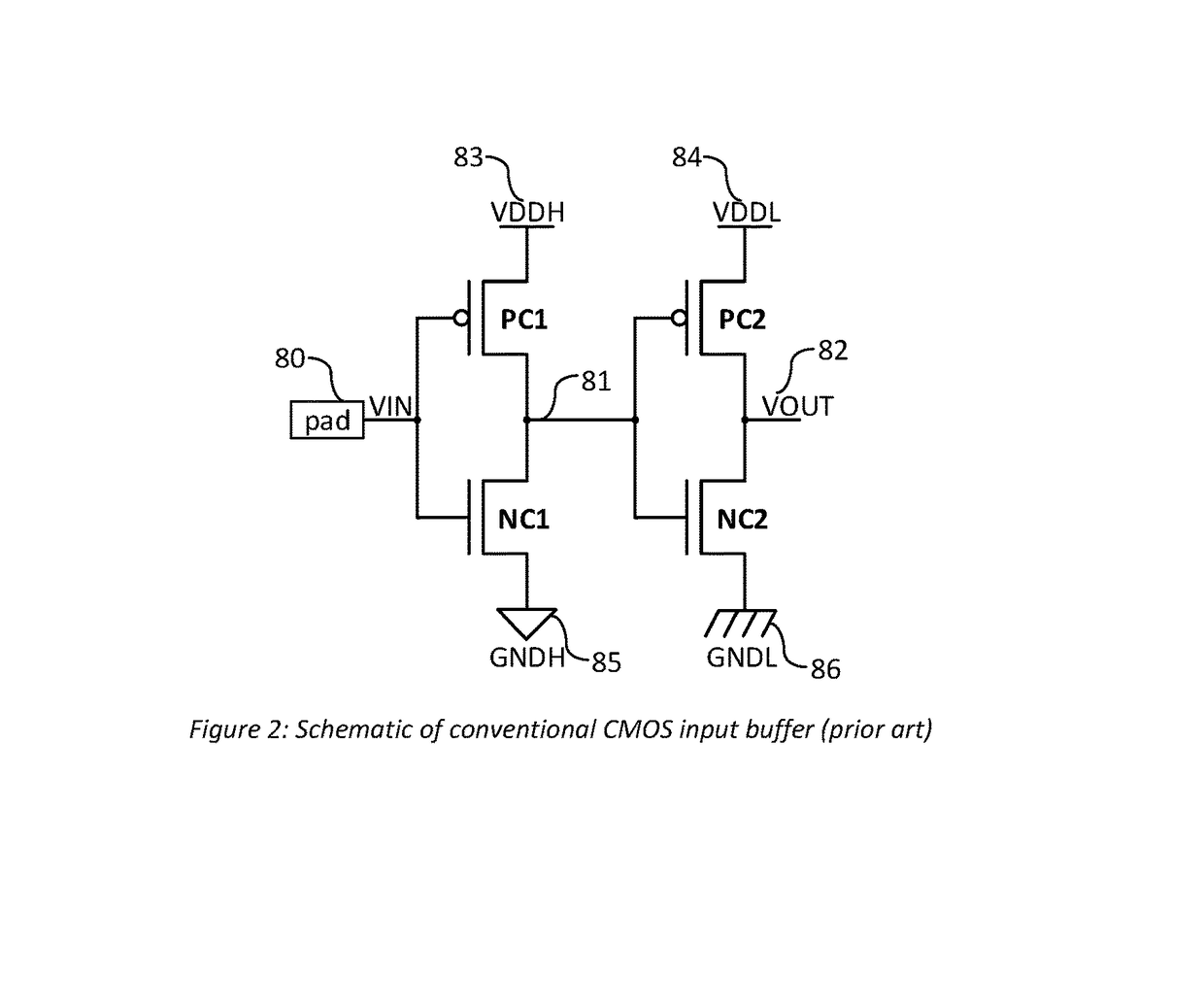

CMOS input buffer with low supply current and voltage down shifting

ActiveUS9935636B1Current consumptionImprove noise marginPower reduction in field effect transistorsLogic circuits coupling/interface using field-effect transistorsHysteresisDown shifting

A method for implementing a CMOS input buffer that consumes very low current even when input levels are less than full swing. An additional optional stage enables conversion to very low voltage swing. The circuit can be manufactured with a standard CMOS processing technology and with high immunity to variation of process parameters. The circuit provides some hysteresis response, enhancing the input voltage margin.

Owner:NXP ISRAEL LTD

Select logic for low voltage swing circuits

InactiveUS6922082B2Digital storageElectric pulse generatorEngineeringElectrical and Electronics engineering

Owner:INTEL CORP

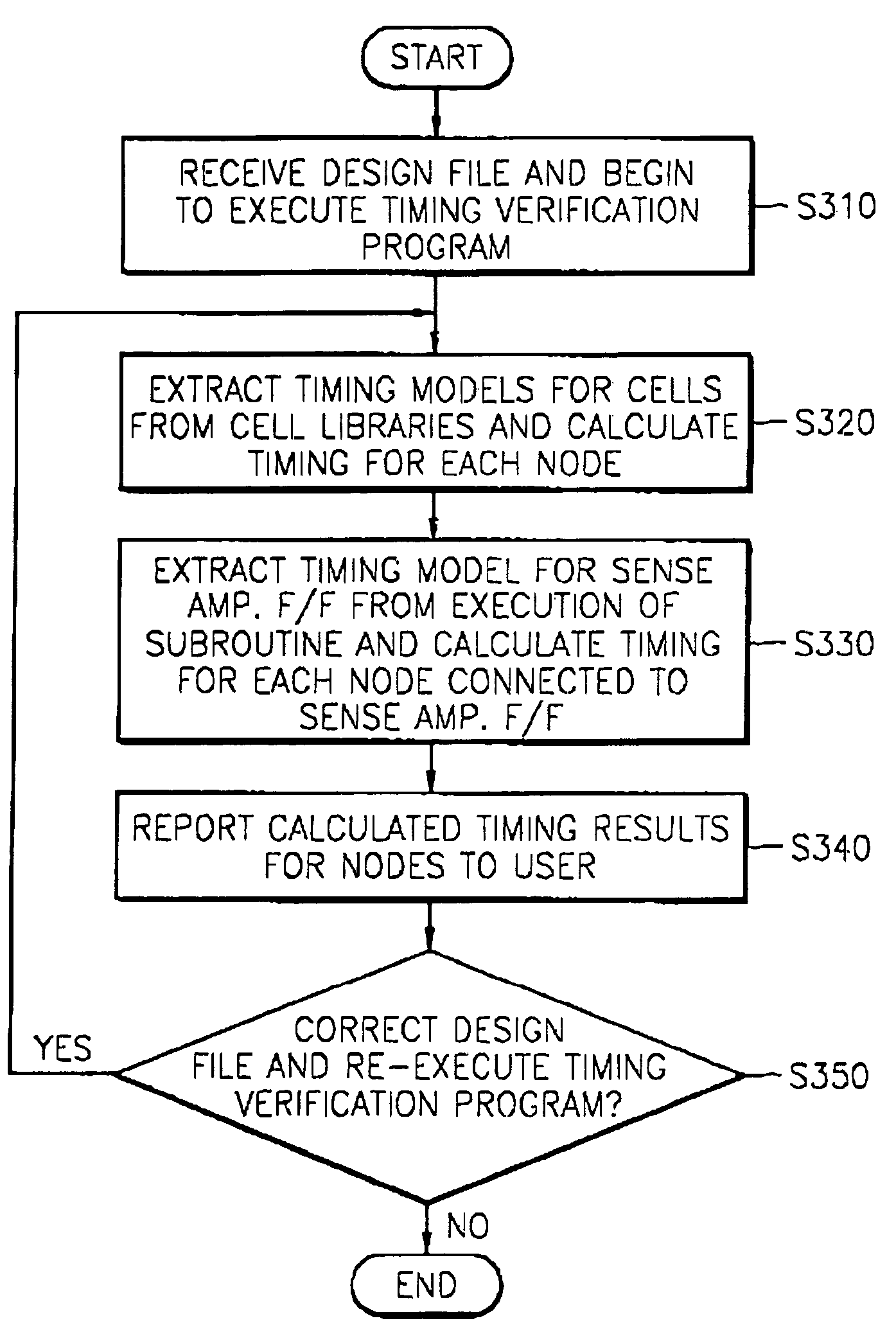

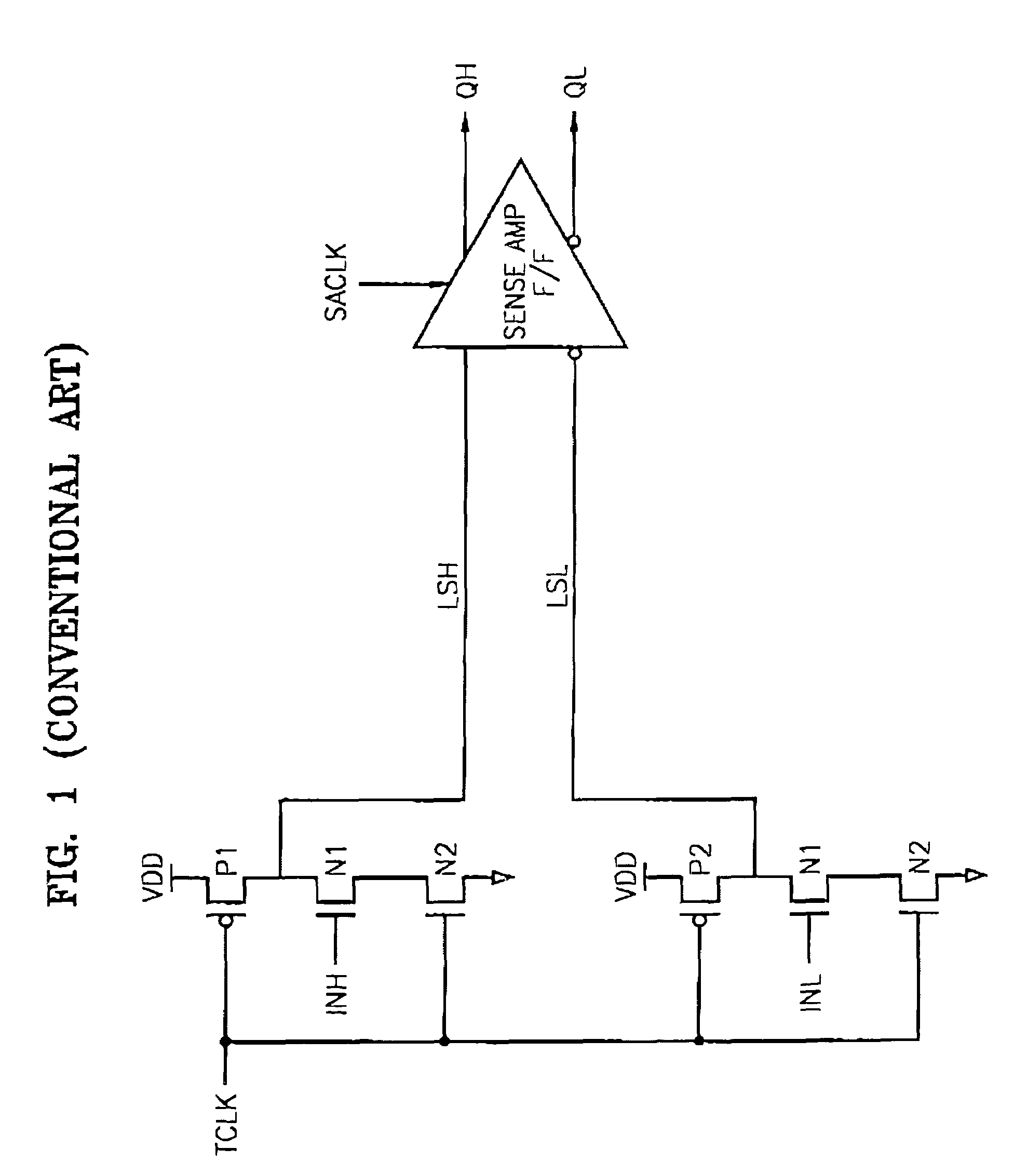

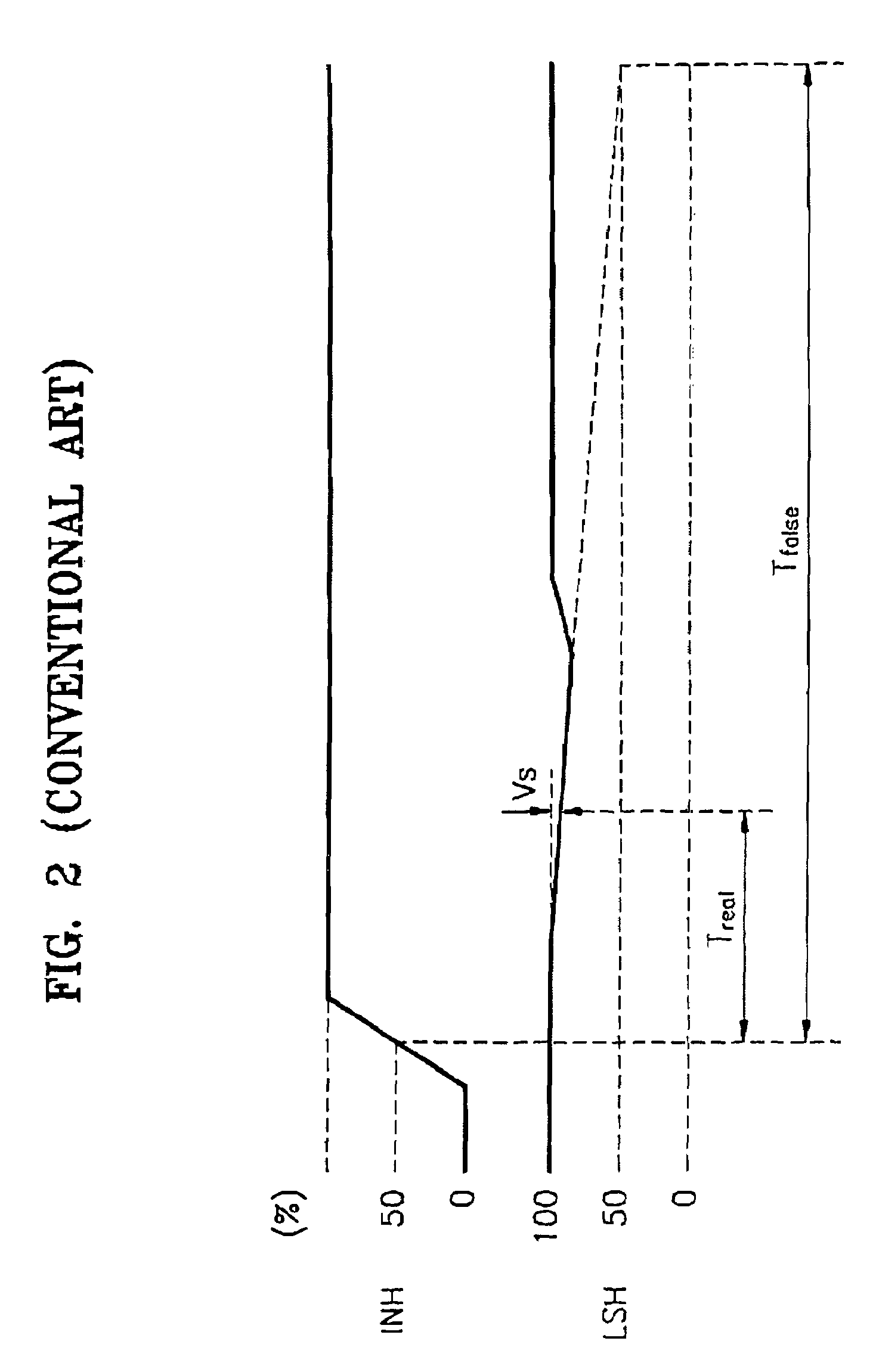

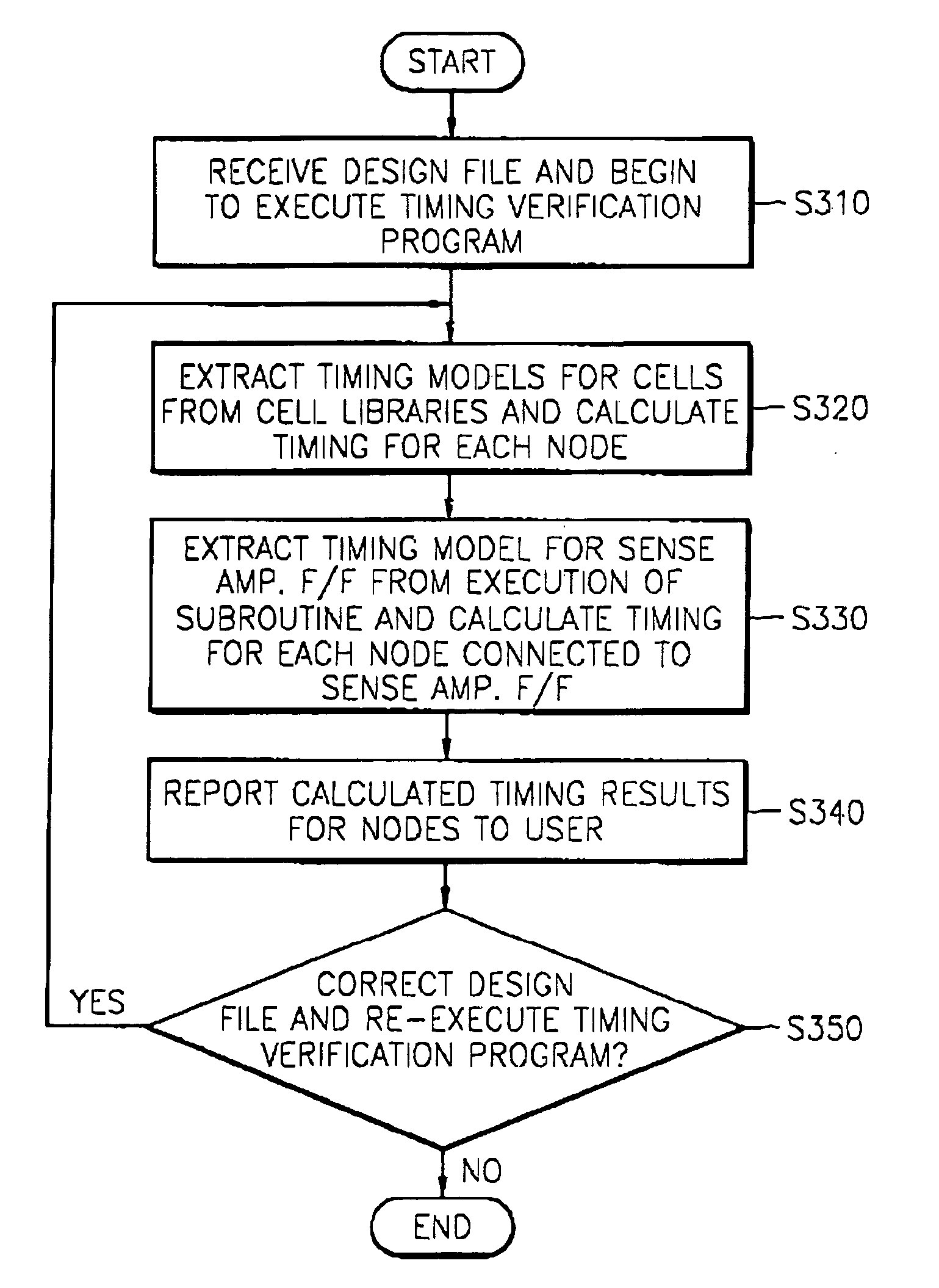

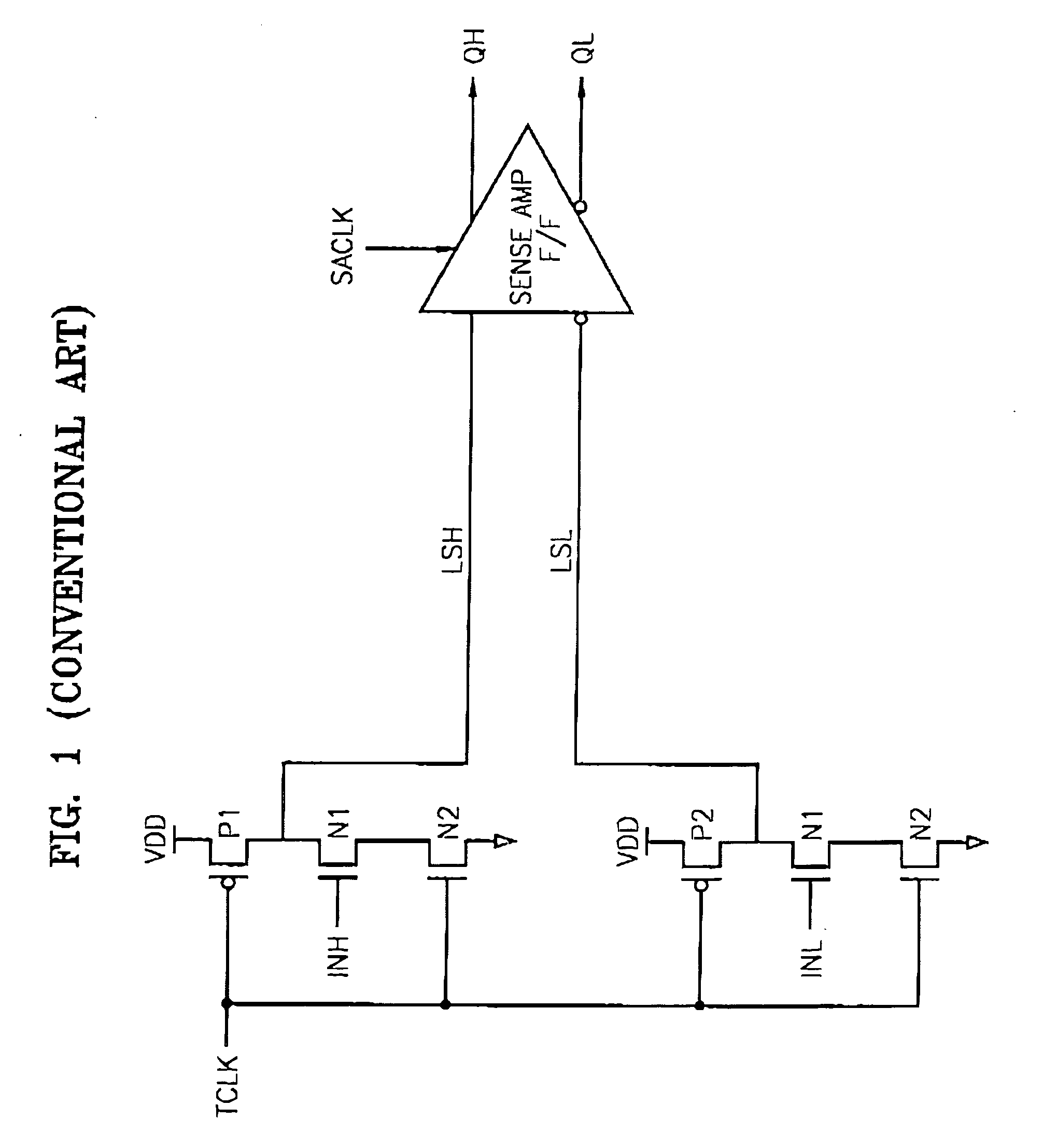

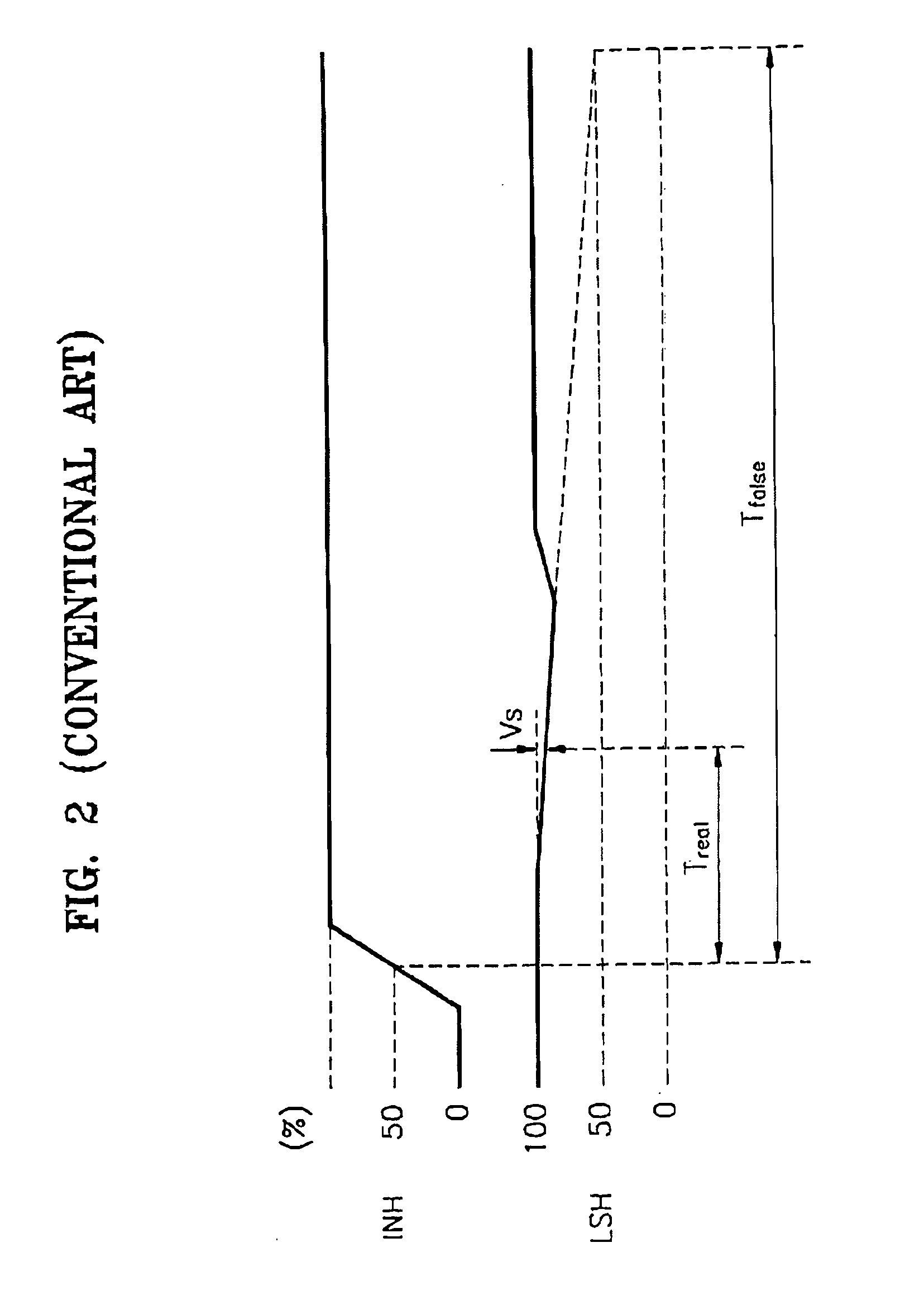

Low voltage swing bus analysis method using static timing analysis tool

InactiveUS7043382B2Simple and accurate timing analysis verificationDigital circuit testingCurrent/voltage measurementStatic timing analysisAnalysis method

A low voltage swing bus analysis method using a static timing analysis (STA) tool, which provides simple and accurate timing analysis verification. The low voltage swing bus analysis method is used in a static timing analysis (STA) tool. The STA tool receives a design file which executes the timing verification program then extracts the timing model for each cell, present in a design file during execution of the timing verification program, and calculates a timing for each node. The STA tool extracts a timing model for a sense amplifying flip flop, among cells present in the design file during execution of the timing verification program, from execution of a subroutine and calculating a timing for each node connected to the sense amplifying flip flop. The STA tool outputs the calculated timings.

Owner:SAMSUNG ELECTRONICS CO LTD

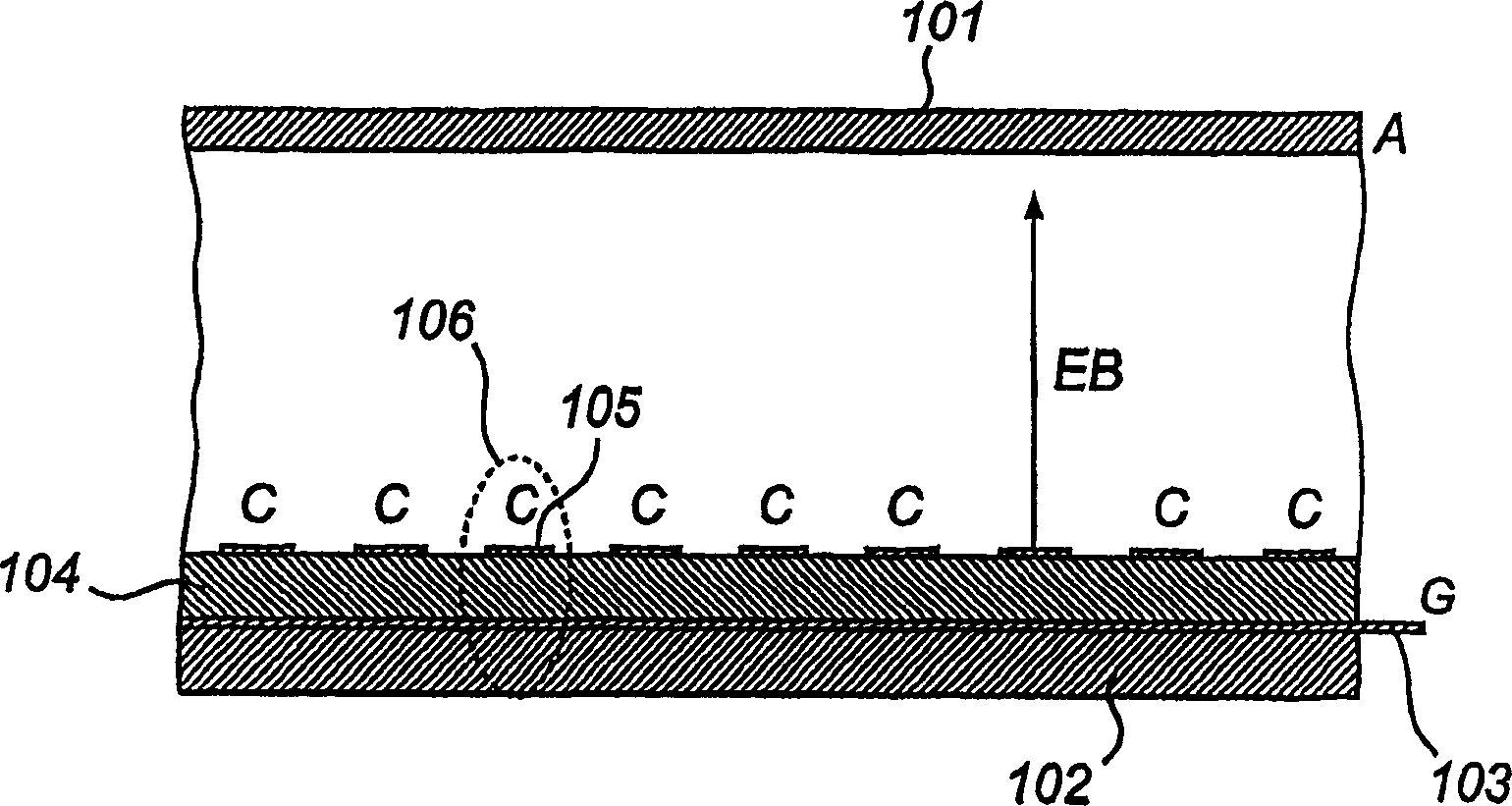

Display device

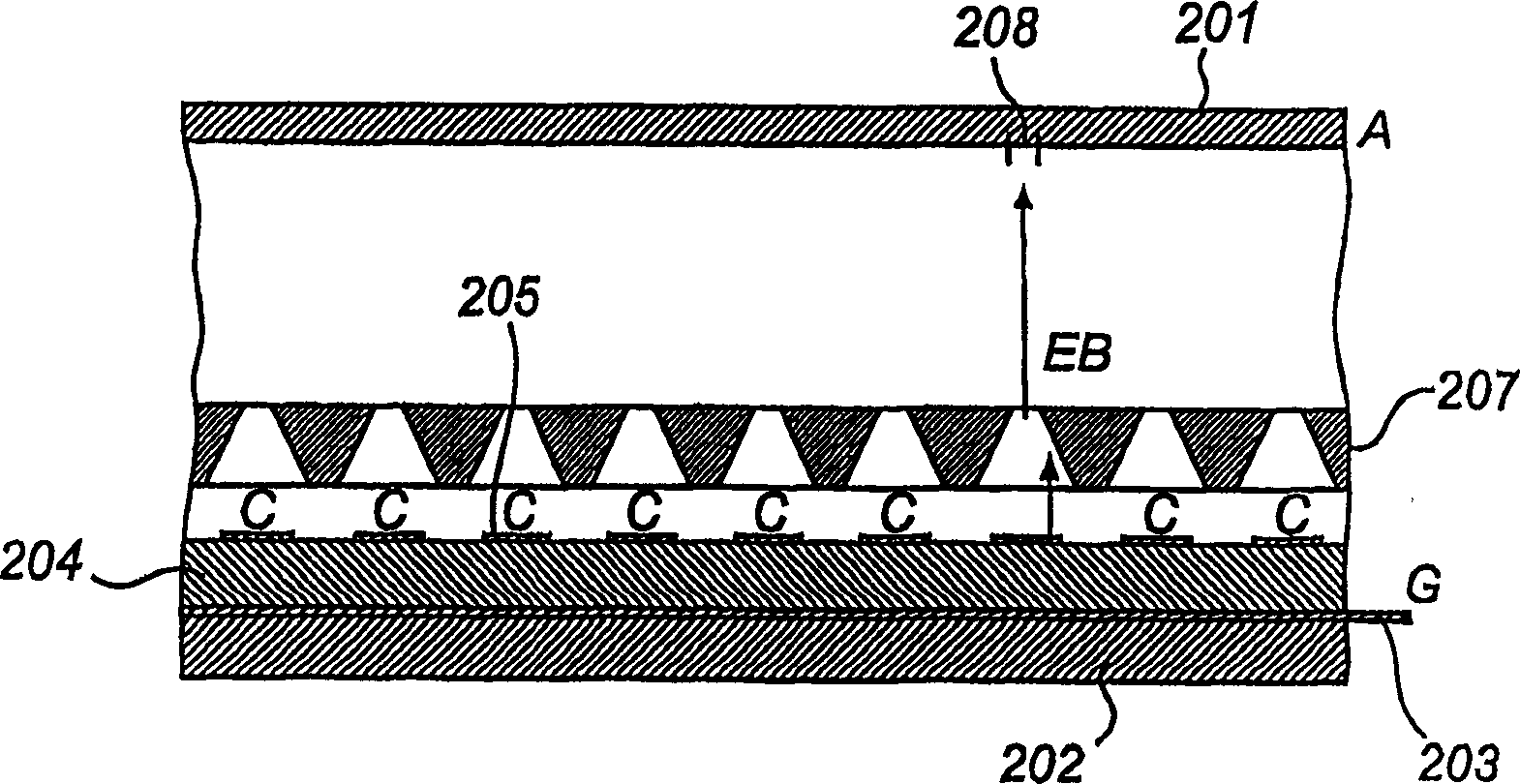

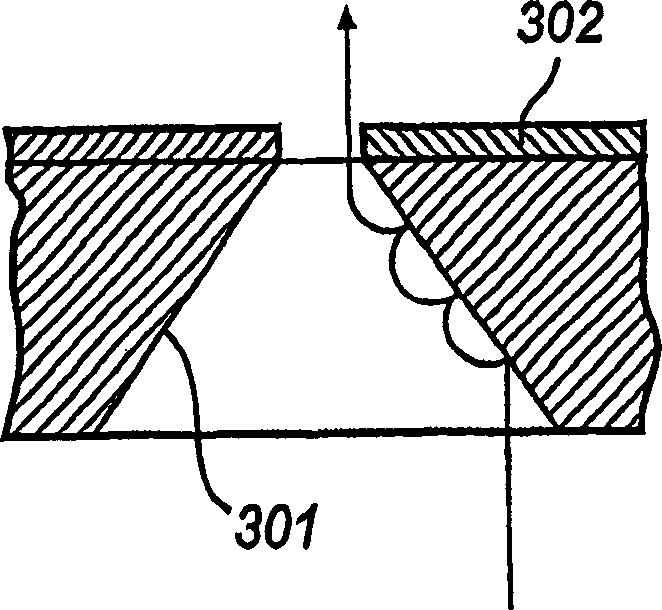

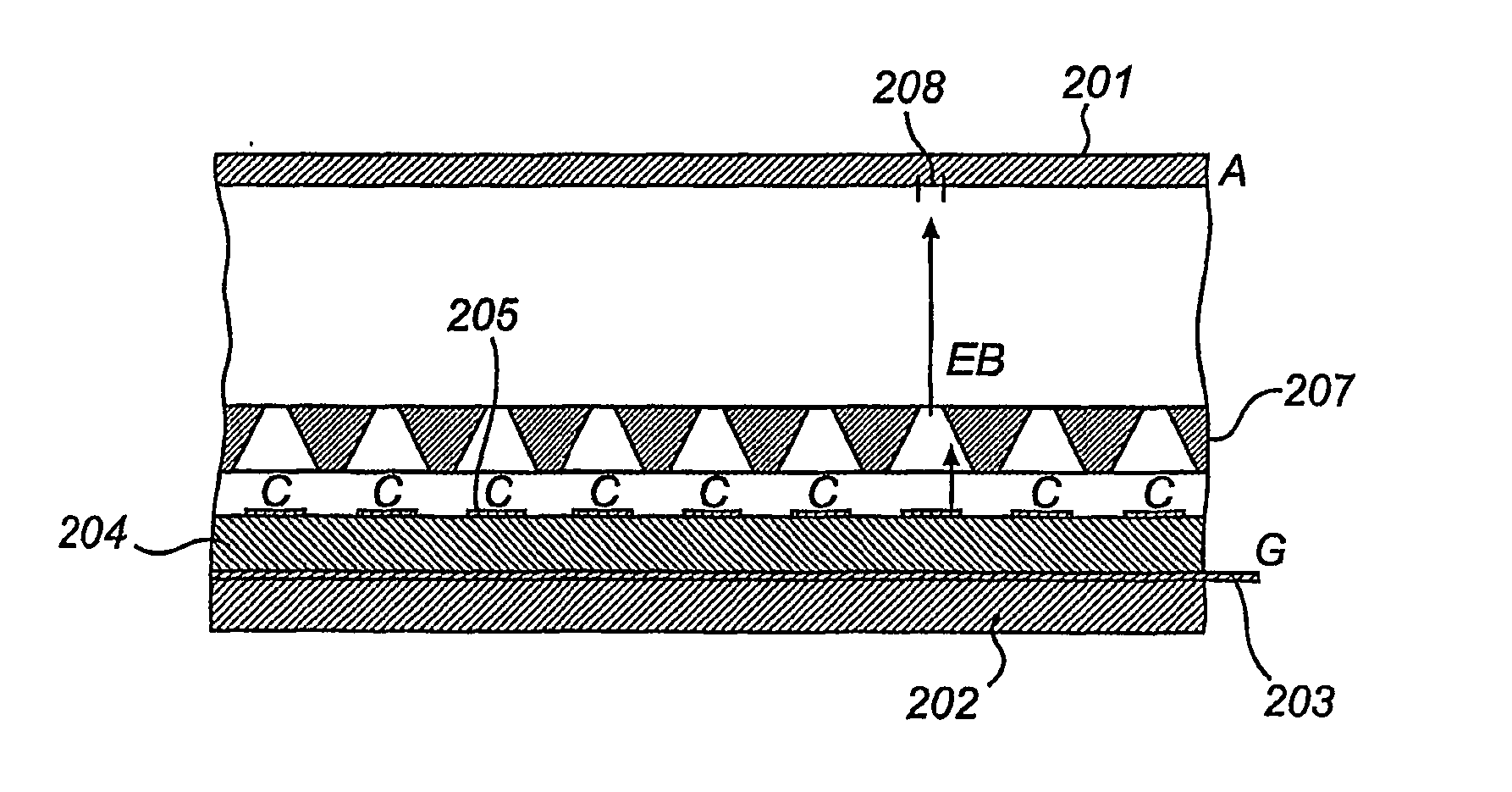

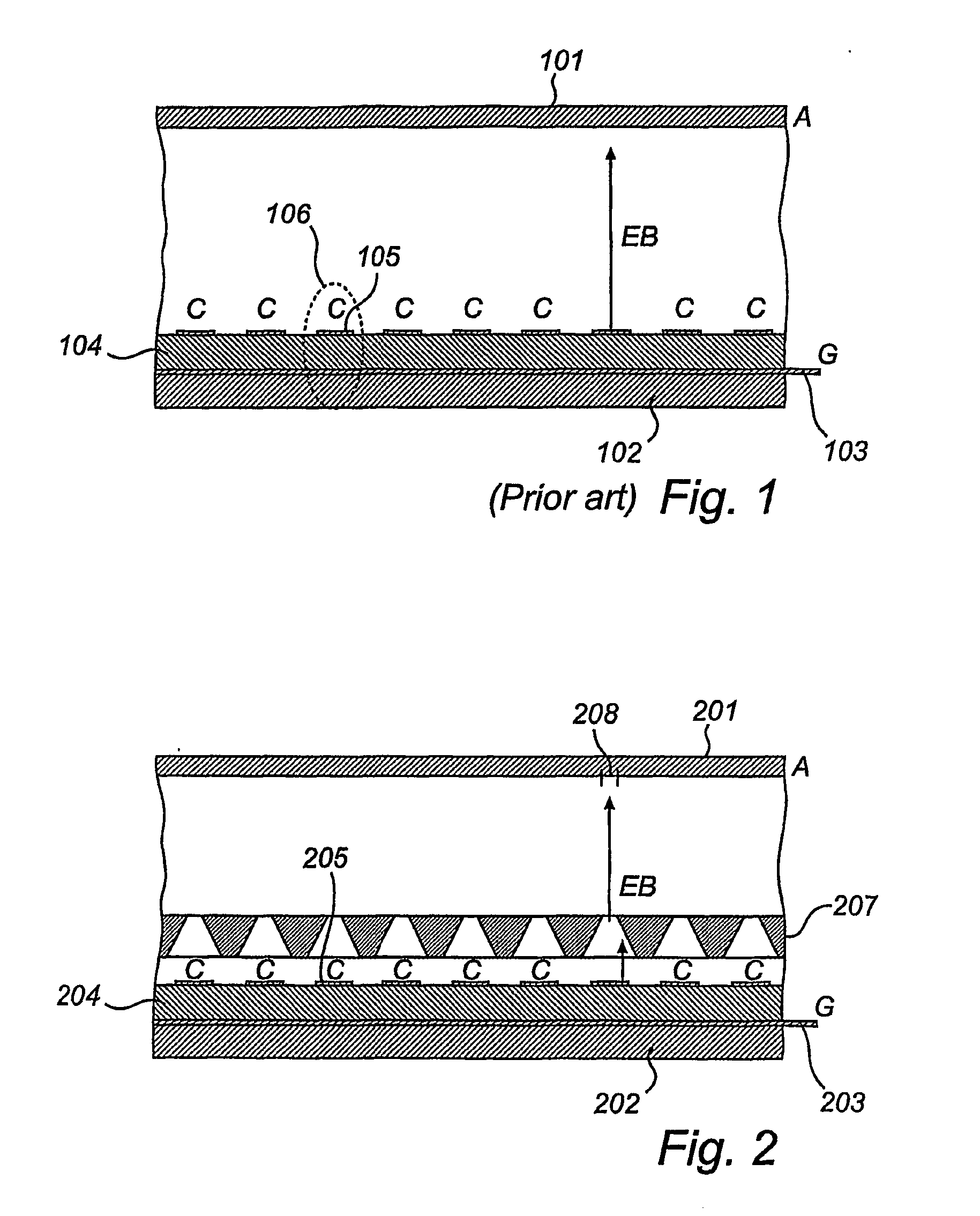

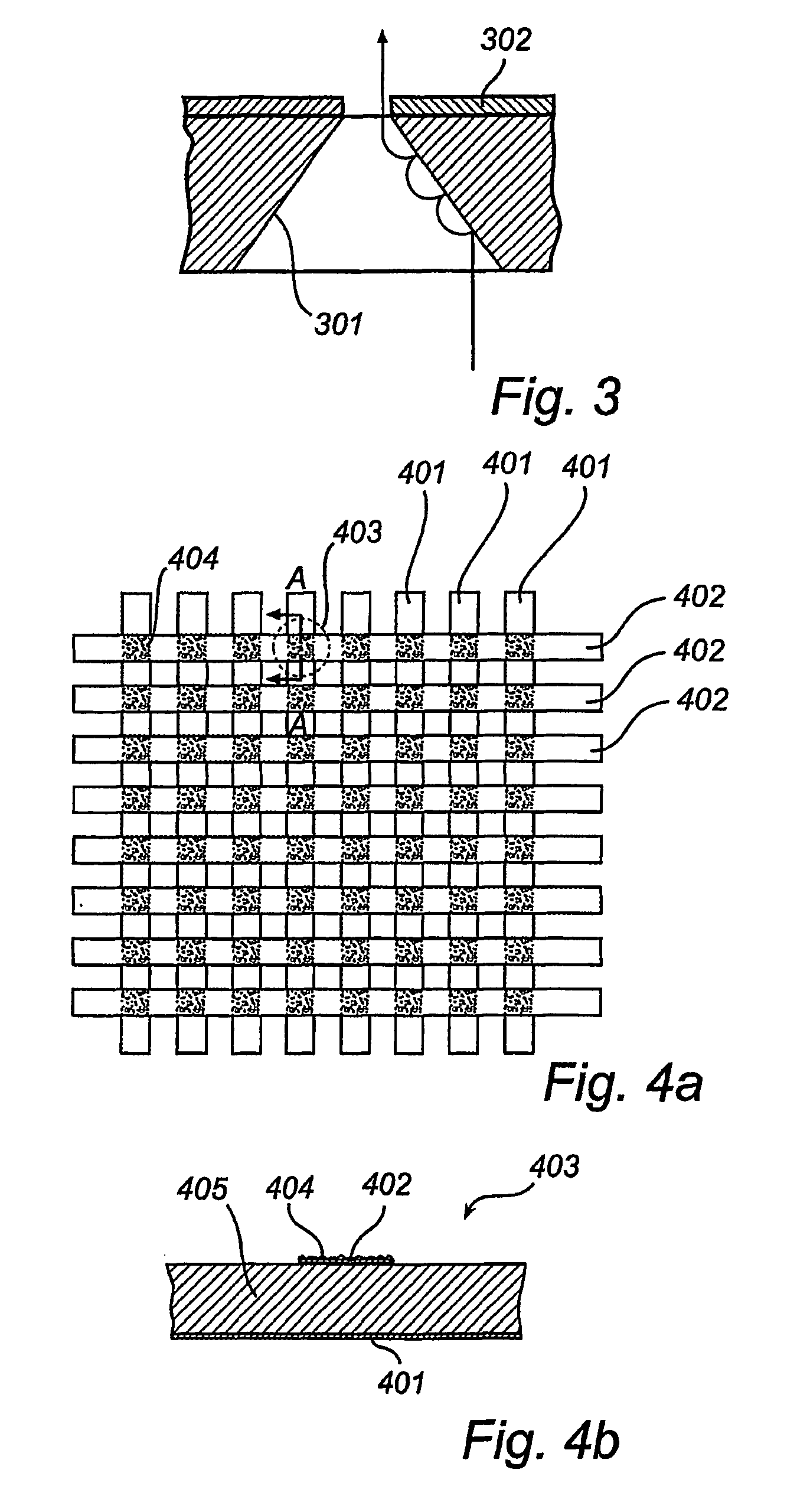

InactiveCN1726578AElectrode and associated part arrangementsImage/pattern display tubesDisplay deviceElectron

The invention relates to a display device having under-gate emitters, i.e. emitters where the gates (203) are arranged under the cathodes (205), beneath an insulating layer (204). In order to protect the emitters from a high electric field from an anode (A), an electron guidance element (207) is placed between the emitters and the anode. This allows a relatively low voltage swing to be used for controlling the electron emission from the emitters from the on-state to the off-state.

Owner:KONINK PHILIPS ELECTRONICS NV +1

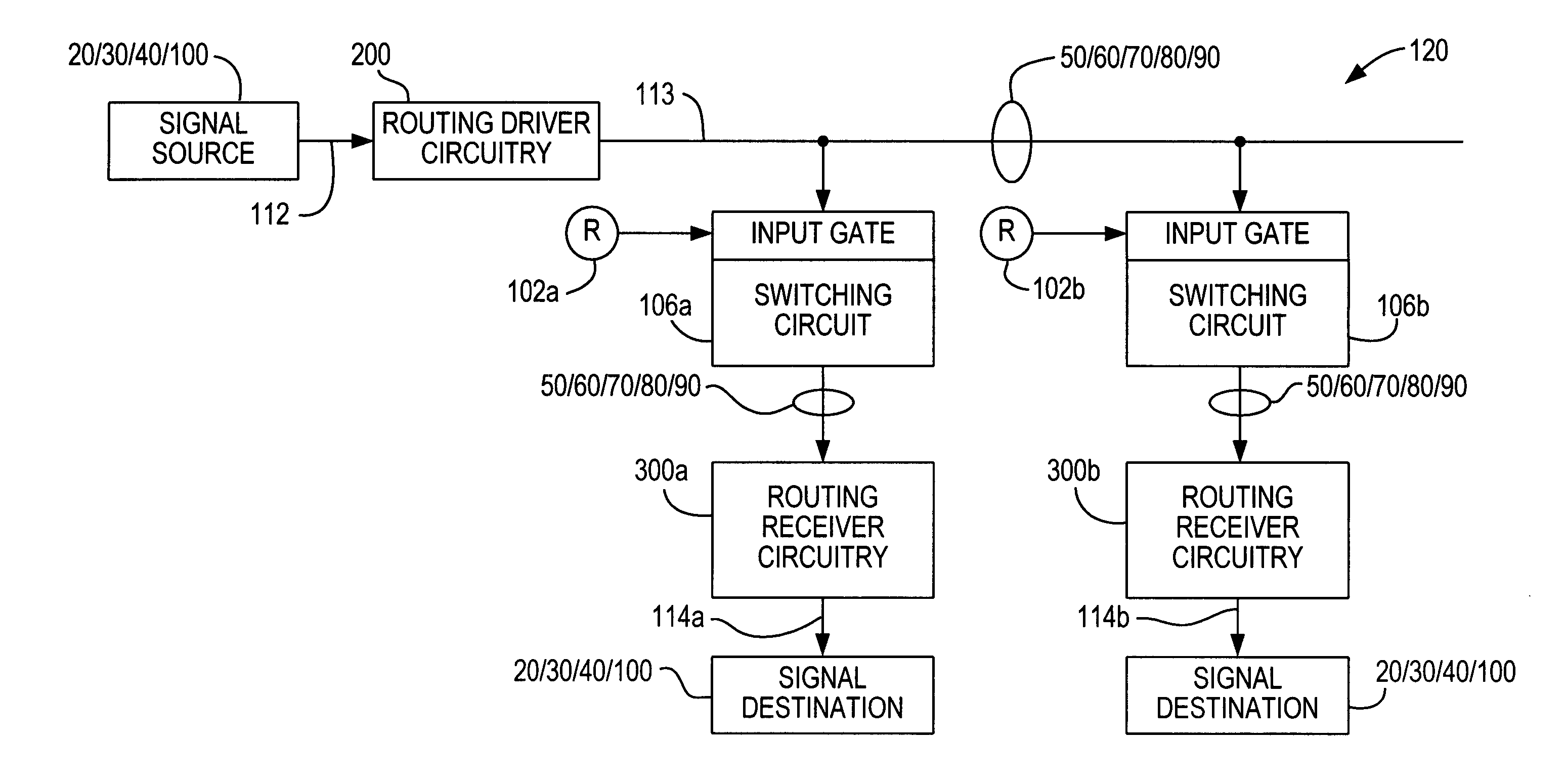

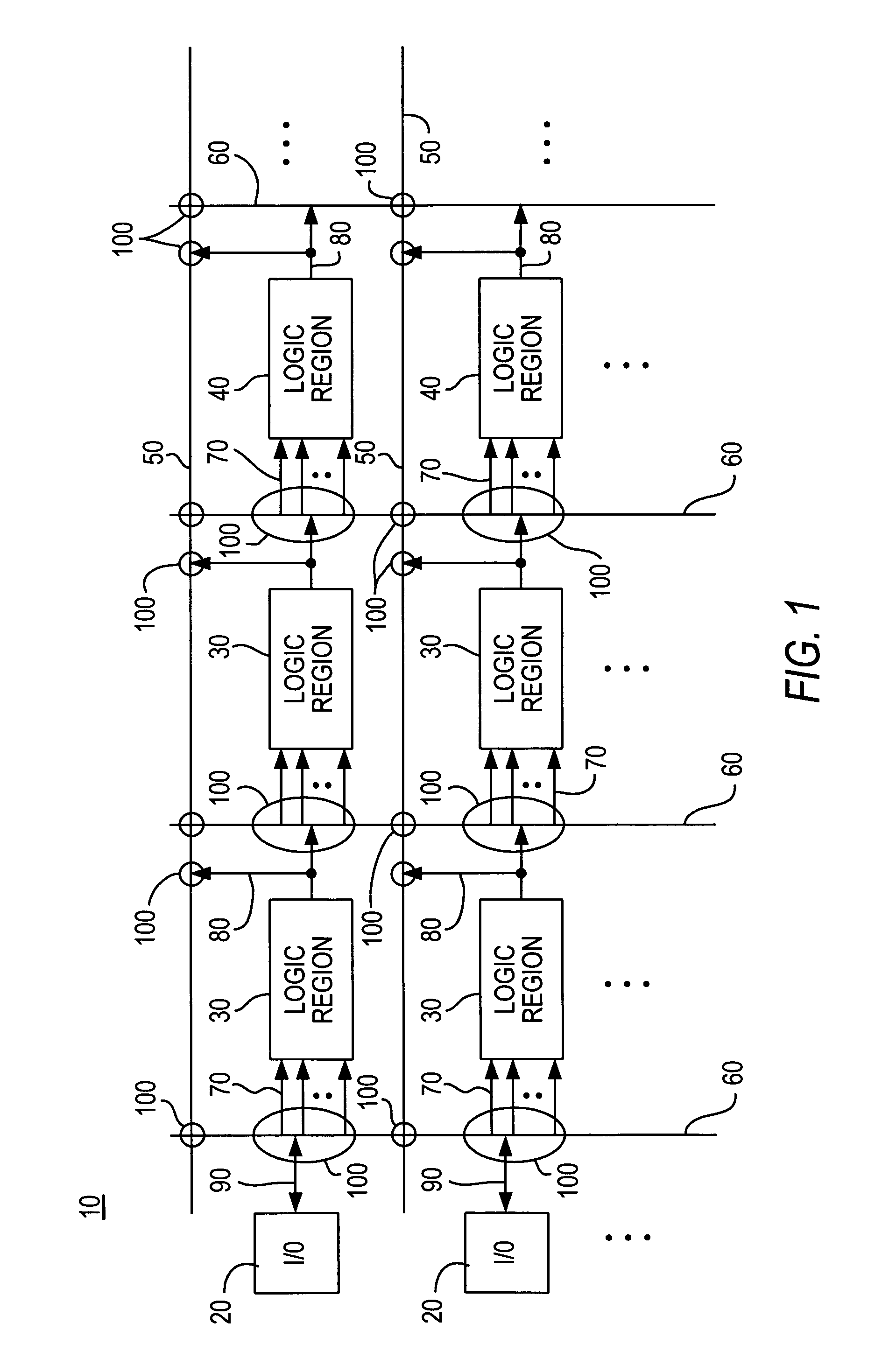

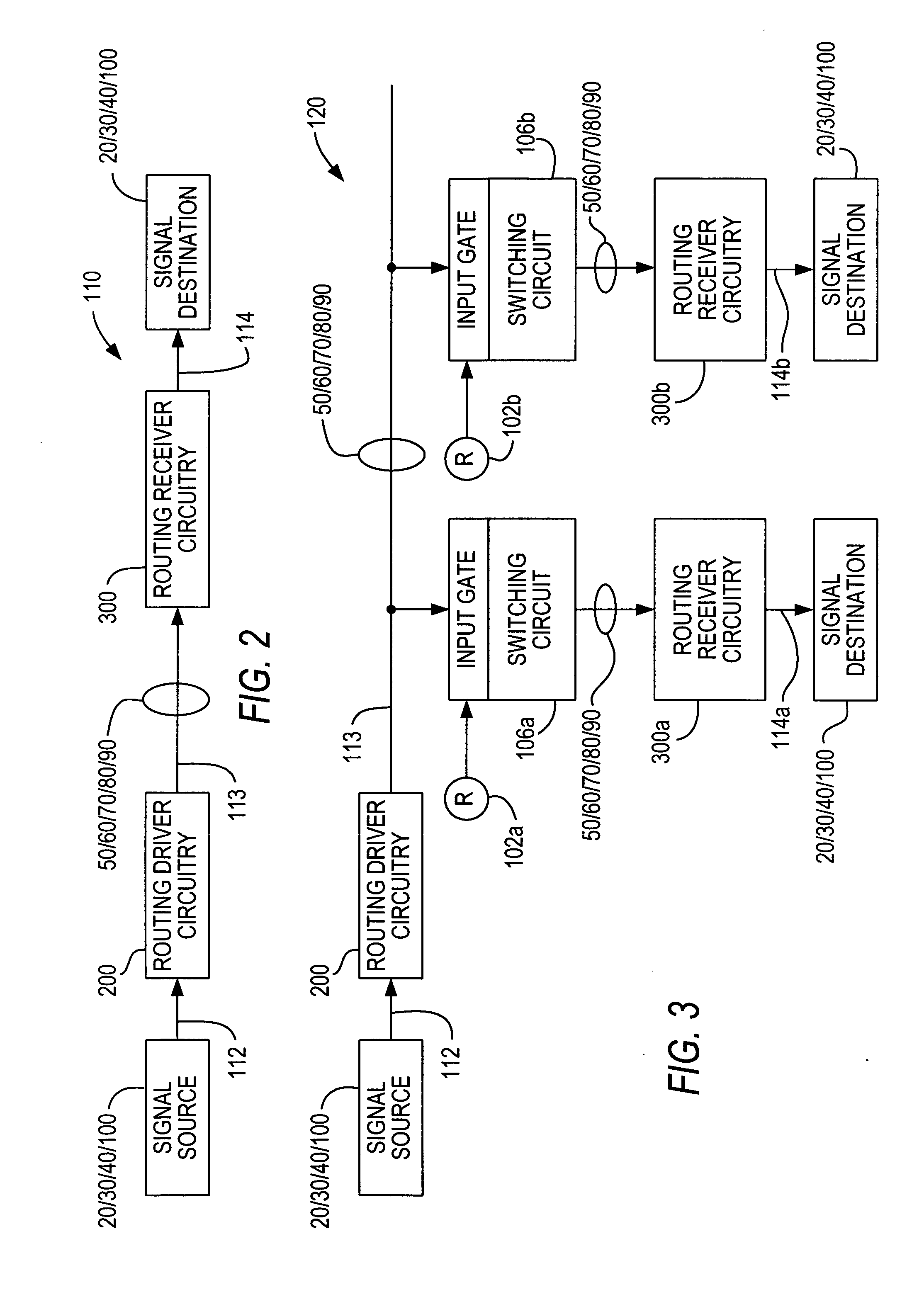

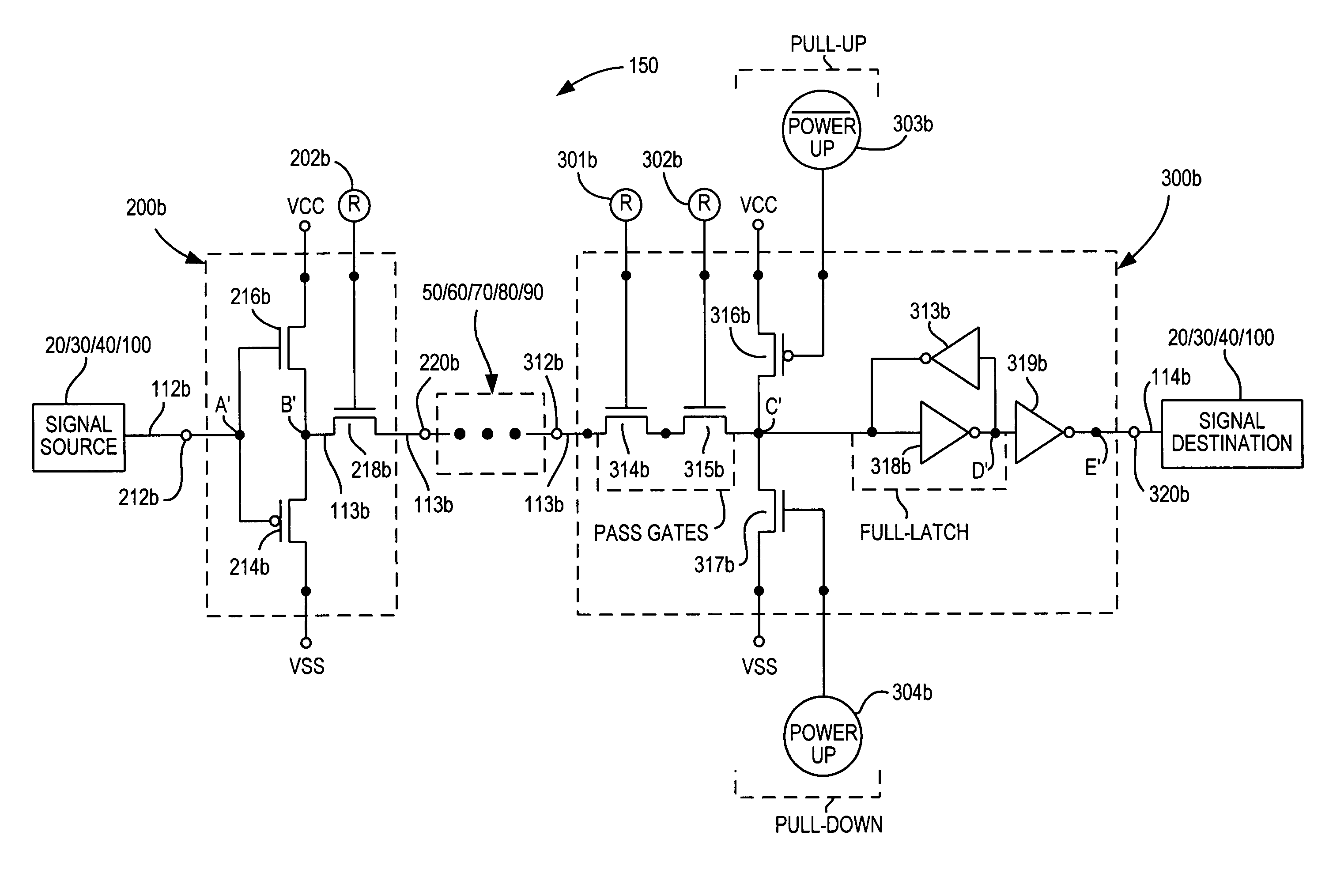

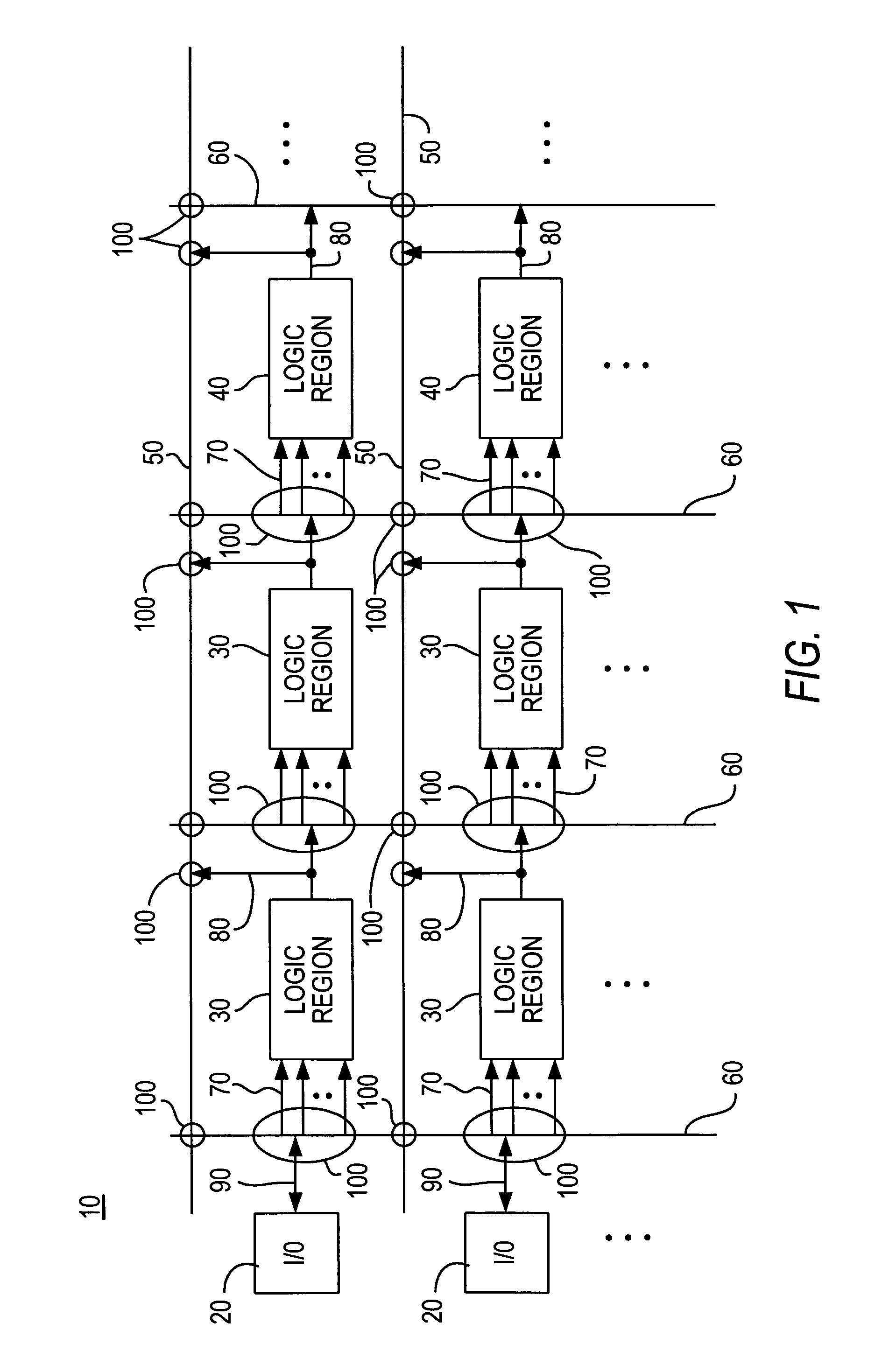

Methods of reducing power in programmable logic devices using low voltage swing for routing signals

InactiveUS20060158220A1Reduce power consumptionReduce the amount requiredPower reduction in field effect transistorsSolid-state devicesProgrammable logic deviceInterconnection

Reduced voltage swing signal path circuitry is provided that lowers the internal signaling power consumption of the interconnection resources of a programmable logic device. The reduced voltage swing signal path circuitry includes a reversed routing driver circuitry to limit the voltage range of the output signal of the driver circuitry.

Owner:ALTERA CORP

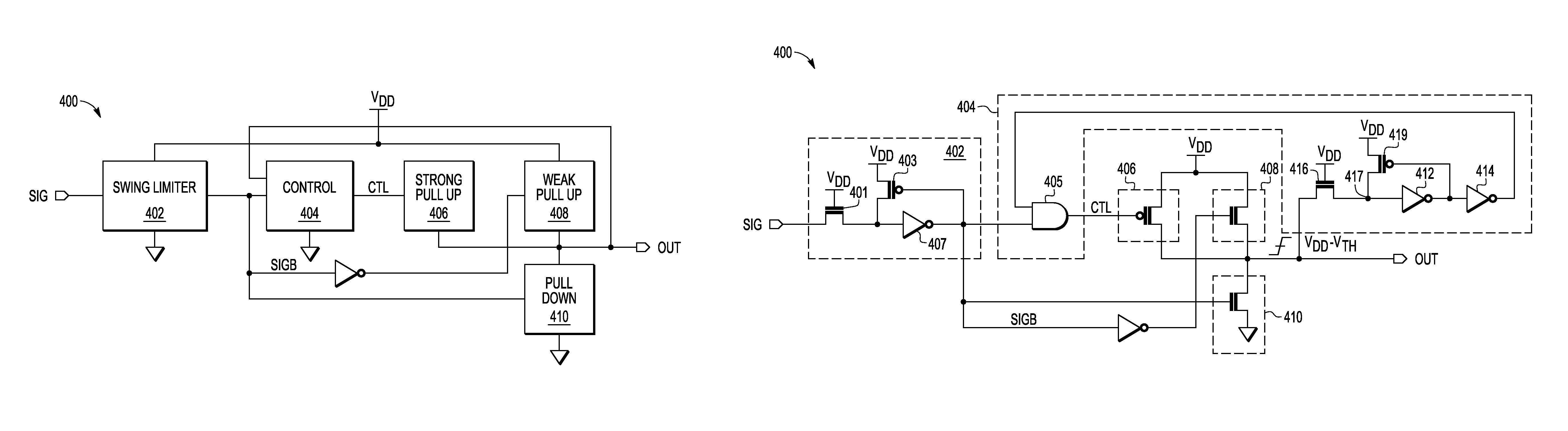

Low voltage swing buffer

Owner:NXP USA INC

Display device

InactiveUS20070052337A1Reduce the impactImprove emission effectElectrode and associated part arrangementsImage/pattern display tubesDisplay deviceElectron

The invention relates to a display device having under-gate emitters, i.e. emitters where the gates (203) are arranged under the cathodes (205), beneath an insulating layer (204). In order to protect the emitters from a high electric field from an anode (A), an electron guidance element (207) is placed between the emitters and the anode. This allows a relatively low voltage swing to be used for controlling the electron emission from the emitters from the on-state to the off-state.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV +1

Methods of reducing power in programmable logic devices using low voltage swing for routing signals

InactiveUS7262634B2Reduce power consumptionReduce the amount requiredPower reduction in field effect transistorsSolid-state devicesProgrammable logic deviceInterconnection

Reduced voltage swing signal path circuitry is provided that lowers the internal signaling power consumption of the interconnection resources of a programmable logic device. The reduced voltage swing signal path circuitry includes a reversed routing driver circuitry to limit the voltage range of the output signal of the driver circuitry.

Owner:ALTERA CORP

Low voltage swing pad driver and receiver

InactiveUS7305045B2Reduce distortion problemsMinimize distortionModulation with suppressed carrierAmplitude-modulated carrier systemsCurrent driverFull scale

Low voltage swing pad driver and receiver. A transmitter portion and a receiver portion are implemented within various devices that communicate using low voltage swing pads communicatively coupled via a trace. The transmitter portion of one device generates a current signal that is pushed / pulled to a low voltage swing pad and is then passed across the trace to another low voltage swing pad. The transmitter portion includes a current driver that outputs the current signal to the low voltage swing pads, and the receiver portion includes a trans-impedance amplifier that transforms the received current signal into a voltage signal. The low voltage swing pad driver and receiver generates a relatively low voltage swing when compared to CMOS full-scale voltage swings thereby significantly reducing the possibility of introducing any noise and / or distortion of data that is communicated via the interface.

Owner:AVAGO TECH INT SALES PTE LTD

Low voltage swing bus analysis method using static timing analysis tool

InactiveUS20040163066A1Digital circuit testingCurrent/voltage measurementStatic timing analysisAnalysis method

A low voltage swing bus analysis method using a static timing analysis (STA) tool, which provides simple and accurate timing analysis verification. The low voltage swing bus analysis method is used in a static timing analysis (STA) tool. The STA tool receives a design file which executes the timing verification program then extracts the timing model for each cell, present in a design file during execution of the timing verification program, and calculates a timing for each node. The STA tool extracts a timing model for a sense amplifying flip flop, among cells present in the design file during execution of the timing verification program, from execution of a subroutine and calculating a timing for each node connected to the sense amplifying flip flop. The STA tool outputs the calculated timings.

Owner:SAMSUNG ELECTRONICS CO LTD

Low voltage swing buffer

ActiveUS20160085261A1Power consumption reductionPower supply for data processingSignal onControl signal

An apparatus includes a first circuit of a first type that couples an output node to a first power supply node in response to a first value of a control signal. The apparatus includes a second circuit of a second type to couple the output node to the first power supply node in response to a first value of a first signal having a first voltage swing. The apparatus includes a third circuit of the second type to couple the output node to a second power supply node in response to a second value of the first signal. The apparatus includes a control circuit that generates the control signal based on the first signal and an output signal on the output node. The first, second, and third circuits generate an output signal on the output node. The output signal has a second voltage swing less than the first voltage swing.

Owner:NXP USA INC

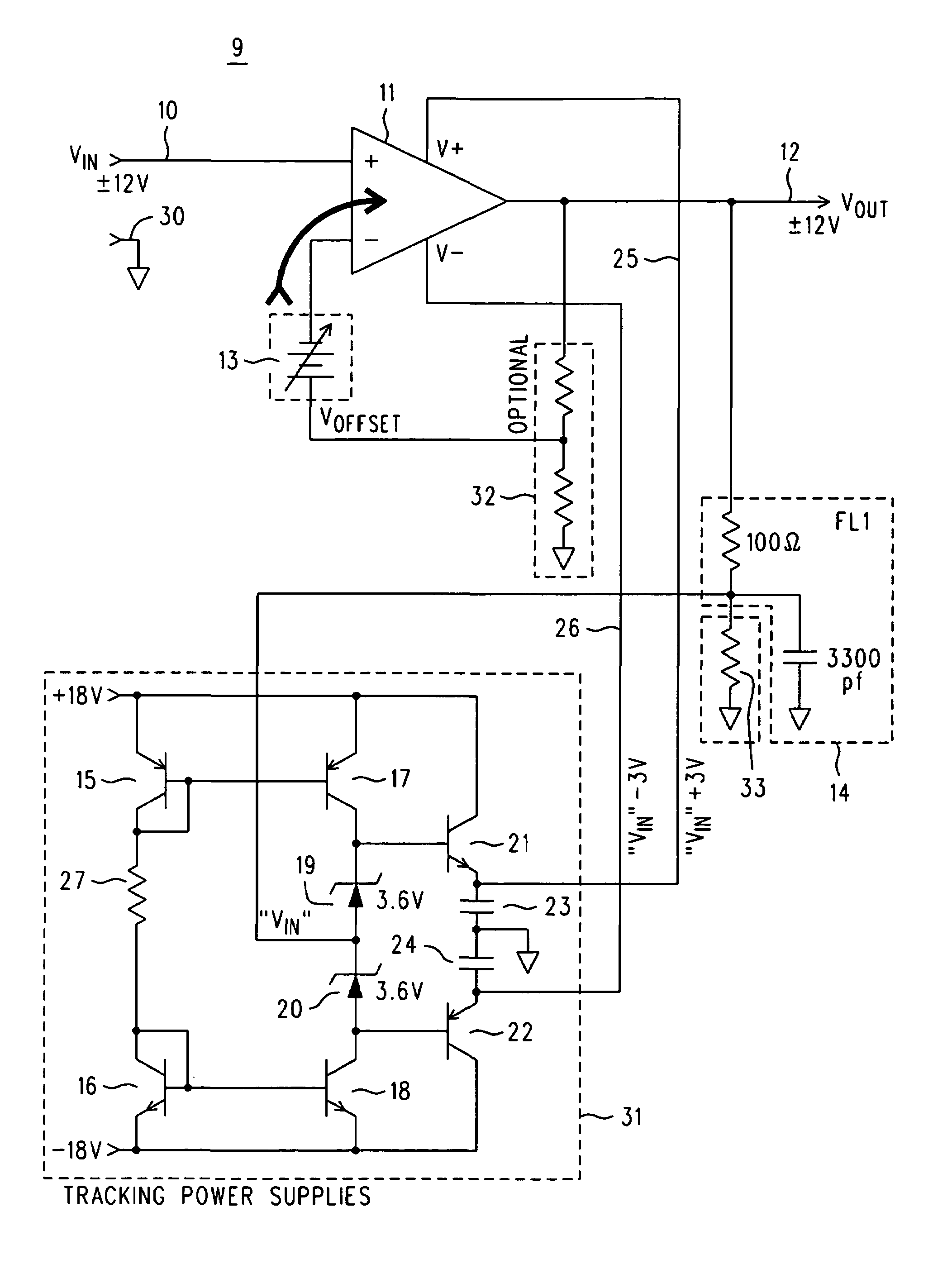

Ultra high linearity amplifier

Owner:KEYSIGHT TECH