Patents

Literature

162 results about "Programming patterns" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In object-oriented programming, a pattern can contain the description of certain objects and object classes to be used, along with their attributes and dependencies, and the general approach to how to solve the problem. Often, programmers can use more than one pattern to address a specific problem.

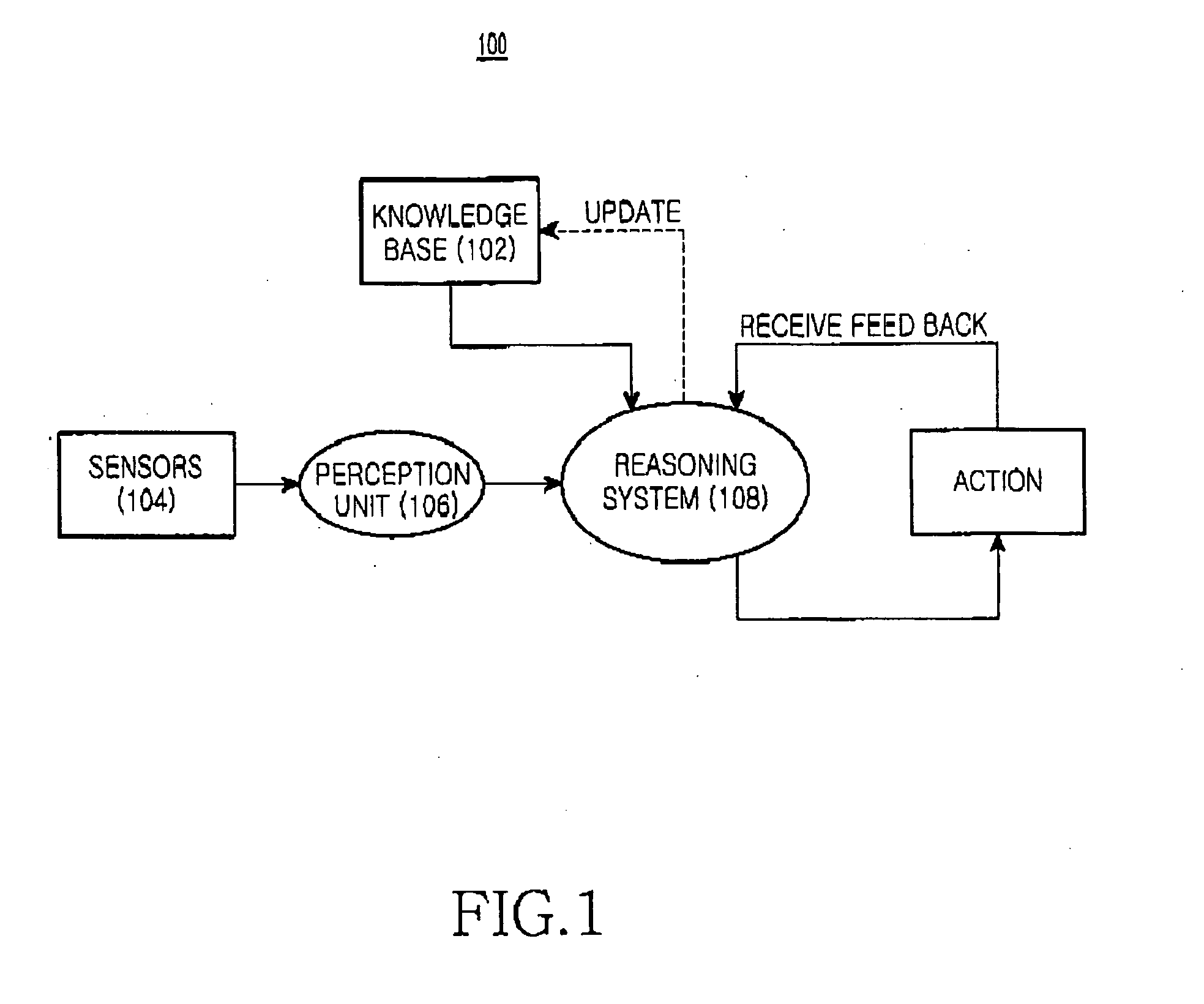

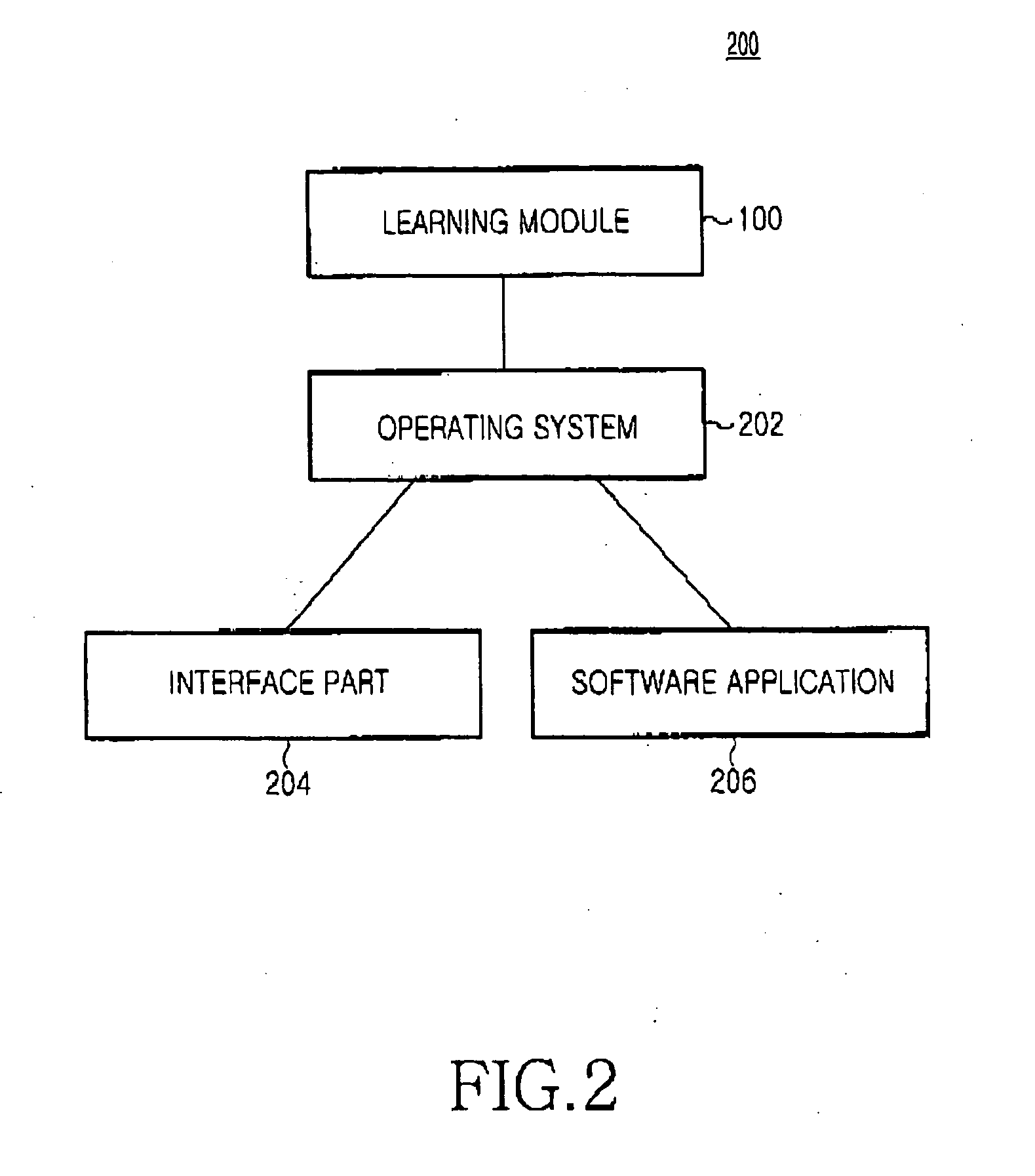

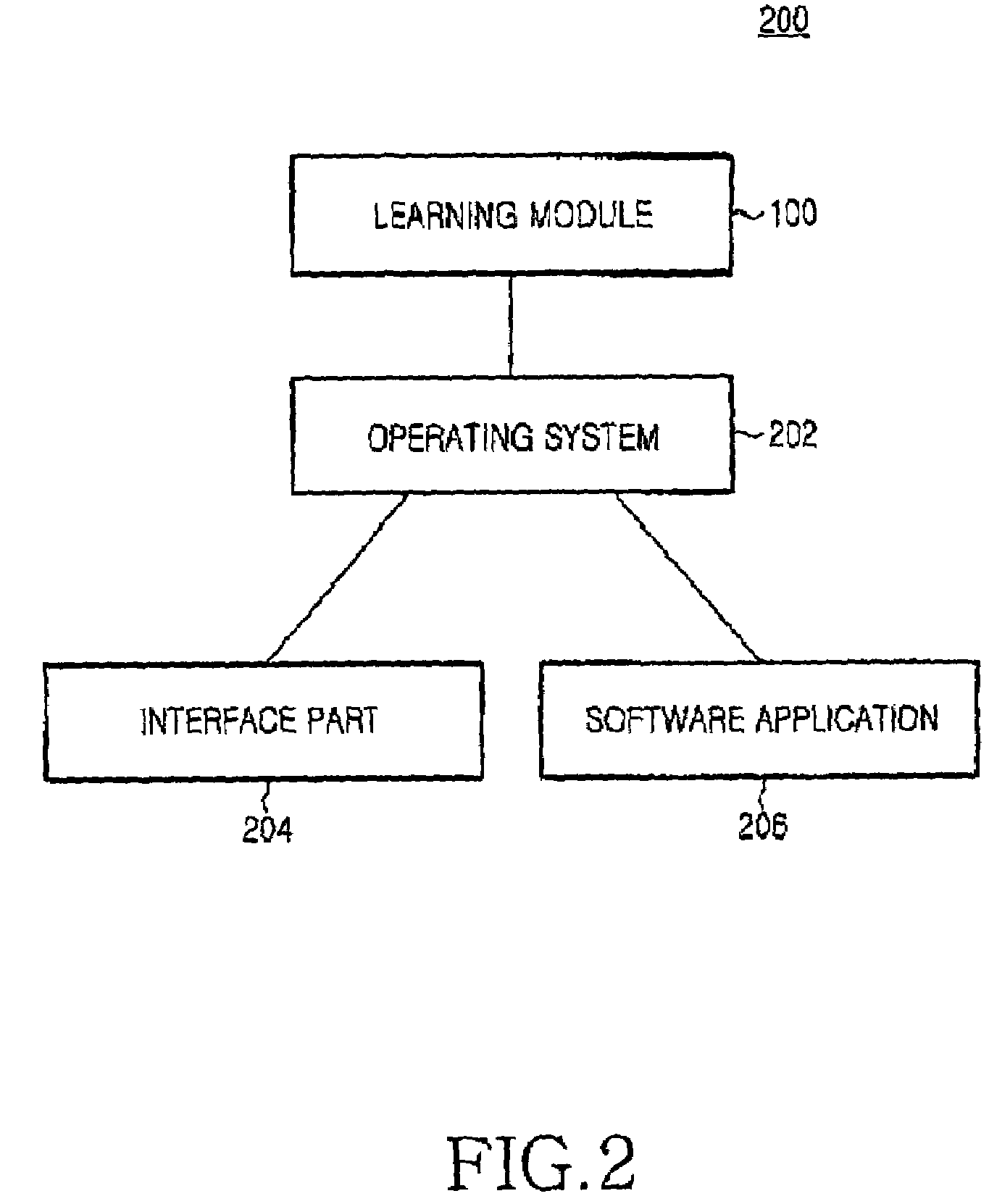

Proactive user interface

InactiveUS20050054381A1Increase sense of intelligenceImprove experienceInput/output for user-computer interactionDevices with sensorDisplay deviceTouchscreen

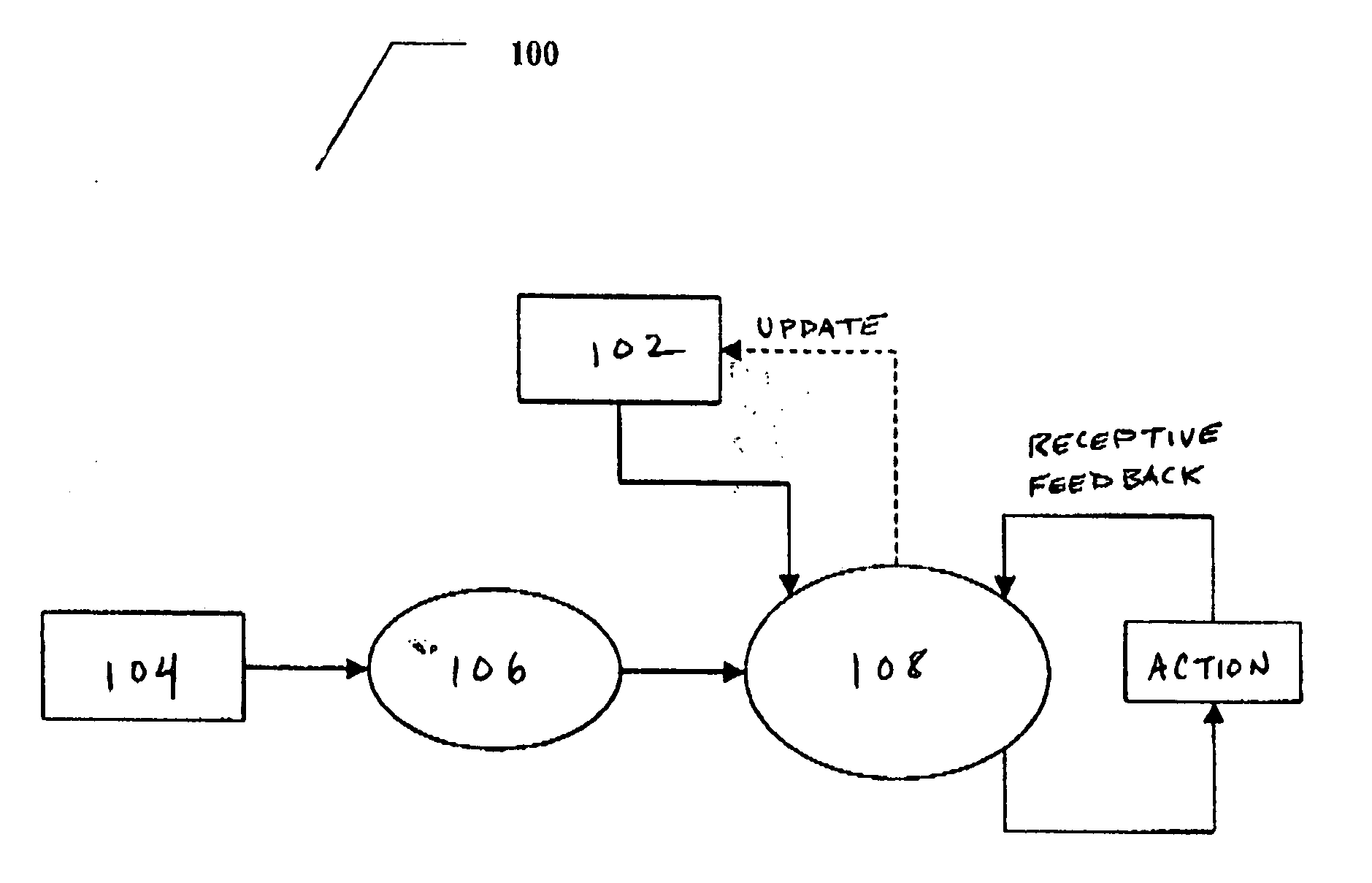

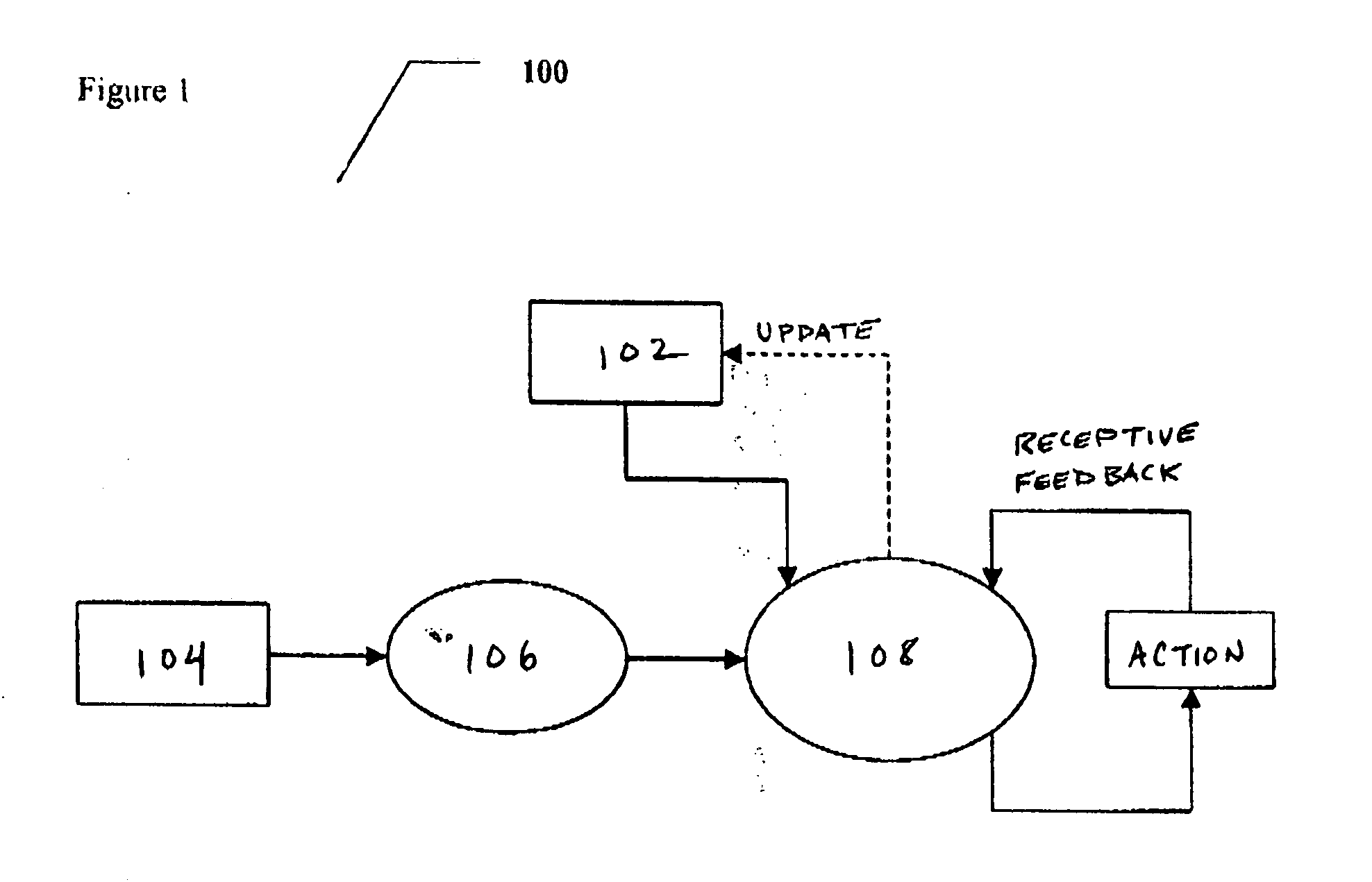

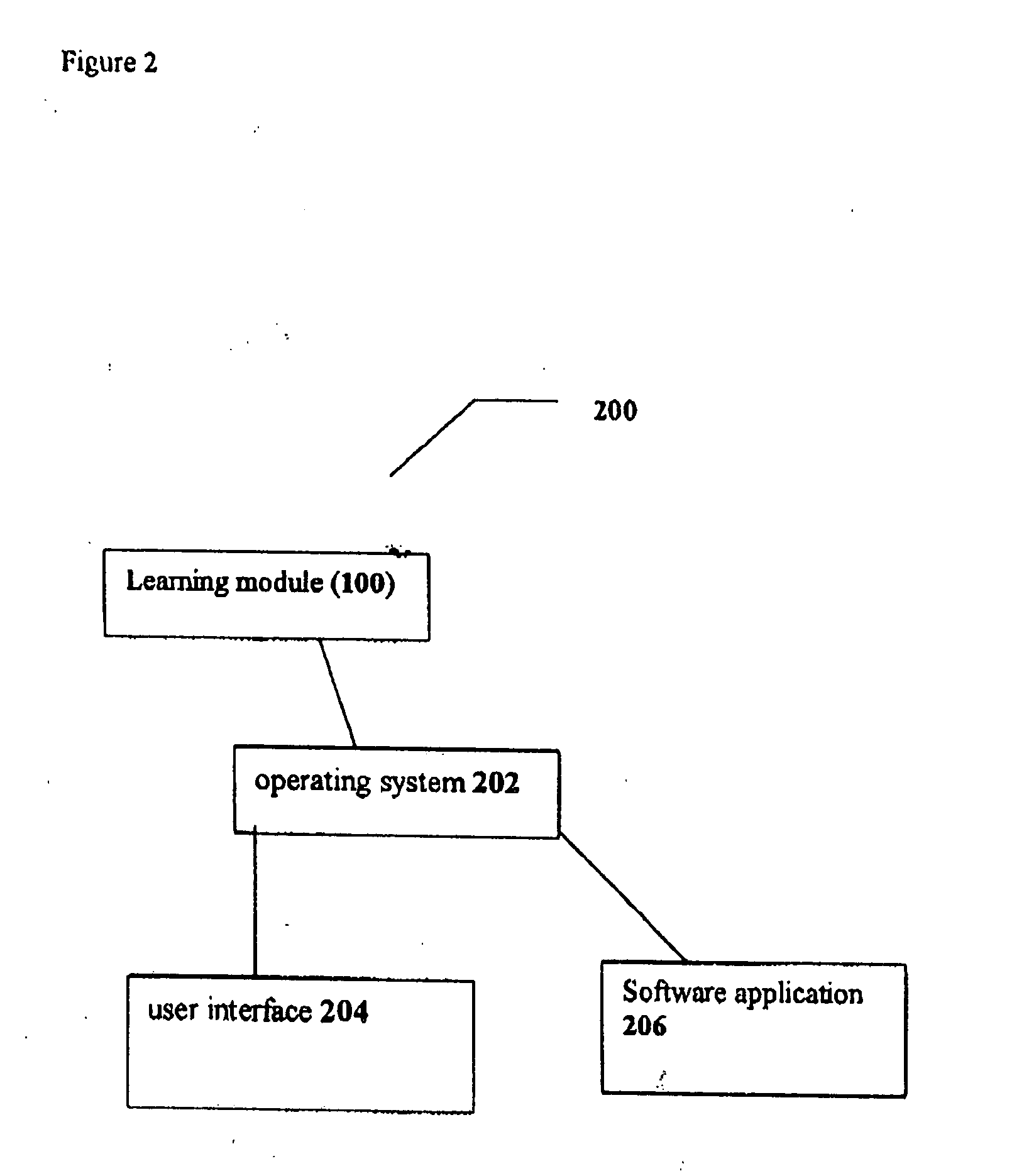

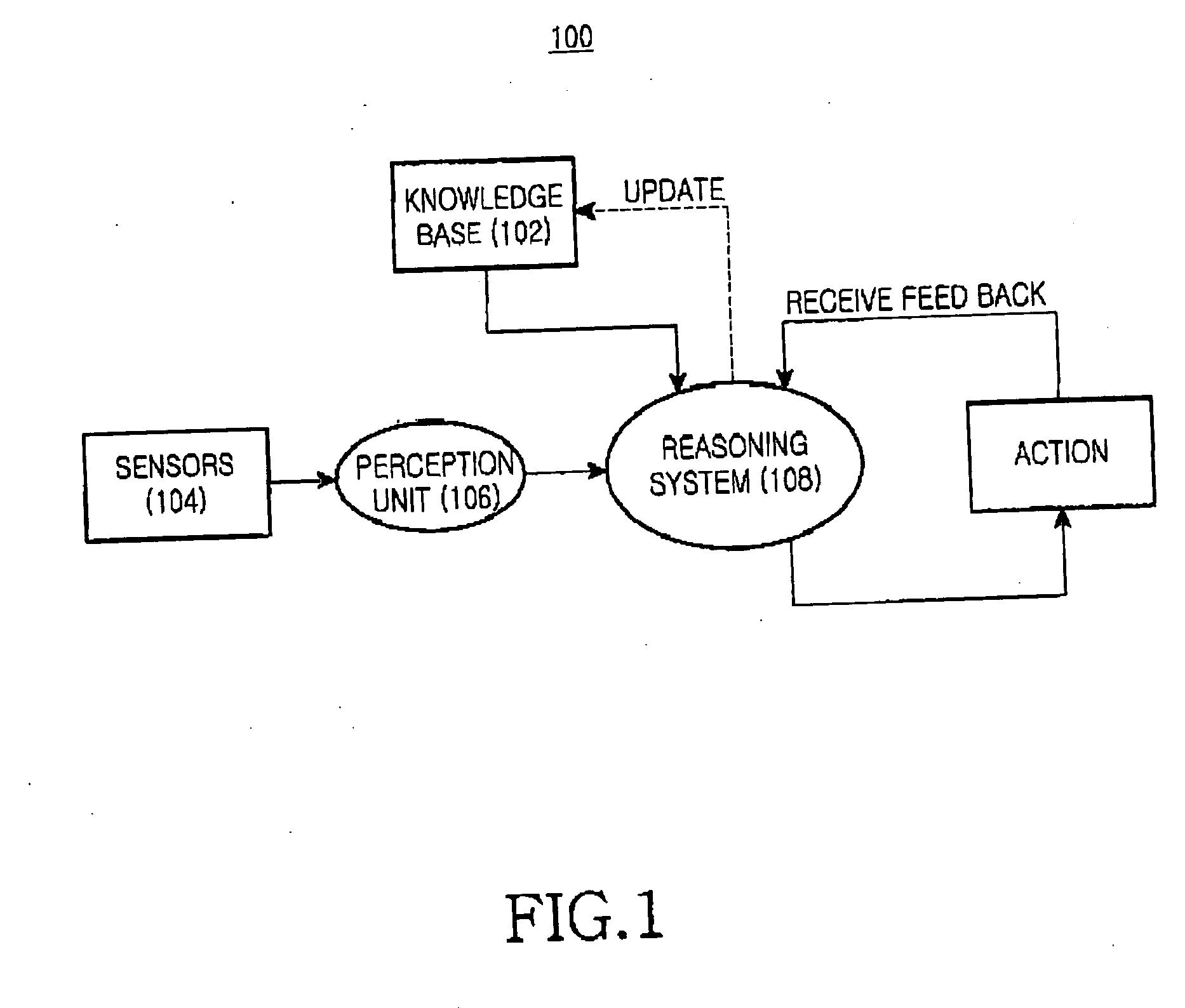

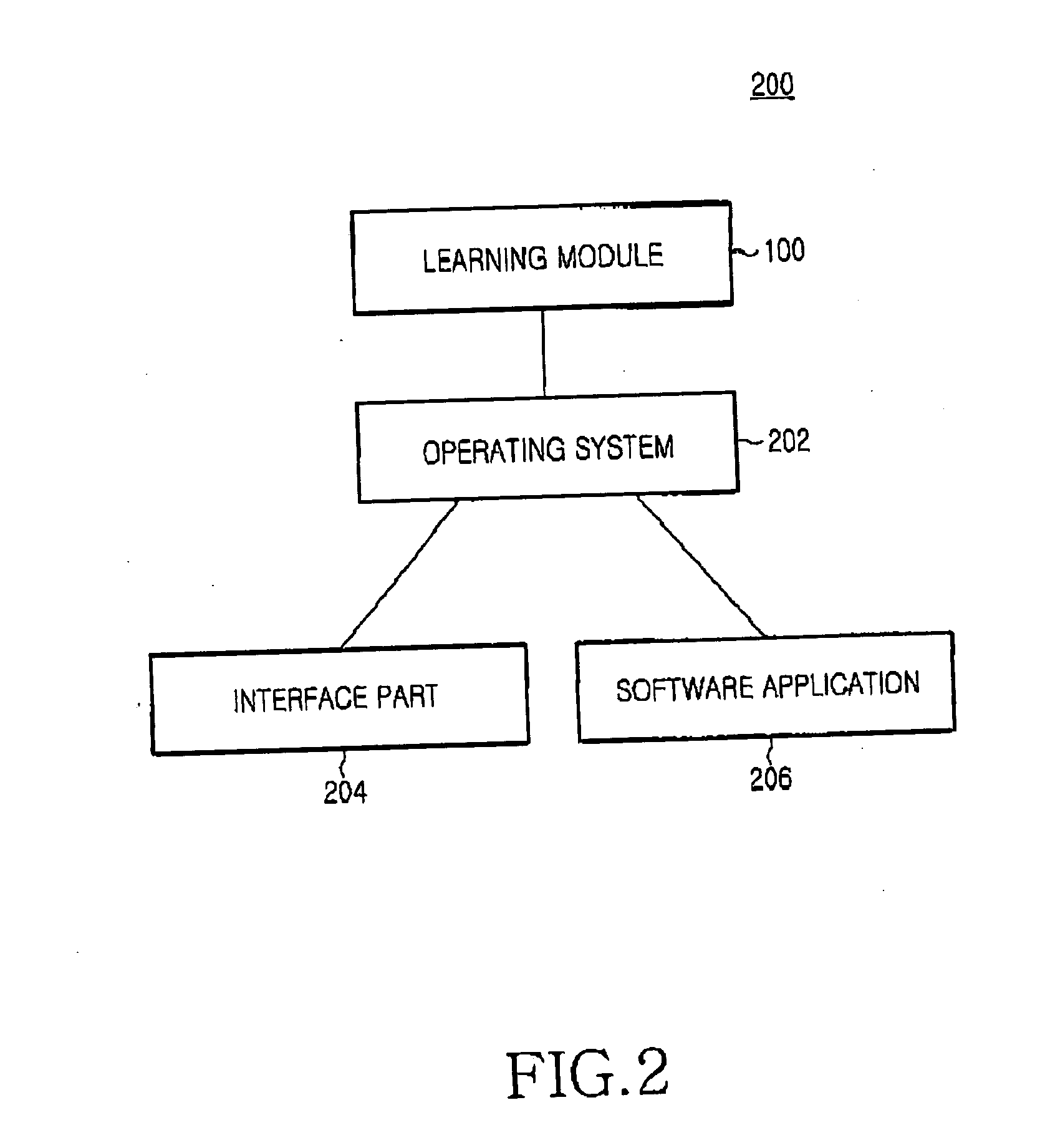

A proactive user interface, which could optionally be installed in (or otherwise control and / or be associated with) any type of computational device. The proactive user interface actively makes suggestions to the user, based upon prior experience with a particular user and / or various preprogrammed patterns from which the computational device could select, depending upon user behavior. These suggestions could optionally be made by altering the appearance of at least a portion of the display, for example by changing a menu or a portion thereof; providing different menus for display; and / or altering touch screen functionality. The suggestions could also optionally be made audibly.

Owner:SAMSUNG ELECTRONICS CO LTD

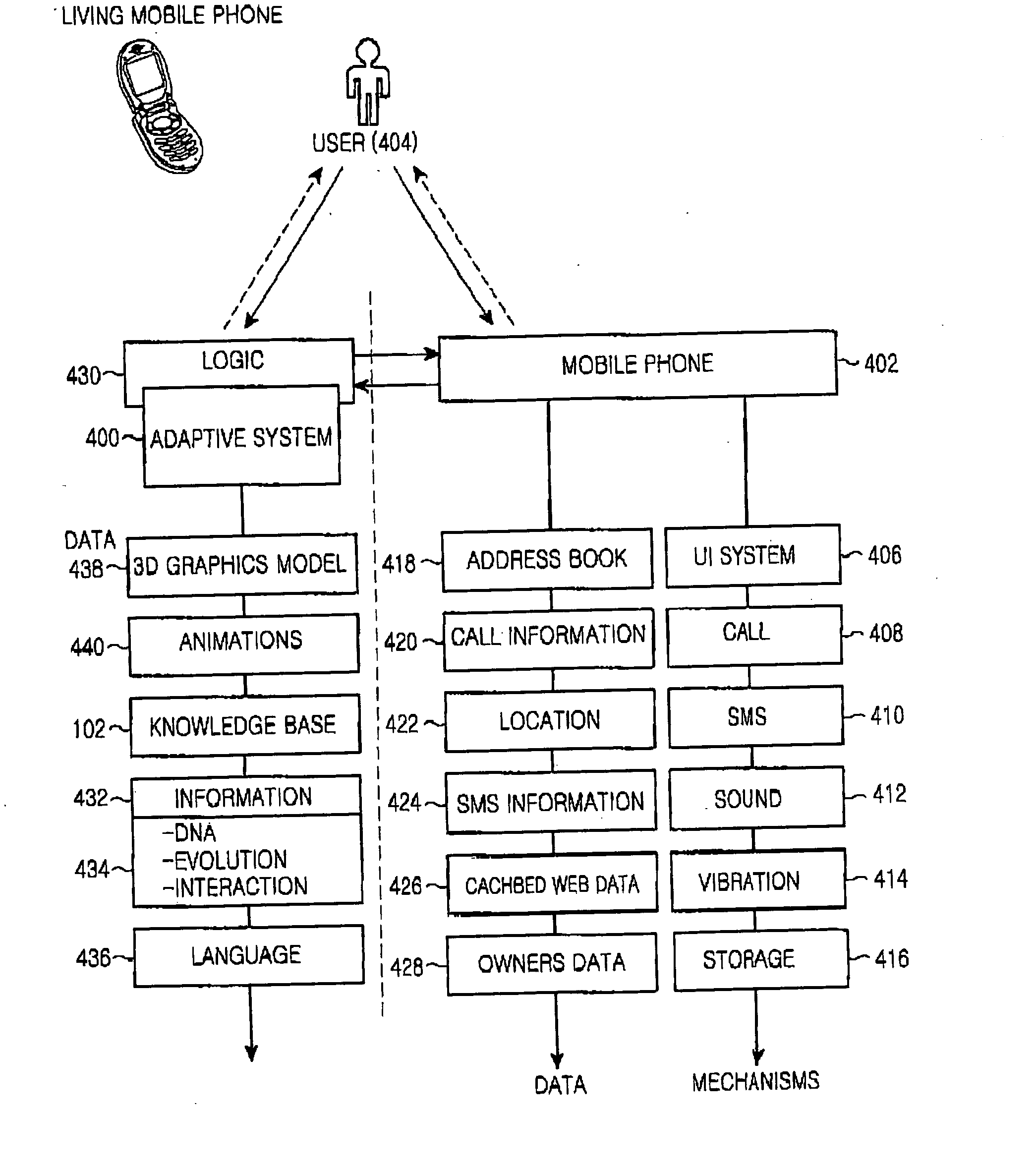

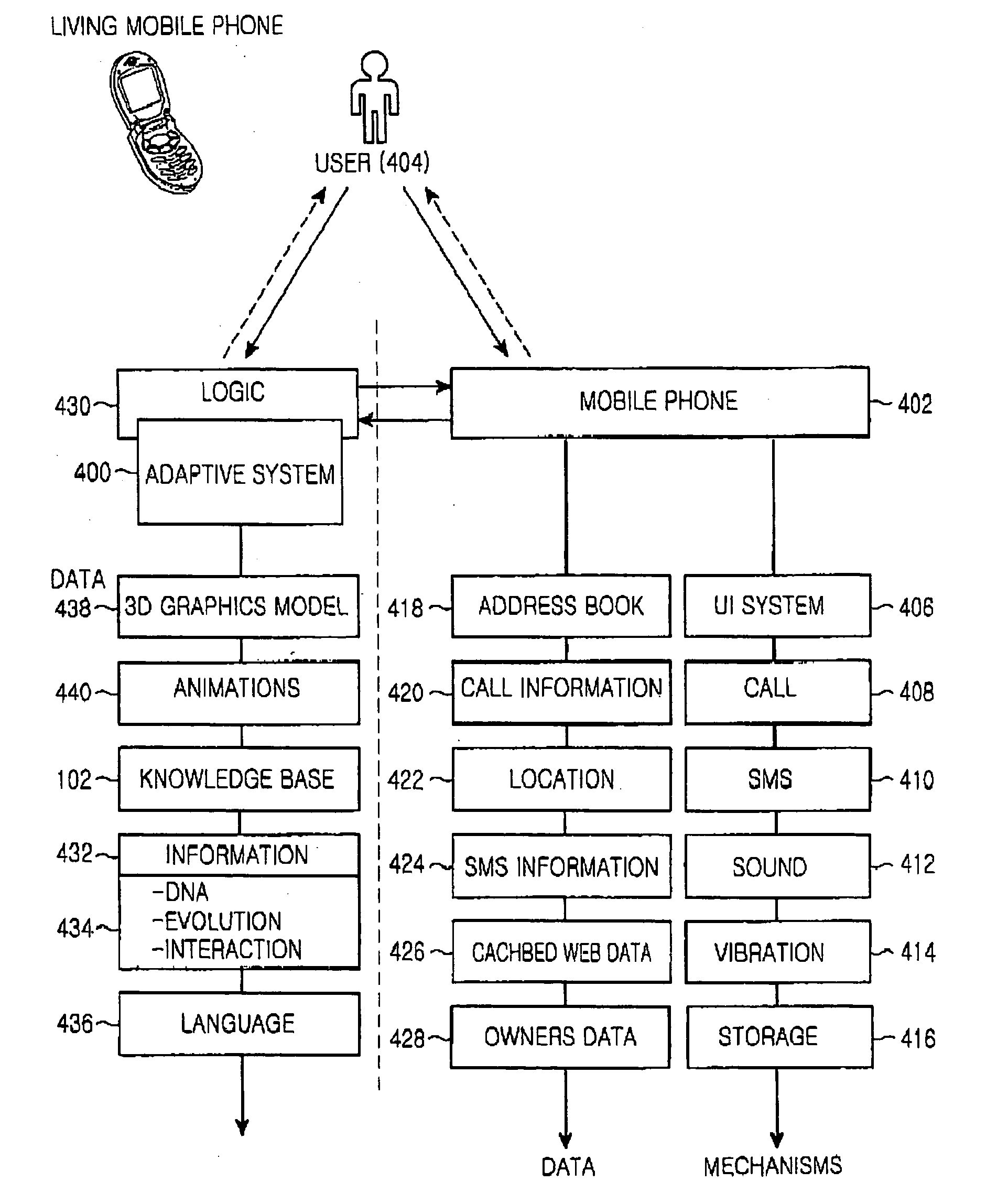

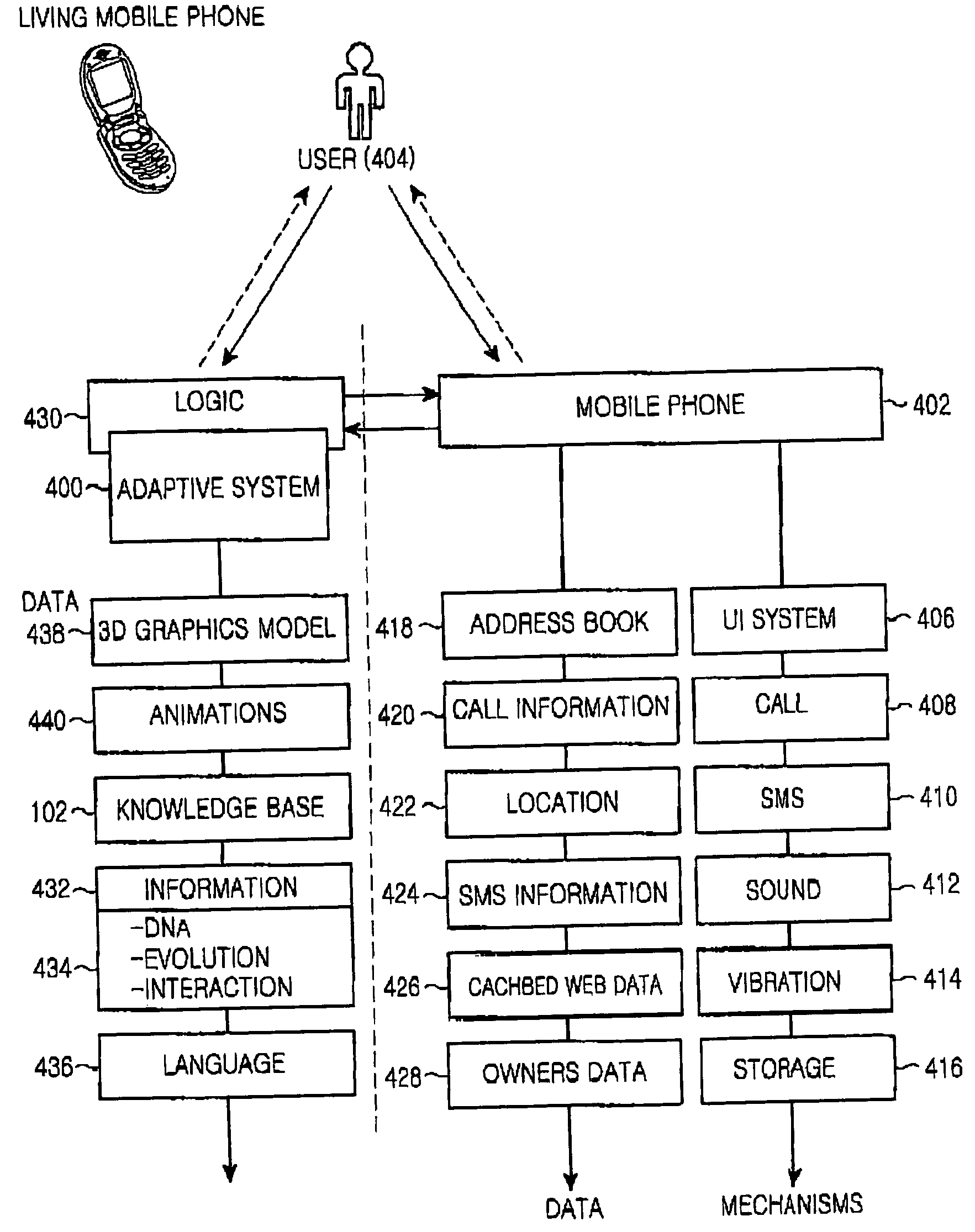

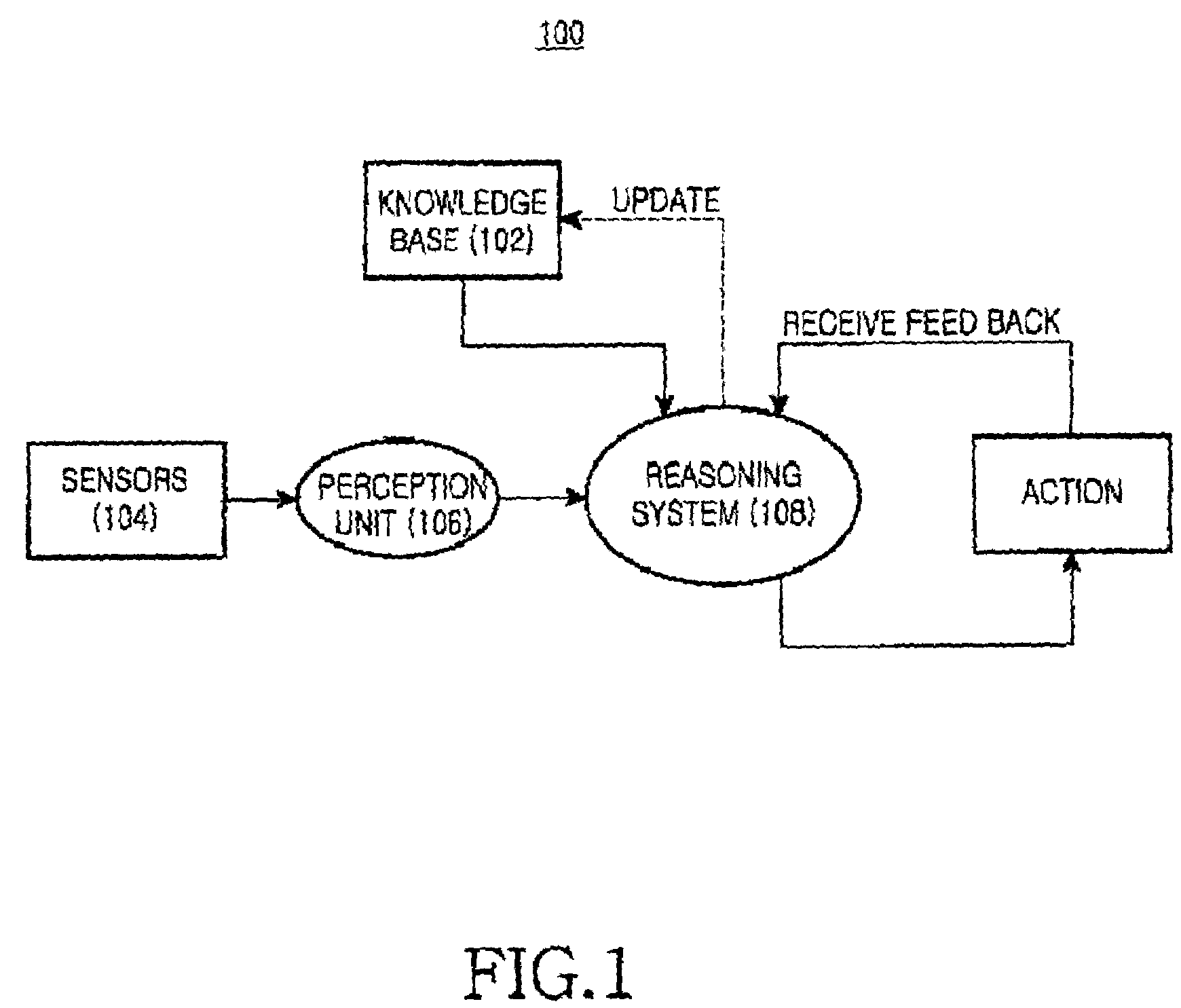

Proactive user interface including emotional agent

ActiveUS20050143138A1Increase sense of intelligenceDevices with sensorSubstation equipmentTouchscreenUser interface

Owner:SAMSUNG ELECTRONICS CO LTD

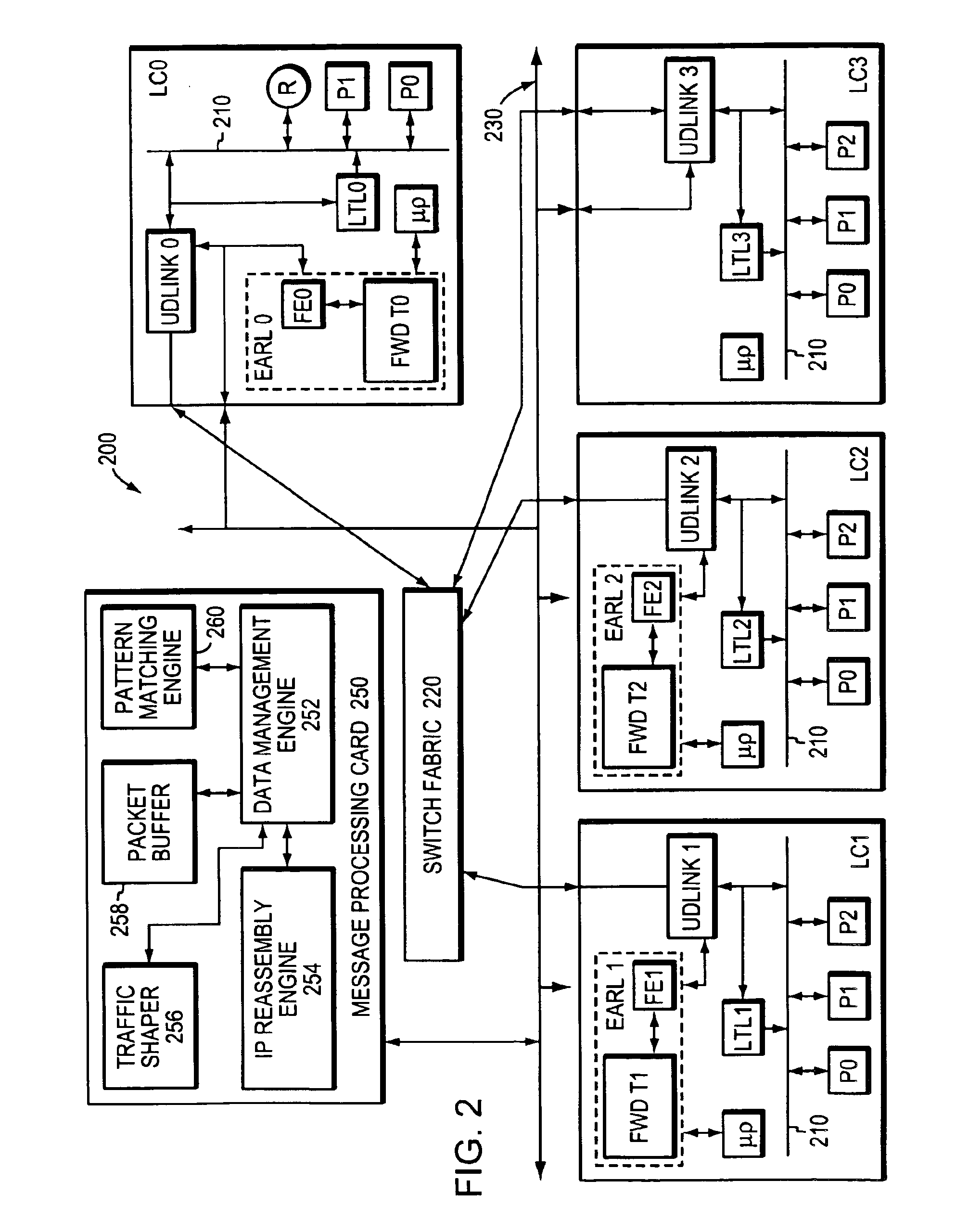

Method and apparatus for high-speed parsing of network messages

InactiveUS6892237B1Efficient analysisIncrease speedMultiple digital computer combinationsData switching networksPattern matchingRandom access memory

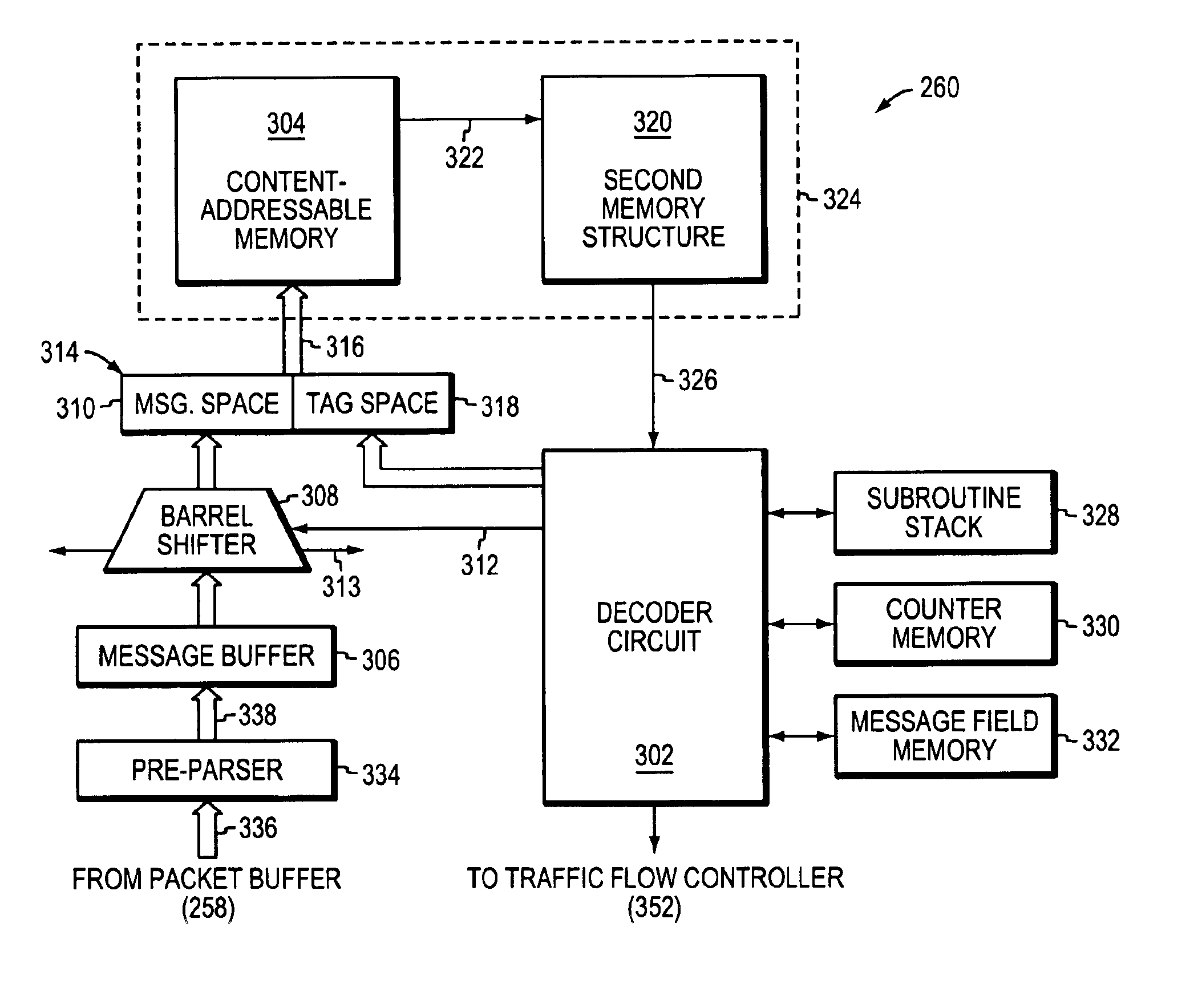

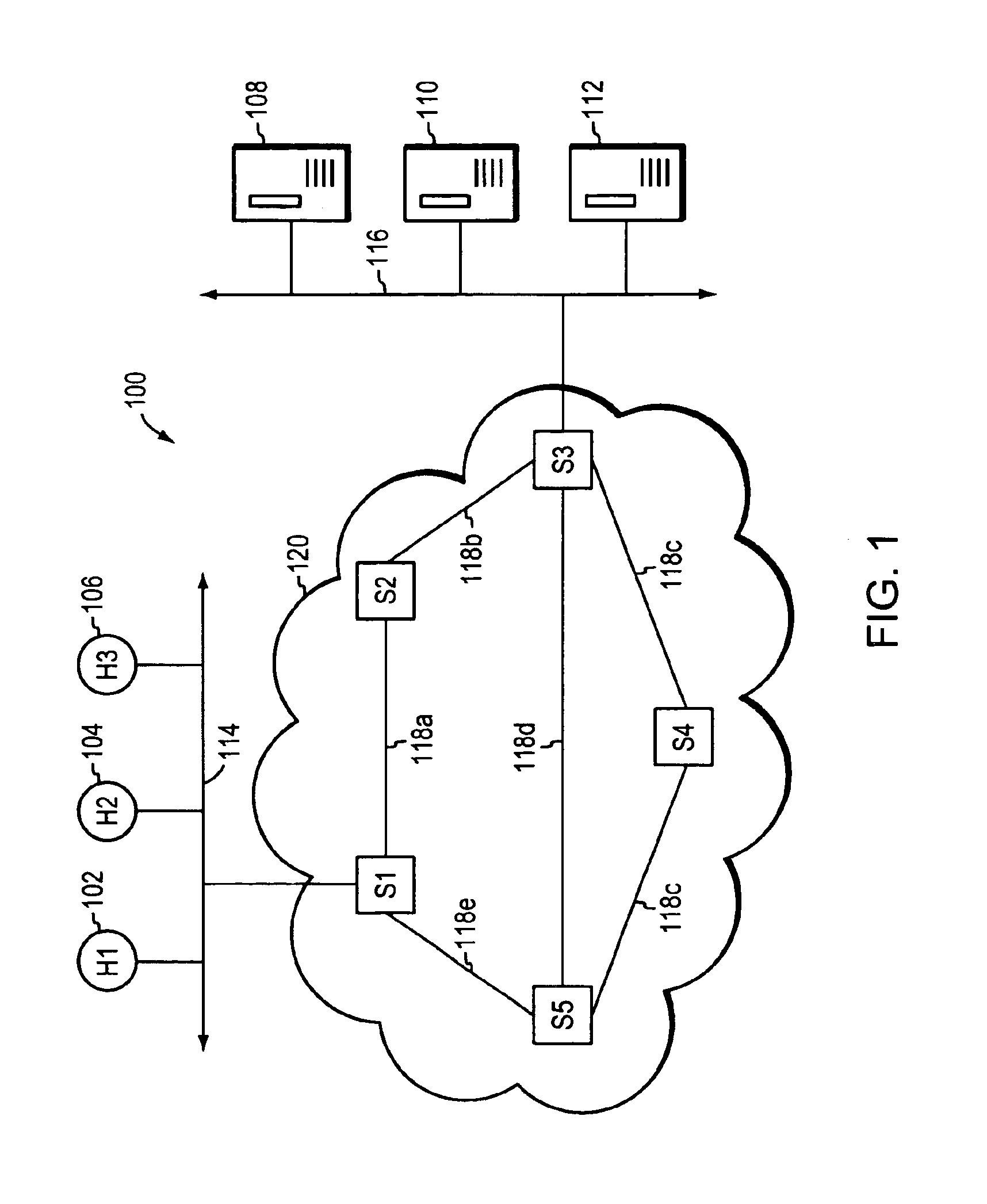

A programmable pattern matching engine efficiently parses the contents of network messages for regular expressions and executes pre-defined actions or treatments on those messages that match the regular expressions. The pattern matching engine is preferably a logic circuit designed to perform its pattern matching and execution functions at high speed, e.g., at multi-gigabit per second rates. It includes, among other things, a message buffer for storing the message being evaluated, a decoder circuit for decoding and executing corresponding actions or treatments, and one or more content-addressable memories (CAMs) that are programmed to store the regular expressions used to search the message. The CAM may be associated with a second memory device, such as a random access memory (RAM), as necessary, that is programmed to contain the respective actions or treatments to be applied to messages matching the corresponding CAM entries. The RAM provides its output to the decoder circuit, which, in response, decodes and executes the specified action or treatment.

Owner:CISCO TECH INC

Proactive user interface including evolving agent

ActiveUS20050118996A1Enhanced interactionImprove user experienceDevices with sensorDigital computer detailsDisplay deviceTouchscreen

A proactive user interface, installed in (or otherwise control and / or be associated with) any type of computational device. The proactive user interface actively makes suggestions to the user, based upon prior experience with a particular user and / or various preprogrammed patterns from which the computational device could select, depending upon user behavior. These suggestions can be made by altering the appearance of at least a portion of the display, for example by changing a menu or a portion thereof; providing different menus for display; and / or altering touch screen functionality. The suggestions can also be made audibly.

Owner:SAMSUNG ELECTRONICS CO LTD

Handling of speech recognition in a declarative markup language

InactiveUS6941268B2Reliably and simply determiningEasy to solveAutomatic exchangesSpeech recognitionSpeech applicationsApplication software

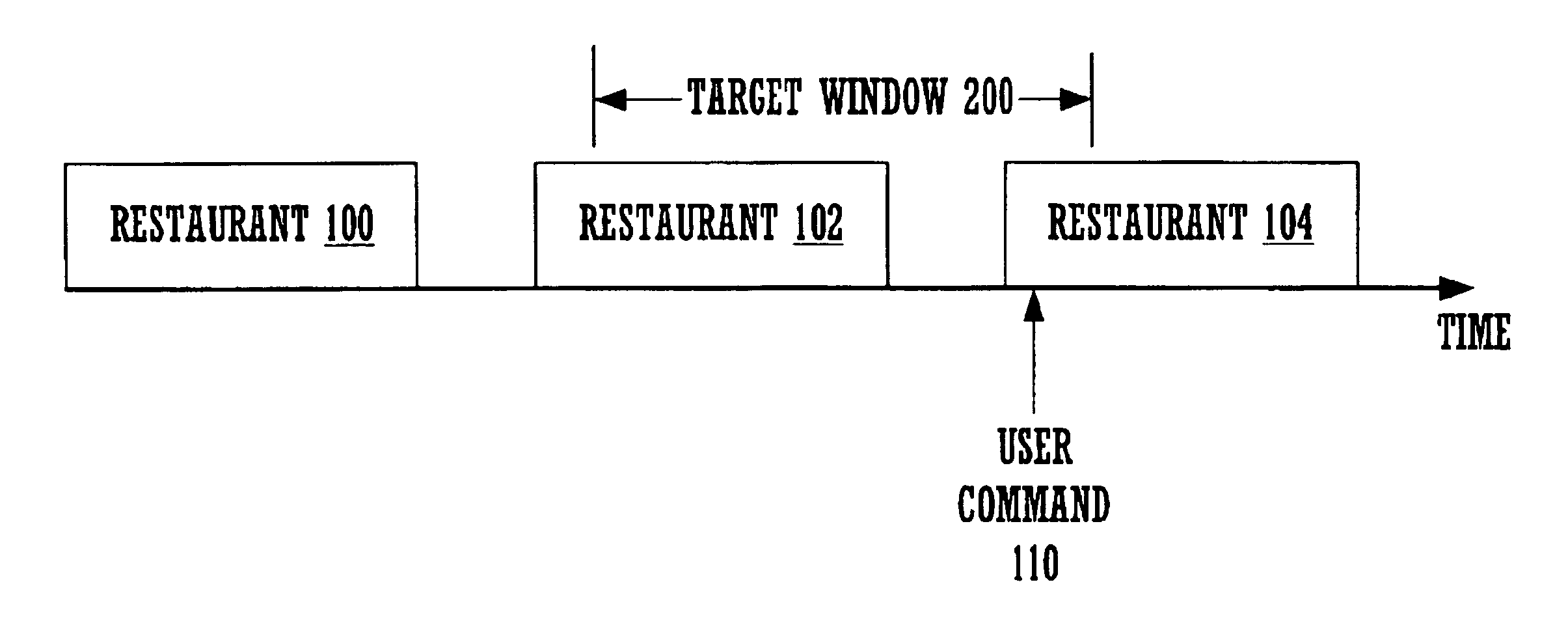

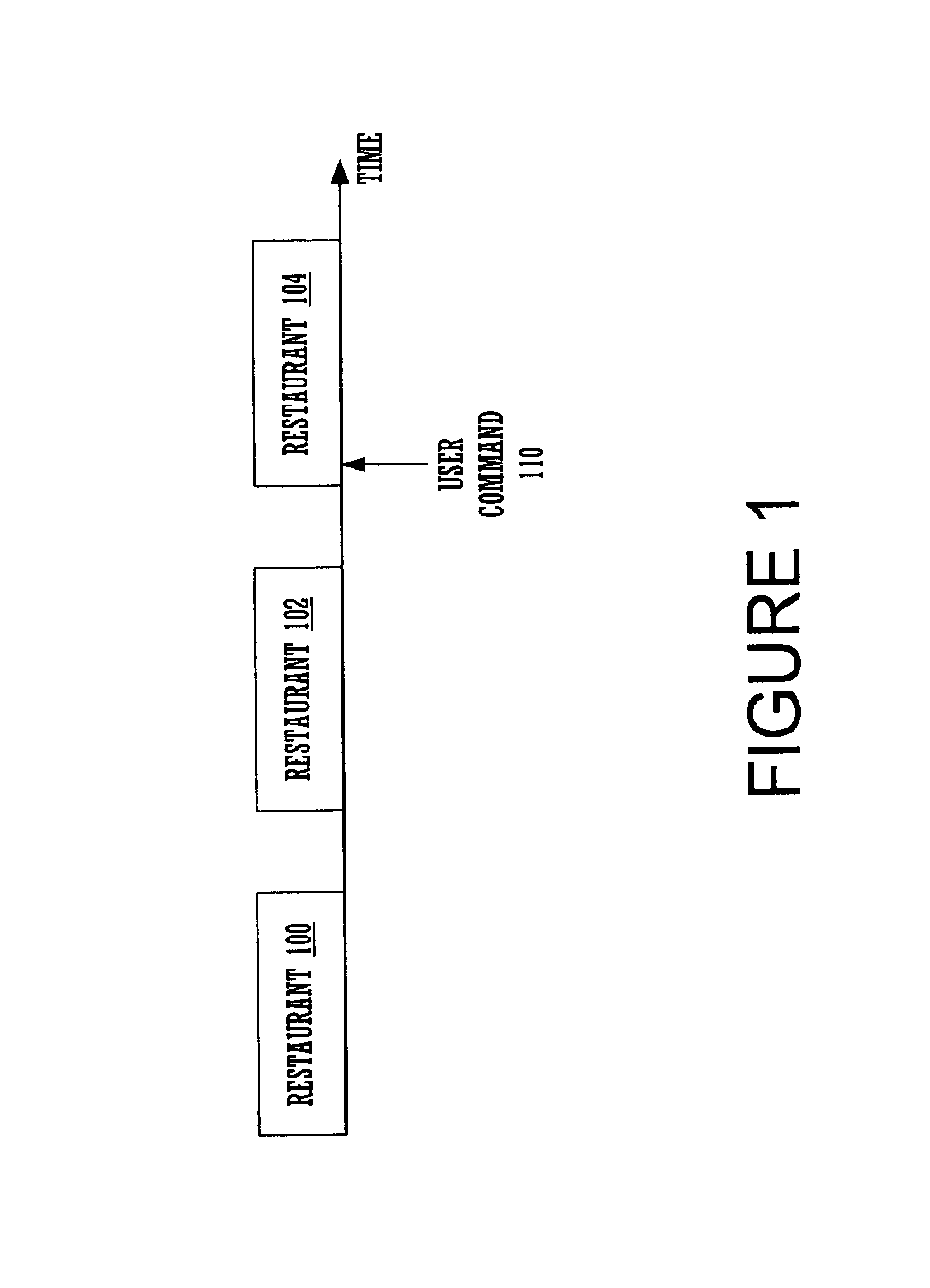

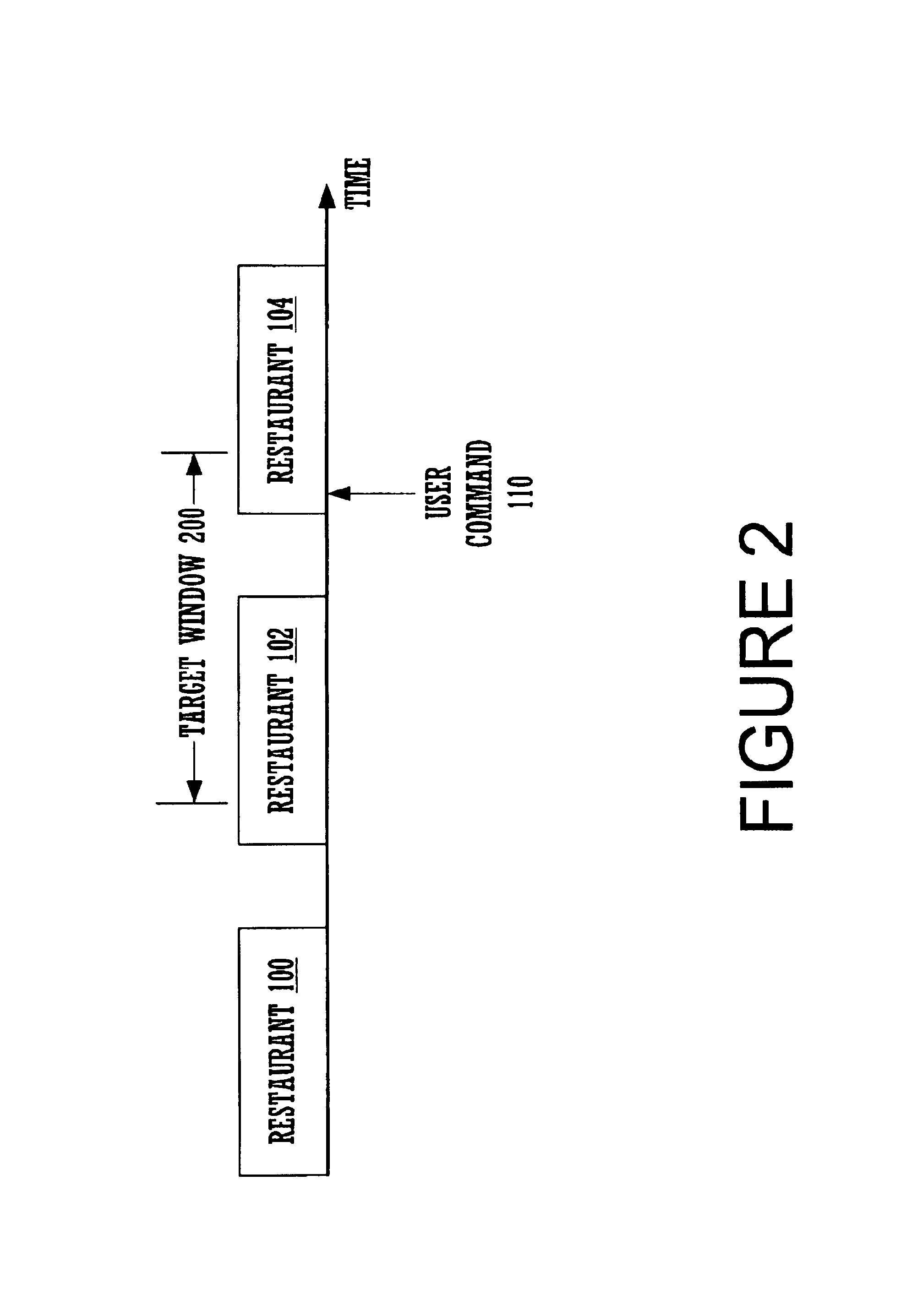

Declarative markup languages for speech applications such as VoiceXML are becoming more prevalent programming modalities for describing speech applications. Present declarative markup languages for speech applications model the running speech application as a state machine with the program specifying the transitions amongst the states. These languages can be extended to support a marker-semantic to more easily solve several problems that are otherwise not easily solved. In one embodiment, a partially overlapping target window is implemented using a mark semantic. Other uses include measurement of user listening time, detection and avoidance of errors, and better resumption of playback after a false barge in.

Owner:MICROSOFT TECH LICENSING LLC

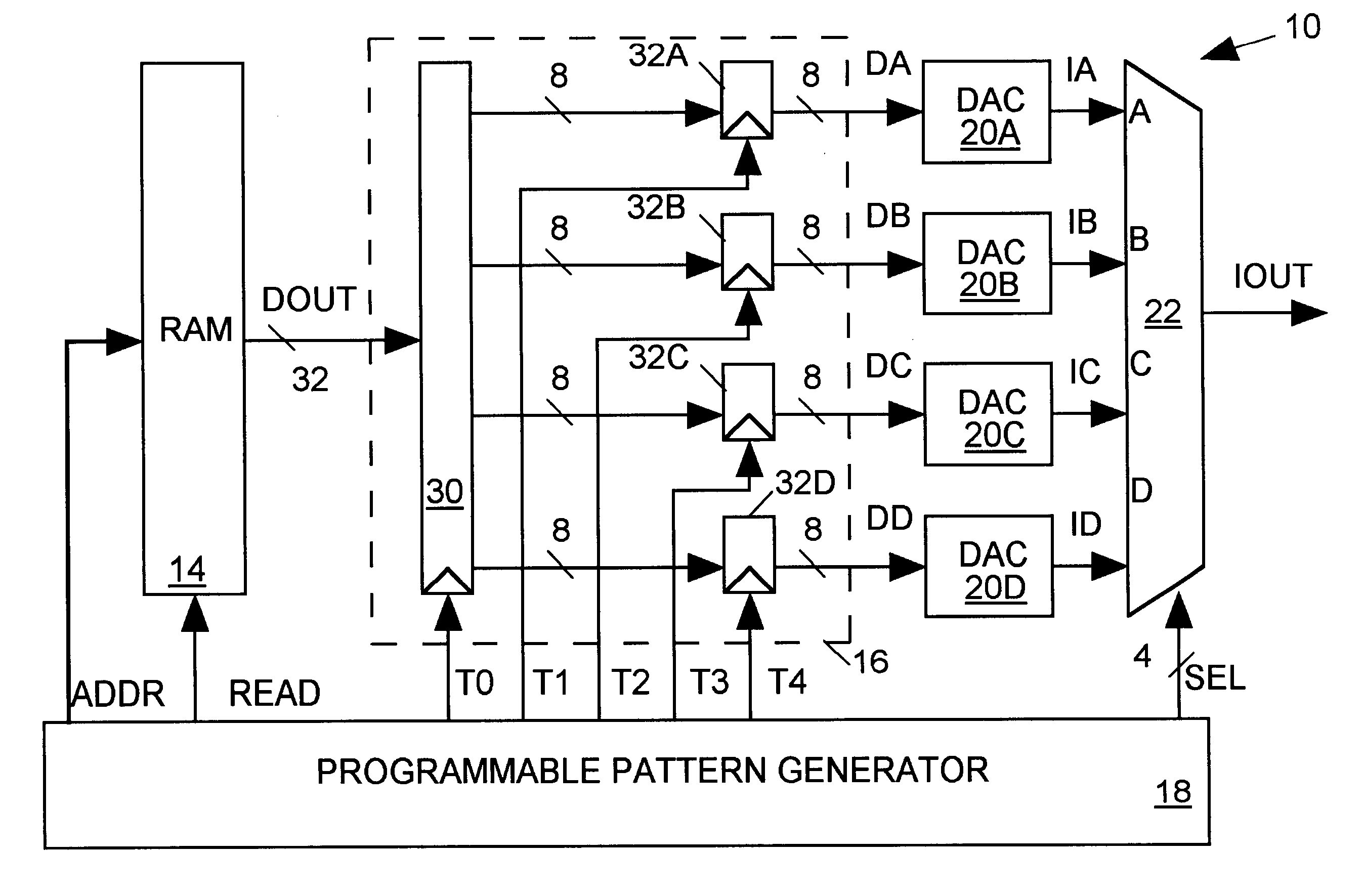

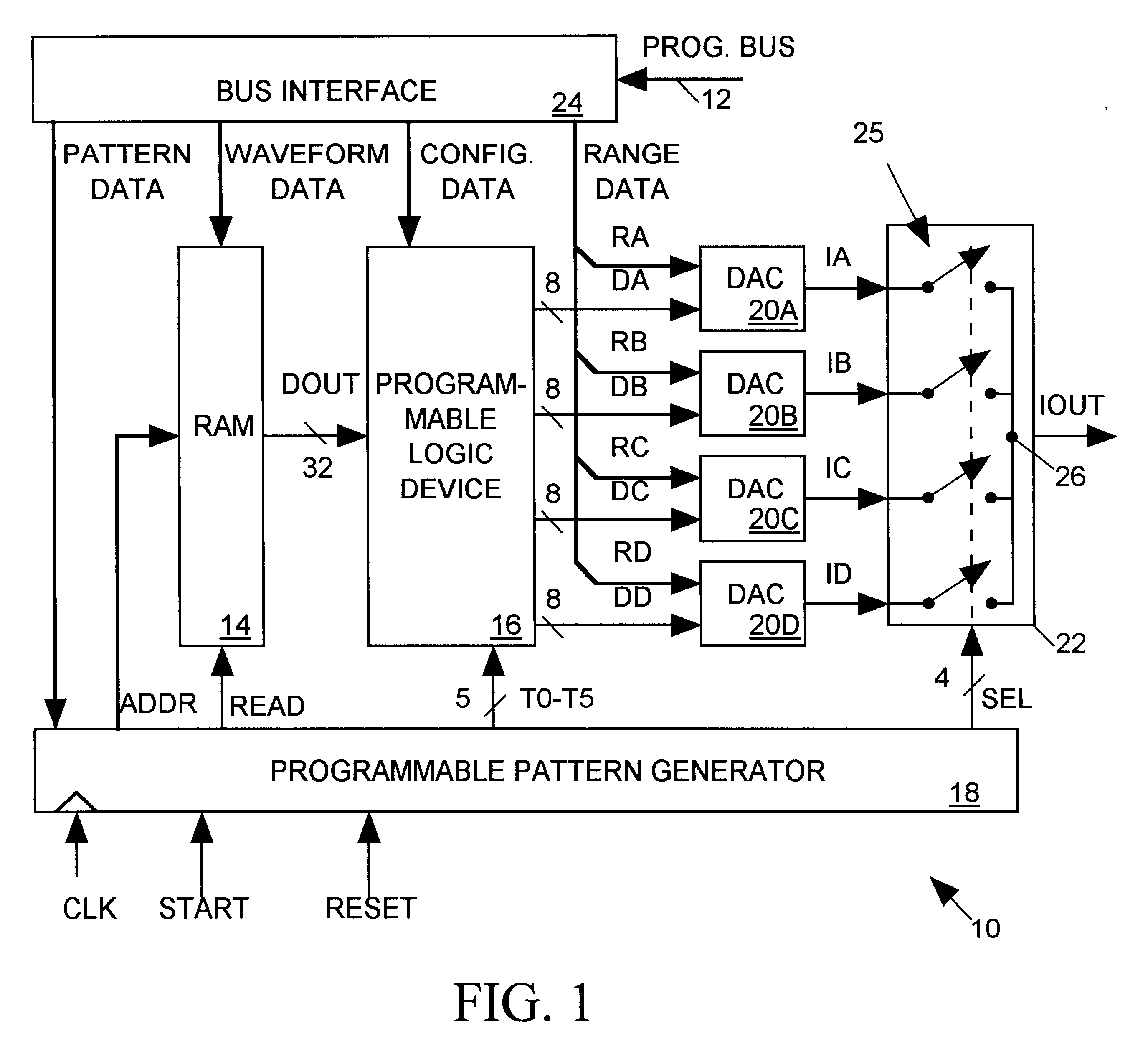

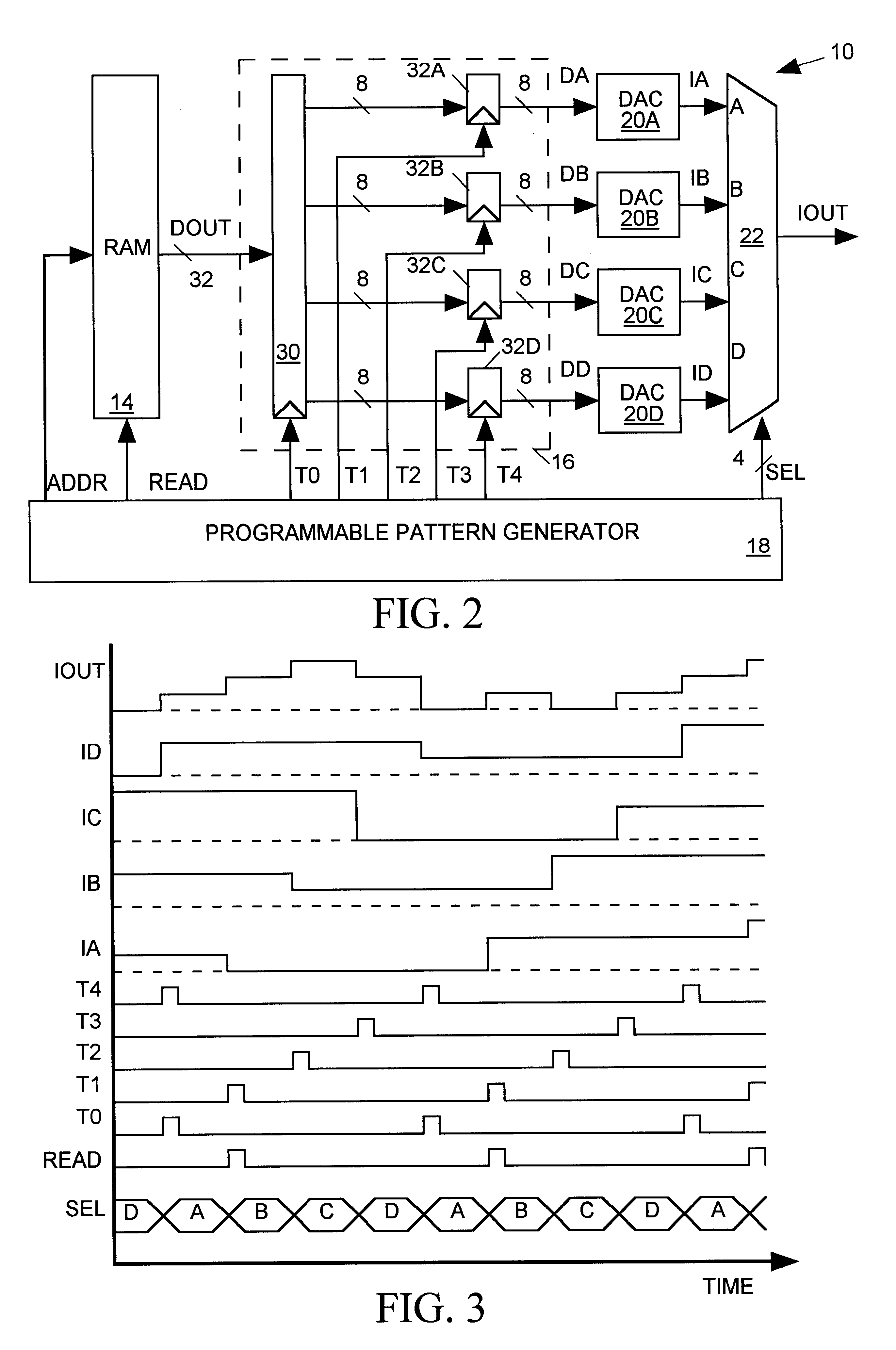

Arbitrary waveform generator having programmably configurable architecture

InactiveUS6356224B1Electric signal transmission systemsOscillations generatorsDigital analog converterMultiplexer

An arbitrary waveform generator (AWG) for producing an analog output current signal includes a random access memory (RAM), a programmable logic device (PLD), a programmable pattern generator, several digital-to analog converters (DACS) and a current multiplexer. The RAM store data sequences representing the analog waveform to be generated. The pattern generator read addresses the RAM causing it to sequentially read out its stored data sequence to the PLD. The PLD routes selected fields of each data sequence word to one or more of the DACs in response to timing signals provided by the pattern generator. Each DAC produces an output current of magnitude determined by its input waveform and range data. The pattern generator also signals the analog multiplexer to sum currents produced by one or more selected DACs to produce the AWG output waveform. The nature of the AWG output waveform is flexibly determined by the nature of the data sequence and the frequency at which it is read out of the RAM, the manner in which the PLD routes the data sequence to the DACs, the value of the range data supplied to each DAC, and the output pattern generated by the pattern generator. The flexible AWG architecture permits the AWG to be appropriately configured for various combinations of output waveform frequency, bandwidth and resolution requirements.

Owner:CREDENCE SYSTEMS

Proactive user interface including emotional agent

ActiveUS7725419B2Increase sense of intelligenceImprove experienceDevices with sensorSubstation equipmentDisplay deviceTouchscreen

A proactive user interface, installed in (or otherwise control and / or be associated with) any type of computational device. The proactive user interface actively makes suggestions to the user, based upon prior experience with a particular user and / or various preprogrammed patterns from which the computational device could select, depending upon user behavior. These suggestions could be made by altering the appearance of at least a portion of the display, for example by changing a menu or a portion thereof; providing different menus for display; and / or altering touch screen functionality. The suggestions could also be made audibly.

Owner:SAMSUNG ELECTRONICS CO LTD

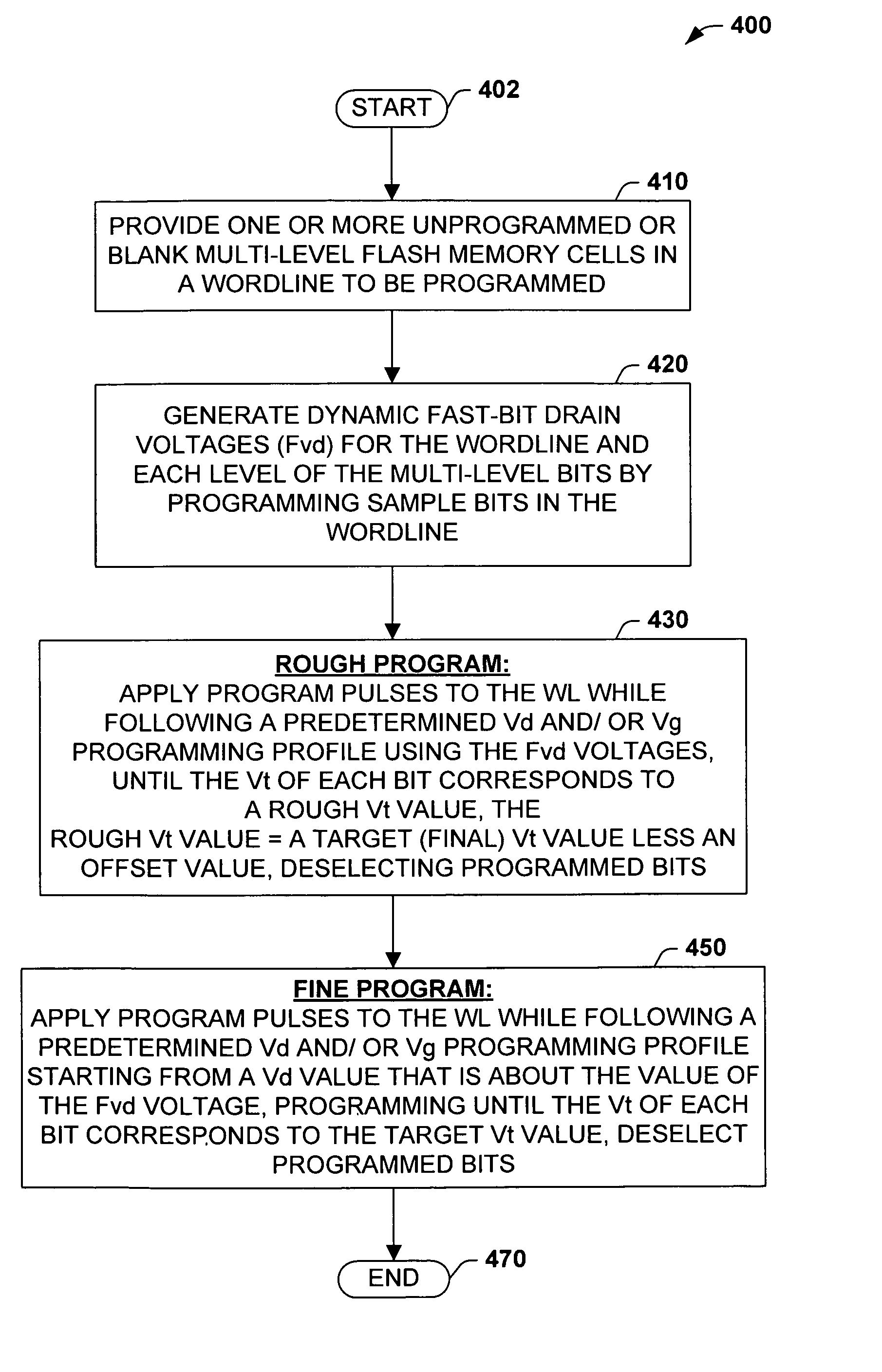

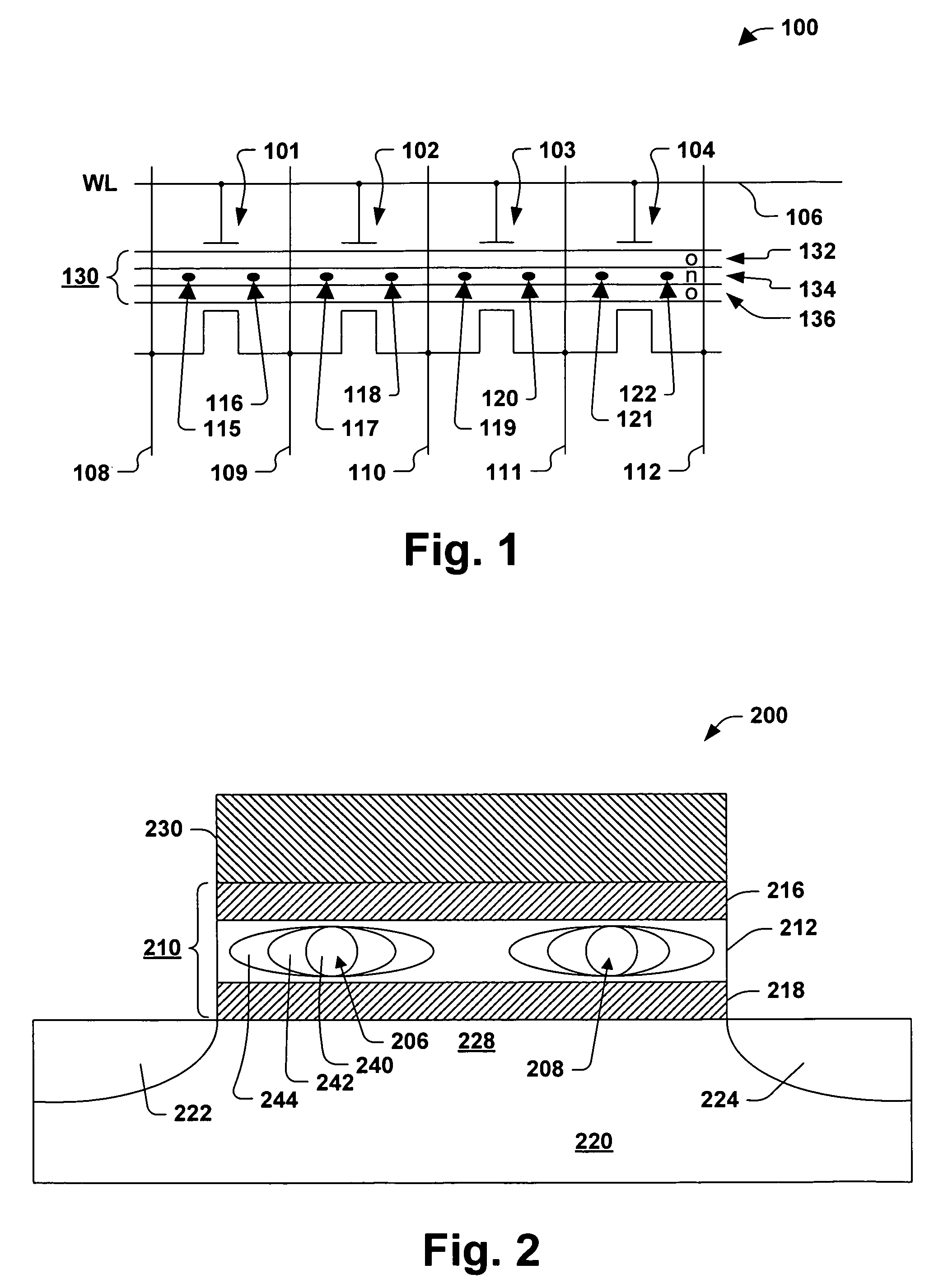

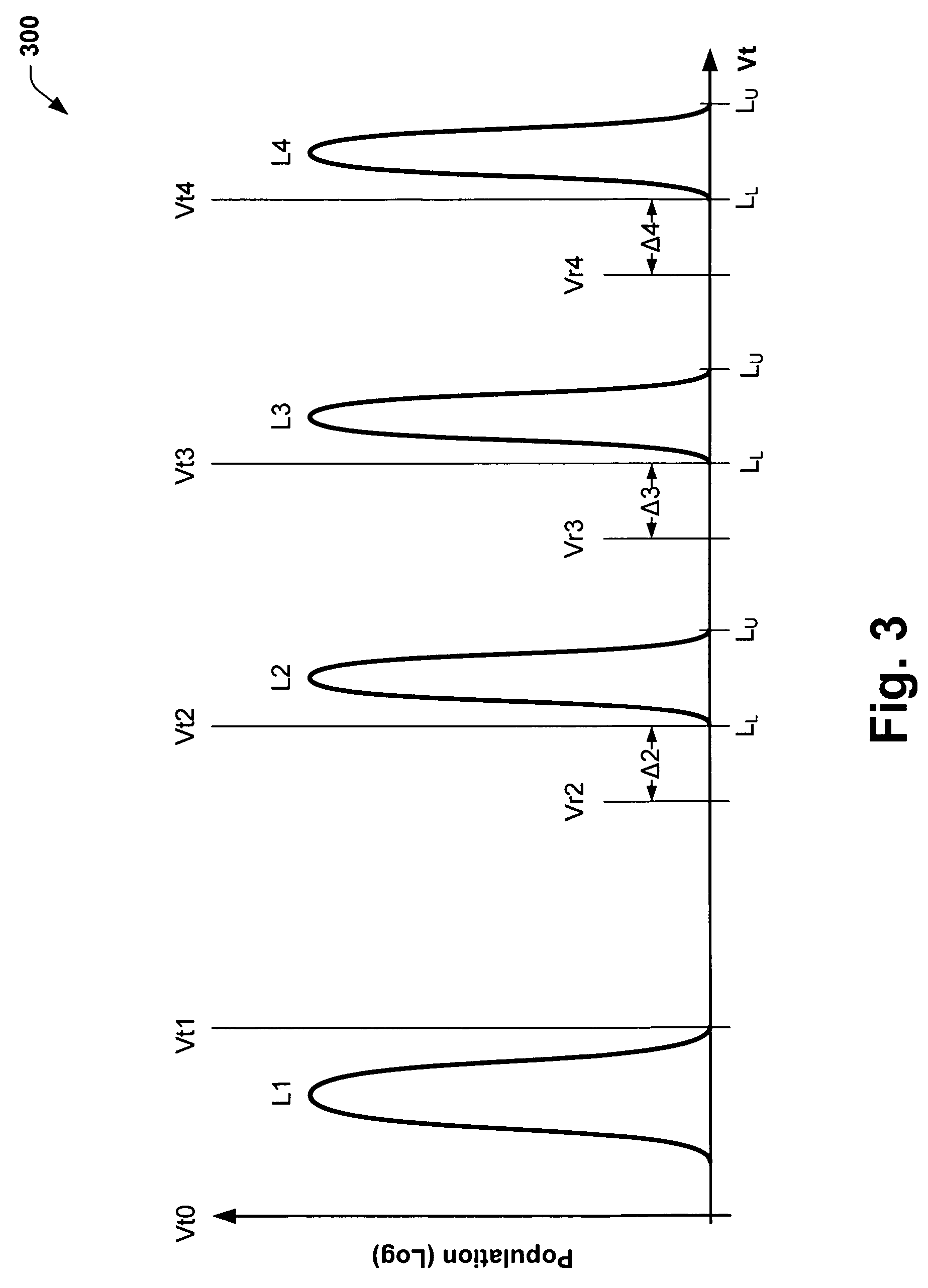

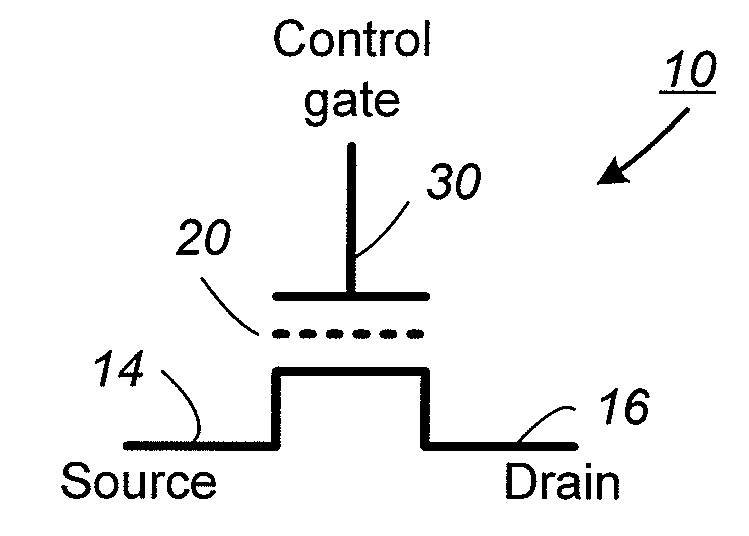

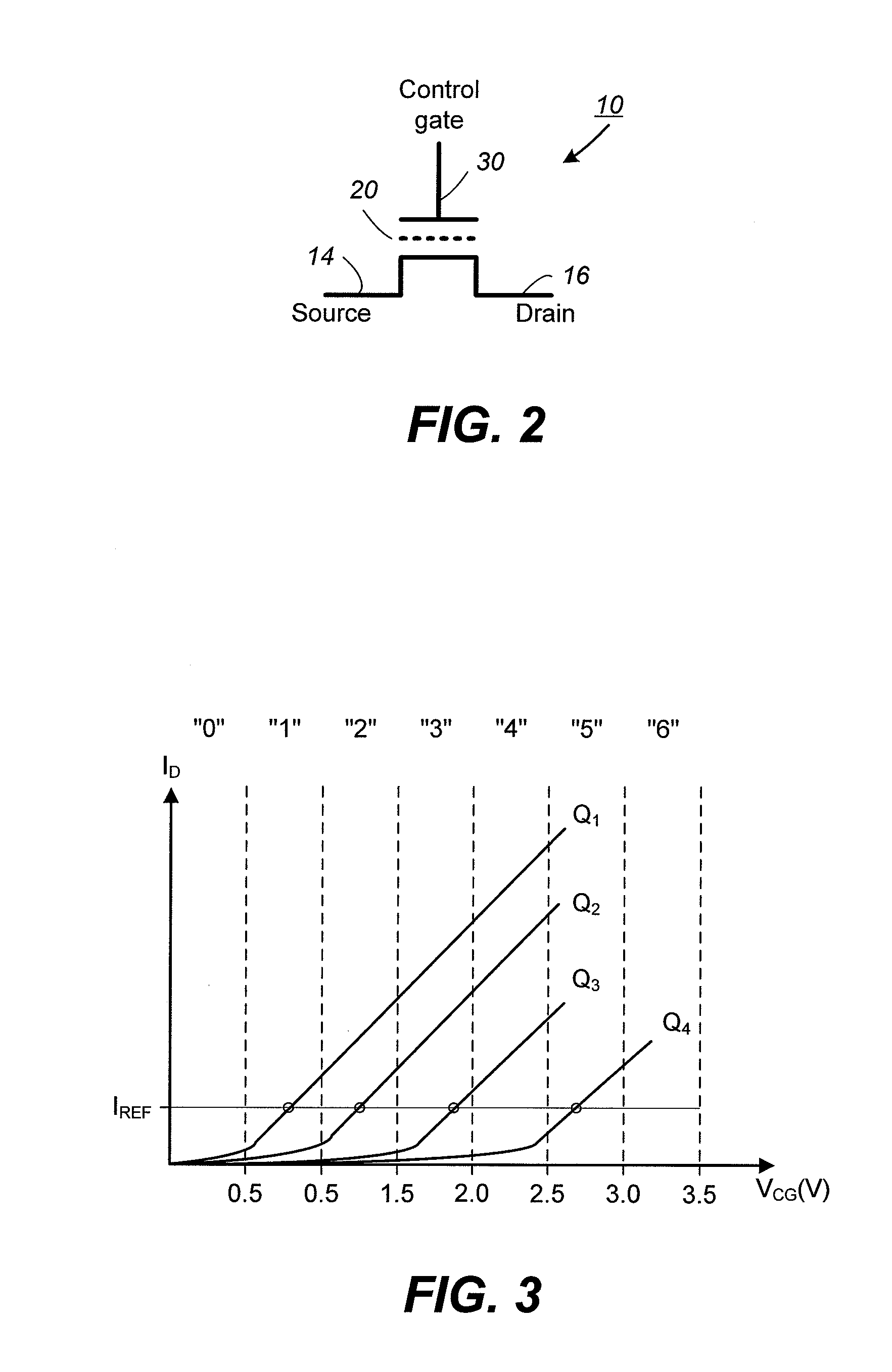

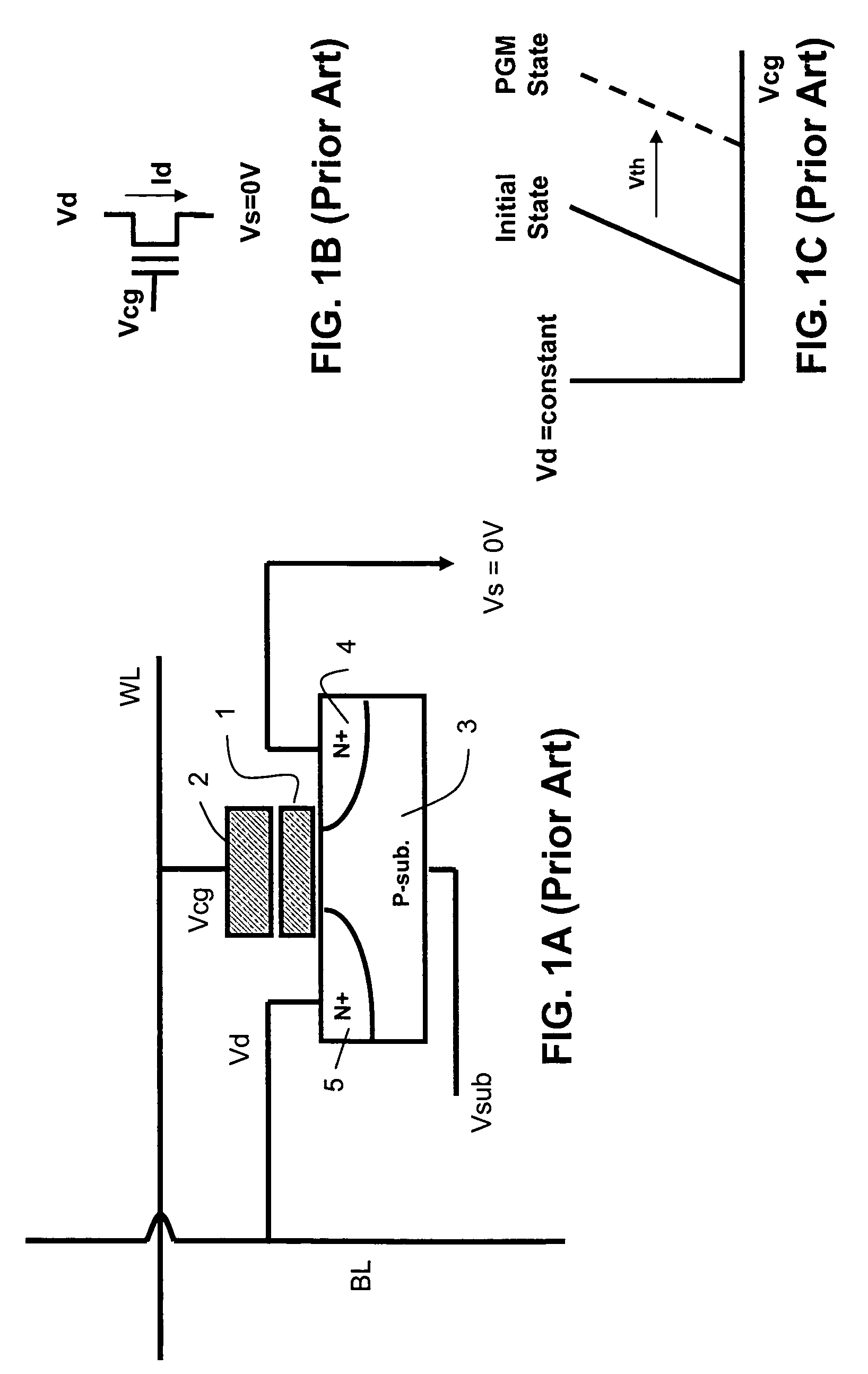

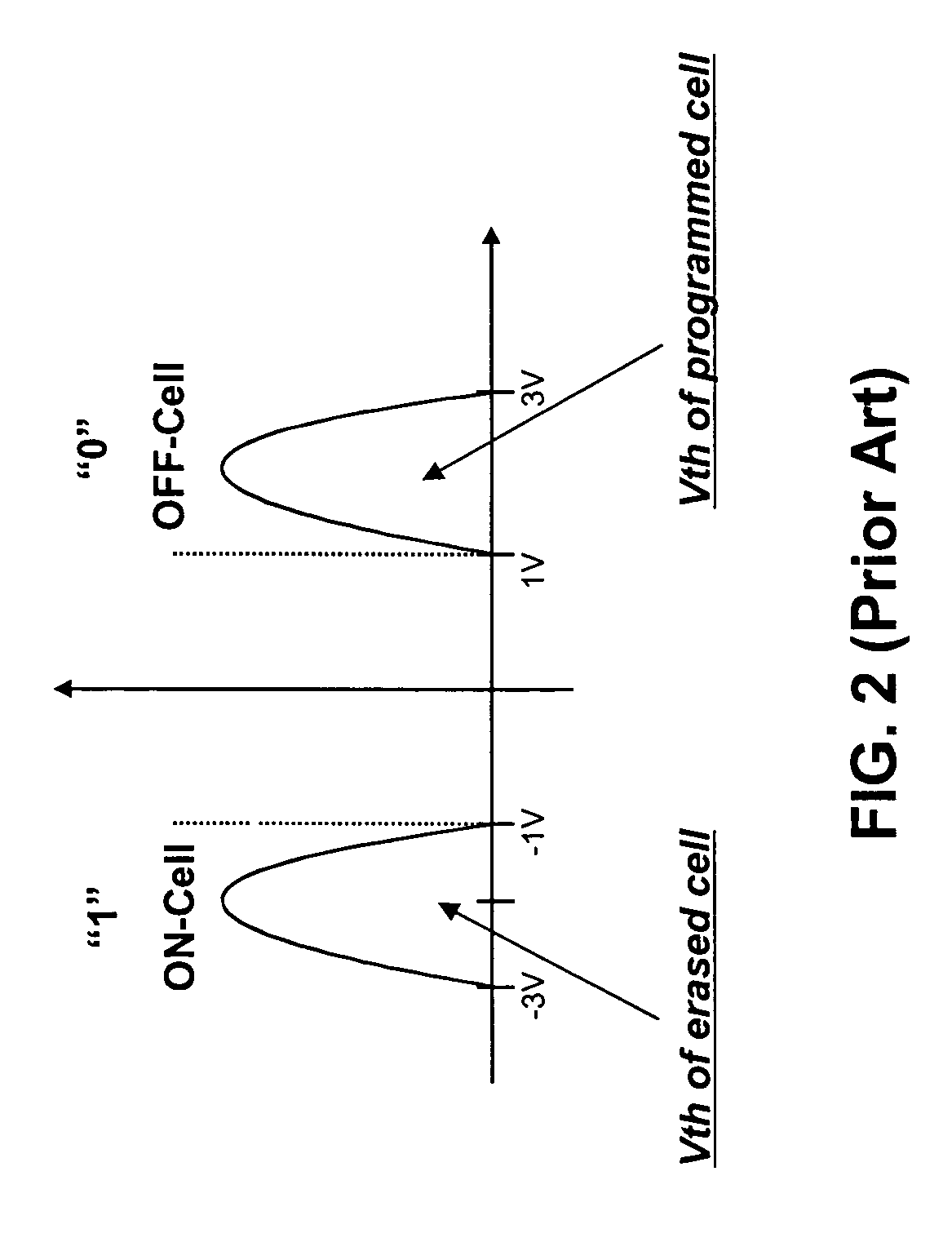

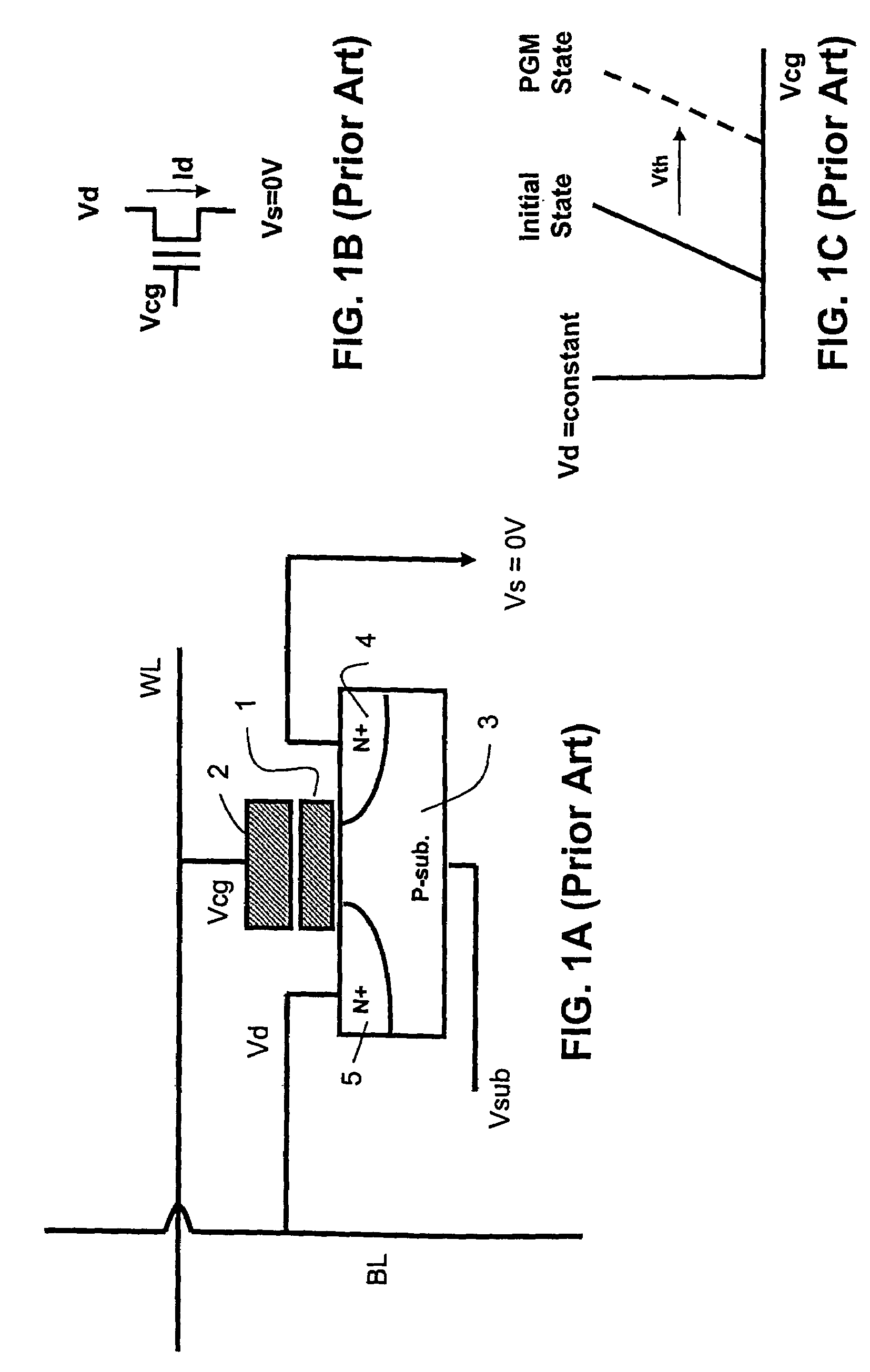

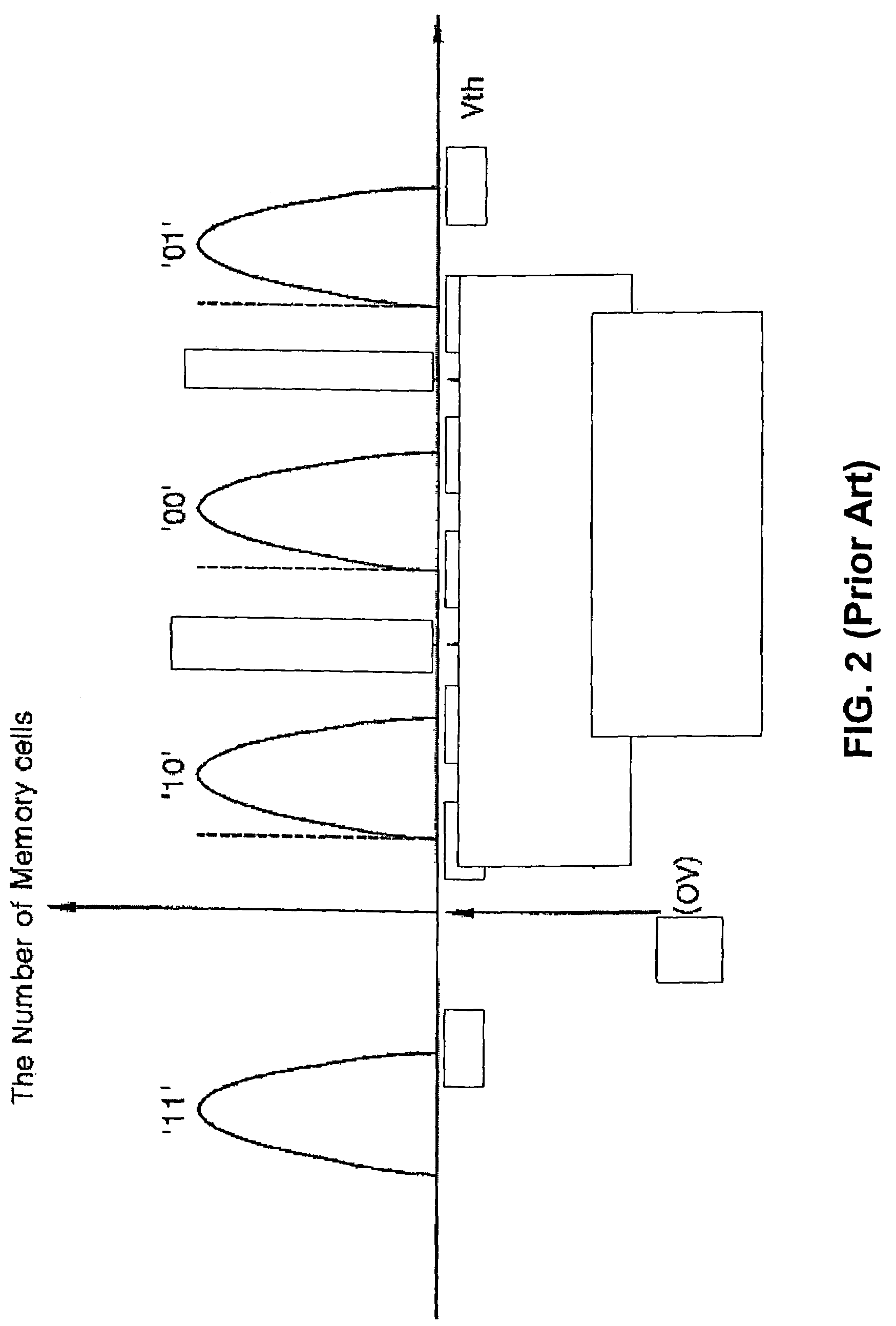

Multi-level ONO flash program algorithm for threshold width control

Methods of programming a wordline of multi-level flash memory cells (MLB) having three or more data levels per bit corresponding to three or more threshold voltages are provided. The present invention employs an interactive program algorithm that programs the bits of the wordline of memory cells in two programming phases, comprising a rough programming phase and a fine programming phase to achieve highly compact Vt distributions. In one example, cell bit-pairs that are to be programmed to the same program pattern are selected along a wordline. Groups of sample bits are chosen for each wordline to represent each possible program level. The sample bits are then programmed to determine a corresponding drain voltage at which each sample group is first programmed. This fast-bit drain voltage (Fvd) for each program level essentially provides a wordline specific program characterization of the Vt required for the remaining bits of that wordline. In the rough programming phase, the bits of core cells are then programmed from a starting point that is relative to (e.g., slightly less than or equal to) the fast-bit Vd and according to a predetermined Vd and Vg profile of programming pulses. The bits of the complementary bit-pairs are alternately programmed in this way until the Vt of the bits attains a rough Vt level, which is offset lower than the final target threshold voltage level. Then in the second fine programming phase, the bits of the MLB cells of the wordline are further programmed with another predetermined Vd and Vg profile of programming pulses until the final target threshold voltage is achieved. The Vd and Vg profiles of programming pulses may further be tailored to accommodate the various bit-pair program pattern combinations possible. In this way, the bits of each wordline are fine-tune programmed to a data state to achieve a more precise Vt distribution, while compensating for the effects of complementary bit disturb.

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

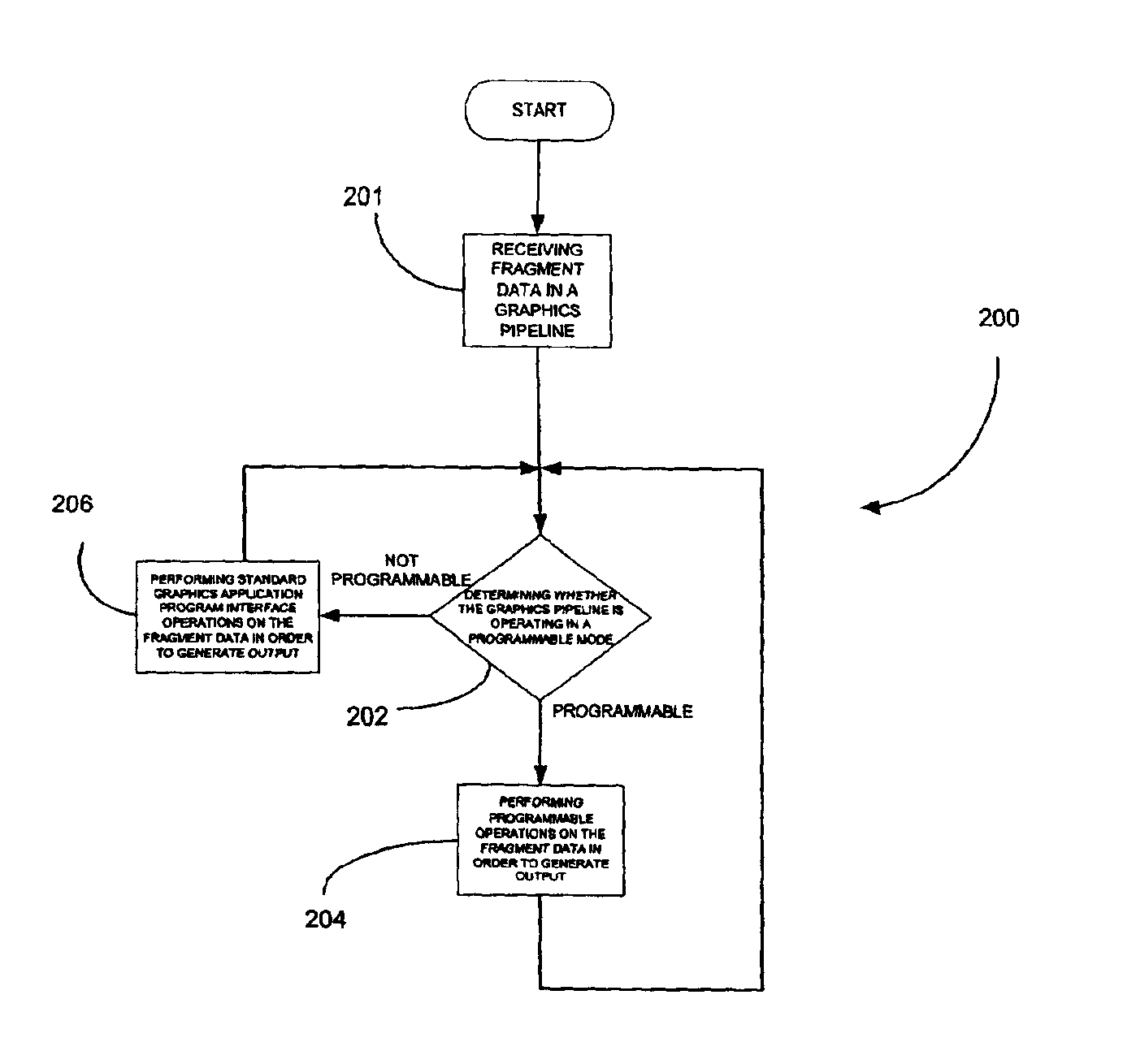

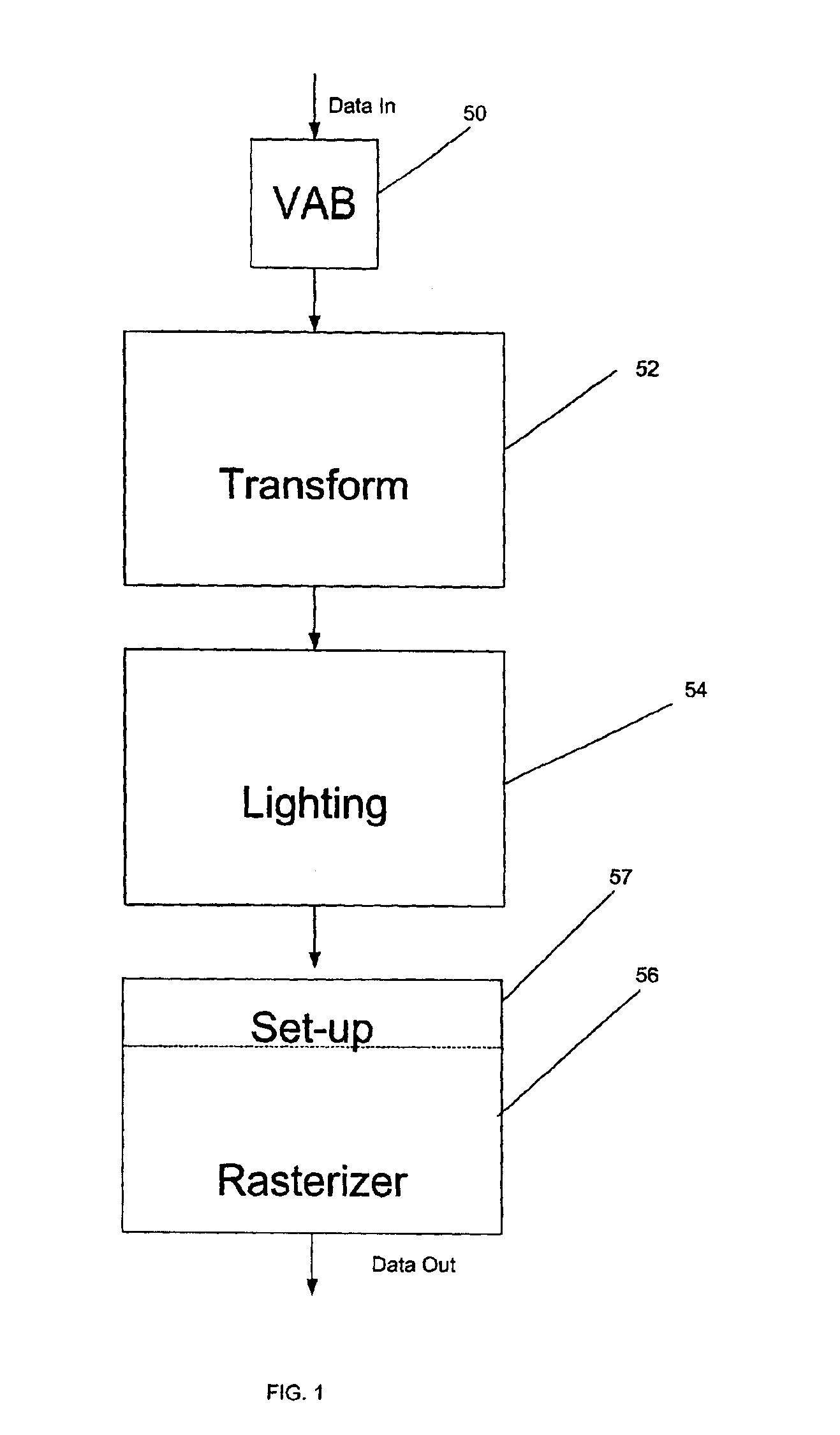

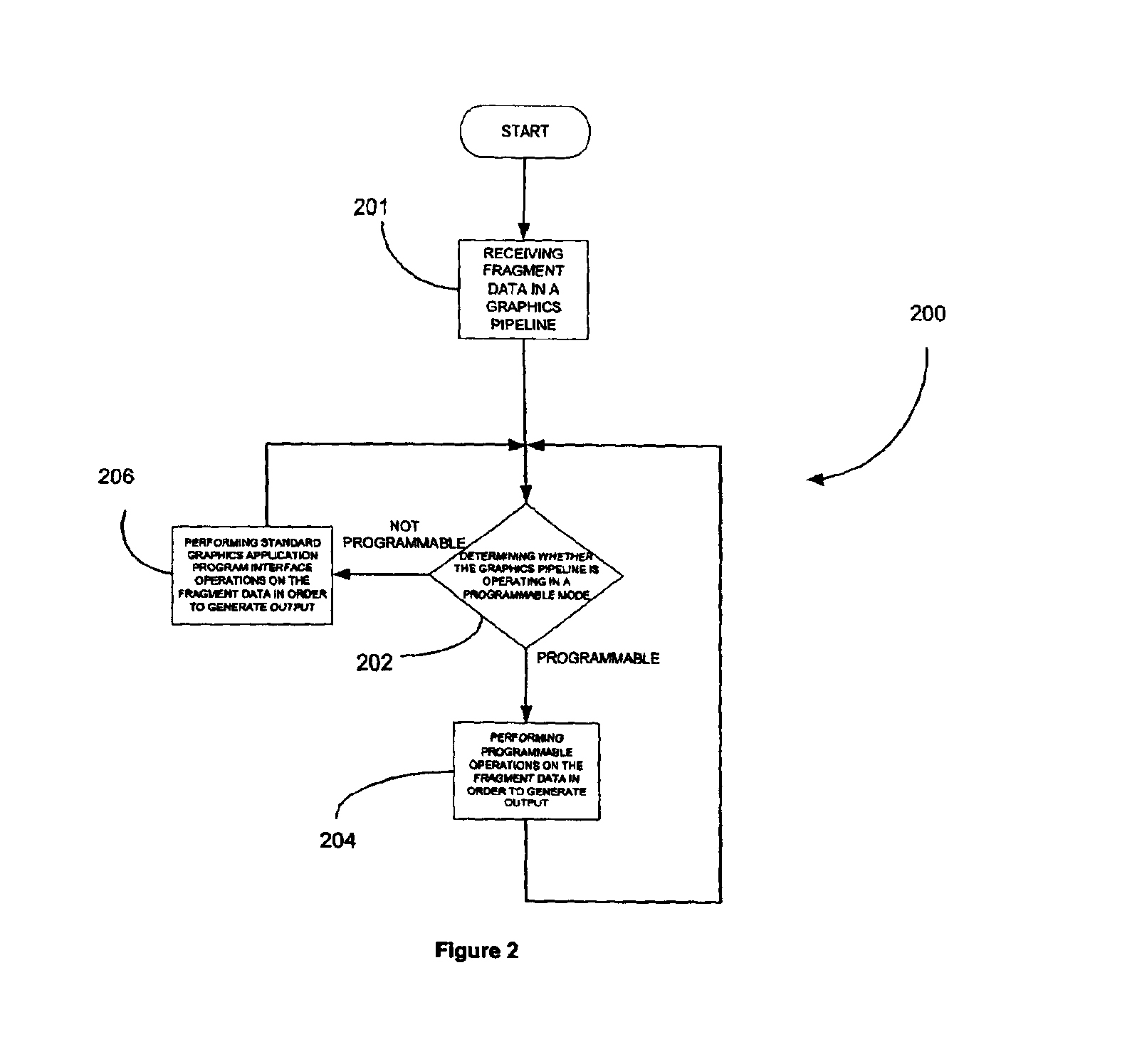

System, method and computer program product for programmable fragment processing in a graphics pipeline

InactiveUS6982718B2Cathode-ray tube indicatorsProcessor architectures/configurationGraphicsFragment processing

A system, method and computer program product are provided for programmable processing of fragment data in a computer hardware graphics pipeline. Initially, fragment data is received in a hardware graphics pipeline. It is then determined whether the hardware graphics pipeline is operating in a programmable mode. If it is determined that the hardware graphics pipeline is operating in the programmable mode, programmable operations are performed on the fragment data in order to generate output. The programmable operations are performed in a manner / sequence specified in a graphics application program interface. If it is determined that the hardware graphics pipeline is not operating in the programmable mode, standard graphics application program interface (API) operations are performed on the fragment data in order to generate output.

Owner:NVIDIA CORP

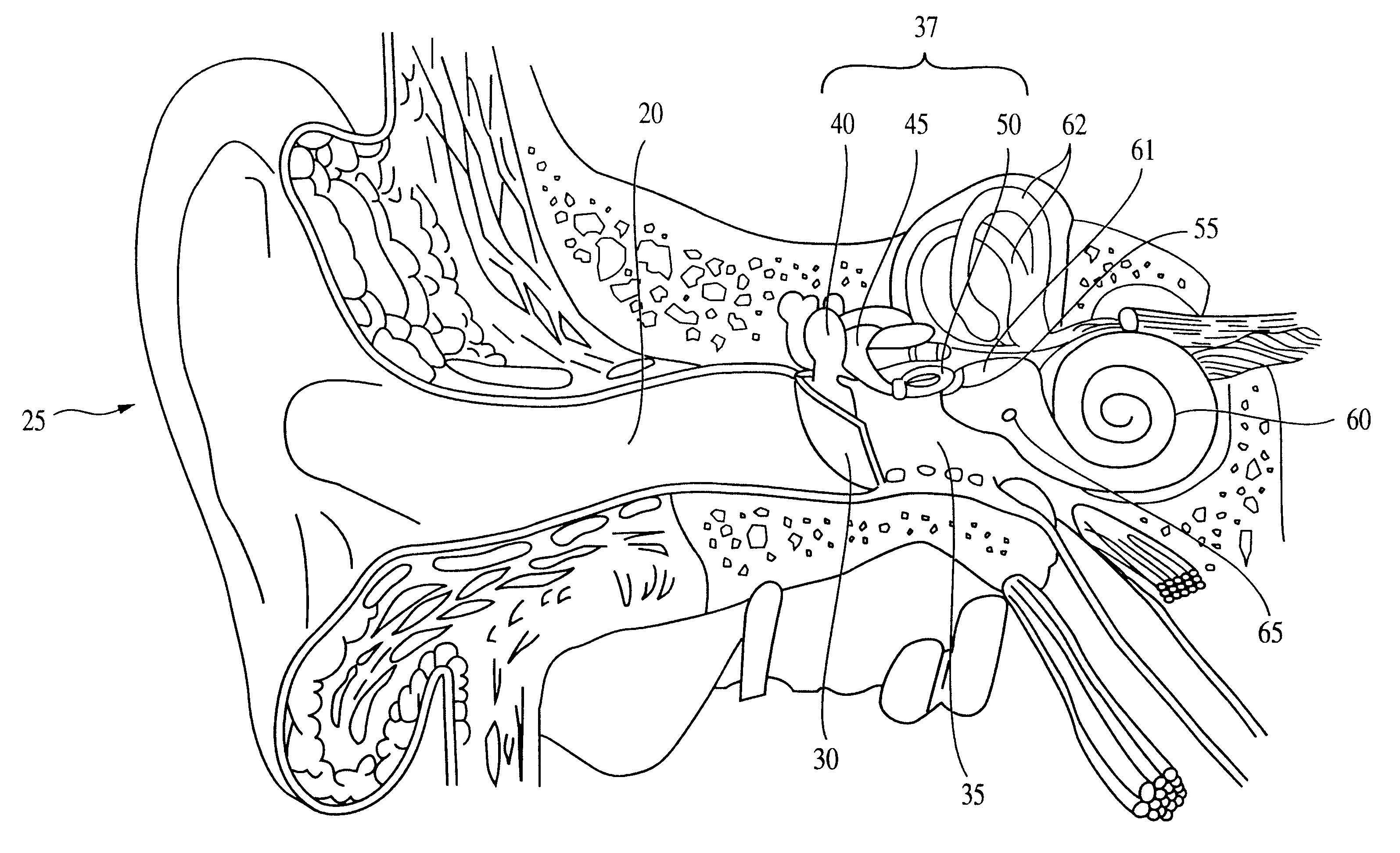

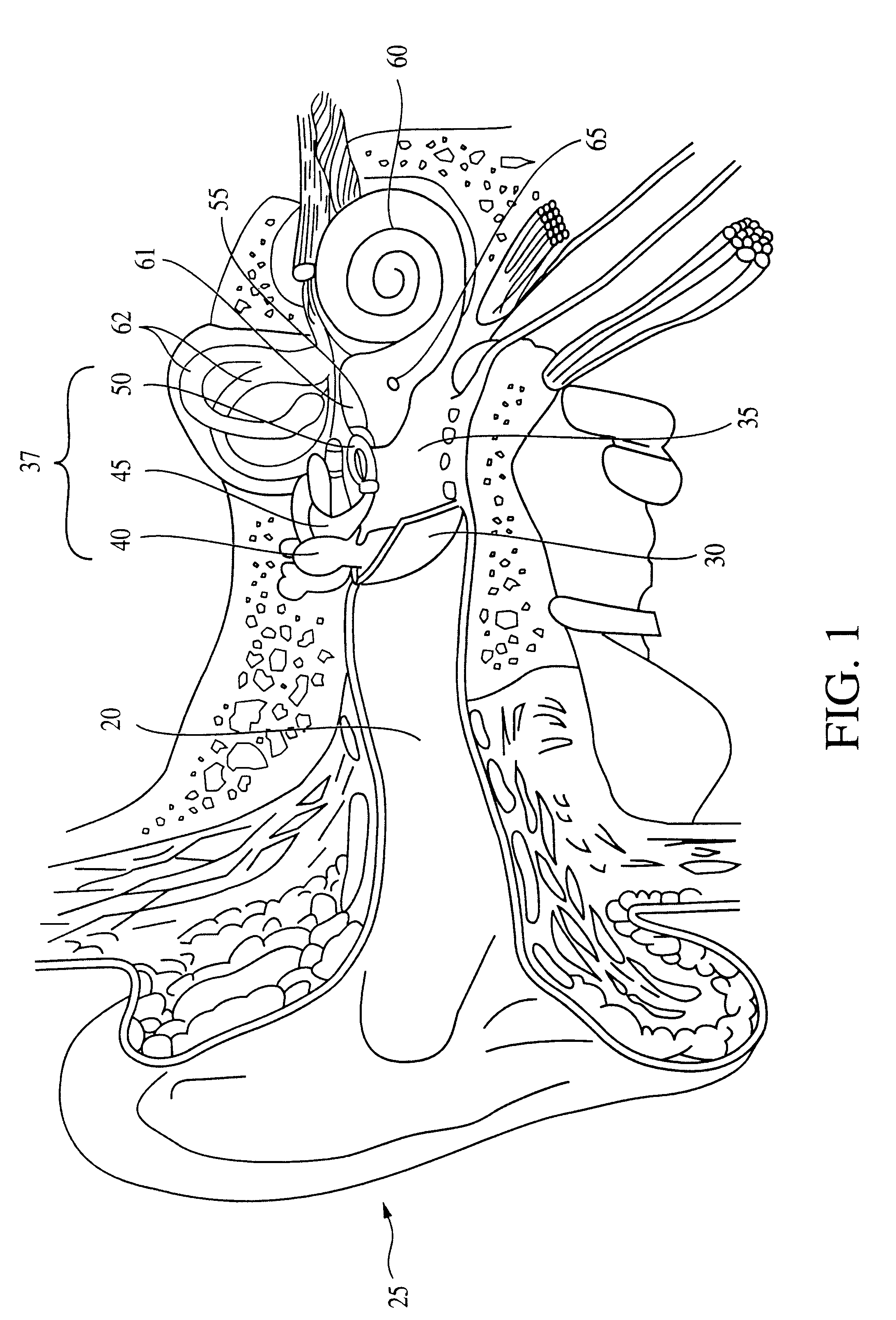

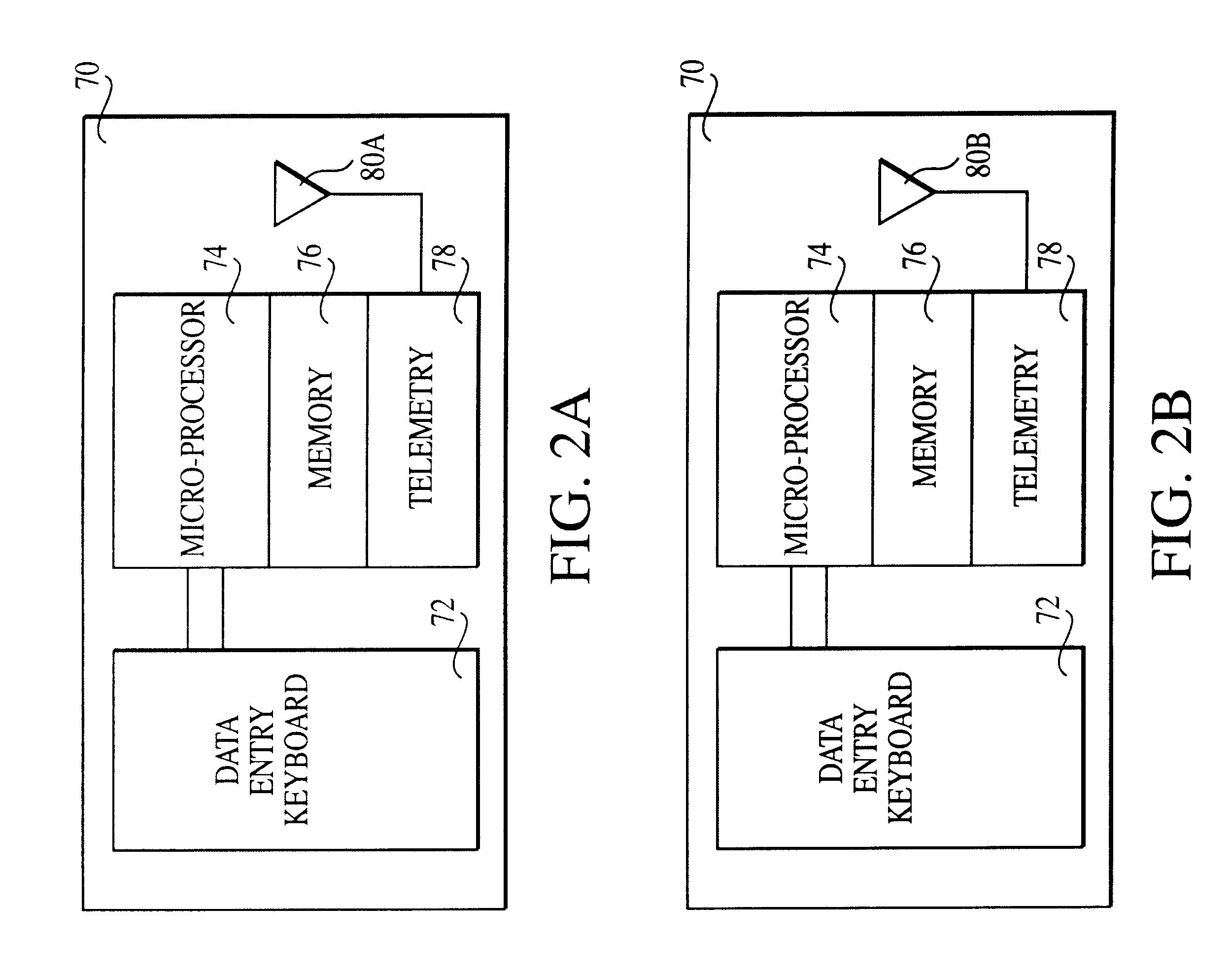

Method and apparatus for a programmable implantable hearing aid

InactiveUS6390971B1Reduce non-critical visitPromoting patient freedomElectrotherapyDeaf aid adaptationHand heldTransducer

The invention discloses a programmable implantable hearing aid including built-in electronics being in wireless communications with a hand-held programmer. The programmer transmits digital code signals of the type including RF, infrared and ultrasonic, based on selected parameter settings. A receiver accepts the signals for transmission to an input transducer in the middle ear. The input transducer collects the middle ear's response to the signals and transmits it to a circuit in the implanted hearing aid. The circuit searches for specific programming patterns and decodes the signals to effectuate the desired adjustment in the hearing aid. The conditioned signals are then transferred to an output transducer to operate the device at the adjusted signal level and condition. The invention enables both a patient and doctor to make unlimited number of adjustments in the implanted hearing aid without invasive surgery.

Owner:ST CROIX MEDICAL

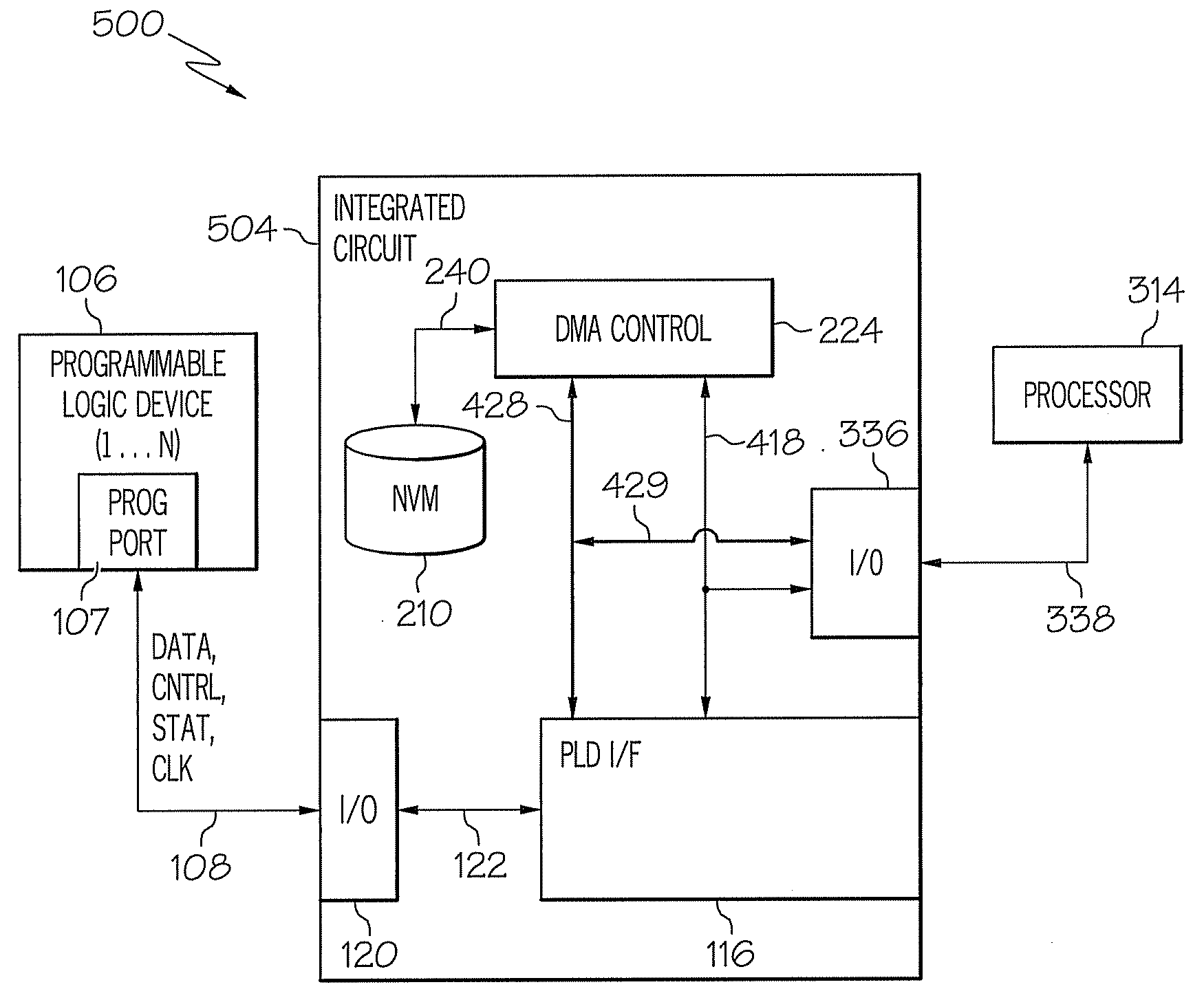

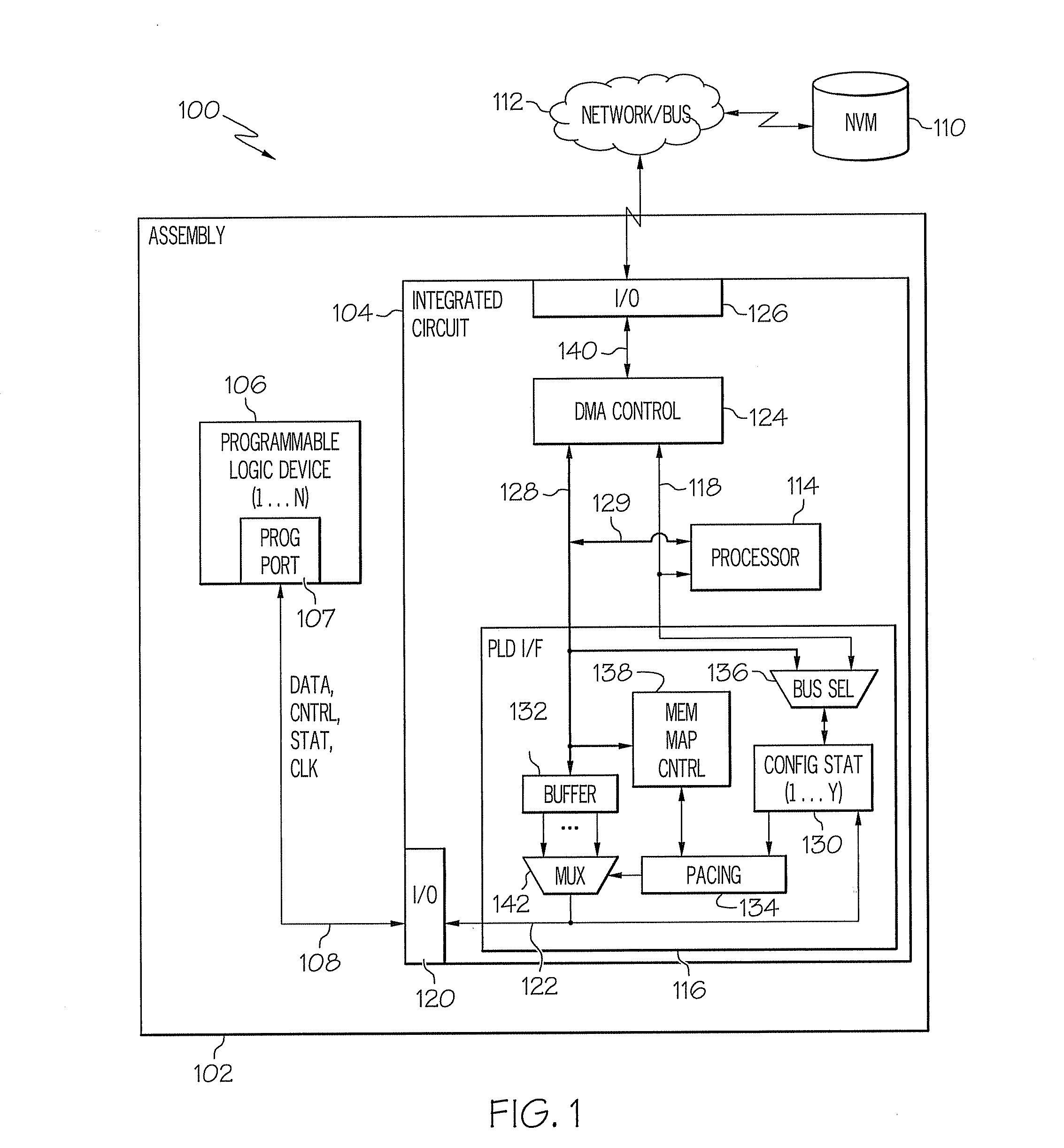

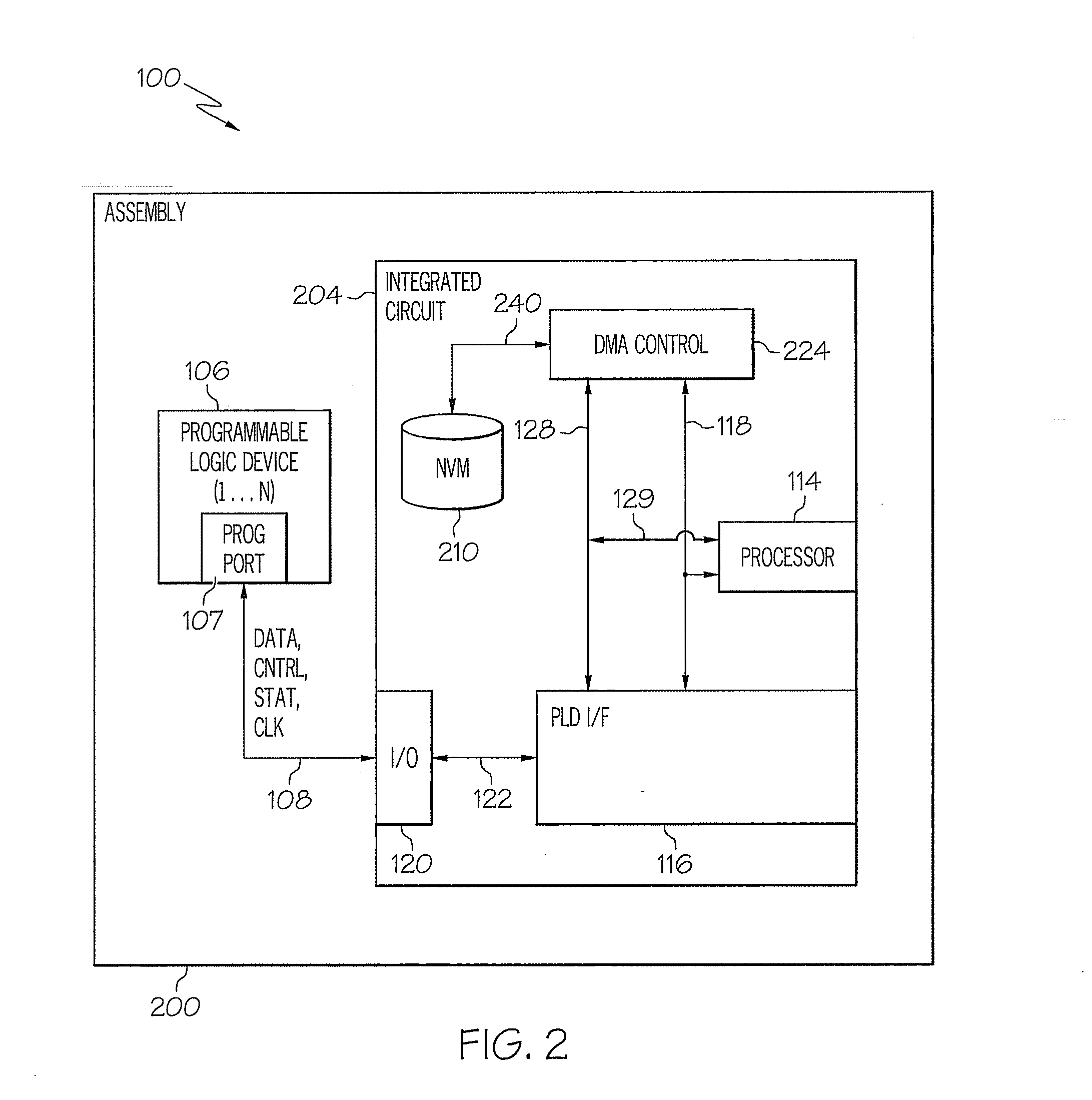

Methods, systems, and computer program products for using direct memory access to initialize a programmable logic device

ActiveUS20080186052A1Special data processing applicationsLogic circuits using elementary logic circuit componentsDirect memory accessProgrammable logic device

Methods, systems, and computer program products for using direct memory access (DMA) to initialize a programmable logic device (PLD) are provided. A method includes manipulating a control line of the PLD to configure the PLD in a programming mode, receiving PLD programming data from a DMA control at a DMA speed, and writing the PLD programming data to a data buffer. The method also includes reading the PLD programming data from the data buffer, and transmitting the PLD programming data to a programming port on the PLD at a PLD programming speed.

Owner:GLOBALFOUNDRIES US INC

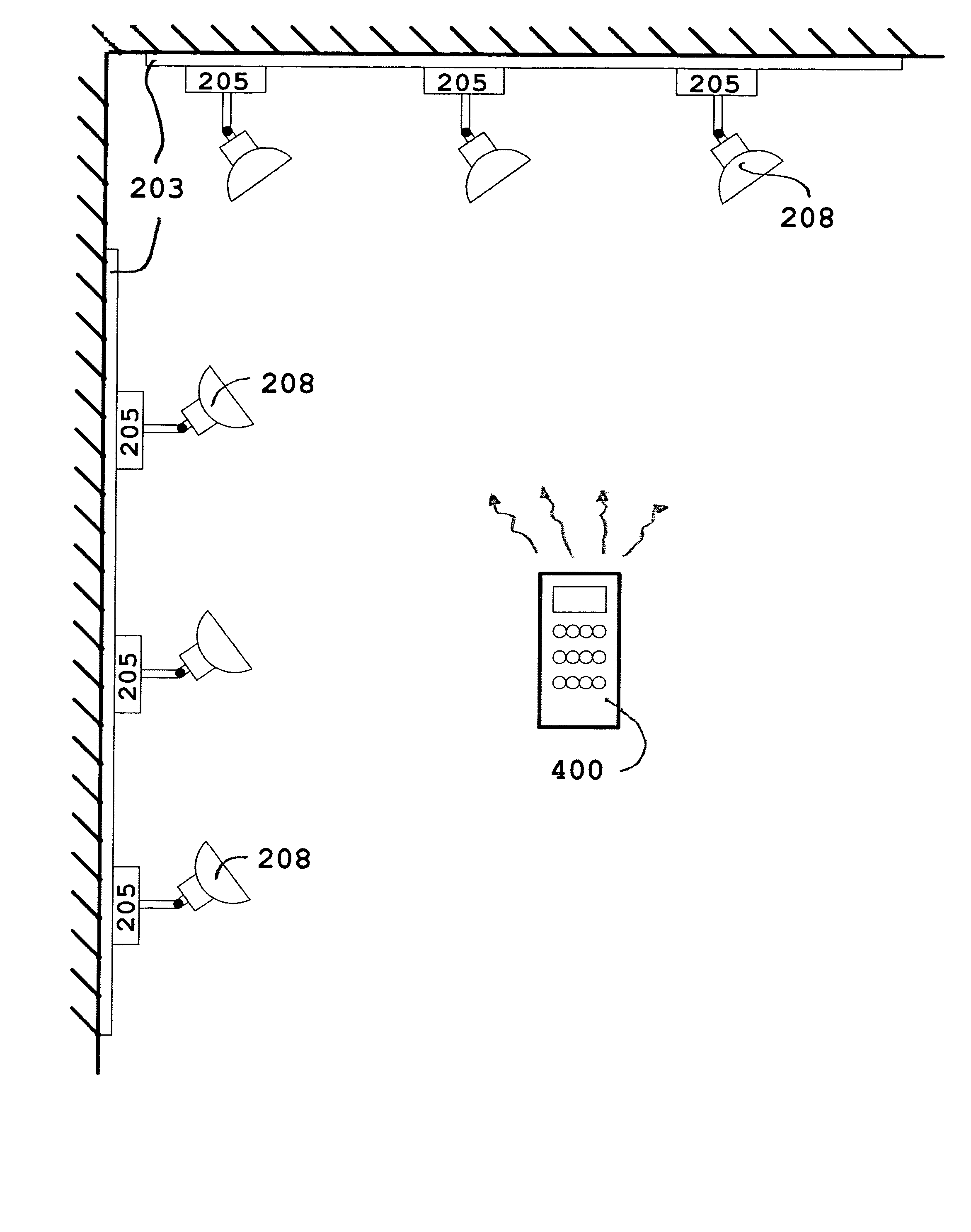

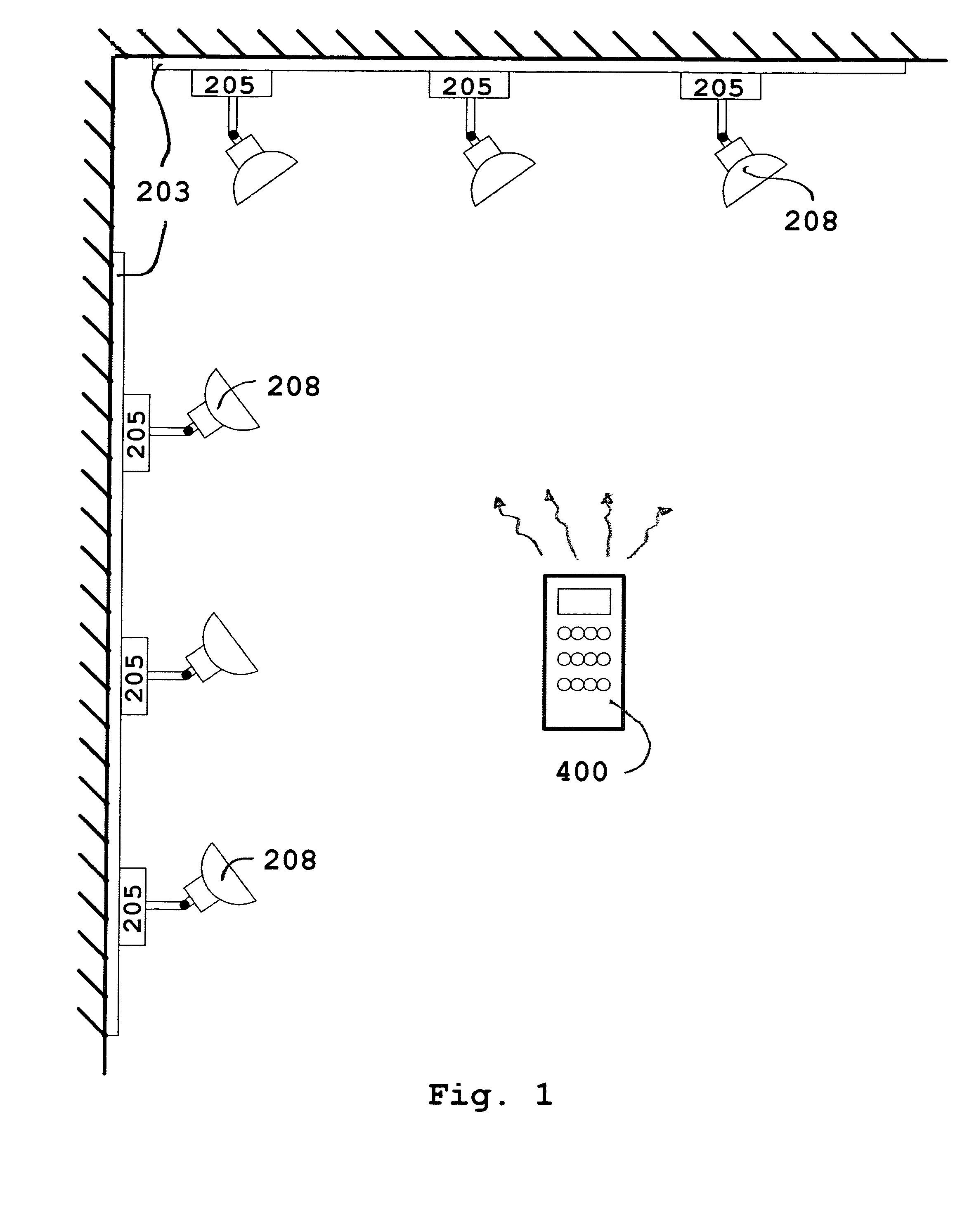

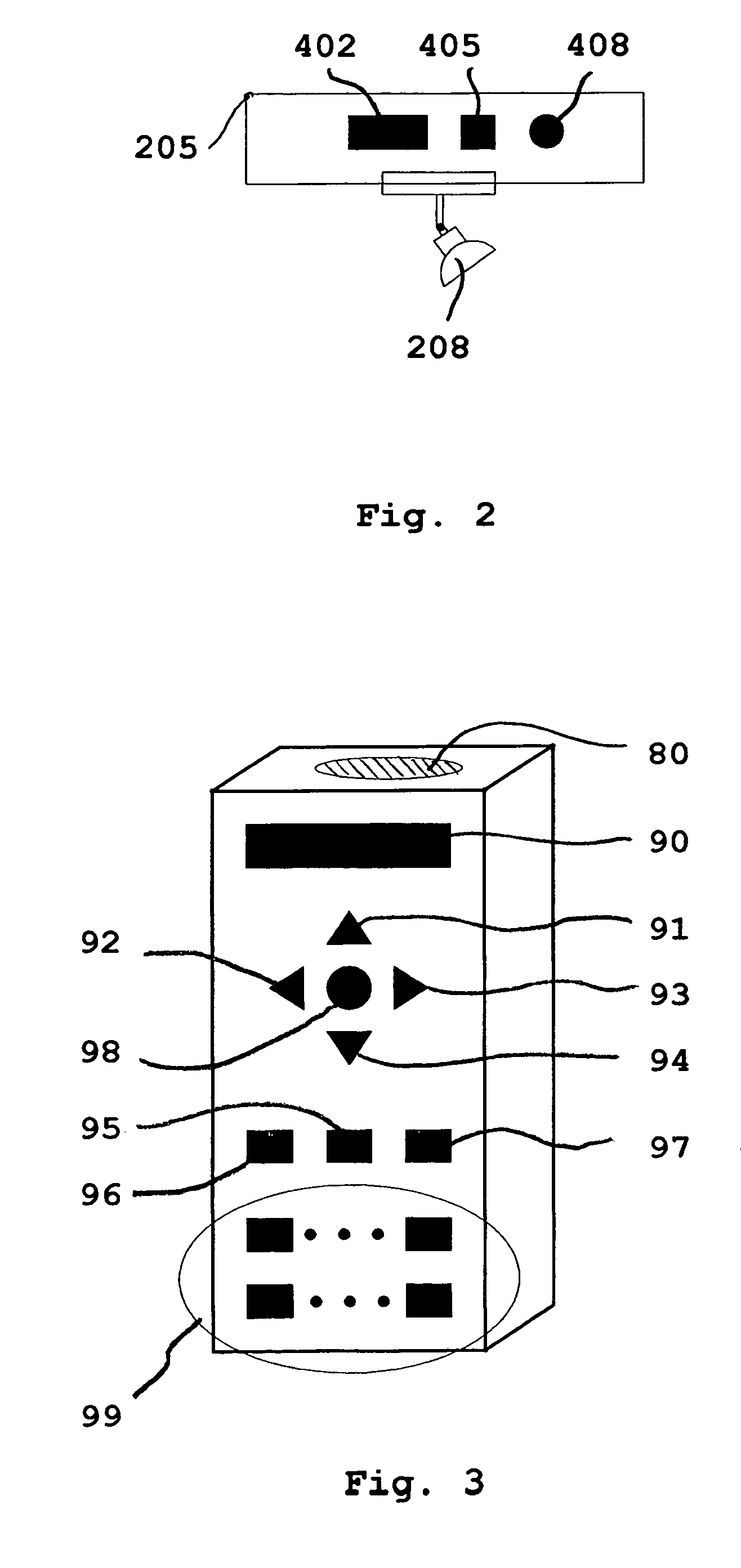

Remote controlled intelligent lighting system

InactiveUS7355523B2Reduce usageDifferent effectElectric signal transmission systemsPoint-like light sourceIntelligent lightingLight equipment

An addressable lighting device and control system uses a user-actuable infrared or radio frequency operated remote control(s) to selectively or collectively generate an electronic address for the addressable lighting device on which the device will respond to all future signals from the remote control corresponding to that electronic address. The addressable lighting device has a programming mode for setting the address and a working mode for receiving control signals on the set address and correspondingly setting the desired intensity level of light. The addressable device may have the address set and changed locally (manually) or remotely using the remote control to switch modes, thereby avoiding the problems, expenses and mistakes associated with using dual in-line package (DIP) switches, binary, hex rotary switches, or thumbwheel switches normally used to set each one of the system's unit's unique address.

Owner:SID ALBERTO

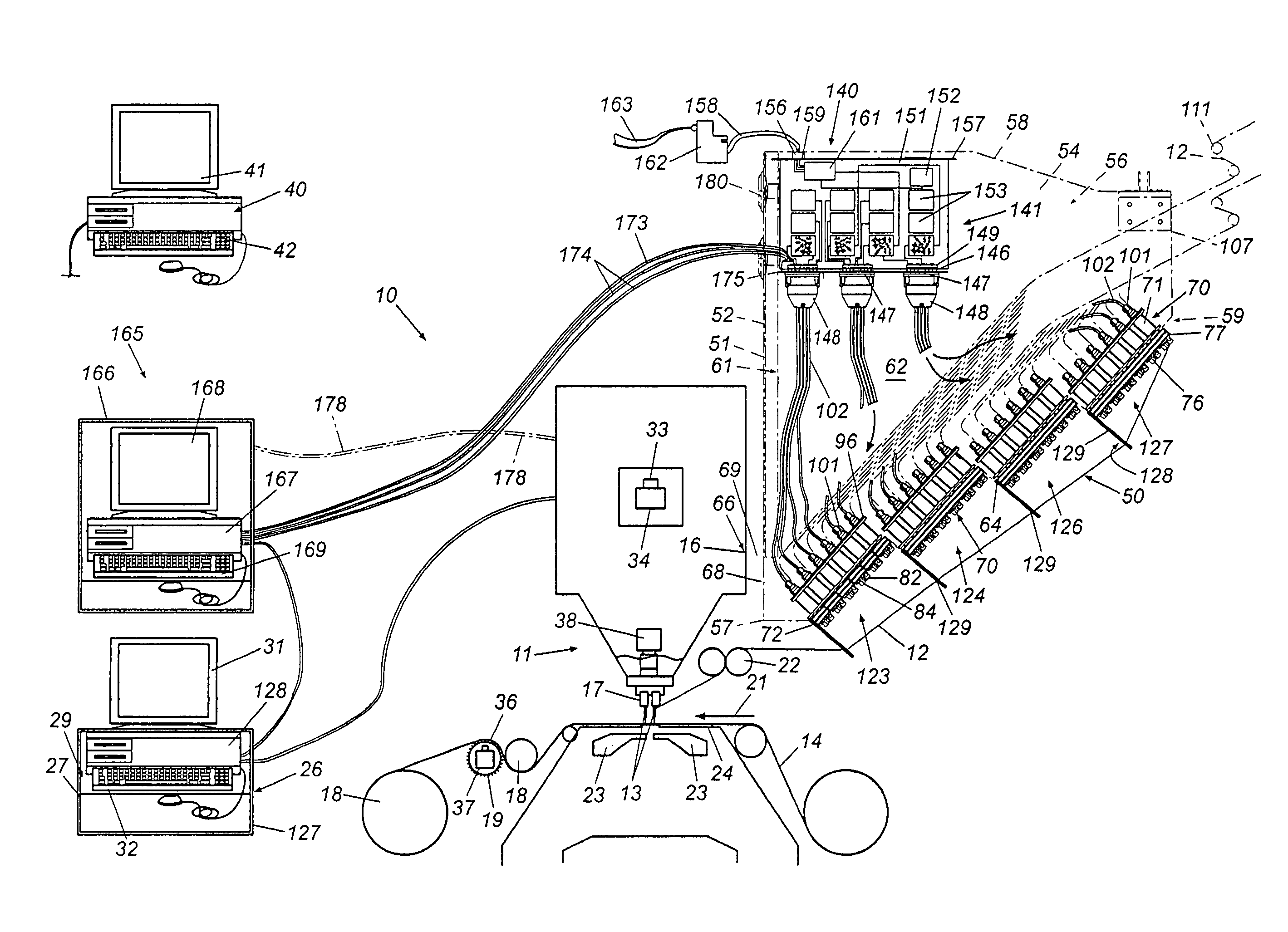

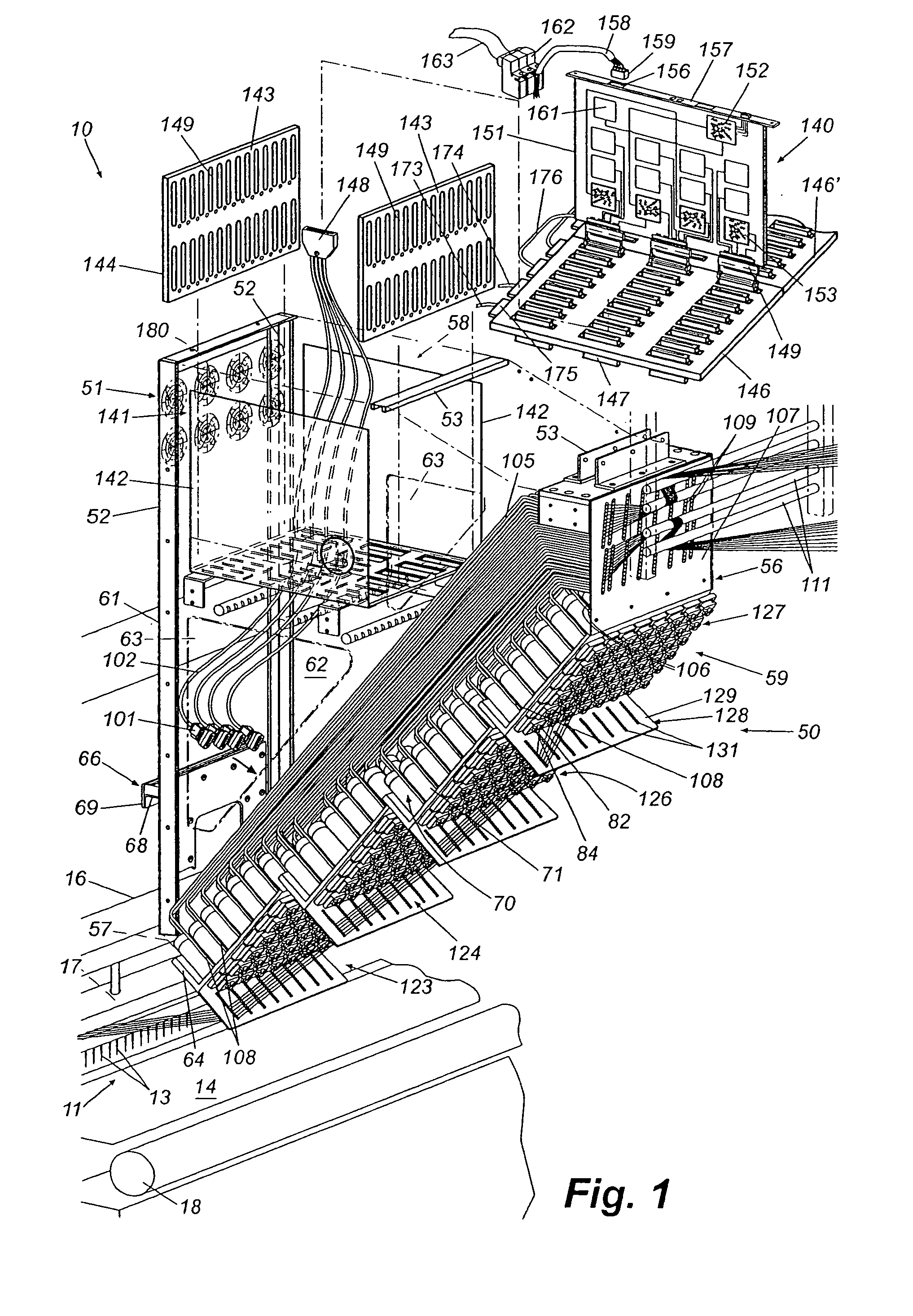

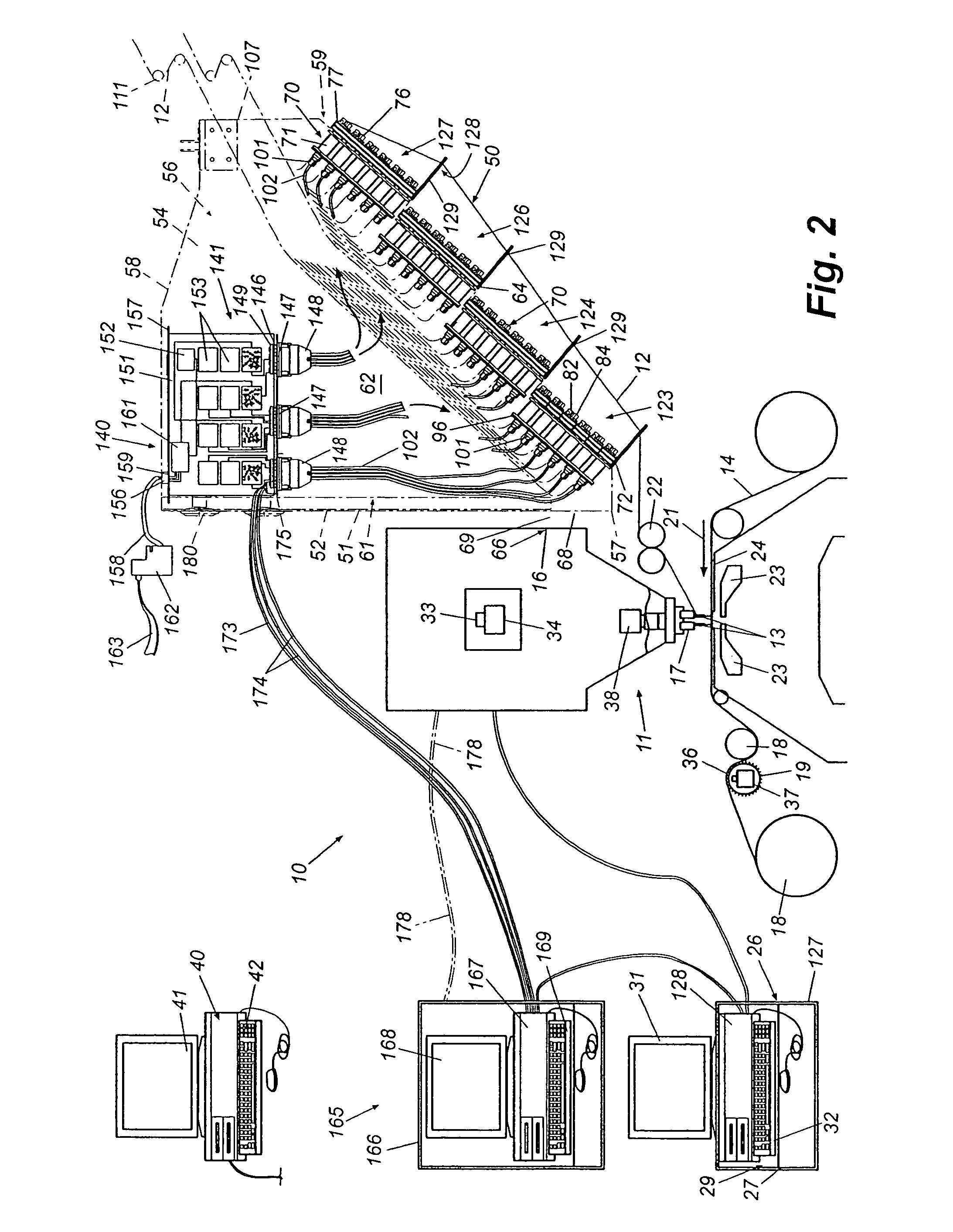

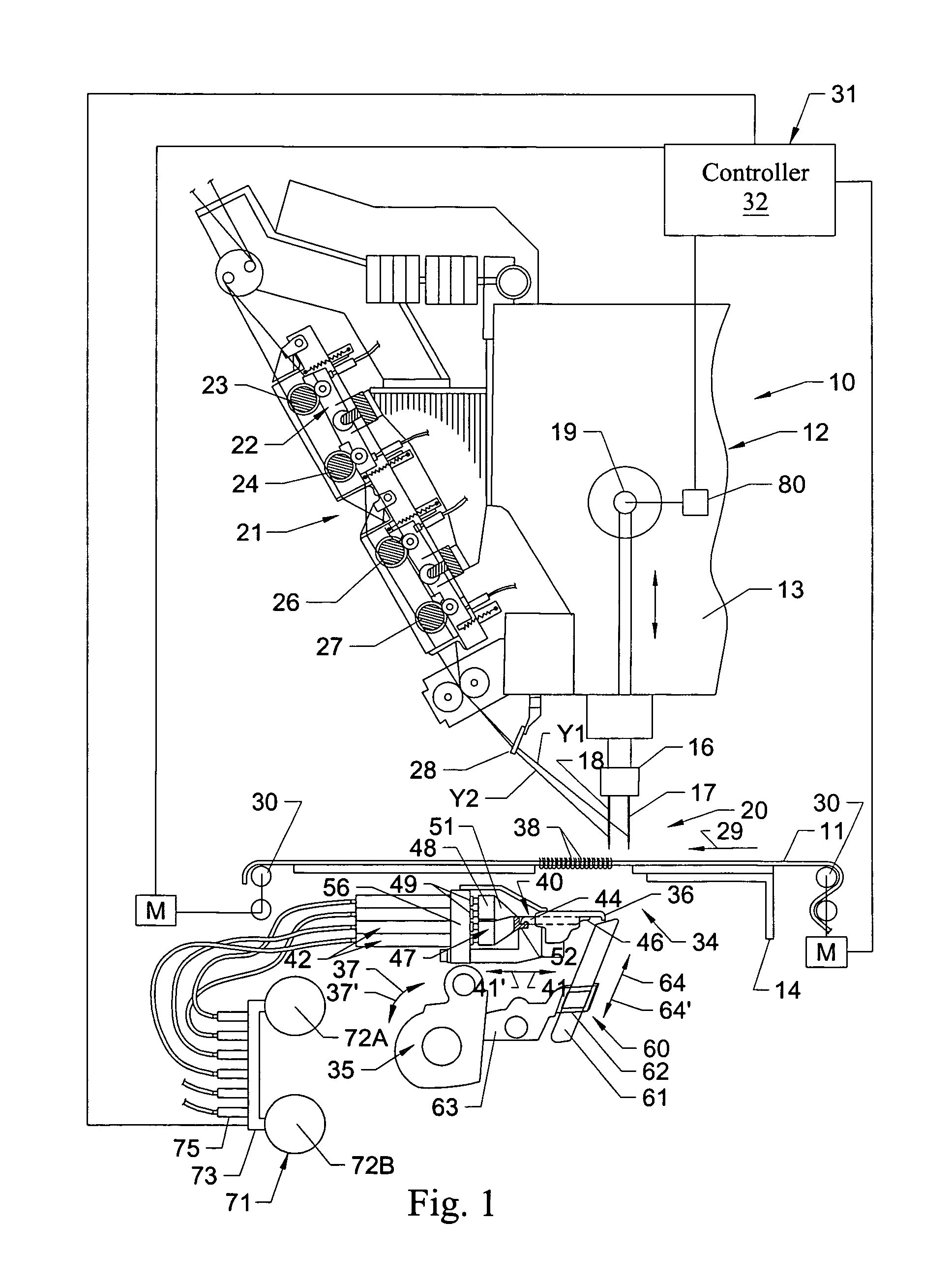

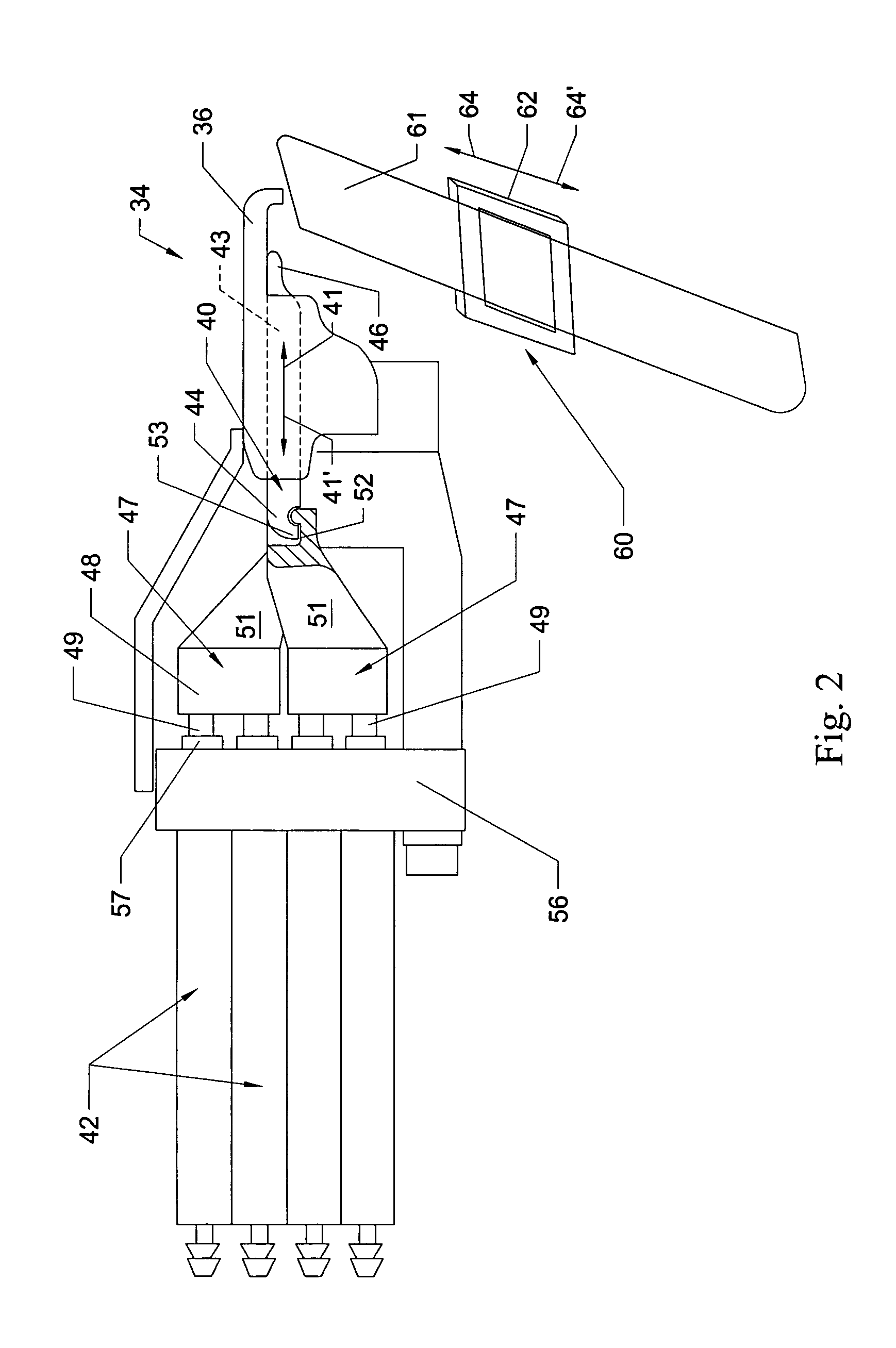

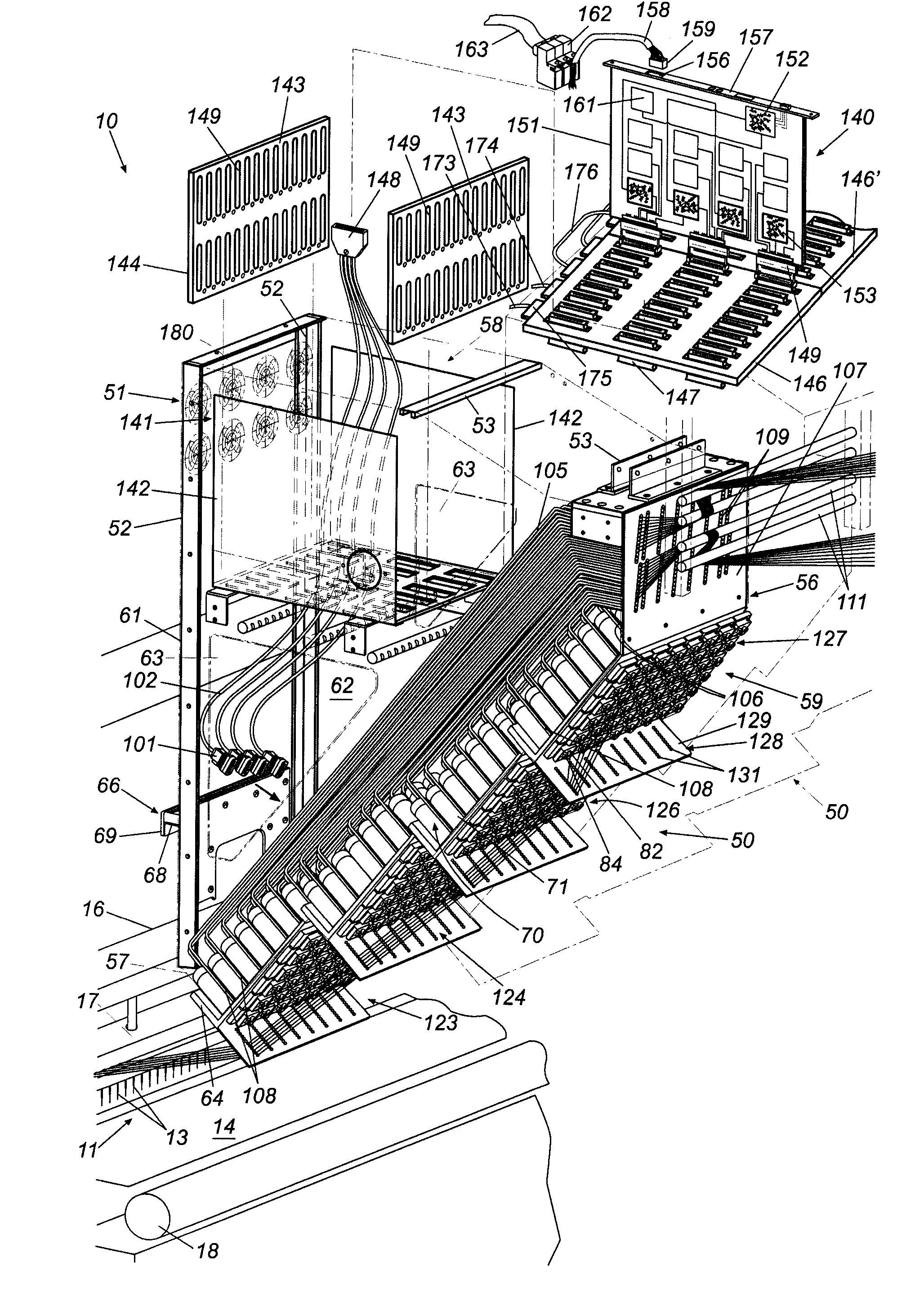

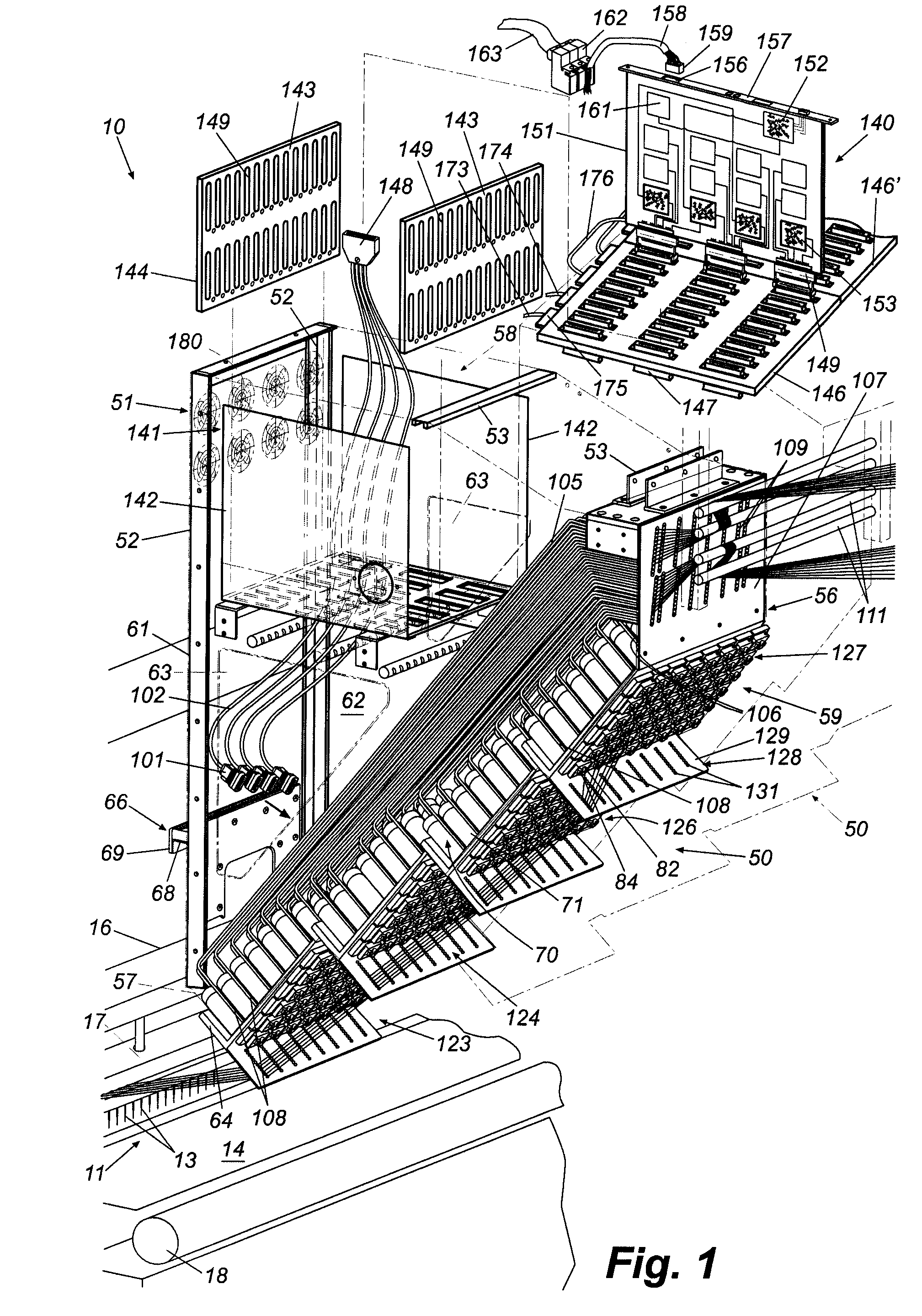

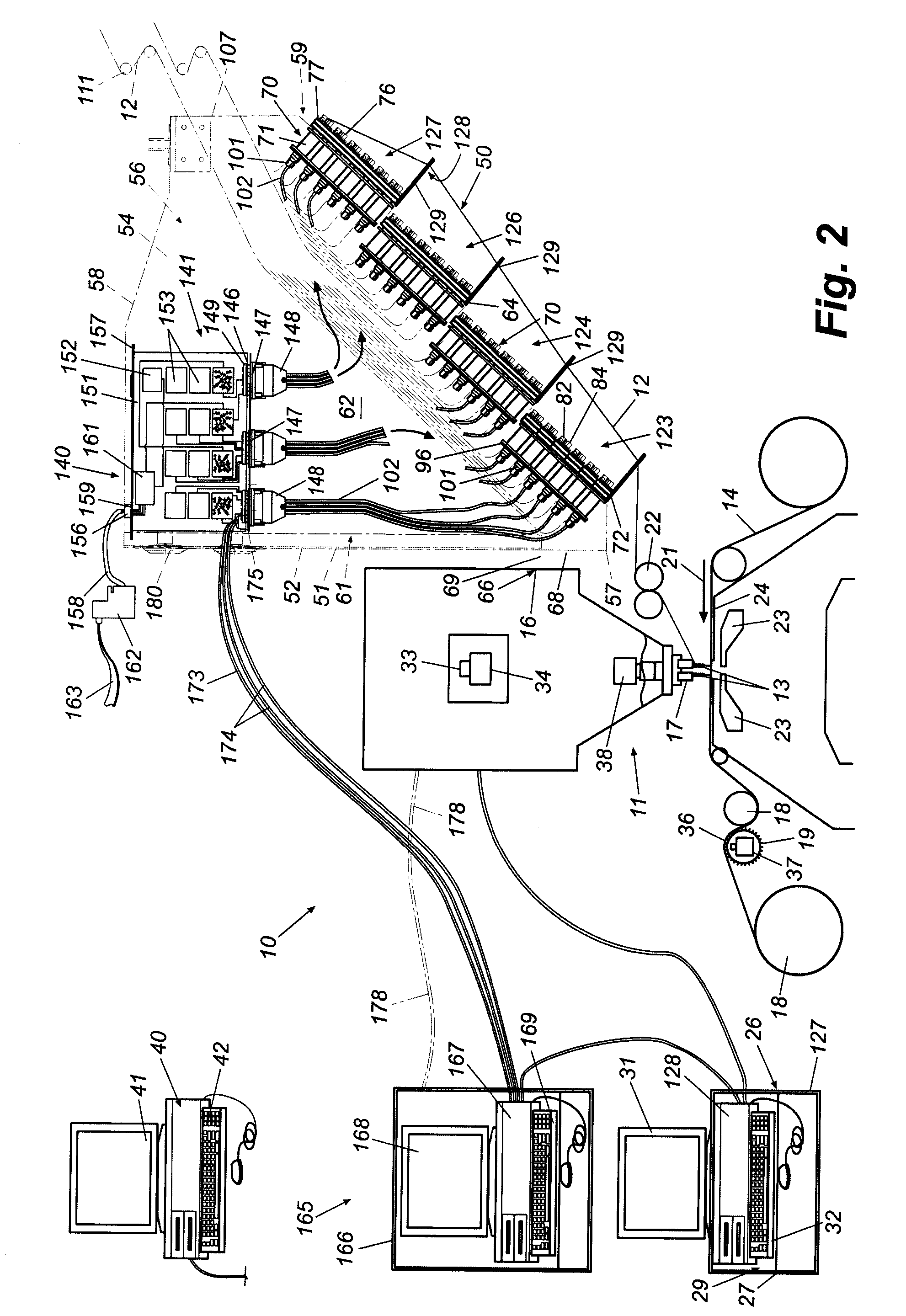

Yarn feed system for tufting machines

InactiveUS7096806B2Improve precisionEasy to controlTufting apparatusYarnElectrical and Electronics engineering

A yarn feed system, enabling the control of individual yarns to the needles of a tufting machine, and which system can be manufactured as a substantially standardized unit or attachment that can be removably mounted to a tufting machine. The yarn feed unit includes a series of yarn feed devices for feeding each of the yarns to the needles of the tufting machine, and a series of yarn feed controllers that monitor and control the operation of the yarn feed devices to control the feeding of the yarns to the needles according to programmed pattern instructions.

Owner:CARD MONROE

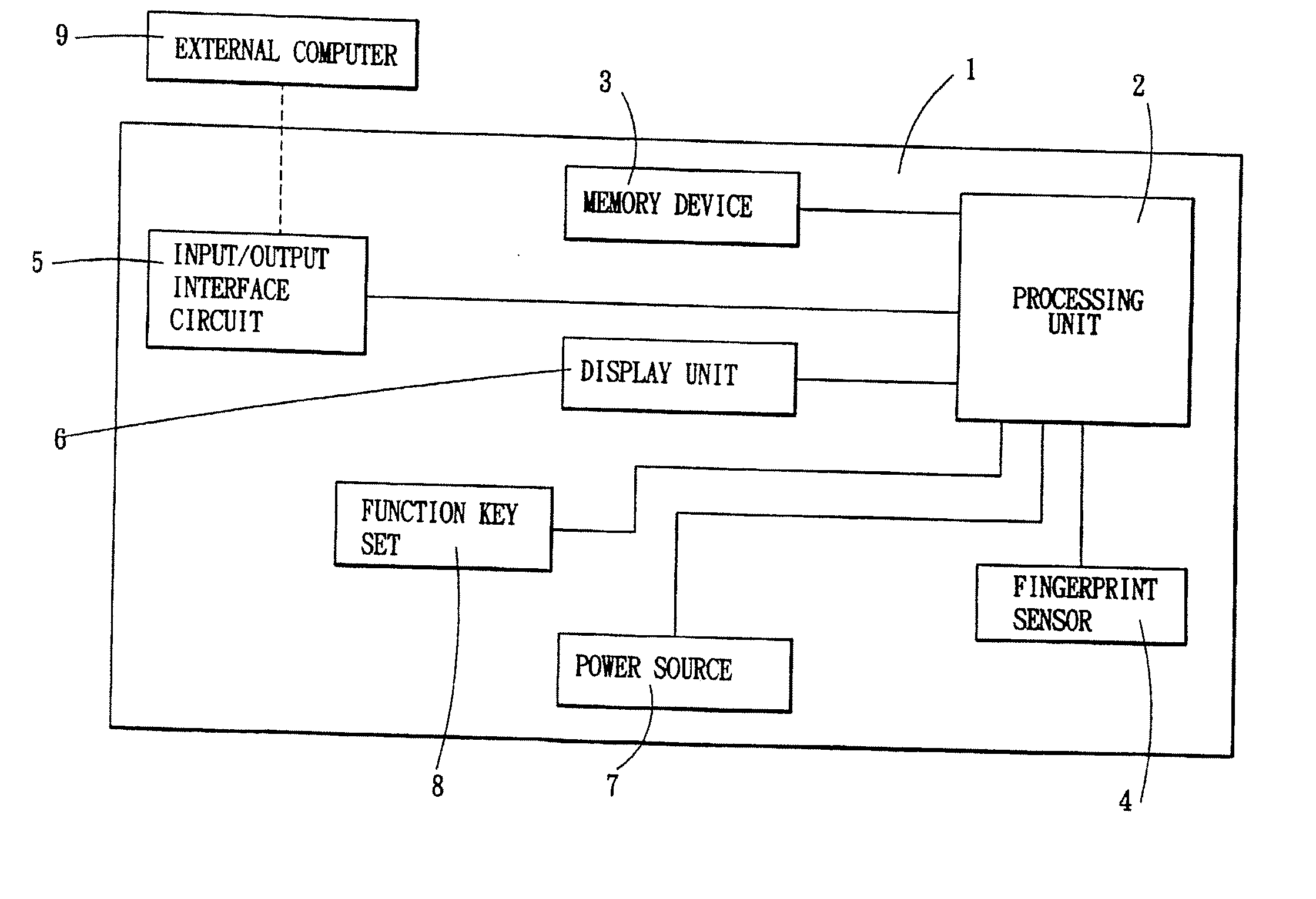

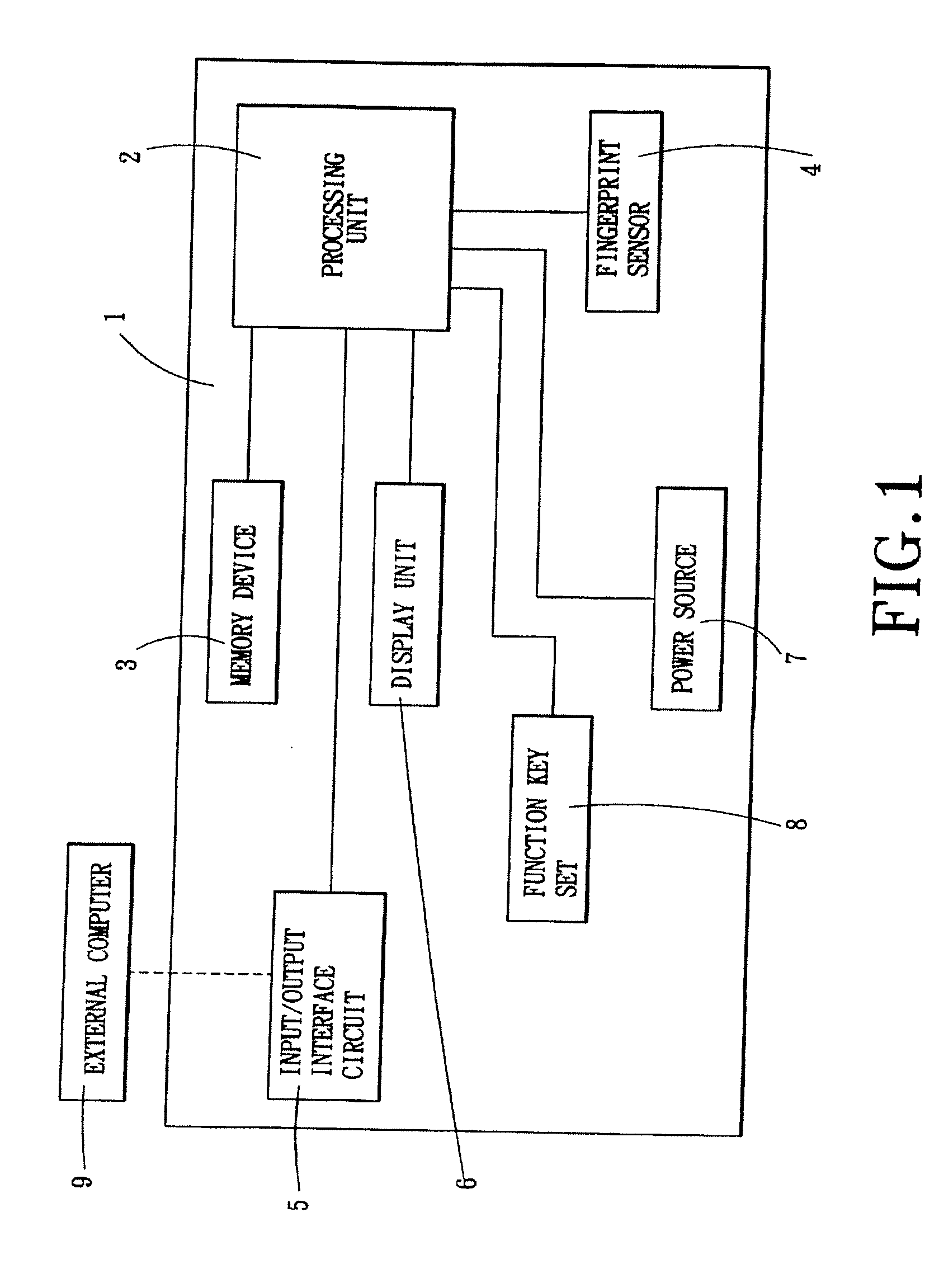

Electronic Data Storage Medium With Fingerprint Verification Capability

An electronic data storage medium is adapted to be accessed by a data terminal, and includes a processing unit connected to a memory device that stores a data file and security reference data possessed by a person authorized to access the data file, and an input-output interface circuit activable so as to establish communication with the data terminal. The processing unit is operable selectively in a programming mode and a data retrieving mode. The electronic data storage medium also includes a function key set for manually switching the electronic data storage medium between the programming mode and the data retrieving mode.

Owner:SUPER TALENT ELECTRONICS

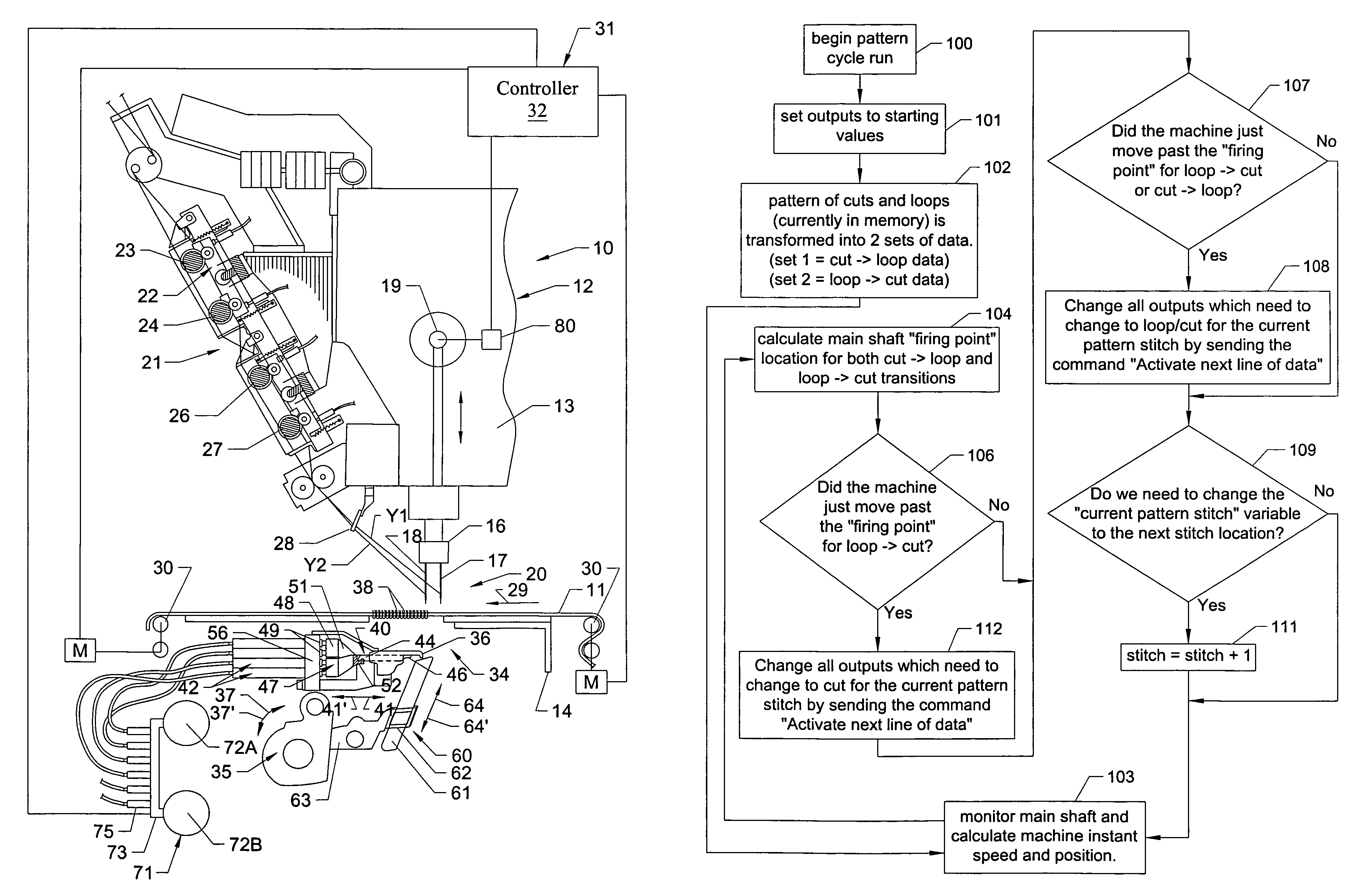

Control assembly for tufting machine

A tufting machine and a method of controlling a tufting machine for forming cut and loop pile tufts of yarns in a backing material that includes a hook assembly having a series of hooks / loopers and a series of clips independently moveable between extended and retracted positions. The movement of the clips between their extended and retracted positions is selectively activated to cause transitions from cut pile tufts to loop pile tufts and loop pile tufts to cut pile tufts according to programmed pattern information.

Owner:CARD MONROE

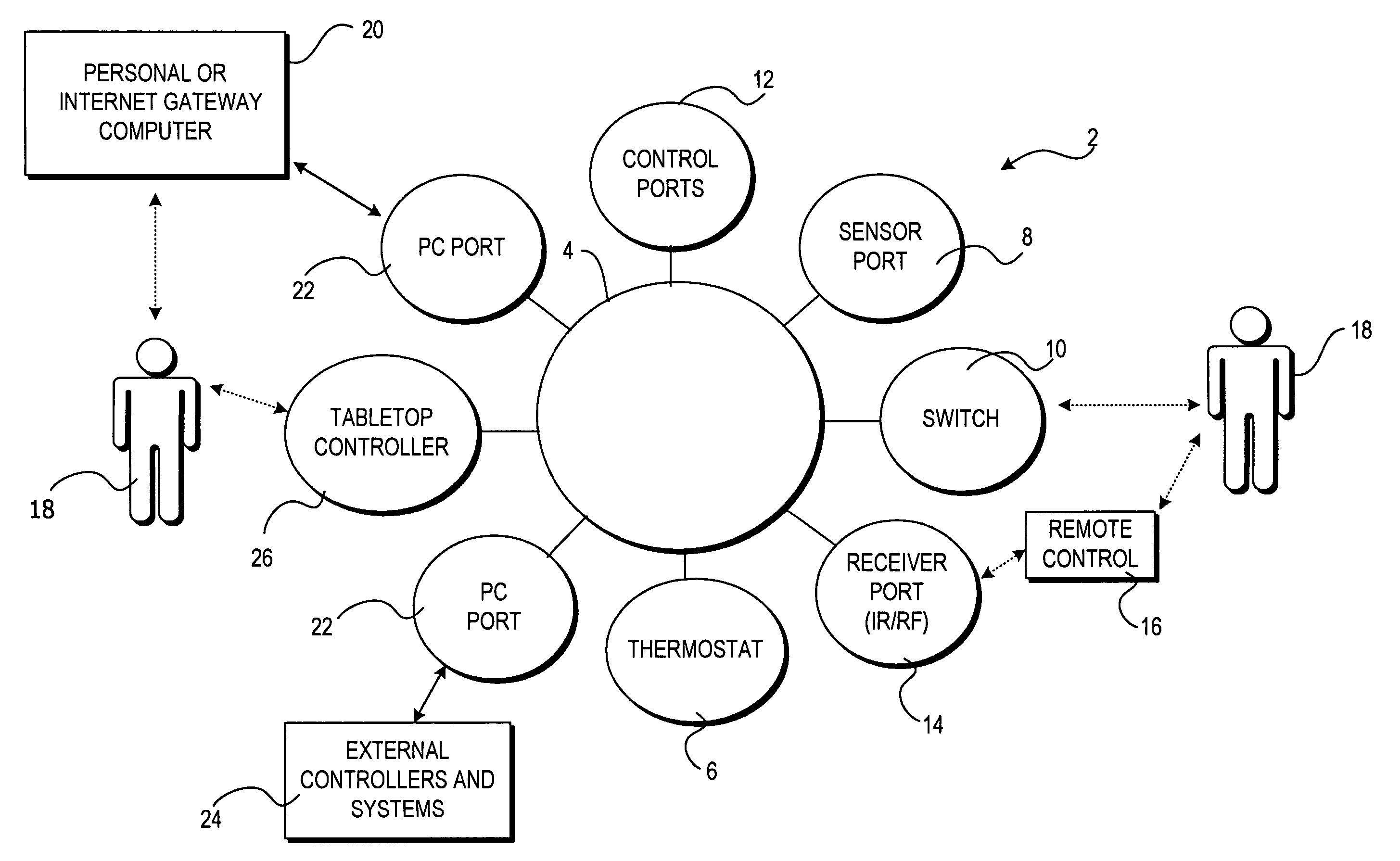

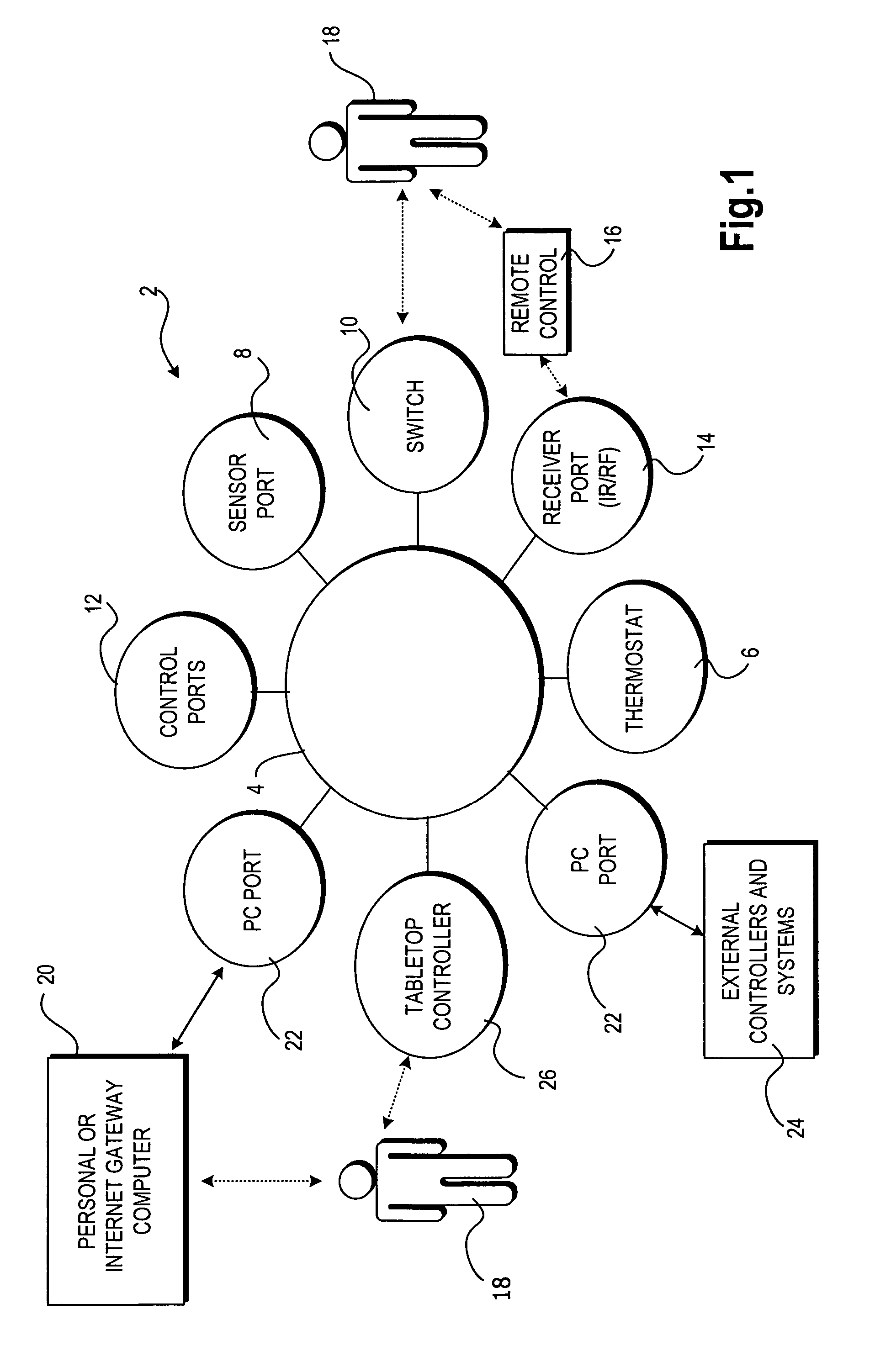

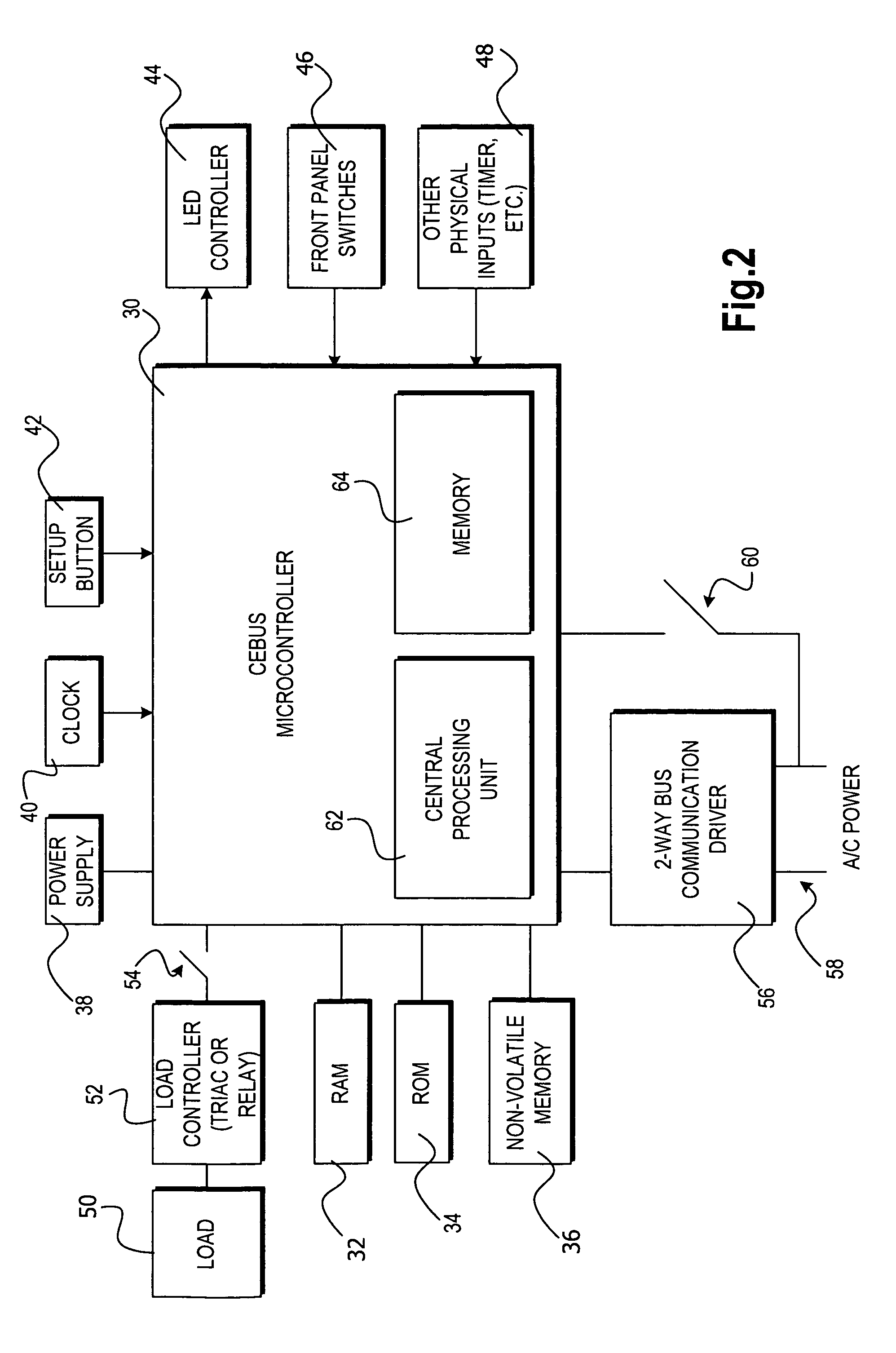

Method and apparatus for providing distributed scene programming of a home automation and control system

InactiveUS6970751B2Reduce rateShorten the timeComputer controlSimulator controlControl systemSystem programming

A method and apparatus for providing a simple user interface for programming scenes and multi-way groups in a home automation and control system is provided. Each device participating in the home automation and control system is equipped with control logic for providing the simple programming interface. Through the control logic, each device maintains its status in a system-wide programming mode and retains knowledge of its inclusion or exclusion in the current scene or multi-way group being programmed. When any device in the system receives indications that affect the system programming mode, such as a press on one of the buttons on the devices, the device broadcasts a notification message to all devices within the home automation and control system. The message maintains the integrity of the system programming mode. Each device knows when a scene or multi-way group being programmed is finally captured and the programming of a new scene or multi-way group has started.

Owner:MICROSOFT TECH LICENSING LLC

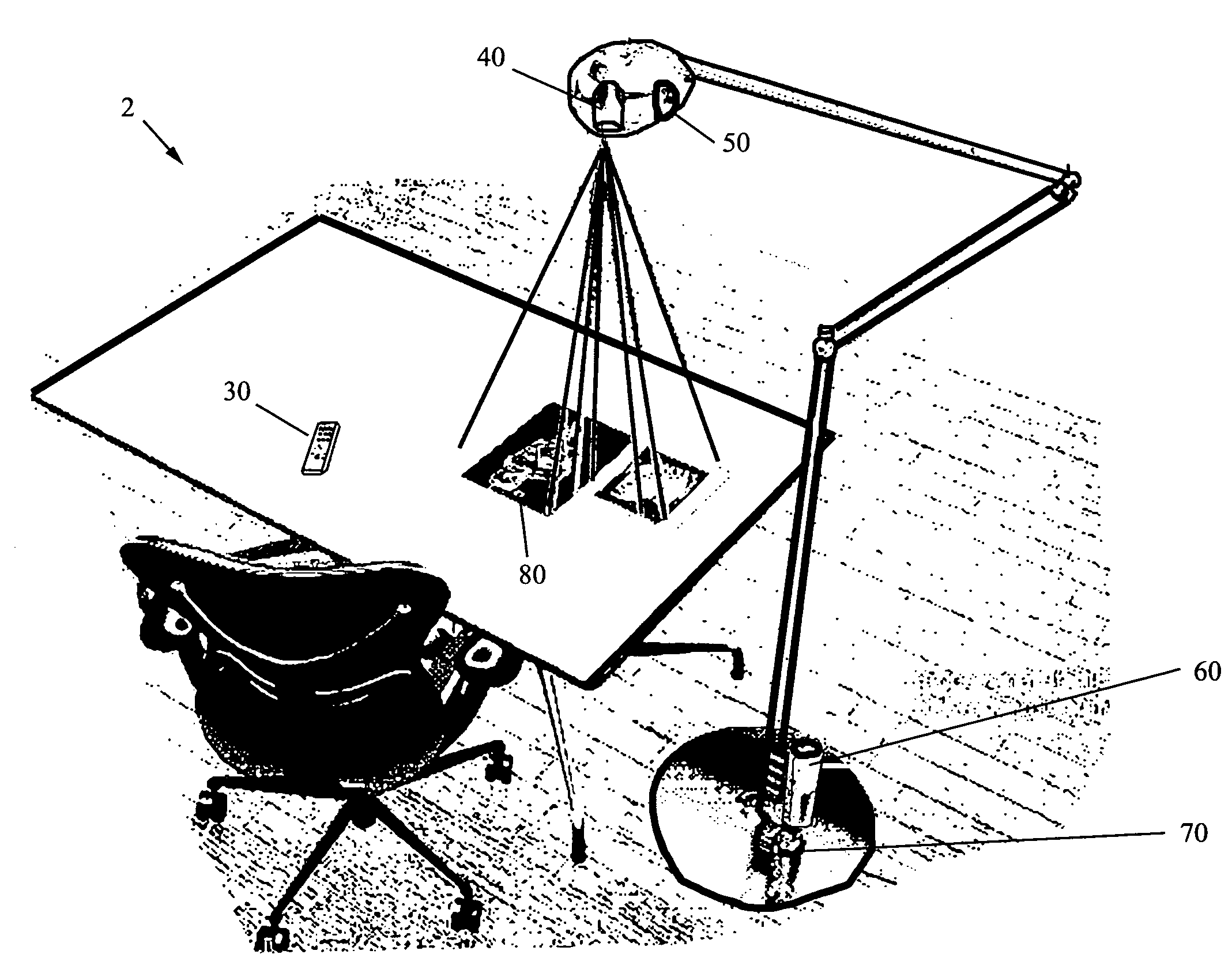

Semantic light

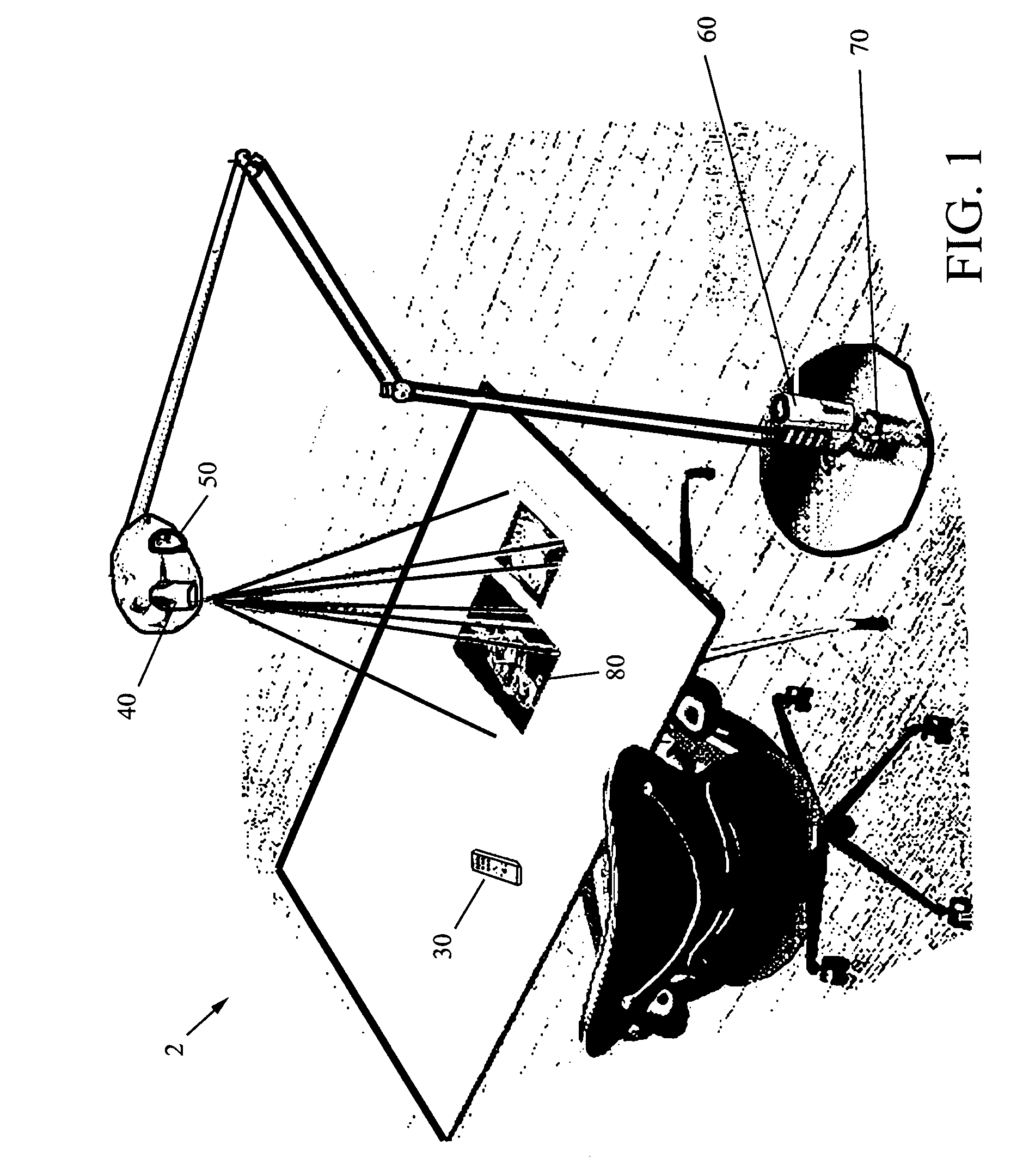

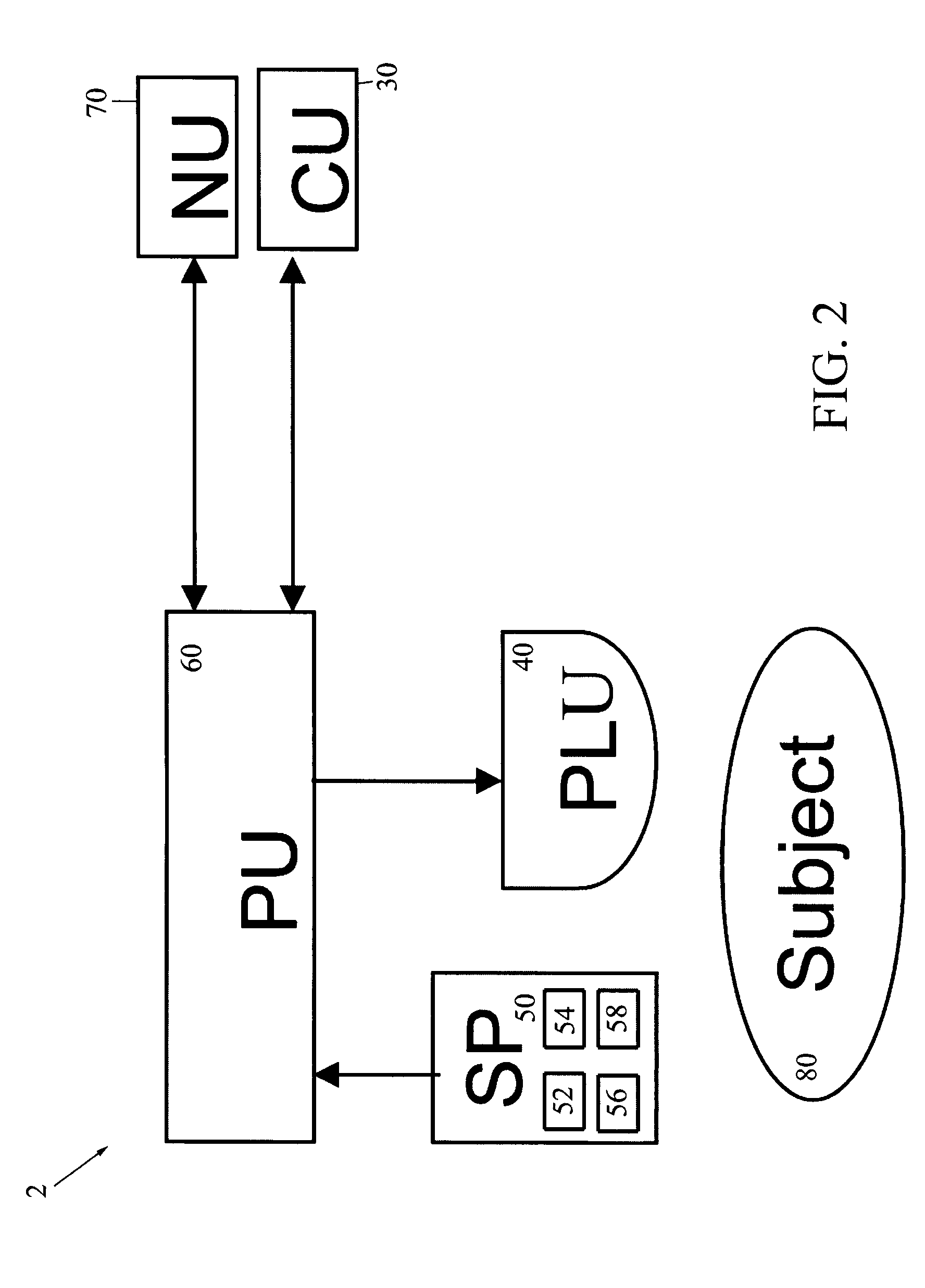

A lighting system for delivering a dynamic, fully customized, and automatic illumination to a subject. The lighting system comprises a programmable light unit for emitting a programmed pattern and spectra of illumination, a sensor pod comprising an array of sensors for detecting ambient lighting conditions and subject characteristics, a control unit for allowing a user to program the lighting system, and a processing unit for analyzing data from the sensor pod and control unit to construct an optimal lighting profile in accordance therewith. The lighting system generates light in accordance with the lighting profile which is fully optimized in spectrum, intensity, color, contrast, temperature, angle, and focus for any given environment, subject and task.

Owner:SEGALL ZARY

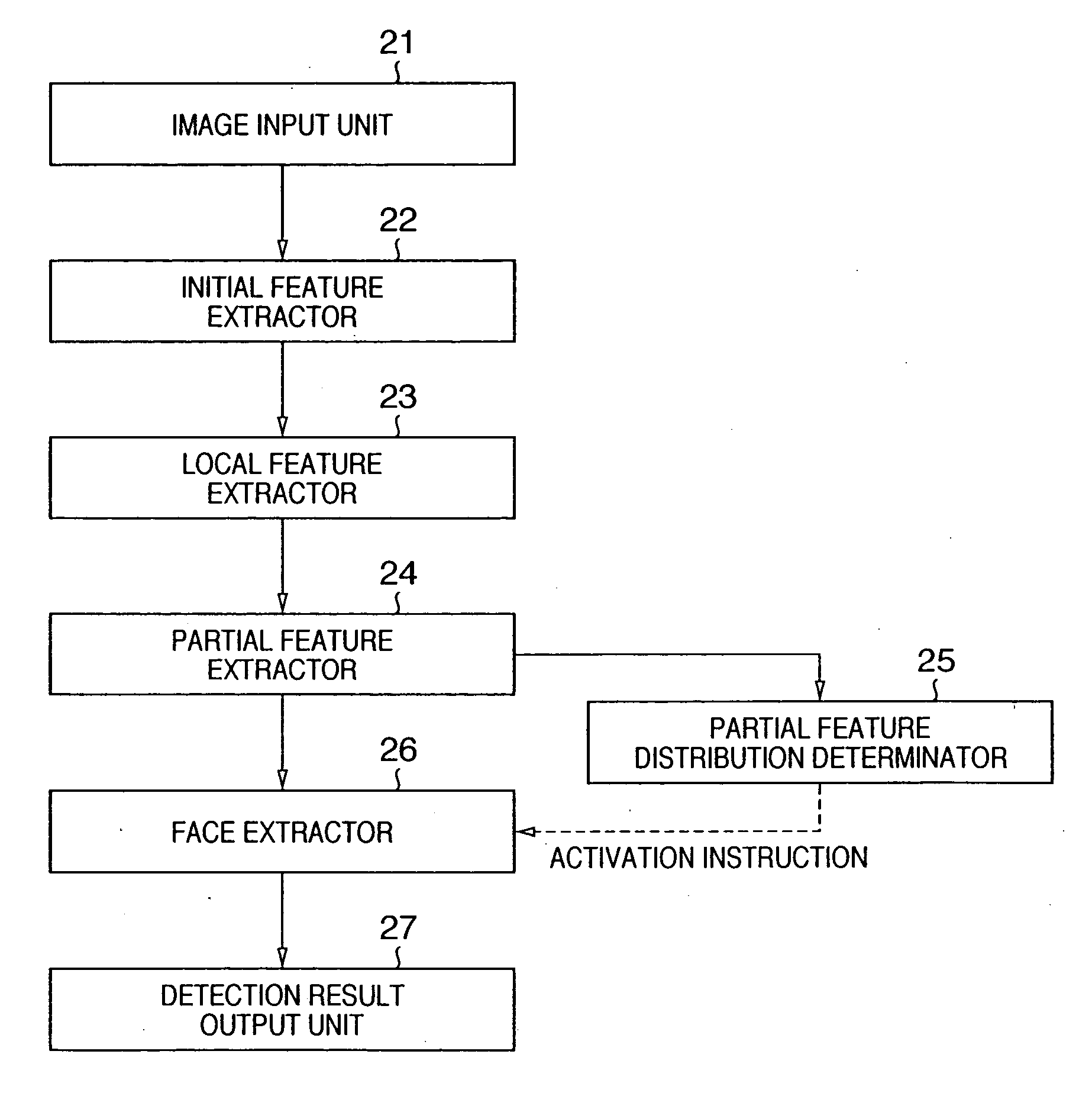

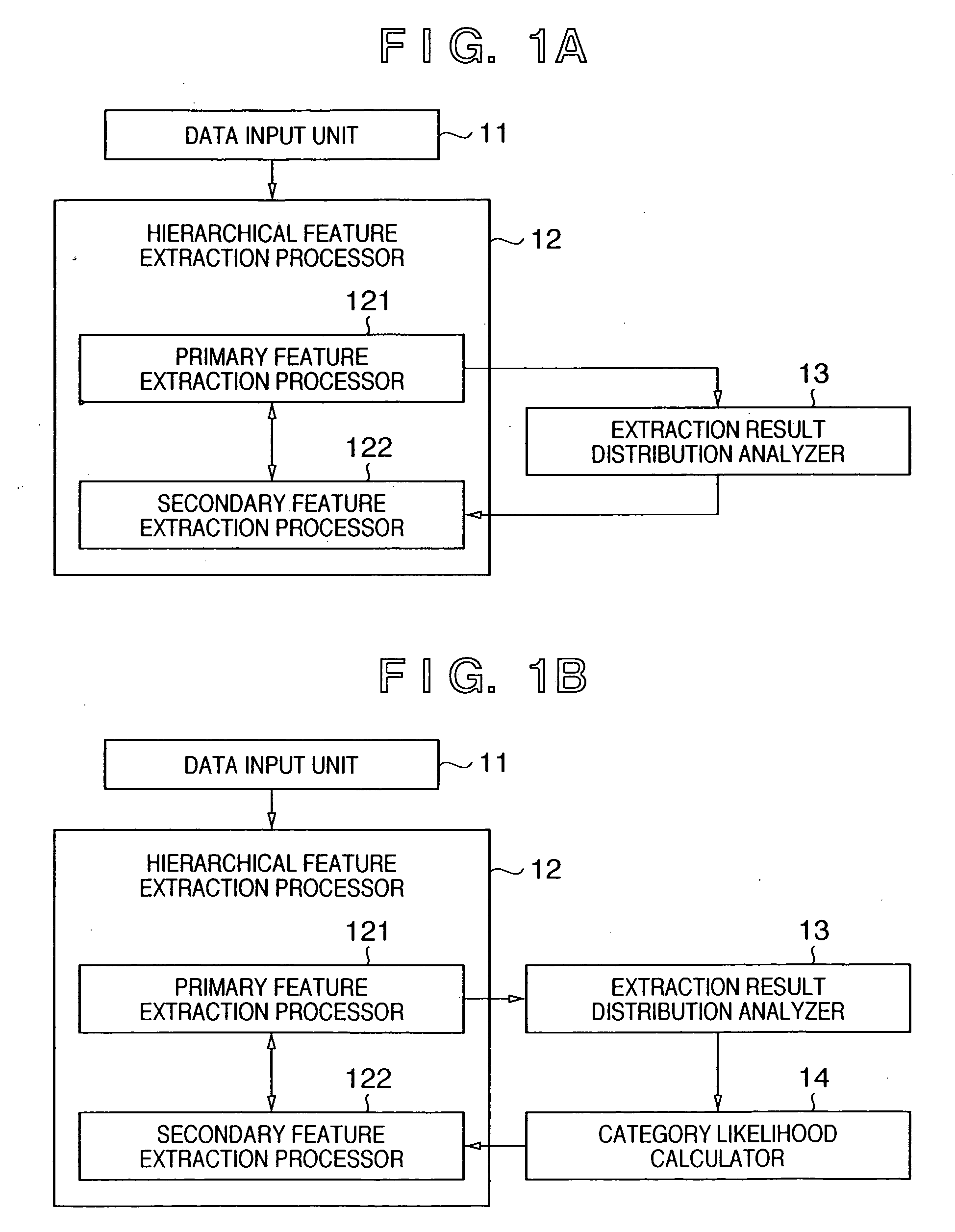

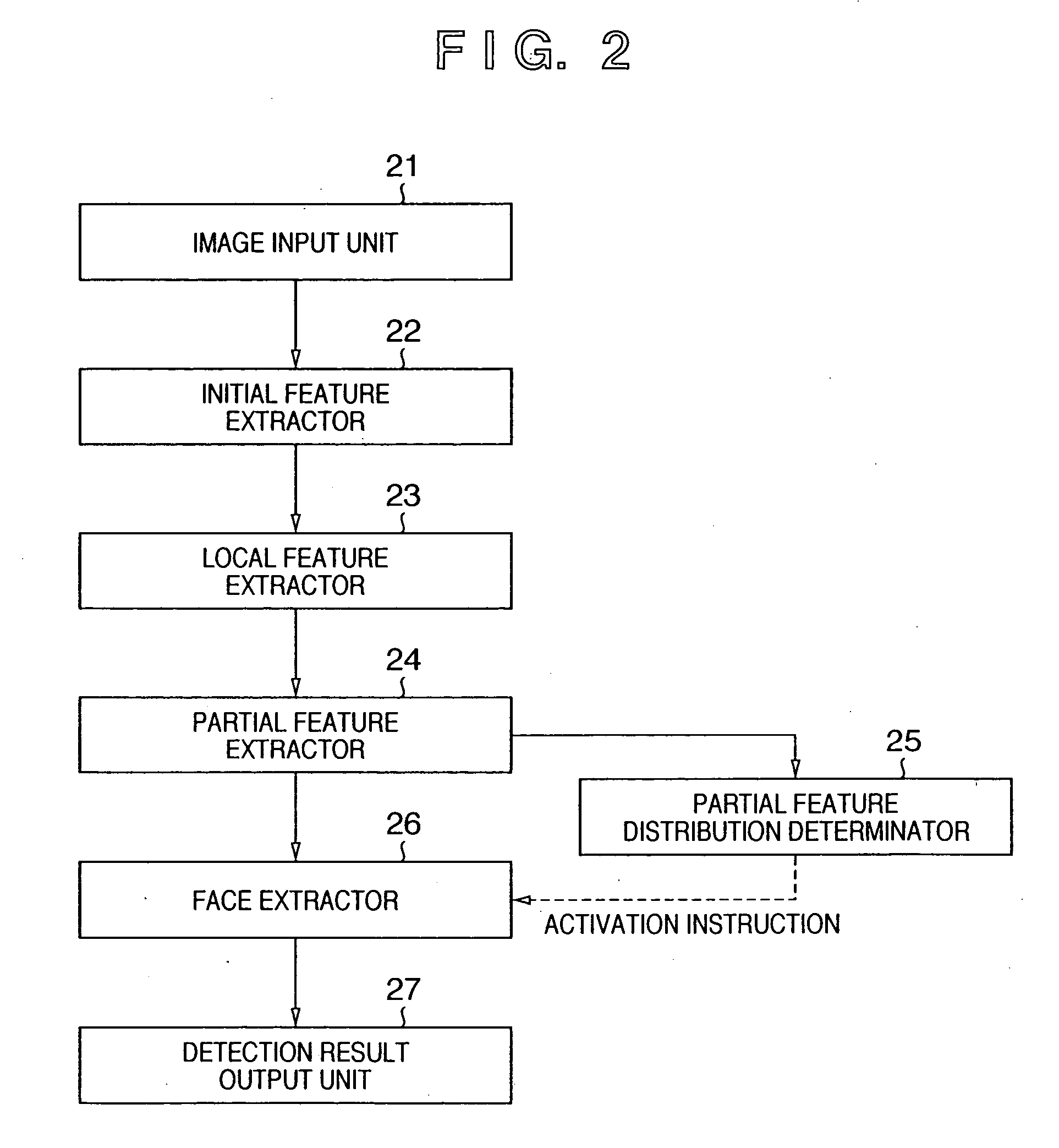

Pattern identification method, apparatus, and program

ActiveUS20060074653A1Reduce processing costsReduce the possibilityCharacter and pattern recognitionSpeech recognitionFeature extractionProcessing cost

Pattern recognition capable of robust identification for the variance of an input pattern is performed with a low processing cost while the possibility of identification errors is decreased. In a pattern recognition apparatus which identifies the pattern of input data from a data input unit (11) by using a hierarchical feature extraction processor (12) which hierarchically extracts features, an extraction result distribution analyzer (13) analyzes a distribution of at least one feature extraction result obtained by a primary feature extraction processor (121). On the basis of the analytical result, a secondary feature extraction processor (122) performs predetermined secondary feature extraction.

Owner:CANON KK

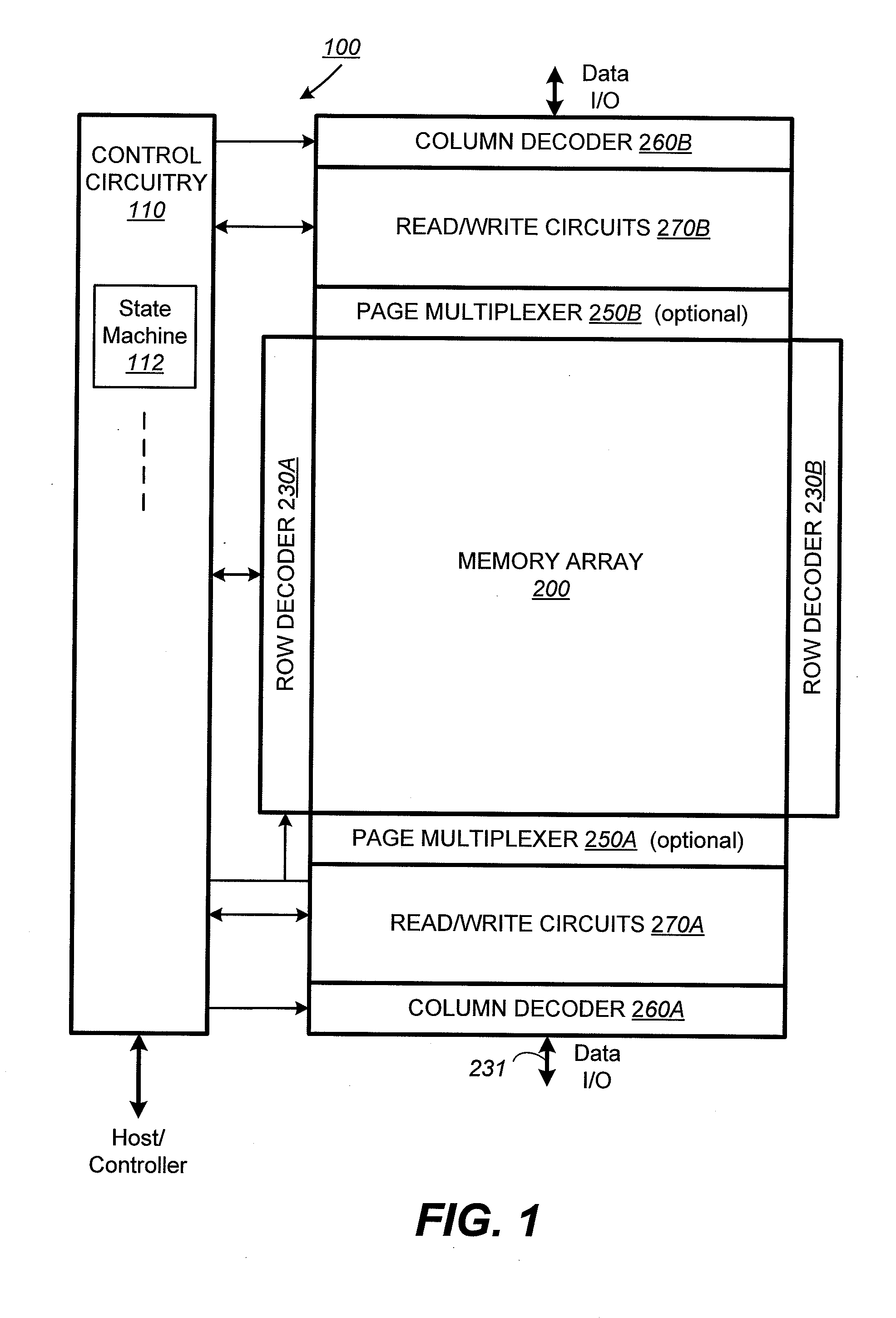

Non-Volatile Memory with Predictive Programming

ActiveUS20080253193A1Improve performanceRead-only memoriesDigital storageCheck pointComputer science

In a nonvolatile memory having an array of memory cells, wherein the memory cells are individually programmable to one of a range of threshold voltage levels, there is provided a predictive programming mode in which a predetermined function predicts what programming voltage level needs to be applied in order to program a given memory cell to a given target threshold voltage level. In this way, no verify operation needs to be performed, thereby greatly improving the performance of the programming operation. In a preferred embodiment, the predetermined function is linear and is calibrated for each memory cell under programming by one or more checkpoints. A checkpoint is a set of coordinates on the predetermined function determined by a conventional programming mode employing alternating program and verify operations.

Owner:SANDISK TECH LLC

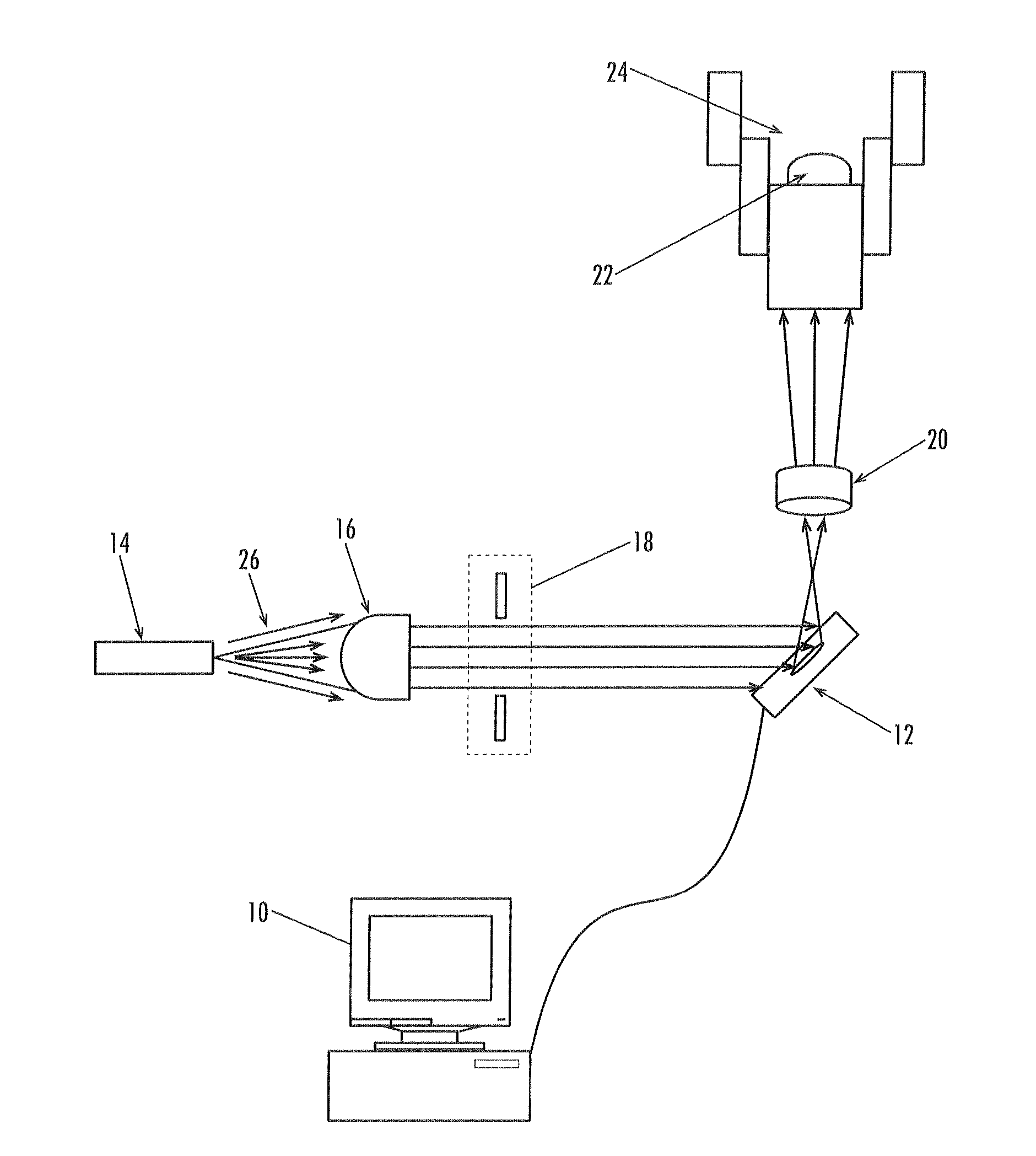

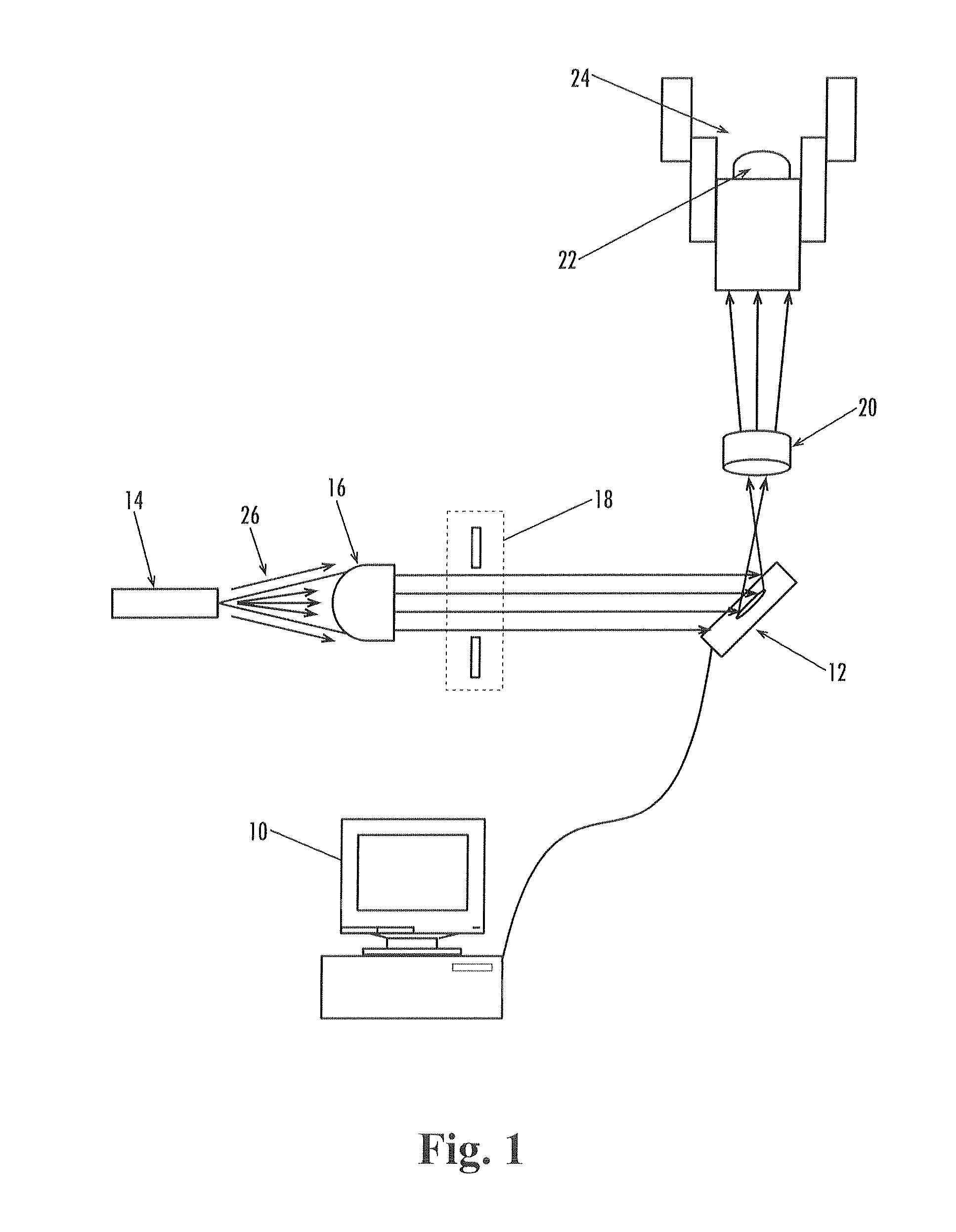

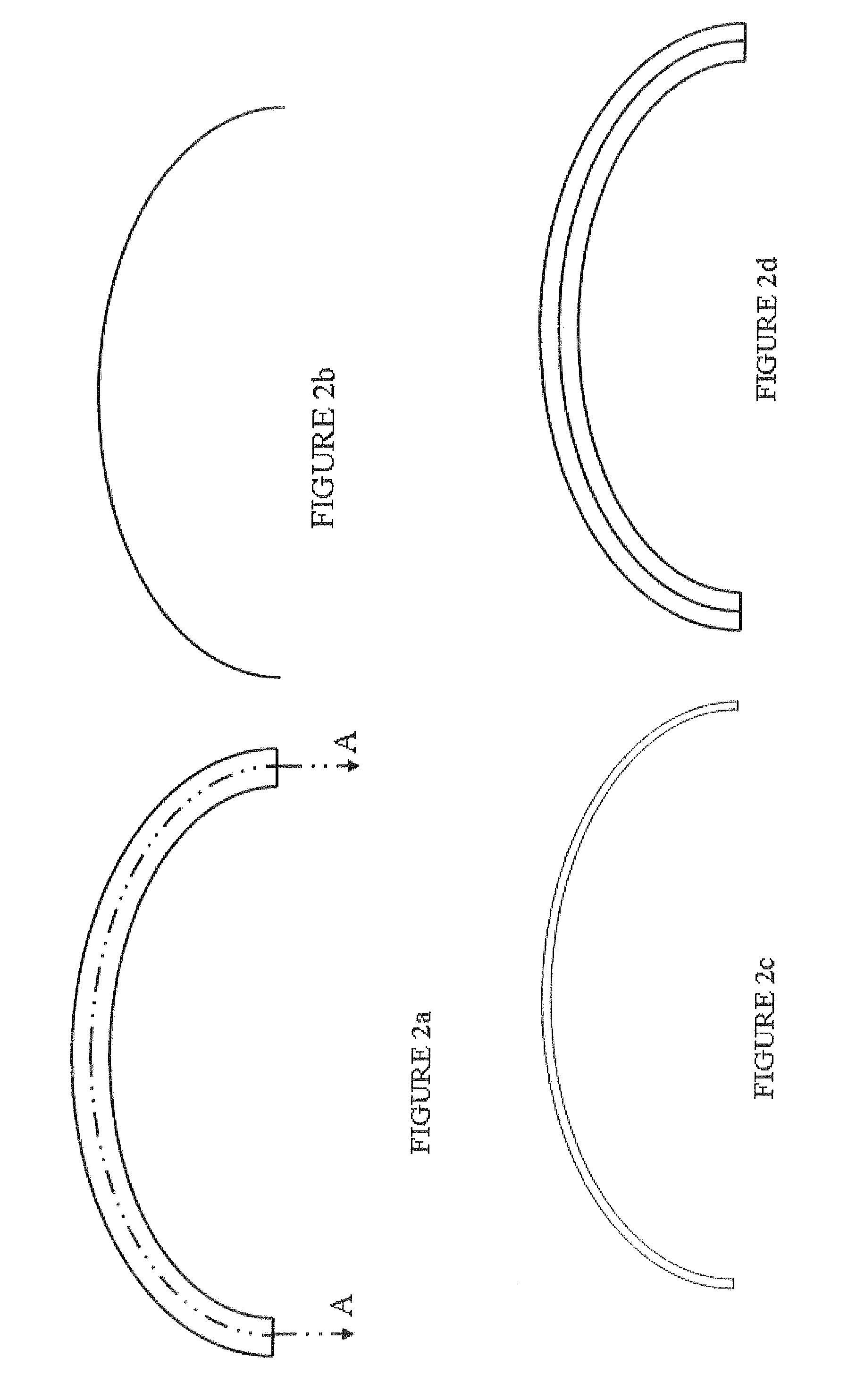

Method for Making Ophthalmic Devices Using Single Mold Stereolithography

InactiveUS20090250828A1Easy to adaptCost-effective mannerAdditive manufacturing apparatusOptical articlesMathematical modelLens materials

A method for manufacturing an ophthalmic lens comprising introducing a volume of photocurable lens material into a container, wherein said container comprises a mold surface. The method further comprises creating a digital 3-D mathematical model defining corrective needs of an eye and projecting programmed patterns of UV light through said mold via a pattern generator, wherein said programmed patterns of UV light cure said photocurable lens material into a lens shape defined by said mold surface and said digital model.

Owner:NOVARTIS AG +1

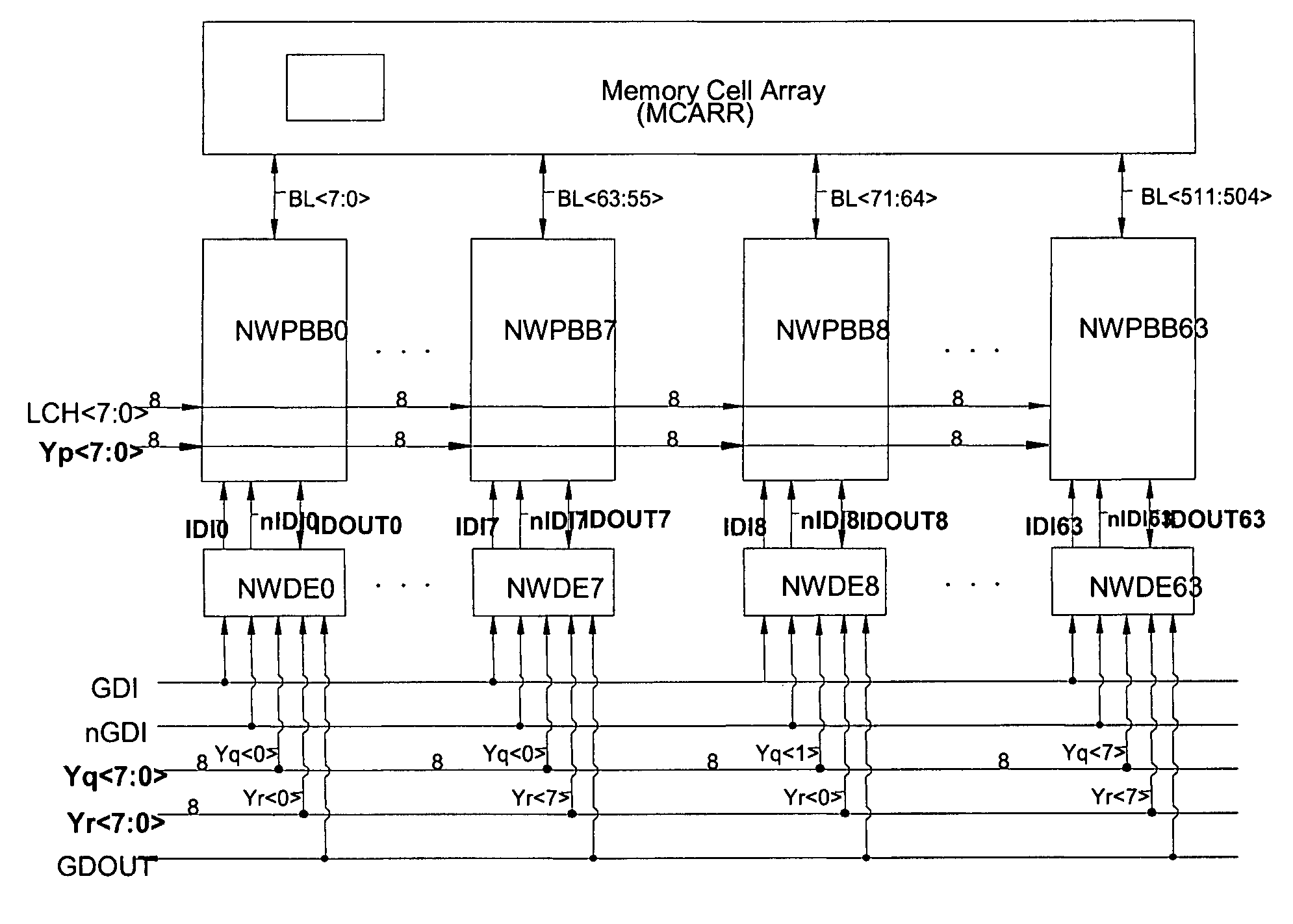

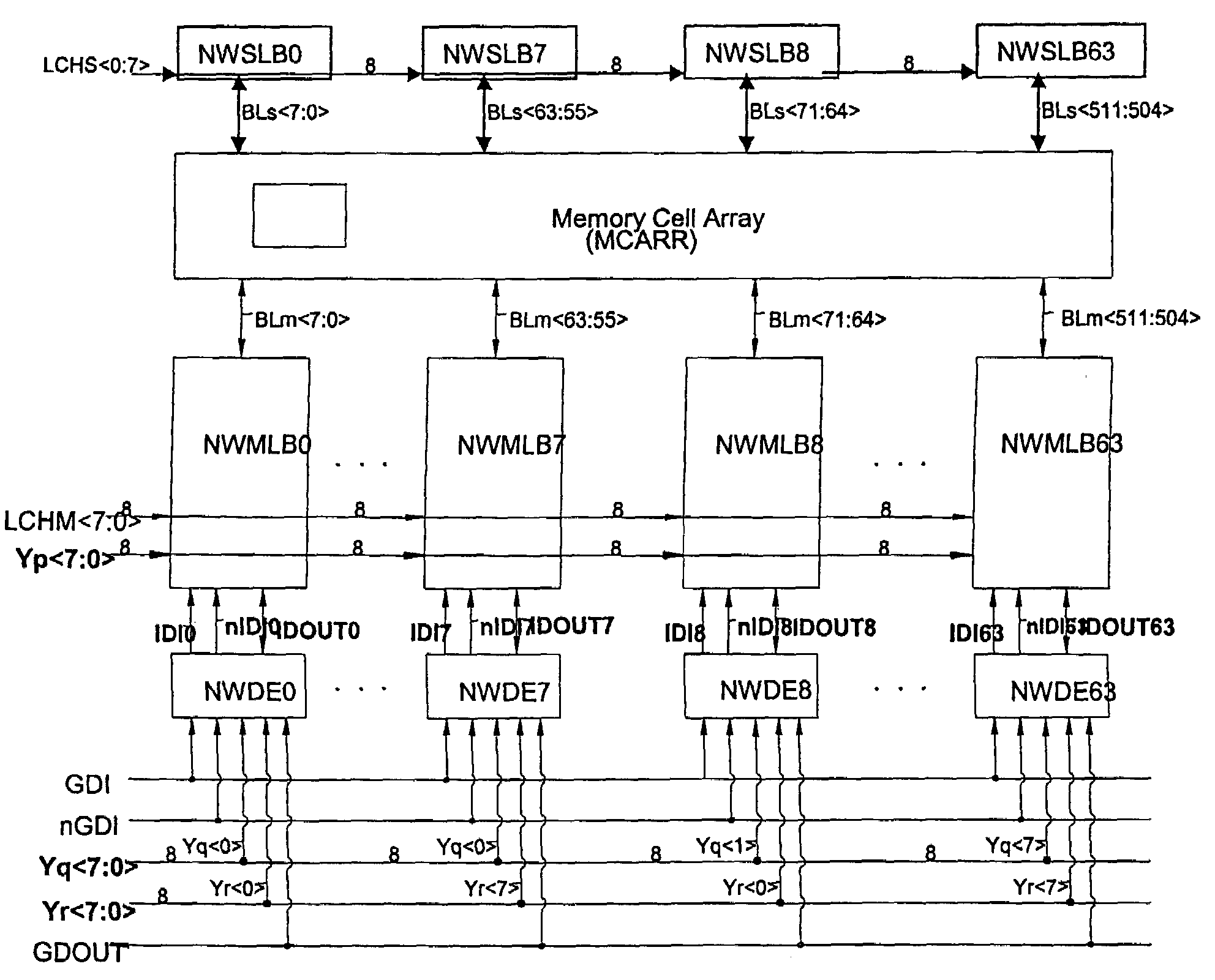

Page-buffer and non-volatile semiconductor memory including page buffer

In one aspect, a non-volatile memory device is provided which is operable in a programming mode and a read mode. The memory device includes a memory cell array which includes a plurality of non-volatile memory cells, a plurality of word lines, and a plurality of bit lines. The memory device further includes an internal data output line for outputting data read from the bit lines of the memory array, and a page buffer operatively connected between a bit line of the memory cell array and the internal data output line. The page buffer includes a sense node which is selectively connected to the bit line, a latch circuit having a latch node which is selectively connected to the sense node, a latch input path which sets a logic voltage of the latch node in the programming mode and the read mode, and a latch output path which is separate from the latch input path and which sets as logic voltage of the internal date output line according to the logic voltage of the latch node.

Owner:SAMSUNG ELECTRONICS CO LTD

Page buffer and multi-state nonvolatile memory device including the same

According to one aspect, a memory cell array includes a bit line connected to a plurality of nonvolatile memory cells, where the nonvolatile memory cells are selectively programmable in any one of at least first, second, third and fourth threshold voltage states, and where the first, second, third and fourth threshold voltage states correspond to four different data values defined by first and second bits. A page buffer circuit stores a logic value as main latch data and is responsive to a main latch signal to selectively flip the logic value of the main latch data according to a voltage level of the bit line. A sub-latch circuit stores a logic value as sub-latch data and is responsive to a sub-latch signal to selectively flip the logic value of the sub-latch data according to the voltage level of the bit line. The memory device is operable in a read mode which reads the threshold voltage state of the non-volatile memory cells and a programming mode which programs the threshold voltage state of the non-volatile memory cells, wherein the page buffer circuit is selectively responsive to the sub-latch data to inhibit flipping of the logic value of the main latch data in the programming mode.

Owner:SAMSUNG ELECTRONICS CO LTD

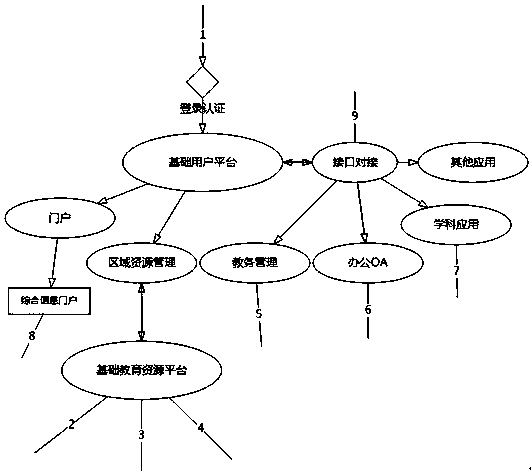

Regional-education cloud resource sharing platform

InactiveCN107784489AImprove efficiencyAddress imbalancesOffice automationService systemProgramming patterns

The invention relates to a regional-education cloud platform and an education method. The regional-education cloud platform mainly comprises a comprehensive information portal, a teacher-student management space, a cloud platform application center, a regional big data analysis platform, an integration system set, a public cloud resource library and a regional resource converging manager. The whole platform system is of an SOA distributed architecture based on a cloud architecture mode and adopts a B / S development programming mode, and all parts are set or installed on a hardware computer of aplatform so as to form an organic integer and are in electrical connection or software connection. A local server does not need to be established by each school during the regional-education cloud construction, and all data are acquired from a cloud end, so that the cost for deploying local server of the scheme is omitted, the construction efficiency is increased, the expense of information fundis saved, meanwhile, the sharing and common construction of localized characteristic teaching services and resources are provided, and an educational informationalized public service system covering the local region is formed.

Owner:兰州乐智教育科技有限责任公司

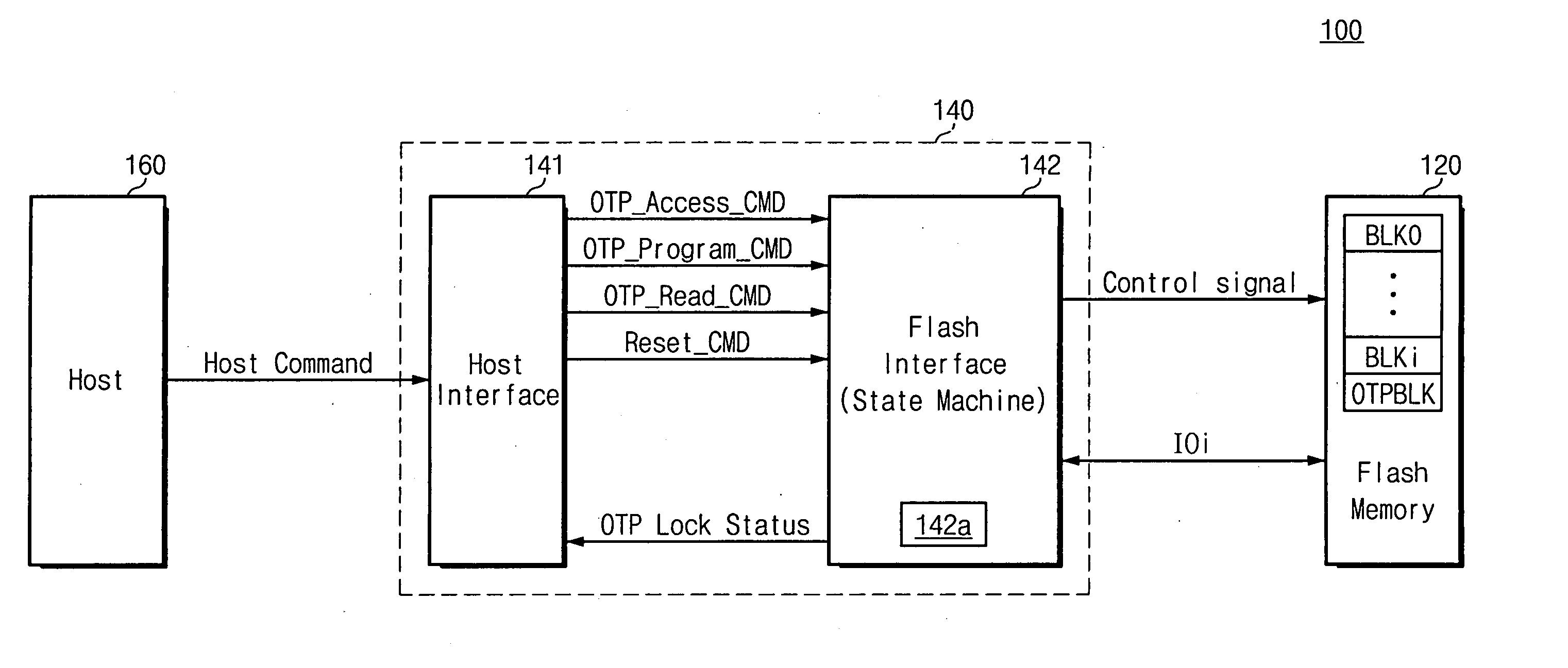

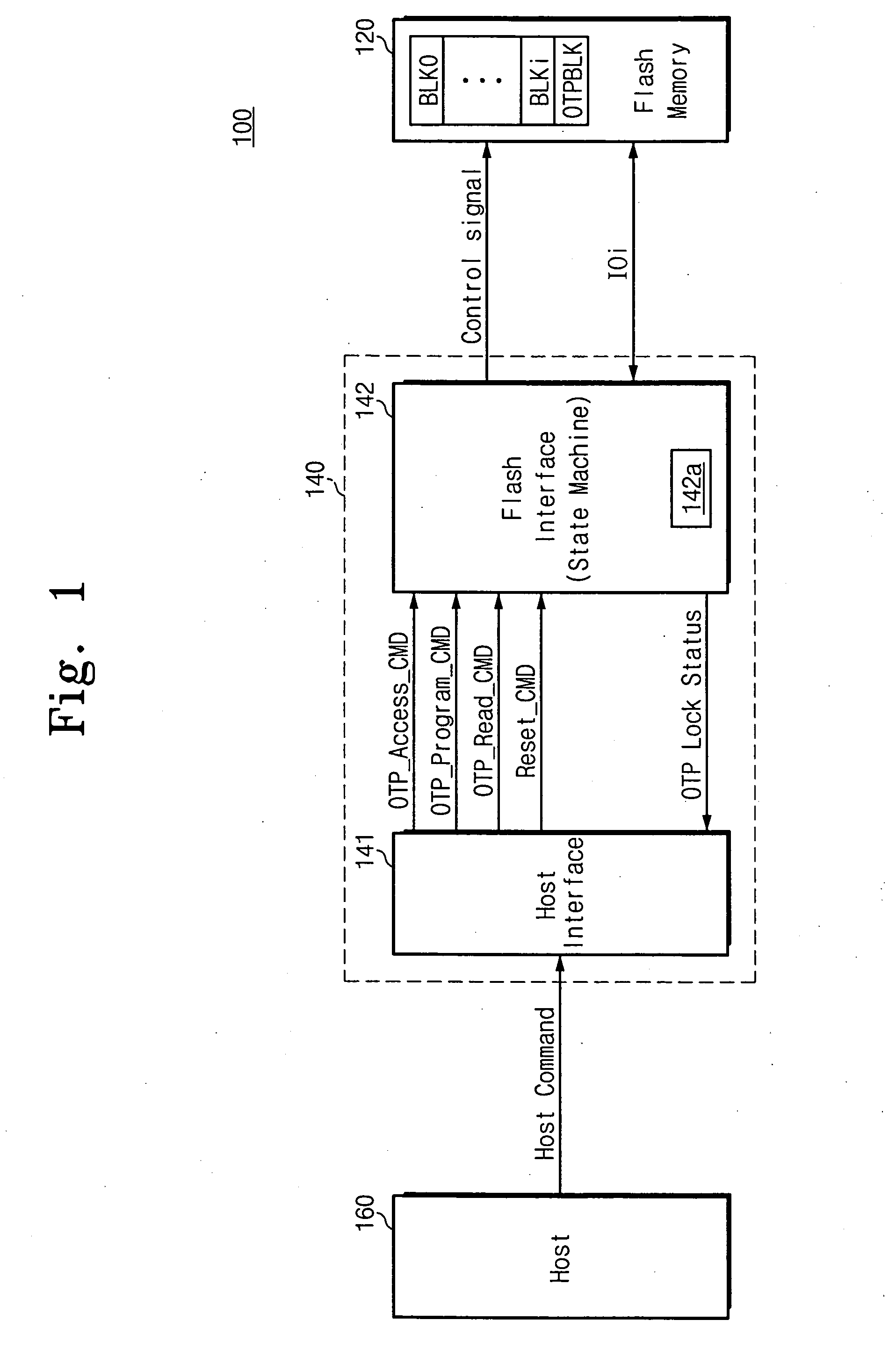

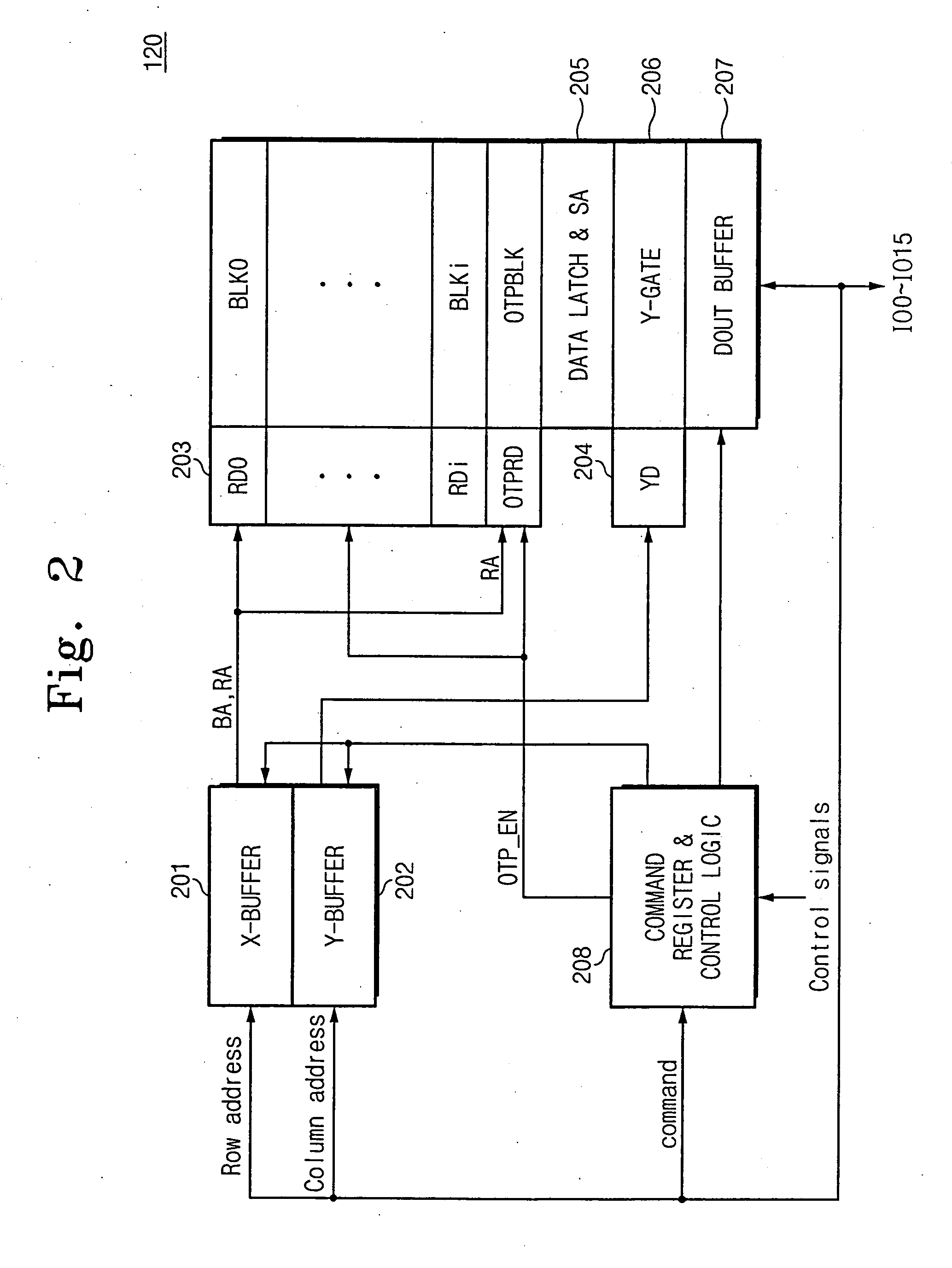

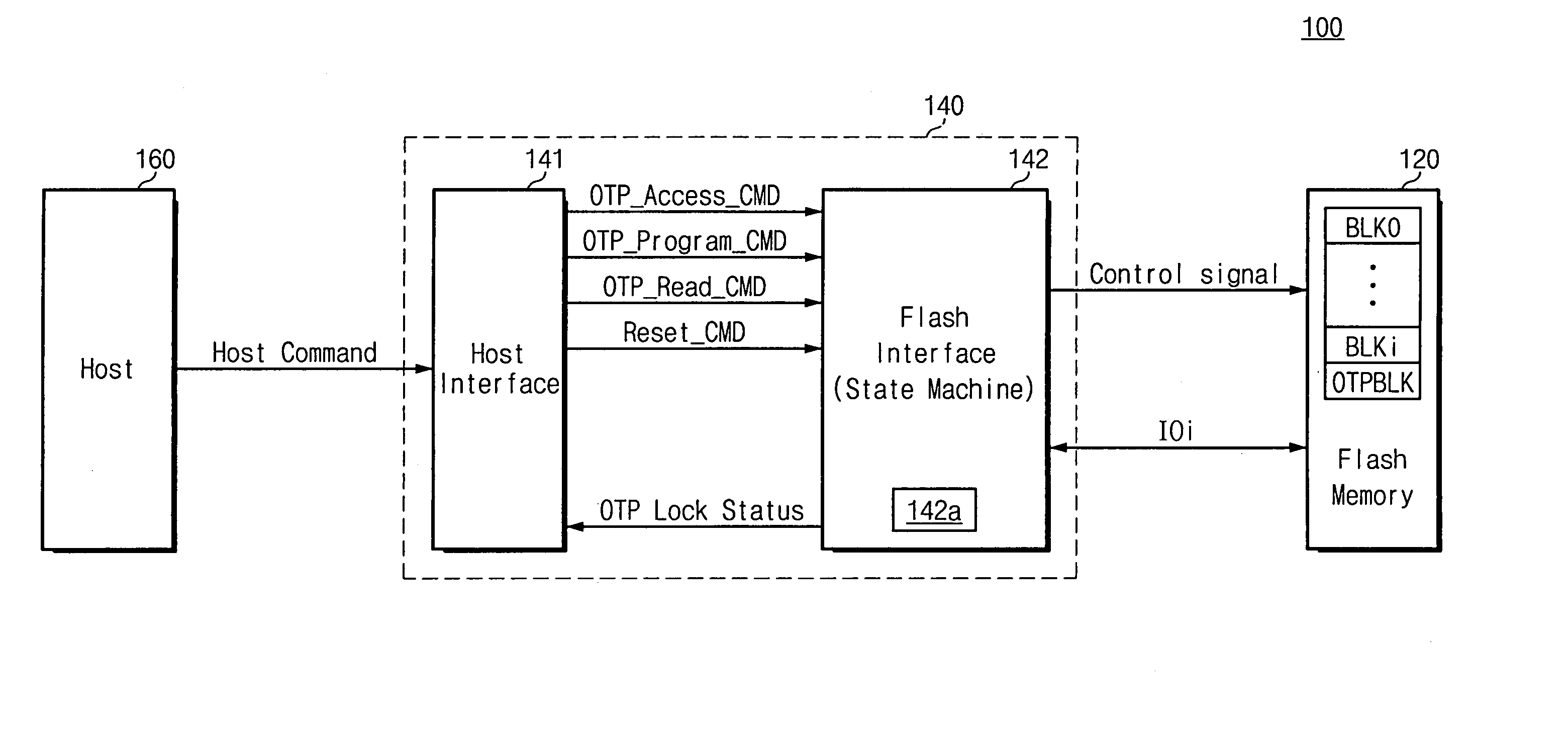

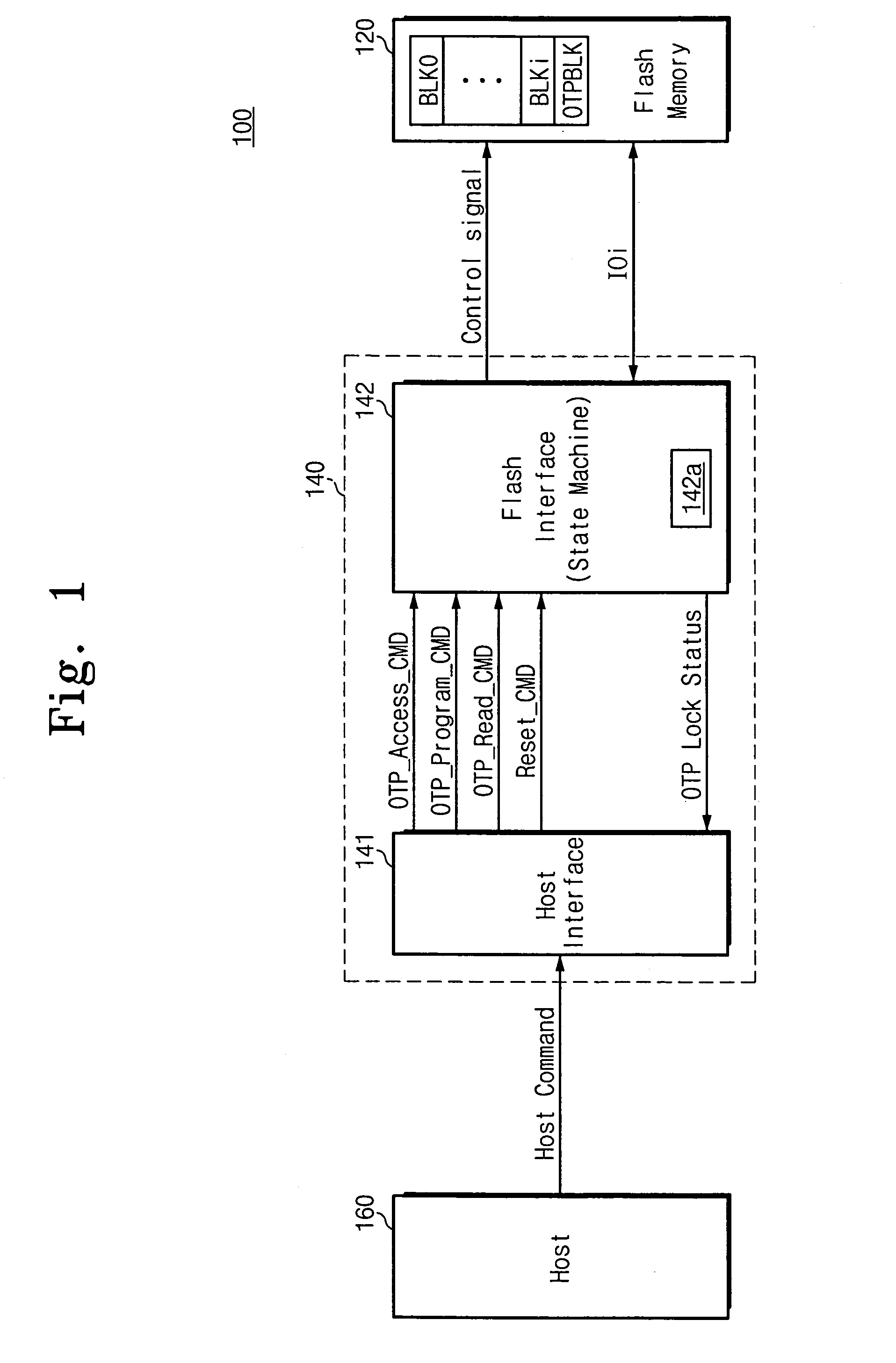

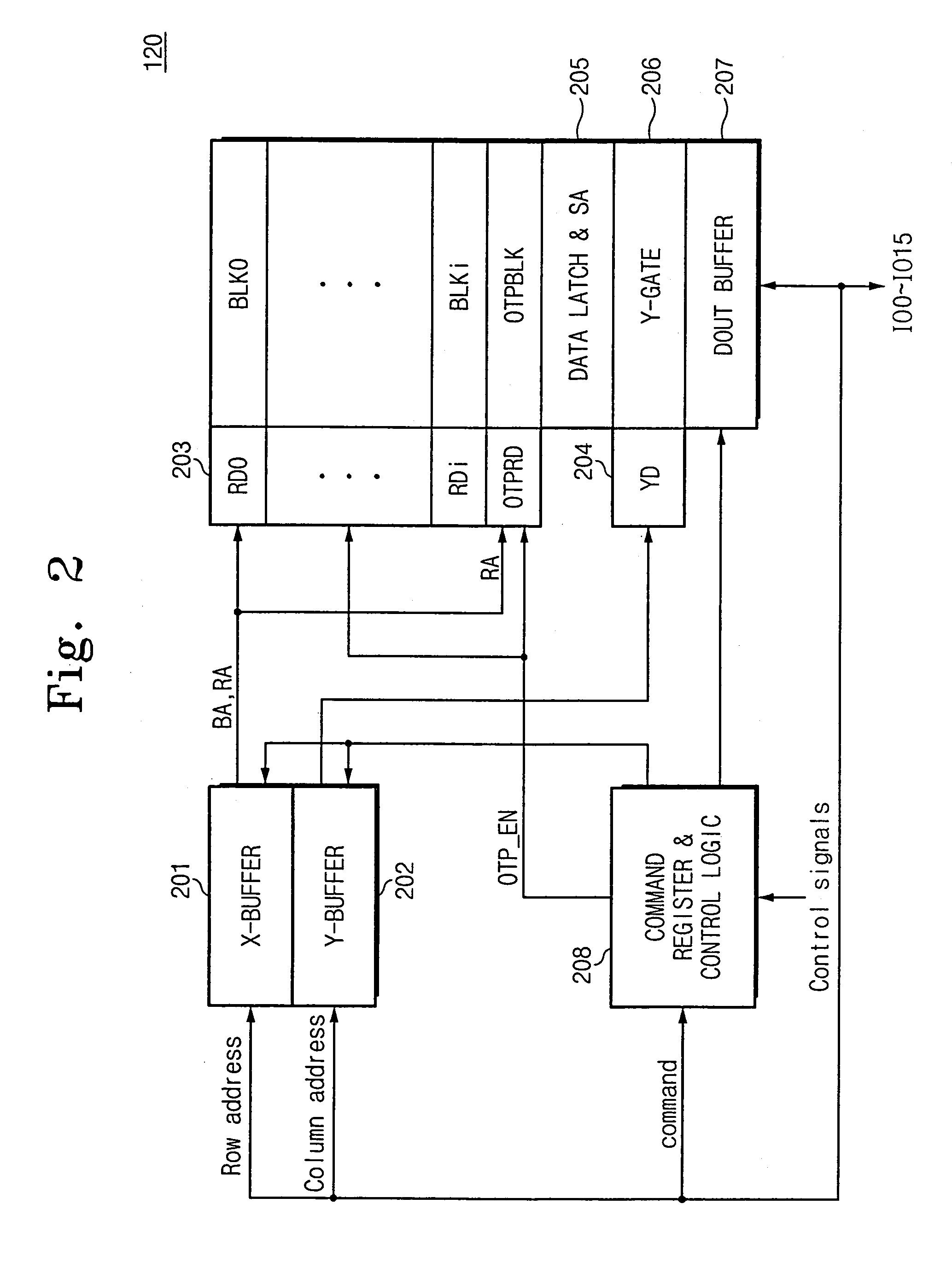

Memory system having flash memory where a one-time programmable block is included

InactiveUS20050105331A1Cut off accessRead-only memoriesDigital storageData informationComputer science

A memory system includes a flash memory device and an interface device. The flash memory device includes a one-time programmable block where protection data information is stored in a predetermined region, and the interface device includes a register for storing one-time programmable lock status information to indicate whether the one-time programmable block is programmed. When a program / erase command is applied externally in a one-time programmable mode, the interface device having the one-time programmable lock status information indicates whether the one-time programmable block is programmed. If the one-time programmable lock status information indicates that the one-time programmable block is programmed, the interface device cuts off an external access to the one-time programmable block.

Owner:SAMSUNG ELECTRONICS CO LTD

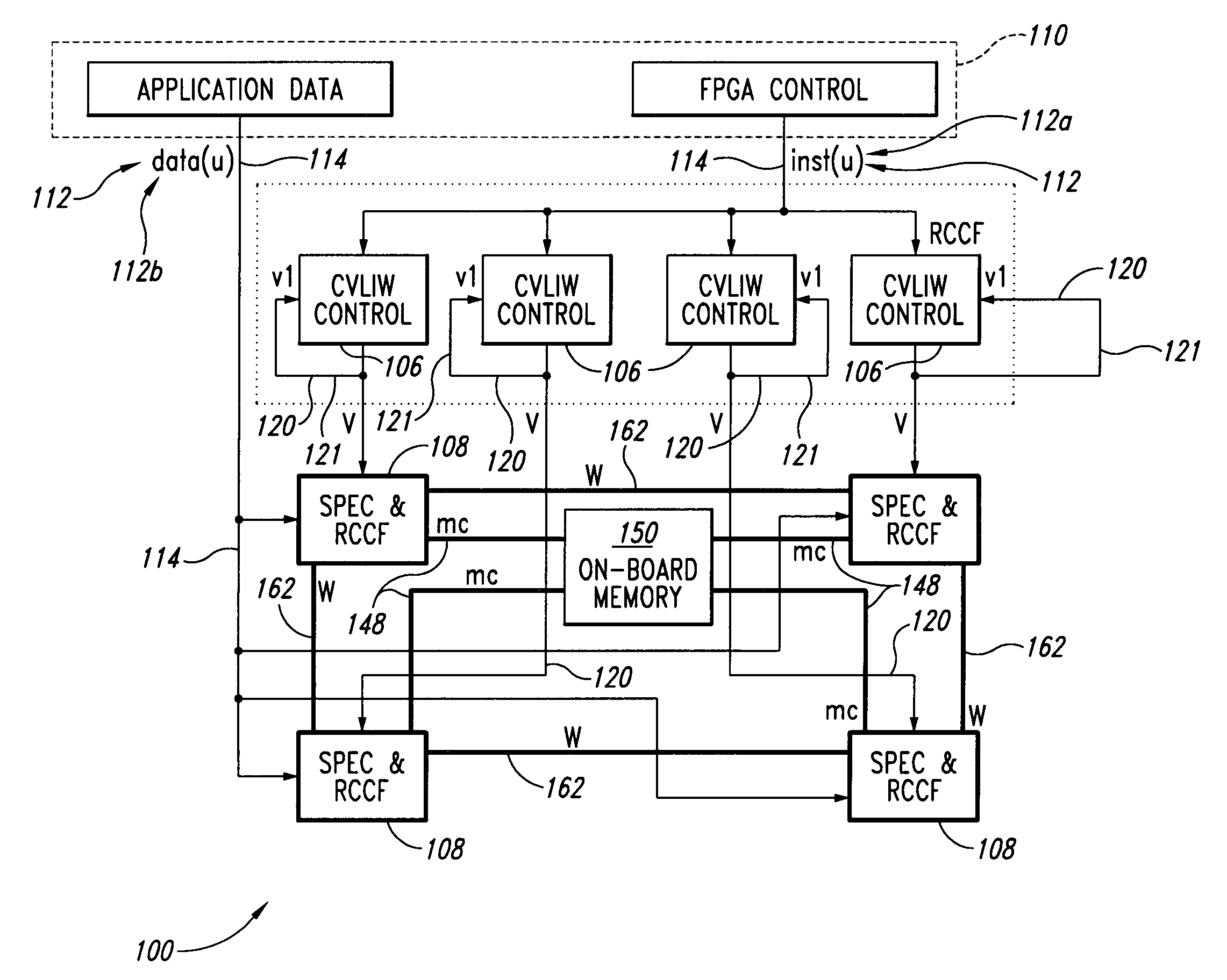

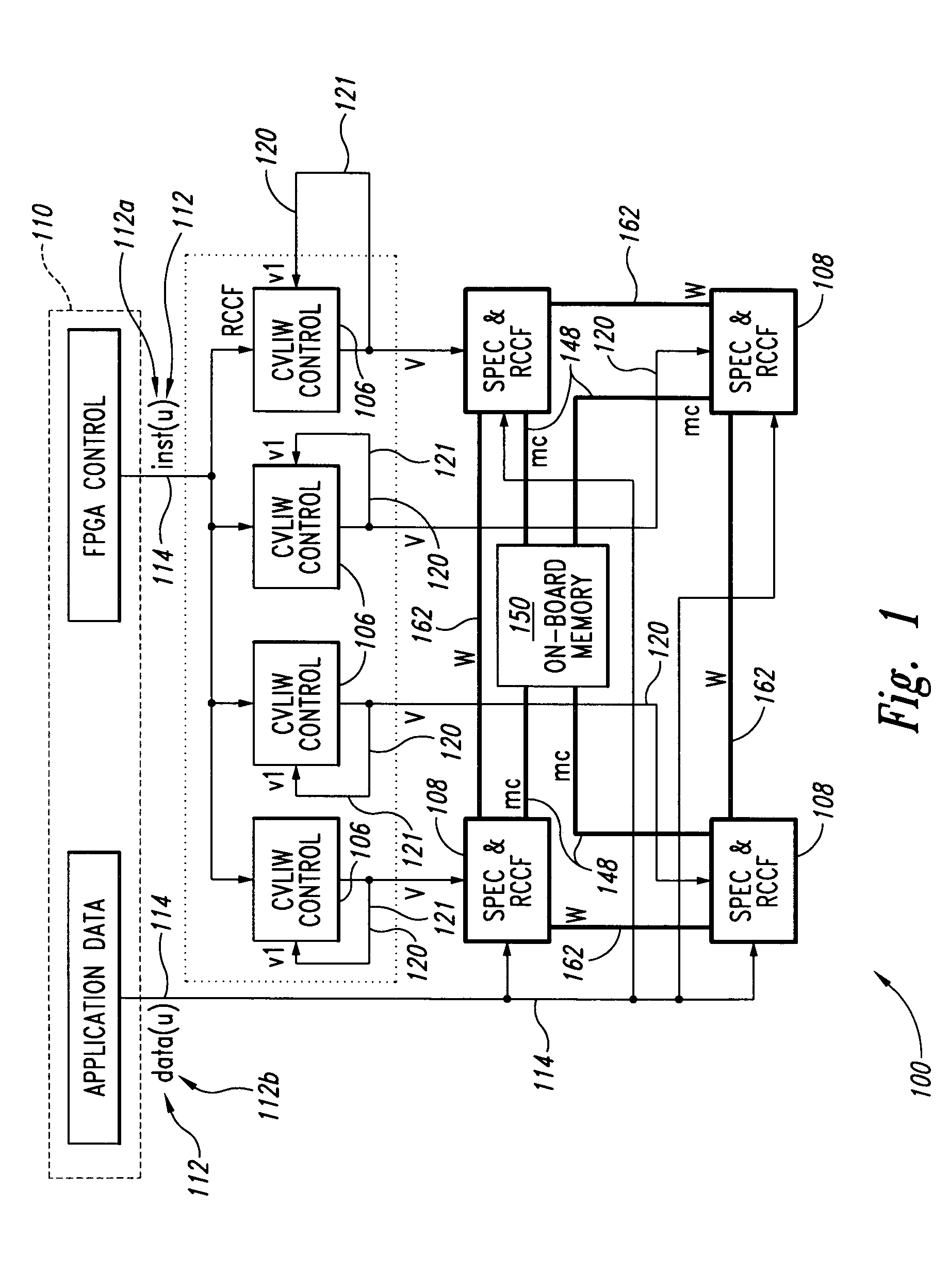

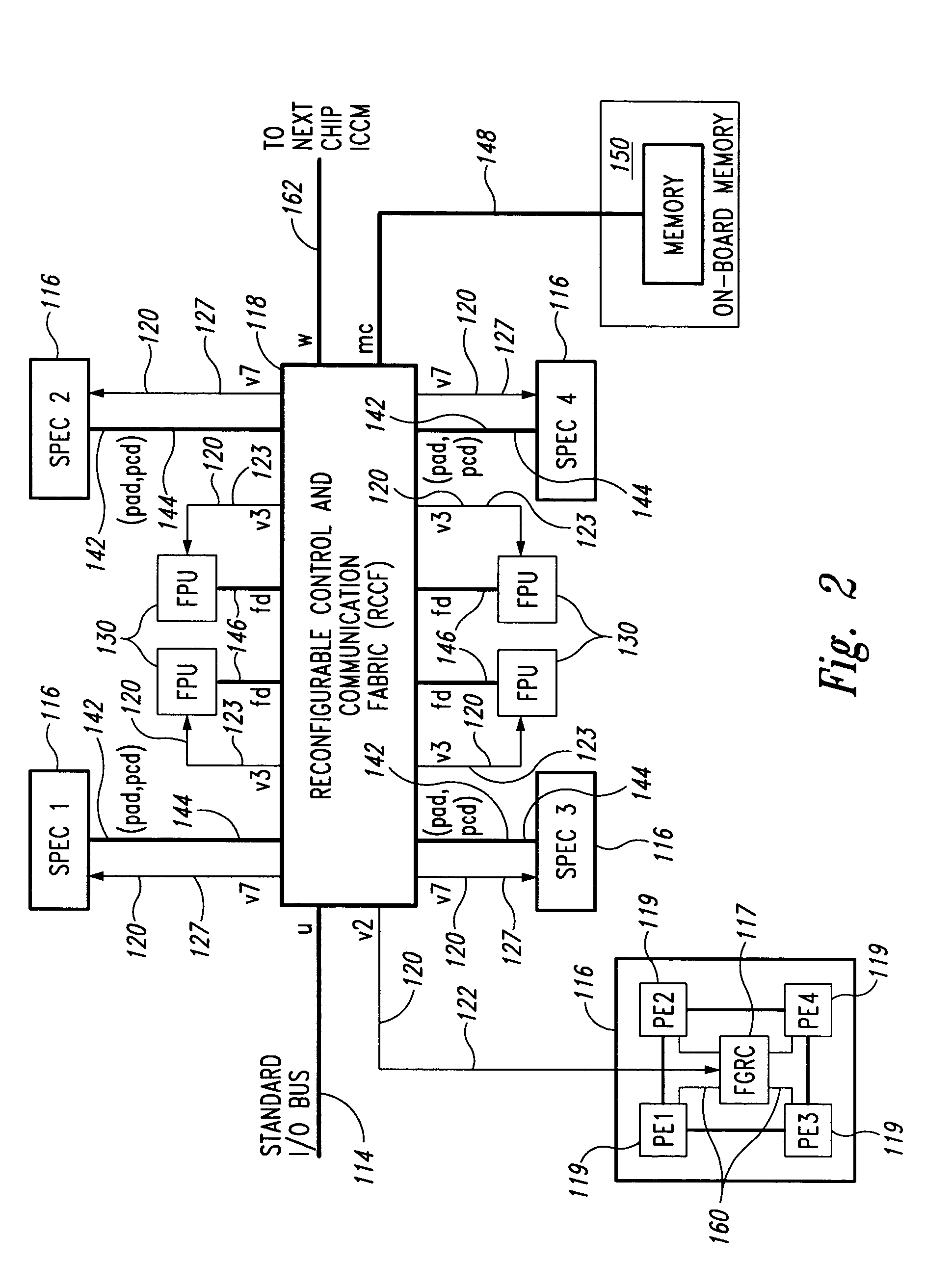

Super-reconfigurable fabric architecture (SURFA): a multi-FPGA parallel processing architecture for COTS hybrid computing framework

InactiveUS7299339B2Single instruction multiple data multiprocessorsMemory adressing/allocation/relocationBus interfaceProcessing element

A field programmable gate array includes a virtual bus interface that receives a control word from a host processor over a standard I / O bus. A configurable very long instruction word (VLIW) controller receives the control word via virtual bus interface signals mapped from the virtual bus interface. A reconfigurable communication and control fabric controls the data paths and programming modes of single instruction-multiple data (SIMD) processing element cells. The configurable VLIW controller has an interface with the reconfigurable communication and control fabric. SIMD processing element cells are controlled by the configurable VLIW controller through the reconfigurable communication and control fabric via the interface.

Owner:THE BOEING CO

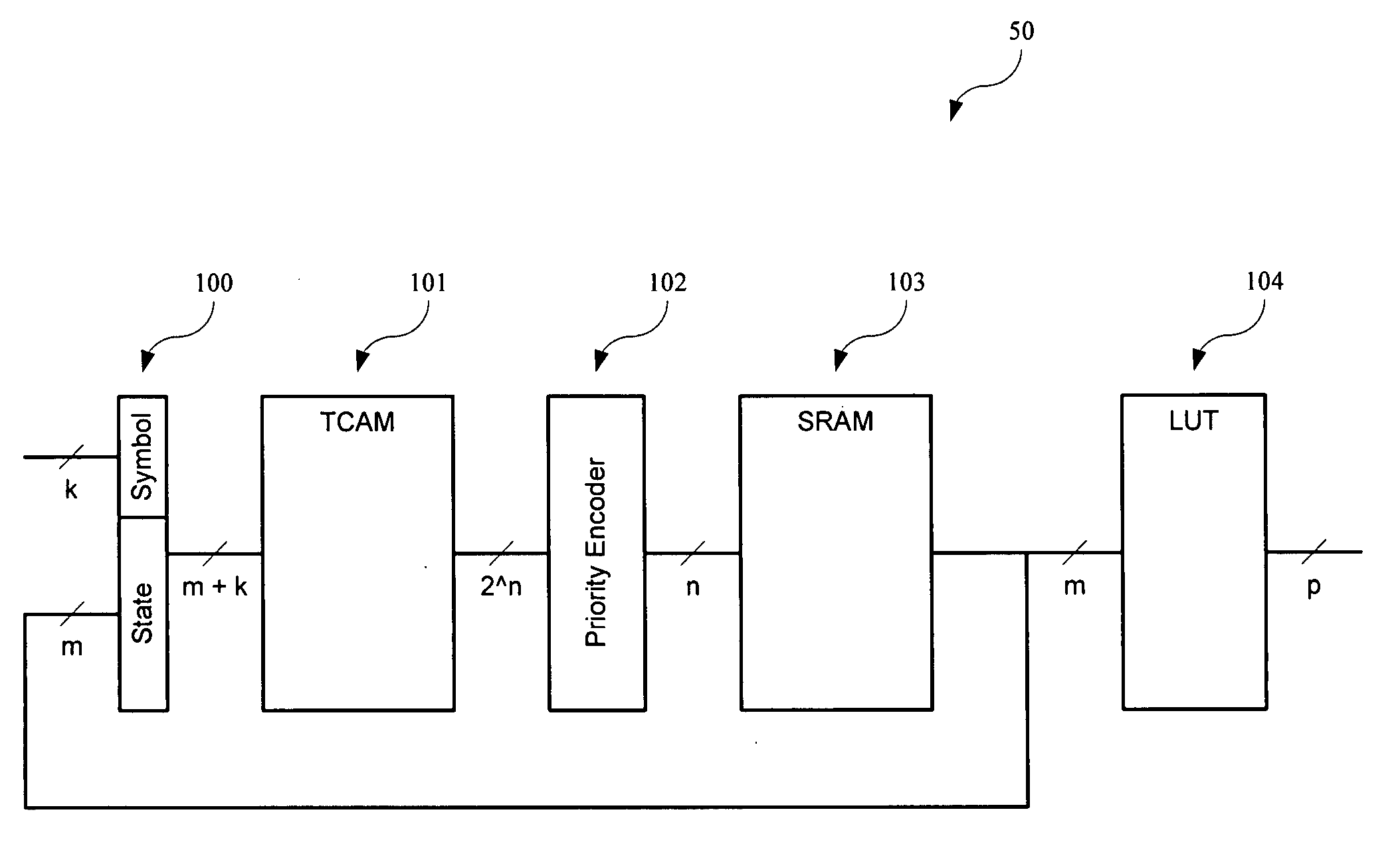

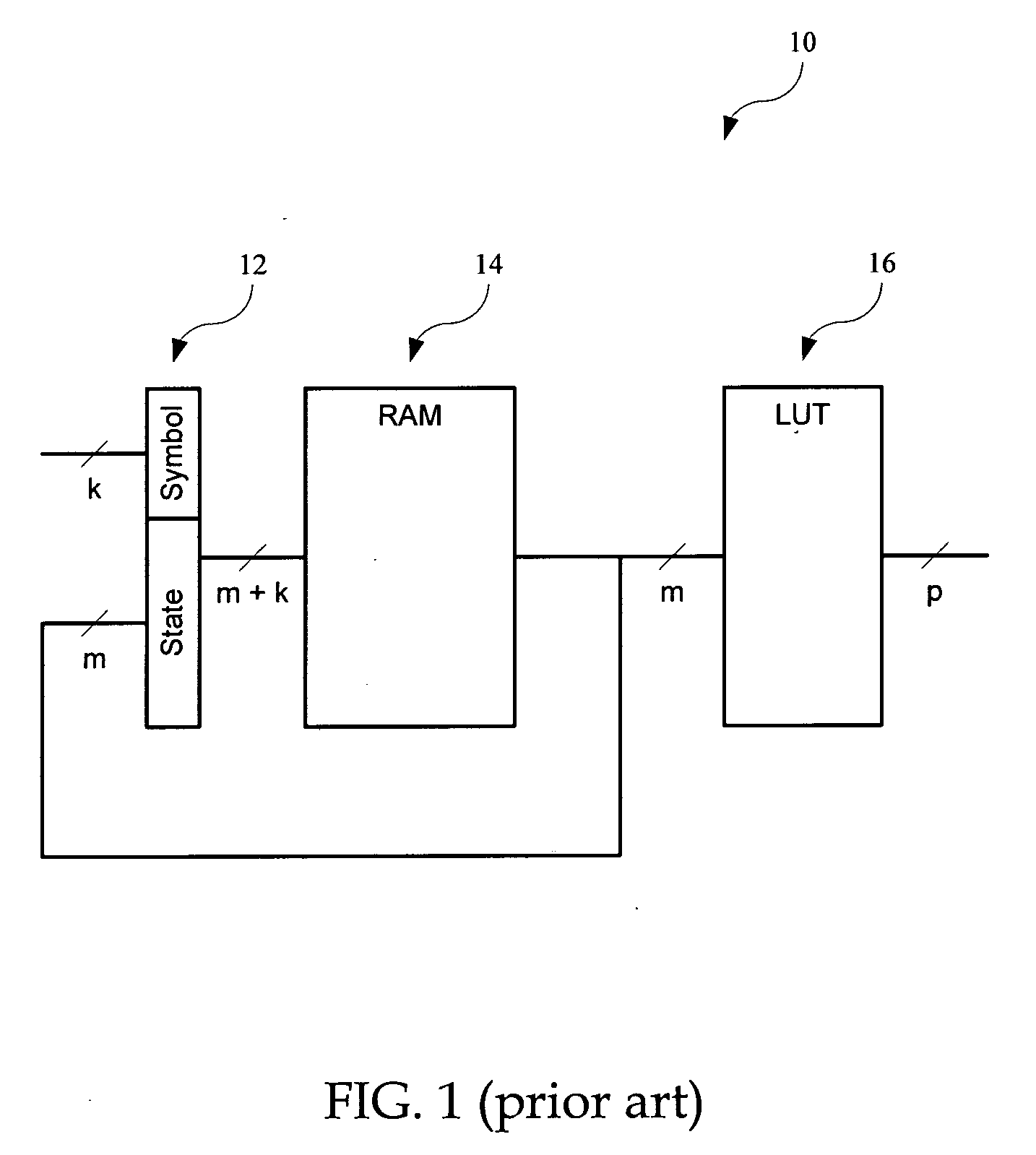

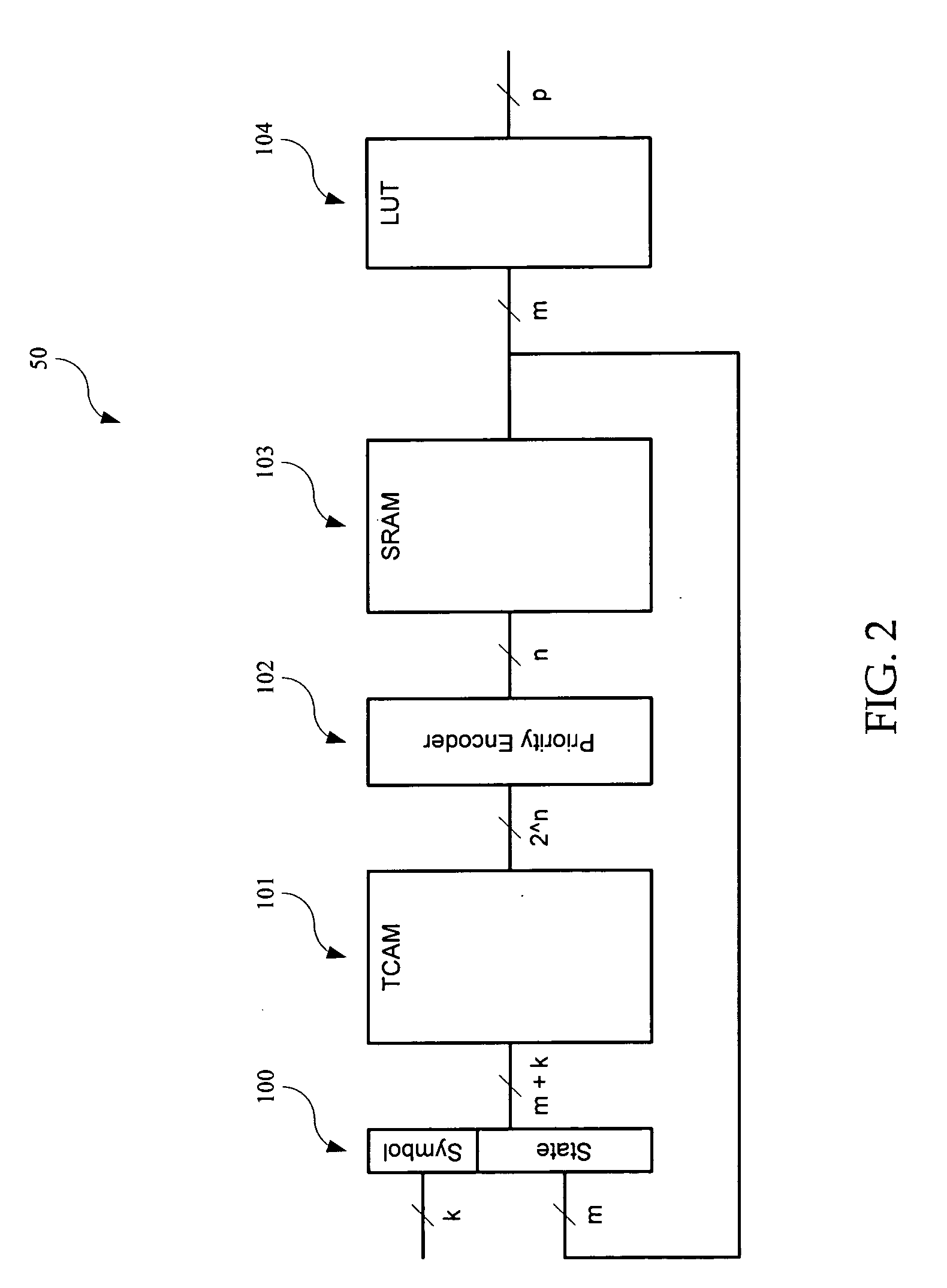

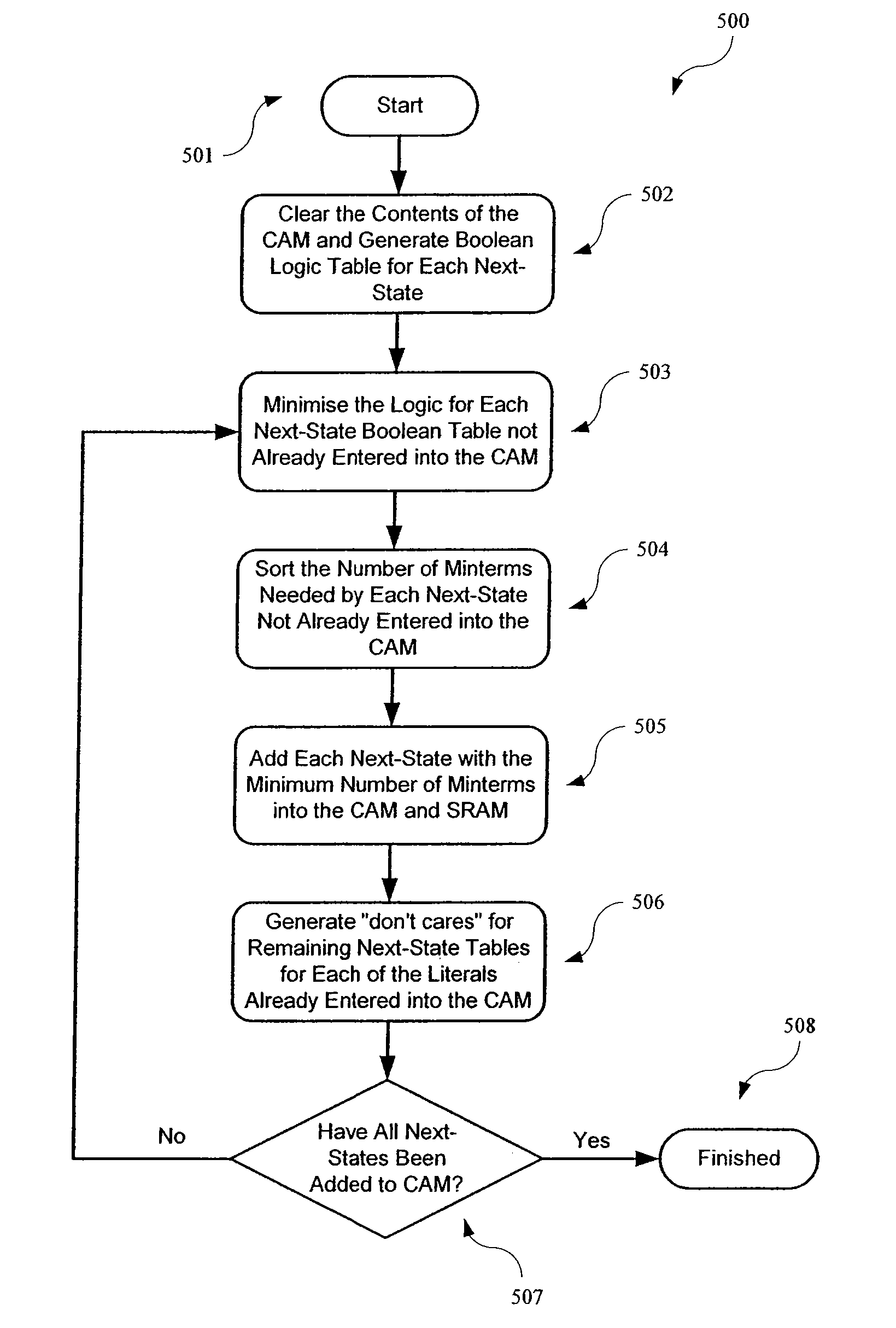

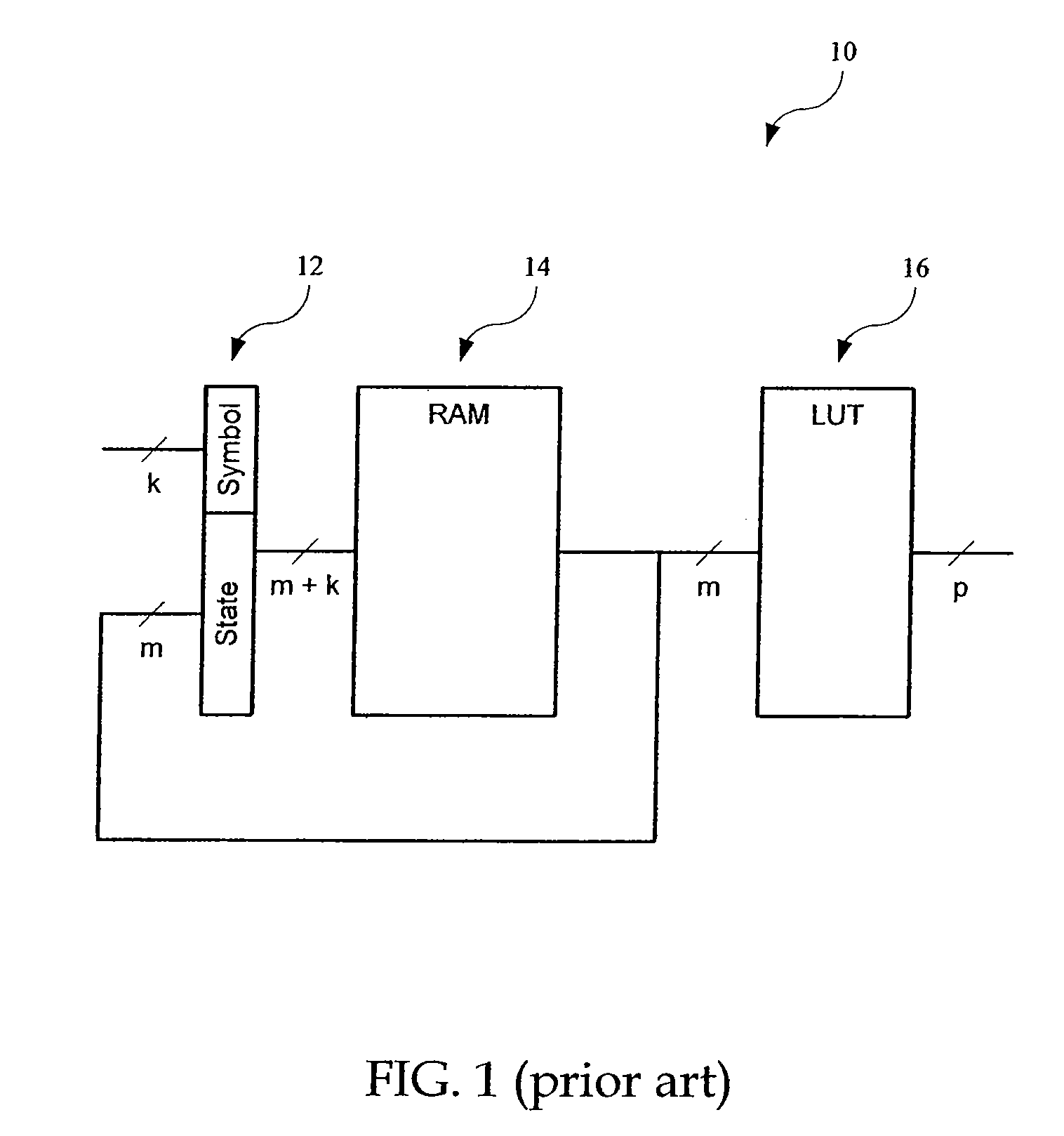

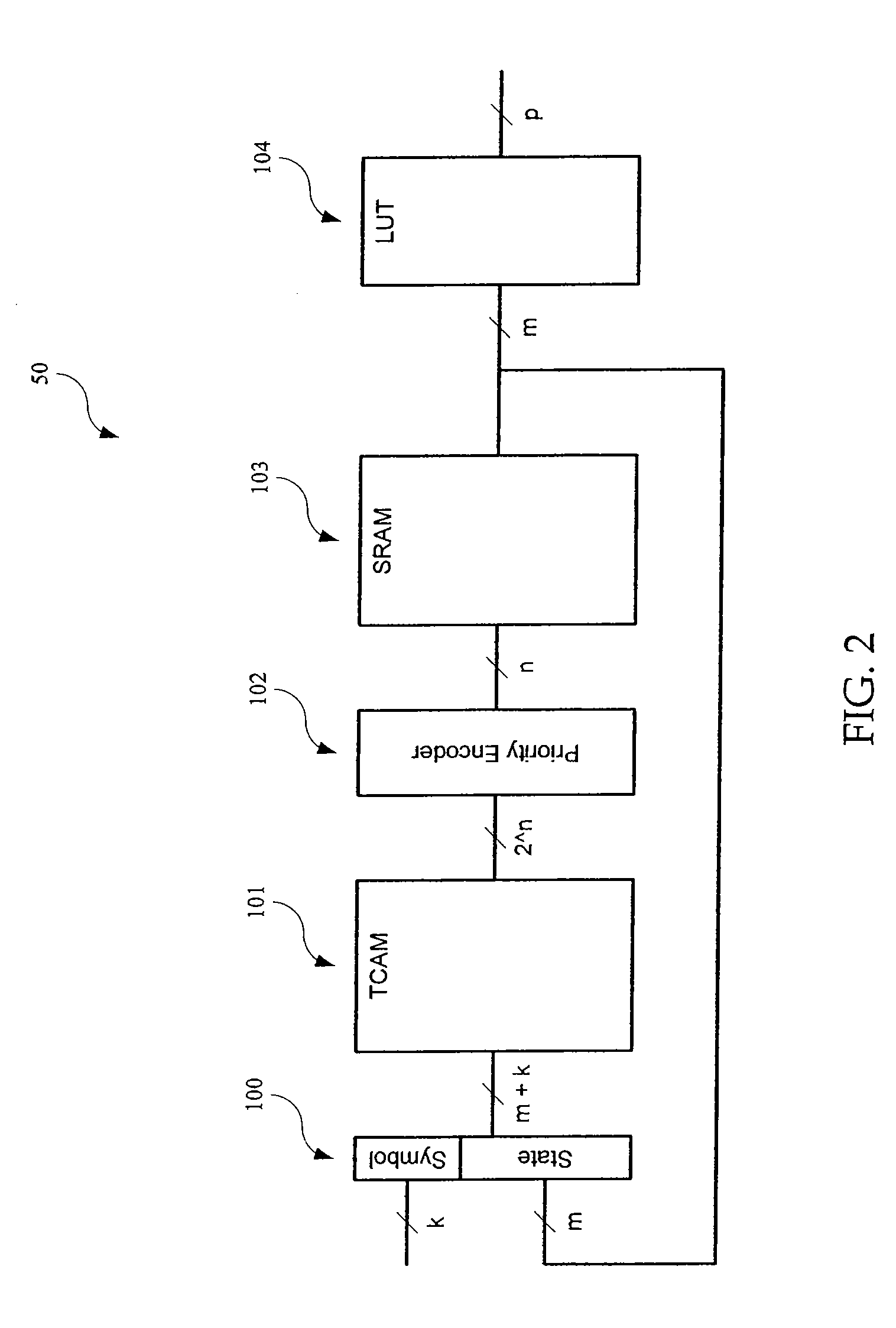

Apparatus and method for memory efficient, programmable, pattern matching finite state machine hardware

InactiveUS20060120137A1Reduce memory requirementsMinimize the numberComputer security arrangementsData switching by path configurationStatic random-access memoryPattern matching

A programmable finite state machine (FSM) includes, in part, first and second memories, and a selection circuit coupled to each of the memories. Upon receiving a (k+m)-bit word representative of the k-bit input symbol and the m-bit current state, the first memory supplies one ore more matching transition rules stored therein. The selection circuit selects the most specific of the supplied rules. The transition rules are stored in the first memory in a ranking order of generality. The second memory receives the selected transition rule and supplies the next state of the FSM. The first memory may be a ternary content addressable memory and the second memory may be a static random access memory. The contents of both the content addressable memory and the static random memory is determined by an algorithm which minimizes the number of terms required to represent the next-state transition functions.

Owner:INTEL CORP +1

Yarn Feed System for Tufting Machines

InactiveUS20060272564A1Easy to controlImprove precisionTufting apparatusDigital differential analysersYarnEngineering

A yarn feed system, enabling the control of individual yarns to the needles of a tufting machine, and which system can be manufactured as a substantially standardized unit or attachment that can be removably mounted to a tufting machine. The yarn feed unit includes a series of yarn feed devices for feeding each of the yarns to the needles of the tufting machine, and a series of yarn feed controllers that monitor and control the operation of the yarn feed devices to control the feeding of the yarns to the needles according to programmed pattern instructions.

Owner:CARD MONROE

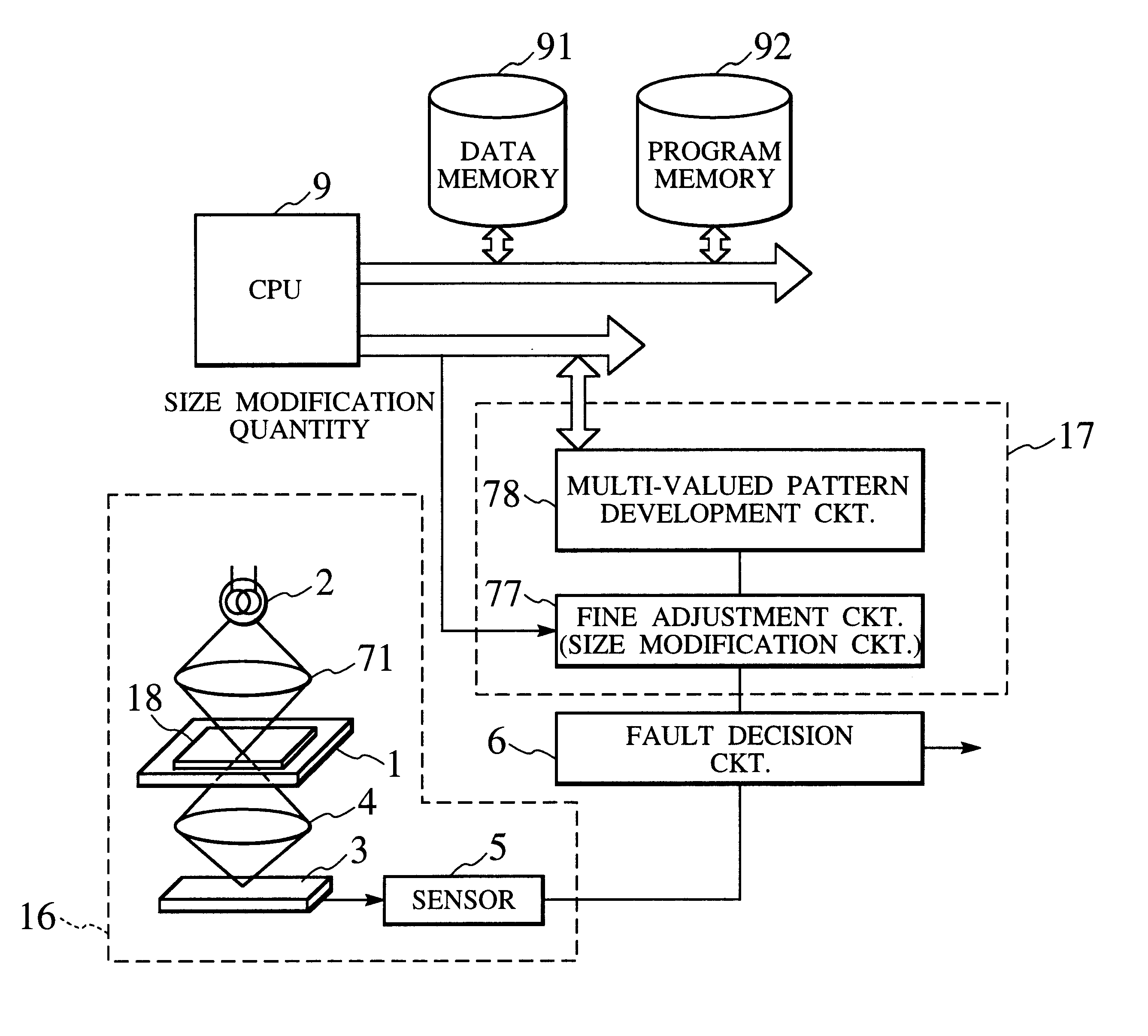

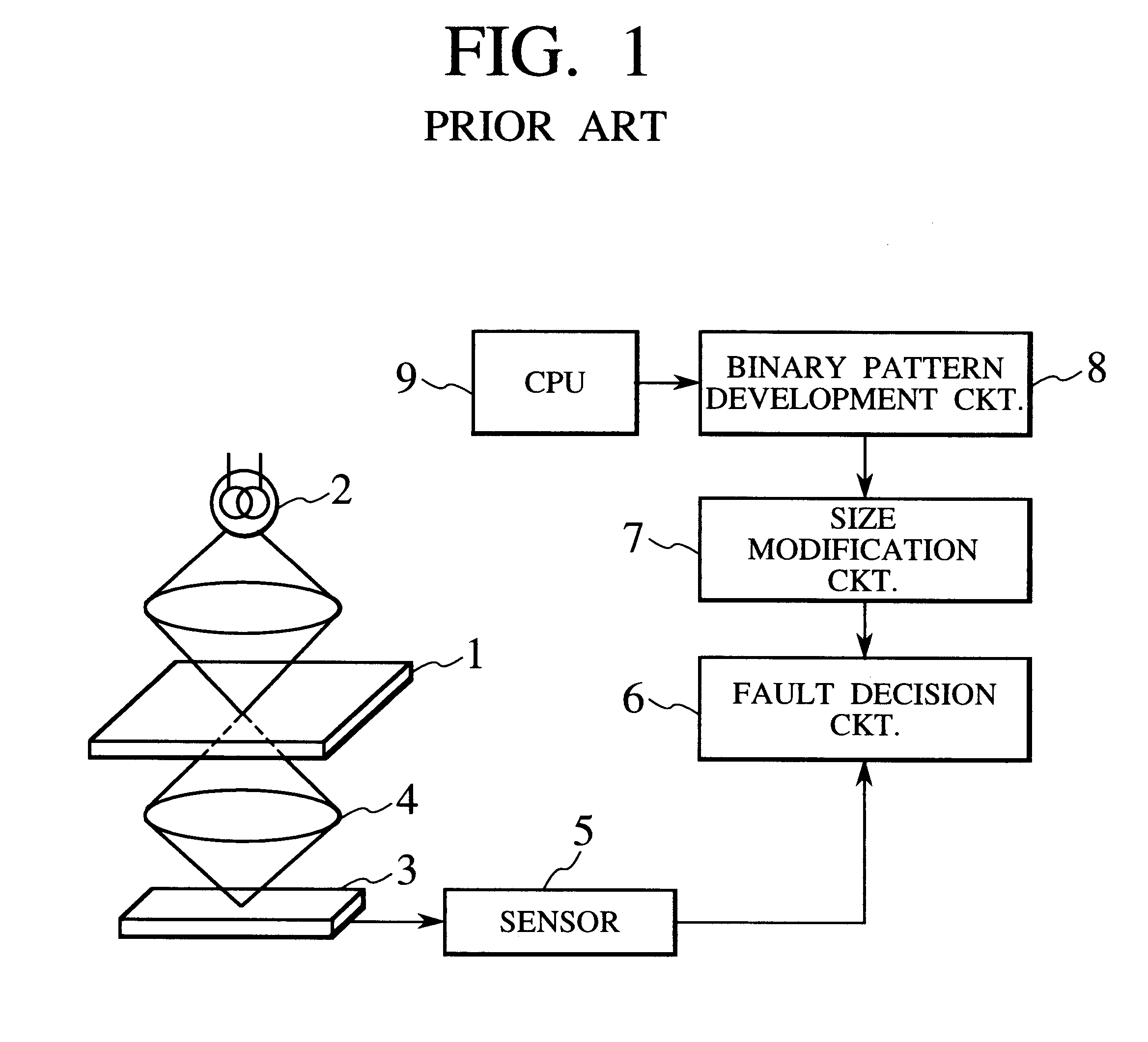

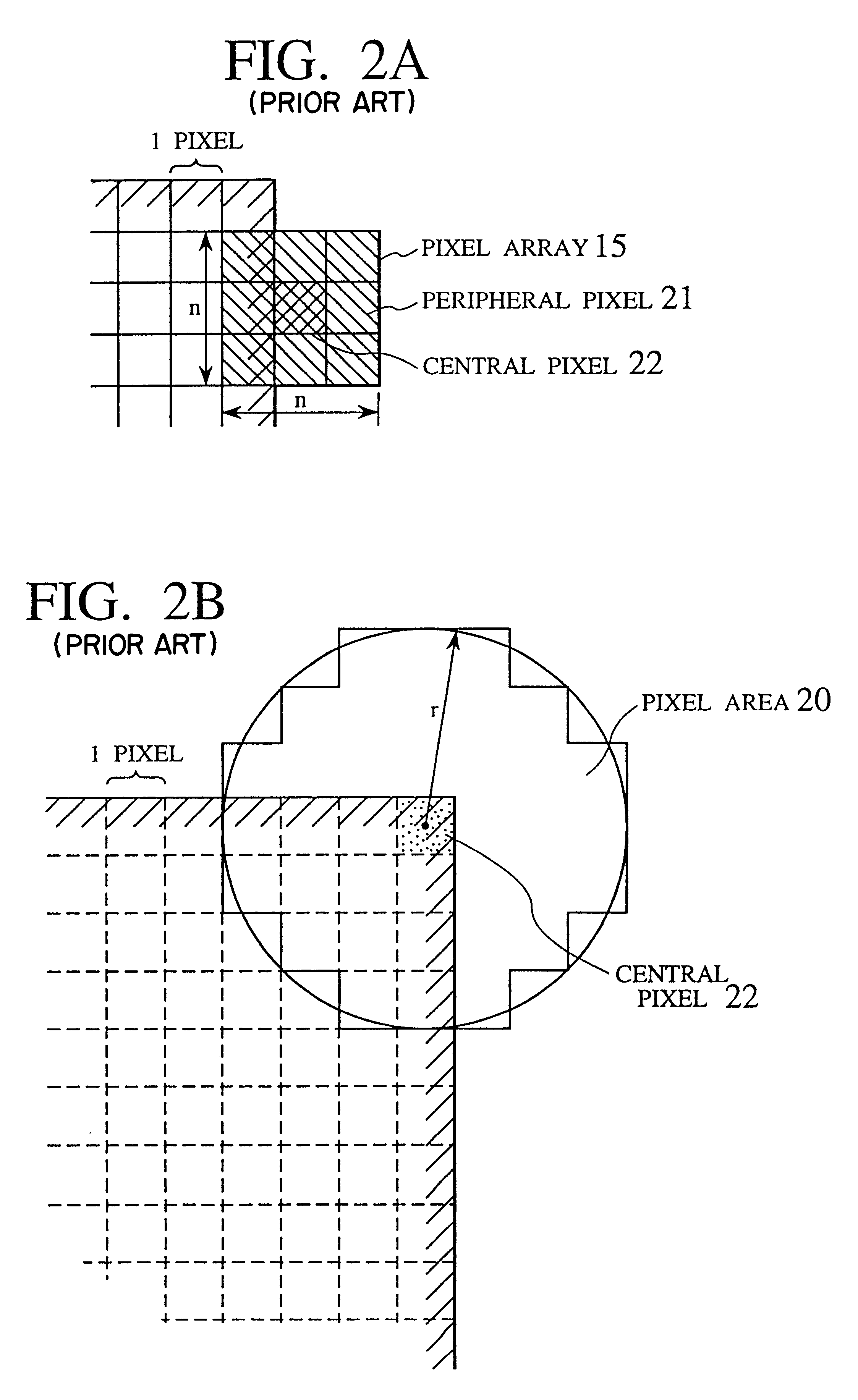

Pattern inspection equipment, pattern inspection method, and storage medium storing pattern inspection program

Pattern inspection equipment has at least a measured data generation unit for generating measured data from patterns that have been delineated on a sample according to design data, a reference data generation unit for generating reference data used to inspect the patterns from gradational data expressed in multiple gradation levels, and a fault decision circuit for comparing the measured data with the reference data. The reference data generation unit has a multi-valued pattern development circuit for developing the design data into the gradational data and a fine adjustment circuit for finely shifting the positions or adjusting the curvatures of pattern edges in the pattern constructed with the gradational data. The fine adjustment of the pattern edges is necessary to cope with slightly displaced edges and rounded corners of the actual patterns on the sample. These slightly displaced edges and rounded corners are caused through mask manufacturing processes and are frequently smaller than the size of a sensor pixel. To adjust the reference data to the displaced edges, a size modification circuit detects a maximum value in a specified area in the gradational data and modifies the size of the pattern constructed with the gradational data. To adjust the reference data to match with the actual rounded corners, a corner rounding circuit rounds corners in the pattern constructed with the gradational data. Also provided is a pattern inspection method for developing the design data into the gradational data, adjusting the gradational data to displaced edges and rounded corners of the actual patterns and preparing the reference data, and testing the patterns for faults. Further provided is a storage medium for storing a pattern inspection program for realizing the pattern inspection method.

Owner:KK TOSHIBA

Apparatus and method for generating state transition rules for memory efficient programmable pattern matching finite state machine hardware

InactiveUS7219319B2Reduce memory requirementsMinimize the numberTransmissionSpecial data processing applicationsStatic random-access memoryPattern matching

A programmable finite state machine (FSM) includes, in part, first and second memories, and a selection circuit coupled to each of the memories. Upon receiving a (k+m)-bit word representative of the k-bit input symbol and the m-bit current state, the first memory supplies one ore more matching transition rules stored therein. The selection circuit selects the most specific of the supplied rules. The transition rules are stored in the first memory in a ranking order of generality. The second memory receives the selected transition rule and supplies the next state of the FSM. The first memory may be a ternary content addressable memory and the second memory may be a static random access memory. The contents of both the content addressable memory and the static random memory is determined by an algorithm which minimizes the number of terms required to represent the next-state transition functions.

Owner:SENSORY NETWORKS +1

Memory system having flash memory where a one-time programmable block is included

A memory system includes a flash memory device and an interface device. The flash memory device includes a one-time programmable block where protection data information is stored in a predetermined region, and the interface device includes a register for storing one-time programmable lock status information to indicate whether the one-time programmable block is programmed. When a program / erase command is applied externally in a one-time programmable mode, the interface device having the one-time programmable lock status information indicates whether the one-time programmable block is programmed. If the one-time programmable lock status information indicates that the one-time programmable block is programmed, the interface device cuts off an external access to the one-time programmable block.

Owner:SAMSUNG ELECTRONICS CO LTD