Patents

Literature

128results about How to "Reduce phase difference" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

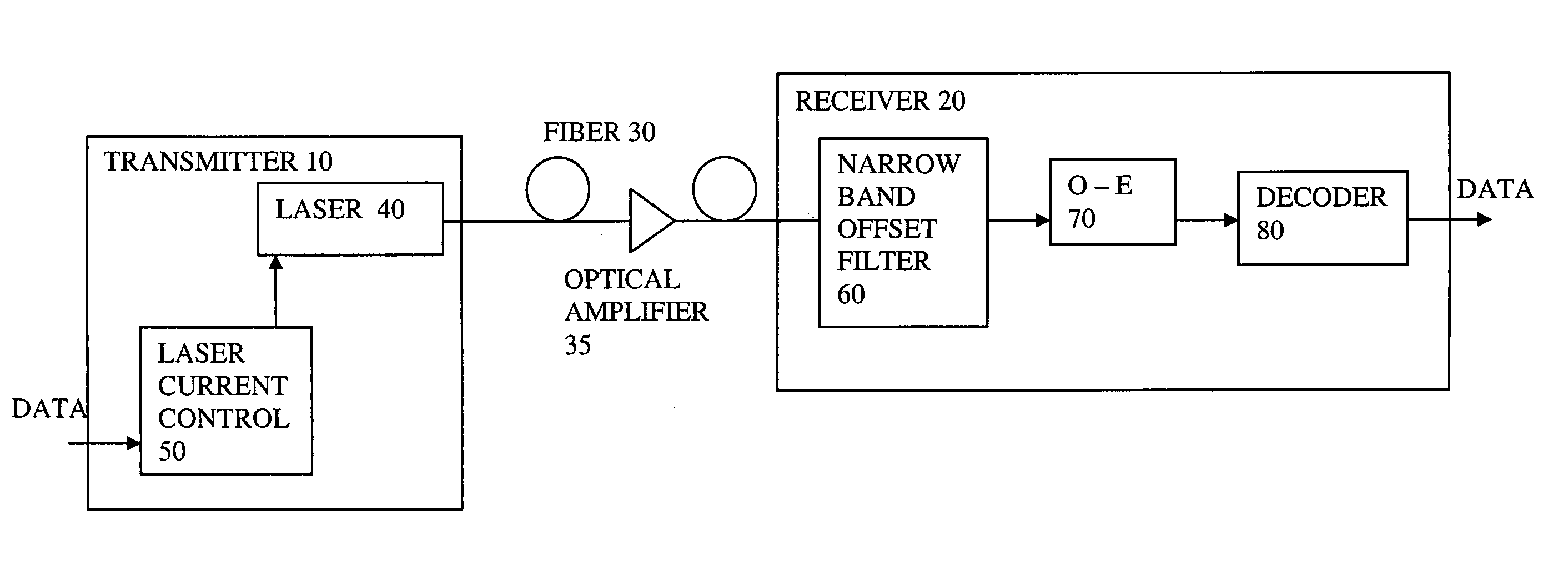

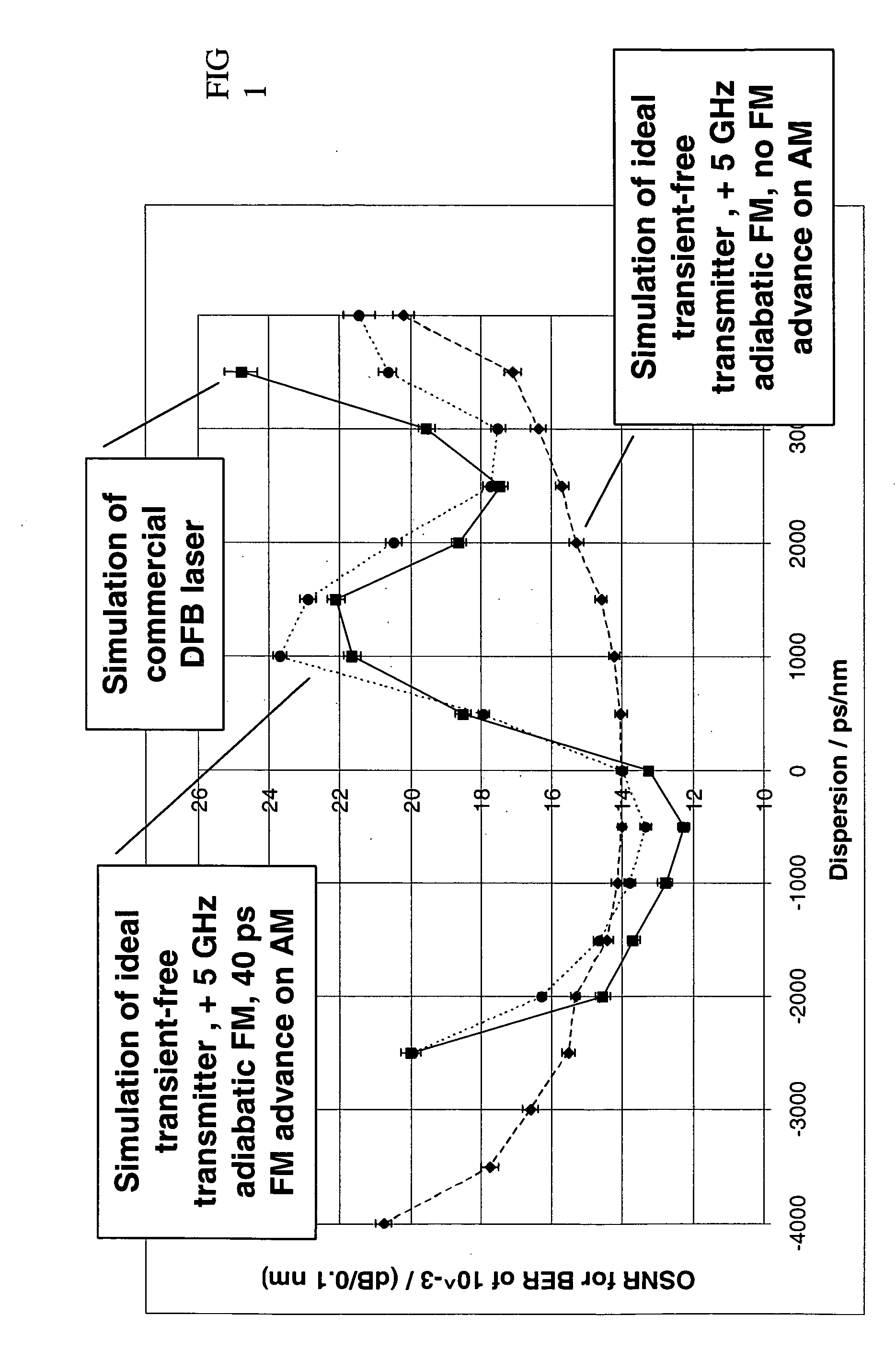

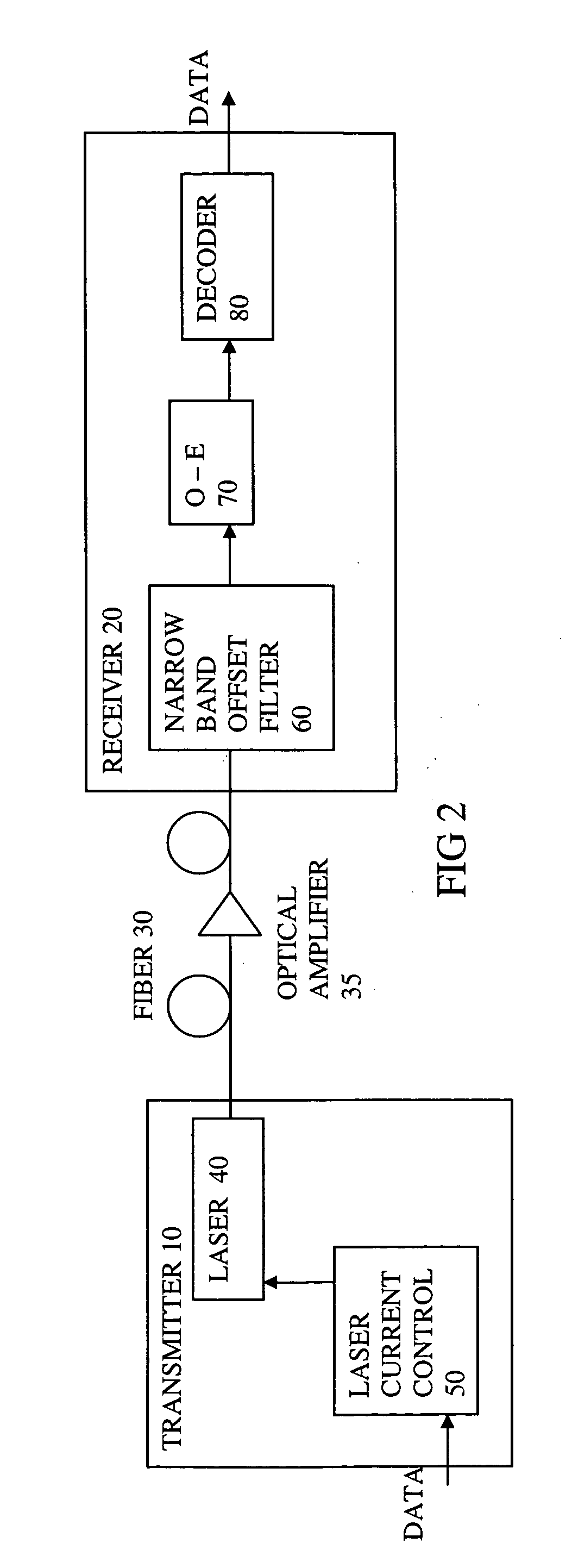

Filter to improve dispersion tolerance for optical transmission

InactiveUS20050271394A1Reduce phase differenceInexpensive optical filteringElectromagnetic transmittersFrequency spectrumPhase difference

An optical transmission system has a directly modulated laser for modulating data directly on an optical signal, and a narrow band optical filter having a band center frequency offset from a central optical frequency of the optical signal, to reduce the phase difference between FM and AM of the modulated optical signal, the filter having a bandwidth sufficiently narrow to substantially remove frequencies outside a spectrum of adiabatic frequency chirp resulting from the modulation, combined with Fourier broadening caused by the data modulation. This is a cost effective way of improving the dispersion tolerance to give greatly improved system reach and to make it practical to use directly modulated lasers with existing NDSF. The narrow band filter can be located at the transmitter or the receiver, and can have a center frequency locked to a feature in the frequency spectrum of the laser.

Owner:NORTEL NETWORKS LTD

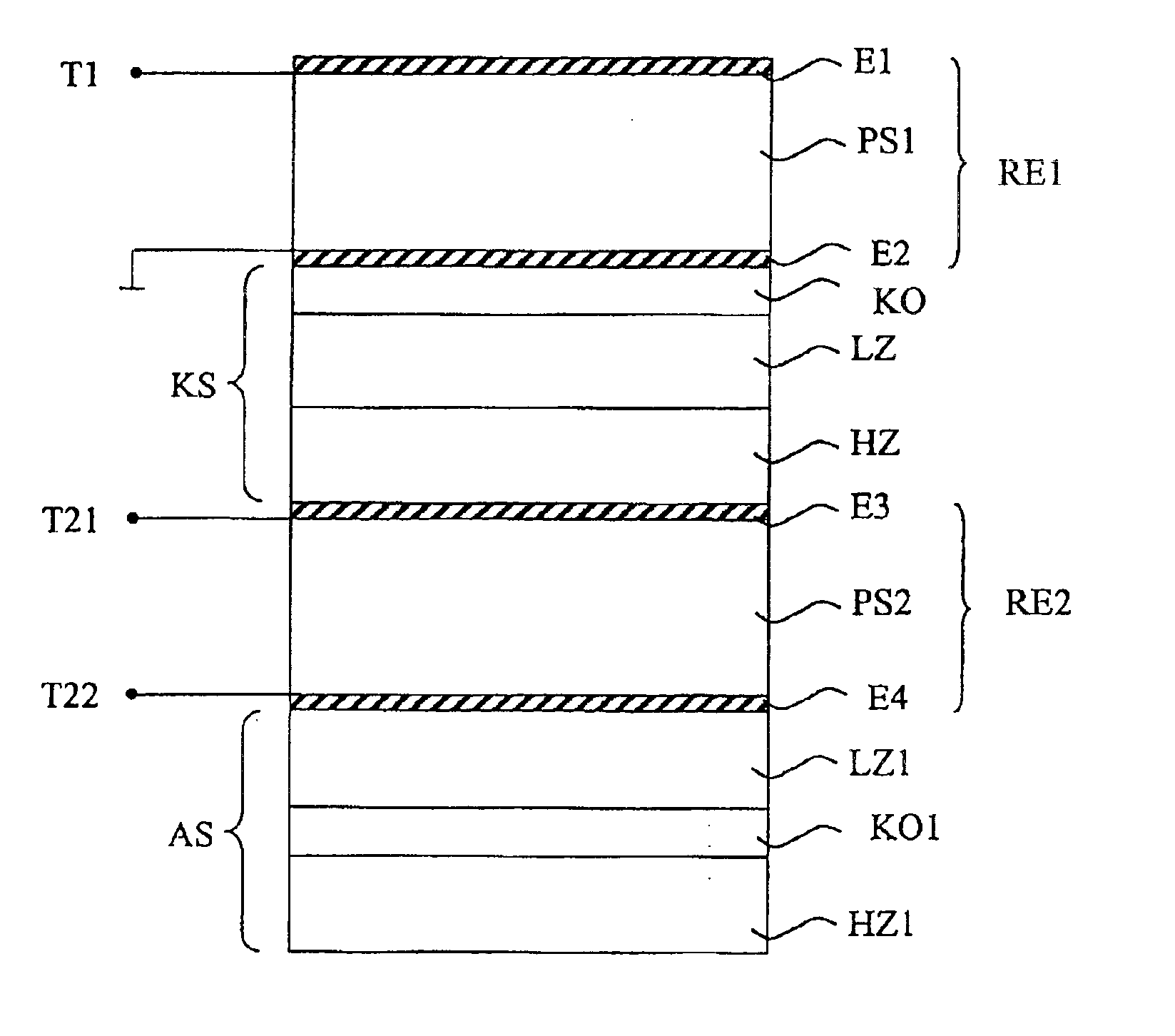

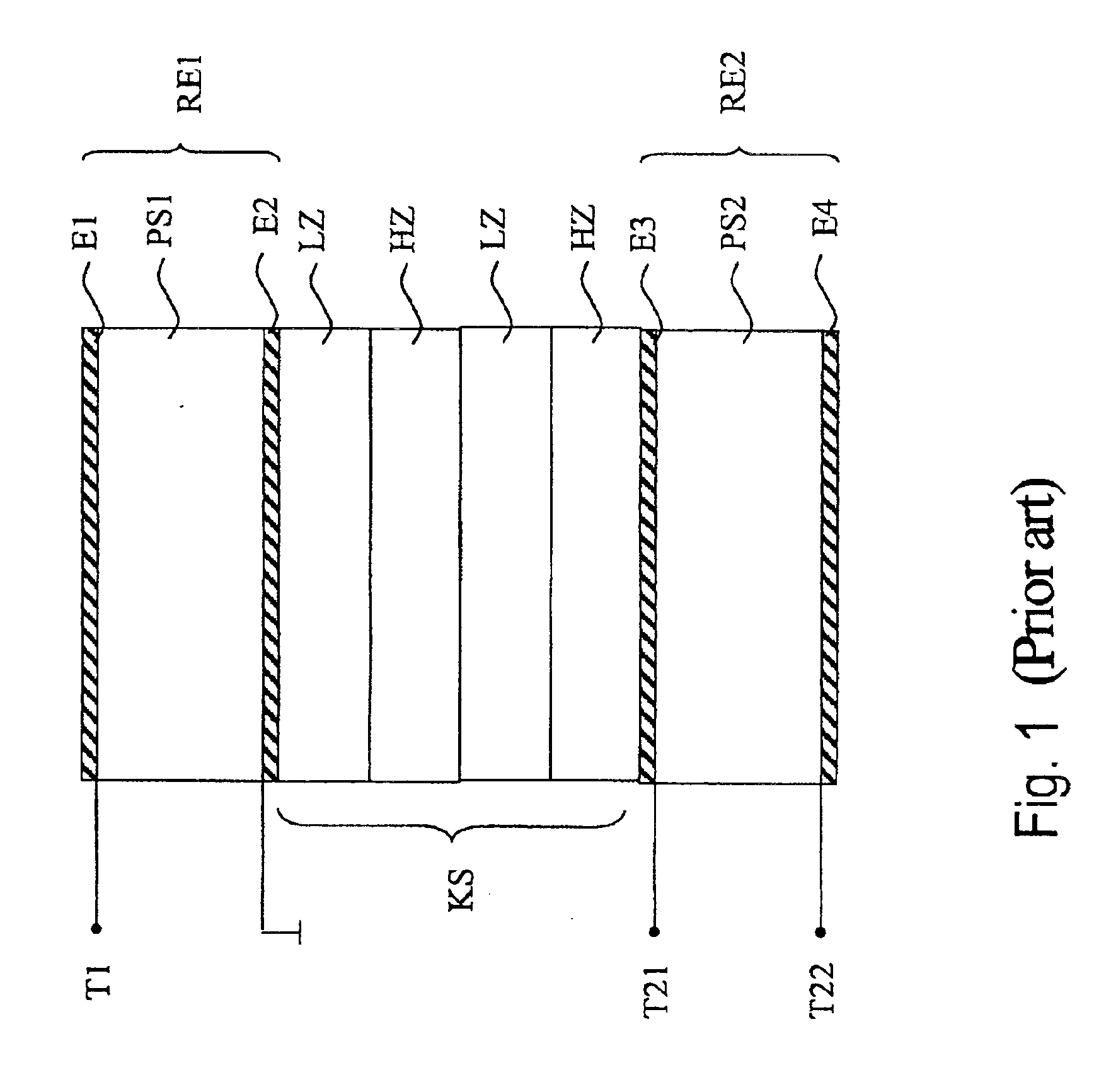

Component operating with bulk acoustic waves, and having asymmetric/symmetrical circuitry

ActiveUS6917261B2Reduce phase differenceBalance-unbalance networksPiezoelectric/electrostriction/magnetostriction machinesCouplingPhase difference

A component operating with bulk acoustic waves has two Bulk Acoustic Wave (BAW) resonators that are stacked and are acoustically coupled to one another, with a first resonator being connected to an asymmetric port, and a second resonator being connected to a symmetrical port. The acoustic coupling is provided by a partially permeable coupling layer system, which has an alternating sequence of at least two λ / 4 mirror layers with different acoustic impedance. The coupling layer system furthermore has a compensation layer, which has an approximate thickness of λ / 8. The compensation layer according to the invention makes it possible to match any discrepancy in the phase difference (which is caused by reflections on the mirror layers) from the predetermined 180° between the connections of the symmetrical port to approximately 180°.

Owner:SNAPTRACK

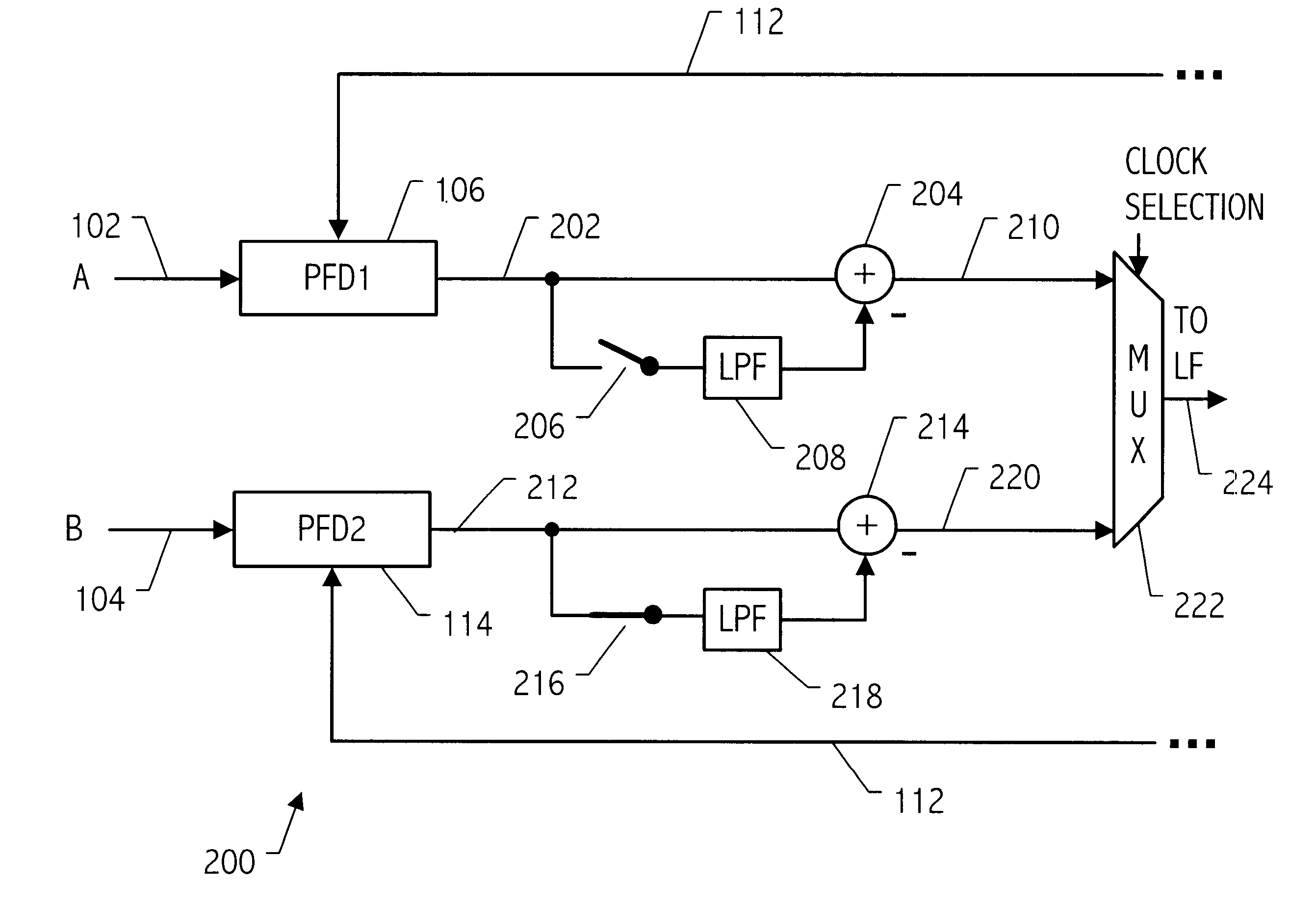

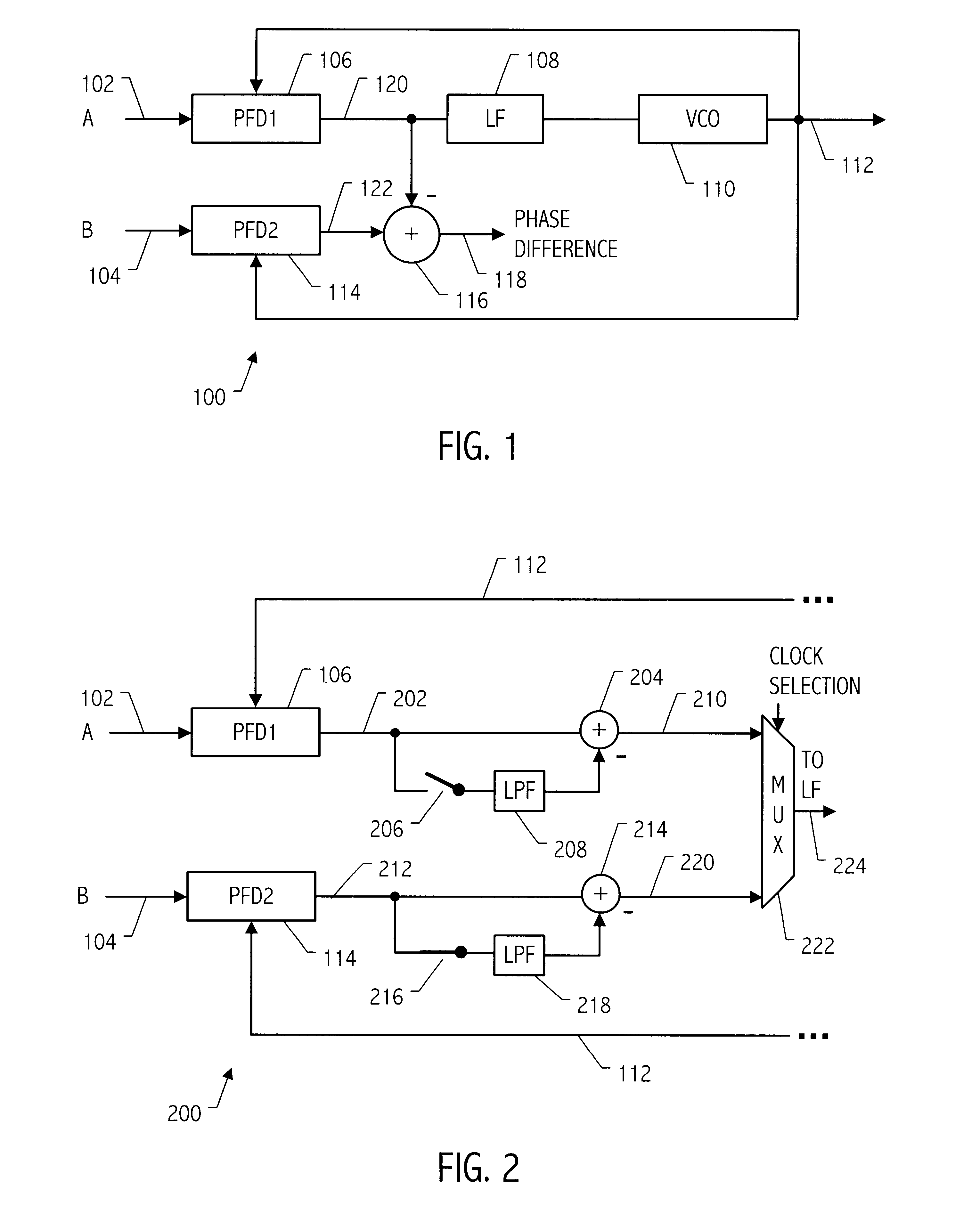

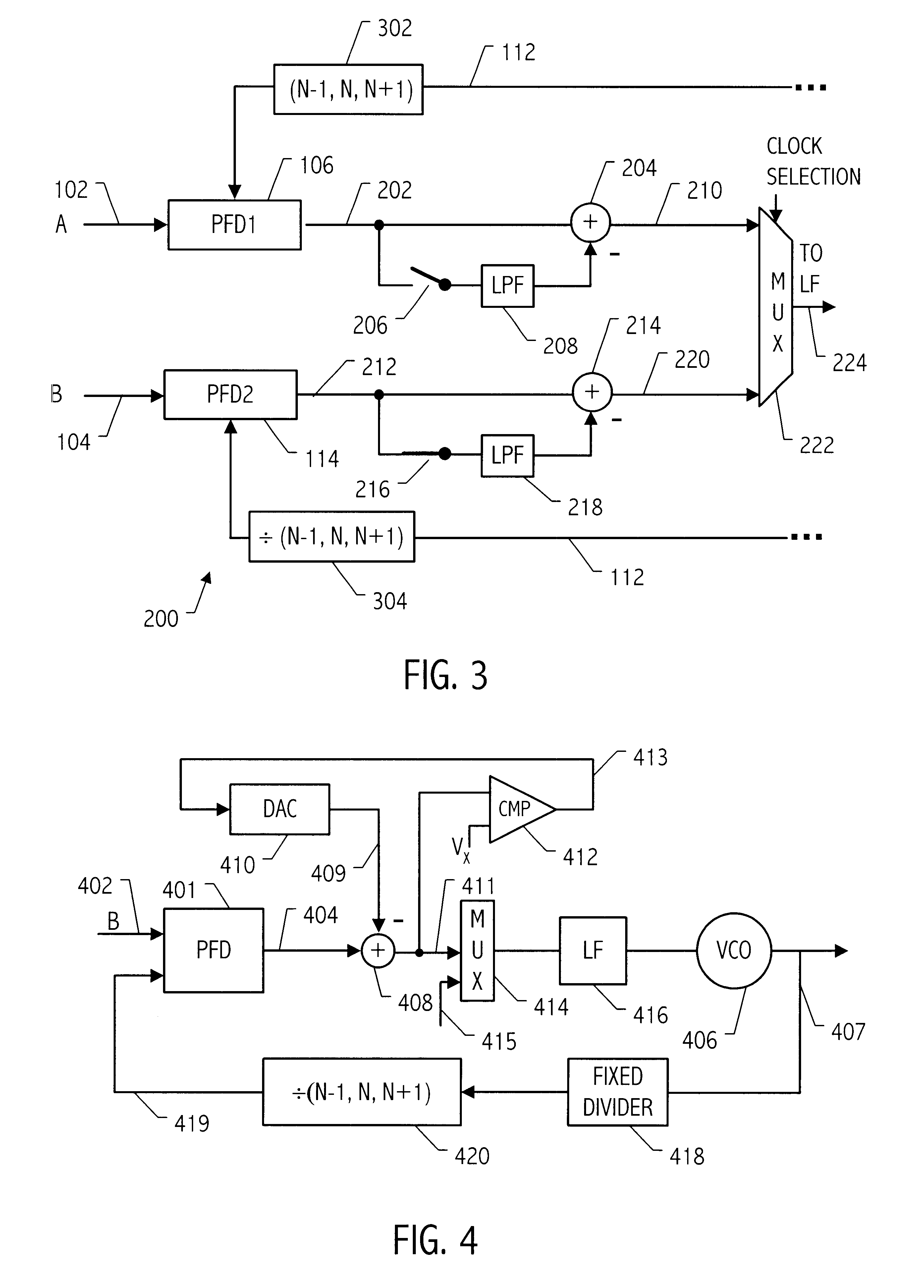

Method and apparatus for switching between input clocks in a phase-locked loop

InactiveUS6741109B1Reduce phase differencePulse automatic controlTime-division multiplexPhase-locked loopMultiple input

A phase-locked loop receives multiple input clocks, one of which is selected for use by the PLL at any one time. The phase difference(s) between non-selected input clocks and a feedback signal of the PLL, is monitored and stored. When a switch occurs to using a non-selected clock as the input clock of the PLL, the stored phase difference, typically a DC offset value, is injected into the phase-locked loop to compensate for the phase difference between the clocks.

Owner:XENOGENIC DEV LLC

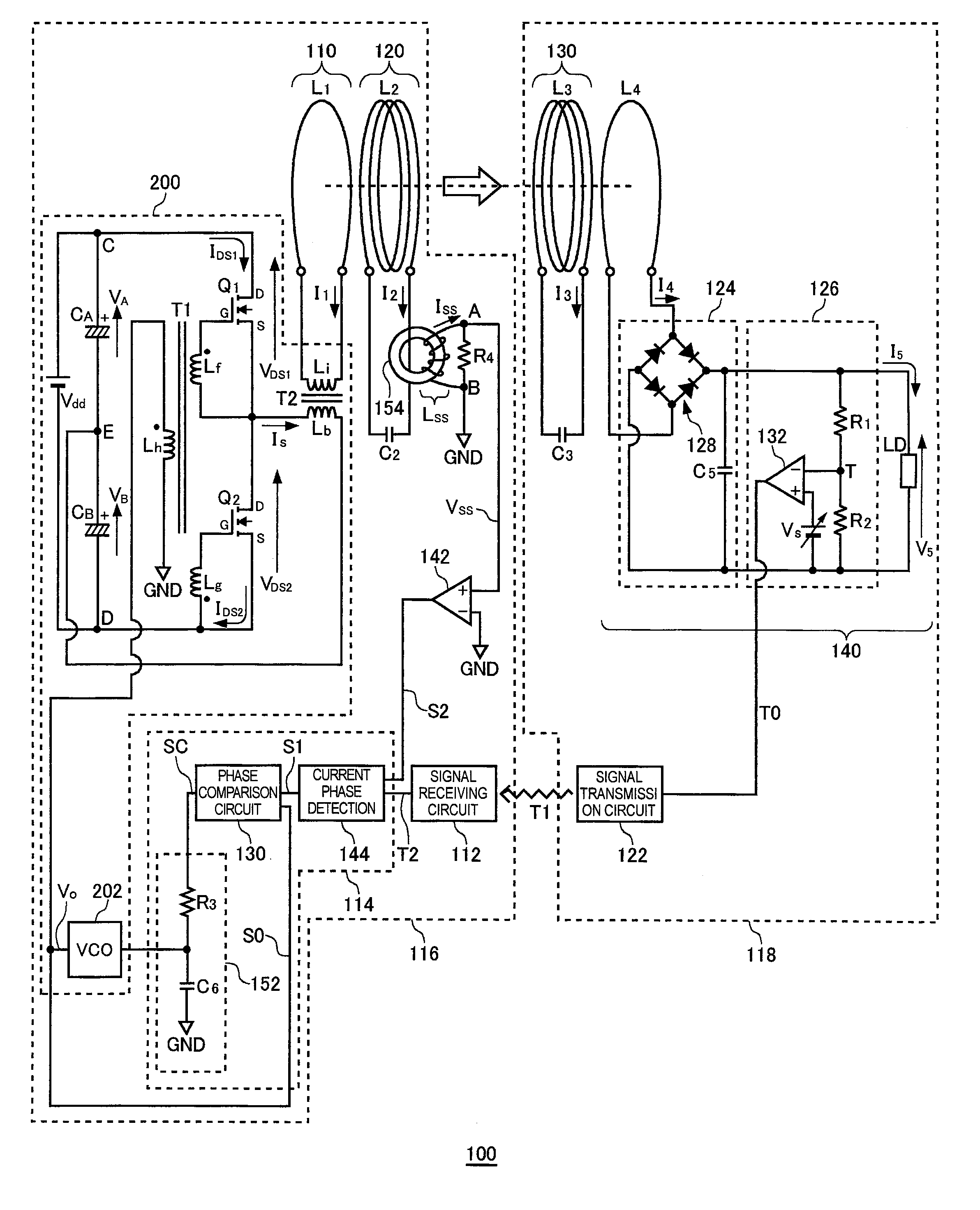

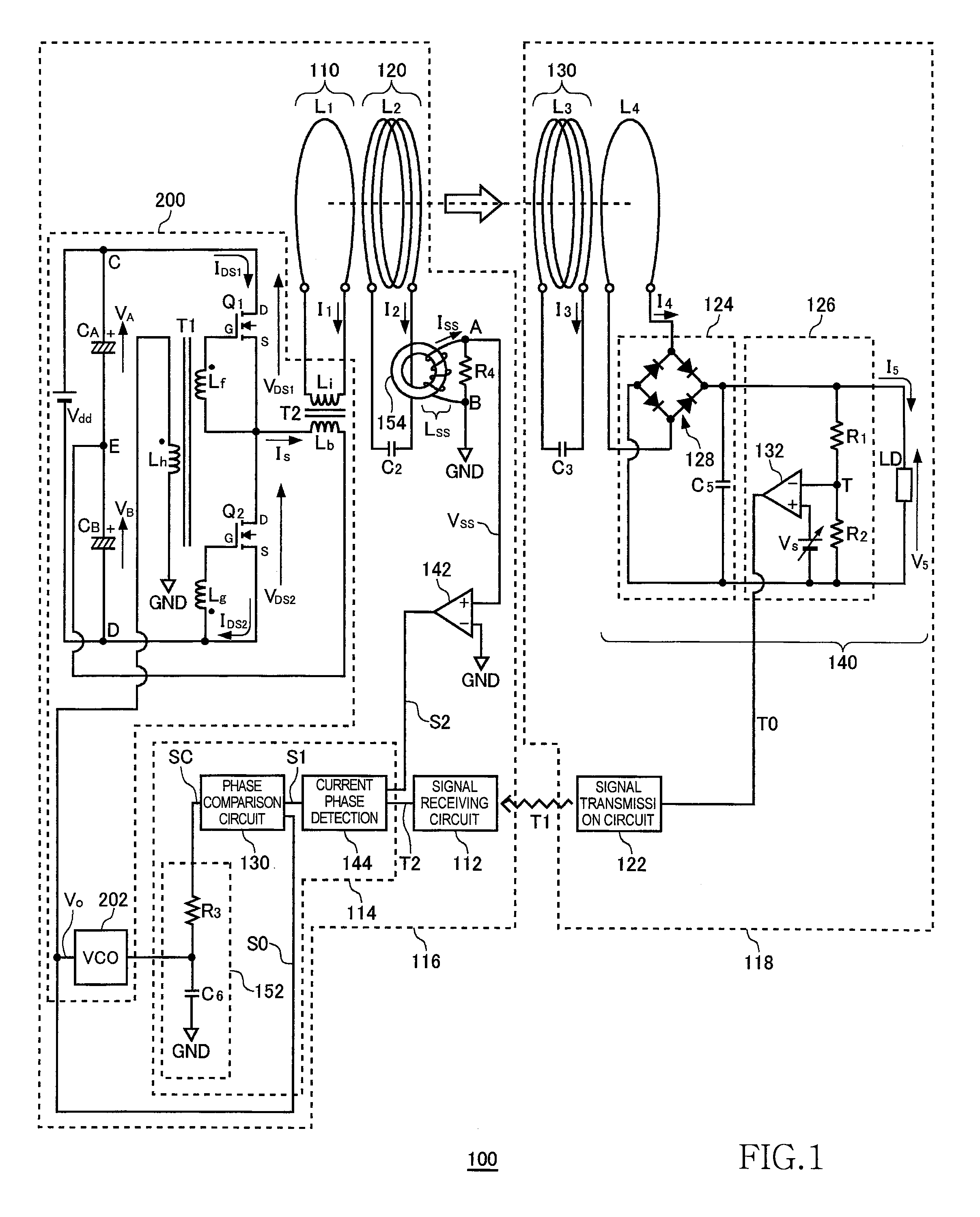

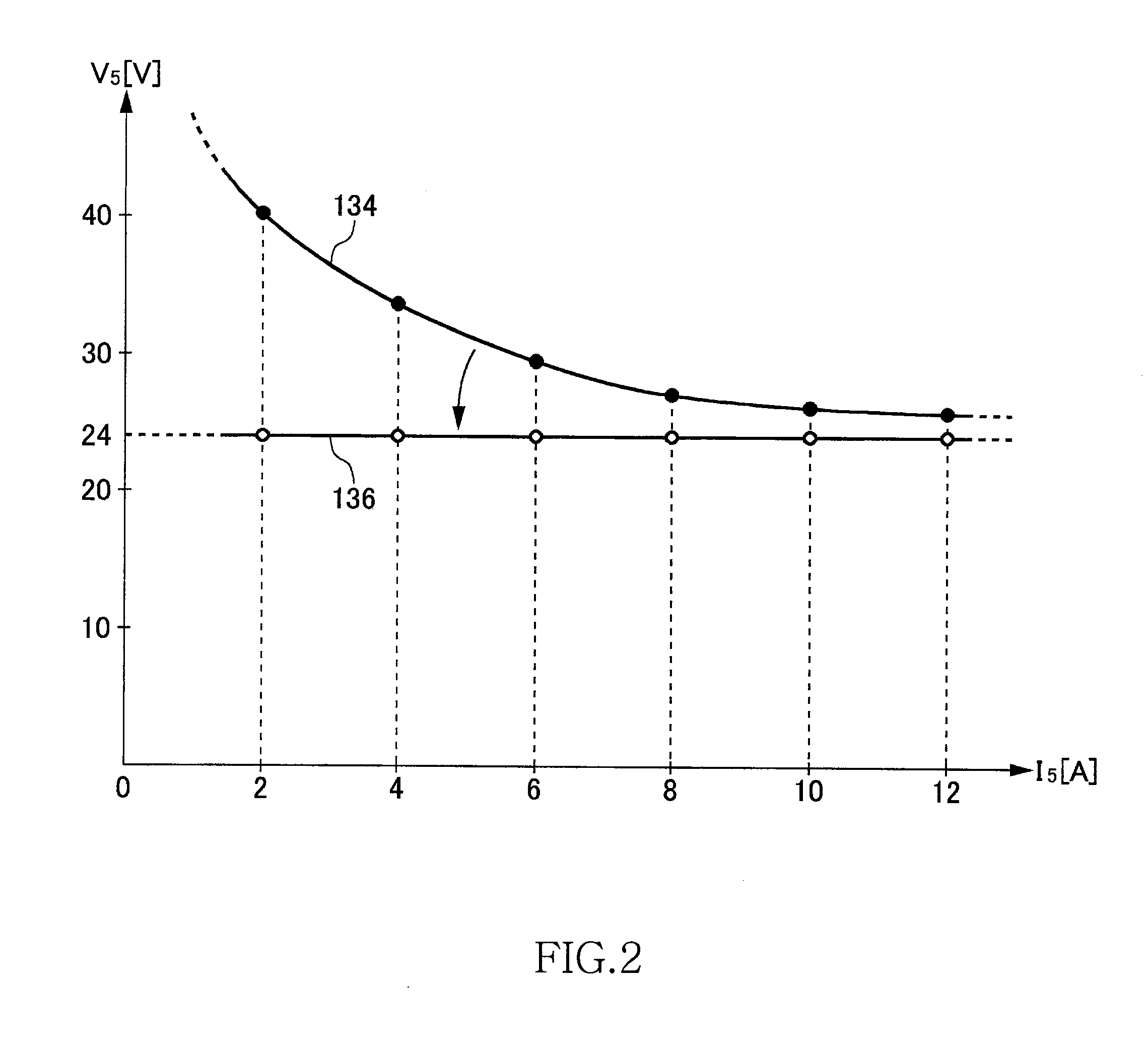

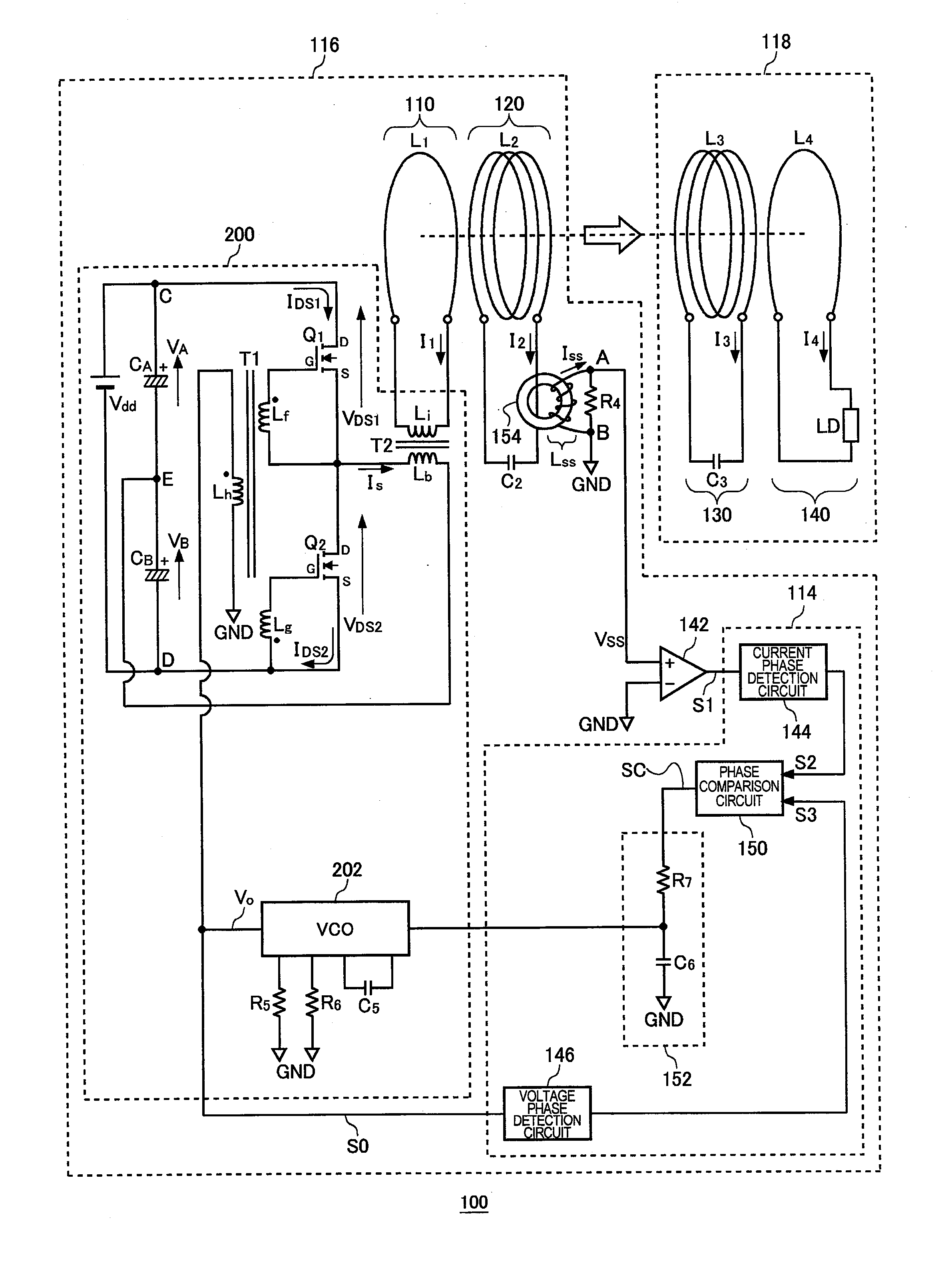

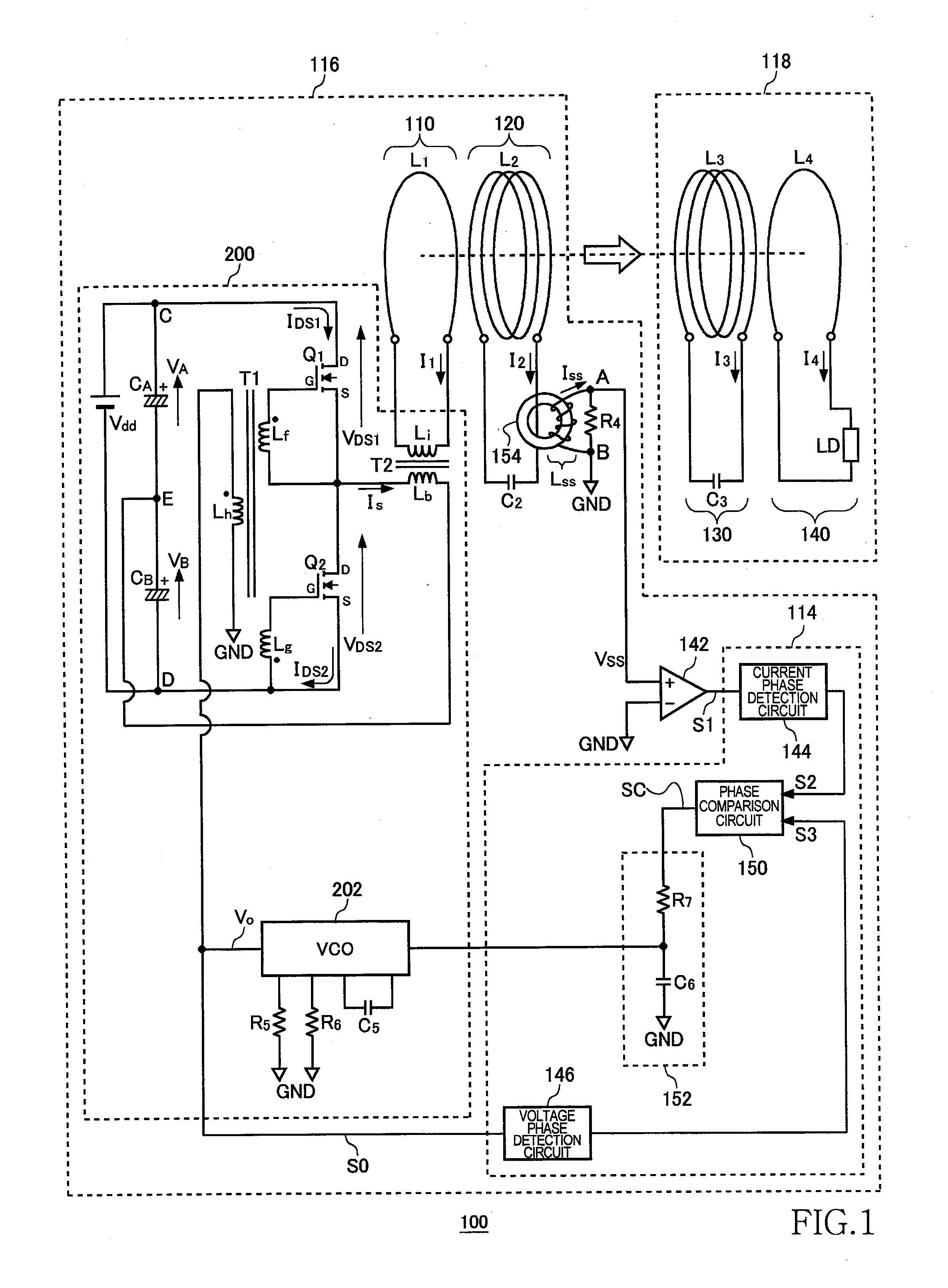

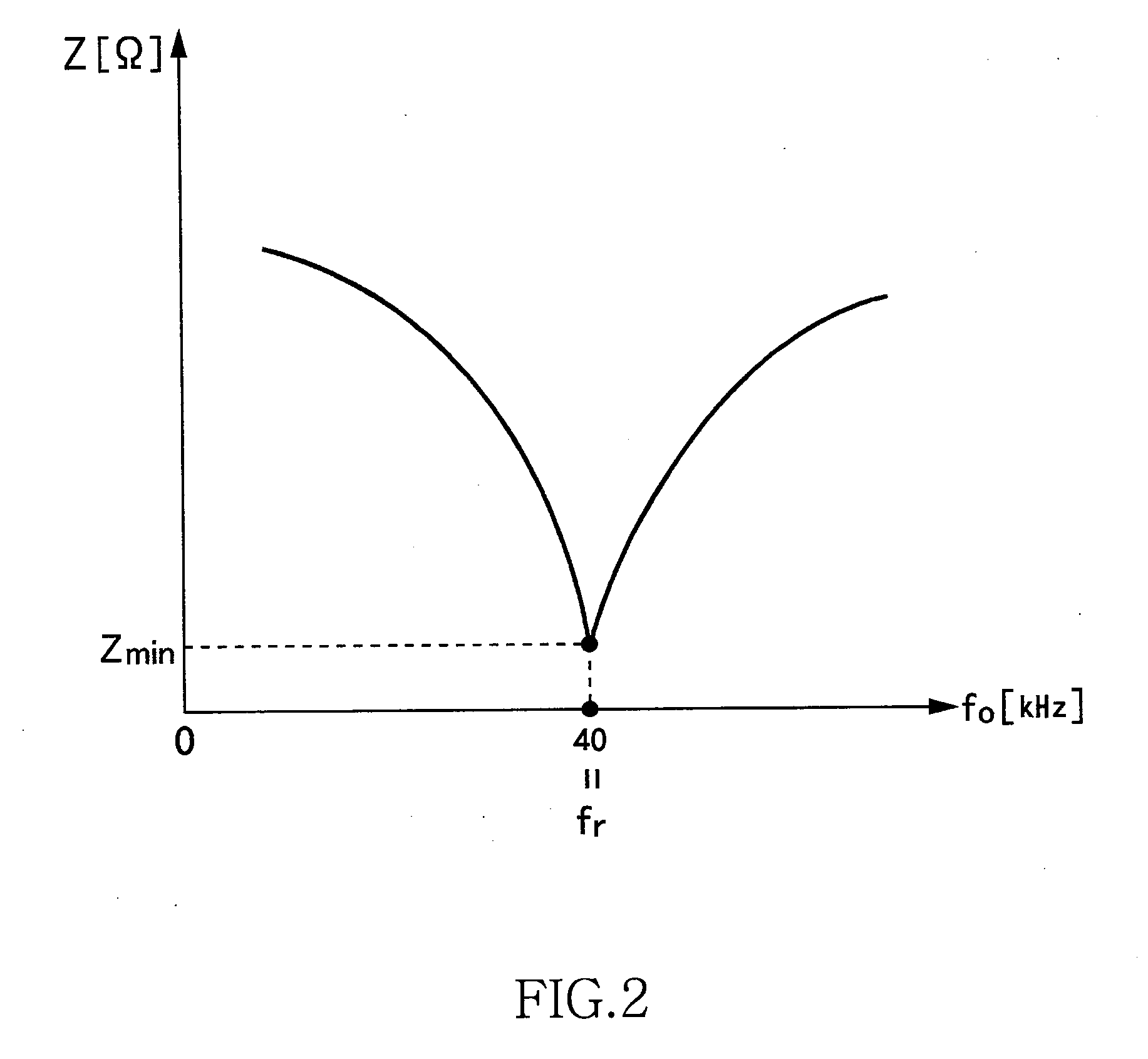

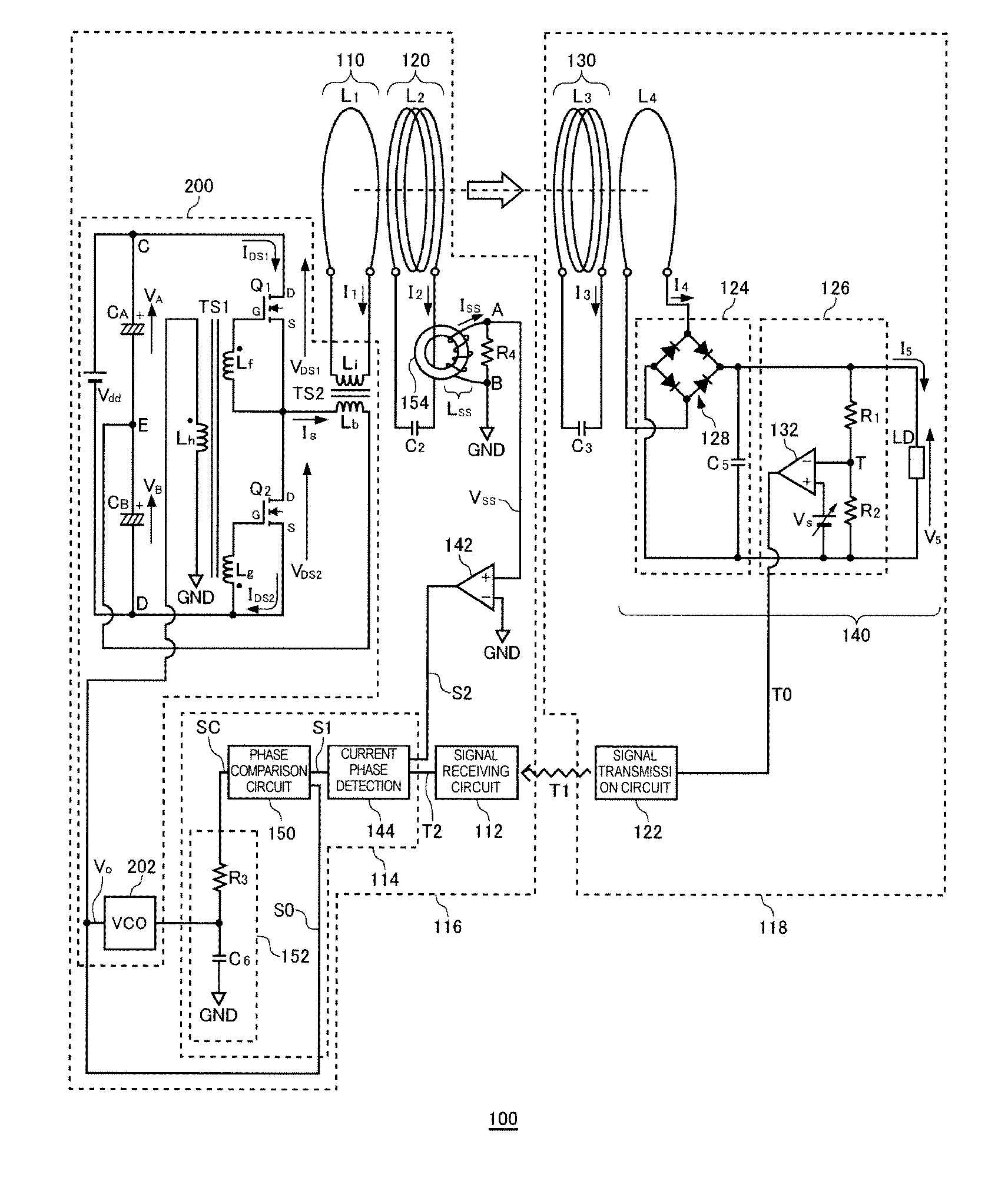

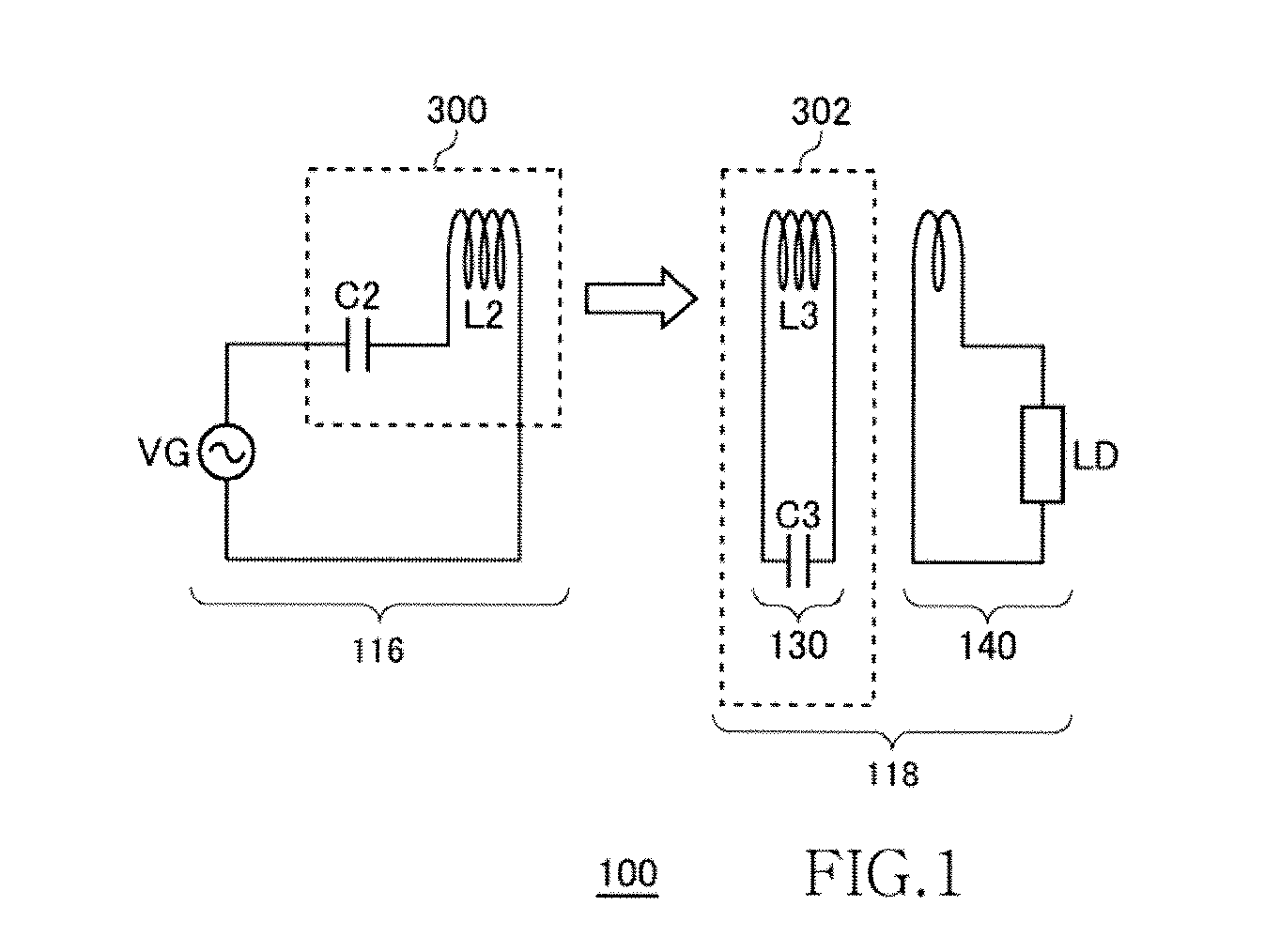

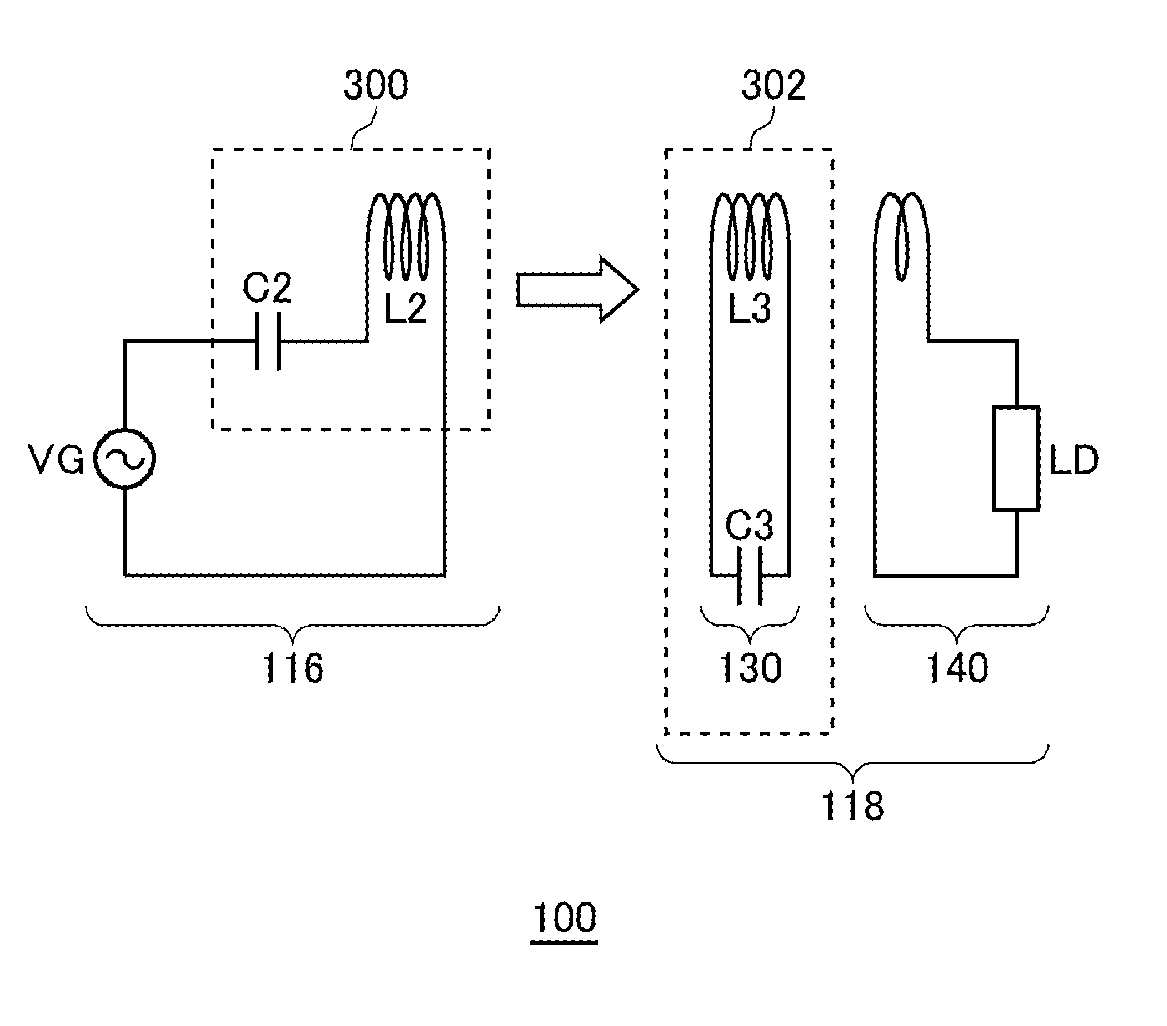

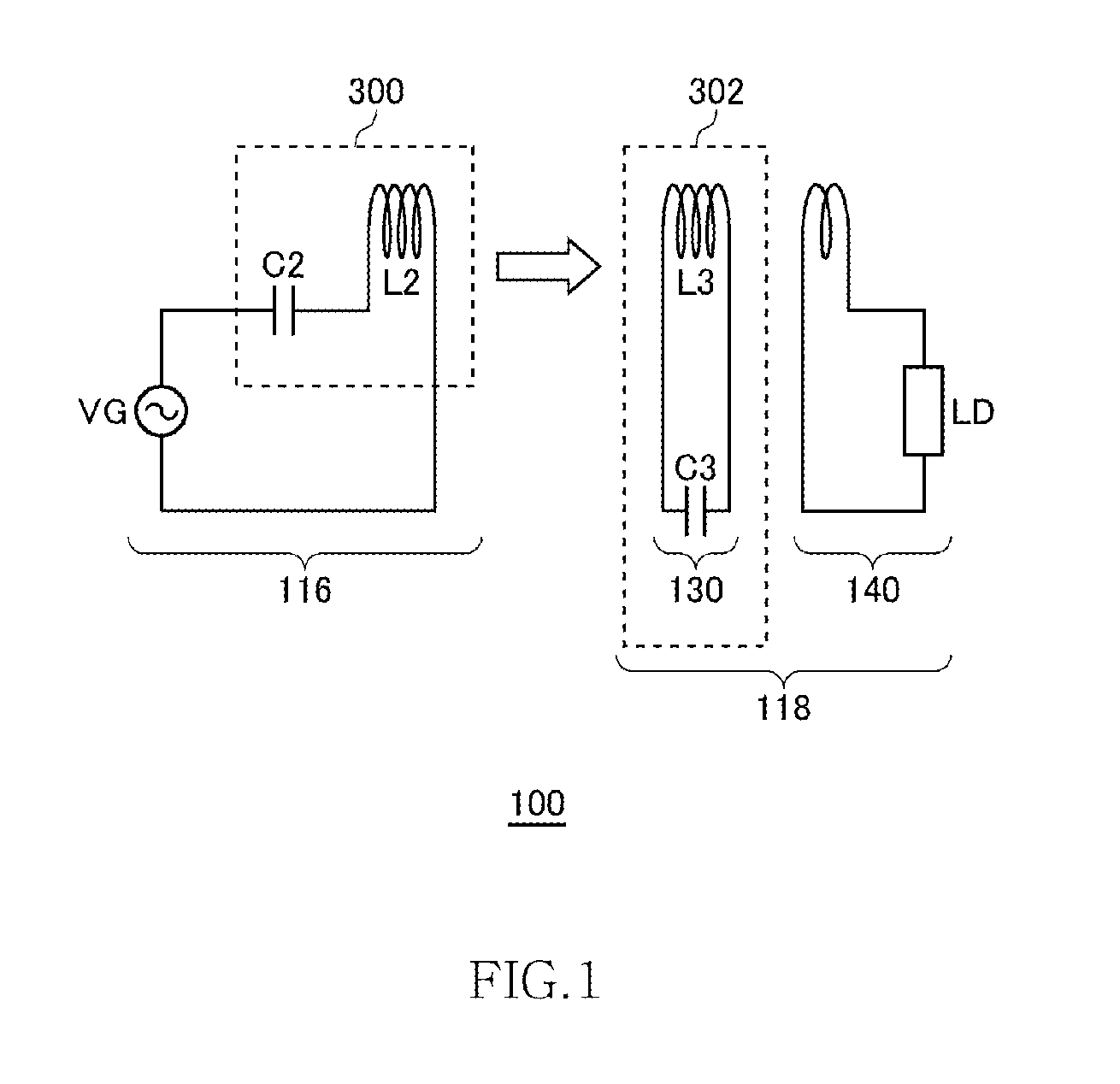

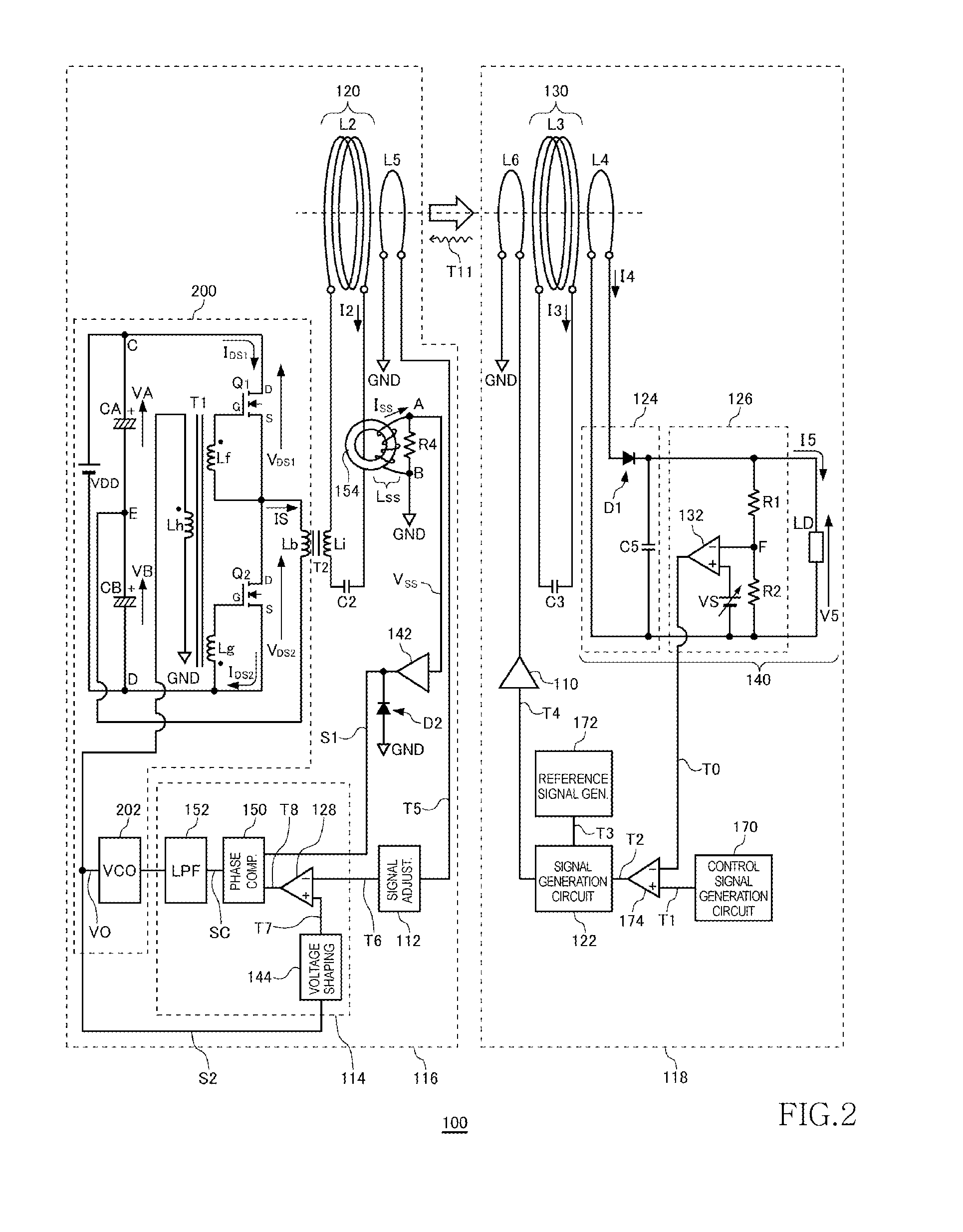

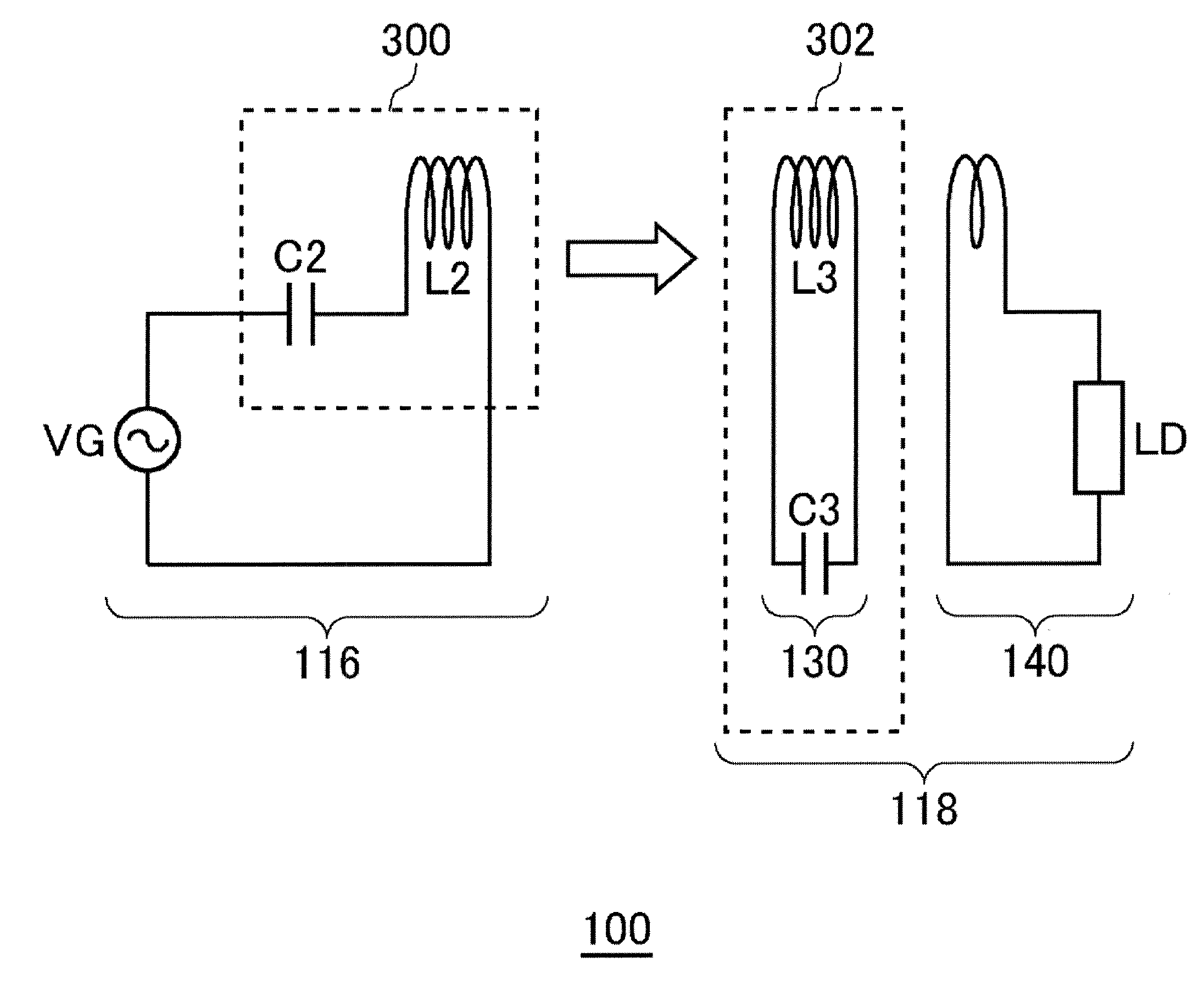

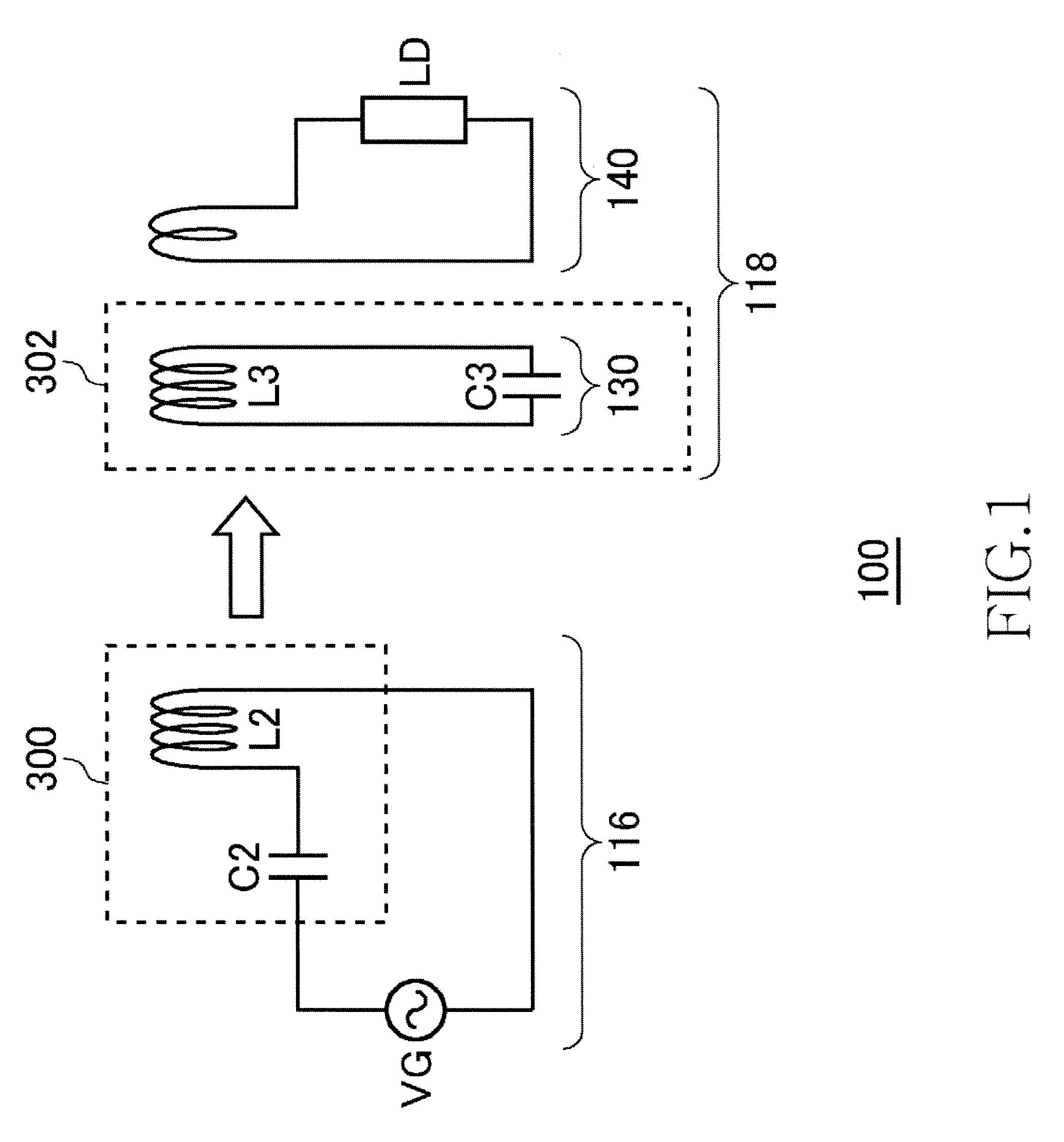

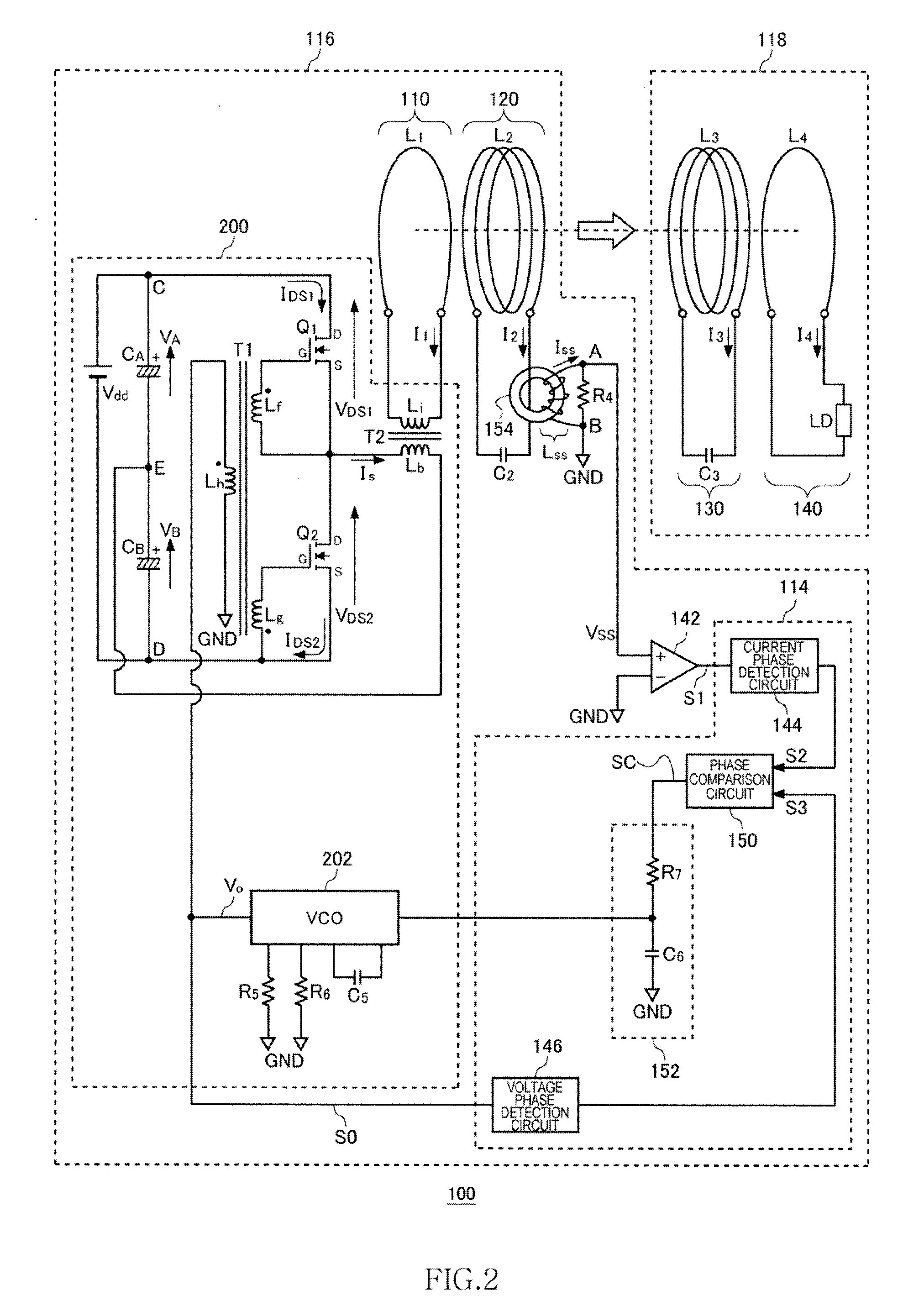

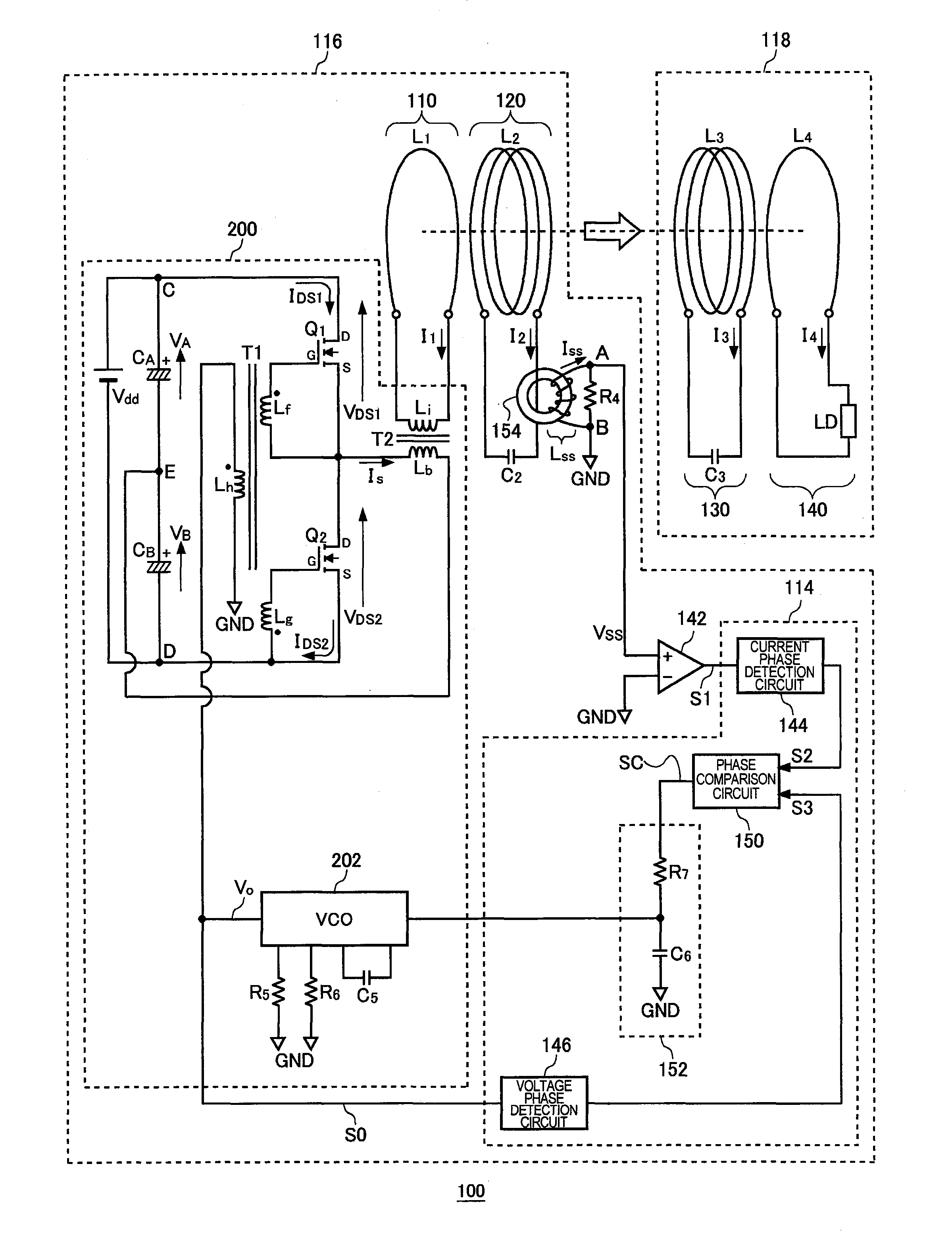

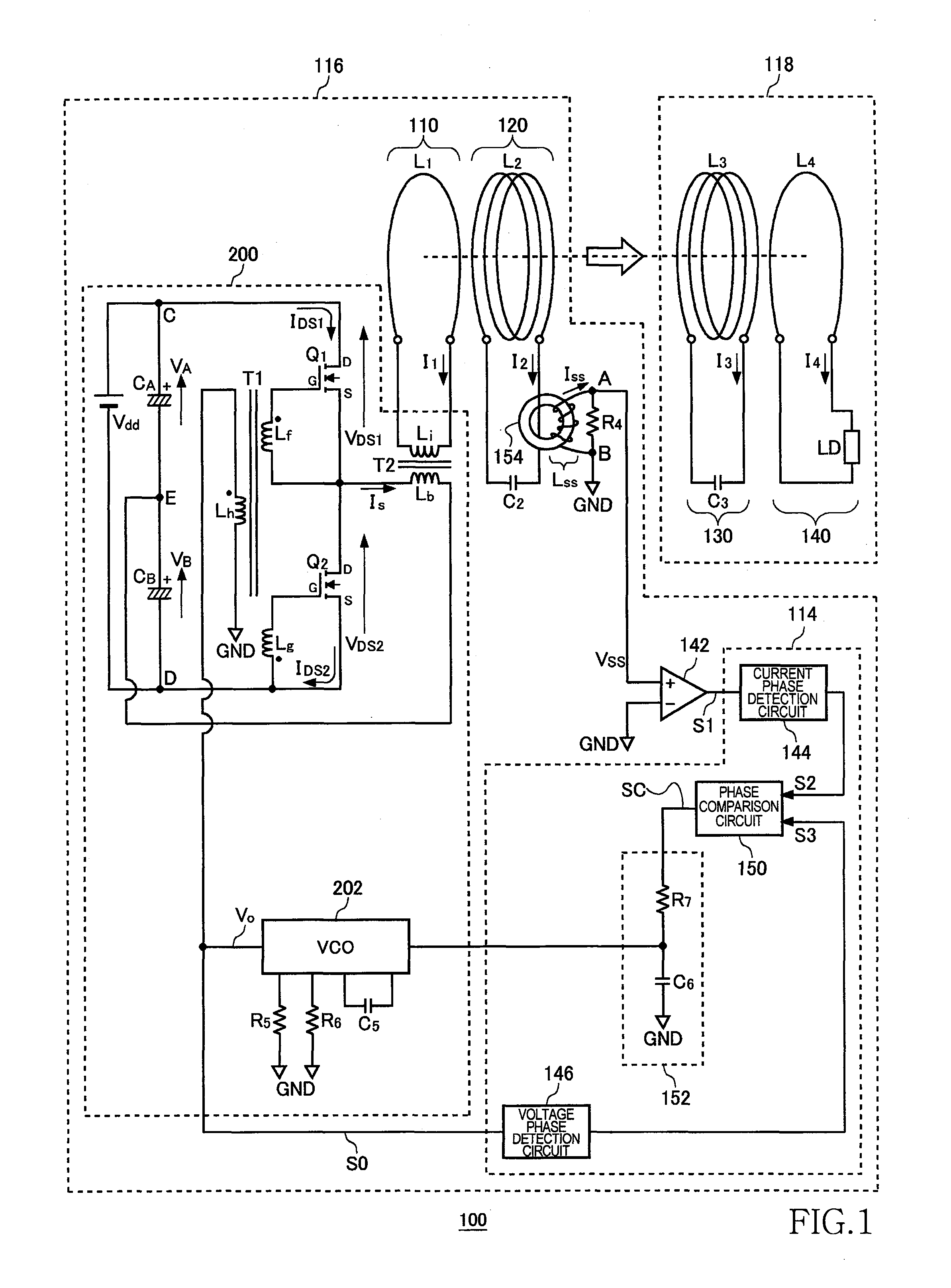

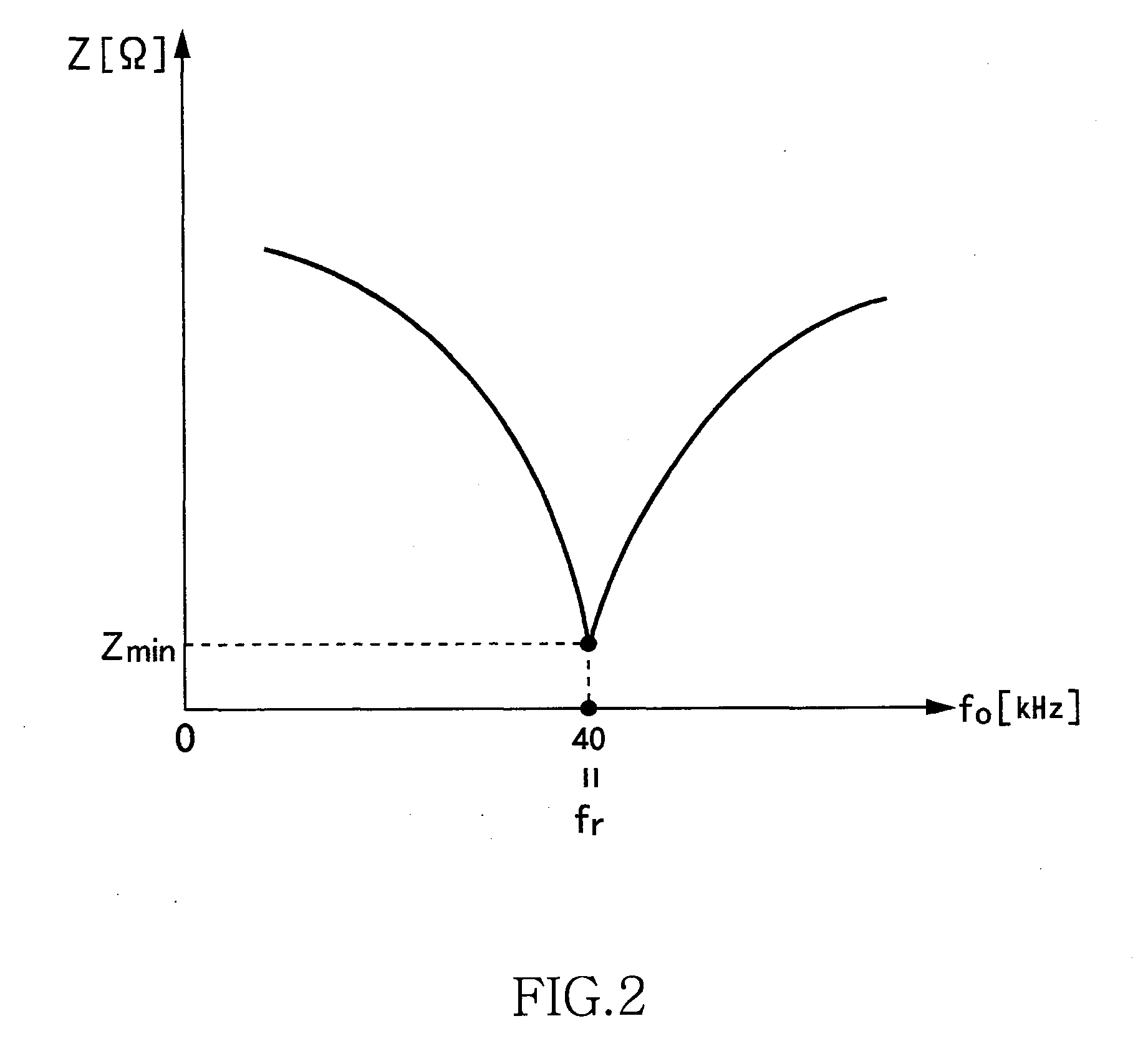

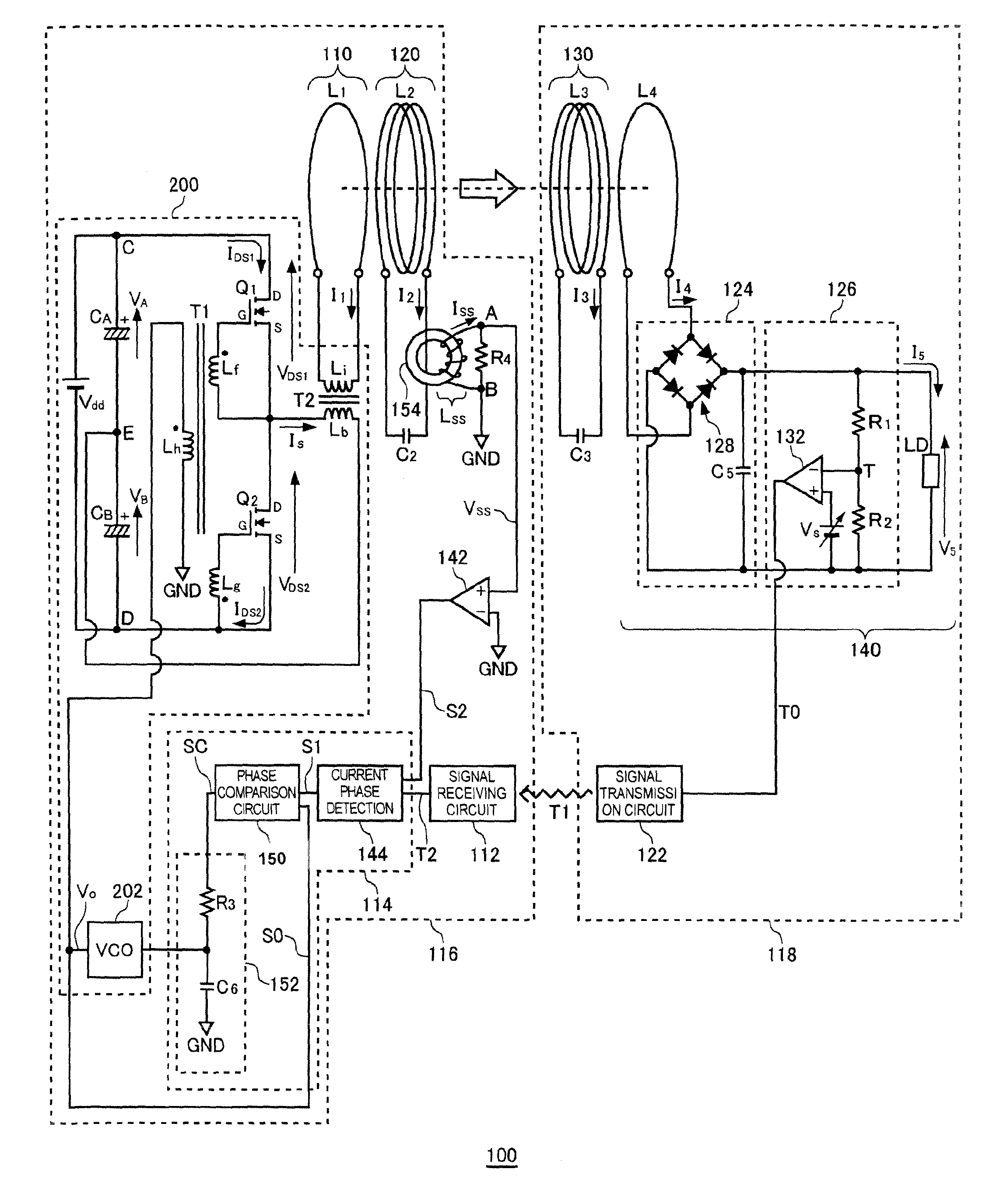

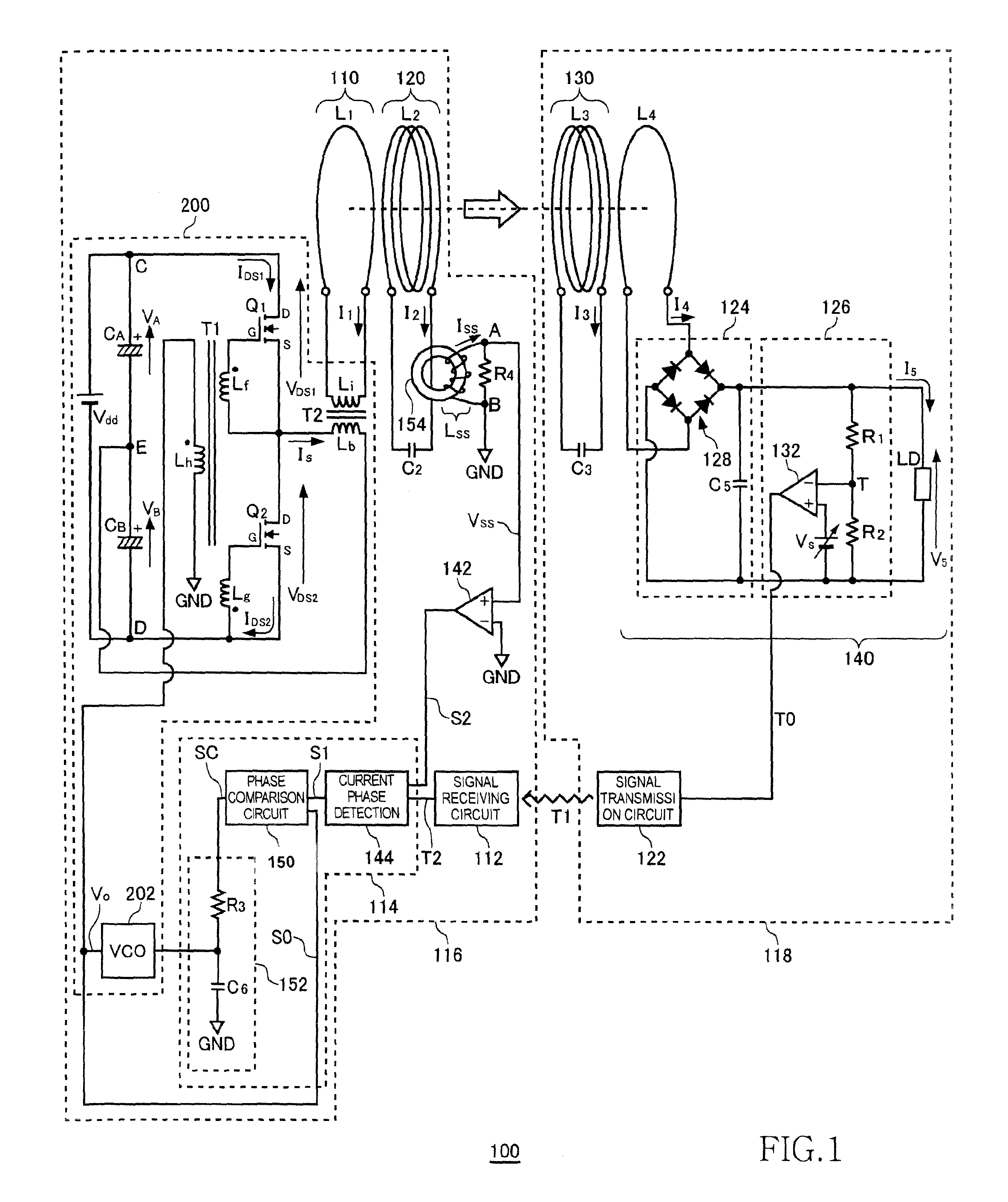

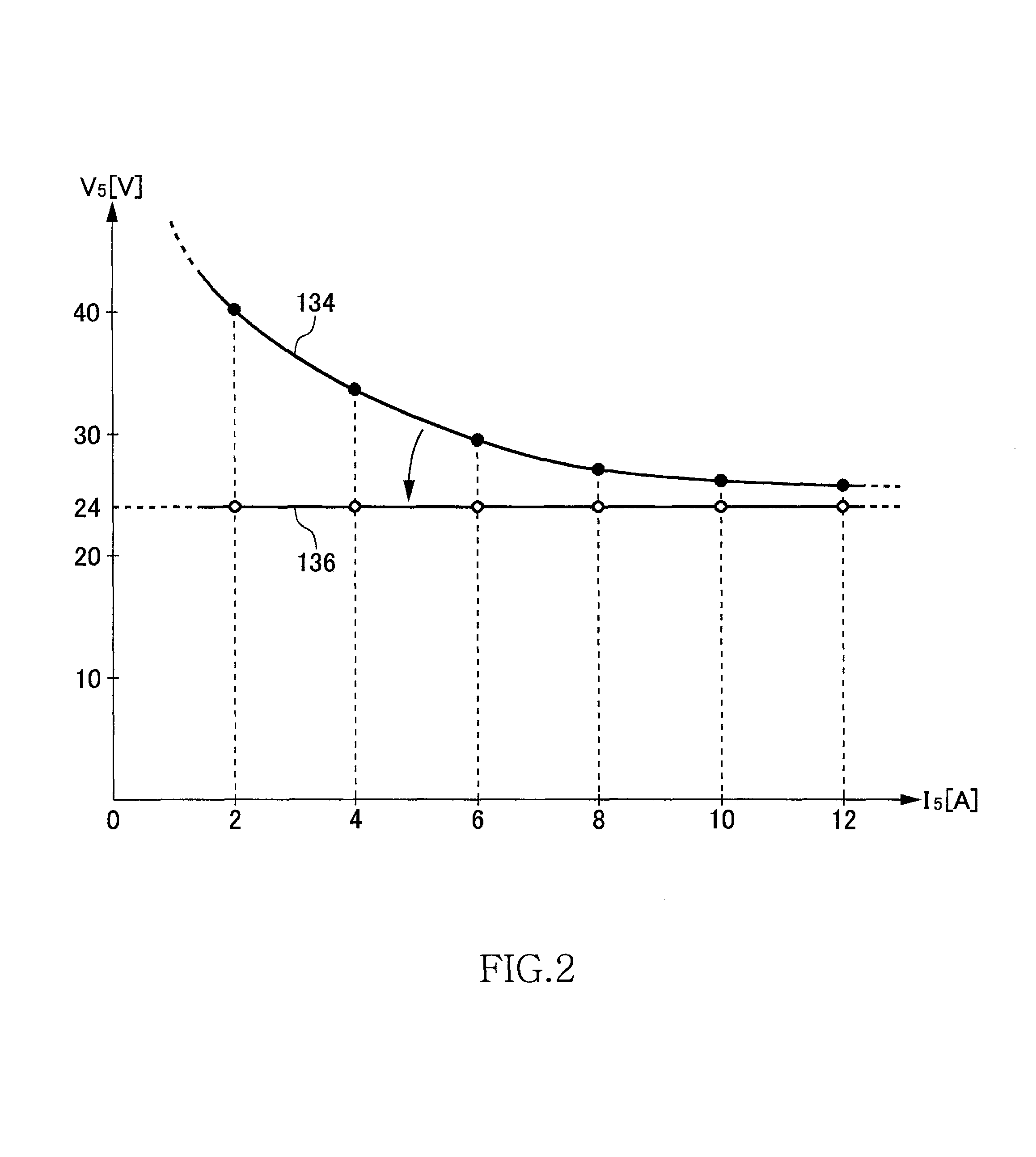

Wireless power feeder, wireless power receiver, and wireless power transmission system

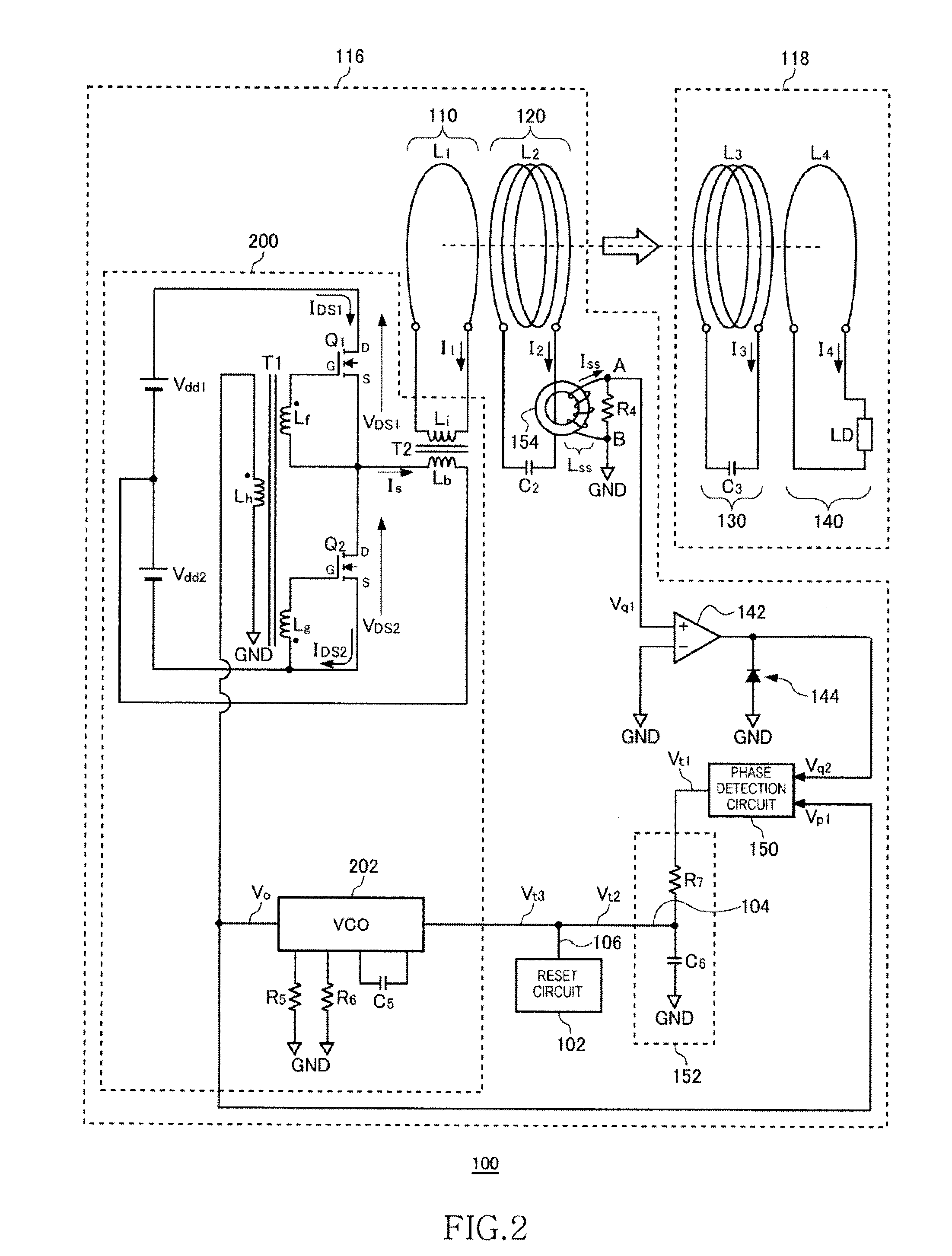

ActiveUS20110127846A1Effective controlConvenient and stableElectromagnetic wave systemTransformersElectric power transmissionResonance

Power is fed from a feeding coil L2 to a receiving coil L3 by magnetic resonance. A VCO 202 alternately turns ON / OFF switching transistors Q1 and Q2 at a drive frequency fo, whereby AC power is fed to the feeding coil L2, and then the AC power is fed from the feeding coil L2 to the receiving coil L3. A phase detection circuit 114 detects a phase difference between the current phase and voltage phase, and the VCO 202 adjusts the drive frequency fo such that the phase difference becomes zero. When load voltage is changed, the detected current phase value is adjusted with the result that the drive frequency fo is adjusted.

Owner:TDK CORPARATION

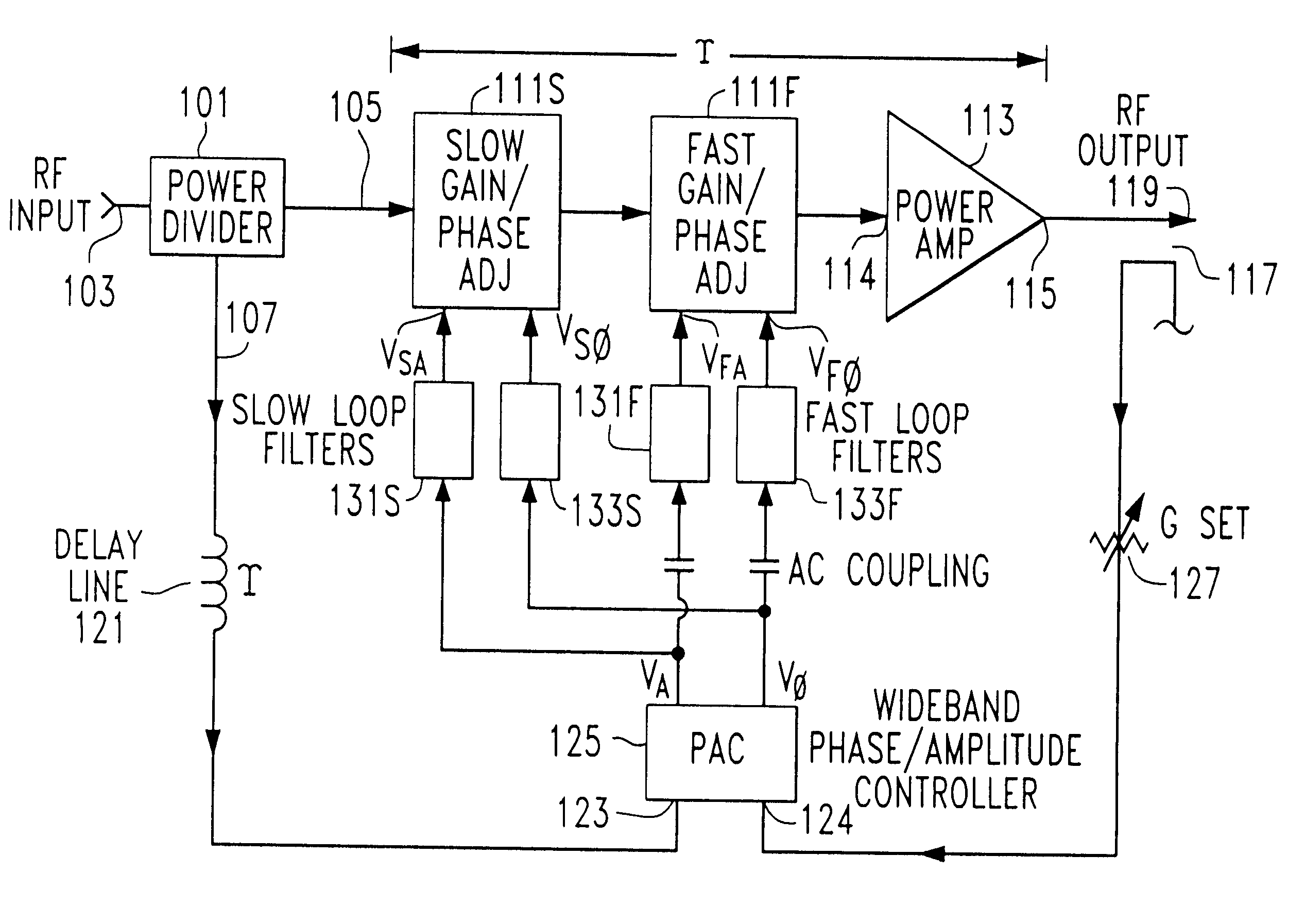

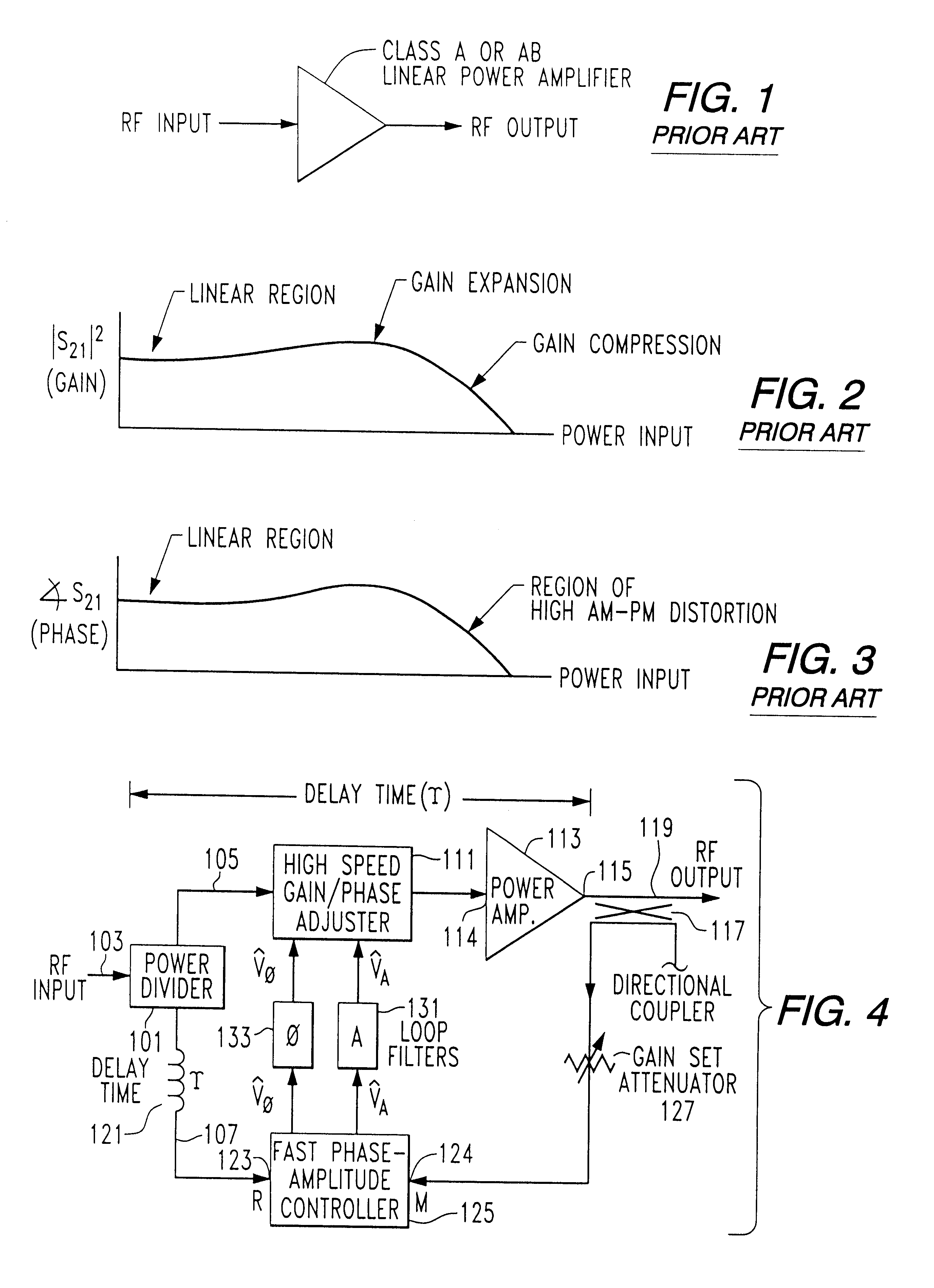

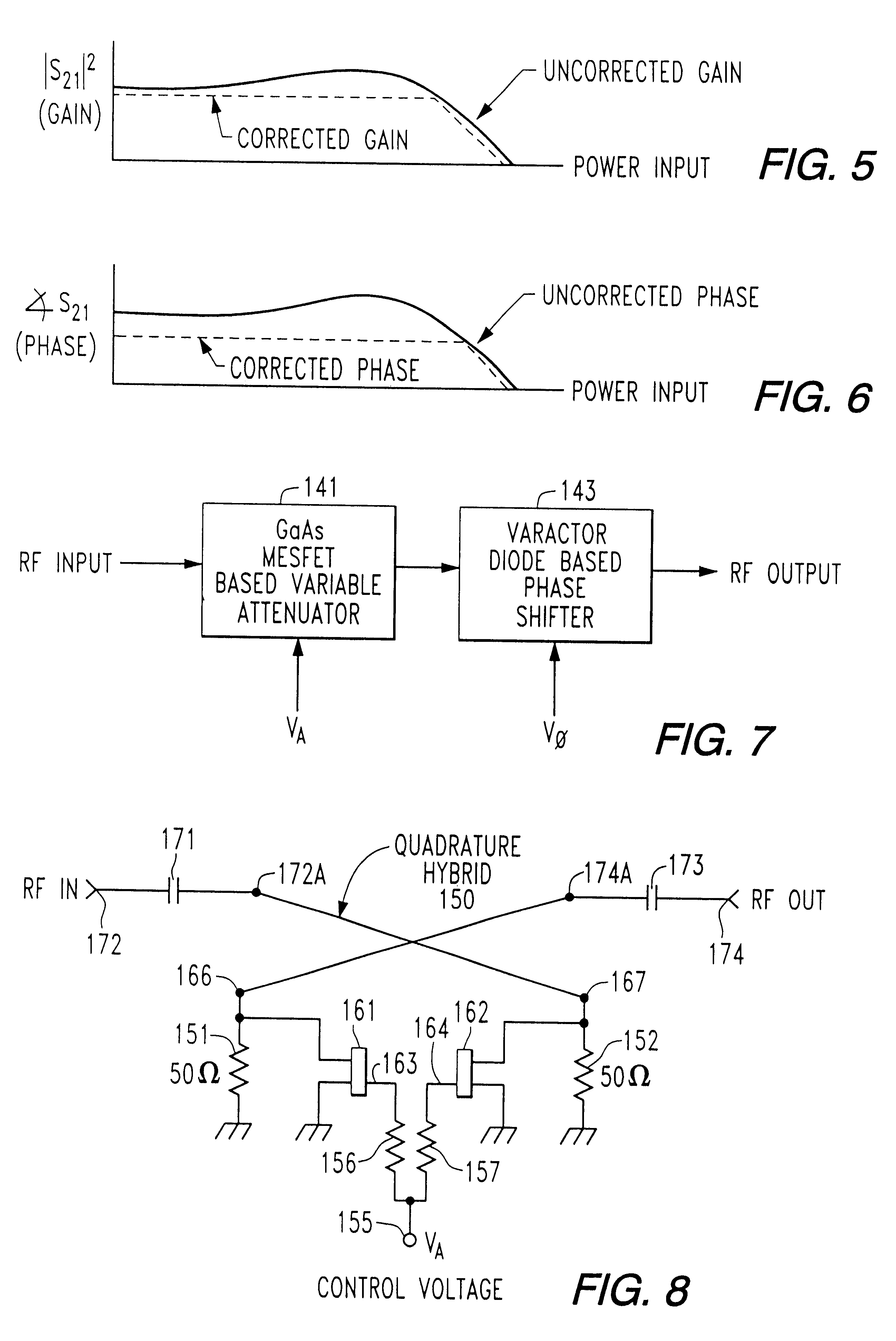

Polar envelope correction mechanism for enhancing linearity of RF/microwave power amplifier

InactiveUSRE37407E1Modest bandwidthImprove linearityAmplifier modifications to reduce non-linear distortionElectric devicesPhase distortionAudio power amplifier

Linearity of an RF / microwave power amplifier is enhanced by an amplitude and phase distortion correction mechanism based upon signal envelope feedback, that operates directly on the RF signal passing through the power amplifier. A phase-amplitude controller responds to changes in gain and phase through the RF / microwave power amplifier signal path caused by changes in RF input power, DC power supply voltages, time, temperature and other variables, and controls the operation of a gain and phase adjustment circuit, so as to maintain constant gain and transmission phase through the RF / microwave power amplifier.

Owner:INTEL CORP

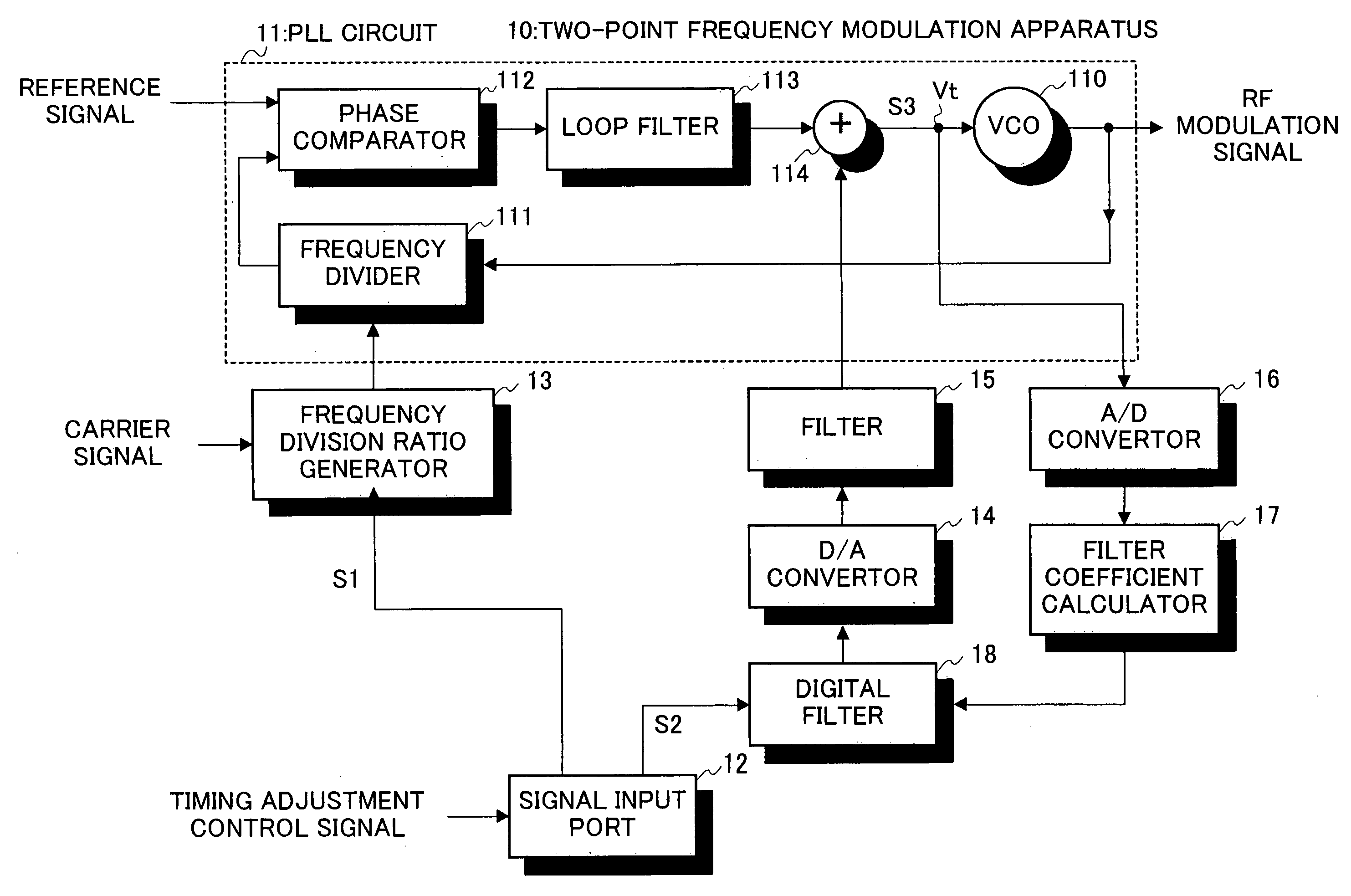

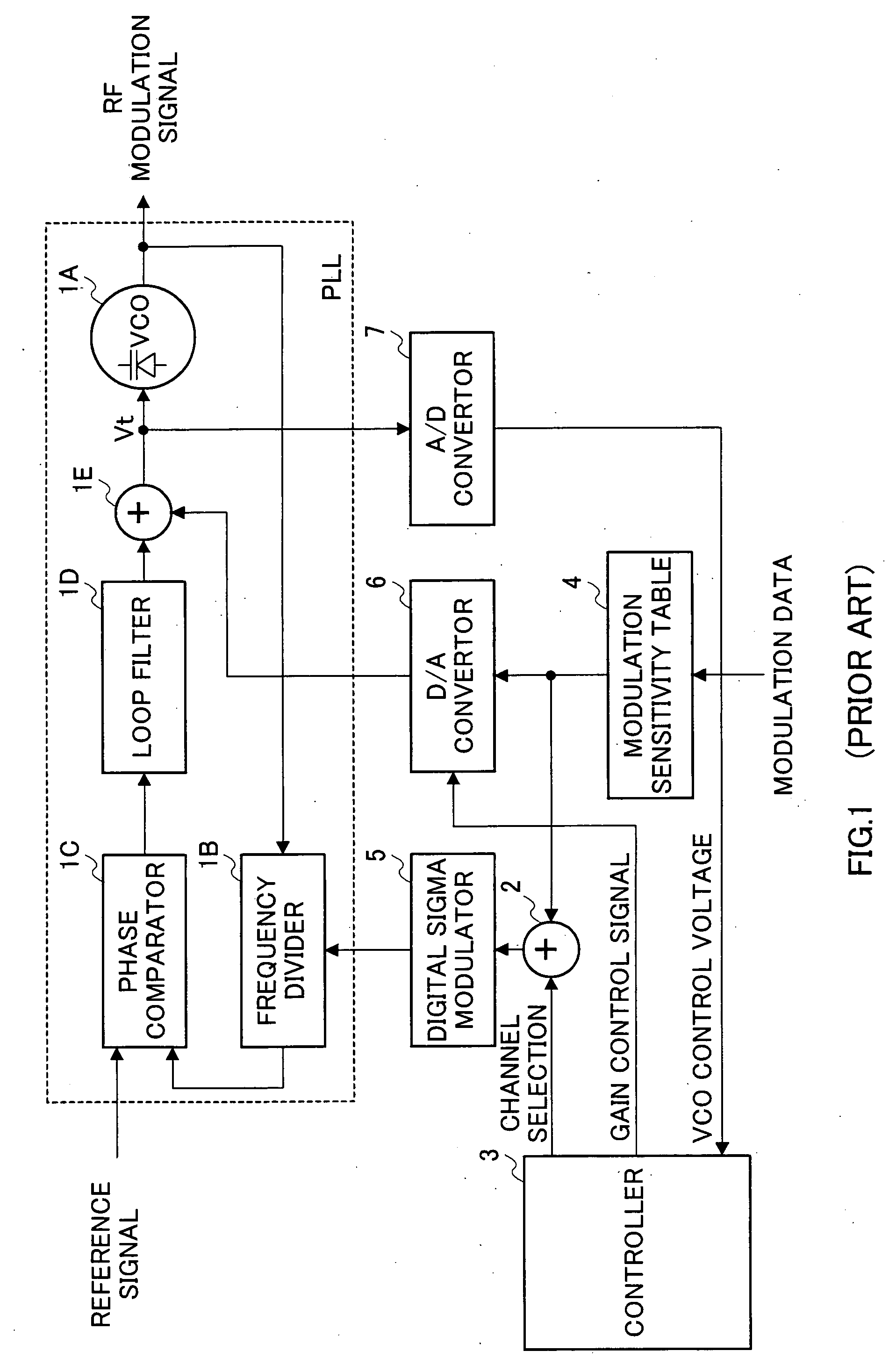

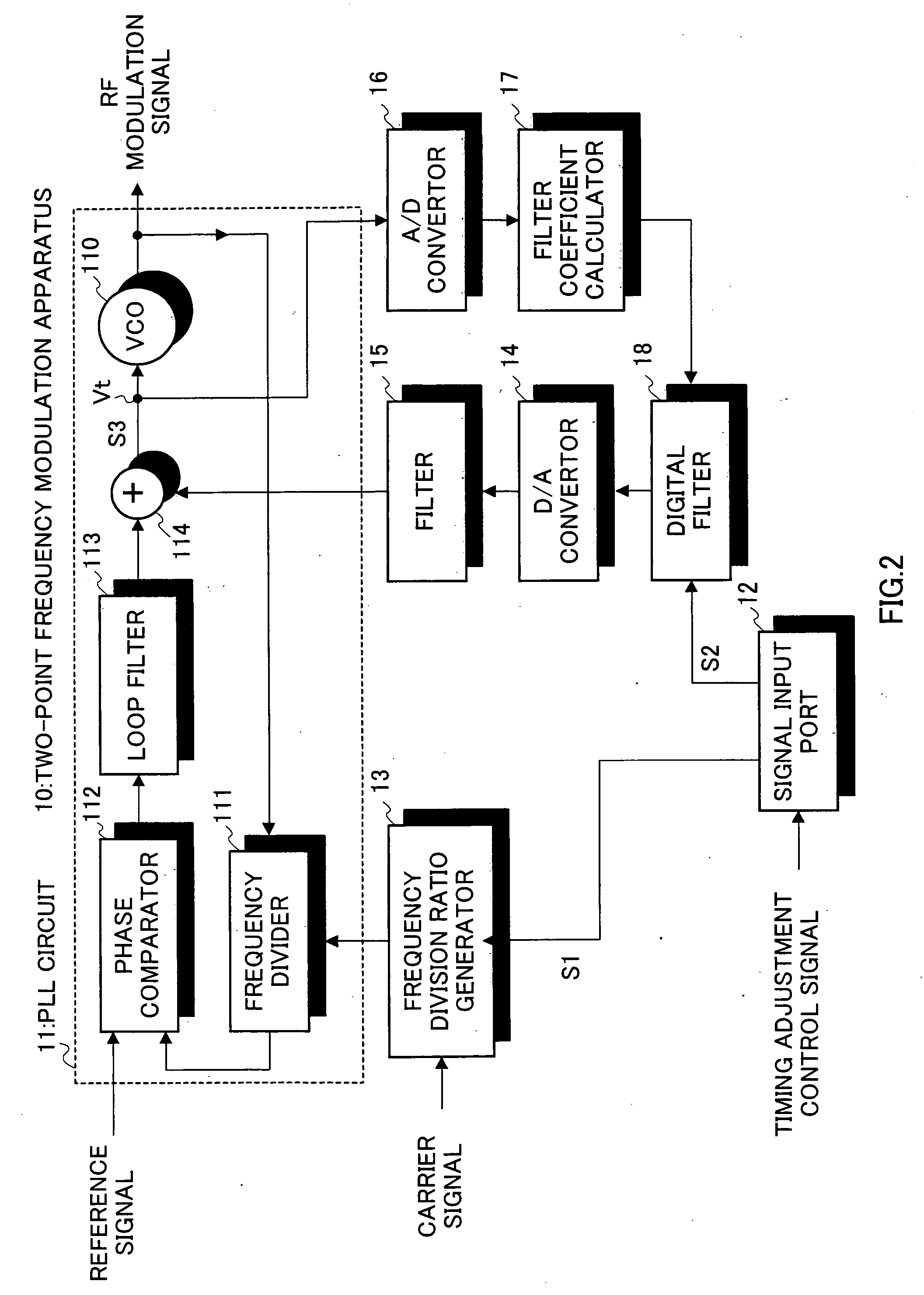

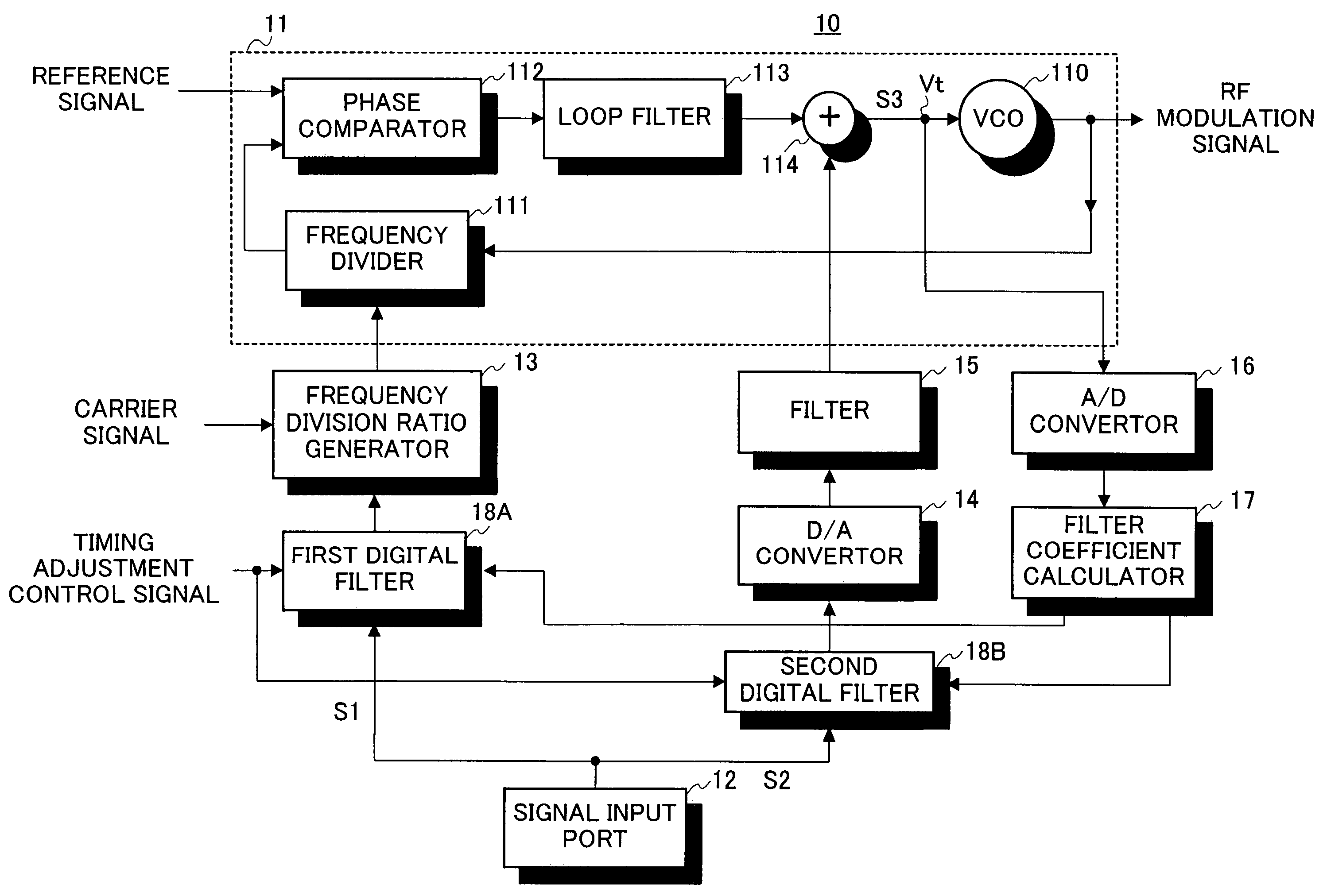

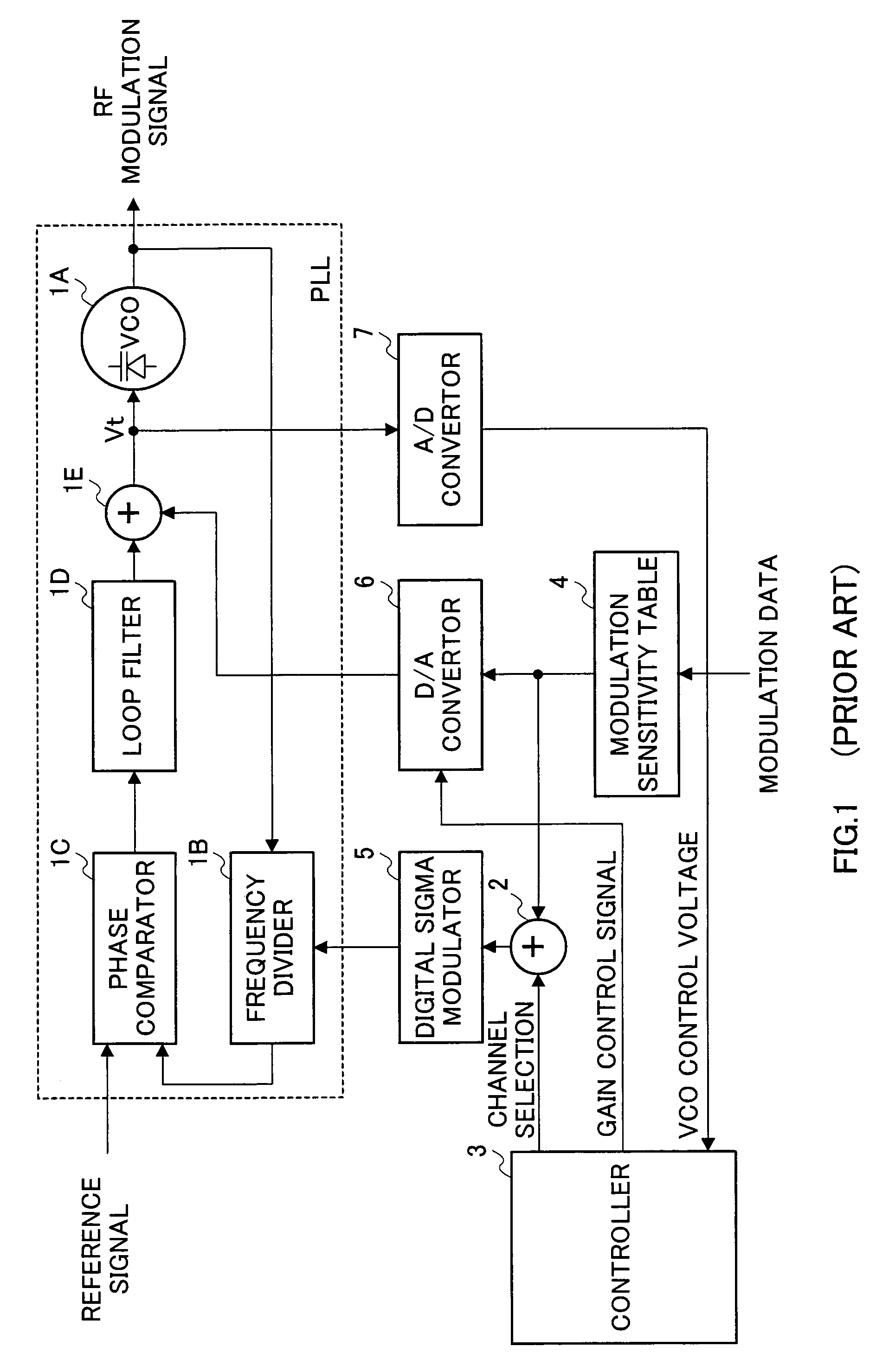

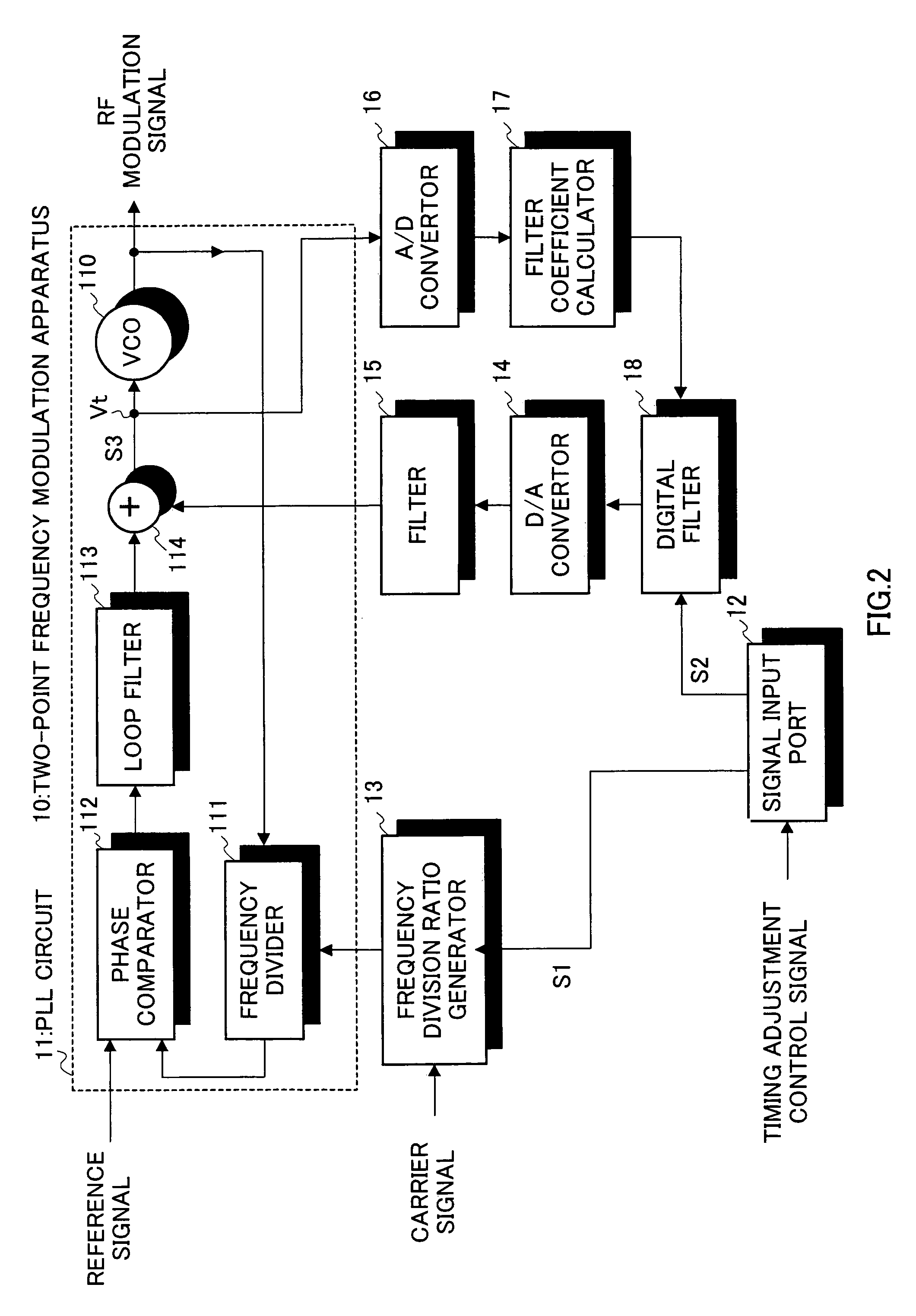

Two-point frequency modulation apparatus, wireless transmitting apparatus, and wireless receiving apparatus

InactiveUS20050232385A1Reduces input timing differenceHigh modulation accuracyPulse automatic controlAngle modulation detailsLoop filterPhase difference

A two-point frequency modulation apparatus is provided that reduces input timing difference and improves modulation accuracy. Two-point frequency modulation apparatus 10 has: PLL circuit 11; frequency division ratio generator 13 that generates the frequency division ratio in frequency divider 111 based on first digital baseband signal S1 and carrier signal; adder 114 that adds second digital baseband signal S2 to the output signal of loop filter 113; a delay index calculator (filter coefficient calculator 17) that calculates the delay index based on the magnitude of change in the amplitude of the output signal of adder 114; and a delay adjuster (digital filter 18) that shifts the phase of one of first digital baseband signal S1 and second digital baseband signal S2 according to the delay index so as to reduce the phase difference.

Owner:PANASONIC CORP

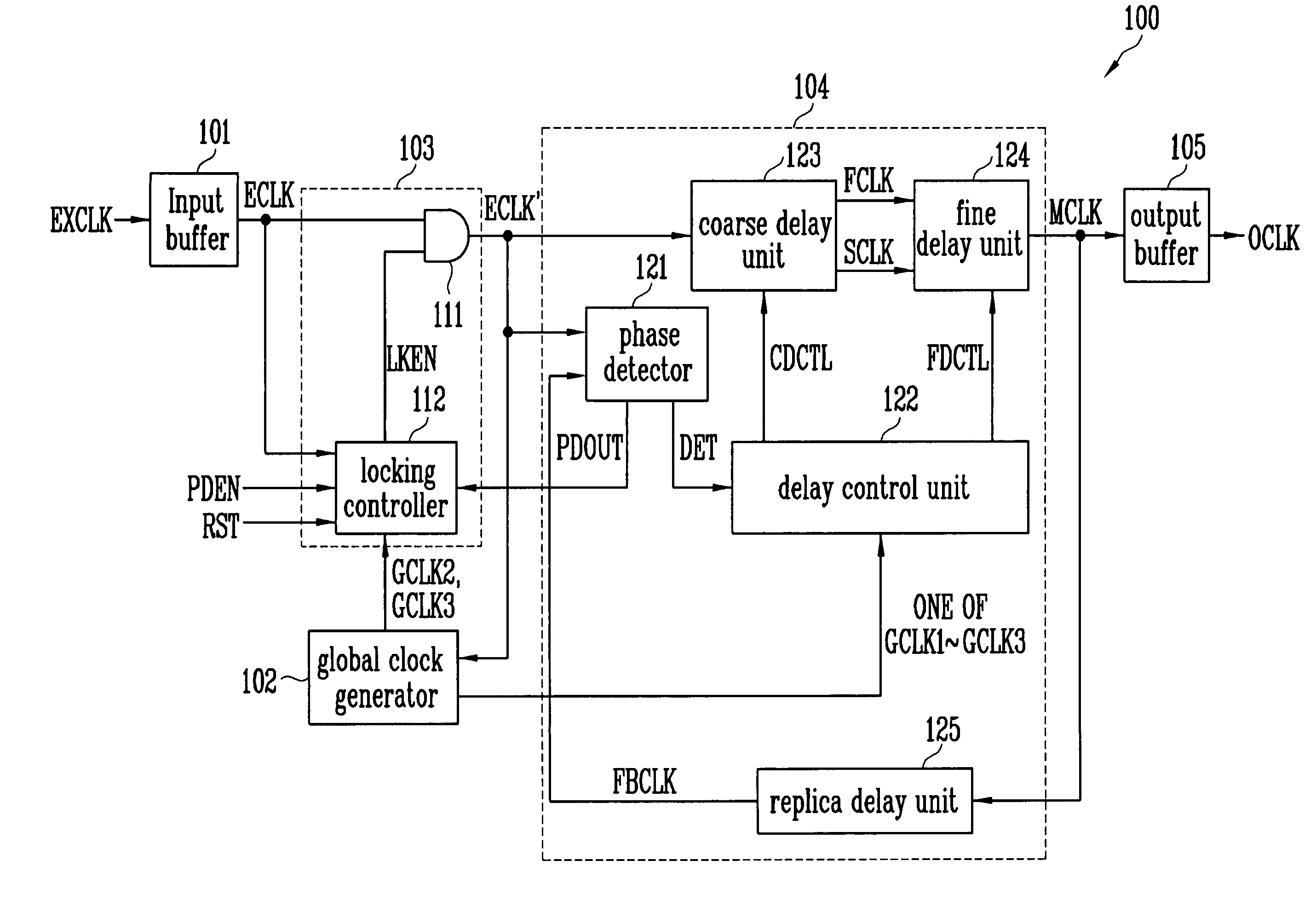

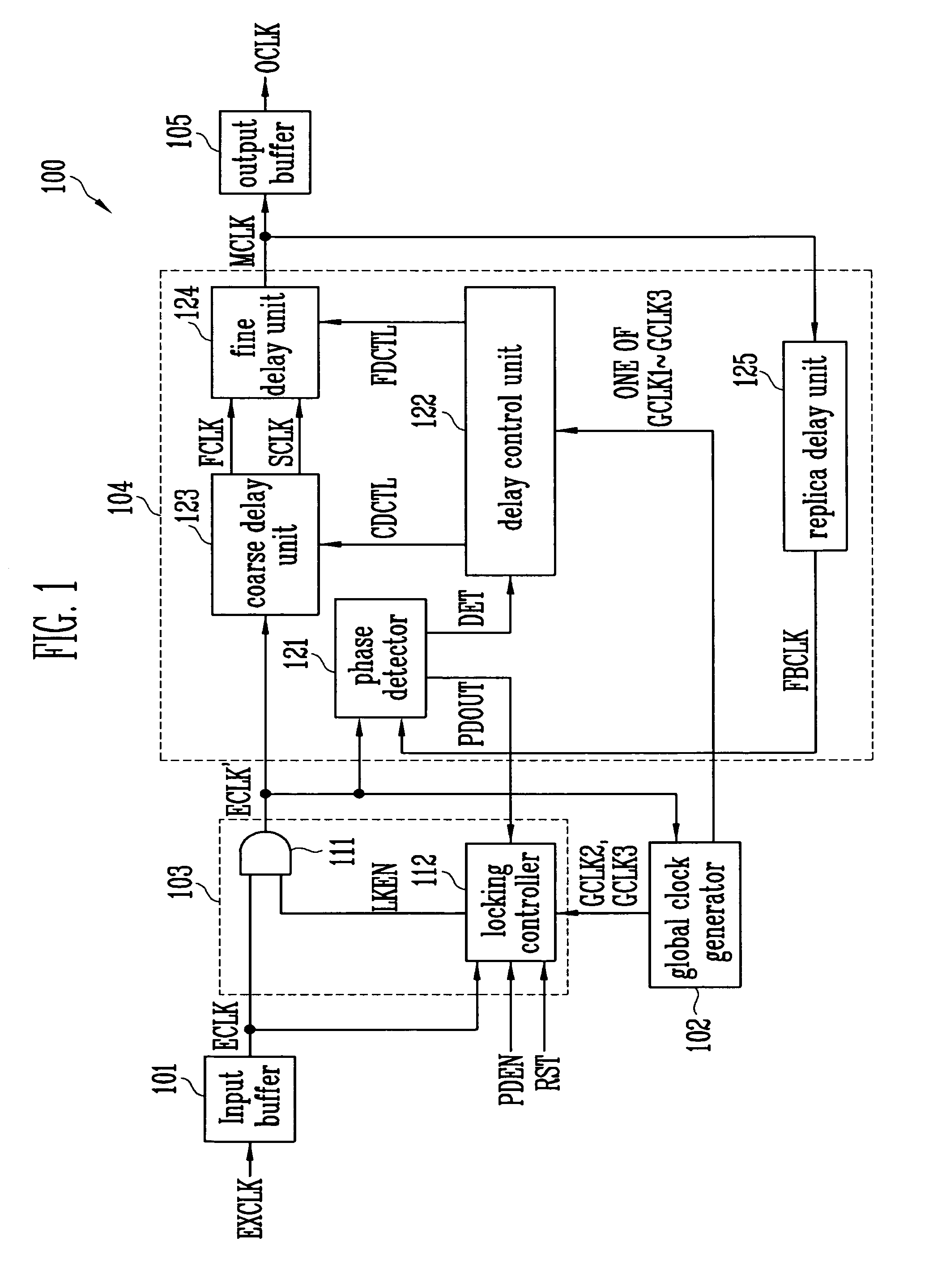

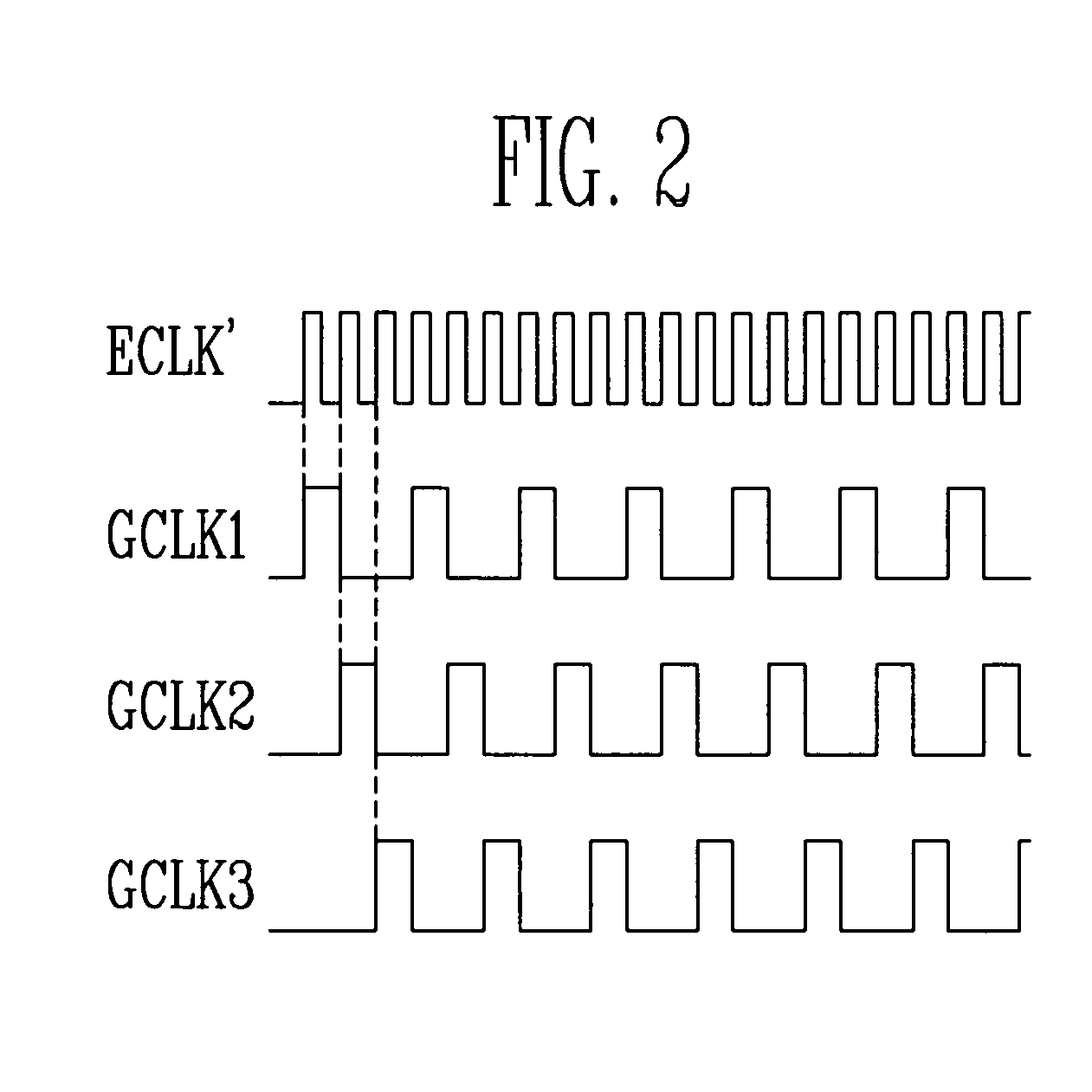

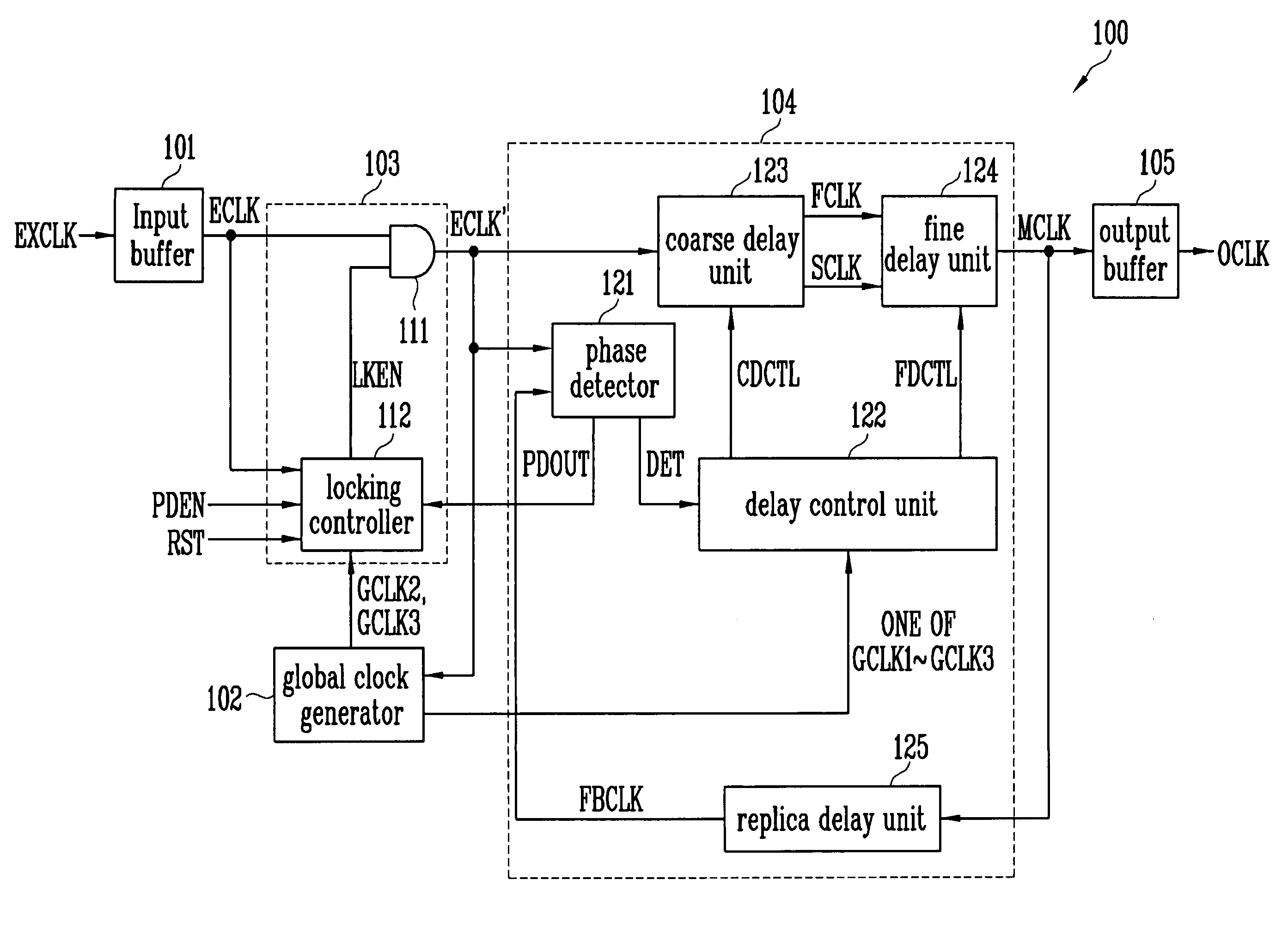

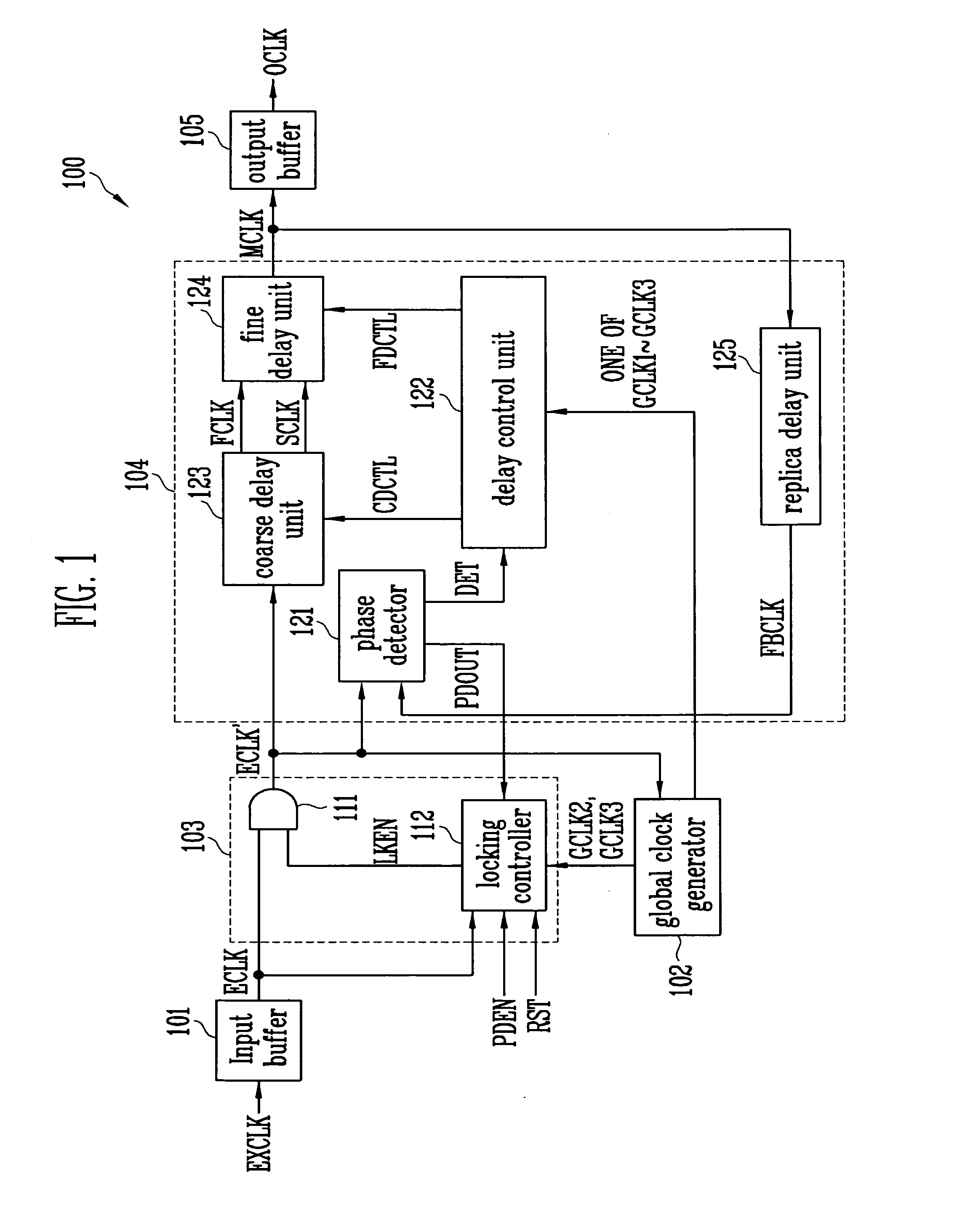

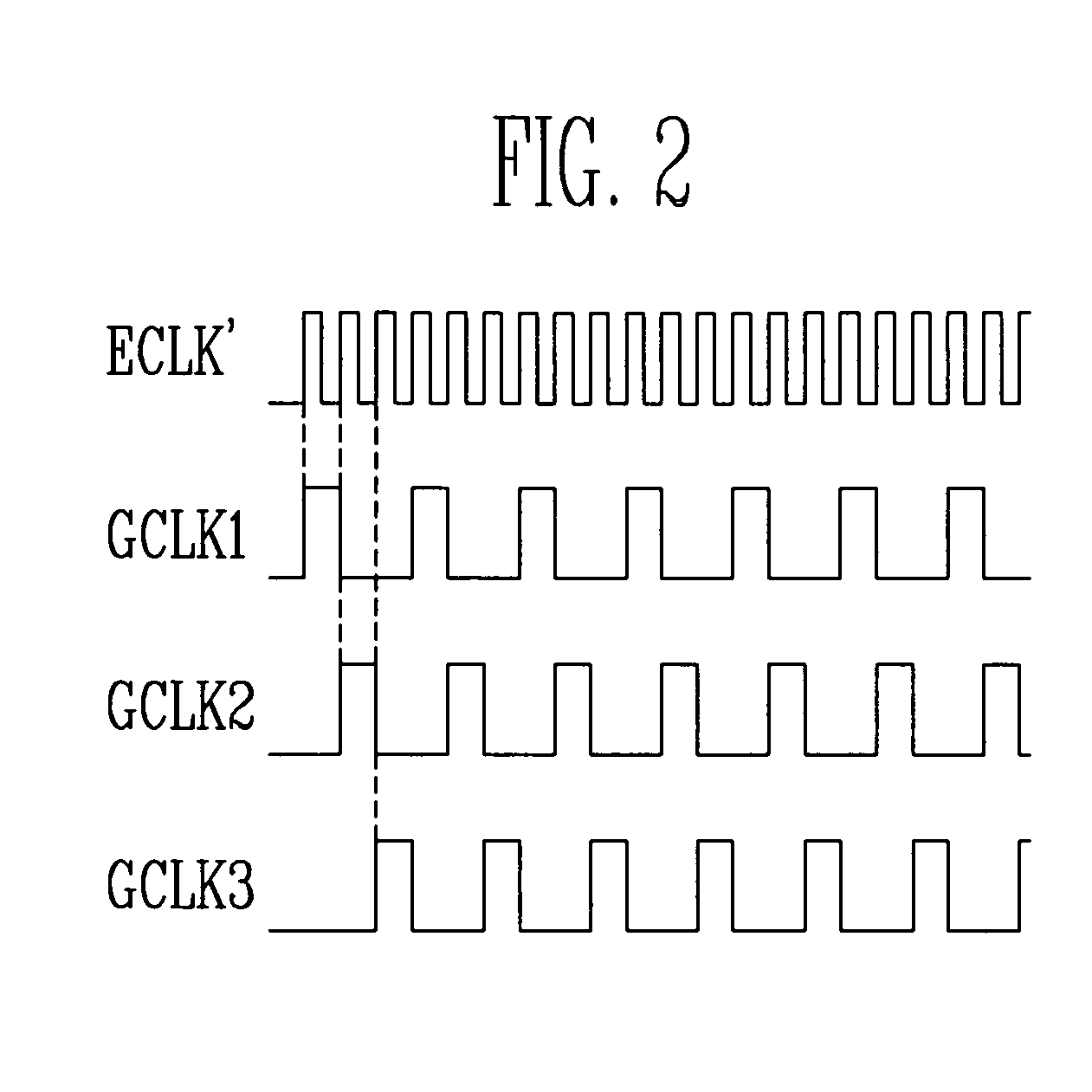

Delay locked loop with a function for implementing locking operation periodically during power down mode and locking operation method of the same

ActiveUS7388415B2Reduce power consumptionHigh speedPulse automatic controlElectricityPhase difference

A Delay Locked Loop (DLL) having a function of periodically executing a locking operation during a power down mode and a locking operation method of the same, which includes a global clock generator, a clock delay unit, and a power down control unit. The power down control unit, in response to some of a plurality of global clock signals, a phase detection signal, and a power down signal, outputs an input clock signal to each of the global clock generator and the clock delay unit. During the power down mode, the clock delay unit is enabled to periodically carry out the locking operation whenever it receives the input clock signal. Therefore, a consumed power of the DLL can be decreased during the power down mode, and a phase difference between an external clock signal and an internal clock signal during the power down mode can be decreased by the periodical locking operation of the clock delay unit, so that the DLL can operate at a fast speed after the power down mode.

Owner:SK HYNIX INC

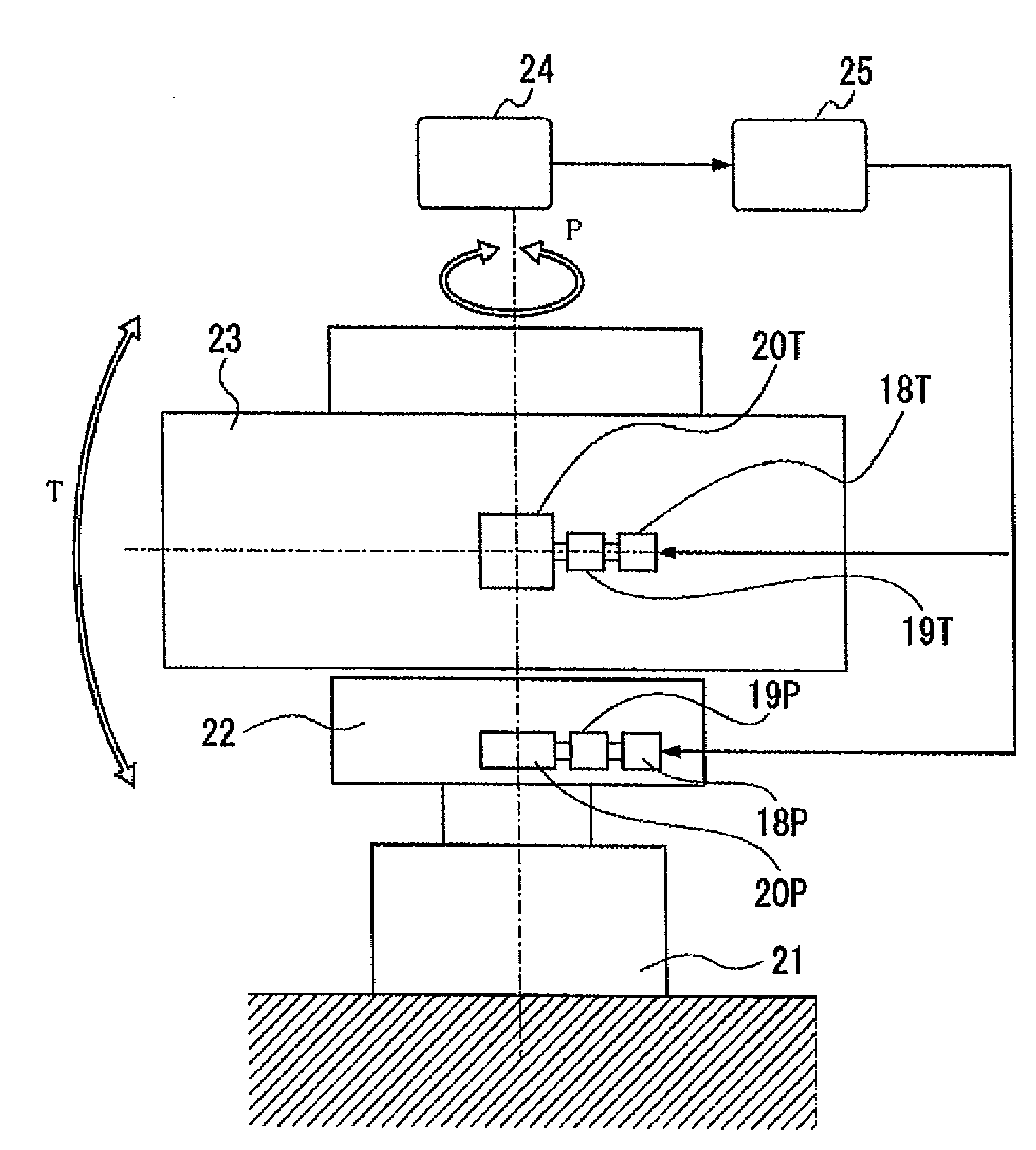

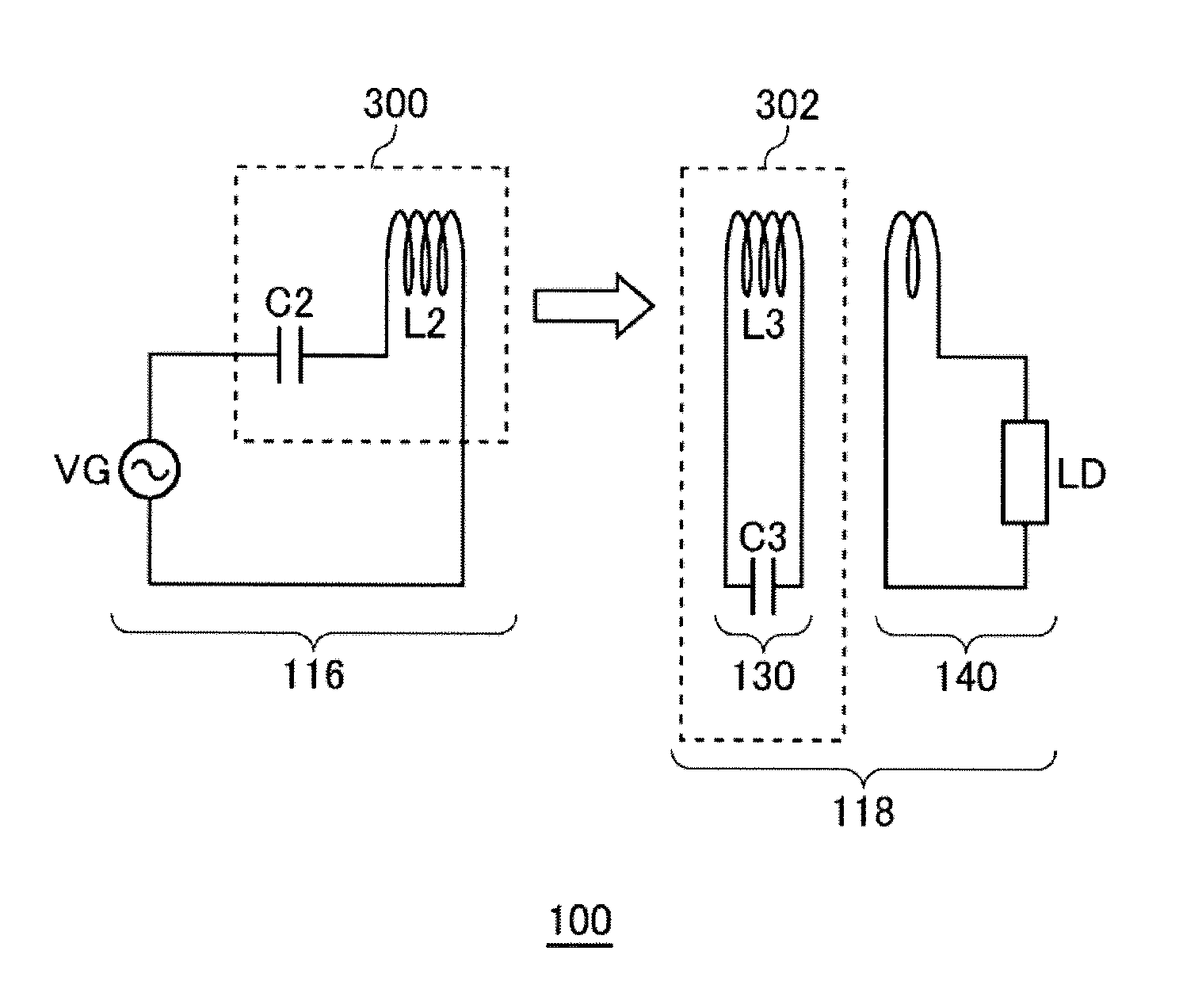

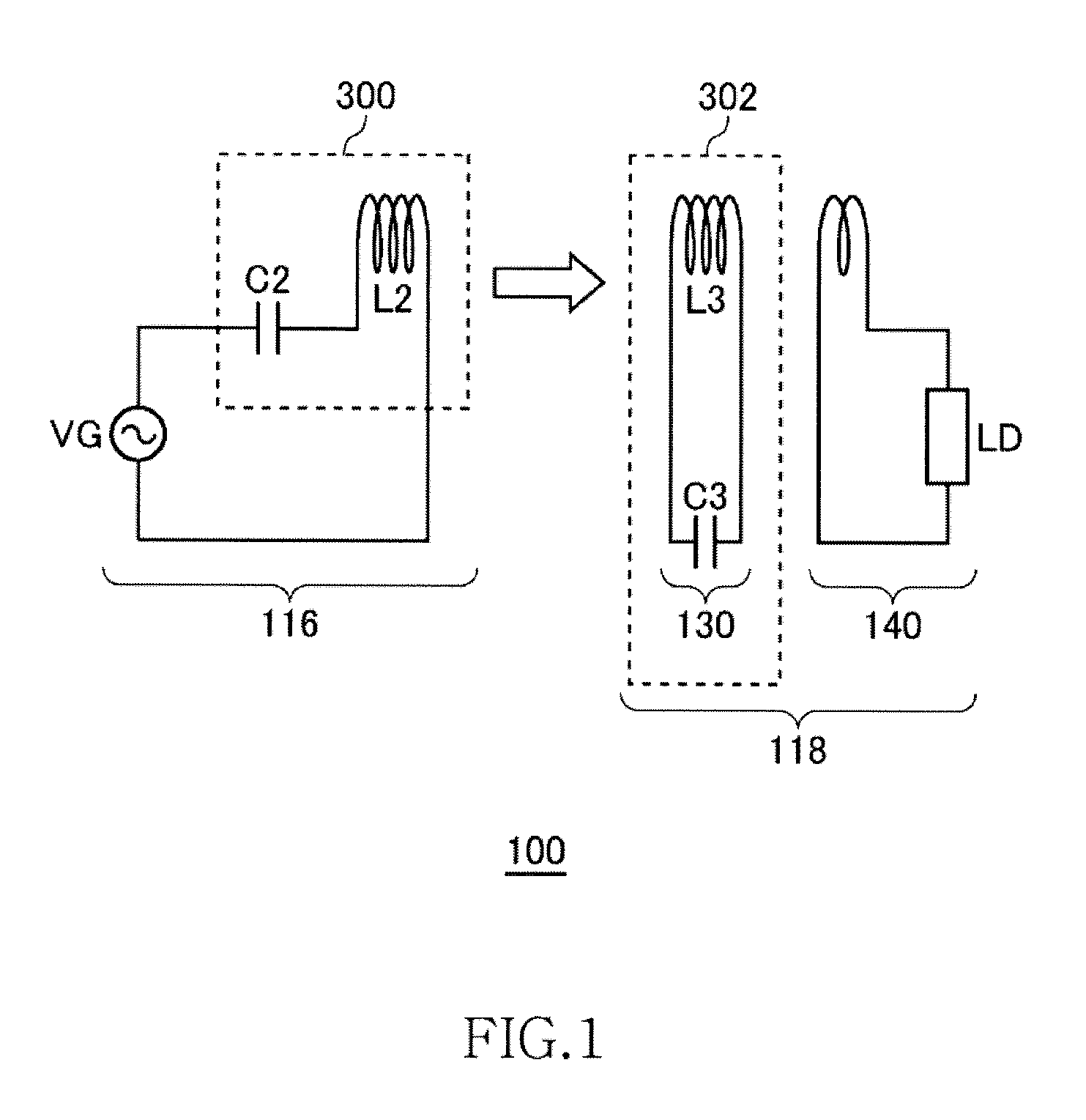

Wireless power feeder, wireless power transmission system, and table and table lamp using the same

ActiveUS20110101791A1Easy to perform controlEfficient powerBatteries circuit arrangementsElectromagnetic wave systemElectric power transmissionResonance

Power is fed from a feeding coil L2 to a receiving coil L3 by magnetic resonance. A VCO alternately turns ON / OFF switching transistors Q1 and Q2 at a drive frequency fo, whereby AC current is fed to the feeding coil L2, and then the AC current is fed from the feeding coil L2 to the receiving coil L3. A phase detection circuit detects a phase difference between the current phase and voltage phase, and the VCO adjusts the drive frequency fo such that the phase difference becomes zero. In a current phase detection circuit and a voltage phase detection circuit, detection values of the current and voltage phases can be changed, respectively and intentionally.

Owner:TDK CORPARATION

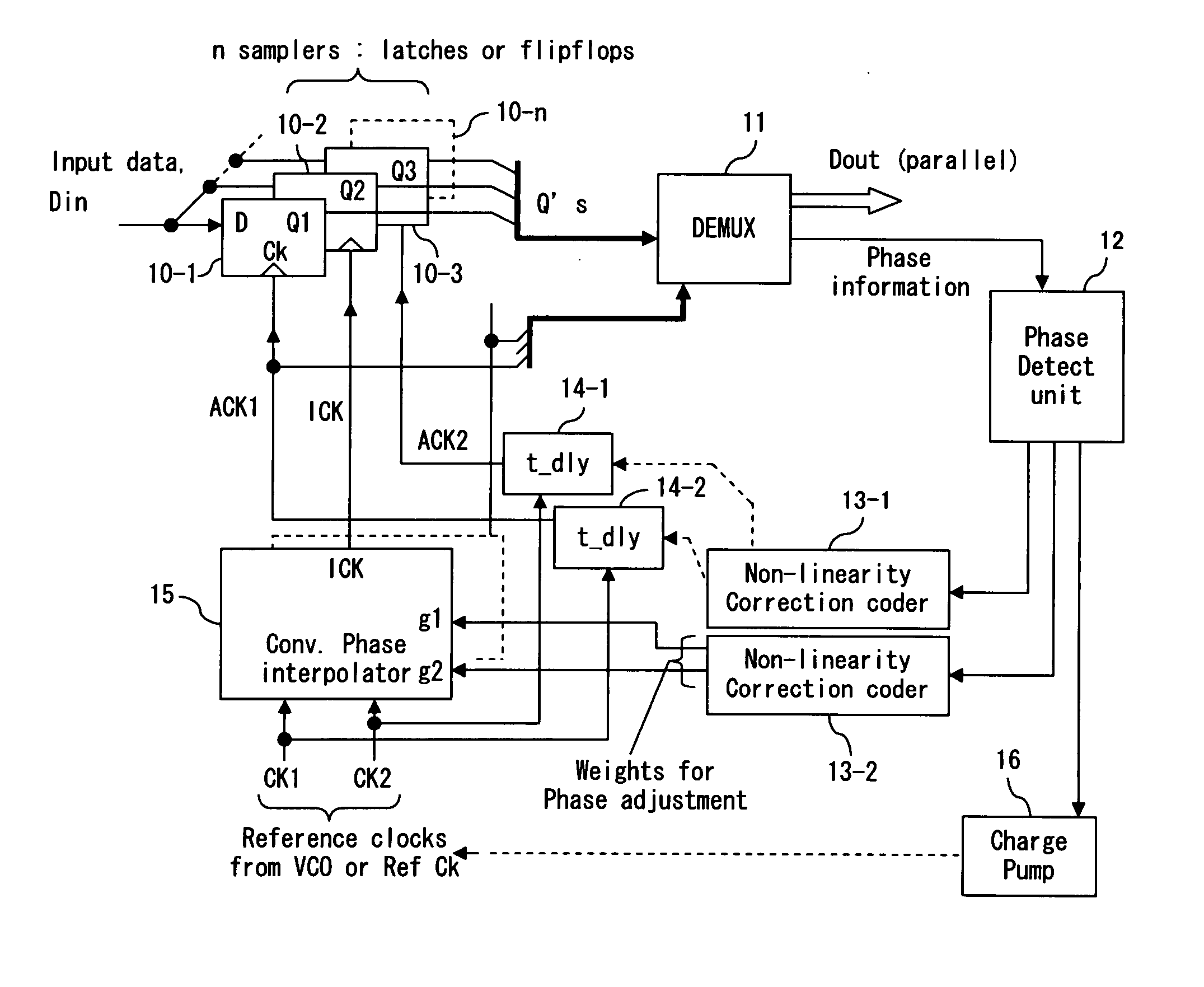

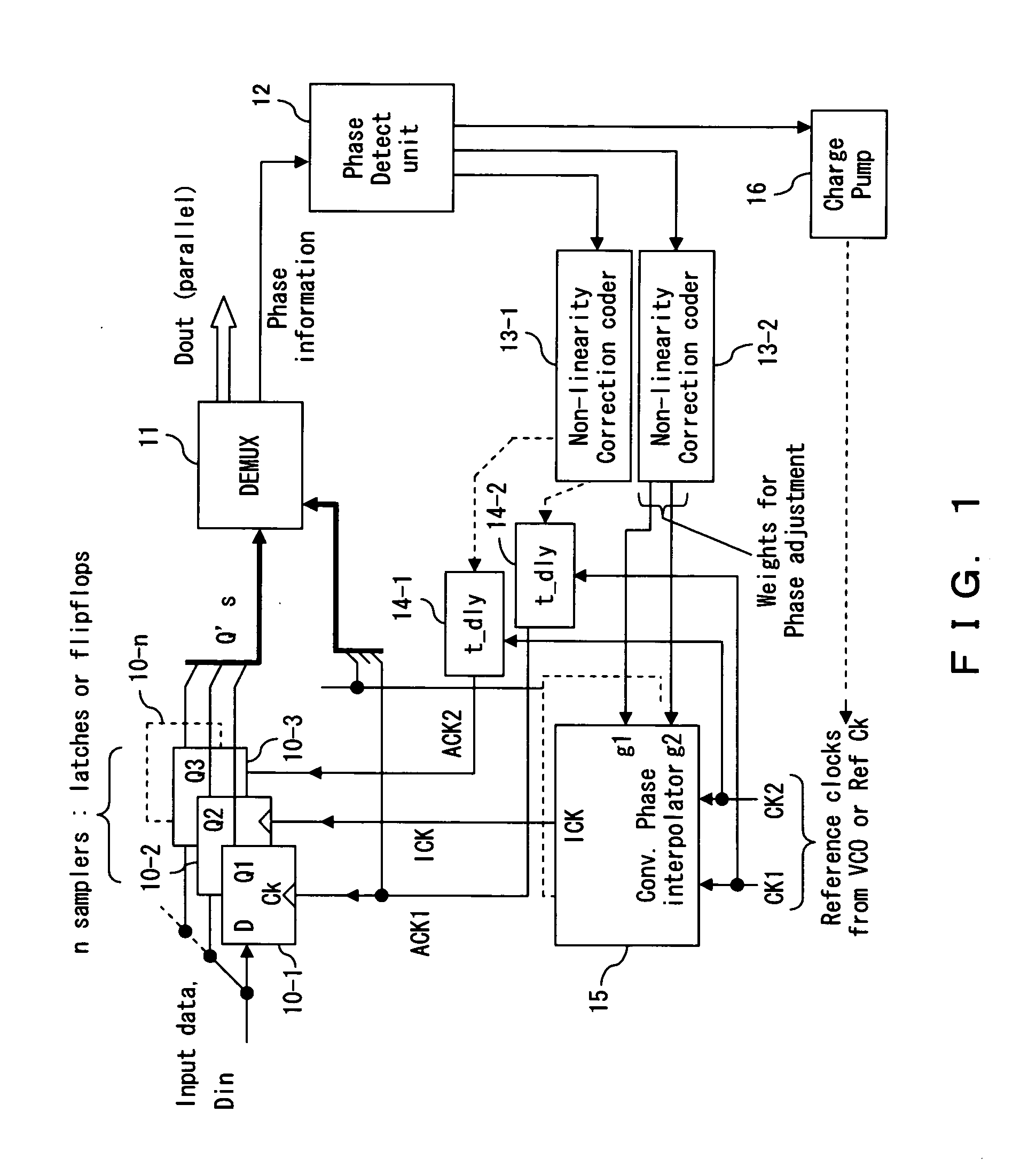

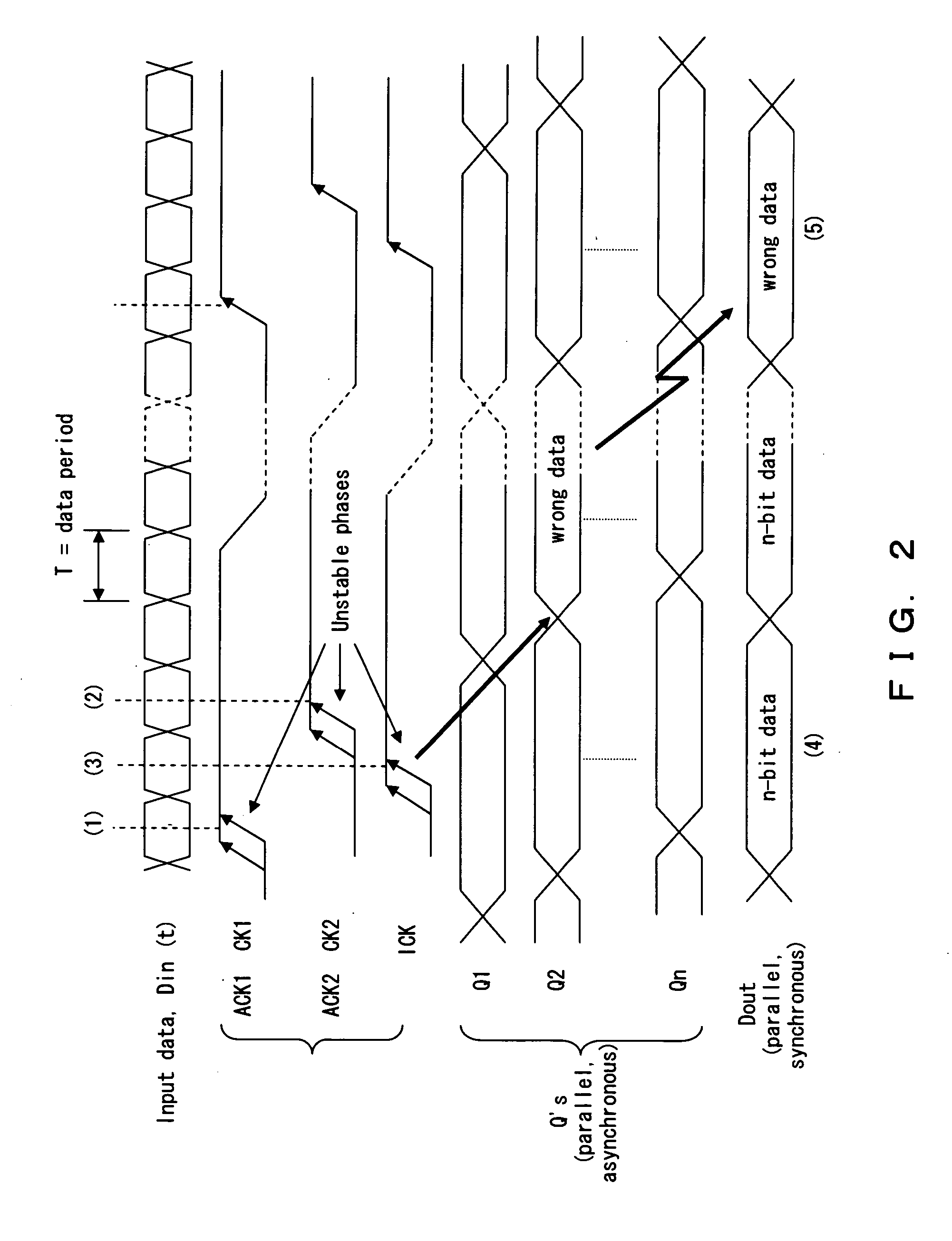

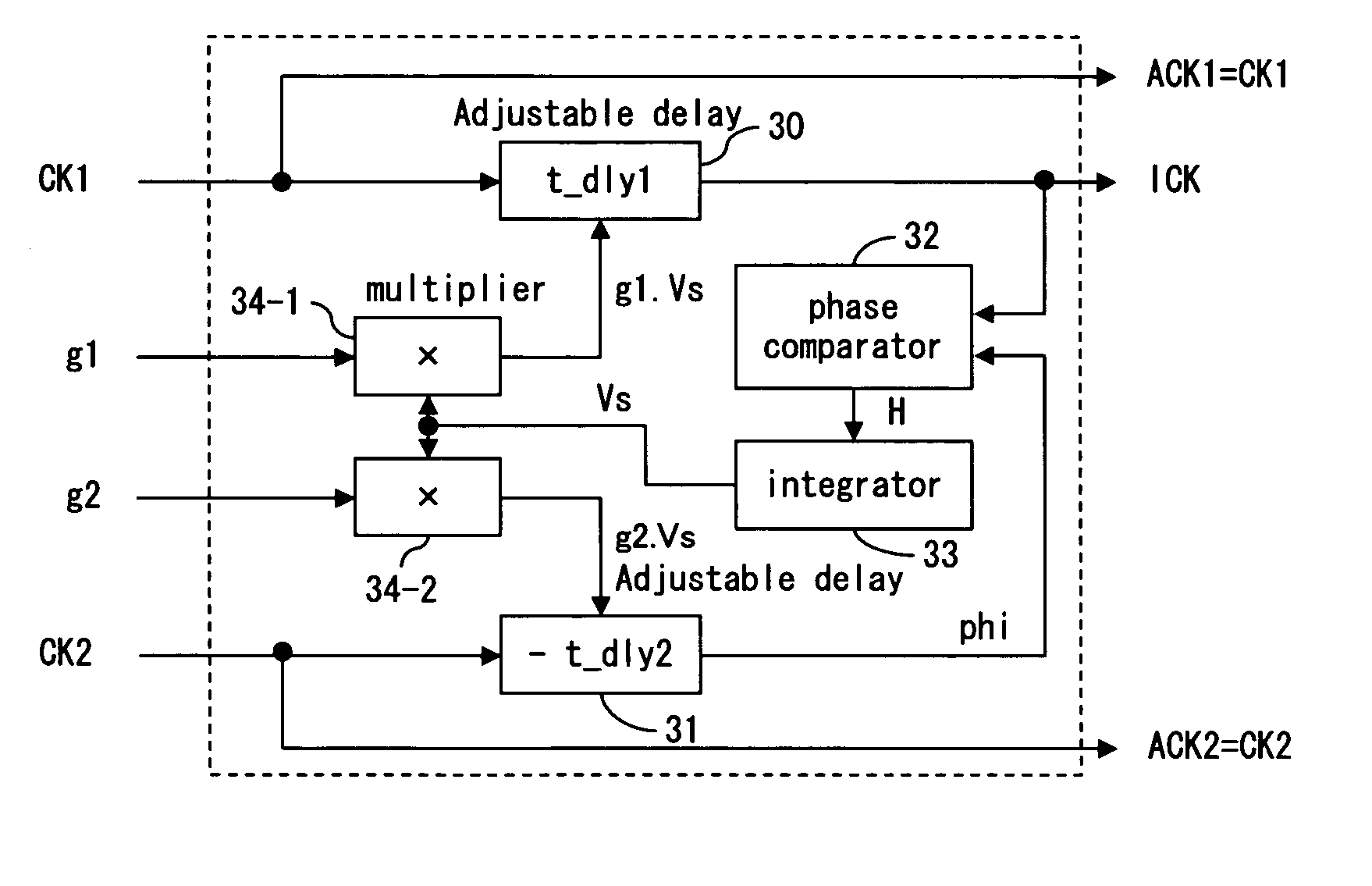

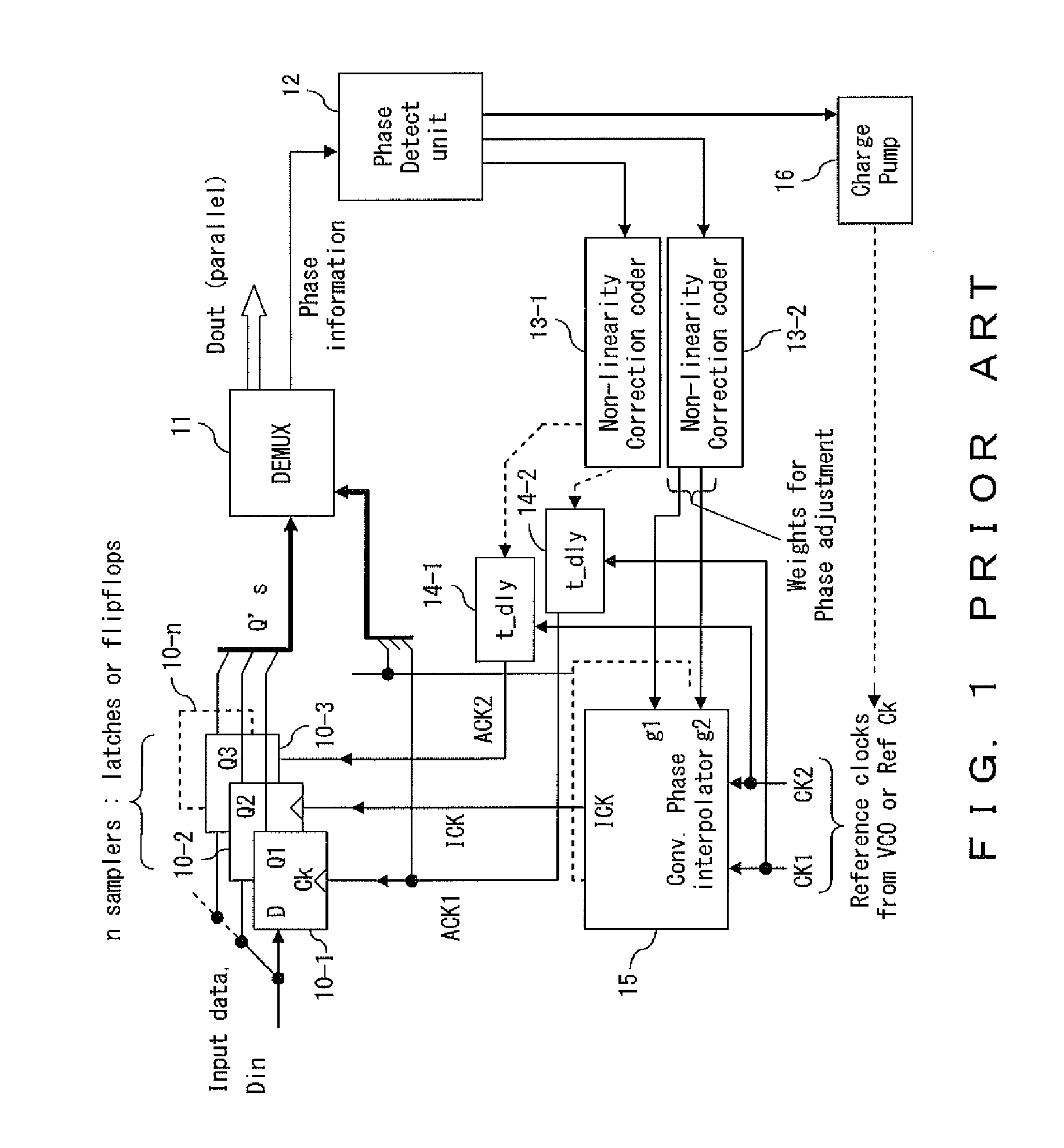

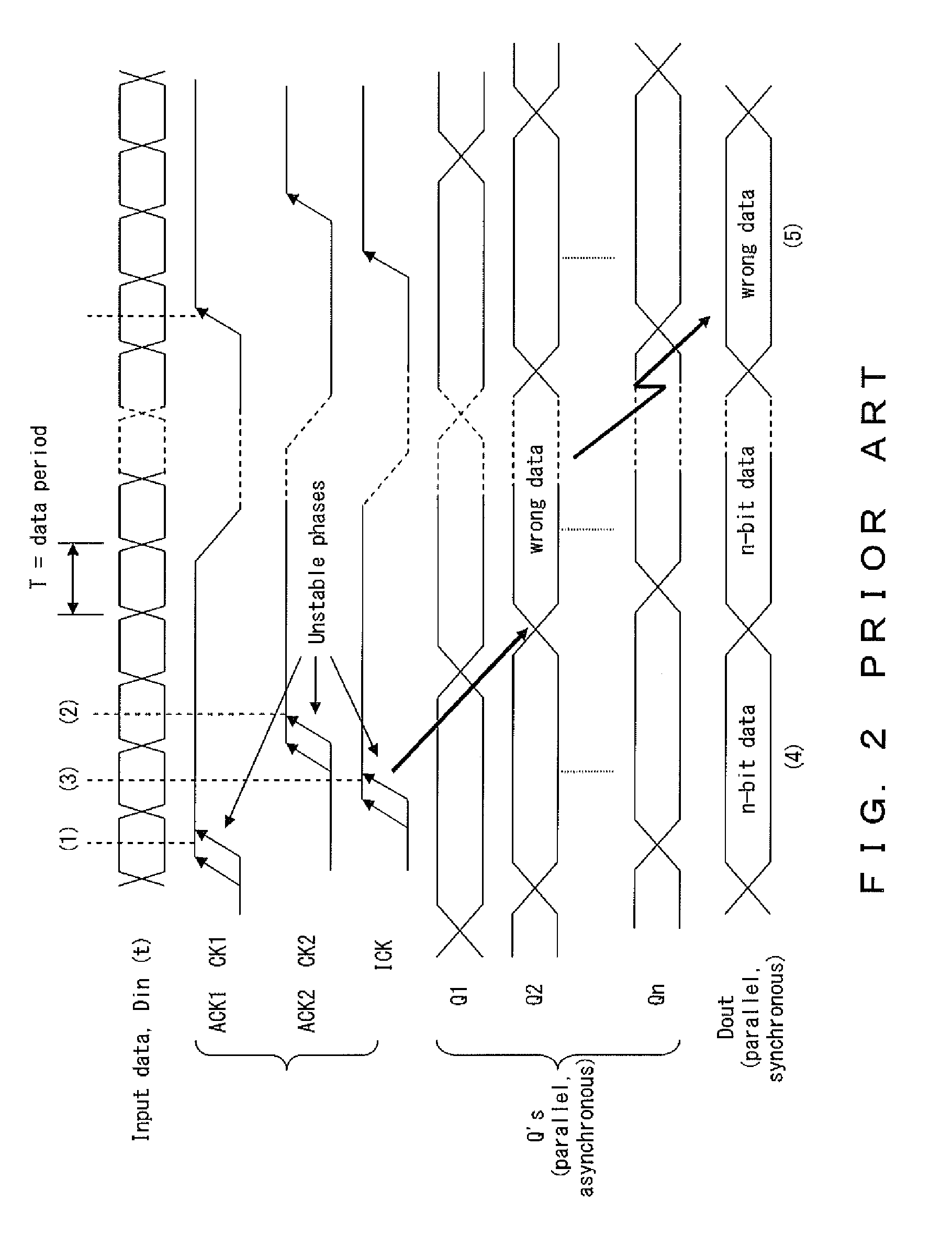

Phase interpolator with adaptive delay adjustment

InactiveUS20070146014A1Small and simple configurationReduce phase differencePulse automatic controlPulse train pattern monitoringIntegratorPhase difference

The phase interpolator includes two adjustable delays 30 and 31, phase comparator 32 which detects a phase difference between a signal delayed by the adjustable delay 30 and a signal delayed by the adjustable delay 31, an integrator 33 which integrates the outputs of the phase comparator 32 and multipliers 34-1 and 34-2 which set a control voltage for the adjustable delays 30 and 31. The feedback loop comprising phase comparator 32 and integrator 33 controls a delay amount of the adjustable delay 30 thereby securing a phase relation between {ACK1, ACK2} and ICK to achieve a stable ICK phase.

Owner:FUJITSU LTD

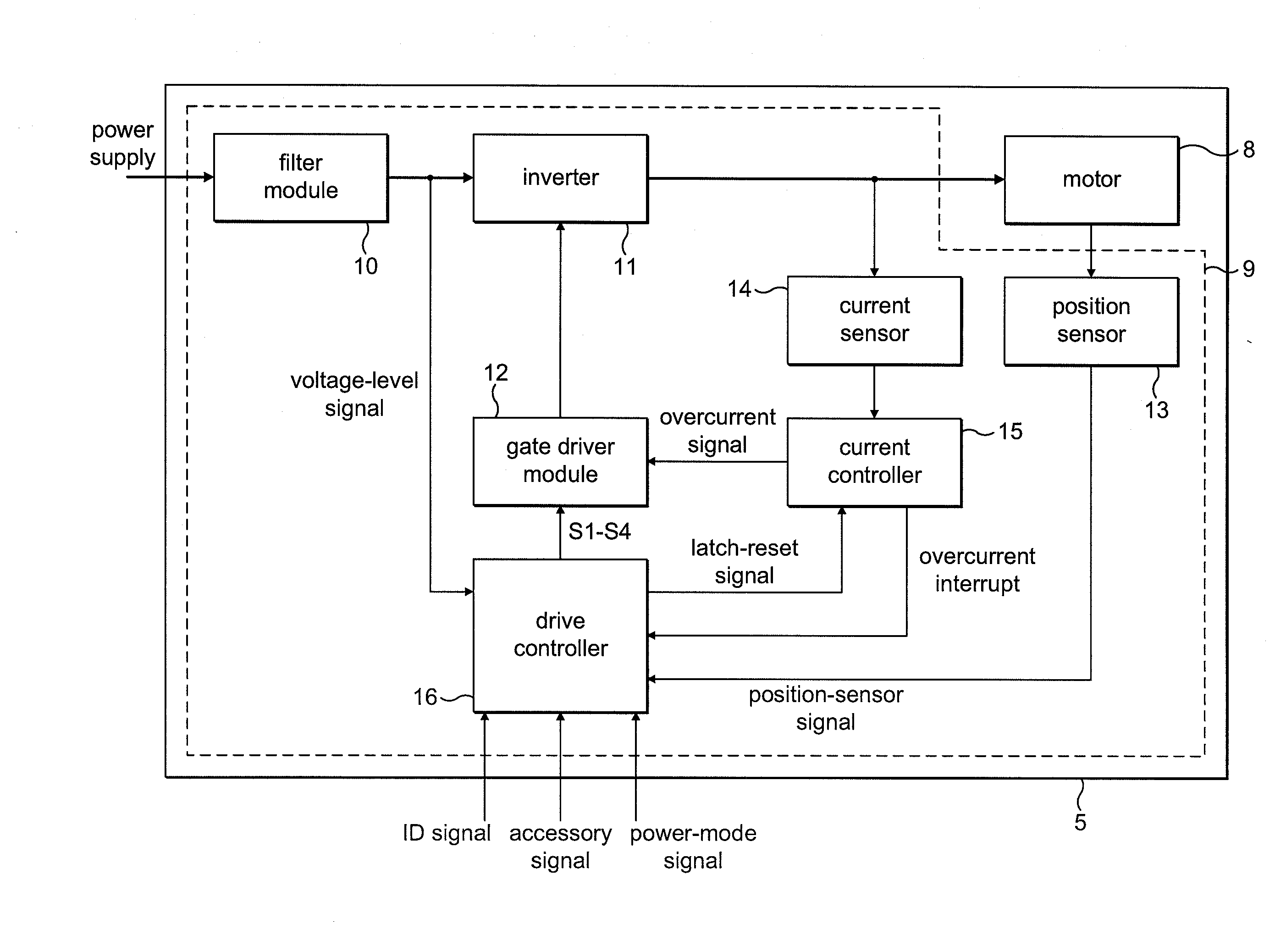

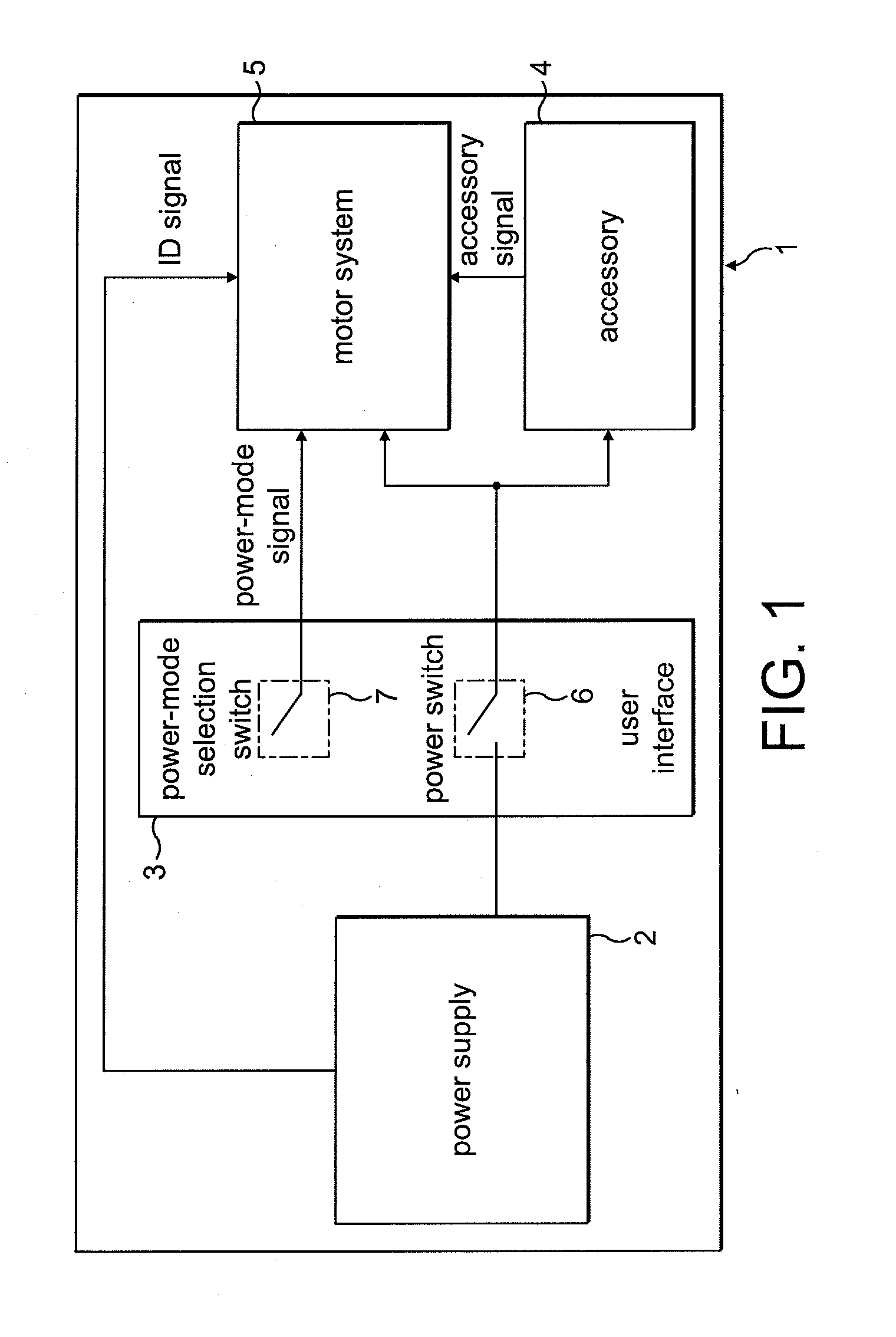

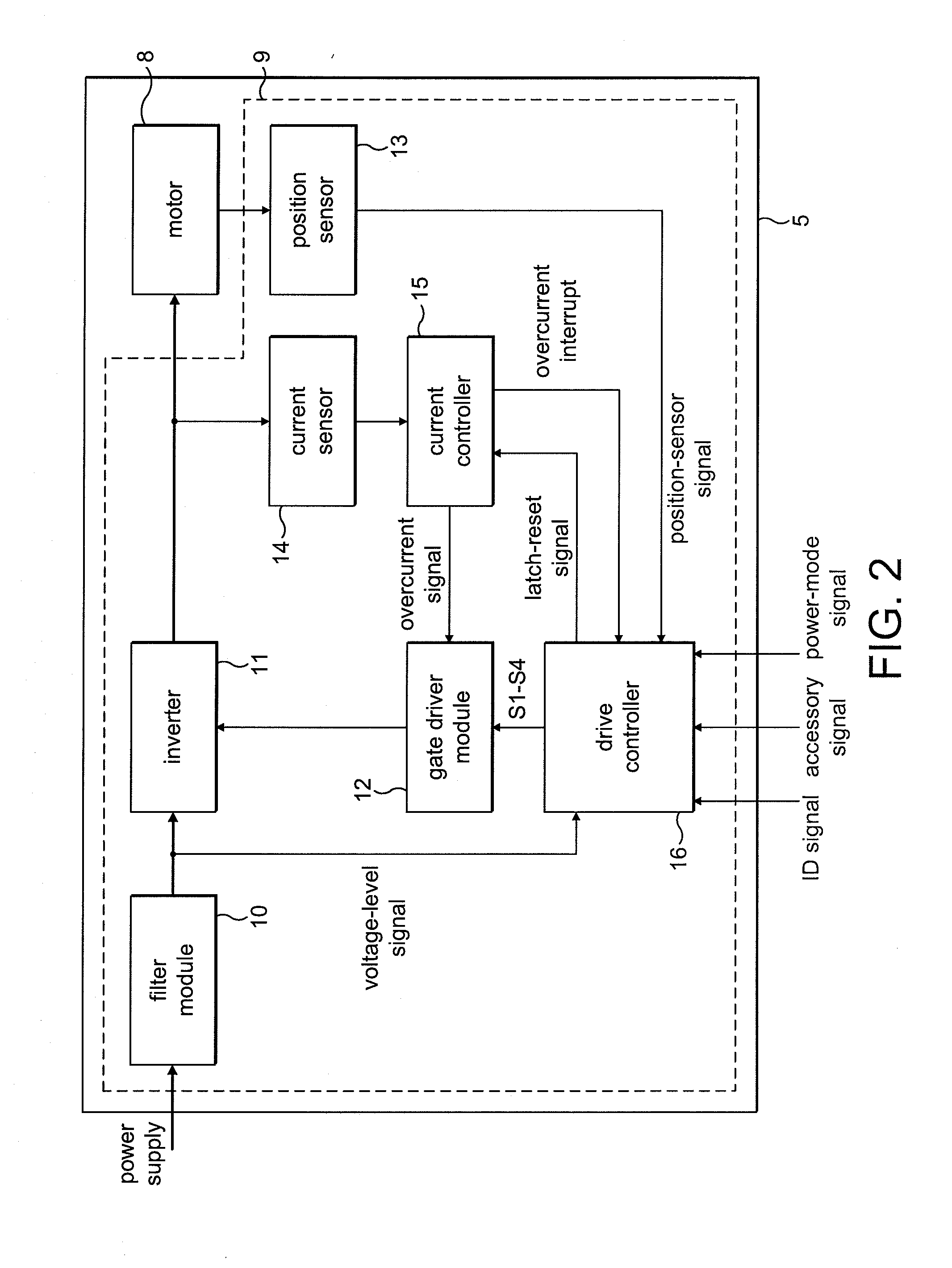

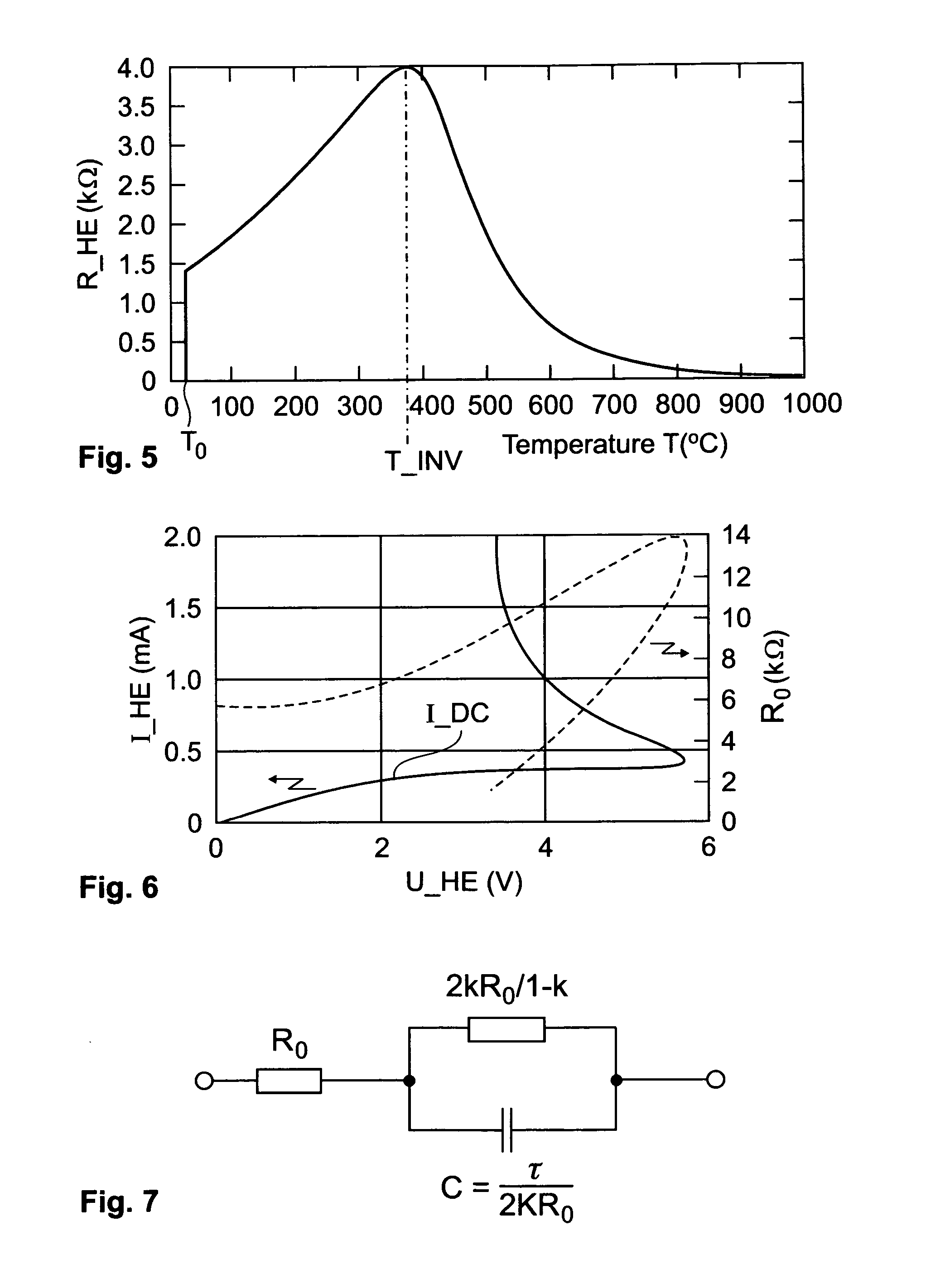

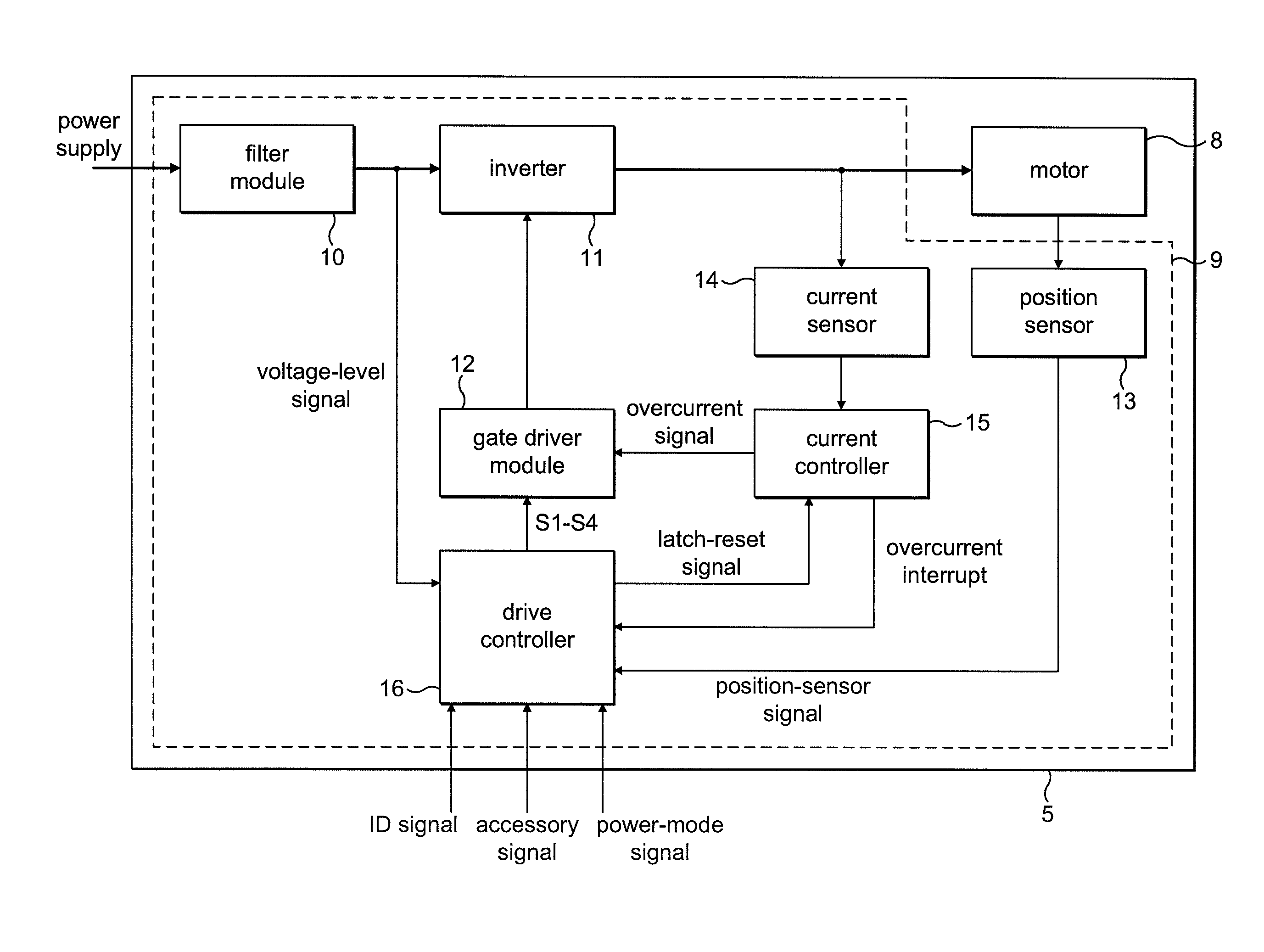

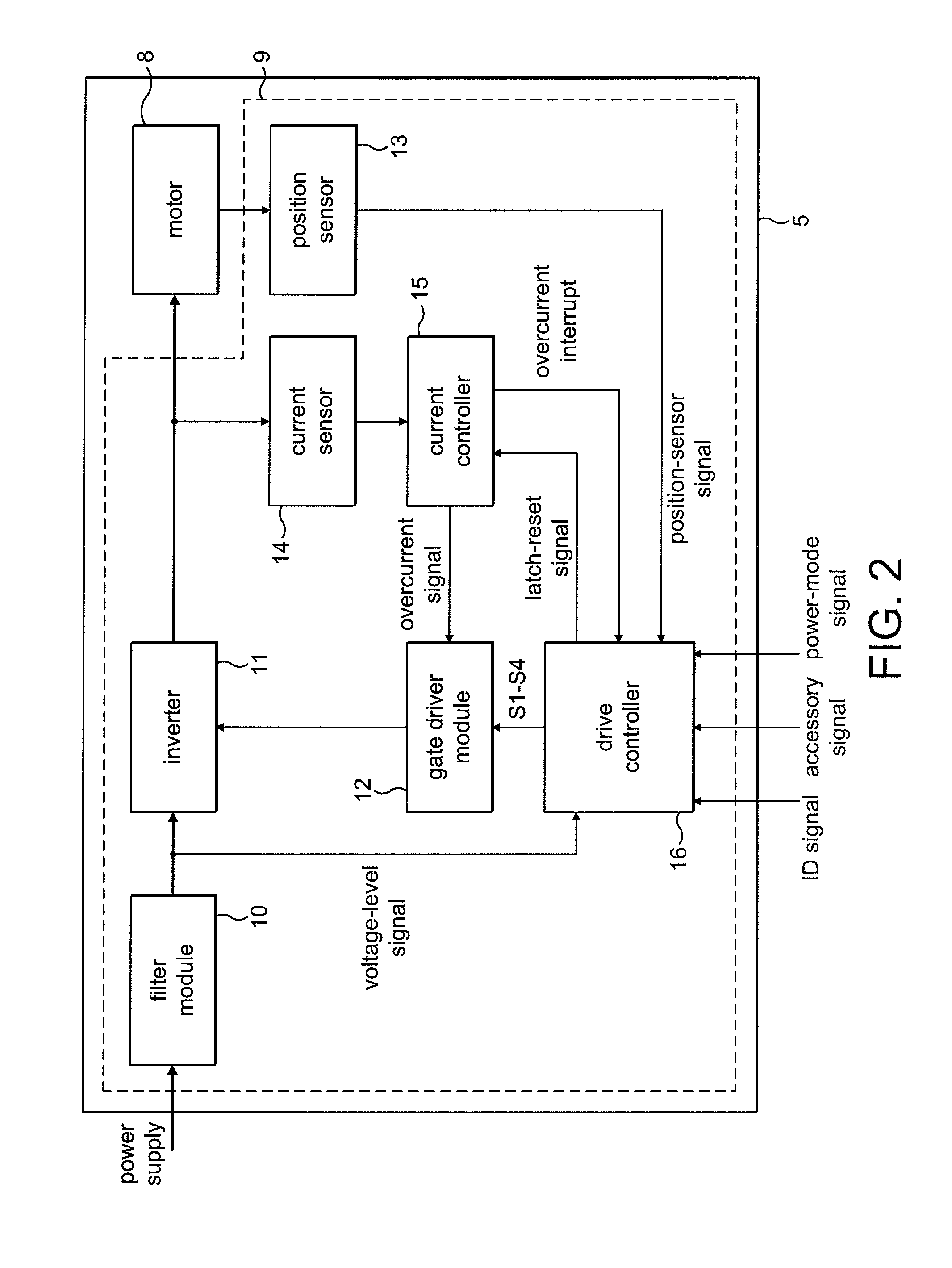

Control system for an electric machine

ActiveUS20100253262A1Improve performanceNarrow speed rangeMotor/generator/converter stoppersSynchronous motors startersElectric machineControl system

A control system for an electric machine, the control system including a position sensor and a drive controller. The drive controller generates one or more control signals for exciting a winding of the electric machine in response to edges of a signal output by the position sensor. The times at which the control signals are generated by the drive controller are corrected by a position-sensor offset that is fixed over an operating speed range of the electric machine.

Owner:DYSON TECH LTD

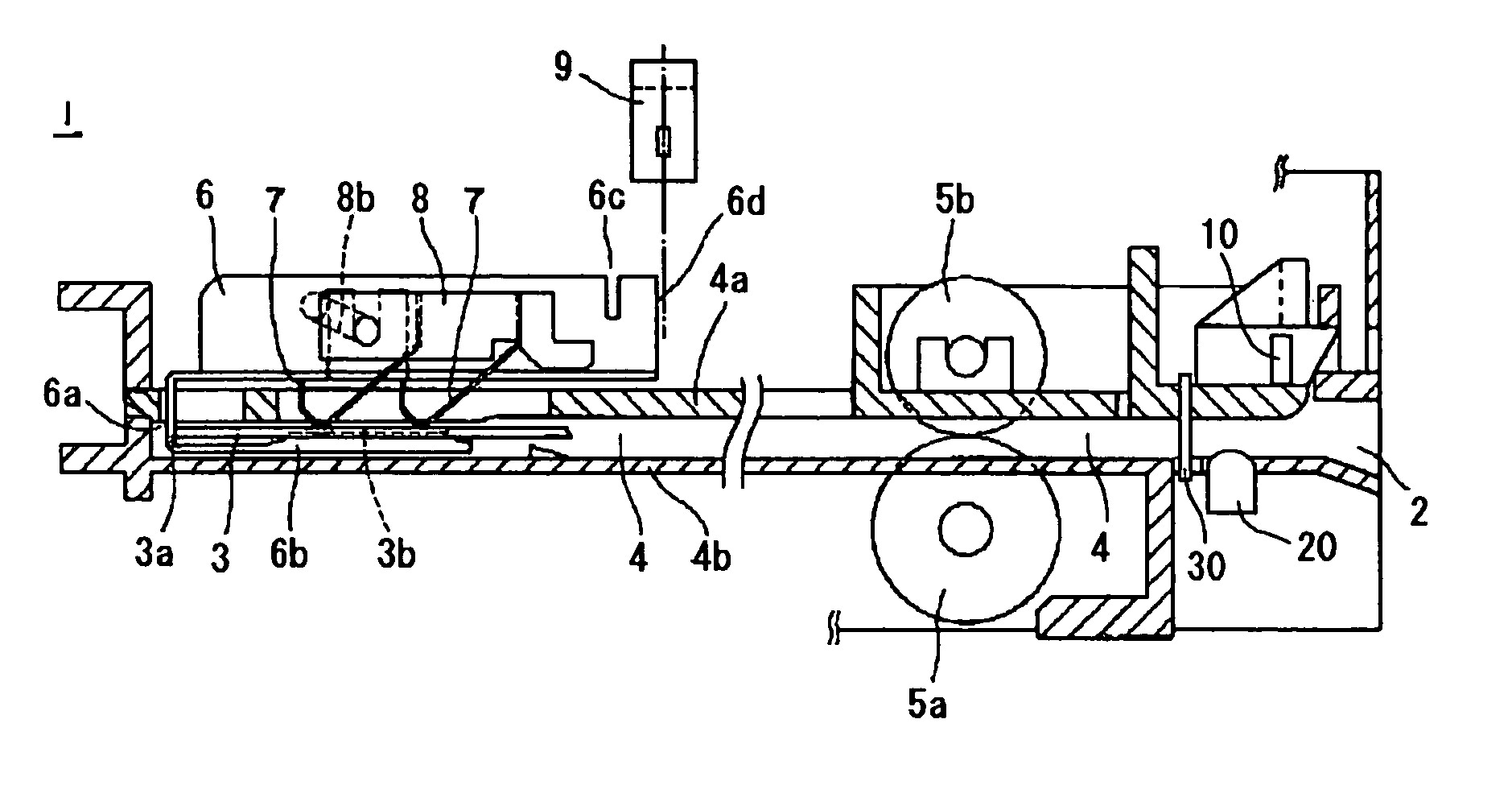

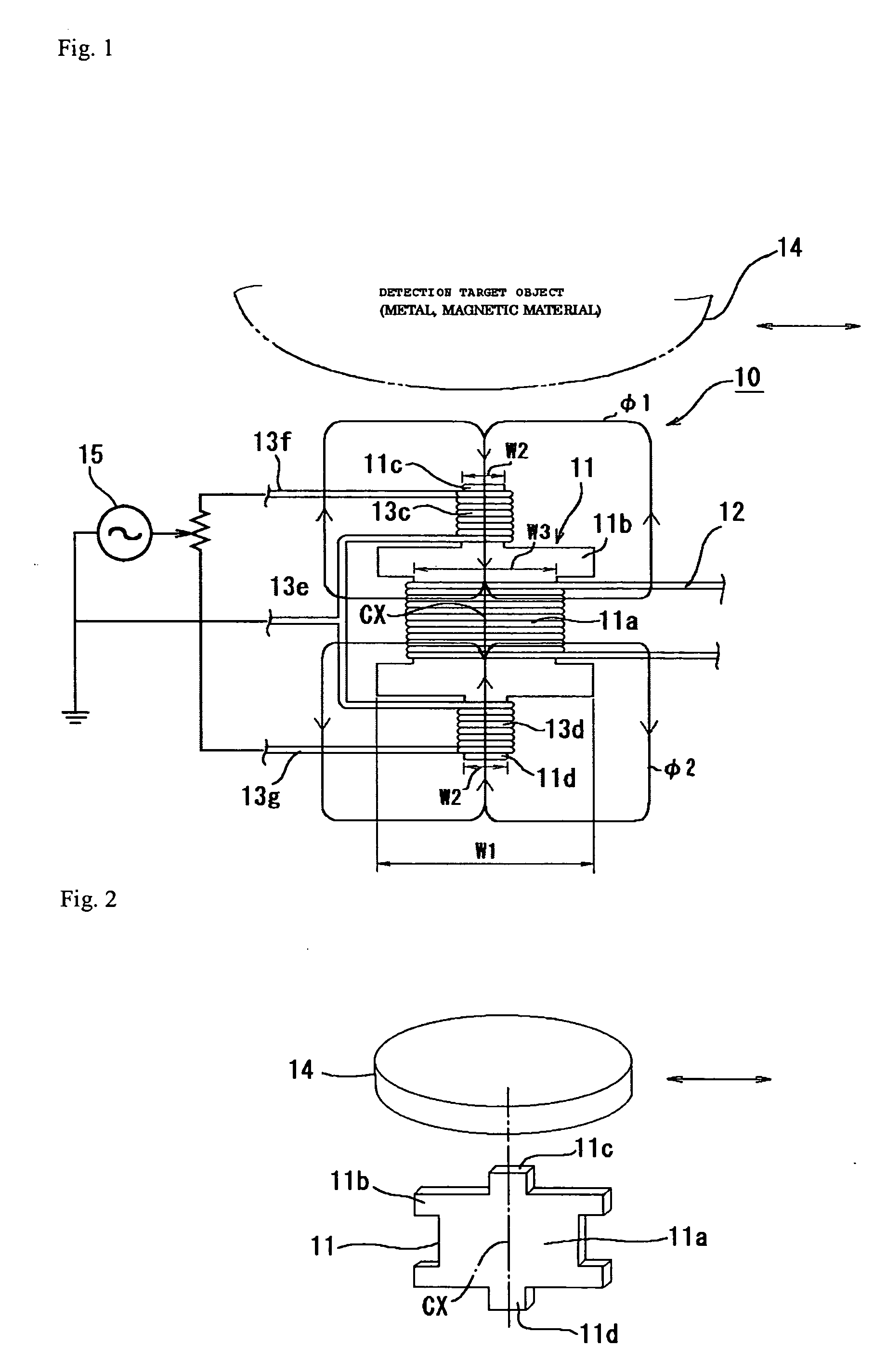

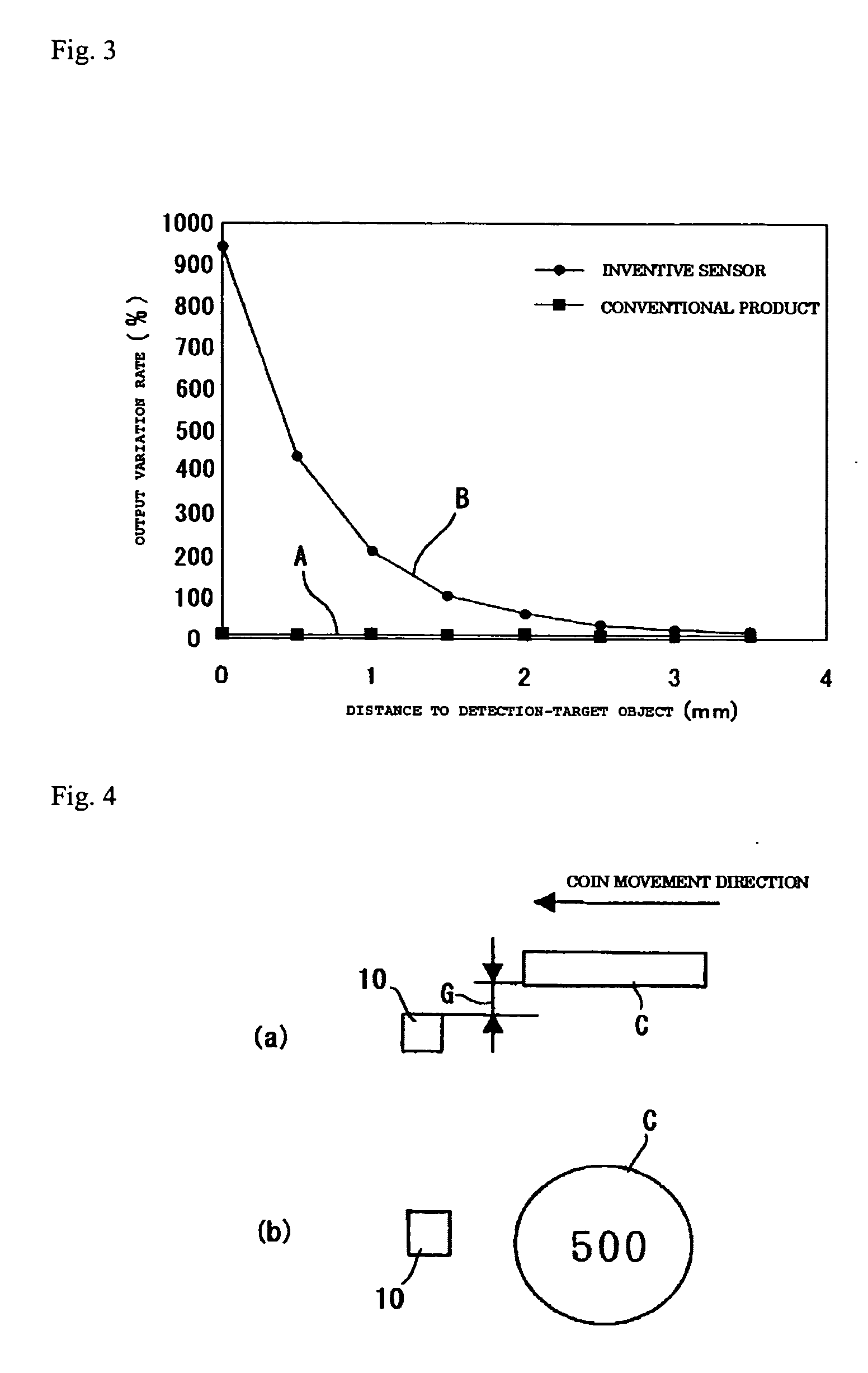

Object sensor and ic card reader with the object sensor

InactiveUS20050218227A1Precise positioningIncrease mutation rateConveying record carriersSensing record carriersElectrical resistance and conductanceCard reader

The present invention provides an object sensor configured such that excitation coils (13c and 13d) and a detection coil (12) are separately disposed, and the detection is performed in accordance with the balance between the excitation coils (13c and 13d) in a pair, a residual variation amount after the impedance due to a DC resistance part and the like has been offset and removed is obtained at high sensitivity with excellent linearity while using a small core body (11), regardless of the impedance including a DC resistance part. Additionally, the object sensor to be used as an inlet sensor is located in an appropriate position on a more upstream side than the read / write position in an insertion direction of the IC card. A contact terminal portion of the IC card is sensed whereby to detect the validity of the card inserted into the apparatus from a card insertion slot. Thereby, steady detection operations can be implemented for the presence or absence of the IC card, notwithstanding environmental temperature variations. The invention further provides an IC card reader configured such that a plurality of inlet sensors for detecting the type of an inserted card is provided in appropriate positions more upstream than the read / write position in a card insertion direction, wherein when an unusable card or the like is inserted, a control operation of closing shutter means can be performed, thereby enabling illegal action with the card to be prevented.

Owner:SANKYO SEIKI MFG CO LTD

Delay locked loop with a function for implementing locking operation periodically during power down mode and locking operation method of the same

ActiveUS20070188206A1Reduce power consumptionHigh speedPulse automatic controlElectricityPhase difference

A Delay Locked Loop (DLL) having a function of periodically executing a locking operation during a power down mode and a locking operation method of the same, which includes a global clock generator, a clock delay unit, and a power down control unit. The power down control unit, in response to some of a plurality of global clock signals, a phase detection signal, and a power down signal, outputs an input clock signal to each of the global clock generator and the clock delay unit. During the power down mode, the clock delay unit is enabled to periodically carry out the locking operation whenever it receives the input clock signal. Therefore, a consumed power of the DLL can be decreased during the power down mode, and a phase difference between an external clock signal and an internal clock signal during the power down mode can be decreased by the periodical locking operation of the clock delay unit, so that the DLL can operate at a fast speed after the power down mode.

Owner:SK HYNIX INC

Wireless power feeder, wireless power receiver, and wireless power transmission system

ActiveUS20120043825A1Efficiently controlling transmitted powerEffective controlElectromagnetic wave systemTransformersElectric power transmissionPower flow

Power is fed from a feeding coil L2 to a receiving coil L3 by magnetic resonance. A VCO 202 alternately turns ON / OFF switching transistors Q1 and Q2 at a drive frequency fo, whereby AC power is fed to the feeding coil L2, and then the AC power is fed from the feeding coil L2 to the receiving coil L3. A phase detection circuit 114 detects a phase difference between the current phase and voltage phase, and the VCO 202 adjusts the drive frequency fo such that the phase difference becomes zero. When load voltage is changed, the detected current phase value is adjusted with the result that the drive frequency fo is adjusted.

Owner:TDK CORPARATION

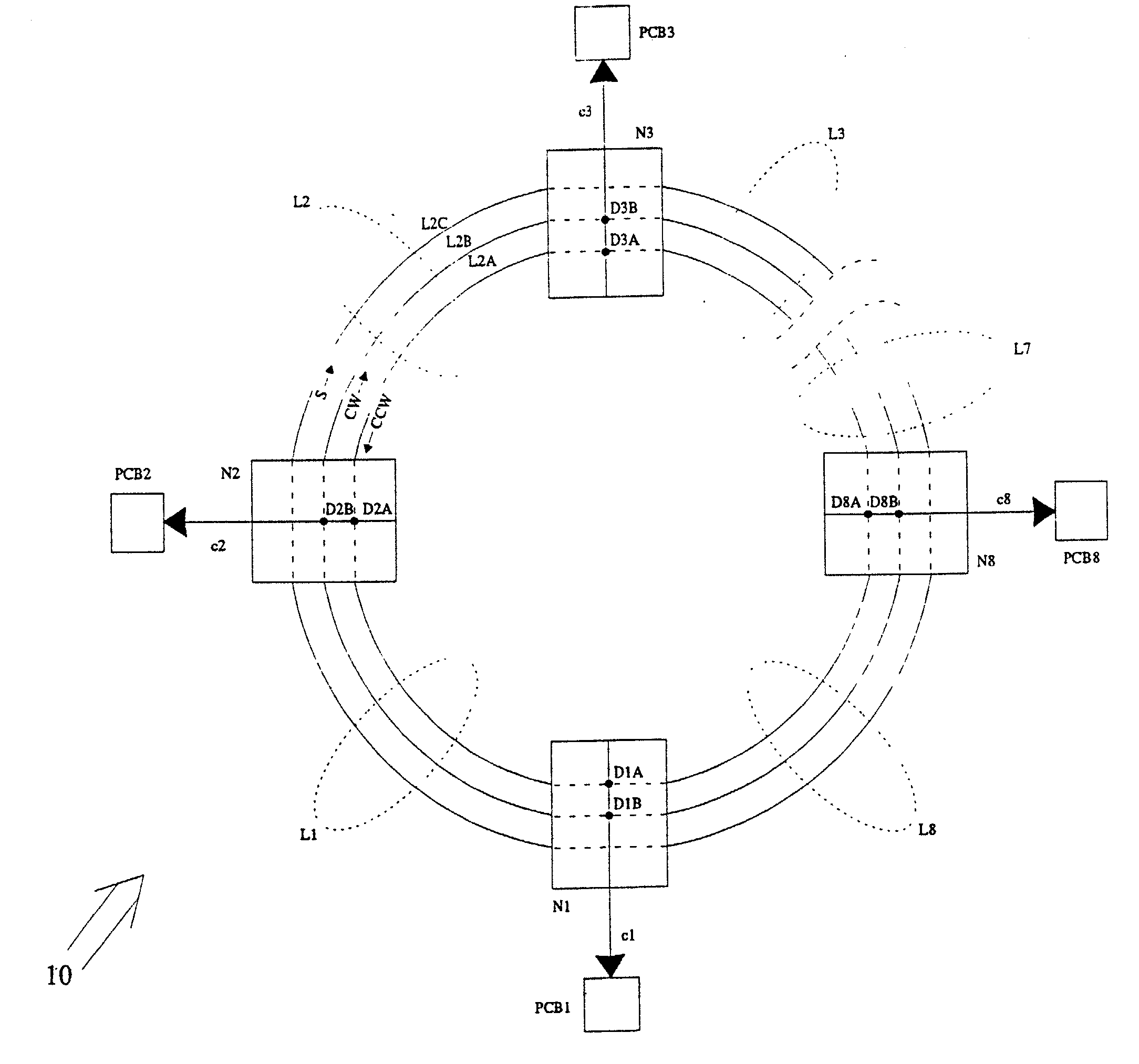

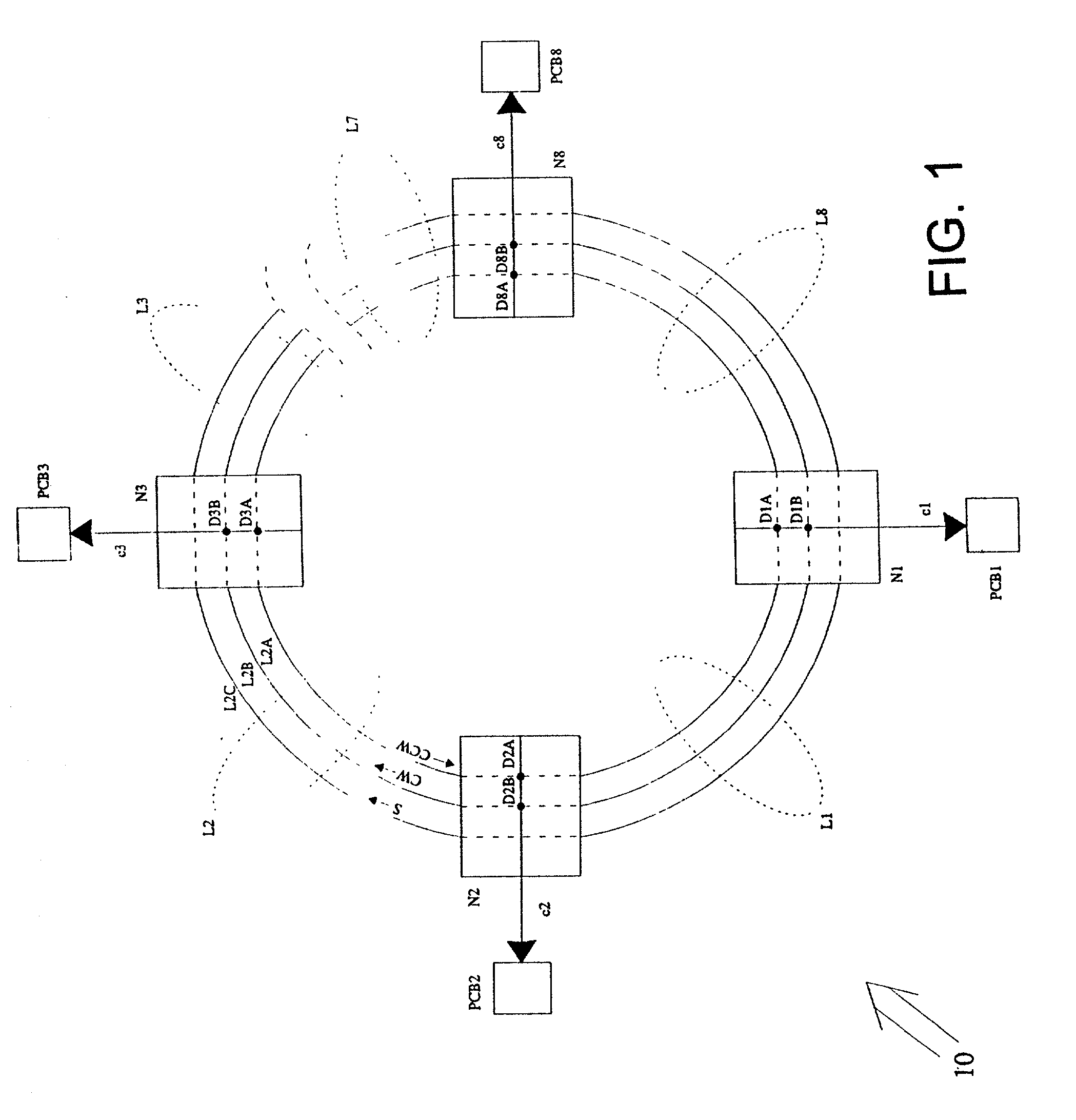

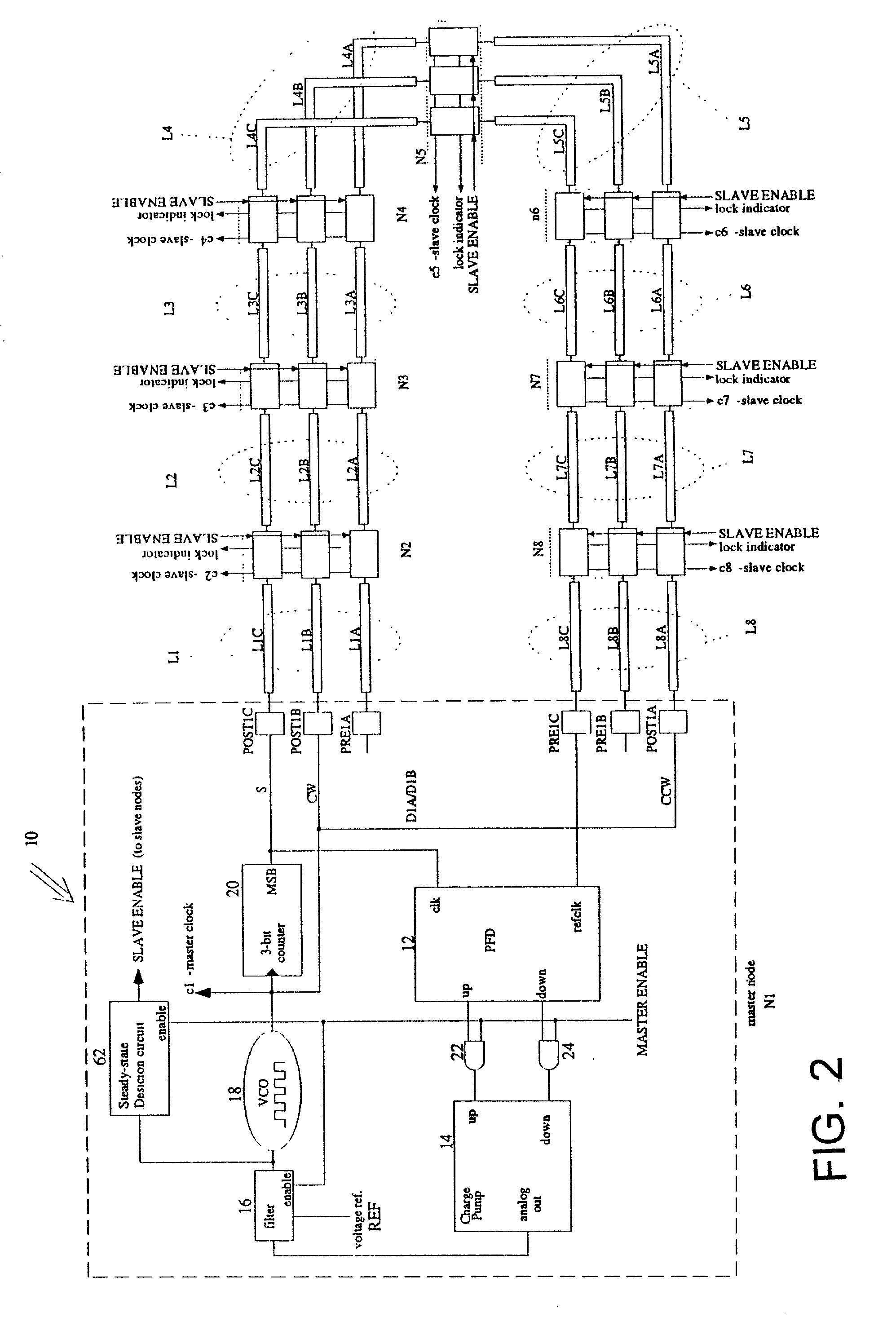

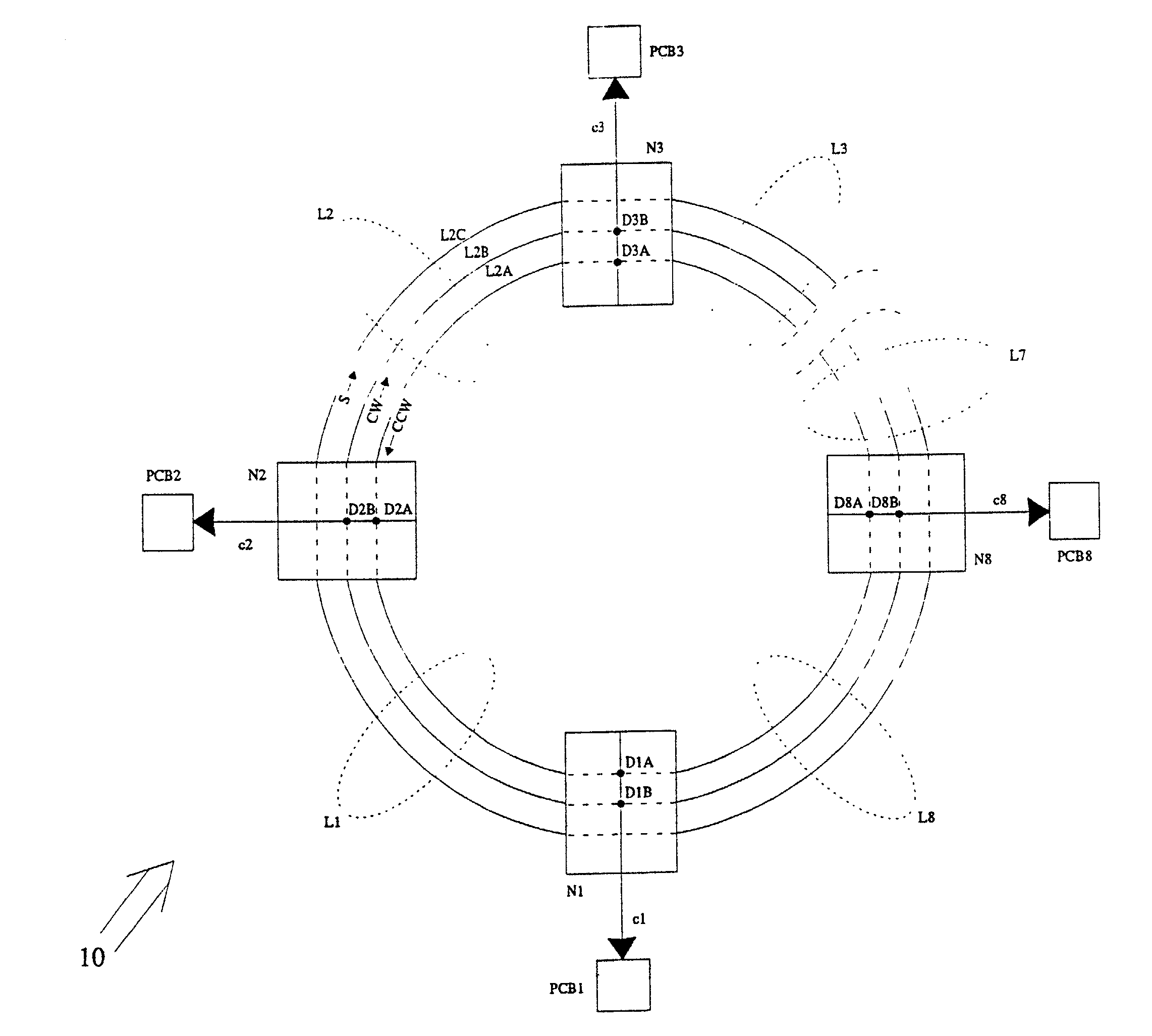

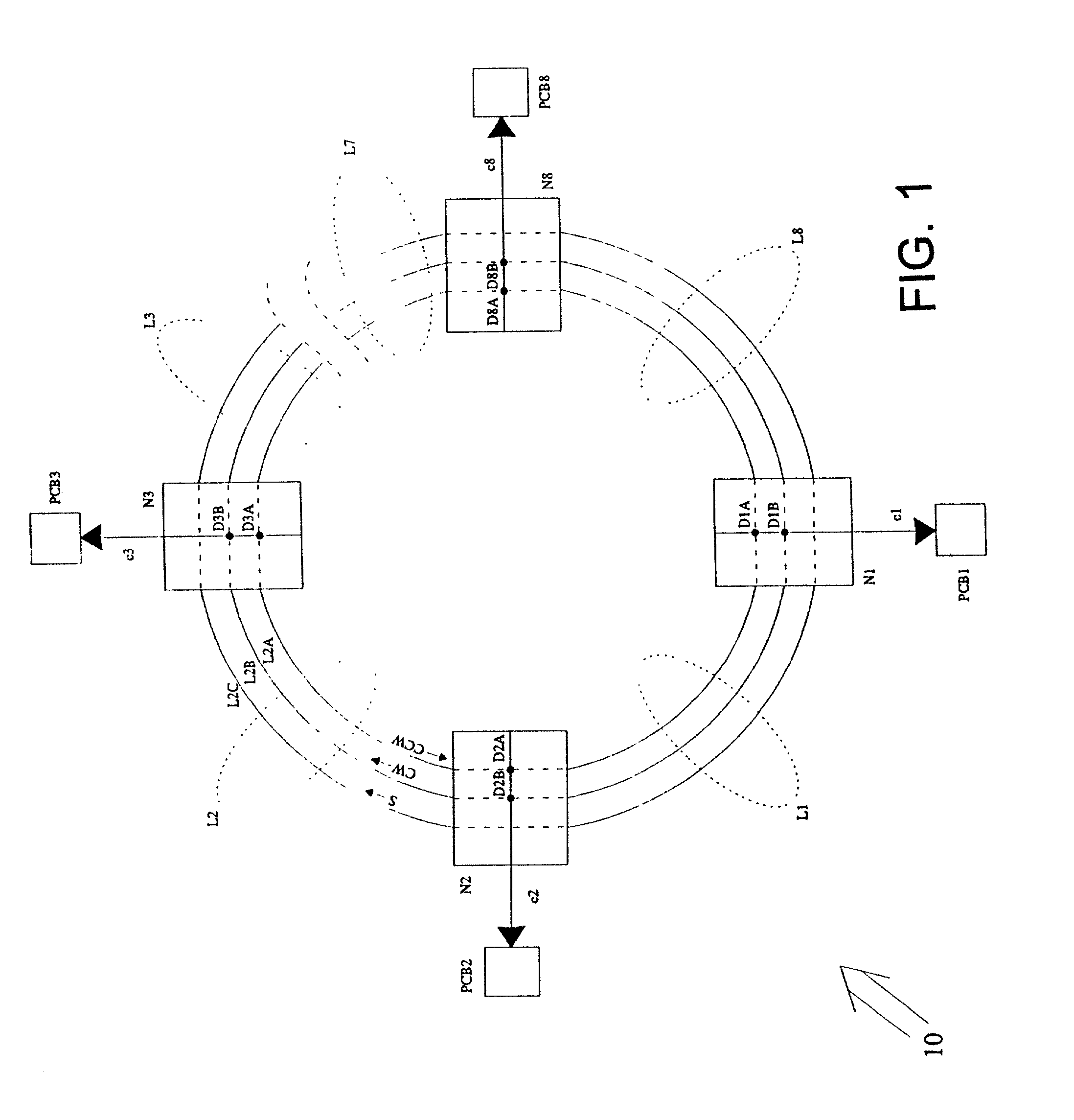

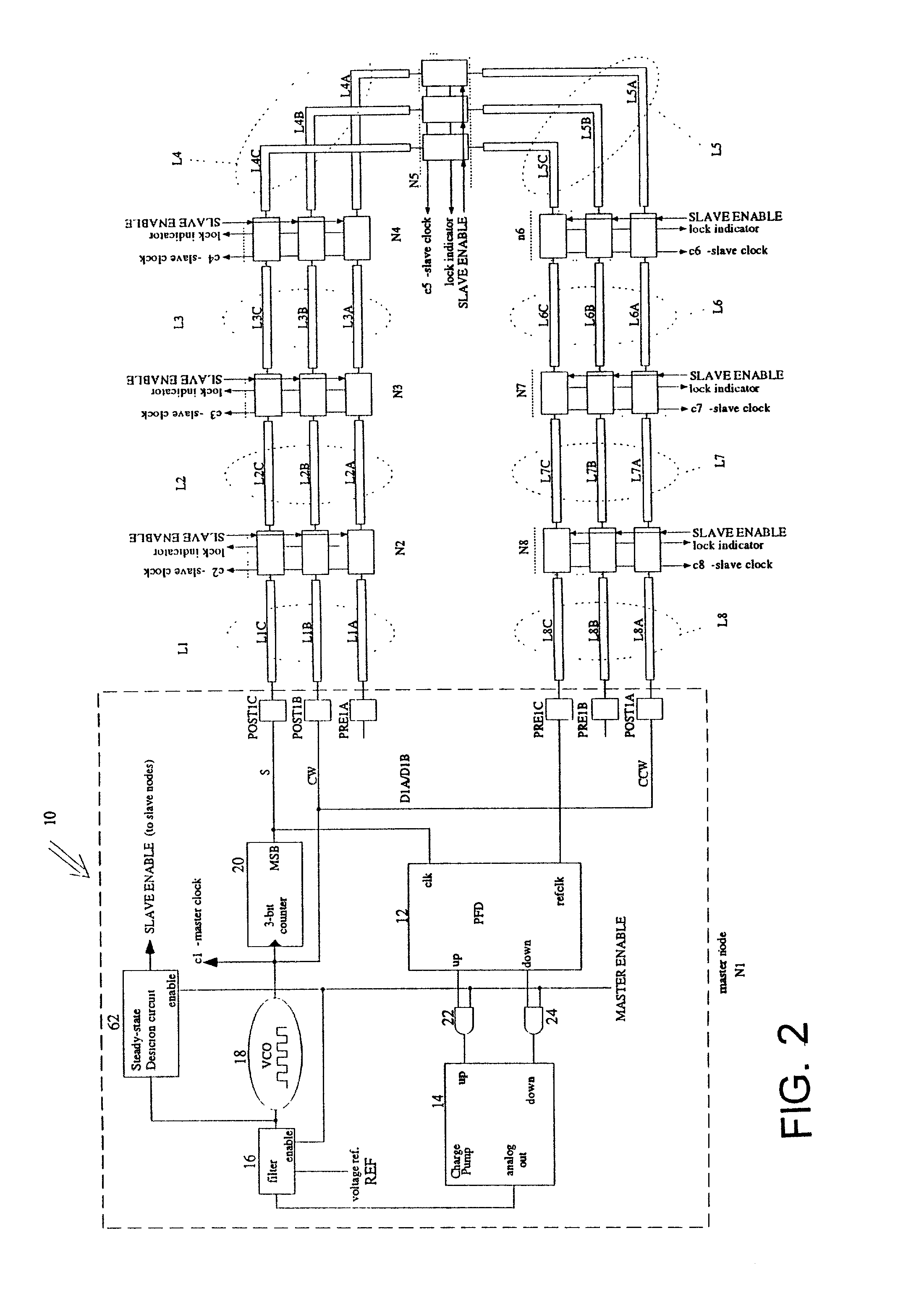

Method and apparatus for distributed synchronous clocking

InactiveUS20020031199A1Reduce phase differenceIncrease the number ofRepeater/relay circuitsActive radio relay systemsTelecommunicationsArrival time

To synchronize clock signals in spatially distributed nodes in a large, synchronous electronic, optical, optoelectronic or wireless system, a master node generates two identical pulse trains and propagates them to a plurality of slave nodes via first and second propagation channels, respectively, so that a pair of pulses, one from each pulse train, arrive at each slave node simultaneously, travelling in opposite directions. Each slave node generates a clock signal event when the pair of pulses arrive substantially simultaneous. When the pulses in the two channels do not arrive simultaneously, the slave node adjusts delays in each propagation channel so as to adjust arrival times of subsequent pairs of pulses. The delays may comprise pre-delays upstream of the detection point and post-delays downstream of the detection point, any increment in a pre-delay being compensated by an equal decrement in the post-delay in the same propagation channel.

Owner:MCGILL UNIV

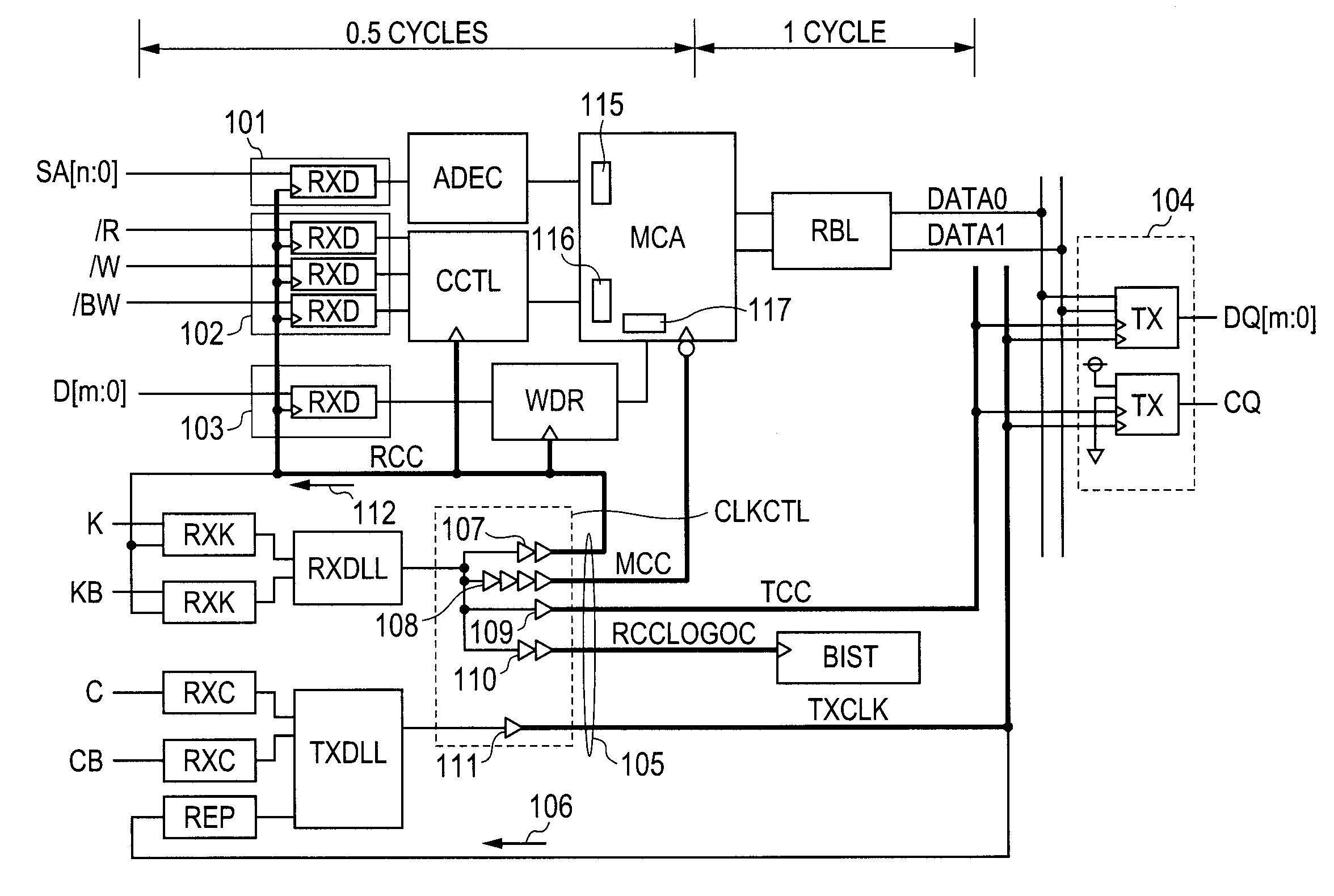

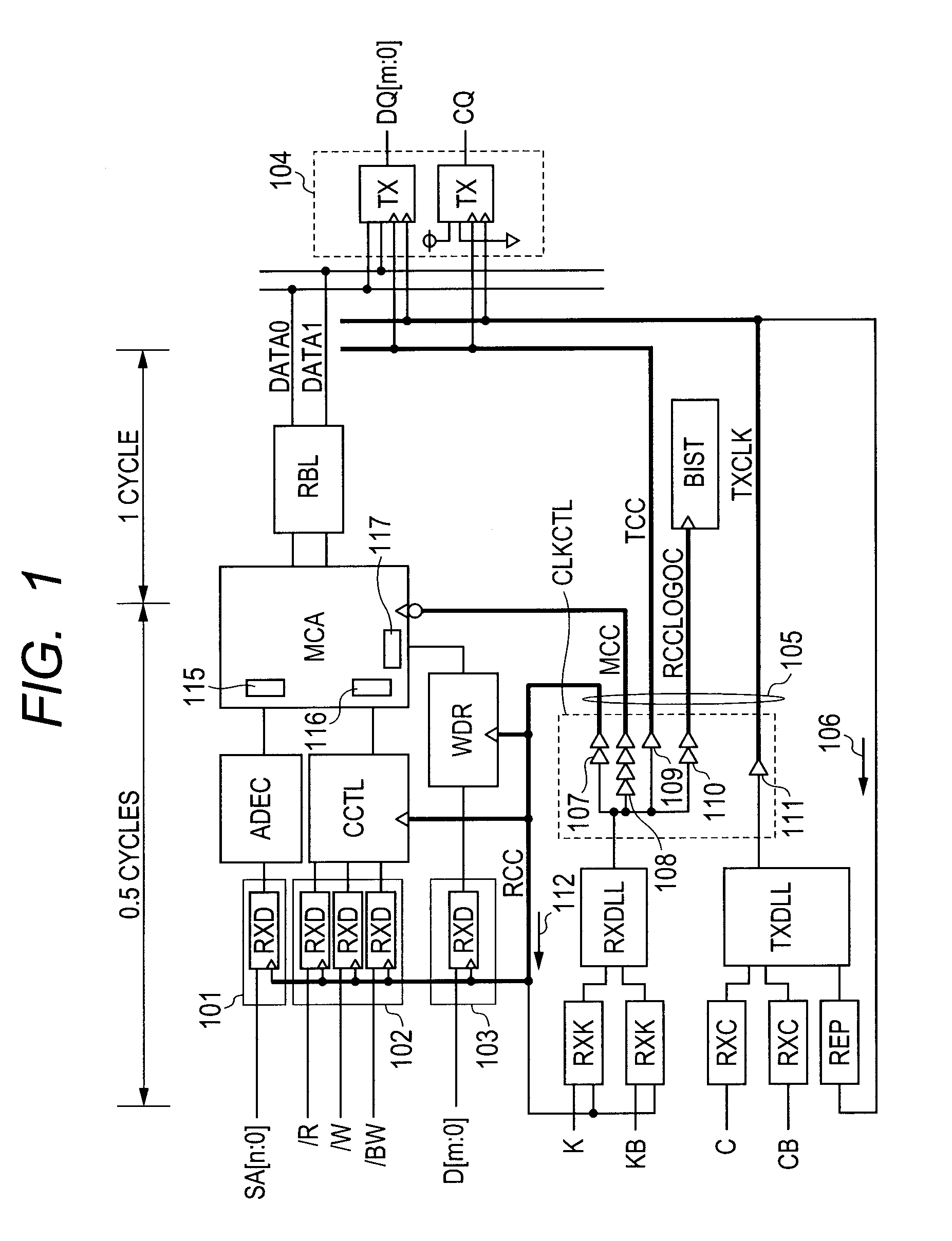

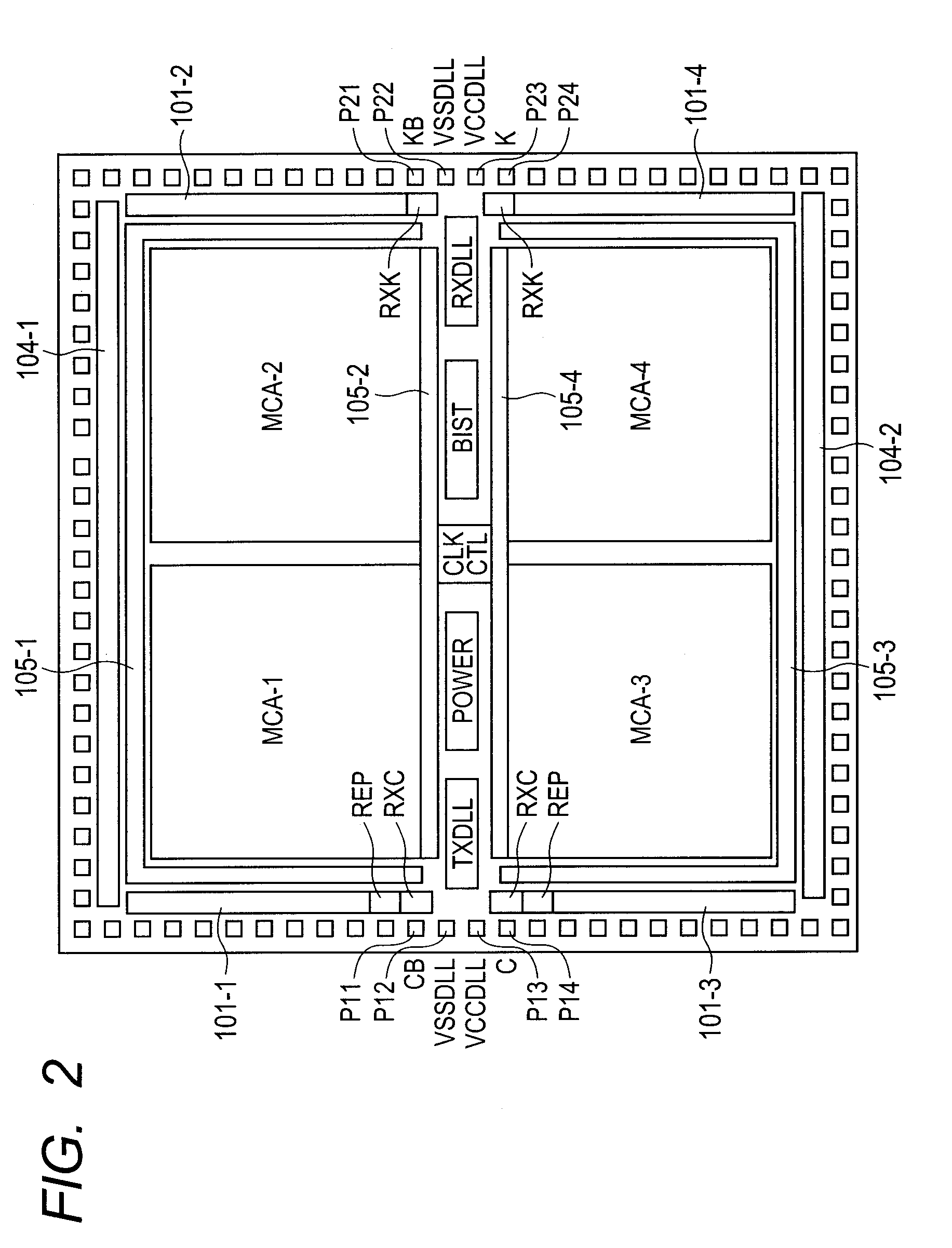

Semiconductor storage device

InactiveUS20100322022A1Lower latencyRun at high speedDigital storagePhase differenceSemiconductor storage devices

The present invention is directed to realize high-speed operation and low latency of a semiconductor storage device employing the QDR method. A memory cell array, a first buffer, a second buffer, a first circuit, a second circuit, a first DLL circuit, and a second DLL circuit are provided. The first DLL circuit generates a first internal clock signal so as to reduce a phase difference between a first clock signal fetched via the first buffer and the first internal clock signal transmitted to the first circuit. The second DLL circuit generates the second internal clock signal so as to reduce a phase difference between the second clock signal fetched via the second buffer and the second internal clock signal transmitted to the second circuit. With the configuration, input setup and hold time can be shortened, and the frequency of the clock signal can be further increased.

Owner:RENESAS ELECTRONICS CORP

Wireless power feeder, wireless power receiver, and wireless power transmission system

ActiveUS20110227420A1Easy to controlConvenient and stableNear-field transmissionElectromagnetic wave systemElectric power transmissionPower flow

Power is fed from a power feeding coil L2 to a power receiving coil L3 by magnetic resonance. A VCO 202 alternately turns ON / OFF switching transistors Q1 and Q2 at a drive frequency fo, whereby AC power is supplied to the power feeding coil L2, and then the AC power is supplied from the power feeding coil L2 to the power receiving coil L3. A phase detection circuit 114 detects a phase difference between current and voltage phases, and the VCO 202 adjusts the drive frequency fo such that the phase difference becomes zero. When load voltage is changed, the detected voltage phase value is adjusted with the result that the drive frequency fo is adjusted.

Owner:TDK CORPARATION

Wireless power feeder, wireless power transmission system, and table and table lamp using the same

ActiveUS20110260548A1Easy to perform controlEasy can be high levelElectromagnetic wave systemTransformersElectric power transmissionPower flow

Power is fed from a feeding coil L2 to a receiving coil L3 by magnetic resonance. A VCO alternately turns ON / OFF switching transistors Q1 and Q2 at a drive frequency fo, whereby AC current is fed to the feeding coil L2, and then the AC current is fed from the feeding coil L2 to the receiving coil L3. A phase detection circuit detects a phase difference between the current phase and voltage phase, and the VCO adjusts the drive frequency fo such that the phase difference becomes zero. In a current phase detection circuit and a voltage phase detection circuit, detection values of the current and voltage phases can be changed, respectively and intentionally.

Owner:TDK CORPARATION

Method and apparatus for distributed synchronous clocking

InactiveUS7035269B2Mitigate, the shortcomingsReduce phase differenceRepeater/relay circuitsActive radio relay systemsArrival timePulse sequence

A method and an apparatus are provided for synchronizing clock signals in spatially distributed nodes in large, synchronous electronic, optical, optoelectronic or wireless systems, such as systems comprising arrays of microprocessors and memories, and telecommunication systems. The nodes comprise a master node and a plurality of slave nodes. The master node generates first and second identical pulse trains and propagates them to the slave nodes via a first and second propagation channels, respectively, so that a pair of pulses, one from each pulse train, arrive at each slave node substantially simultaneously, travelling in opposite directions. Each slave node generates a clock signal event in response to the substantially simultaneous arrival of each pair of pulses. The master node maintains the rate of the two pulse trains such that there are “pN” pulses in each propagation channel at any time, where “N” is the number of nodes and “p” is an integer. Adjustable delays are provided at each slave node, disposed in each propagation channel. When the pulses in the two channels do not arrive simultaneously, the slave node adjusts the delay units so as reduce differences in the arrival times of subsequent pairs of pulses. The delay units may comprise pre-delay units upstream of the detection point and post-delay unit downstream of the detection point, any increment in a pre-delay being compensated by an equal decrement in the post-delay in the same propagation channel.

Owner:MCGILL UNIV

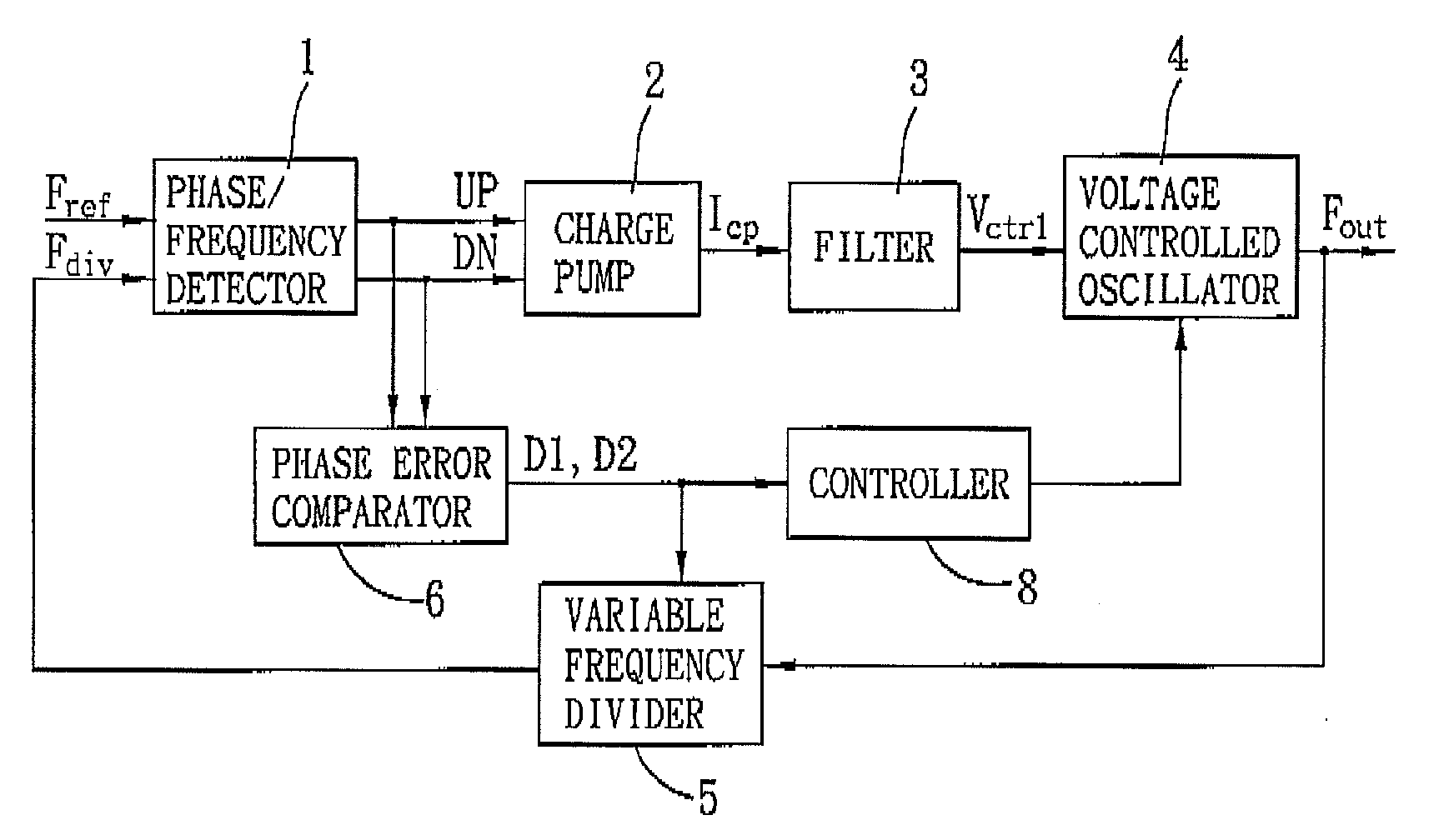

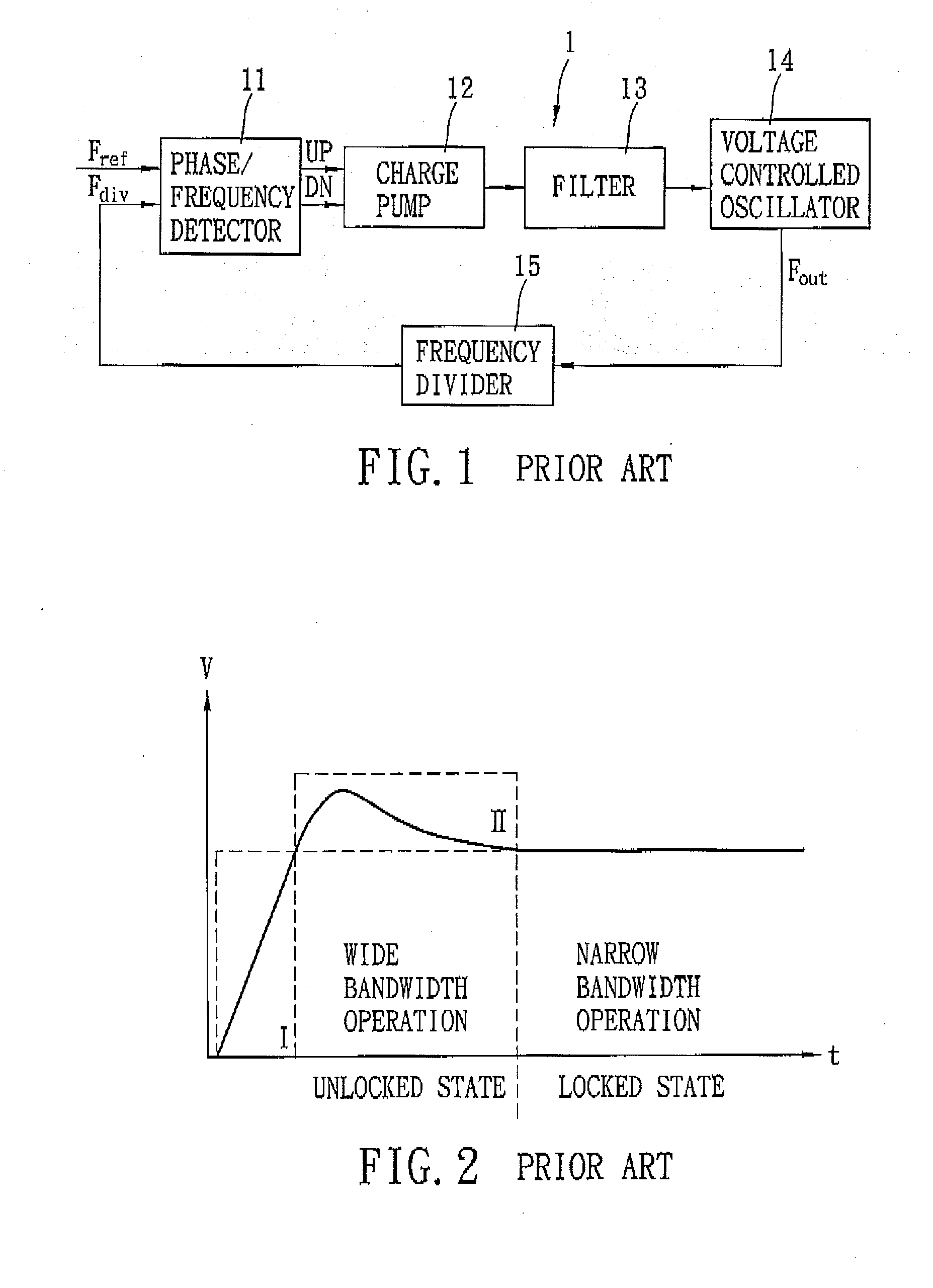

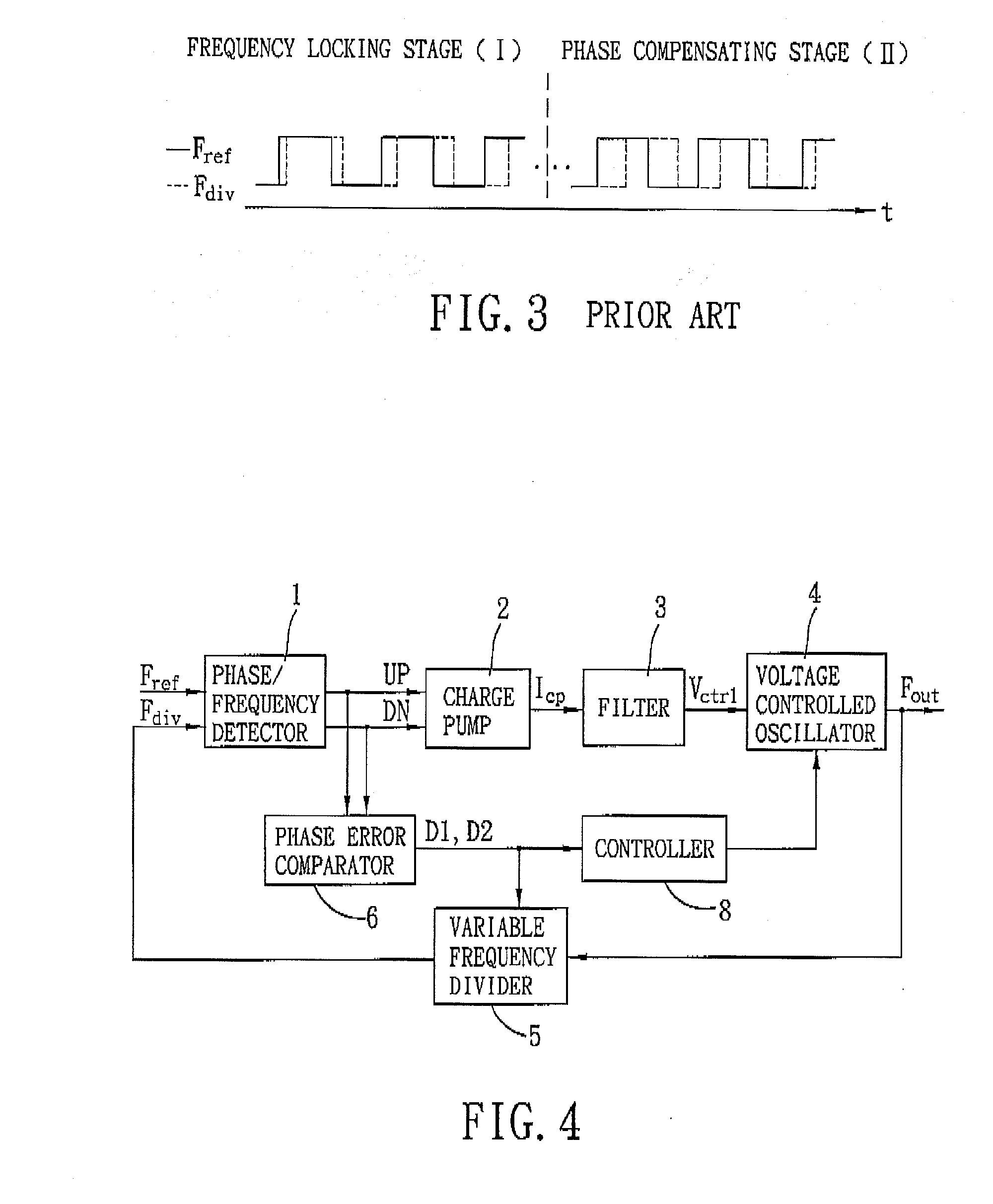

Phase locked loop capable of fast locking

ActiveUS20100183109A1Reduce phase differencePulse automatic controlAngle demodulation by phase difference detectionPhase differenceEngineering

A phase locked loop includes a voltage controlled oscillator operable to generate an output signal corresponding to a reference signal in response to a control voltage signal outputted by a filter in response to a current signal, and a variable frequency divider operable to perform frequency division on the output signal using a variable divisor so as to generate a divided feedback signal. A charge pump outputs the current signal in response to a phase detecting output from a phase / frequency detector indicating phases of the divided feedback signal and the reference signal. A phase error comparator outputs, in accordance with the phase detecting output, a digital output indicating whether the divided feedback signal lags or leads the reference signal and further indicating a phase difference between the divided feedback signal and the reference signal. The variable frequency divider determines a value of the variable divisor in accordance with the digital output to reduce the phase difference between the divided feedback signal and the reference signal .

Owner:NAT TAIWAN UNIV

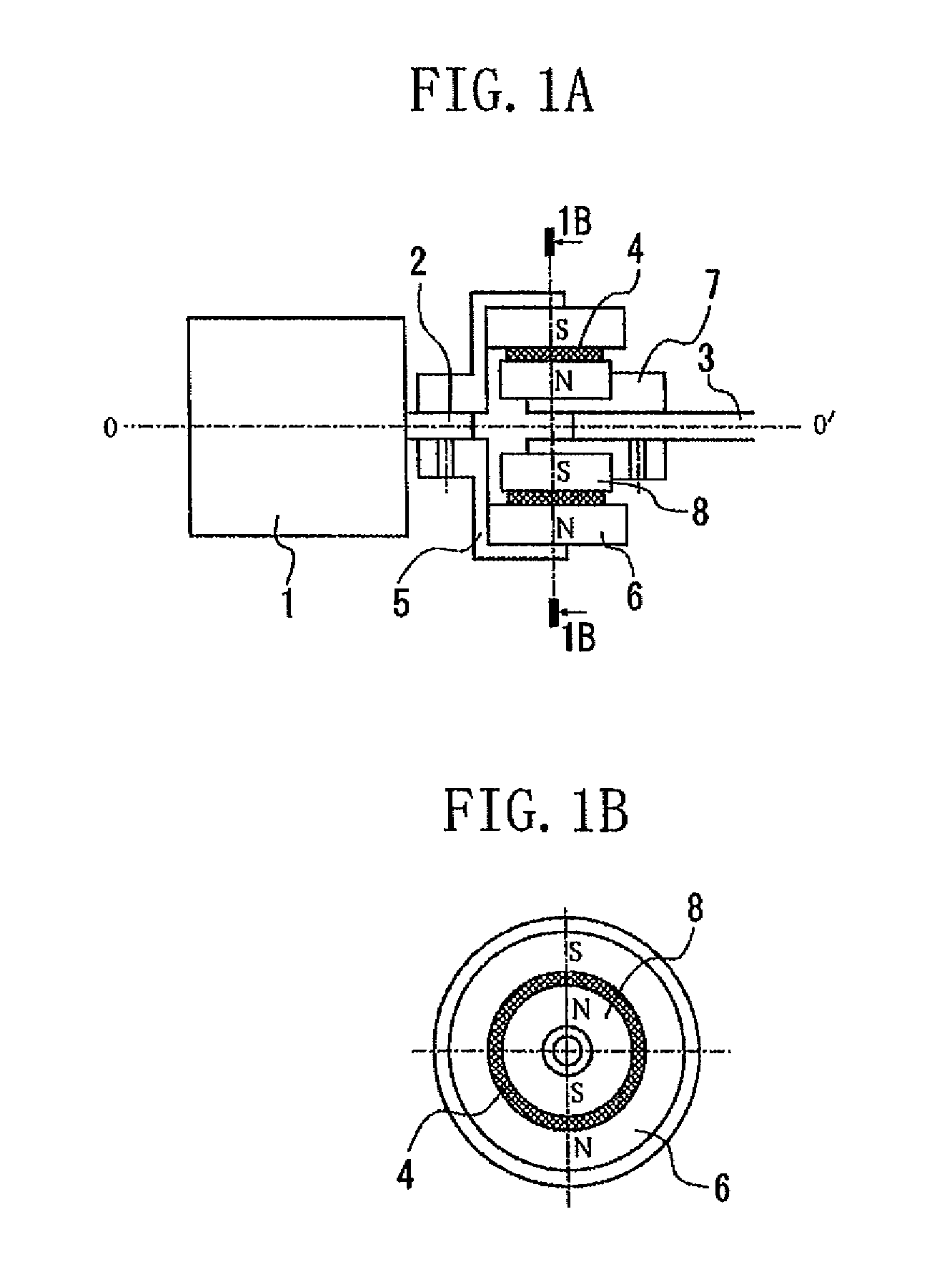

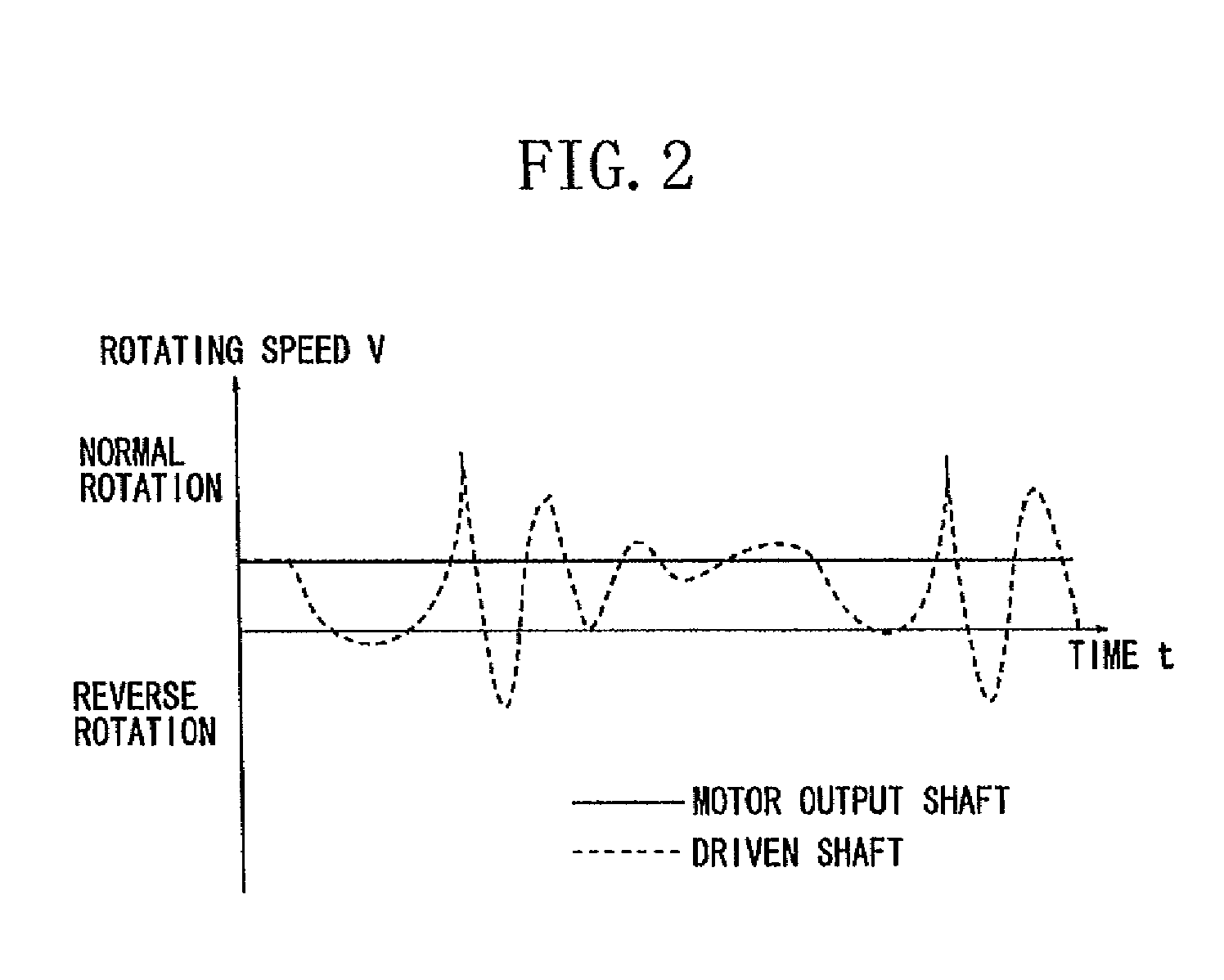

Magnetic coupling and camera platform using magnetic coupling

InactiveUS20080207336A1Reduce vibrationMaintain performanceDynamo-electric brakes/clutchesSlip couplingDrive shaftCoupling

A coupling configured to transmit rotation of a drive shaft to a driven shaft by magnetic force includes a drive portion configured to rotate integrally with the drive shaft, a driven portion configured to rotate integrally with the driven shaft, and a buffer member located in contact with both the drive portion and the driven portion.

Owner:CANON KK

Phase interpolator with adaptive delay adjustment

InactiveUS7772898B2Small and simple configurationReduce phase differencePulse automatic controlSingle output arrangementsIntegratorPhase difference

The phase interpolator includes two adjustable delays 30 and 31, phase comparator 32 which detects a phase difference between a signal delayed by the adjustable delay 30 and a signal delayed by the adjustable delay 31, an integrator 33 which integrates the outputs of the phase comparator 32 and multipliers 34-1 and 34-2 which set a control voltage for the adjustable delays 30 and 31. The feedback loop comprising phase comparator 32 and integrator 33 controls a delay amount of the adjustable delay 30 thereby securing a phase relation between {ACK1, ACK2} and ICK to achieve a stable ICK phase.

Owner:FUJITSU LTD

Wireless power feeder, wireless power transmission system, and table and table lamp using the same

ActiveUS8581444B2Efficient powerEasy can be high levelBatteries circuit arrangementsTransformersElectric power transmissionResonance

Power is fed from a feeding coil L2 to a receiving coil L3 by magnetic resonance. A VCO alternately turns ON / OFF switching transistors Q1 and Q2 at a drive frequency fo, whereby AC current is fed to the feeding coil L2, and then the AC current is fed from the feeding coil L2 to the receiving coil L3. A phase detection circuit detects a phase difference between the current phase and voltage phase, and the VCO adjusts the drive frequency fo such that the phase difference becomes zero. In a current phase detection circuit and a voltage phase detection circuit, detection values of the current and voltage phases can be changed, respectively and intentionally.

Owner:TDK CORPARATION

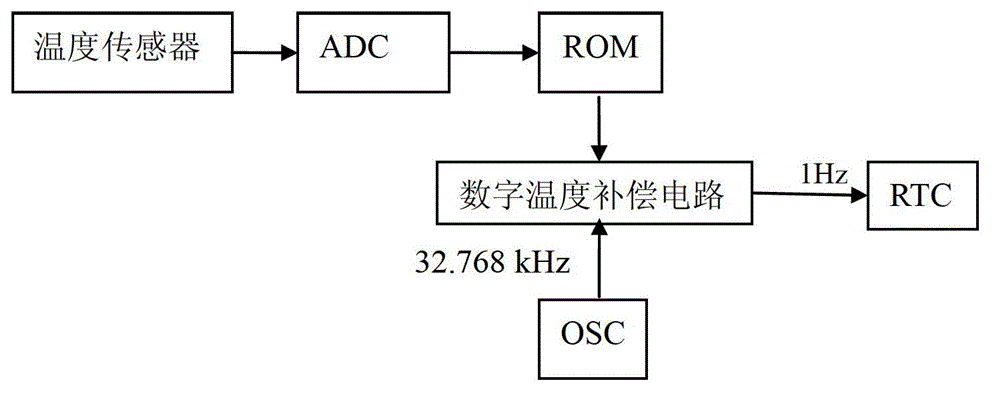

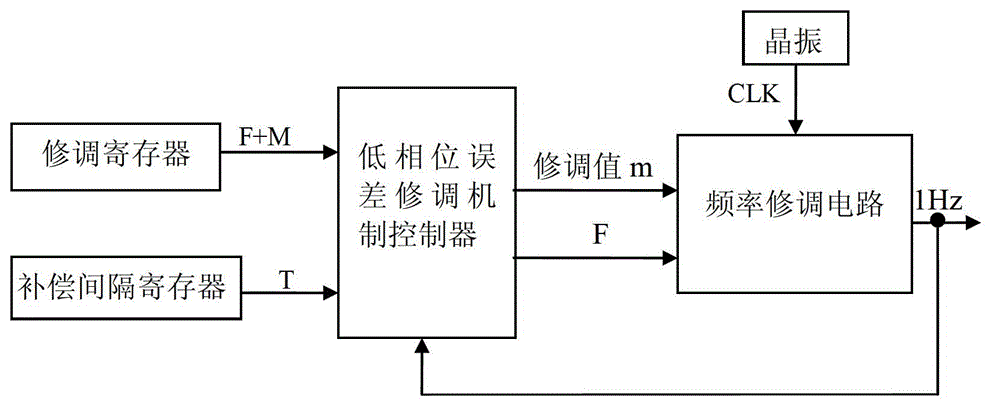

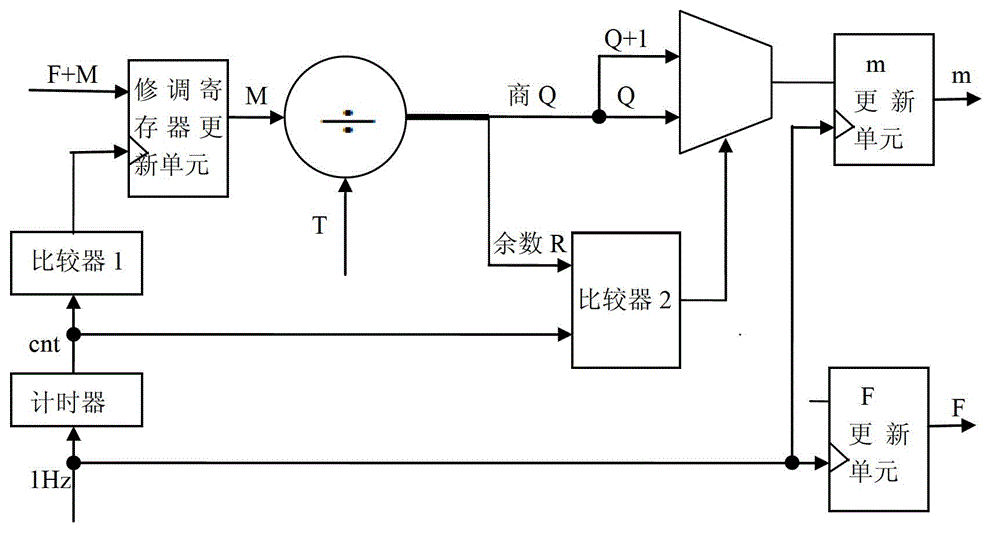

Temperature compensation system for real-time clock and method

ActiveCN102981551AReduce phase errorReduce phase differenceGenerating/distributing signalsReal-time clockClock rate

The invention discloses a temperature compensation system for a real-time clock. The temperature compensation system for the real-time clock comprises a repairing regulating register, a compensation interval register, a low-phase error repairing regulating mechanism controller, a crystal oscillator and a frequency repairing regulating circuit, wherein the repairing regulating register is used for storing an increasing and reducing pulse flag bit F and a repairing regulating data M; the compensation interval register is used for storing a compensation interval time value T; the low-phase error repairing regulating mechanism controller connected with the repairing regulating register is used for outputting a repairing regulating value m of a present second clock within the compensation interval time value T by judging the second clock corresponding to the compensation under the present state according to the size of the repairing regulating data; the crystal oscillator is used for generating a clock frequency; and the frequency repairing regulating circuit connected with a clock generator and the low-phase error repairing regulating mechanism controller is used for performing a pulse increasing and reducing operation on the clock outputted by the crystal oscillator according to the increasing and reducing pulse flag bit F and finally outputting an accurate low-phase error 1Hz clock when the repairing regulating value m of the present second clock is received by the frequency repairing regulating circuit.

Owner:PERICOM TECH (SHANGHAI) CO LTD

Wireless power feeder, wireless power receiver, and wireless power transmission system

ActiveUS8729735B2Effective controlConvenient and stableElectromagnetic wave systemTransformersElectric power transmissionPower flow

Power is fed from a feeding coil L2 to a receiving coil L3 by magnetic resonance. A VCO 202 alternately turns ON / OFF switching transistors Q1 and Q2 at a drive frequency fo, whereby AC power is fed to the feeding coil L2, and then the AC power is fed from the feeding coil L2 to the receiving coil L3. A phase detection circuit 114 detects a phase difference between the current phase and voltage phase, and the VCO 202 adjusts the drive frequency fo such that the phase difference becomes zero. When load voltage is changed, the detected current phase value is adjusted with the result that the drive frequency fo is adjusted.

Owner:TDK CORPARATION

Wireless power feeder and wireless power transmission system

ActiveUS20120001494A1Reliable trackingVoltage differenceTransformersCircuit arrangementsResonancePhase difference

Power is transmitted from a feeding coil L2 to a receiving coil L3 by magnetic resonance. A VCO 202 alternately turns ON / OFF switching transistors Q1 and Q2 to feed AC current to the feeding coil L2, whereby the AC power is fed from the feeding coil L2 to the receiving coil L3. An AC magnetic field generated by AC current IS flowing in the feeding coil L2 causes inductive current ISS to flow in a detection coil LSS. A phase detection circuit 150 compares the phase of AC voltage generated by the VCO 202 and phase of the inductive current ISS to detect the phase difference between voltage and current phases and generates phase difference indicating voltage indicating the magnitude of the phase difference. The reset circuit 102 forcibly reduces the phase difference indicating voltage when the phase difference indicating voltage exceeds a predetermined threshold.

Owner:TDK CORPARATION

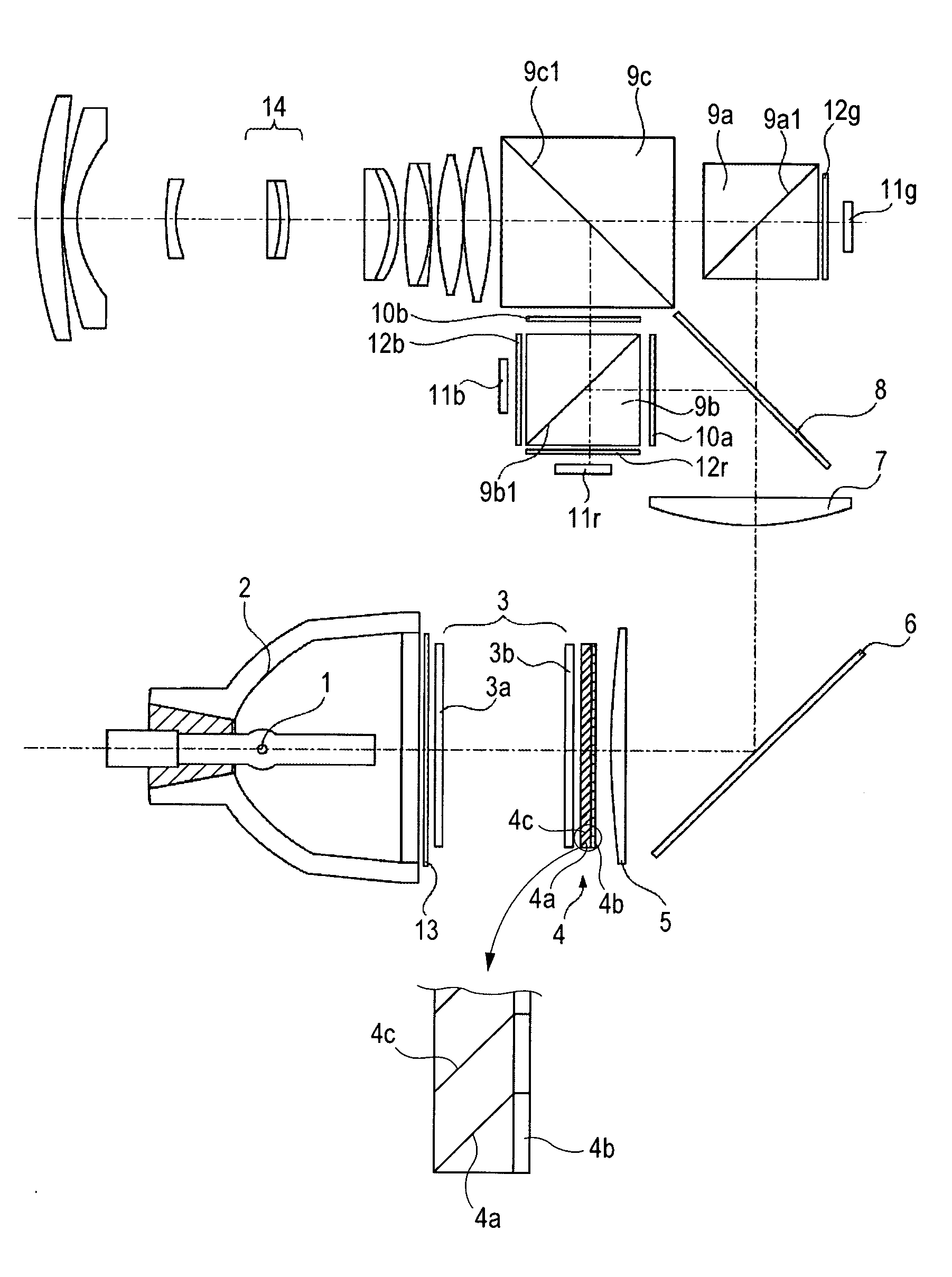

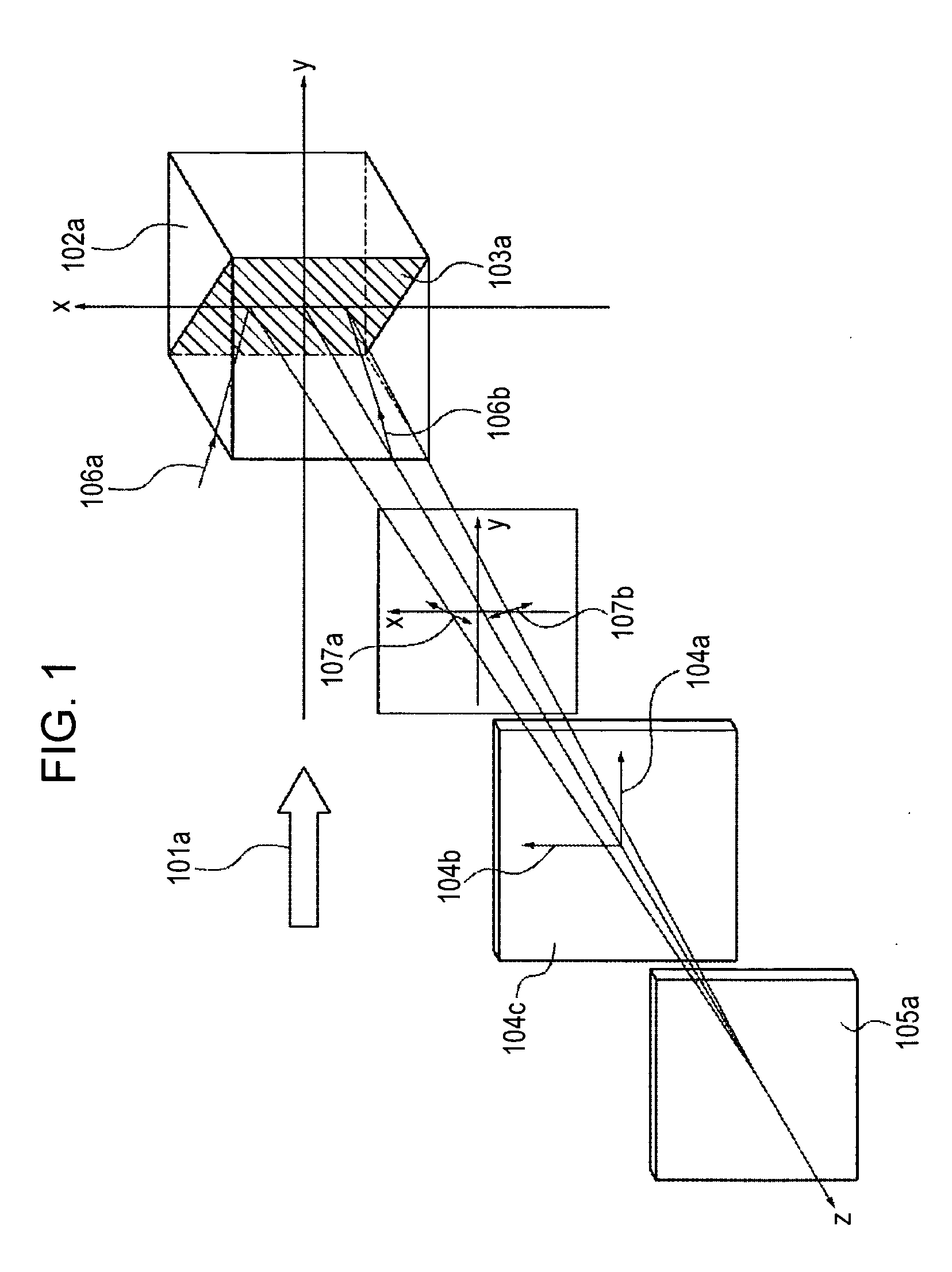

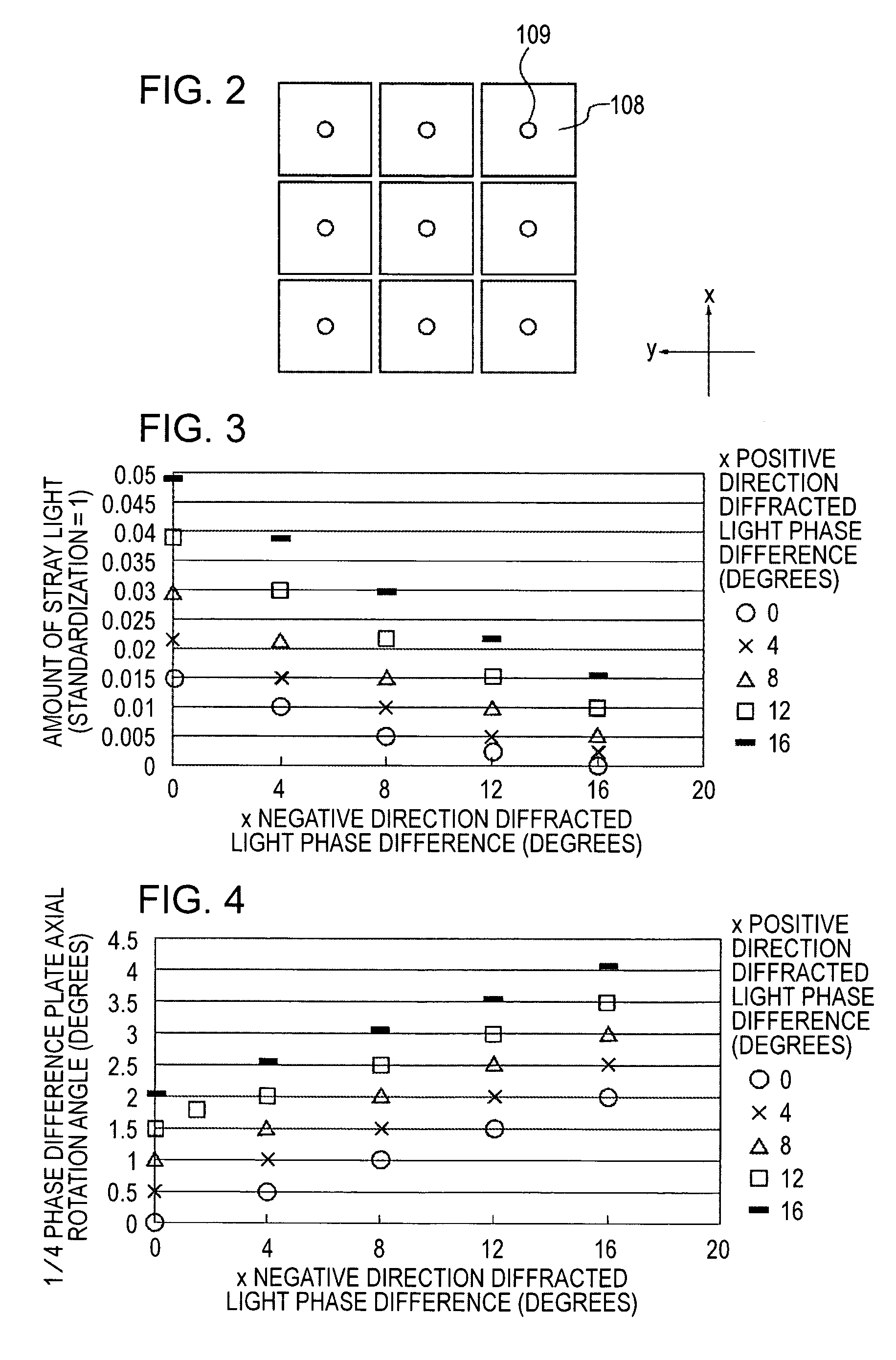

Reflective liquid crystal display apparatus

InactiveUS20060061712A1Easy to optimizeReduce lightTelevision system detailsColor television detailsBeam splitterLiquid-crystal display

At least one exemplary embodiment is directed to a reflective liquid crystal display apparatus which comprises: a polarization beam splitter having a polarization split film used as both a polarizer and an analyzer; a reflective liquid crystal display device; a quarter wave plate; and a projection optical system; where the absolute value of phase difference of diffracted light generated by the reflective liquid crystal display device in a black display state is reduced by the phase difference of the quarter wave plate, and thus the amount of stray light of the diffracted light guided from the polarizing beam splitter to the projection optical system decreases.

Owner:CANON KK

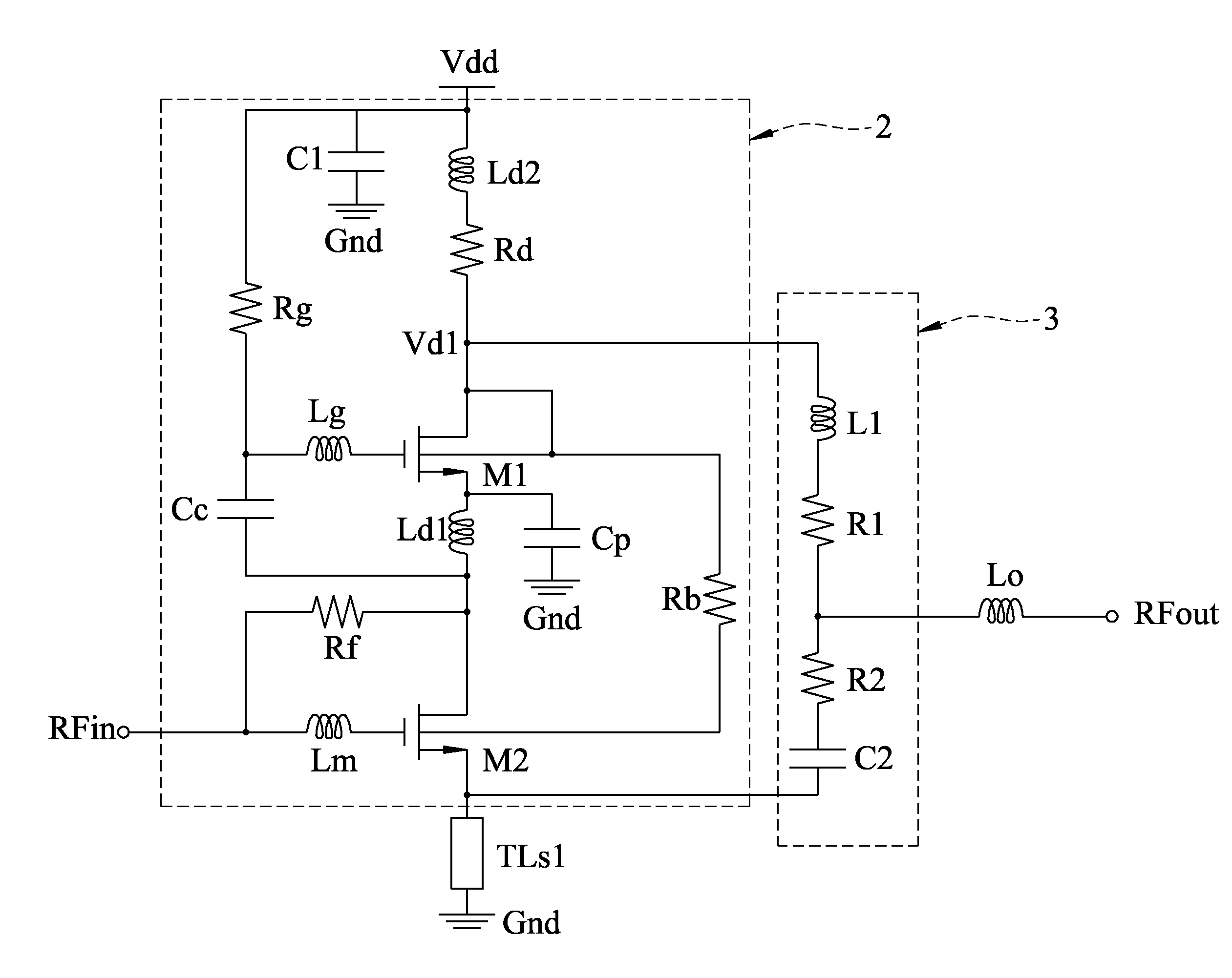

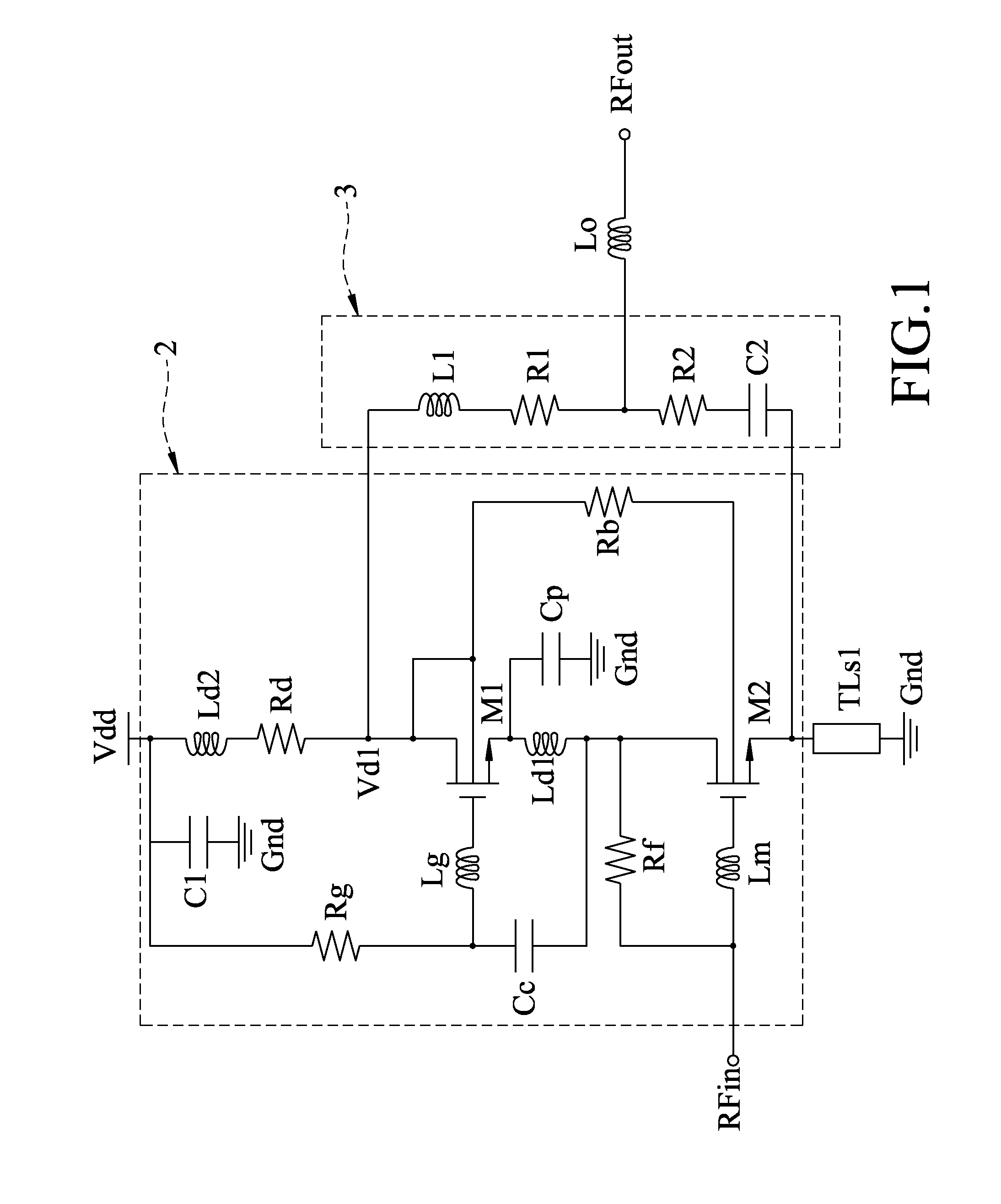

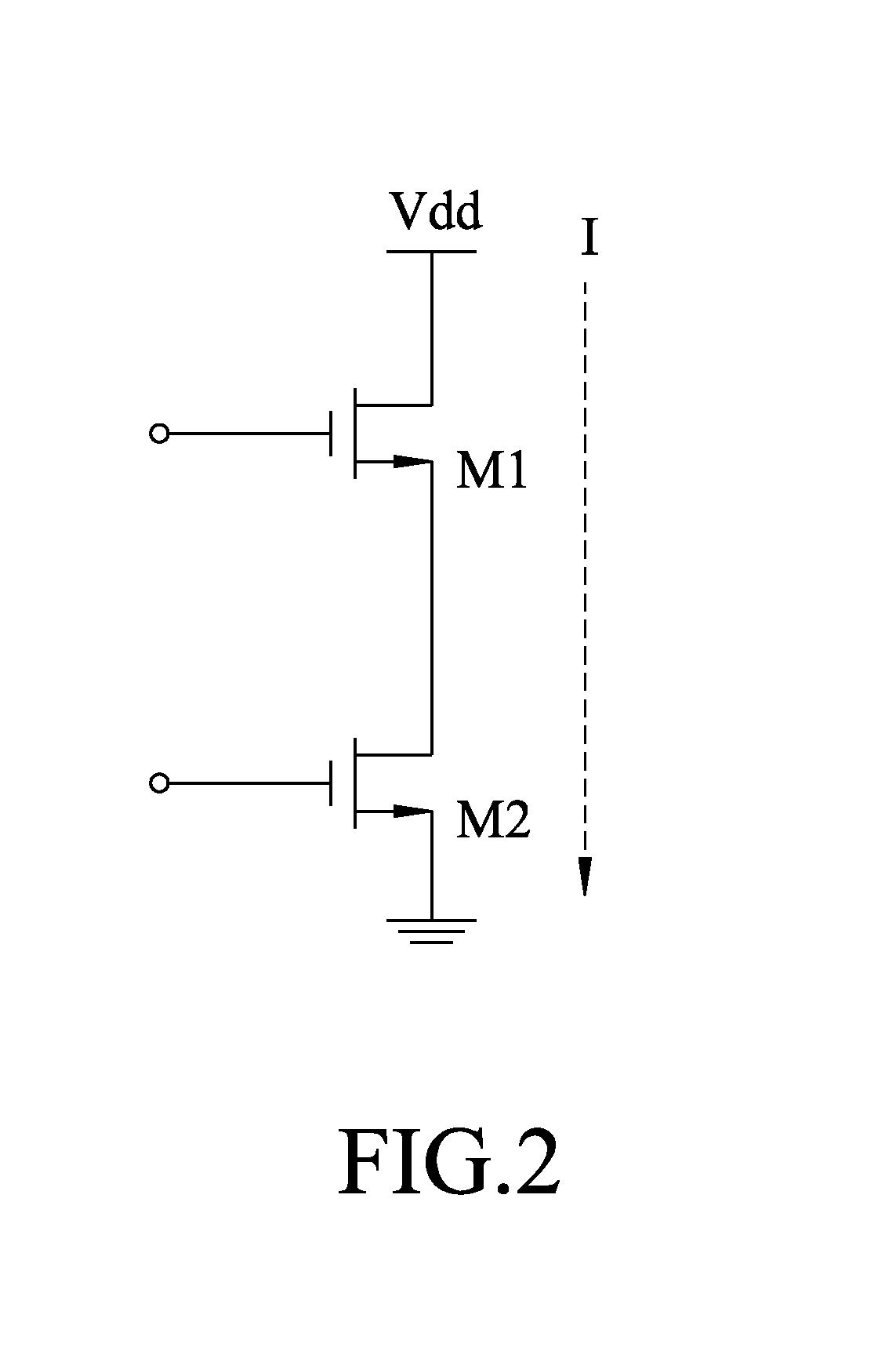

Ultra-wideband low-noise amplifier circuit with low power consumption

InactiveUS20150048889A1Reduce phase differenceHigh gainAmplifier with semiconductor-devices/discharge-tubesAmplifier modifications to reduce detrimental impedenceUltra-widebandAudio power amplifier

An ultra-wideband low-noise amplifier circuit with low power consumption includes a cascode amplifier circuit module and an output combining circuit module. The cascode amplifier circuit module receives an input signal, and outputs a first output signal and a second output signal. The output combining circuit module receives the first output signal and the second output signal, and applies respective phase shifts to the first output signal and the second output signal for reducing a phase difference between the first output signal and the second output signal, so as to obtain a combined output signal.

Owner:NATIONAL CHI NAN UNIVERSITY

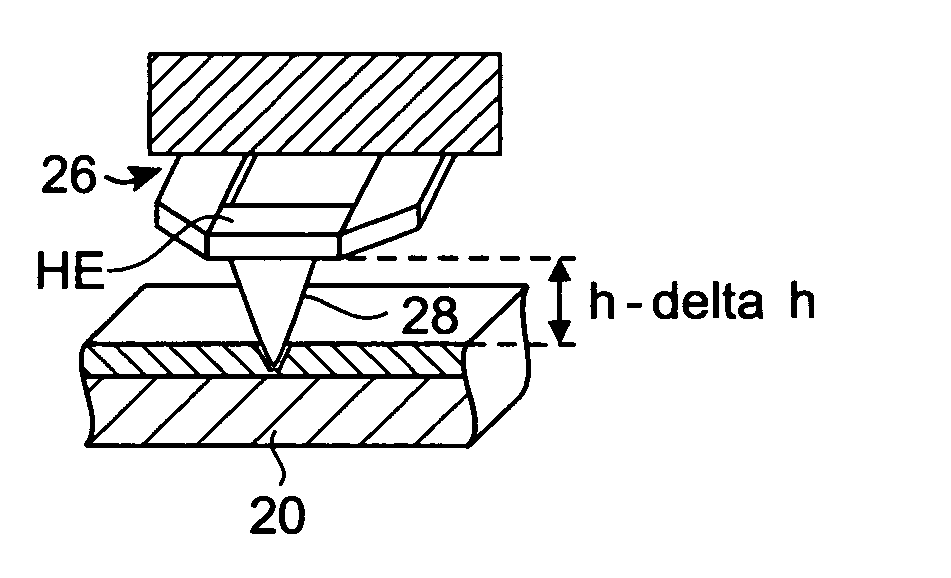

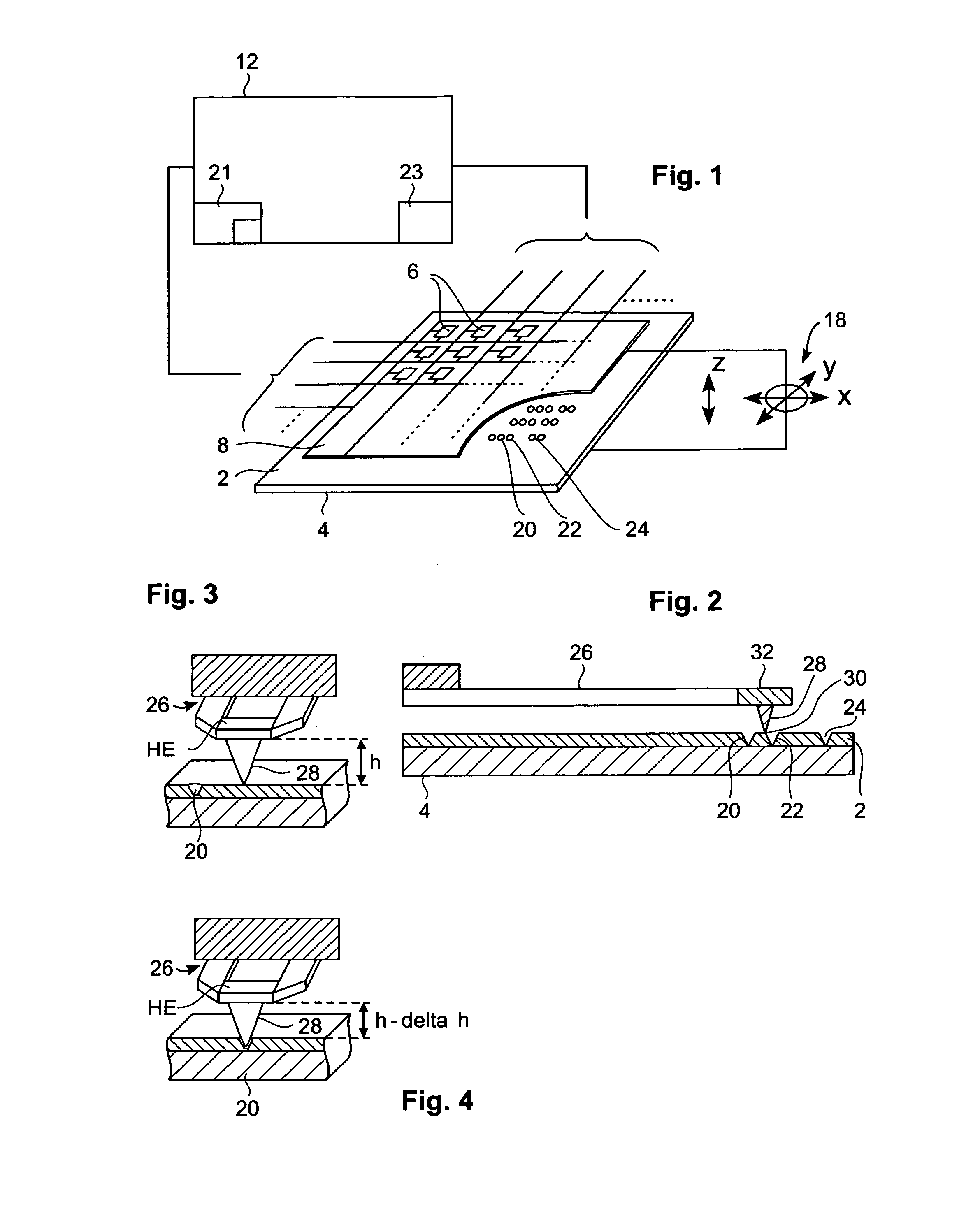

Device and method for sensing a position of a probe

InactiveUS20070063141A1Superior stability and phase noise performanceReduce phase differenceMaterial analysis using wave/particle radiationElectrical measurement instrument detailsThermal relaxation timeHeating element

Owner:GLOBALFOUNDRIES INC

Control system for an electric machine

ActiveUS8350508B2Efficient powerAlignment toleranceMotor/generator/converter stoppersSynchronous motors startersElectric machineControl system

A control system for an electric machine, the control system including a position sensor and a drive controller. The drive controller generates one or more control signals for exciting a winding of the electric machine in response to edges of a signal output by the position sensor. The times at which the control signals are generated by the drive controller are corrected by a position-sensor offset that is fixed over an operating speed range of the electric machine.

Owner:DYSON TECH LTD

Two-point frequency modulation apparatus, wireless transmitting apparatus, and wireless receiving apparatus

InactiveUS7333582B2Reduces input timing differenceHigh modulation accuracyPulse automatic controlModulated-carrier systemsLoop filterPhase difference

A two-point frequency modulation apparatus is provided that reduces input timing difference and improves modulation accuracy. Two-point frequency modulation apparatus 10 has: PLL circuit 11; frequency division ratio generator 13 that generates the frequency division ratio in frequency divider 111 based on first digital baseband signal S1 and carrier signal; adder 114 that adds second digital baseband signal S2 to the output signal of loop filter 113; a delay index calculator (filter coefficient calculator 17) that calculates the delay index based on the magnitude of change in the amplitude of the output signal of adder 114; and a delay adjuster (digital filter 18) that shifts the phase of one of first digital baseband signal S1 and second digital baseband signal S2 according to the delay index so as to reduce the phase difference.

Owner:PANASONIC CORP