Patents

Literature

30 results about "Diffuse field" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Diffuse field principle. Theoretically, diffuse field is defined as a Sound pressure field where there is no privileged direction of the energy. In other words, when sound pressure is the same everywhere in the room. This is obtained with large rooms with no absorbent materials on walls, ceiling or floor. Diffusion is enhanced in asymmetric rooms.

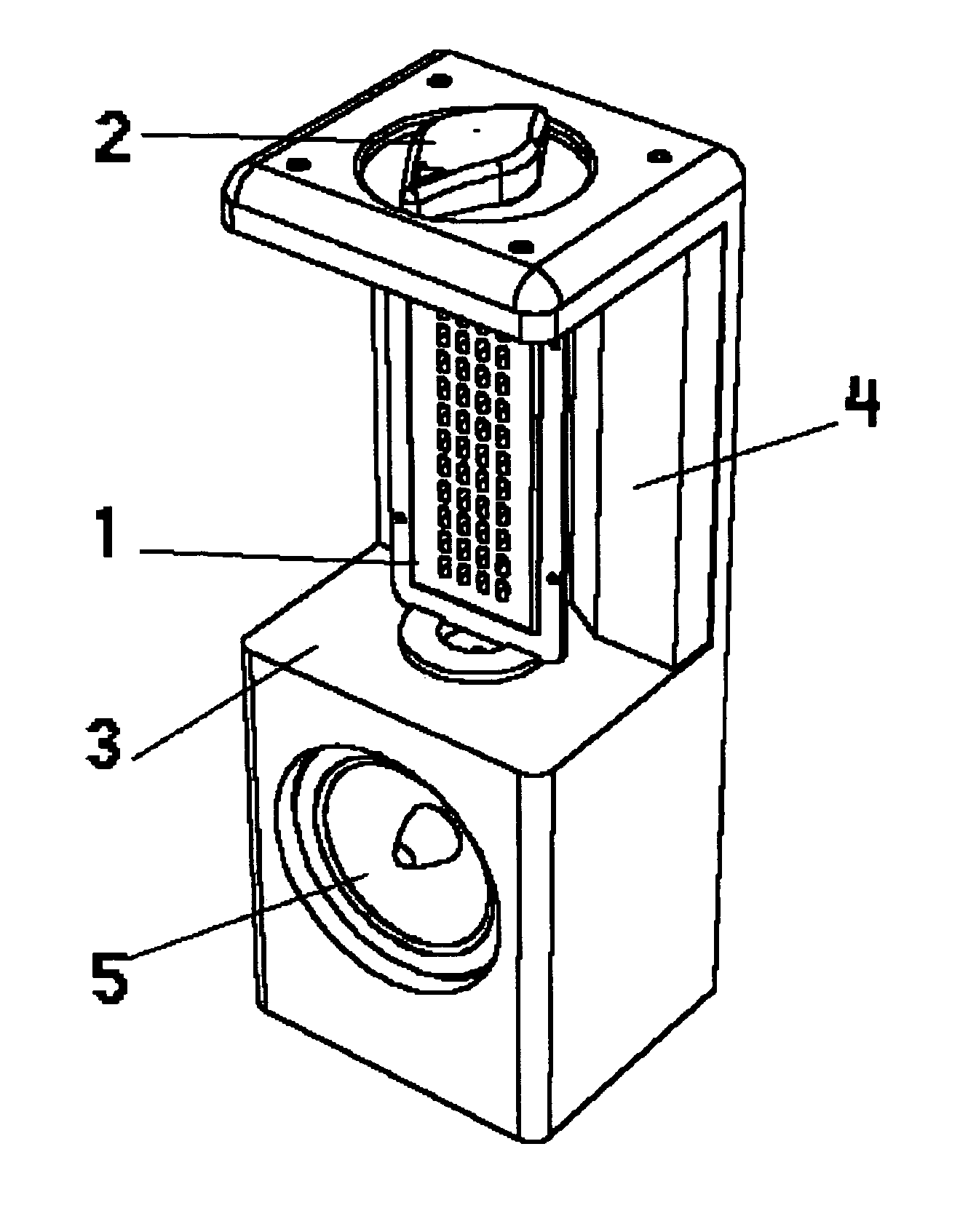

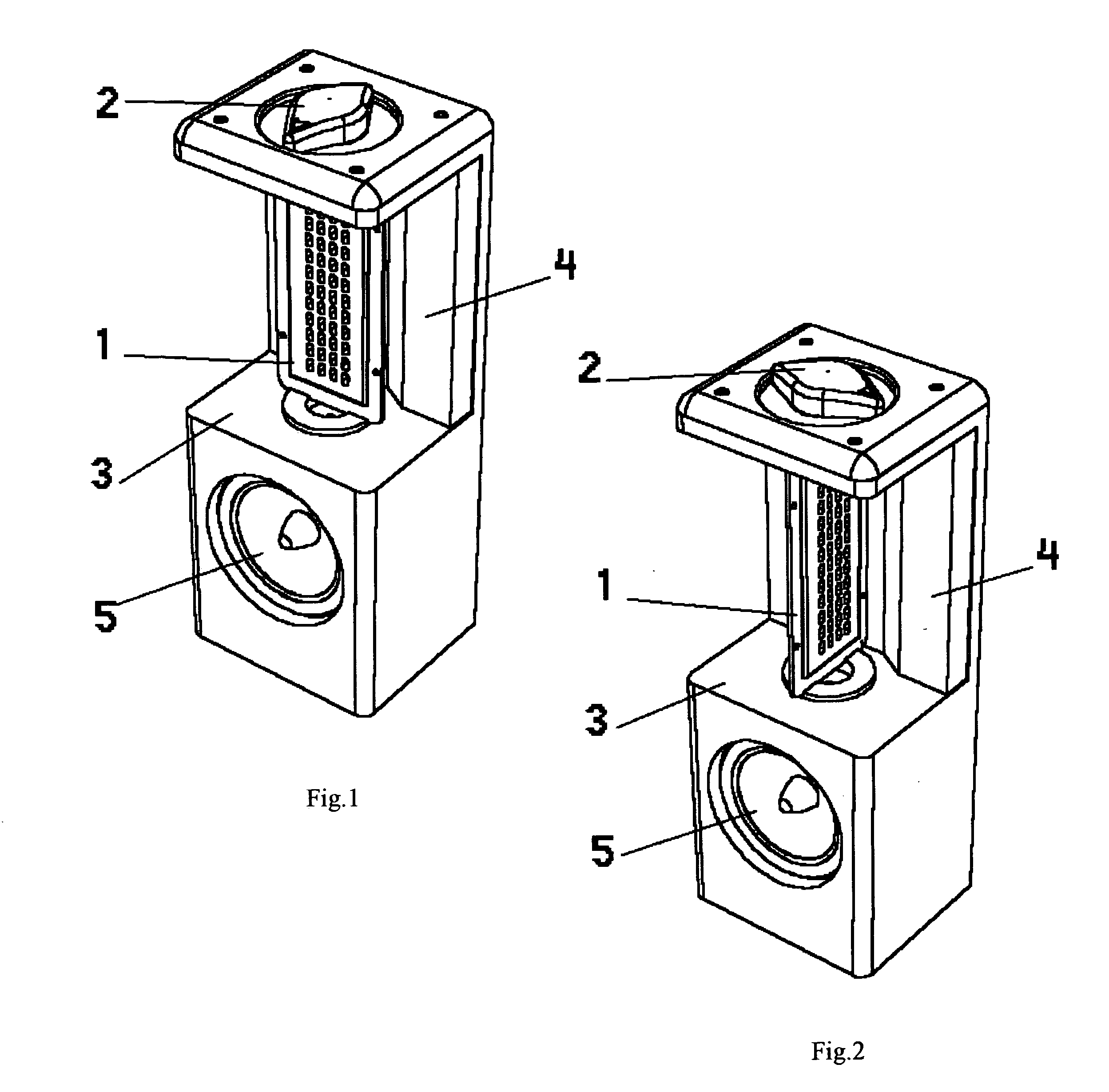

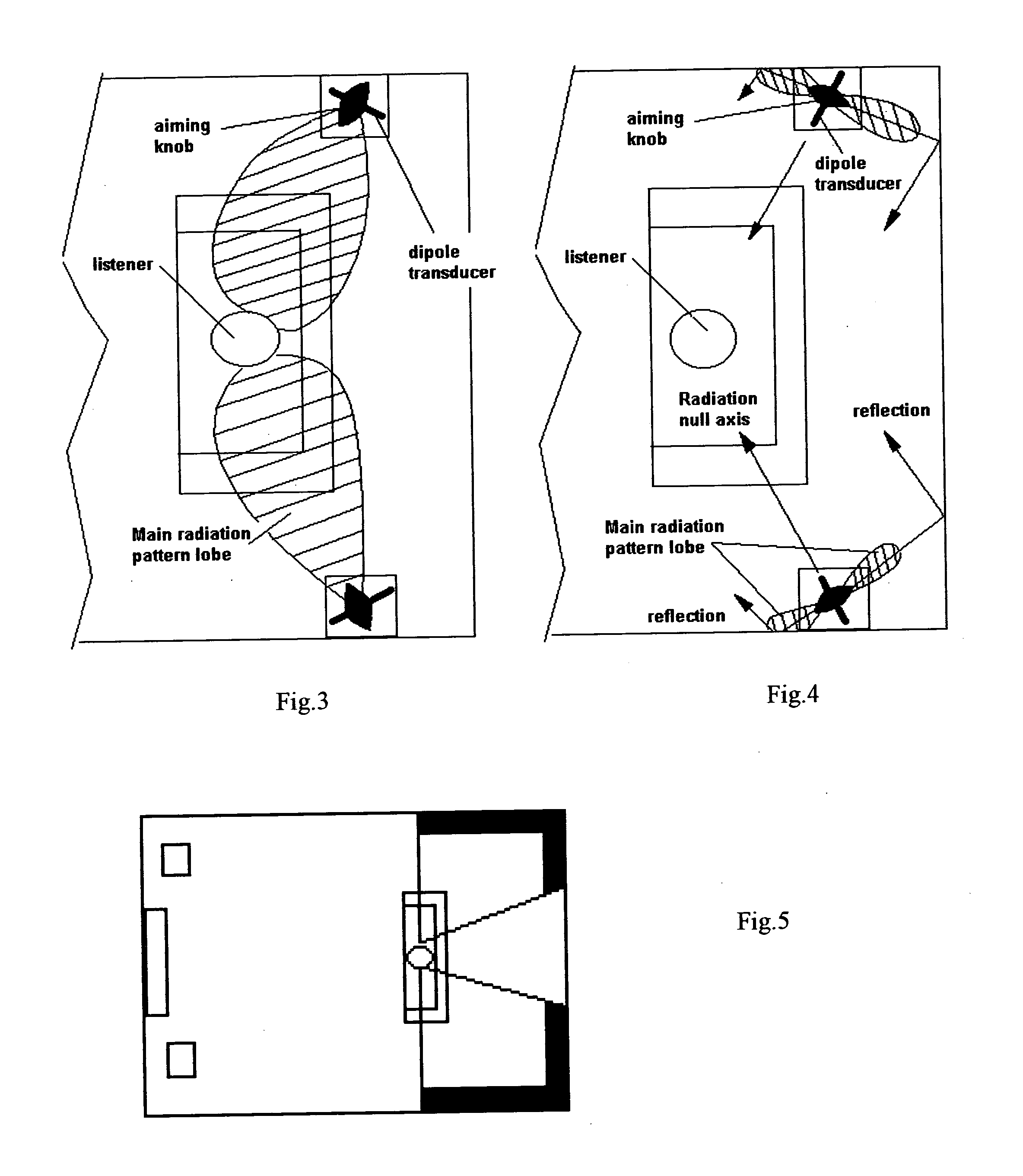

Loudspeaker with variable radiation pattern

InactiveUS20060050907A1More freedom for in room designAcceptable performanceBending wave transducersFrequency/directions obtaining arrangementsDiffuse fieldTransducer

The invention is a loudspeaker for use in home theater or multi-channel sound systems that includes an enclosure, a wideband transducer, a sound absorbing pad and an aiming knob. The wideband transducer is rotatably mounted in the enclosure so that the wideband transducer can be rotated around its vertical axis and an aiming knob mechanically coupled to the wideband transducer. The wideband transducer has a front side and a rear side open so that said wideband transducer operates as a dipole transducer. The aiming knob controls the rotation angle of the dipole transducer. The loudspeaker uses the dipole transducer to create either a diffuse field or direct radiating surround sound.

Owner:LEVITSKY IGOR

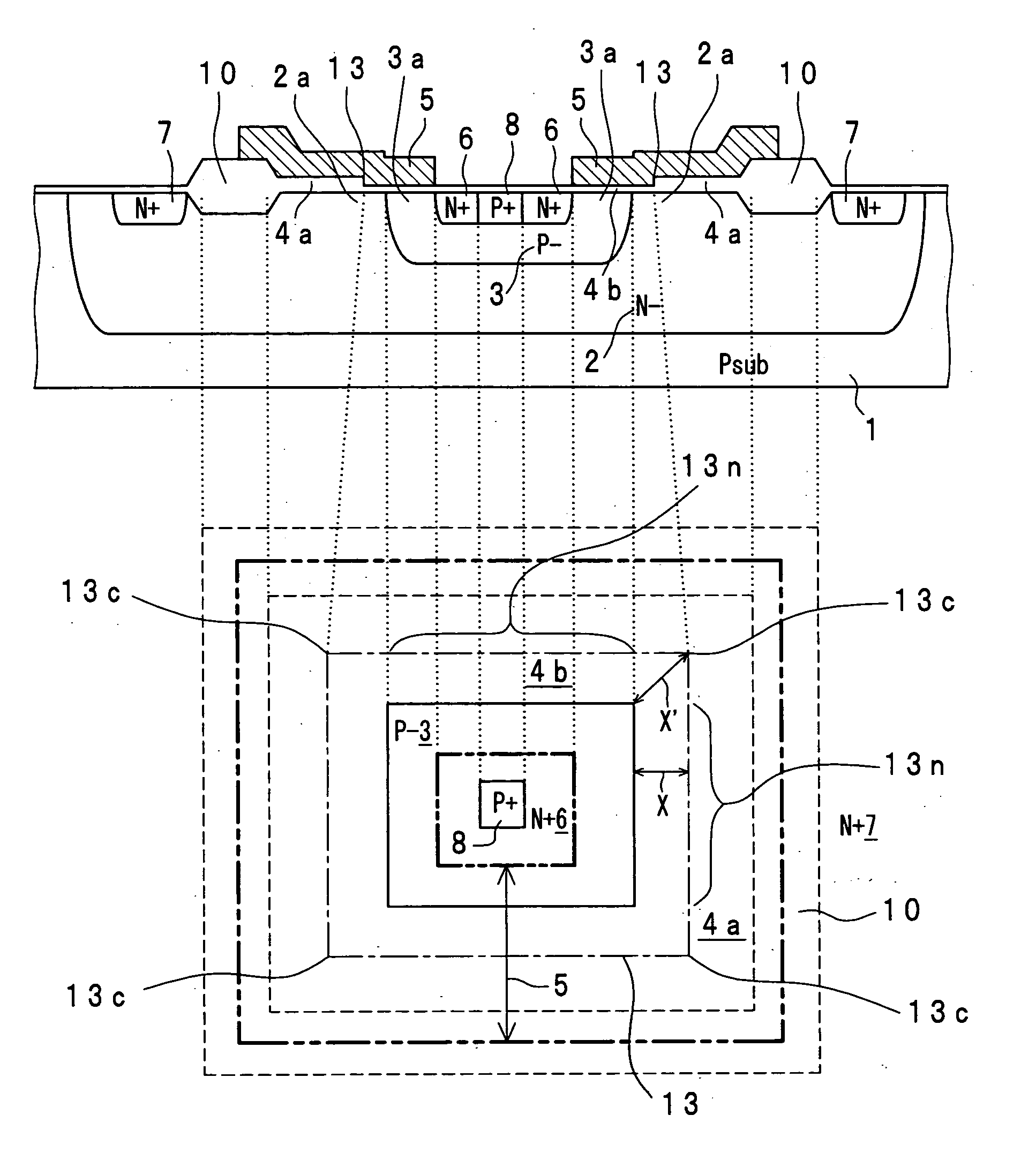

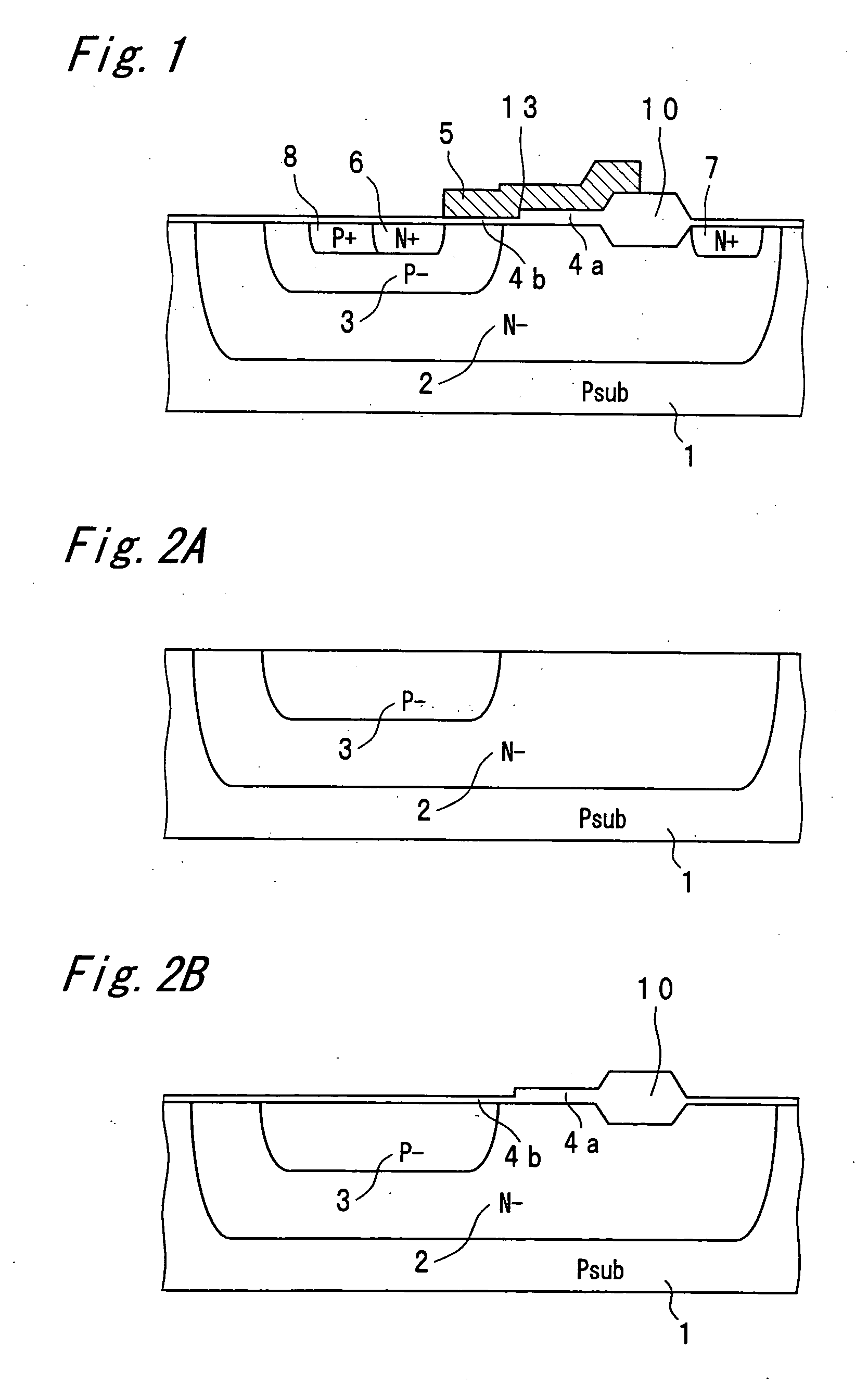

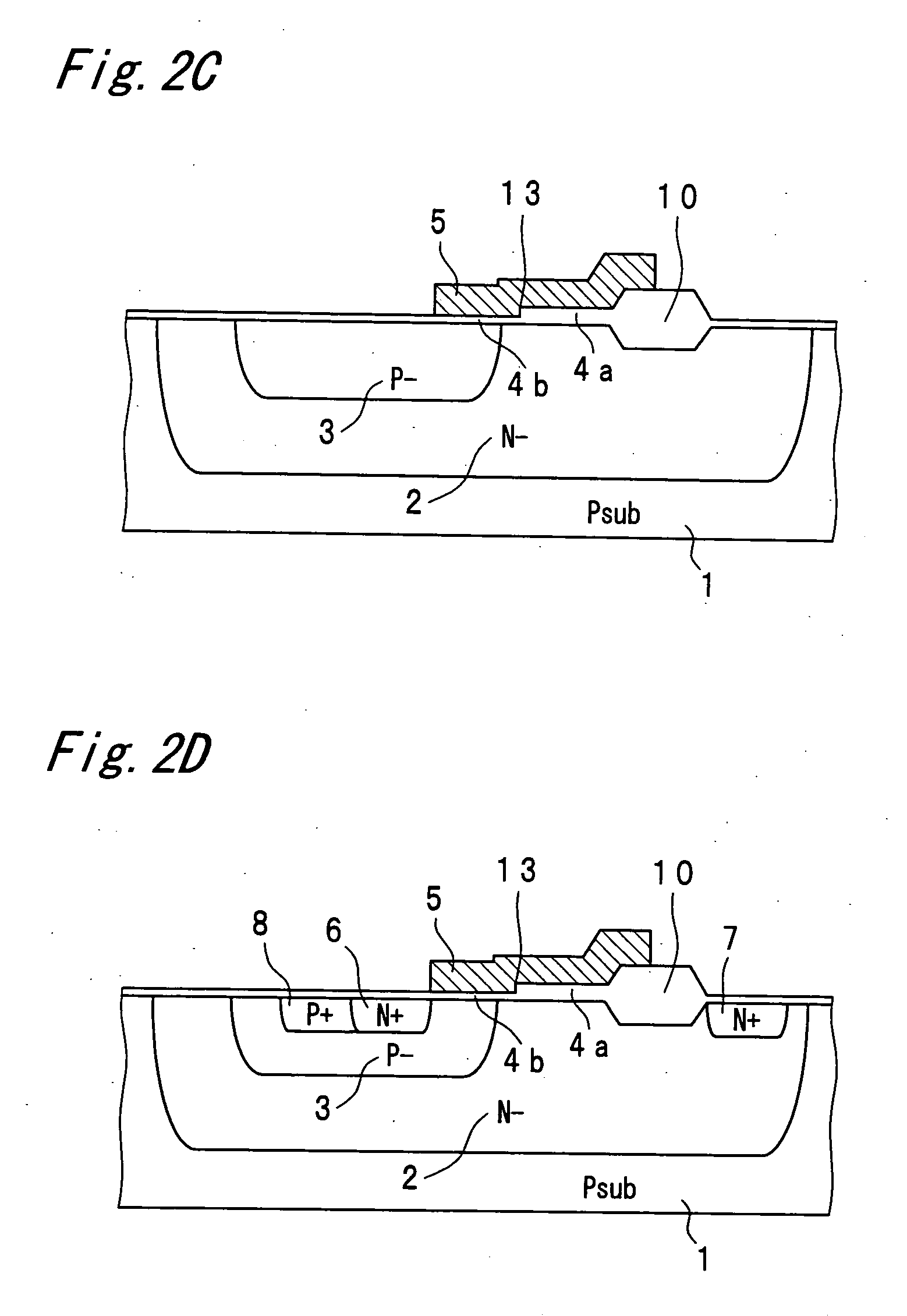

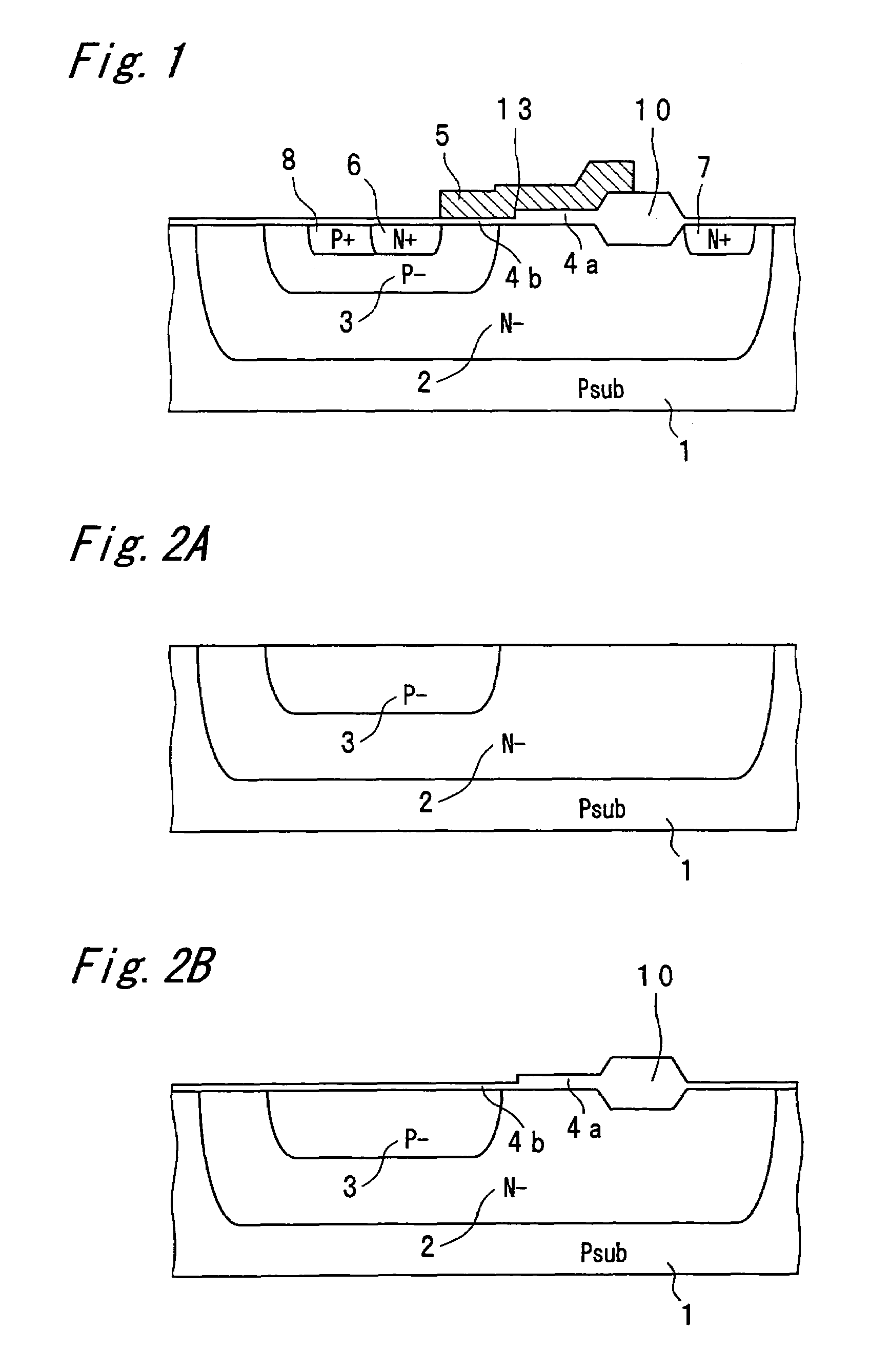

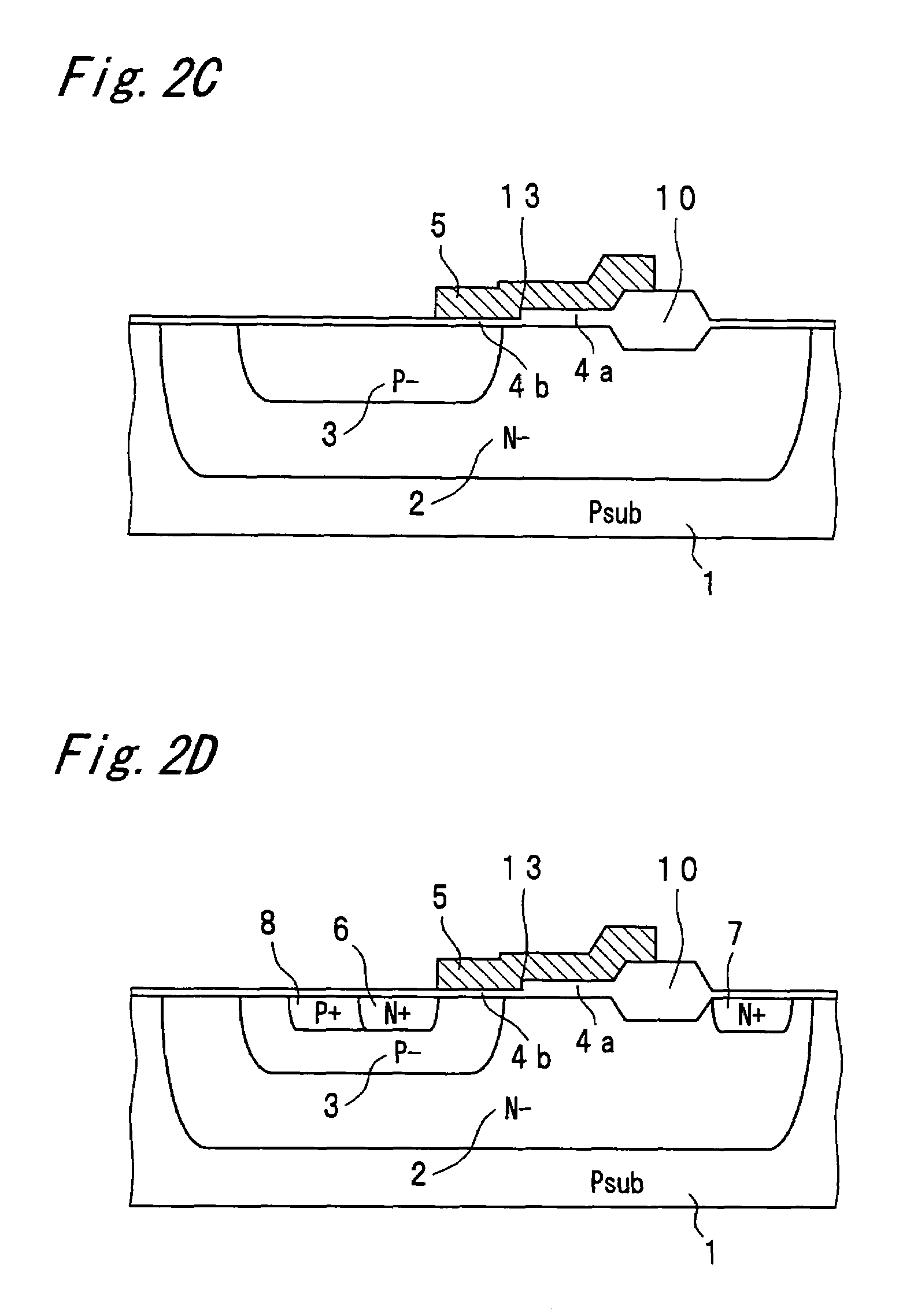

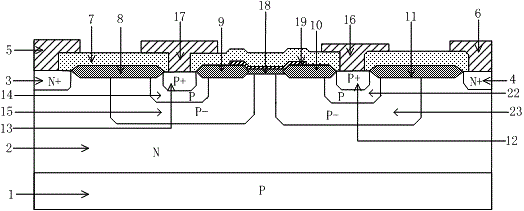

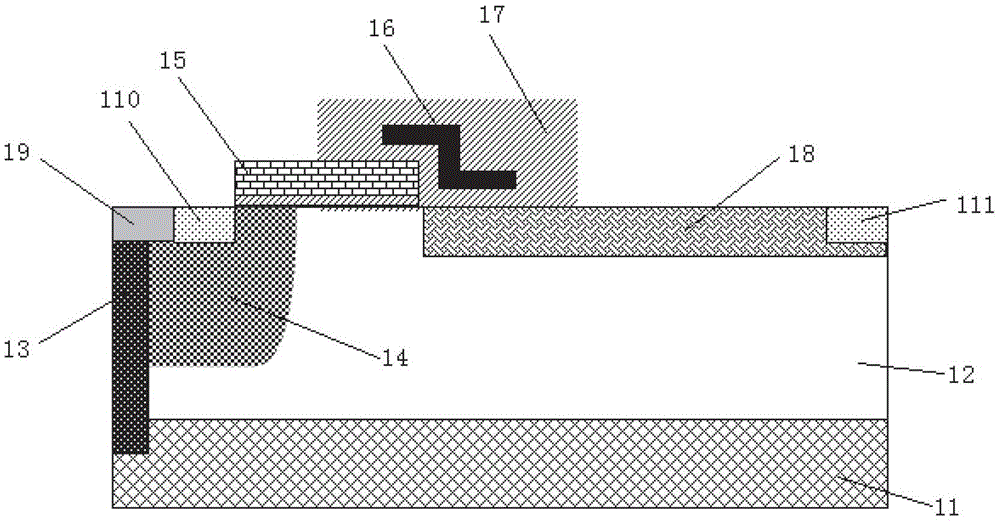

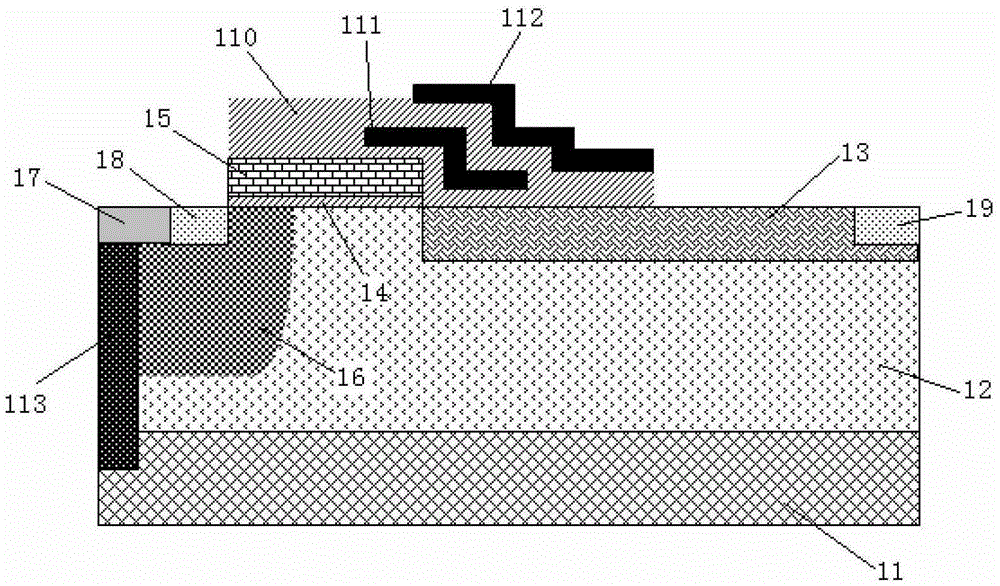

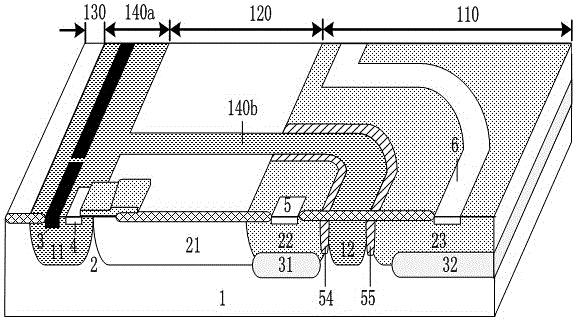

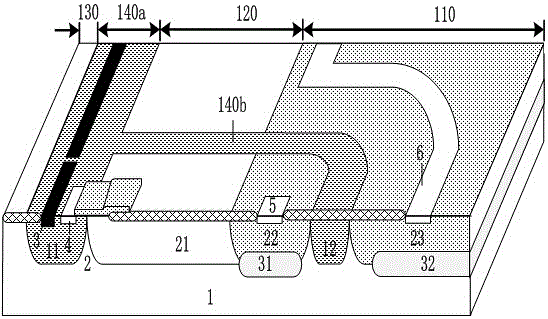

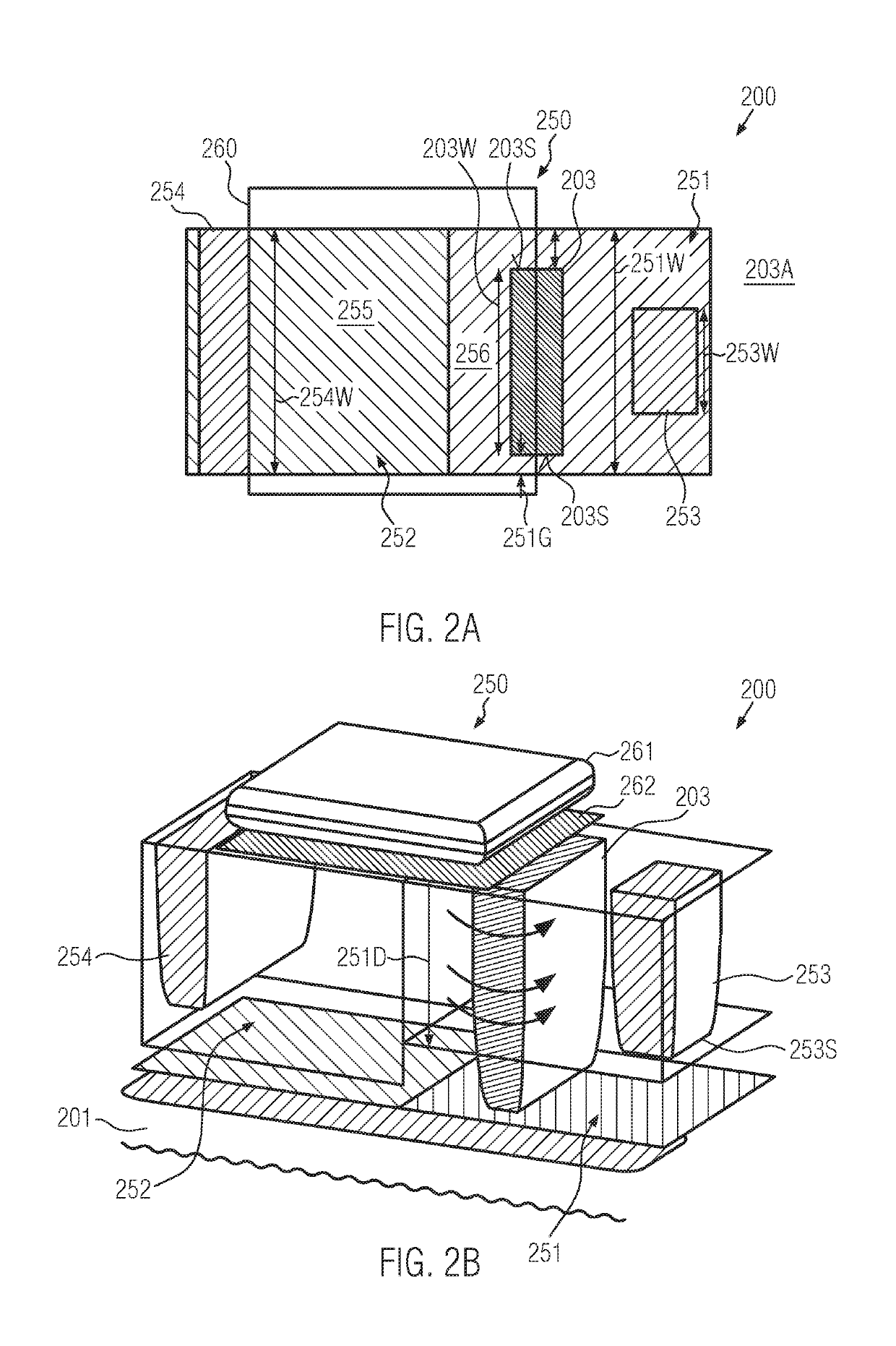

Lateral double-diffused field effect transistor and integrated circuit having same

InactiveUS20070063271A1Improve breakdown voltageLower on-resistanceTransistorSolid-state devicesDiffuse fieldField-effect transistor

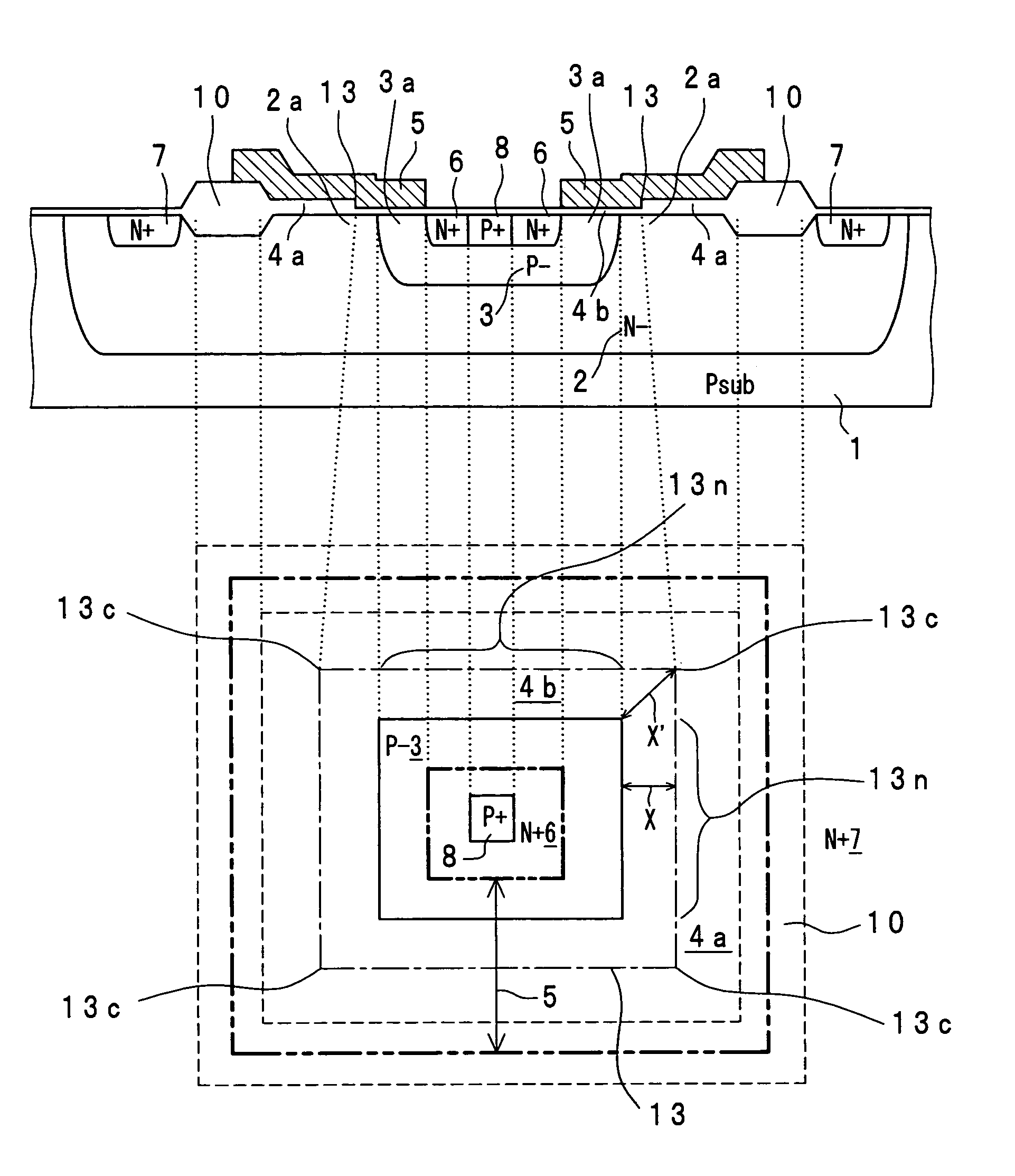

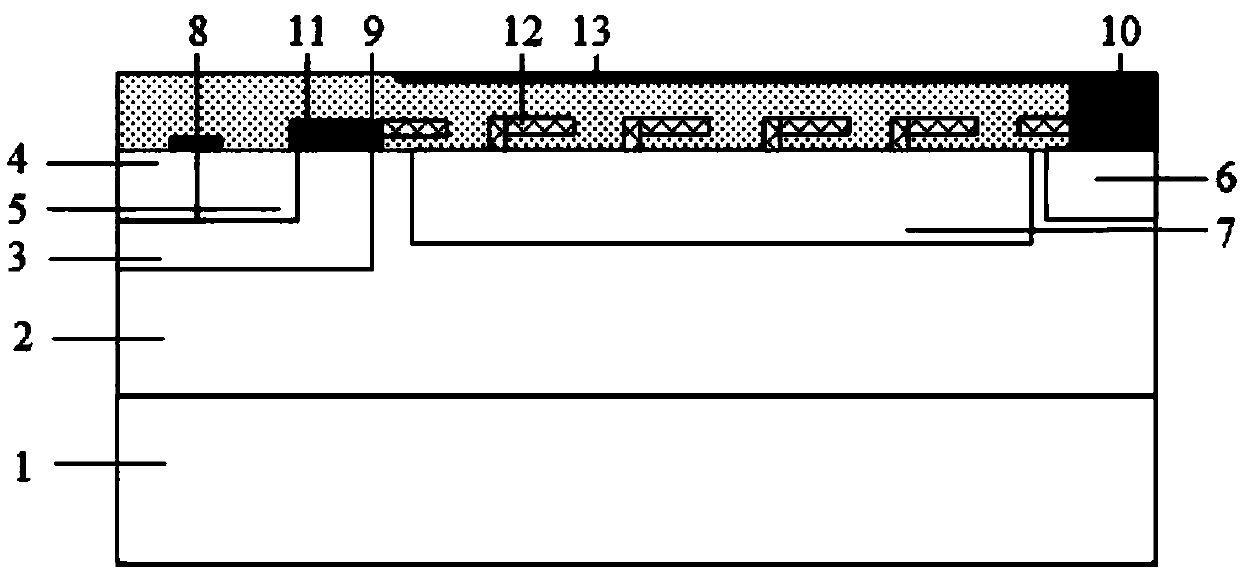

In a lateral double-diffused field effect transistor of the present invention, a gate insulating film includes a first gate insulating film covering a source diffusion layer up to a region beyond the pattern of a body diffusion layer and a second gate insulating film having a film thickness larger than that of the first gate insulating film and covering a region closer to a drain diffusion layer than the region covered by the first gate insulating film. A boundary between the first gate insulating film and the second gate insulating film is composed of a straight portion parallel to a side of the pattern of the body diffusion layer and a corner portion surrounding an vertex of the pattern of the body diffusion layer from a distance. A distance between the vertex of the pattern of the body diffusion layer and the corner portion of the boundary is equal to or smaller than a distance between the side of the pattern of the body diffusion layer and the straight portion of the boundary.

Owner:SHARP KK

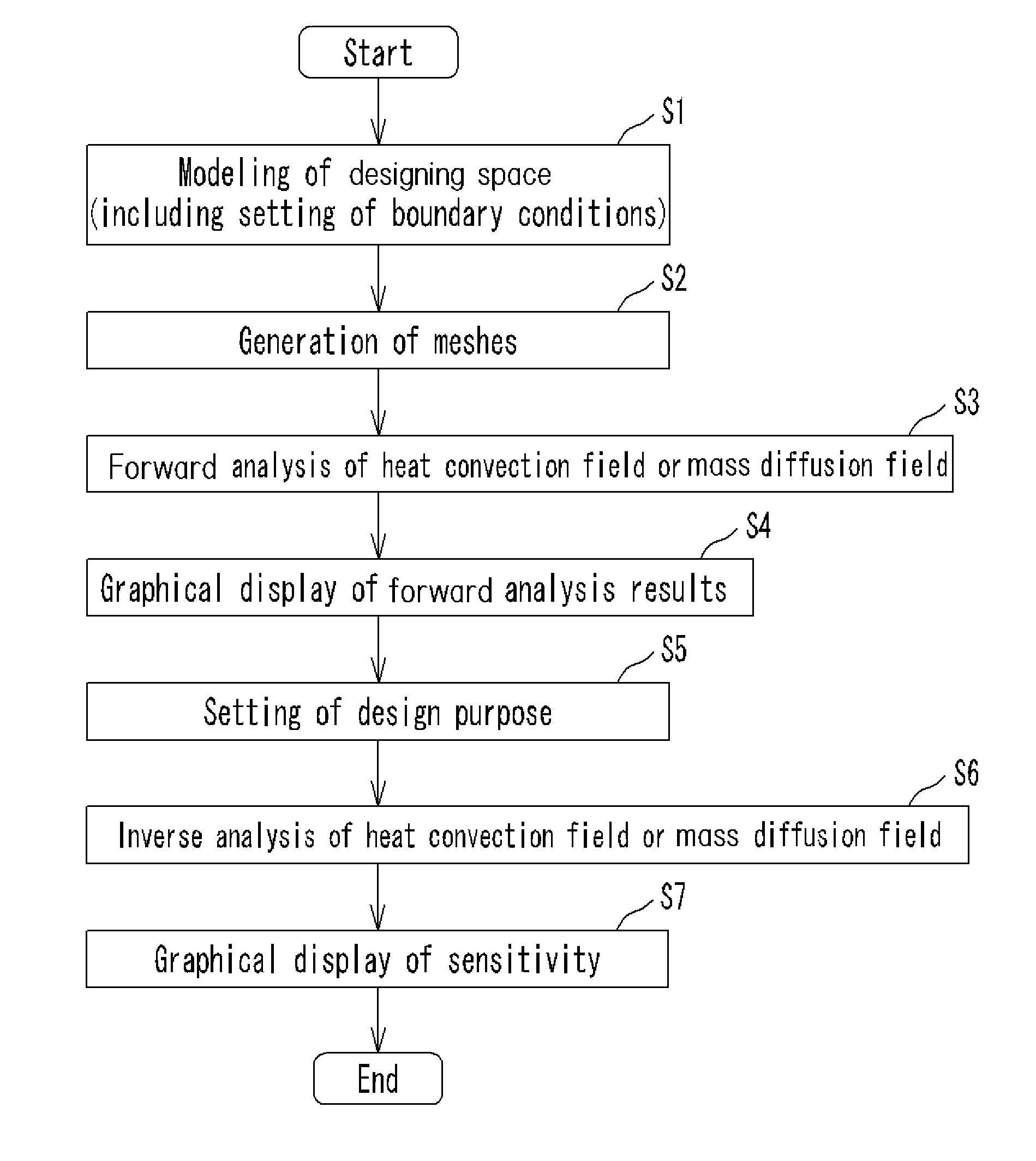

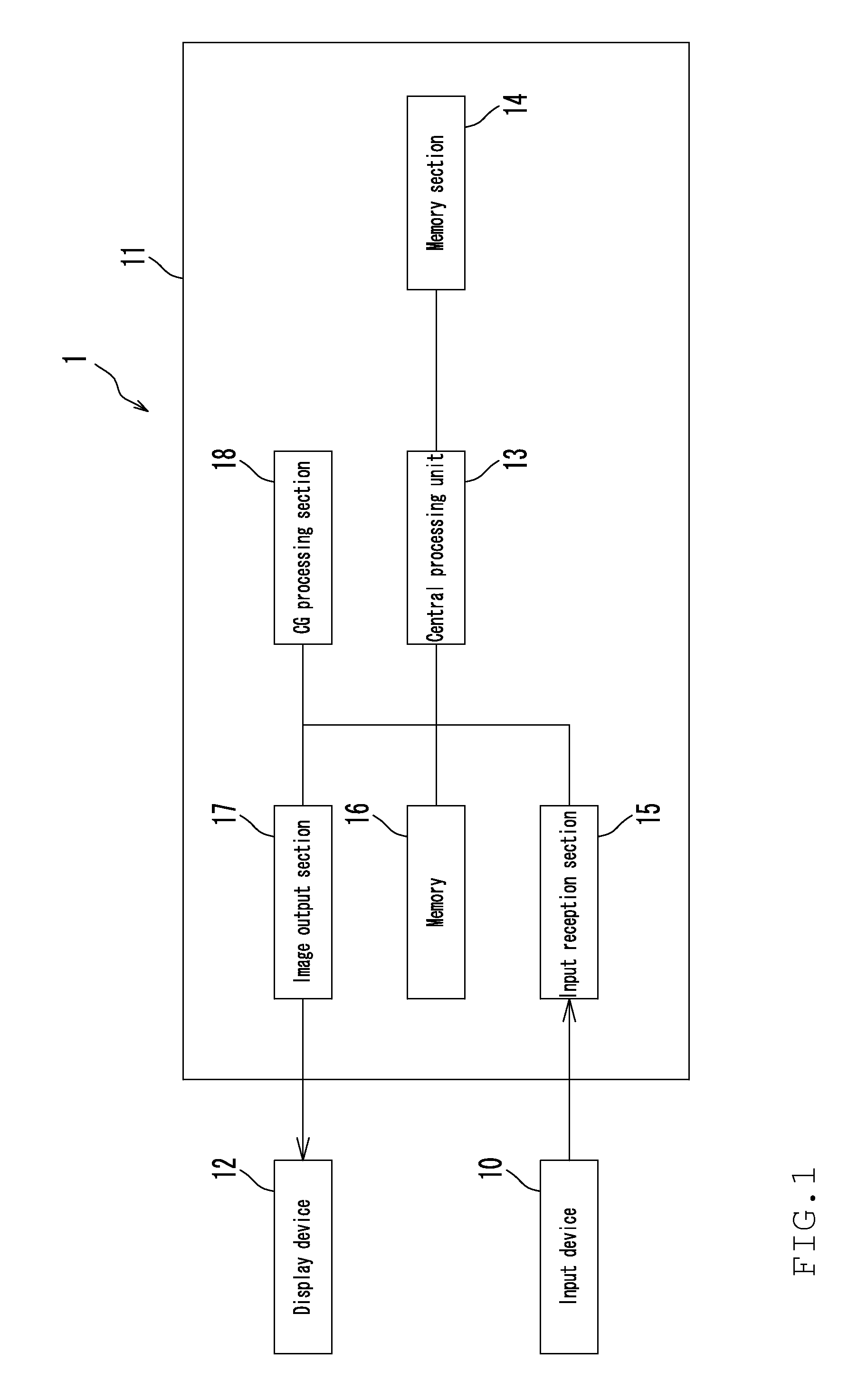

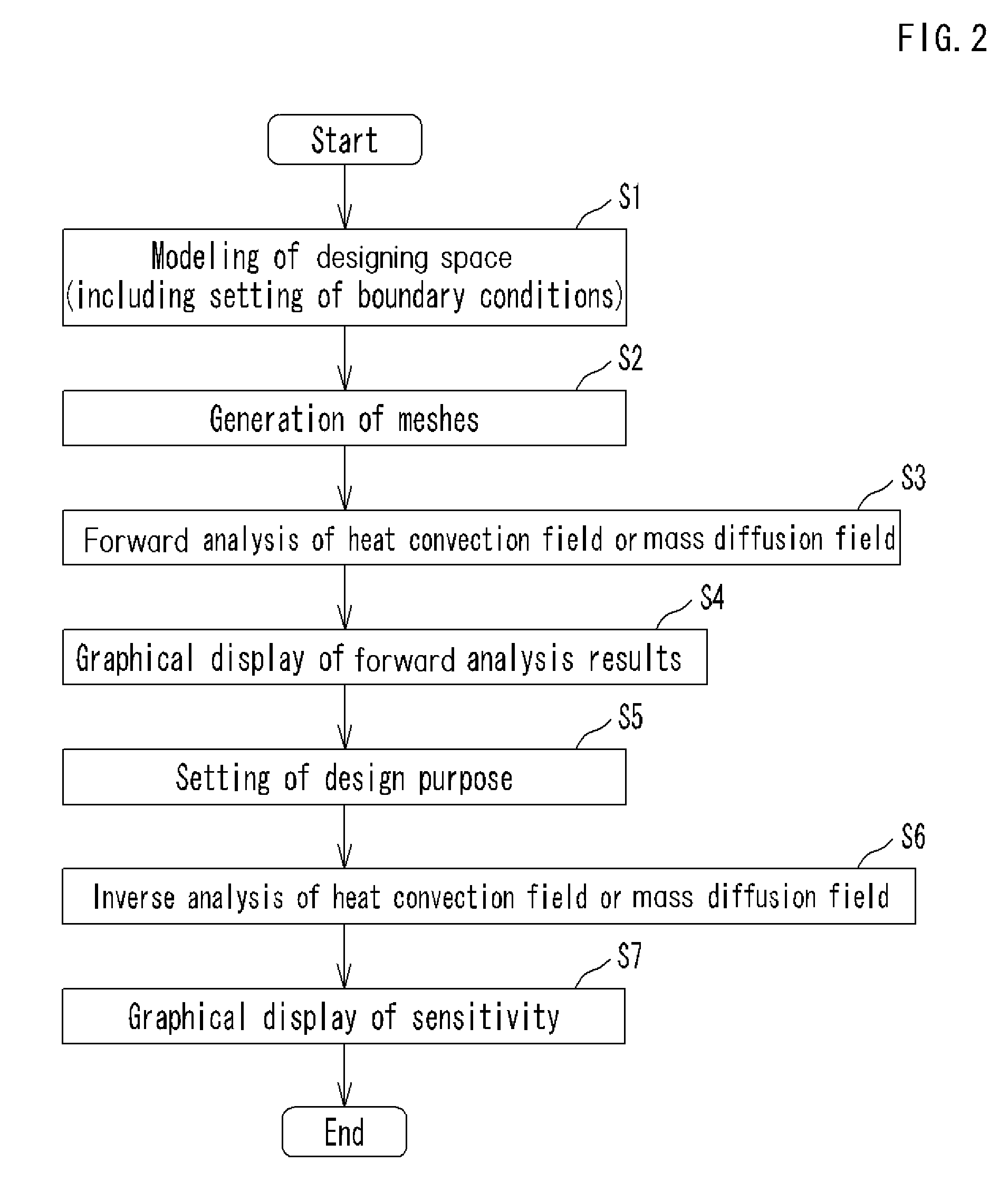

Design support method, design support system, and design support program for heat convection field

ActiveUS20090276193A1Reduces number of time of numericalShorten the timeGeometric CADDesign optimisation/simulationGraphicsDesign support system

A highly convenient design support method and design support system for a heat convection field or a mass diffusion field which significantly reduce the number of times of numerical simulation required to examine the designing parameters for achieving the design purpose. The design support method includes a forward analysis step of analyzing the heat convection field or the mass diffusion field by solving an equation of the heat convection field or the mass diffusion field based on an initially set value of a designing parameter, an inverse analysis step of analyzing a sensitivity defined by a change ratio of the design purpose to a designing parameter change by solving an adjoint equation corresponding to the design purpose based on the set design purpose, and a sensitivity display step of displaying information on the sensitivity analyzed by inverse analysis step as a graphic image on the display device.

Owner:OSAKA UNIV +1

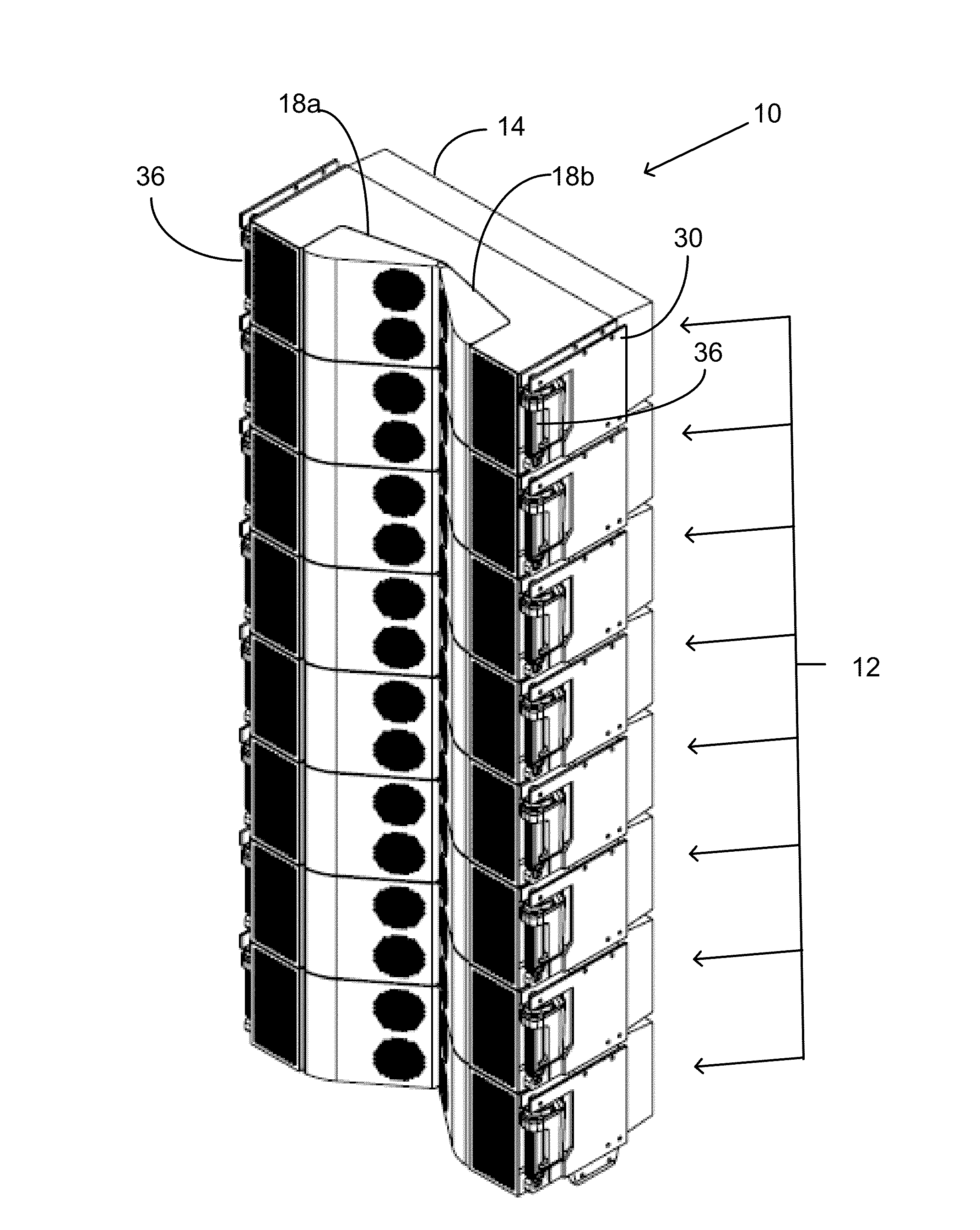

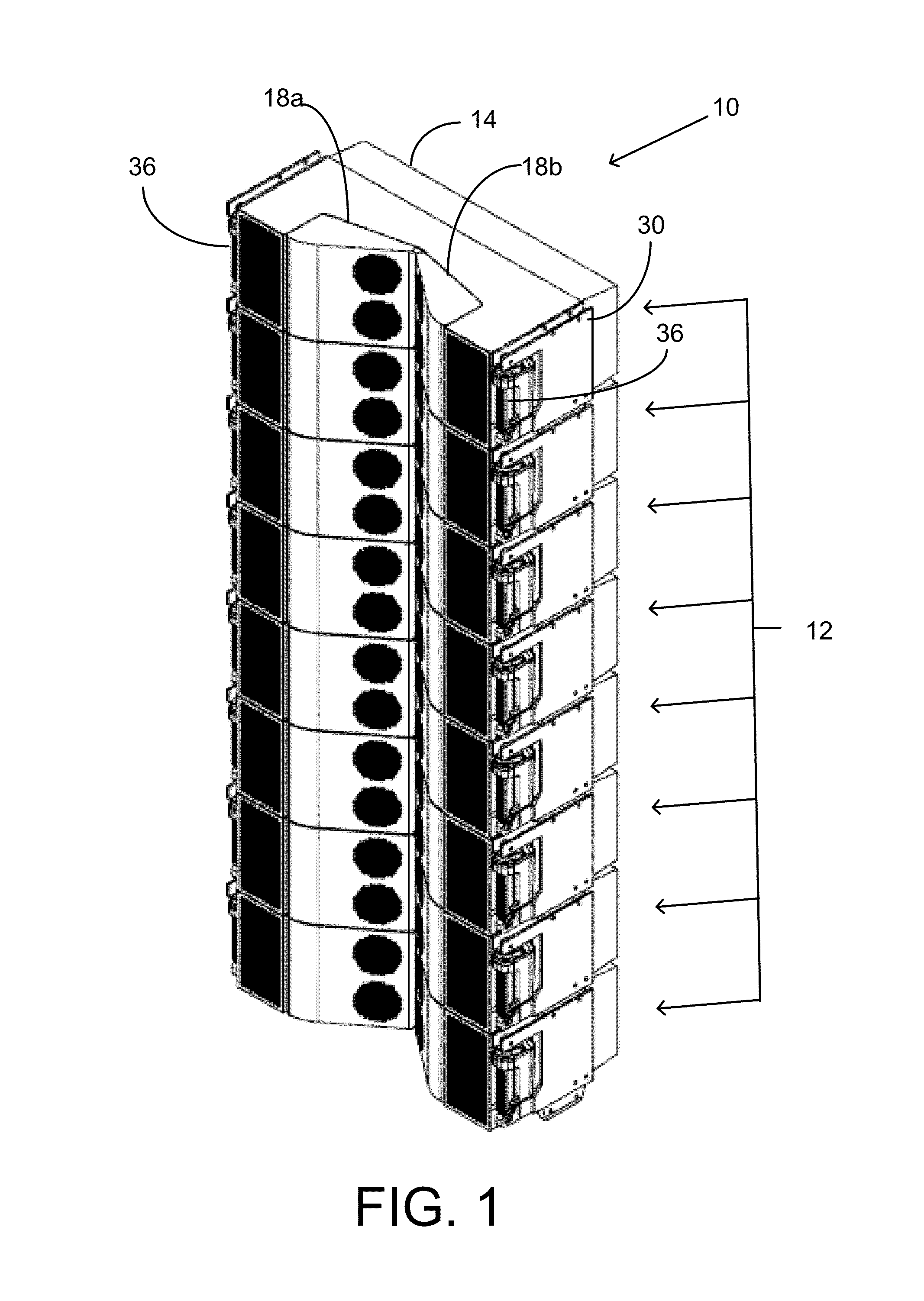

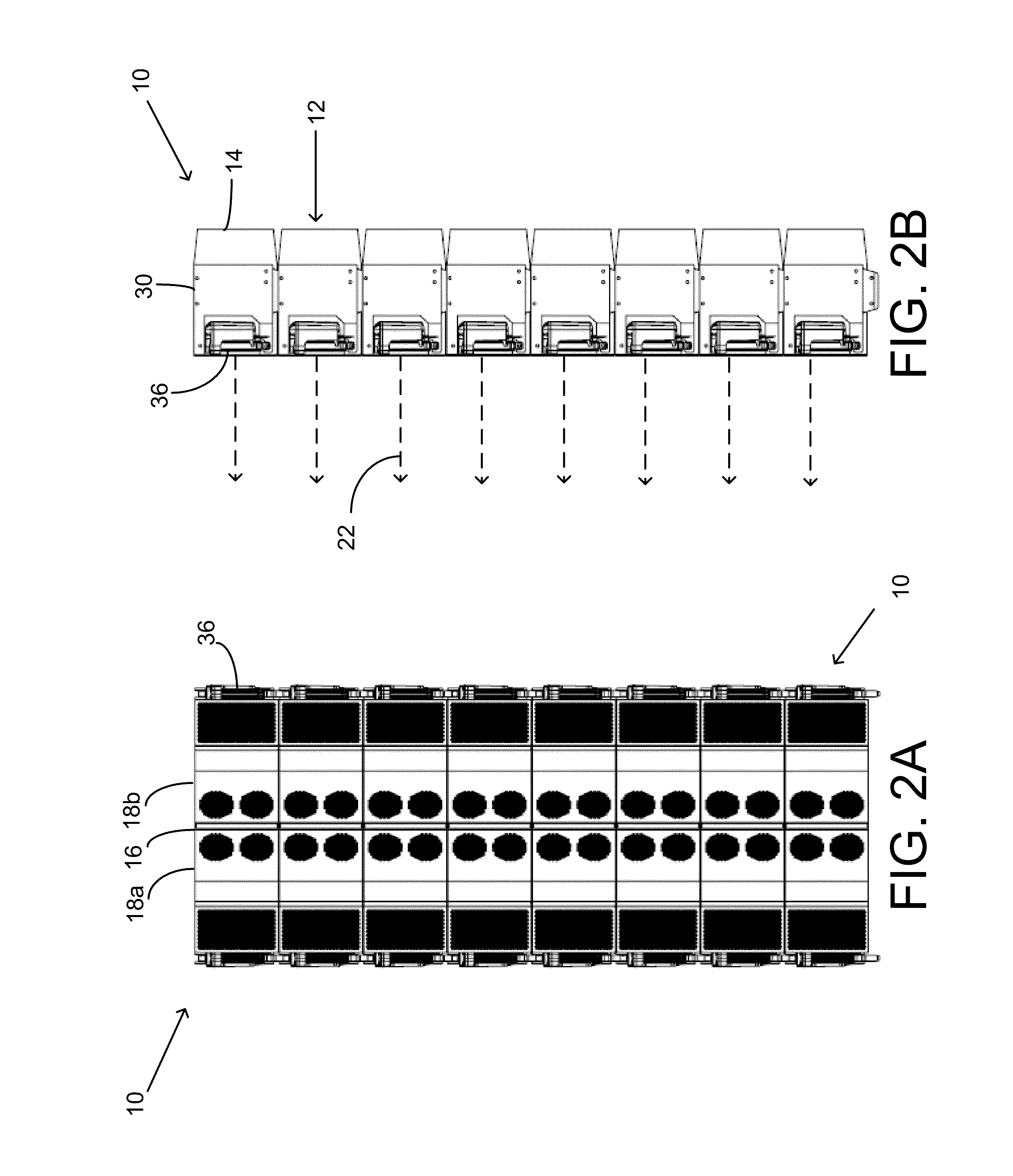

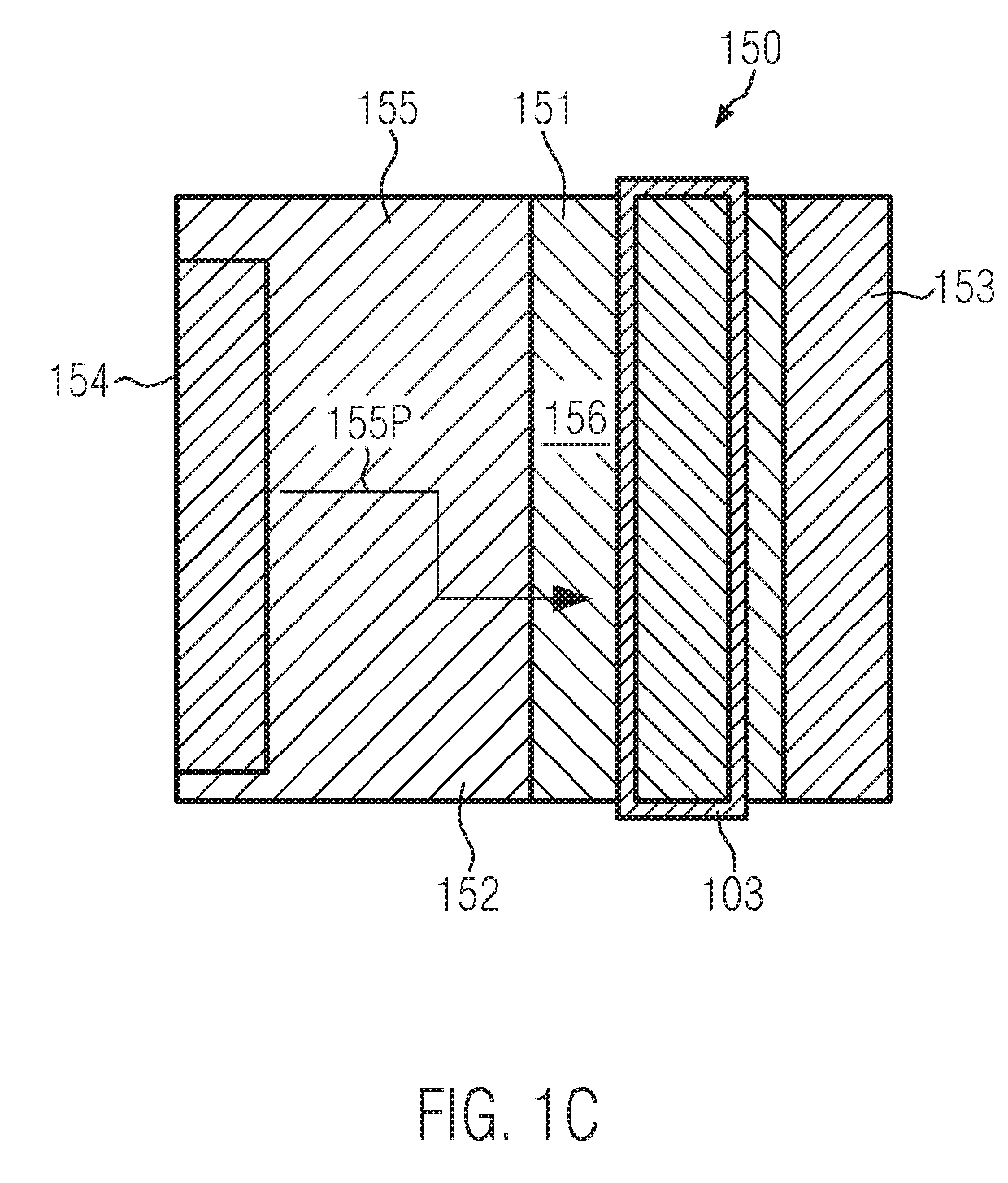

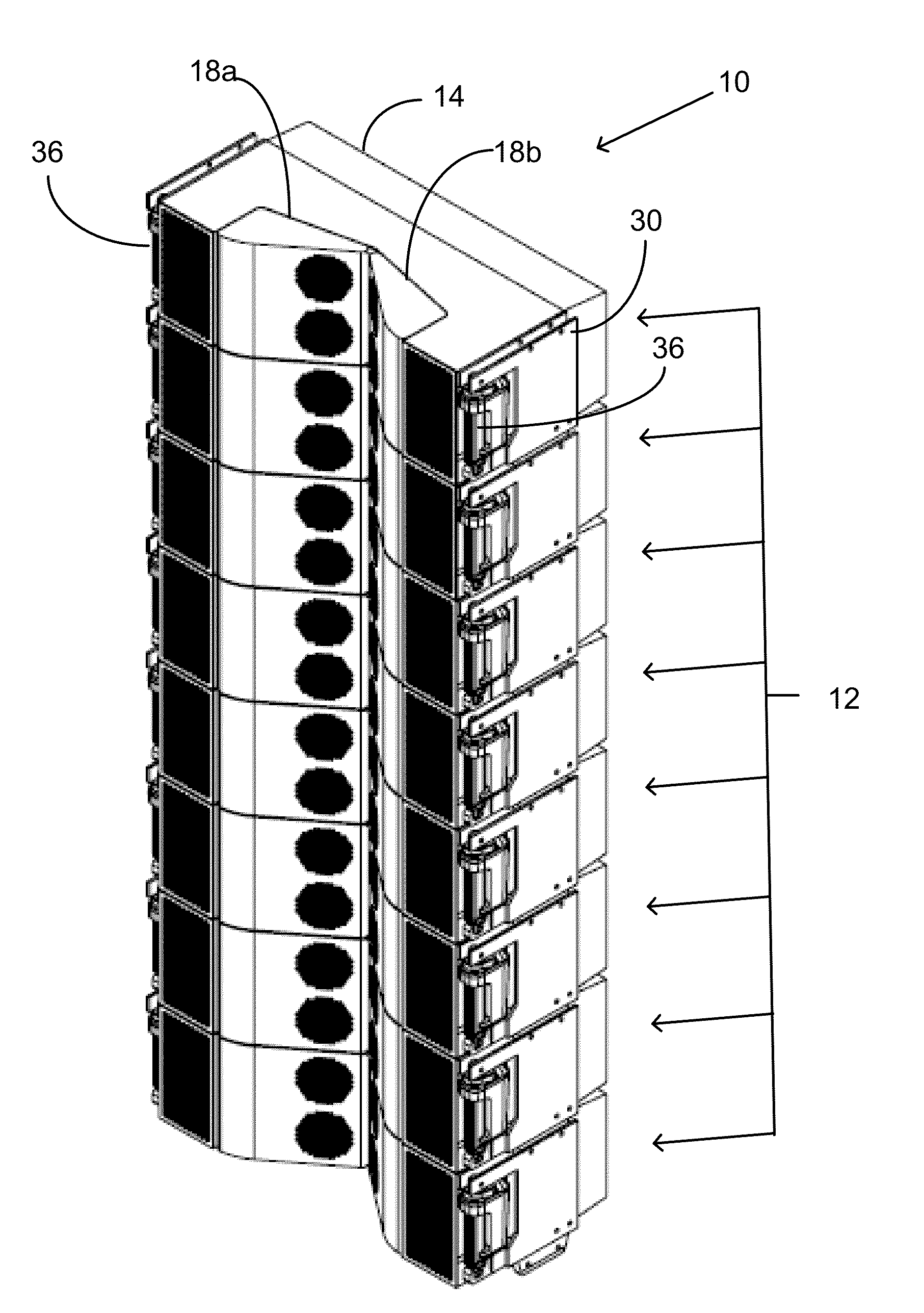

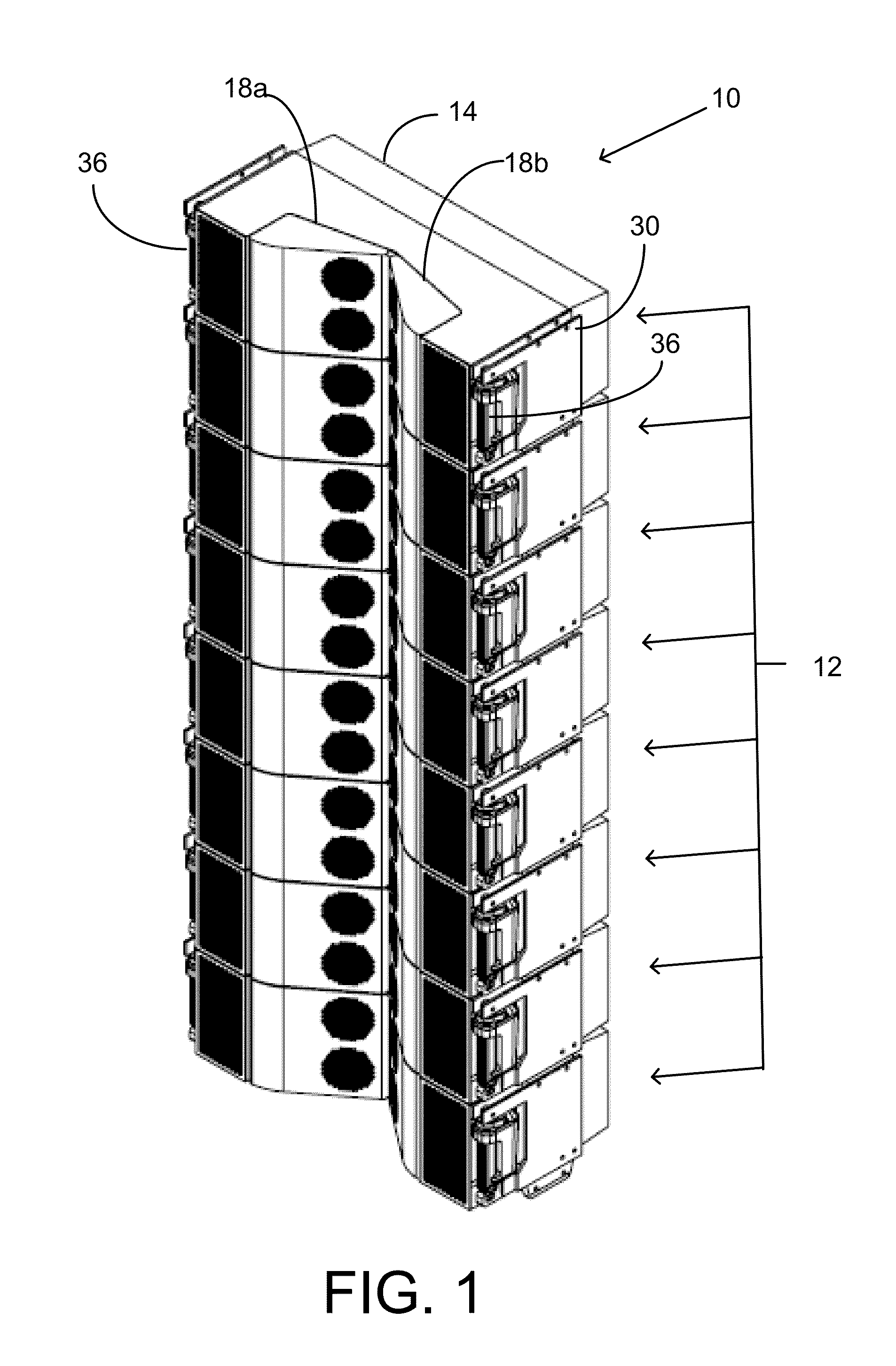

Vertical line array loudspeaker mounting and adjustment system

ActiveUS20140353074A1Reduce forceLoudspeaker casing supportsPublic address systemsJoystickDiffuse field

The invention relates to a loudspeaker mounting and adjustment system and method for installing and operating a professional audio system used in a stadium, concert hall or the like. The system comprises a vertical array of loudspeaker cabinets that can be suspended from a ceiling and that enables the horizontal and vertical angle of the sound dispersion field to be adjusted remotely and / or automatically while the system is suspended. Each loudspeaker cabinet is connected to a vertically adjacent loudspeaker cabinet via a pair of levers located on either side of the cabinet that control the angle between adjacent loudspeaker cabinets. A linear actuator is connected to each lever for controlling the lever position. Each loudspeaker cabinet also comprises a waveguide with at least one actuator for modifying the waveguide angle and thus the horizontal angle of the sound dispersion field.

Owner:PK SOUND CORP

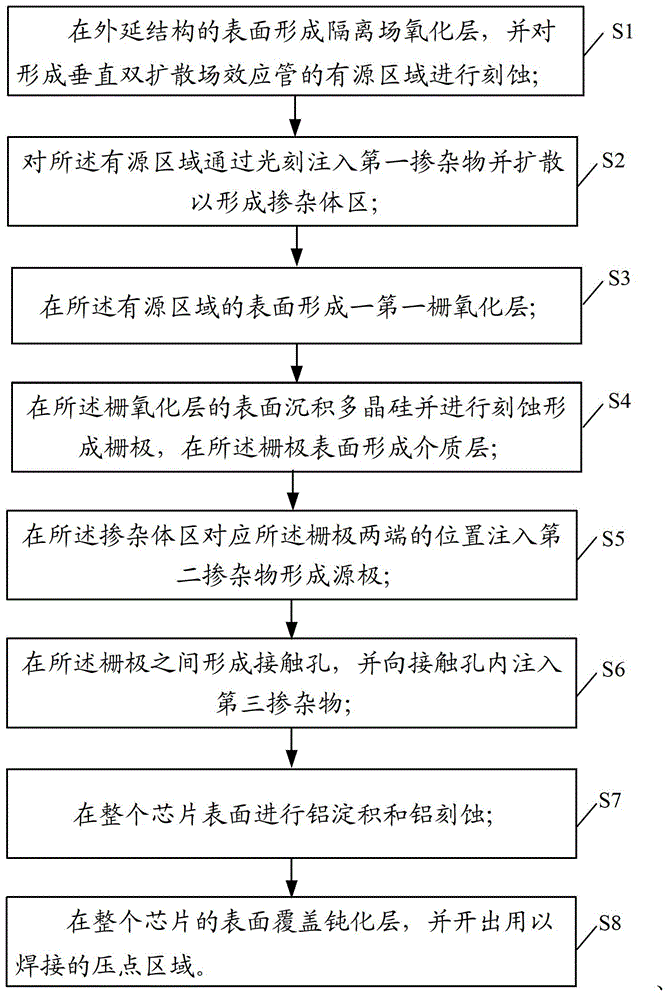

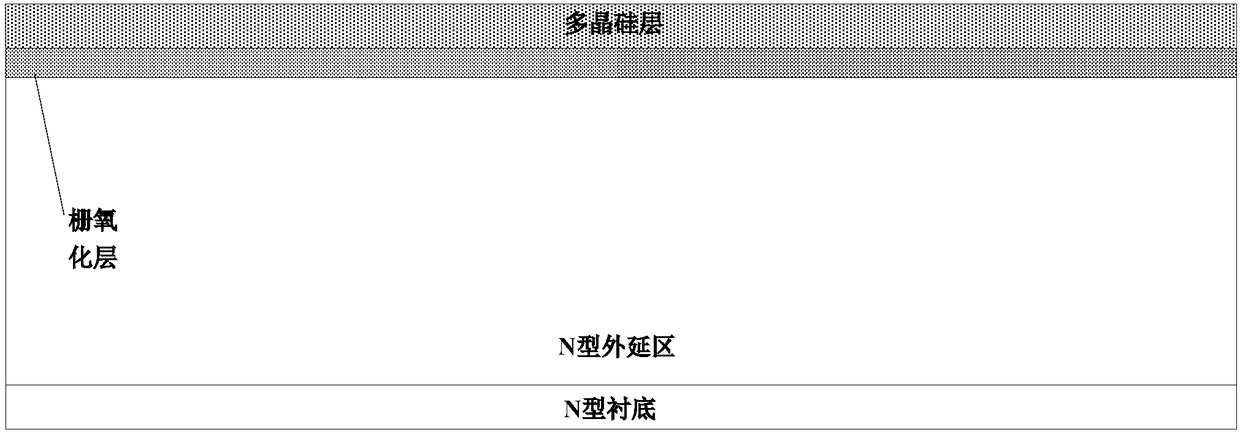

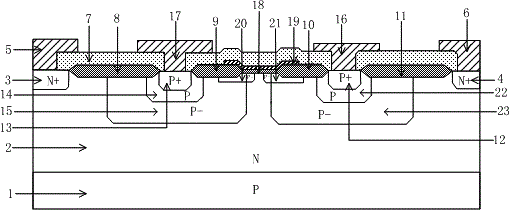

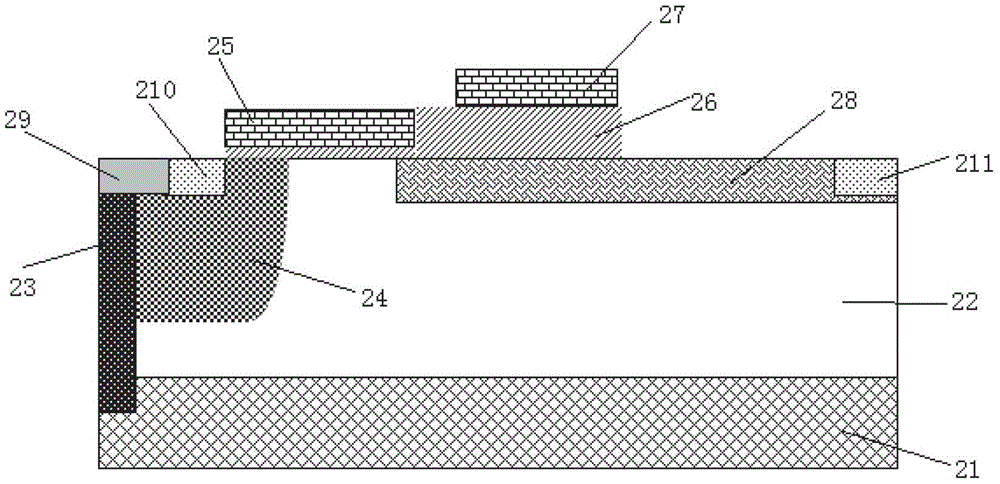

Vertical double-diffused field-effect tube and manufacturing process thereof

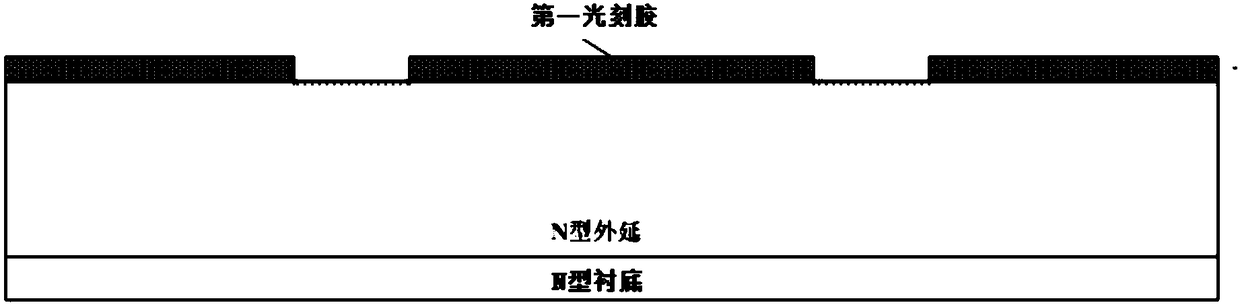

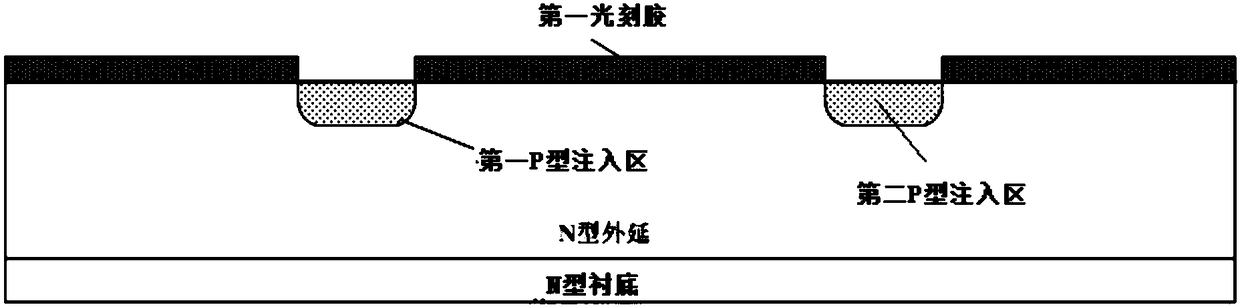

ActiveCN103151268ABreakdown voltage does not dropIncrease the number of photolithographySemiconductor/solid-state device manufacturingSemiconductor devicesDiffuse fieldEngineering

The invention provides a vertical double-diffused field-effect tube and a manufacturing process thereof. In the technical process, after a dopant region is formed, polycrystalline silicon is accumulated to form a grid; and the photoetching frequency is improved, but a photoetching plate is shared for two-time photoetching to reduce production cost. In the manufacturing process for a depletion type vertical double-diffused field-effect tube, the channel injection for the depletion tube is non self-aligned injection, so the breakdown voltage of the vertical double-diffused field-effect tube cannot be reduced, and an electric leakage problem is solved.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

Lateral double-diffused field effect transistor and integrated circuit having same

InactiveUS7485924B2Improve breakdown voltageLower on-resistanceTransistorSolid-state devicesDiffuse fieldField-effect transistor

Owner:SHARP KK

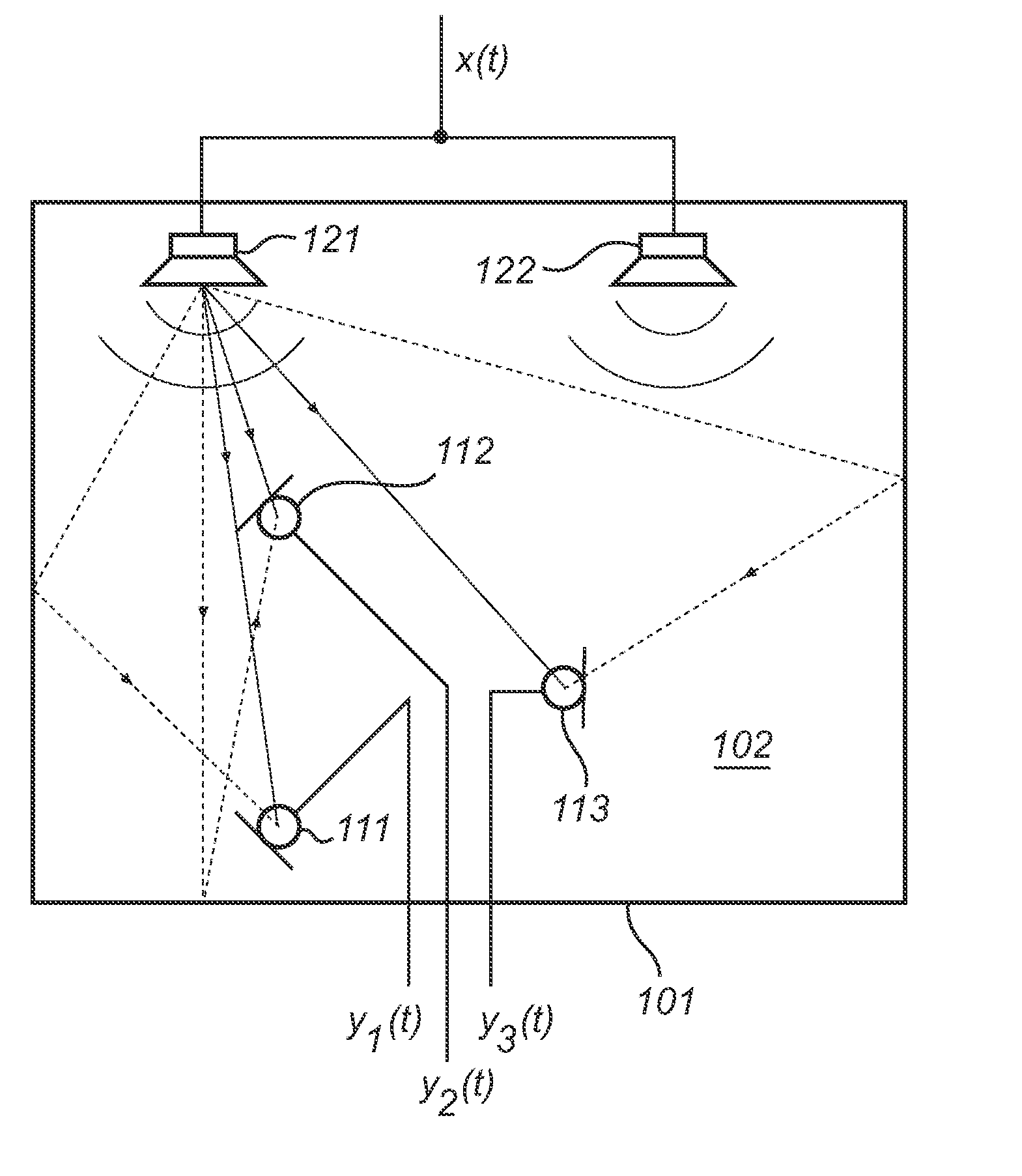

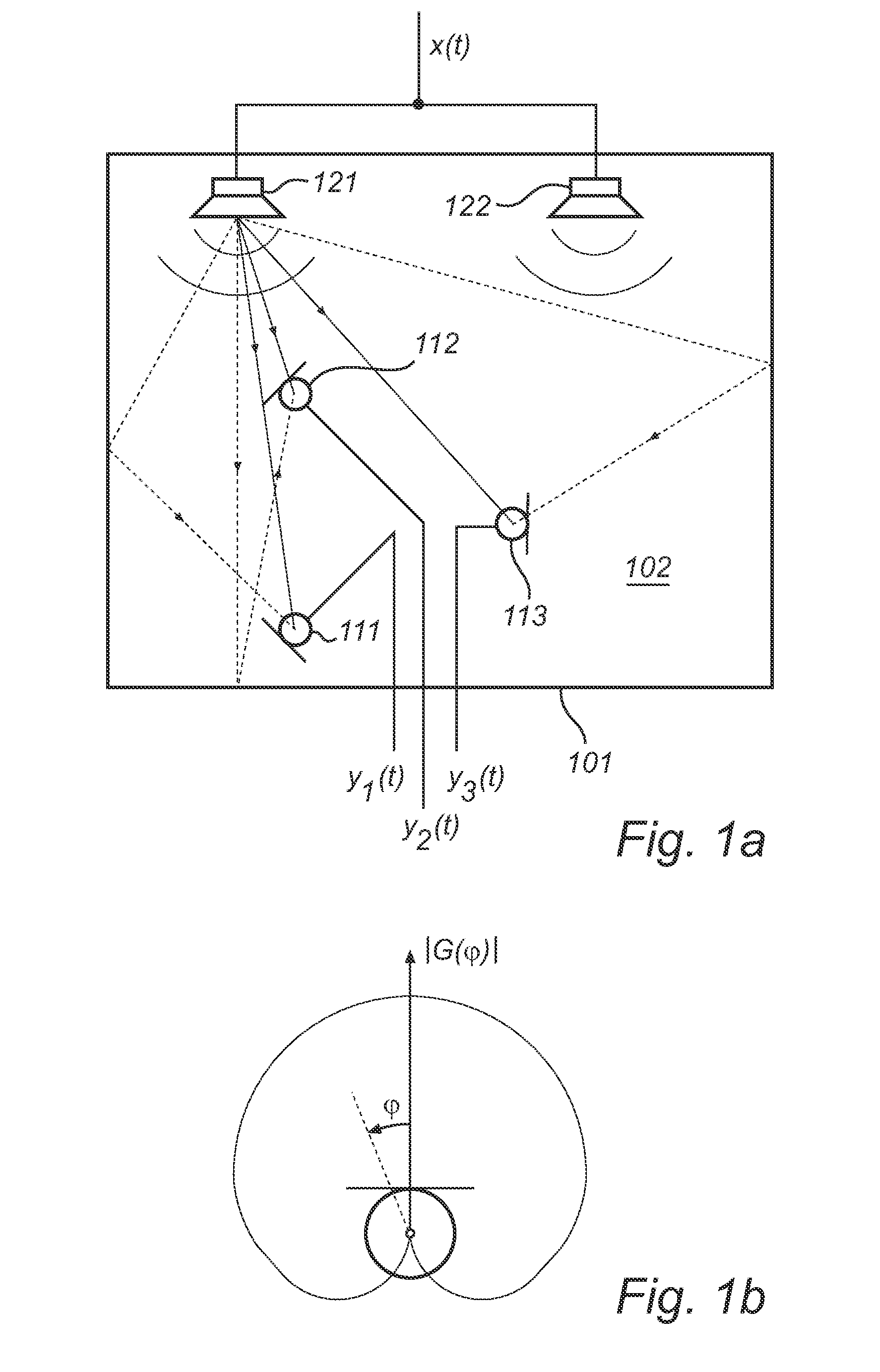

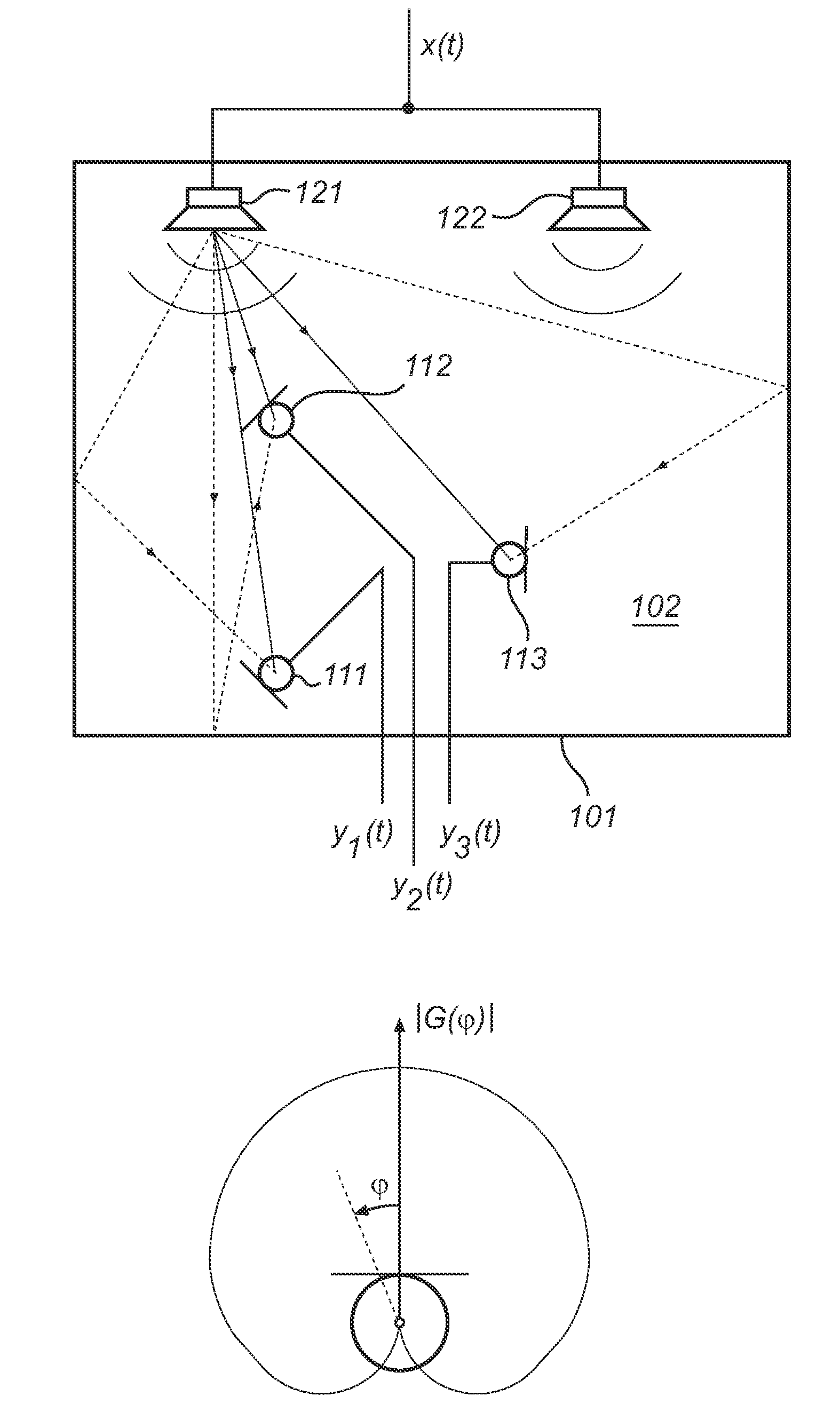

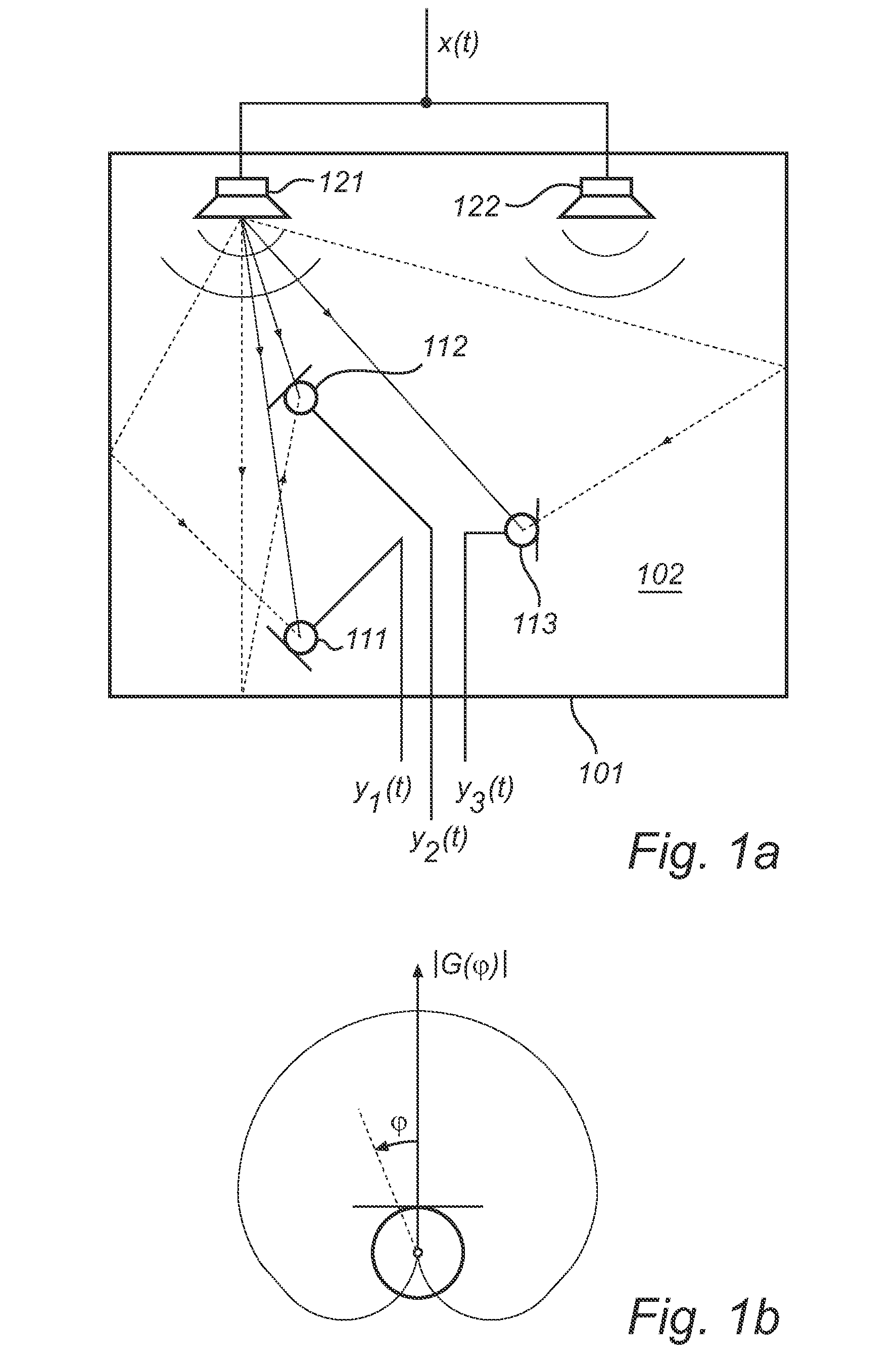

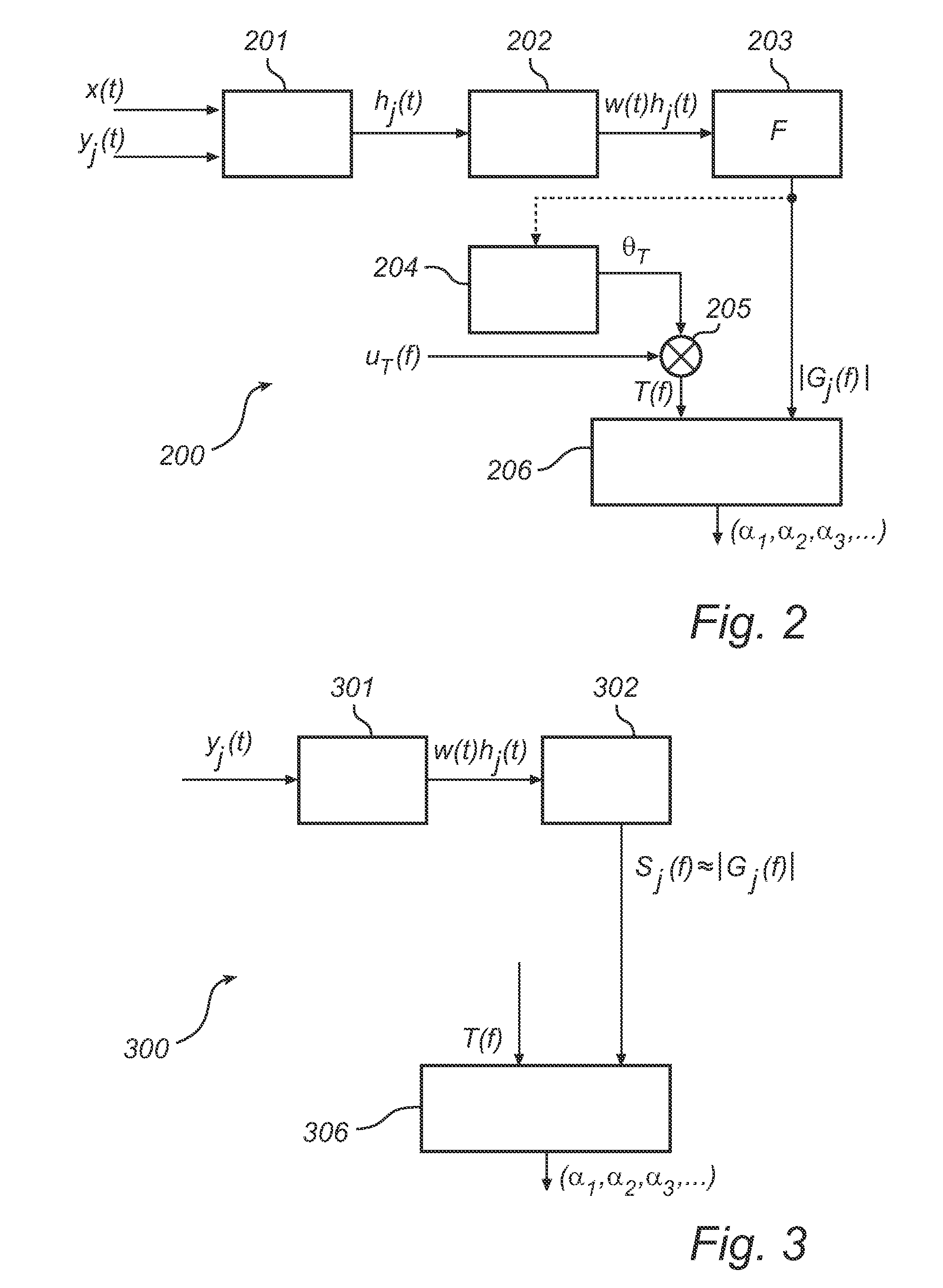

Conferencing Device Self Test

A plurality of acoustic sensors in a non-anechoic environment are calibrated with the aim of removing manufacturing tolerances and degradation over time but preserving position-dependent differences between the sensors, The sensors are excited by an acoustic stimulus which has either time-dependent characteristics or finite duration. The calibration is to be based on diffuse-field excitation only, in which indirect propagation (including single or multiple reflections) dominate over any direct-path excitation. For this purpose, the calibration process considers only a non-initial portion of sensor outputs and / or of an impulse response derived there-from. Based on these data, a frequency-dependent magnitude response function is estimated and compared with a target response function, from which a calibration function is derived.

Owner:DOLBY LAB LICENSING CORP

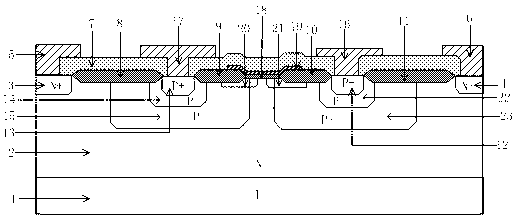

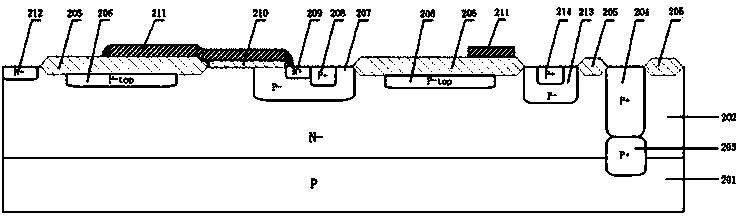

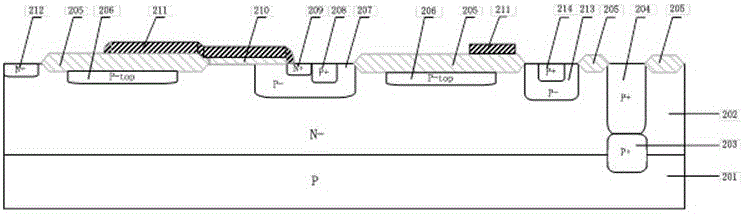

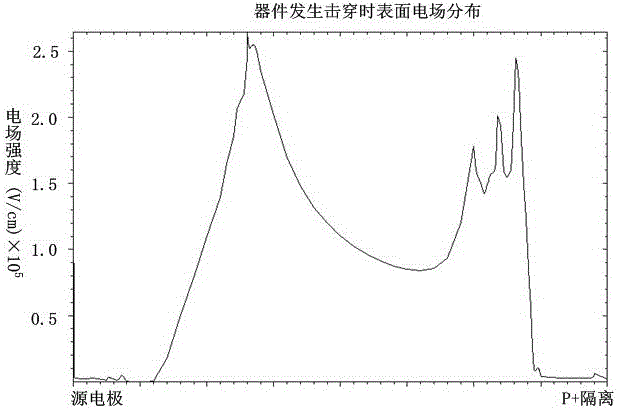

High-robustness P type symmetric laterally double-diffused field effect transistor

InactiveCN103280462AImprove the problem of insufficient electrostatic discharge capacityMaximum lattice temperature dropSemiconductor devicesBody contactLow voltage

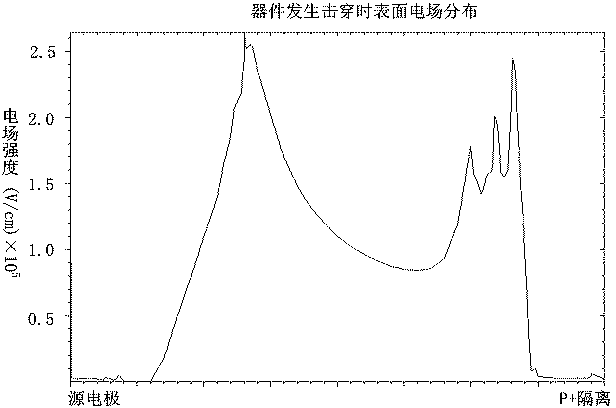

The invention discloses a high-robustness P type symmetric laterally double-diffused field effect transistor, which comprises a P type substrate, wherein an N type epitaxial layer is arranged on the P type substrate; two P type drift traps, two P type buffer traps and two N type body contact regions are arranged in the N type epitaxial layer; a P type drain region and a P type source region are arranged in the P type buffer trap respectively; the surface of the N type epitaxial layer is provided with a gate oxide layer and a field oxide layer; the surface of the gate oxide layer is provided with a polycrystalline silicon gate; the surfaces of the field oxide layer, the N type body contact regions, the P type source region, the polycrystalline silicon gate and the P type drain region are provided with passivation layers; the high-robustness P type symmetric laterally double-diffused field effect transistor is characterized in that the surfaces of the two P type drift traps are also provided with a photo-etching plate shared with the low-voltage P type trap; first and second shallow P type traps formed by low-energy ion implantation are adopted; and the surface electric field distribution is effectively optimized at the region, the highest lattice temperature is reduced, the secondary breakdown current is improved and the robustness of the device in an ESD (Electronic Static Discharge) process is enhanced.

Owner:SOUTHEAST UNIV

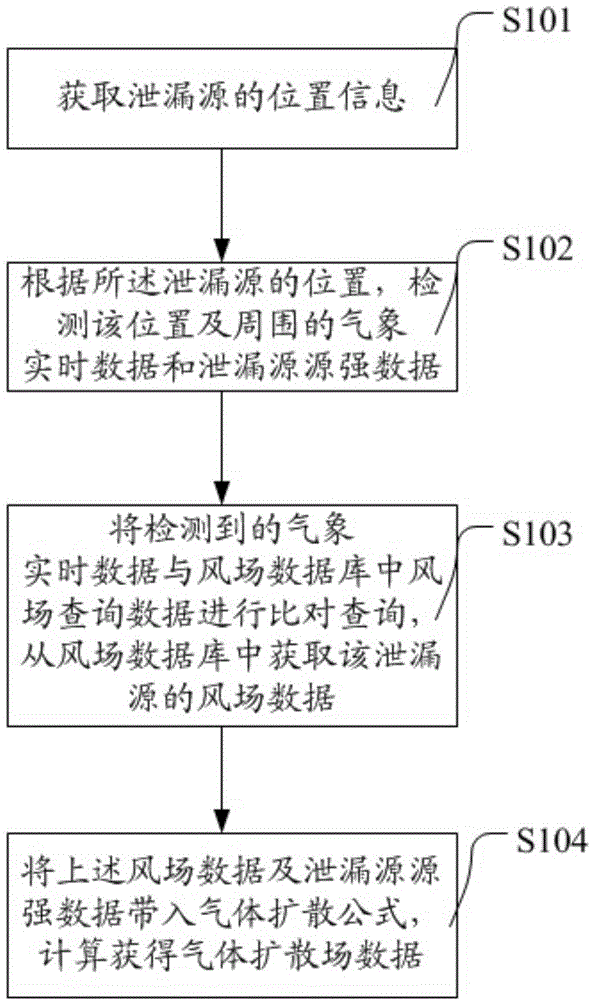

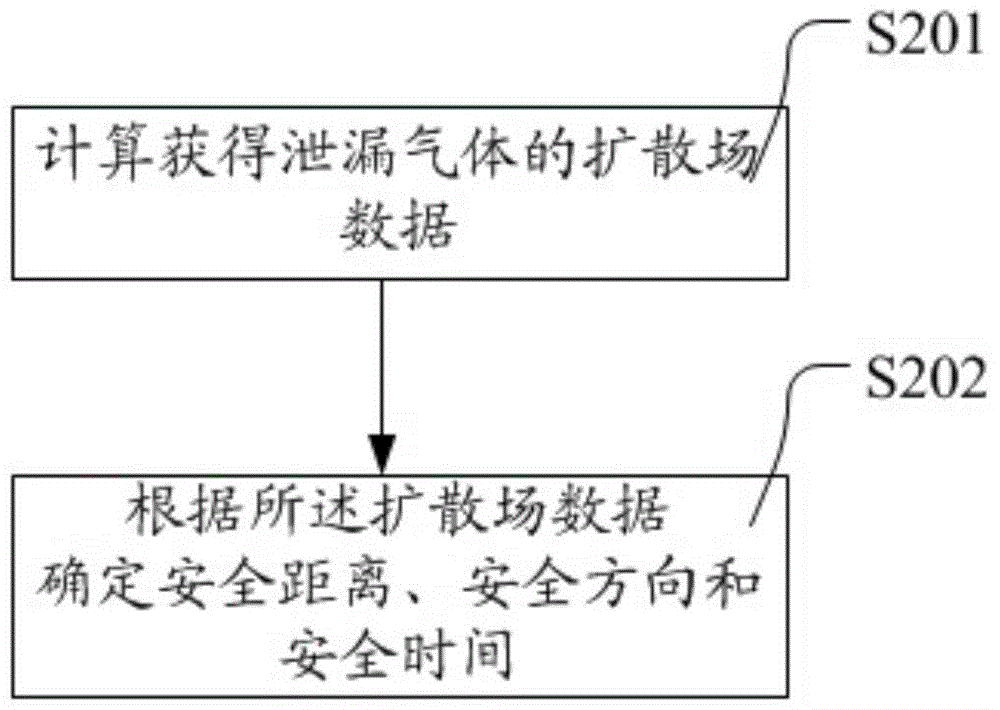

Three-dimensional simulation method and emergency evacuation method for gas leakage and diffusion

ActiveCN104091001AThe acquisition process is fast and efficientSpecial data processing applications3D modellingDiffusionThree dimensional simulation

The invention discloses a three-dimensional simulation method and an emergency evacuation method for gas leakage and diffusion. The three-dimensional simulation method includes acquiring location information of a leakage source; according to the location of the leakage source, acquiring meteorological real-time data and leakage source strong data measured form the periphery; comparing and querying the meteorological real-time data with wind-field query data in a wind field database; acquiring wind field data of the leakage source from the wind field database; and introducing the wind field data and the leakage source strong data into a gas diffusion formula to calculate wind file data of the periphery of the leakage source. According to the three-dimensional simulation method, by the wind field database, the wind field data of the periphery of the leakage source is rapidly and efficiently queried and acquired, and the conventional step of wind field calculation is omitted, thus three-dimensional simulation field data are acquired within the shortest time, and requirements of chemical industrial parks and industrial enterprises for emergency systems are met in the new situation.

Owner:CHINA ACAD OF SAFETY SCI & TECH

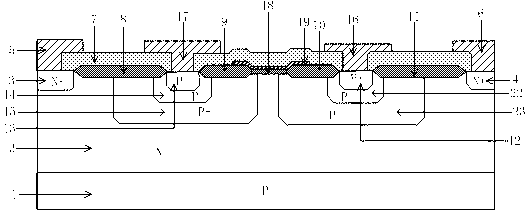

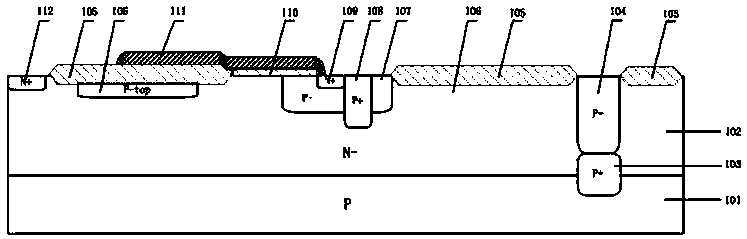

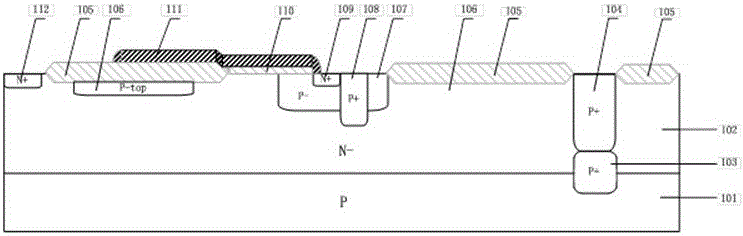

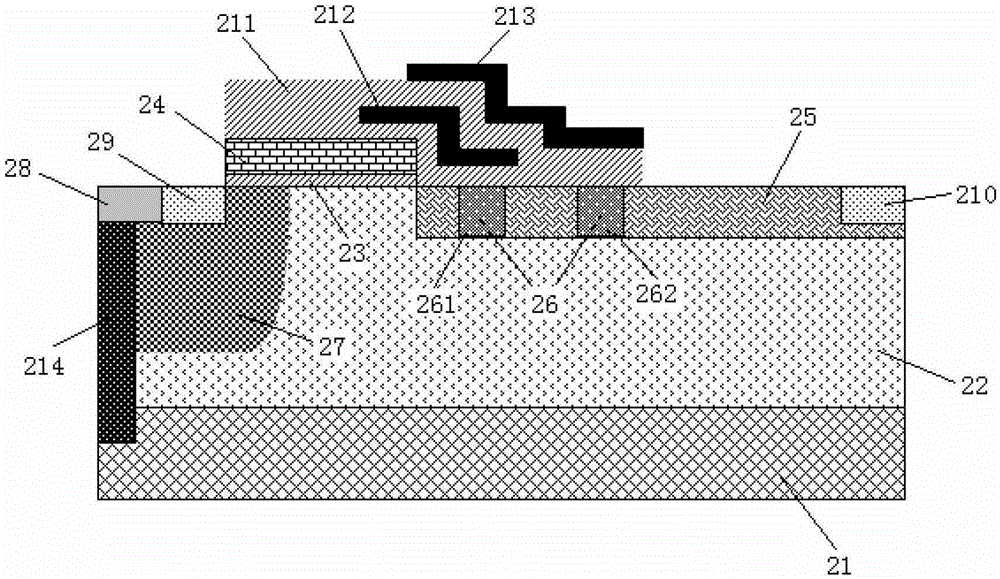

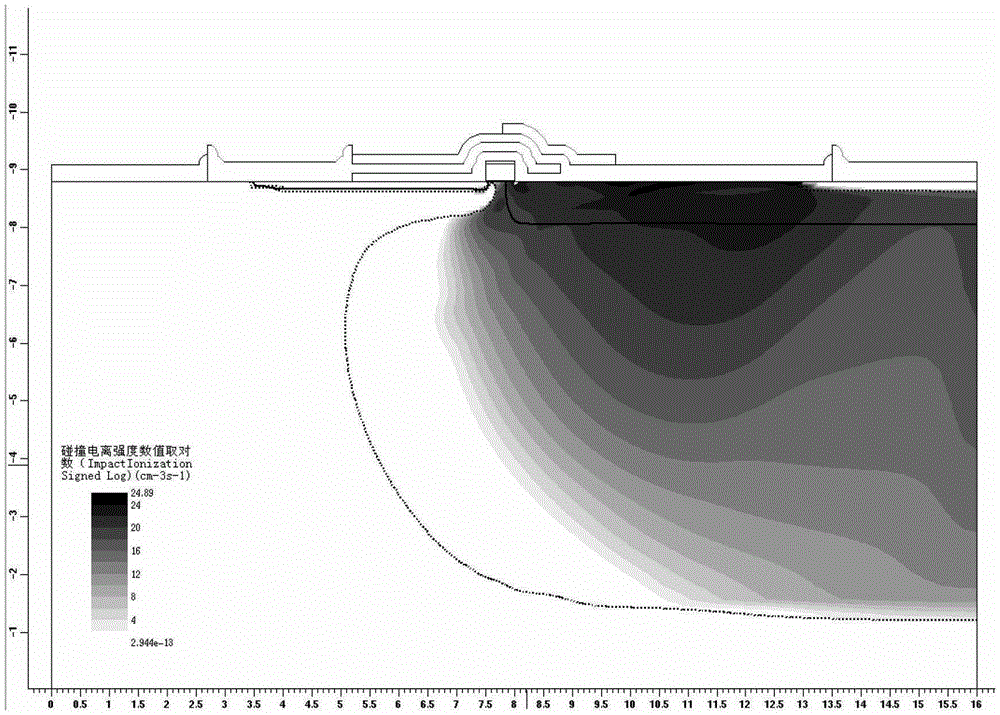

High-sided transverse double diffused field effect transistor

ActiveCN104037231AIncreased avalanche breakdown voltageReduce surface electric fieldSemiconductor devicesDiffuse fieldBody area

The invention discloses a high-sided transverse double diffused field effect transistor. The high-sided transverse double diffused field effect transistor comprises a P type substrate, an N- epitaxial layer, a P+ buried layer, a P+ P-N junction isolation, field oxygen, a P- top layer, P- body areas, a P- body area contact P+, an N+ source electrode, a gate oxygen layer, a polycrystalline silicon gate electrode and an N+ drain electrode, wherein the N- epitaxial layer is arranged above the P type substrate; the P+ buried layer and the P+ P-N junction isolation are arranged at one side of the N- epitaxial layer and are used to isolate different types of devices; furthermore, another P- body area is arranged between the P- body area and the P+ P-N junction isolation; the body area contact P+ is arranged in the P- body area; the P- top layer is arranged between the P- body area and the another P- body area. According to the high-sided transverse double diffused field effect transistor disclosed by the invention, an avalanche breakdown voltage between the source electrode and the substrate is greatly increased, that is, an isolation performance is greatly improved, so that application in the field which requires relatively high working voltage is satisfied.

Owner:ZHEJIANG UNIV

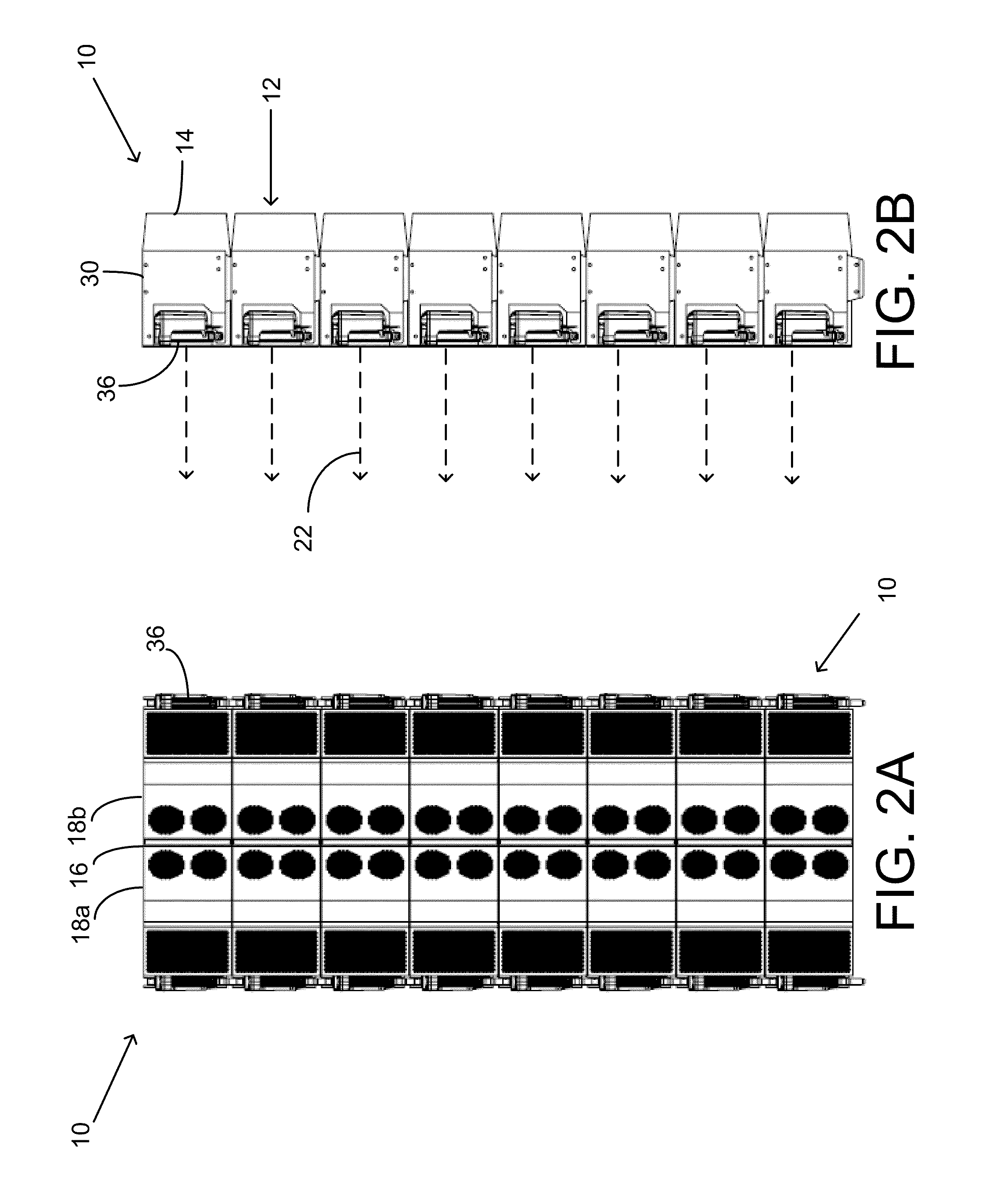

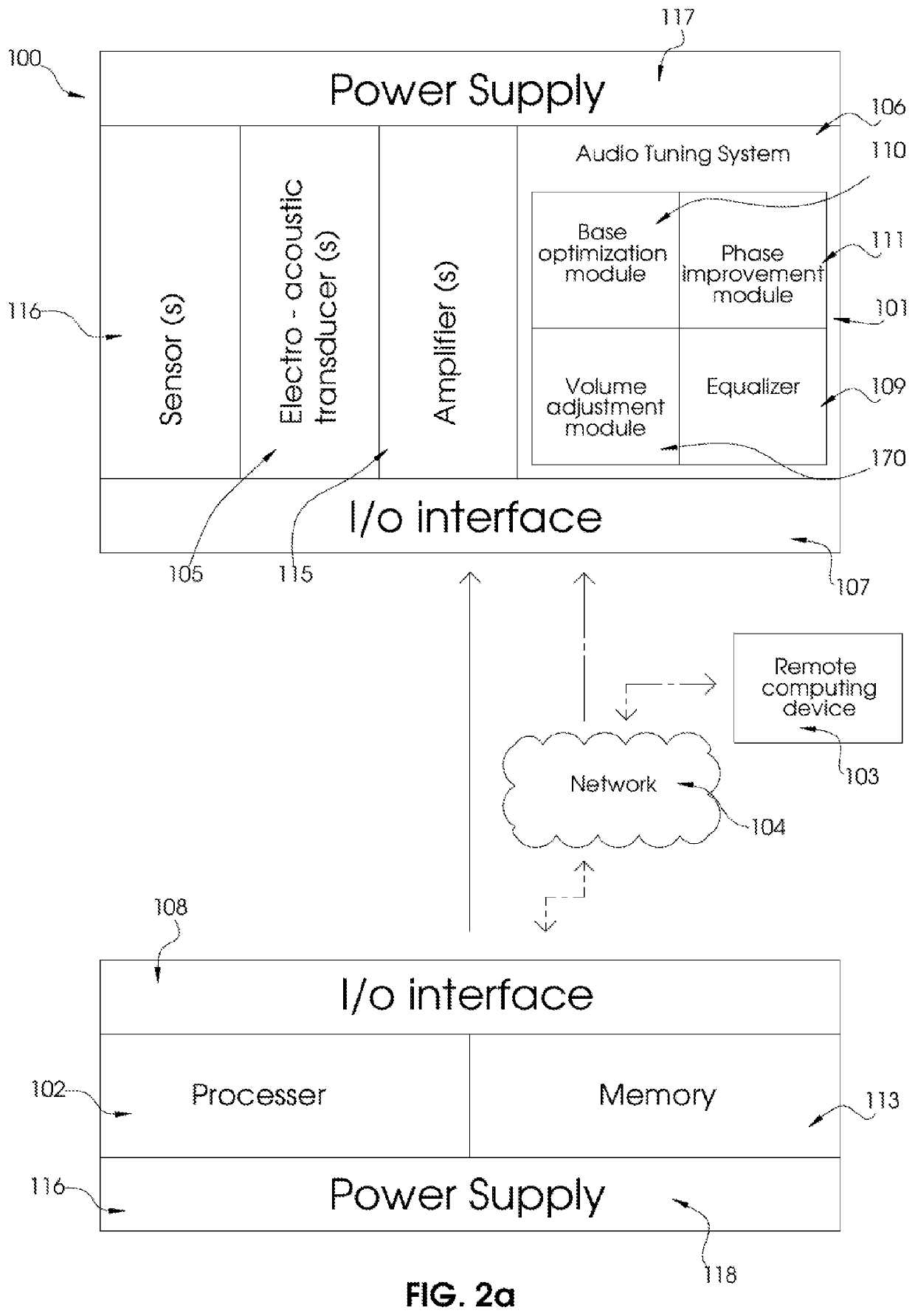

Improvements in or relating to audio systems

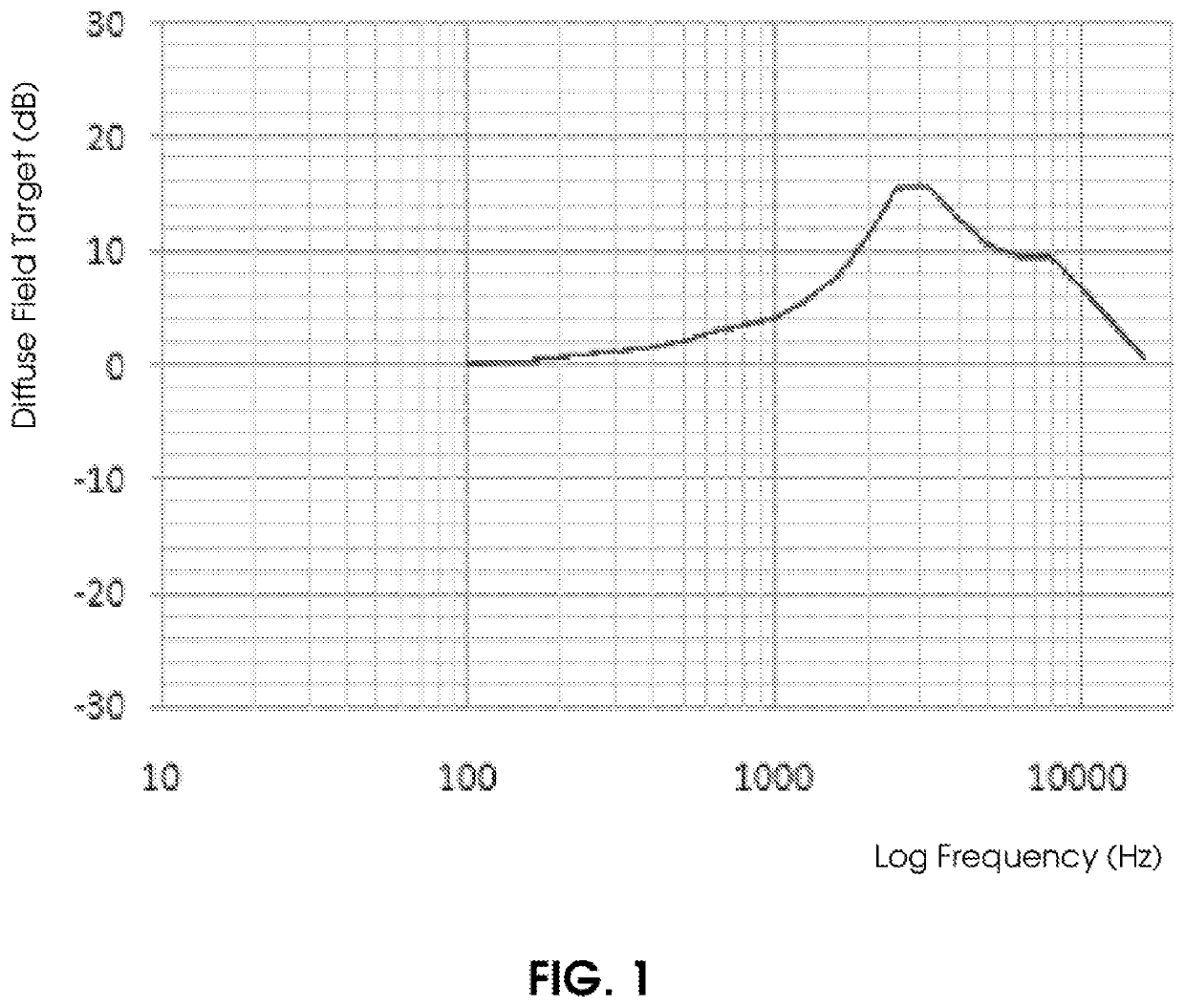

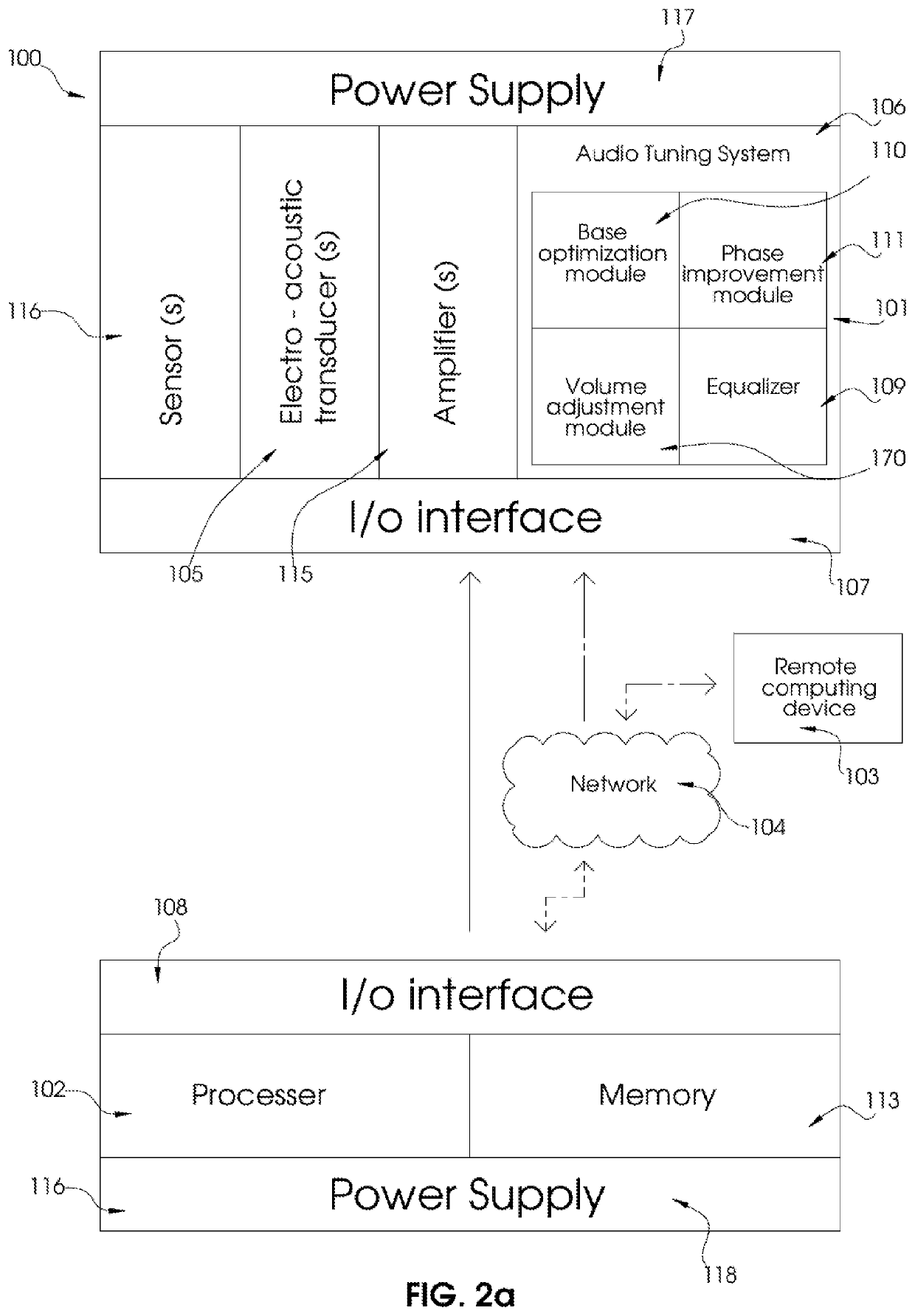

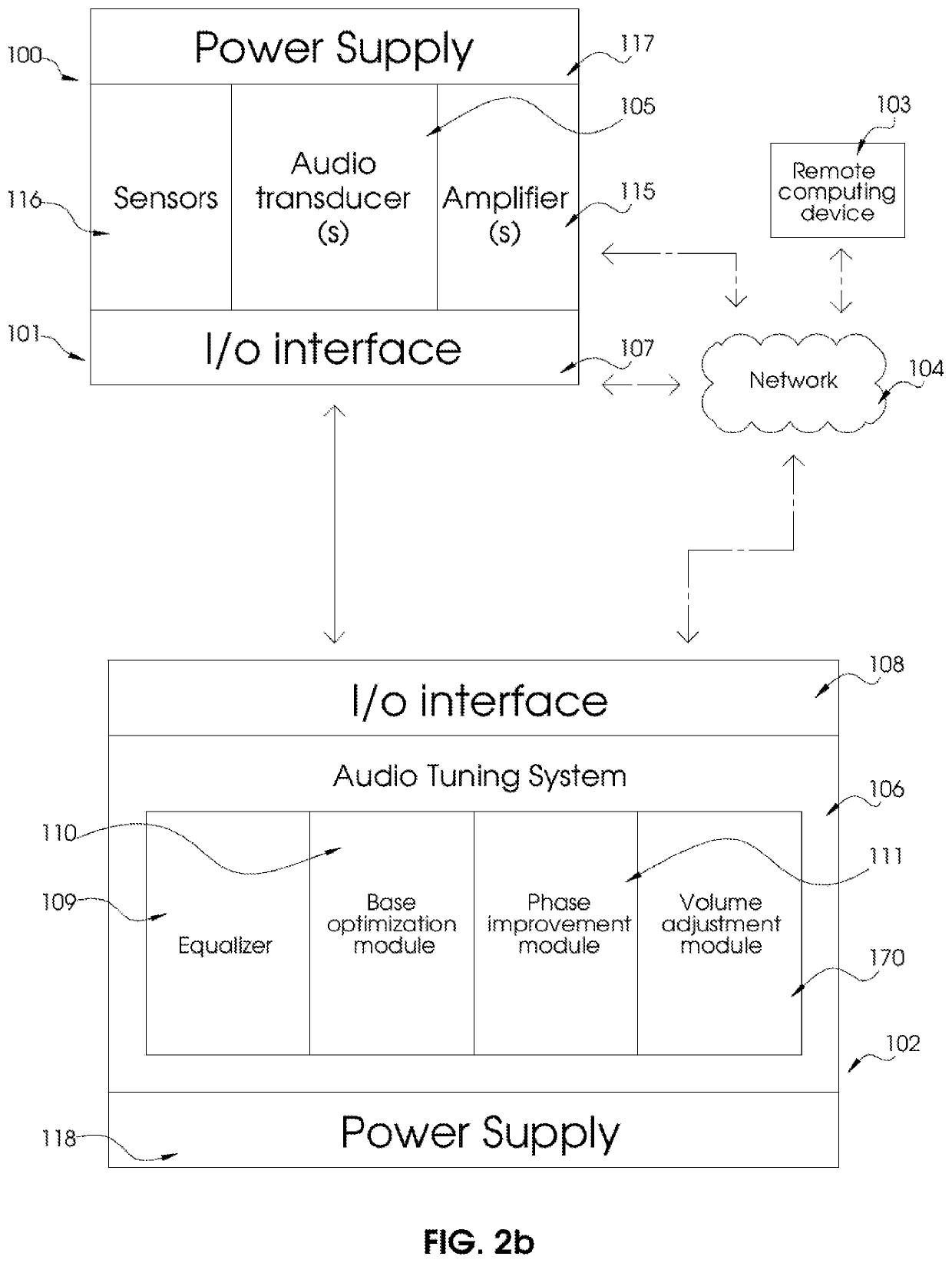

ActiveUS20200092647A1Control flowReduce mechanical transmissionLoudspeaker transducer fixingHeadphones for stereophonic communicationTransducerDiffuse field

The invention relates to audio transducer technology, including audio tuning systems to be utilised in personal audio devices, such as headphone, earphones, mobile phones and the like. The audio tuning system optimises the frequency response of the personal audio device by using Diffuse Field curve characteristics. The audio transducers of the personal audio device incorporate low resonance designs, including low resonance transducer and diaphragm suspensions to further optimise the sound quality of the device. The invention also relates to an audio transducer diaphragm construction that includes a three-dimensional lattice which may be utilised in any audio transducer application.

Owner:WING ACOUSTICS LTD

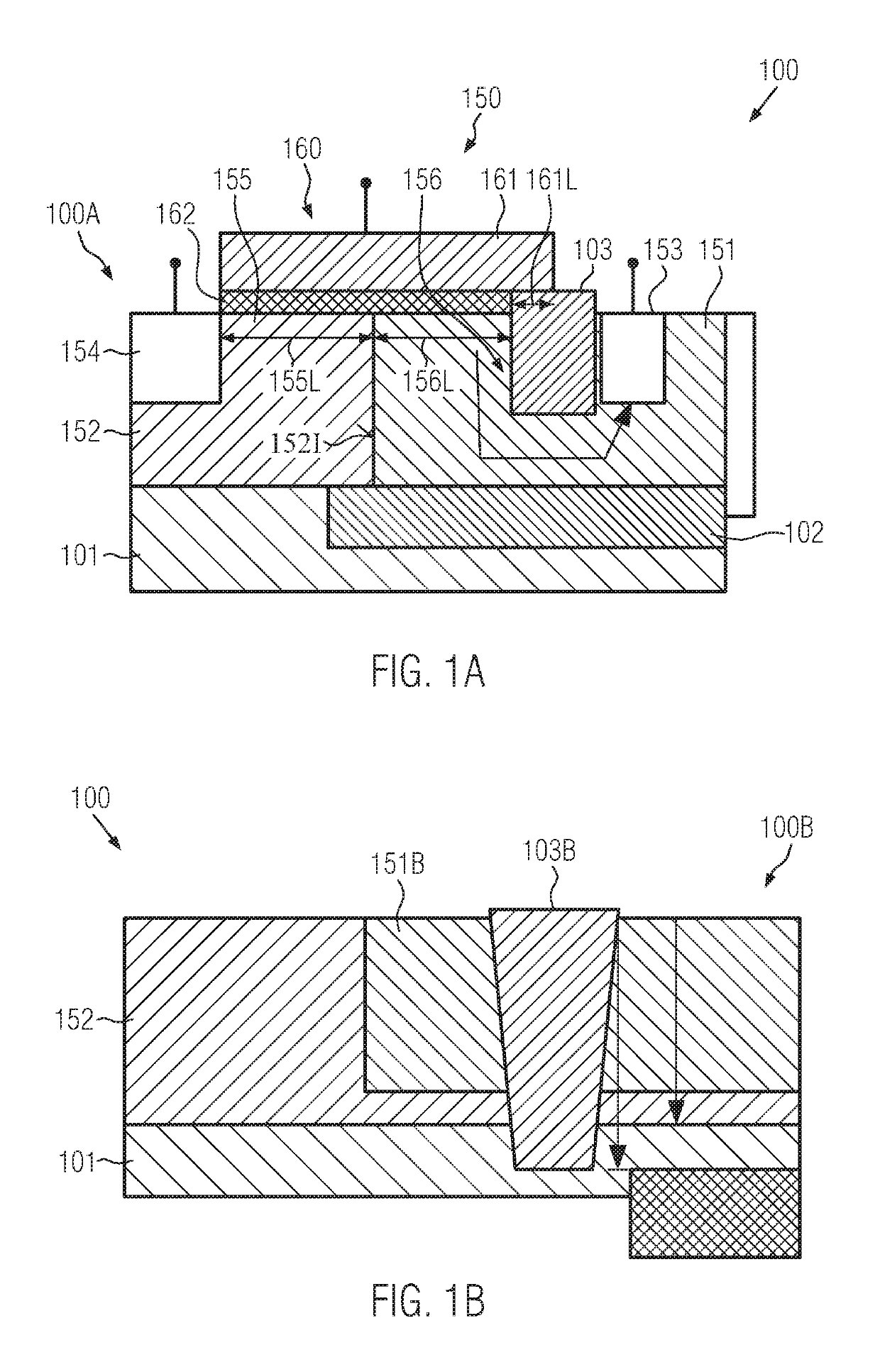

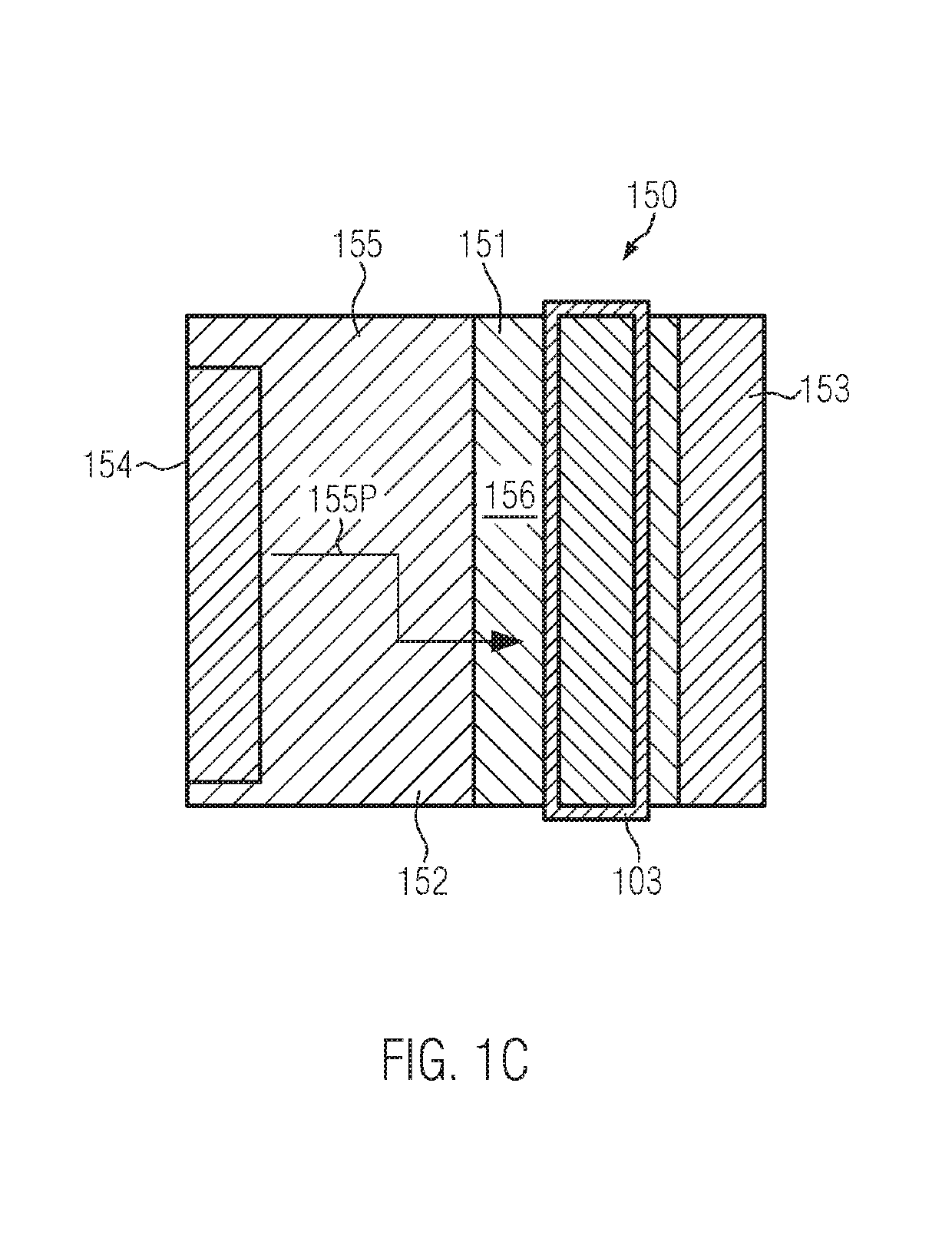

Laterally diffused field effect transistor and a method of manufacturing the same

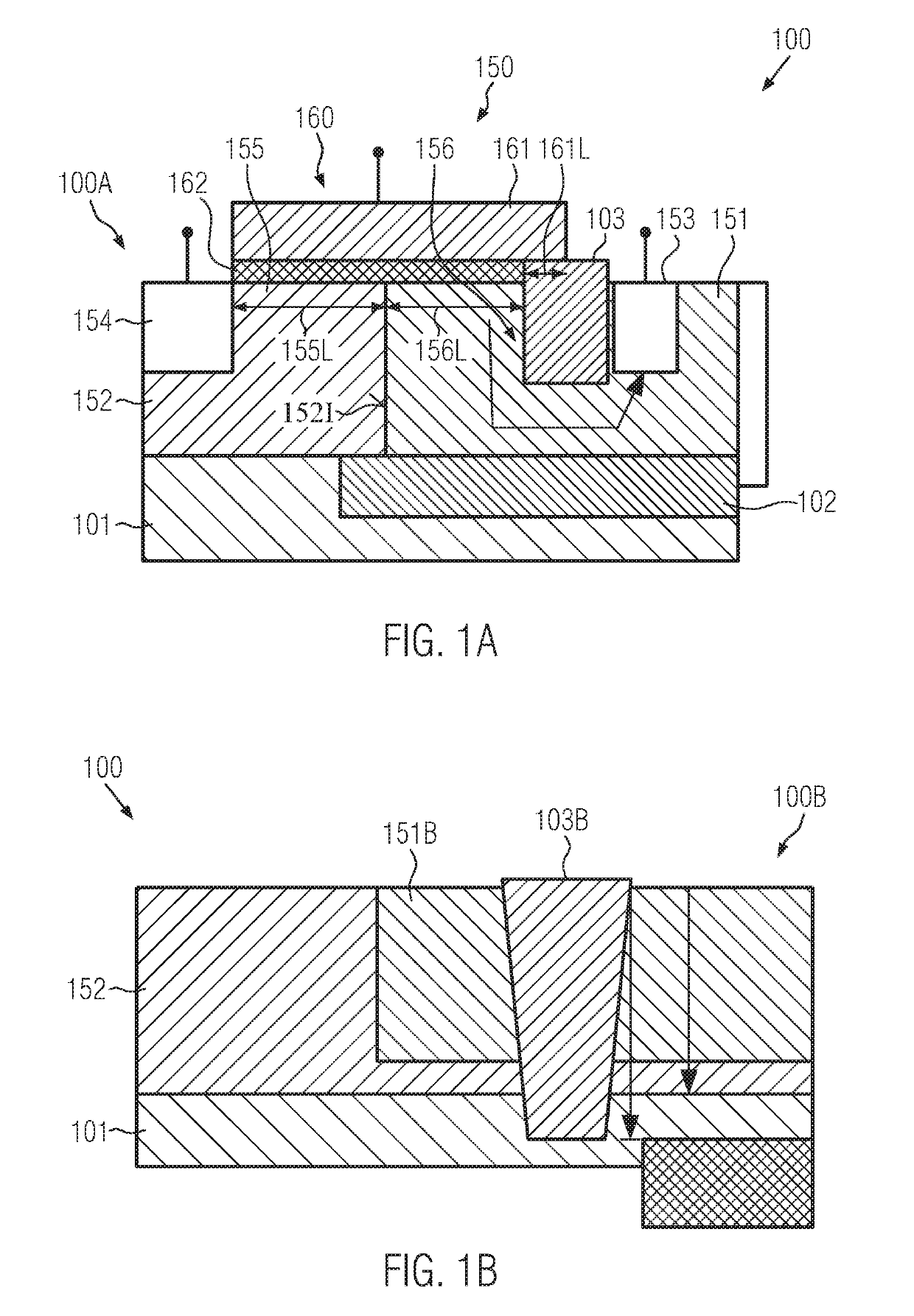

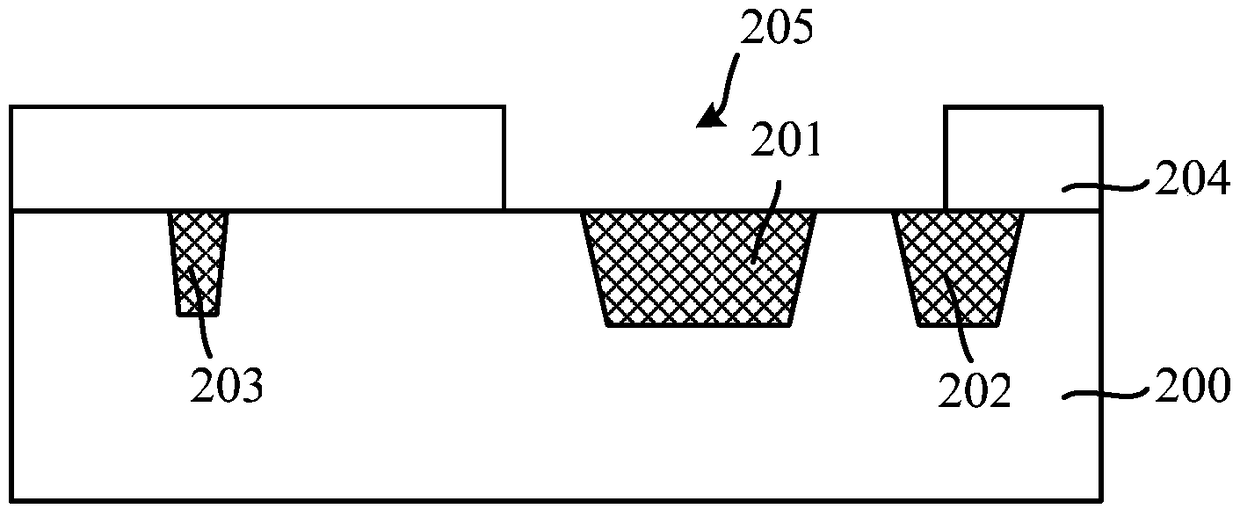

ActiveUS20190245080A1Improve performanceIsolation is requiredSemiconductor devicesDiffuse fieldField-effect transistor

An LDFET may be formed on the basis of manufacturing platforms designed for forming sophisticated small signal transistor elements. To this end, sidewall areas of trench isolation regions laterally positioned within the drift region may be used as current paths, thereby achieving increased design flexibility, since efficient current paths may still be established, even if the trench isolation regions have to extend into the substrate material due to design criteria determined by the sophisticated small signal transistor elements. In some illustrative embodiments, isolation of P-LDFETs with respect to the P-substrate may be accomplished without requiring a deep well implantation.

Owner:GLOBALFOUNDRIES US INC

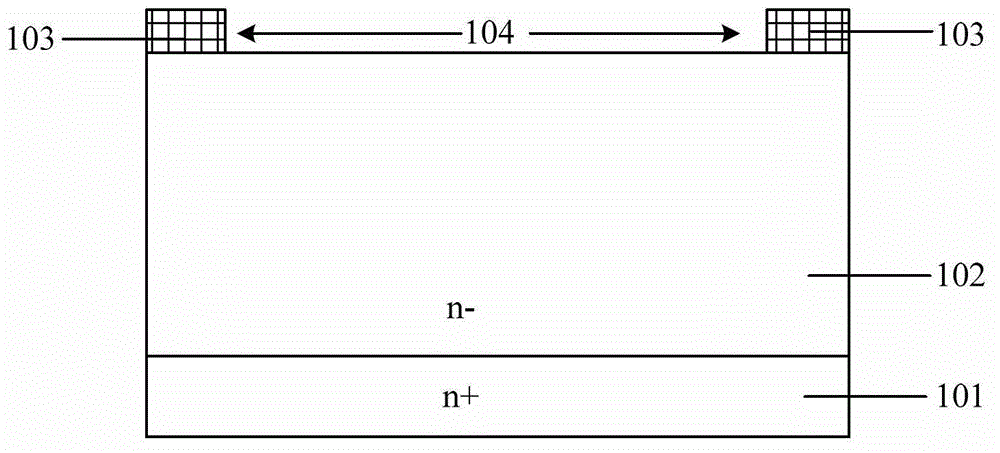

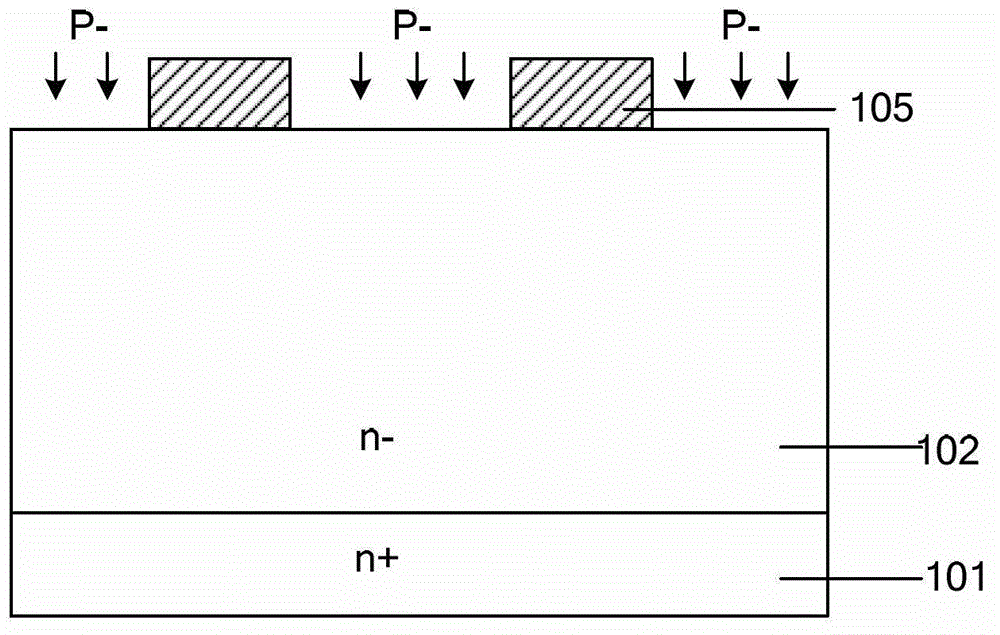

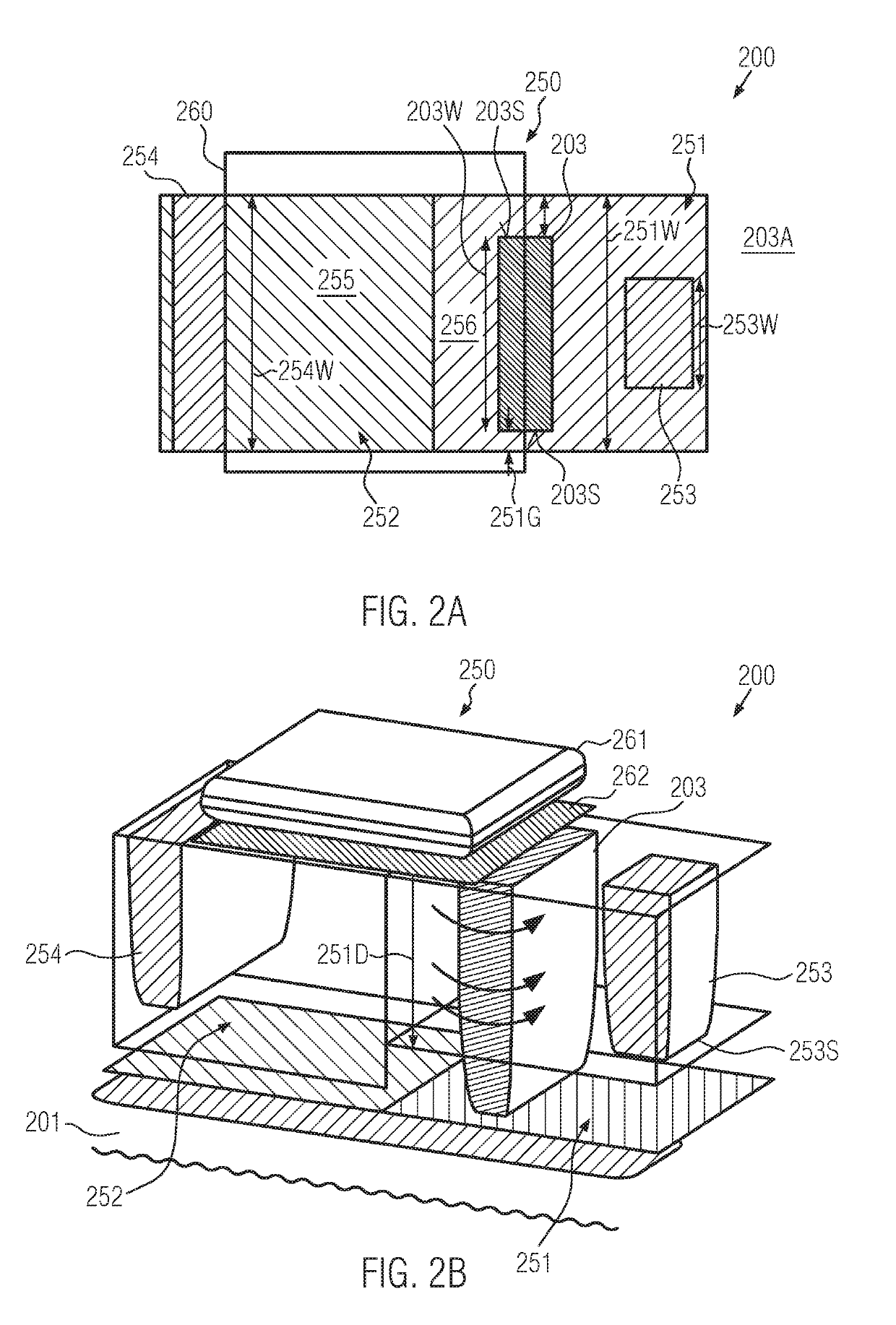

Vertical double-diffused field effect transistor and preparation method thereof

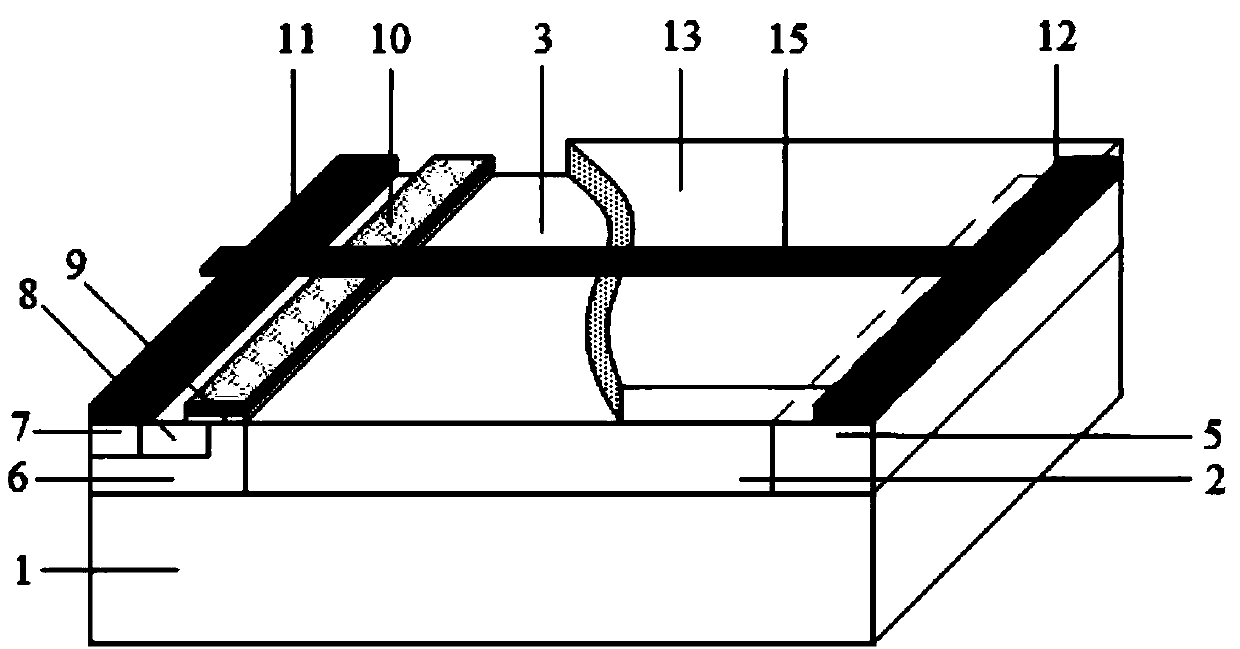

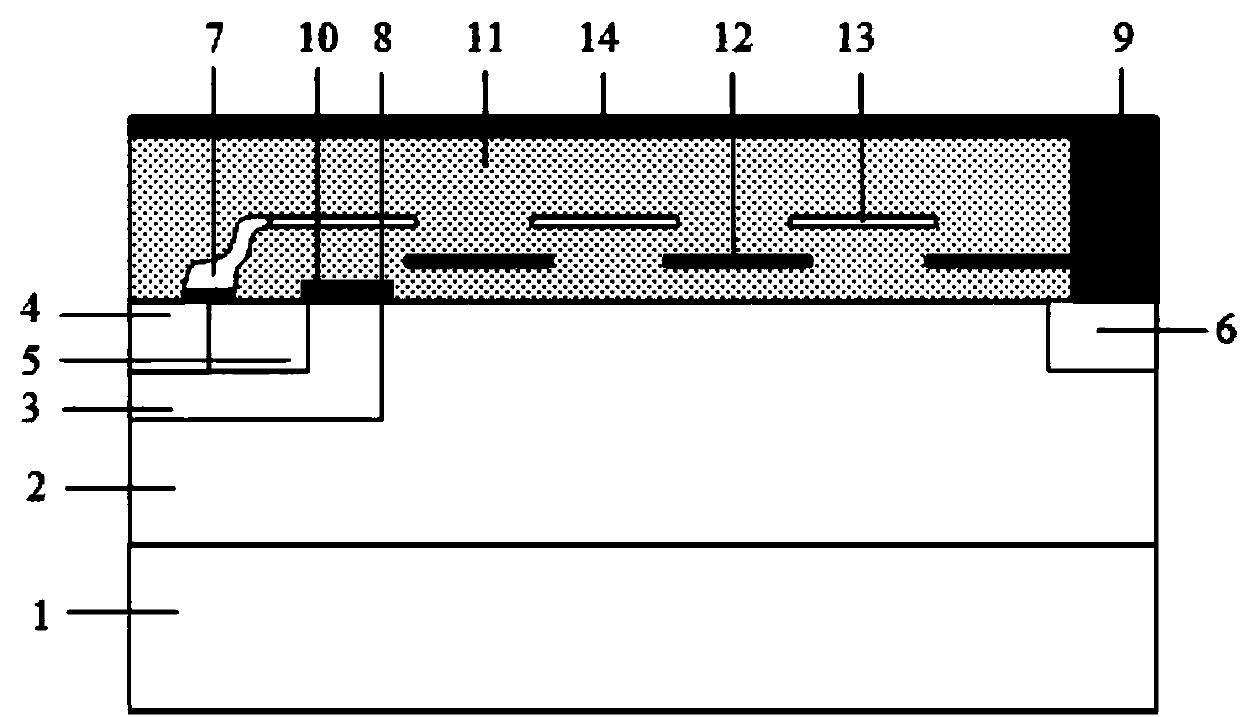

ActiveCN108110056AImprove performanceImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesDiffuse fieldSilicon oxide

A vertical double-diffused field effect transistor includes an N-type substrate, an N-type epitaxial layer formed on the N-type substrate, first and second P-type implanted regions formed on the surface of the N-type epitaxial layer, a P-type epitaxial layer formed on the N-type epitaxial layer and the first and second P-type implanted regions, first and second N-type implanted regions formed on the surface of the P-type epitaxial layer and corresponding to the first and second P-type implanted regions respectively, a silicon oxide layer formed in the P-type epitaxial layer and the first and second N-type implanted regions, first and second trenches passing through the silicon oxide layer and the first N-type implanted region and extending into the first and second P-type implanted regionsrespectively; silicon oxide formed in the inner walls of the first and the second trenches and connected with the silicon oxide layer, openings passing through the silicon oxide layer between the first and the second trenches and corresponding to the P-type epitaxial layer and the first and second N-type implanted regions, and polycrystalline silicon formed on the surface of the silicon oxide layer in the first and second trenches.

Owner:SHANGHAI XINLONG SEMICON TECH CO LTD

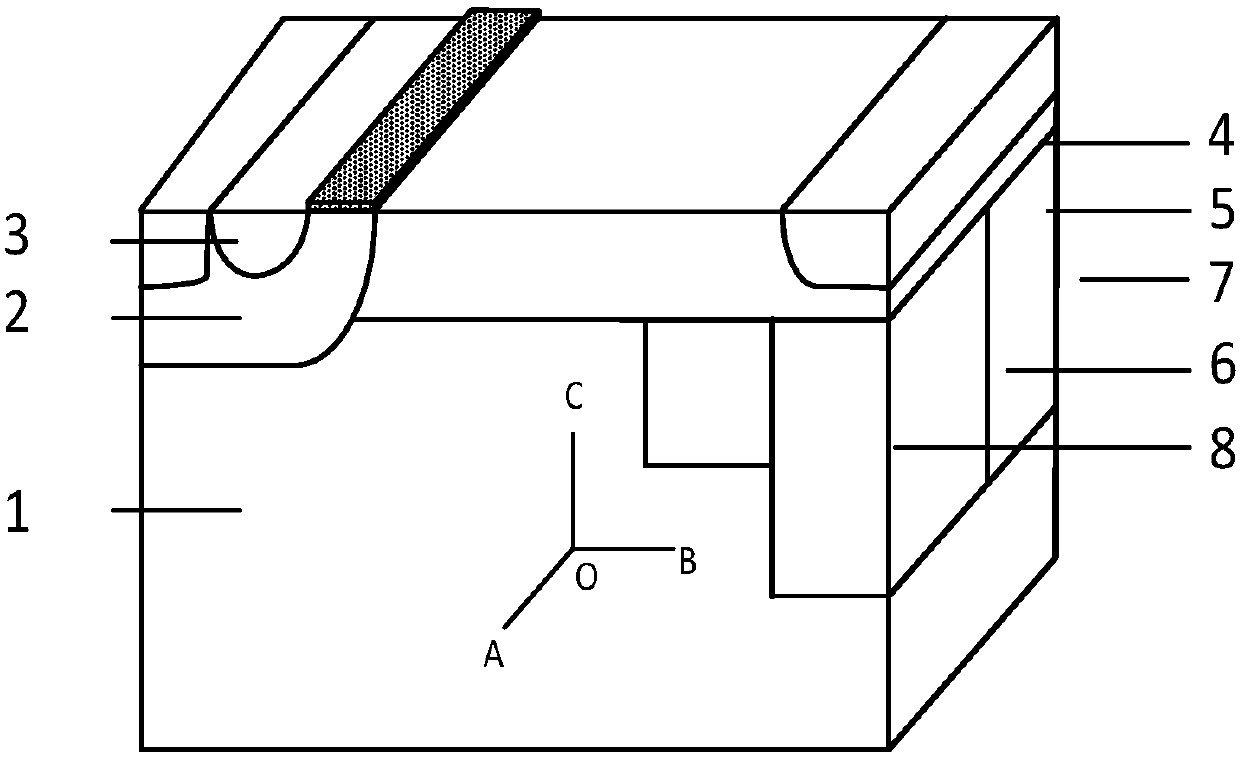

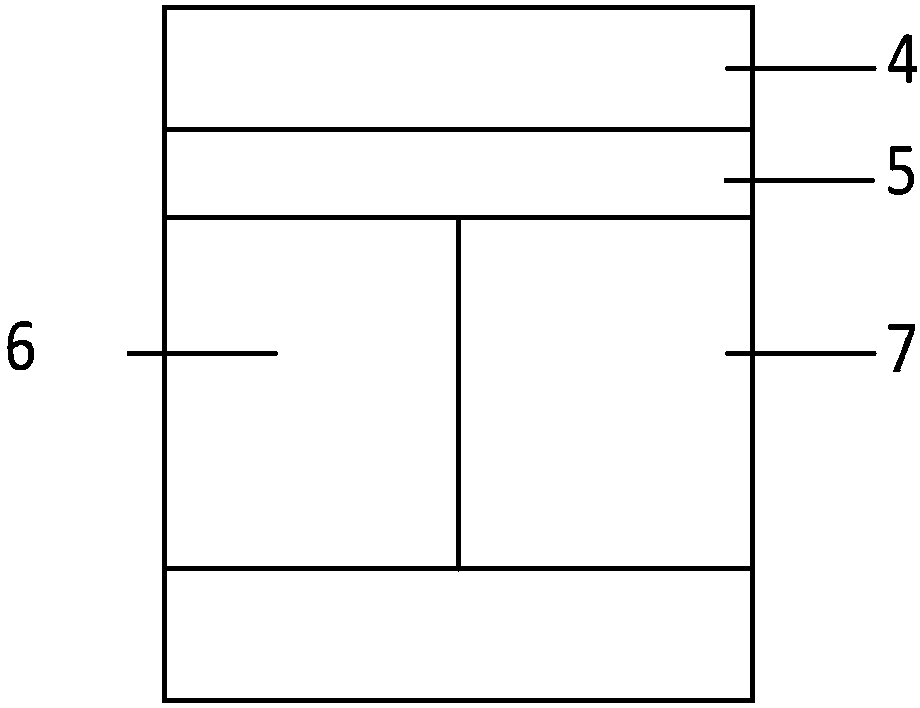

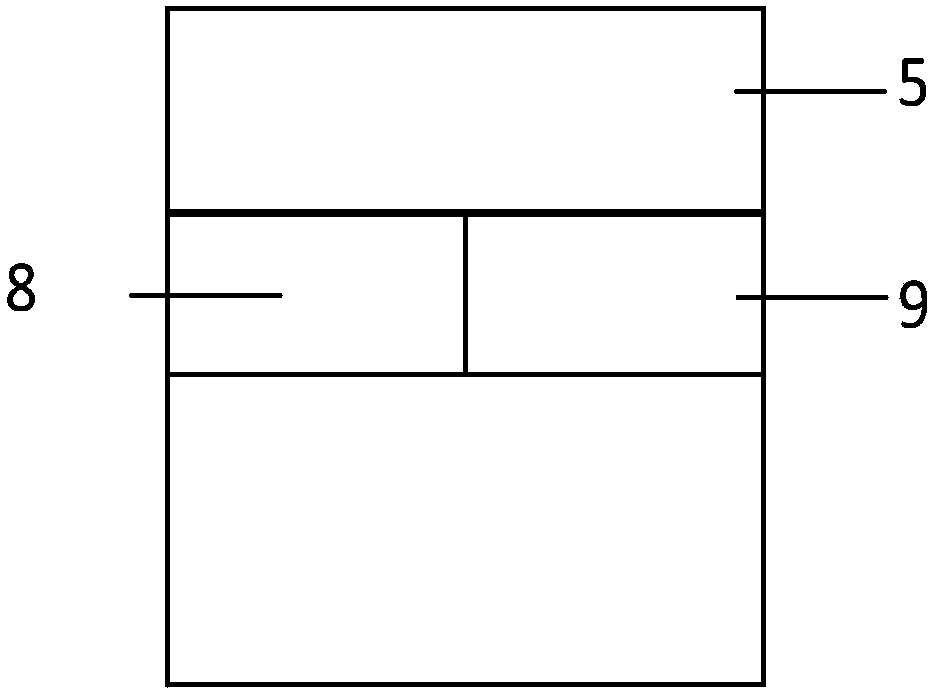

Transverse power device high-voltage interconnection structure

ActiveCN107863387AImprove pressure resistanceReduce the impactSemiconductor devicesLDMOSDiffuse field

The invention provides a transverse power device high-voltage interconnection structure. An insulator area having a high dielectric constant is introduced into a drift region of a power device; and surface electrical field distribution caused by high-voltage interconnection is modulated by utilizing the area, thereby greatly enhancing voltage endurance capability of the device during high-voltageinterconnection and improving performance of the deice. The transverse power device high-voltage interconnection structure can be applied to a laterally-diffused field effect transistor LDMOS, a lateral PN diode or a lateral insulated gate bipolar transistor LIGBT, and is simple in process and low in cost.

Owner:NANJING UNIV OF POSTS & TELECOMM +1

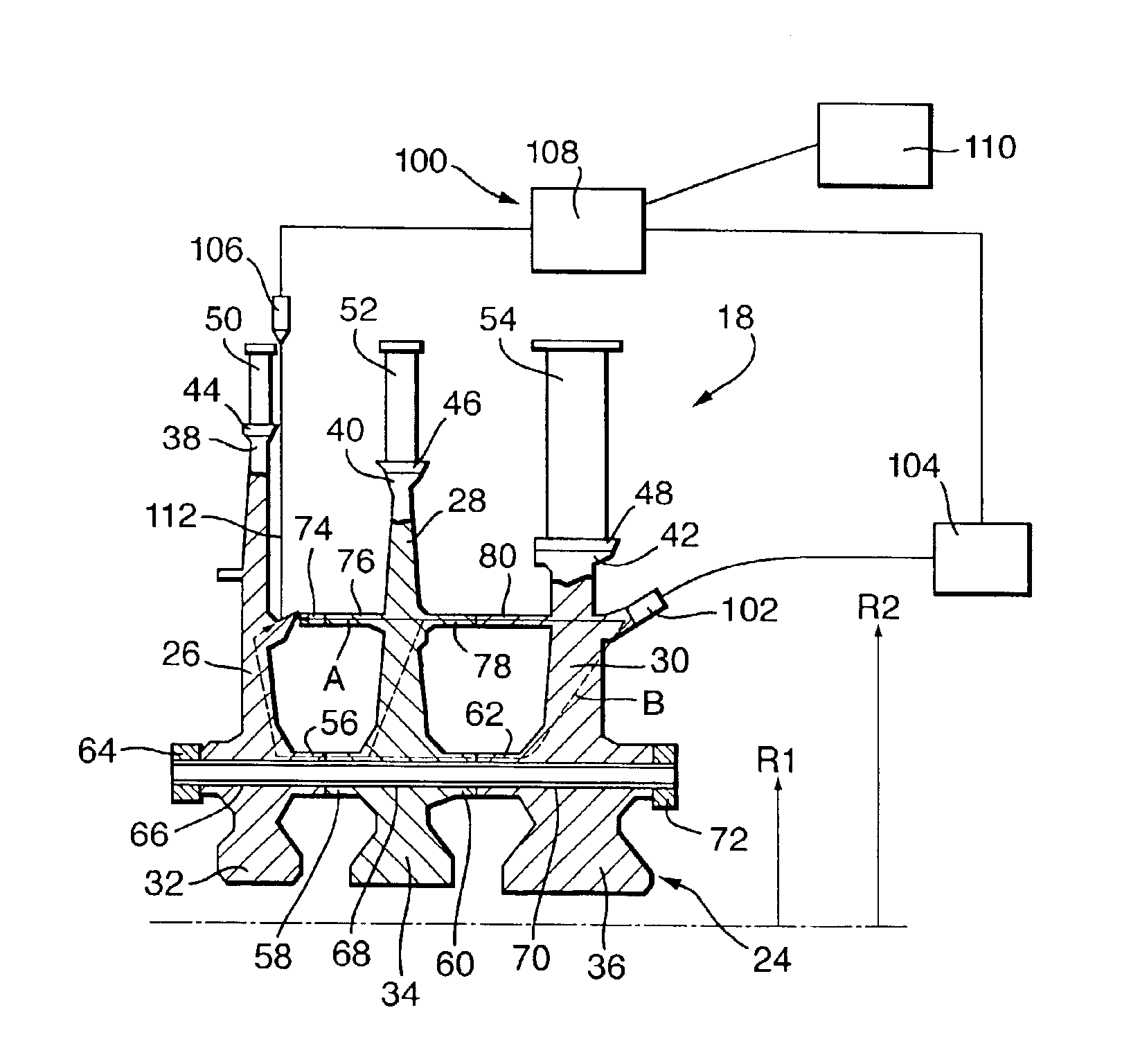

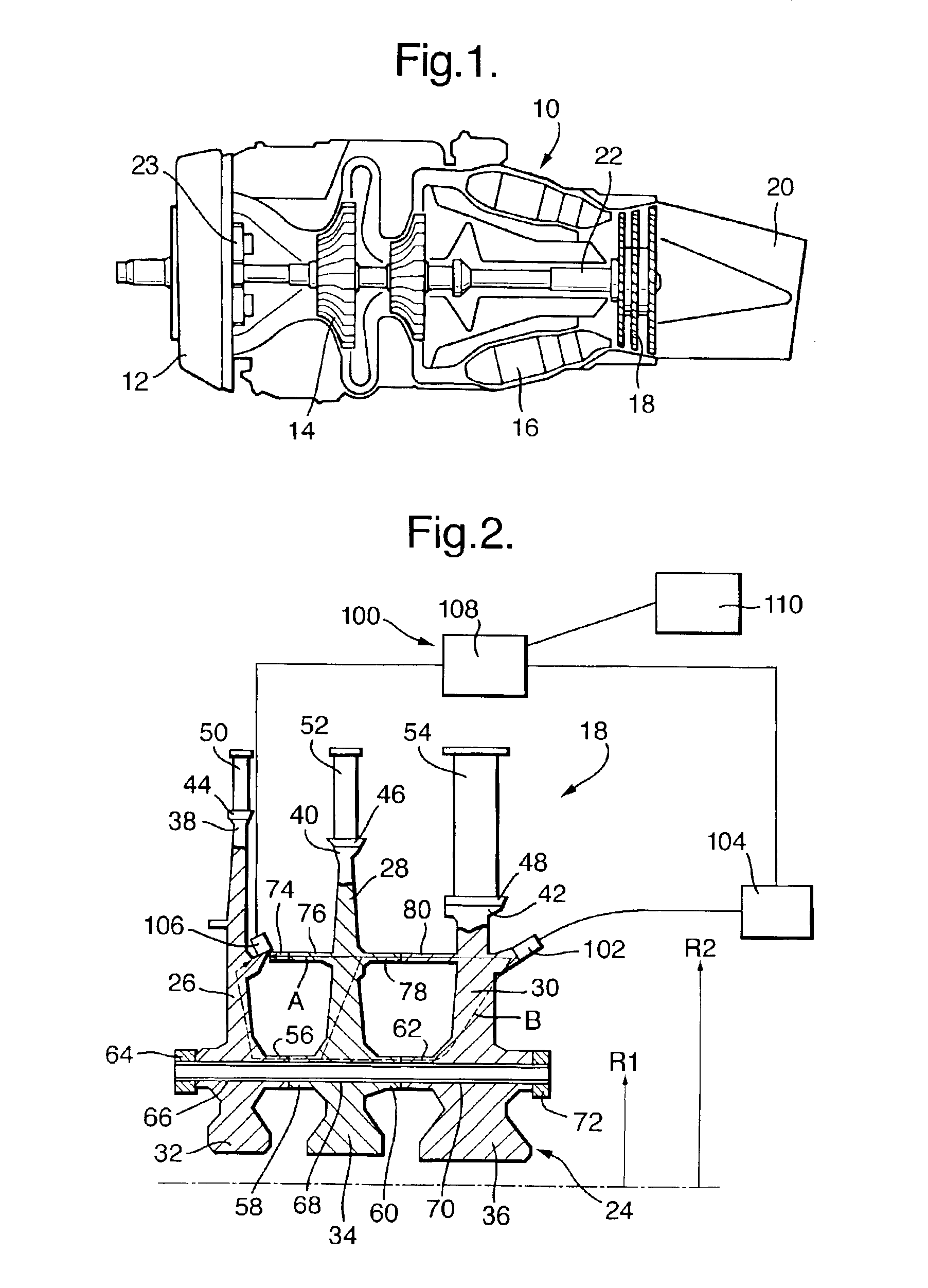

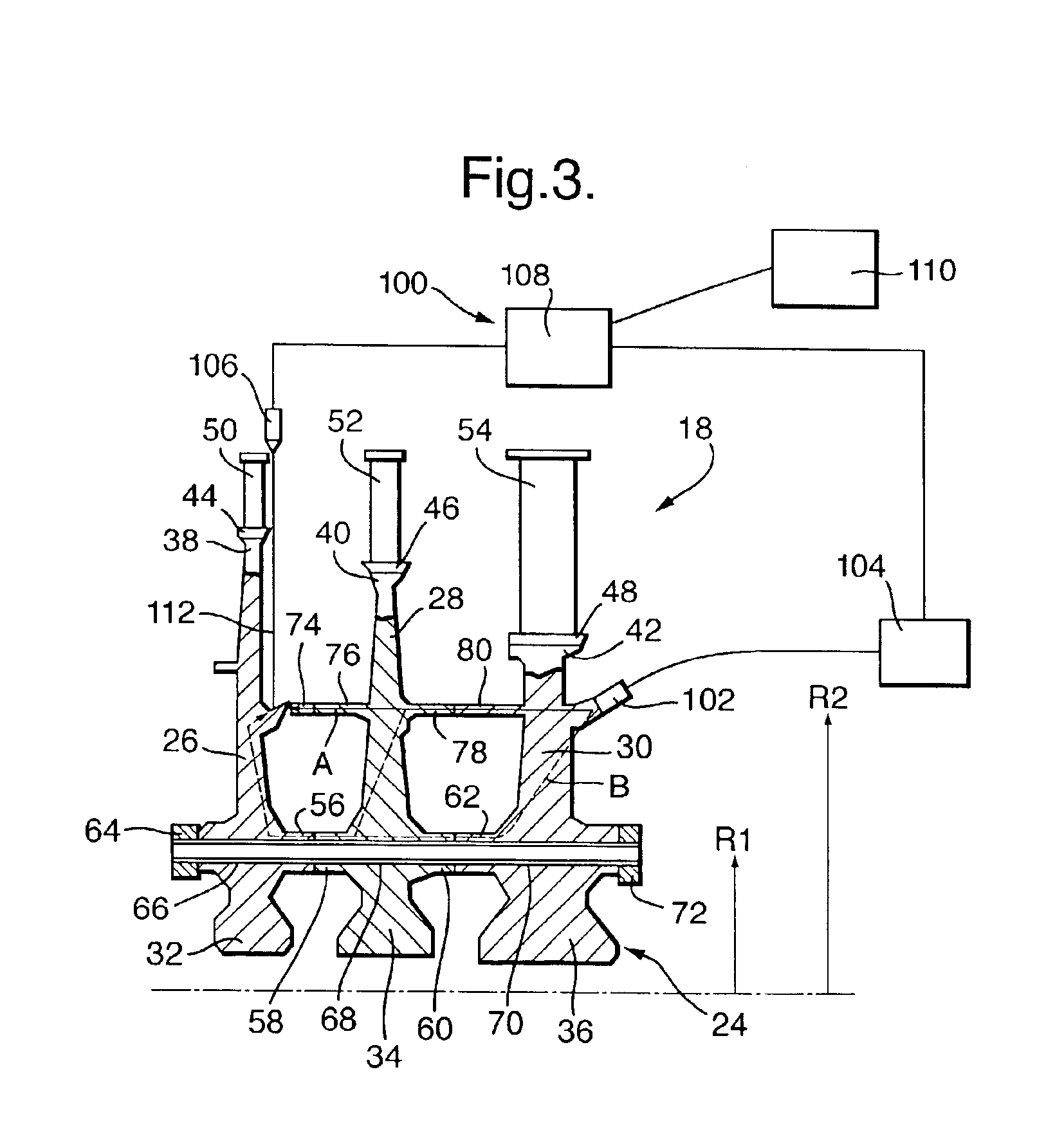

Method of detecting a change in the structure of a complex shape article

InactiveUS6899519B2PropellersAnalysing solids using sonic/ultrasonic/infrasonic wavesSonificationUltrasonic sensor

A method of detecting the change in the structure of a turbine rotor uses the steps of injecting an ultrasonic signal into the turbine rotor at a first position using a first ultrasonic transducer to produce a diffuse field ultrasonic signal in the rotor; detecting the signal in the rotor at a second position using a second ultrasonic transducer measuring the time for the signal to travel from the first ultrasonic transducer to the second ultrasonic transducer and comparing the measured time for the diffuse field ultrasonic signal to travel from the first ultrasonic transducer to the second ultrasonic transducer with a stored time for the diffuse field ultrasonic signal to travel from the first ultrasonic transducer to the second ultrasonic transducer to determine if there is a change in the structure of the turbine rotor.

Owner:ROLLS ROYCE PLC

Vertical line array loudspeaker mounting and adjustment system

The invention relates to a loudspeaker mounting and adjustment system and method for installing and operating a professional audio system used in a stadium, concert hall or the like. The system comprises a vertical array of loudspeaker cabinets that can be suspended from a ceiling and that enables the horizontal and vertical angle of the sound dispersion field to be adjusted remotely and / or automatically while the system is suspended. Each loudspeaker cabinet is connected to a vertically adjacent loudspeaker cabinet via a pair of levers located on either side of the cabinet that control the angle between adjacent loudspeaker cabinets. A linear actuator is connected to each lever for controlling the lever position. Each loudspeaker cabinet also comprises a waveguide with at least one actuator for modifying the waveguide angle and thus the horizontal angle of the sound dispersion field.

Owner:PK SOUND CORP

Bass optimization for audio systems and devices

ActiveUS11166100B2Reduce mechanical transmissionLoudspeaker transducer fixingHeadphones for stereophonic communicationTransducerDiffuse field

The invention relates to audio transducer technology, including audio tuning systems to be utilised in personal audio devices, such as headphone, earphones, mobile phones and the like. The audio tuning system optimises the frequency response of the personal audio device by using Diffuse Field curve characteristics. The audio transducers of the personal audio device incorporate low resonance designs, including low resonance transducer and diaphragm suspensions to further optimise the sound quality of the device. The invention also relates to an audio transducer diaphragm construction that includes a three-dimensional lattice which may be utilised in any audio transducer application.

Owner:WING ACOUSTICS LTD

Radio frequency lateral double diffused field effect transistor and its manufacturing method

ActiveCN104282762BSimple processReduce output capacitanceSemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingCapacitanceDouble diffusion

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

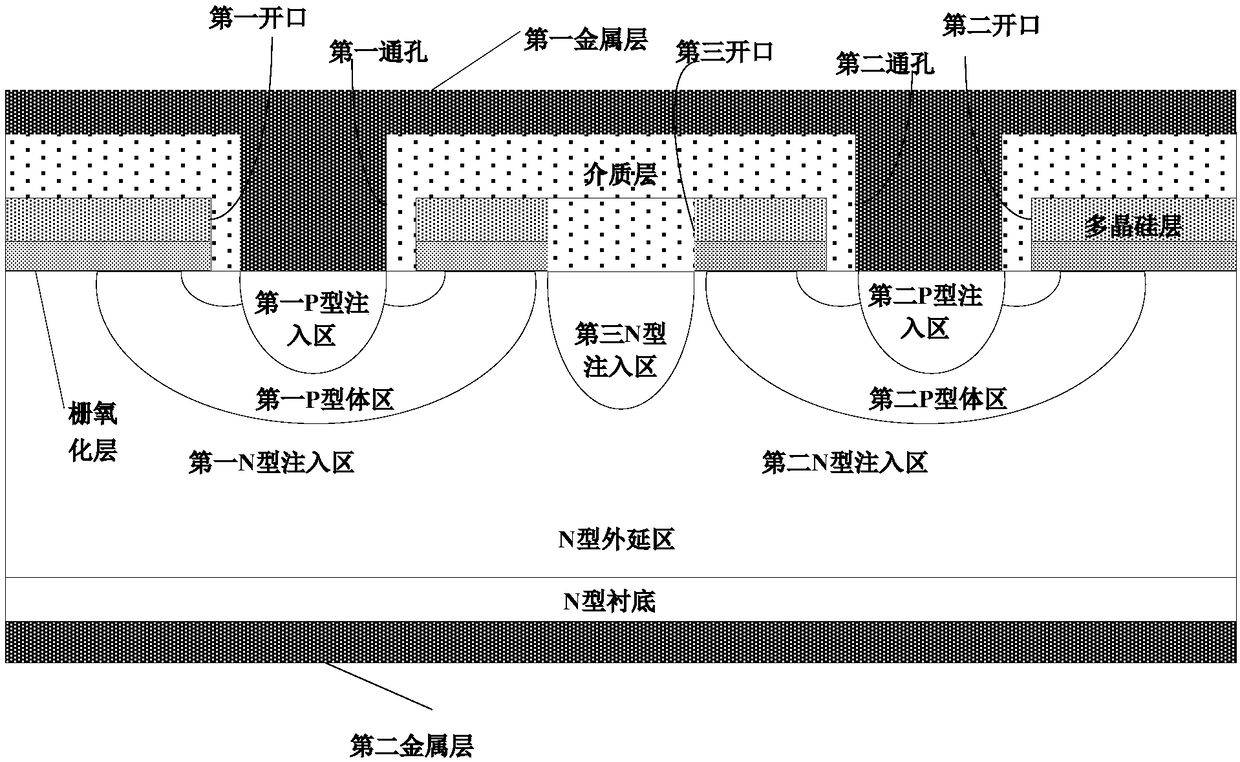

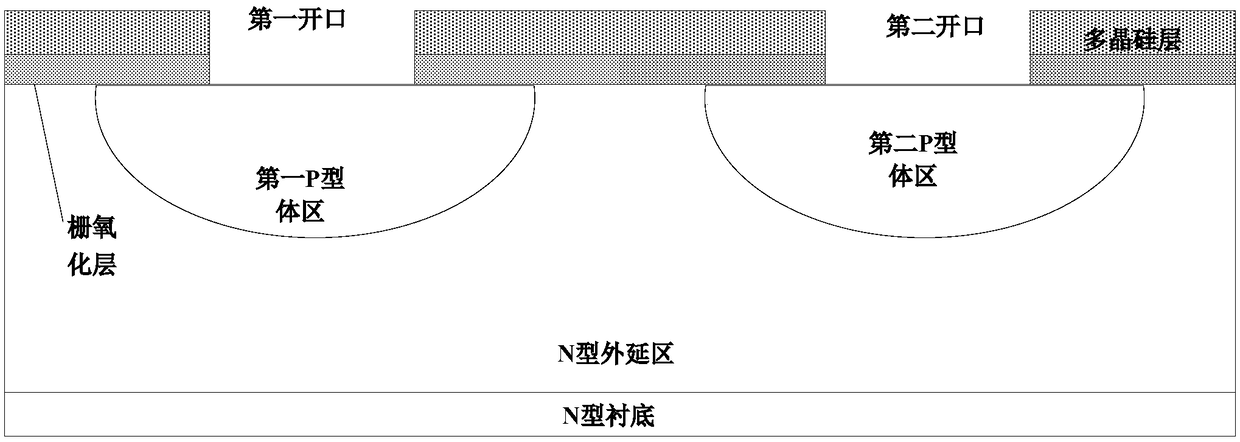

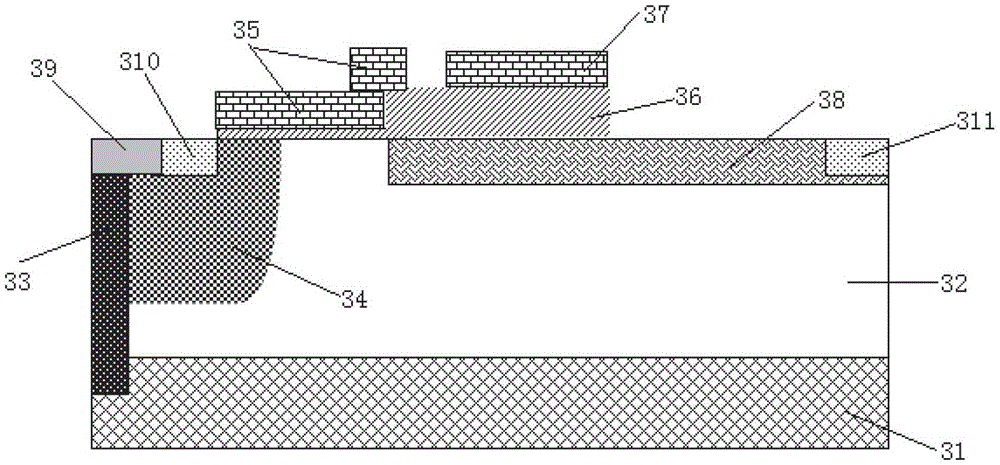

Vertical double-diffused field-effect transistor and fabrication method thereof

InactiveCN108198860AReduce the size of parasitic capacitanceLower resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDiffuse fieldField-effect transistor

A vertical double-diffused field-effect transistor comprises an N-type substrate, an N-type epitaxial region, a first P-type body region, a second P-type body region, two first N-type injection regions, two second N-type injection regions, a third N-type injection region, a first P-type injection region, a second P-type injection region, a grid oxide layer, a poly-silicon layer, a dielectric layer, a first through hole and a second through hole, wherein the first P-type body region and the second P-type body region are formed on a surface of the N-type epitaxial region, the two first N-type injection regions are arranged on a surface of the first P-type body region, the two second N-type injection regions are arranged on a surface of the second P-type body region, the third N-type injection region is arranged on a surface of the N-type epitaxial region, the first P-type injection region is arranged between the two first N-type injection regions, the second P-type injection region is arranged between the two second N-type injection regions, the grid oxide layer and the poly-silicon layer are sequentially formed on the N-type epitaxial region, the first P-type body region, the secondP-type body region, the first N-type injection region and the second N-type injection region, the dielectric layer is formed on the poly-silicon layer and on the first N-type injection region, the second N-type injection region and the third N-type injection region, the first through hole penetrates through the dielectric layer and is corresponding to the first N-type injection region and the first P-type injection region, and the second through hole penetrates through the dielectric layer and is corresponding to the second N-type injection region and the second P-type injection region.

Owner:深圳市金誉半导体股份有限公司

A high-side lateral double-diffused field-effect transistor

ActiveCN104037231BIncreased avalanche breakdown voltageReduce surface electric fieldSemiconductor devicesDouble diffusionBody area

The invention discloses a high-sided transverse double diffused field effect transistor. The high-sided transverse double diffused field effect transistor comprises a P type substrate, an N- epitaxial layer, a P+ buried layer, a P+ P-N junction isolation, field oxygen, a P- top layer, P- body areas, a P- body area contact P+, an N+ source electrode, a gate oxygen layer, a polycrystalline silicon gate electrode and an N+ drain electrode, wherein the N- epitaxial layer is arranged above the P type substrate; the P+ buried layer and the P+ P-N junction isolation are arranged at one side of the N- epitaxial layer and are used to isolate different types of devices; furthermore, another P- body area is arranged between the P- body area and the P+ P-N junction isolation; the body area contact P+ is arranged in the P- body area; the P- top layer is arranged between the P- body area and the another P- body area. According to the high-sided transverse double diffused field effect transistor disclosed by the invention, an avalanche breakdown voltage between the source electrode and the substrate is greatly increased, that is, an isolation performance is greatly improved, so that application in the field which requires relatively high working voltage is satisfied.

Owner:ZHEJIANG UNIV

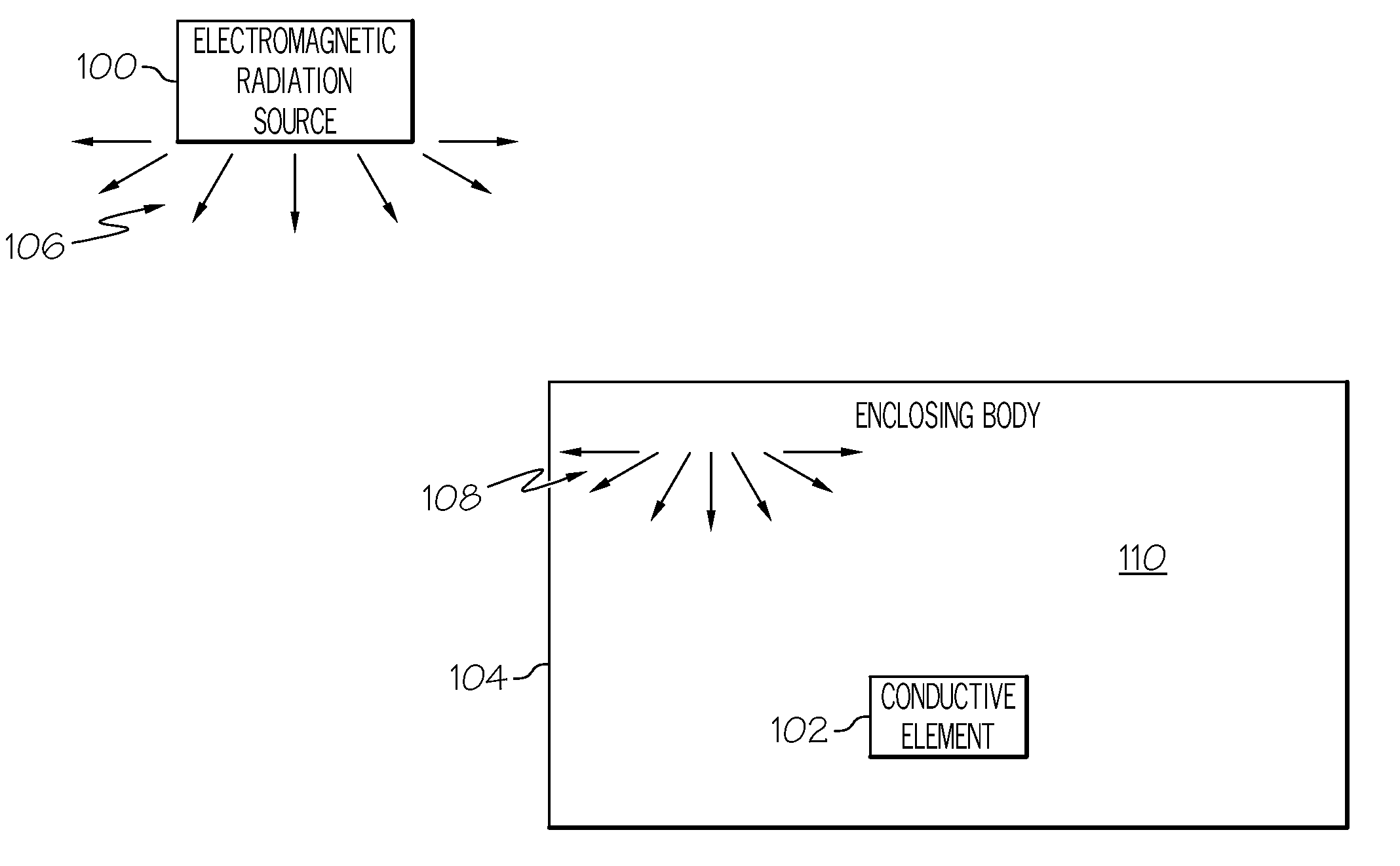

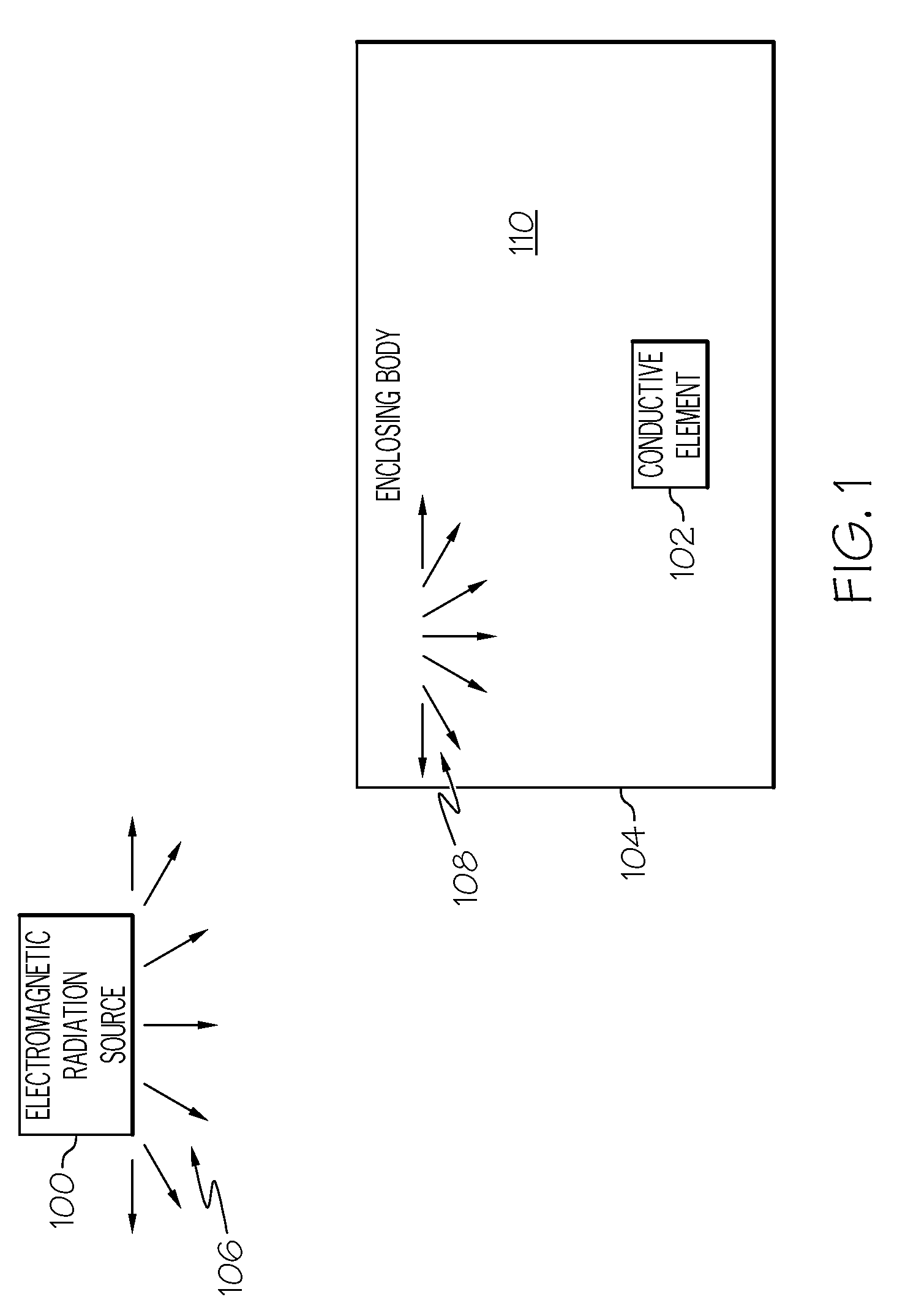

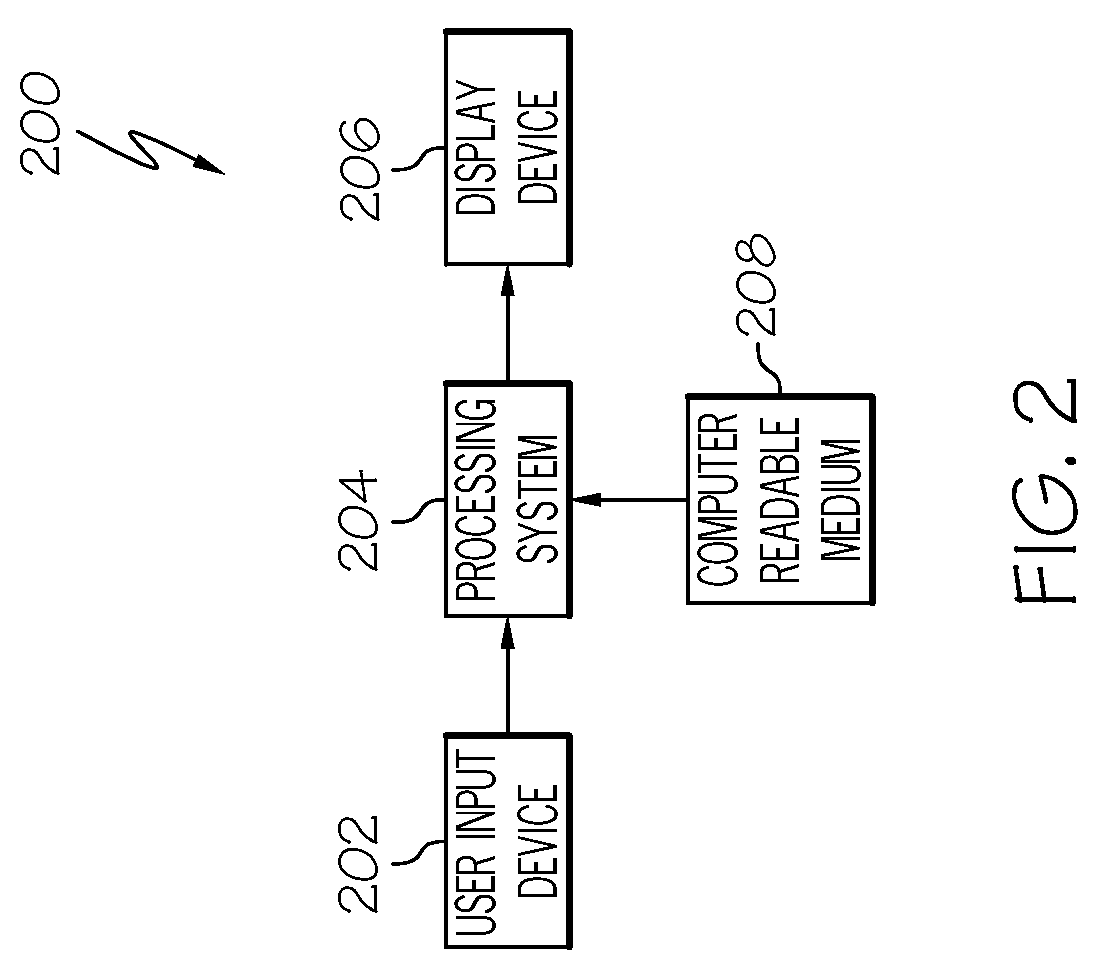

Induced field determination using diffuse field reciprocity

Methods and systems are provided for determining the surface electromagnetic impedance of a conductive element and applying the diffuse field reciprocity principle using that surface electromagnetic impedance to determine electric fields induced in the conductive element. An exemplary method involves determining a surface electromagnetic impedance matrix for the conductive element based on its physical dimensions and an excitation frequency for an incident electromagnetic wavefield, applying diffuse field reciprocity to determine a metric indicative of an induced field based on the surface electromagnetic impedance matrix and an energy metric for the incident electromagnetic wavefield, and displaying a graphical representation of the metric on a display device.

Owner:DASSAULT SYSTEMES SIMULIA CORP +1

A Highly Robust P-Type Symmetric Lateral Double-Diffused Field-Effect Transistor

InactiveCN103280462BImprove the problem of insufficient electrostatic discharge capacityMaximum lattice temperature dropSemiconductor devicesLow voltageBody contact

The invention discloses a high-robustness P type symmetric laterally double-diffused field effect transistor, which comprises a P type substrate, wherein an N type epitaxial layer is arranged on the P type substrate; two P type drift traps, two P type buffer traps and two N type body contact regions are arranged in the N type epitaxial layer; a P type drain region and a P type source region are arranged in the P type buffer trap respectively; the surface of the N type epitaxial layer is provided with a gate oxide layer and a field oxide layer; the surface of the gate oxide layer is provided with a polycrystalline silicon gate; the surfaces of the field oxide layer, the N type body contact regions, the P type source region, the polycrystalline silicon gate and the P type drain region are provided with passivation layers; the high-robustness P type symmetric laterally double-diffused field effect transistor is characterized in that the surfaces of the two P type drift traps are also provided with a photo-etching plate shared with the low-voltage P type trap; first and second shallow P type traps formed by low-energy ion implantation are adopted; and the surface electric field distribution is effectively optimized at the region, the highest lattice temperature is reduced, the secondary breakdown current is improved and the robustness of the device in an ESD (Electronic Static Discharge) process is enhanced.

Owner:SOUTHEAST UNIV

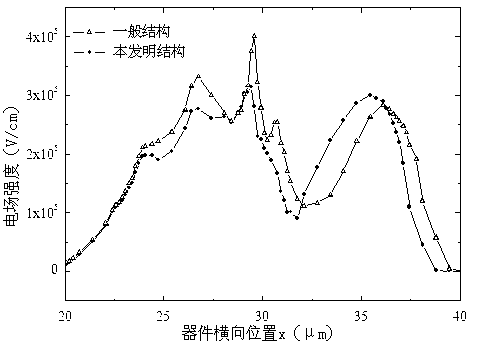

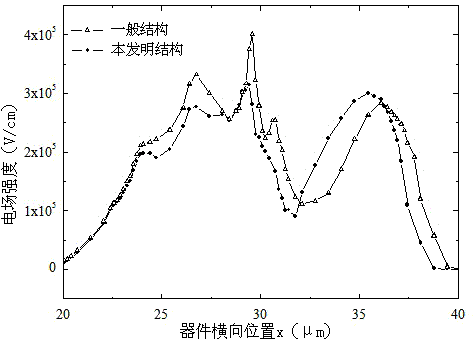

Wide-bandgap semiconductor lateral double-diffused field effect transistor with transverse and longitudinal electric field simultaneous optimization function

InactiveCN107623039AExtended longitudinal space charge regionImprove breakdown voltageSemiconductor devicesLDMOSPartial charge

The invention discloses a wide-bandgap semiconductor lateral double-diffused field effect transistor with a transverse and longitudinal electric field simultaneous optimization function. An assisted depletion substrate buried layer is arranged below a drift region at the drain end, and a substrate buried layer with partial charge compensation is arranged in a substrate area below the drift regionof LDMOS and near the assisted depletion substrate buried layer. A new electric field peak is introduced to the surface transverse electric field of the device, so that the surface transverse electricfield of the device is distributed more uniformly, and the surface transverse electric field of the device is well optimized. A new electric field peak is also introduced to the inside longitudinal electric field distribution of the device, which further optimizes the inside longitudinal electric field. The structure breaks through the voltage saturation phenomenon caused by the limited longitudinal withstand voltage. Most importantly, the surface transverse electric field and the inside longitudinal electric field can be optimized simultaneously, and the breakdown voltage of the device is greatly improved.

Owner:XIDIAN UNIV

Conferencing device self test

A plurality of acoustic sensors in a non-anechoic environment are calibrated with the aim of removing manufacturing tolerances and degradation over time but preserving position-dependent differences between the sensors, The sensors are excited by an acoustic stimulus which has either time-dependent characteristics or finite duration. The calibration is to be based on diffuse-field excitation only, in which indirect propagation (including single or multiple reflections) dominate over any direct-path excitation. For this purpose, the calibration process considers only a non-initial portion of sensor outputs and / or of an impulse response derived there-from. Based on these data, a frequency-dependent magnitude response function is estimated and compared with a target response function, from which a calibration function is derived.

Owner:DOLBY LAB LICENSING CORP

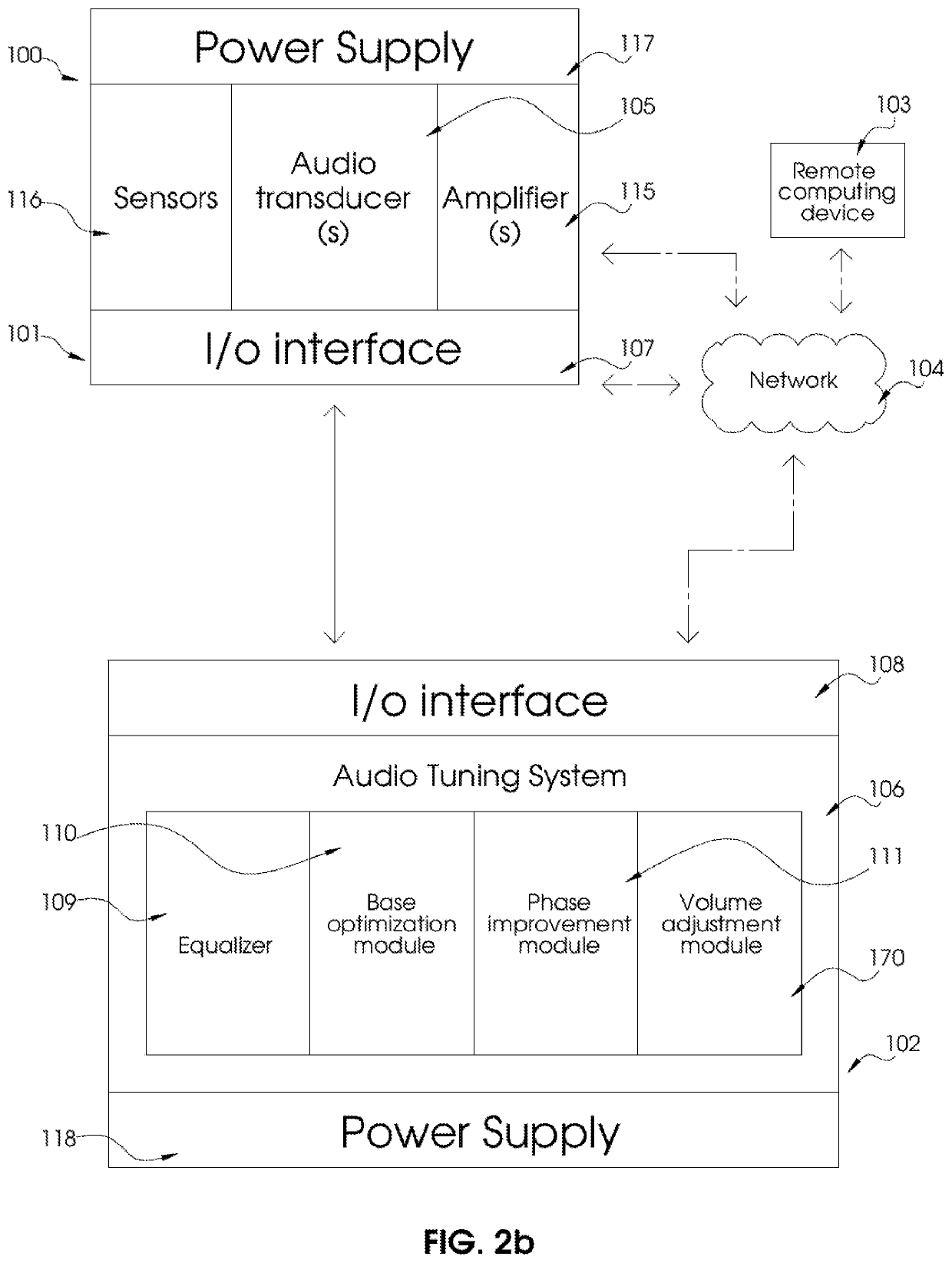

Radio frequency lateral double diffused field effect transistor and its manufacturing method

ActiveCN103035724BQuality improvementIncreased durabilitySemiconductor/solid-state device detailsSolid-state devicesDouble diffusionDiffuse field

The invention discloses a radio frequency lateral double-diffusion field effect transistor, which comprises a polysilicon gate and a Faraday shielding layer, and the Faraday shielding layer is a polysilicon Faraday shielding layer. The RF lateral double-diffusion field-effect transistor of the present invention adopts the structure of the polysilicon Faraday shielding layer. Compared with the traditional preparation process of the Faraday shielding layer, the preparation process is simple, and only one thermal oxidation process is added, and the oxide layer under the Faraday shielding layer is reduced once. Deposition and metal deposition and etching process, the quality of the oxide layer under the Faraday shielding layer prepared by this method is better than that of the ordinary Faraday shielding layer grown by deposition, thereby enhancing the durability of the device; and this Compared with common metal Faraday shielding layer devices, the invented device has the same breakdown voltage, on-resistance and other characteristics. At the same time, the stepped gate structure prepared by this method can also play a role in suppressing hot carrier injection (HCI).

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

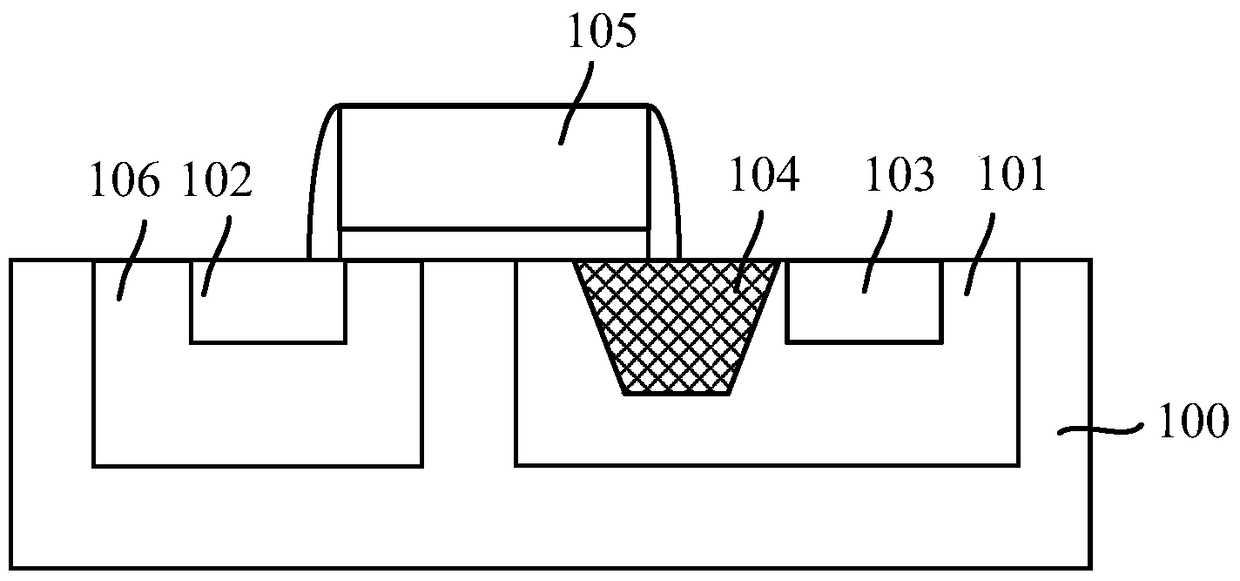

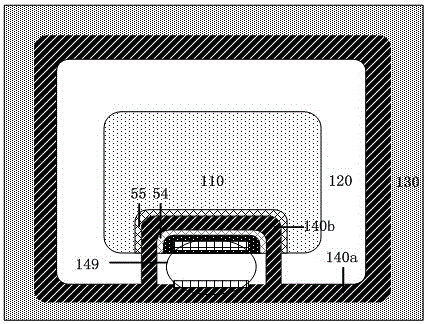

Lateral double diffused field effect transistor and method of forming the same

ActiveCN105448979BReduce dynamic lossReduce sizeSemiconductor/solid-state device manufacturingSemiconductor devicesDouble diffusionDiffuse field

A lateral double diffused field effect transistor and its forming method. The lateral double diffused field effect transistor comprises: a semiconductor substrate doped with impurity ions of a first conductivity type; a first shallow trench located in the semiconductor substrate Trench isolation structure; a drift region located in the semiconductor substrate, the drift region surrounds the first shallow trench isolation structure, the drift region is doped with impurity ions of a second conductivity type, the second conductivity type is opposite to the first conductivity type ; An inversion doped region located in the drift region, the depth of the inversion doped region is less than the depth of the drift region, and the inversion doped region is doped with impurity ions of the first conductivity type; The body region in the semiconductor substrate is doped with impurity ions of the first conductivity type; a gate structure is formed on the semiconductor substrate, one end of the gate structure extends above the body region, and the other end extends to the first above the shallow trench isolation structure. The gate-to-drain parasitic capacitance of the lateral double-diffused field effect transistor is reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP

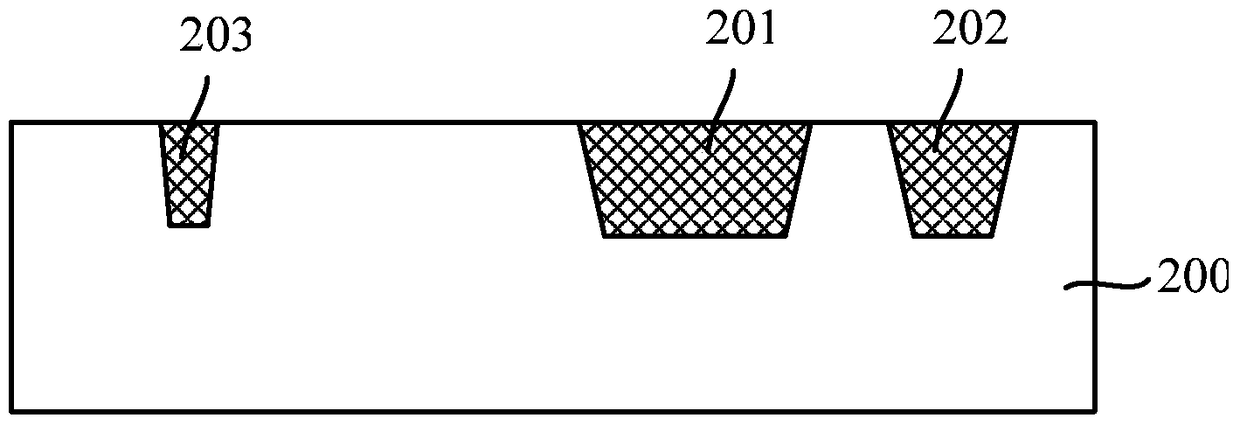

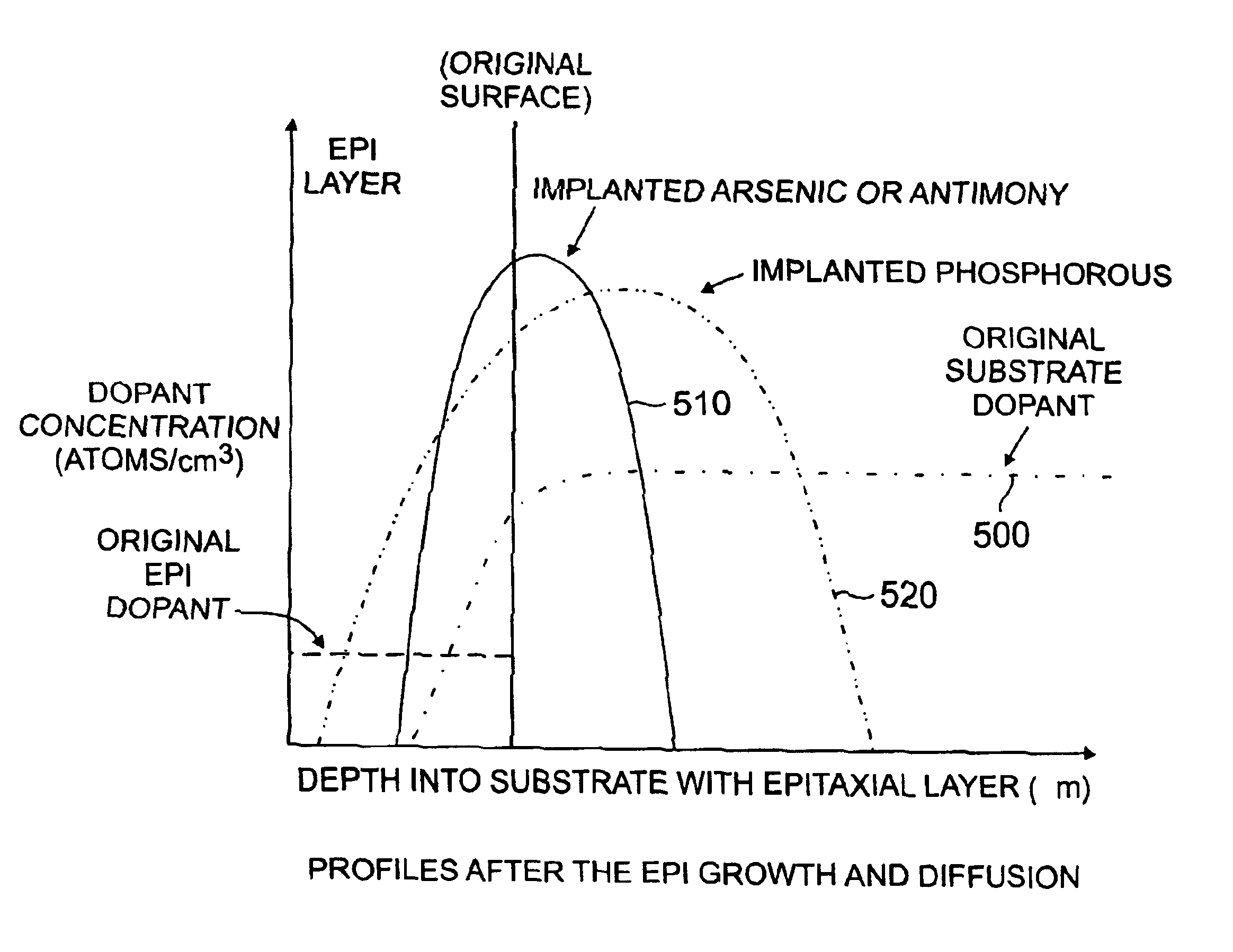

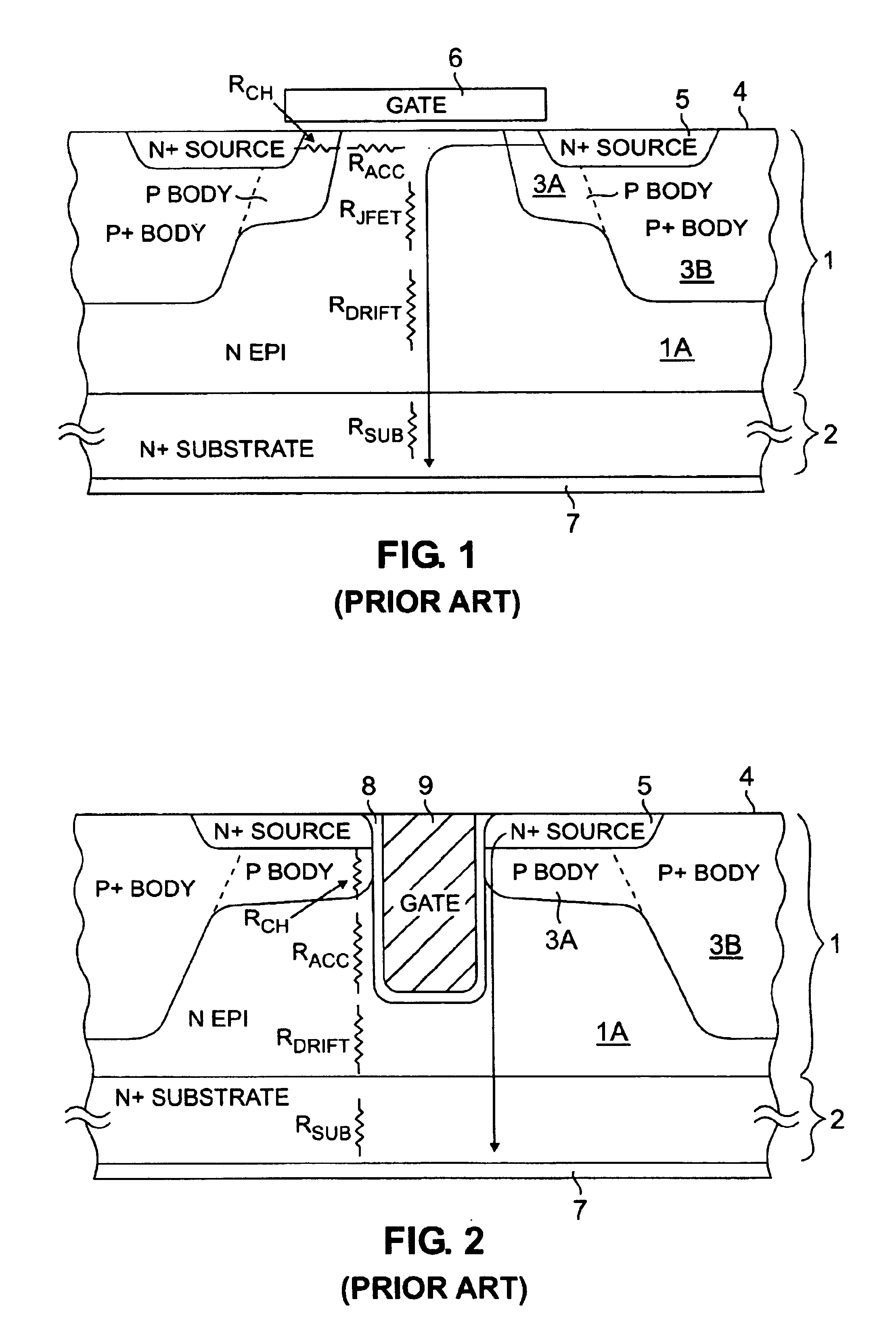

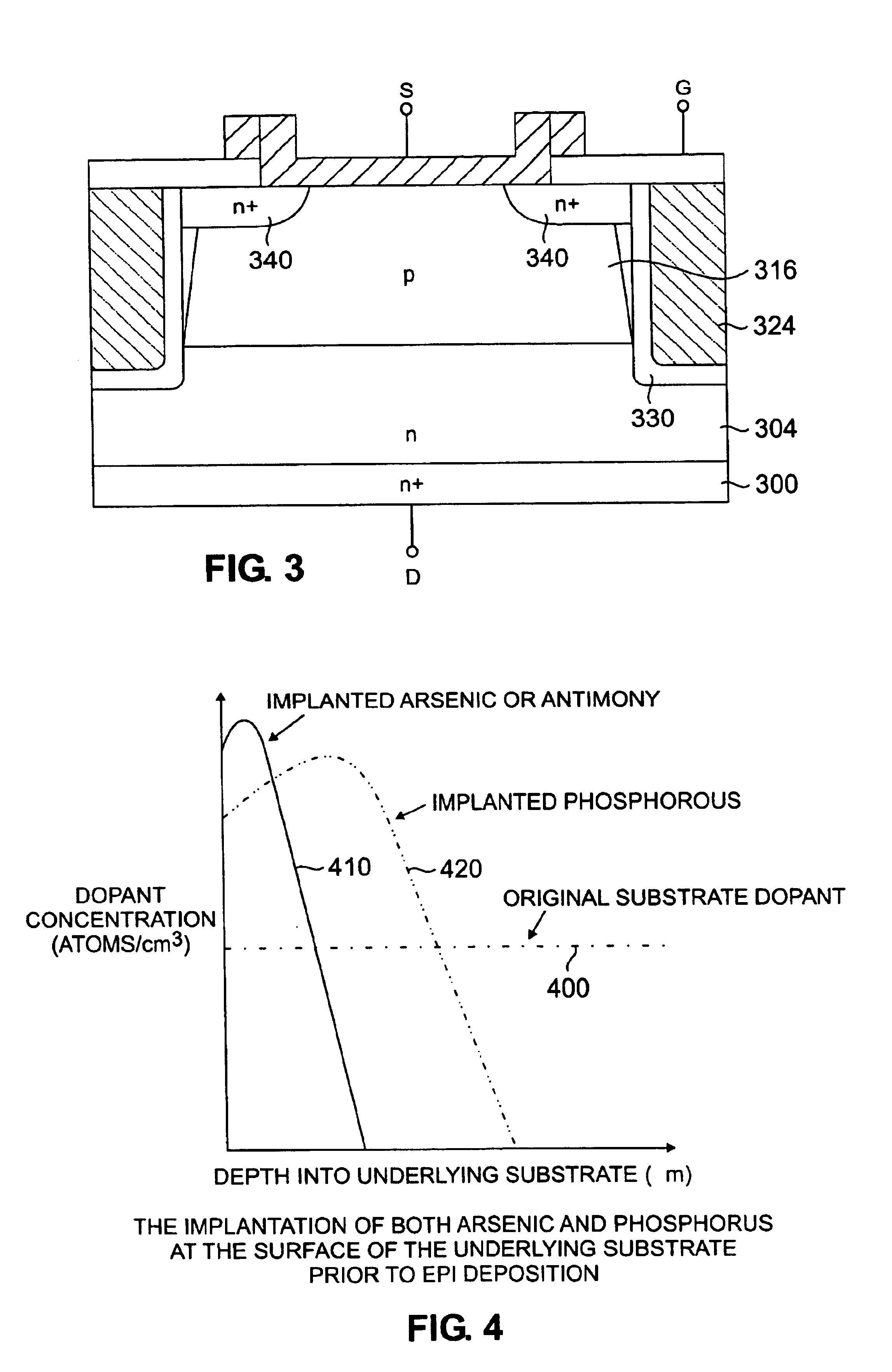

Double diffused field effect transistor having reduced on-resistance

InactiveUS6921938B2Semiconductor/solid-state device manufacturingSemiconductor devicesDiffuse fieldField-effect transistor

A double diffused field effect transistor and a method of forming the same is provided. The method begins by providing a substrate of a first conductivity type. Next, at least one dopant species, also of the first conductivity type, is introduced into a surface of the substrate so that the substrate has a nonuniform doping profile. An epitaxial layer of the first conductivity type is formed over the substrate and one or more body regions of a second conductivity type are formed within the epitaxial layer. A plurality of source regions of the first conductivity type are then formed within the body regions. Finally, a gate region is formed, which is adjacent to the body regions.

Owner:GEN SEMICON

Radio frequency lateral double diffused field effect transistor and its manufacturing method

ActiveCN103035731BLower on-resistanceImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesDouble diffusionDiffuse field

The invention discloses a radio frequency lateral double-diffusion field effect transistor, which comprises a P-type substrate, a P-type epitaxial layer is grown on the P-type substrate, a lightly doped drift region is formed in the P-type epitaxial layer, and A first layer of Faraday shield and a second layer of Faraday shield are arranged above the P-type epitaxial layer, and two second NLDD implantation regions are also included in the lightly doped drift region, respectively located in the first layer of Faraday shield and below the second layer of the Faraday shield. The invention can obtain performance exceeding that of the device with the original structure, realize higher breakdown voltage (higher than 120V), and reduce the on-resistance of the device with the original structure at the same time. At the same time, the invention also discloses a manufacturing method of the transistor.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Isolation structure of a high-voltage driving circuit and its preparation method

ActiveCN104167434BPrevent punch-throughGuaranteed withstand voltageSemiconductor/solid-state device manufacturingSemiconductor devicesDiffuse fieldEngineering

The invention discloses an isolation structure of a high-voltage driving circuit and a preparation method thereof. The improvement over the traditional isolation structure lies in that one N-type well region is respectively filled on both sides of the second P-type well region, thereby improving the isolation performance. While ensuring the withstand voltage of the isolation structure, the invention suppresses the punch-through leakage between the high voltage region and the drain terminal of the lateral diffusion field effect transistor in the isolation structure.

Owner:WUXI CHIPOWN MICROELECTRONICS

Laterally diffused field effect transistor and a method of manufacturing the same

ActiveUS10475921B2Improve performanceIsolation is requiredSemiconductor devicesPower flowDiffuse field

An LDFET may be formed on the basis of manufacturing platforms designed for forming sophisticated small signal transistor elements. To this end, sidewall areas of trench isolation regions laterally positioned within the drift region may be used as current paths, thereby achieving increased design flexibility, since efficient current paths may still be established, even if the trench isolation regions have to extend into the substrate material due to design criteria determined by the sophisticated small signal transistor elements. In some illustrative embodiments, isolation of P-LDFETs with respect to the P-substrate may be accomplished without requiring a deep well implantation.

Owner:GLOBALFOUNDRIES U S INC