Patents

Literature

97 results about "Dram capacitor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

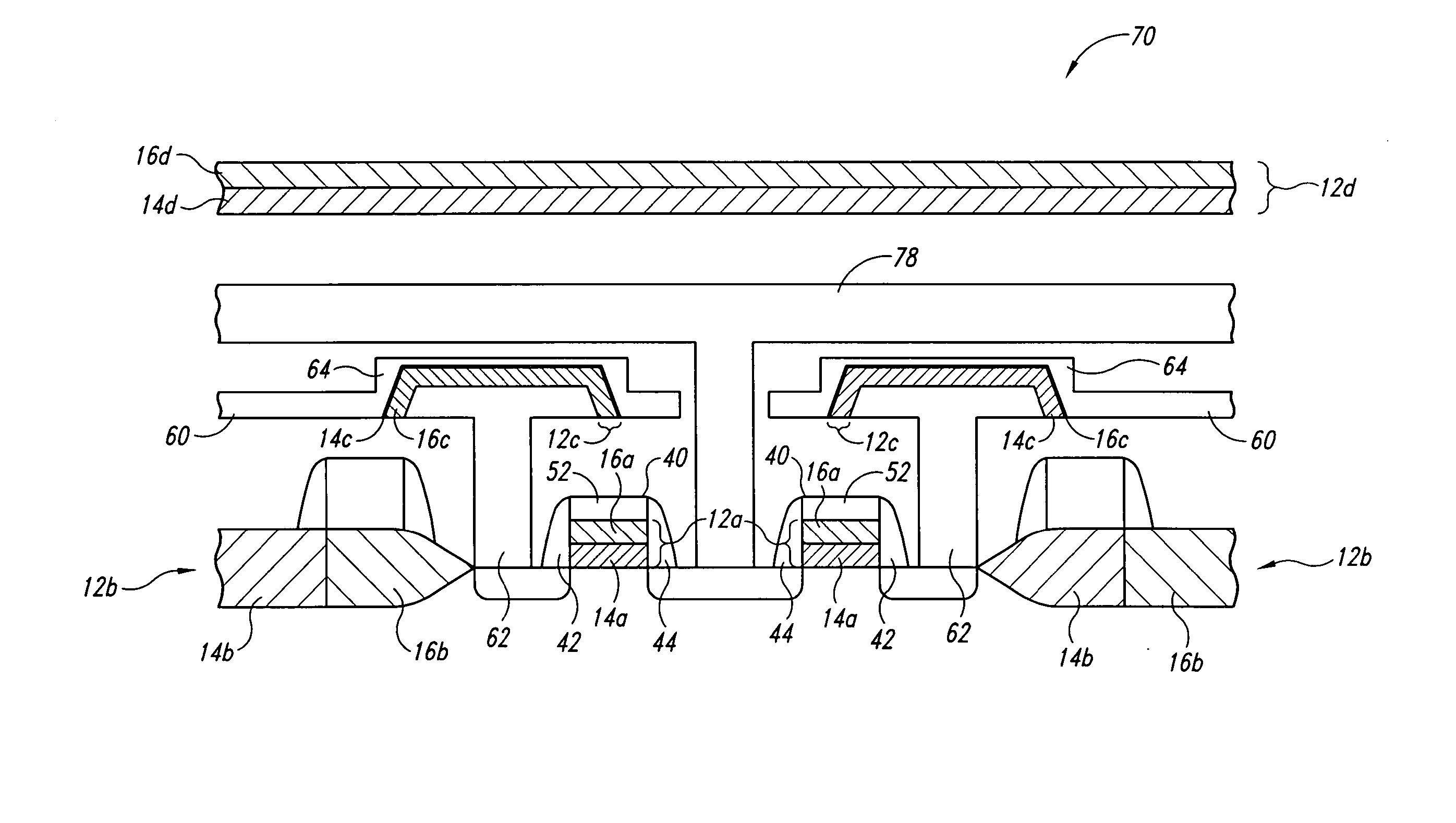

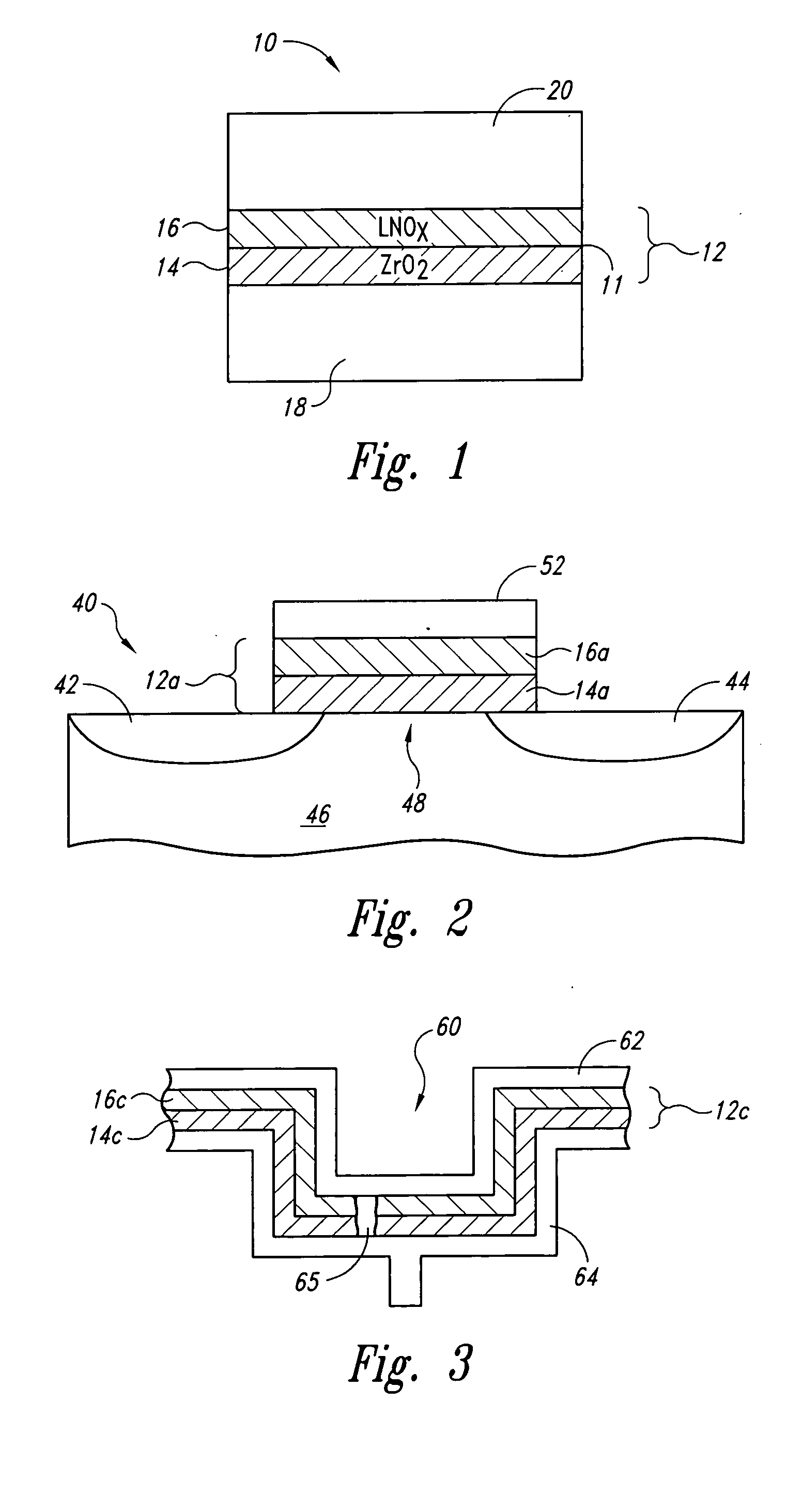

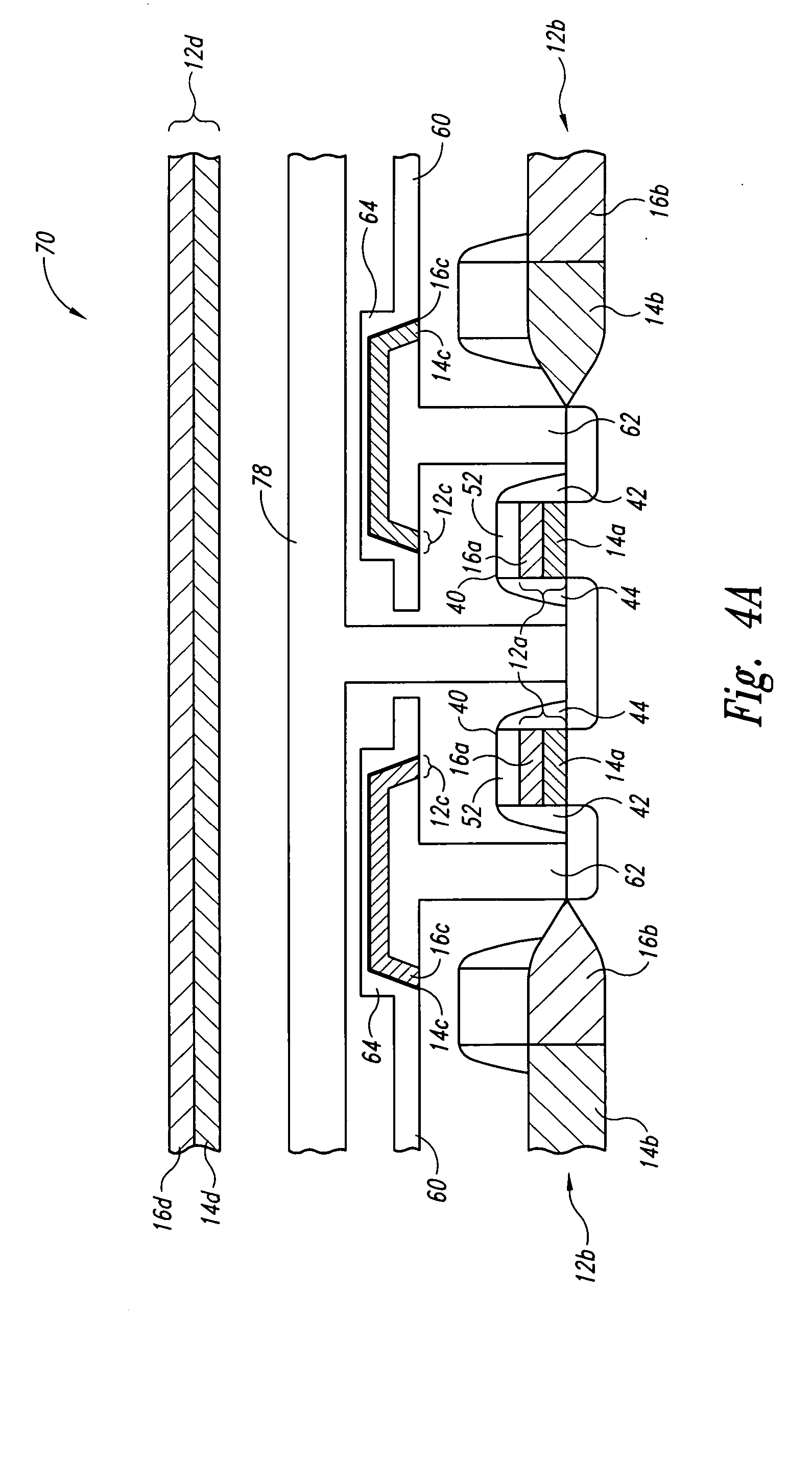

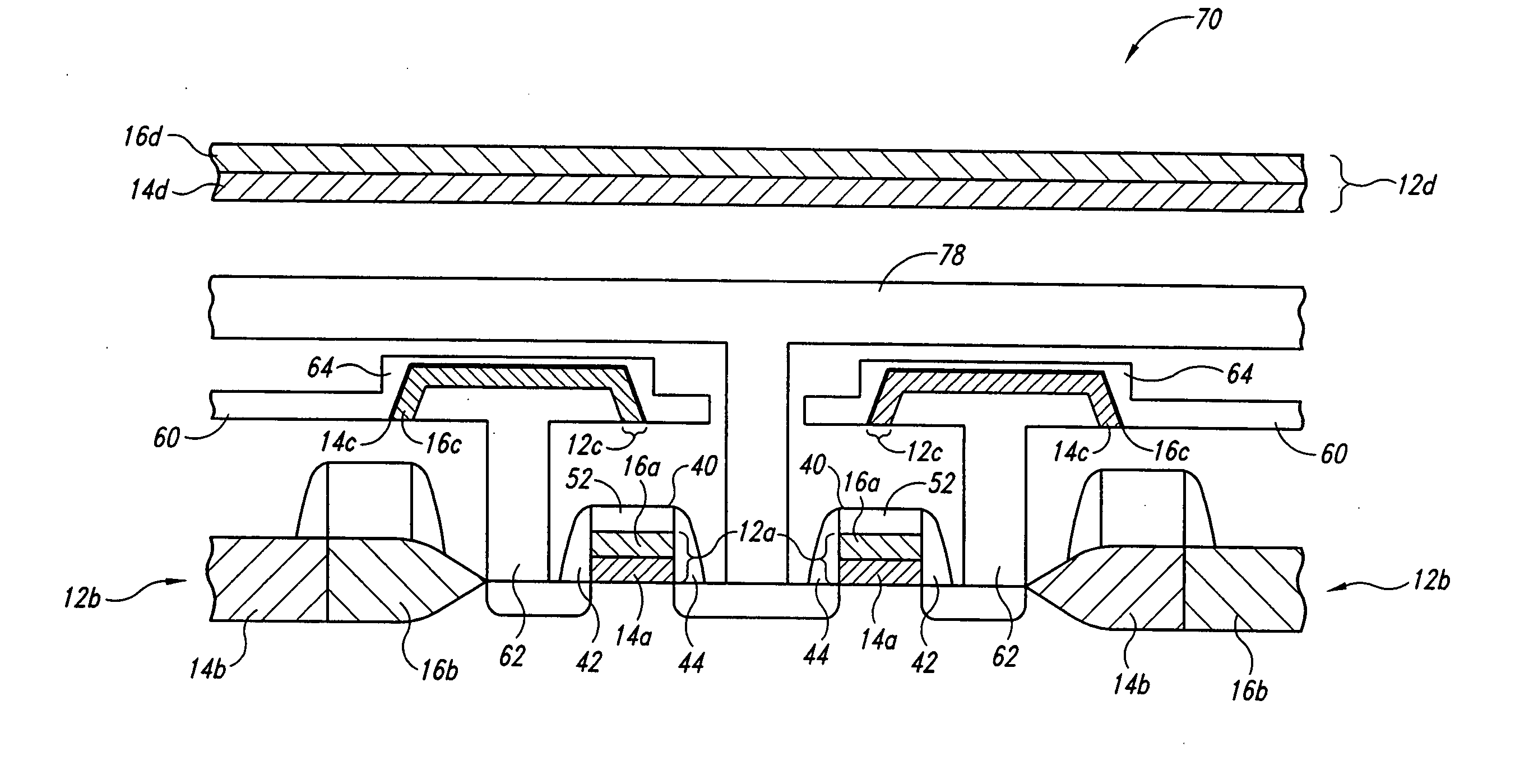

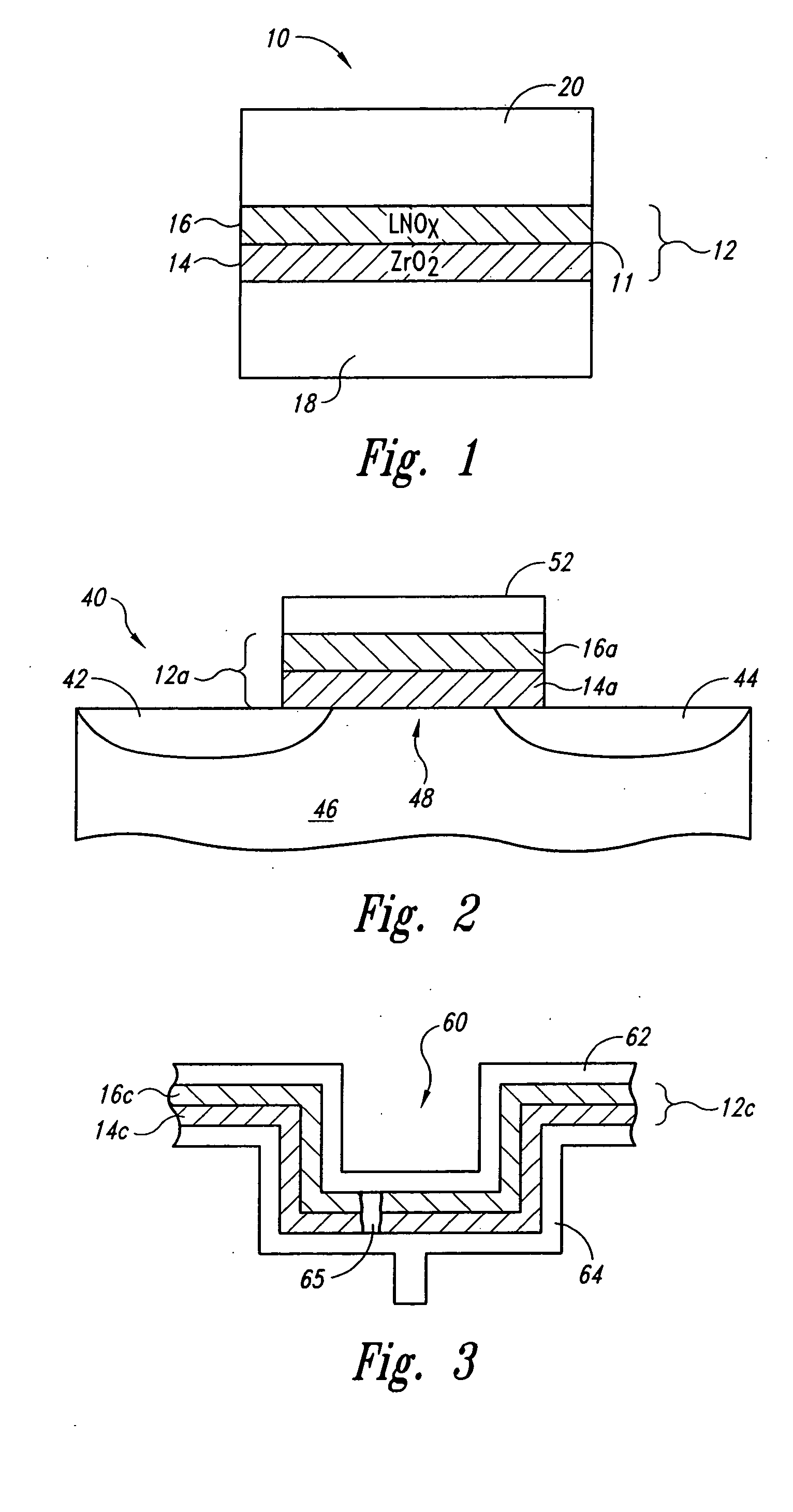

Lanthanide oxide/zirconium oxide atomic layer deposited nanolaminate gate dielectrics

The invention provides a laminated dielectric layer for semiconductor devices formed by a combination of ZrO2 and a lanthanide oxide on a semiconductor substrate and methods of making the same. In certain methods, the ZrO2 is deposited by multiple cycles of reaction sequence atomic layer deposition (RS-ALD) that includes depositing a ZrI4 precursor onto the surface of the substrate in a first pulse followed by exposure to H2O / H2O2 in a second pulse, thereby forming a thin ZrO2 layer on the surface. After depositing the ZrO2 layer, the lanthanide oxide layer is deposited by electron beam evaporation. The composite laminate zirconium oxide / lanthanide oxide dielectric layer has a relatively high dielectric constant and can be formed in layers of nanometer dimensions. It is useful for a variety of semiconductor applications, particularly for DRAM gate dielectric layers and DRAM capacitors.

Owner:MICRON TECH INC

Lanthanide oxide/zirconium oxide atomic layer deposited nanolaminate gate dielectrics

The invention provides a laminated dielectric layer for semiconductor devices formed by a combination of ZrO2 and a lanthanide oxide on a semiconductor substrate and methods of making the same. In certain methods, the ZrO2 is deposited by multiple cycles of reaction sequence atomic layer deposition (RS-ALD) that includes depositing a ZrI4 precursor onto the surface of the substrate in a first pulse followed by exposure to H2O / H2O2 in a second pulse, thereby forming a thin ZrO2 layer on the surface. After depositing the ZrO2 layer, the lanthanide oxide layer is deposited by electron beam evaporation. The composite laminate zirconium oxide / lanthanide oxide dielectric layer has a relatively high dielectric constant and can be formed in layers of nanometer dimensions. It is useful for a variety of semiconductor applications, particularly for DRAM gate dielectric layers and DRAM capacitors.

Owner:AHN KIE +1

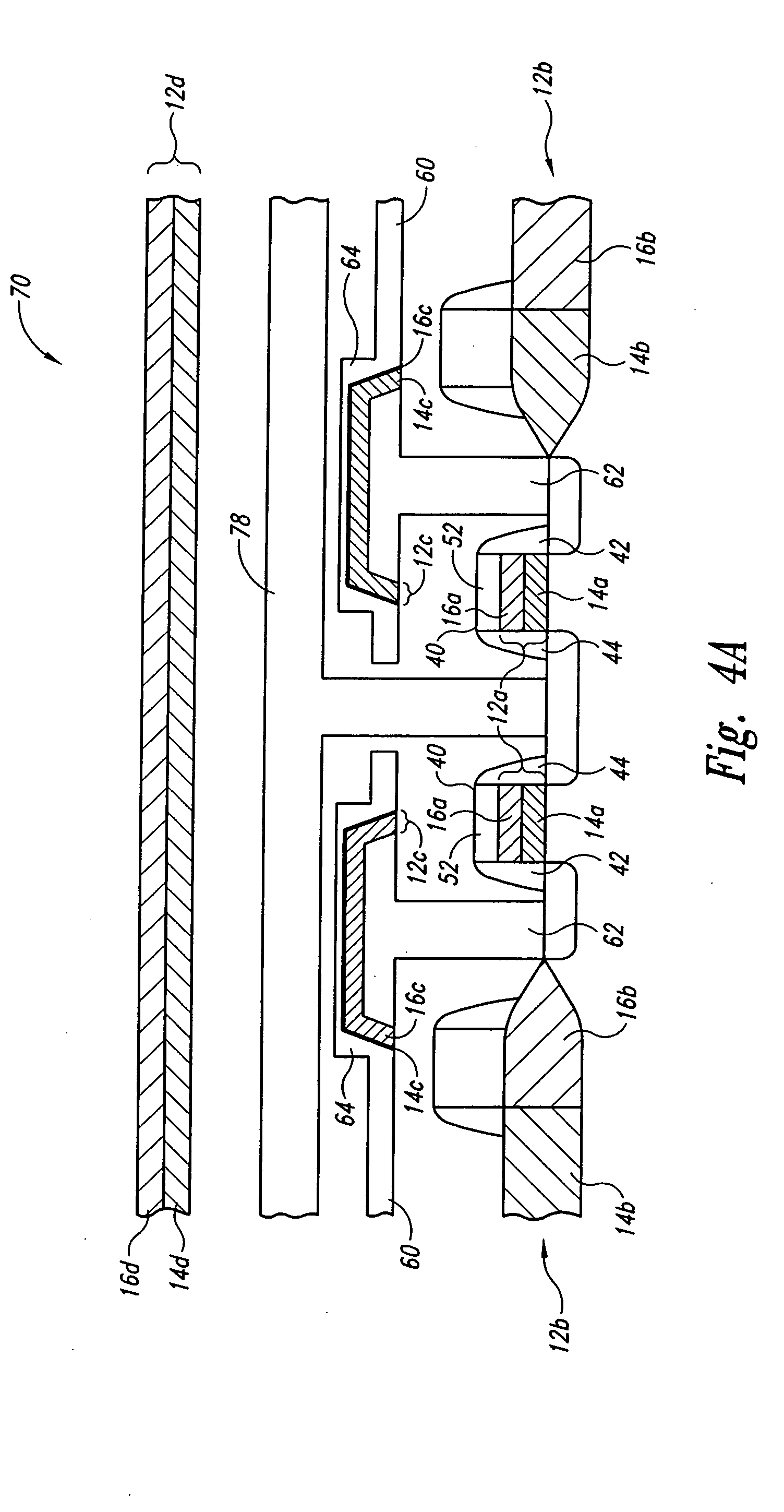

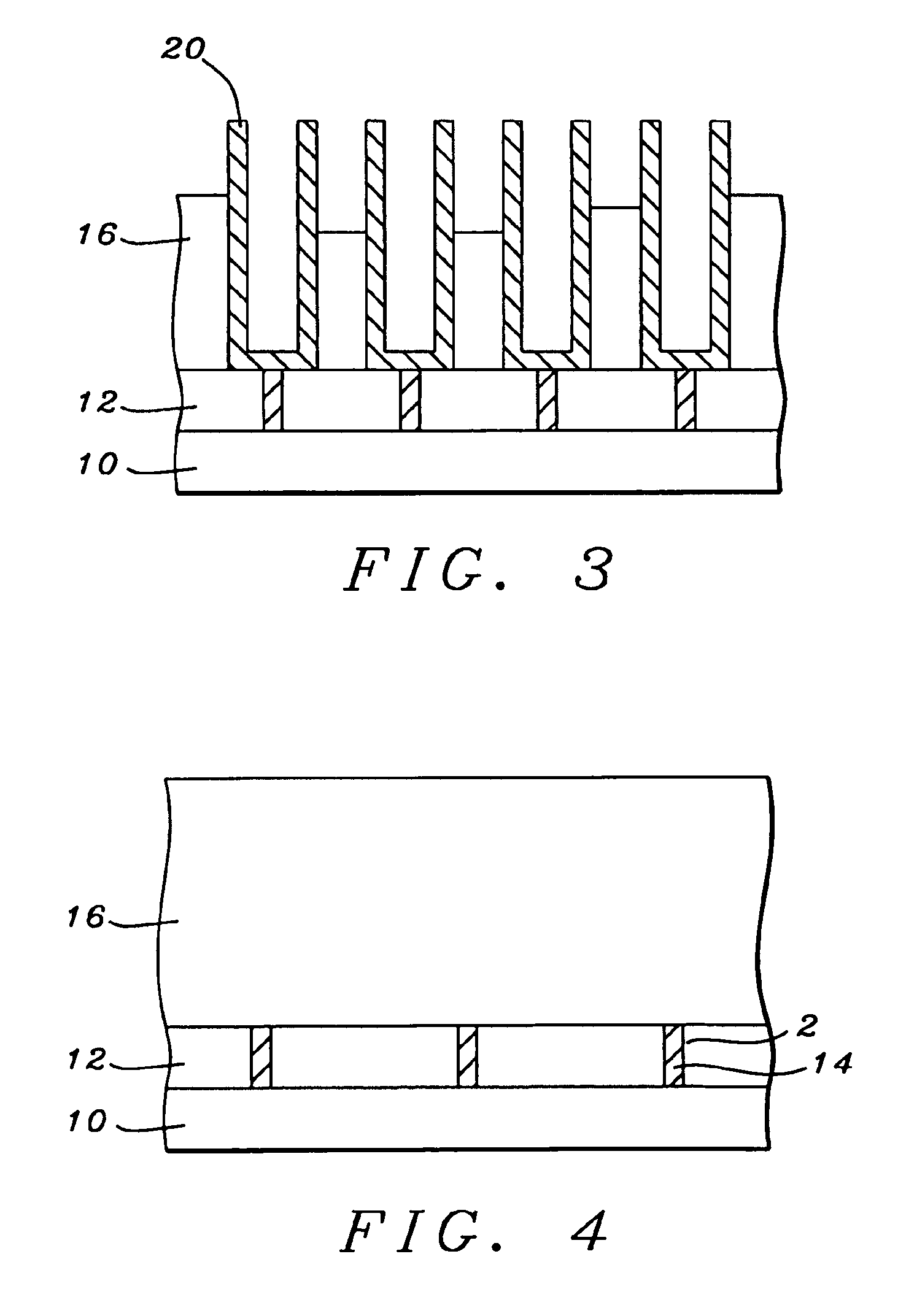

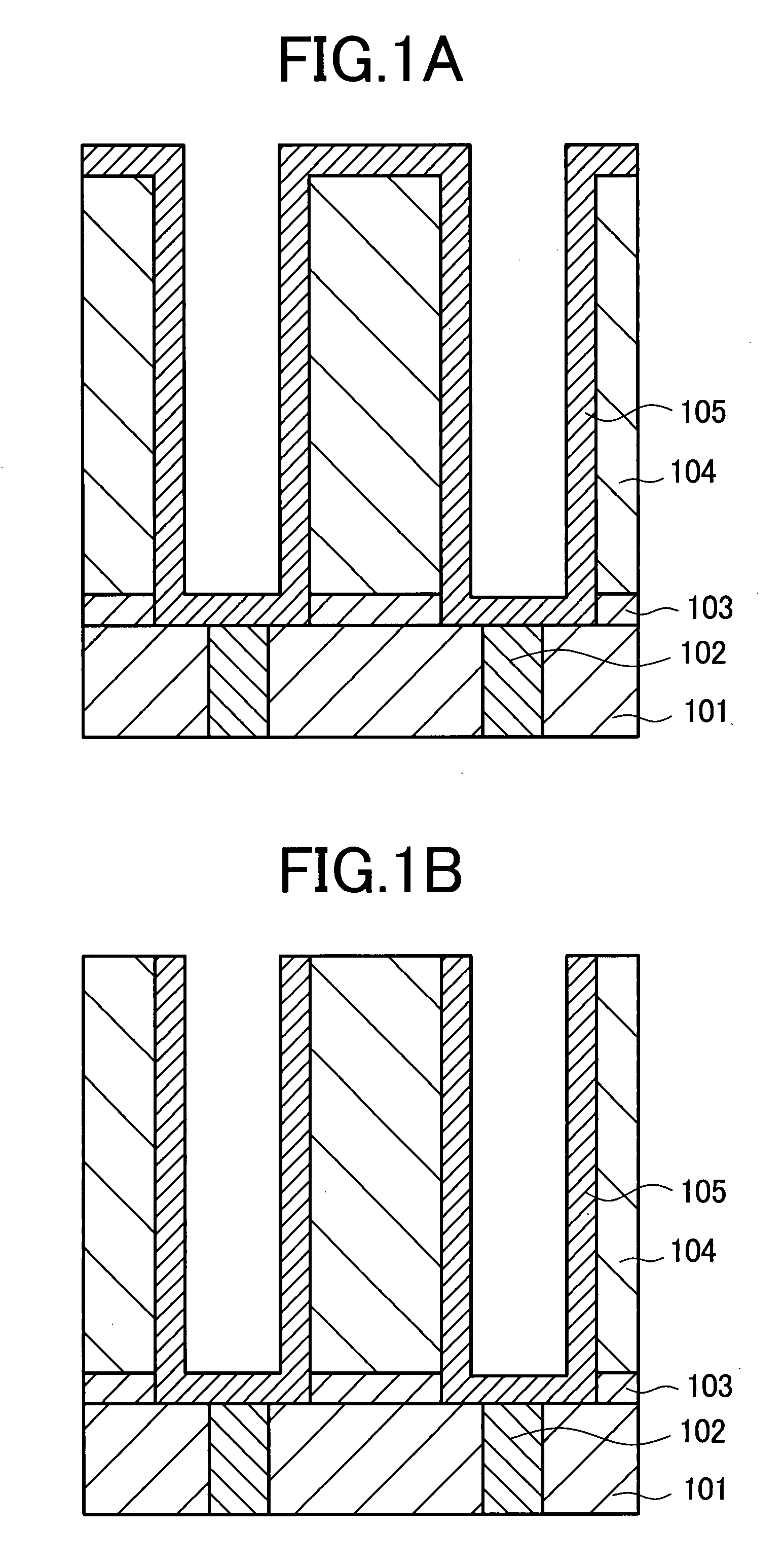

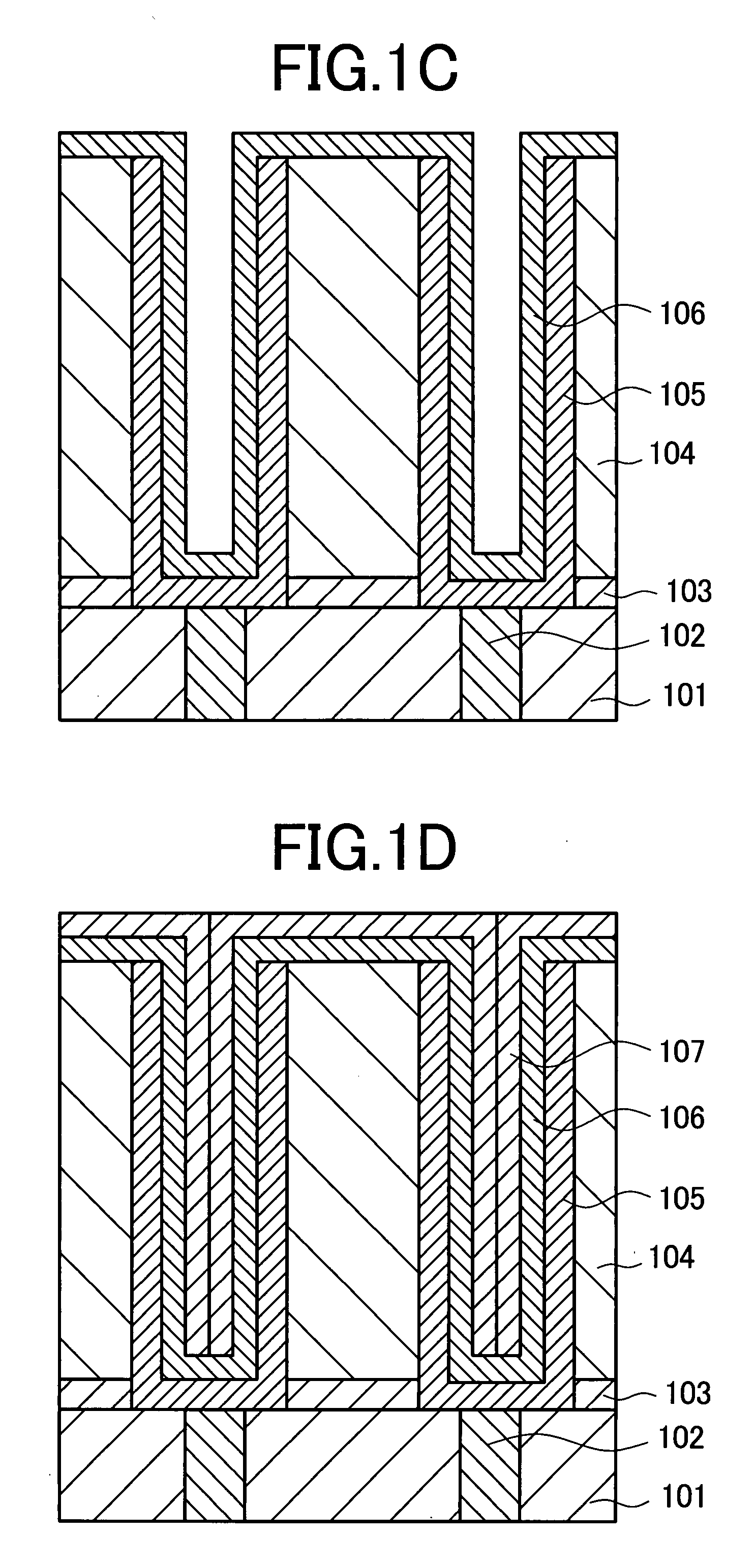

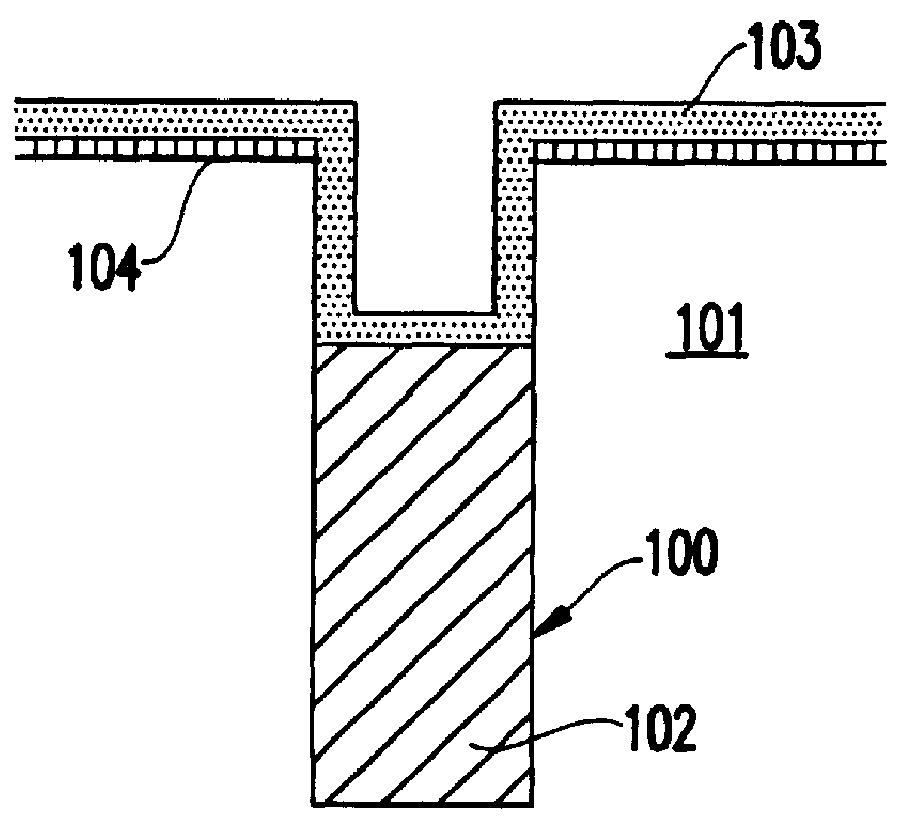

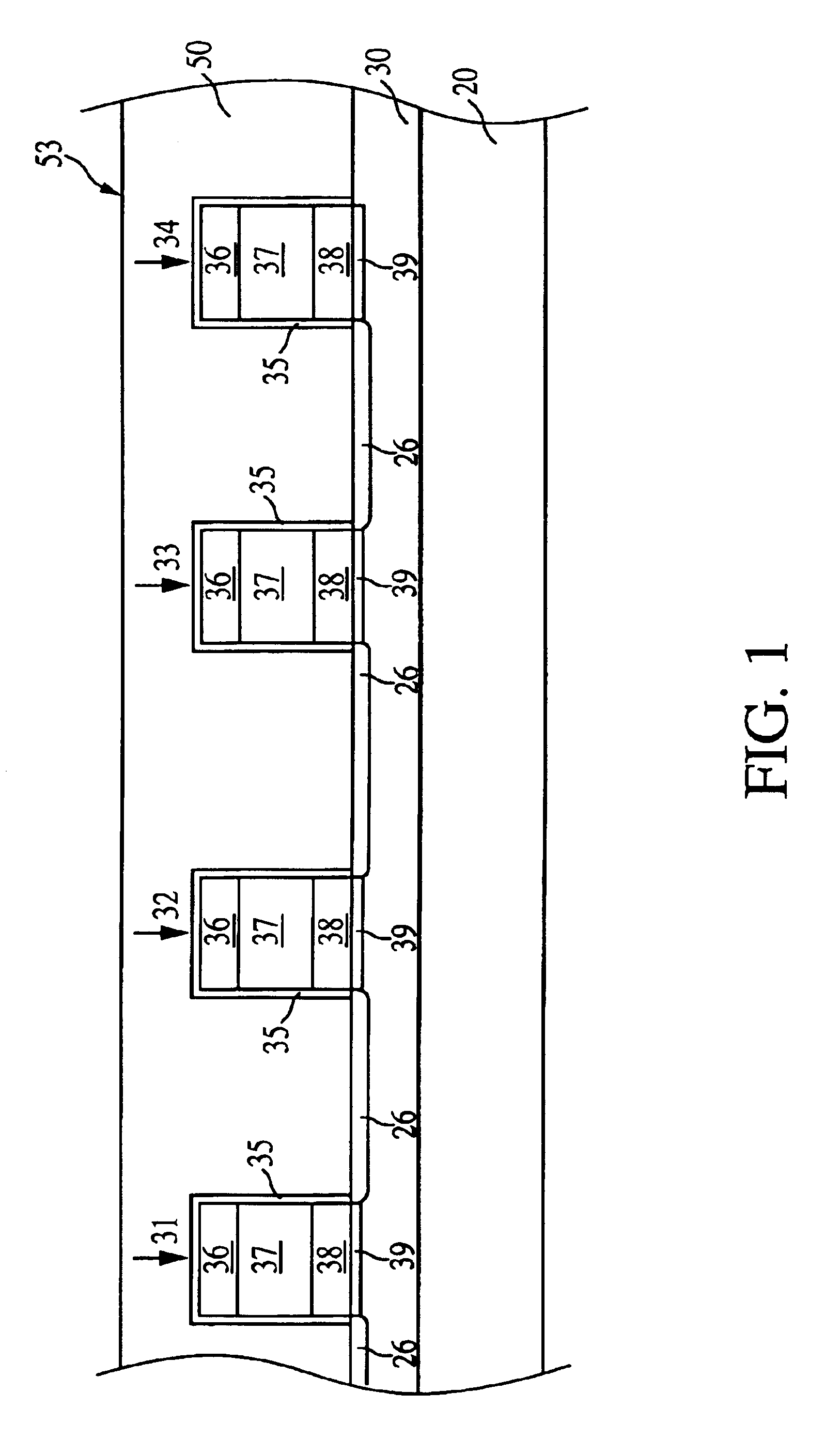

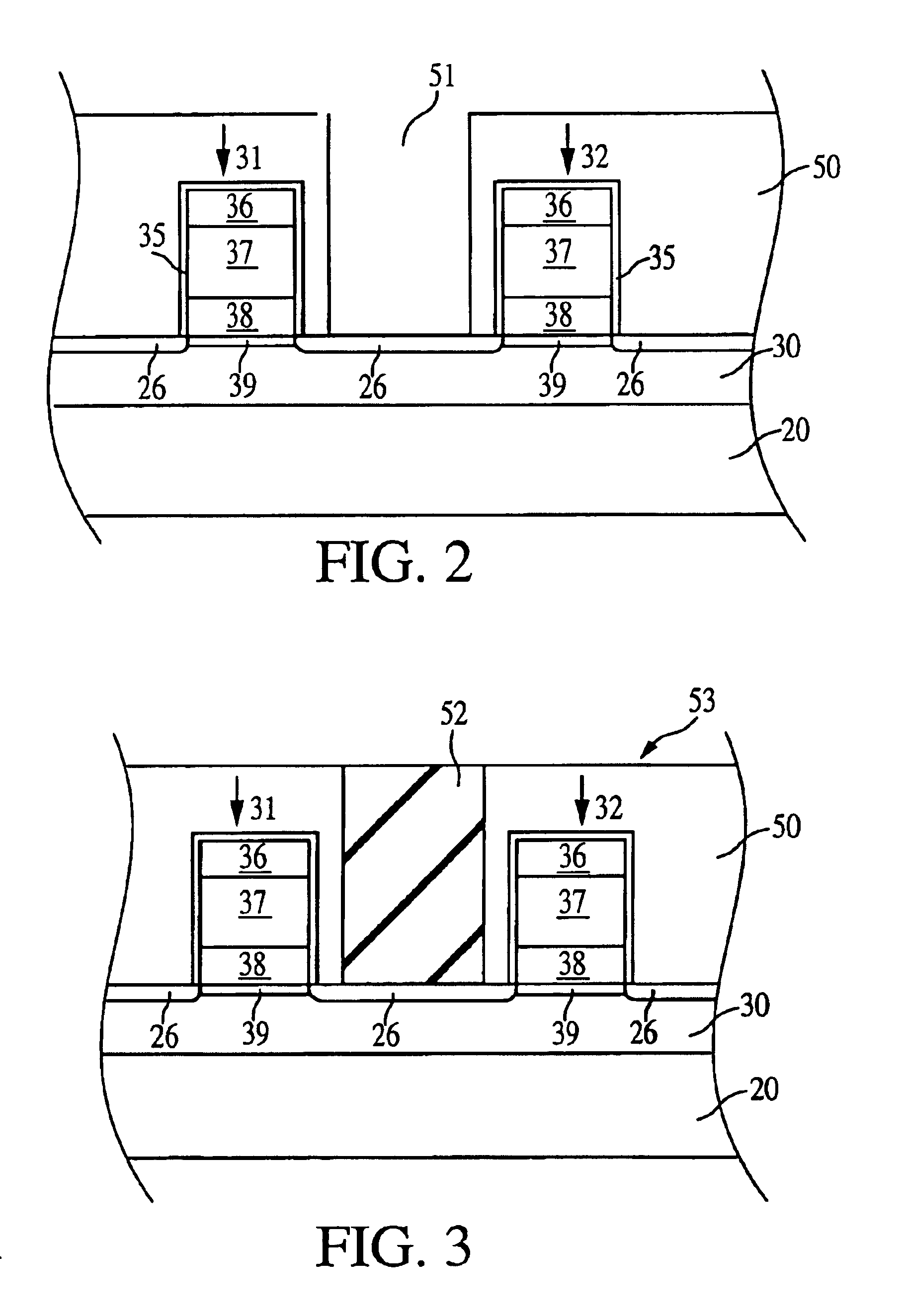

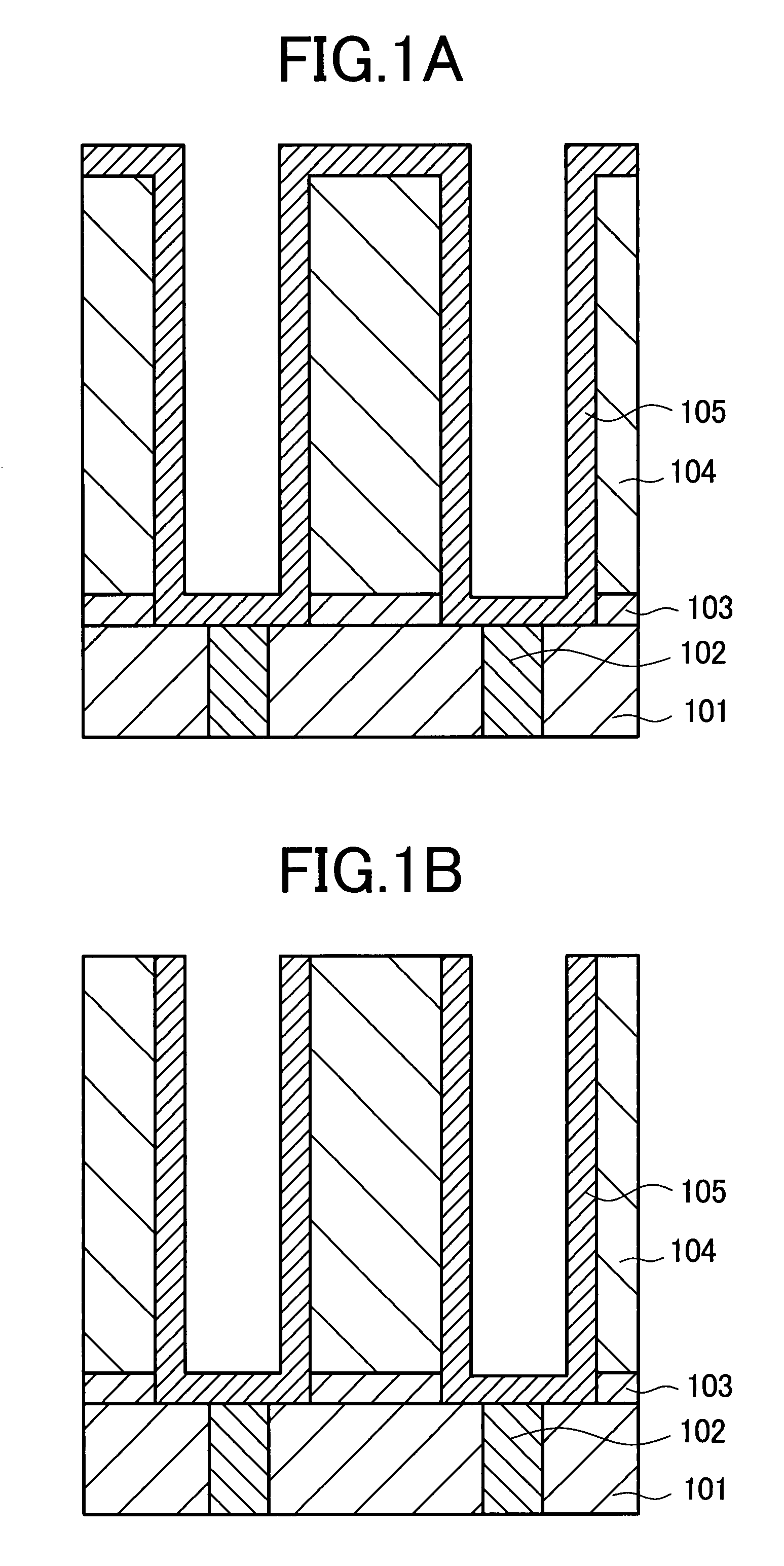

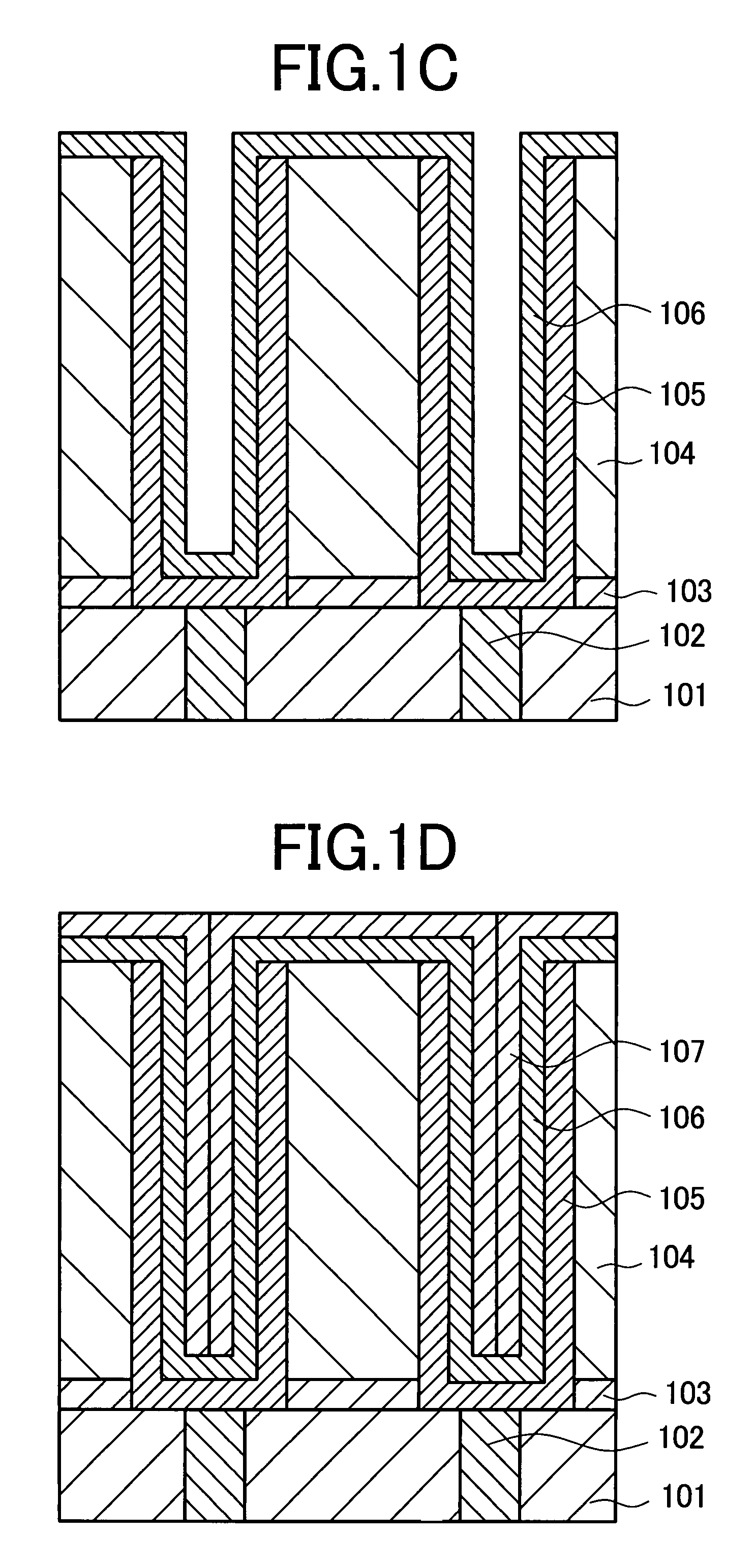

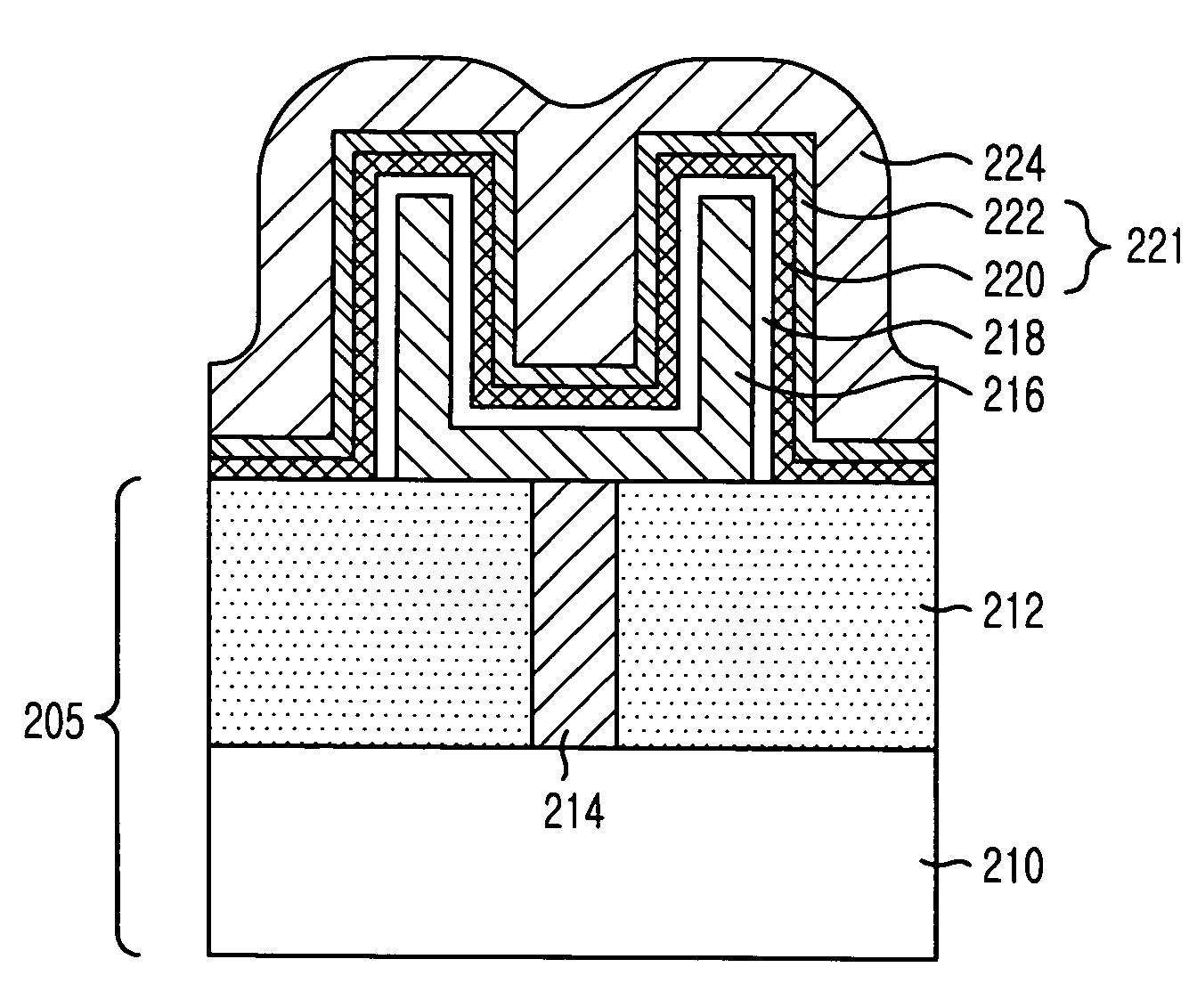

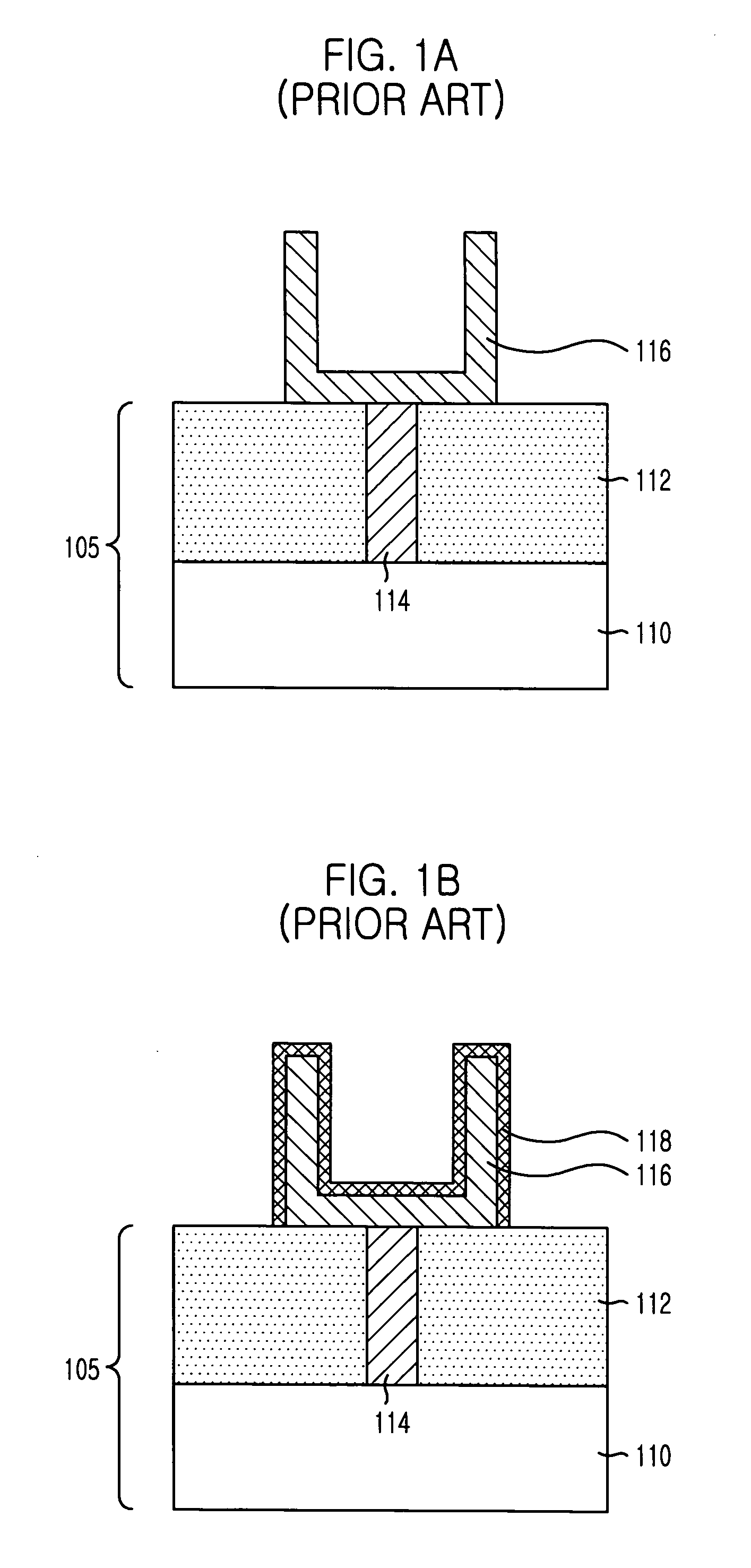

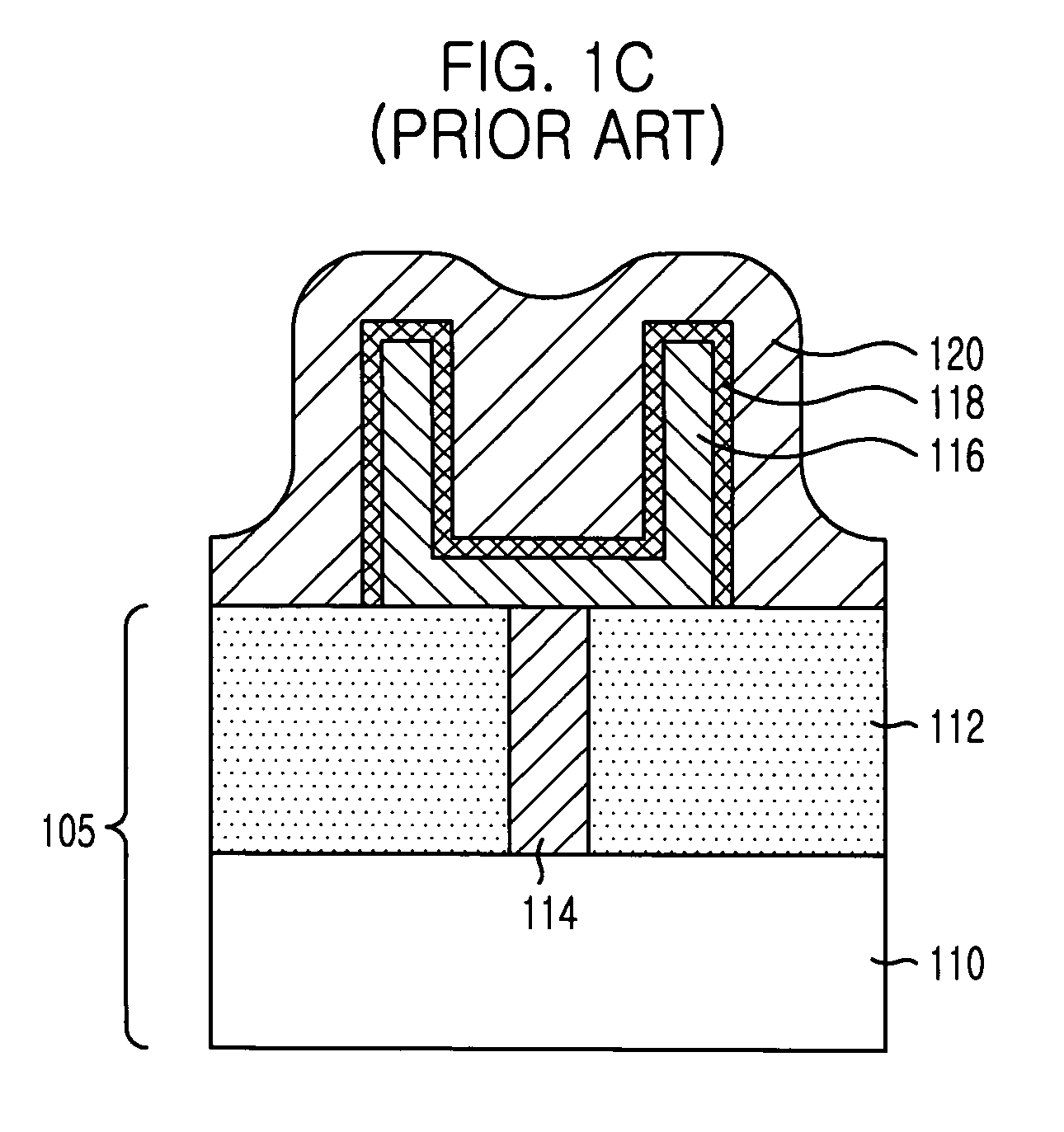

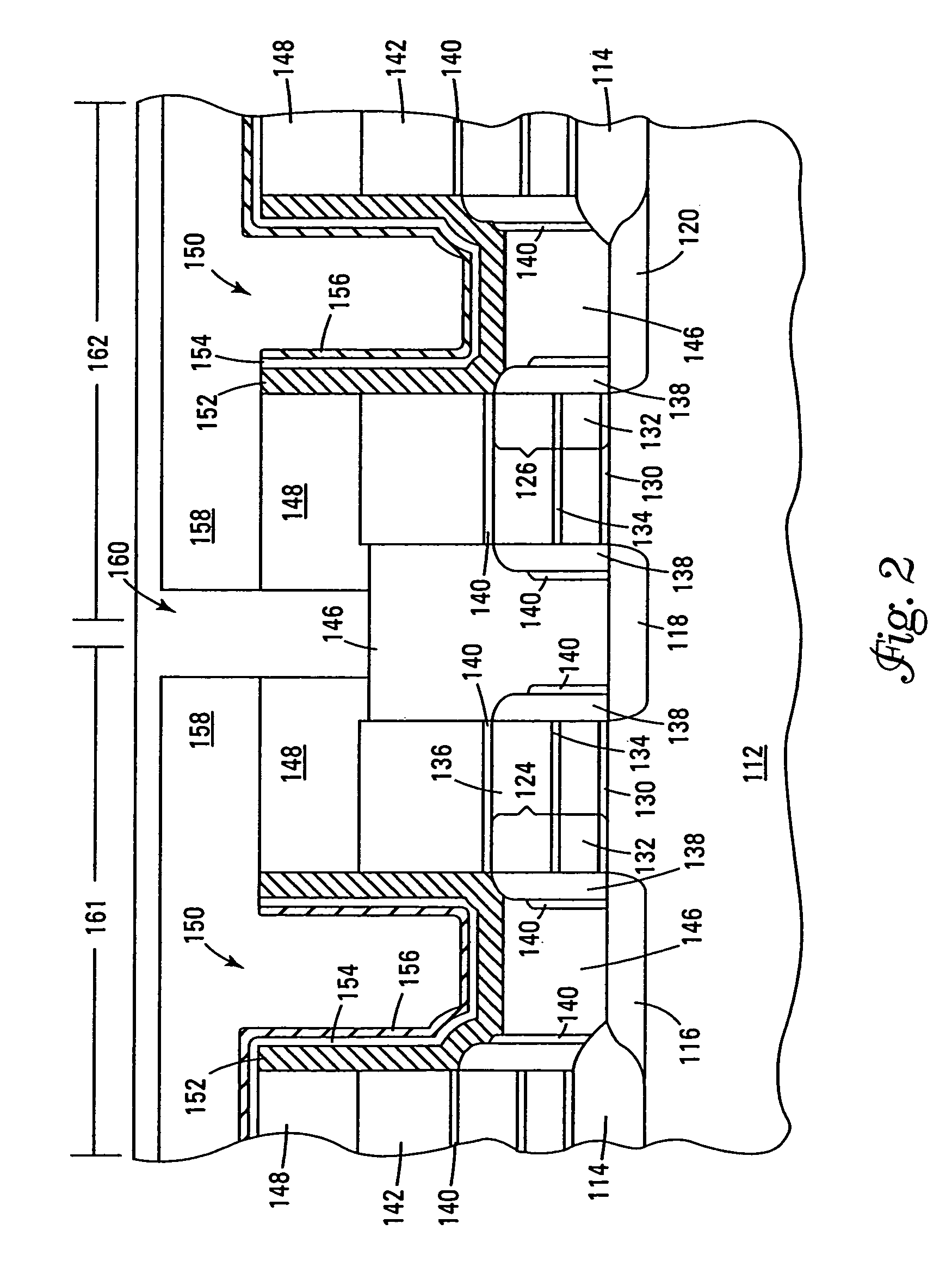

Method of forming DRAM capacitors with protected outside crown surface for more robust structures

A method for fabricating a high-density array of crown capacitors with increased capacitance while reducing process damage to the bottom electrodes is achieved. The process is particularly useful for crown capacitors for future DRAM circuits with minimum feature sizes of 0.18 micrometer or less. A conformal conducting layer is deposited over trenches in an interlevel dielectric (ILD) layer, and is polished back to form capacitor bottom electrodes. A novel photoresist mask and etching are then used to pattern the ILD layer to provide a protective interlevel dielectric structure between capacitors. The protective structures prevent damage to the bottom electrodes during subsequent processing. The etching also exposes portions of the outer surface of bottom electrodes for increased capacitance (>50%). In a first embodiment the ILD structure is formed between pairs of adjacent bottom electrodes, and in a second embodiment the ILD structure is formed between four adjacent bottom electrodes.

Owner:TAIWAN SEMICON MFG CO LTD

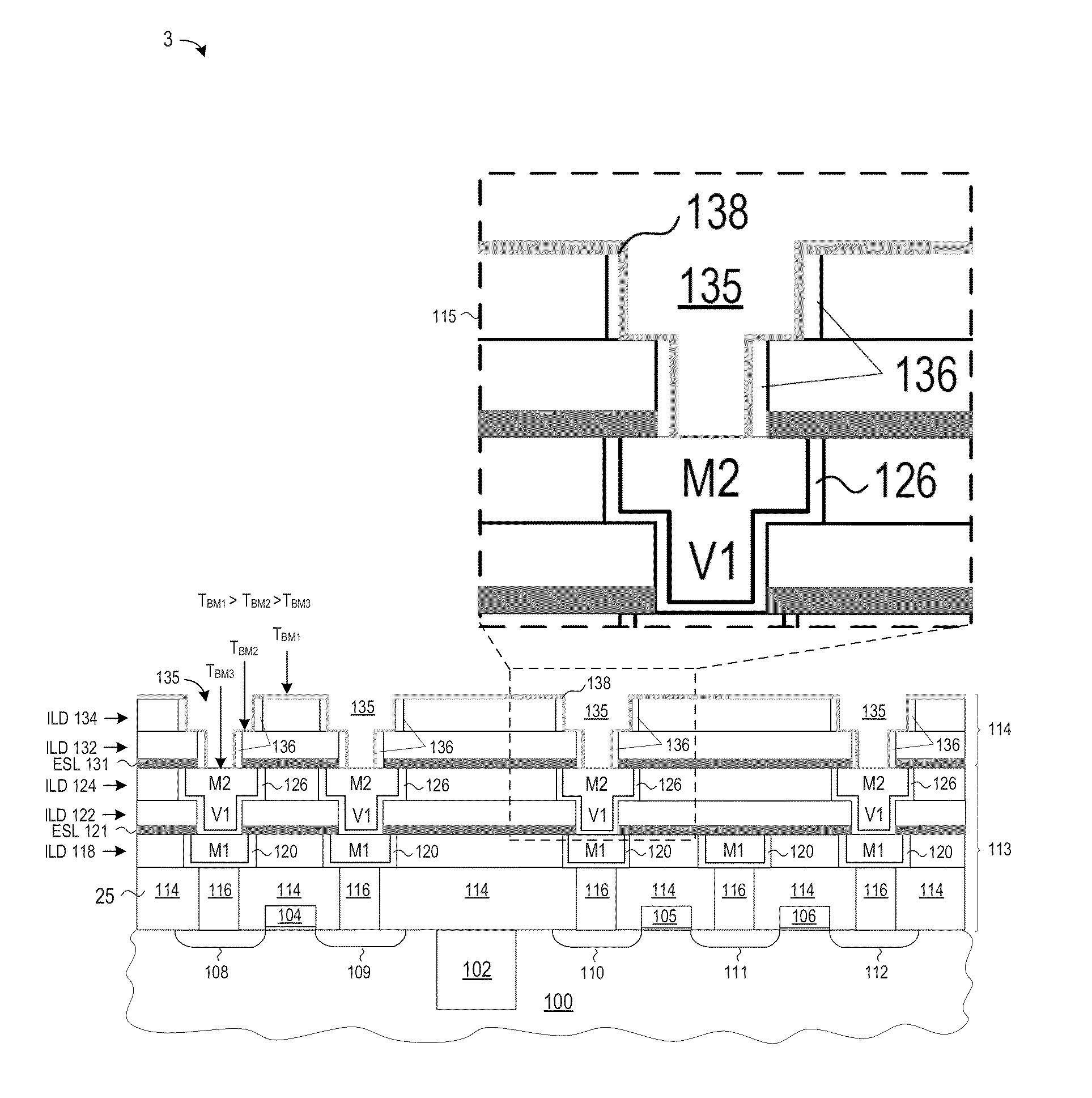

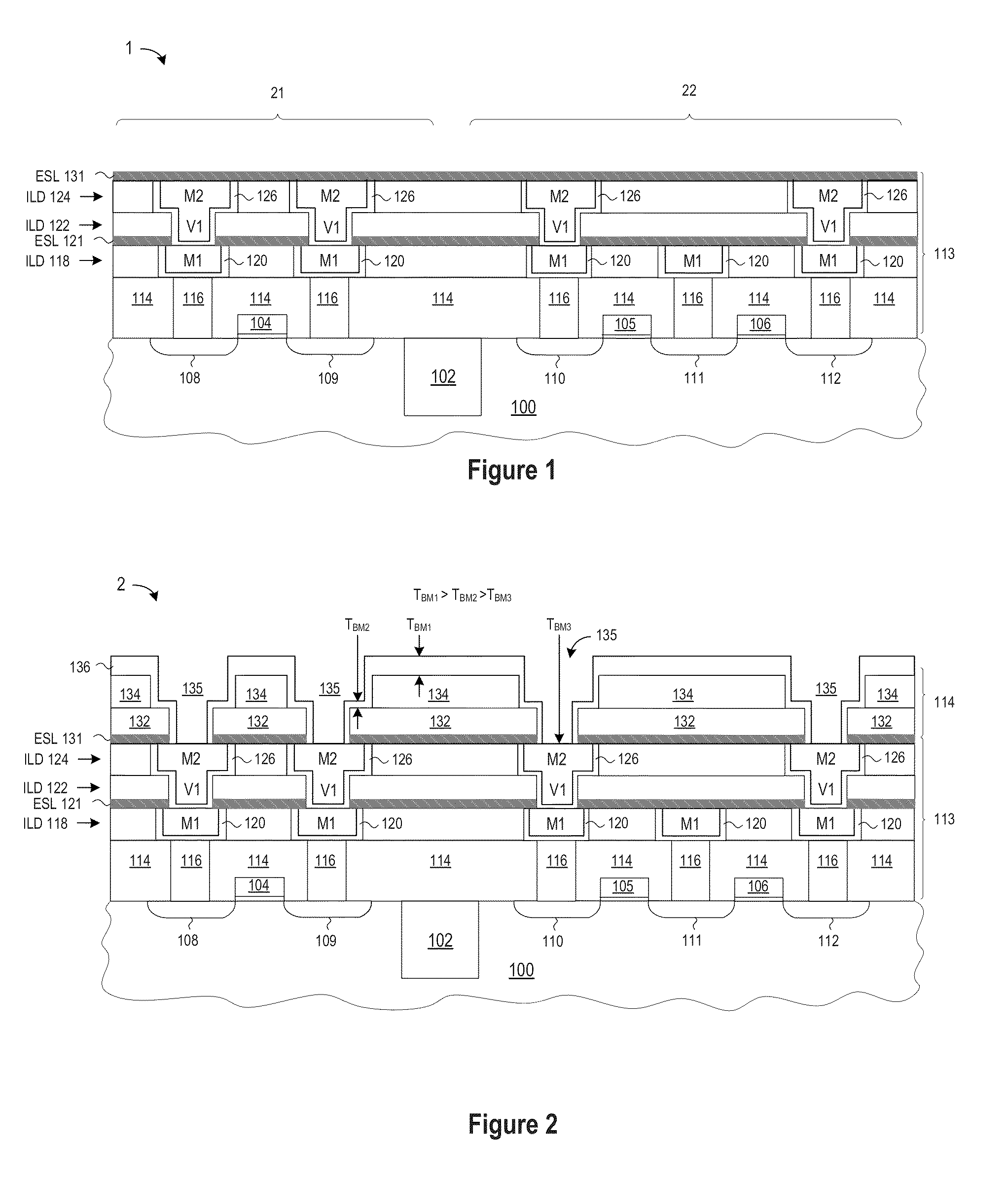

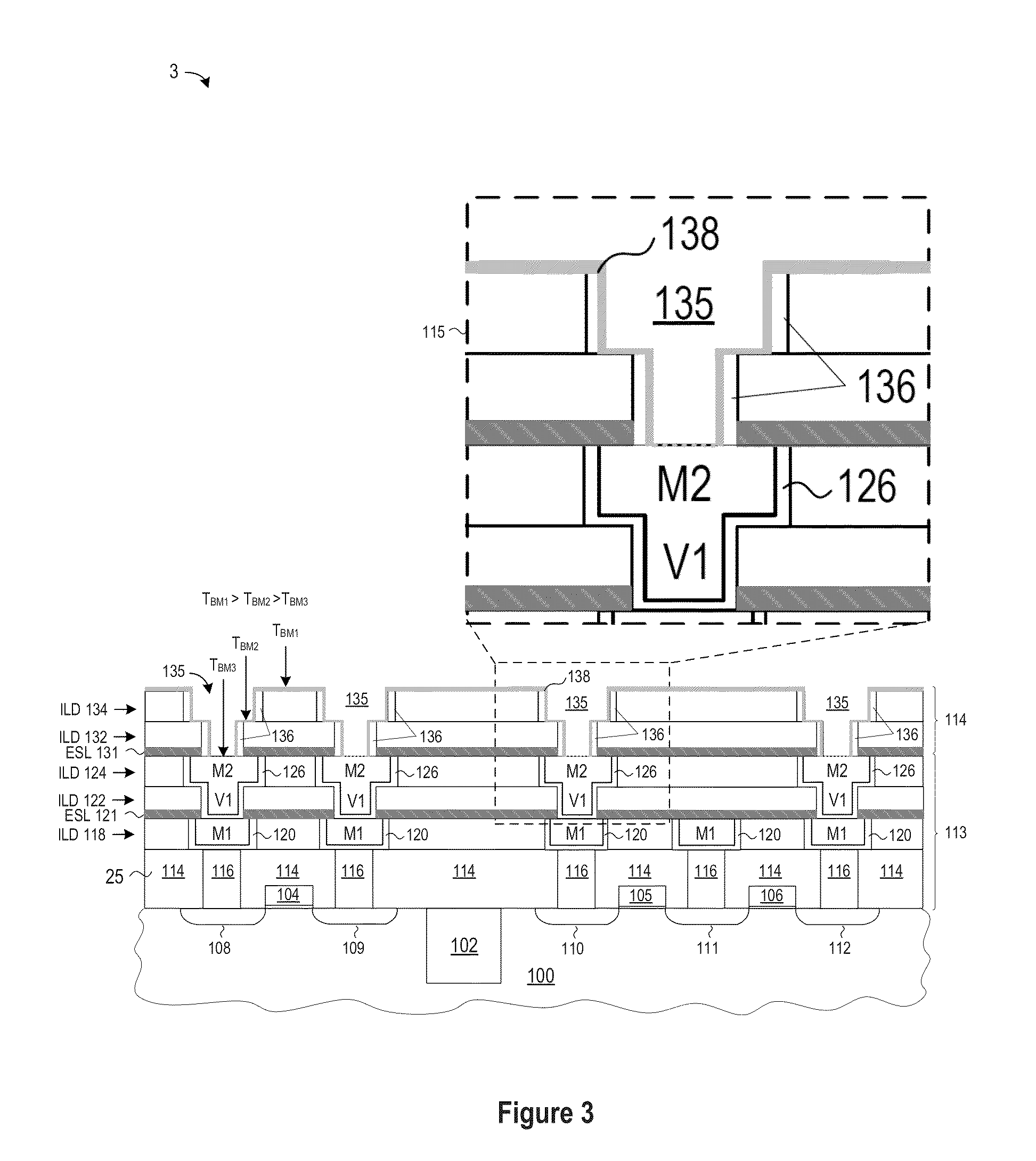

Cost Effective Method of Forming Embedded DRAM Capacitor

ActiveUS20150102461A1TransistorSemiconductor/solid-state device detailsCapacitanceCopper interconnect

A high capacitance embedded metal interconnect capacitor and associated fabrication processes are disclosed for using a directional barrier metal formation sequence in a dual damascene copper process to form multi-layer stacked copper interconnect structure having reduced barrier metal layer formation at the bottom of each via hole so that the multi-layer stacked copper interconnect structure may be readily removed and replaced with high capacitance MIM capacitor layers.

Owner:MOSAID TECH

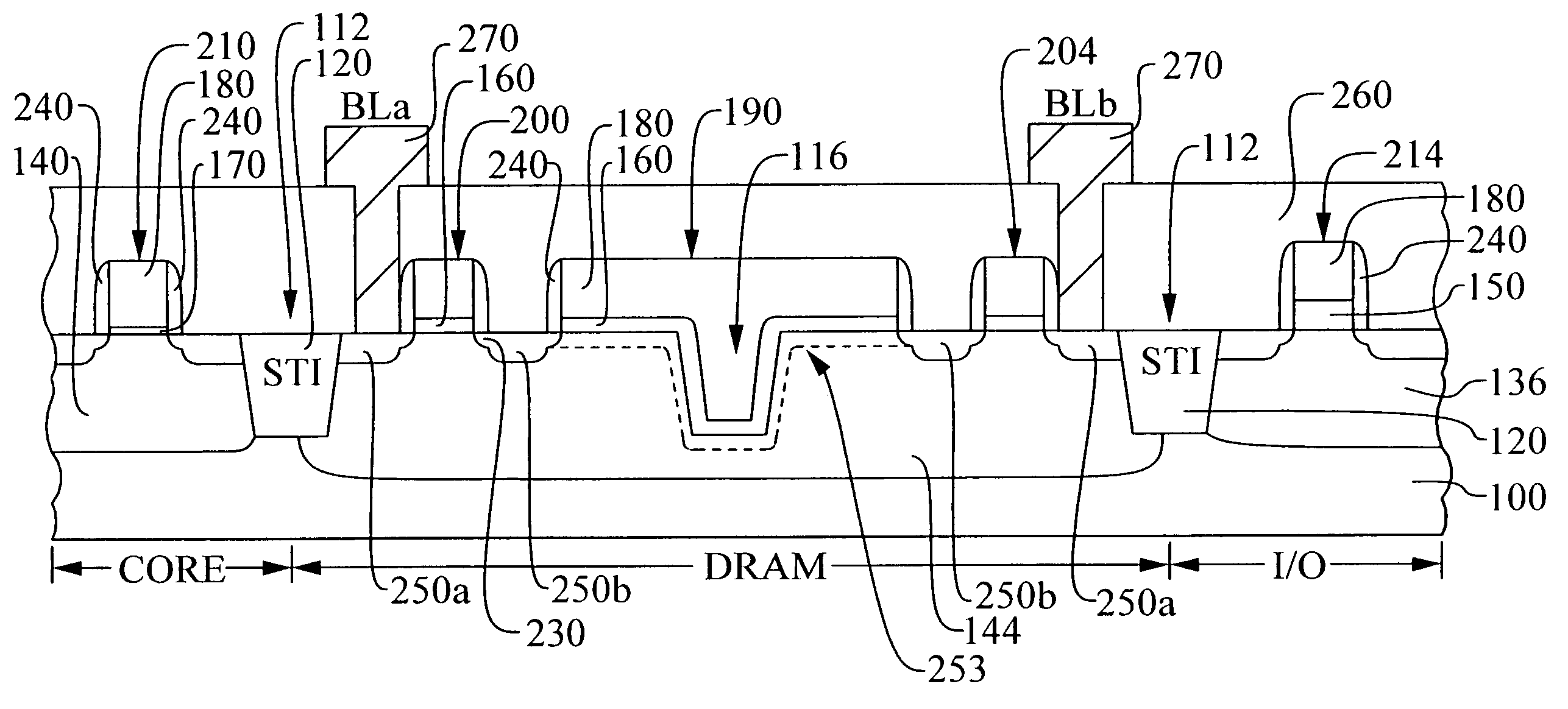

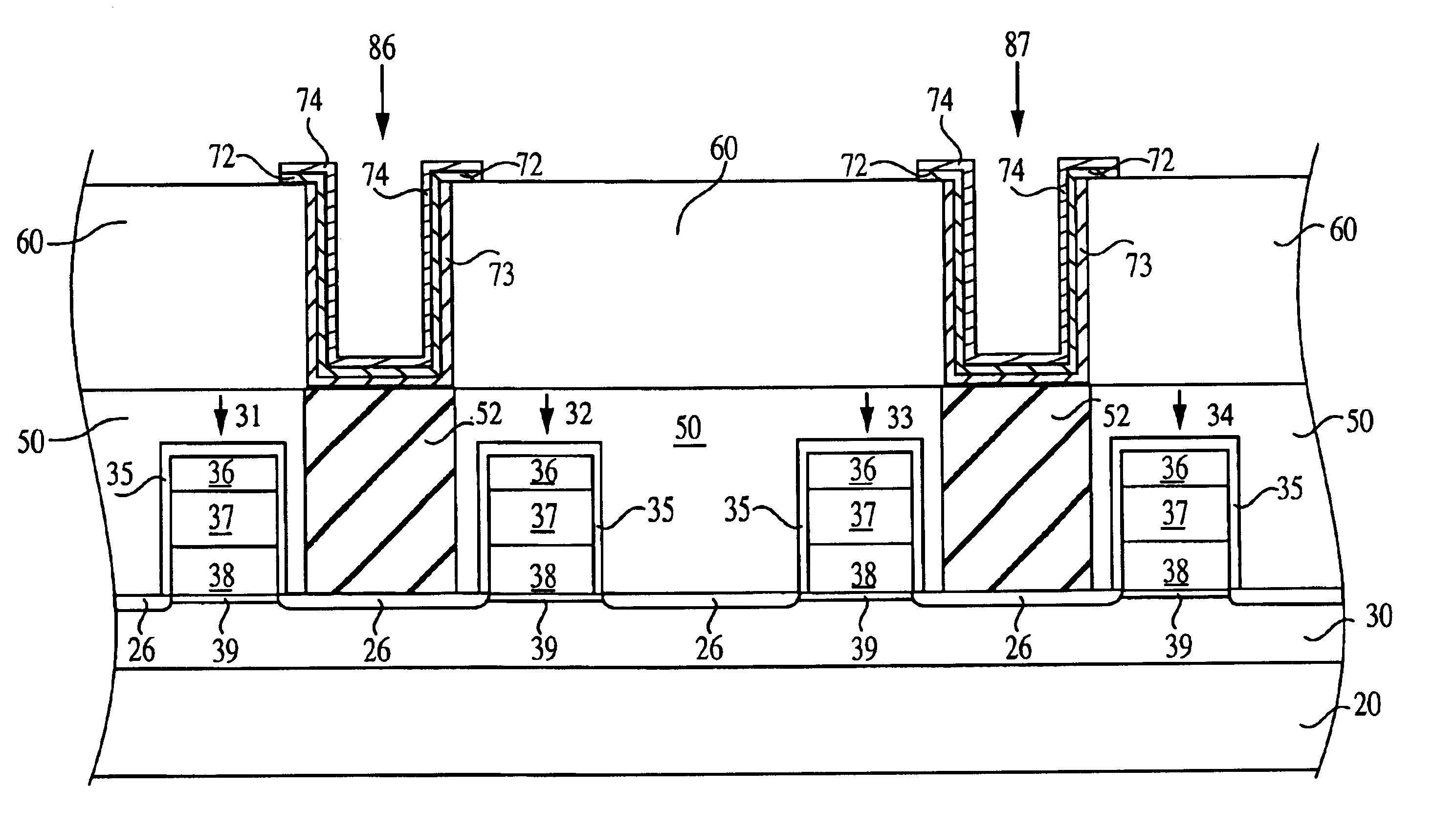

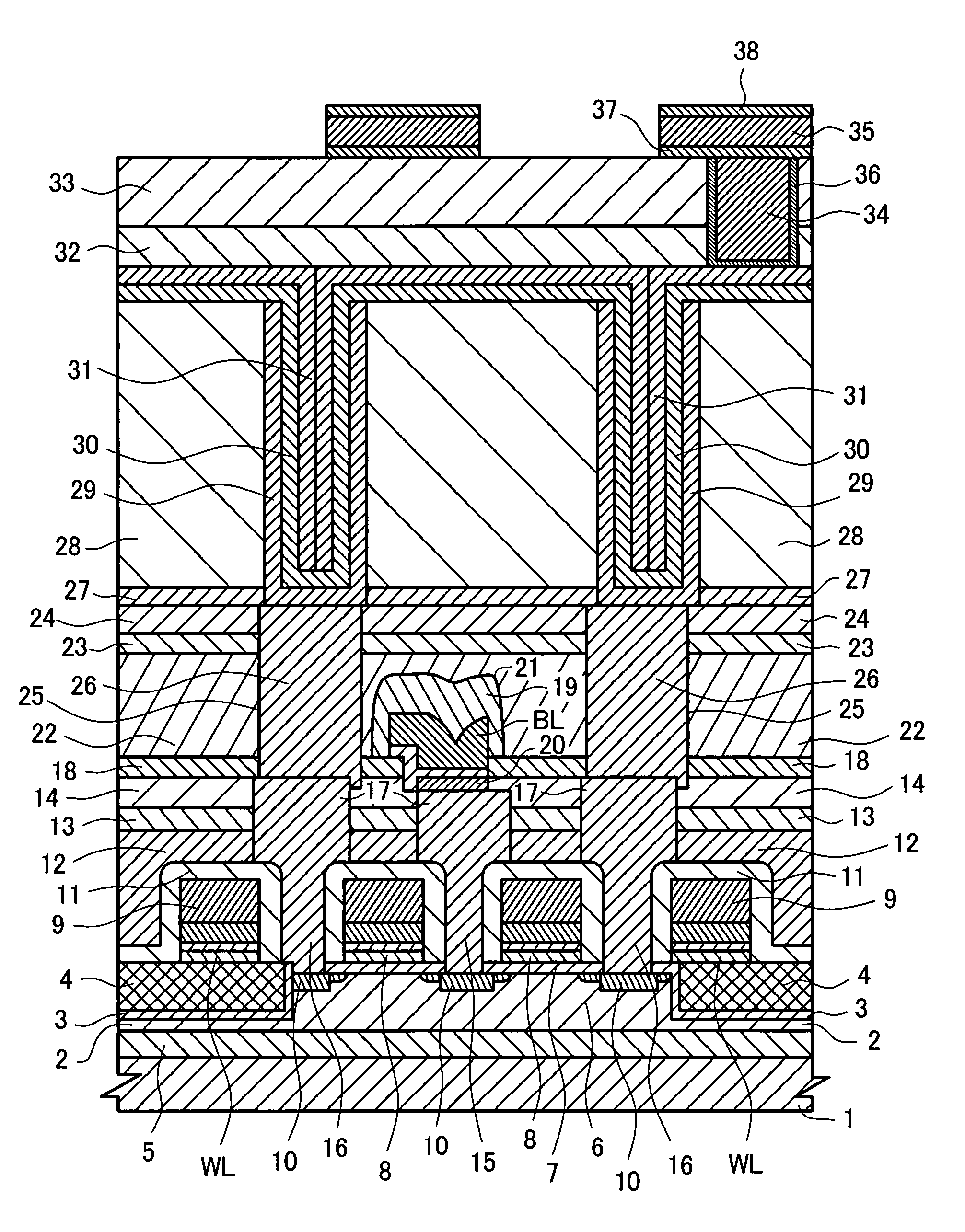

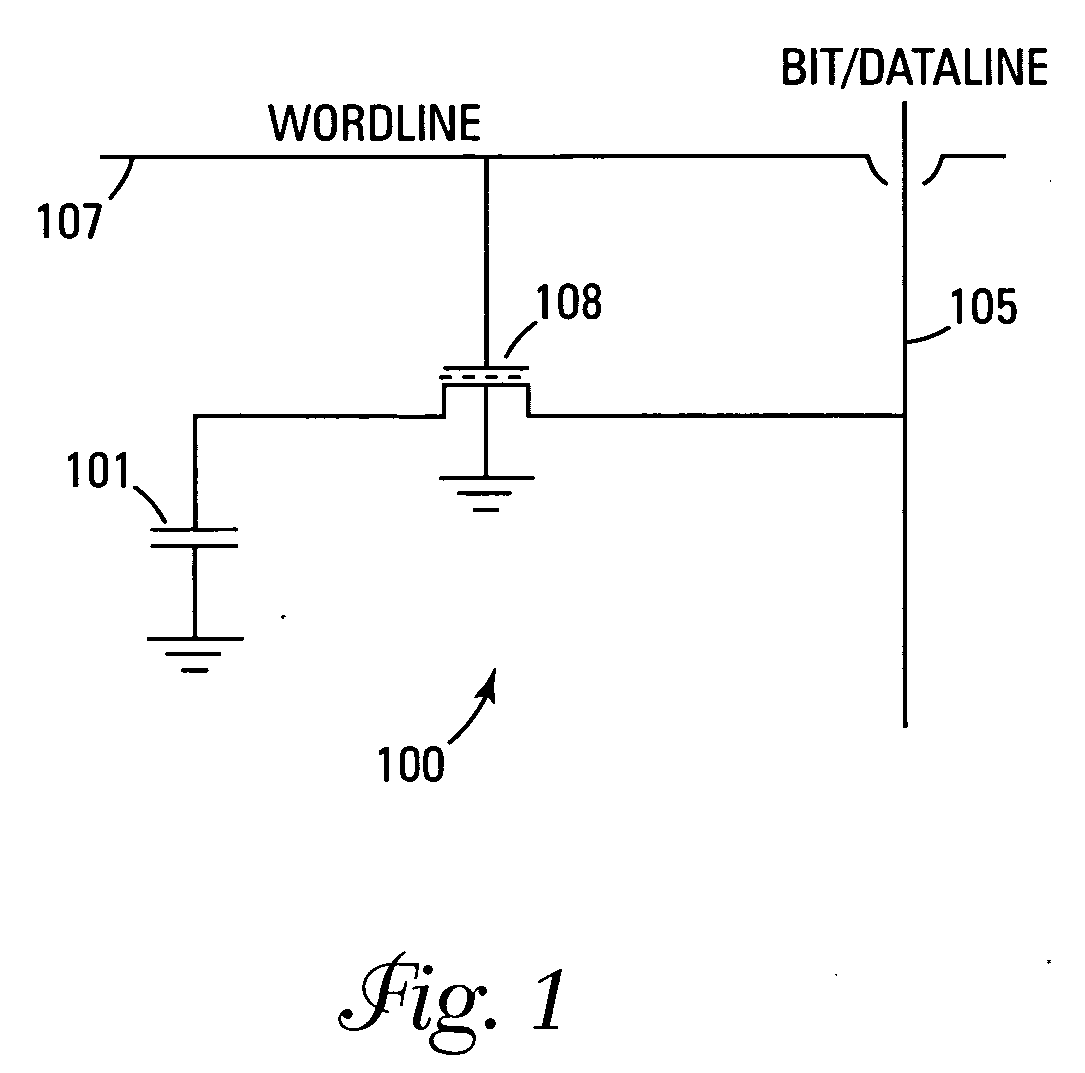

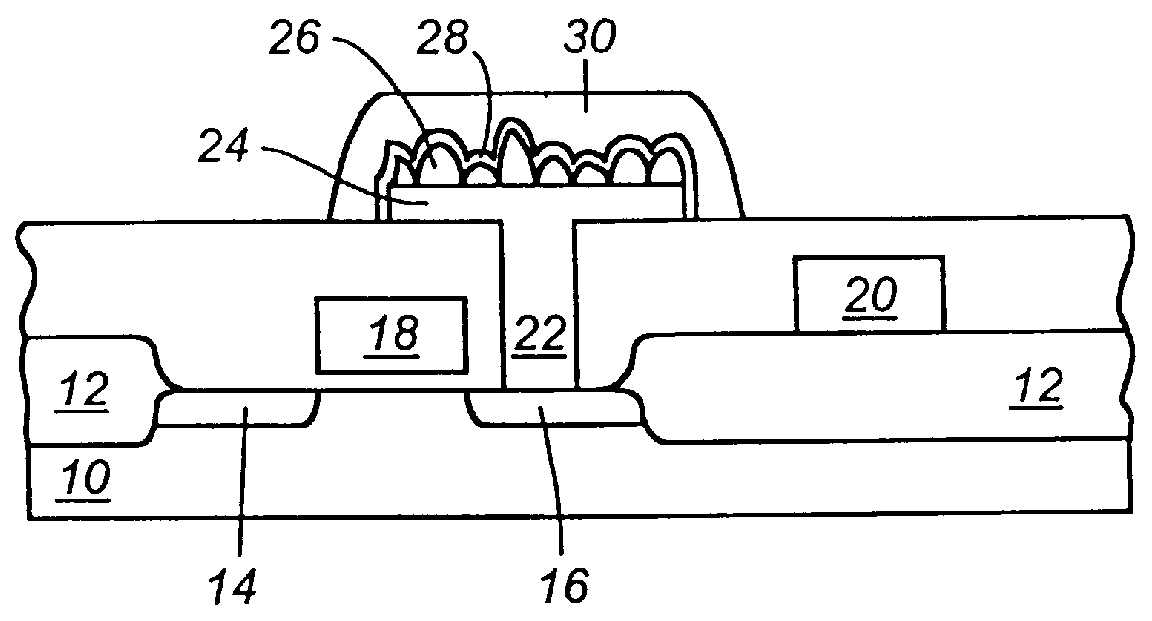

Embedded dual-port DRAM process

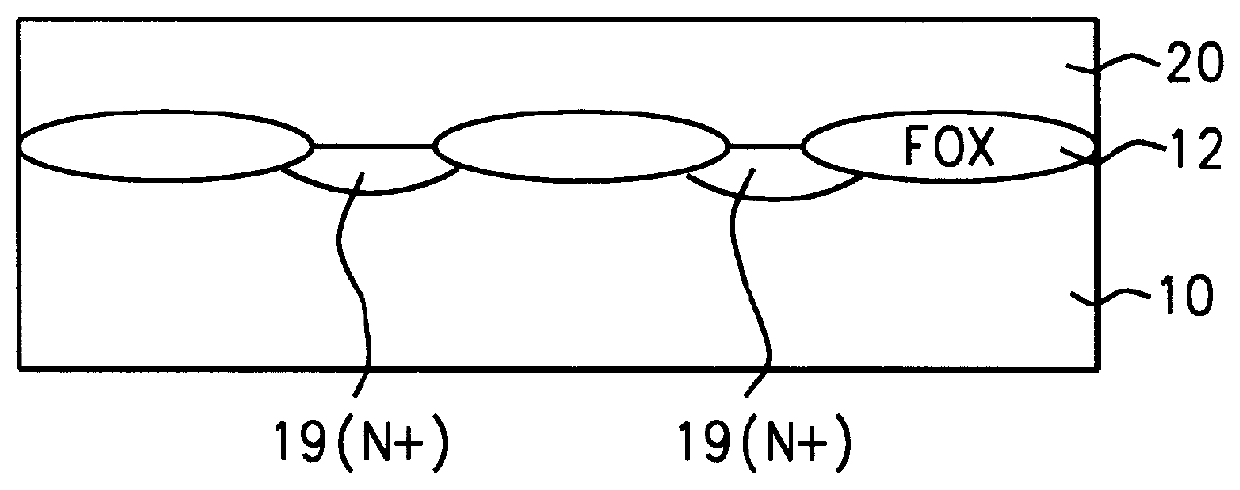

InactiveUS7091543B2Minimal cell areaIncrease speedTransistorSolid-state devicesIon implantationTransistor

A new method to form DRAM cells in an integrated circuit device is achieved. The method comprises providing a substrate. A plurality of STI regions is formed in the substrate. The STI regions comprise trenches in the substrate. The trenches are filled with a first dielectric layer. All of the first dielectric layer is etched away from a first group of the STI regions to form open trenches while leaving the first dielectric layer in a second group of the STI regions. A second dielectric layer is formed overlying the substrate and lining the open trenches. A conductive layer is deposited overlying the second dielectric layer and completely filling the open trenches. The conductive layer is patterned to define DRAM transistor gates and to define DRAM capacitor top plates. Thereafter, ions are implanted into the substrate to form source and drain regions for the transistors.

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor memory device

ActiveUS20070228427A1Increasing oxygen coordination numberHigh dielectric constantTransistorSolid-state devicesDielectricEngineering

HfO2 films and ZrO2 films are currently being developed for use as capacitor dielectric films in 85 nm technology node DRAM. However, these films will be difficult to use in 65 nm technology node or later DRAM, since they have a relative dielectric constant of only 20-25. The dielectric constant of such films may be increased by stabilizing their cubic phase. However, this results in an increase in the leakage current along the crystal grain boundaries, which makes it difficult to use these films as capacitor dielectric films. To overcome this problem, the present invention dopes a base material of HfO2 or ZrO2 with an oxide of an element having a large ion radius, such as Y or La, to increase the oxygen coordination number of the base material and thereby increase its relative dielectric constant to 30 or higher even when the base material is in its amorphous state. Thus, the present invention provides dielectric films that can be used to form DRAM capacitors that meet the 65 nm technology node or later.

Owner:HITACHI LTD

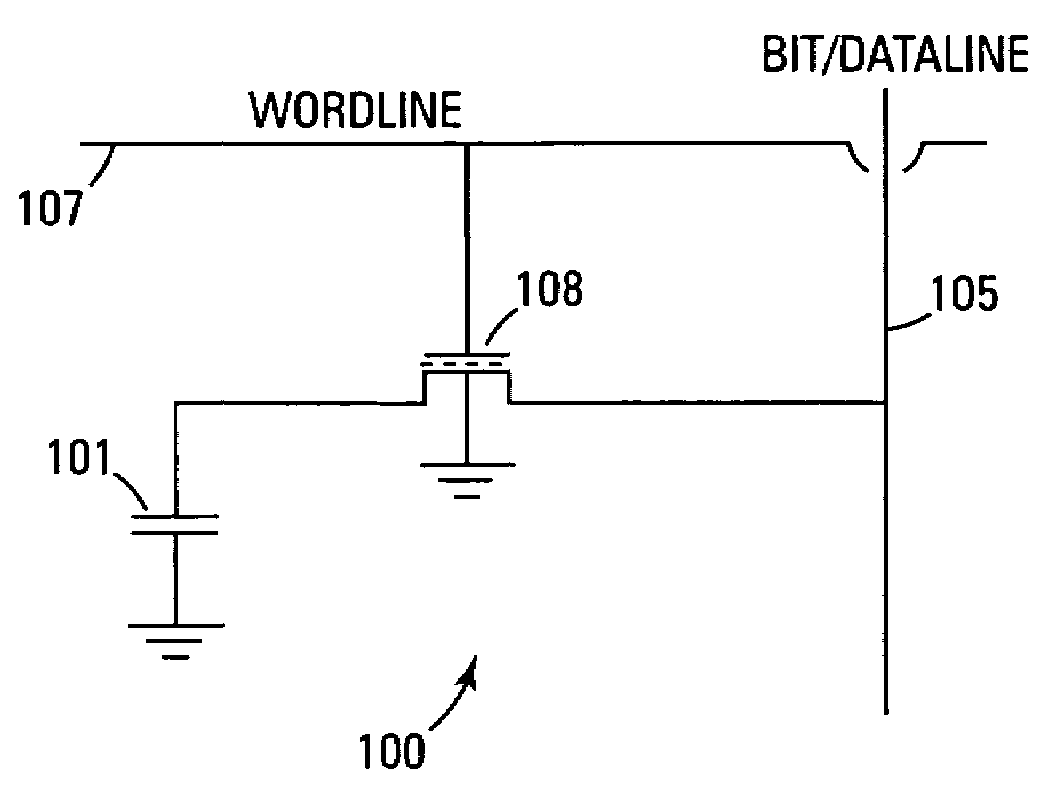

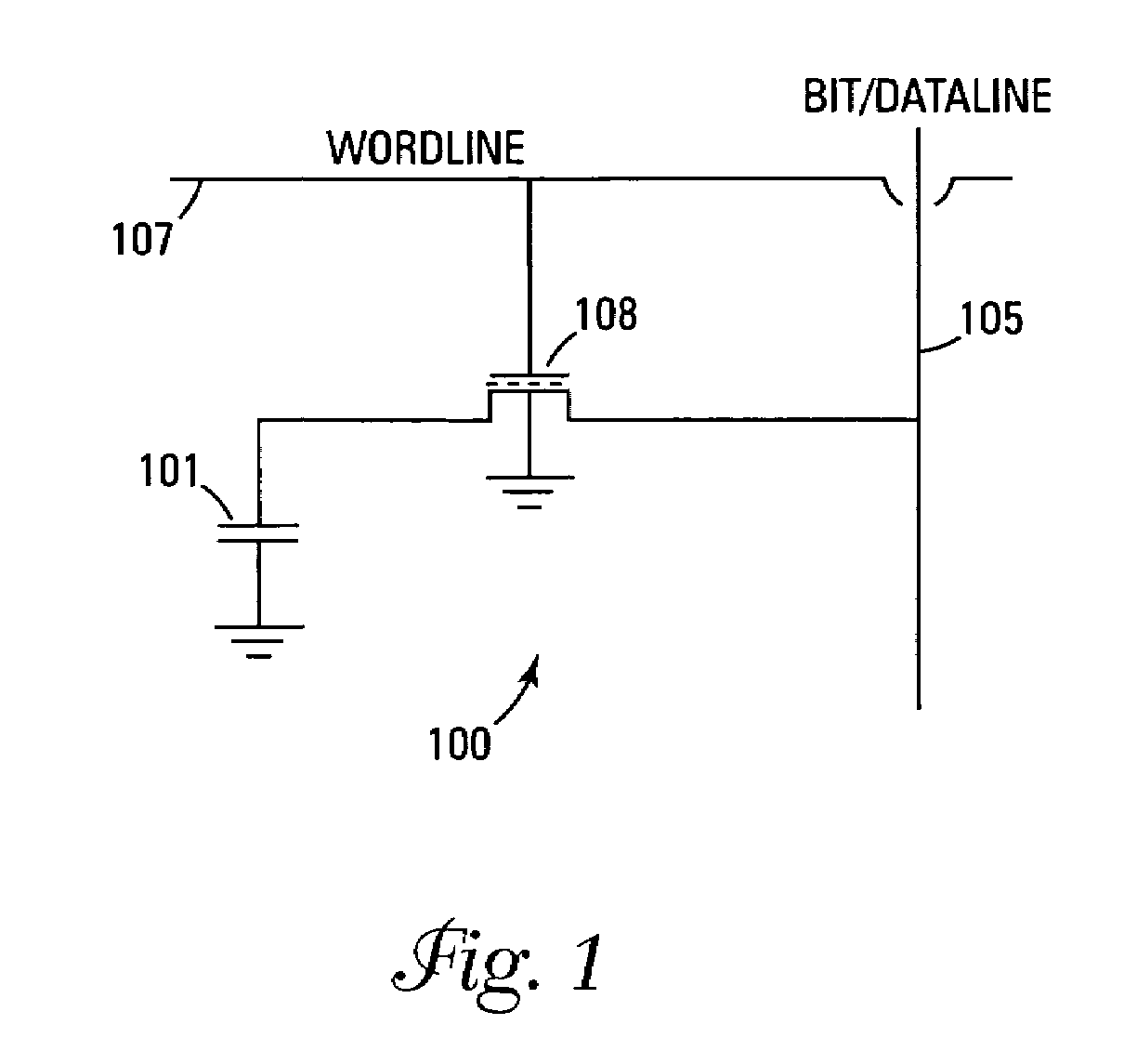

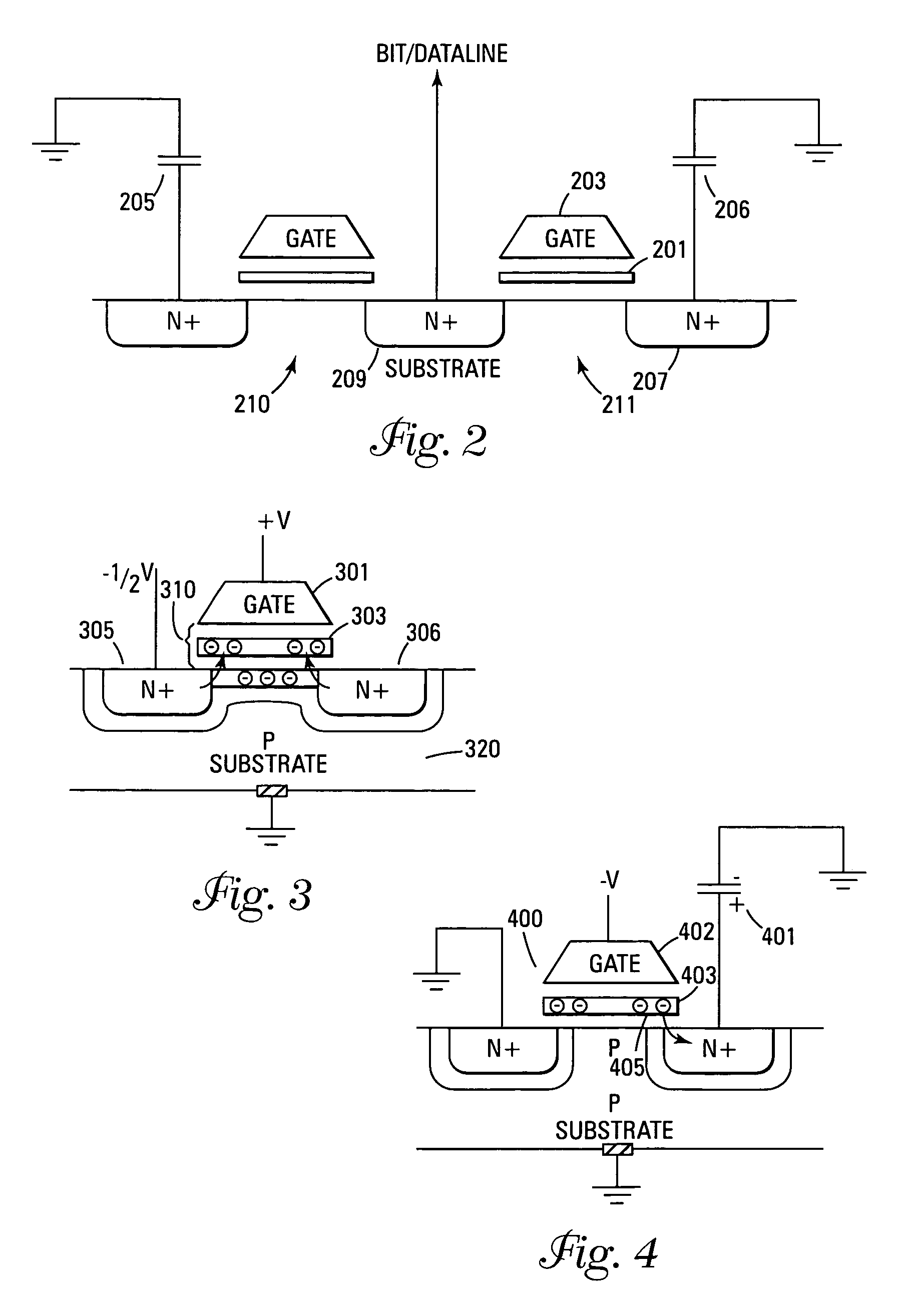

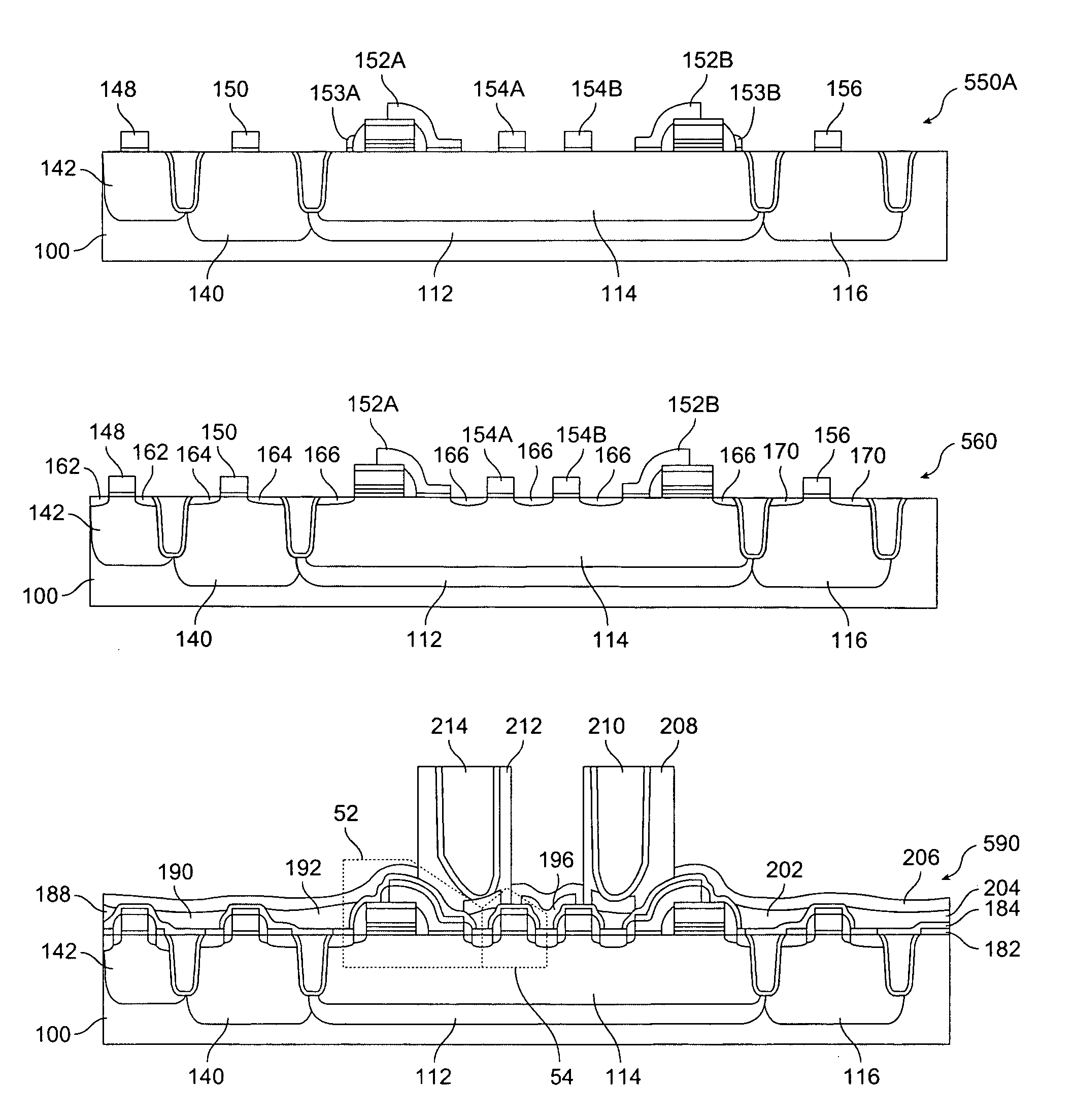

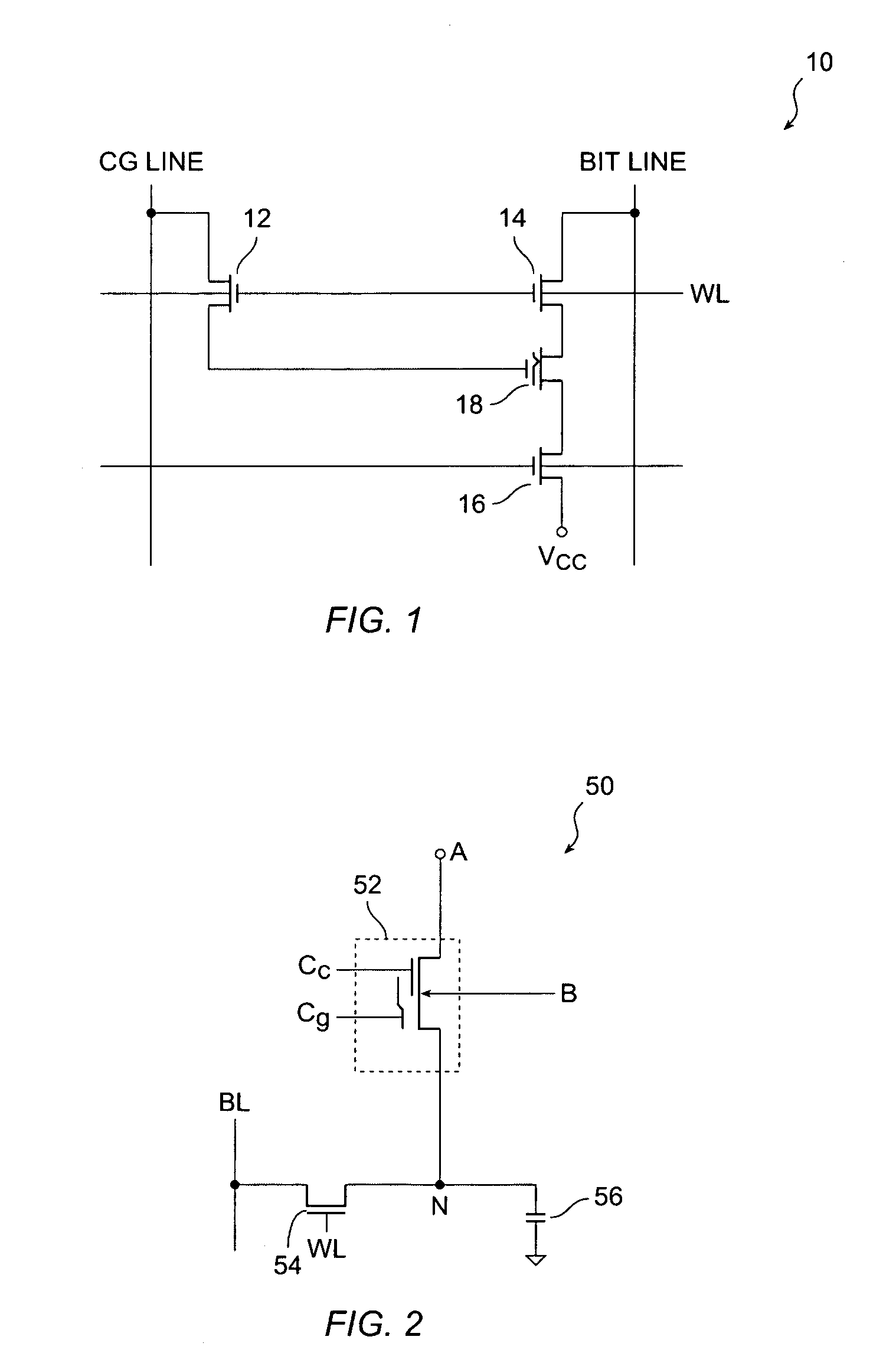

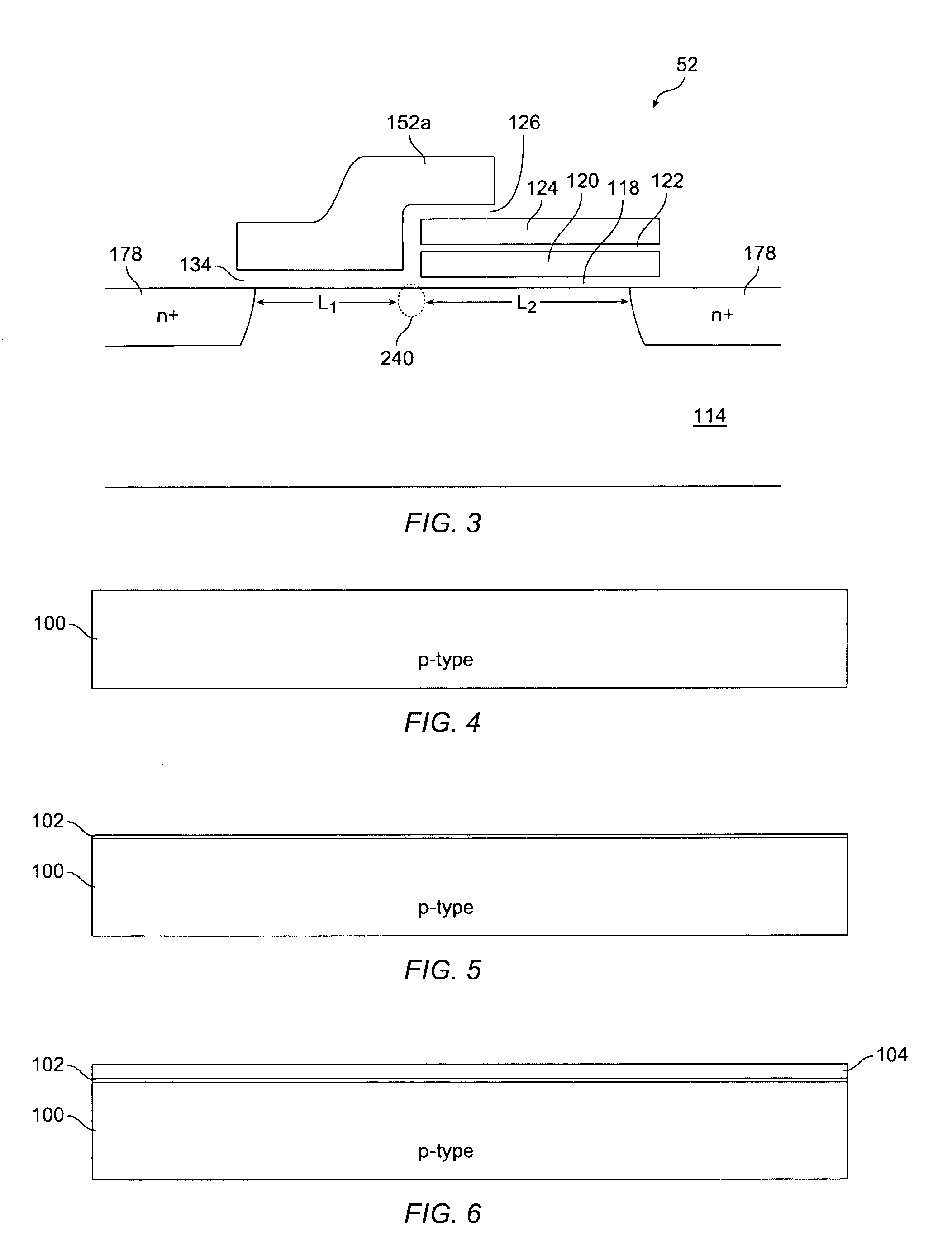

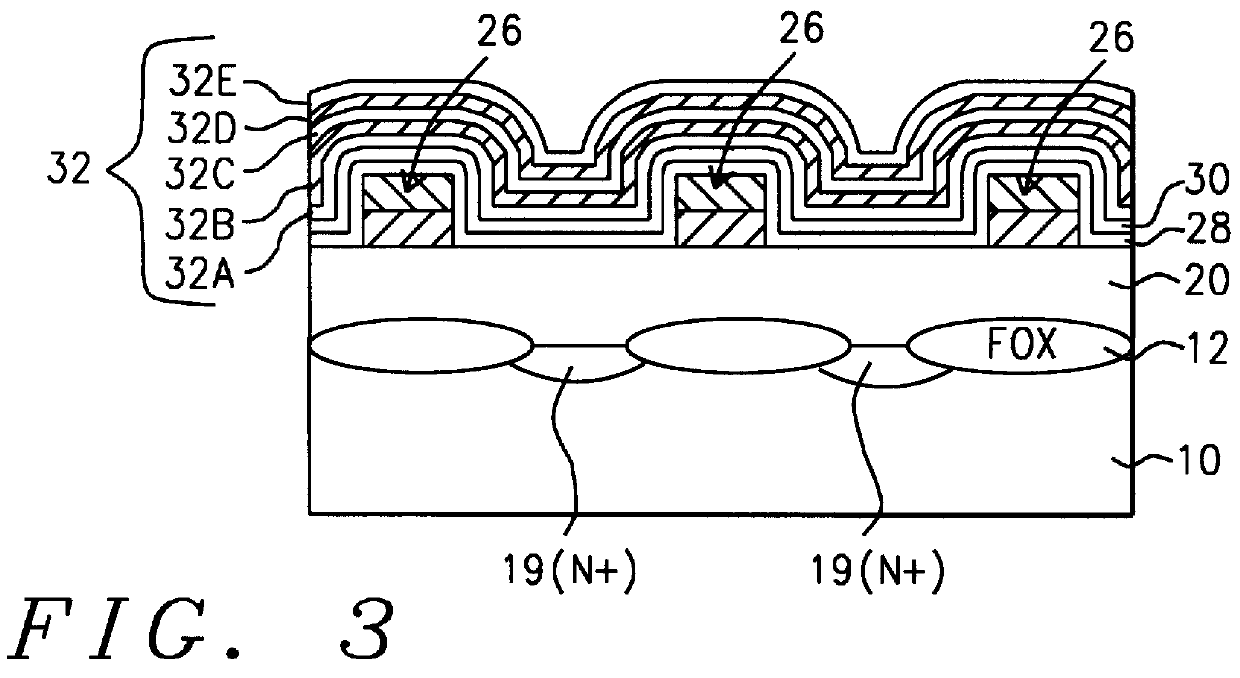

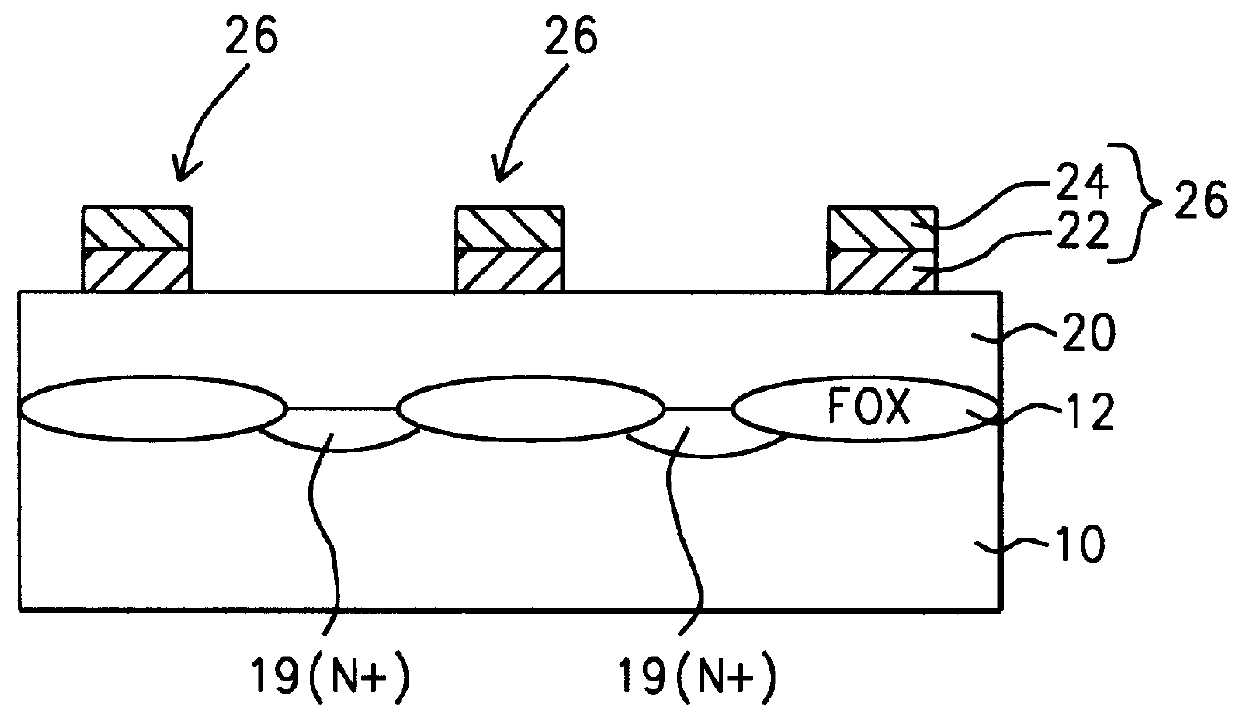

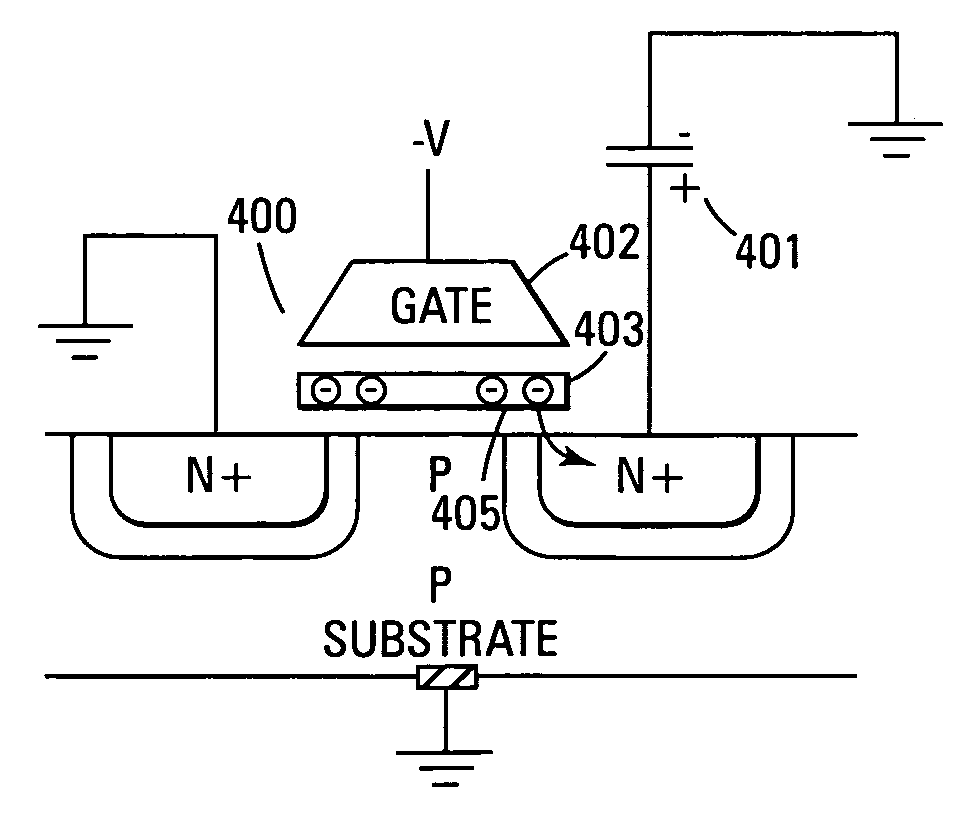

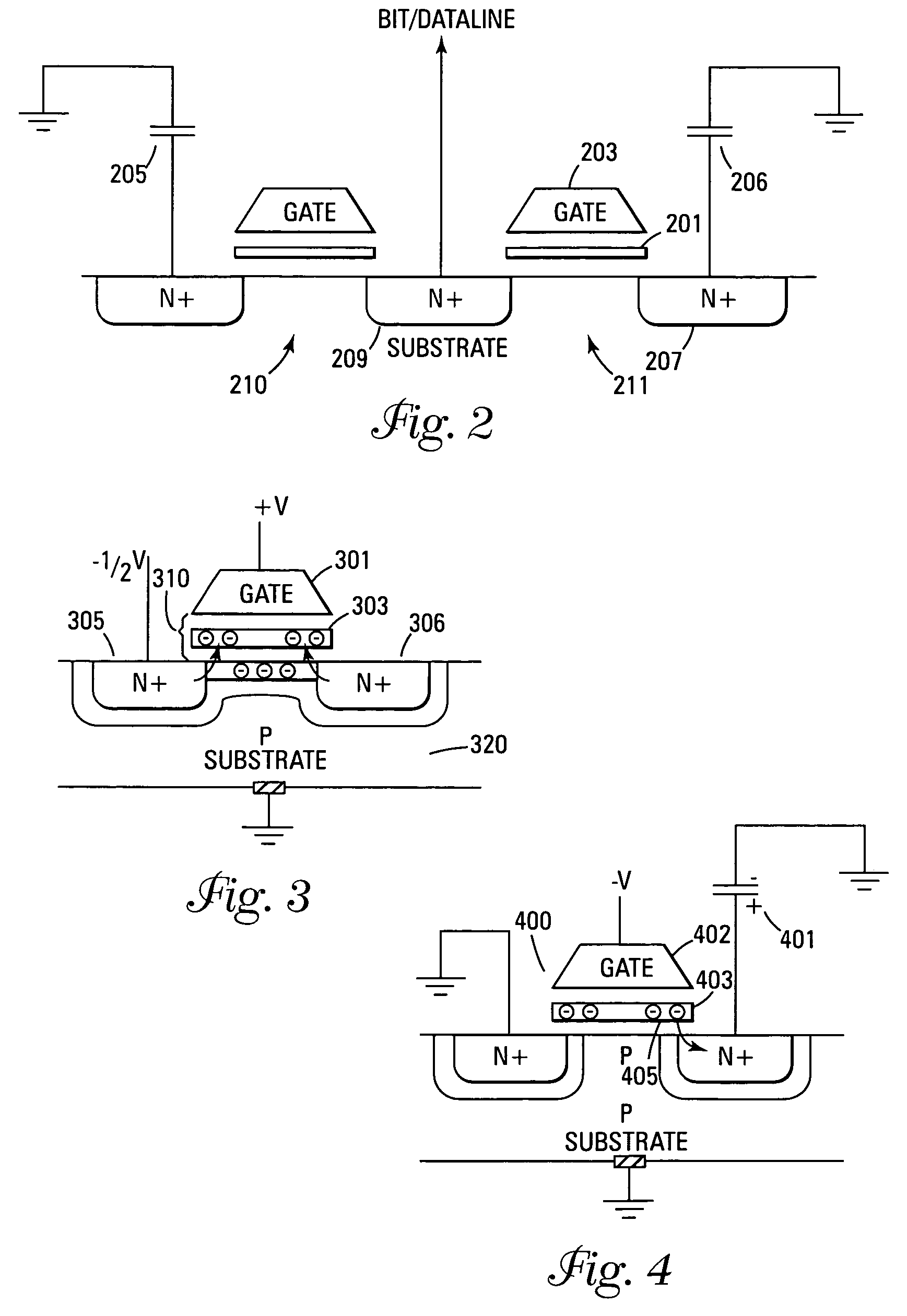

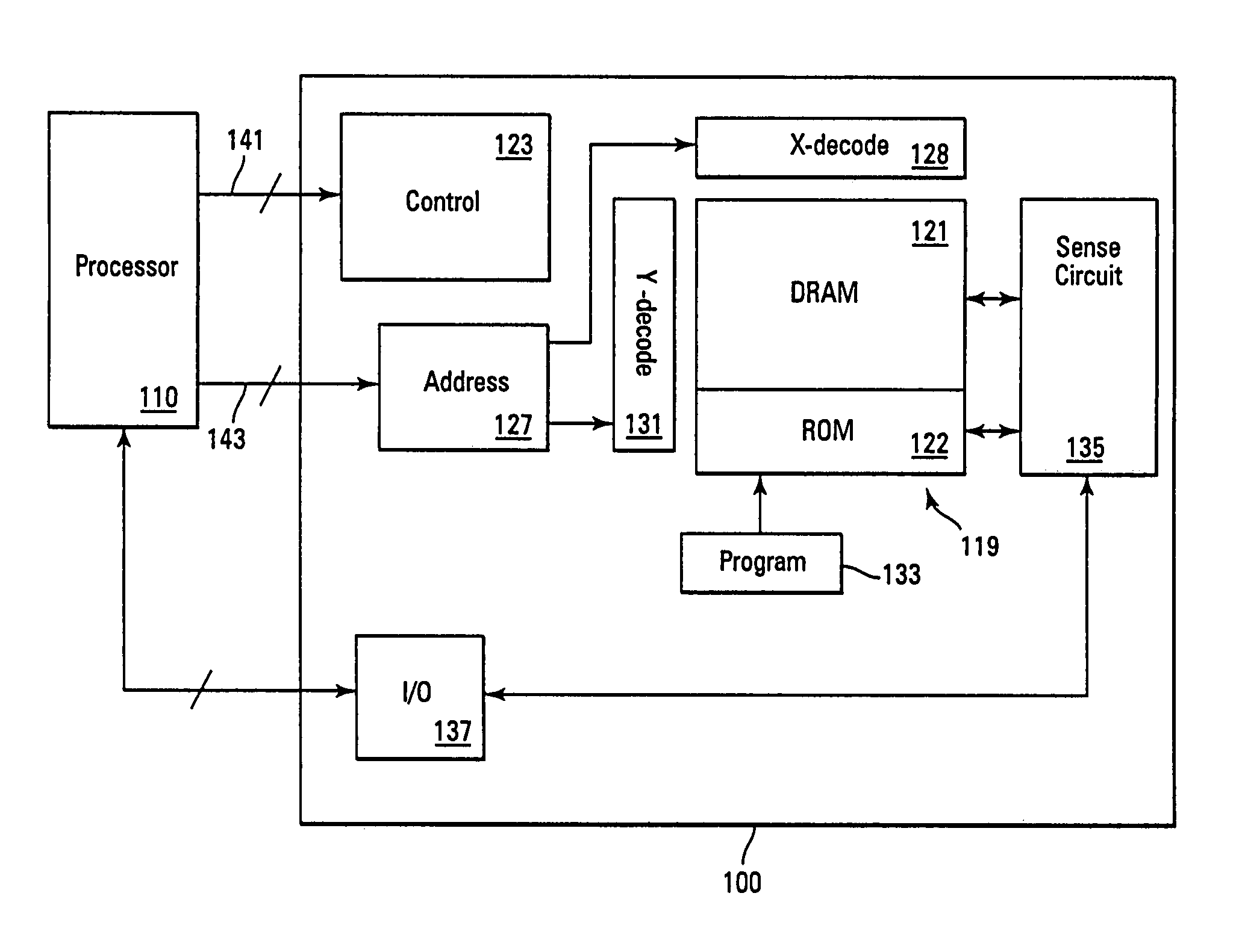

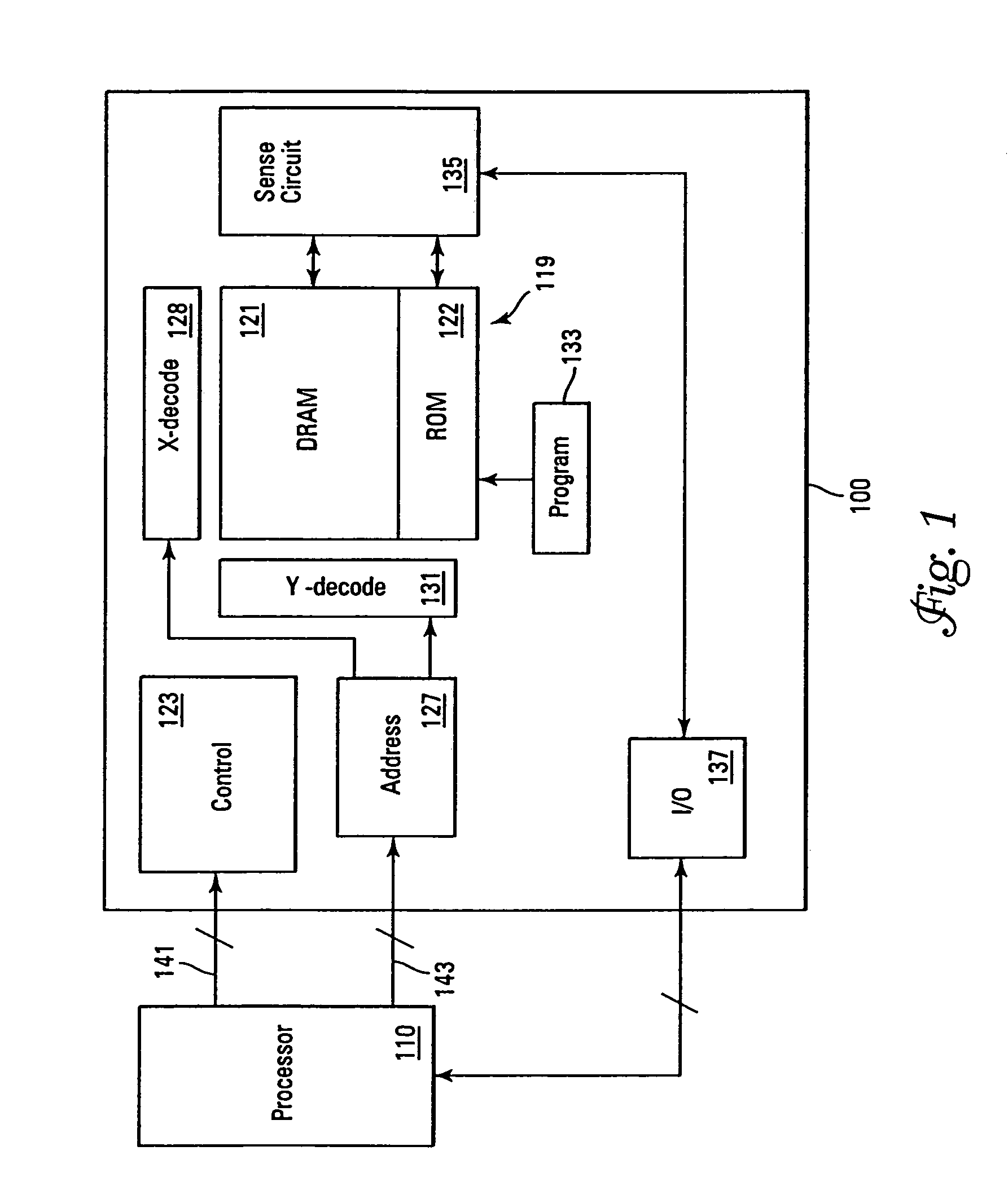

NROM flash memory cell with integrated DRAM

InactiveUS6952366B2Digital storageSpecial data processing applicationsStatic random-access memoryMultiple modes

A memory device that is comprised of a dynamic random access memory (DRAM) capacitor and a nitride read only memory (NROM) transistor. The memory device provides multiple modes of operation including a DRAM mode using the capacitor and a non-volatile random access memory mode using the NROM transistor. The device is comprised of two source / drain regions between which a gate insulator layer is formed. A control gate, coupled to a word line, is formed on top of the gate insulator. The DRAM capacitor is coupled to one of the source / drain regions while the second source / drain region is coupled to a bit line that is eventually coupled to a sense amplifier for reading the state or states of the memory device.

Owner:MICRON TECH INC

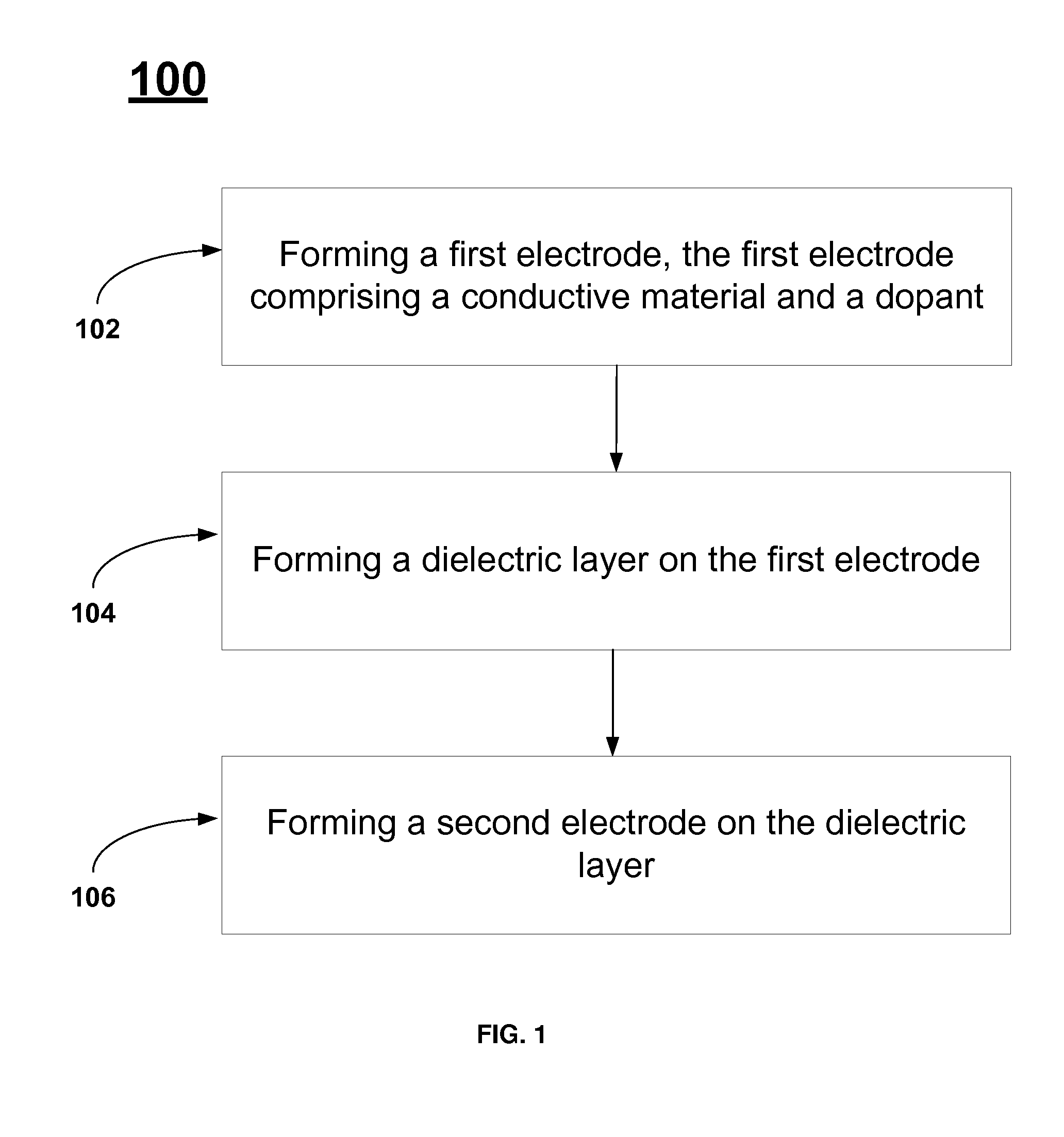

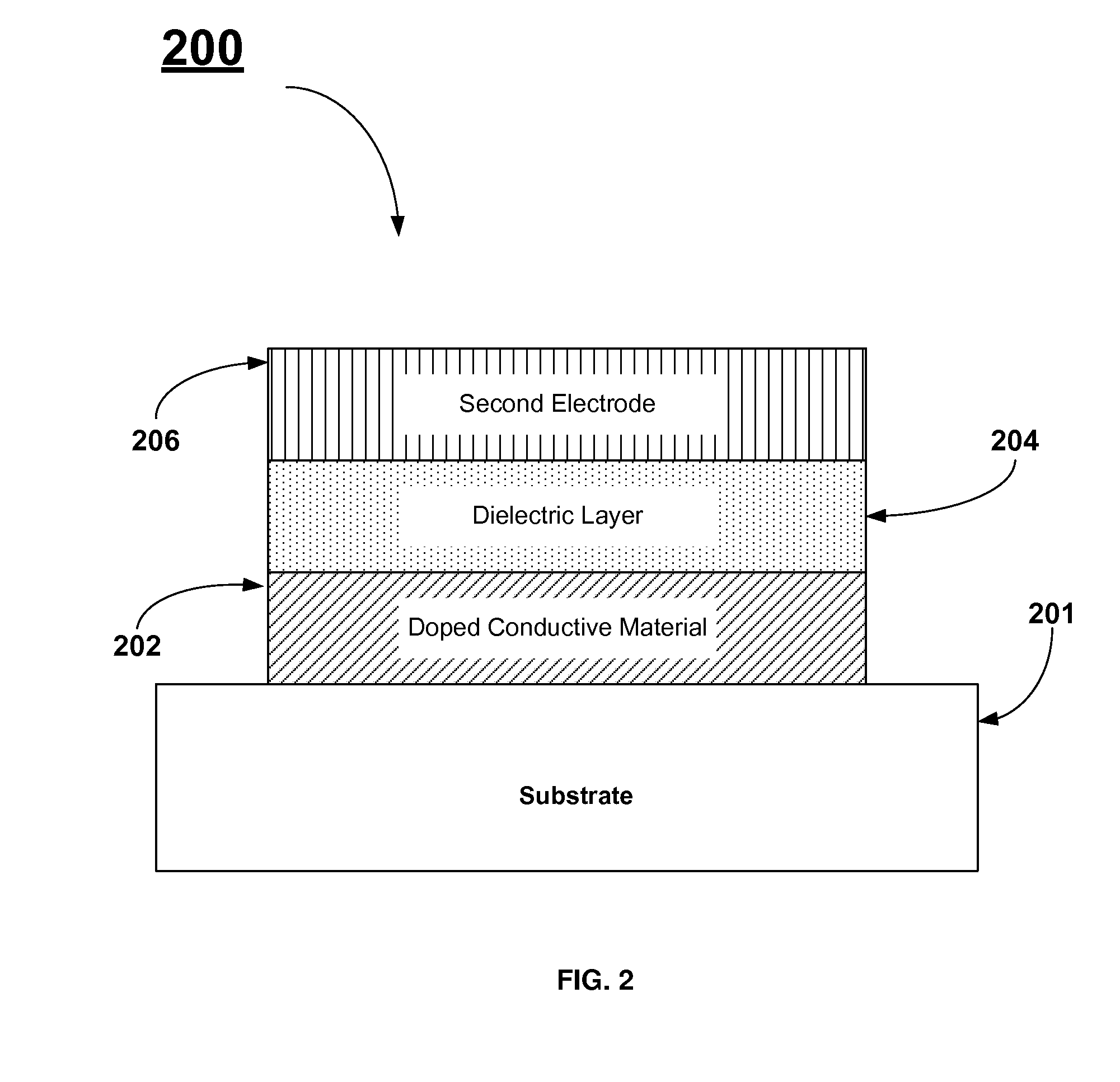

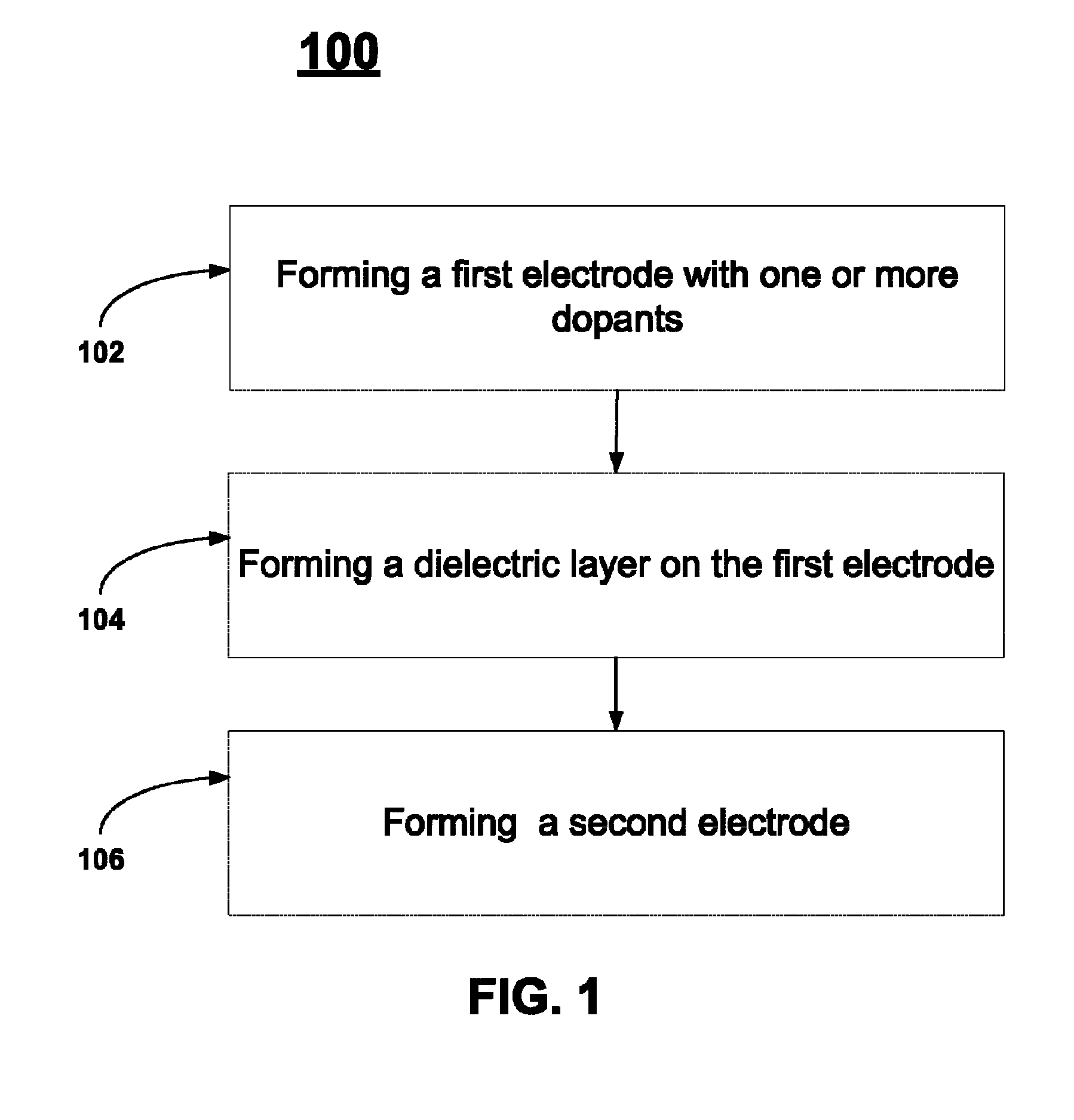

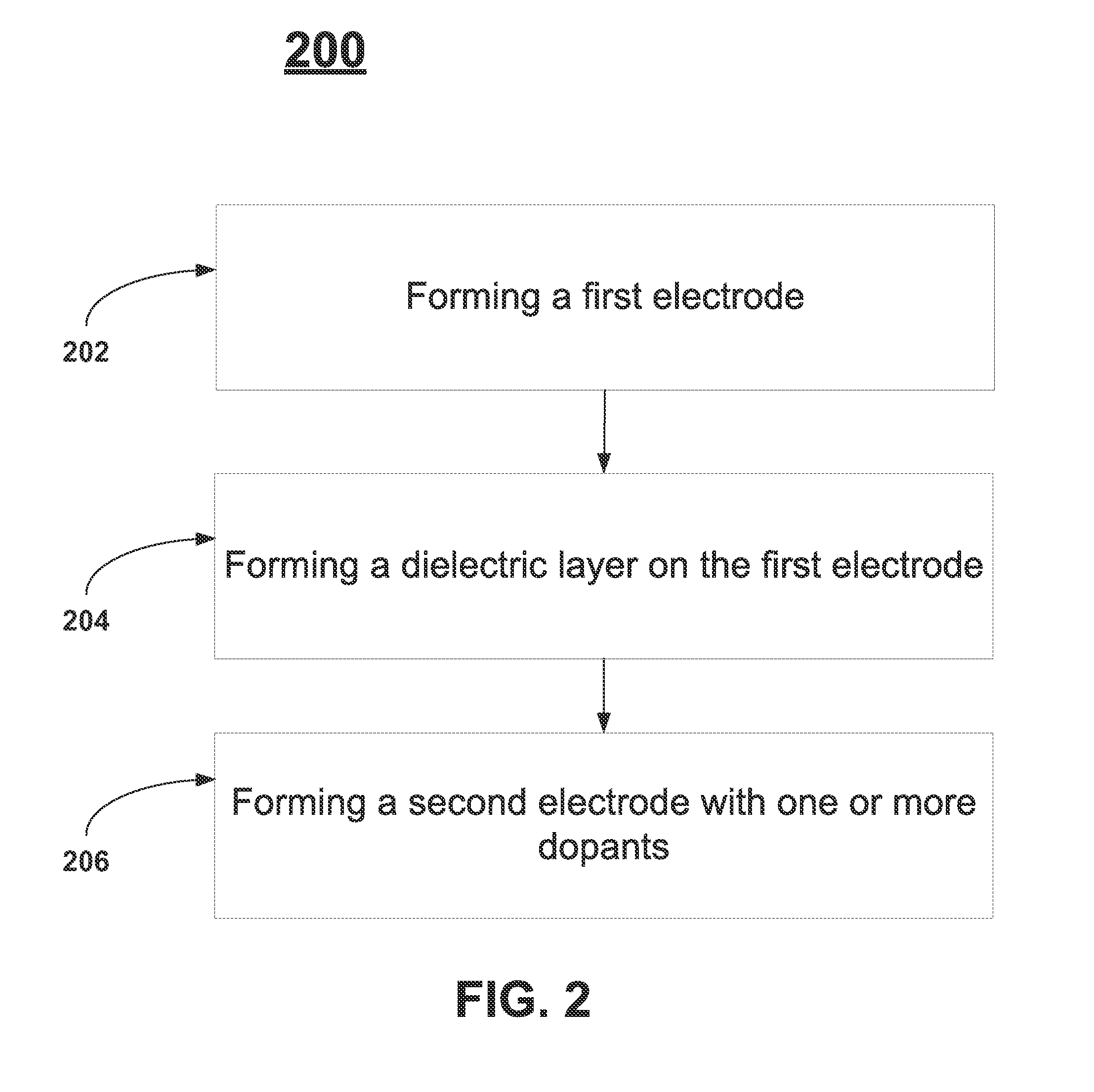

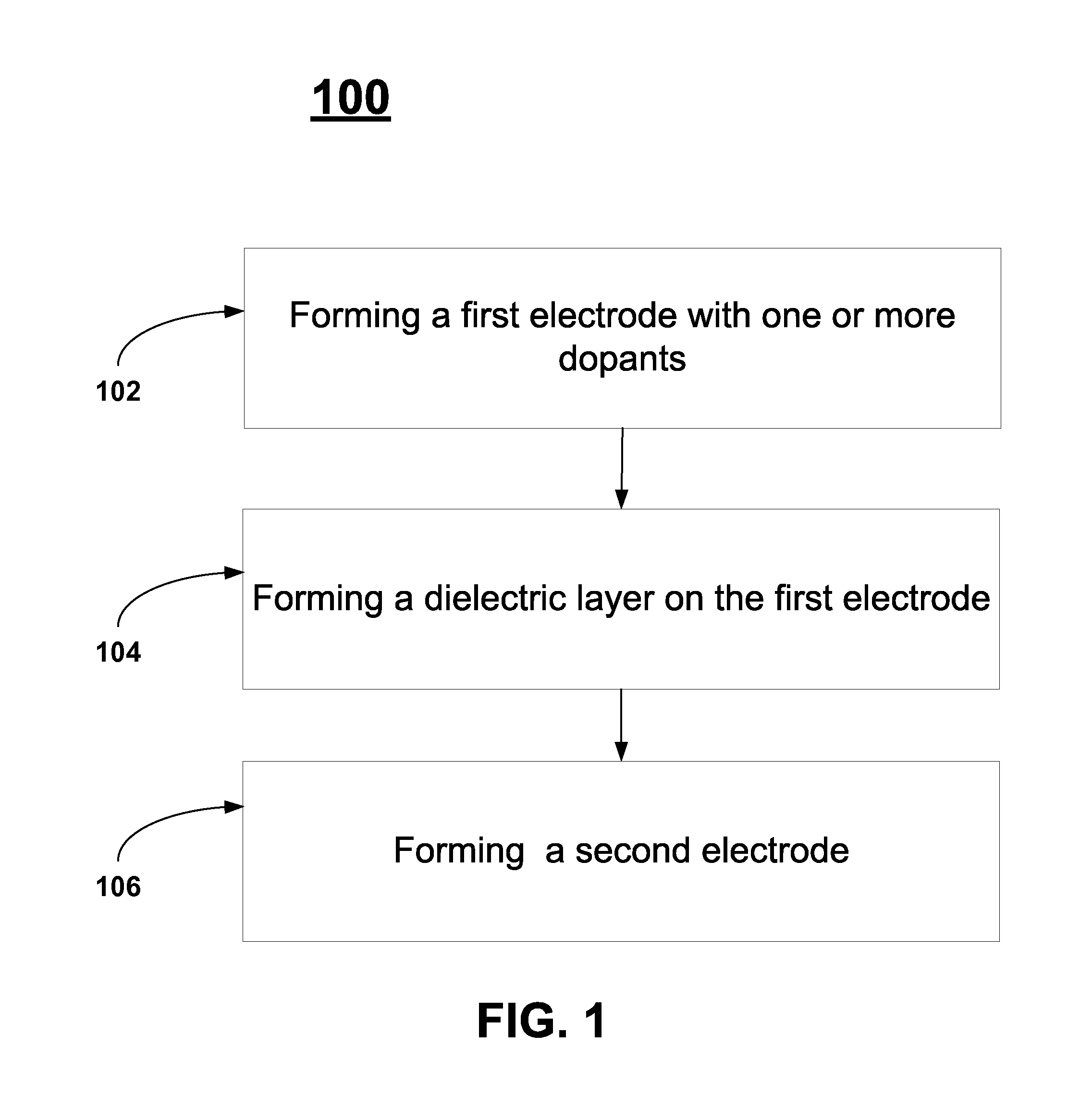

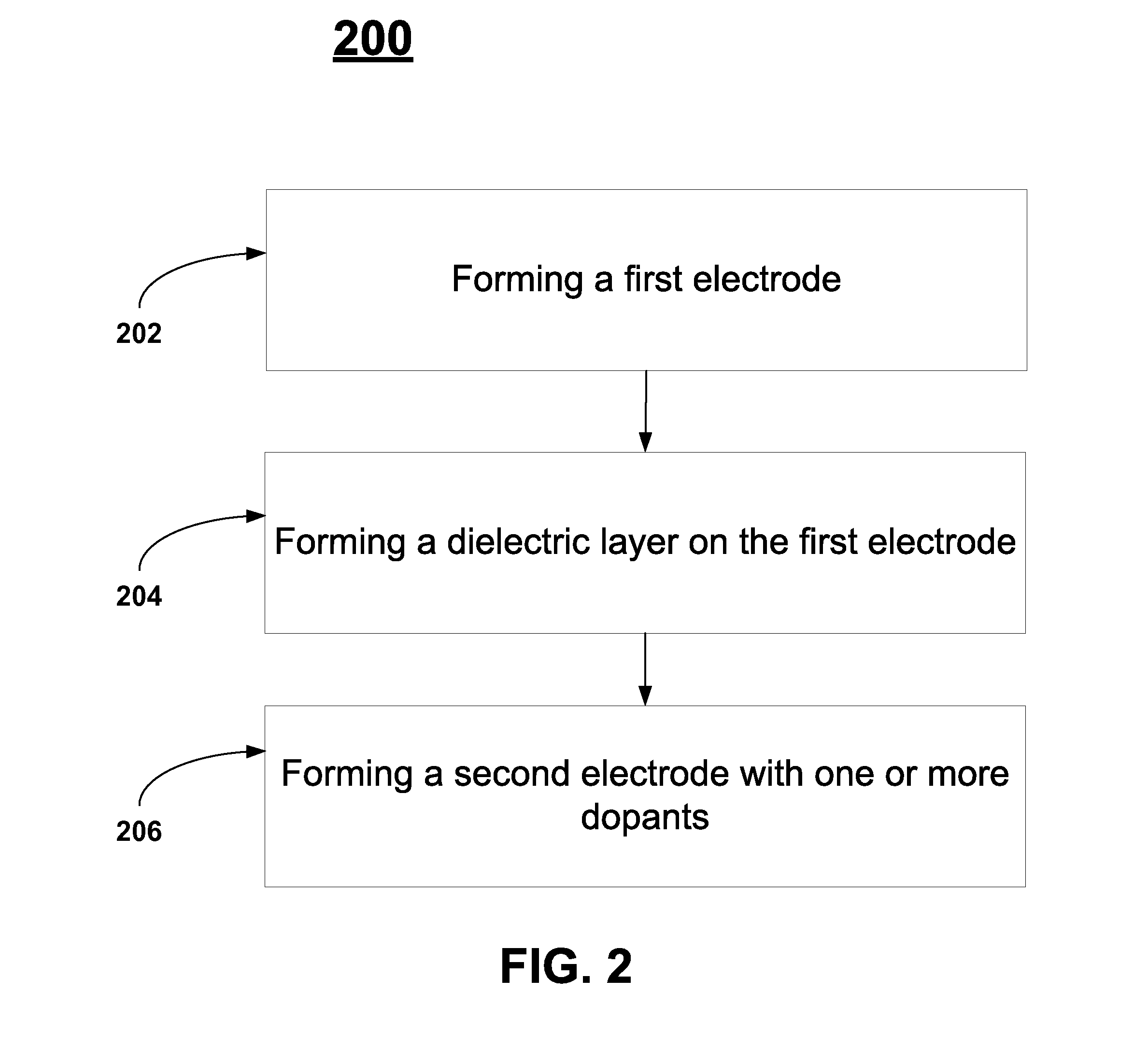

Method for fabricating a dram capacitor having increased thermal and chemical stability

A method for fabricating a dynamic random access memory (DRAM) capacitor includes forming a first electrode film. The first electrode film comprises a conductive binary metal compound and a dopant. The dopant may have a uniform or non-uniform concentration within the first electrode film. A high-k dielectric film is formed over the first electrode film. A second electrode film is formed over the dielectric film. The second electrode film comprises a conductive binary metal compound and a dopant. The dopant may have a uniform or non-uniform concentration within the second electrode film. The dopants and their distribution are chosen so that the crystal structure of the surface of the electrode is not degraded if the electrode is to be used as a templating structure for subsequent layer formation. Additionally, the dopants and their distribution are chosen so that the work function of the electrodes is not degraded.

Owner:INTERMOLECULAR +1

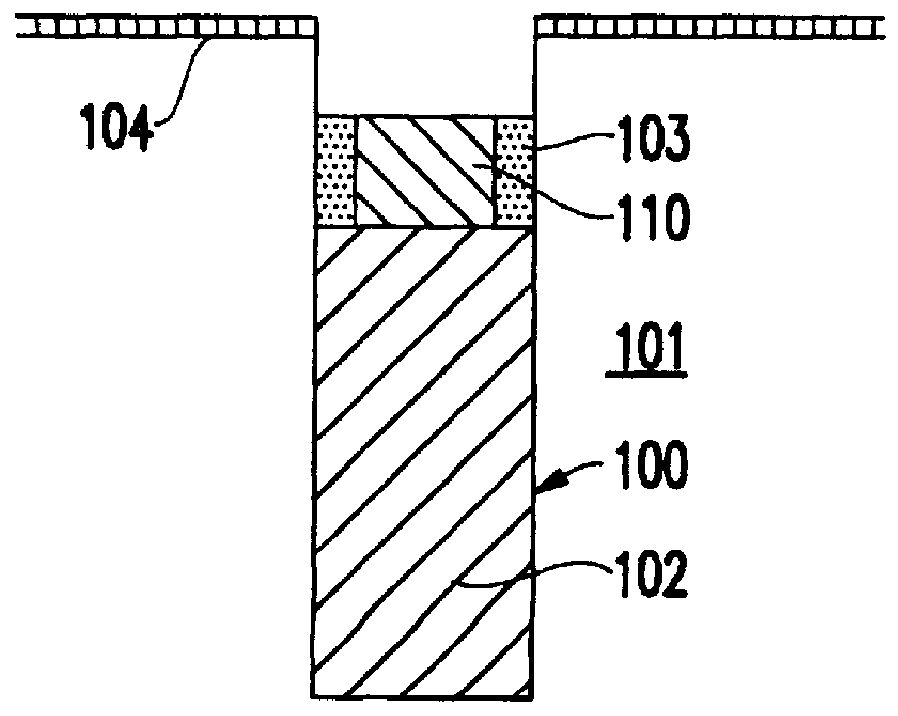

Method for making DRAM capacitor strap

A method of forming a trench capacitor comprises steps of forming a trench in a substrate, partially filling the trench with a first conductive material, lining a portion of the trench above the first conductive material with a collar material, etching the collar material to a strap depth below a top of the trench, and filling the trench with a second conductive material, wherein a portion of the second conductive material positioned between the strap depth and the top of the trench comprises a buried strap.

Owner:INFINEON TECH AG +1

Electro-mechanically polished structure

InactiveUS6867448B1Improve machining accuracyTransistorSemiconductor/solid-state device detailsMaterials scienceMetal

A method of patterning a metal surface by electro-mechanical polishing is disclosed. A metal surface is placed in fluid communication with an abrasive surface of a pad. The two surfaces are moved relative to each other, in acidic fluid which contains abrasive particles. An electrical circuit is formed between the metal surface and abrasive pad and a current is supplied to the circuit. The patterned surface then is processed into a useful feature such as a bottom electrode for a DRAM capacitor.

Owner:ROUND ROCK RES LLC

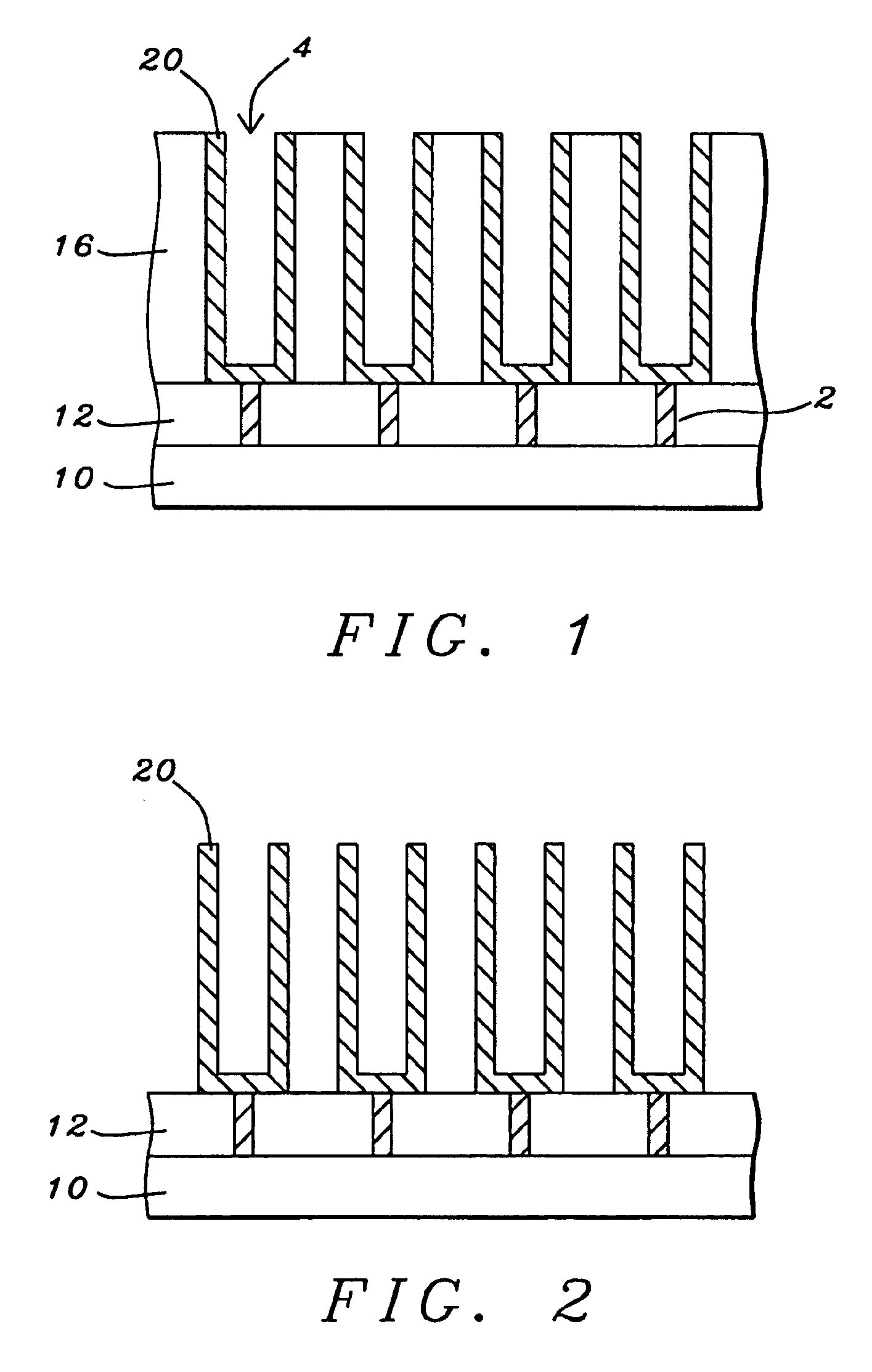

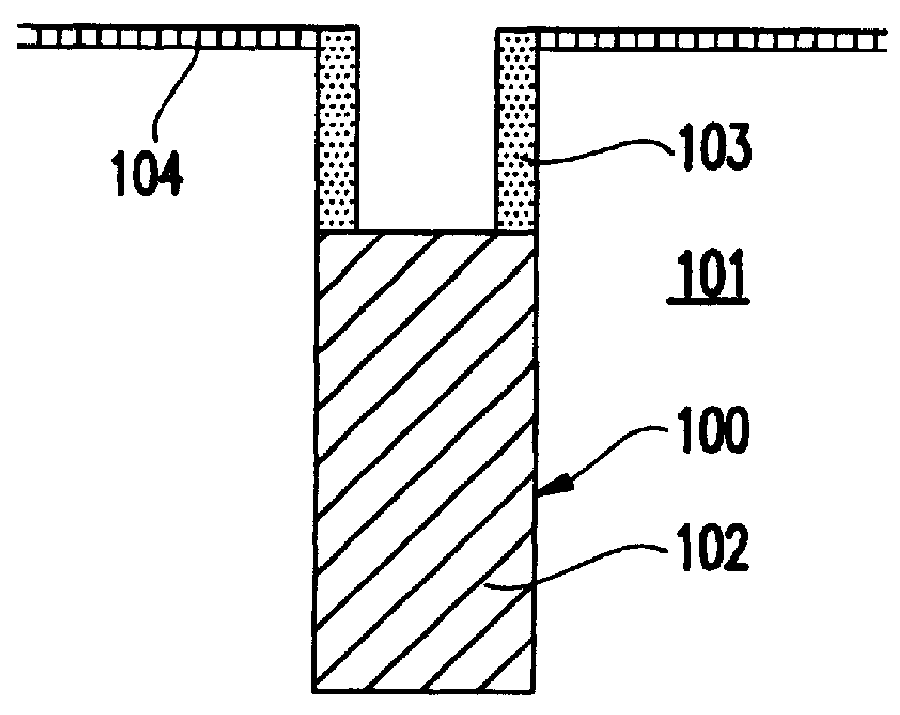

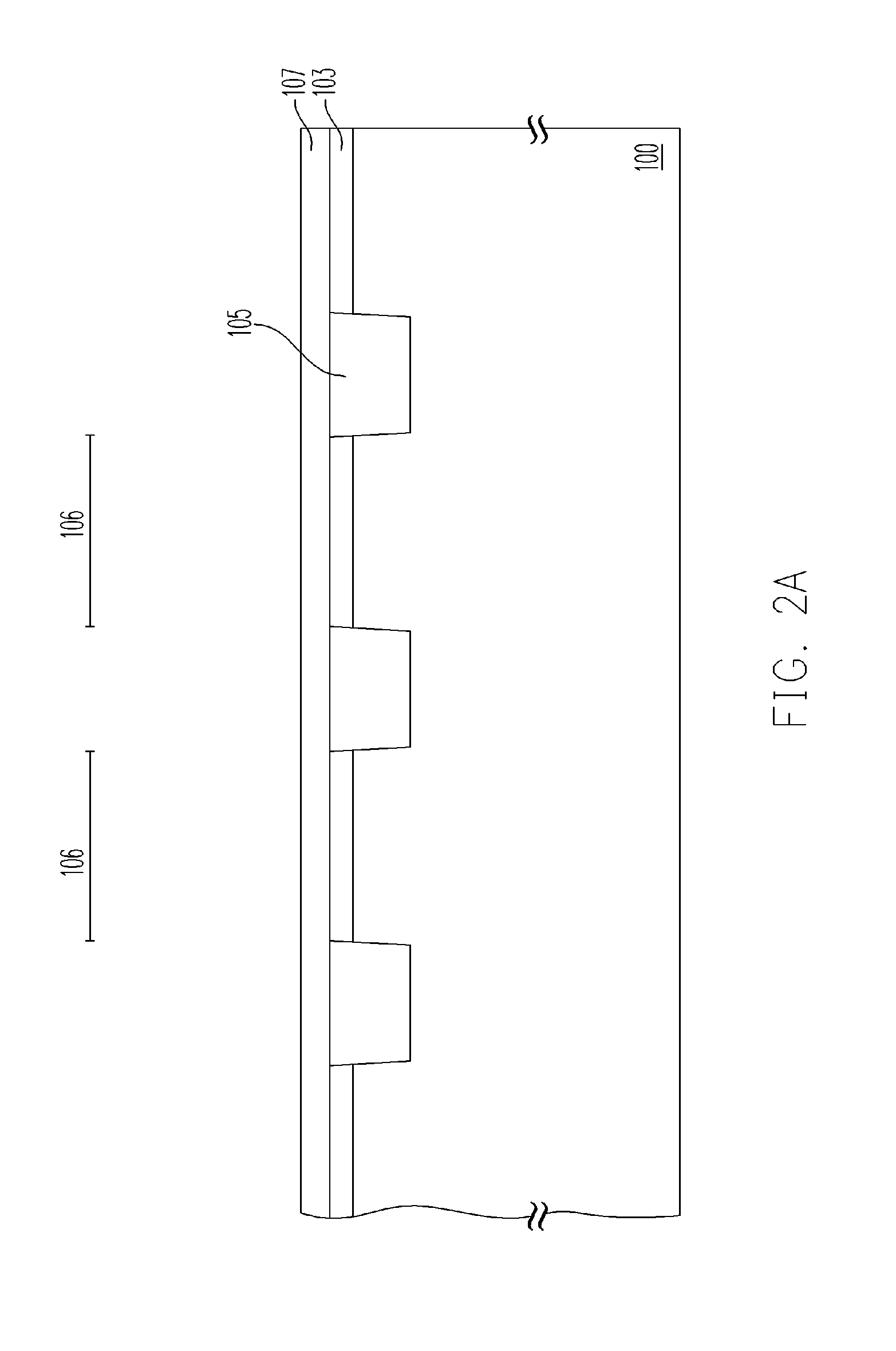

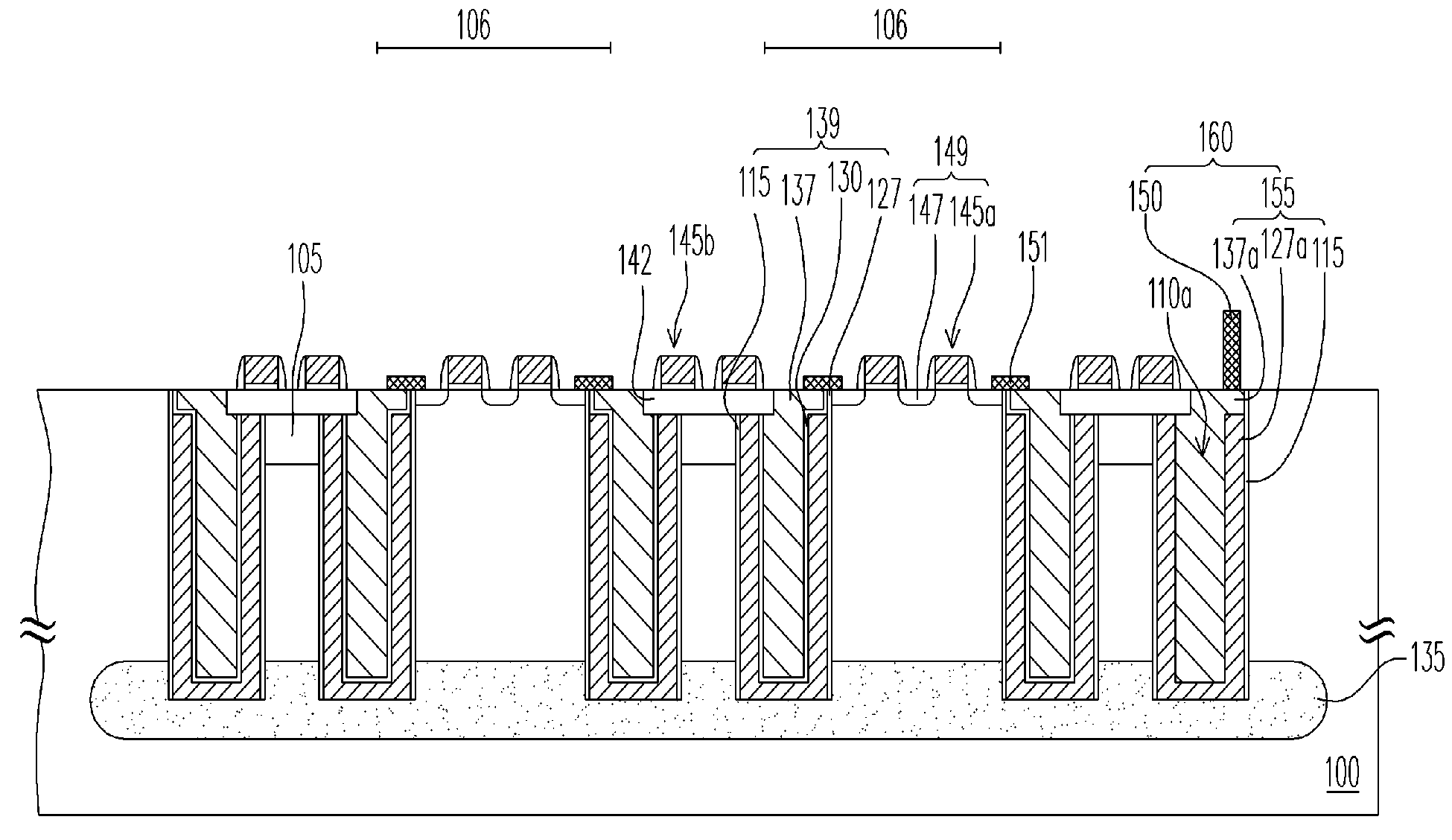

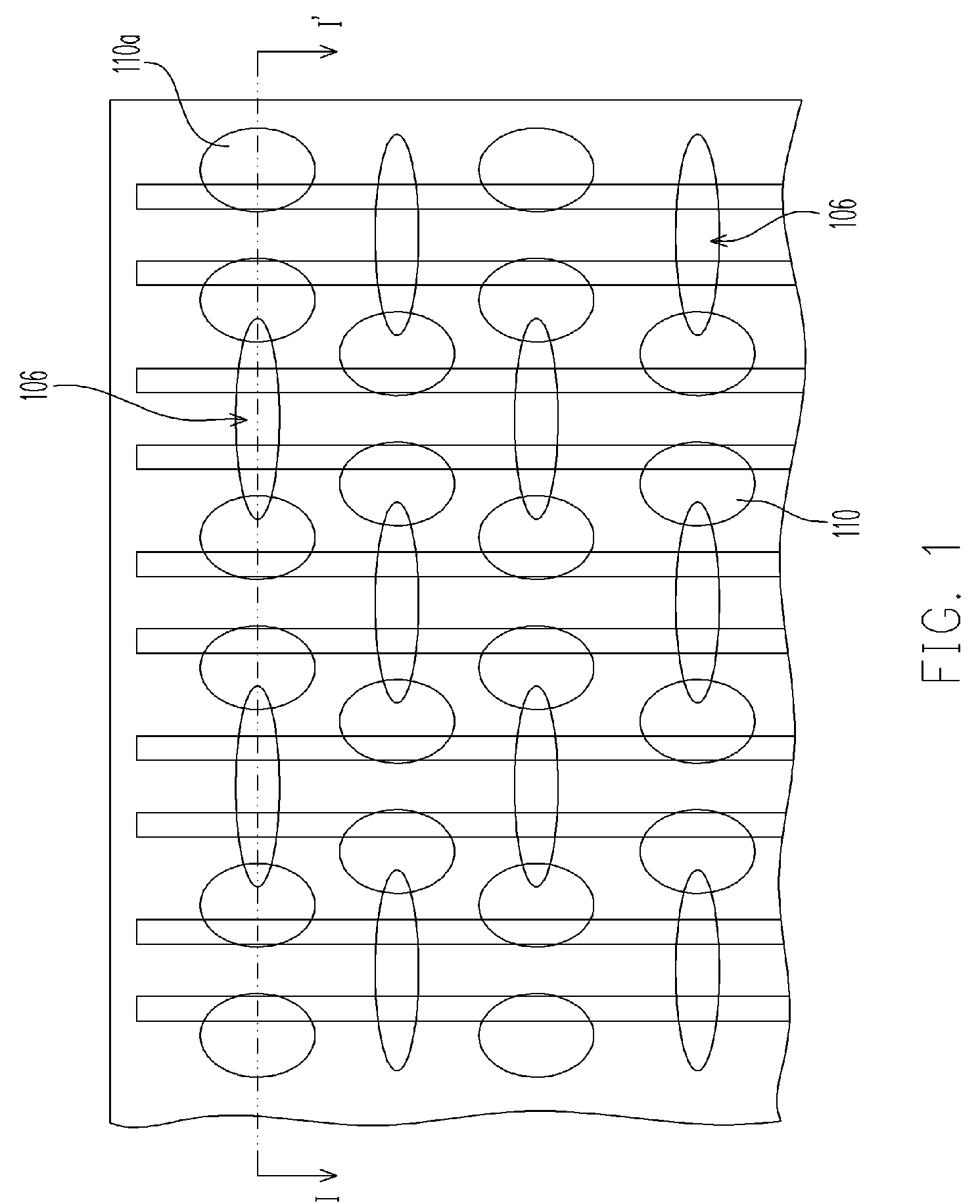

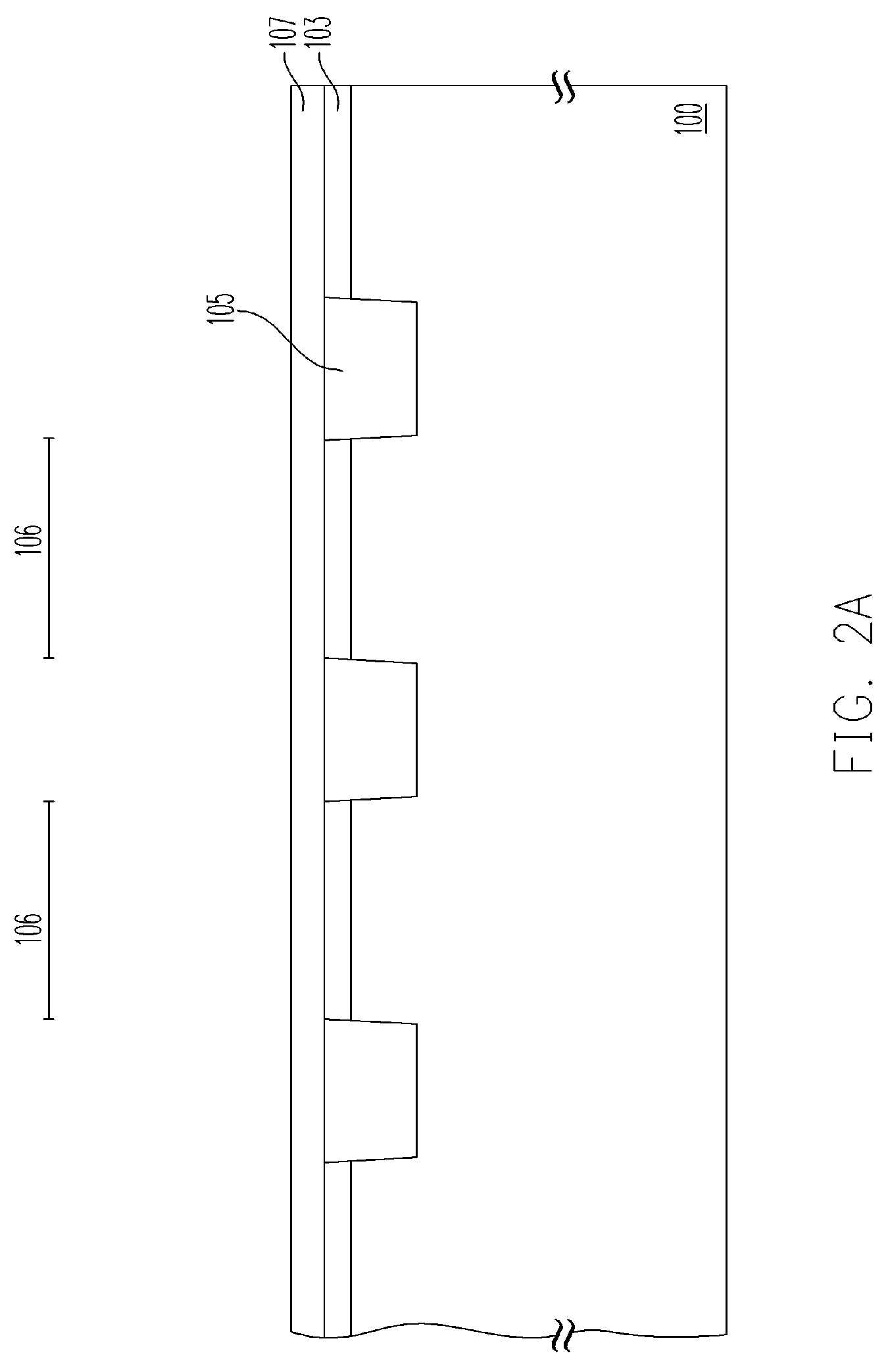

Pick-up structure for dram capacitors and dram process

A pick-up structure for DRAM capacitors and a DRAM process are described. A substrate with trenches therein is provided, wherein the trenches include a first trench and the sidewall of each of the trenches is formed with a dielectric layer thereon. A conductive layer is formed on the surfaces of the substrate and the trenches, and then a patterned photoresist layer is formed on the conductive layer filling in the trenches and further covering the first trench. The exposed conductive layer is removed to form bottom electrodes in the trenches, and then the patterned photoresist layer is removed. A capacitor dielectric layer is formed on each bottom electrode, and then top electrodes are formed on the substrate filling up the trenches. A contact is then formed on the bottom electrode in the first trench, electrically connecting the substrate via the bottom electrode.

Owner:UNITED MICROELECTRONICS CORP

Pick-up structure for DRAM capacitors

A pick-up structure for DRAM capacitors and a DRAM process are described. A substrate with trenches therein is provided, wherein the trenches include a first trench and the sidewall of each of the trenches is formed with a dielectric layer thereon. A conductive layer is formed on the surfaces of the substrate and the trenches, and then a patterned photoresist layer is formed on the conductive layer filling in the trenches and further covering the first trench. The exposed conductive layer is removed to form bottom electrodes in the trenches, and then the patterned photoresist layer is removed. A capacitor dielectric layer is formed on each bottom electrode, and then top electrodes are formed on the substrate filling up the trenches. A contact is then formed on the bottom electrode in the first trench, electrically connecting the substrate via the bottom electrode.

Owner:UNITED MICROELECTRONICS CORP

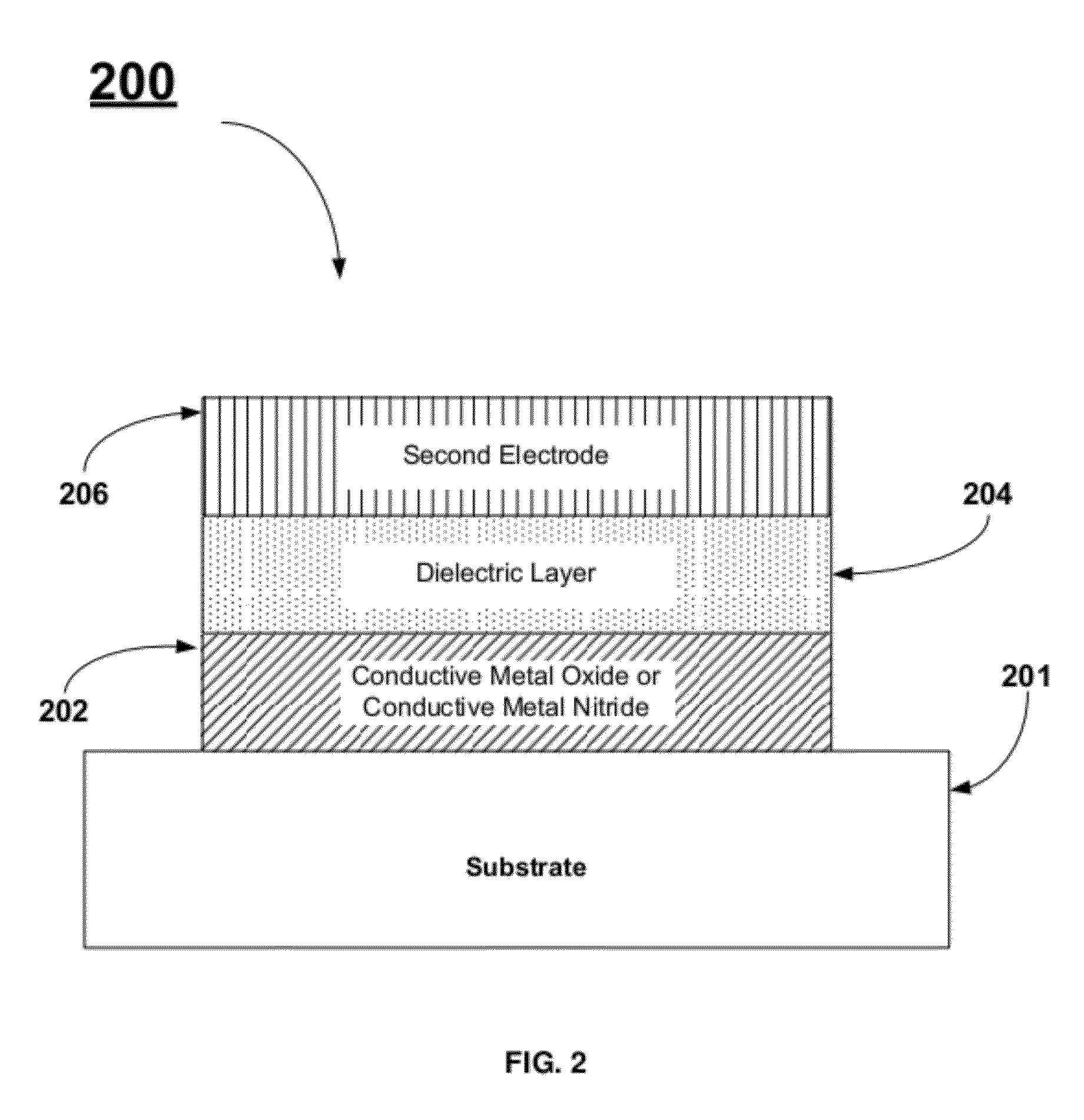

Interfacial layer for dram capacitor

InactiveUS20130071988A1Increase heightSolid-state devicesSemiconductor/solid-state device manufacturingDielectricInterface layer

A method for reducing leakage current in DRAM capacitor stacks by introducing dielectric interface layers between the electrodes and the bulk dielectric material. The dielectric interface layers are typically amorphous dielectric materials with a k value between about 10 and about 30 and are less than about 1.5 nm in thickness. Advantageously, the thickness of each of the dielectric interface layers is less than 1.0 nm. In some cases, only a single dielectric interface layer is used between the bulk dielectric material and the second electrode.

Owner:INTERMOLECULAR +1

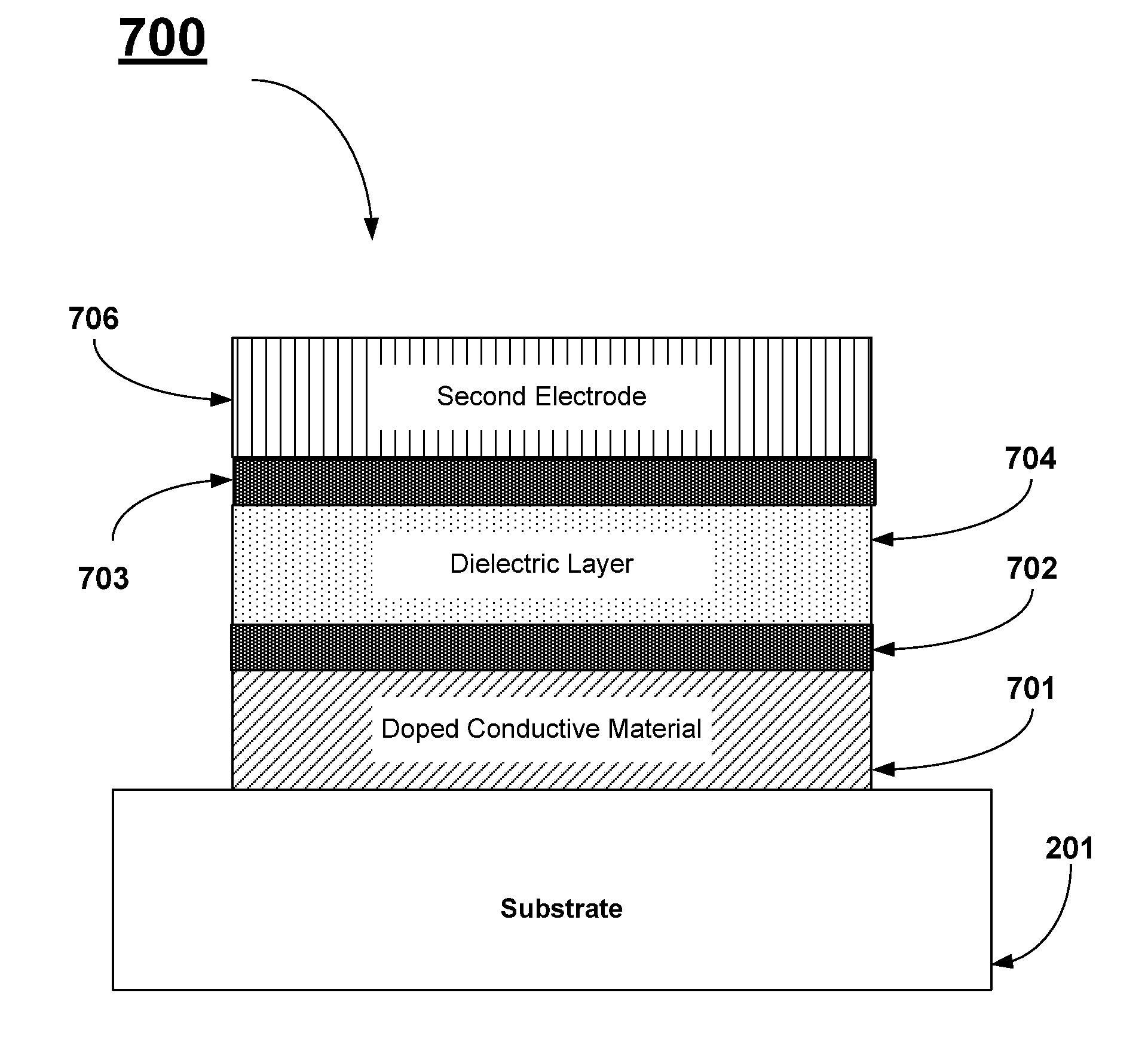

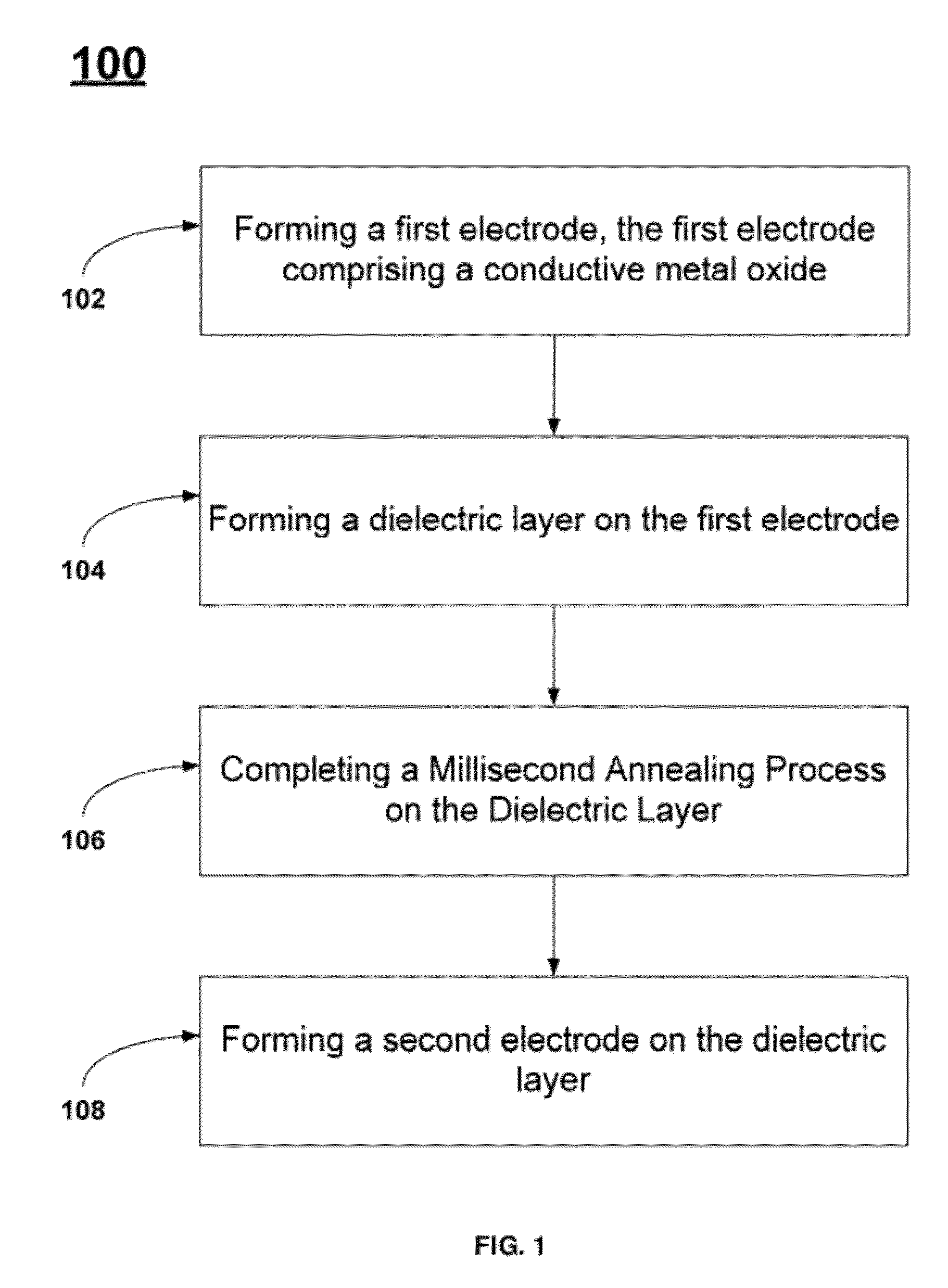

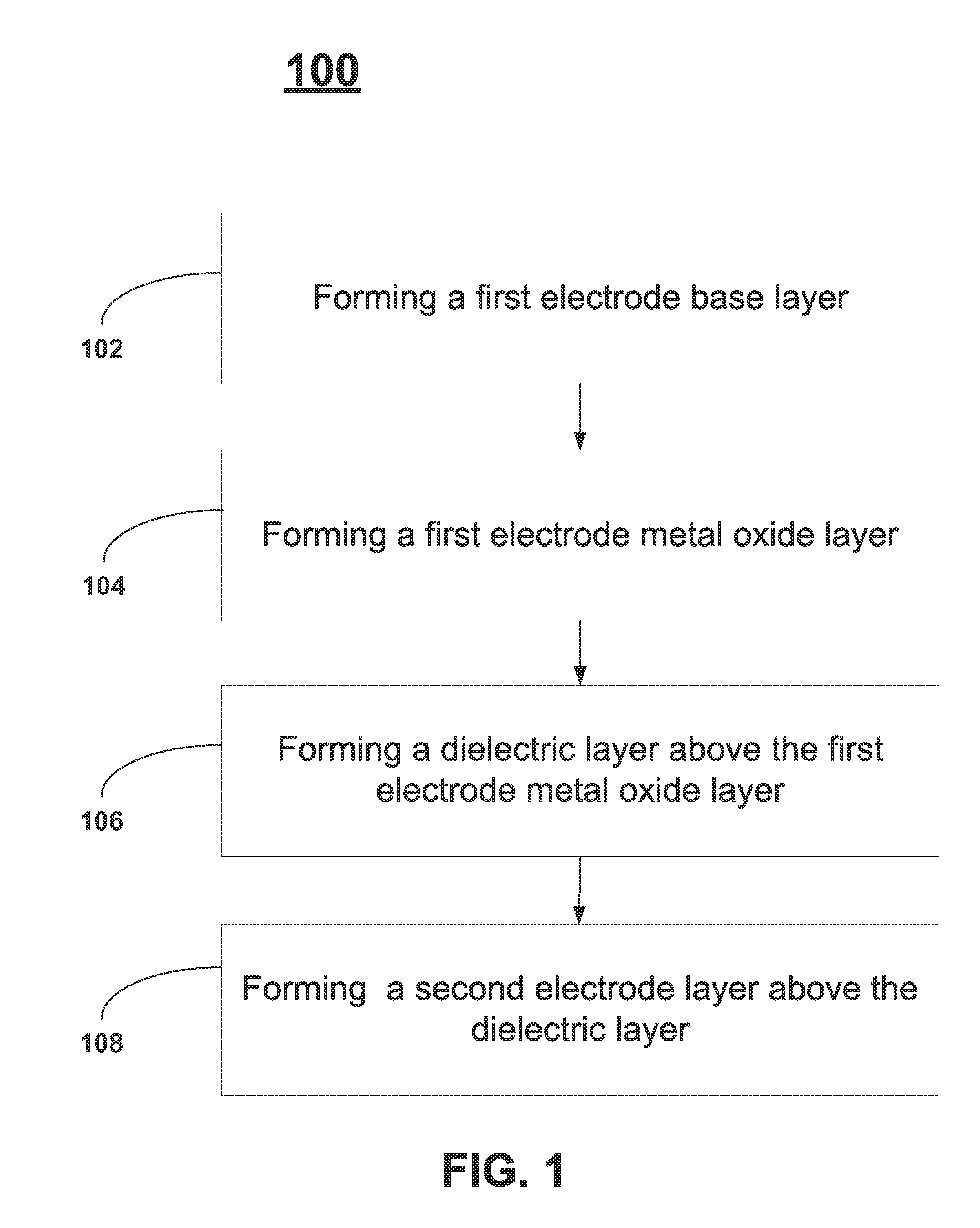

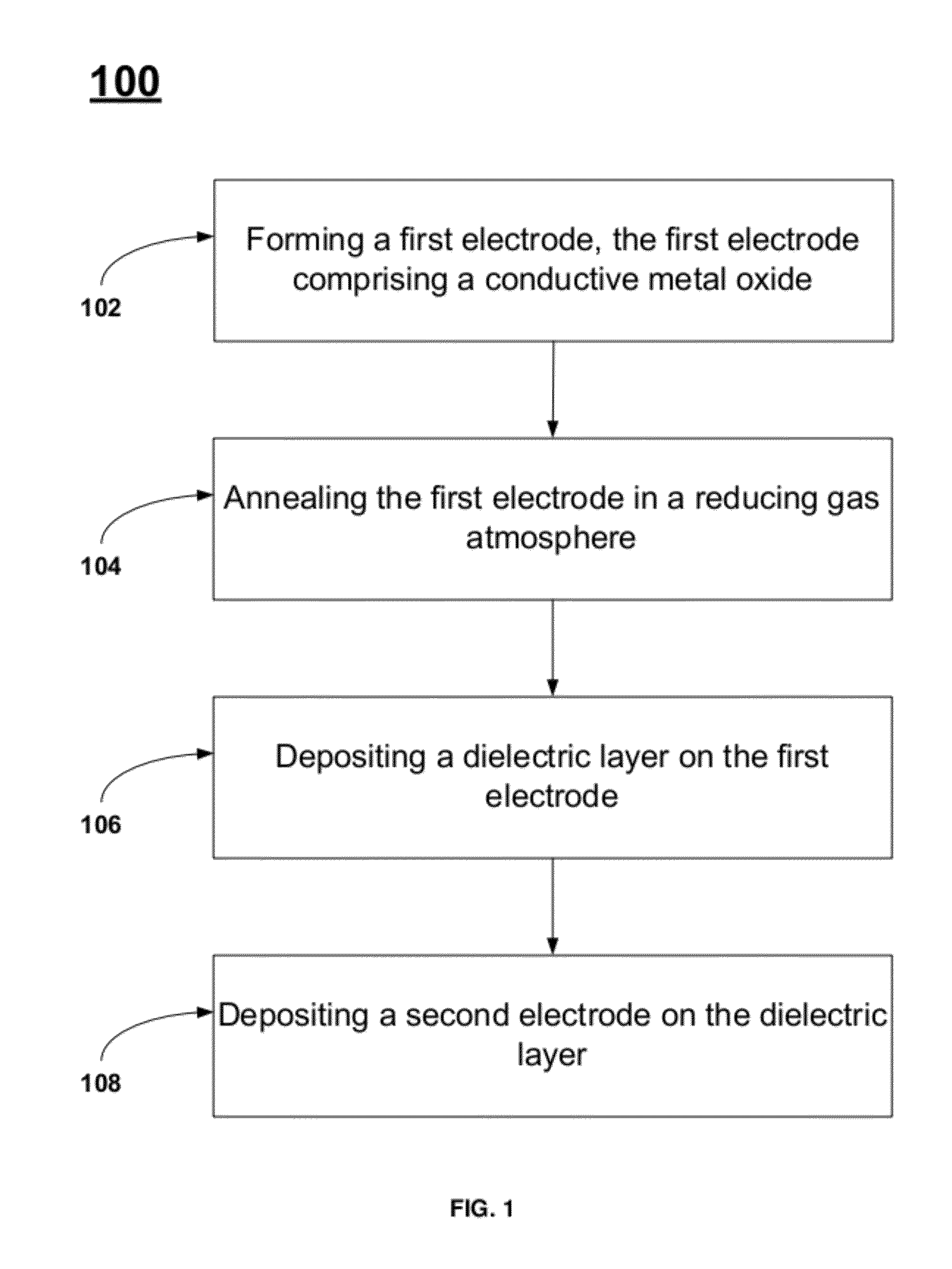

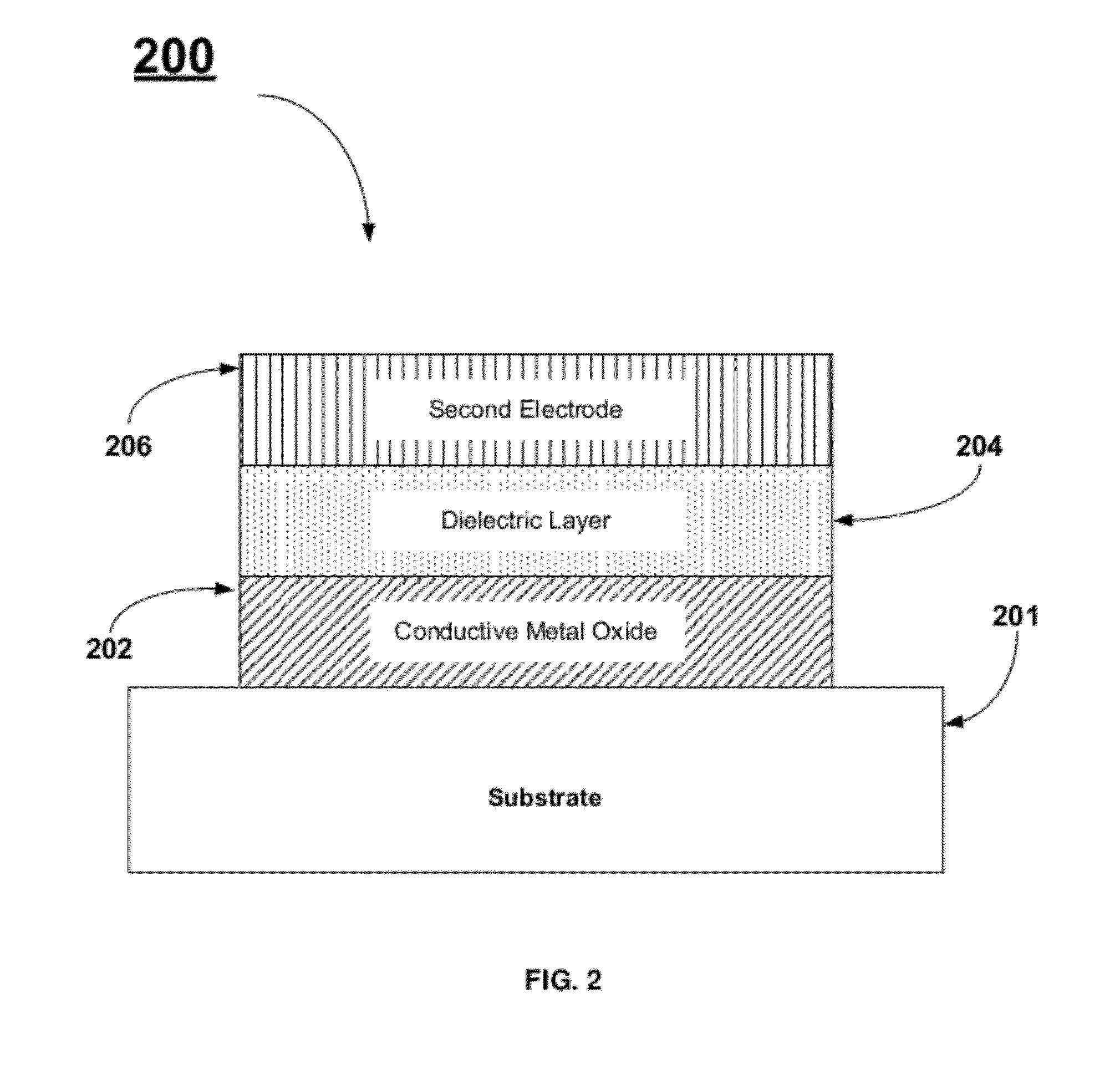

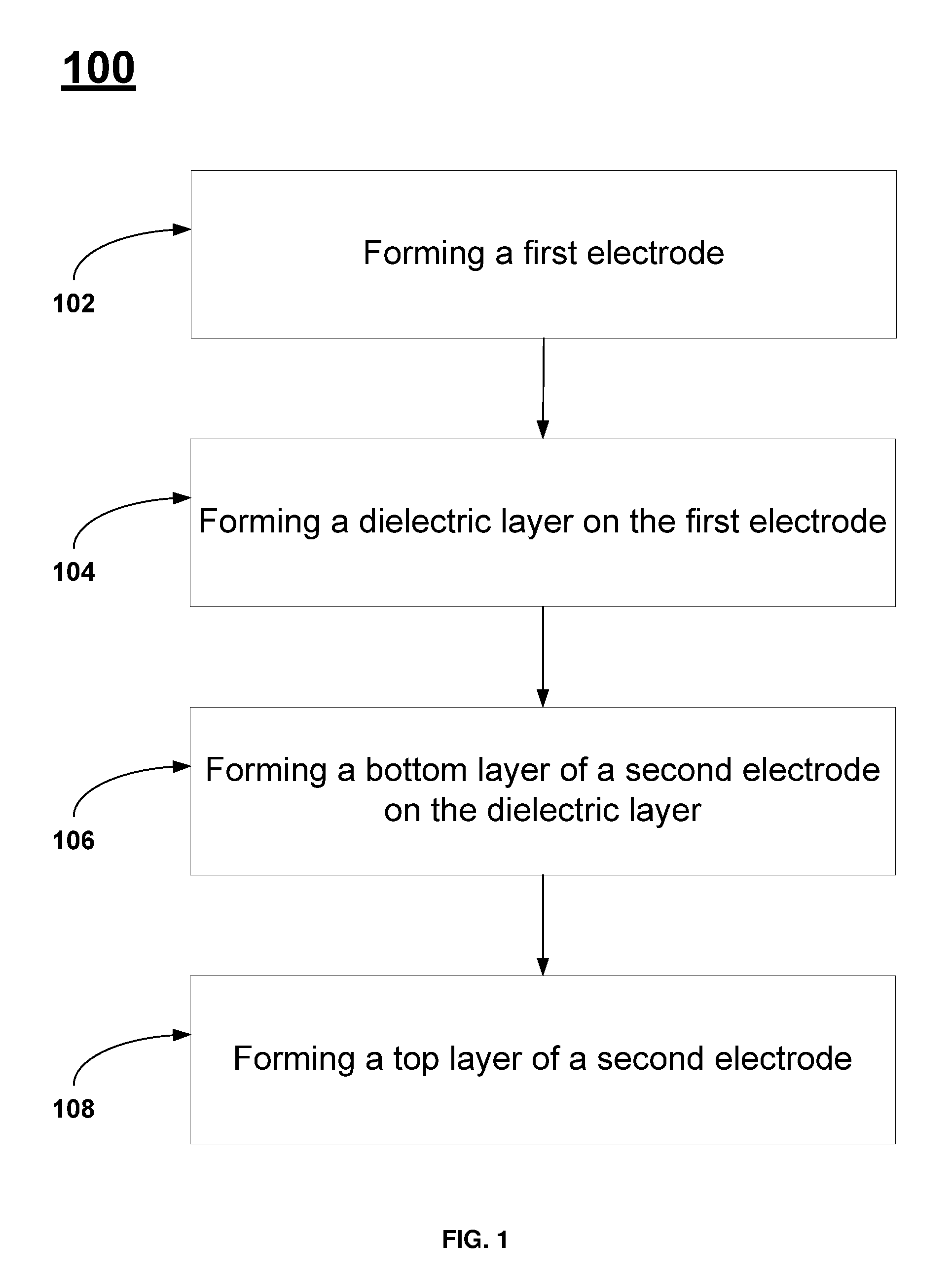

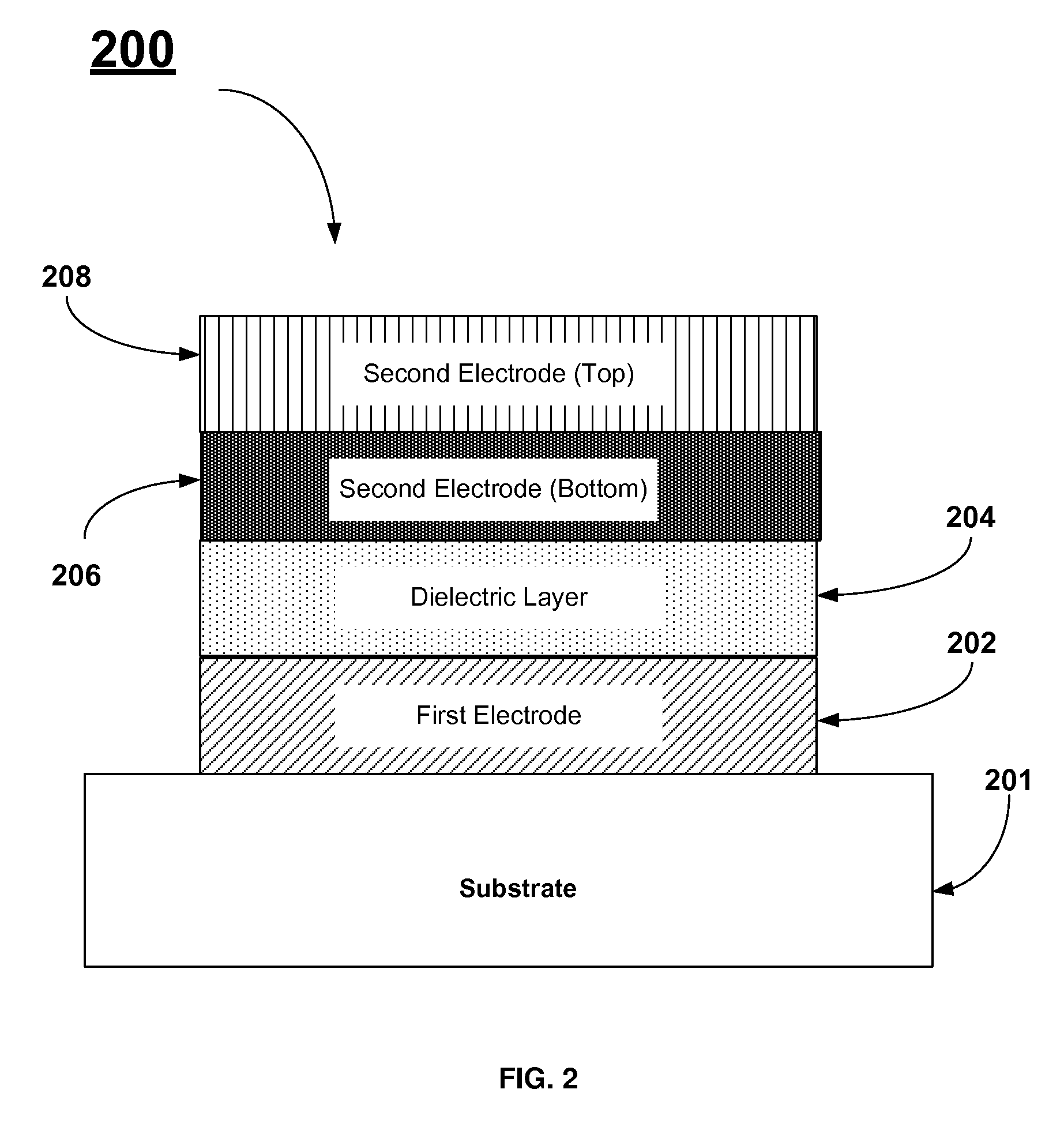

Method for fabricating a dram capacitor

InactiveUS20120309160A1Semiconductor/solid-state device manufacturingCapacitorsOxygen vacancyOptoelectronics

A method for fabricating a dynamic random access memory (DRAM) capacitor stack is disclosed wherein the stack includes a first electrode, a dielectric layer, and a second electrode. The first electrode is formed from a conductive binary metal. A dielectric layer is formed over the first electrode. The dielectric layer is subjected to a milliseconds anneal process that serves to crystallize the dielectric material and decrease the concentration of oxygen vacancies.

Owner:INTERMOLECULAR +1

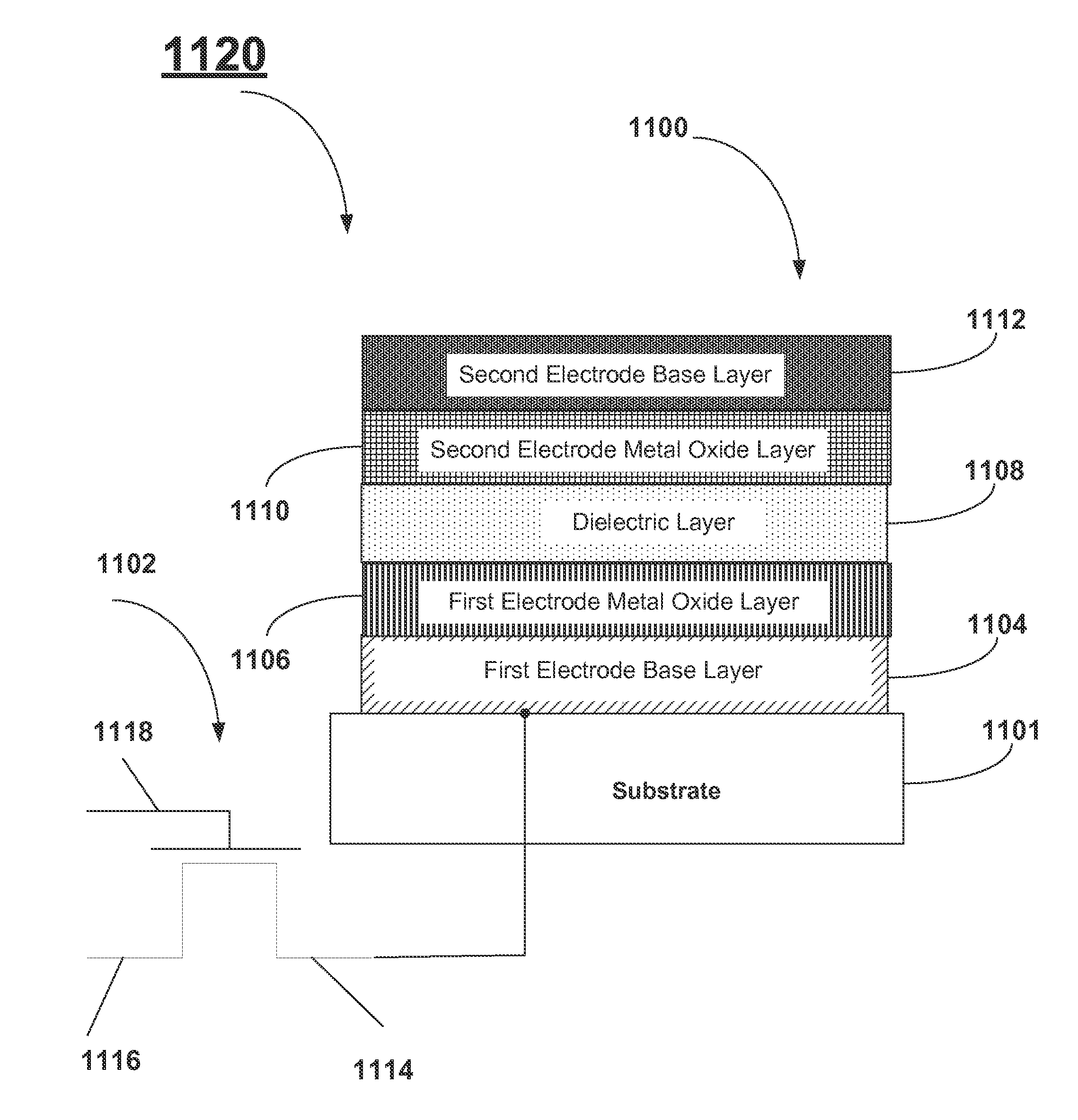

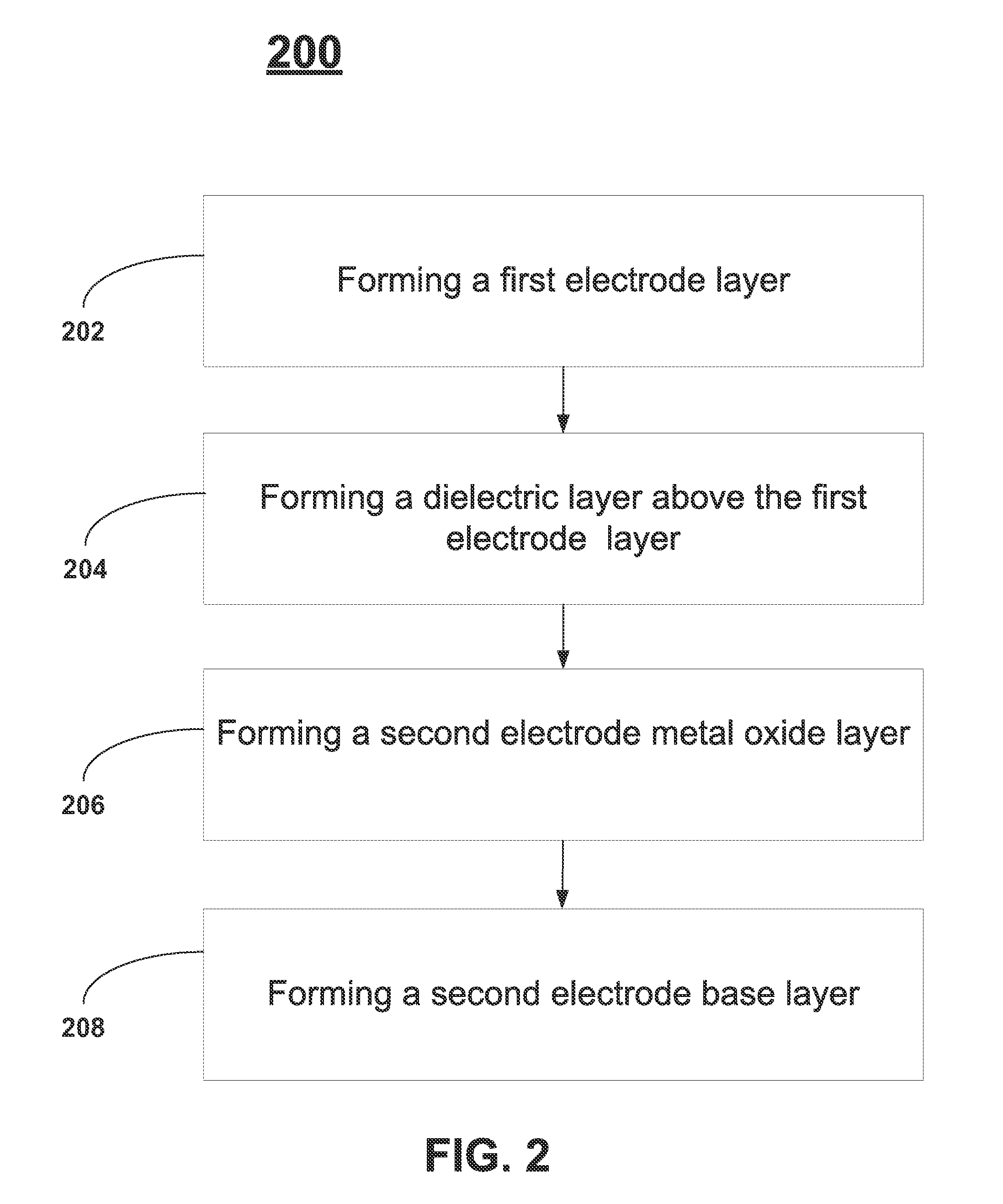

Methods to Improve Leakage for ZrO2 Based High K MIM Capacitor

InactiveUS20140187015A1Solid-state devicesSemiconductor/solid-state device manufacturingMetal-insulator-metalOptoelectronics

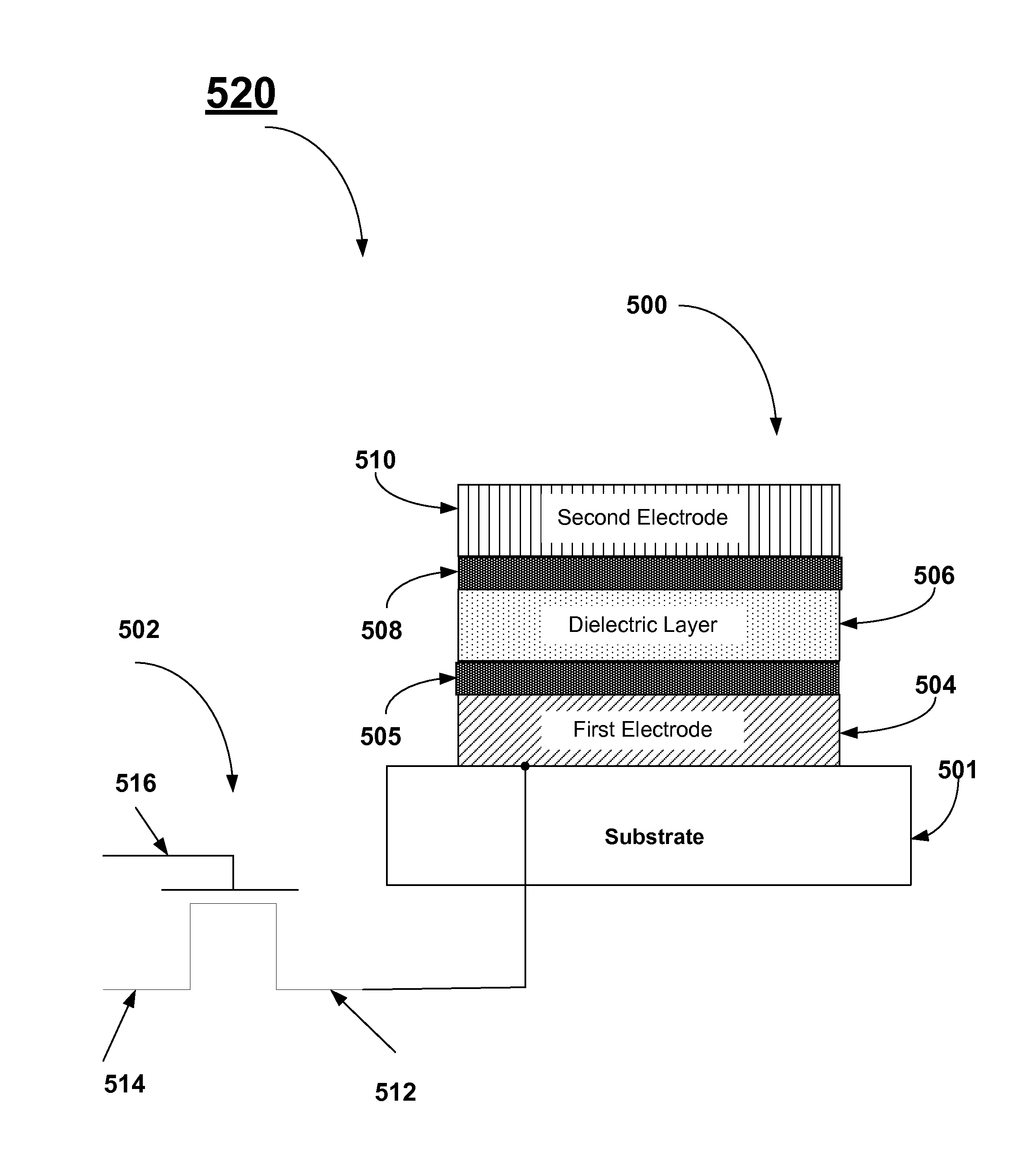

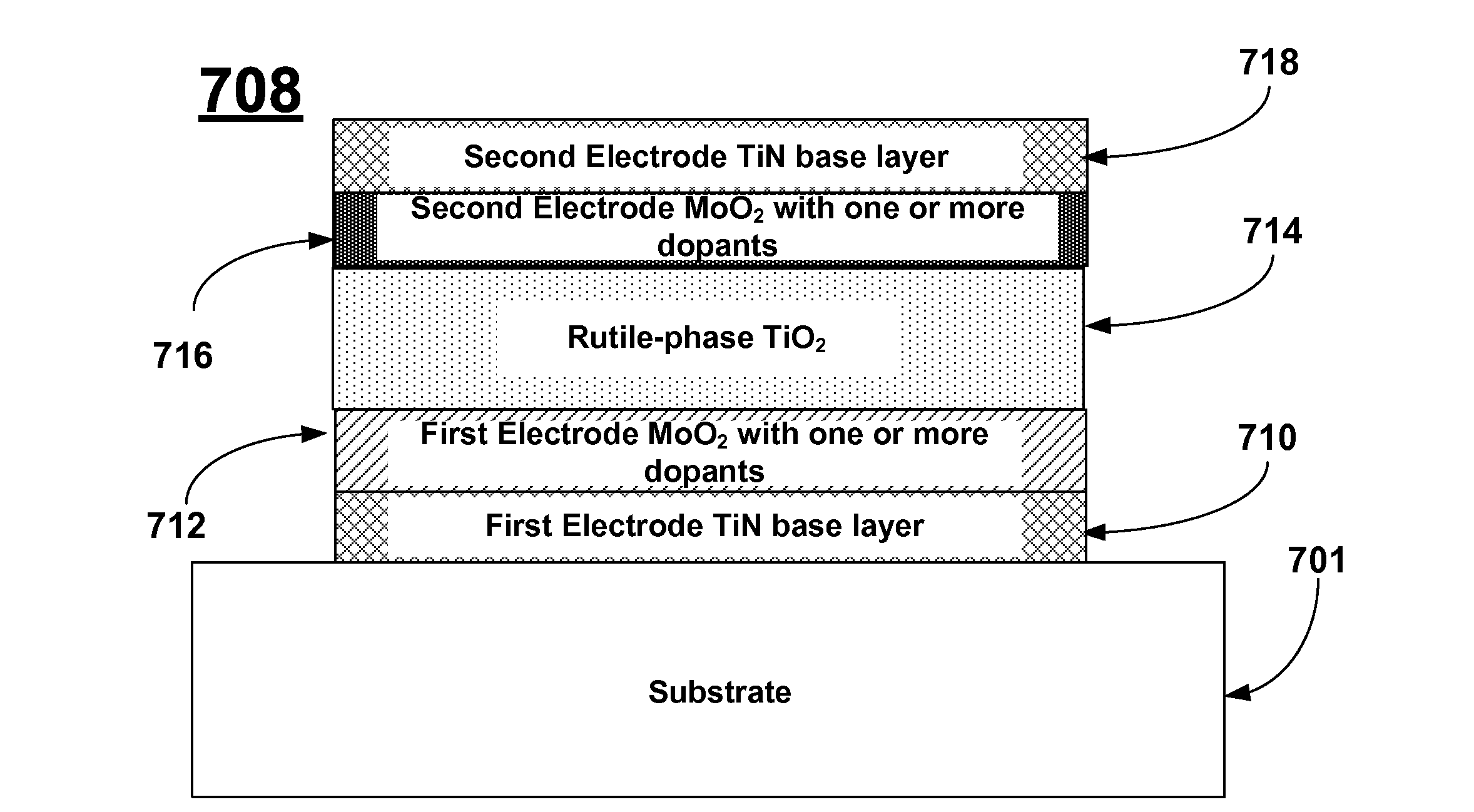

A first electrode layer for a Metal-Insulator-Metal (MIM) DRAM capacitor is formed wherein the first electrode layer contains a conductive base layer and conductive metal oxide layer. A second electrode layer for a Metal-Insulator-Metal (MIM) DRAM capacitor is formed wherein the second electrode layer contains a conductive base layer and conductive metal oxide layer. In some embodiments, both the first electrode layer and the second electrode layer contain a conductive base layer and conductive metal oxide layer.

Owner:INTERMOLECULAR +1

Method of manufacturing non-volatile DRAM

InactiveUS7232717B1Solid-state devicesSemiconductor/solid-state device manufacturingVarying thicknessPolysilicon gate

A method of forming a non-volatile DRAM includes, in part: forming p-well and an n-well between two trench isolation regions formed in a semiconductor substrate, forming a polysilicon control gate of the non-volatile device disposed in the non-volatile DRAM, forming a first oxide spacer above portions of the body region and adjacent said first control gate, forming gate oxide layers of varying thicknesses above the body region, forming the guiding gate of the non-volatile device and the gate of an associated passgate transistor, forming LDD implant regions of the non-volatile device and the associated pass-gate transistor, forming source / drain regions of the non-volatile device and the associated pass-gate transistor, depositing a dielectric layer over the polysilicon guiding gate of the non-volatile device and the polysilicon gate of the associated passgate transistor, forming polysilicon landing pads, and forming polysilicon vertical walls defining capacitor plates of the non-volatile DRAM capacitor.

Owner:O2IC

Semiconductor memory device

ActiveUS7728376B2High dielectric constantIncrease semaphoreTransistorSolid-state devicesDielectricEngineering

HfO2 films and ZrO2 films are currently being developed for use as capacitor dielectric films in 85 nm technology node DRAM. However, these films will be difficult to use in 65 nm technology node or later DRAM, since they have a relative dielectric constant of only 20-25. The dielectric constant of such films may be increased by stabilizing their cubic phase. However, this results in an increase in the leakage current along the crystal grain boundaries, which makes it difficult to use these films as capacitor dielectric films. To overcome this problem, the present invention dopes a base material of HfO2 or ZrO2 with an oxide of an element having a large ion radius, such as Y or La, to increase the oxygen coordination number of the base material and thereby increase its relative dielectric constant to 30 or higher even when the base material is in its amorphous state. Thus, the present invention provides dielectric films that can be used to form DRAM capacitors that meet the 65 nm technology node or later.

Owner:HITACHI LTD

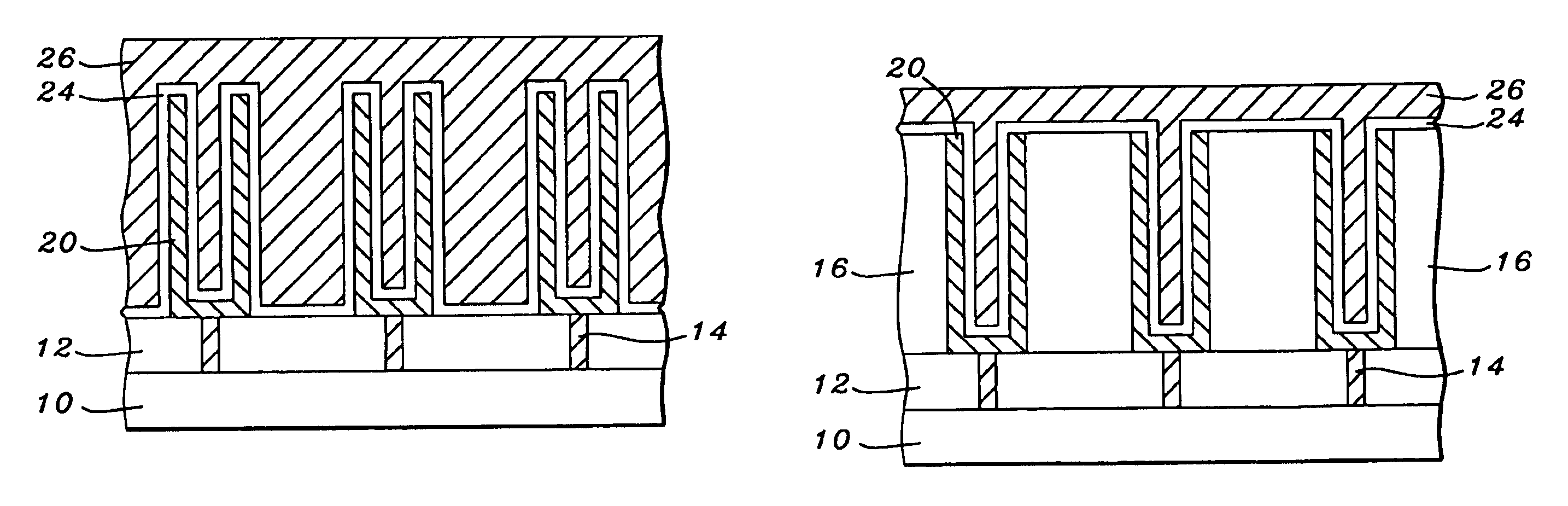

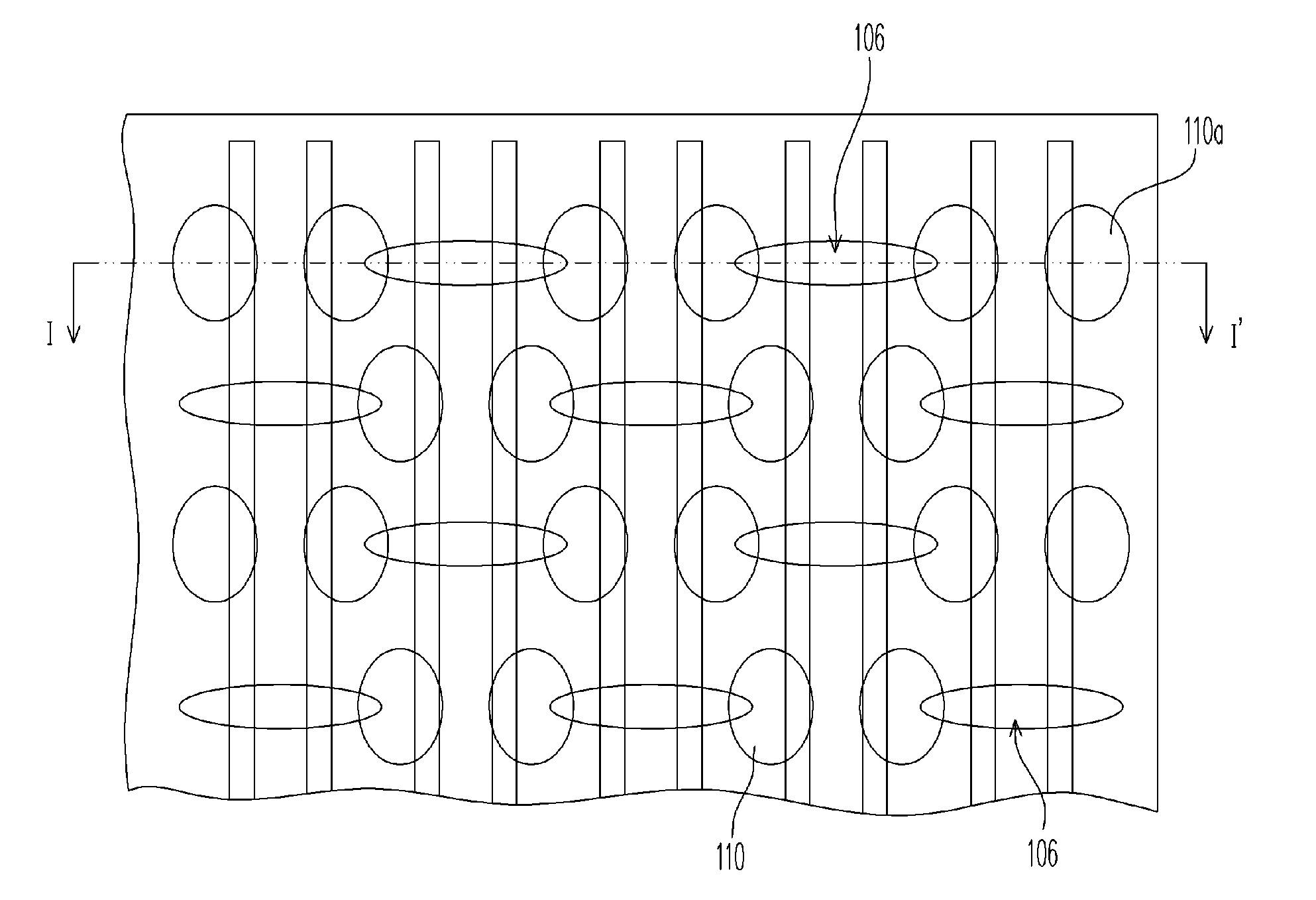

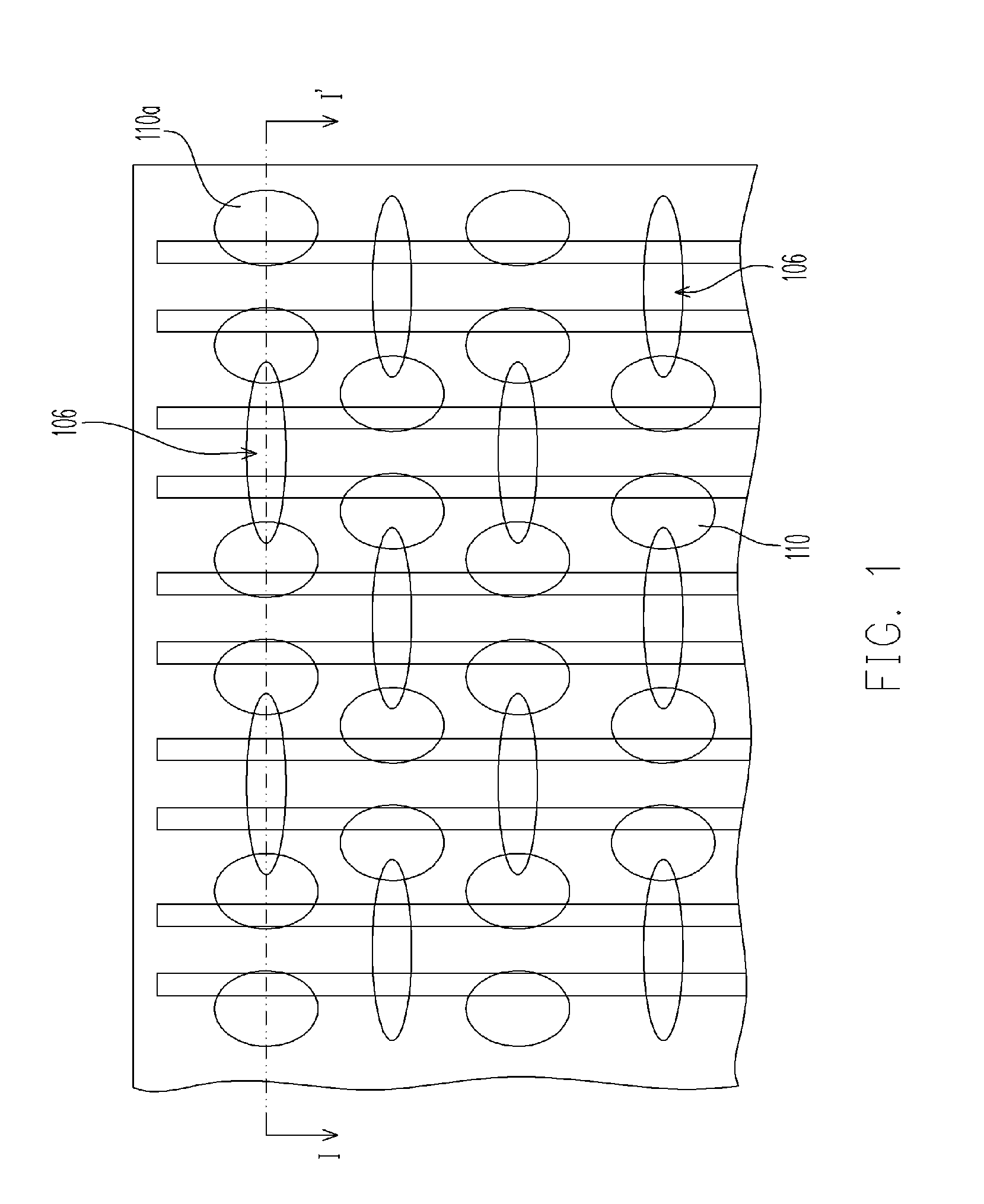

Method for making y-shaped multi-fin stacked capacitors for dynamic random access memory cells

InactiveUS6083790ACost-effective manufacturing processTransistorSolid-state devicesCapacitanceBit line

An array of DRAM cells having Y-shaped multi-fin stacked capacitors with increased capacitance is achieved. A planar first insulating layer is formed over the semi-conductor devices on the substrate. Polycide bit lines are formed on the first insulating layer, and a second insulating layer and a silicon nitride (Si3N4) etch-stop layer are conformally deposited. A multilayer, composed of a alternating insulating and polysilicon layers, is conformally deposited over the bit lines. Capacitor node contact openings are etched in the multilayer and in the underlying layers to the substrate. A fourth polysilicon layer is deposited sufficiently thick to fill the node contact openings and to form the node contacts. The multilayer is then patterned to leave portions over the node contacts, and an isotropic etch is used to remove the insulating layers exposed in the sidewalls of the patterned multilayer to provide Y-shaped multi-fin capacitor bottom electrodes over the bit lines. These Y-shaped multi-fin capacitors increase the capacitance by 37% over T-shaped multi-fin capacitors. The DRAM capacitors are then completed by forming an interelectrode dielectric layer on the bottom electrodes and by depositing a fifth polysilicon layer to form the capacitor top electrodes.

Owner:TAIWAN SEMICON MFG CO LTD

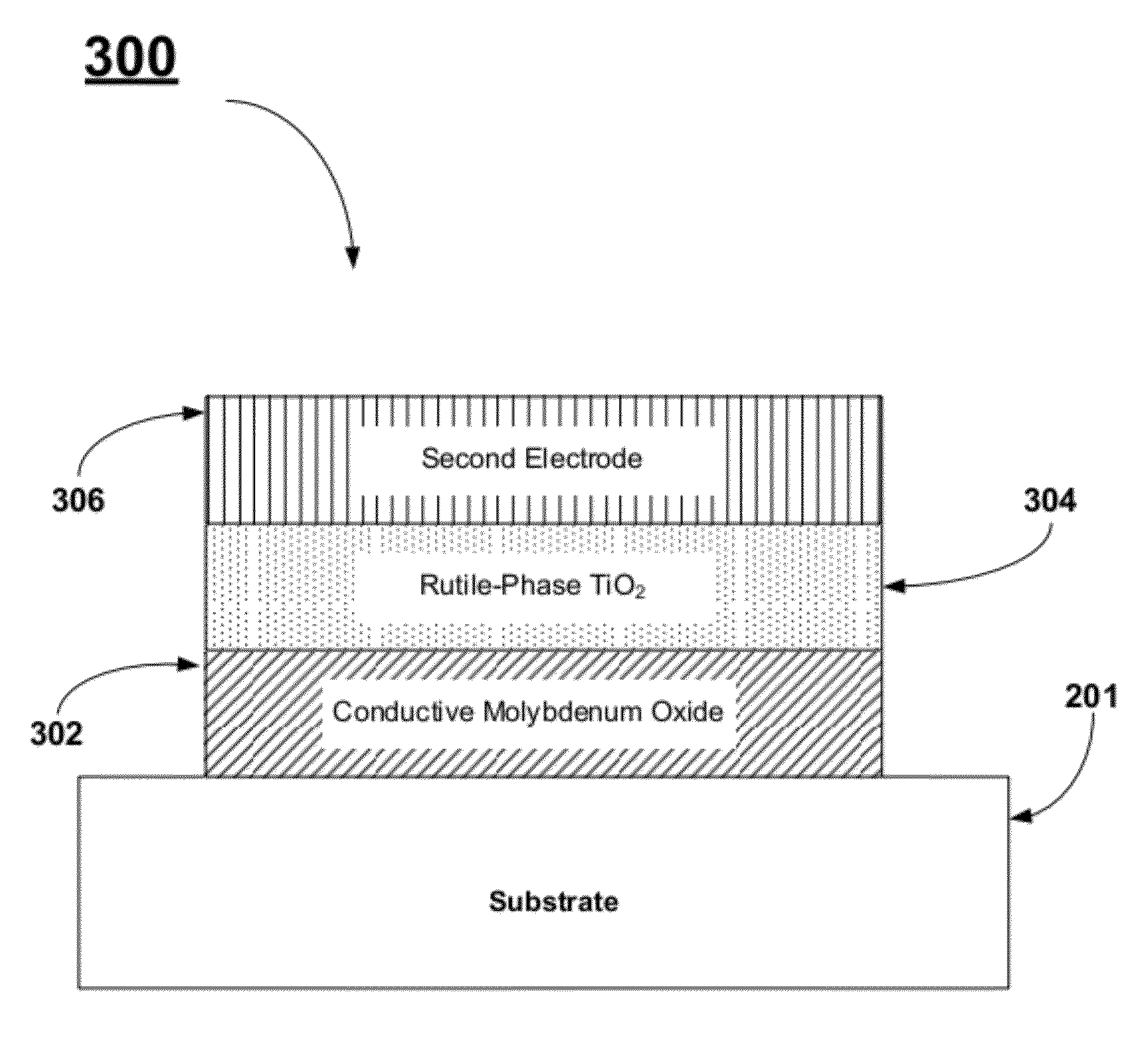

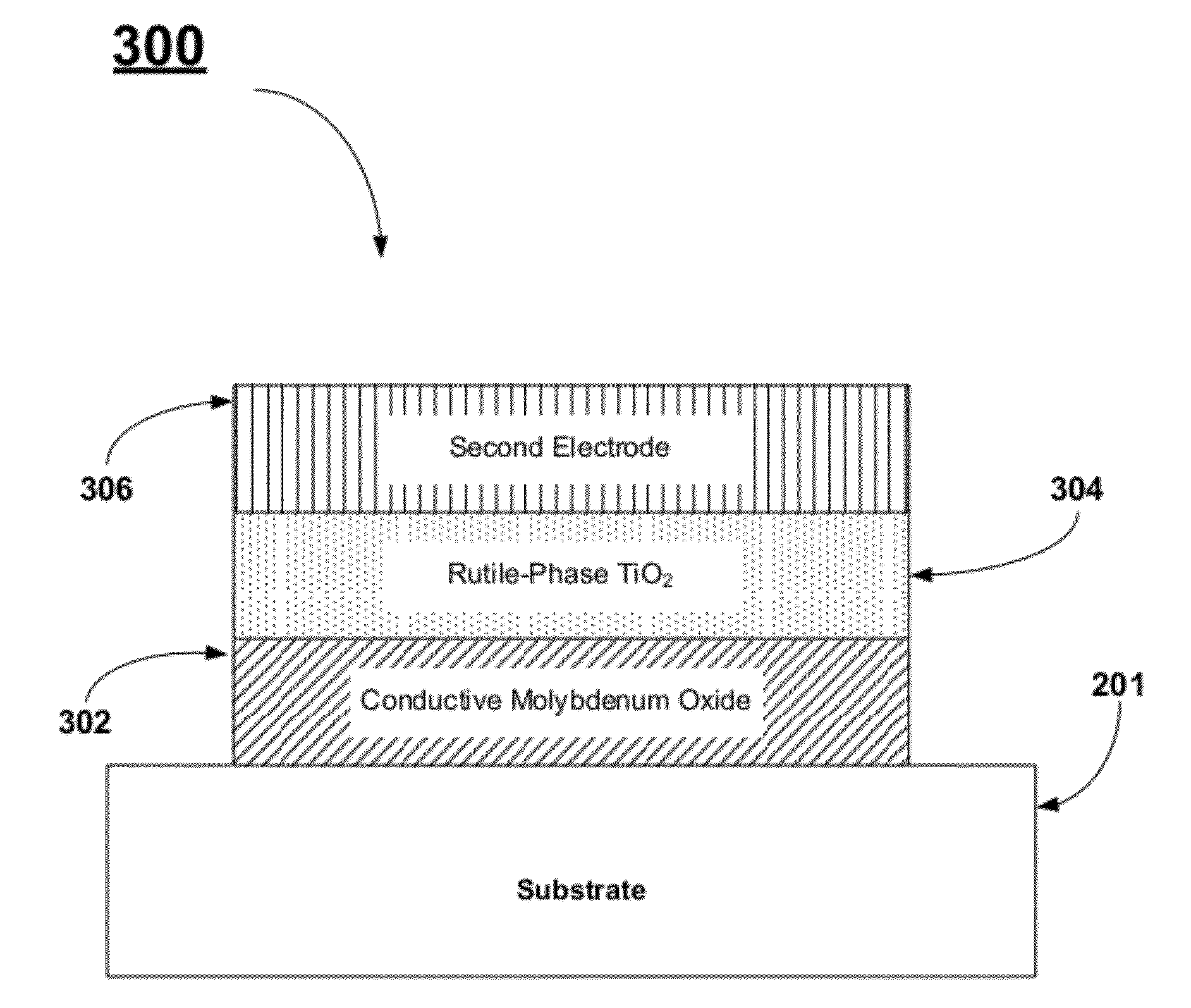

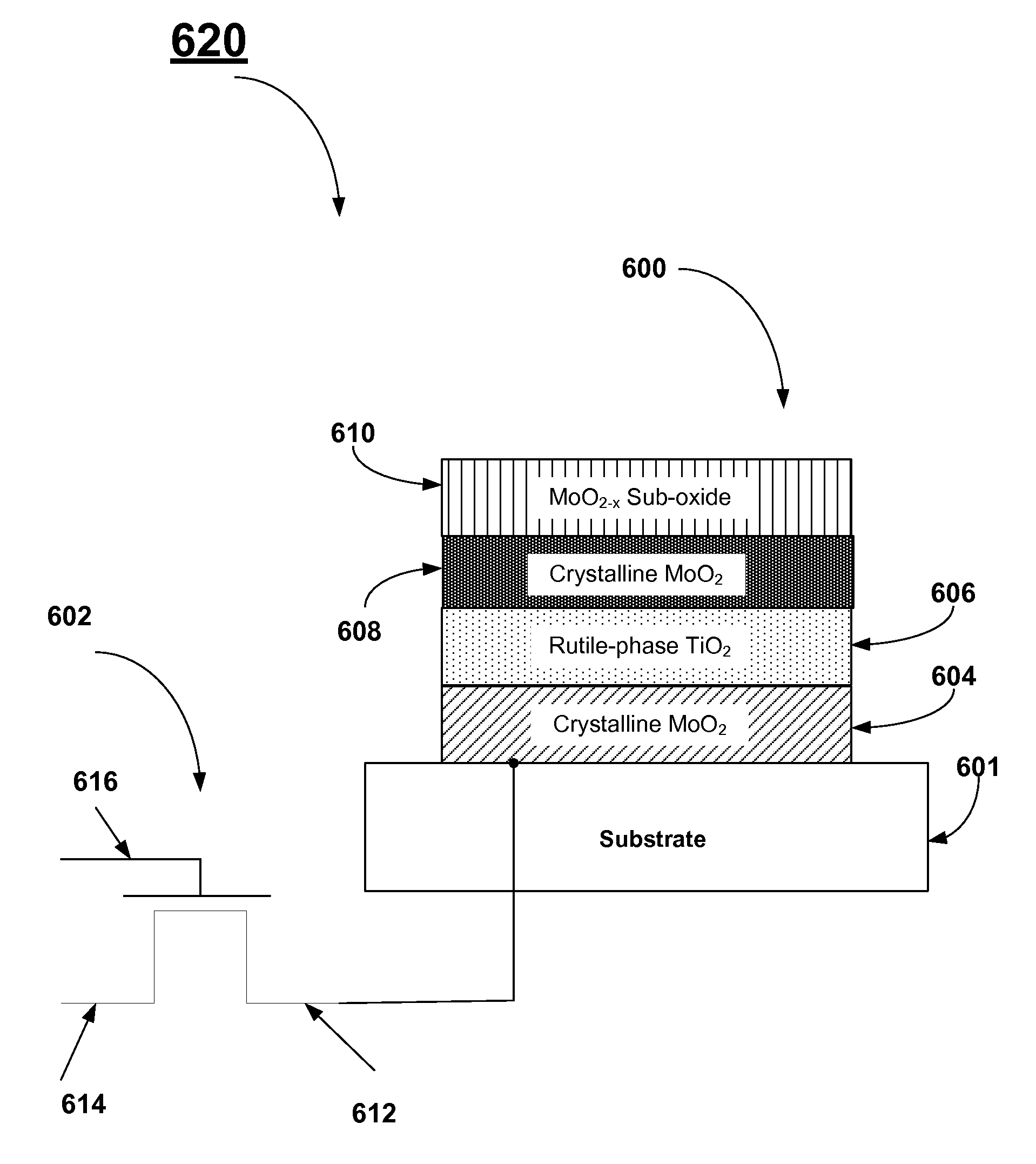

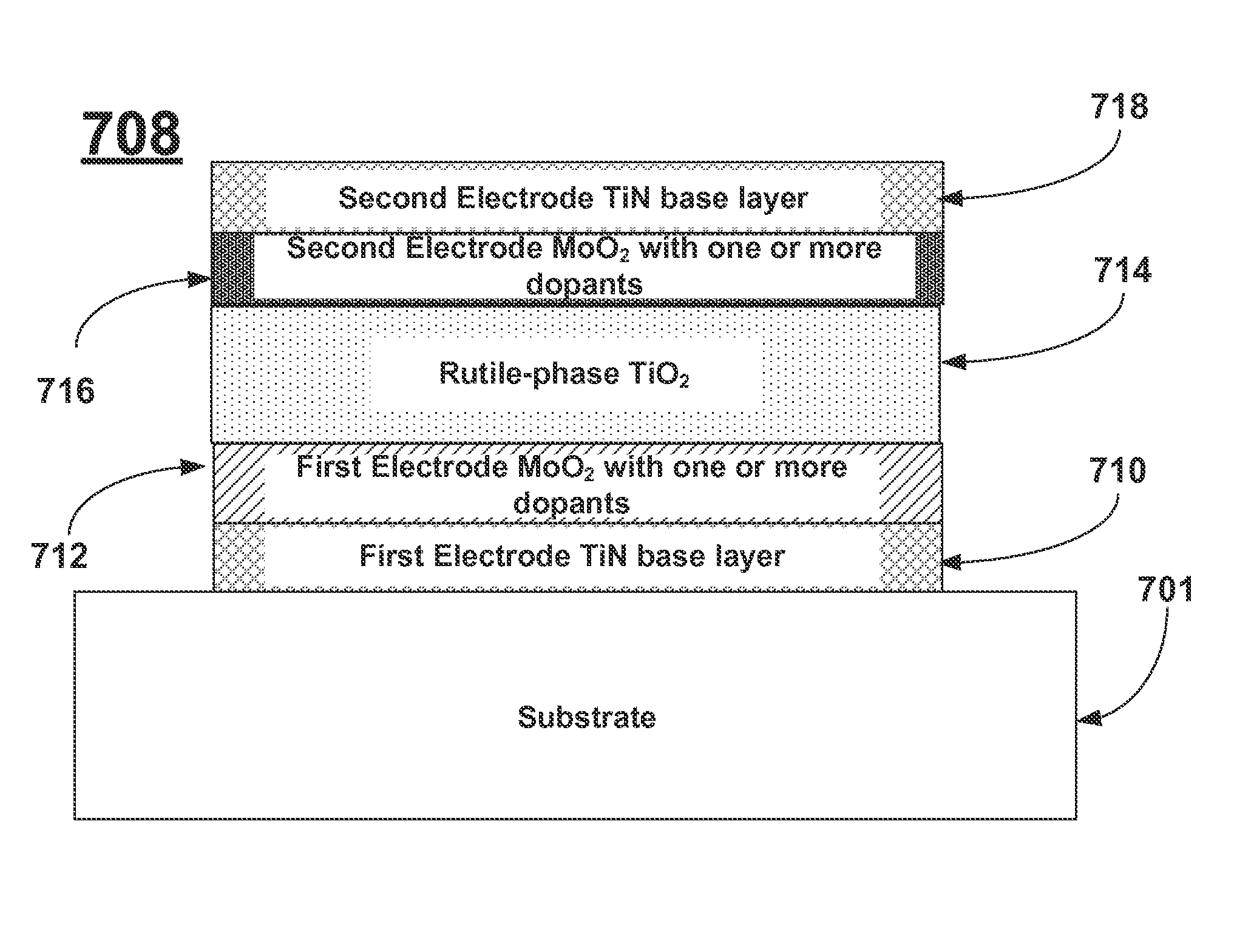

Method for fabricating a dram capacitor

A method for fabricating a dynamic random access memory (DRAM) capacitor stack is disclosed wherein the stack includes a first electrode, a dielectric layer, and a second electrode. The first electrode is formed from a conductive binary metal compound and the conductive binary metal compound is annealed in a reducing atmosphere to promote the formation of a desired crystal structure. The binary metal compound may be a metal oxide. Annealing the metal oxide (i.e. molybdenum oxide) in a reducing atmosphere may result in the formation of a first electrode material (i.e. MoO2) with a rutile-phase crystal structure. This facilitates the formation of the rutile-phase crystal structure when TiO2 is used as the dielectric layer. The rutile-phase of TiO2 has a higher k value than the other possible crystal structures of TiO2 resulting in improved performance of the DRAM capacitor.

Owner:INTERMOLECULAR +1

Method for manufacturing semiconductor capacitor having double dielectric layer therein

ActiveUS6962845B2Enhancing charge capacitanceHigh breakdown strengthTransistorSolid-state devicesCapacitanceActive matrix

The method for manufacturing a DRAM capacitor is employed to enhance charge capacitance and electrical endurance of the DRAM capacitor by structuring a double dielectric layer of aluminum oxide (Al2O3) and hafnium oxide (HfO2). The method includes steps of: preparing an active matrix including a semiconductor substrate, an ILD formed on the semiconductor substrate and a storage node obtained after patterning the ILD into a predetermined configuration; forming a bottom electrode on top faces of the storage node and portions of the ILD; forming a diffusion barrier on an exposed surface of the bottom electrode; forming a double dielectric layer including an aluminum oxide layer and a hafnium oxide layer, wherein the aluminum oxide layer and the hafnium oxide layer are formed on the diffusion barrier in succession; carrying out an annealing process for recovering dielectric properties of the aluminum oxide layer and the hafnium oxide layer; and forming a top electrode on the hafnium oxide layer.

Owner:SK HYNIX INC

Molybdenum oxide top electrode for dram capacitors

InactiveUS20120322221A1Prevent oxidationSemiconductor/solid-state device manufacturingCapacitorsCrystal structureOxygen

A metal oxide bilayer second electrode for a MIM DRAM capacitor is formed wherein the layer of the electrode that is in contact with the dielectric layer (i.e. bottom layer) has a desired composition and crystal structure. An example is crystalline MoO2 if the dielectric layer is TiO2 in the rutile phase. The other component of the bilayer (i.e. top layer) is a sub-oxide of the same material as the bottom layer. The top layer serves to protect the bottom layer from oxidation during subsequent PMA or other DRAM fabrication steps by reacting with any oxygen species before they can reach the bottom layer of the bilayer second electrode.

Owner:INTERMOLECULAR +1

NROM flash memory cell with integrated dram

InactiveUS20050174847A1Digital storageSpecial data processing applicationsMultiple modesRead-only memory

A memory device that is comprised of a dynamic random access memory (DRAM) capacitor and a nitride read only memory (NROM) transistor. The memory device provides multiple modes of operation including a DRAM mode using the capacitor and a non-volatile random access memory mode using the NROM transistor. The device is comprised of two source / drain regions between which a gate insulator layer is formed. A control gate, coupled to a word line, is formed on top of the gate insulator. The DRAM capacitor is coupled to one of the source / drain regions while the second source / drain region is coupled to a bit line that is eventually coupled to a sense amplifier for reading the state or states of the memory device.

Owner:MICRON TECH INC

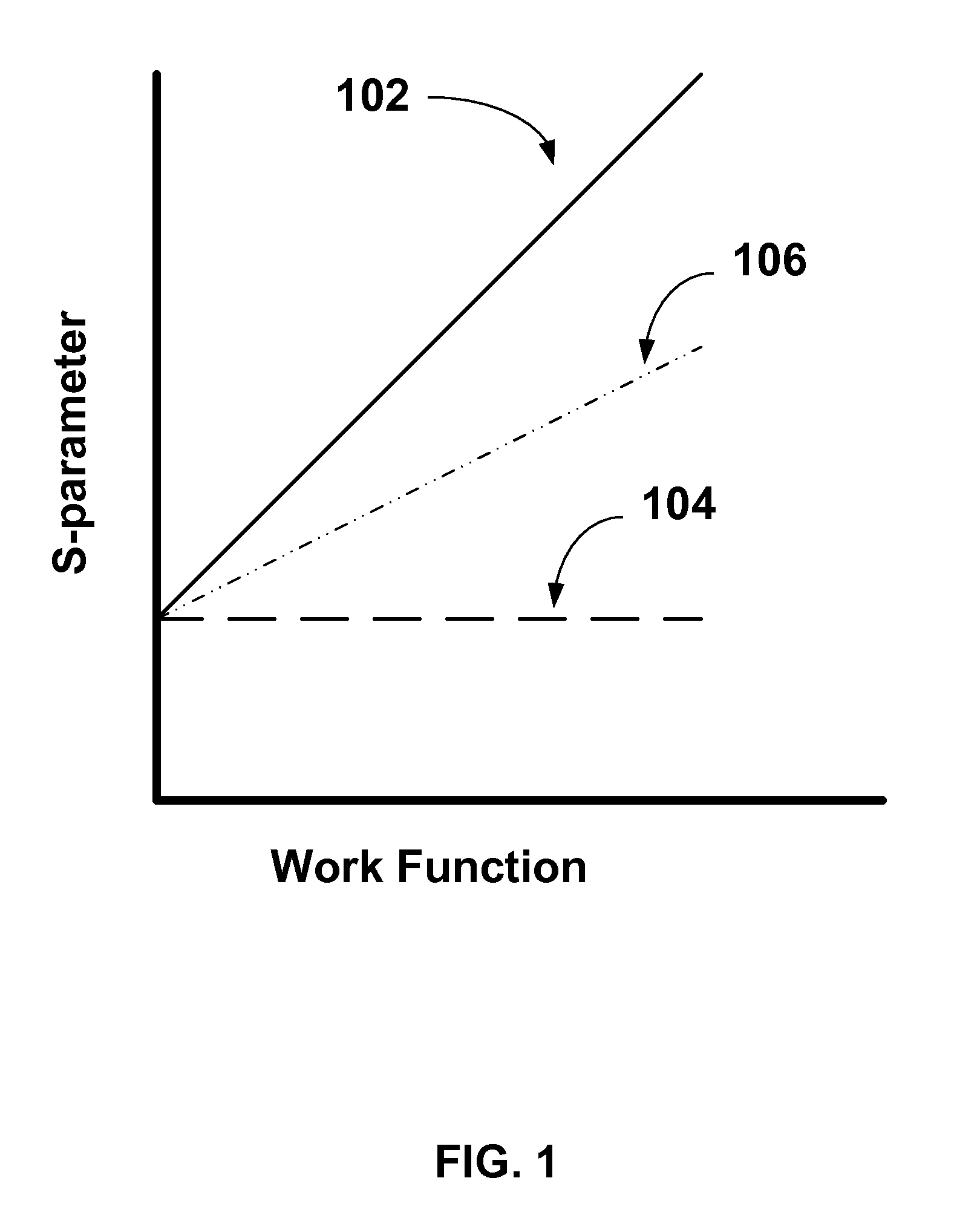

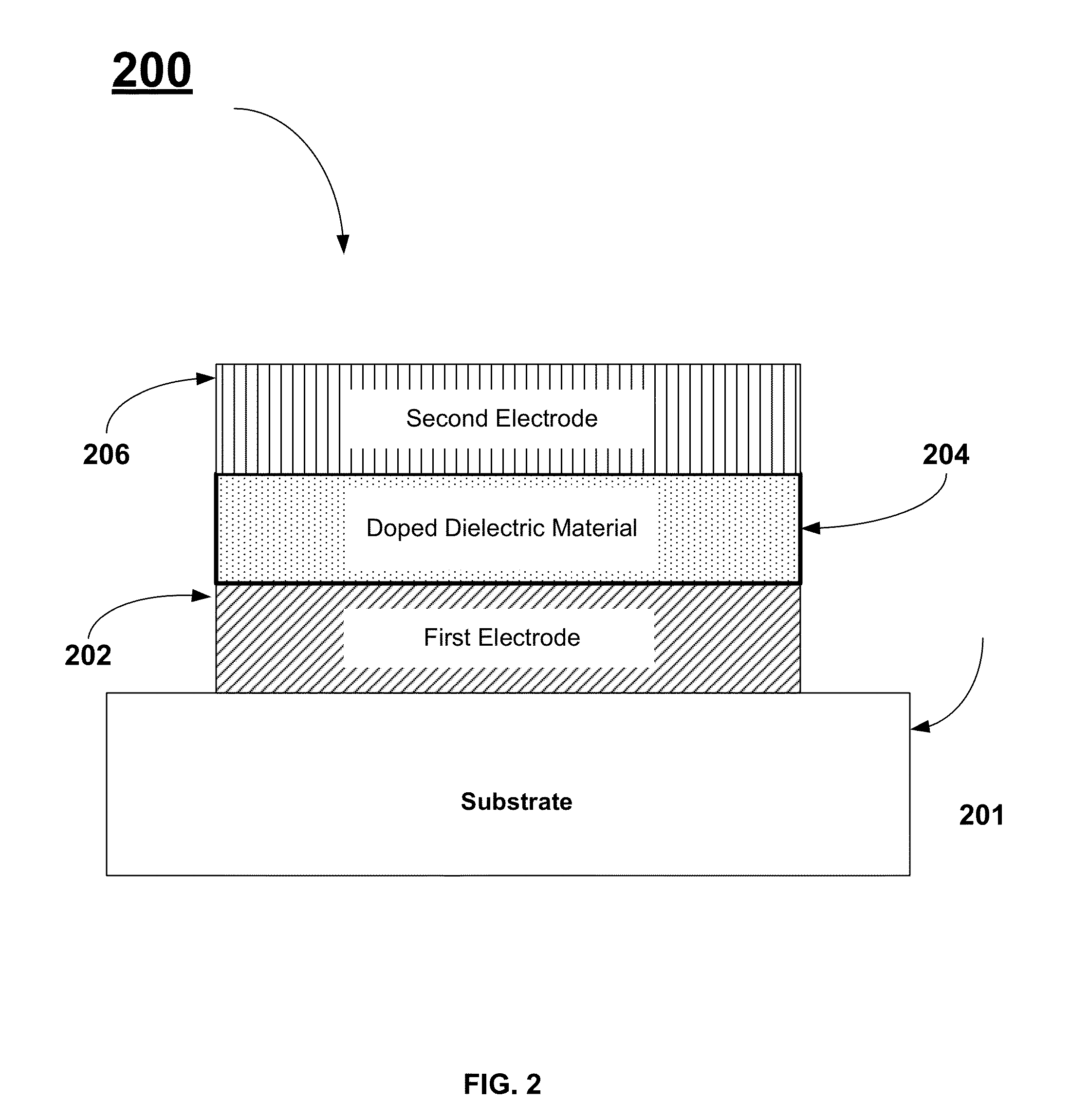

Enhanced non-noble electrode layers for DRAM capacitor cell

InactiveUS8581318B1Reduce leakage currentAlters resistivityTransistorSolid-state devicesDopantWork function

A metal oxide first electrode material for a MIM DRAM capacitor is formed wherein the first and / or second electrode materials or structures contain layers having one or more dopants up to a total doping concentration that will not prevent the electrode materials from crystallizing during a subsequent anneal step. Advantageously, the electrode doped with one or more of the dopants has a work function greater than about 5.0 eV. Advantageously, the electrode doped with one or more of the dopants has a resistivity less than about 1000 μΩcm. Advantageously, the electrode materials are conductive molybdenum oxide.

Owner:INTERMOLECULAR

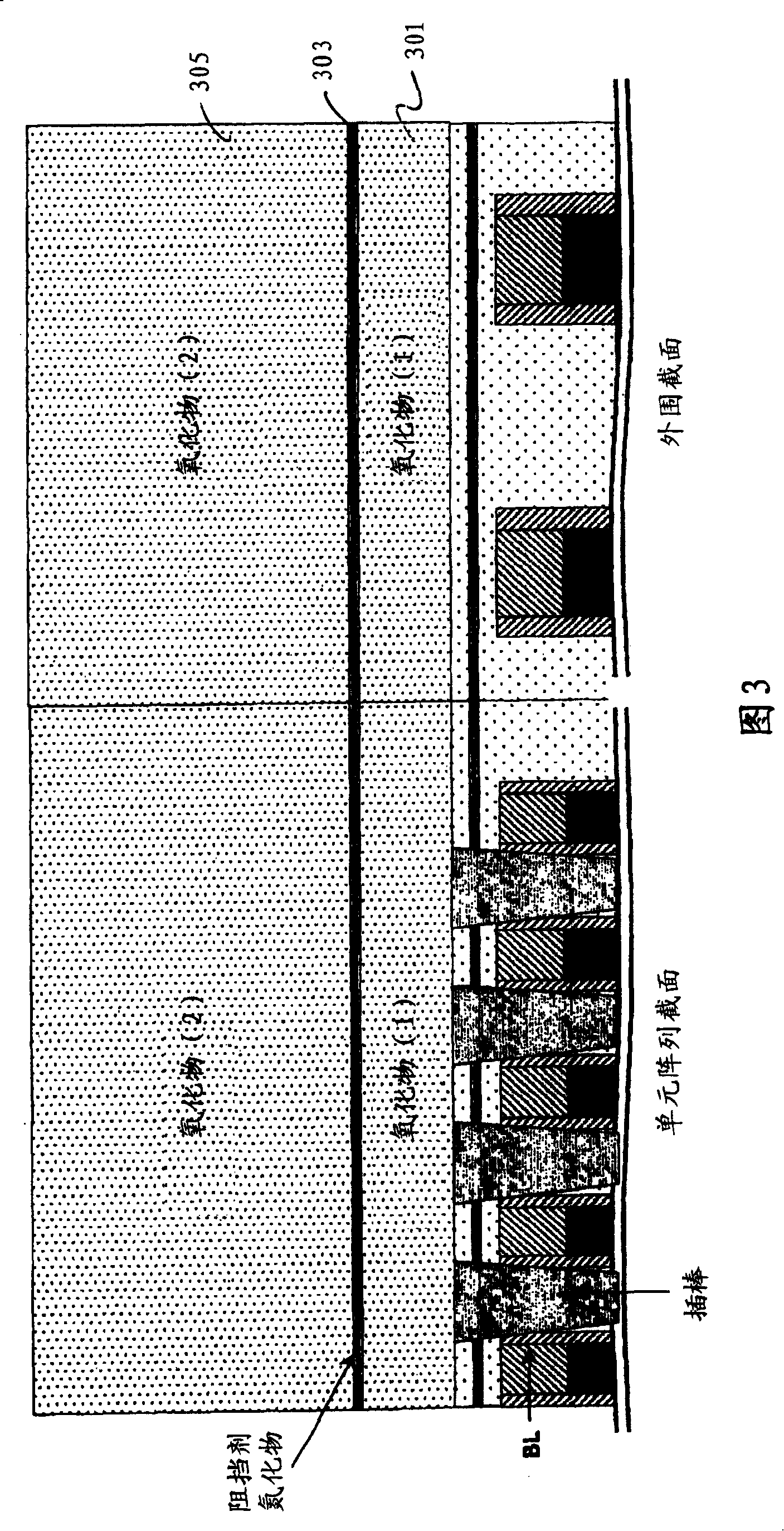

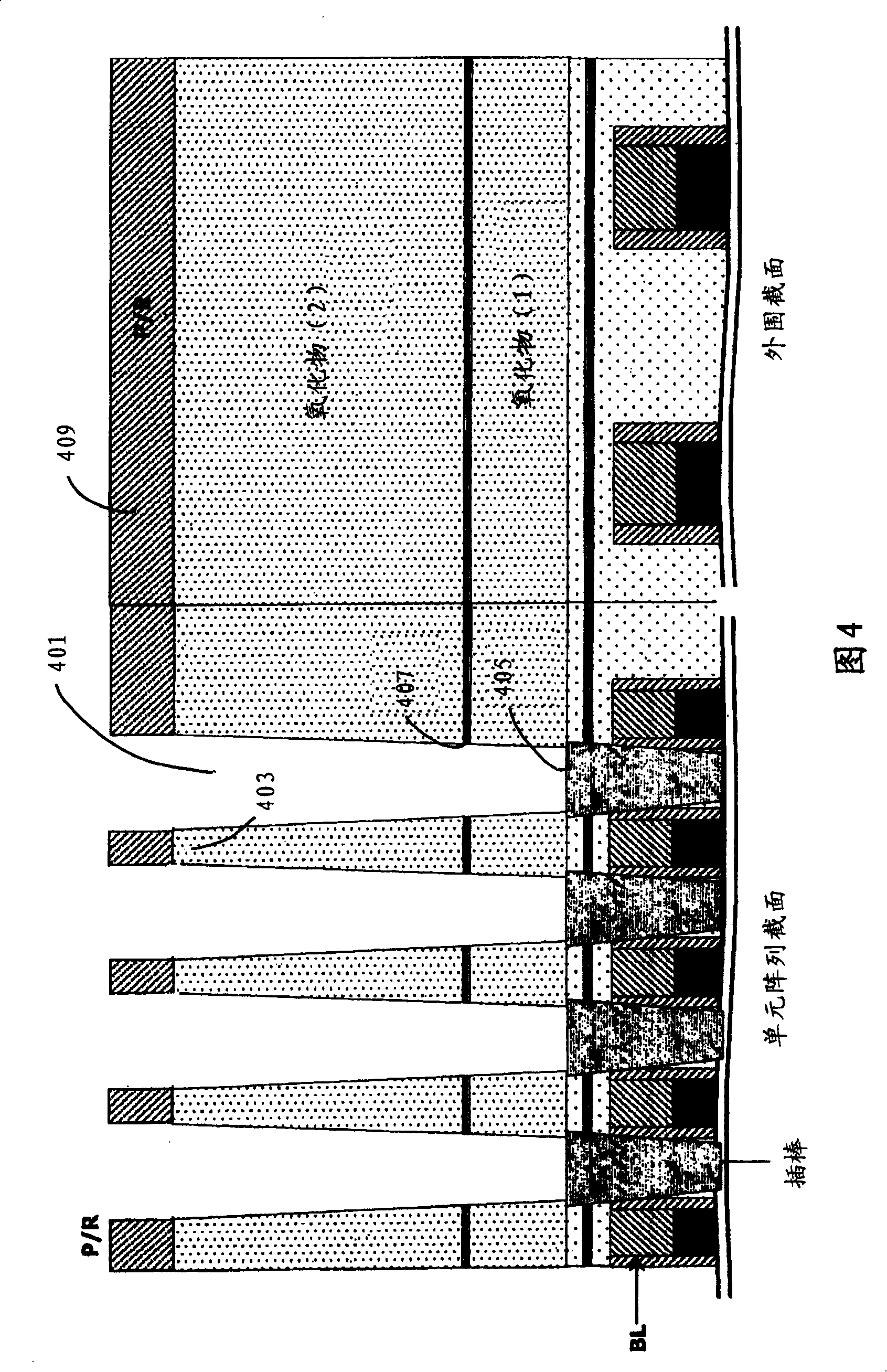

Method for manufacturing DRAM capacitor structure and formed structure

ActiveCN101211853AImprove device yieldEasy process integrationTransistorSolid-state devicesSemiconductorMask layer

The invention relates to a method for forming a capacitor structure used for a dynamic random access memory. The method comprises the steps as follows: a cover semiconductor substrate is formed; a first dielectric layer of a cover device is formed; a via hole in the first dielectric layer is formed; a first oxide layer covering the first dielectric layer is formed; a barrier layer covering the first oxide layer is formed; a second oxide layer covering the barrier layer is formed; a groove region which passes through a part of the second oxide layer, a part of the barrier layer and a part of the first oxide layer is formed; a bottom electrode structure is formed to sketch out the groove region; a mask layer is used for protecting the bottom electrode structure and selectively removing the second oxide layer and up to the barrier layer which has etching and resisting effect to expose the external region of the bottom electrode structure; dielectric layers of the capacitor which cover the external region of the bottom electrode structure and the internal region of the bottom electrode structure are formed; a plate of the upper capacitor which covers the dielectric layers of the capacitor is formed to form the capacitor structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

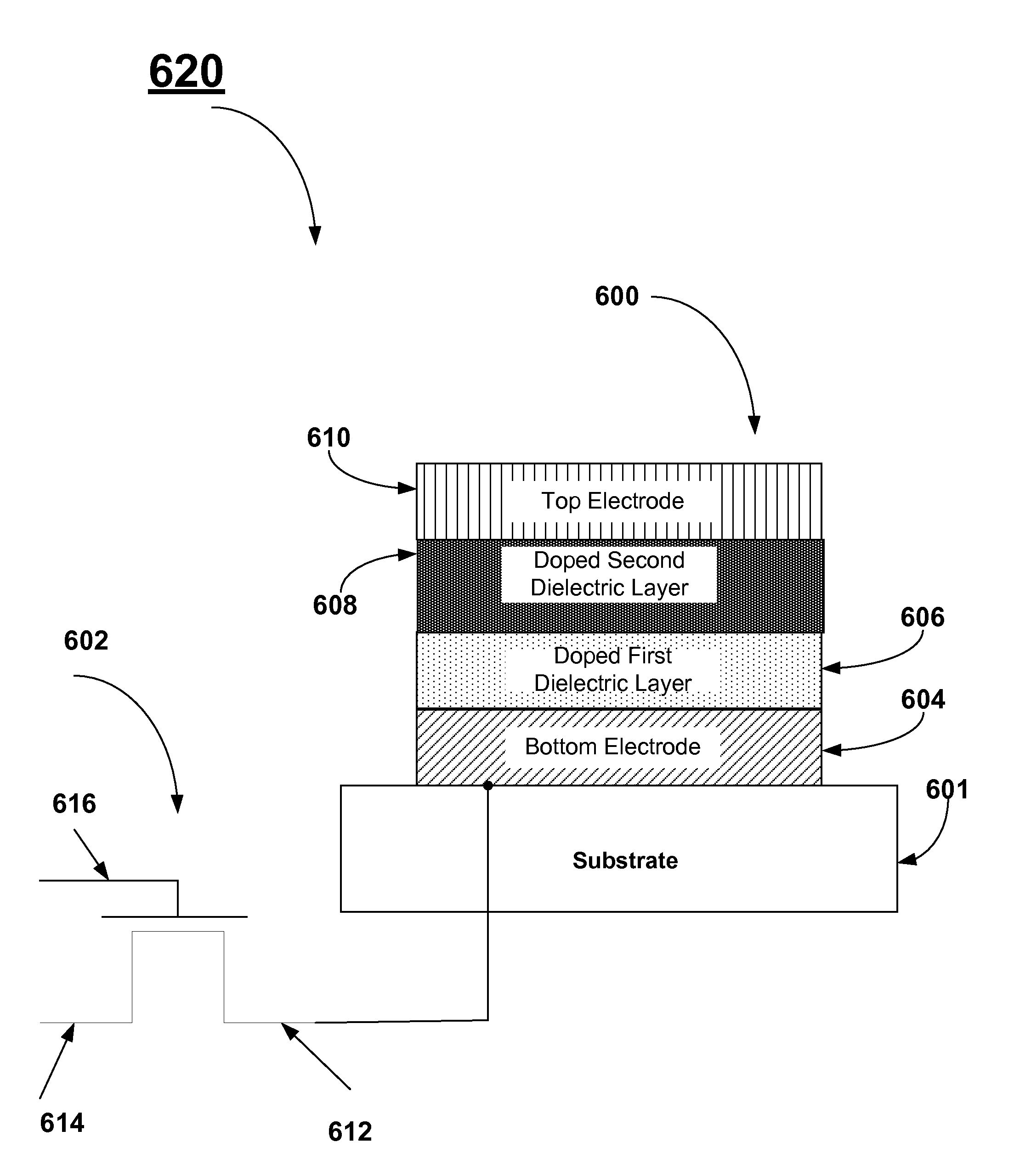

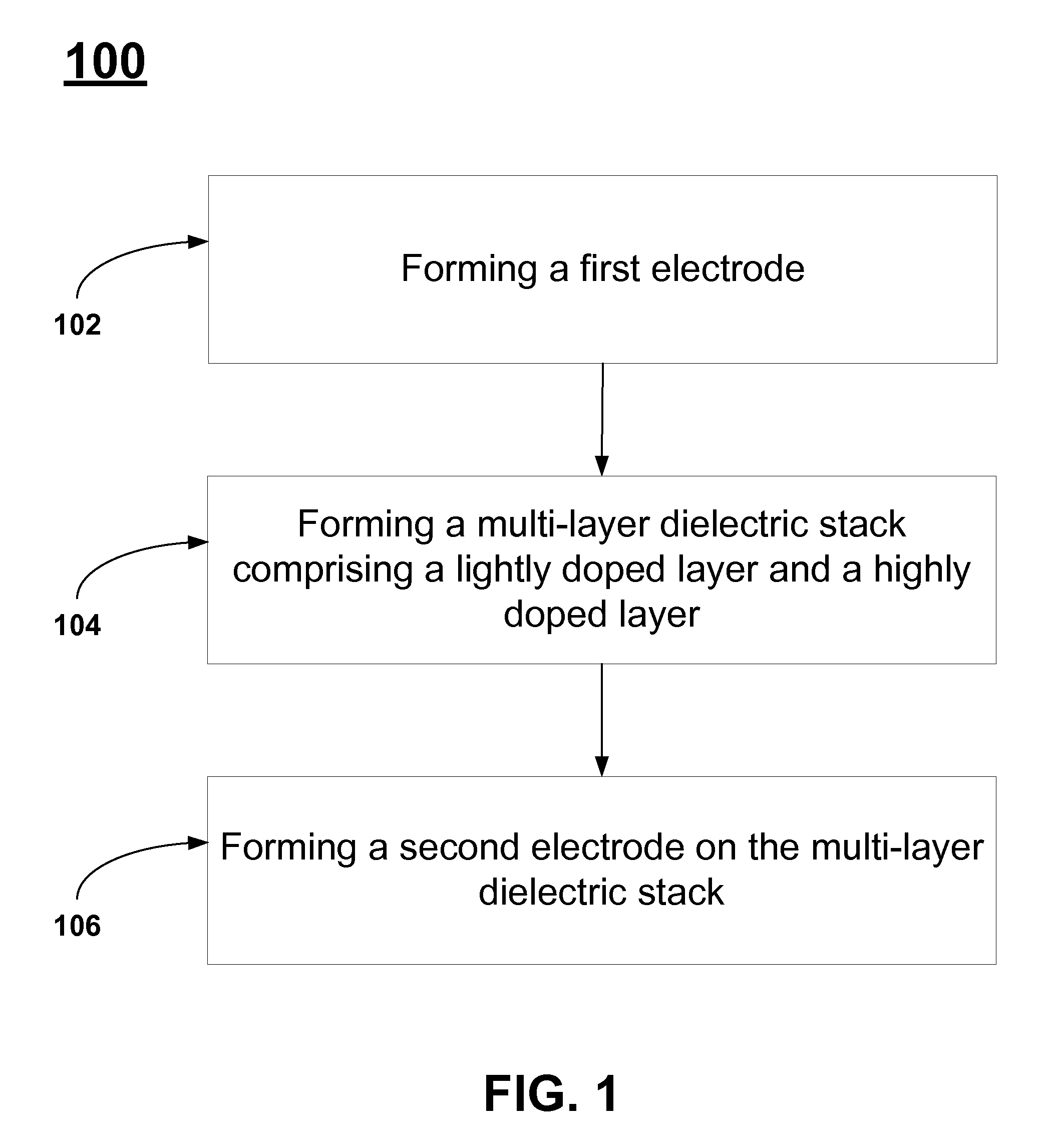

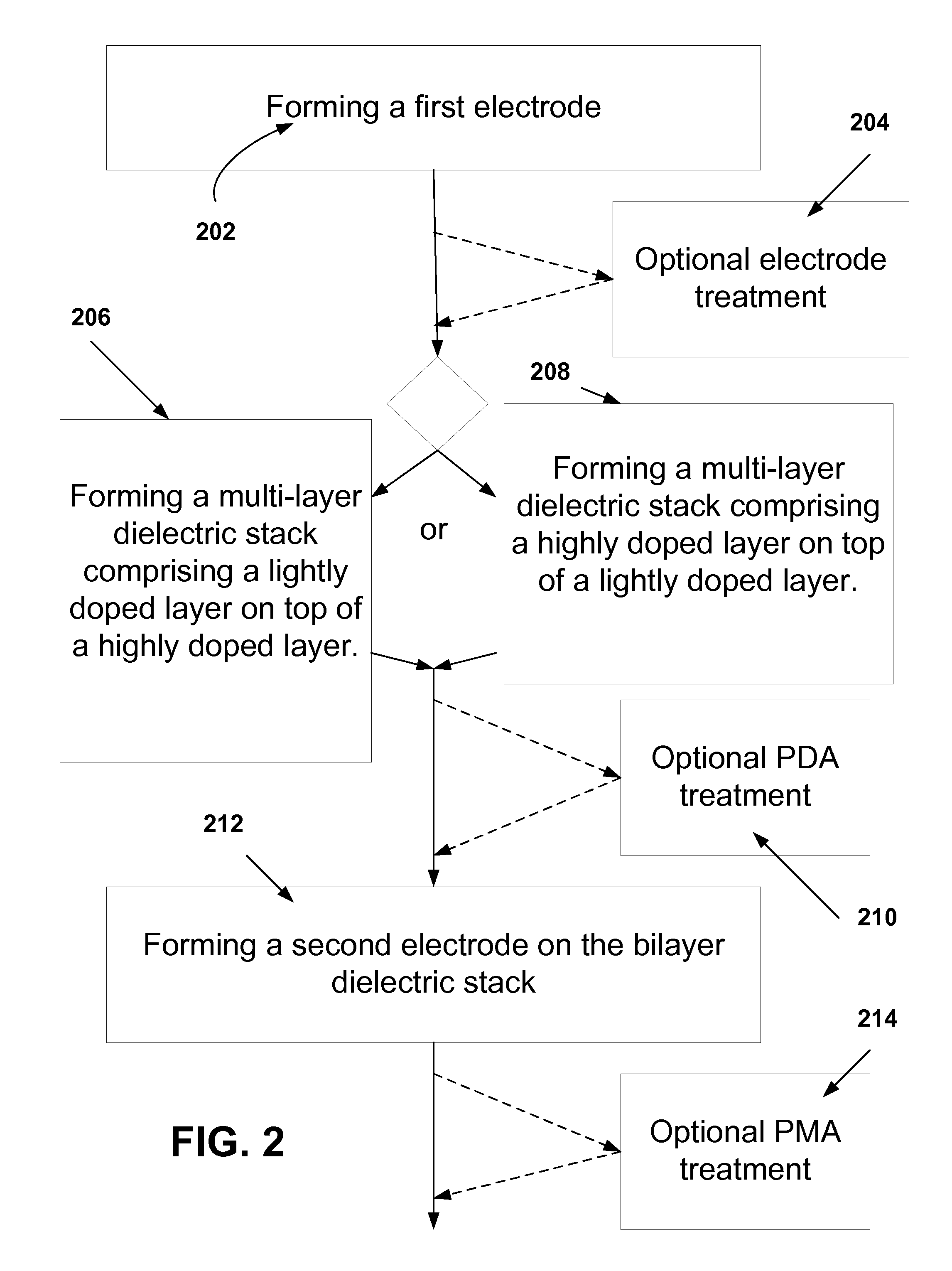

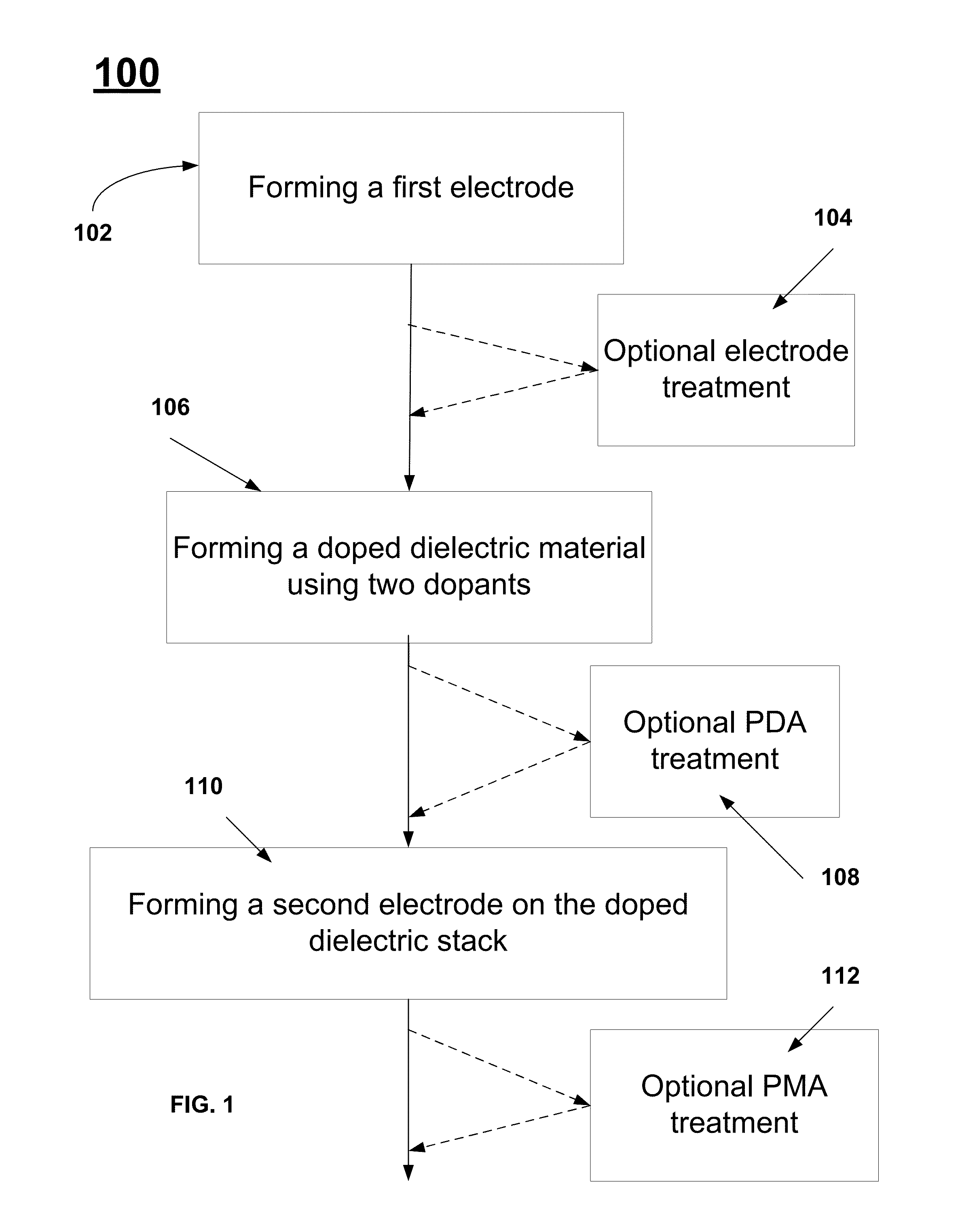

High performance dielectric stack for dram capacitor

A method for fabricating a DRAM capacitor stack is described wherein the dielectric material is a multi-layer stack formed from a highly-doped material combined with a lightly or non-doped material. The highly-doped material remains amorphous with a crystalline content of less than 30% after an annealing step. The lightly or non-doped material becomes crystalline with a crystalline content of equal to or greater than 30% after an annealing step. The dielectric multi-layer stack maintains a high k-value while minimizing the leakage current and the EOT value.

Owner:INTERMOLECULAR +1

ROM embedded DRAM with anti-fuse programming

A ROM embedded DRAM provides ROM cells that can be electrically programmed to a data state using DRAM capacitor memory cells. Numerous techniques for reading the memory cells are provided if a single state memory is desired. For example, bias techniques allow un-programmed ROM cells to be read accurately. In one embodiment, the memory includes program circuitry to short capacitor plates together by breaking down an intermediate dielectric layer using anti-fuse programming techniques.

Owner:MICRON TECH INC

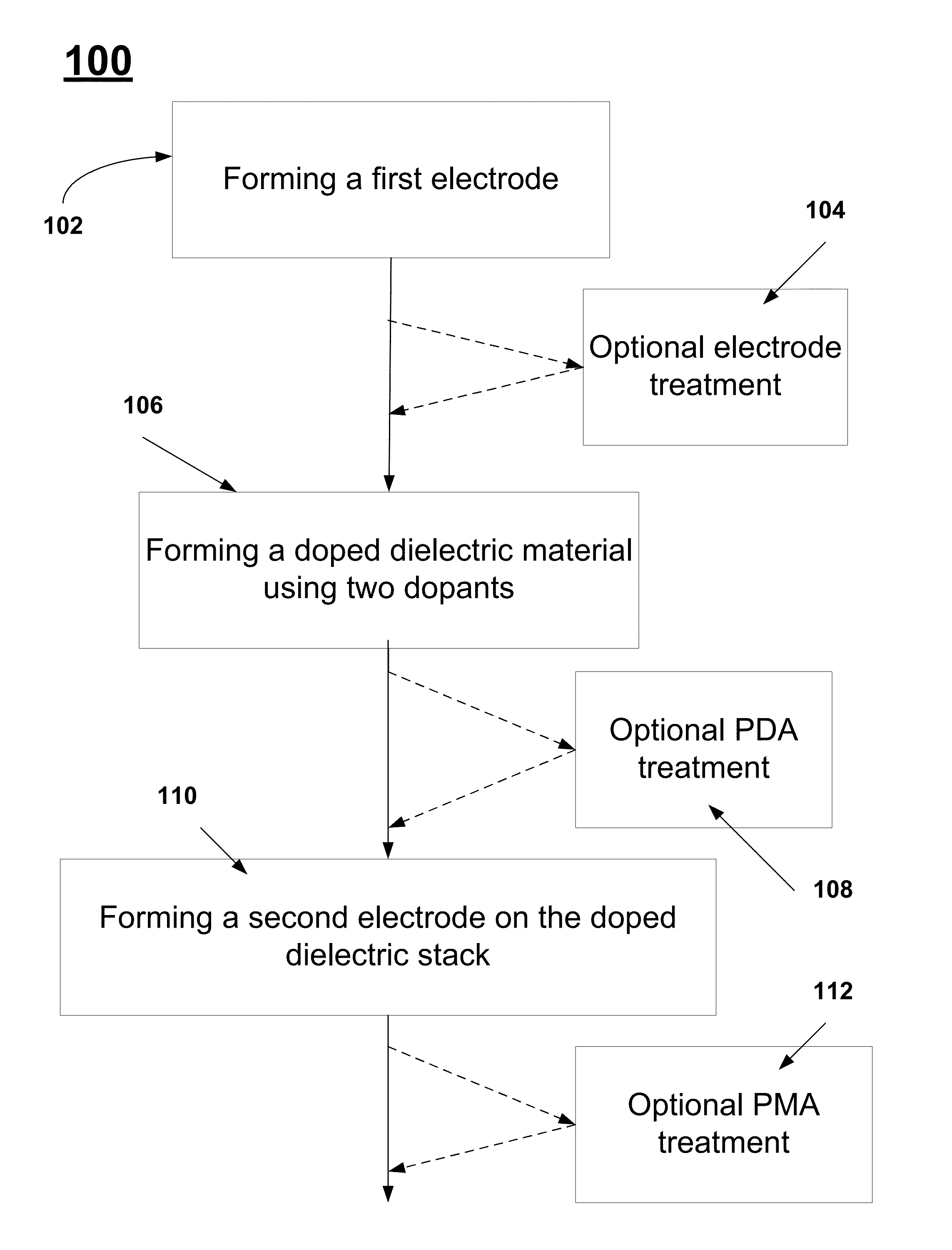

Doping approach of titanium dioxide for dram capacitors

InactiveUS20130052790A1Reduce leakage currentIncreased polarizationSemiconductor/solid-state device manufacturingCapacitorsSolubilityDopant

A method for fabricating a DRAM capacitor stack is described wherein the dielectric material is a doped material formed from a first dopant in concert with a second dopant wherein the second dopant has a different physical size from the first dopant and the presence of the second dopant influences the solubility of the first dopant in the dielectric material. The dielectric material maintains a high k-value while minimizing the leakage current and the EOT value

Owner:INTERMOLECULAR +1

Enhanced non-noble electrode layers for dram capacitor cell

InactiveUS20130330902A1Reduce leakage currentAlters resistivitySemiconductor/solid-state device manufacturingCapacitorsDopantWork function

A metal oxide first electrode material for a MIM DRAM capacitor is formed wherein the first and / or second electrode materials or structures contain layers having one or more dopants up to a total doping concentration that will not prevent the electrode materials from crystallizing during a subsequent anneal step. Advantageously, the electrode doped with one or more of the dopants has a work function greater than about 5.0 eV. Advantageously, the electrode doped with one or more of the dopants has a resistivity less than about 1000 μΩ cm. Advantageously, the electrode materials are conductive molybdenum oxide.

Owner:INTERMOLECULAR +1

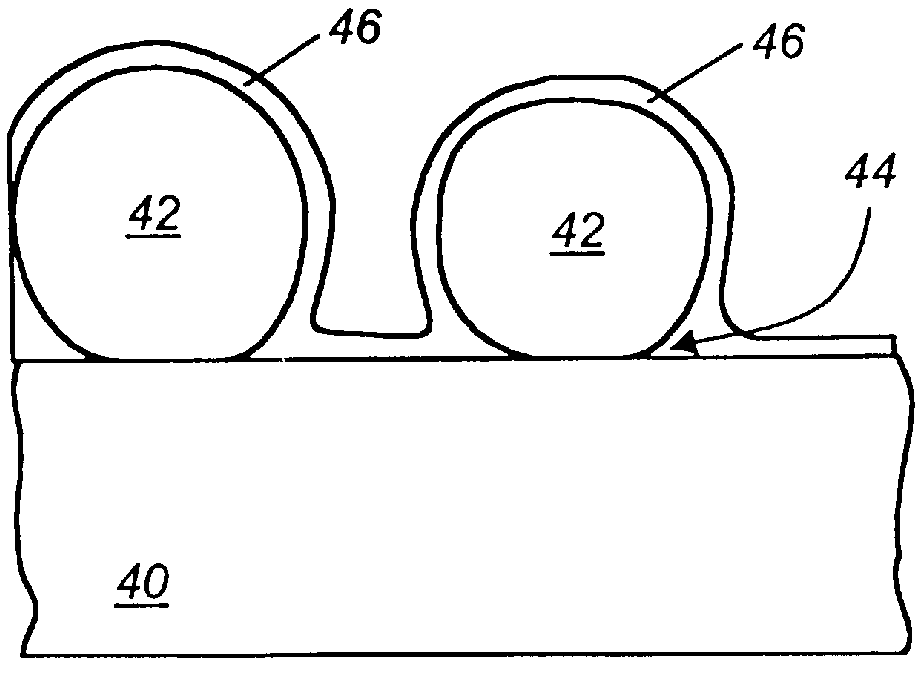

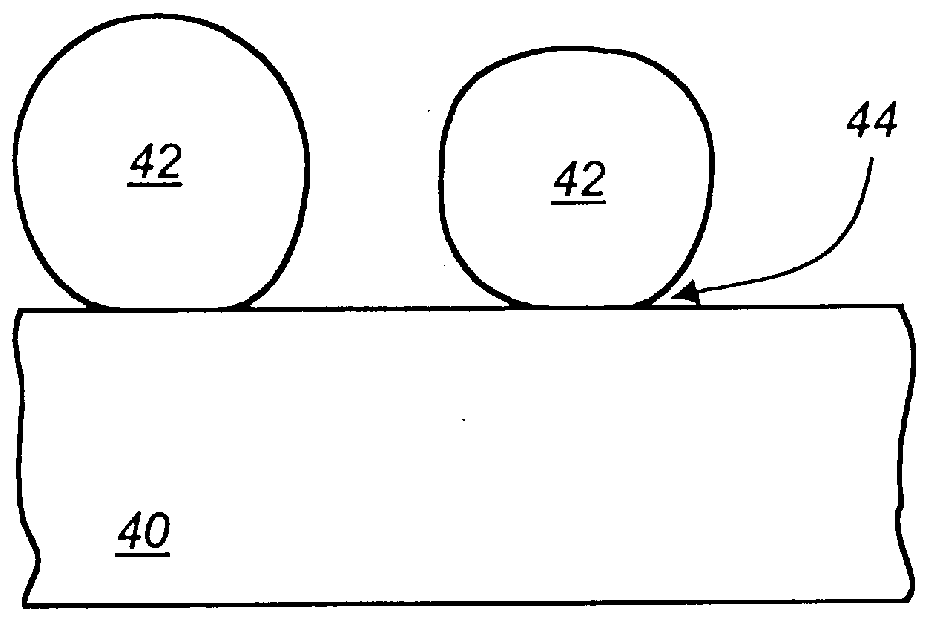

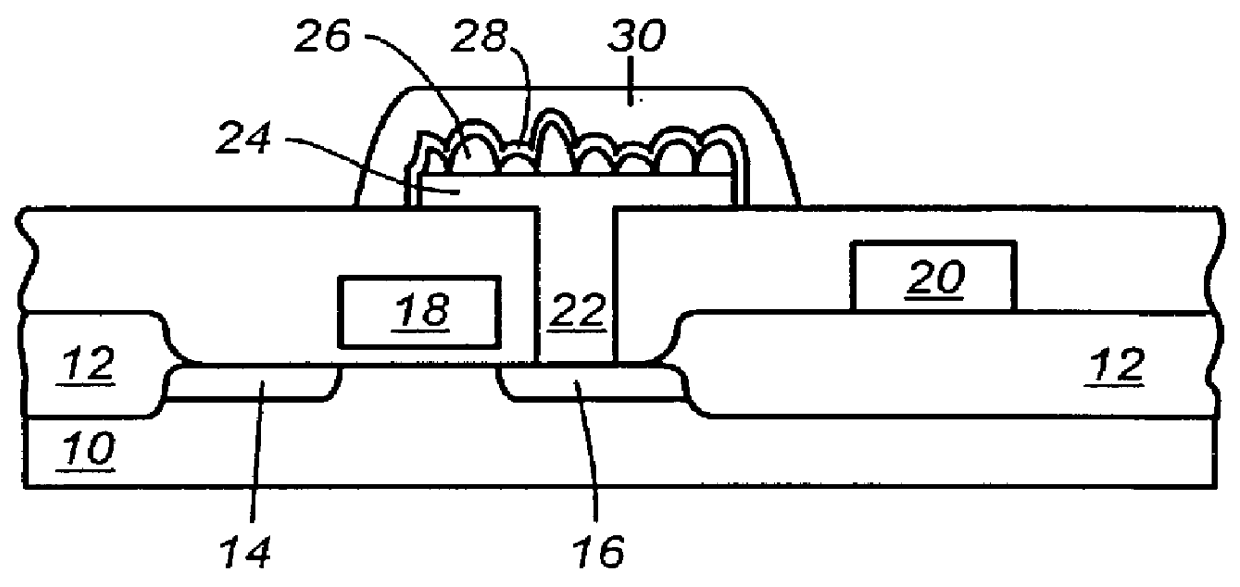

Process for rounding an intersection between an HSG-SI grain and a polysilicon layer

InactiveUS6013555ASolid-state devicesSemiconductor/solid-state device manufacturingThin layerAmorphous silicon

The capacitor of a DRAM cell is formed by depositing a layer of doped polysilicon, patterning the layer of doped polysilicon to define the extent of the capacitor's lower electrode and depositing a layer of hemispherical-grained silicon (HSG-Si) on the layer of doped polysilicon. A thin layer of amorphous silicon is then formed over the HSG-Si layer. This textured polysilicon structure forms the lower electrode of the DRAM capacitor. A dielectric layer is formed on the lower electrode, and an upper electrode is formed from a second layer of doped polysilicon. As-formed HSG-Si grains tend to form sharp intersections with the polysilicon layers on which they grow. When these HSG-Si grains are exposed to a thermal oxidation environment, poor quality oxides are formed at the sharp corners between the HSG-Si grains and the doped polysilicon layer. The poor quality oxides at the sharp corners between the HSG-Si grains and the doped polysilicon layer break down comparatively readily, and appears to cause leakage currents in capacitors having HSG-Si electrodes. By growing a thin amorphous silicon layer over the surface of the HSG-Si layer, the intersection between the HSG-Si grains and the layer of polysilicon is rounded. Subsequent growth of a thermal oxide, or the formation of other dielectric layers, provides a more reliable capacitor.

Owner:UNITED MICROELECTRONICS CORP

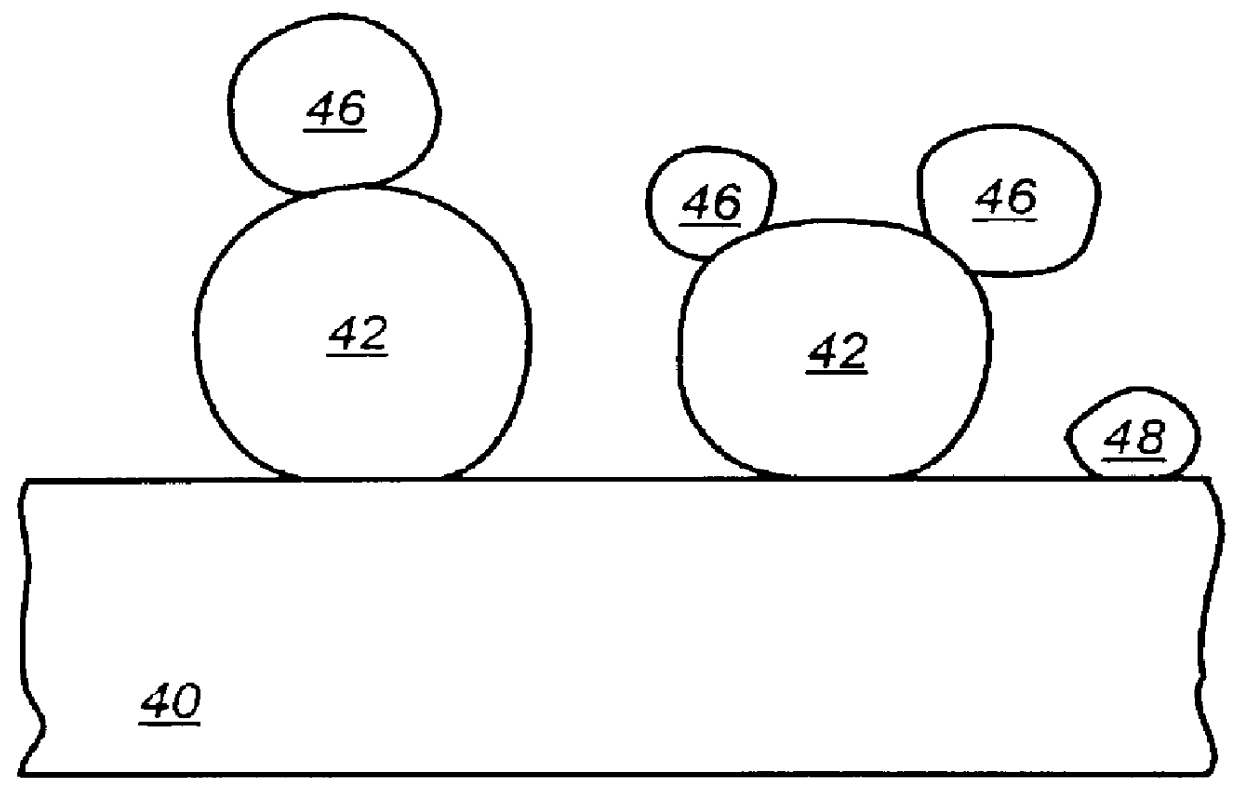

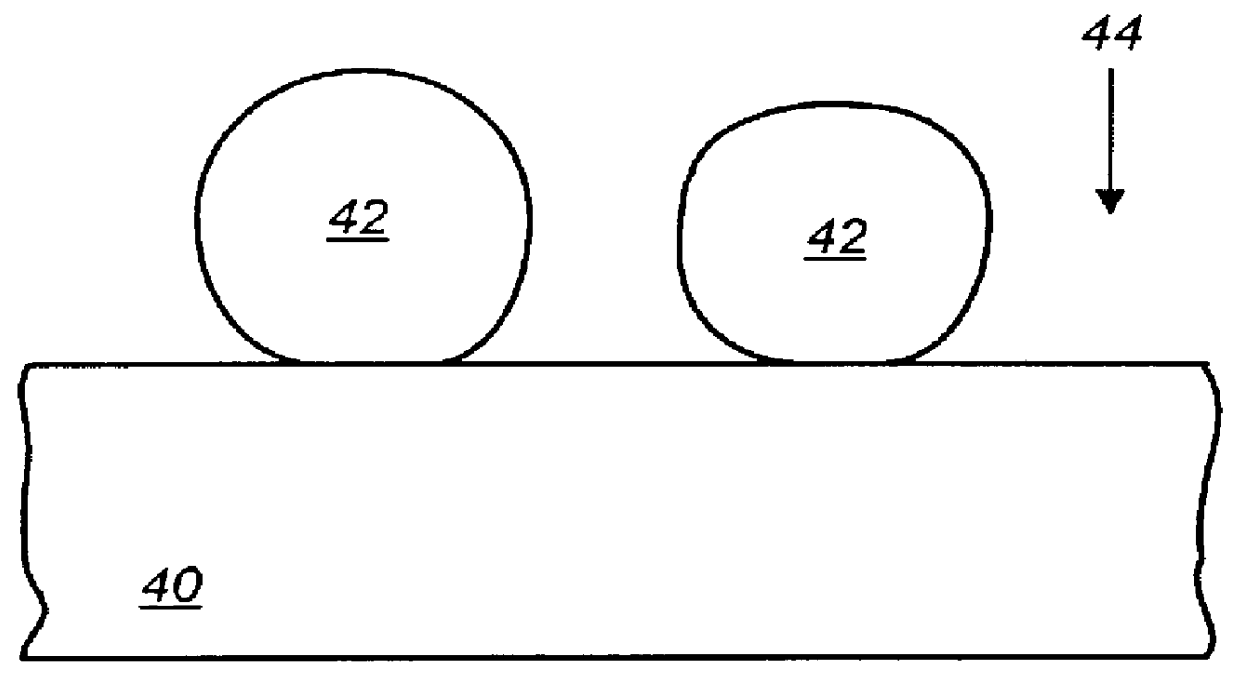

Method for increasing capacitance

The capacitor of a DRAM cell is formed by depositing a layer of doped polysilicon, patterning the layer of doped polysilicon to define the extent of the capacitor's lower electrode and then depositing a first layer of hemispherical-grained silicon (HSG-Si) on the layer of doped polysilicon. Growth of the first layer of HSG-Si is interrupted and then a second layer of HSG-Si is grown. In one aspect, growth of the first layer of HSG-Si may be interrupted by either cooling the deposition substrate or stopping deposition for a period of time and then reinitiating deposition to provide a second layer of HSG-SI on the surface of the electrode. The interruption of the growth of the first layer, whether by cooling or by delay, is sufficient if the reinitiated growth initiates in a manner that is independent of the first process; i.e., the second layer of HSG-Si grows independently. In a different aspect of the invention, growth of the first layer may be interrupted by removing the electrode from the deposition system and performing an etch back operation. After the etch back operation, the electrode is reintroduced to the deposition system and a second layer of HSG-Si is grown on the etched surface. This textured silicon structure forms the lower electrode of the DRAM capacitor.

Owner:AISAWA TECH